Patents

Literature

5036results about How to "Increase storage capacity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

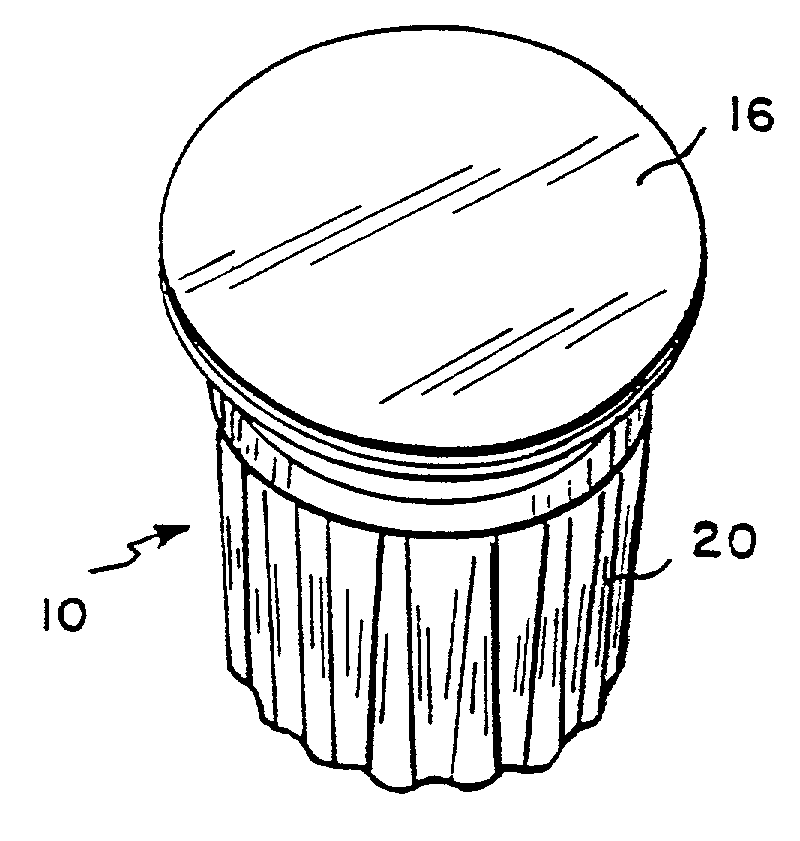

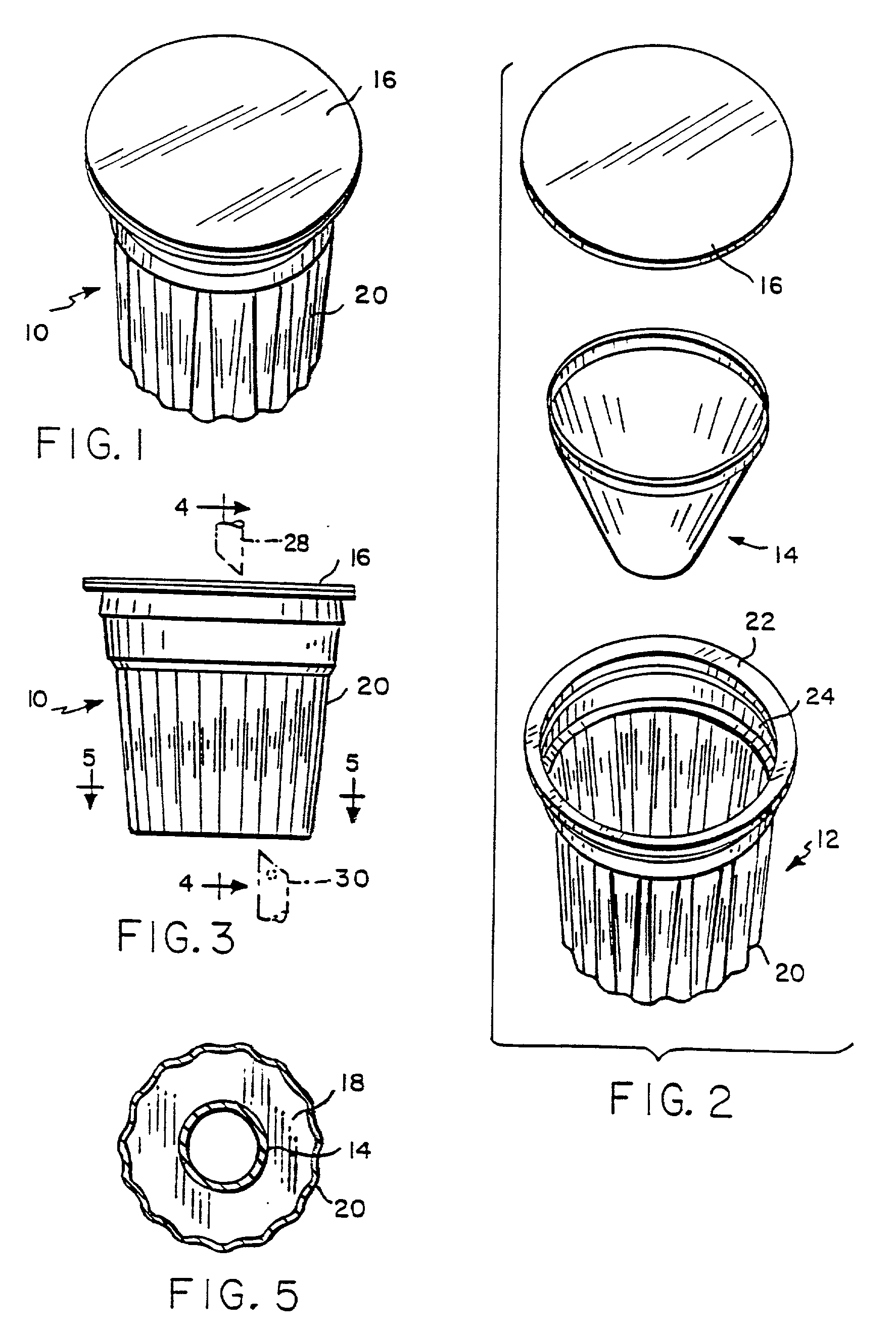

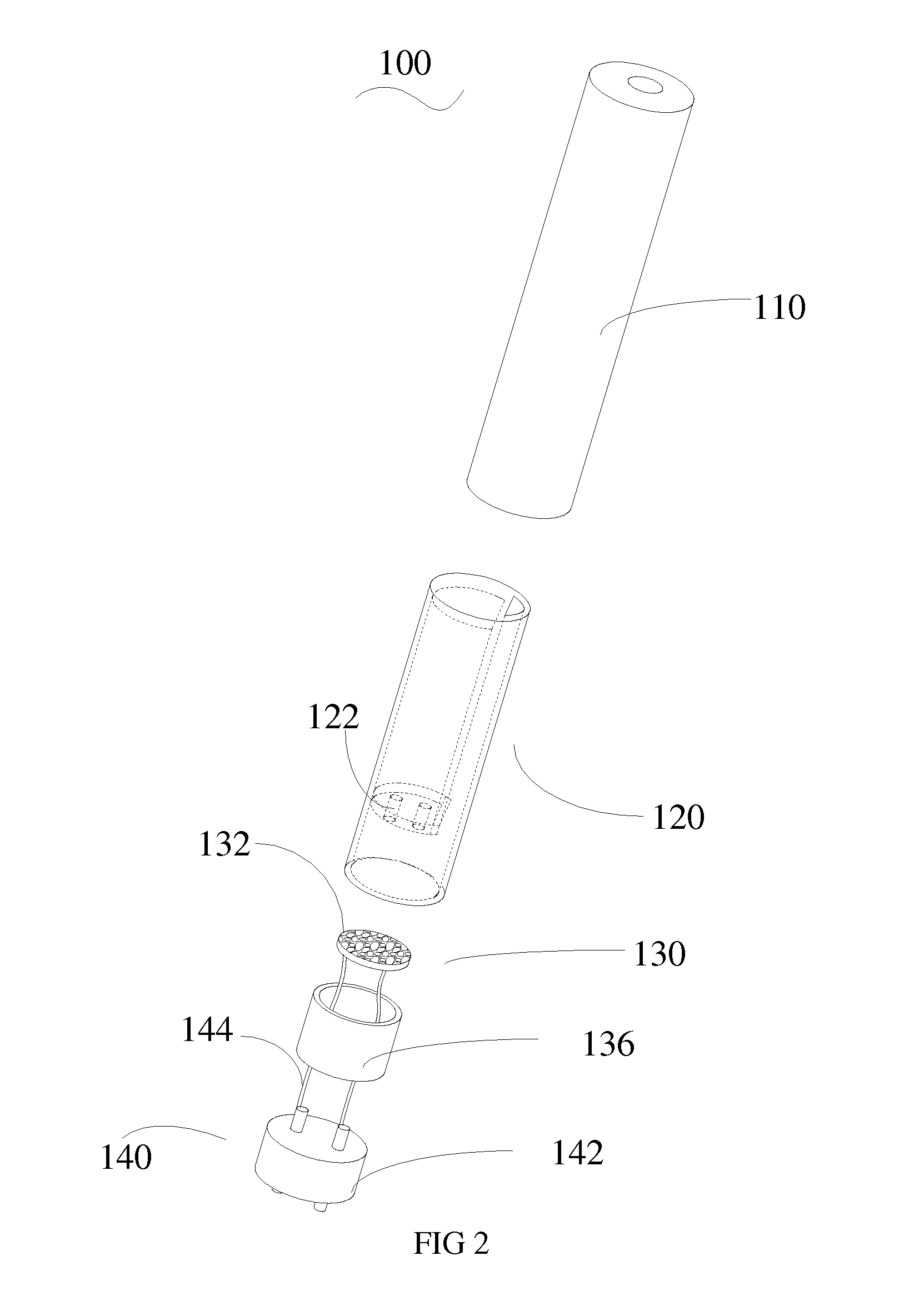

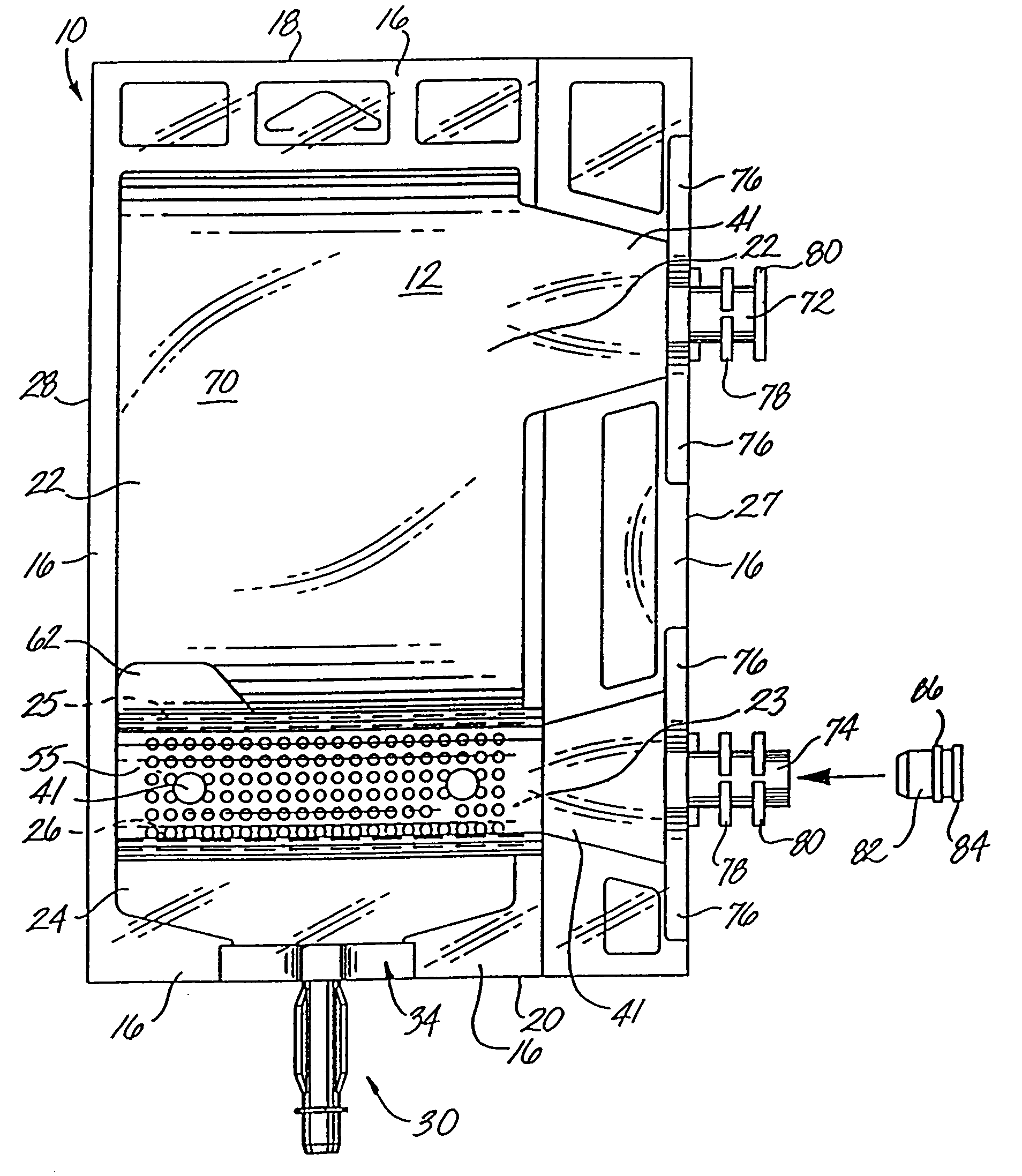

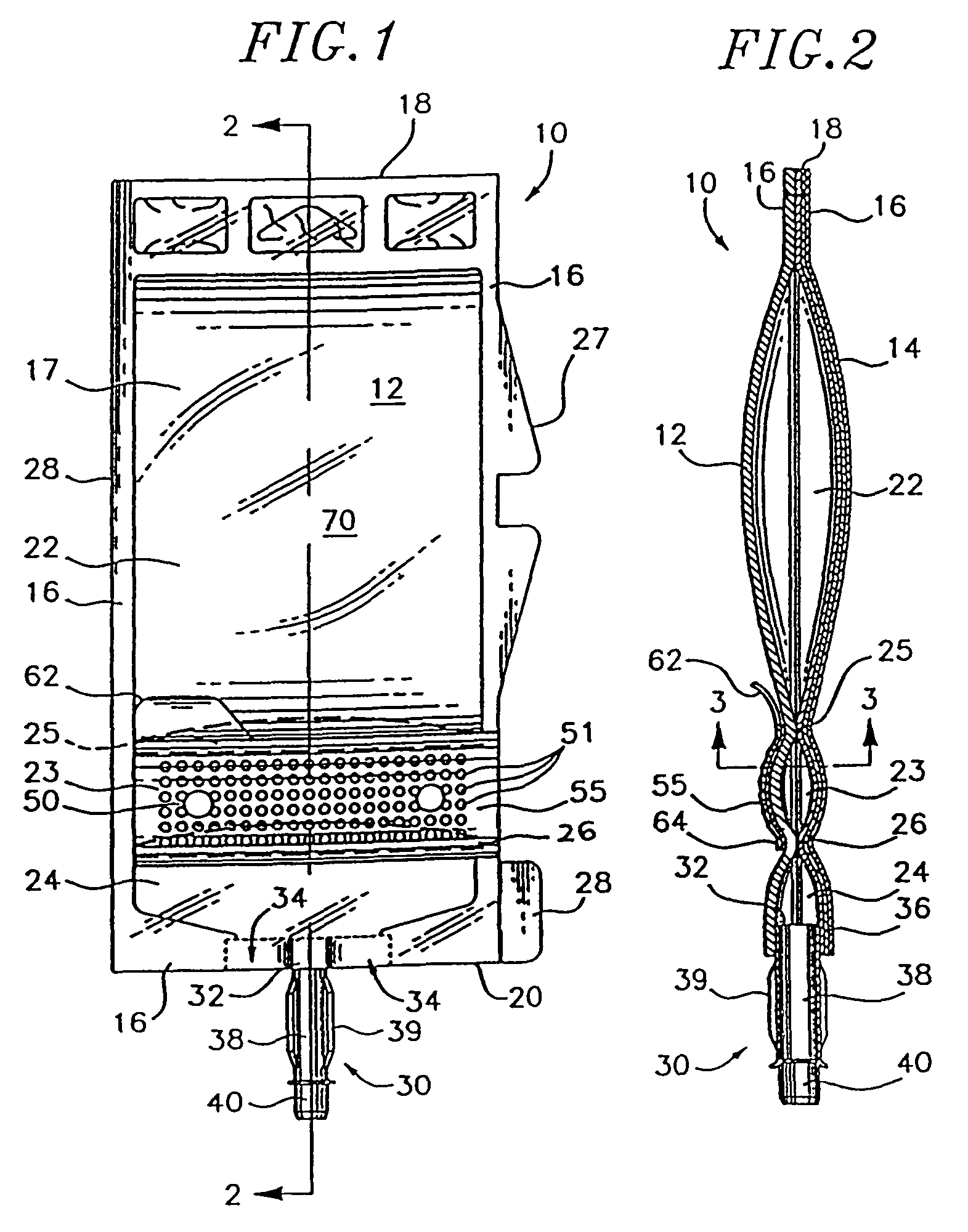

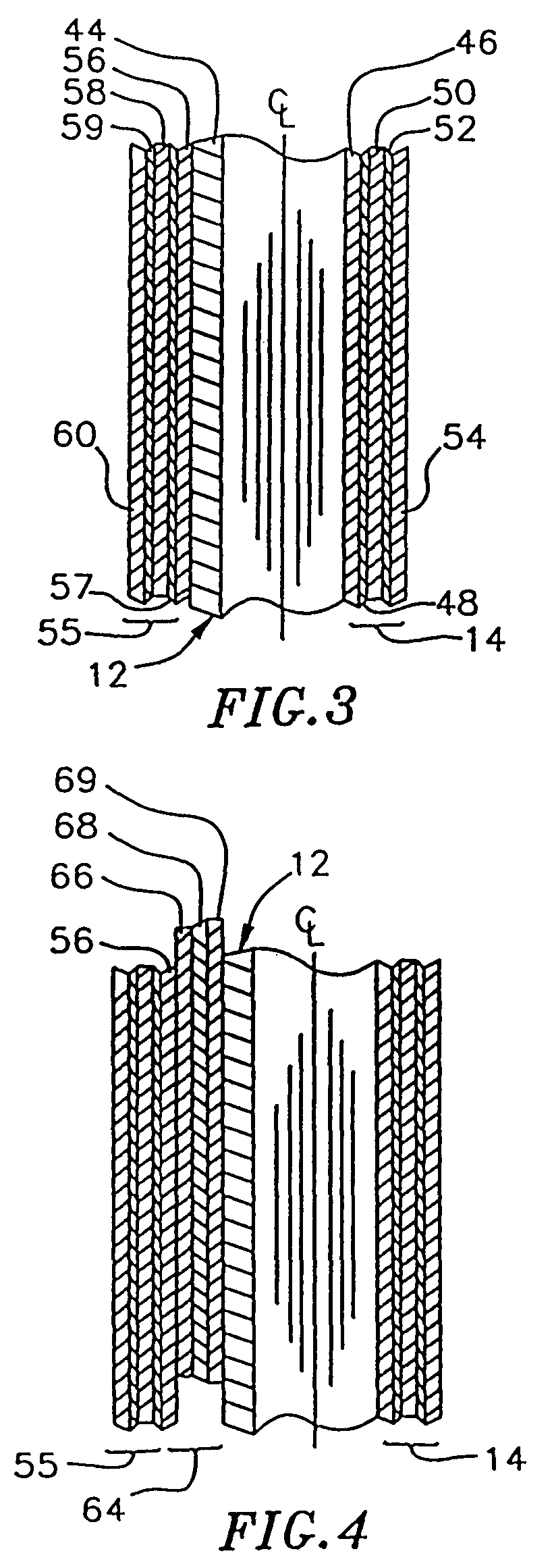

Beverage filter cartridge

InactiveUS6645537B2Increase storage capacityImprove the immunityReady-for-oven doughsBeverage vesselsMechanical engineeringEngineering

Owner:KEURIG GREEN MOUNTAIN INC

System for card to card transfer of monetary values

InactiveUS6394343B1Less incentiveIncrease valueComplete banking machinesFinanceSmart cardData transmission

A smart card stores monetary values and selectively transfers monetary values to and receives monetary values from a compatible smart card. The smart card includes a data storage device that stores data representing monetary values. Control circuitry controls the transfer of the monetary values into the data storage device and controls the transfer of the monetary values out of the data storage device. A data transfer interface couples directly to a like interface on the compatible card to enable data to be transferred between the smart card and the compatible card. A system for electronic transfer of monetary values includes first and second smart cards. Each of the first and second smart cards includes a data storage device that stores data representing monetary values.

Owner:BERG JON N +1

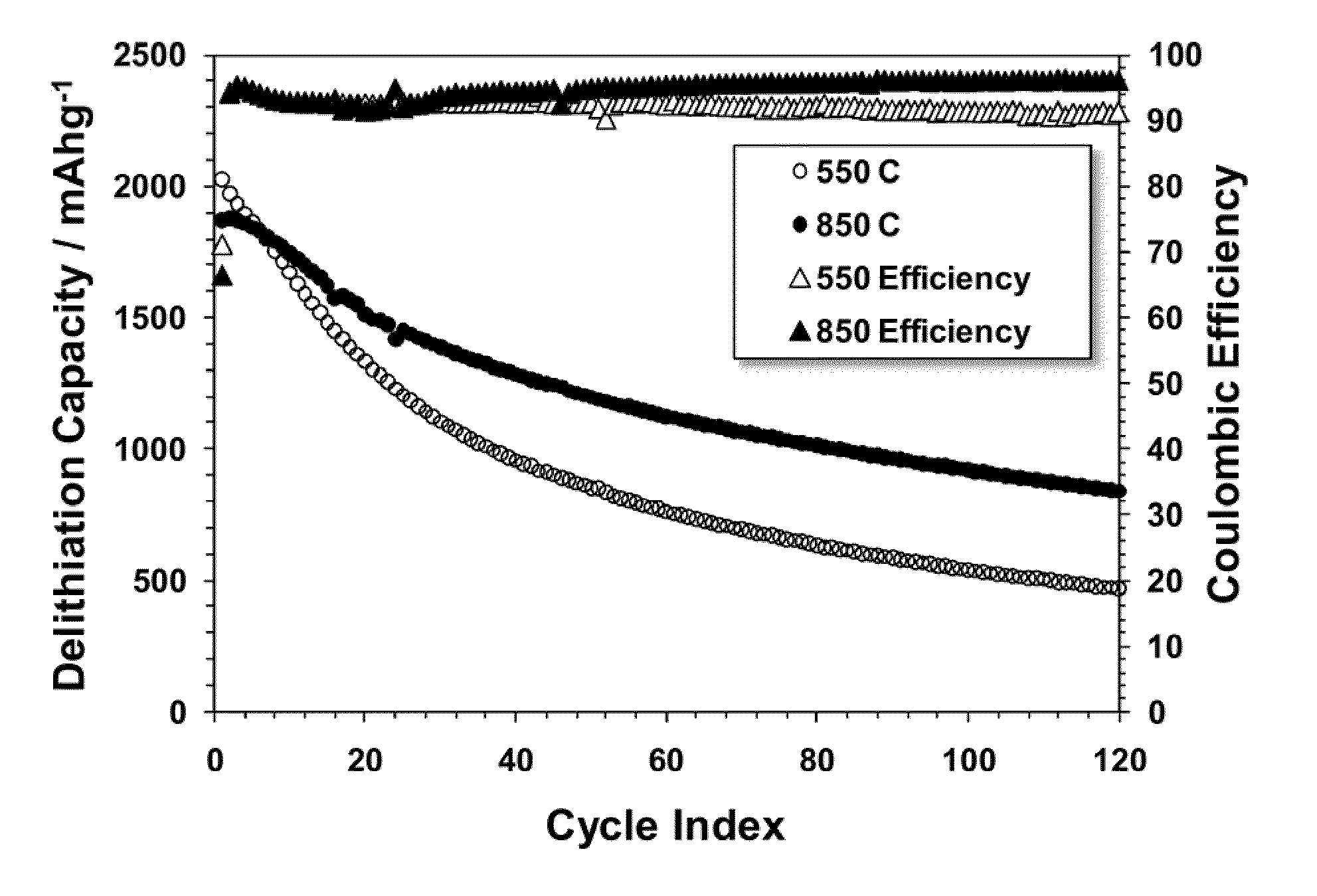

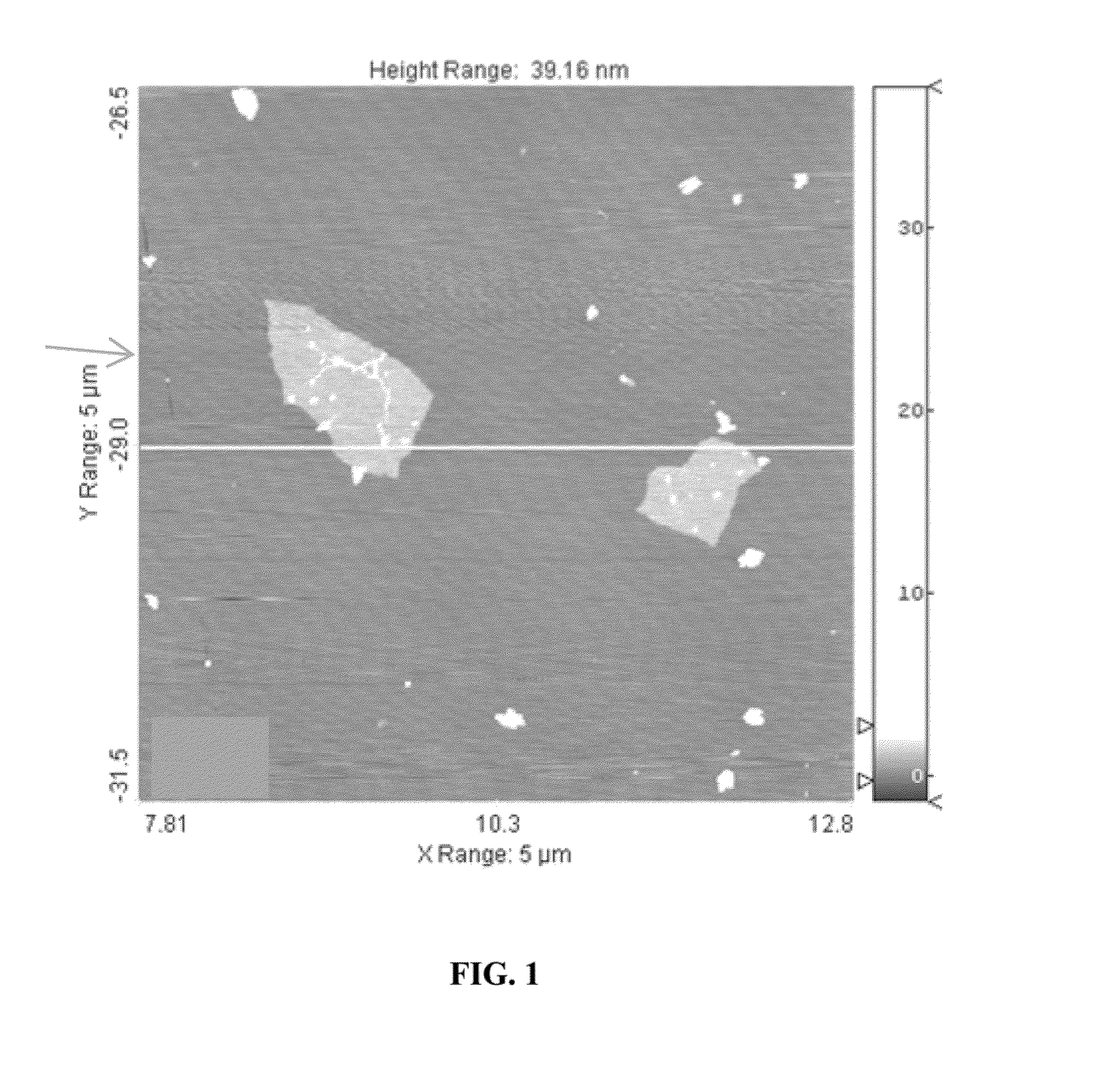

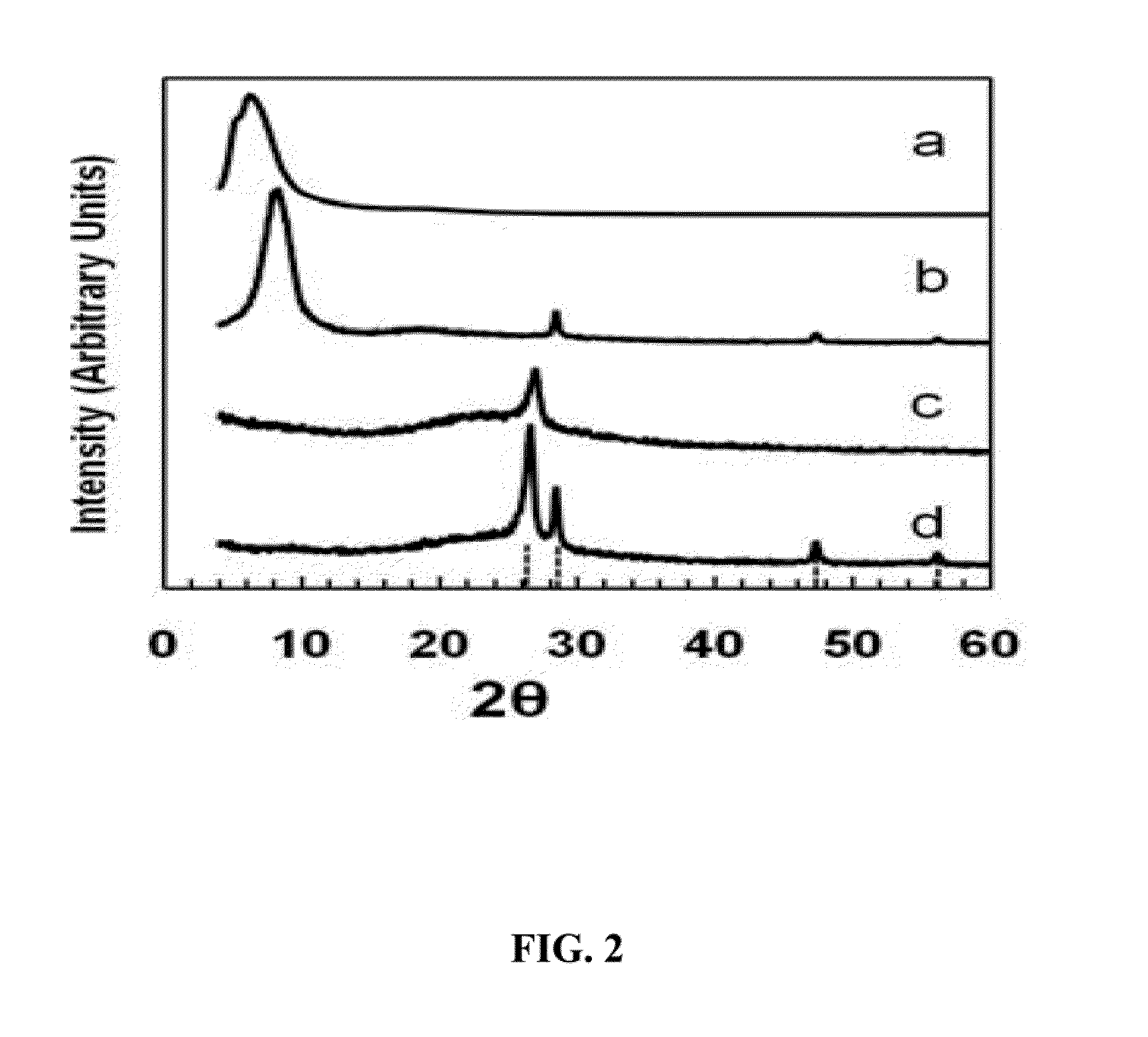

Electrode material comprising graphene composite materials in a graphite network formed from reconstituted graphene sheets

ActiveUS20110111303A1Weight increaseIncrease storage capacityConductive materialNon-conductive material with dispersed conductive materialGraphiteCvd graphene

A durable electrode material suitable for use in Li ion batteries is provided. The material is comprised of a continuous network of graphite regions integrated with, and in good electrical contact with a composite comprising graphene sheets and an electrically active material, such as silicon, wherein the electrically active material is dispersed between, and supported by, the graphene sheets.

Owner:NORTHWESTERN UNIV

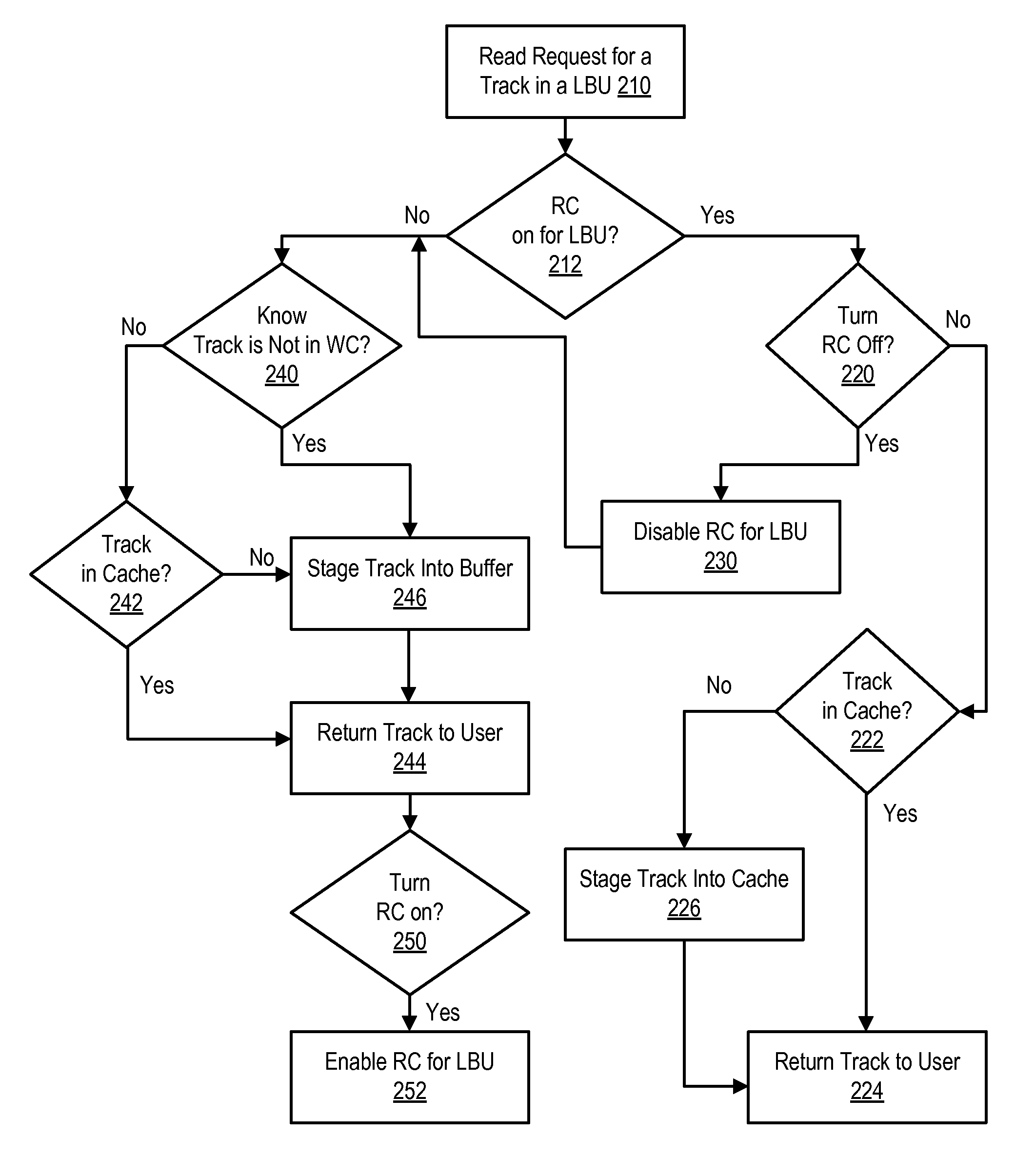

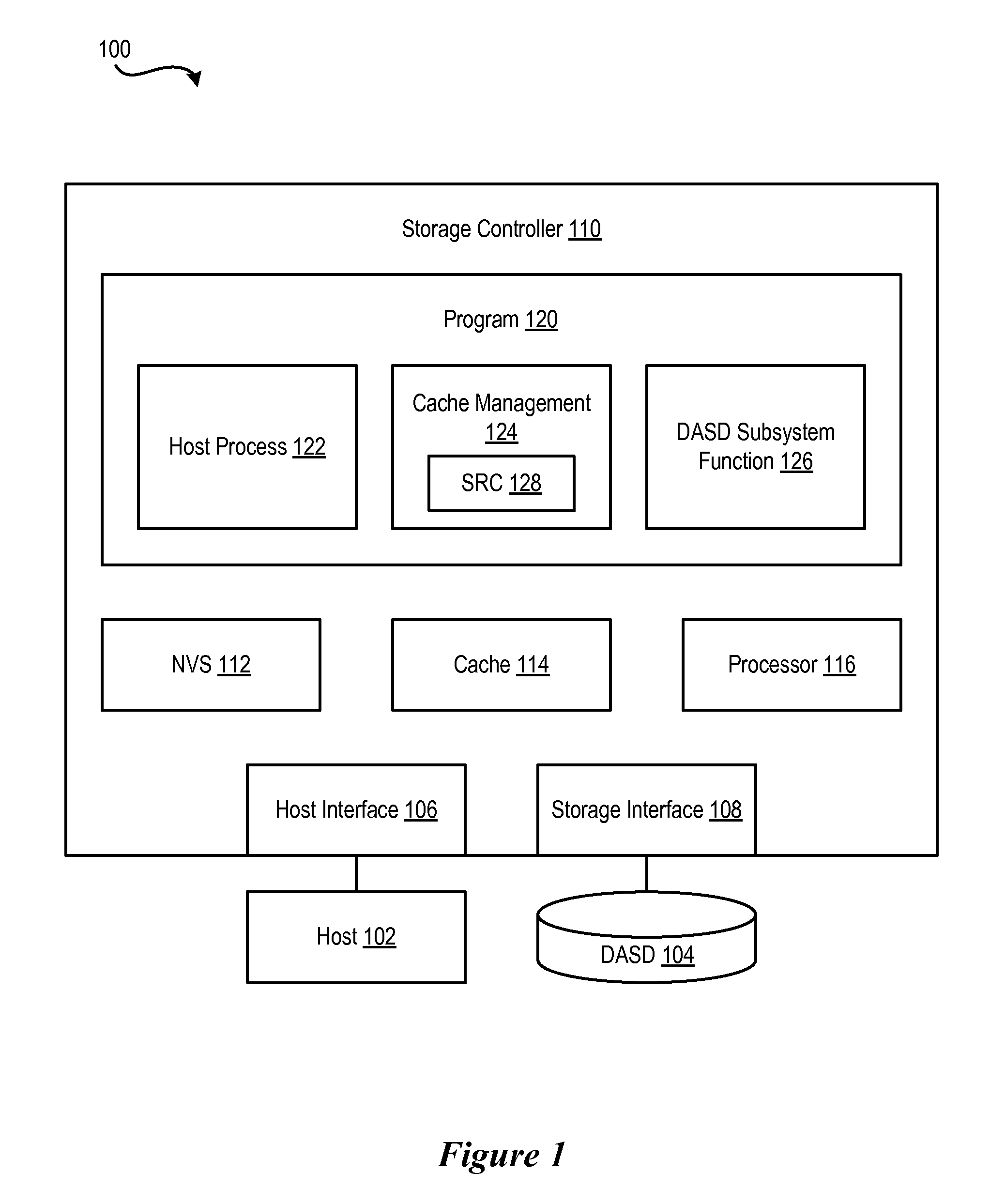

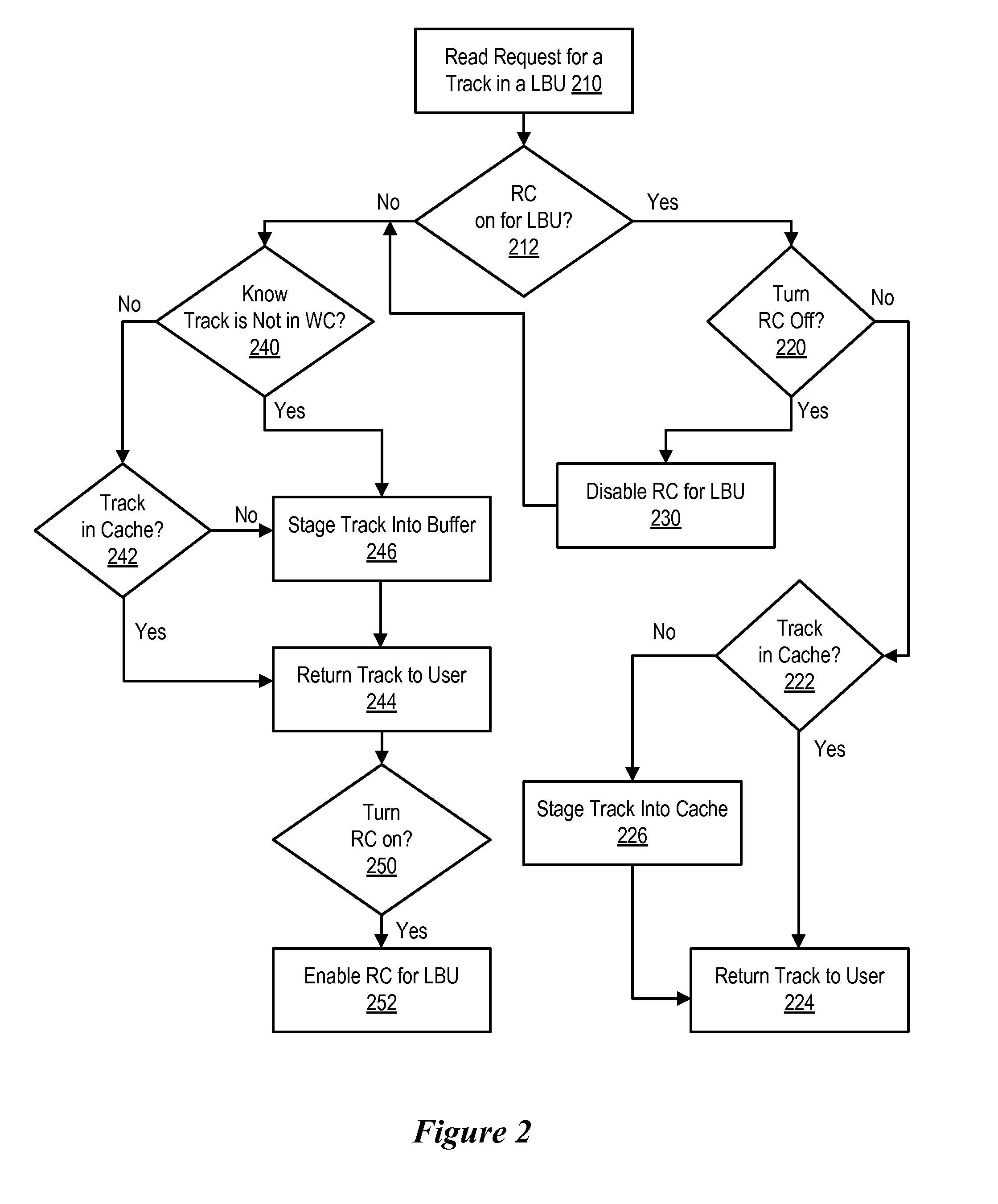

Method for Selectively Enabling and Disabling Read Caching in a Storage Subsystem

InactiveUS20090037662A1Improve performanceLow cache hit ratioMemory adressing/allocation/relocationCache hit rateWorkload

A mechanism for selectively disabling and enabling read caching based on past performance of the cache and current read / write requests. The system improves overall performance by using an autonomic algorithm to disable read caching for regions of backend disk storage (i.e., the backstore) that have had historically low cache hit ratios. The result is that more cache becomes available for workloads with larger hit ratios, and less time and machine cycles are spent searching the cache for data that is unlikely to be there.

Owner:IBM CORP

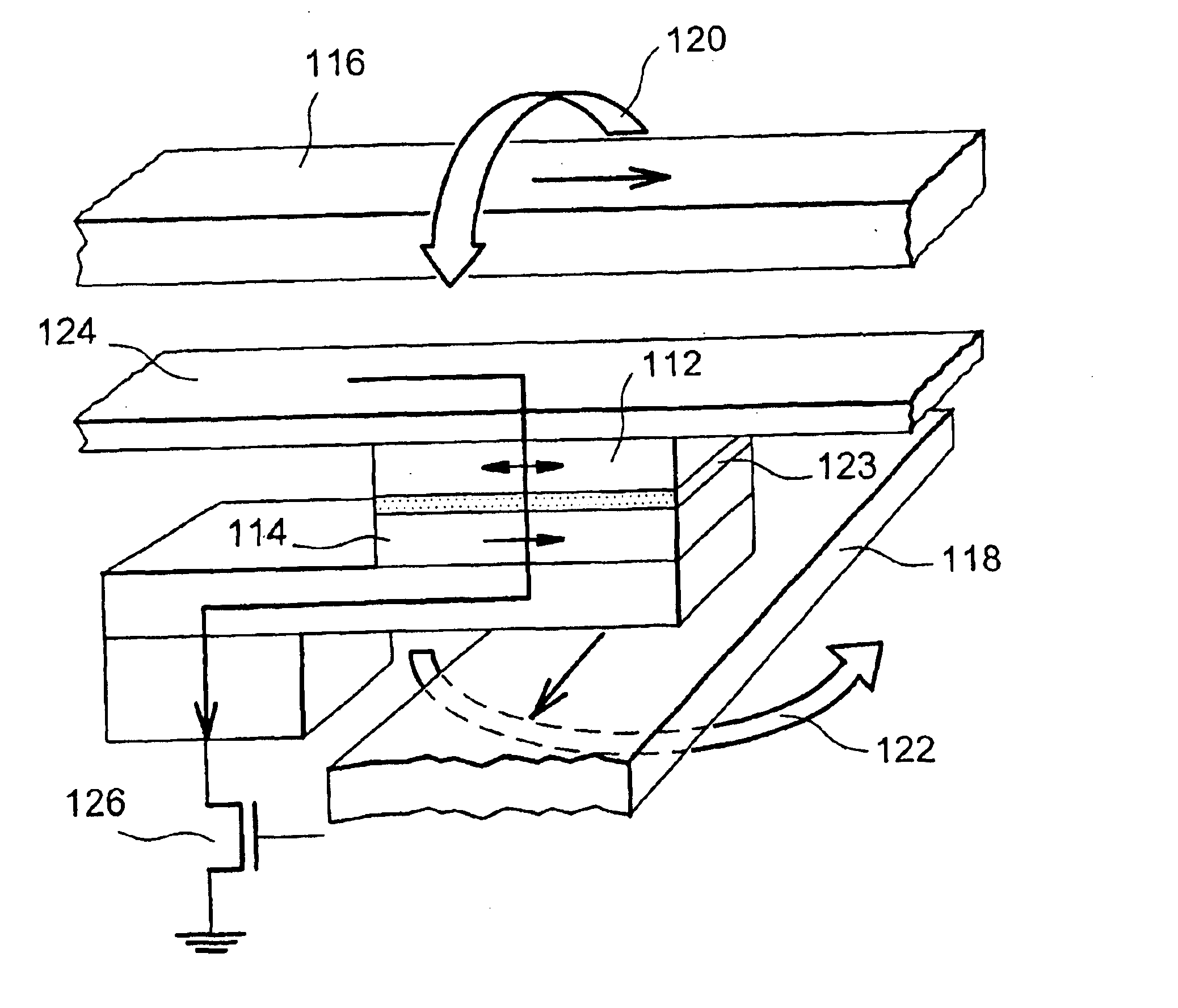

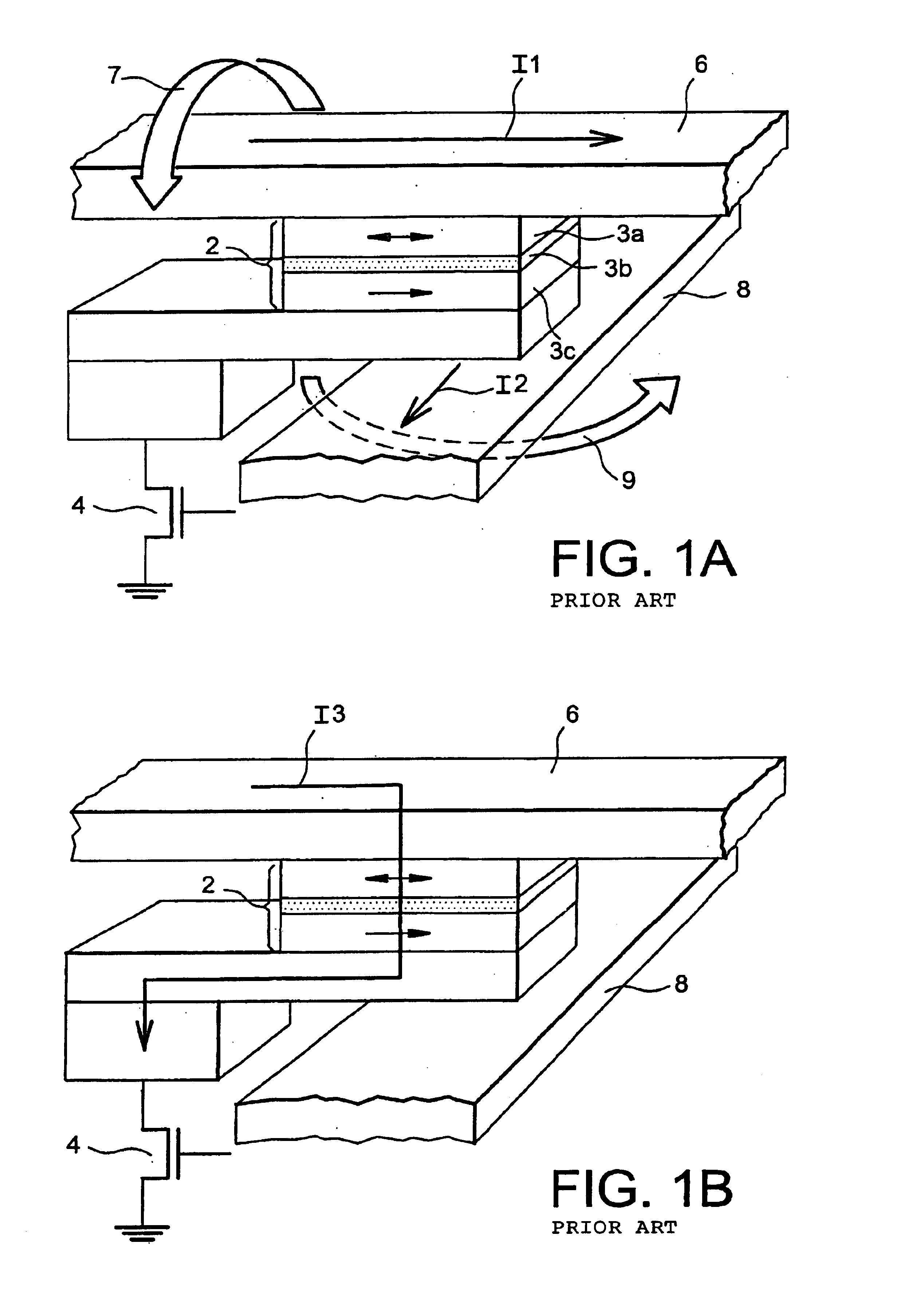

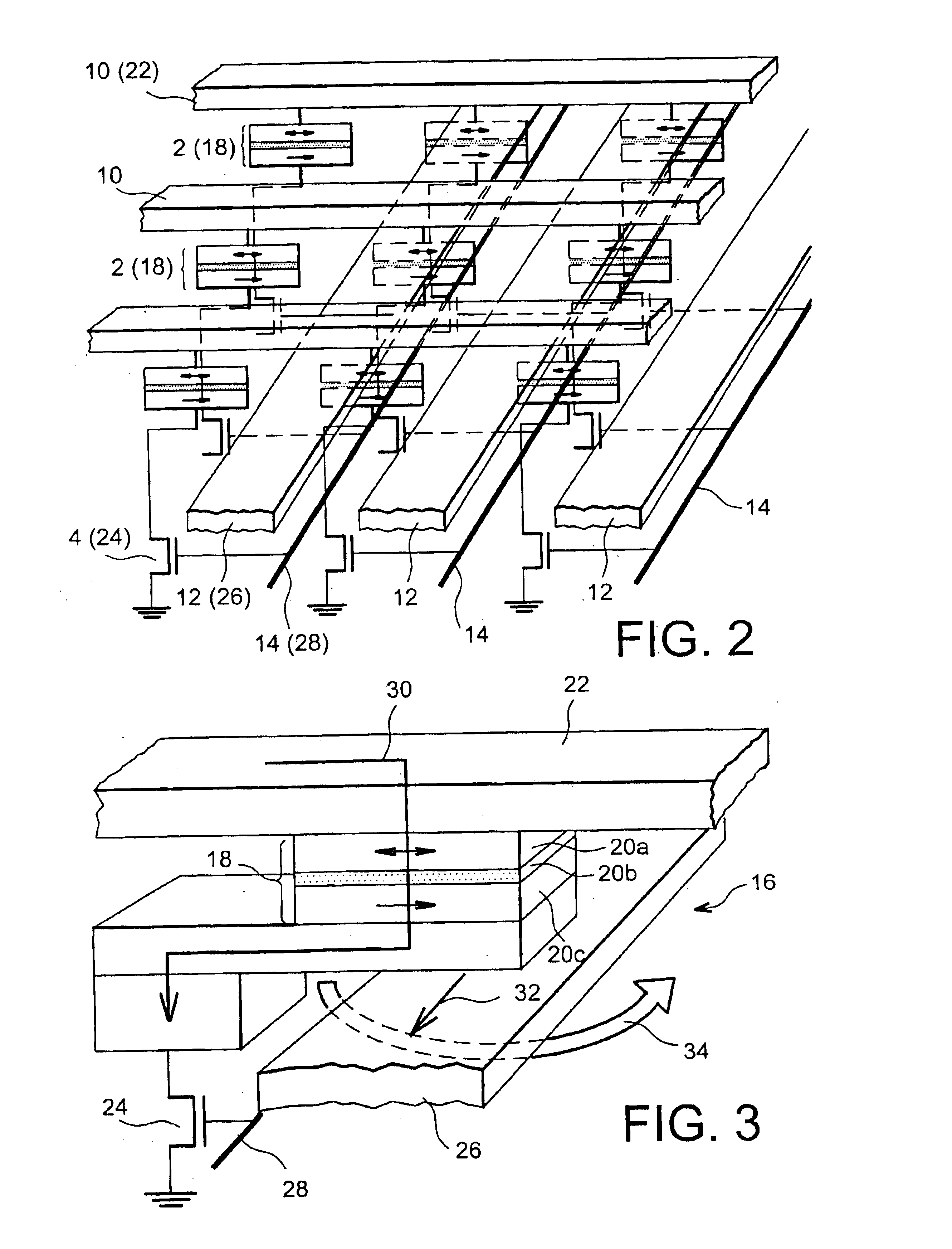

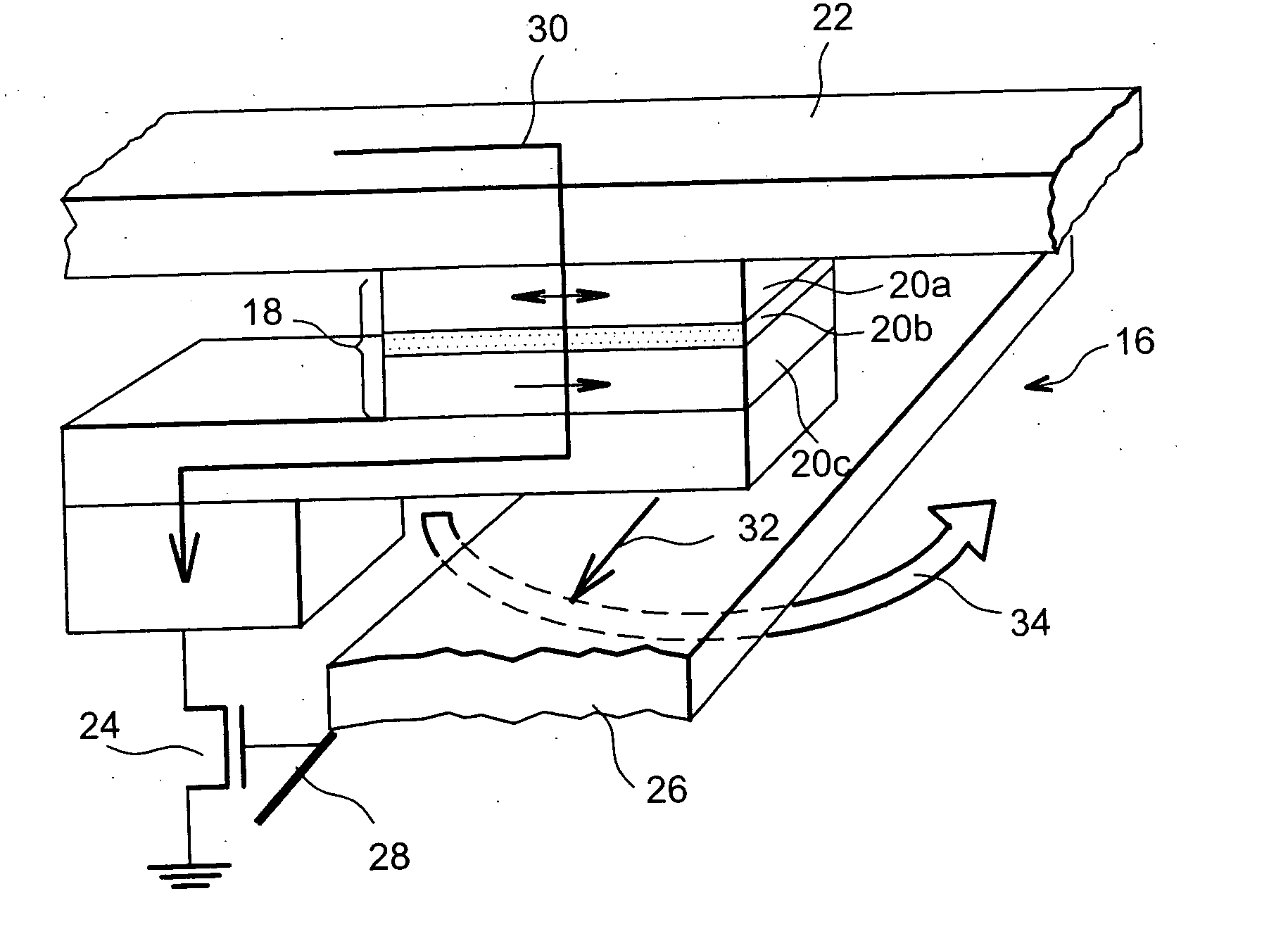

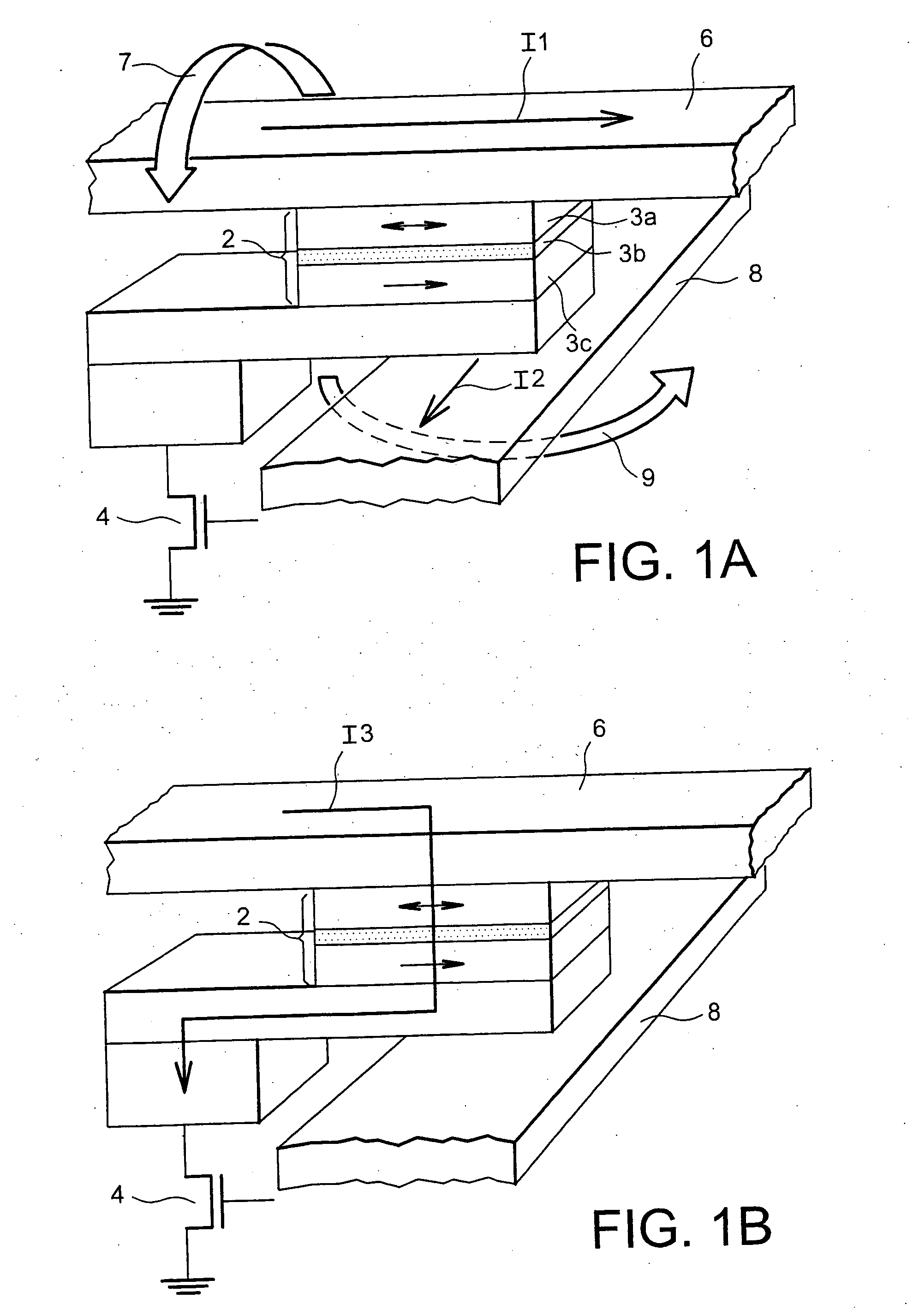

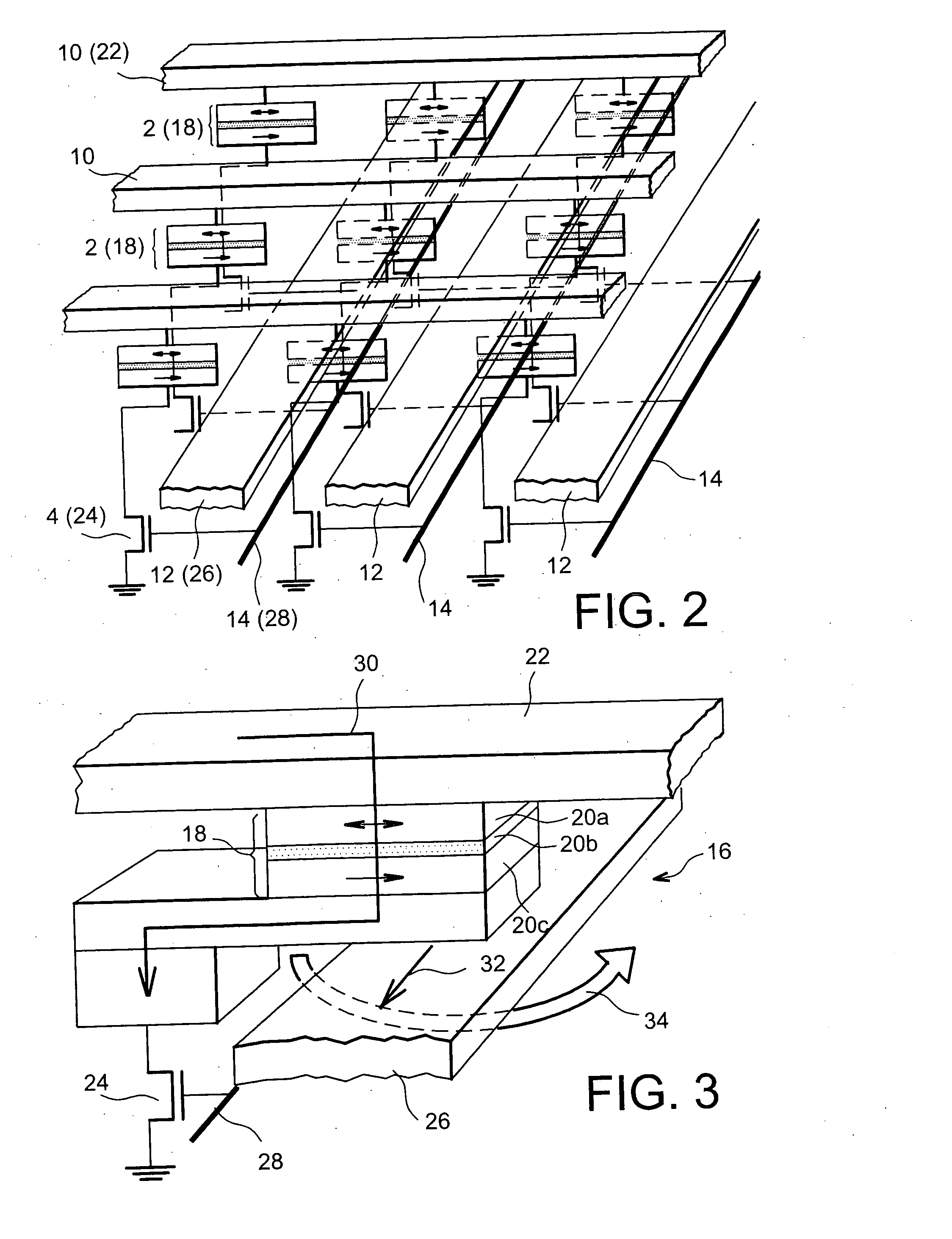

Magnetic tunnel junction magnetic device, memory and writing and reading methods using said device

InactiveUS6950335B2Good reproducibilityEliminate errorsNanomagnetismMagnetic-field-controlled resistorsMagnetizationSemiconductor

Magnetic tunnel junction magnetic device (16) for writing and reading uses a reference layer (20c) and a storage layer (20a) separated by a semiconductor or insulating layer (20b). The blocking temperature of the magnetisation of the storage layer is less than that of the reference layer. The storage layer is heated (22, 24) above the blocking temperature of its magnetisation. A magnetic field (34) is applied (26) to it orientating its magnetization with respect to that of the reference layer without modifying the orientation of the reference layer.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

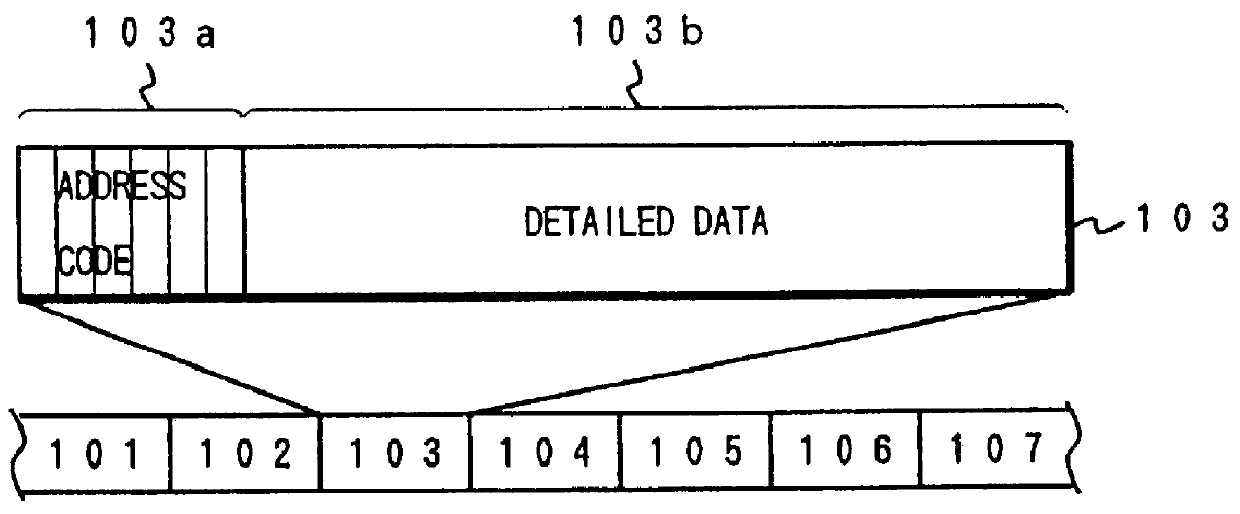

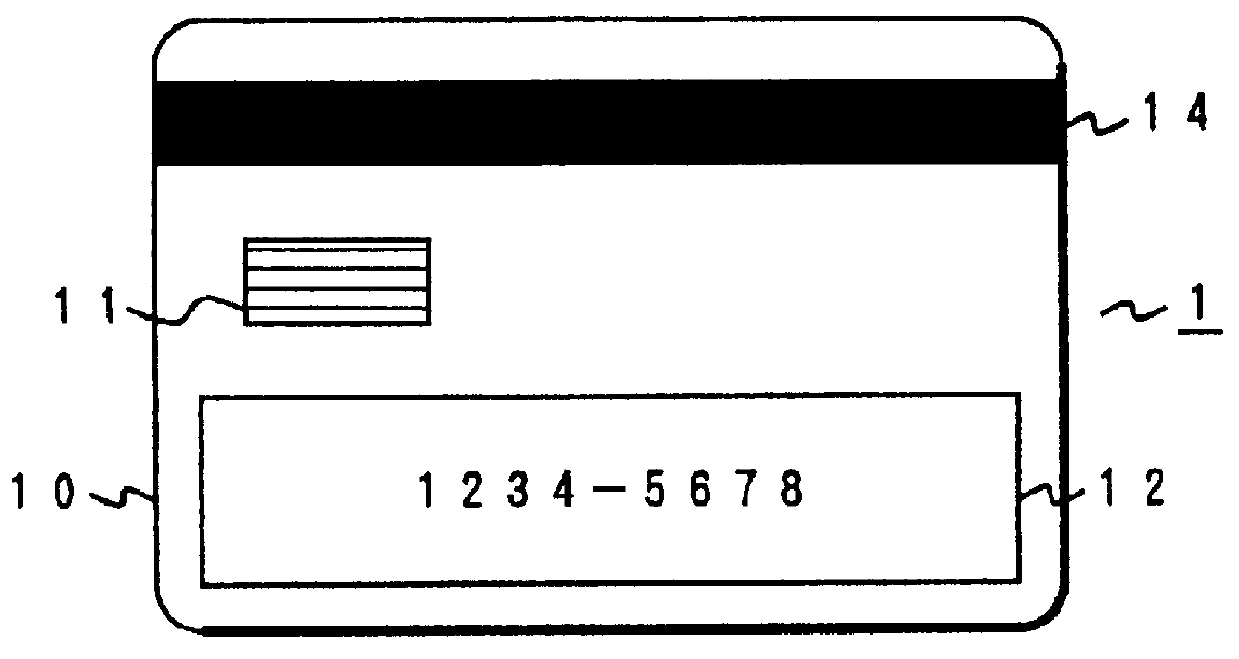

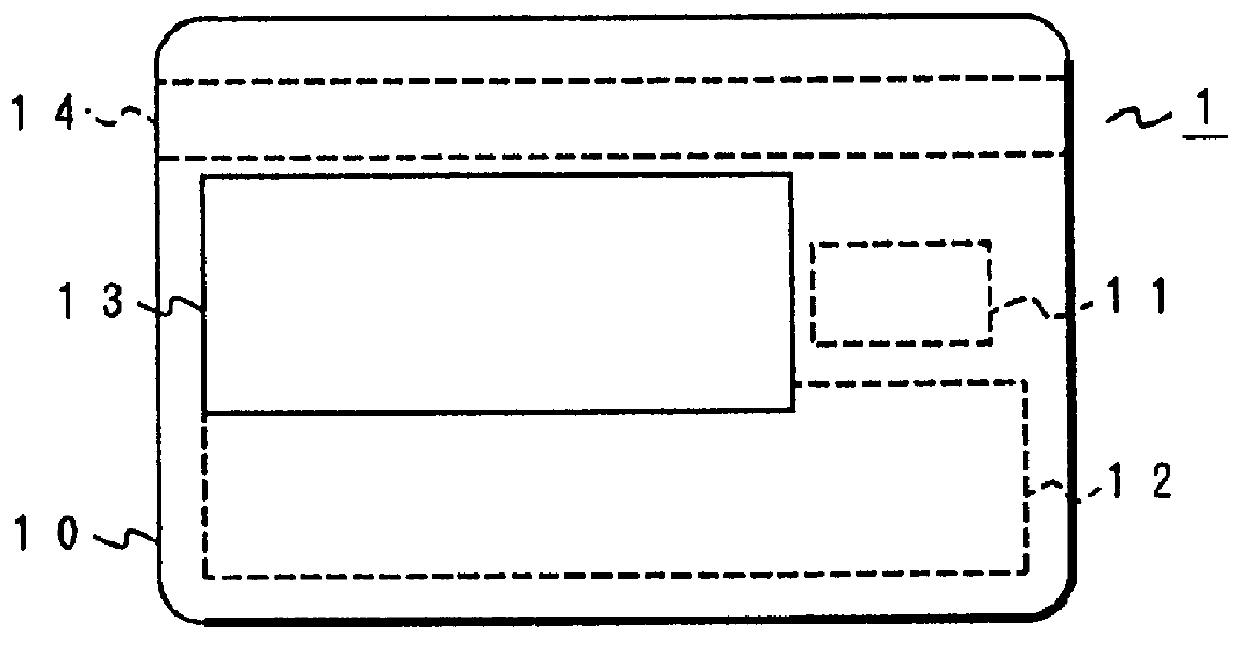

Electronic bankbook and processing system for financial transaction information using electronic bankbook

InactiveUS6029887AImprove security levelImprove securityComplete banking machinesFinanceReceiptSemiconductor memory

PCT No. PCT / JP95 / 01427 Sec. 371 Date Mar. 18, 1996 Sec. 102(e) Date Mar. 18, 1996 PCT Filed Jul. 18, 1995 PCT Pub. No. WO96 / 02890 PCT Pub. Date Feb. 1, 1996The object of the present invention is to propose an account bankbook, a money transfer card, a receipt file, and a checkbook utilizing an optical card, an IC card, or a hybrid optical / IC card. On the surface of a resin card base board 1 are formed an IC chip 11, an optical recording sheet 13, a magnetic stripe 14, and an embossment 12. In a semiconductor memory within the IC chip 11 are written validation keys, search keys, payee information, the upper limit amount of a check, and a program for processing transaction data. Access restrictions corresponding to various applications are imposed upon these data. The history of various cash transactions is recorded in the optical recording sheet 13. These records are of write-once type and rewriting or deletion thereof is impossible.

Owner:N T T DATA TSUSHIN KK

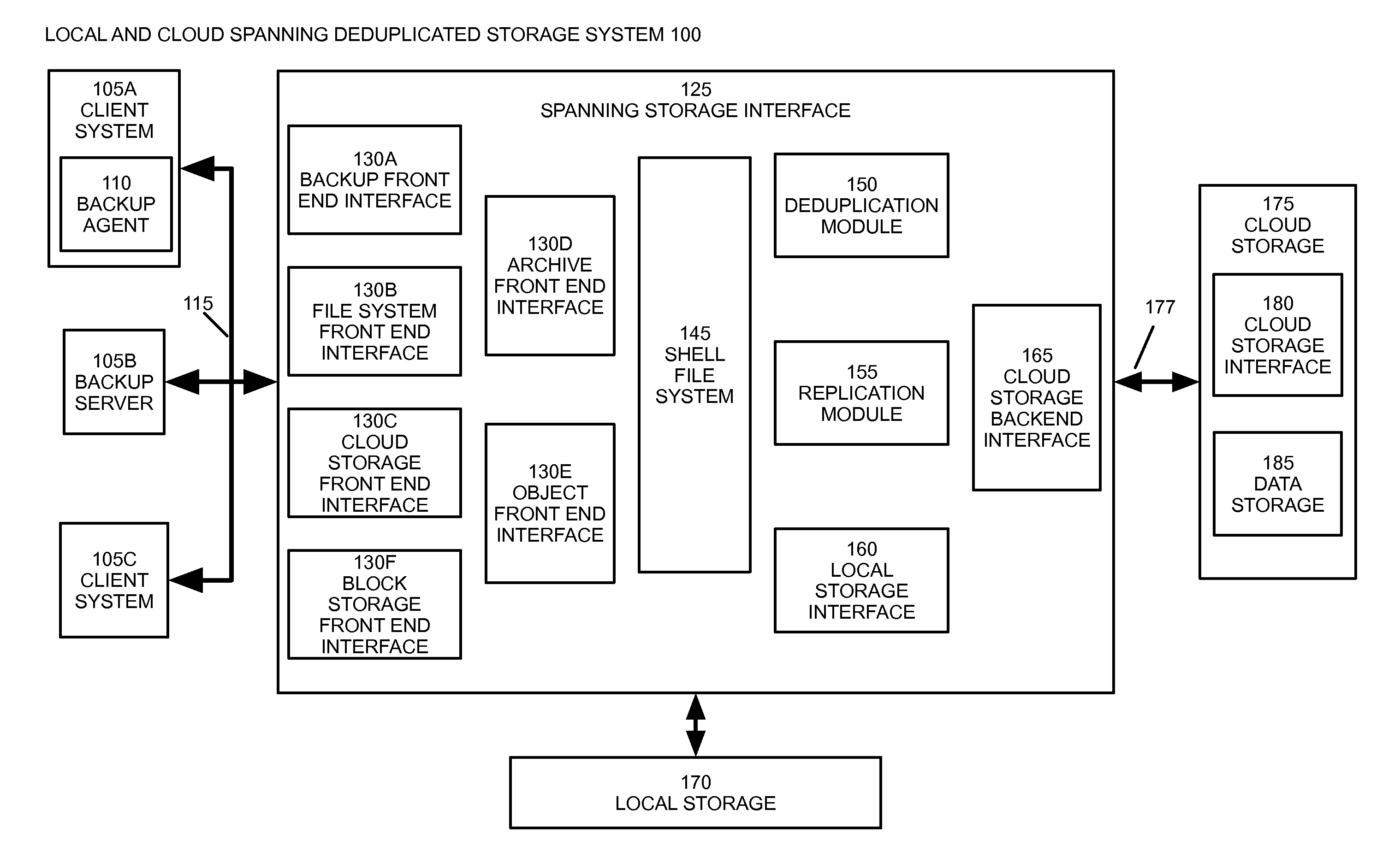

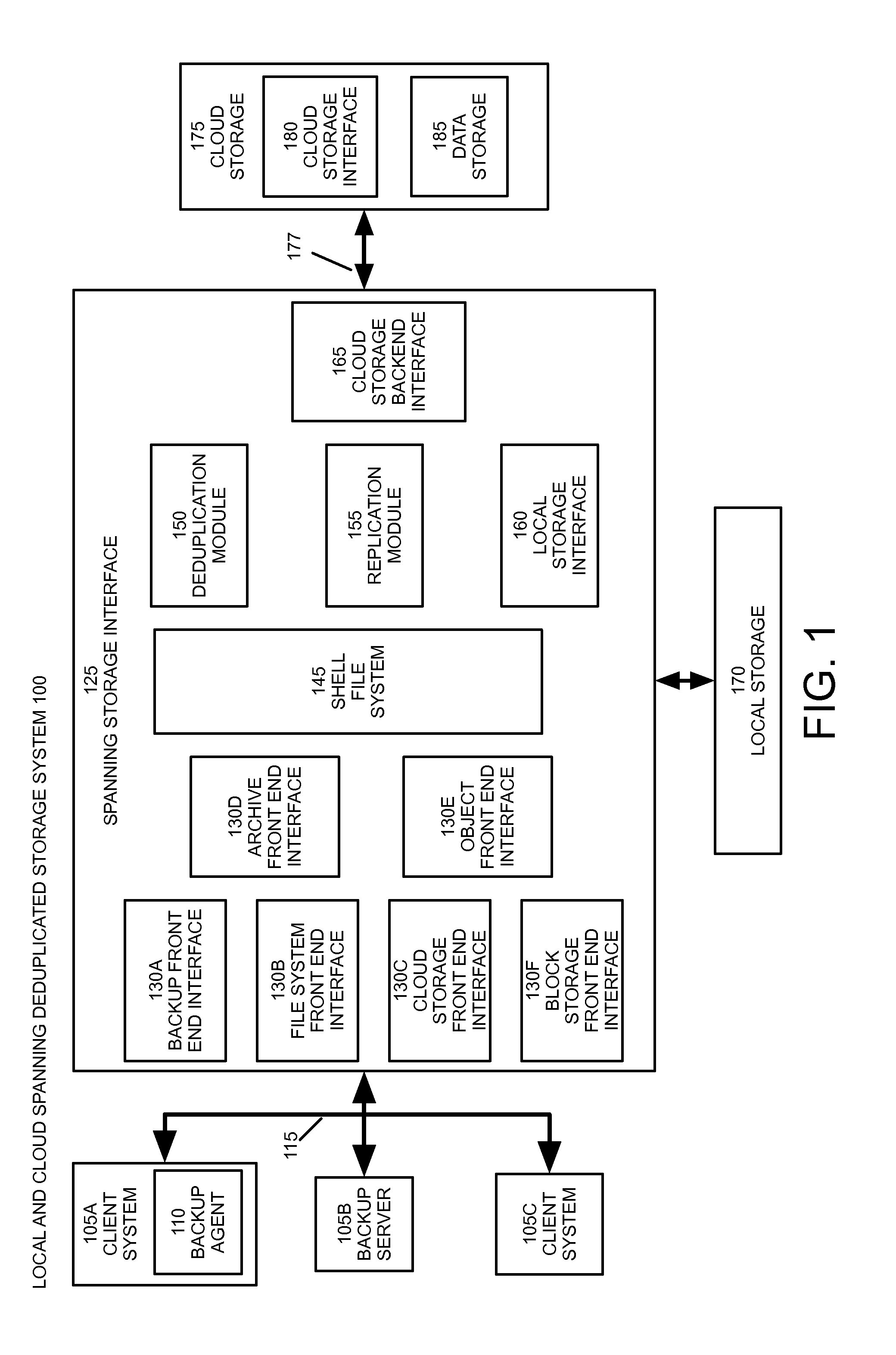

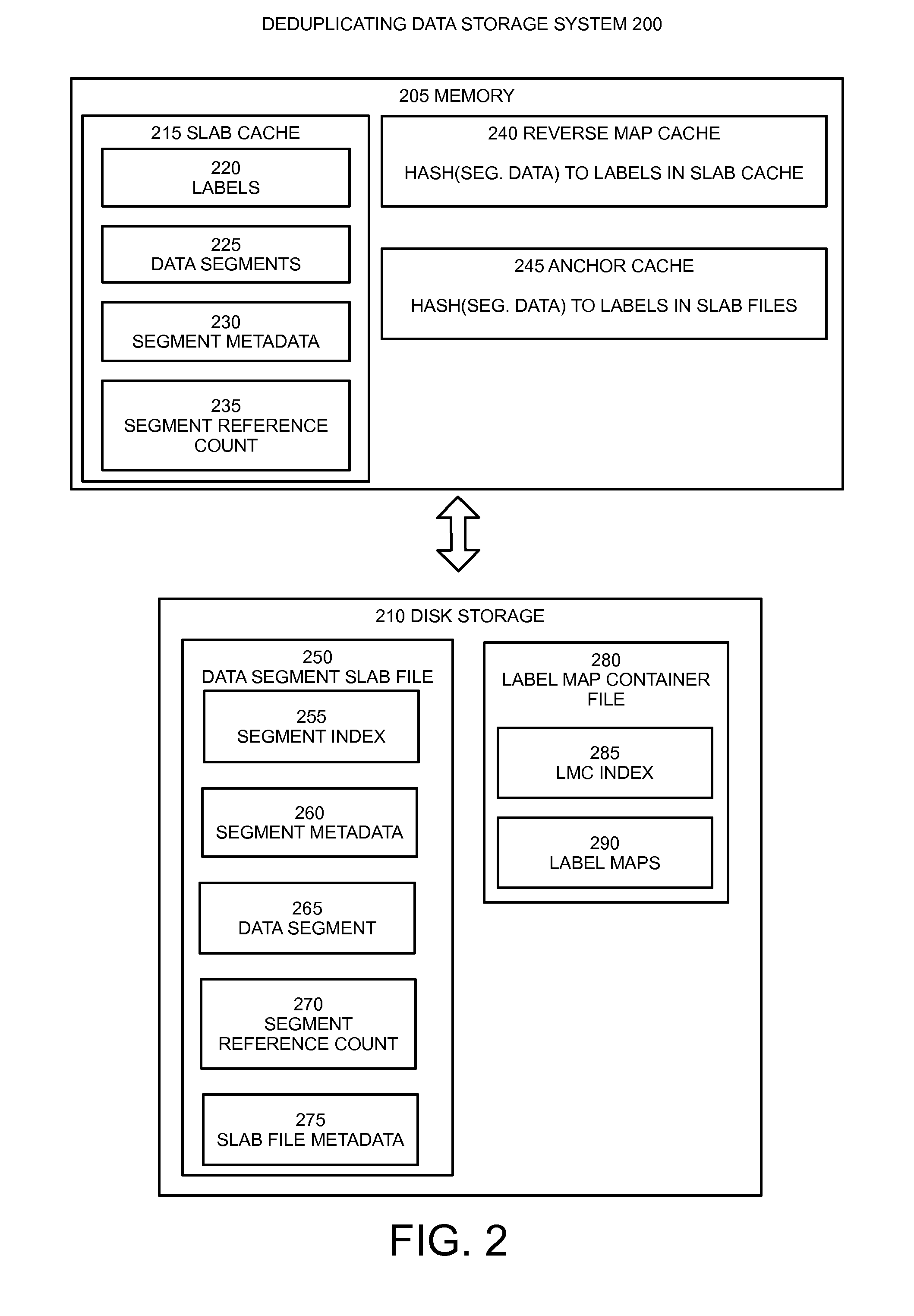

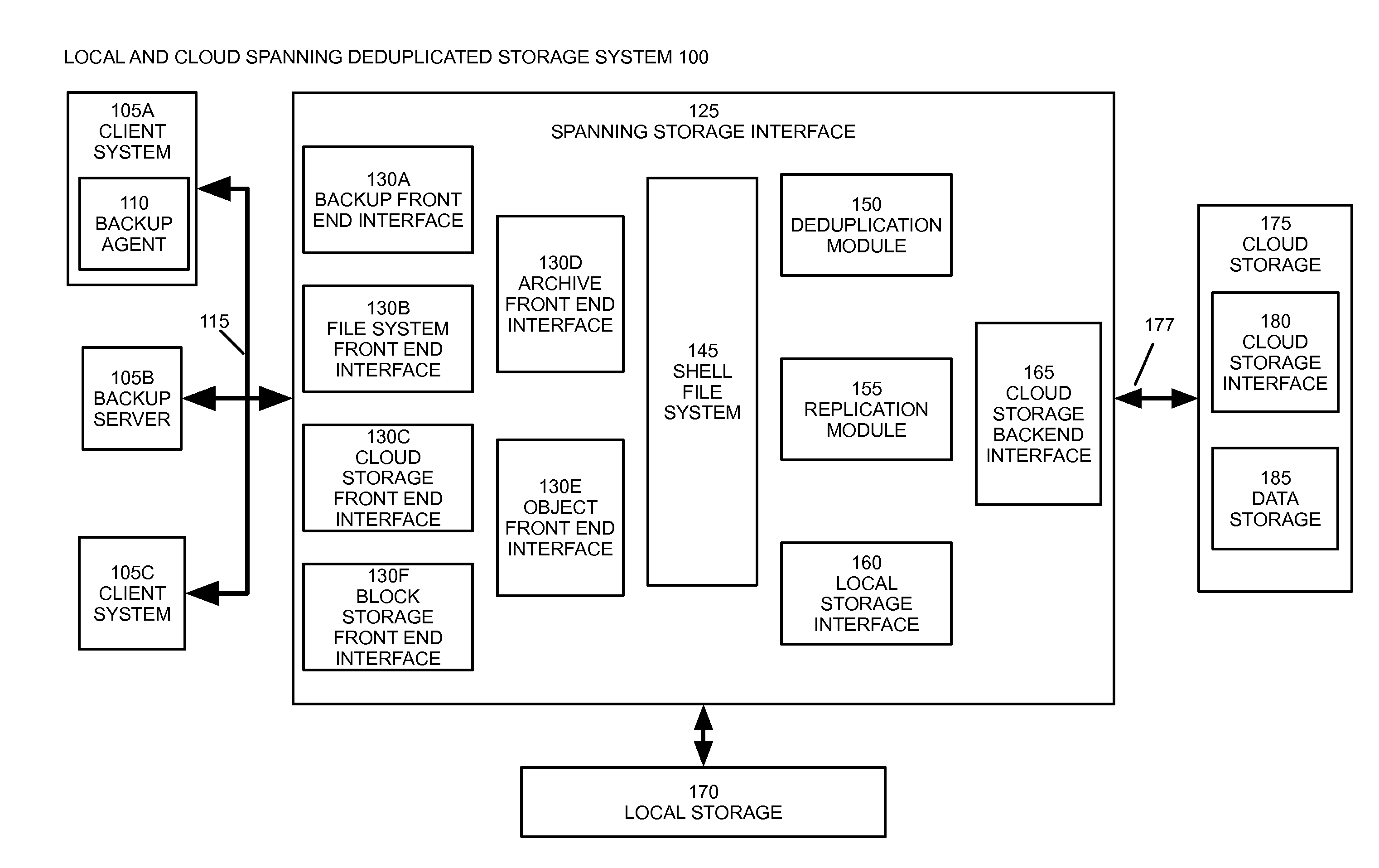

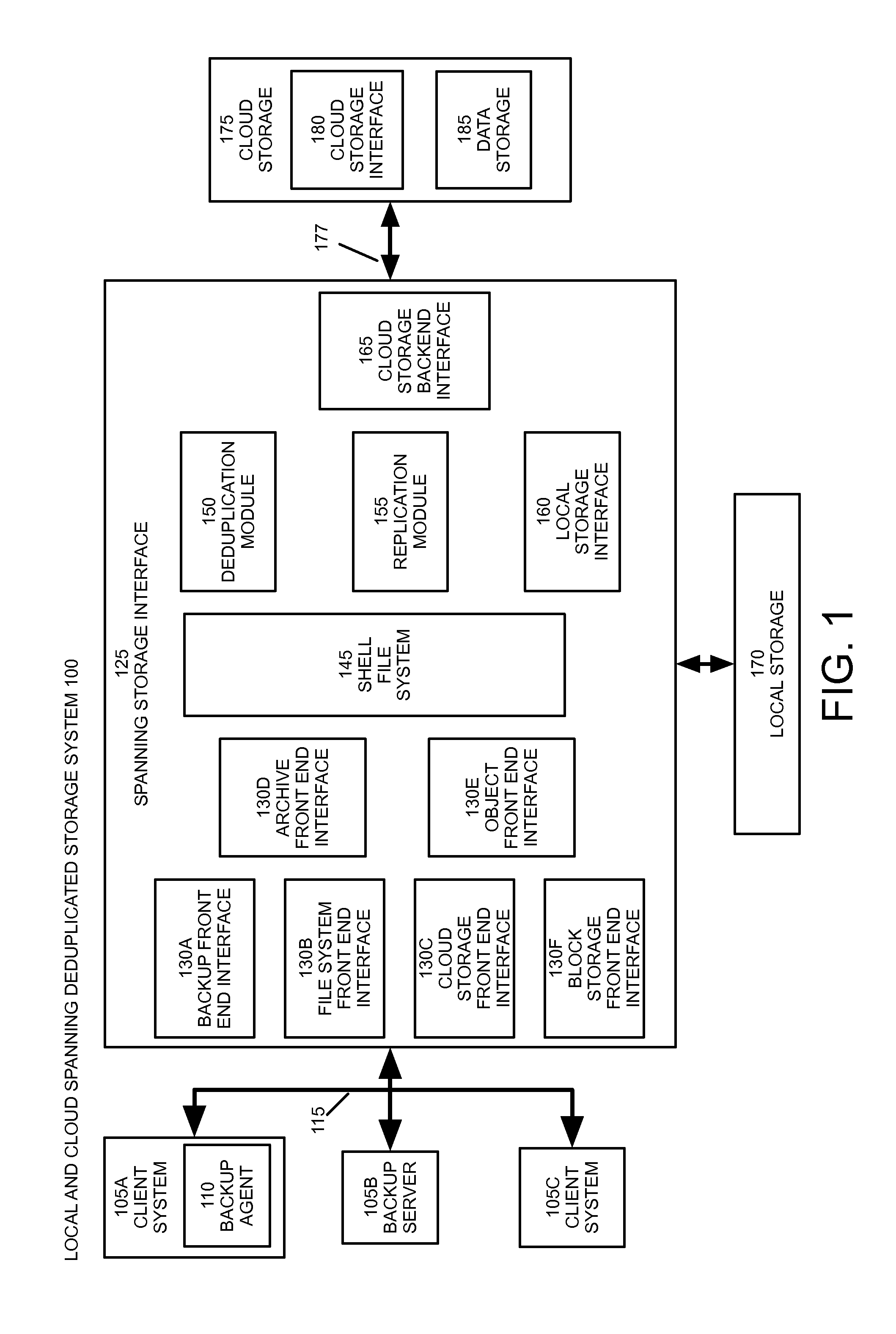

Disaster recovery using local and cloud spanning deduplicated storage system

InactiveUS20110161723A1Improve data access performanceImproved performance benefitDigital data information retrievalSpecial data processing applicationsClient-sideCloud storage

A spanning storage interface facilitates the use of cloud storage services by storage clients and may perform data deduplication. The spanning storage interface may include local storage for caching data from storage clients. A disaster recovery application includes at least first and second spanning storage interfaces at first and second network locations. The second spanning storage interface is provided for at least disaster recovery operations. The second spanning storage interface includes second local storage for improving data access performance. A copy of the local cache of the first spanning storage interface is transferred to the second local storage while the first network location is operating. In the event of a disaster affecting the first network location, the second spanning storage interface can provide data access to the first network location's data with improved performance from using the copy of local cache in the second local storage.

Owner:RIVERBED TECH INC

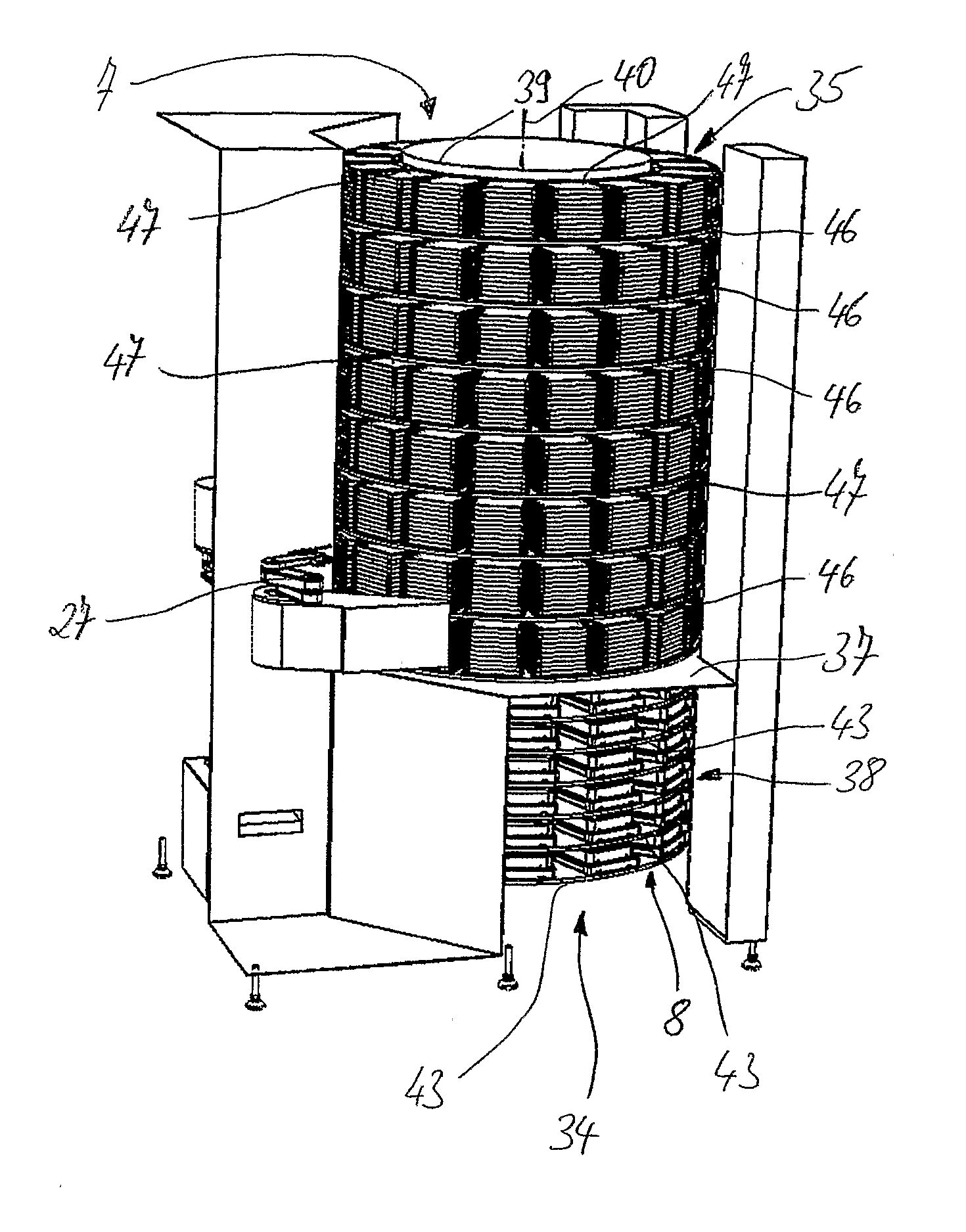

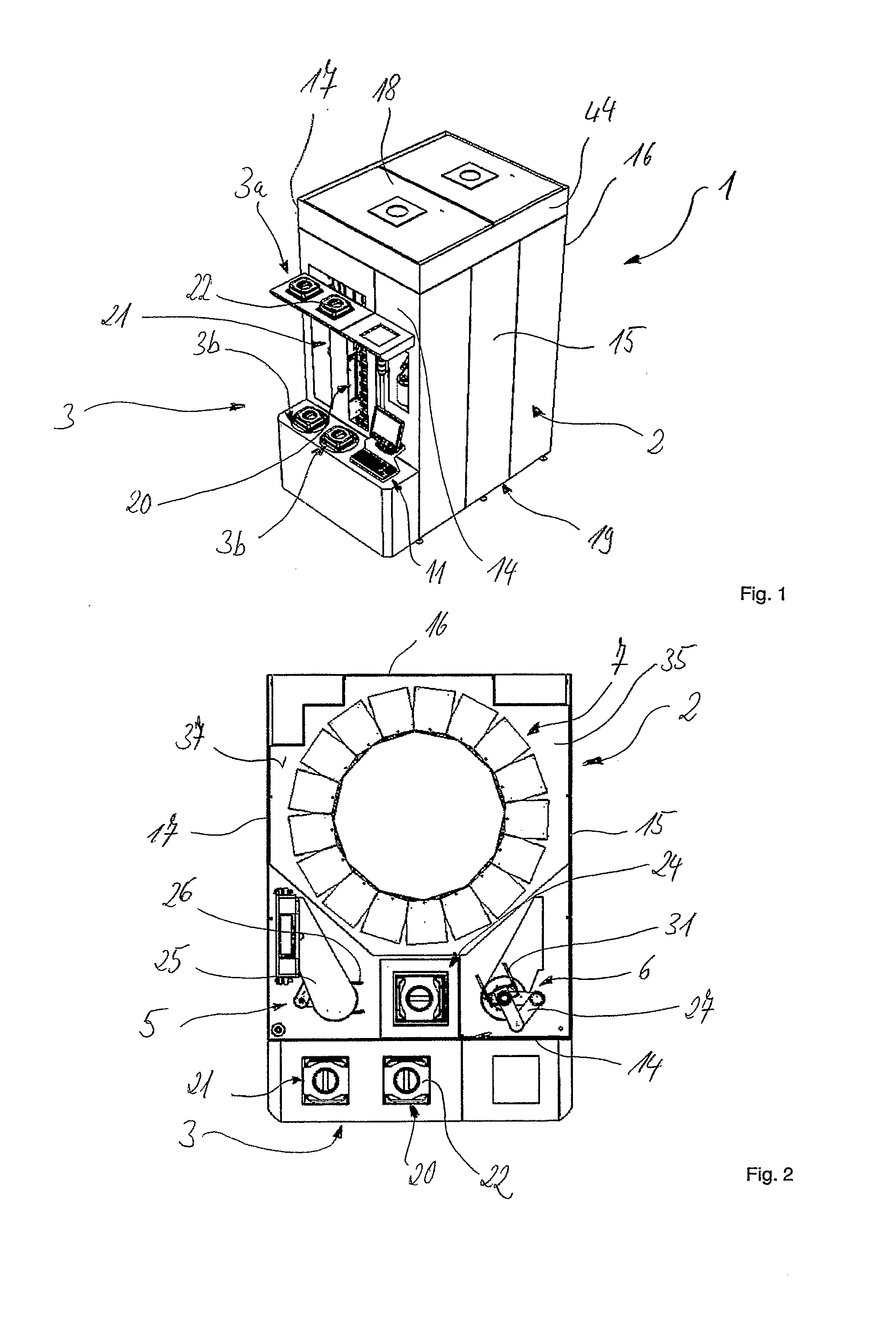

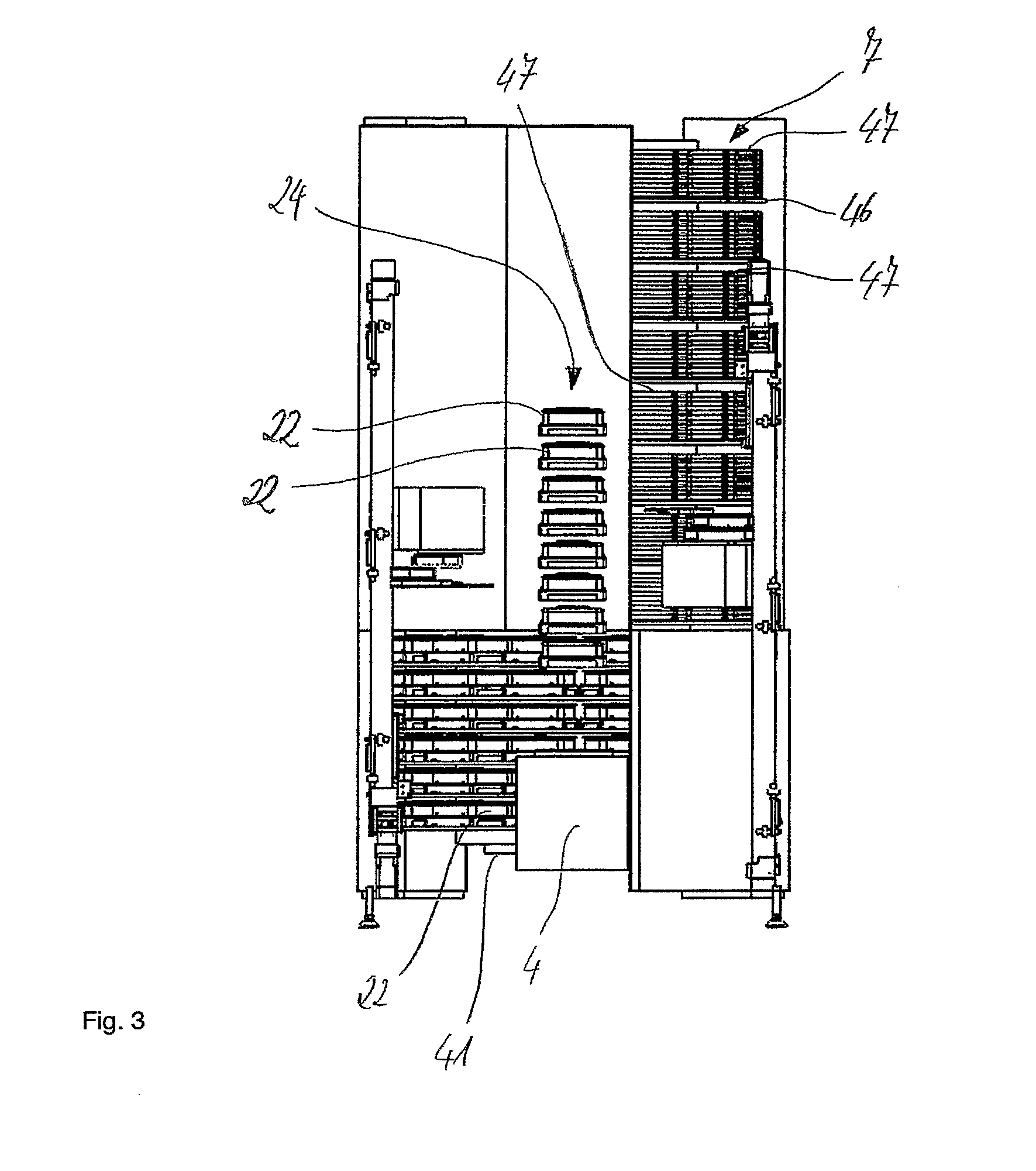

Apparatus for storage of objects from the field of manufacture of electronic components

ActiveUS20120027547A1Avoid pollutionFew stepsSemiconductor/solid-state device manufacturingLoading/unloadingAir atmosphereEngineering

A storage apparatus for objects in the manufacture of substrates, in particular of substrates for electronic components, is provided with a housing which forms at least one closed area for storage of the objects. The storage apparatus also has a pure air device by which a pure air atmosphere can be produced at least within a section of the housing. Using at least one input / output device for the storage apparatus, objects can be passed into the interior of the housing or removed from the interior, in which case the objects can be handled by at least one handling device in the interior of the housing, and object receptacles are provided within the housing, in which objects can be temporarily stored outside transport containers. In order to require a position area which is as small as possible for a storage apparatus such as this, despite it having a high storage capacity, the invention provides that two areas which are arranged at least partially one above the other are formed in the same housing of the storage apparatus, with a first area for an object storage device, and a second area for a transport container storage device.

Owner:BOOKS AUTOMATION US LLC +2

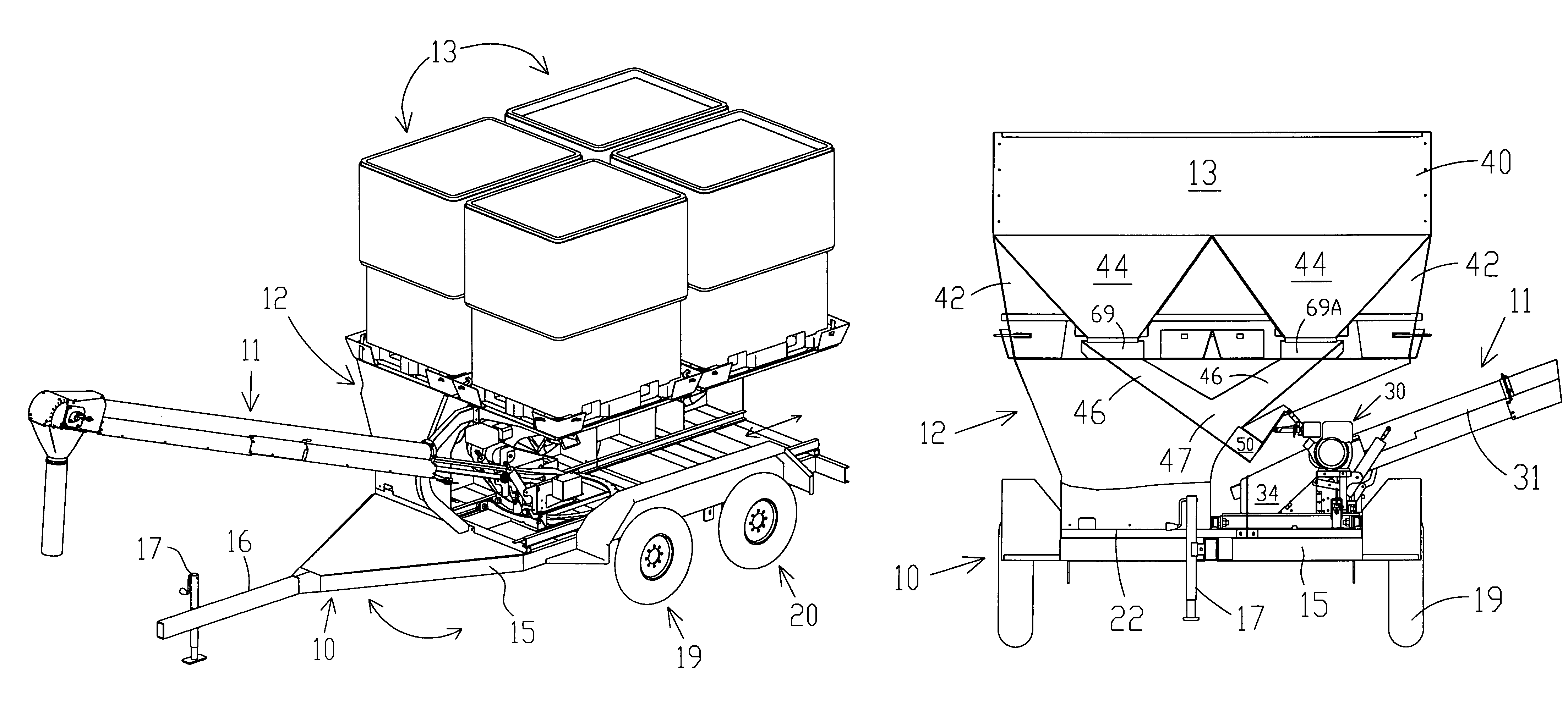

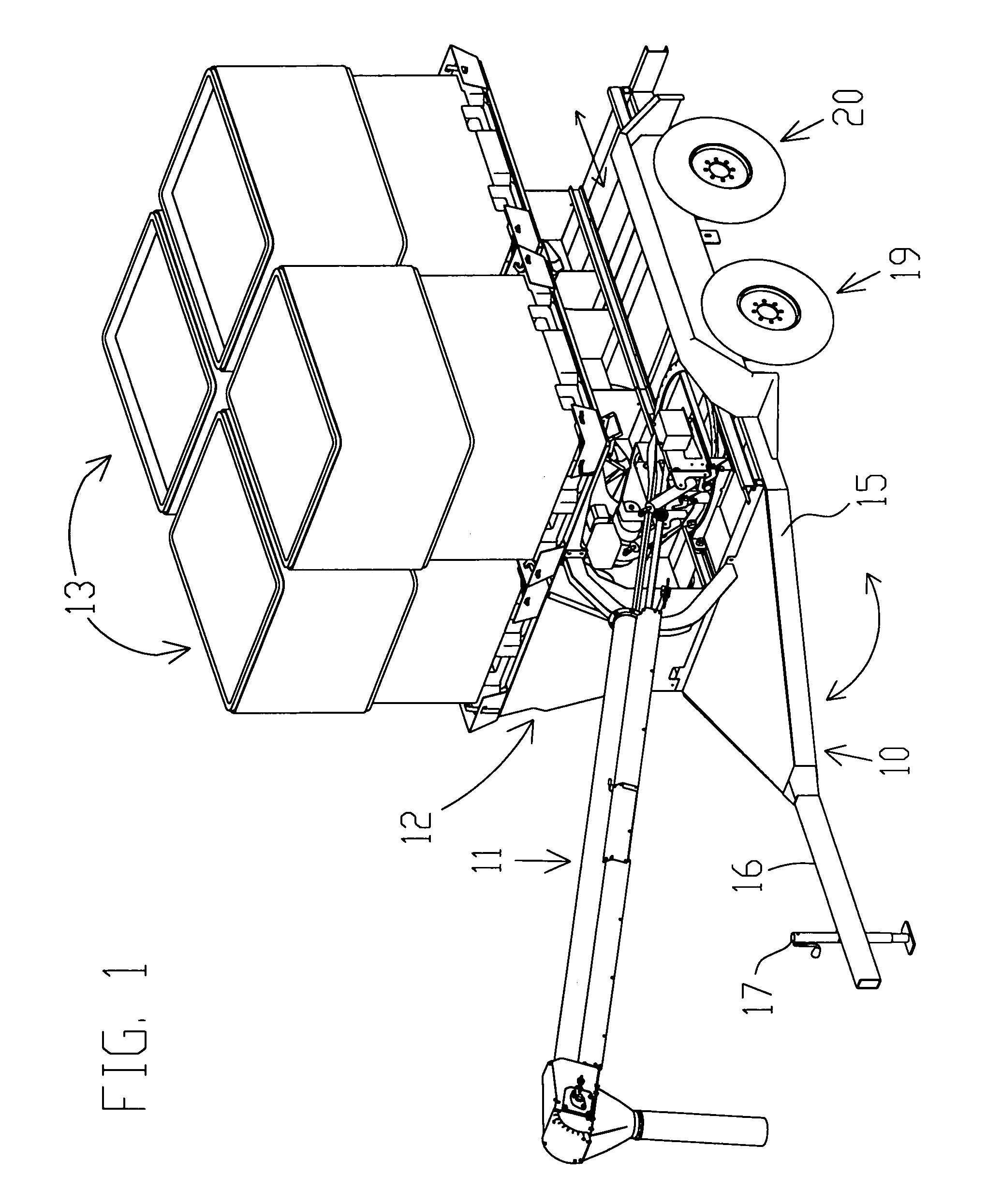

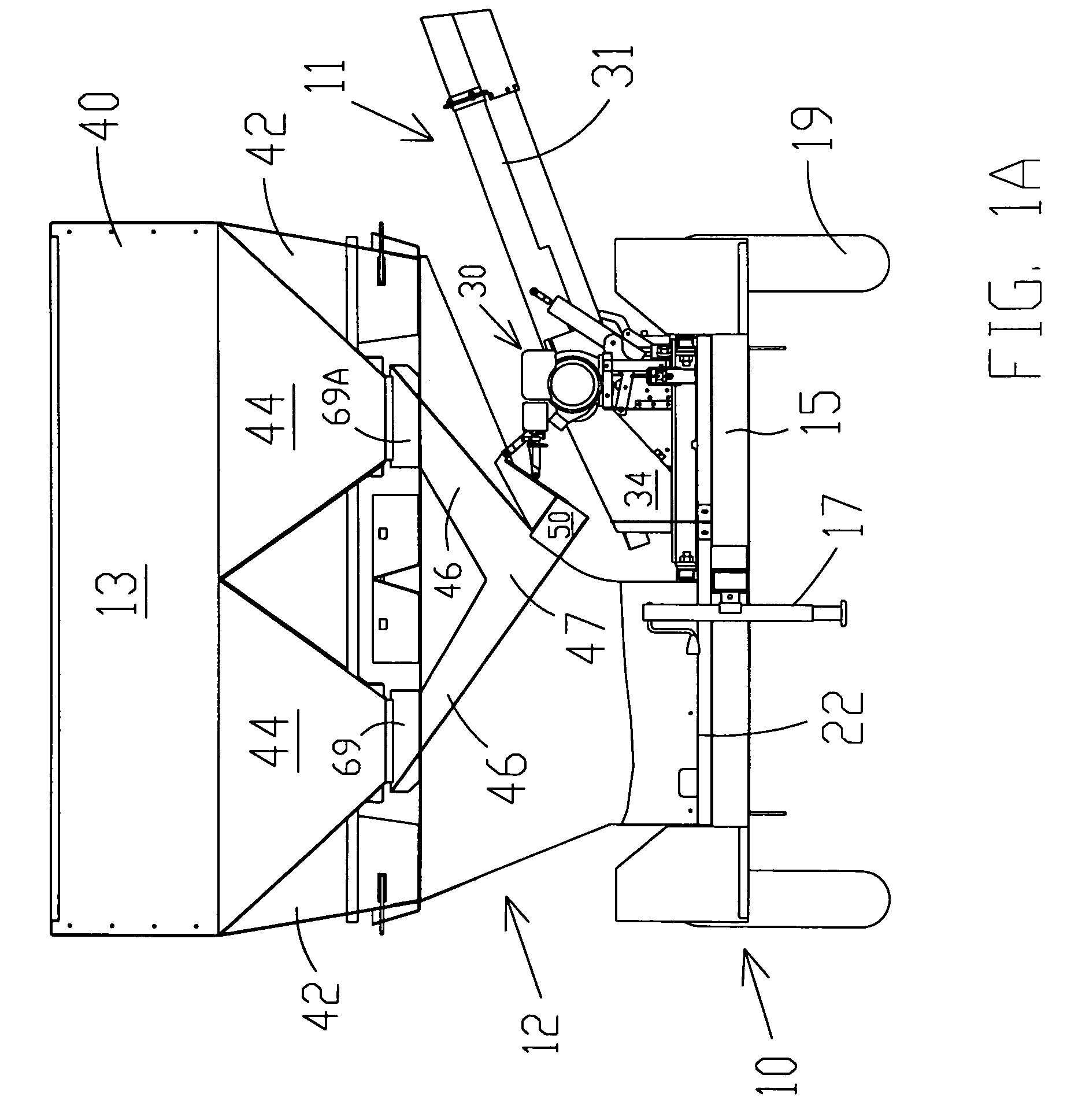

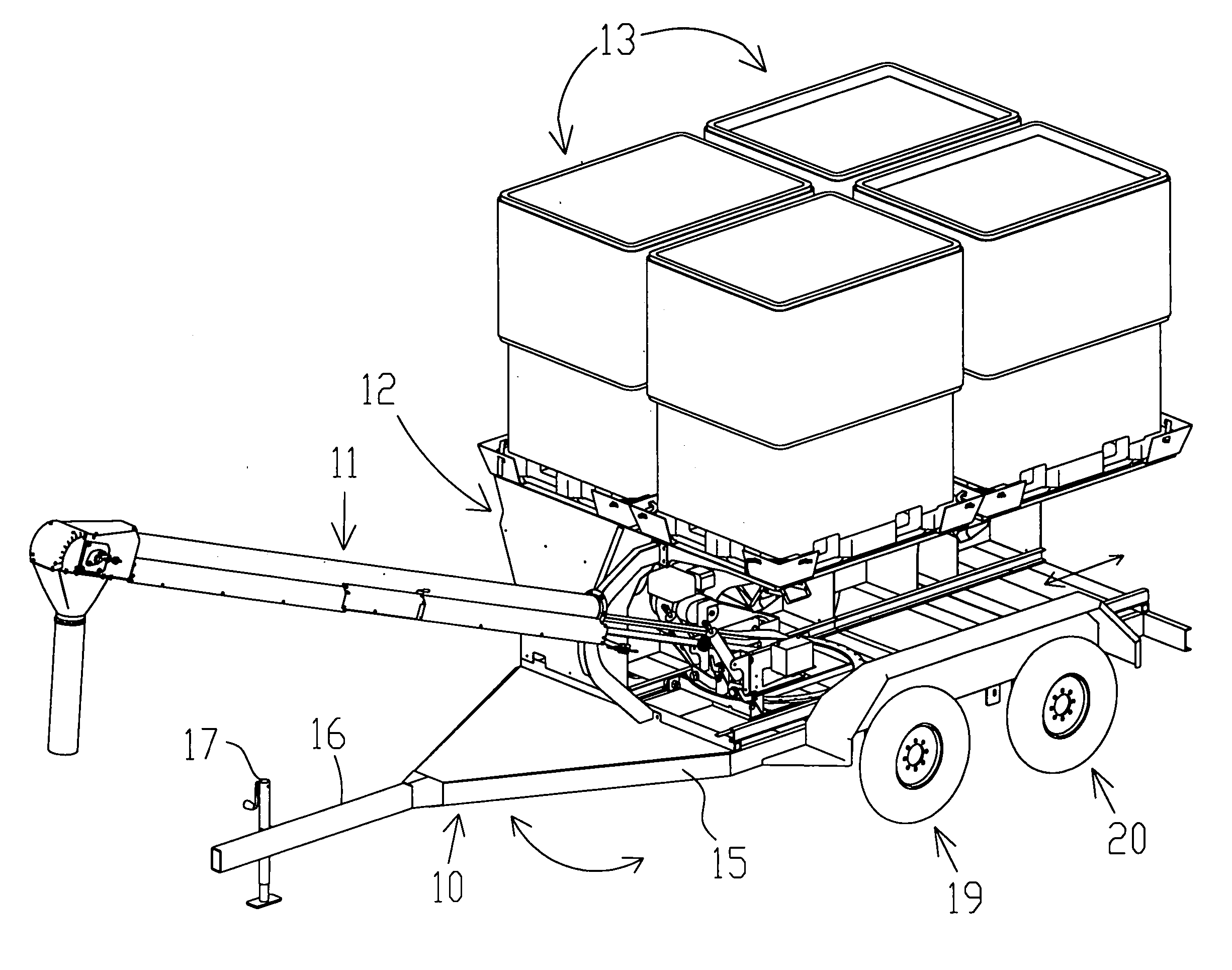

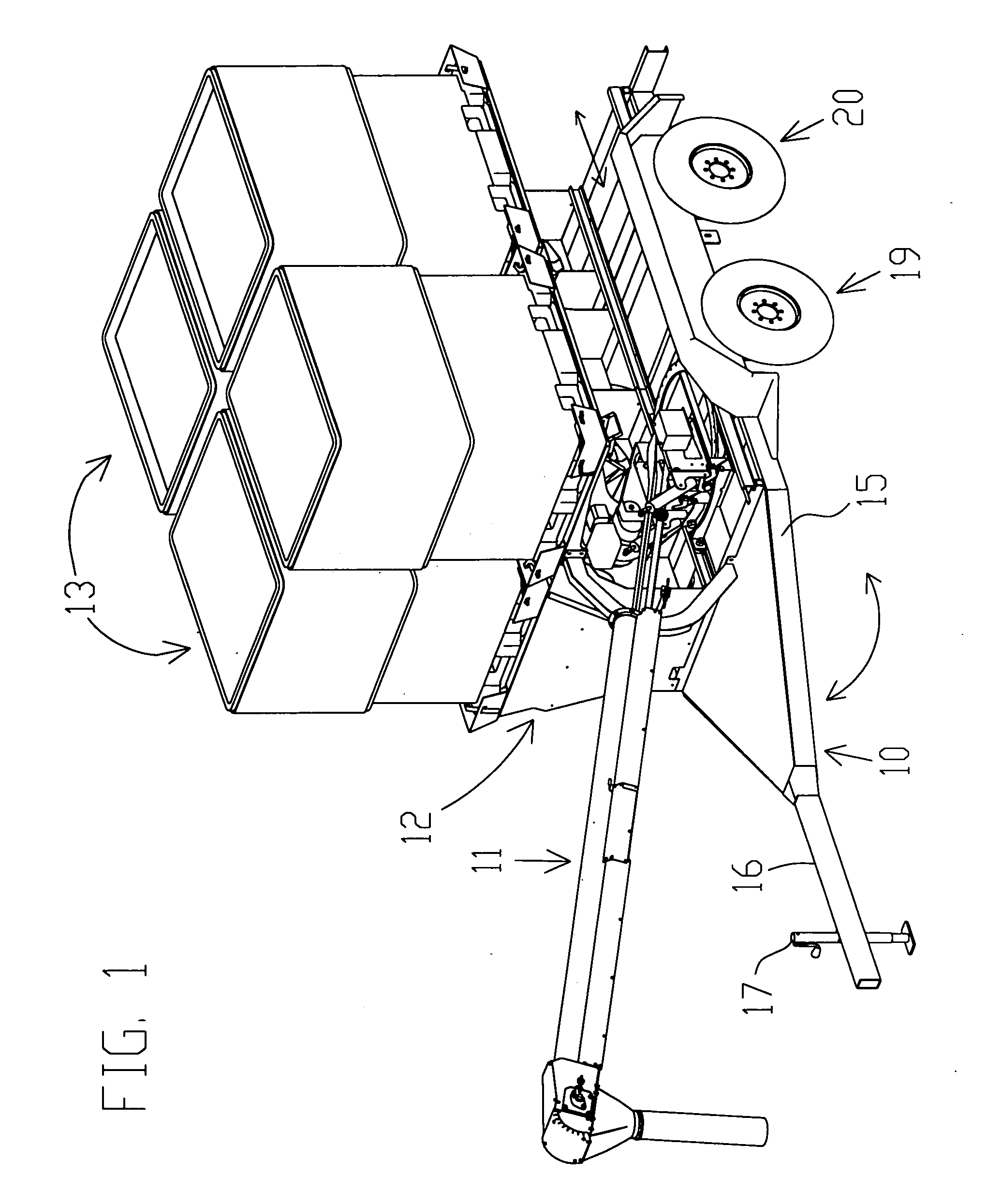

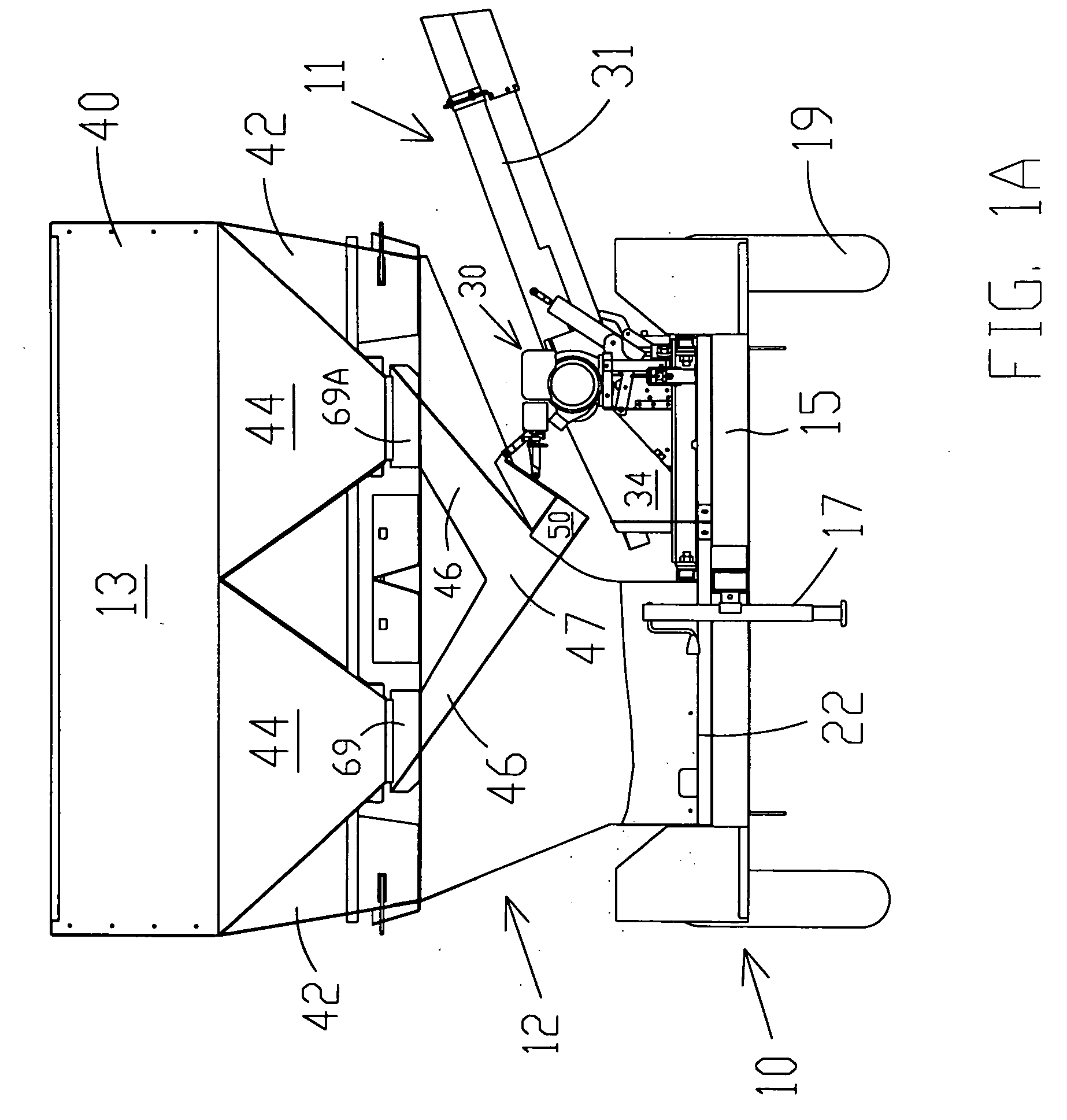

Agricultural seed tender with modular storage containers

ActiveUS7500817B2Improve economyIncrease storage capacityConveyorsMovable measuring chambersComputer moduleEngineering

Owner:MERIDIAN MFG

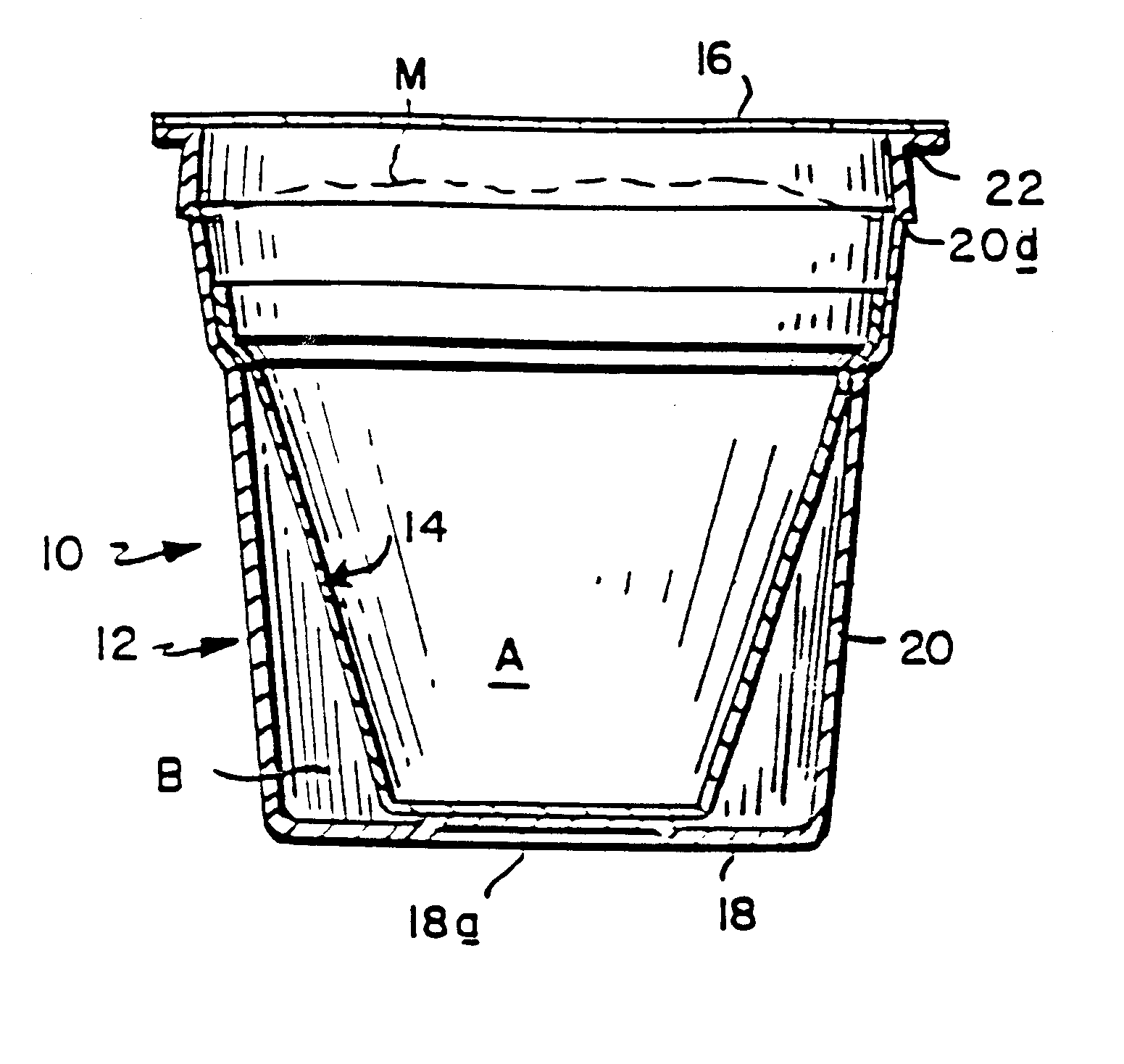

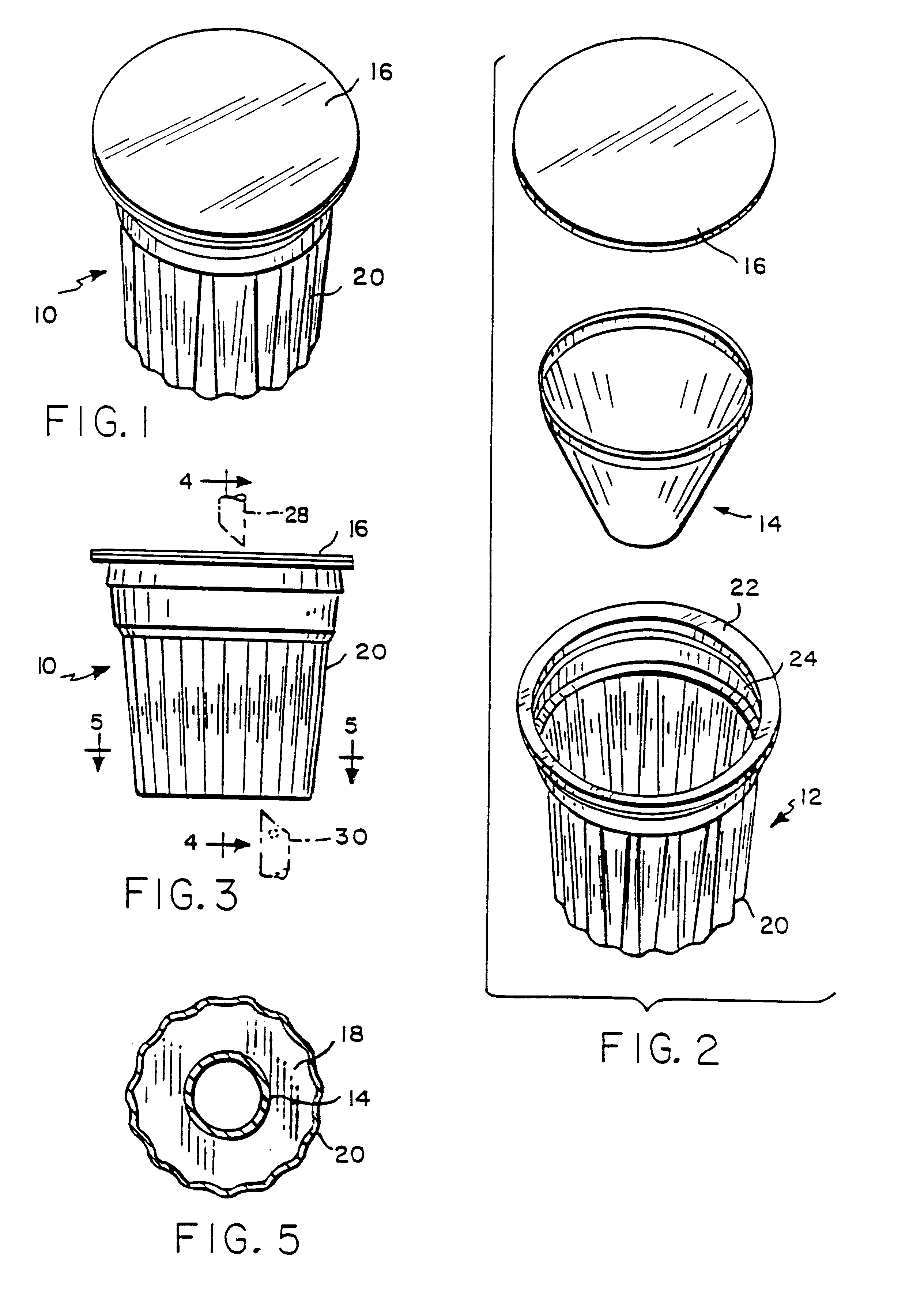

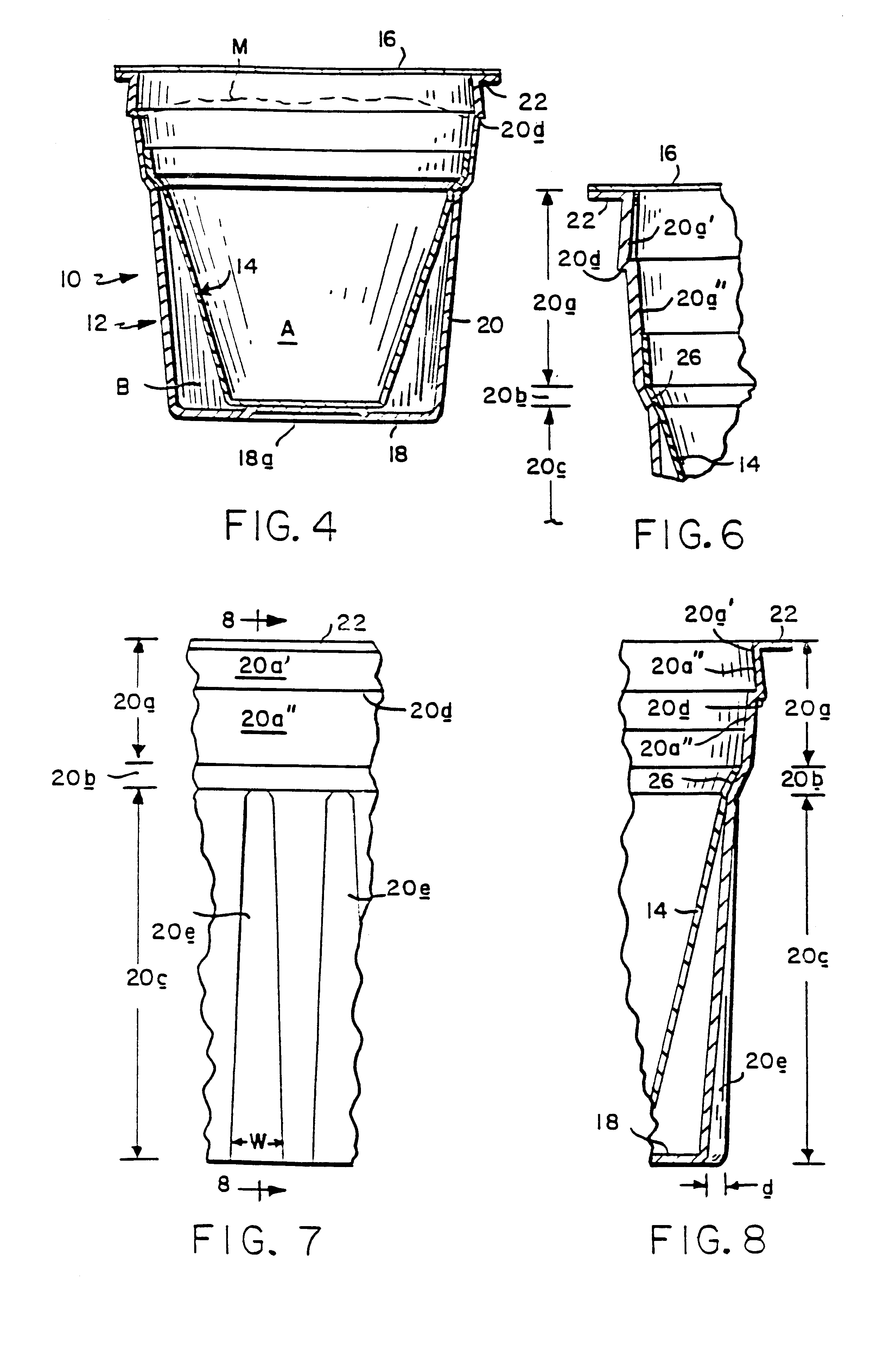

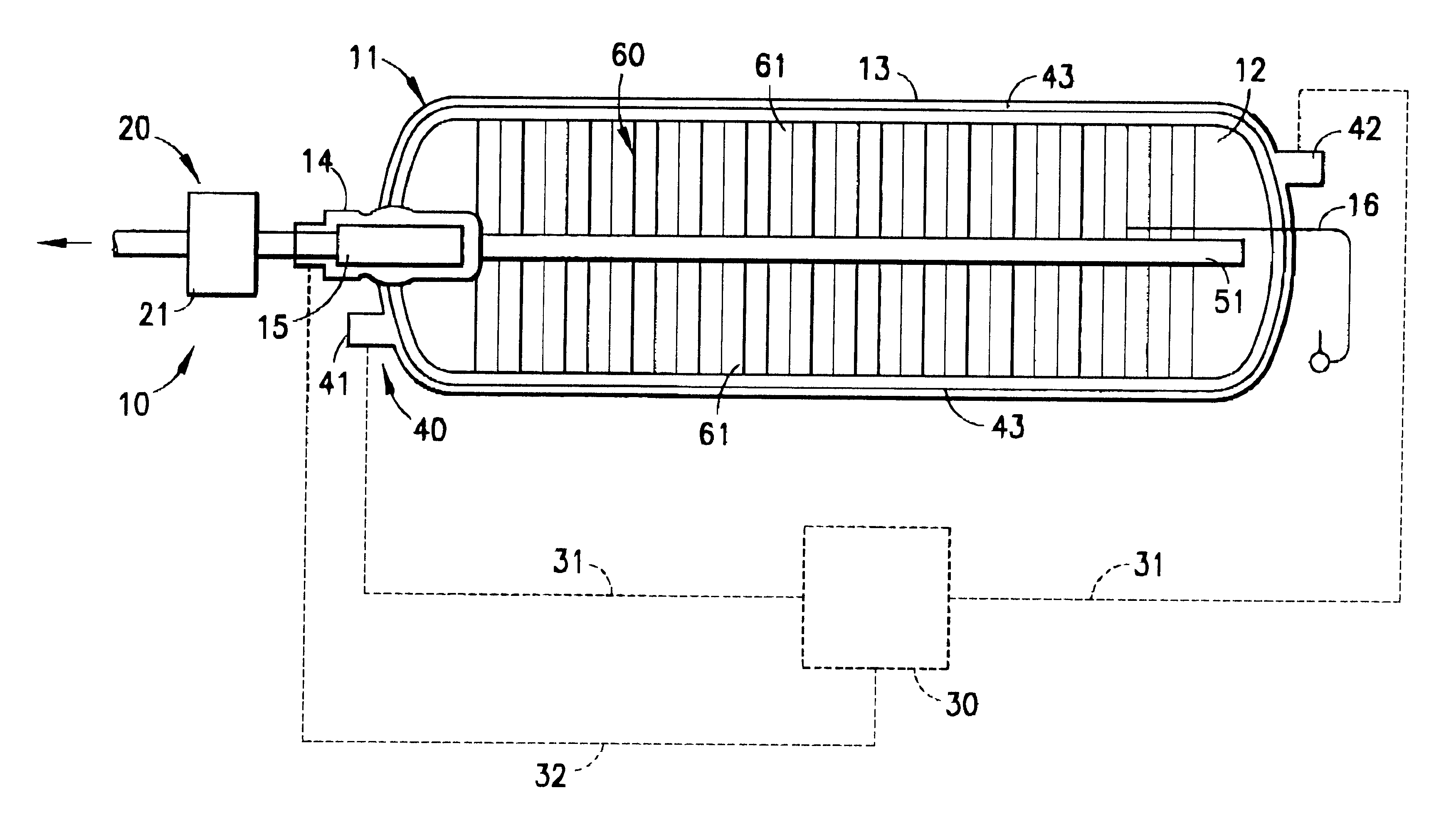

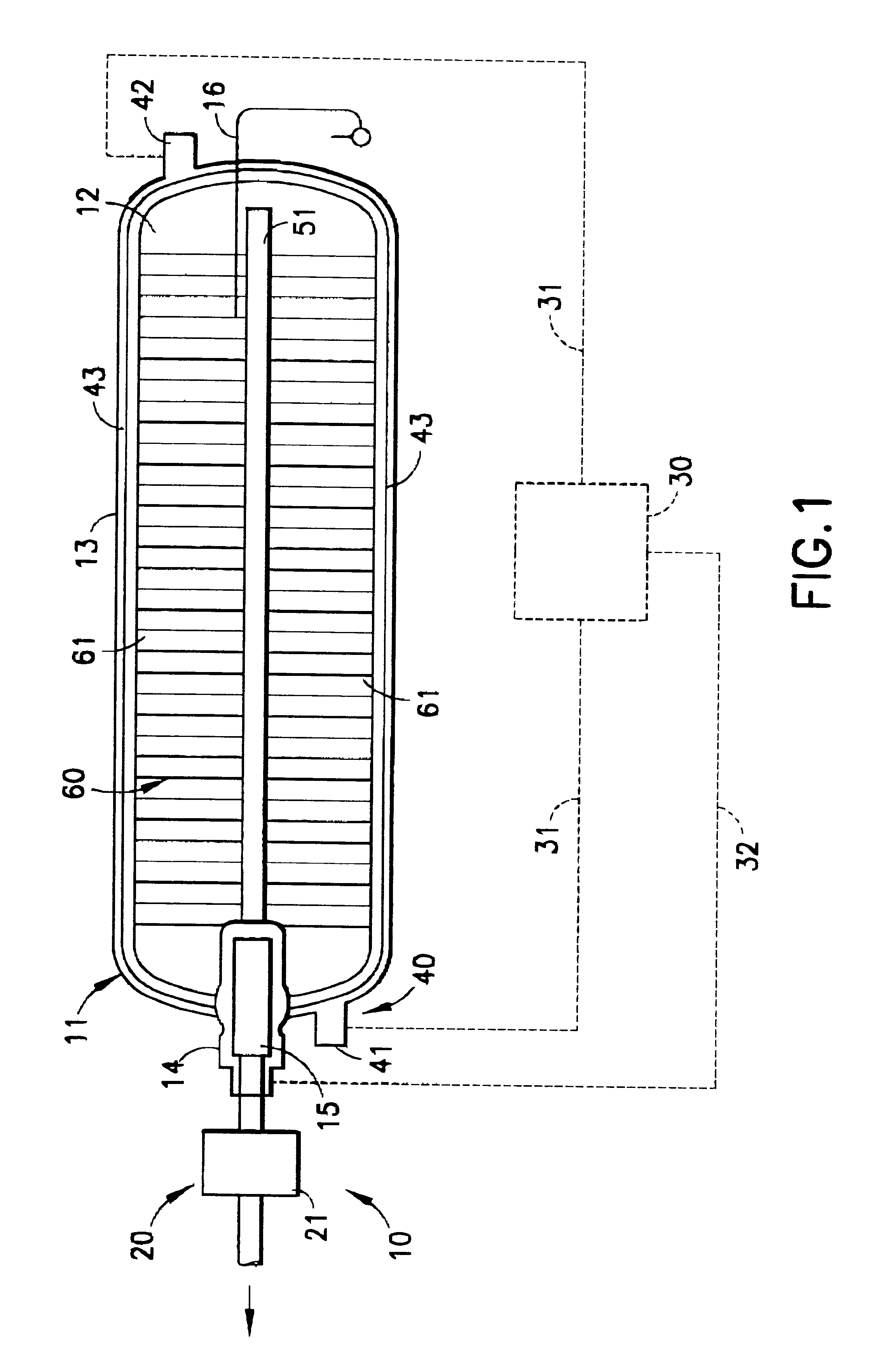

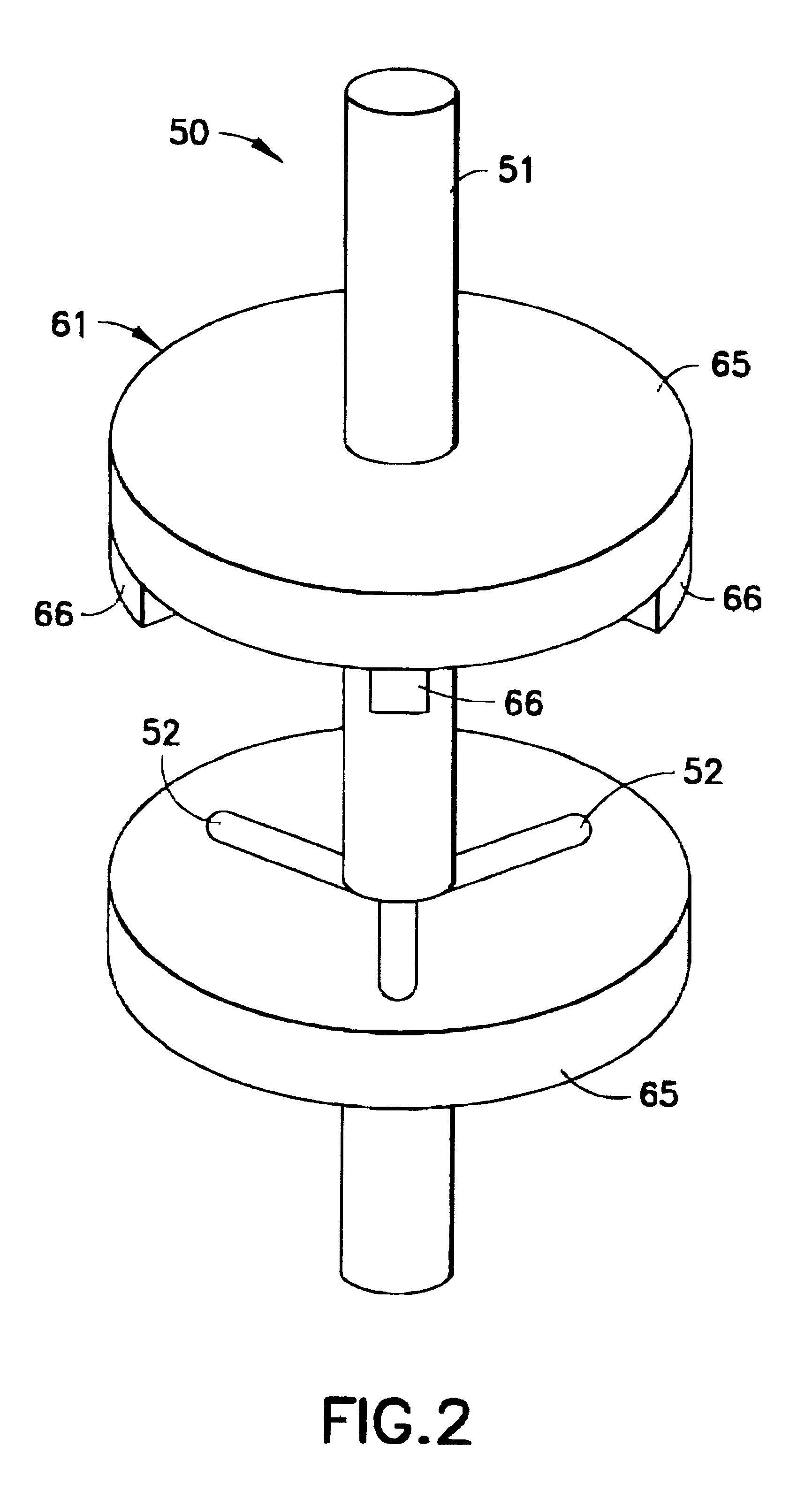

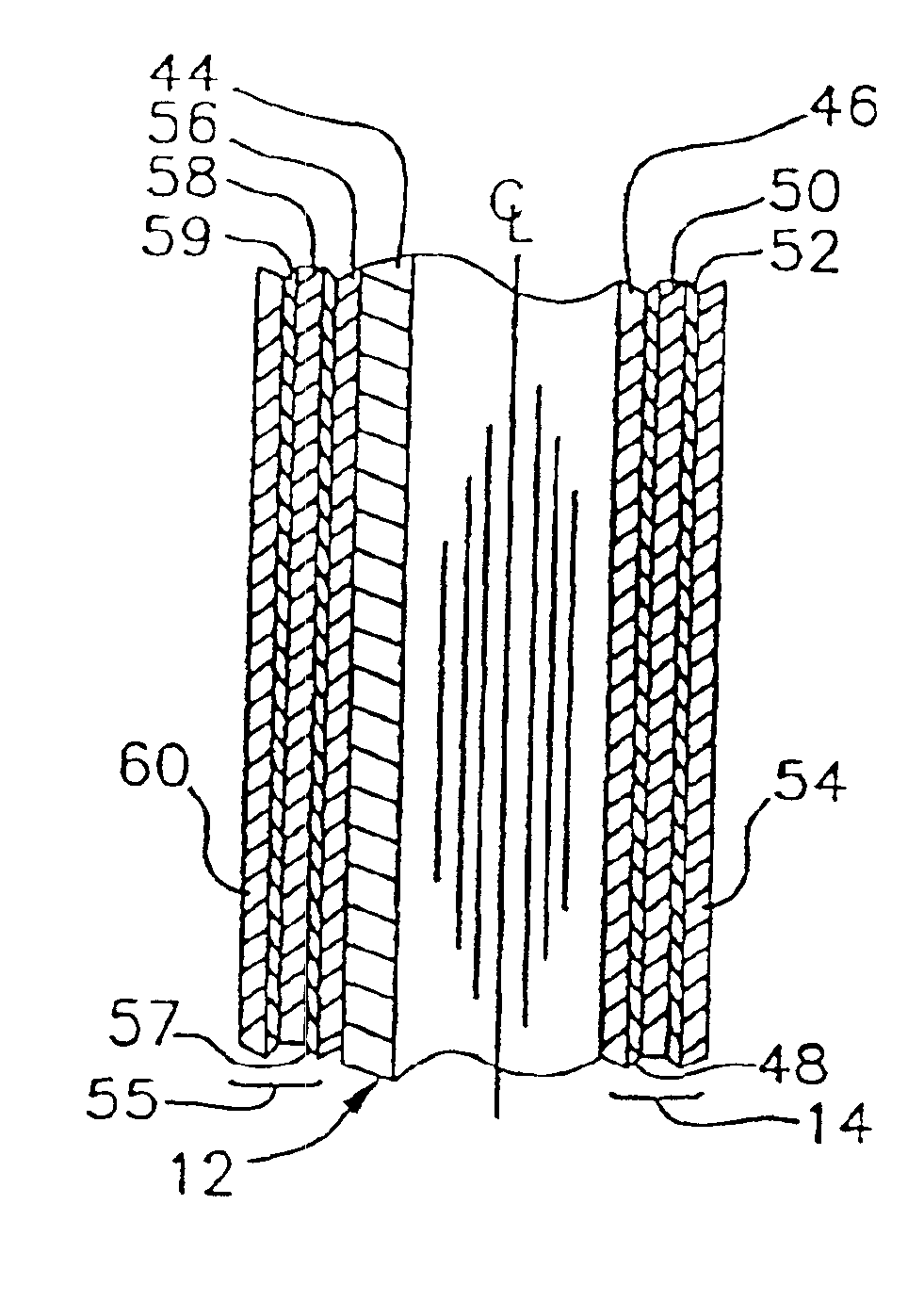

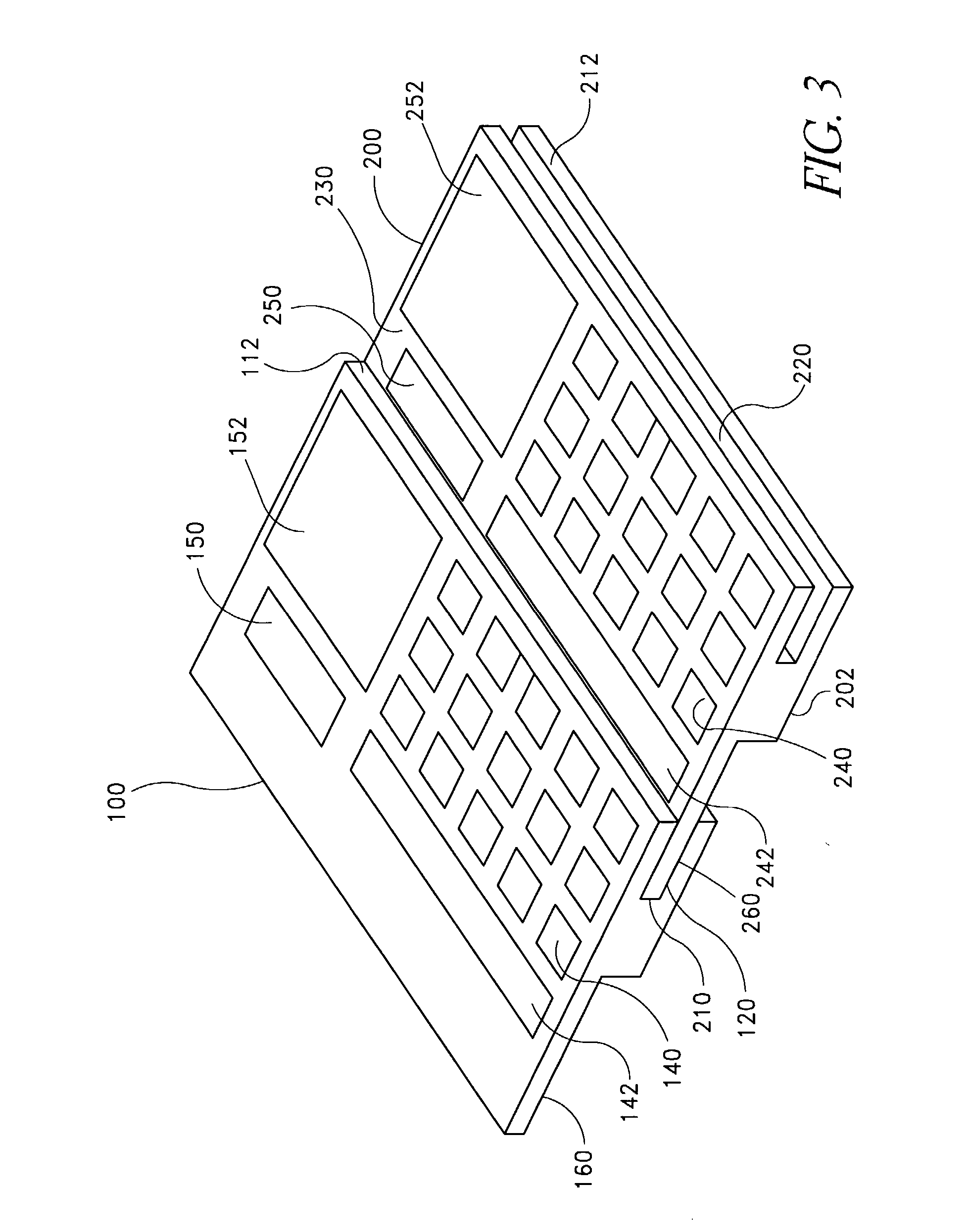

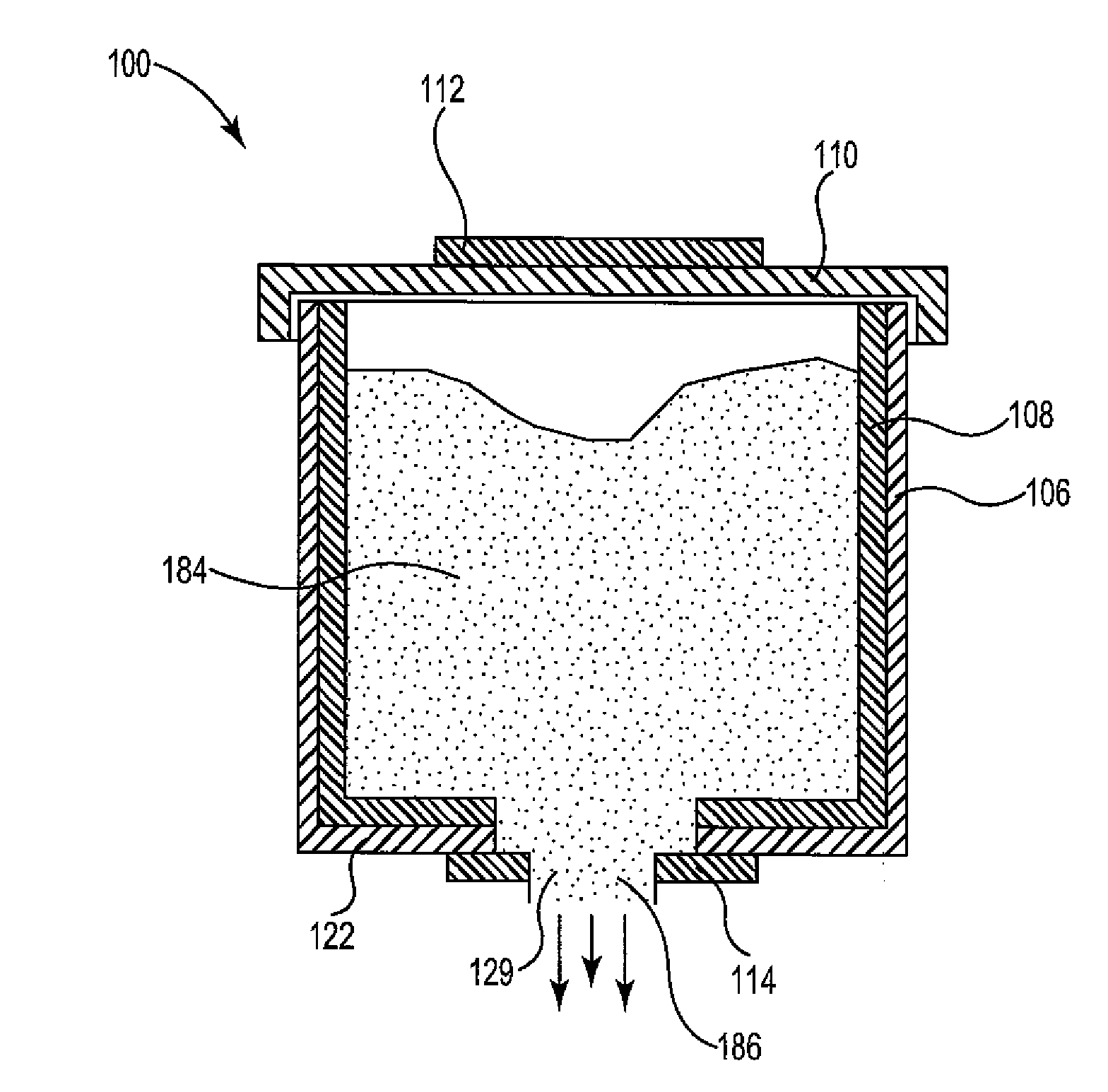

Beverage filter cartridge

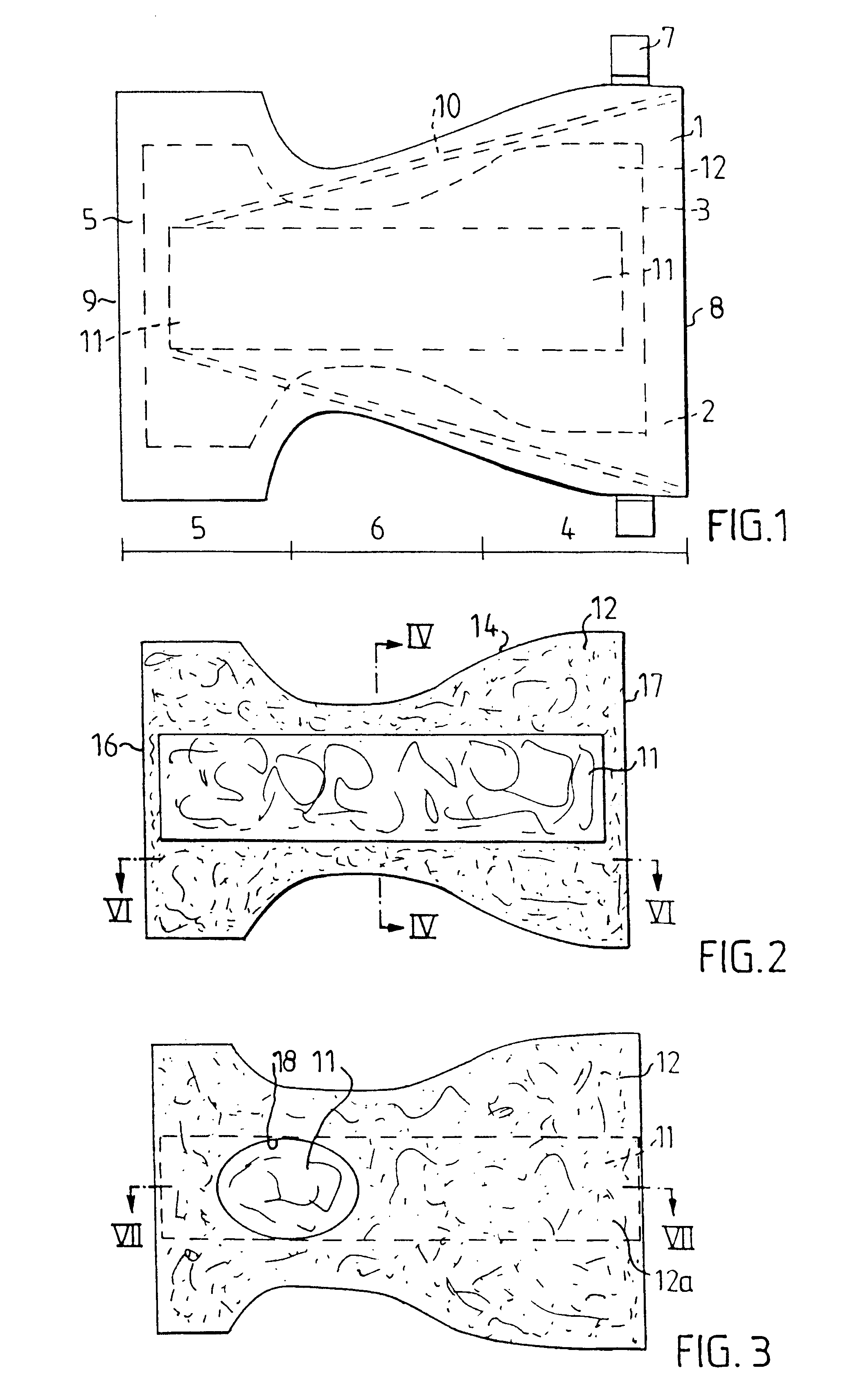

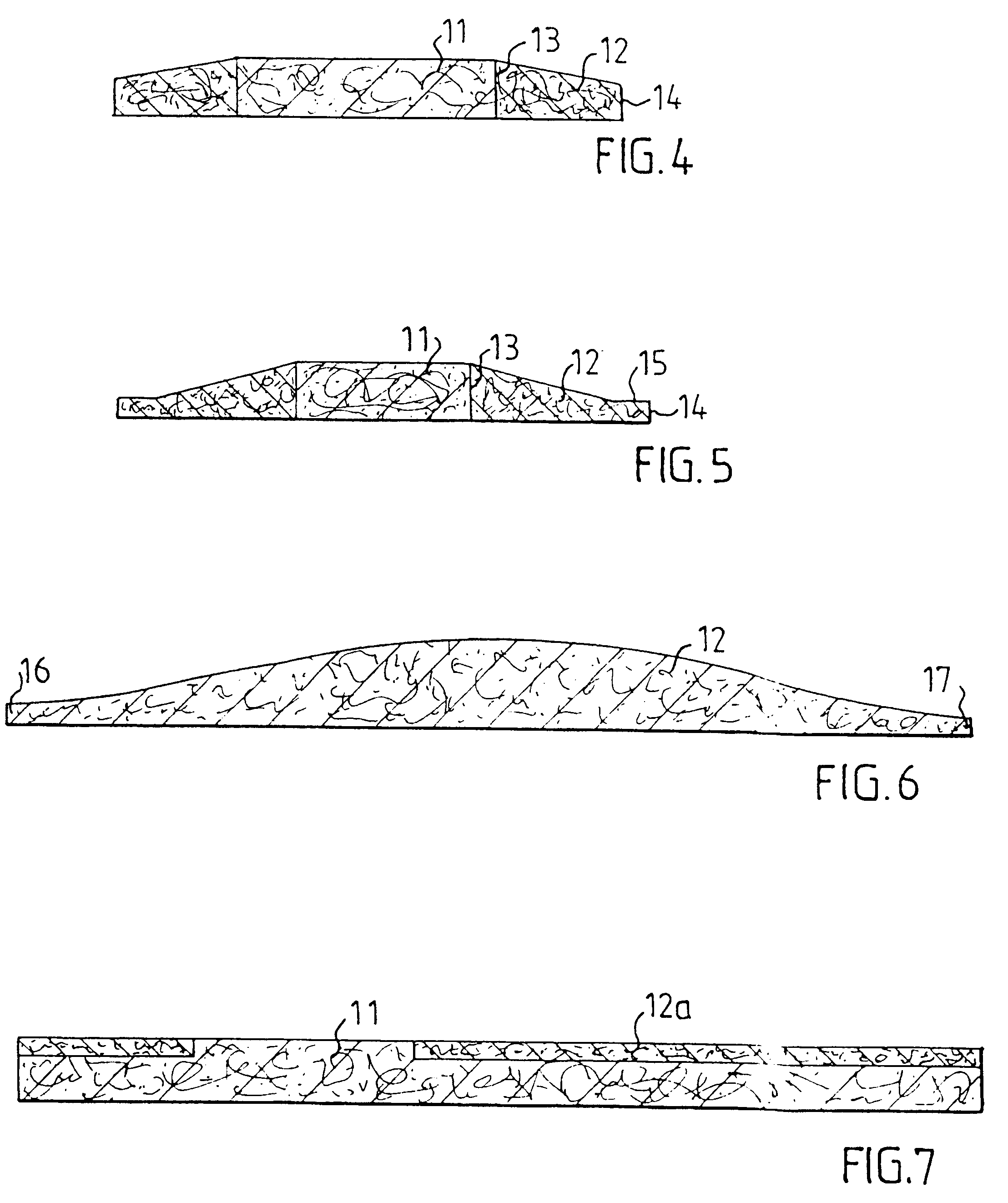

InactiveUS20020020659A1Increase storage capacityImprove the immunityLoose filtering material filtersCartridge filtersEngineeringMechanical engineering

A beverage filter cartridge includes a cup-shaped outer container with a bottom and a side wall extending upwardly from the bottom wall to a circular rim surrounding an upper opening. The side wall has an upper section extending downwardly from the rim to an intermediate section, and a tapered lower section configured to provide a plurality of circumferentially spaced flutes extending downwardly from the intermediate section to the bottom wall. A filter element subdivides the interior of the container into first and second chambers. A beverage medium is stored in the first chamber. A cover is joined to the side wall at the rim to close the upper opening. The cover is yieldably piercable to accommodate an injection of liquid into the first chamber for combination with the beverage medium to produce a beverage. The filter element is permeable to accommodate a flow of the beverage from the first chamber into the second chamber, and the bottom wall is yieldably piercable to accommodate an outflow of the beverage from the second chamber to the exterior of the cartridge.

Owner:KEURIG GREEN MOUNTAIN INC

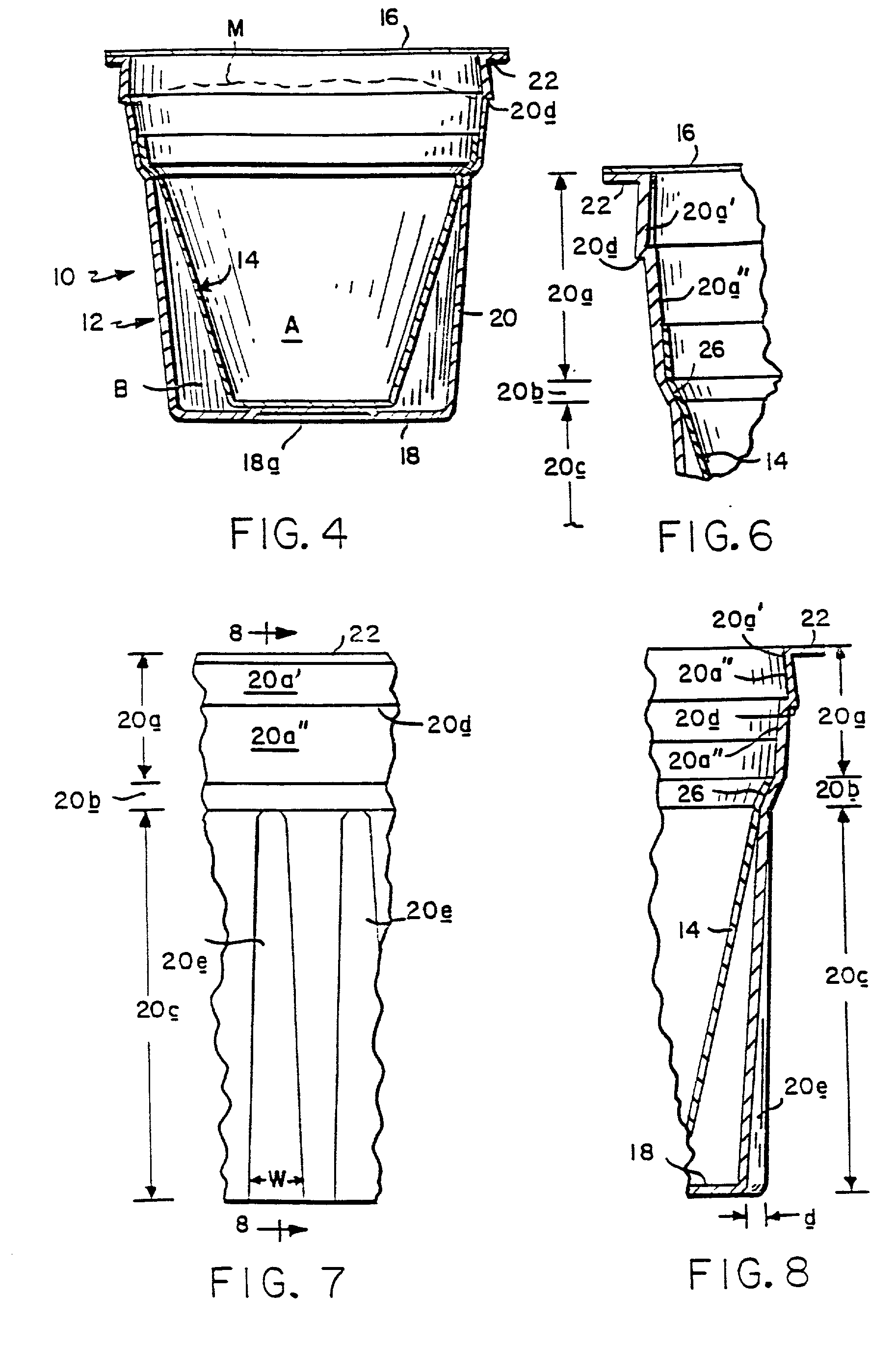

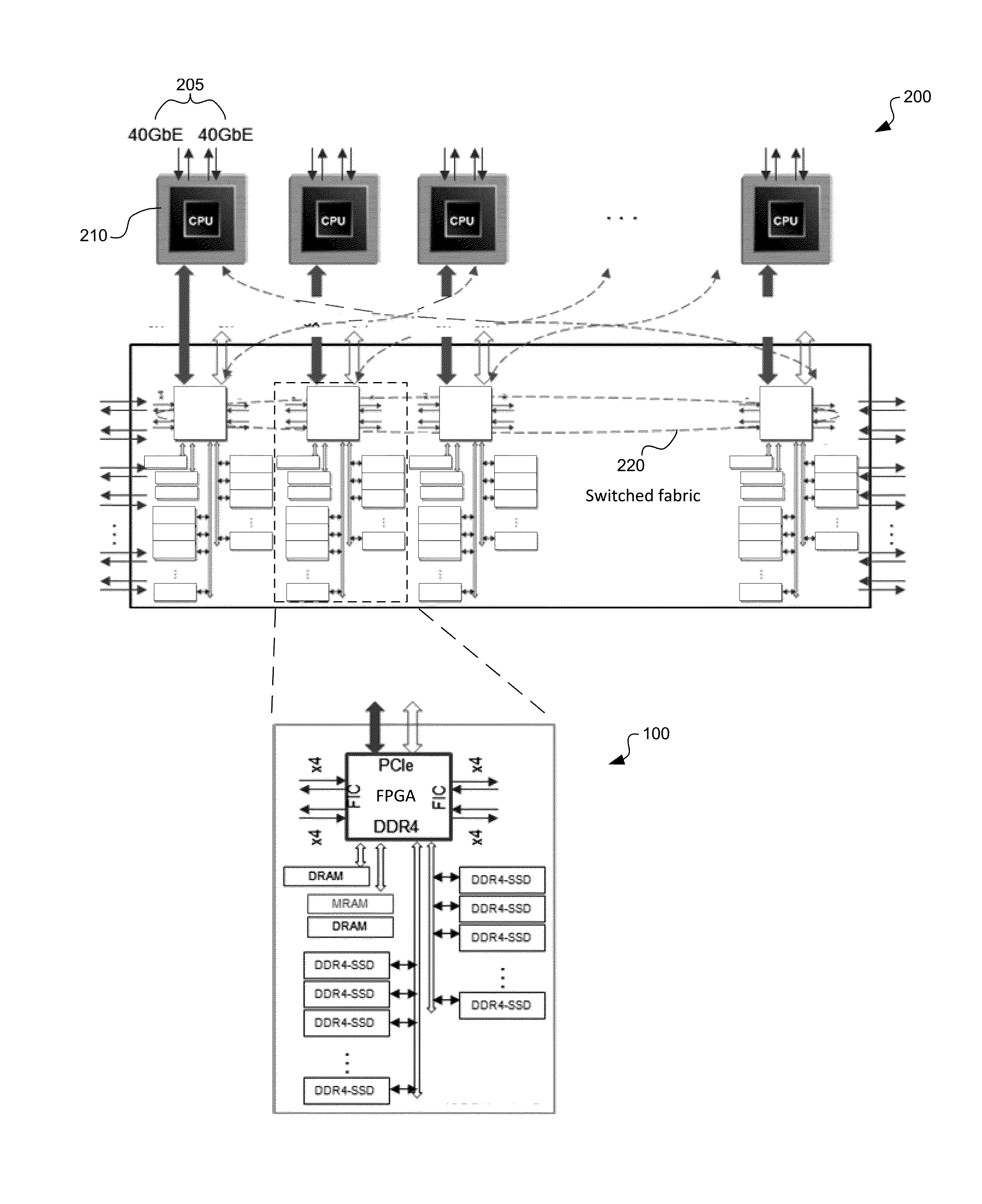

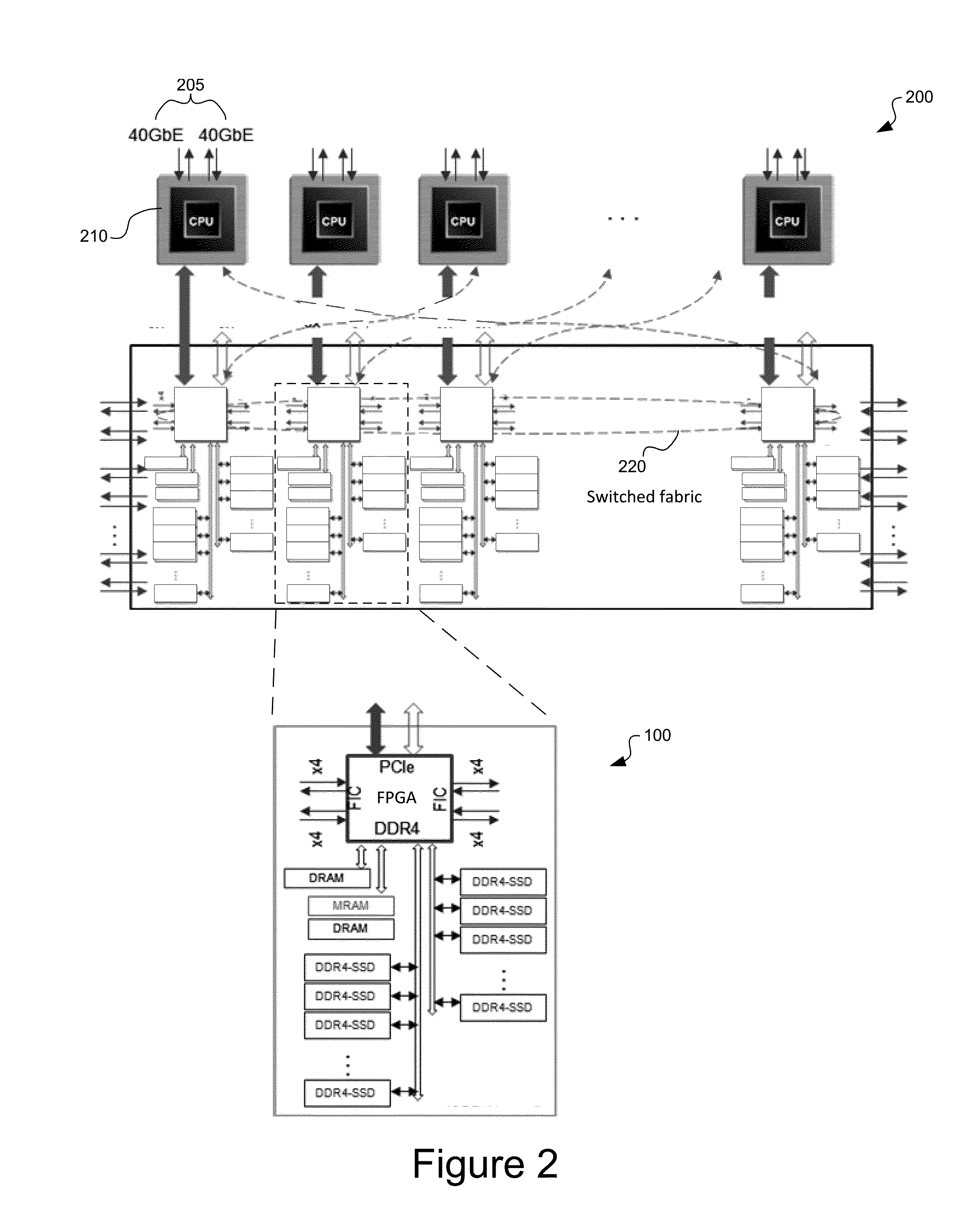

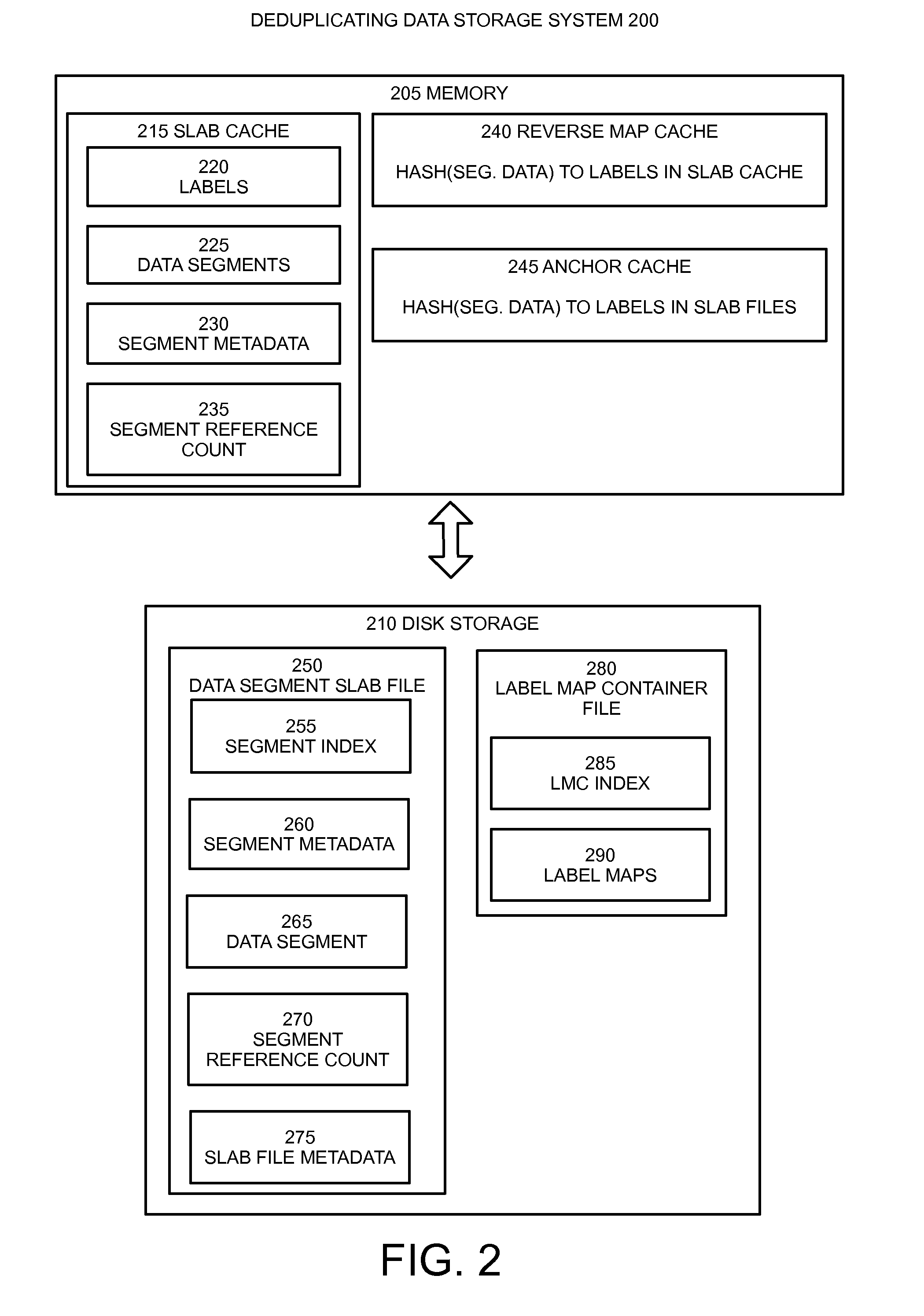

Rdma-ssd dual-port unified memory and network controller

ActiveUS20150254003A1Increase storage capacityLower latencyMemory architecture accessing/allocationInput/output to record carriersMagnetic reluctanceData memory

System and method for a unified memory and network controller for an all-flash array (AFA) storage blade in a distributed flash storage clusters over a fabric network. The unified memory and network controller has 3-way control functions including unified memory buses to cache memories and DDR4-AFA controllers, a dual-port PCIE interconnection to two host processors of gateway clusters, and four switch fabric ports for interconnections with peer controllers (e.g., AFA blades and / or chassis) in the distributed flash storage network. The AFA storage blade includes dynamic random-access memory (DRAM) and magnetoresistive random-access memory (MRAM) configured as data read / write cache buffers, and flash memory DIMM devices as primary storage. Remote data memory access (RDMA) for clients via the data caching buffers is enabled and controlled by the host processor interconnection(s), the switch fabric ports, and a unified memory bus from the unified controller to the data buffer and the flash SSDs.

Owner:FUTUREWEI TECH INC

Wan-optimized local and cloud spanning deduplicated storage system

InactiveUS20110161291A1Easy to useImprove performanceDigital data information retrievalDigital data processing detailsCloud baseClient-side

A spanning storage interface facilitates the use of cloud storage services by storage clients. The spanning storage interface presents one or more data interfaces to storage clients at a network location, such as file, object, data backup, archival, and storage block based interfaces. The data interfaces allows storage clients to store and retrieve data using non-cloud based protocols. The spanning storage interface may perform data deduplication on data received from storage clients. The spanning storage interface may transfer the deduplicated version of the data to the cloud storage service. The spanning storage interface may include local storage for storing a copy or all or a portion of the data from storage clients. The local storage may be used as a local cache of frequently accessed data, which may be stored data in its deduplicated form.

Owner:NETWORK APPLIANCE INC

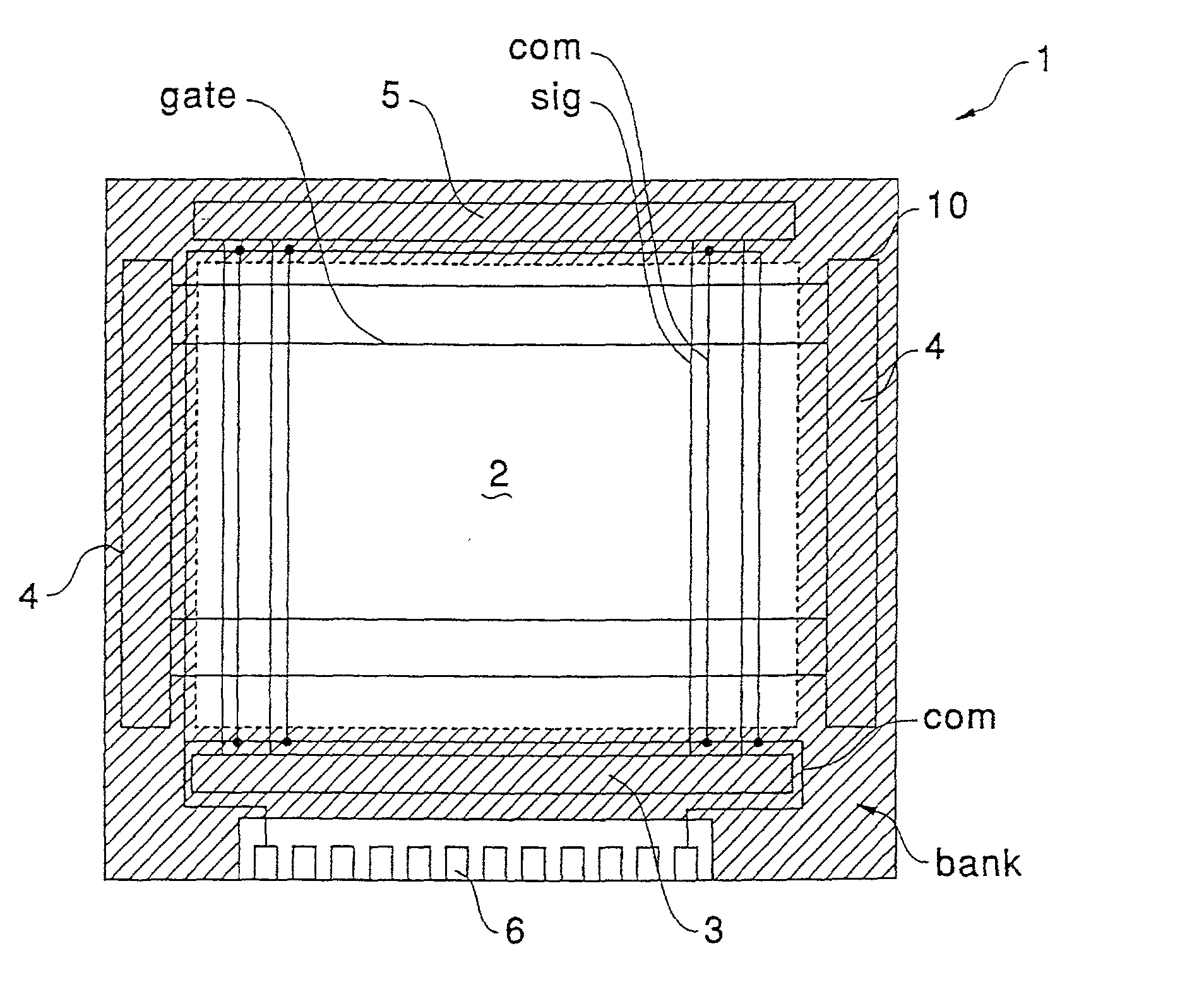

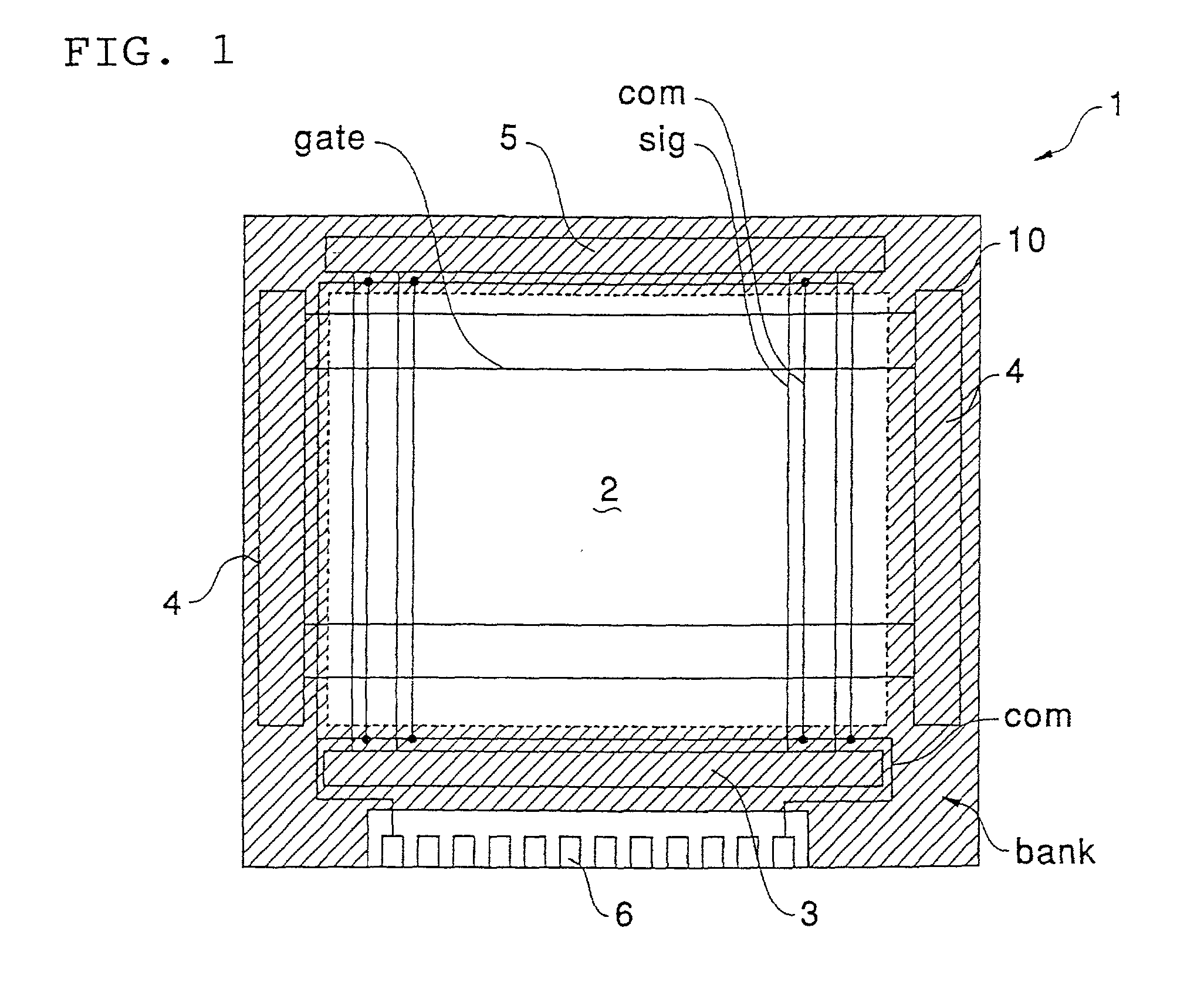

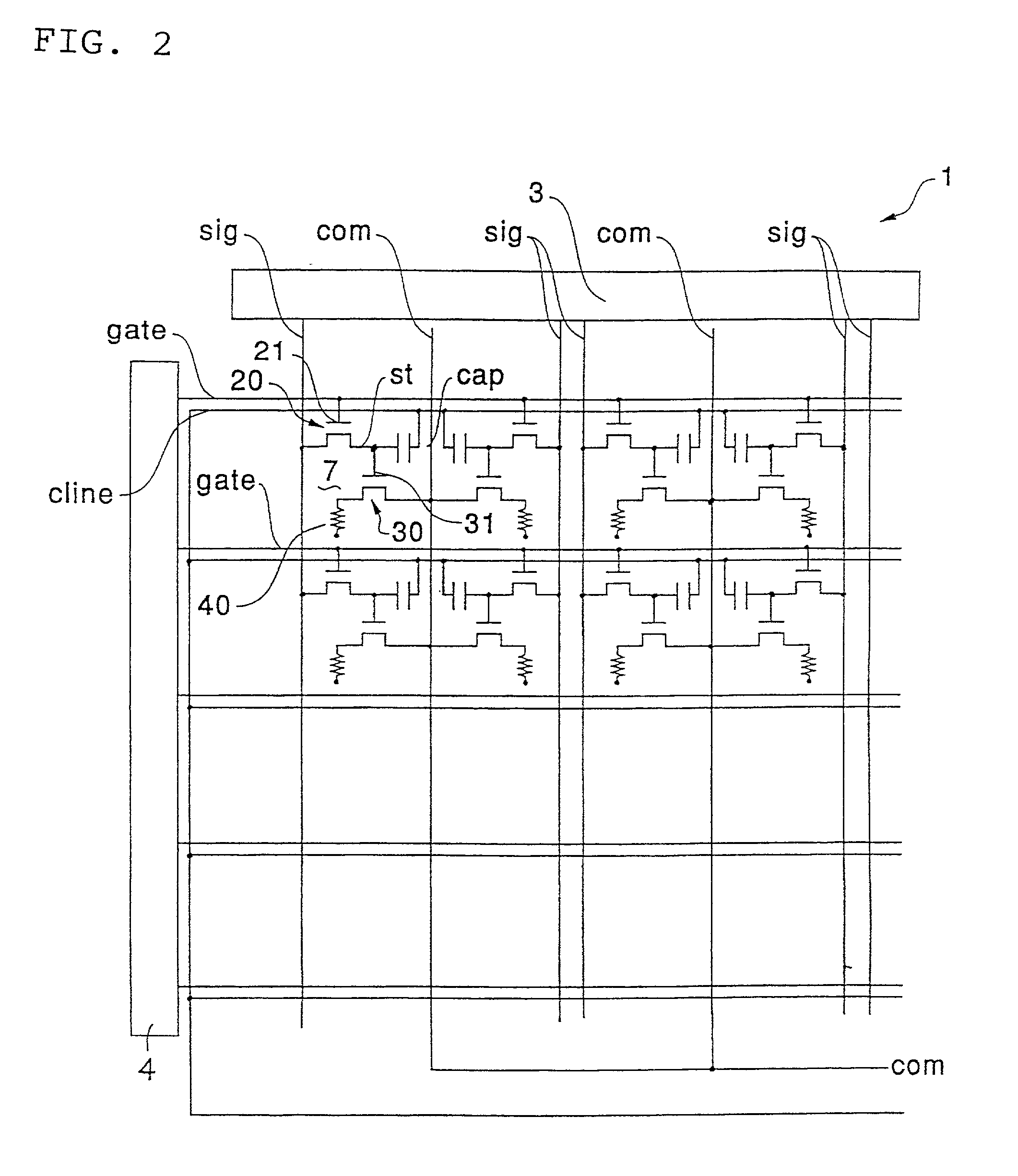

Display apparatus

InactiveUS20020024493A1Increase storage capacityIncrease emission luminanceStatic indicating devicesElectroluminescent light sourcesVIT signalsN channel

A display apparatus, that includes current driving type luminescent elements, has a driving system that takes the conduction types of TFTs to control the emission of the luminescent elements into consideration. In order to reduce driving voltage and improve display quality simultaneously, the arrangement is provided such that if the second TFT (30) which performs the "on-off" function of the current for the luminescent element (40) is of an N channel type, the potential of the common power supply line ("com") is lowered below the potential of the opposite electrode ("op") of the luminescent element (40) to obtain a higher gate voltage ("Vgcur"). In this case, if the first TFT (20) connected to the gate of the second TFT (30) is of a P channel type, when using the potential of the potential-holding electrode ("st") at the "on" state as a reference, potentials of the scanning signal ("Sgate") at the lower potential and the common power supply line ("com") are rendered of the same polarities with respect to this potential of the potential-holding electrode ("st"). Therefore, the potential of the image signal ("data") to turn "on" can be shifted within the range of the driving voltage in the display apparatus (1) in the direction to reduce resistances at the "on" states of the first TFT (20) and the second TFT (30) to reduce driving voltage and improve display quality.

Owner:INTELLECTUAL KEYSTONE TECH

Agricultural seed tender with modular storage containers

ActiveUS20060180062A1Improve economyImprove stabilityConveyorsMovable measuring chambersEngineeringAdemetionine

A trailer having support wheels and a frame adapted to be hitched to a truck, includes a support track extending longitudinally for supporting an unload conveyor. The conveyor is mounted by a turret to the support track and, thus, to the trailer frame, permitting the turret to move in a fore-to-aft direction, as well as to rotate about the vertical for about 180°, providing flexibility in use as well as transport and storage. A support module, carrying at least one storage container is mounted on the trailer frame. The storage containers may be provided in a number of different sizes and they may be arranged in various configurations suiting the user's needs. The turret is positioned along the track beneath a desired seed container, which may then be unloaded by the conveyor to fill a planter seed box or grain drill, or for other seed handling applications.

Owner:MERIDIAN MFG

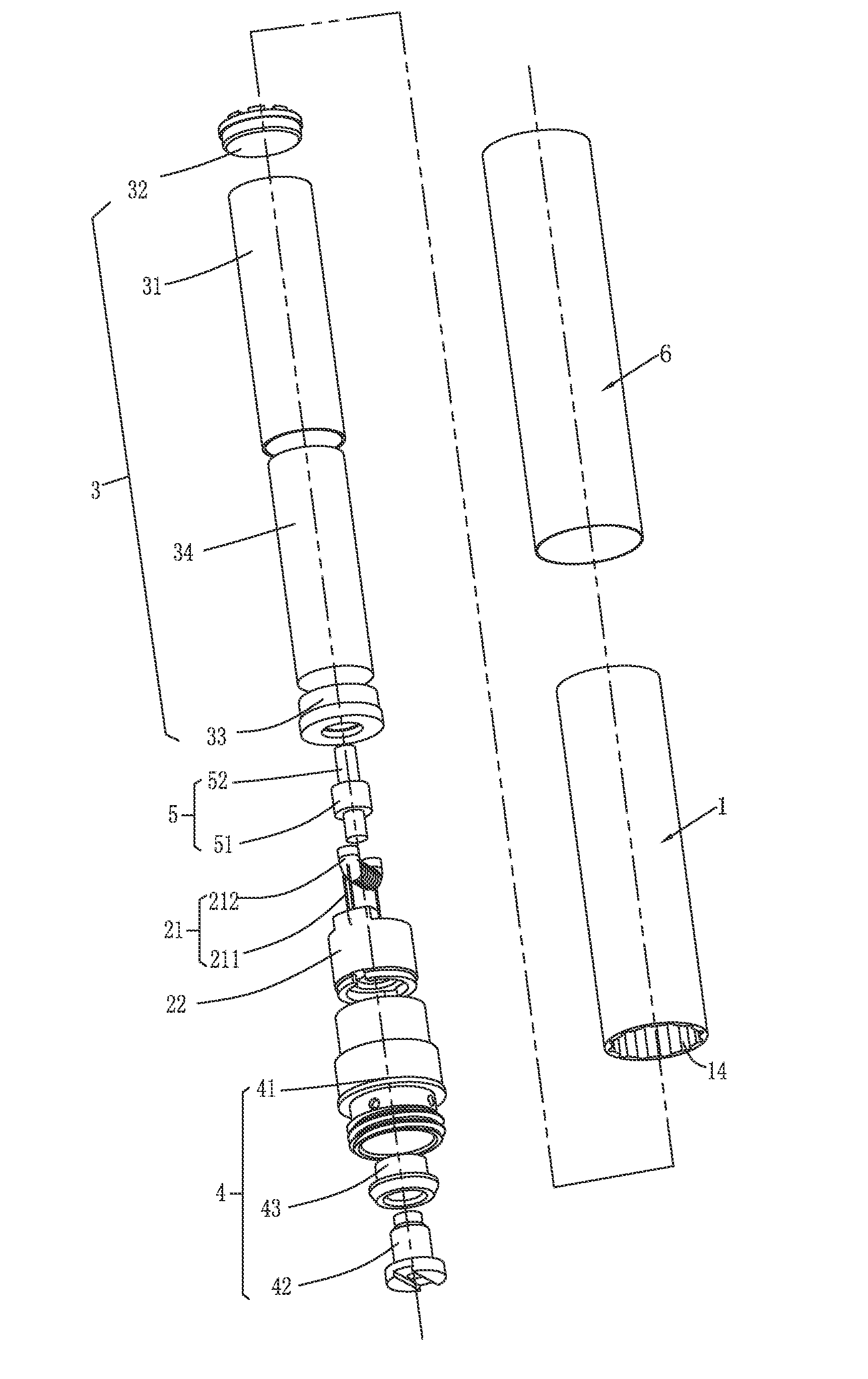

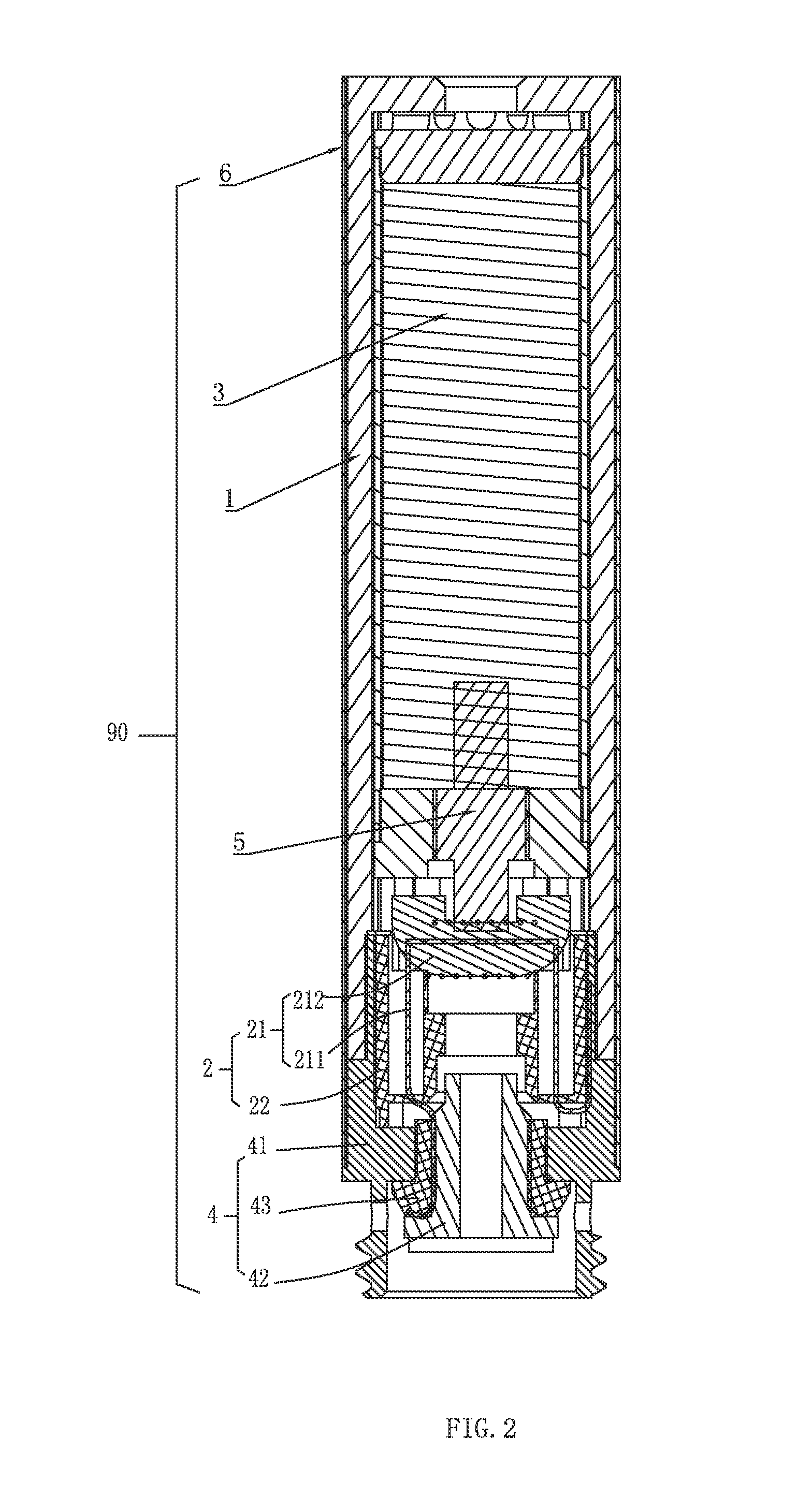

Electronic Cigarette and Soft Absorption Stem Thereof

InactiveUS20140182610A1Compact internal structureUnique smoke pathTobacco pipesTobacco devicesElectronic cigaretteSoft materials

A soft absorption stem for an electronic cigarette is provided, comprising a sleeve, a cigar liquid tank disposed inside the sleeve, an atomization device and a liquid guiding component. The sleeve is made of soft material; a plurality of venting slots is extended axially from one end of the sleeve to the other end thereof and disposed on an inner wall of the sleeve; the sleeve includes a mouthpiece end and a connection end; a suction hole communicating with the venting slots is provided on the mouthpiece end; smoke produced by atomization of the atomization device flows out of the sleeve from the venting slots across the suction hole. The electronic cigarette makes the user more comfortable when holding the sleeve in hand and containing in mouth, having more compact internal construction, having unique smoke path, and having increased cigar liquid storage capacity.

Owner:HUIZHOU KIMREE TECH

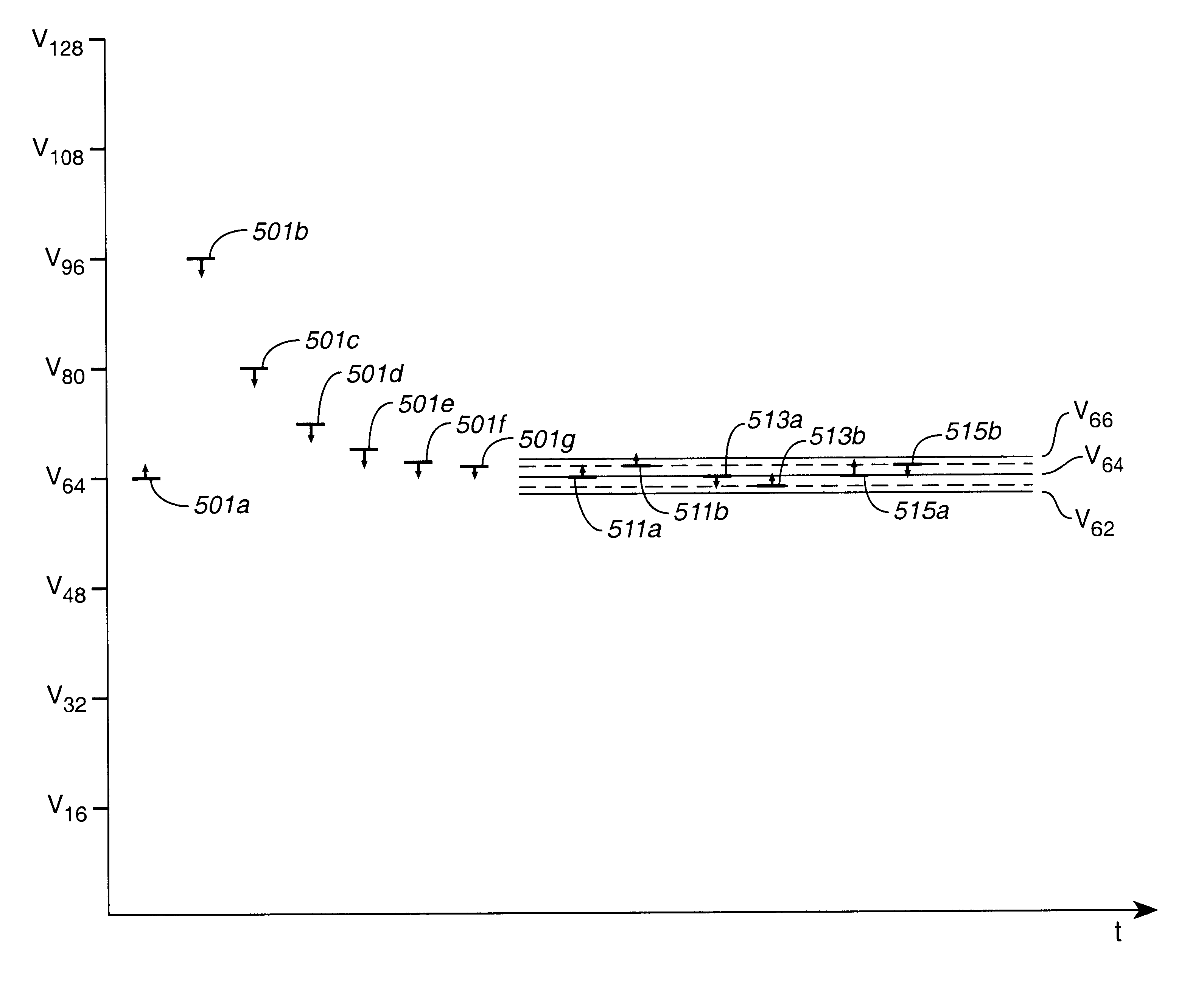

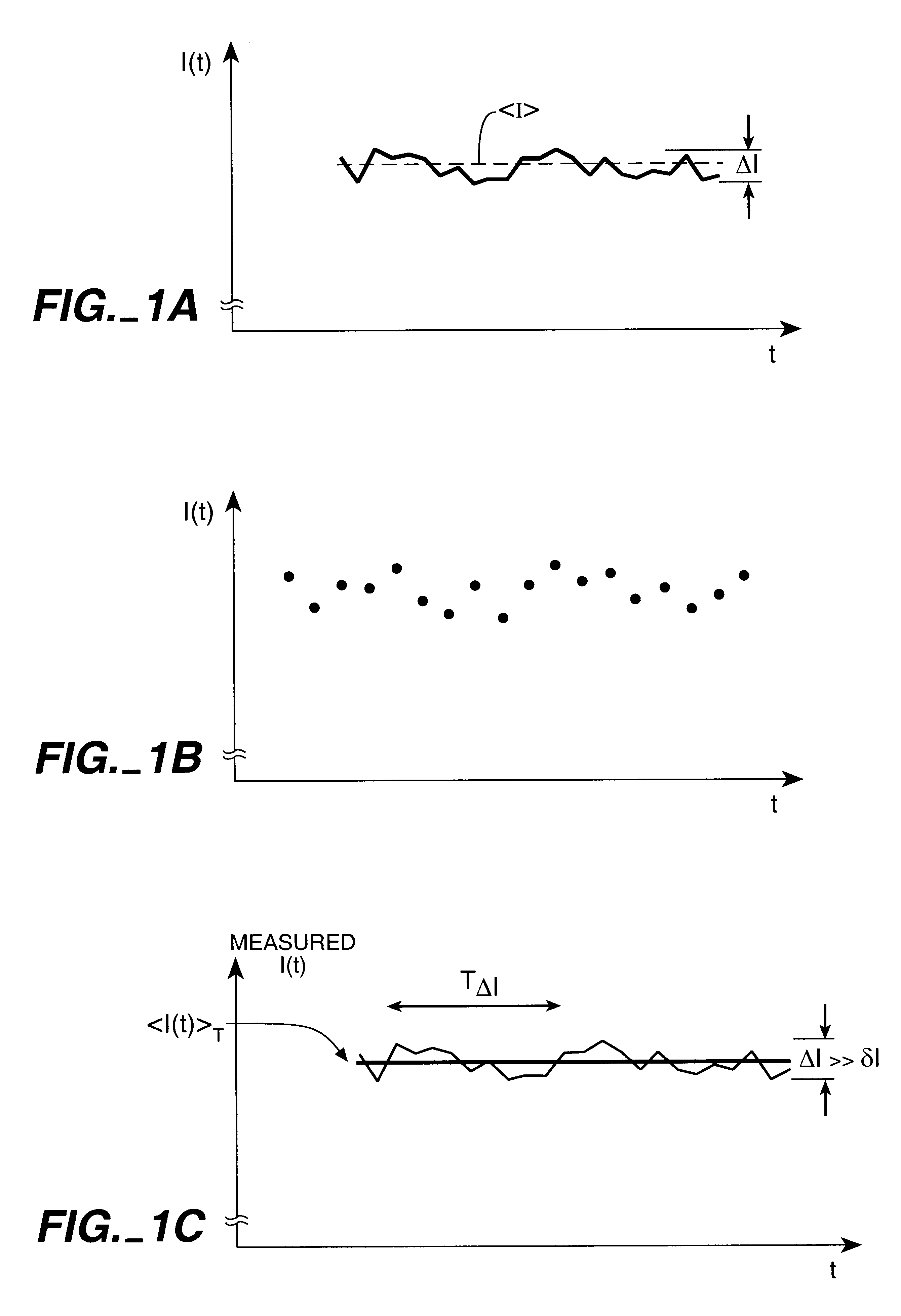

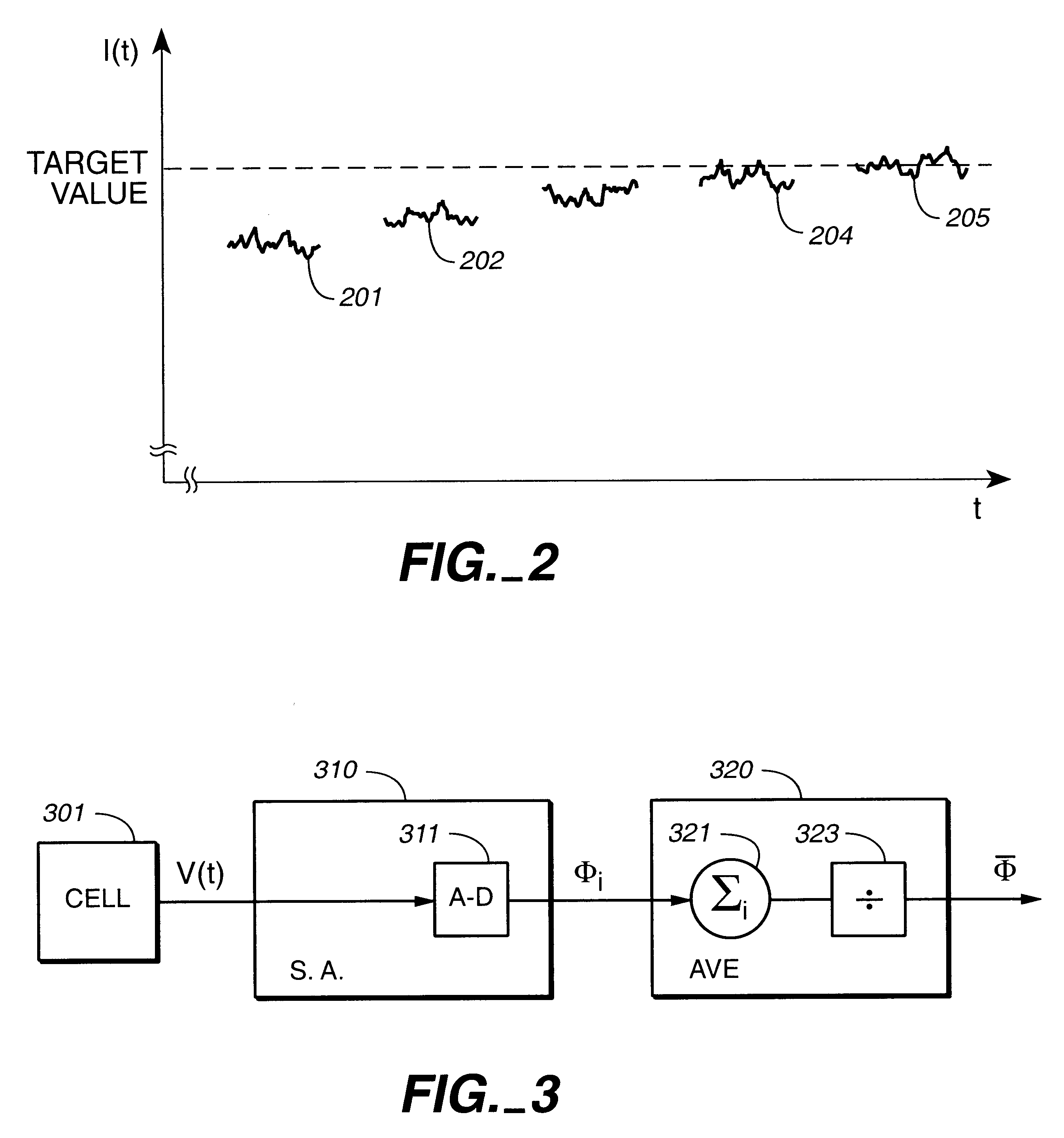

Reducing the effects of noise in non-volatile memories through multiple reads

InactiveUS6621739B2Increase storage capacityReduce physical sizeRead-only memoriesDigital storageNormal modeOperation mode

Storage elements are read multiple times and the results are accumulated and averaged for each storage element to reduce the effects of noise or other transients in the storage elements and associated circuits that may adversely affect the quality of the read. Several techniques may be employed, including: A full read and transfer of the data from the storage device to the controller device for each iteration, with averaging performed by the controller; a full read of the data for each iteration, with the averaging performed by the storage device, and no transfer to the controller until the final results are obtained; one full read followed by a number of faster re-reads exploiting the already established state information to avoid a full read, followed by an intelligent algorithm to guide the state at which the storage element is sensed. These techniques may be used as the normal mode of operation, or invoked upon exception condition, depending on the system characteristics. A similar form of signal averaging may be employed during the verify phase of programming. An embodiment of this technique would use a peak-detection scheme. In this scenario, several verify checks are performed at the state prior to deciding if the storage element has reached the target state. If some predetermined portion of the verifies fail, the storage element receives additional programming. These techniques allow the system to store more states per storage element in the presence of various sources of noise.

Owner:SANDISK TECH LLC

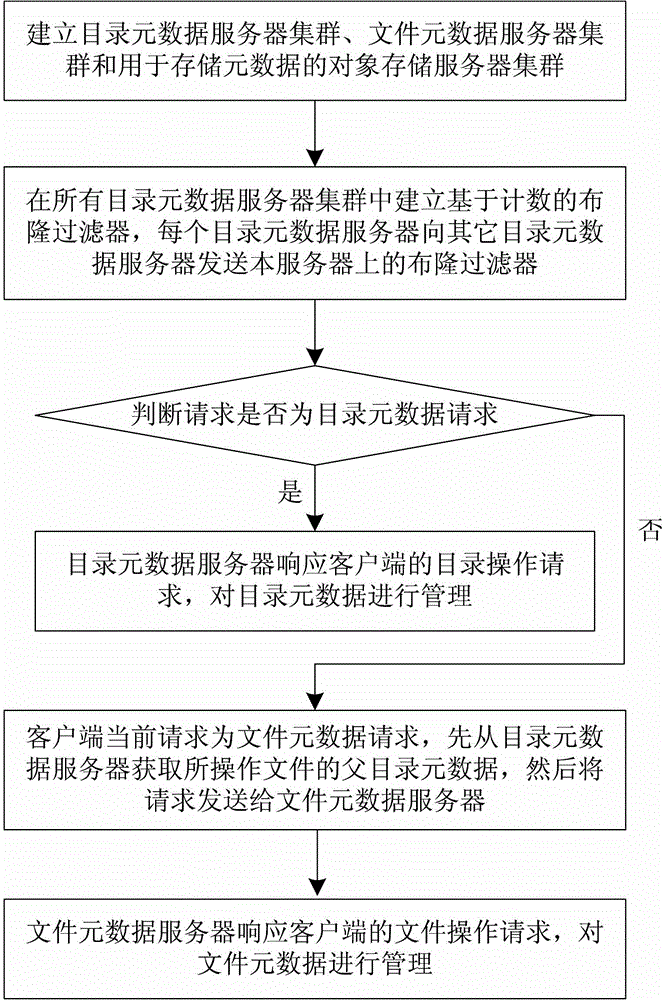

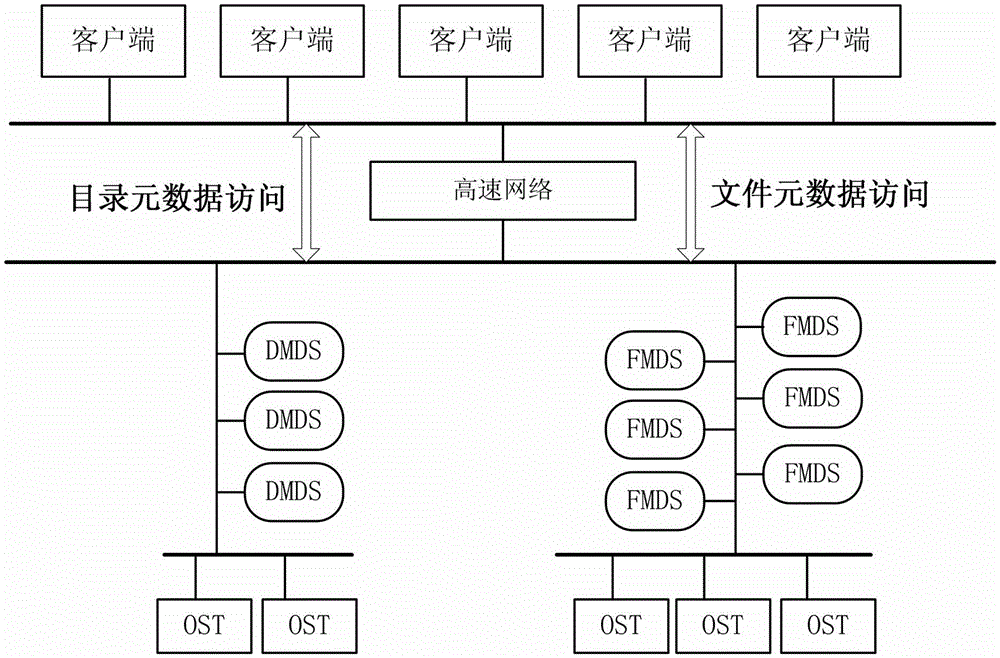

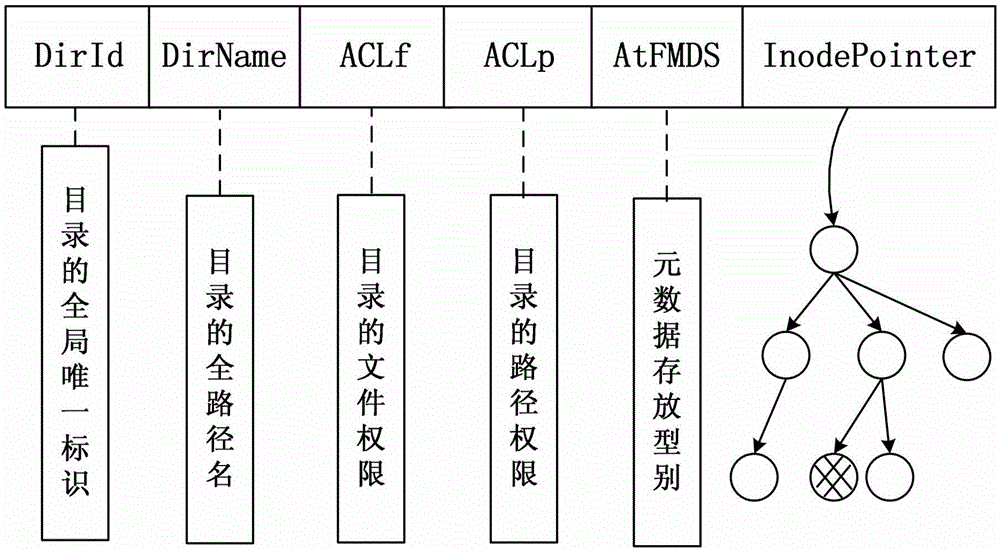

Distributed file system metadata management method facing to high-performance calculation

ActiveCN103150394AInhibit migrationLoad balancingTransmissionSpecial data processing applicationsDistributed File SystemMetadata management

The invention discloses a distributed file system metadata management method facing to high-performance calculation. The method comprises the following steps of: 1) establishing a catalogue metadata server cluster, a file metadata server cluster and an object storage server cluster; 2) establishing a global counting-based bloom filter in the catalogue metadata server cluster; 3) when the operation request of a client side arrives, skipping to execute step 4) or 5); 4) enabling the catalogue metadata server cluster to respond to the catalogue operation request of the client side to manage the catalogue metadata; and 5) enabling the file metadata server cluster to respond to the file operation request of the client side to manage the file metadata data. According to the distributed file system metadata management method disclosed by the invention, the metadata transferring problem brought by catalogue renaming can be effectively solved, and the distributed file system metadata management method has the advantages of high storage performance, small maintenance expenditure, high load, no bottleneck, good expansibility and balanced load.

Owner:NAT UNIV OF DEFENSE TECH

Absorbent structure that has a high degree of utilization

InactiveUS6441268B1Improve acquisitionImprove storage propertiesLayered productsBaby linensVolumetric Mass DensityBiomedical engineering

An absorbent structure in an absorbent article, such as a diaper, an incontinence guard, a sanitary napkin or like article. The structure includes a liquid-acquisition and liquid-dispersing core of high bulk, porous material. The core is in liquid communication with a liquid storage part that surrounds the core at least along its longitudinally extending side-edges and which has a mean pore size that is smaller than the mean pore size of the high bulk, porous core. The density of the liquid storage part increases in a direction out towards the longitudinally extending side-edges of the absorbant structure.

Owner:SCA HYGIENE PROD AB

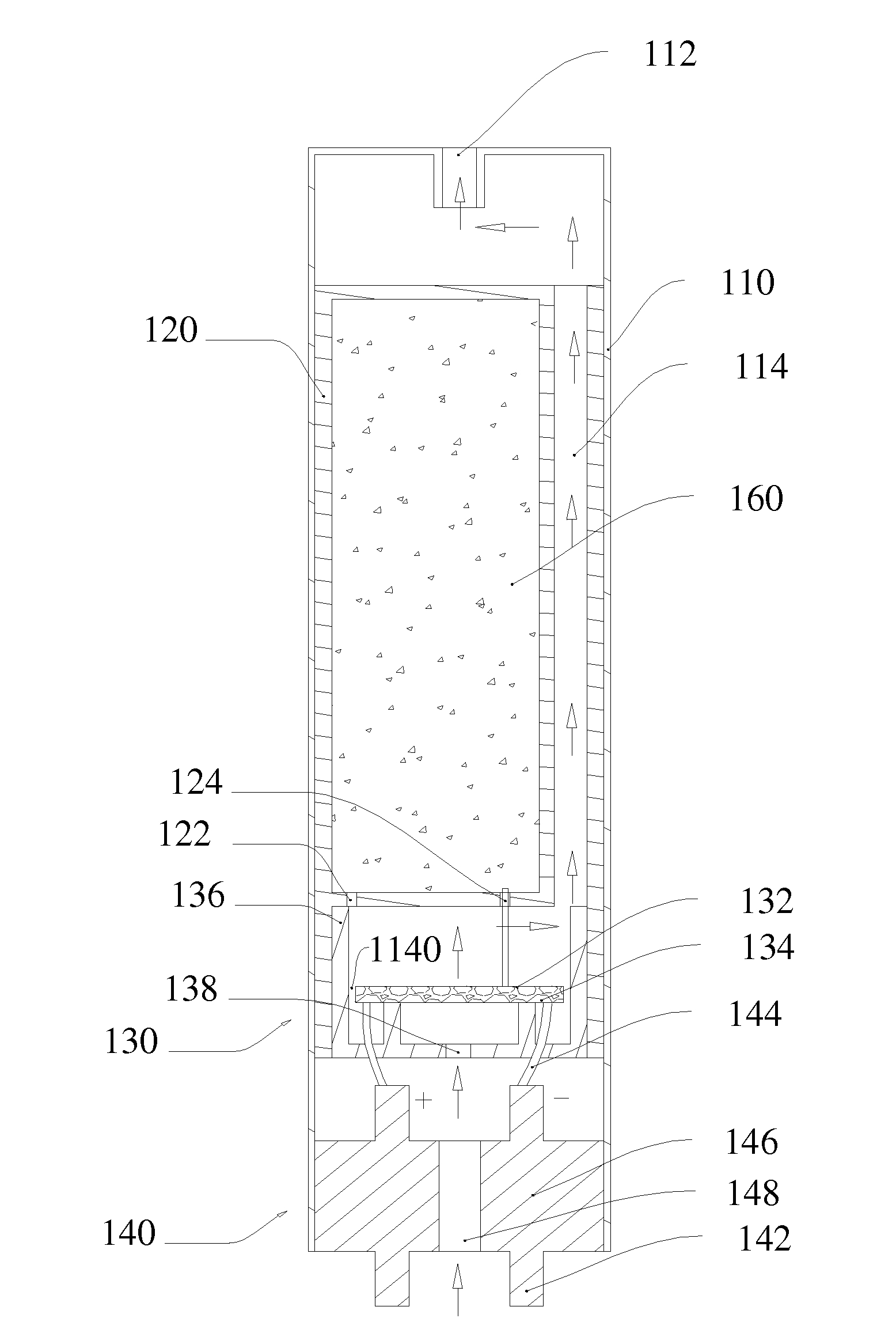

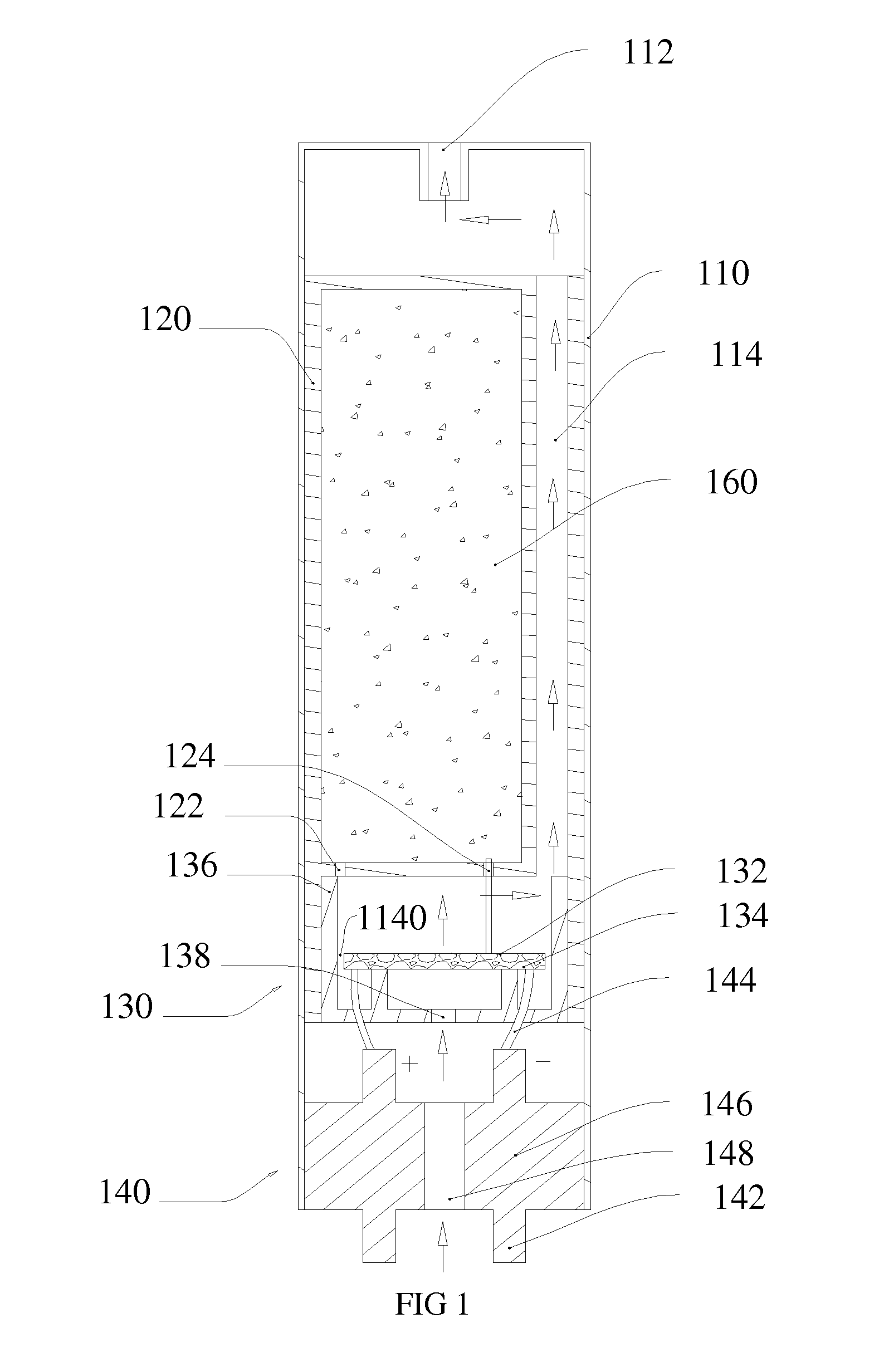

Electronic cigarette

ActiveUS20150090279A1Easily inhale smokeProne to feverTobacco pipesTobacco devicesEngineeringElectronic cigarette

An electronic cigarette is provided, which includes: a housing, a liquid reservoir, and an atomizer assembly. The housing has a chimney formed therein; the liquid reservoir is used for storing liquid; the atomizer assembly received in the housing. The atomizer assembly includes a heating plate capable of absorbing liquid. An outer surface of the heating plate is in contact with the air in the chimney.

Owner:SHENZHEN SMOORE TECH LTD

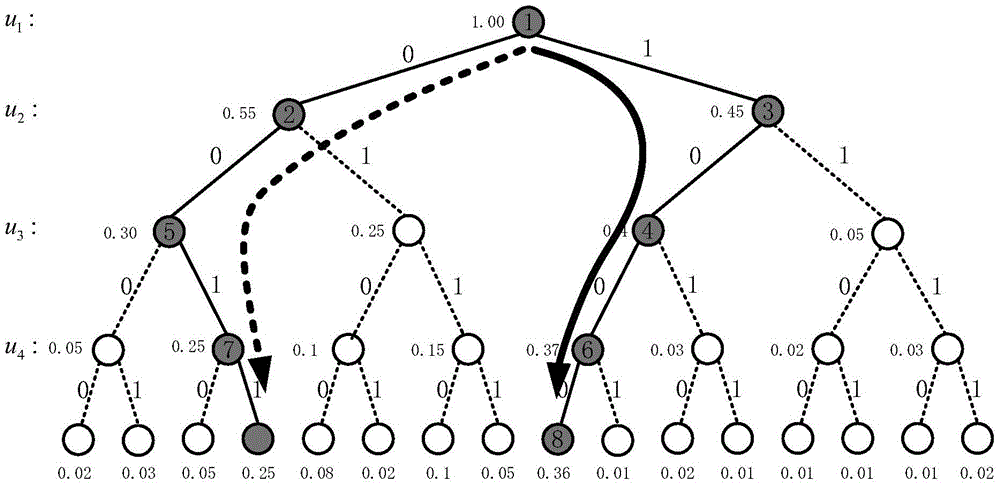

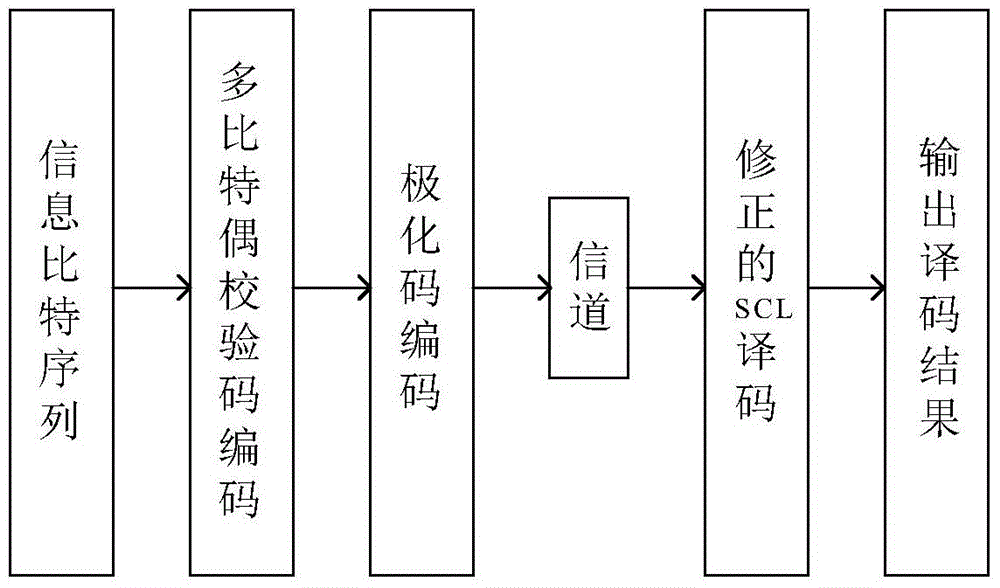

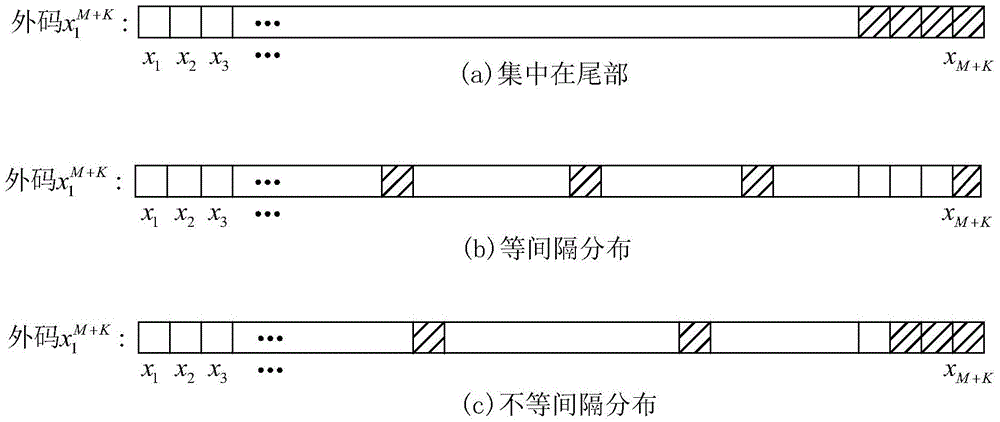

Polarization code and multi-bit even parity check code cascaded error correction coding method

ActiveCN105680883AImprove error correction performanceBreakthrough in error correction performanceCode conversionError correction/detection by combining multiple code structuresComputer hardwareError correction coding

The invention discloses a polarization code and multi-bit even parity check code cascaded error correction coding method. The method comprises the steps: a transmitting end encoder utilizes a multi-bit even parity check code as an outer code, and utilizes a polarization code as an inner code; a receiving end decoder decodes by utilizing a modified successive cancellation list (SCL) decoding algorithm. On the aspect of error correction performance, comparing with the prior art utilizing middle-short code length non-cascaded polarization codes of the SCL decoding algorithm, the polarization code and multi-bit even parity check code cascaded error correction coding method has the advantages that frame error rate performance of a system can be remarkably improved, and a maximum likelihood bound (ML Bound), which cannot be broken through by the SCL decoding algorithm, can be remarkably broken through. On the aspect of engineering realization, according to the polarization code and multi-bit even parity check code cascaded error correction coding method, the outer code utilizes the multi-bit even parity check code, which is simple to code; the modified SCL decoding algorithm is utilized to decode, bit decision and even parity check are combined to be carried out in a decoding process, and compared with the original SCL decoding algorithm, the method provided by the invention does not increase the decoding complexity, and facilitates the engineering realization.

Owner:HUAZHONG UNIV OF SCI & TECH

Device for storing compressed gas

InactiveUS6432176B1Reduce storage timeIncrease storage capacityMaterial nanotechnologyHydrogenNMR - Nuclear magnetic resonanceProcess engineering

A closed storage reservoir has at least one feed and discharge line for compressed gas and, in its interior, a gas flow control system which connects the feed and discharge line to a solid filling for storing the compressed gas in the interior. To ensure the highest possible specific storage capacity of the device and to enable the device to be used as a tank system for a fuel cell, the solid filling comprises carbon nanostructures which are joined to form larger, cohesive conglomerates. A device for measuring the filling level of the compressed gas in the storage vessel may be a device for measuring the nuclear magnetic resonance or a device for measuring the mass flow rates of the compressed gas. A temperature sensor and a heating / cooling device having an inlet connection piece and an outlet connection piece for a heating / cooling medium and a cooling passage connected to the connection pieces are provided in order to set a defined temperature in the storage vessel.

Owner:MANNESMANN AG

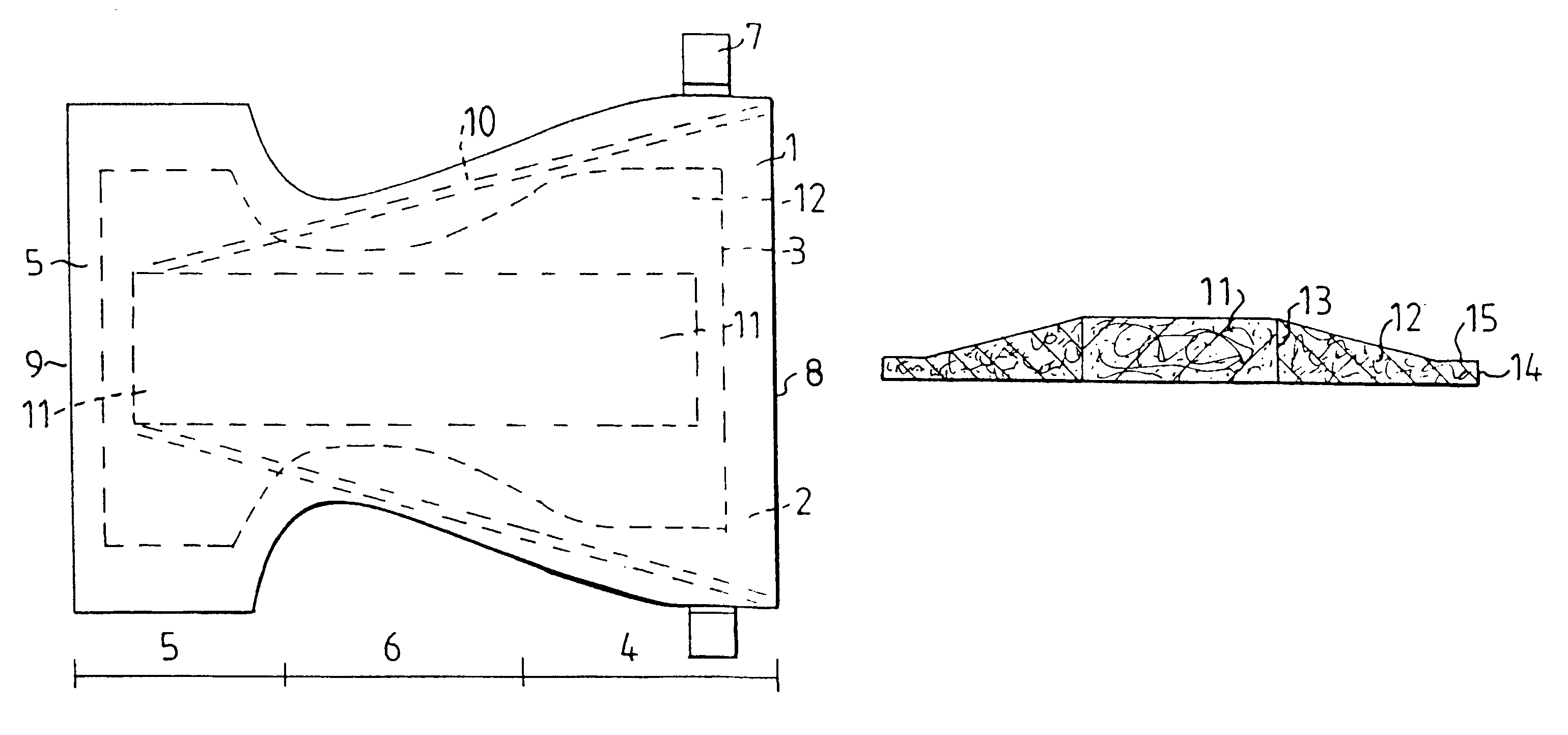

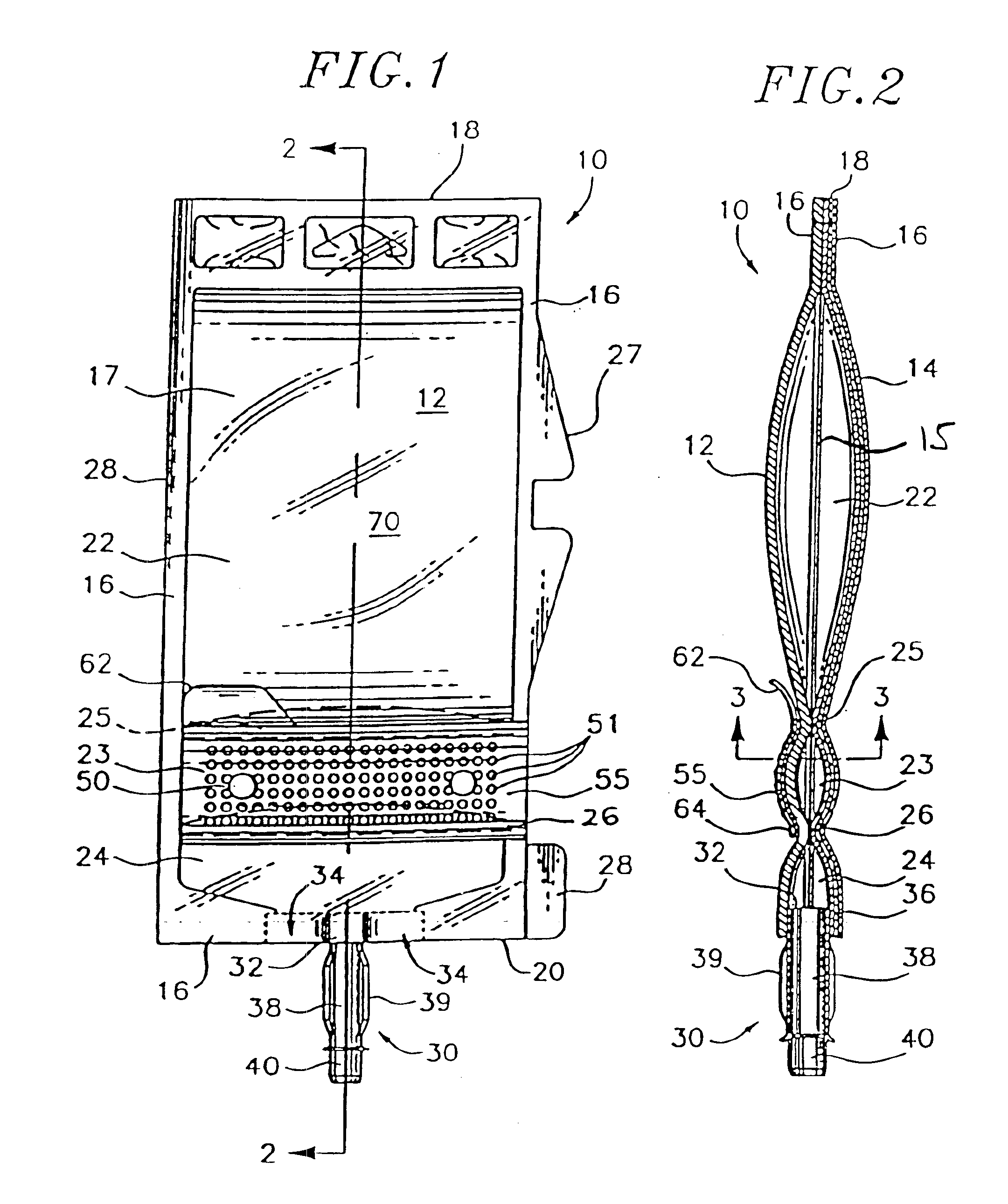

Flexible multi-compartment container with peelable seals and method for making same

InactiveUS6846305B2Increase capacityIncrease storage capacityWrappersMedical devicesThermoplasticDiluent

A flexible container is provided for the storage and administration of medical solutions. The container incorporates a transparent front sheet made from a planar layer of a polymer and an opposing rear sheet. The rear sheet is made from a planar laminate layer. The front and rear sheets are sealed together along a common peripheral edge to form a volume enclosure. The volume enclosure is constructed of materials having high oxygen and moisture barrier properties which allows the container thermoplastic to be stored for extended periods of time without degrading the contents. The volume enclosure is then inflated with a pressurized gas to permanently stretch the front and rear sheets outwardly and to thereby increase the volume capacity of the container. An alternative embodiment of the container incorporates multiple compartments, separated by peelable seals, for containing a diluent and a medicament. The seals are ruptured by manipulation of the container to thereby mix the contents together for delivery through standard IV arrangement to a patient.

Owner:B BRAUN MEDICAL

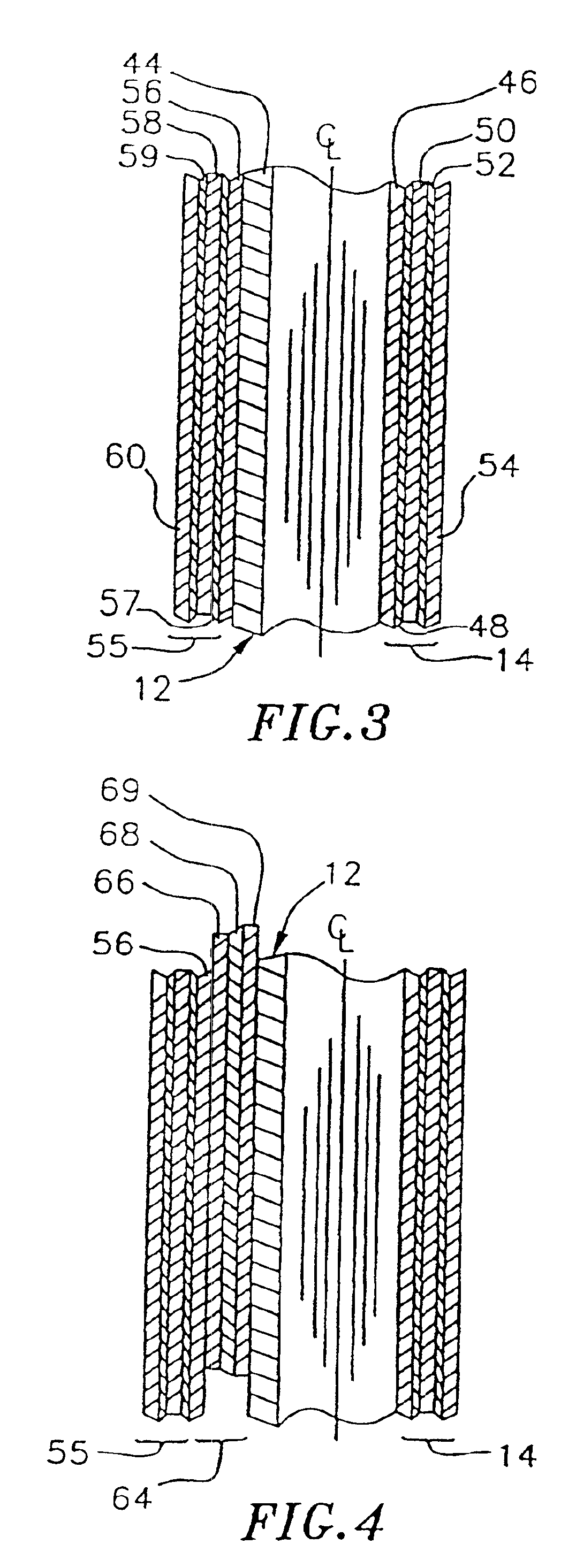

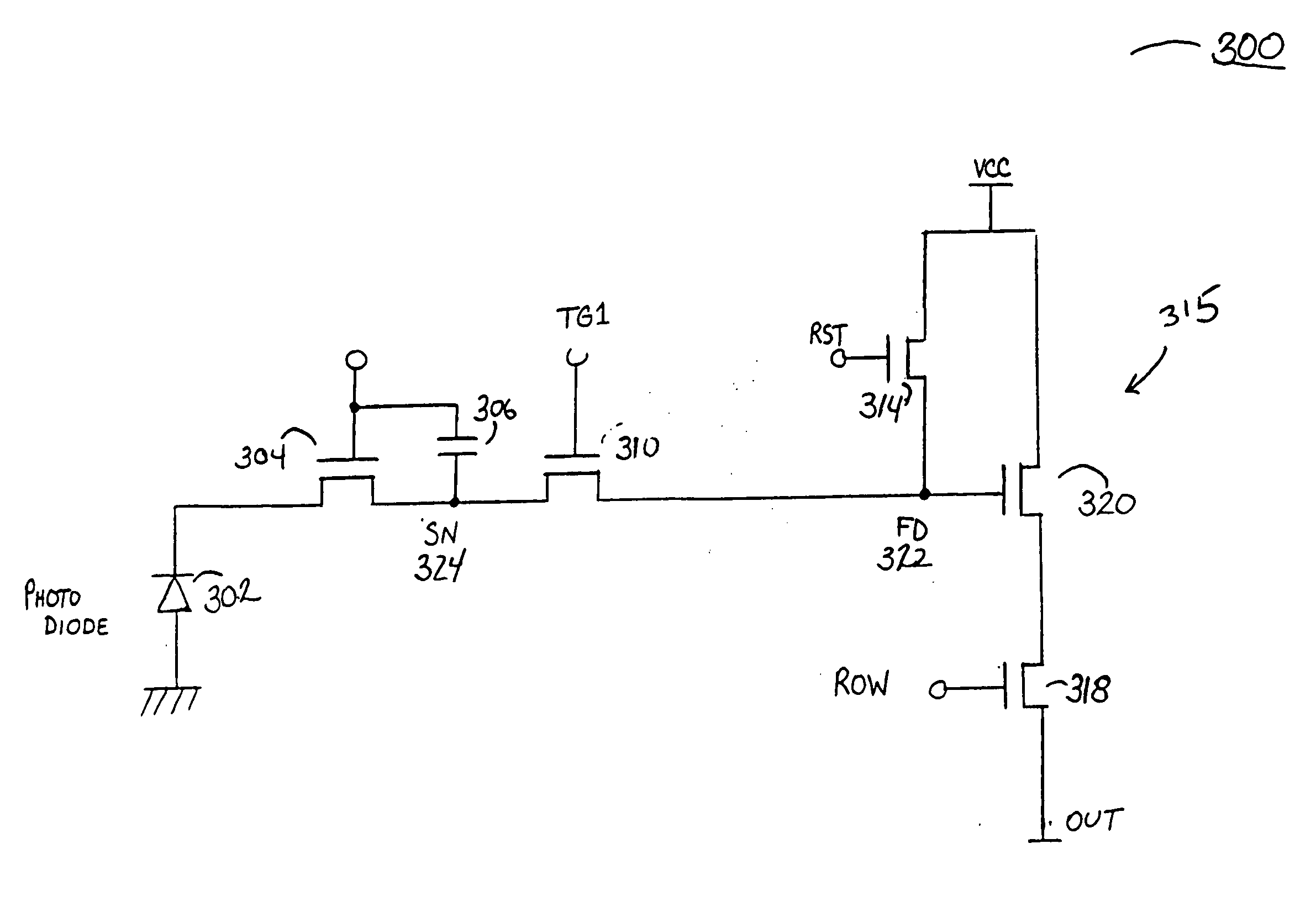

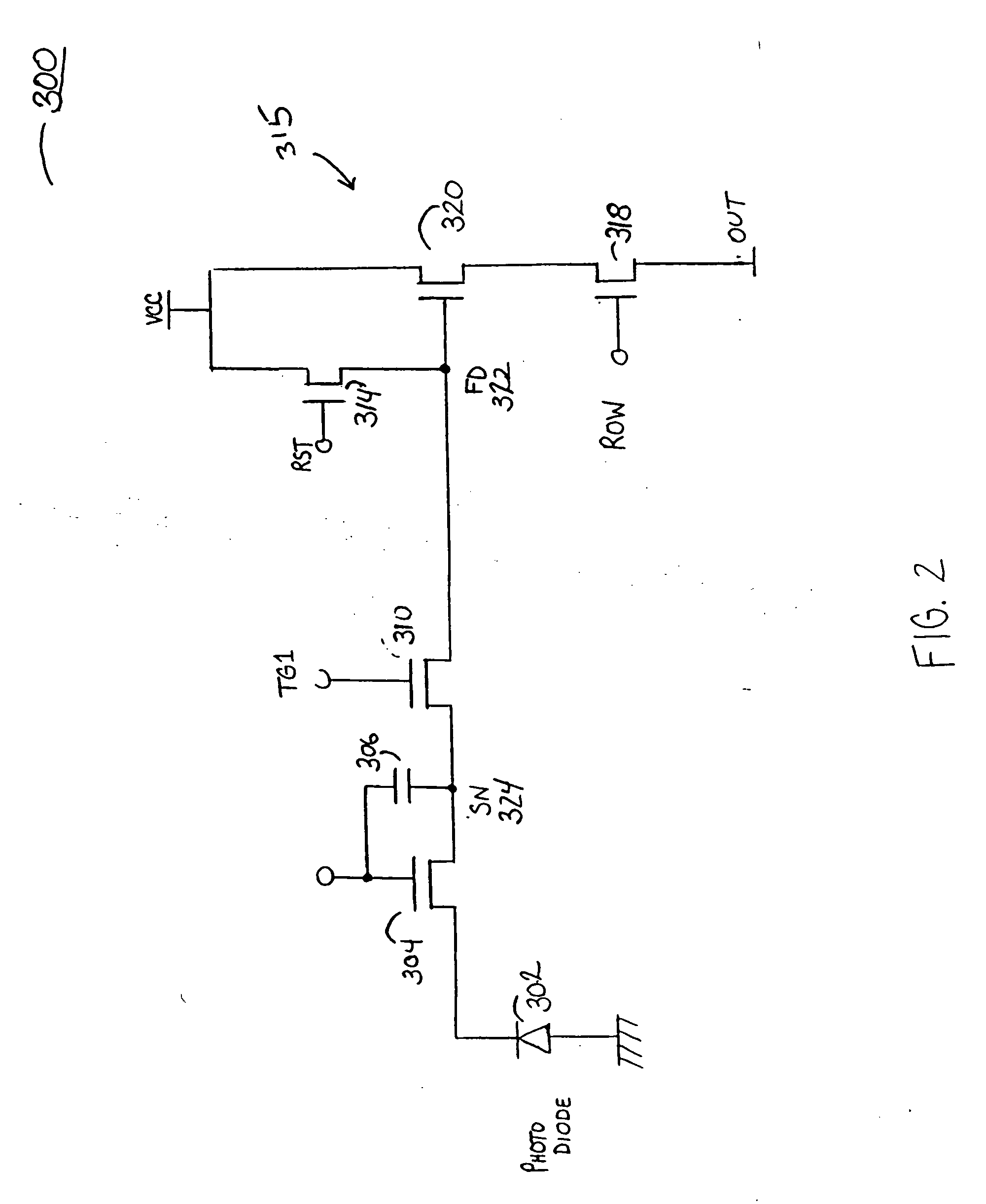

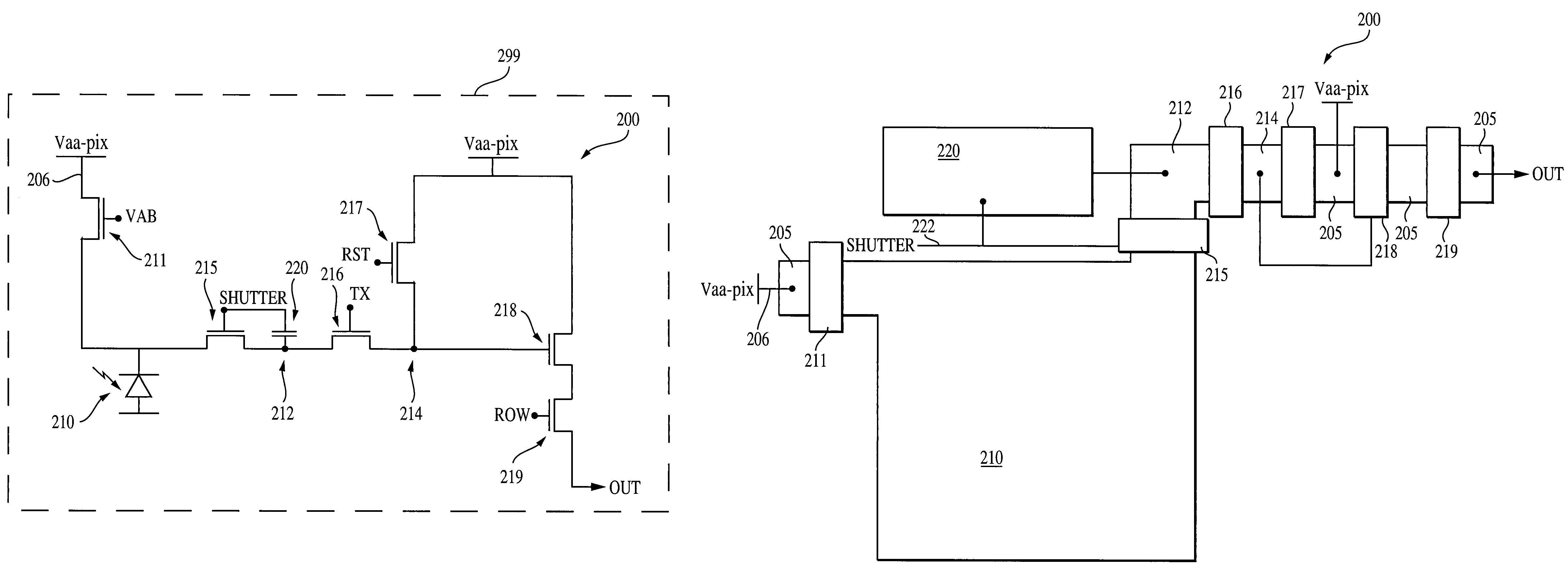

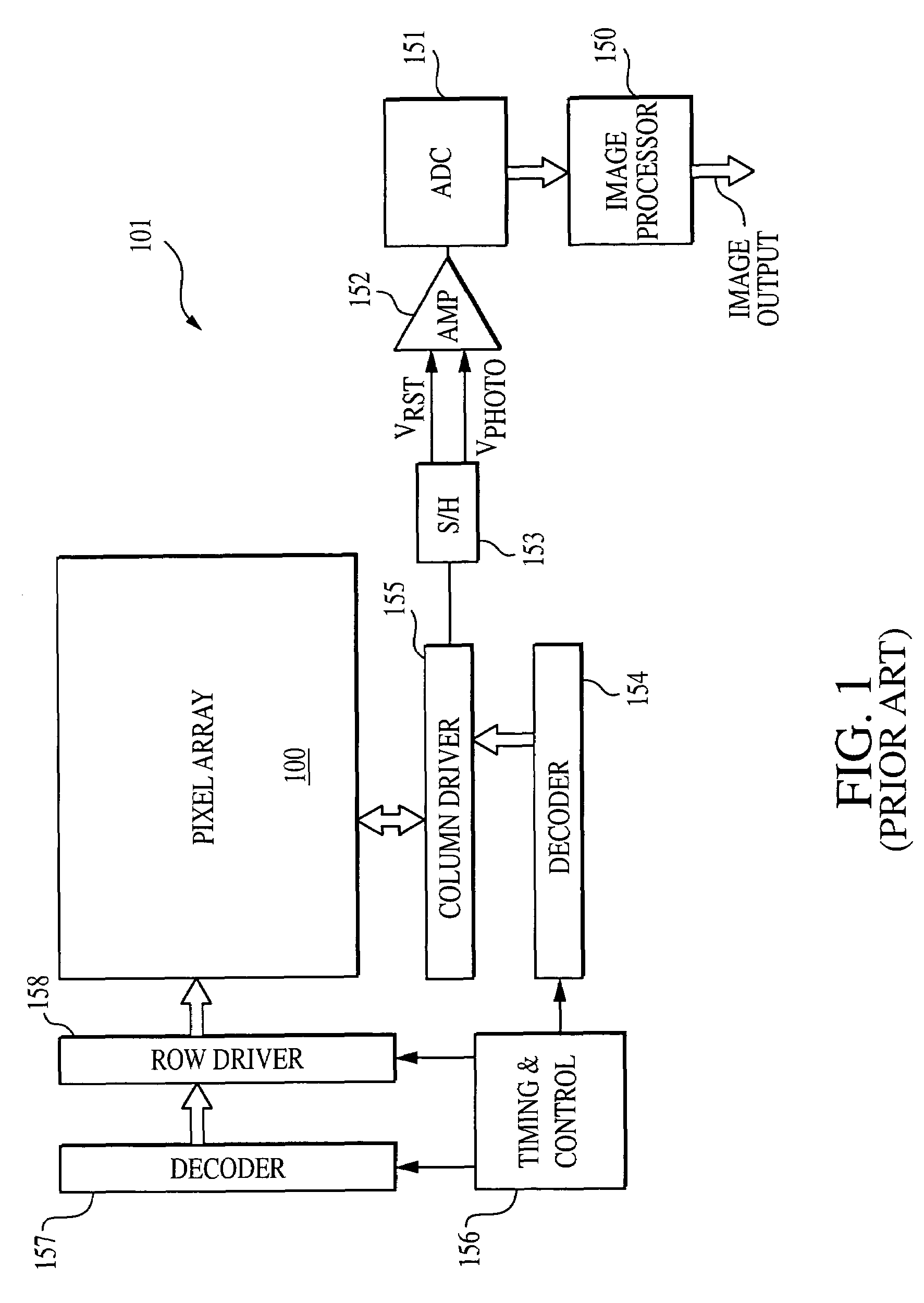

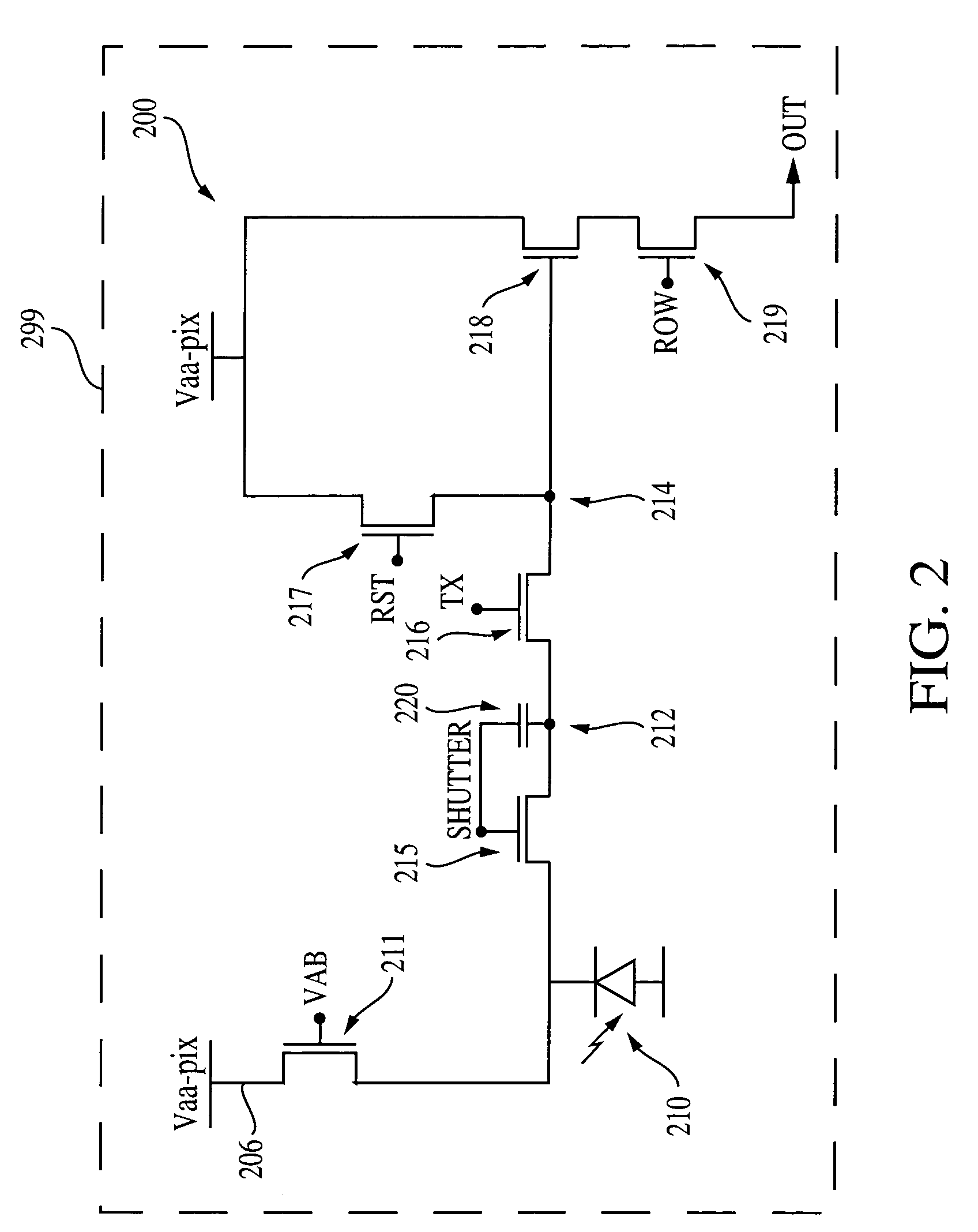

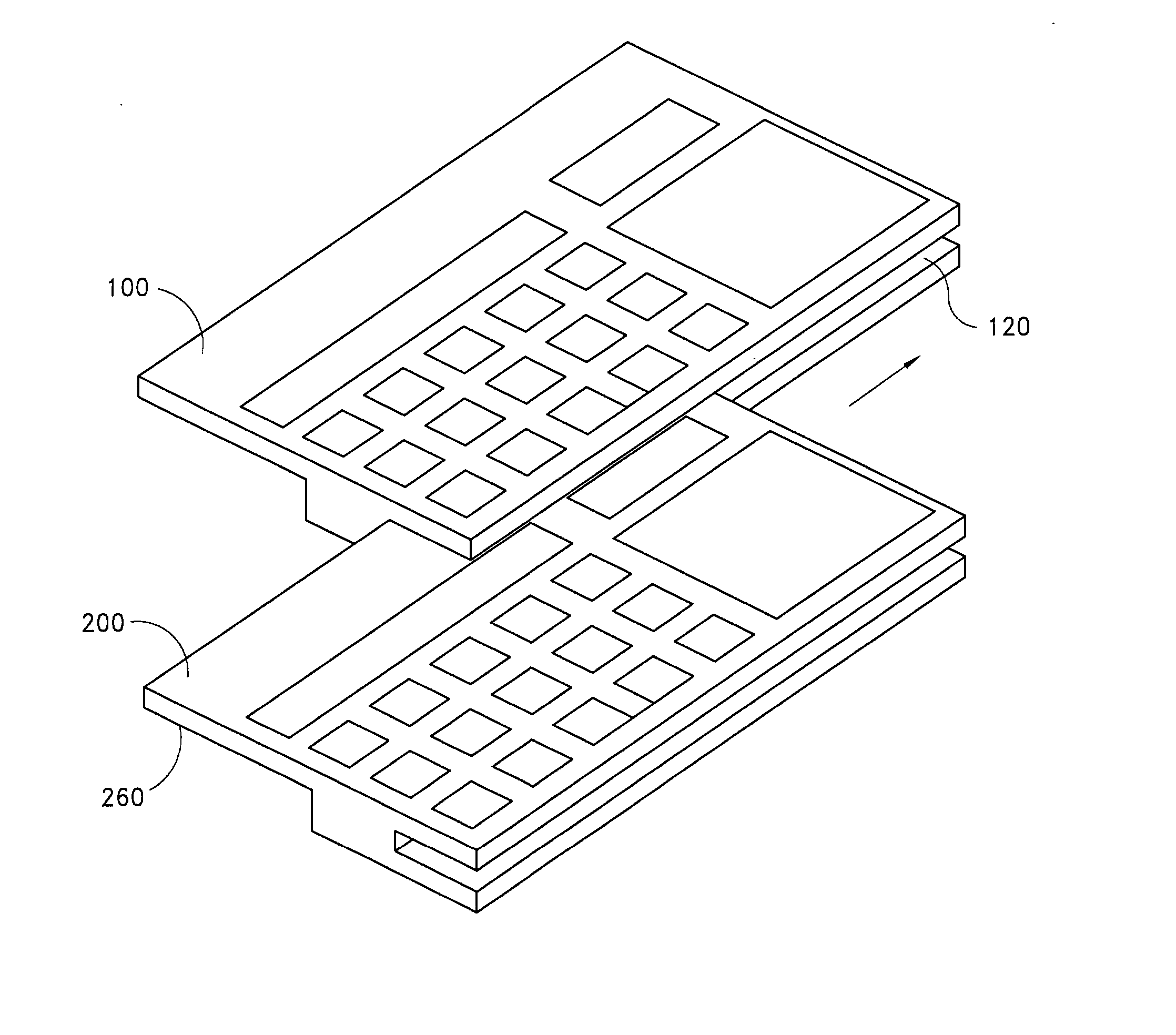

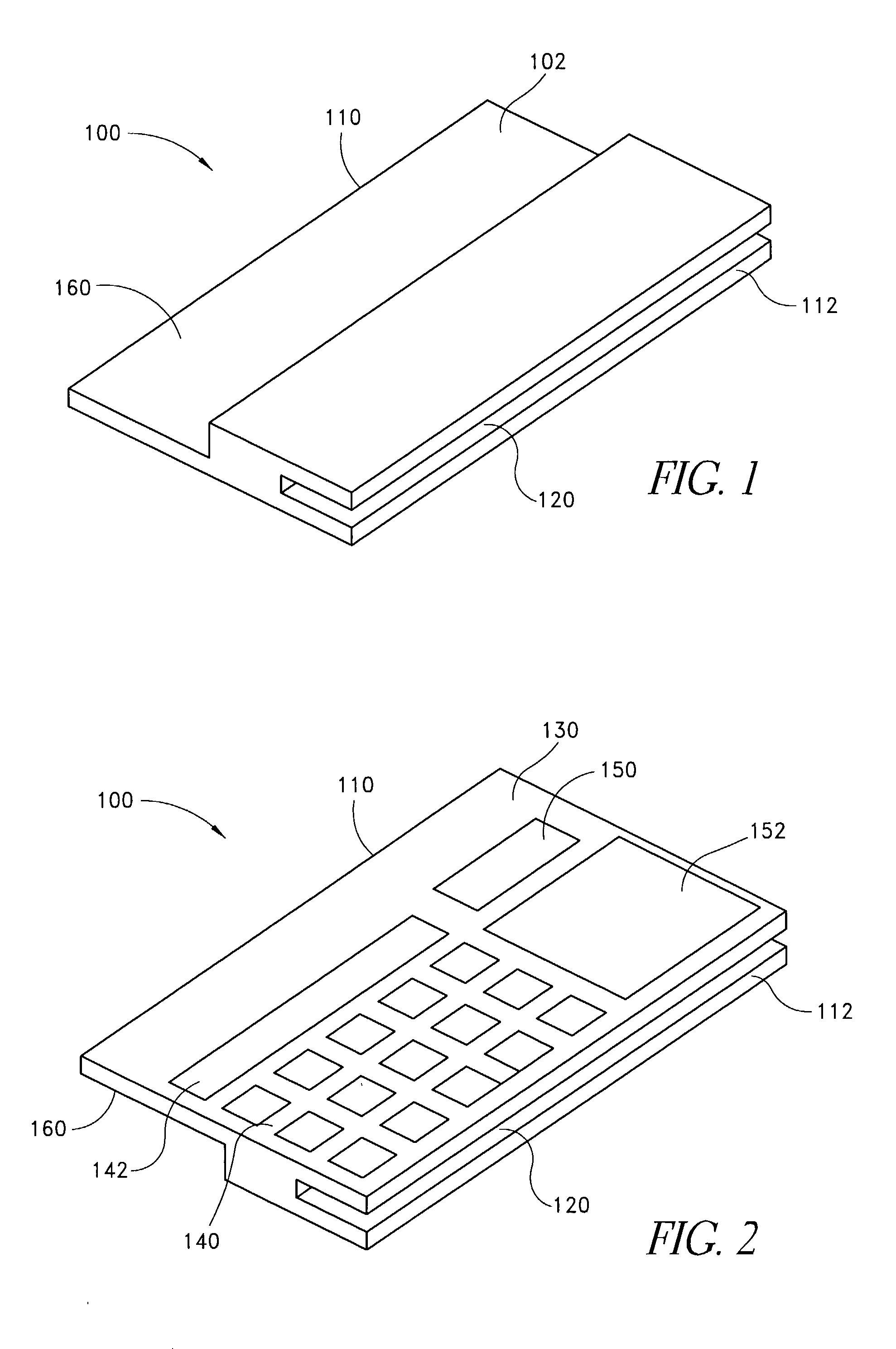

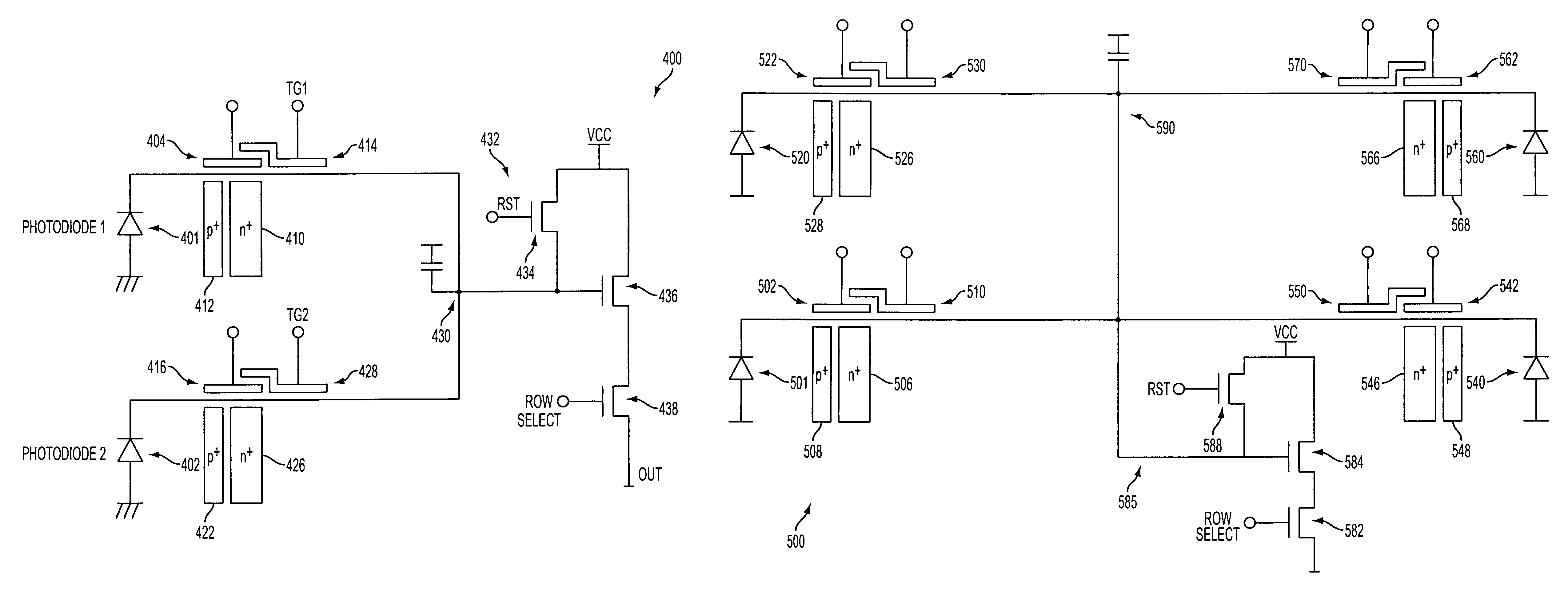

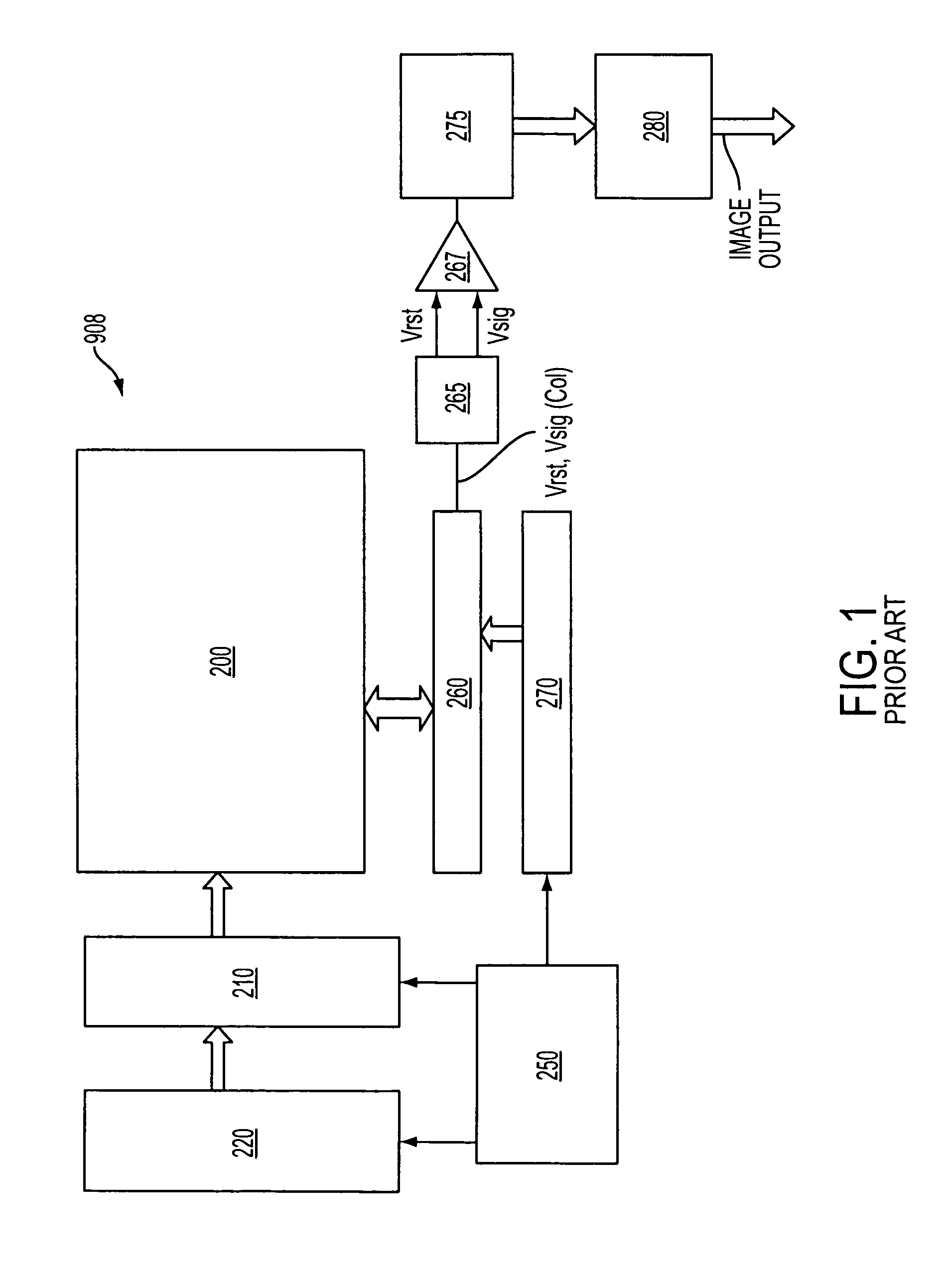

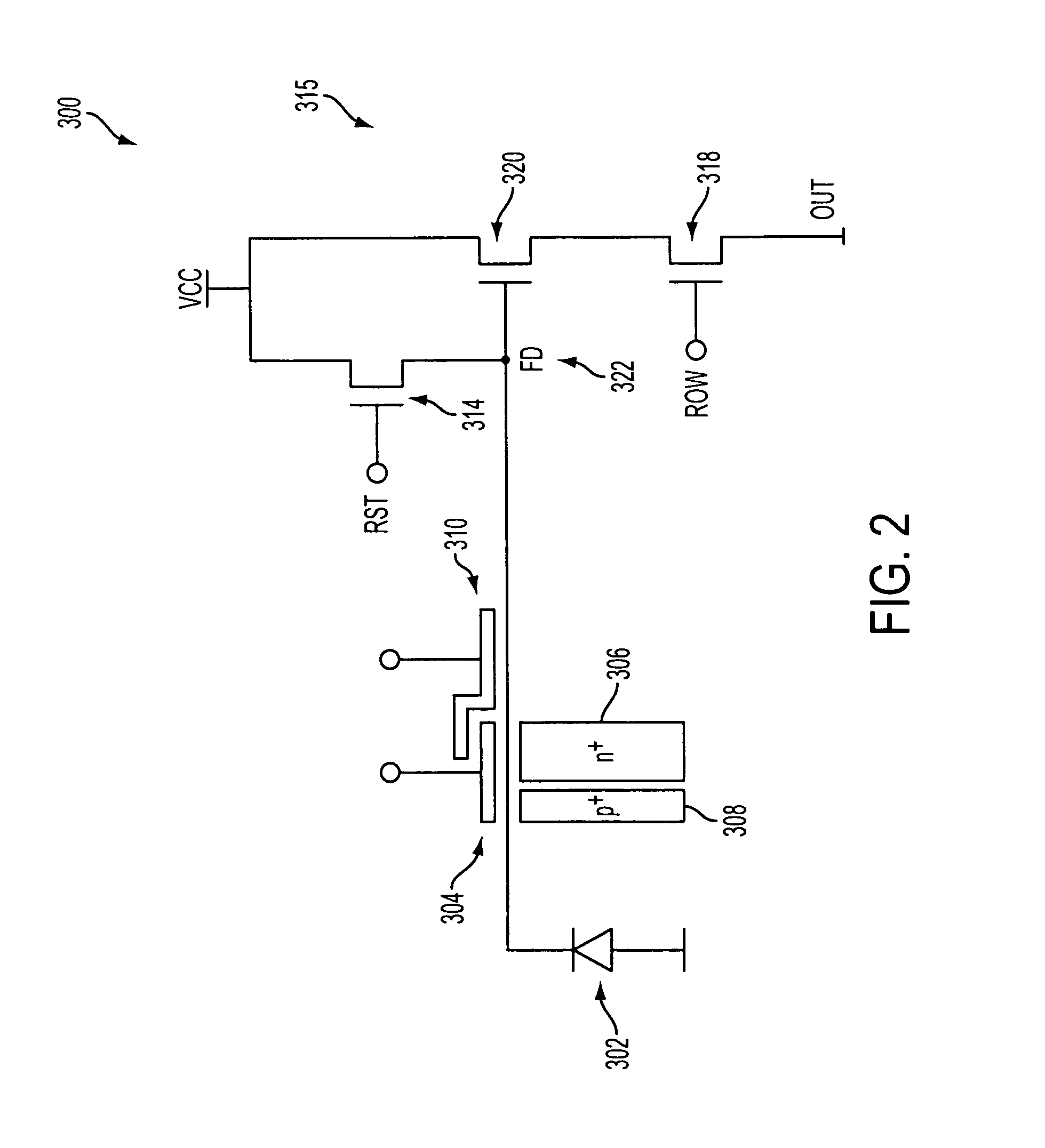

Image sensor with a capacitive storage node linked to transfer gate

ActiveUS20050110884A1Increases charge generating areaIncrease costTelevision system detailsTelevision system scanning detailsCapacitanceCMOS

A CMOS imaging system with increased charge storage capacitance of pixels yet decreased physical size, kTC noise and active area. A capacitor is linked to the transfer gate and provides a storage node for a pixel, allowing for kTC noise reduction prior to readout. The pixel may be operated with the shutter gate on during the integration period to increase the amount of time for charge storage by a pixel.

Owner:APTINA IMAGING CORP

Magnetic device with magnetic tunnel junction, memory array and read/write methods using same

InactiveUS20050002228A1Good reproducibilityEliminate errorsNanomagnetismMagnetic-field-controlled resistorsSemiconductorTunnel junction

Magnetic tunnel junction magnetic device, memory and writing and reading methods using said device. Said device (16) comprises a reference layer (20c) and a storage layer (20a) separated by a semiconductor or insulating layer (20b). The blocking temperature of the magnetisation of the storage layer is less than that of the reference layer. The device further comprises means (22, 24) for heating the storage layer above the blocking temperature of its magnetisation and means (26) for applying to it a magnetic field (34) orientating its magnetisation in relation to that of the reference layer without modifying the orientation of said reference layer.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

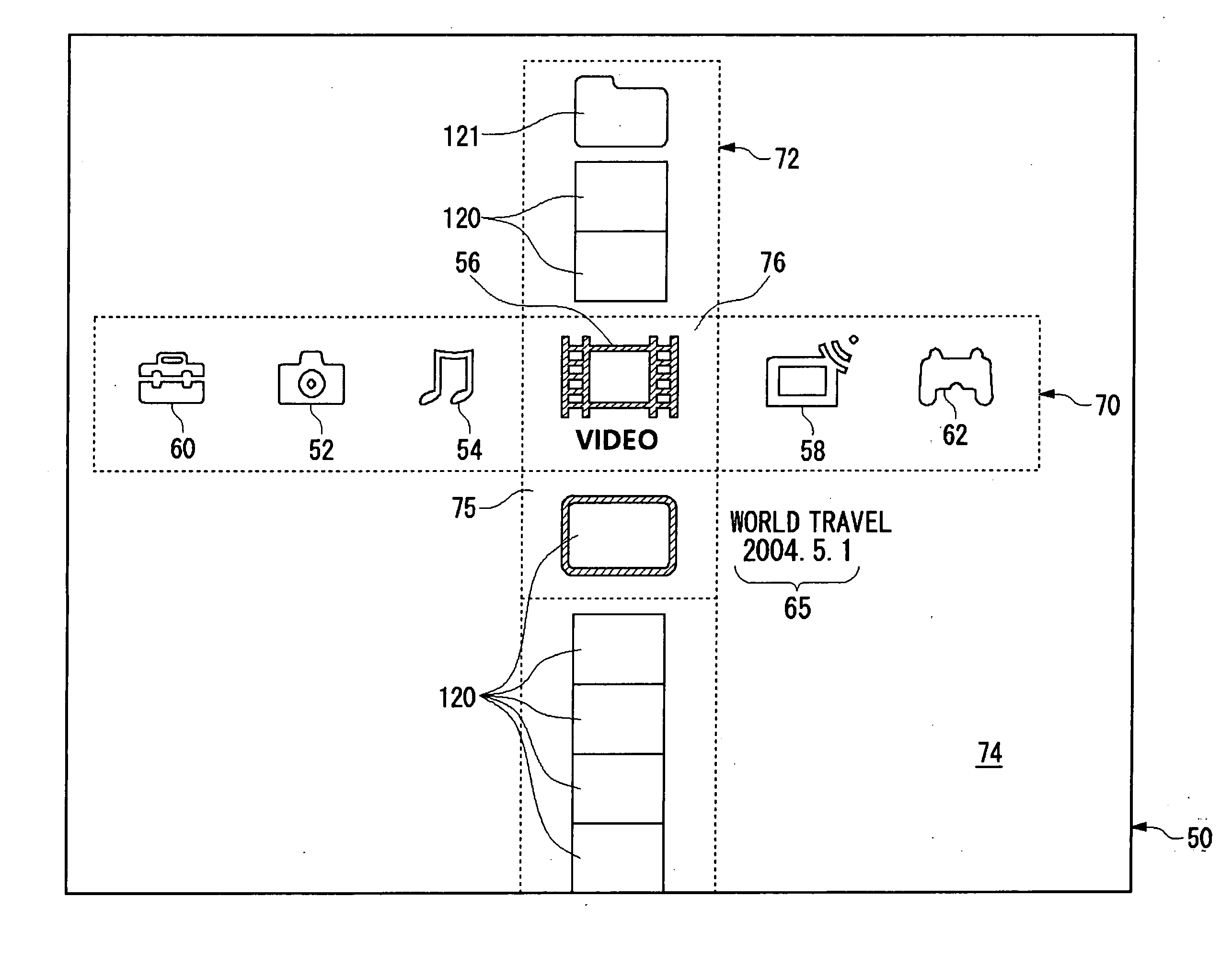

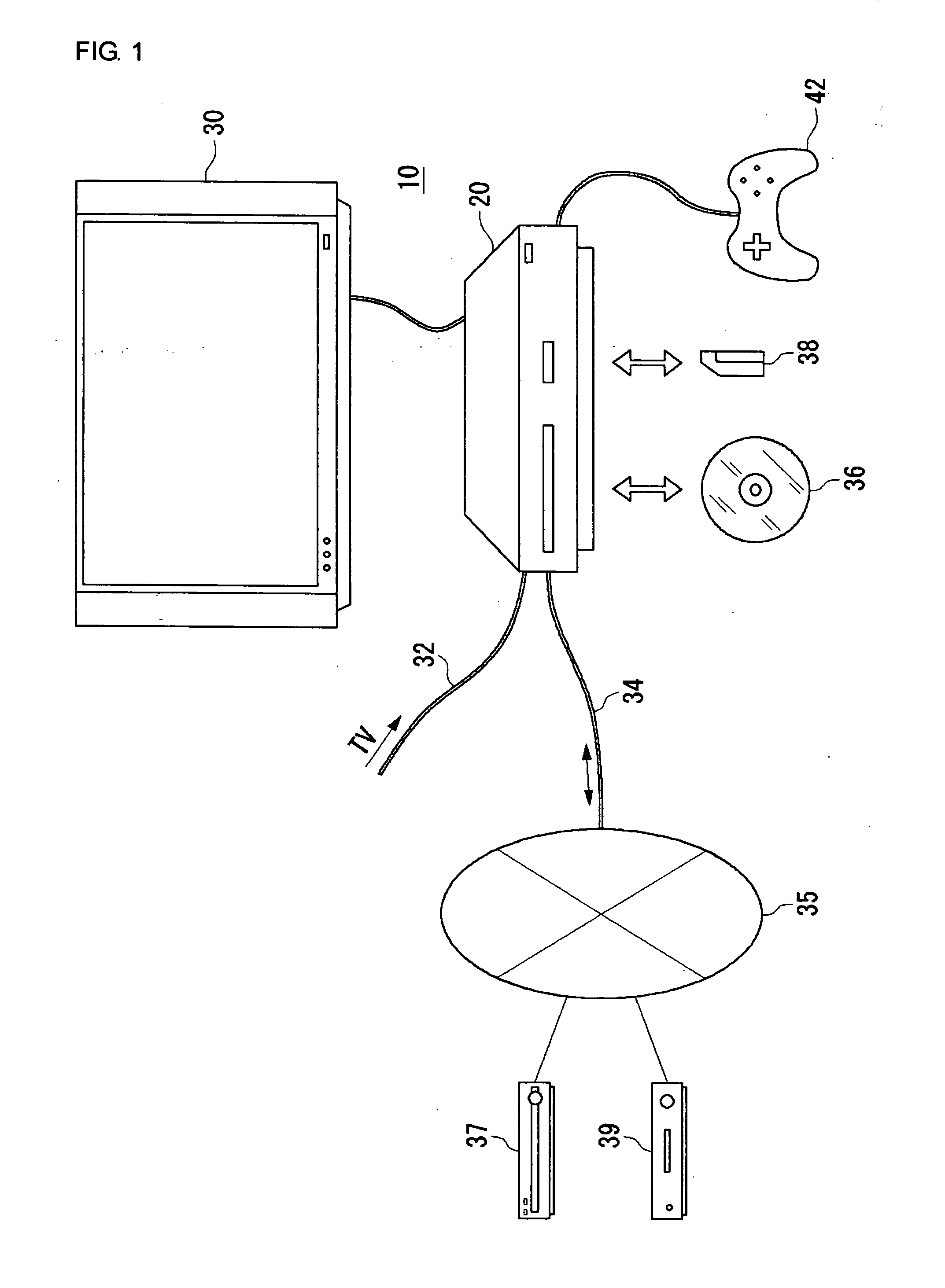

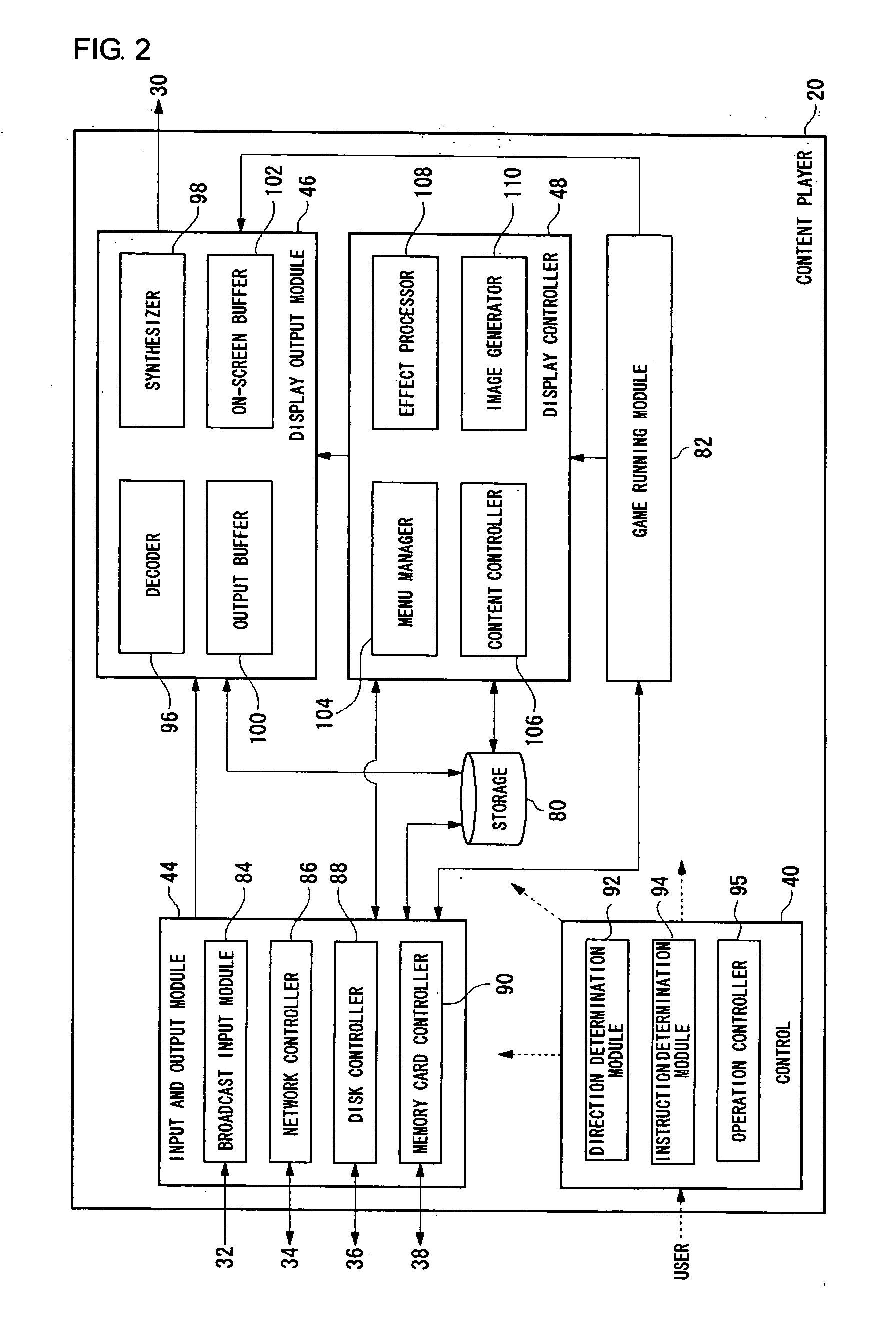

Content Reproduction Device and Menu Screen Display Method

InactiveUS20070266411A1Increase the number ofImprove efficiencyTelevision system detailsColor television detailsTelevision screenHome appliance

Favorable visual appearance and ease of operation are required in the user interface of digital home appliances using a television screen. An array of function icons including multiple function icons representing respective types of media that can be played and an array of content icons including multiple content icons representing items of contents that can be played are displayed practically at the center of an on-screen menu such that the arrays intersect. A moving image icon, which is a function icon displayed in an area of intersection in which the array of function icons and the array of content icons intersect, is highlighted by a color different from that of the other function icons and by an enlarged view. In the array of content icons, the hierarchy of the contents is visually represented.

Owner:SONY COMPUTER ENTERTAINMENT INC +1

Anti-blooming storage pixel

ActiveUS7332786B2Increase storage capacityImprove signal-to-noise ratioTelevision system detailsTelevision system scanning detailsElectronic shutterFloating diffusion

Embodiments of the present invention provide pixel cells with increased storage capacity, which are capable of anti-blooming operations. In an exemplary embodiment a pixel cell has an electronic shutter that transfers charge generated by a photo-conversion device to a storage node before further transferring the charge to the pixel cell's floating diffusion node. Each pixel cell also includes an anti-blooming transistor for directing excess charge out of each respective pixel cell, thus preventing blooming. Additionally, two or more pixel cells of an array may share a floating diffusion node and reset and readout circuitry.

Owner:APTINA IMAGING CORP

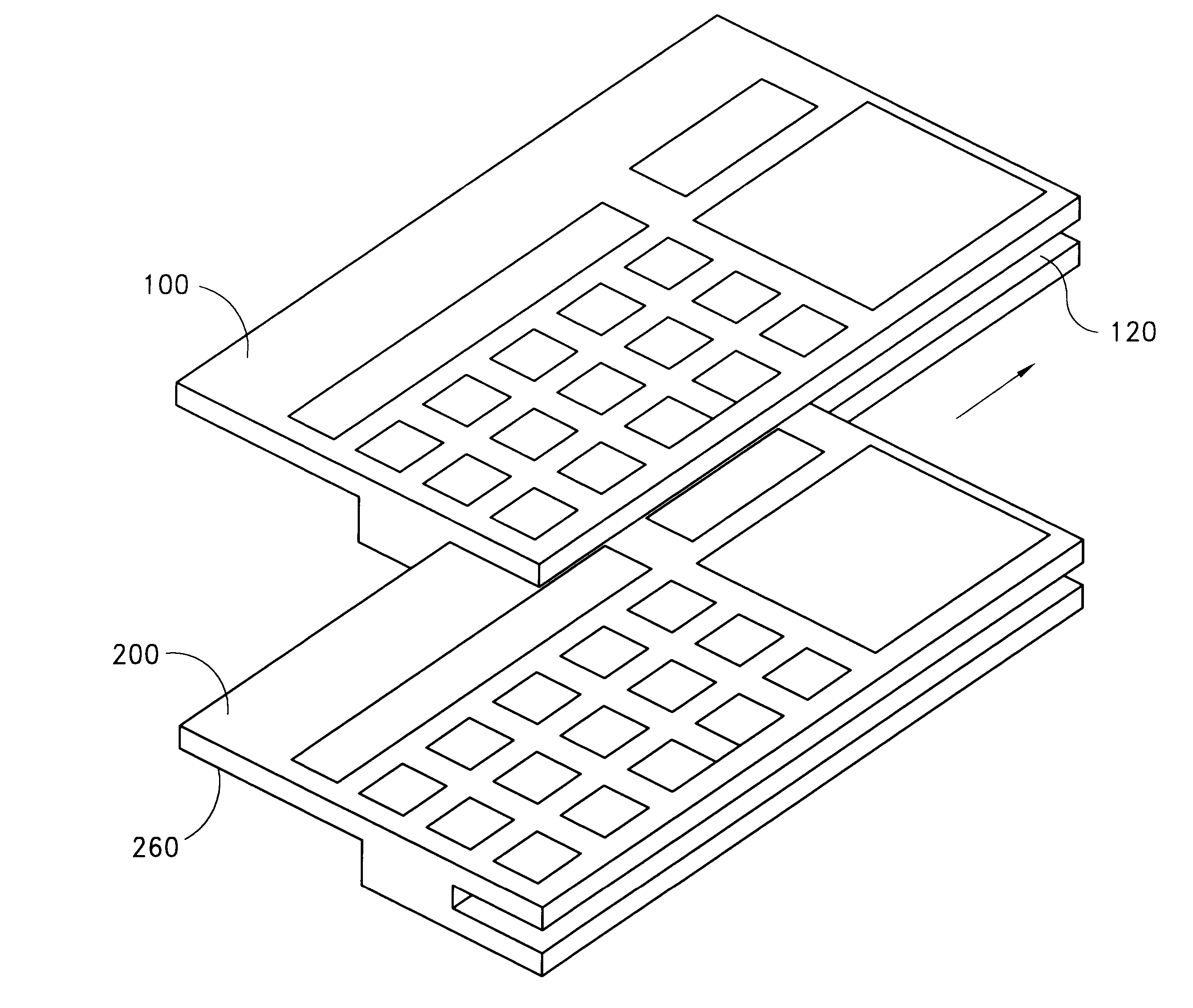

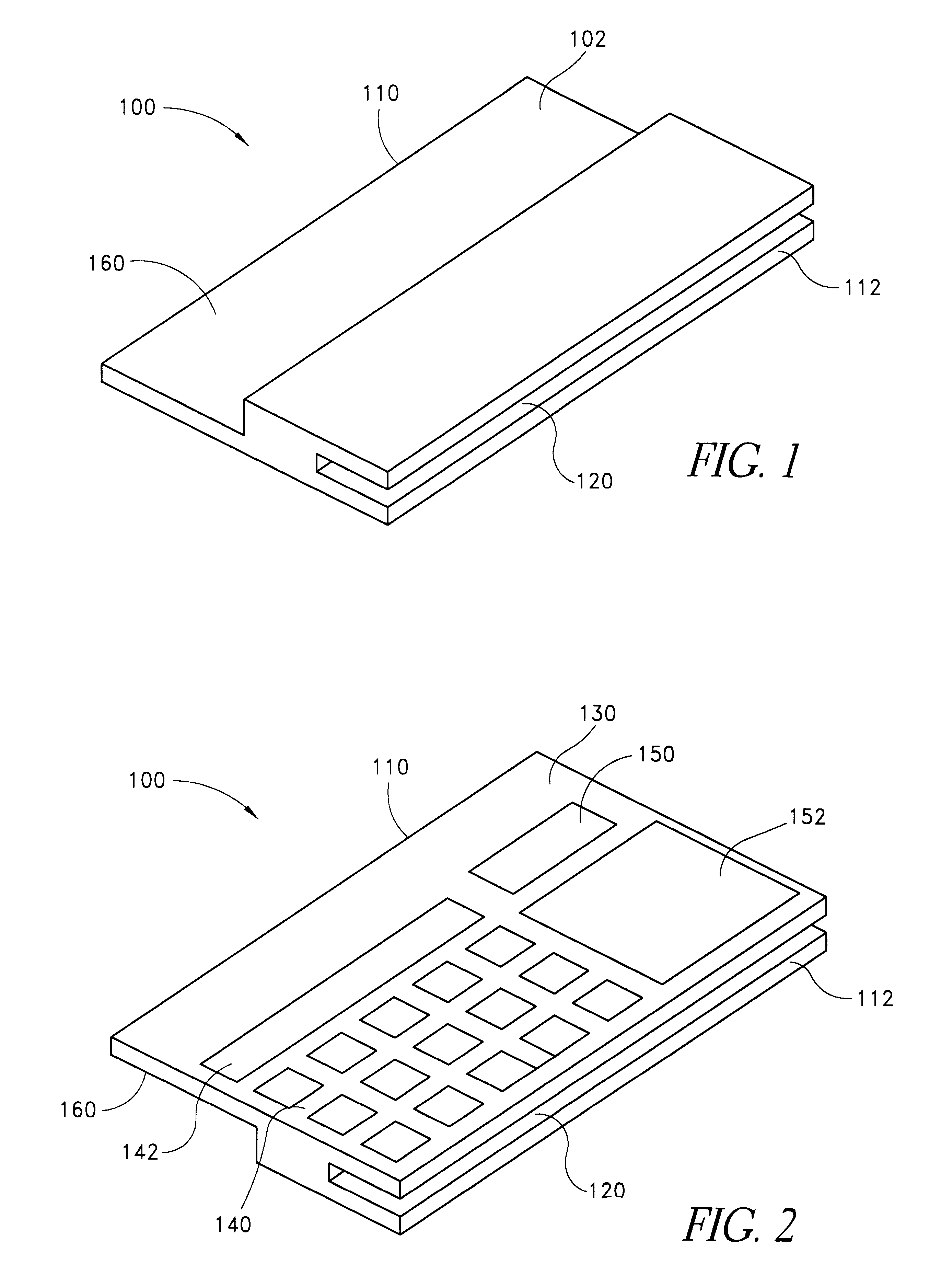

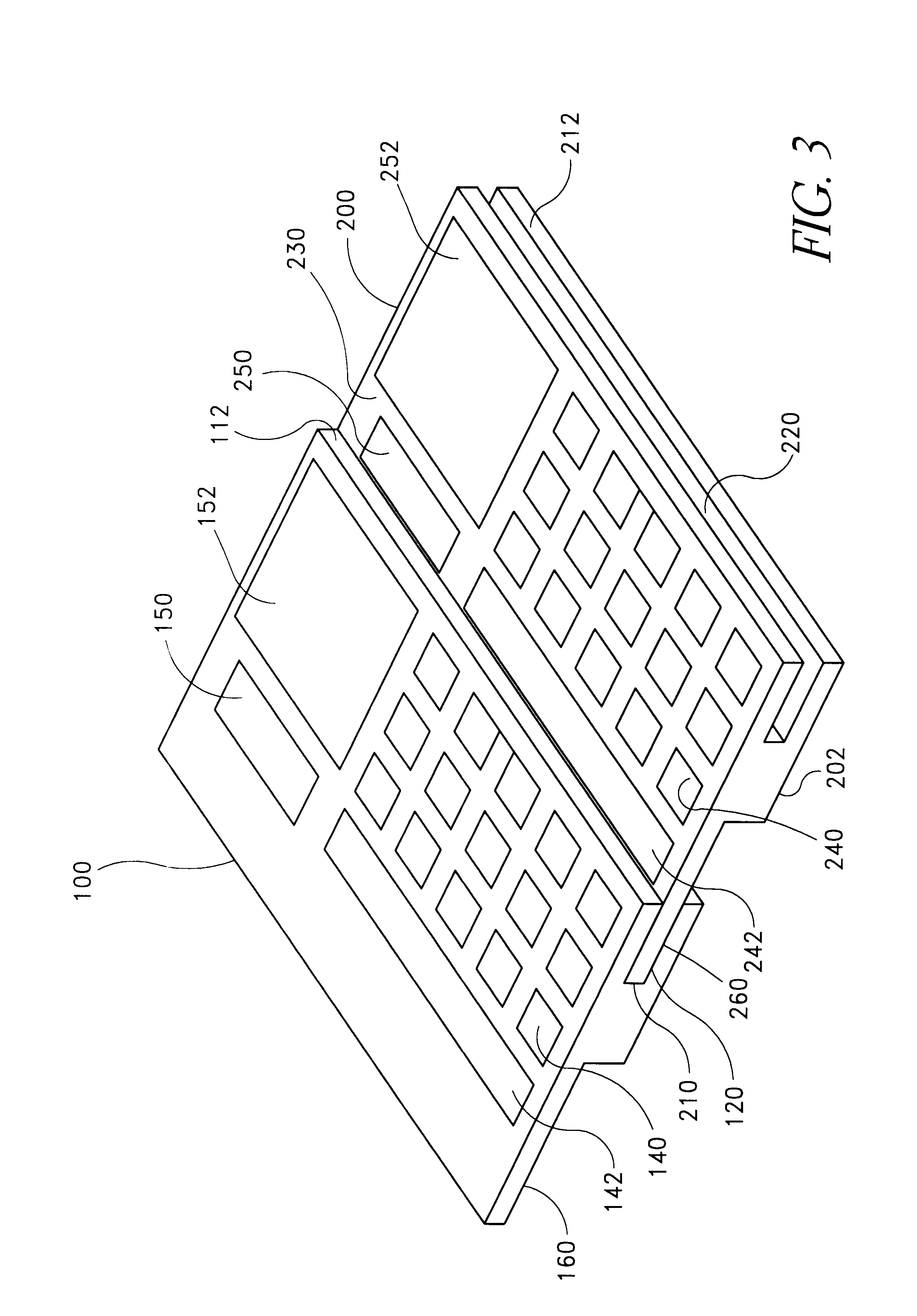

System for card to card transfer of secure data

InactiveUS20020130187A1Security and ease of carryingEase and immediacy of useMemory record carrier reading problemsPayment architectureControl systemSmart card

A smart card stores secure data, such as monetary values, and selectively transfers the secure data to or receives the secure data from a compatible smart card. The smart card includes a data storage device that stores the secure data. An identification input system receives identification input from a user. Control circuitry is responsive to the identification input to transfer secure data into the data storage device from a compatible smart card or to transfer secure data out of the data storage device to a compatible smart card when the control system determines from the identification input that the transfer is authorized. A data transfer interface in an edge of one card couples directly to a like interface in a slot of the other card to enable the secure data to be transferred between the two cards when the two cards are moved relative to each other.

Owner:BERG JON N +1

Container system for hydraulic fracturing proppants

InactiveUS20150086307A1Large storage capacityIncrease storage capacityLoadersLarge containersEngineeringHydraulic fracturing proppants

Described herein is an improved container for storing, shipping, and dispensing proppant materials used in hydraulic fracturing operations. The container systems incorporate stretchable hopper structures in the container. The hopper expands and contracts responsive to the amount of proppant material held in the container. When the container is filled with a sufficient amount of proppant, the hopper stretches to expand the storage volume. When the sufficient amount of proppant material is dispensed from the container, the hopper contracts to lift and dispense the container contents.

Owner:PROPPANT EXPRESS SOLUTIONS LLC

Flexible multi-compartment container with peelable seals and method for making same

InactiveUS6996951B2Increase storage capacityIncrease capacityEnvelopes/bags making machineryBoxes/cartons making machineryThermoplasticDiluent

A flexible container is provided for the storage and administration of medical solutions. The container incorporates a transparent front sheet made from a planar layer of a polymer and an opposing rear sheet. The rear sheet is made from a planar laminate layer. The front and rear sheets are sealed together along a common peripheral edge to form a volume enclosure. The volume enclosure is constructed of materials having high oxygen and moisture barrier properties which allows the container thermoplastic to be stored for extended periods of time without degrading the contents. The volume enclosure is then inflated with a pressurized gas to permanently stretch the front and rear sheets outwardly and to thereby increase the volume capacity of the container. An alternative embodiment of the container incorporates multiple compartments, separated by peelable seals, for containing a diluent and a medicament. The seals are ruptured by manipulation of the container to thereby mix the contents together for delivery through standard IV arrangement to a patient.

Owner:B BRAUN MEDICAL

Image sensor with a gated storage node linked to transfer gate

ActiveUS7443437B2Increase storage capacityReduce noiseTelevision system detailsTelevision system scanning detailsCMOSEngineering

A CMOS imaging system with increased charge storage of pixels yet decreased physical size, kTC noise and active area. A storage node is connected to the transfer gate and provides a storage node for a pixel, allowing for kTC noise reduction prior to readout. The pixel may be operated with the shutter gate on during the integration period to increase the amount of time for charge storage by a pixel.

Owner:SAMSUNG ELECTRONICS CO LTD