Patents

Literature

470 results about "Error correction coding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

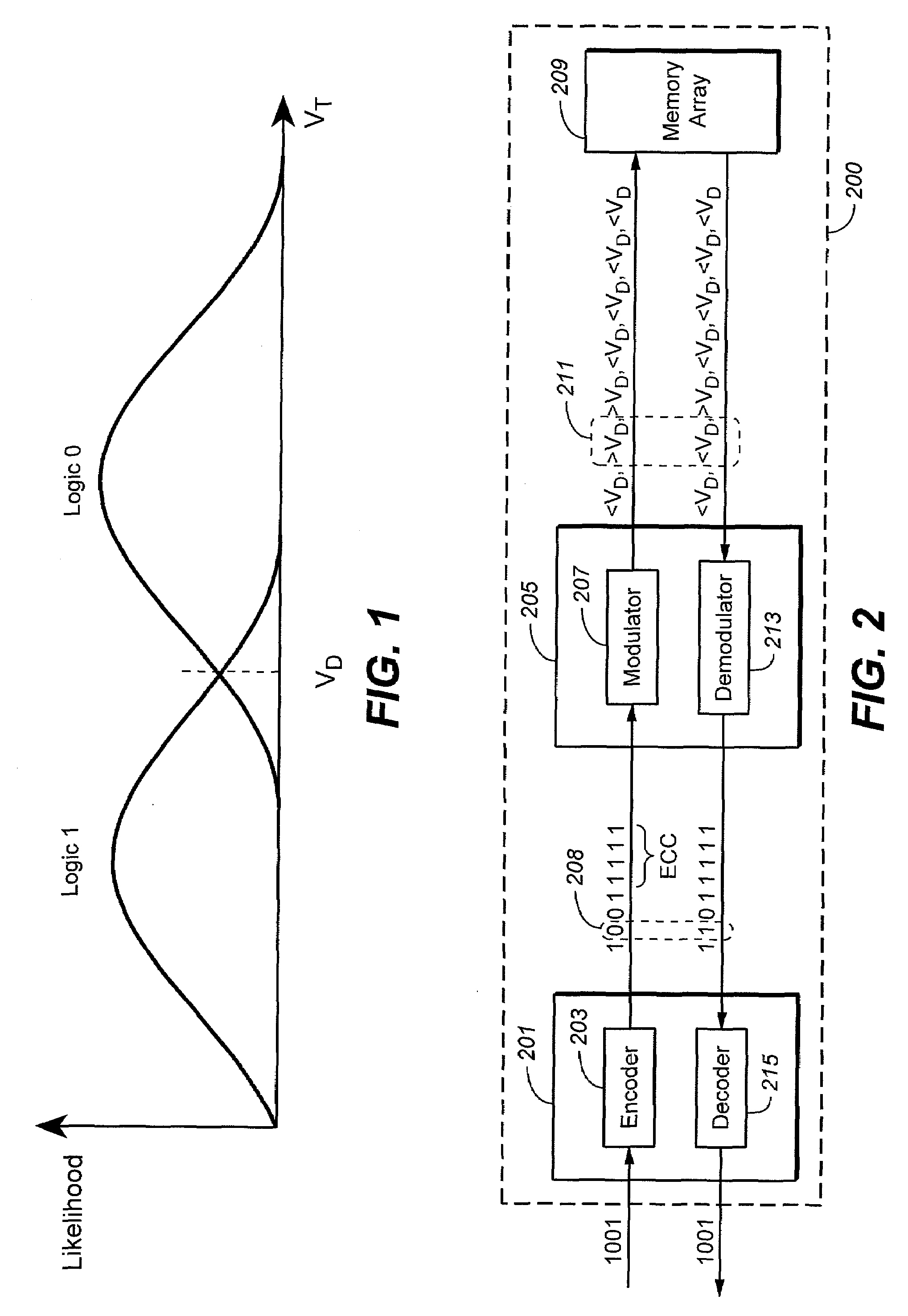

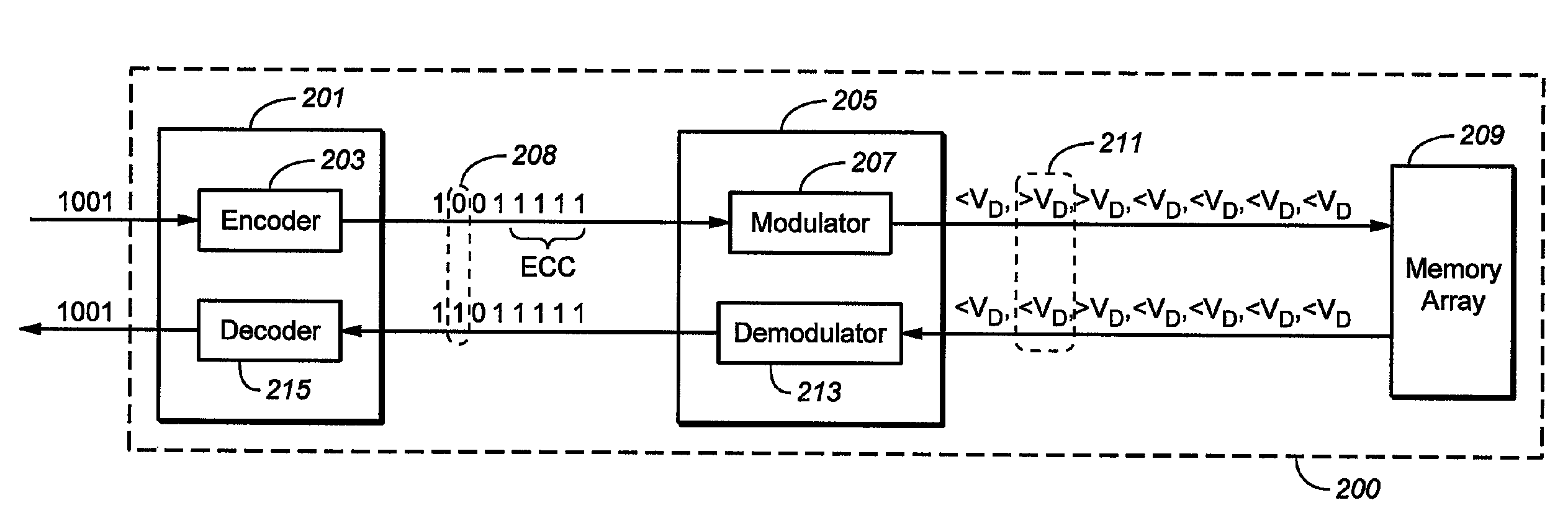

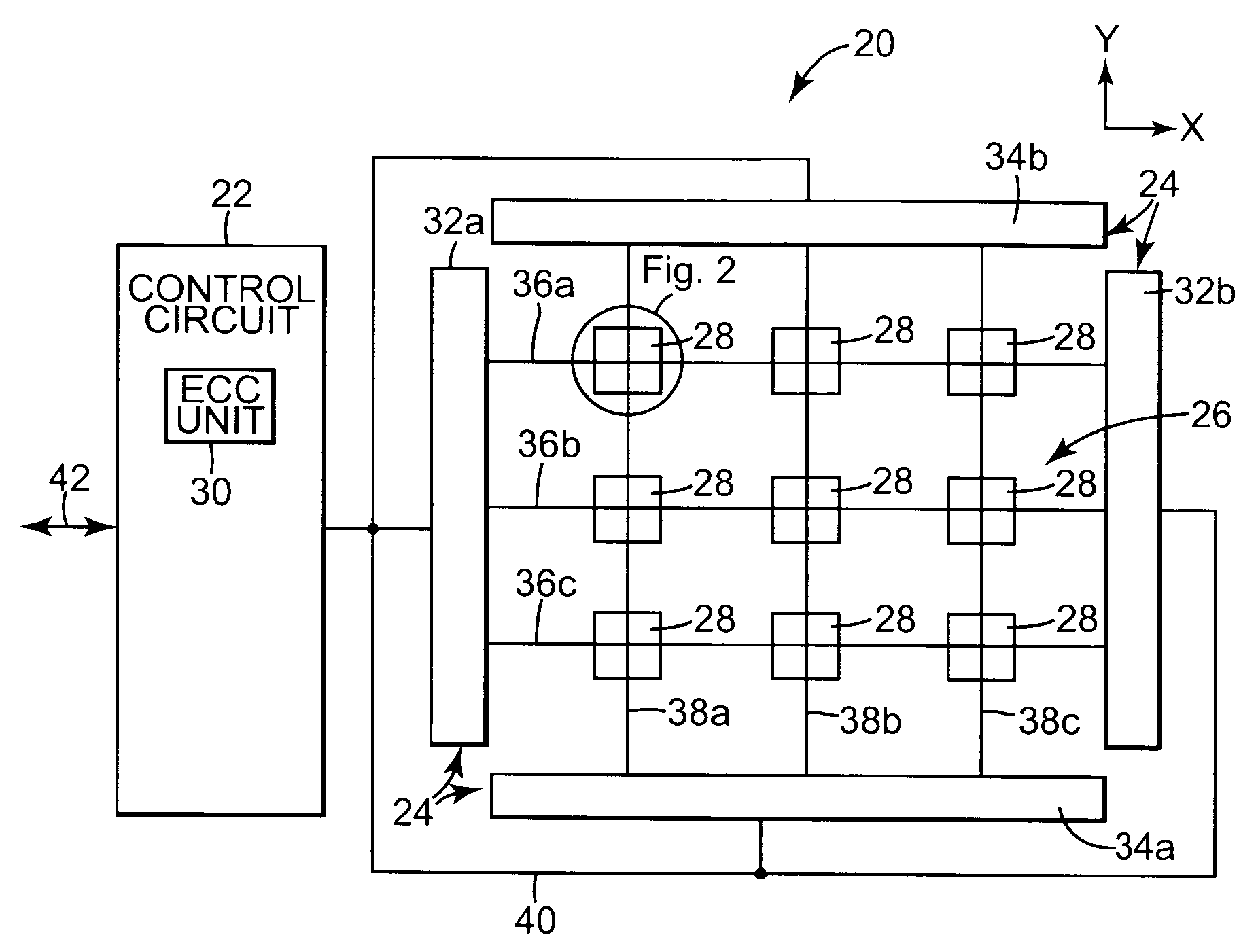

Combined distortion estimation and error correction coding for memory devices

ActiveUS20090024905A1Improve performanceData representation error detection/correctionError detection/correctionCalculation errorDistortion

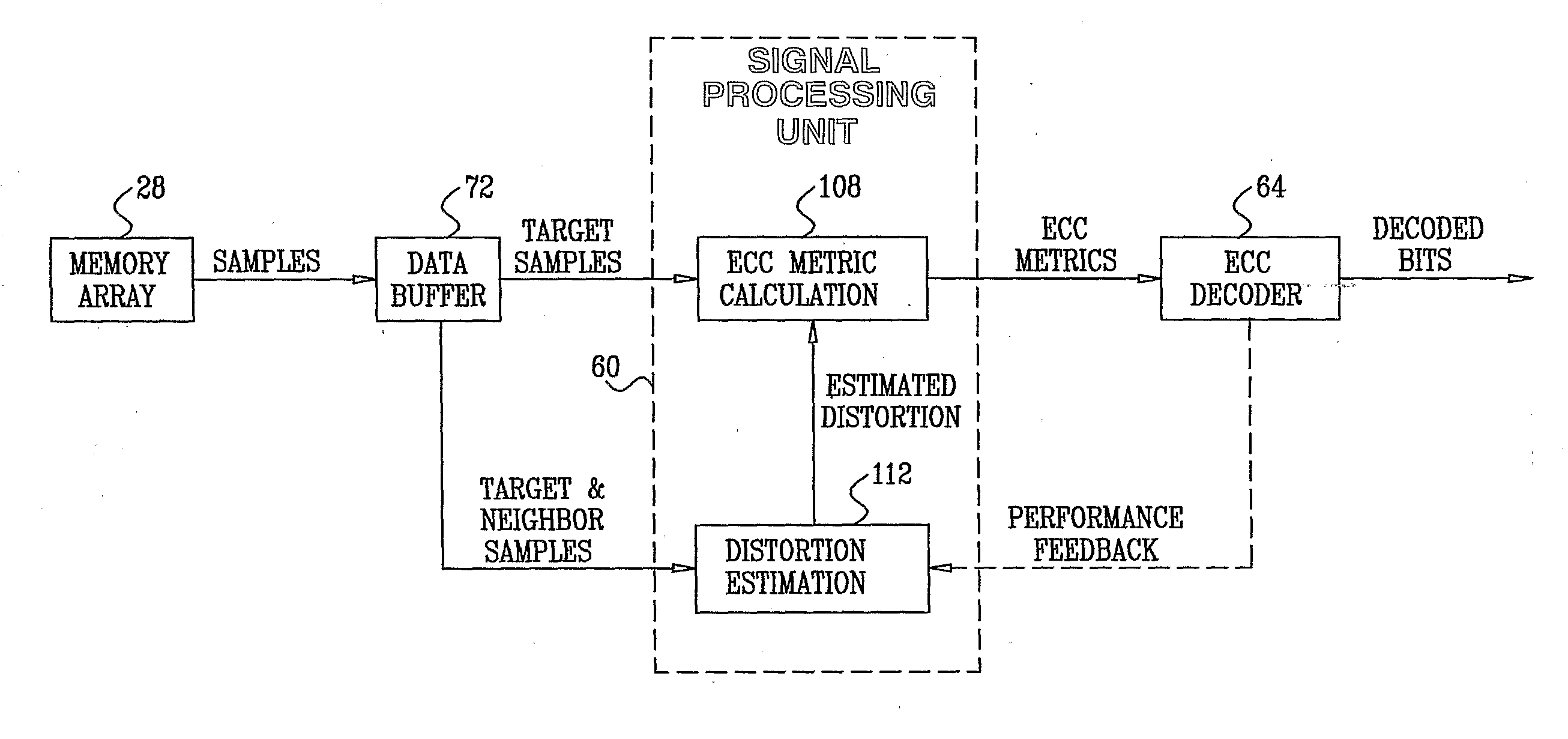

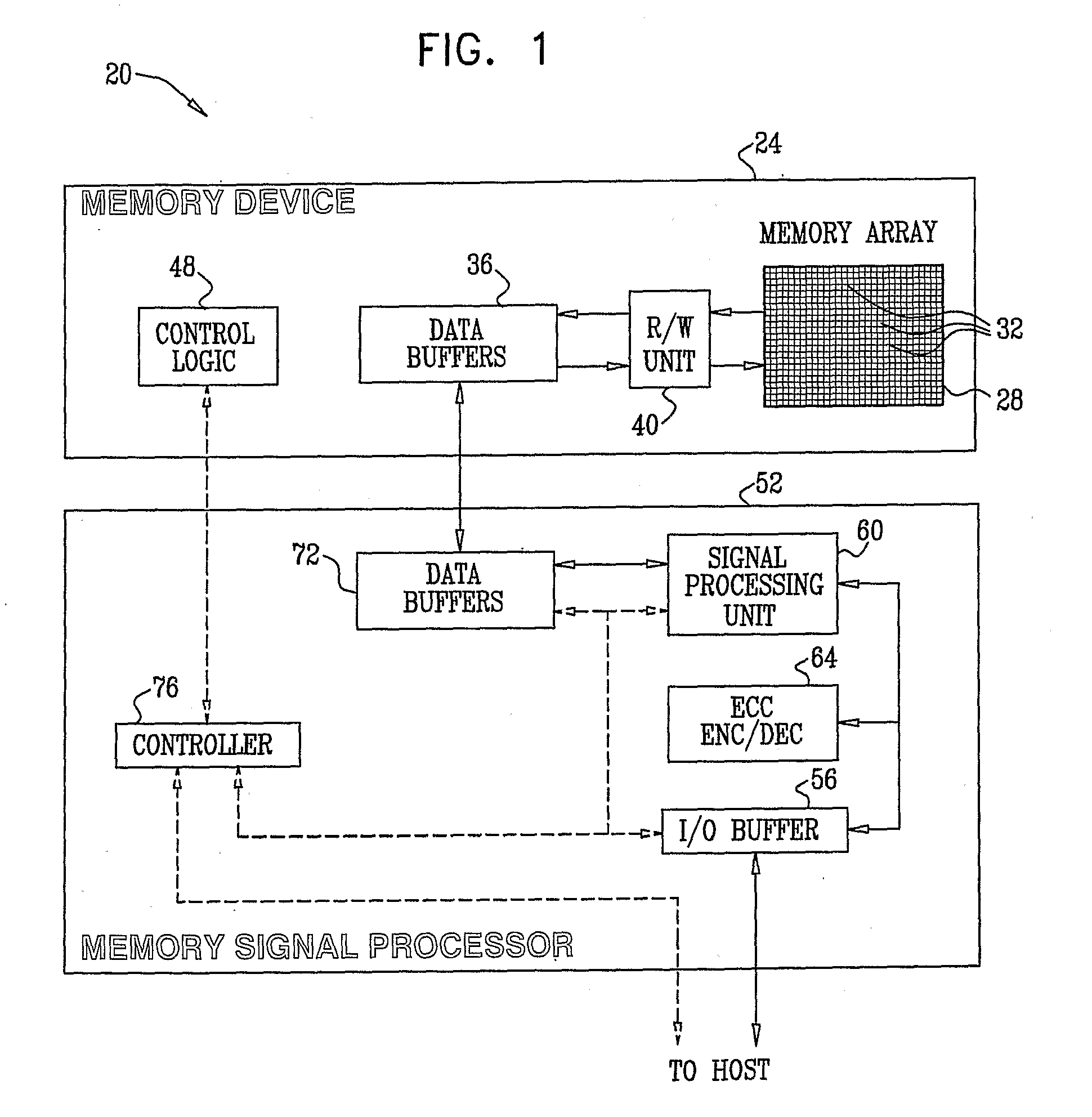

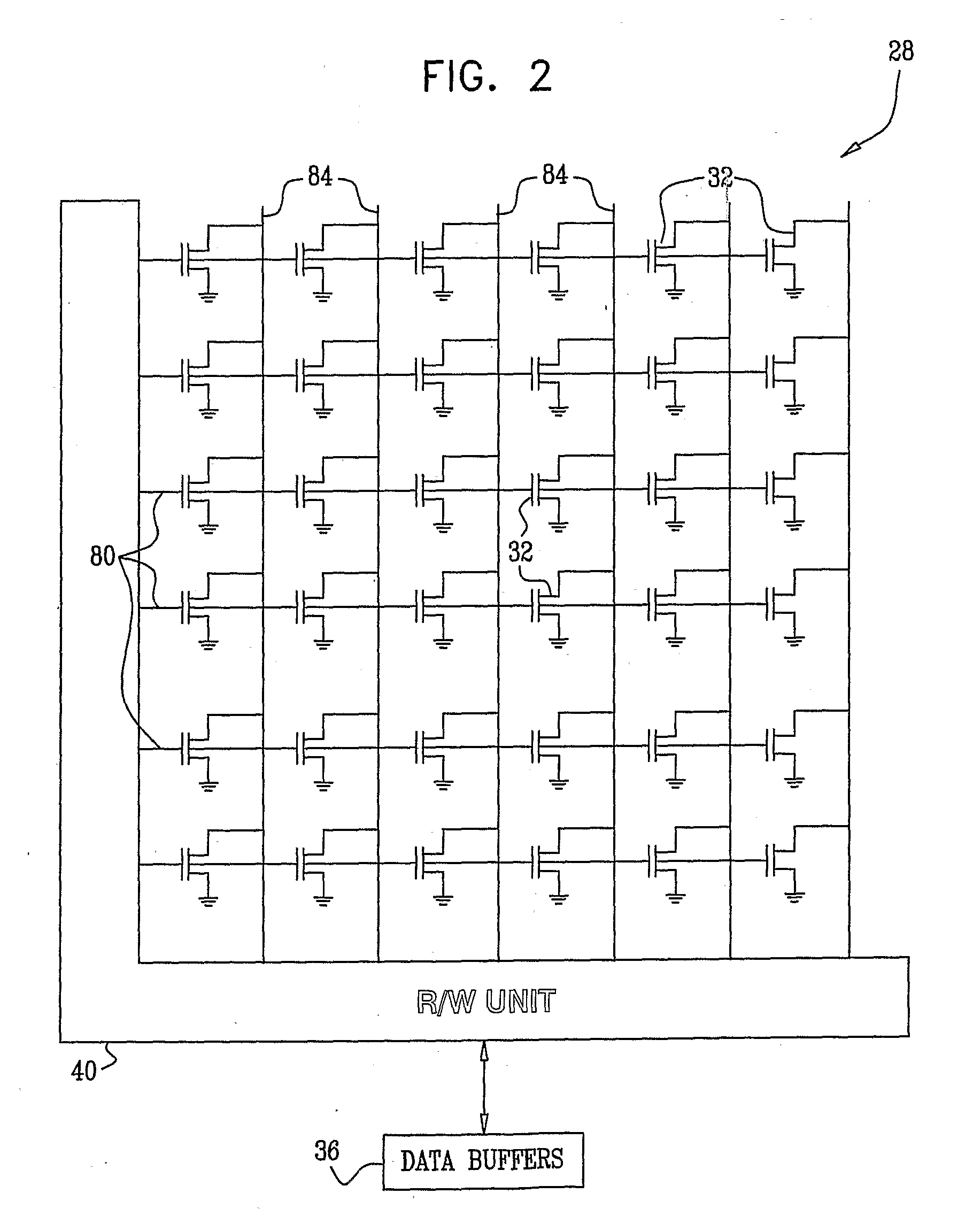

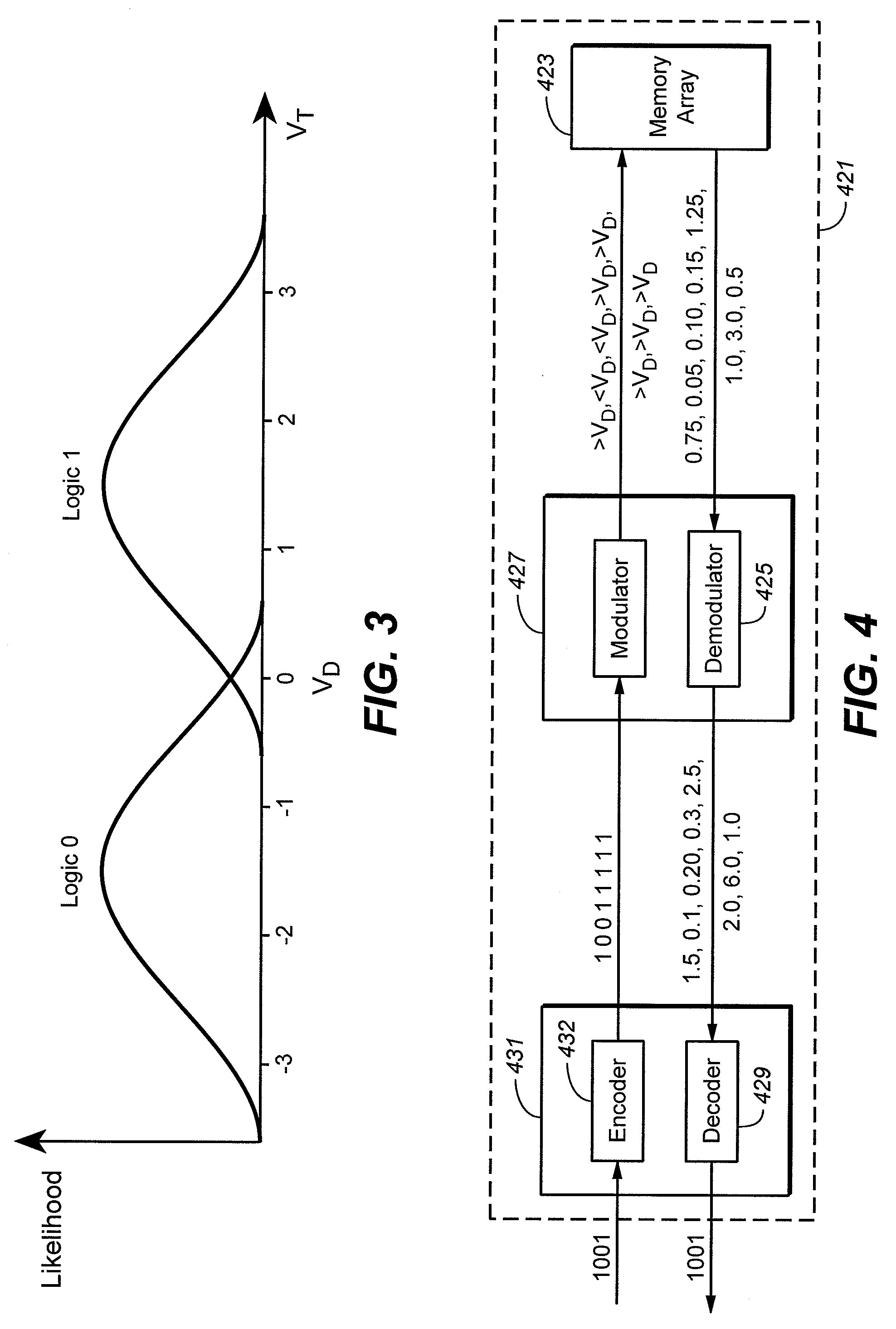

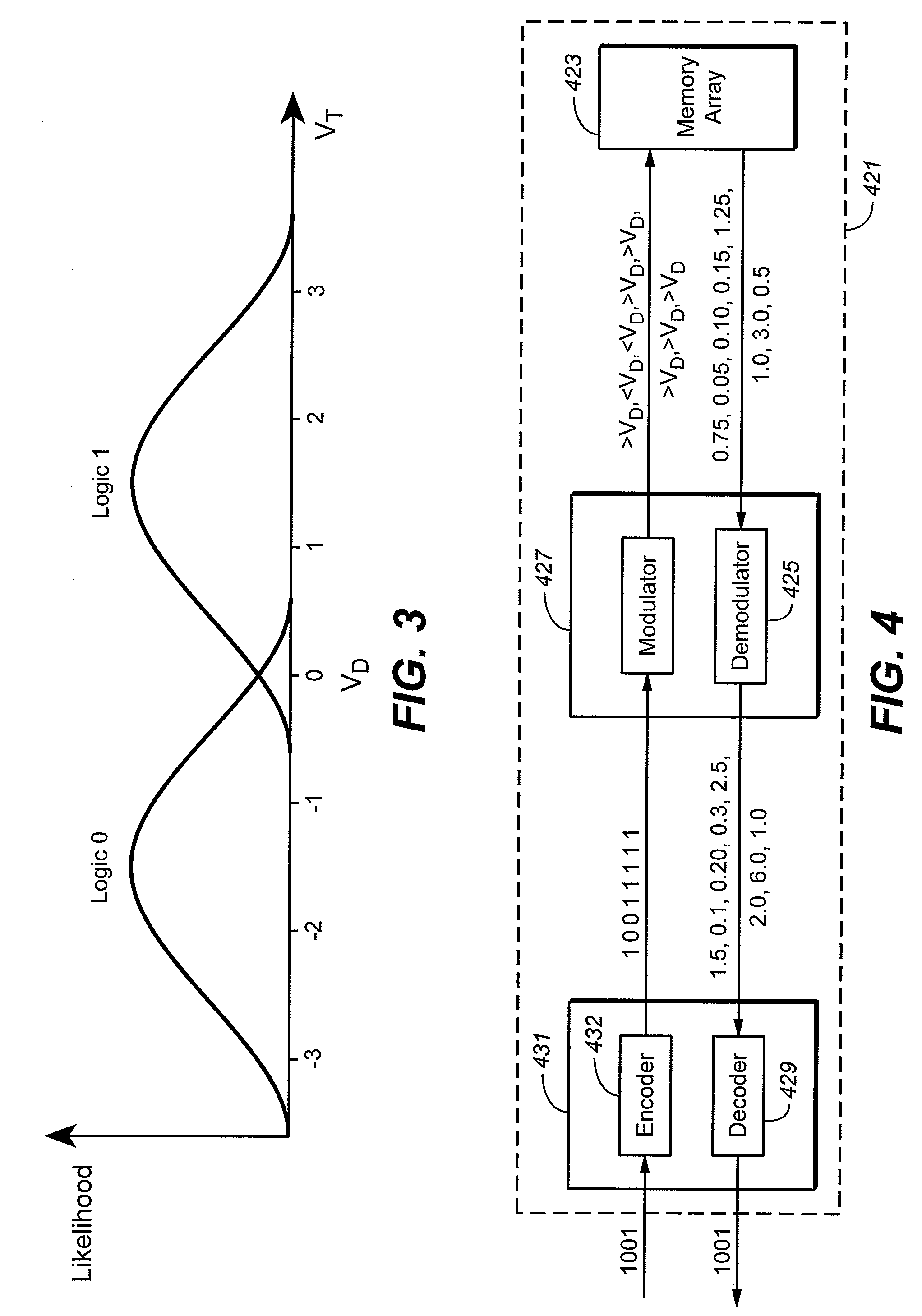

A method for operating a memory device (24) includes encoding data using an Error Correction Code (ECC) and storing the encoded data as first analog values in respective analog memory cells (32) of the memory device. After storing the encoded data, second analog values are read from the respective memory cells of the memory device in which the encoded data were stored. At least some of the second analog values differ from the respective first analog values. A distortion that is present in the second analog values is estimated. Error correction metrics are computed with respect to the second analog values responsively to the estimated distortion. The second analog values are processed using the error correction metrics in an ECC decoding process, so as to reconstruct the data.

Owner:APPLE INC

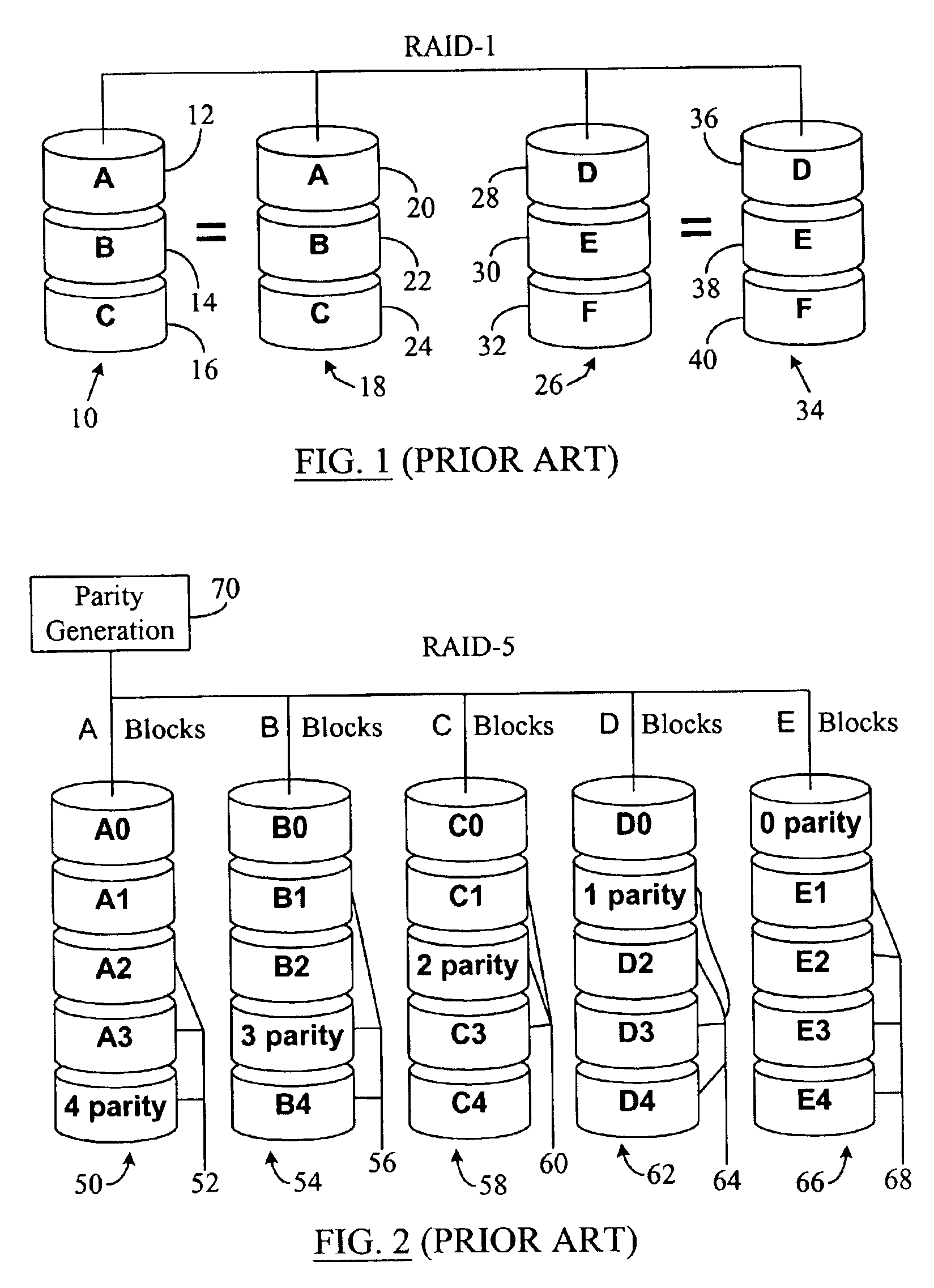

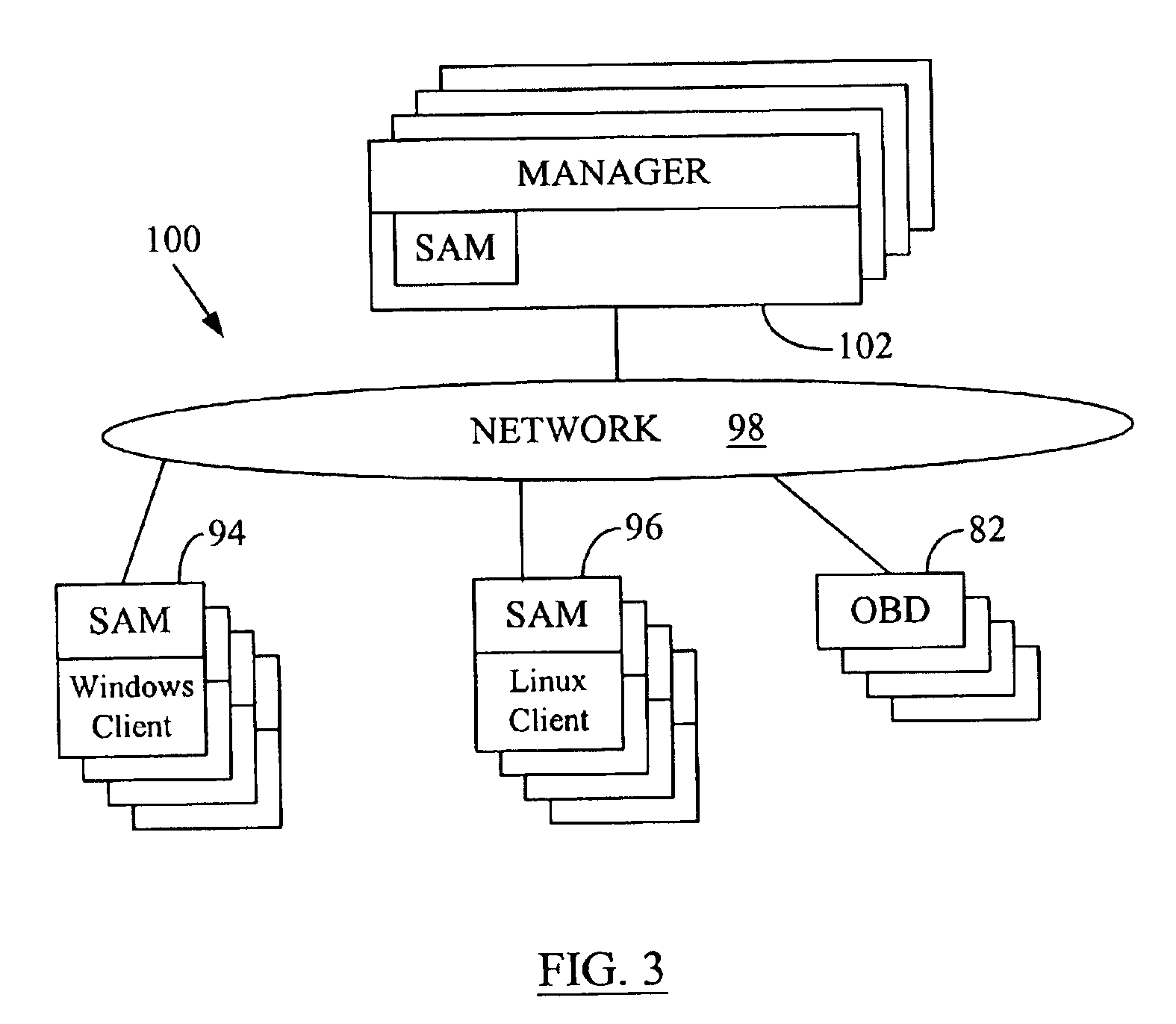

Data file migration from a mirrored RAID to a non-mirrored XOR-based RAID without rewriting the data

InactiveUS6985995B2Improve performanceImprove reliabilityData processing applicationsMemory loss protectionRAIDObject based

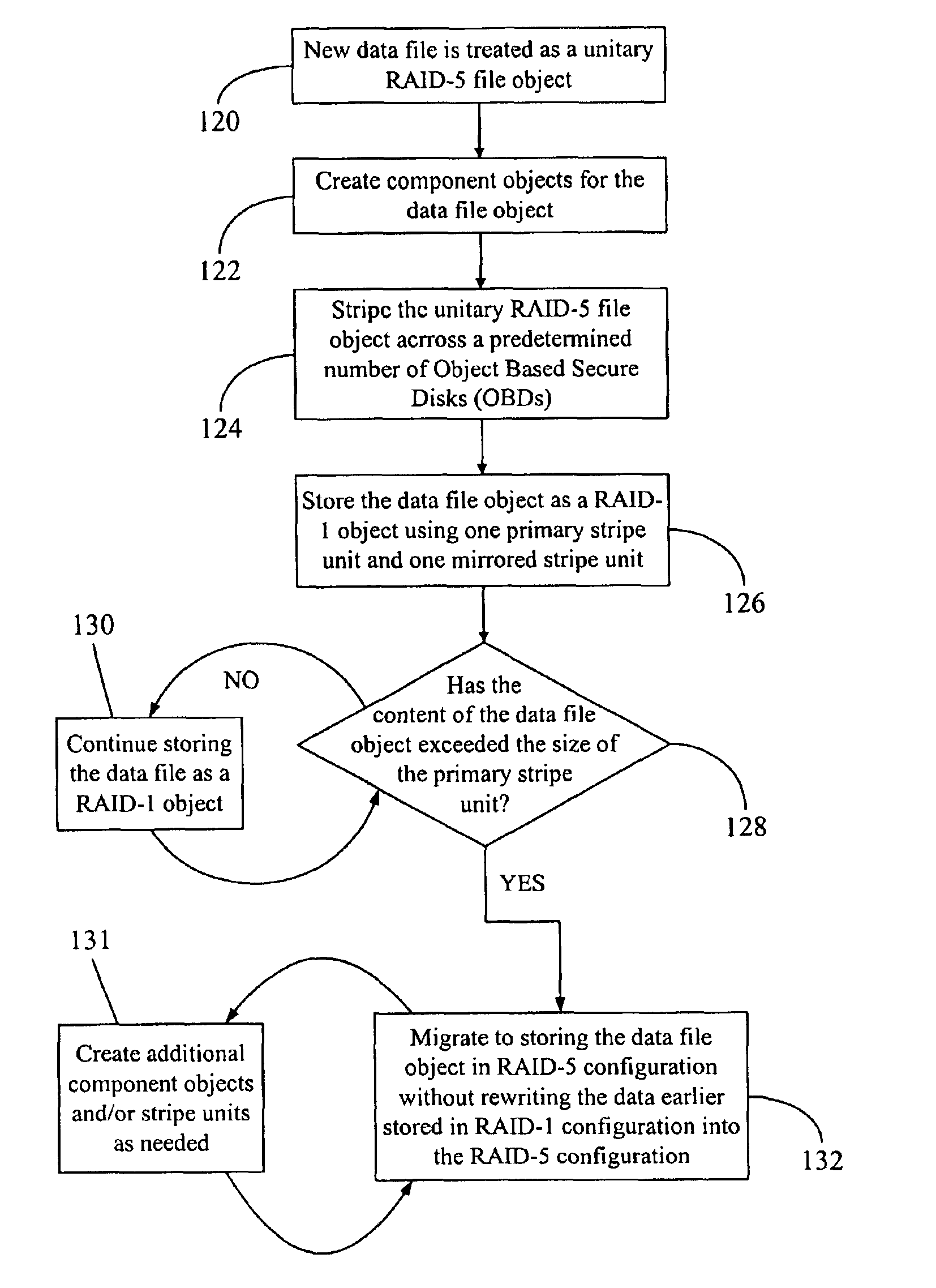

A data storage methodology wherein a data file is initially stored in a format consistent with RAID-1 and RAID-X and then migrated to a format consistent with RAID-X and inconsistent with RAID-1 when the data file grows in size beyond a certain threshold. Here, RAID-X refers to any non-mirrored storage scheme employing XOR-based error correction coding (e.g., a RAID-5 configuration). Each component object (including the data objects and the parity object) for the data file is configured to be stored in a different stripe unit per object-based secure disk. Each stripe unit may store, for example, 64 KB of data. So long as the data file does not grow beyond the size threshold of a stripe unit (e.g., 64 KB), the parity stripe unit contains a mirrored copy of the data stored in one of the data stripe units because of the exclusive-ORing of the input data with “all zeros” assumed to be contained in empty or partially-filled stripe units. When the file grows beyond the size threshold, the parity stripe unit starts storing parity information instead of a mirrored copy of the file data. Thus, the data file can be automatically migrated from a format consistent with RAID-1 and RAID-X to a format consistent with RAID-X and inconsistent with RAID-1 without the necessity to duplicate or rewrite the stored data.

Owner:PANASAS INC

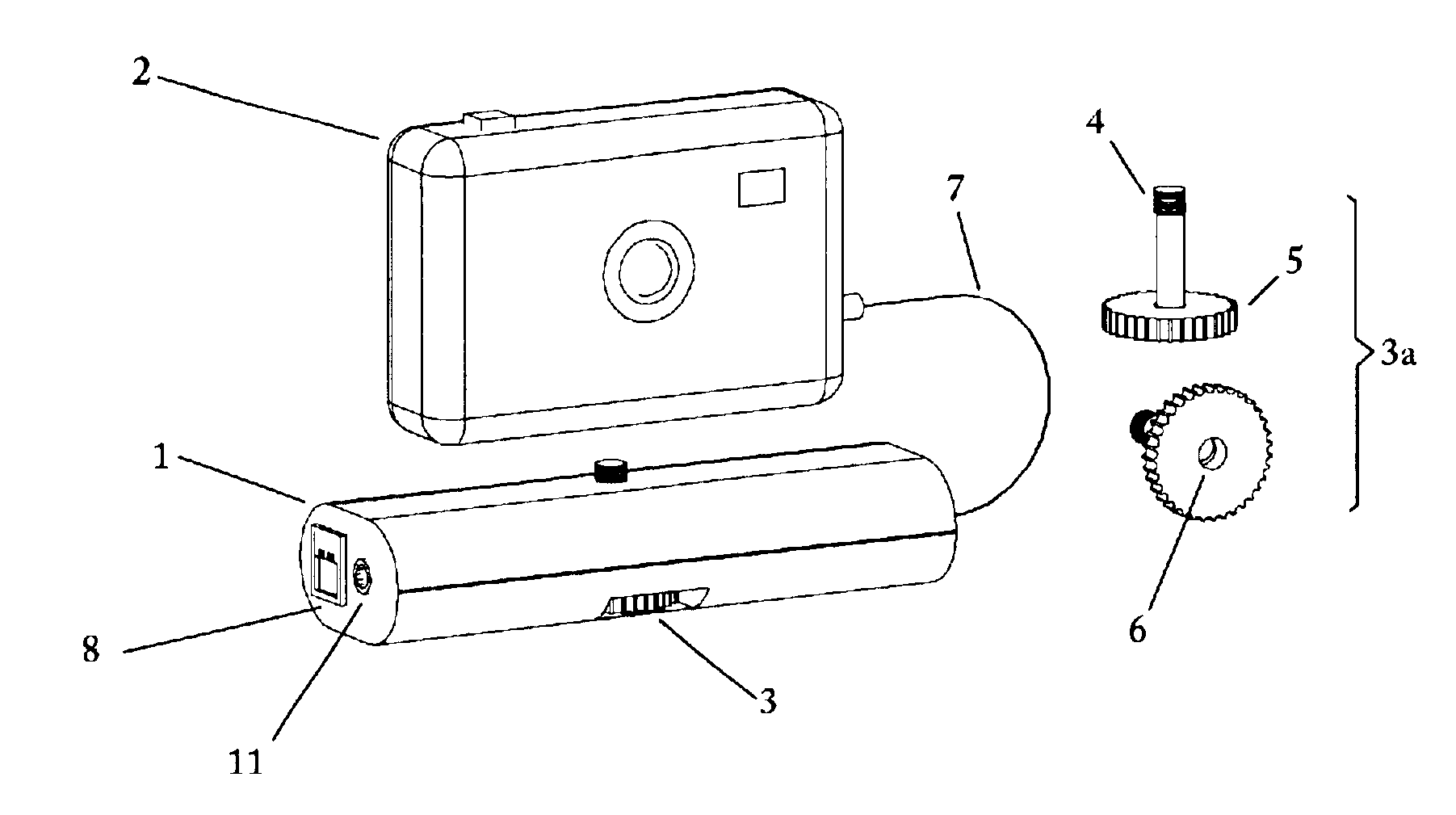

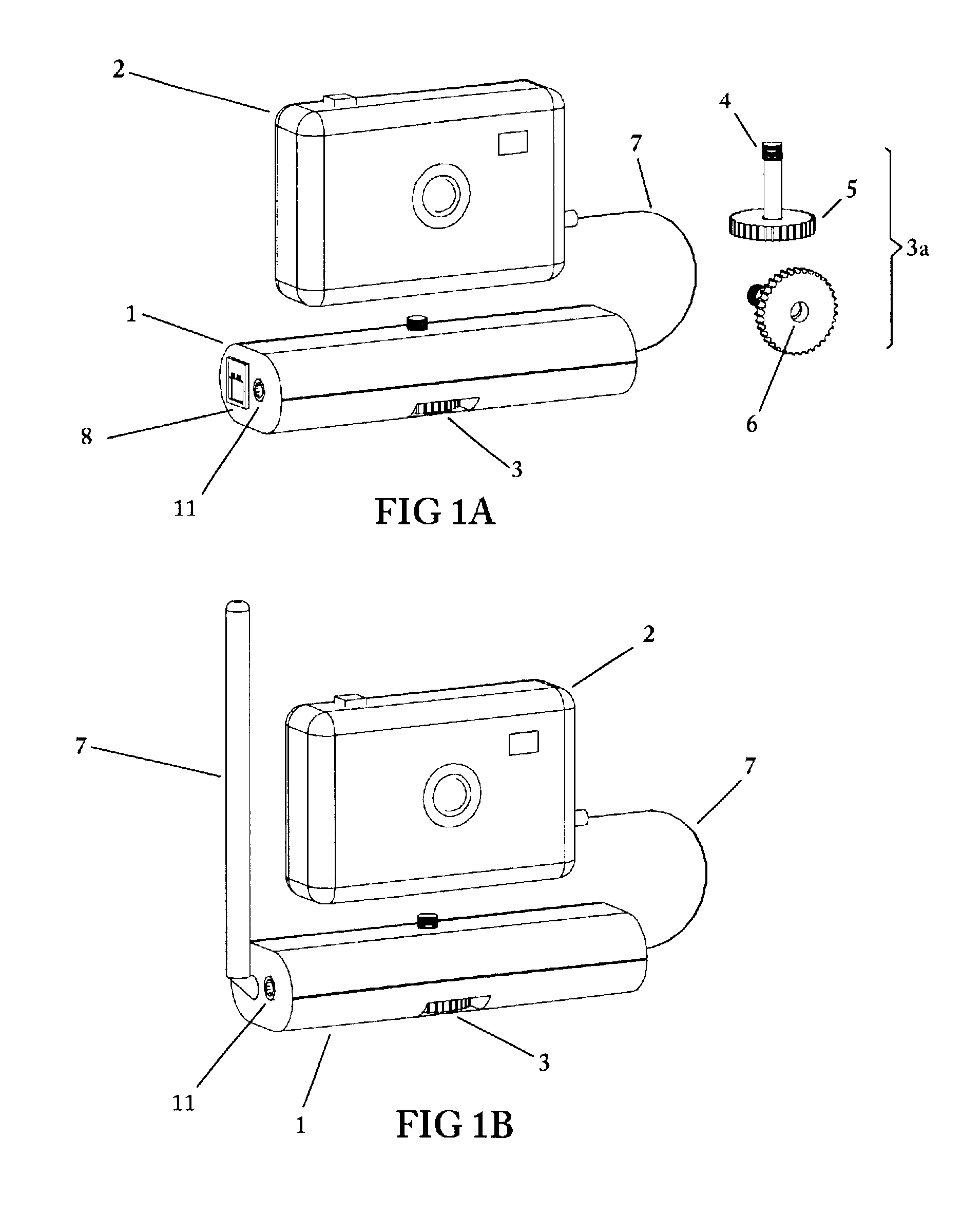

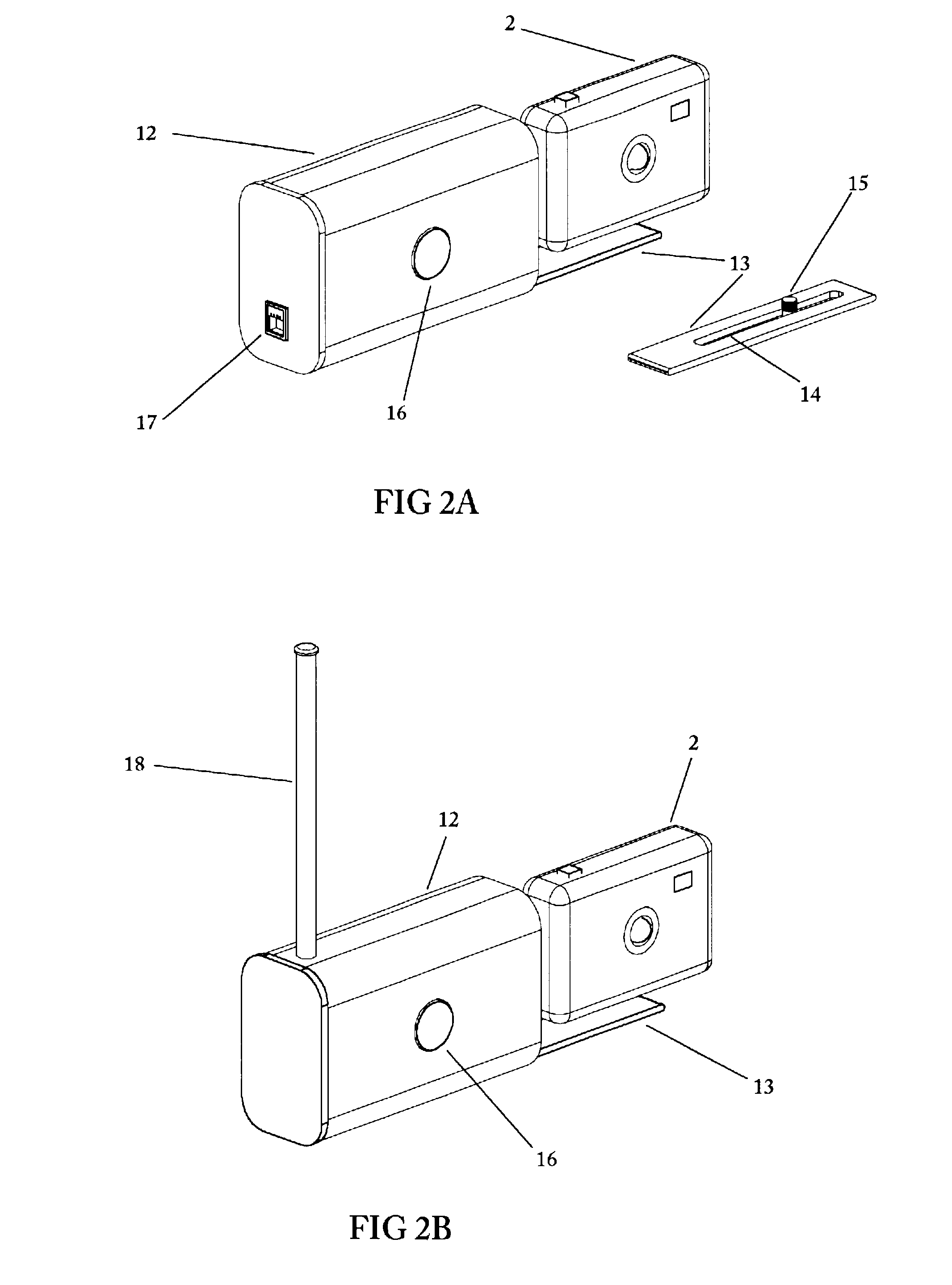

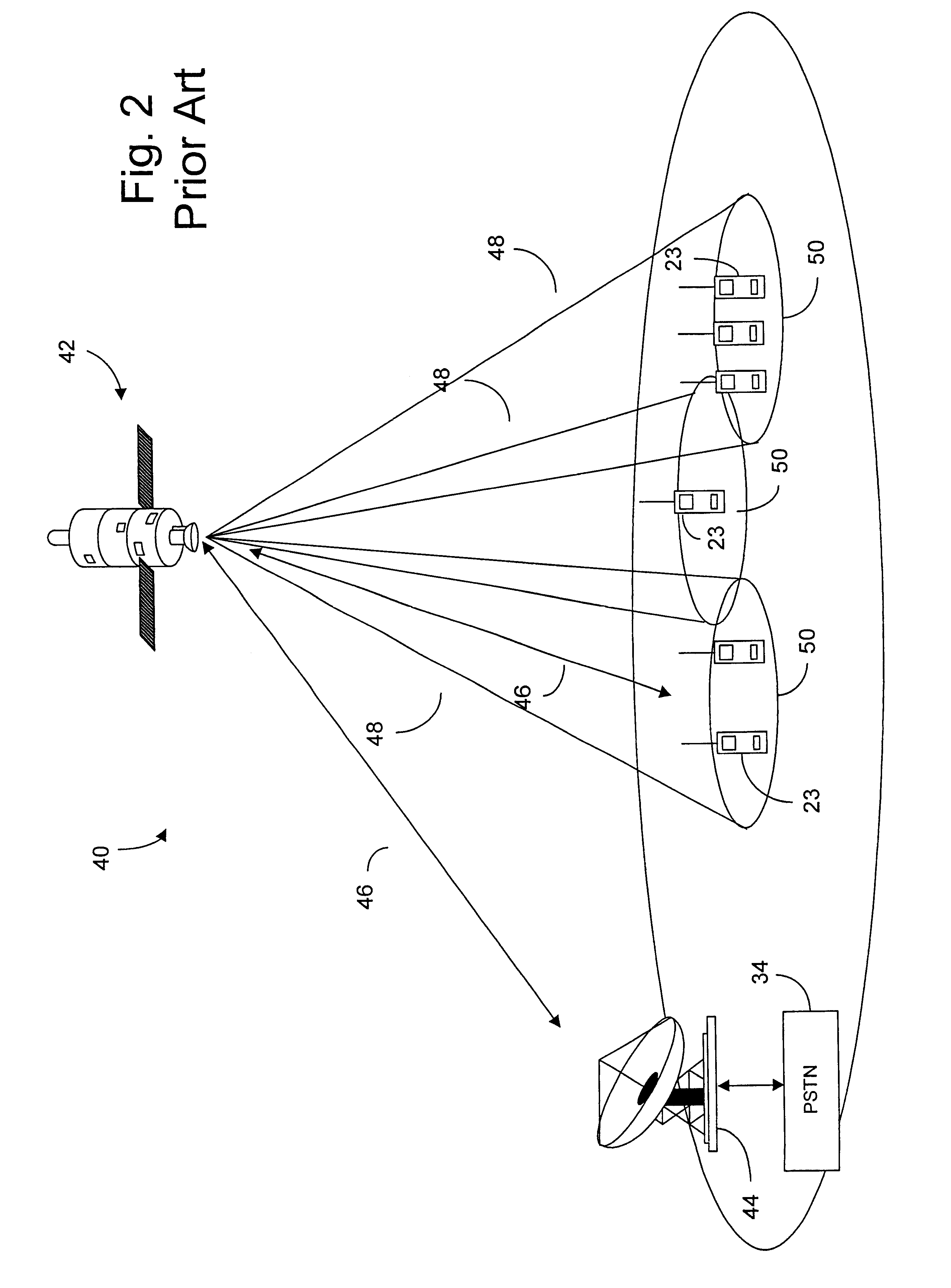

Remote camera relay controller method and apparatus

InactiveUS6400903B1Reduce transmit powerReduction in Eb/NoTelevision system detailsProjector film strip handlingModem deviceTelecommunications link

A remote camera relay method and apparatus for remotely operating a self-contained, unattended digital camera over a communications link. Format conversion means are included for transparently relaying control signals and remote image data between a local host processor and the remotely located digital camera, independently of specific camera command and image protocols. It thereby functions as a universal remote image transmission adapter, operable as an attachment for use with self-contained digital cameras. A portable enclosure is provided for accommodating the remote relay communications and control electronics and for attaching a hand-held digital camera thereto. Further means are included for remotely actuating the pan and tilt orientation of the camera in accordance with field-of-view selection commands. Data rate conversion and error correction coding are included for providing reliable, low power image forwarding. The communications channel could be a dial-up telephone system, a network connection, modem, an infra-red link or a wireless RF link, for example. Additional control means are provided for remotely selecting the camera field of view for image capture, and includes the ability to access only those subsets of image scenes for which viewing permissions are authorized. A further mode of operation includes protocol training whereby host photographing commands are captured by the remote relay invention during on-line operation, then replayed at programmed times resulting in automatic scheduled remote image capture. Power management is provided for maximizing operating time when used in low power, portable, battery operation.

Owner:CONOVAL PAUL

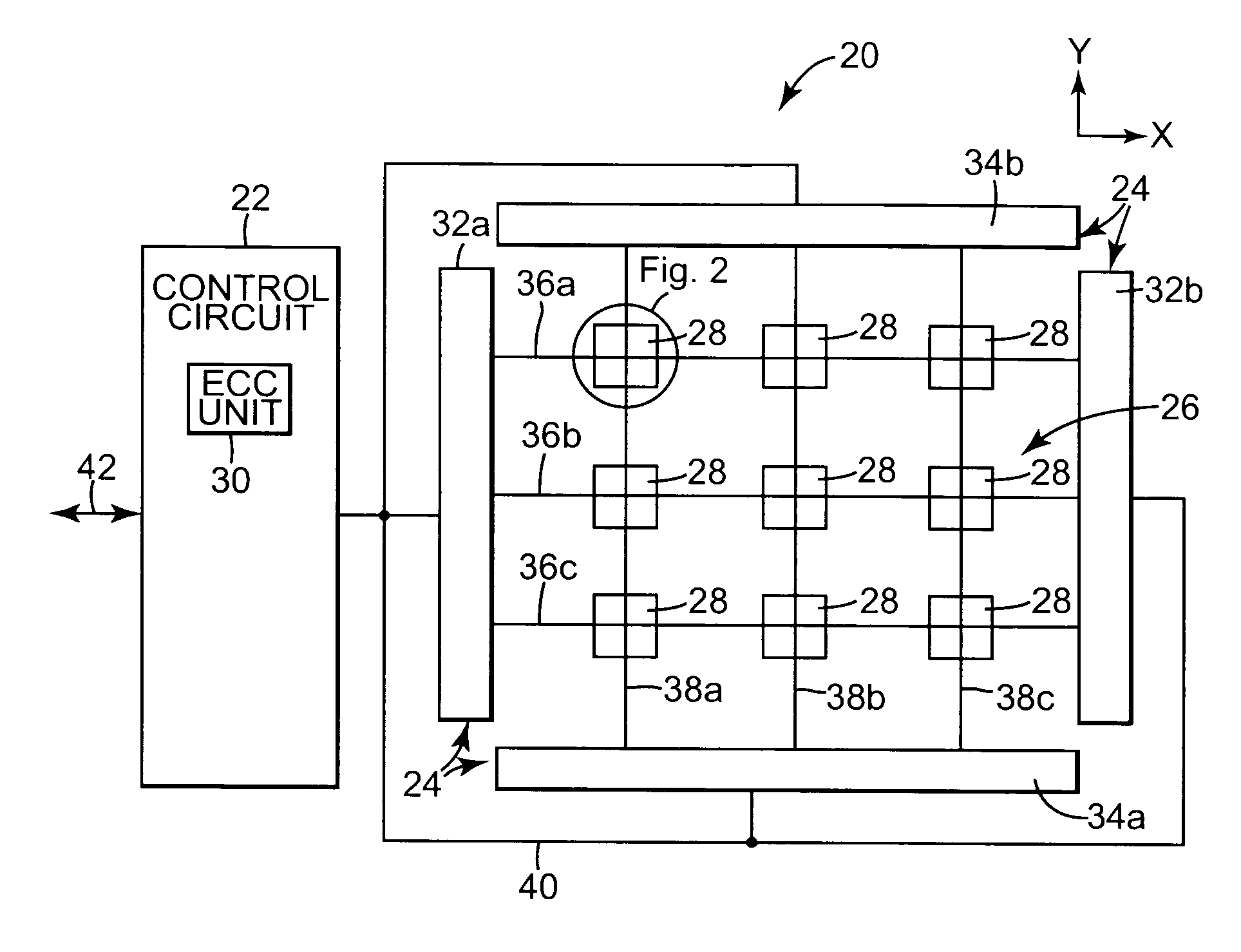

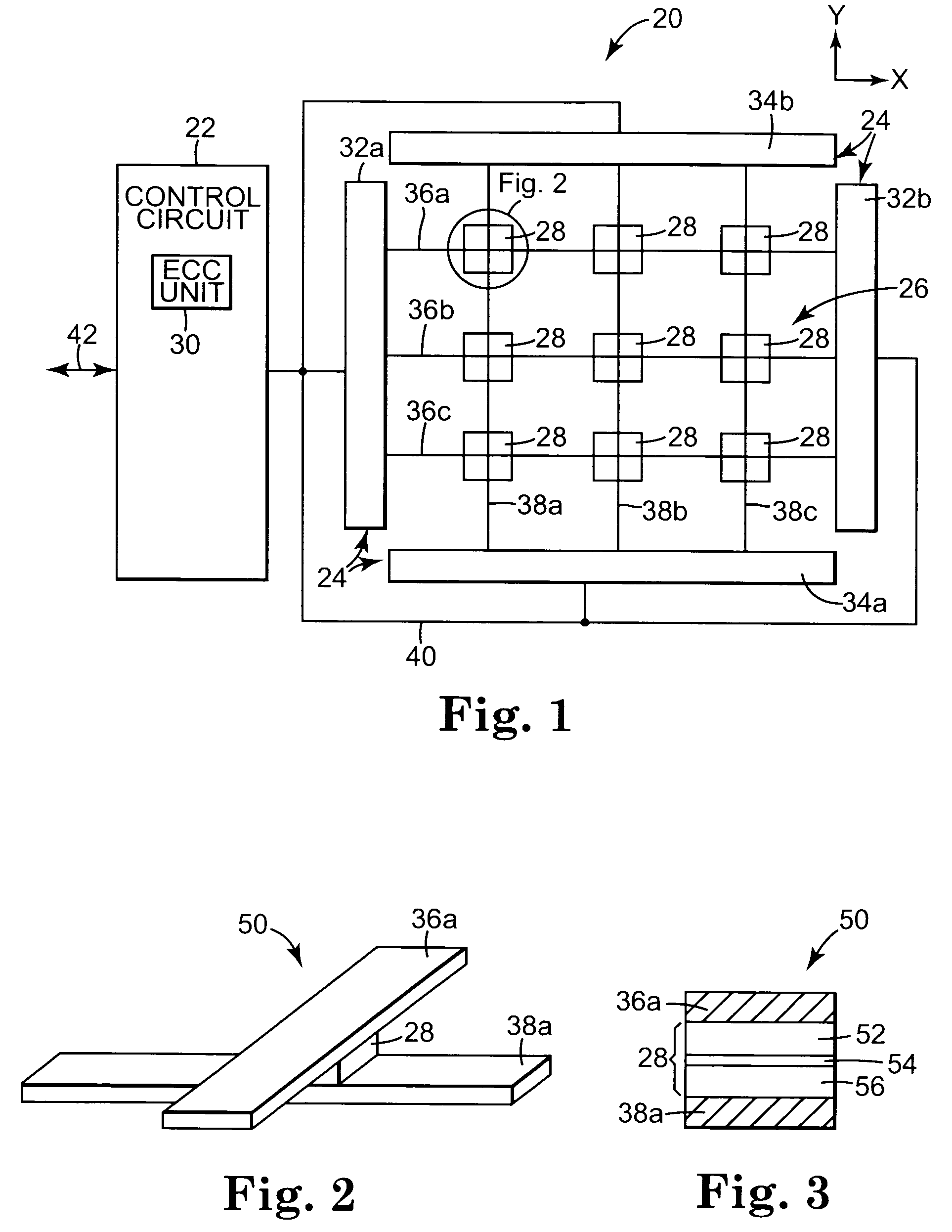

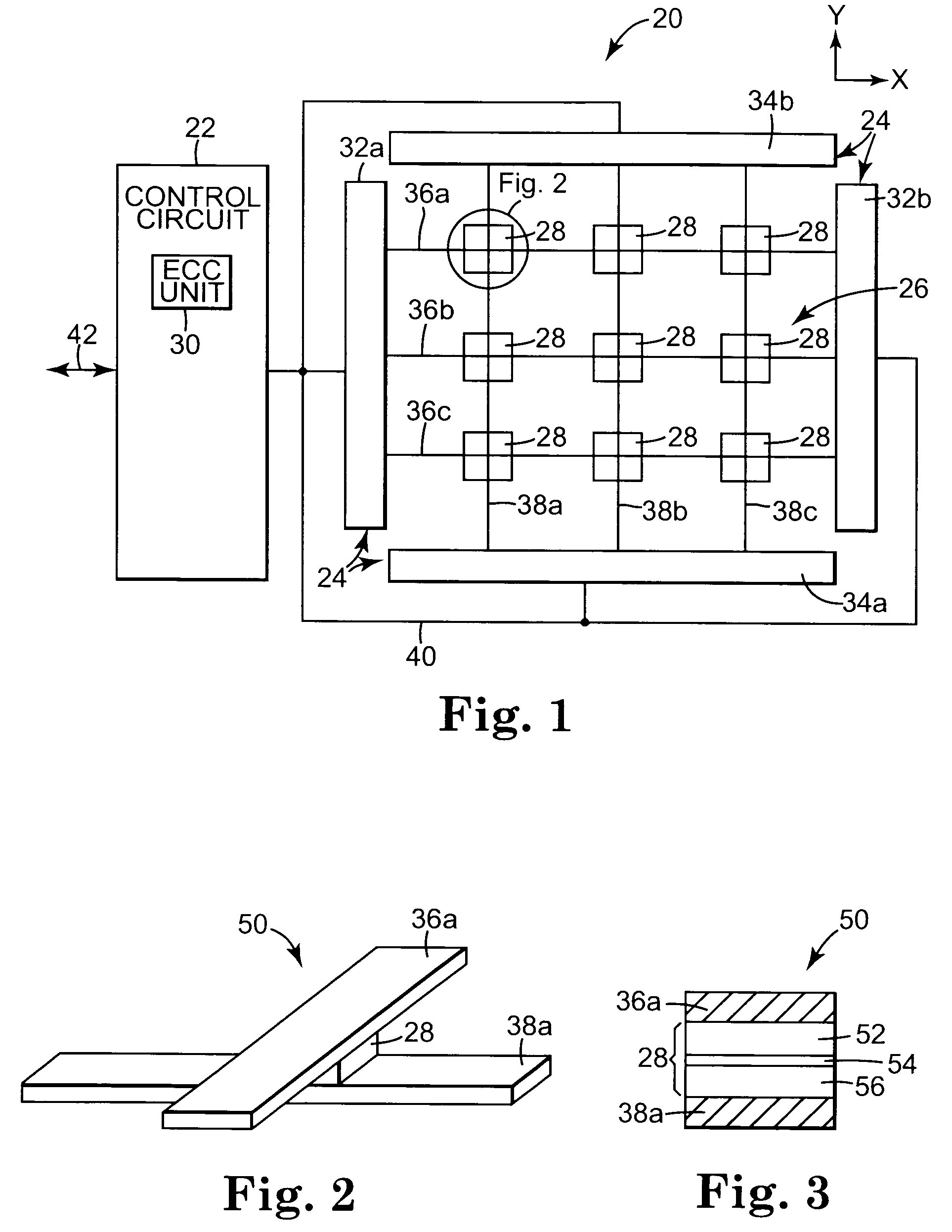

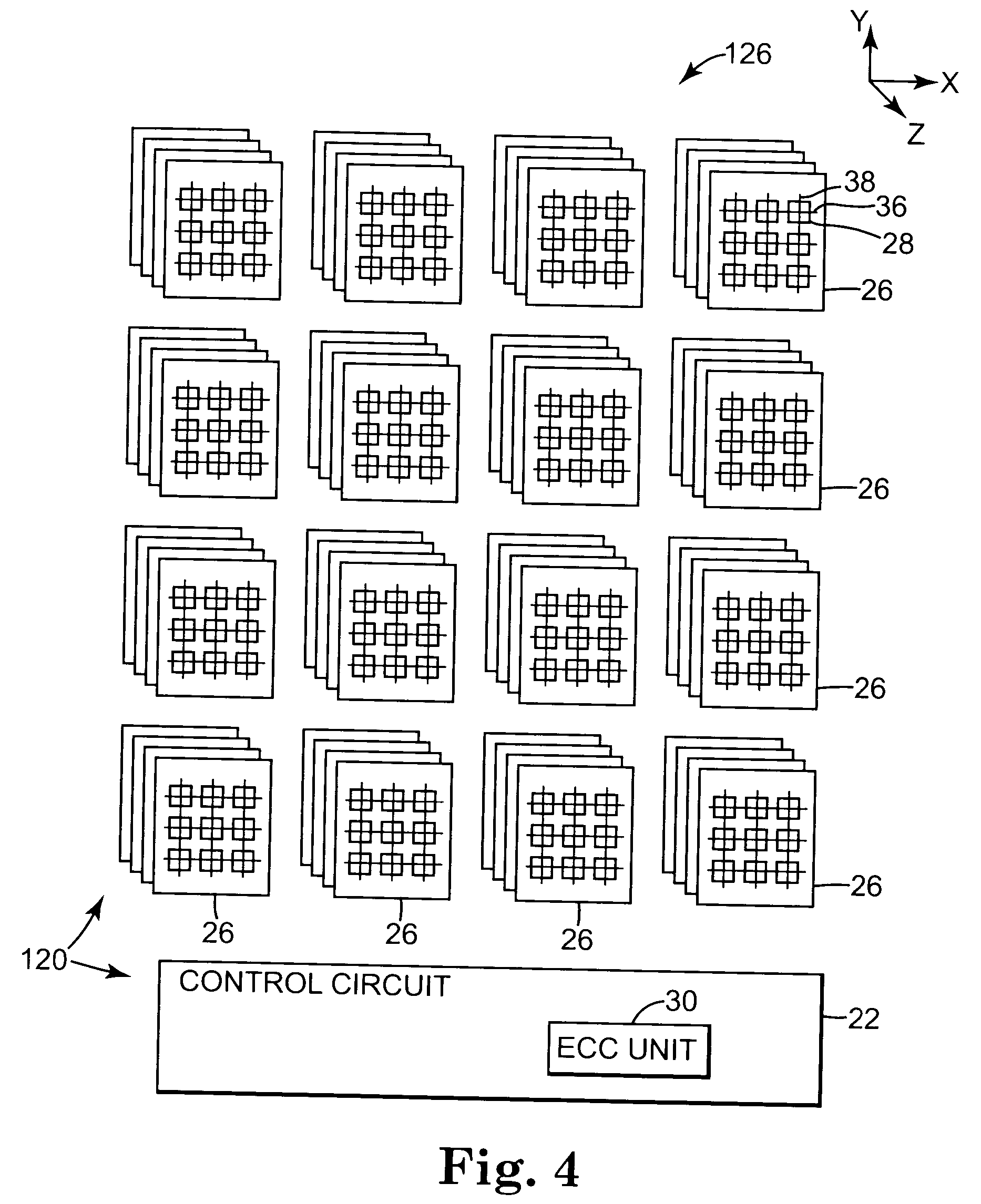

Magnetic memory with error correction coding

Embodiments of the present invention are implemented in memory systems. In one embodiment, the memory comprises an array of memory cells and a control circuit. The control circuit is configured to read error correction coded data from the array of memory cells, provide error correction code decoding to selected error correction coded data and discard unused error correction code parity data of unselected error correction coded data.

Owner:SAMSUNG ELECTRONICS CO LTD

Watermark payload encryption methods and systems

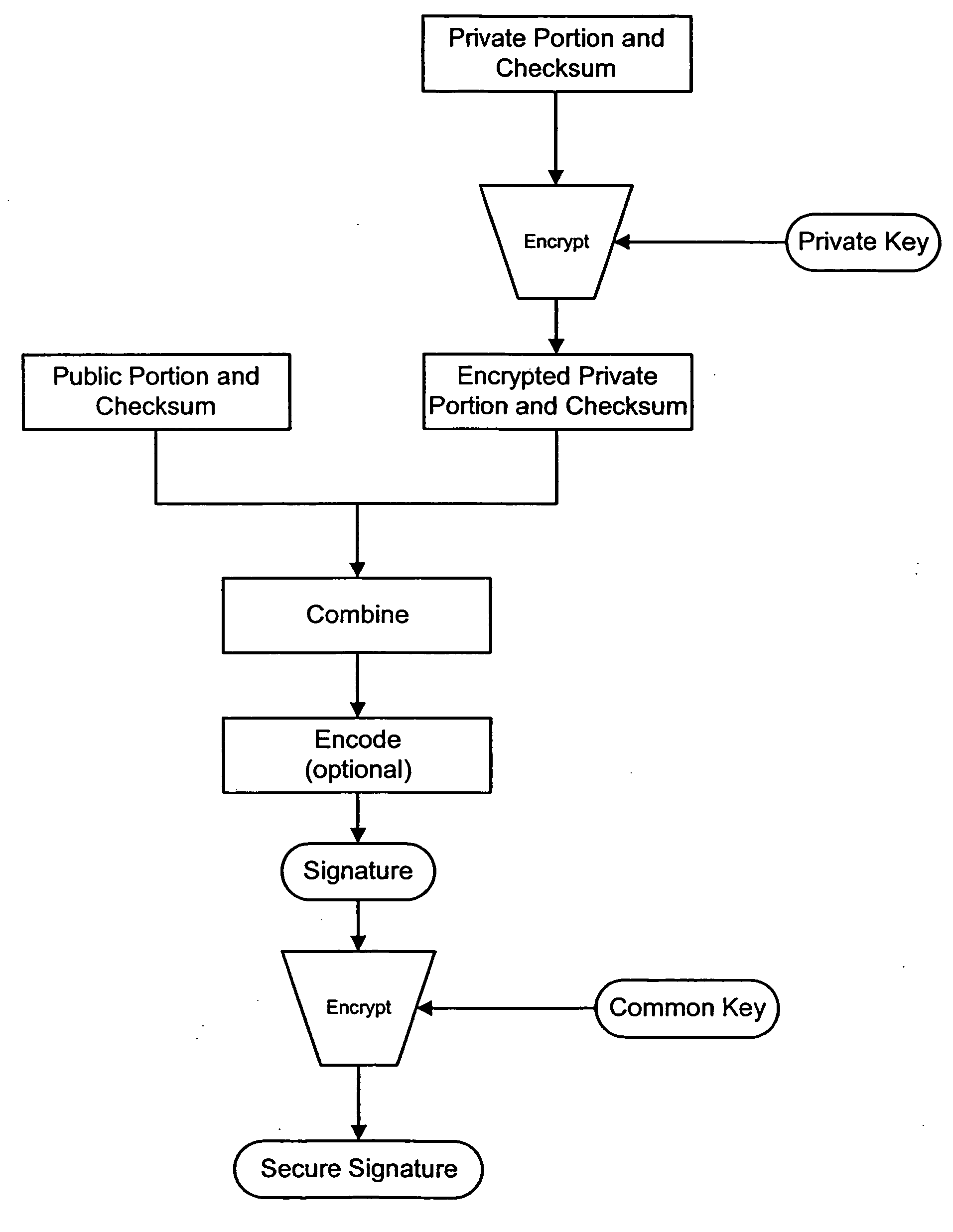

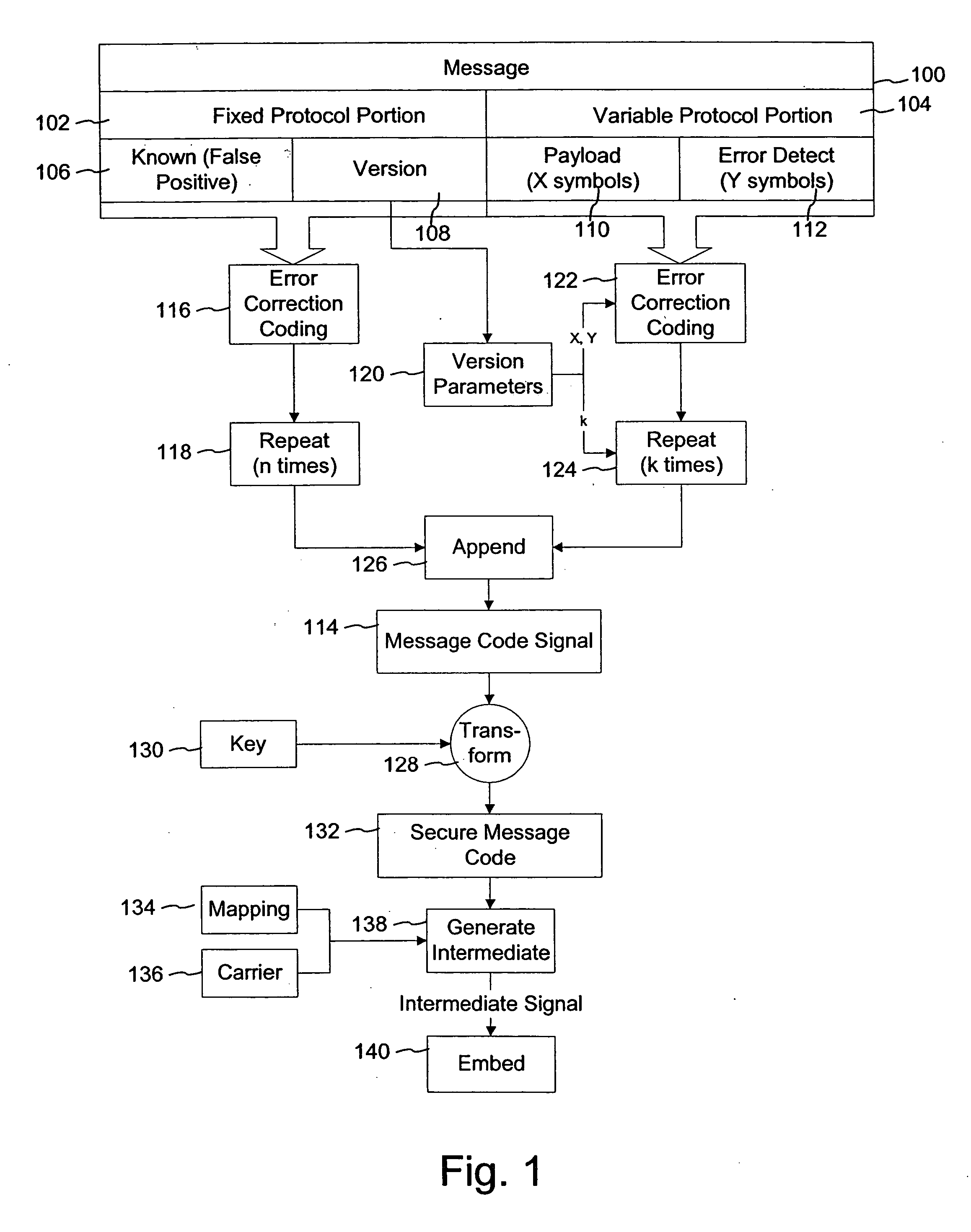

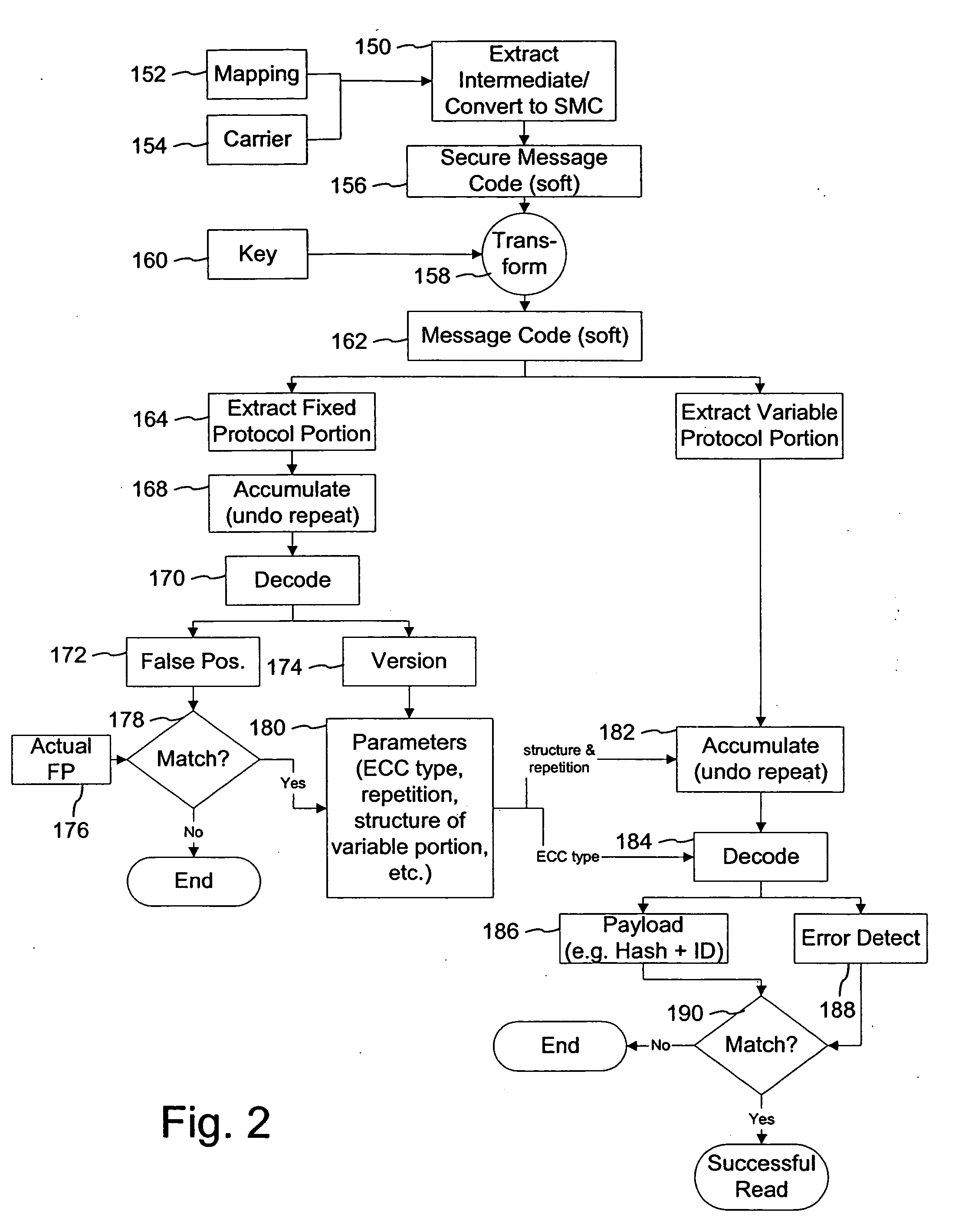

InactiveUS20050271246A1User identity/authority verificationCharacter and pattern recognitionInternet privacyChecksum

The present invention provides a method of securing messages steganographically embedded in media (e.g., printed or electronic objects, audio and video). In one implementation, a message includes a first portion and a second portion. The first portion includes a first message and a first checksum, which are encrypted with a private key. The encrypted first portion is combined with the second portion. The second portion includes a second message and as second checksum. The combined encrypted first portion and the second portion form a signature. The signature is encrypted with a common or universal key, perhaps after error correction coding. The private key is uniquely associated with an entity such as a document issuing jurisdiction. In another implementation, a method appends information to a watermark message received from a remote device. The information preferably corresponds to the remote device or to a user of the remote device. In yet another implementation, a method provides standardized watermark payloads from various input data, regardless of the size of the input data.

Owner:DIGIMARC CORP

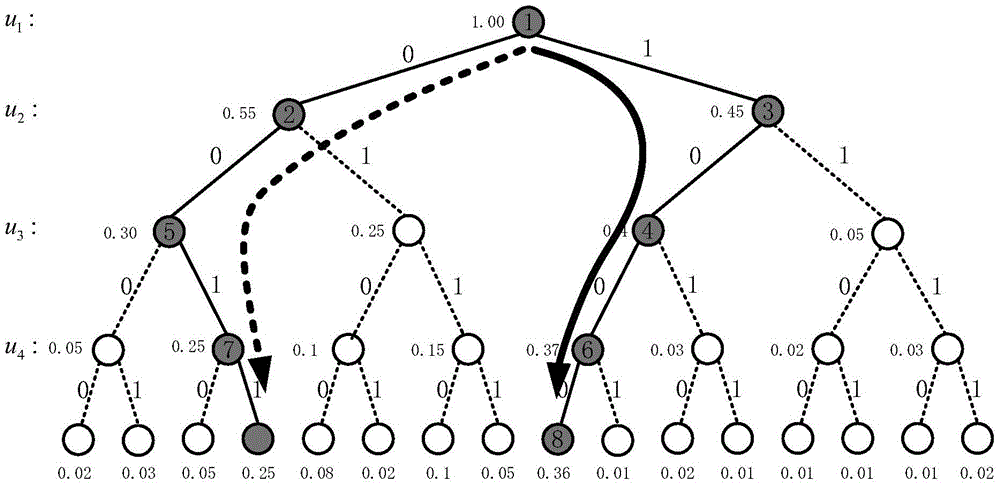

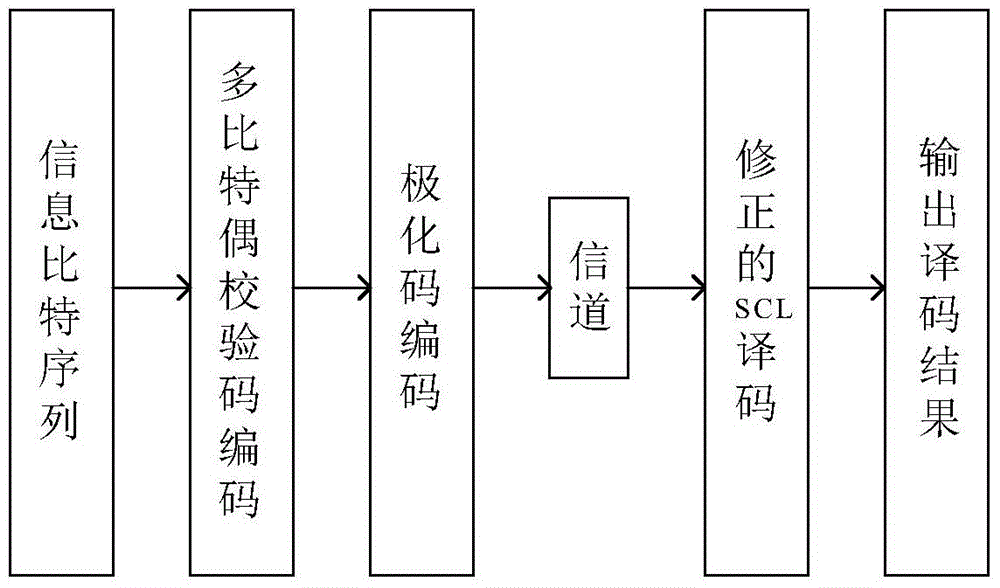

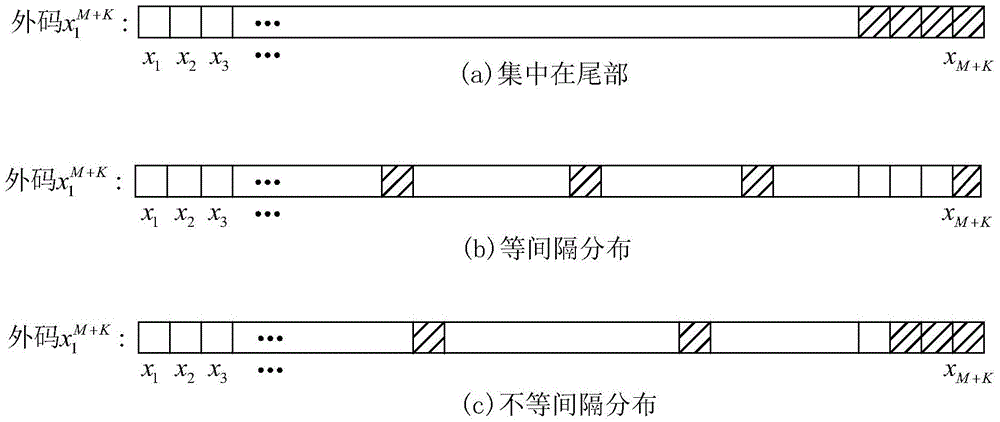

Polarization code and multi-bit even parity check code cascaded error correction coding method

ActiveCN105680883AImprove error correction performanceBreakthrough in error correction performanceCode conversionError correction/detection by combining multiple code structuresComputer hardwareError correction coding

The invention discloses a polarization code and multi-bit even parity check code cascaded error correction coding method. The method comprises the steps: a transmitting end encoder utilizes a multi-bit even parity check code as an outer code, and utilizes a polarization code as an inner code; a receiving end decoder decodes by utilizing a modified successive cancellation list (SCL) decoding algorithm. On the aspect of error correction performance, comparing with the prior art utilizing middle-short code length non-cascaded polarization codes of the SCL decoding algorithm, the polarization code and multi-bit even parity check code cascaded error correction coding method has the advantages that frame error rate performance of a system can be remarkably improved, and a maximum likelihood bound (ML Bound), which cannot be broken through by the SCL decoding algorithm, can be remarkably broken through. On the aspect of engineering realization, according to the polarization code and multi-bit even parity check code cascaded error correction coding method, the outer code utilizes the multi-bit even parity check code, which is simple to code; the modified SCL decoding algorithm is utilized to decode, bit decision and even parity check are combined to be carried out in a decoding process, and compared with the original SCL decoding algorithm, the method provided by the invention does not increase the decoding complexity, and facilitates the engineering realization.

Owner:HUAZHONG UNIV OF SCI & TECH

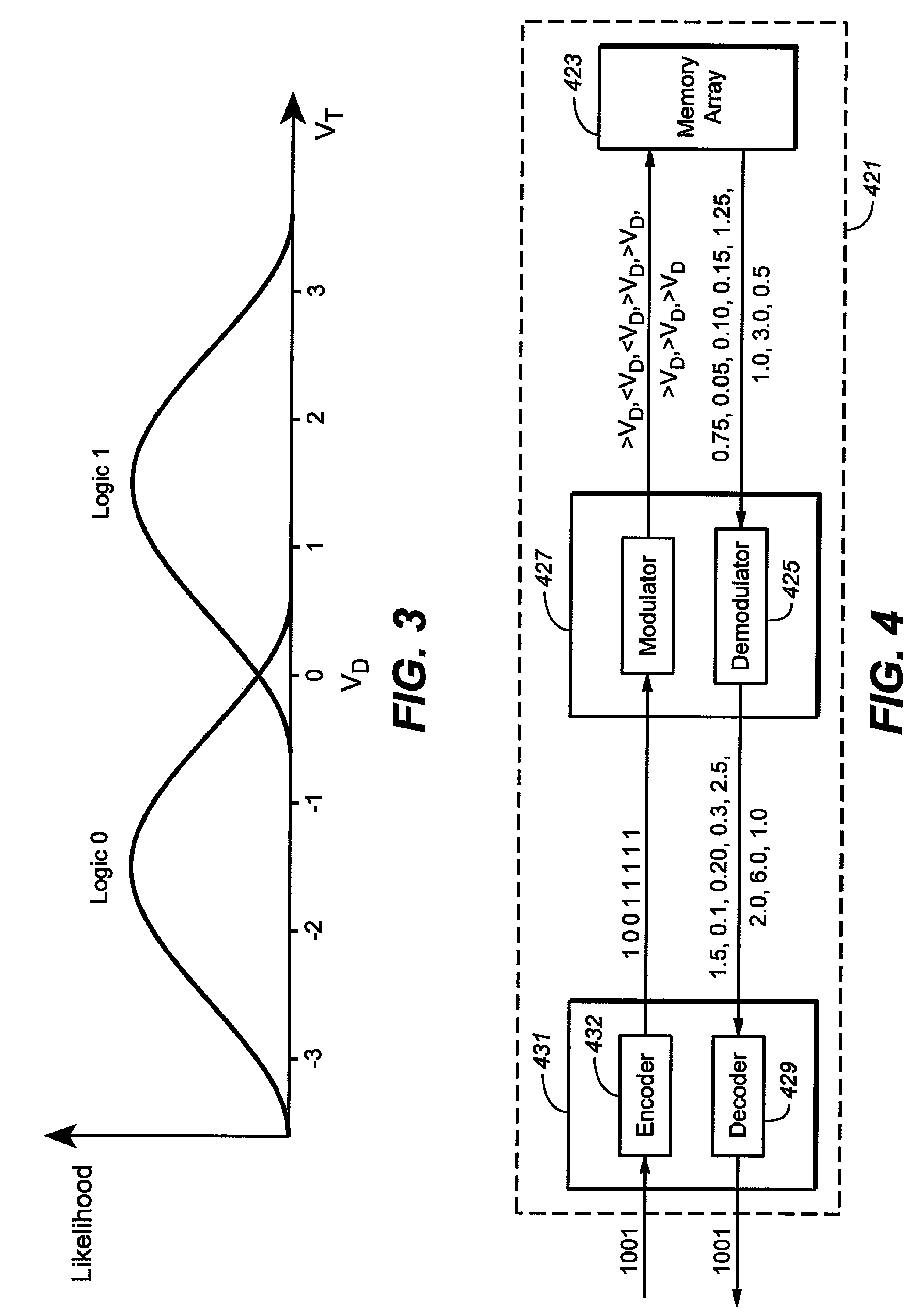

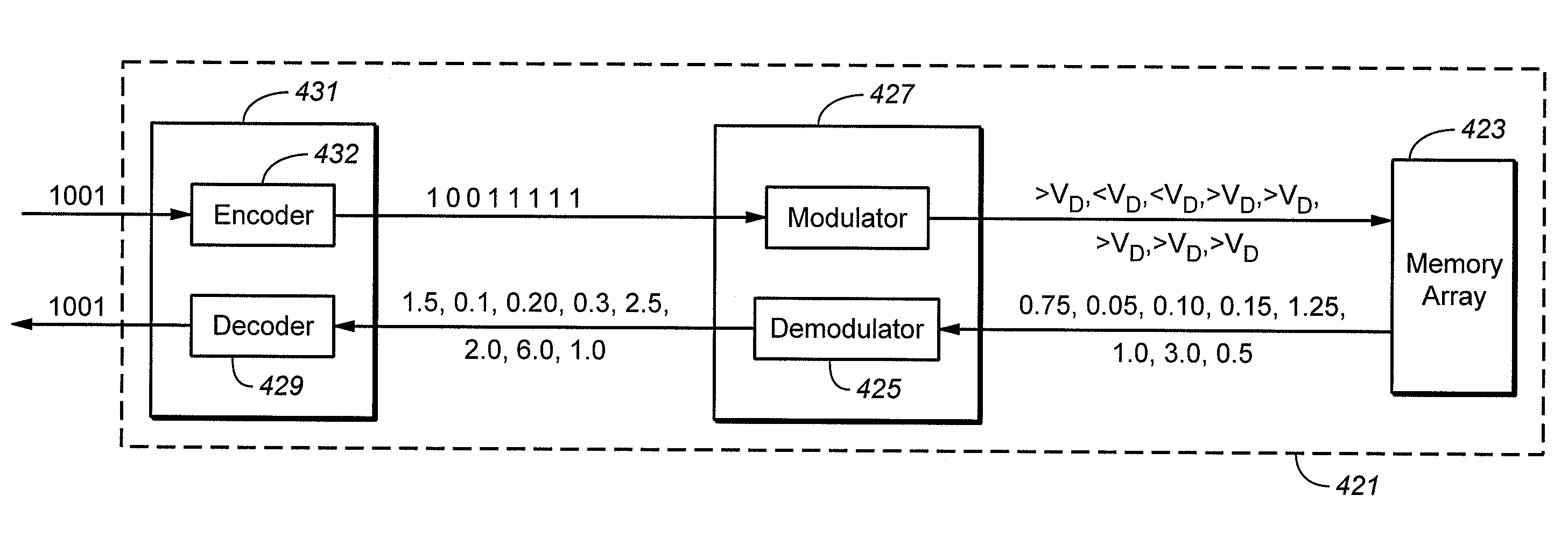

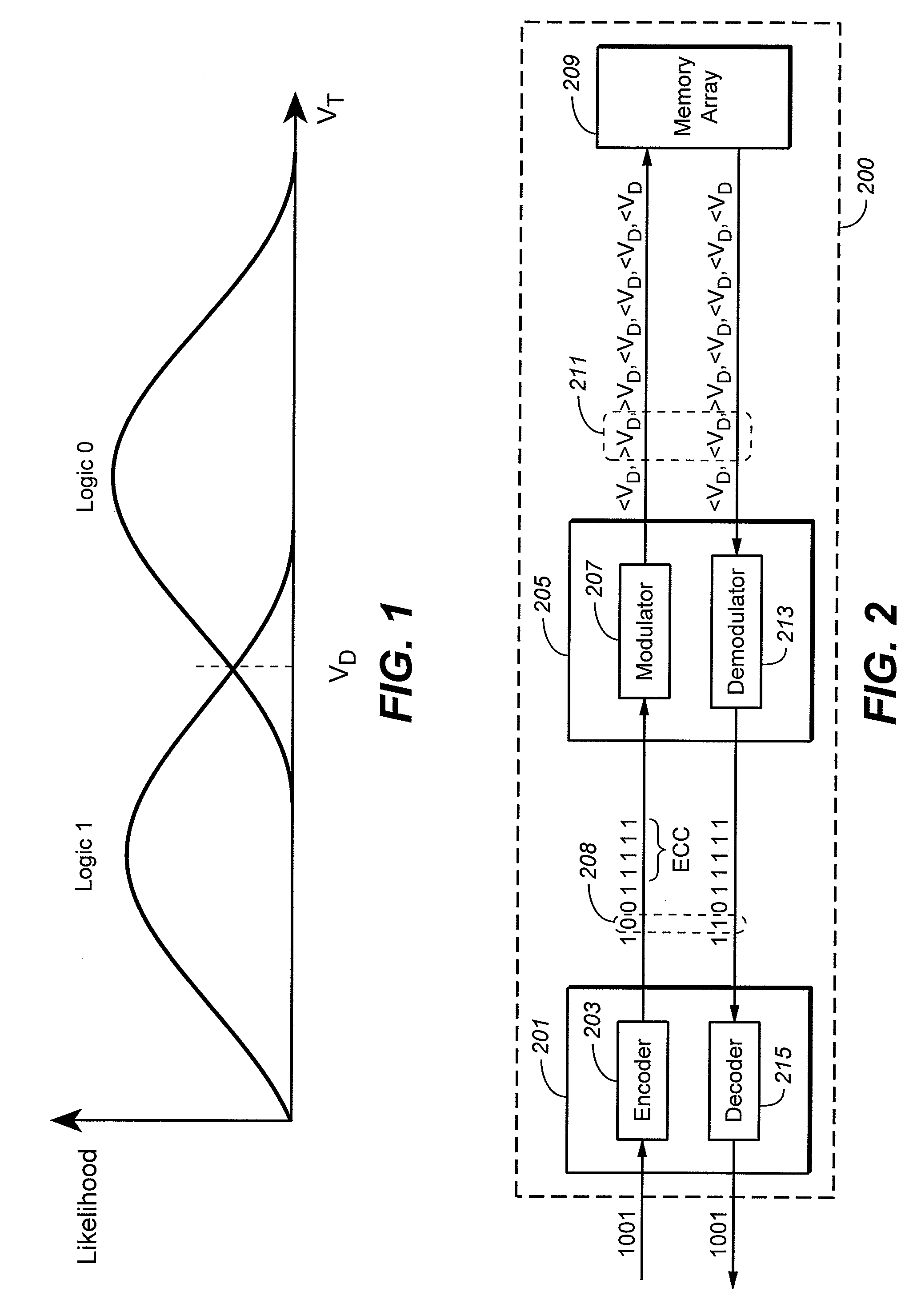

Nonvolatile Memory With Modulated Error Correction Coding

Owner:SANDISK TECH LLC

Partial Page Fail Bit Detection in Flash Memory Devices

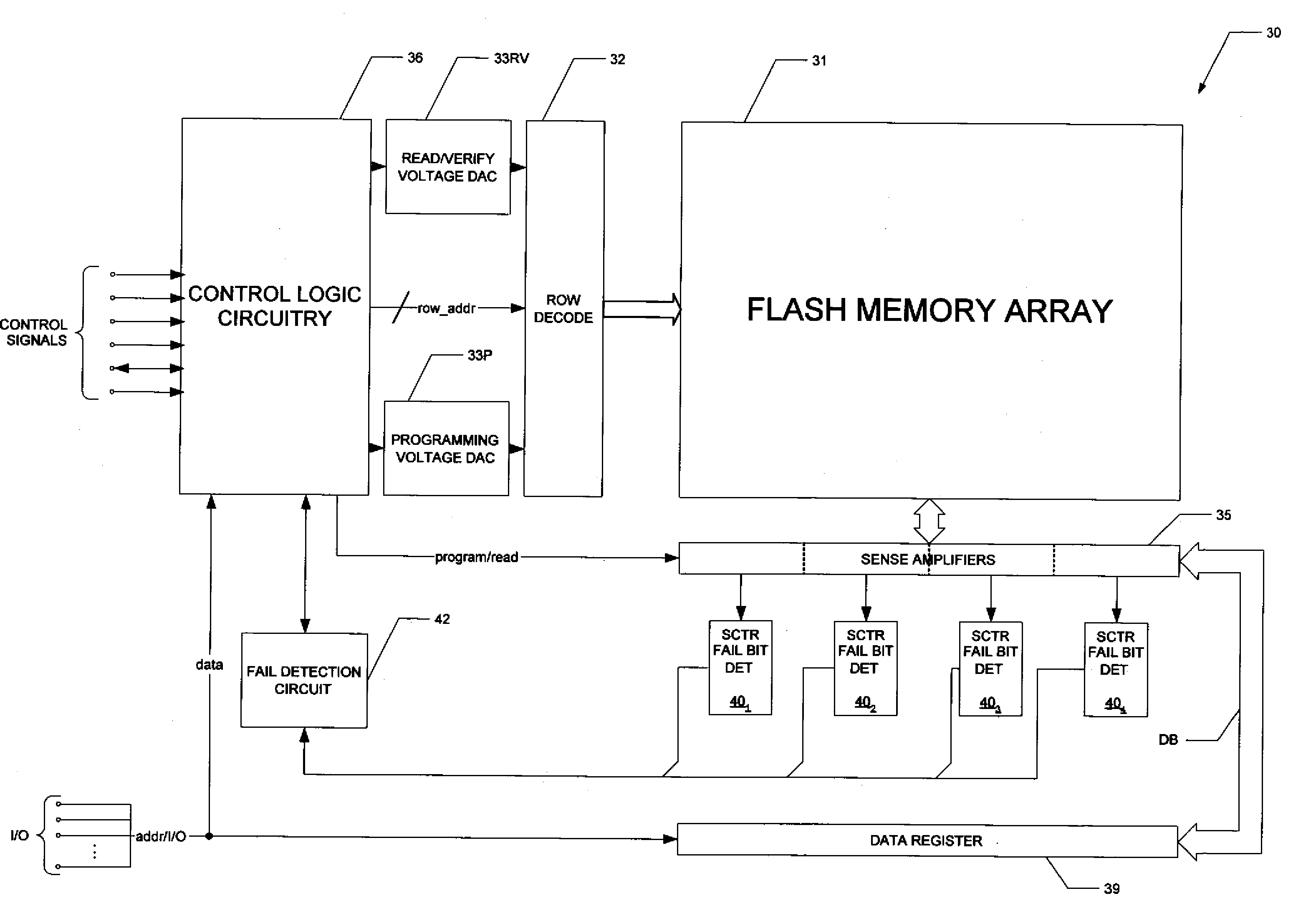

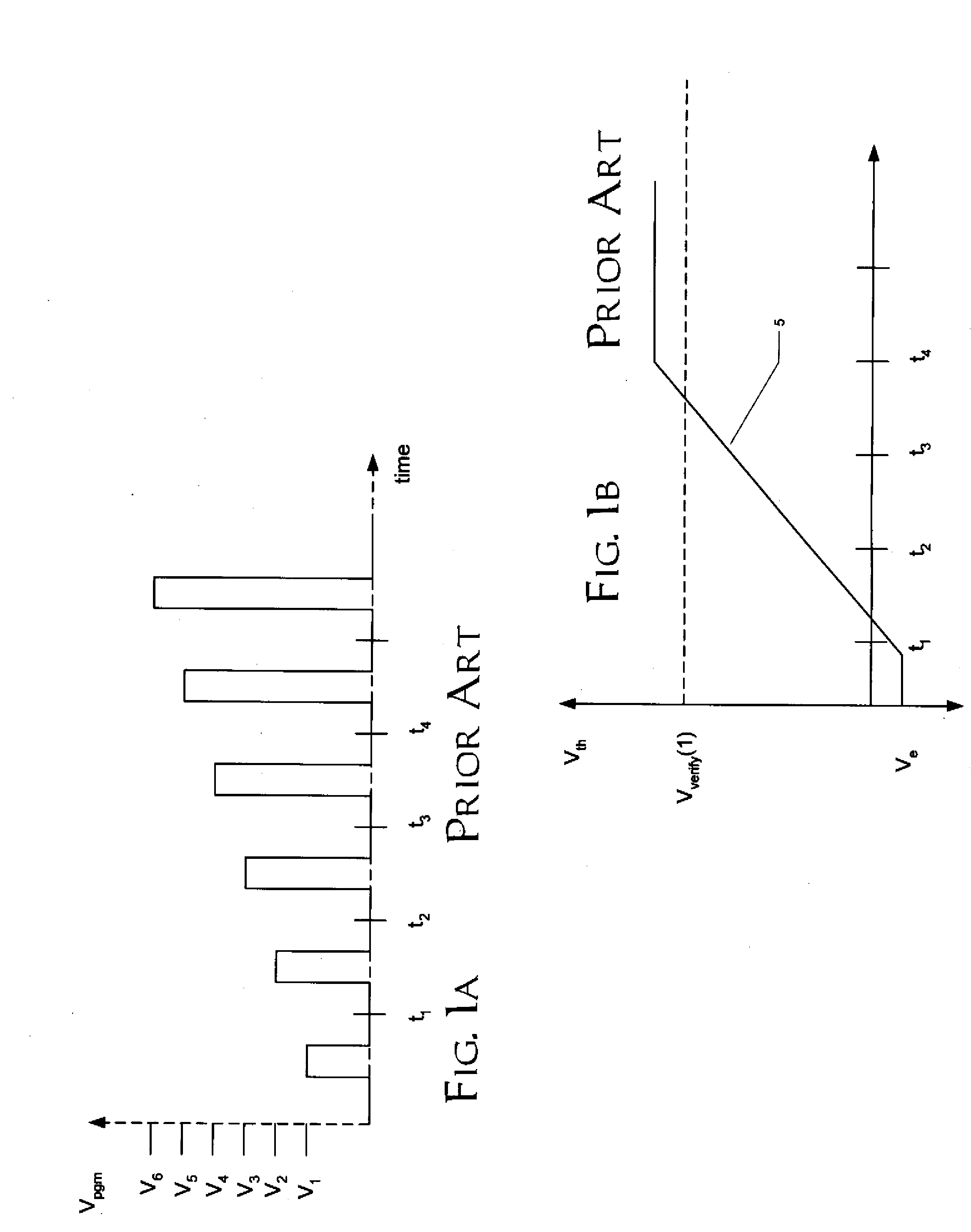

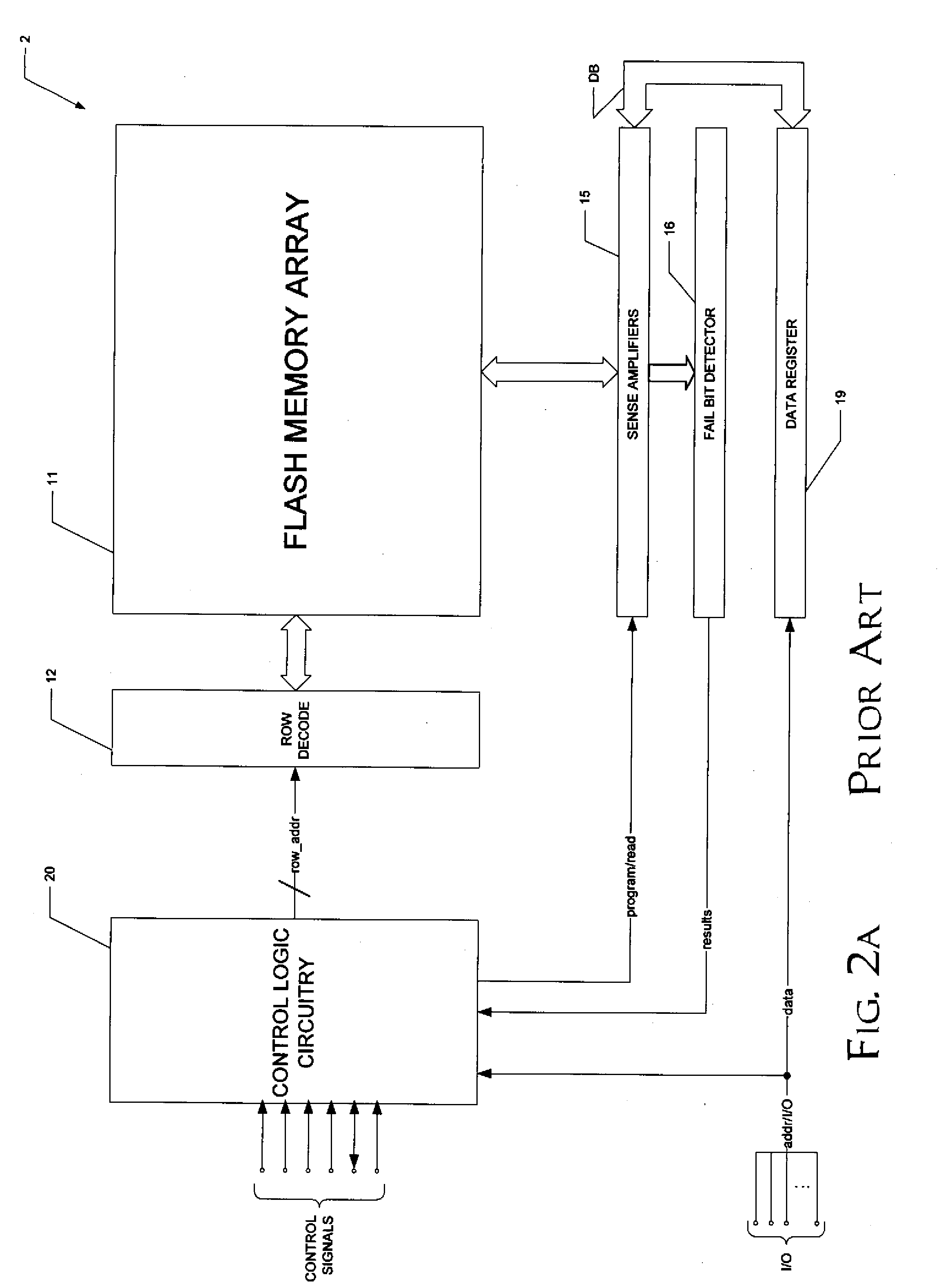

ActiveUS20080002468A1Improve efficiencyEarly terminationError detection/correctionRead-only memoriesDetection thresholdError correction coding

A flash memory device, and a method of operating the same, is disclosed. The array of the flash memory device is arranged in pages of memory cells, each page having memory cells associated into groups of memory cells within the page for purposes of fail bit detection in program verification. For example, these groups may correspond to sectors within the page. In a programming operation, the verify process determines whether each group of memory cells within the page has fewer than a selected ignore bit limit for the sector. If not, additional programming is required for the insufficiently programmed cells in the page. By applying a fail bit detection threshold for each of multiple groups within the page, the efficiency of error correction coding in the flash memory is improved. A similar verify and fail bit detection approach may be used in erase and soft programming operations.

Owner:SANDISK TECH LLC

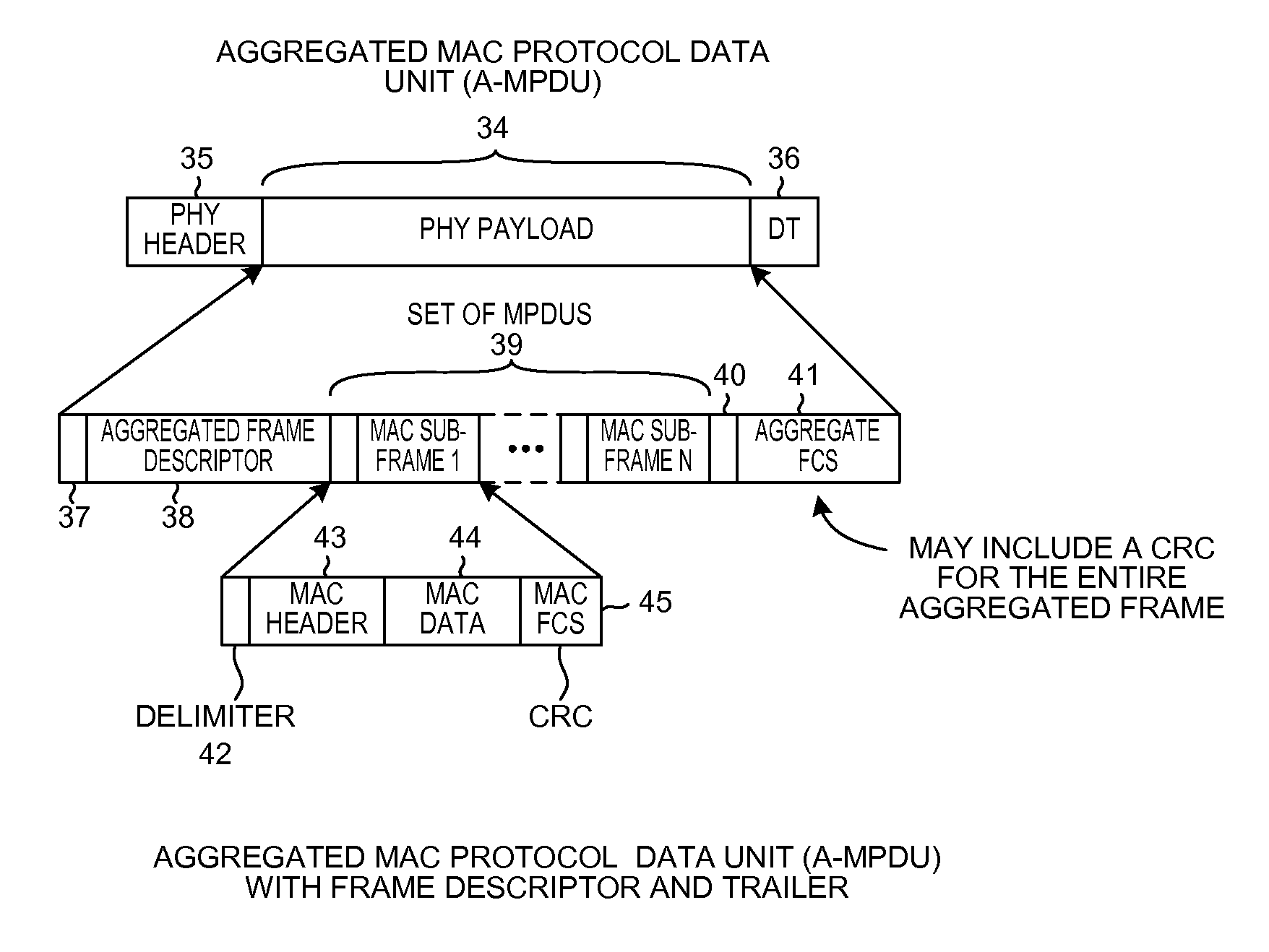

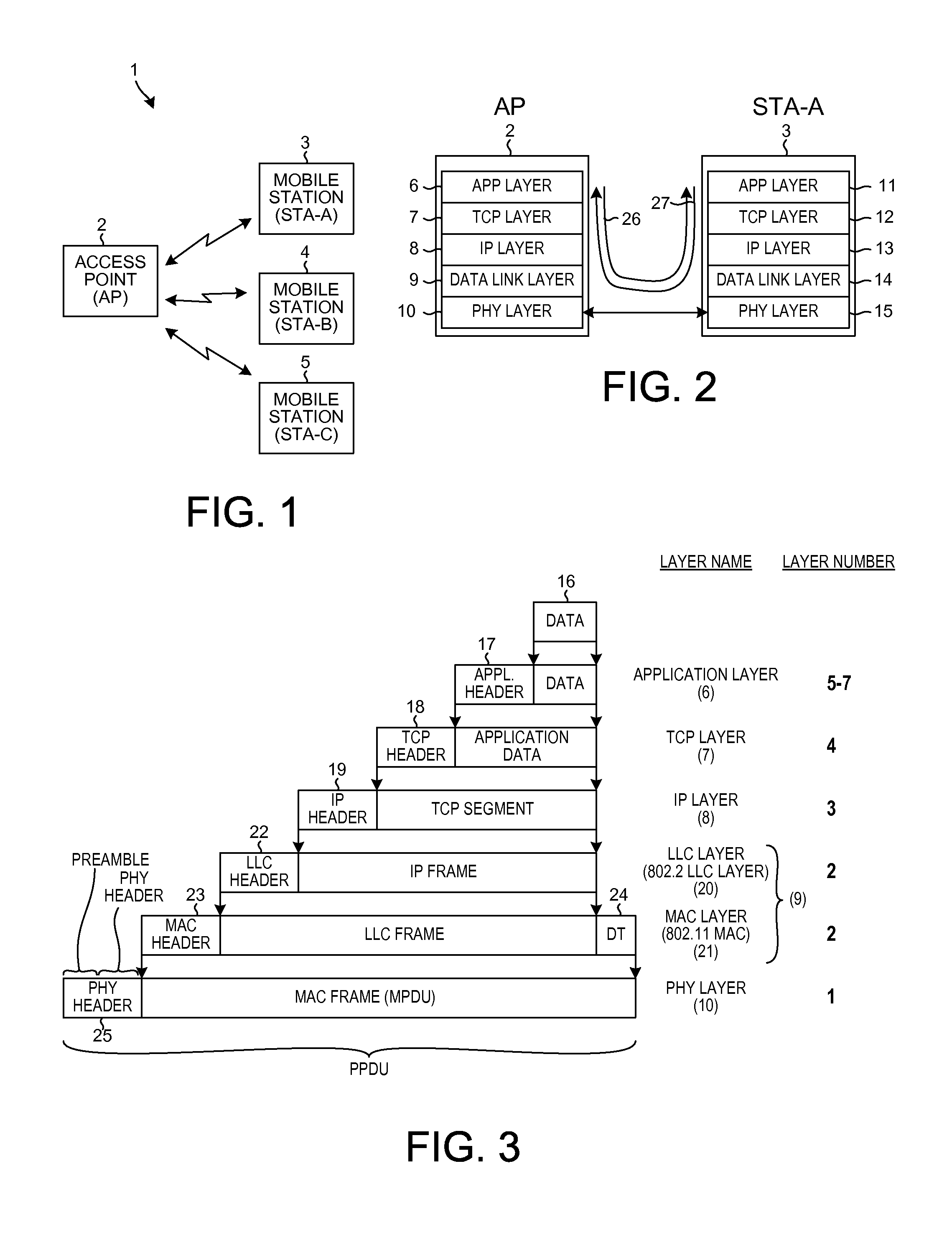

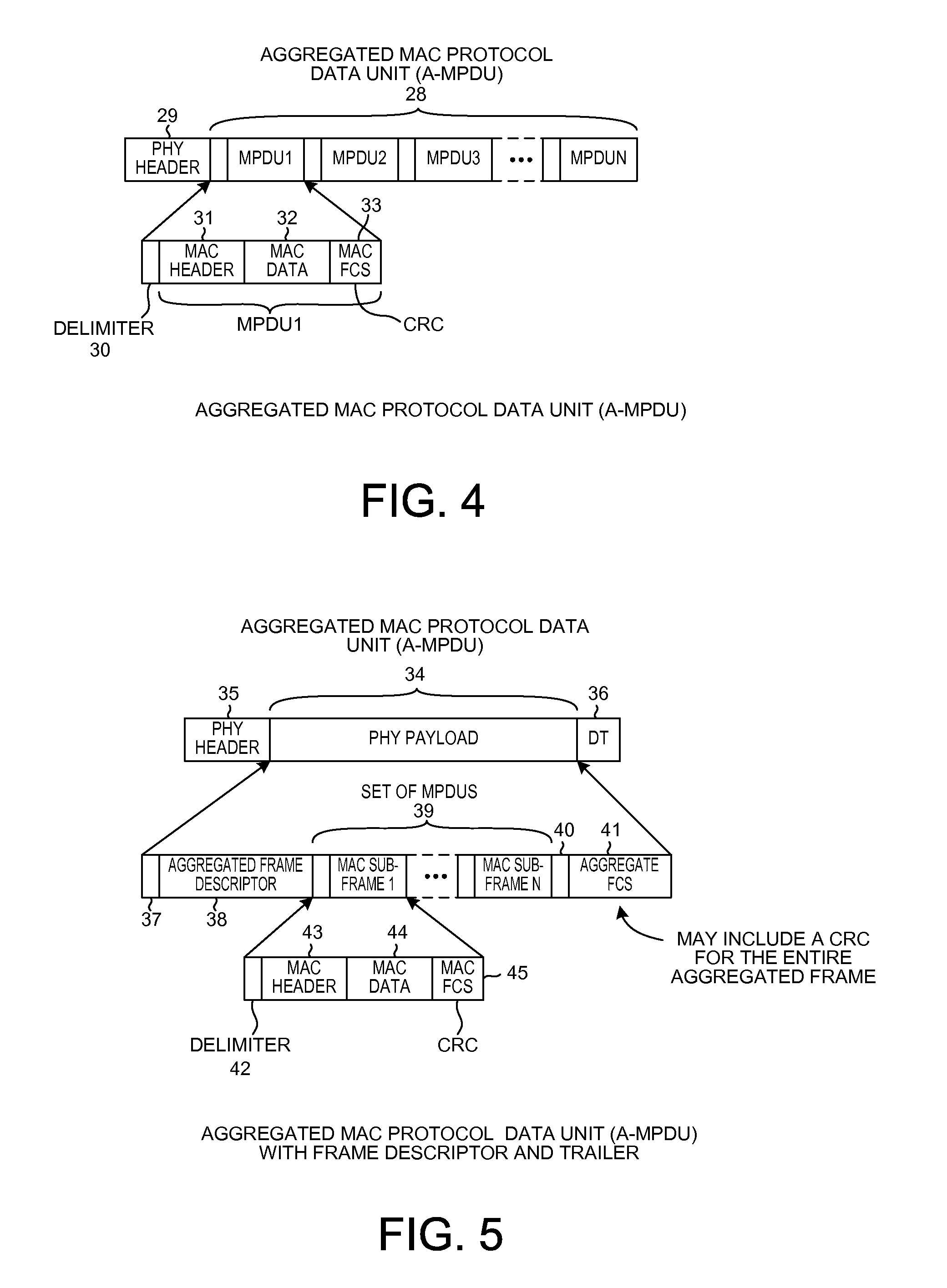

Packet-level erasure protection coding in aggregated packet transmissions

InactiveUS20120117446A1Code conversionError correction/detection using block codesComputer hardwareFountain code

In a first aspect, an aggregated packet (A-MPDU) includes packets (MPDUs) and EC-Blocks (Error Correction Blocks) containing error correction coding information. A transmitter uses a Fountain coding scheme (for example, Raptor or RaptorQ) to generate the error correction coding information from the MPDUs. If a receiver detects an error in a received MPDU, then the receiver uses the error correction coding information from the EC-Blocks to correct the error. In a second novel aspect, a determination is made as to whether a change in error rate is more likely due to collisions or to a low SNR. If the determination is that the change is due to collisions then the MCS index is adjusted to restore a target error rate, whereas if the determination is that the change is due to a low SNR then the number of EC-Blocks per A-MPDU is adjusted to restore the target error rate.

Owner:QUALCOMM INC

Methods of modulating error correction coding

Owner:SANDISK TECH LLC

Methods of Modulating Error Correction Coding

Owner:SANDISK TECH LLC

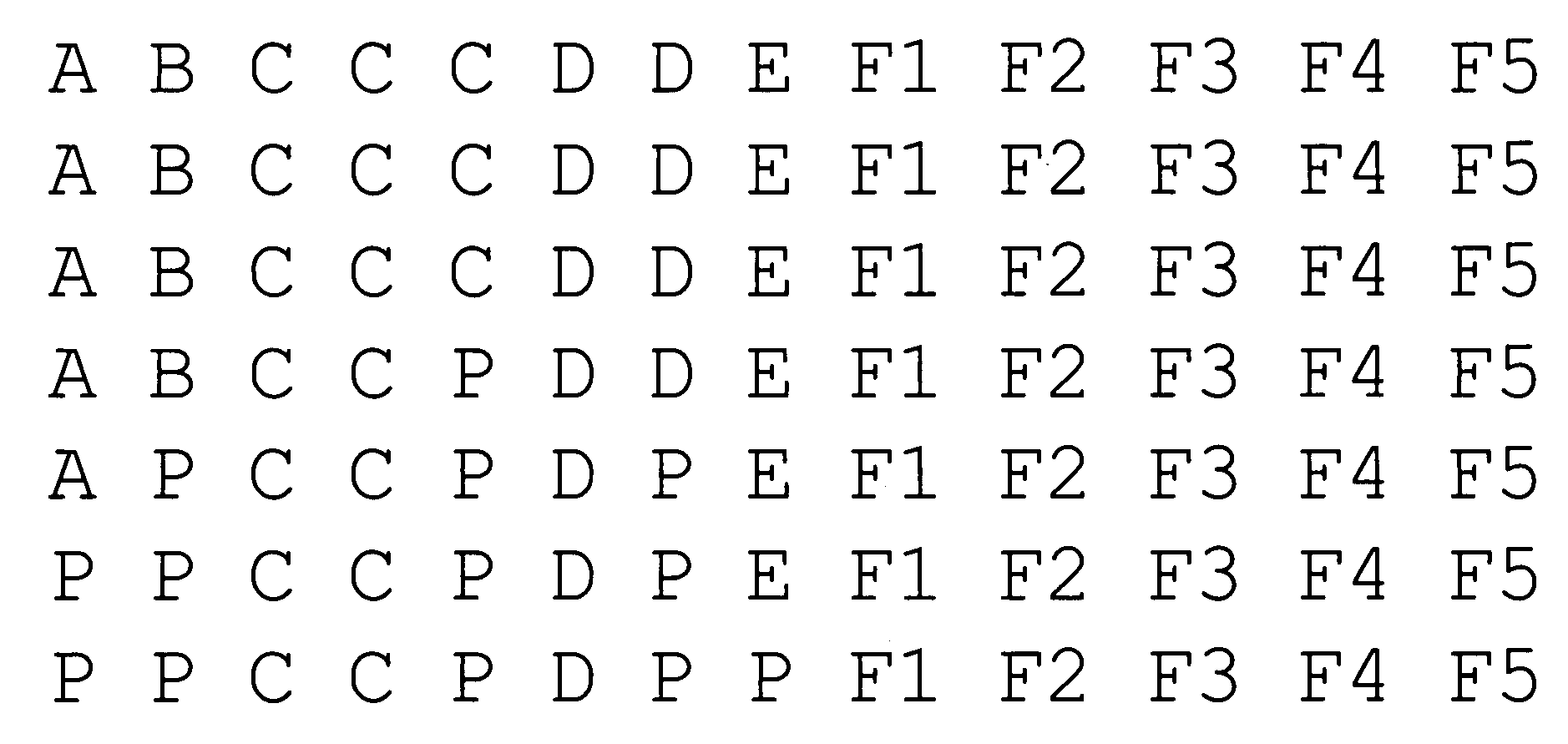

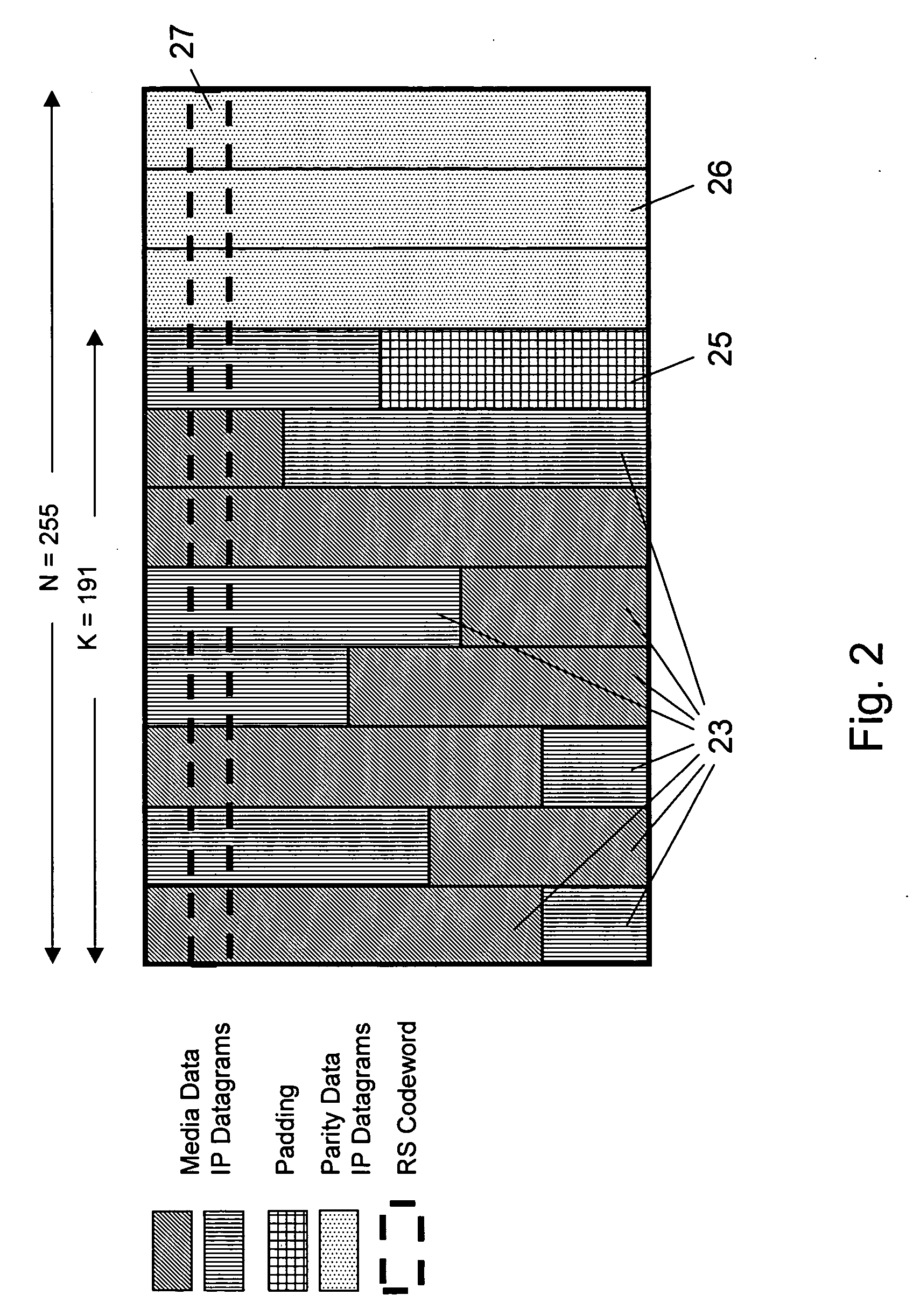

Efficient source blocking algorithm for FEC for MBMS streaming

InactiveUS20060077890A1Frequency-division multiplex detailsTransmission systemsBlock numberCorrection code

A hybrid-padding approach for arranging variable size data packets for error correction encoding and decoding is disclosed. The approach can involve arranging the data packets in columns and rows and selecting the row size to minimize the amount of padding required. If data packet is smaller than the number of rows the data packet is inserted into the column and the remaining rows are padded. If the data packet is larger than the number of rows, the data packet is allowed to span multiple columns with the last column being padded if necessary. The data packets can include parameters, such as a source block number, packet length, and starting column number, and the error correction packets can include parameters, such as, a source block number an N, a K, the starting column number, and the number of row, to signal the hybrid-padding message.

Owner:NOKIA CORP

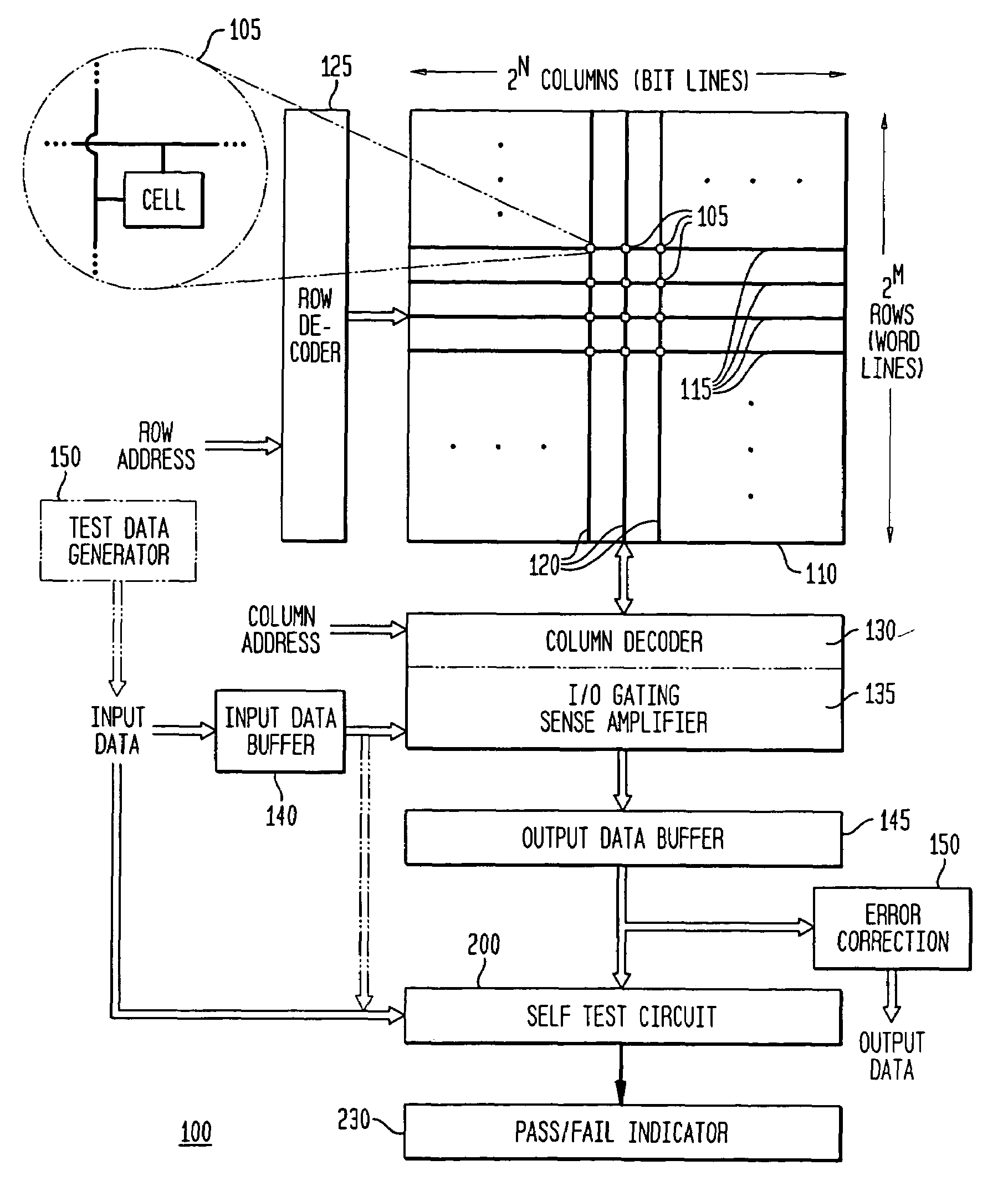

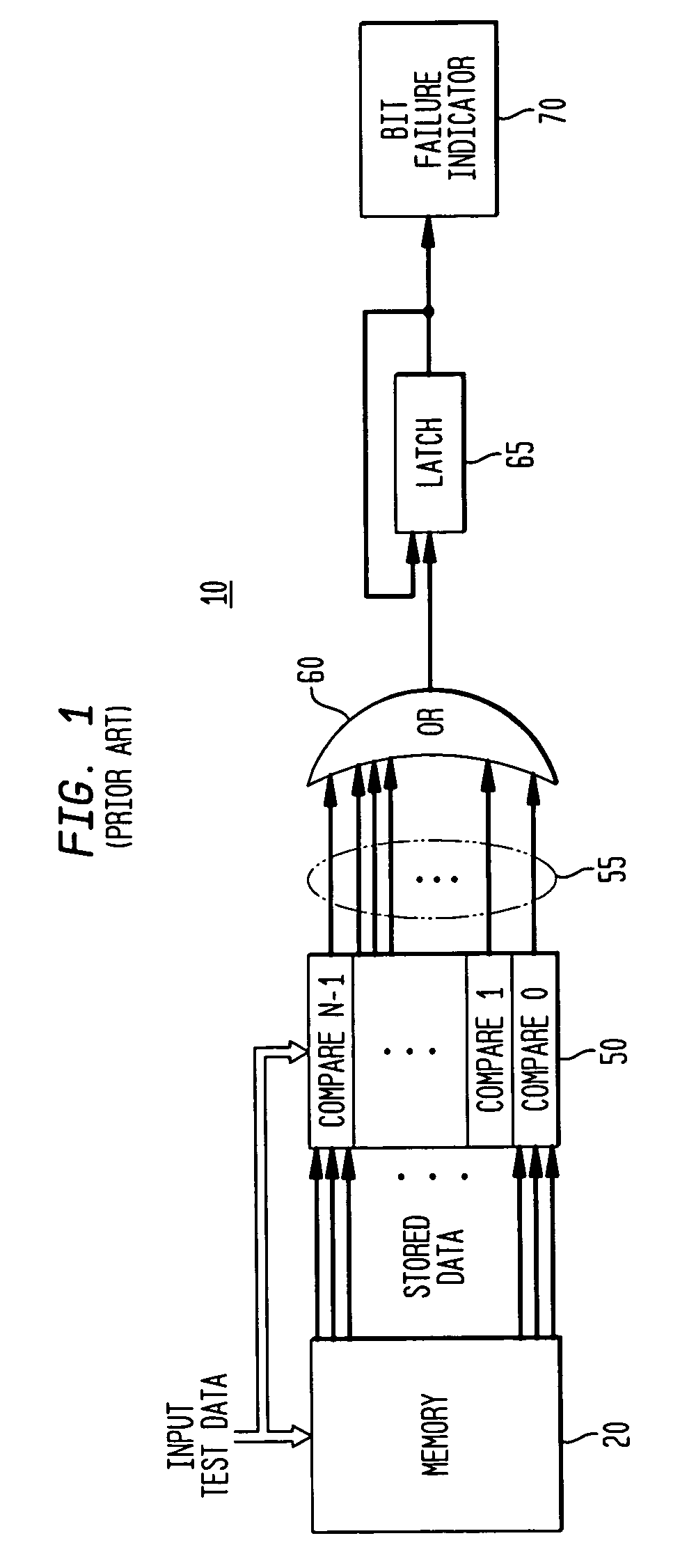

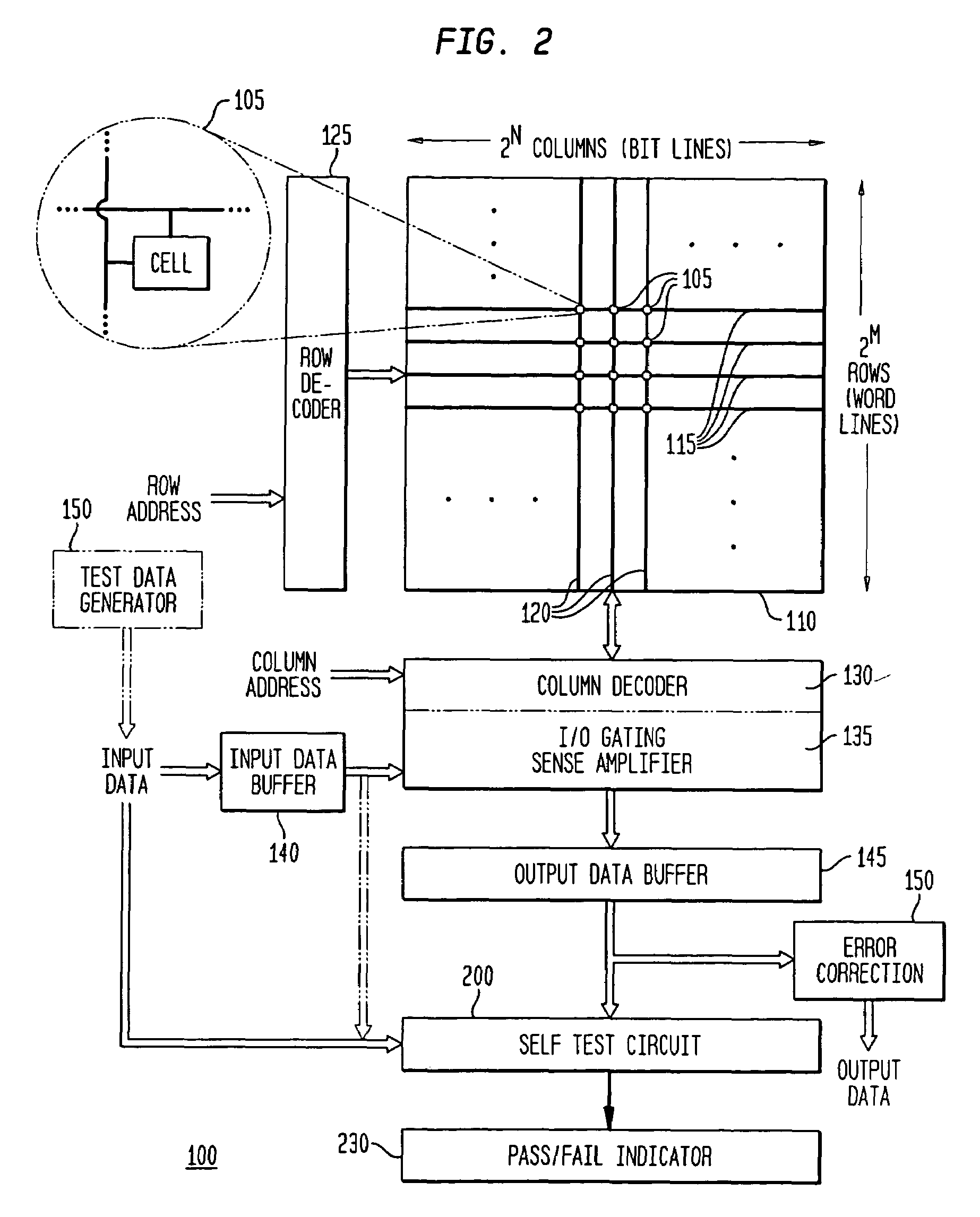

Built-in self test for memory arrays using error correction coding

InactiveUS7254763B2Increased and improved IC manufacturing yieldShorten test timeElectronic circuit testingError detection/correctionIntegratorControl circuit

A memory self-testing system, apparatus, and method are provided which allow for testing for a plurality of bit errors and passing memory arrays having an error level which is correctable using selected error correction coding. An exemplary system embodiment includes a memory array, a comparator, an integrator, and a test control circuit. The memory array is adapted to store input test data and output stored test data during a plurality of memory read and write test operations. The comparator compares the input test data and the stored test data for a plurality of bit positions, and provides a corresponding error signal when the stored test data is not identical to the input test data for each bit position of the plurality of bit positions. The integrator receives the corresponding error signal and maintains the corresponding error signal for each bit position during the plurality of test operations. The test control circuit provides a fail signal when a predetermined level of corresponding error signals have been provided for the plurality of bit positions.

Owner:AVAGO TECH INT SALES PTE LTD

Magnetic memory with error correction coding

Embodiments of the present invention are implemented in memory systems. In one embodiment, the memory comprises an array of memory cells and a control circuit. The control circuit is configured to read error correction coded data from the array of memory cells, provide error correction code decoding to selected error correction coded data and discard unused error correction code parity data of unselected error correction coded data.

Owner:SAMSUNG ELECTRONICS CO LTD

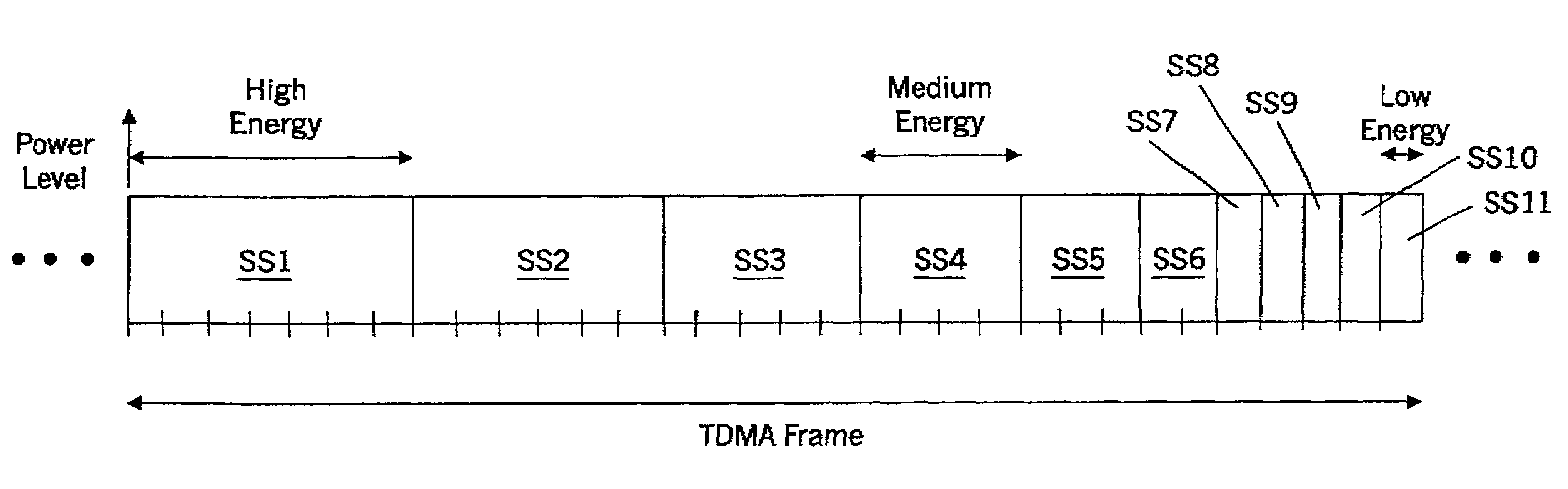

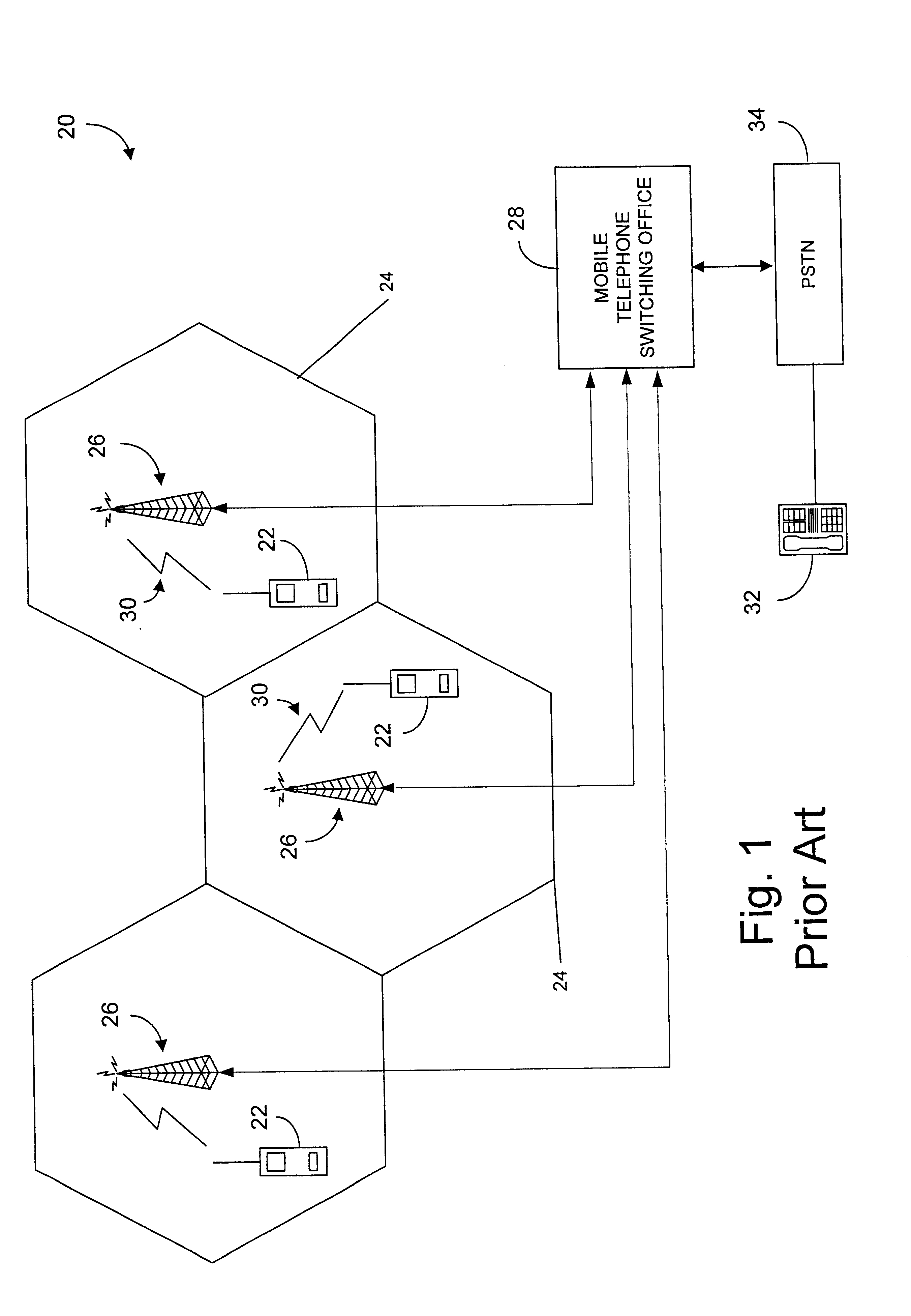

Methods for wirelessly communicating time division multiple access (TDMA) data using adaptive multiplexing and coding

InactiveUS6873613B1Time-division multiplexRadio/inductive link selection arrangementsMultiplexingTime division multiple access

Data is wirelessly transmitted from a base station, and / or wirelessly received at a plurality of subscriber stations that are at a plurality of distances from the base station using a Time Division Multiple Access (TDMA) frame by transmitting a same amount of data to each of the subscriber stations at a same power level during the TDMA frame while varying at least one other parameter as a function of the distance of the respective subscriber station from the base station. The at least one other parameter may be an amount of error correction coding, a sub-period duration in the TDMA frame, a number of modulation symbols from a set of modulation symbols and / or a number of sub-periods of the TDMA frame.

Owner:ERICSSON INC

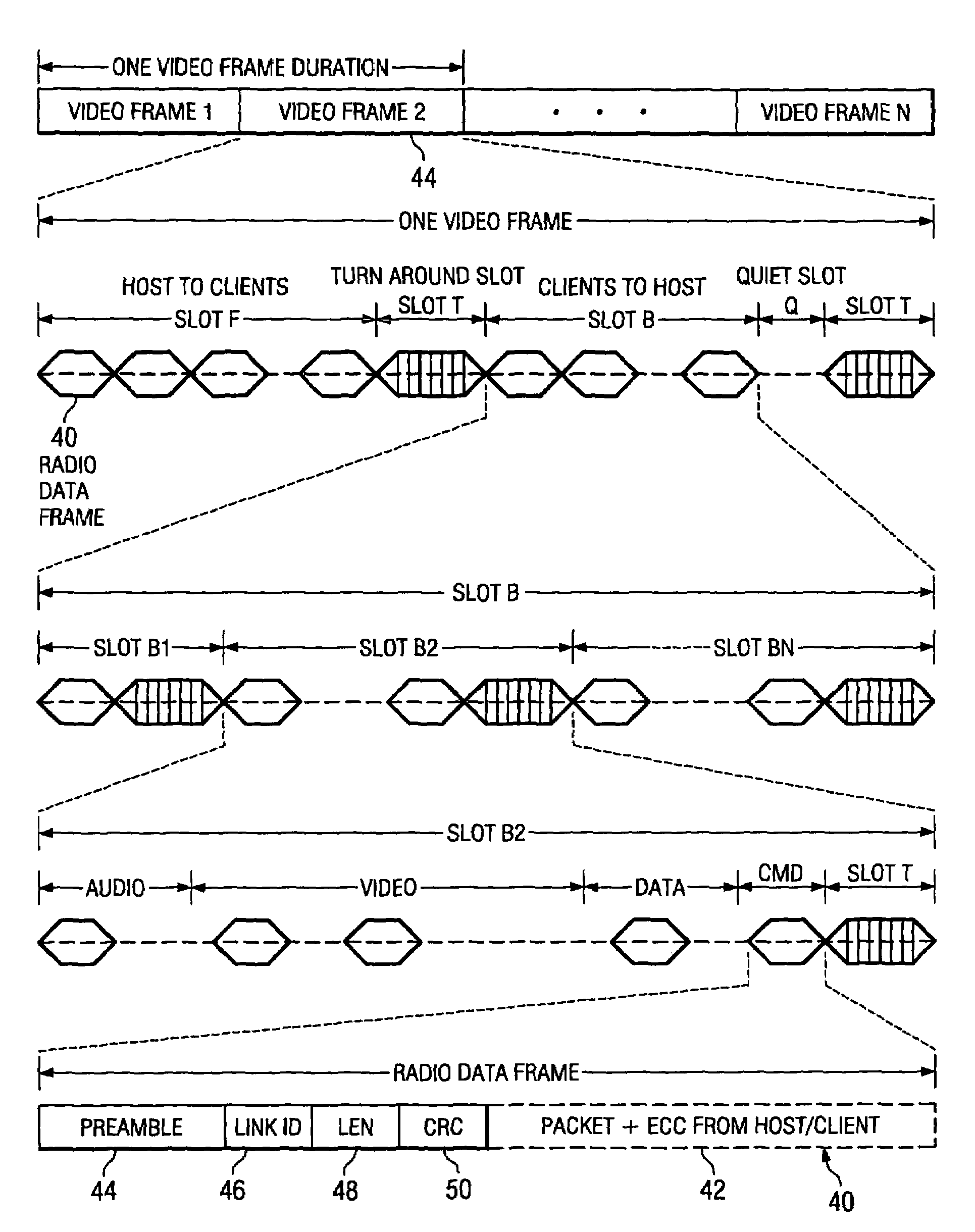

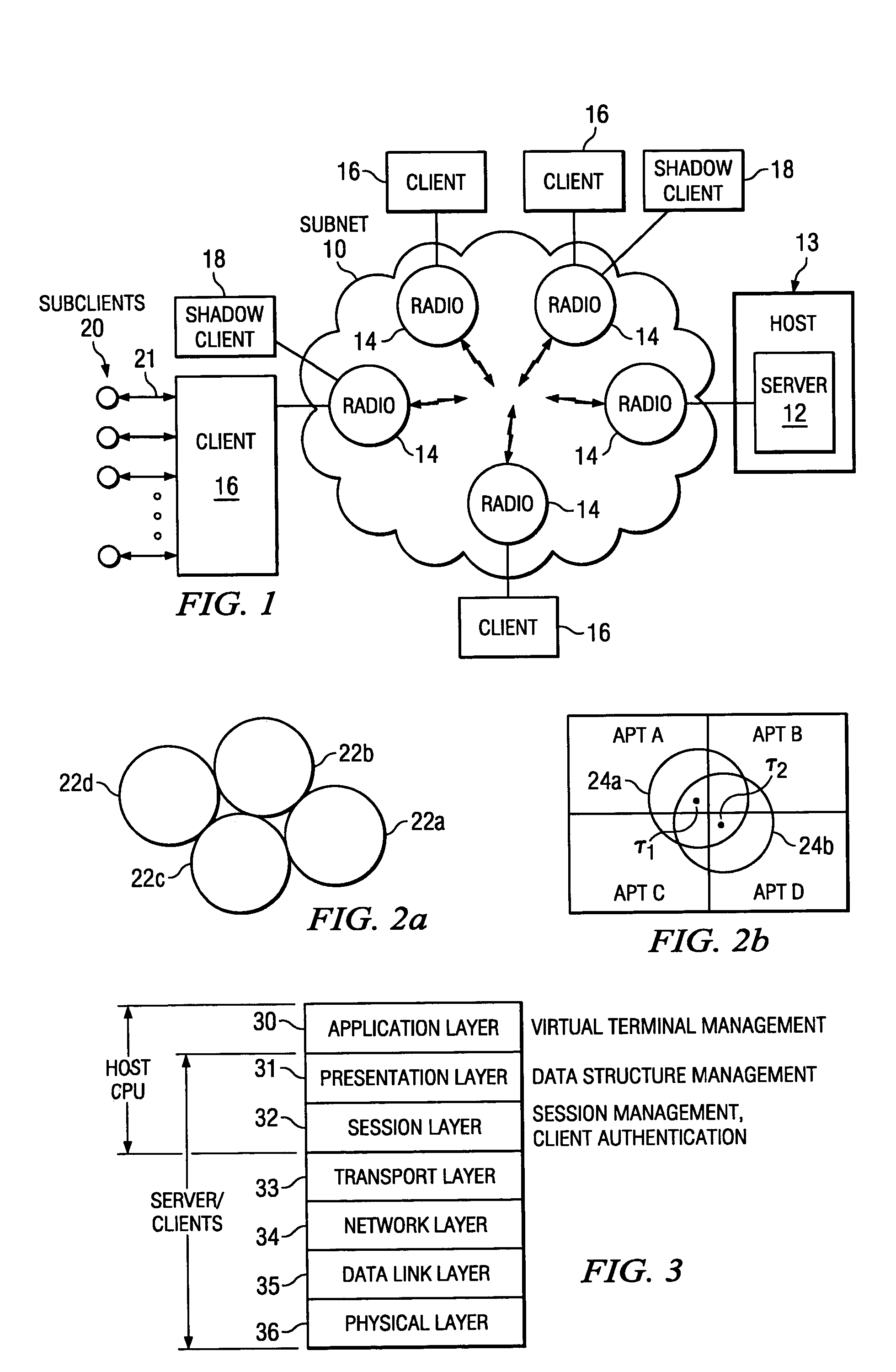

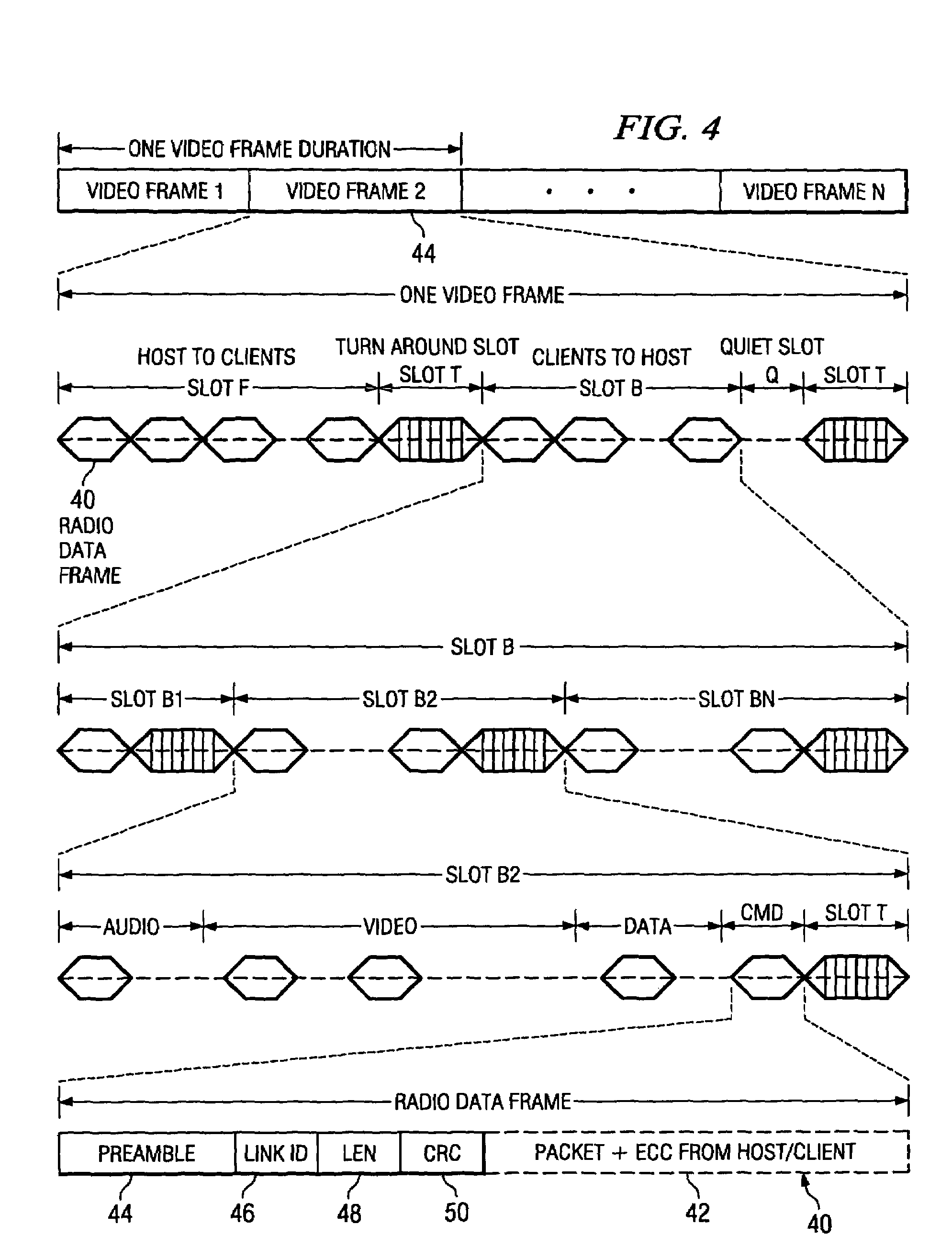

Method and apparatus for controlling communication within a computer network

InactiveUS7251231B2Network traffic/resource managementNetwork topologiesReverse timeControl communications

A communication channel is controlled so as to dynamically accommodate network client requests for access thereto. The communication channel may be supported on a wireless link, such as a spread spectrum wireless link, and client requests for access thereto may be dynamically accommodated by allocating time slots for client transmissions on the wireless link. Providing a quiet time slot within which clients may request access to the communication channel may accommodate various client requests for access to the communication channel. These quiet slots may exist with other forward and reverse time slots which are superimposed on the communication channel, each forward and reverse time slot including one or more data frames. The forward and reverse time slots are preferably fixed, but negotiable, time periods. Each of the data frames may include a plurality of data packets, each of the data packets being variable in length. Preferably, each of the data packets includes error correction coding information as well as information which may be used to synchronize pseudo-random number generators of a transmitter and a receiver operating according to the communication protocol. Each of the data frames may further include link identification information that uniquely identifies a wireless link supporting the communication protocol.

Owner:CIRRUS LOGIC INC

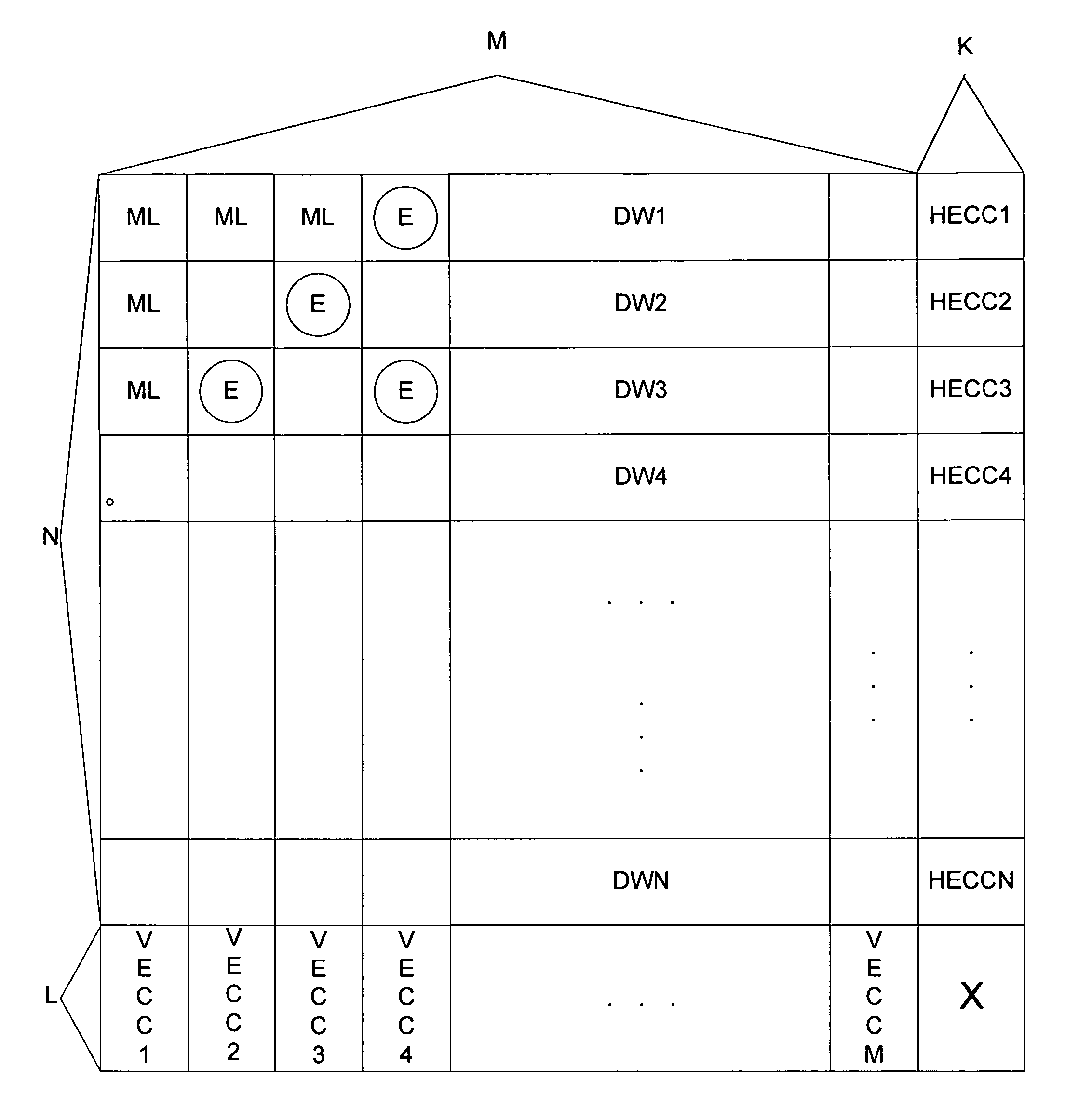

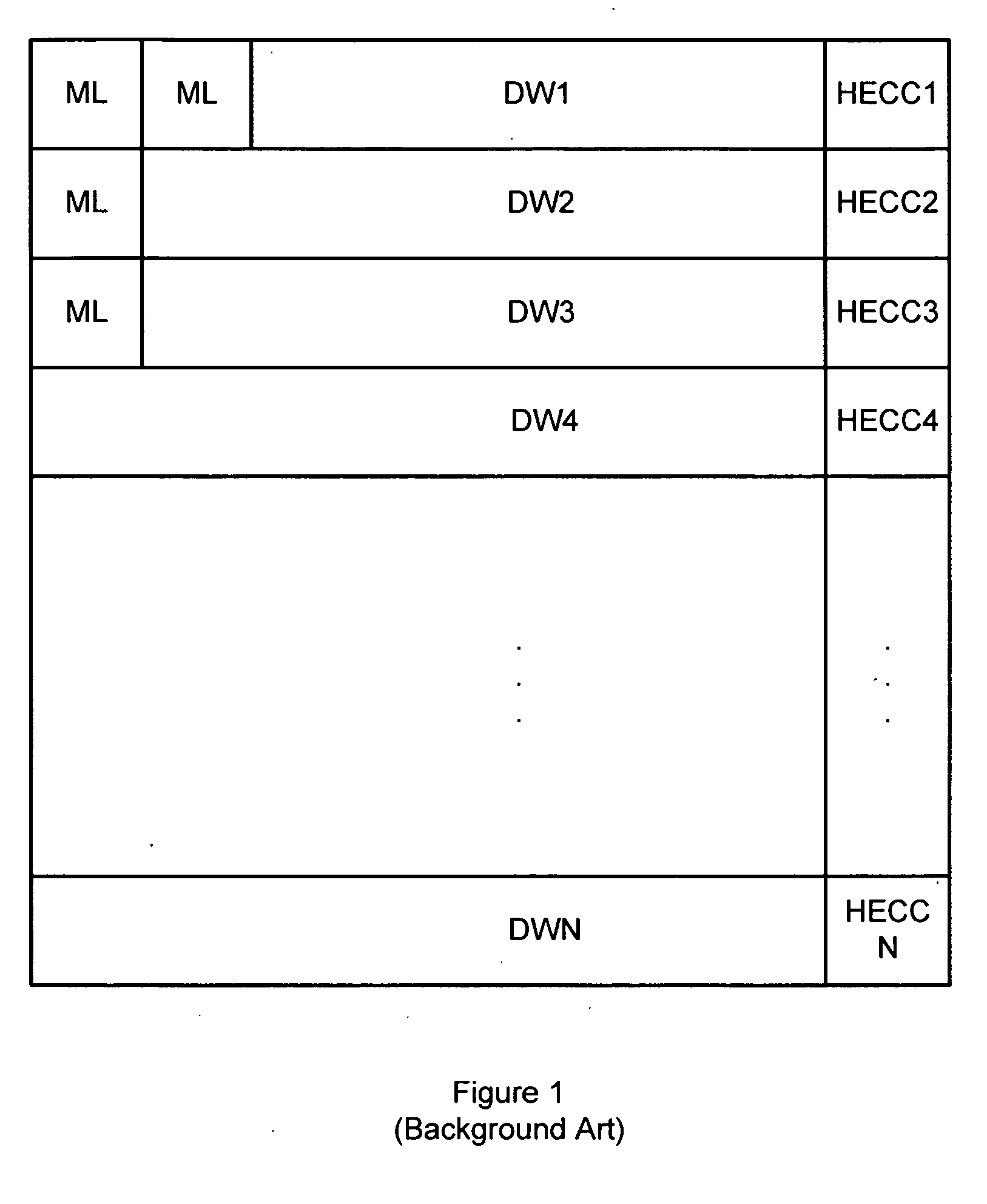

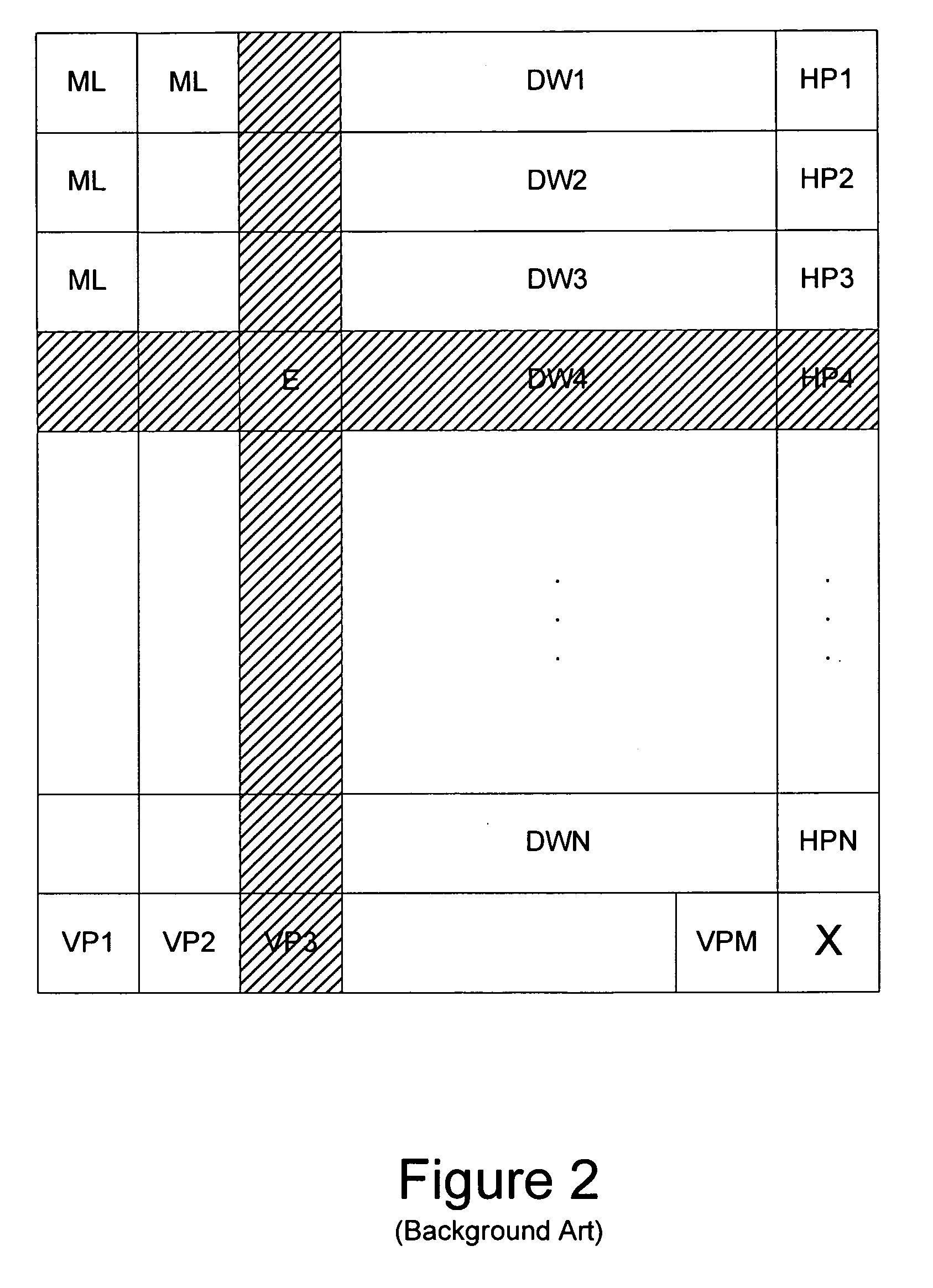

Horizontal and vertical error correction coding (ECC) system and method

InactiveUS20060256615A1Error detection/correctionRead-only memoriesMemory controllerHorizontal and vertical

A method and system detects and corrects errors in data bits of data words stored in a system memory. Each data word includes a plurality of data bits and the method includes generating a horizontal error correcting code for each data word. Vertical error correcting codes are generated, with each vertical error correcting code being generated using a particular bit from all of the data words. Each vertical and horizontal error correcting code is stored in the system memory. Vertical scrubbing is performed using the vertical error correcting codes to detect and possibly correct errors in the data words and horizontal scrubbing is performed using the horizontal error correcting codes to detect and correct errors in the data words. The vertical scrubbing may be done automatically either through suitable hardware contained on memory modules in the system memory or by a memory controller.

Owner:HEWLETT PACKARD DEV CO LP

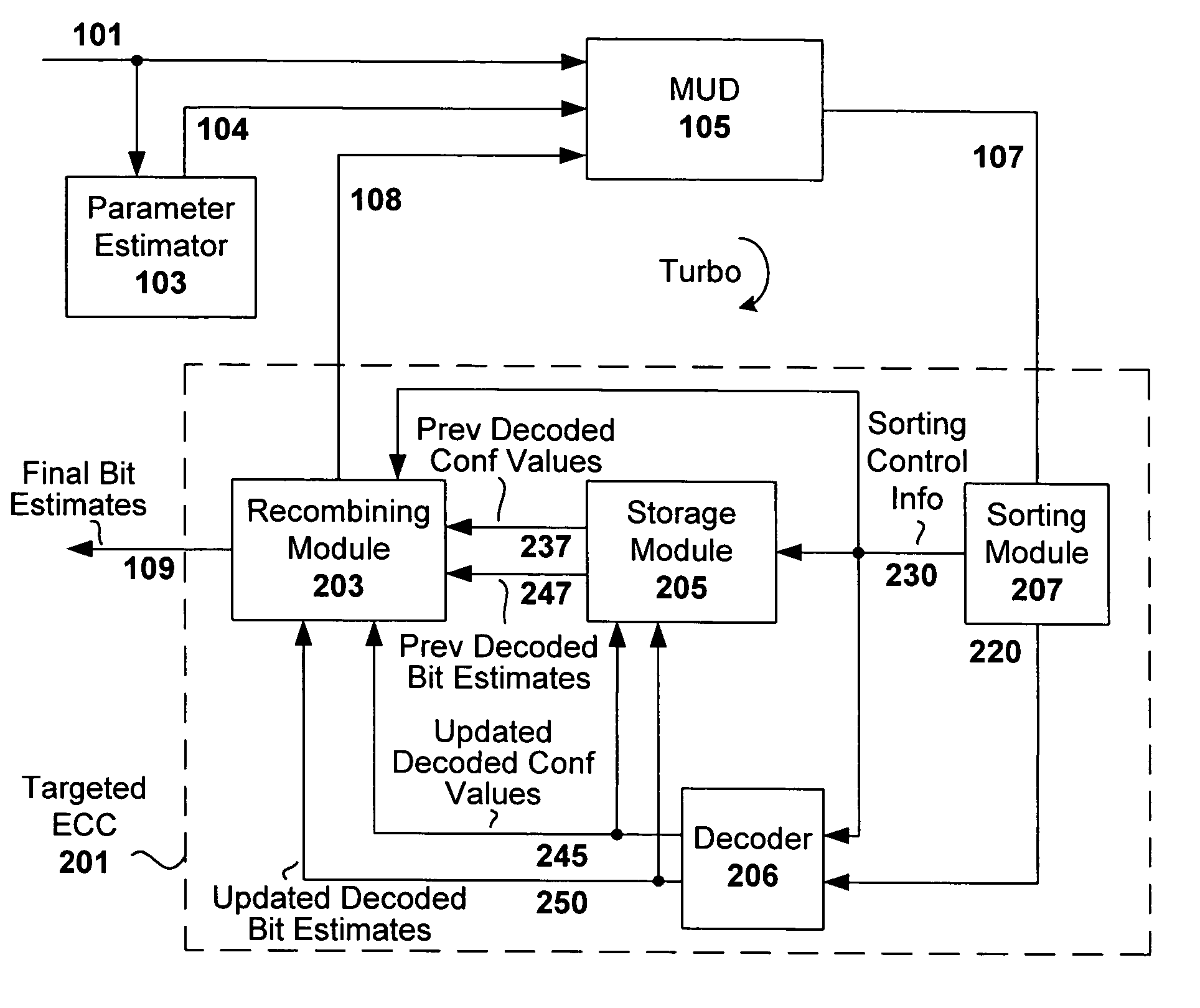

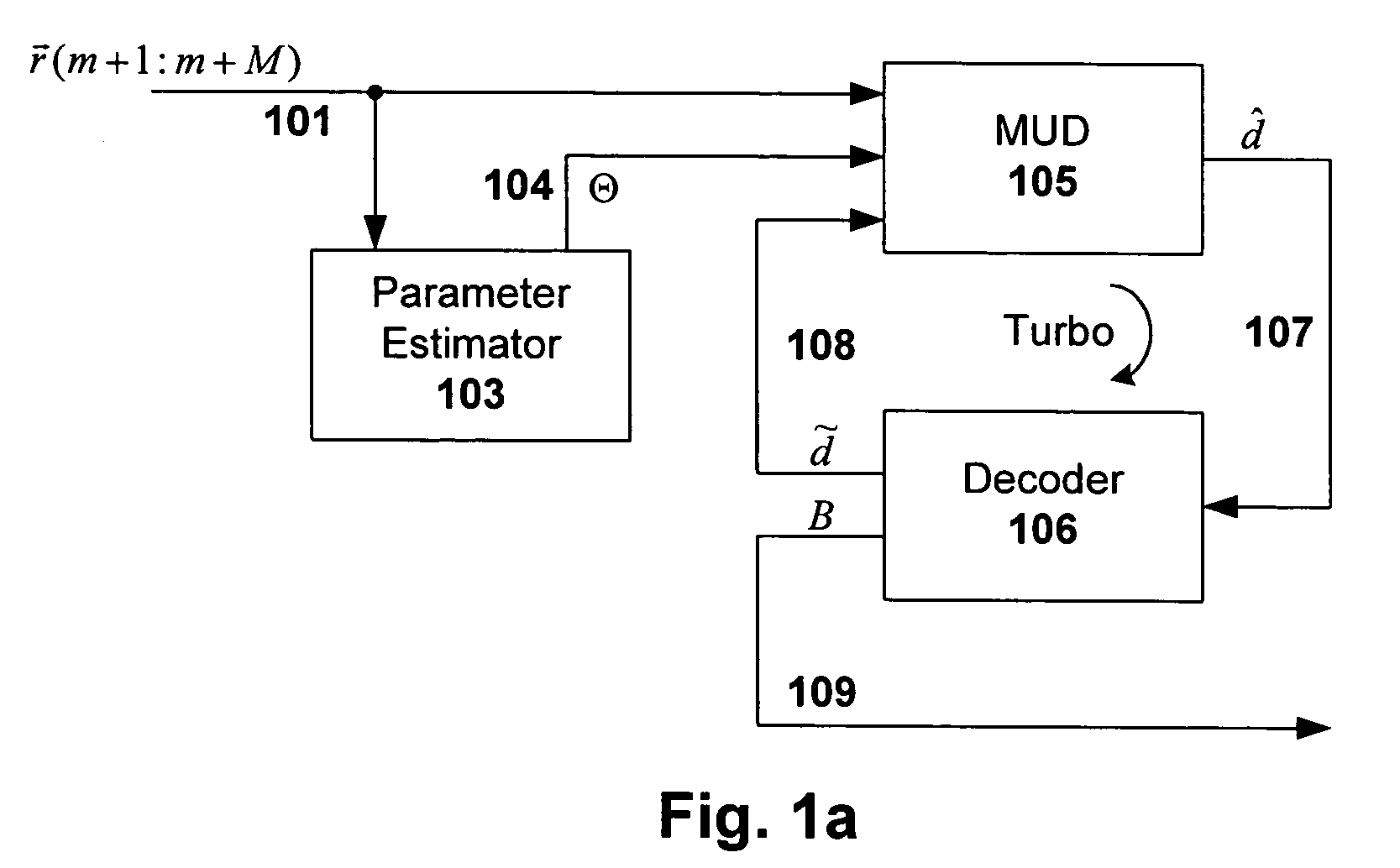

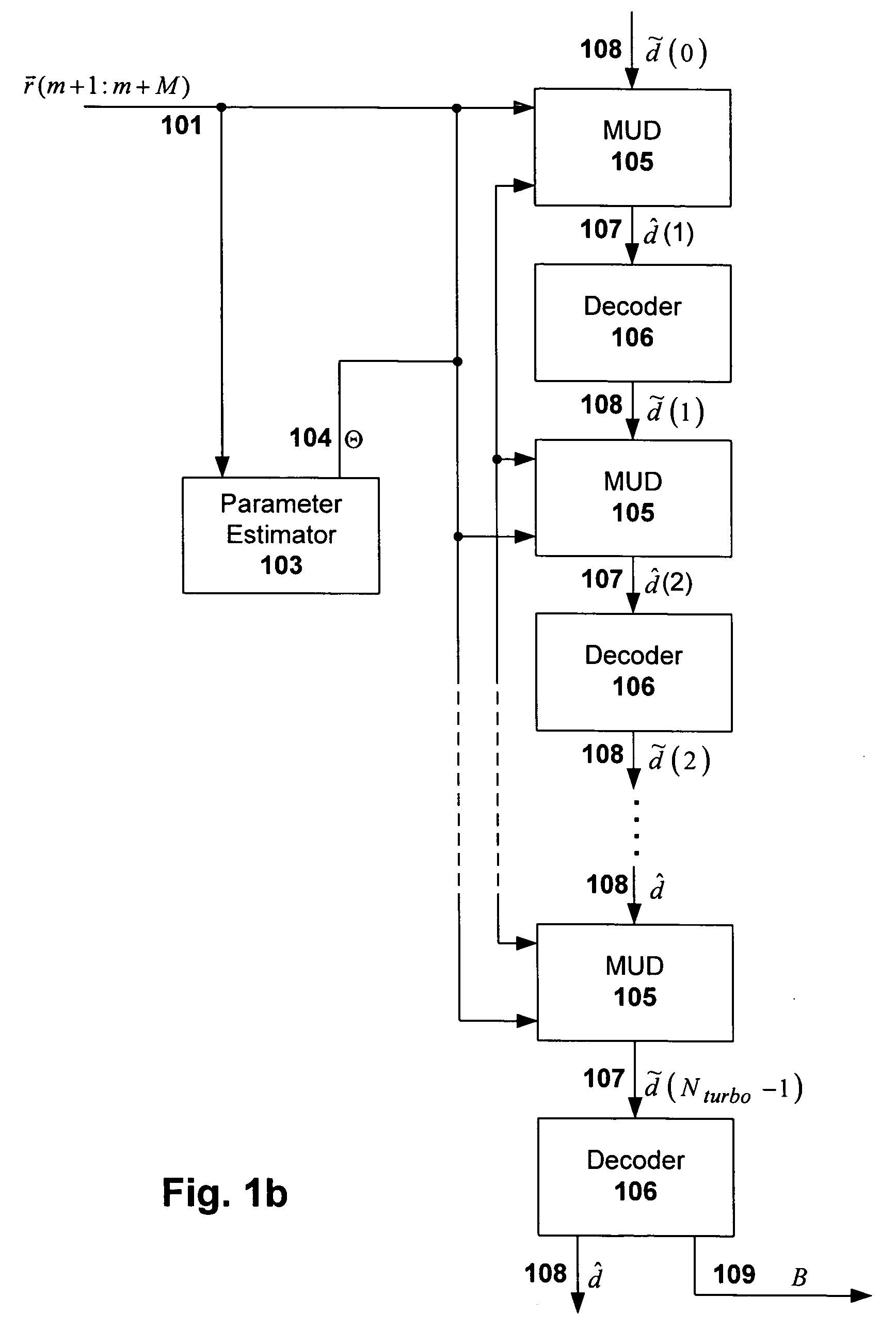

Multiuser detection with targeted error correction coding

InactiveUS7092464B2Reducing error correction complexityReducing error correction coding complexityJoint error correctionOther decoding techniquesMultiuser detectionQuality of service

An error correction decoding (ECC) processing scheme is disclosed that reduces computational complexity normally associated with multiuser detection (e.g., TurboMUD) solutions, without causing degradation in quality of service or decreasing the total throughput. Error correction decoding algorithms are applied only to portions of the estimates that were affected by the immediately previous MUD update process. Even though the MUD and / or ECC updating is targeted so as to reduce complexity of each iteration, all of the estimates are maintained and remain candidates for future updates. As such, there is no negative impact real-time or future performance. This targeting approach can be used in conjunction with many variations of MUD, including full-complexity or reduced complexity, and may include MUD with confidence ordering or voting, and other techniques for facilitating efficient and effective MUD processing.

Owner:COLLISION COMM INC

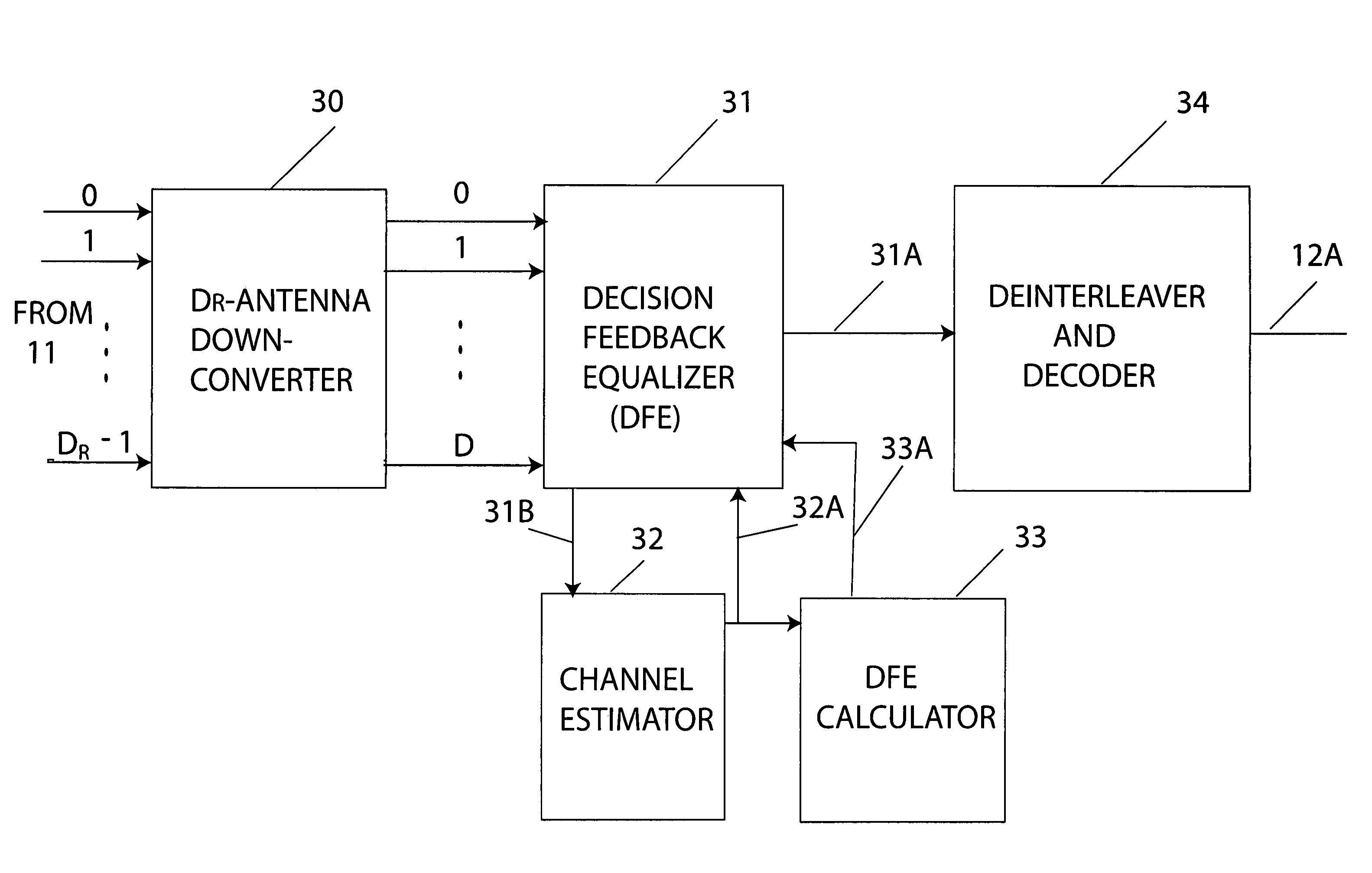

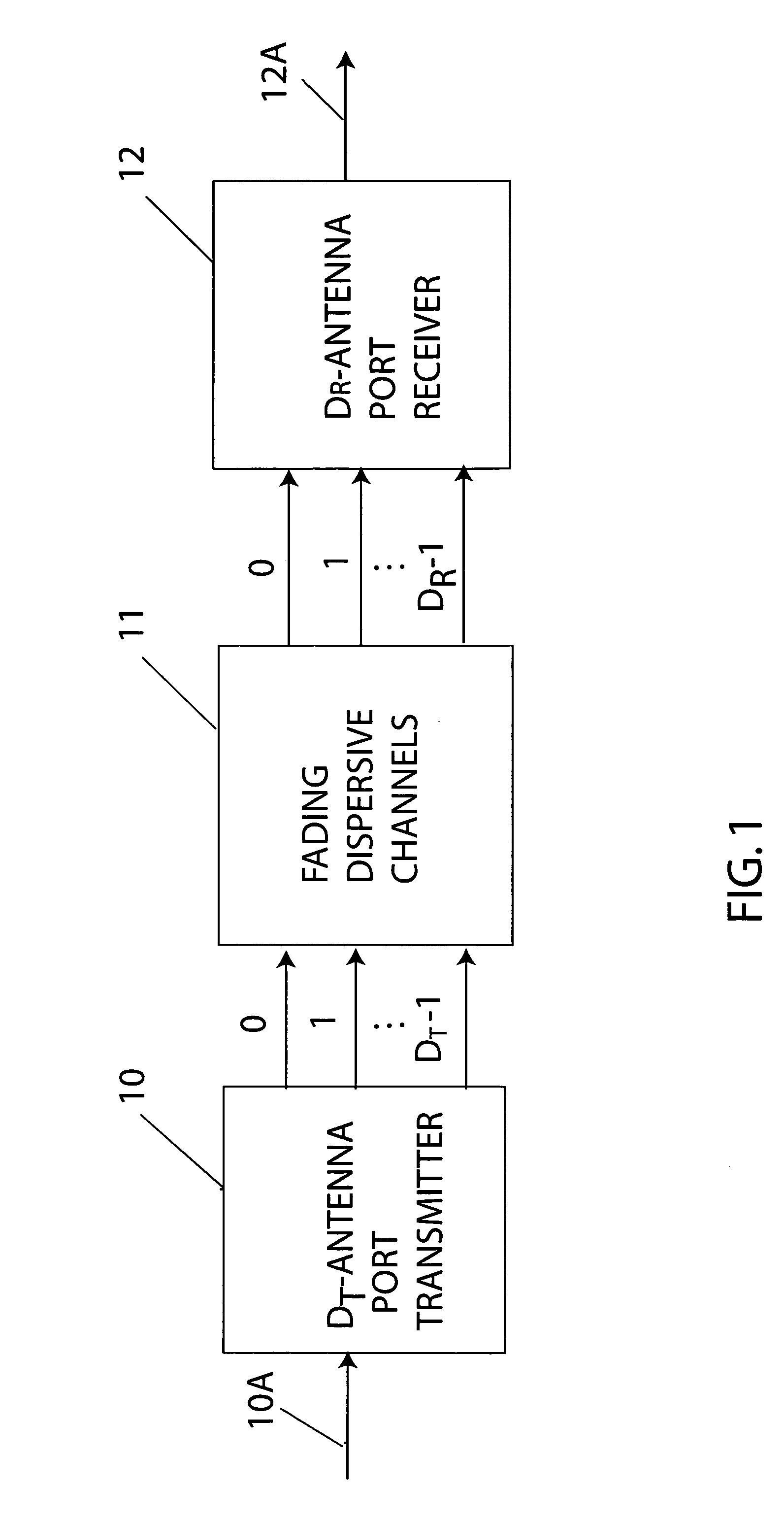

Technique for adaptive equalization in band-limited high data rate communication over fading dispersive channels

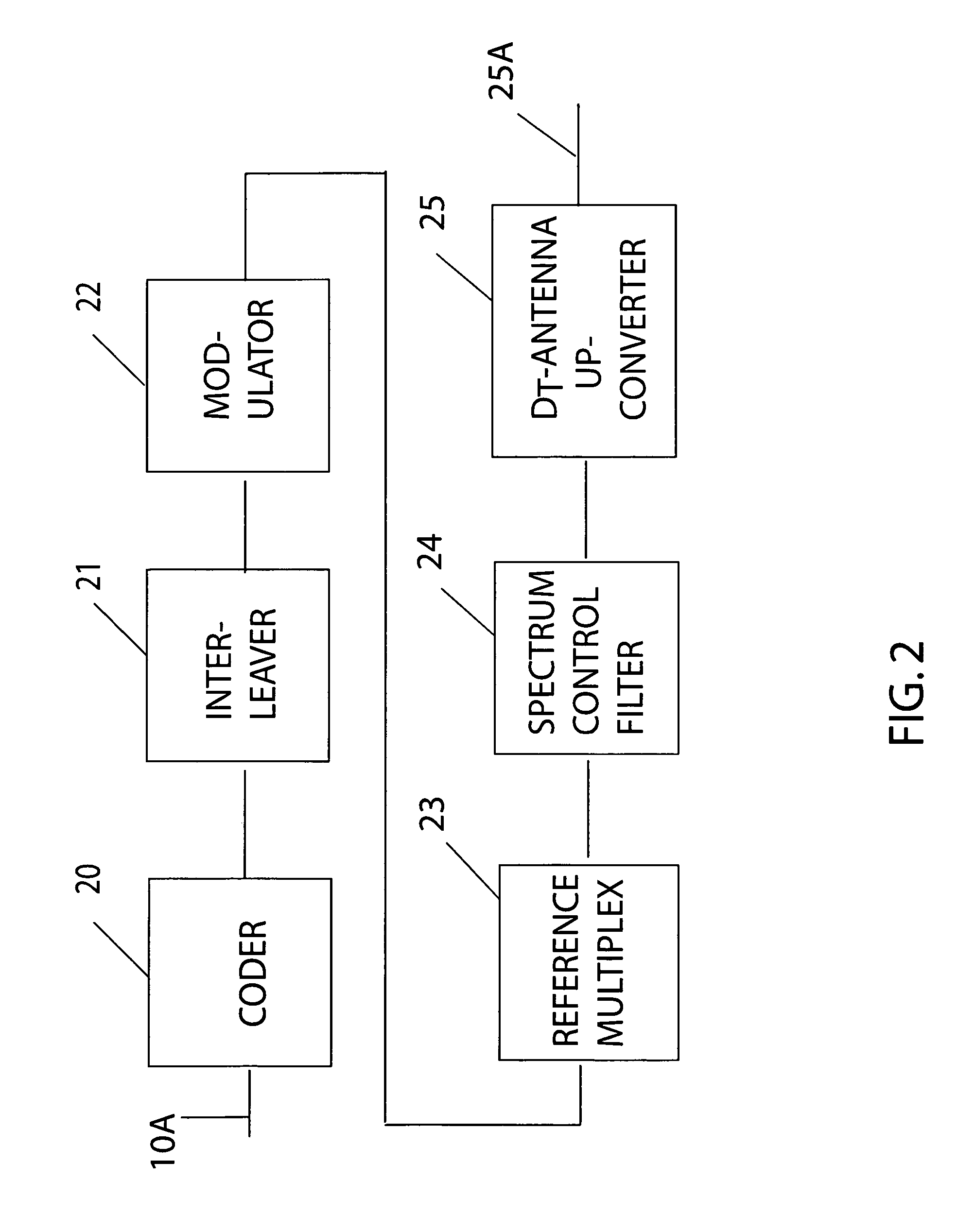

InactiveUS7590204B2Quality improvementEasy to adaptAmplitude-modulated carrier systemsDiversity/multi-antenna systemsDigital dataFrequency spectrum

In high data rate communication applications where digital data information is error-corrected coded and interleaved and transmitted with spectral limitations over fading dispersive channels, a method and receiver is described that incorporates channel estimation and decision-feedback equalization. Channel estimation is accomplished within a receiver time block with locally generated reference symbol sequences. The parameters of the decision-feedback equalizer (DFE) are computed directly from the channel estimates. The DFE is an optimum finite length realization that includes effects from spectrum control filtering, a space-time block coder (STBC) on multiple transmit antennas, multiple receiver diversity signals, and the fading dispersive channel. The DFE includes a matched filter, forward filter, backward filter, and detector. A symbol combiner within the matched filter produces a P+1 dimensional signal that provides ideal cancellation of P intersymbol interferers in the forward filter. When P is selected to meet an intersymbol interference (ISI) criterion, all desired signal energy is collected and all ISI can be ideally cancelled. The DFE processes received signals within the receiver time block to produce information symbol estimates that are subsequently deinterleaved and error-correction decoded to recover the transmitted digital data information. Deinterleaving over multiple receiver time blocks further compensates for channel estimation variations from block to block. Additionally the STBC and DFE are used in a quadruple angle diversity technique requiring only a single antenna at each terminal of a troposcatter link to provide performance approaching that of a nonfading satellite link.

Owner:MONSEN PETER

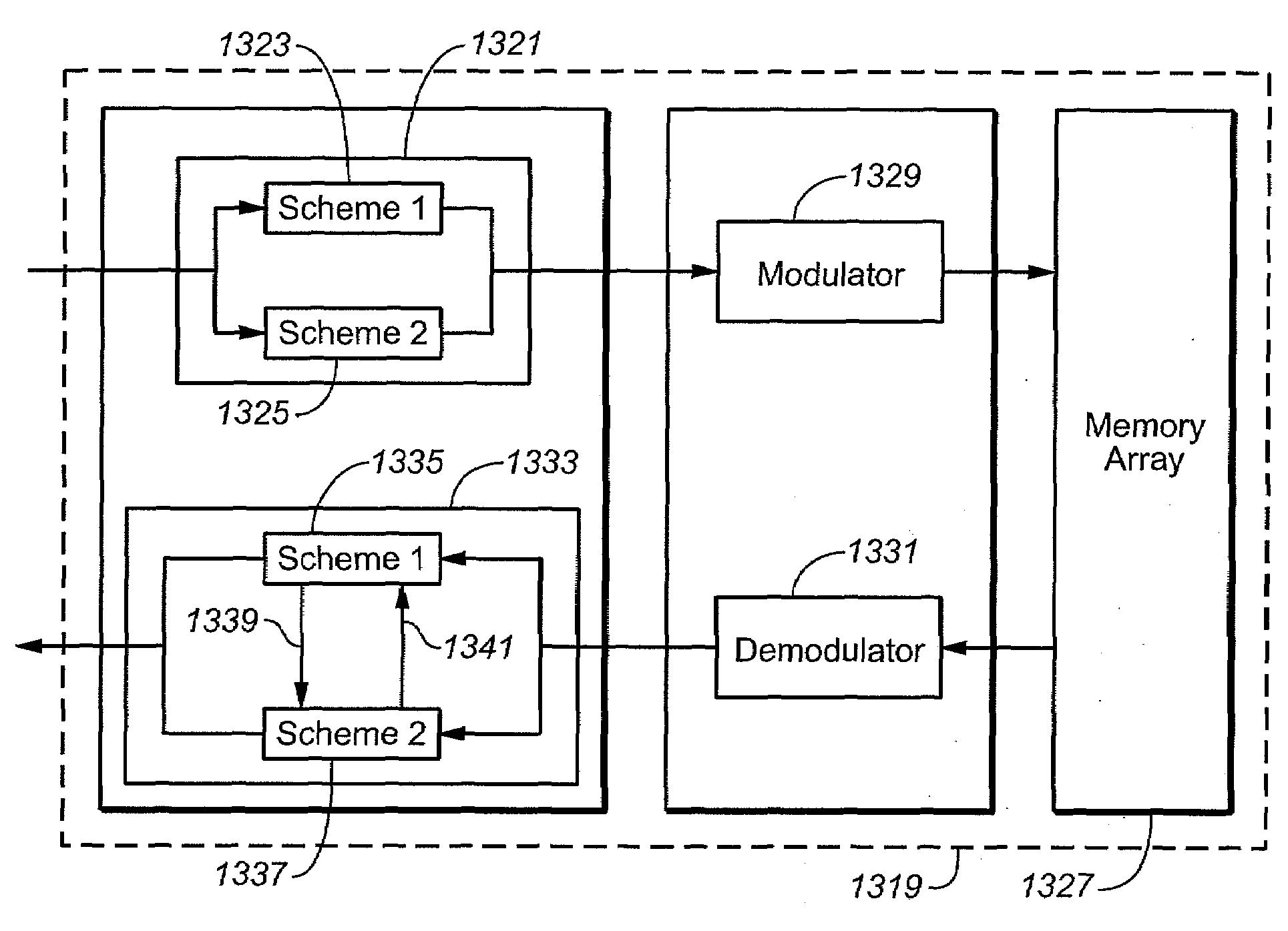

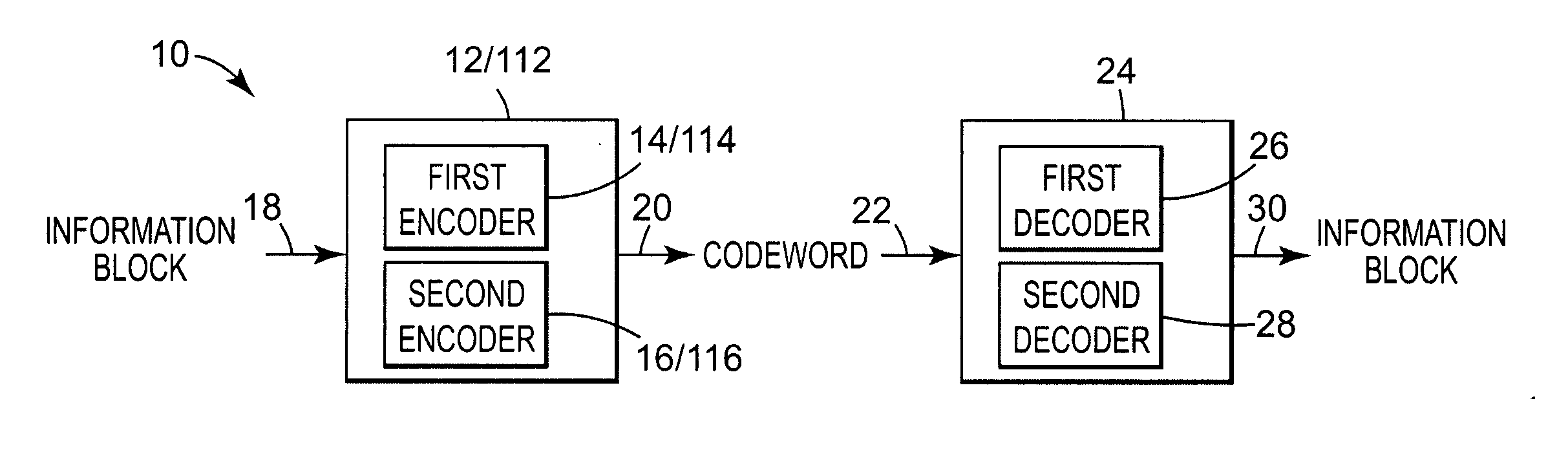

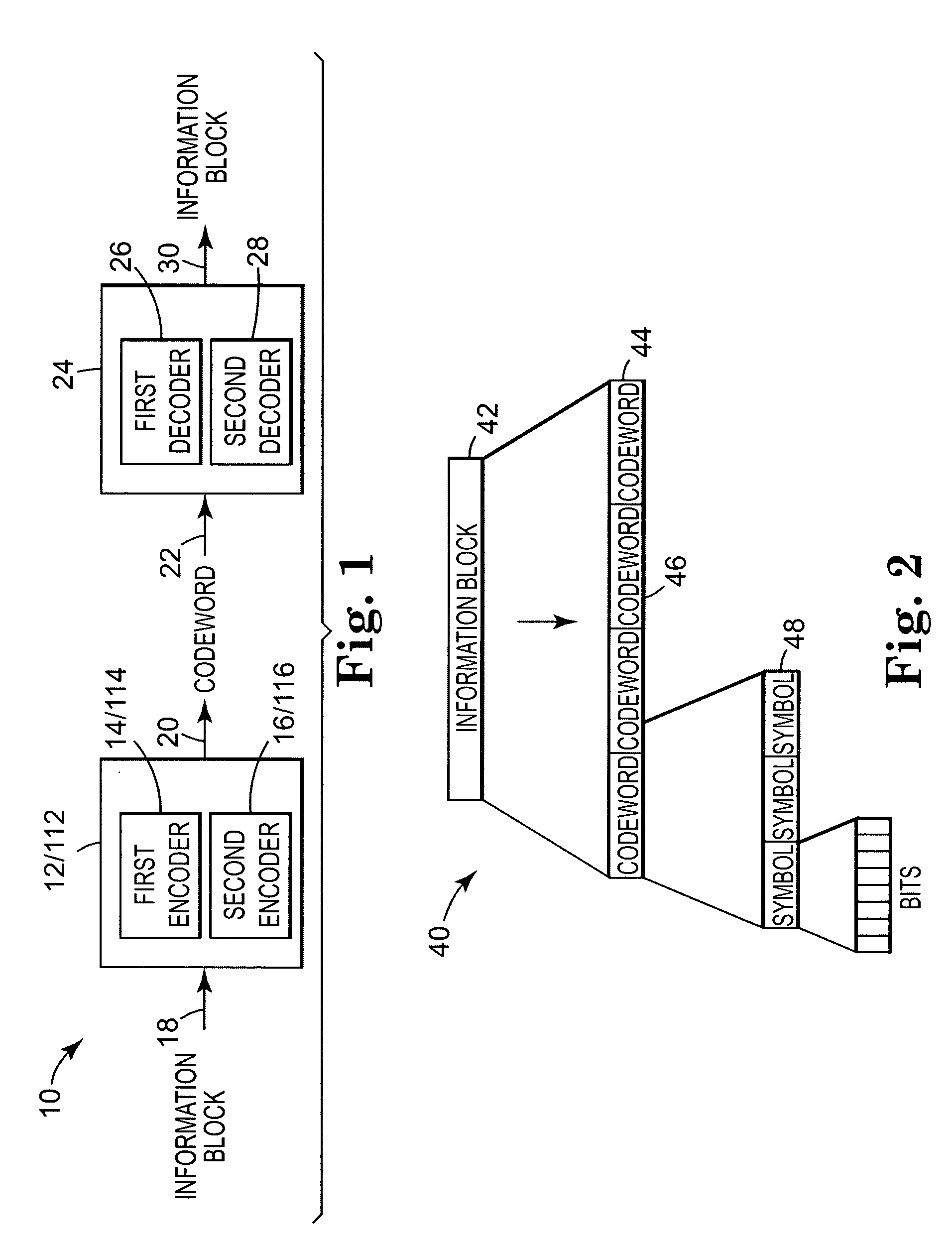

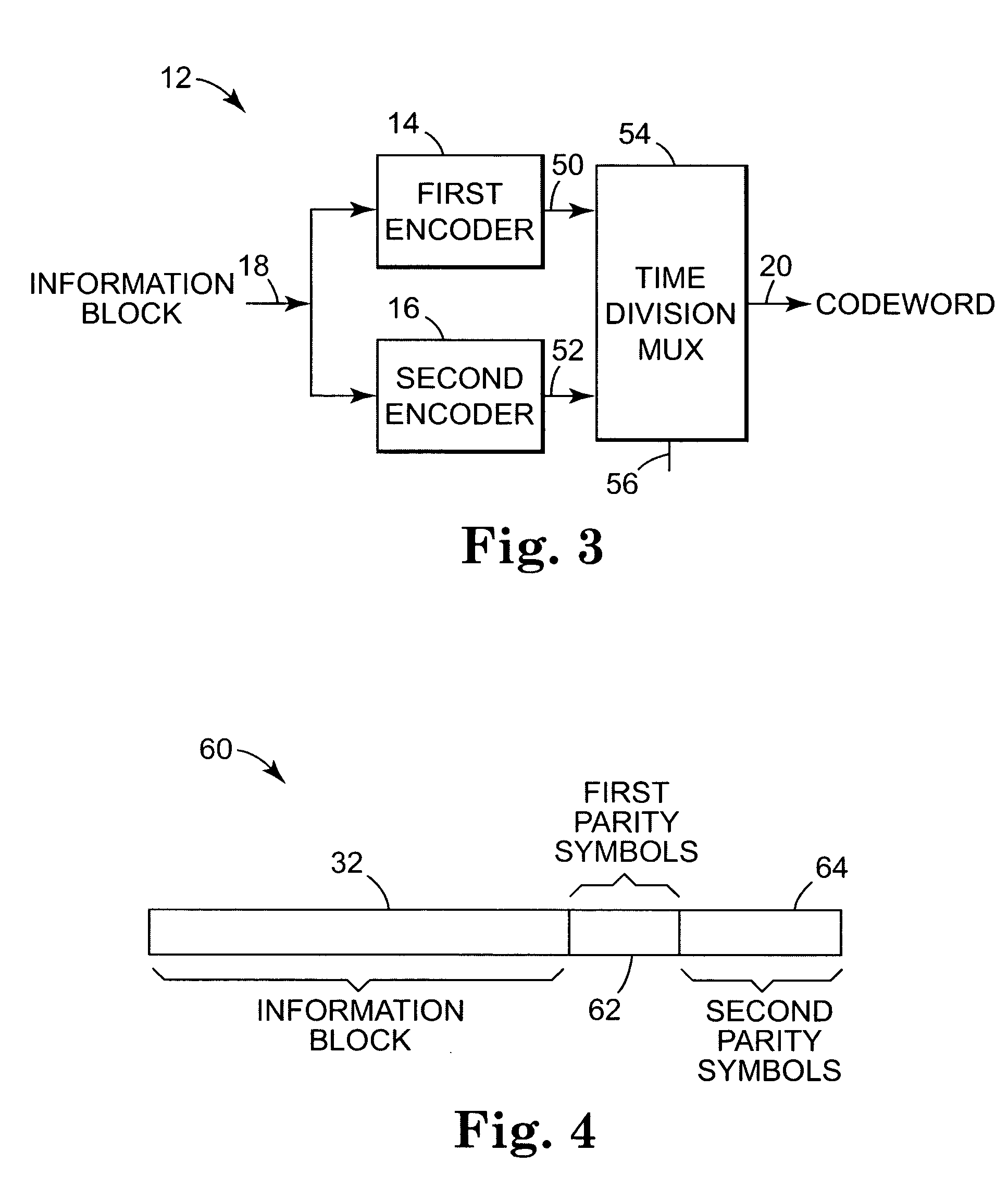

System for error correction coding and decoding

ActiveUS20050193312A1Improve abilitiesError correction/detection using convolutional codesOther decoding techniquesComputer hardwareError correction coding

A system for error correction coding and decoding information is disclosed. In one embodiment, the first and second encoders are each configured to encode the information, wherein the second encoder has a higher capability than the first encoder. First and second decoders are configured to recover the information, wherein the second decoder recovers the information encoded by the second encoder only if the first decoder cannot recover the information.

Owner:SAMSUNG ELECTRONICS CO LTD

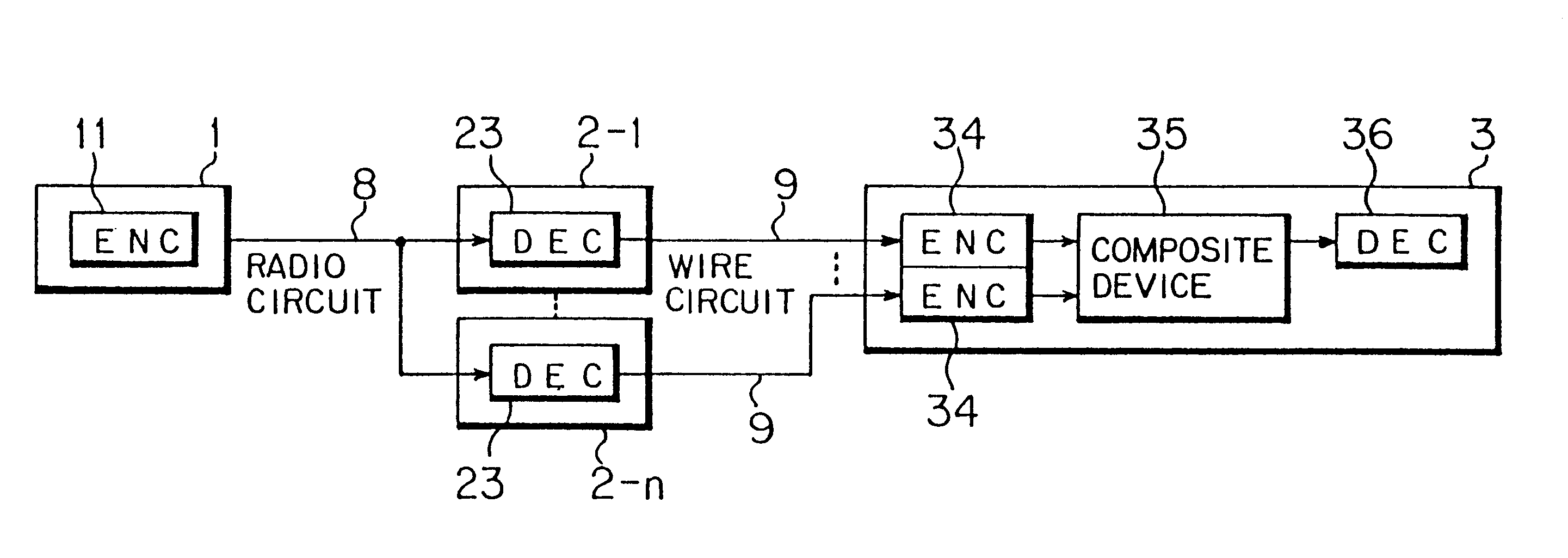

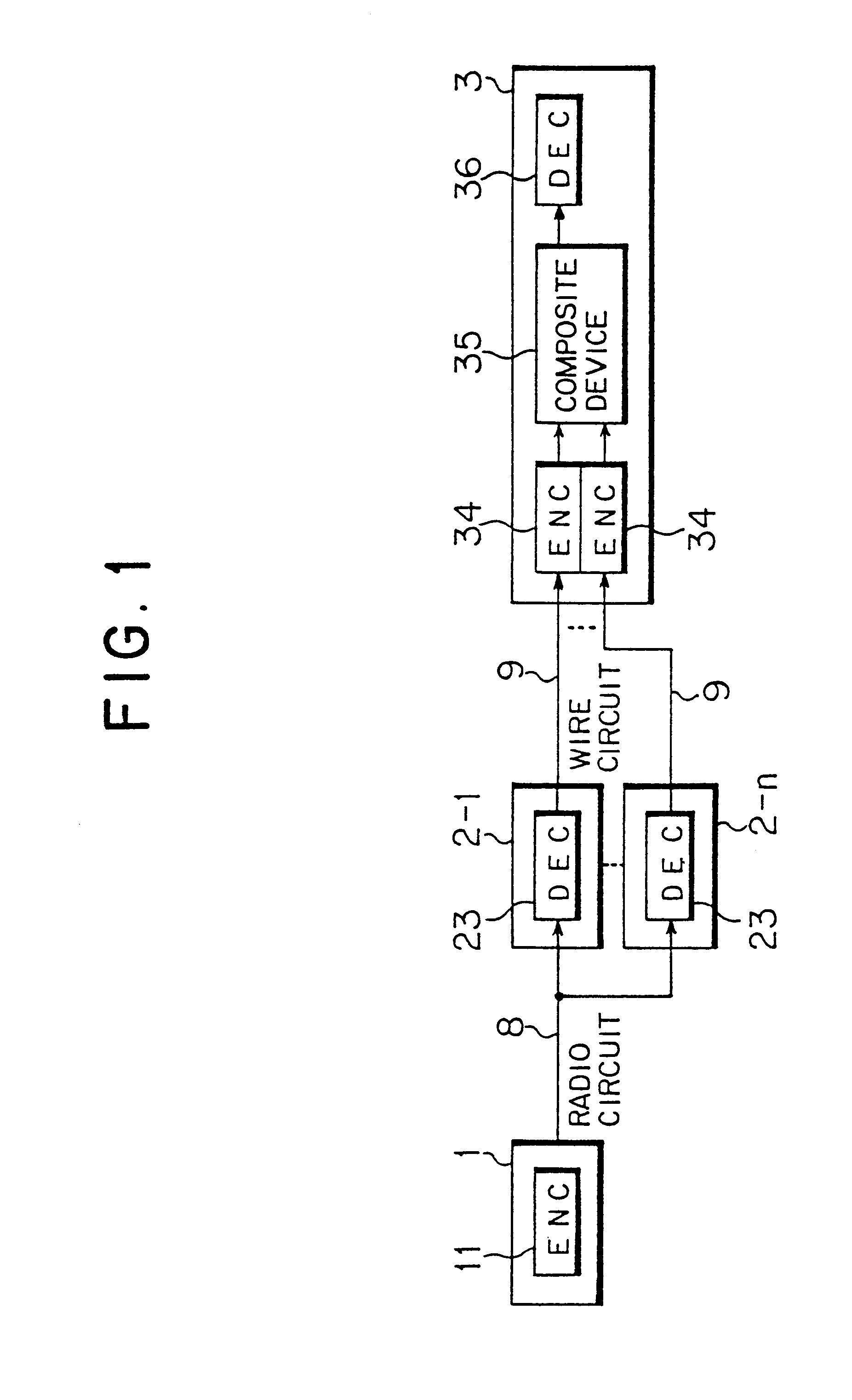

Base station host apparatus used in mobile communication system which employs a site diversity receiving method and a signal processing method

InactiveUS6320852B1Data representation error detection/correctionSpatial transmit diversityDiversity schemeSignal processing

A technique used in a mobile communications system. A mobile terminal station transmits a signal subjected to an error-correction encoding processing. Each of a plurality of base stations receives the signal transmitted from the mobile terminal station via the wireless line, performs an error-correction decoding processing for the received signal, and transmits an error-correction decoded signal to a base-station host apparatus via the wired line. The base-station host apparatus performs an error-correction encoding processing for each of the signals received from the base stations, composes the thus error-correction encoded signals into one signal, and performs an error-correction decoding processing for the composed signal. The technique can improve the error rate of a received signal without increasing the amount of signal data flowing between the base stations and the base-station host apparatus.

Owner:FUJITSU LTD

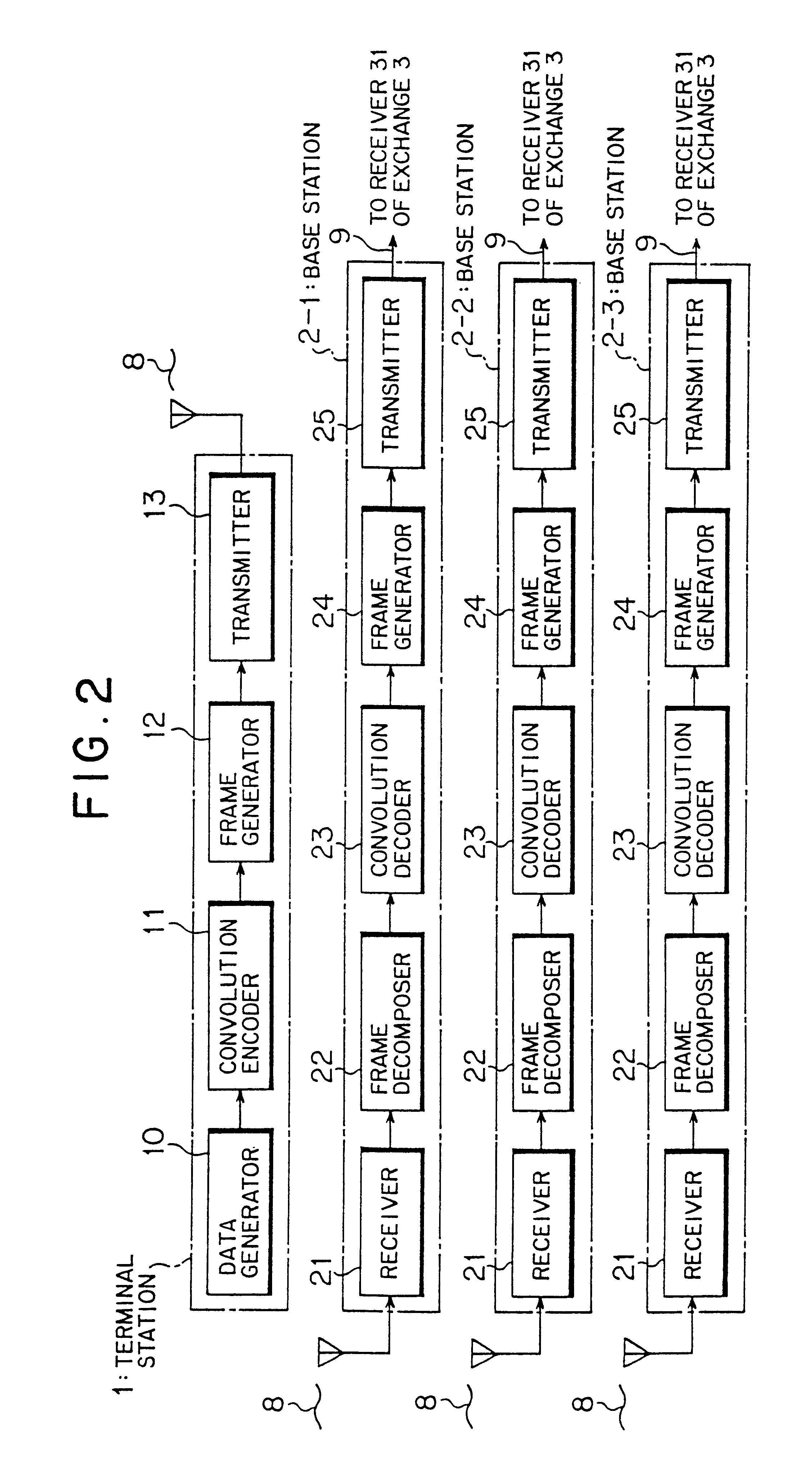

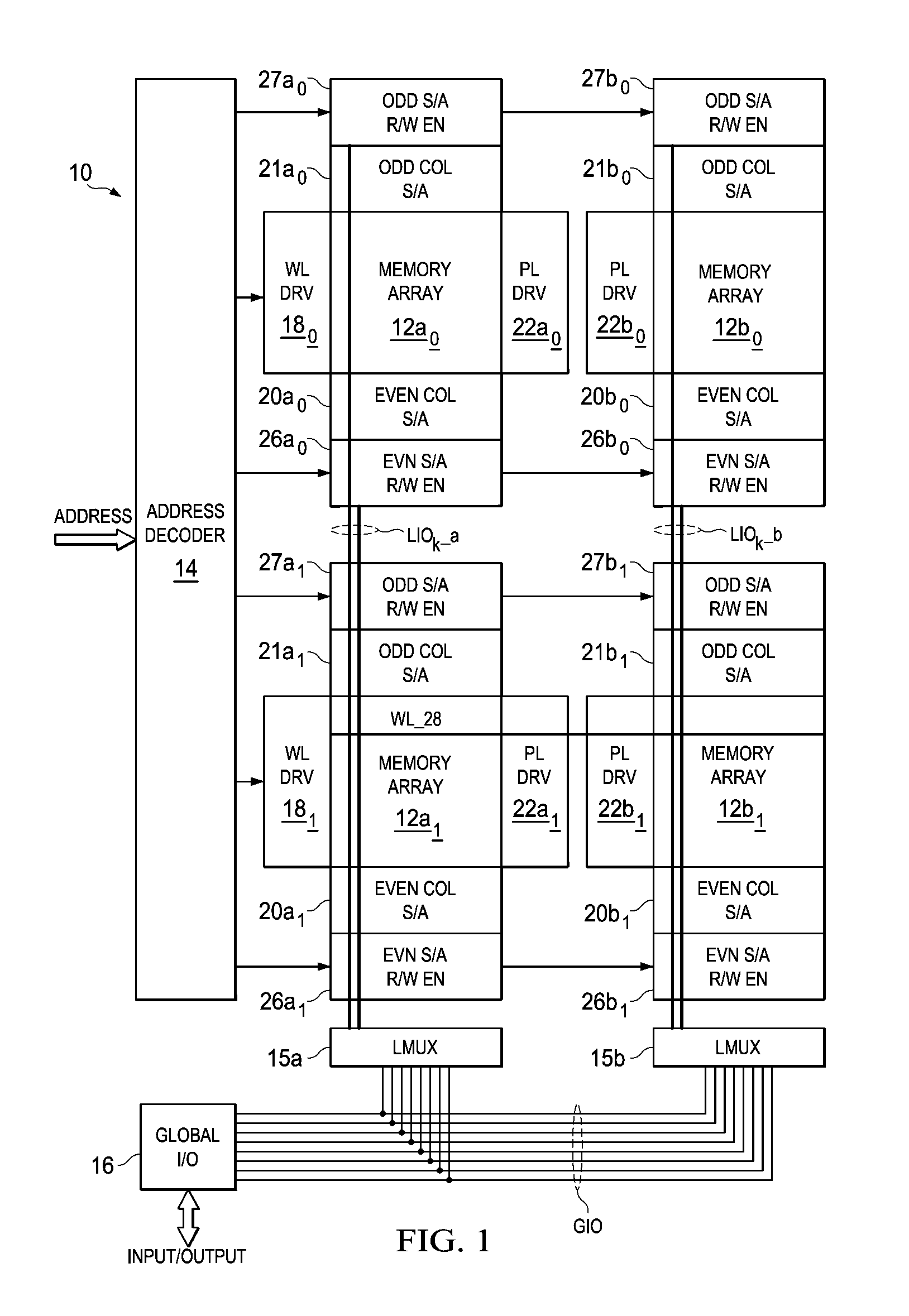

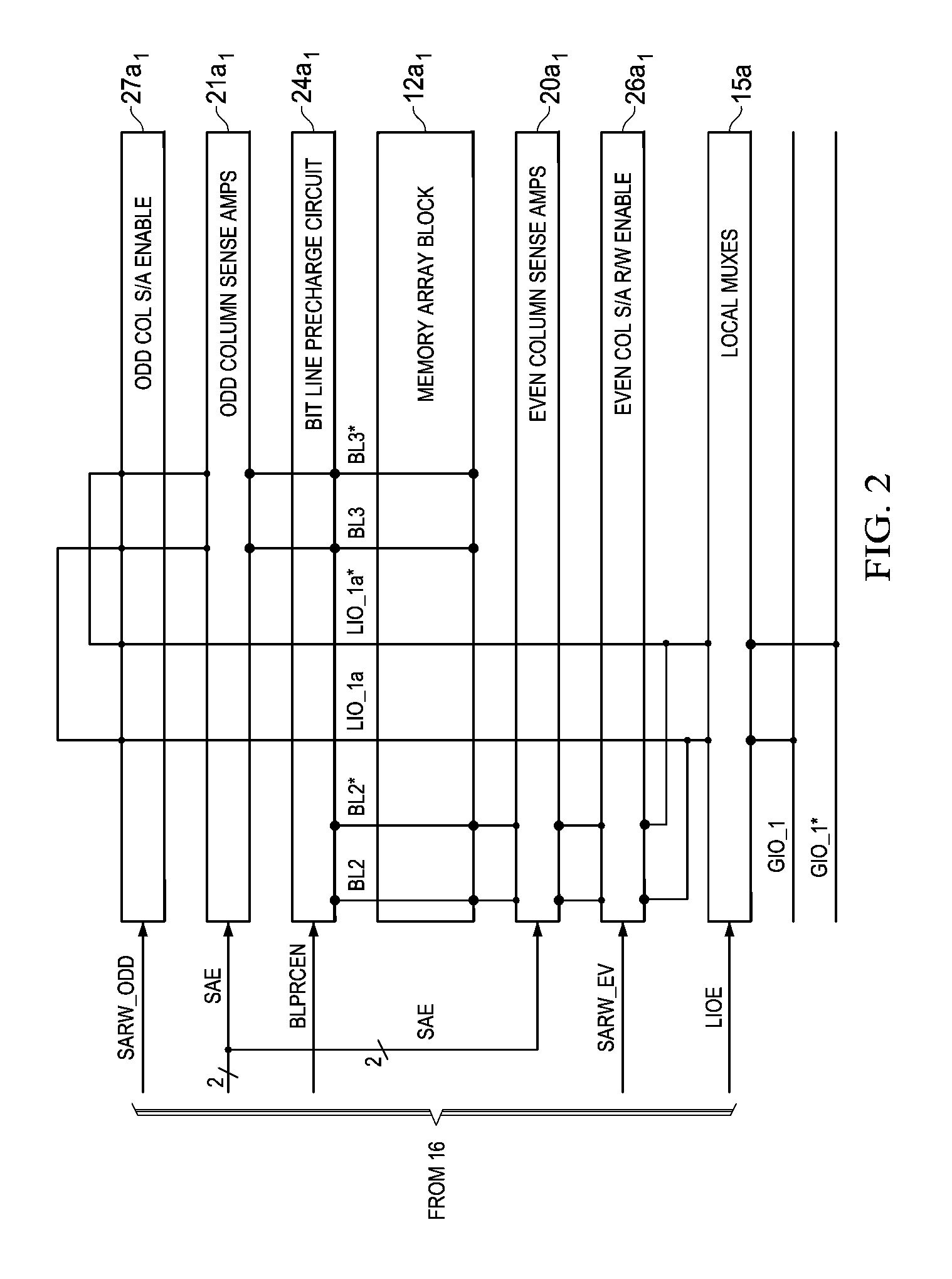

Data Path Read/Write Sequencing for Reduced Power Consumption

ActiveUS20110035644A1Reduce power consumptionIncrease the areaCode conversionDigital storageAudio power amplifierRandom access memory

A solid-state memory such as a ferroelectric random access memory (FeRAM) with multiplexed internal data bus and reduced power consumption on data transfer. The memory stores data in the form of multi-byte data words with error correction coding (ECC). In a page mode read / write operation, data states stored in memory cells of the selected row are sensed by sense amplifiers arranged in first and second banks, which are associated with first and second groups of columns. The first bank of sense amplifiers, associated with the first group of columns and containing the ECC value, are coupled to to the internal bus, followed by coupling the second bank of sense amplifiers associated with the second group of columns to the internal bus. The internal bus is then placed in tri-state, following which the internal data bus is driven with data to be written into the second group of columns in that same row, that data latched into the second bank of sense amplifiers. The internal bus is then driven with the data to be written to the first group of columns in the row, and latched into the first bank of sense amplifiers. To the extent that the data in the second group of columns does not change from the read to write operations, power consumption otherwise necessary for switching the internal bus is avoided.

Owner:TEXAS INSTR INC

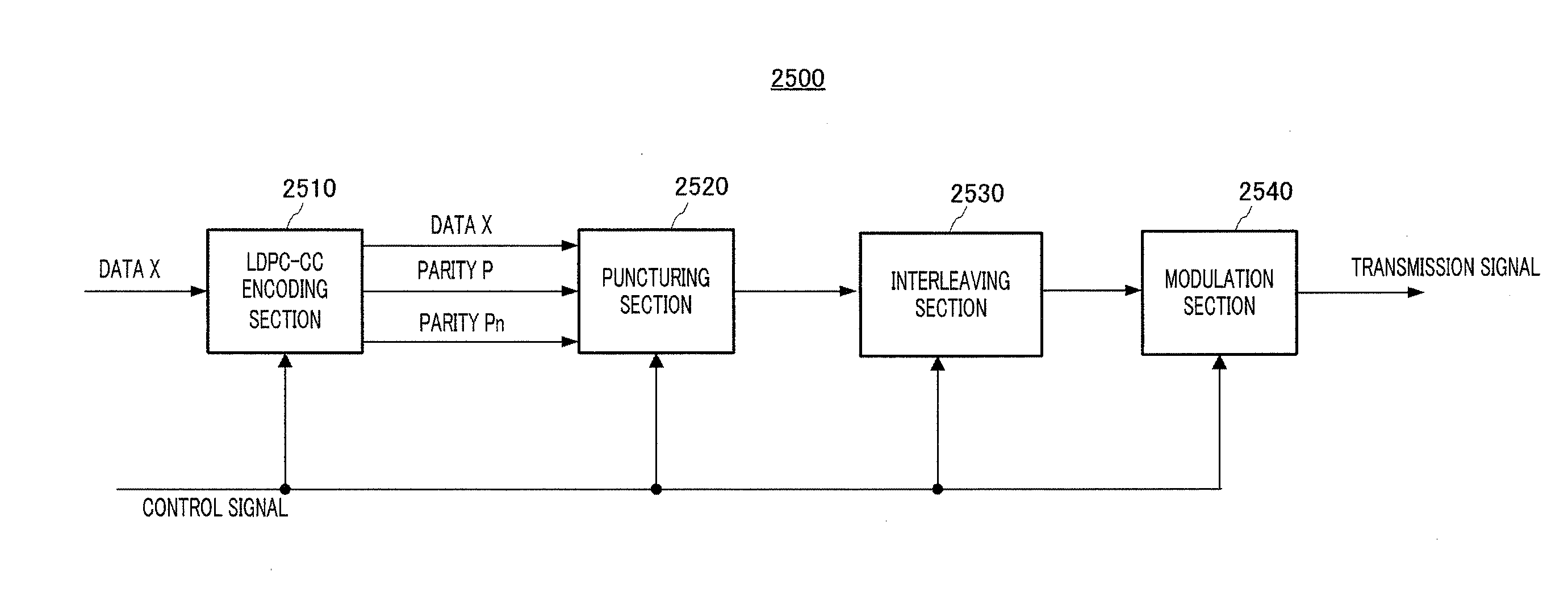

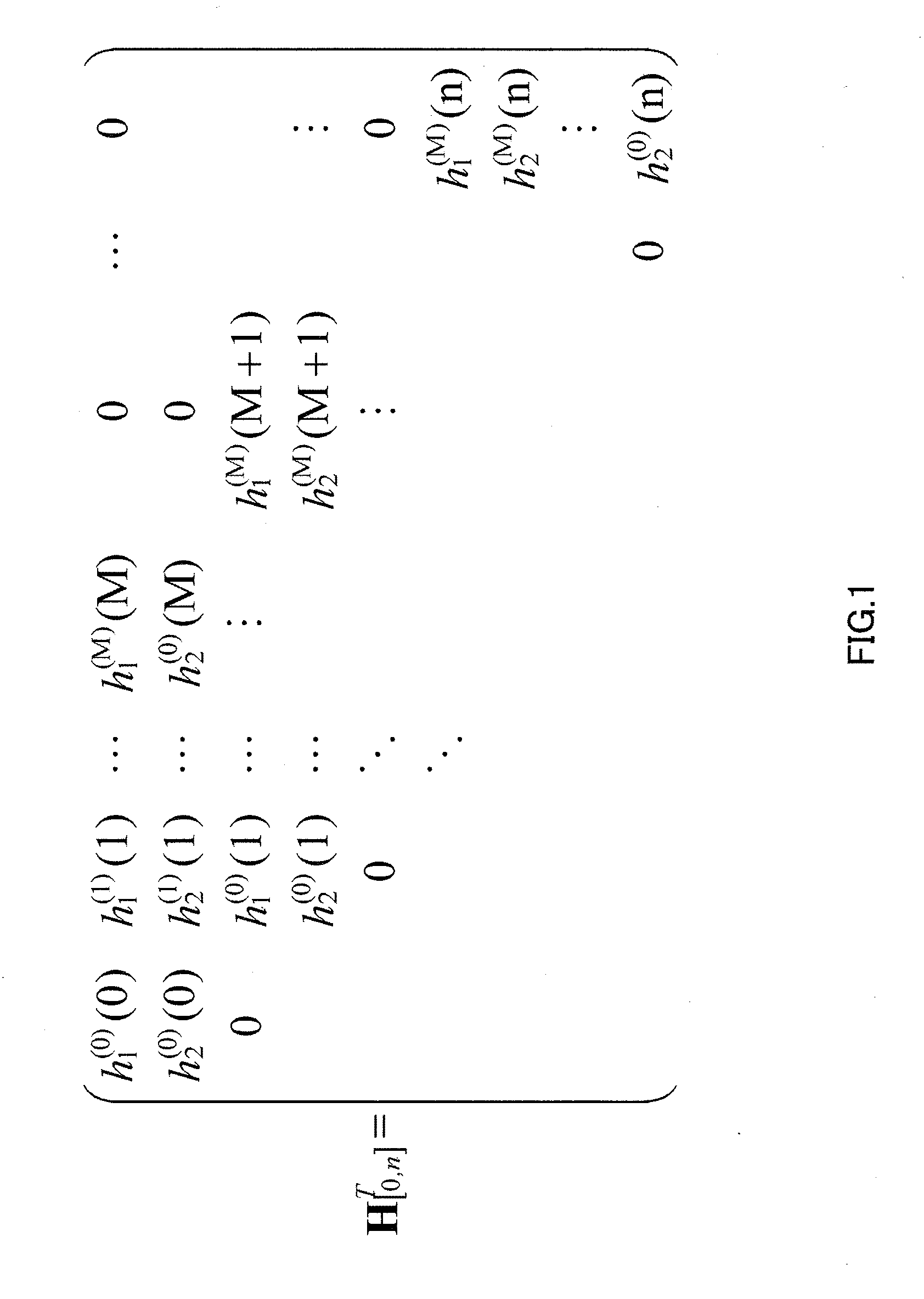

Encoding method, encoder, and decoder

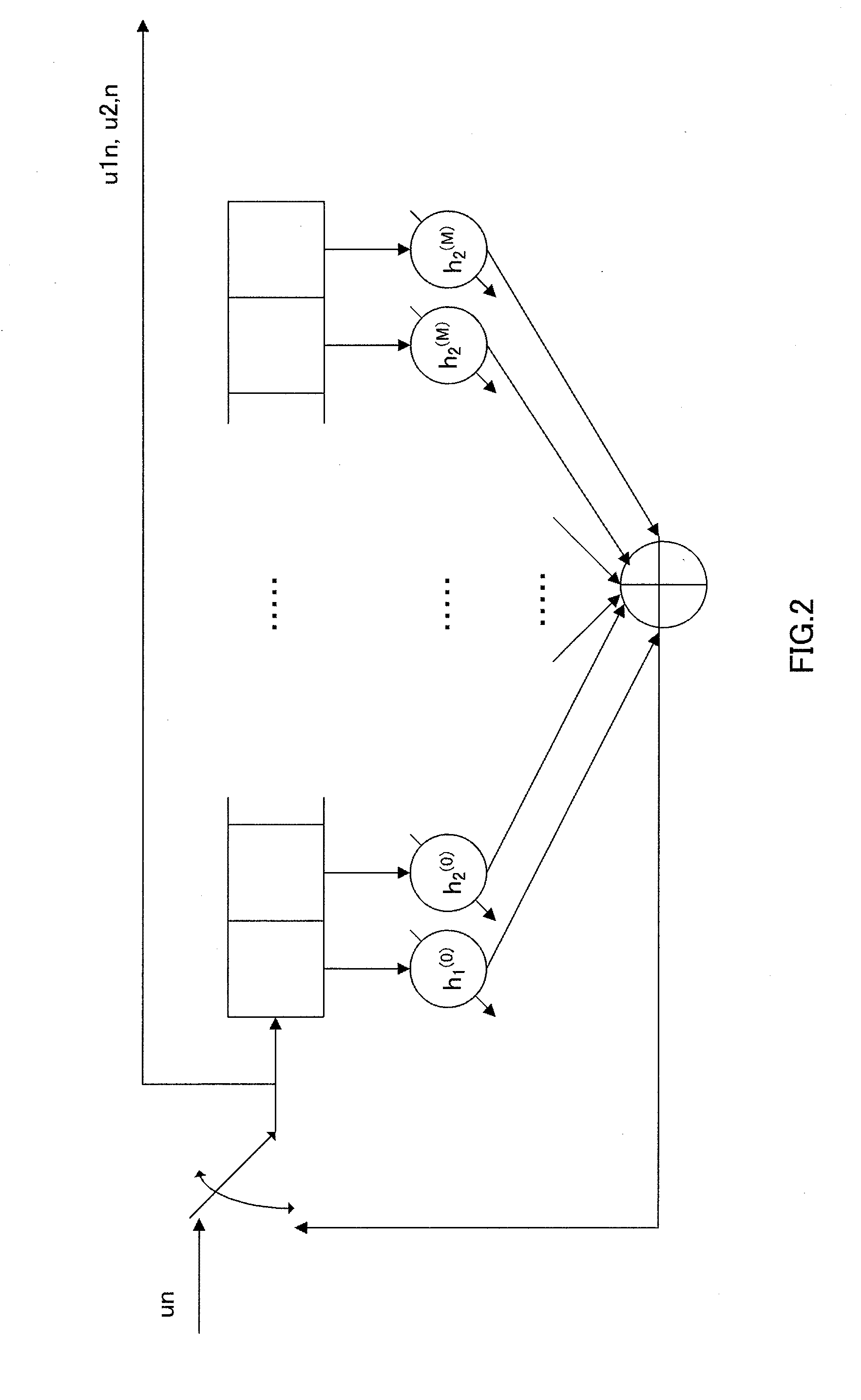

ActiveUS20100205511A1Good reception qualityImprove reception qualityError correction/detection using convolutional codesError preventionLinear operationConvolution

A low-density parity check convolution code (LDPC-CC) is made, and a signal sequence is sent after subjected to an error-correcting encodement using the low-density parity check convolution code. In this case, a low-density parity check code of a time-variant period (3g) is created by linear operations of first to 3g-th (letter g designates a positive integer) parity check polynomials and input data.

Owner:PANASONIC CORP

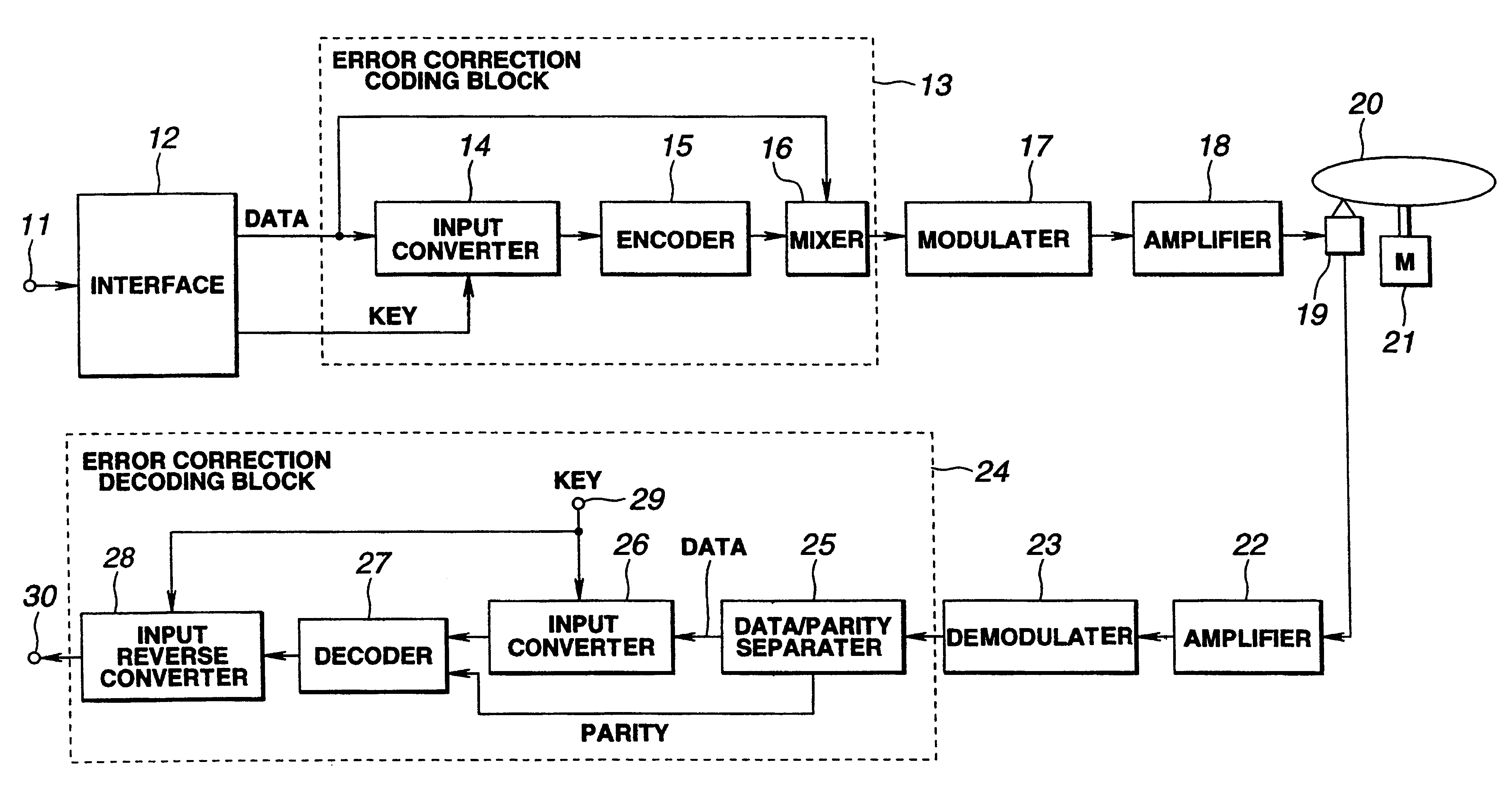

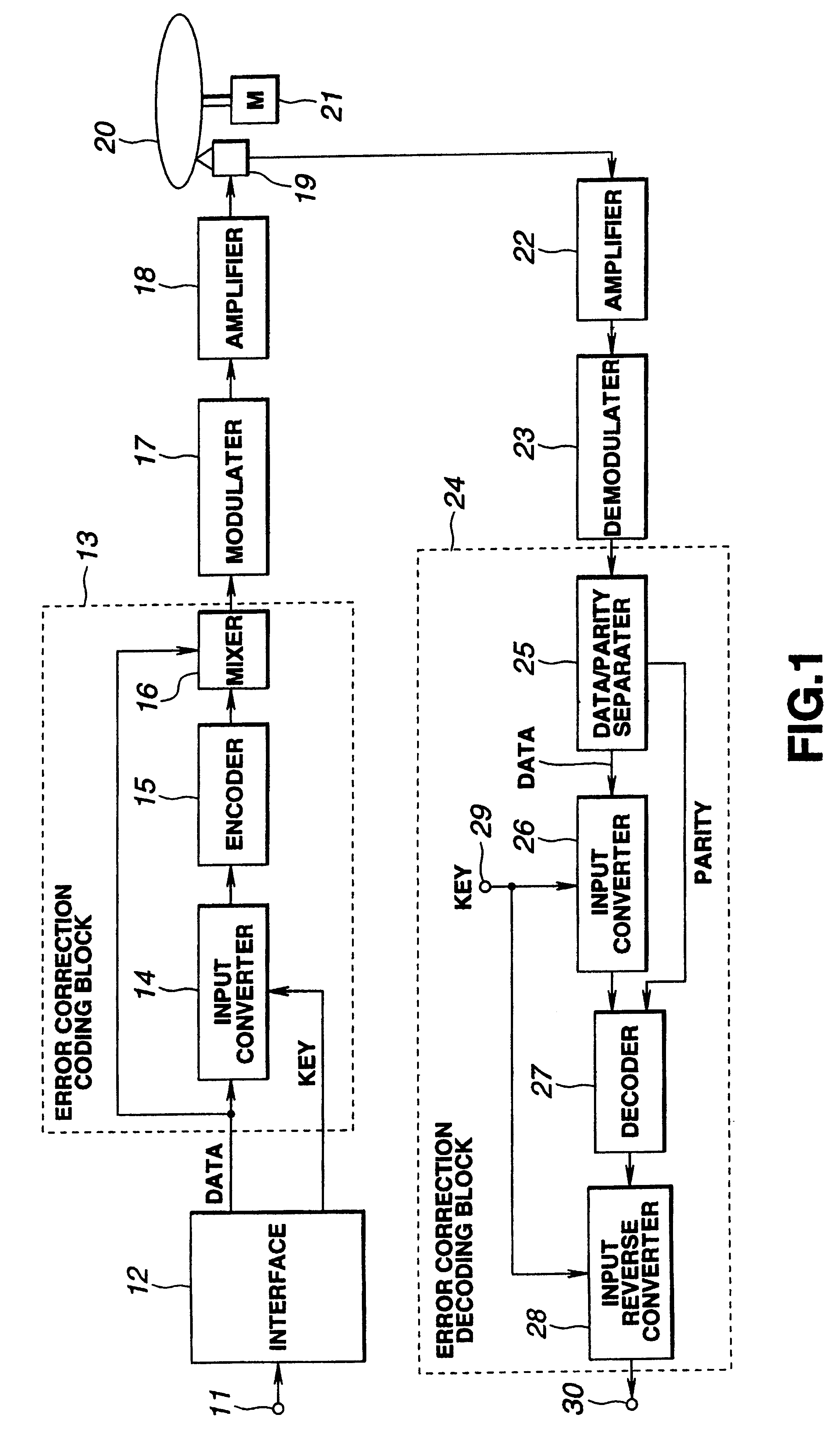

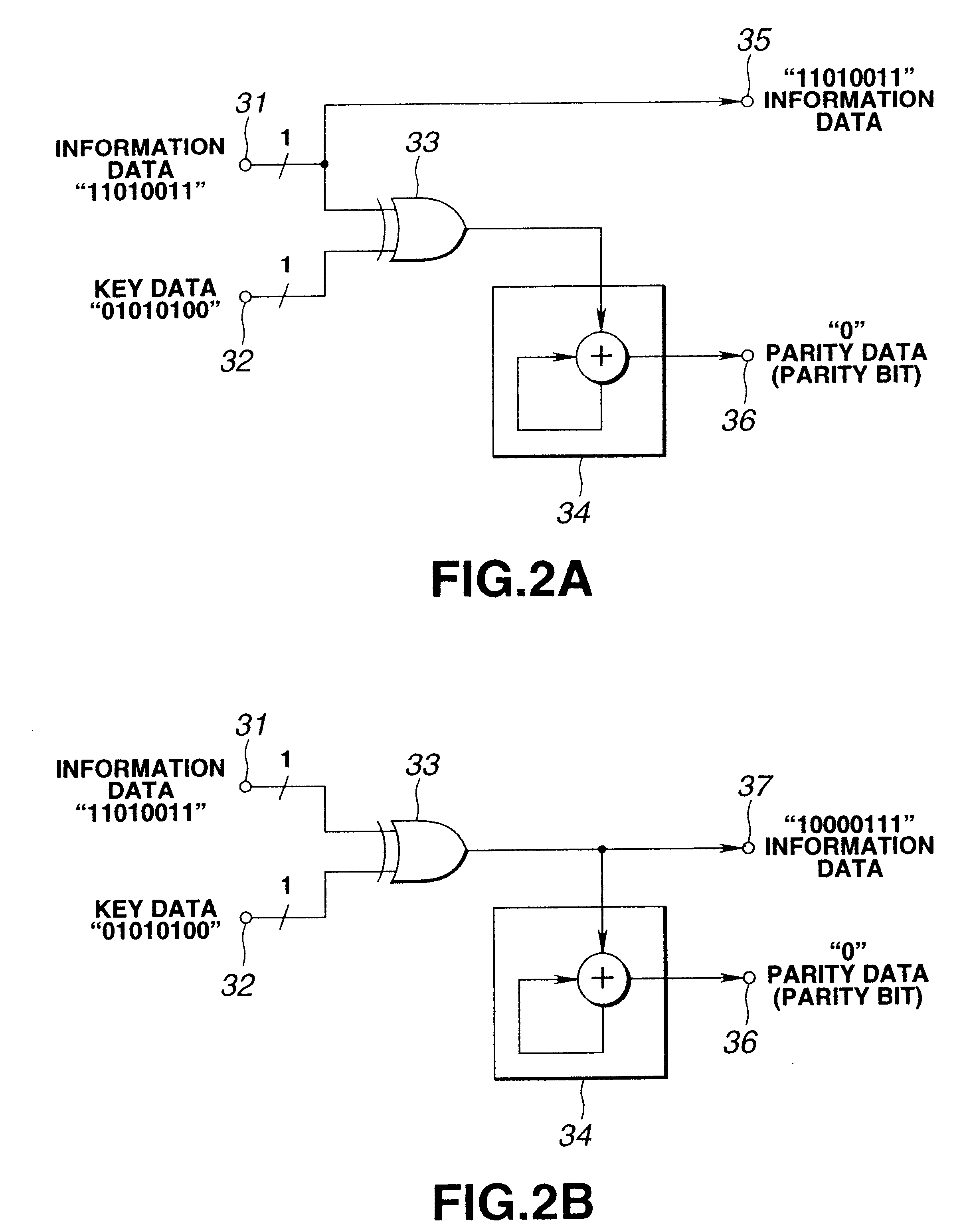

Method for transmitting data apparatus for recording data medium for recording data and apparatus for reproducing data

InactiveUS6463153B1Improve data securityDigital data processing detailsUnauthorized memory use protectionInterface circuitsCoding block

A data transmitting method, a data recording apparatus, a data record medium and a data reproducing apparatus are provided to disallow the encryption to be easily decoded and keep the secrecy of key information higher. The data transmitting apparatus includes an error correction coding process block. In the block, an input converting circuit operates to perform a logic operation with respect to the information data from an interface circuit according to the key data. The converted information data is sent to an encoder for generating parity data. This parity data is mixed in a mixing circuit with information data before conversion. The error correction coding block operates to send the resulting data to a modulating circuit for modulating the data. The modulated data is recorded on a disk record medium.

Owner:SONY CORP

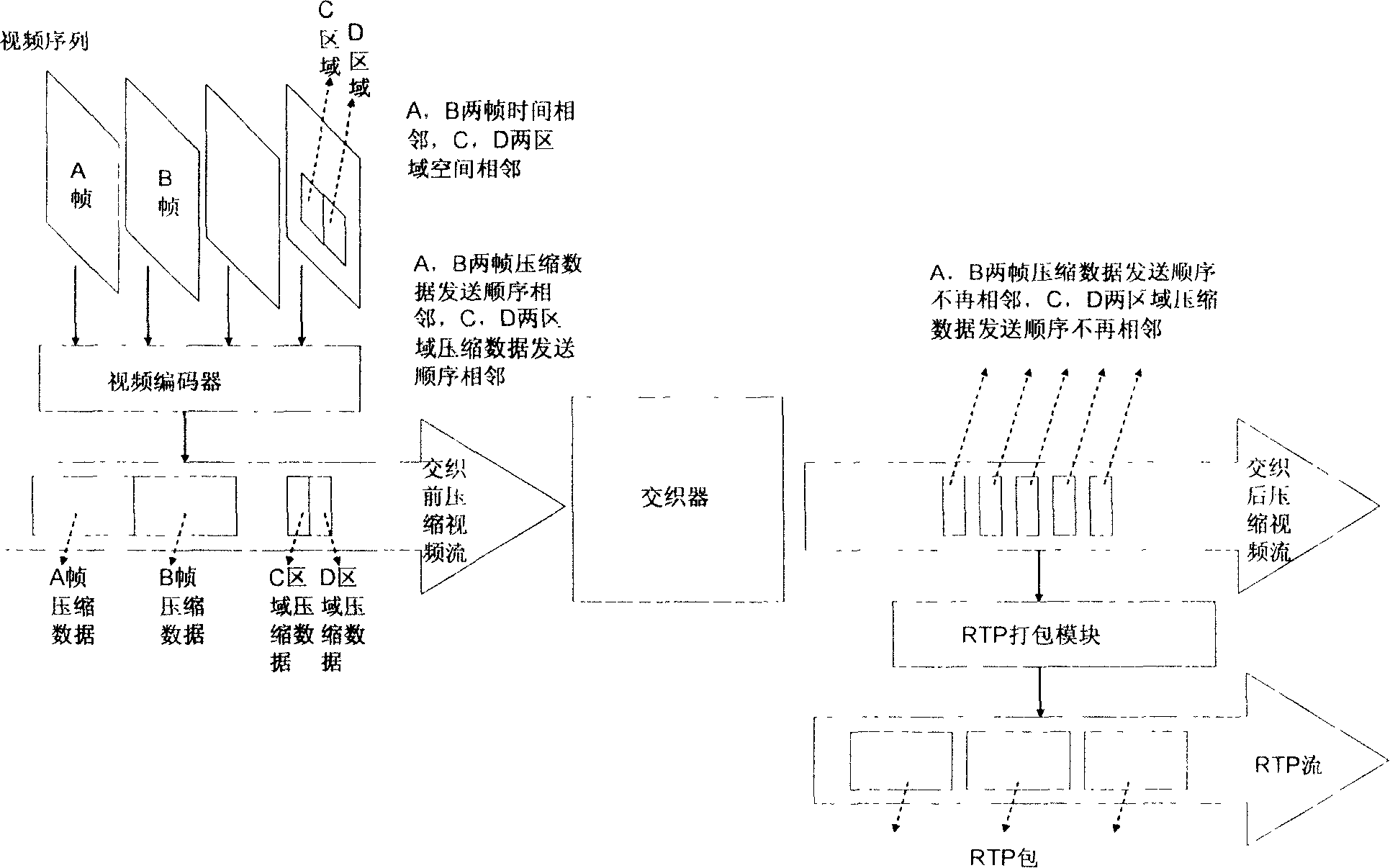

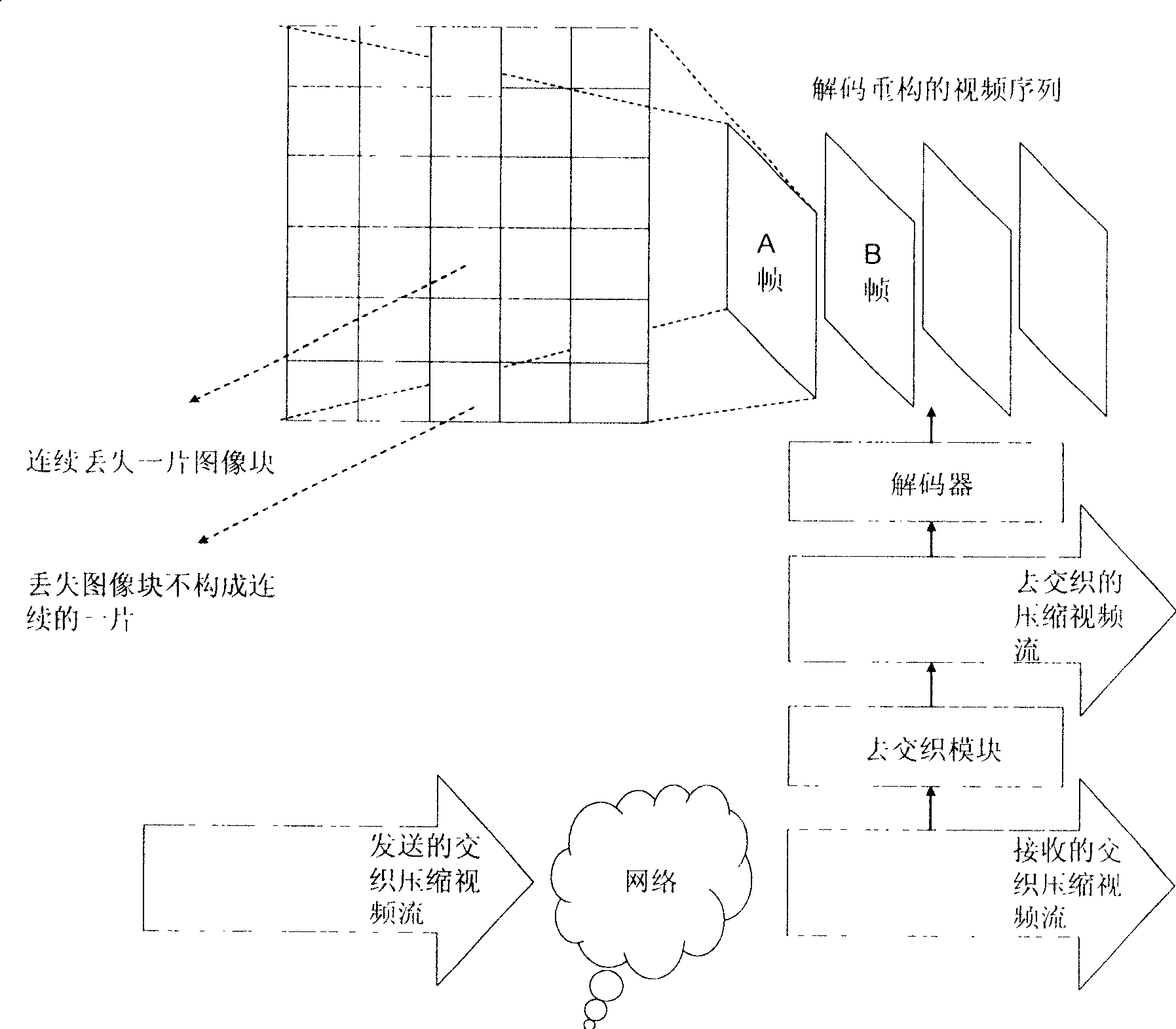

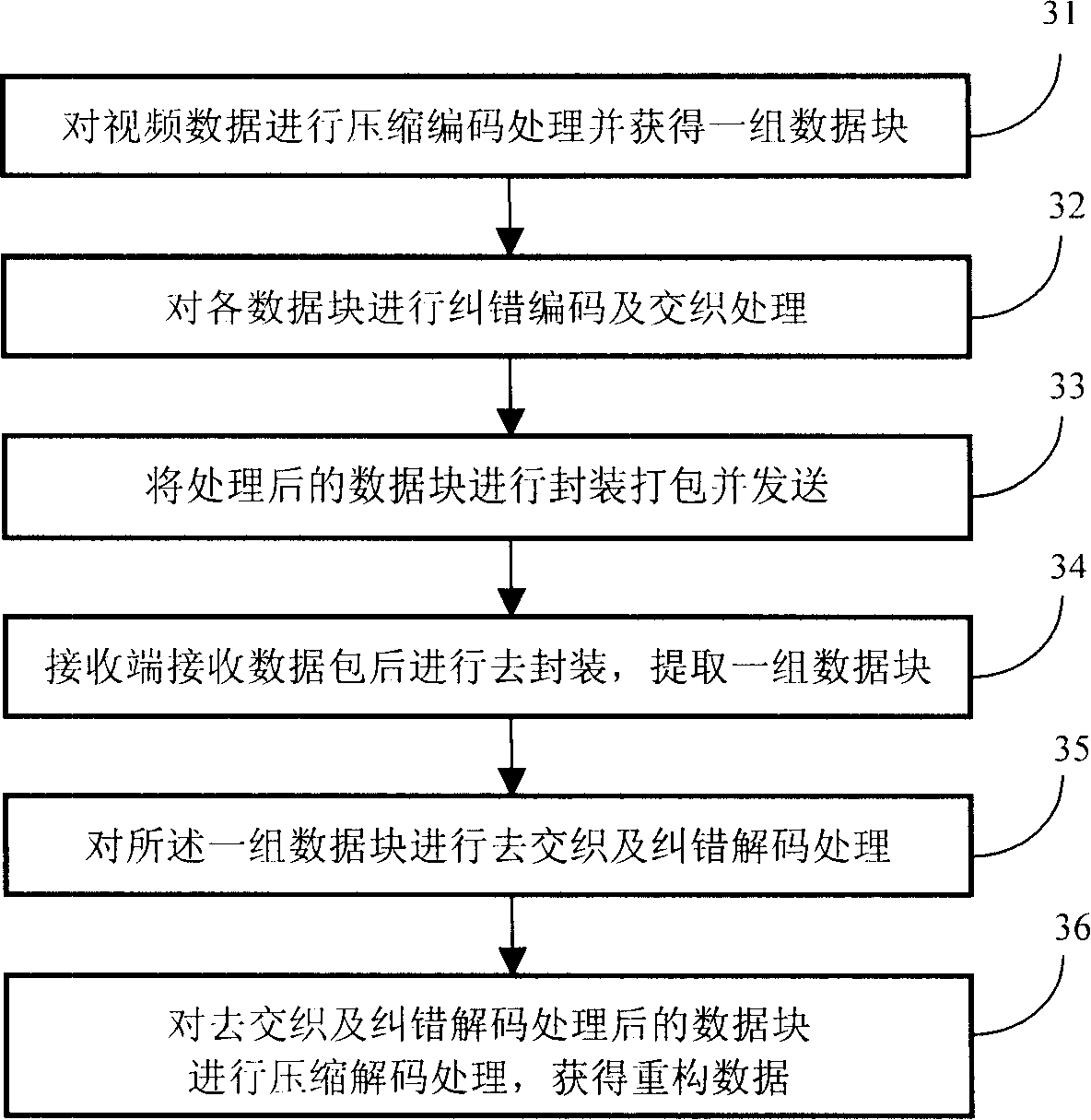

Method, device and system for transmitting video data

InactiveCN101166273AImprove delivery qualityImprove experienceTelevision systemsDigital video signal modificationPacket lossData shipping

The invention includes following steps: first, carrying out compressed encoding process for video data to be transmitted so as to obtain multiple data blocks after encoding process; then, carrying out error correction coding process for the said multiple data blocks to obtain corresponding checking blocks; finally, carrying out interlacing process for the said data blocks and the checking blocks, as well as packing, packaging, and transmitting the interlaced data blocks and checking blocks. In the invention, since it is lower correlativity between data blocks packaged in same or successive interlaced data packets, thus even if packet loss occurs in the transmission, the possibility that the receiving end is unable to decode the received data is reduced greatly. The invention raises quality for transferring video data through IP network, wireless network etc, where packet loss exists.

Owner:HUAWEI TECH CO LTD

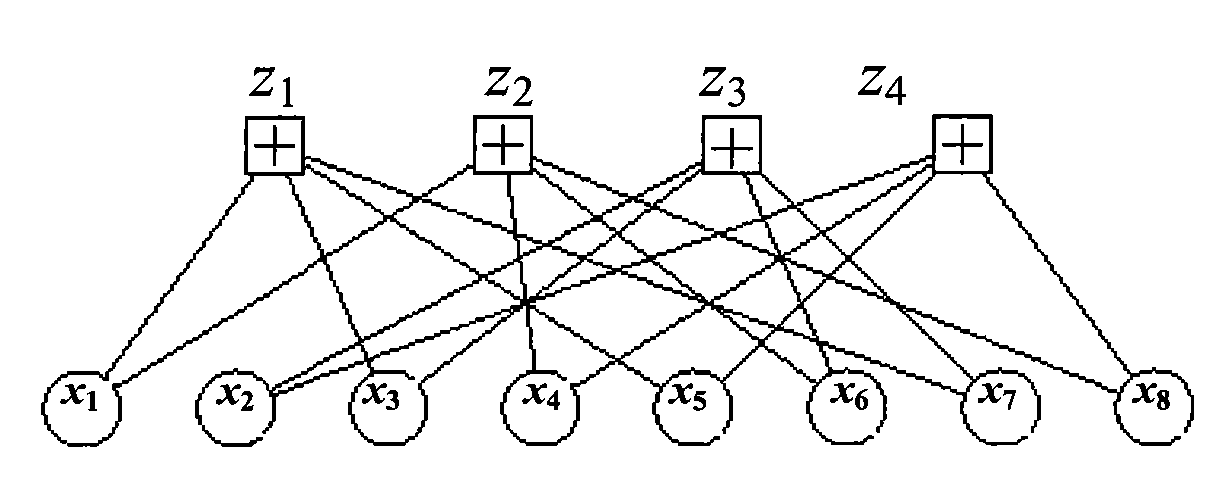

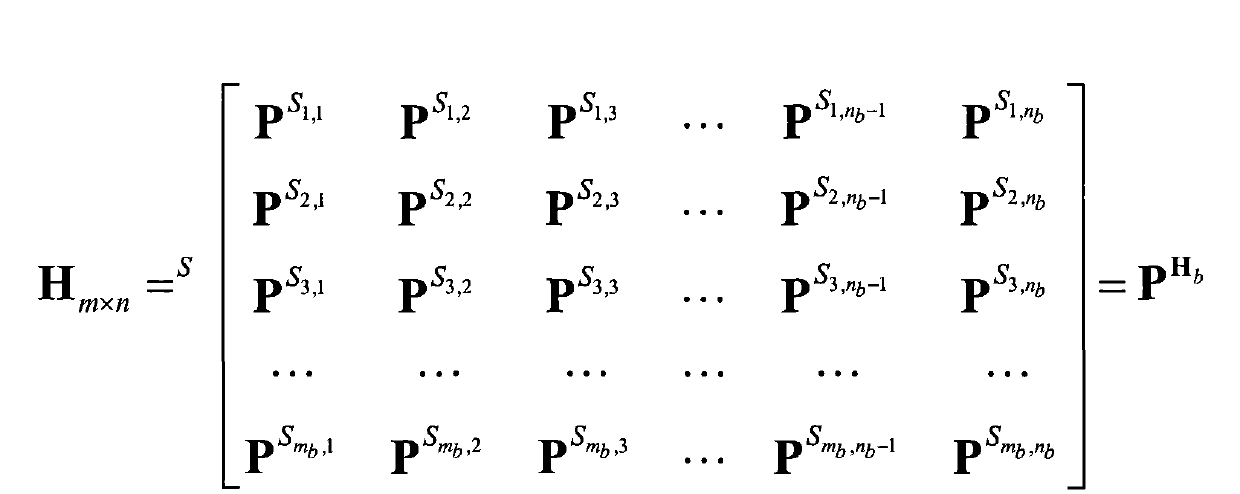

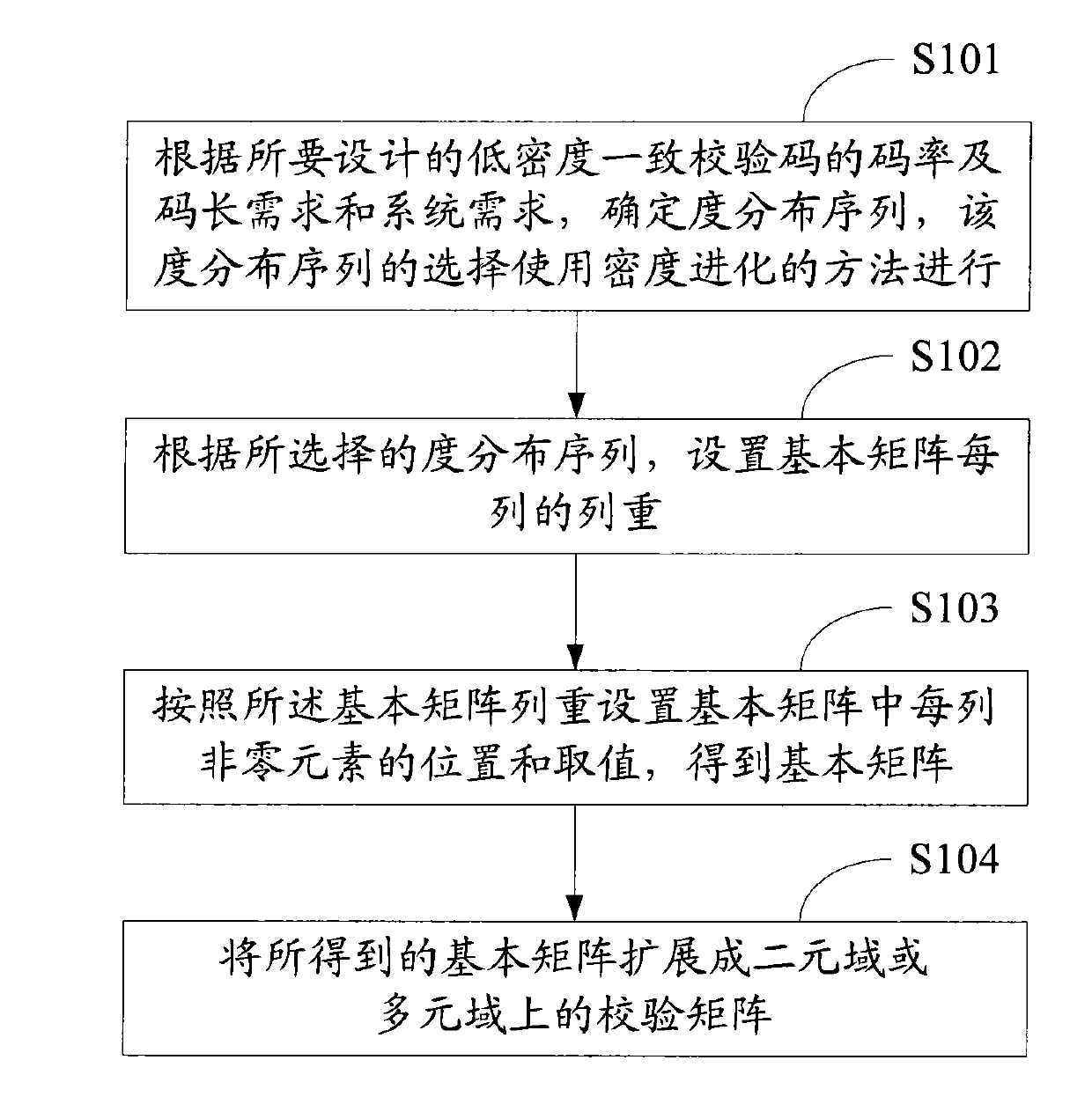

Method and device for generating and coding quasi-cyclic LDPC code

ActiveCN101662290AError correction/detection using multiple parity bitsCode conversionAlgorithmSystem requirements

The invention relates to the technical filed of the error correction and coding of communication and information systems and discloses a method for generating a quasi-cyclic low density parity check code. The method comprises the following steps: according to the requirements on code rate and code length of the low density parity check code to be designed and system requirements, determining a degree distribution sequence which is selected by adopting a density evolution method; setting the column weight of each column of a basic matrix according to the selected degree distribution sequence; setting the positions and values of non-zero elements in each column in the basic matrix according to the column weights of the basic matrix to obtain the basic matrix; and expanding the obtained basic matrix into a check matrix. At the same time, the invention also discloses a method for coding the quasi-cyclic low density parity check code and provides corresponding devices. The methods and the devices provided by the embodiment of the invention enable finally obtained code words to effectively reduce influences of cycle overlapping.

Owner:HONOR DEVICE CO LTD

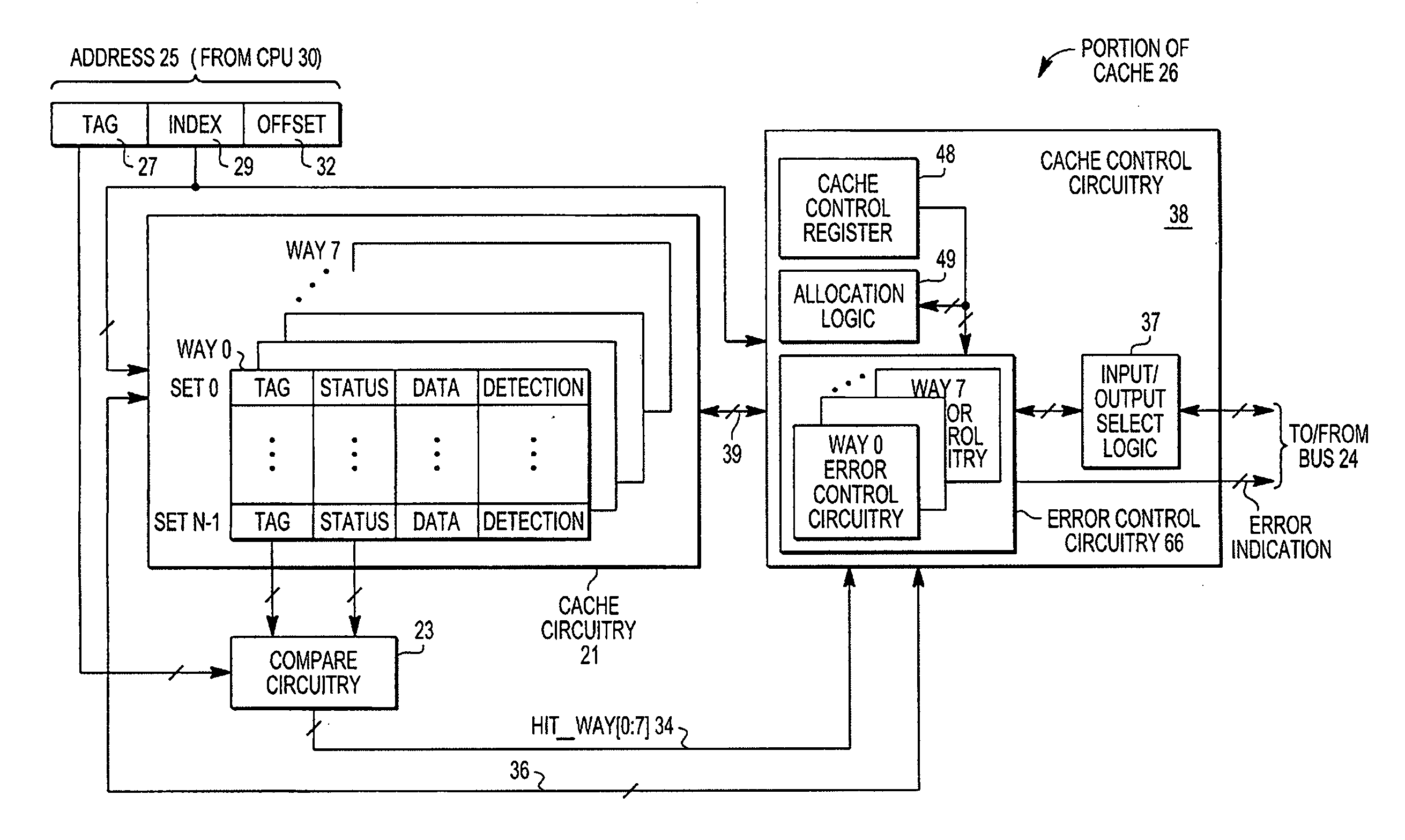

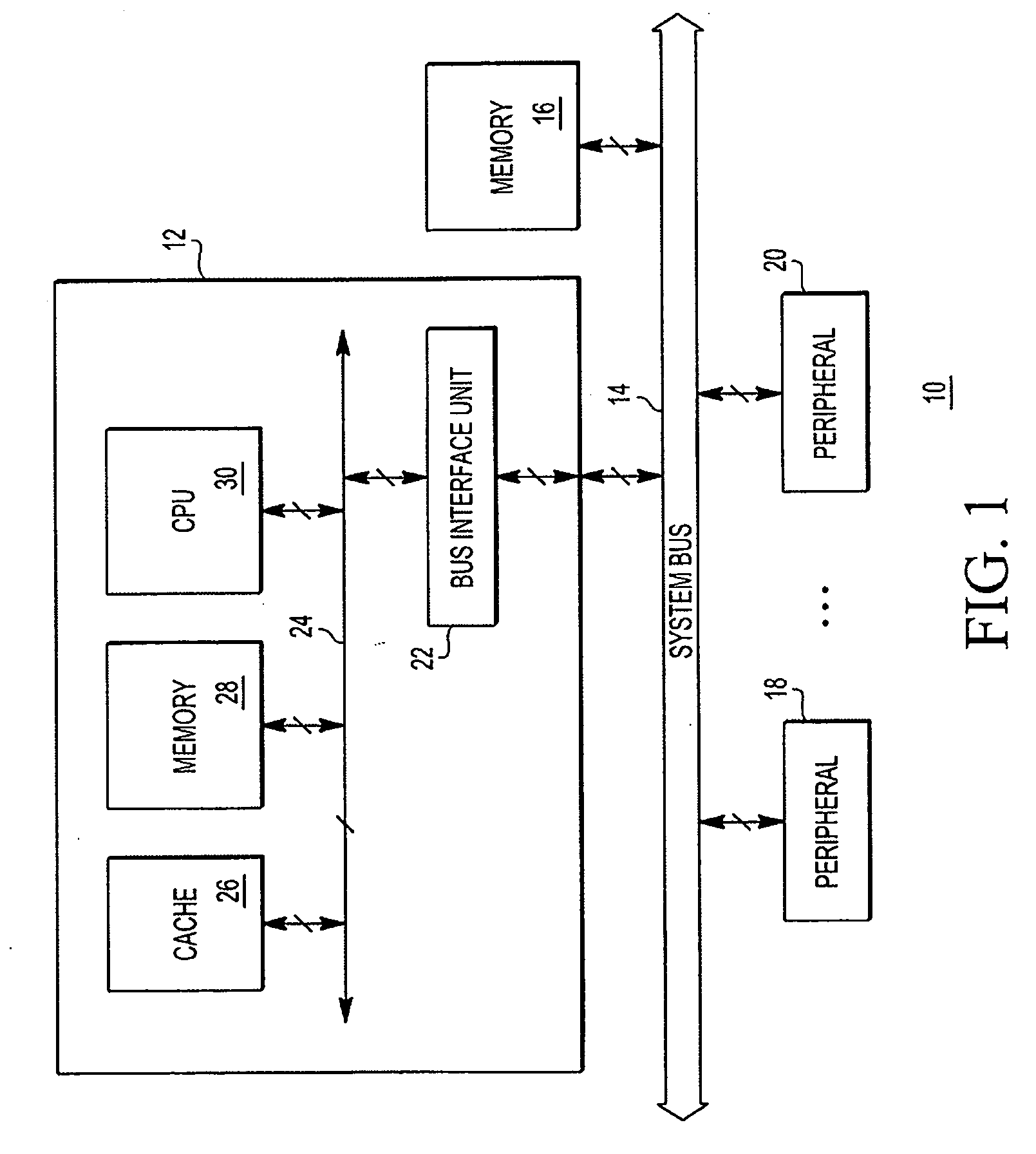

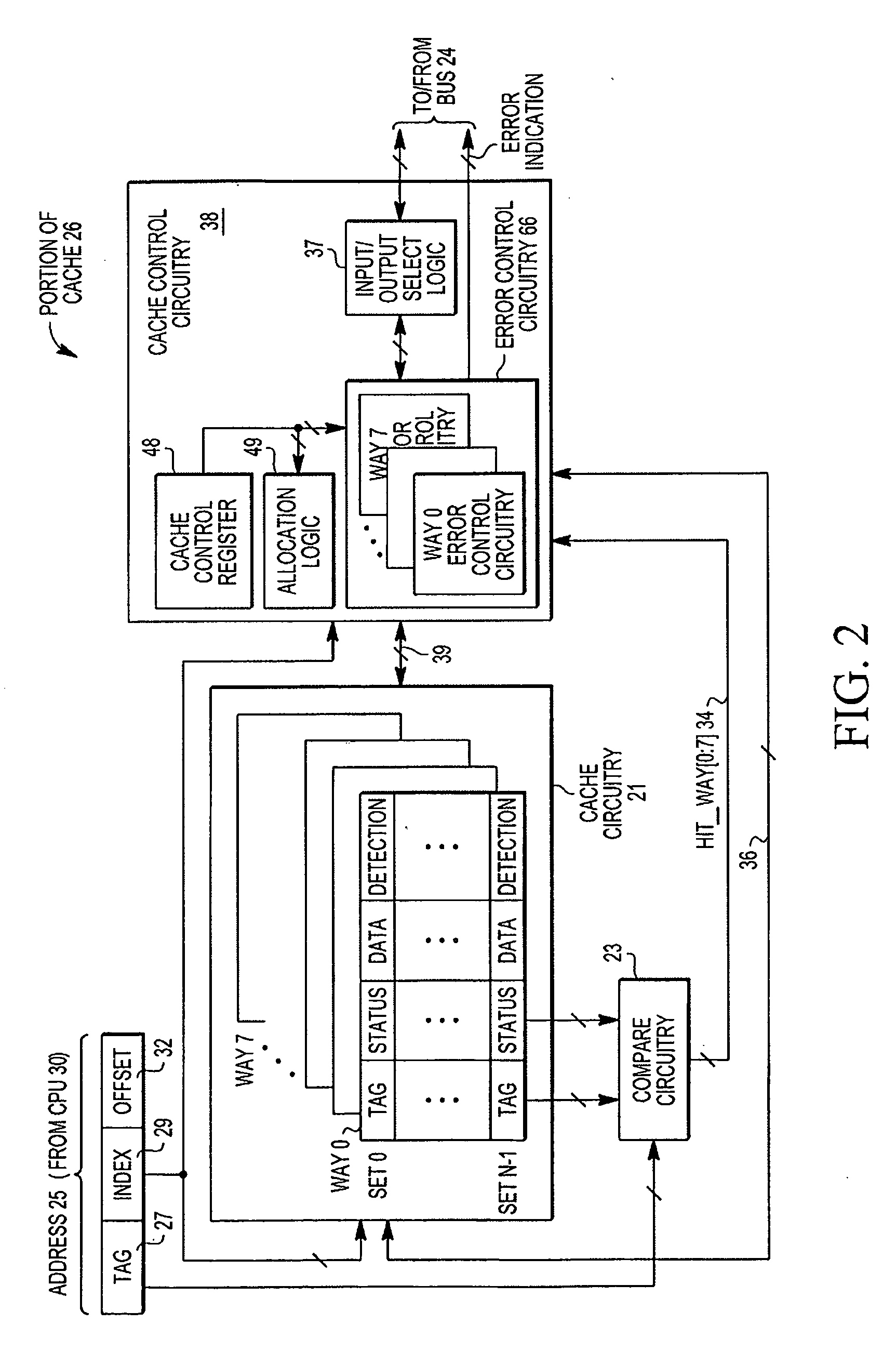

Implementation of multiple error detection schemes for a cache

A cache includes a plurality of cache lines, where each cache line includes a detection type field, corresponding cache data field, a detection field, and a corresponding tag field. The detection type field indicates an error detection scheme from a plurality of error detection schemes currently in use for the corresponding cache data field. One example of an error detection scheme is a multiple bit error detection scheme (e.g. an error detection coding (EDC) or an error correction coding (ECC)). Another type is a single bit error detection scheme (e.g. parity error detection). The detection bits field stores parity bits if parity error detection is used. The detection bits field stores checking bits if EDC coding is used.

Owner:NORTH STAR INNOVATIONS

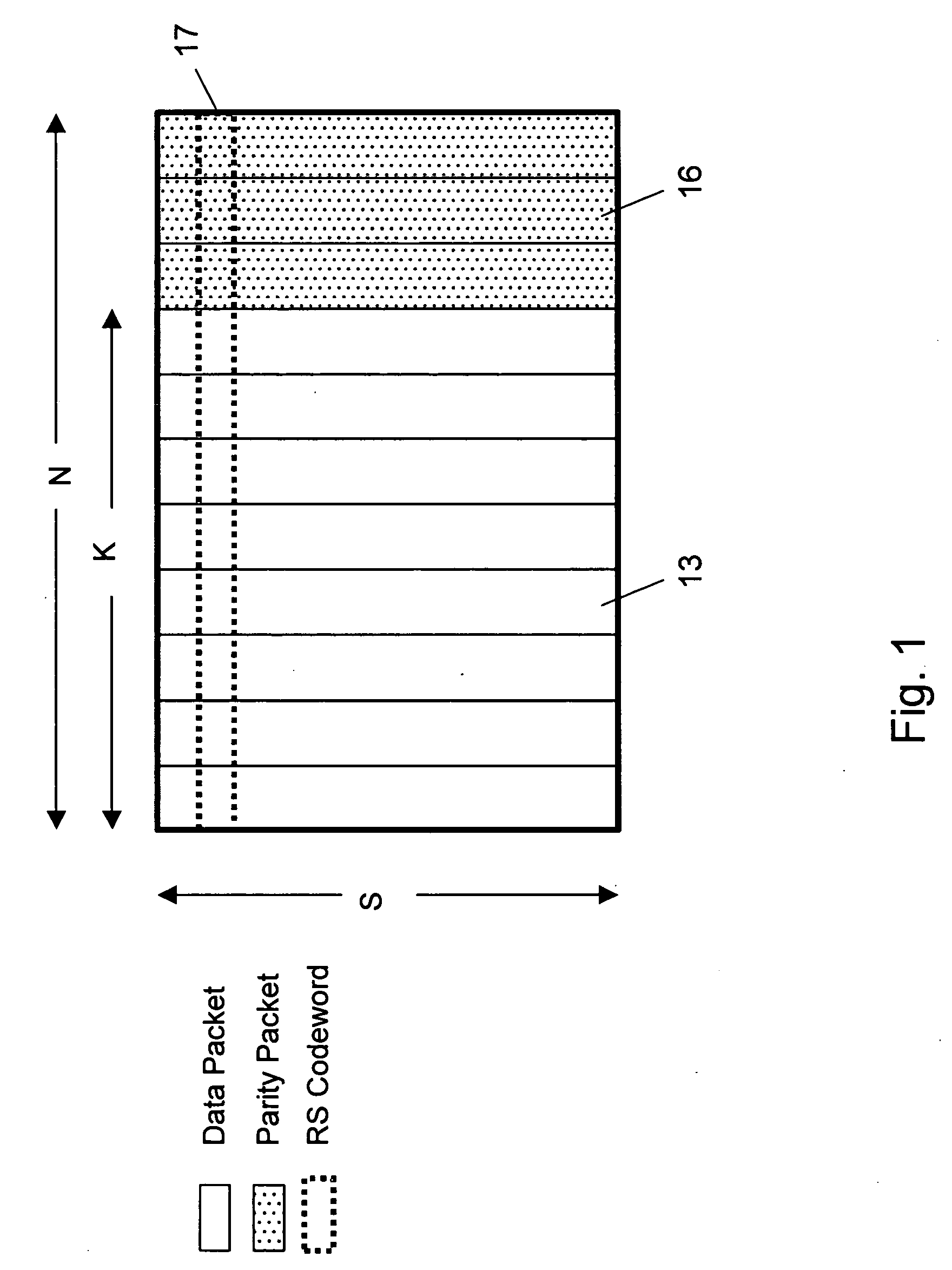

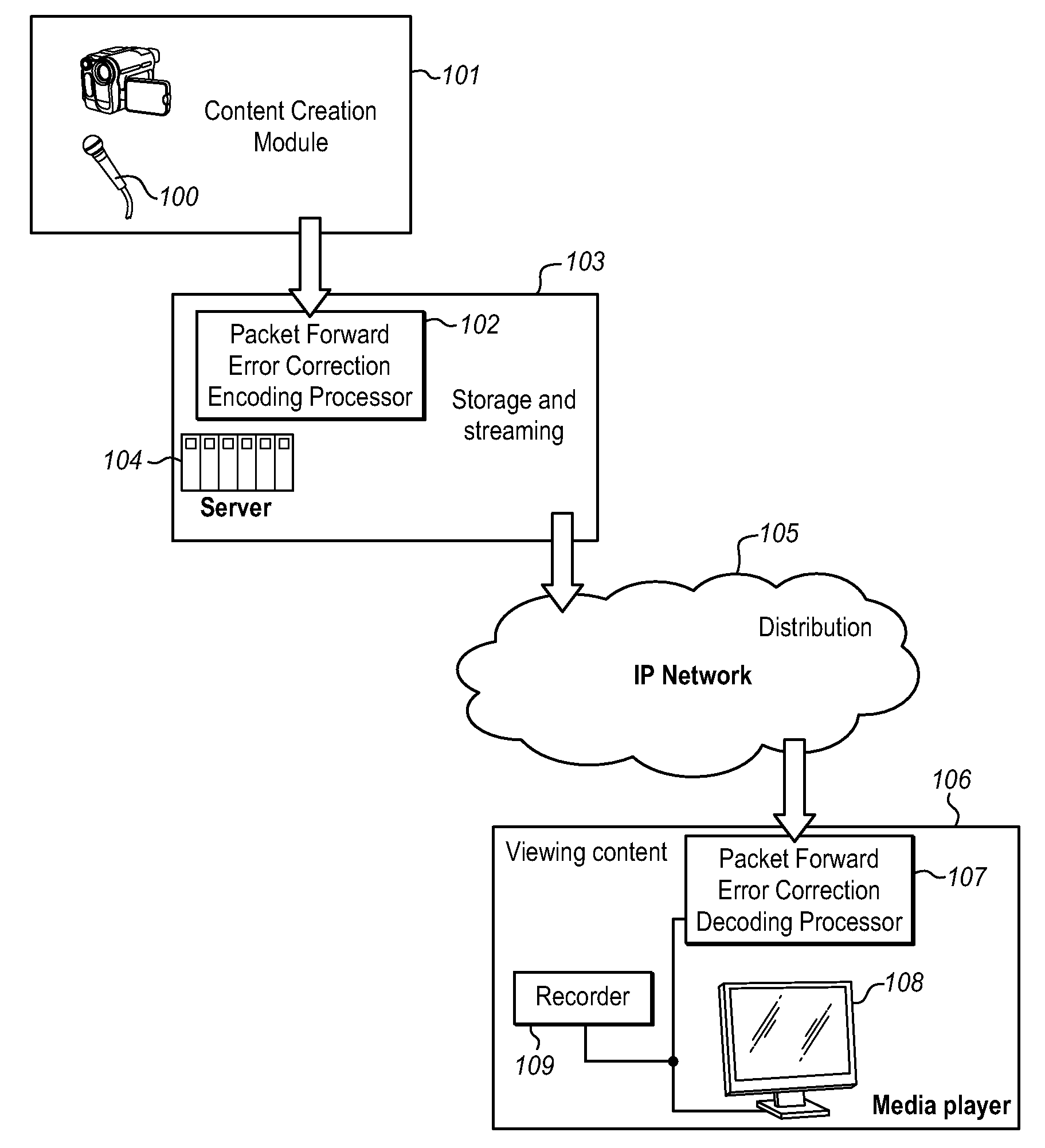

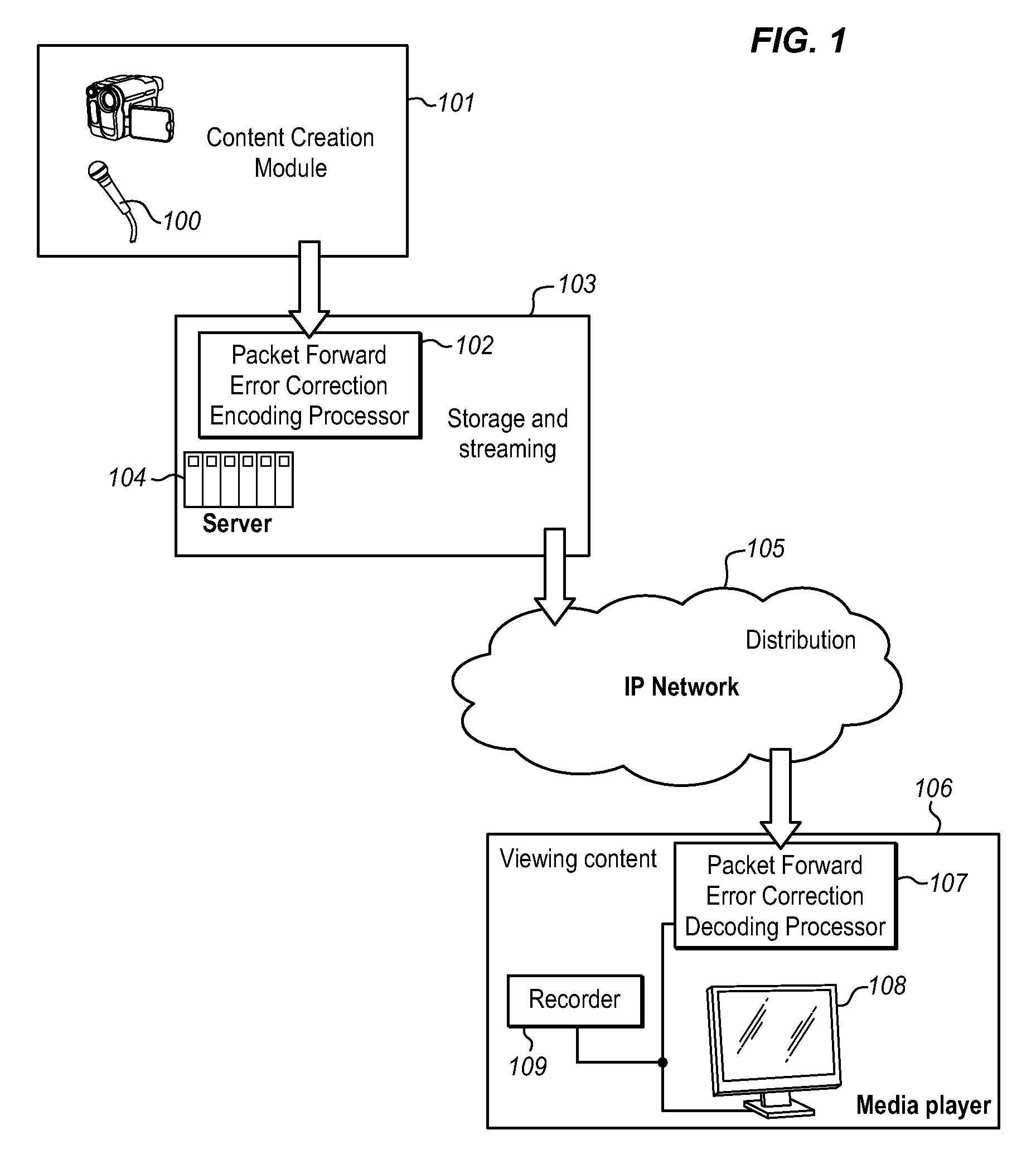

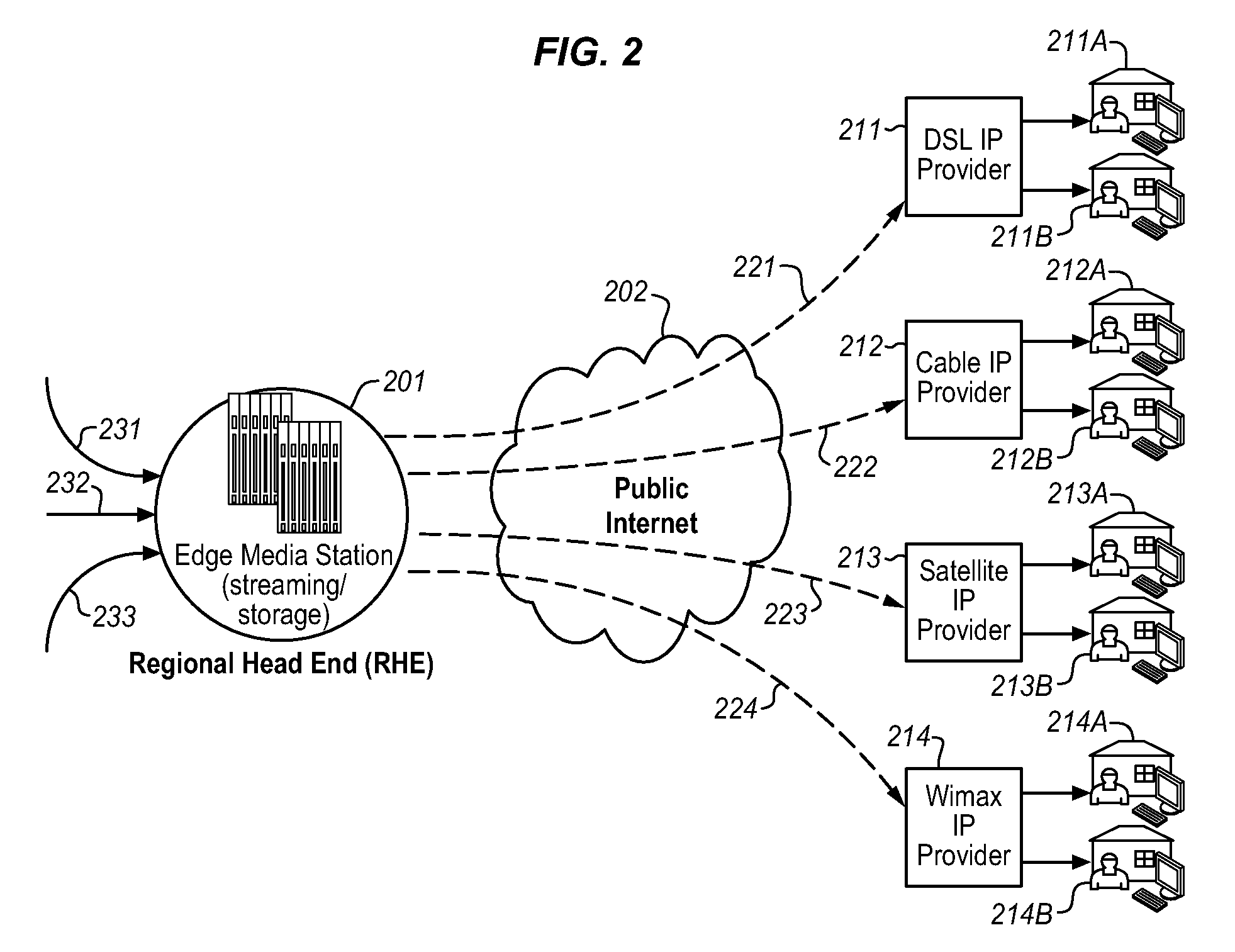

Universal packet loss recovery system for delivery of real-time streaming multimedia content over packet-switched networks

InactiveUS20090222709A1Reliable end-to-end network deliveryImprove transmission reliabilityError detection/correctionCode conversionPacket lossTransport layer

The Universal Packet Loss Recovery System is capable of recovering end-to-end network packet losses to obtain reliable end-to-end network delivery of multimedia streaming content over Internet Protocol (IP) networks, where packet losses appear above the transport layer. This system incorporates the use of Packet Forward Error Correction Coding (FEC) with packet interleaving processing prior to transport. Packet FEC Coding is an error correction coding method at the packet level which improves link transmission reliability. At the source end of the packet-switching network, the Packet FEC Coding scheme encodes a stream of transport multimedia content packets by including redundant packets to allow for recovery of lost packets by the Packet FEC Coding decoder at the user end of the packet-switching network. Since lost packets appear only above the transport layer in the IP network protocol stack, Packet FEC Coding can be viewed as a transport layer or application layer coding method.

Owner:COMM CODING

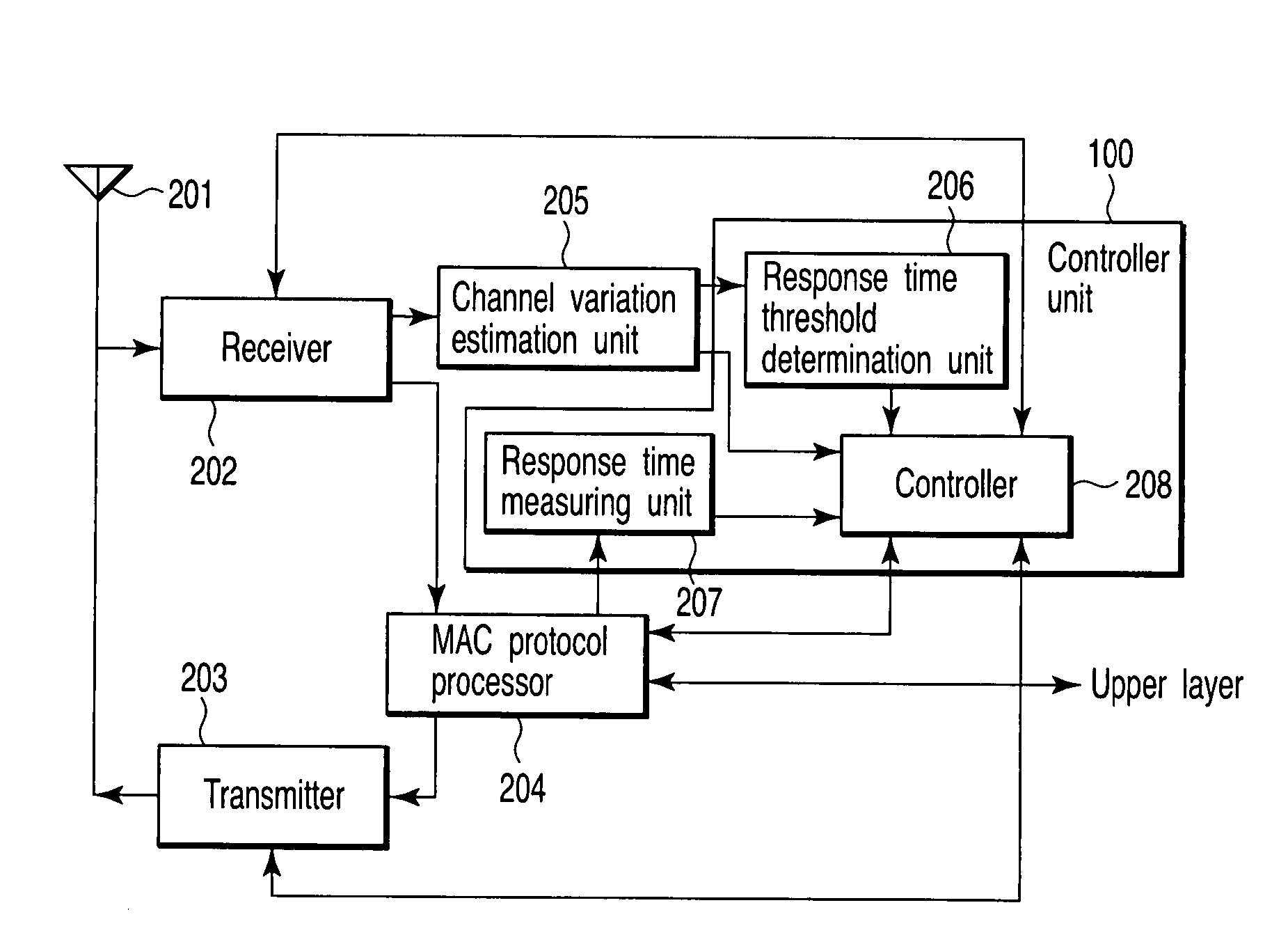

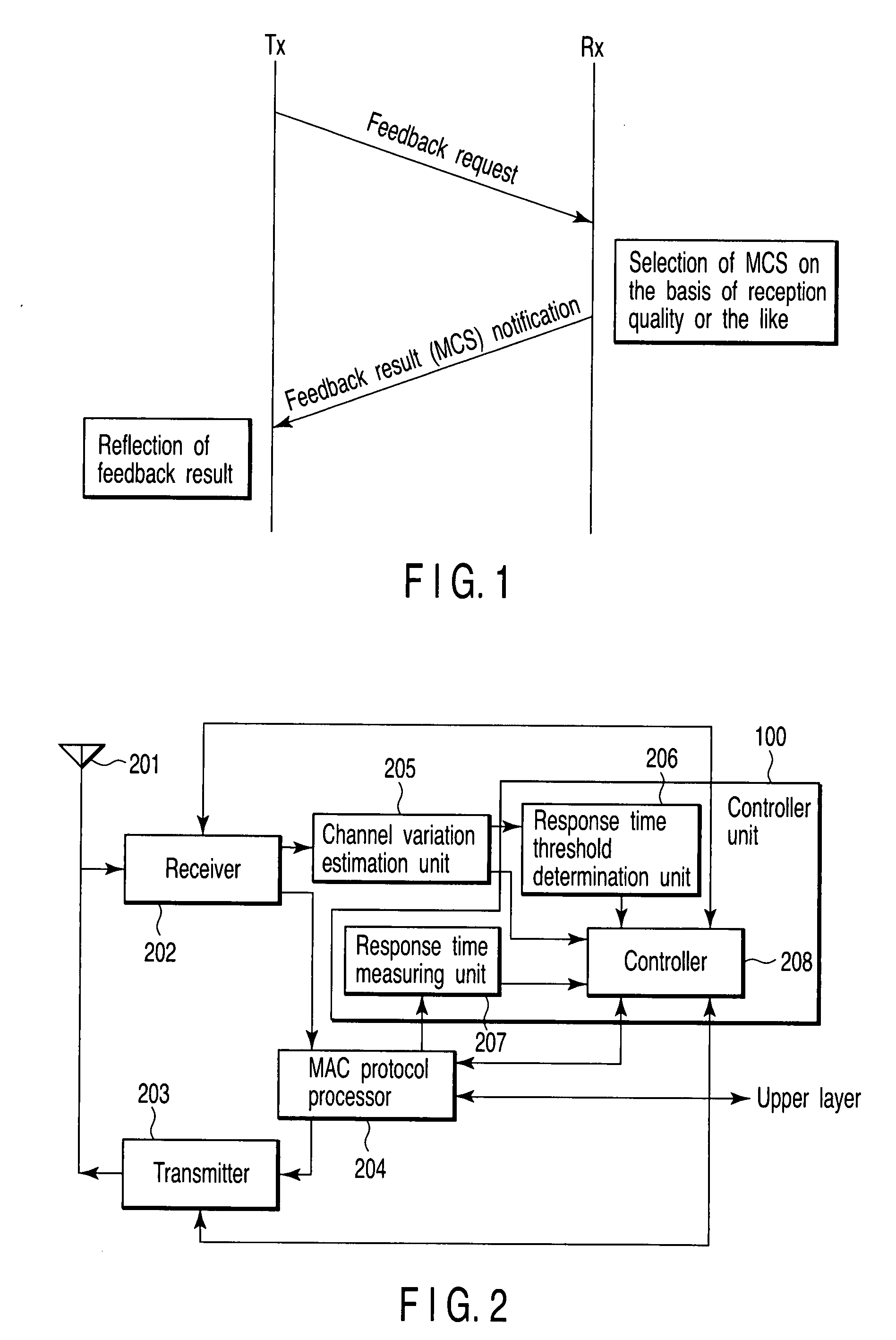

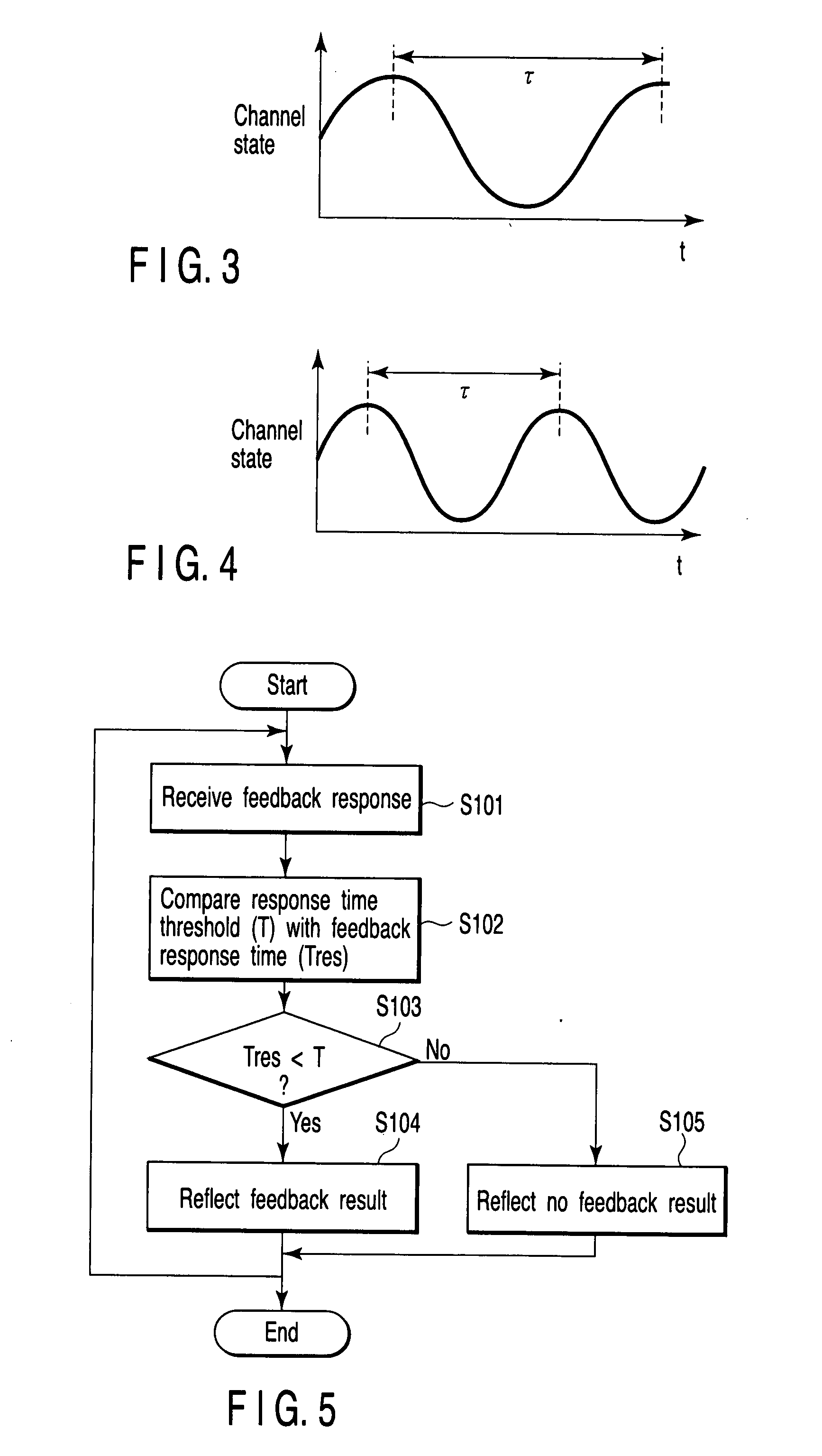

Wireless communication apparatus and transmission control method

ActiveUS20070291829A1Receivers monitoringFrequency-division multiplex detailsTransmitterRequest–response

A wireless communication apparatus includes a transmitter and a receiver, and determines a modulation and error correction coding scheme used by the transmitter. The apparatus estimates a degree of channel variation, transmits, by the transmitter, a first frame for requesting response information necessary to select the modulation and error correction coding scheme, measures a response time between a instant when the transmitter transmits the first frame and a instant when the receiver receives a second frame including the response information, determines a threshold value of the response time for determining reliability of the response information, based on the degree of channel variation, and determines the modulation and error correction coding scheme selected based on the response information included in the second frame received by the receiver in the response time shorter than the threshold value.

Owner:PALMIRA WIRELESS AG

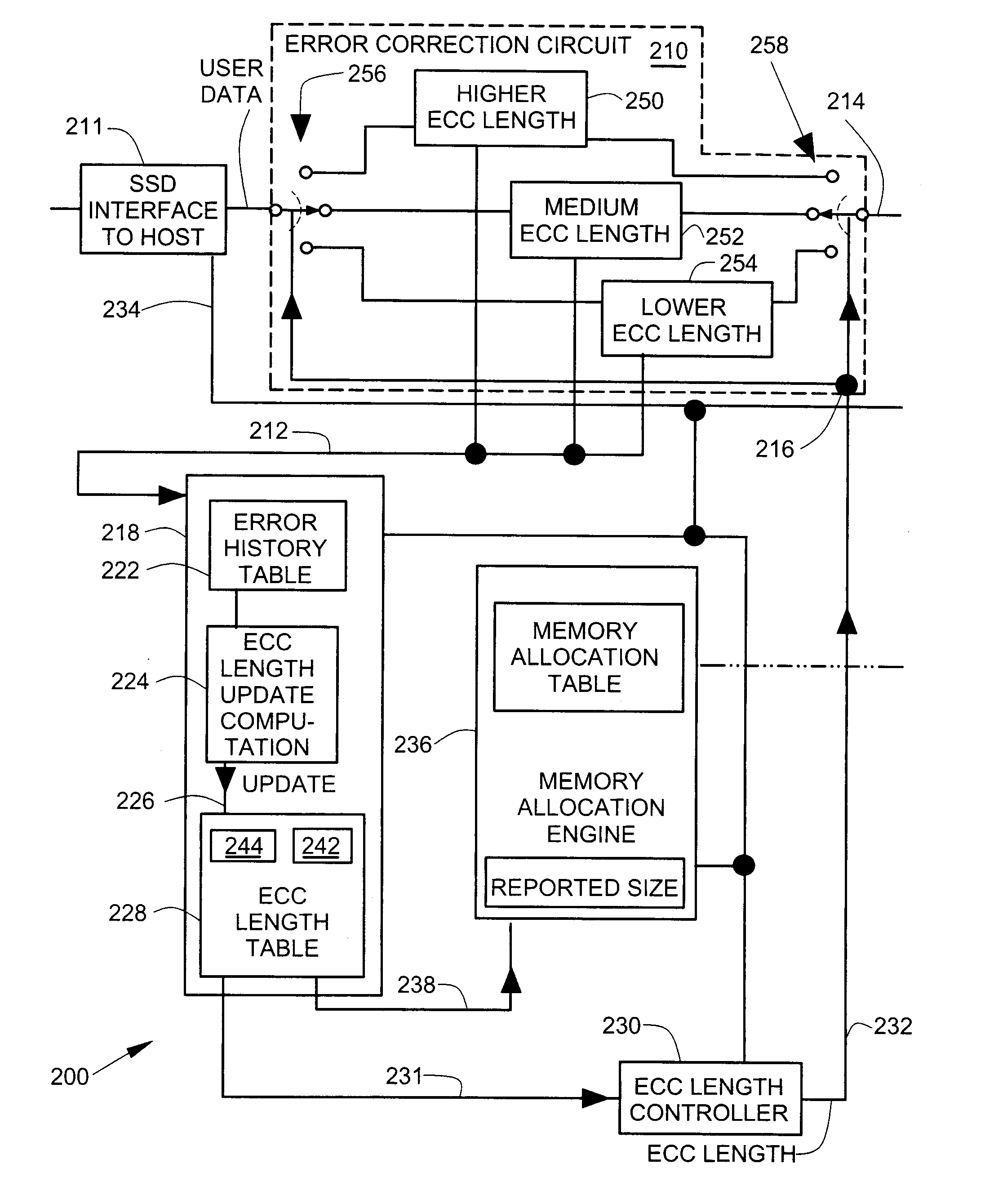

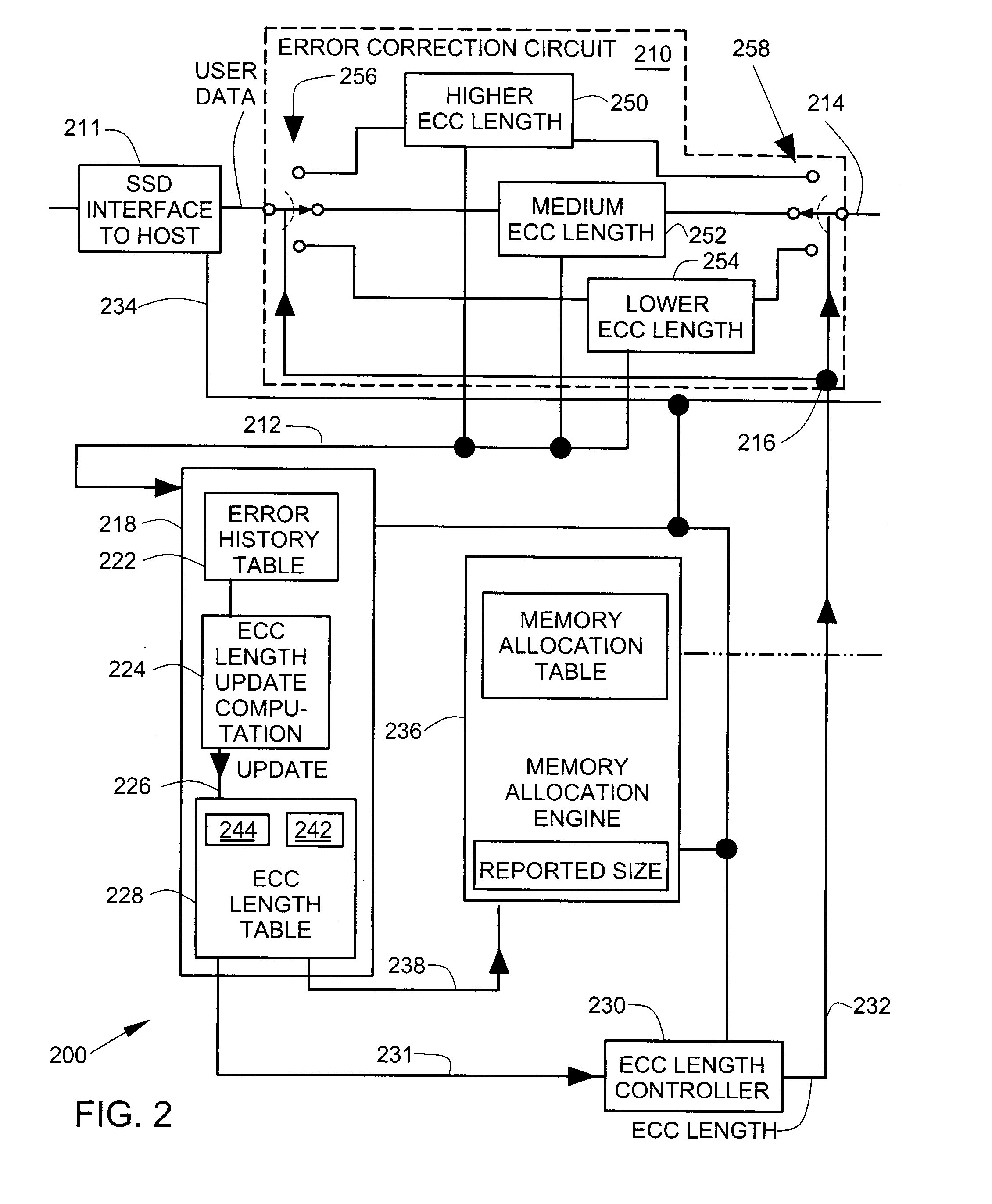

Adjustable error correction code length in an electrical storage device

ActiveUS20110191654A1Code conversionError correction/detection using block codesComputer hardwareParallel computing

Owner:SEAGATE TECH LLC