Patents

Literature

182 results about "Analog memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

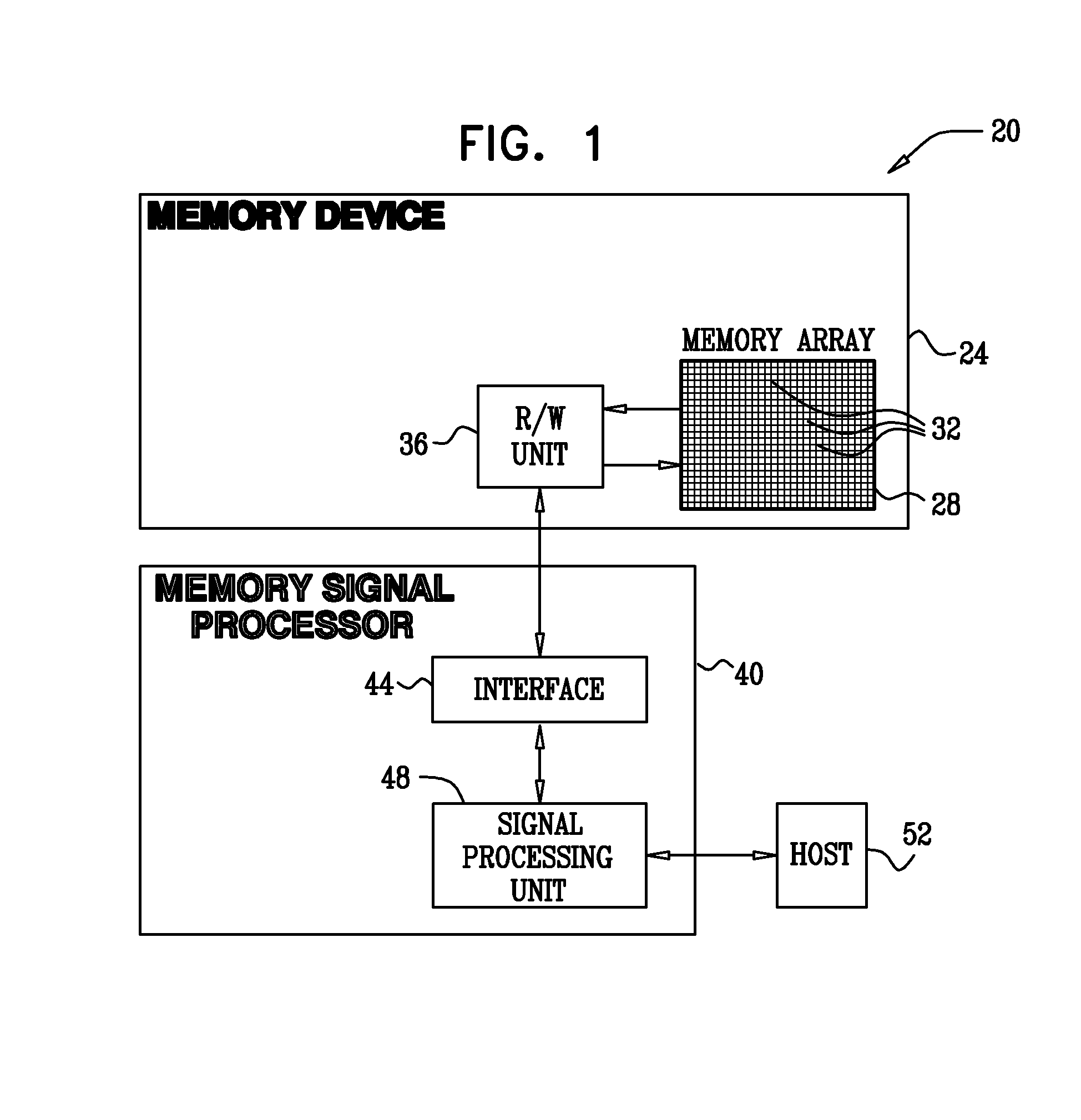

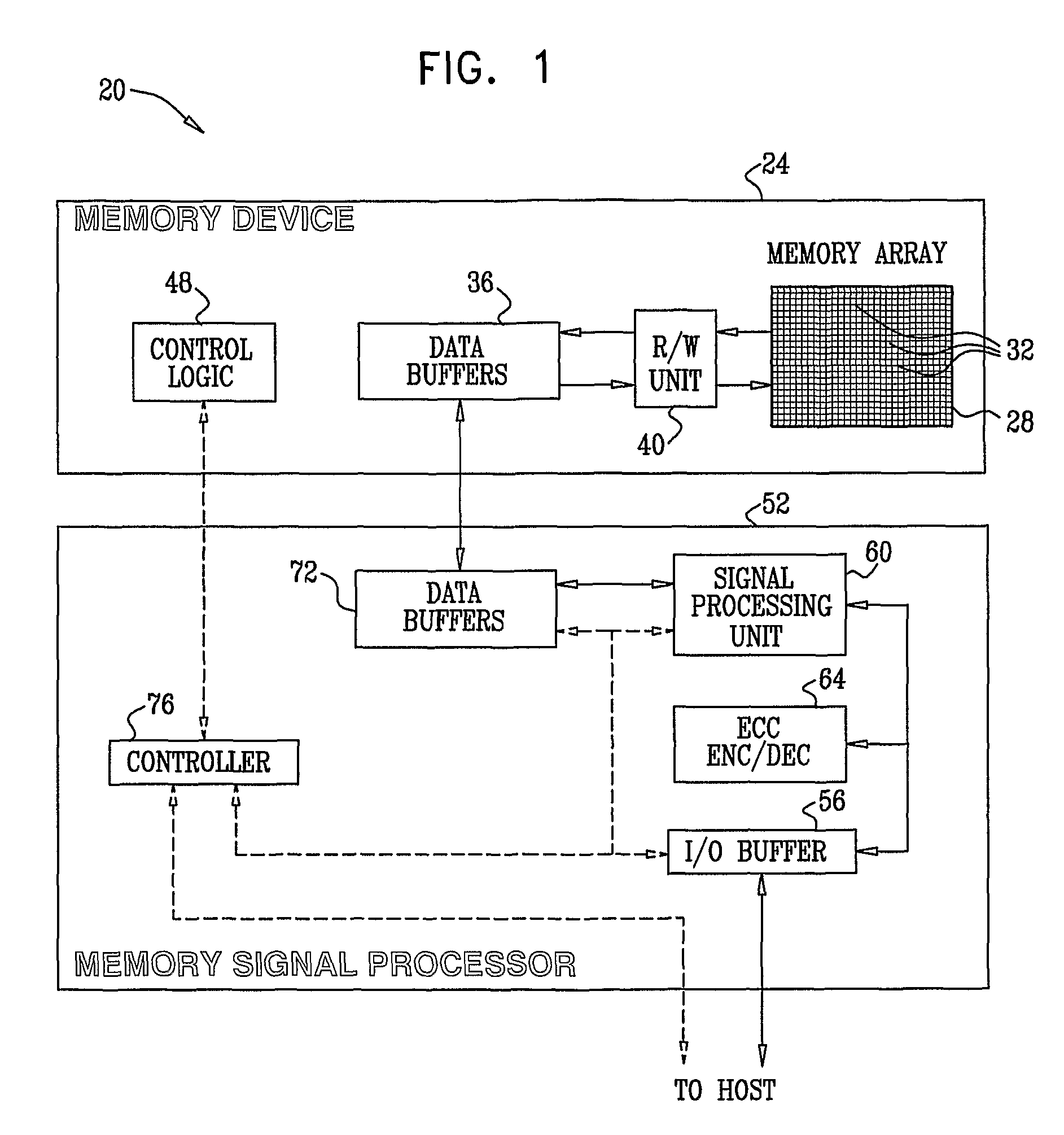

Combined distortion estimation and error correction coding for memory devices

ActiveUS20090024905A1Improve performanceData representation error detection/correctionError detection/correctionCalculation errorDistortion

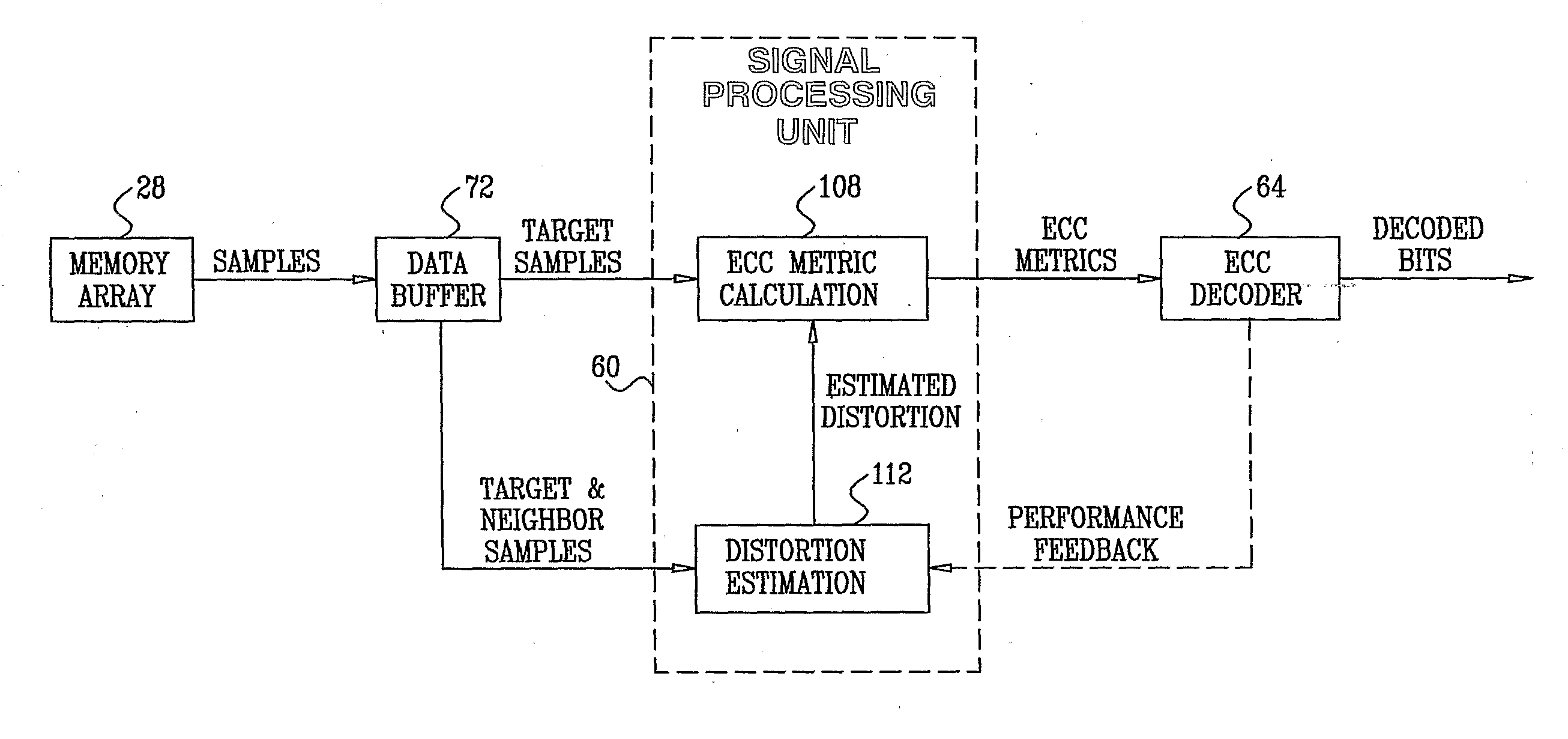

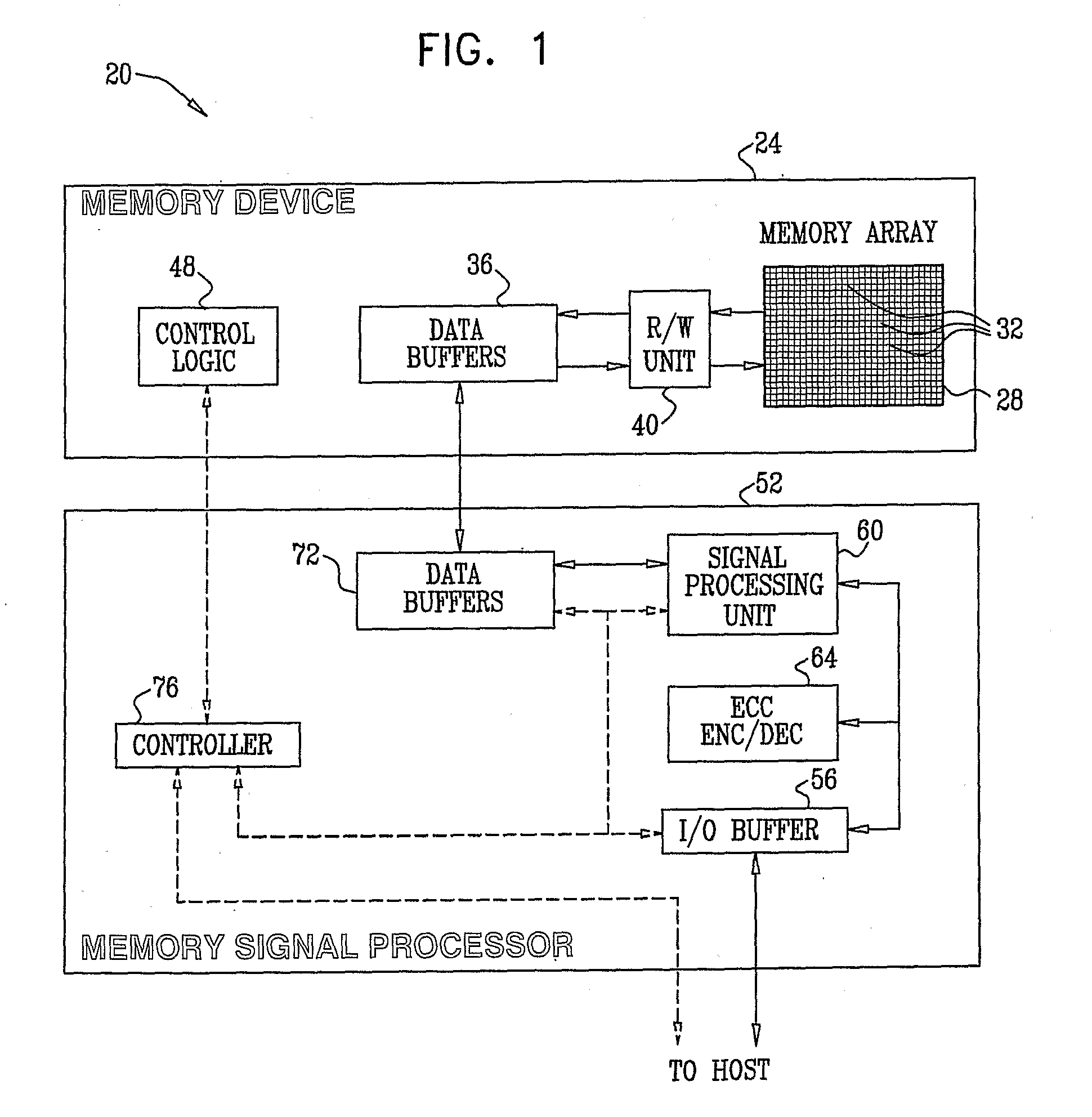

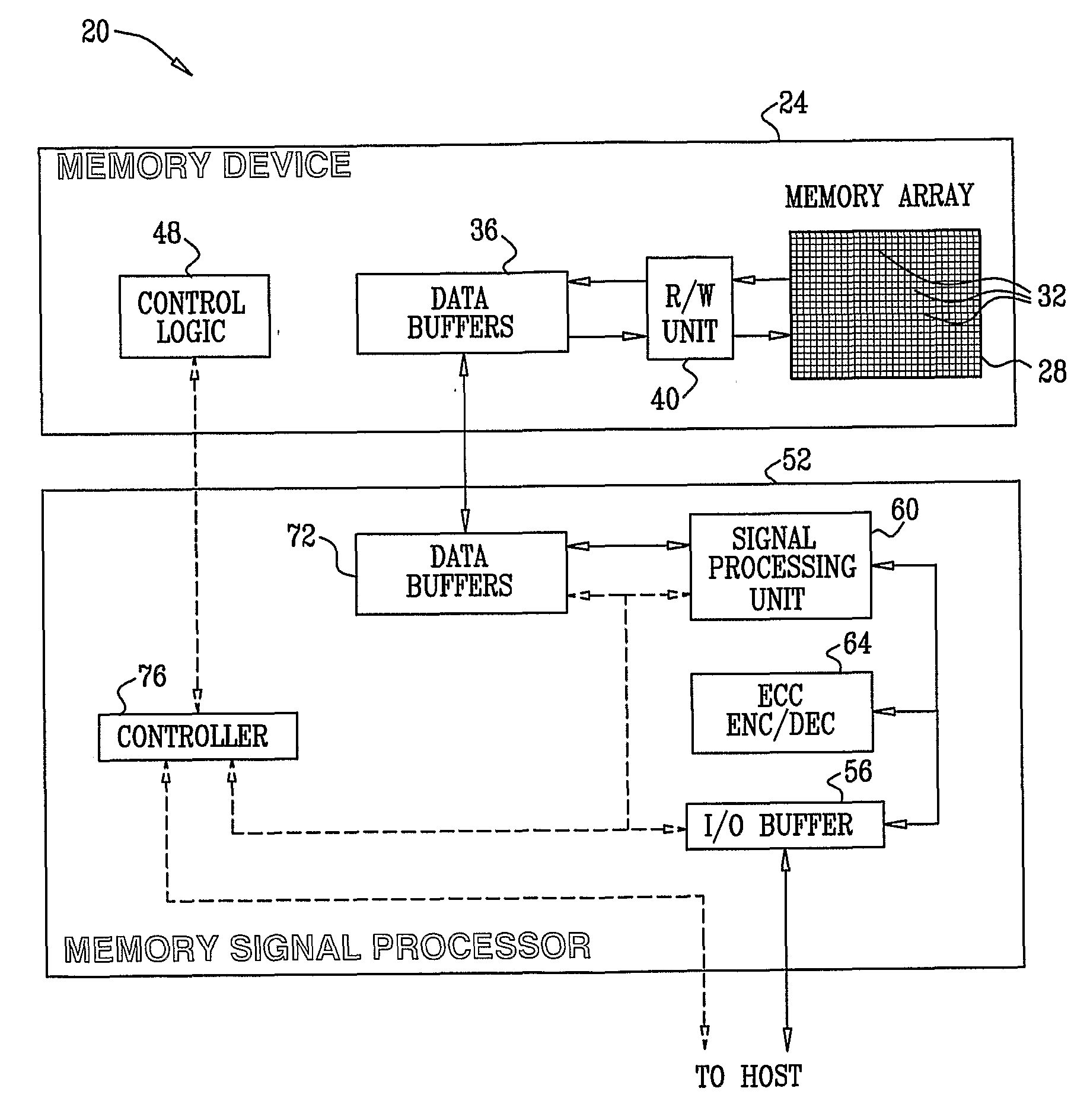

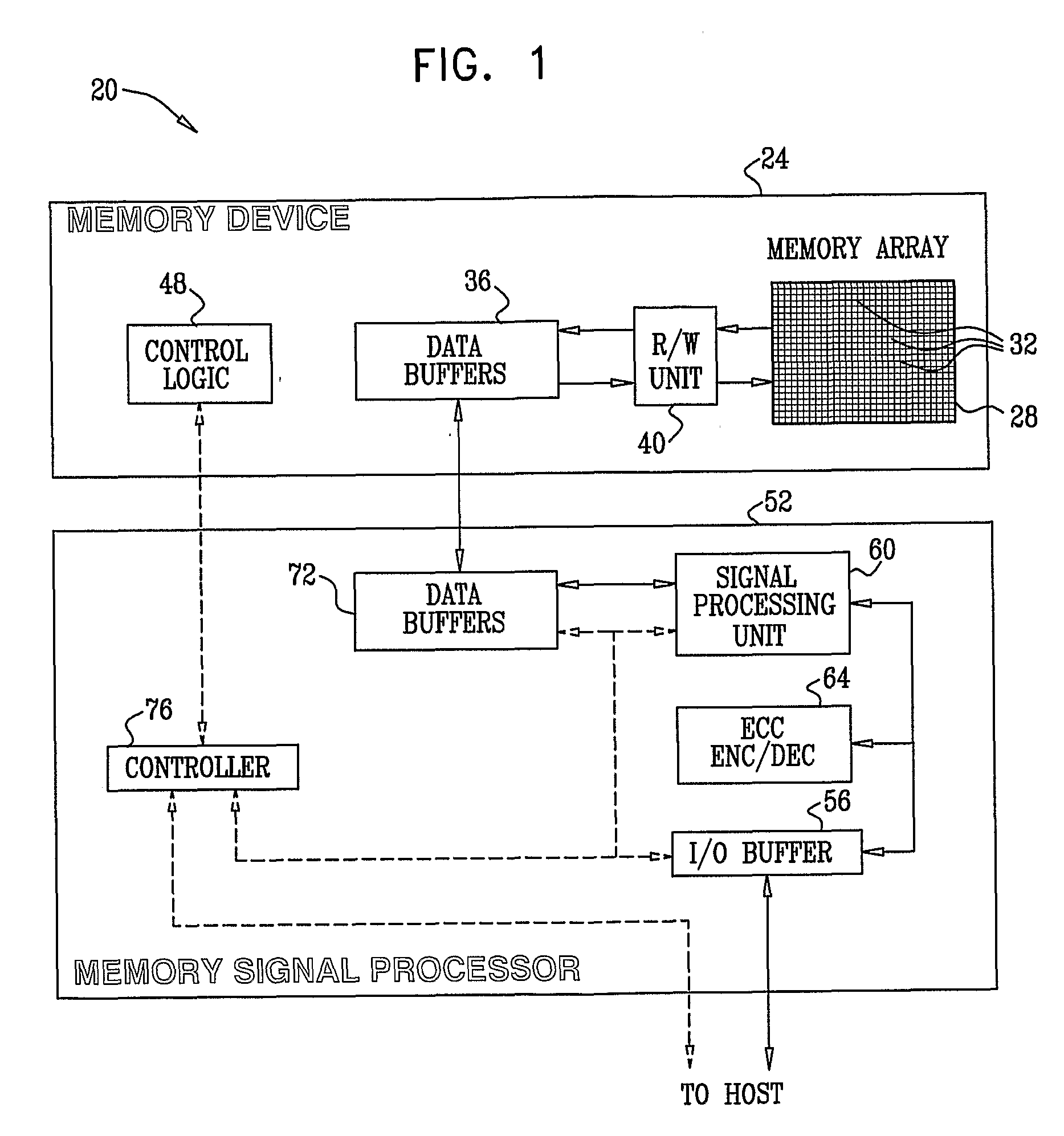

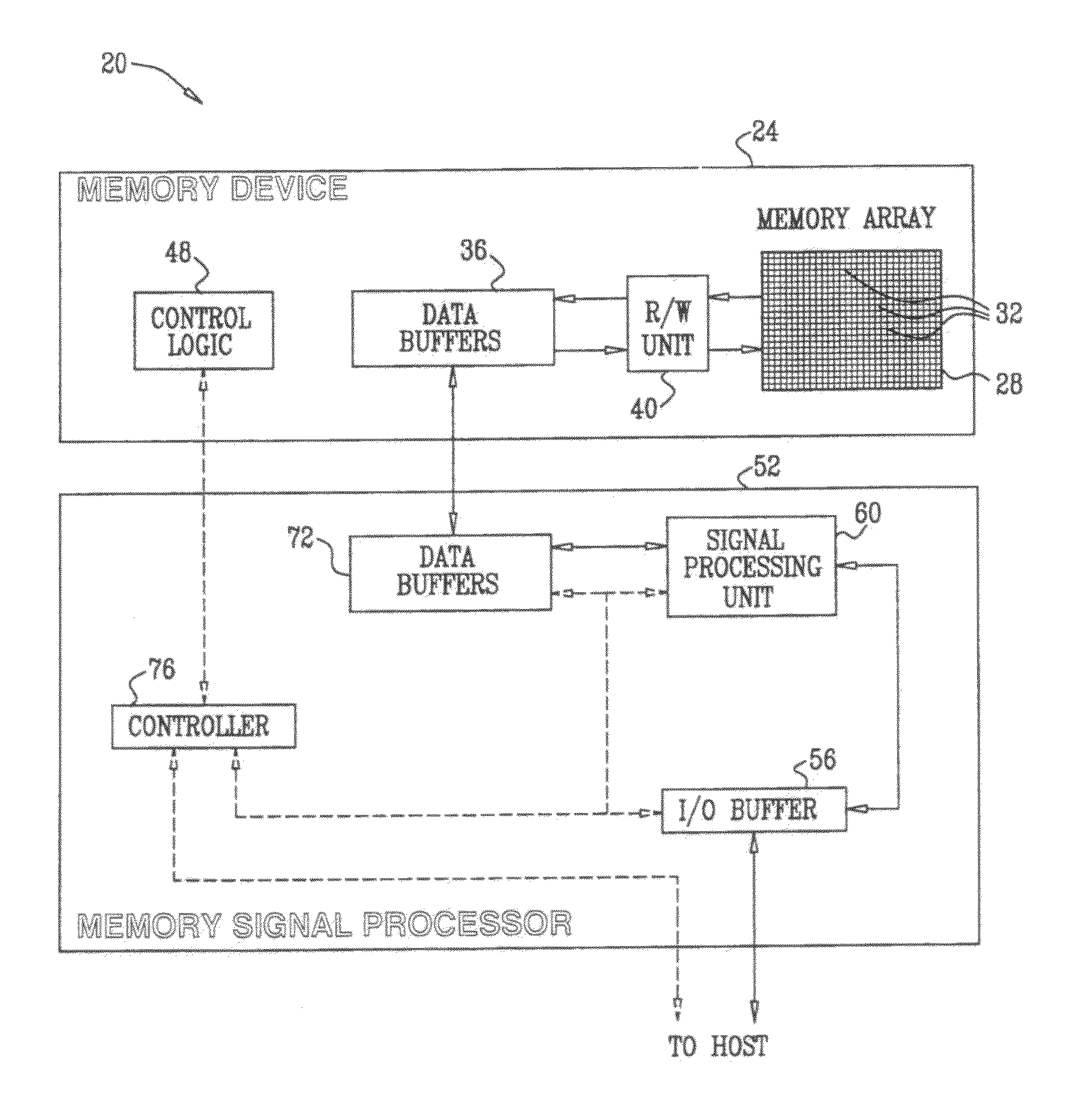

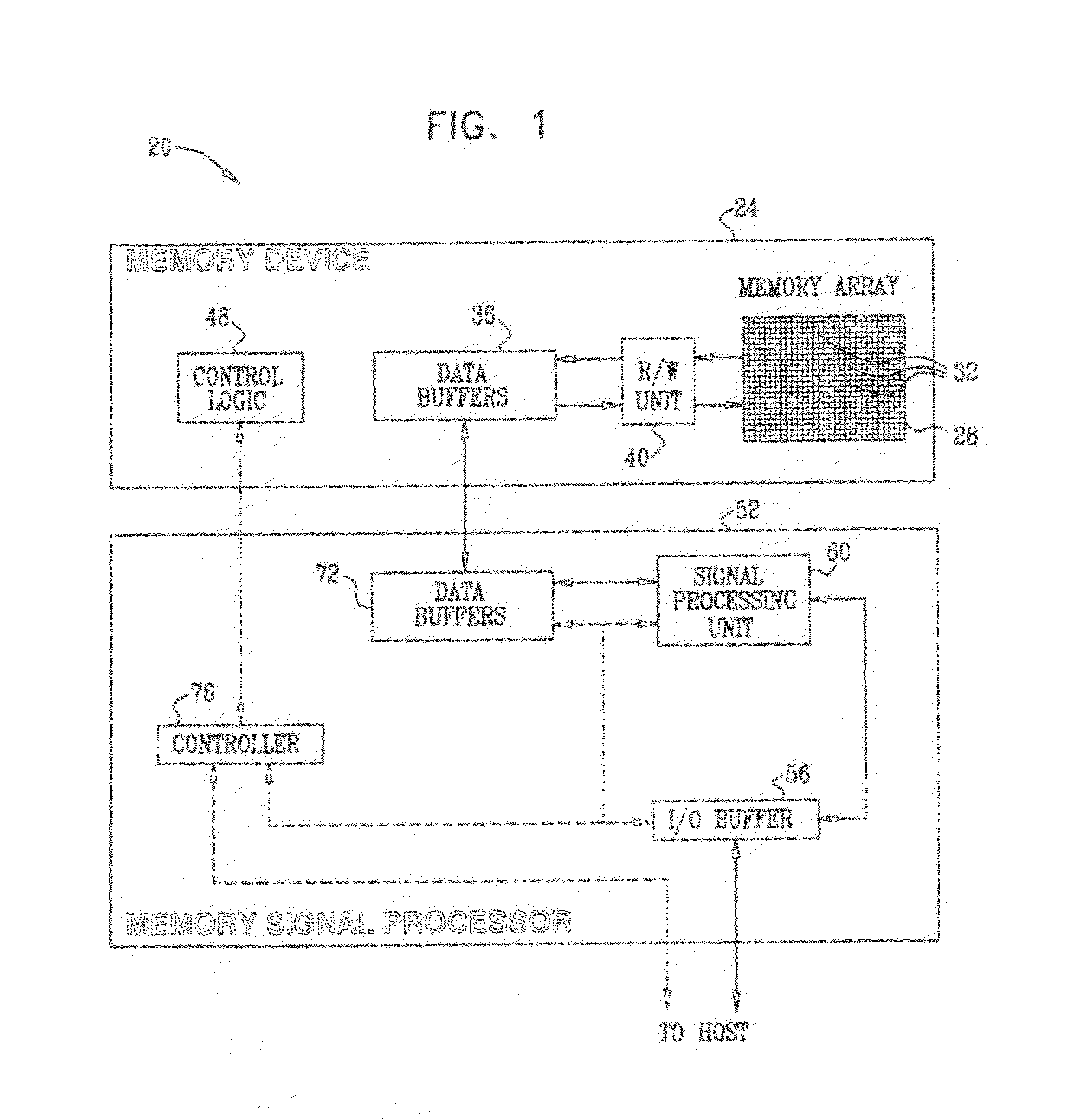

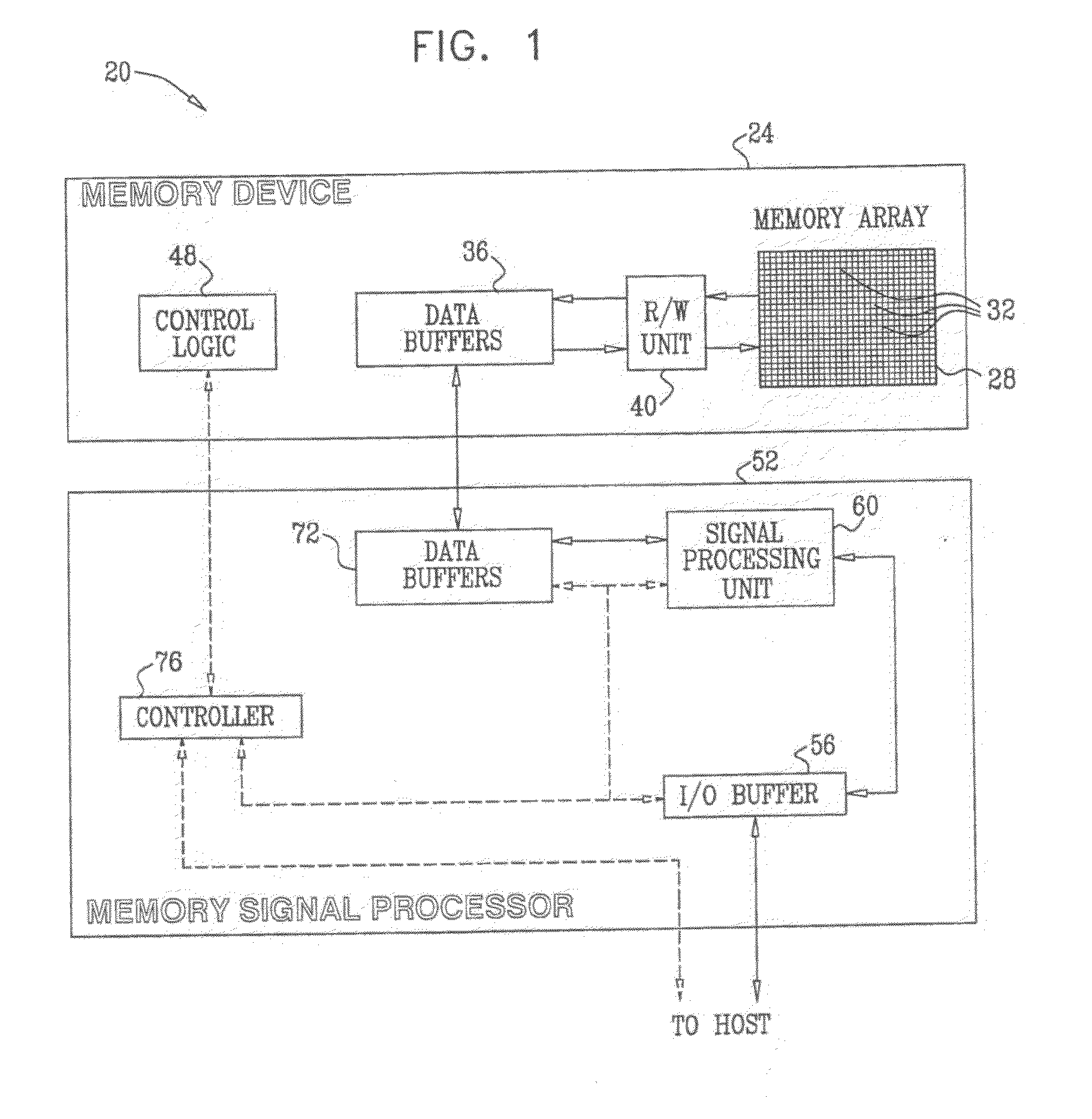

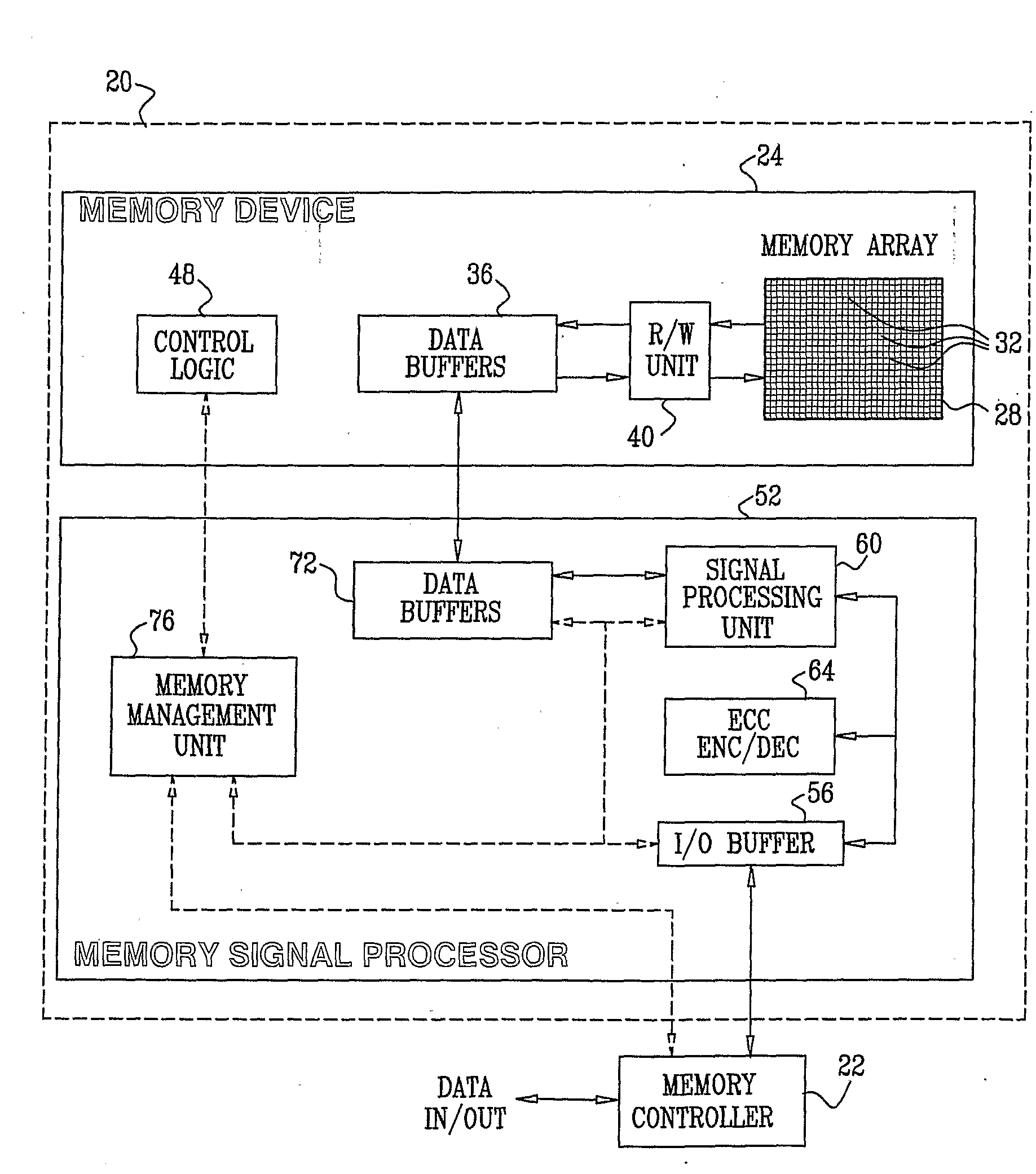

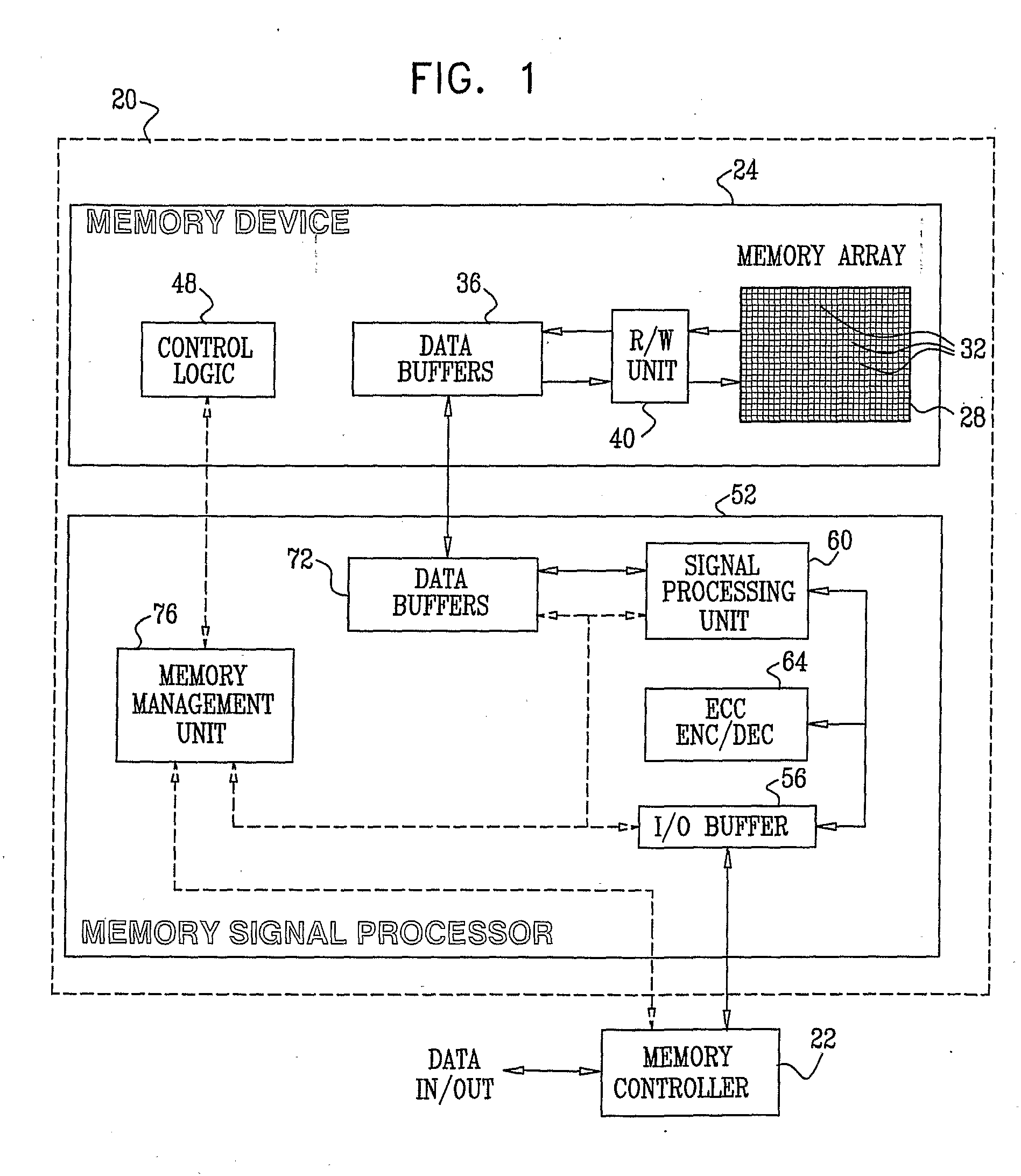

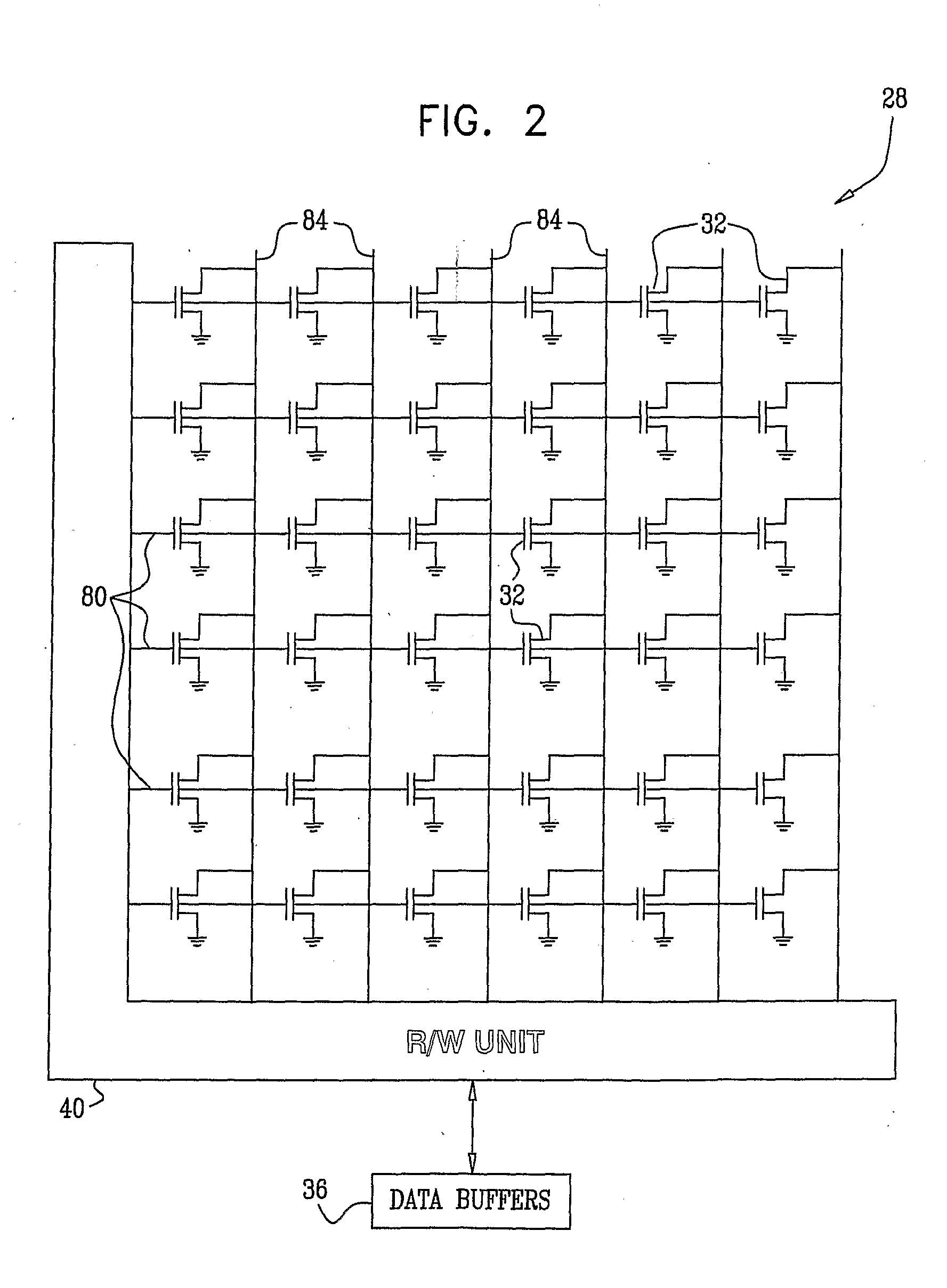

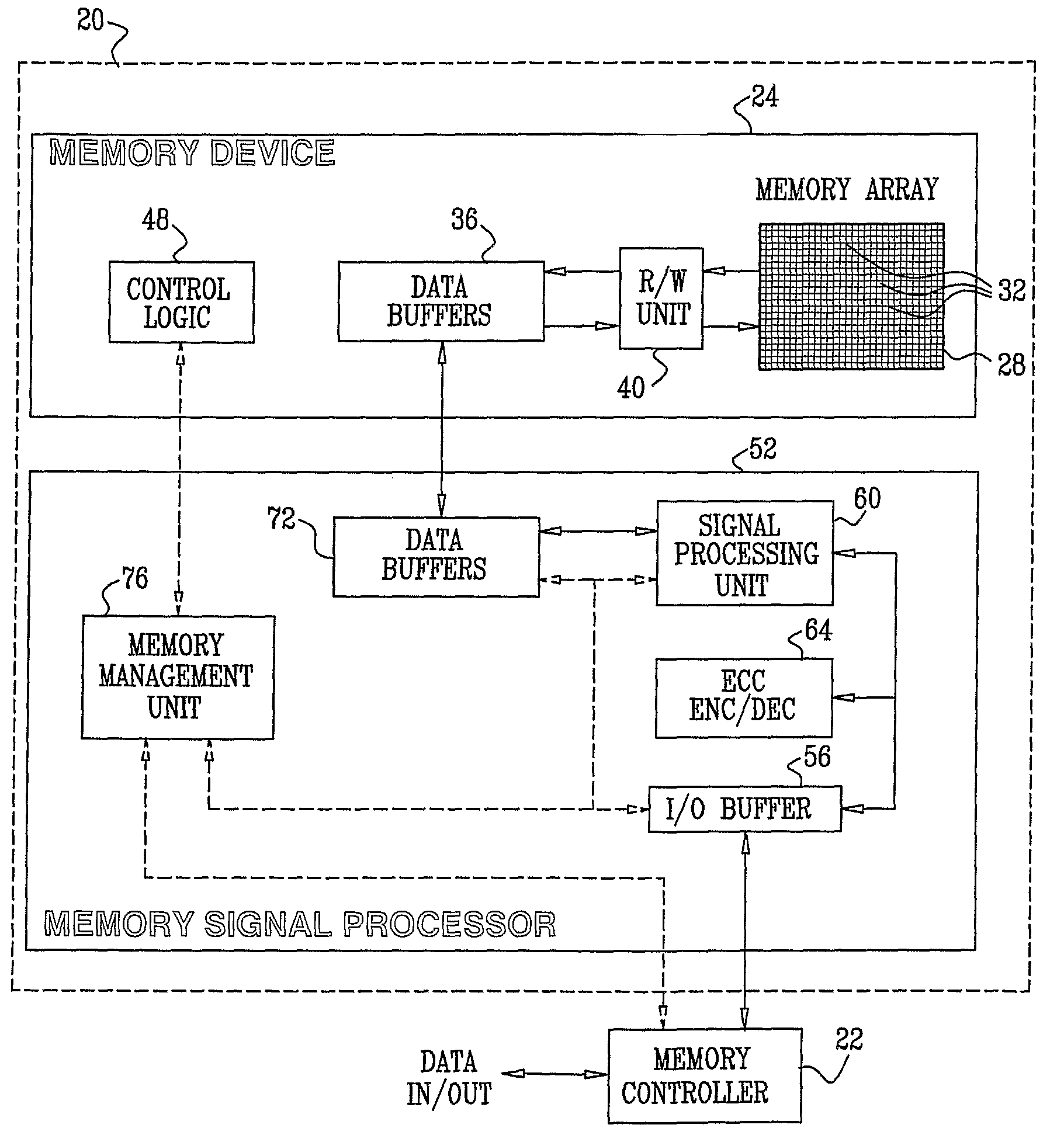

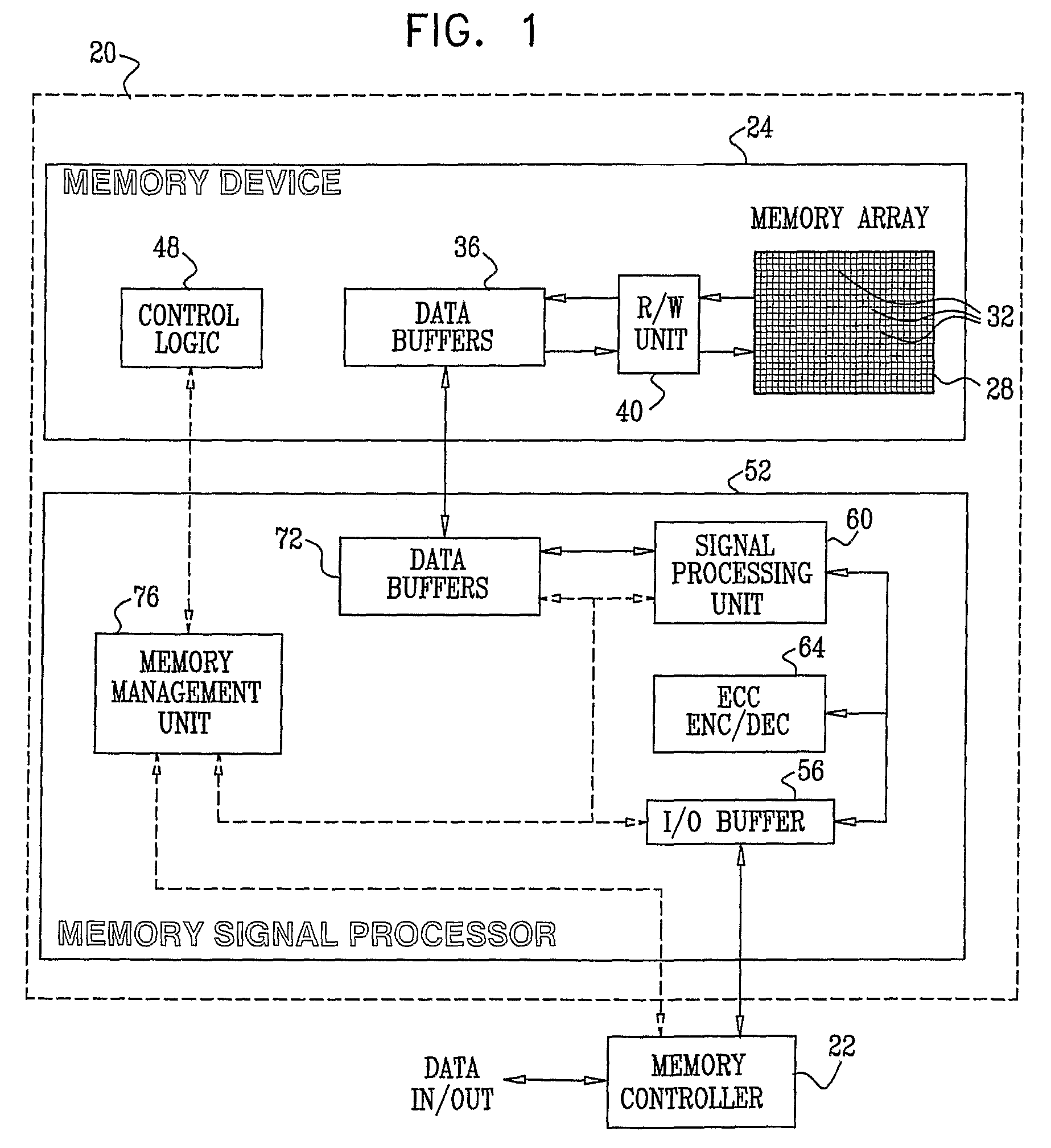

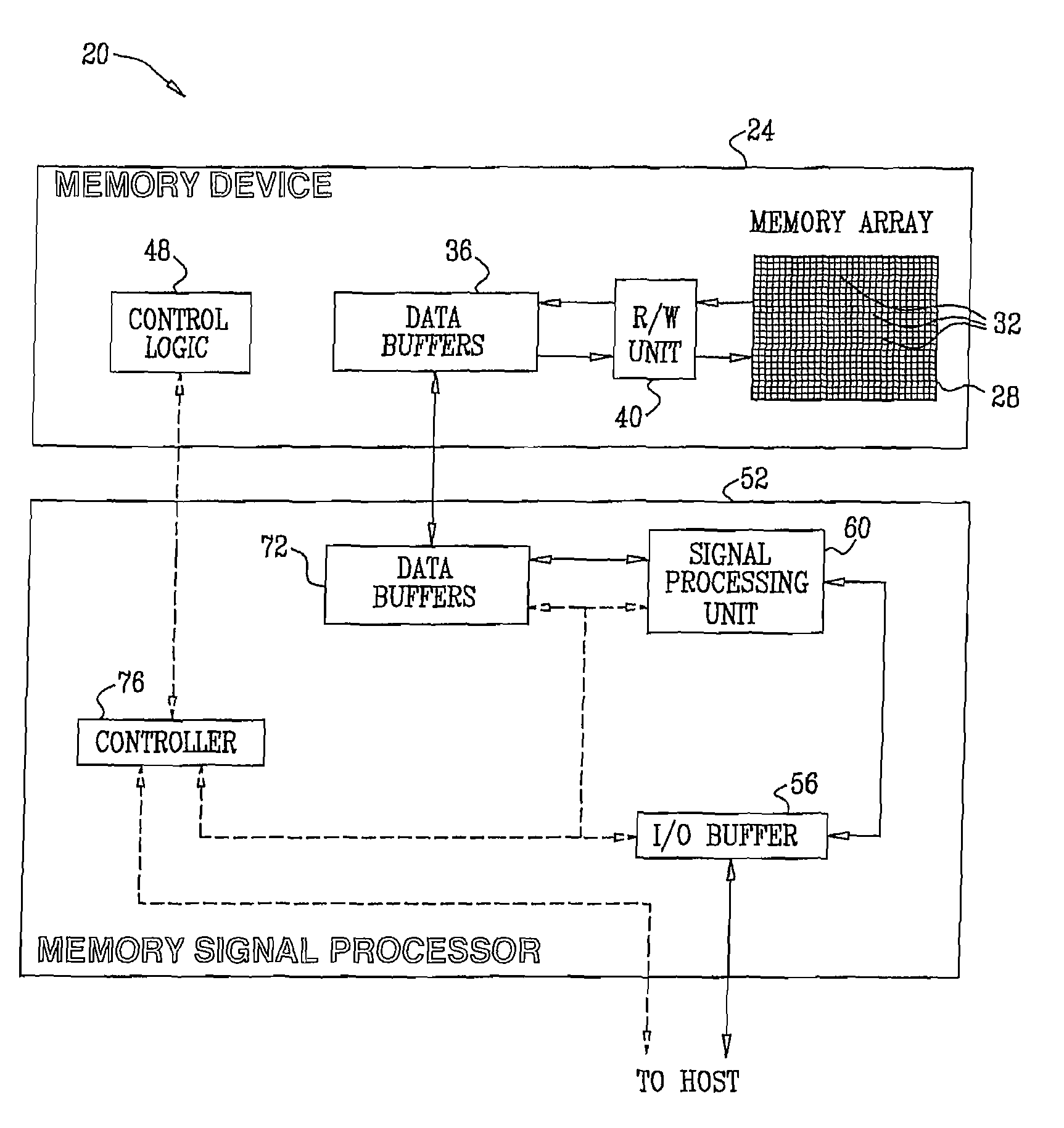

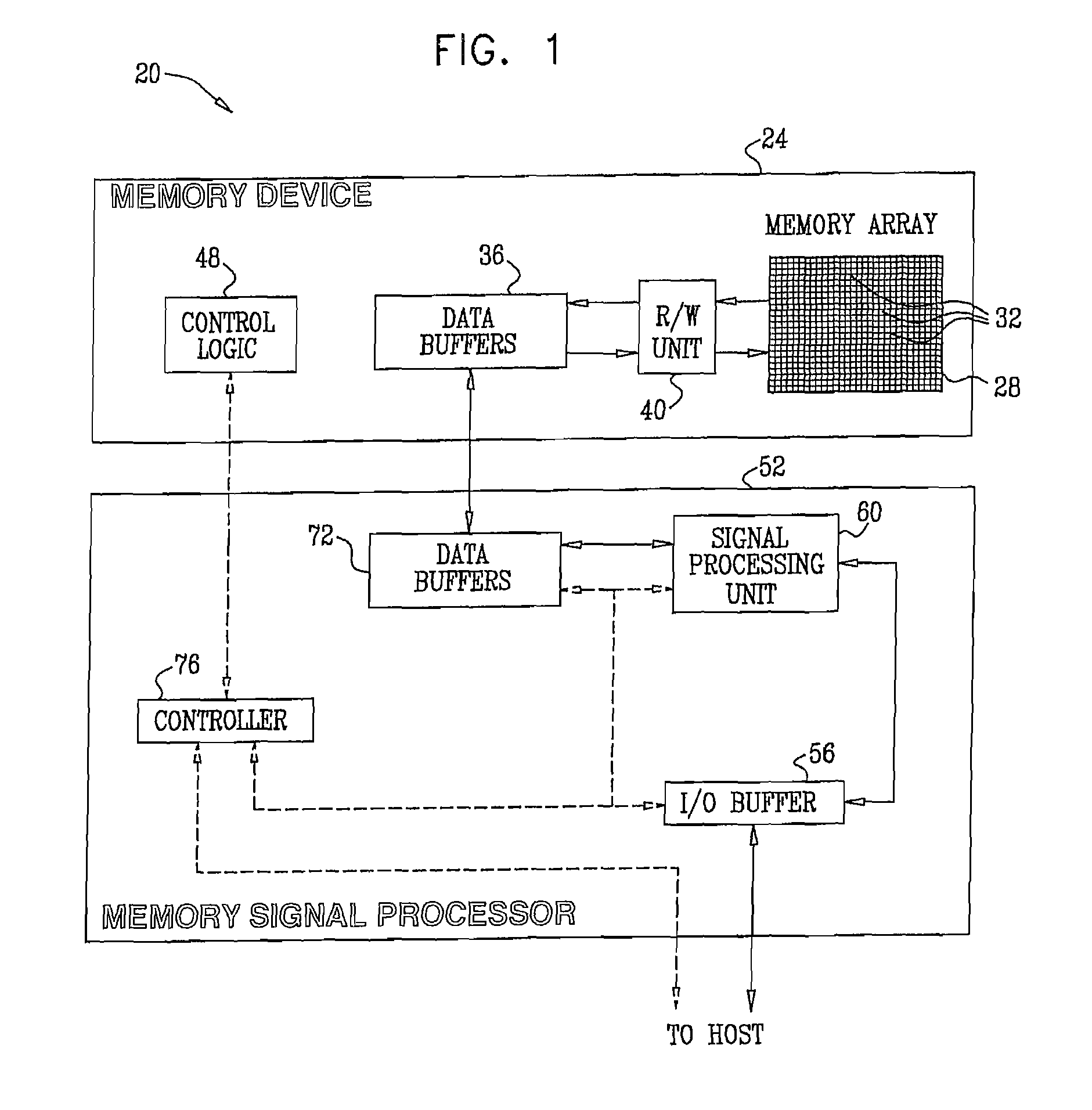

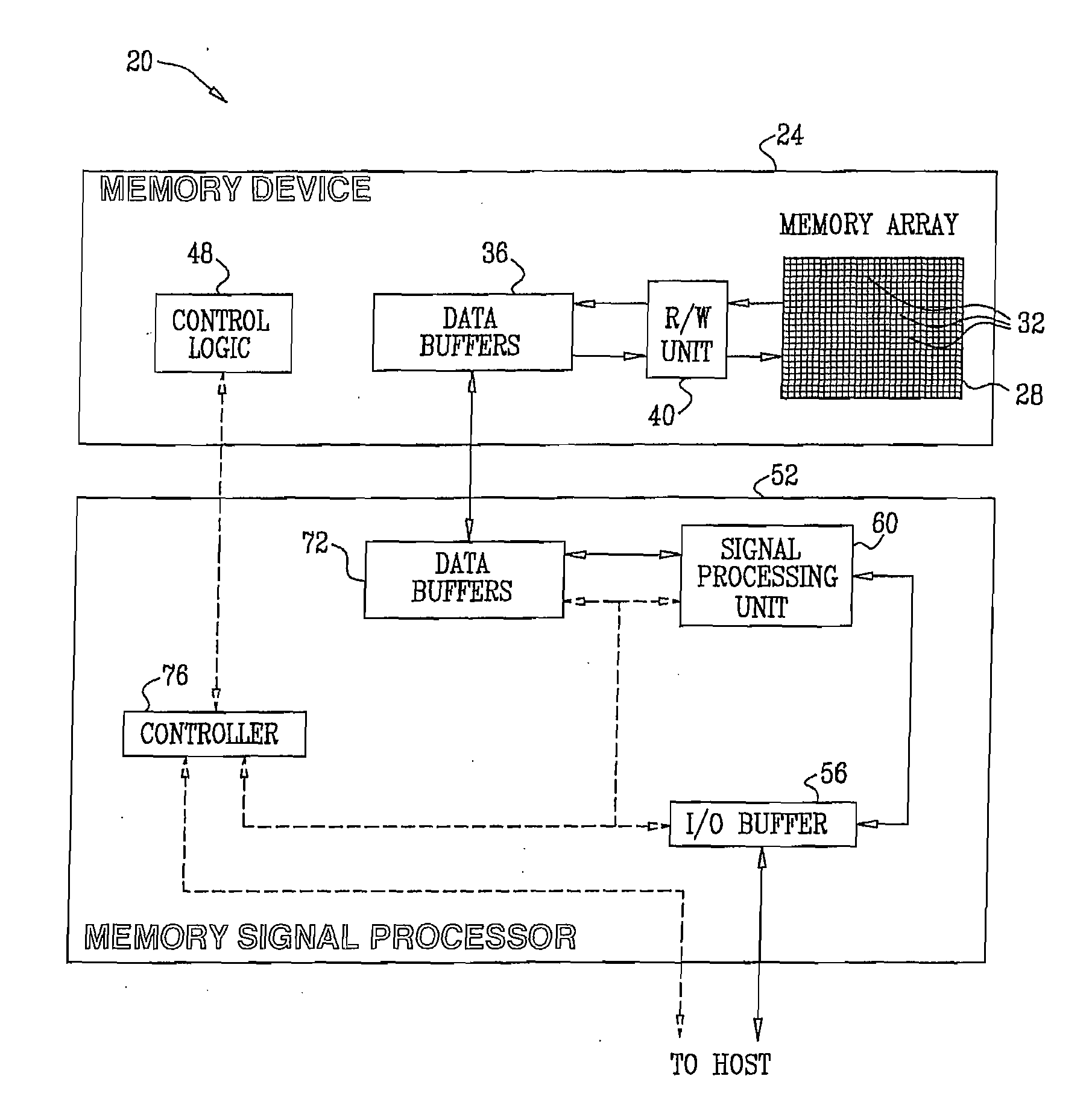

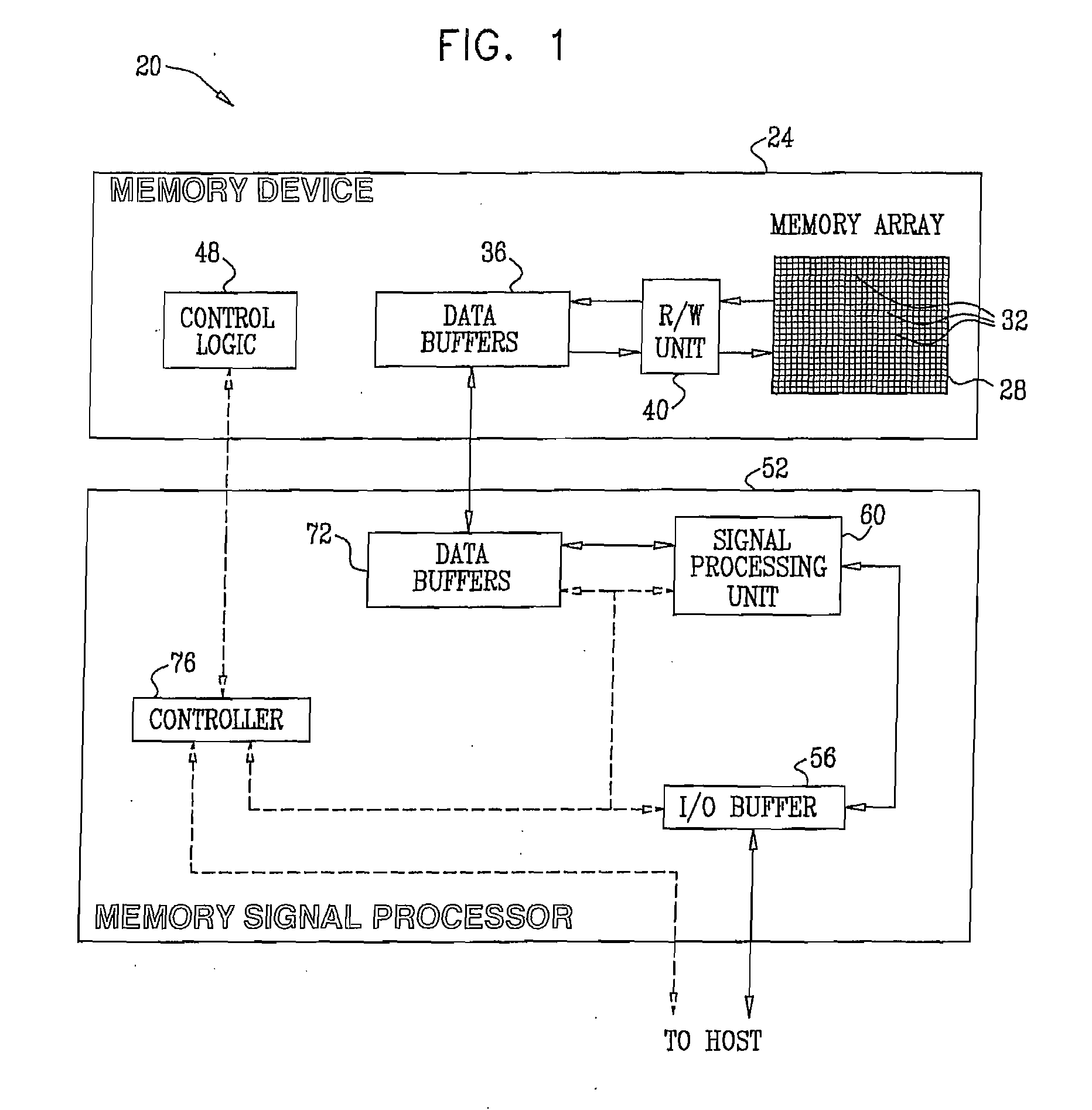

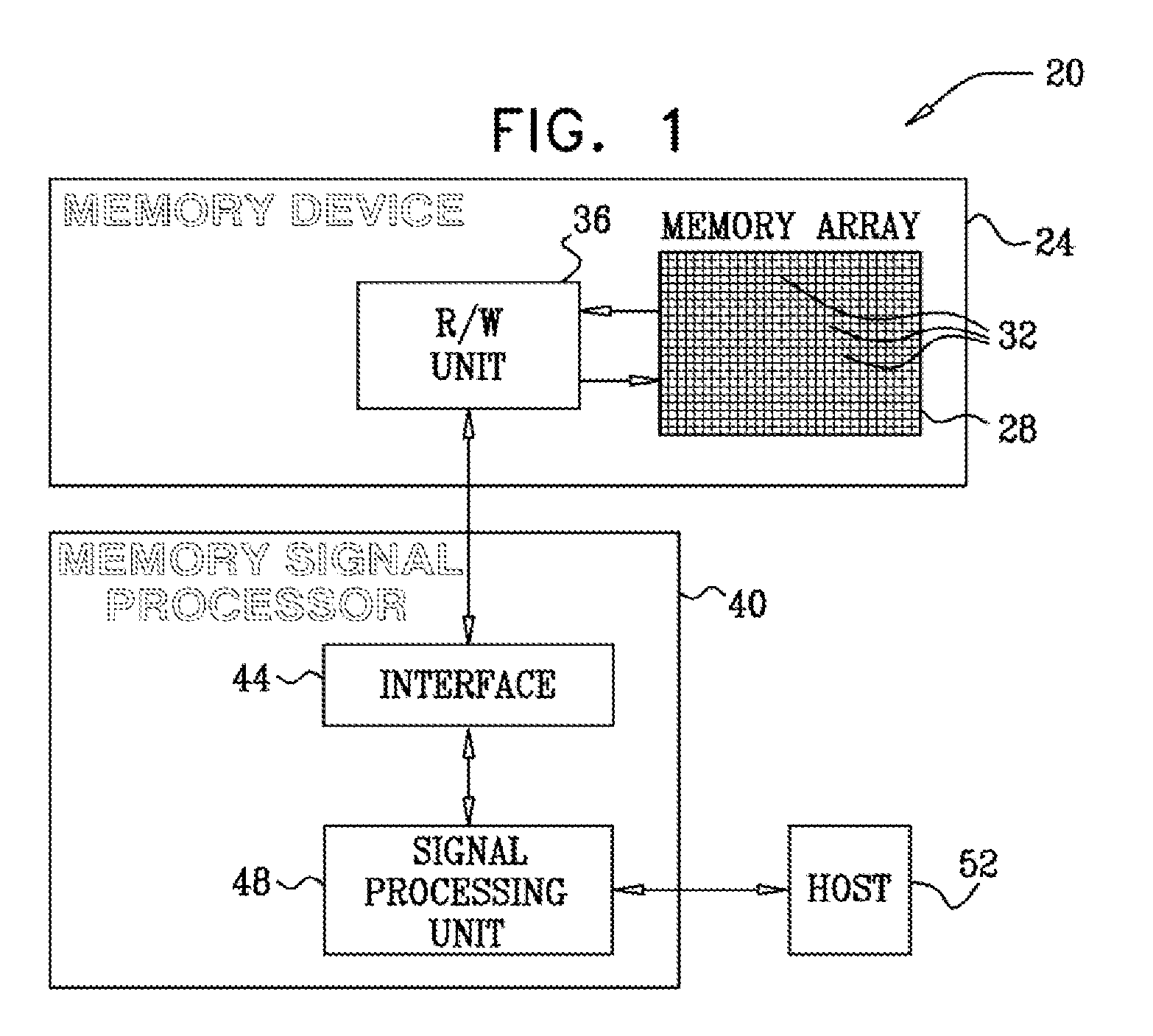

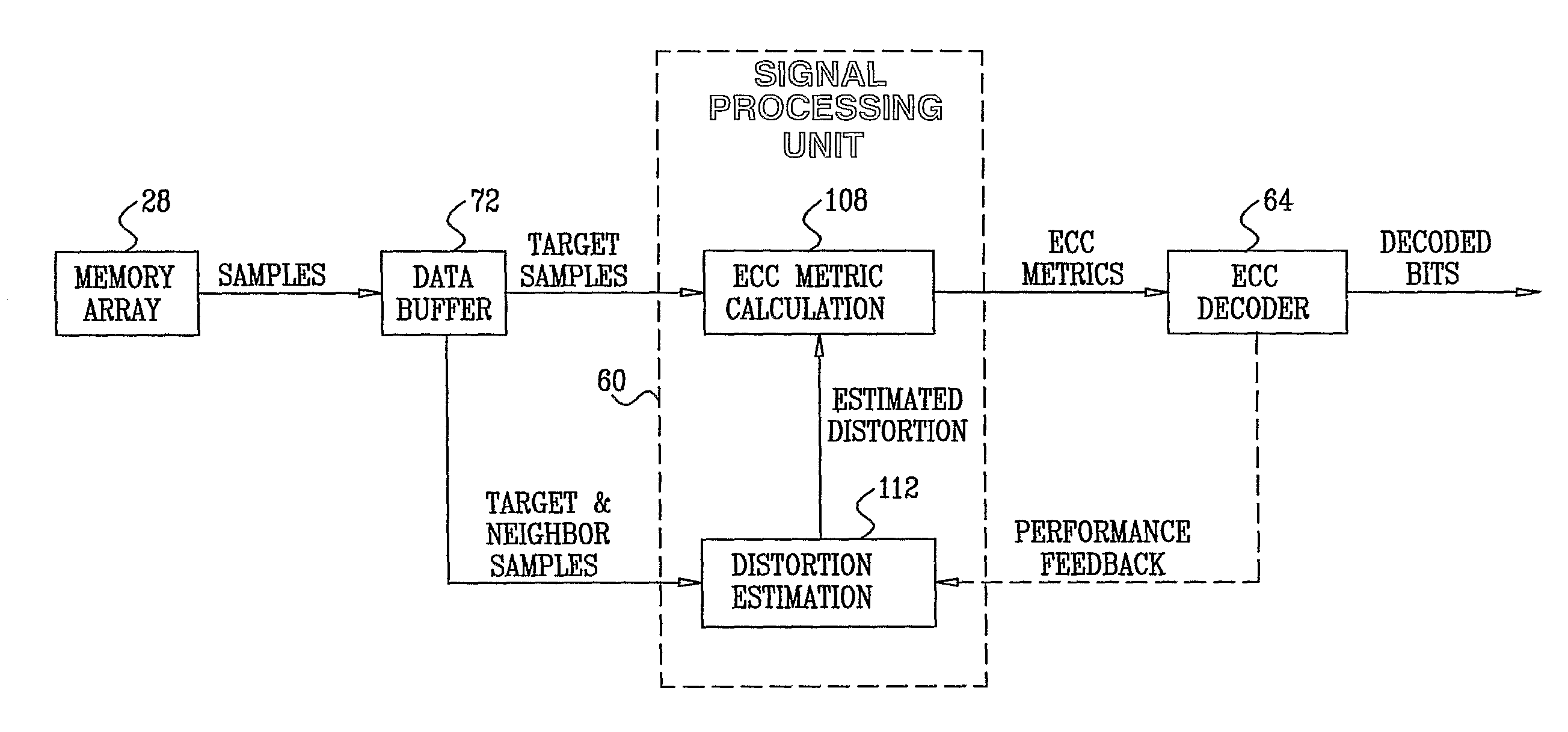

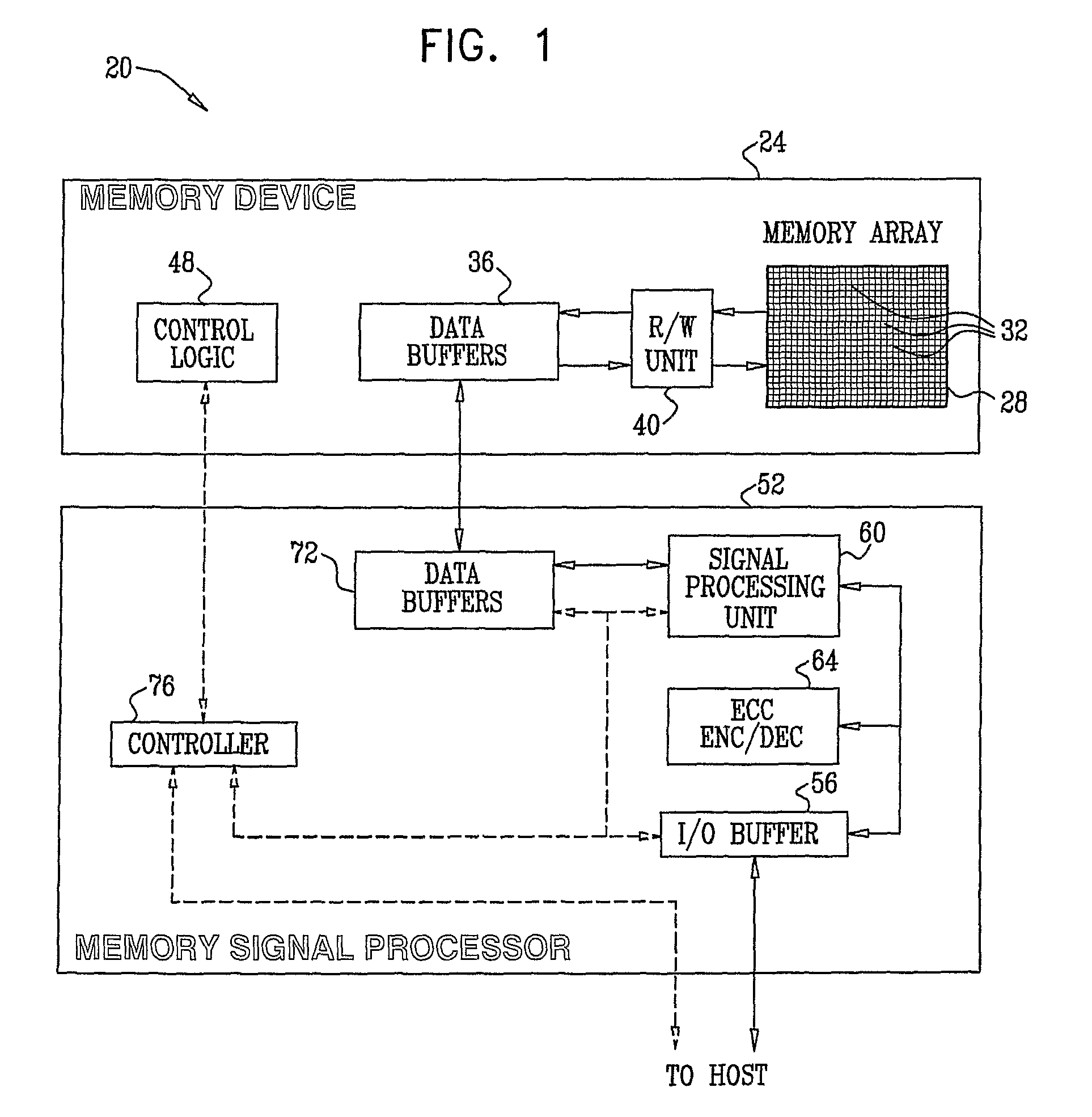

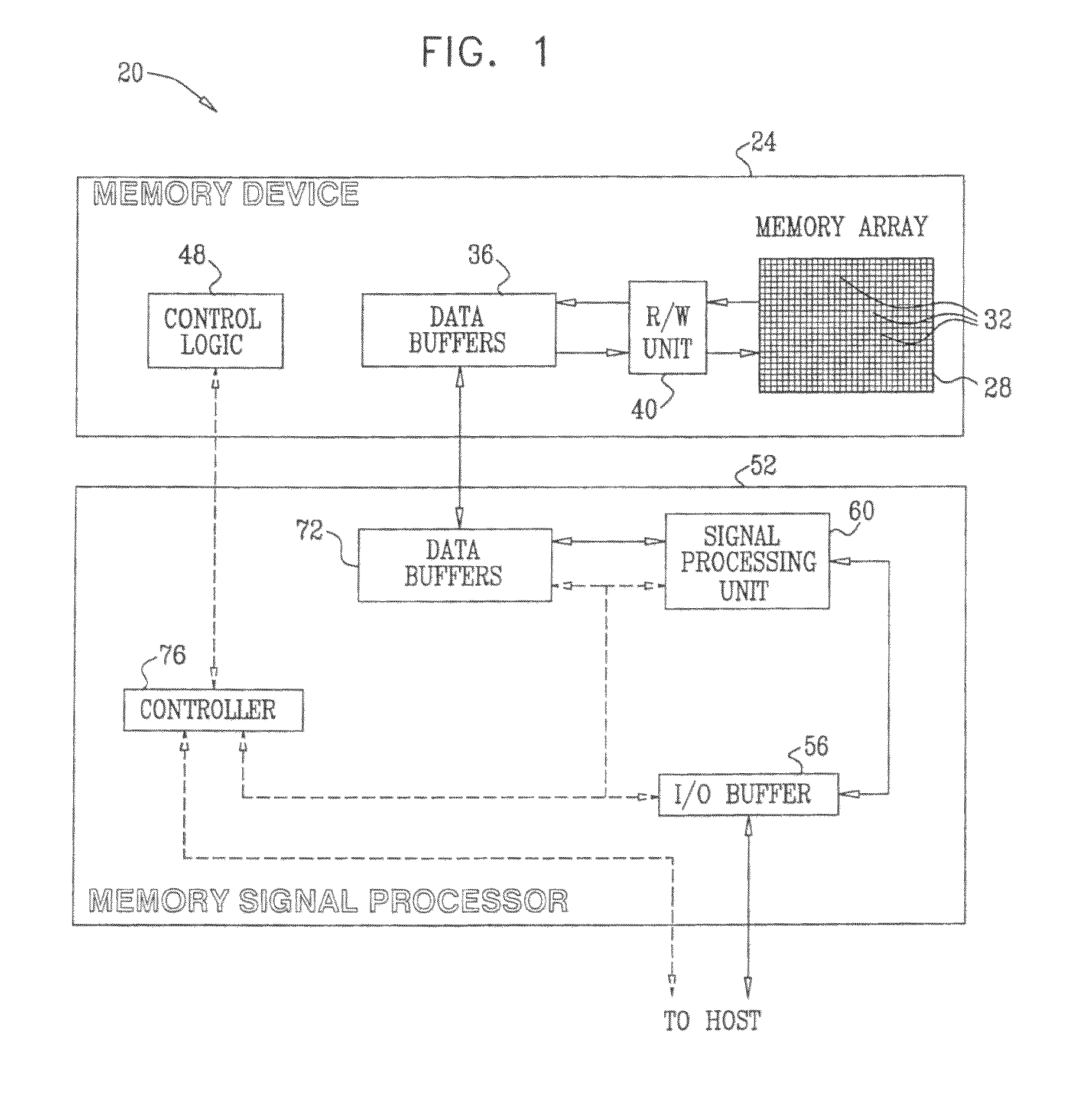

A method for operating a memory device (24) includes encoding data using an Error Correction Code (ECC) and storing the encoded data as first analog values in respective analog memory cells (32) of the memory device. After storing the encoded data, second analog values are read from the respective memory cells of the memory device in which the encoded data were stored. At least some of the second analog values differ from the respective first analog values. A distortion that is present in the second analog values is estimated. Error correction metrics are computed with respect to the second analog values responsively to the estimated distortion. The second analog values are processed using the error correction metrics in an ECC decoding process, so as to reconstruct the data.

Owner:APPLE INC

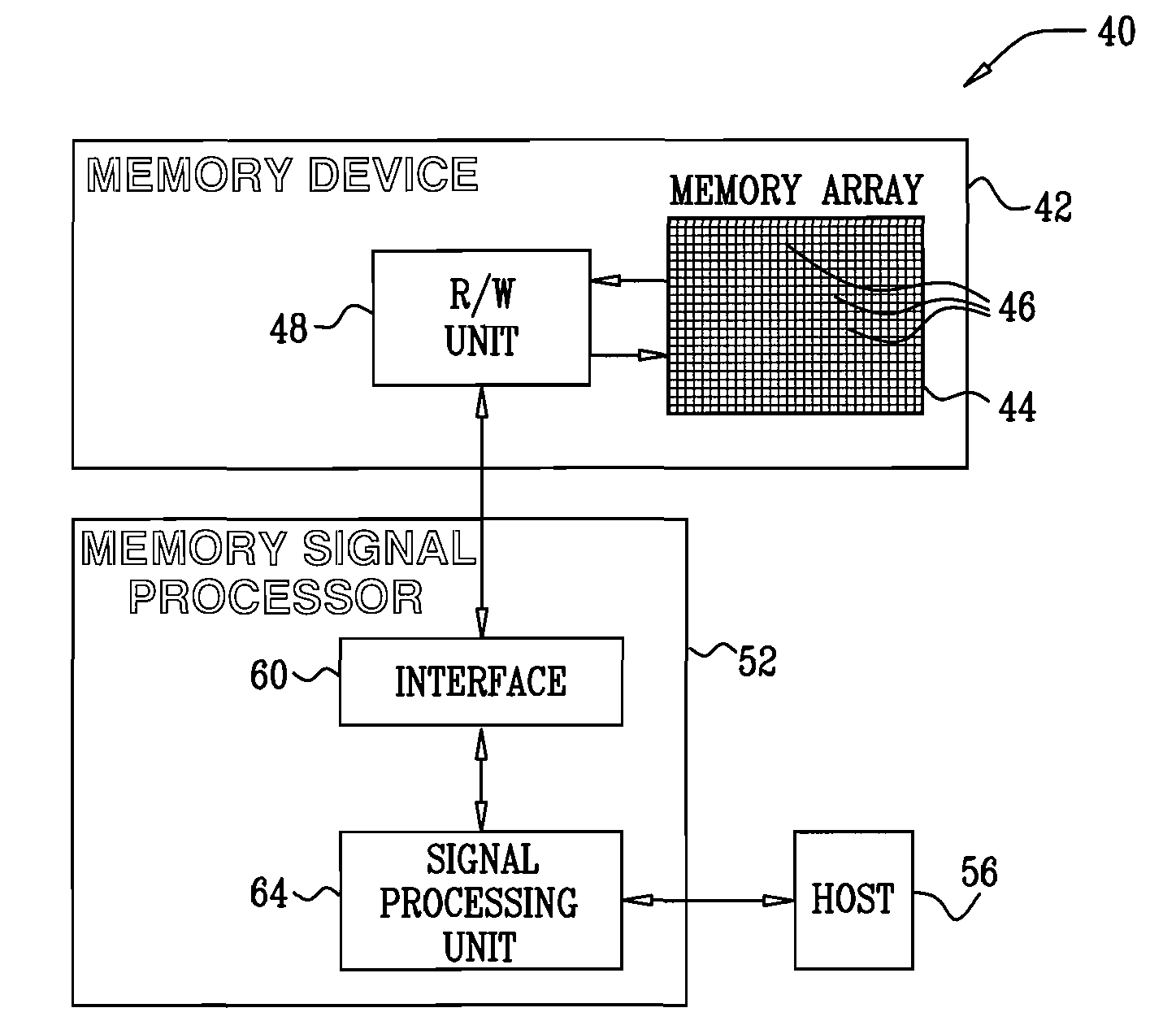

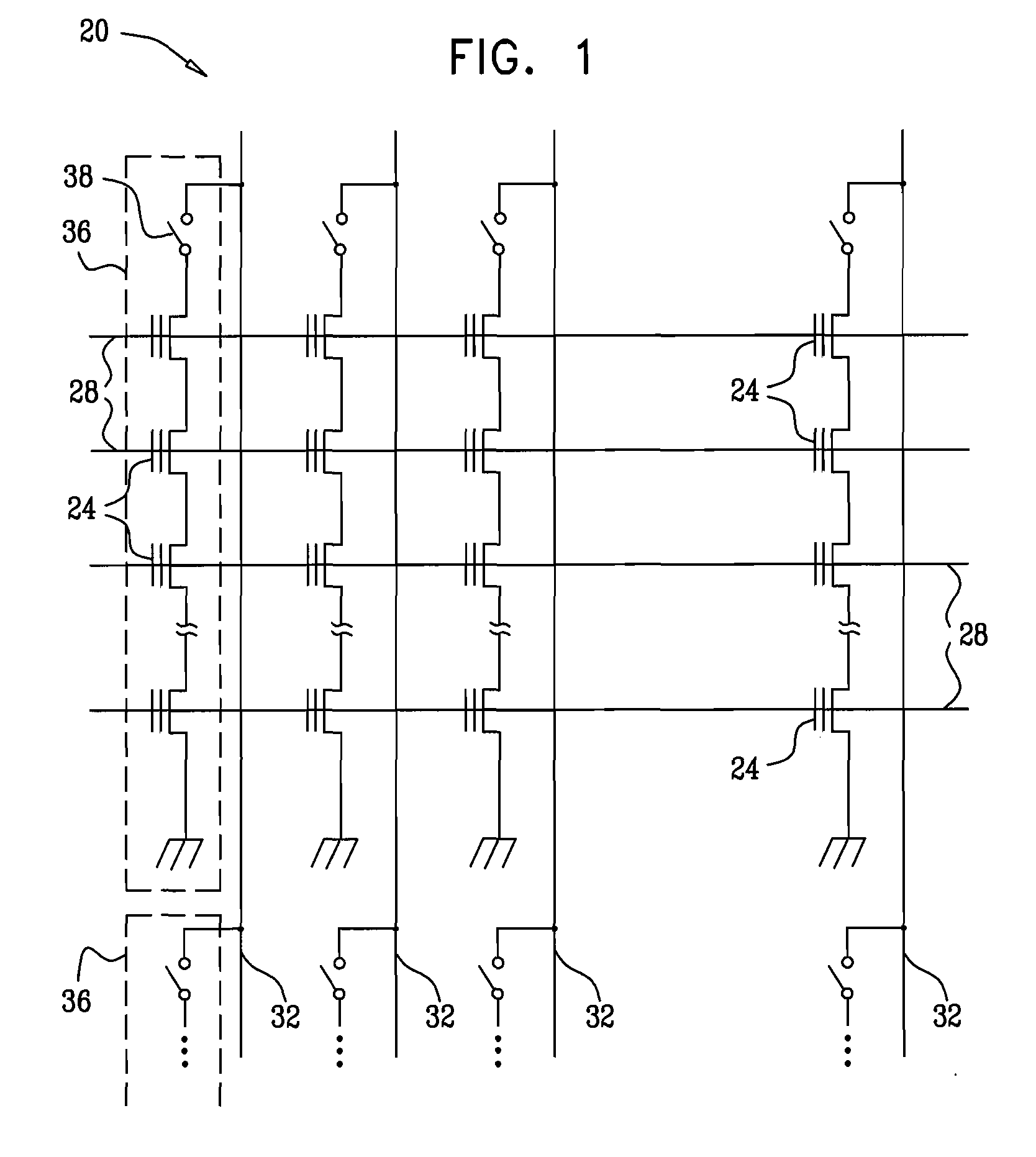

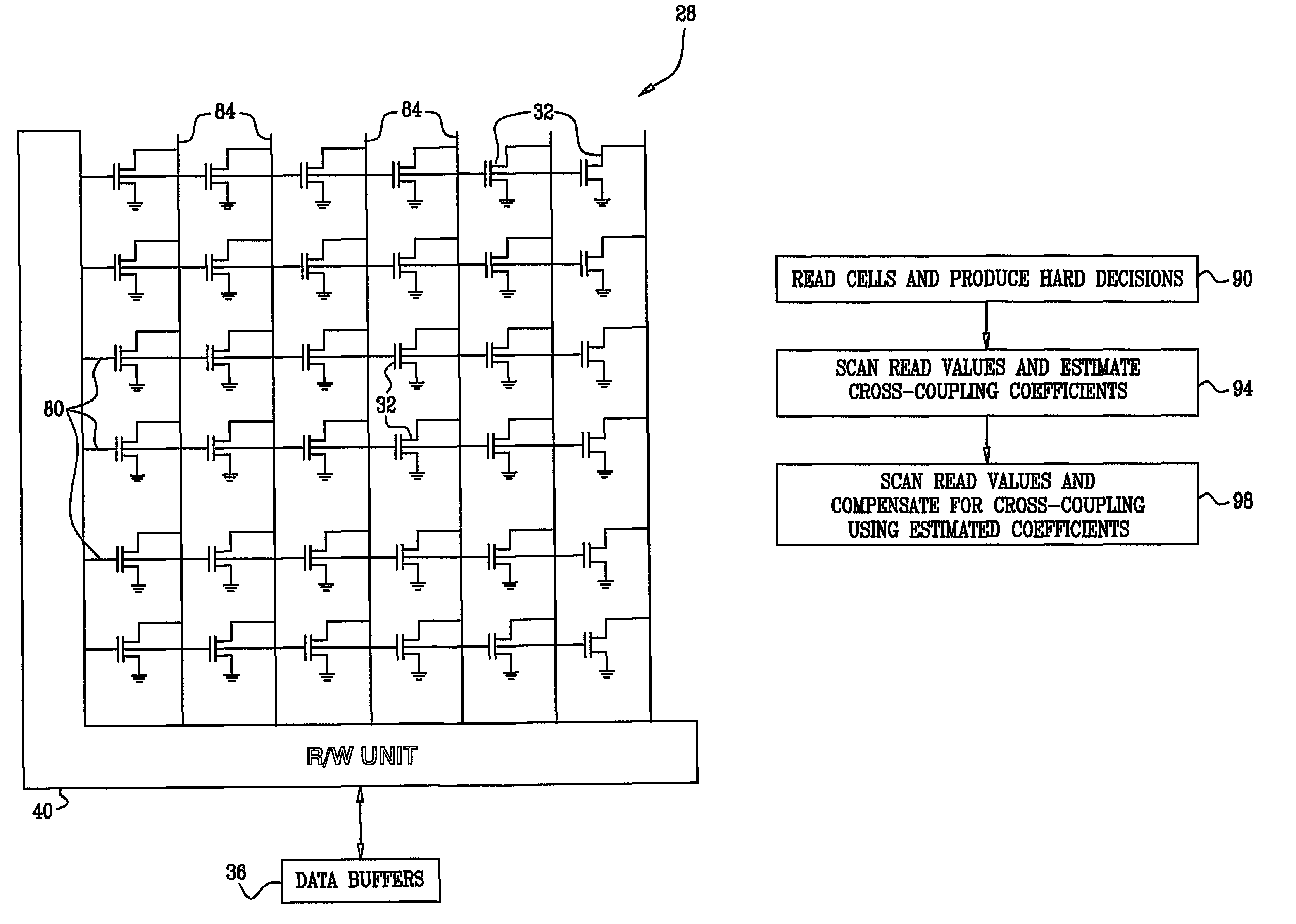

Distortion Estimation And Cancellation In Memory Devices

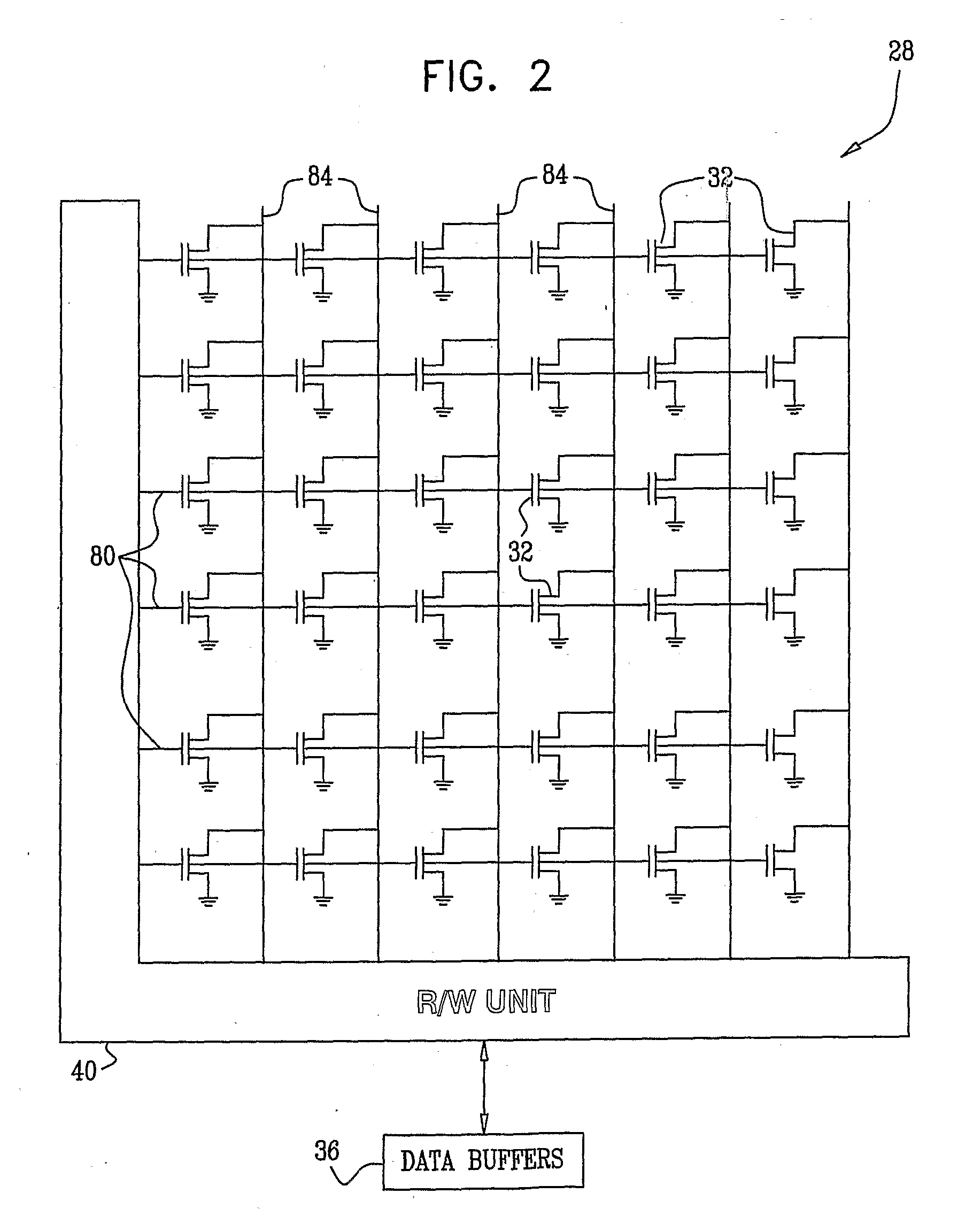

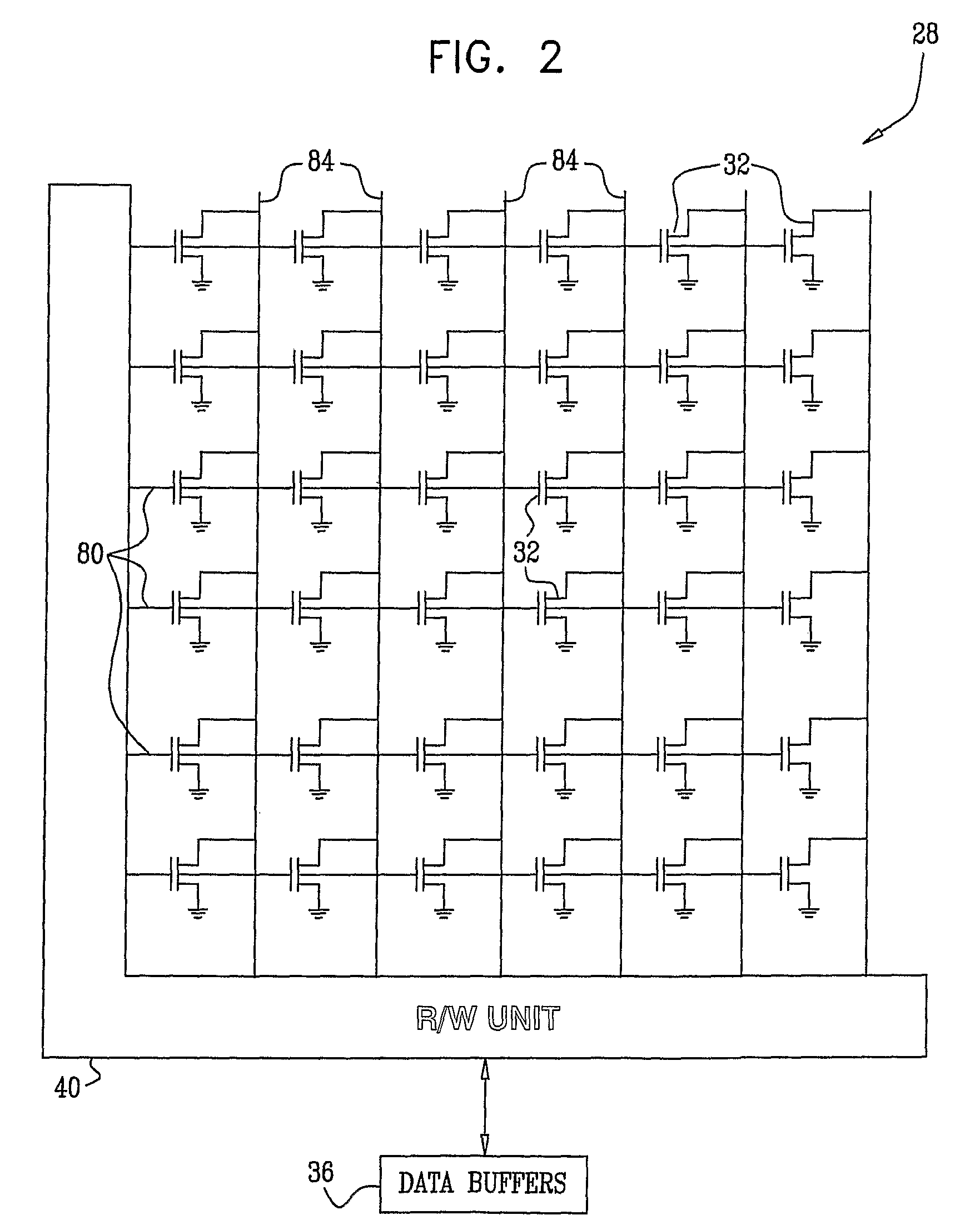

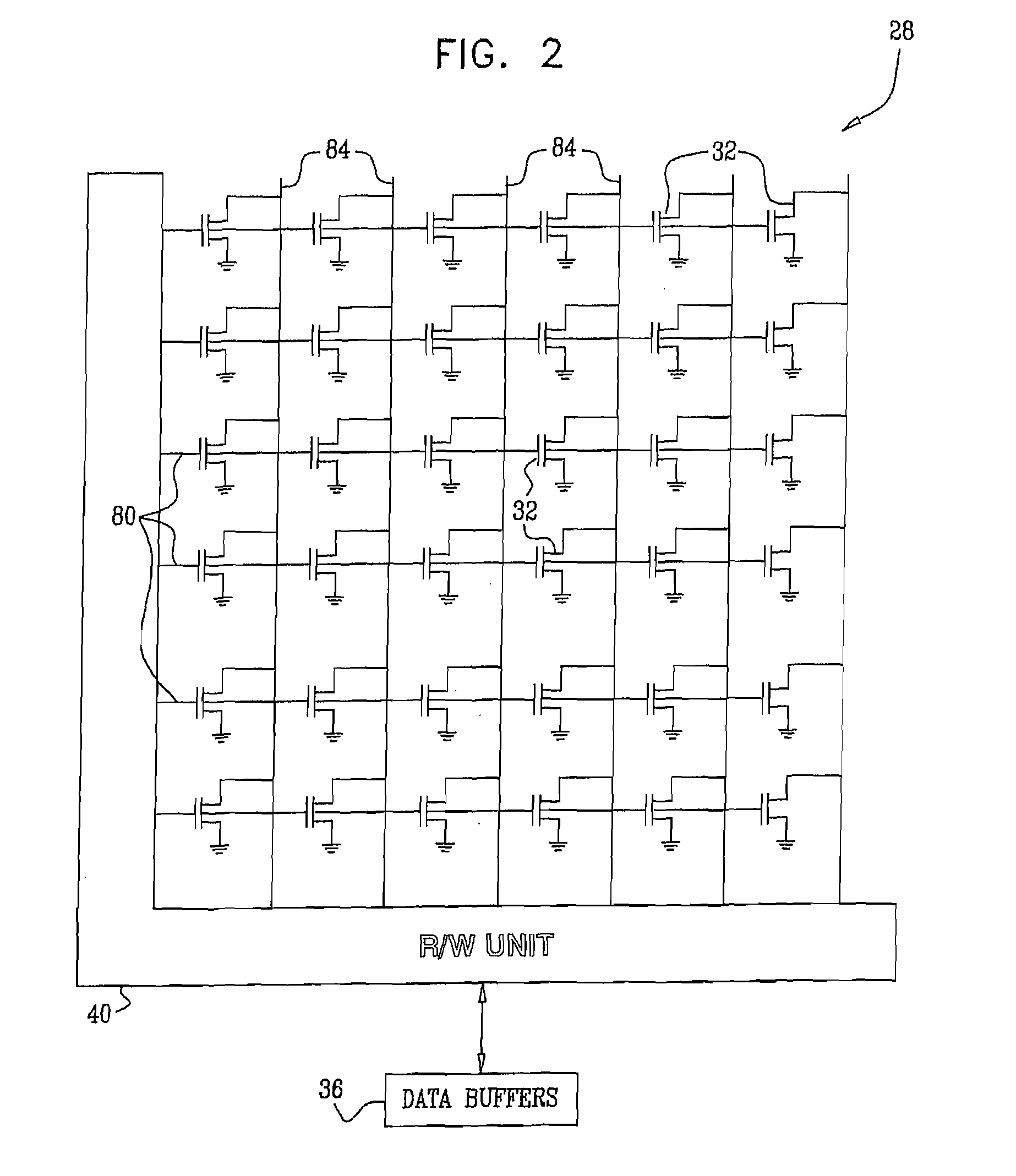

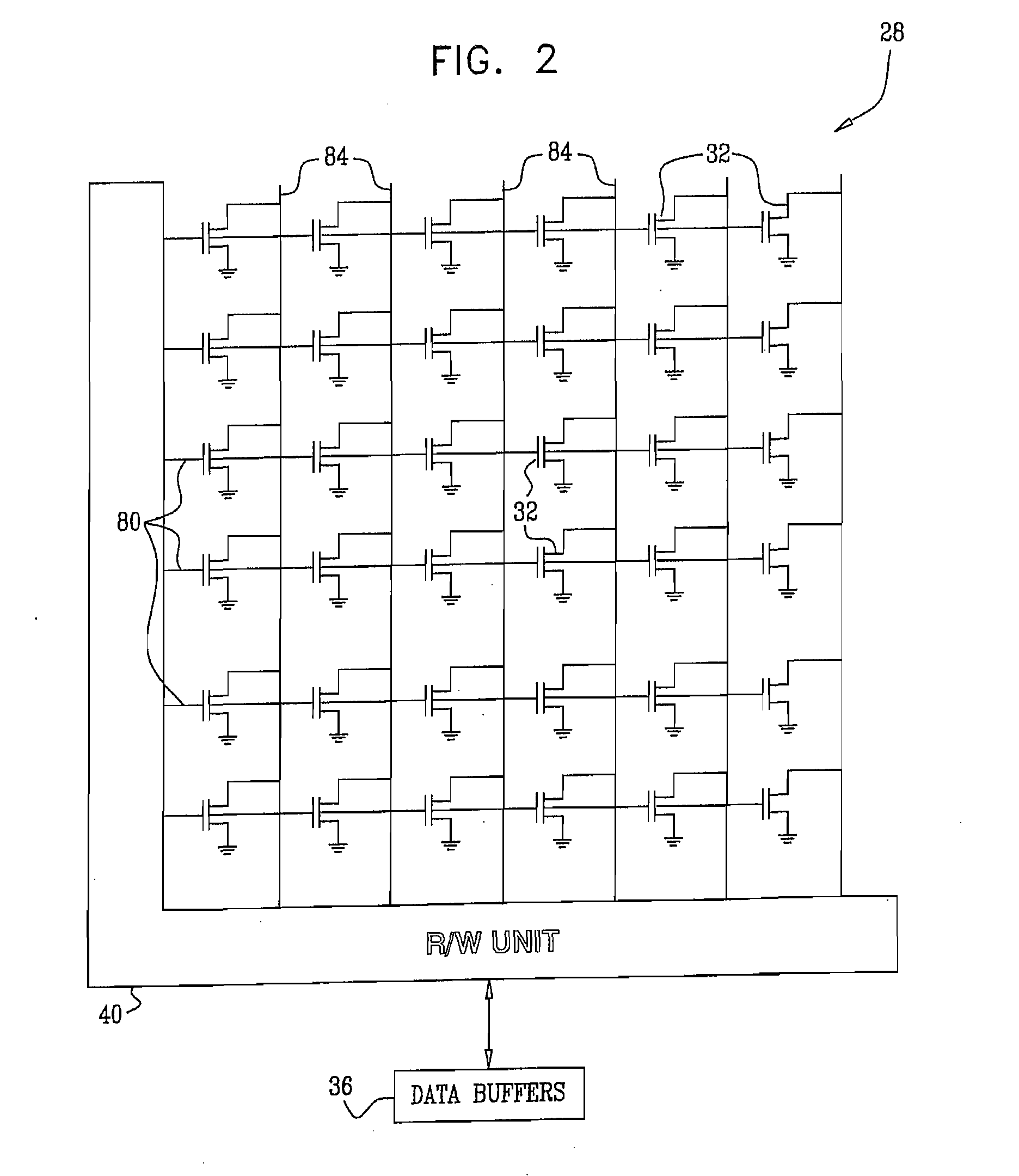

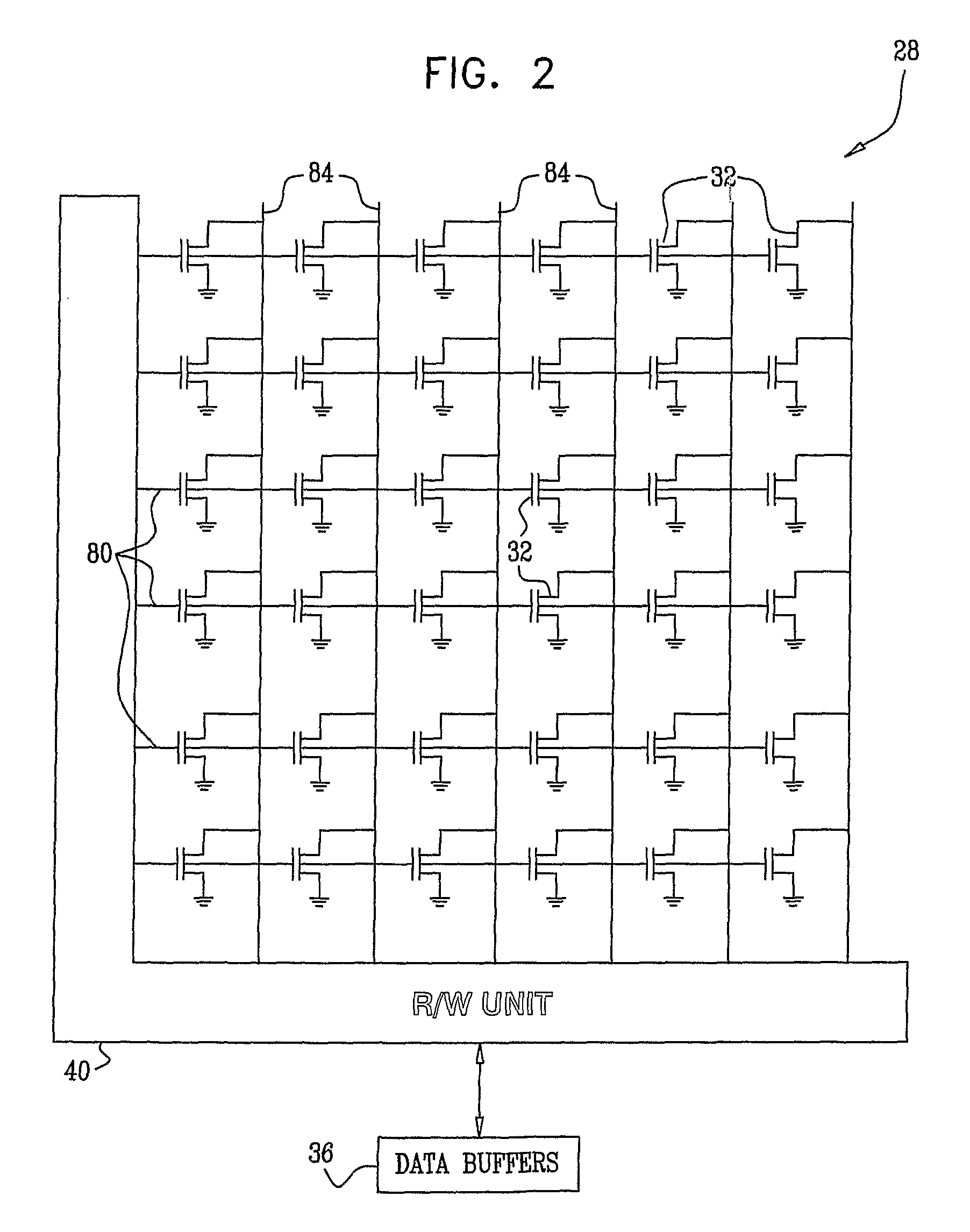

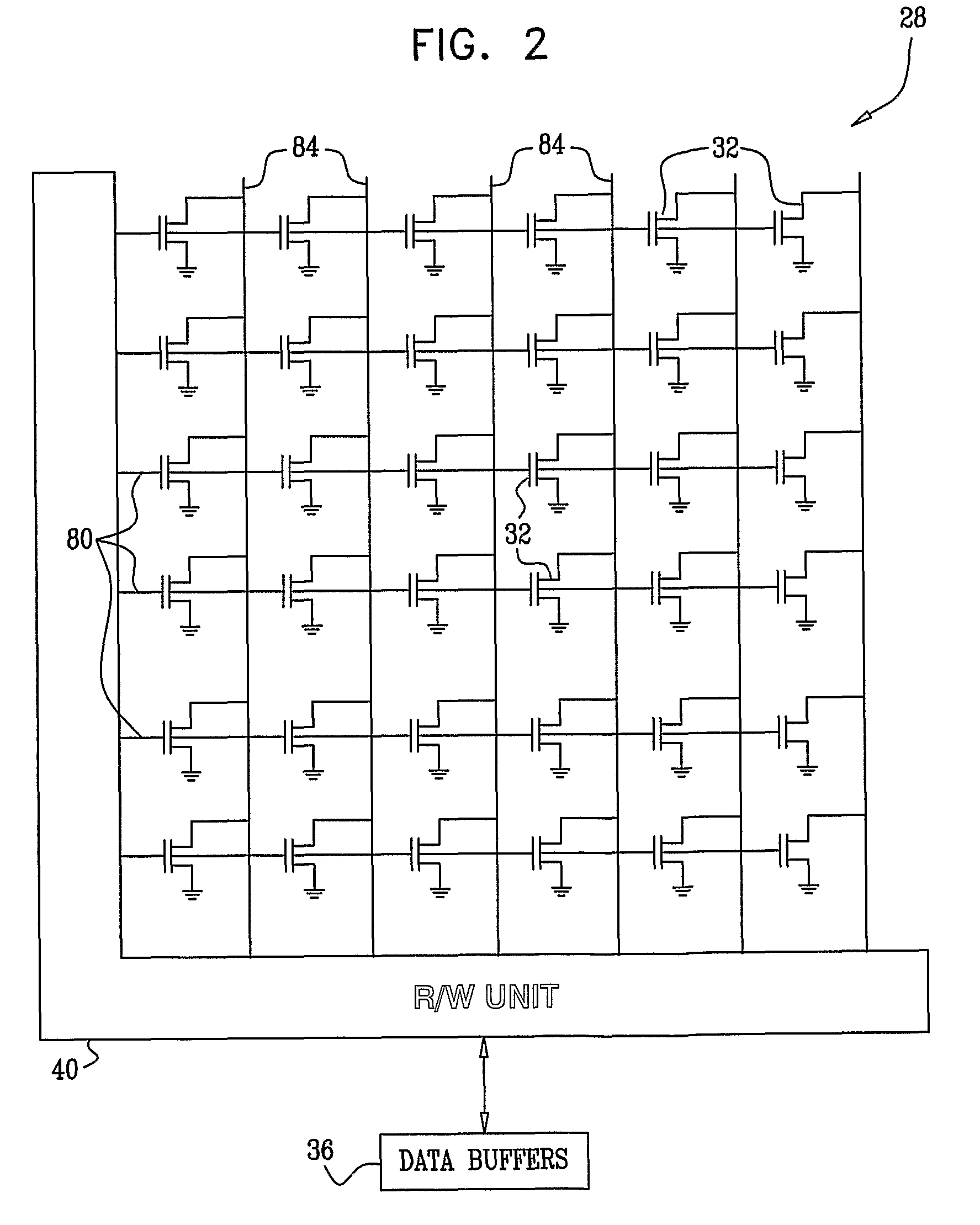

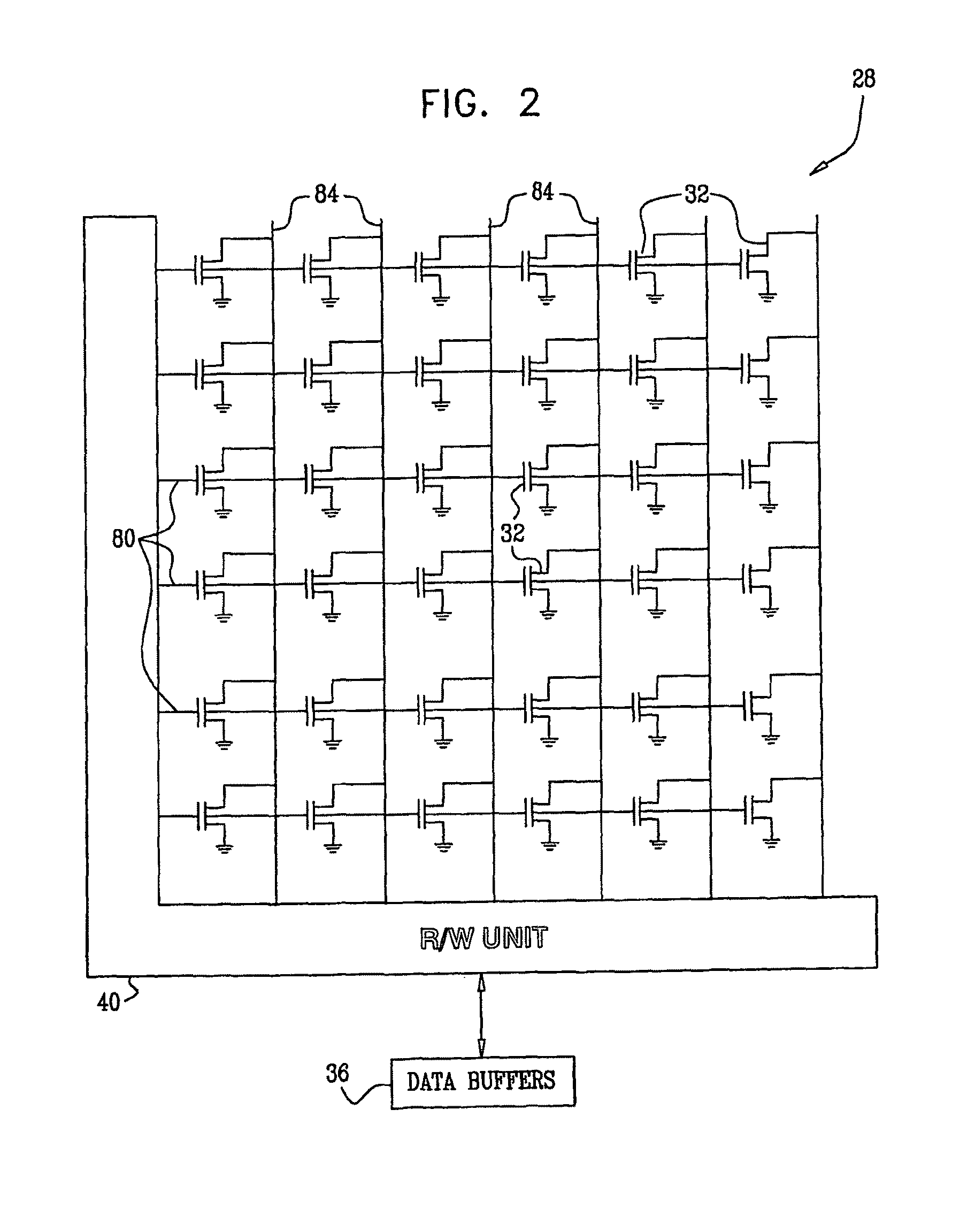

A method for operating a memory (28) includes storing data in a group of analog memory cells (32) of the memory as respective first voltage levels. After storing the data, second voltage levels are read from the respective analog memory cells. The second voltage levels are affected by cross-coupling interference causing the second voltage levels to differ from the respective first voltage levels. Cross-coupling coefficients, which quantify the cross-coupling interference among the analog memory cells, are estimated by processing the second voltage levels. The data stored in the group of analog memory cells is reconstructed from the read second voltage levels using the estimated cross-coupling coefficients.

Owner:APPLE INC

Automatic defect management in memory devices

ActiveUS20100115376A1Code conversionError correction/detection using block codesAlternative methodsComputer science

A method for storing data in a memory (28) that includes analog memory cells (32) includes identifying one or more defective memory cells in a group of the analog memory cells. An Error Correction Code (ECC) is selected responsively to a characteristic of the identified defective memory cells. The data is encoded using the selected ECC and the encoded data is stored in the group of the analog memory cells. In an alternative method, an identification of one or more defective memory cells among the analog memory cells is generated. Analog values are read from the analog memory cells in which the encoded data were stored, including at least one of the defective memory cells. The analog values are processed using an ECC decoding process responsively to the identification of the at least one of the defective memory cells, so as to reconstruct the data.

Owner:APPLE INC

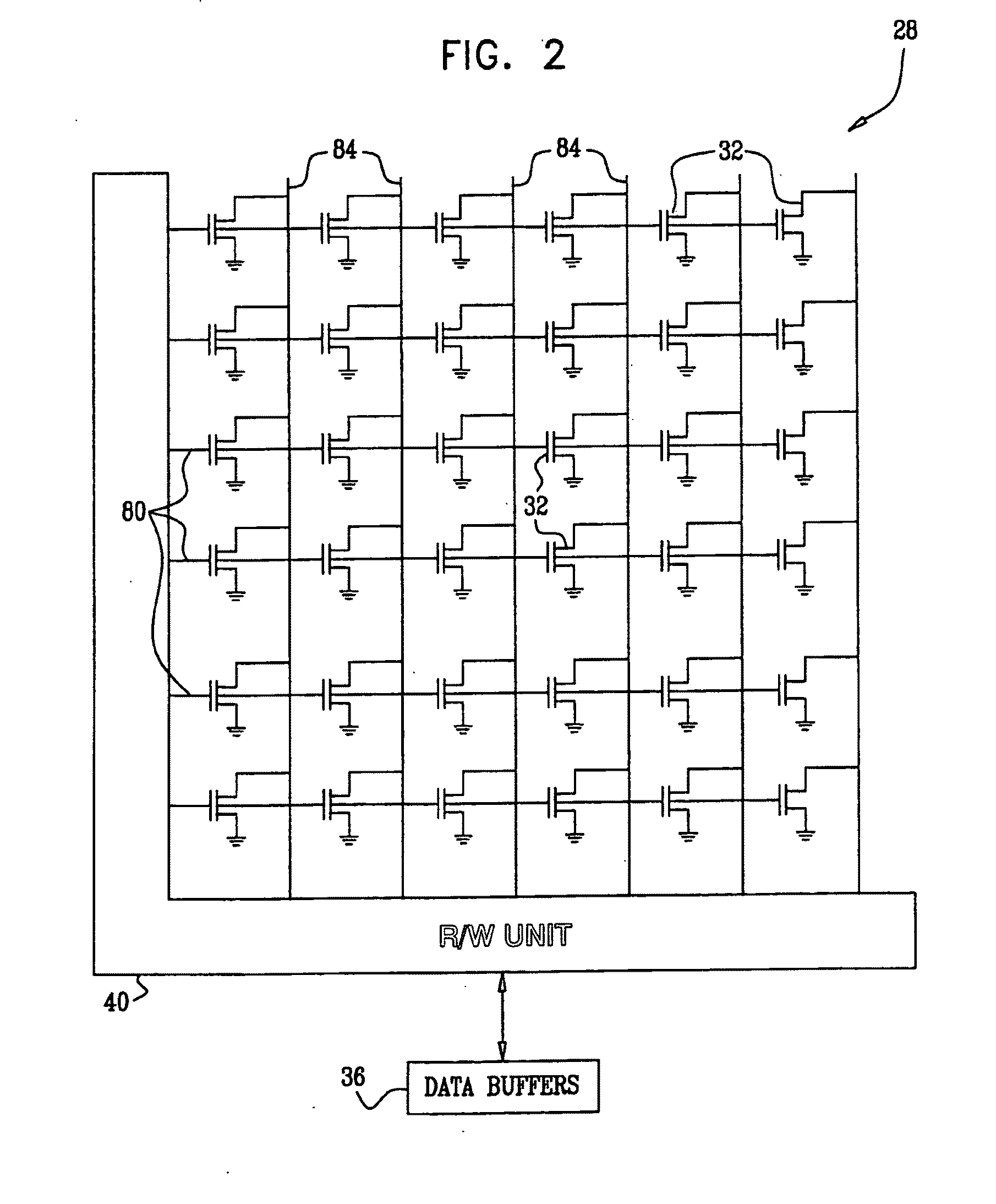

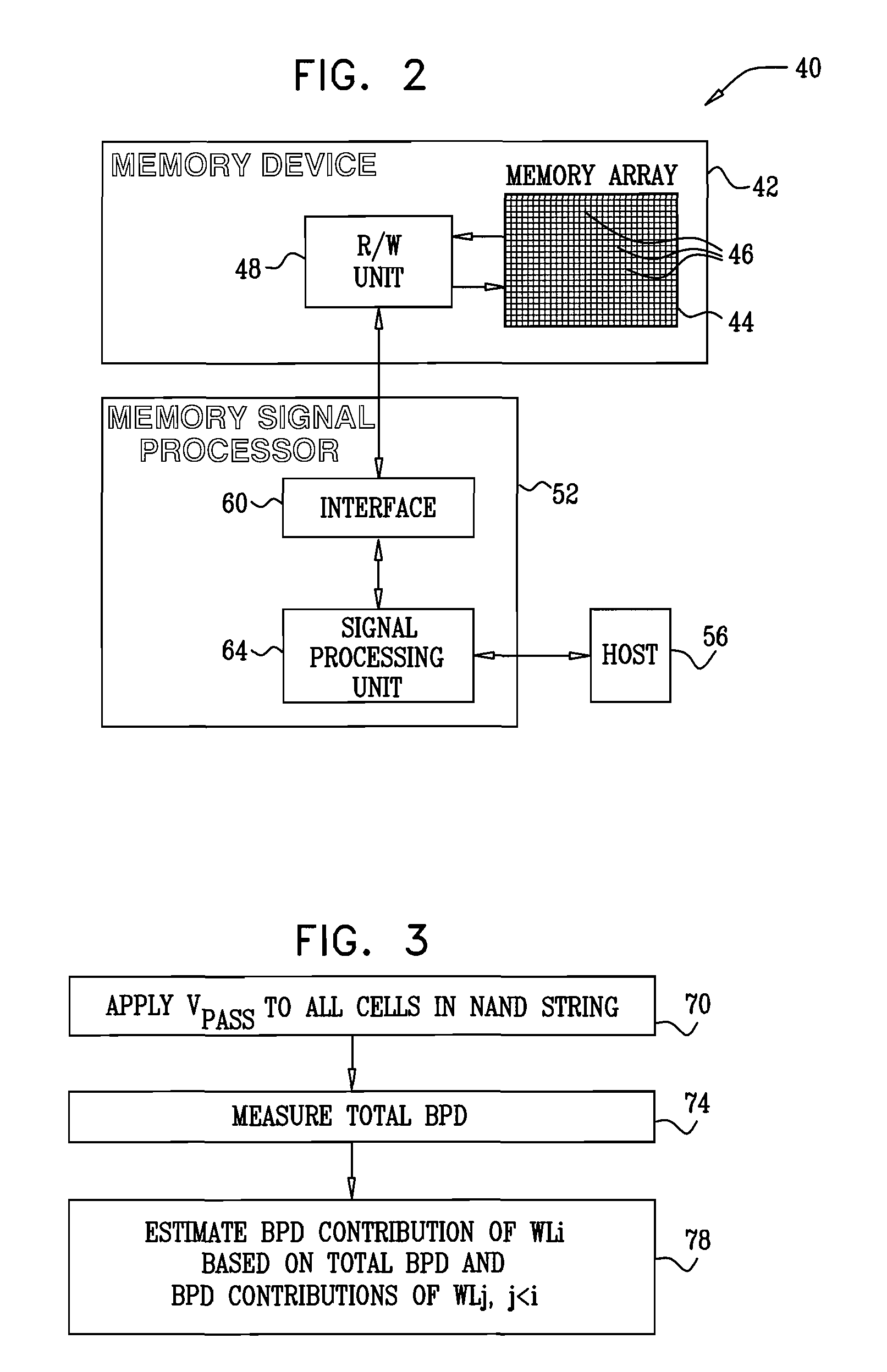

Reduction of back pattern dependency effects in memory devices

ActiveUS20080219050A1High voltageError detection/correctionElectric analogue storesParallel computingDistortion

A method for operating a memory that includes multiple analog memory cells includes storing data in the memory by writing first storage values to the cells, so as to cause the cells to hold respective electrical charge levels. After storing the data, second storage values are read from at least some of the cells, including at least one interfered cell that belongs to a group of cells. A Back Pattern Dependency (BPD) distortion caused by the electrical charge levels of one or more interfering cells in the group to at least one of the second storage values read from the at least one interfered cell is detected and canceled. The second storage values, including the at least one of the second storage values in which the BPD distortion was canceled, are processed so as to reconstruct the data.

Owner:APPLE INC

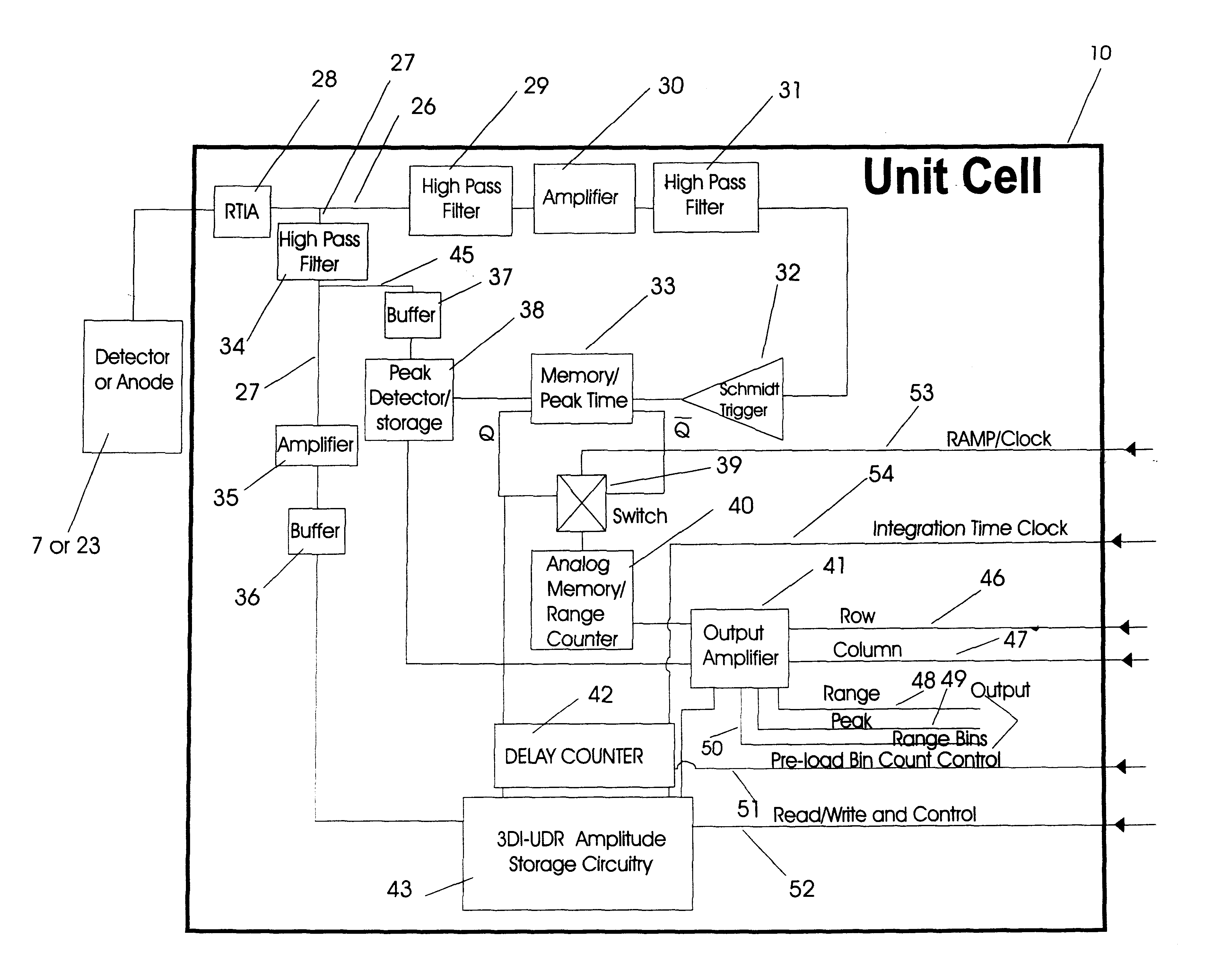

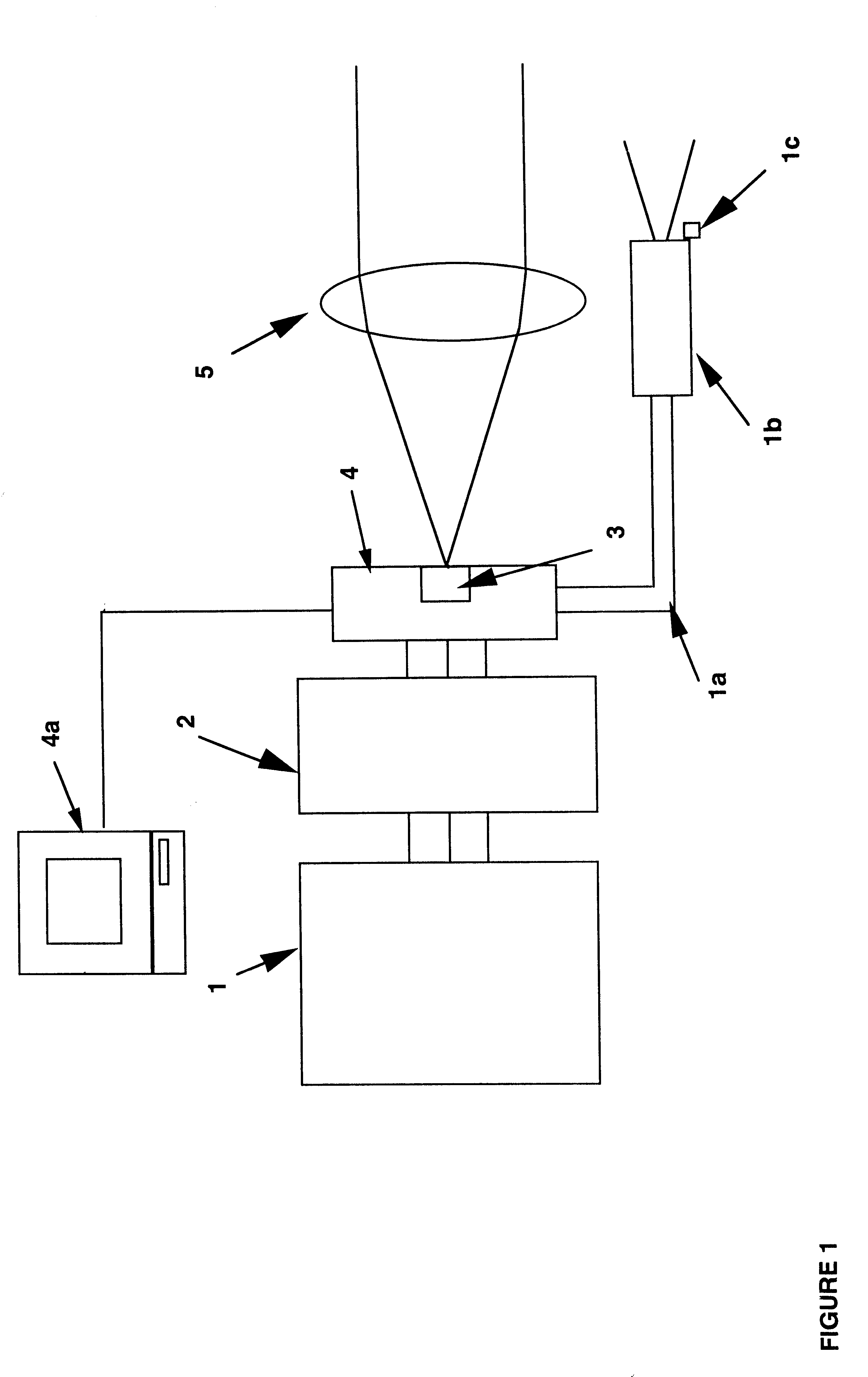

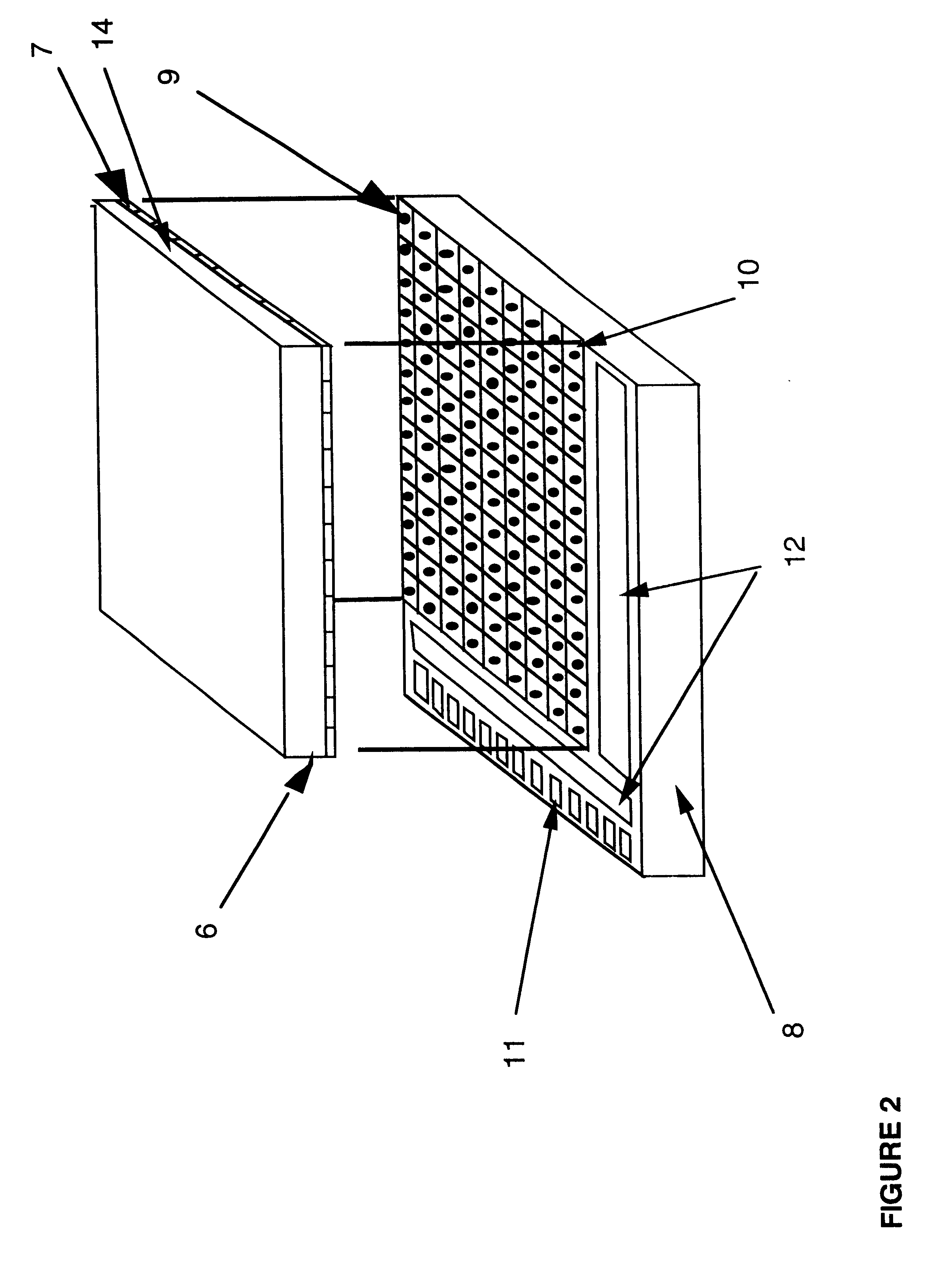

3-D imaging multiple target laser radar

InactiveUS6414746B1Accurately determineOptical rangefindersSolid-state devicesElectronIntegrated circuit

A three dimensional imaging device is presented which uses a single pulse from a pulsed light source to detect objects which are obscured by camouflage, fog or smoke but otherwise enveloped by a light-transmitting medium. The device simultaneously operates in two modes, light reflected from the nearest object is processed to form a three-dimensional image by an array of pixels. This first image is based upon the light-pulse transit time recorded in each pixel. Each pixel also contains a high-speed analog memory that sequentially stores reflected signals at a repeated time interval. The first reflection acts as a time base that controls when the analog memory begins or ends the storage sequence. The first return could be from a camouflage net and the amplitudes of the return signals, after the first return, would then be from objects behind the net. Computer processing these amplitudes reveals the three-dimensional nature of the obscured objects.The device consists of the pulsed light source, optics for collecting the reflected light, a sensor for detecting the light and converting it to electrical data, drive and output electronics for timing and signal conditioning of data generated by the sensors and a computer for processing the sensor data and converting it to a three dimensional image. The sensor collects and processes the light data in a unique manner, first converting it to electricity by a number of alternate detector technologies and then using integrated circuit chips which consist of a two dimensional array of electronic pixels also called unit cells. The two dimensional array defines two dimensions of the image. Stored within each unit cells is data associated with the third dimension, ranges of targets, and amplitudes of target reflections. This data is read out of the integrated circuit chip in the time interval between laser pulses to a processing computer. The processing computer corrects the data and, by means of computer algorithms specific to the device, converts the data to a three-dimensional image of one or more targets. This image may be viewed or processed electronically to isolate targets.

Owner:CONTINENTAL AUTONOMOUS MOBILITY US LLC

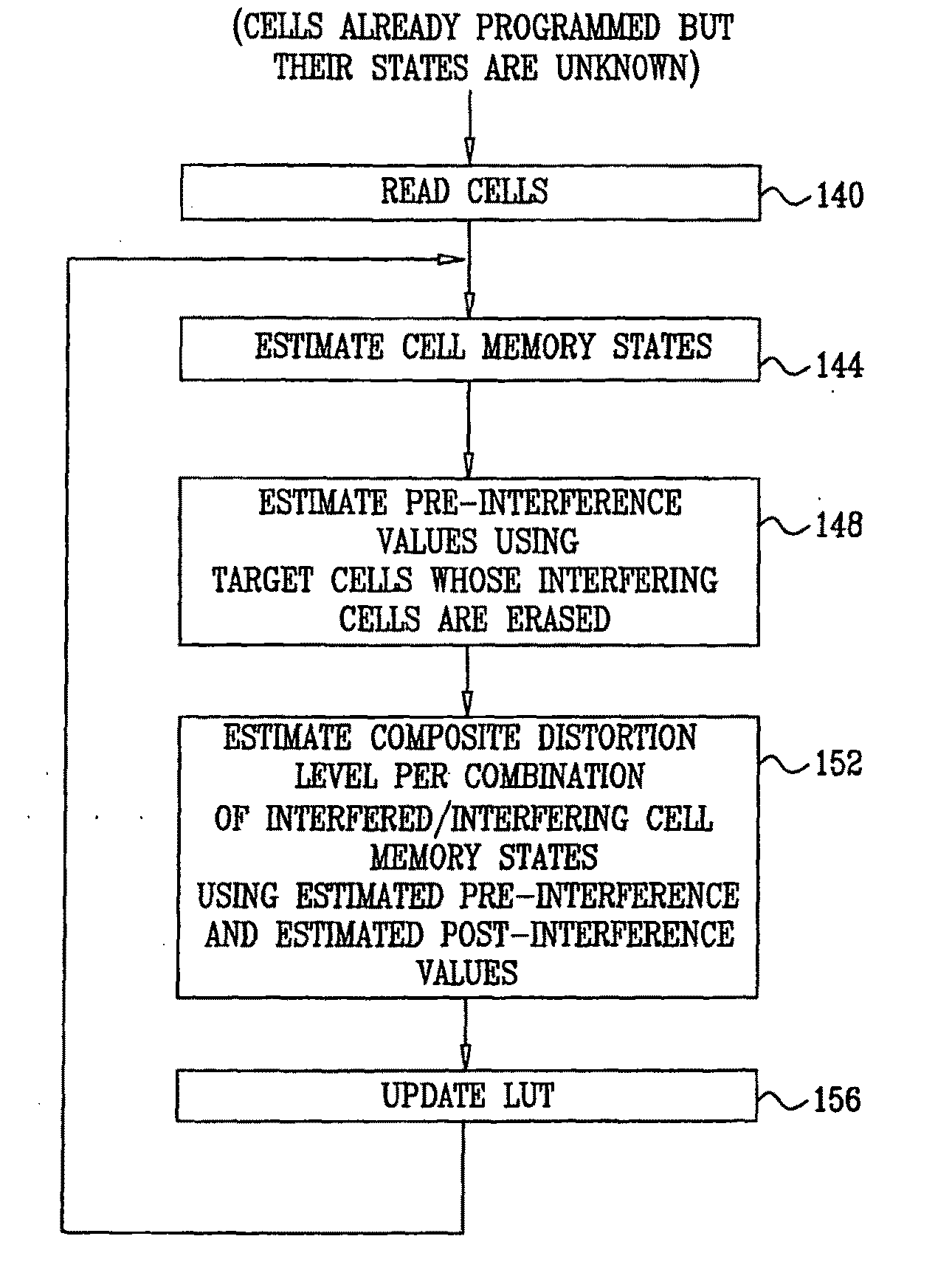

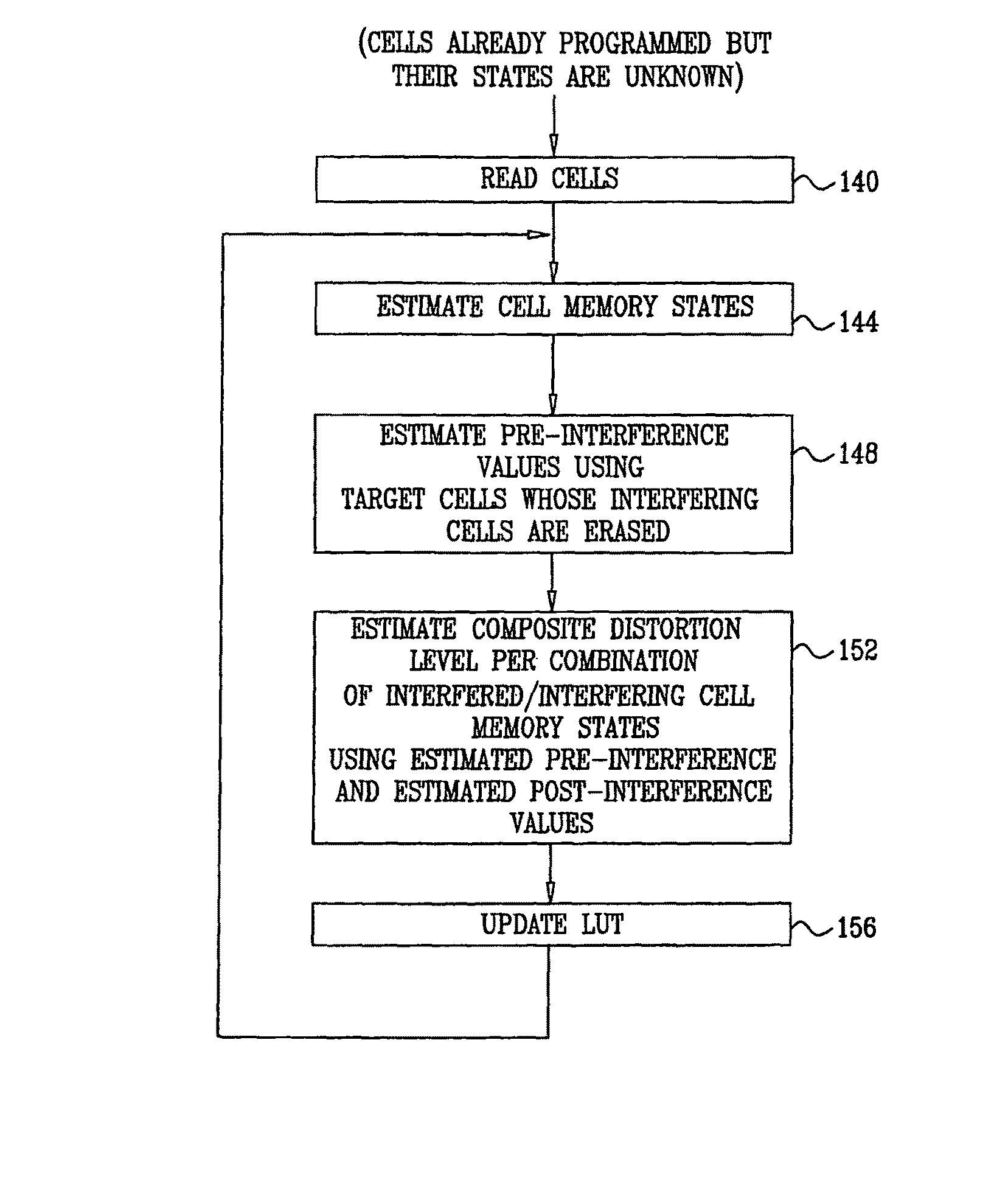

Estimation of non-linear distortion in memory devices

A method for operating a memory (24) includes storing data in analog memory cells (32) of the memory by writing respective analog values to the analog memory cells. A set of the analog memory cells is identified, including an interfered cell having a distortion that is statistically correlated with the respective analog values of the analog memory cells in the set. A mapping is determined between combinations of possible analog values of the analog memory cells in the set and statistical characteristics of composite distortion levels present in the interfered memory cell. The mapping is applied so as to compensate for the distortion in the interfered memory cell.

Owner:APPLE INC

Reducing programming error in memory devices

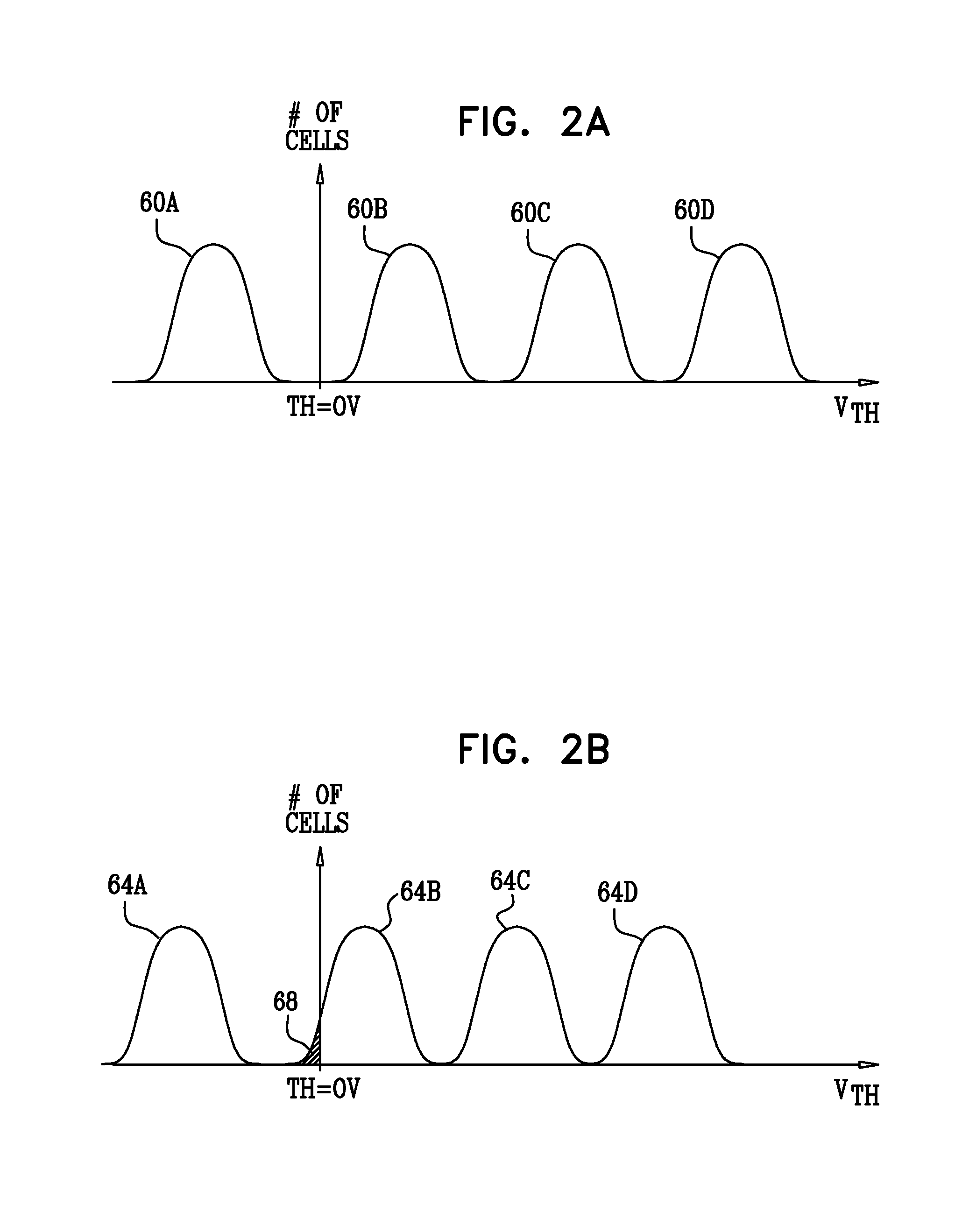

InactiveUS20090103358A1Multiplex system selection arrangementsElectric analogue storesComputer scienceVoltage

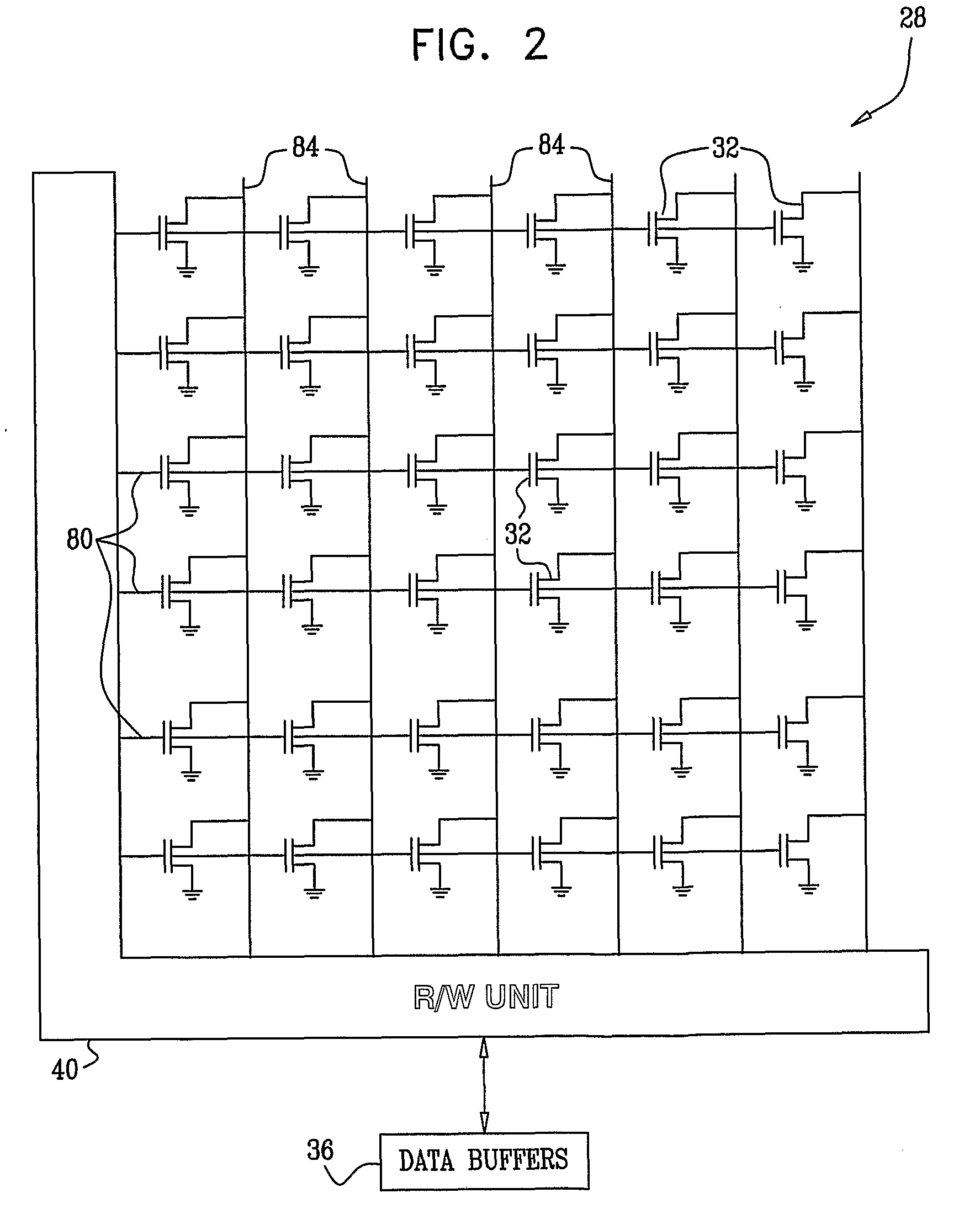

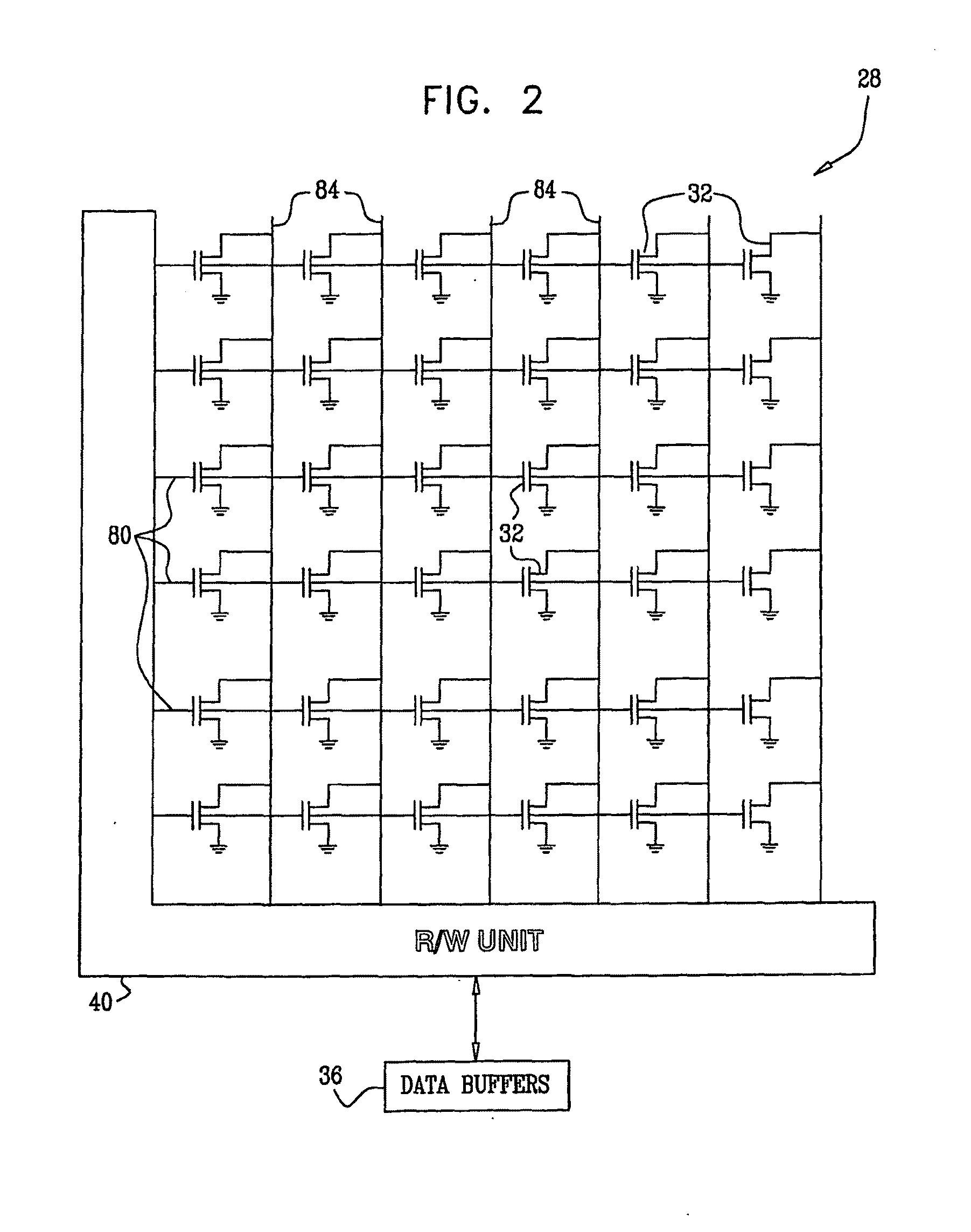

A method for storing data in an array (28) of analog memory cells (32) includes defining a constellation of voltage levels (90A, 90B, 90C, 90D) to be used in storing the data. A part of the data is written to a first analog memory cell in the array by applying to the analog memory cell a first voltage level selected from the constellation. After writing the part of the data to the first analog memory cell, a second voltage level that does not belong to the constellation is read from the first analog memory cell. A modification to be made in writing to one or more of the analog memory cells in the array is determined responsively to the second voltage level, and data are written to the one or more of the analog memory cells subject to the modification.

Owner:APPLE INC

Reducing programming error in memory devices

InactiveUS7697326B2Multiplex system selection arrangementsElectric analogue storesComputer scienceVoltage

A method for storing data in an array (28) of analog memory cells (32) includes defining a constellation of voltage levels (90A, 90B, 90C, 90D) to be used in storing the data. A part of the data is written to a first analog memory cell in the array by applying to the analog memory cell a first voltage level selected from the constellation. After writing the part of the data to the first analog memory cell, a second voltage level that does not belong to the constellation is read from the first analog memory cell. A modification to be made in writing to one or more of the analog memory cells in the array is determined responsively to the second voltage level, and data are written to the one or more of the analog memory cells subject to the modification.

Owner:APPLE INC

Reading memory cells using multiple thresholds

A method for operating a memory (28) includes storing data, which is encoded with an Error Correction Code (ECC), in analog memory cells (32) of the memory by writing respective analog input values selected from a set of nominal values to the analog memory cells. The stored data is read by performing multiple read operations that compare analog output values of the analog memory cells to different, respective read thresholds so as to produce multiple comparison results for each of the analog memory cells. At least two of the read thresholds are positioned between a pair of the nominal values that are adjacent to one another in the set of the nominal values. Soft metrics are computed responsively to the multiple comparison results. The ECC is decoded using the soft metrics, so as to extract the data stored in the analog memory cells.

Owner:APPLE INC

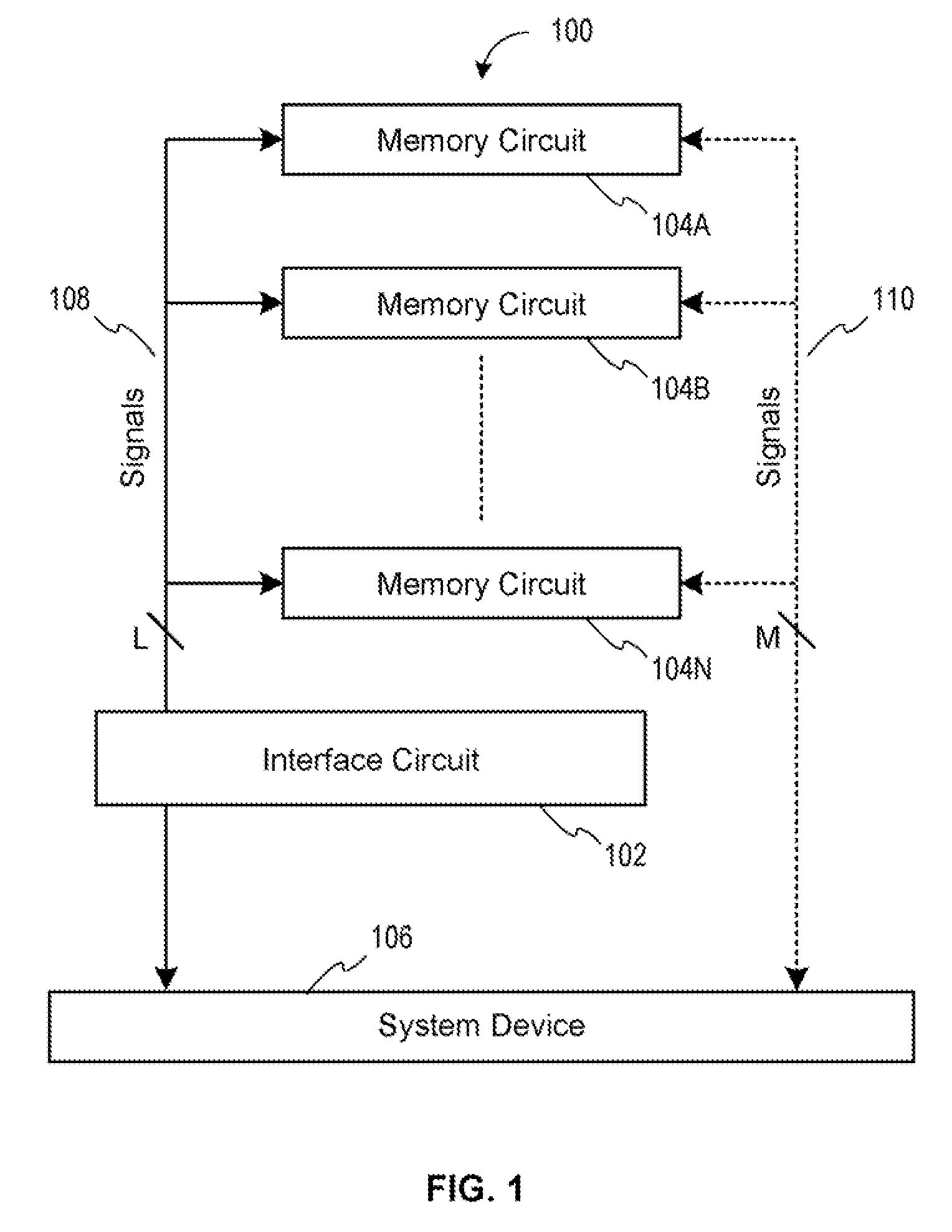

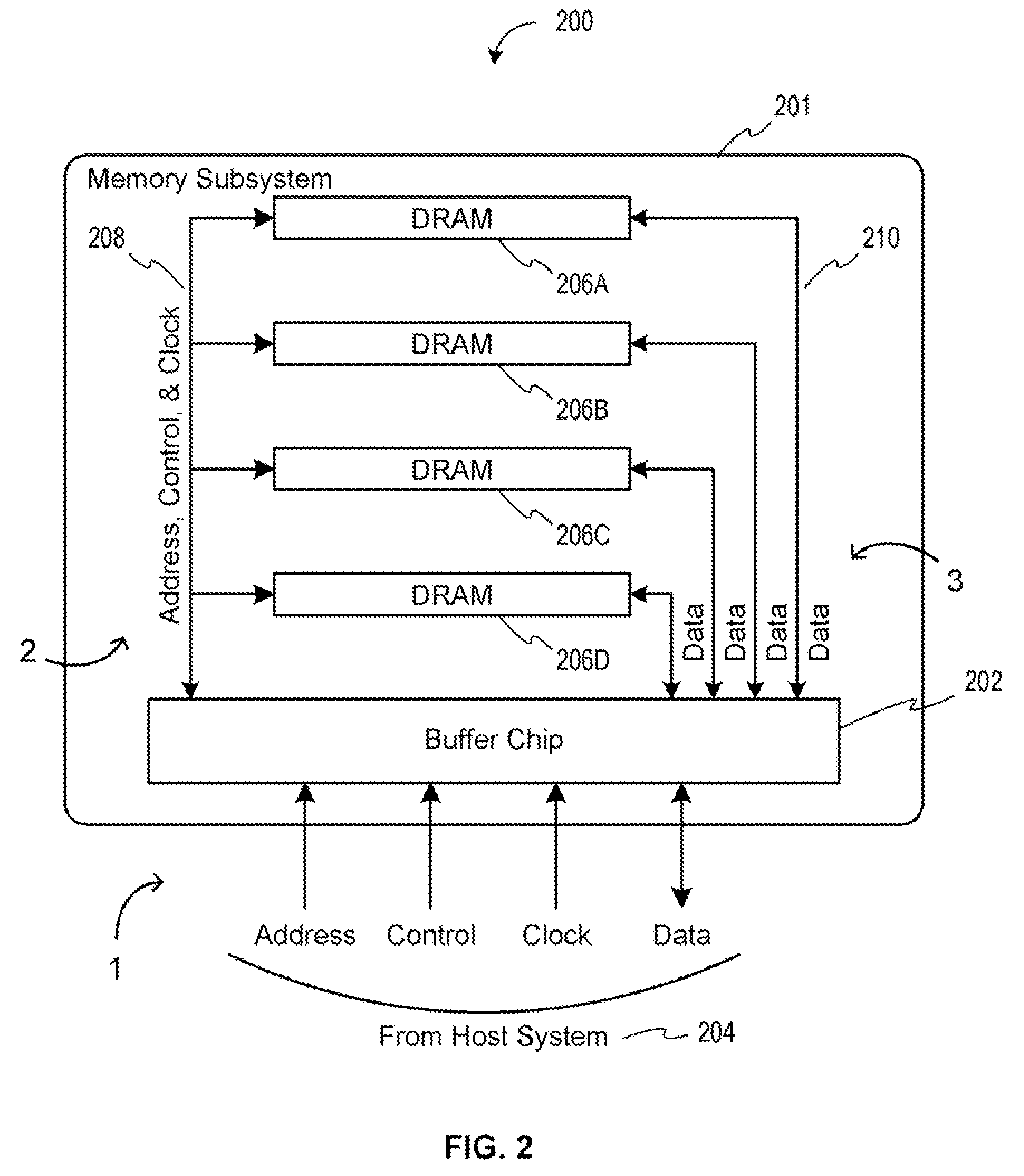

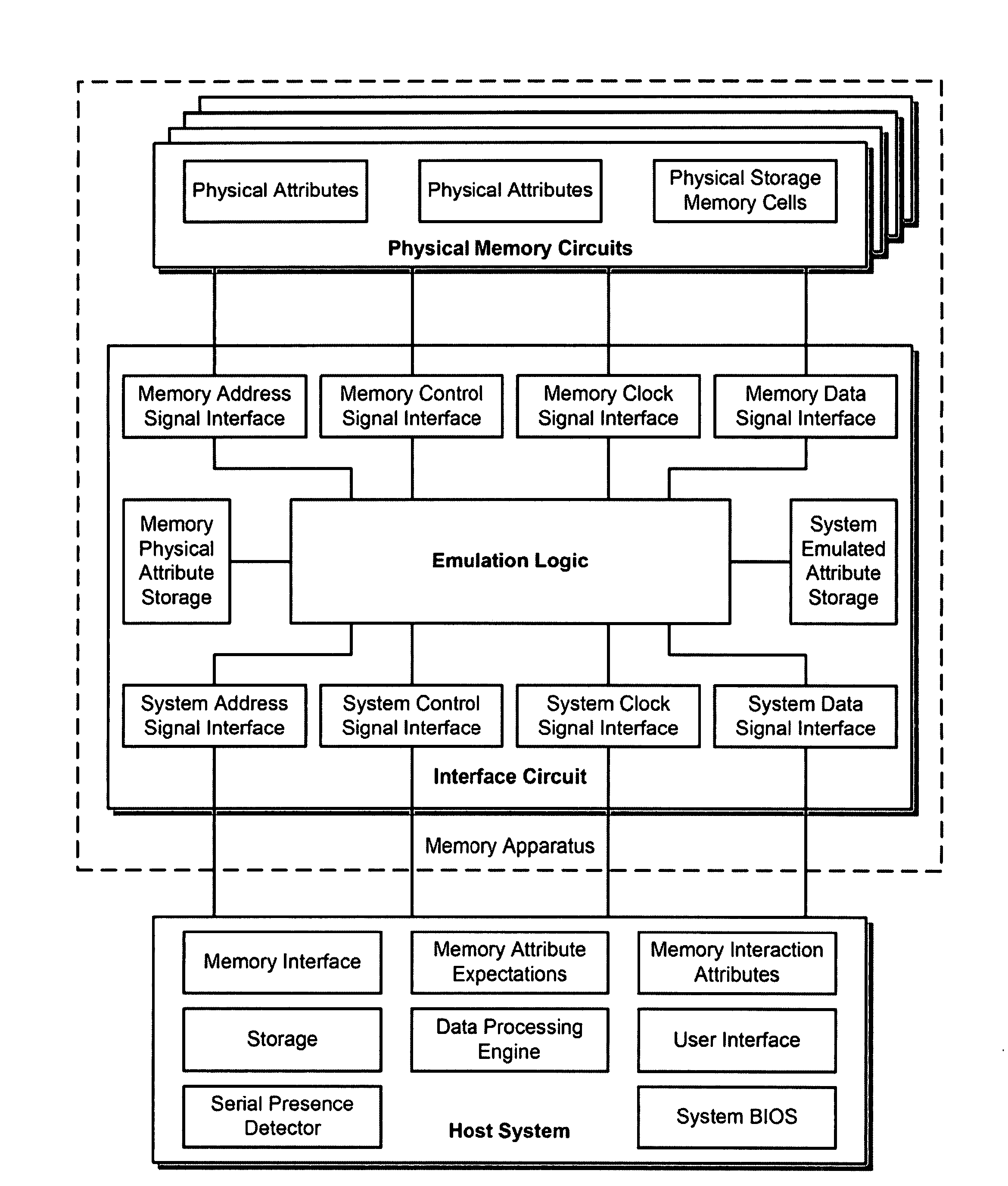

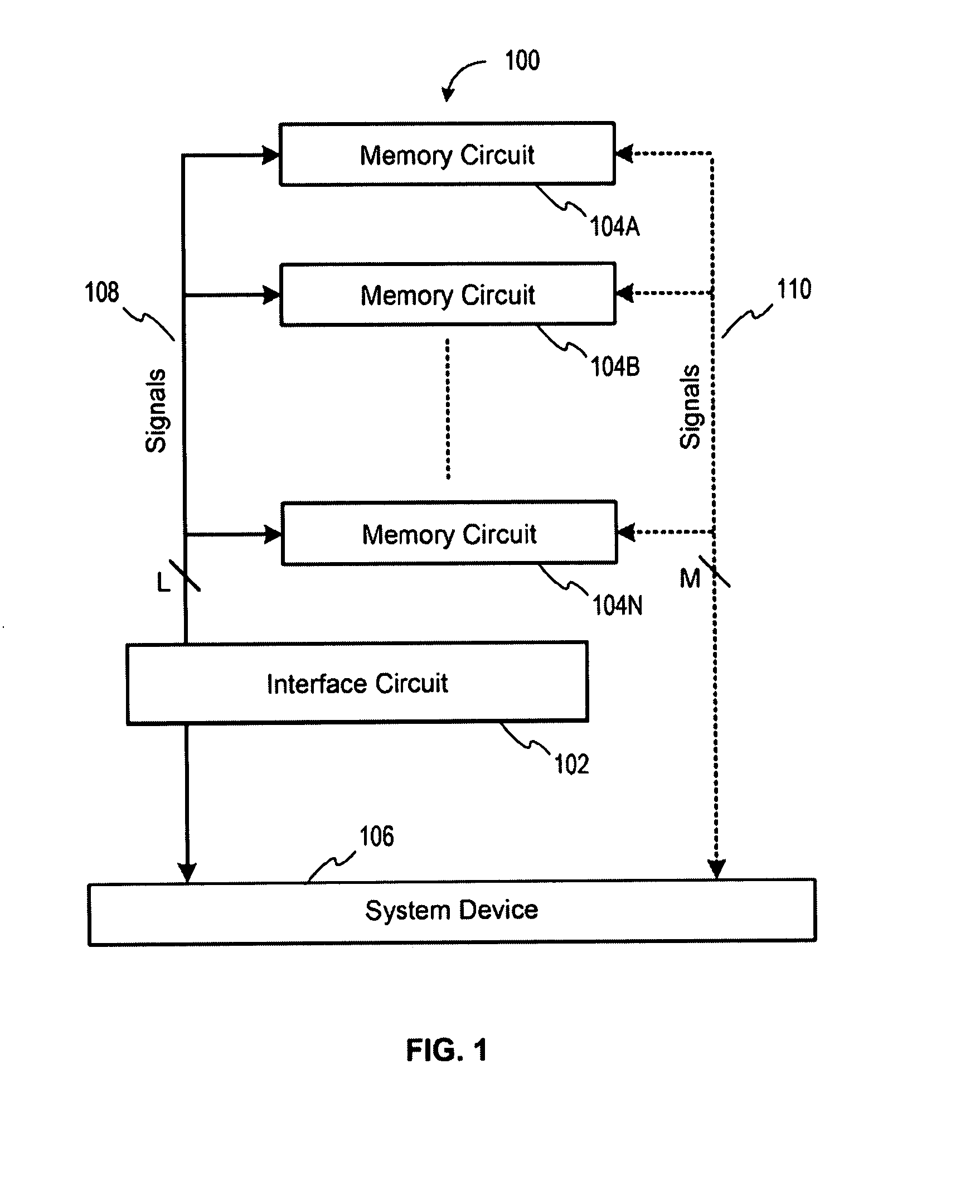

System and method for simulating an aspect of a memory circuit

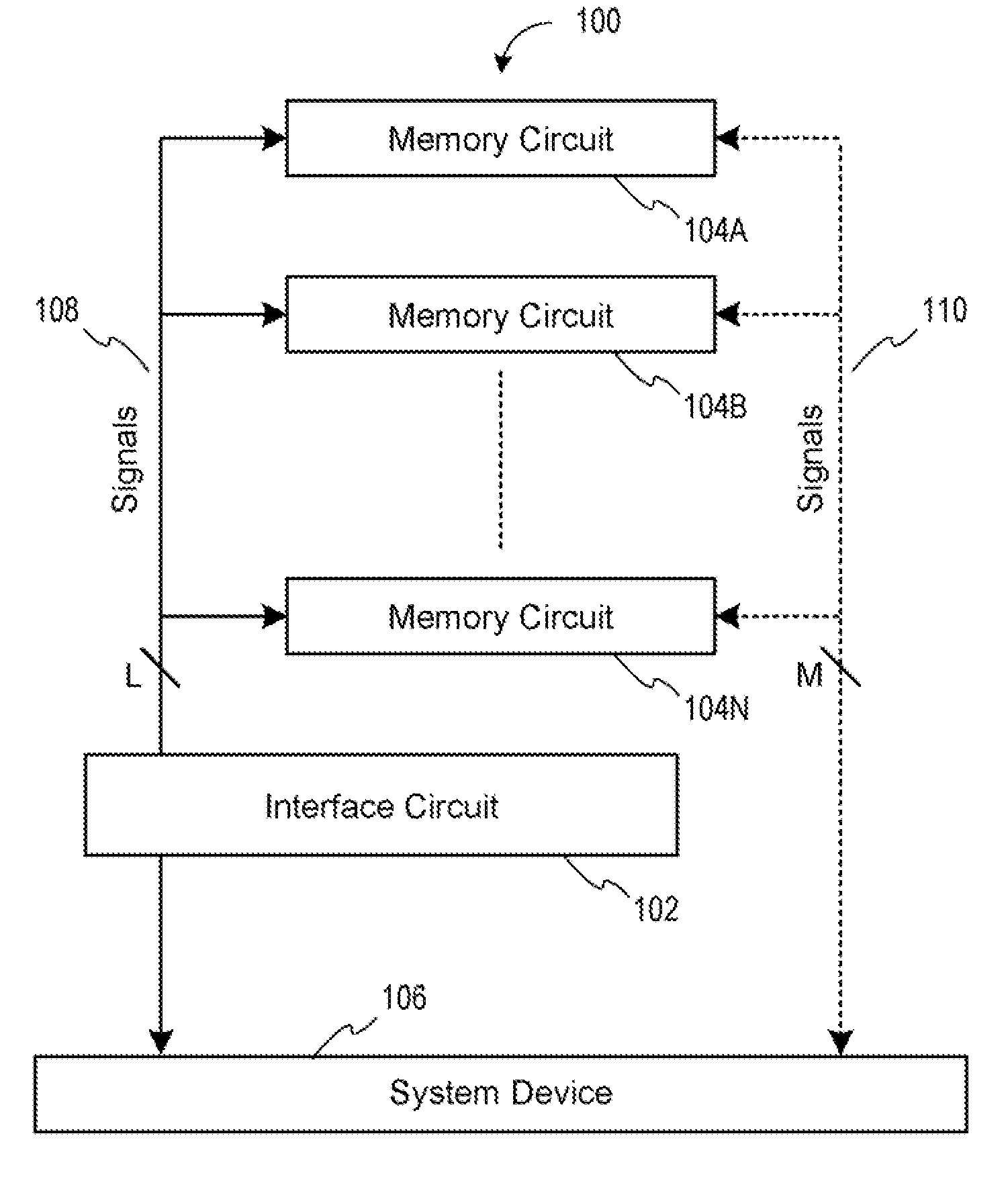

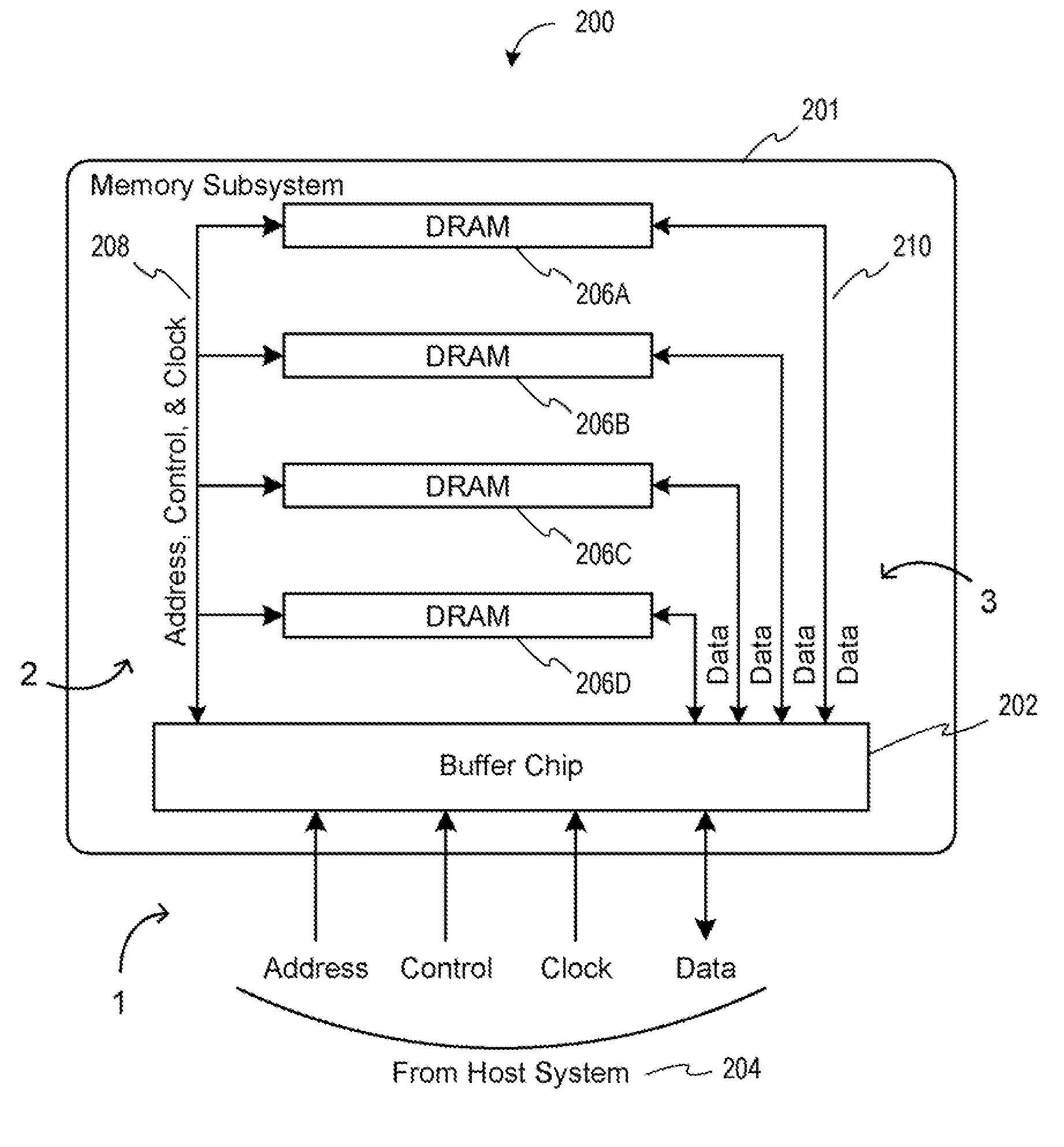

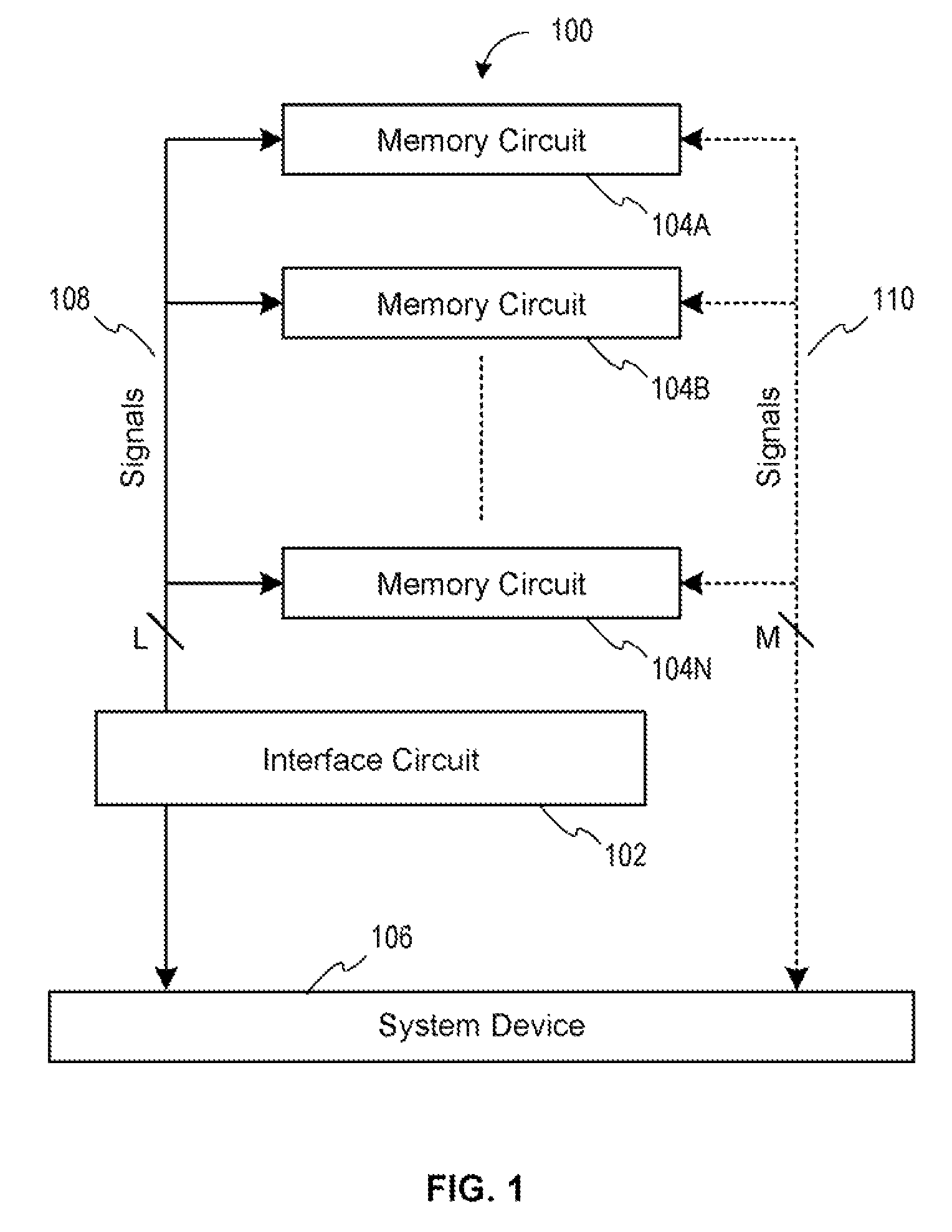

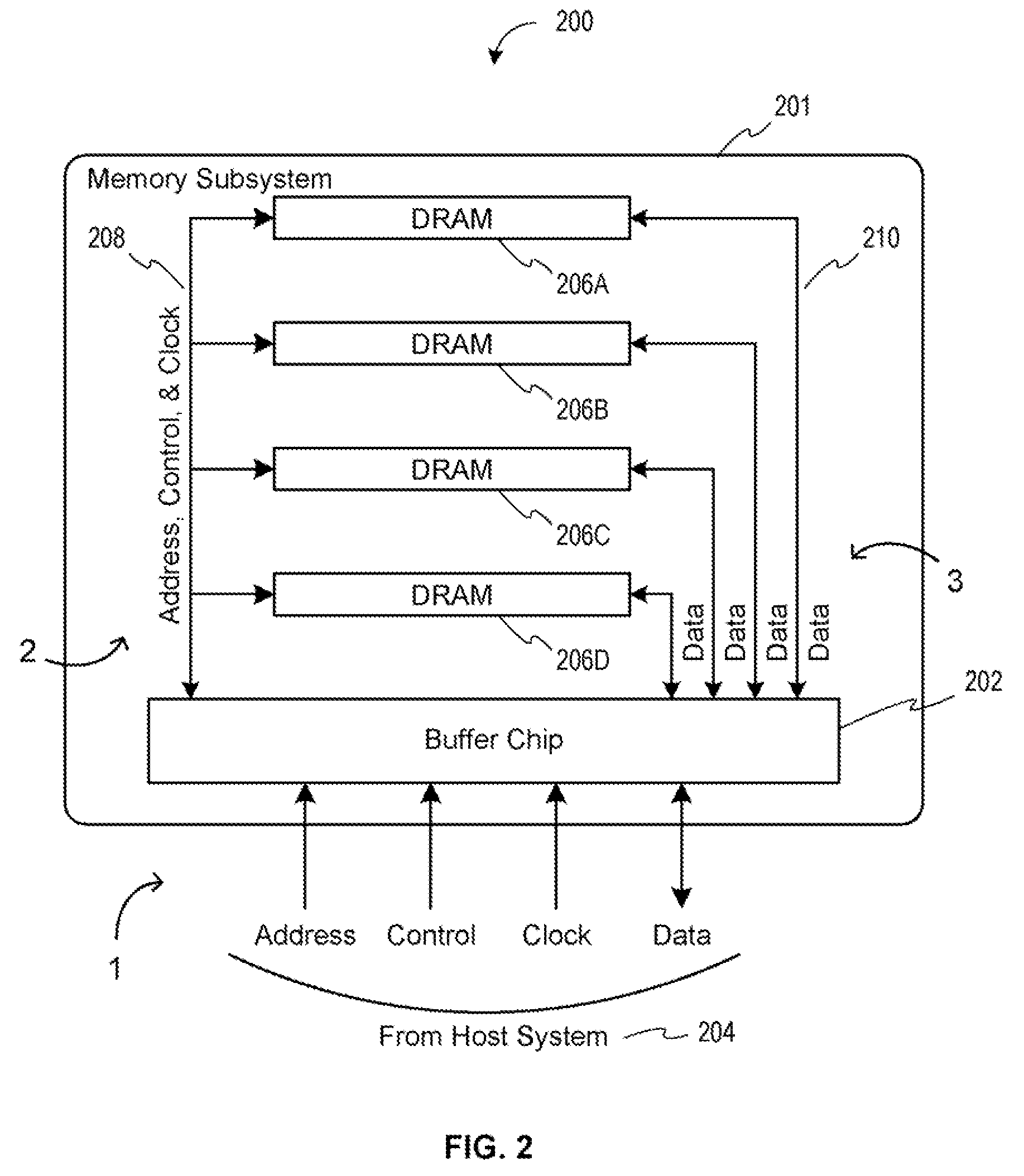

A memory subsystem is provided including an interface circuit adapted for coupling with a plurality of memory circuits and a system. The interface circuit is operable to interface the memory circuits and the system for emulating at least one memory circuit with at least one aspect that is different from at least one aspect of at least one of the plurality of memory circuits. Such aspect includes a signal, a capacity, a timing, and / or a logical interface.

Owner:GOOGLE LLC

System and method for simulating an aspect of a memory circuit

A memory subsystem is provided including an interface circuit adapted for coupling with a plurality of memory circuits and a system. The interface circuit is operable to interface the memory circuits and the system for emulating at least one memory circuit with at least one aspect that is different from at least one aspect of at least one of the plurality of memory circuits. Such aspect includes a signal, a capacity, a timing, and / or a logical interface.

Owner:GOOGLE LLC

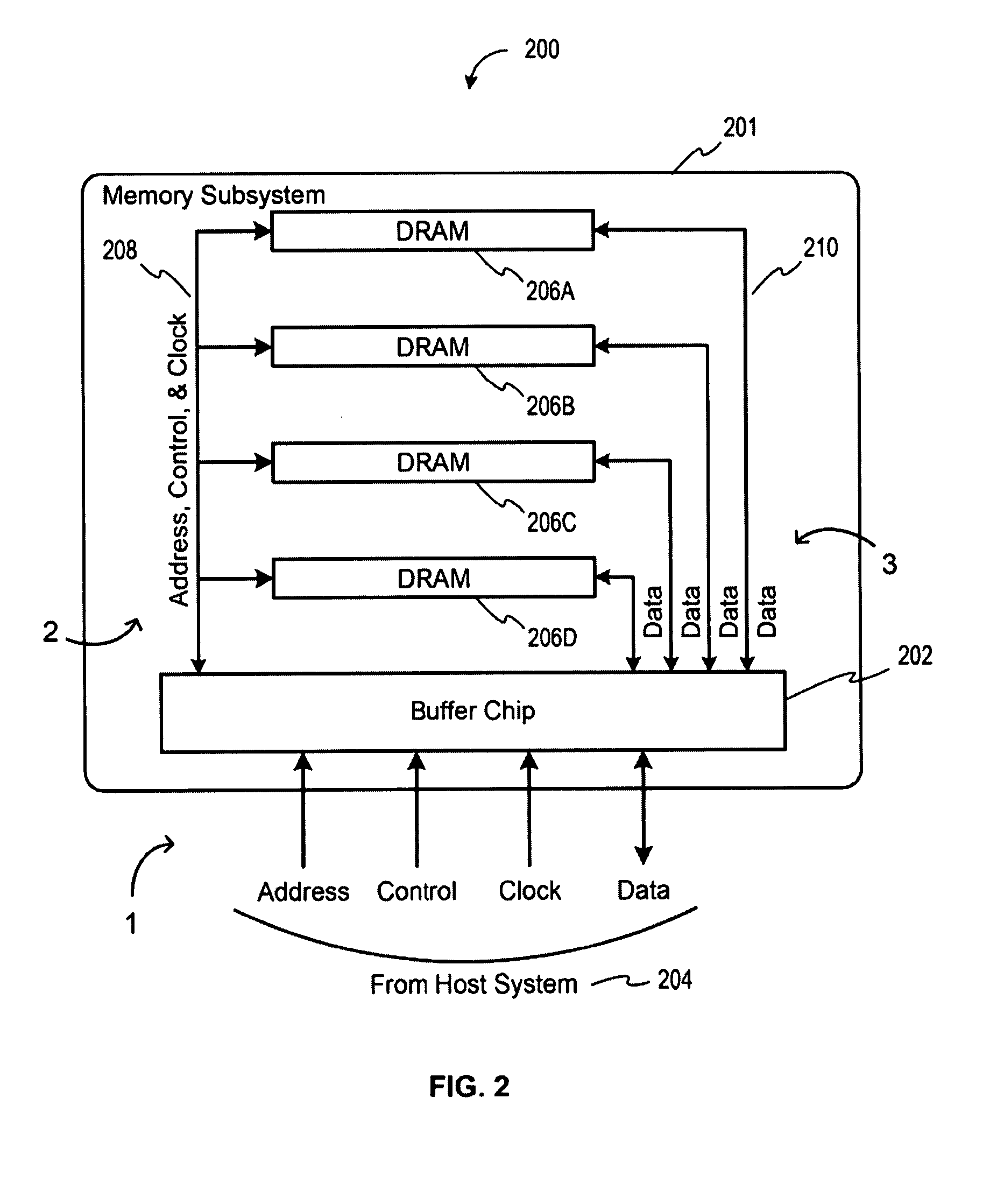

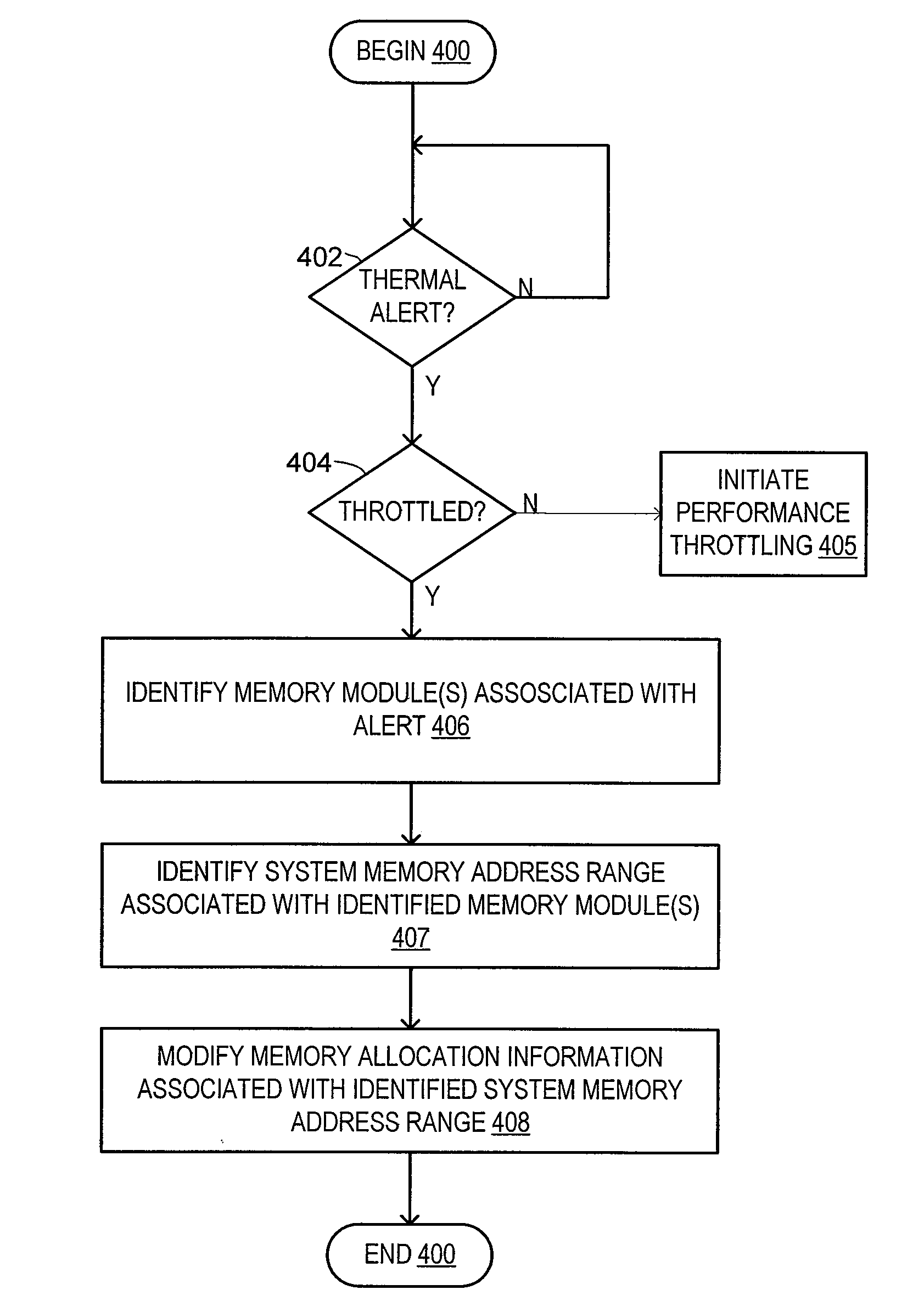

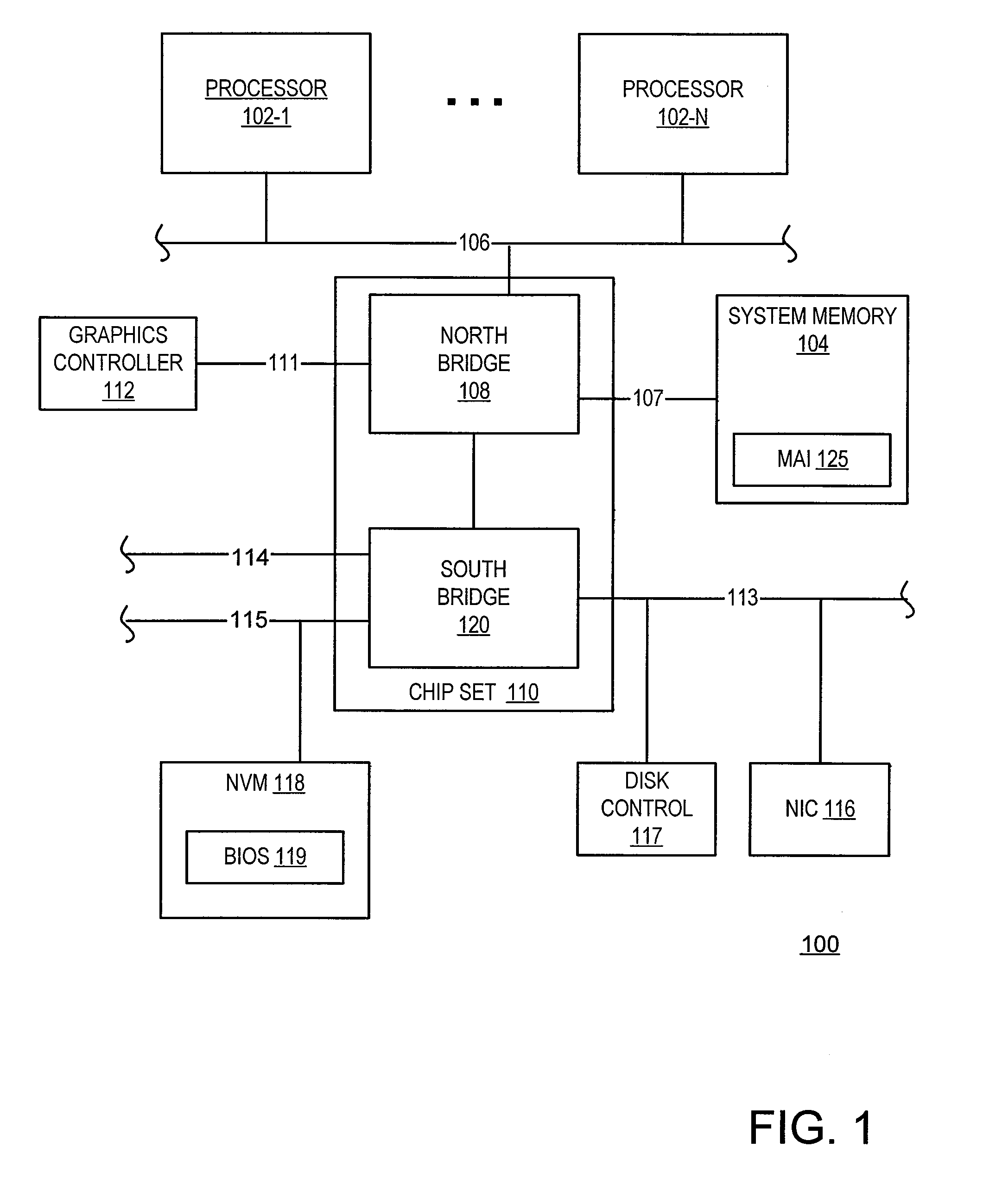

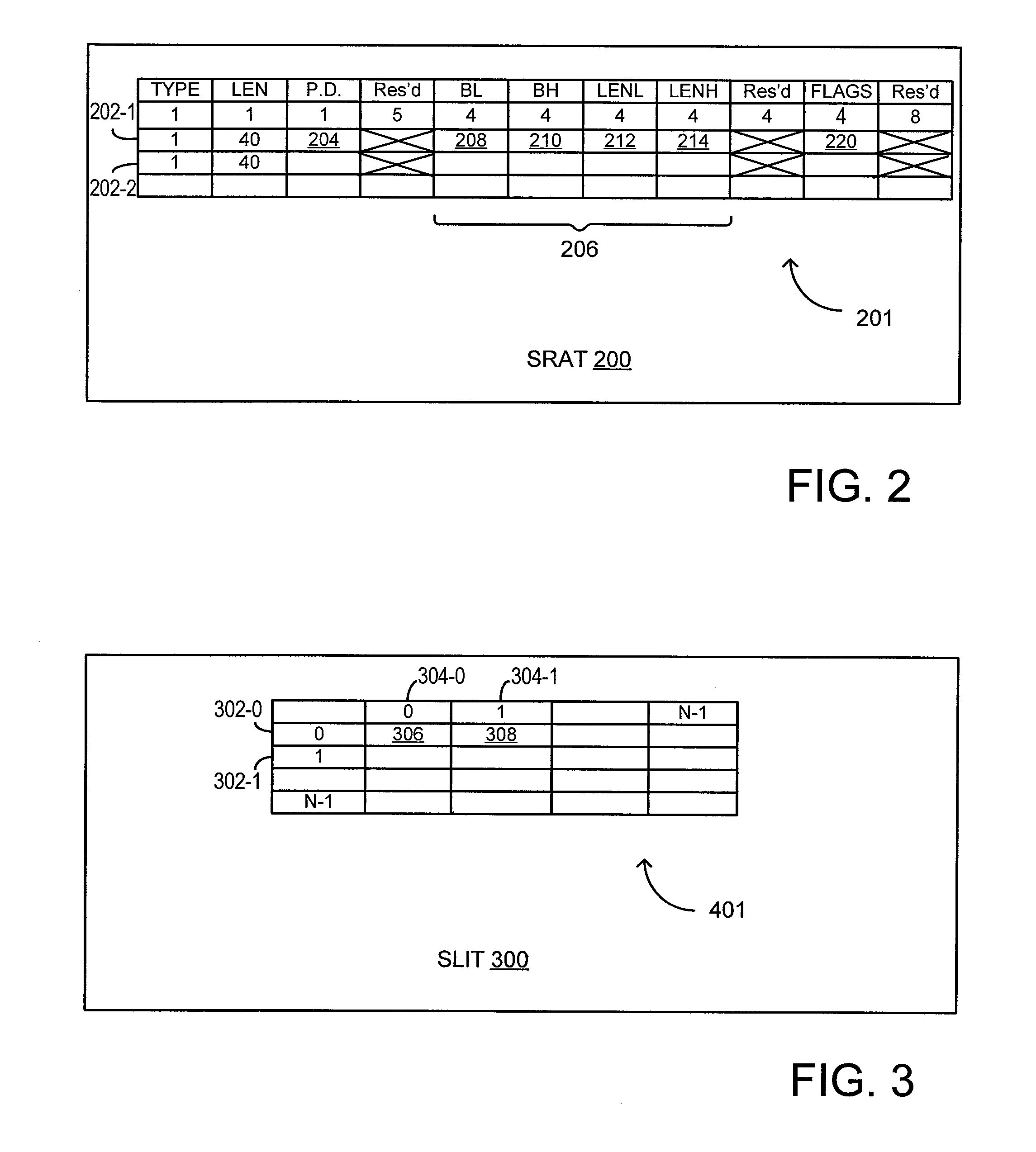

Thermal control of memory modules using proximity information

ActiveUS20080052483A1Recover thermallyReduce total usageDigital data processing detailsMemory systemsInformation processingOperational system

An information handling system includes a processor having access to a system memory. The system is operable to detect a thermal alert and identify an associated portion of system memory. The system may then modify memory allocation information used by an operating system to allocate system memory. When the thermal alert indicates a rising memory module temperature that exceeds a specified threshold, the modification of the memory allocation information causes the memory to appear to be more “distant” from the system processor(s) and thereby allocated less preferentially than other memory. If the temperature continues to rise beyond a higher threshold, a second modification of the memory allocation information is performed to simulate a “hot eject” of the memory module. As the memory module cools, the memory allocation information can be restored to simulate a hot add of the memory module and to restore the proximity of the memory module.

Owner:DELL PROD LP

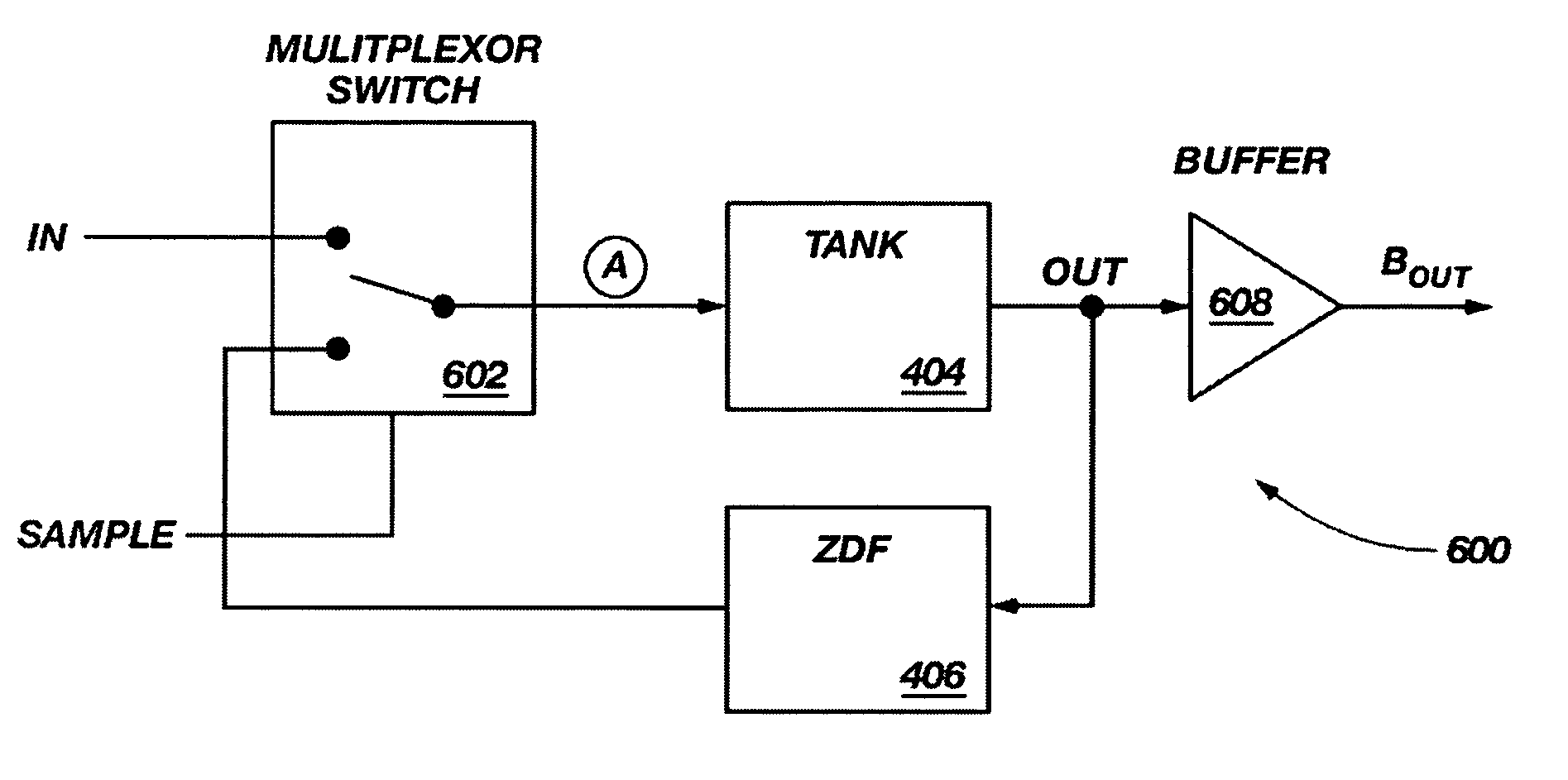

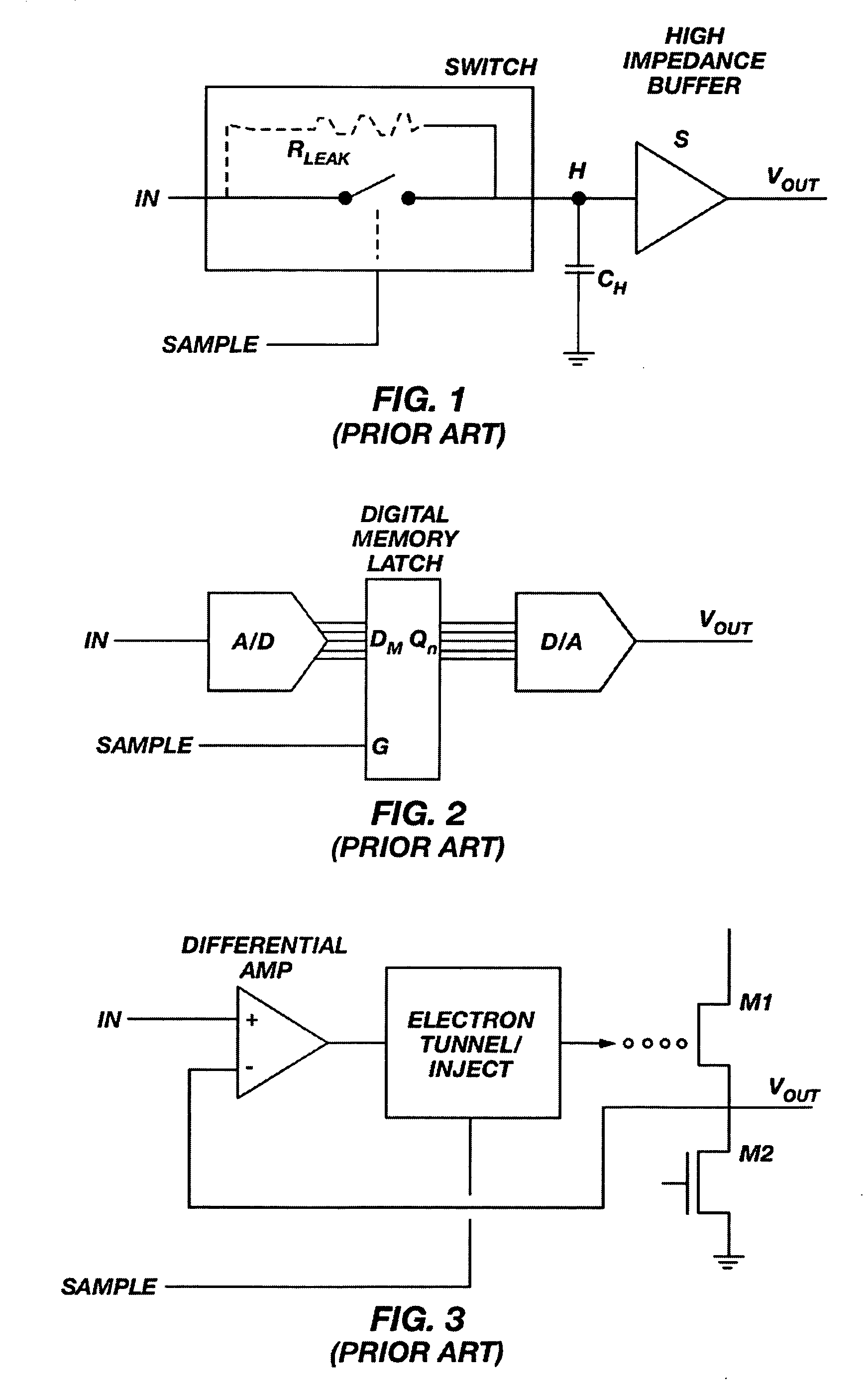

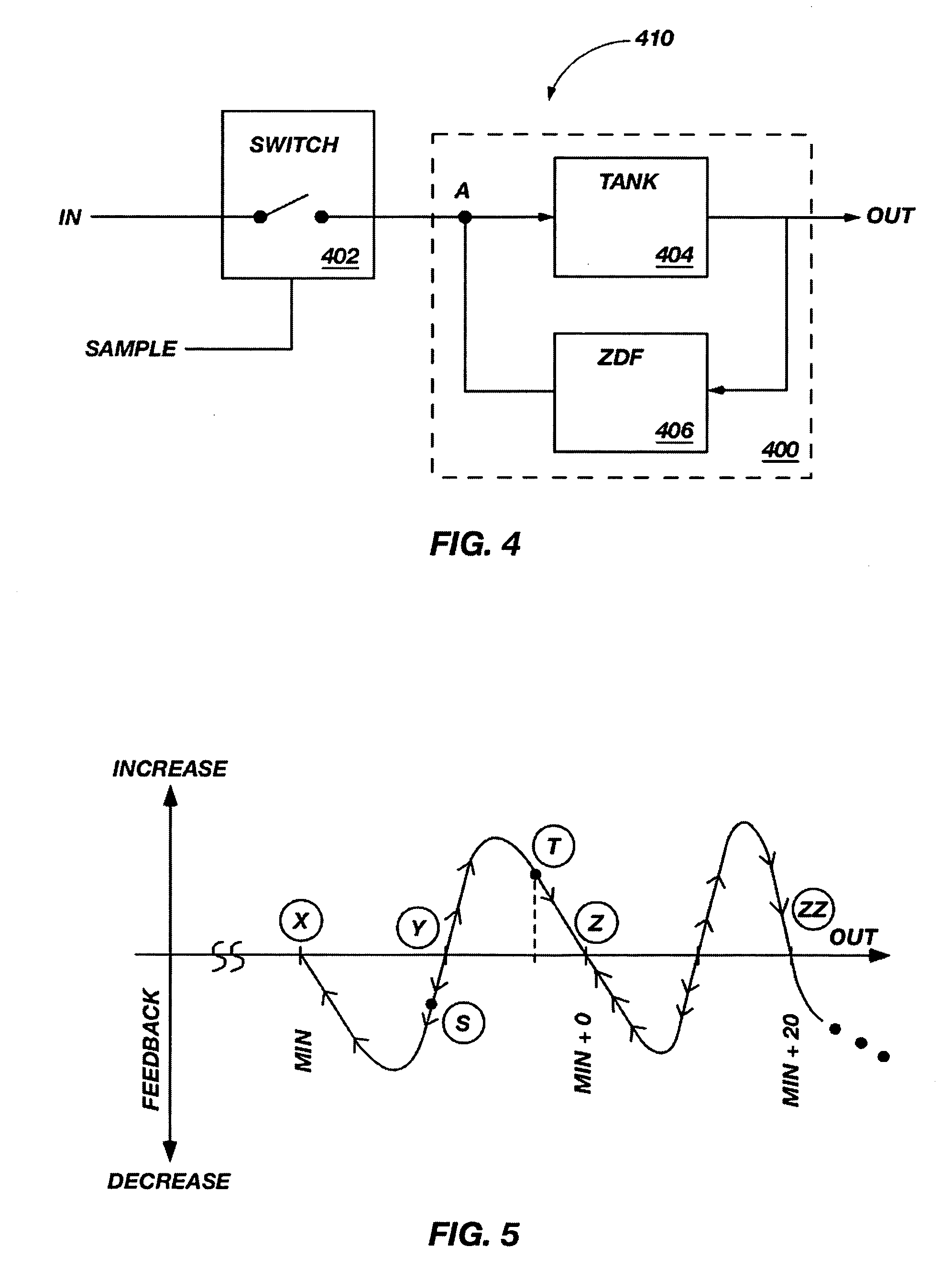

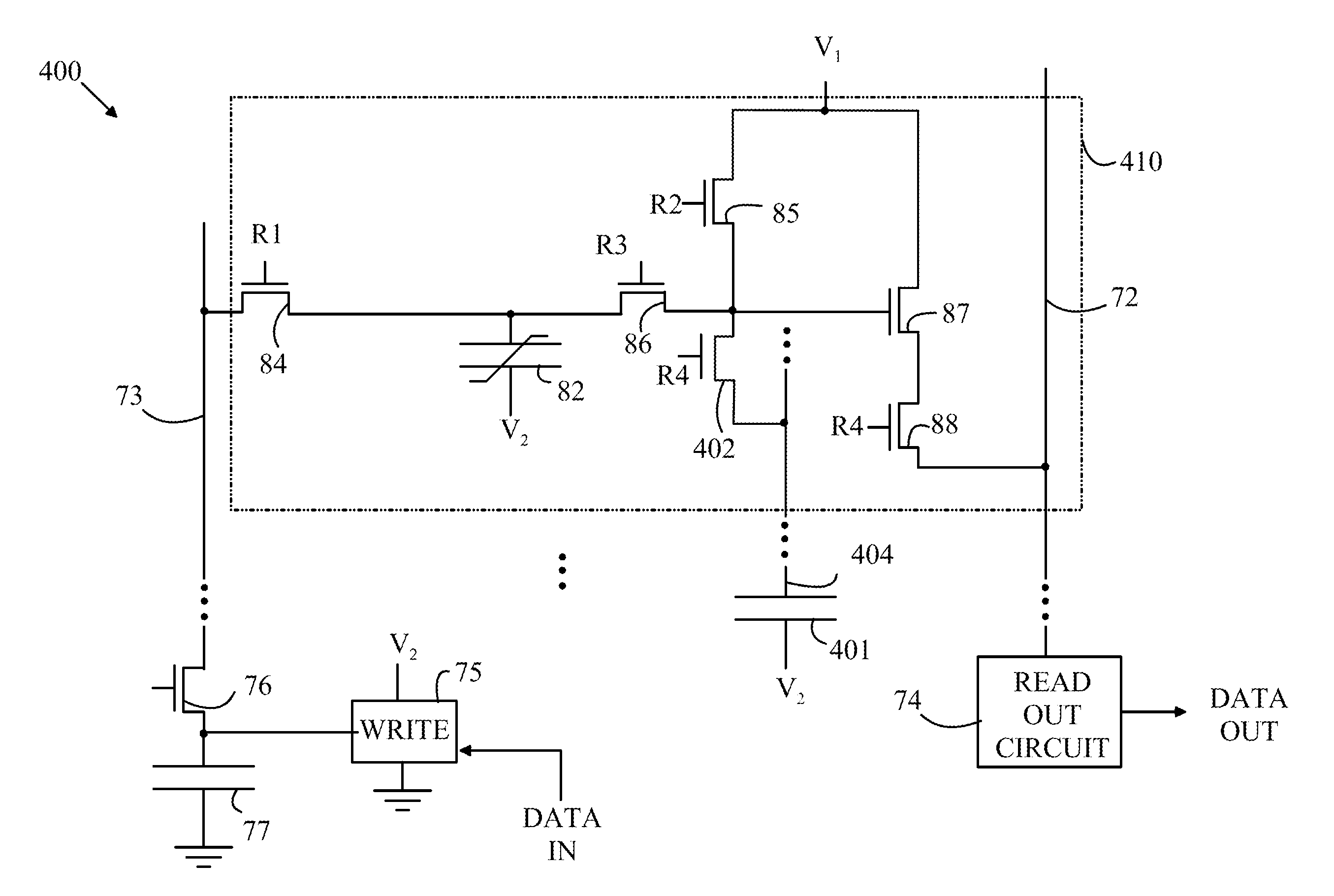

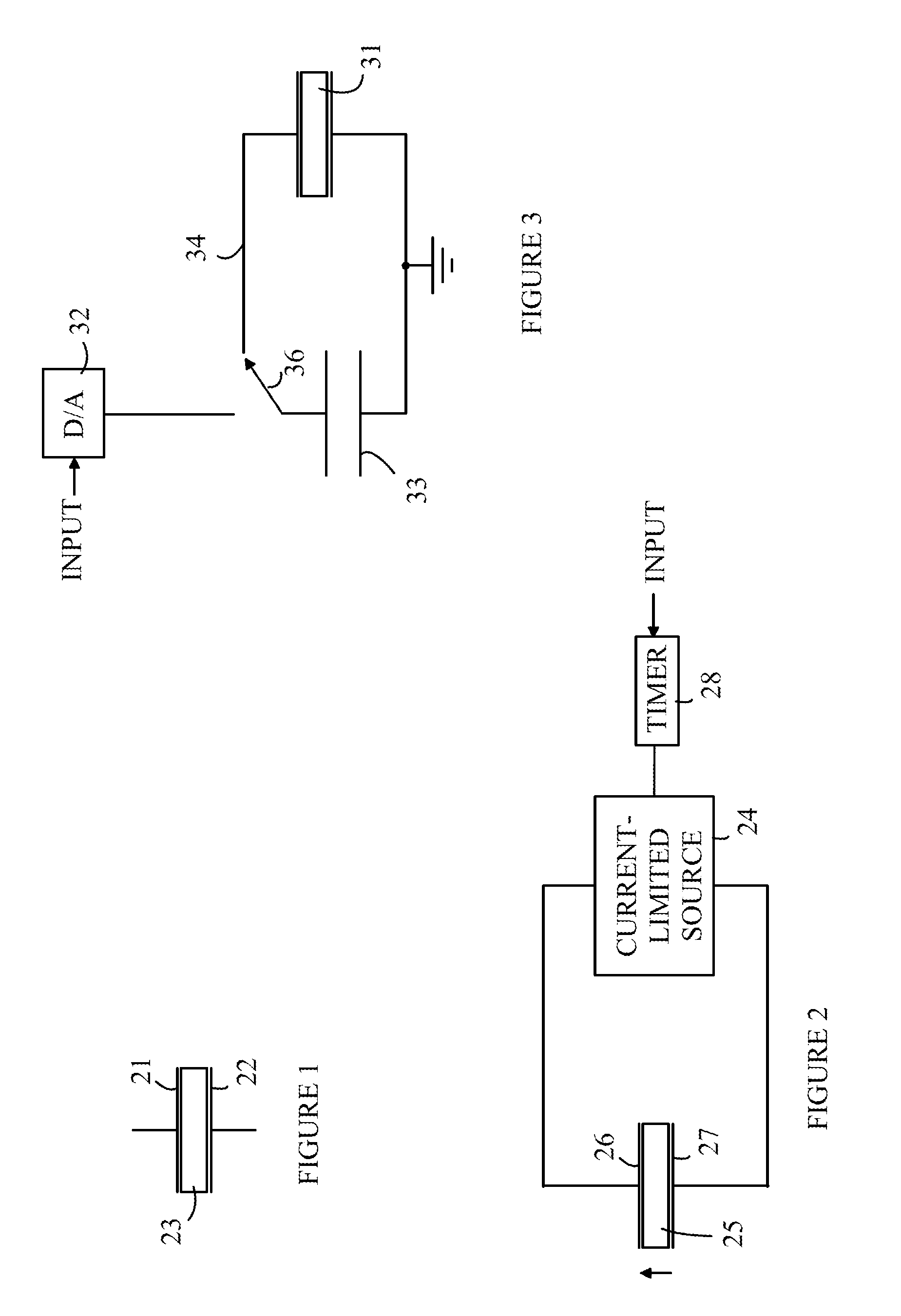

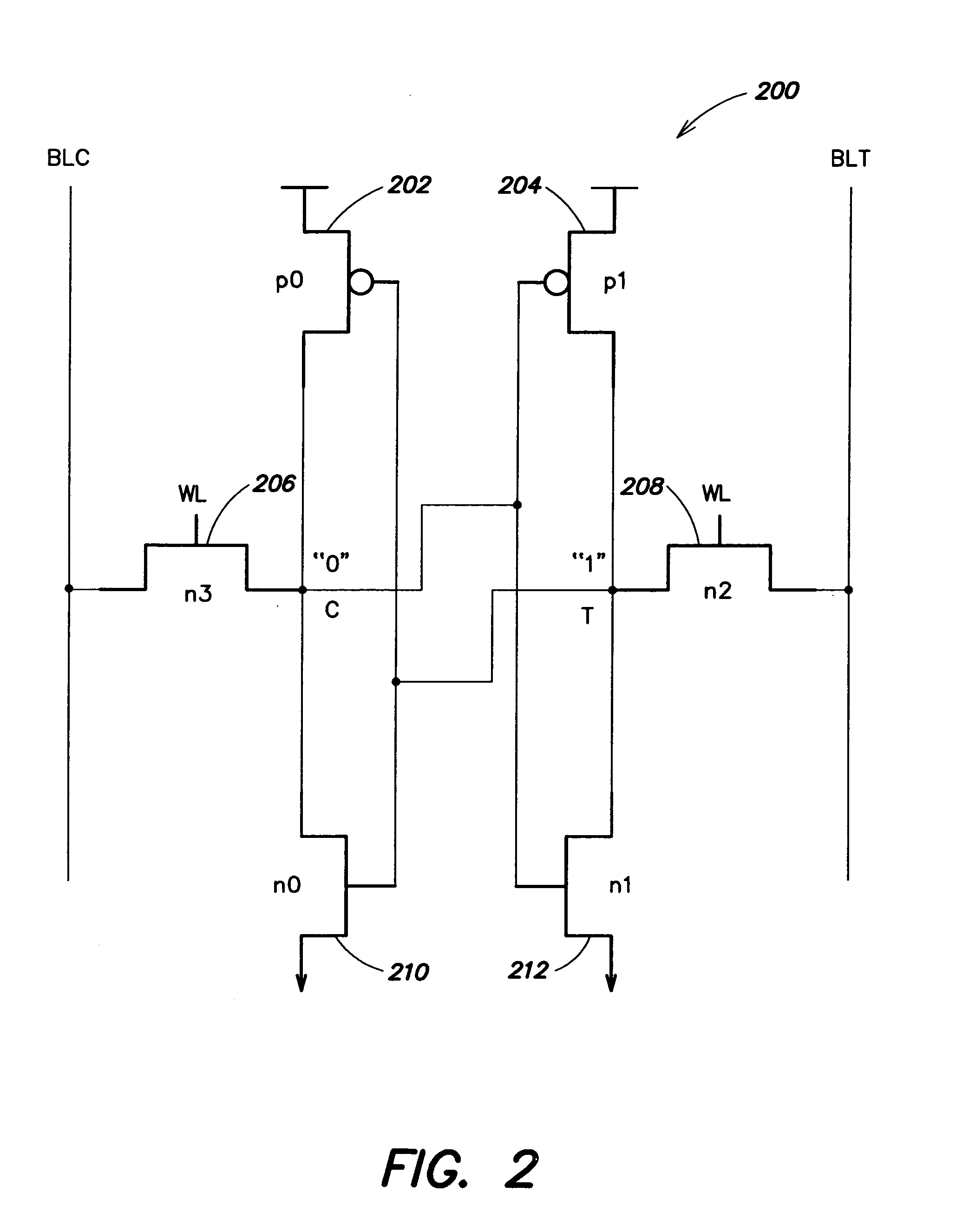

Zero drift analog memory cell, array and method of operation

A zero-drift analog memory (ZDAM) cell that indefinitely maintains an output signal at a discrete voltage while the memory circuit is powered, wherein the memory circuit receives an input signal, passes the input signal to a storage element upon receiving an assertion signal, maintains an output signal at a level of the input signal when the assertion signal is removed, and utilizes a zero-drift transfer function feedback loop on the output signal to maintain the output signal. A memory array including a plurality of ZDAM cells and method of operation are also disclosed.

Owner:VODAFONE AG

Reading memory cells using multiple thresholds

A method for operating a memory (28) includes storing data, which is encoded with an Error Correction Code (ECC), in analog memory cells (32) of the memory by writing respective analog input values selected from a set of nominal values to the analog memory cells. The stored data is read by performing multiple read operations that compare analog output values of the analog memory cells to different, respective read thresholds so as to produce multiple comparison results for each of the analog memory cells. At least two of the read thresholds are positioned between a pair of the nominal values that are adjacent to one another in the set of the nominal values. Soft metrics are computed responsively to the multiple comparison results. The ECC is decoded using the soft metrics, so as to extract the data stored in the analog memory cells.

Owner:APPLE INC

System and method for simulating an aspect of a memory circuit

A memory subsystem is provided including an interface circuit adapted for coupling with a plurality of memory circuits and a system. The interface circuit is operable to interface the memory circuits and the system for emulating at least one memory circuit with at least one aspect that is different from at least one aspect of at least one of the plurality of memory circuits. Such aspect includes a signal, a capacity, a timing, and / or a logical interface.

Owner:GOOGLE LLC

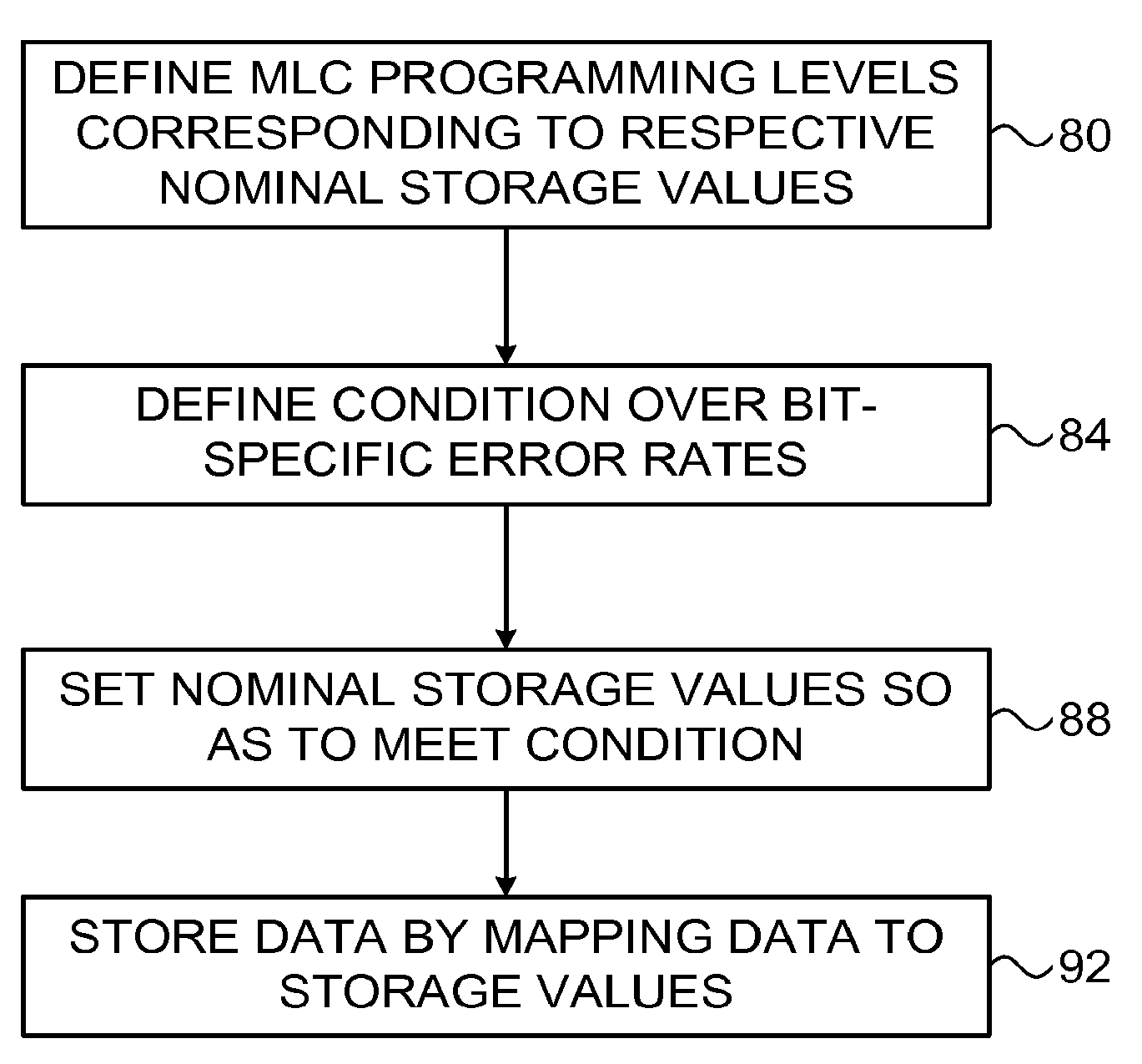

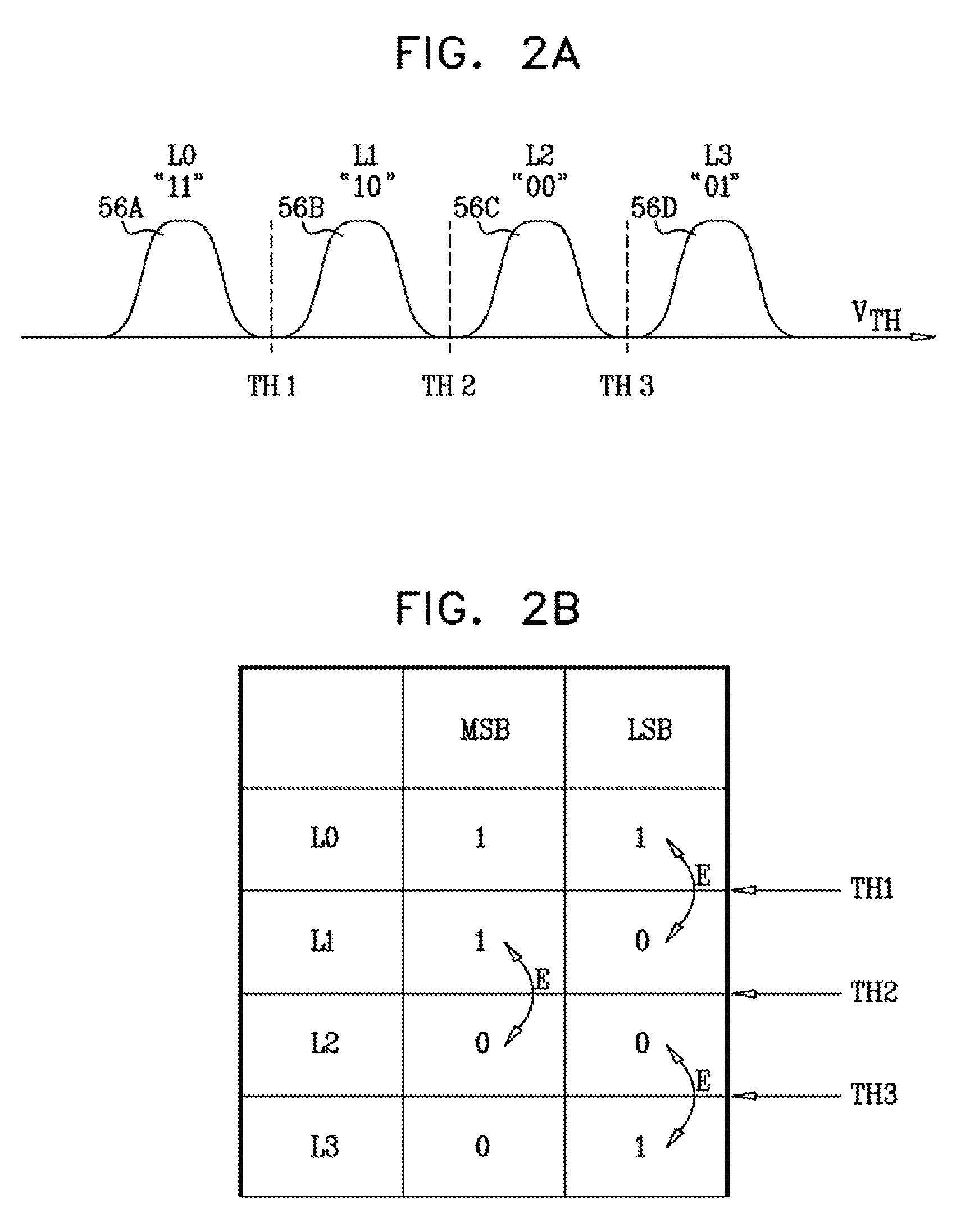

Memory device with non-uniform programming levels

InactiveUS7925936B1Reduce spacingHigh error rateError preventionTransmission systemsData storingComputer science

A method for storing data in a memory, which includes a plurality of analog memory cells, includes defining programming levels that represent respective combinations of at least first and second bits and are represented by respective nominal storage values. The data is stored by mapping the data to storage values selected from among the nominal storage values and writing the storage values to the memory cells. A condition is defined over two or more bit-specific error rates applicable respectively to at least the first and second bits. The bit-specific error rates include a first bit-specific error rate computed over the data stored by the first bits and a second bit-specific error rate computed, separately from the first bit-specific error rate, over the data stored by the second bits. The nominal storage values are set based on the bit-specific error rates so as to meet the condition.

Owner:APPLE INC

Combined distortion estimation and error correction coding for memory devices

ActiveUS8156403B2Improve performanceData representation error detection/correctionError detection/correctionCalculation errorForward error correction

Owner:APPLE INC

Analog memories utilizing ferroelectric capacitors

A ferroelectric memory having a plurality of ferroelectric memory cells, each ferroelectric memory cell including a ferroelectric capacitor is disclosed. The ferroelectric memory includes read and write lines and a plurality of ferroelectric memory cell select buses, one select bus corresponding to each of the ferroelectric memory cells. Each of the ferroelectric memory cells includes first and second gates for connecting the ferroelectric memory cell to the read line and the write line, respectively, in response to signals on the ferroelectric memory cell select bus corresponding to that ferroelectric memory cell. A write circuit causes a charge to be stored in the ferroelectric capacitor of the ferroelectric memory cell currently connected to the write line, the charge having a value determined by a data value having at least three states. A read circuit measures the charge stored in the ferroelectric capacitor of the ferroelectric memory cell currently connected to the read line to generate an output value, the output value corresponding to one of the states.

Owner:RADIANT TECH

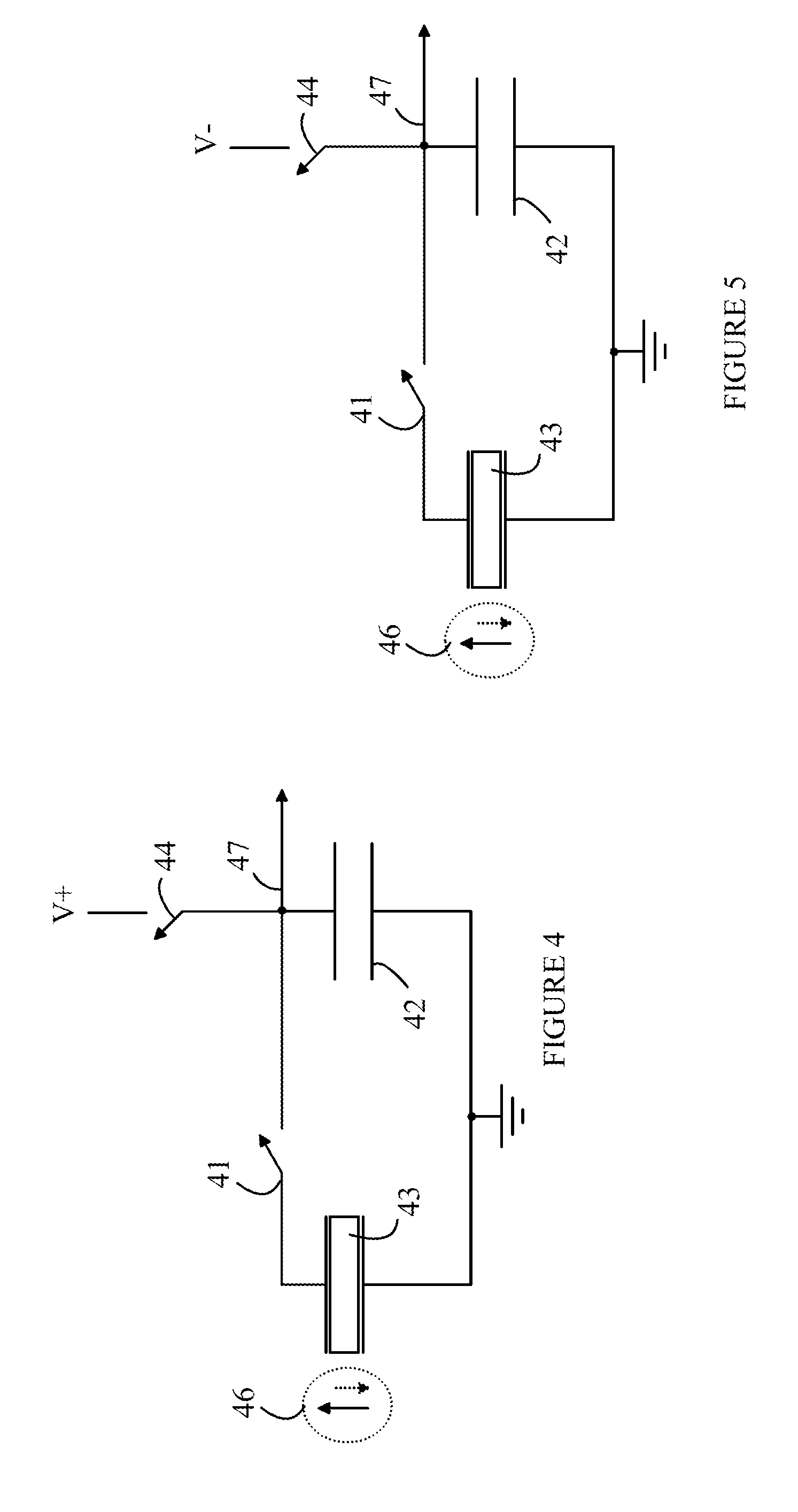

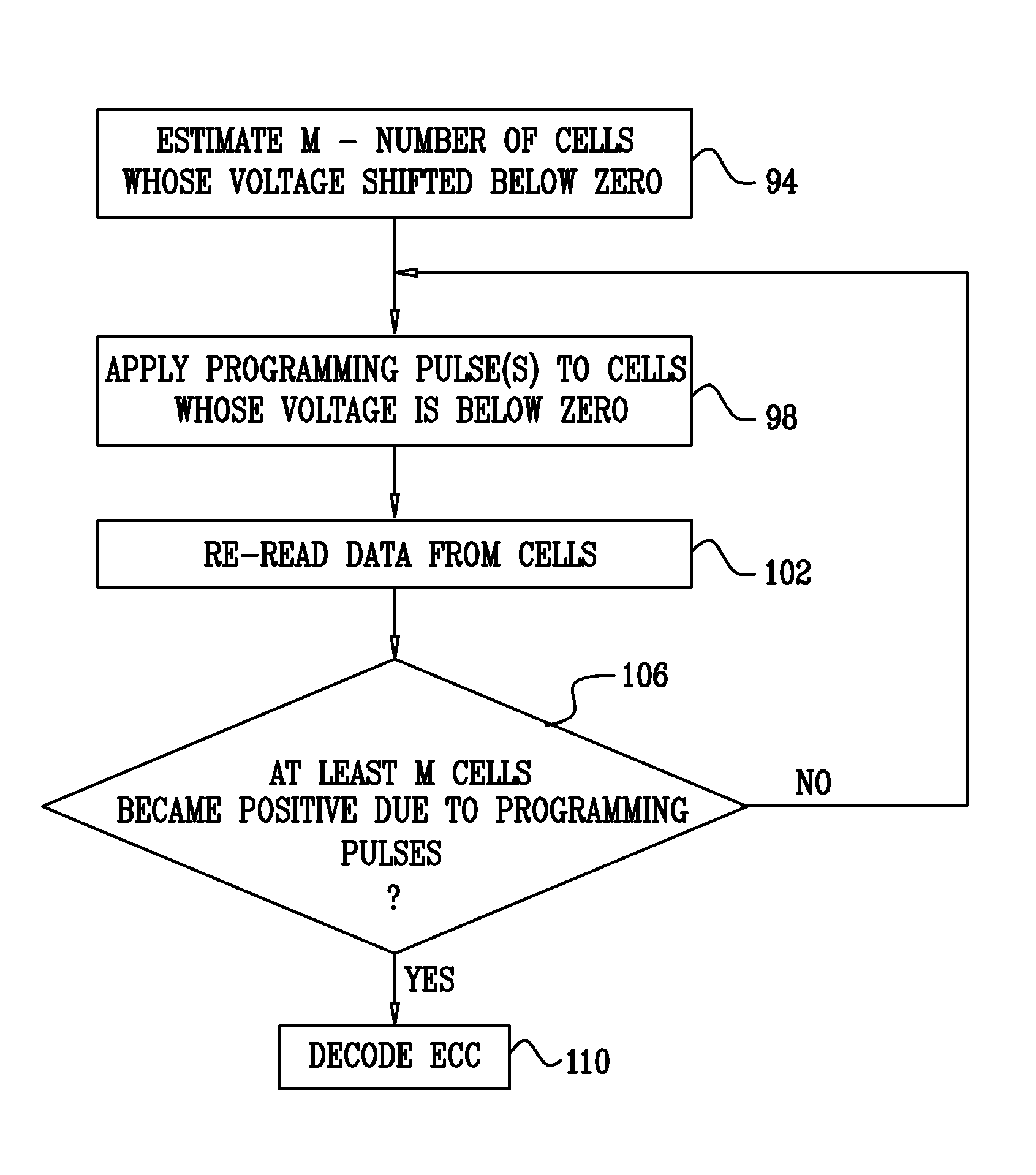

Compensation for voltage drifts in analog memory cells

A method for data storage includes storing data in a group of analog memory cells by writing respective first storage values into the memory cells. After storing the data, respective second storage values are read from the memory cells. A subset of the memory cells, in which the respective second storage values have drifted below a minimum readable value, is identified. The memory cells in the subset are operated on, so as to cause the second storage values of at least one of the memory cells in the subset to exceed the minimum readable value. At least the modified second storage values are re-read so as to reconstruct the stored data.

Owner:APPLE INC

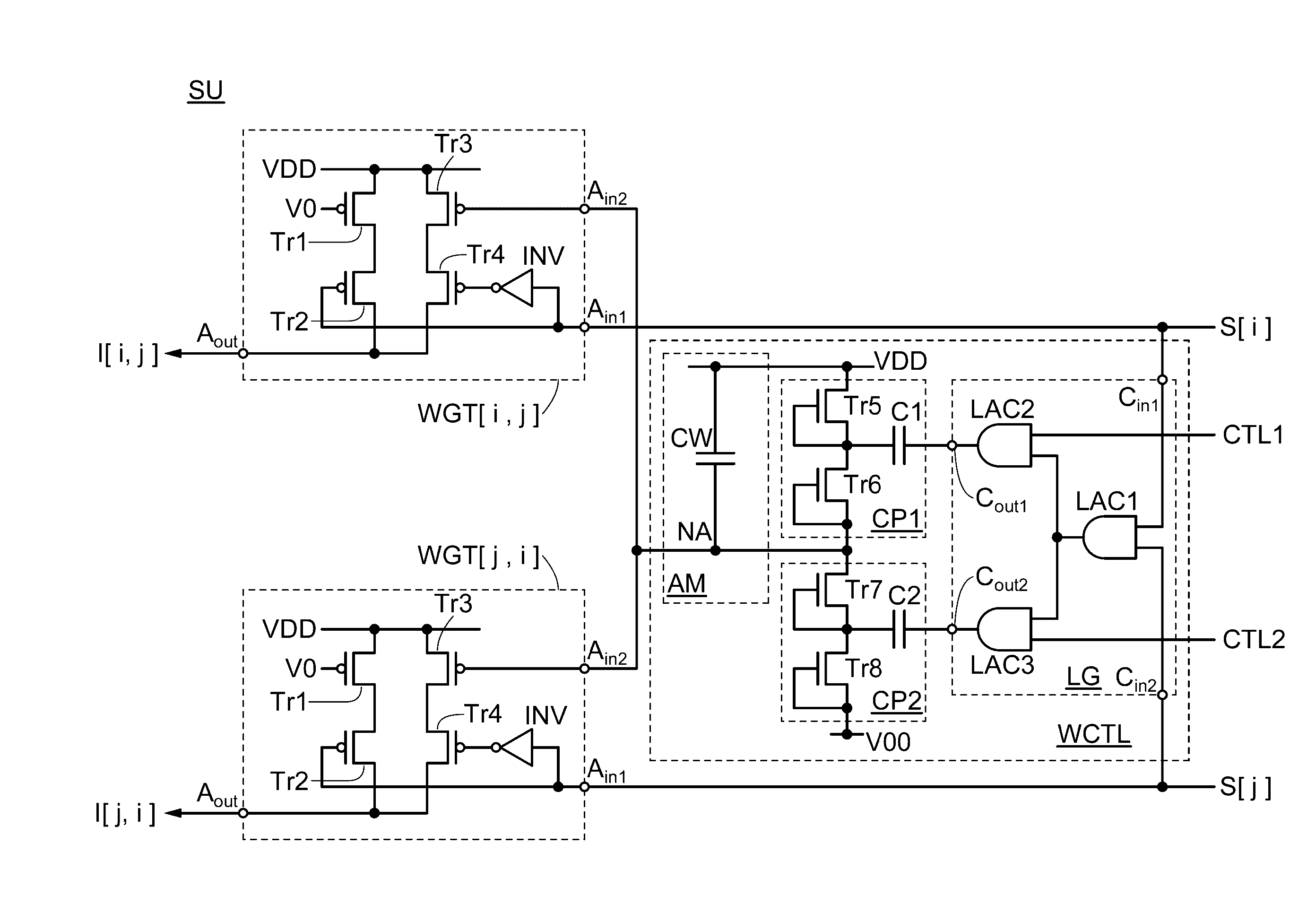

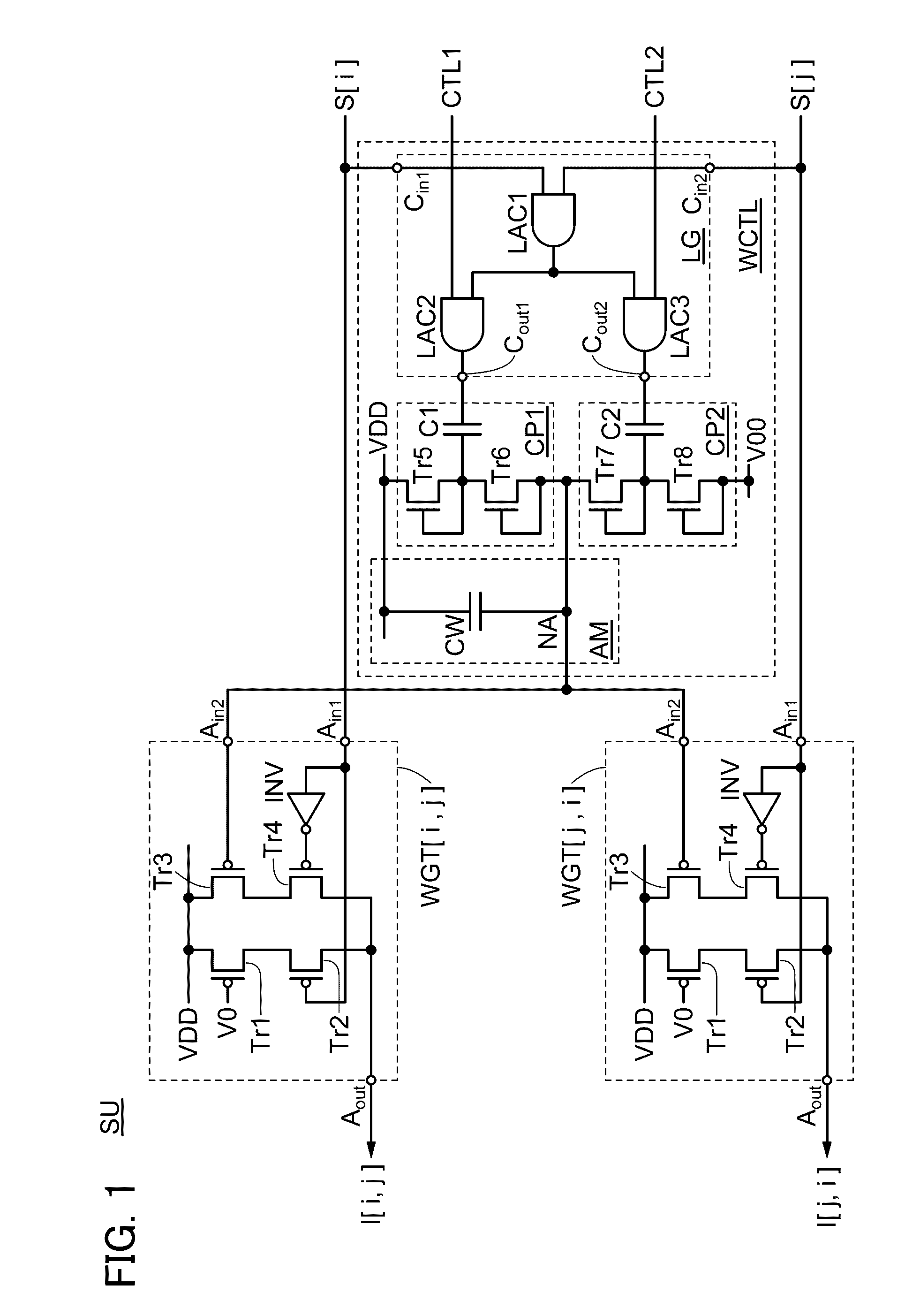

Semiconductor device or electronic device including the semiconductor device

InactiveUS20170063351A1Reduce circuit sizeReduce power consumptionTransistorSolid-state devicesHopfield networkData compression

To provide a semiconductor device with a small circuit size and low power consumption or an electronic device including the semiconductor device and compressing a large volume of image data. A semiconductor device of a Hopfield neural network is formed using neuron circuits and synapse circuits. The synapse circuit includes an analog memory and a writing control circuit, and the writing control circuit is formed using a transistor including an oxide semiconductor in a channel formation region. Thus, data retention lifetime of the analog memory can be extended and refresh operation for data retention can be omitted, so that power consumption of the semiconductor device can be reduced. The semiconductor device enables judgement whether learned image data and arbitrary image data match, are similar, or mismatch by comparing video data. Thus, motion compensation prediction, which is one of data compression methods, can be employed for image data.

Owner:SEMICON ENERGY LAB CO LTD

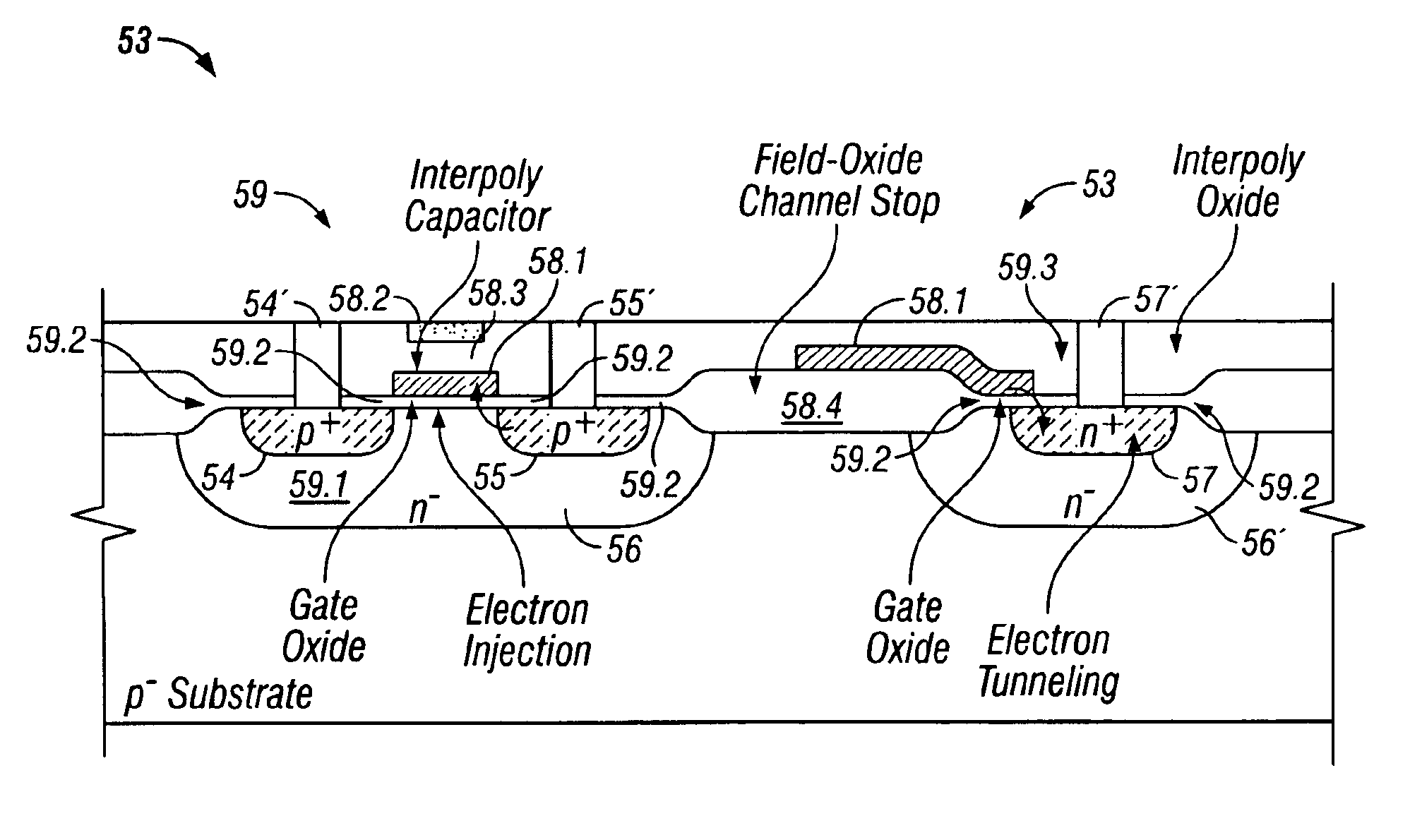

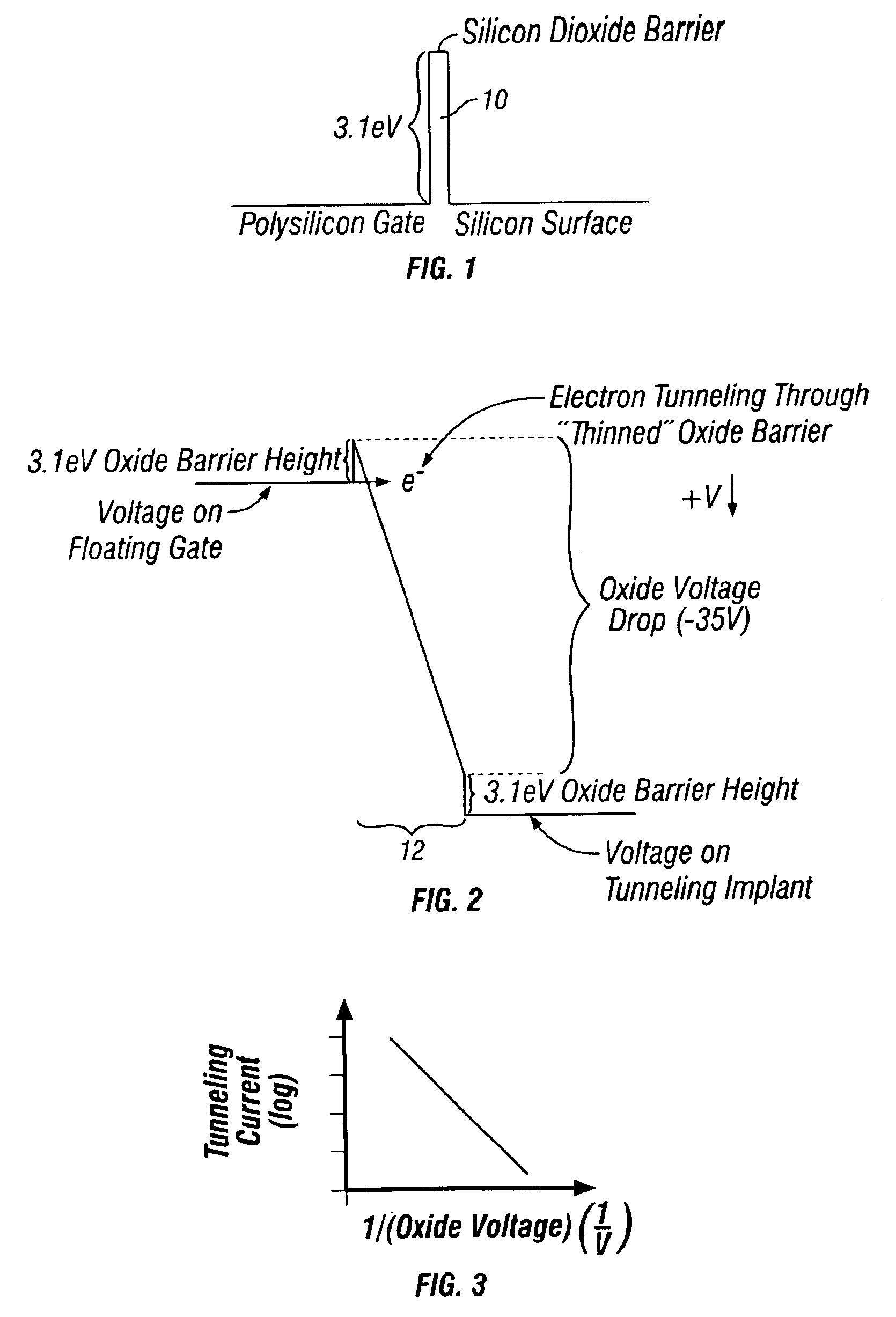

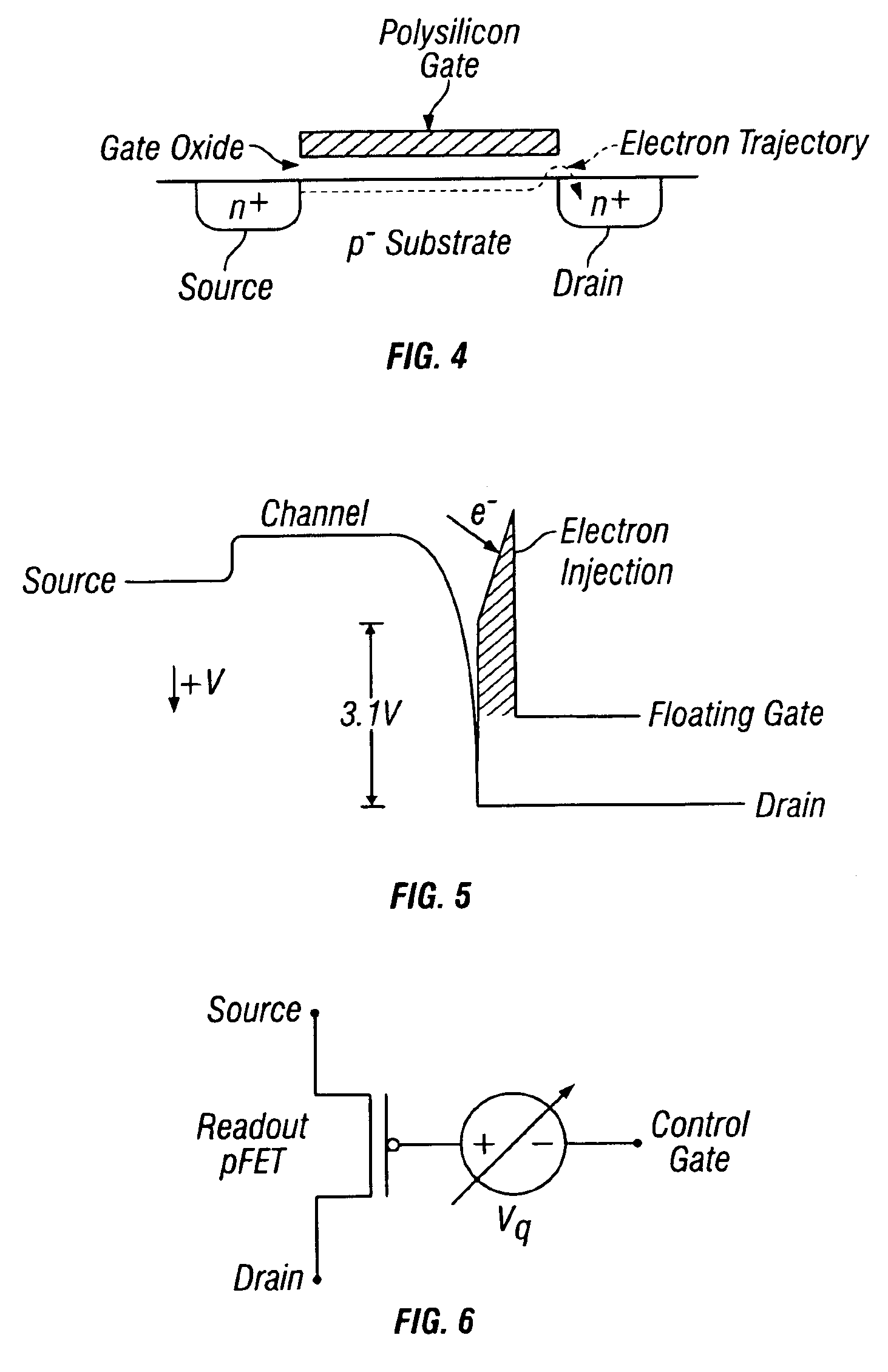

Floating-gate semiconductor structures

Hot-electron injection driven by hole impact ionization in the channel-to-drain junction of a p-channel MOSFET provides a new mechanism for writing a floating-gate memory. Various pFET floating-gate structures use a combination of this mechanism and electron tunneling to implement nonvolatile analog memory, nonvolatile digital memory, or on-line learning in silicon. The memory is nonvolatile because the devices use electrically isolated floating gates to store electronic charge. The devices enable on-line learning because the electron injection and tunneling mechanisms that write the memory can occur during normal device operation. The memory updates and learning are bidirectional because the injection and tunneling mechanisms add and remove electrons from the floating gate, respectively. Because the memory updates depend on both the stored memory and the pFETs terminal voltages, and because they are bidirectional, the devices can implement on-line learning functions.

Owner:SYNOPSYS INC +1

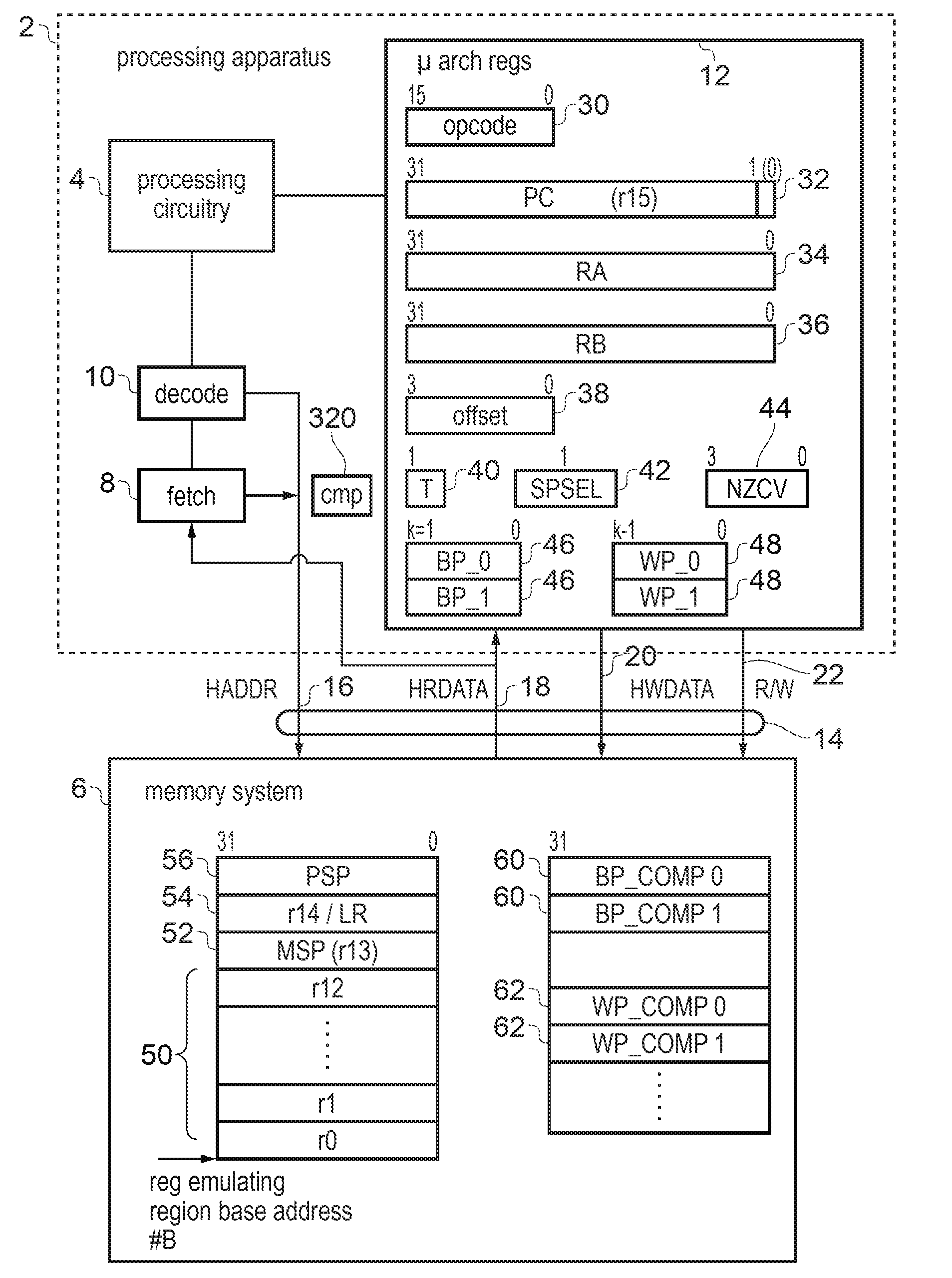

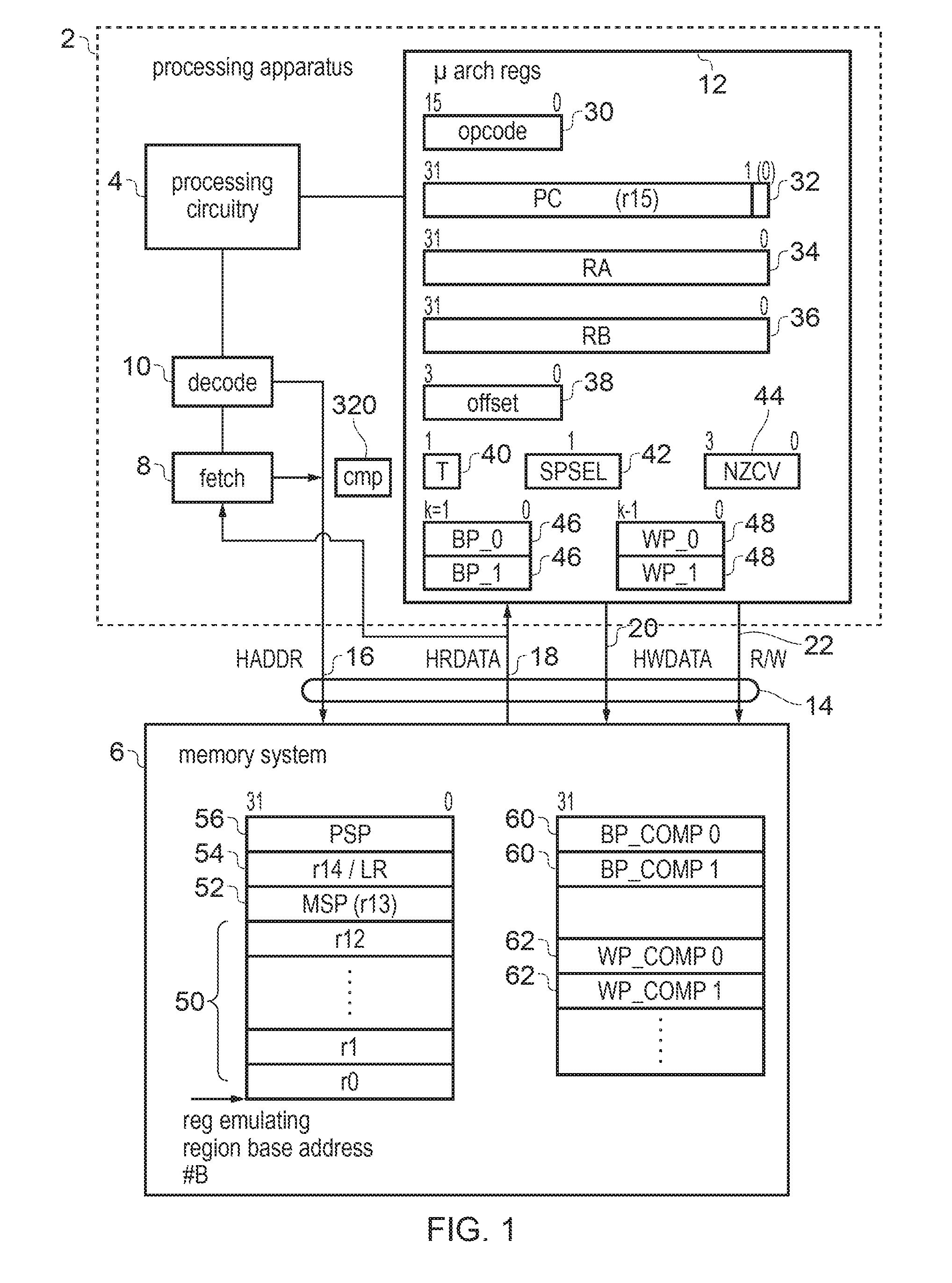

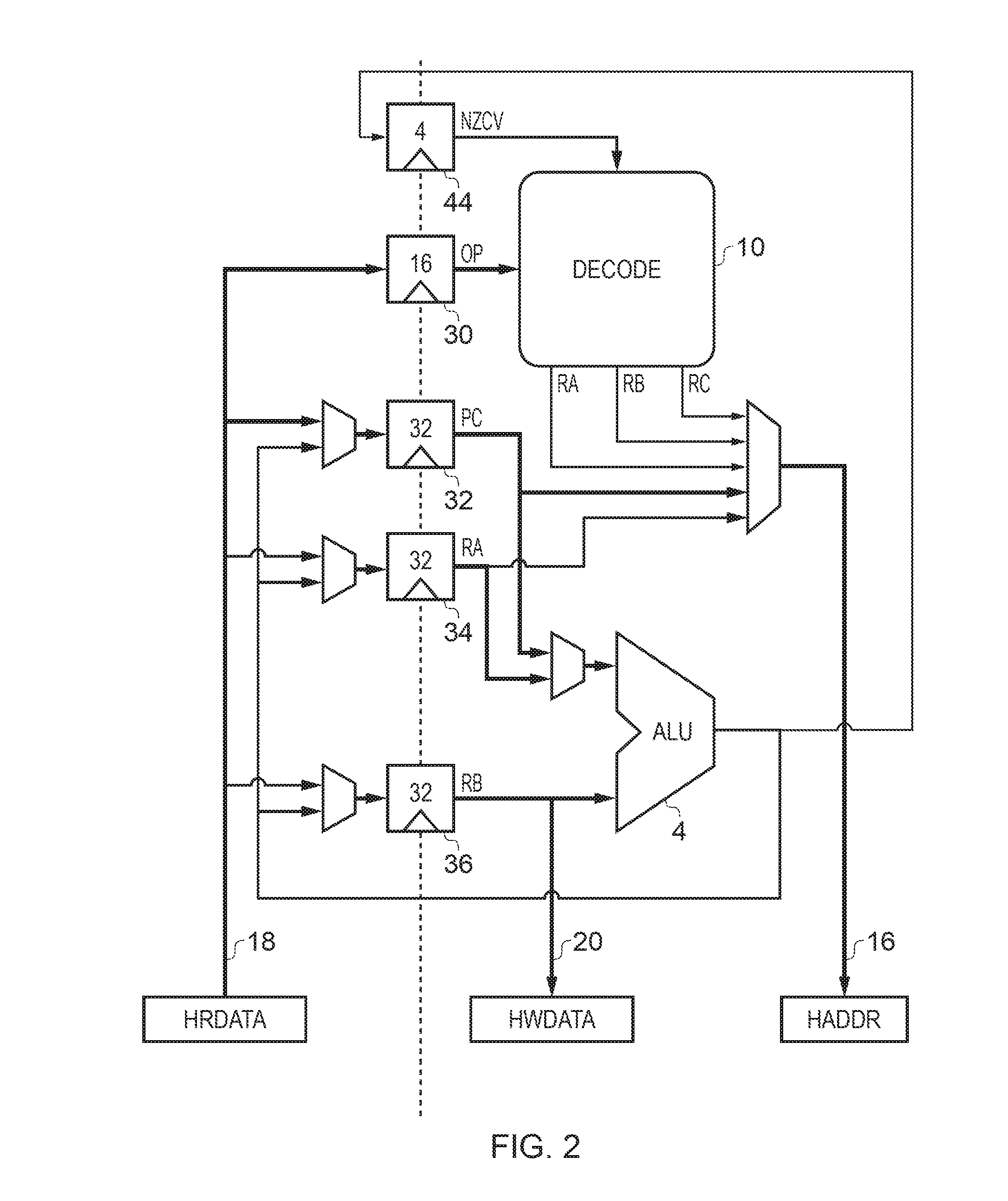

Apparatus with reduced hardware register set

InactiveUS20170031685A1Register arrangementsConcurrent instruction executionProgram instructionParallel computing

An apparatus comprises processing circuitry for processing program instructions according to a predetermined architecture defining a number of architectural registers accessible in response to the program instructions. A set of hardware registers is provided in hardware. A storage capacity of the set of hardware registers is insufficient for storing all the data associated with the architectural registers of the pre-determined architecture. Control circuitry is responsive to the program instructions to transfer data between the hardware registers and at least one register emulating memory location in memory for storing data corresponding to the architectural registers of the architecture.

Owner:ARM LTD

Distortion estimation and cancellation in memory devices

A method for operating a memory (28) includes storing data in a group of analog memory cells (32) of the memory as respective first voltage levels. After storing the data, second voltage levels are read from the respective analog memory cells. The second voltage levels are affected by cross-coupling interference causing the second voltage levels to differ from the respective first voltage levels. Cross-coupling coefficients, which quantify the cross-coupling interference among the analog memory cells, are estimated by processing the second voltage levels. The data stored in the group of analog memory cells is reconstructed from the read second voltage levels using the estimated cross-coupling coefficients.

Owner:APPLE INC

Estimation of non-linear distortion in memory devices

A method for operating a memory (24) includes storing data in analog memory cells (32) of the memory by writing respective analog values to the analog memory cells. A set of the analog memory cells is identified, including an interfered cell having a distortion that is statistically correlated with the respective analog values of the analog memory cells in the set. A mapping is determined between combinations of possible analog values of the analog memory cells in the set and statistical characteristics of composite distortion levels present in the interfered memory cell. The mapping is applied so as to compensate for the distortion in the interfered memory cell.

Owner:APPLE INC

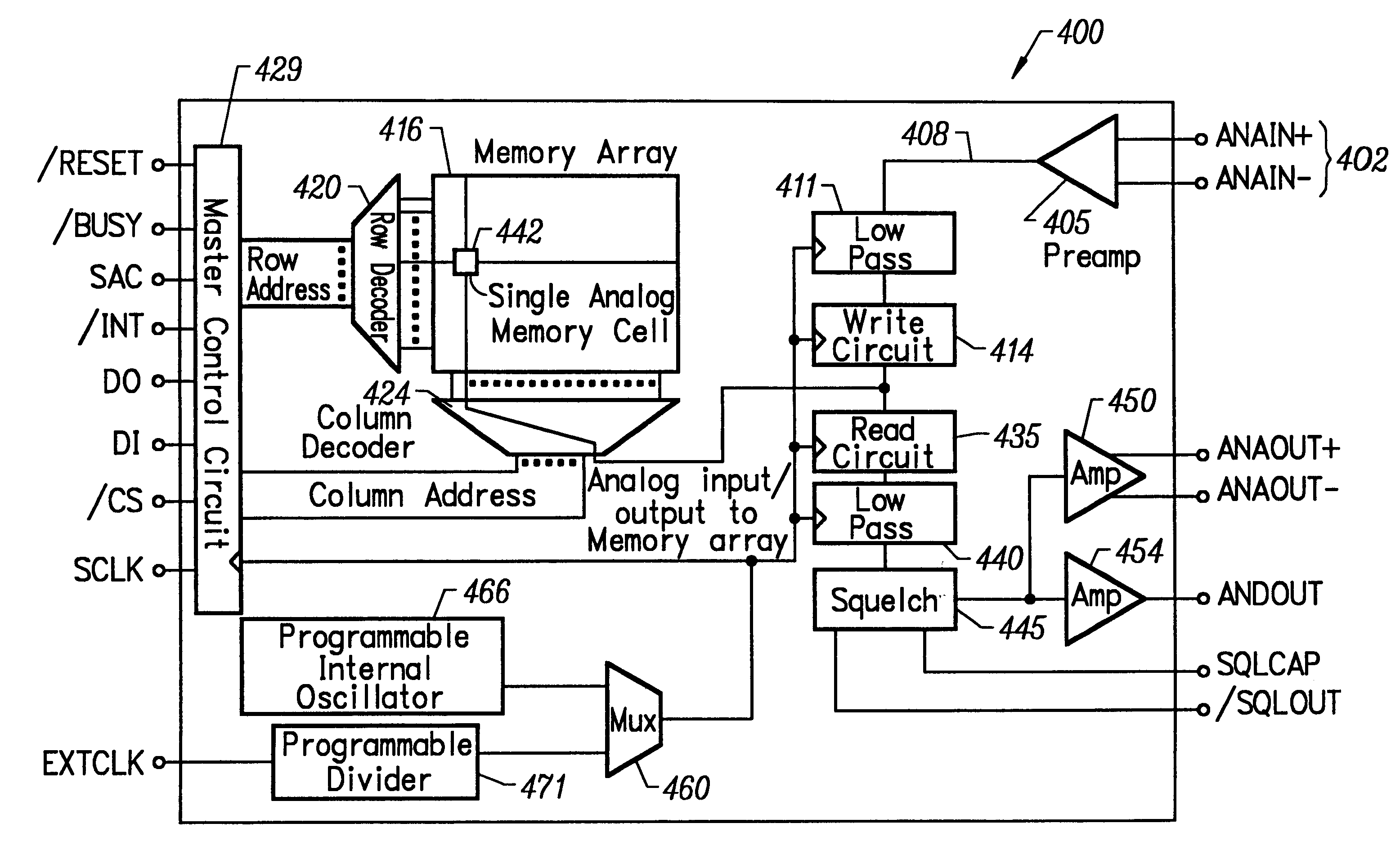

Analog memory IC with fully differential signal path

InactiveUS6185119B1High precisionImproved noise suppressionElectric analogue storesRead-only memoriesDifferential signalingAnalog signal

An integrated circuit memory is capable of storing analog information without the need for A / D conversion. Samples of a analog signal input are stored in nonvolatile memory cells. The integrated circuit is also capable of storing digital information in digital form. The sampling rate at which the analog signal input is sampled is user selectable. An internal signal path of the integrated circuit memory is differential, which enhances the precision with which the analog signal is stored in the memory cells.

Owner:SANDISK CORP

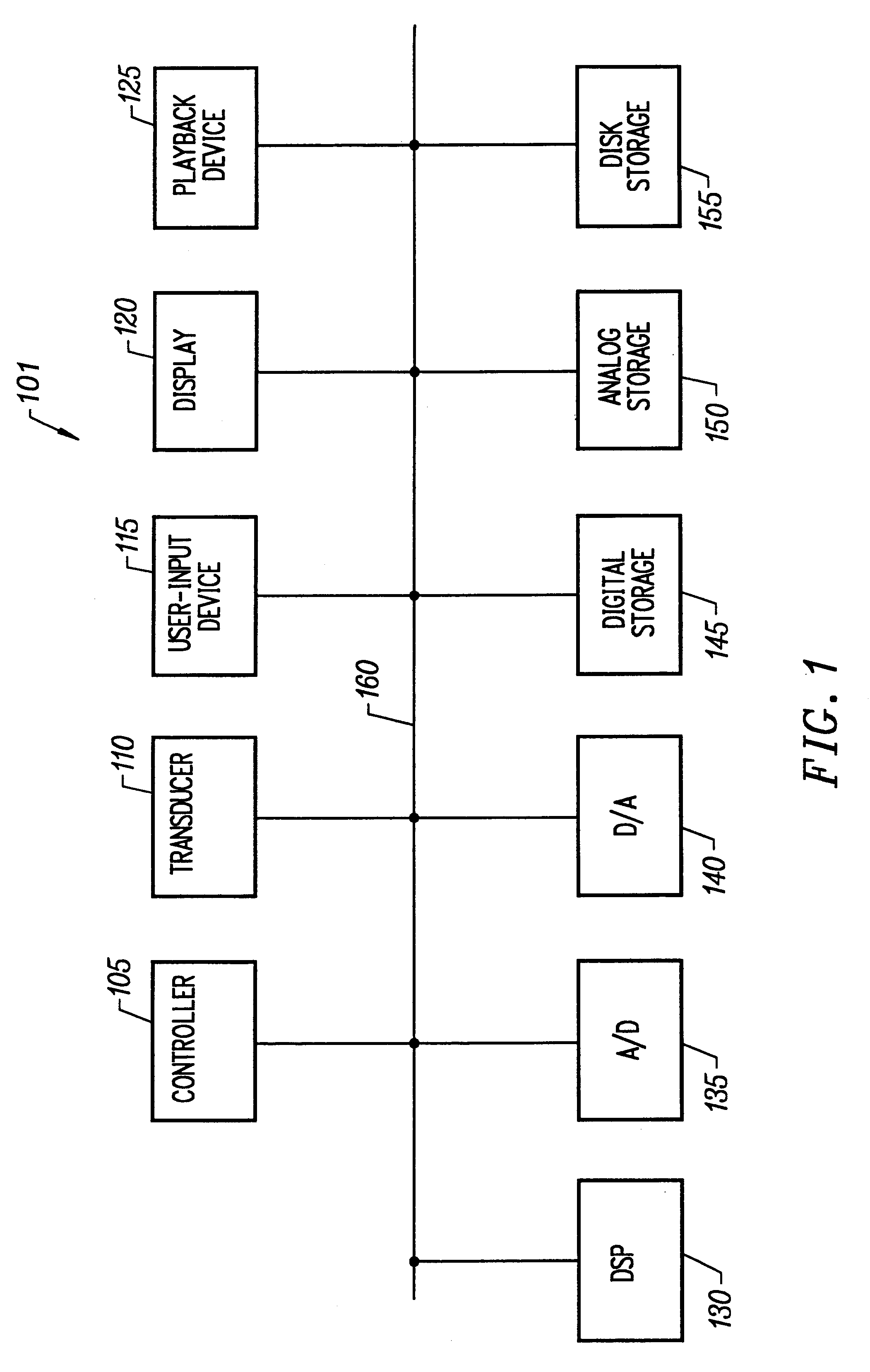

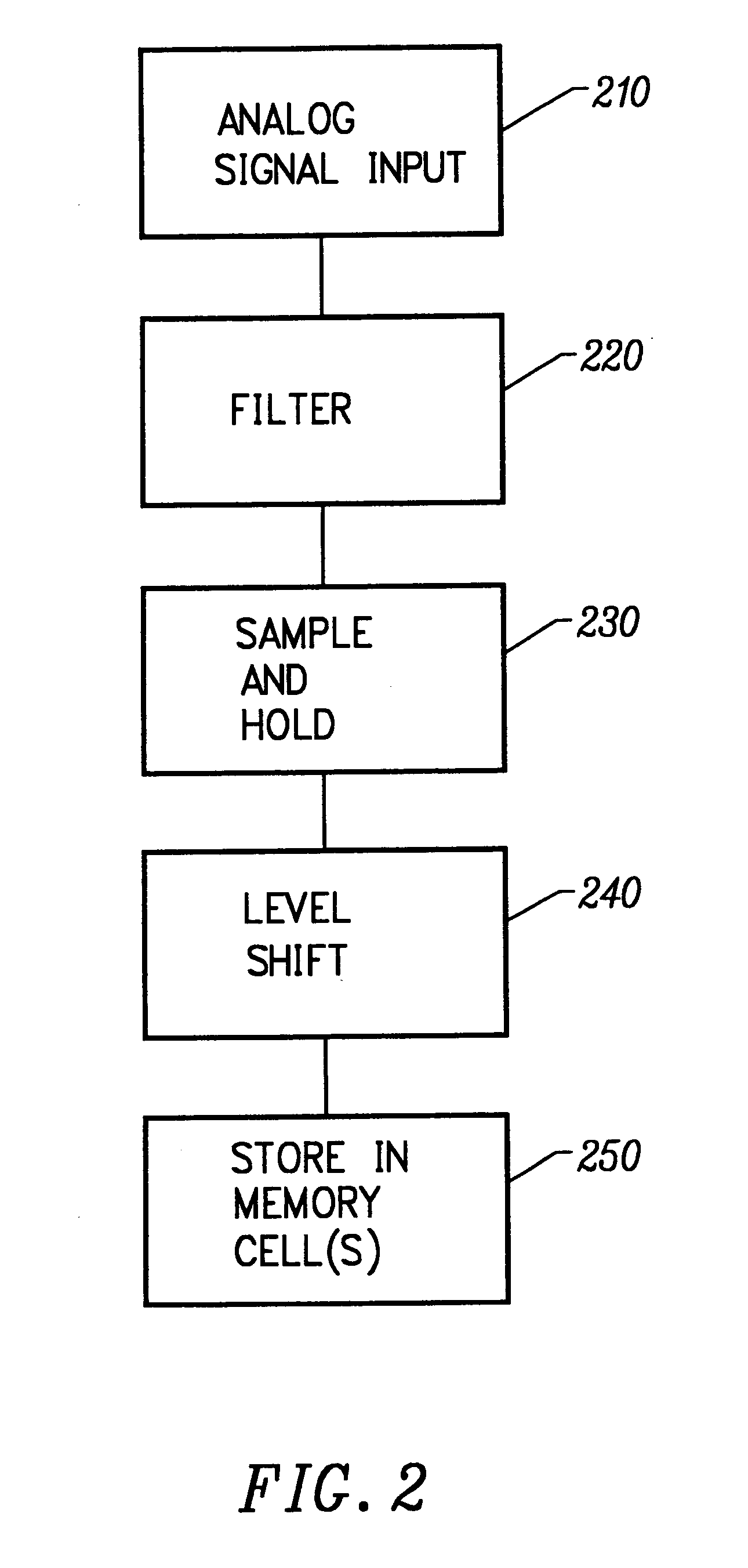

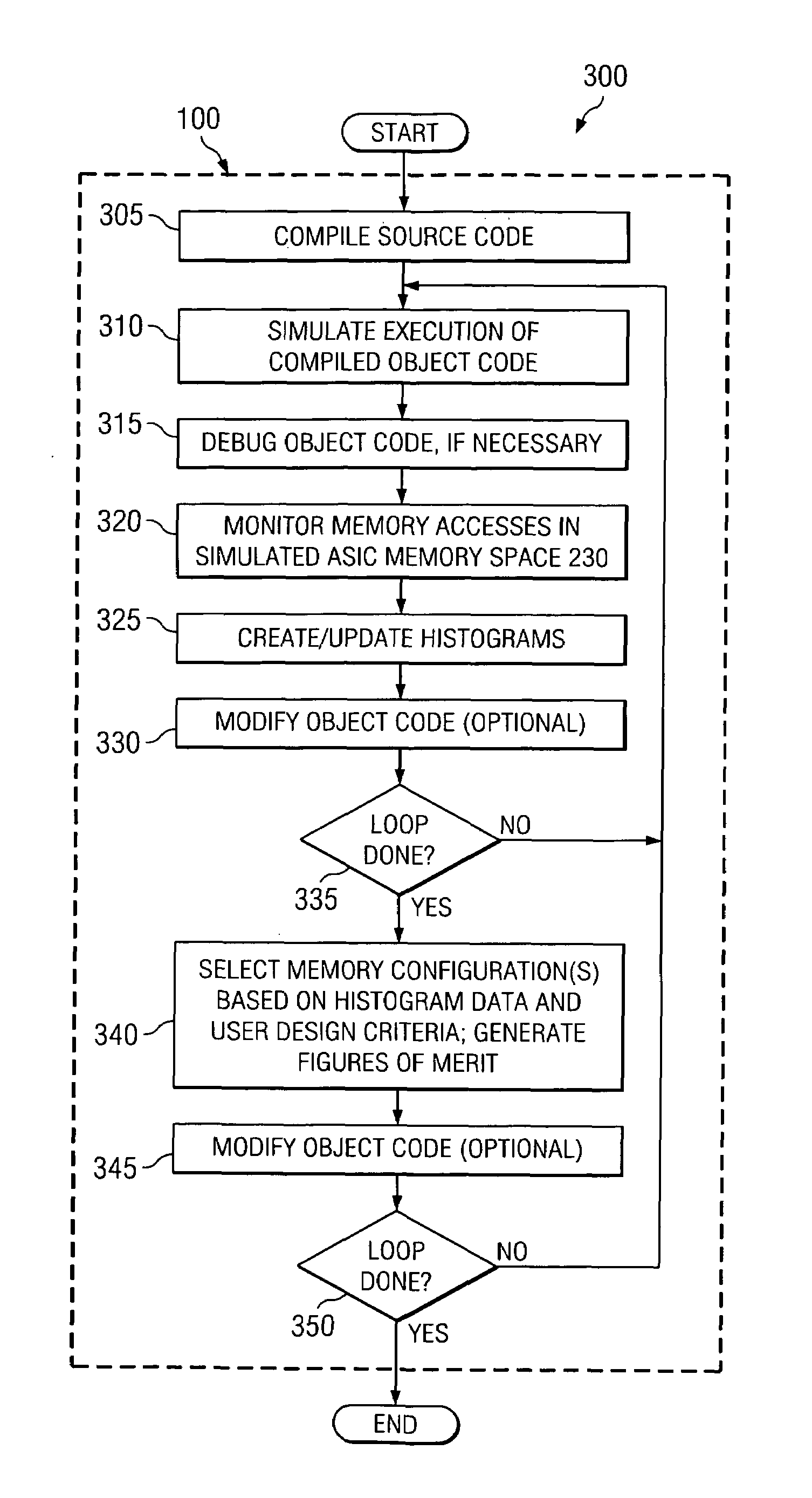

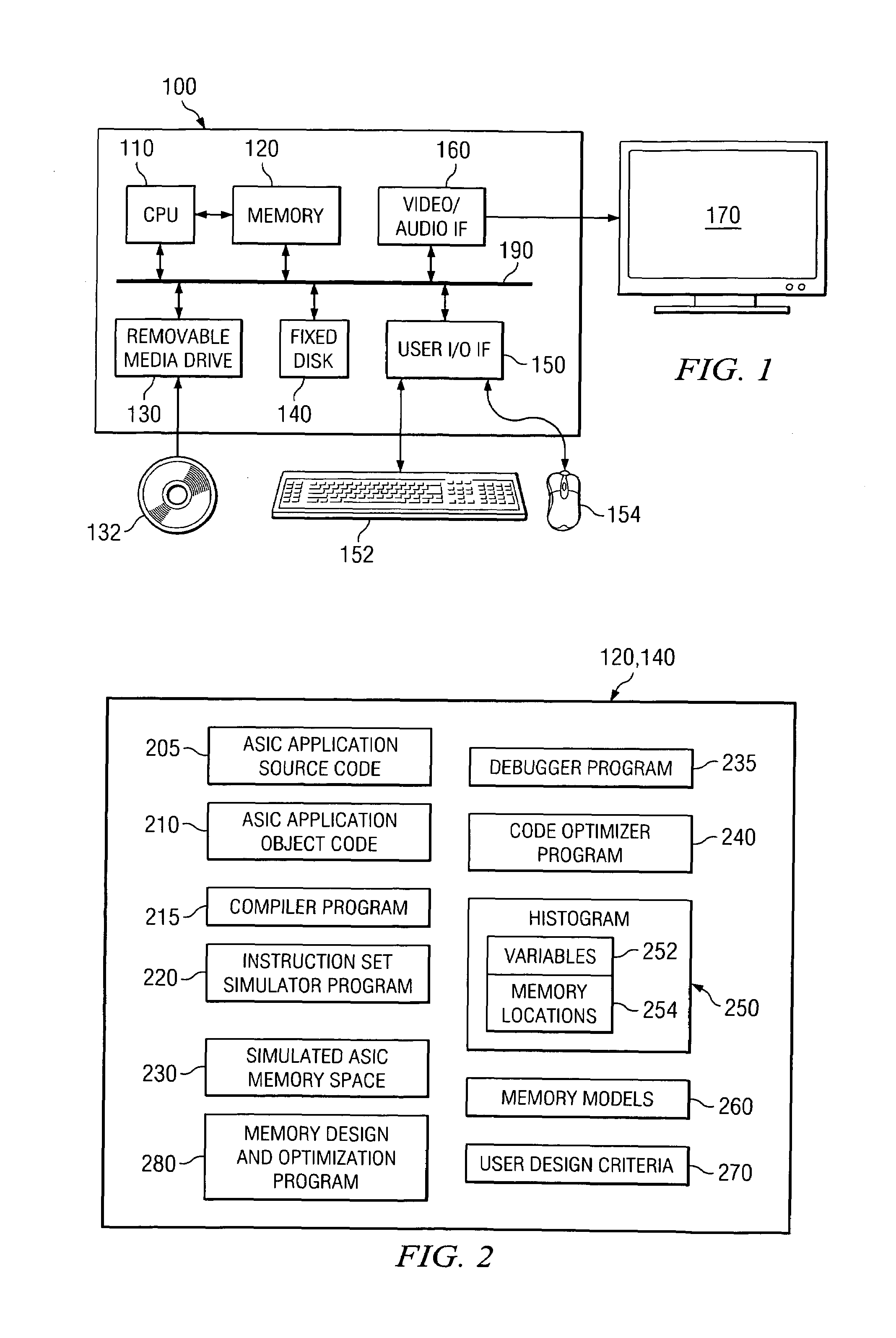

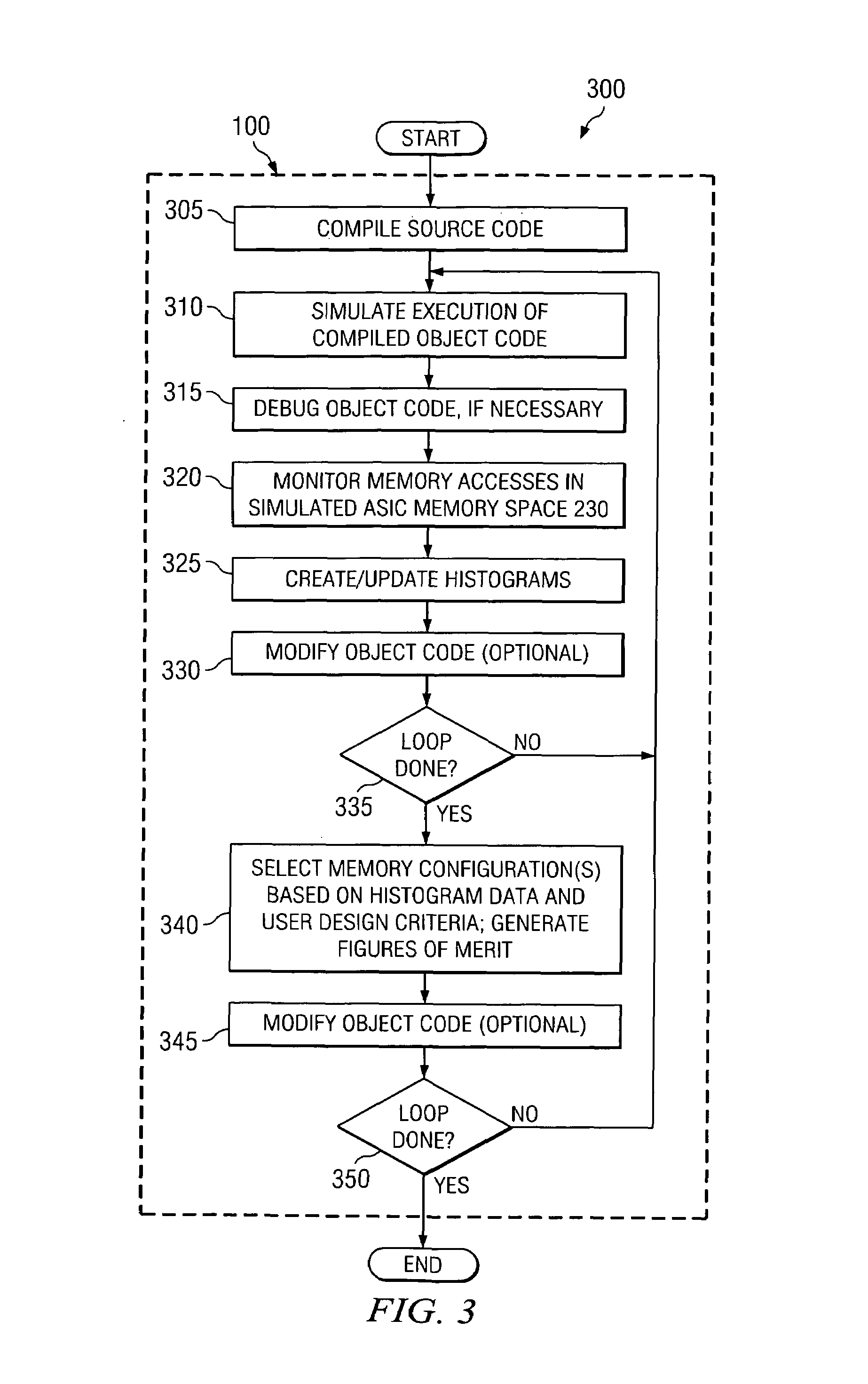

System and method for designing and optimizing the memory of an embedded processing system

InactiveUS7412369B1Error detection/correctionAnalogue computers for electric apparatusData processing systemAnalog controller

There is disclosed an apparatus for designing and optimizing a memory for use in an embedded processing system. The apparatus comprises: 1) a simulation controller for simulating execution of a test program to be executed by the embedded processing system; 2) a memory access monitor for monitoring memory accesses to a simulated memory space during the simulated execution of the test program, wherein the memory access monitor generates memory usage statistical data associated with the monitored memory accesses; and 3) a memory optimization controller for comparing the memory usage statistical data and one or more predetermined design criteria associated with the embedded processing system and, in response to the comparison, determining at least one memory configuration capable of satisfying the one or more predetermined design criteria.

Owner:STMICROELECTRONICS SRL

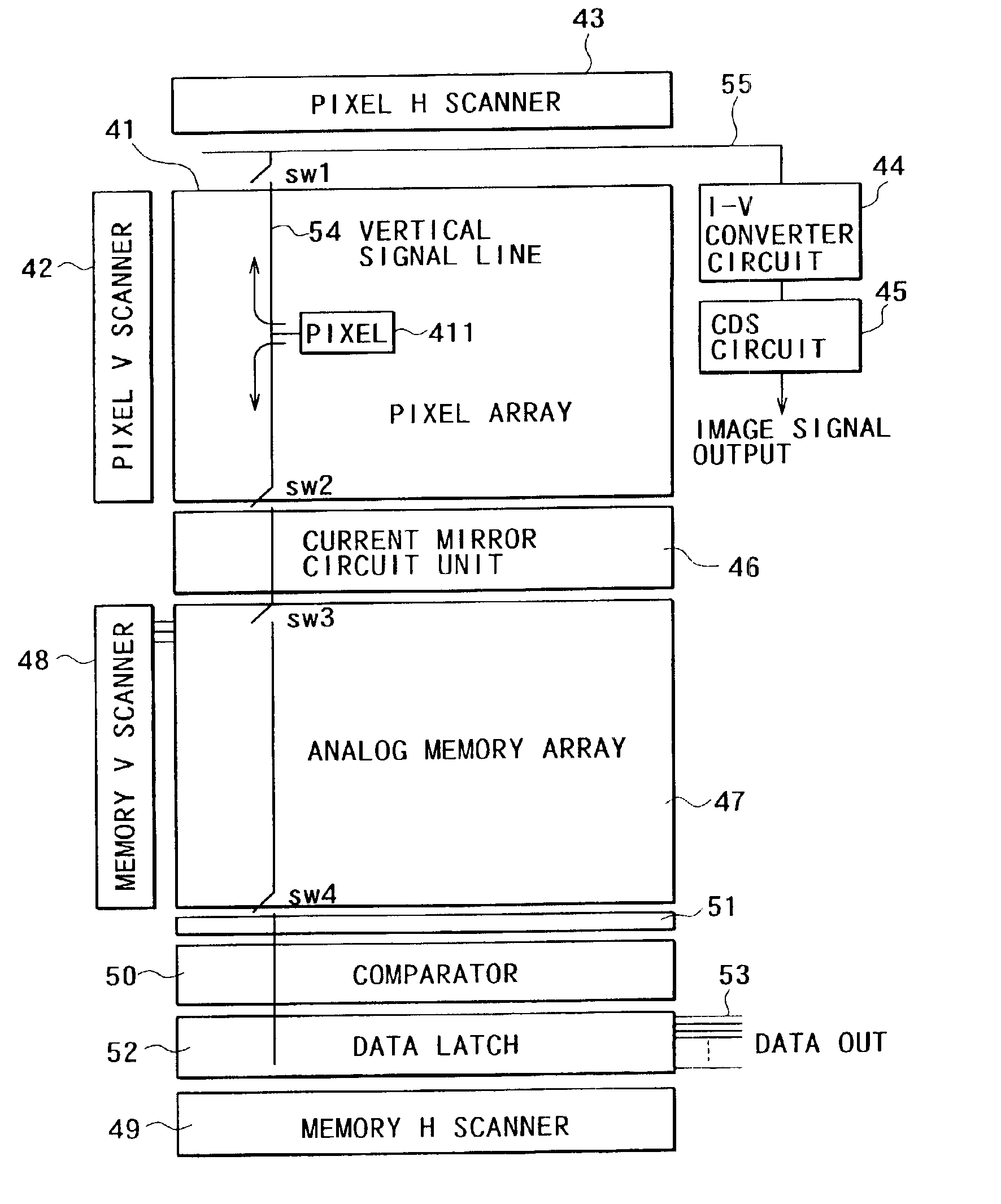

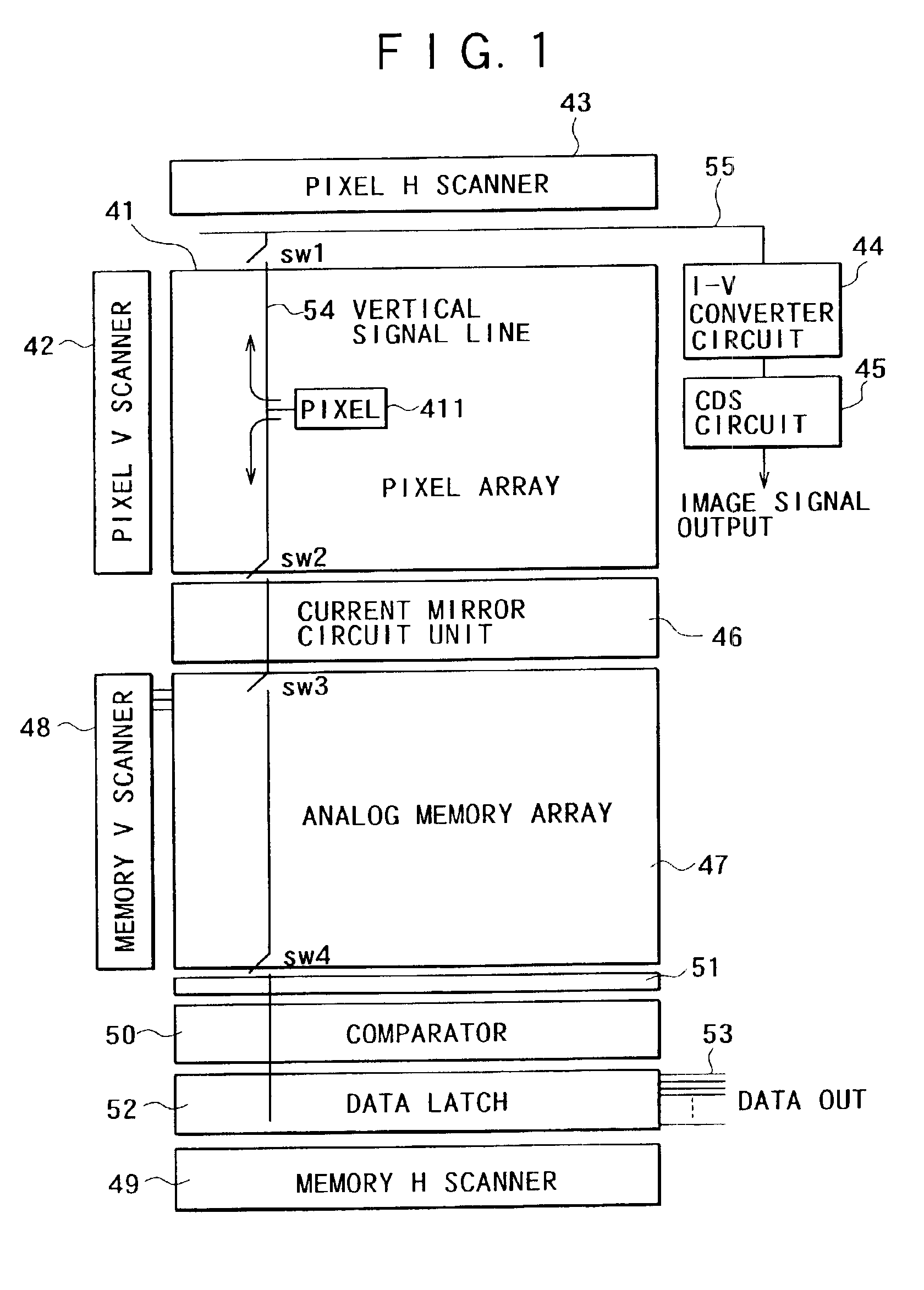

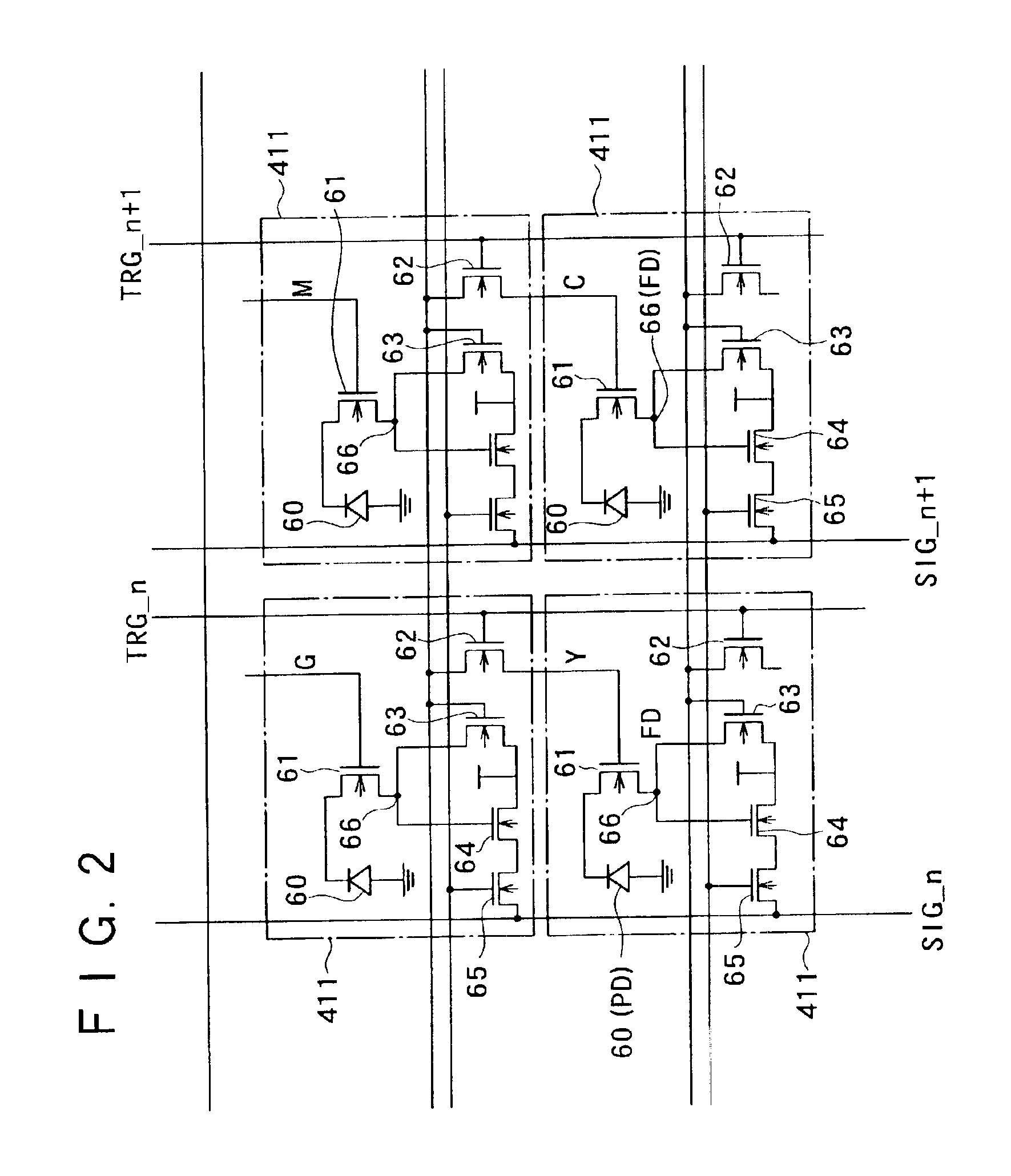

Solid-state image pickup apparatus and control method thereof

InactiveUS6858827B2Increase heightSmall apparatus sizeTelevision system detailsOptical rangefindersSignal processing circuitsImaging quality

An arithmetic circuit, which is retained by each pixel in a conventional image sensor, is shared by each column. Signal processing circuits of different configurations are provided on signal transmission paths in an upward direction and a downward direction of a vertical signal line for extracting an image signal from each pixel, whereby image output processing and arithmetic processing are performed completely separately by the different circuit blocks. Thus, image quality of an actual image is improved and optimum design for arithmetic processing is made possible. Specifically, an I-V converter circuit unit, a CDS circuit unit and the like are provided on the image output side. A current mirror circuit unit, an analog memory array unit, a comparator unit, a bias circuit unit, a data latch unit, an output data bus unit and the like are provided on the arithmetic processing side.

Owner:SONY CORP

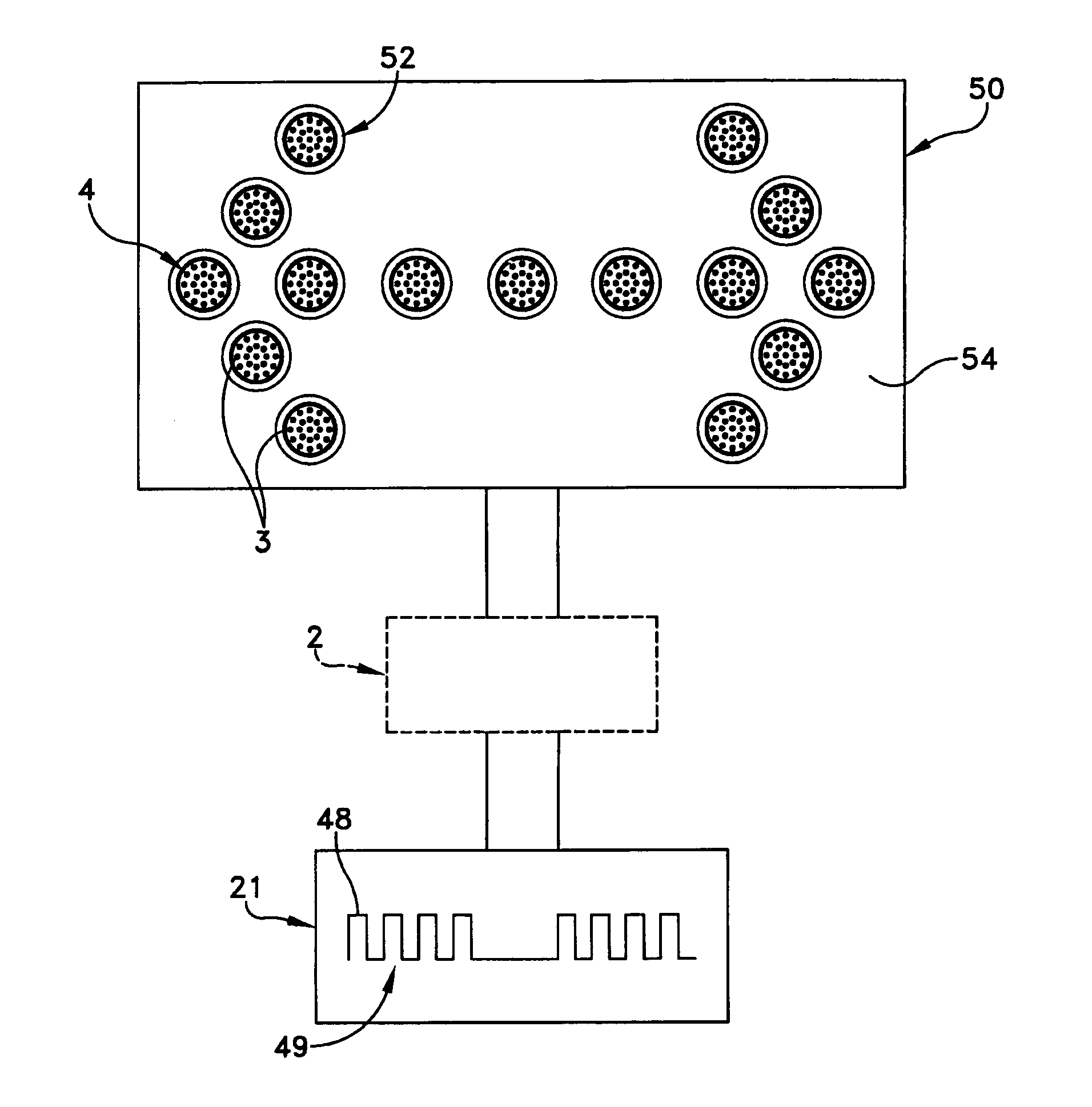

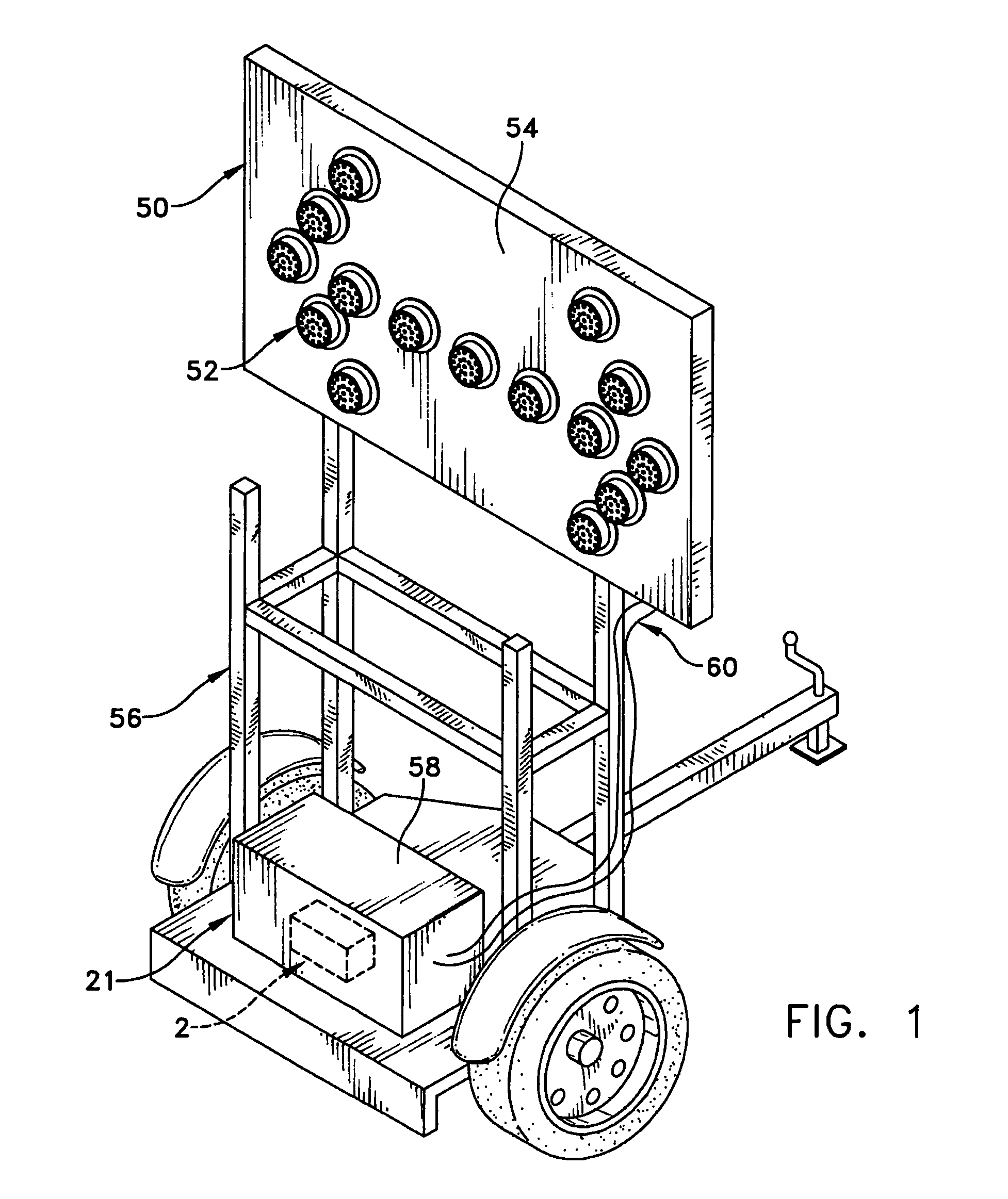

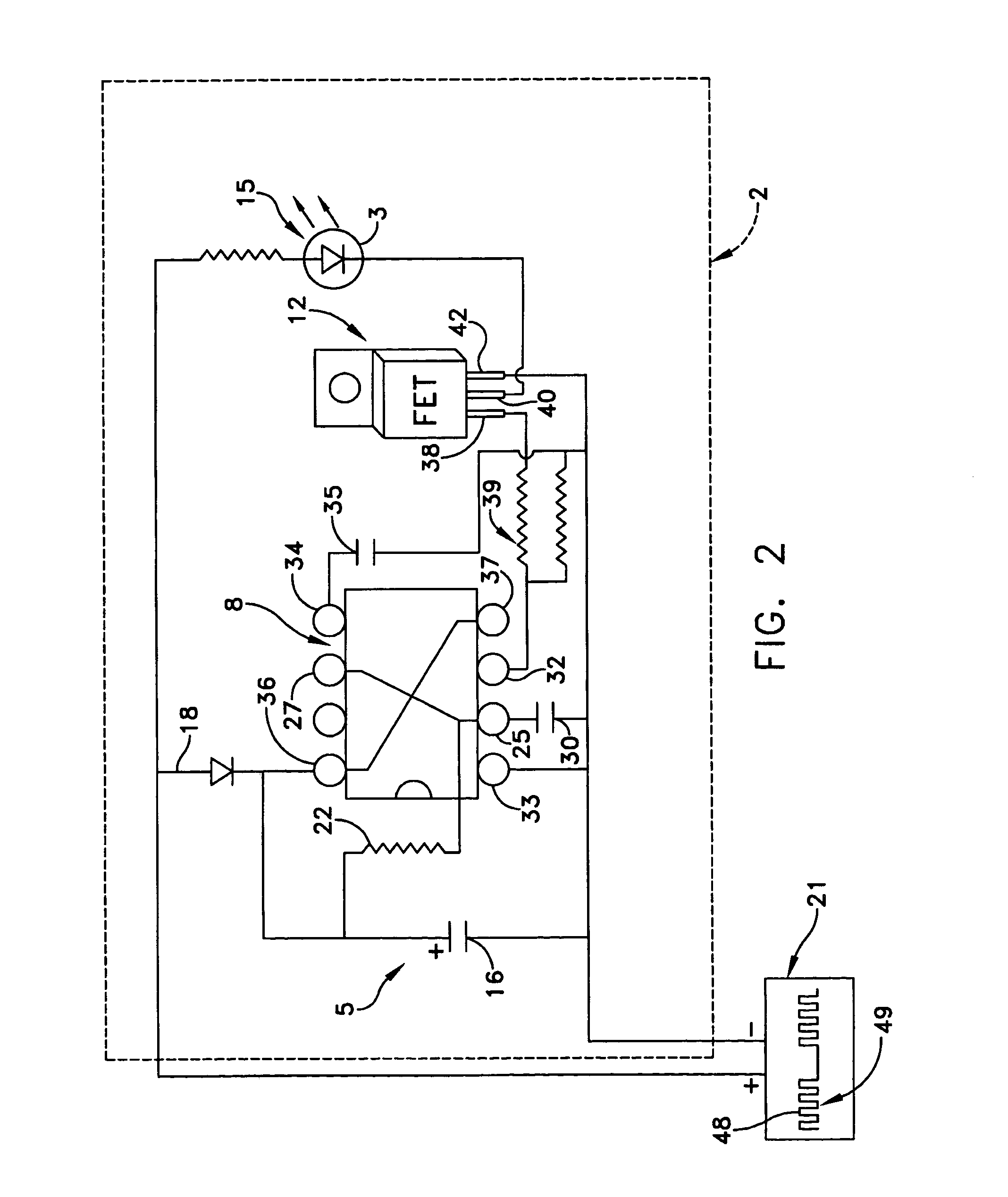

Burst pulse circuit for signal lights and method

A circuit is provided for over-driving a super-luminescent light emitting diode having a maximum forward continuous current rating. A power supply provides a pulse width modulated signal to an analog memory connected to the power supply and a pulse generator. The pulse generator includes a window comparator engaged with the analog memory, and is responsive to a portion of the pulse width modulated signal. A power driver that is controlled by the output of the pulse generator, is operably connected with the super-luminescent light emitting diode and with the power supply so as to energize the super-luminescent light emitting diode with a current that is above the maximum forward continuous current rating by between two and ten times that rated current. A signal is also provided along with a method of over-driving a super-luminescent light emitting diode.

Owner:TRAFCON INDS

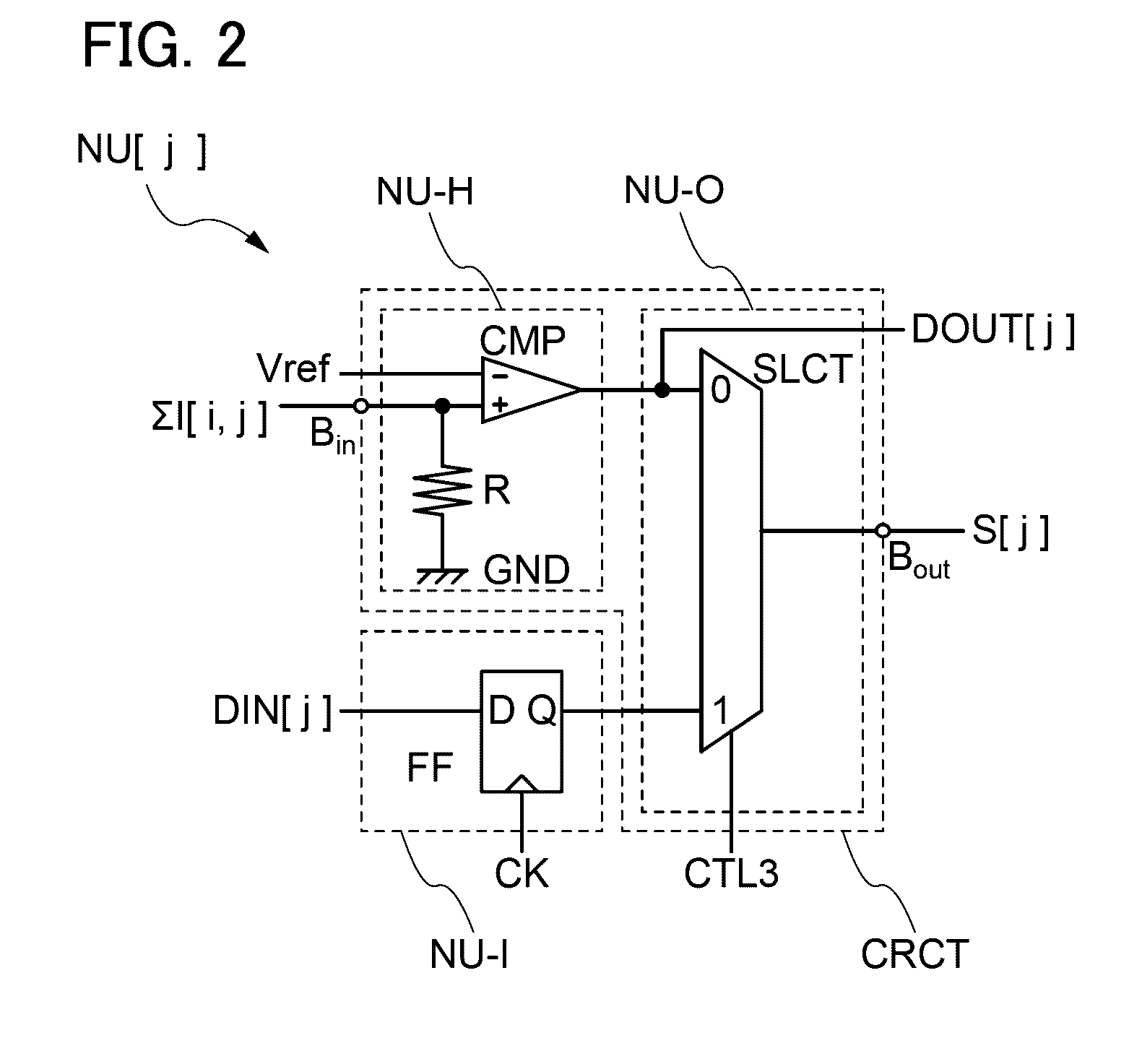

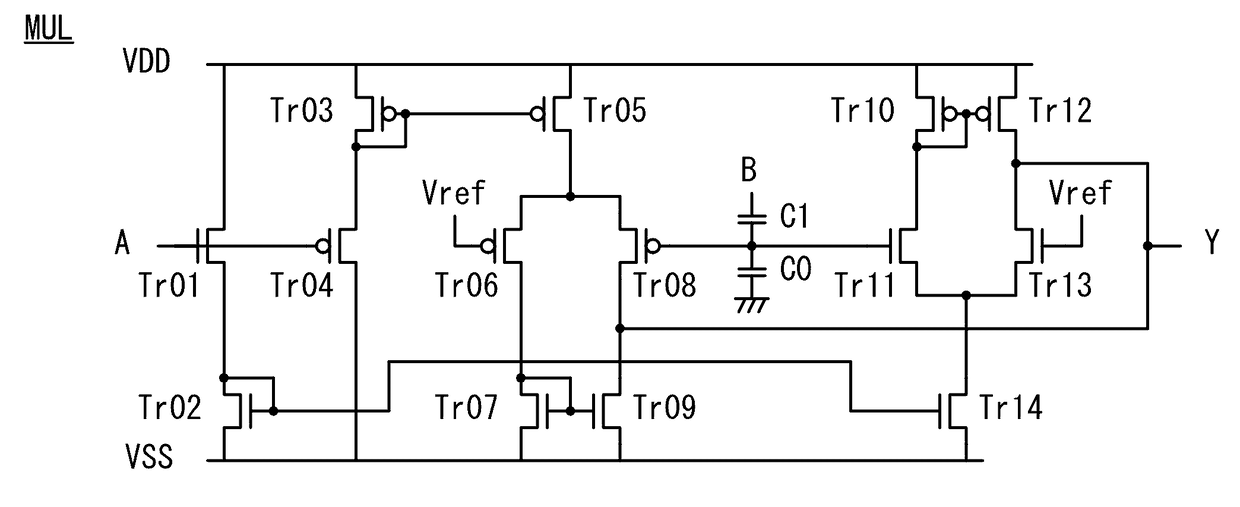

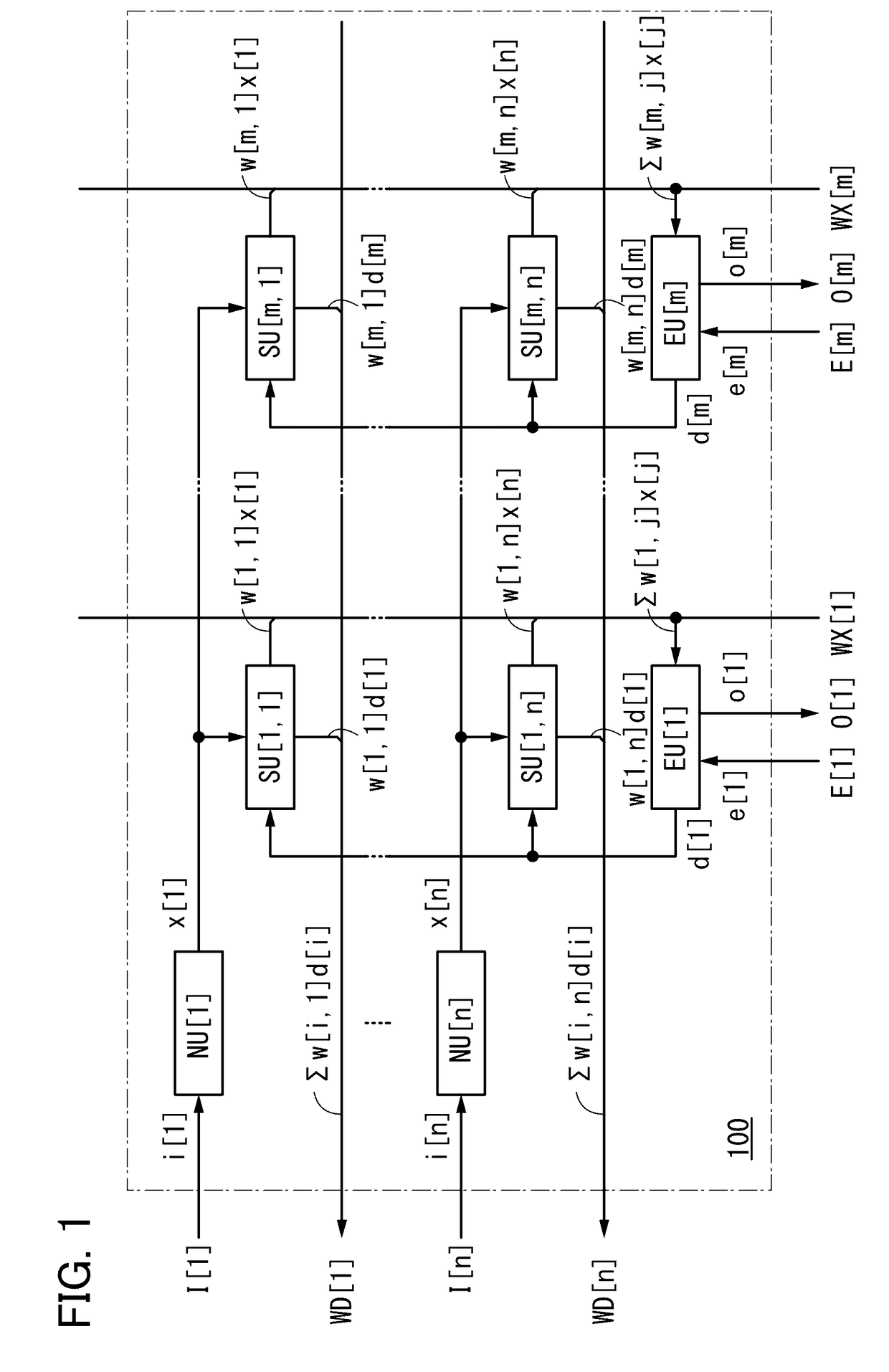

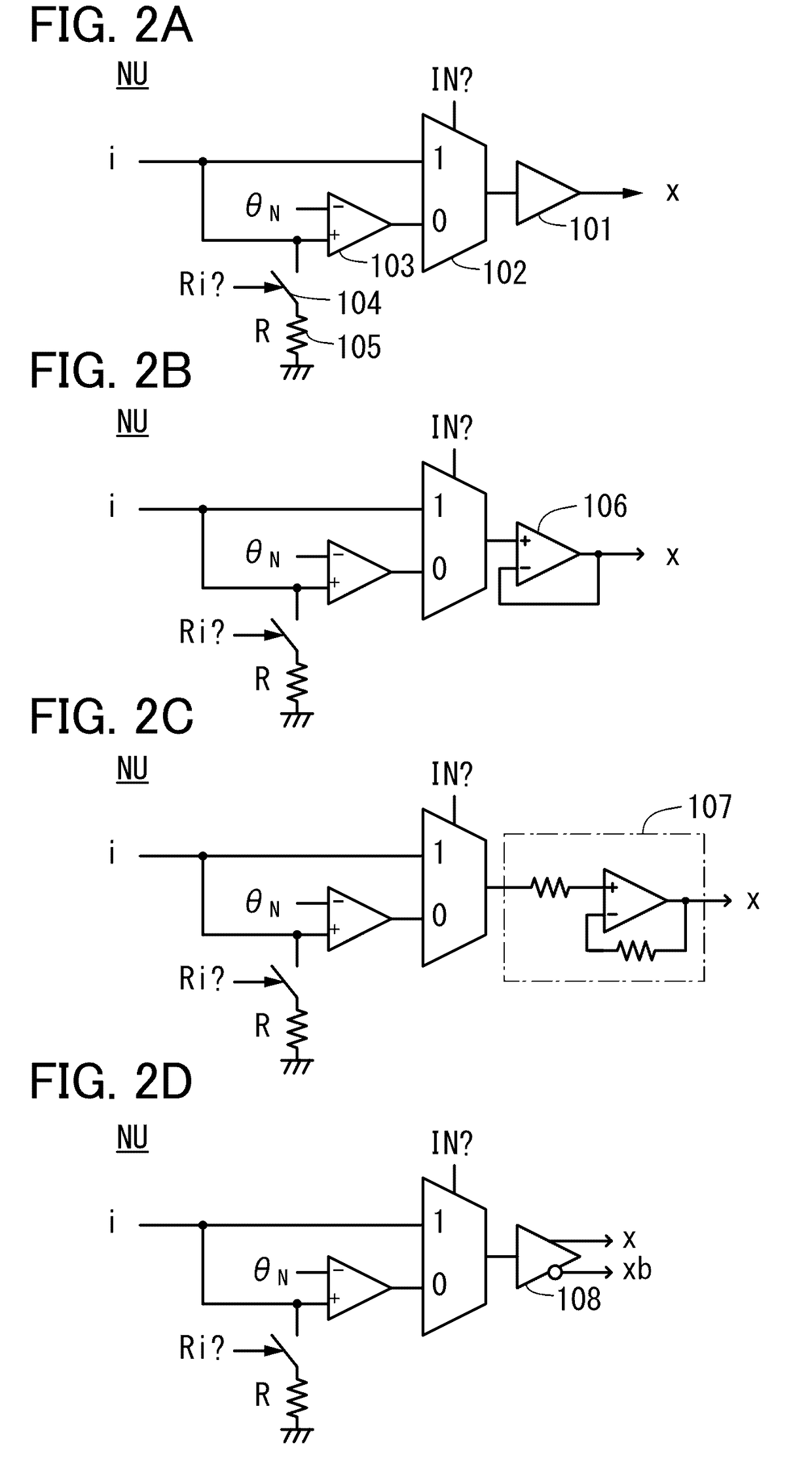

Semiconductor device and electronic device

ActiveUS20170116512A1Novel configurationReduce chip areaElectric analogue storesDigital storageSynapseNeuron circuit

A neuron circuit can switch between two functions: as an input neuron circuit, and as a hidden neuron circuit. An error circuit can switch between two functions: as a hidden error circuit, and as an output neuron circuit. A switching circuit is configured to be capable of changing the connections between the neuron circuit, a synapse circuit, and the error circuit. The synapse circuit includes an analog memory that stores data that corresponds to the connection strength between the input neuron circuit and the hidden neuron circuit or between the hidden neuron circuit and the output neuron circuit, a writing circuit that changes the data in the analog memory, and a weighting circuit that weights an input signal in reaction to the data of the analog memory and outputs the weighted output signal. The analog memory includes a transistor comprising an oxide semiconductor with extremely low off-state current.

Owner:SEMICON ENERGY LAB CO LTD

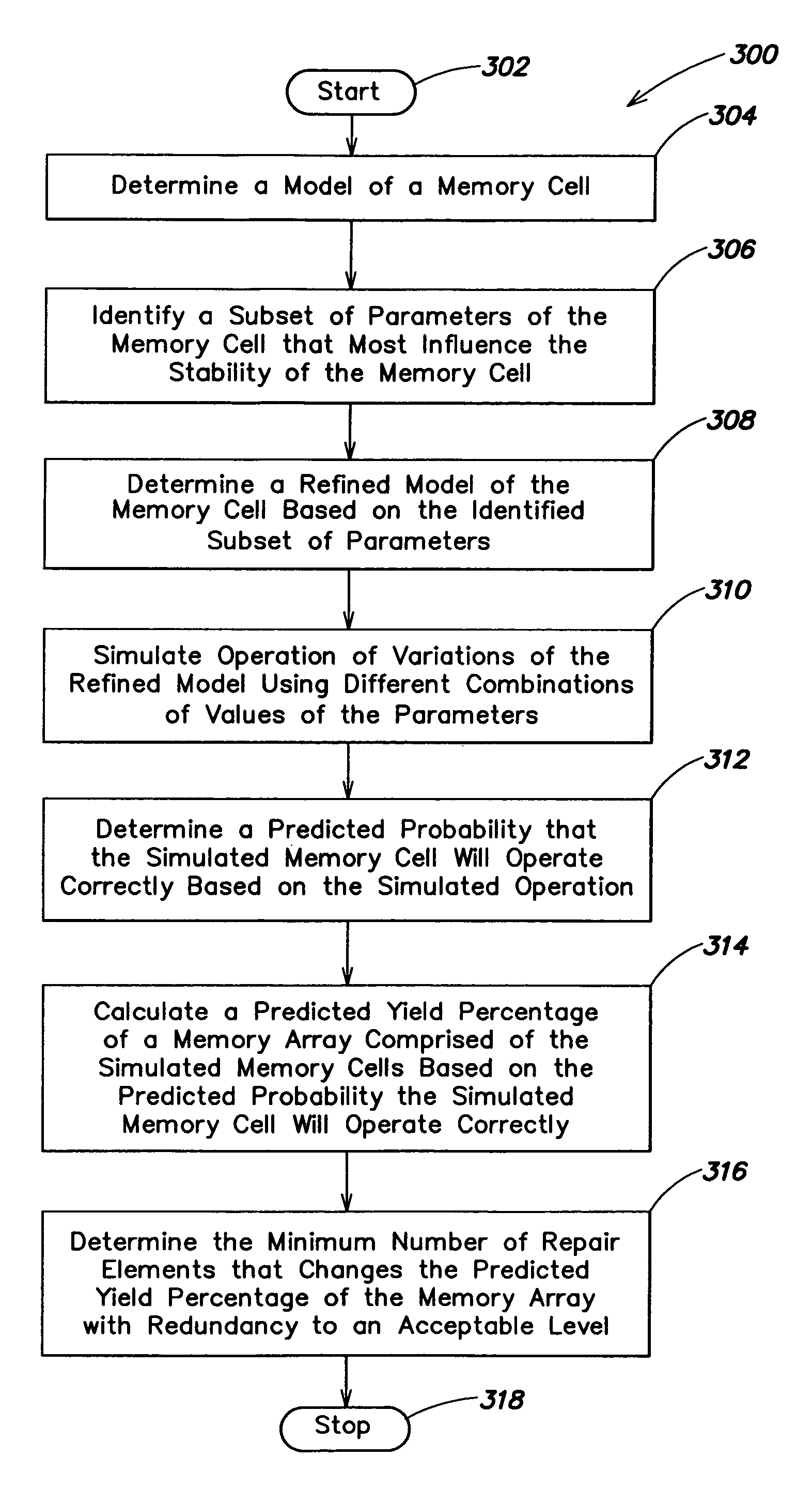

Apparatus and methods for predicting and/or calibrating memory yields

InactiveUS20070044049A1Detecting faulty computer hardwareElectrical testingParallel computingMemory array

An apparatus and methods for predicting and / or for calibrating memory yields due to process defects and / or device variations, including determining a model of a memory cell, identifying a subset of parameters associated with the model, determining and executing a refined model using the parameters, determining a predicted probability the simulated memory cell will be operational based on the simulated operation of the refined model, determining yield prediction information from the predicted probability, and determining the minimum number of repair elements to include in a memory array design to insure a desired yield percentage based on the yield prediction information.

Owner:GLOBALFOUNDRIES INC