Patents

Literature

1734 results about "Embedded processing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Associating data with images in imaging systems

InactiveUS7010144B1Data processing applicationsUser identity/authority verificationExternal storageImage capture

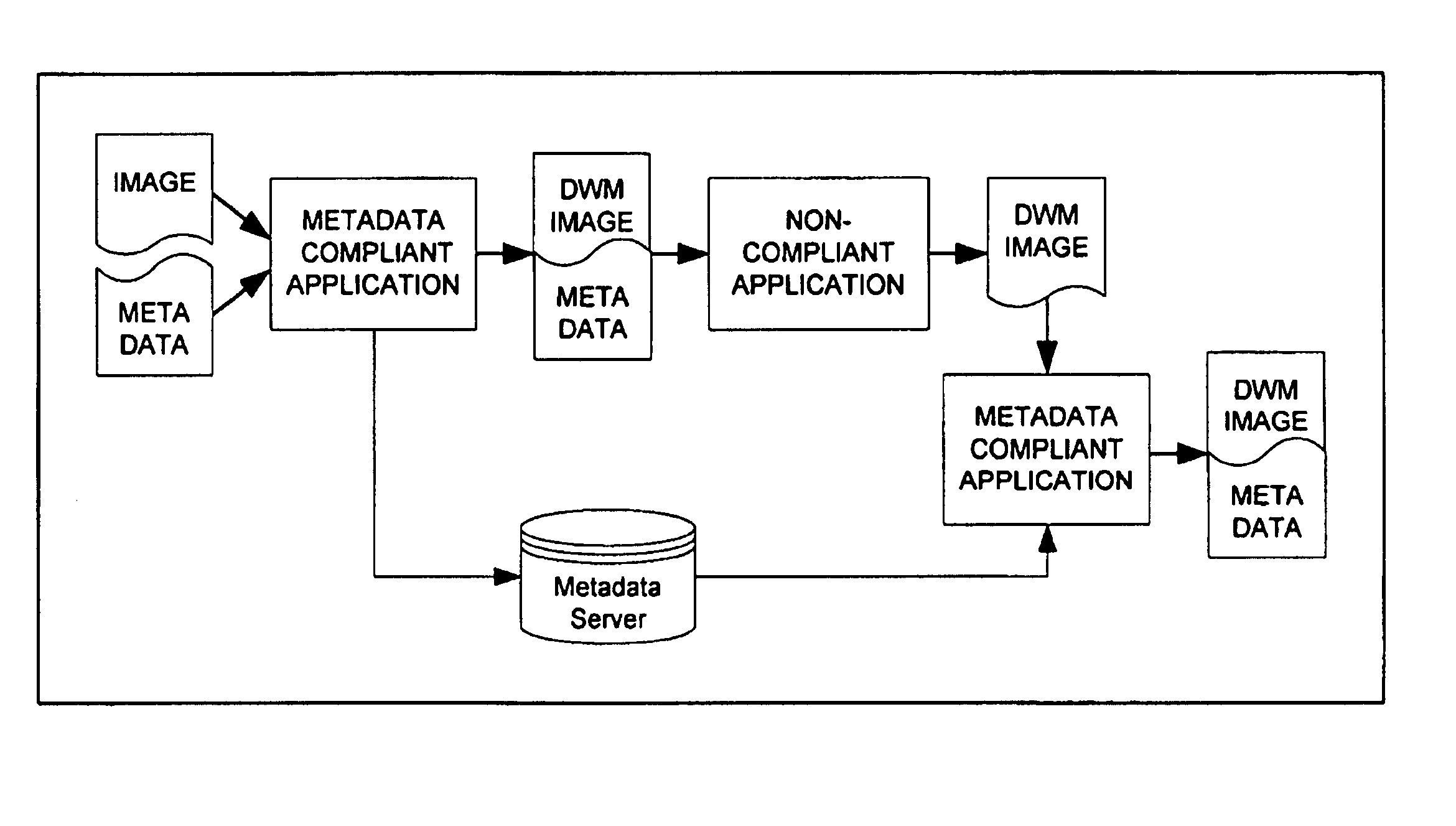

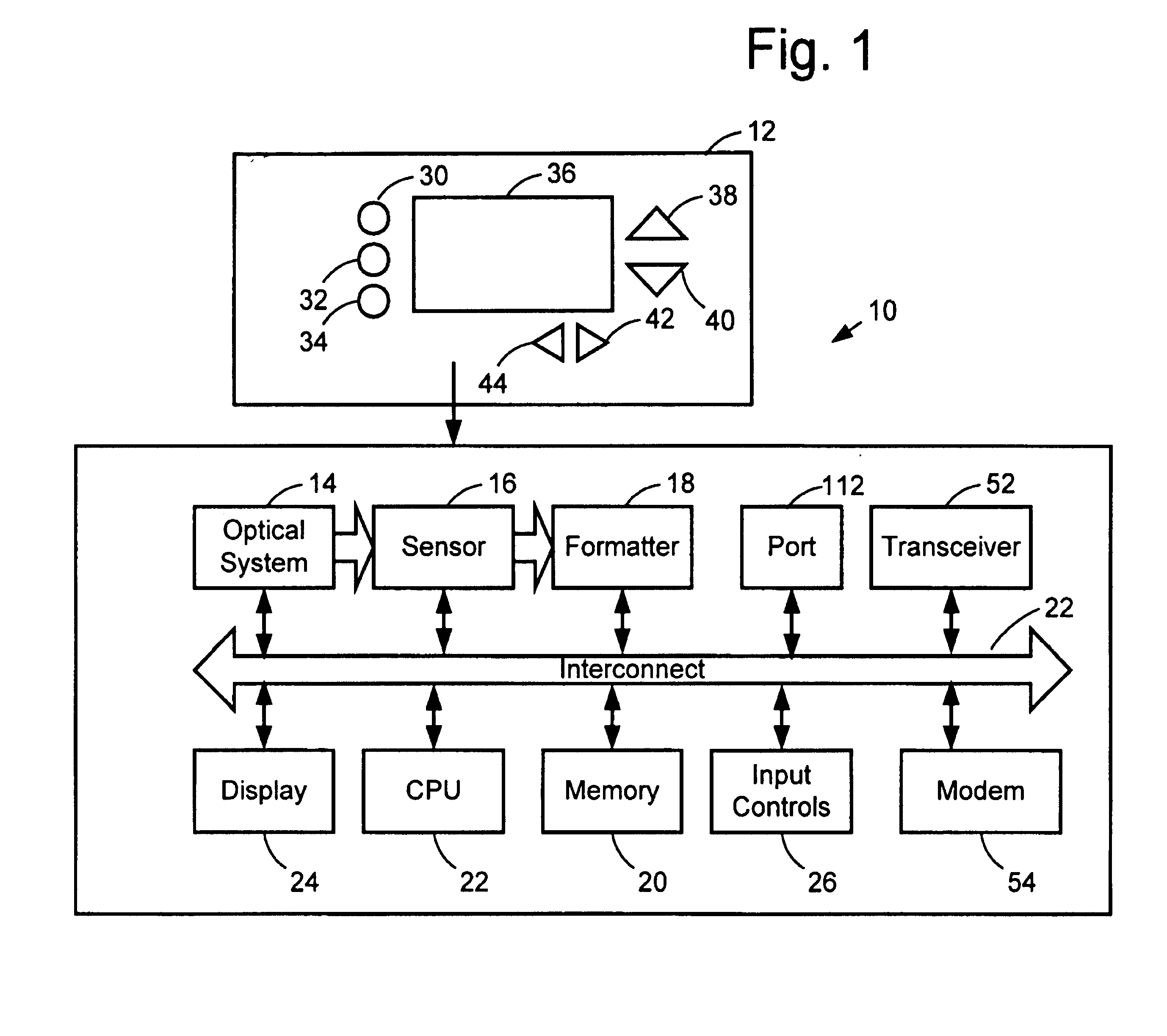

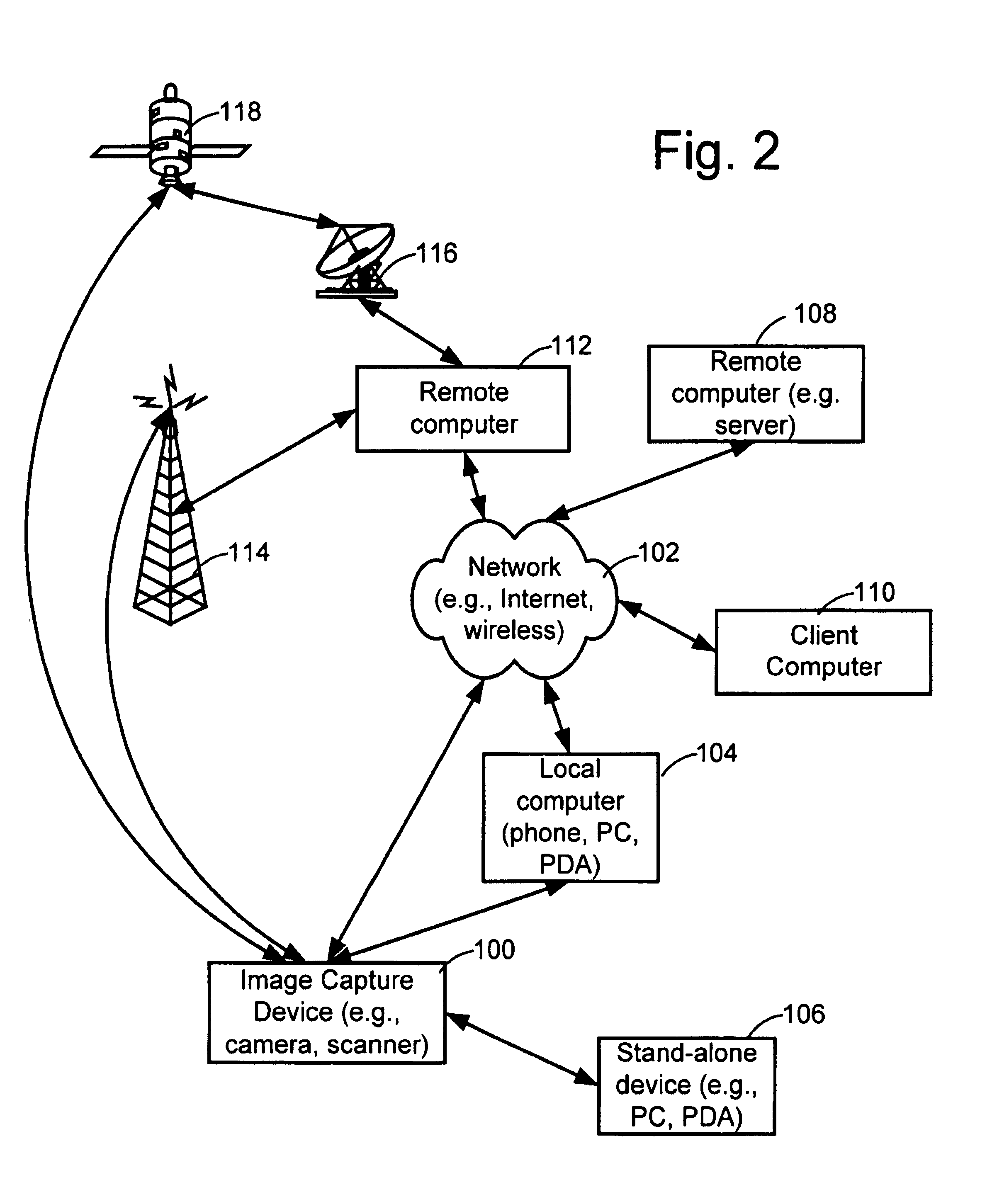

A steganographic embedder associates data with an image by encoding the data, a link to the data, or a combination of both into the image. The embedder may be located in an image capture device or an external process or device. In one application, for example, an embedder process steganographically encodes data into an image as part of the process of uploading the image from the image capture device to external storage.

Owner:DIGIMARC CORP

Universal Game Monitoring Unit and System

ActiveUS20110230260A1Increase excitementRich gaming experienceApparatus for meter-controlled dispensingVideo gamesControl systemInternal os

An embedded user interface incorporated into a gaming device, the gaming device including a gaming presentation of a base game and a gaming processor for controlling the base game. The embedded user interface includes: a player tracking interface and an embedded processor. The player tracking interface includes (or is associated with) a display screen and enables display of a system game to a user, presentation of information to the user, and reception of information from the user. The embedded processor employs an internal operating system and communicates with the gaming processor, enables control of the system game, control of player tracking information, and control of non-gaming information. In one embodiment, the embedded user interface enables control of a system game of which at least a portion of the system game is presented physically external to the embedded user interface. In another embodiment, the embedded user interface enables control of a system gaming indicator that is physically external to the embedded user interface. In still another embodiment, communication between a game processor and an embedded user interface is only enabled through the gaming network and is not direct enabled via a direct connection.

Owner:LNW GAMING INC

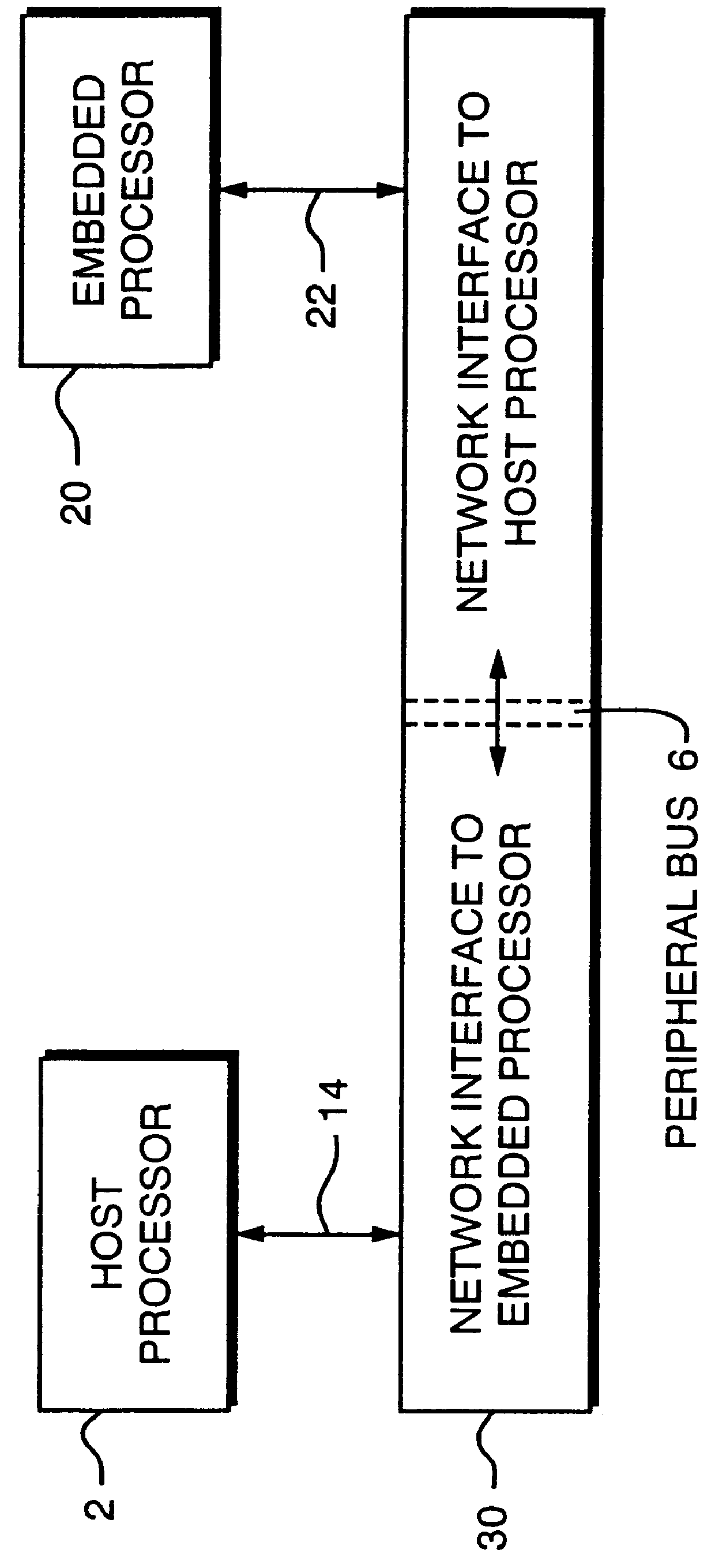

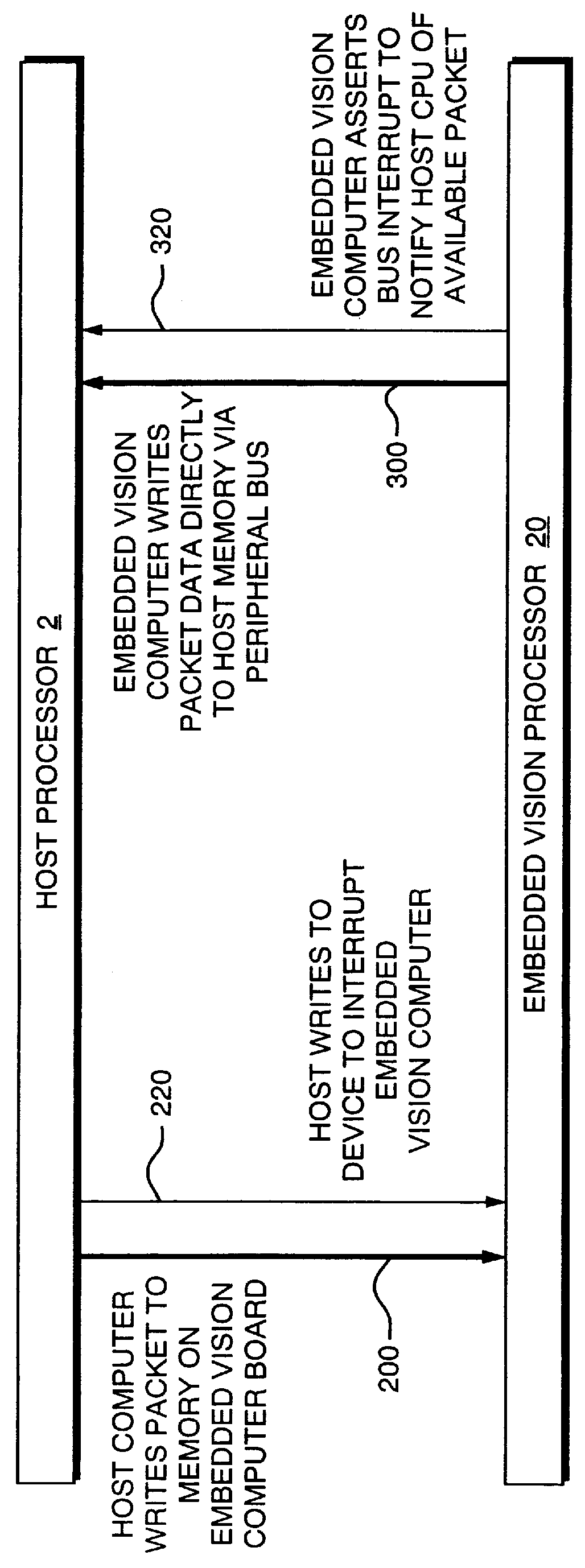

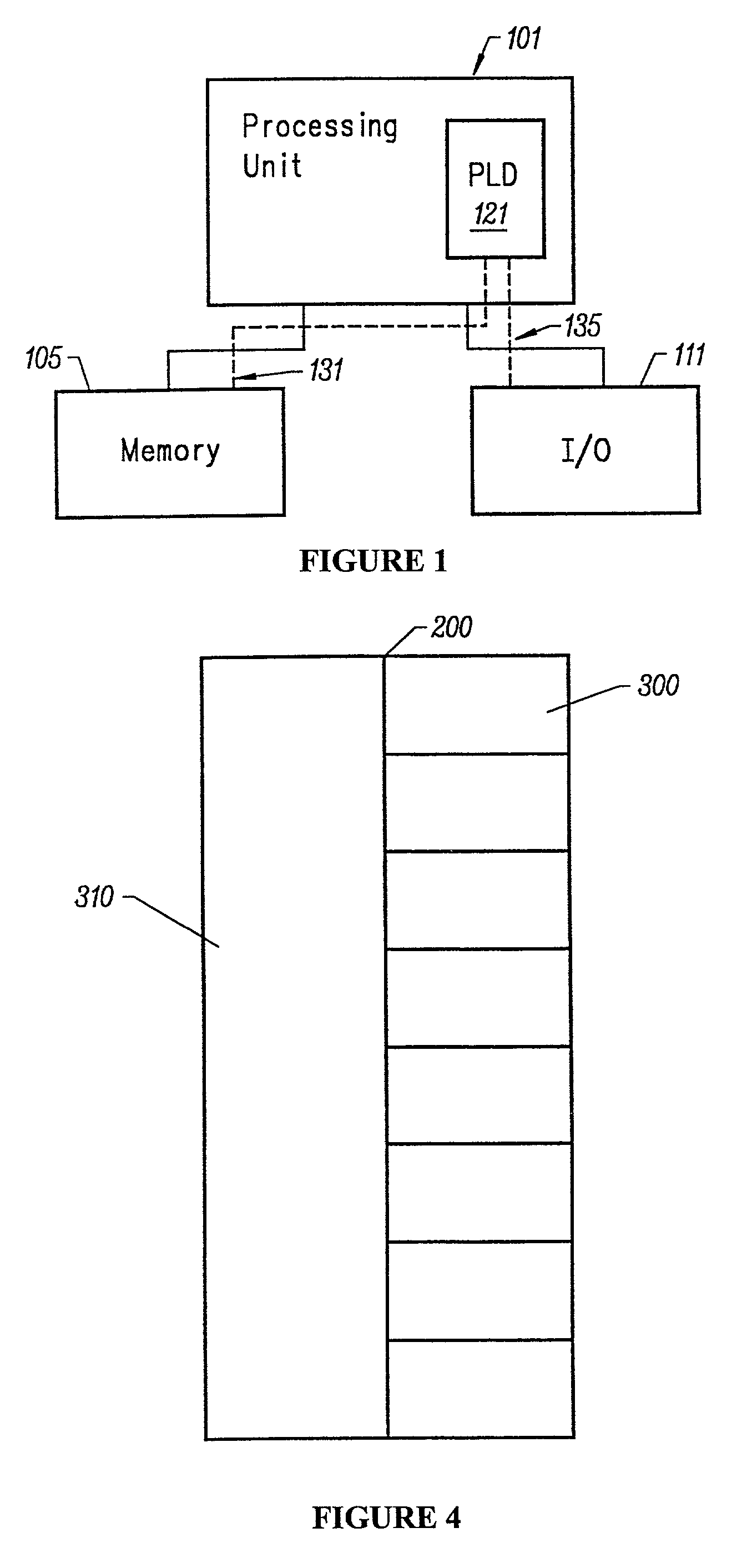

Apparent network interface for and between embedded and host processors

InactiveUS6058434ASignificant comprehensive benefitsMultiple digital computer combinationsElectric digital data processingPerformance enhancementWeb service

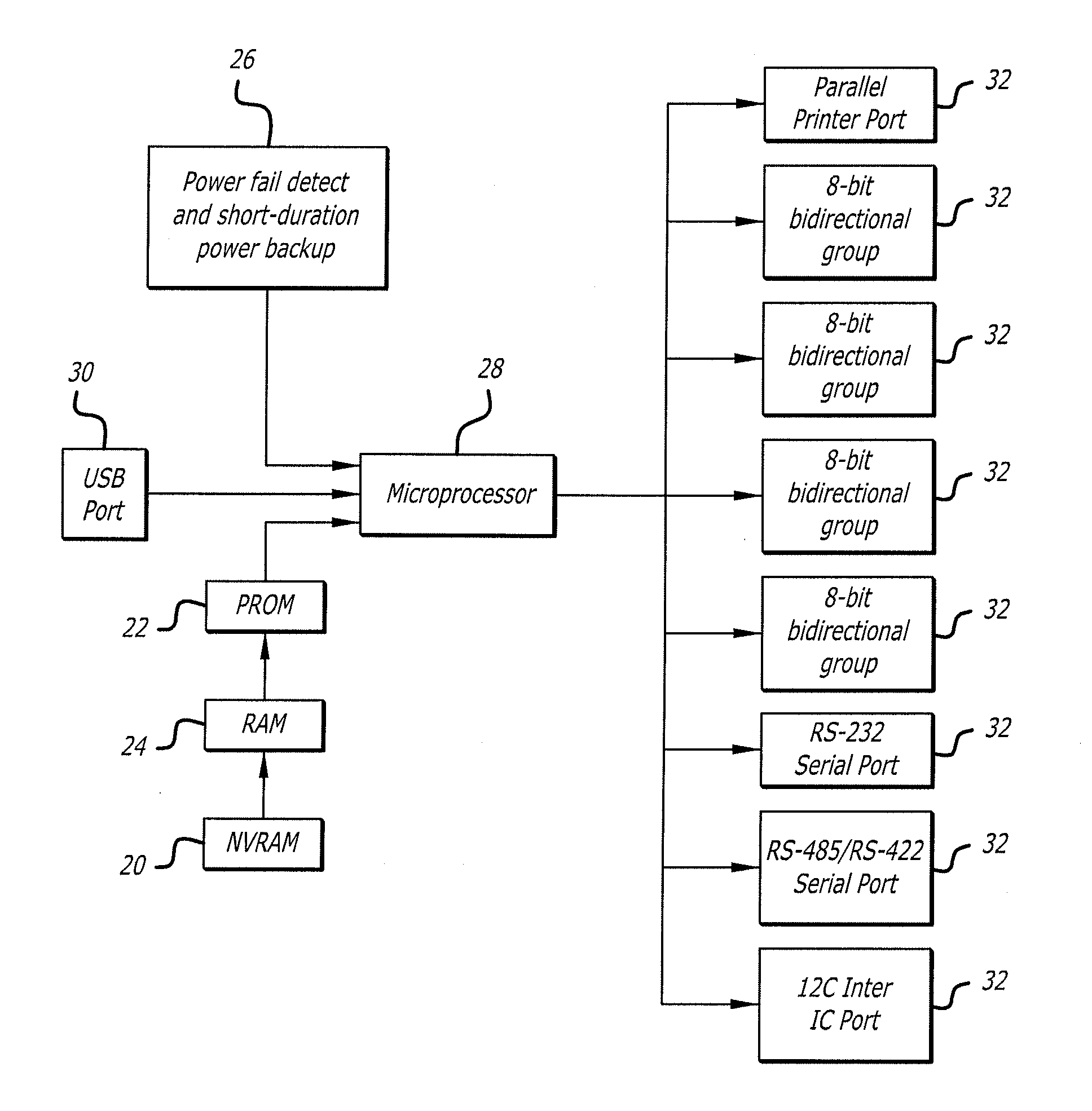

An apparent network interface permits one processor such as a processor embedded within a larger processing system (an embedded processor) to communicate to a host processor or other processors and devices on the network to which the embedded processor is attached, using standard network communication mechanisms / protocols such as TCP / IP, NFS, FTP, HTTP, etc. The web server protocol HTTP is particularly useful because it permits the embedded computer to publish a user interface for remote monitoring and remote control using a standard web browser application. The invention provides the host computer with an apparent network interface that appears to be a standard network device, such as an Ethernet interface card. This apparent interface communicates directly with the embedded processor, which appears to be a device on this apparent network. Significant cost savings and performance enhancements are realized by implementing the communication directly over the host computer's peripheral bus rather than using standard network hardware such as Ethernet hardware.

Owner:MICROSCAN SYSTEMS

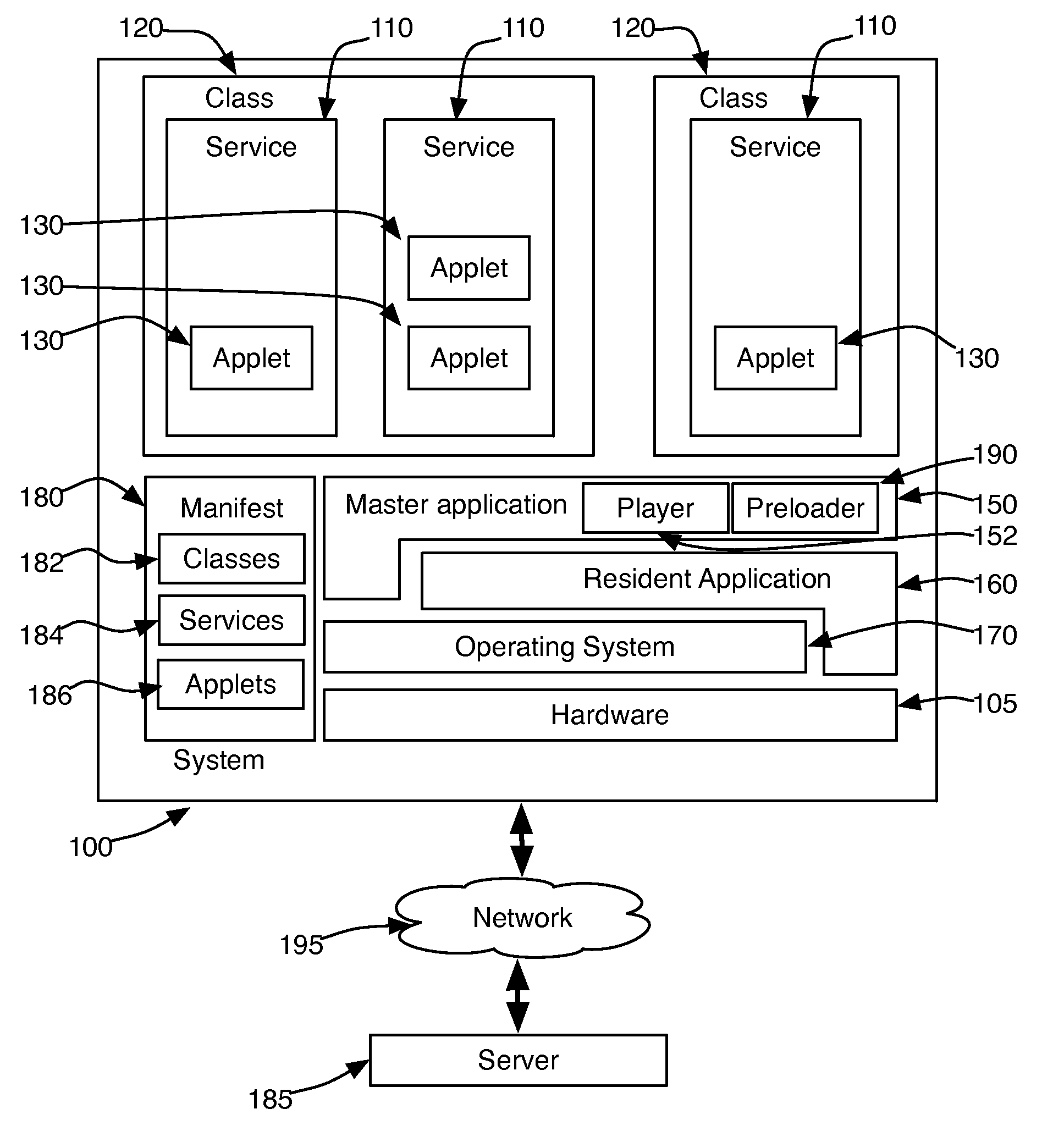

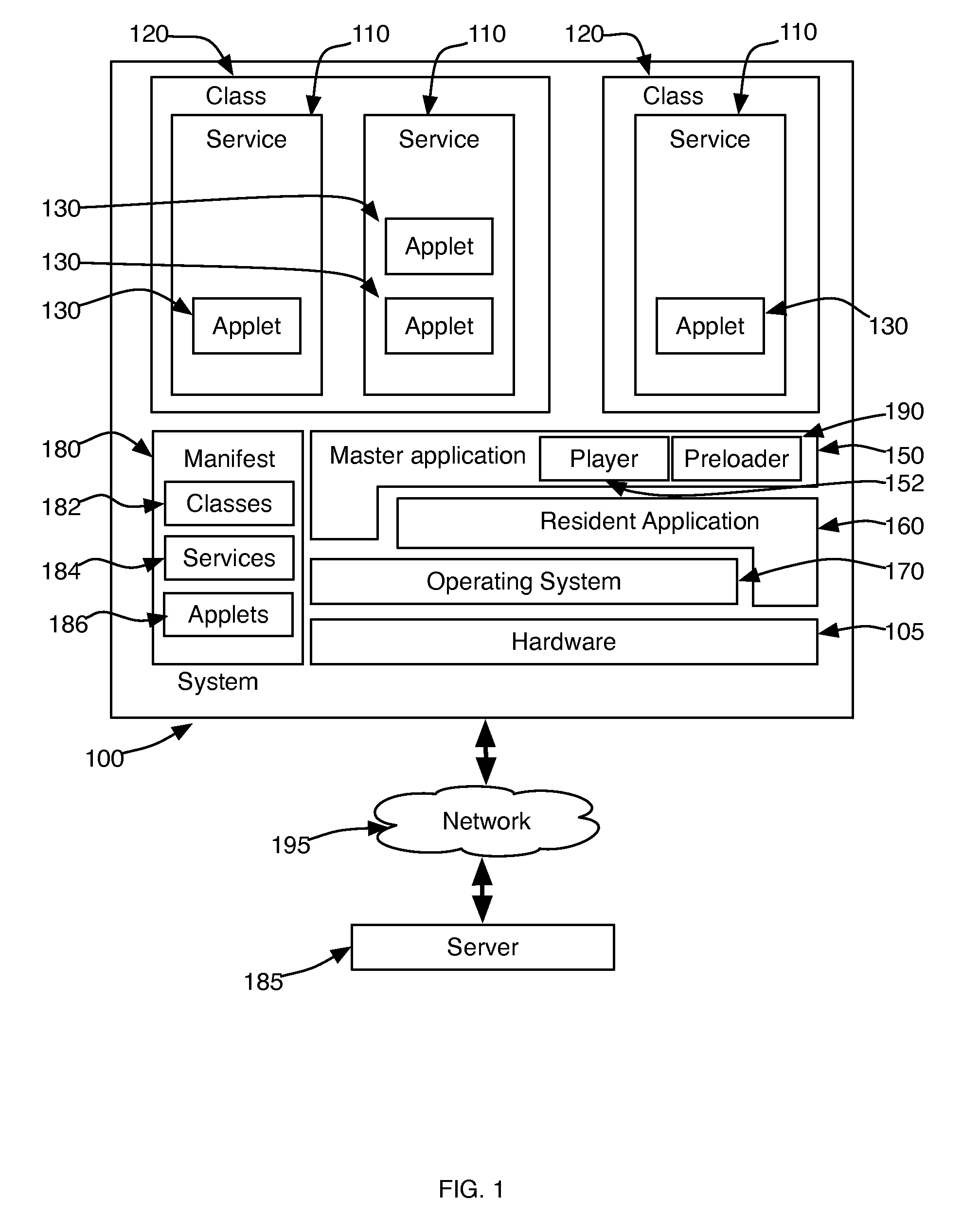

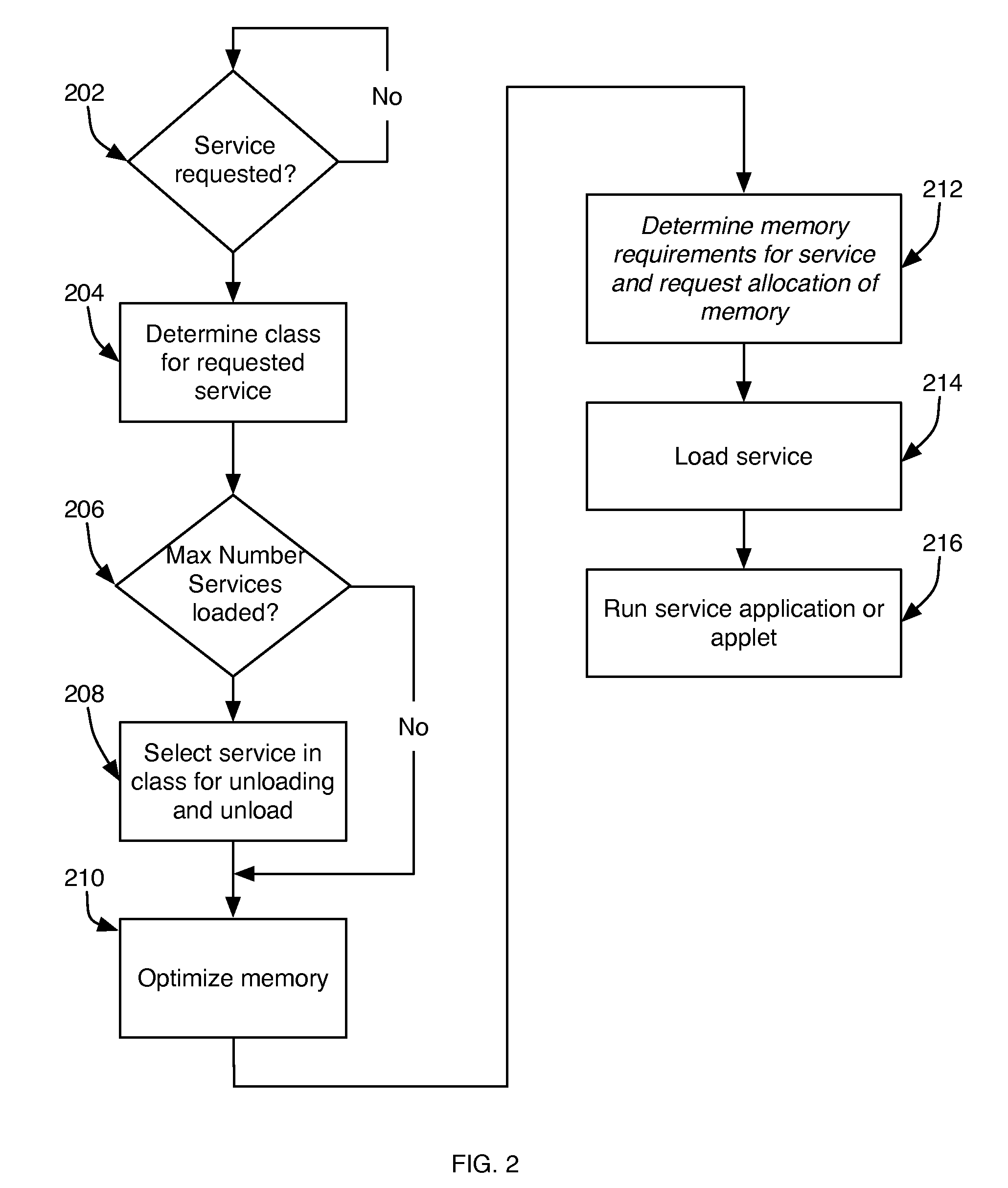

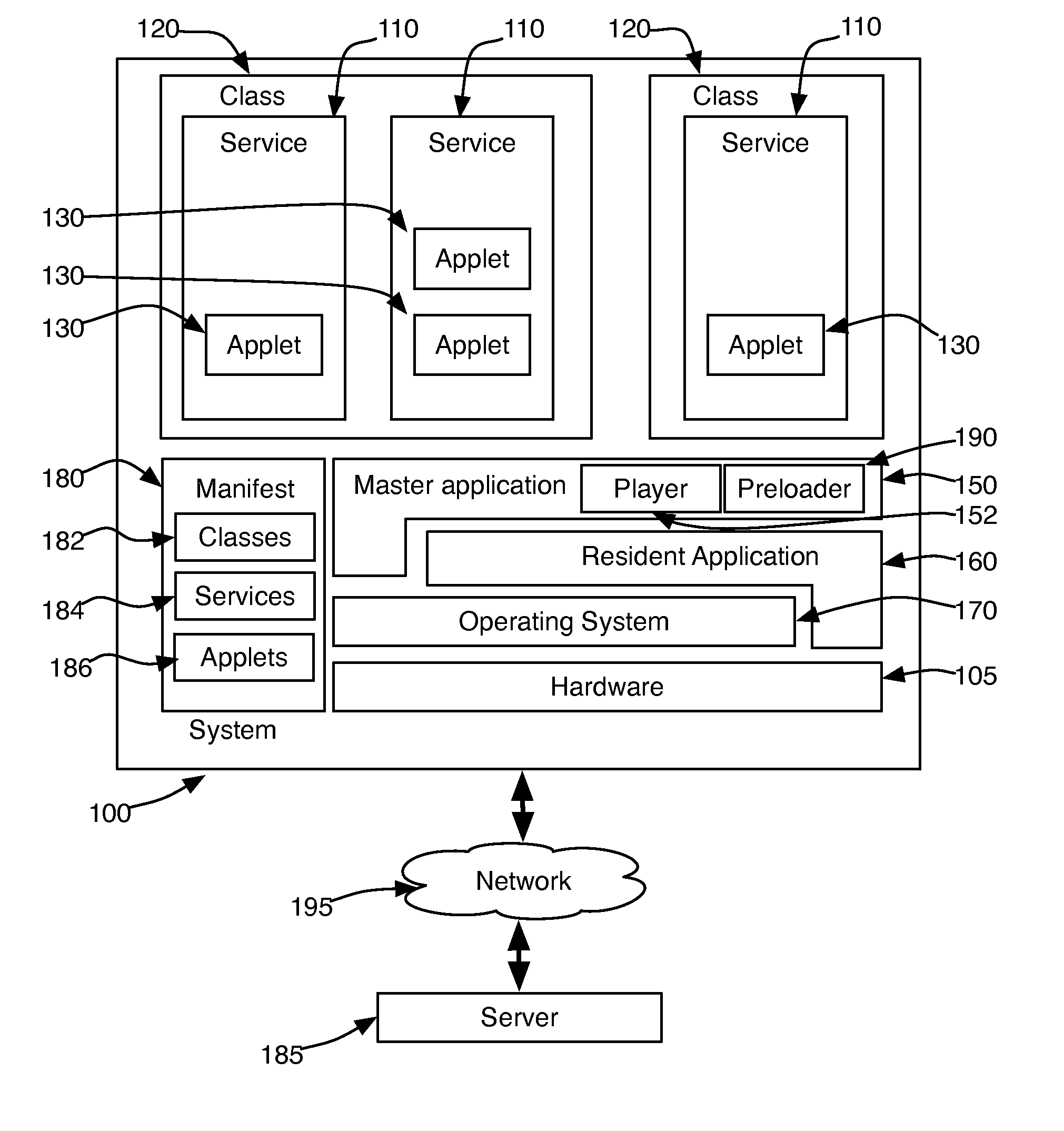

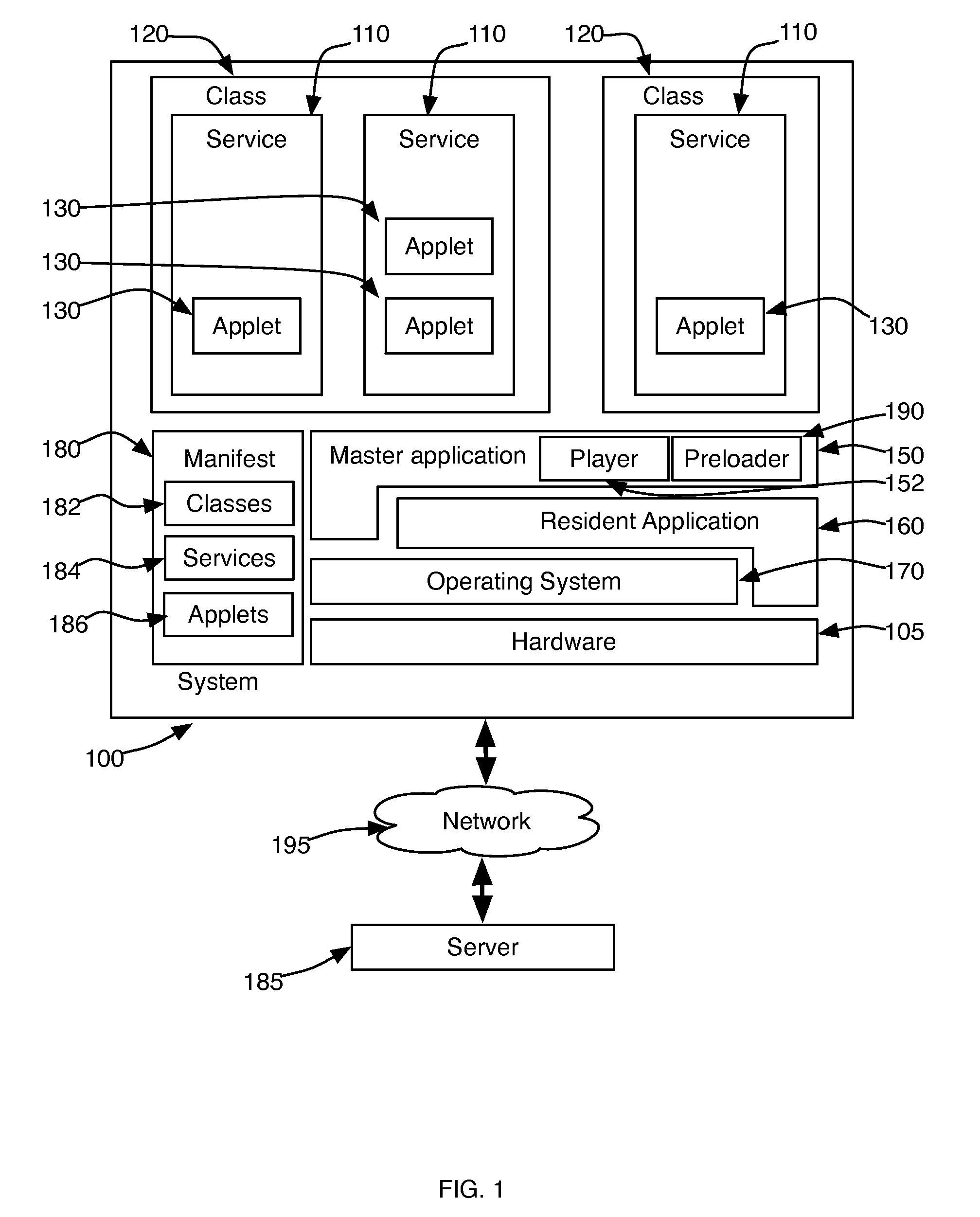

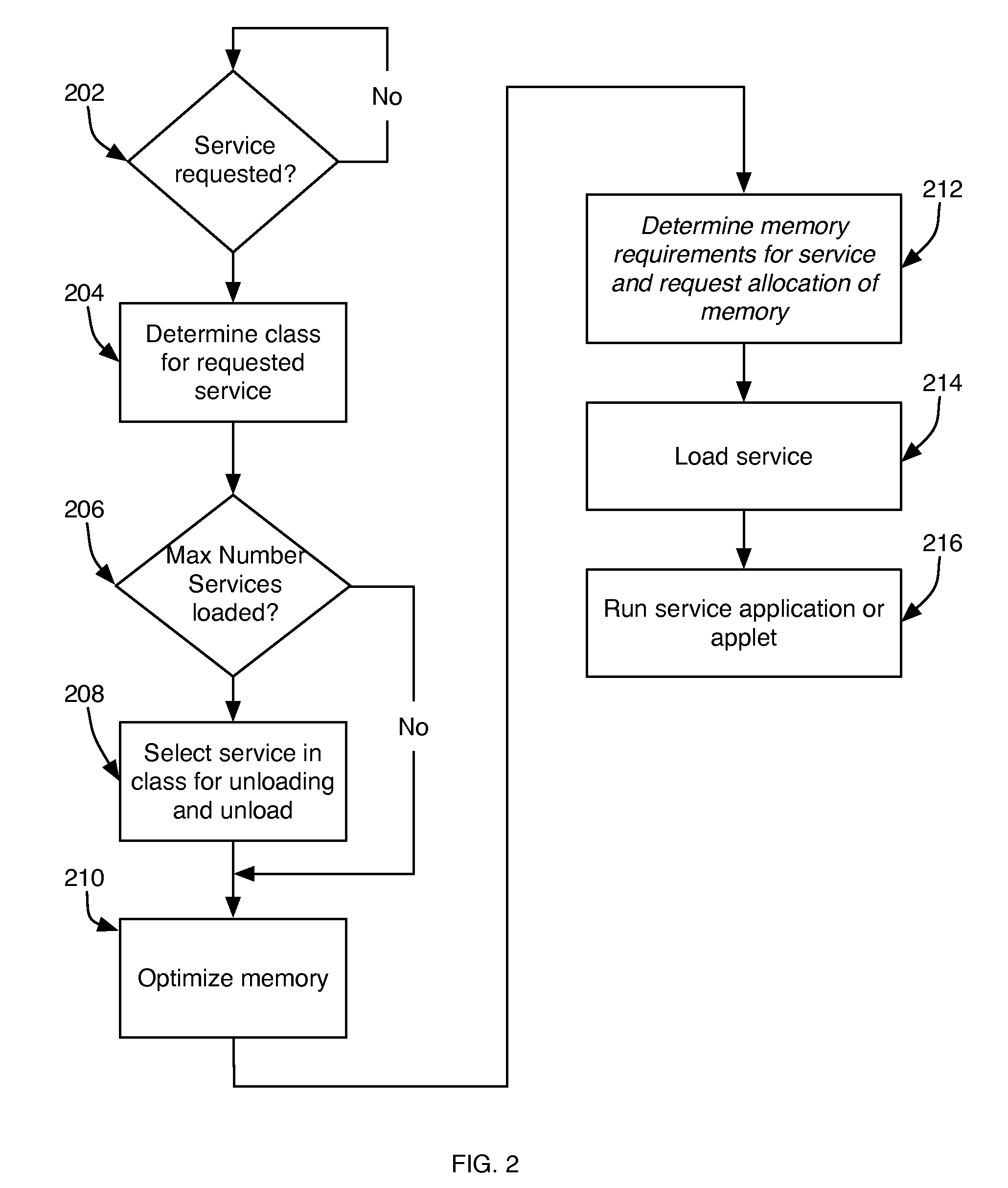

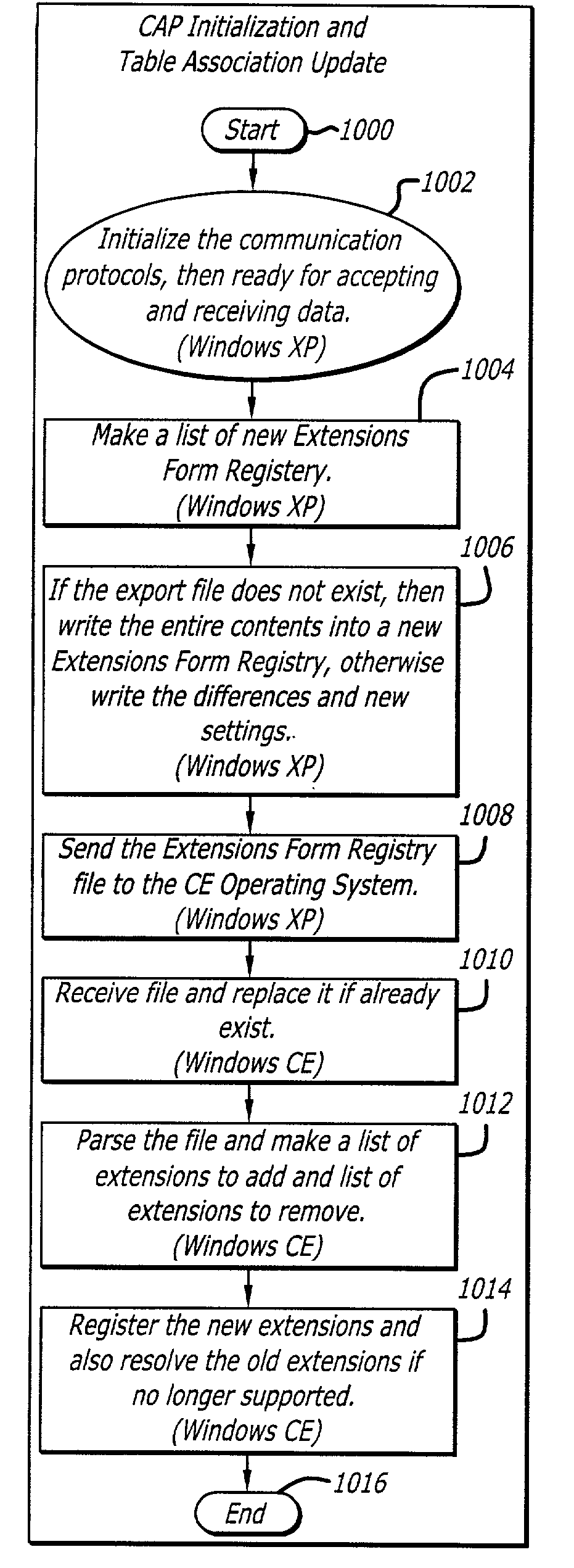

Management of Software Implemented Services in Processor-Based Devices

InactiveUS20090013157A1Reduce memory fragmentationShorten activation timeDigital computer detailsMultiprogramming arrangementsSatellite televisionApplication software

A service management system for devices with embedded processor systems manages use of memory by programs implementing the services by assigning services to classes and limiting the number of services per class that can be loaded into memory. Classes enable achieving predictable and stable system behavior, defining the services and service classes in a manifest that is downloaded to embedded devices operating on a network, such as a cable or satellite television network, telephone or computer network, and permit a system operator, administrator, or manager to manage the operation of the embedded devices while deploying new services implemented with applications downloaded from the network when the service is requested by a user.

Owner:BLUESTREAK TECH INC

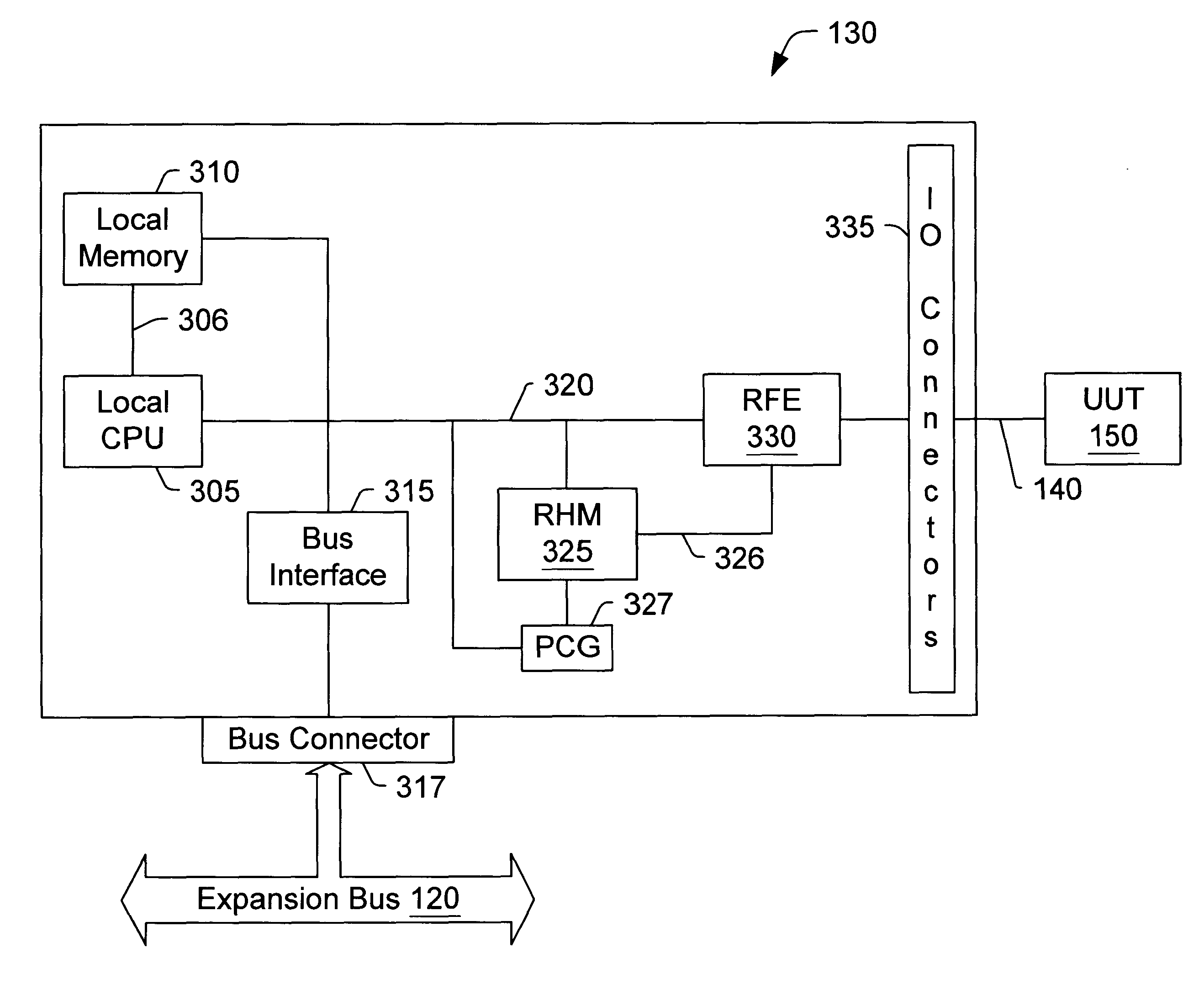

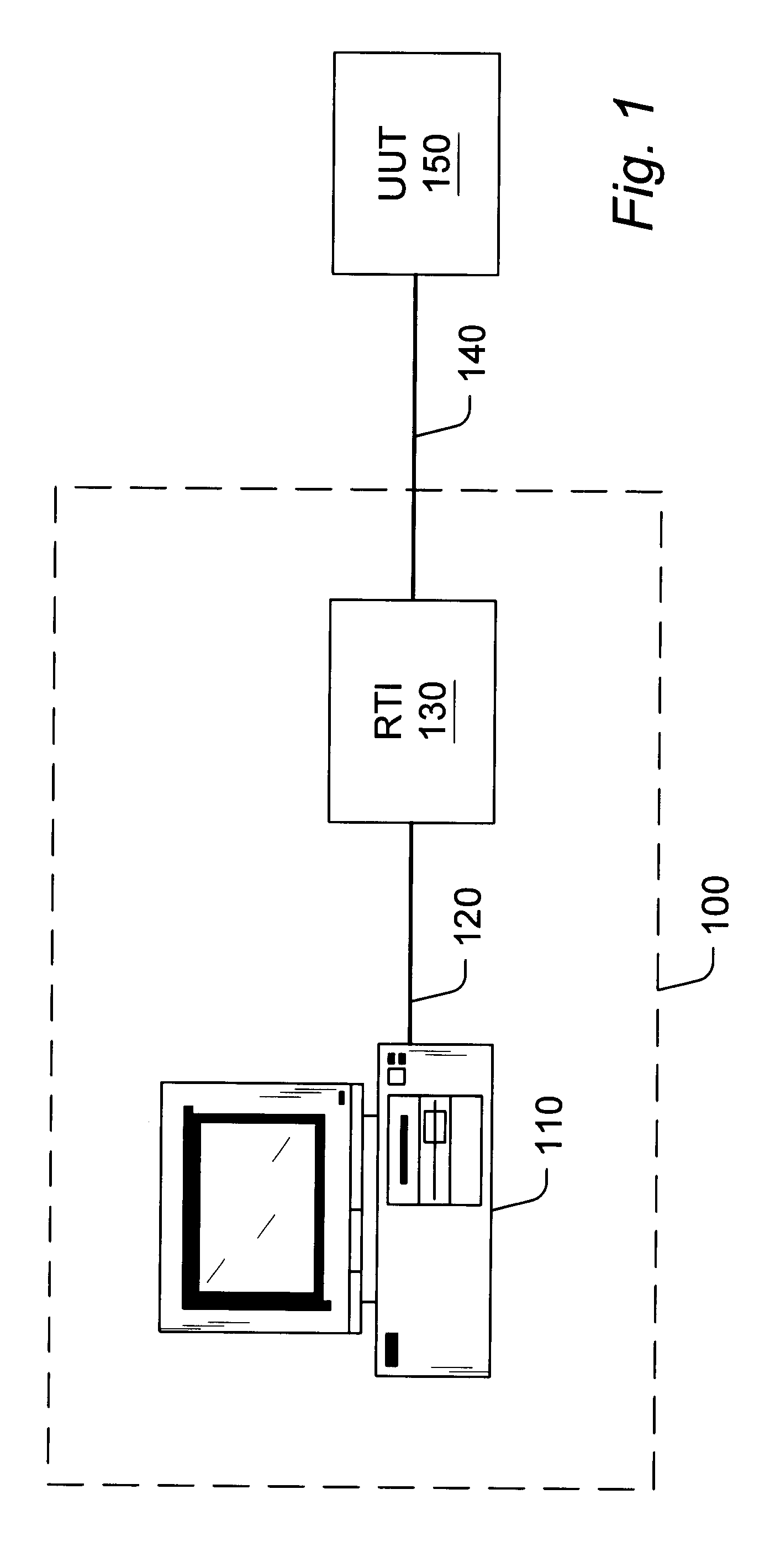

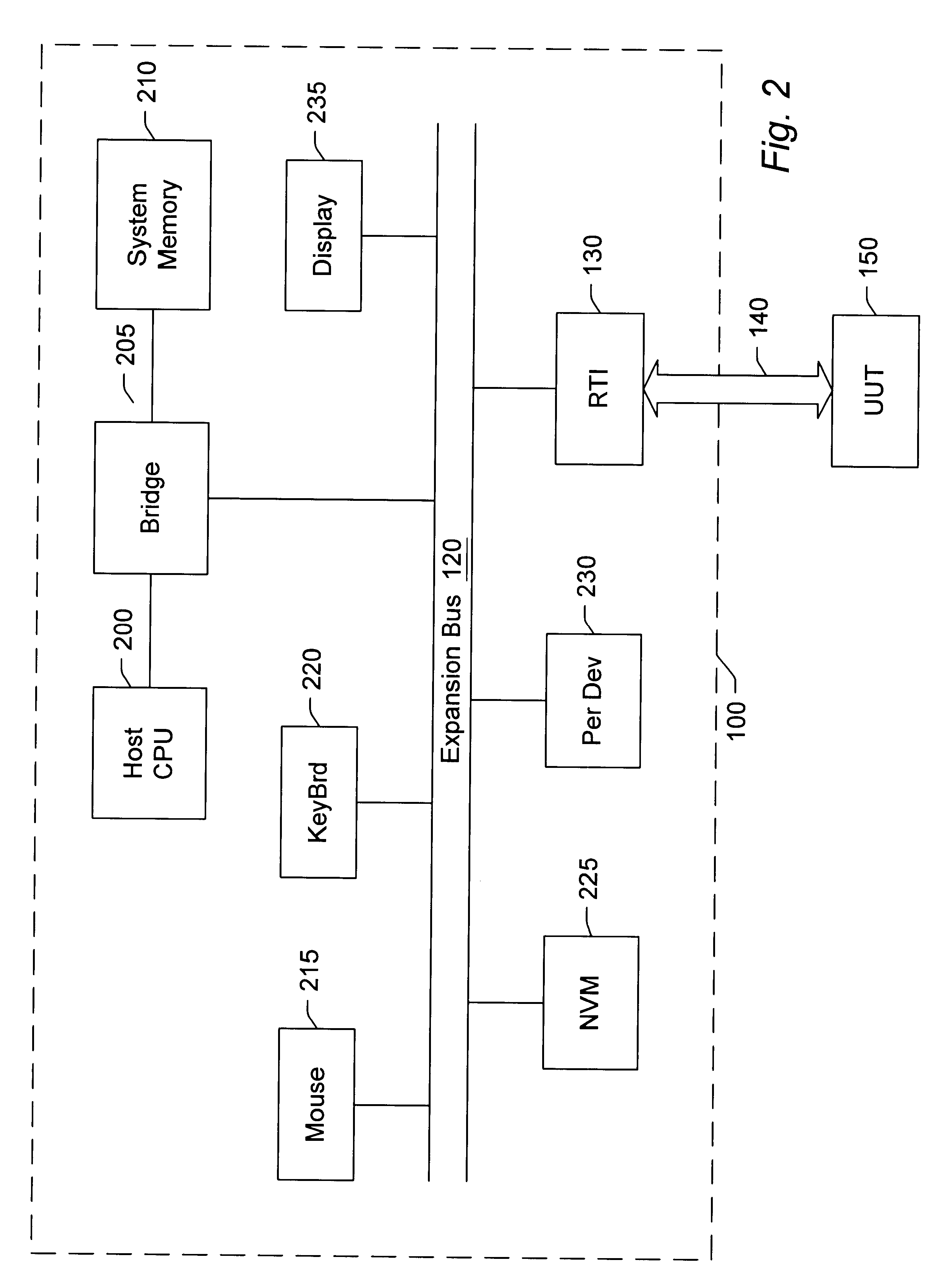

Reconfigurable test system

A reconfigurable test system including a host computer coupled to a reconfigurable test instrument. The reconfigurable test instrument includes reconfigurable hardware-i.e. a reconfigurable hardware module with one or more programmable elements such as Field Programmable Gate Arrays for realizing an arbitrary hardware architecture and a reconfigurable front end with programmable transceivers for interfacing with any desired physical medium-and optionally, an embedded processor. A user specifies system features with a software configuration utility which directs a component selector to select a set of software modules and hardware configuration files from a series of libraries. The modules are embedded in a host software driver or downloaded for execution on the embedded CPU. The configuration files are downloaded to the reconfigurable hardware. The entire selection process is performed in real-time and can be changed whenever the user deems necessary. Alternatively, the user may create a graphical program in a graphical programming environment and compile the program into various software modules and configuration files for host execution, embedded processor execution, or programming the reconfigurable hardware.

Owner:NATIONAL INSTRUMENTS

Management of software implemented services in processor-based devices

InactiveUS8522249B2Shorten activation timeAvoid timeDigital computer detailsMultiprogramming arrangementsSatellite televisionService allocation

A service management system for devices with embedded processor systems manages use of memory by programs implementing the services by assigning services to classes and limiting the number of services per class that can be loaded into memory. Classes enable achieving predictable and stable system behavior, defining the services and service classes in a manifest that is downloaded to embedded devices operating on a network, such as a cable or satellite television network, telephone or computer network, and permit a system operator, administrator, or manager to manage the operation of the embedded devices while deploying new services implemented with applications downloaded from the network when the service is requested by a user.

Owner:BLUESTREAK TECH INC

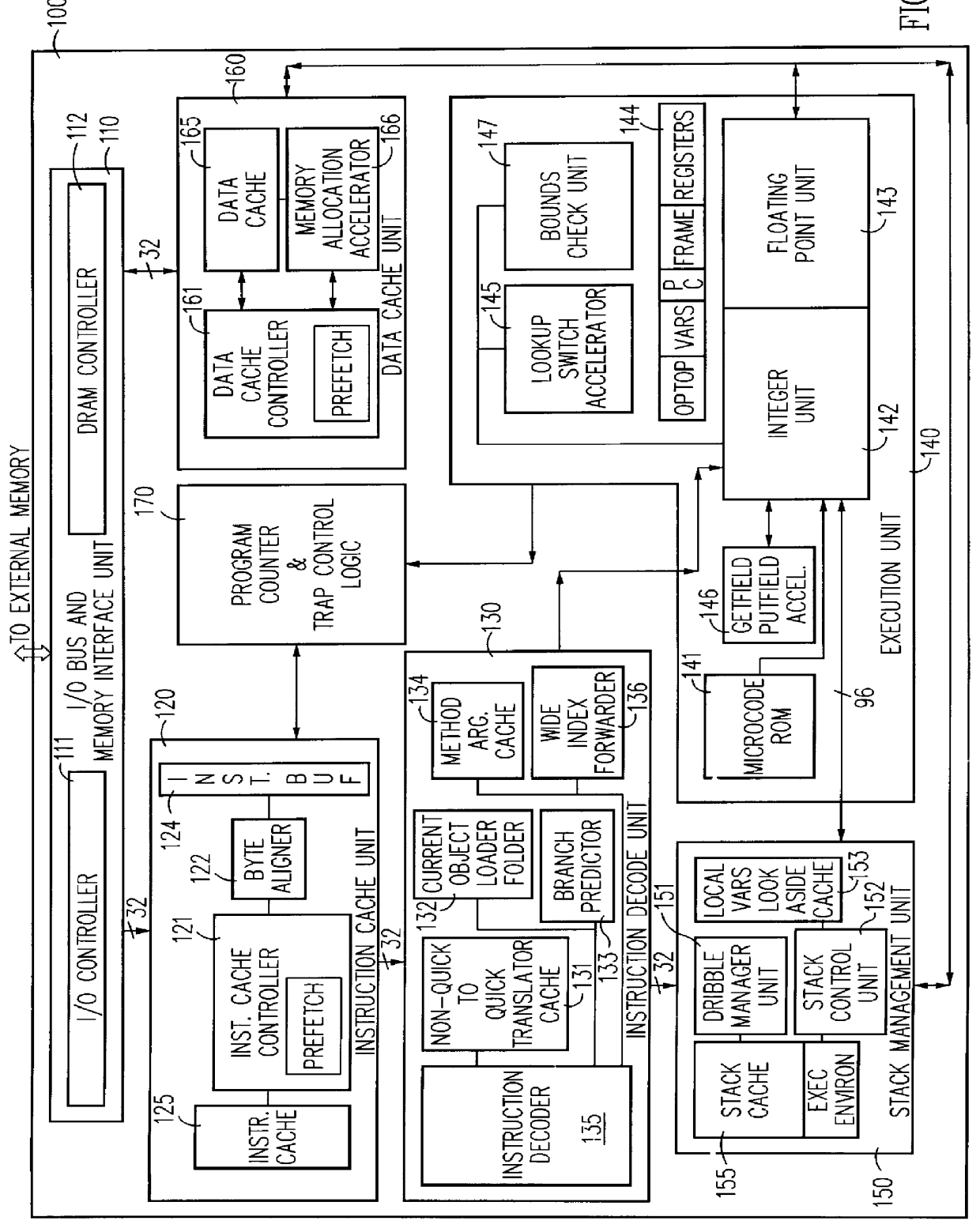

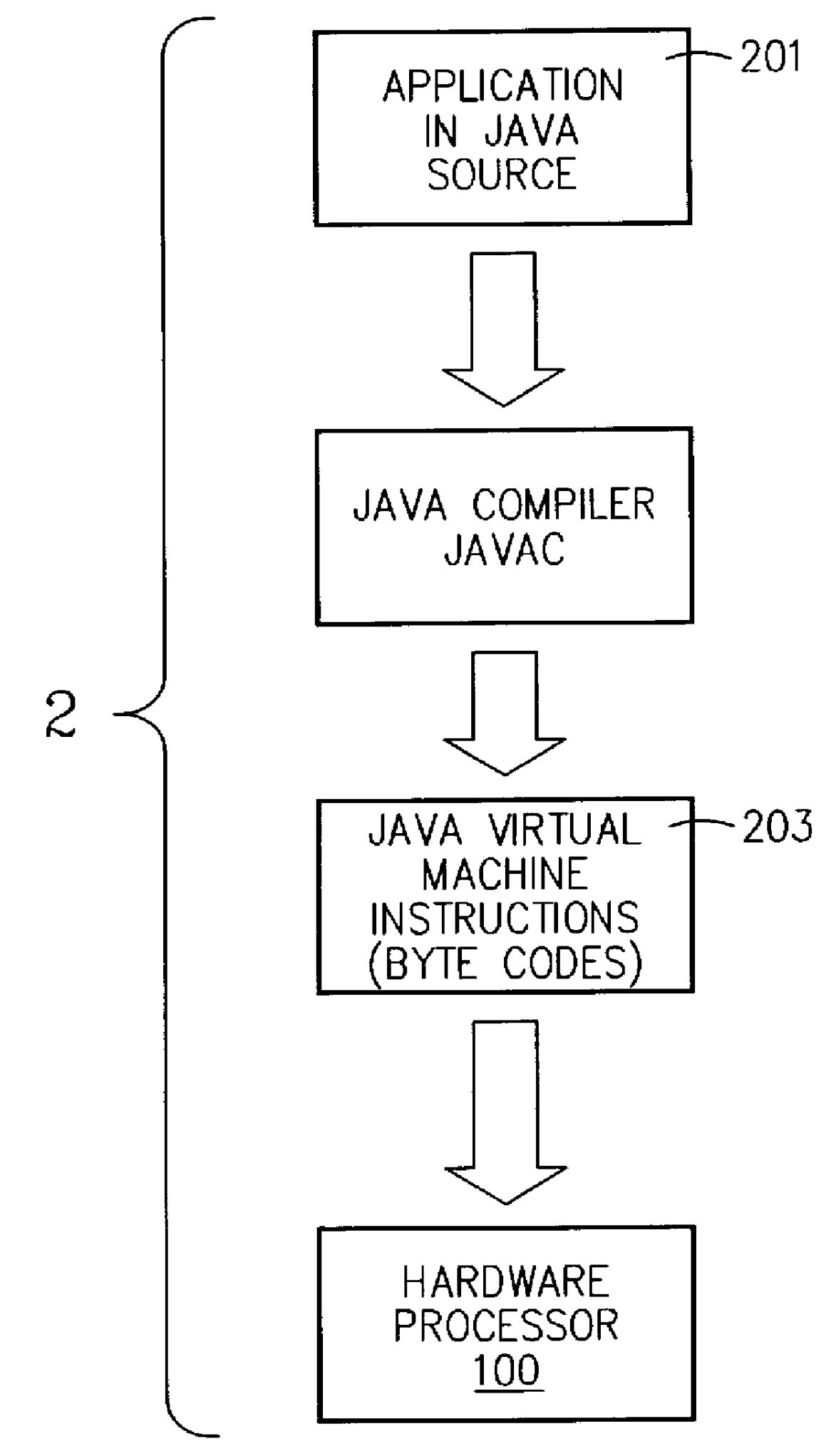

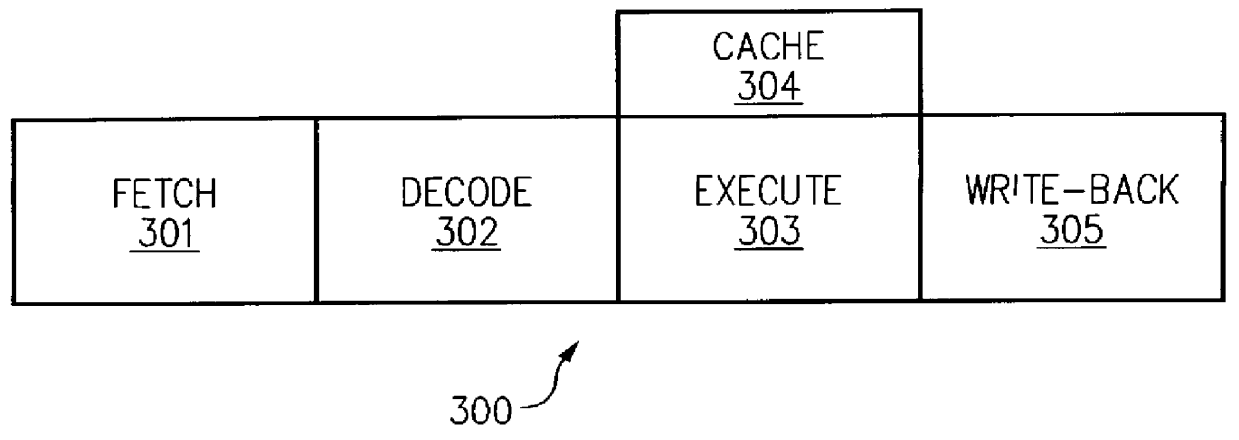

Hardware virtual machine instruction processor

InactiveUS6021469AProhibitive expenseLow costMemory architecture accessing/allocationEnergy efficient ICTThe InternetCellular telephone

A hardware virtual machine instruction processor directly executes virtual machine instructions that are processor architecture independent. The hardware processor has high performance; is low cost; and exhibits low power consumption. The hardware processor is well suited for portable applications. These applications include, for example, an Internet chip for network appliances, a cellular telephone processor, other telecommunications integrated circuits, or other low-power, low-cost applications such as embedded processors, and portable devices.

Owner:ORACLE INT CORP

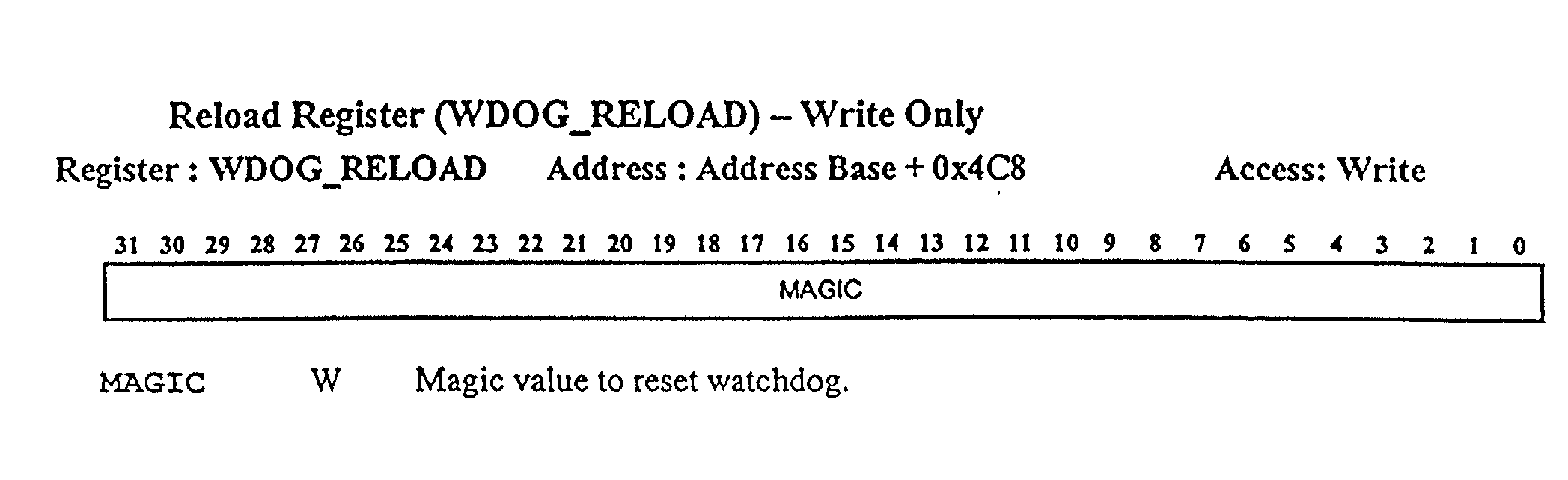

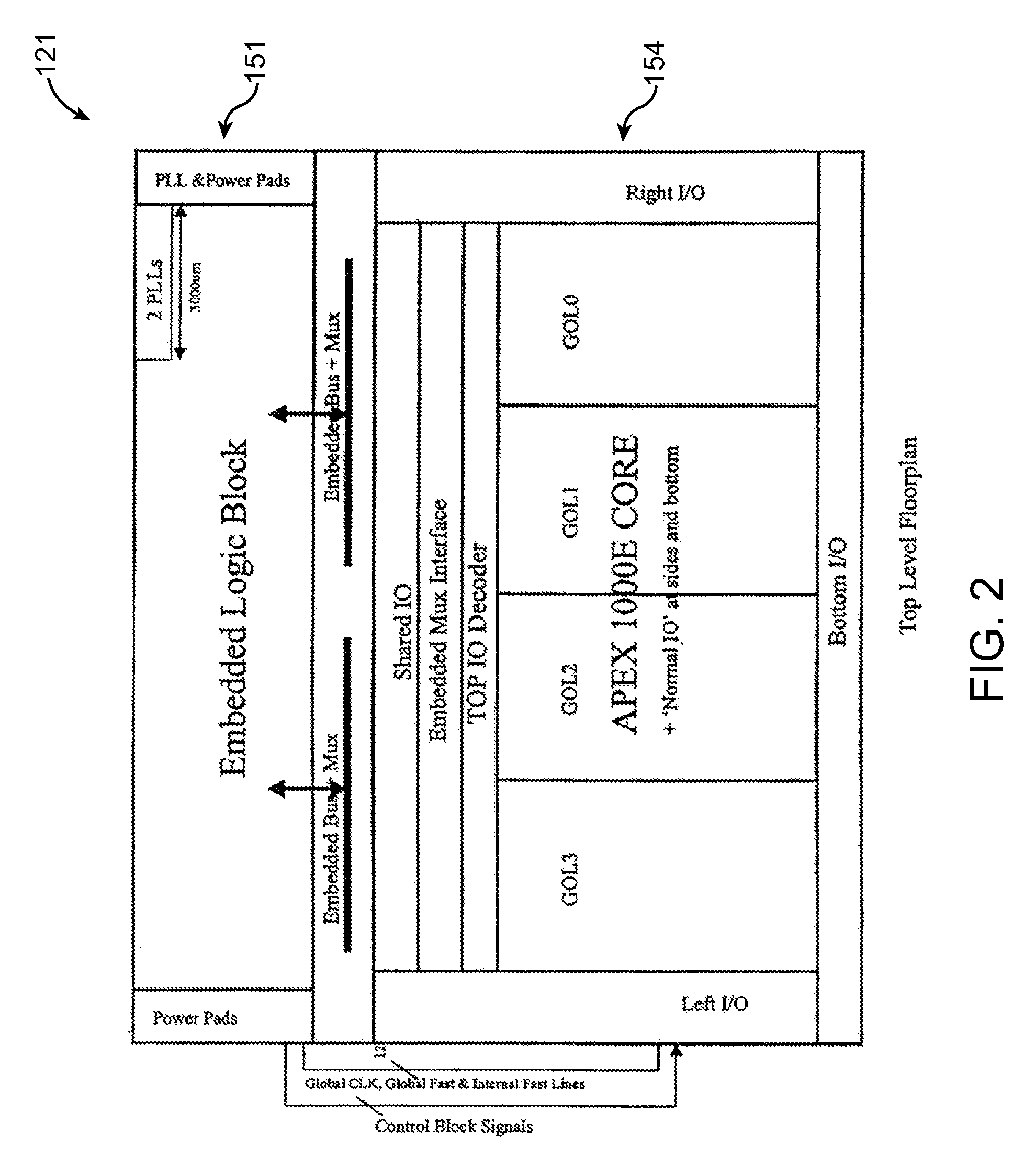

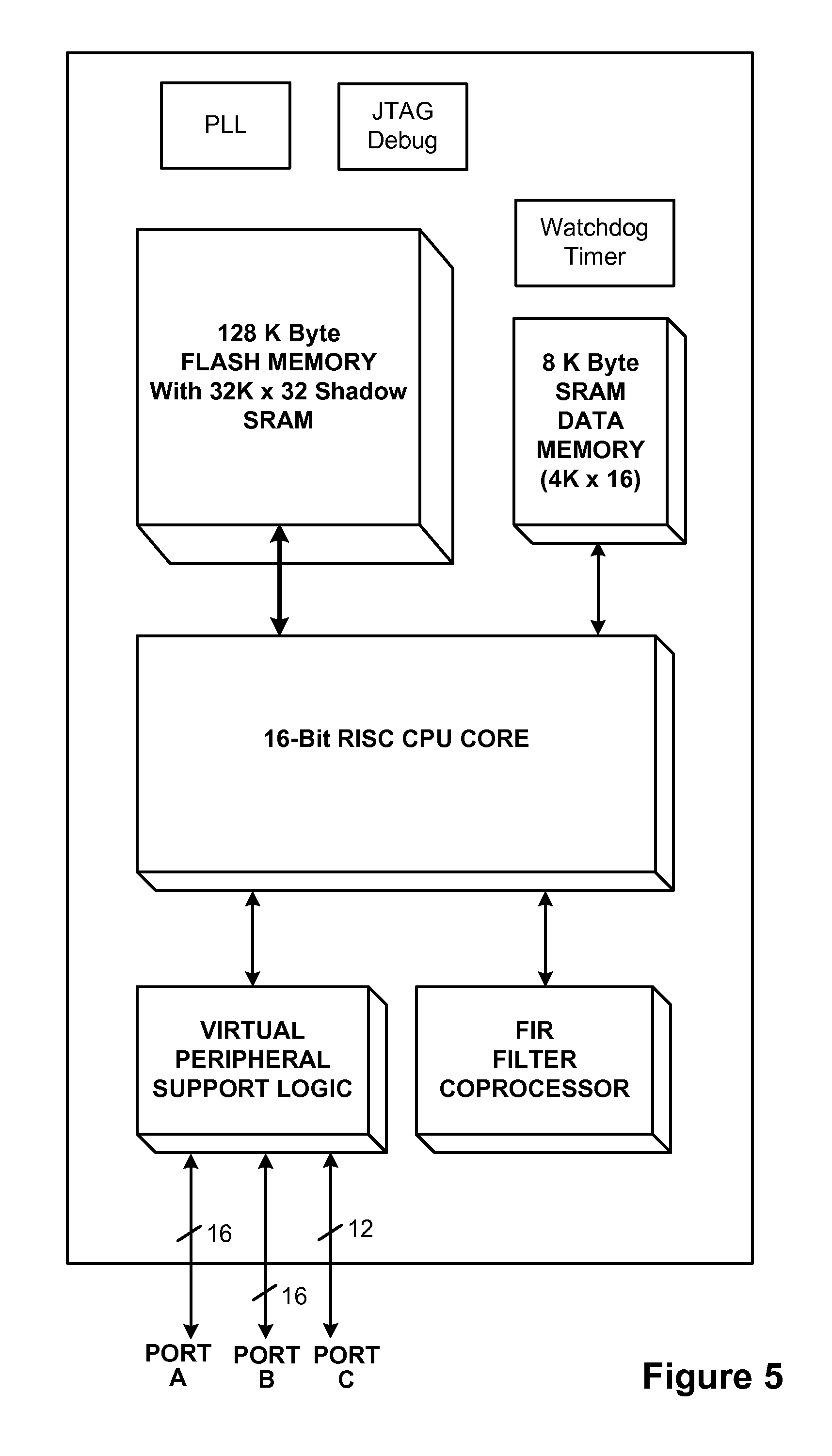

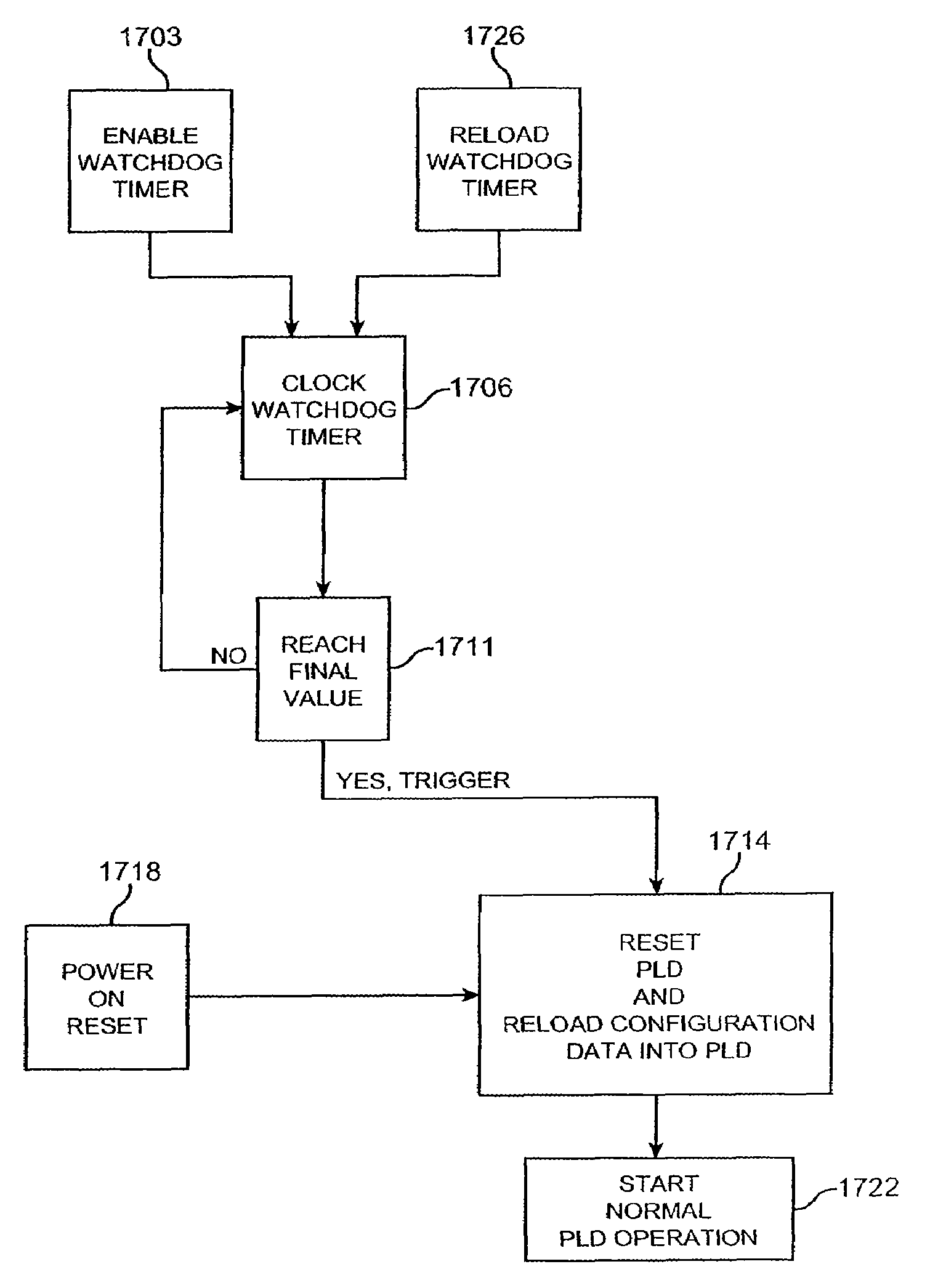

Embedded processor with watchdog timer for programmable logic

InactiveUS7340596B1Digital computer detailsData resettingProgrammable logic deviceProcessor register

A programmable logic integrated circuit has an embedded processor with a watchdog timer circuit. The watchdog timer circuit is used to detect software or hardware failures. In one implementation, the watchdog timer circuit includes a counter register that advances (e.g., incremented or decremented) with each clock. To prevent the watchdog timer circuit from becoming triggered, the watchdog timer circuit should be reset or reloaded by software. For example, the count register may be reset to a value to start the count over. If the count register is allowed to count to a final or maximum value, the watchdog timer circuit will become triggered, generating a triggered signal that causes the programmable logic integrated circuit to be reset. A reset causes a reloading of the configuration data used to program the programmable logic and embedded processor portions of the integrated data. The configuration data may be stored in an external nonvolatile storage memory.

Owner:ALTERA CORP

Novel personal electronics device

First (embedded) and second (non-embedded) processors are energized by an energy source in a hand-held device. The second processor performs functions requiring more power than those performed by the first processor. The second processor is normally asleep and is awakened by the first processor and is empowered, when awakened, to perform functions. Only the portions of the second processor required to perform these functions are activated. Protocols for functions to be performed by the second processor are provided initially to the second processor and are processed in the second processor. They are then transferred to the first processor for storage. When the second processor is activated to perform functions represented by a protocol, the protocol is transferred to the second processor and the functions are performed by the second processor.

Owner:ARM LTD

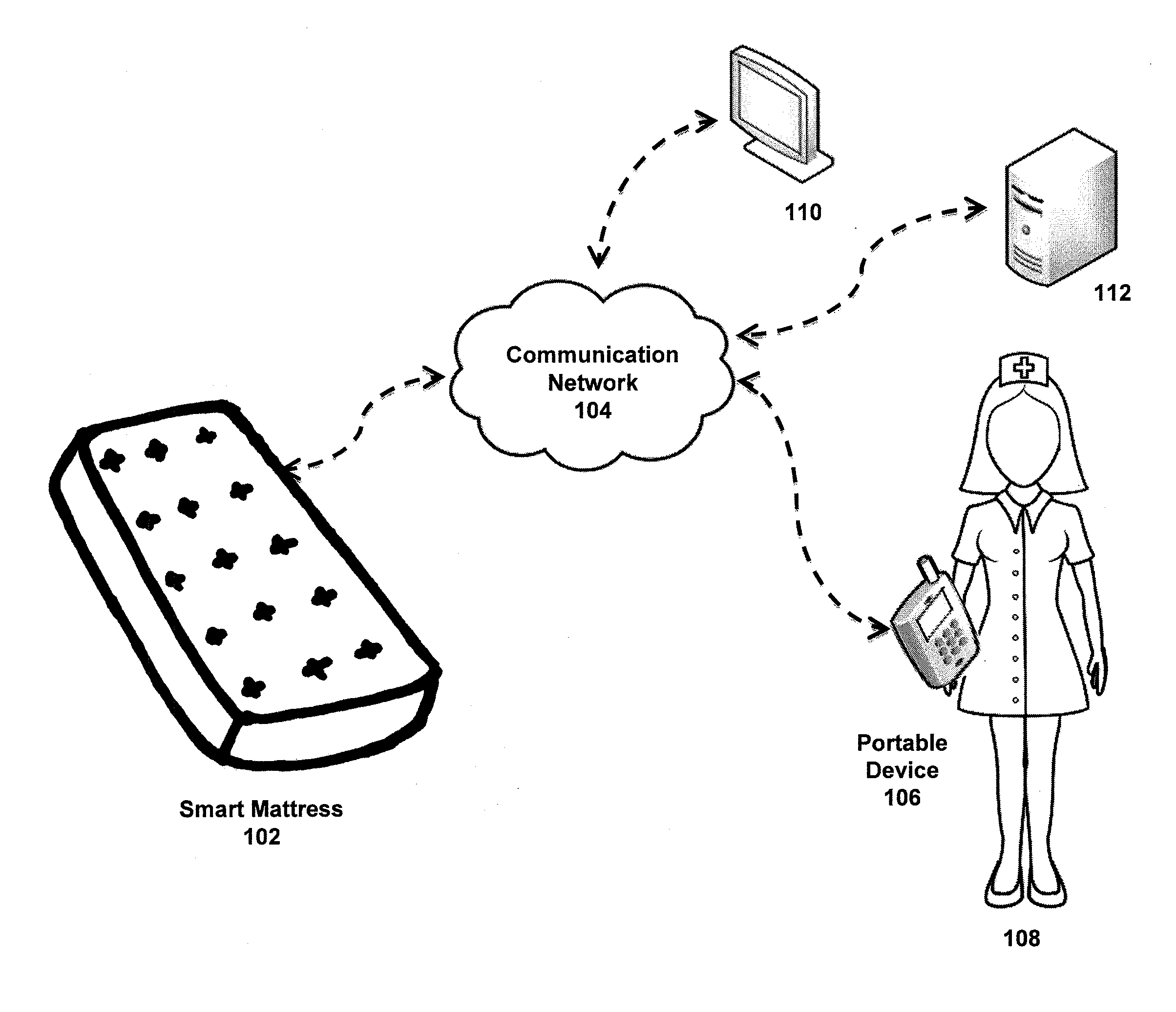

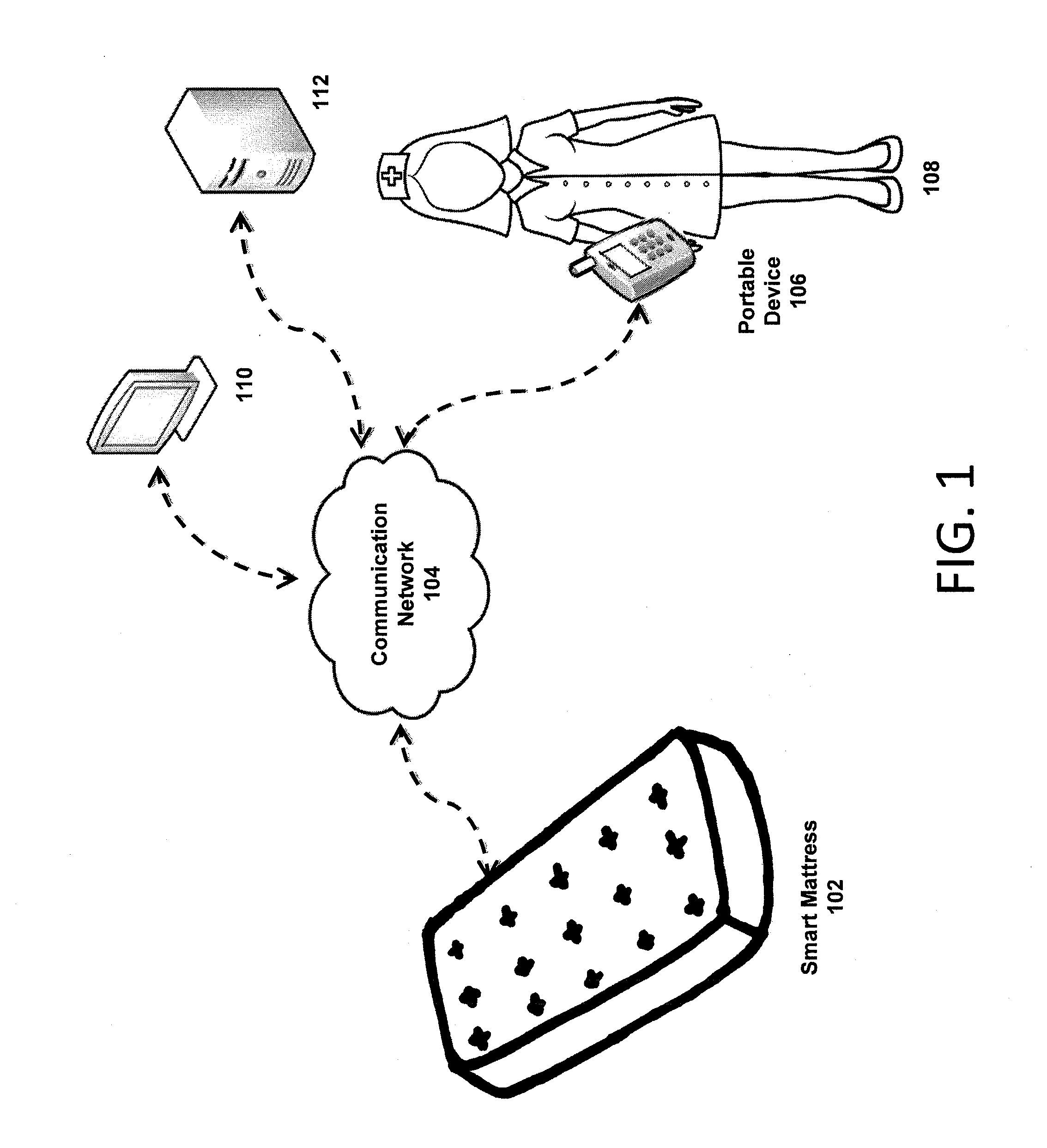

Smart mattress

InactiveUS20120053423A1Good flexibilityAdvanced technologyChildren furnitureDiagnostic recording/measuringBed-riddenCare giver

Systems and methods are disclosed for a self-contained Smart Mattress which is capable of monitoring the vital statistics of a patient in real time, analyzing the data using an embedded processor, storing patient identification and information, producing an electronic medical report and communicating any data to the caregiver or computer server using wireless technology, such as Bluetooth® Technology. Due to the self-contained nature of the mattress, it is also ideal for use as an emergency evacuation mattress for bed-ridden patients.

Owner:EVACUSLED

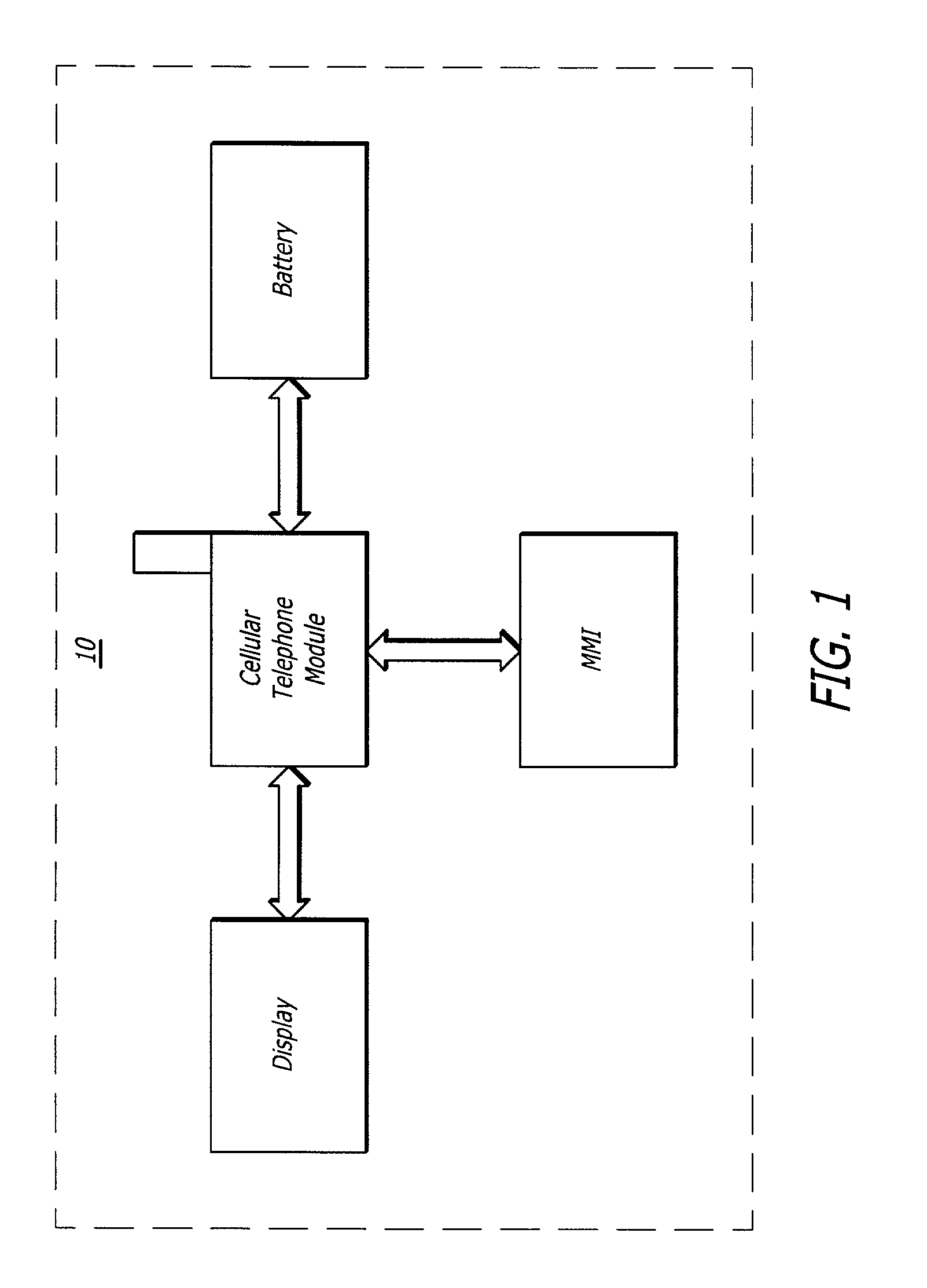

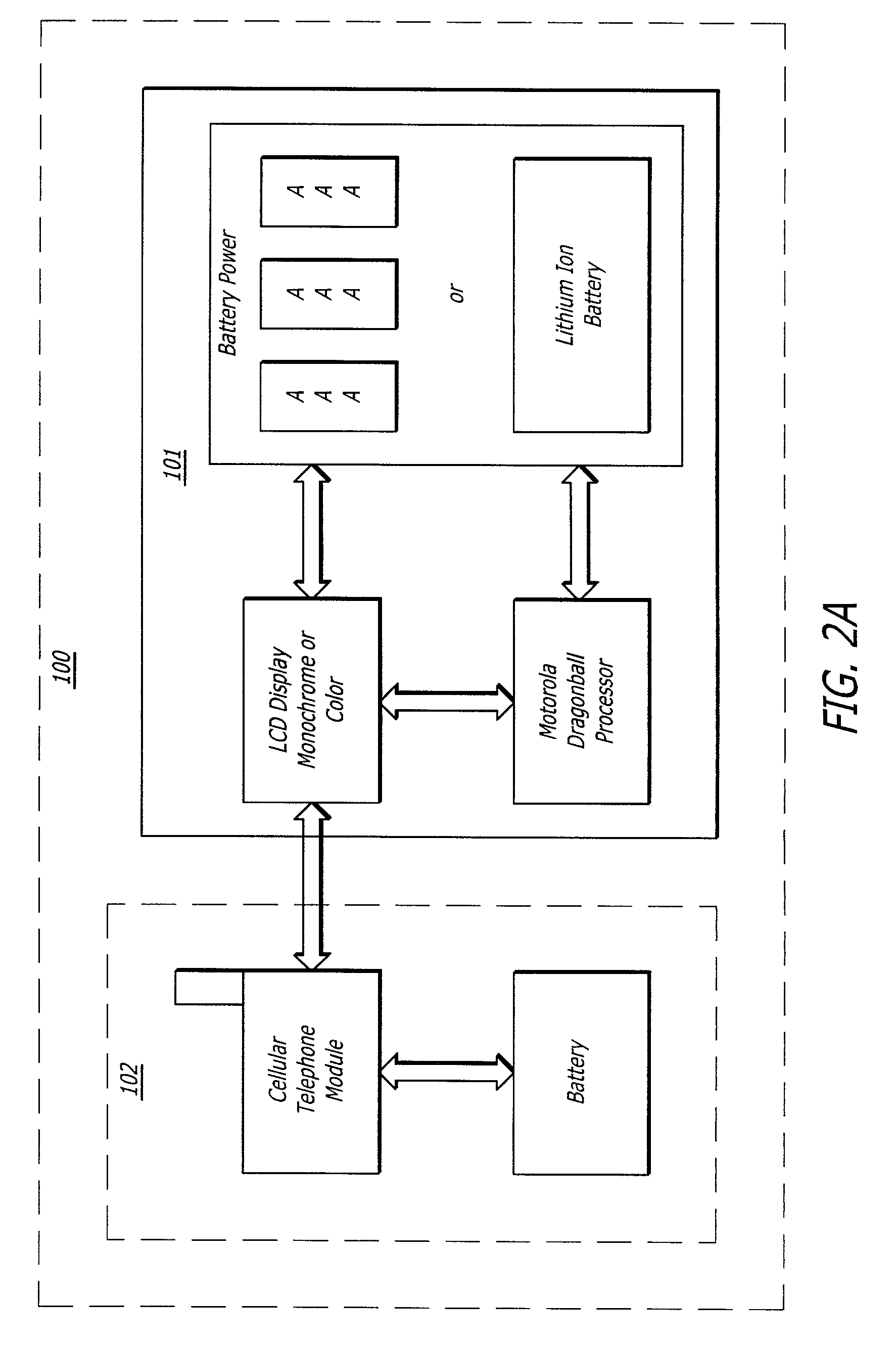

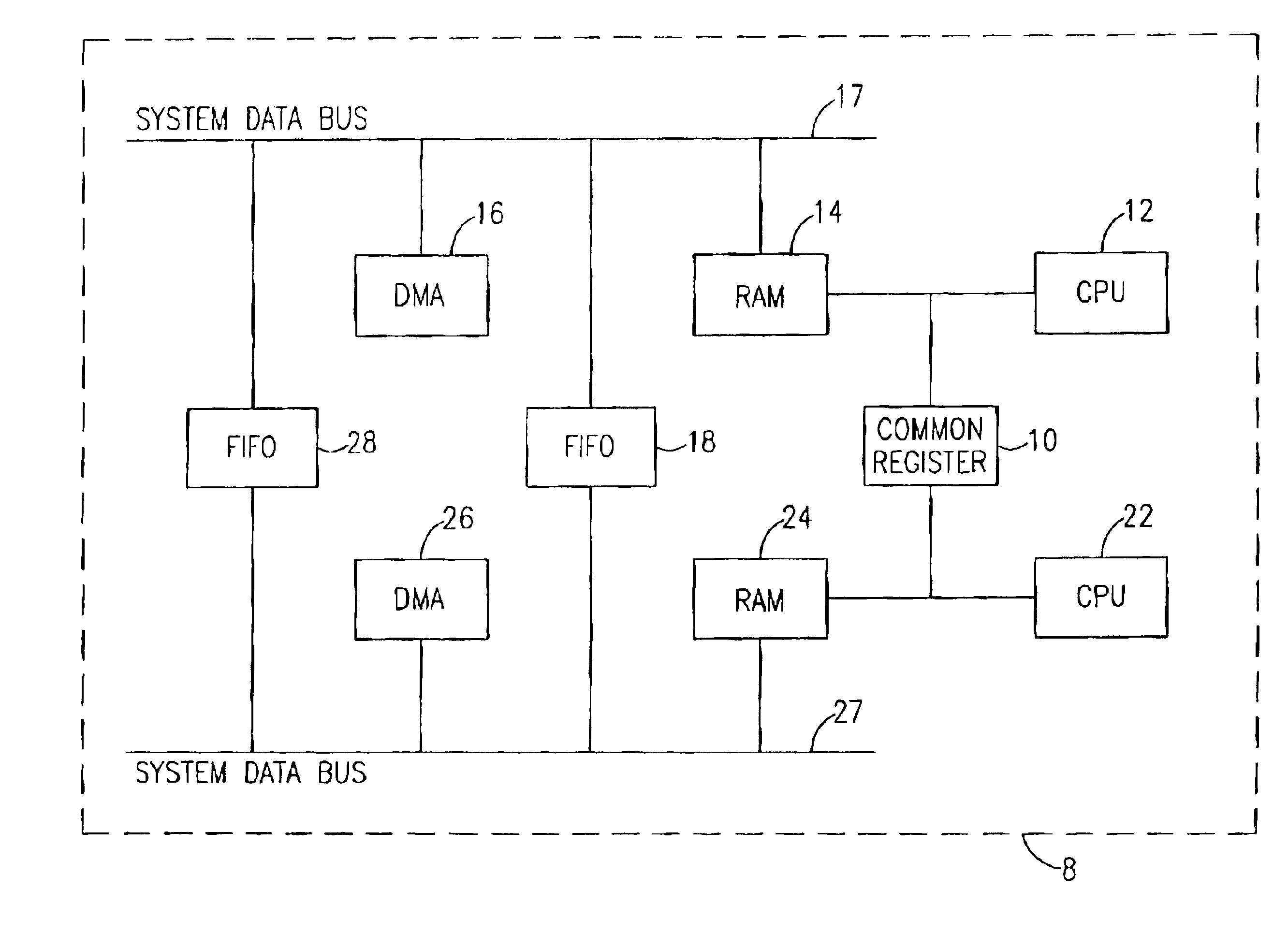

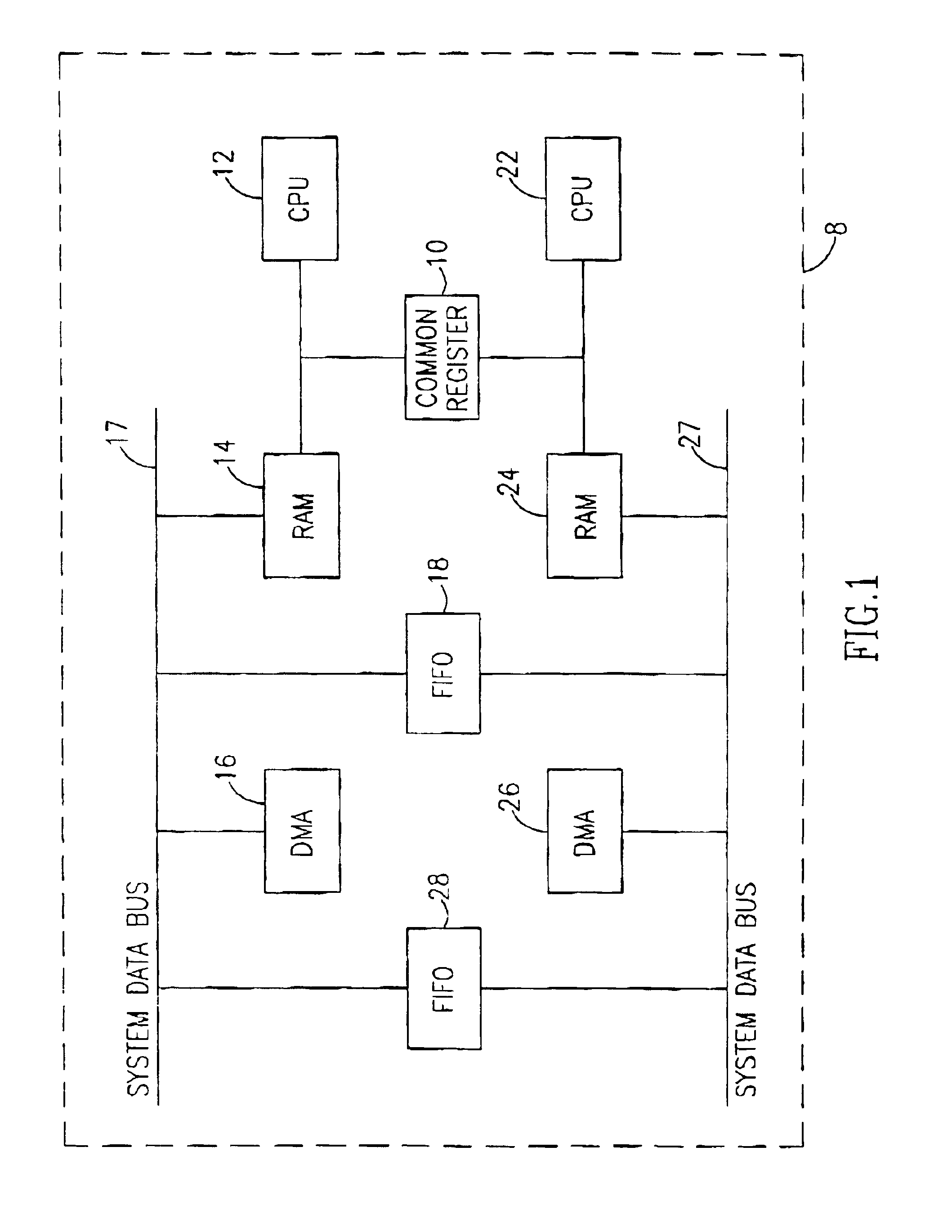

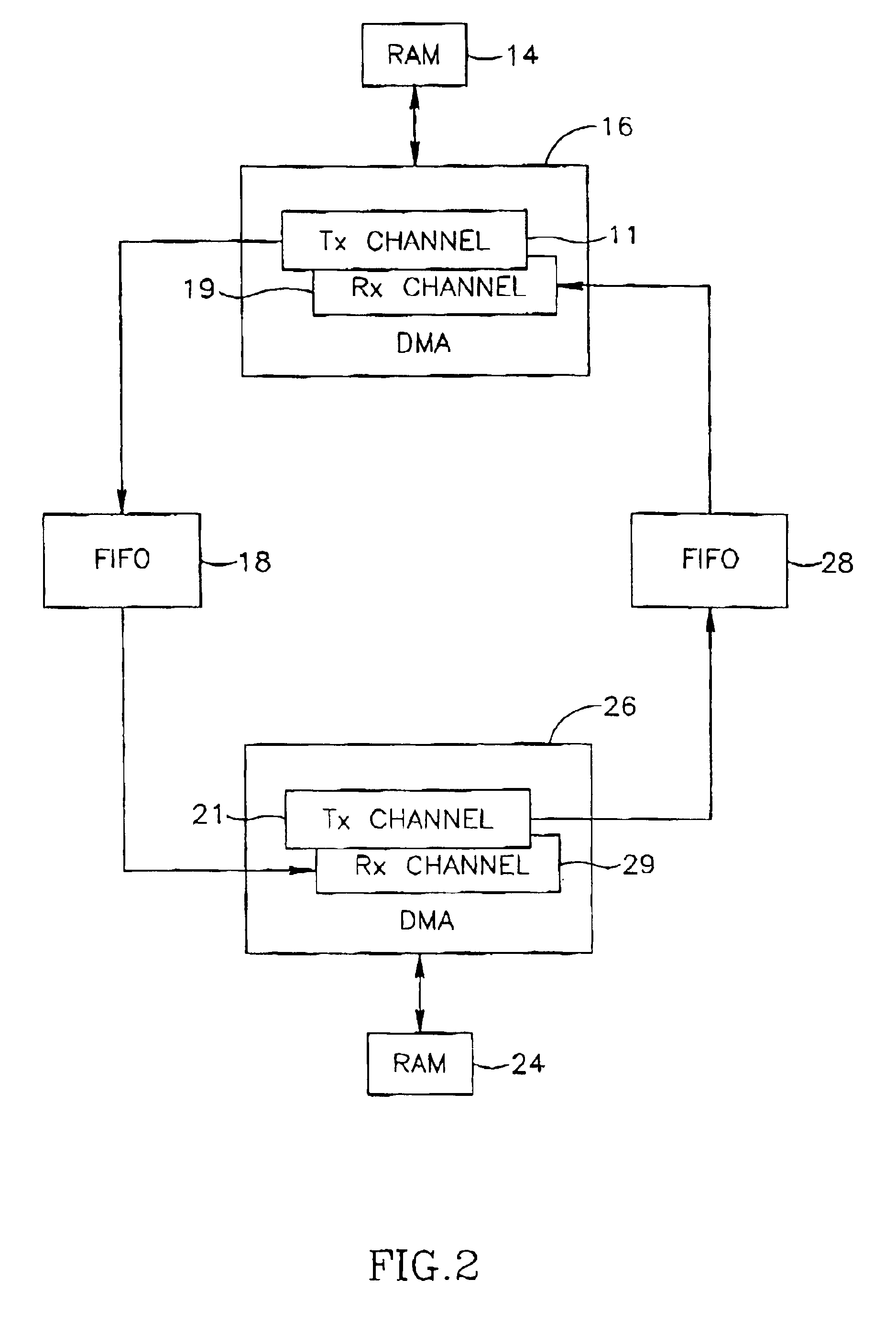

Communication between two embedded processors

A system including at least two processing units embedded on a chip able to communicate with each other and to generally independently control access to data from memory on the chip.

Owner:INTEL CORP

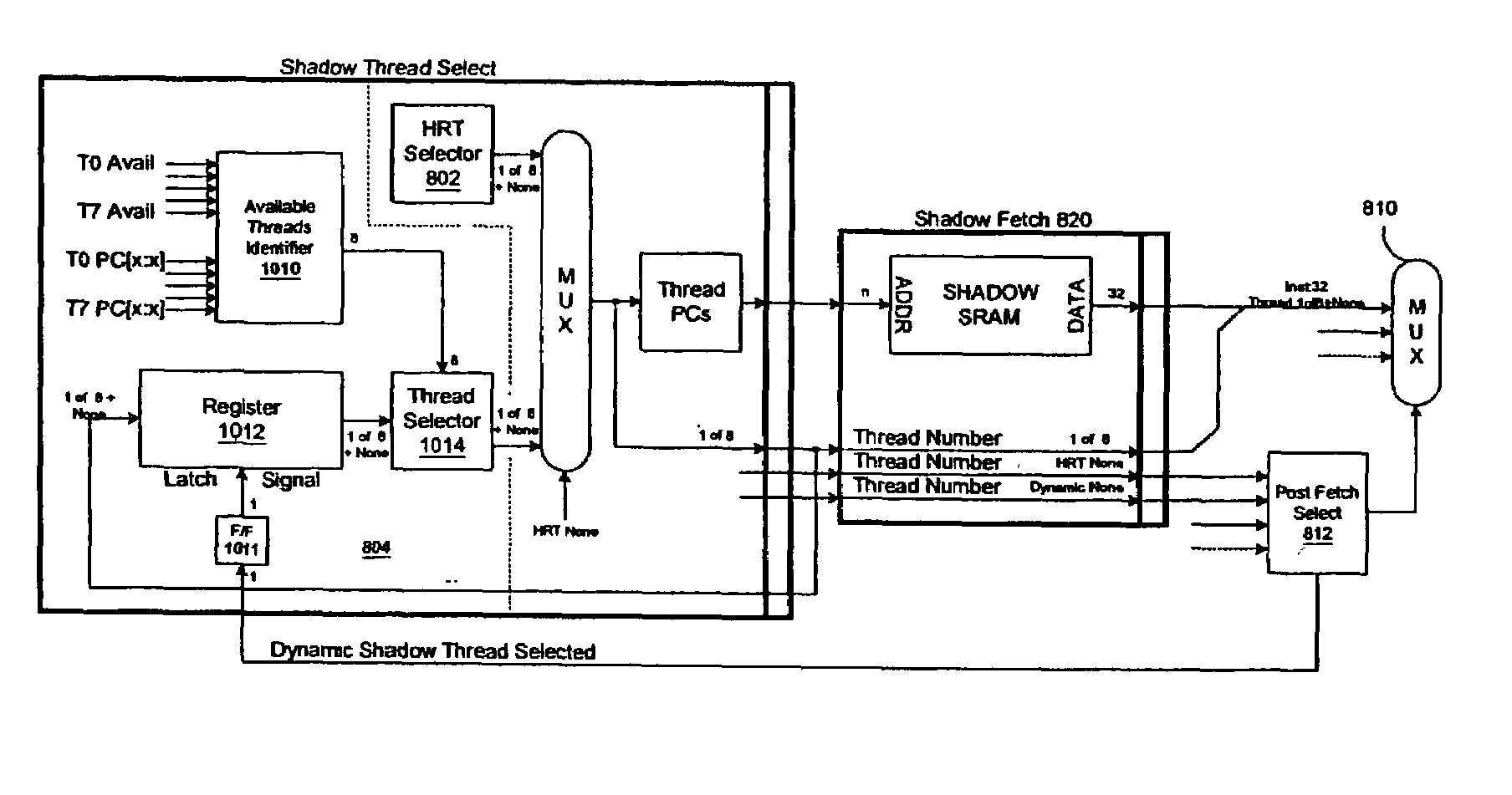

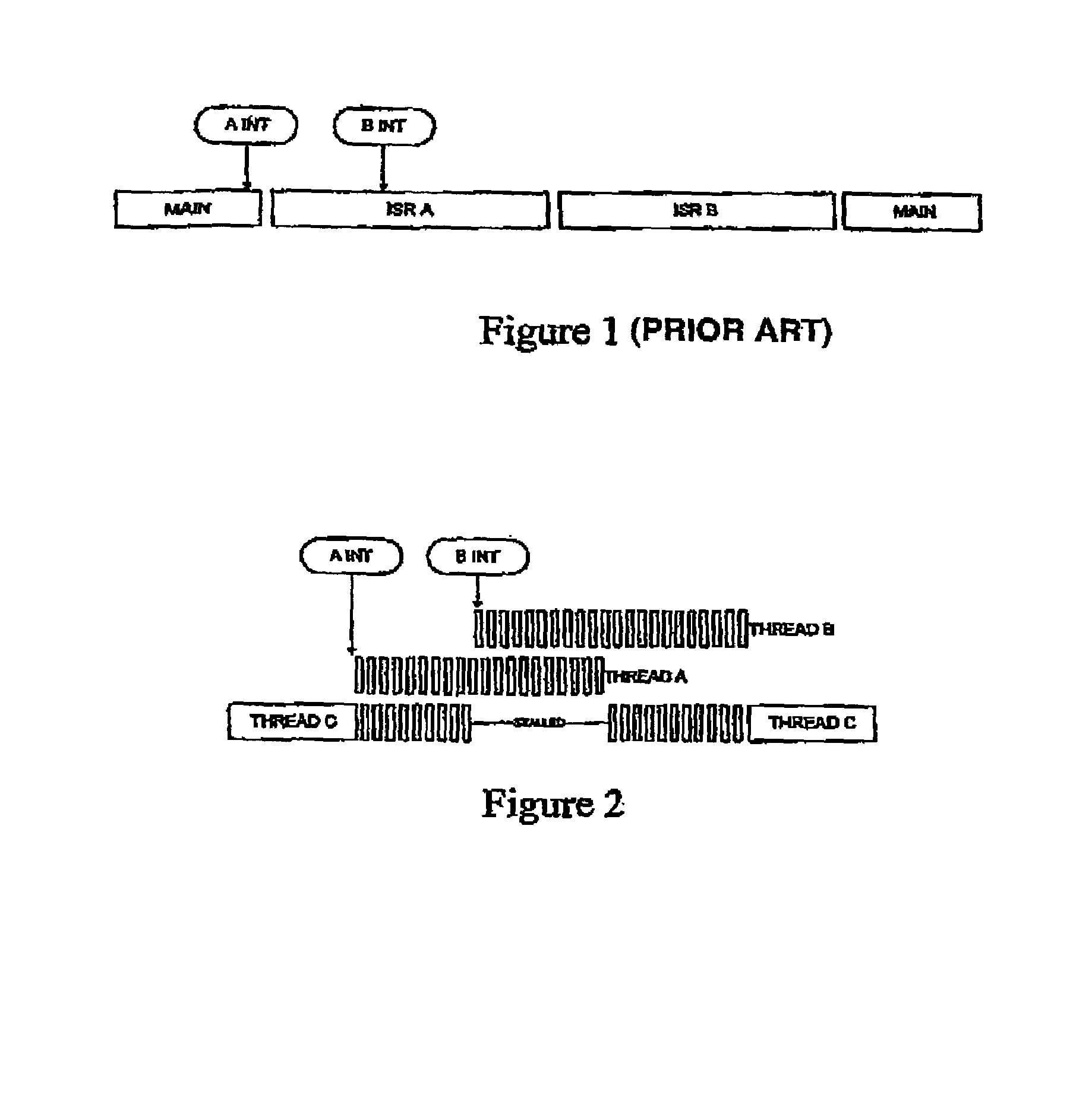

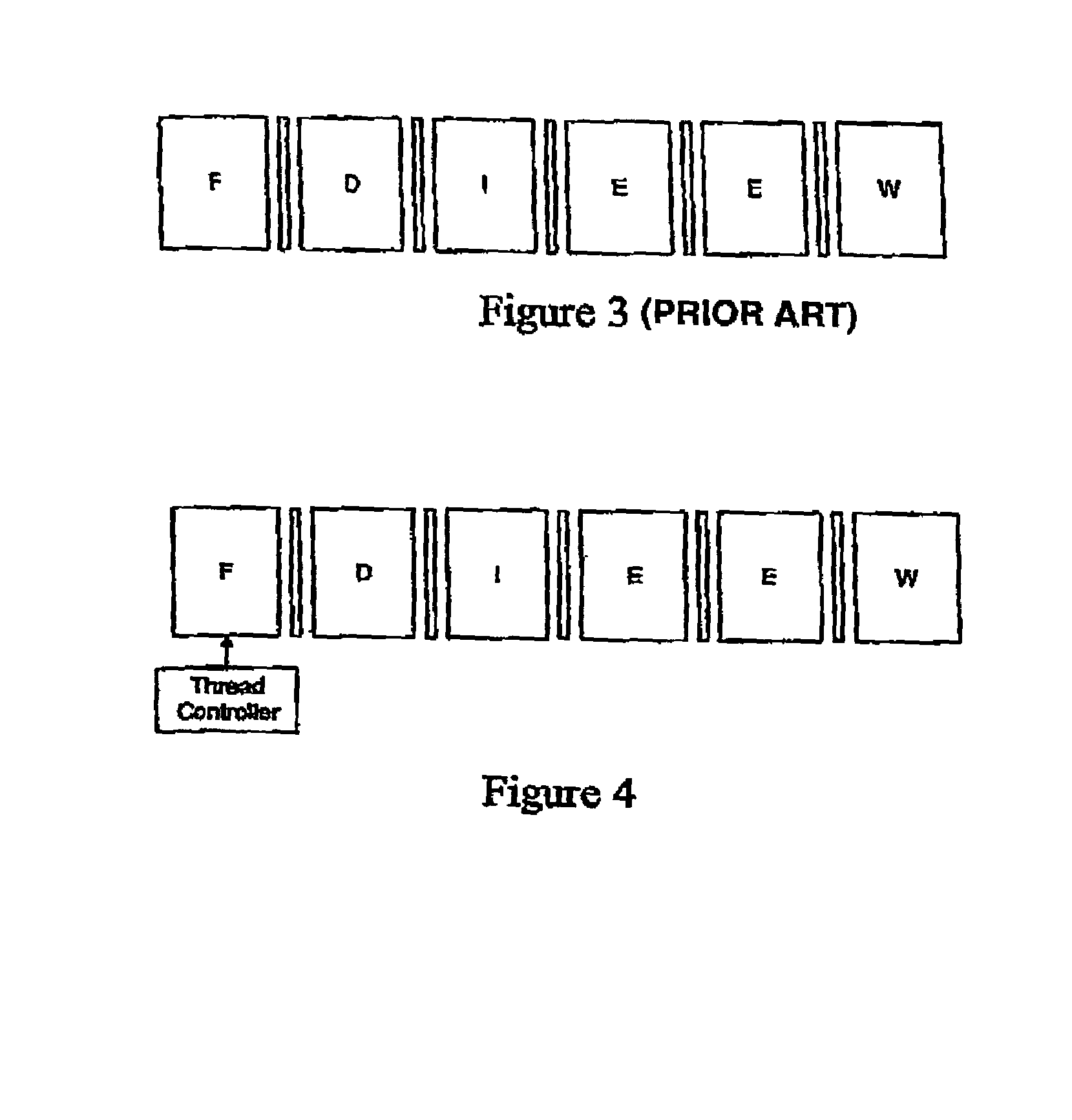

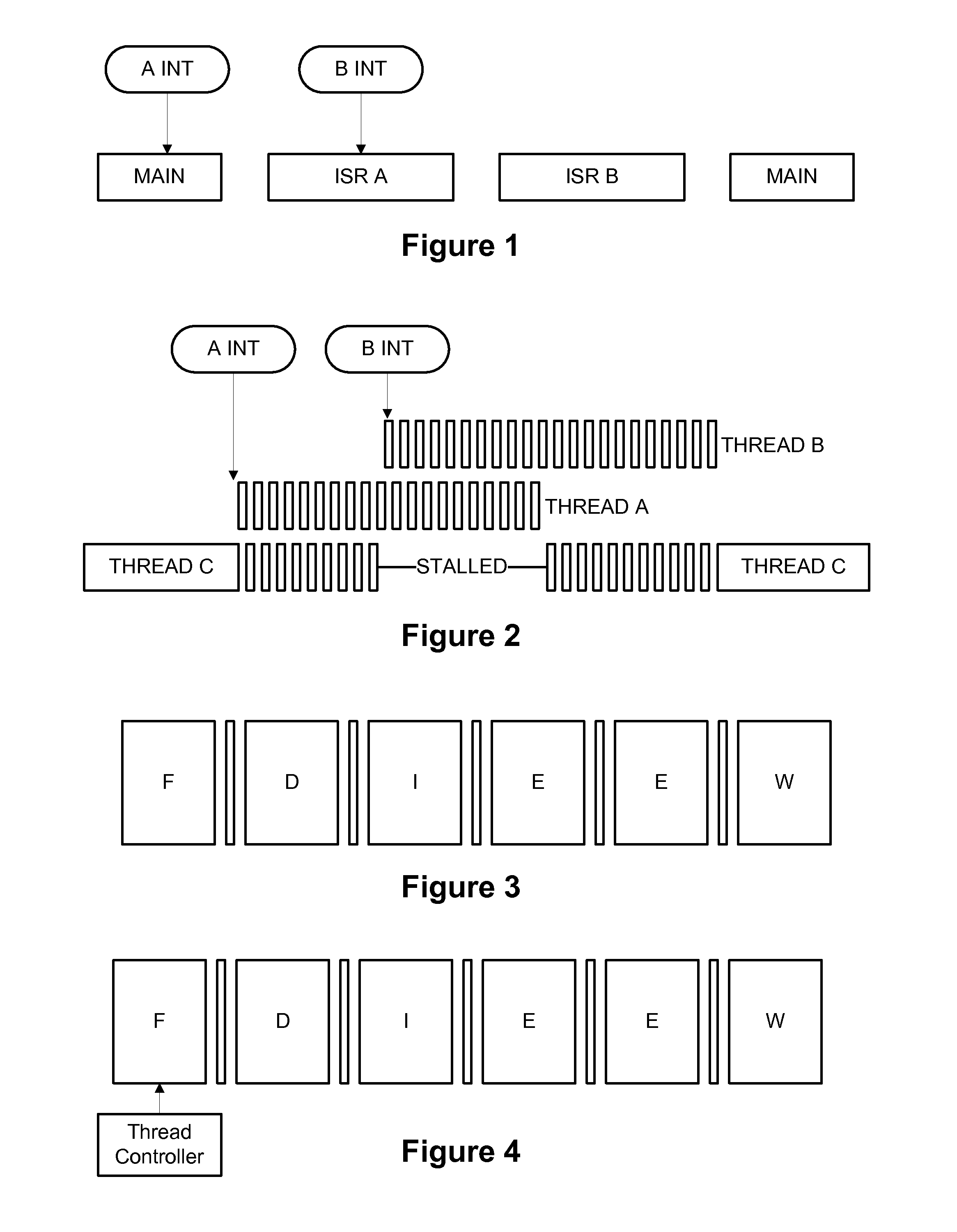

System and method for instruction level multithreading scheduling in a embedded processor

A system and method for enabling multithreading in a embedded processor, invoking zero-time context switching in a multithreading environment, scheduling multiple threads to permit numerous hard-real time and non-real time priority levels, fetching data and instructions from multiple memory blocks in a multithreading environment, and enabling a particular thread to modify the multiple states of the multiple threads in the processor core.

Owner:MAYFIELD XI +9

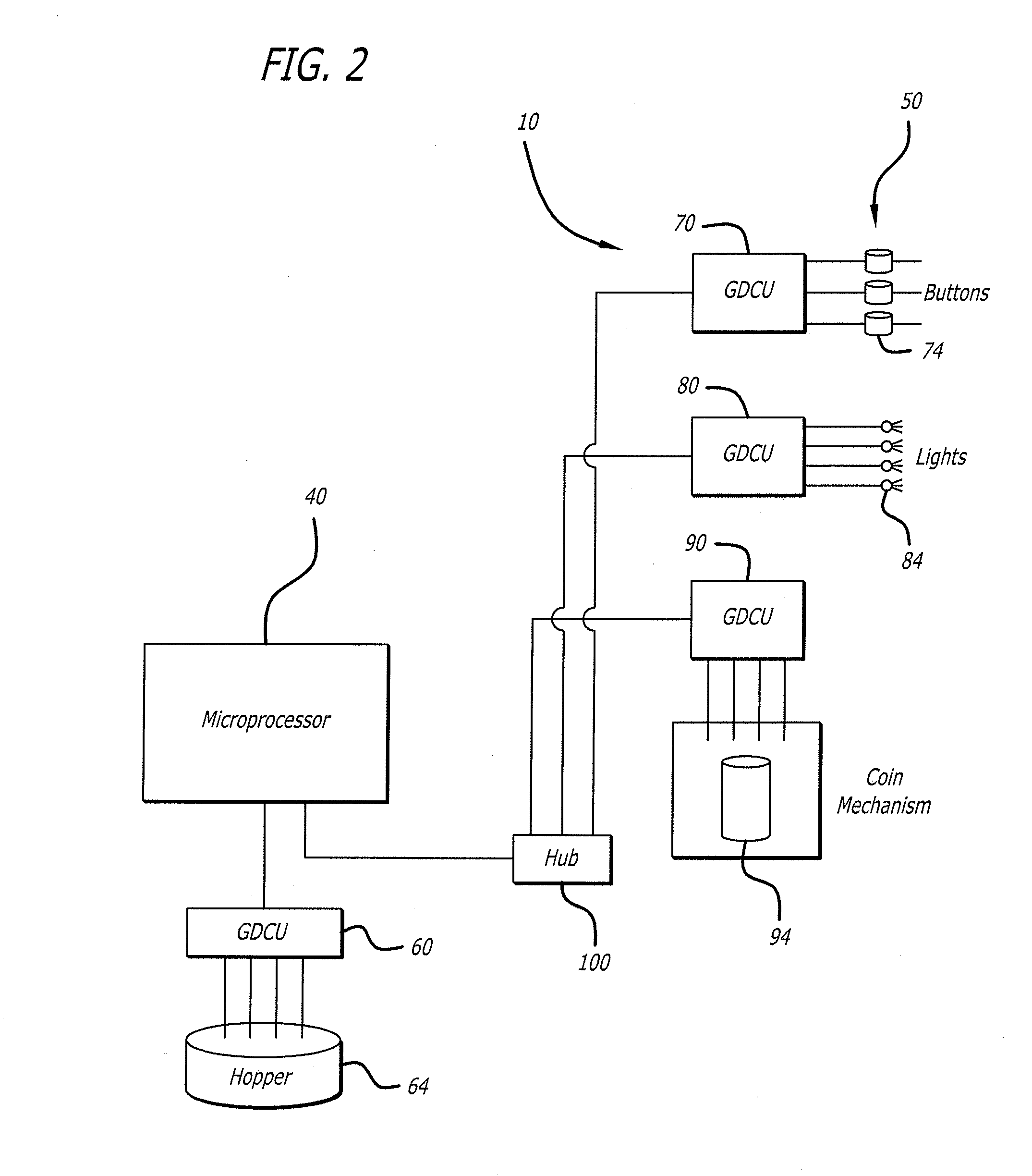

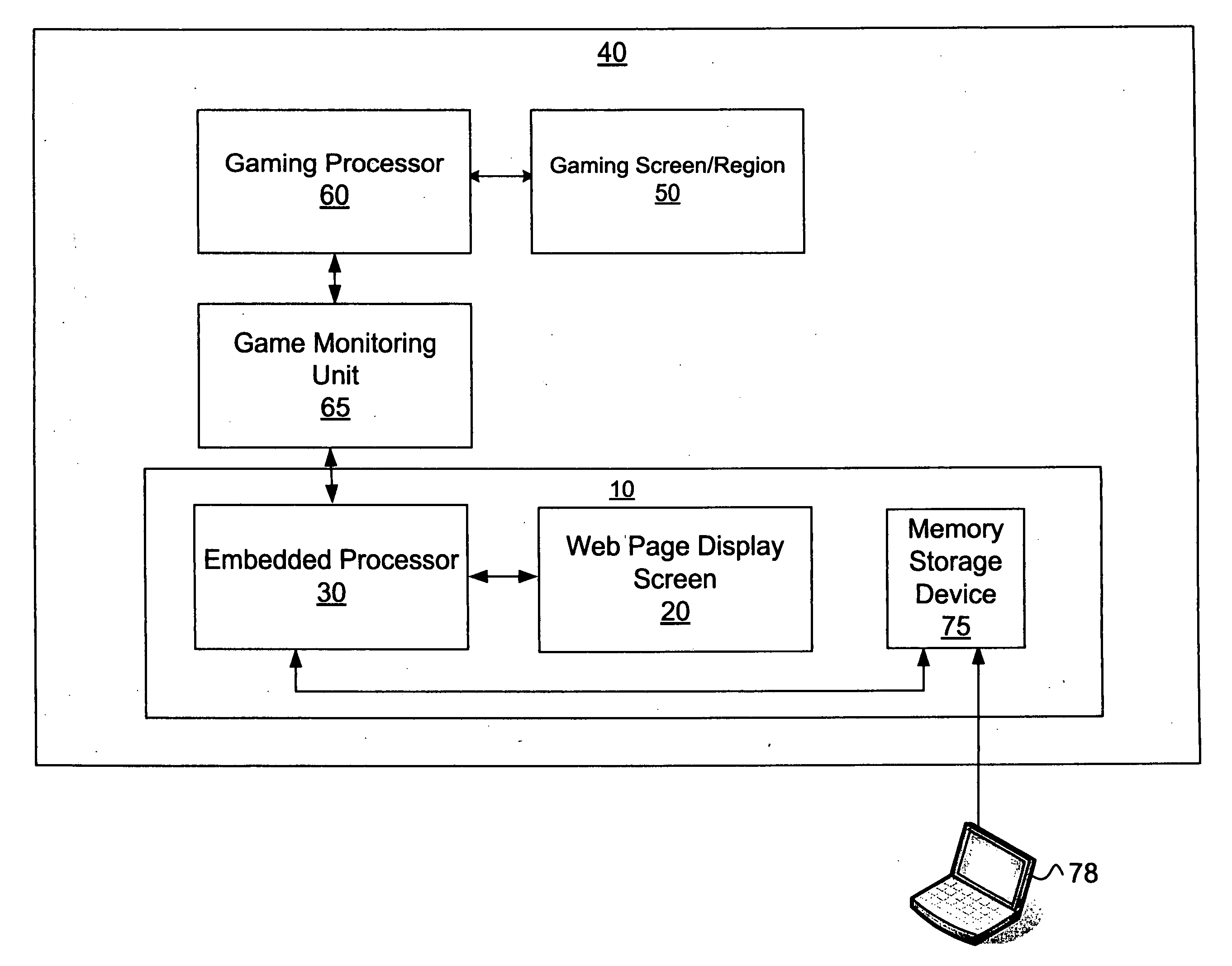

User interface system and method for a gaming machine

InactiveUS20060068906A1Increase excitementRich gaming experienceApparatus for meter-controlled dispensingVideo gamesOperational systemDisplay device

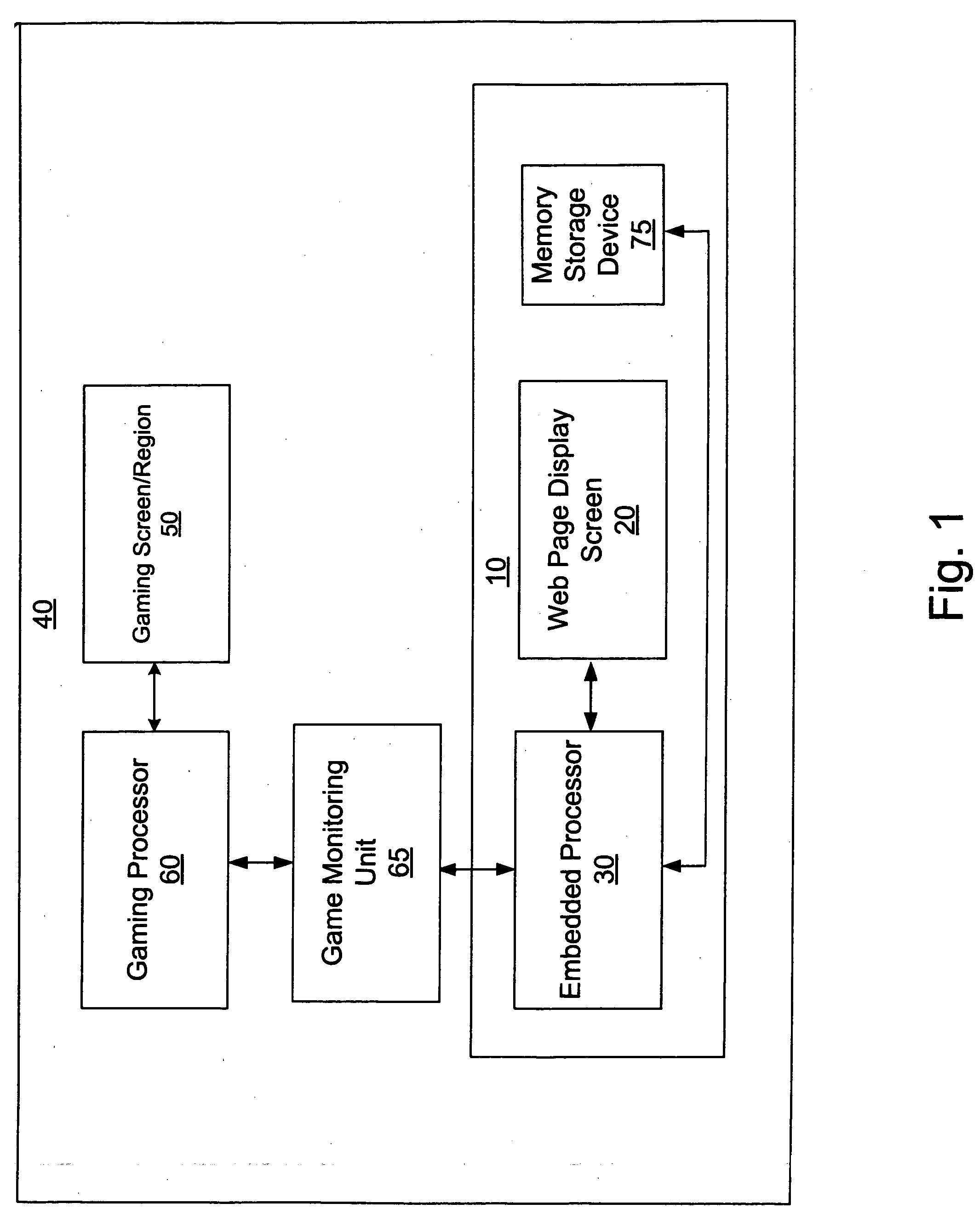

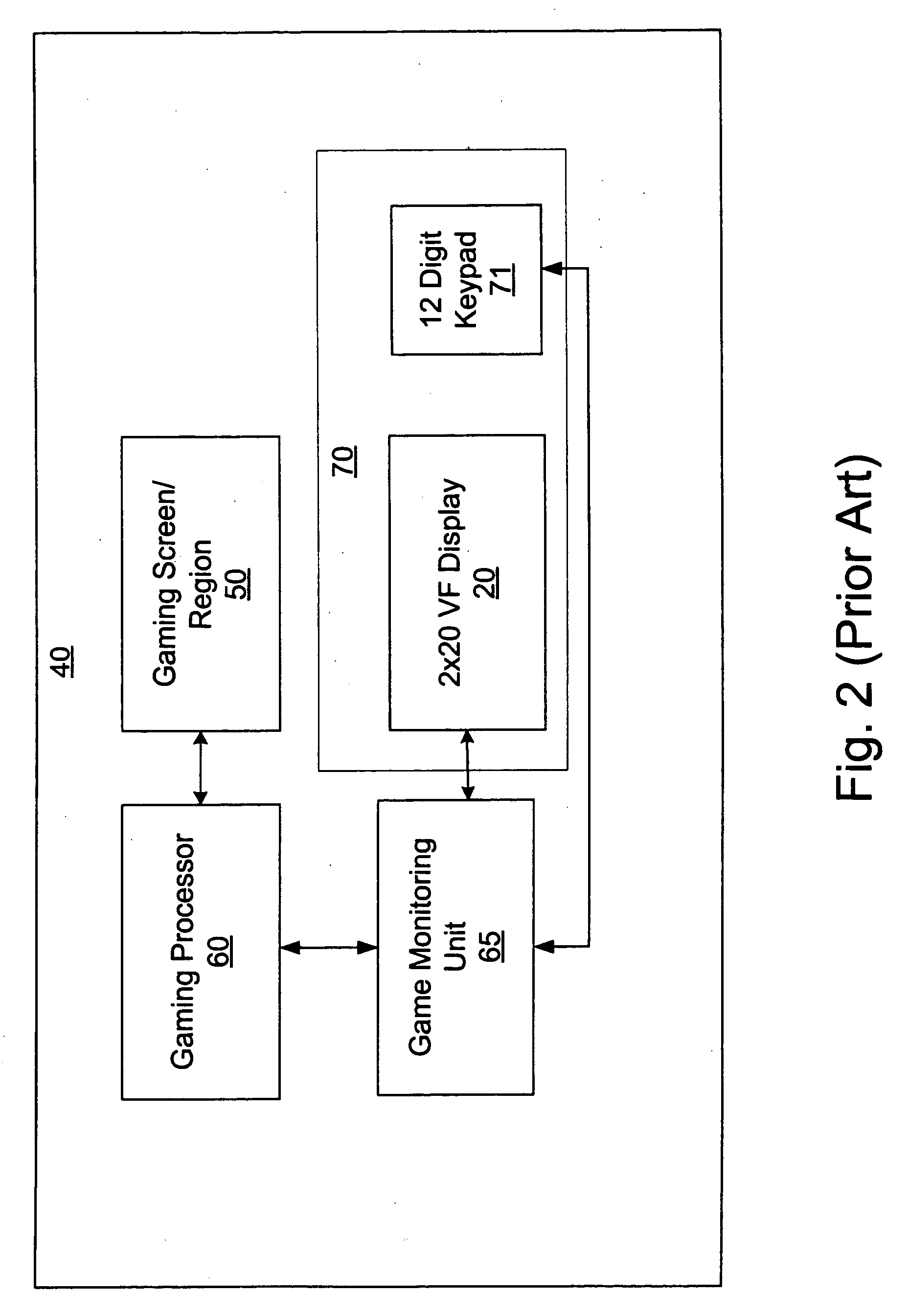

An embedded additional user interface 10 includes a web page display screen 20 and an embedded processor 30, and is incorporated into a gaming machine 40 that in turn includes a gaming screen 50 and a gaming processor 60. The embedded processor 30 employs an internal operating system and communicates with the gaming processor 60. The embedded processor reads incoming data, translates the data into a web authoring language, and maps the data to the web page display screen. The display screen 20 presents web page information to a user via the display screen, thereby increasing user excitement by providing a richer gaming experience. This provides a dramatic improvement over traditional system components 70 (input / output peripherals) that have been used in the past to access service and system information, such as a 2-line, 20-character VF display and a 12-digit keypad.

Owner:BALLY GAMING INC

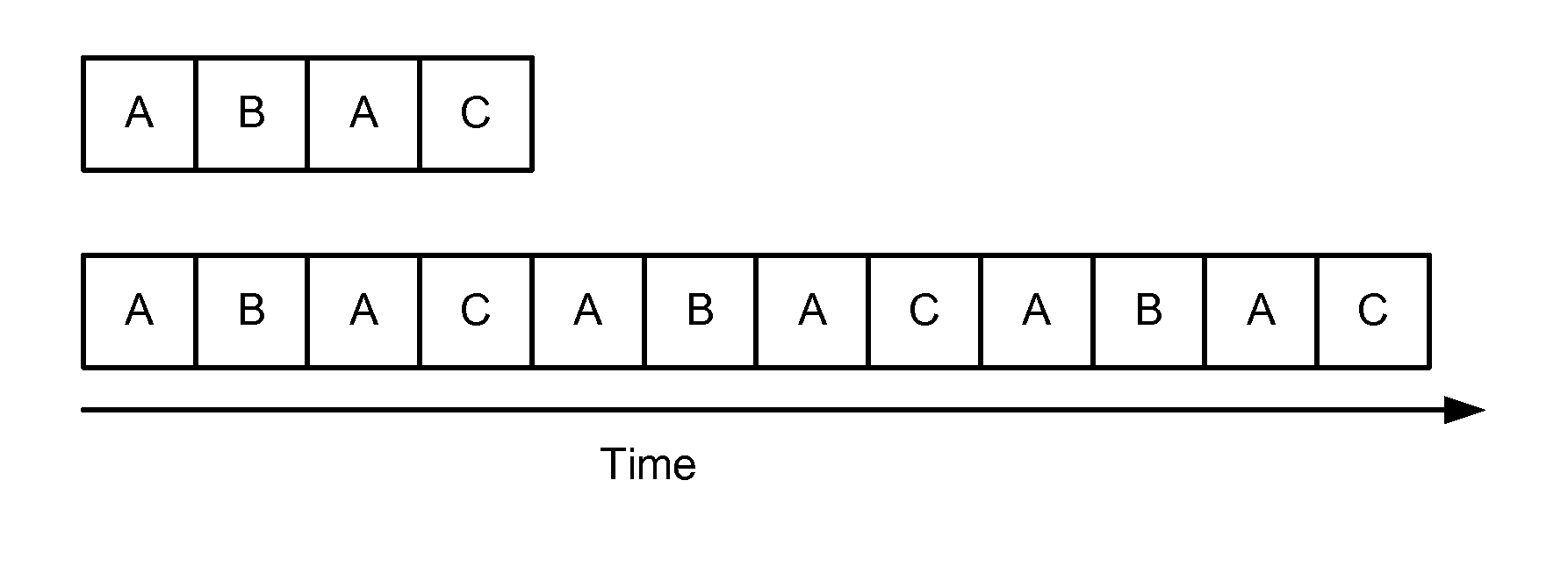

Instruction-level multithreading according to a predetermined fixed schedule in an embedded processor using zero-time context switching

A system and method for enabling multithreading in a embedded processor, invoking zero-time context switching in a multithreading environment, scheduling multiple threads to permit numerous hard-real time and non-real time priority levels, fetching data and instructions from multiple memory blocks in a multithreading environment, and enabling a particular thread to modify the multiple states of the multiple threads in the processor core.

Owner:MAYFIELD XI +8

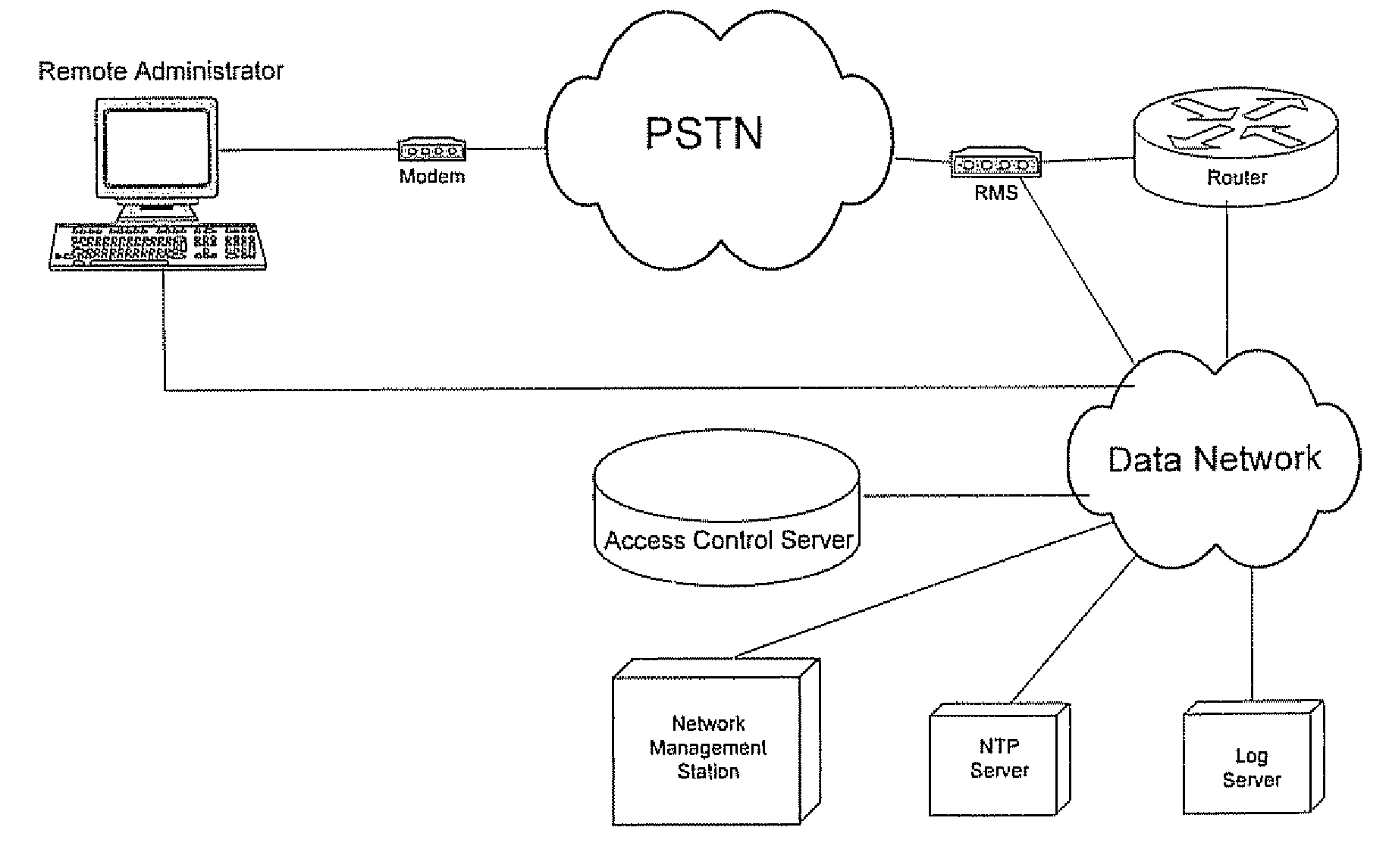

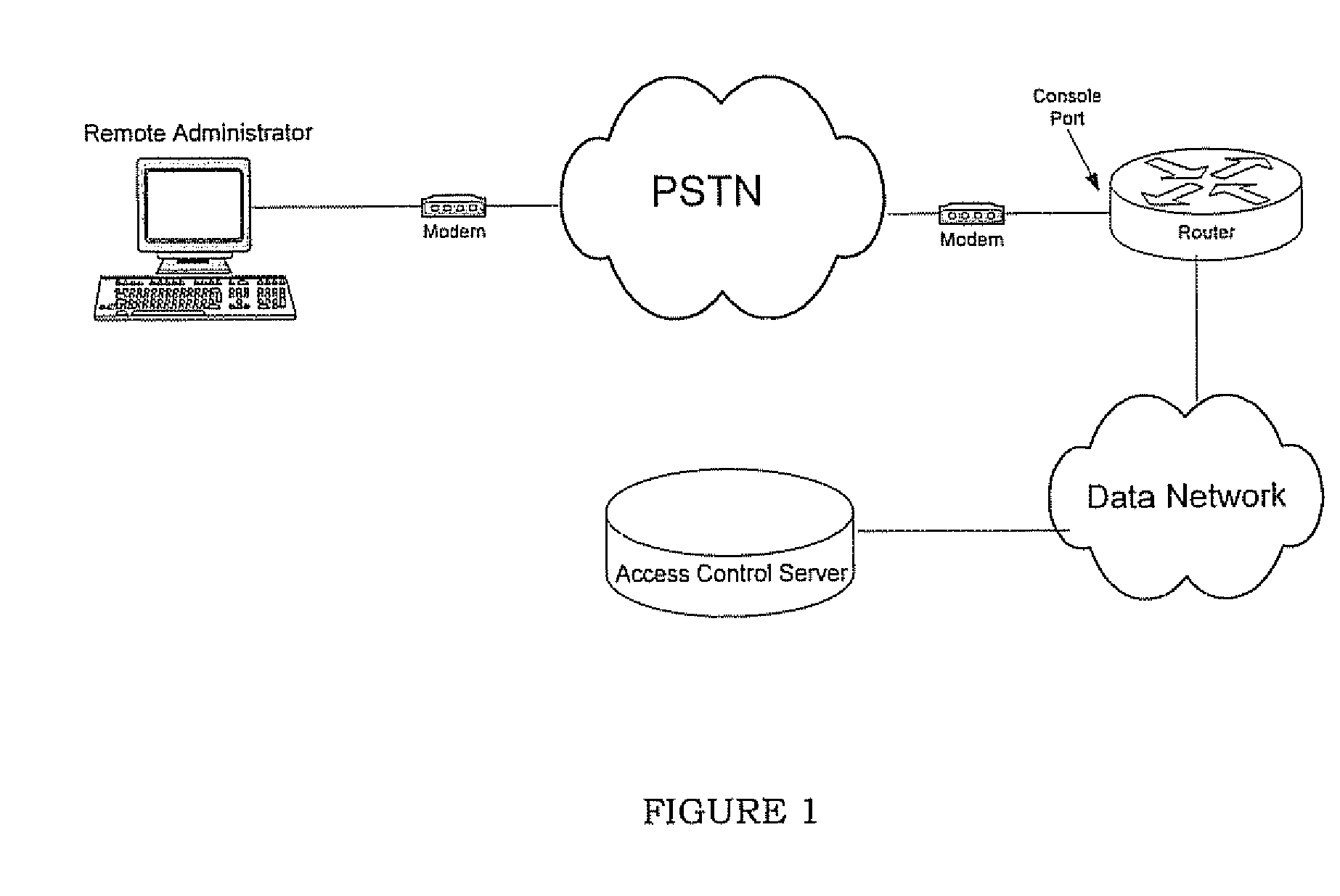

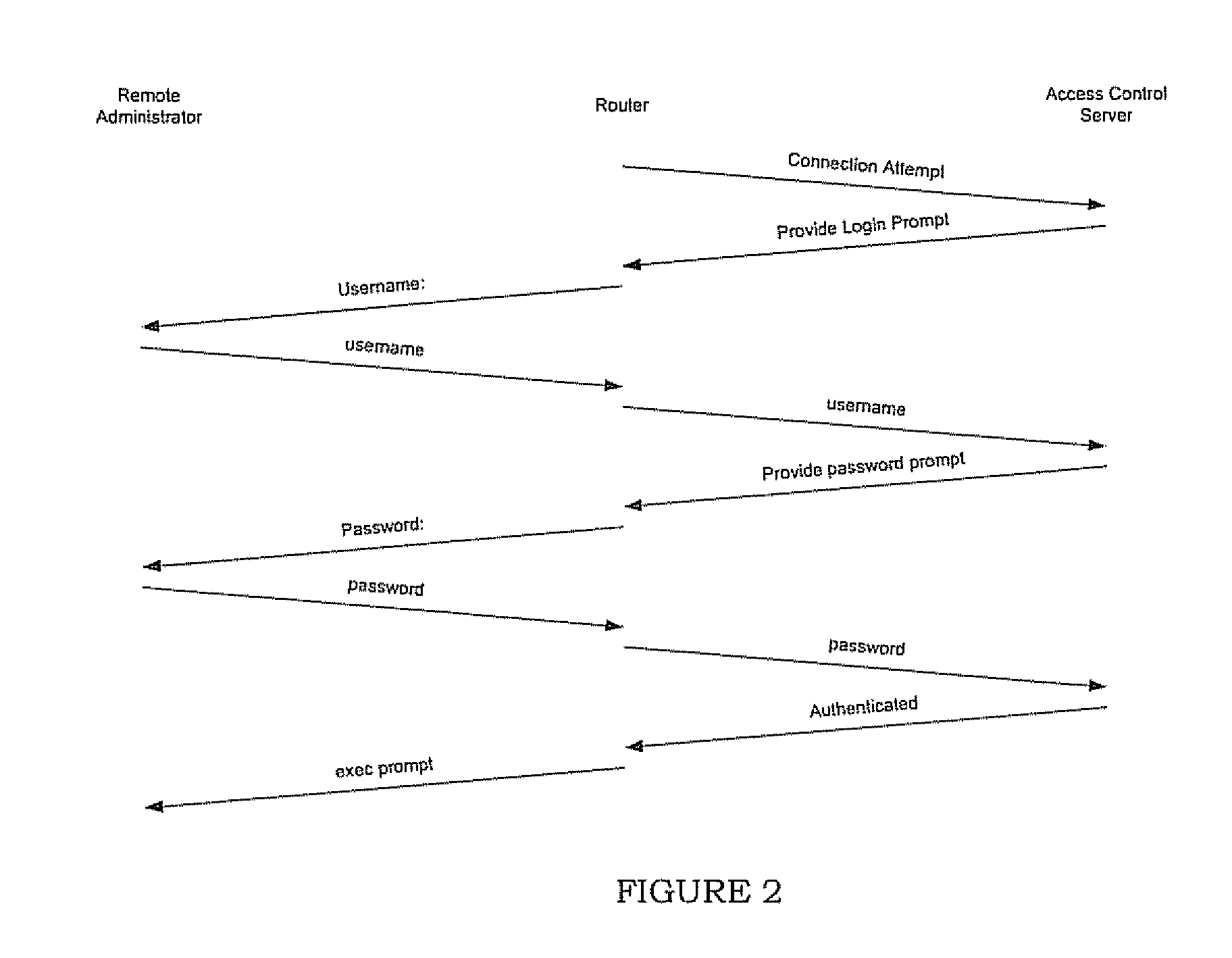

Out-of-band remote management station

InactiveUS20070130334A1Eliminate security concernsProtect informationDigital computer detailsSupervisory/monitoring/testing arrangementsCommunications systemEngineering

A management system for a computer data network comprises a remote management station connected to an analog communication system and connected to a device console port of a co-located computer device. The remote management station comprises (a) an embedded processor, (b) a connecting means to the analog communication system, and (c) a connecting means to the device console port. The remote management station is configured to detect a user connecting to or disconnecting from the device console port via the remote management station. The remote management station is configured for one or more of the following: (a) logging the user off the device console port when the user disconnects or is disconnected from the console port; (b) logging a previous user off the device console port before allowing a new user to access the device console port; or (c) monitoring messages sent to the device console port.

Owner:INFINITE BAY TELECOM LIABILITY +1

NAND Flash-based data recording method and recording controller

InactiveCN102169462AReduce usageImprove acceleration performanceInput/output to record carriersMemory adressing/allocation/relocationStatic random-access memoryControl signal

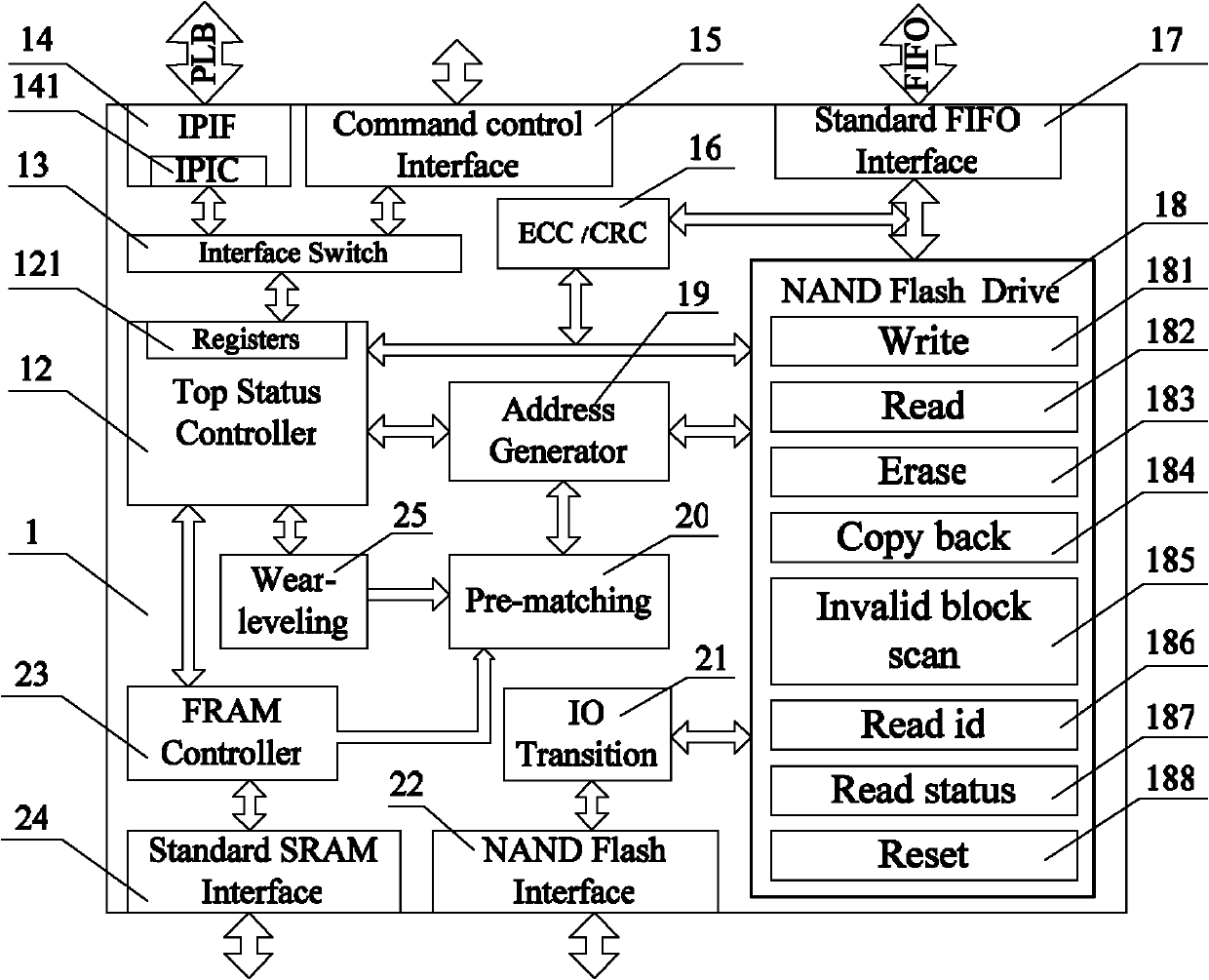

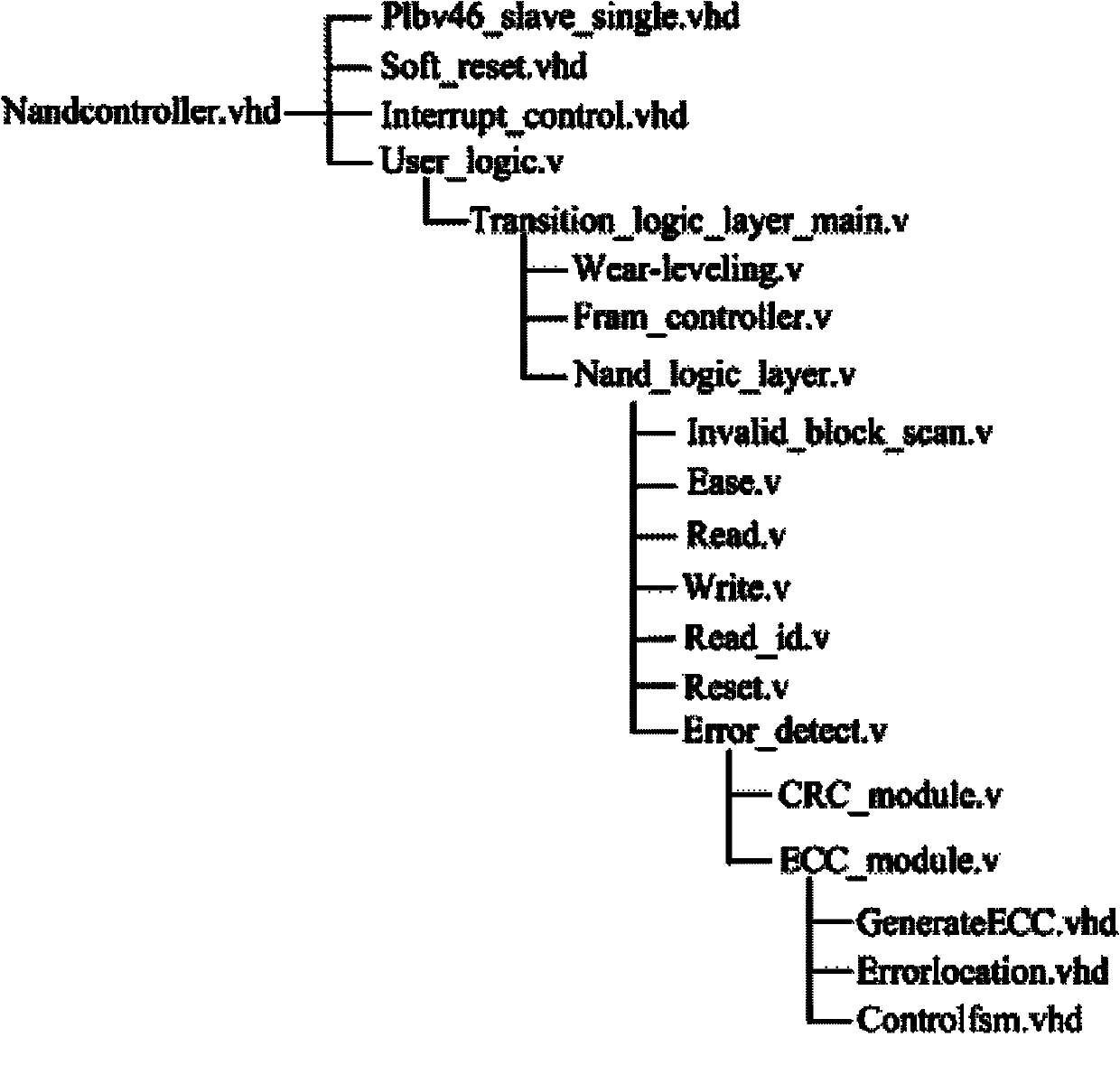

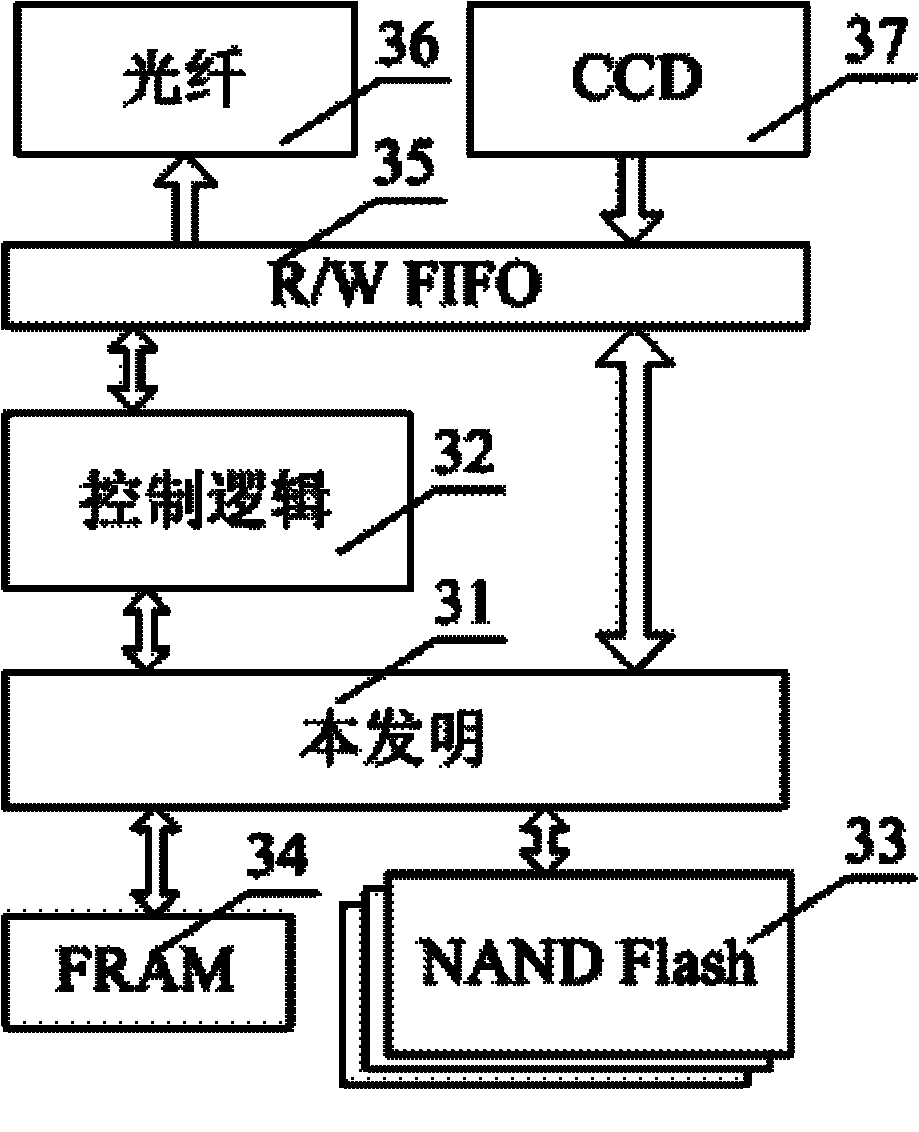

The invention discloses an NAND Flash-based data recording method and an NAND Flash-based data recording controller. The method comprises the following methods: a hardware bad block management method comprising the following steps of: when a sudden bad block appears, jumping to a next matched valid block without time delay to continuously record, and finally writing the data lag of a page before the bad block appears back to the jumped valid block; a hardware balance method comprising the following step of: starting the erasing-writing operation in succession to the last erasing-writing address so that the erasing-writing times of each block of the NAND Flash is approximately equal; and an input output (IO) expansion method comprising the following steps of: converting data bit width and switching control signals so that a single NAND Flash driver can control multiple chips and multiple groups of NAND Flashes. The controller comprises a ferroelectric random access memory (FRAM) controller, a top state controller, a loss equalizer, an interface switching module, a pre-matching module, an address generating module, a register set, a data verification module, a standard first in first out (FIFO) interface, a standard static random access memory (SRAM) interface, a command control interface and the NAND Flash driver. The whole controller can be mounted on a processor local bus (PLB) of an embedded processor, and data conversion between a control signal and a state signal can be performed through the command control interface and an external module.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

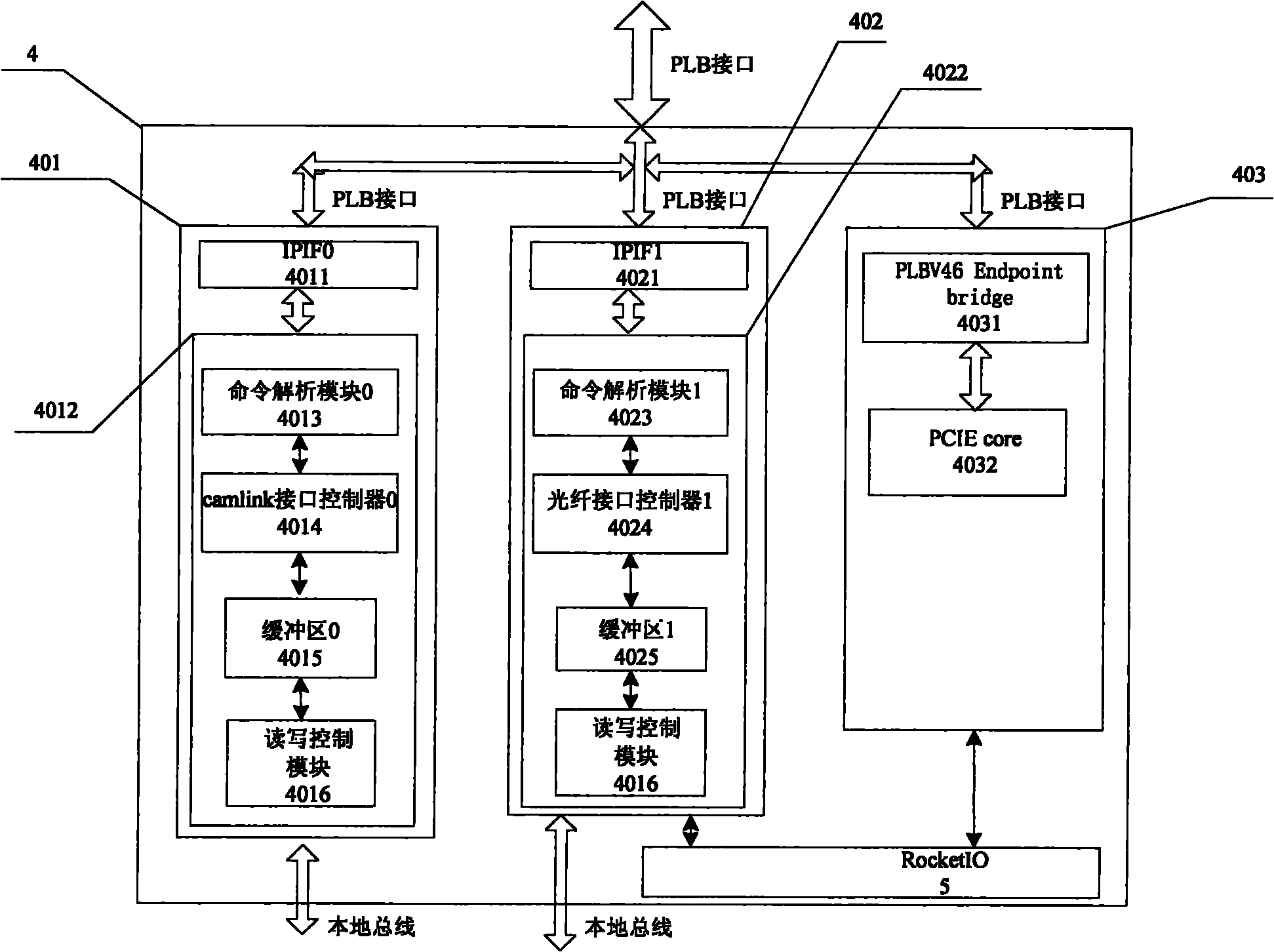

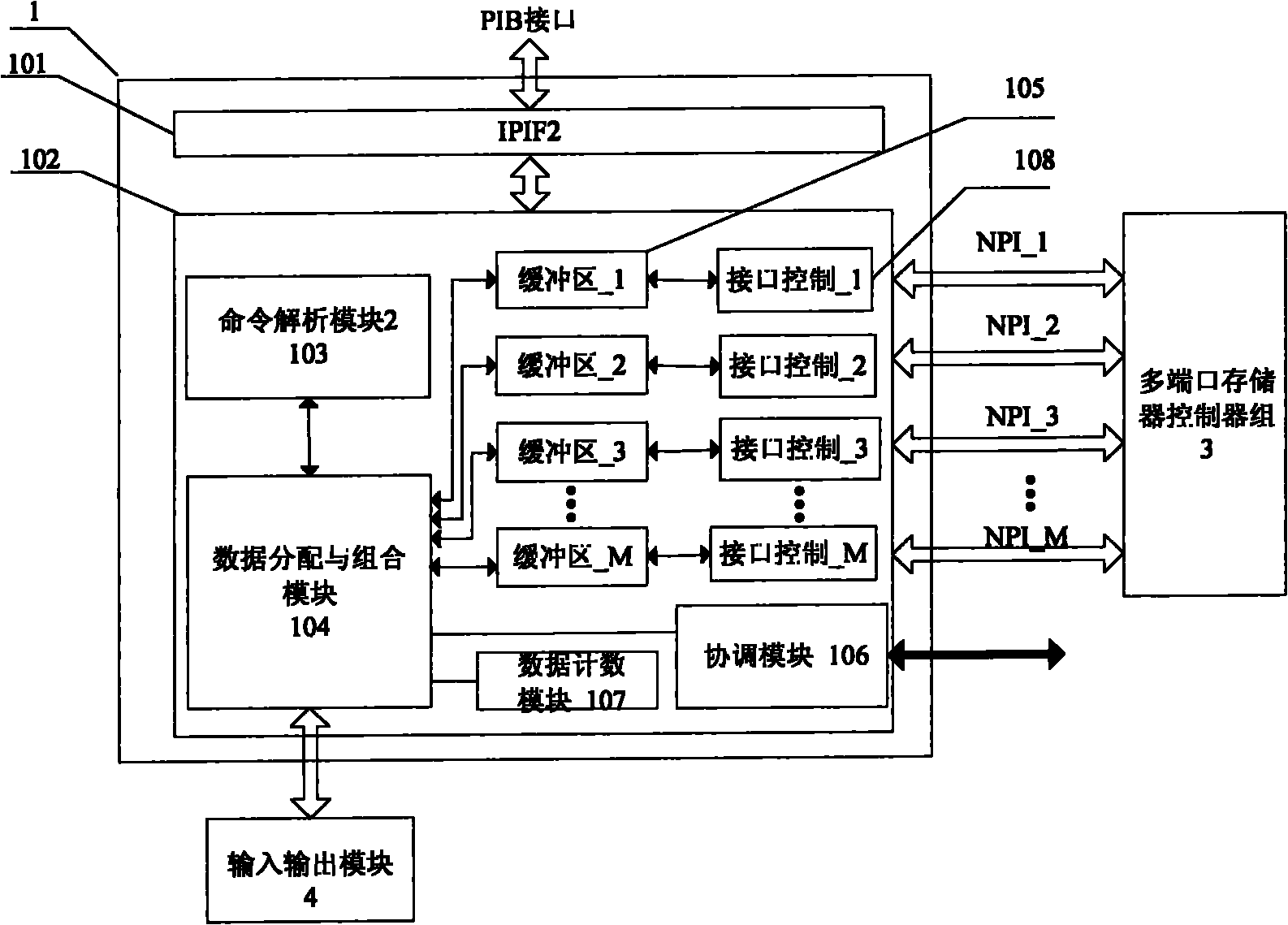

High speed storage and transmission device based on FPGA

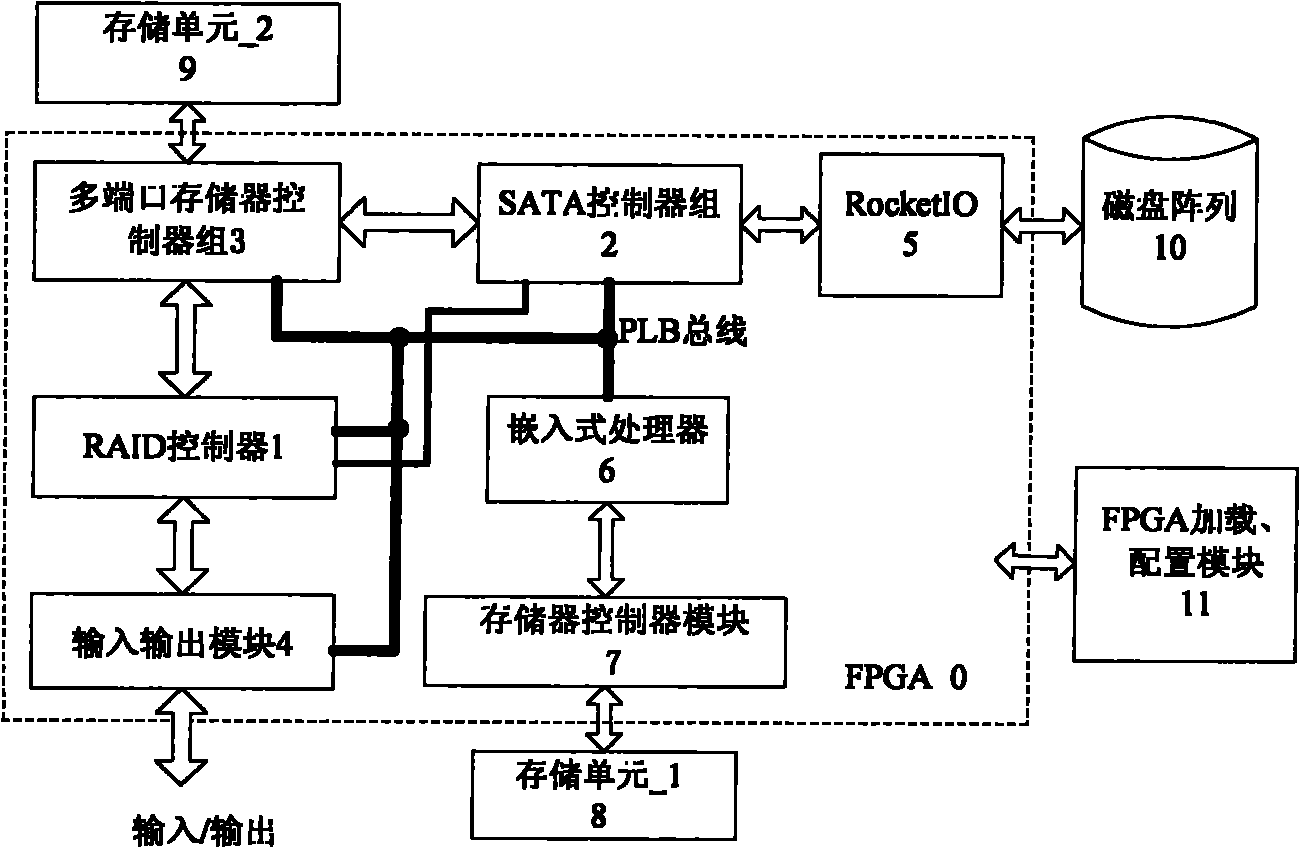

The invention provides a high speed data storing or reading method and device based on FPGA, the method and device belong to the computer field and the storage field. The device comprises an RAID controller (1), an SATA controller group (2), a multi-port memory controller group (3), an input output module (4), a RocketIO (5), an embedded processor (6), a memory controller module (7), a memory cell _1 (8), a memory cell _2 (9), a disk array (10) and an FPGA loading and configuring module (11). The modules 1-7 are realized in FPGA, and the modules 1-4 are connected with the embedded processor by a PLB bus. The embedded processor is taken as a core processing unit and coordinates and controls the entire system to operate. The device can simultaneously control a plurality of hard disks, and RAID0 and RAID1 can be realized by software configuration. The device is provided with a camlink interface, a PCIE interface and a fiber interface. The device reduces peripheral ASIC chip and PCB area and has the advantages of miniaturization, low power consumption and wide application.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

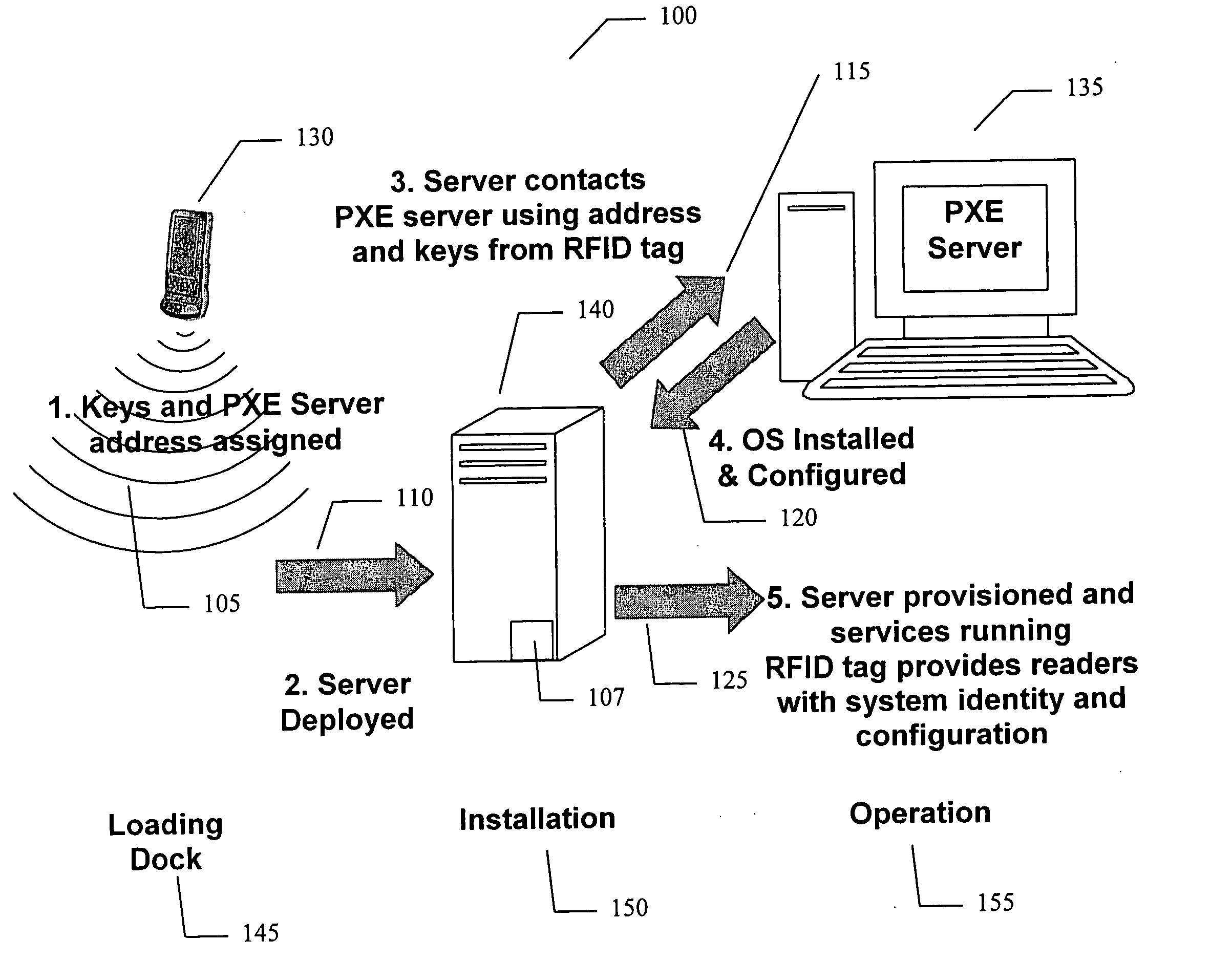

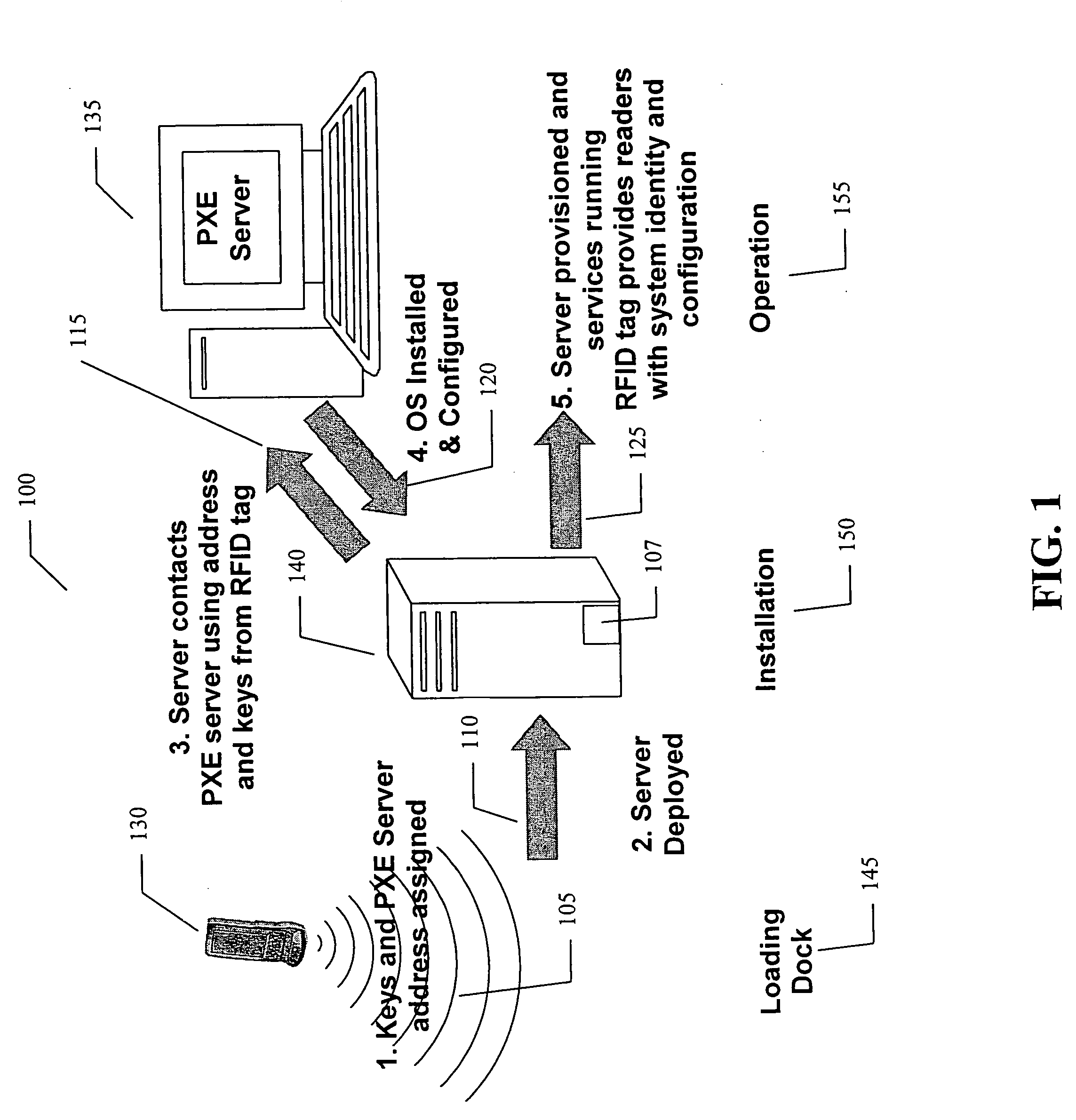

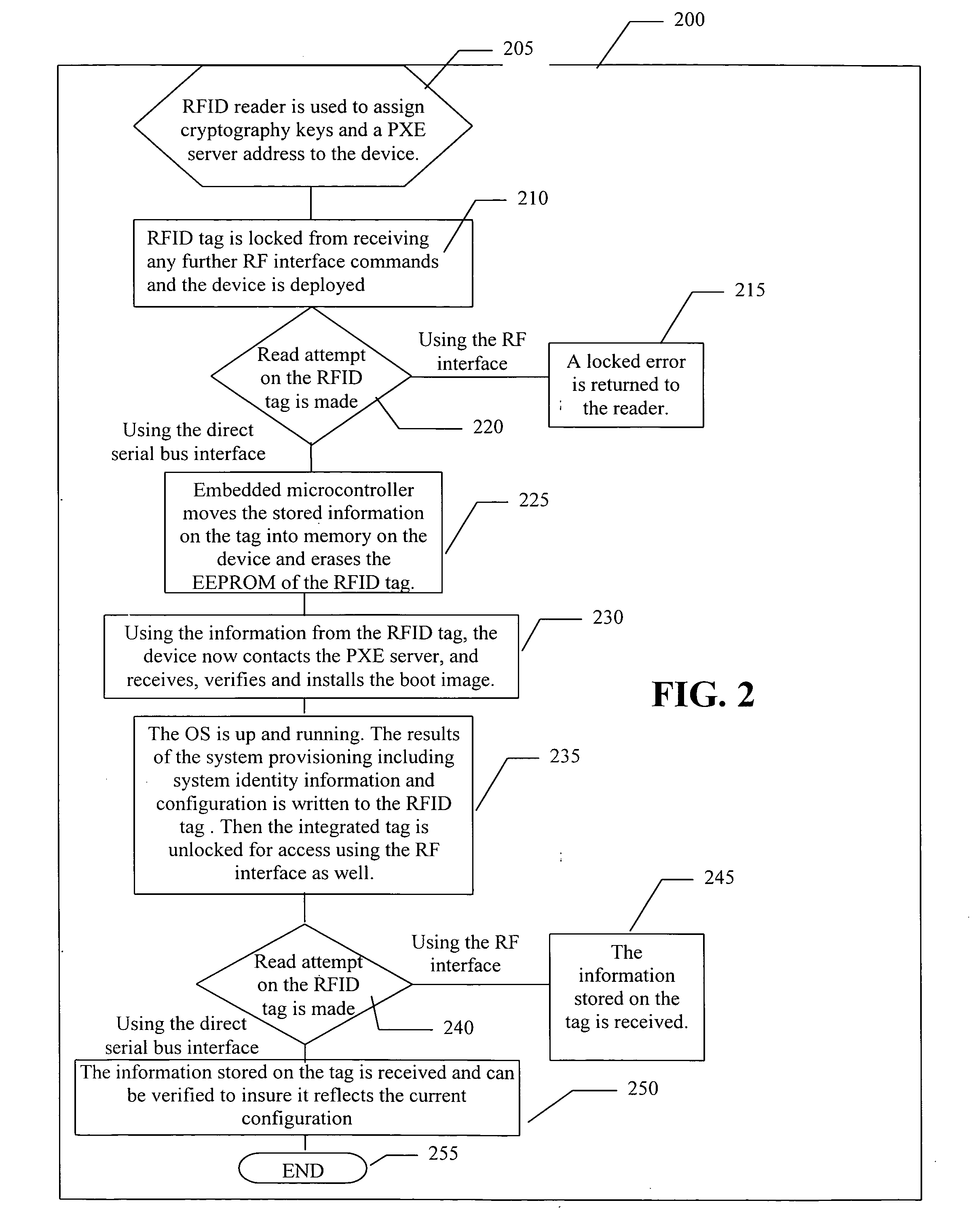

Apparatus and method capable of secure wireless configuration and provisioning

An embodiment of the present invention provides an apparatus, comprising an RFID tag interfaced with the apparatus, the RFID tag enables wireless provisioning and configuration of the apparatus and may be a passive read / write RFID tag. The apparatus may be, in one embodiment, a platform such as a client or server and the passive RFID tag may be interfaced with the platform such that the tag's EEPROM can also be read from or written to by the platform using a wired serial connection. The apparatus may further comprise a host processor with an operating system (OS) and an embedded microcontroller, the embedded microcontroller may have access to dynamic and non-volatile memory capable of operating independently of the host processor and OS and with direct access to a network interface, wherein the RFID tag may be read from or written to by either a RFID reader or the platform via a direct connection to the embedded processor.

Owner:UNM RAINFOREST INNOVATIONS

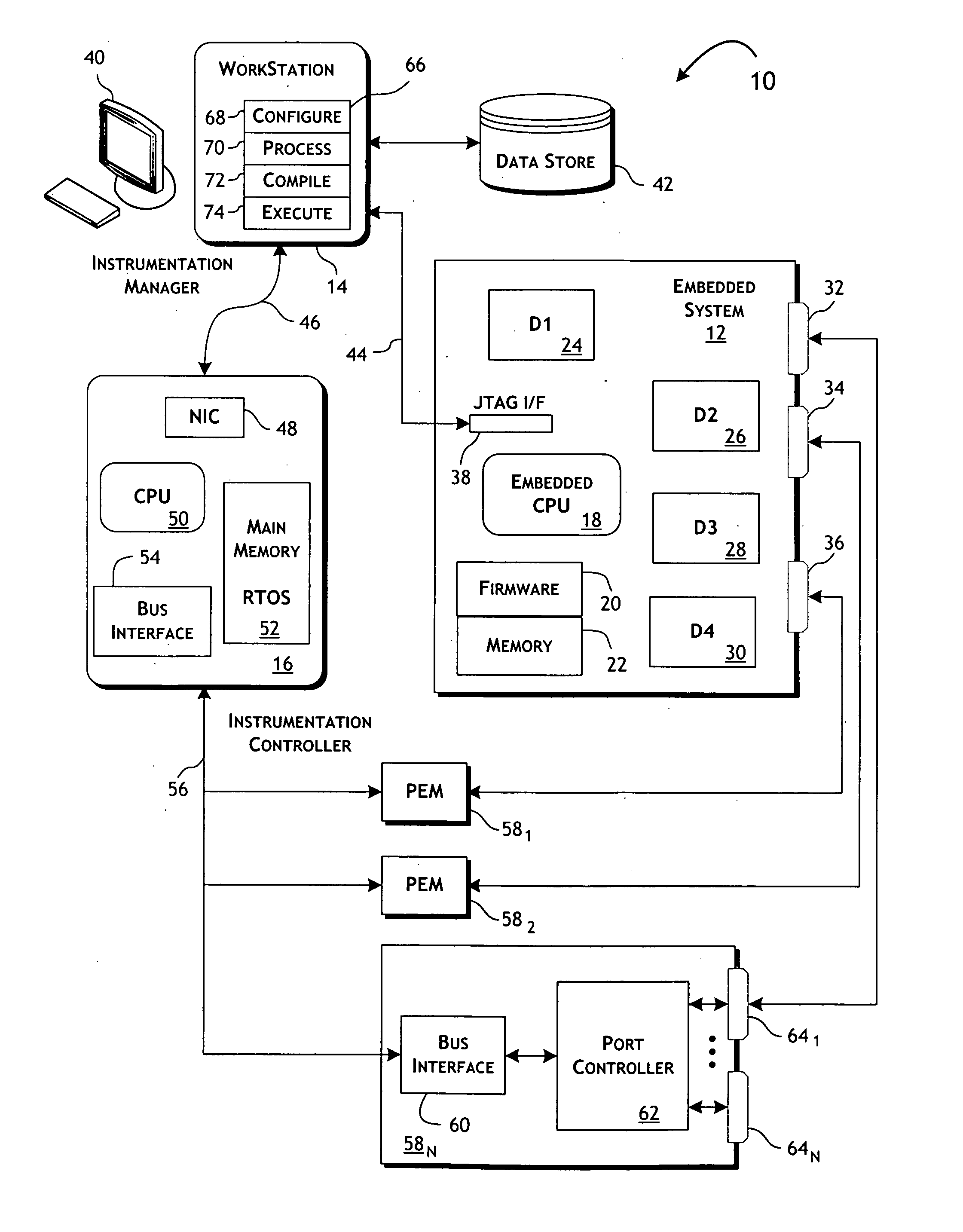

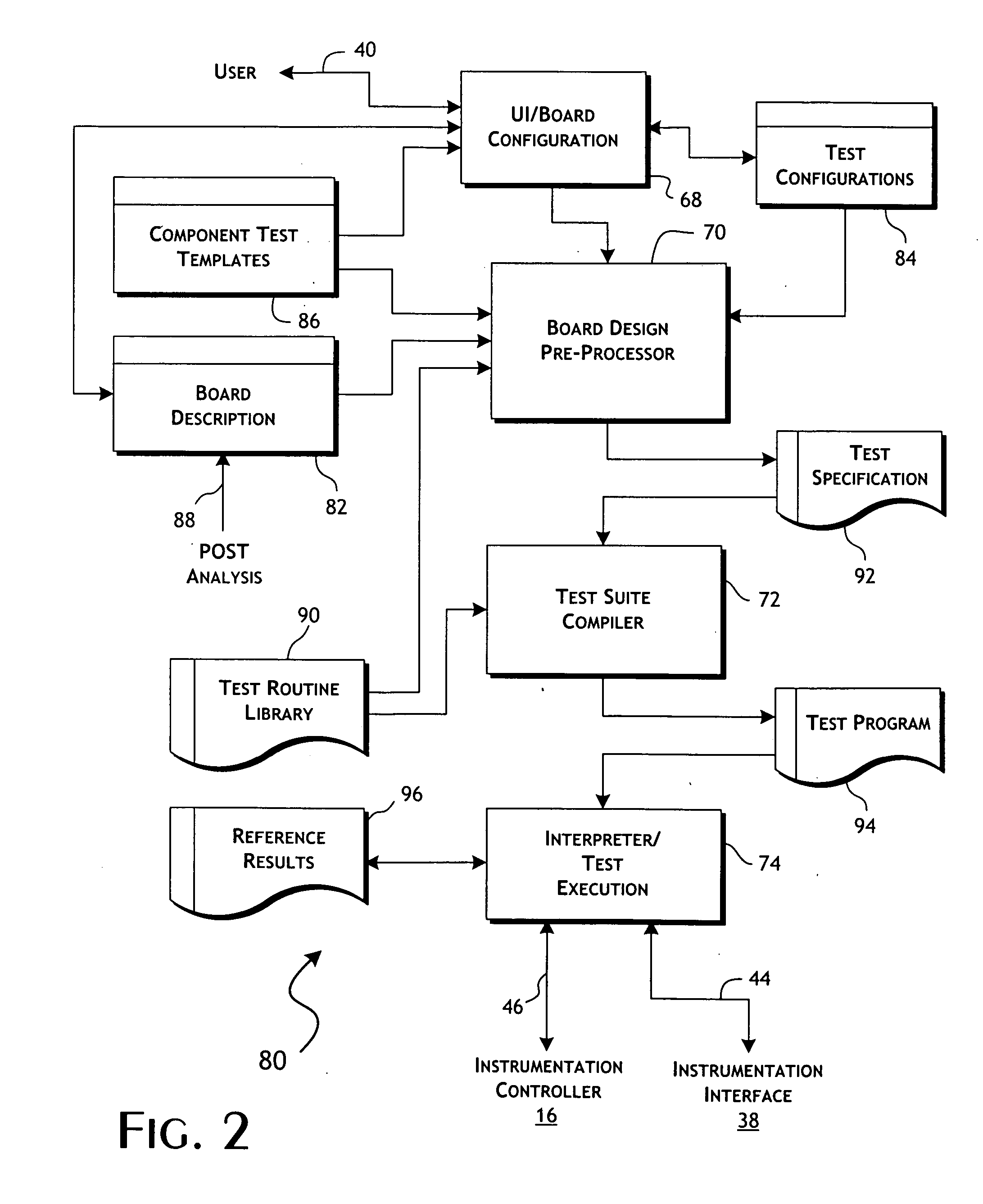

System and methods for functional testing of embedded processor-based systems

InactiveUS20070011522A1Test directlyElectronic circuit testingError detection/correctionSpecific testFunctional testing

Functional testing of an embedded system is performed by a test control system that implements a peripheral emulation module to interface with an externally accessible port of the embedded system. The test control system implements a test generation processor that operates to autonomously resolve abstracted component templates and embedded system description data, specific to the embedded system, to produce a corresponding specific test program. The test control system executes the test program to drive operation of the embedded processor unit to cause transfer of test data through the external interface, which is then autonomously compared to reference data derived through the execution of the test program and specific to the embedded system, whereby the comparison results reflect the correct operation of the embedded system.

Owner:DENNISTON WILLIAM B

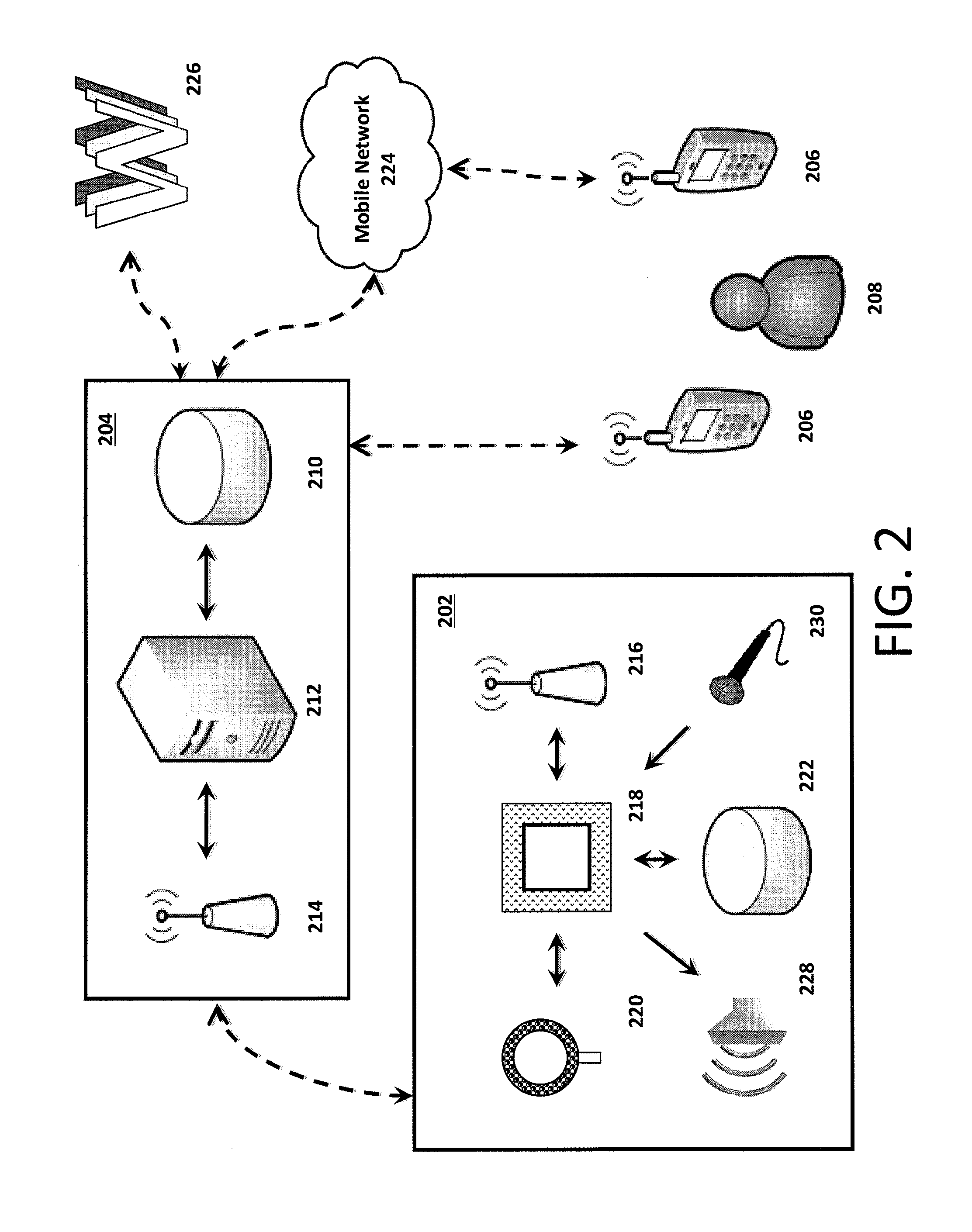

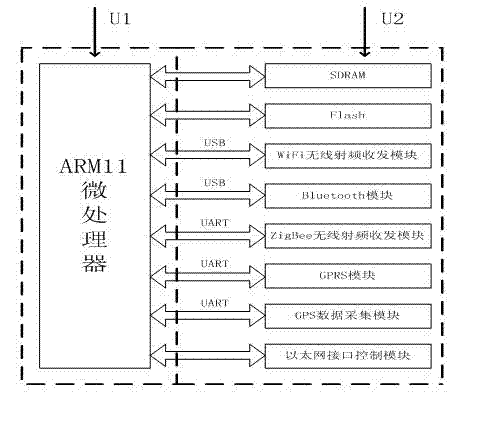

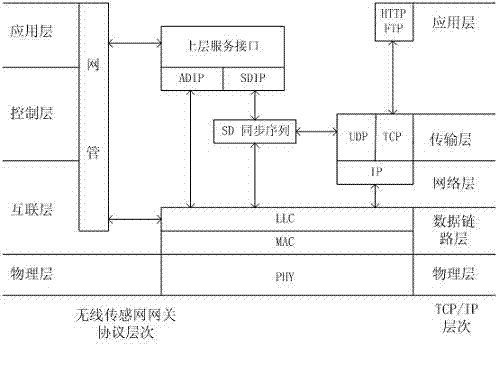

Multi-protocol multi-interface wireless sensor network gateway

InactiveCN102448202AImprove anti-interference abilityReduce power consumptionHigh level techniquesWireless communicationGeneral Packet Radio ServiceTransceiver

The invention discloses a multi-protocol multi-interface wireless sensor network gateway and relates to the technical field of a wireless sensor network. The gateway mainly consists of an embedded processor, an SDRAM (Synchronous Dynamic Random Access Memory), a Flash memory, a WiFi (Wireless Fidelity) wireless radio frequency transceiver module, a ZigBee wireless radio frequency transceiver module, a GPRS (General Packet Radio Service) module, a Bluetooth module, a GPS (Global Positioning System) data acquisition module and an Ethernet interface control module. A networked operating system Linux is used as an operating system of the multi-protocol multi-interface wireless sensor network gateway and can be compatible with a TCP / IP (Transmission Control Protocol / Internet Protocol) protocol IPv6 (Internet Protocol Version 6). The multi-protocol multi-interface wireless sensor network gateway has the advantages that conversion among various protocols is completed by treatment of a design protocol conversion program; the multi-protocol multi-interface wireless sensor network gateway can be used for setting up networks with various architectures, interconnecting the networks with various architectures and transmitting data; various network access schemes are provided for the wireless sensor network; the multi-protocol multi-interface wireless sensor network gateway has strong anti-interference capability, low power consumption and small volume; and portable equipment is provided for interconnection among the networks with various architectures and building of an integrated network.

Owner:CHINA UNIV OF MINING & TECH

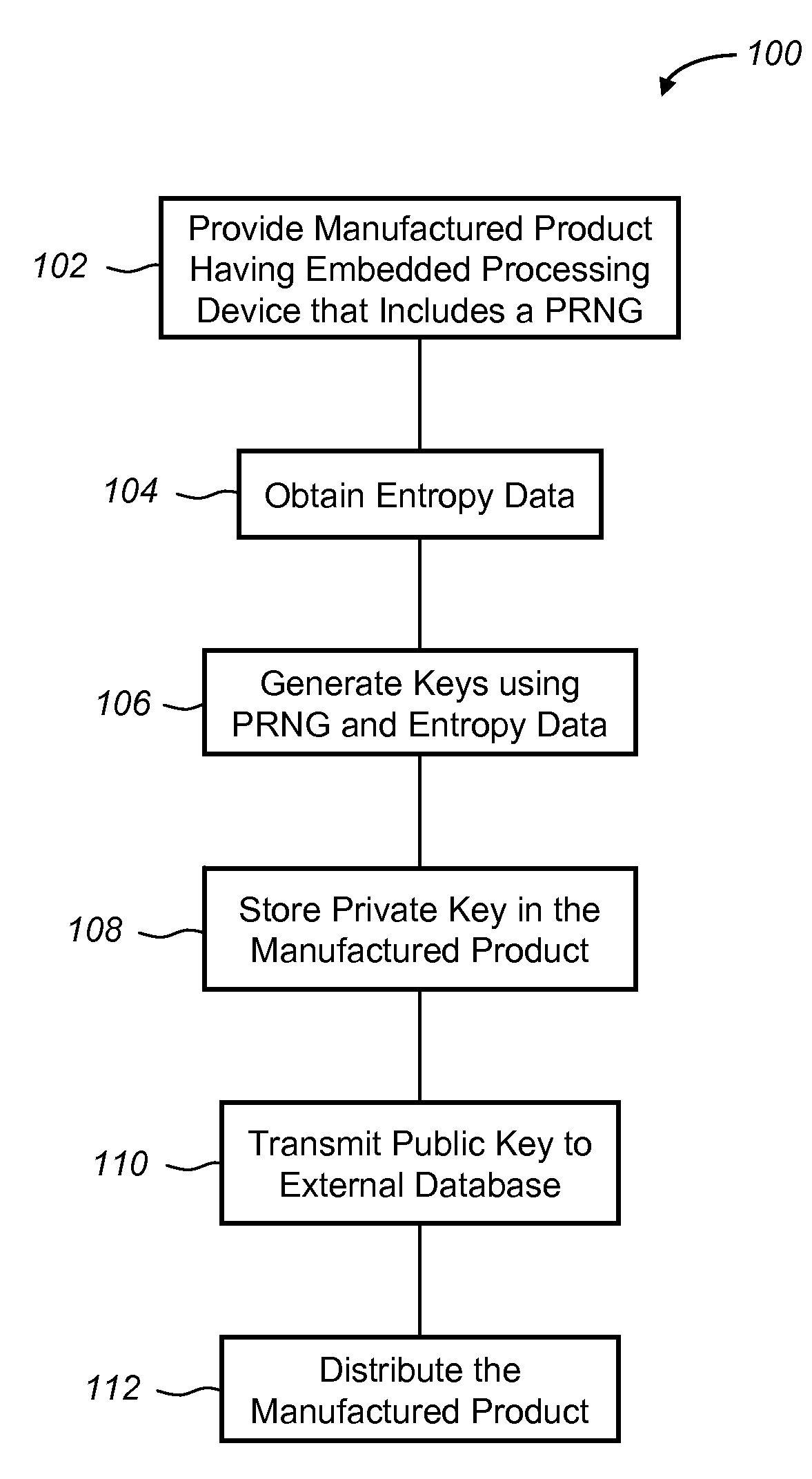

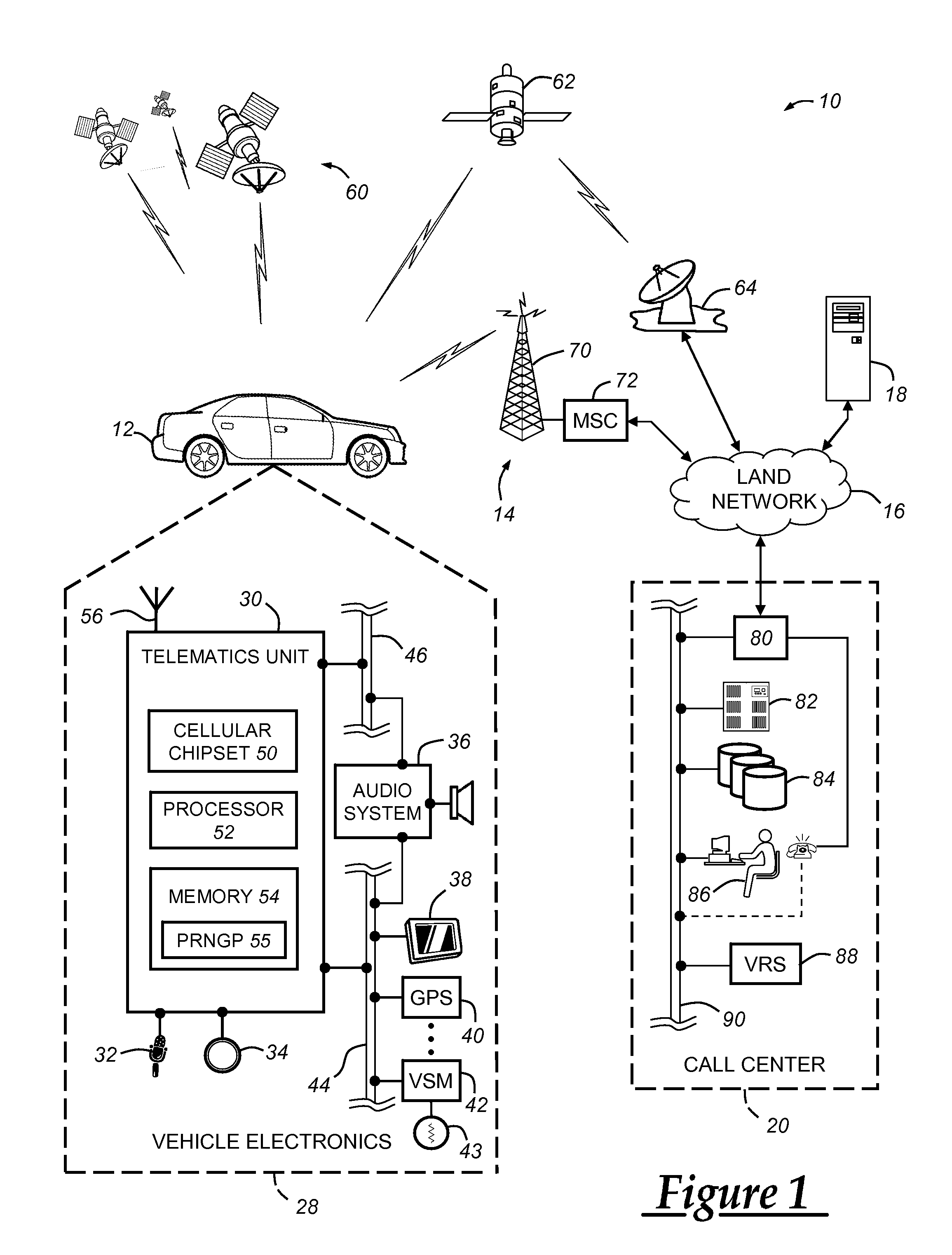

Production of cryptographic keys for an embedded processing device

ActiveUS20090323967A1Avoid dataKey distribution for secure communicationPublic key for secure communicationUnique identifierCryptographic nonce

A system and method for producing cryptographic keys for use by an embedded processing device within a manufactured product. A pseudo random number generator is seeded with entropy data gathered by the embedded device, and the result is used to generate a public-private key pair. The process can be carried out during manufacturing so that the public key of each manufactured product can be stored in a database along with a unique identifier for the embedded device associated with the key. In one particular example, a vehicle having an installed telematics unit uses the key generating process to self-generate keys using entropy data available to the vehicle.

Owner:GENERA MOTORS LLC

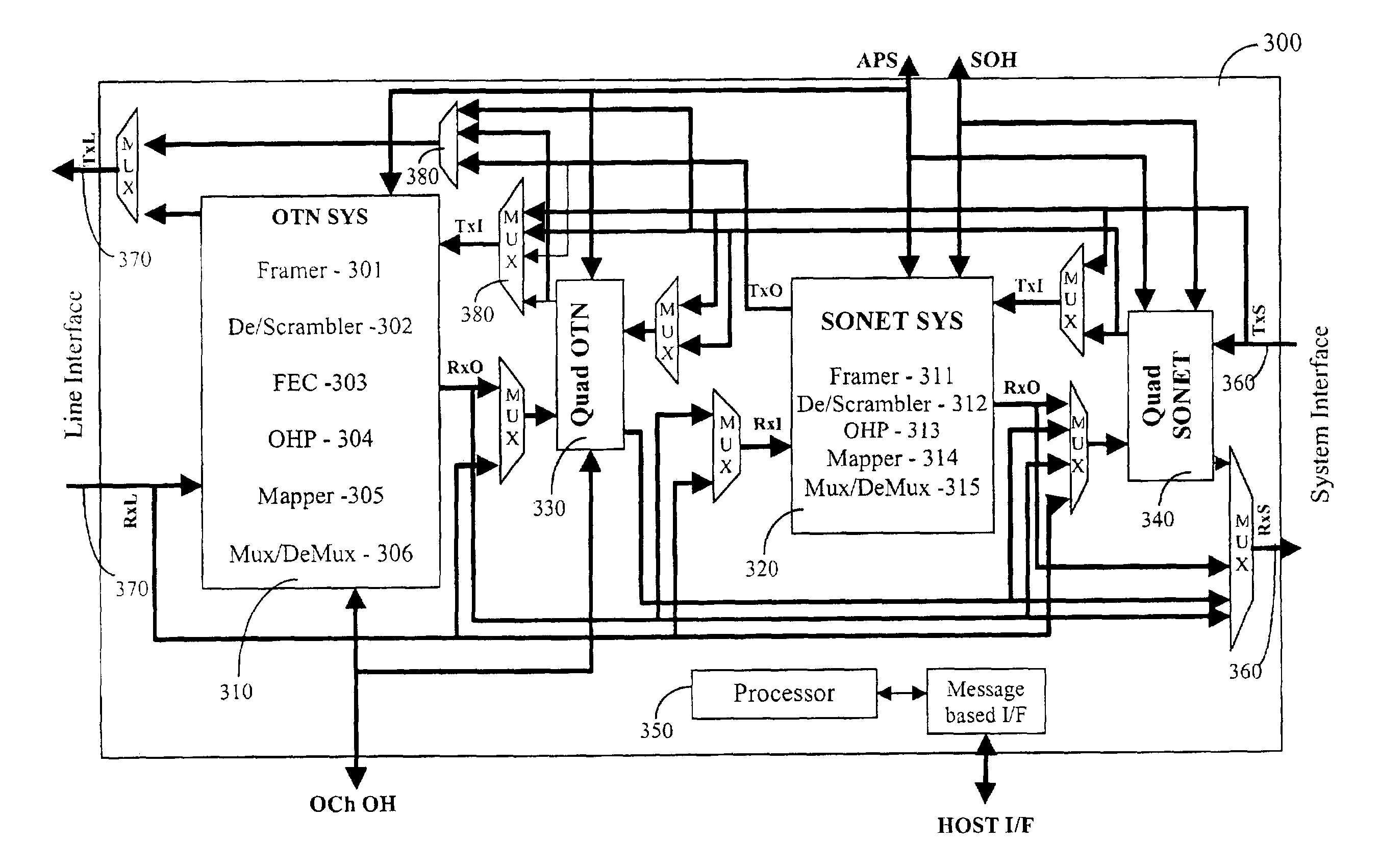

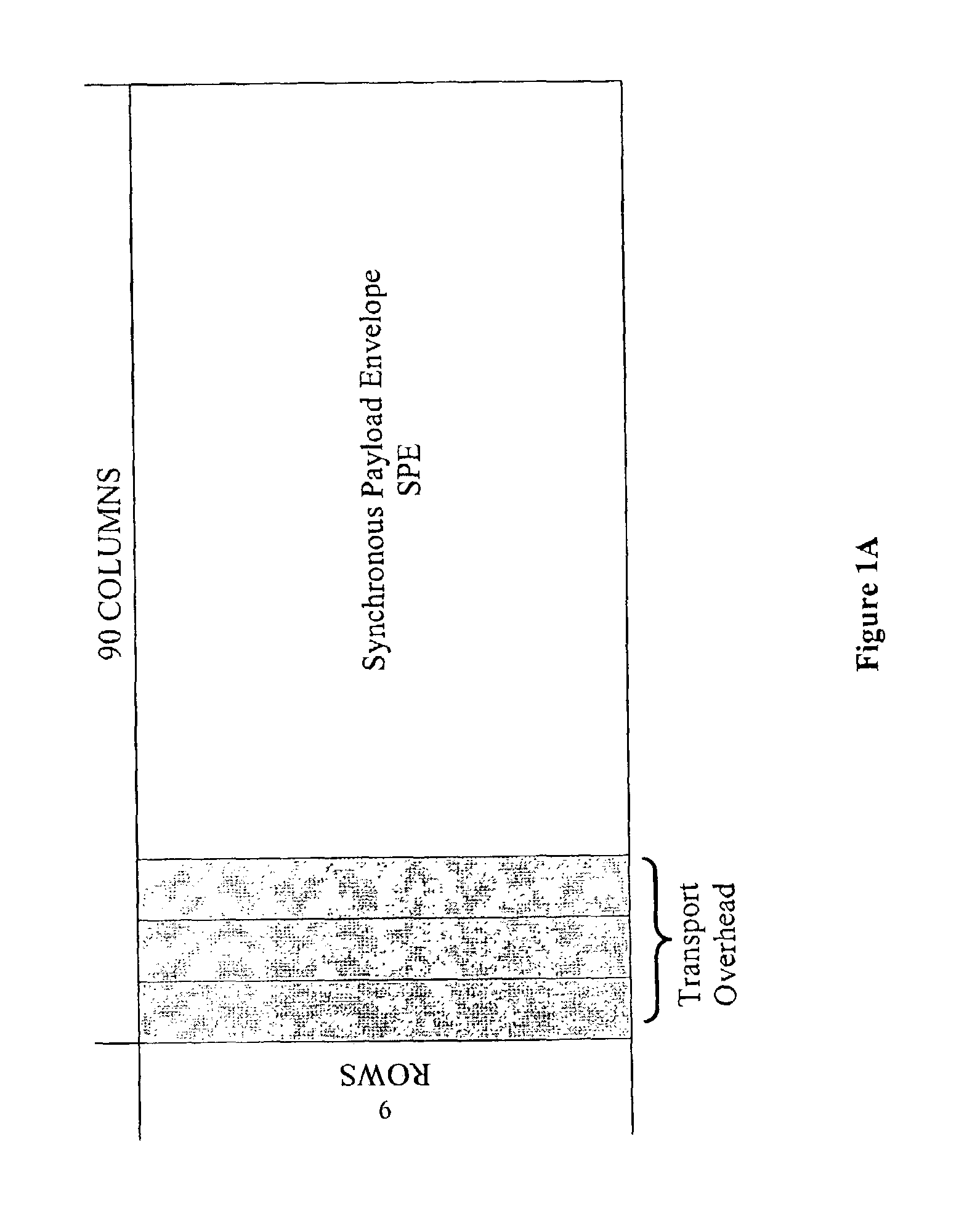

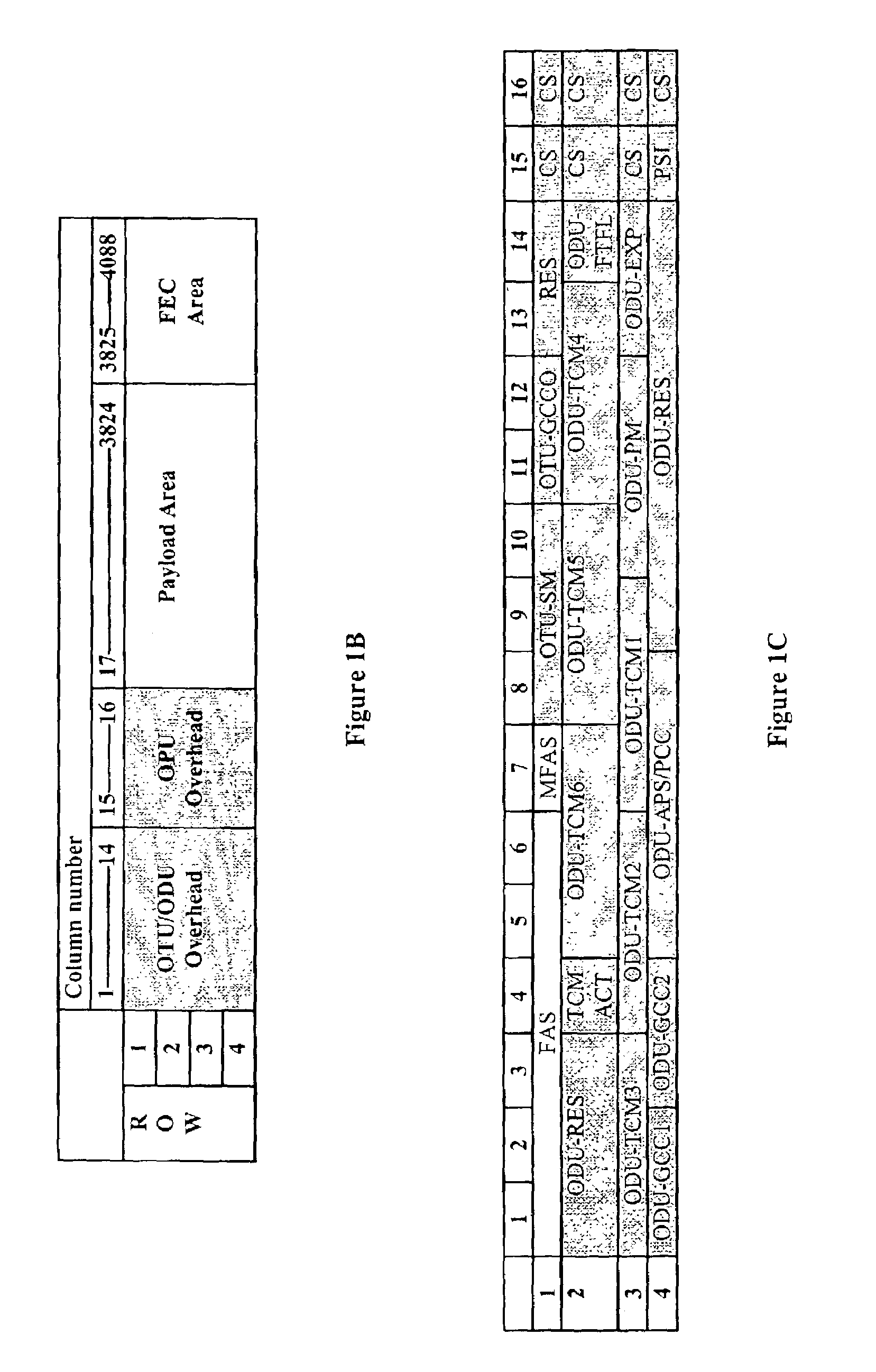

Combined SONET/SDH and OTN architecture

ActiveUS7106968B2Effective maintenanceEfficient settingsTime-division multiplexMultiple digital computer combinationsMultiplexingComputer architecture

Architecture for efficient processing of the evolving OTN transmission technology, standardized under ITU-T G.709, in conjunction with existing and emerging SONET / SDH protocol signals, standardized under ANSI T1.105 / ITU-T G.707. The new architecture allows processing the SONET / SDH signals, and / or OTN signals, and / or SONET / SDH mapped into OTN signals more efficiently. The architecture further allows processing and multiplexing of lower order signals into a higher order signal such as quad OC-192 into OC-768 or quad OC-192 into OPU3 and OTU3. This architecture uses an embedded processor to process some of the signals' overhead in software, contributing to an additional level of flexibility in the processing. This architecture enables customization and allowing for future standard updates and upgrades. The architecture can be upgraded to SONET OC-3072, SDH STM-1024 and OTU4, which currently are not standardized. The architecture can also be used for the implementation of SONET OC-192 with OTN OTU2.

Owner:TRANSWITCH LICENSING LLC

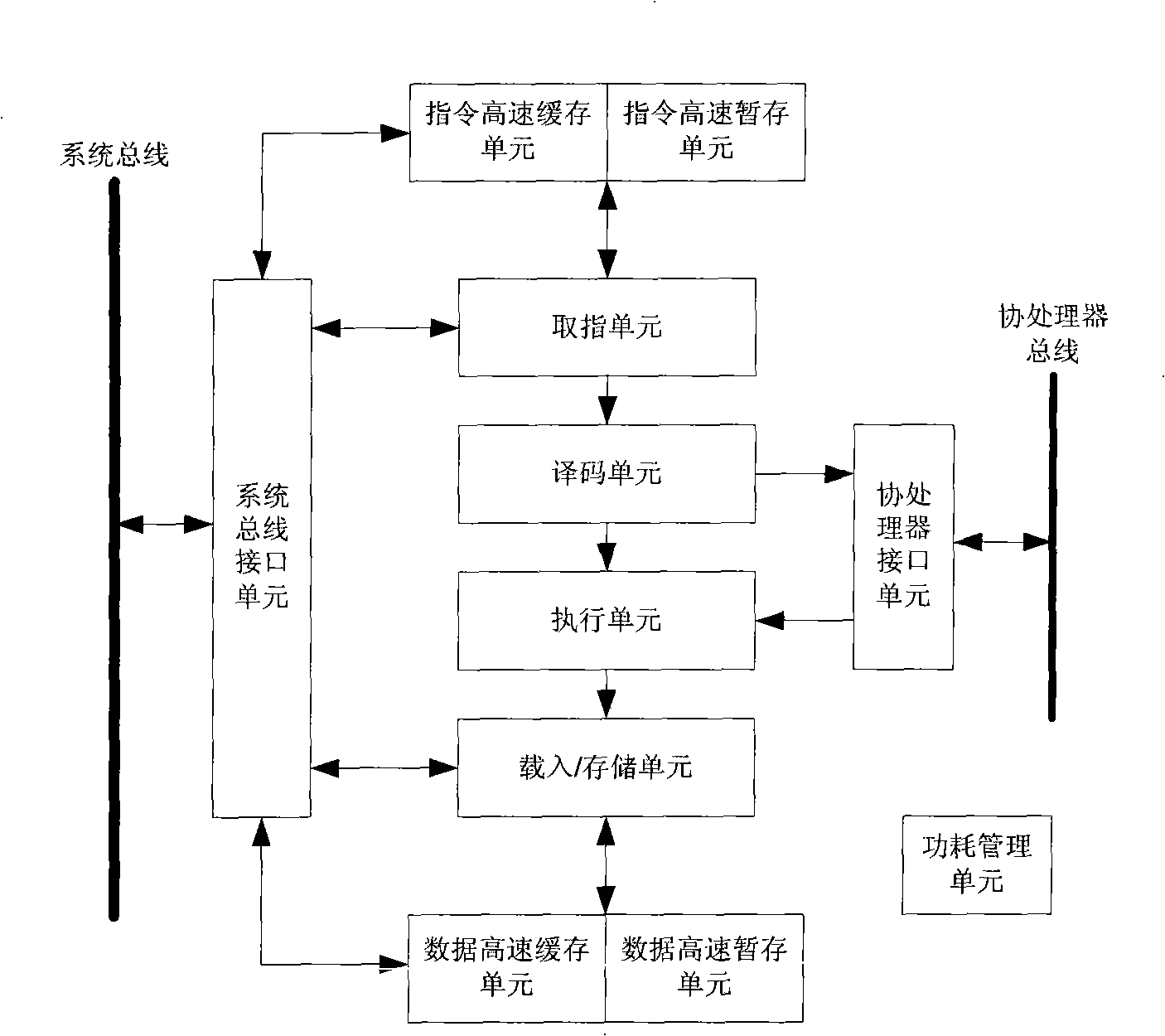

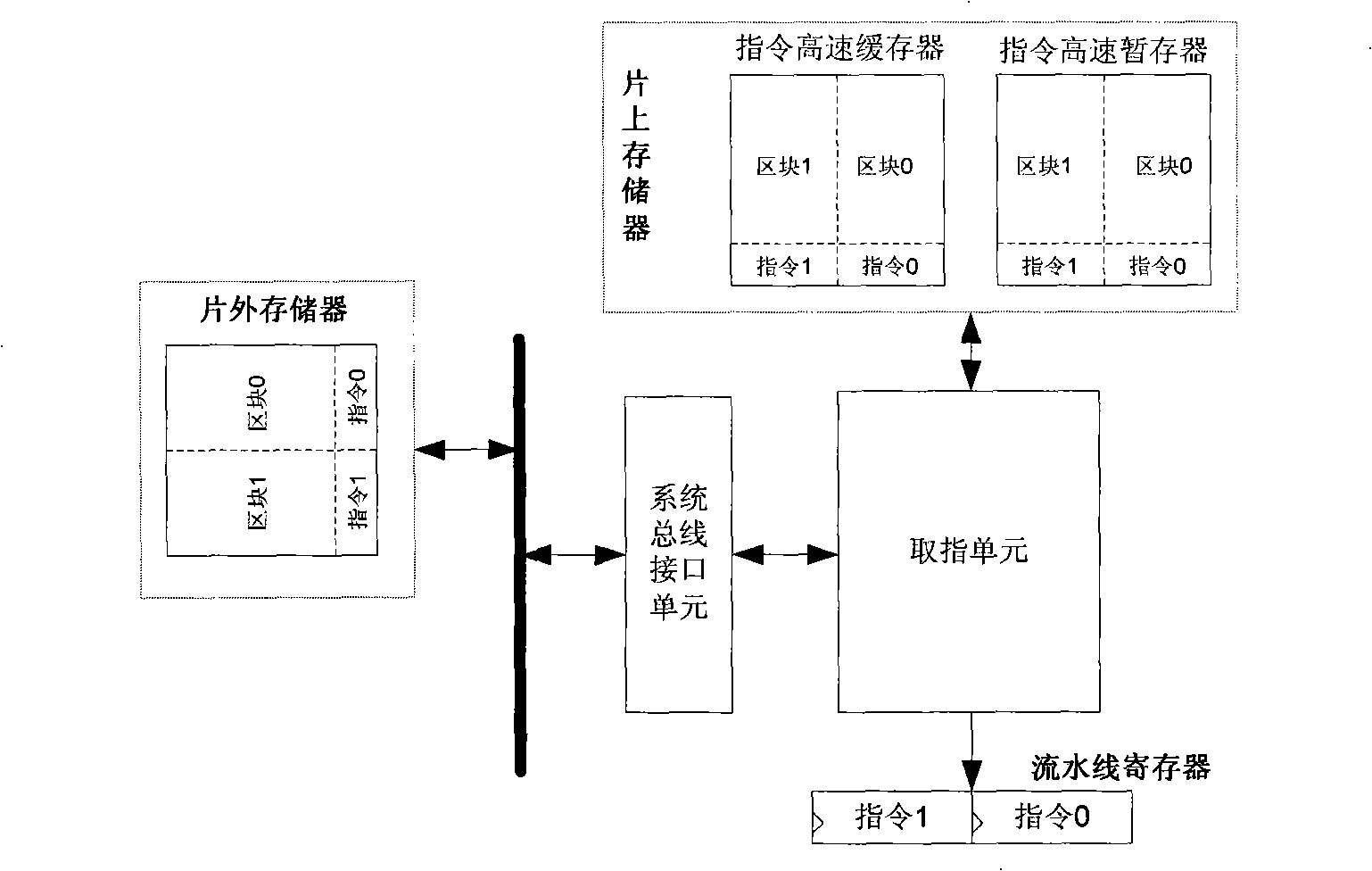

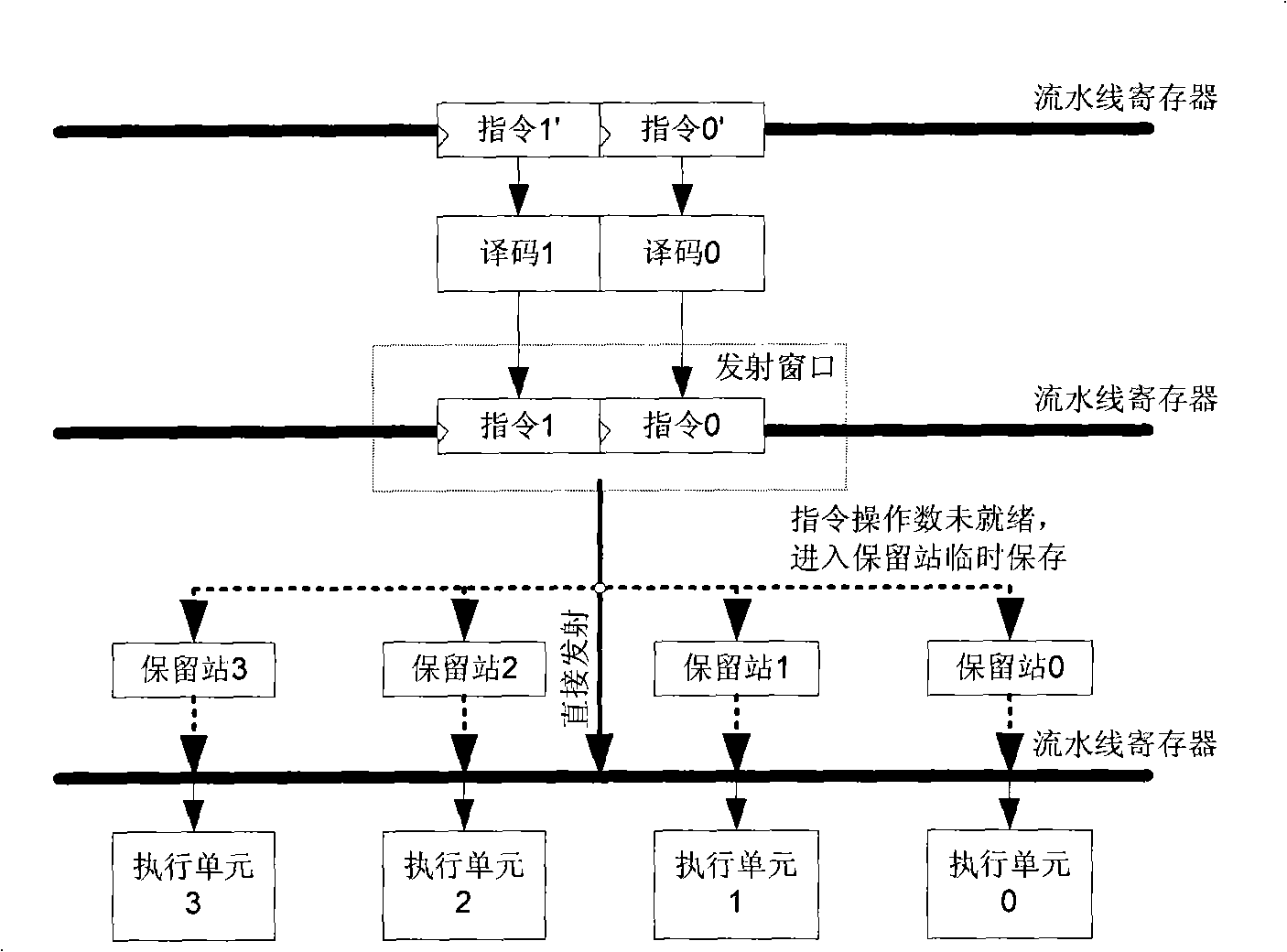

High-performance low-power-consumption embedded processor based on command dual-transmission

ActiveCN101526895AImprove parallel processing capabilitiesAchieve leapfrog developmentConcurrent instruction executionPower supply for data processingAssembly lineExecution control

The invention provides a high-performance low-power-consumption embedded processor based on command dual-transmission, comprising a command fetching unit, a two-way decoding unit, a transmitting unit, a command dispatch execution control unit, a command executing unit and a loading / storing unit; wherein the command fetching unit is used for pre-fetching two commands in a single clock cycle and sending the commands into an assembly line; the two-way decoding unit is used for parallelly decoding the two commands in the single clock cycle; the transmitting unit is used for parallelly transmitting the two commands in the single clock cycle; the command dispatch execution control unit is used for dynamically adjusting the command dispatch according to the computing load and controlling execution according to an out-of-order execution mechanism; the command executing unit is used for computing the results of the commands; and the loading / storing unit is used for ensuring that when the commands are absent, sequent commands can successfully occupy the assembly line and visit the data memory on the disc and the data memory outside the disc. The invention can improve the performance of the embedded processor and reduce the cost under the precondition of low power consumption.

Owner:C SKY MICROSYST CO LTD

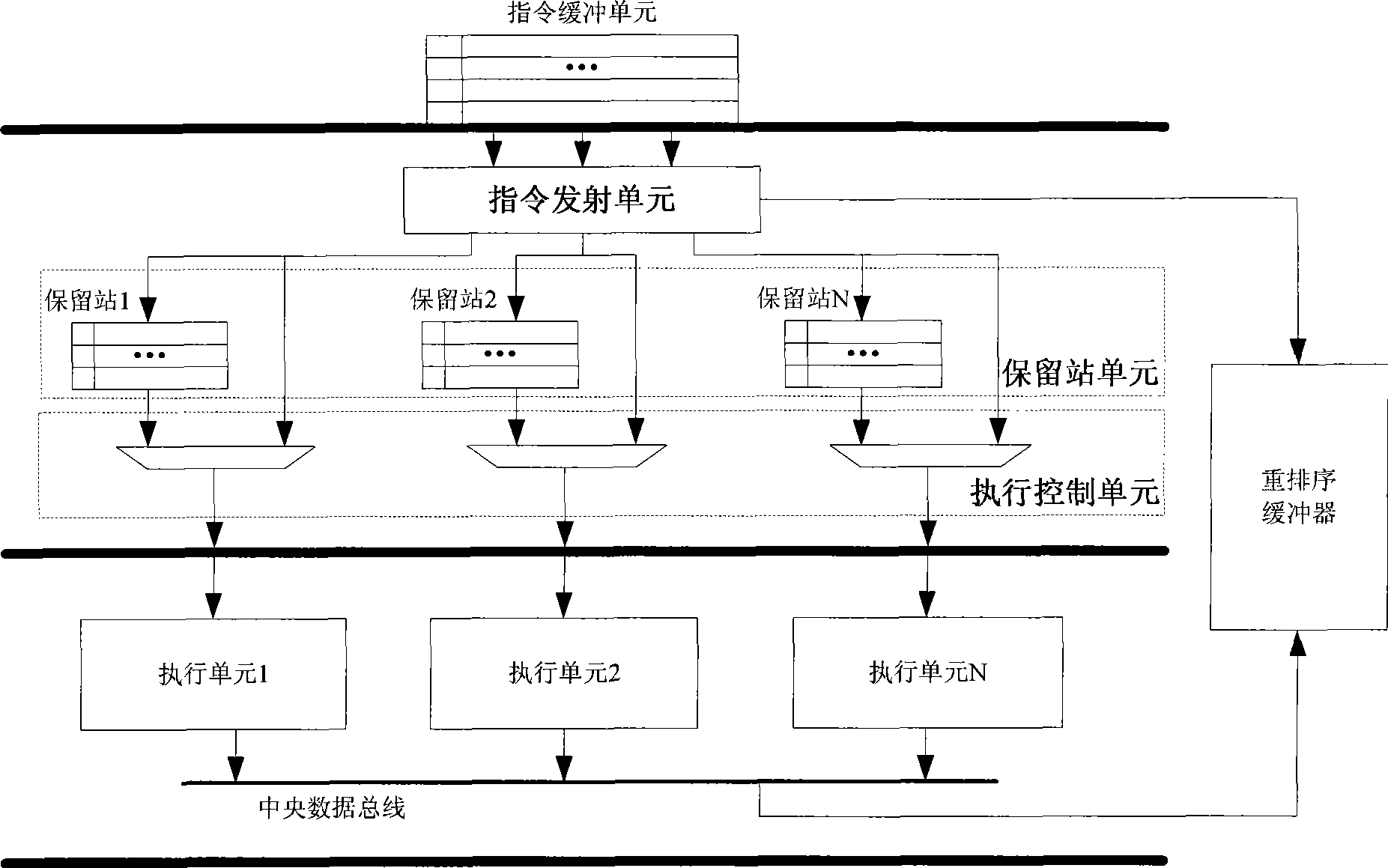

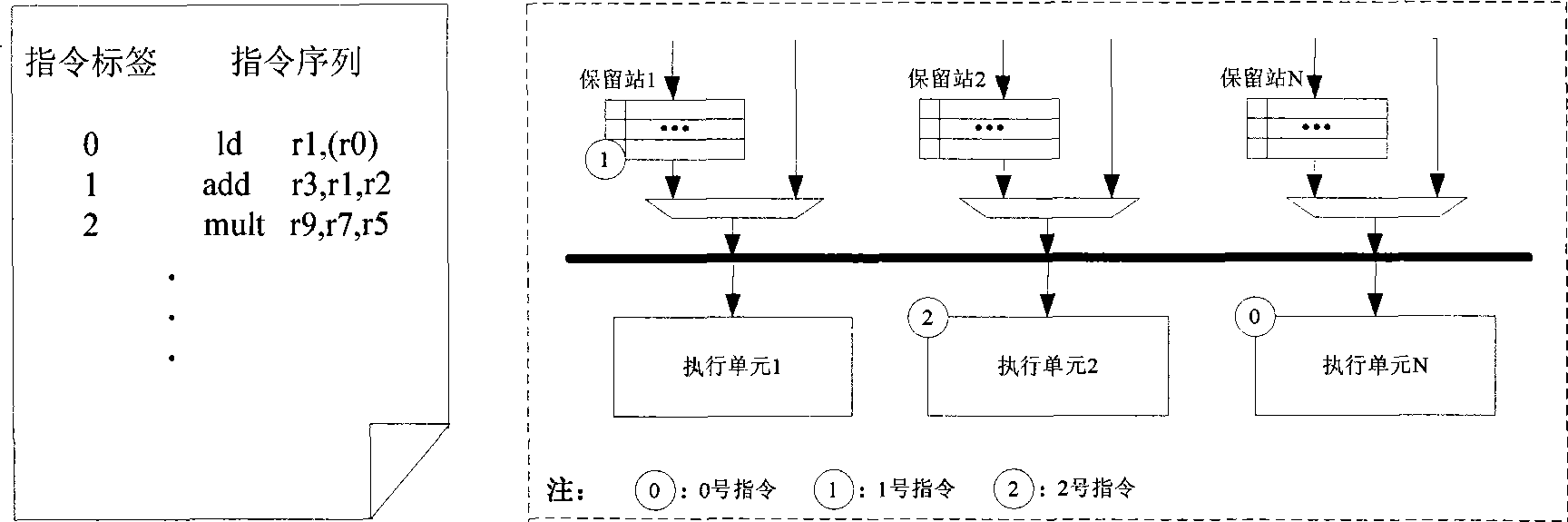

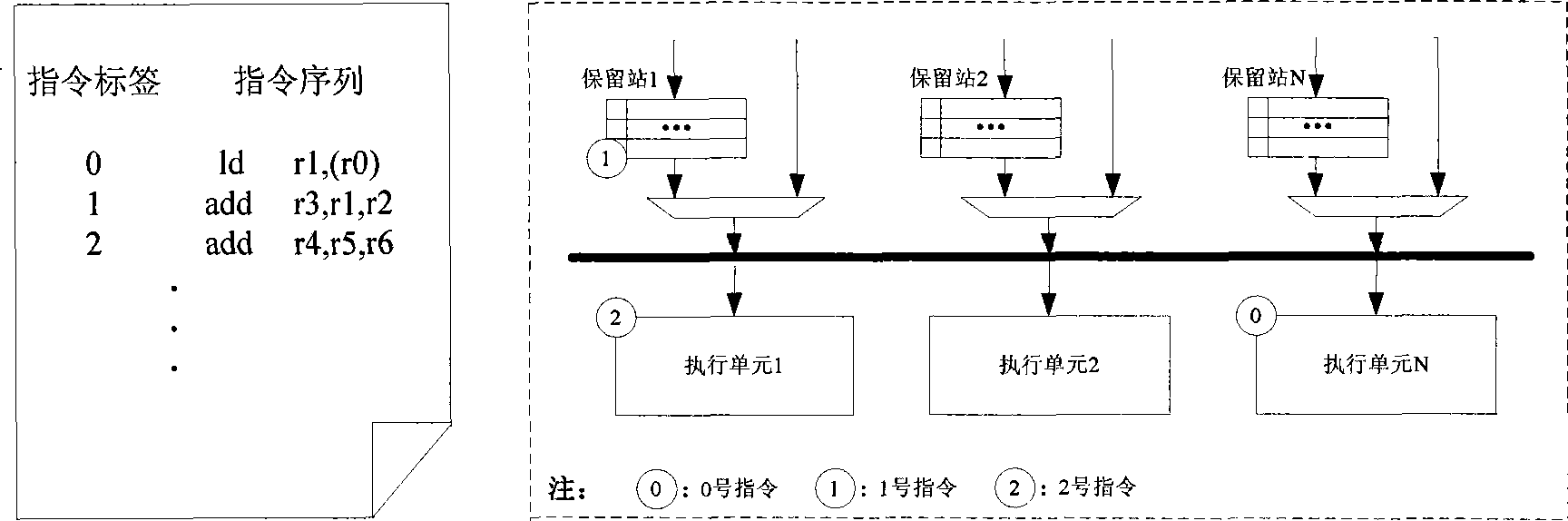

Out-of-order execution control device of built-in processor

InactiveCN101477454AImprove performanceSimplify Bypass LogicConcurrent instruction executionReservation stationProcessor register

The invention relates to a device of an embedded processor, which can control the out-of-order execution. The device comprises a transmit unit, a reservation station register unit and an execution control unit. The transmit unit is used for storing a decoded instruction on a pipeline register, and sending an instruction in a single-clock-cycle manner; the reservation station register unit is used for temporarily storing an instruction for generating for generating a pause when the sent instruction generates a pause because of the related conflict of write / read data, and conducting the bypass monitoring on operands; the execution control unit is used for monitoring the working condition of each execution unit in a real time manner, and dynamically distributing the instruction in the reservation station register unit or the current transmitted instruction according to the information returned by each execution unit. The invention has the advantages of simple design, easy realization and remarkable promotion of the performance of the embedded processor.

Owner:ZHEJIANG UNIV

Embedded processor with watchdog timer for programmable logic

InactiveUS7350178B1Data resettingAerodynamics improvementProcessor registerProgrammable logic device

Owner:ALTERA CORP

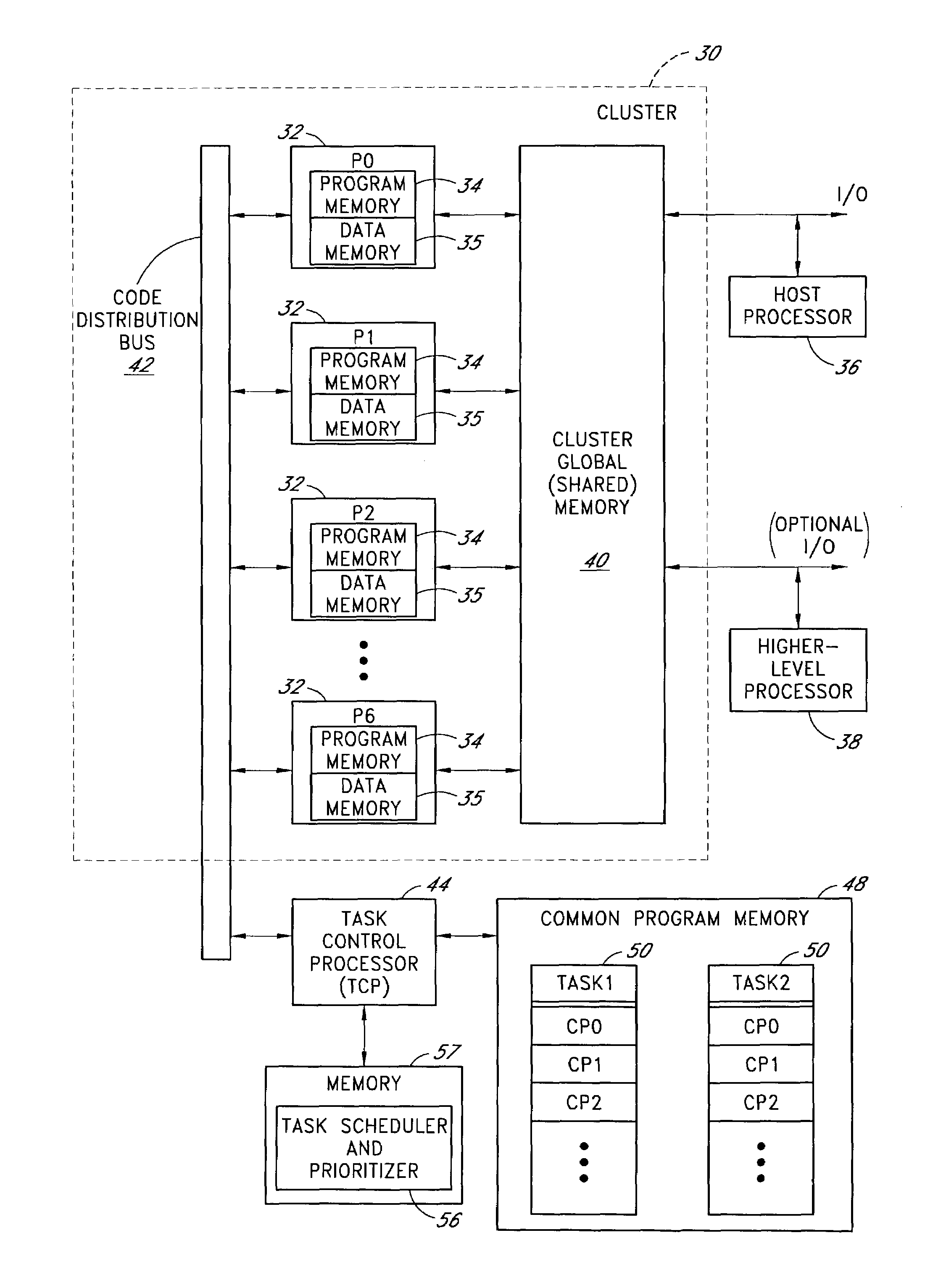

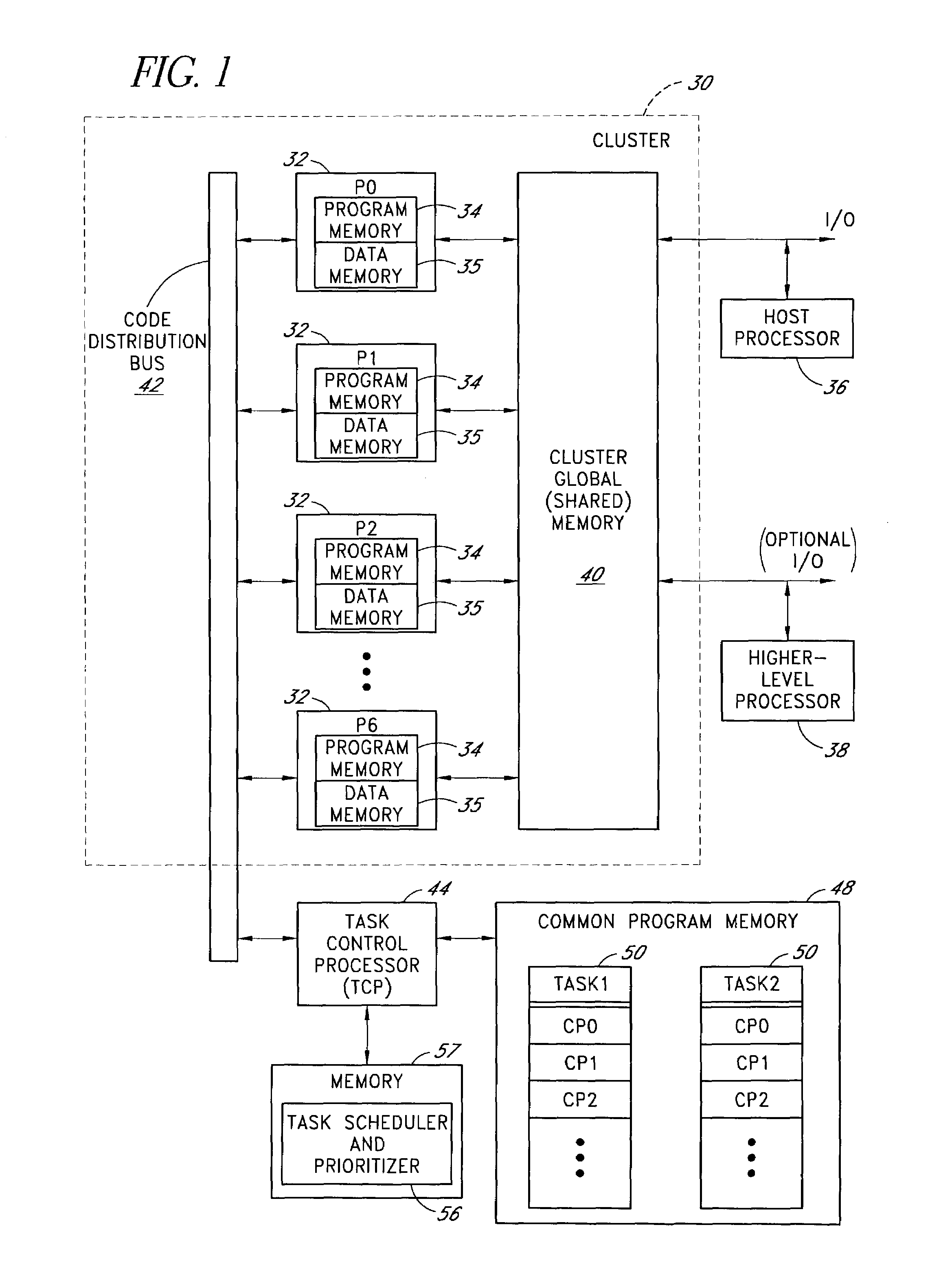

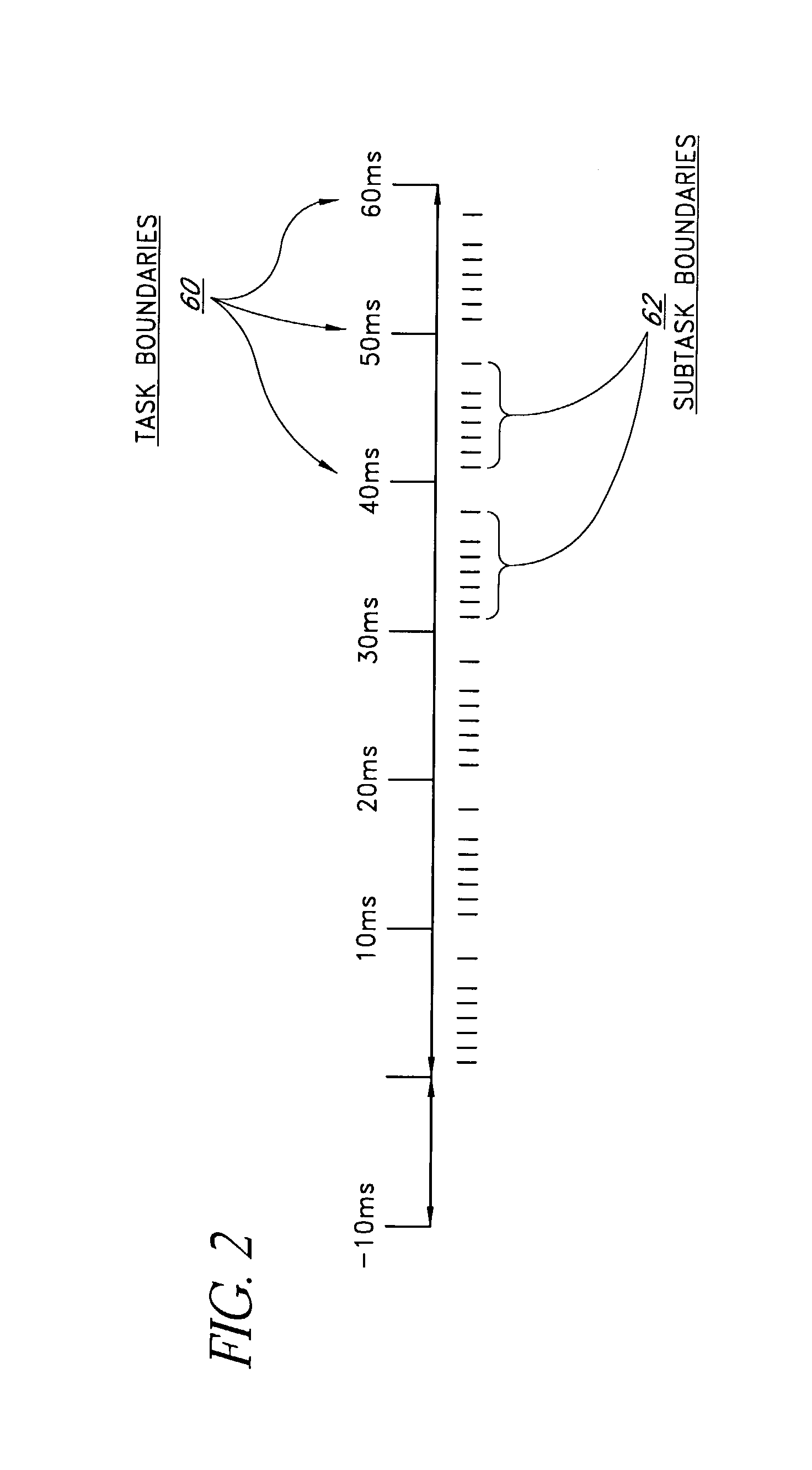

Processor cluster architecture and associated parallel processing methods

ActiveUS6959372B1High level of performanceGeneral purpose stored program computerProgram loading/initiatingCode distributionComputer science

A parallel processing architecture comprising a cluster of embedded processors that share a common code distribution bus. Pages or blocks of code are concurrently loaded into respective program memories of some or all of these processors (typically all processors assigned to a particular task) over the code distribution bus, and are executed in parallel by these processors. A task control processor determines when all of the processors assigned to a particular task have finished executing the current code page, and then loads a new code page (e.g., the next sequential code page within a task) into the program memories of these processors for execution. The processors within the cluster preferably share a common memory (1 per cluster) that is used to receive data inputs from, and to provide data outputs to, a higher level processor. Multiple interconnected clusters may be integrated within a common integrated circuit device.

Owner:NVIDIA CORP

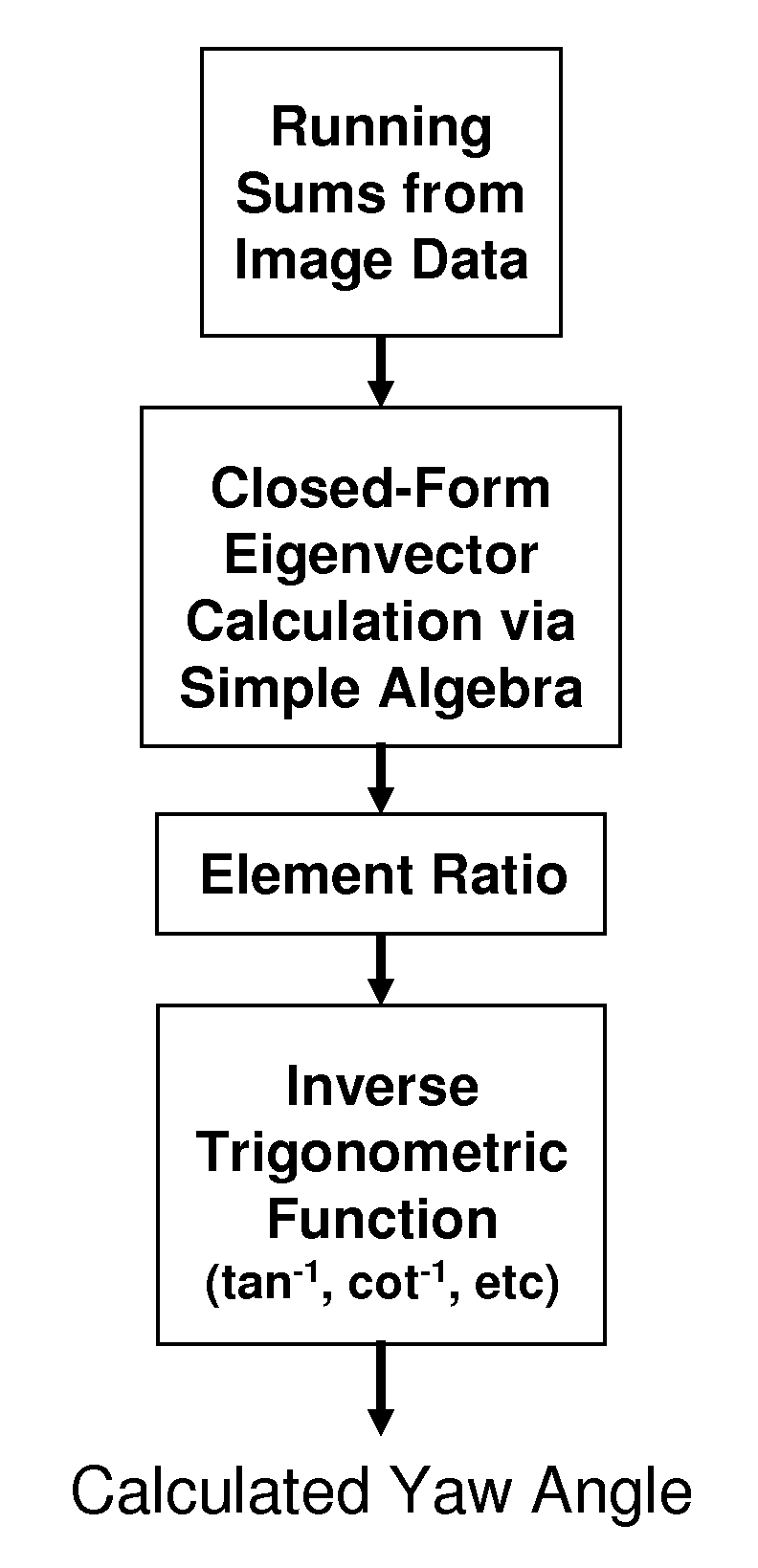

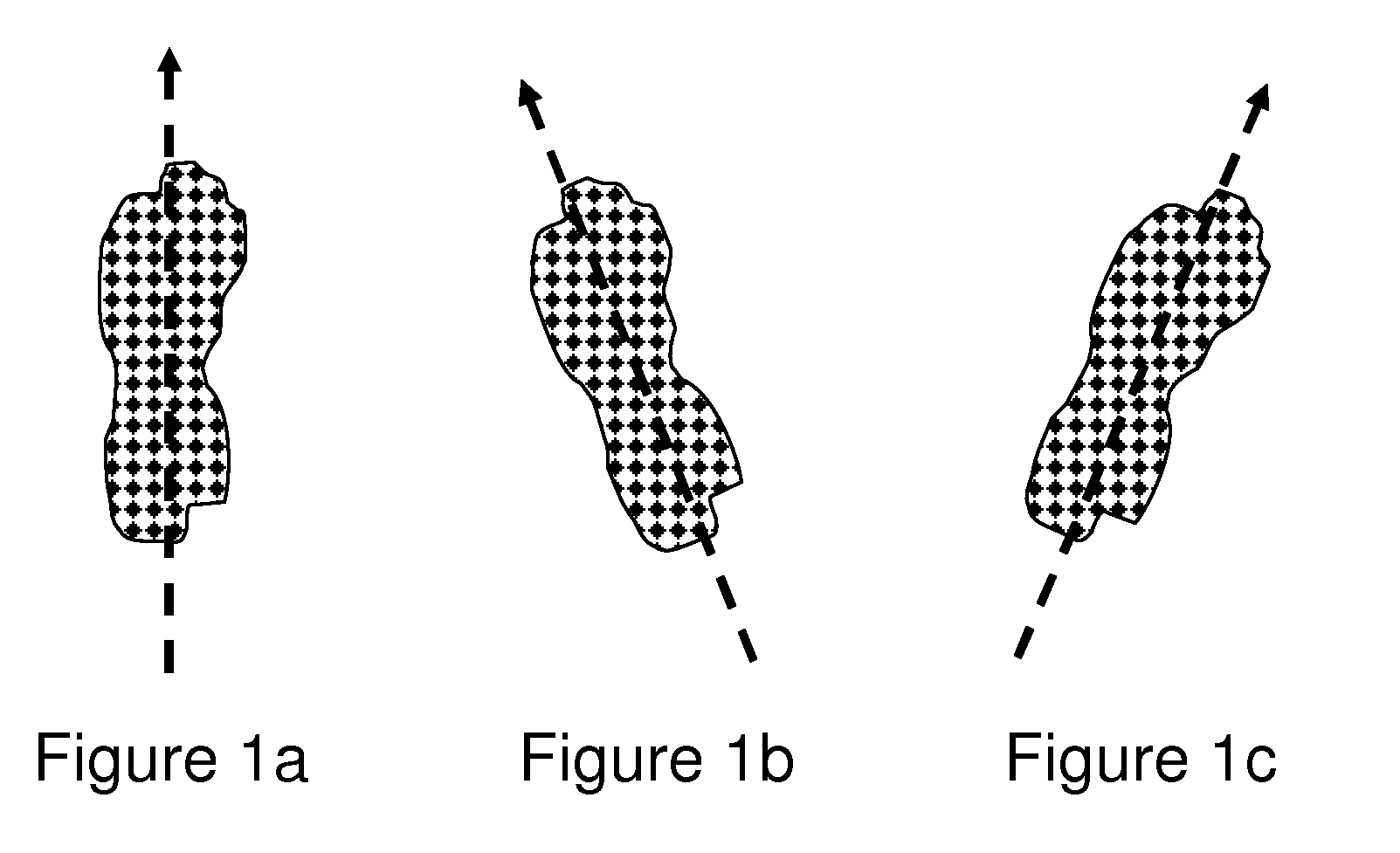

High-performance closed-form single-scan calculation of oblong-shape rotation angles from binary images of arbitrary size using running sums

A method for performing a high-performance closed-form single-scan calculation of oblong-shape rotation angles from binary images of arbitrary size on a processor using running sums is disclosed. Running sums are calculated and stored throughout each scan, and the results are obtained in closed form by simple post-scan computation. An algorithmic embodiment may execute on one or more hardware processors with limited or constrained computation power, available instruction cycles, available memory, etc. Exemplary hardware processors are found in one or more CPUs of a desktop, laptop, tablet, or handheld computing device, and may be an embedded processor or a signal processor chip. The resulting method may be used for touch or optical user interfaces, real-time image recognition, real-time machine vision, and other purposes.

Owner:NRI R&D PATENT LICENSING LLC

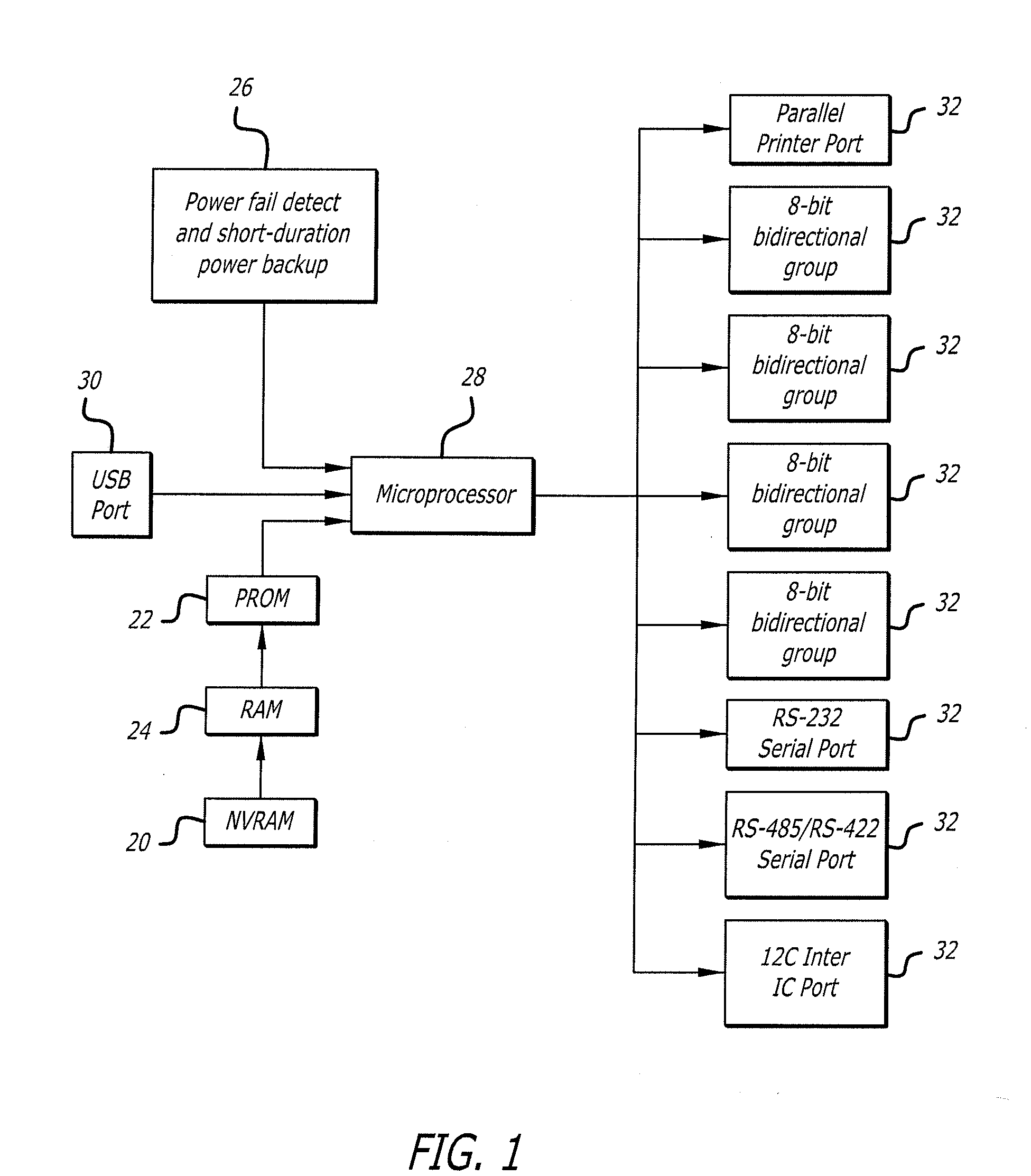

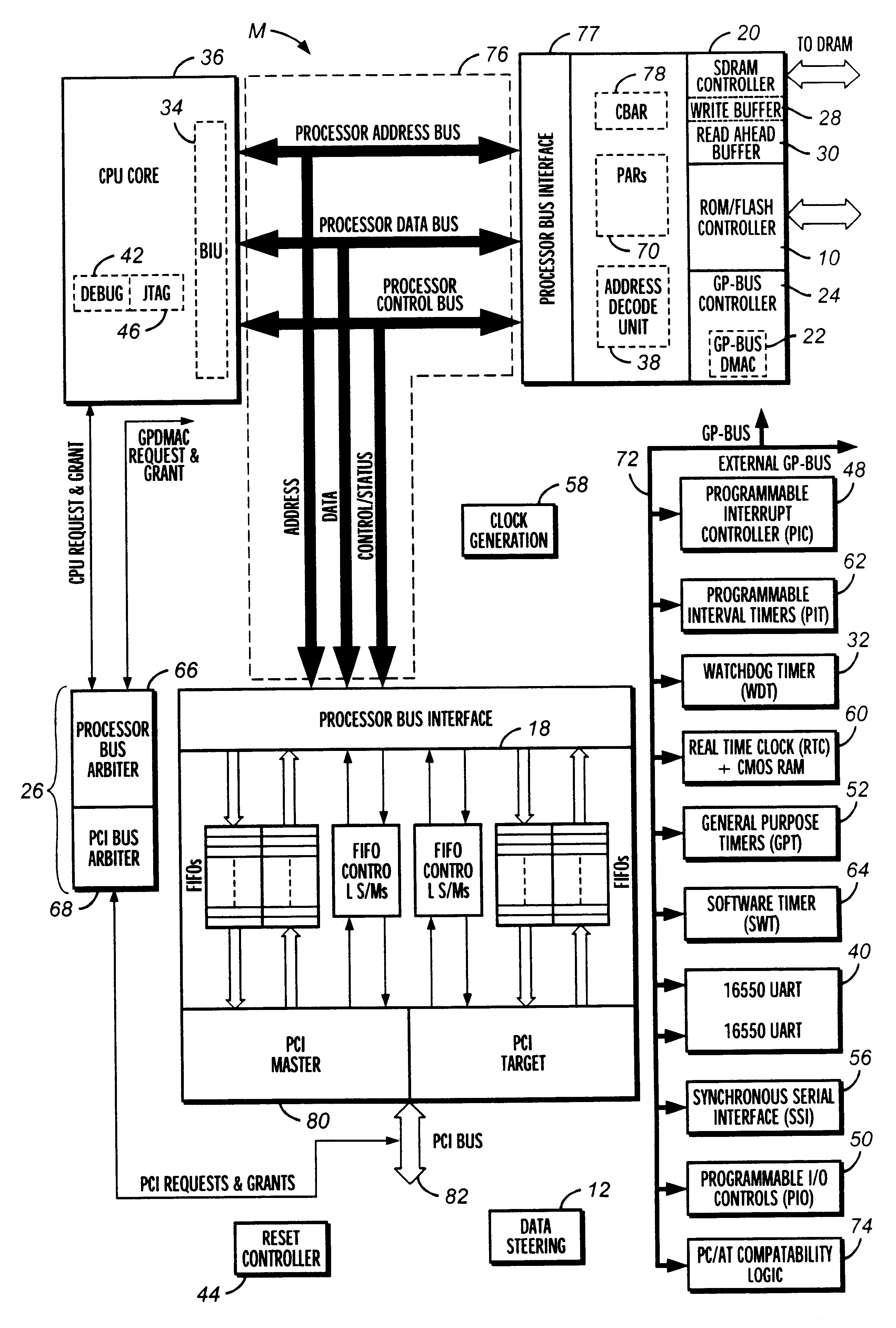

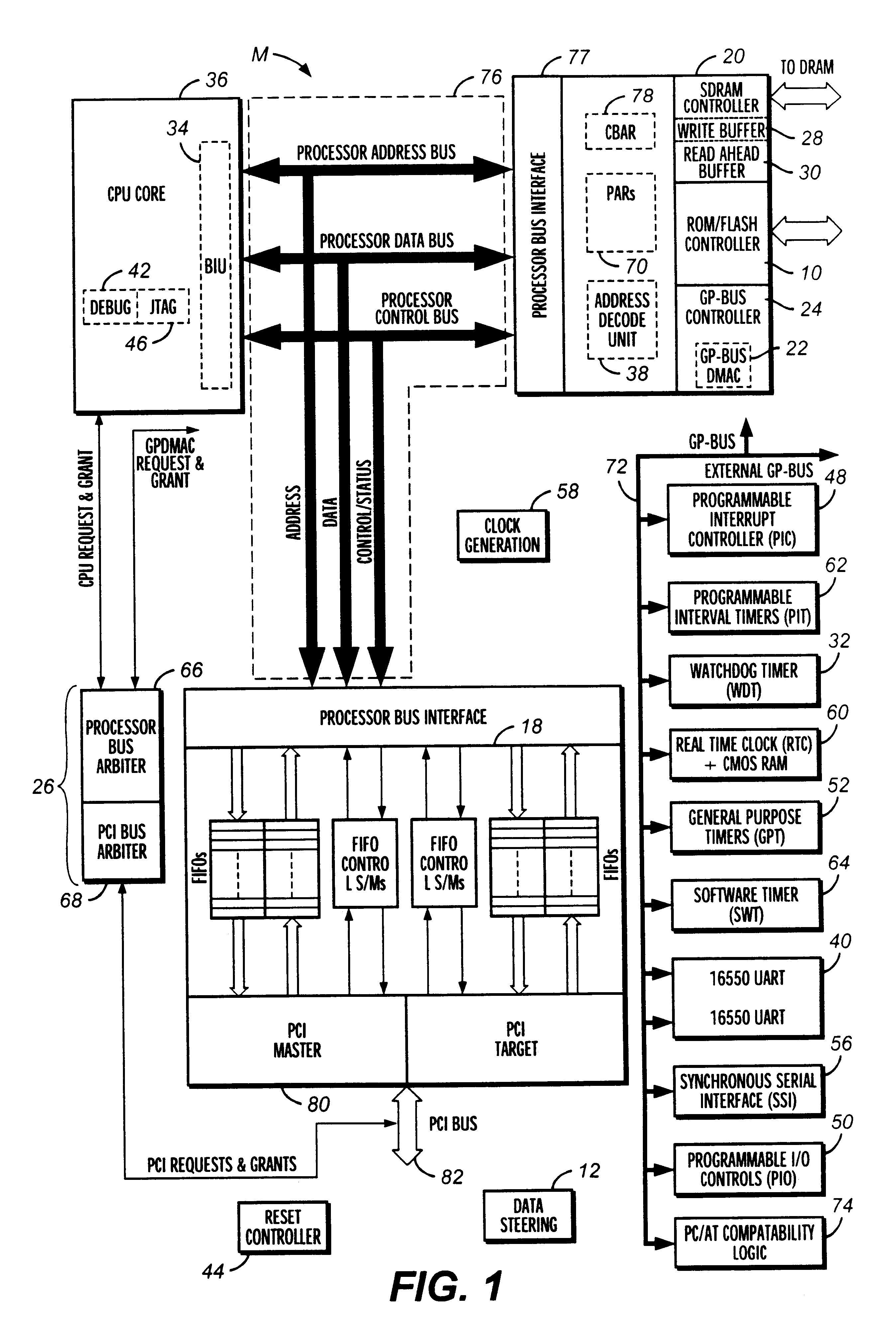

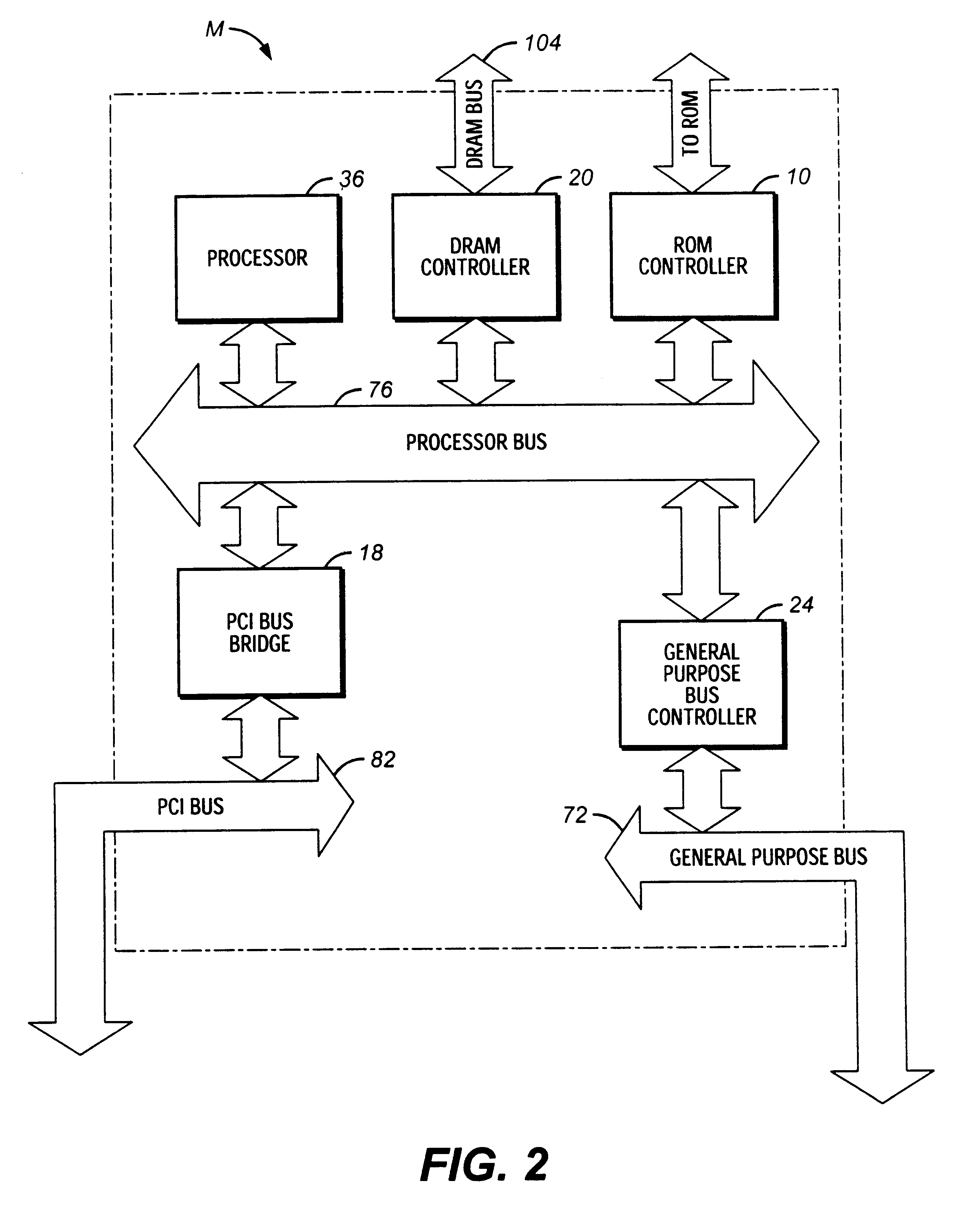

Flexible microcontroller architecture

A microcontroller provides a flexible architecture to readily support both general embedded applications and communications applications. The microcontroller includes an embedded processor, a relatively low-speed general purpose peripheral bus controller, a relatively high-speed peripheral bus host bridge, a primary memory controller, and a secondary memory controller, each coupled to a processor bus. The general purpose peripheral bus controller is coupled to a relatively low-speed general purpose peripheral bus which is coupled to a plurality of integrated general purpose peripherals. The relatively high-speed peripheral bus host bridge is coupled to a relatively high-speed peripheral bus capable of supporting a plurality of communication-oriented peripherals. The secondary memory controller shares an address bus with the general purpose peripheral bus controller and shares a data bus with either the primary memory controller or the general purpose peripheral bus controller. The control timing of the secondary memory controller is independent of the control timing of the general purpose peripheral bus controller. Also, a processor arbiter is coupled to the embedded processor, and a relatively high-speed peripheral bus arbiter is coupled to the peripheral bus host bridge. Aside from the microcontroller, an embedded system can include a relatively low-speed general purpose peripheral bus and a relatively high-speed peripheral bus, both external to the microcontroller. The external relatively lowspeed general purpose bus can be coupled to the relatively low-speed general purpose peripheral bus controller, and the external relatively high-speed peripheral bus can be coupled to the relatively high-speed peripheral bus host bridge.

Owner:ADVANCED MICRO DEVICES INC

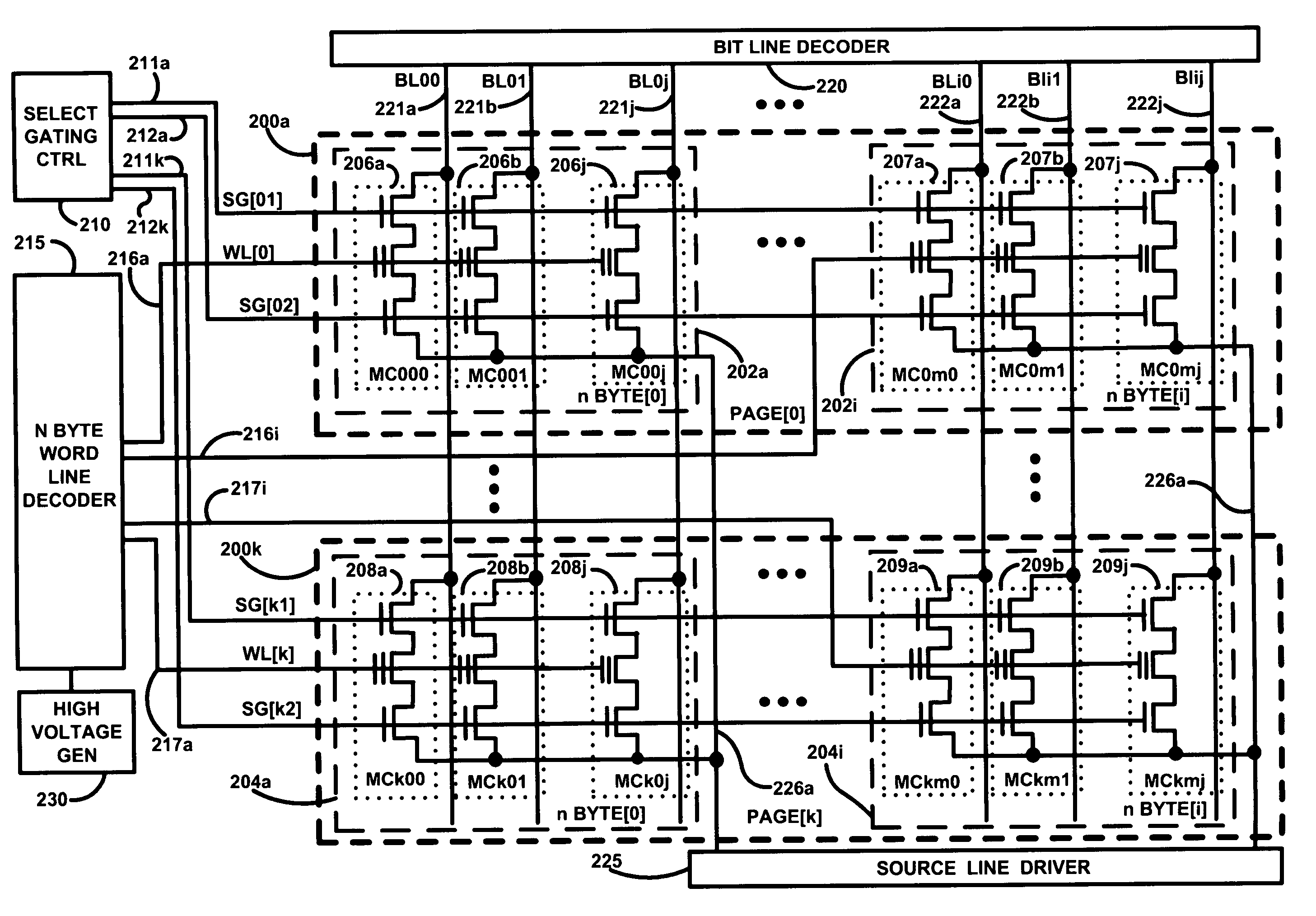

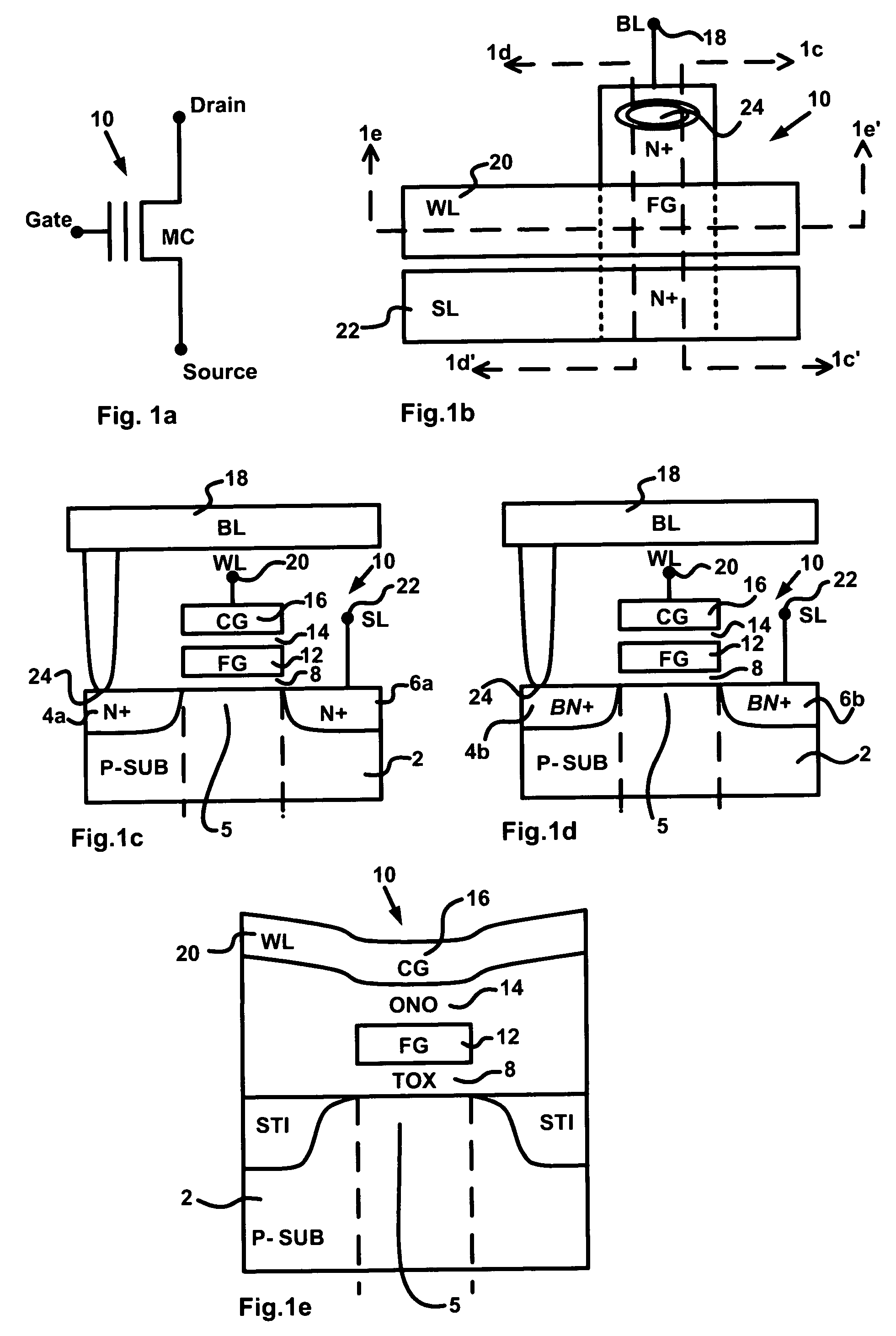

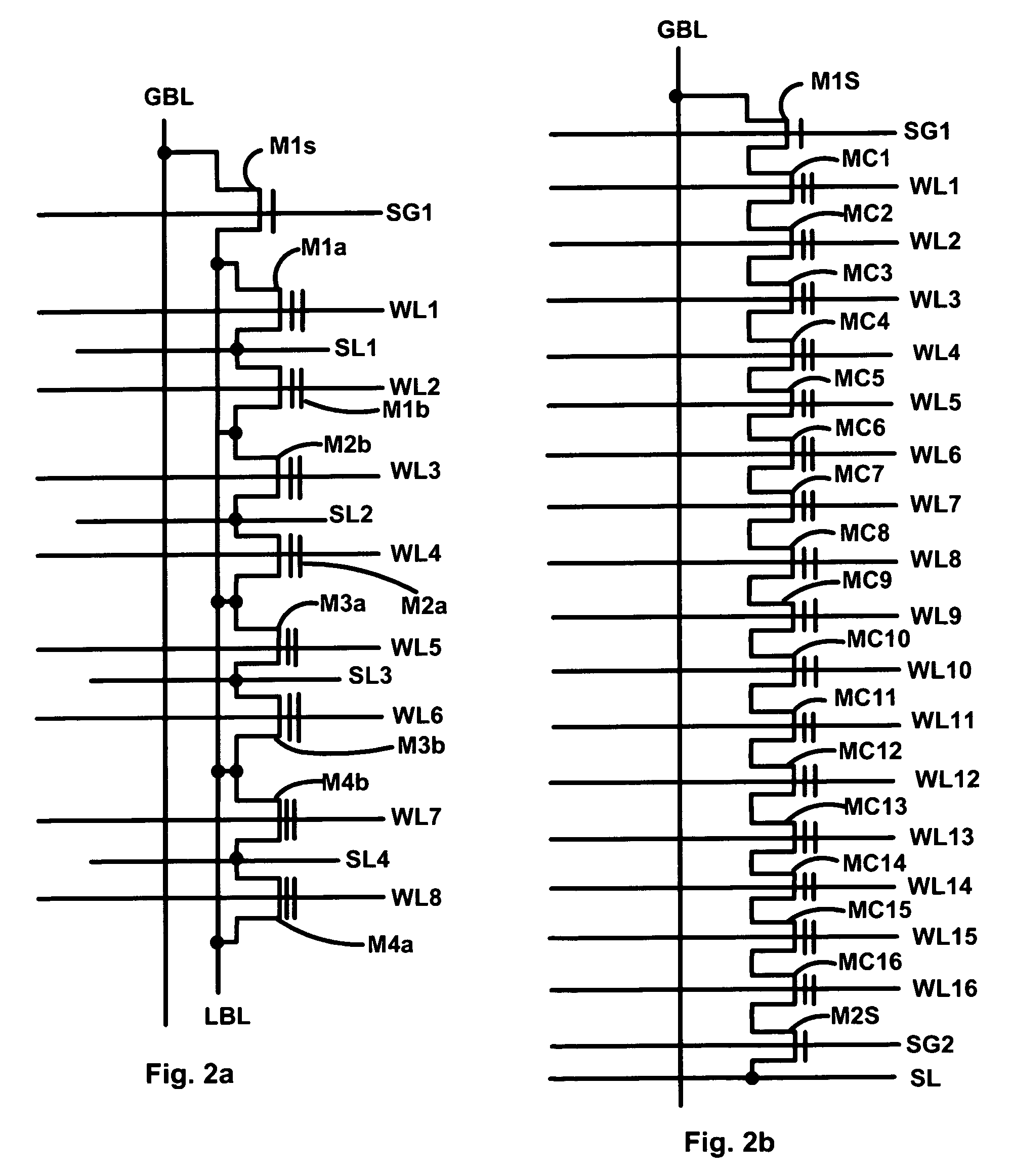

Novel combination nonvolatile integrated memory system using a universal technology most suitable for high-density, high-flexibility and high-security sim-card, smart-card and e-passport applications

A combination EEPROM, NOR-type Flash and NAND-type Flash nonvolatile memory contains memory cells in which a floating gate transistor forms a NAND-type Flash nonvolatile memory cell, forms a NOR-type Flash nonvolatile memory cells and with one or two select transistors forms a two and three transistor EEPROM cell. The nonvolatile memory cells use a large positive programming voltage (+18V) applied to the word lines or select gating lines for programming the memory cells and a large negative erasing voltage (−18V) applied to the word lines or select gating lines for erasing the memory cells. The NOR-type Flash nonvolatile memory array is used to store code of embedded processor programs or application programs for smart cards. The EEPROM array is preferably used to store byte alterable data and NAND-type Flash nonvolatile memory array is used to store personalized biometric data such as Iris, DNA, facial picture and finger prints.

Owner:CALLAHAN CELLULAR L L C

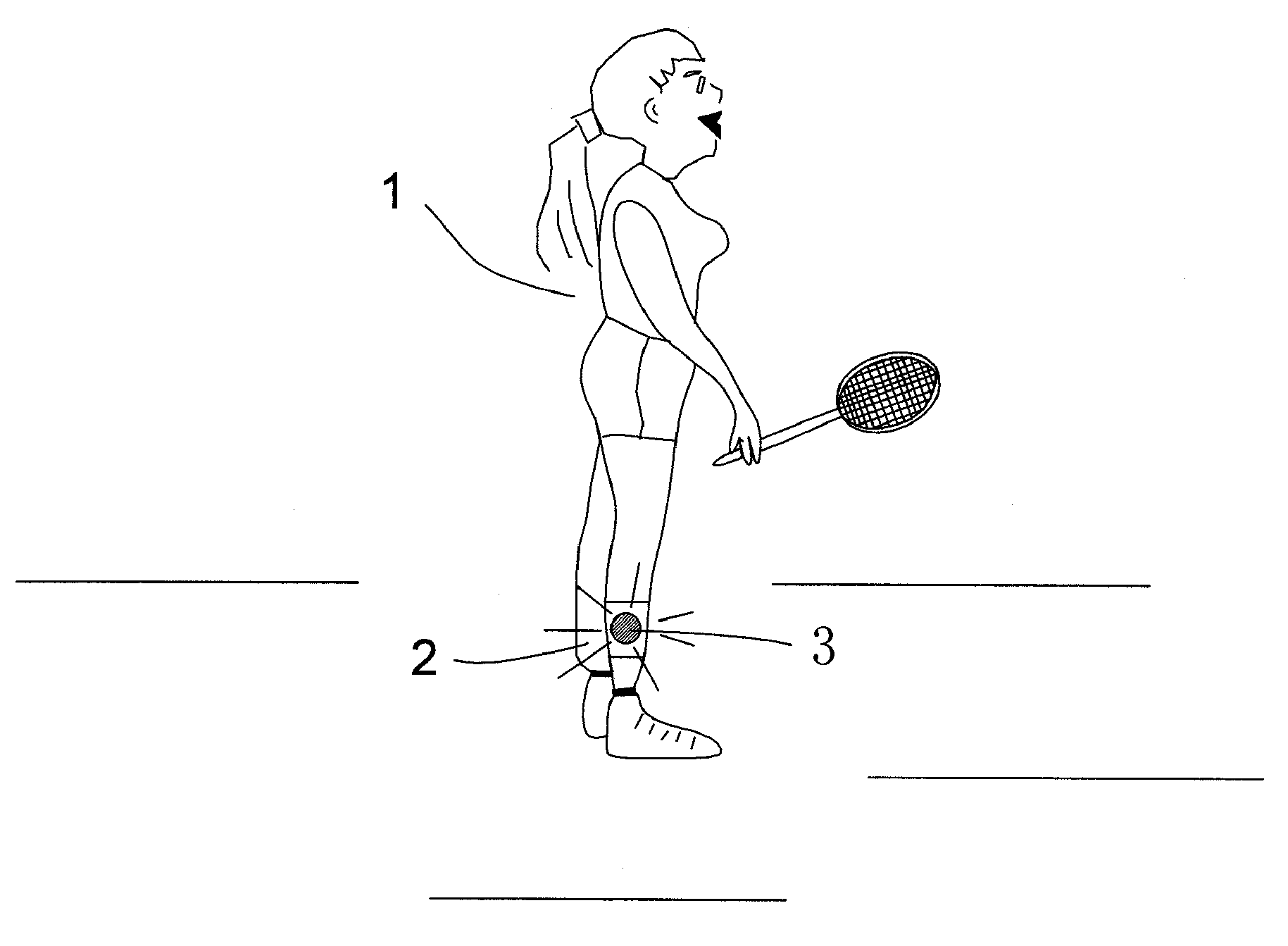

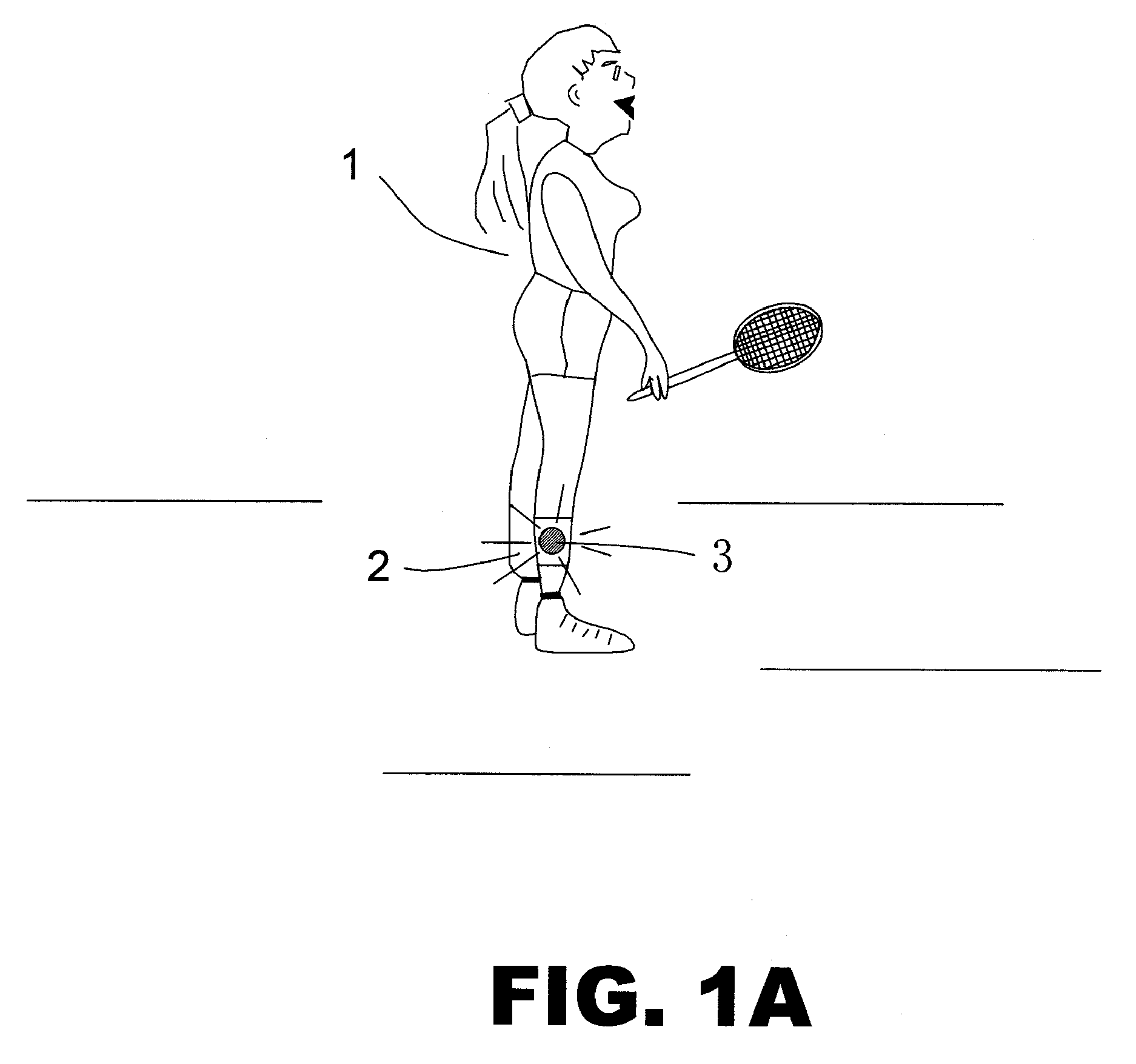

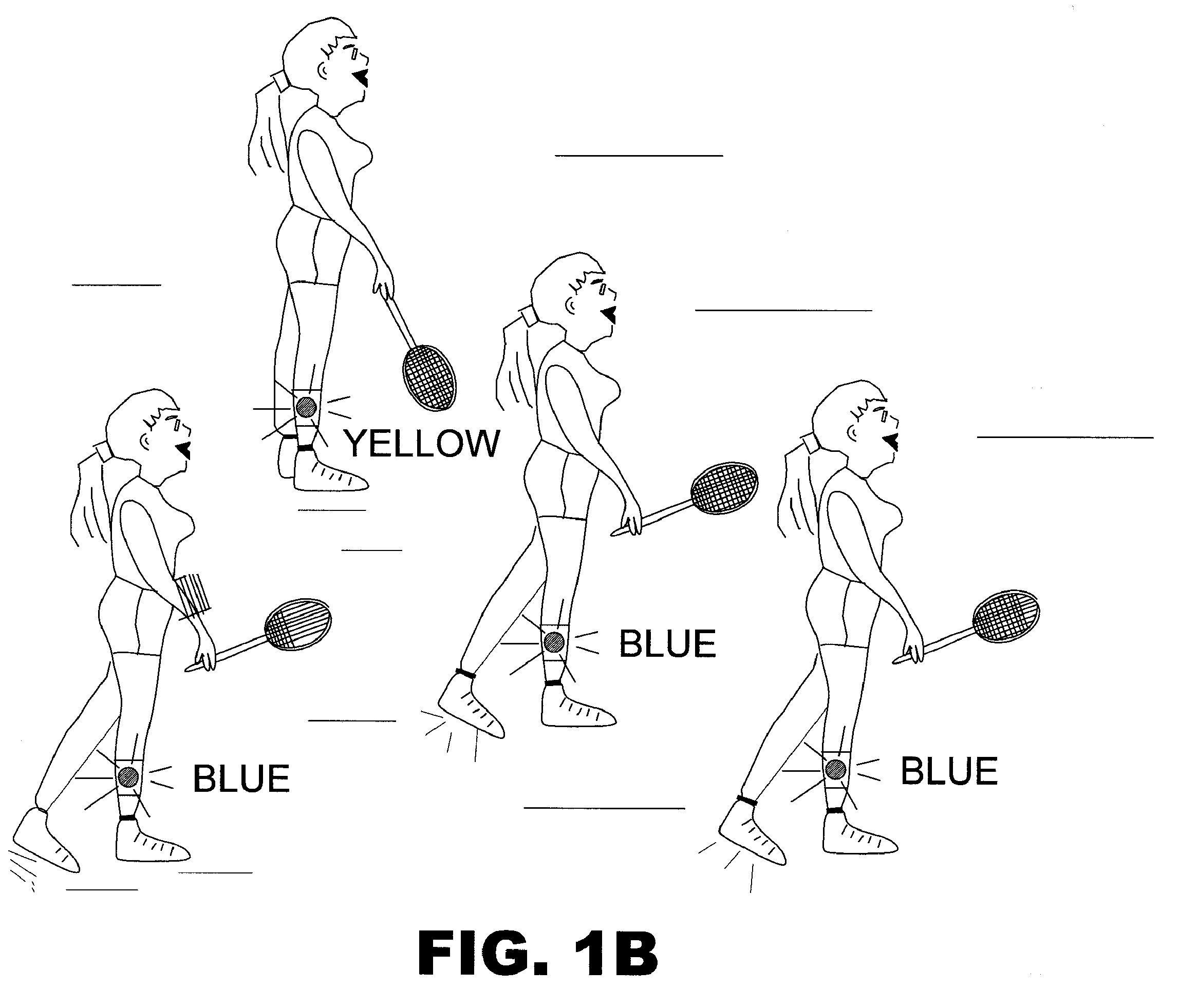

Sports training system

InactiveUS8043173B2Increase heart rateImprove fitnessSwimming detailsBall sportsEngineeringColored light

A training system used in sports or other training that where a participant wears a device with a visual indicator such as a device emitting colored light and an optional signaling device like a vibrator or beeper. The device can be worn on the head, elbow, wrist, waist, knee, ankle or foot or be part of an participant's attire. The device can optionally be embedded in or on a shoe. A motion or position sensor can cause the visual indicator to change color or indication when the wearer is not moving correctly. Also, in some embodiments, a vibration can signal can be commanded by a coach or instructor to show that the player is not properly moving. An embedded processor can optionally set up various rhythm patterns used in practice. The device, wherever it is worn or disposed, can optionally be controlled remotely by a coach or instructor using a wireless transmission such as digital or analog radio or light to establish certain rhythms or to signal certain participants. The coach can send different signals to different devices worn by different participants. In a particular shoe embodiment, each of a pair of shoes can optionally communicate with the other member of the pair wirelessly so that a processor in one of the shoes can coordinate a rhythm pattern of vibration or beeping signals between the shoes.

Owner:MENALAGHA NASRIN +2