Patents

Literature

3187 results about "Test program" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

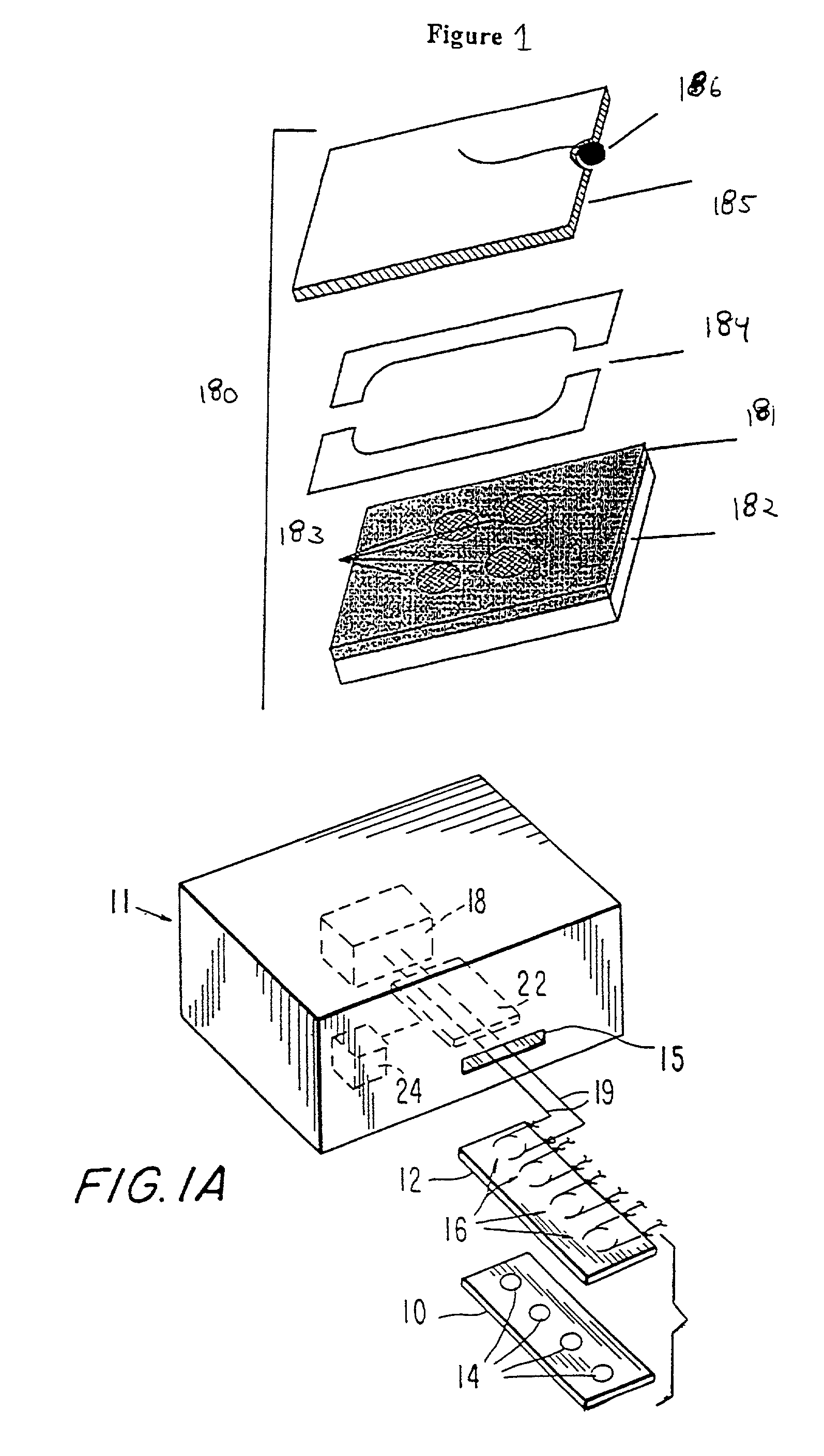

Multi-array multi-specific electrochemiluminescence testing

InactiveUS6673533B1Bioreactor/fermenter combinationsMaterial nanotechnologyAnalyteElectrochemiluminescence

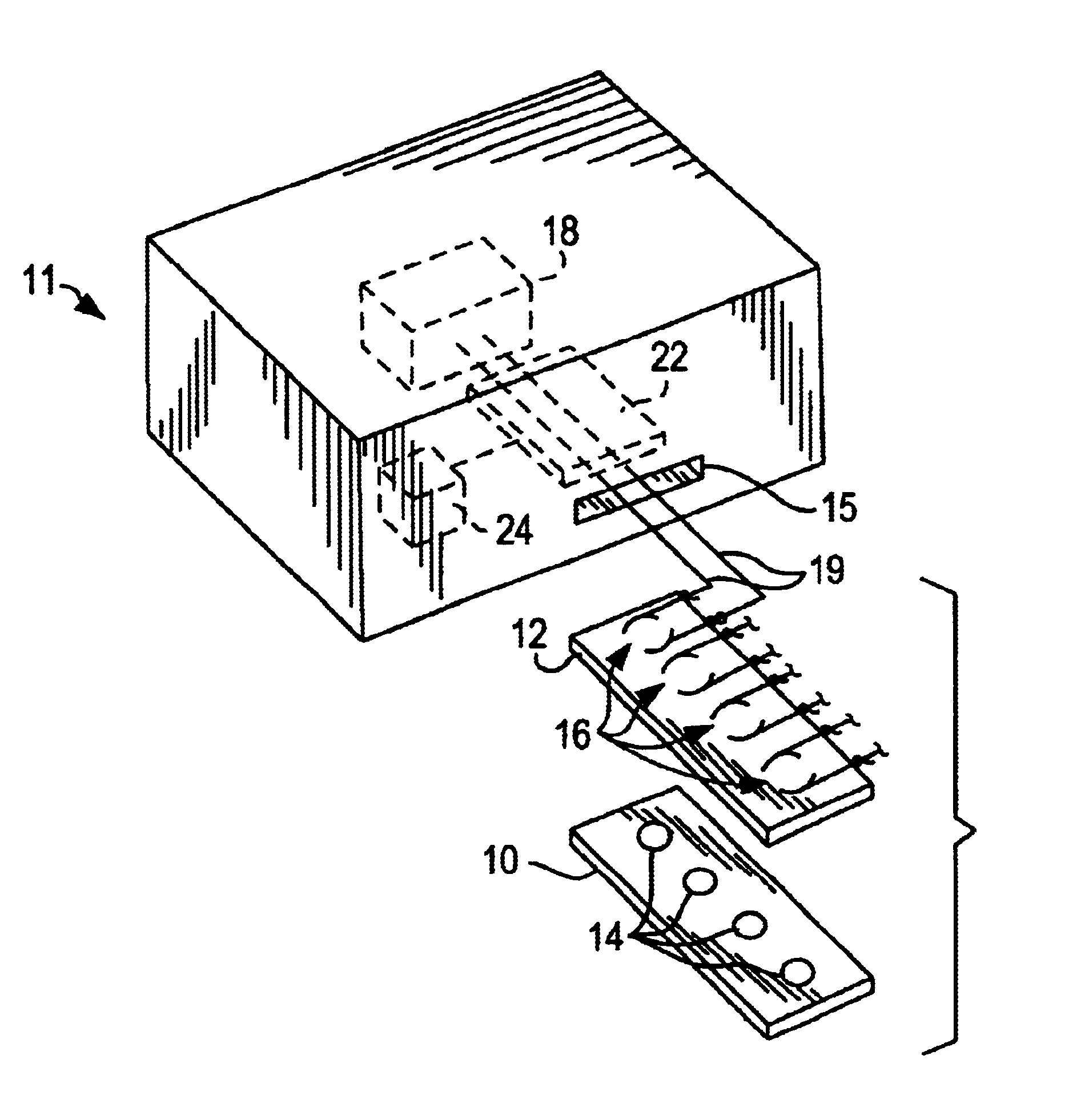

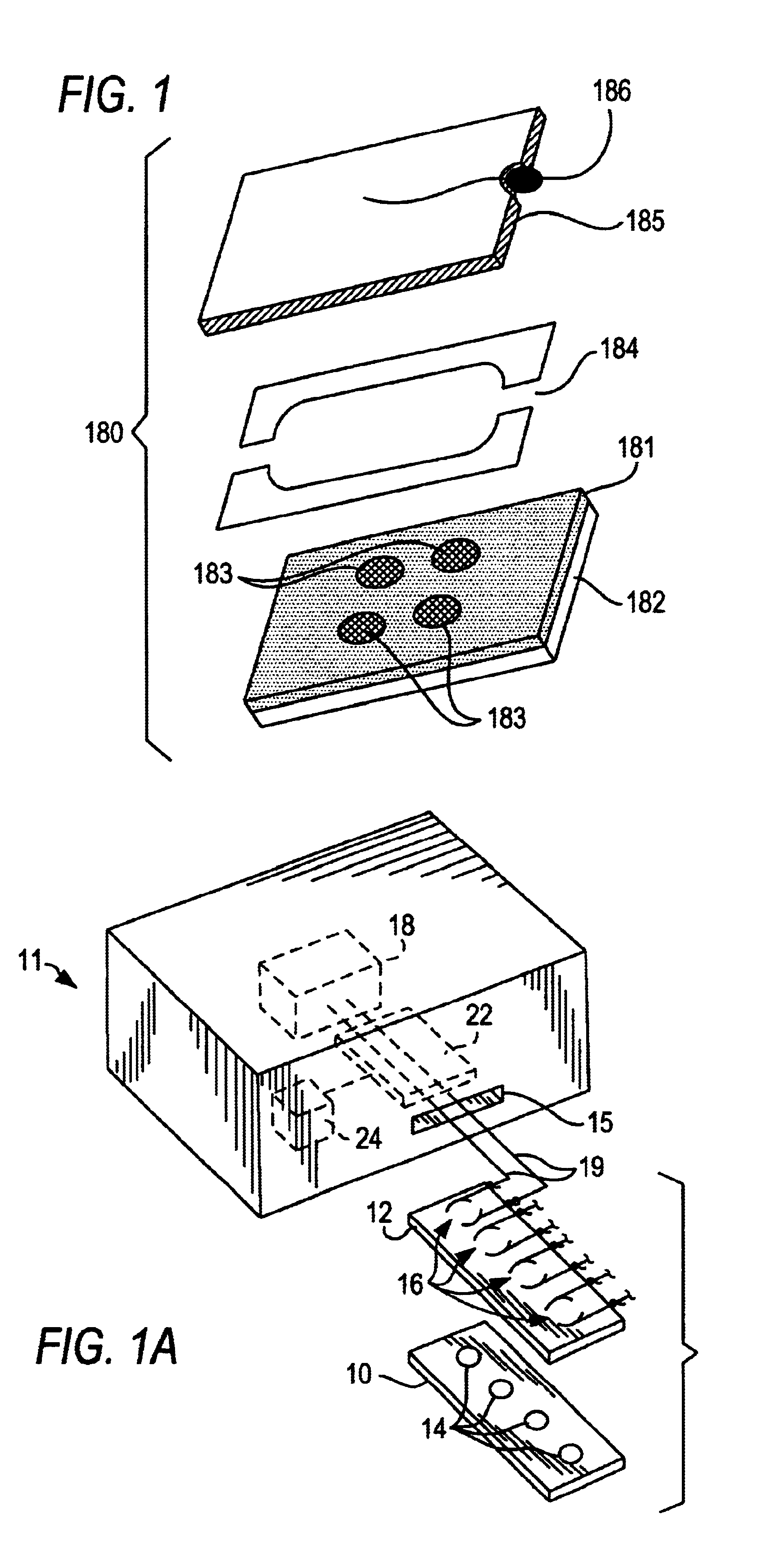

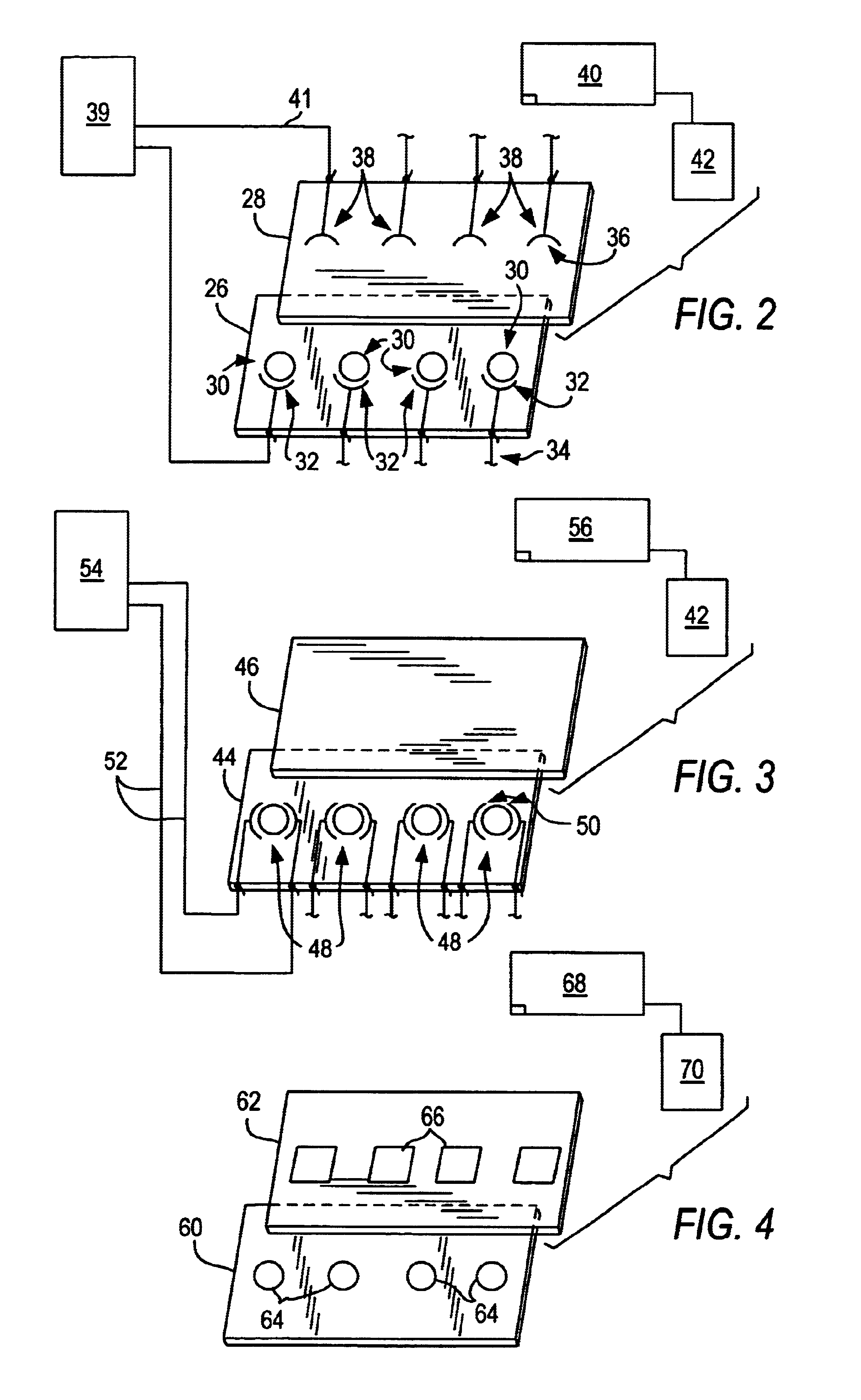

Materials and methods are provided for producing patterned multi-array, multi-specific surfaces for use in diagnostics. The invention provides for electrochemiluminescence methods for detecting or measuring an analyte of interest. It also provides for novel electrodes for ECL assays. Materials and methods are provided for the chemical and / or physical control of conducting domains and reagent deposition for use multiply specific testing procedures.

Owner:MESO SCALE TECH LLC

Voice recognition virtual test engineering assistant

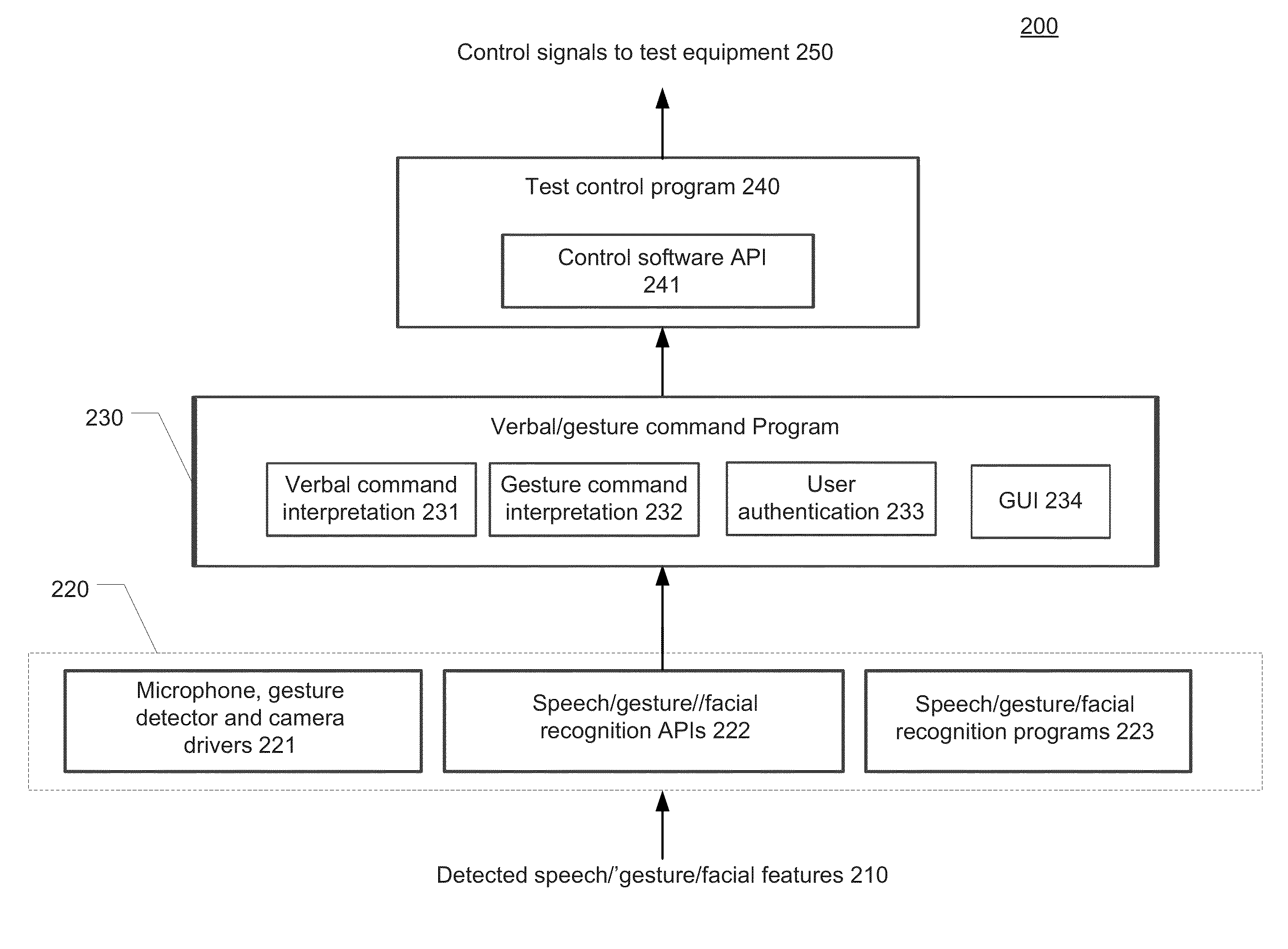

ActiveUS20140344627A1Improve user interactionEliminating operator potential mischievous unwanted behaviorFunctional testingExecution for user interfacesComputer hardwareControl software

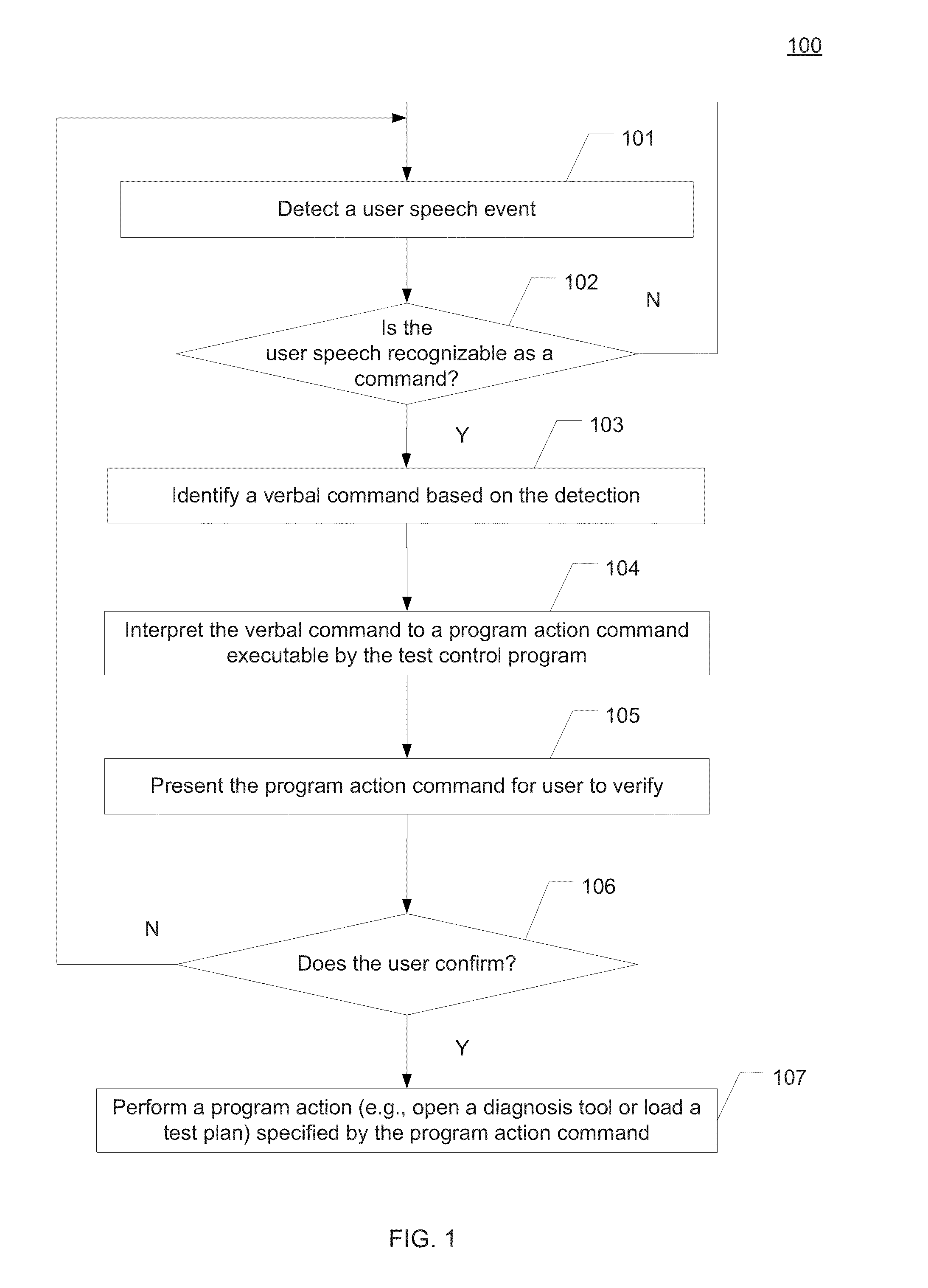

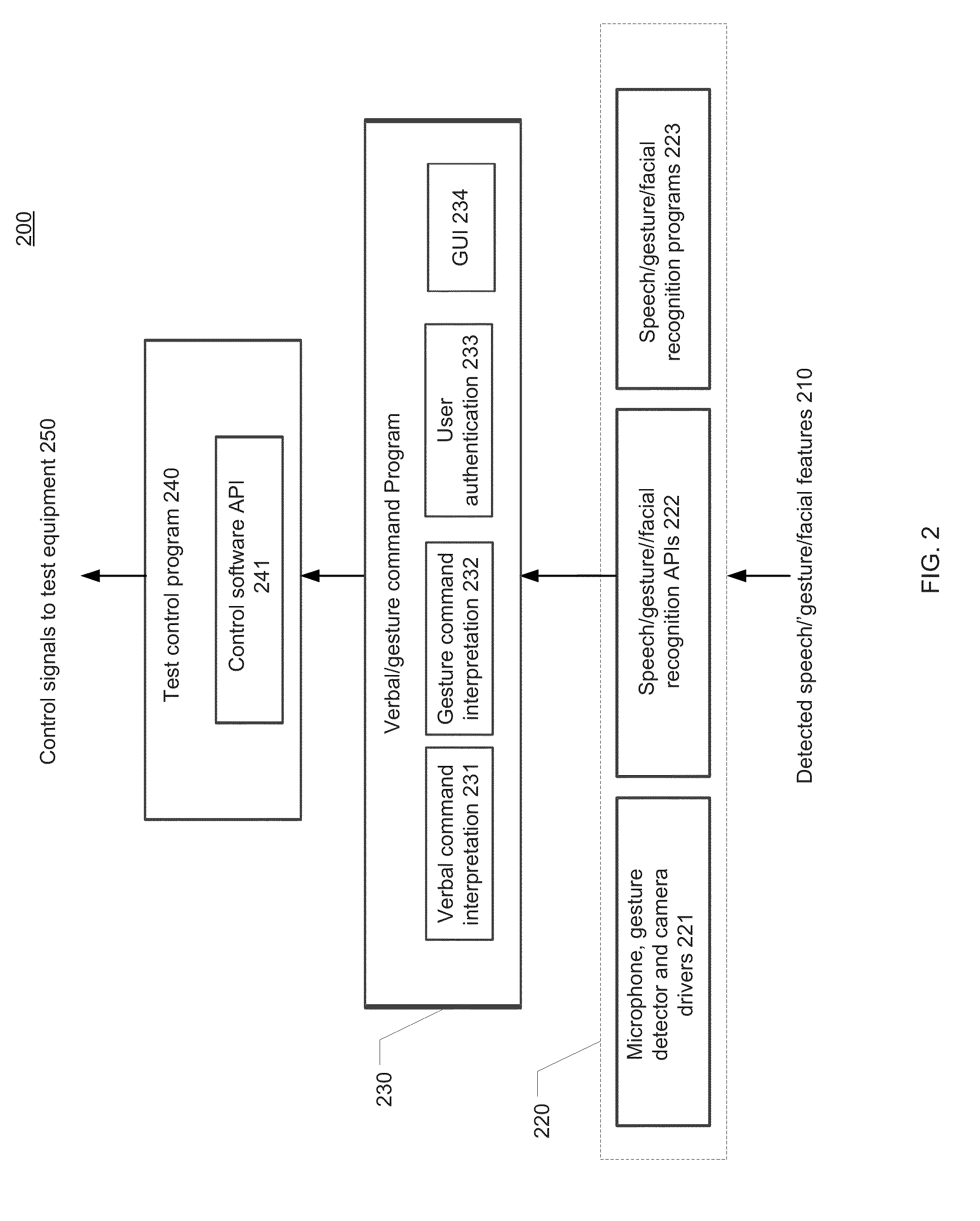

System and method of systems and methods of controlling an IC test equipment in response to verbal commands issued by test equipment users. A control apparatus according to the present disclosure includes a speech detection device operable to detect verbal commands and test control software configured to control operations of the test equipment. The control software is added with verbal command recognition capabilities. Program action commands defined in the test control software are associated with respective recognizable verbal commands. Upon a recognizable verbal command is detected, it is interpreted into the corresponding program action command which triggers the intended test program actions. The control apparatus may also have a gesture detection device, through which user gesture commands can be detected and interpreted into corresponding program actions commands.

Owner:ADVANTEST CORP

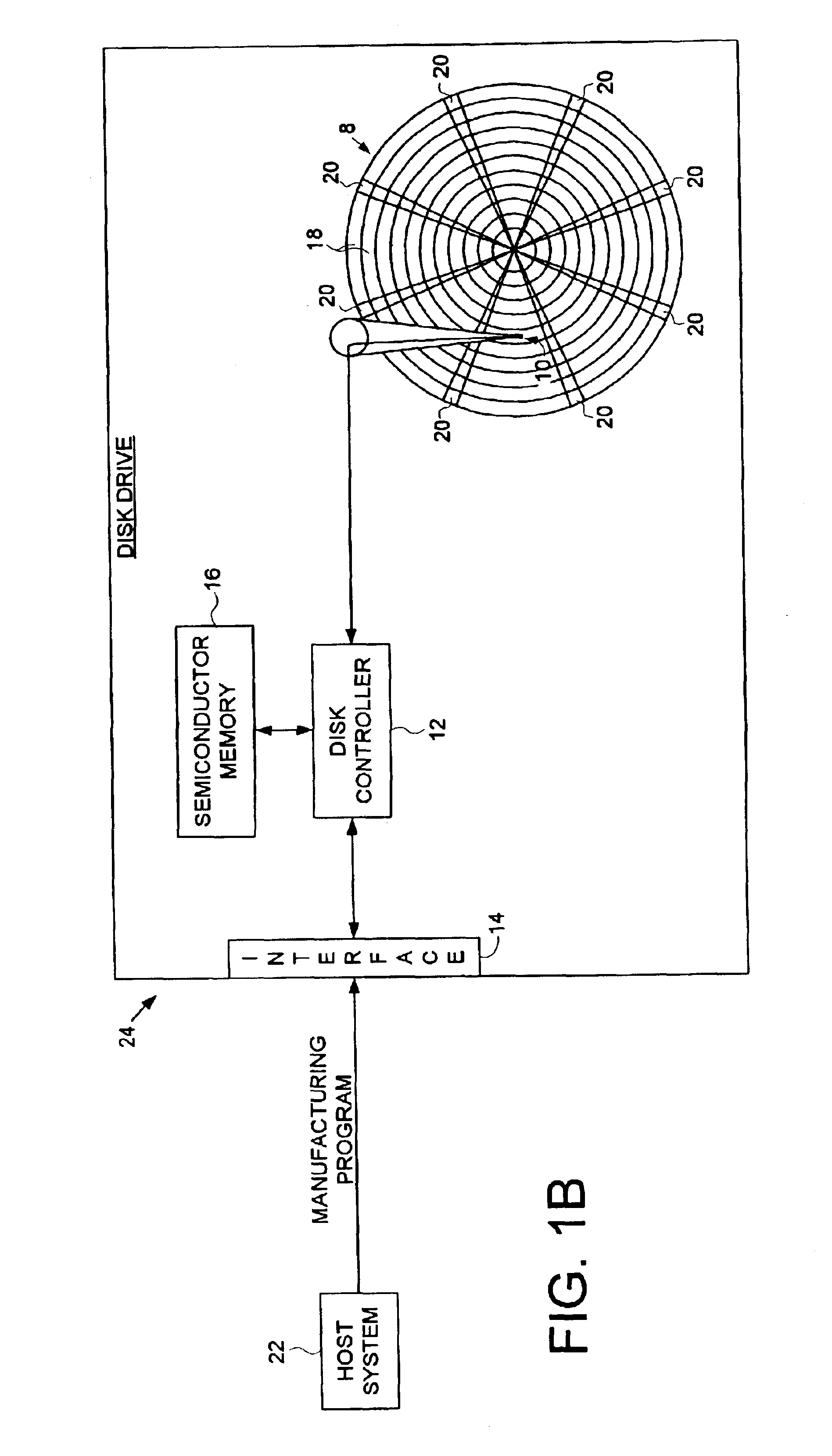

Disk drive executing a manufacturing program internally by executing disk commands through a vector

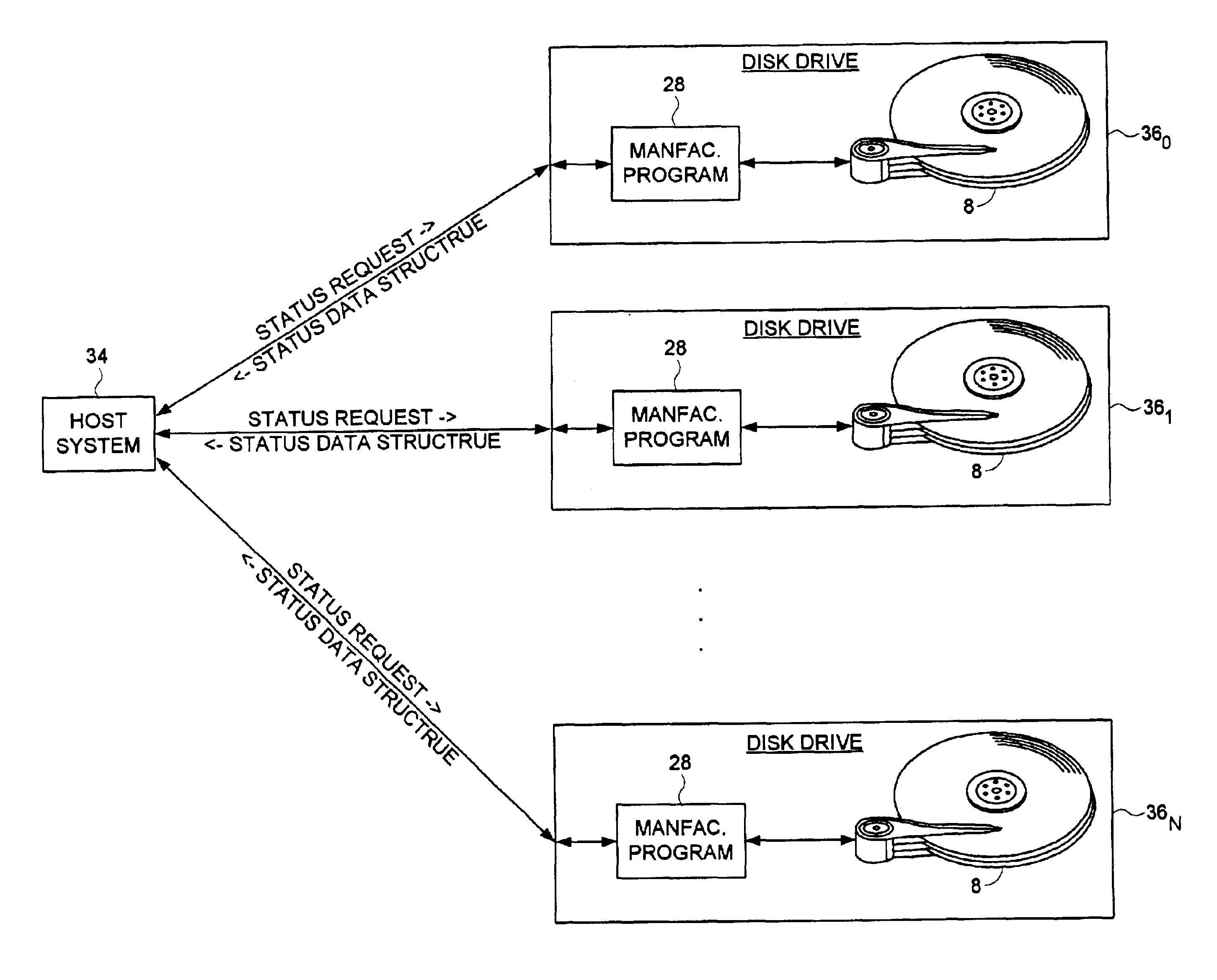

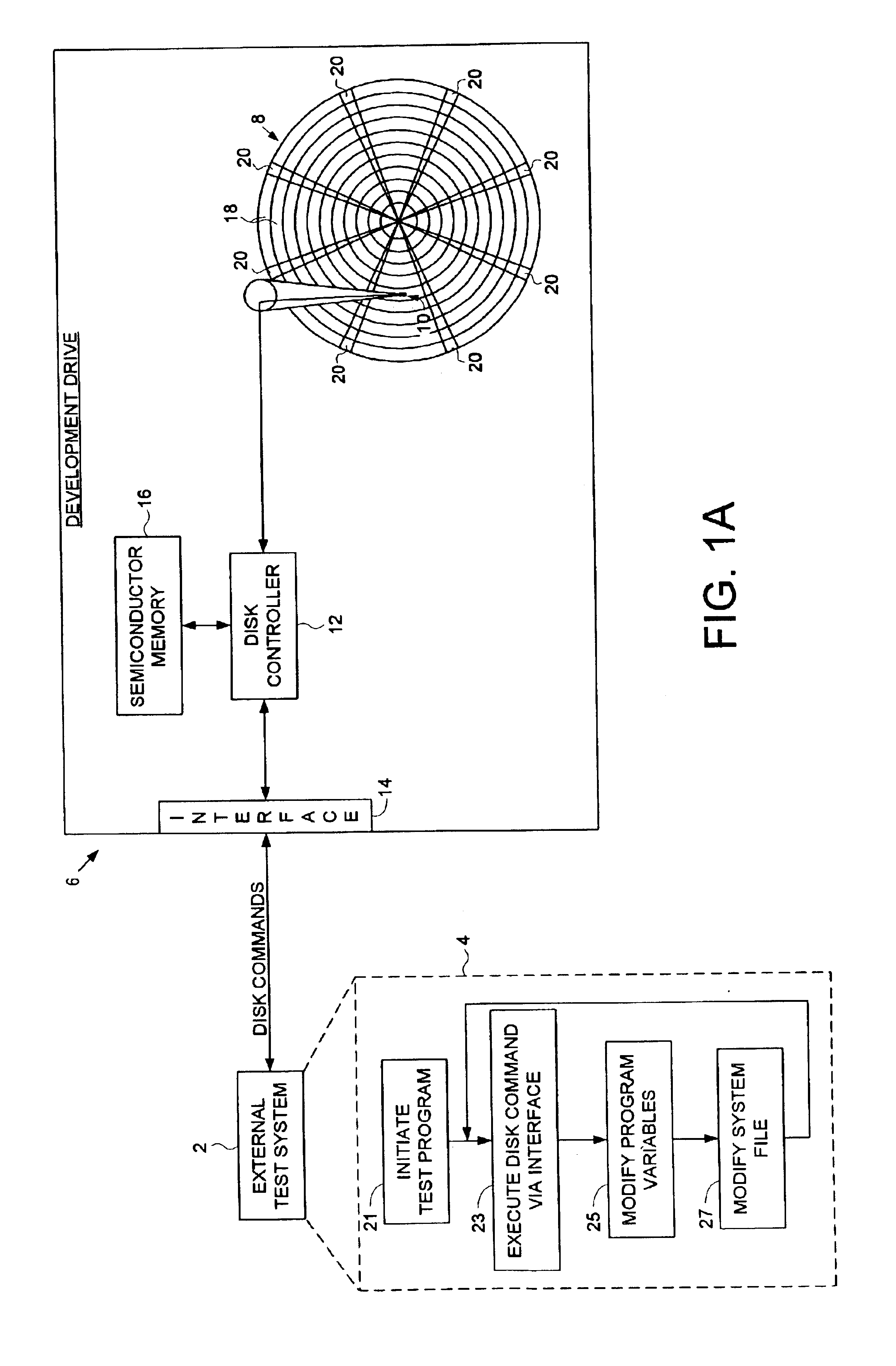

A disk drive is disclosed for executing a drive operating program and a manufacturing program during a manufacturing process. An external test system executes a test program comprising platform independent executable code segments and host interface executable code segments. The external test system for executing the host interface executable code segments to send disk commands to a development drive. The manufacturing program comprises the platform independent executable code segments of the test program and disk access executable code segments. The drive operating program comprises a disk access procedure for processing disk commands and a disk access vector for calling the disk access procedure. The disk access executable code segments of the manufacturing program execute disk commands by calling the disk access procedure of the drive operating program through the disk access vector.

Owner:WESTERN DIGITAL TECH INC

Multi-array, multi-specific electrochemiluminescence testing

Materials and methods are provided for producing patterned multi-array, multi-specific surfaces for use in diagnostics. The invention provides for electrochemiluminescence methods for detecting or measuring an analyte of interest. It also provides for novel electrodes for ECL assays. Materials and methods are provided for the chemical and / or physical control of conducting domains and reagent deposition for use multiply specific testing procedures.

Owner:MESO SCALE TECH LLC

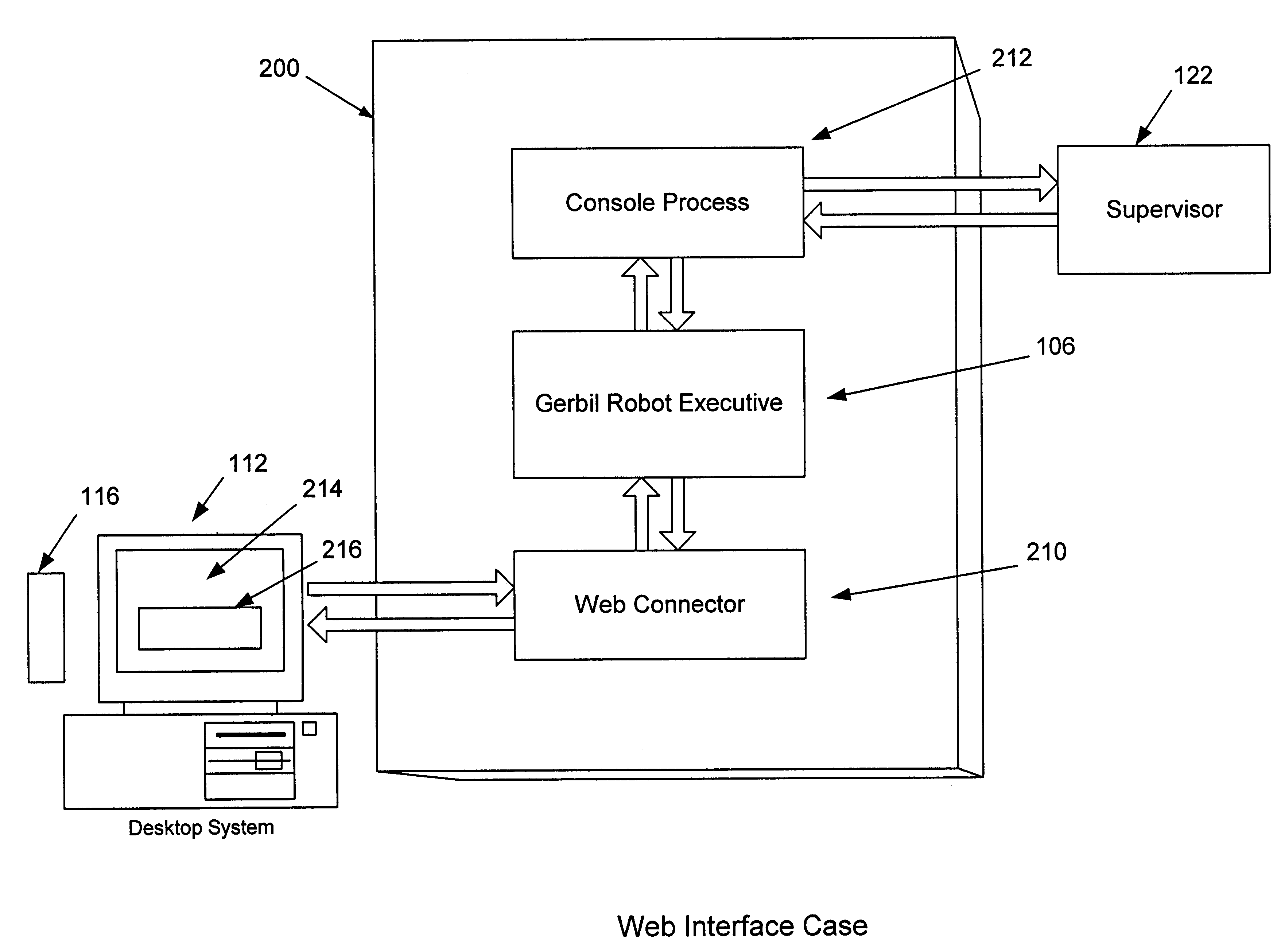

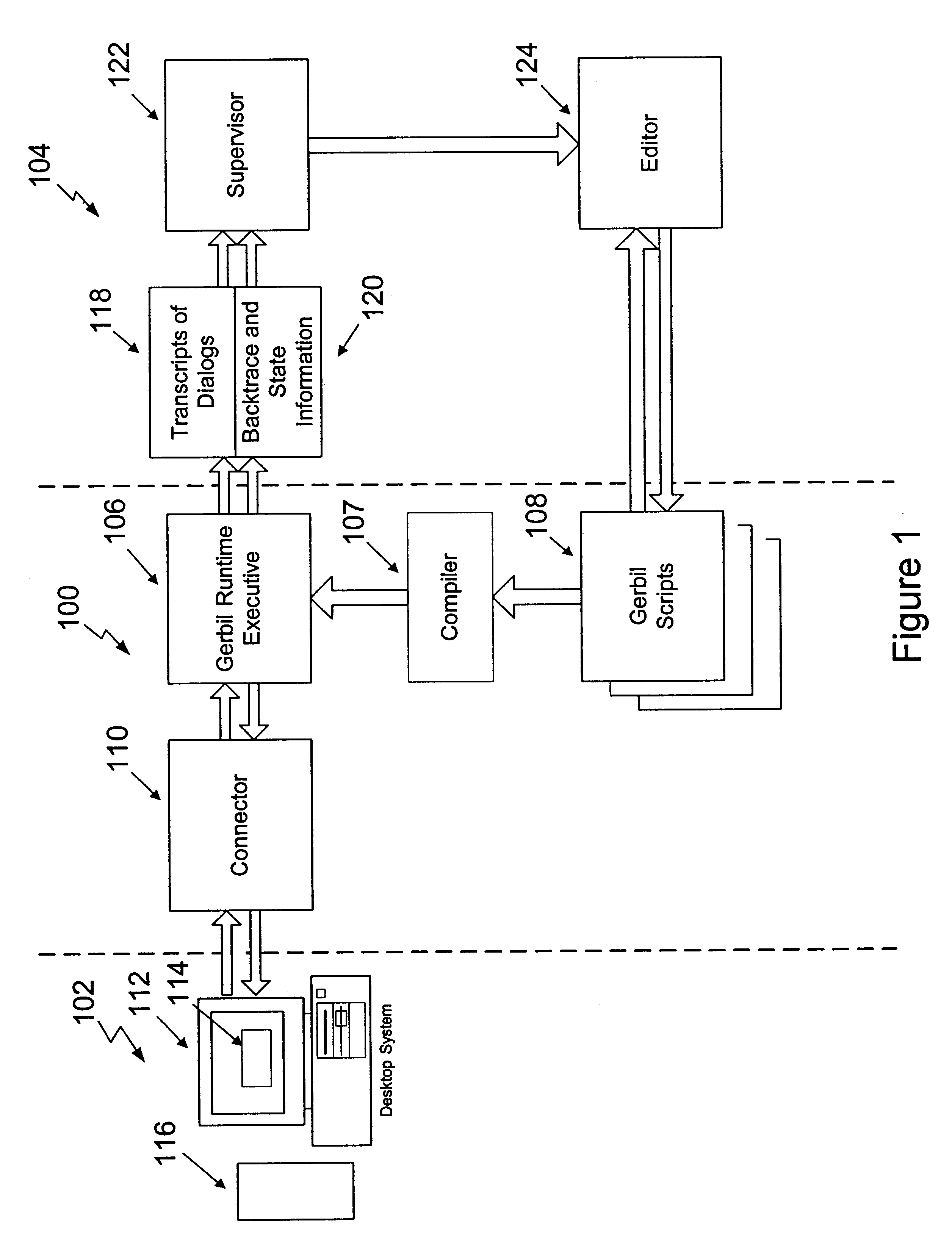

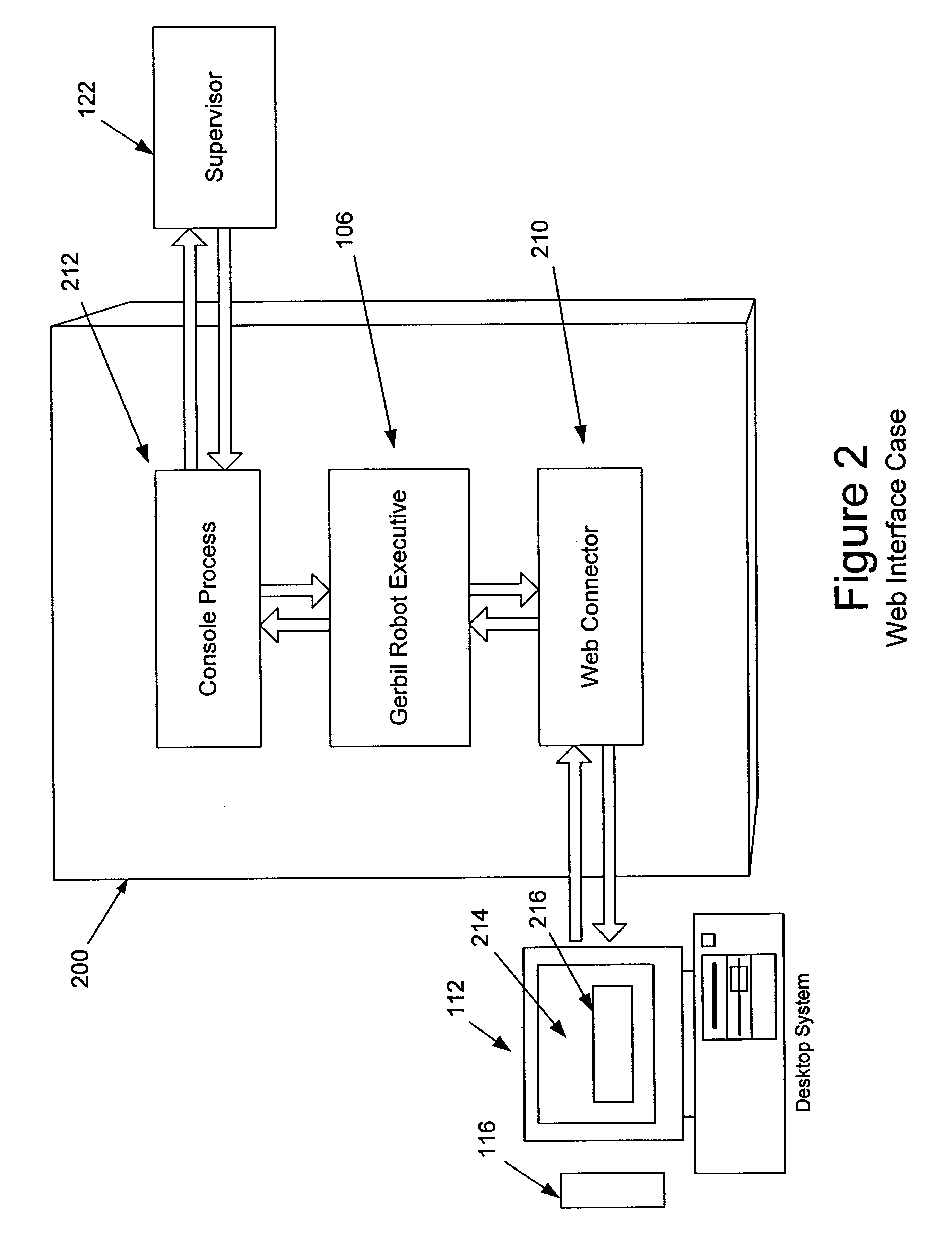

System and method for automatically verifying the performance of a virtual robot

In an automated interface program designed to interact and communicate with users, said program executing actions when a category among a predefined set of categories is activated, a method is disclosed for automatically verifying the performance of said program, the steps of said method comprising: specifying inputs under which the program should be tested; associating said inputs with conditions within categories in the program, each said condition comprising at least one response which could be given if said condition is satisfied; executing said program under at least one said input; determining whether the associated condition is satisfied upon said input; and determining whether the response associated with said condition is given upon said input. In another aspect of the present invention, the test inputs are embedded within the script itself, and specifically, within categories that can be automatically listed upon compilation of the script. Such list of test inputs can then be automatically executed to test the program. The execution of a test input can be used to check whether the test input activated the category in which the test input is embedded. The response given upon execution of a test input can then determine whether other categories are erroneously activated; or whether inputs, other than the test input, erroneously activate the category associated with the test input.

Owner:MICRO FOCUS LLC

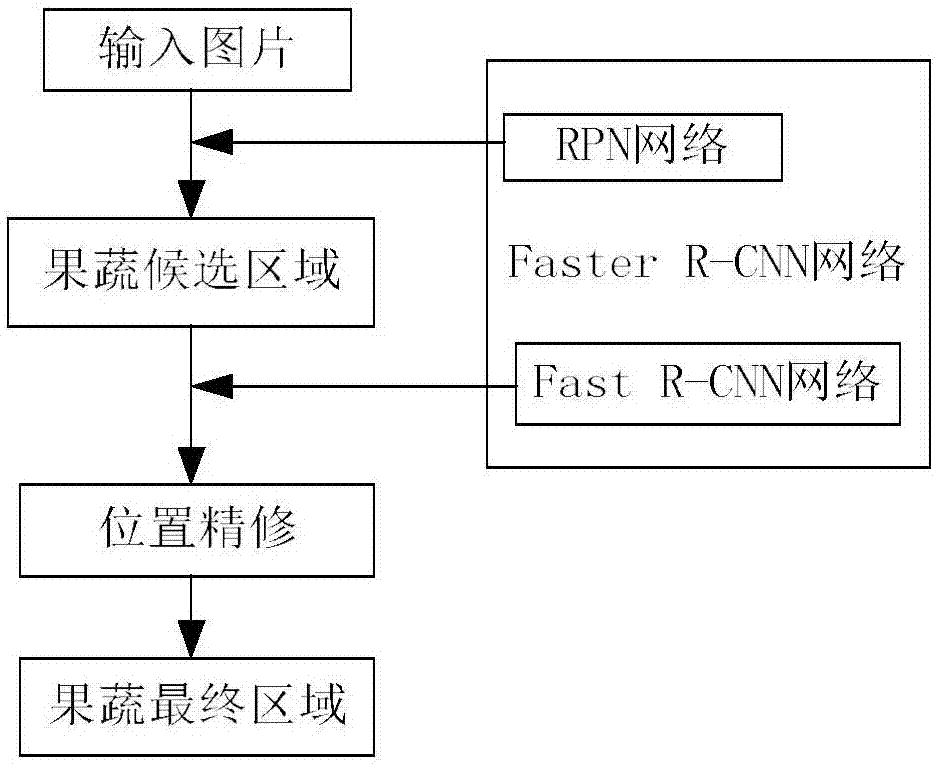

Fruit and vegetable detection method based on deep learning

InactiveCN107451602AImprove detection accuracyGuaranteed qualityCharacter and pattern recognitionAngular pointTest tests

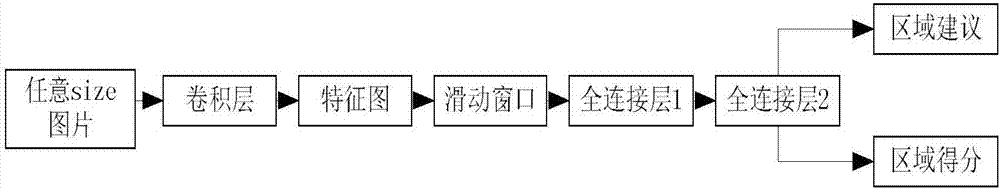

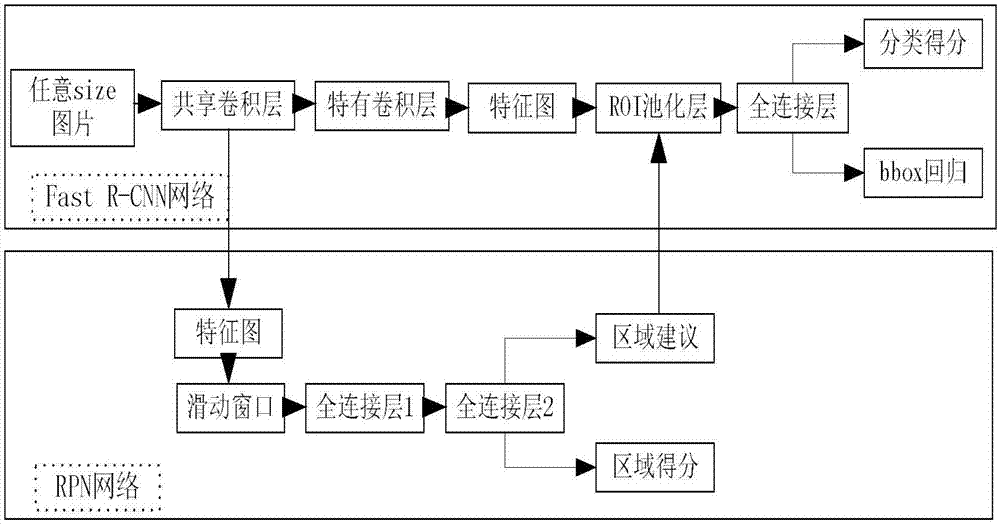

The invention discloses a fruit and vegetable detection method based on deep learning. The method comprises the following steps that: S1: firstly, preprocessing data, and carrying out manual calibration on an original picture in advance to obtain a segmentation tag, wherein the calibration means the coordinates of the left upper angular point and the right lower angular point of a target frame in the original picture, and the tag is used for judging whether a target in each calibration frame is a fruit and vegetable and determining the category of the fruit and vegetable; S2: secondly, training the data, taking the original picture and the picture tag as a training set of a deep learning neural network, and combining with a RPN (Region Proposal Network) and a Fast R-CNN to train the data to obtain a final fruit and vegetable detection model; and S3: finally, testing test data, calling a final fruit and vegetable detection model and a test program, carrying out fruit and vegetable detection on a test picture, and analyzing a final fruit and vegetable detection model effect through the observation of a test result.

Owner:ZHEJIANG UNIV OF TECH

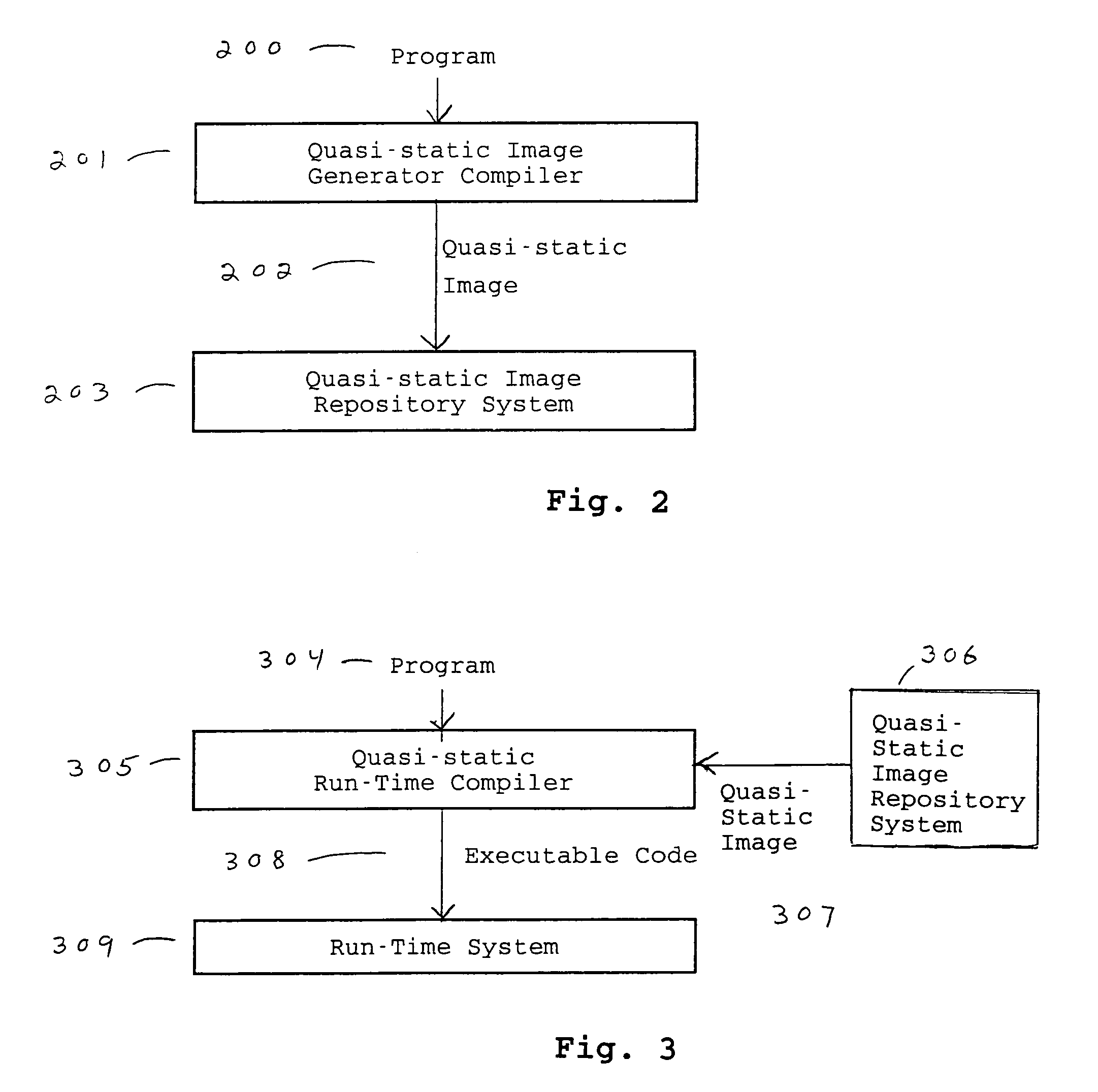

Method for compiling program components in a mixed static and dynamic environment

InactiveUS6973646B1Simple methodReduce the amount requiredUser identity/authority verificationProgram controlProgramming languageDynamic compilation

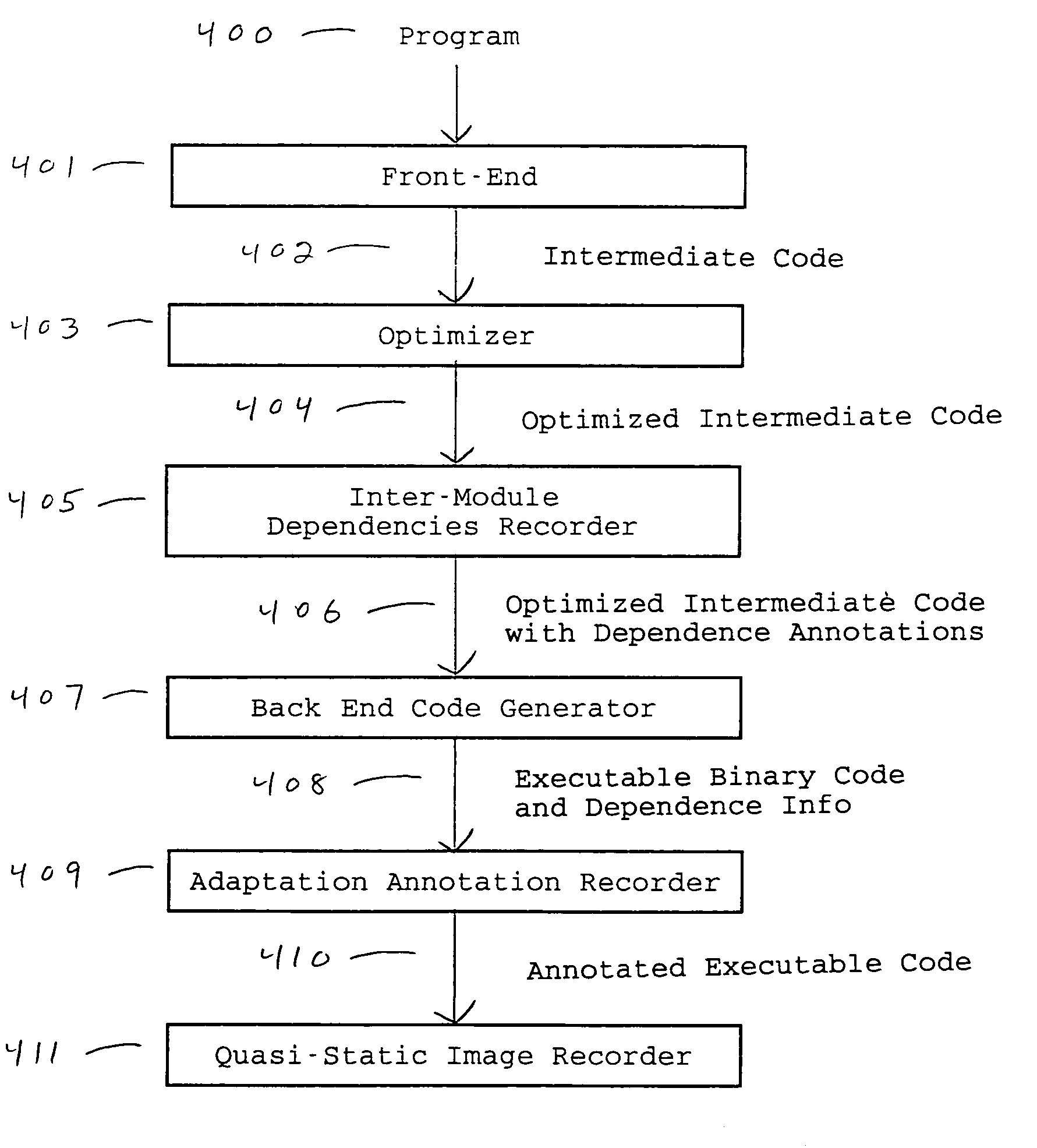

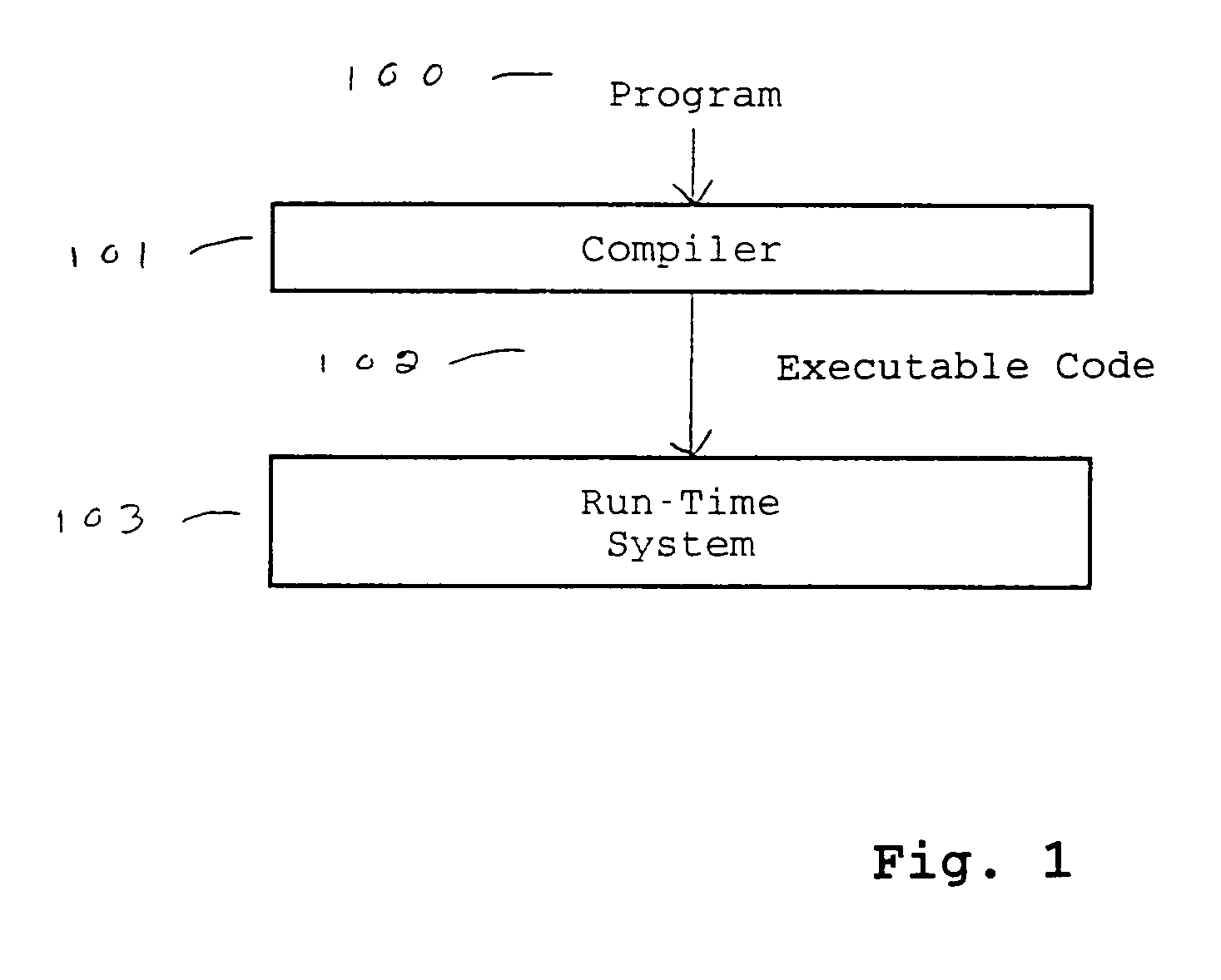

This invention describes a method and several variants for compiling programs or components of programs in a mixed static and dynamic environment, so as to reduce the amount of time and memory spent in run-time compilation, or to exercise greater control over testing of the executable code for the program, or both. The invention involves generating persistent code images prior to program execution based on static compilation or dynamic compilation from a previous run, and then, adapting those images during program execution. We describe a method for generating auxiliary information in addition to the executable code that is recorded in the persistent code image. Further, we describe a method for checking the validity of those code images, adapting those images to the new execution context, and generating new executable code to respond to dynamic events, during program execution. Our method allows global interprocedural optimizations to be performed on the program, even if the programming language supports, or requires, dynamic binding. Variants of the method show how one or several of the features of the method may be performed. The invention is particularly useful in the context of implementing Java Virtual Machines, although it can also be used in implementing other programming languages.

Owner:IBM CORP

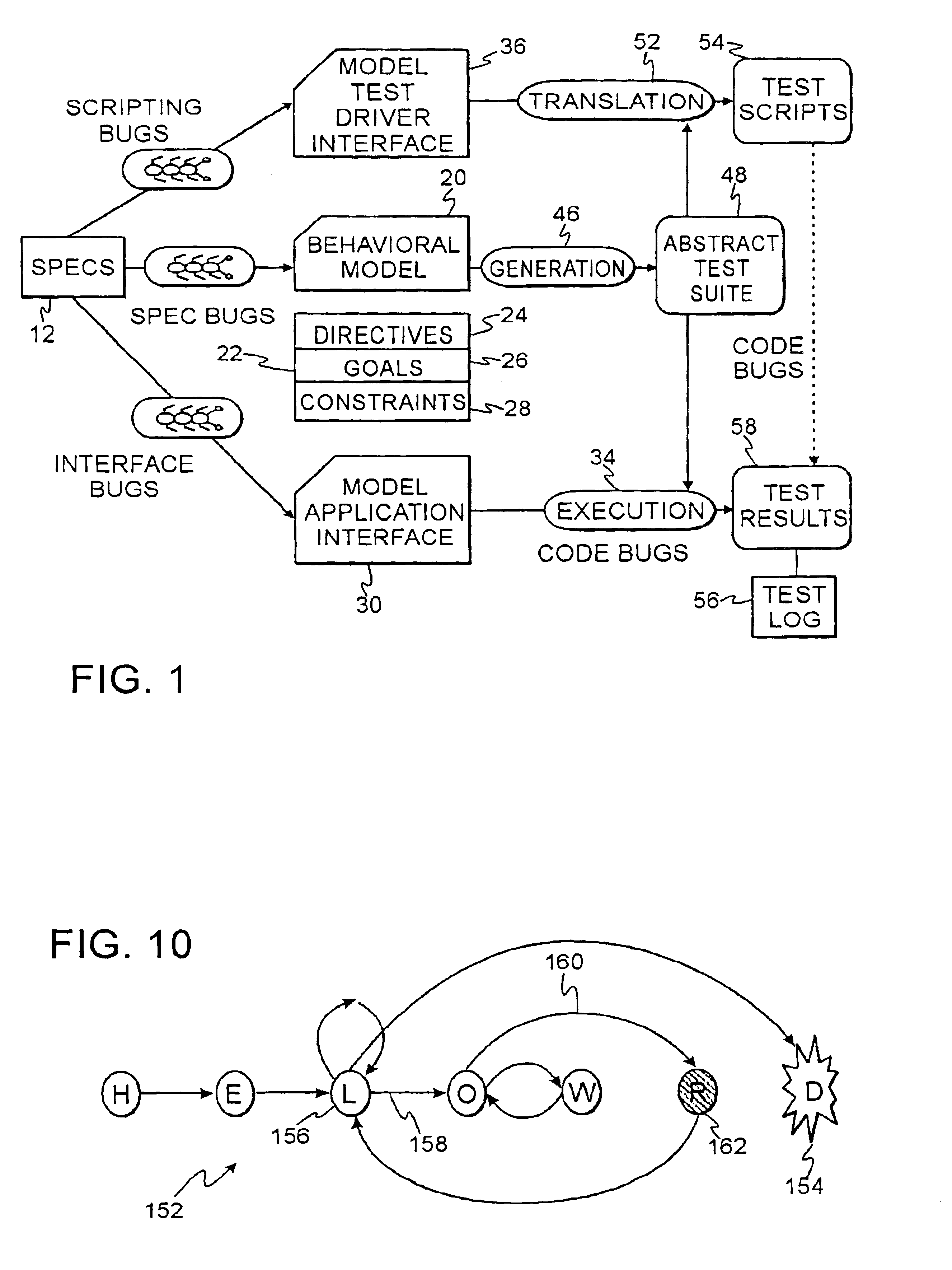

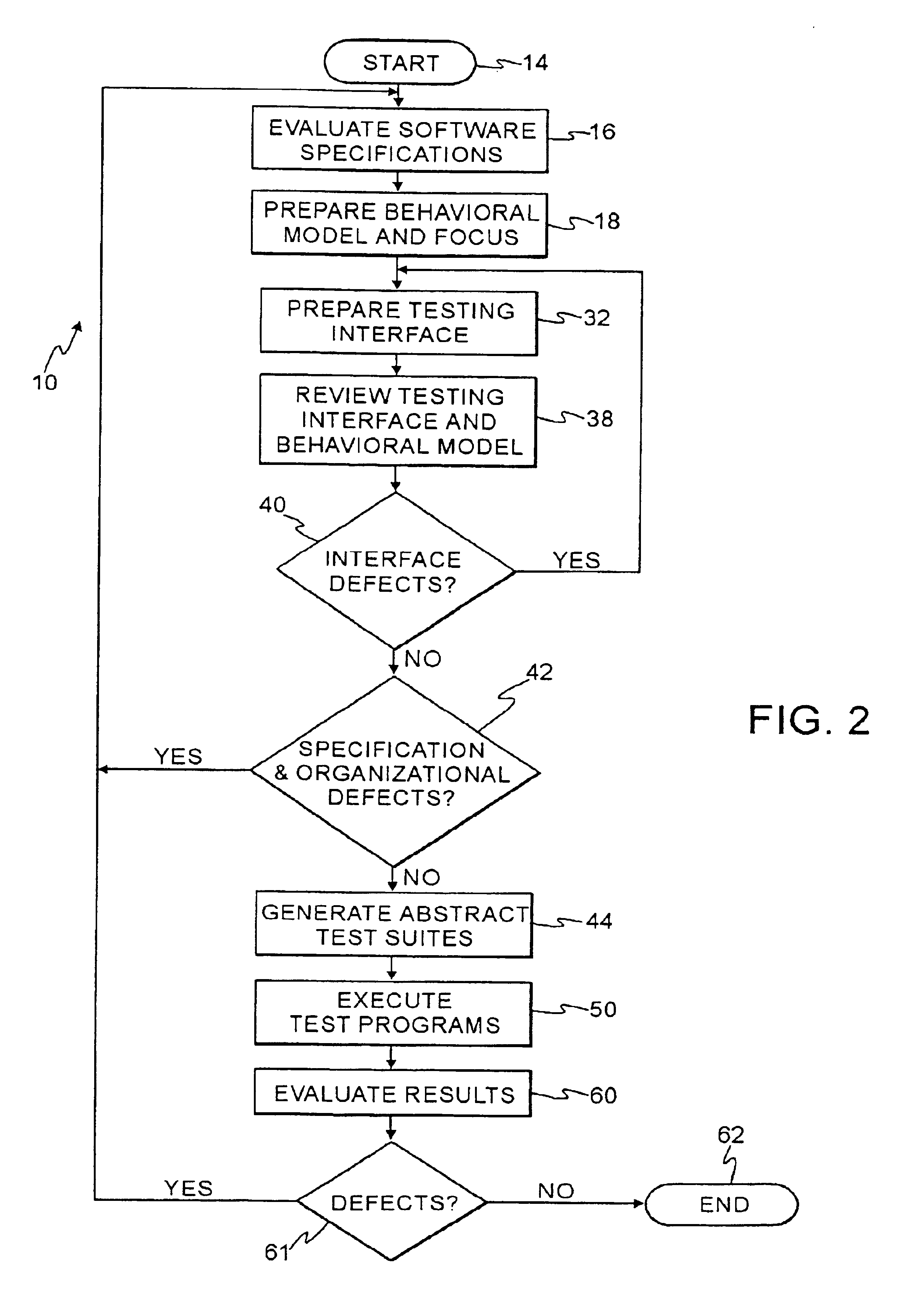

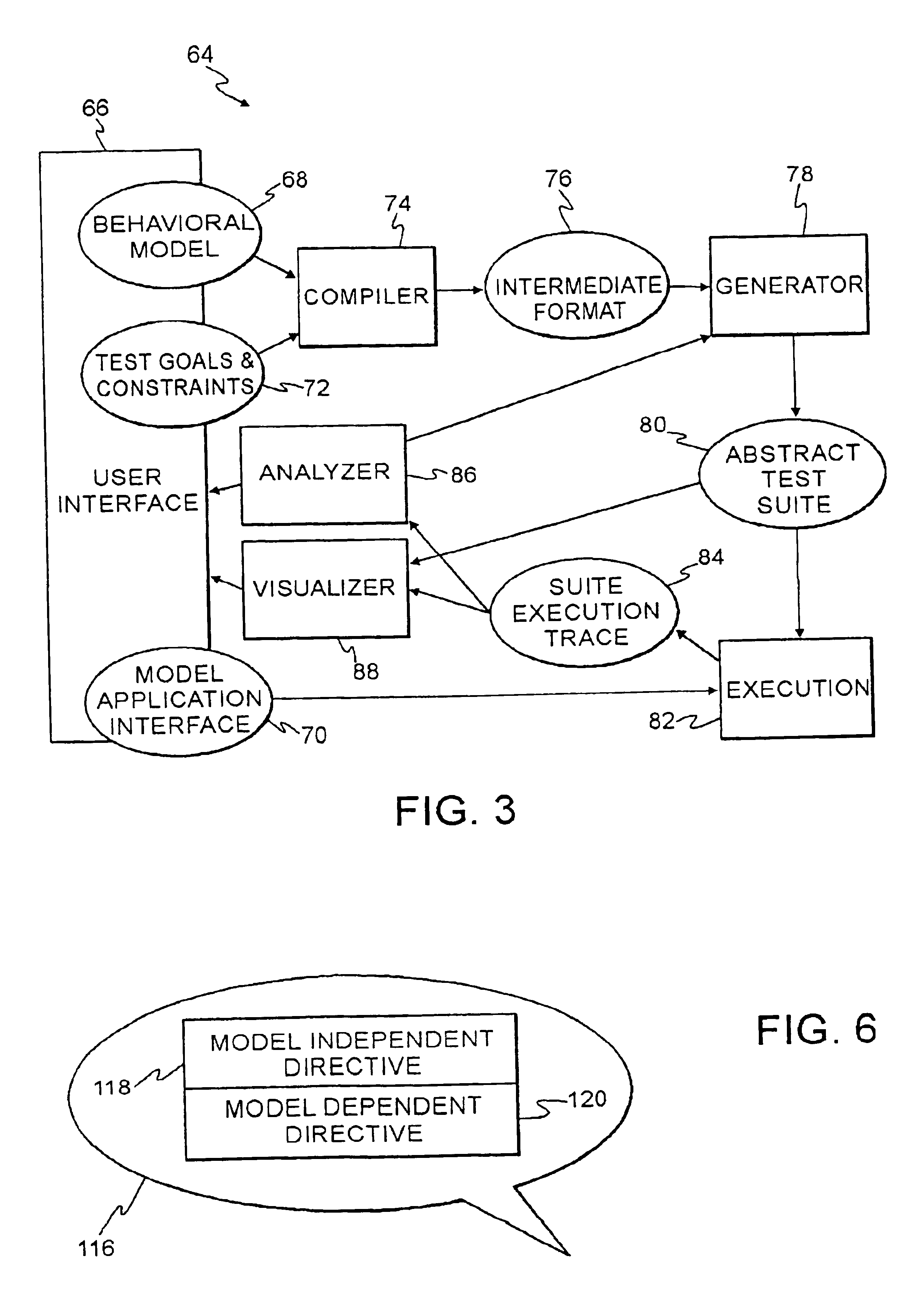

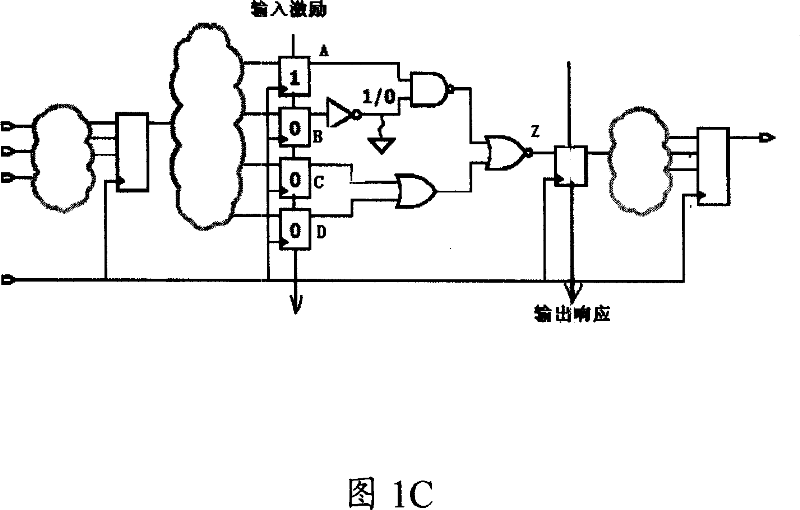

Technique using persistent foci for finite state machine based software test generation

InactiveUS6944848B2Reduce in quantitySoftware testing/debuggingSpecific program execution arrangementsTest suiteTheoretical computer science

A system for automatic generation of test programs employs test generation foci linked to a finite state machine behavioral model of a software application under test to produce abstract test suites that are executed by an execution engine. The foci include directive expressions that tag coverage variables of the behavioral model. The execution engine operates until the tagged coverage variables have assumed all their possible values. Both the behavioral models and the foci are archivable and can be retrieved and reused independently.

Owner:IBM CORP

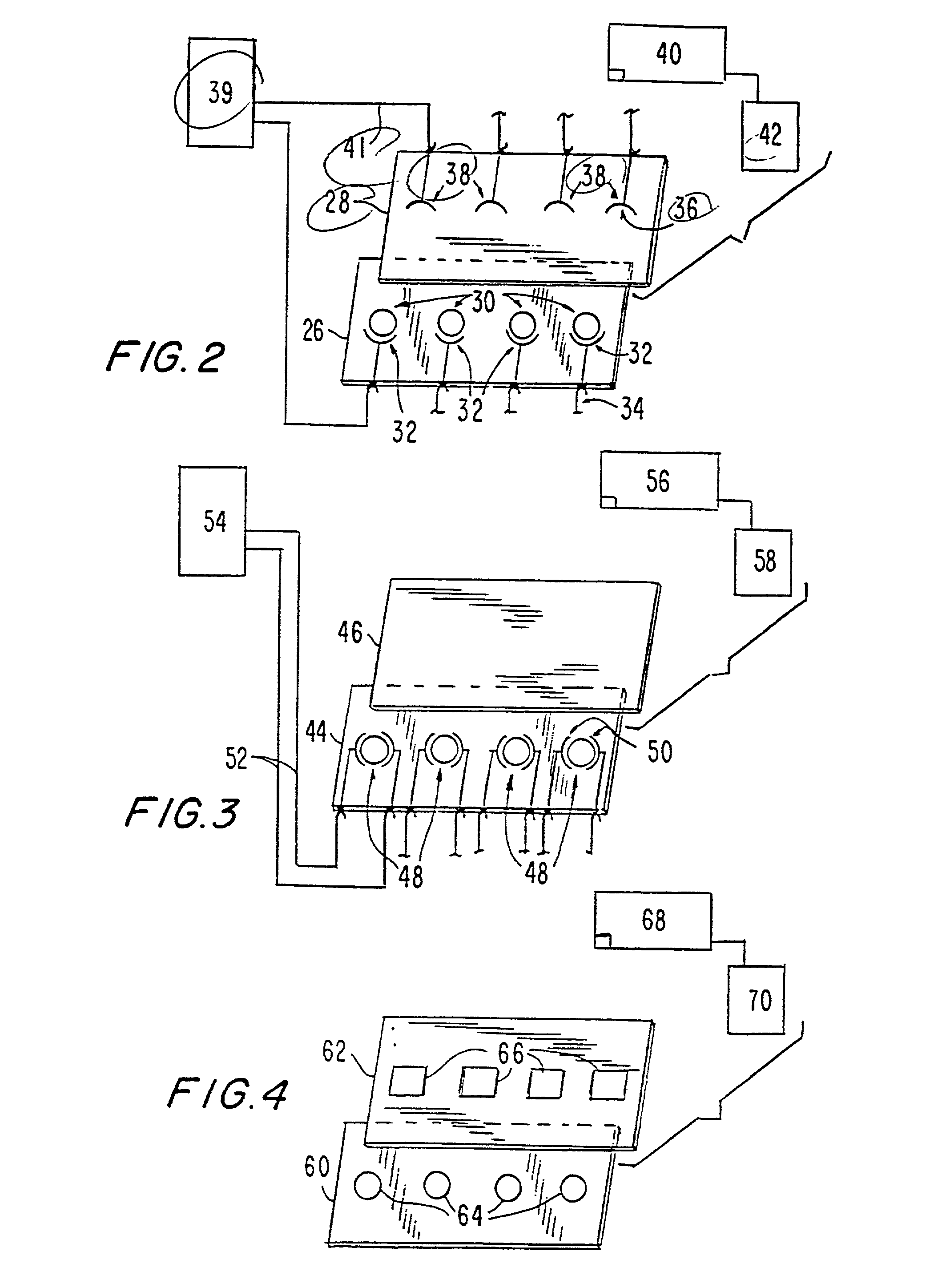

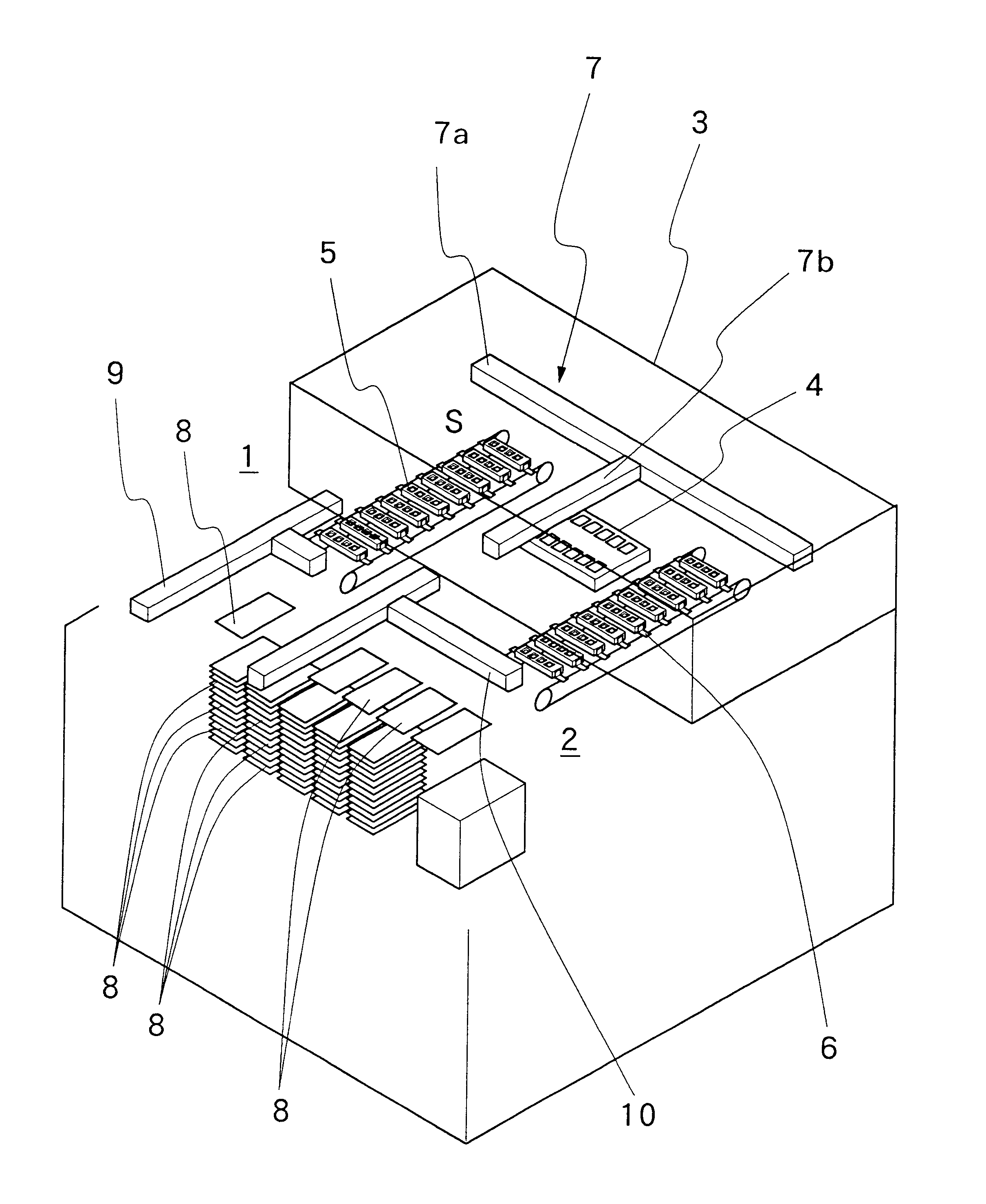

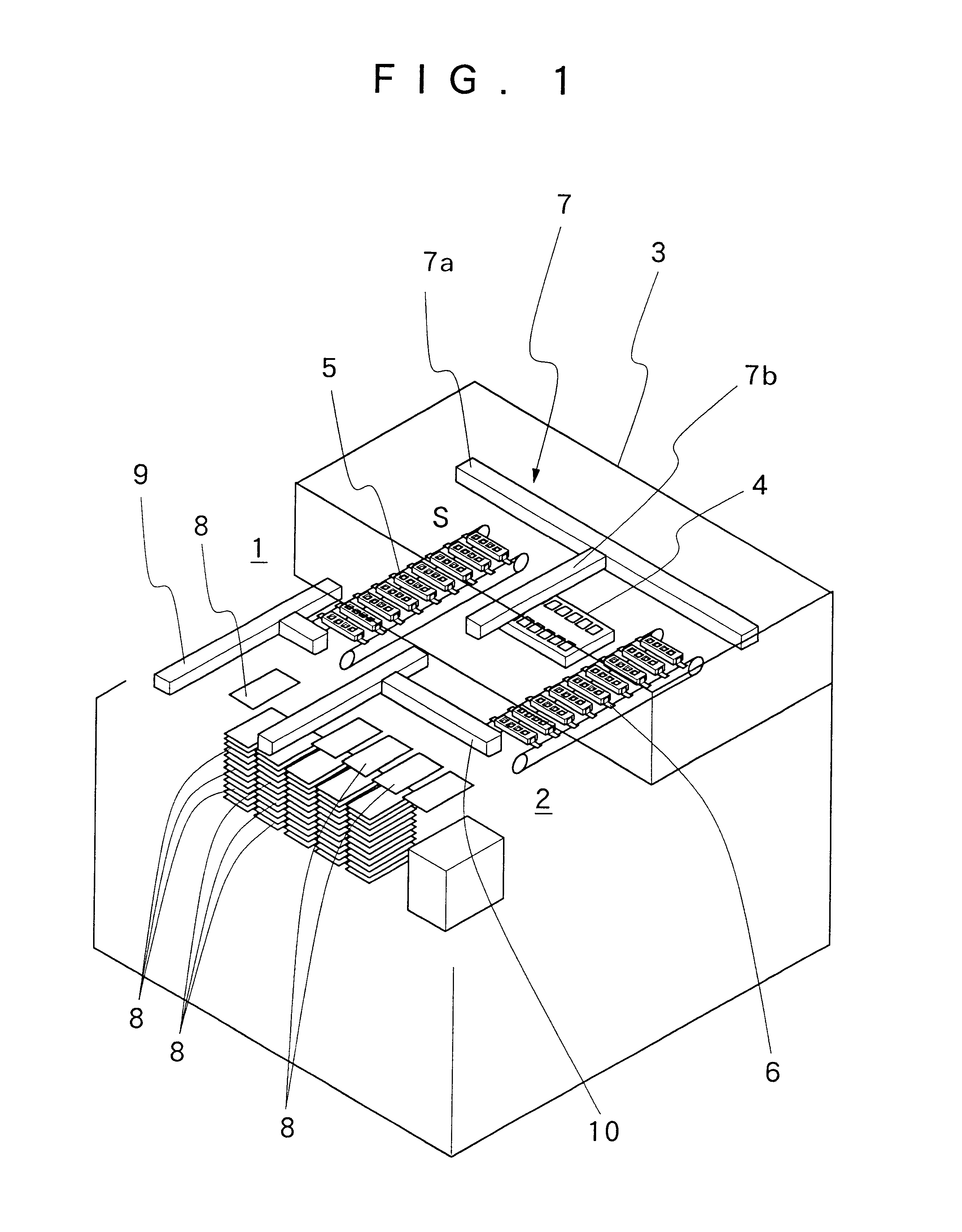

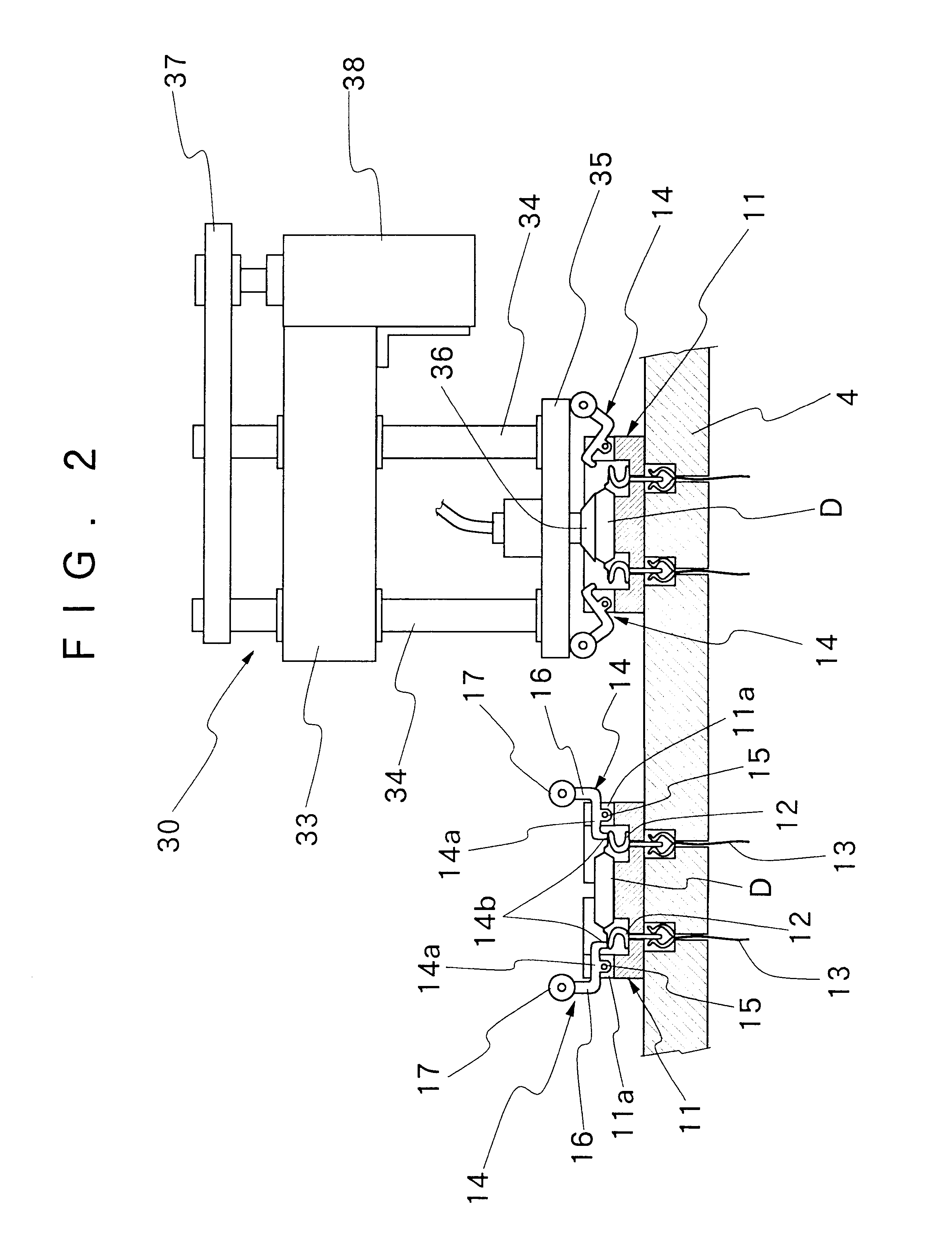

Method and apparatus for testing IC device

InactiveUS6515470B2Semiconductor/solid-state device testing/measurementDigital data processing detailsElectricityEngineering

For testing electrical properties of packaged IC devices, there is provided an apparatus which includes a test board which is located at a testing station and provided with a plural number of contacting sockets for connecting individual IC devices to an IC tester separately and independently of each other, a loader which is located at a loading station and adapted to feed untested IC devices toward the test board, an unloader which is located at an unloading station and adapted to discharge tested IC devices from the test board at the testing station, and a device transfer mechanism which is movable across the testing station to transfer untested IC devices from the loader to the test board and also to transfer tested IC devices from the test board to the unloader. Upon detecting completion of a test on one of IC devices in one socket of the test board, a fresh untested IC device is transferred to the testing station to replace the tested IC device. As soon as the fresh IC device is set in position in that socket, execution of a test program is started with respect to that socket on the test board.

Owner:HITACHI ELECTRONICS ENG CO LTD

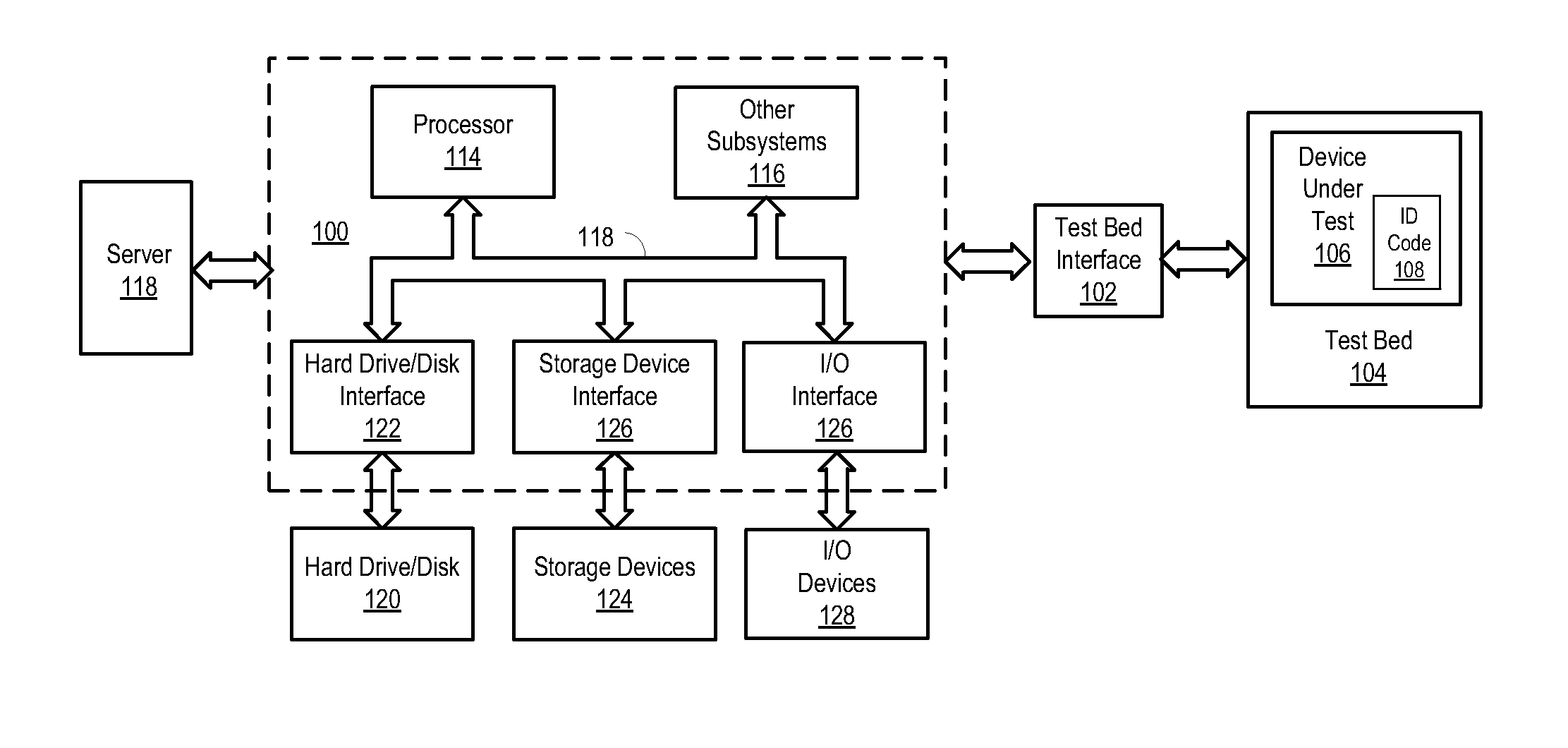

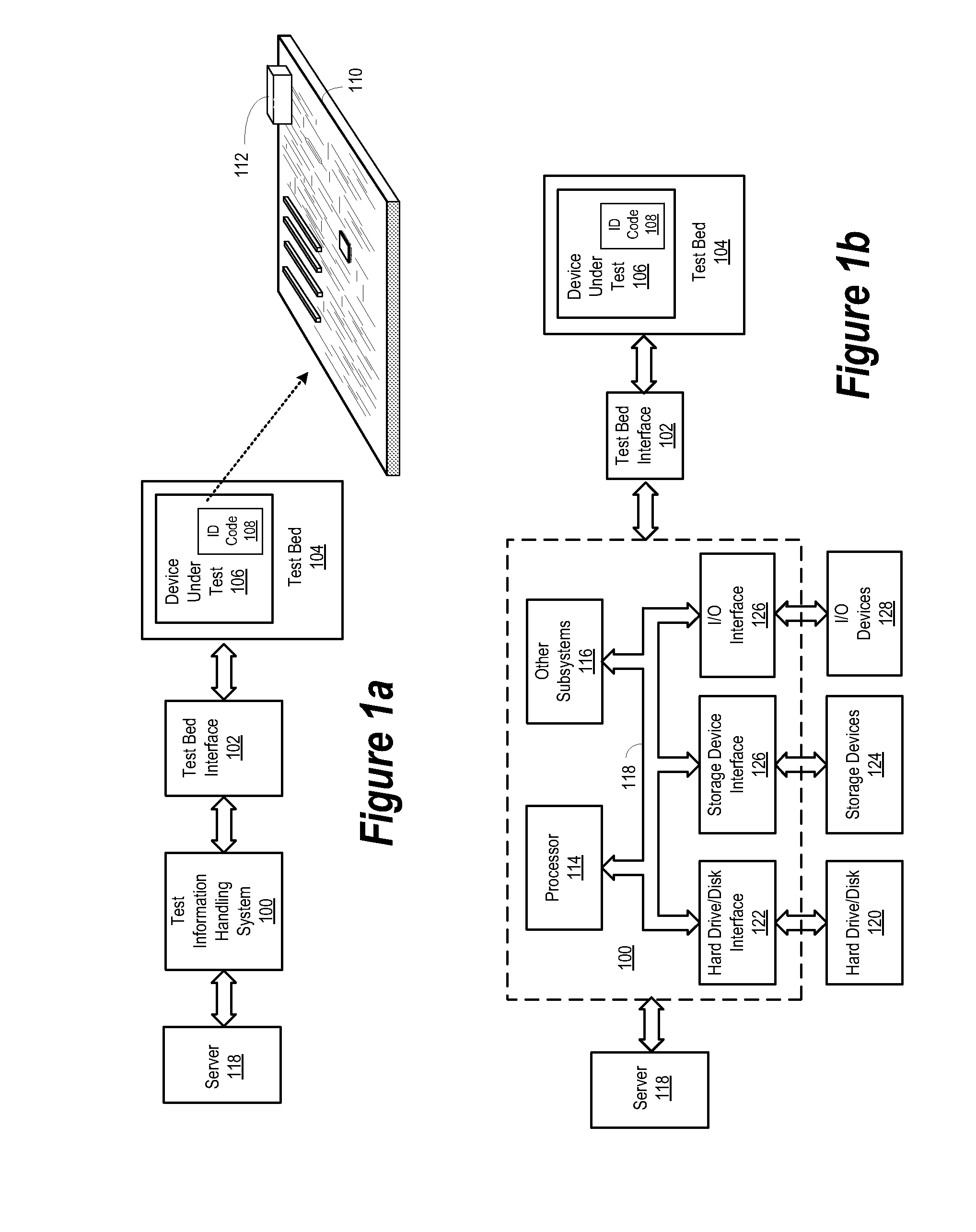

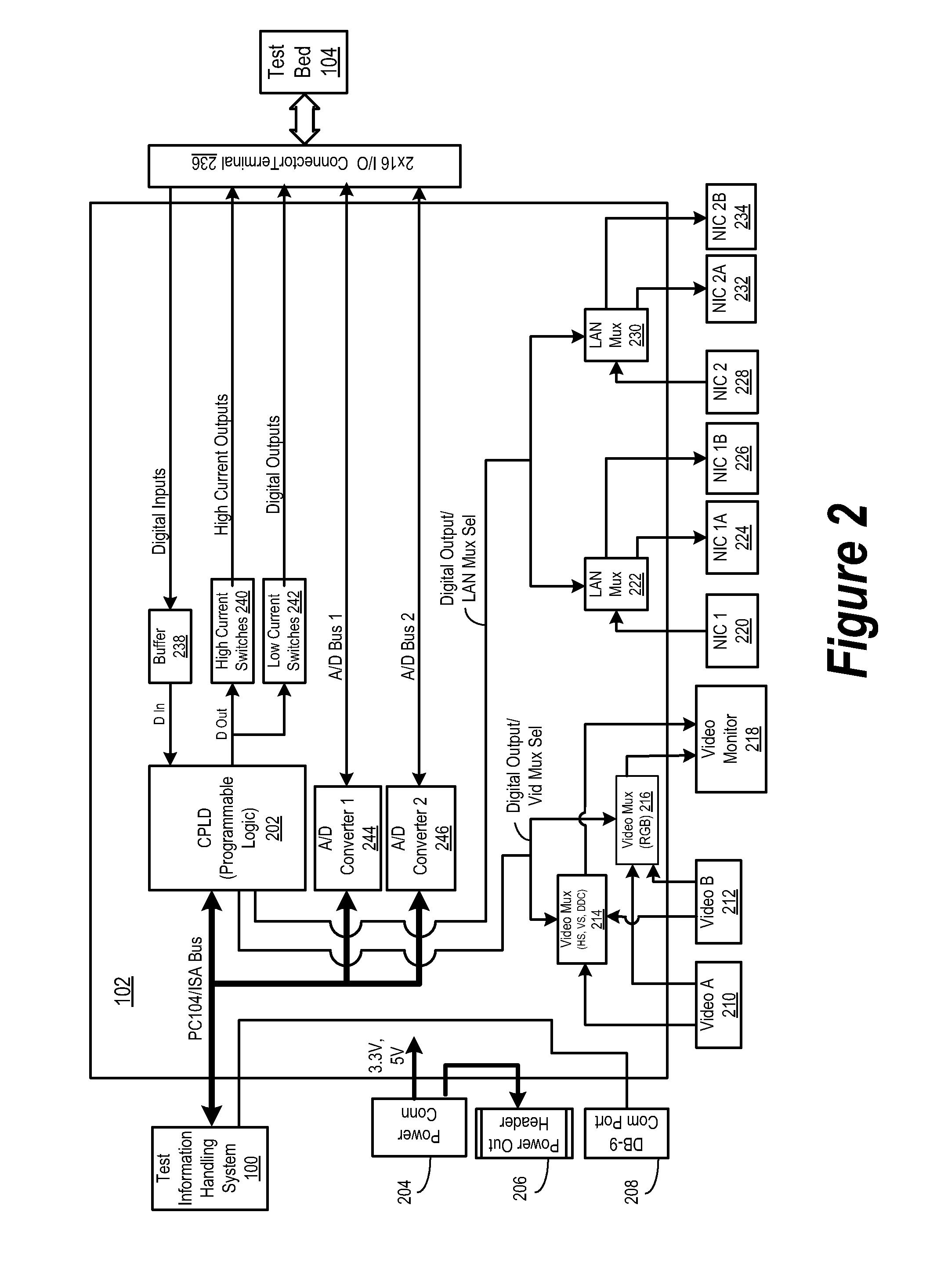

System and method for testing information handling system components

InactiveUS20080262759A1Quickly and easily swappedElectrical testingSpecial data processing applicationsControl signalHandling system

A system and method is disclosed for testing components used in the manufacture of information handling systems. In embodiments of the invention, a device-under-test (DUT) comprises a DUT identifier code. The DUT is operably coupled to a test bed. An information handling system is operable to use the identifier code to select and execute a predetermined test program to generate a plurality of test commands. A test bed interface is operable to receive the test commands and to generate a plurality of test control signals therefrom to perform a predetermined set of tests of said DUT.

Owner:DELL PROD LP

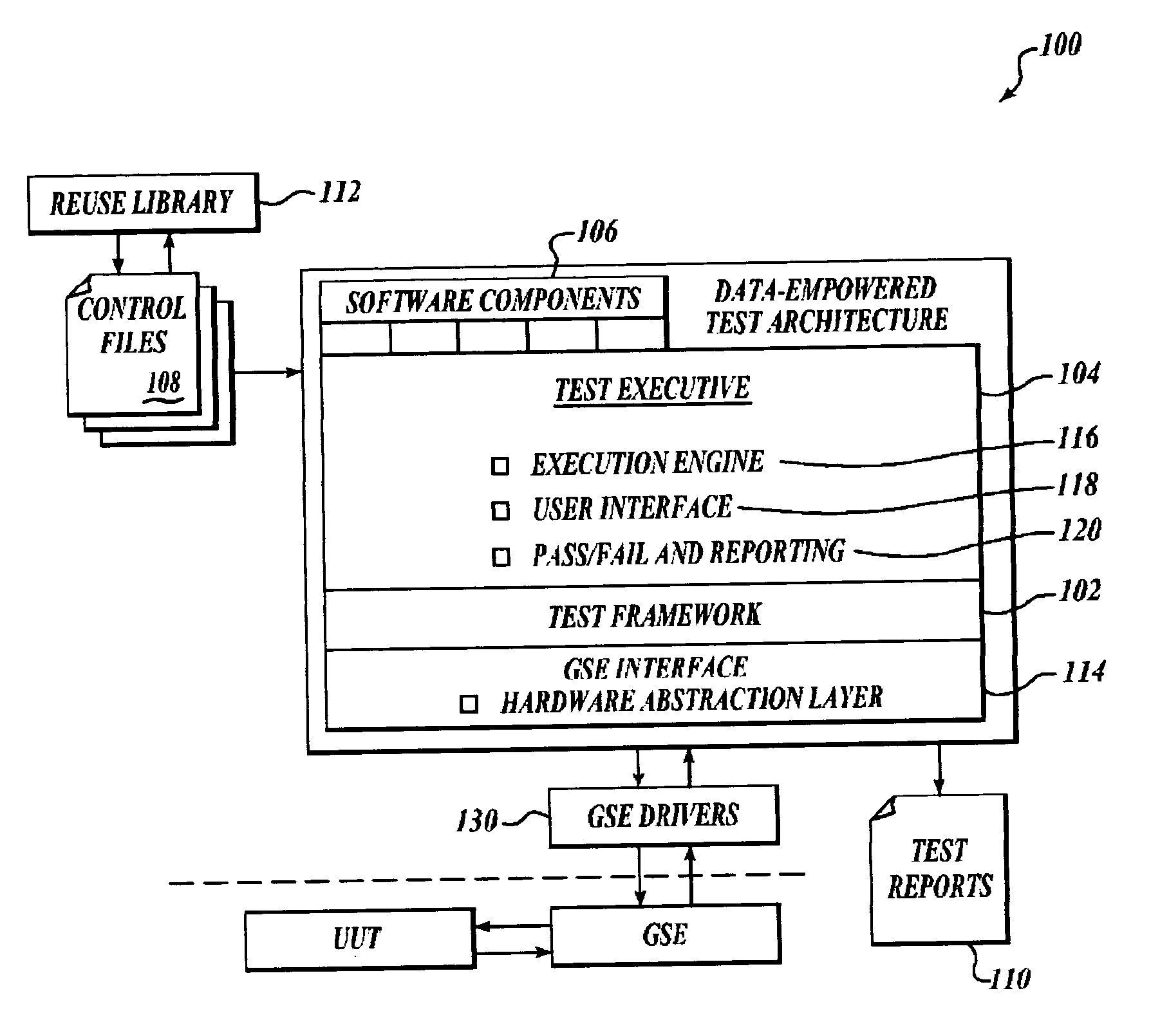

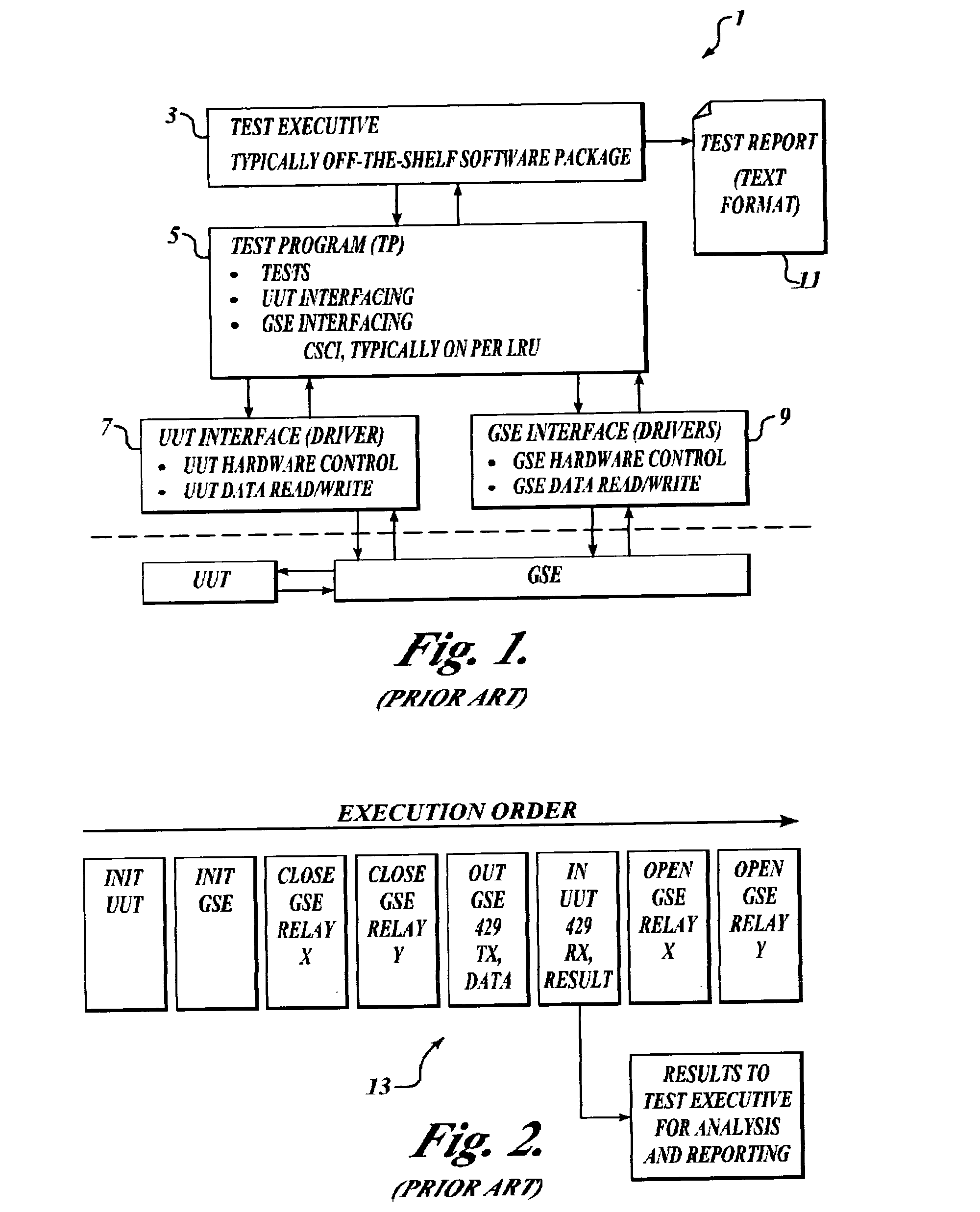

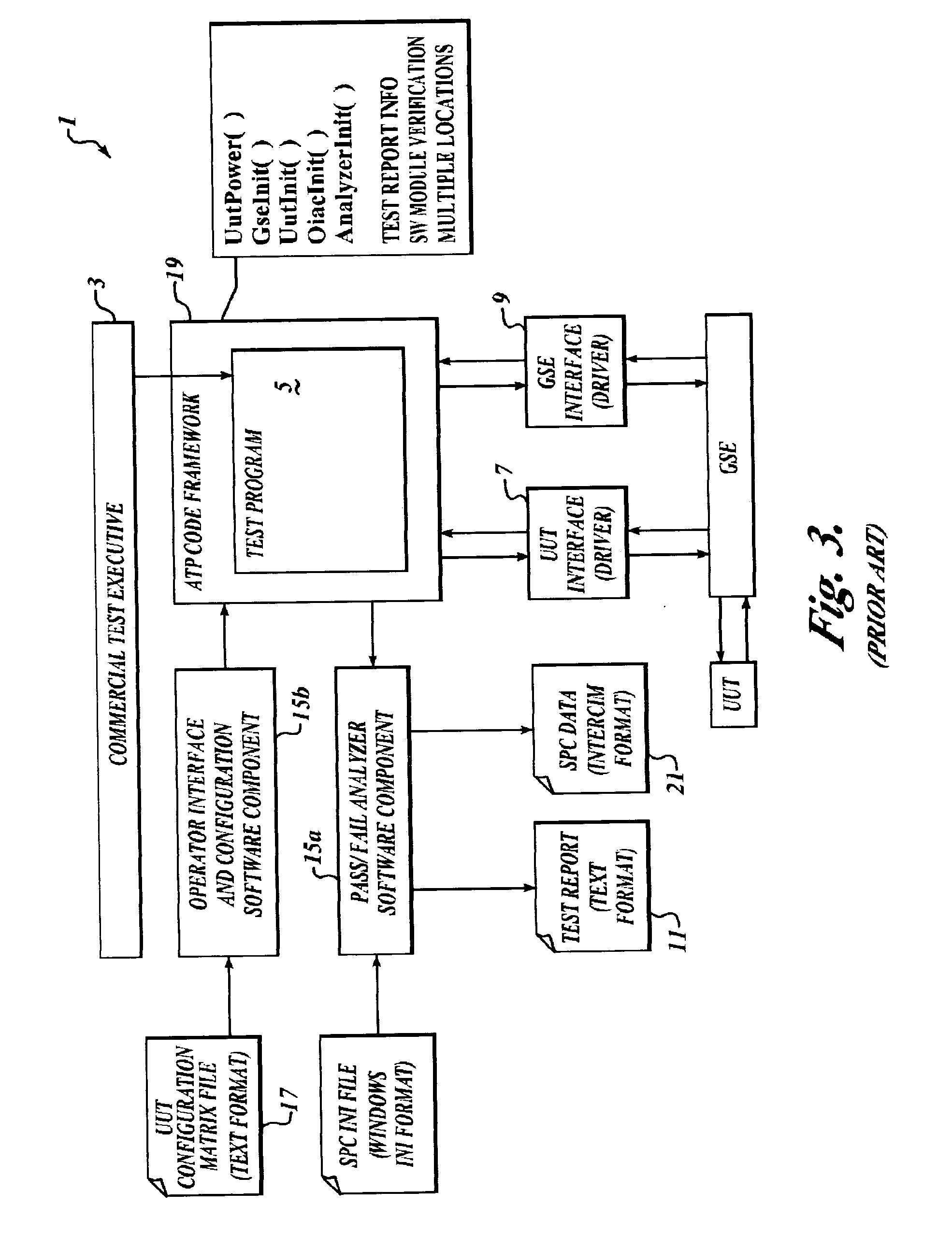

Data empowered laborsaving test architecture

InactiveUS20050097515A1Easy to operateOvercome limitationsError detection/correctionSpecific program execution arrangementsComputer hardwareTest frame

A test program development method embodied in a data-empowered test program architecture including a test executive software module; a test framework software module having externally configurable generic software code and being coupled for interaction with the test executive software module; a plurality of software components in a software components module coupled for interaction with the test framework software module and structured for outputting one or more test reports; and one or more external control files coupled for configuring the generic software code of the test framework software module.

Owner:HONEYWELL INT INC

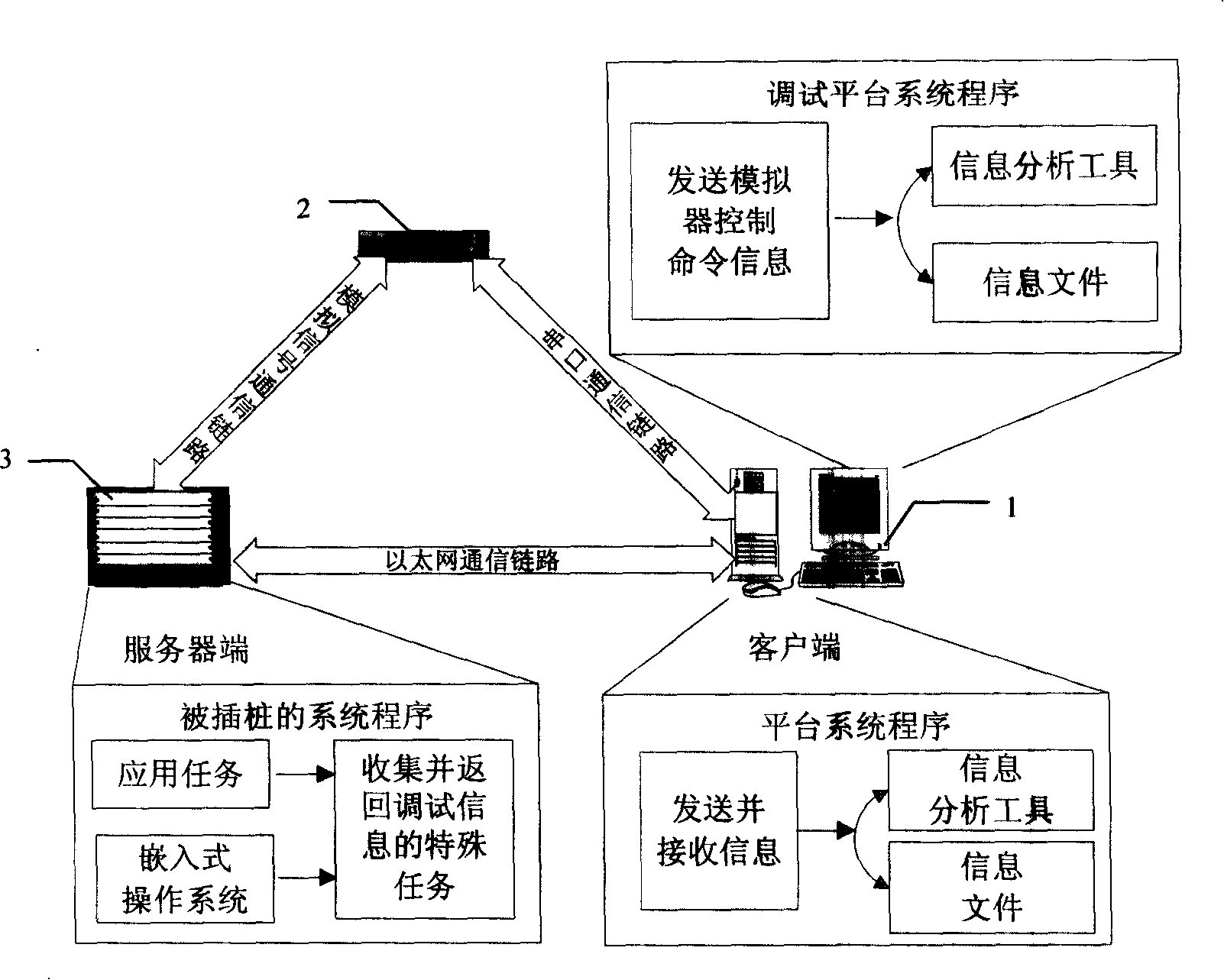

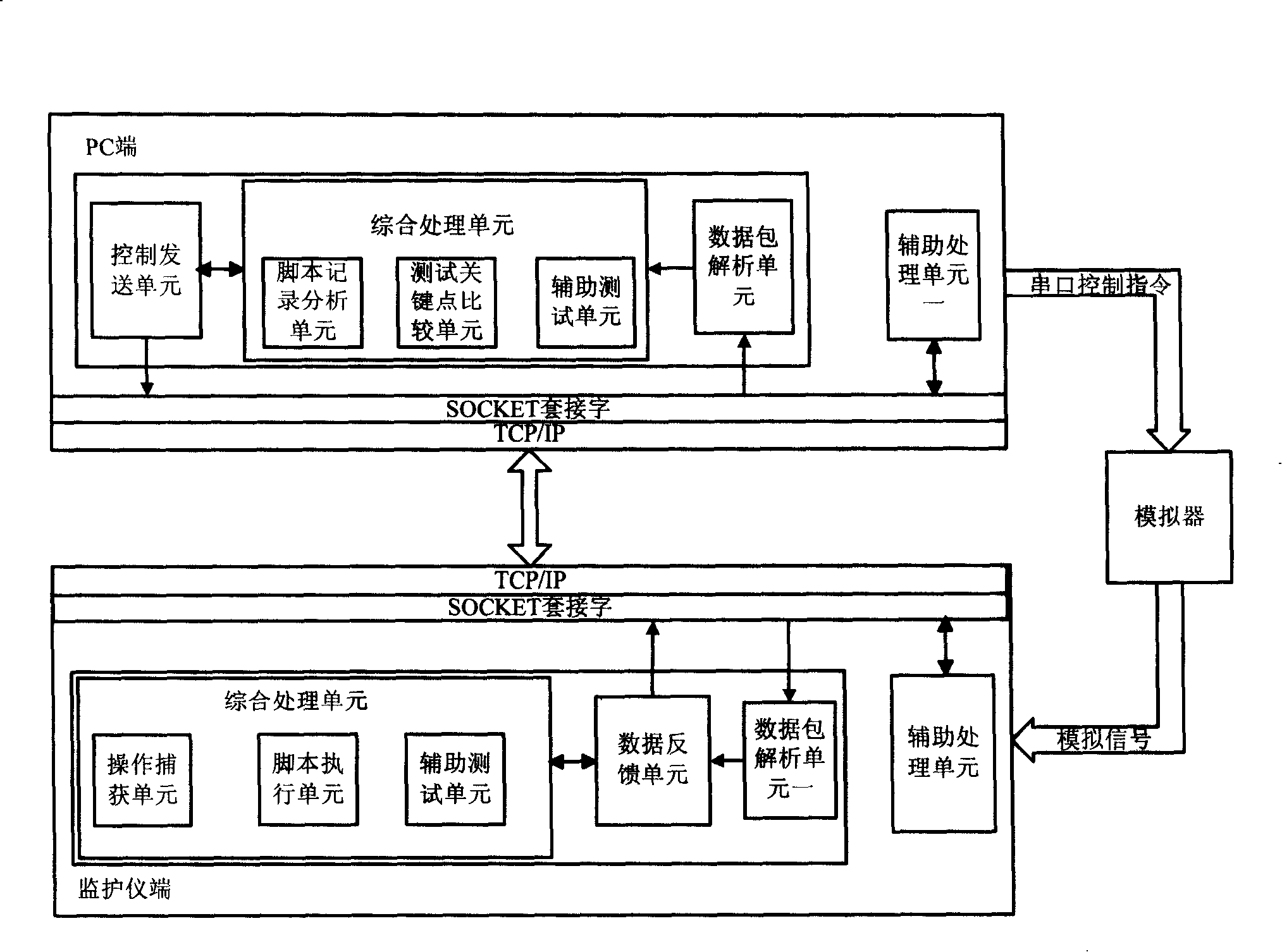

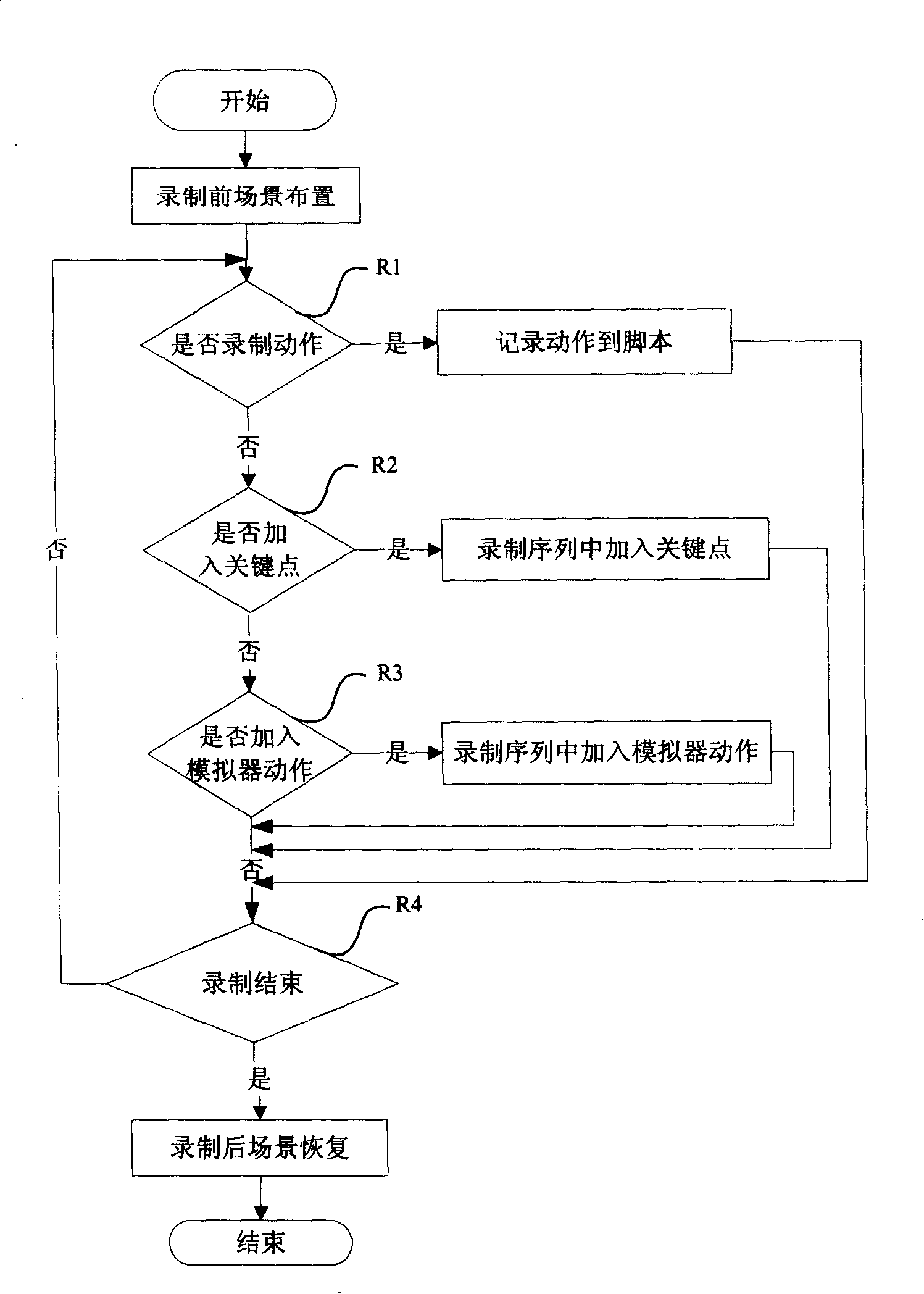

Embedded software test method and system

InactiveCN101241466AHigh speedImprove test efficiencySoftware testing/debuggingTest efficiencyTest script

Owner:SHENZHEN MINDRAY BIO MEDICAL ELECTRONICS CO LTD

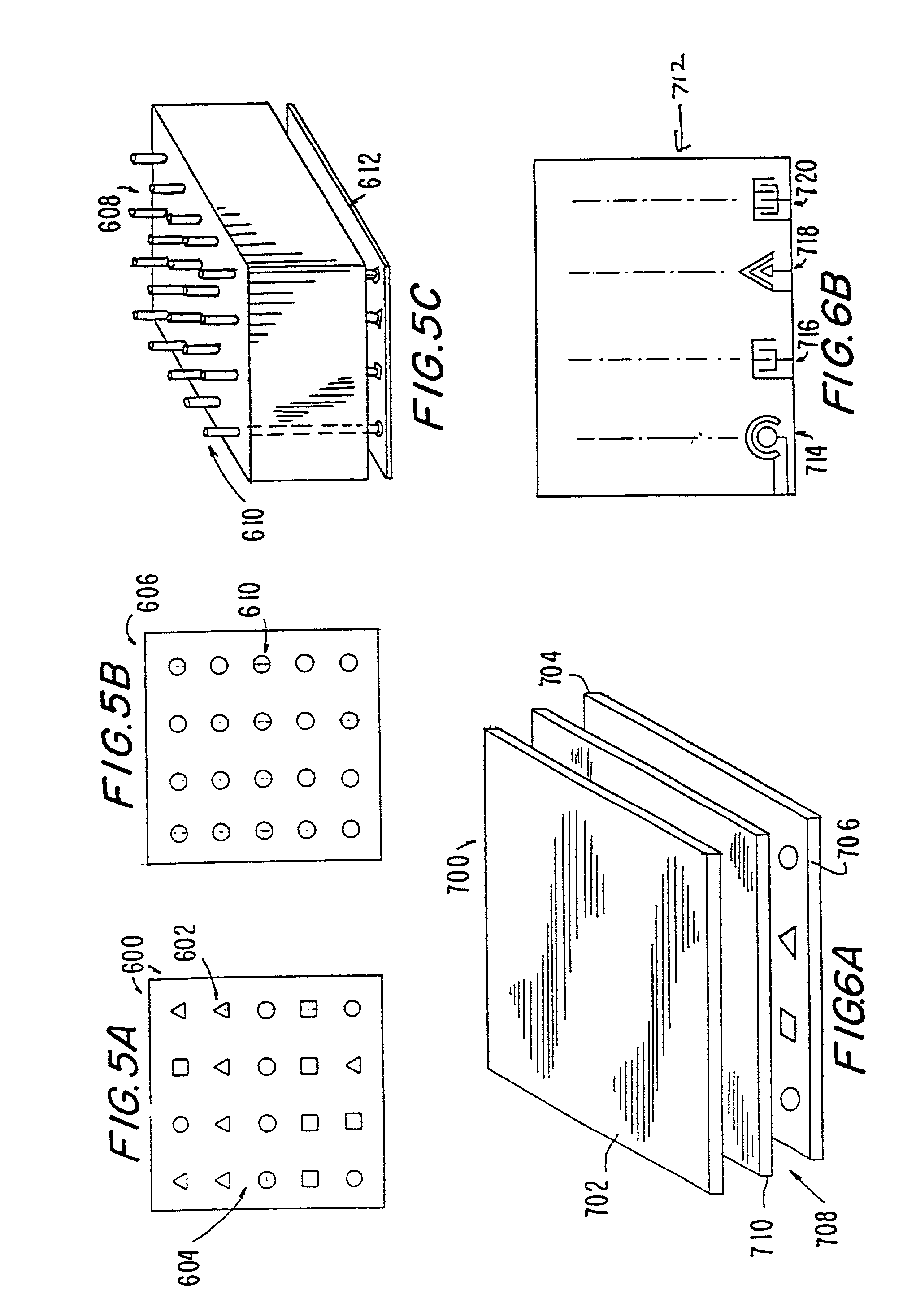

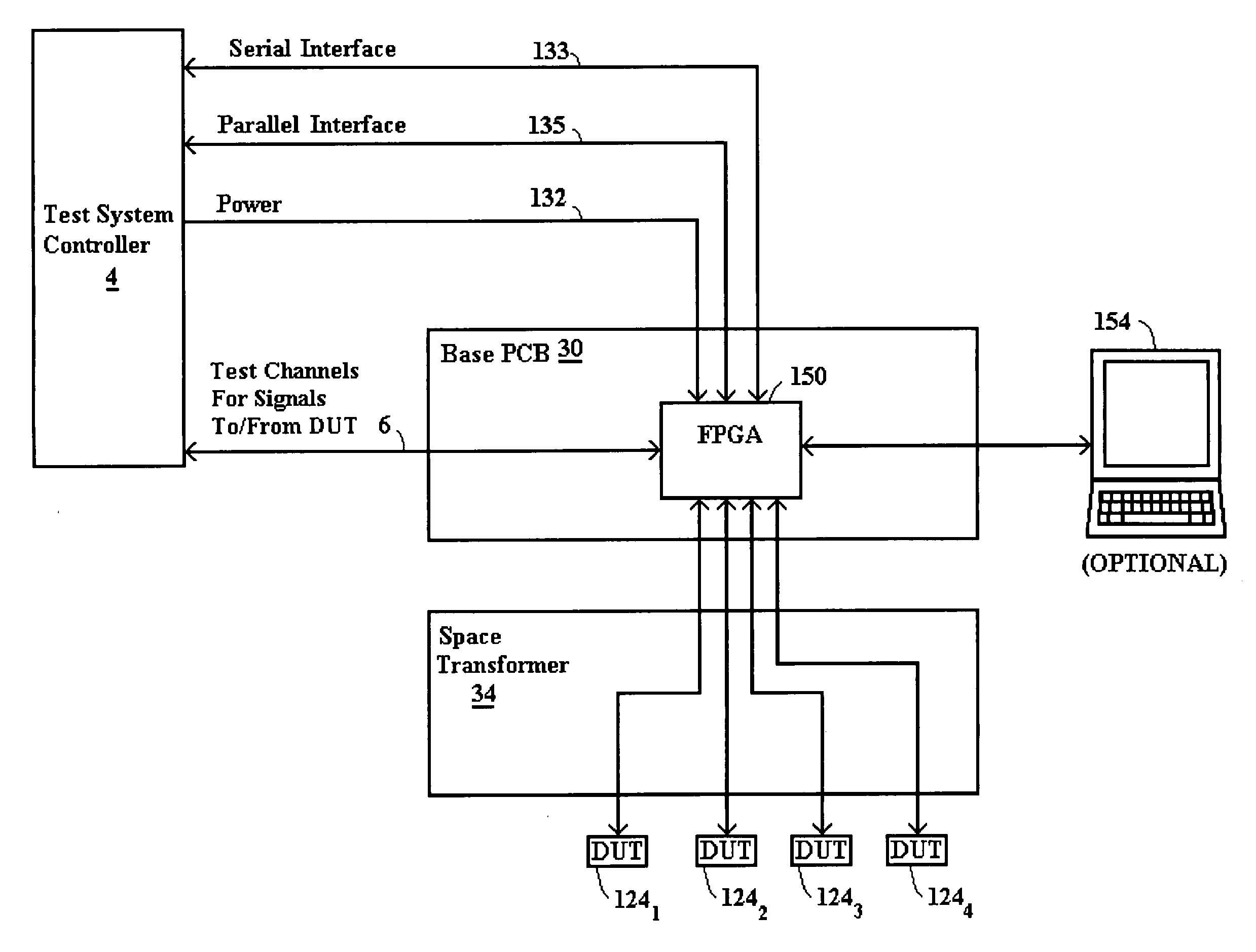

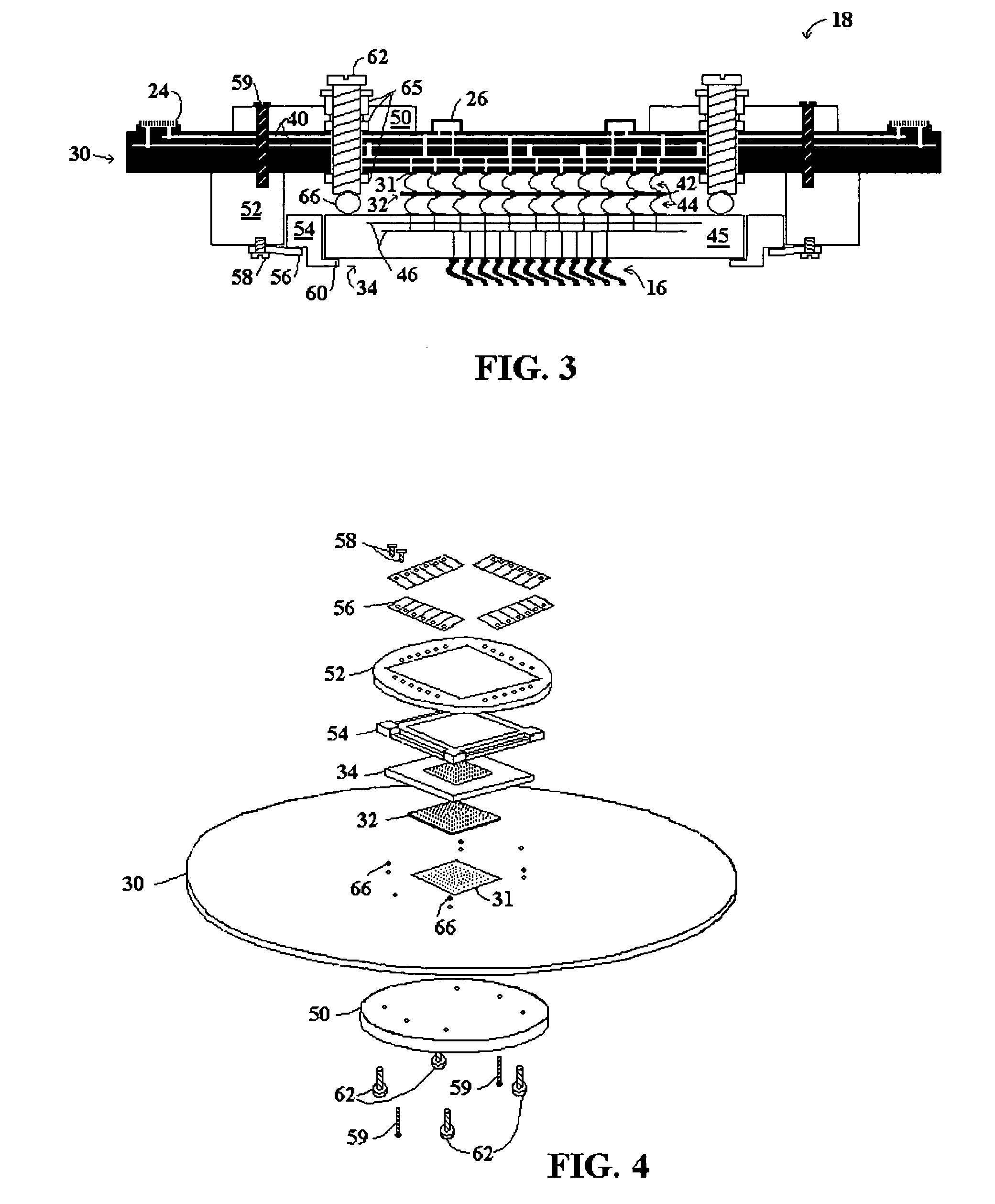

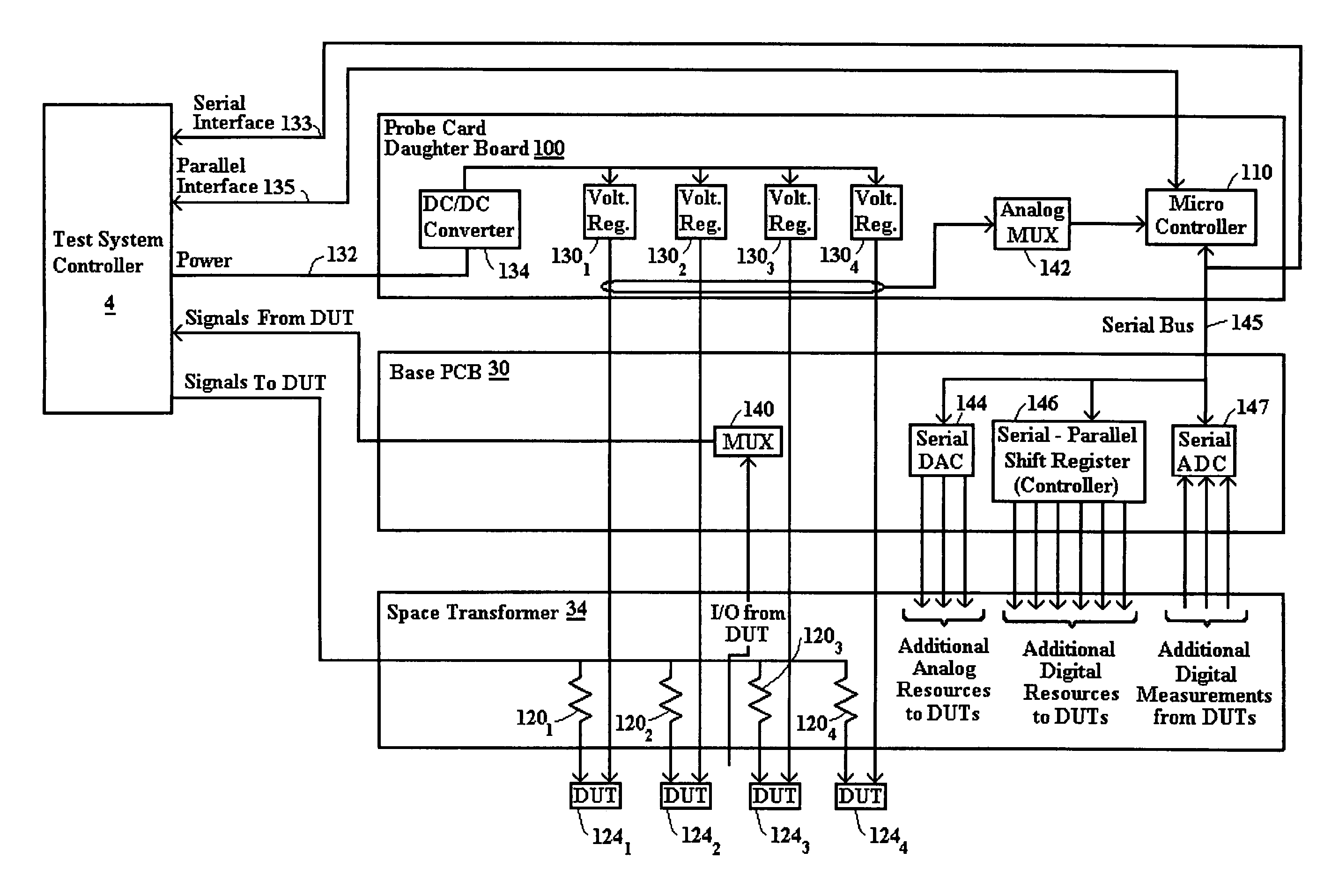

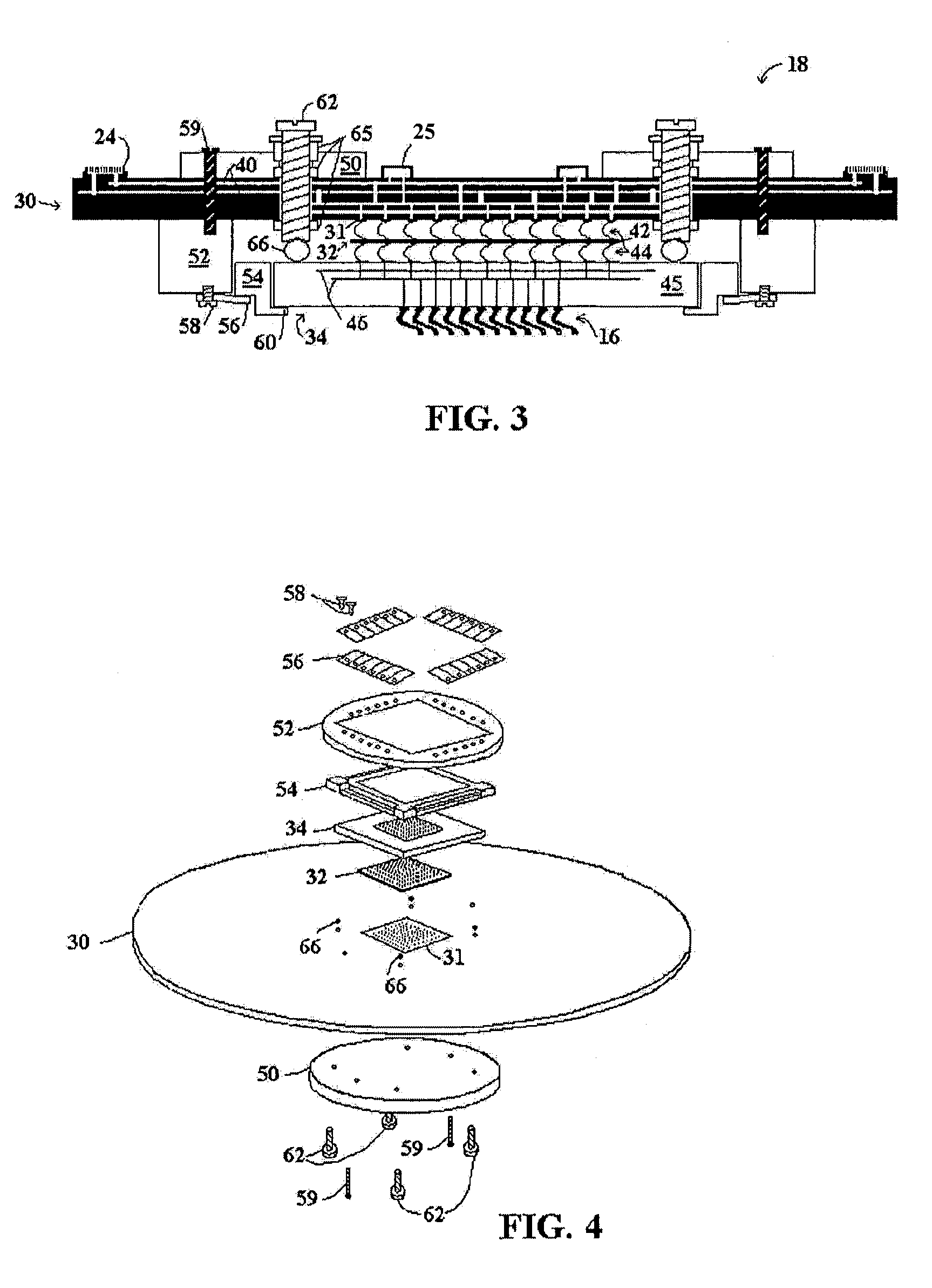

Programmable devices to route signals on probe cards

InactiveUS20060170435A1Great switching densityLong life cycleSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsProbe cardTest engineer

A probe card of a wafer test system includes one or more programmable ICs, such as FPGAs, to provide routing from individual test signal channels to one of multiple probes. The programmable ICs can be placed on a base PCB of the probe card, or on a daughtercard attached to the probe card. With programmability, the PCB can be used to switch limited test system channels away from unused probes. Programmability further enables a single probe card to more effectively test devices having the same pad array, but having different pin-outs for different device options. Reprogrammability also allows test engineers to re-program as they are debugging a test program. Because the programmable IC typically includes buffers that introduce an unknown delay, in one embodiment measurement of the delay is accomplished by first programming the programmable IC to provide a loop back path to the test system so that buffer delay can be measured, and then reprogramming the programmable IC now with a known delay to connect to a device being tested.

Owner:FORMFACTOR INC

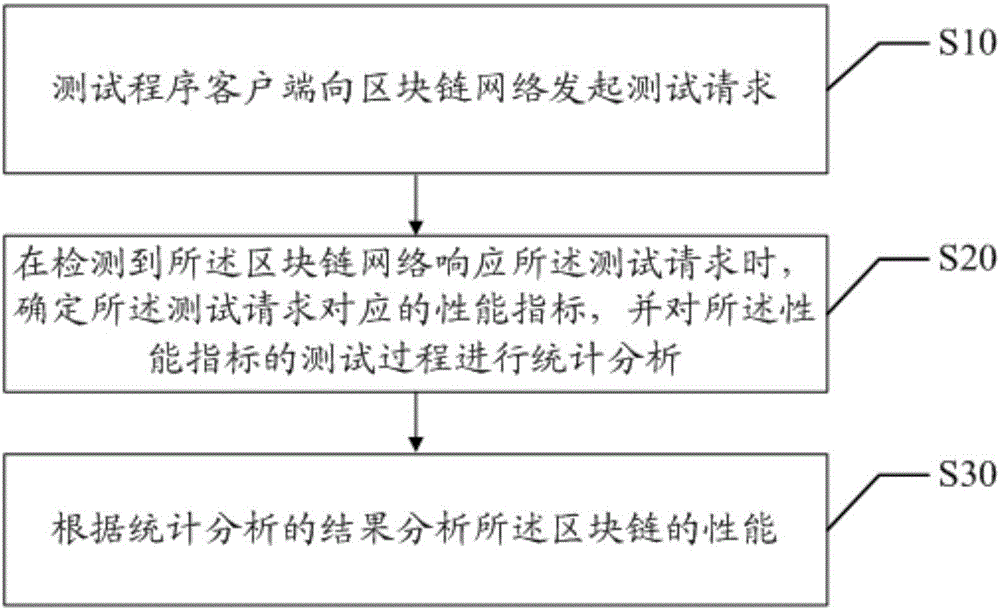

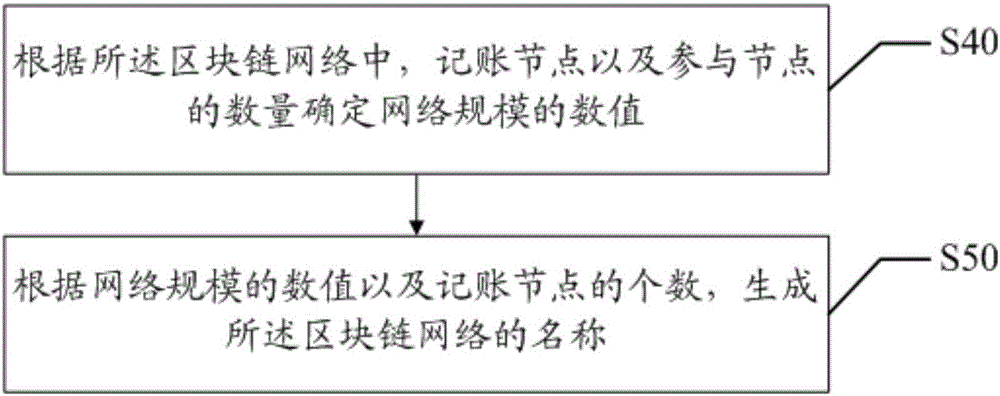

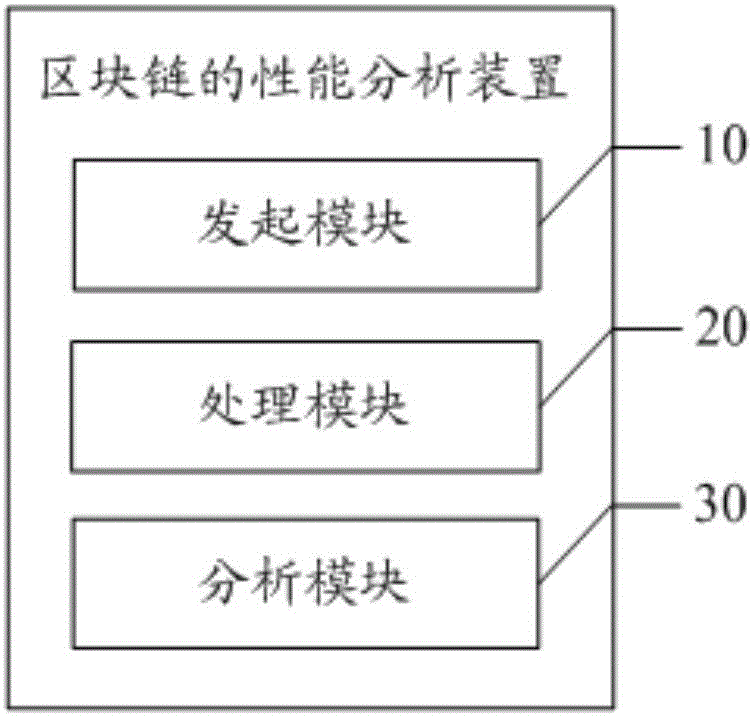

Performance analysis method and device for block chain

ActiveCN106598824AImprove accuracyIncrease diversityHardware monitoringStatistical analysisPerformance index

The invention discloses a performance analysis method for a block chain. The method is applied to a block chain network, the block chain network comprises a plurality of server nodes and is deployed with a test program client, and the performance analysis method for the block chain comprises the steps of: the test program client sending a test request to the block chain network; when detecting that the block chain network responds to the test request, determining a performance index corresponding to the test request, performing statistical analysis on the test process of the performance index, and analyzing the performance of the block chain according to the statistical analysis result. The invention further discloses a performance analysis device for a block chain. The method and the device improve the performance analysis accuracy of the block chain network by deep analysis on a plurality of performance indexes of the block chain network.

Owner:WEBANK (CHINA)

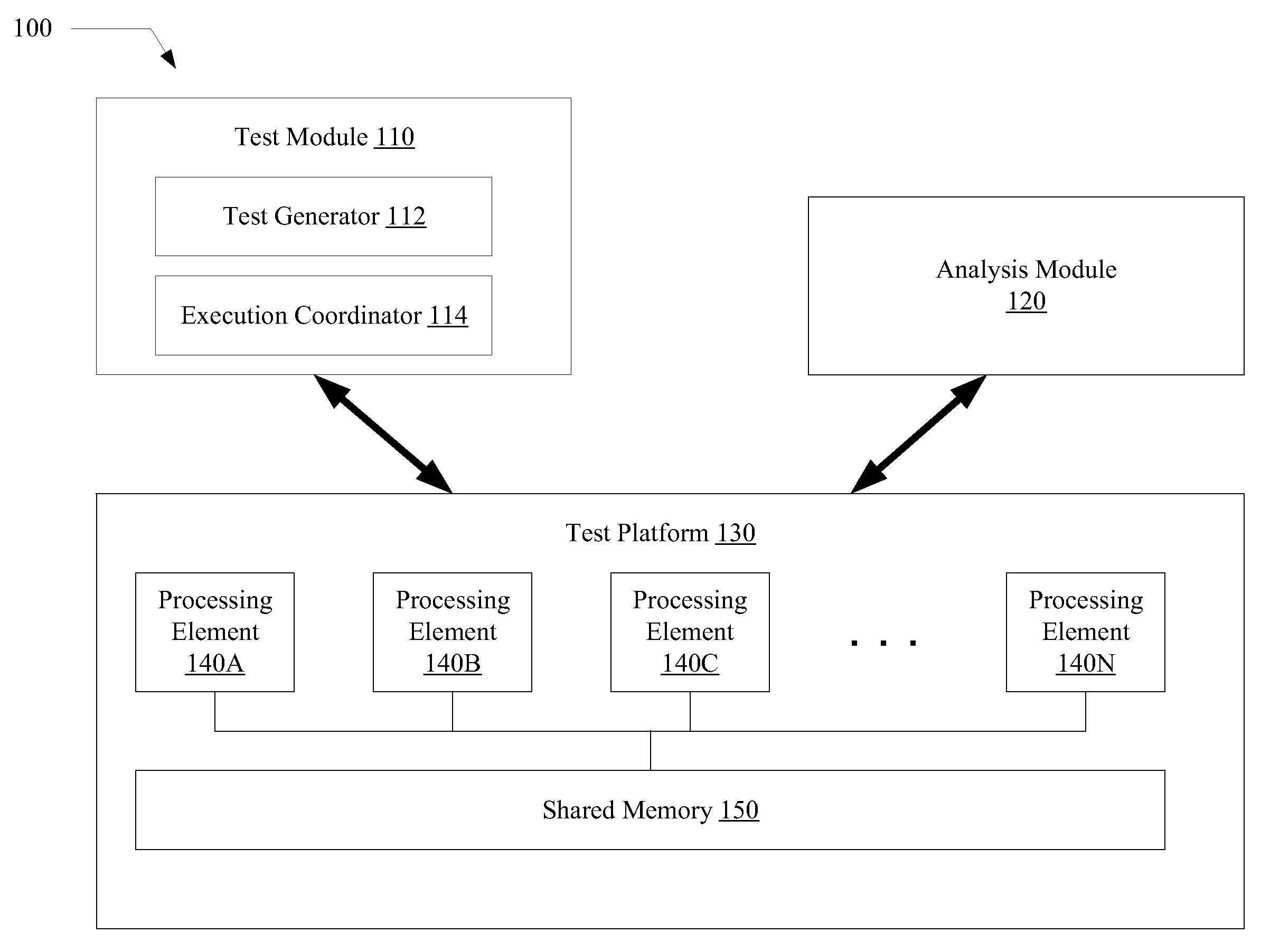

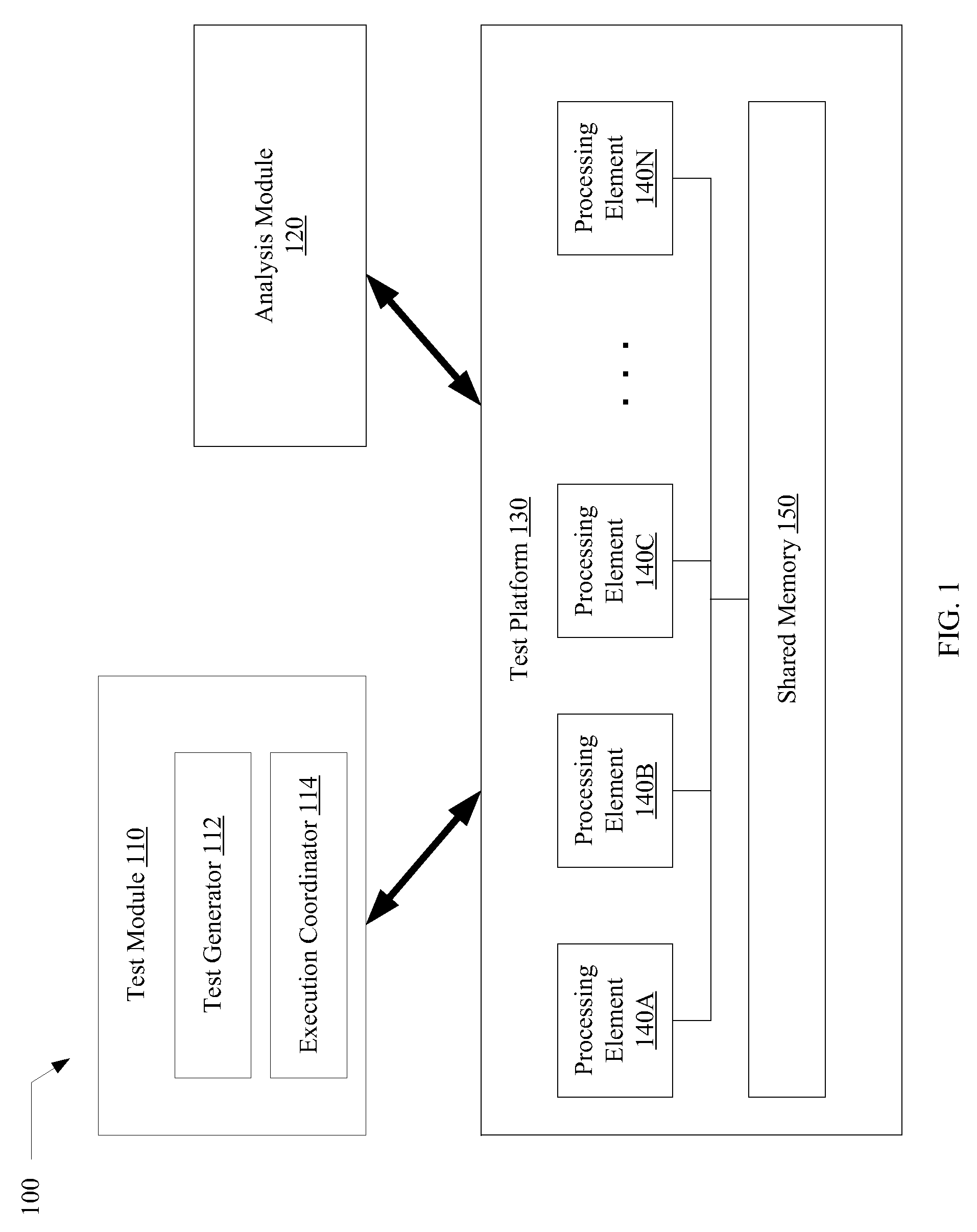

Verification of memory consistency and transactional memory

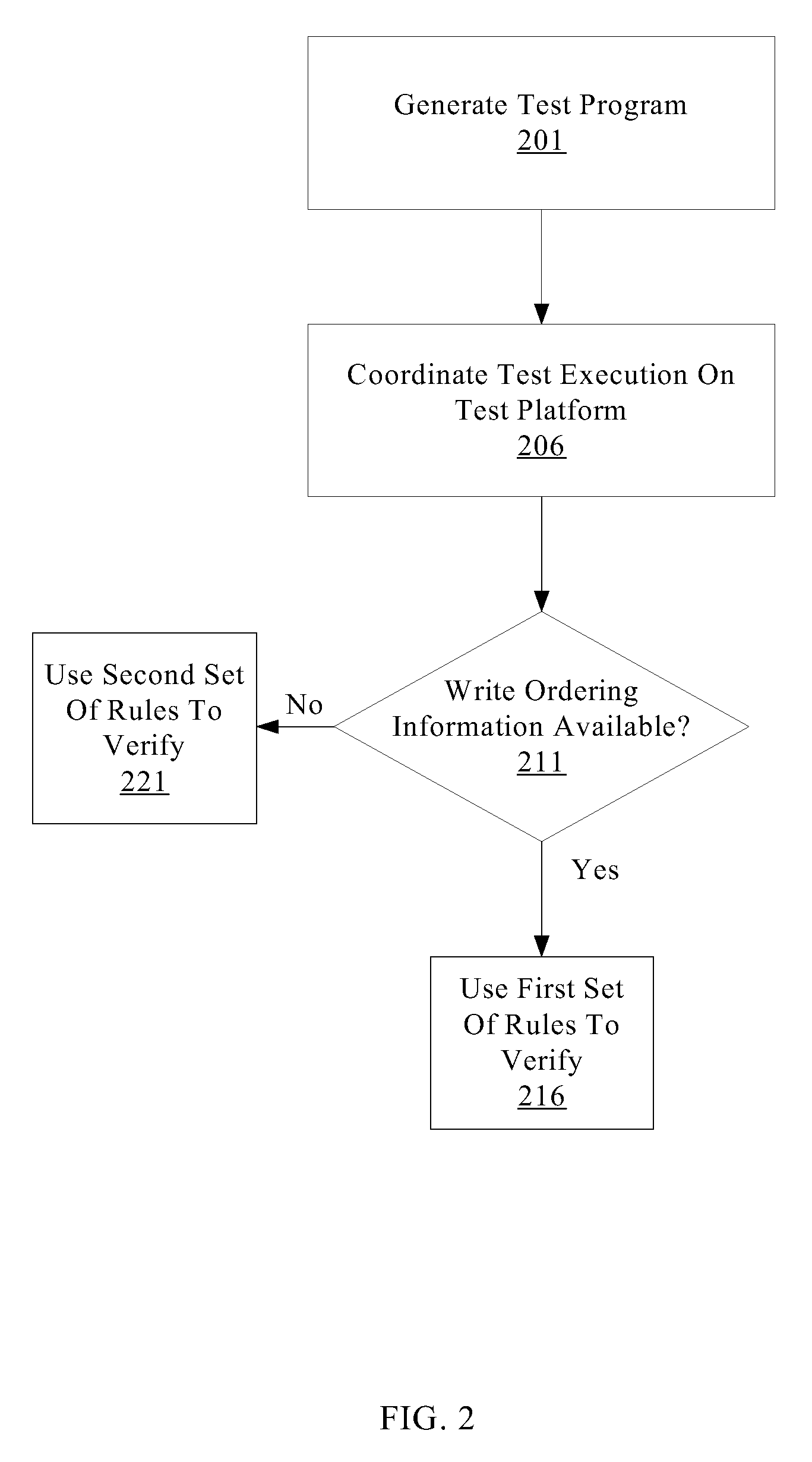

A system for efficiently verifying compliance with a memory consistency model includes a test module and an analysis module. The test module may coordinate an execution of a multithreaded test program on a test platform. If the test platform provides an indication of the order in which writes from multiple processing elements are performed at shared memory locations, the analysis module may use a first set of rules to verify that the results of the execution correspond to a valid ordering of events according to a memory consistency model. If the test platform does not provide an indication of write ordering, the analysis module may use a second set of rules to verify compliance with the memory consistency model. Further, a backtracking search may be performed to find a valid ordering if such ordering exists or show that none exists and, hence, confirm whether or not the results comply with the given memory consistency model.

Owner:ORACLE INT CORP

Method and apparatus for programmable generation of traffic streams

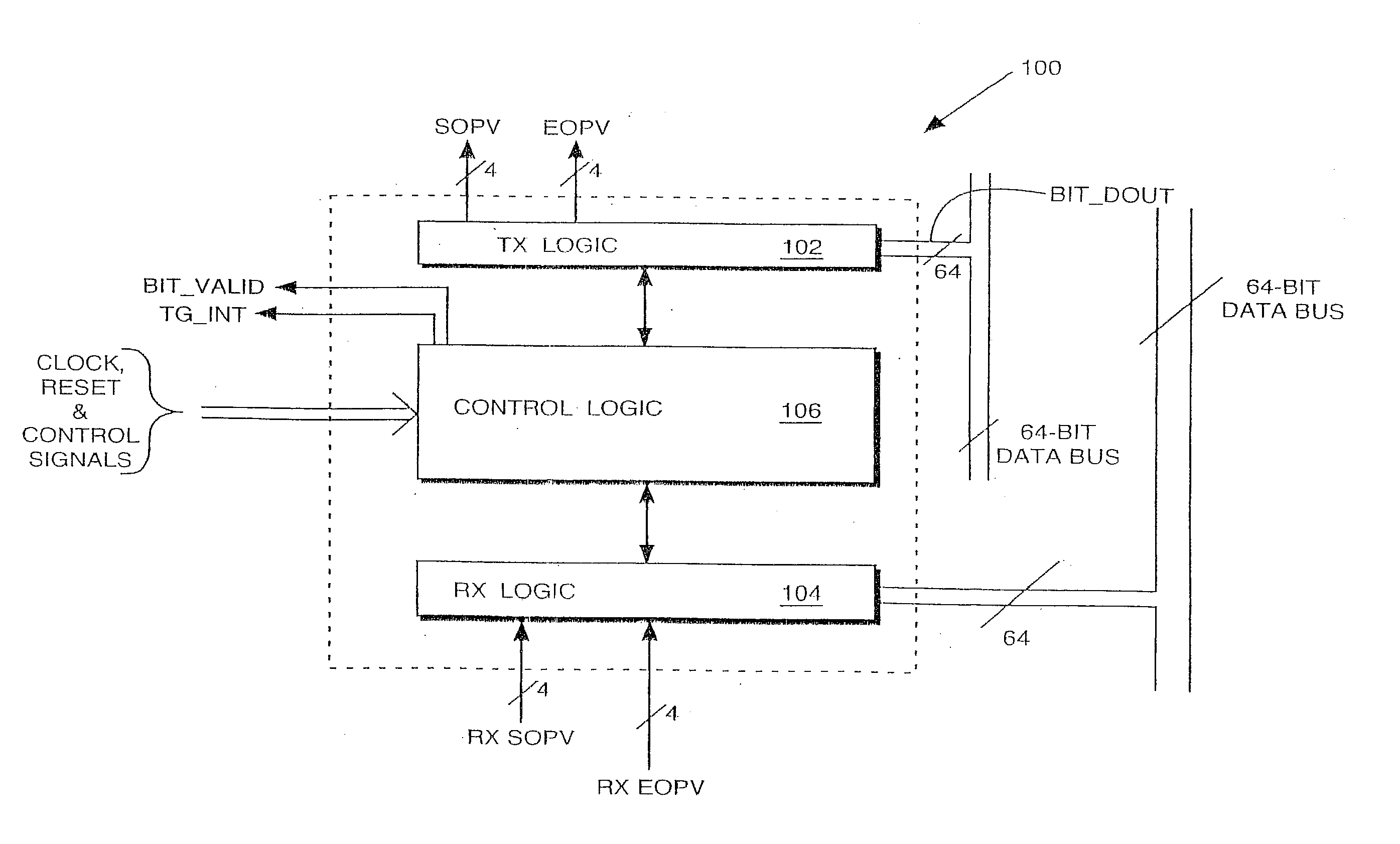

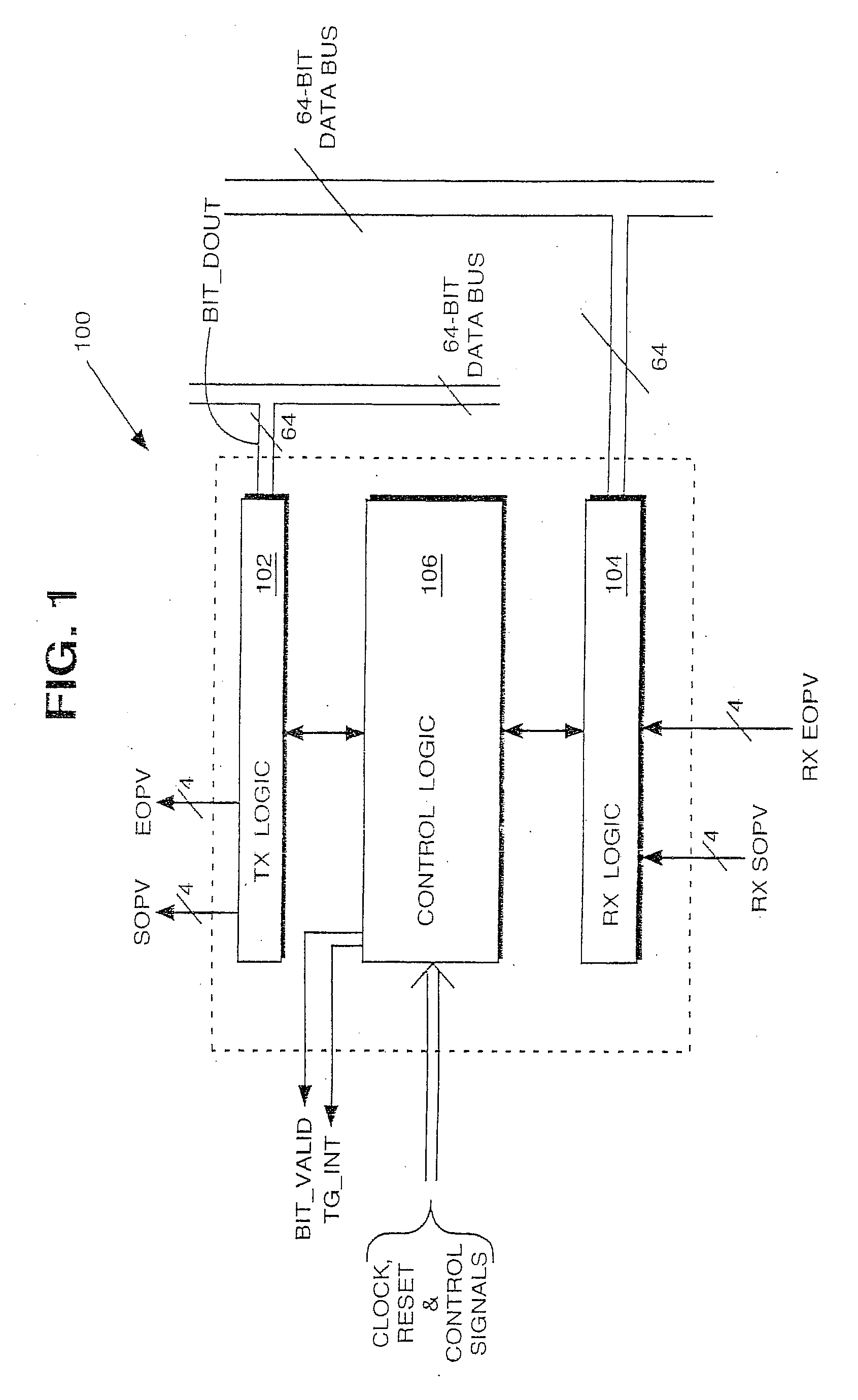

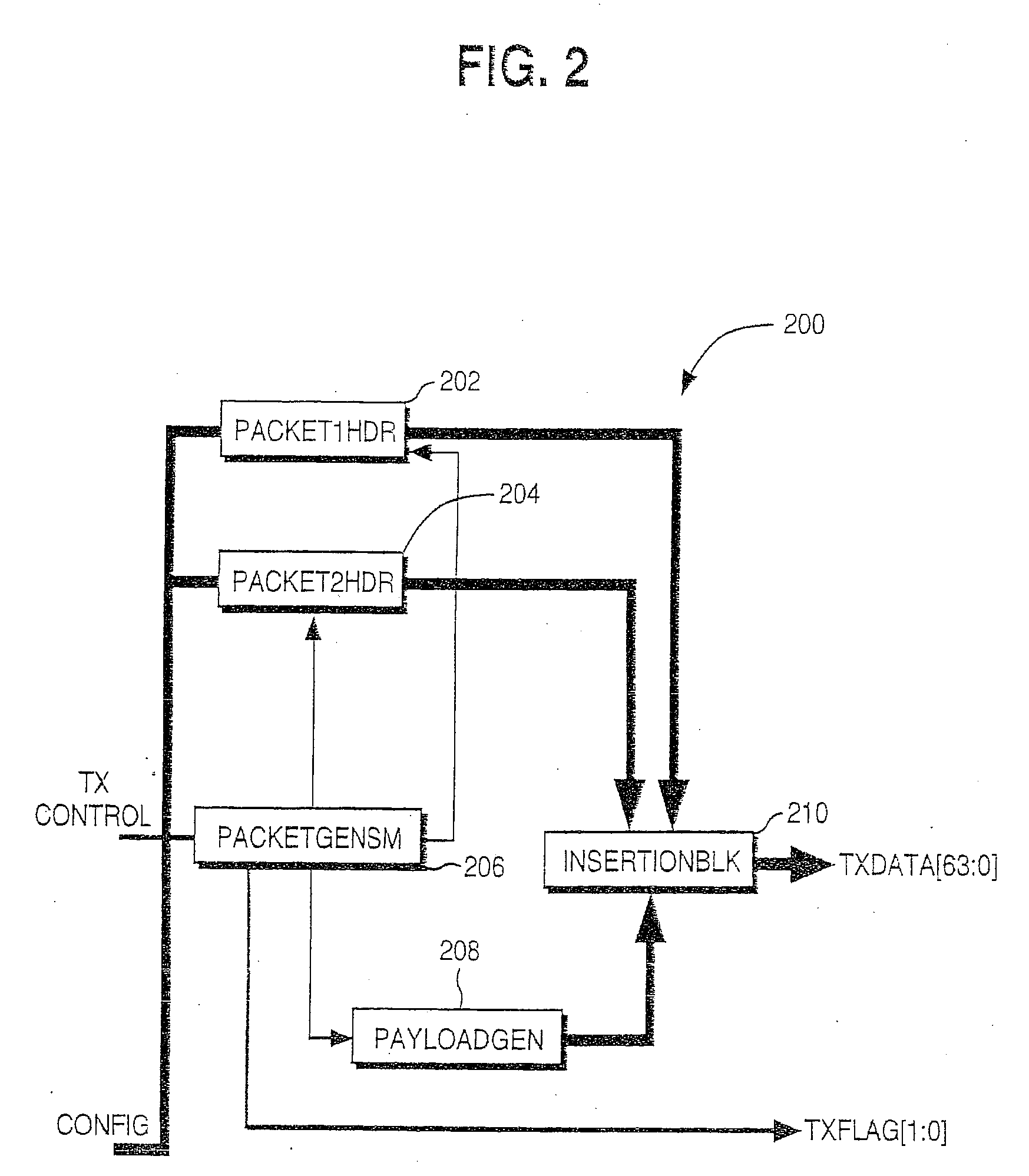

Methods and apparatus provide single or multi-port, flexible, cost-effective, built-in self-test capabilities for network communications equipment, such as for example switches, and programmably generate, and subsequently analyze, one or more sequences of test packets, wherein the test packets simulate at least two flows of traffic. Such test packets can have programmable headers, payloads, and duty cycle. A line card embodying the present invention may generate its own traffic pattern, which may be similar or identical, to traffic patterns observed on Internet backbones. These traffic patterns may contain a bimodal distribution of control packets interspersed with data packets wherein the control packets and data packets are relatively short and long respectively. A plurality of test packet generators / receivers can be deployed in a network communications device having a plurality of ports. In such a configuration, test generator / receiver is associated with each of the plurality of ports. Under software control, test packets can be sent from at least any one of the plurality of ports to at least any other one of the plurality of ports. In this way, an in-circuit testing procedure may be implemented without having to disconnect line cards from the switch and connect the switch to expensive external test equipment.

Owner:XYLON LLC

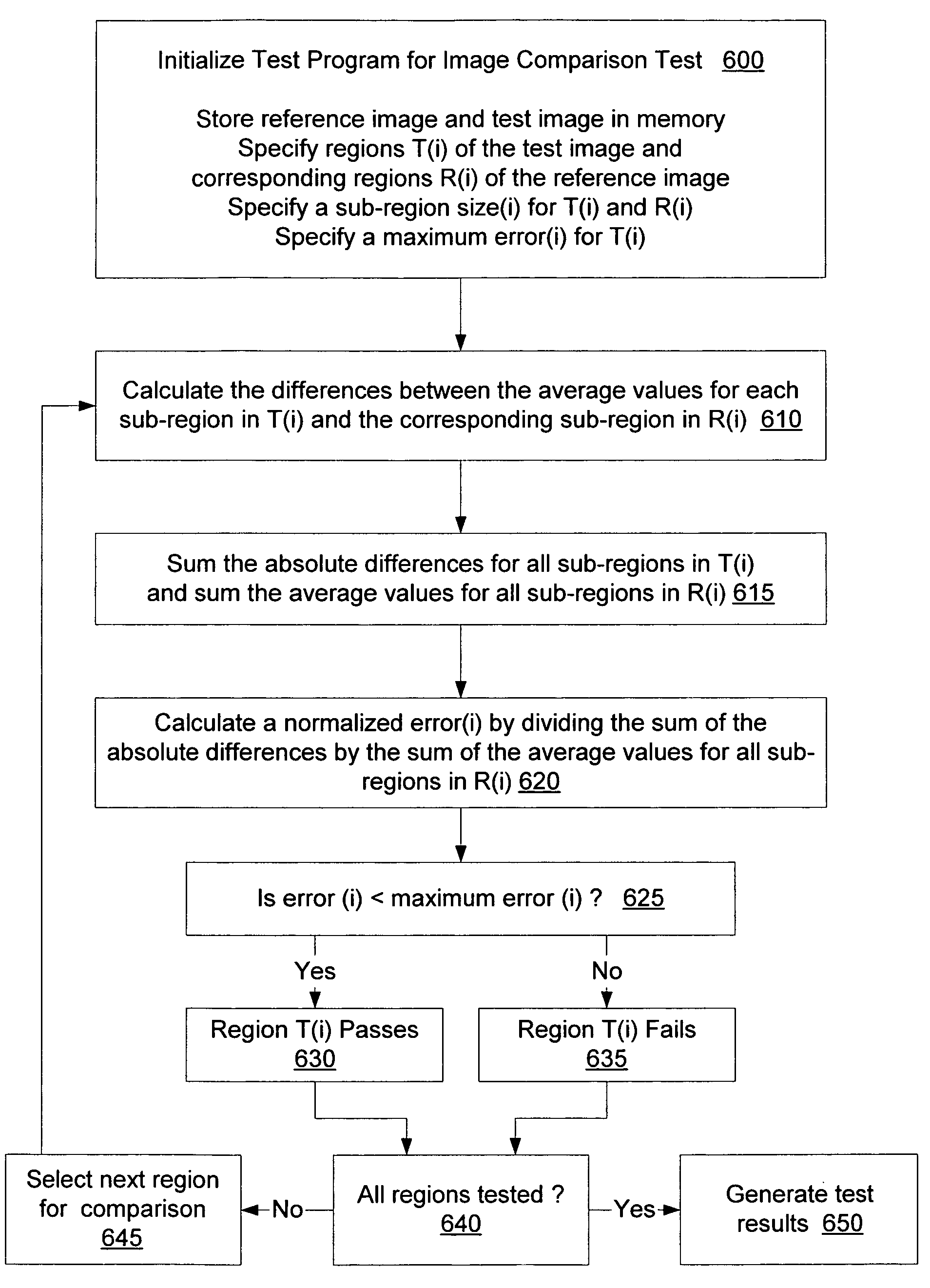

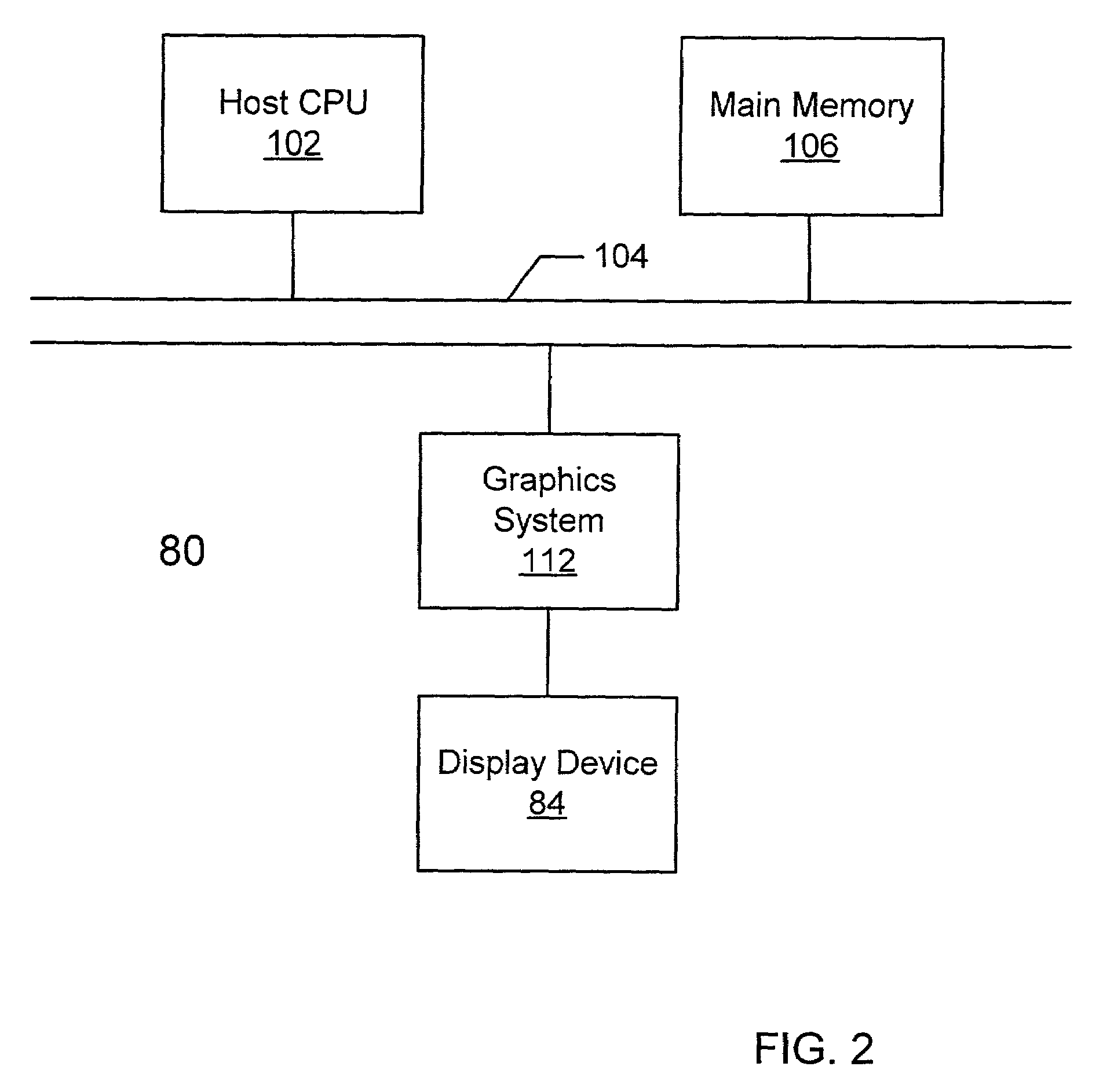

Method and apparatus for global image quantification verification

ActiveUS7092572B2Reduce in quantityEffectively blurredImage analysisCharacter and pattern recognitionGraphicsMaximum error

A method and apparatus are disclosed for testing the accuracy of digital test images generated by a computer graphics program executed on a computer graphics system. A test program is utilized to compare the test image with a reference image. The user defines regions of interest and a maximum error for each region. This allows the user to focus on a particular object or group of objects. Global image quantification verification generates one measurement of error or image difference for each region of the test image. Each region is divided into sub-regions and an average color value is calculated for each sub-region and the corresponding sub-region in the reference image. The differences between the averages for corresponding sub-regions in the test and reference images are calculated. A test image region may be unacceptably different from a reference image if a normalized sum of the absolute differences exceeds the maximum error.

Owner:ORACLE INT CORP

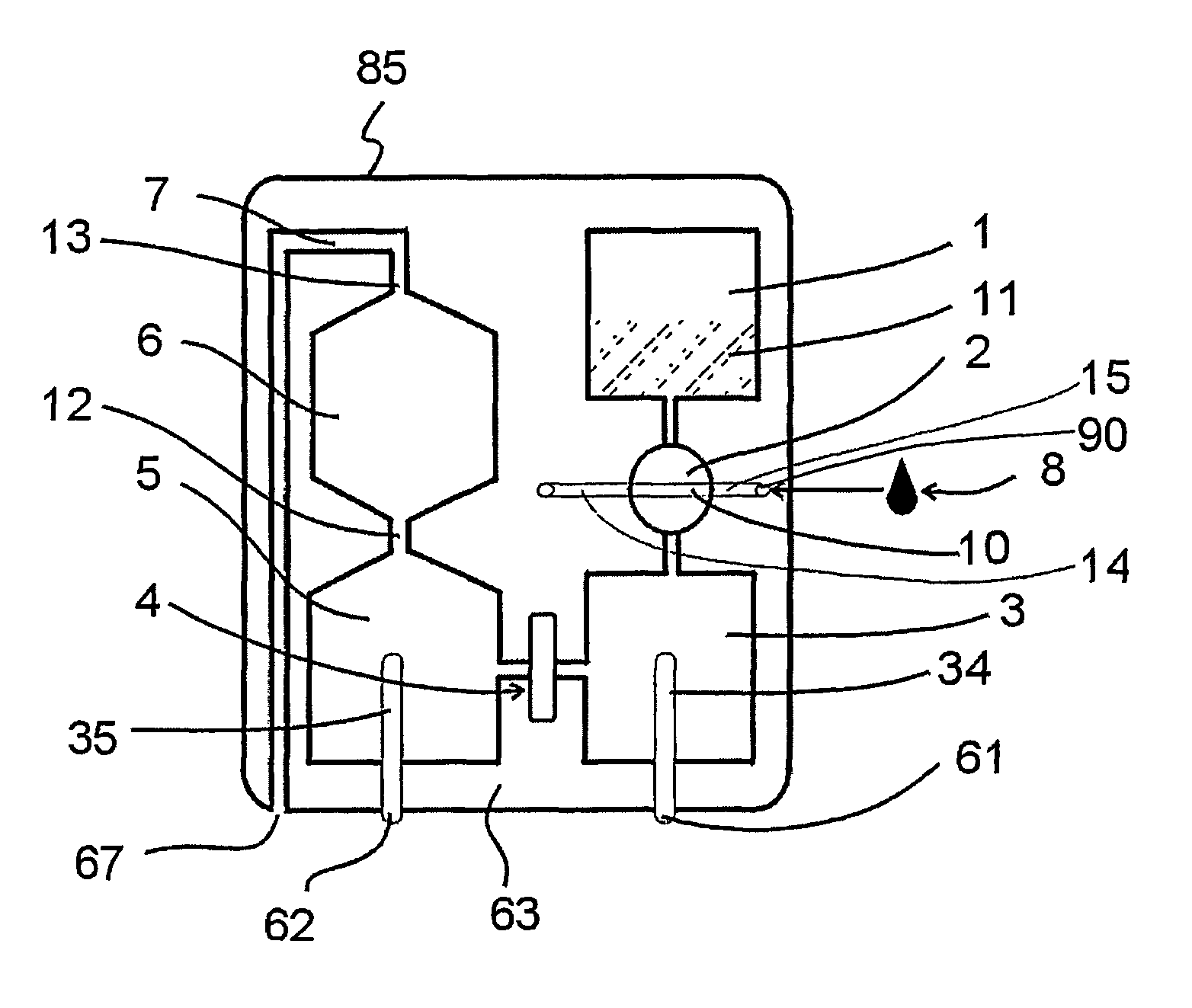

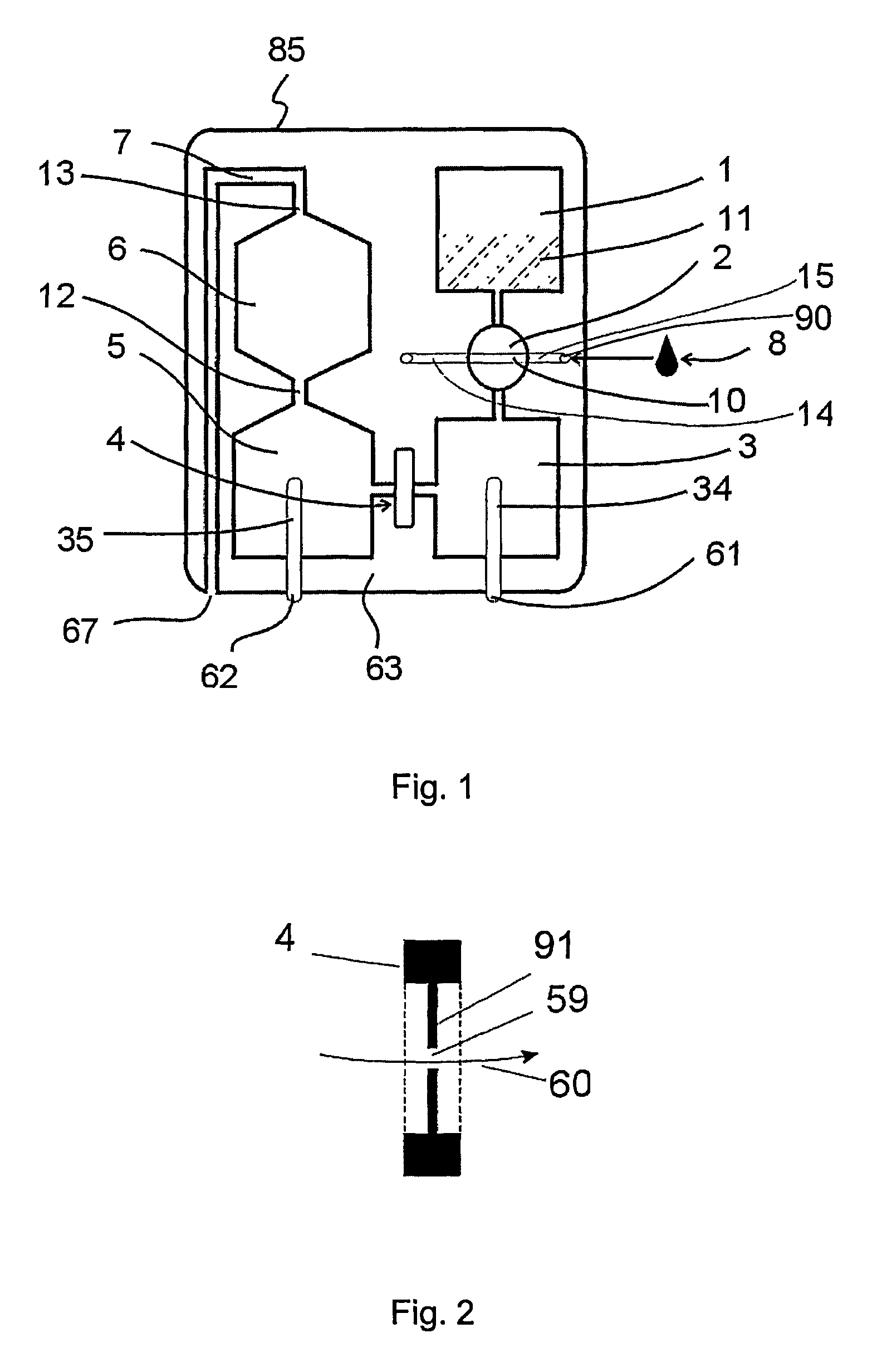

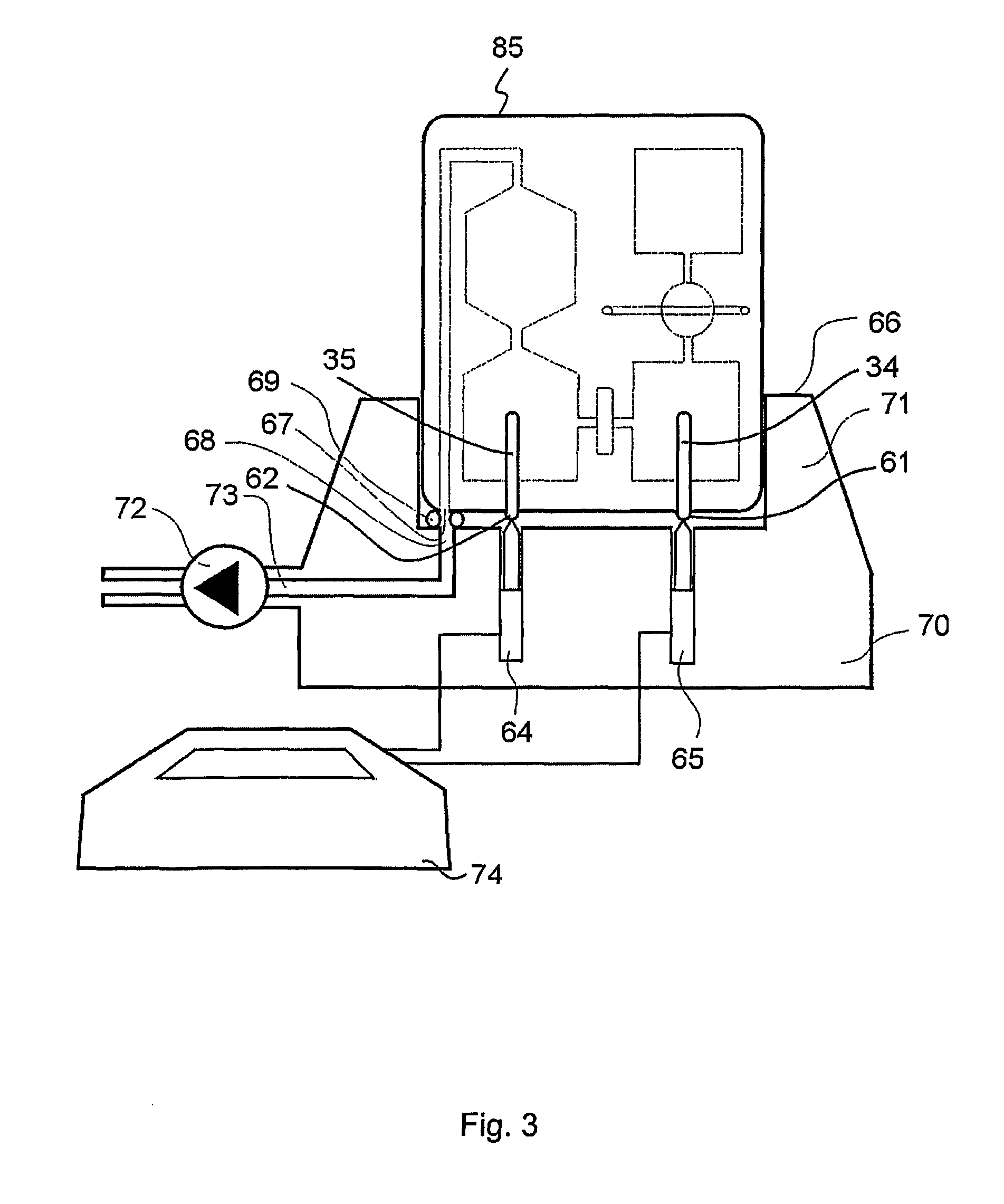

Disposable cartridge for characterizing particles suspended in a liquid

InactiveUS7771658B2Facilitate drainingBioreactor/fermenter combinationsBiological substance pretreatmentsSingle useEngineering

A disposable cartridge for characterizing particles suspended in a liquid, especially a self-contained disposable cartridge for single-use analysis, such as for single-use analysis of a small quantity of whole blood. The self-contained disposable cartridge facilitates a straightforward testing procedure, which can be performed by most people without any particular education. Furthermore, the apparatus used to perform the test on the cartridge is simple, maintenance free, and portable.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

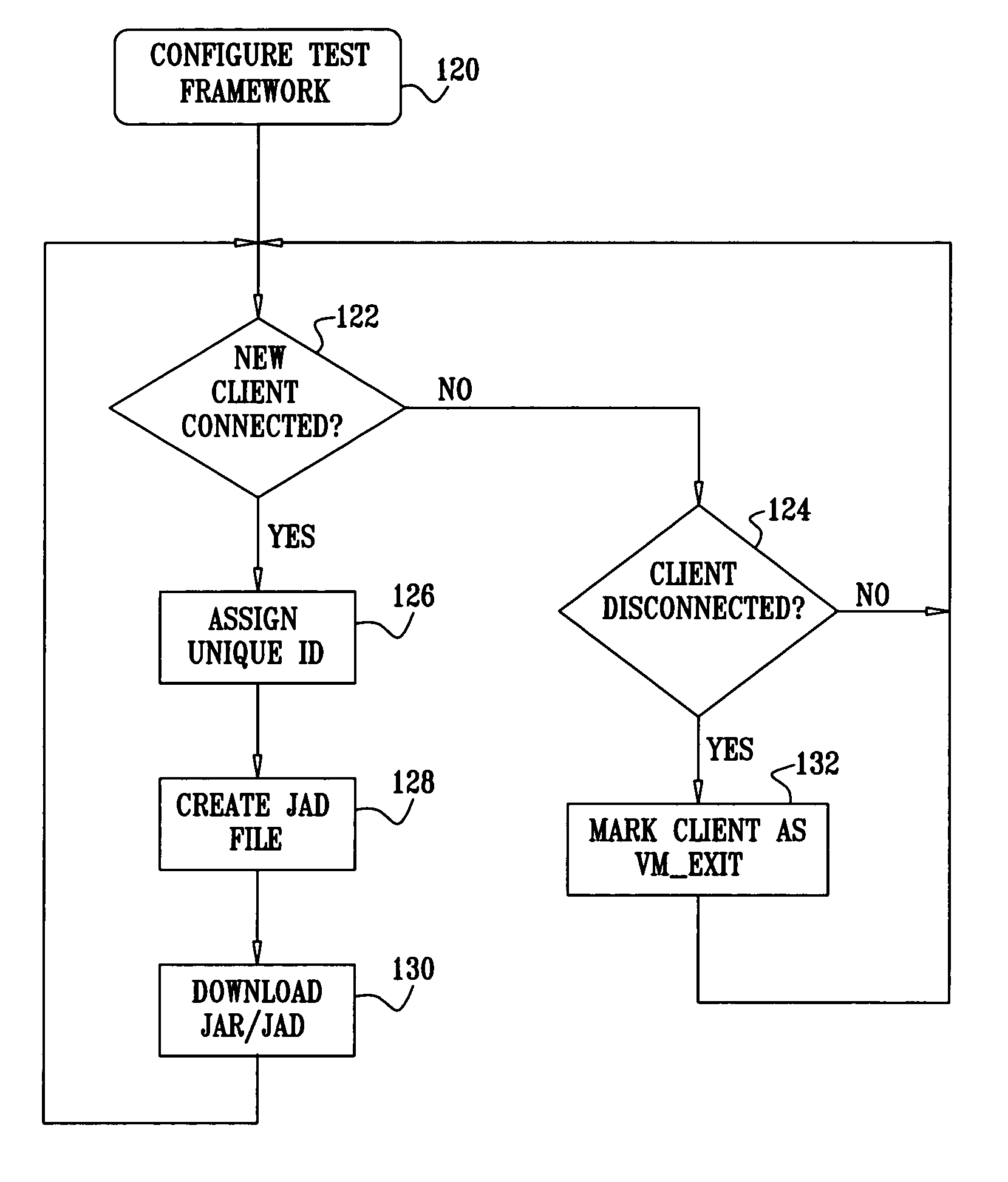

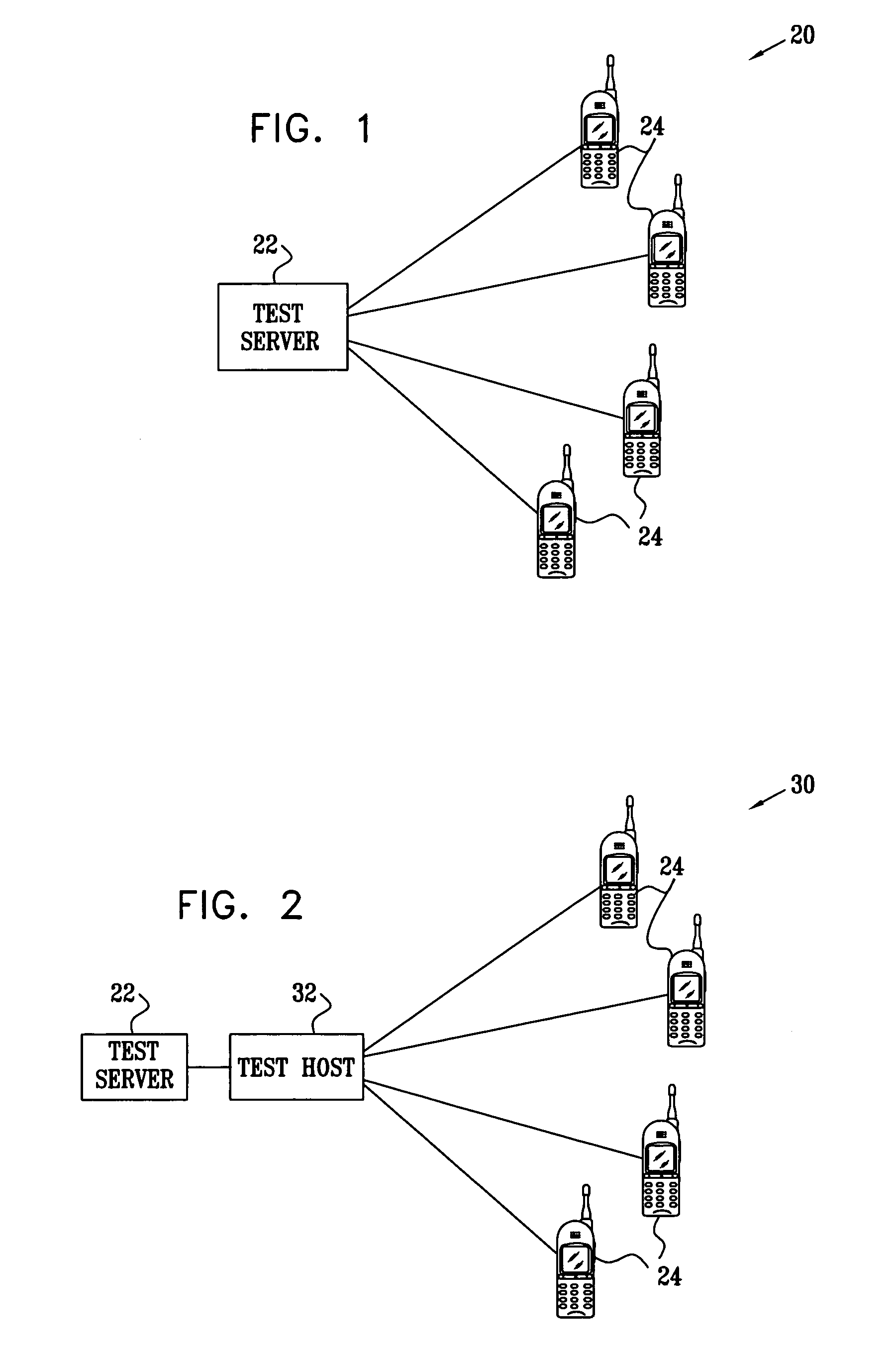

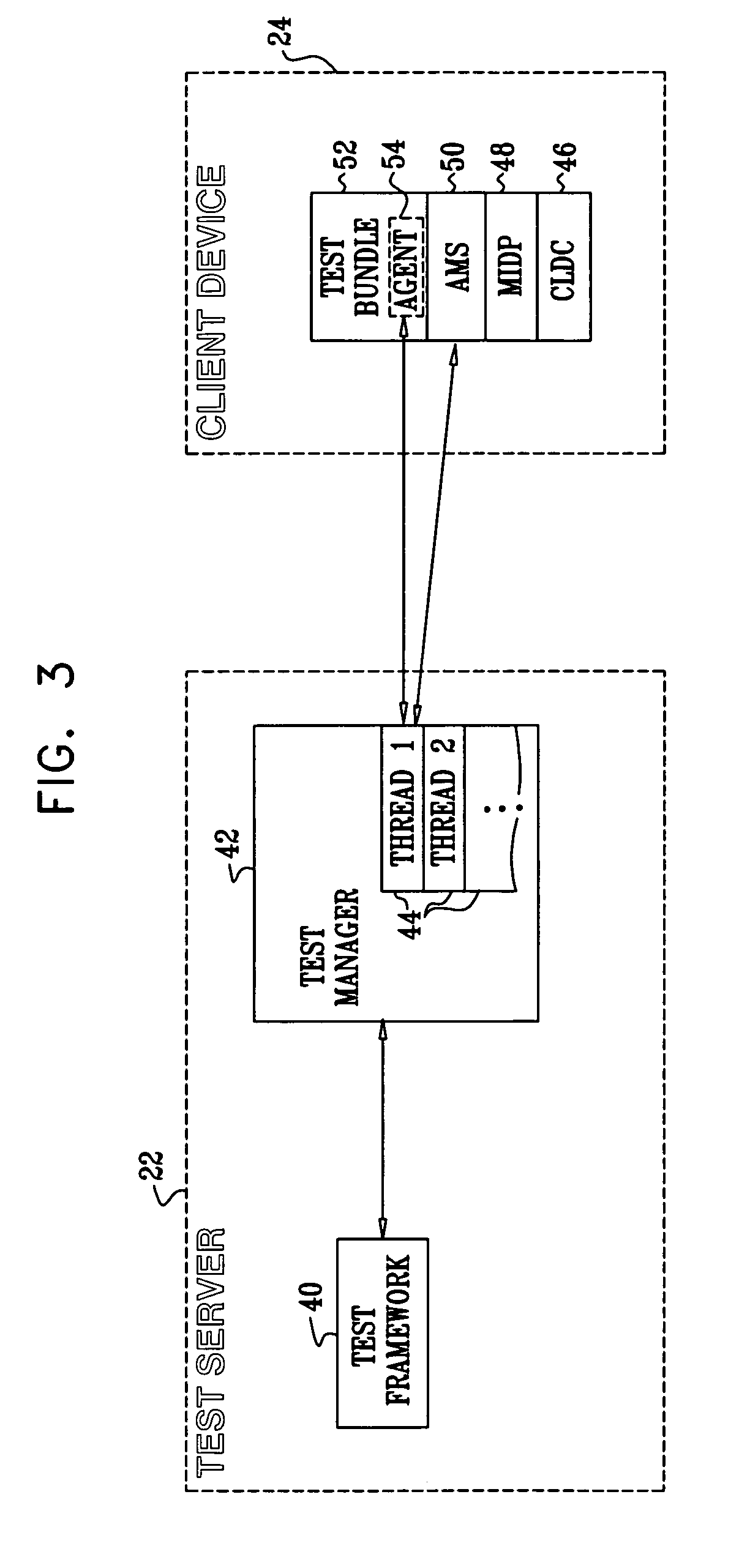

Dynamic distribution of test execution

ActiveUS7334162B1Less timeReduce running timeDetecting faulty hardware by remote testSpecific program execution arrangementsUnique identifierTest execution

Computing devices are tested by providing a suite of test programs on a server for execution by a plurality of identical computing devices that are coupled to the server. A respective unique identifier is assigned to each of the plurality of the computing devices, for use in communicating with the server. The test programs are downloaded from the server for execution by the computing devices coupled thereto, so that at different computing devices execute different test programs substantially simultaneously. The server receives messages from the computing devices with respect to execution of the test programs, each of the messages containing the respective unique identifier, and controls the execution of the test programs in the suite based on the messages. The server dynamically distributes the test programs to a changing population of the computing devices, optimizing the distribution so as to minimize the time to complete the suite.

Owner:ORACLE INT CORP

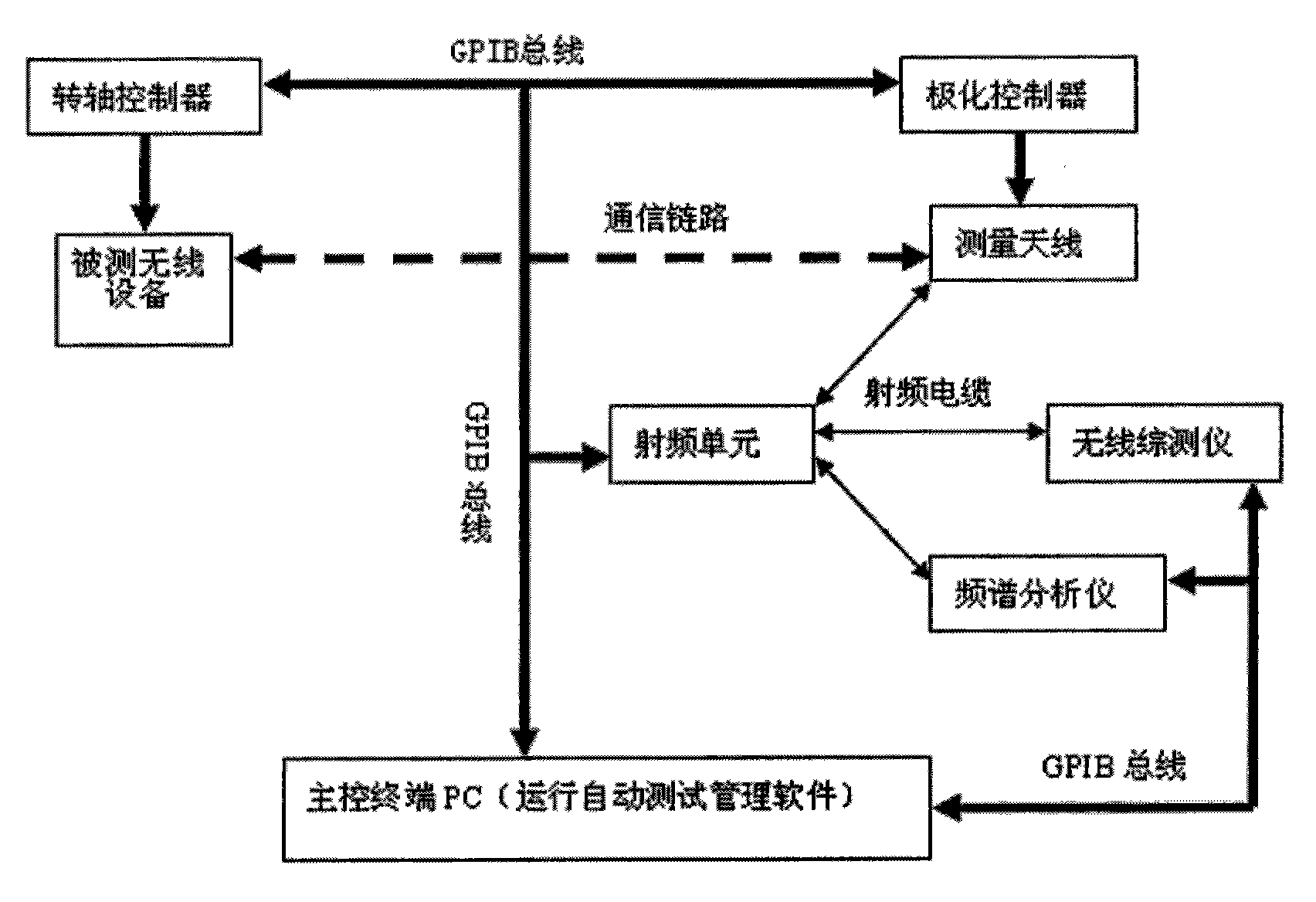

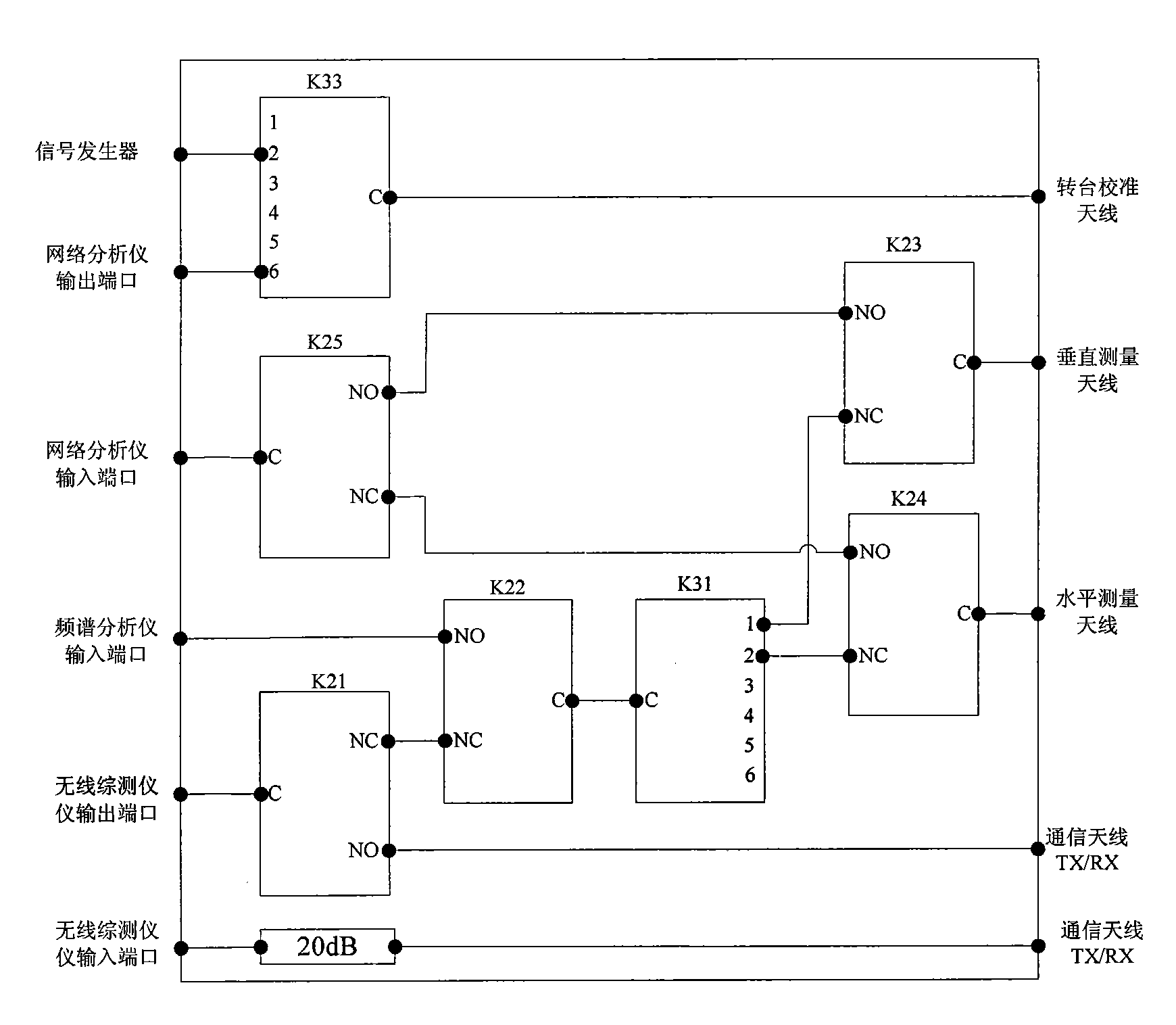

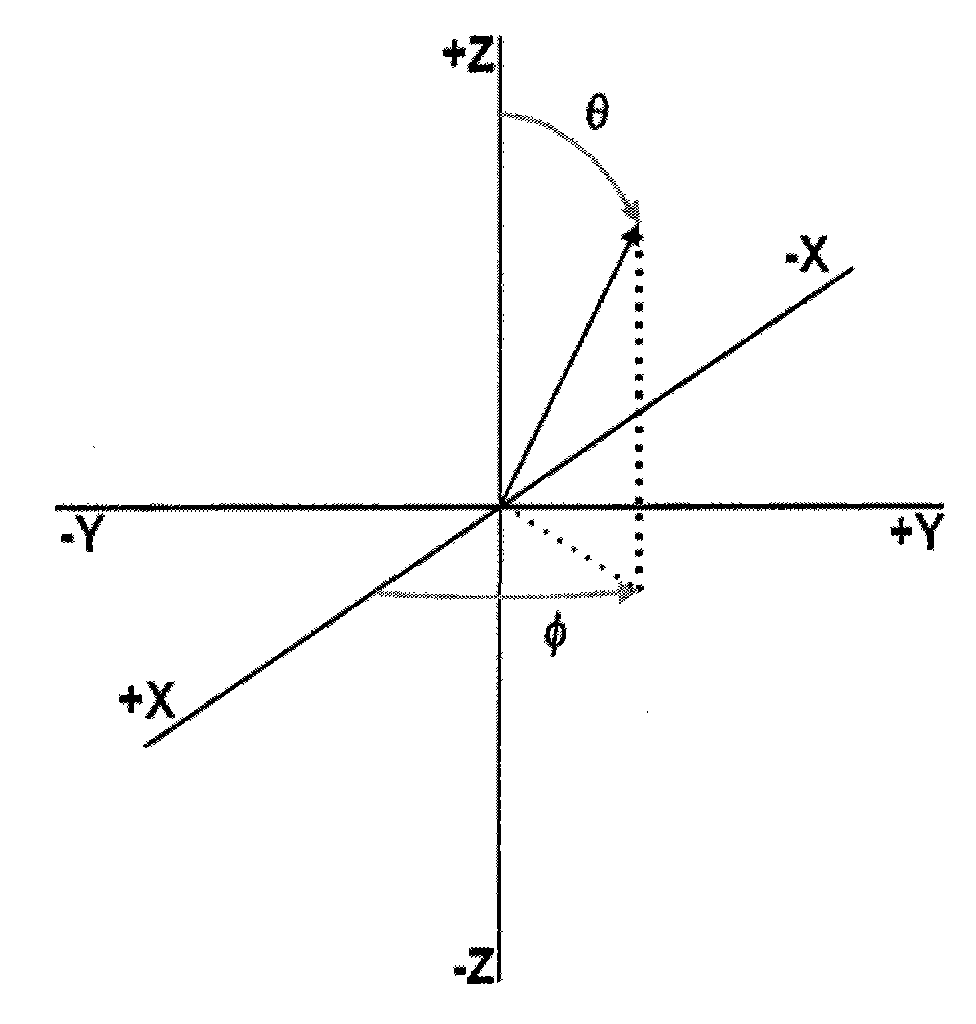

Multi-wireless access technology based over-the-air test system and test method thereof

InactiveCN101605350AAll test typesWide coverageEnergy efficient ICTTransmission monitoringTelecommunications linkSpectrum analyzer

A multi-wireless access technology based over-the-air test system, used for evaluating over-the-air index of a wireless terminal device, has the principle of putting a device to be tested in a three-dimensional space, and establishing a communication link with a base station simulator (namely wireless communications test set); controlling Phi, Theta axles (two axles perpendicular to each other) to rotate according to set step, performing measurement on various angle positions; measuring spherical effective Total Radiated Power of a moving station in the three-dimensional space and Total Isotropic Sensitivity of a receiver. The system mainly comprises a darkroom, a high-accuracy positioning system and its controller(including a rotating axle controller and a polarization controller), a radio frequency test instrument and a main control terminal computer with automatic test program, wherein the radio frequency instruments comprises a wireless communications test set, a spectrum analyzer, a network analyzer and a radio frequency unit.

Owner:TELECOMM METROLOGY CENT OF MINIST OF IND & INFORMATION TECH

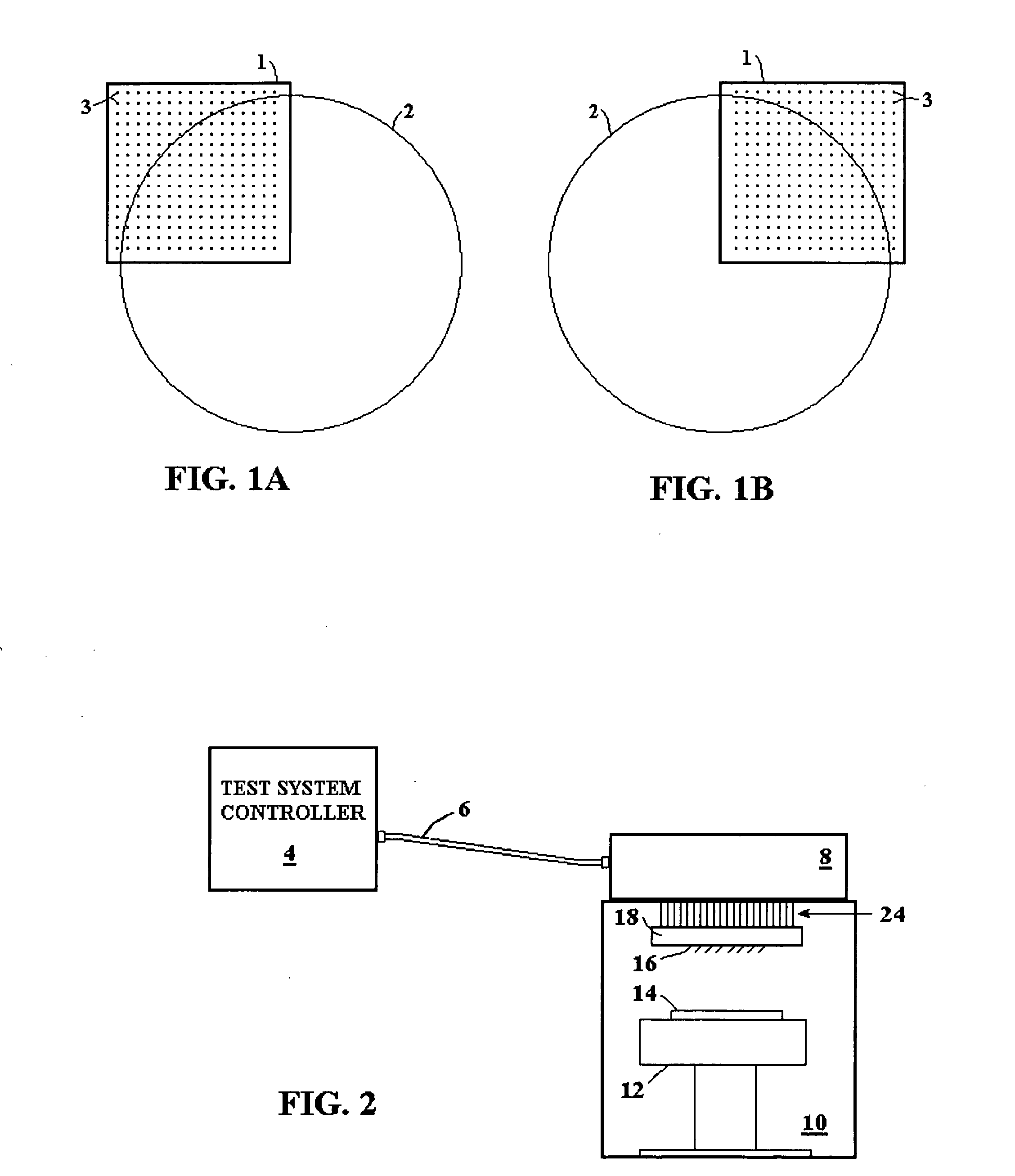

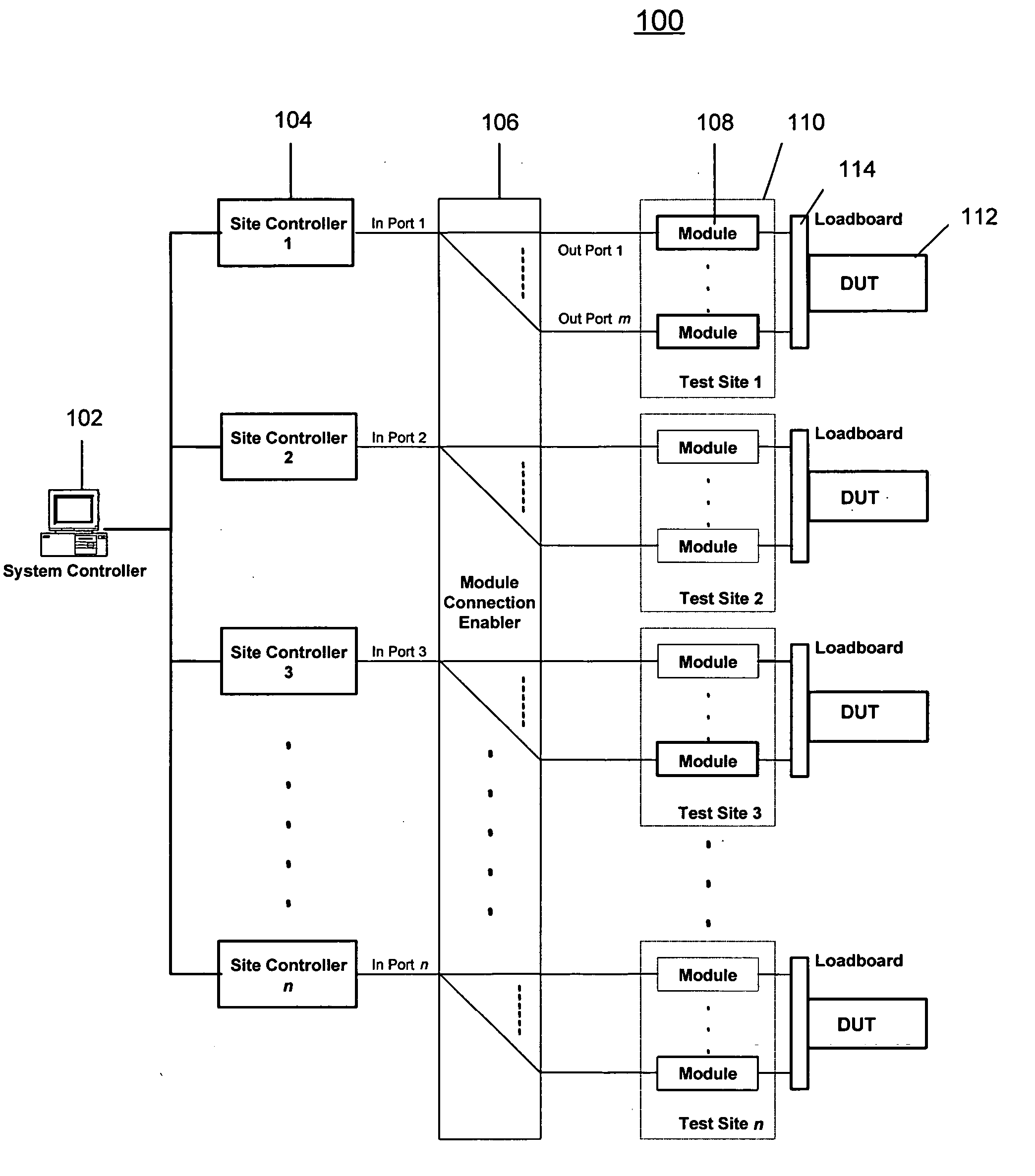

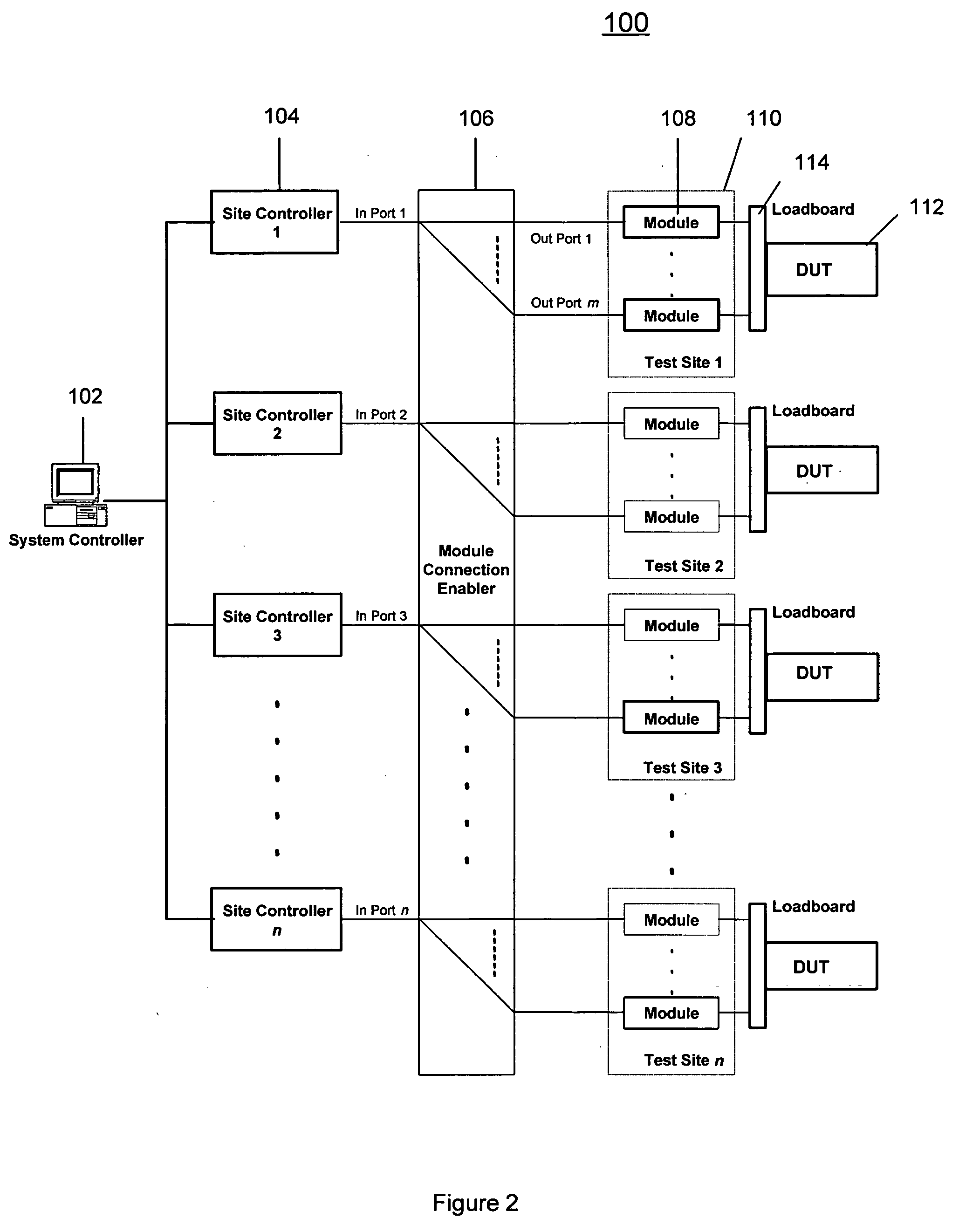

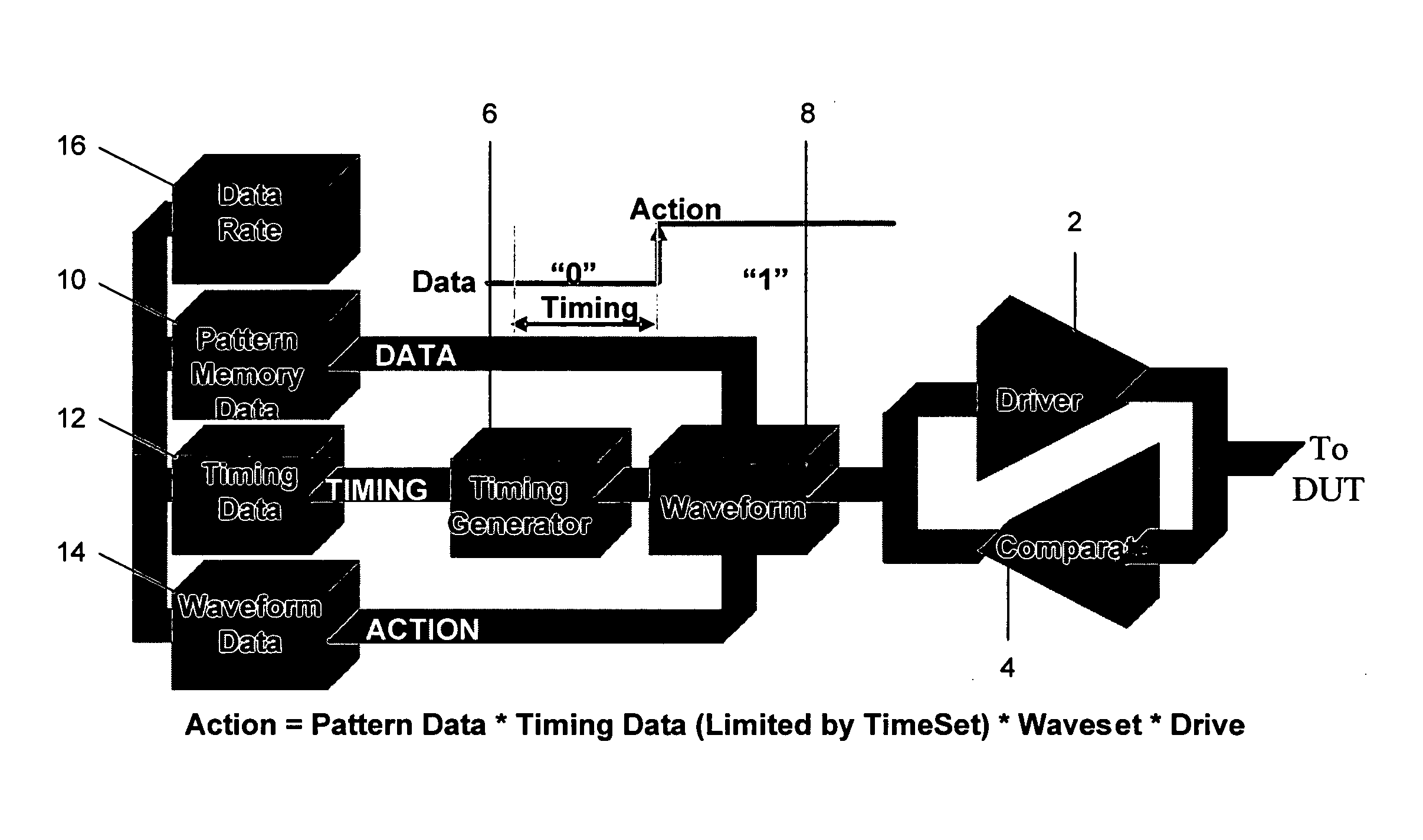

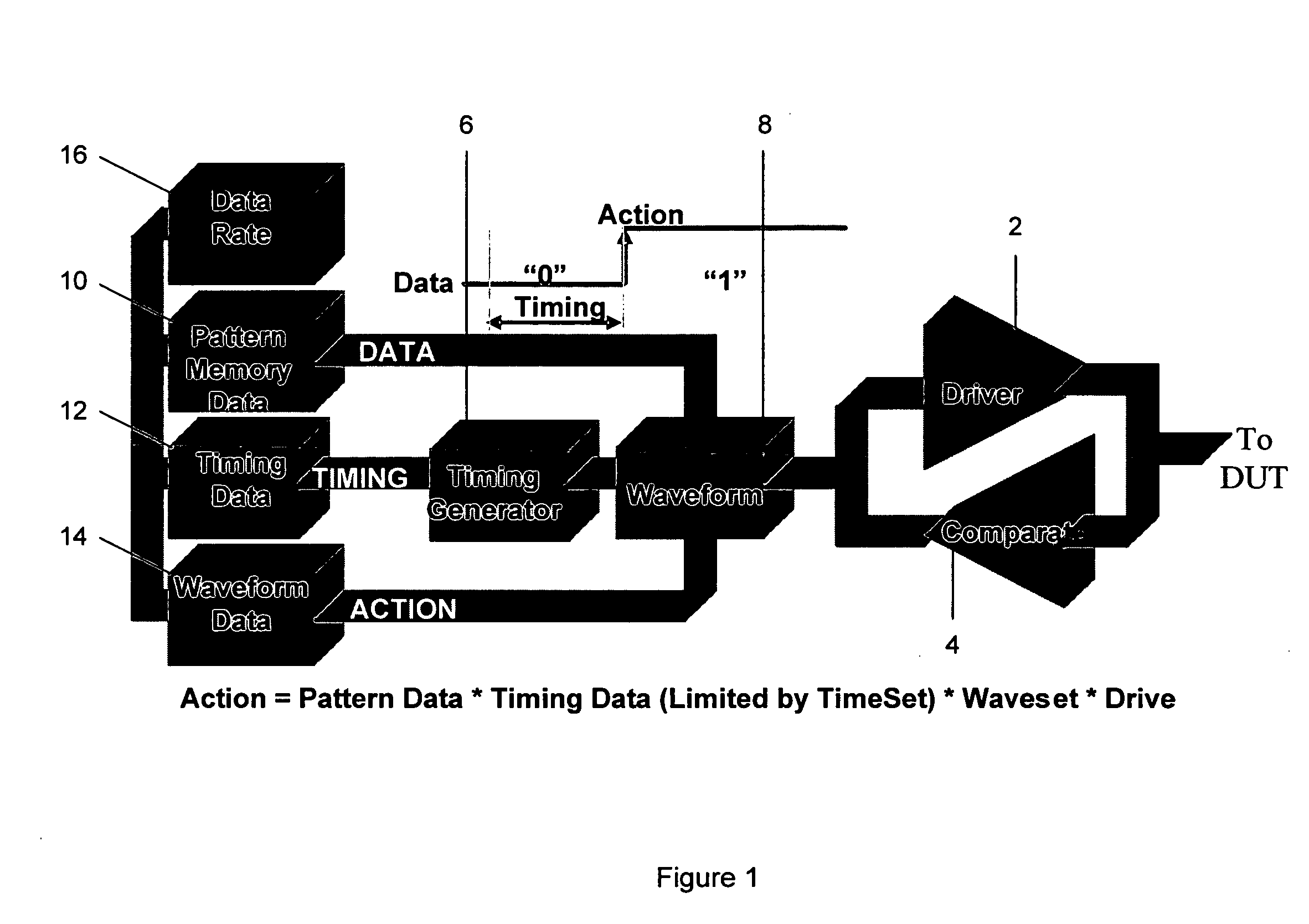

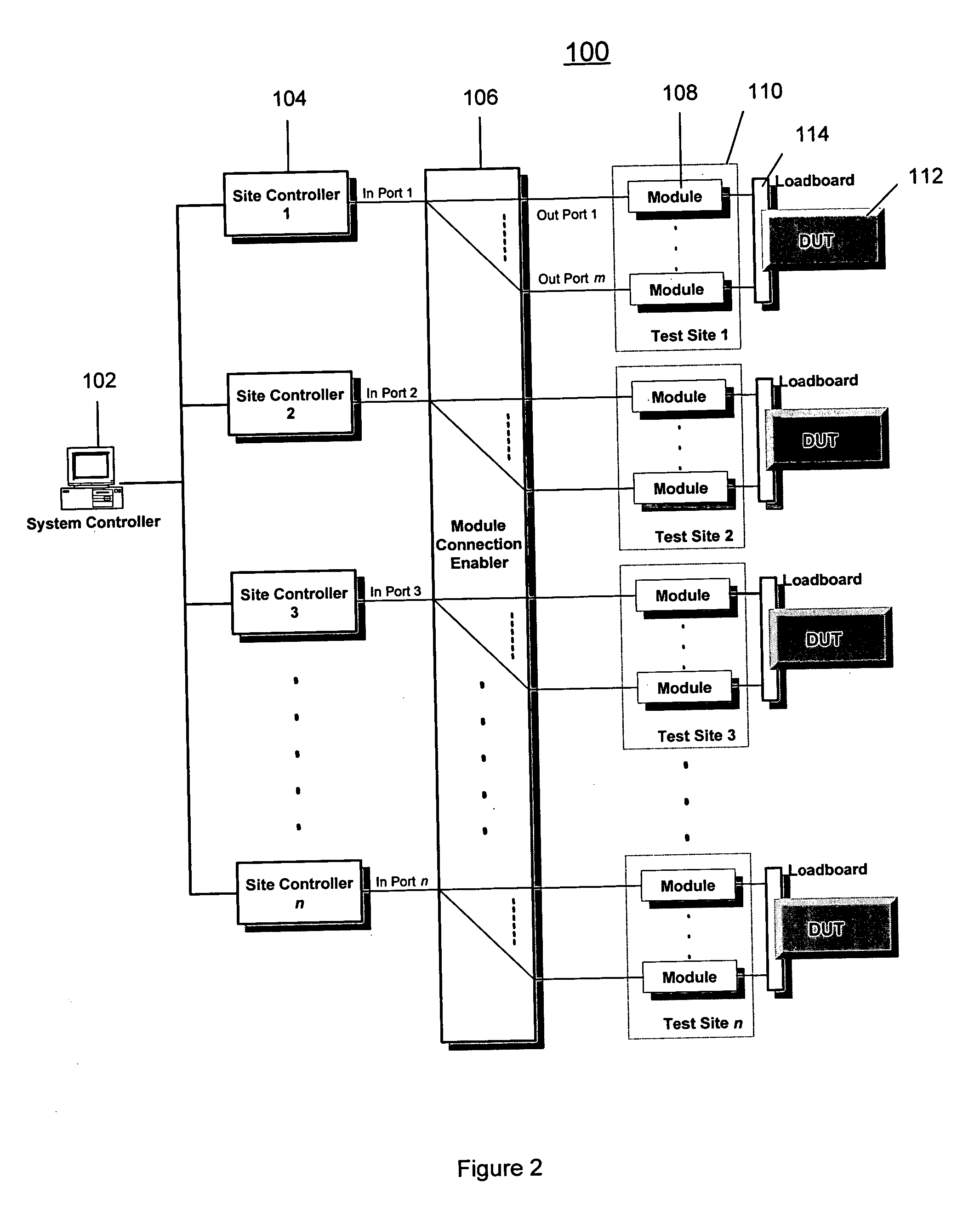

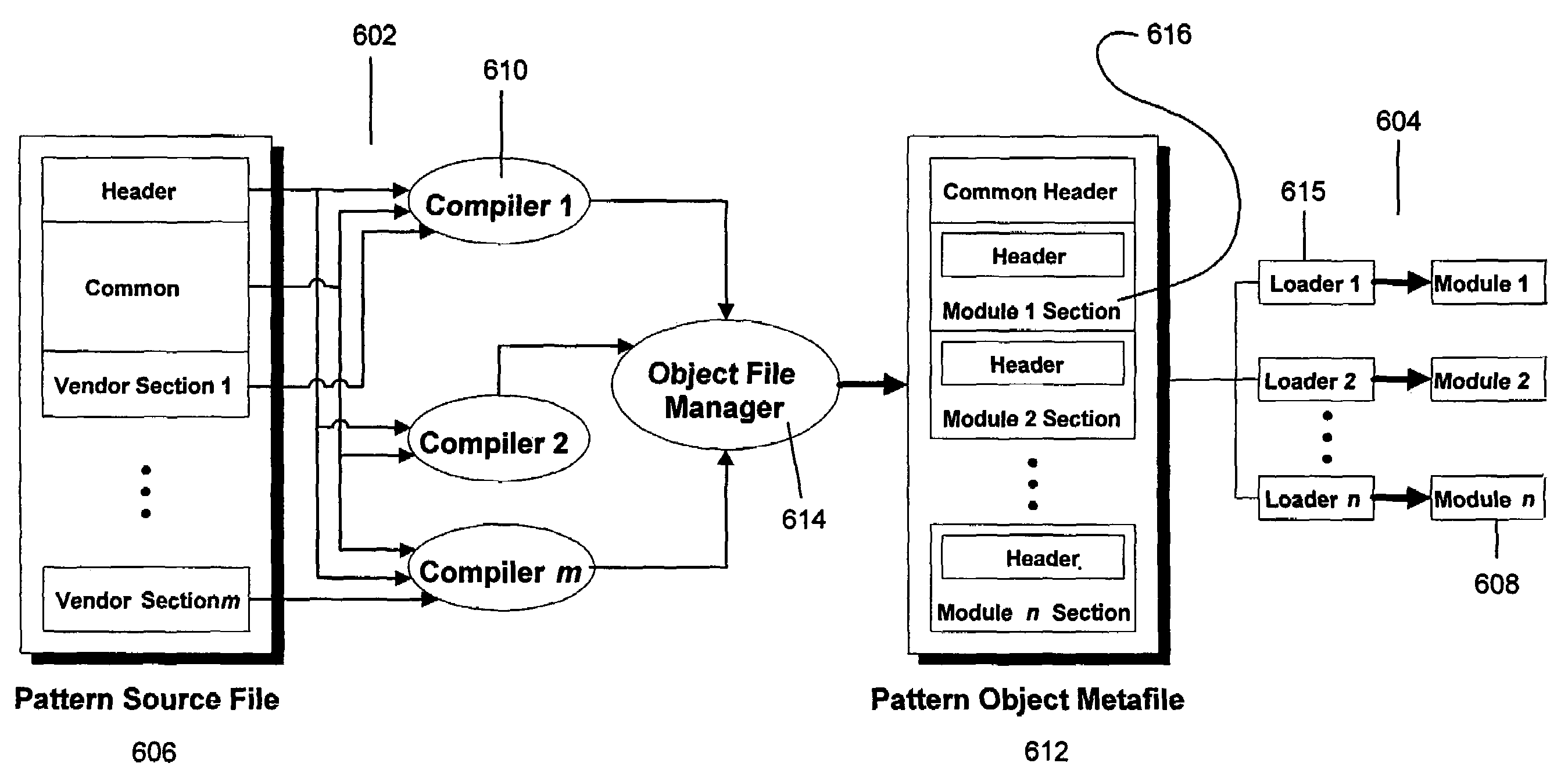

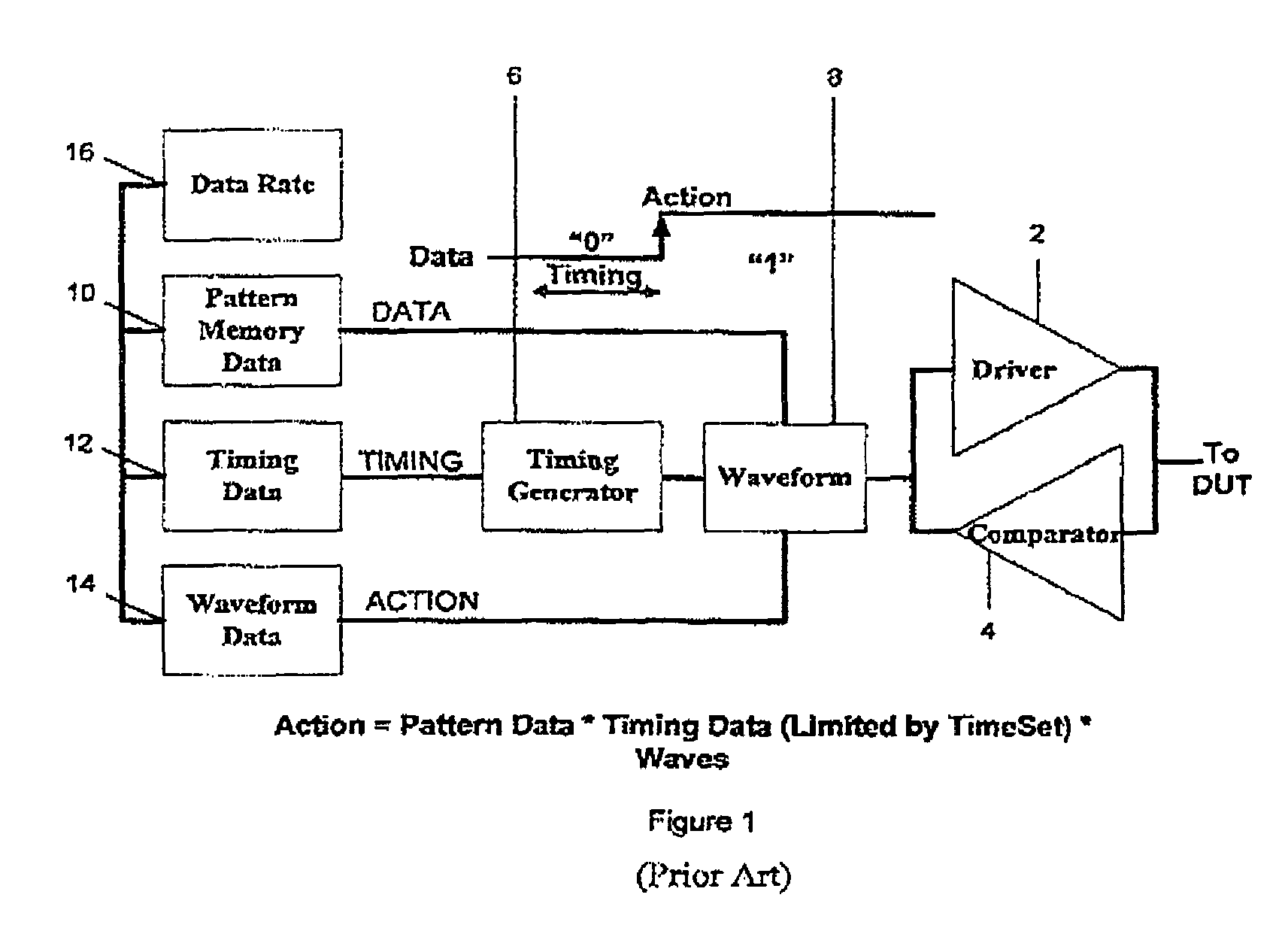

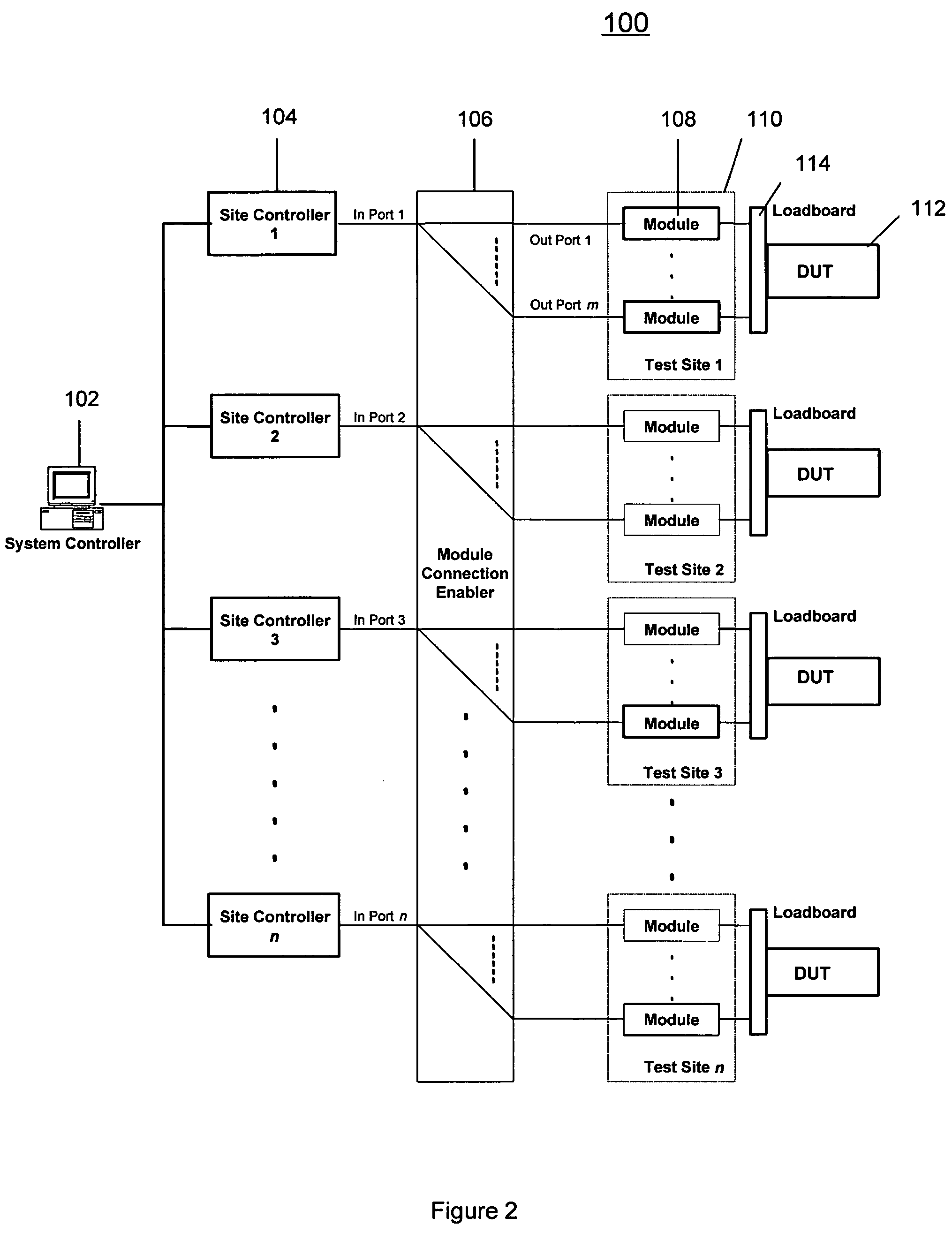

Method and structure to develop a test program for semiconductor integrated circuits

ActiveUS20050154550A1Digital circuit testingResistance/reactance/impedenceModularitySystem controller

A method for managing a pattern object file in a modular test system is disclosed. The method includes providing a modular test system, where the modular test system comprises a system controller for controlling at least one site controller, and where the at least one site controller controls at least one test module and its corresponding device under test (DUT). The method further includes creating an object file management framework for establishing a standard interface between vendor-supplied pattern compilers and the modular test system, receiving a pattern source file, creating a pattern object metafile based on the pattern source file using the object file management framework, and testing the device under test through the test module using the pattern object metafile.

Owner:ADVANTEST AMERICA R & D CENT

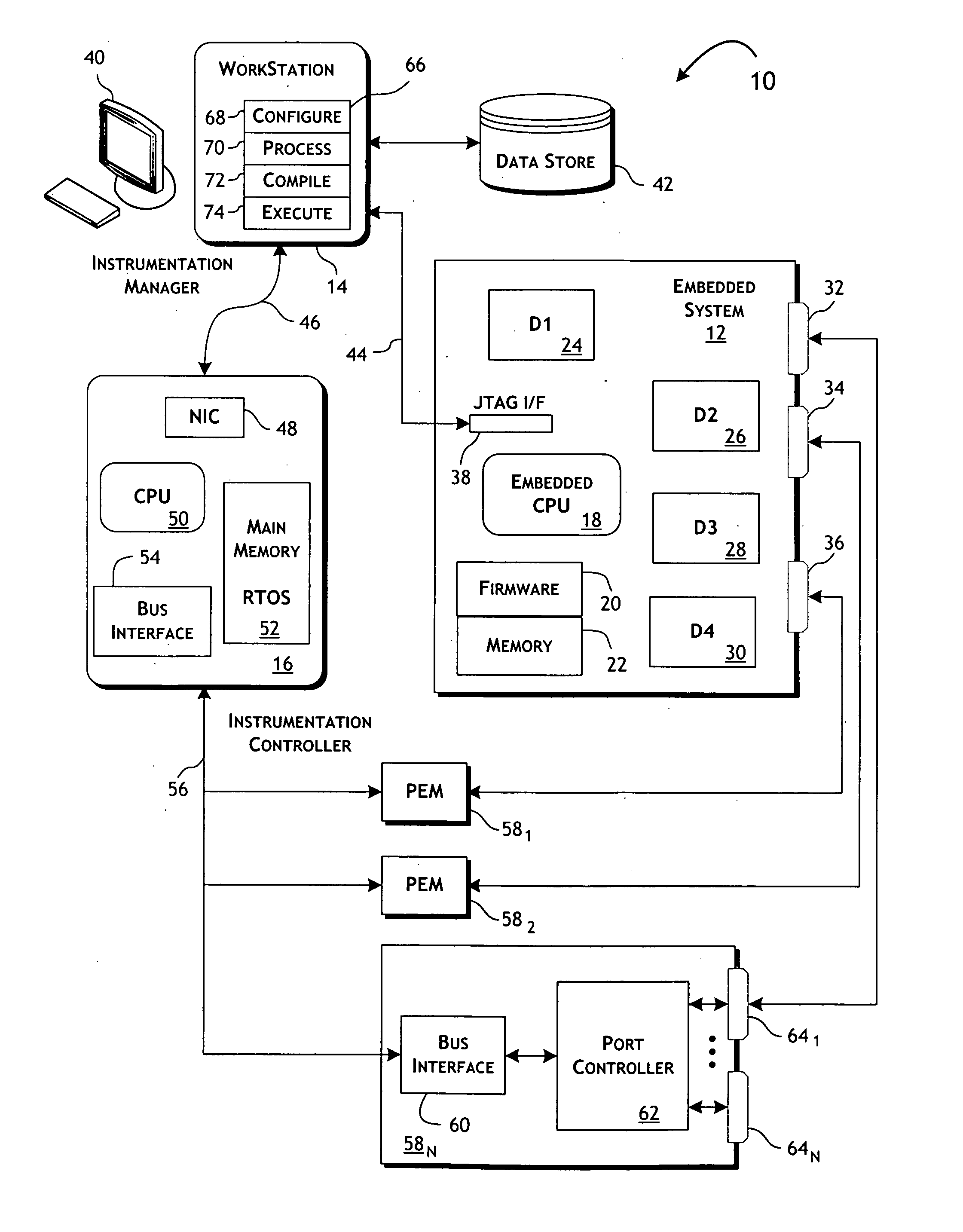

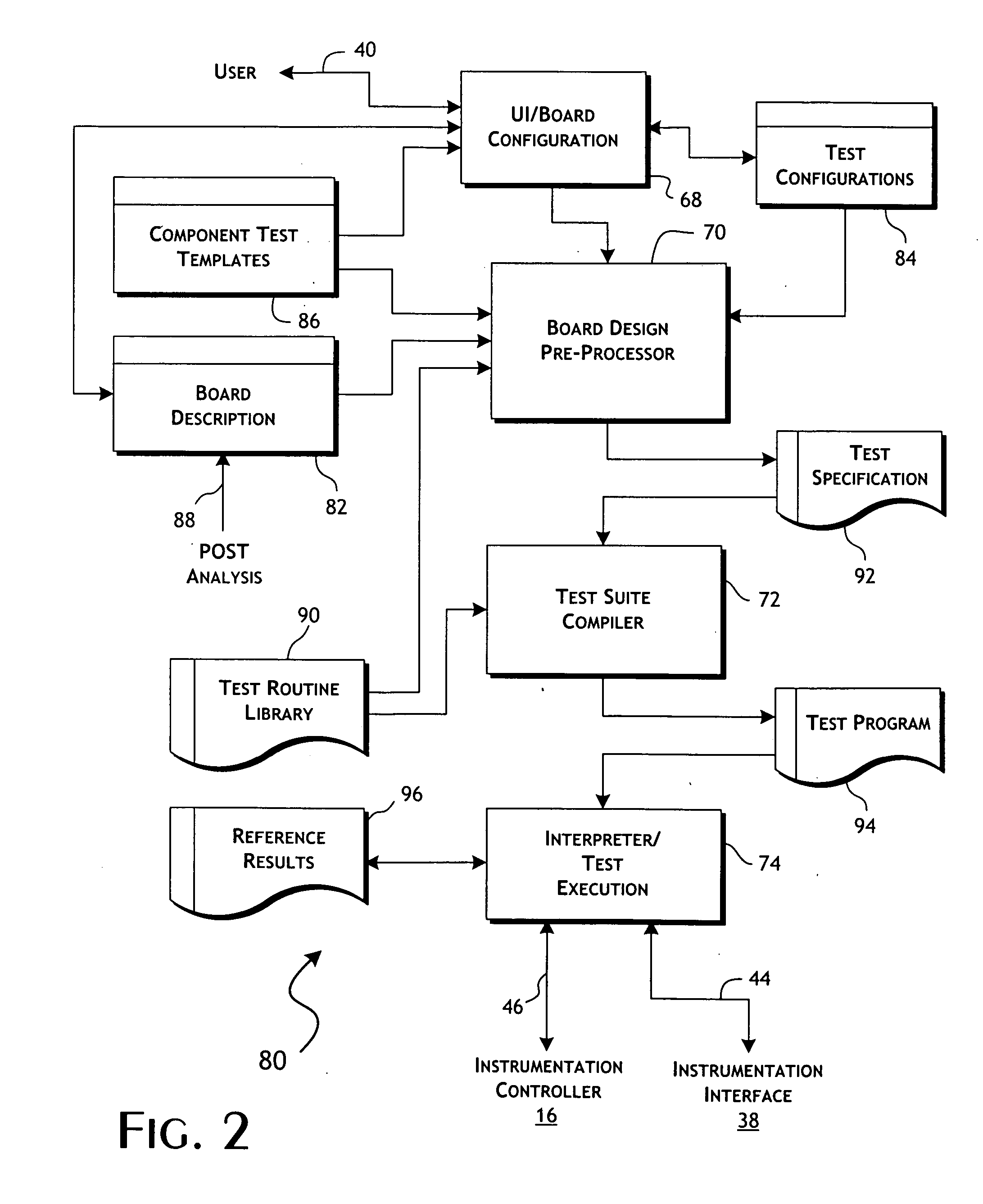

System and methods for functional testing of embedded processor-based systems

InactiveUS20070011522A1Test directlyElectronic circuit testingError detection/correctionSpecific testFunctional testing

Functional testing of an embedded system is performed by a test control system that implements a peripheral emulation module to interface with an externally accessible port of the embedded system. The test control system implements a test generation processor that operates to autonomously resolve abstracted component templates and embedded system description data, specific to the embedded system, to produce a corresponding specific test program. The test control system executes the test program to drive operation of the embedded processor unit to cause transfer of test data through the external interface, which is then autonomously compared to reference data derived through the execution of the test program and specific to the embedded system, whereby the comparison results reflect the correct operation of the embedded system.

Owner:DENNISTON WILLIAM B

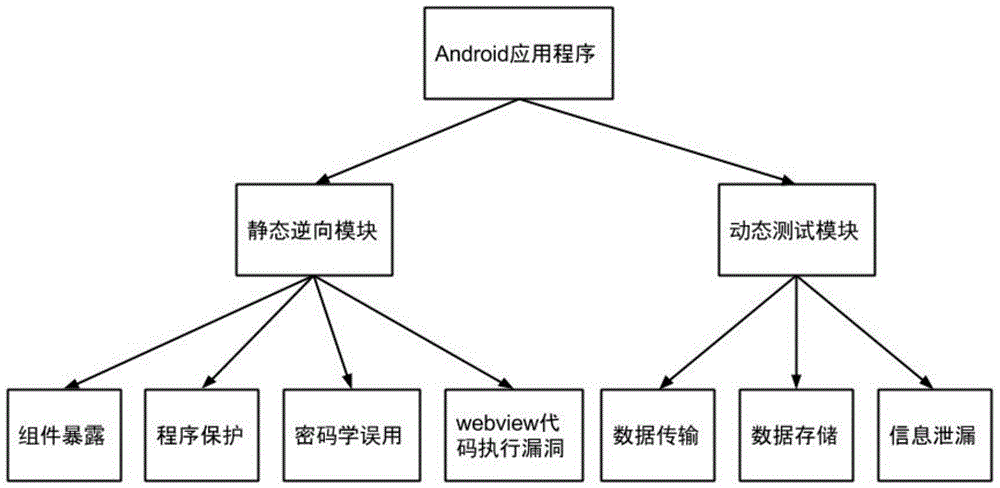

Universal method and universal system for performing safety testing on Android application programs

InactiveCN104484607AReduce false alarm ratePlatform integrity maintainanceApplication softwareSafety testing

The invention discloses a universal method and a universal system for performing safety testing on Android application programs. The universal method comprises the following steps of unpacking and decompiling a to-be-tested program to obtain an XML (extensive markup language) source code; then, through static analysis on configuration files and the code of the to-be-tested program, performing vulnerability detection and safety testing on the aspects of component exposed vulnerability, cryptology misuse, webview code execution vulnerability and code protection; then, performing actual running on the to-be-tested program, and configuring a network detection environment; finally, performing dynamic analysis, and performing dynamic vulnerability detection and the safety testing on three aspects of information leakage, data transmission safety and data storage safety, thus obtaining a vulnerability detection and safety testing report. According to the universal method and the universal system disclosed by the invention, by performing a static analysis and dynamic analysis combination mode on an optional Android application program and through a series of steps of detection and estimation, safety flaws and potential safety hazards existing in the aspects of design and implementation of the application program can be finally given out.

Owner:SHANGHAI JIAO TONG UNIV +1

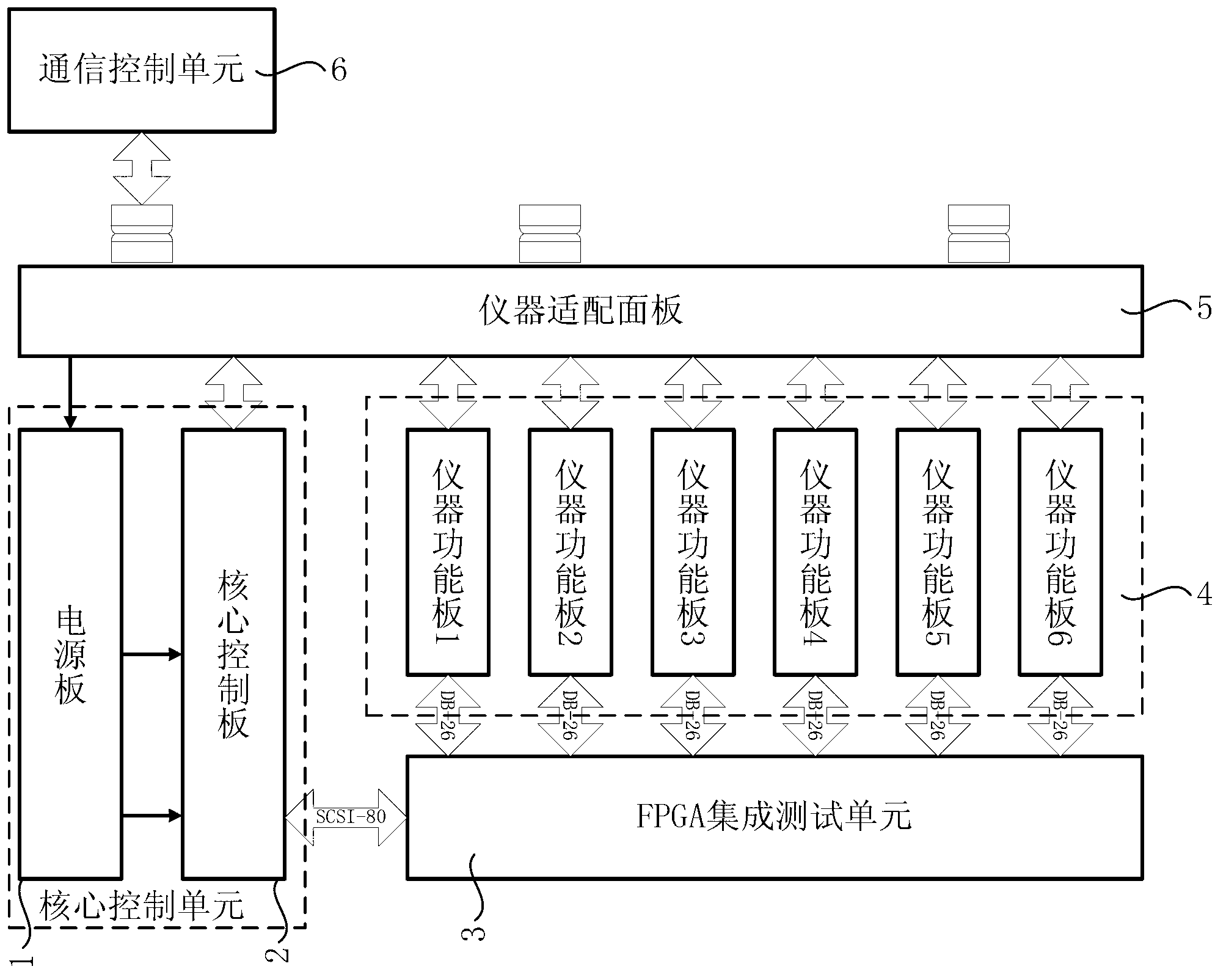

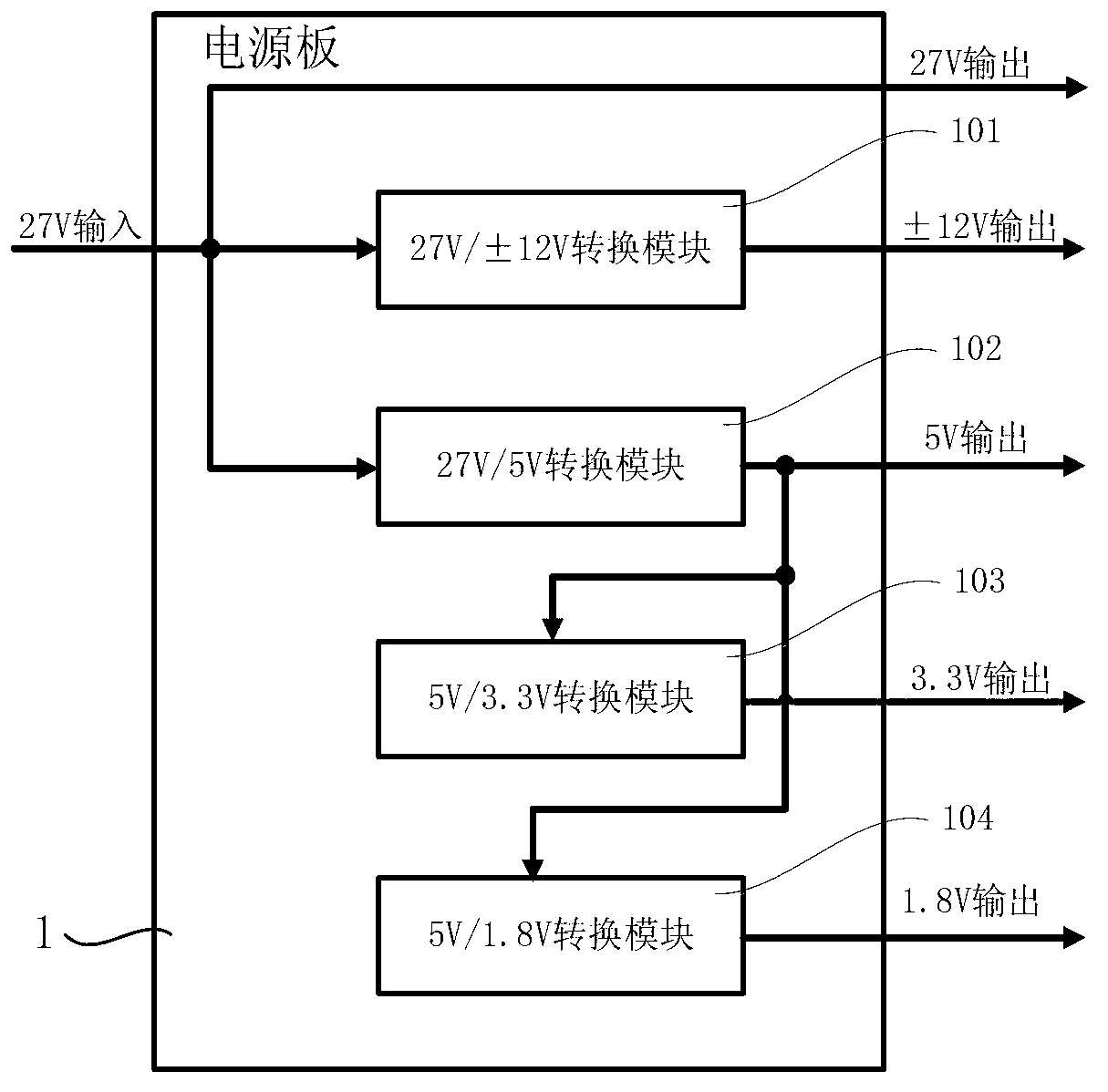

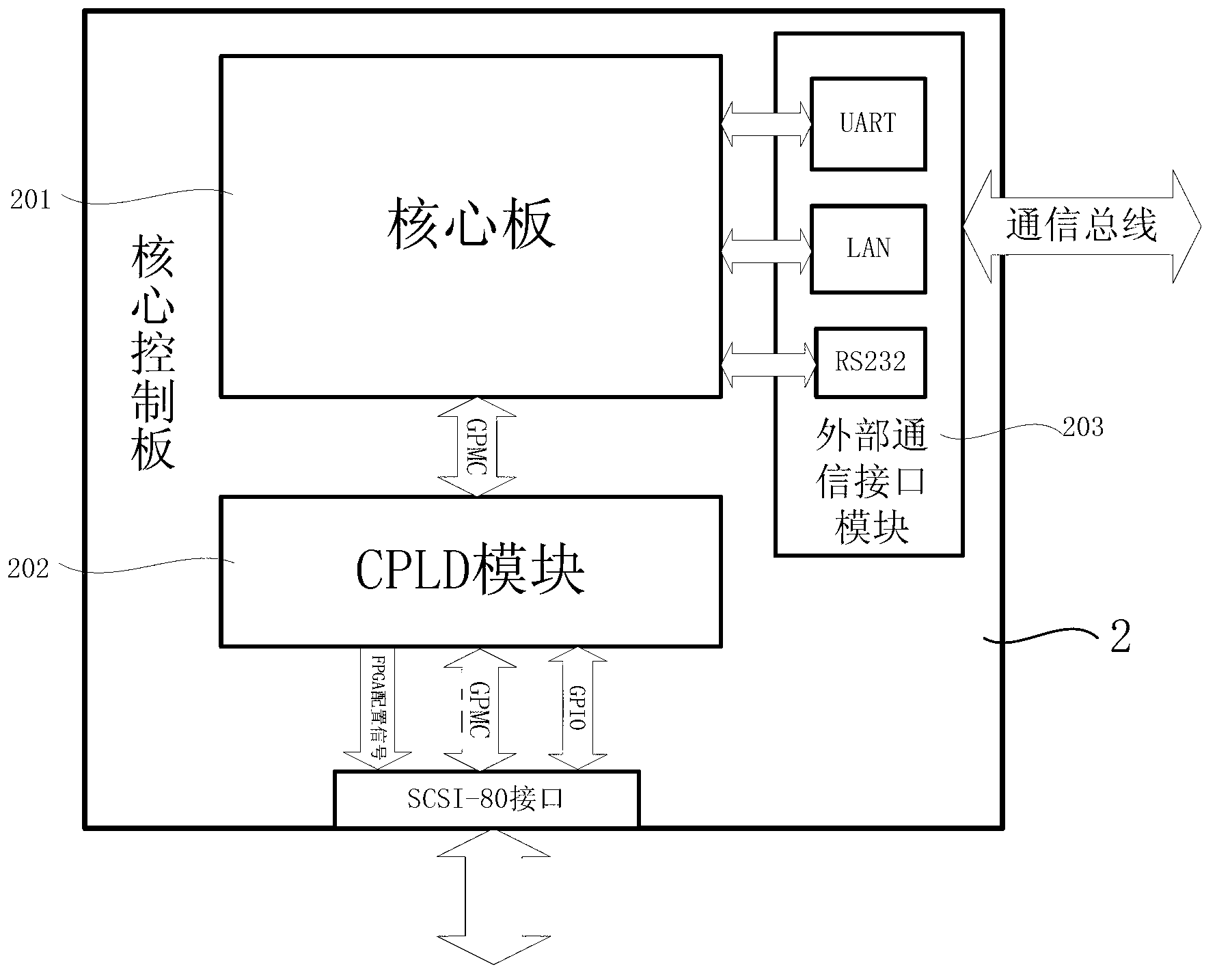

LX I embedded type reconfigurable general test platform capable of being used for on-site test

ActiveCN103257910AEasy for secondary developmentGuaranteed versatilityDetecting faulty computer hardwareInstrument functionWeb service

The invention discloses an LX I embedded type reconfigurable general test platform capable of being used for an on-site test. The test platform mainly comprises a core control unit, an FPGA integrated test unit, an instrument function unit, a test program set, a Web server and the like. Modularized hardware design is reliably and tightly connected with a function module through a compact and firm portable machine box. The core control unit finishes control and communication of a whole system. The integrated test unit mainly completes logic functions of test instruments. The instrument function unit mainly completes conversion of signals. On the basis of LX I standard design, the test platform has multiple communication modes, is suitable for mobile tests, and facilitates secondary development. Hardware is designed in a modularized mode, and is compact in structure, small in size and low in weight. Software meets standards such as IVI, SCPI, ATML and the like, and is strong in generality. The instruments have the strong data processing ability and have functions of multi-channel parallel testing and online reconfiguration of the hardware and the software. What is needed is a browser during use of the instruments, the instruments can be operated remotely and the online reconfiguration of the instruments is achieved.

Owner:BEIHANG UNIV

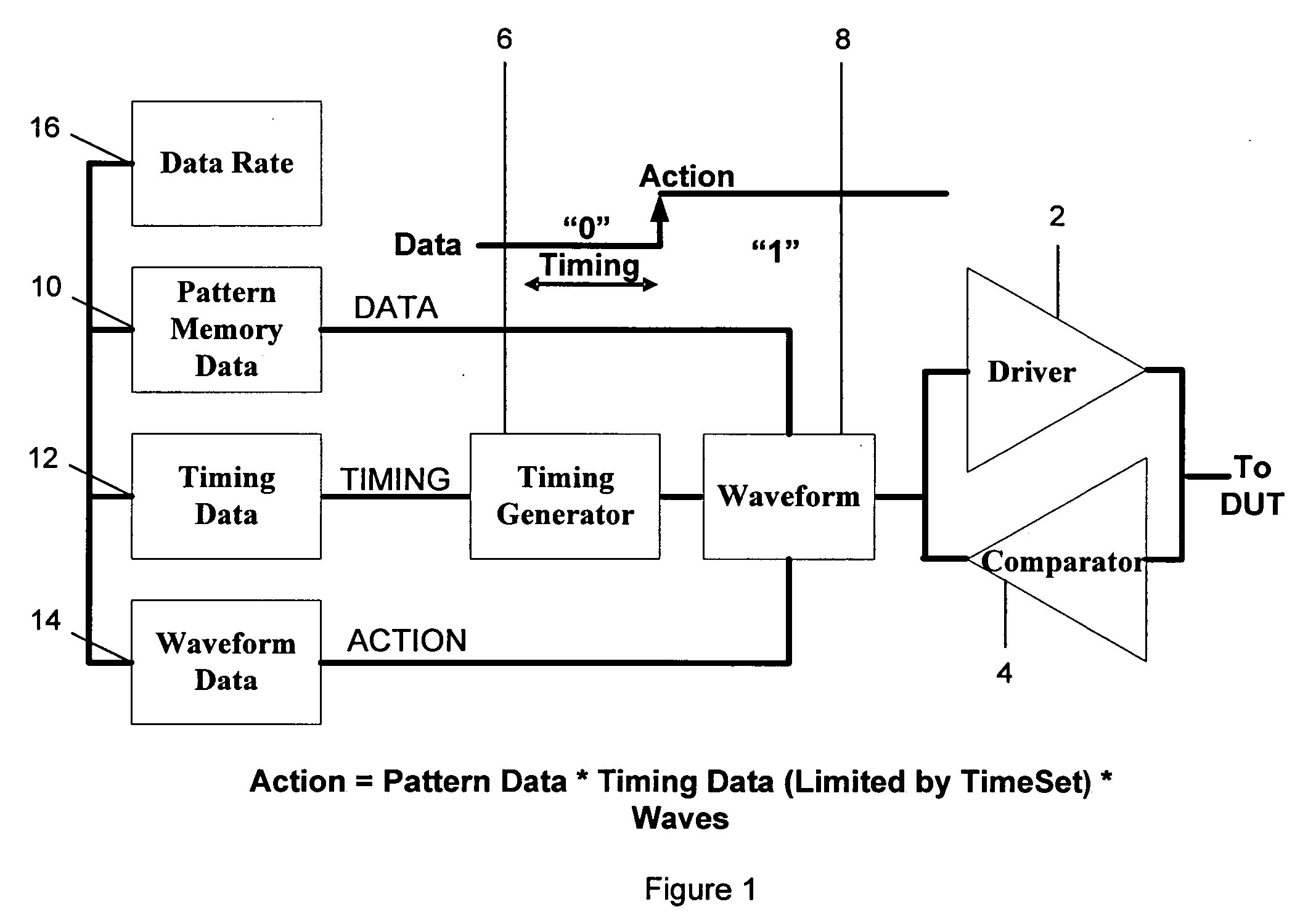

Method and structure to develop a test program for semiconductor integrated circuits

ActiveUS20050154551A1Shorten development timeError is identifiedTransformation of program codeDigital circuit testingProgramming languageSemiconductor

A method for developing a test program for a semiconductor test system is disclosed. The method includes describing a test plan file in a test program language (TPL), where the test plan file describes at least one test of the test program, describing a test class file in a system program language (SPL) and a corresponding pre-header file of the test class file in the TPL, where the test class file describes an implementation of the at least one test of the test program, and generating the test program using the test plan file, the test class file, and the pre-header file.

Owner:ADVANTEST AMERICA R & D CENT

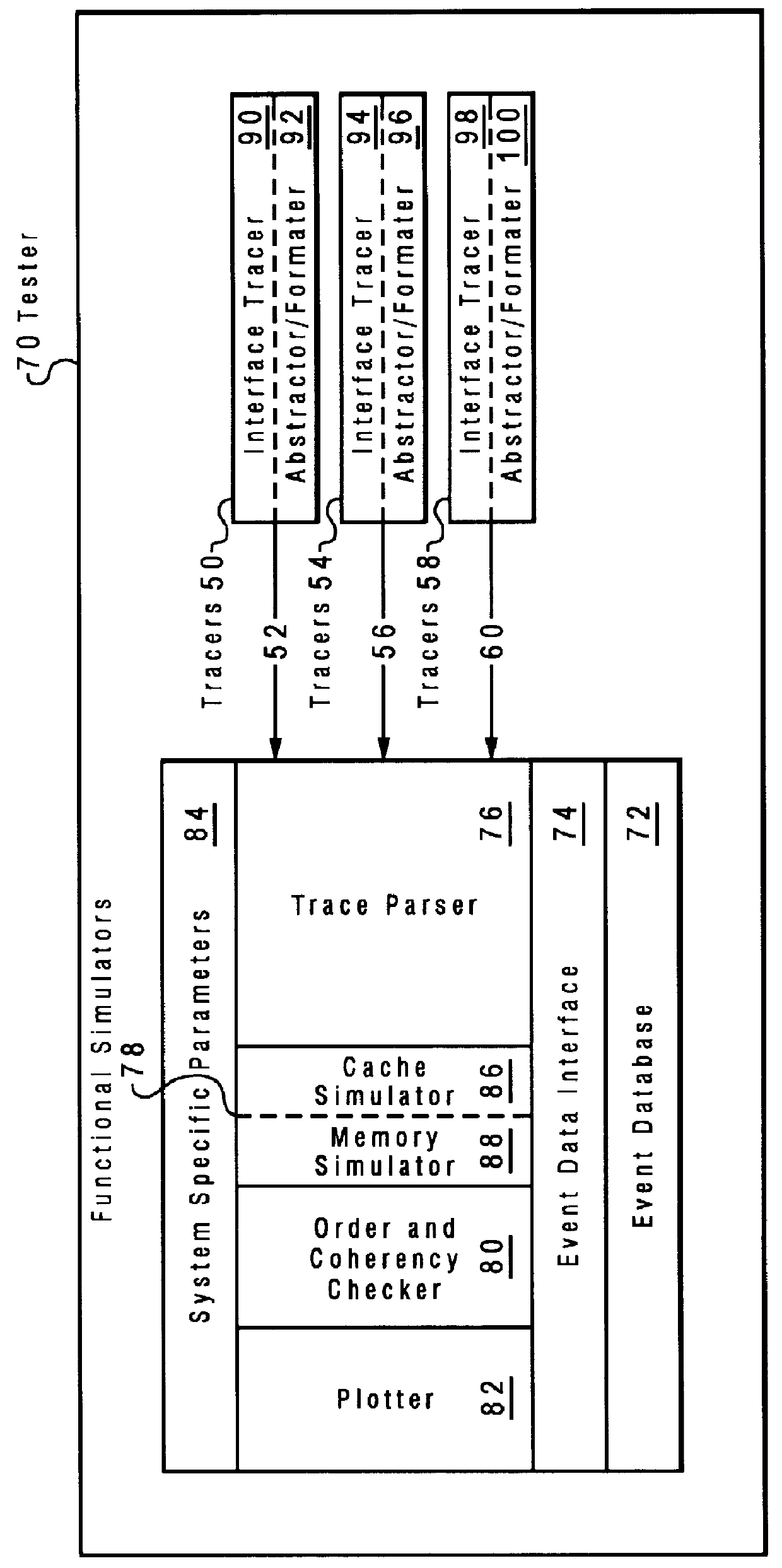

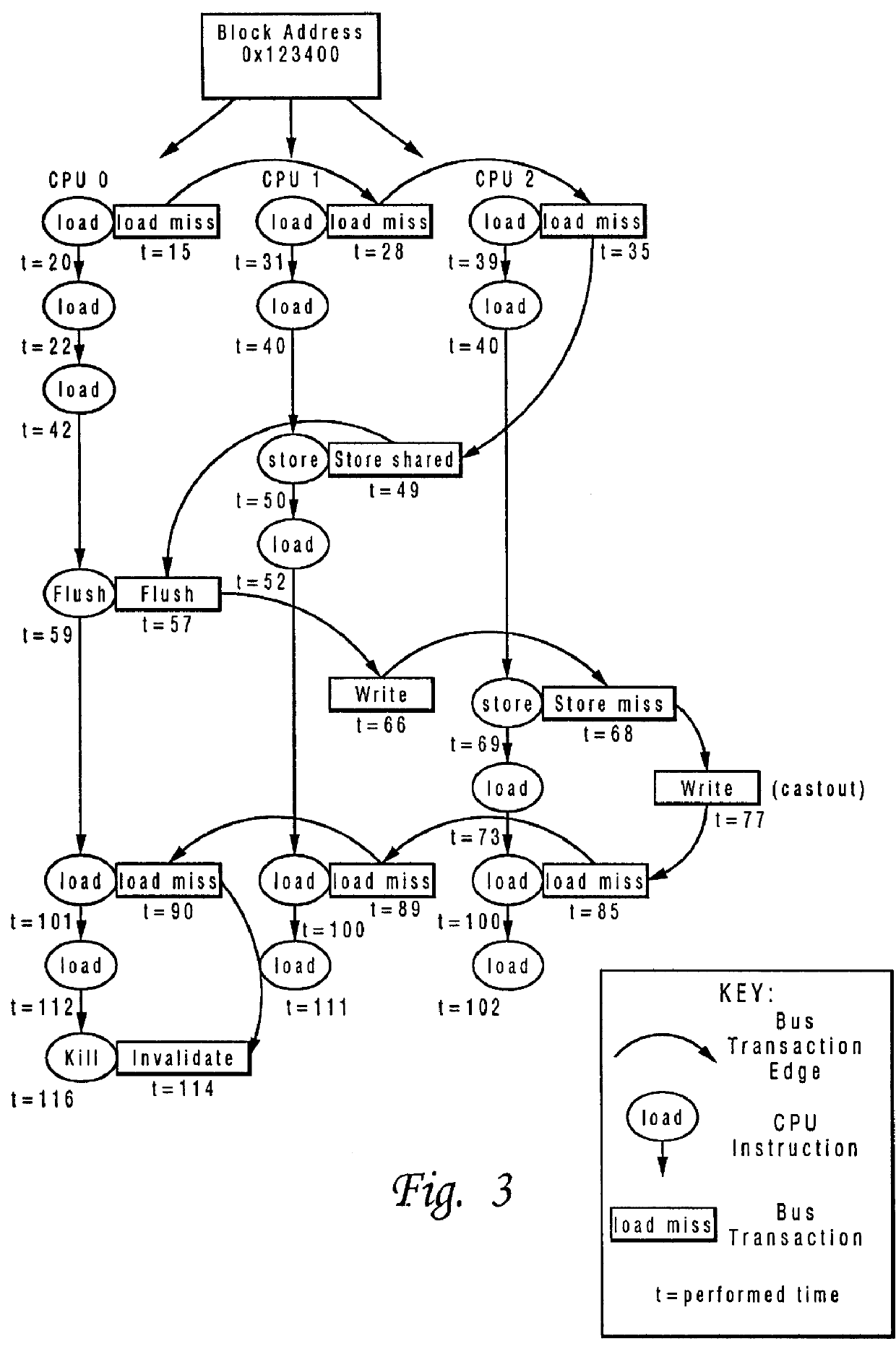

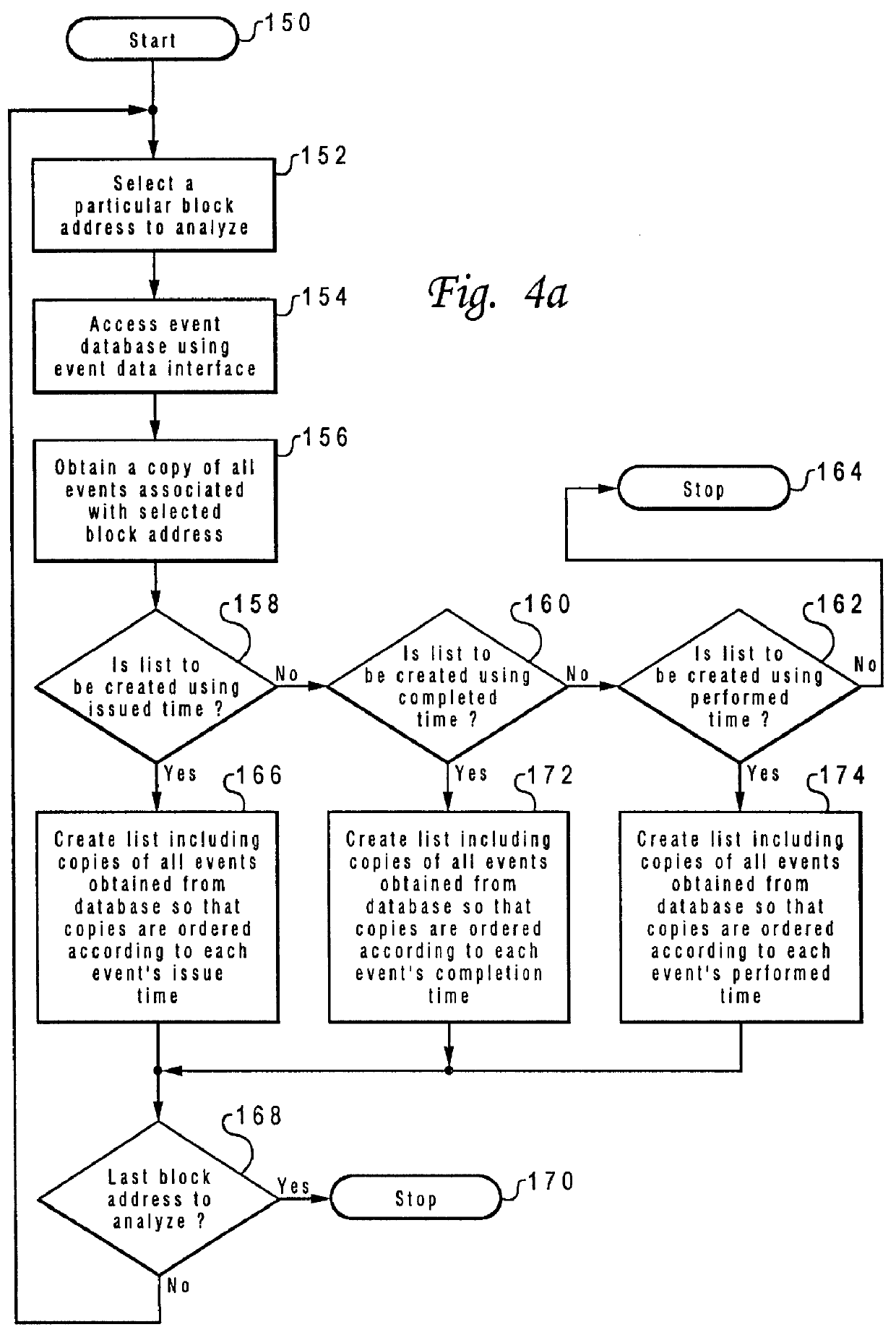

Method and system for testing a multiprocessor data processing system utilizing a plurality of event tracers

A multiprocessor data processing system includes a shared main memory and a plurality of processors connected to the memory utilizing a system bus. Data is transferred utilizing the system bus. The plurality of processors include a first processor and a second processor. The first processor includes a first cache, and the second processor includes a second cache. The multiprocessor data processing system executes a test program. During execution of the test program, a first and a second trace are generated. The first trace is generated by monitoring all events occurring at a first location within the system. The second trace is generated by monitoring all events occurring at a second location within the system. Each event is associated with a time of occurrence of that event. The first trace includes each event which was monitored at the first location and the time associated with each event. The second trace includes each event which was monitored at the second location and the time associated with each event. The first and second traces are stored and utilized to determine if the multiprocessor data processing system is operating correctly.

Owner:IBM CORP

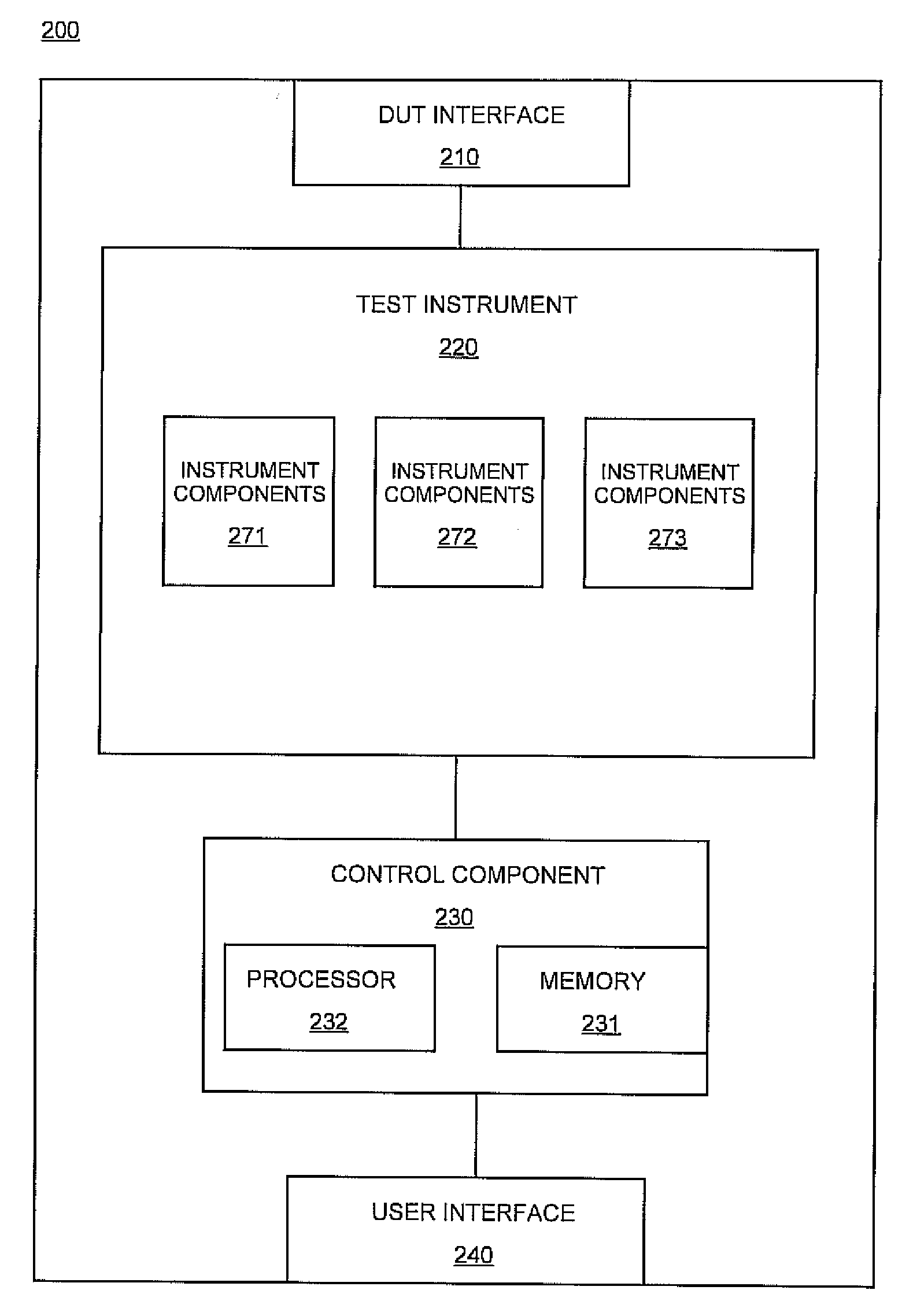

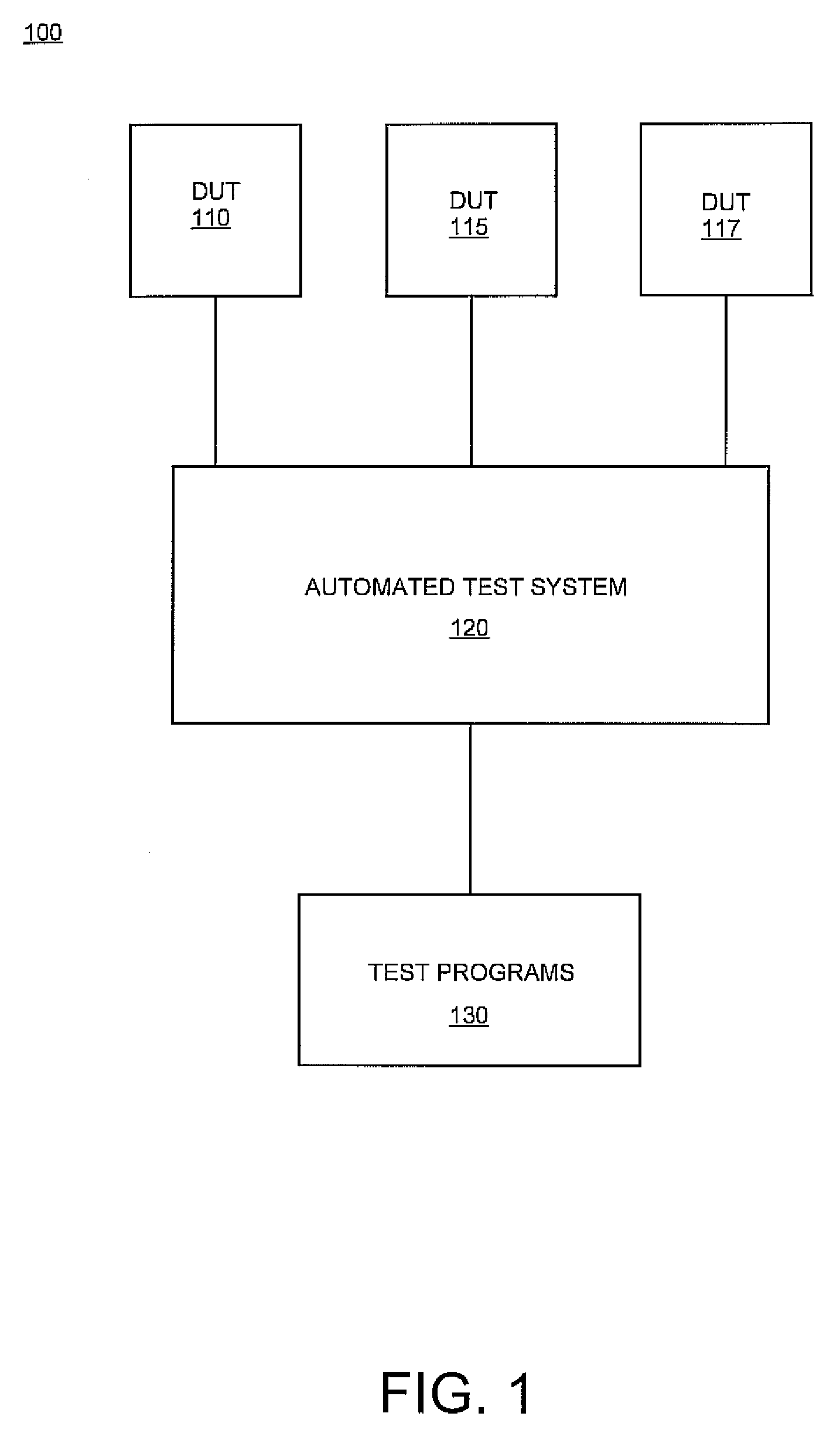

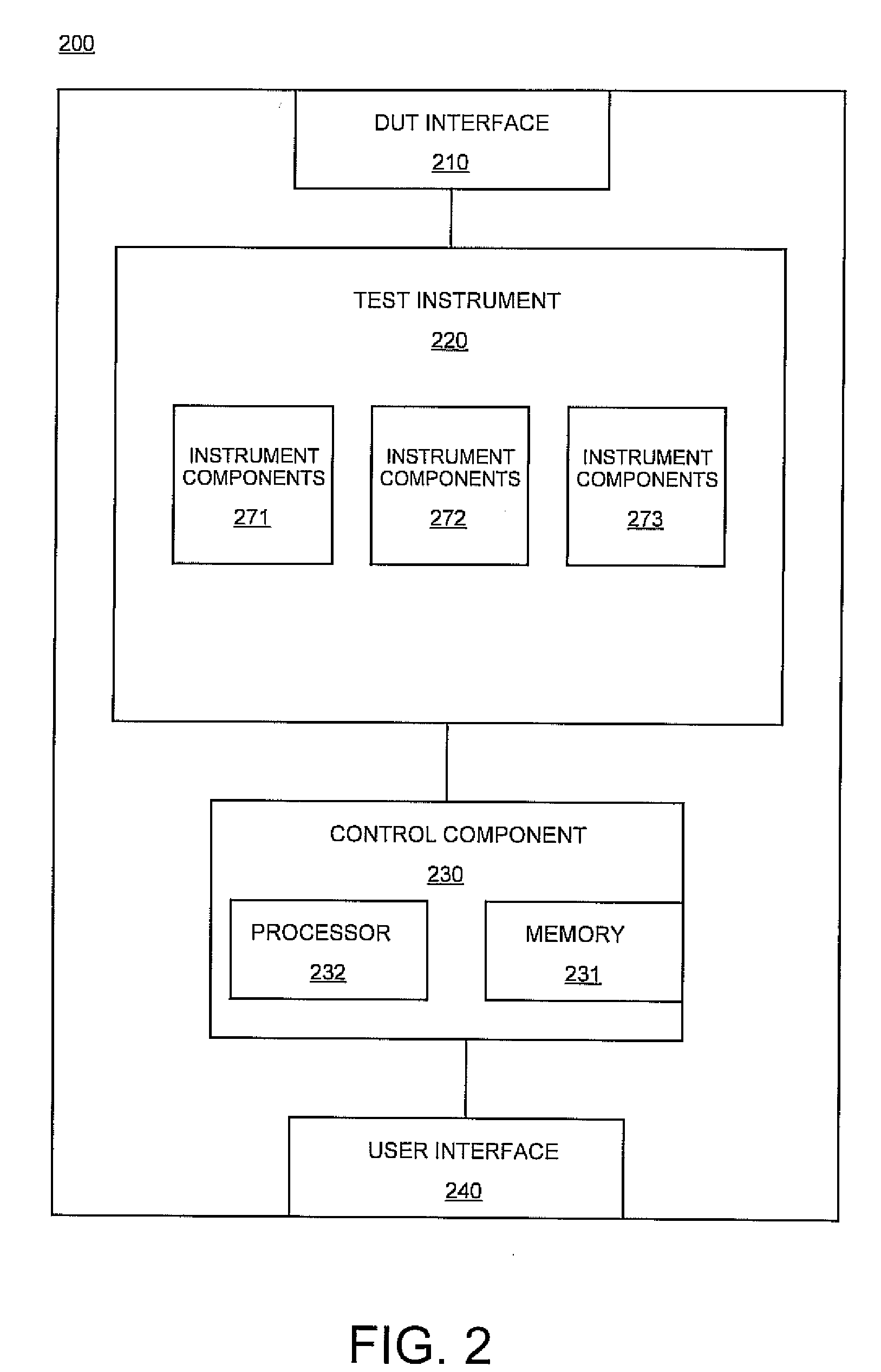

Automated test system and method

InactiveUS20100023294A1Special data processing applicationsAutomated test systemsComputer hardwareEquipment under test

An efficient automated testing system and method are presented. In one embodiment, an automated testing system includes a control component and an automated test instrument for testing a device or a plurality of devices (e.g., packages or wafers containing multiple independent different devices) under test. The automated test instrument component performs testing operation on the device or devices under test (DUT). The control component manages testing activities of a test instrument testing the device under test, including managing implementation of a plurality of test programs loaded as a group. In one exemplary implementation, the automated test system also includes a DUT interface and a user interface. The device under test interface interfaces with a device or devices under test.

Owner:CREDENCE SYSTEMS

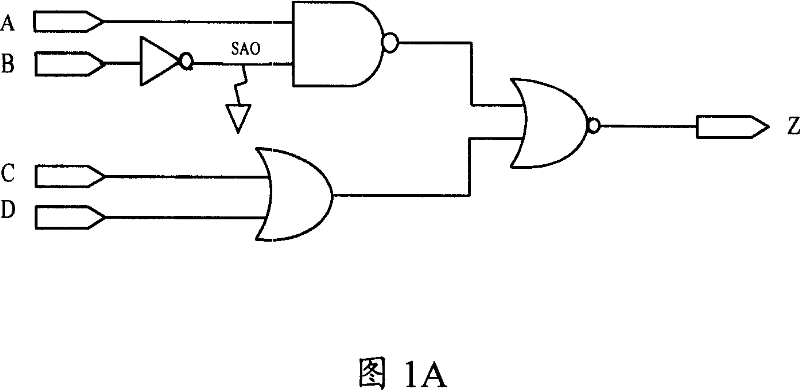

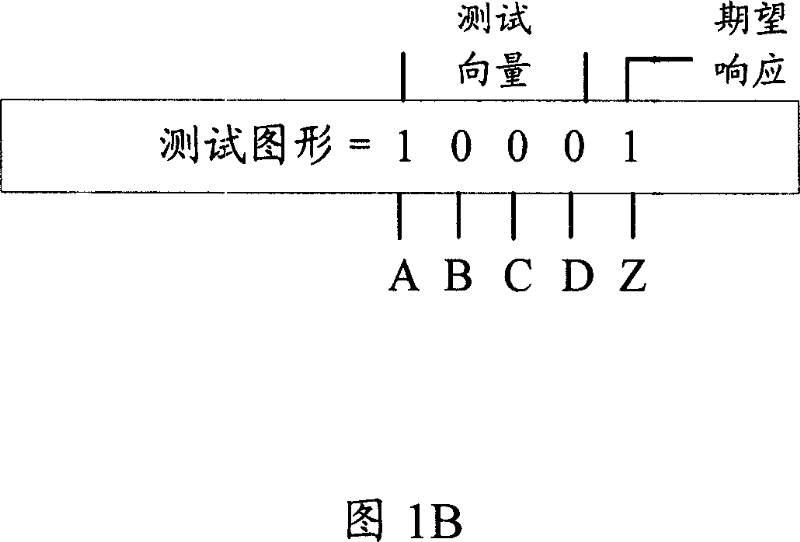

Method and device for testing chip

InactiveCN101038325AEasy to debugReduce testing costsDigital circuit testingTester deviceTest response

The invention discloses a device for testing the chip, including the mutually stand-alone server, simulator, control circuit board and running circuit board, in which: the server is used for creating the test program according to the test tasks, and output to the simulator; the simulator is connected with the server for simulation processing of the test program, and creating the simulation document with test data and sending to the control circuit board; the control circuit board is connected with the simulator for reading the relevant test vectors from the simulation document, and sending this test vector to the running circuit board, and decide whether the relevant chip is in good conditions or not according to the test response feedback from the running circuit board; the running circuit board is connected with the control circuit board for testing the relevant chip according to the test vector from the control circuit board, and sending the test response to the control circuit board. Thus, during the batch production testing of chip, the automatic tester with expensive rent may be not rented, thereby greatly reduce the test cost. The invention still discloses a test method for chip.

Owner:VIMICRO CORP

Probe card assembly including a programmable device to selectively route signals from channels of a test system controller to probes

InactiveUS7245134B2High densityLong life cycleSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsProbe cardTest engineer

Owner:FORMFACTOR INC

Method and structure to develop a test program for semiconductor integrated circuits

ActiveUS7209851B2Digital circuit testingResistance/reactance/impedenceSystem controllerSemiconductor

A method for managing a pattern object file in a modular test system is disclosed. The method includes providing a modular test system, where the modular test system comprises a system controller for controlling at least one site controller, and where the at least one site controller controls at least one test module and its corresponding device under test (DUT). The method further includes creating an object file management framework for establishing a standard interface between vendor-supplied pattern compilers and the modular test system, receiving a pattern source file, creating a pattern object metafile based on the pattern source file using the object file management framework, and testing the device under test through the test module using the pattern object metafile.

Owner:ADVANTEST AMERICA R & D CENT