Patents

Literature

174 results about "Test generator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

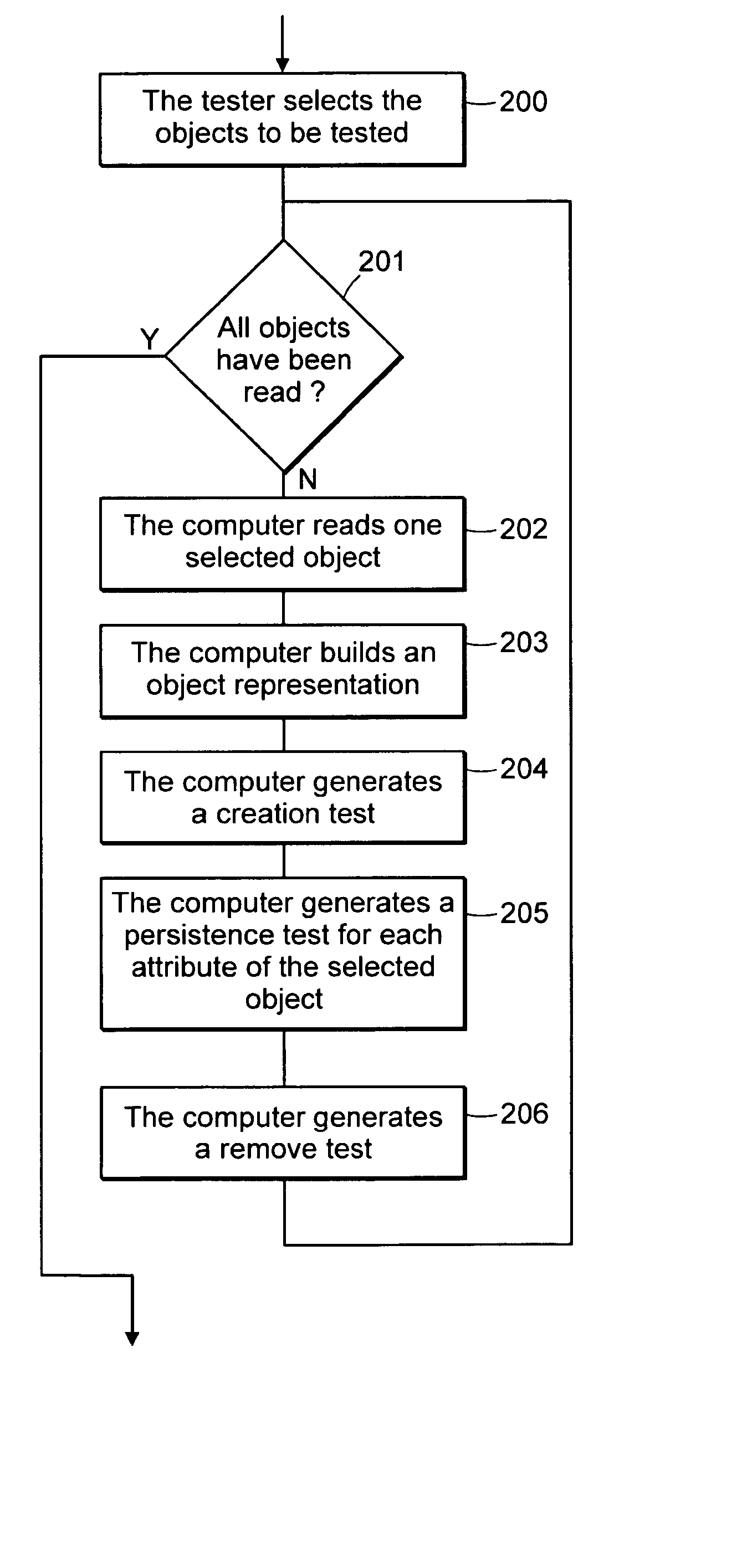

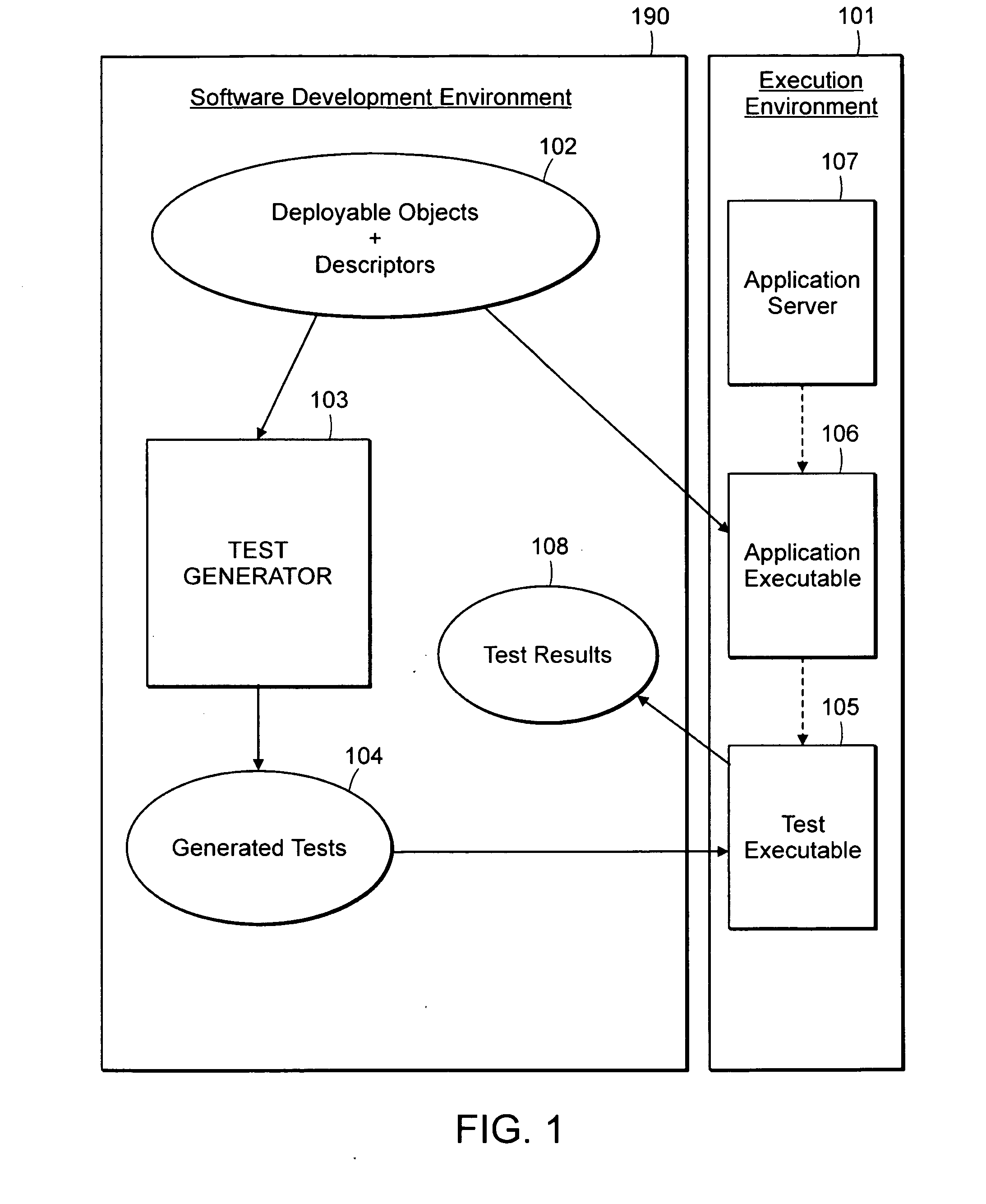

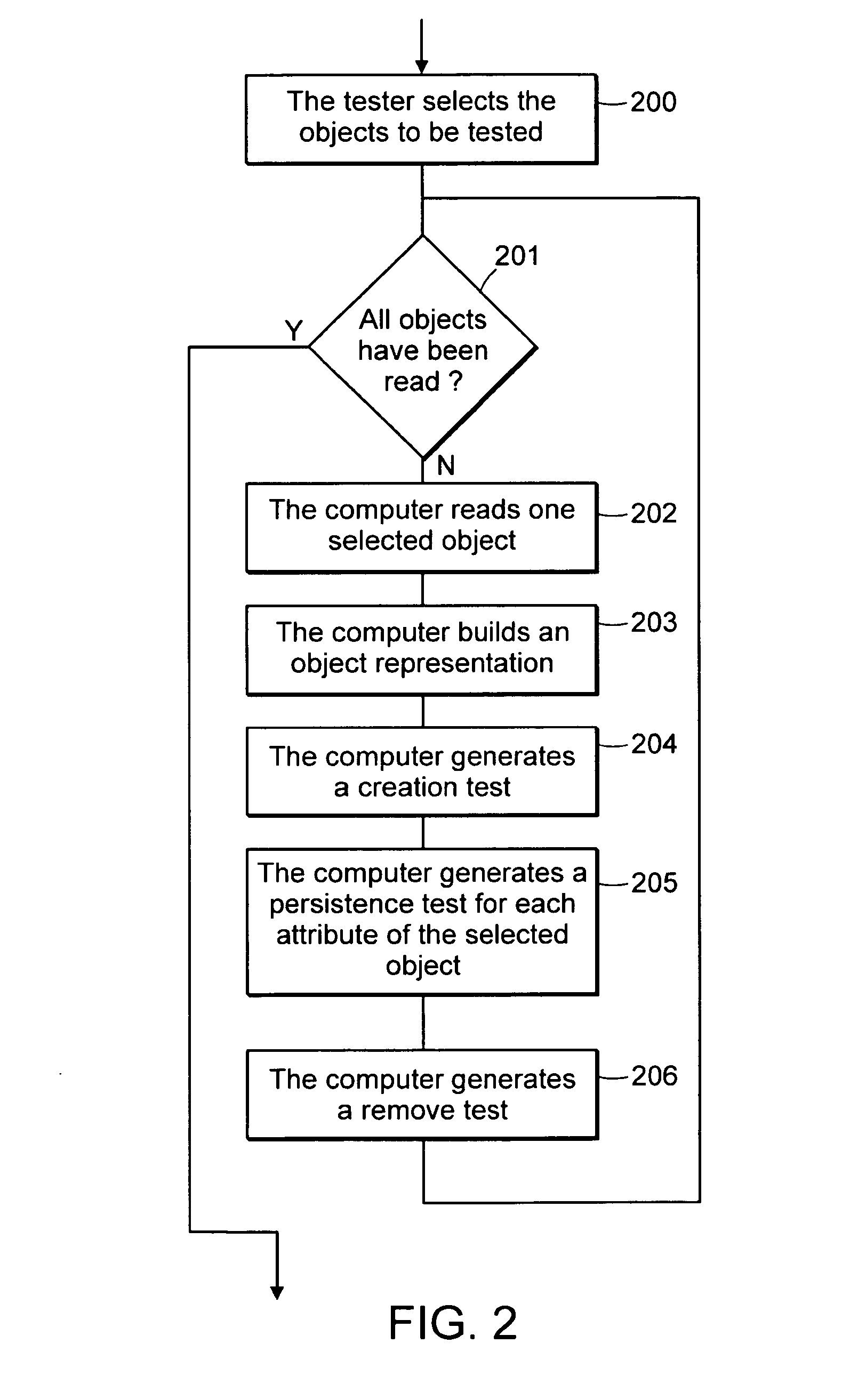

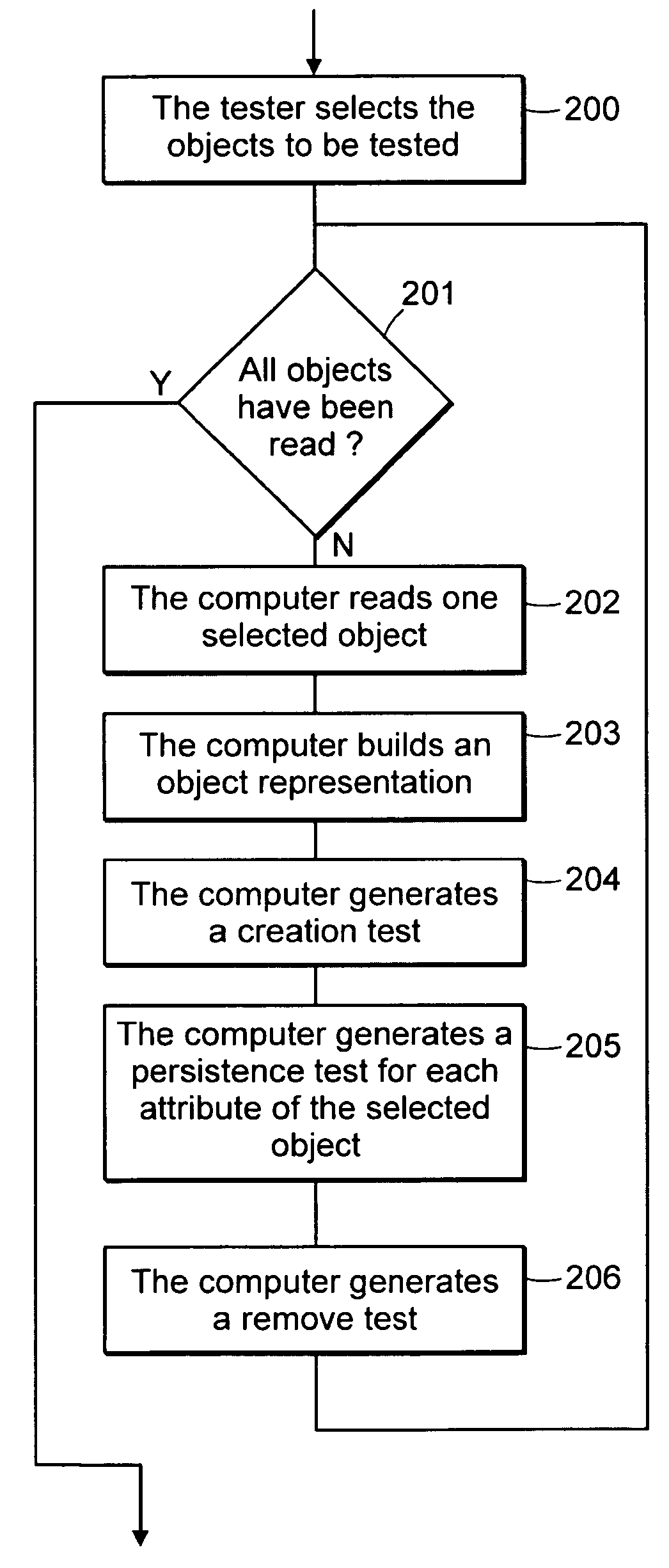

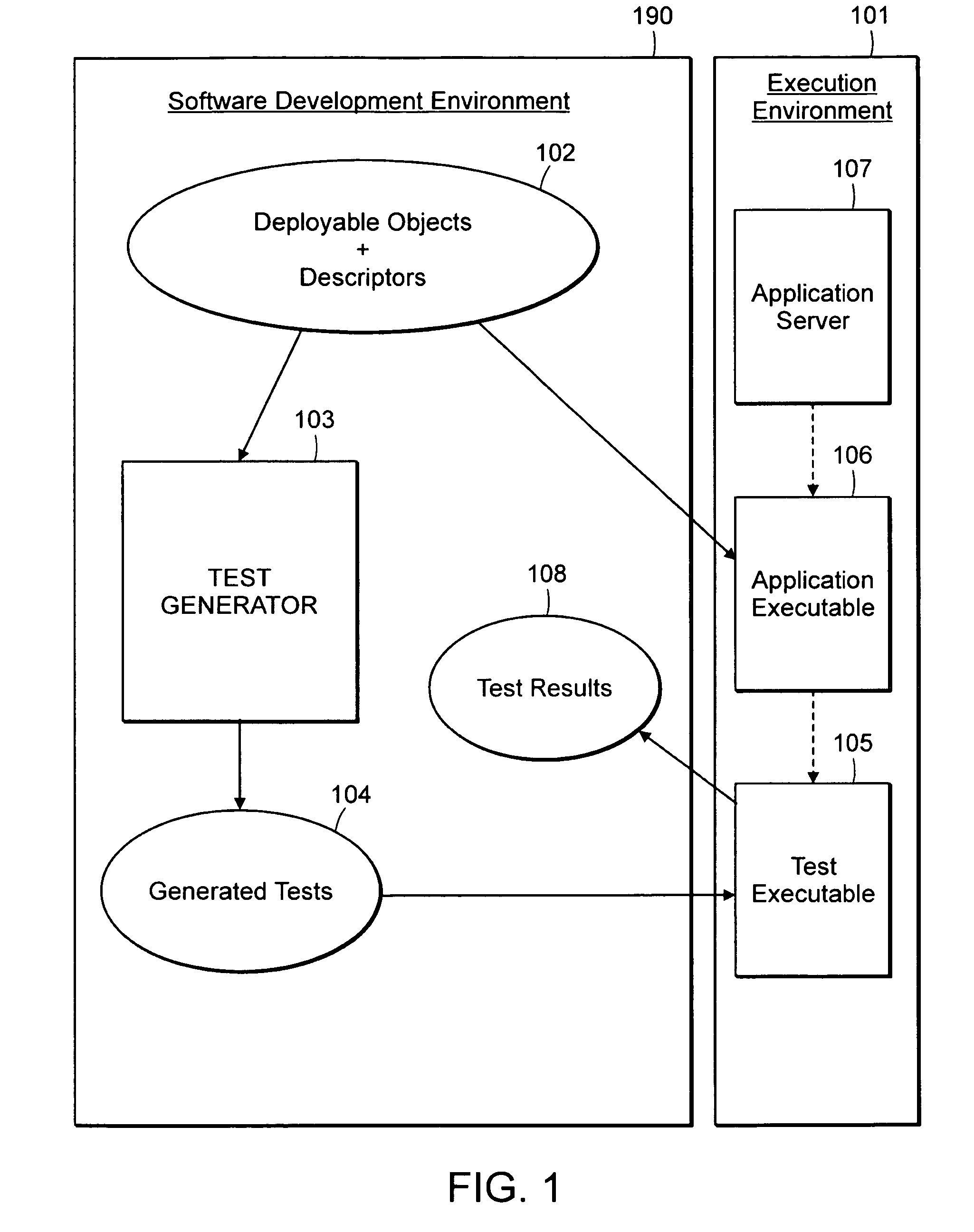

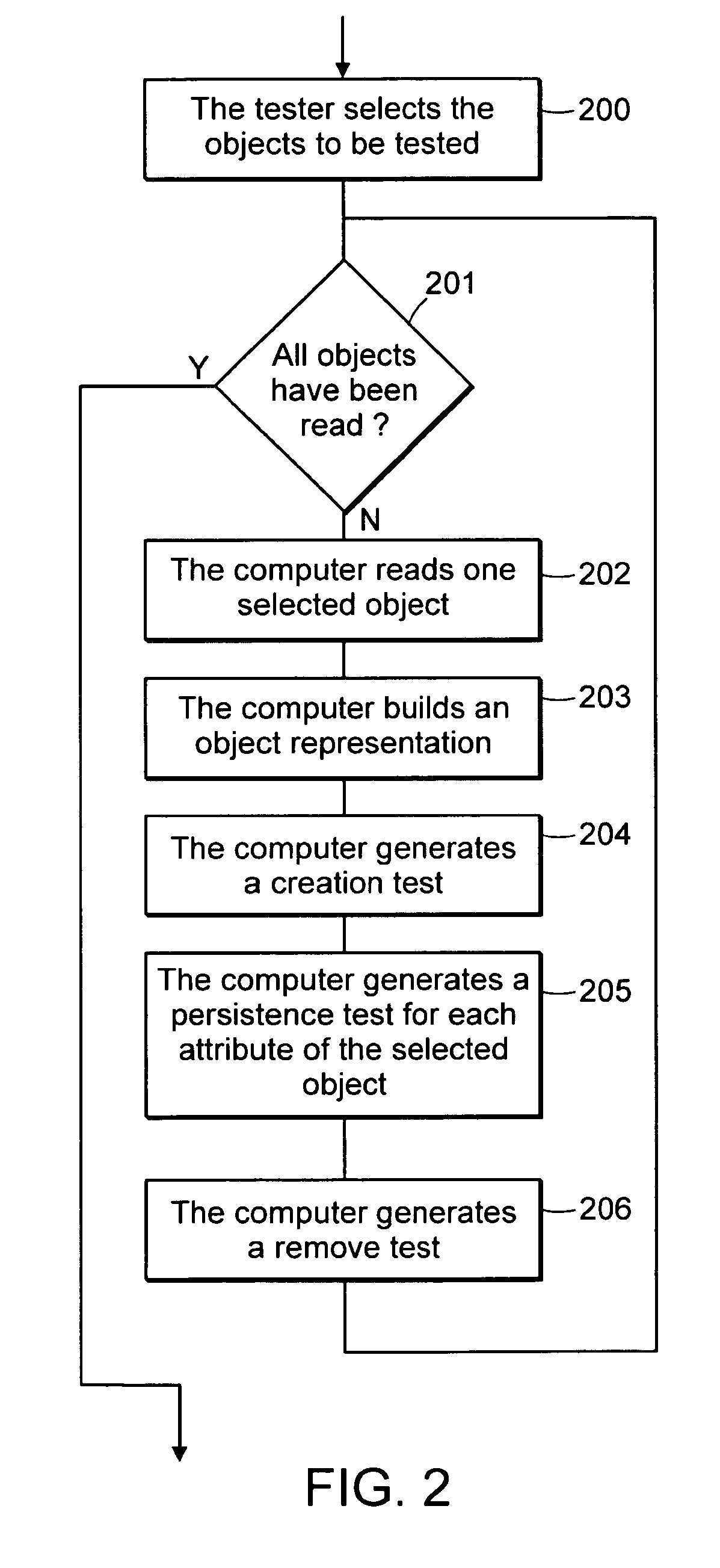

Computer method and system for automatically creating tests for checking software

Computer system and method automatically generates a test source code for checking validity of an application written in an object oriented language. The application includes objects accessible through an interface implementing programming rules and object behavior rules. For each object, the invention extracts object methods and attributes of the object interface which are impacted by the object behavior rules and extracts the object identification. The invention fills the variable fields of a source code template with the extracted information. The template non variable source code is in conformance with the programming rules and implements a scenario for checking a set of object behavior rules; thus the filled template forms a generated test source code. For distributed applications, the specifications may be EJB or CORBA and the Test Generator uses templates for checking the life-cycle (creation, persistency, removal) of deployed objects.

Owner:IBM CORP

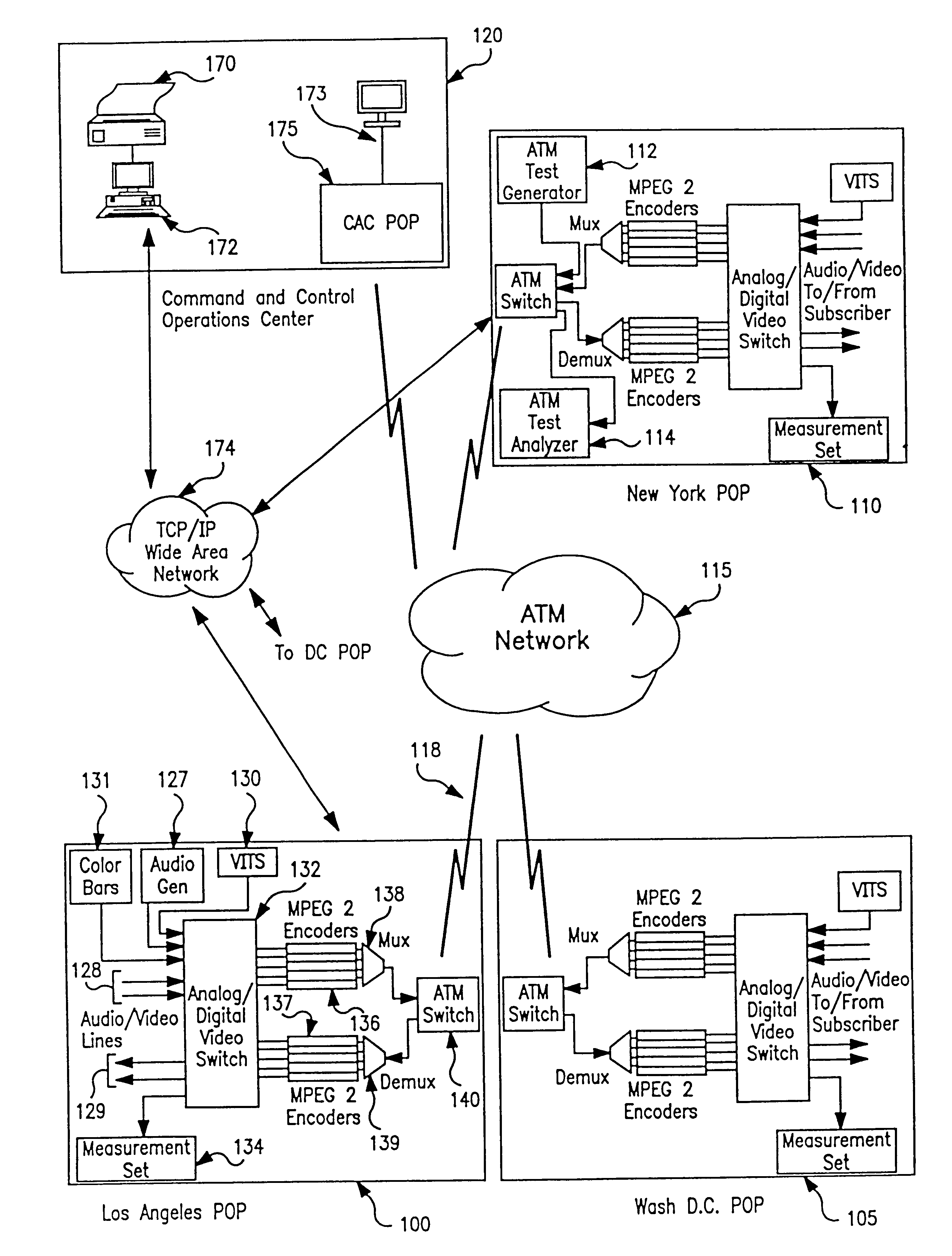

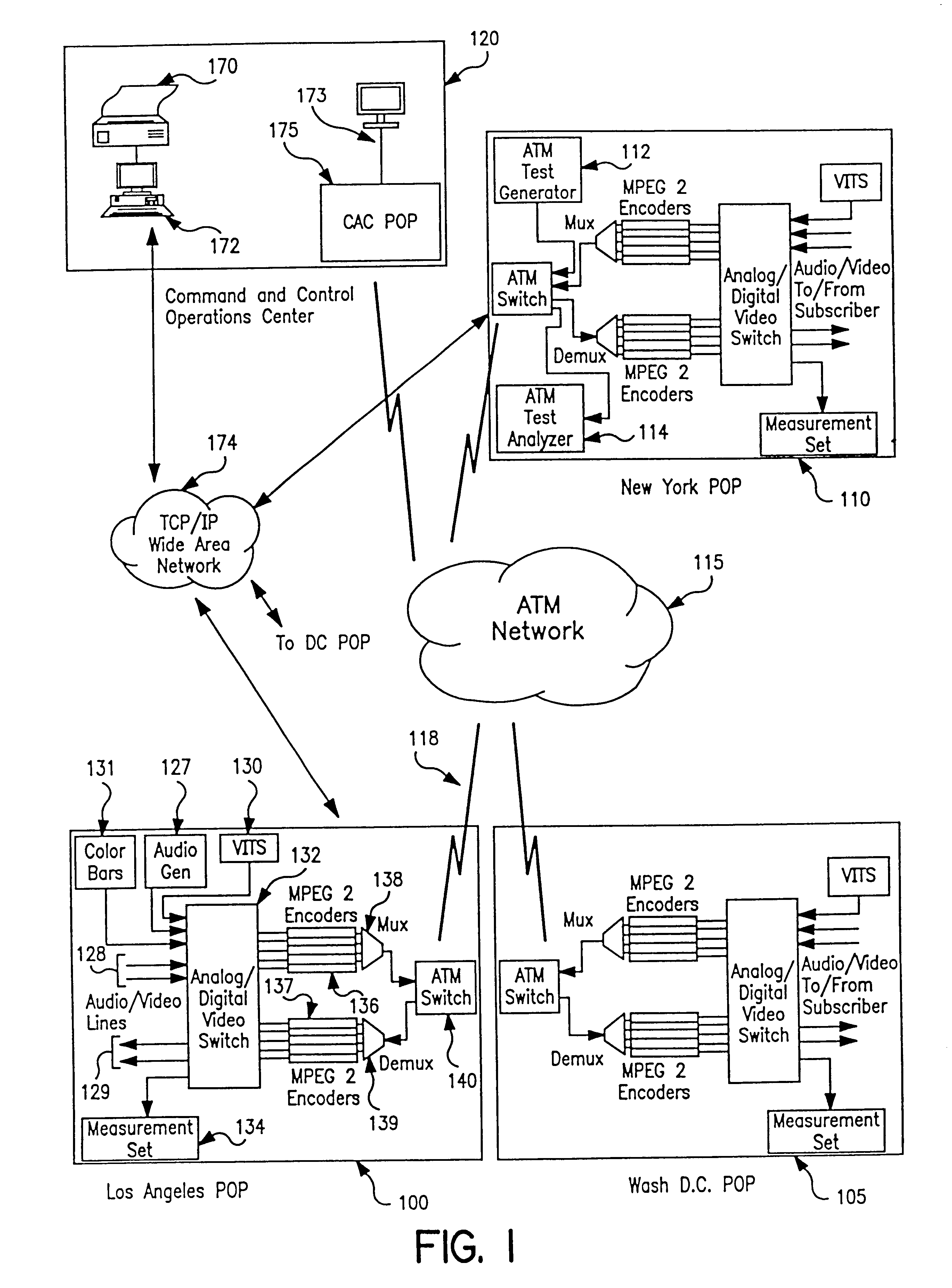

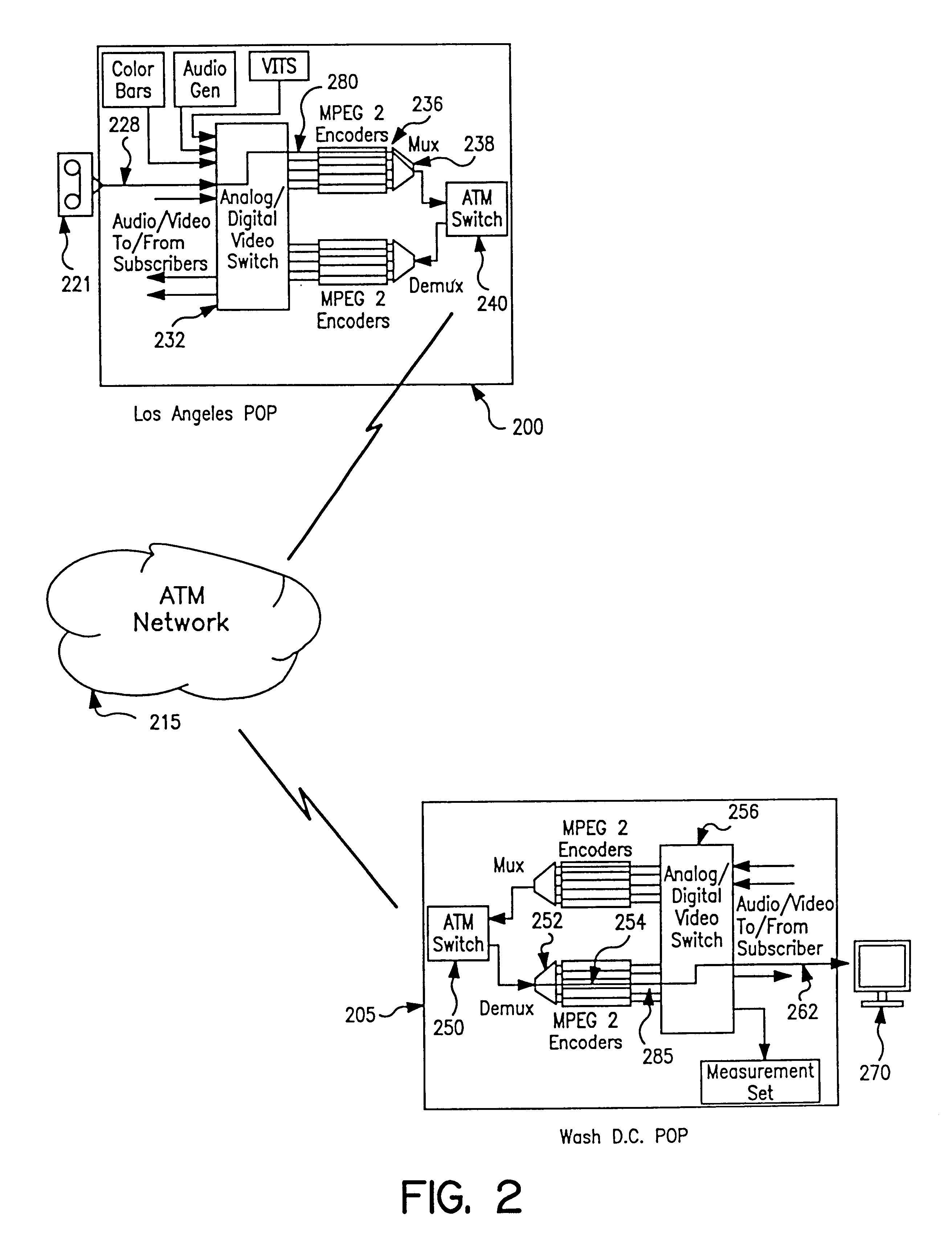

Apparatus and method of in-service audio/video synchronization testing

InactiveUS6414960B1Easy to testTime-division multiplexData switching by path configurationVideo-signal generatorNoise level

An apparatus and method provide non-intrusive in-service testing of audio / video synchronization testing without using traditional audio marker tones. The network includes an A / V synchronous test signal generator which injects video and audio markers into the video and audio non-intrusively and routes the two signals into a switch where they are switched into a channel for encoding and transmission via the ATM network. At the distant end the signal is decoded and routed by a switch into the A / V test generator and measurement set where the markers are detected and the A / V skew calculated, after which the audio and video are routed to the subscriber. The A / V test set signal generator includes a Video Blanking Interval (VBI) test signal generator and a white noise generator, the former injecting a marker into the video signal and the later injecting an audio marker into the audio signal. The video marker is injected into the VBI and broadband, background audio noise to measure the delay between the audio and video components of a broadcast. The marking of the audio is accomplished by gradually injecting white noise into the audio channel until the noise level is 6 dB above the noise floor of the audio receiver. As a precursor A / V sync signal, a small spectrum of the white noise is notched or removed. This signature precludes inadvertent recognition of program audio noise as the audio marker.

Owner:IBM CORP

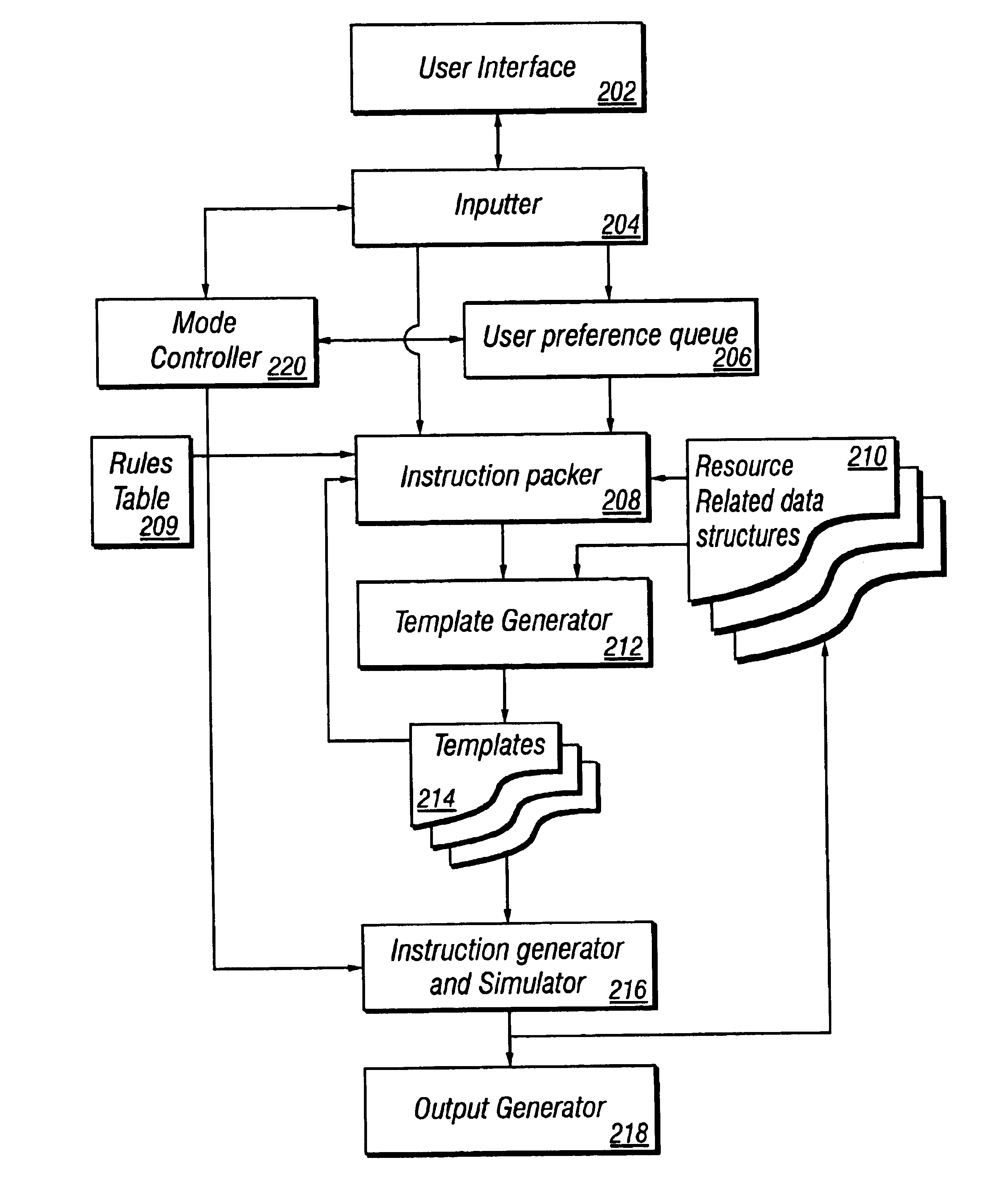

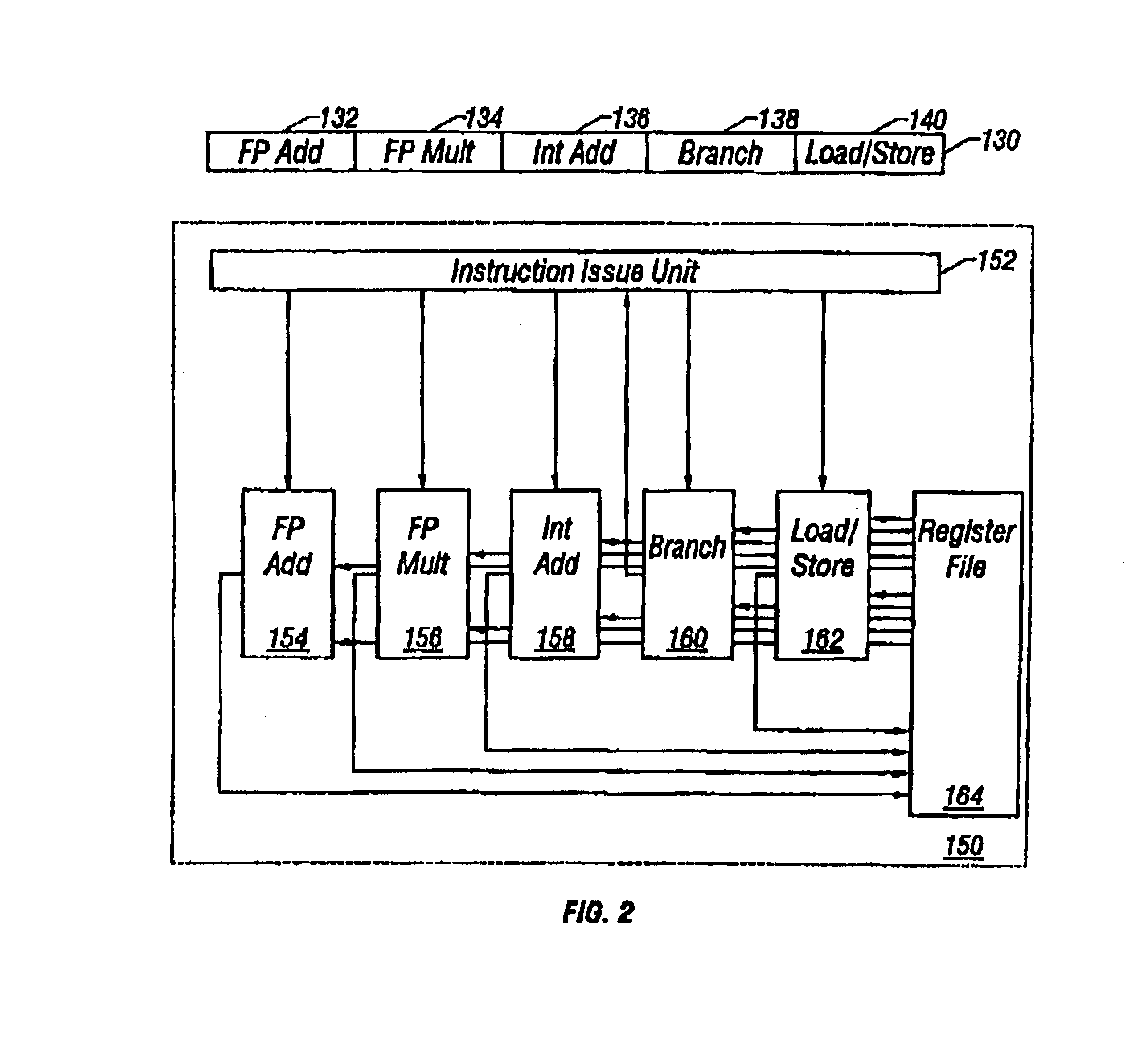

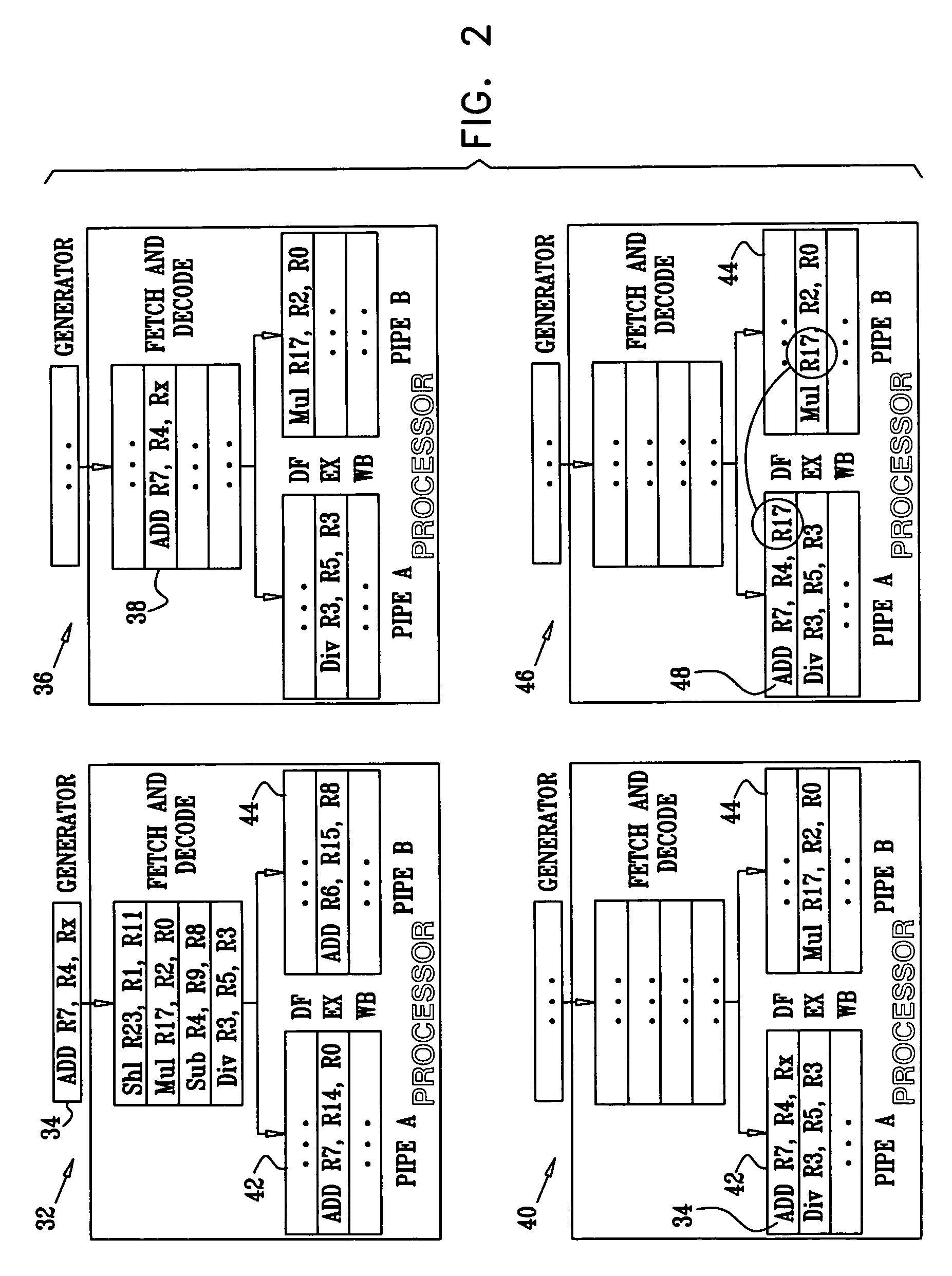

Method and apparatus that simulates the execution of paralled instructions in processor functional verification testing

InactiveUS6871298B1Properly be executeError detection/correctionDigital computer detailsAnalog processorParallel computing

A dynamic test generation method and apparatus enabling verification of the parallel instruction execution capabilities of VLIW processor systems is described. The test generator includes a user preference queue, a rules table, plurality of resource-related data structures, an instruction packer, and an instruction generator and simulator. The present invention generates a test by selecting instructions for parallel execution based upon resource availability as indicated by the resource-related data structures and the processor's instruction grouping rules, simulating the parallel execution of the instructions on a golden model, updating the resource-related data structures, and evaluating the updated architectural state of the golden model.

Owner:ARM INC

Computer method and system for automatically creating tests for checking software

InactiveUS7707553B2Error detection/correctionSoftware engineeringComputerized systemApplication software

Computer system and method automatically generates a test source code for checking validity of an application written in an object oriented language. The application includes objects accessible through an interface implementing programming rules and object behavior rules. For each object, the invention extracts object methods and attributes of the object interface which are impacted by the object behavior rules and extracts the object identification. The invention fills the variable fields of a source code template with the extracted information. The template non variable source code is in conformance with the programming rules and implements a scenario for checking a set of object behavior rules; thus the filled template forms a generated test source code. For distributed applications, the specifications may be EJB or CORBA and the Test Generator uses templates for checking the life-cycle (creation, persistency, removal) of deployed objects.

Owner:INT BUSINESS MASCH CORP

Method and apparatus for programmable generation of traffic streams

Methods and apparatus provide single or multi-port, flexible, cost-effective, built-in self-test capabilities for network communications equipment, such as for example switches, and programmably generate, and subsequently analyze, one or more sequences of test packets, wherein the test packets simulate at least two flows of traffic. Such test packets can have programmable headers, payloads, and duty cycle. A line card embodying the present invention may generate its own traffic pattern, which may be similar or identical, to traffic patterns observed on Internet backbones. These traffic patterns may contain a bimodal distribution of control packets interspersed with data packets wherein the control packets and data packets are relatively short and long respectively. A plurality of test packet generators / receivers can be deployed in a network communications device having a plurality of ports. In such a configuration, test generator / receiver is associated with each of the plurality of ports. Under software control, test packets can be sent from at least any one of the plurality of ports to at least any other one of the plurality of ports. In this way, an in-circuit testing procedure may be implemented without having to disconnect line cards from the switch and connect the switch to expensive external test equipment.

Owner:XYLON LLC

Late binding of variables during test case generation for hardware and software design verification

InactiveUS7003420B2Improves quality and rapidityPerformance penaltyResistance/reactance/impedenceCAD circuit designSoftware designTheoretical computer science

Methods and systems are provided that improve design verification by test generators by delaying assignment of values in the generated stimuli until these values are used in the design. Late binding allows the generator to have a more accurate view of the state of the design, and in order to choose correct values. Late binding can significantly improve test coverage with a reasonable performance penalty as measured by simulation time.

Owner:IBM CORP

Automated test generator

InactiveUS6378088B1Software testing/debuggingEmergency protective arrangements for automatic disconnectionComputer hardwareComputer science

A test generator generates tests by randomly traversing a description of the interface of a program being tested, thereby generating tests that contain randomly selected actions and randomly generated data. When executed, these tests randomly manipulate the program being tested.

Owner:AUTODESK INC

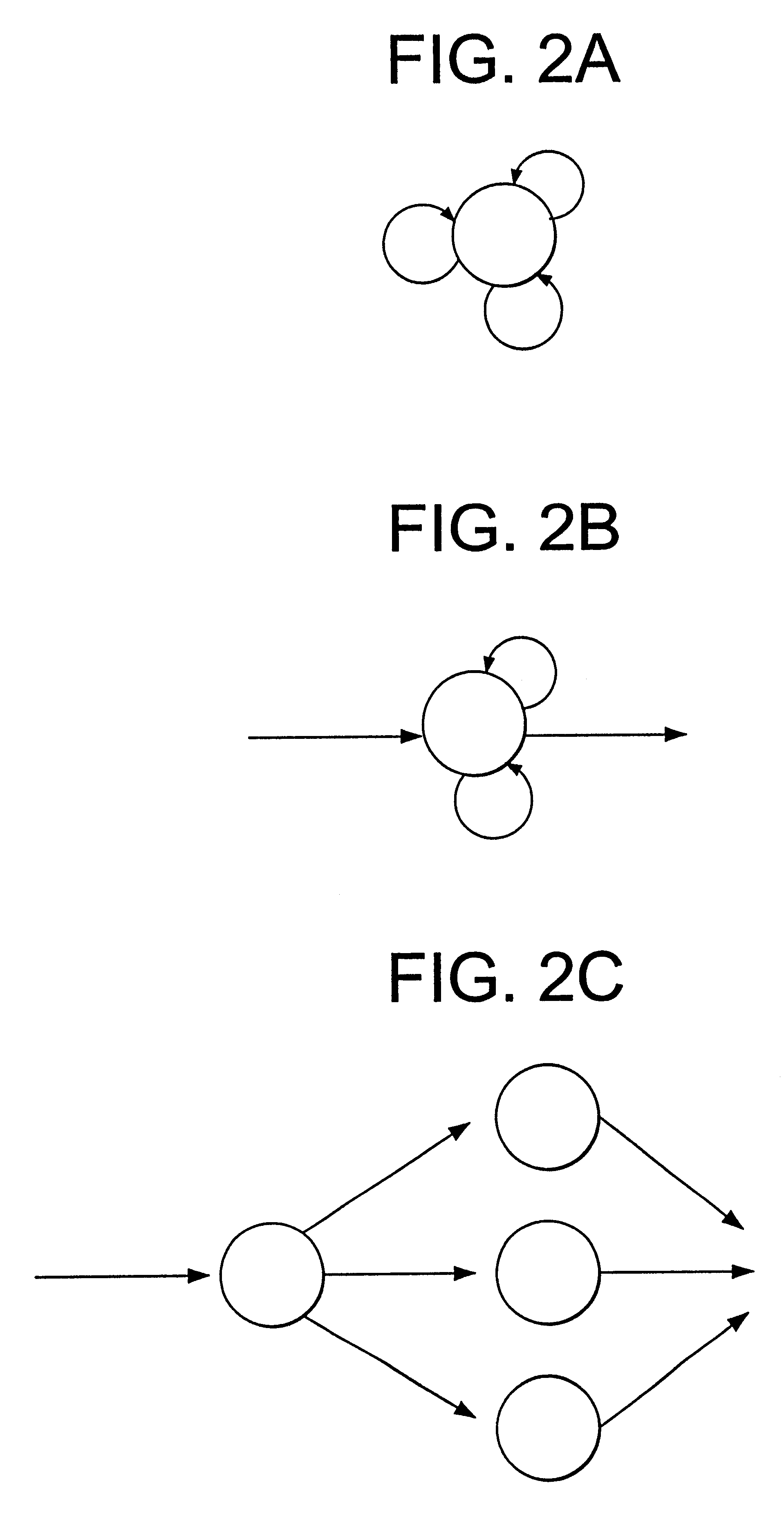

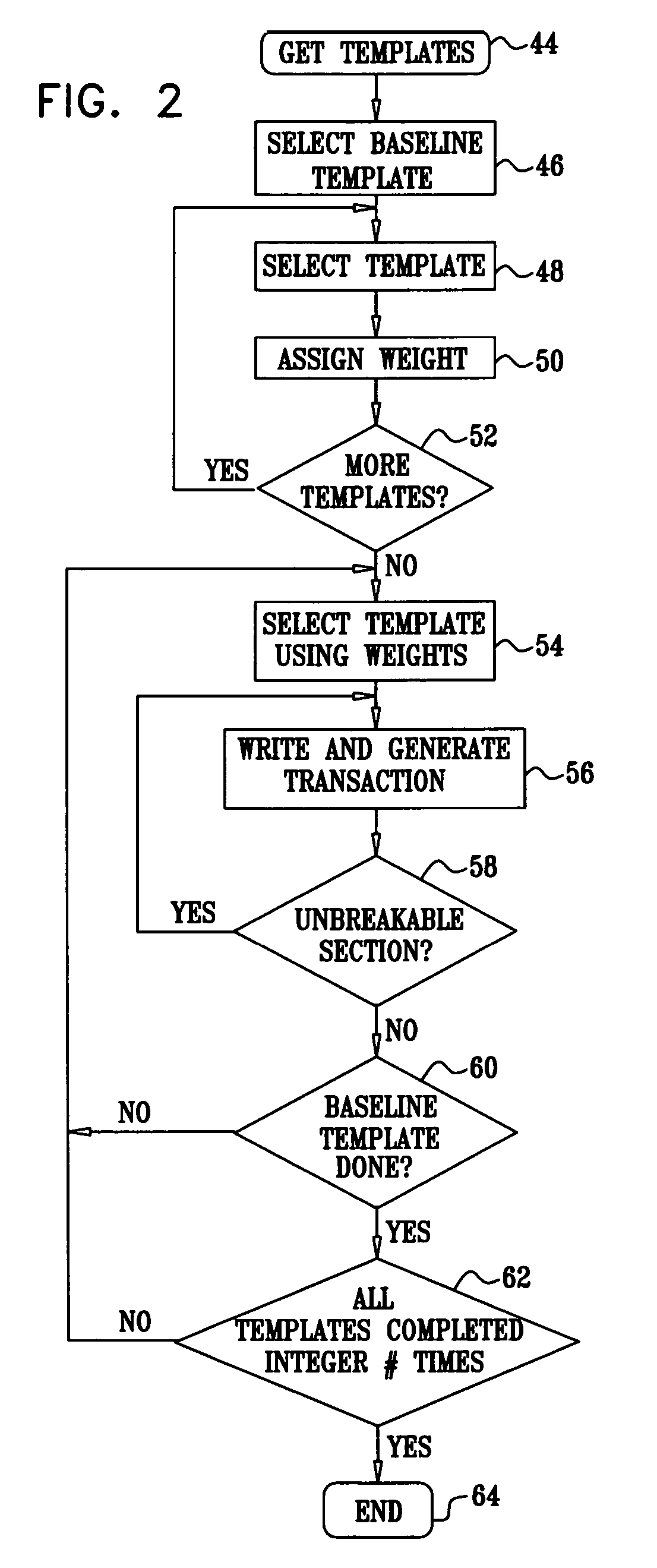

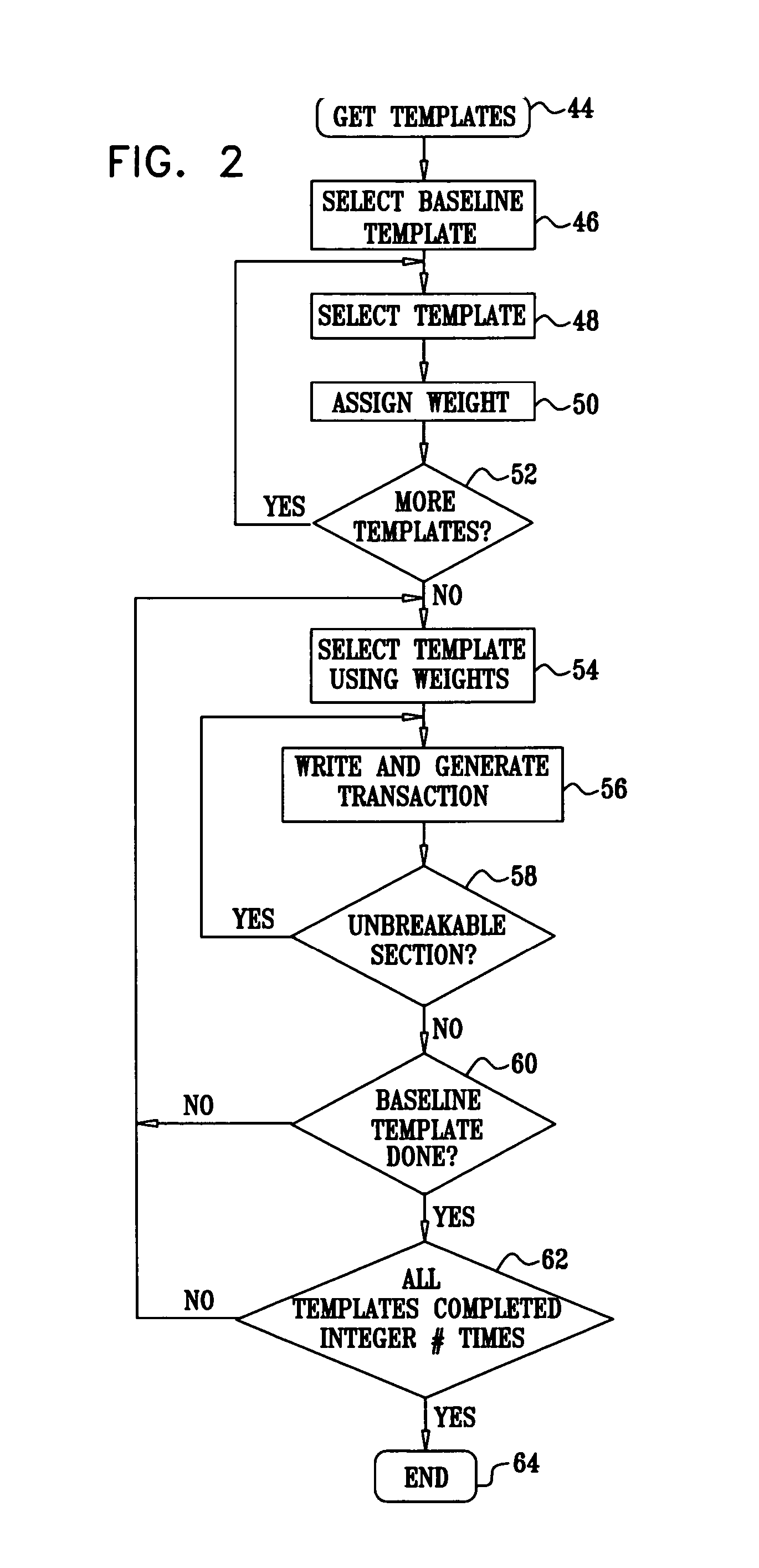

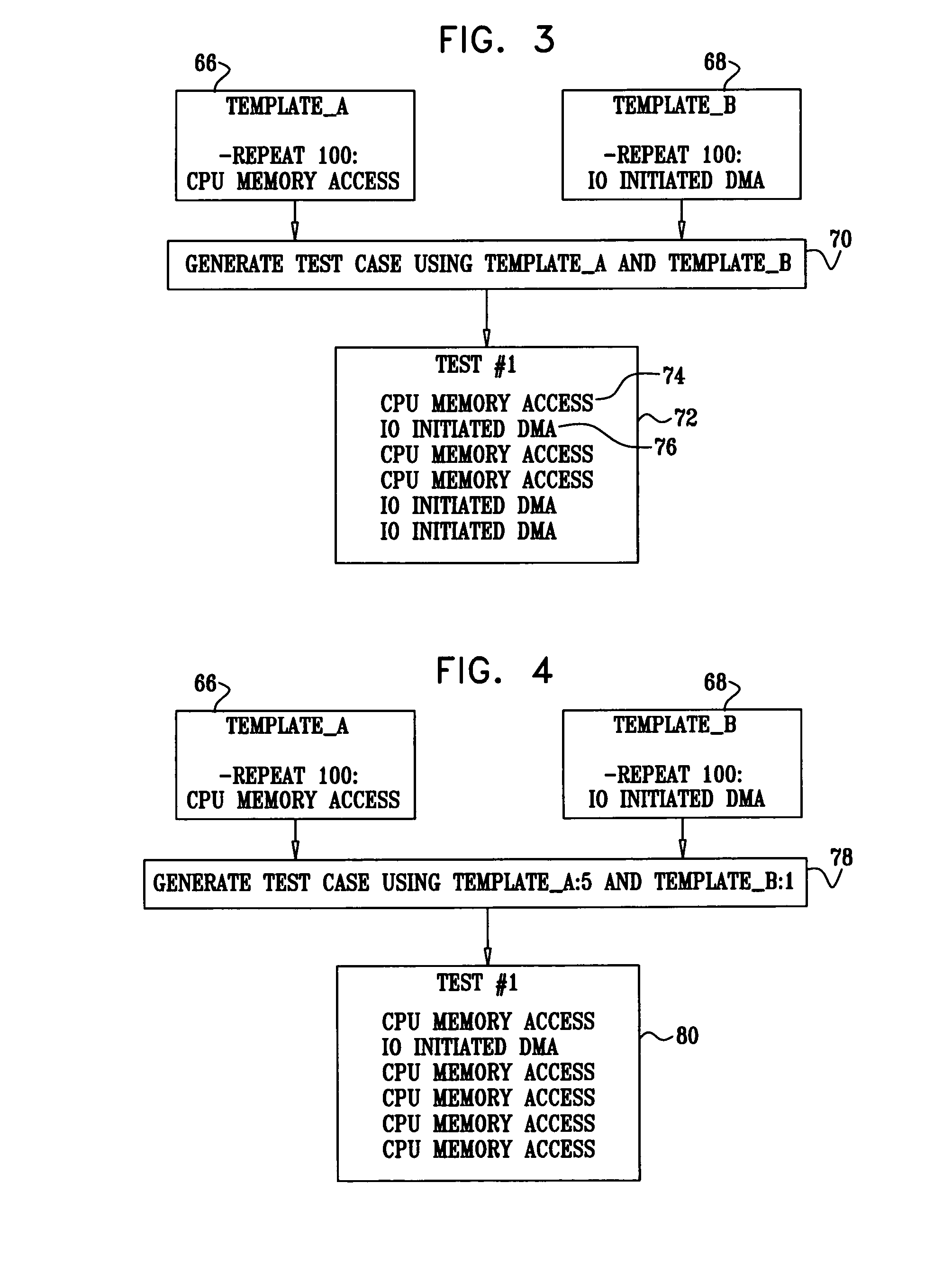

Dynamically interleaving randomly generated test-cases for functional verification

InactiveUS7627843B2Significant effortElectronic circuit testingResistance/reactance/impedenceGeneration processParallel computing

The input for a test generator is a plurality of test templates, each of which typically aims at covering a specific verification task. Test templates direct the production of distinct transactions, which are the atomic functional building blocks of the design-under-verification. Test templates directed to different hardware functions of the scenario are dynamically interleaved. In this way several transactions are combined together in complex statements in order to achieve a complex test scenario. The transactions are submitted to the test generator, which generates test cases, in which the different hardware functions of the scenario are exercised in combinations. Variation among the test cases is achieved through a large number of random decisions made during the generation process.

Owner:GLOBALFOUNDRIES INC

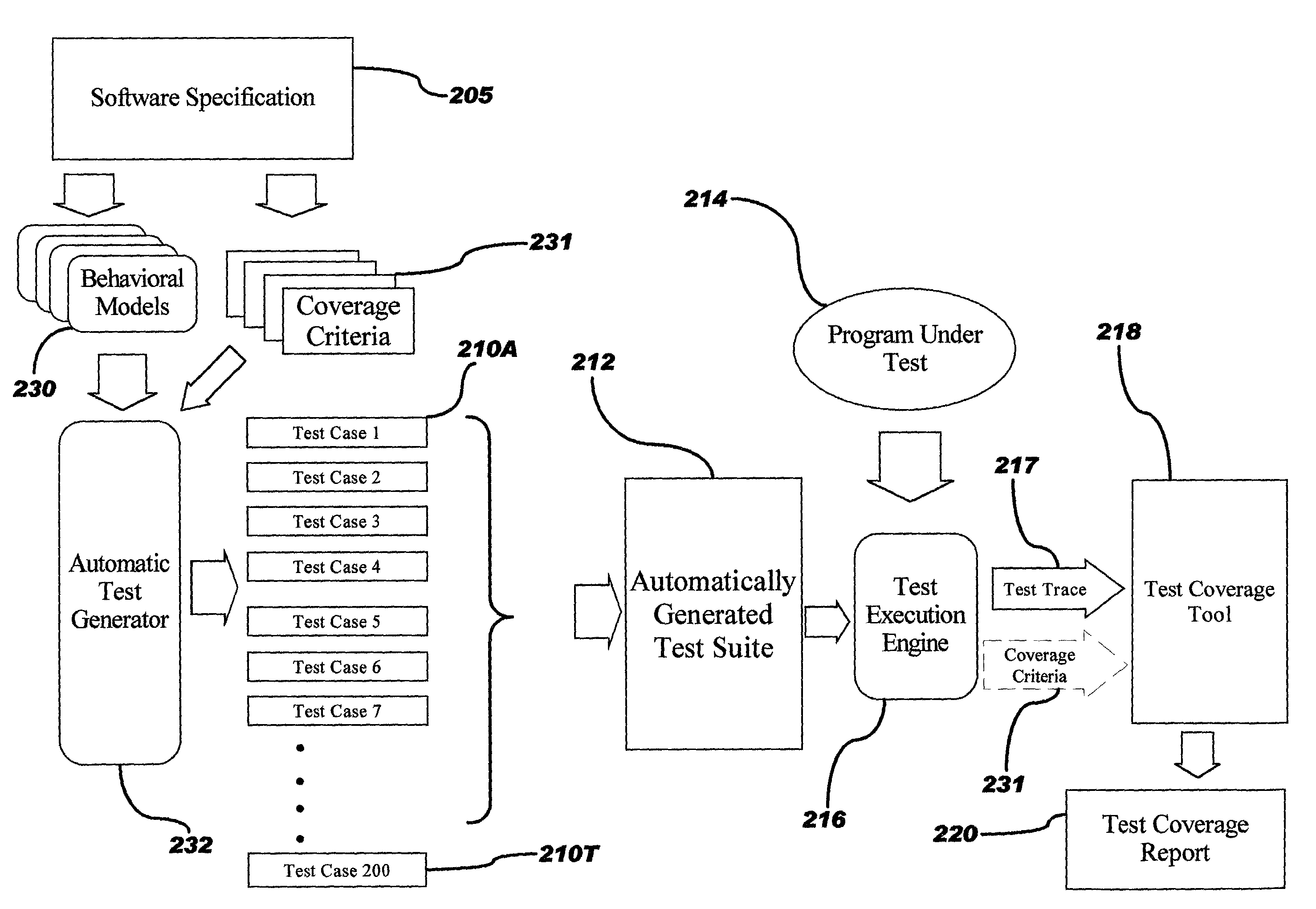

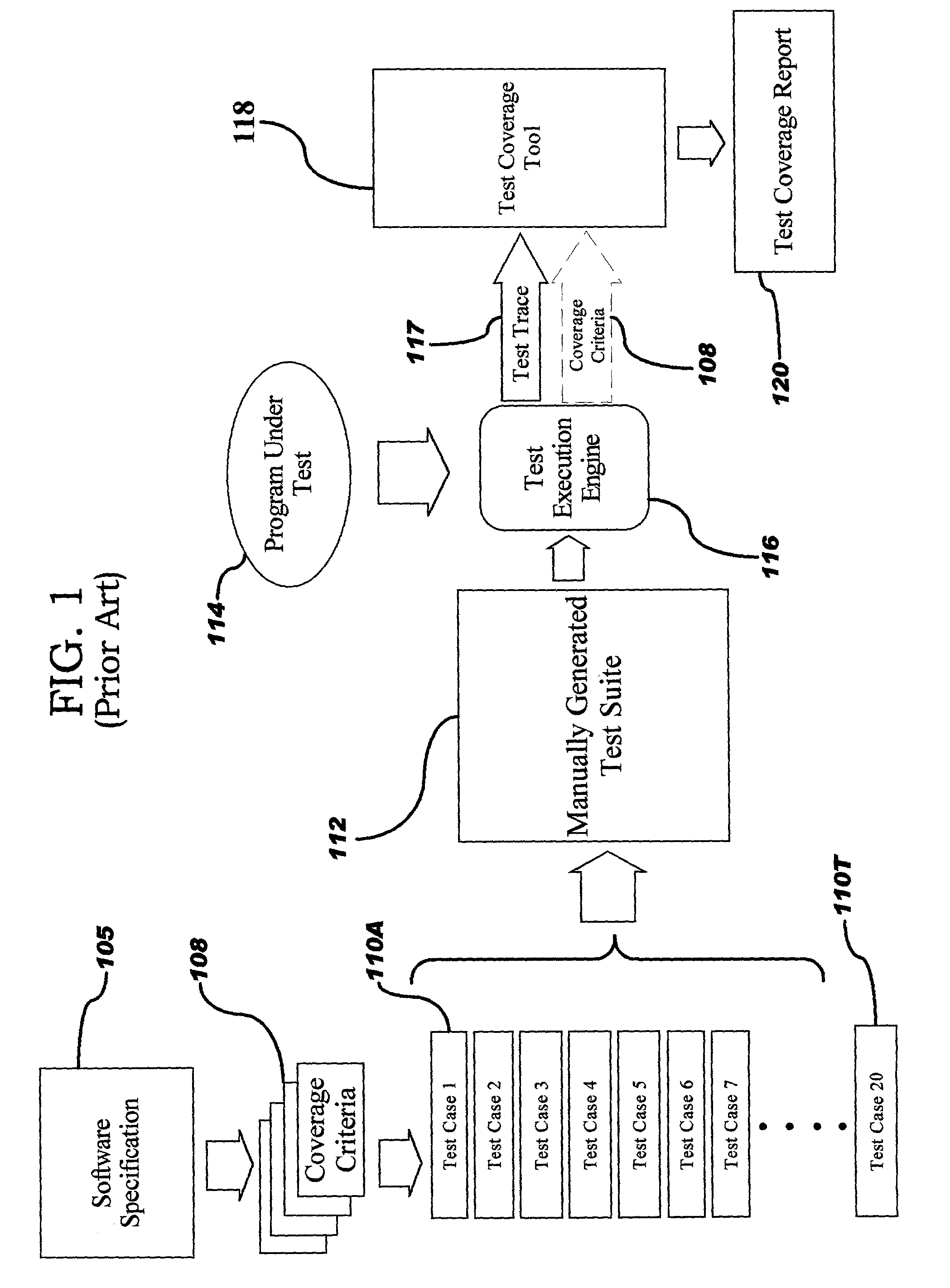

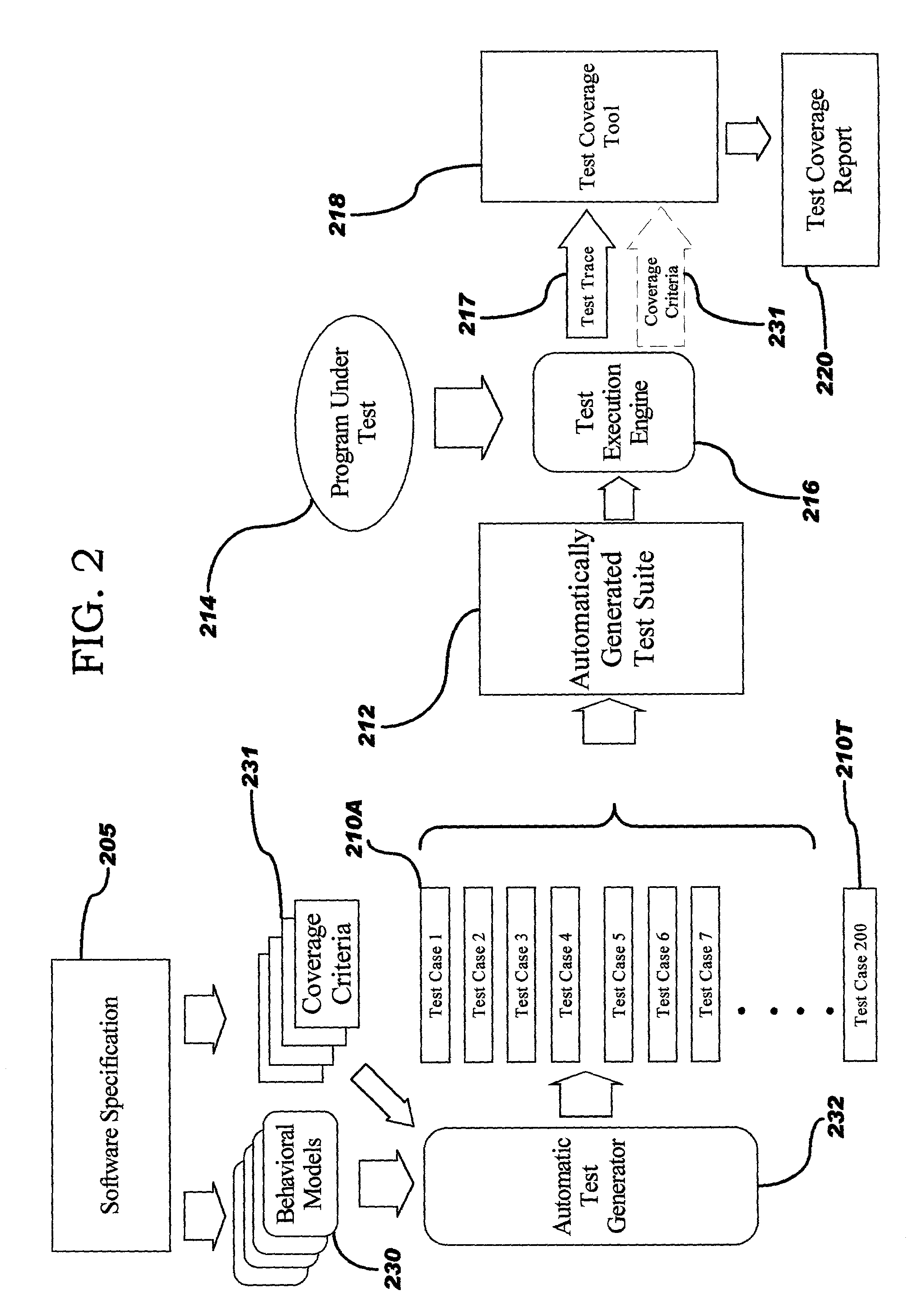

Method and system for integrating test coverage measurements with model based test generation

A test coverage tool provides output that identifies differences between the actual coverage provided by a test suite run on a program under test and the coverage criteria (e.g., the coverage criteria required by the test / development team management). The output from the test coverage tool is generated in the same language that was used to write the coverage criteria that are input to an automated test generator to create the test cases which form the test suite. As a result, the output from the coverage tool can be input back into the automated test generator to cause the generator to revise the test cases to correct the inadequacies. This allows iterative refinement of the test suite automatically, enabling automated test generation to be more effectively and efficiently used with more complex software and more complex test generation inputs.In preferred embodiments, test coverage analysis results of several different test suites, some manually generated and others automatically generated, are used to produce a streamlined automatically-generated test suite and / or to add missing elements to an automatically generated test-suite.

Owner:GLOBALFOUNDRIES INC

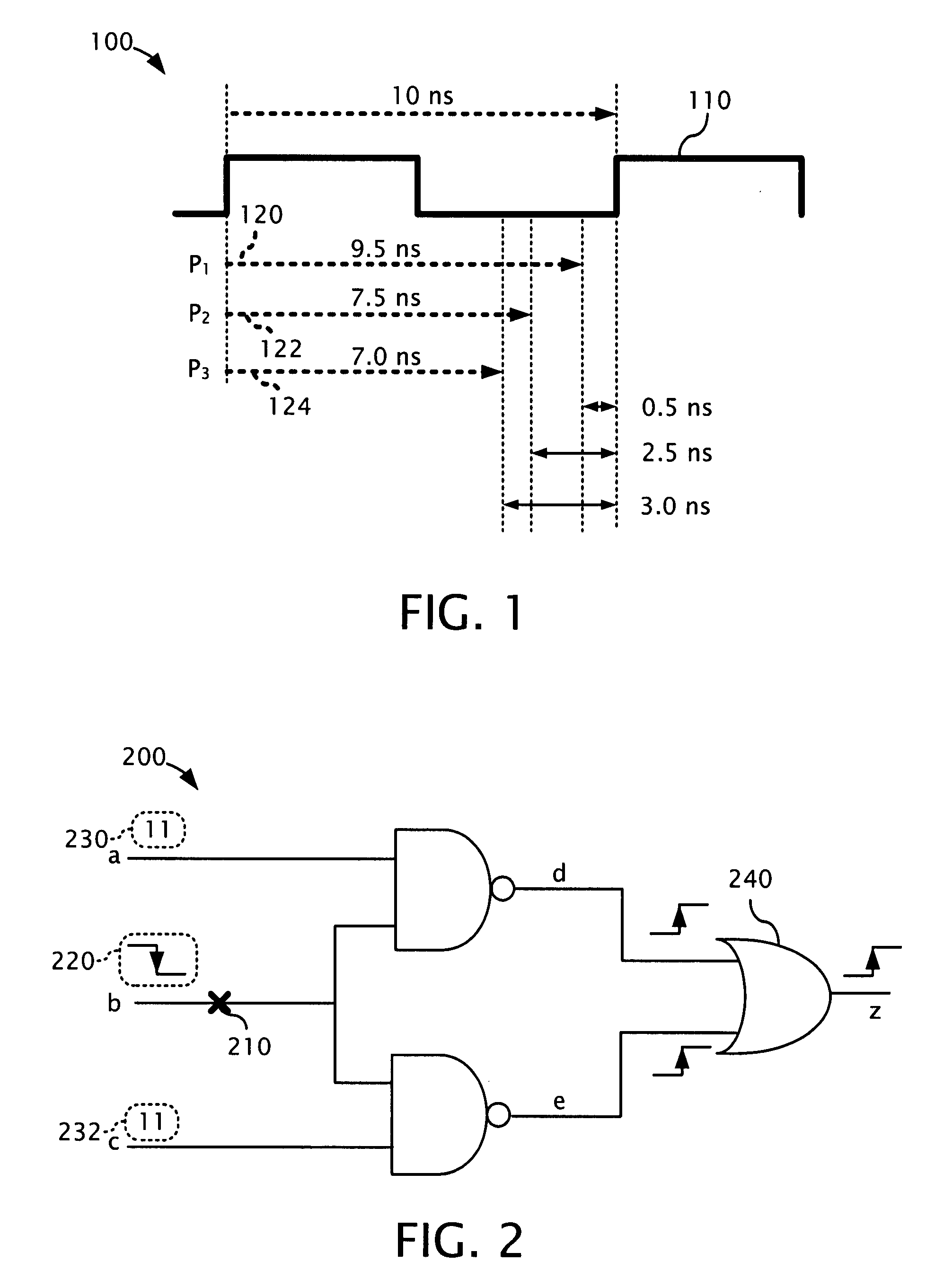

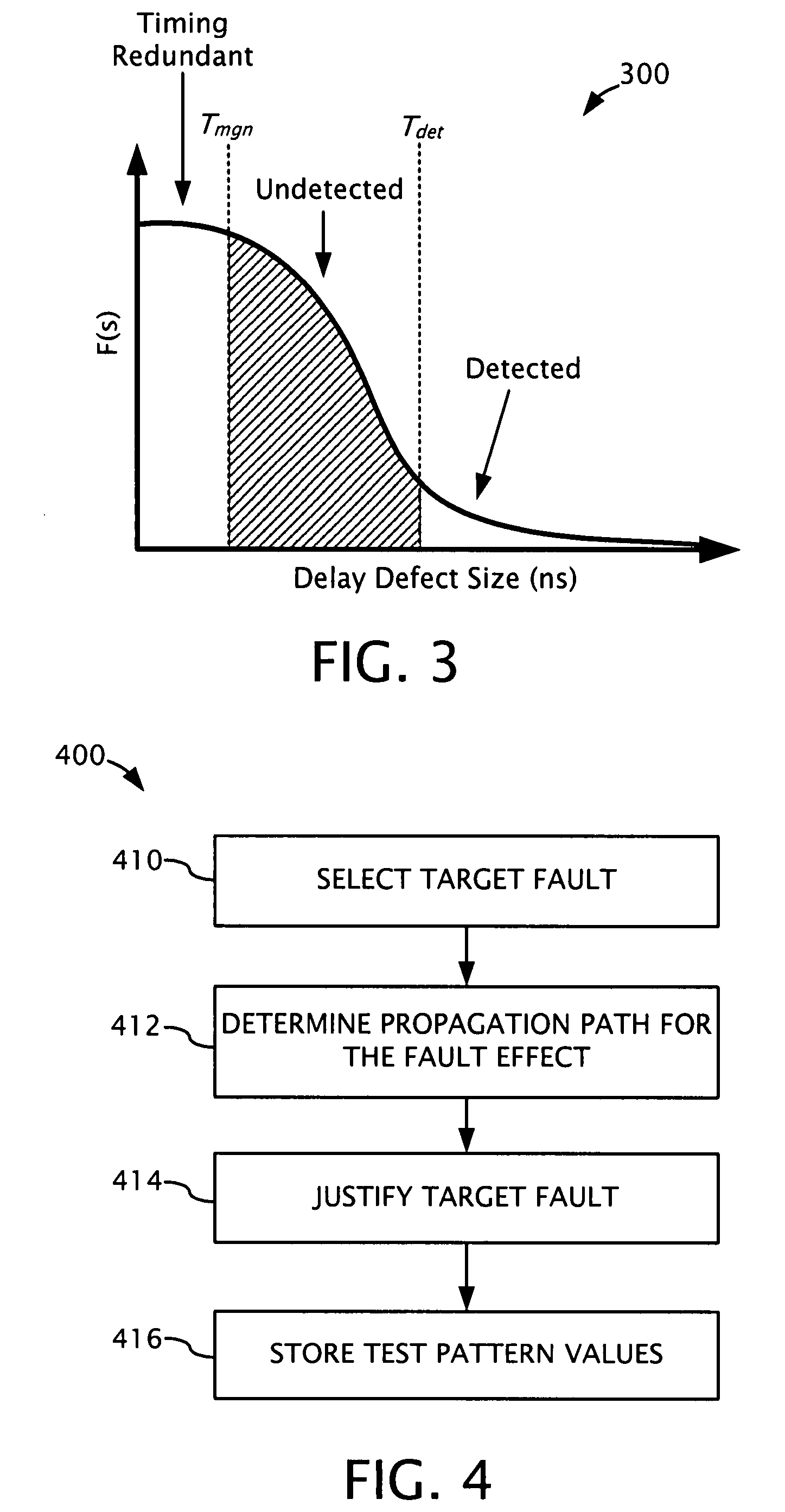

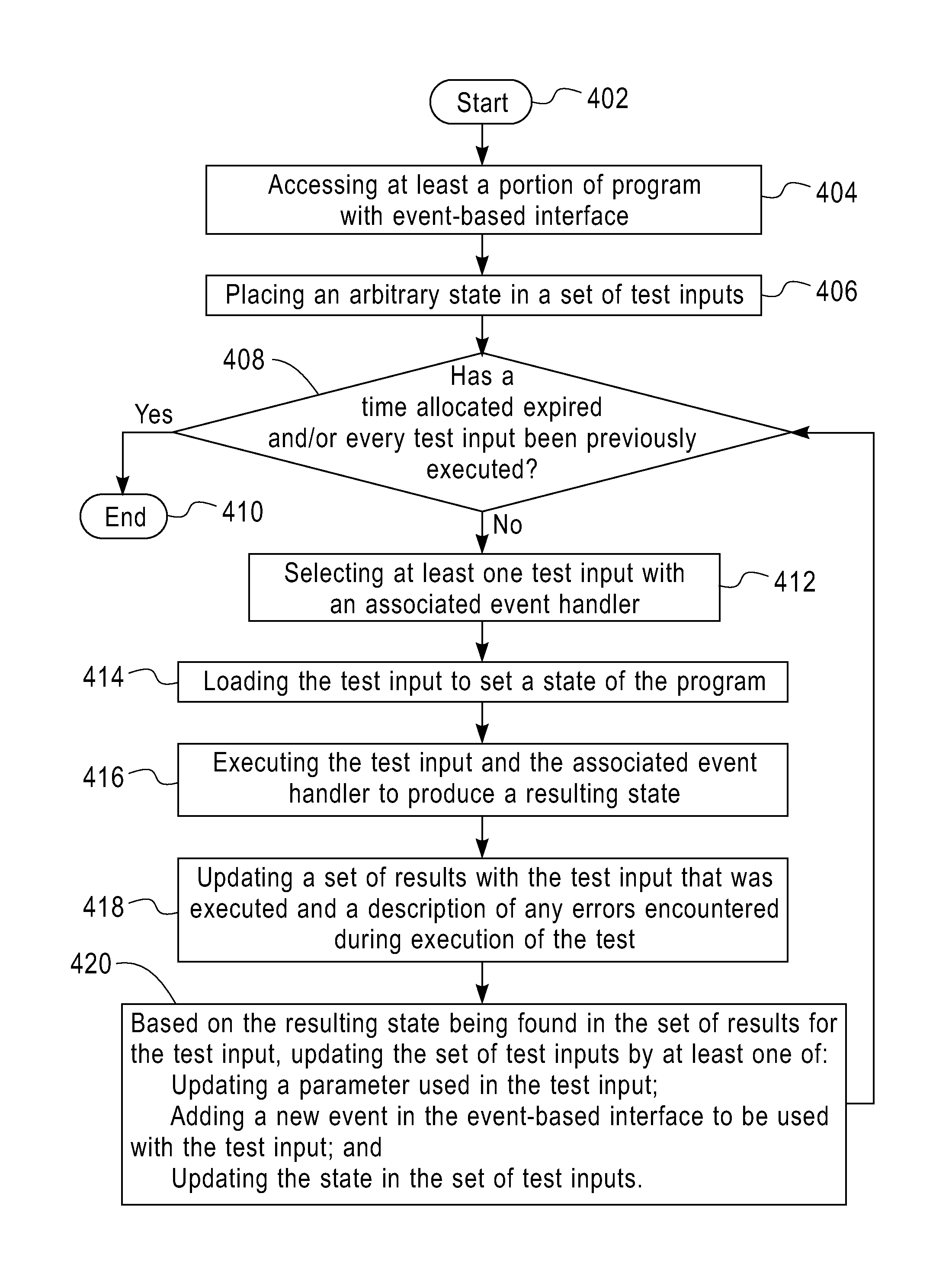

Timing-aware test generation and fault simulation

ActiveUS20070288822A1Quality improvementExpand coverageElectronic circuit testingError detection/correctionTime informationRandom method

Disclosed herein are exemplary methods, apparatus, and systems for performing timing-aware automatic test pattern generation (ATPG) that can be used, for example, to improve the quality of a test set generated for detecting delay defects or holding time defects. In certain embodiments, timing information derived from various sources (e.g. from Standard Delay Format (SDF) files) is integrated into an ATPG tool. The timing information can be used to guide the test generator to detect the faults through certain paths (e.g., paths having a selected length, or range of lengths, such as the longest or shortest paths). To avoid propagating the faults through similar paths repeatedly, a weighted random method can be used to improve the path coverage during test generation. Experimental results show that significant test quality improvement can be achieved when applying embodiments of timing-aware ATPG to industrial designs.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

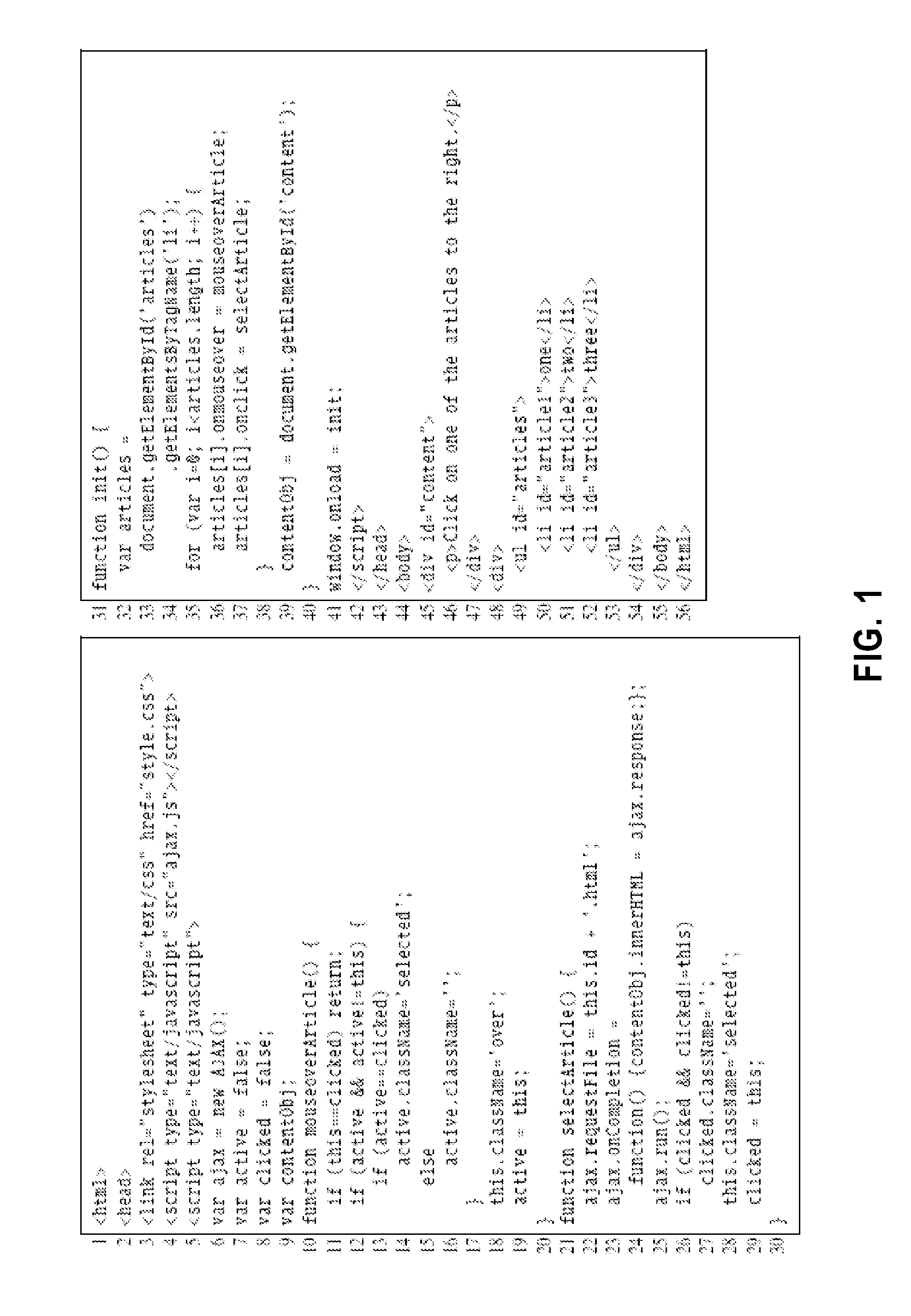

Automated testing of applications with scripting code

InactiveUS20130290786A1Expand coverageIncrease coverageSoftware testing/debuggingComputer programJavaScript

A novel system, computer program product, and method are disclosed for feedback-directed automated test generation for programs, such as JavaScript, in which execution is monitored to collect information that directs the test generator towards inputs that yield increased coverage. Several instantiations of the framework are implemented, corresponding to variations on feedback-directed random testing, in a tool called Artemis.

Owner:IBM CORP

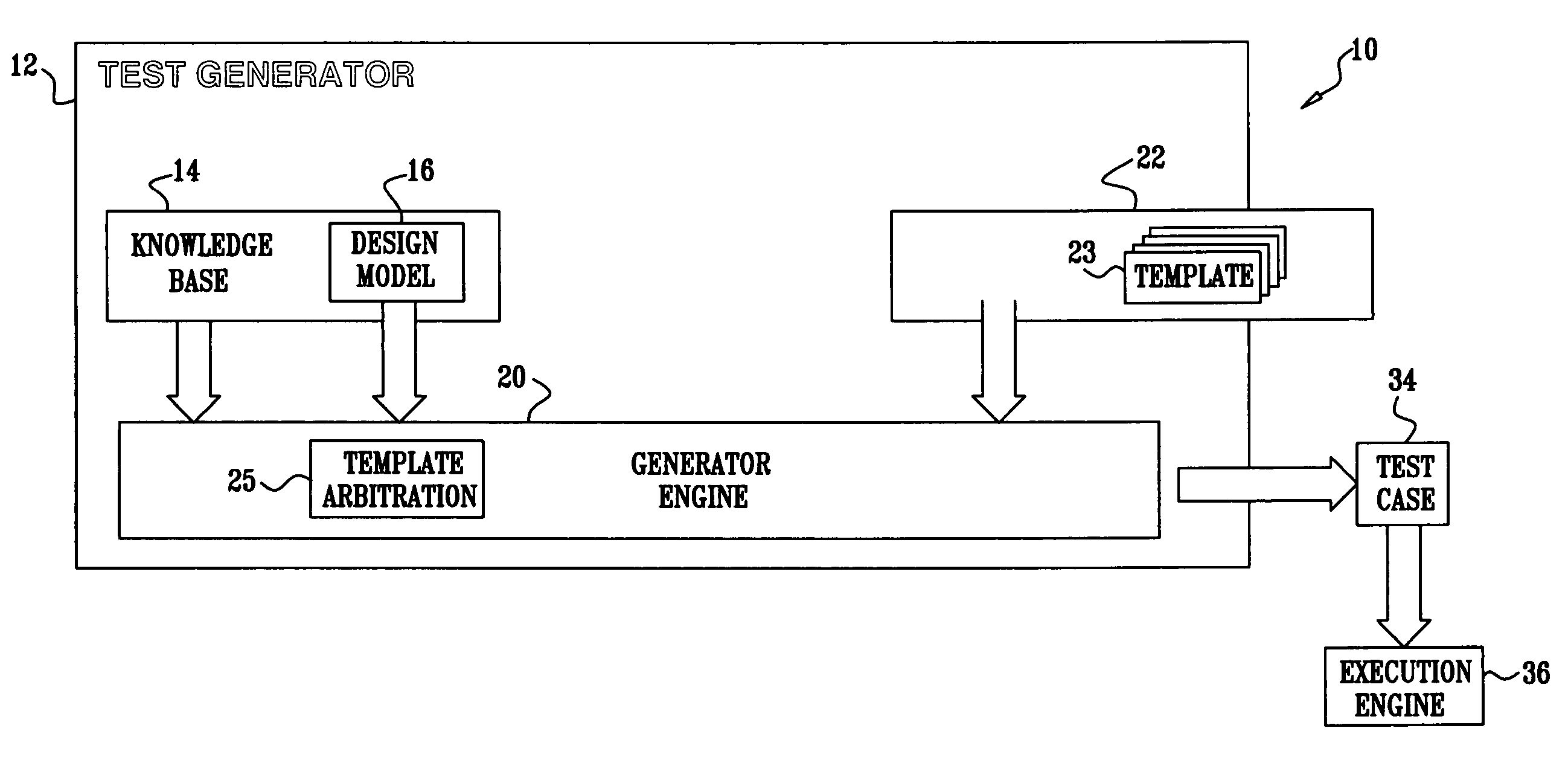

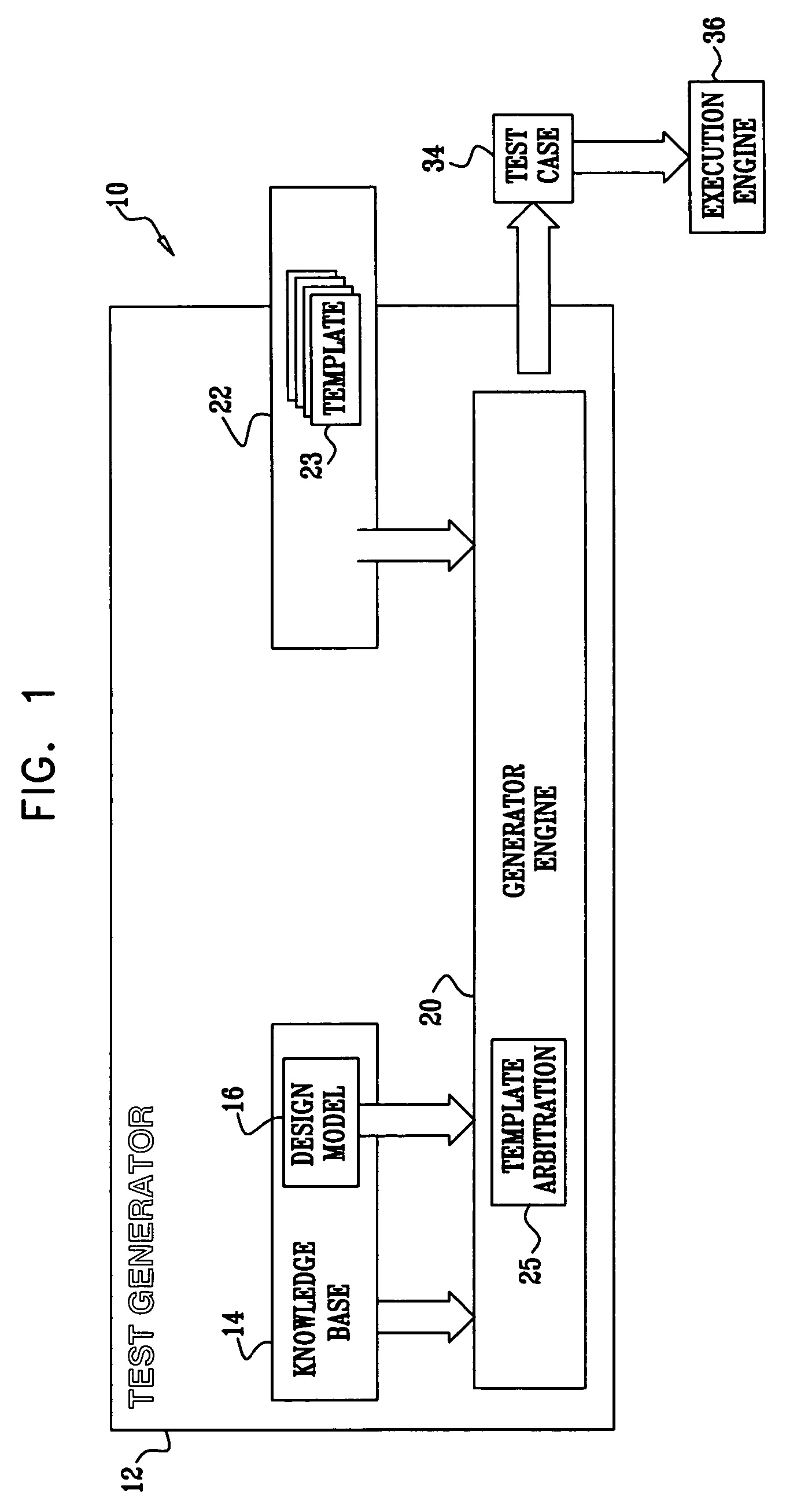

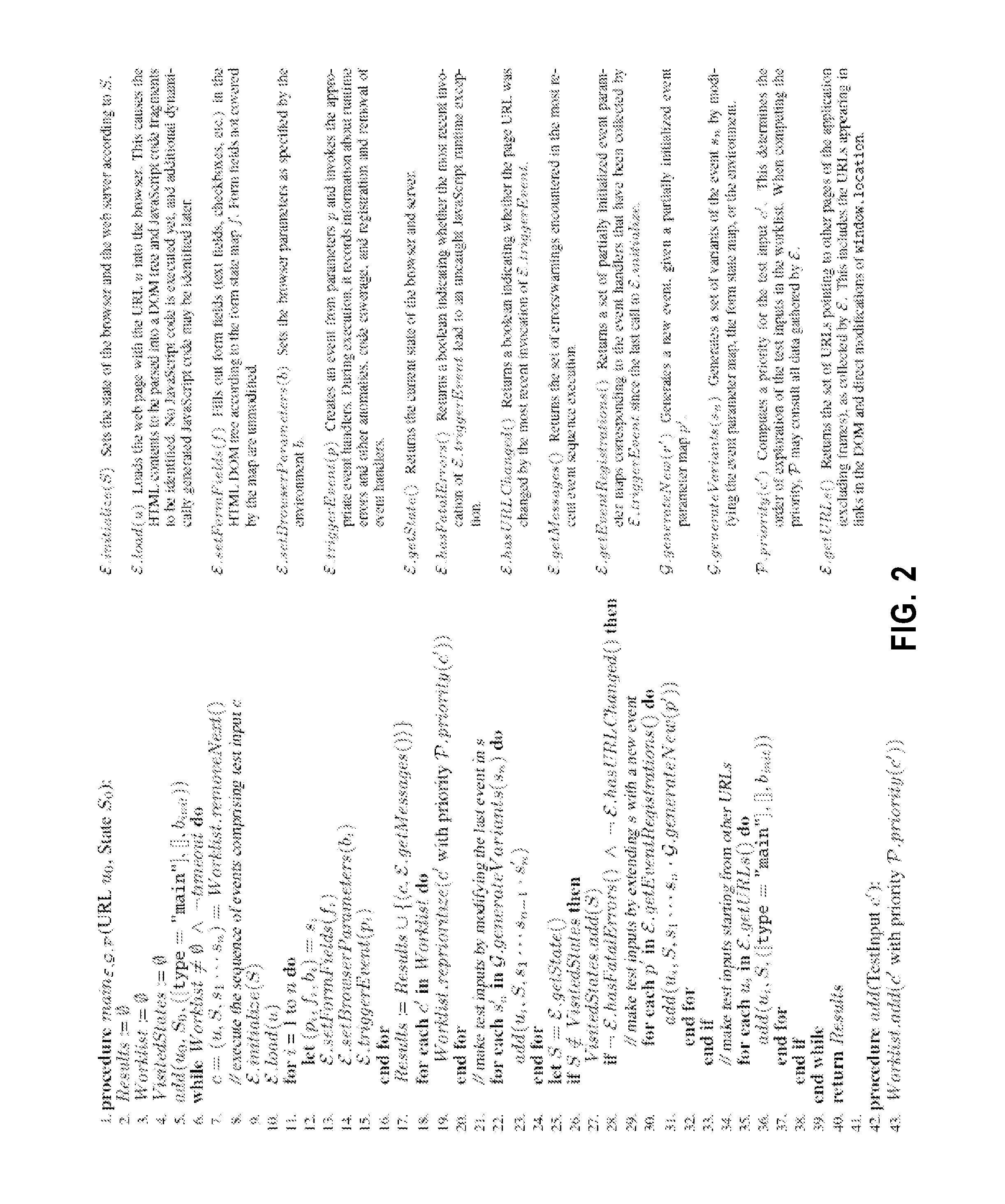

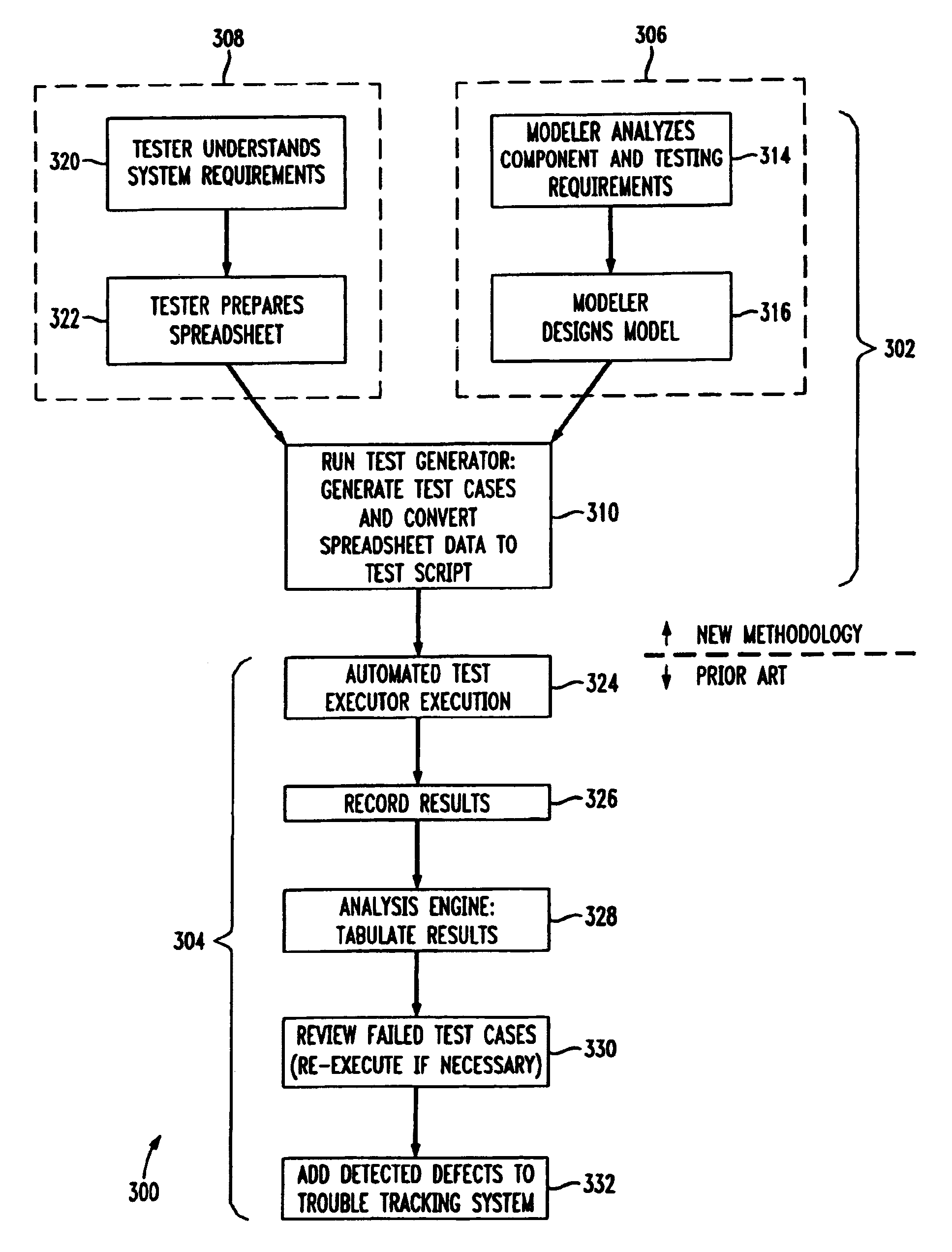

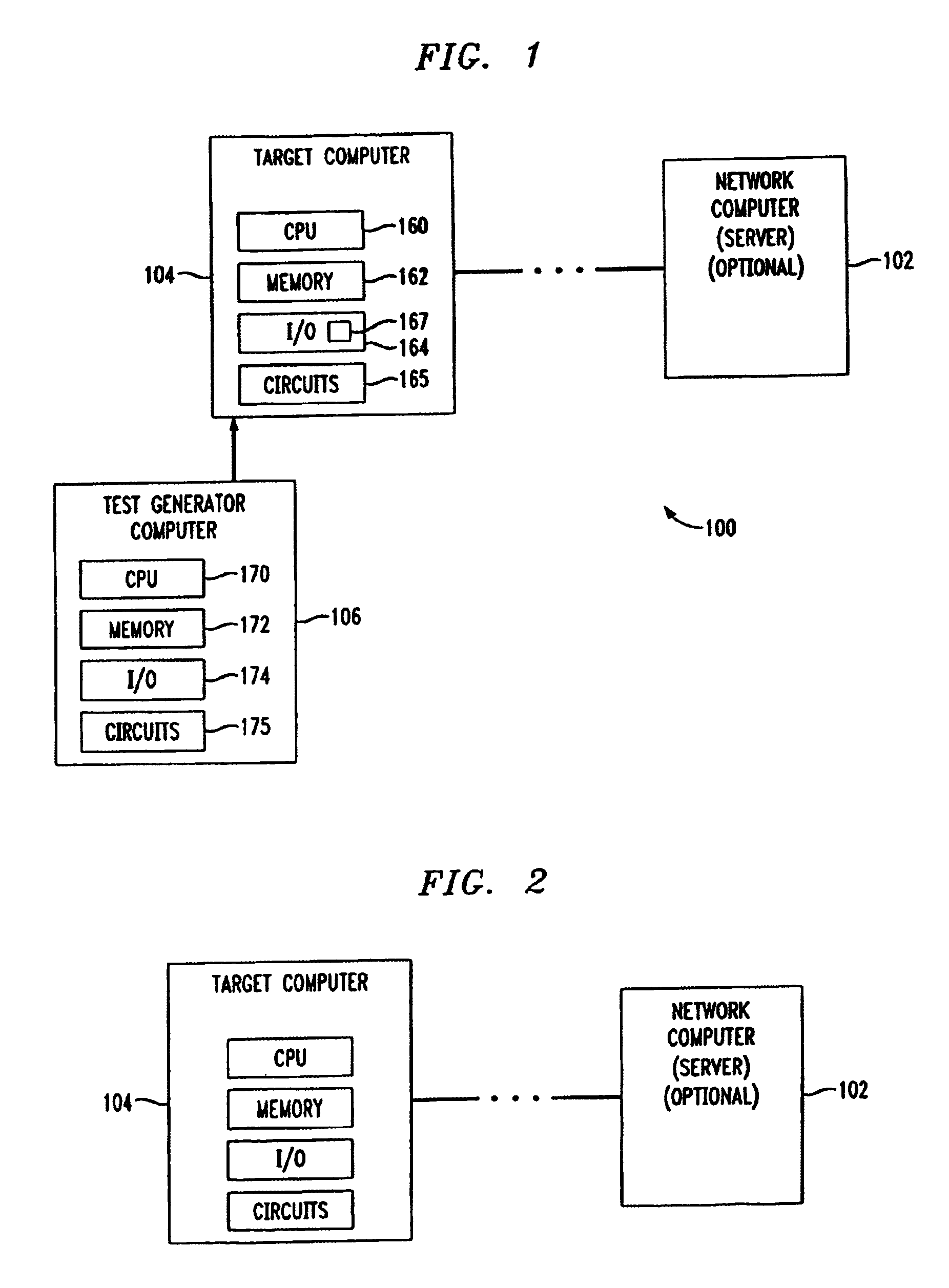

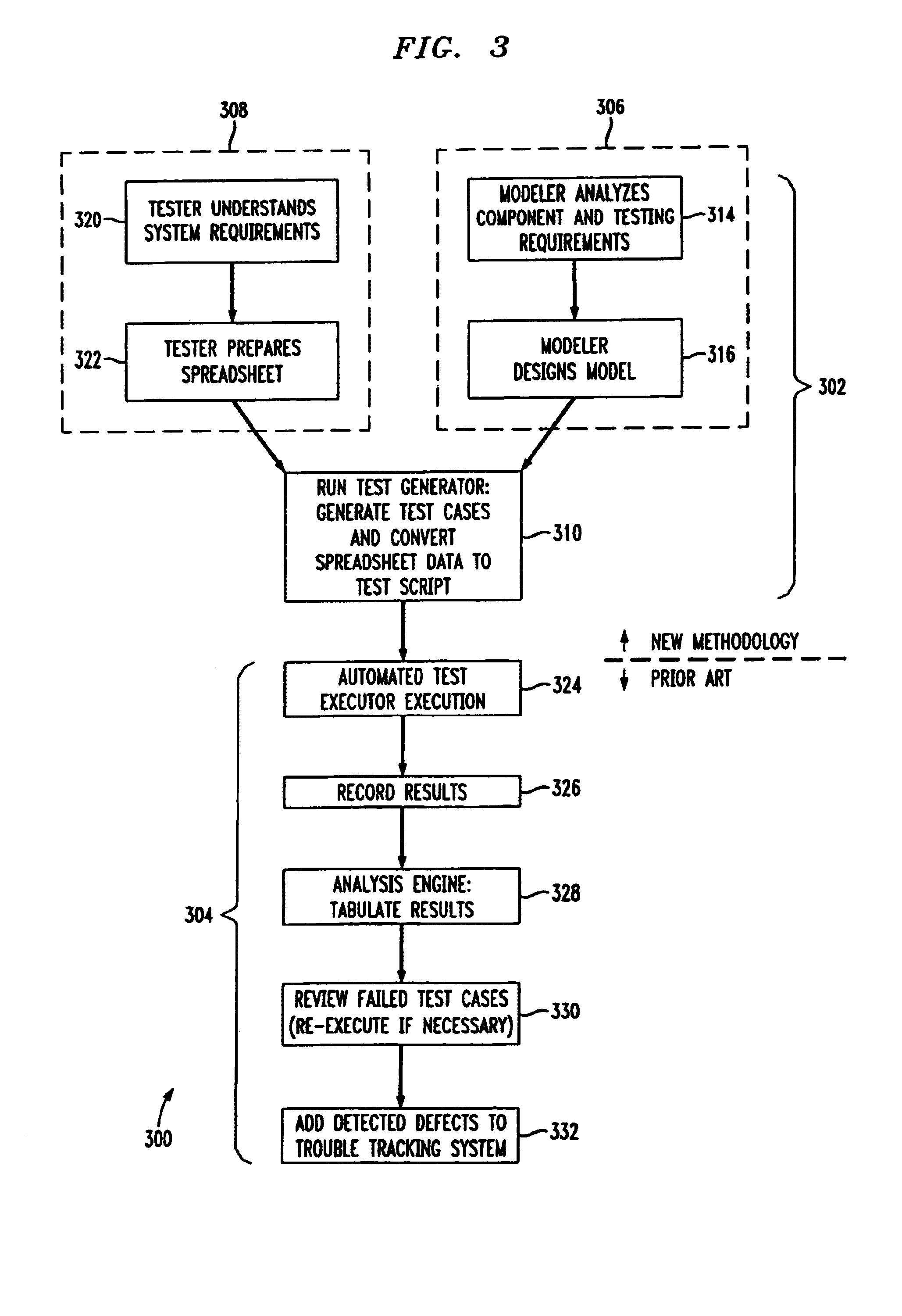

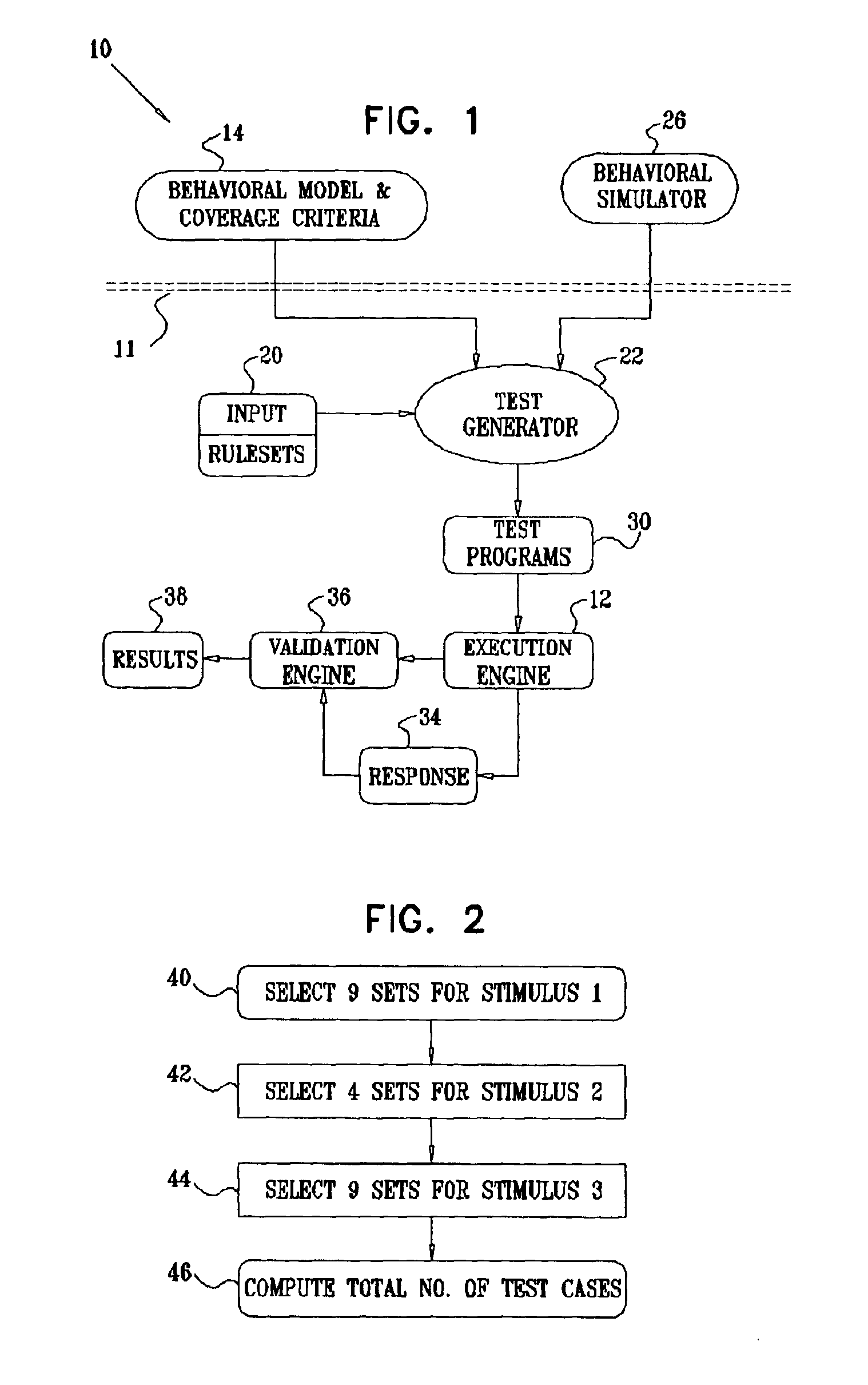

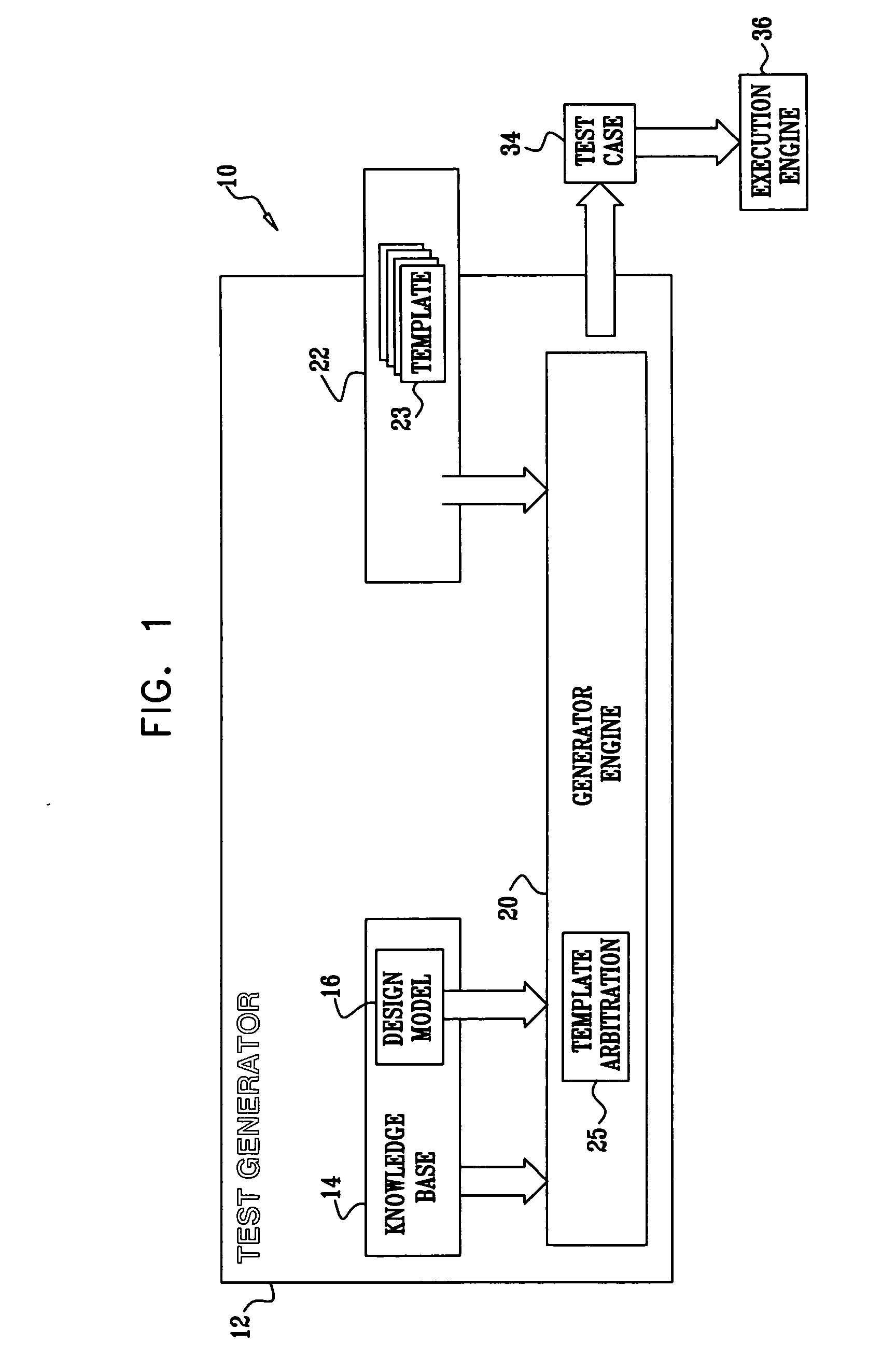

Test generator for converting a model of computer component object behavior and stimulus values to test script

InactiveUS7076713B1Electronic circuit testingError detection/correctionTest scriptTest vector generator

This invention relates to an apparatus and an associated method that tests the response of a computer component. The apparatus includes a modeler, a tester, and a test generator. The modeler provides a model of the computer component object behavior. The tester provides stimulus values to be applied to the computer component object. The test generator converts the model of the computer component object behavior and the stimulus values into test script. The test script can be executed by an automated test executor.

Owner:WSOU INVESTMENTS LLC +1

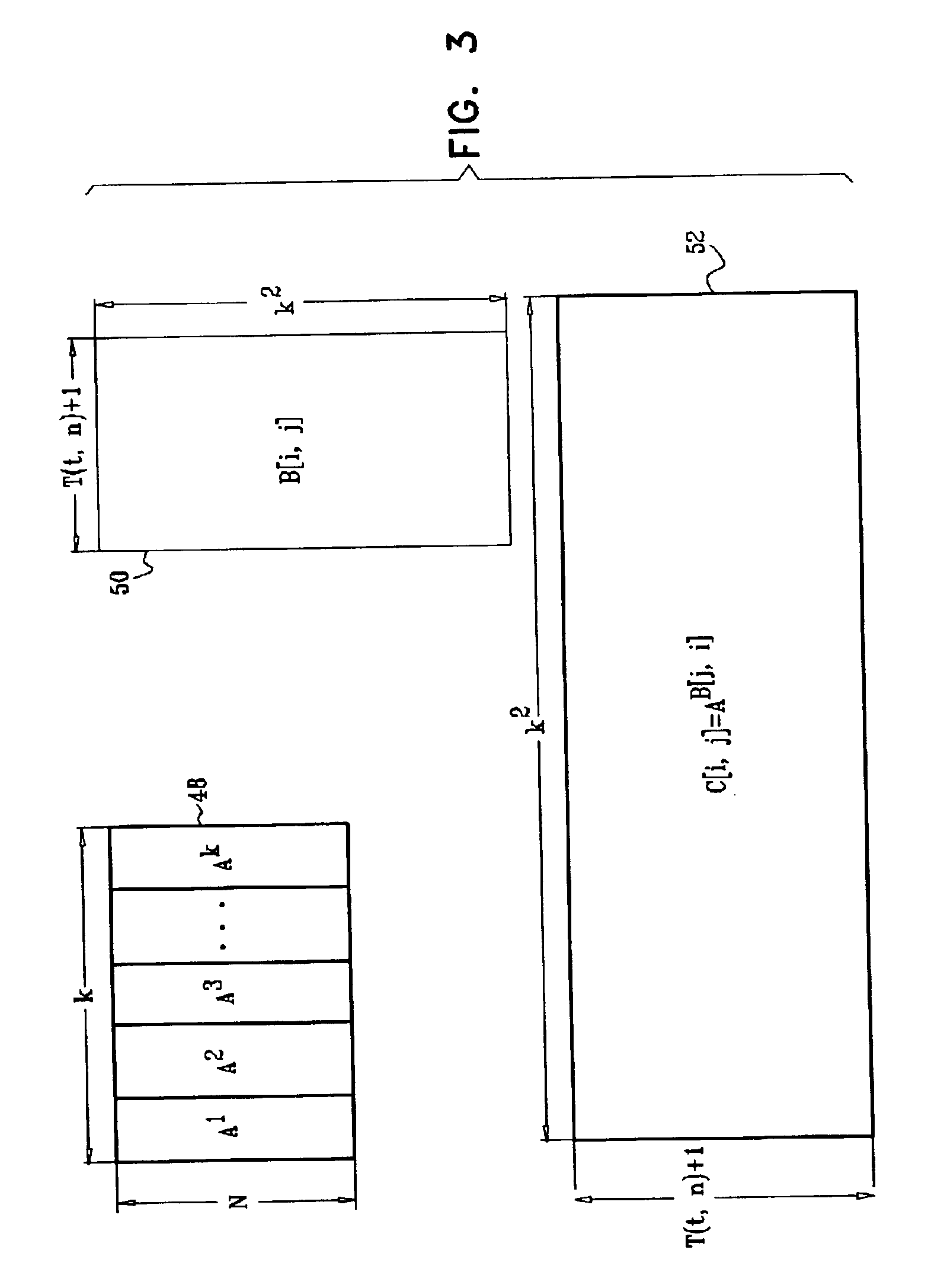

Reducing the complexity of finite state machine test generation using combinatorial designs

InactiveUS7024589B2Generate efficientlyGuaranteed test coverageElectronic circuit testingError detection/correctionTest inputTheoretical computer science

A design verification system generates a small set of test cases, from a finite state machine model of the application under test. The finite state machine is reduced by creating efficient samples of the inputs to the application under test which are prepared by combinatorial input parameter selection. The test cases are generated by finite state machine traversal of the reduced state machine, and tests interacting combinations of input parameters in an efficient way. The technique is integrated into a test generator based on a finite state machine. Using an extended language, partial rulesets are employed to instruct the test generator to automatically employ combinatorial input parameter selection during test generation. Another technique for test case generation is disclosed, which uses combinatorial selection algorithms to guarantee coverage of the system under test from the aspect of interaction between stimuli at different stages or transitions in the test case.

Owner:IBM CORP

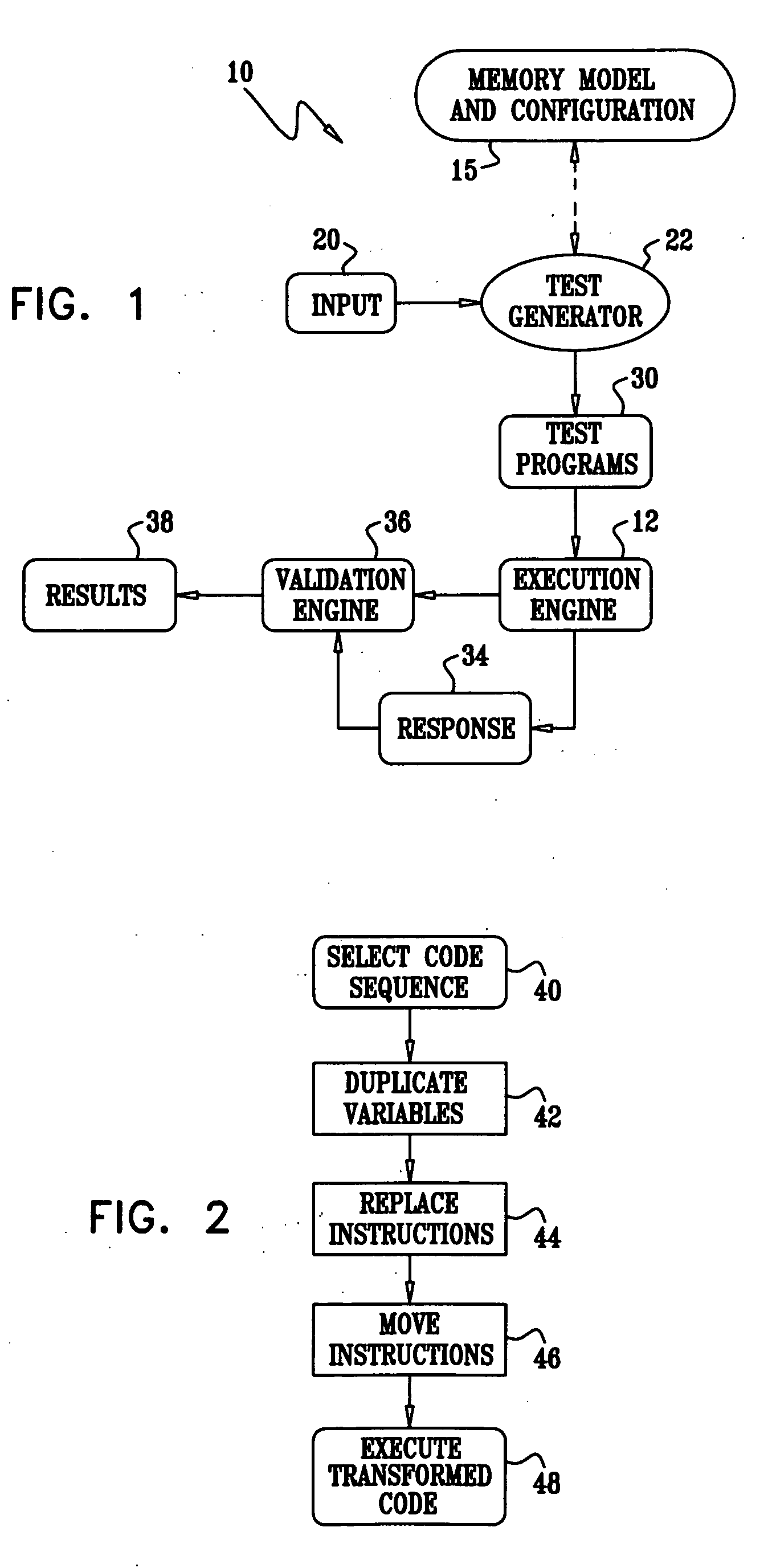

Using code motion and write and read delays to increase the probability of bug detection in concurrent systems

InactiveUS20060161897A1Raise the possibilityError detection/correctionSpecific program execution arrangementsLocal variableParallel computing

A tool is provided for modifying the code of a multi-threaded computer program undergoing testing. The program executes in an environment that has a governing memory model. It is assumed that there is a global heap and a thread-local heap, which are synchronized from time to time. The modifications are of two types: (1) code instructions are reordered while remaining in compliance with the memory model; and (2) thread-local variables are added to functions, together with inserted heap synchronizing instructions. The modified programs are then used by a test generator to prepare test cases for execution. The modifications have the effect of changing the interleavings that occur among different threads, and increase the likelihood of exposing flaws that may become evident under different memory models.

Owner:IBM CORP

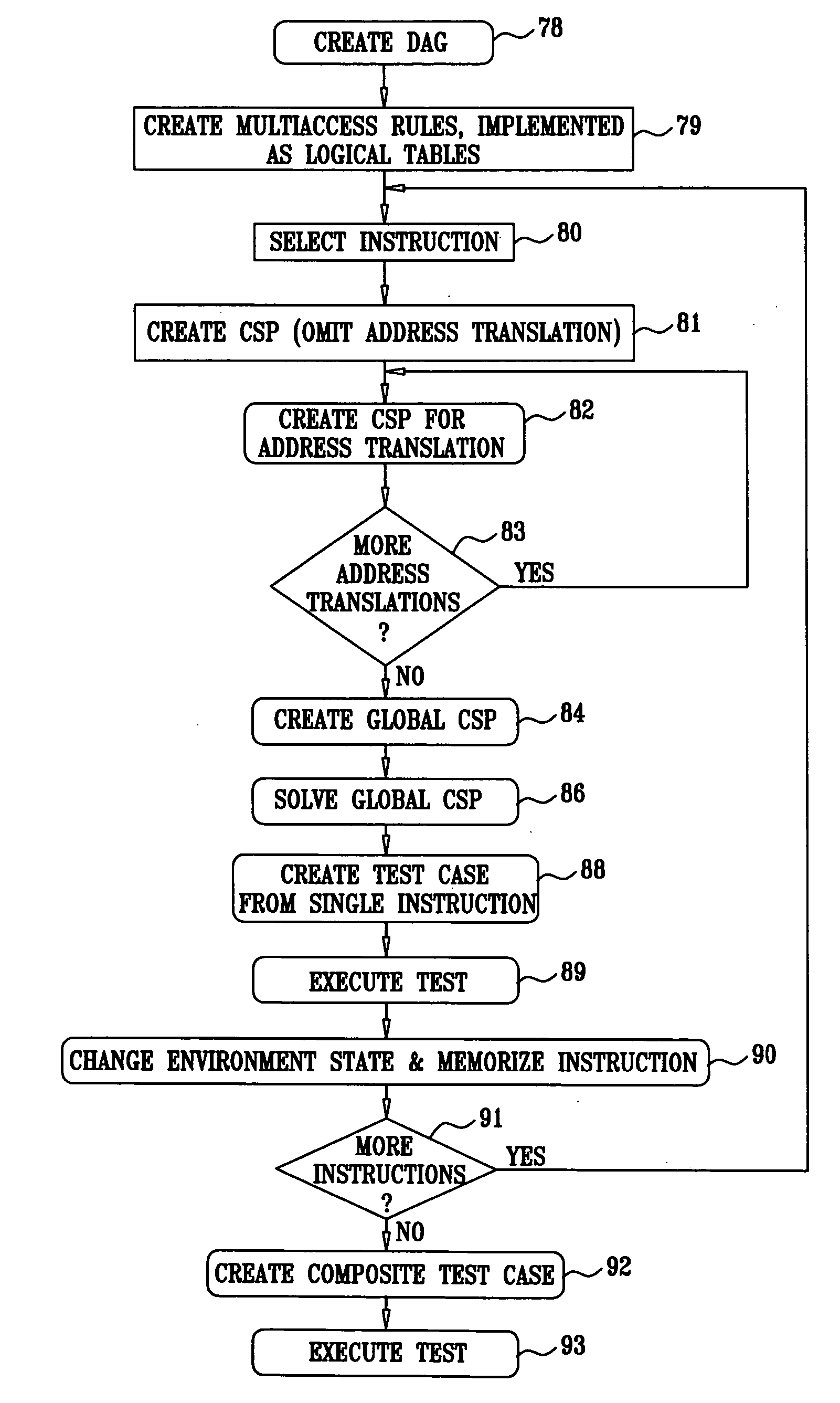

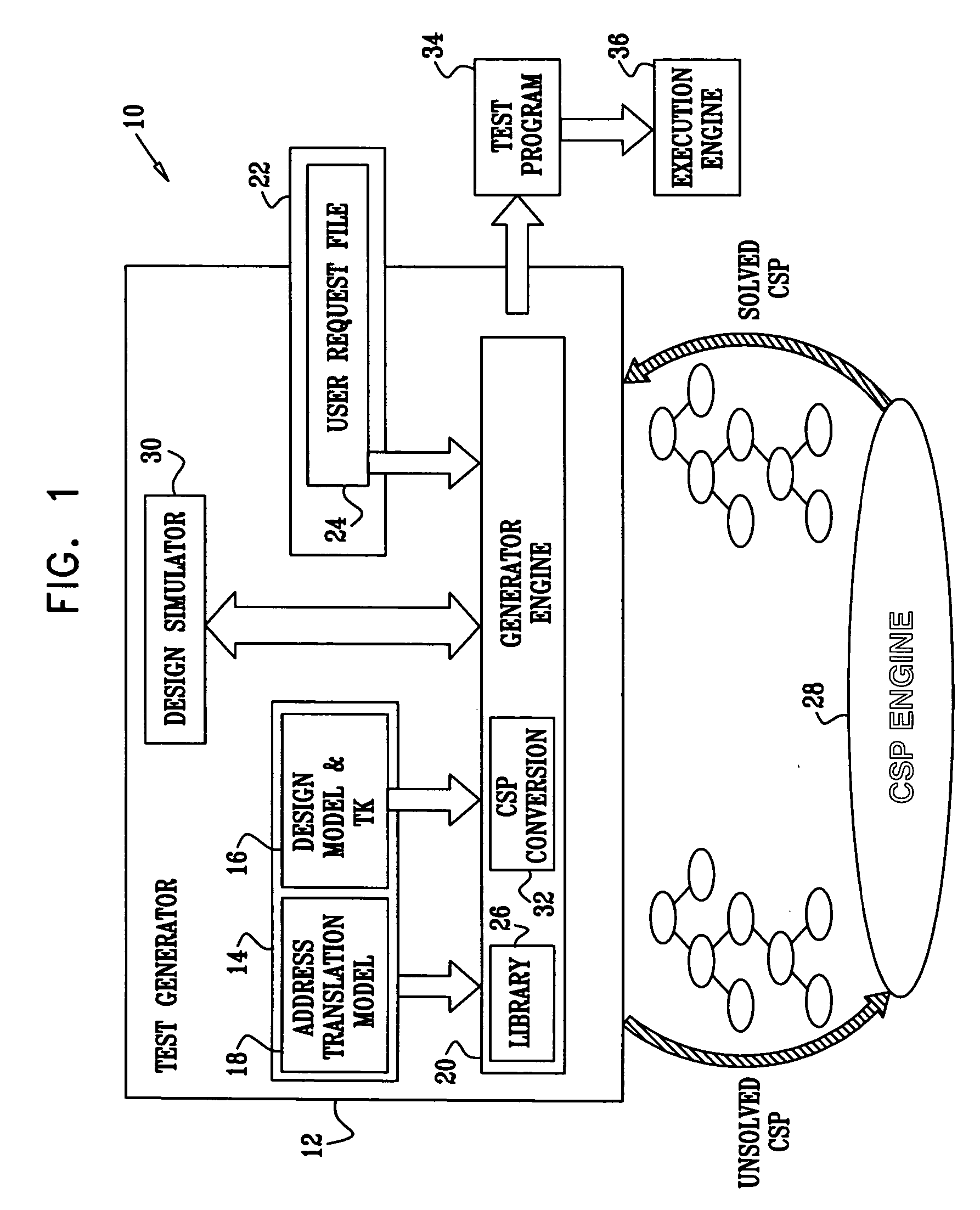

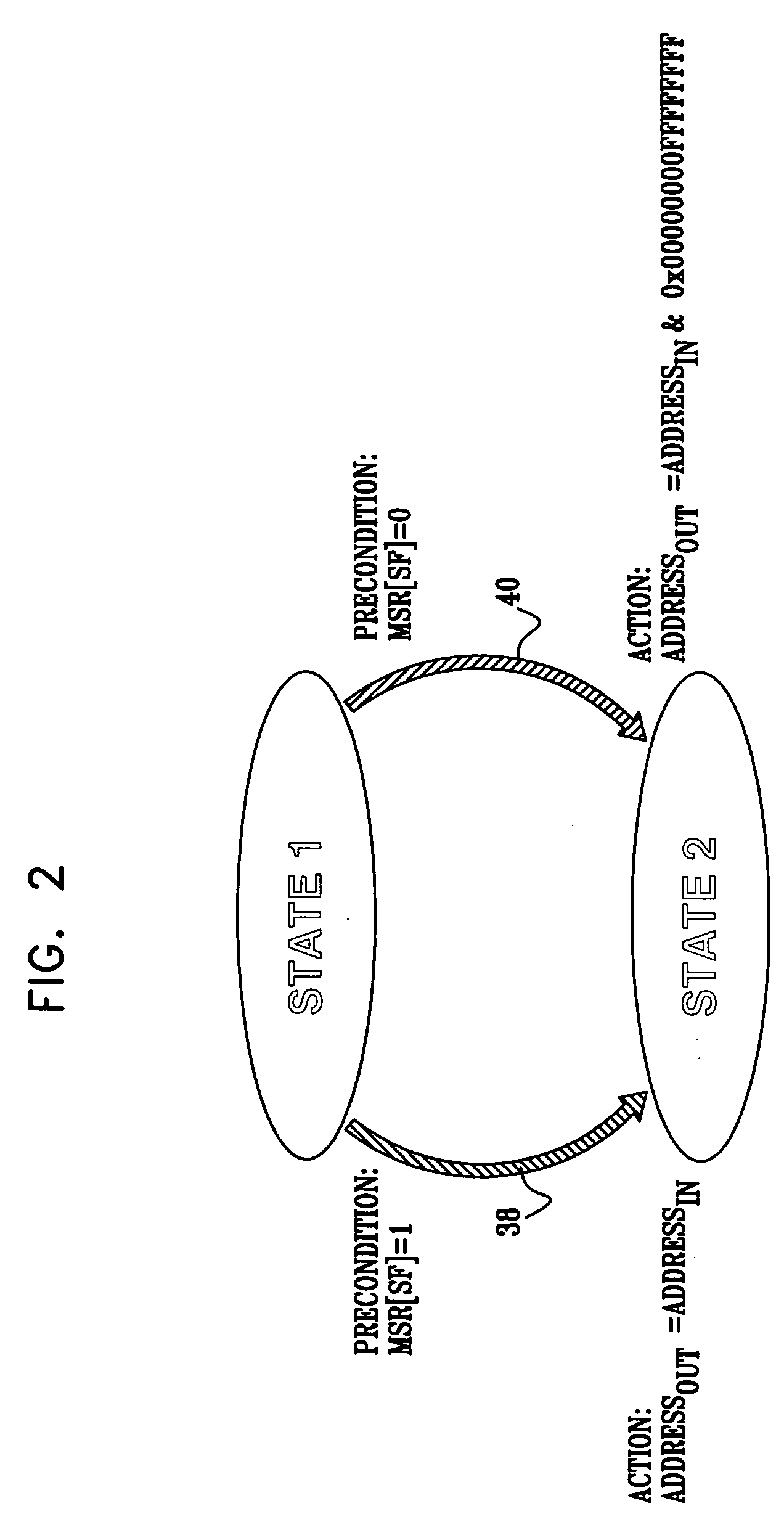

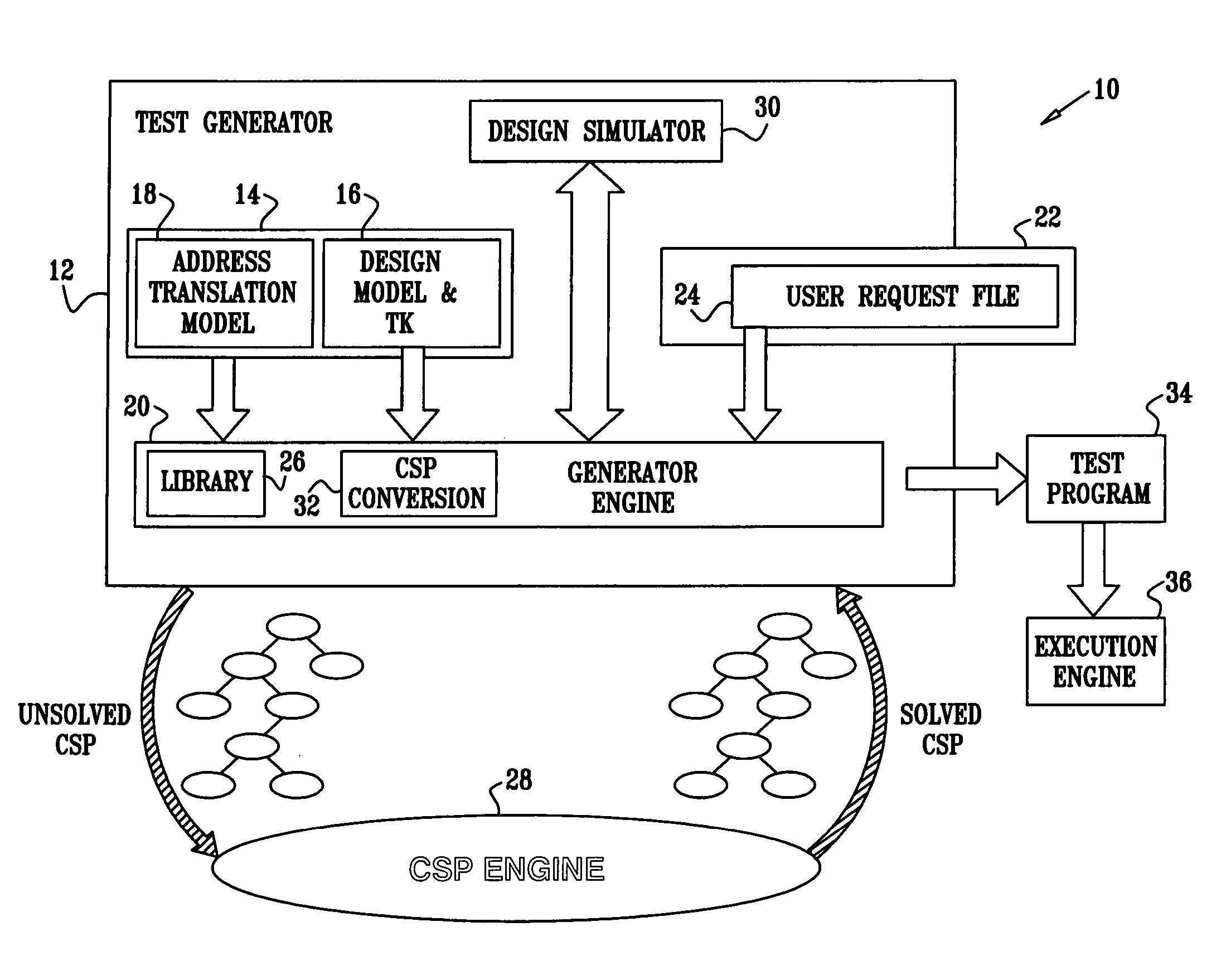

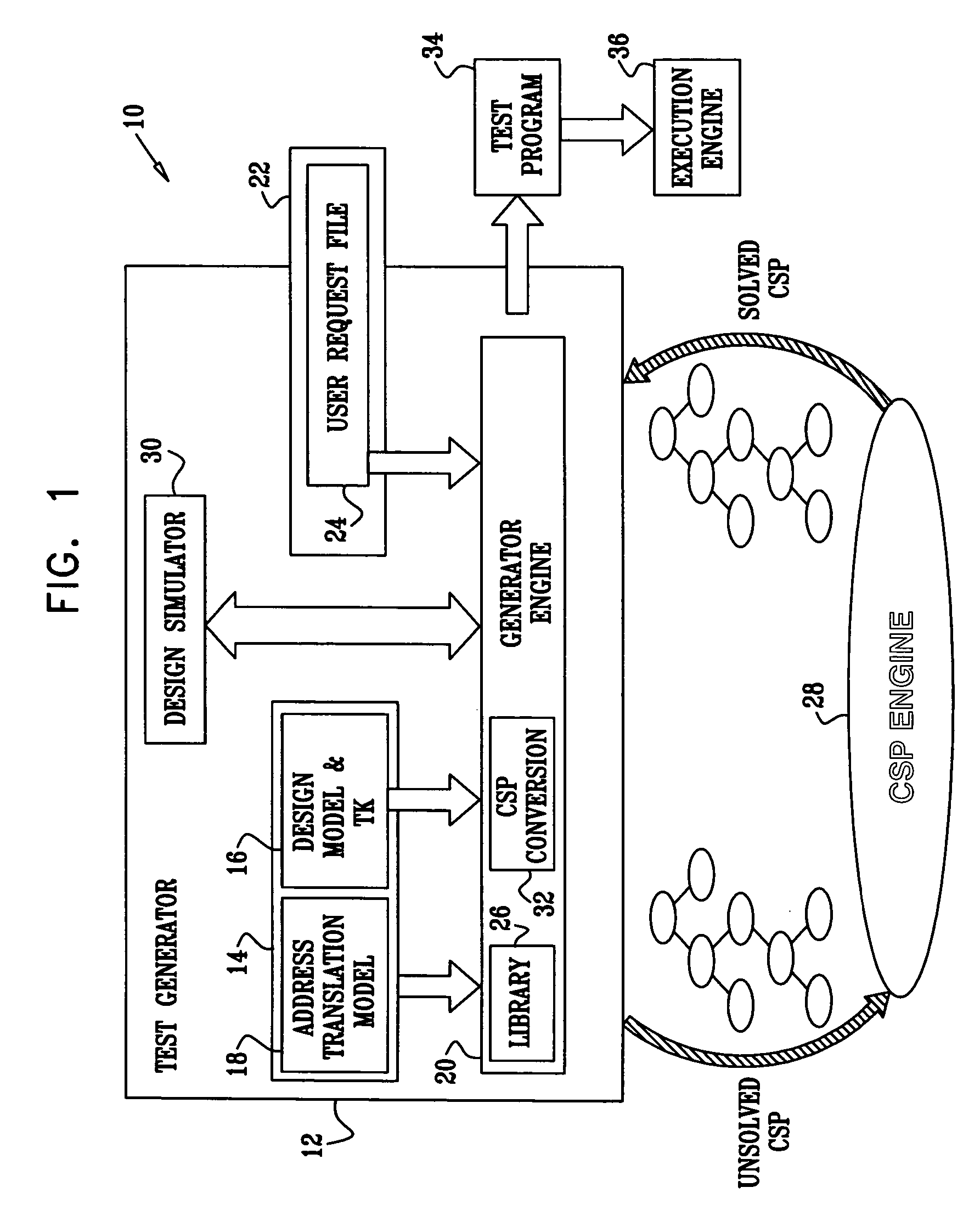

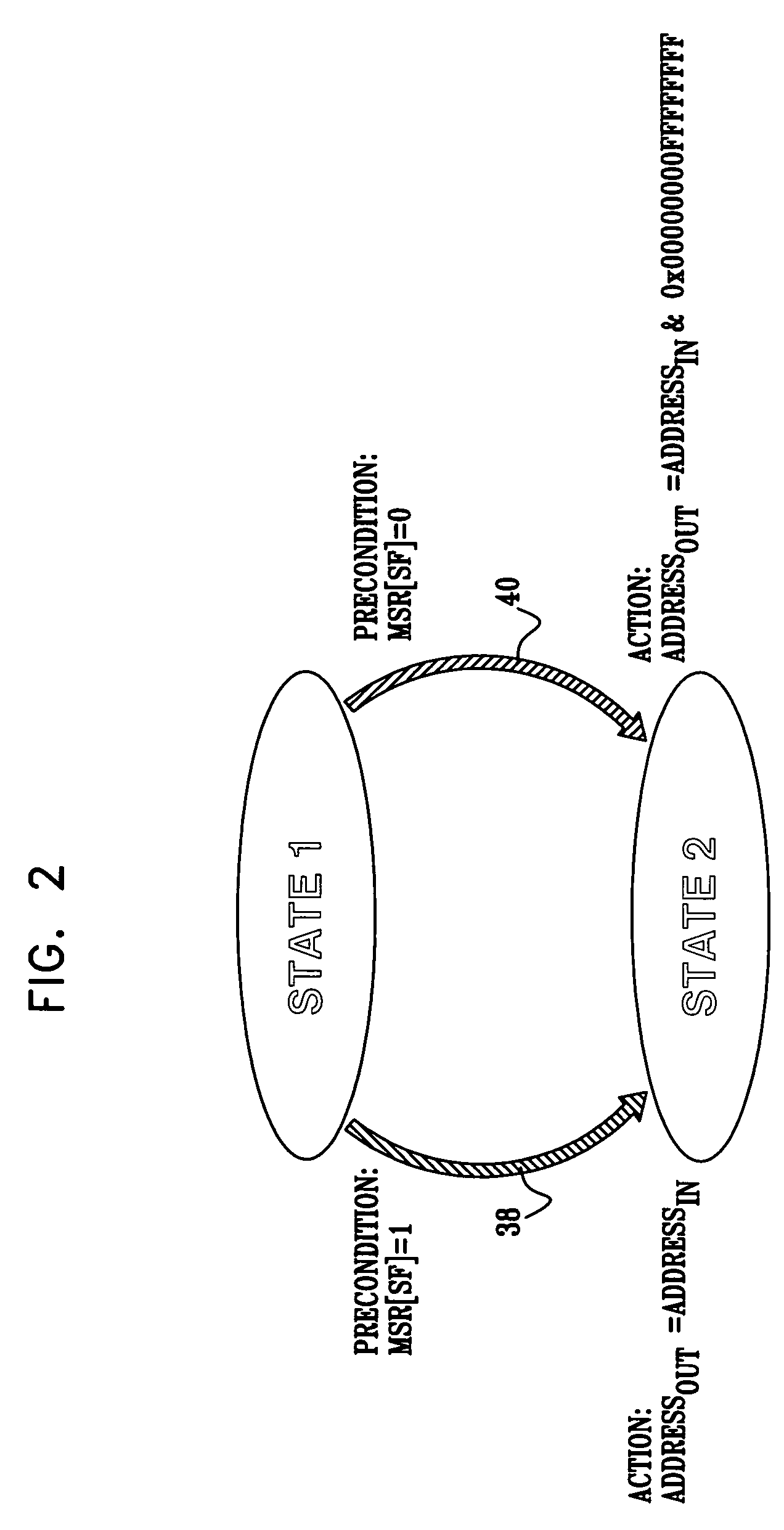

Modeling language and method for address translation design mechanisms in test generation

InactiveUS20050278702A1Large coverageLogical operation testingSoftware simulation/interpretation/emulationConstraint satisfaction problemModeling language

Methods and systems are disclosed that enhance the ability of a test generator to automatically deal with address translation in a processor design, and without need for creating specific code. A model of the address translation mechanism of a design-under-test is represented as a directed acyclic graph and then converted into a constraint satisfaction problem. The problem is solved by a CSP engine, and the solution used to generate test cases for execution. Using the model, testing knowledge can be propagated to models applicable to many different designs to produce extensive coverage of address translation mechanisms.

Owner:GLOBALFOUNDRIES INC

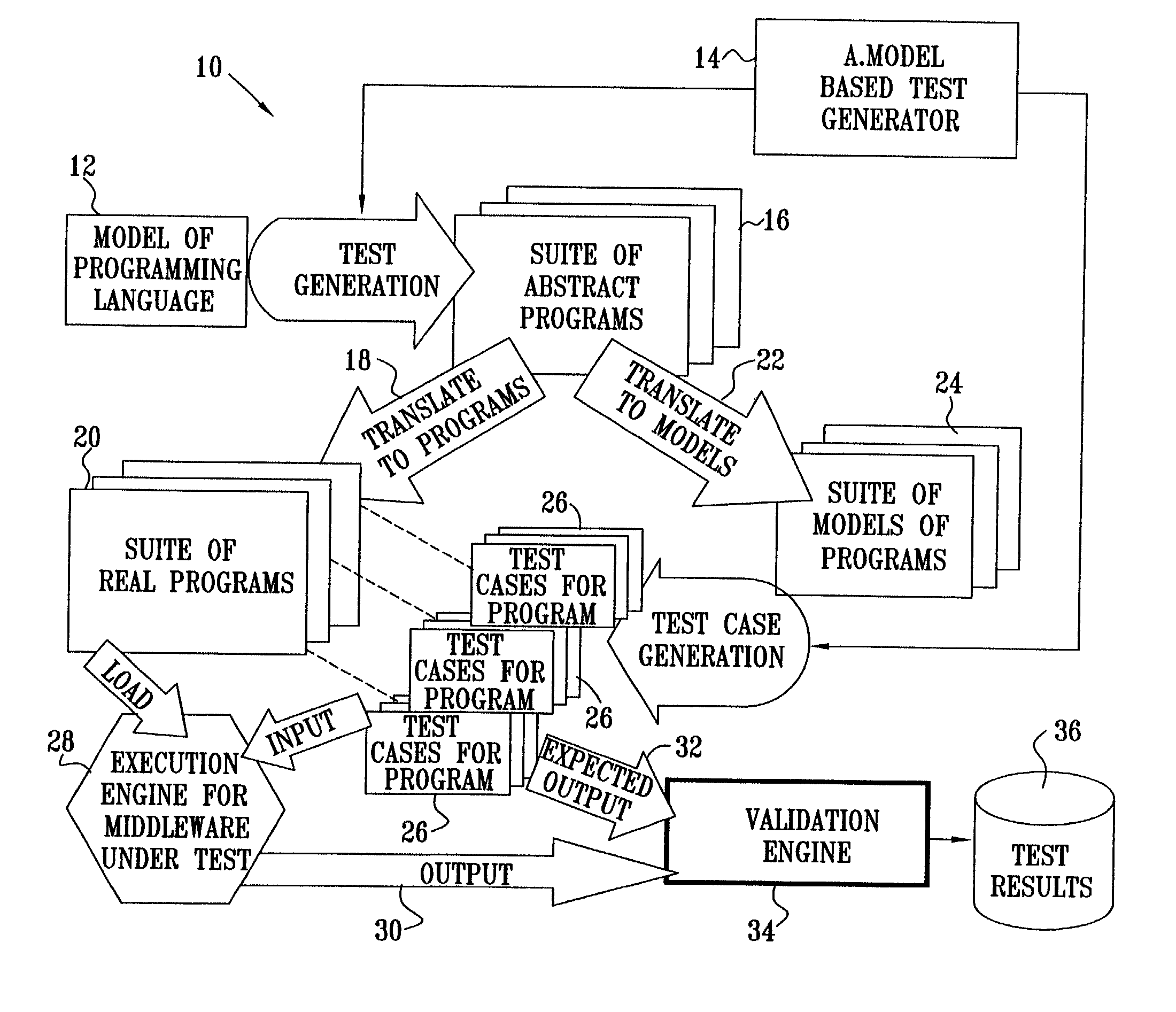

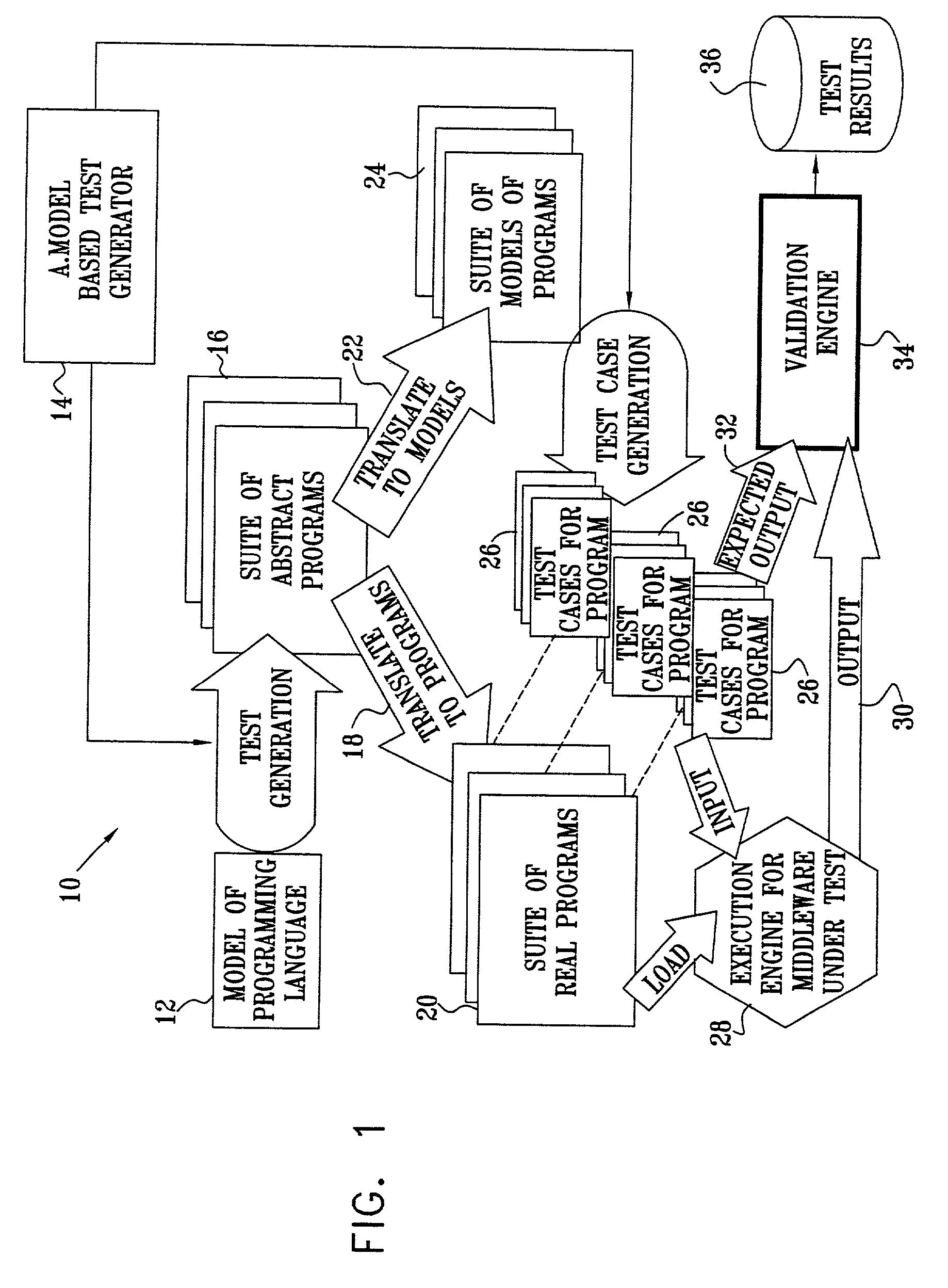

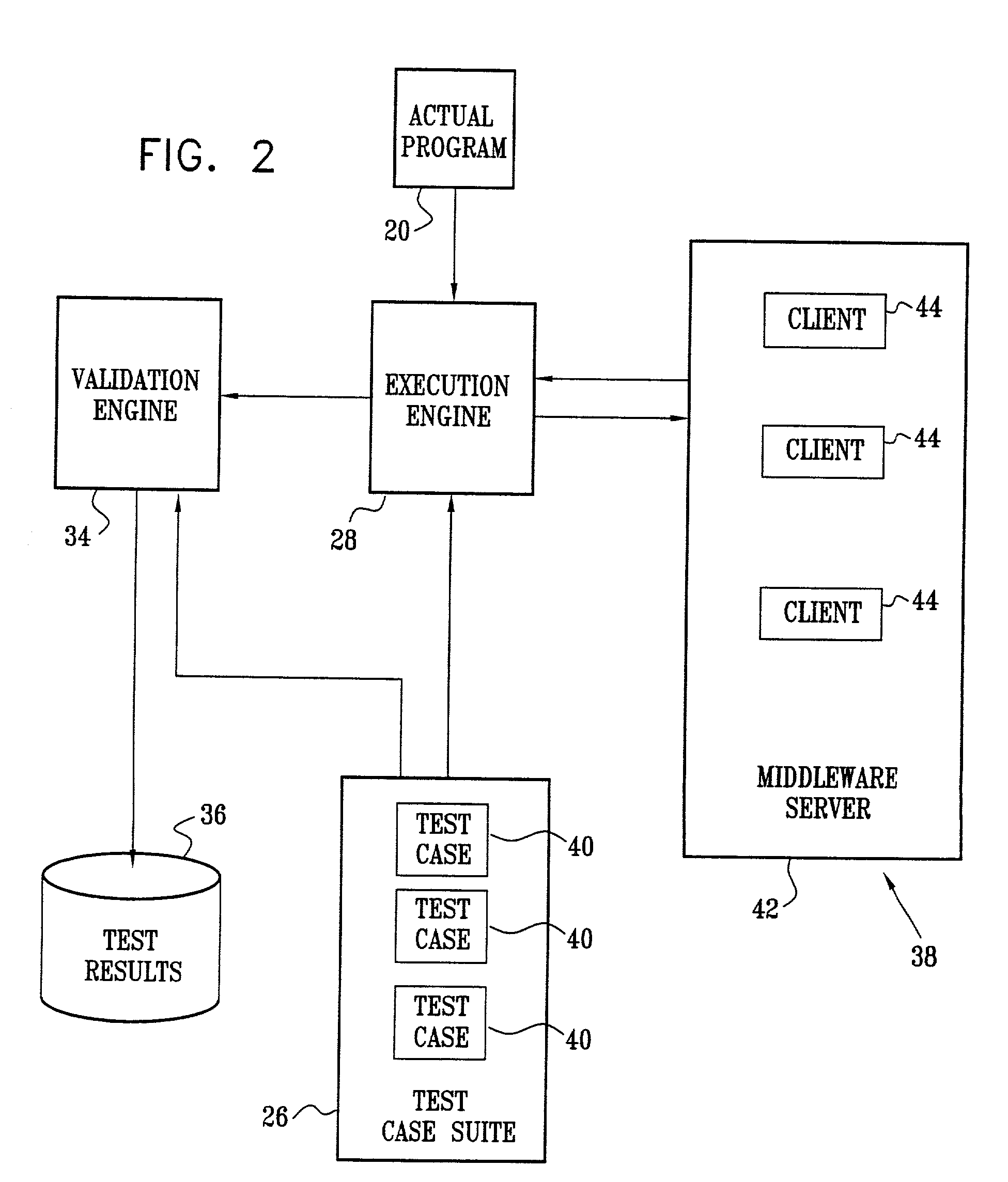

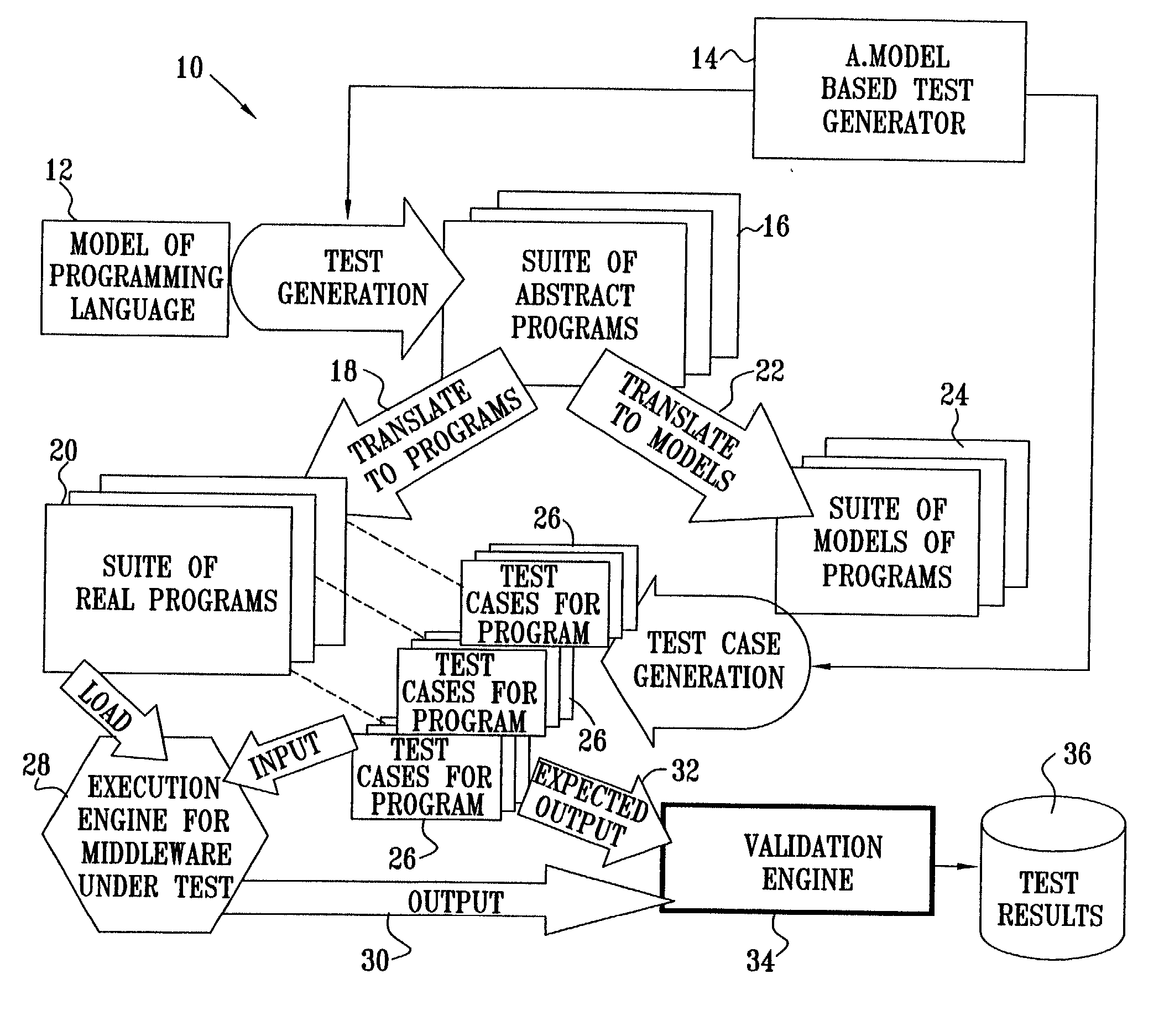

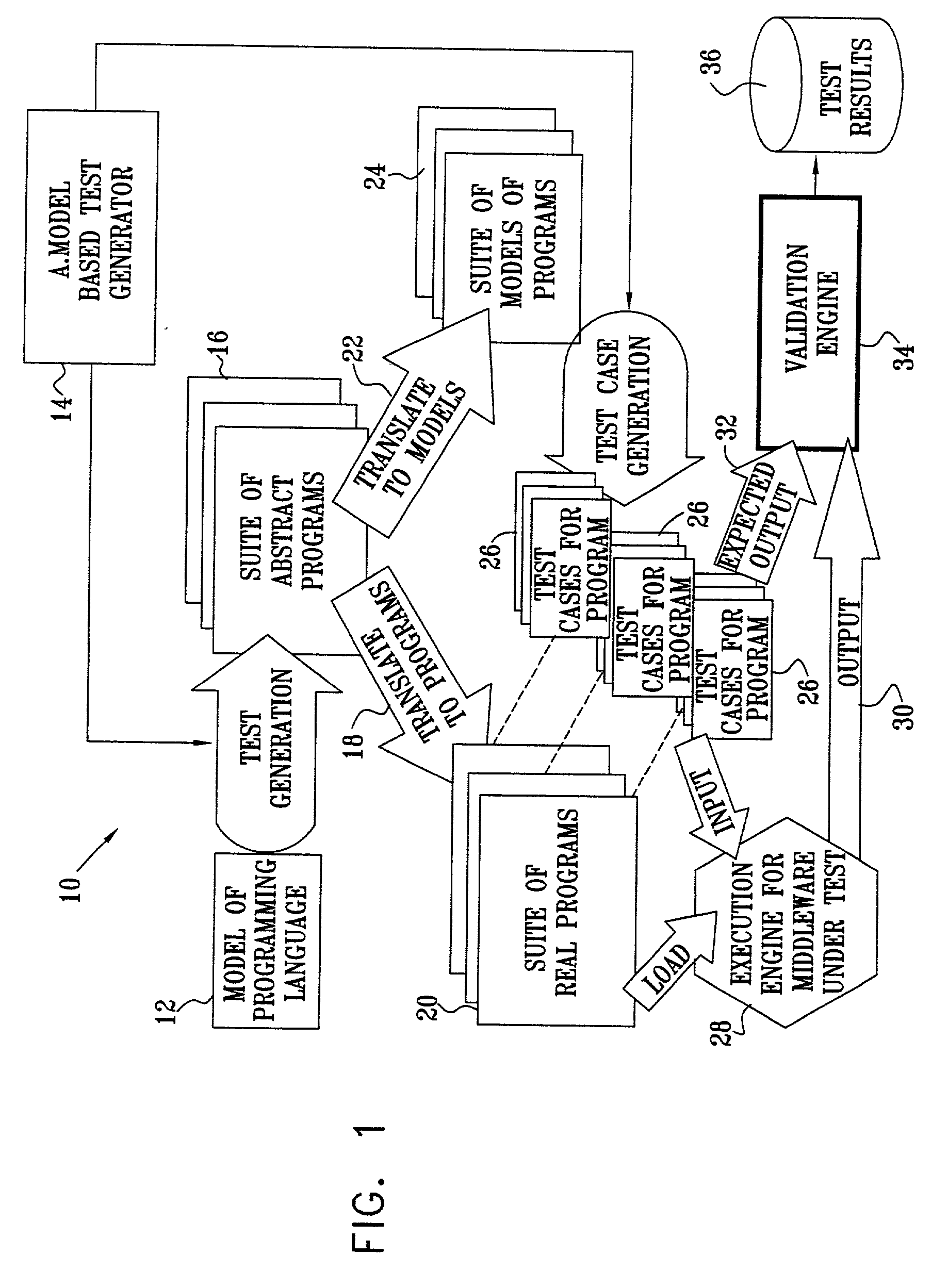

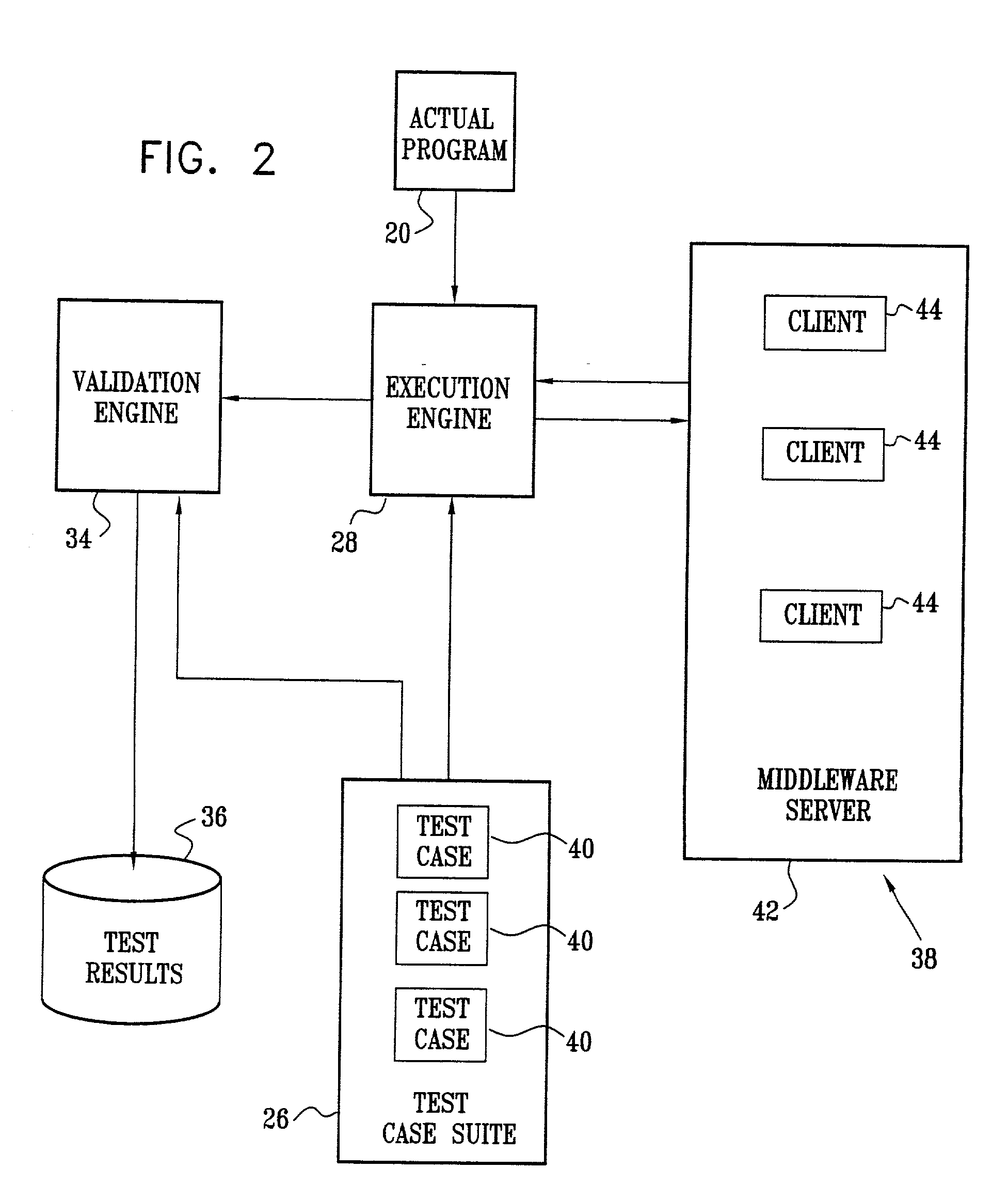

Recursive use of model based test generation for middleware validation

InactiveUS7117484B2Efficient testingSoftware testing/debuggingSpecific program execution arrangementsHigh level modelAbstract program

Owner:LINKEDIN

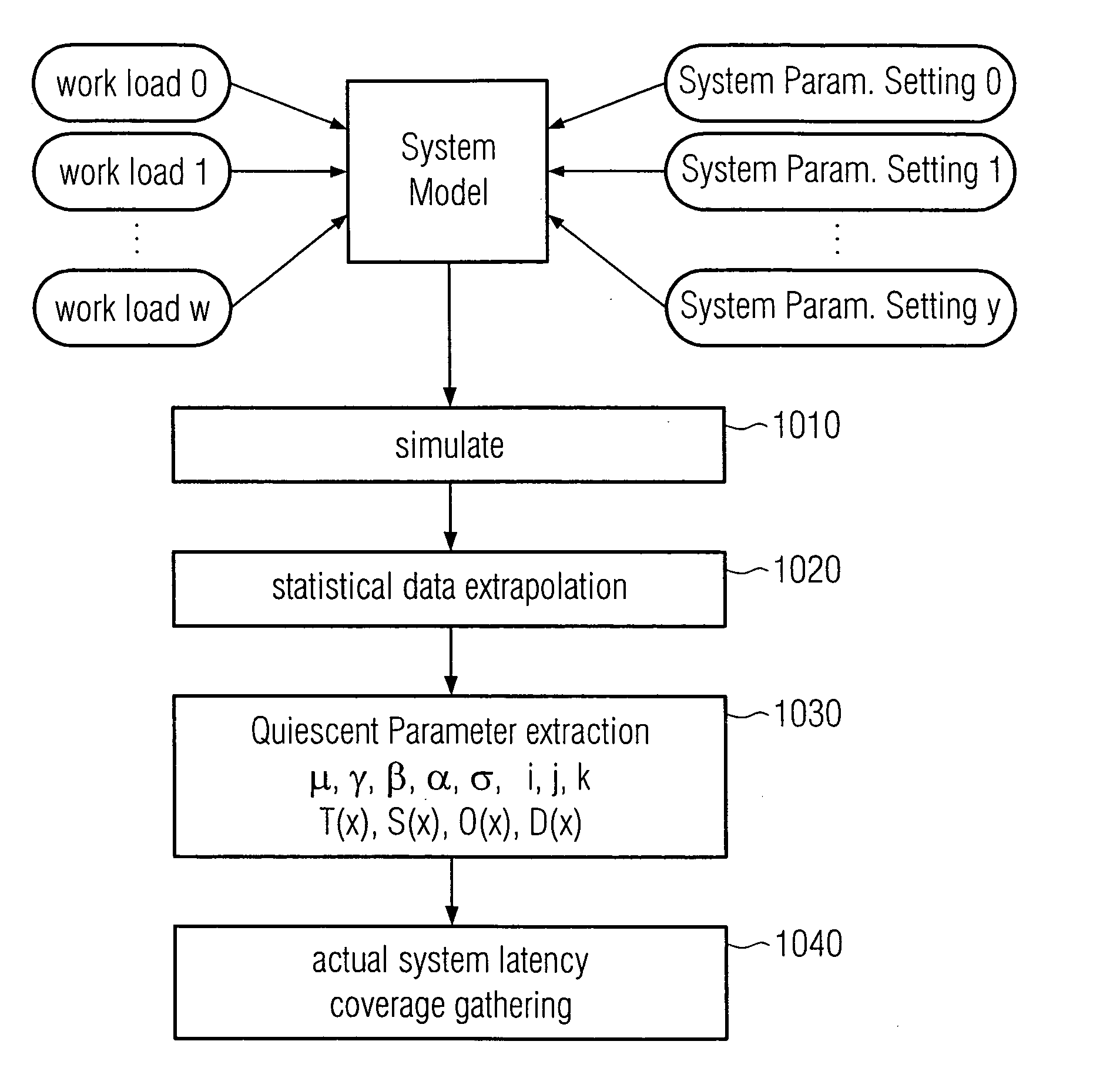

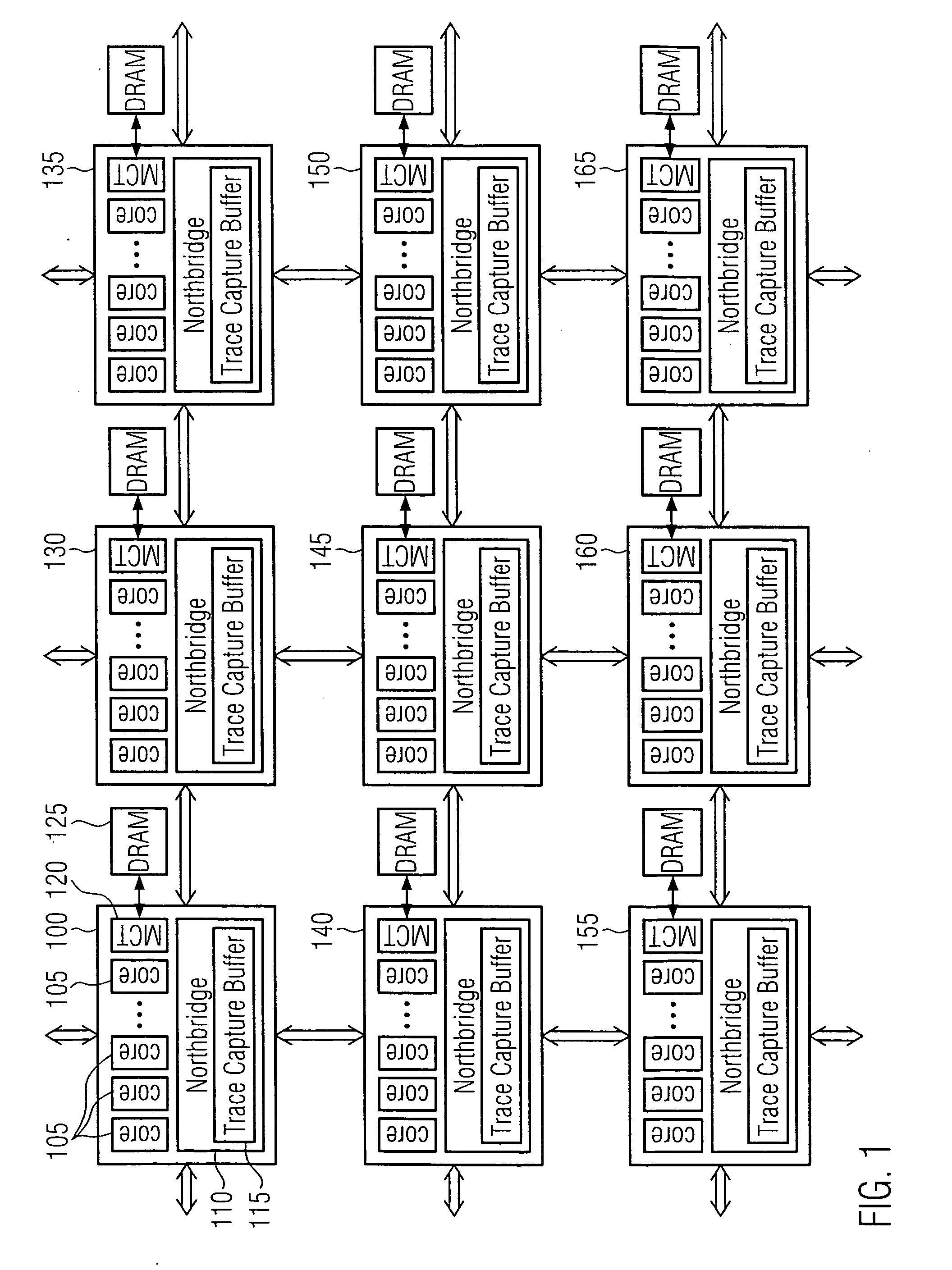

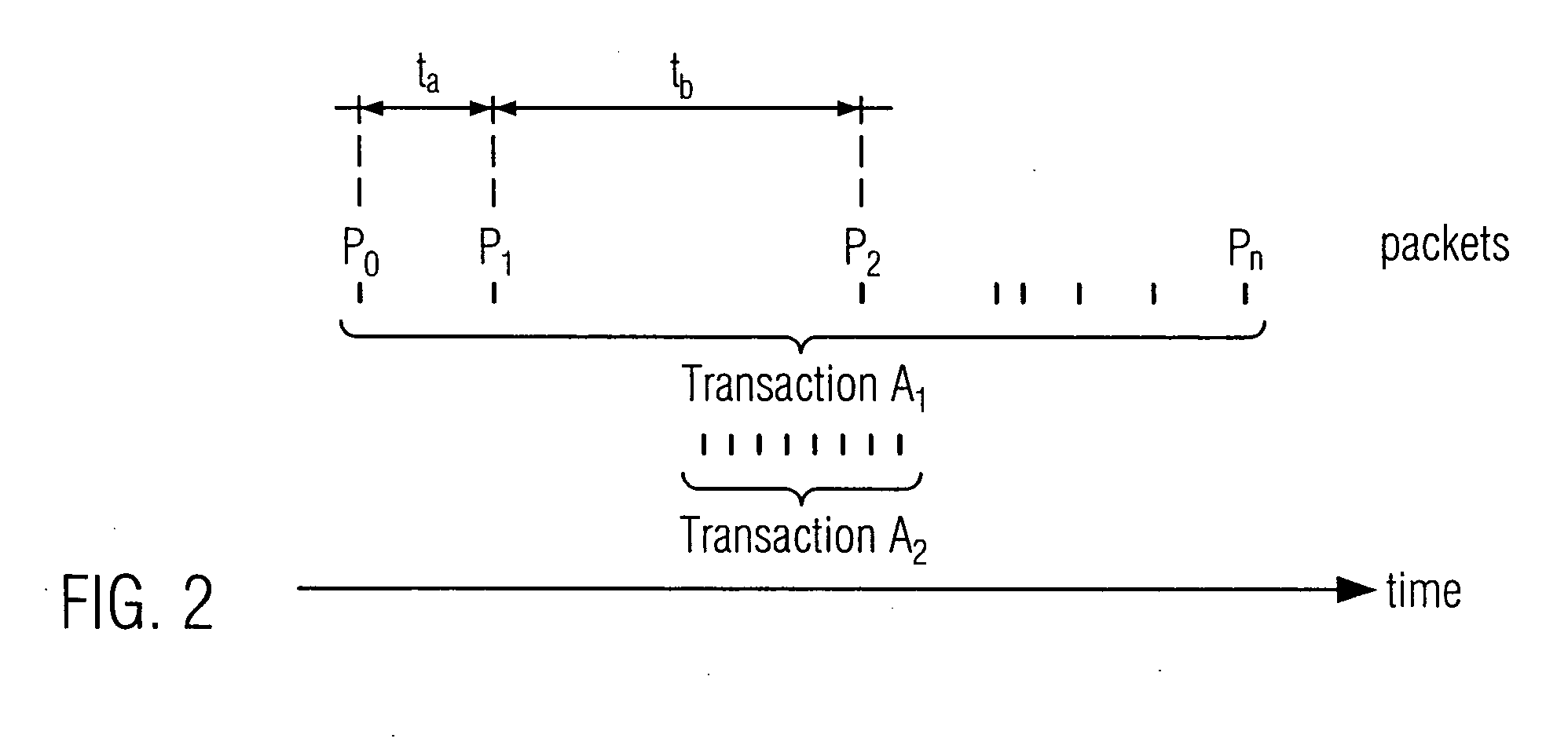

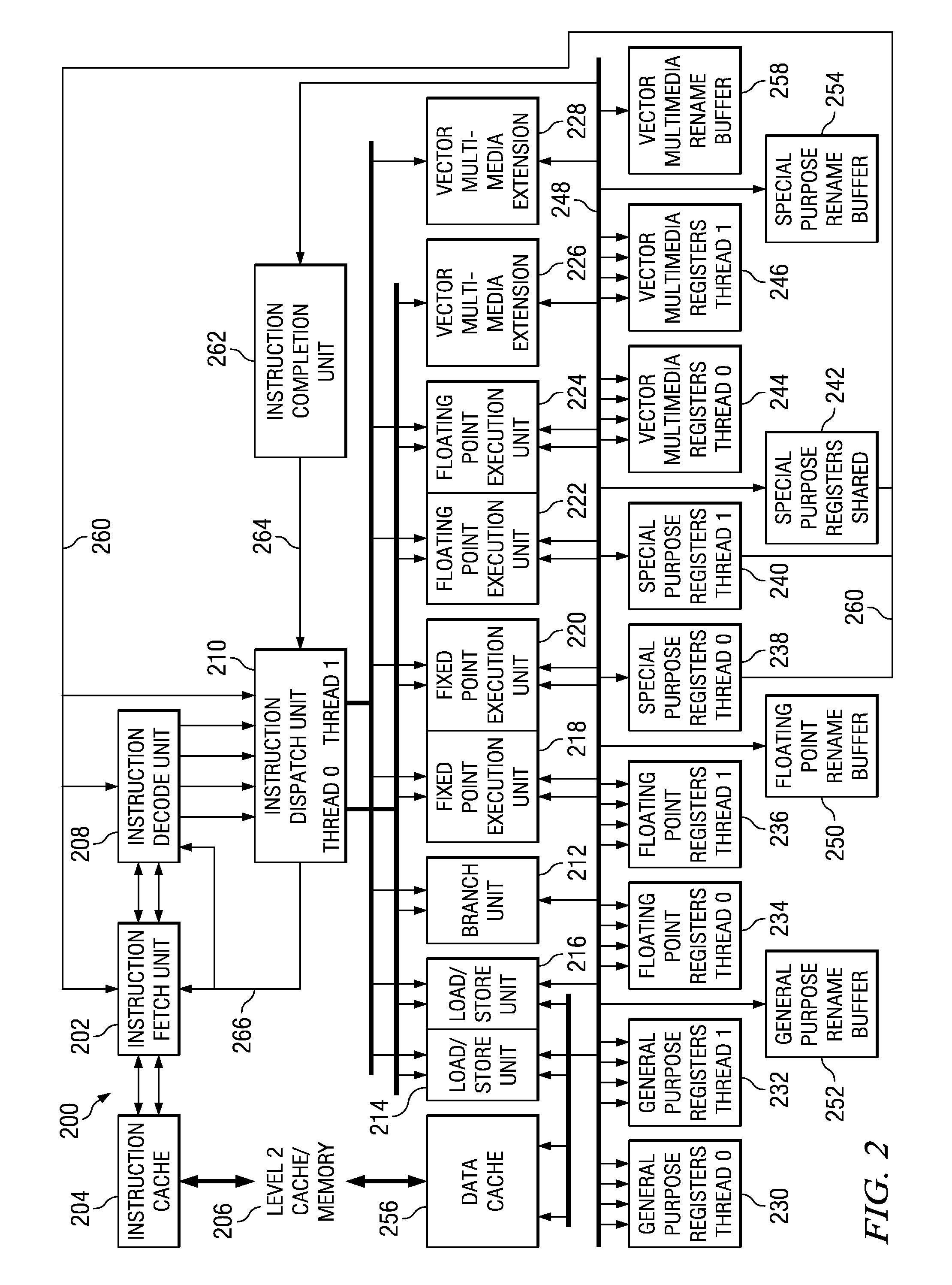

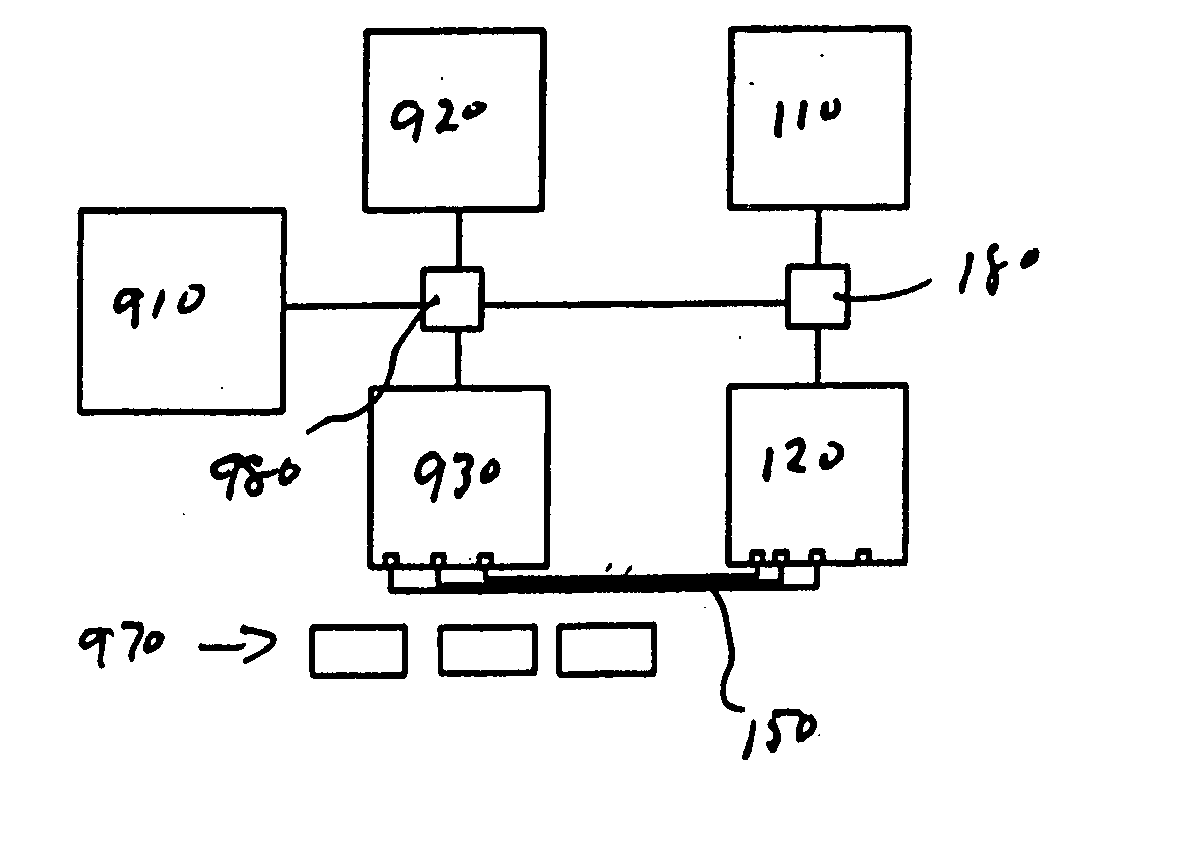

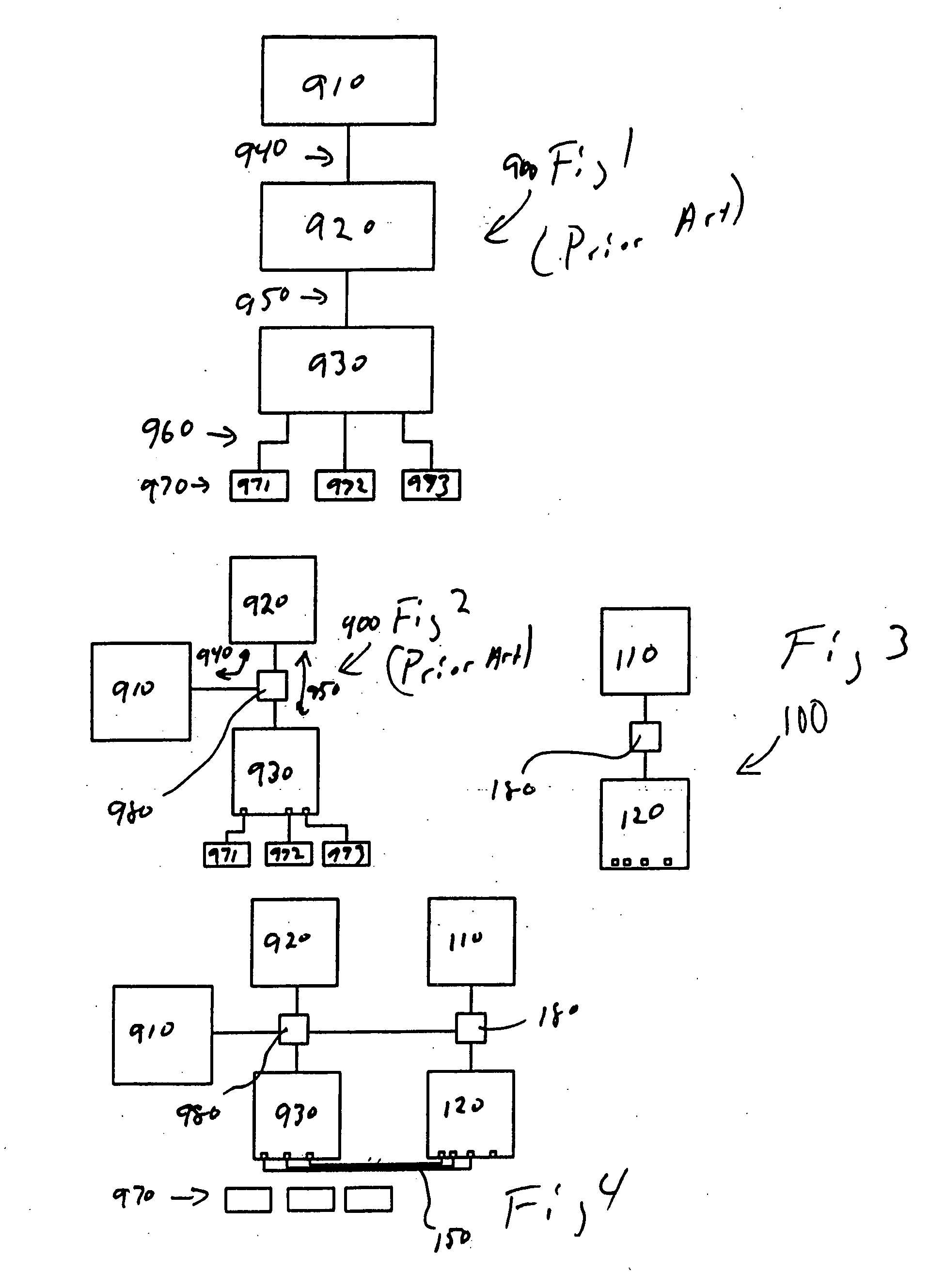

Latency coverage and adoption to multiprocessor test generator template creation

InactiveUS20090064149A1Easy to measureEasy to captureError detection/correctionMultiprogramming arrangementsMulti processorTransaction data

A multi-core multi-node processor system has a plurality of multiprocessor nodes, each including a plurality of microprocessor cores. The plurality of microprocessor nodes and cores are connected and form a transactional communication network. The multi-core multi-node processor system has further one or more buffer units collecting transaction data relating to transactions sent from one core to another core. An agent is included which calculates latency data from the collected transaction data, processes the calculated latency data to gather transaction latency coverage data, and creates random test generator templates from the gathered transaction latency coverage data. The transaction latency coverage data indicates at least the latencies of the transactions detected during collection of the transaction data having a pre-determined latency, and includes, for example, four components for transaction type latency, transaction sequence latency, transaction overlap latency, and packet distance latency. Thus, random test generator templates may be created using latency coverage.

Owner:GLOBALFOUNDRIES INC

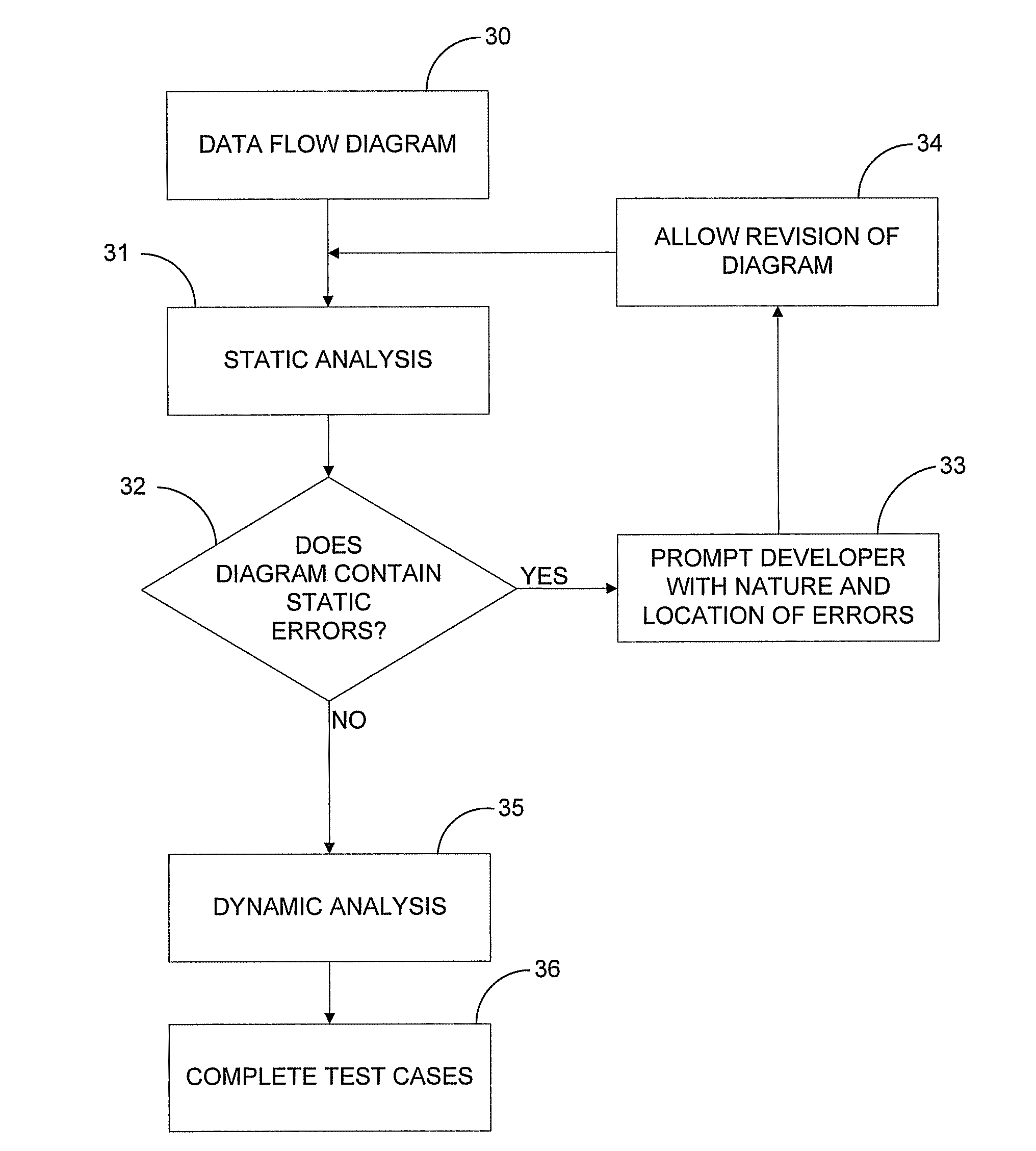

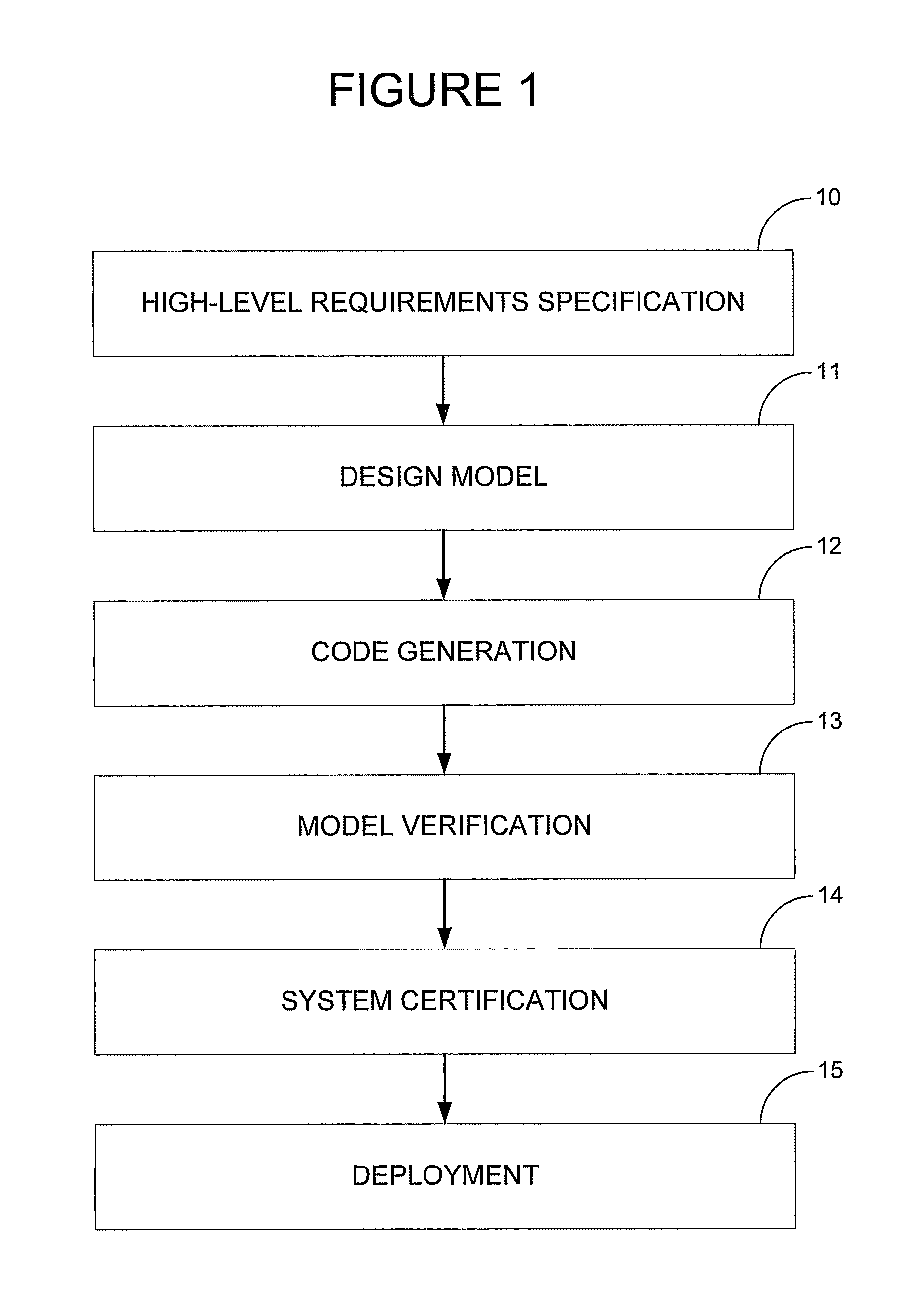

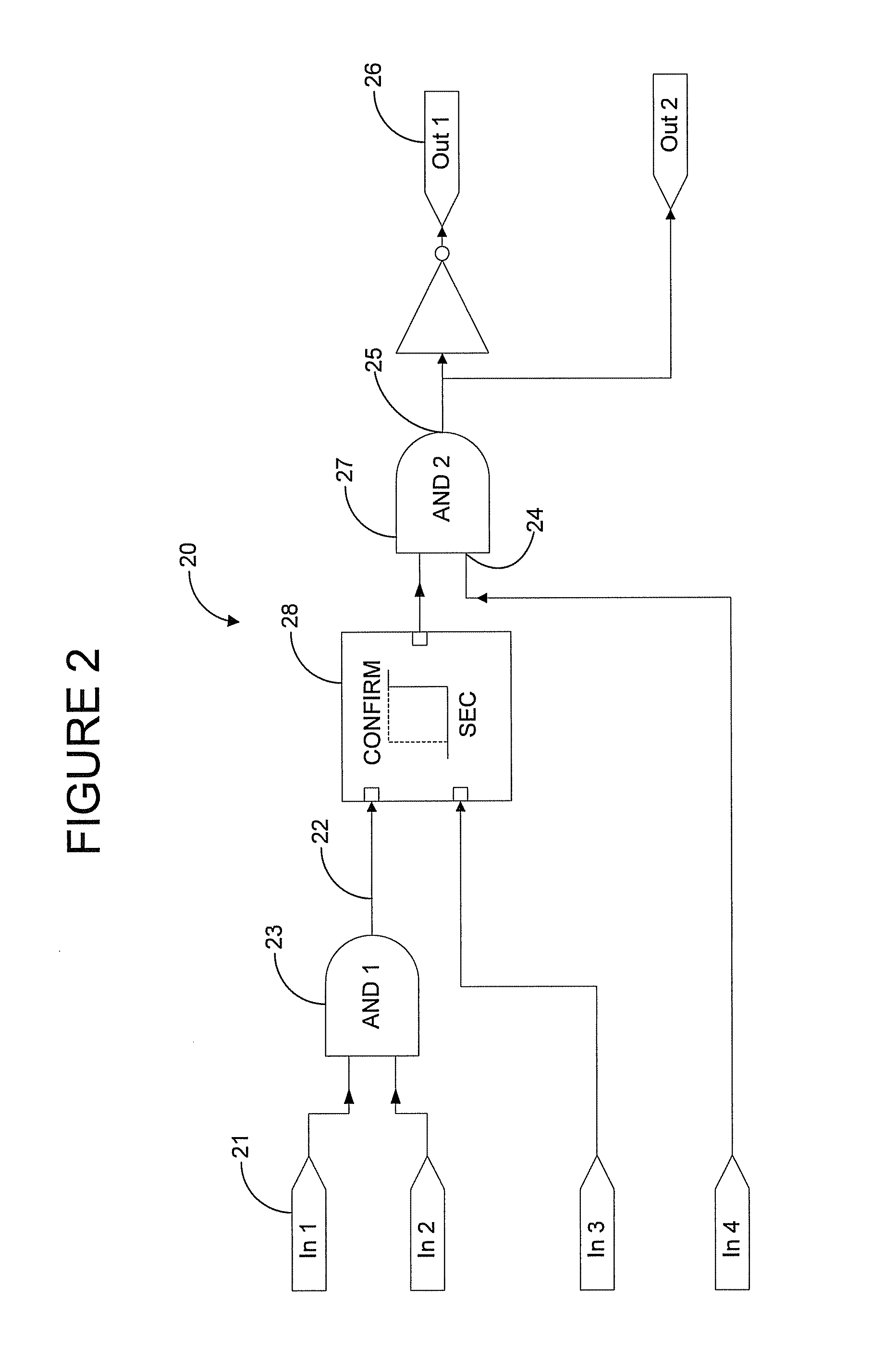

Requirements-based test generation

ActiveUS7644334B2Facilitates meeting DO-178B objectivesReducing resourceElectronic circuit testingError detection/correctionBlock typeTest vector

This test generator takes data flow block diagrams and uses requirements-based templates, selective signal propagation, and range comparison and intersection to generate test cases containing test vectors for those diagrams. The templates are based on the functionality and characteristics of a block type, and each block type has associated templates. These templates provide maps for the creation of test values that verify the functionality of particular instances of that block type. Signal propagation allows the generation of diagram-level test cases that verify particular characteristics of a single embedded block. The methods disclosed for signal propagation utilize range intersection, equivalence classes, and block type formulae to create efficient and complete test cases. This test generation method would preferably be repeated until all blocks in a data flow block diagram were verified in their respective contexts, and it creates test cases that cover multiple time steps.

Owner:HONEYWELL INT INC

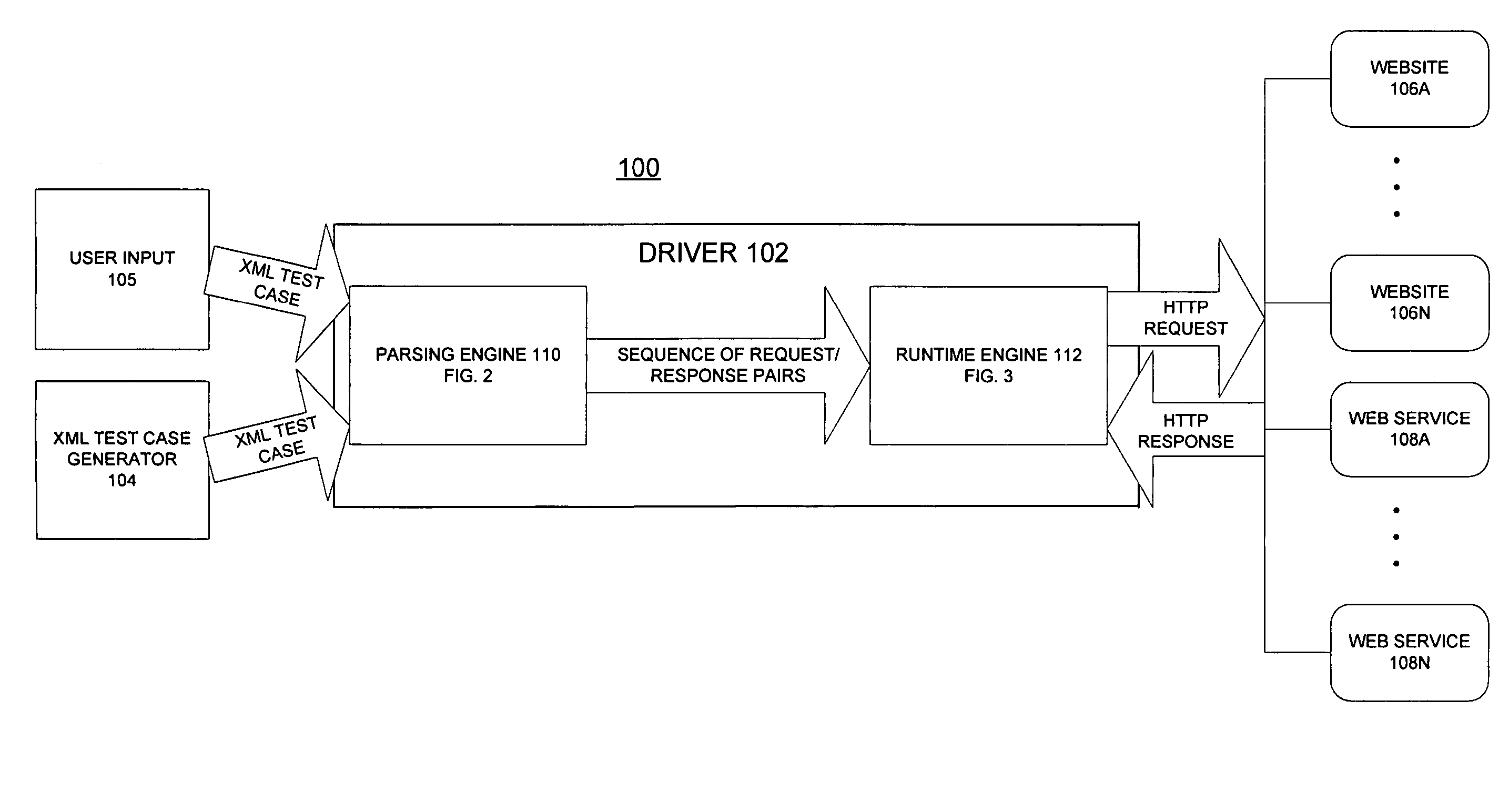

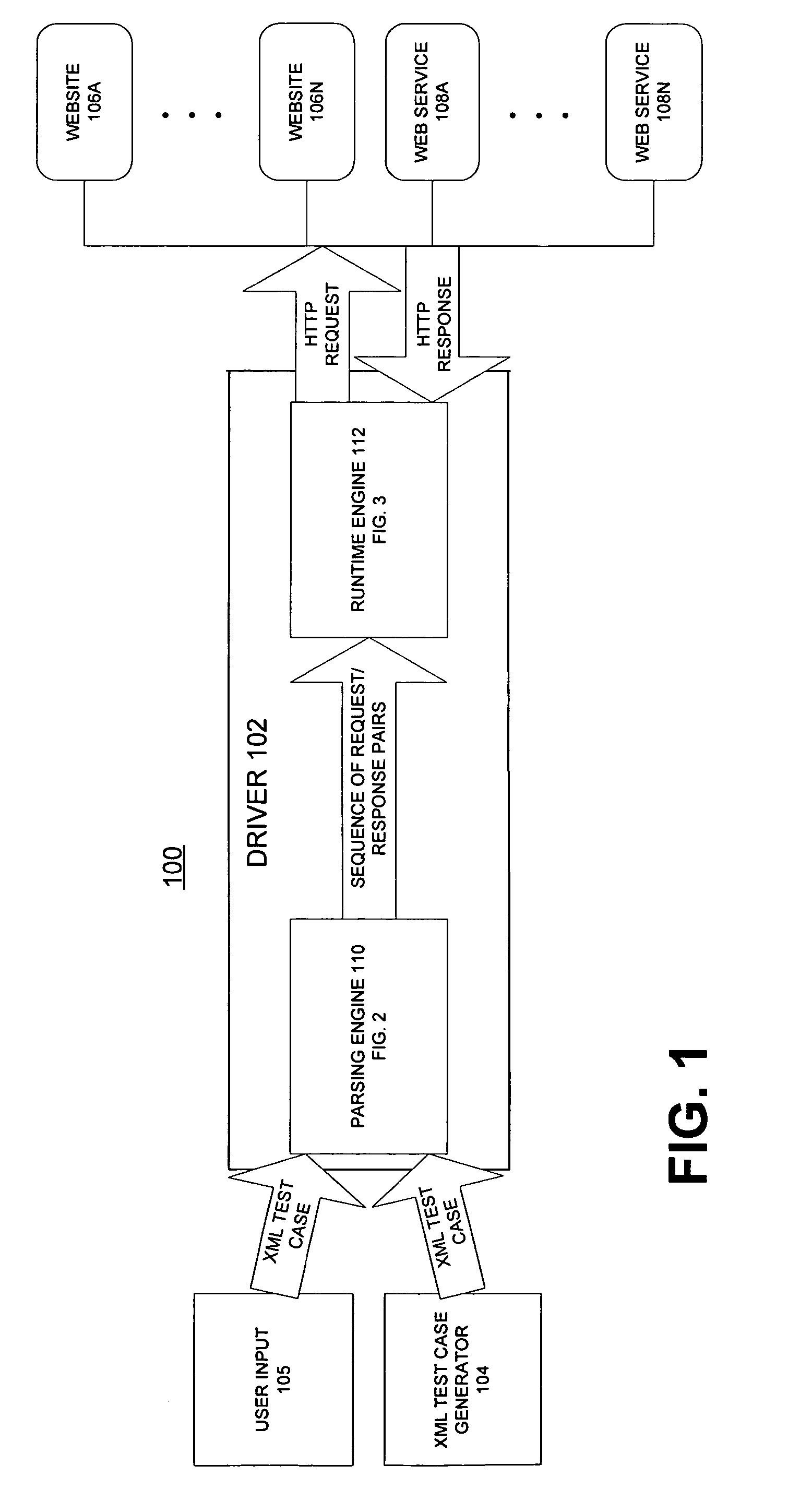

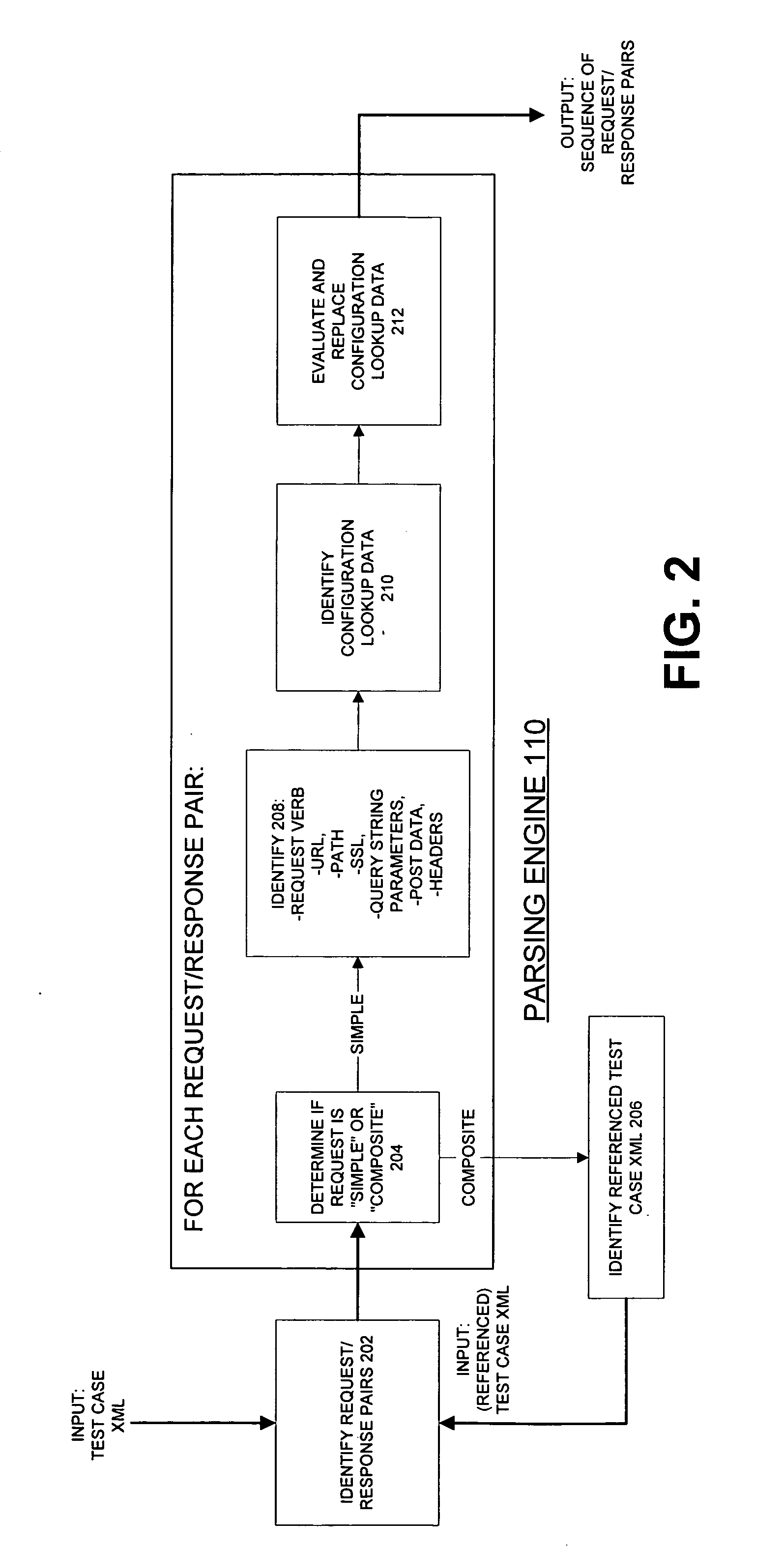

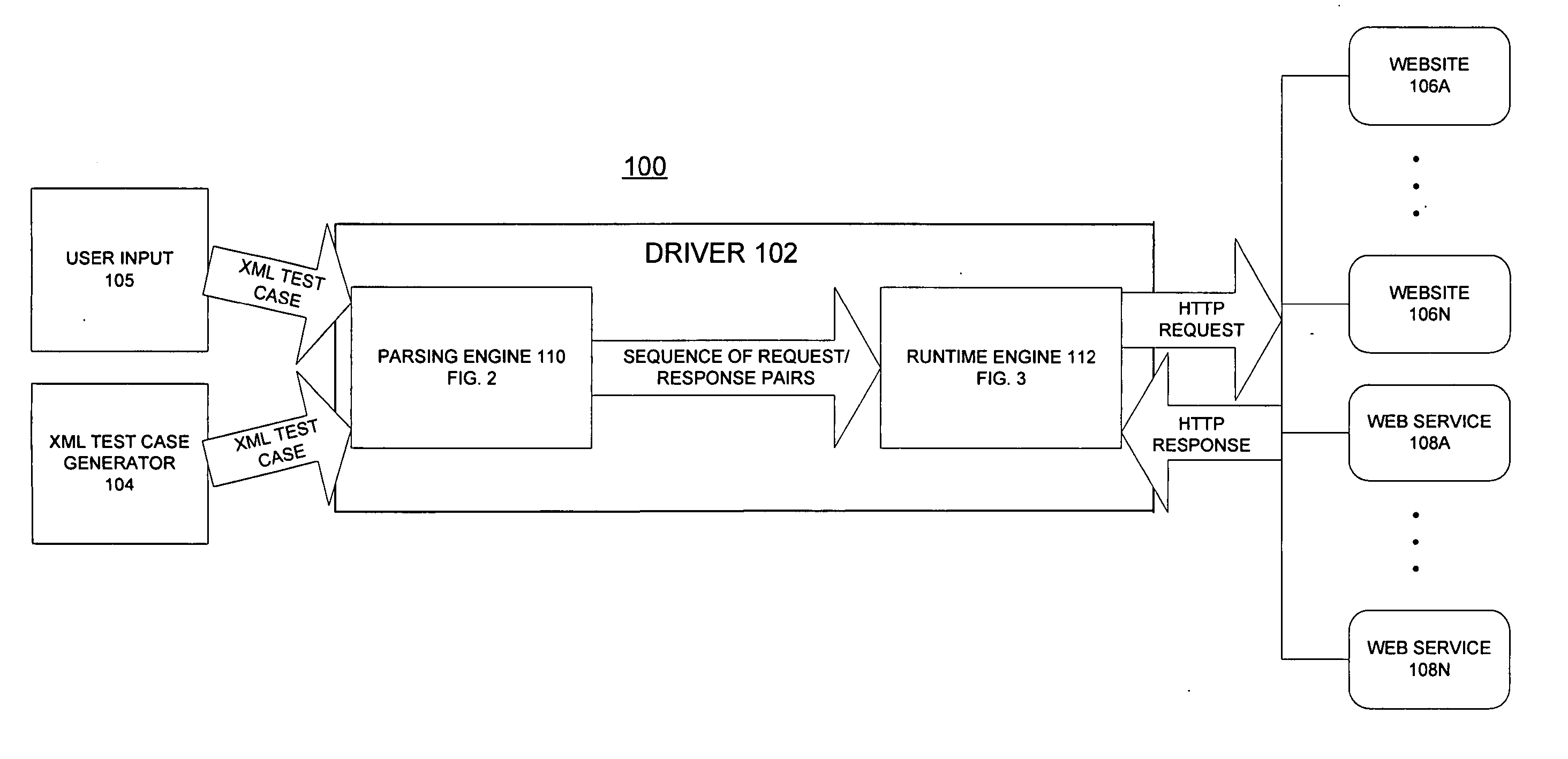

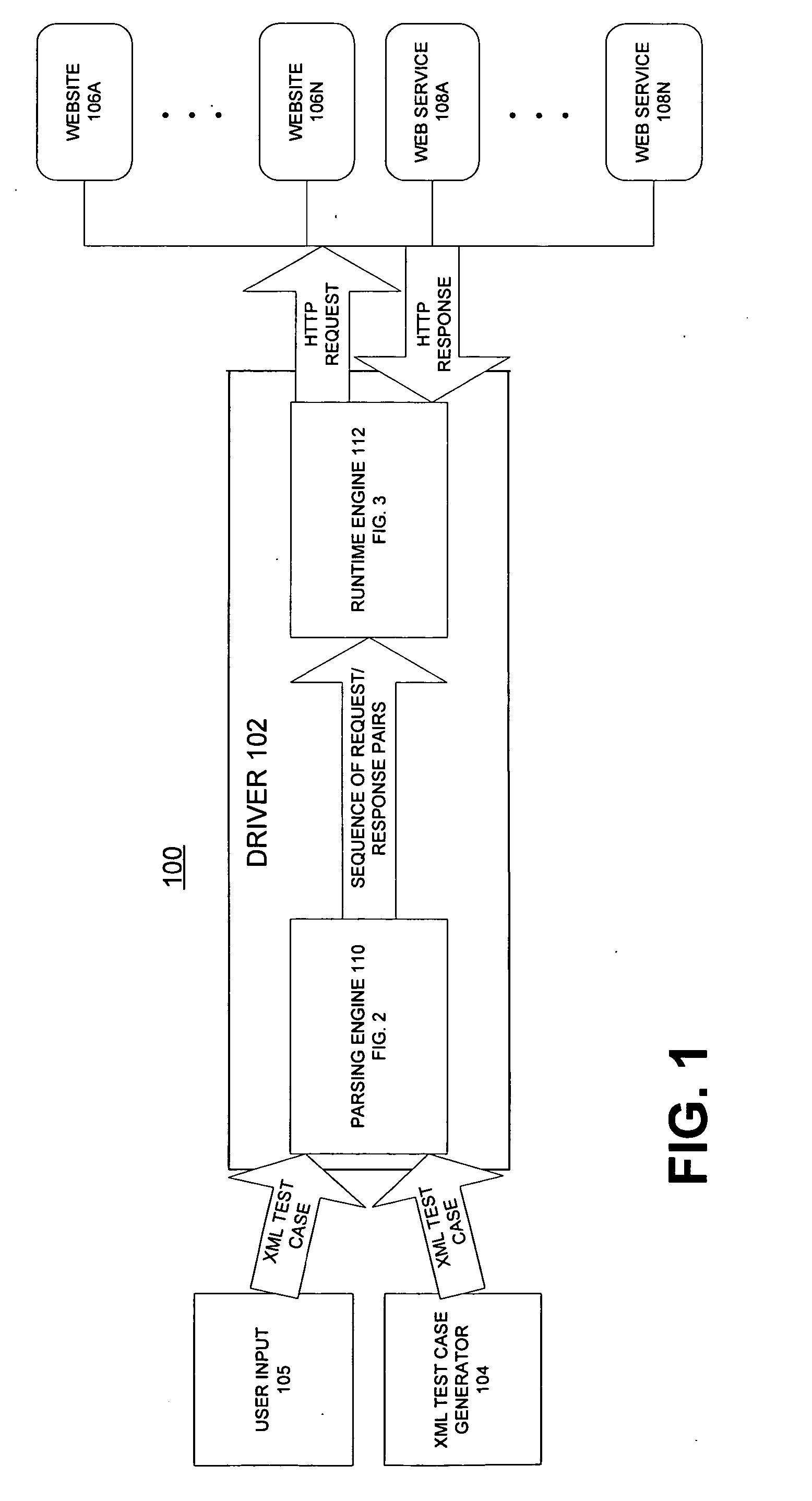

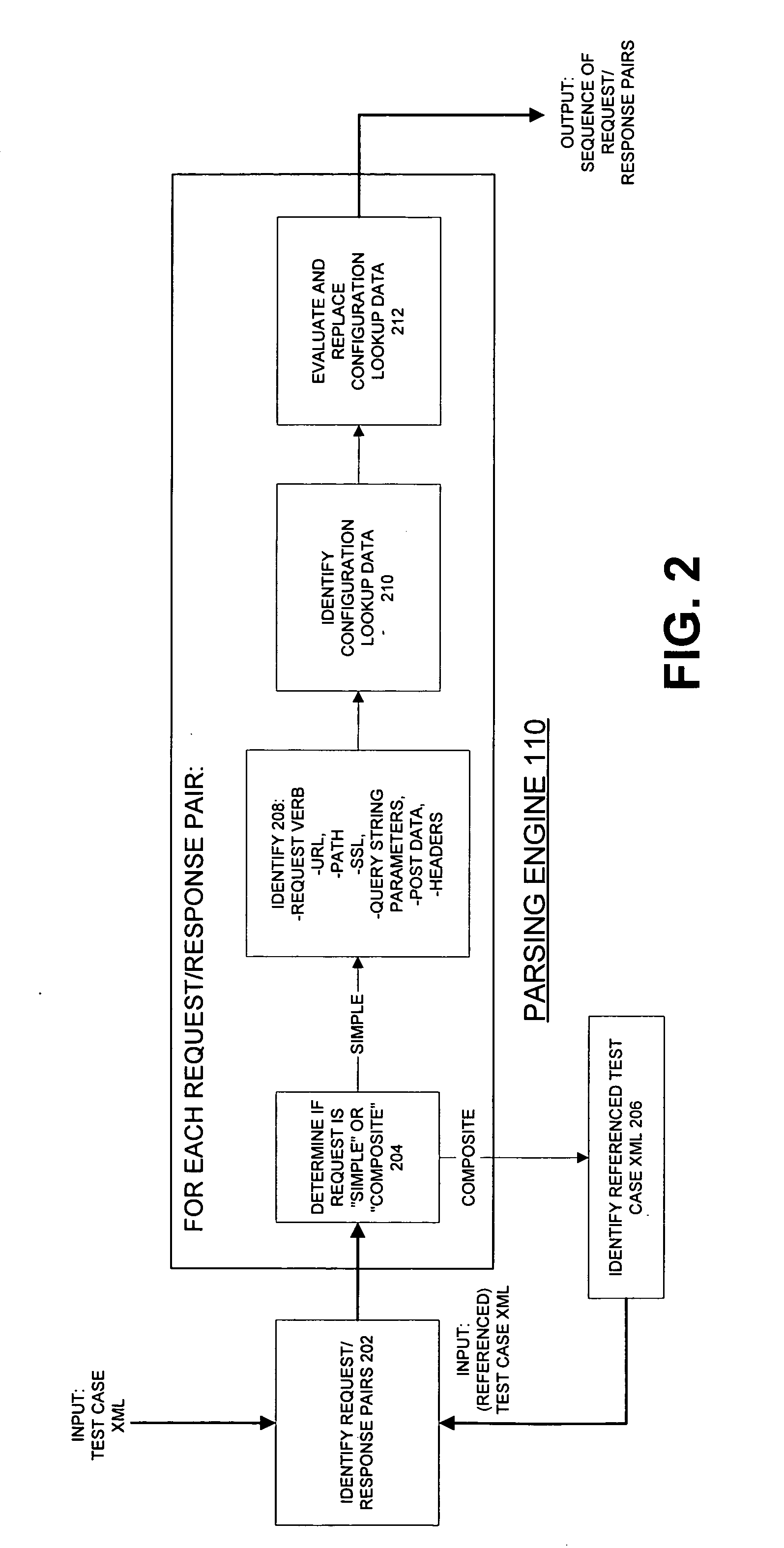

Data driven test automation of web sites and web services

A system, method and data structure for testing a web location including a web site or web service. A test generator or user generates an XML test case and a driver interprets the XML test case into an http request to be sent to the web location as a test.

Owner:MICROSOFT TECH LICENSING LLC

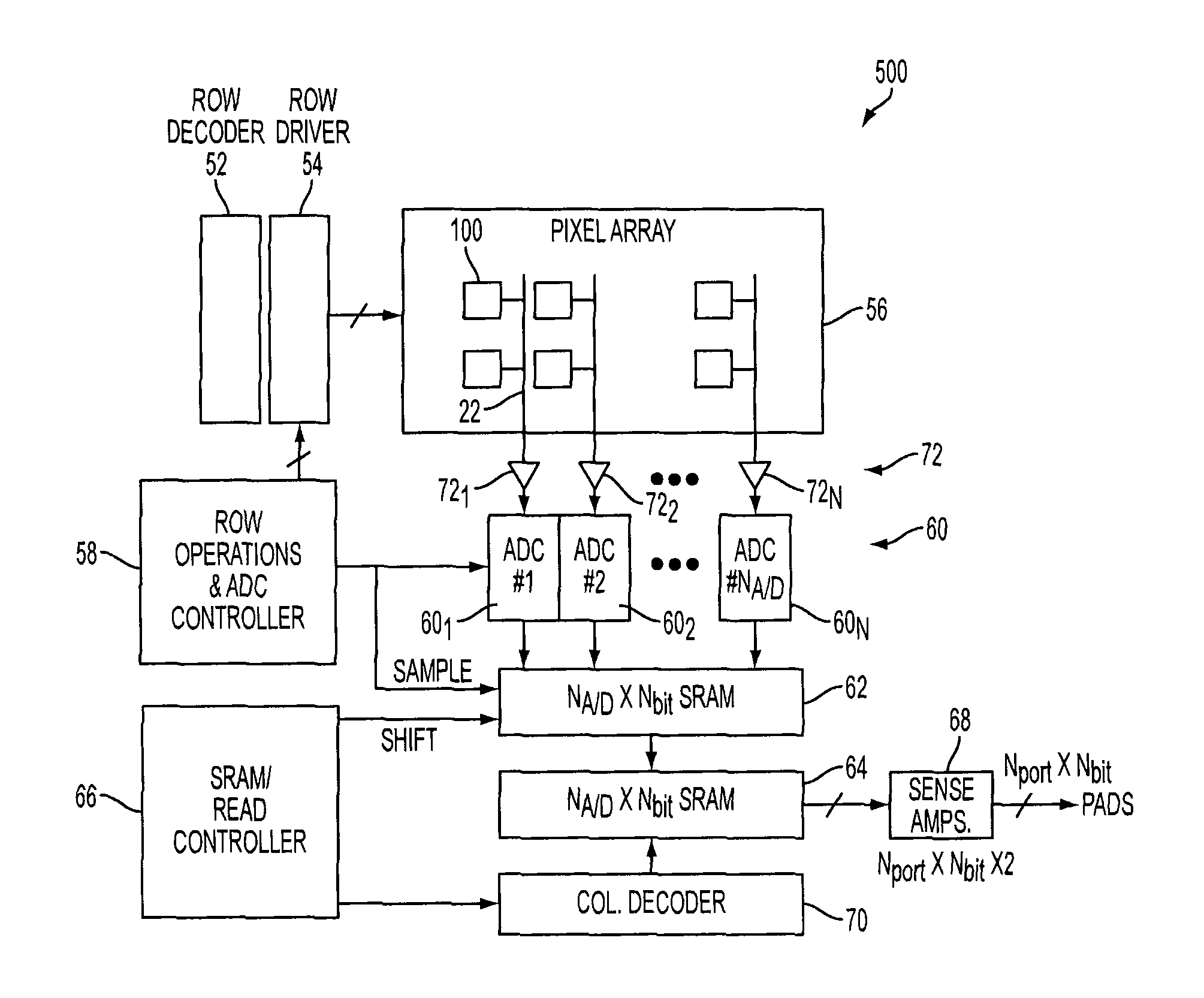

Self test of image signal chain while running in streaming mode

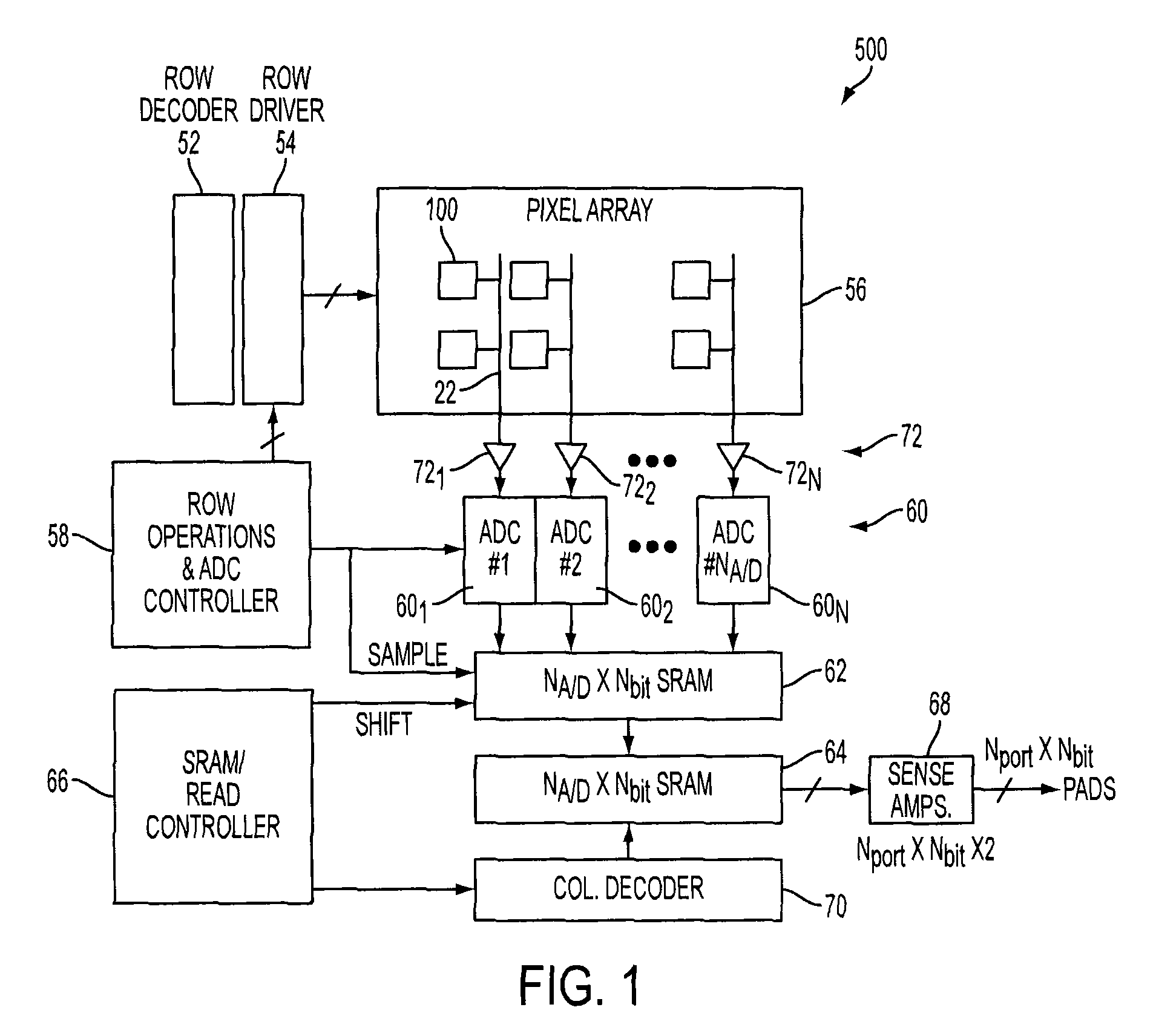

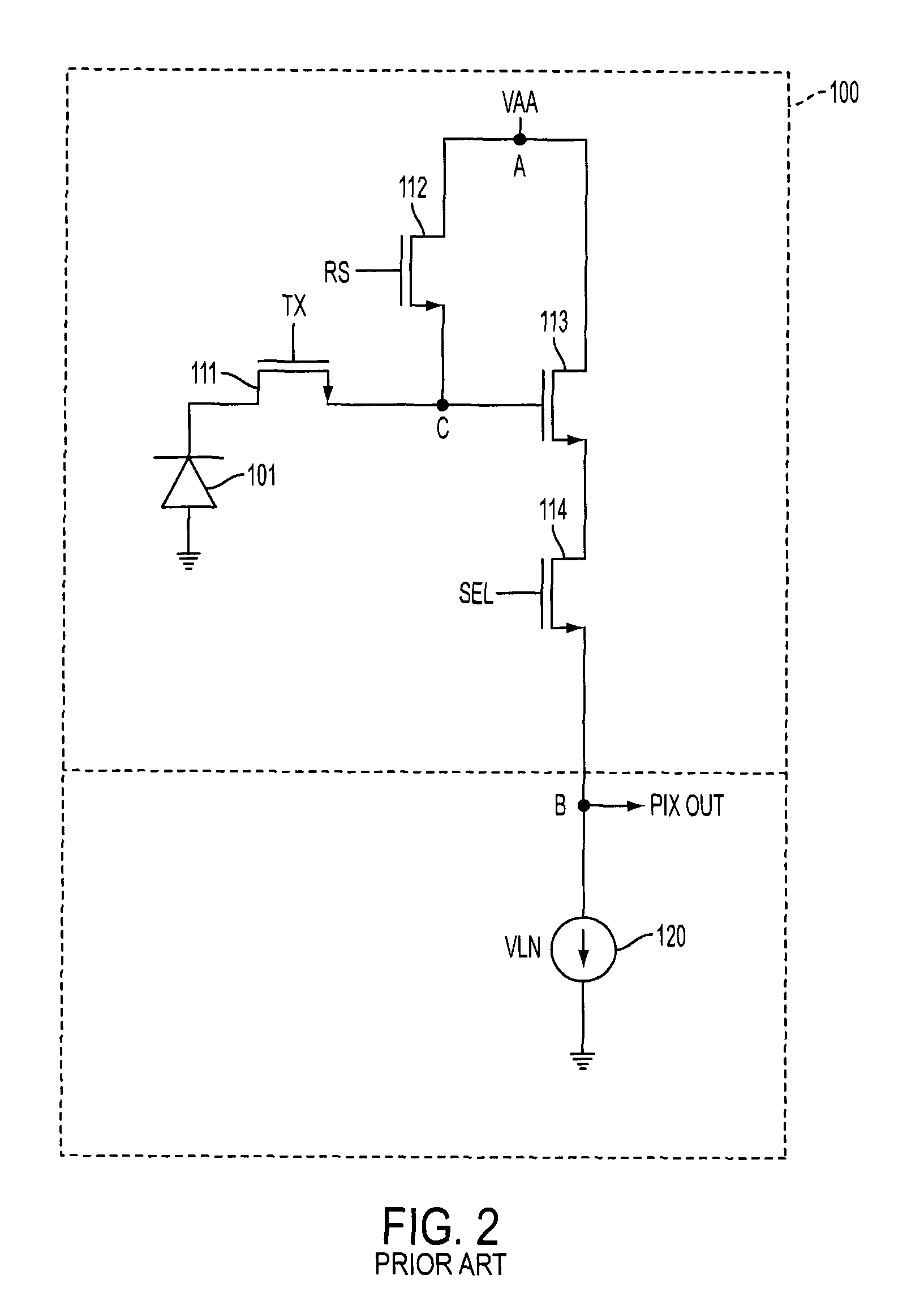

An imager including a self test mode. The imager includes a pixel array for providing multiple pixel output signals via multiple columns; and a test switch for (a) receiving a test signal from a test generator and (b) disconnecting a pixel output signal from a column of the pixel array. The test switch provides the test signal to the column of the pixel array. The test signal includes a test voltage that replaces the pixel output signal. The test signal is digitized by an analog-to digital converter (ADC) and provided to a processor. The processor compares the digitized test signal to an expected pixel output signal. The processor also interpolates the output signal from a corresponding pixel using adjacent pixels, when the test switch disconnects the pixel output signal from the column of the pixel array.

Owner:APTINA IMAGING CORP

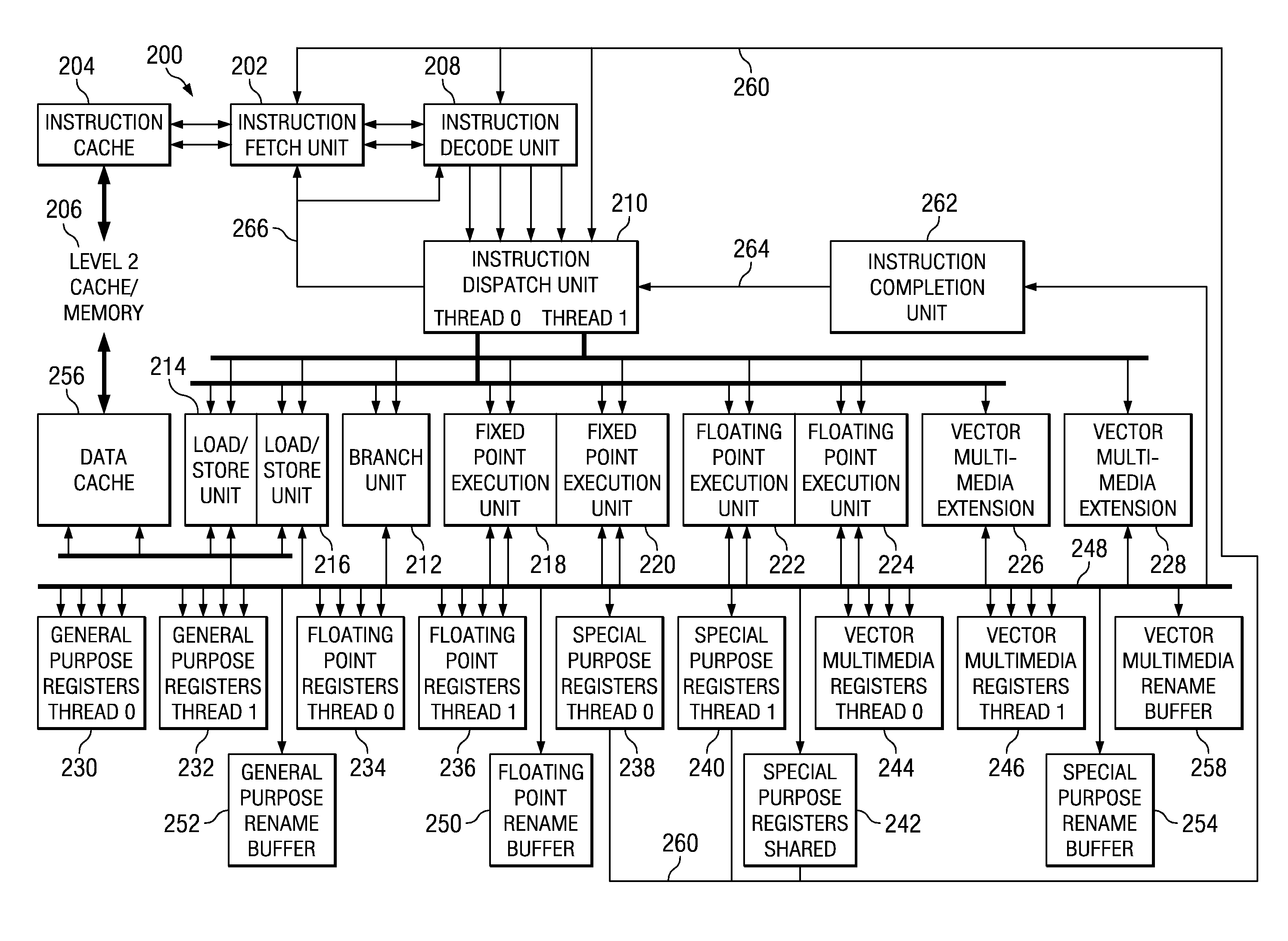

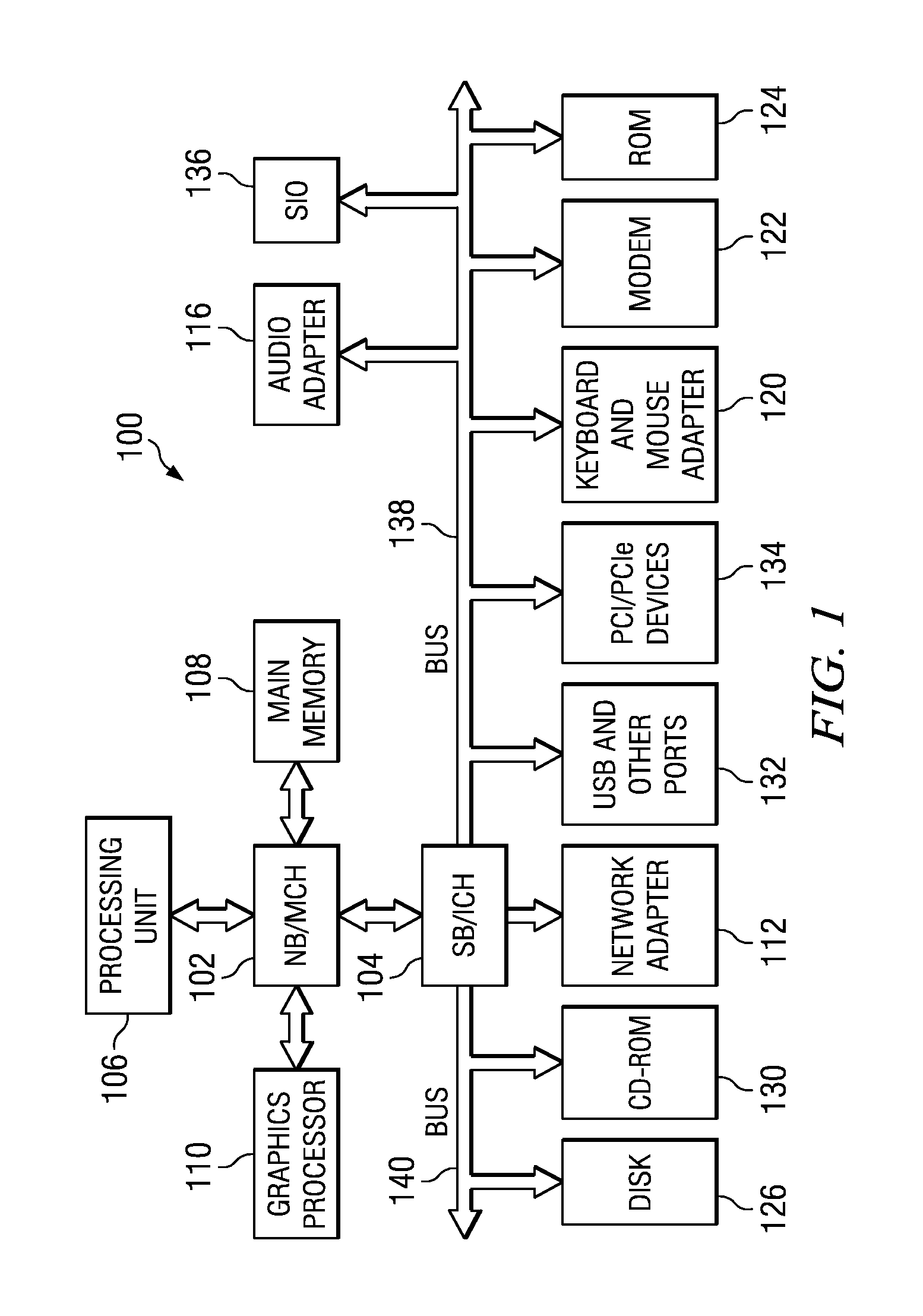

Efficient and Self-Balancing Verification of Multi-Threaded Microprocessors

ActiveUS20100011345A1Error detection/correctionSpecific program execution arrangementsTest generatorInstruction stream

Creating one or more irritator threads on one or more processor cores in a multi-threaded multiprocessor data processing system is provided. A test generator generates non-irritator thread code for execution by a non-irritator thread and irritator thread code for execution by one or more irritator threads of the multi-threaded multiprocessor data processing system. A simulation controller instantiates the non-irritator thread to execute the non-irritator thread code and the one or more irritator threads to execute the irritator thread code. The simulation controller determines if the non-irritator thread has finished execution of the entire instruction stream of the non-irritator thread code. Responsive to the non-irritator thread finishing execution of the entire instruction stream of the non-irritator thread code, the non-irritator thread performs an operation to terminate the execution of the irritator thread code by the one or more irritator threads.

Owner:IBM CORP

Data driven test automation of web sites and web services

A system, method and data structure for testing a web location including a web site or web service. A test generator or user generates an XML test case and a driver interprets the XML test case into an http request to be sent to the web location as a test.

Owner:MICROSOFT TECH LICENSING LLC

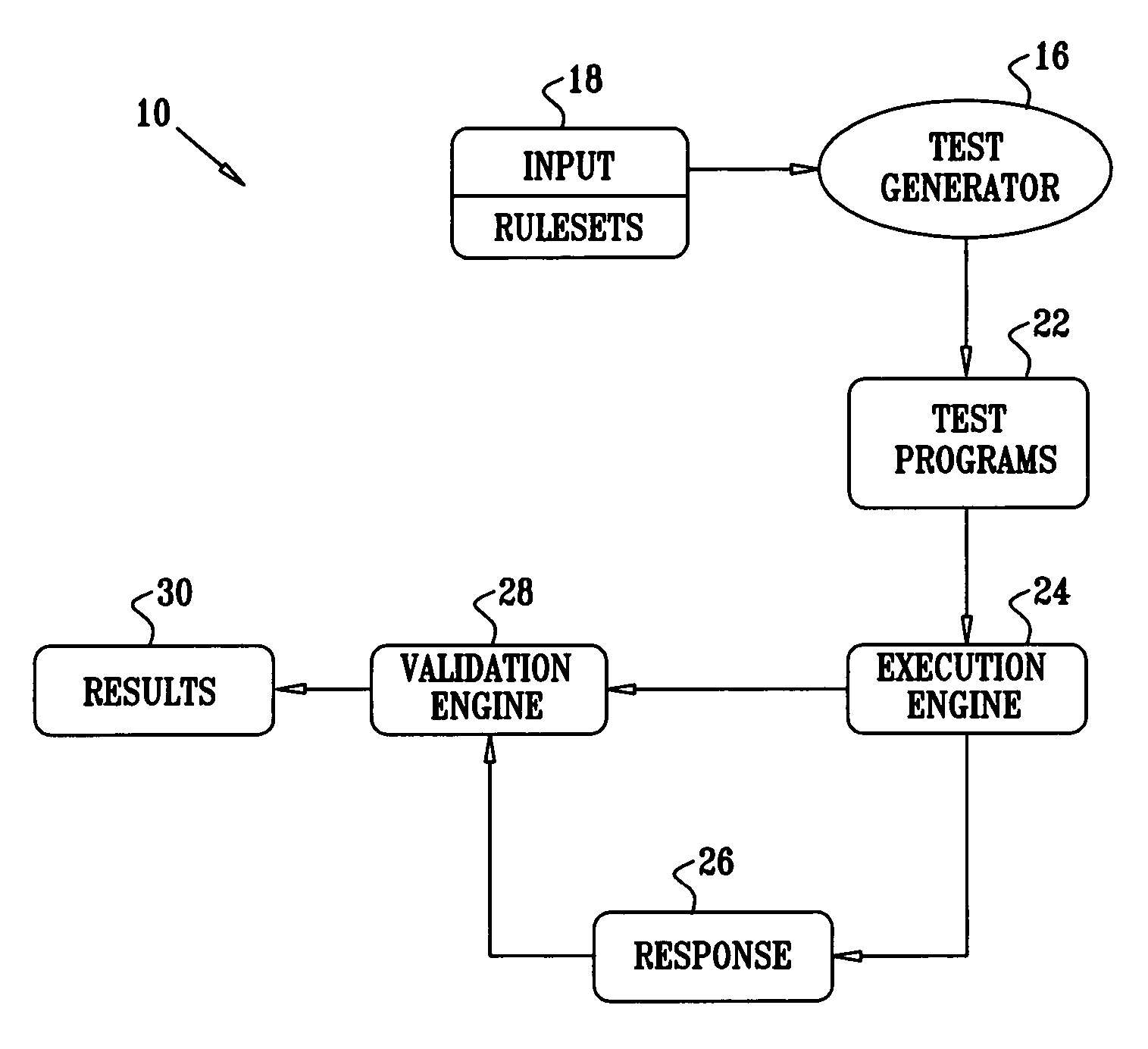

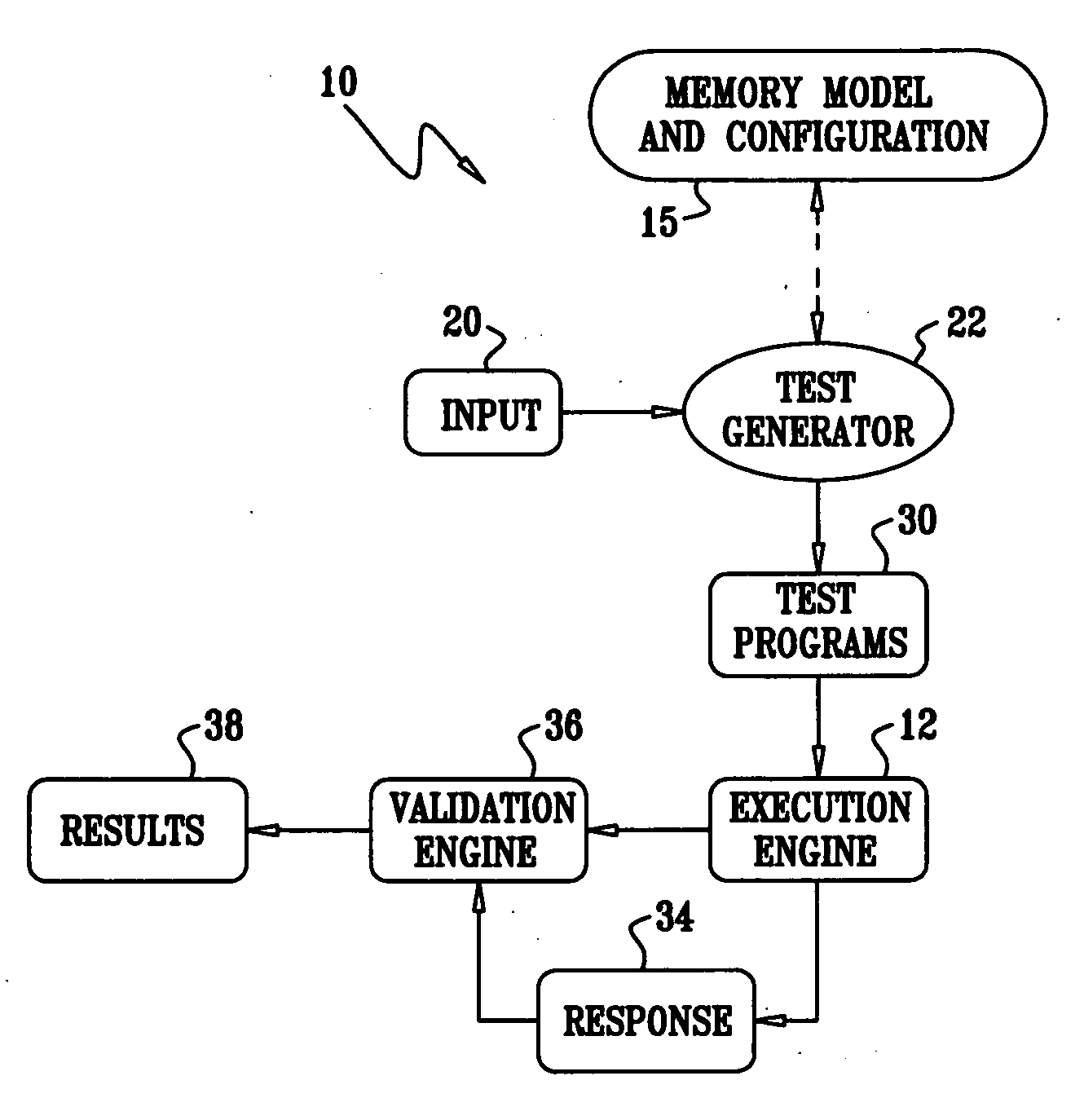

Recursive use of model based test generation for middlevare validation

InactiveUS20030196191A1Software testing/debuggingSpecific program execution arrangementsHigh level modelAbstract program

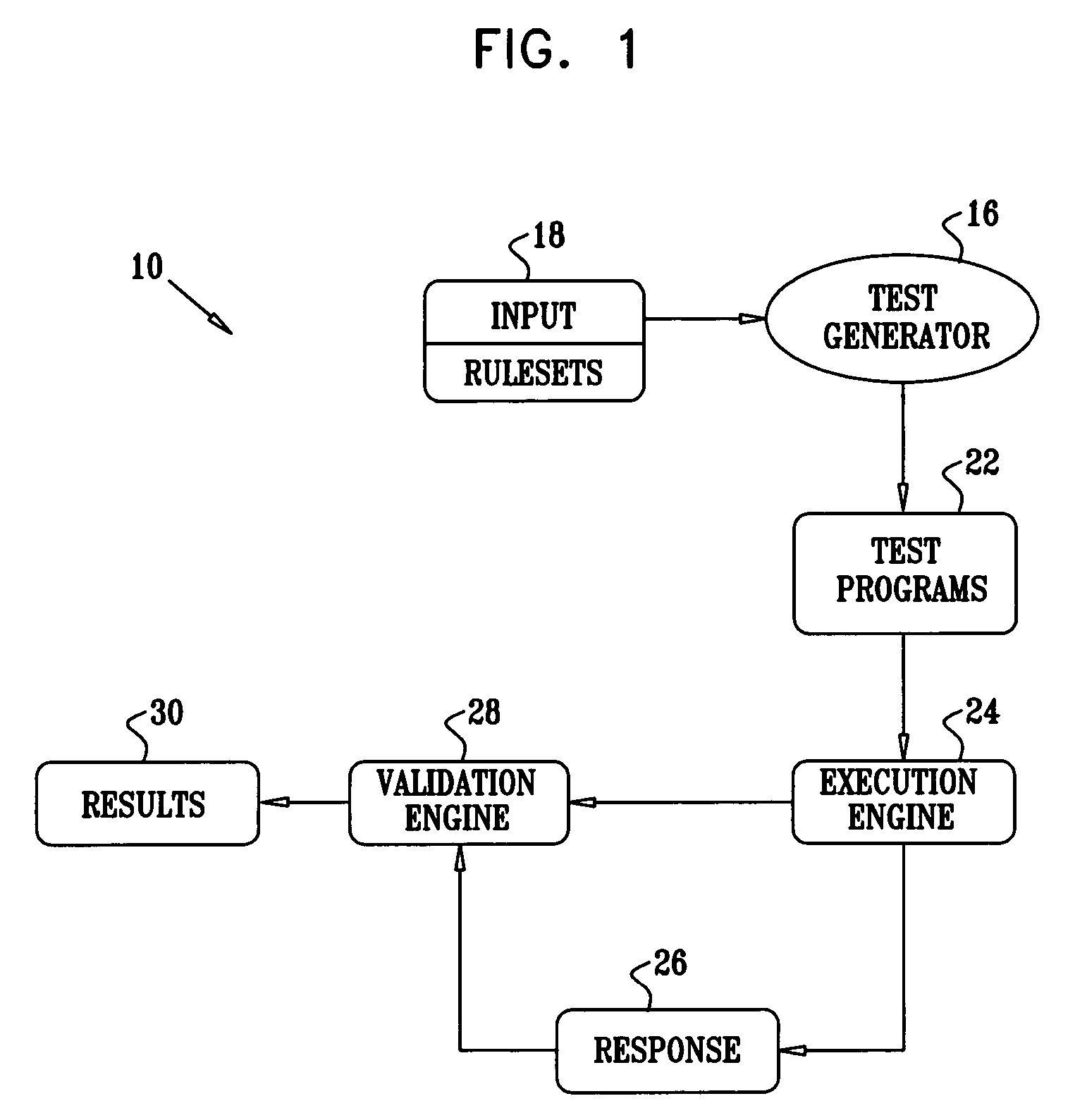

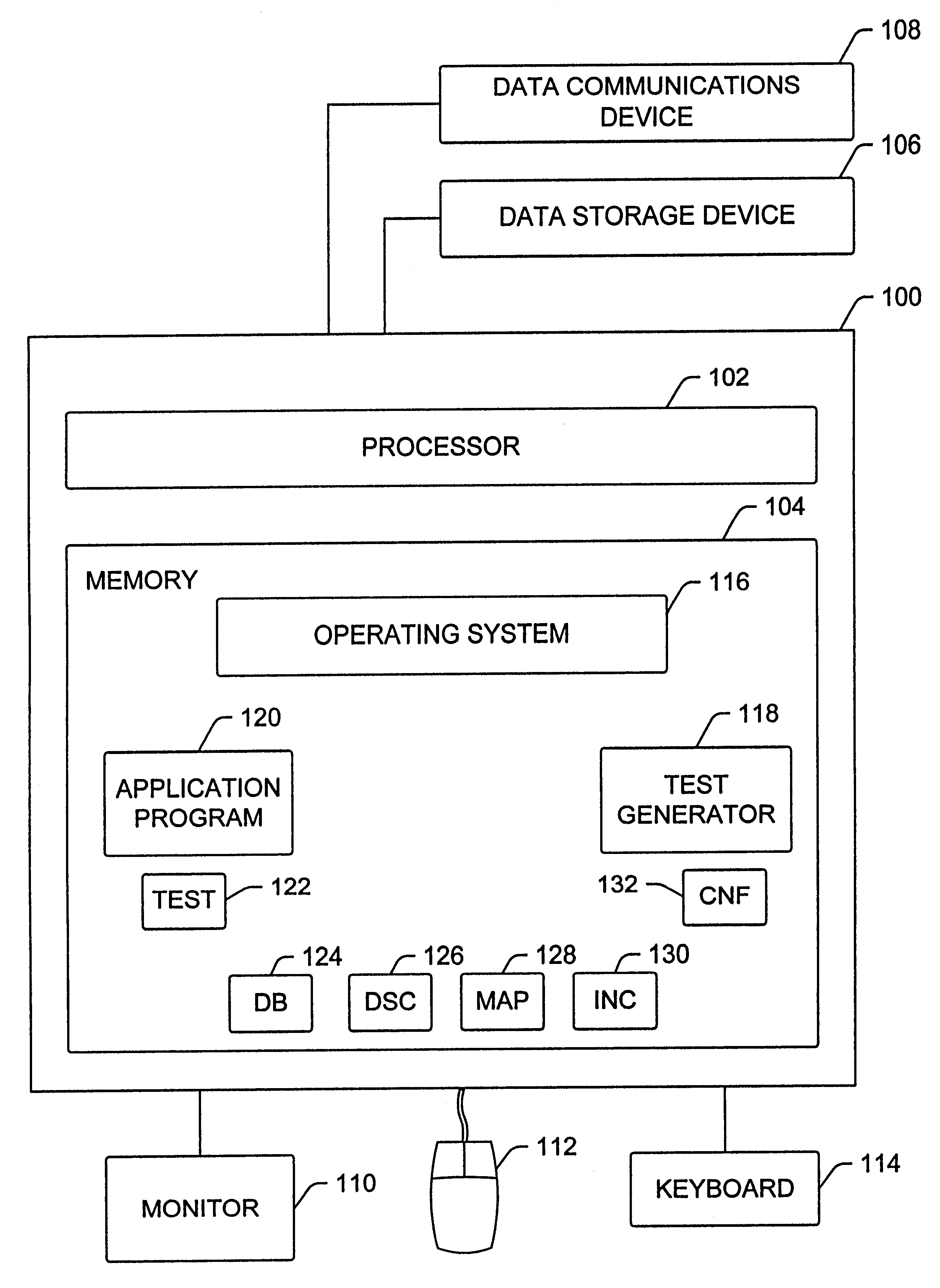

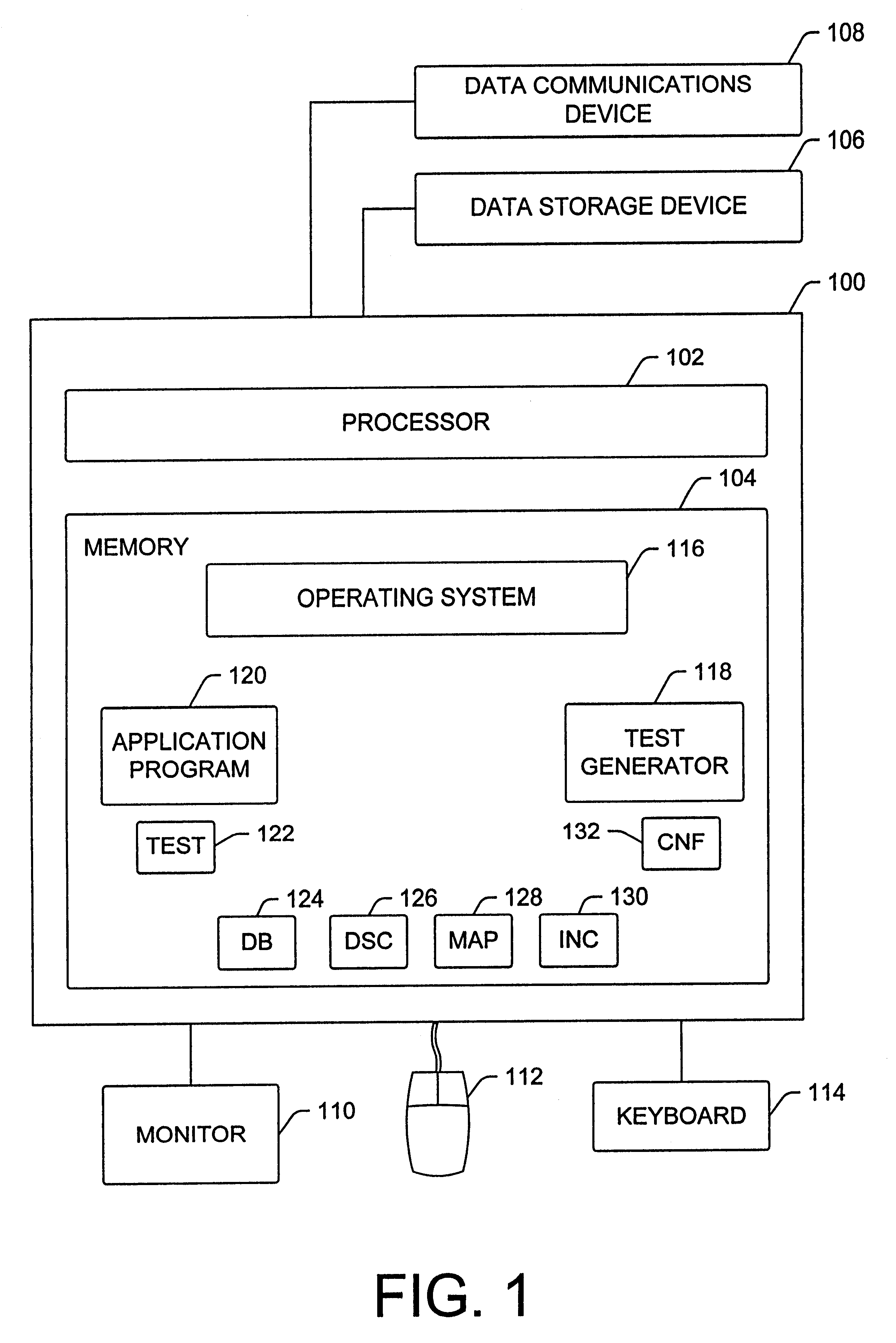

Middleware is validated using a two layered modeling strategy for the generation of test suites. A high level model of the syntax of the programming language used to program the middleware generates a series of high level abstract programs. These high level abstract programs then undergo two separate translations. First they are translated directly into actual test programs, which are expressed in the programming language of the middleware. Second, they are translated into second models of the high level abstract programs. Running the model based test generator again on the second models produces a set of suites of test cases, each test case consisting of data inputs and predicted results for one of the actual test programs. The actual test programs are run repetitively using the middleware execution engine. The results are compared with the predicted results, using a generic validation engine.

Owner:LINKEDIN

Dynamically interleaving randomly generated test-cases for functional verification

InactiveUS20060218513A1Significant effortElectronic circuit testingResistance/reactance/impedenceComputer hardwareGeneration process

The input for a test generator is a plurality of test templates, each of which typically aims at covering a specific verification task. Test templates direct the production of distinct transactions, which are the atomic functional building blocks of the design-under-verification. Test templates directed to different hardware functions of the scenario are dynamically interleaved. In this way several transactions are combined together in complex statements in order to achieve a complex test scenario. The transactions are submitted to the test generator, which generates test cases, in which the different hardware functions of the scenario are exercised in combinations. Variation among the test cases is achieved through a large number of random decisions made during the generation process.

Owner:GLOBALFOUNDRIES INC

Control system simulation, testing, and operator training

InactiveUS20050223120A1Facilitate onsite/plant training of operatorEffective approachCosmonautic condition simulationsElectric testing/monitoringDocumentation procedureControl system

A requirements database and test generator generates tests for functional and field testing and generates requirements documentation, user manuals, operational procedures, instrument data sheets, instrument indices, instrument loop diagrams, validation reports, and test reports, including exception and passing reports. A portable process control simulator system which provides control system users with scenarios that mirror field operation as defined.

Owner:FLUOR TECH CORP

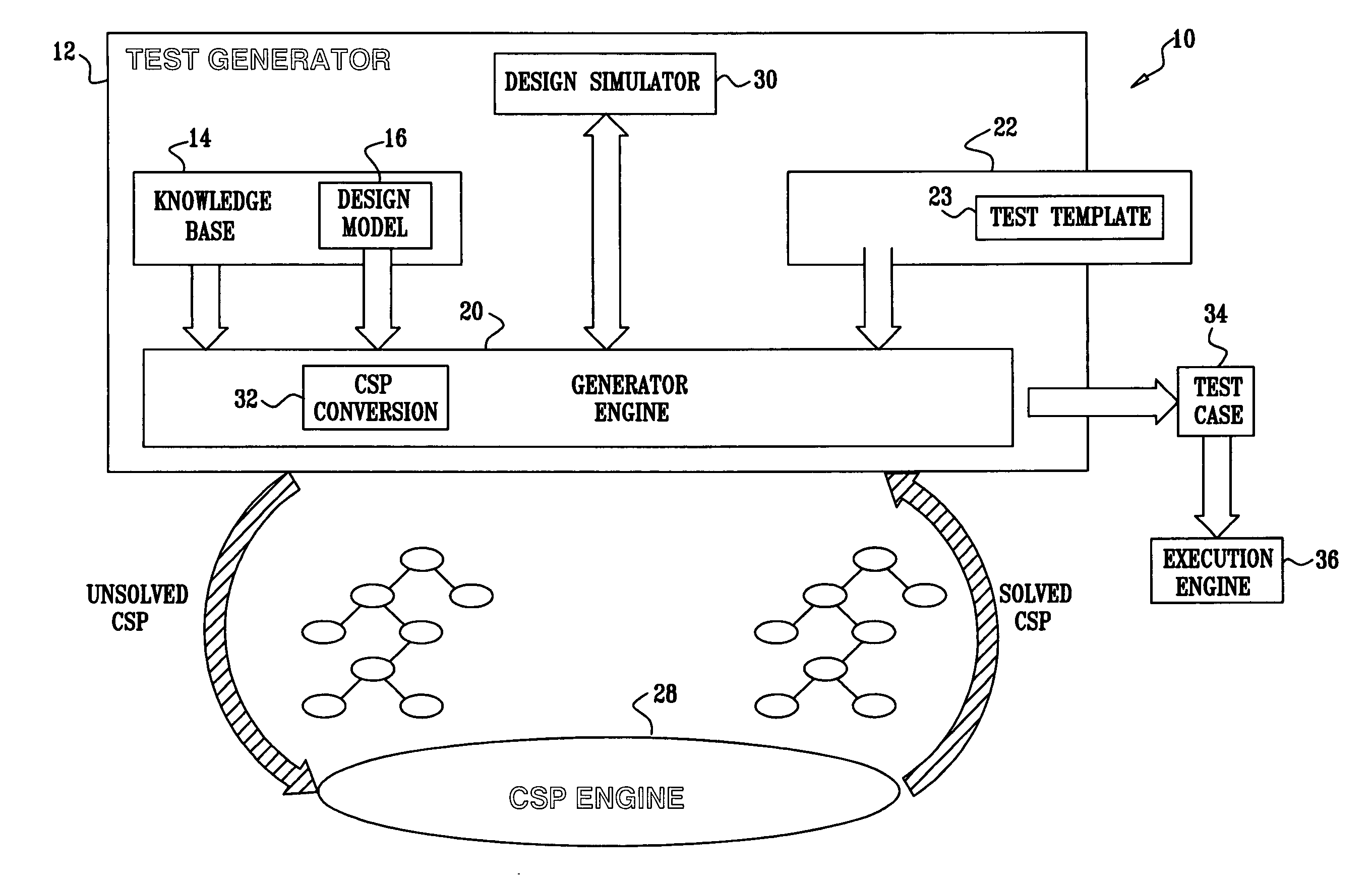

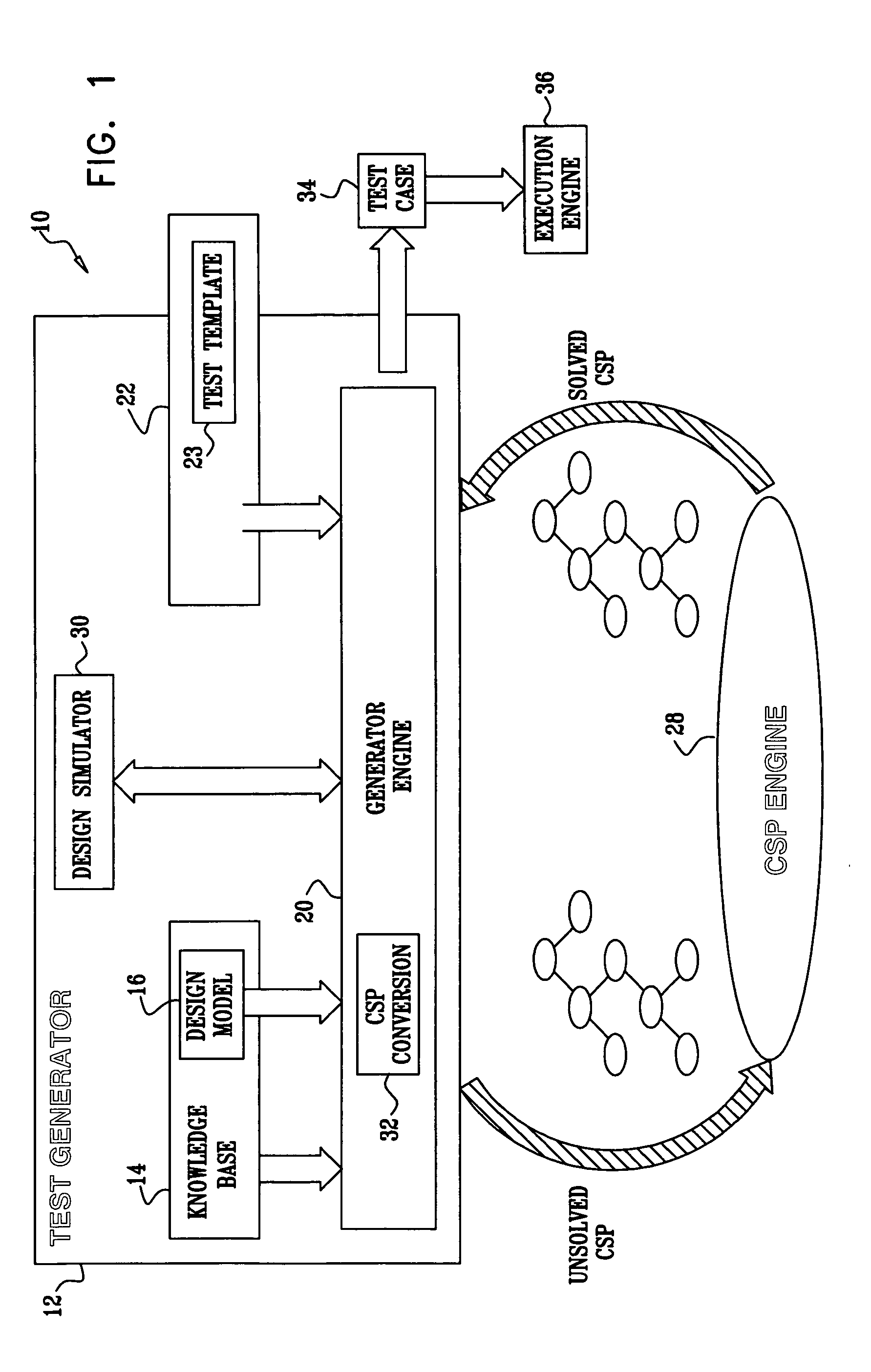

Modeling language and method for address translation design mechanisms in test generation

InactiveUS7370296B2Large coverageLogical operation testingSoftware simulation/interpretation/emulationConstraint satisfaction problemTheoretical computer science

Methods and systems are disclosed that enhance the ability of a test generator to automatically deal with address translation in a processor design, and without need for creating specific code. A model of the address translation mechanism of a design-under-test is represented as a directed acyclic graph and then converted into a constraint satisfaction problem. The problem is solved by a CSP engine, and the solution used to generate test cases for execution. Using the model, testing knowledge can be propagated to models applicable to many different designs to produce extensive coverage of address translation mechanisms.

Owner:GLOBALFOUNDRIES INC

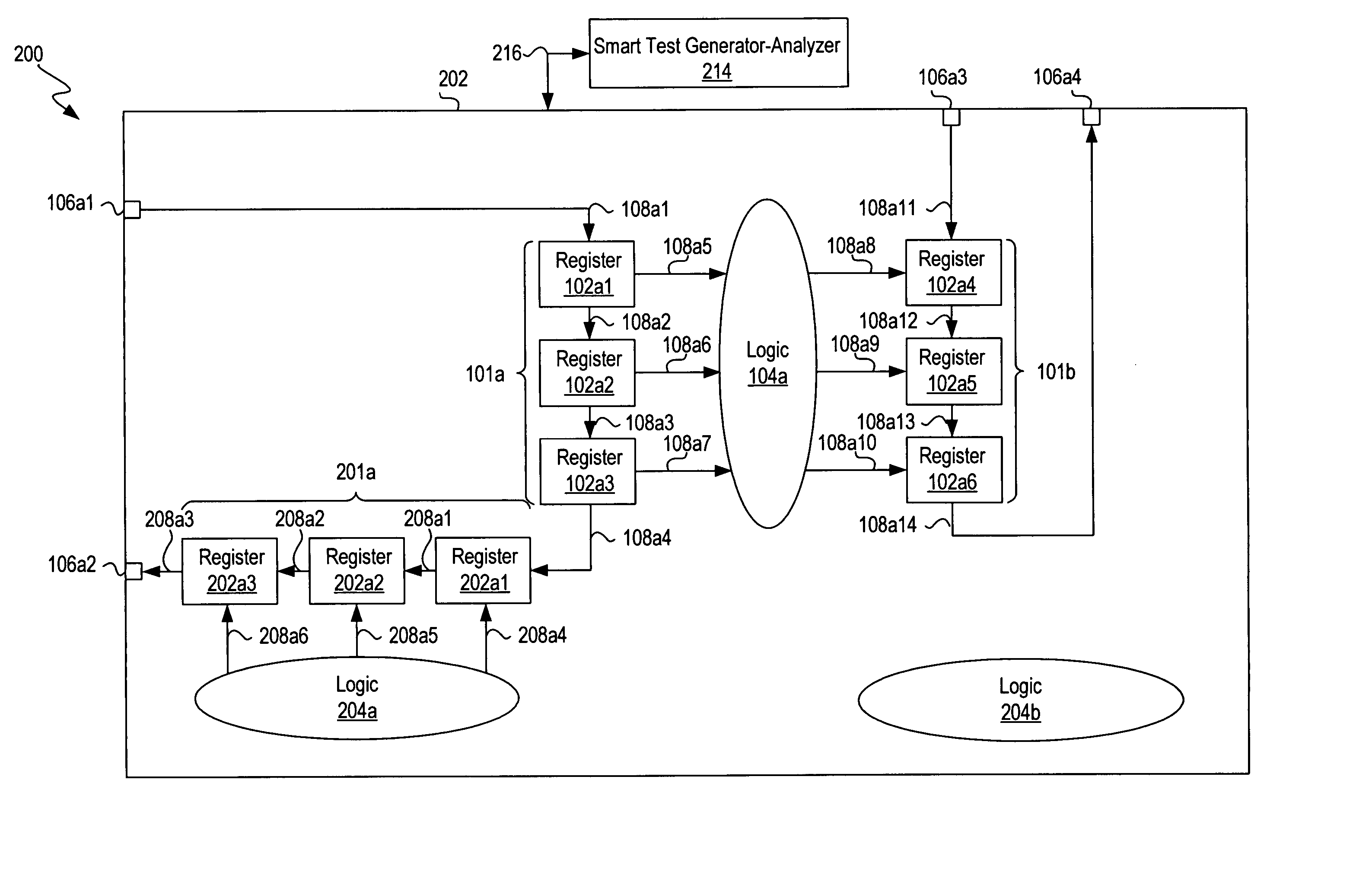

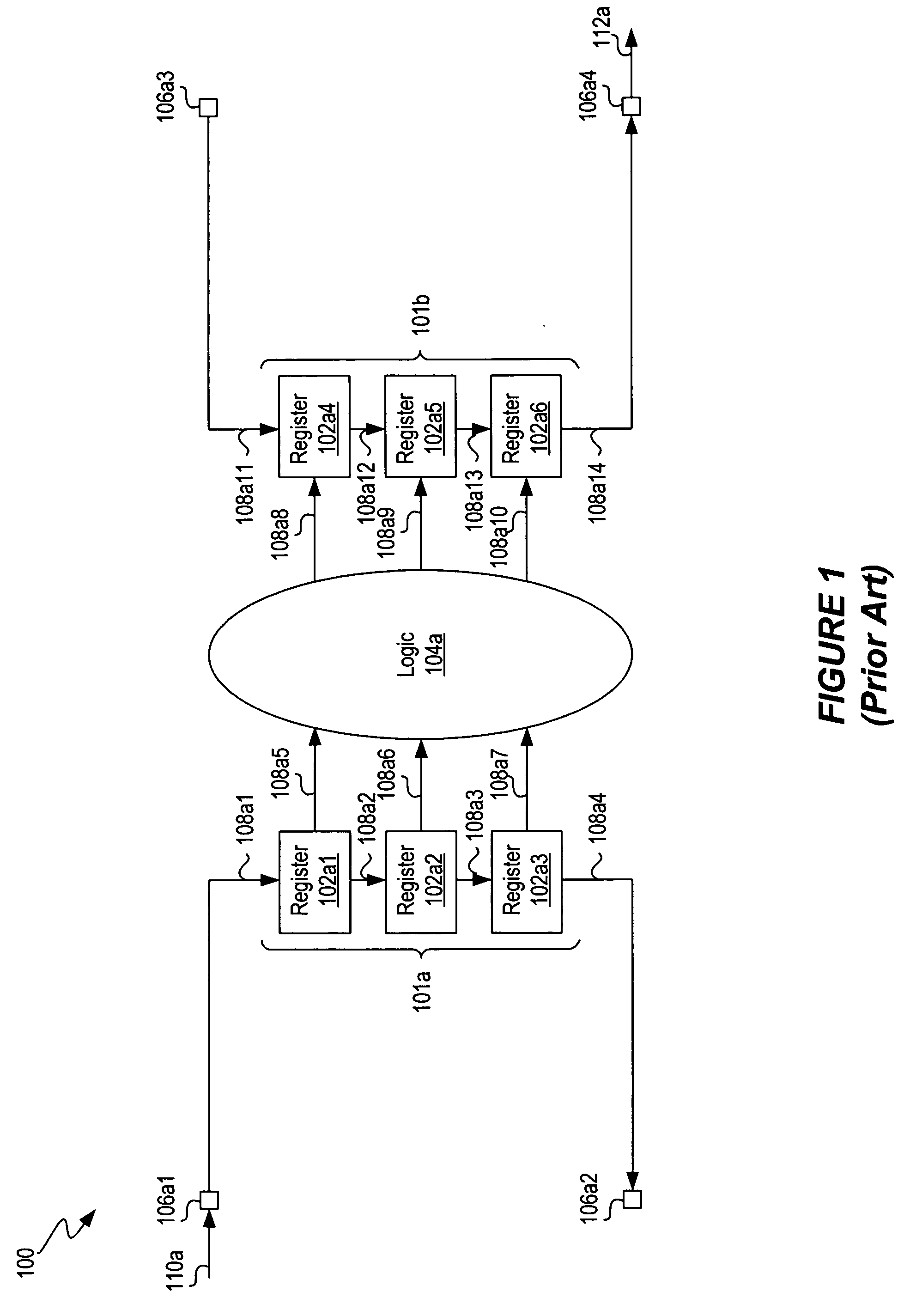

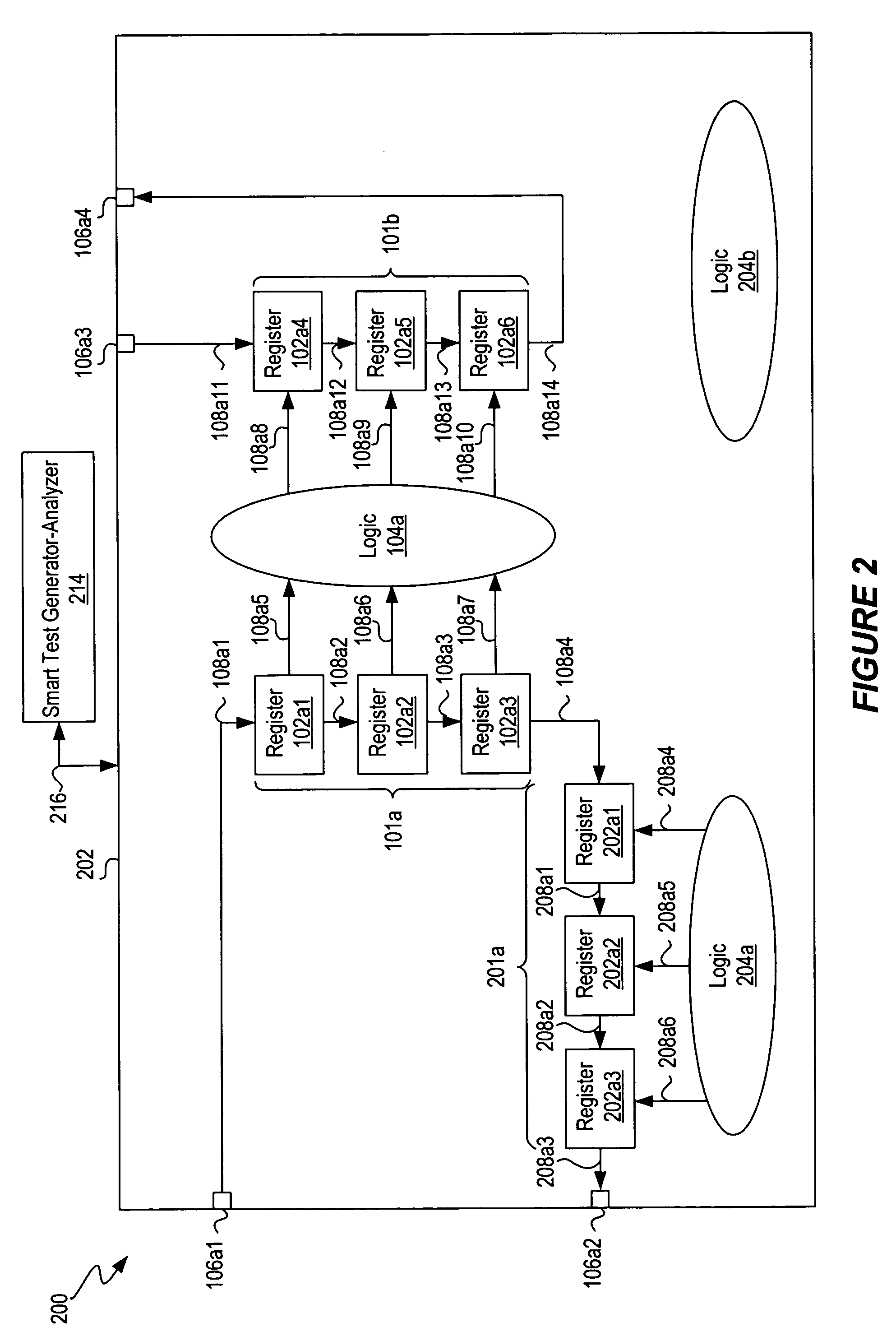

Pipelined scan structures for testing embedded cores

ActiveUS20060282729A1Minimizing impact to die costReduce scan testing timeElectronic circuit testingSystems designProgrammable logic device

A scan testing technique in which test data is pipelined to scan logic within an integrated circuit. In system on a programmable chip (SOPC) designs, pipelines are easily built in the programmable logic device (PLD) logic by configuring programmable interconnects to connect registers in a pipelined manner so that test data can be pipelined to scan the logic under test. In system on a chip (SOC) designs, a smart test generator-analyzer is configured to recursively extract pipeline information from a design-so that test data can be pipelined to scan the logic under test. Generally, test data is pipelined using existing functional logic and / or scan chains. Furthermore, a failure analysis (FA) platform is described. The FA platform is operable to take as its input a failing vector as well as a pipelined scan vector and unroll the pipeline sequence to determine which vector caused the failure.

Owner:ALTERA CORP

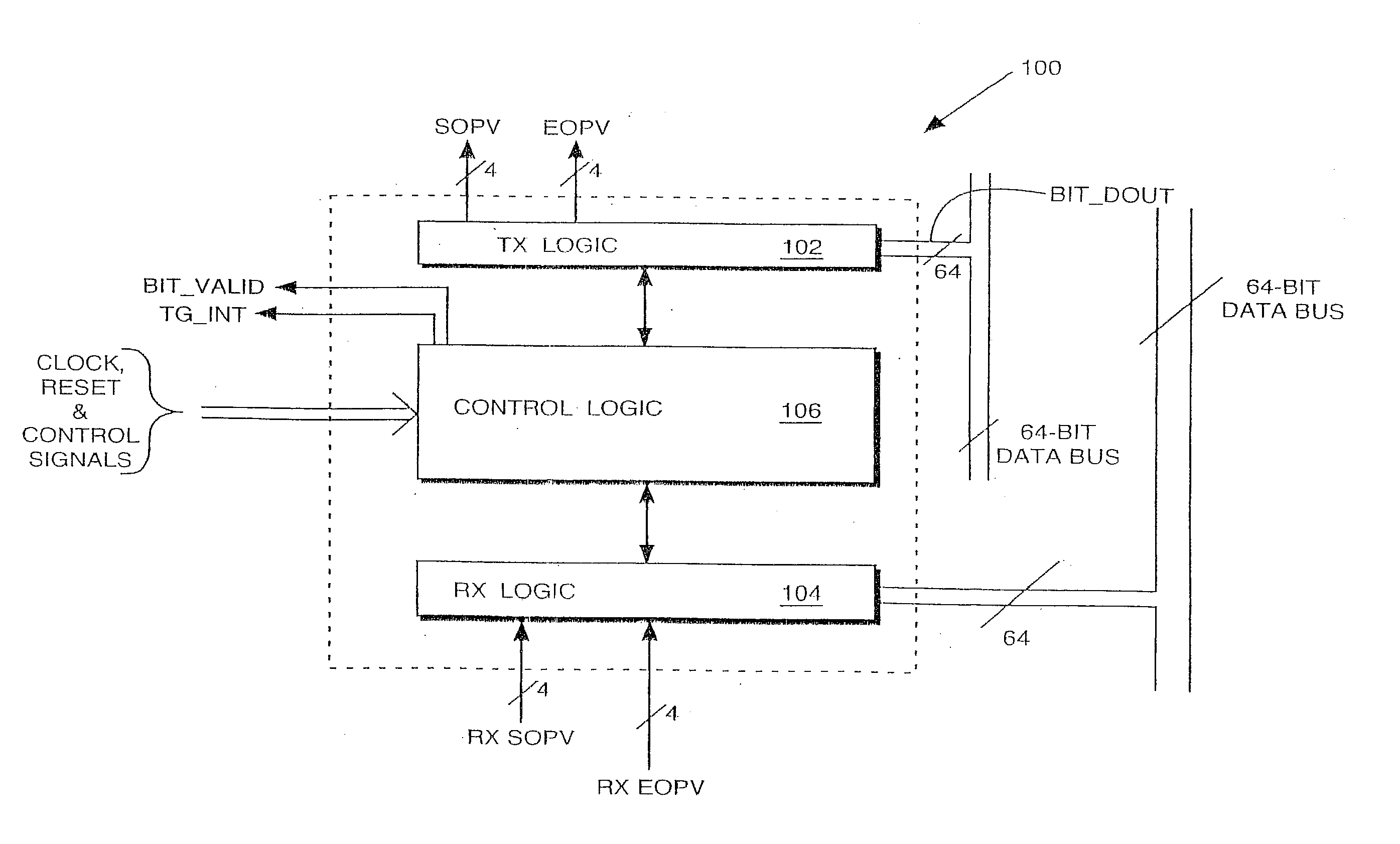

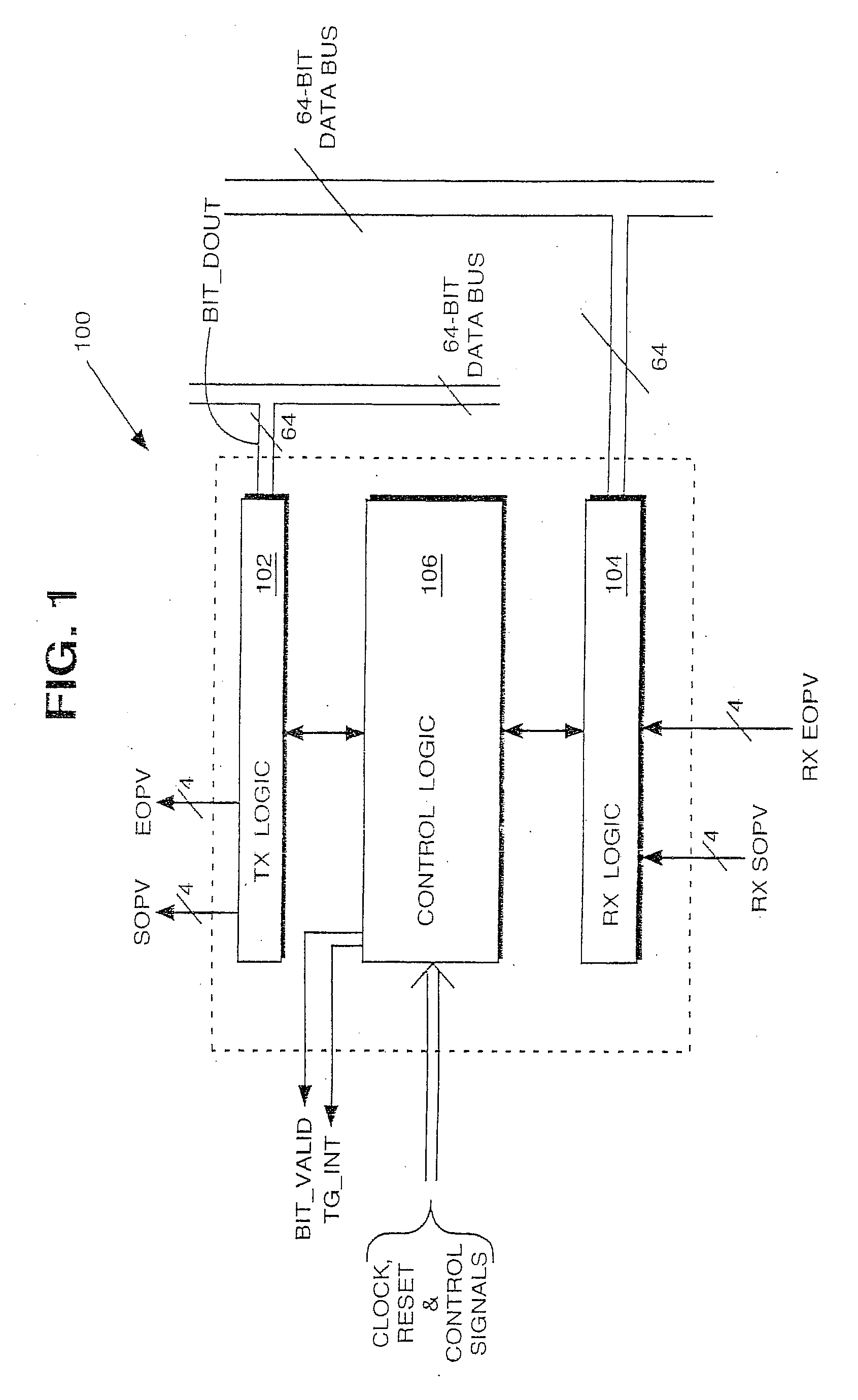

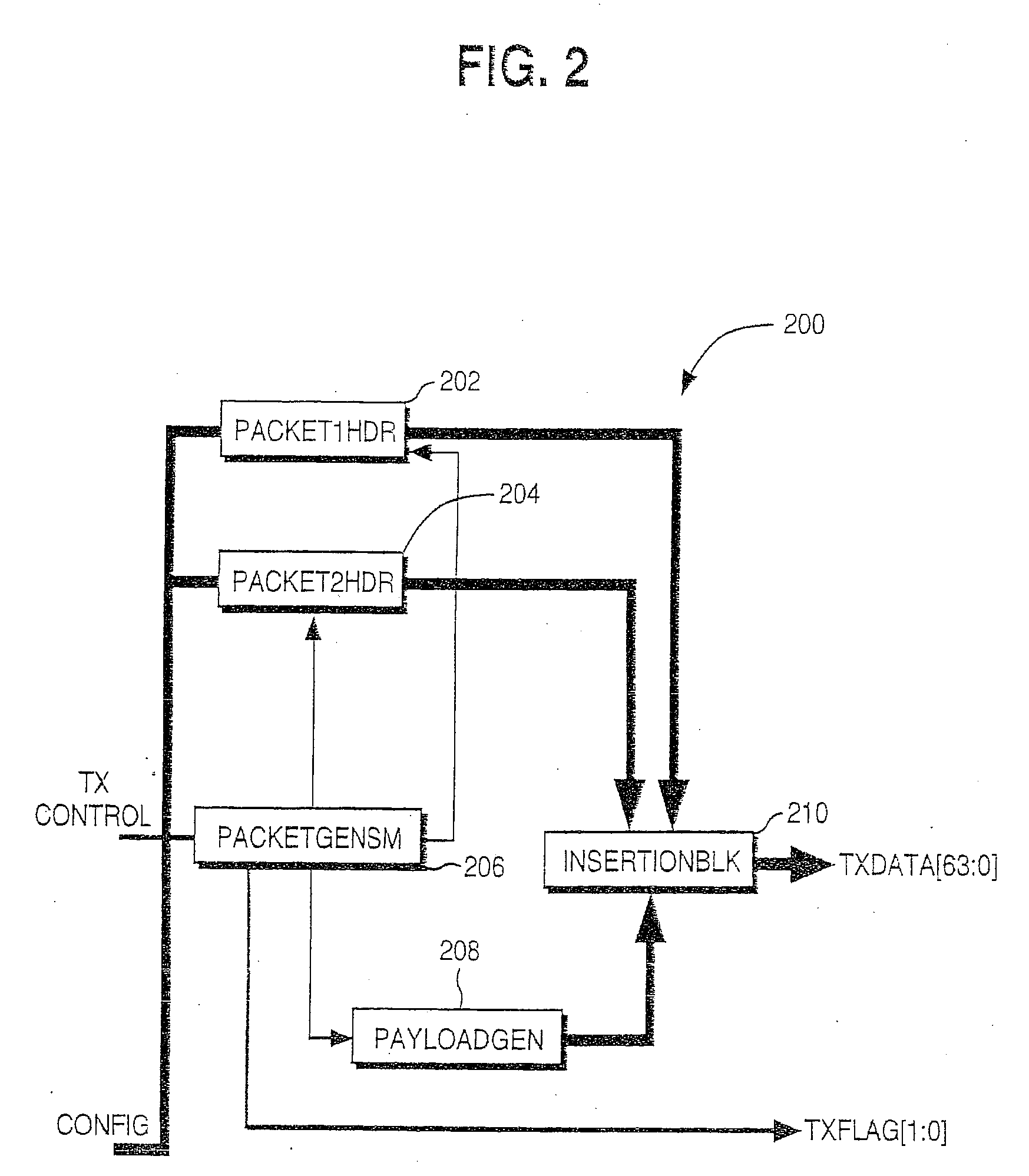

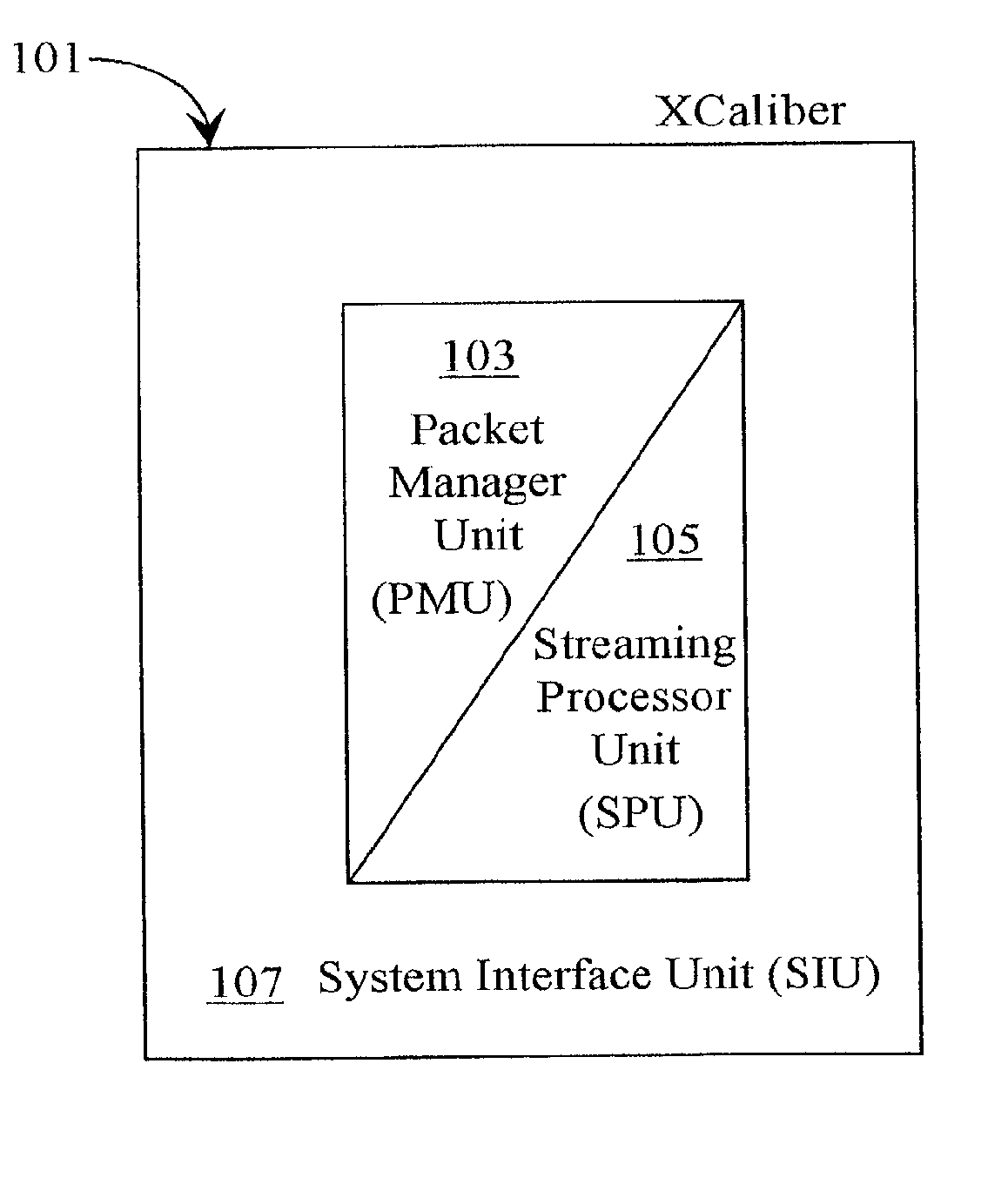

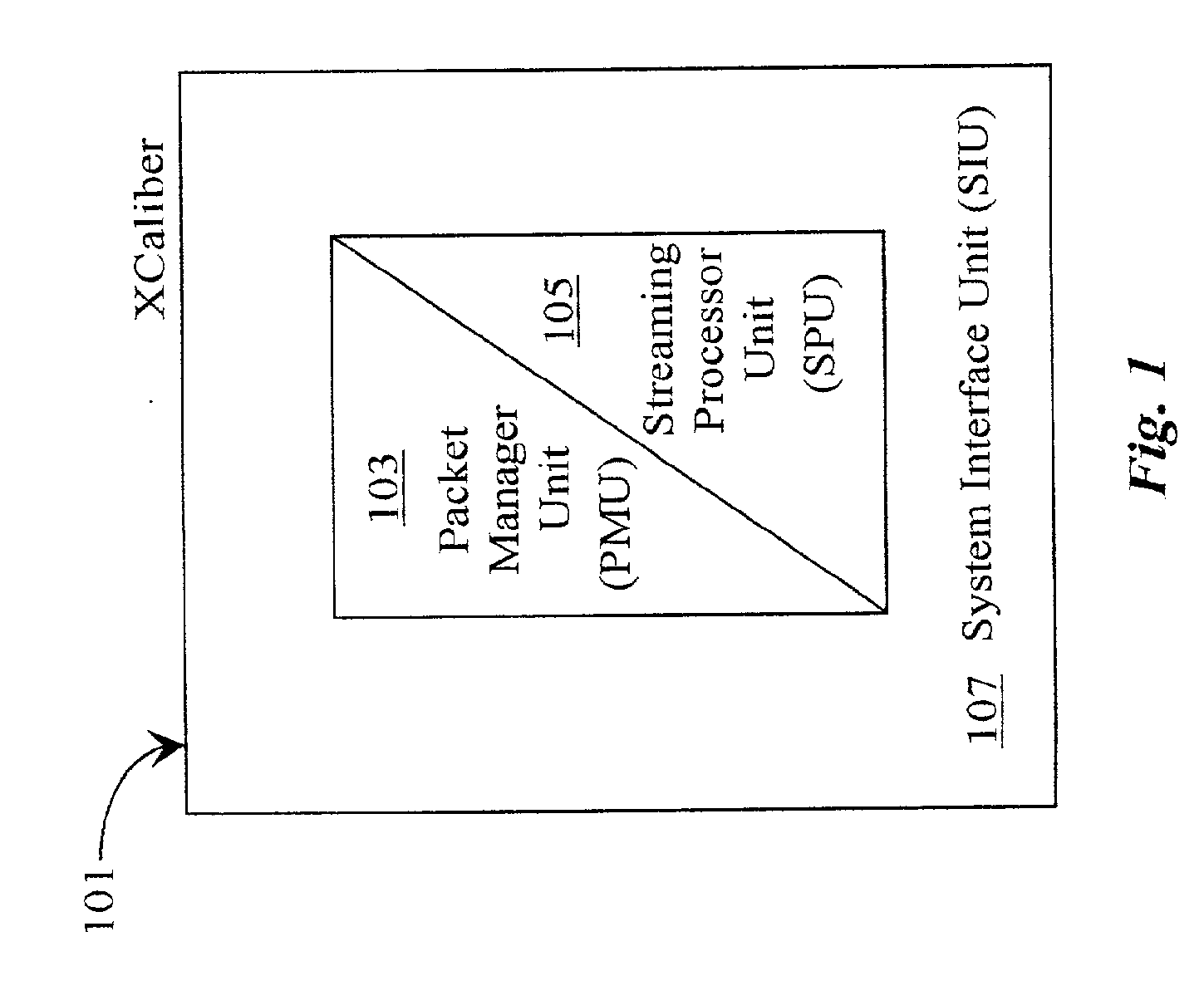

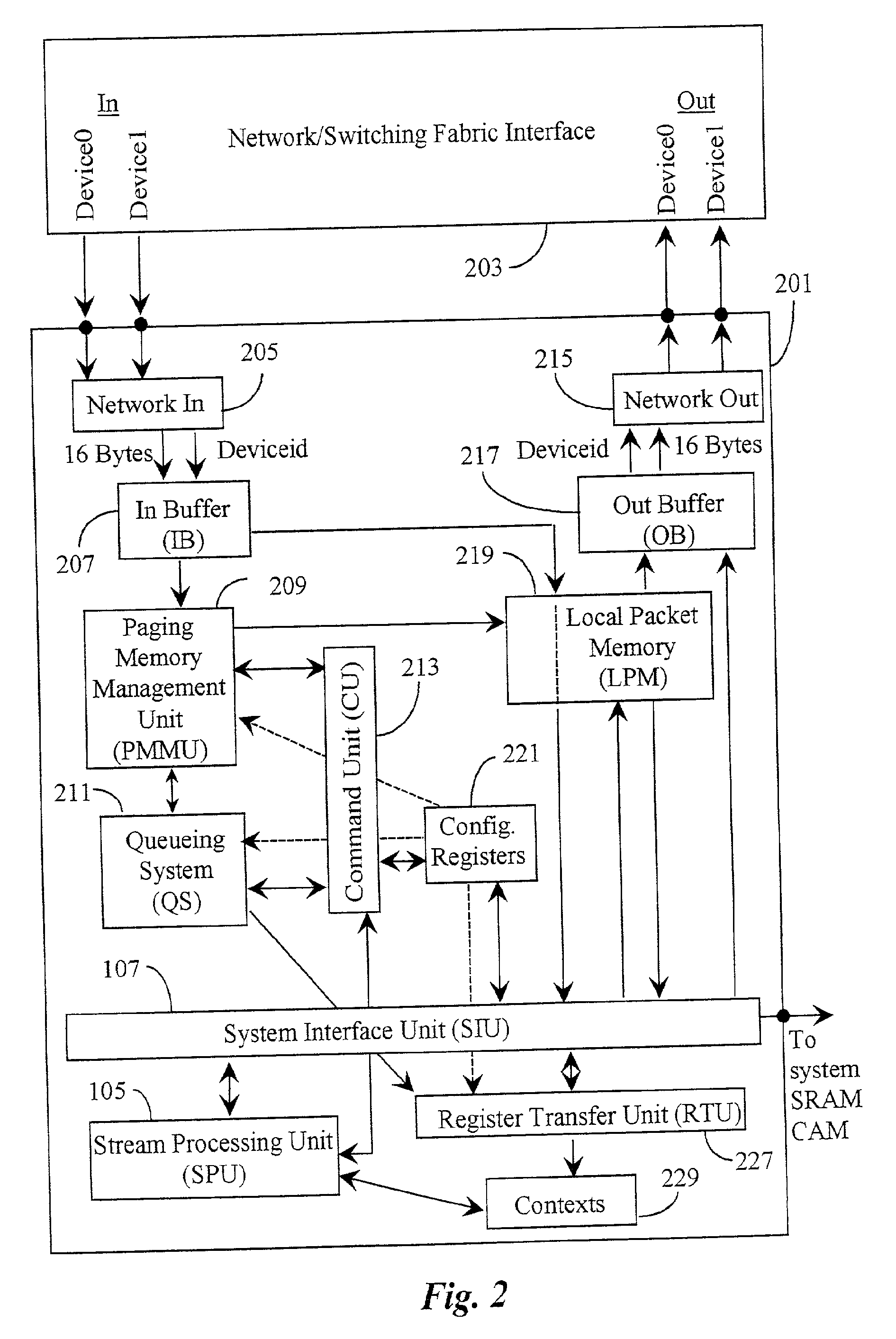

Functional validation of a packet management unit

InactiveUS20070168748A1Cost-effective and reliablePrecise designError detection/correctionProgram controlRandom test generatorUser interface

A validation system is disclosed for validating function of a packet-management unit operationally coupled through a system interface to a processing unit of a processor system. The validation system comprises a user interface for creating an inputting test parameters and test code into the system, a test generator coupled to the user interface, the test generator for generating input packet activity in the form of a packet stream, a model coupled to the test generator for emulating separate and integrated function of the packet management unit, the system interface, and a stream-processing unit and an evaluation software for checking and validating or not validating results. The system validation function relies, in a preferred embodiment, on comparing output results with criteria of the selected test code resulting in an indication of pass or failure of the test. In a preferred embodiment, the system also notifies to cause of failure.

Owner:ARM FINANCE OVERSEAS LTD

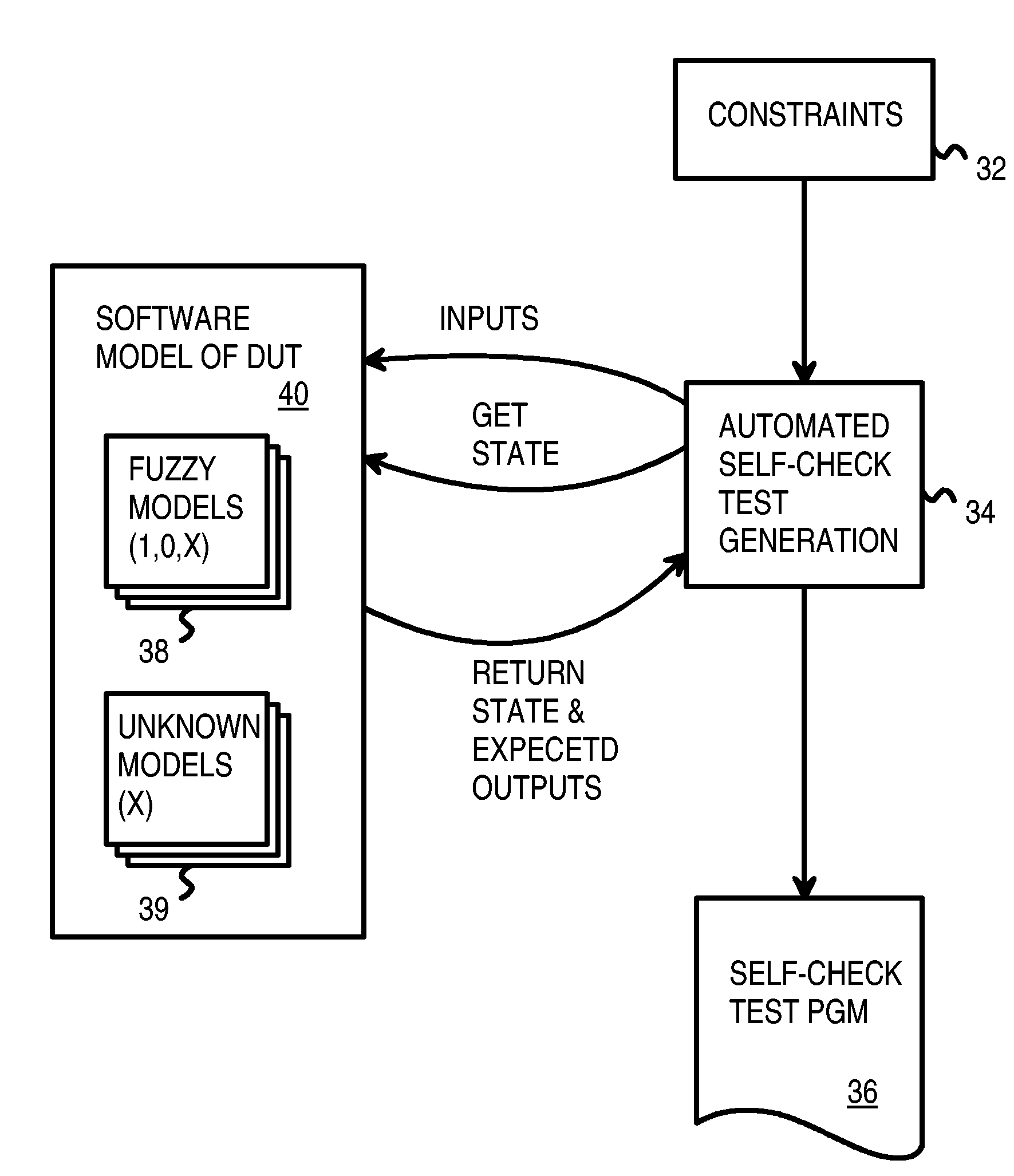

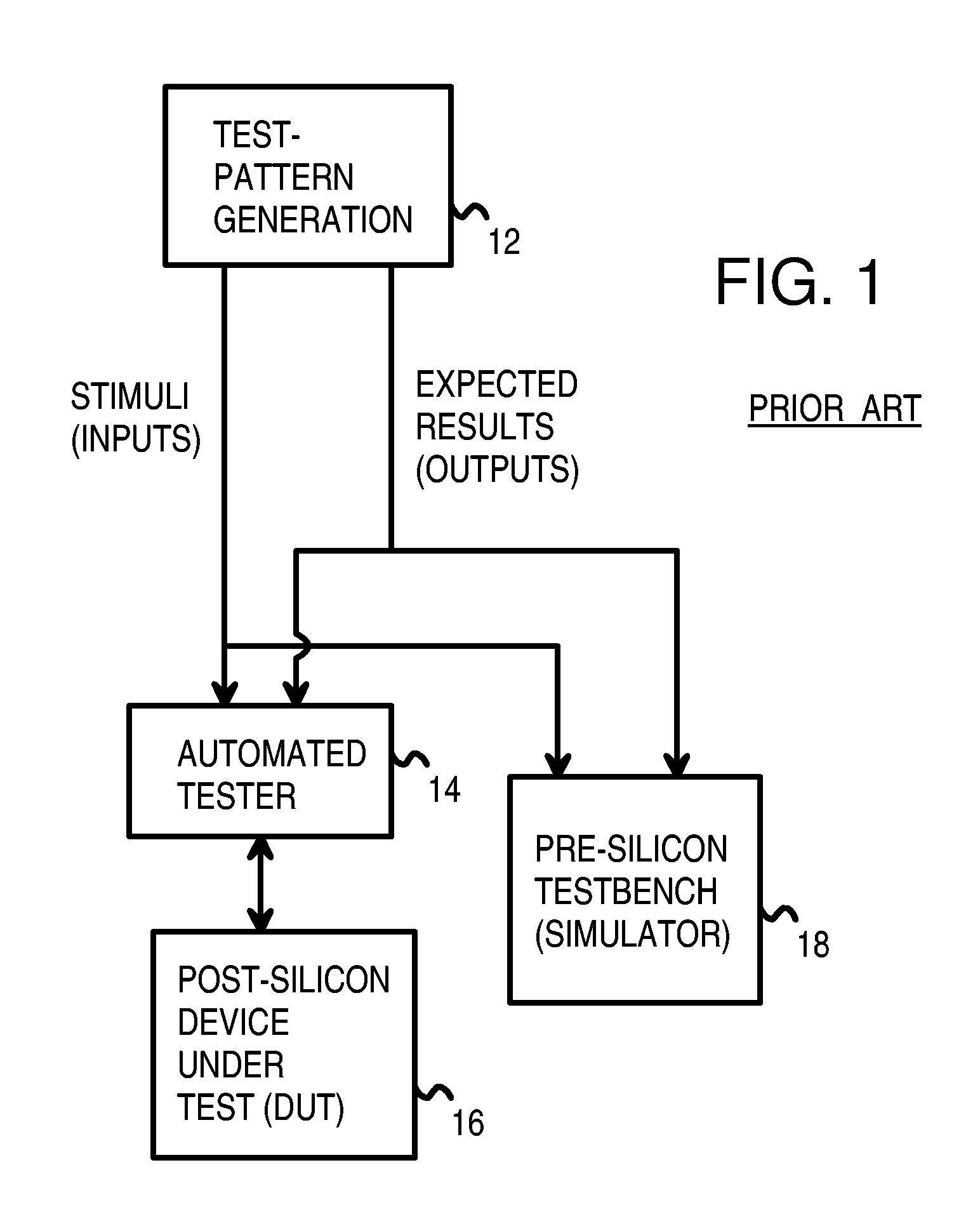

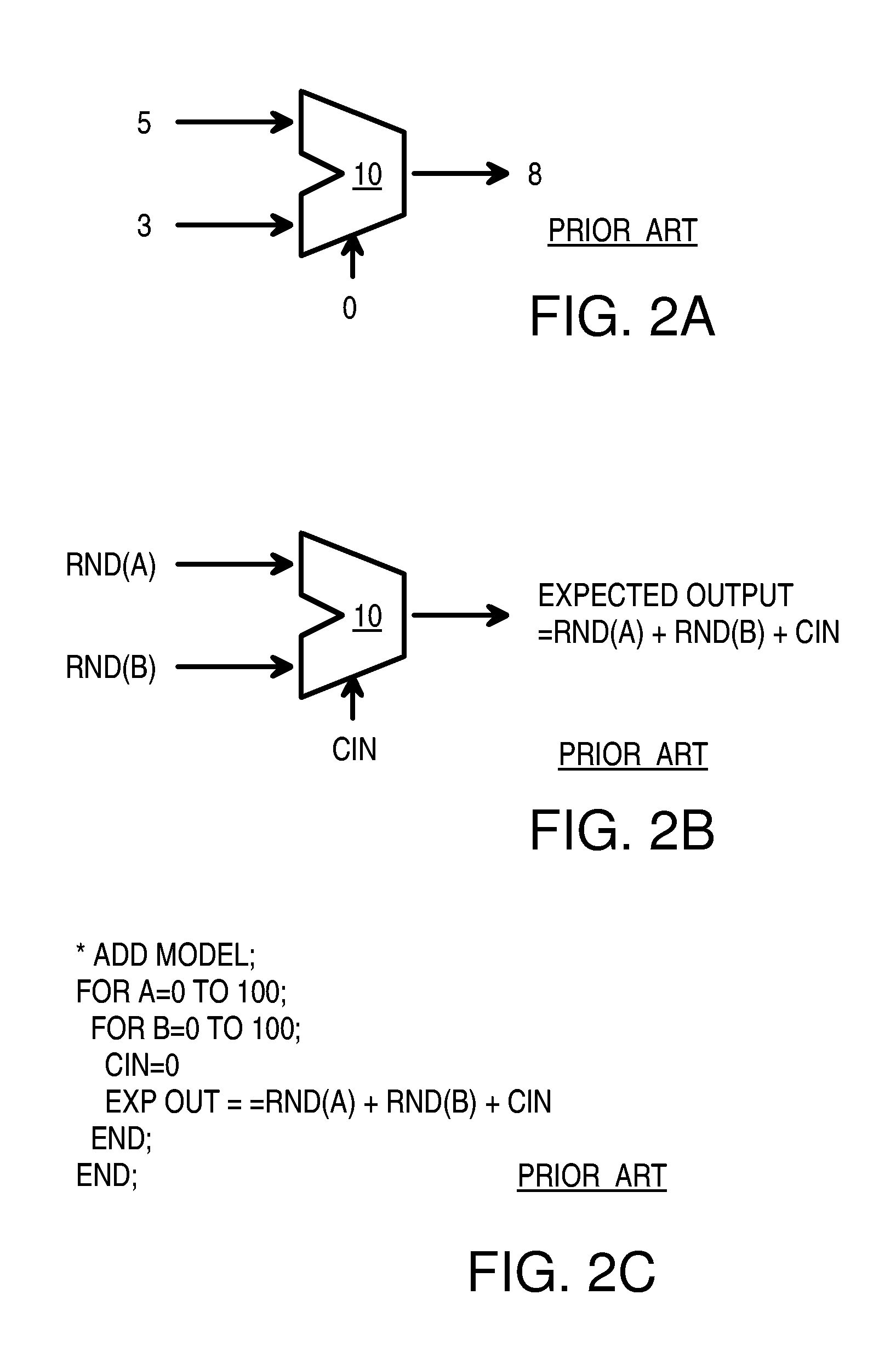

Self-checking test generator for partially-modeled processors by propagating fuzzy states

InactiveUS7483824B1Semiconductor/solid-state device testing/measurementElectronic circuit testingAlgorithmChoice test

A self-checking test generator program creates a self-checking test program that can test a device under test (DUT). The self-checking test generator selects instructions for a test. Selected instructions are executed on a software DUT model to generate results that can be self-checked by other instructions such as compare and branch instructions. The software DUT model has fuzzy models and unknown models for blocks in the DUT. Fuzzy models generate expected outputs for a block of the DUT. Fuzzy models may propagate unknown data from their inputs to their outputs. Unknown models do not predict expected outputs. Instead, unknown models always output unknown (X). Over time, as more of the DUT logic is modeled, unknown models may be replaced with fuzzy models.

Owner:AZUL SYSTEMS

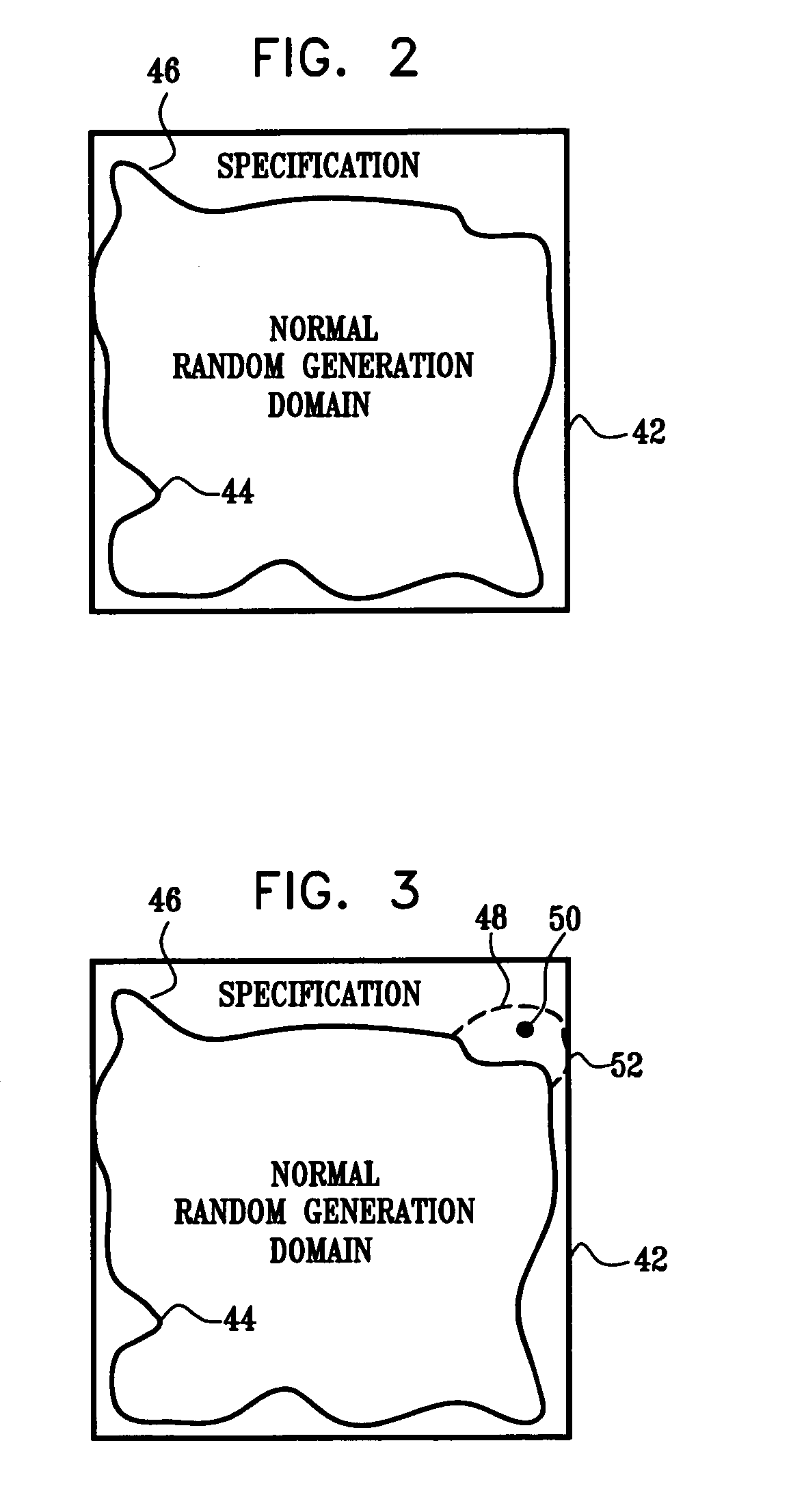

Highly specialized scenarios in random test generation

Improvements in functional verification of a design are achieved by providing a test template that specifies test parameters directed to a function of the design. An exemption mode of operation is associated with a portion of the template, in which constraints and variables associated with the template are revised. The template is an input to a CSP engine, which, in cooperation with a test generator engine, produces test scenarios that lie in an expanded region of the generator's usual operational space. Provision is made for independently enabling and disabling a plurality of exemption modes of operation that are associated with the same or different areas of the template.

Owner:GLOBALFOUNDRIES INC