Patents

Literature

979results about How to "Efficient testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

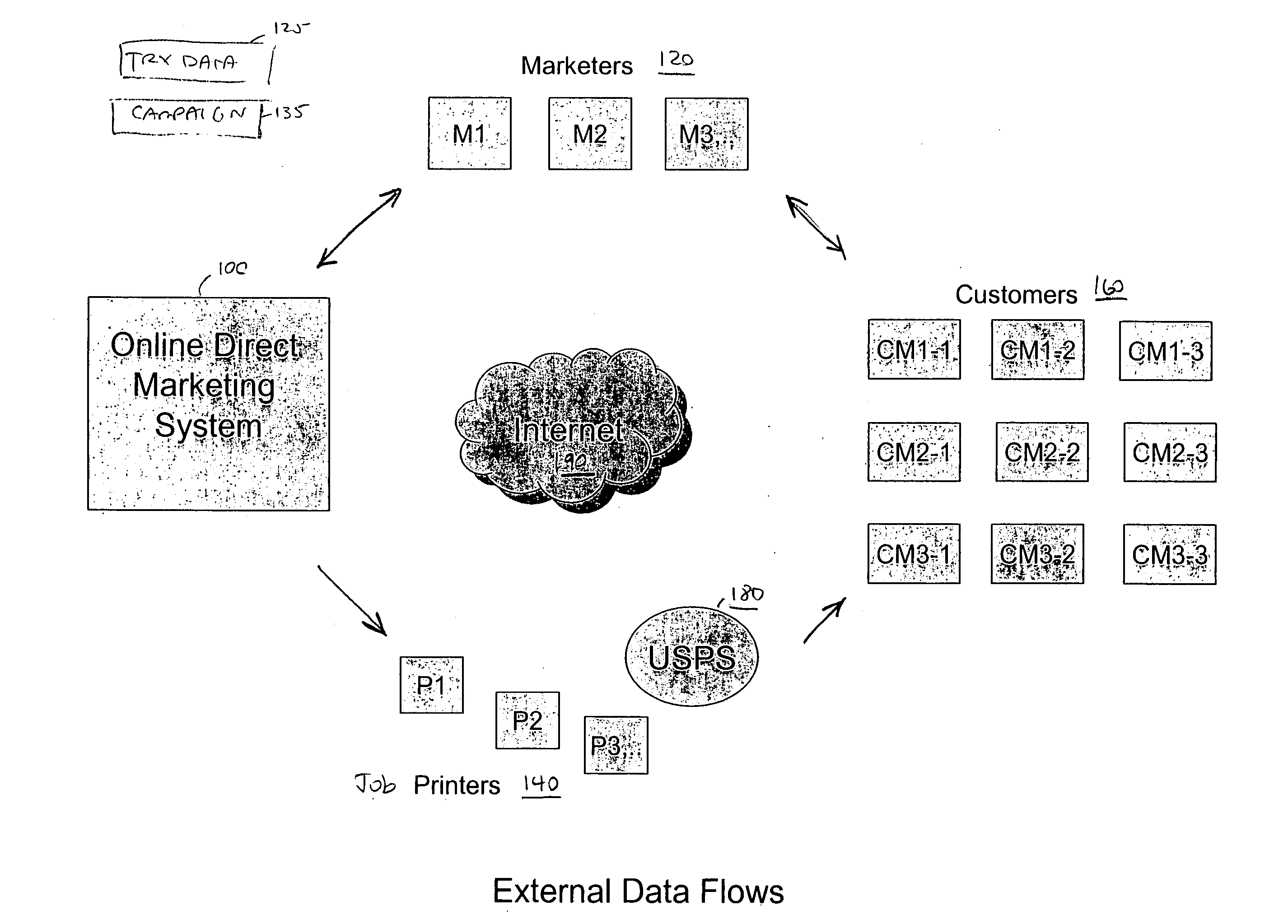

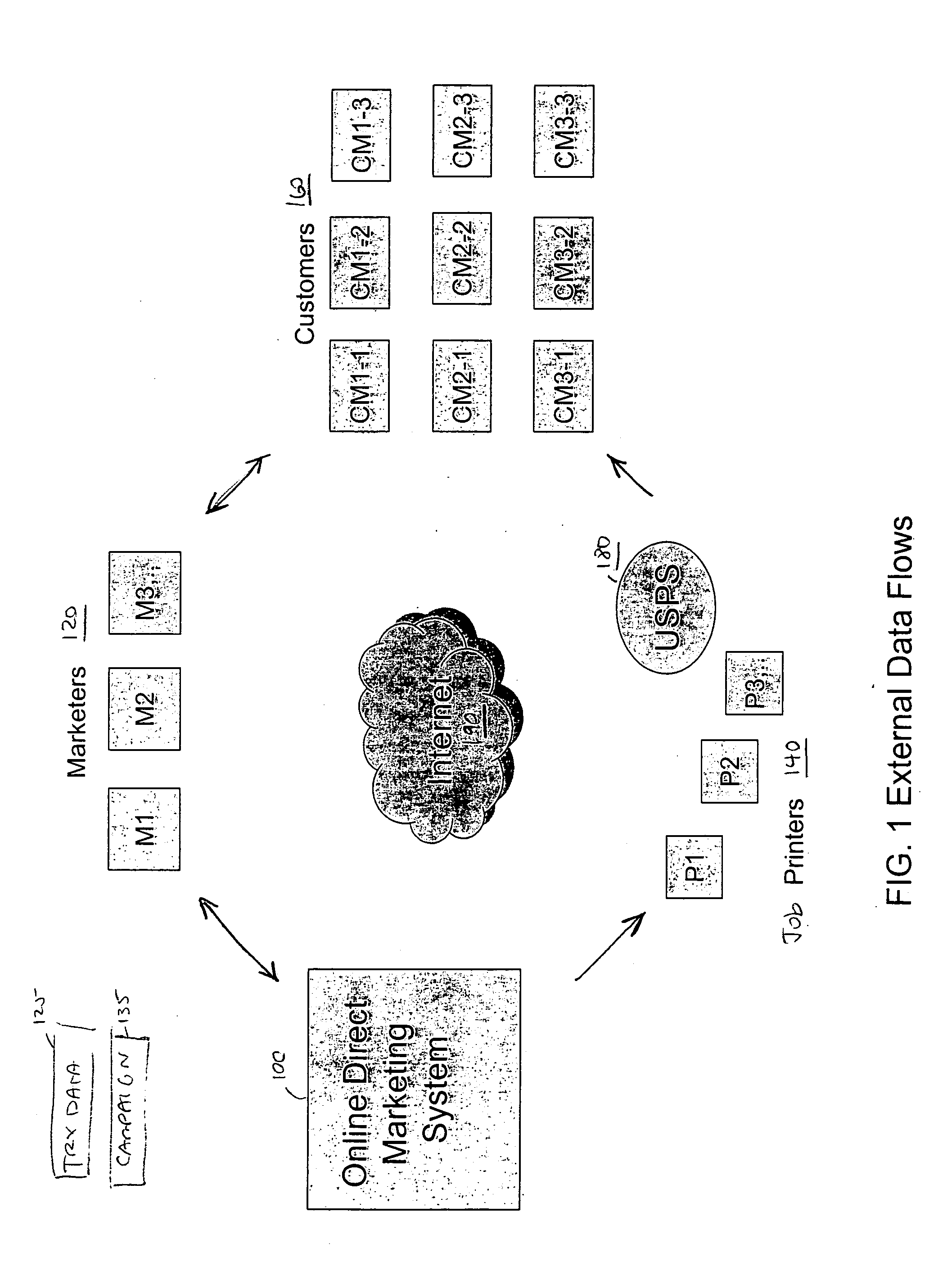

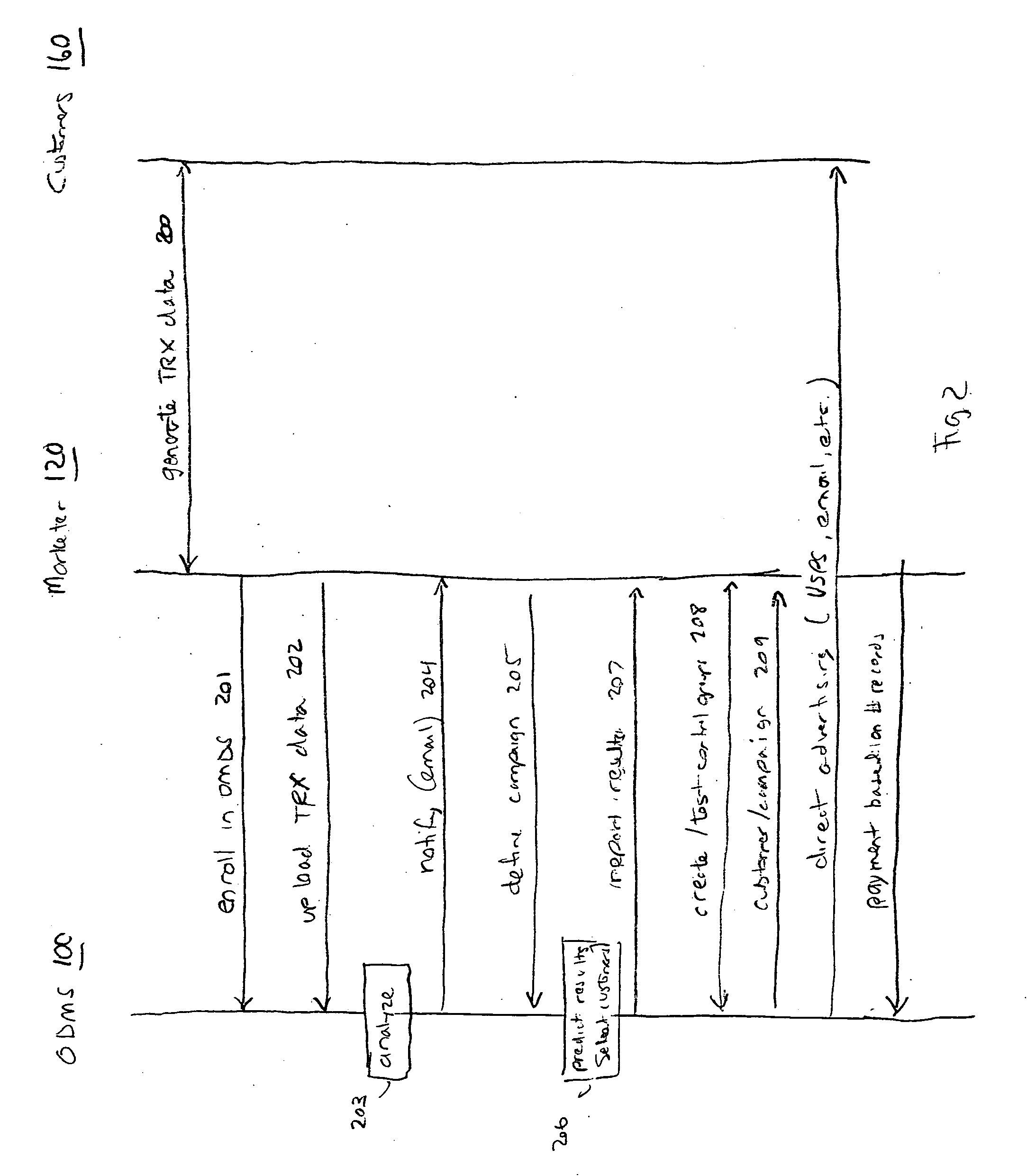

Online direct marketing system

InactiveUS20080065476A1Targeting of customers is improvedImprove accuracyAdvertisementsTransaction dataFinancial transaction

An automated, unified, interactive system and methods for marketing. After a Marketer uploads transaction and customer data, the system automatically analyzes this data to predict at least one of the group consisting of purchase probabilities, likely buyers, up-sell opportunities, cross-sell opportunities, and potential defectors; selects a marketing campaign and customers to target in that marketing campaign, the step of selecting customers being based upon results from the step of analyzing customer and transaction data; predicts anticipated response rate and / or revenue from the marketing campaign; delivers at least one list of the customers to target, wherein the list of customers further comprises customer records; supplies an expert system to test elements of the campaigns such as targeting and offers; and collects fees based on a number of the records downloaded.

Owner:LOYALTY BUILDERS

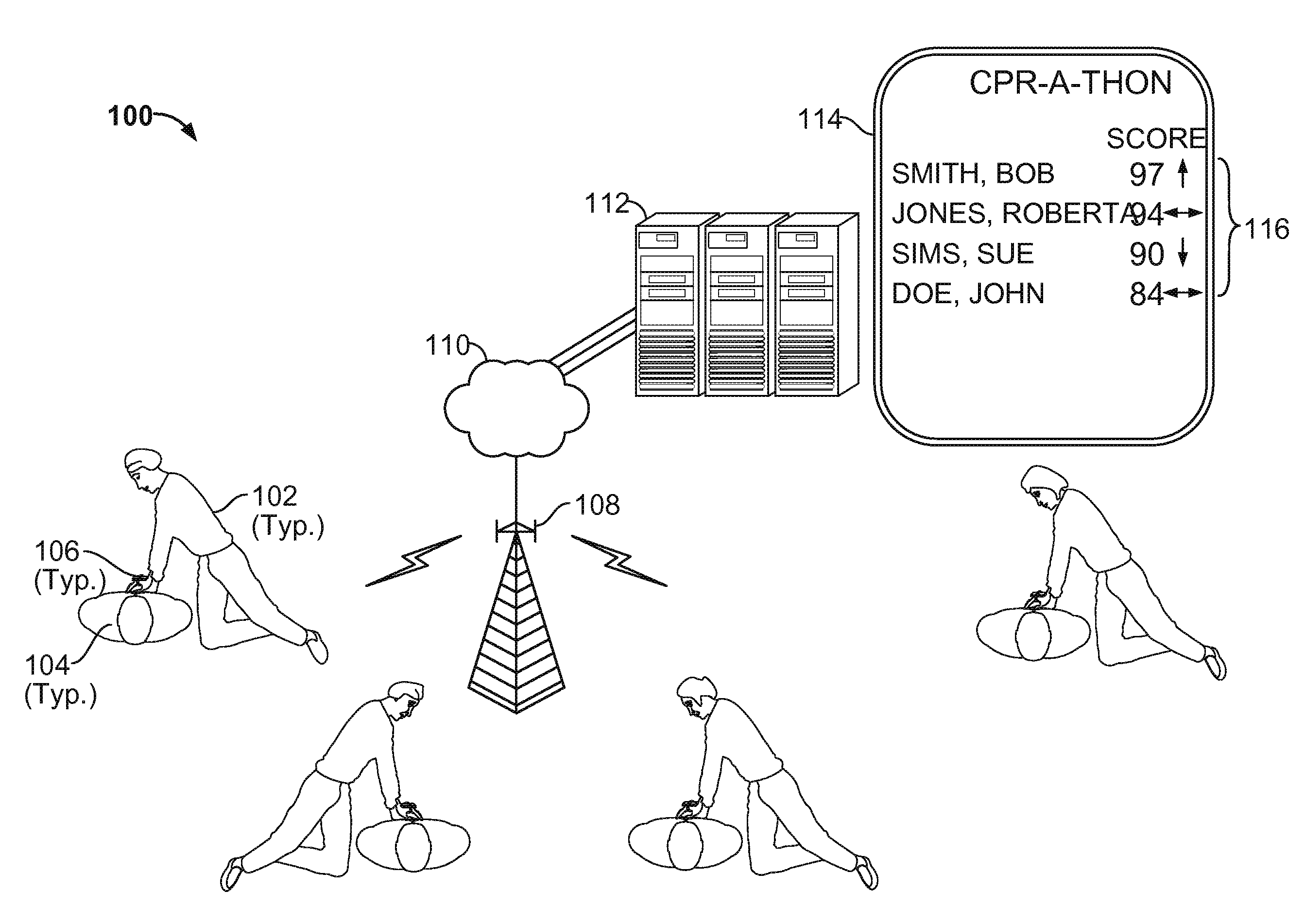

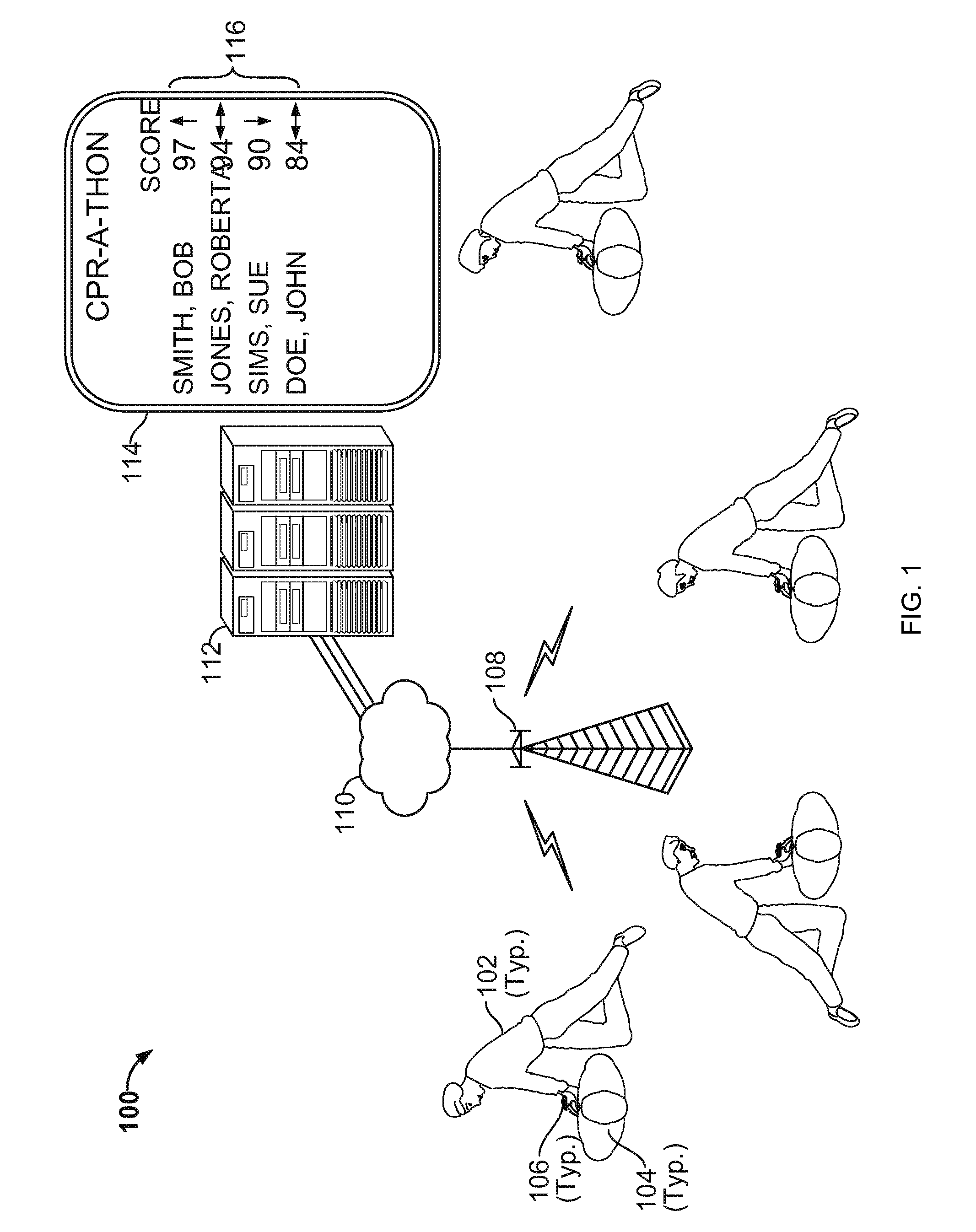

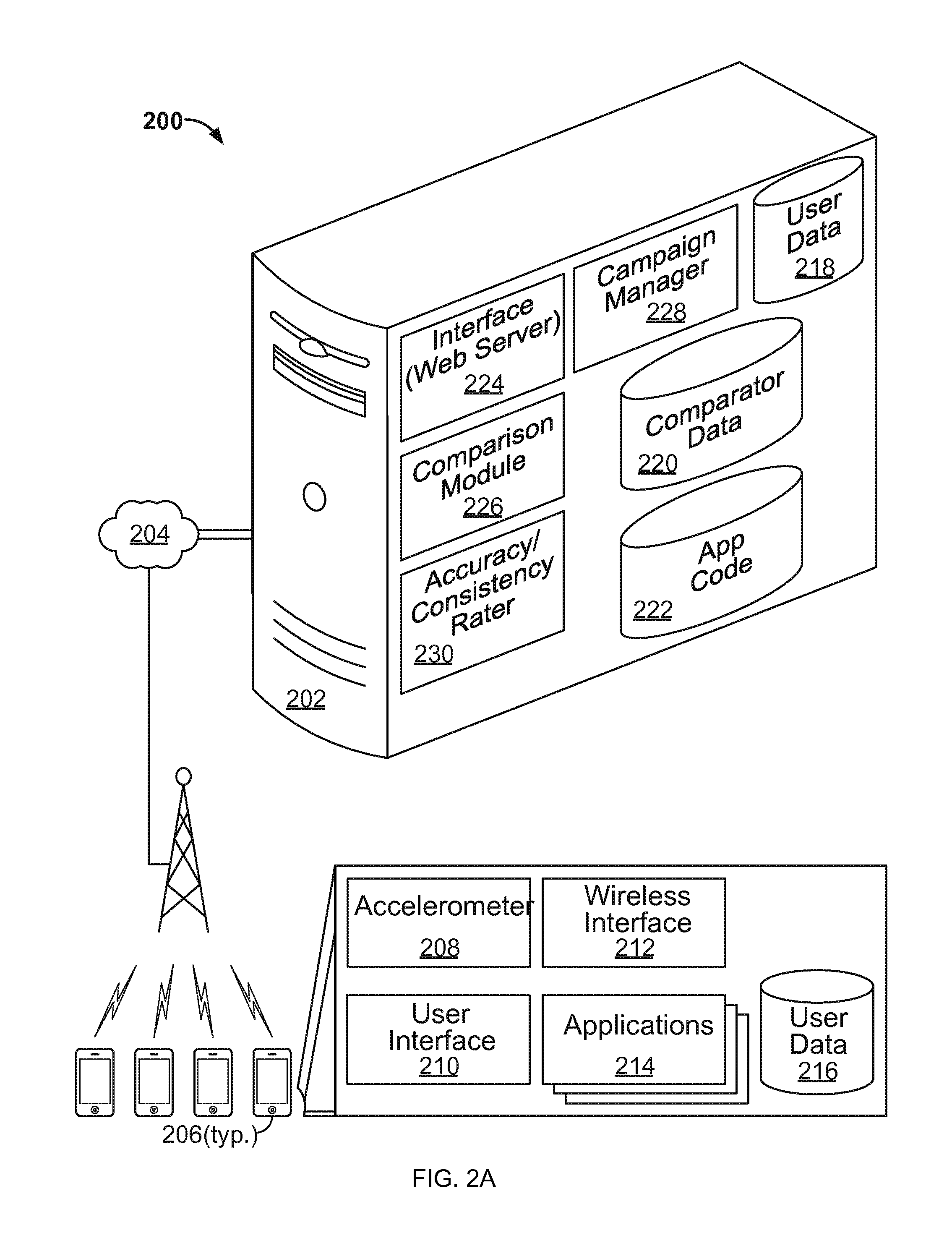

CPR Competition System

InactiveUS20110117529A1Increase the number ofQuality improvementPhysical therapies and activitiesEducational modelsComputer scienceCardiopulmonary resuscitation

A computer-implemented method for managing rescue training includes registering a plurality of individuals as potential rescue trainees through a central computer server system, receiving from computing devices that are remote from the central server system information indicative of rate and depth of compression for ones of the potential rescue trainees, and generating comparative data that reflects performance of CPR chest compressions for a first rescue trainee against other rescue trainees. The method also includes providing the comparative data over a network for review by one or more of the rescue trainees.

Owner:ZOLL MEDICAL CORPORATION

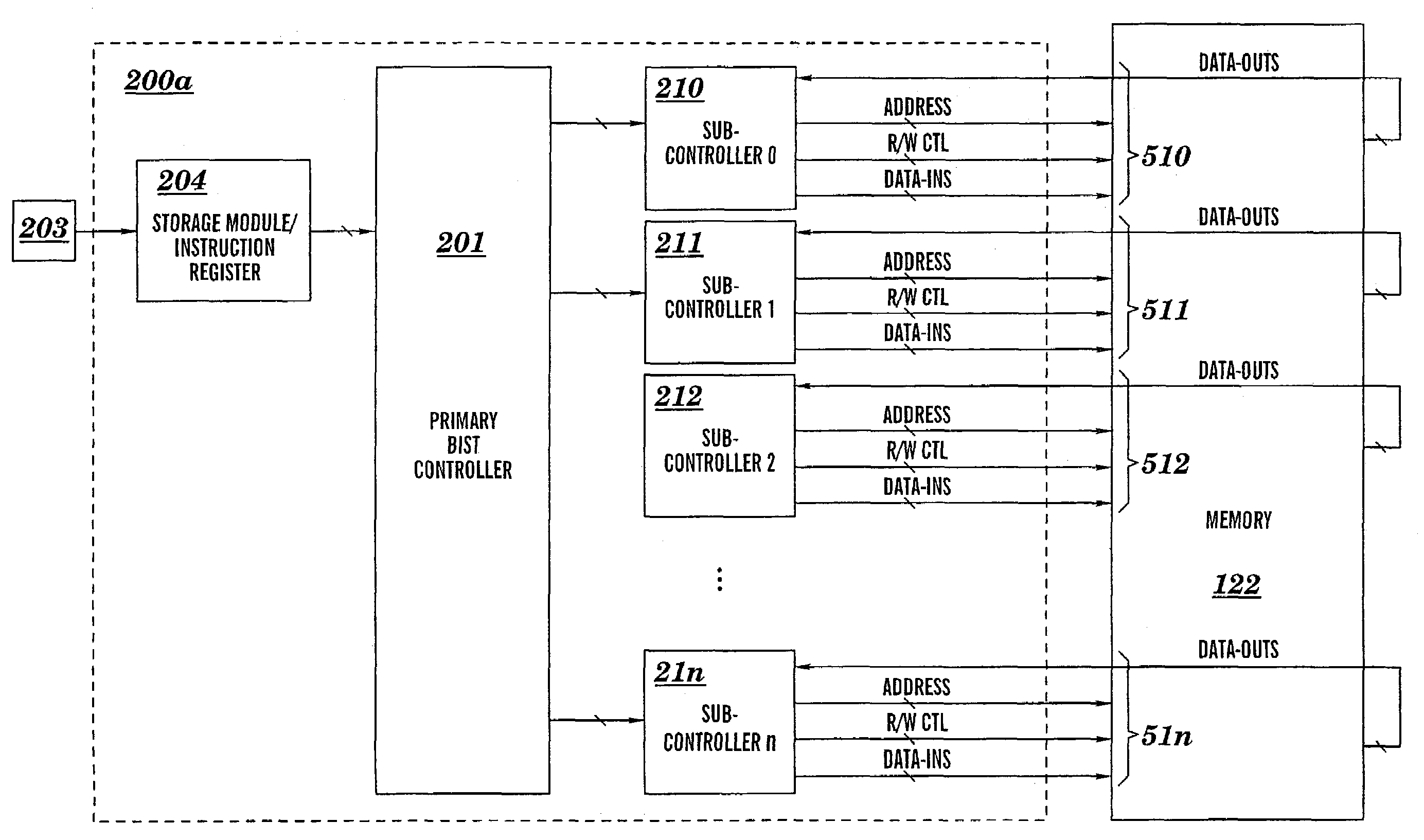

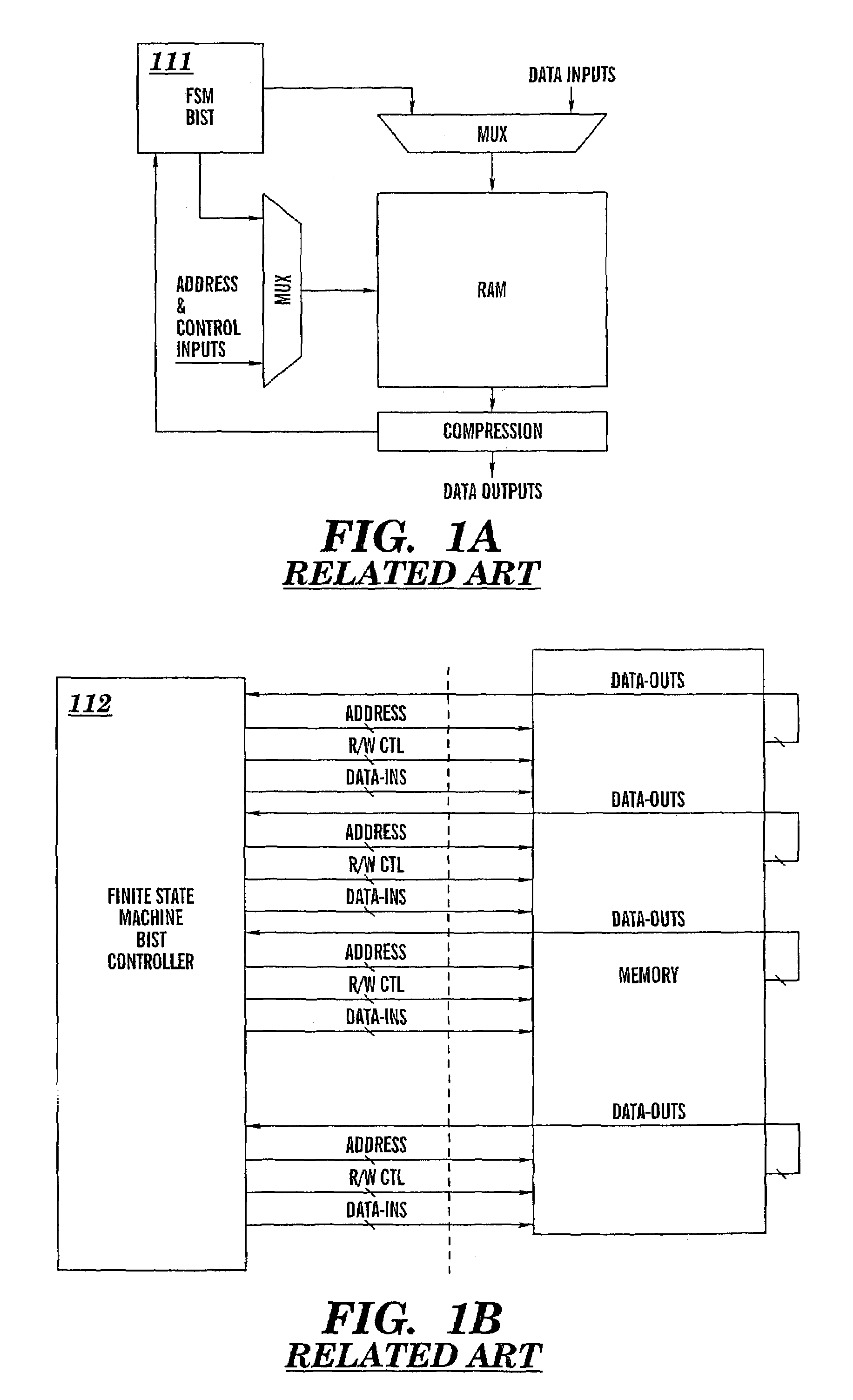

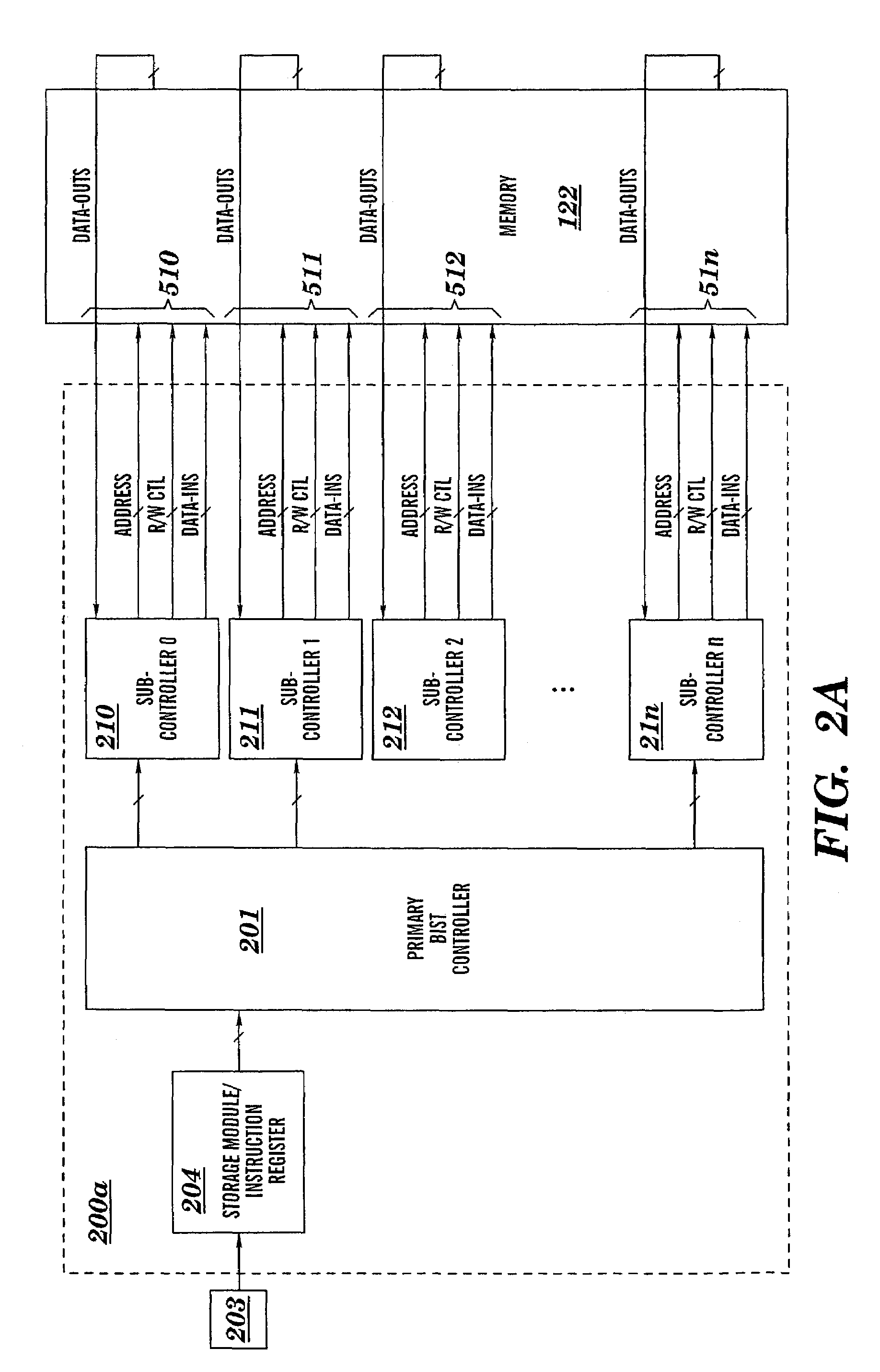

Programable multi-port memory BIST with compact microcode

InactiveUS7168005B2Easy to testIncrease flexibilityElectronic circuit testingFunctional testingAs DirectedMaster controller

A microcode programmable built-in-self-test (BIST) circuit and method for testing a multiported memory via multiple ports, either simultaneously or sequentially, as directed by a microcode instruction word. The microcode instruction word contains a plurality of executable subinstructions and one bit of information that controls whether the test operations prescribed in the plurality of subinstructions shall be executed in parallel or in series. The executable subinstructions are dispatched by a primary controller to subcontrollers which perform test operations at each port according to the subinstructions. The microcode programable BIST architecture flexibly facilitates the testing of multiple devices, multiported devices, including multiported memory structures and complex dependent multiported memory structures. The BIST supports in-situ testing of the functionality of the memory at wafer, module, and burn-in, as well as system-level testing.

Owner:CADENCE DESIGN SYST INC

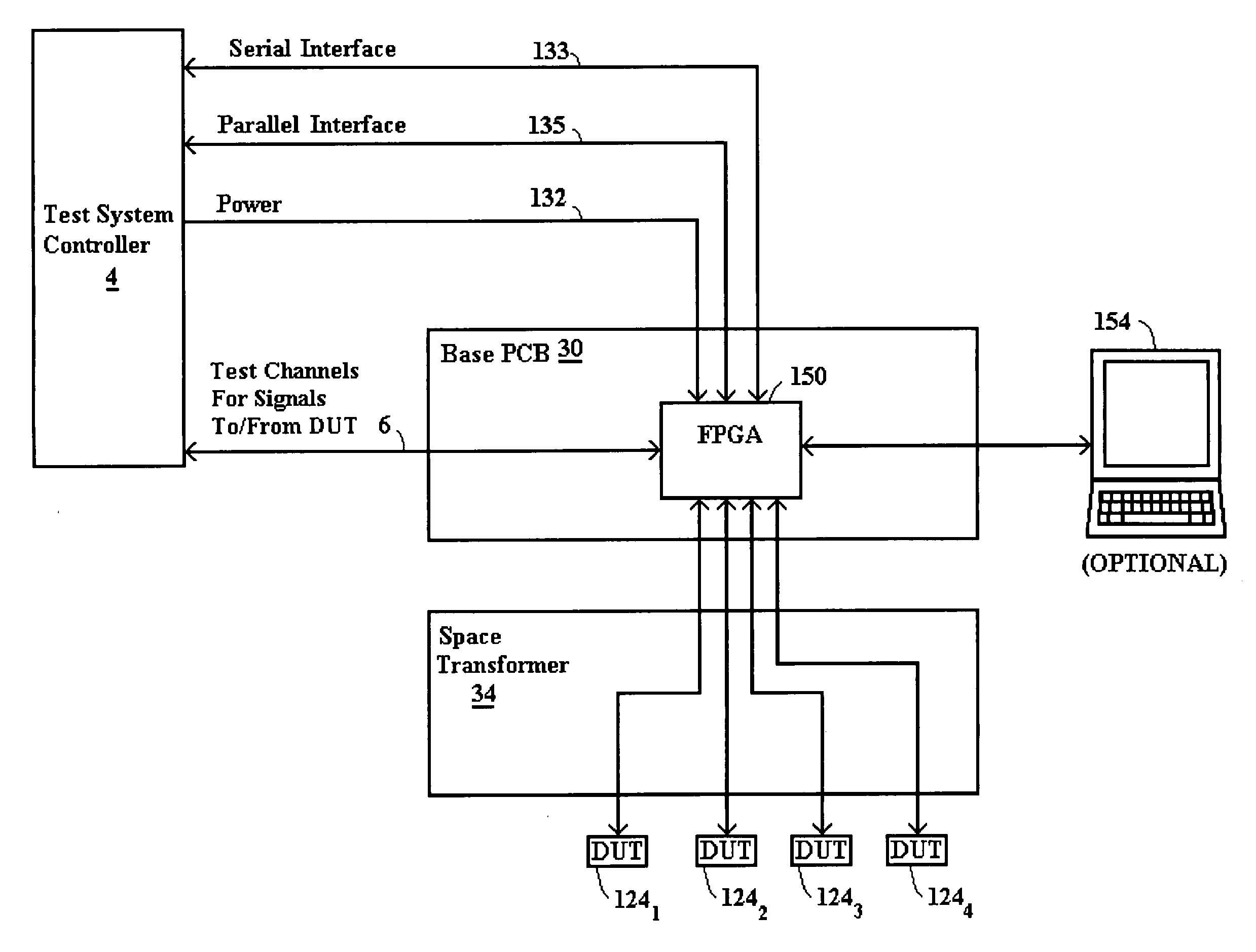

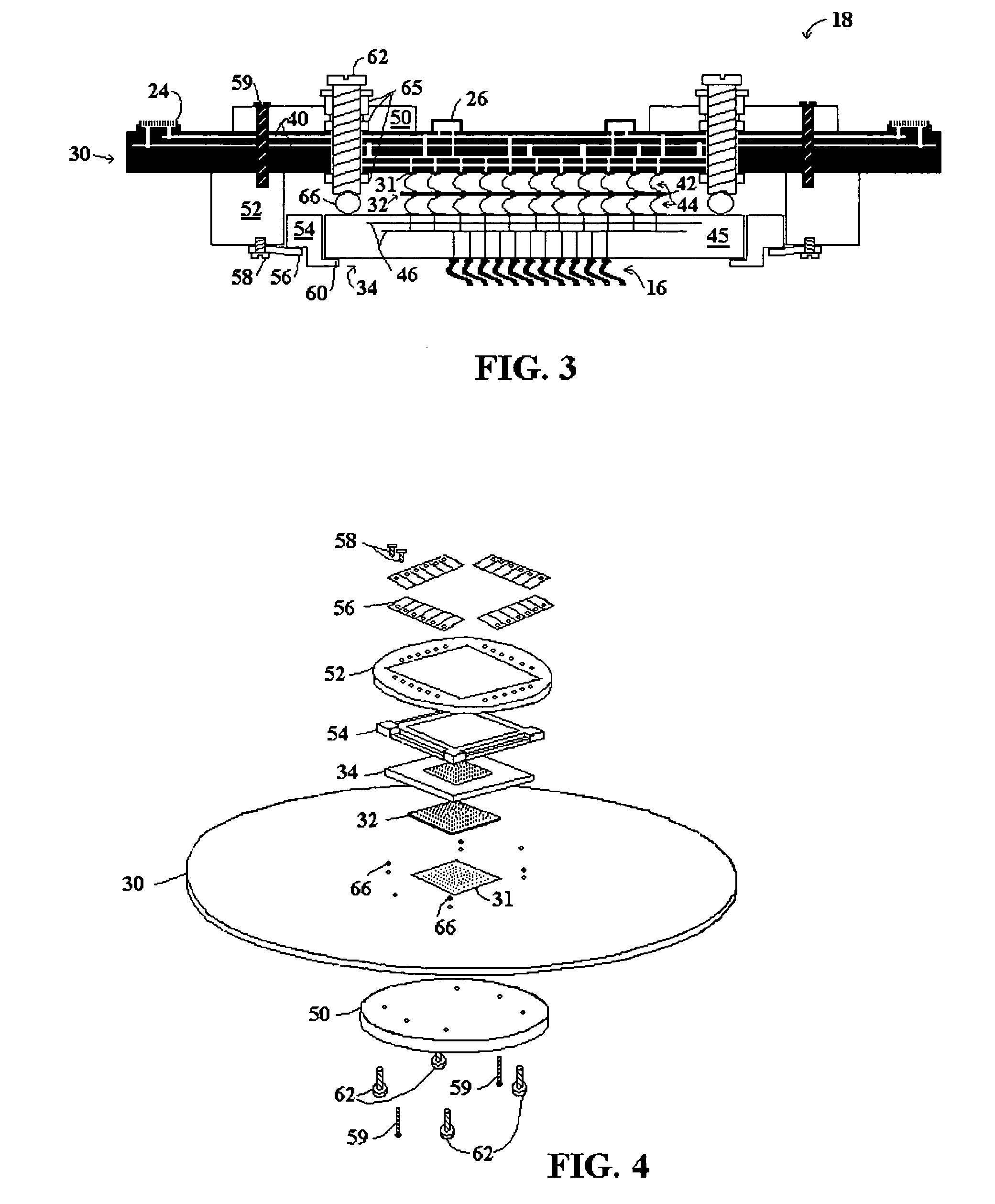

Programmable devices to route signals on probe cards

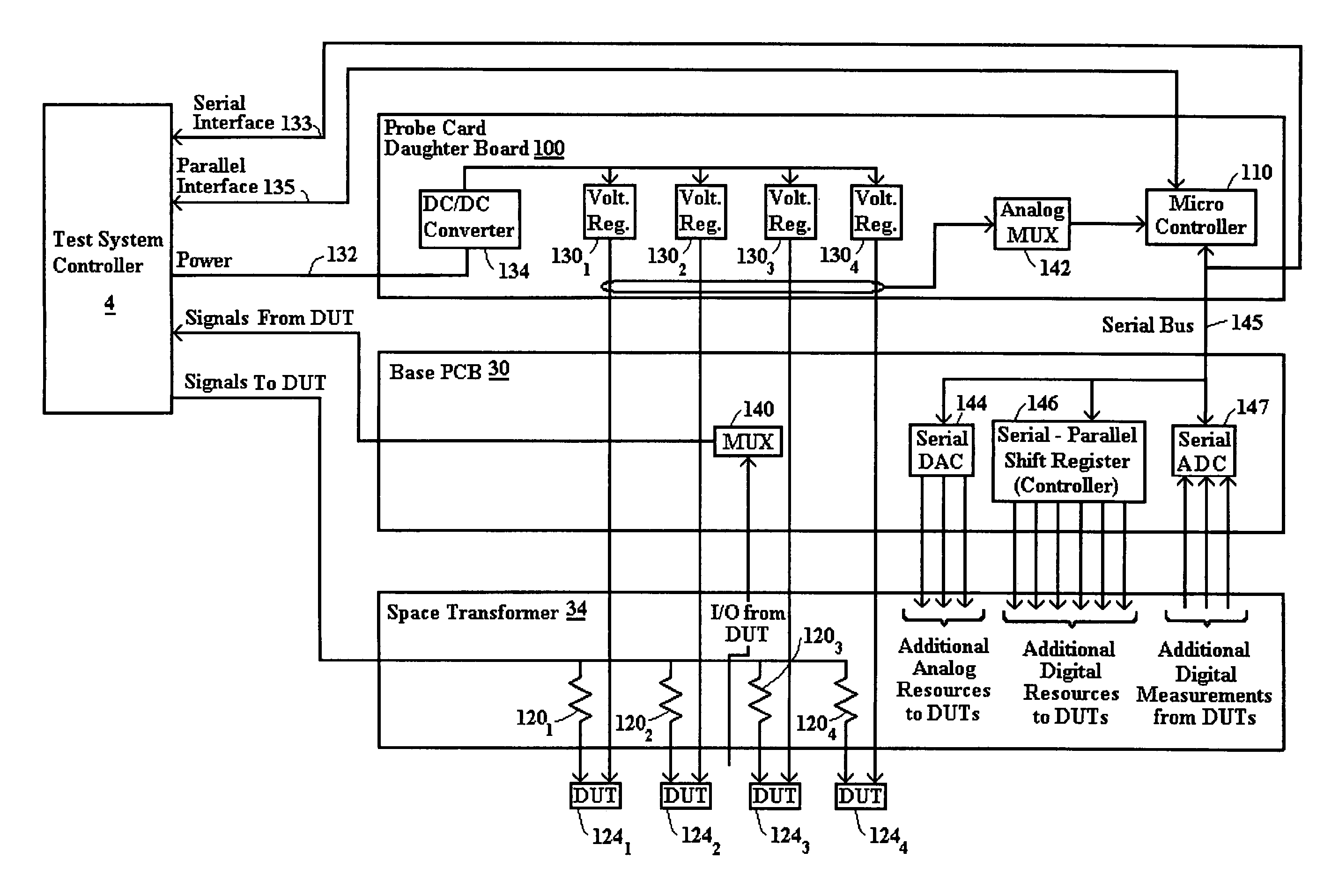

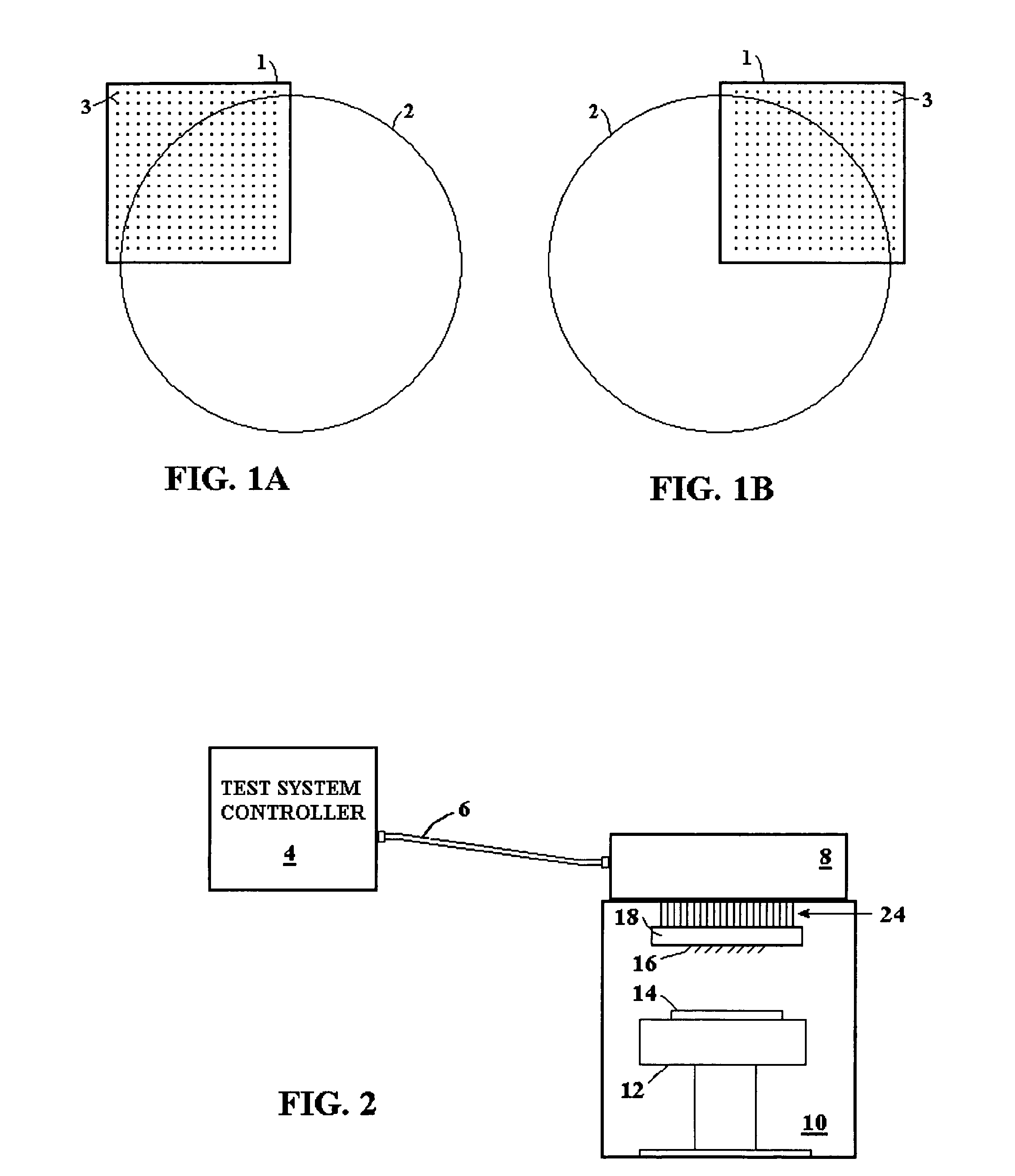

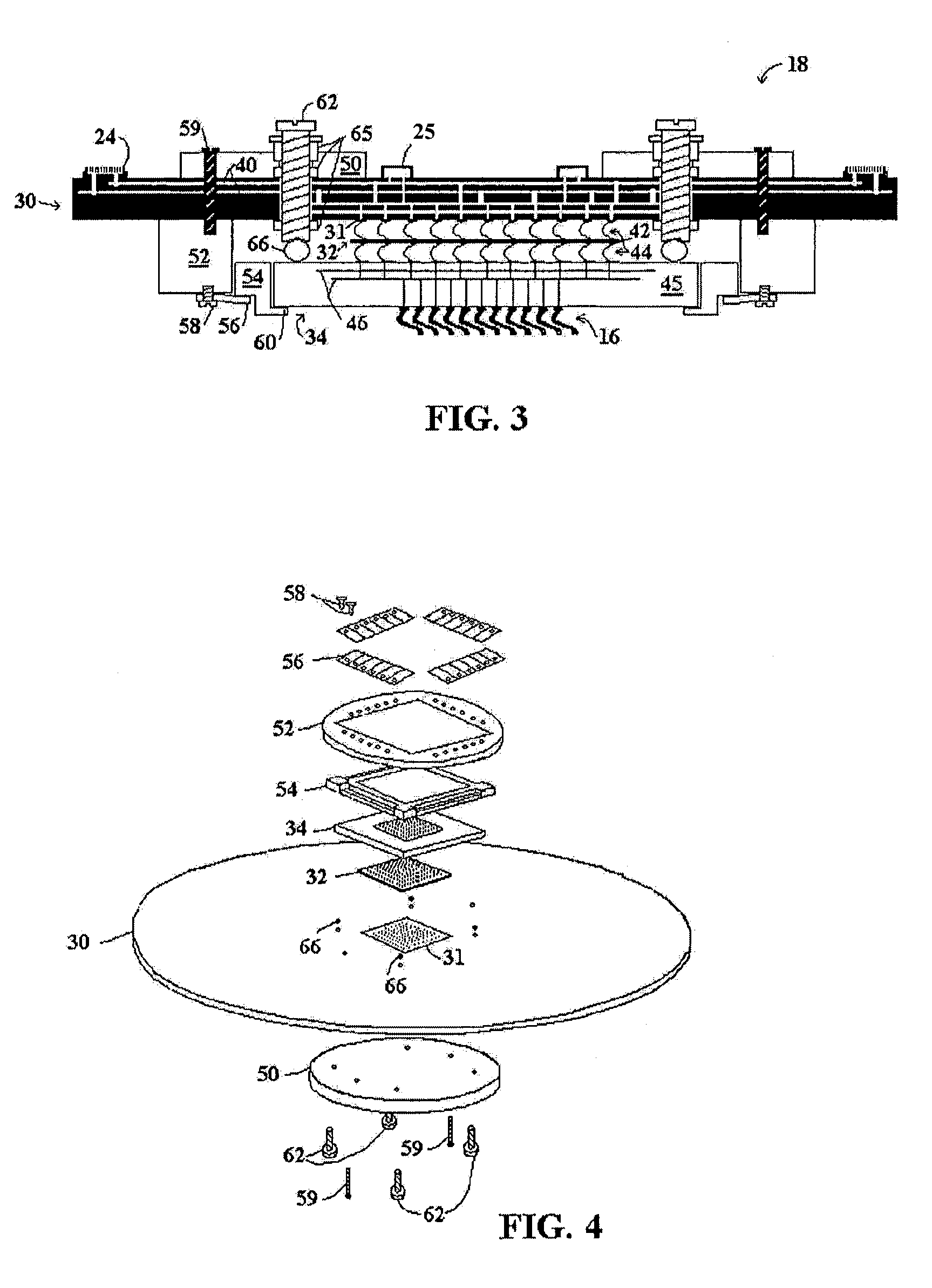

InactiveUS20060170435A1Great switching densityLong life cycleSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsProbe cardTest engineer

A probe card of a wafer test system includes one or more programmable ICs, such as FPGAs, to provide routing from individual test signal channels to one of multiple probes. The programmable ICs can be placed on a base PCB of the probe card, or on a daughtercard attached to the probe card. With programmability, the PCB can be used to switch limited test system channels away from unused probes. Programmability further enables a single probe card to more effectively test devices having the same pad array, but having different pin-outs for different device options. Reprogrammability also allows test engineers to re-program as they are debugging a test program. Because the programmable IC typically includes buffers that introduce an unknown delay, in one embodiment measurement of the delay is accomplished by first programming the programmable IC to provide a loop back path to the test system so that buffer delay can be measured, and then reprogramming the programmable IC now with a known delay to connect to a device being tested.

Owner:FORMFACTOR INC

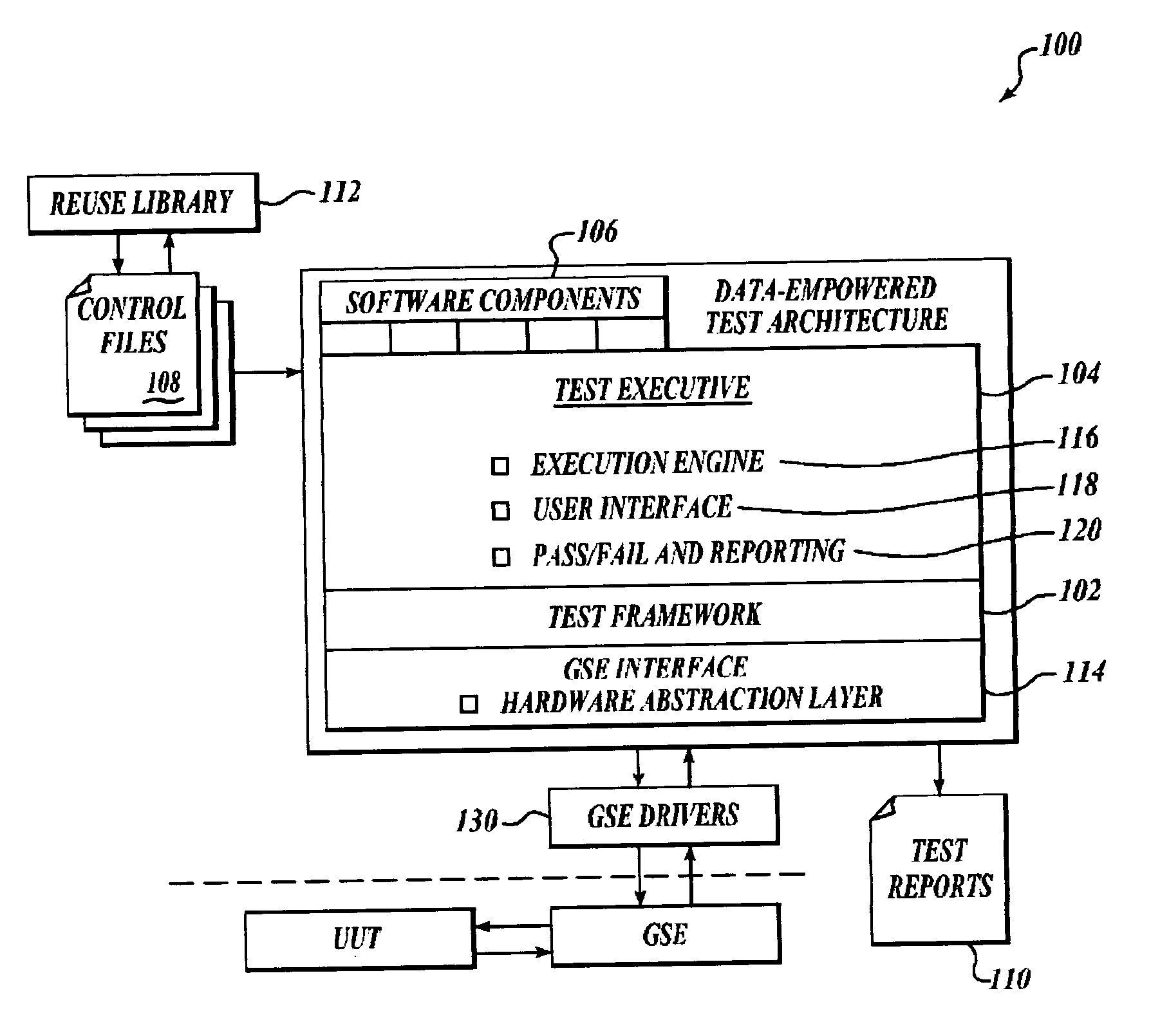

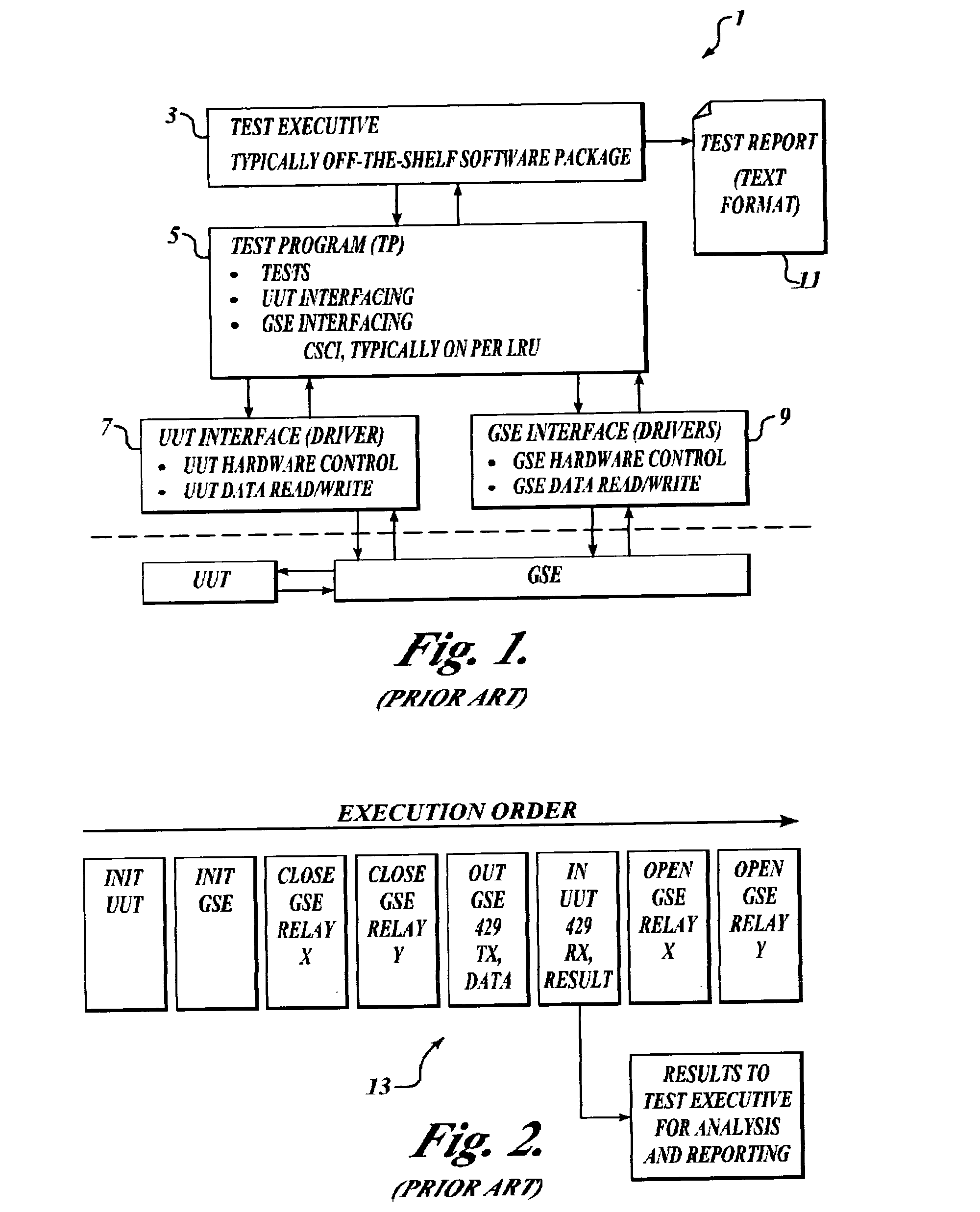

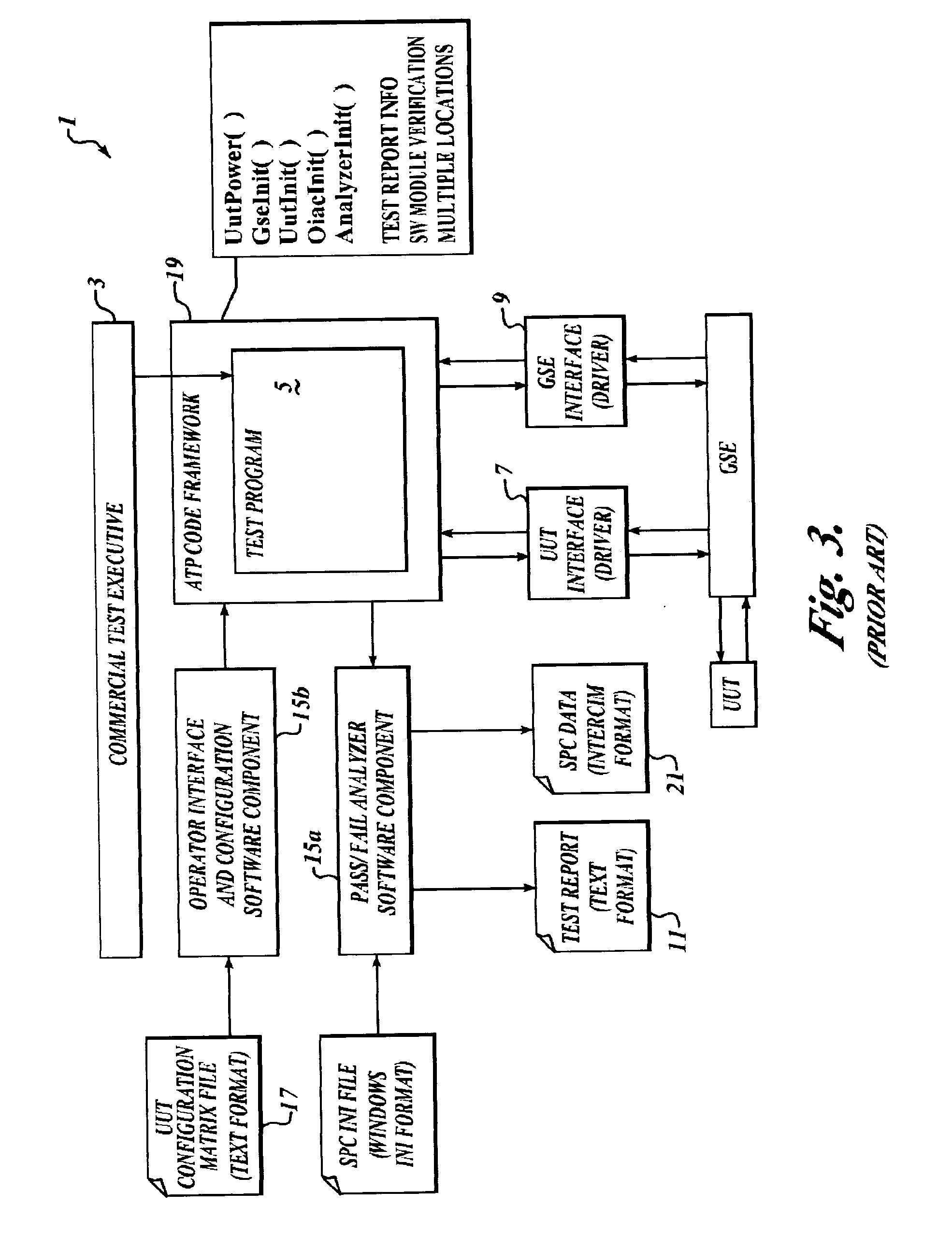

Data empowered laborsaving test architecture

InactiveUS20050097515A1Easy to operateOvercome limitationsError detection/correctionSpecific program execution arrangementsComputer hardwareTest frame

A test program development method embodied in a data-empowered test program architecture including a test executive software module; a test framework software module having externally configurable generic software code and being coupled for interaction with the test executive software module; a plurality of software components in a software components module coupled for interaction with the test framework software module and structured for outputting one or more test reports; and one or more external control files coupled for configuring the generic software code of the test framework software module.

Owner:HONEYWELL INT INC

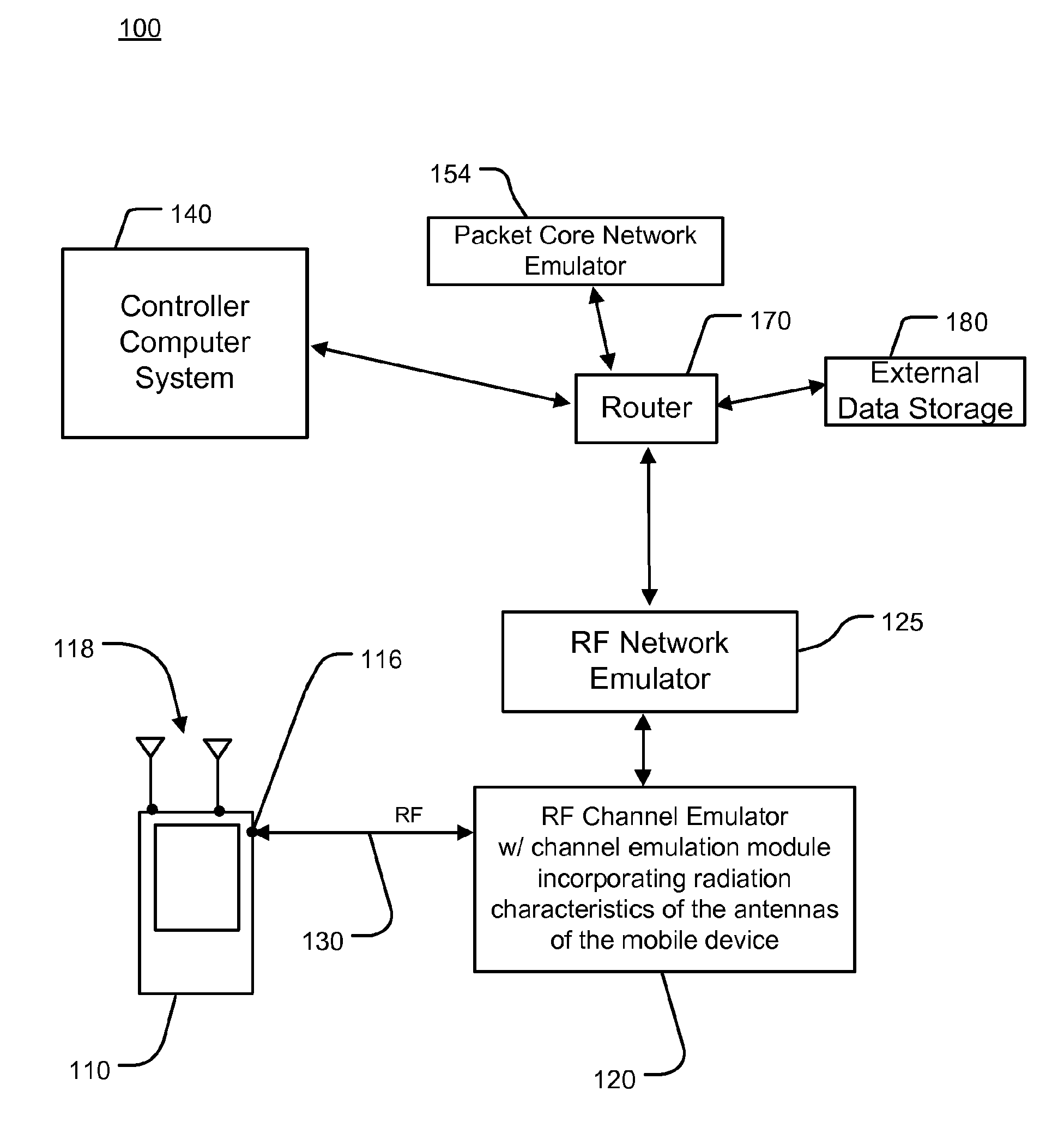

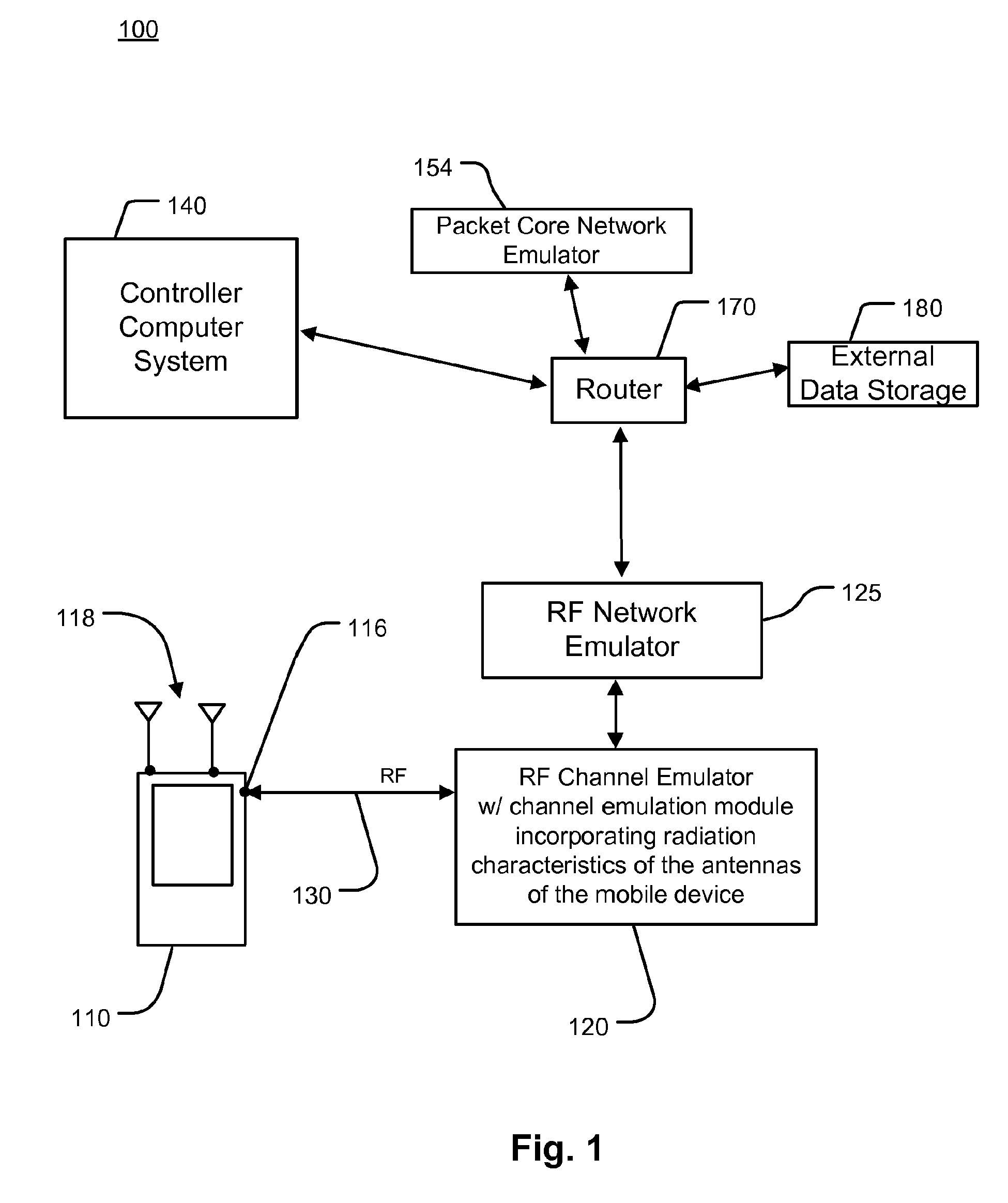

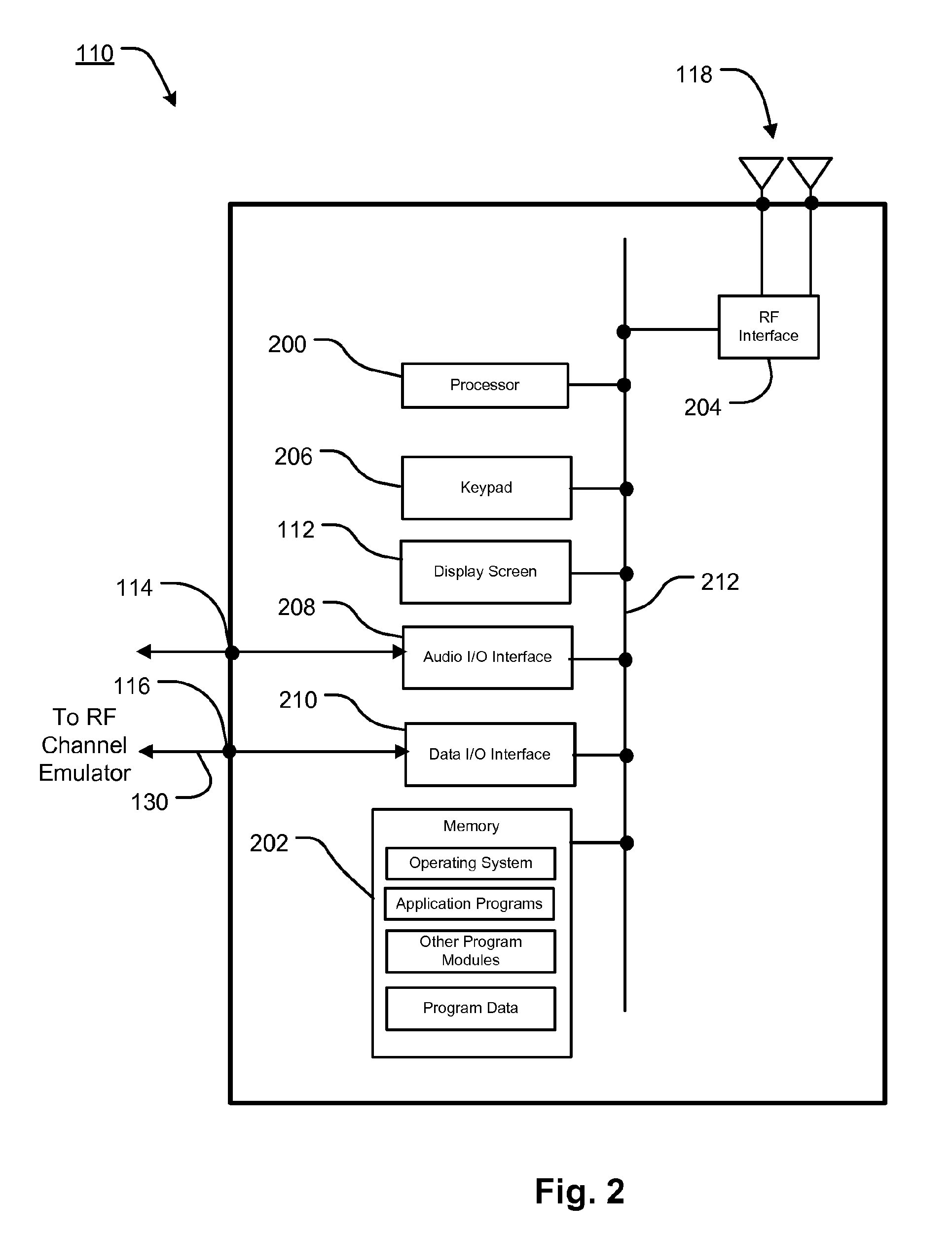

Method and Apparatus for Virtual Desktop OTA

ActiveUS20110306306A1Accurate measurementEasy to useTransmission monitoringWireless communicationEngineeringAnechoic chamber

The present invention relates to testing a mobile device in a lab by providing test signals to the mobile device via a cabled connection which bypasses the actual physical antennas in the mobile device. The test signals emulate a wireless channel and incorporate representative and / or actual measured characteristics of the performance of the antennas in the mobile device. As such, the performance mobile device can be accurately measured without requiring placement in an anechoic chamber, which enables efficient testing over a large set of configurations and underlying conditions.

Owner:SPIRENT COMM

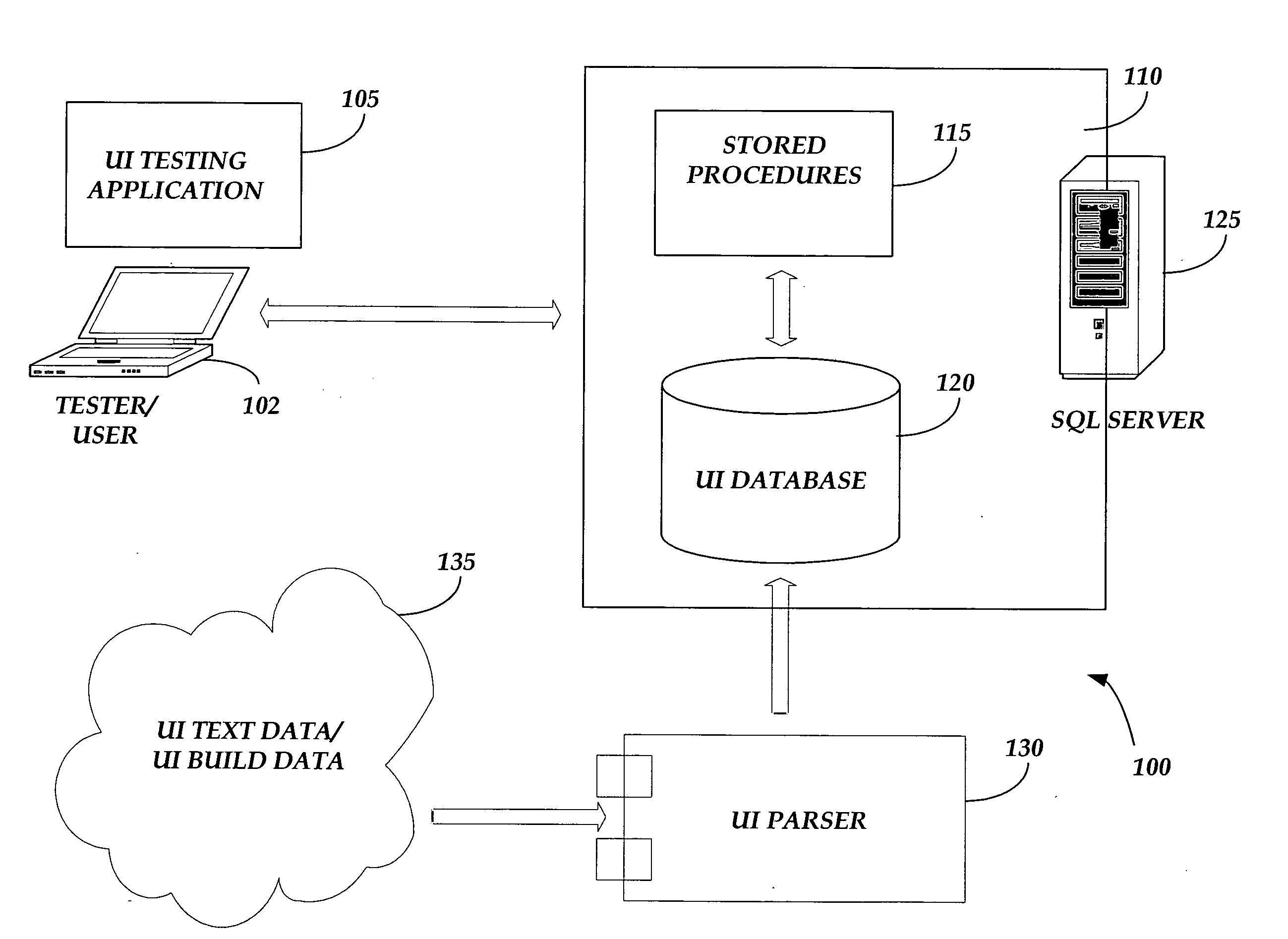

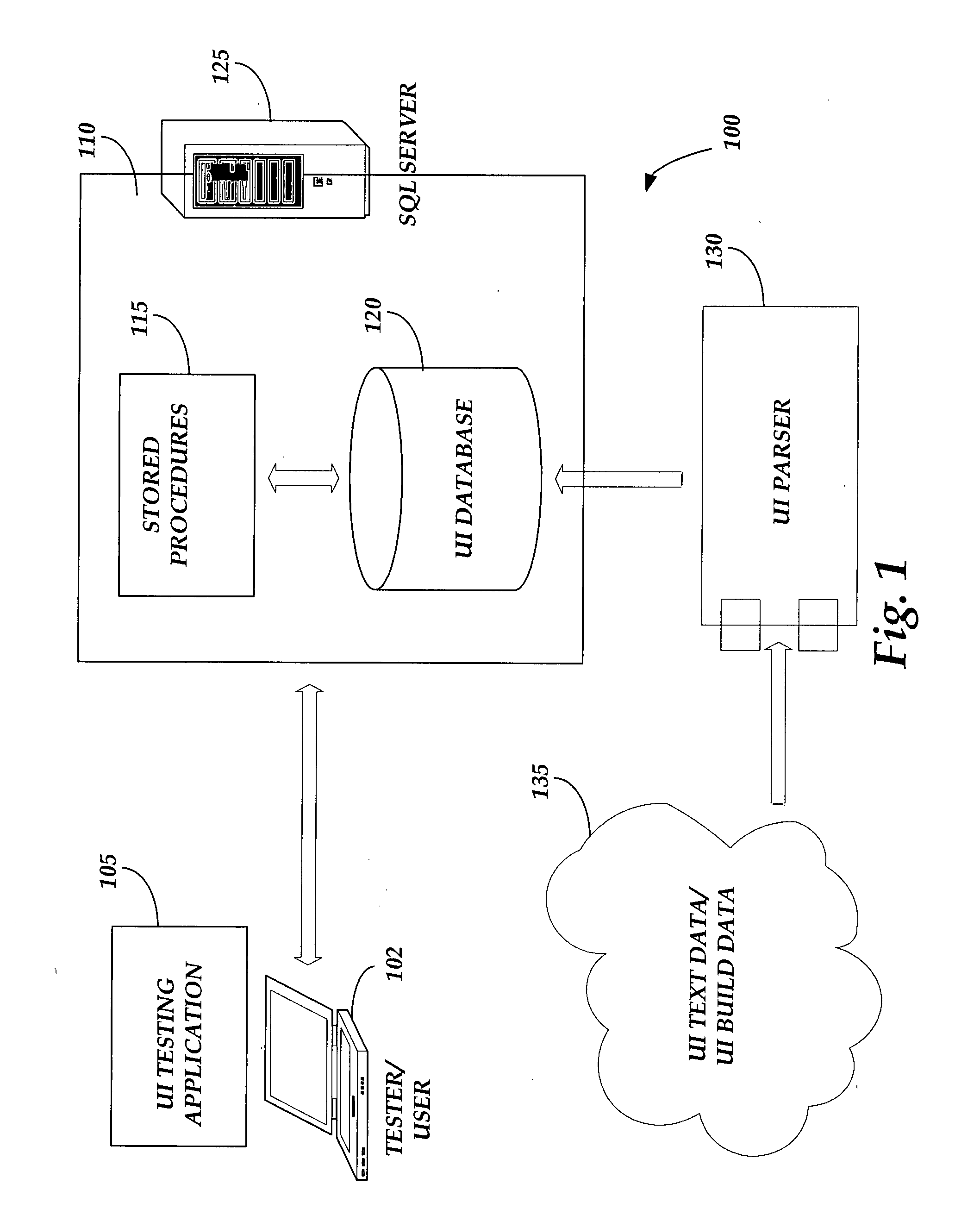

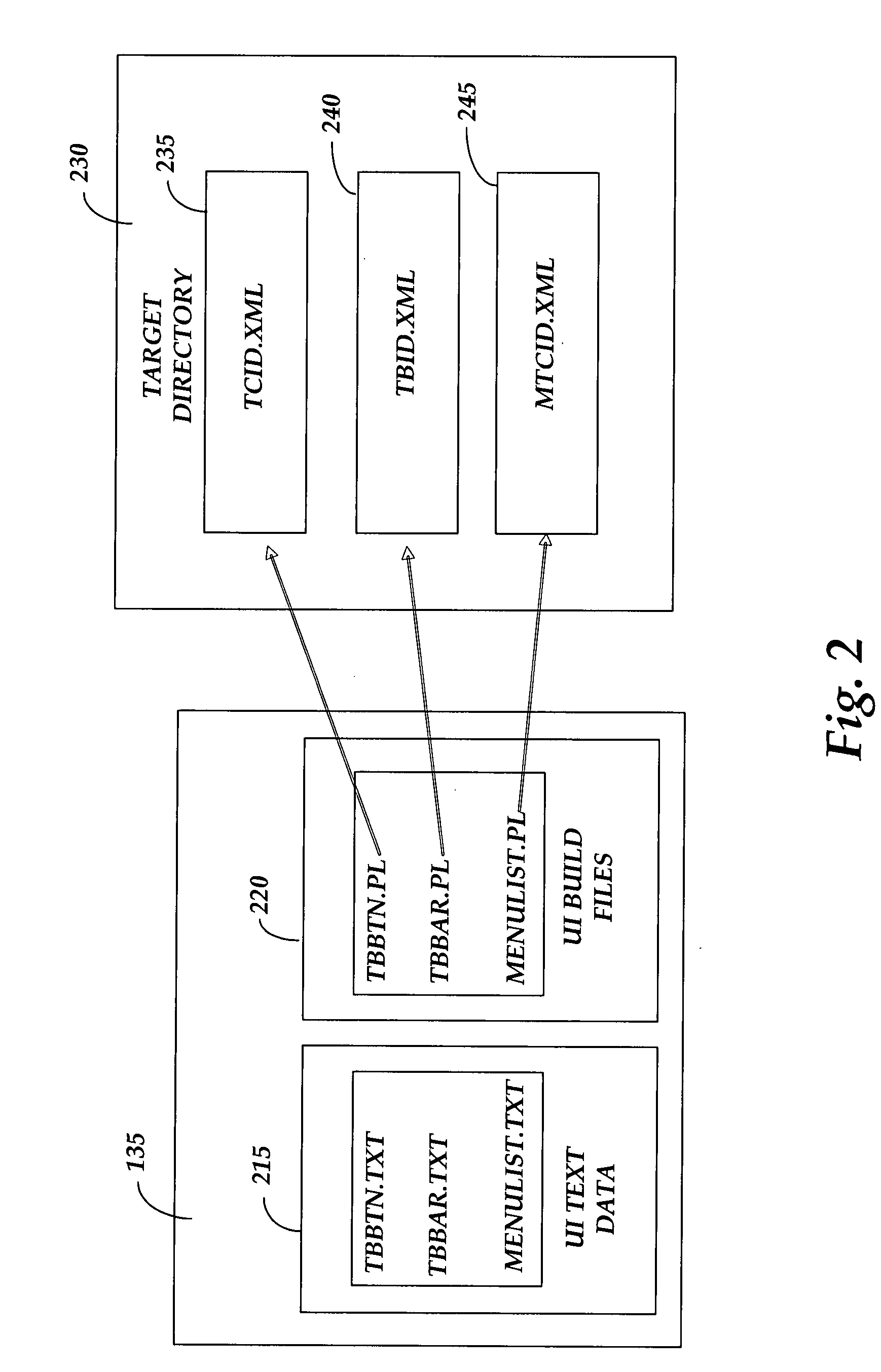

Graphical user interface testing

InactiveUS20080295076A1Efficient testingSoftware testing/debuggingExecution for user interfacesGraphicsGraphical user interface

Graphical user interface testing is provided. User interface (UI) build data and text data are transformed into a testable data format, such as XML, by a UI parser. The transformed UI data may be stored to a backend server where stored procedures and functions may be utilized to analyze the UI data against build differencing procedures, command mapping procedures, comparison to previous or subsequent user interface builds, etc. Additional stored procedures may allow UI testers to query data, create test suites and record testing information for a given UI. A front end testing module may provide a testing user an interface to query the backend database for information on various UI components and to review results for tests conducted on UI data. The front end testing module may also provide an interface for allowing testers to generate and execute new tests for a given user interface.

Owner:MICROSOFT TECH LICENSING LLC

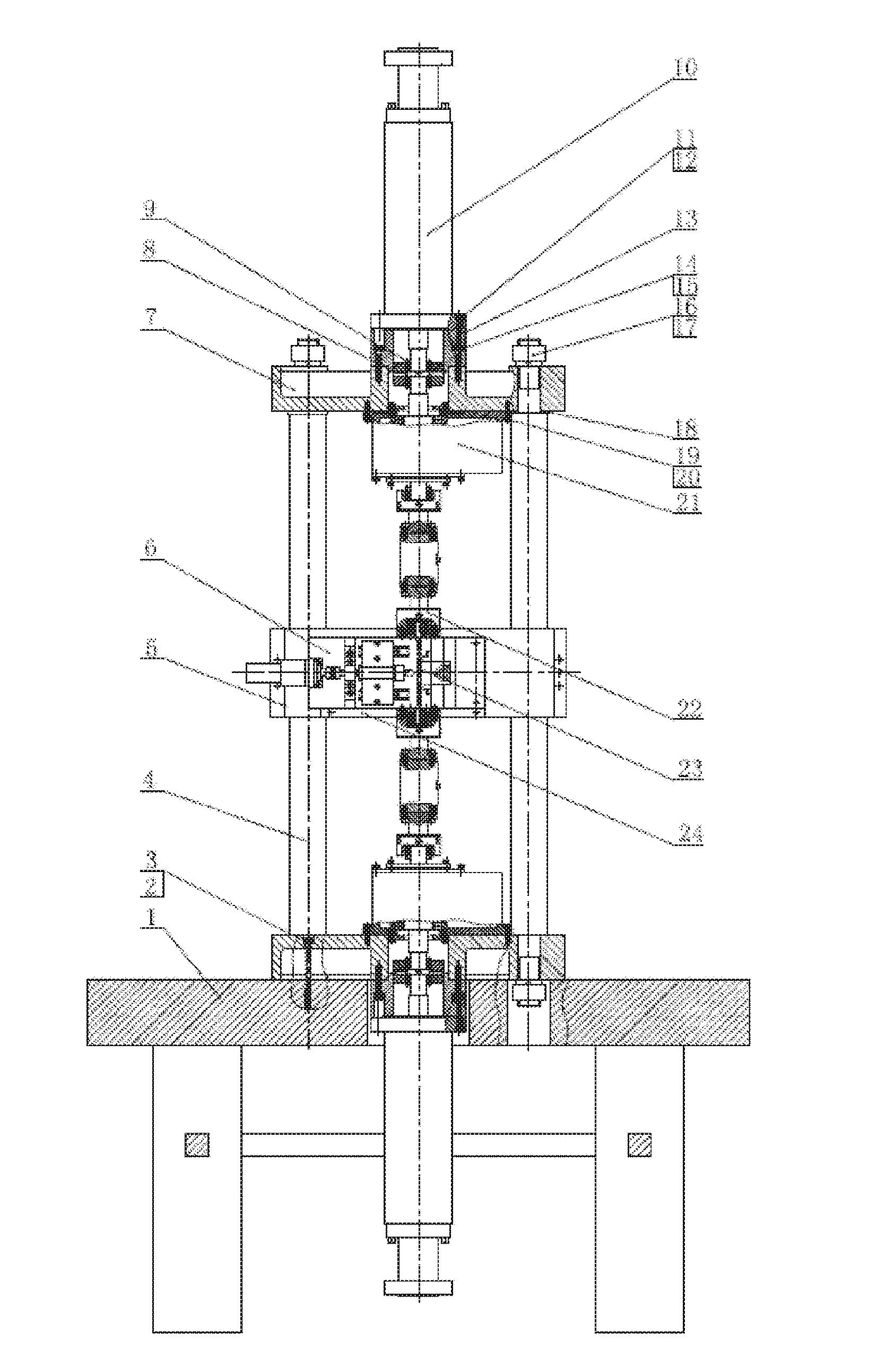

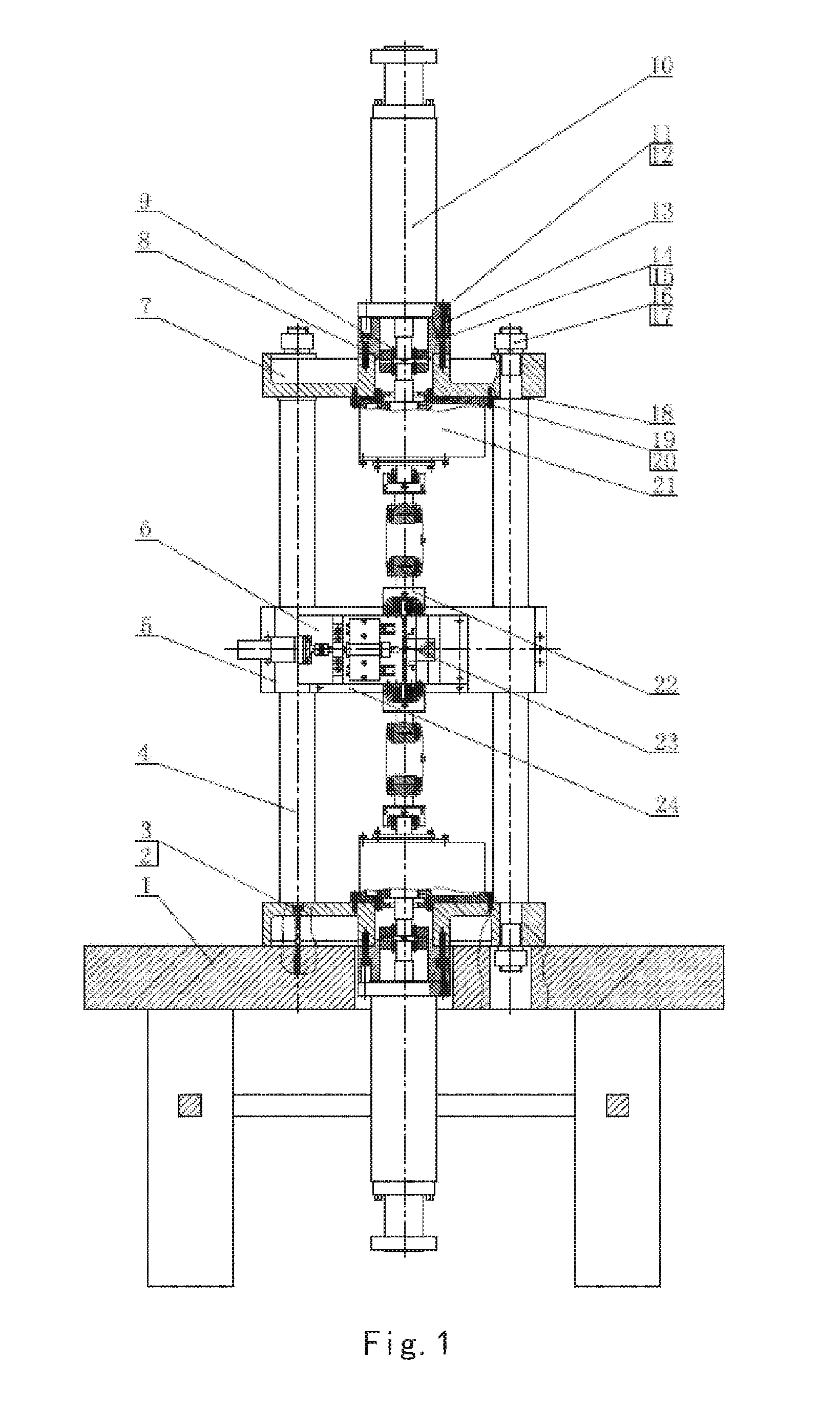

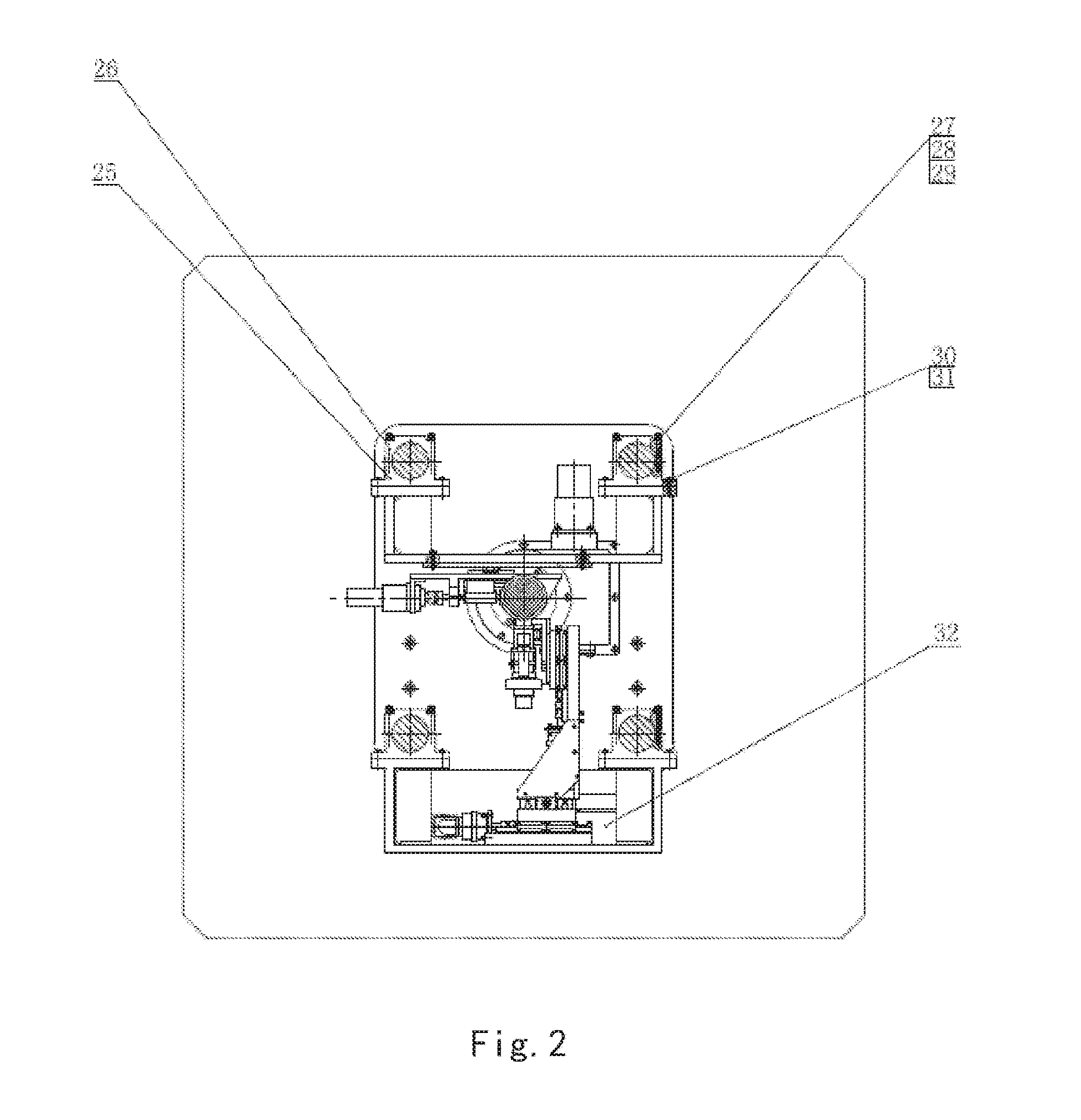

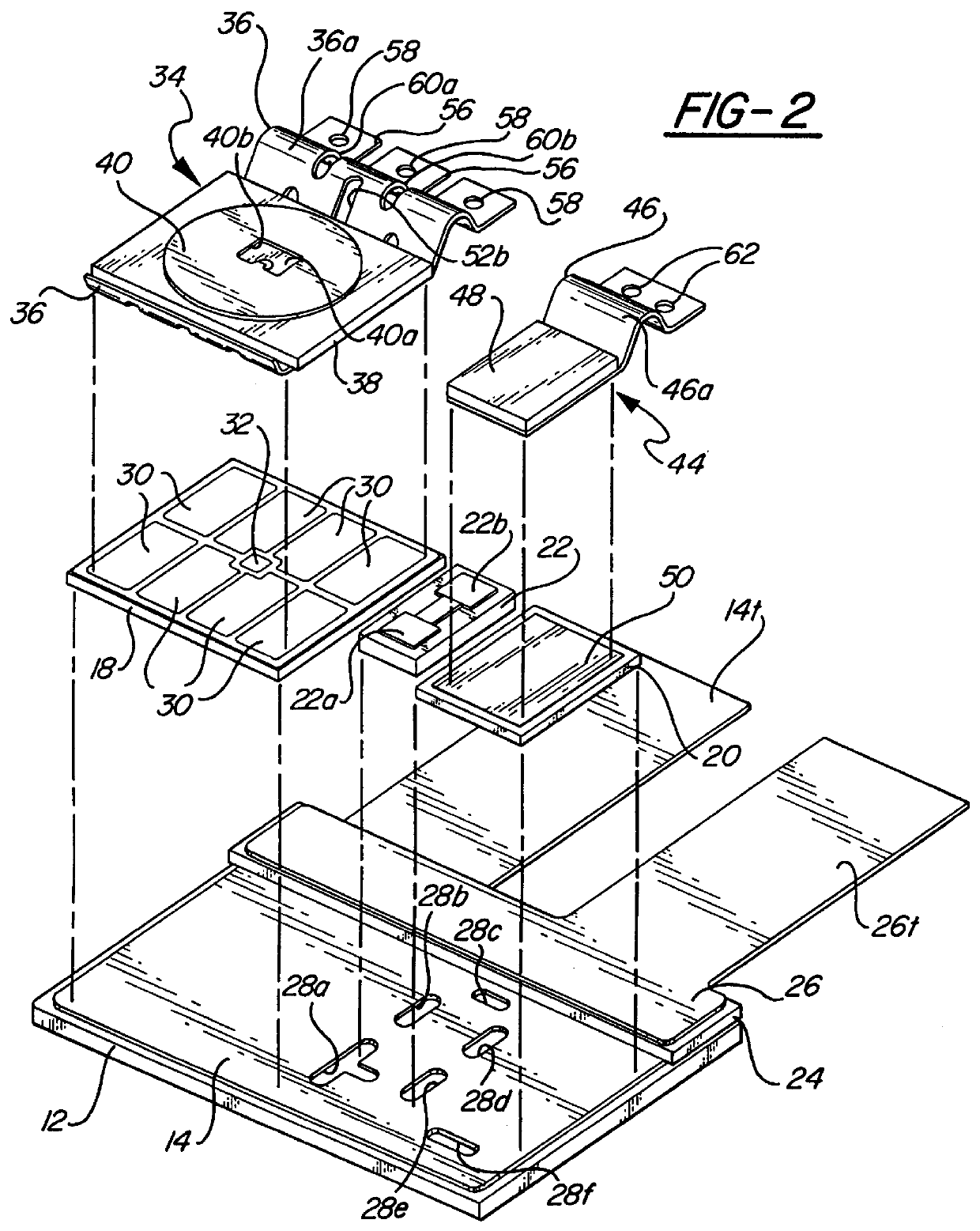

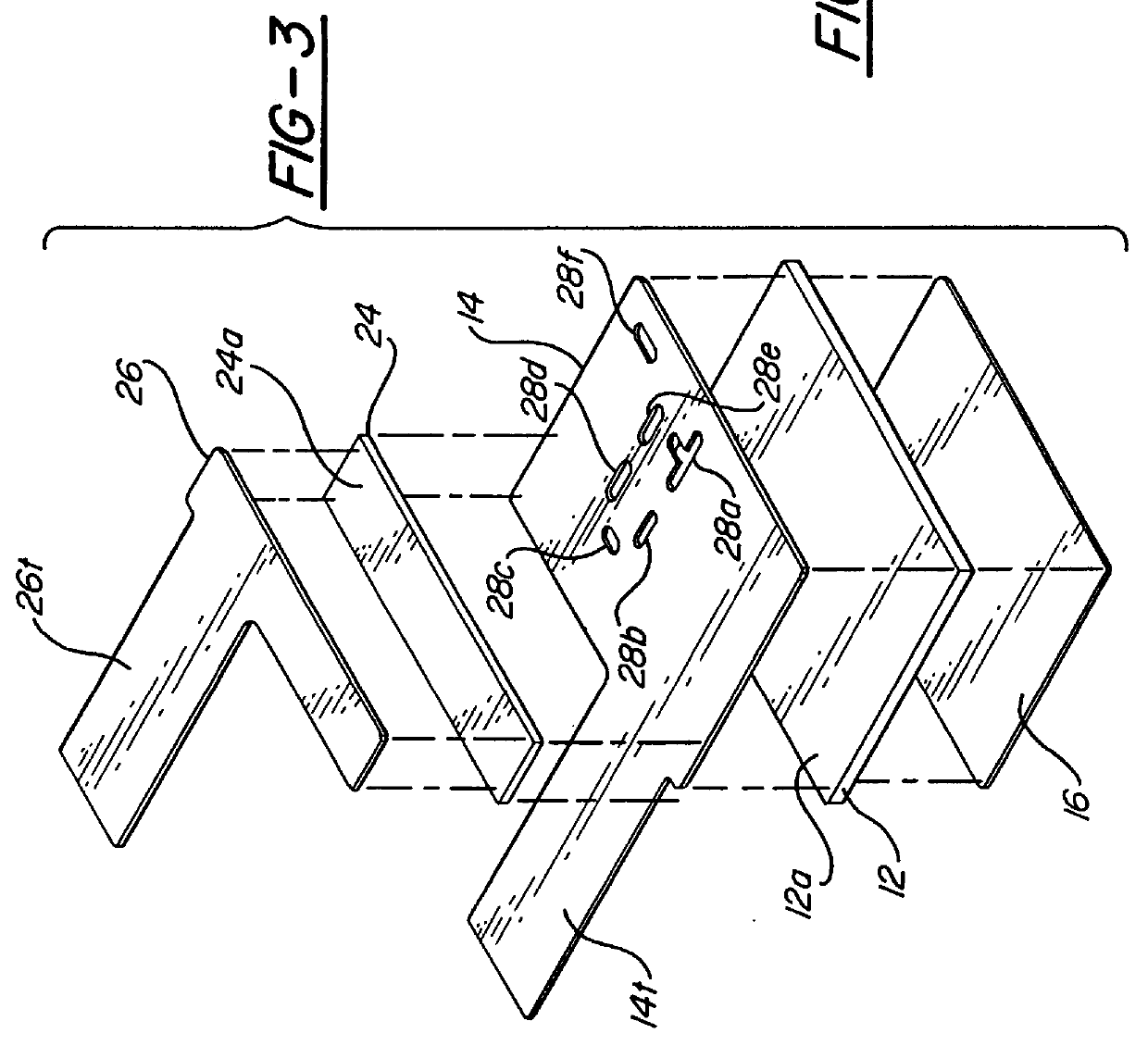

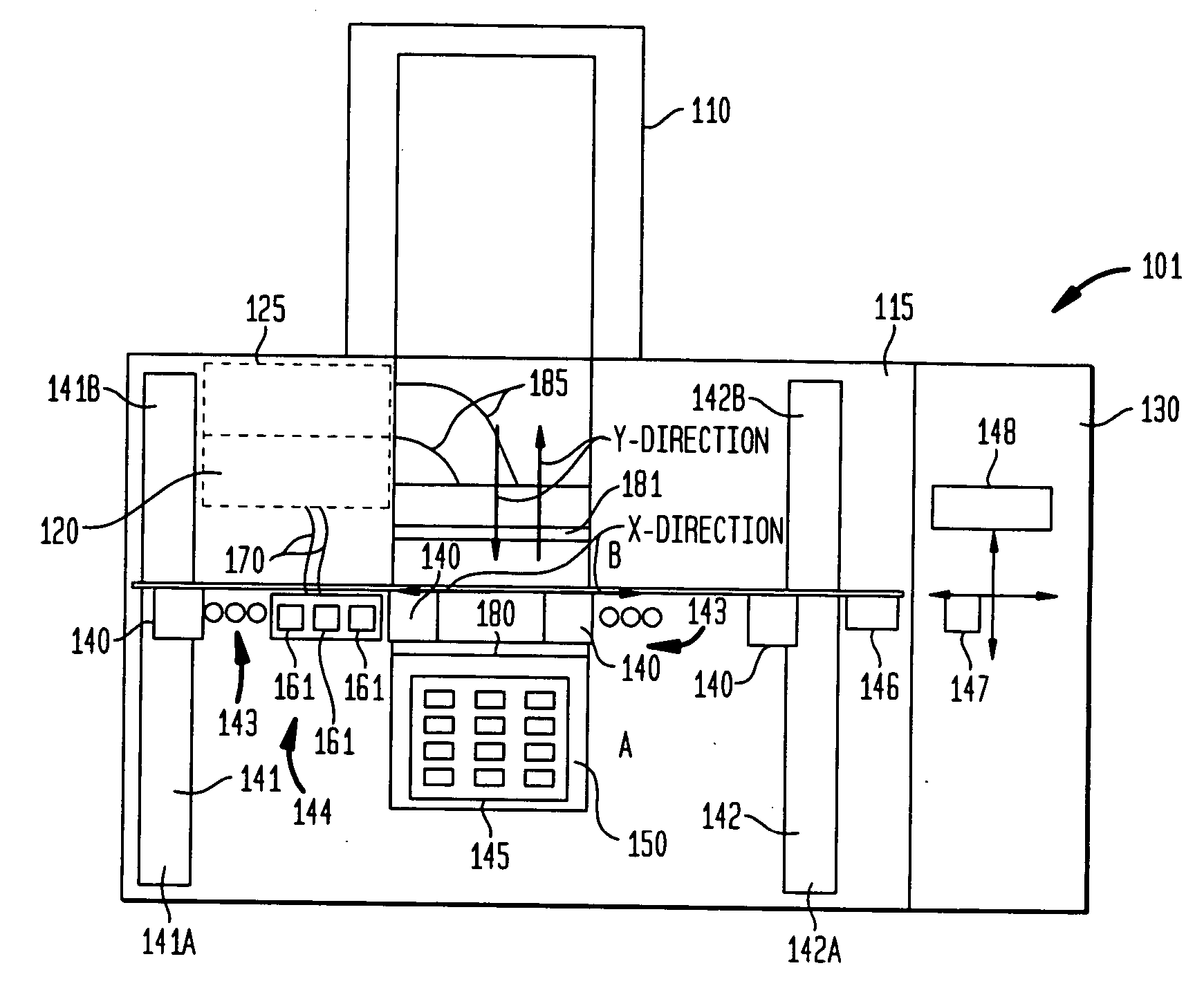

In-situ testing equipment for testing micromechanical properties of material in multi-load and multi-physical field coupled condition

ActiveUS20160216182A1Innovative structureEffective testingMaterial strength using tensile/compressive forcesMaterial strength using steady bending forcesTesting equipmentTest material

An in-situ testing equipment for testing micromechanical properties of a material in a multi-load and multi-physical field coupled condition is disclosed. The equipment comprises a frame supporting module, a tension / compression-low cycle fatigue module, a torsioning module (21), a three-point bending module (6), an impressing module (33), a thermal field and magnetic field application module (34), an in-situ observation module (32) and a clamp body module (22). The frame supporting module provides a structural support for the whole testing equipment, the tension / compression-low cycle fatigue module is arranged at upper and lower ends of the testing equipment, the torsioning module (21) is directly arranged at a front end of the tension / compression-low cycle fatigue module, the three-point bending module (6), the impressing module (33) and the thermal field and magnetic field application module (34) are disposed on a support post at one side of the whole testing equipment through a common replacing component, and the in-situ observation module is disposed on another support post at the other side of the testing equipment. The clamp body module is connected to a front segment of the torsioning module, so as to clamp a test piece. An overall structure of the testing equipment is configured in a vertically symmetrical arrangement achieved by using four support posts. Two identical servo hydraulic cylinders (10) and two torsioning modules (21) are located at the upper and the lower ends of the testing equipment respectively and are used to perform a symmetrical tension / compression test and a symmetrical torsion test on the test piece (23) positioned centrally. The testing equipment is capable of realizing applications of five different types of loads including tension / compression, low cycle fatigue, torsion, bending and impressing, performing an intensive study on micromechanical properties of the material in the multi-load and multi-physical field coupled condition by using built-in electric, thermal and magnetic application modules and the in-situ observation module, and acquiring relations between deformation behavior, mechanism of damage, performance weakening of the material, applied loads and material properties.

Owner:JILIN UNIV

Probe card assembly including a programmable device to selectively route signals from channels of a test system controller to probes

InactiveUS7245134B2High densityLong life cycleSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsProbe cardTest engineer

Owner:FORMFACTOR INC

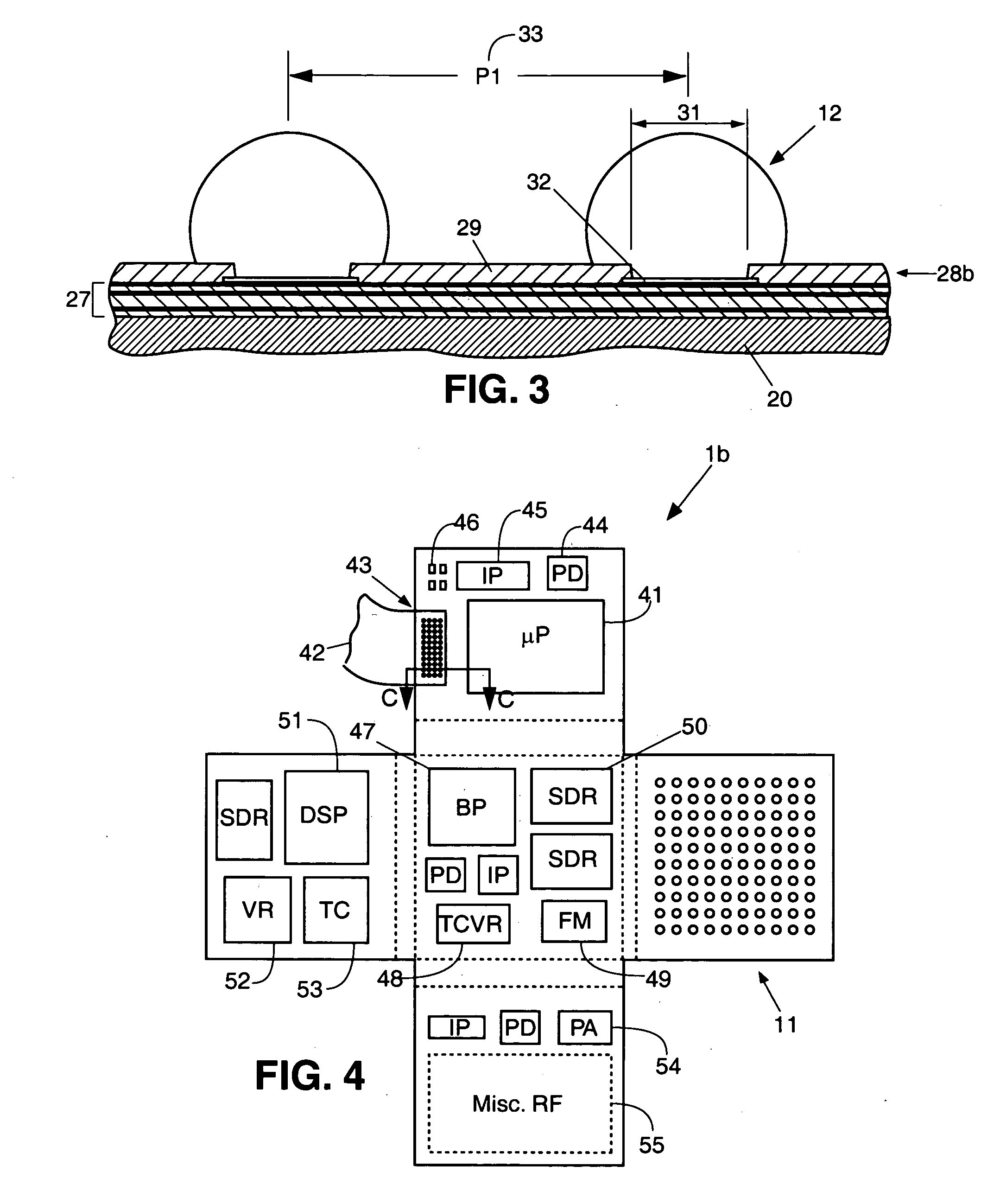

Semiconductor substrate subassembly with alignment and stress relief features

InactiveUS6127727ALow parasitic impedanceEnhance cancellationSemiconductor/solid-state device detailsSolid-state devicesSolderingElectrical conductor

A composite conductor for contacting a semiconductor device chip. A durable substrate subassembly for a high power transistor switching modules. The substrate subassembly is durable because wire bonds to the semiconductor device electrodes are replaced with a soldered metal / ceramic composite conductor. The part of the composite conductor contacting the semiconductor device has a coefficient of thermal expansion close to that of the semiconductor device. The substrate in the substrate subassembly has automatic alignment features. The composite conductor also has automatic alignment features, along with stress relief features. Automatic alignment permits concurrent soldering of the chip to the substrate, and the composite conductor to the chip and to a terminal contact.

Owner:DELPHI TECH IP LTD

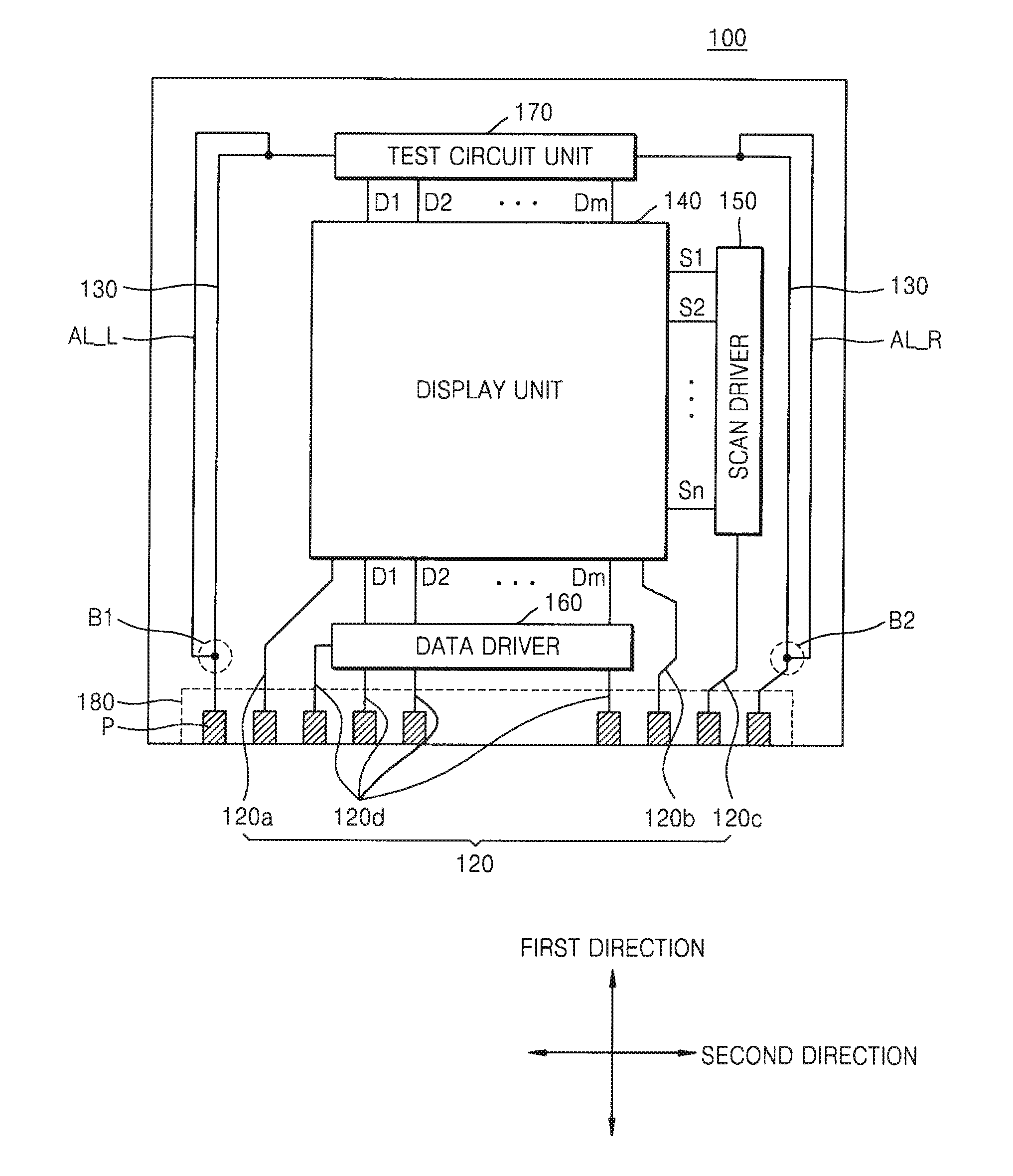

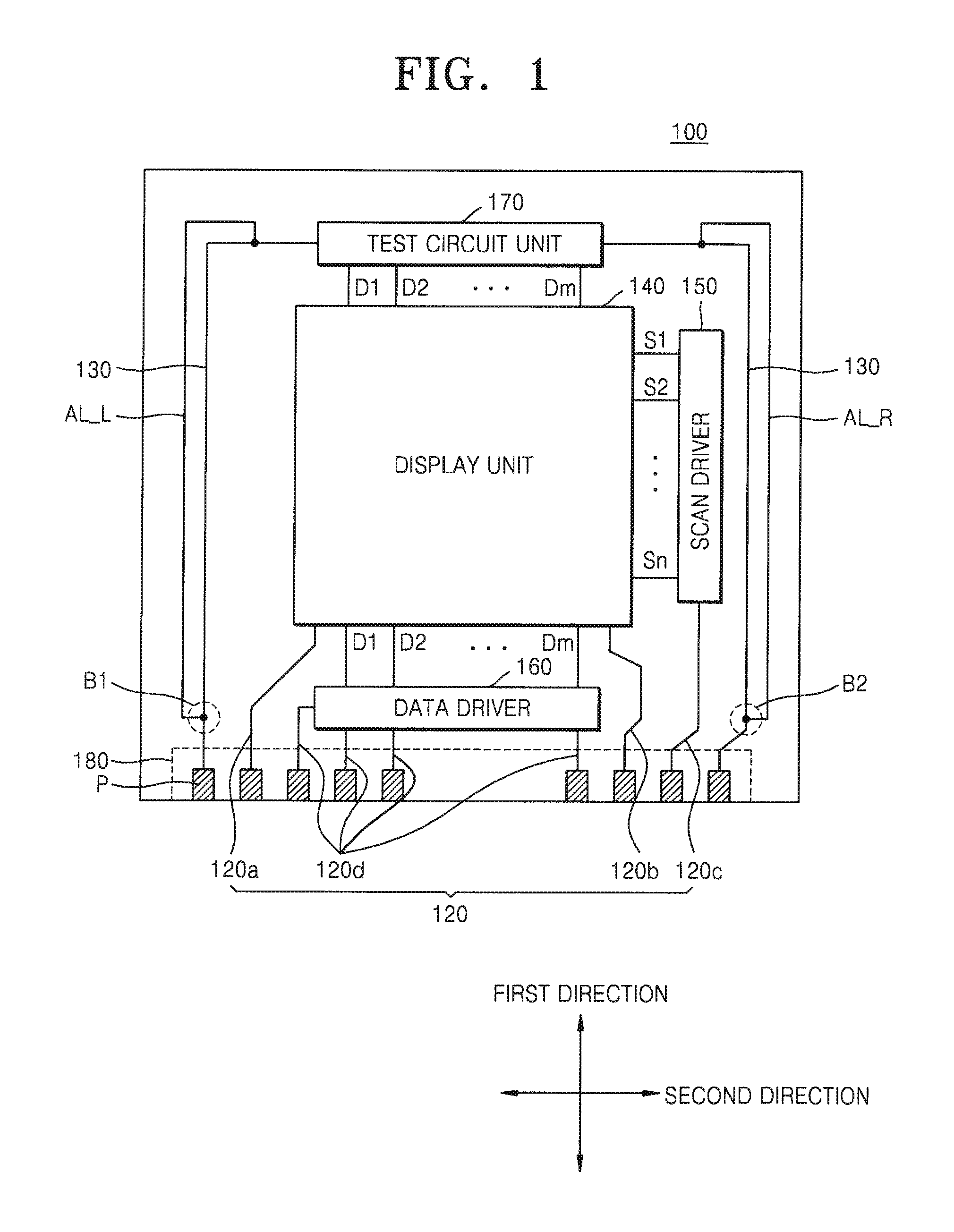

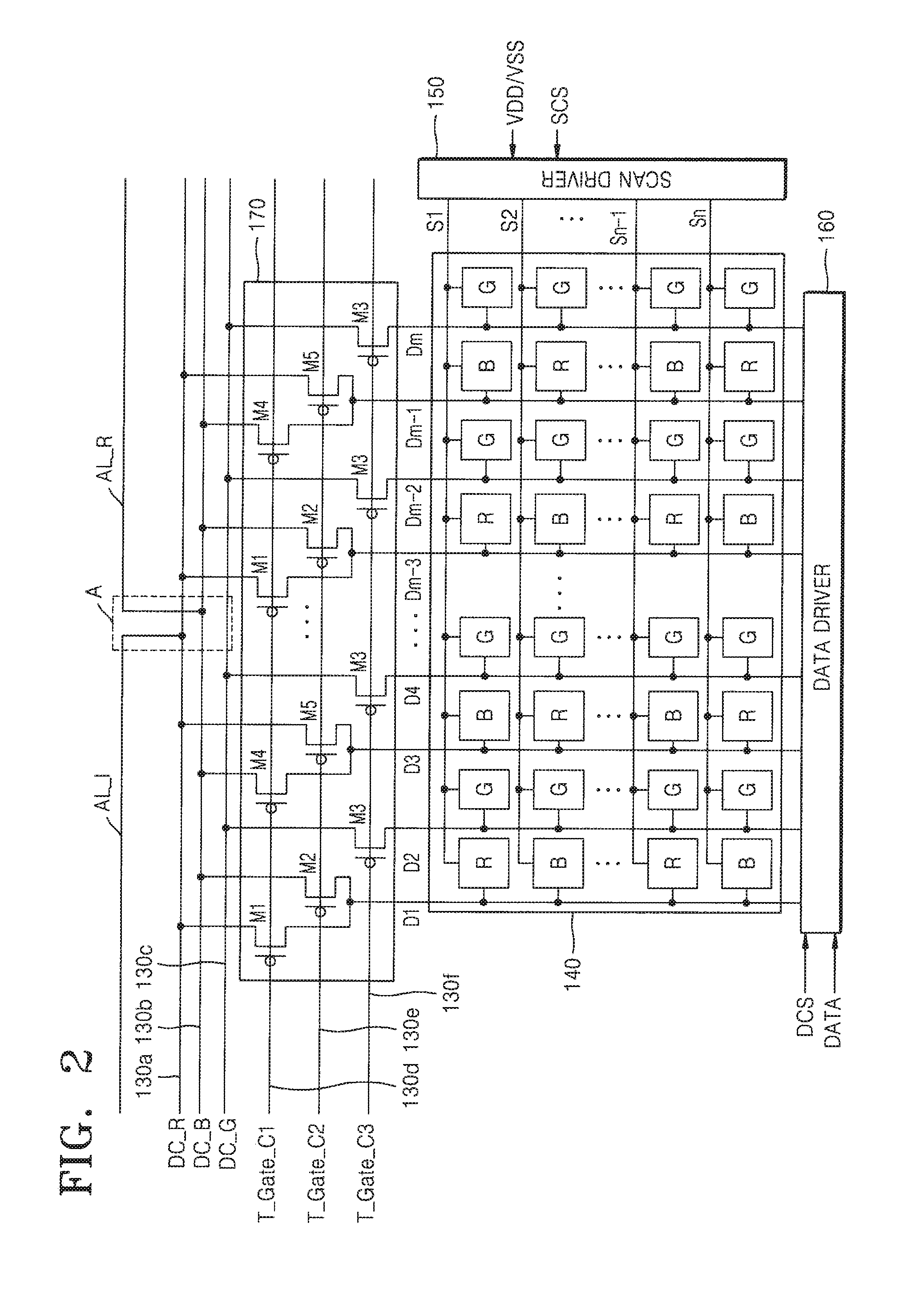

Organic light emitting display panel

ActiveUS20140240521A1High resolution imageEfficient testingStatic indicating devicesTelevision systemsScan lineEngineering

An organic light emitting display panel includes a display unit at crossing regions of scan lines and data lines, the display unit including a plurality of pixels configured to display different colors, the pixels being arranged in a pattern; a test circuit configured to apply a test signal to the plurality of pixels, the test circuit being coupled to one end of the data lines; and an auxiliary line adjacent to a plurality of signal lines for supplying the test signal to the test circuit and coupled to at least one of the plurality of signal lines.

Owner:SAMSUNG DISPLAY CO LTD

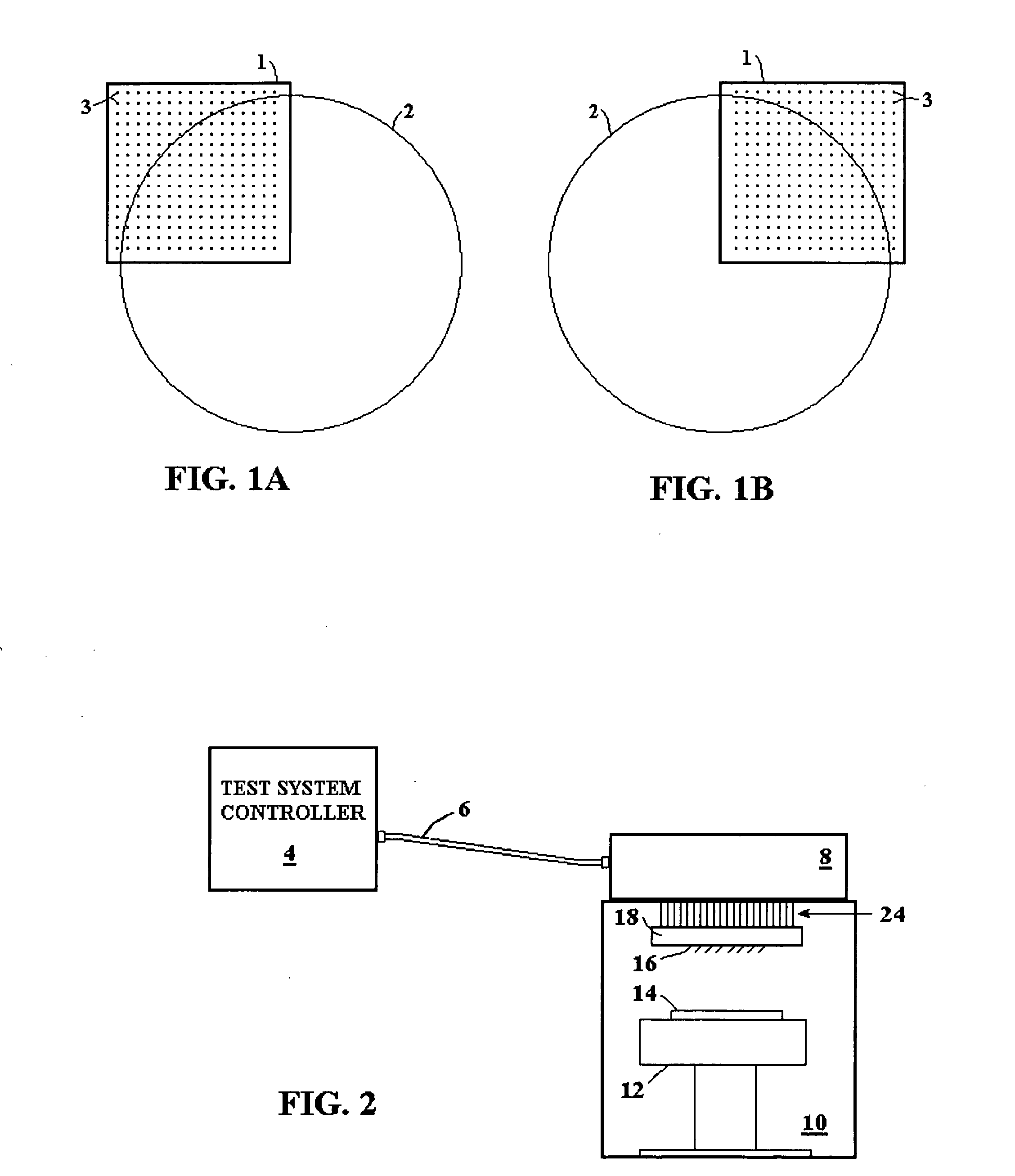

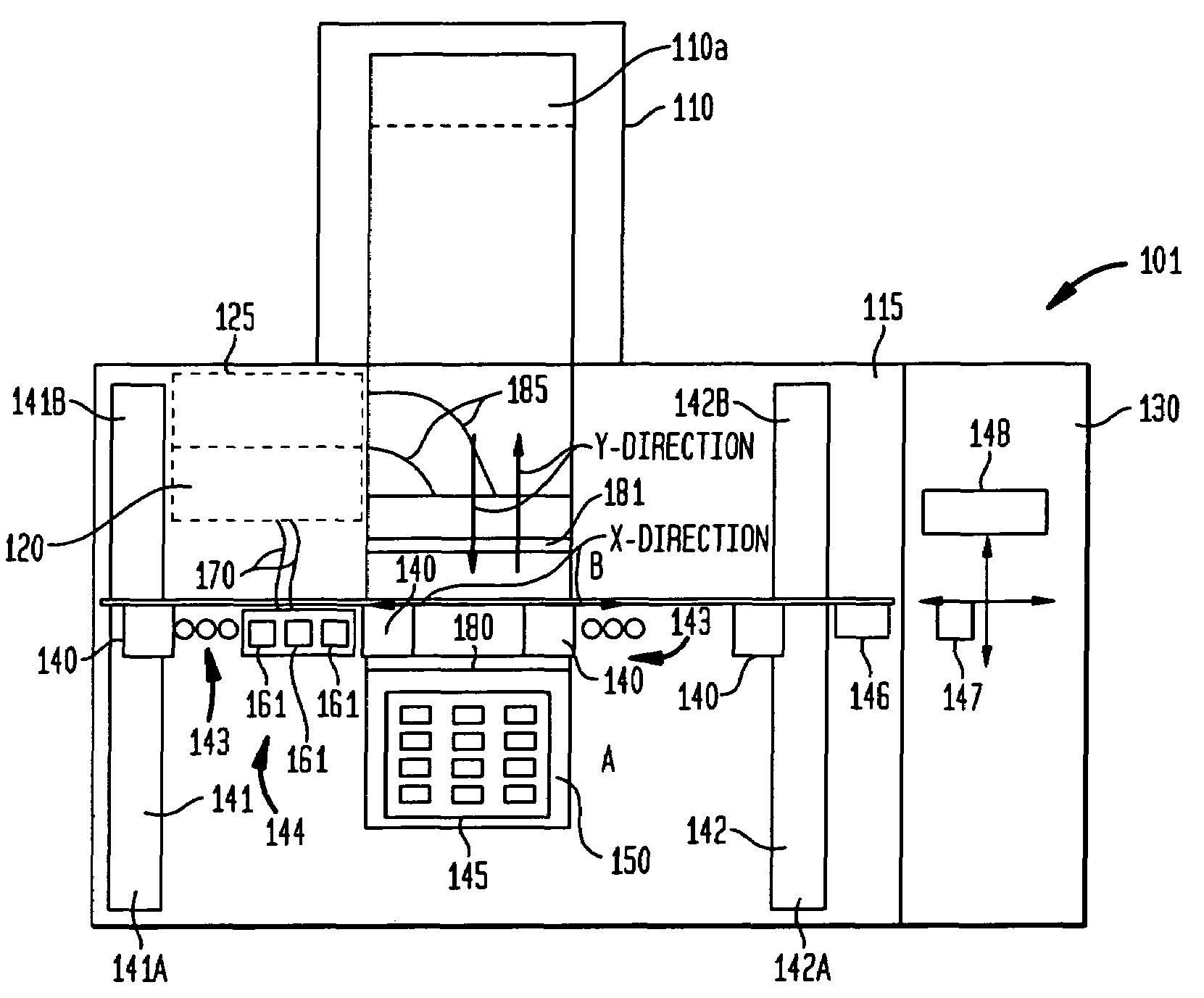

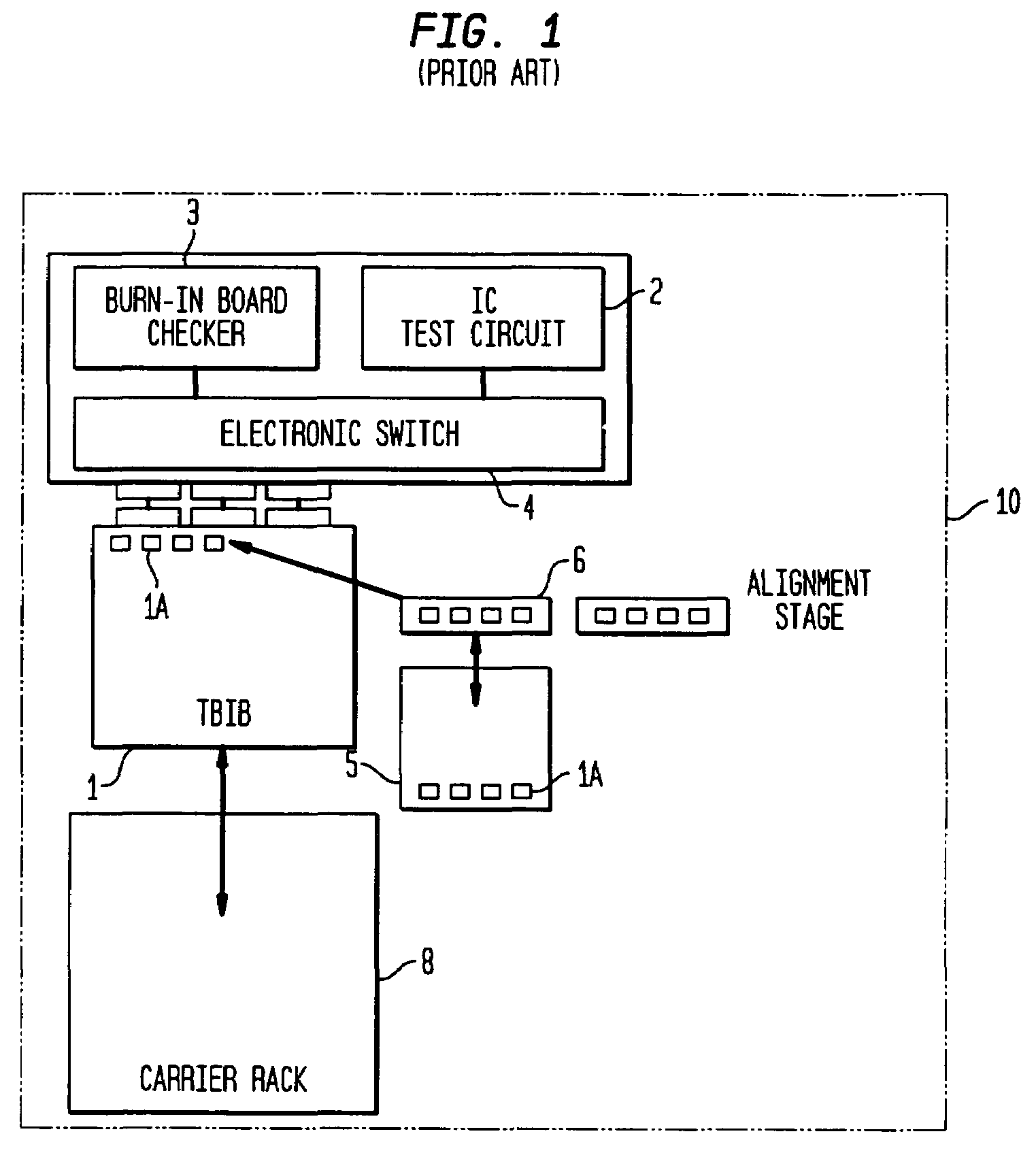

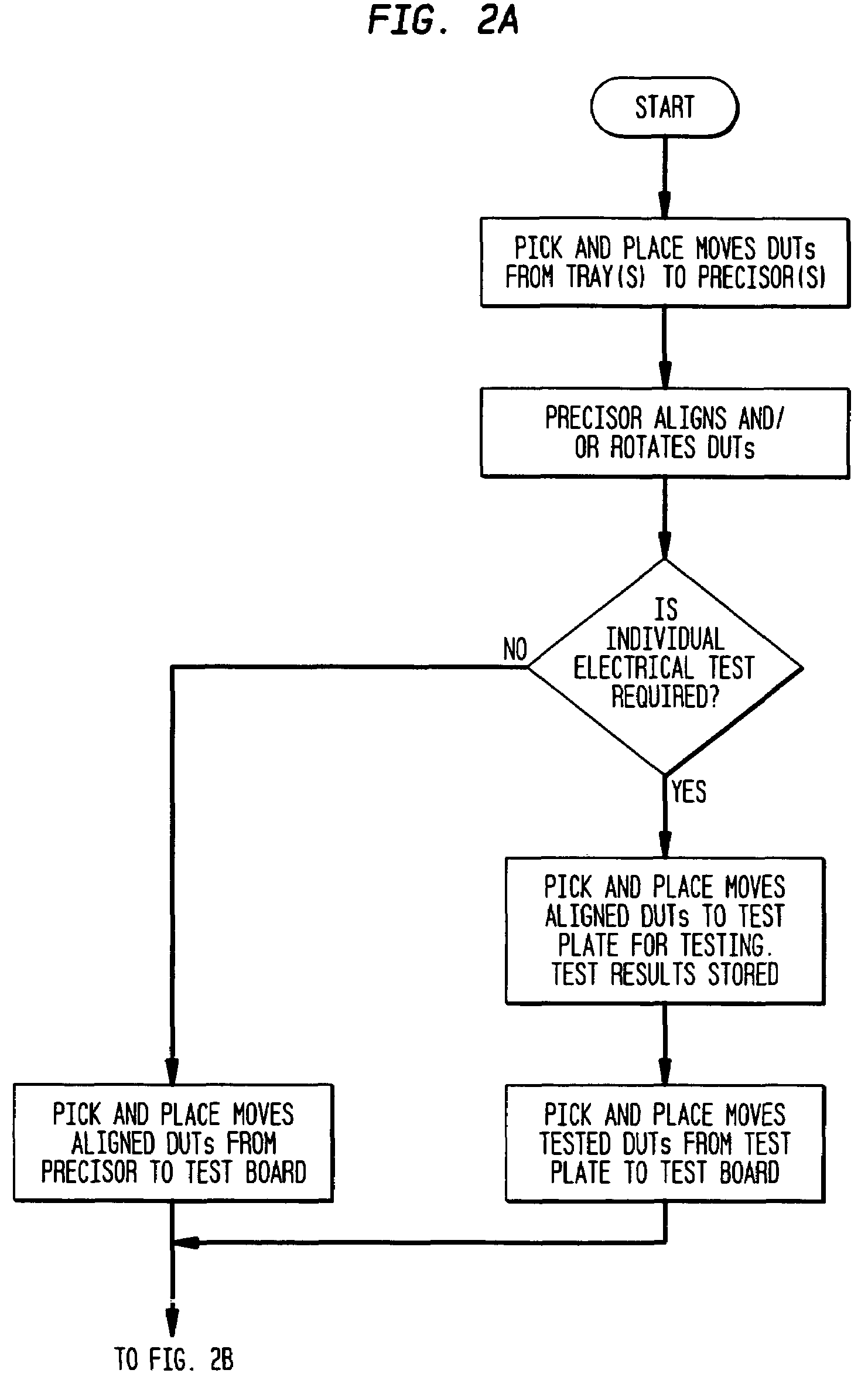

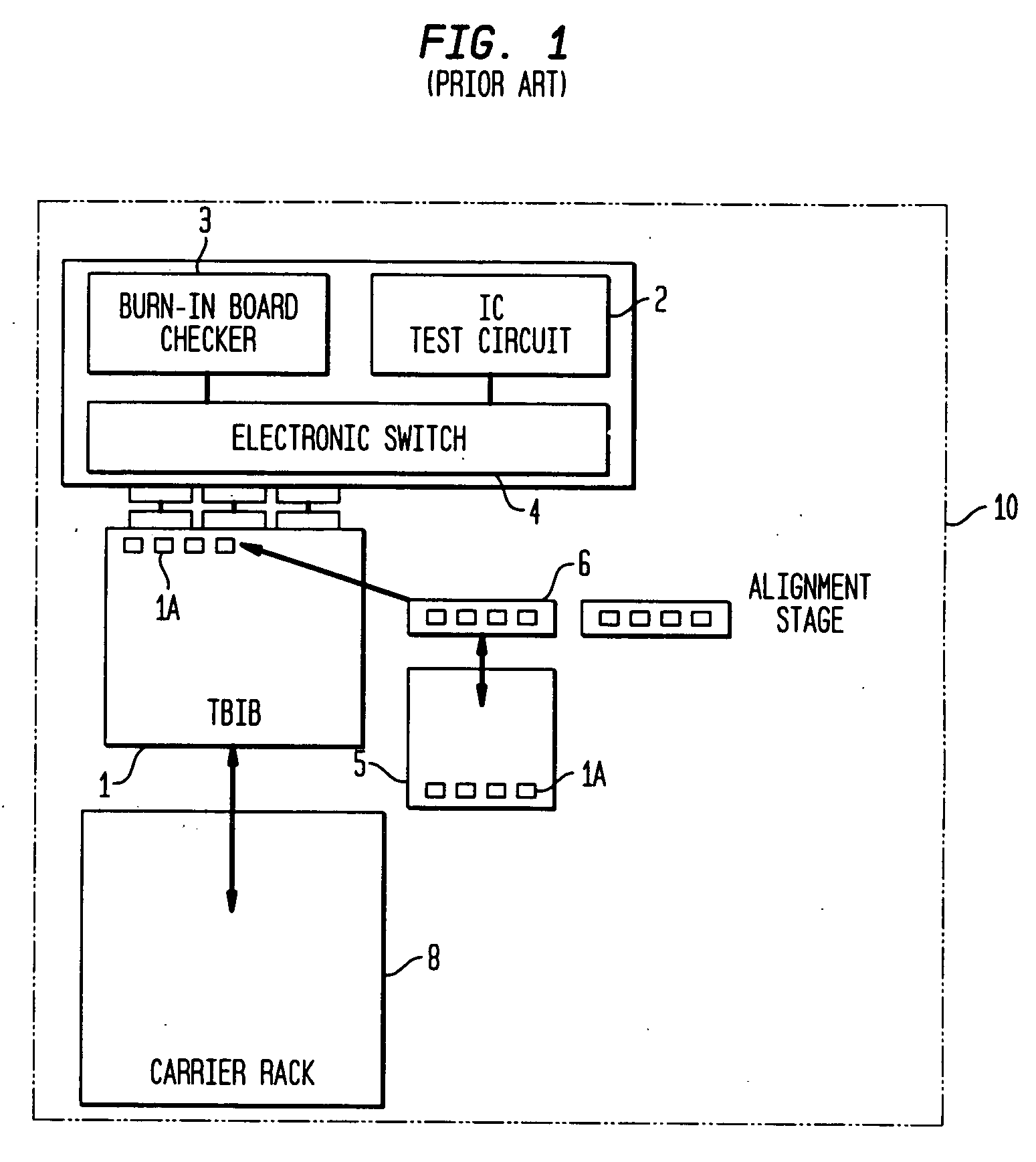

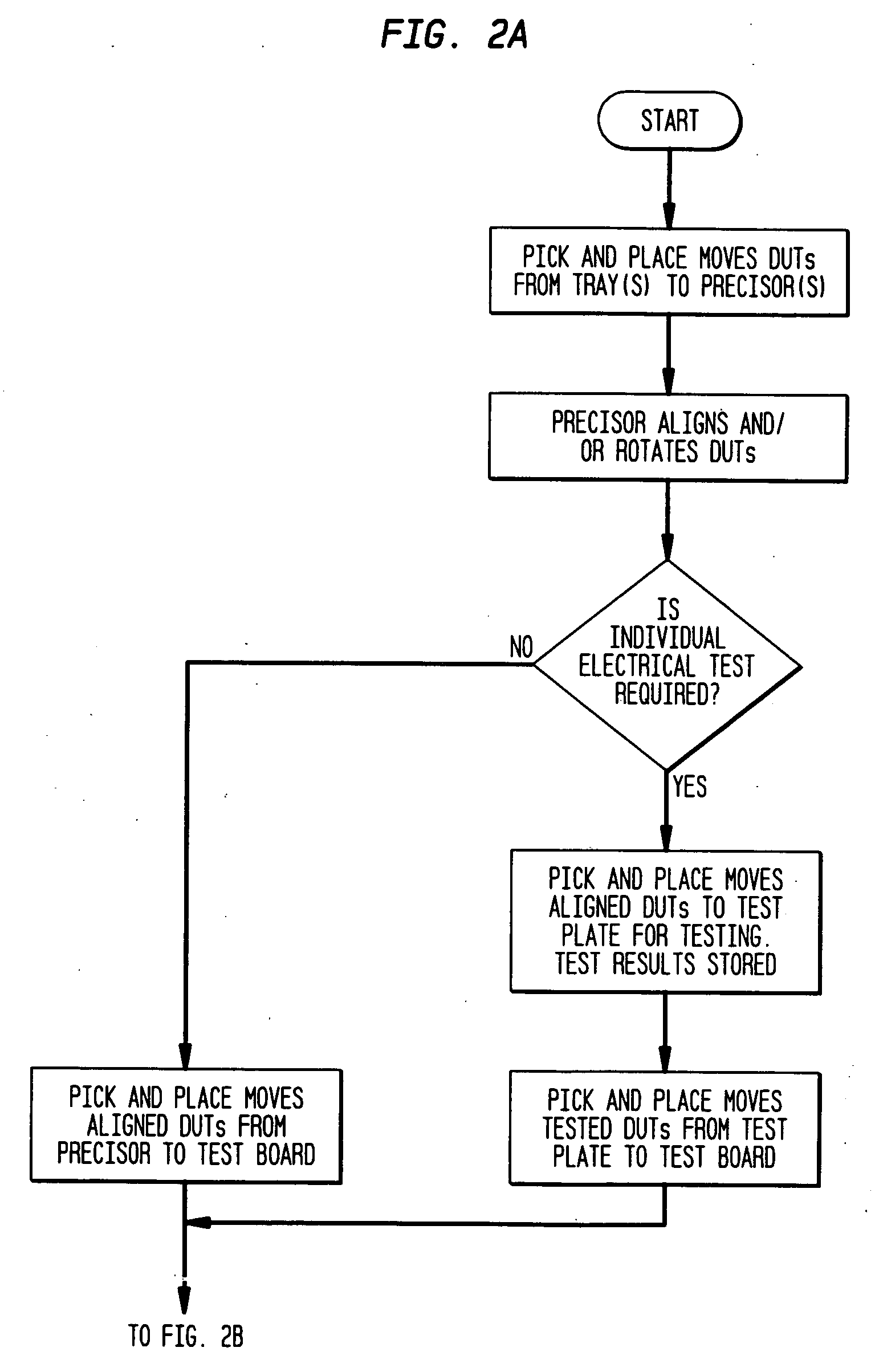

Method for testing semiconductor devices and an apparatus therefor

InactiveUS7151388B2Good flexibilityEfficient loadingSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsElectricityEngineering

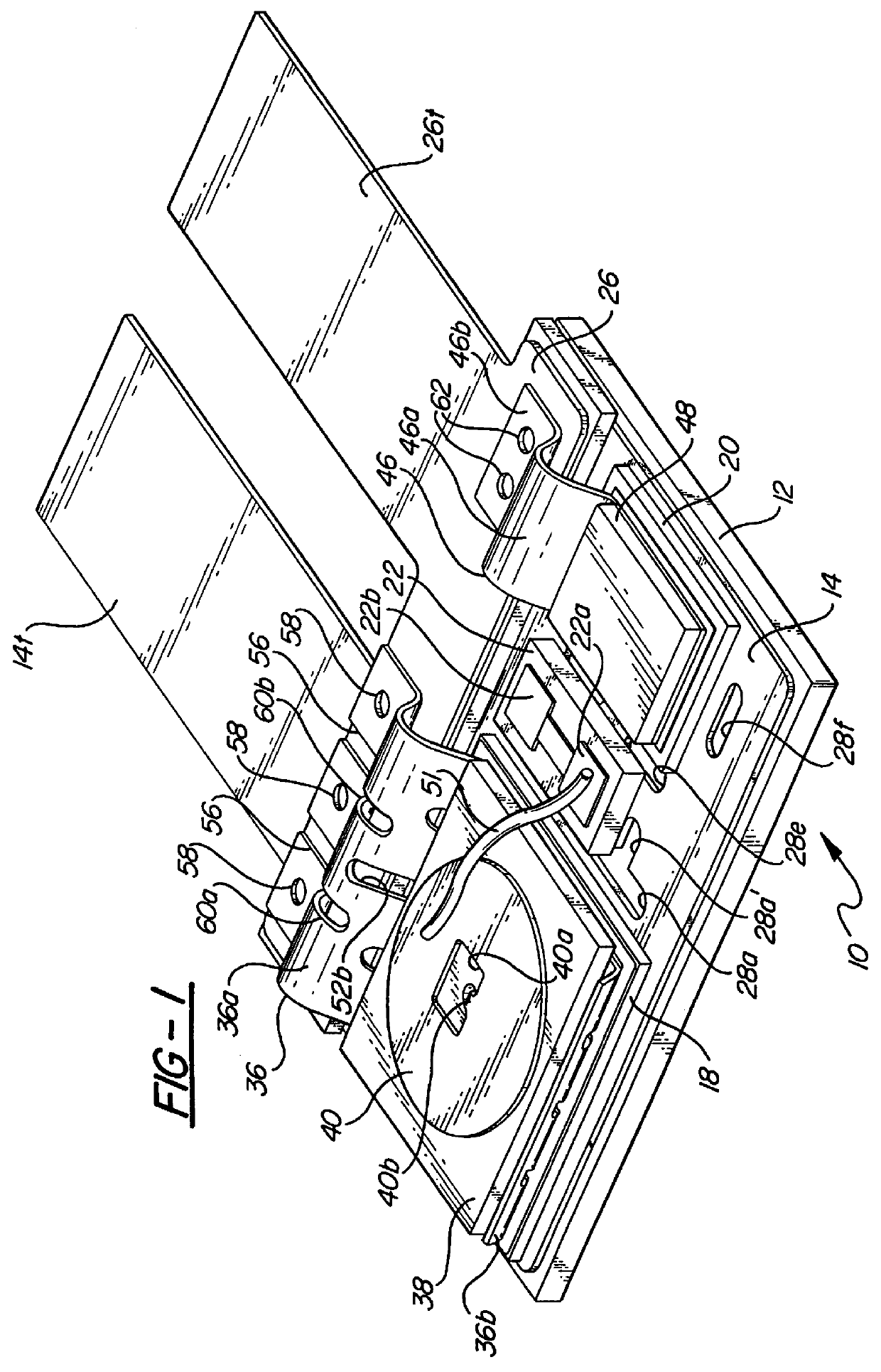

A method for testing integrated circuit devices and loading such devices into a test board for further testing and an apparatus therefor is disclosed. The method allows for selection between two modes of operation. In a first mode, the integrated circuit devices are subjected to an electrical test before being placed into the test board for further testing. In a second mode, the integrated circuit devices are tested after being placed in the test board. The apparatus allows for the selection between the first mode and the second mode. In either mode, information about the tested devices and the sockets in the test board is used to load the test boards intelligently. Intelligent loading means that devices under test (DUTs) are not placed in bad sockets and devices that do test bad are removed from the test board, with an option of replacing the failed DUT with another DUT before subsequent environmental testing of the DUTs in the test board is carried out.

Owner:KES SYST

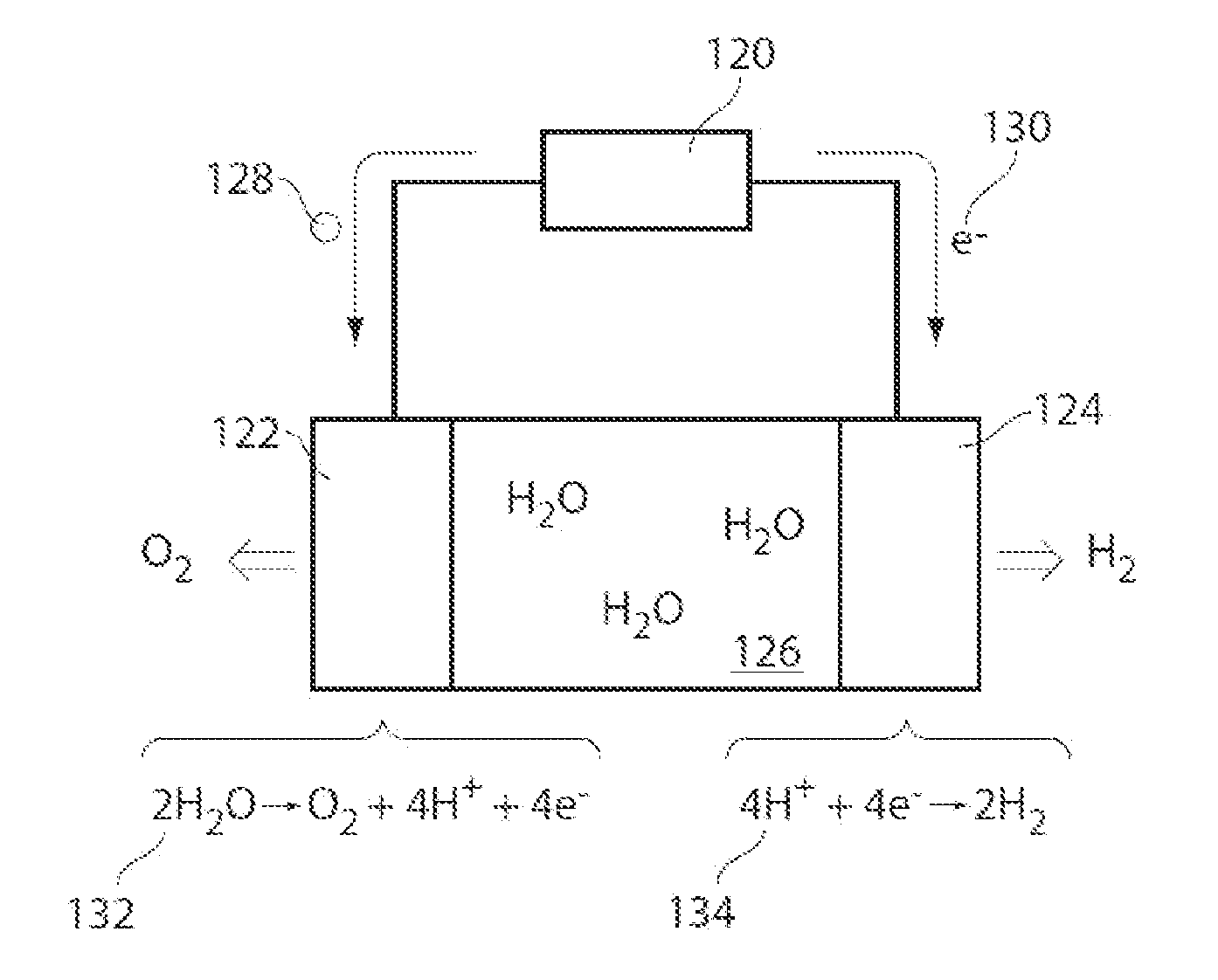

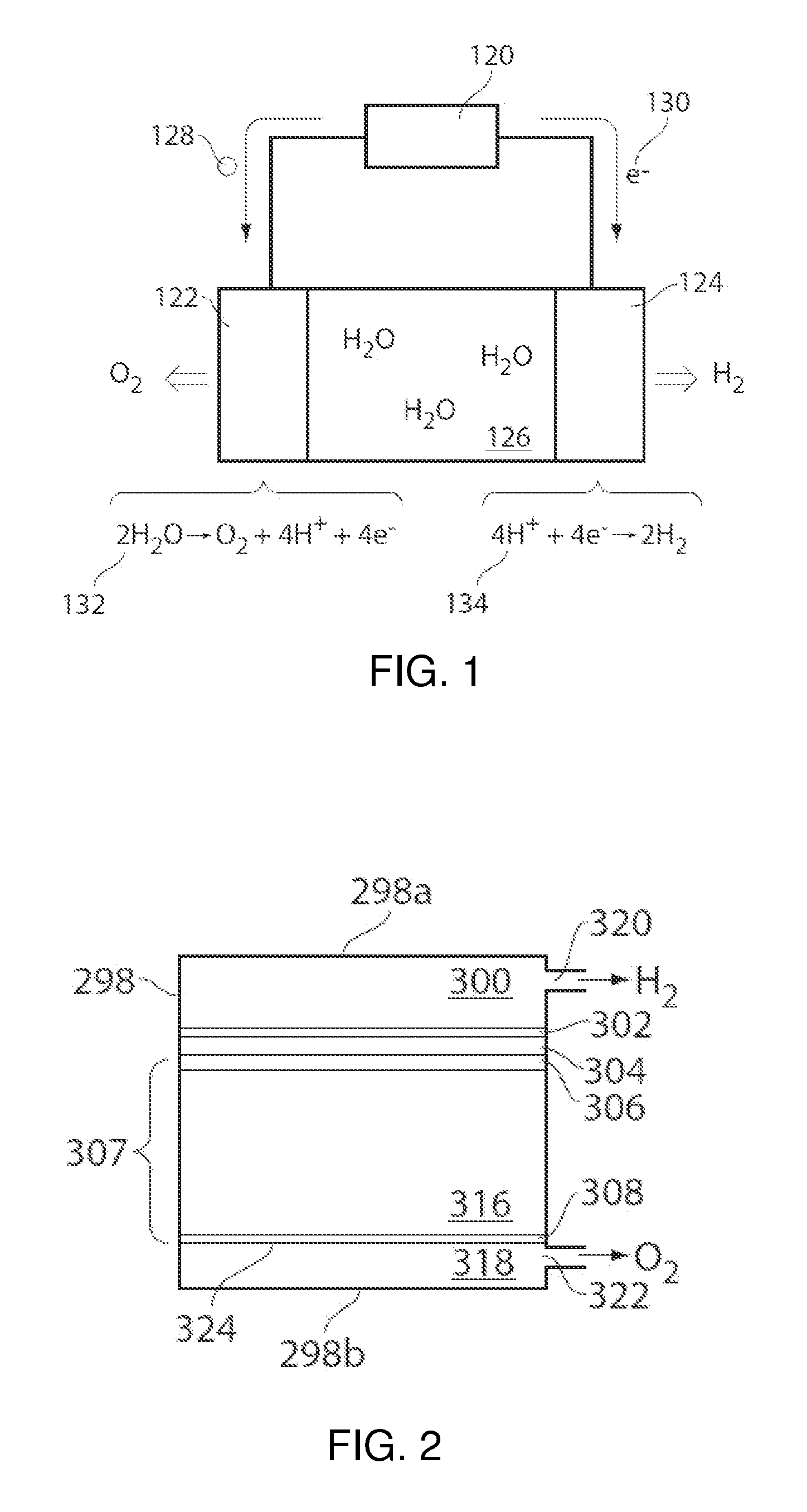

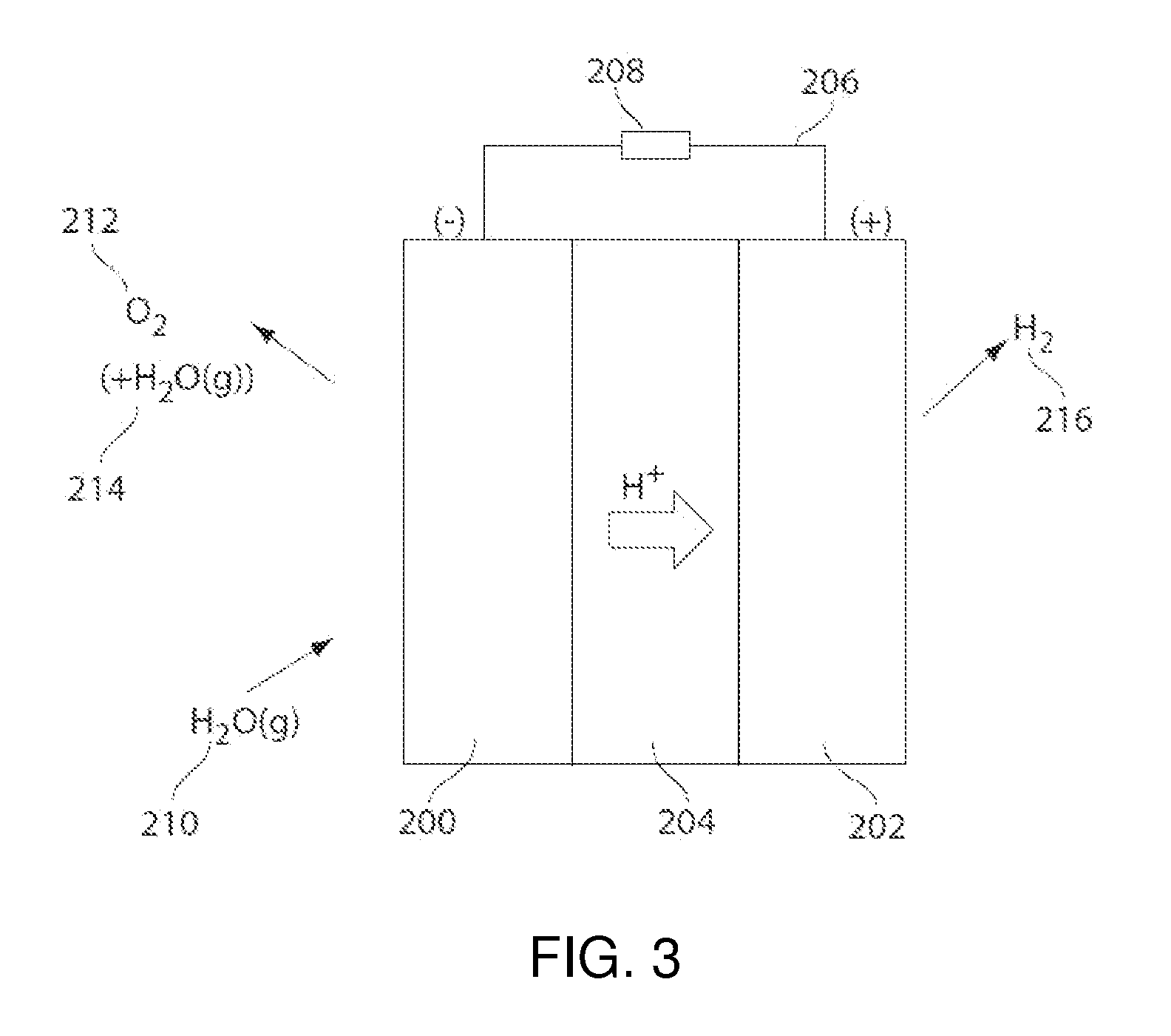

Compositions, electrodes, methods, and systems for water electrolysis and other electrochemical techniques

ActiveUS20110048962A1Increase surface areaEfficient testingPhotography auxillary processesActive material electrodesHydrogenOxygen

Compositions, electrodes, systems, and / or methods for water electrolysis and other electrochemical techniques are provided. In some cases, the compositions, electrodes, systems, and / or methods are for electrolysis which can be used for energy storage, particularly in the area of energy conversion, and / or production of oxygen, hydrogen, and / or oxygen and / or hydrogen containing species. In some embodiments, the water for electrolysis comprises at least one impurity and / or at least one additive which has little or no substantially affect on the performance of the electrode.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

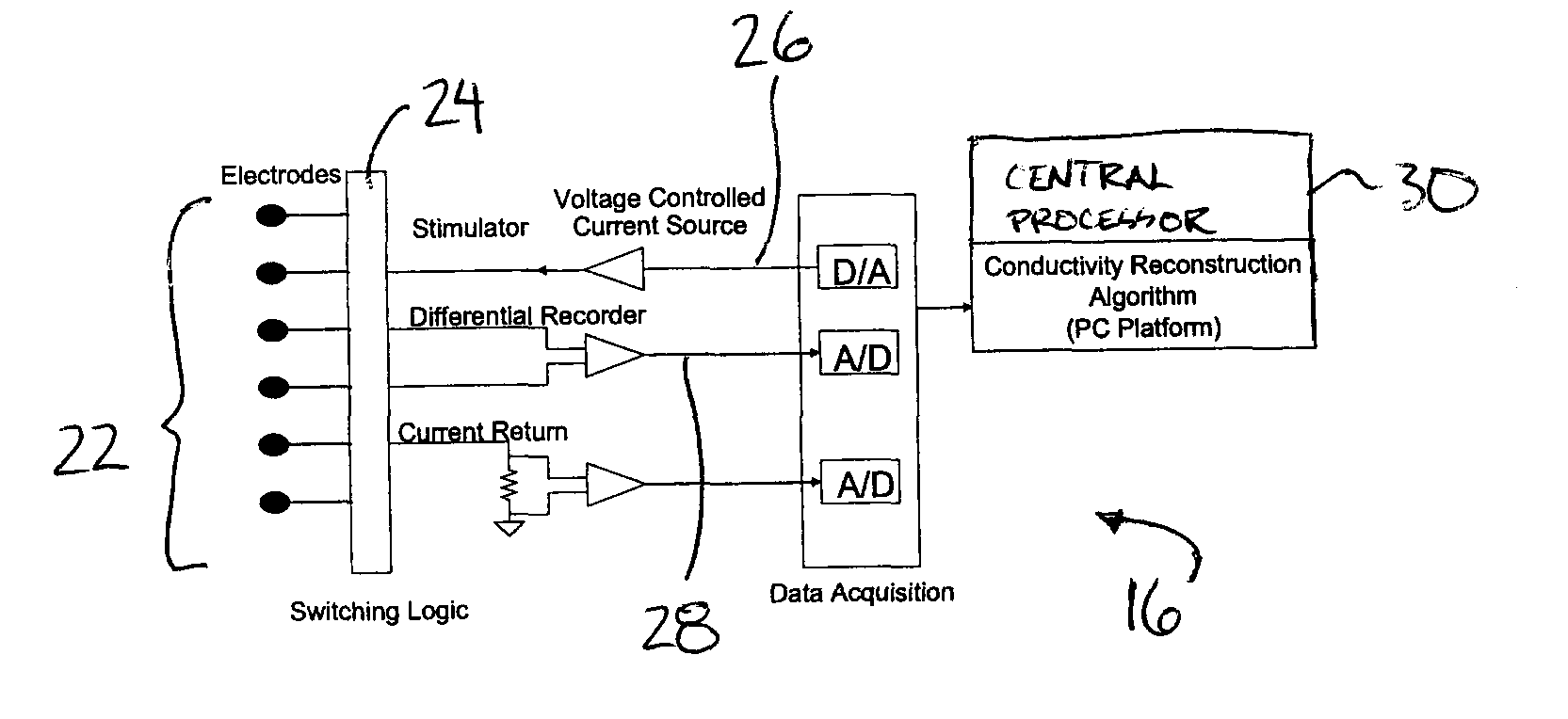

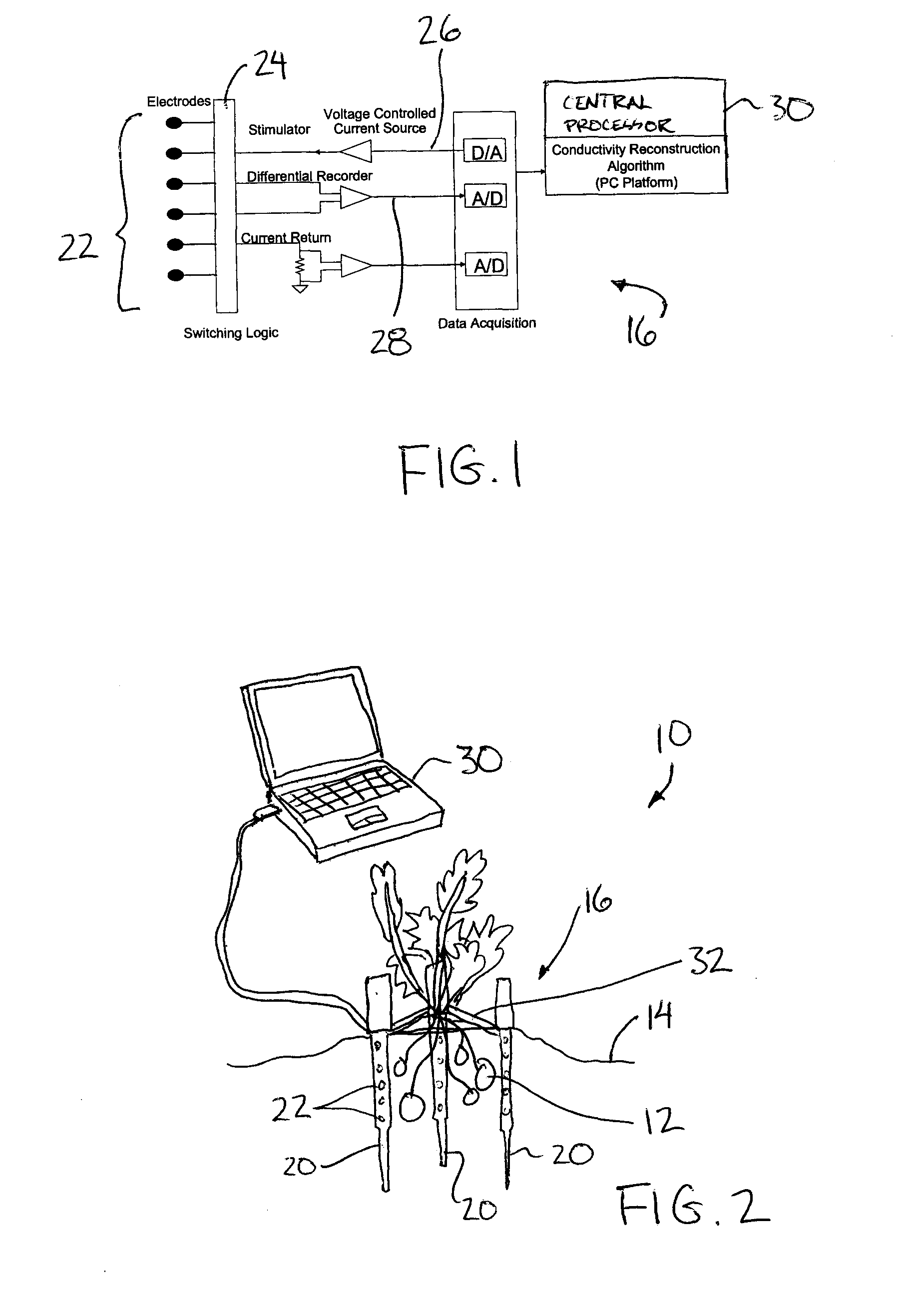

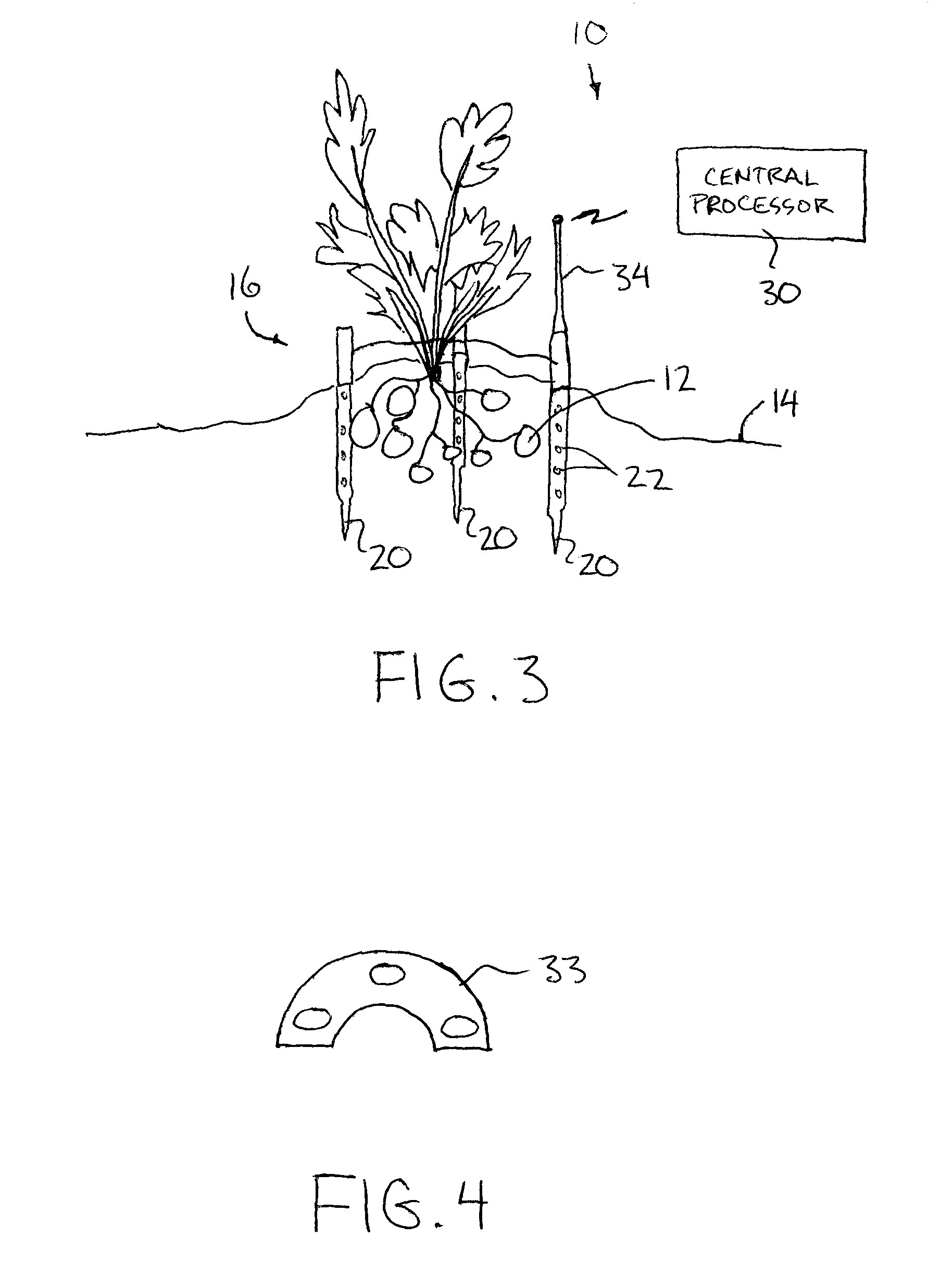

Method and System for Monitoring Growth Characteristics

InactiveUS20090322357A1Efficient NDTMinimize damageResistance/reactance/impedenceMaterial analysis by electric/magnetic meansElectrical resistance and conductanceEngineering

A system monitors growth characteristics of a plant having a root buried in a prescribed volume of ground using a plurality of electrodes inserted into the ground at a known spacing relative to one another in proximity to the root or root-like structure. When electrical current is applied to some of the electrodes, electrical potential is measured at other ones of the electrodes to construct a representation of electrical impedance across the prescribed volume locating the root or root-like structure. Growth characteristics of the soil and the plant, for example root size, root shape, soil moisture content, and the like, can be identified by locating variations of the electrical impedance.

Owner:P & B AGRI TECH INNOVATIONS

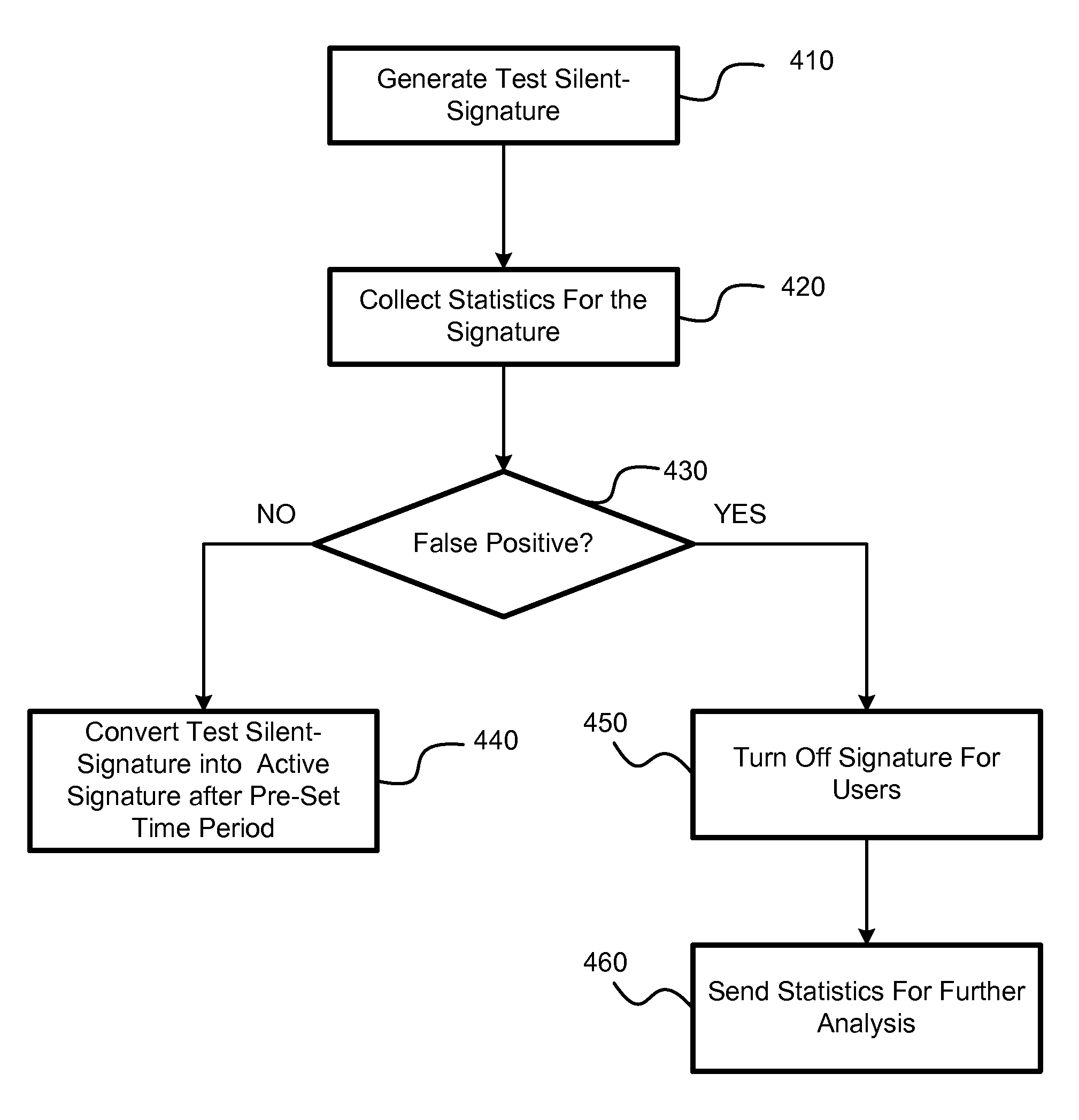

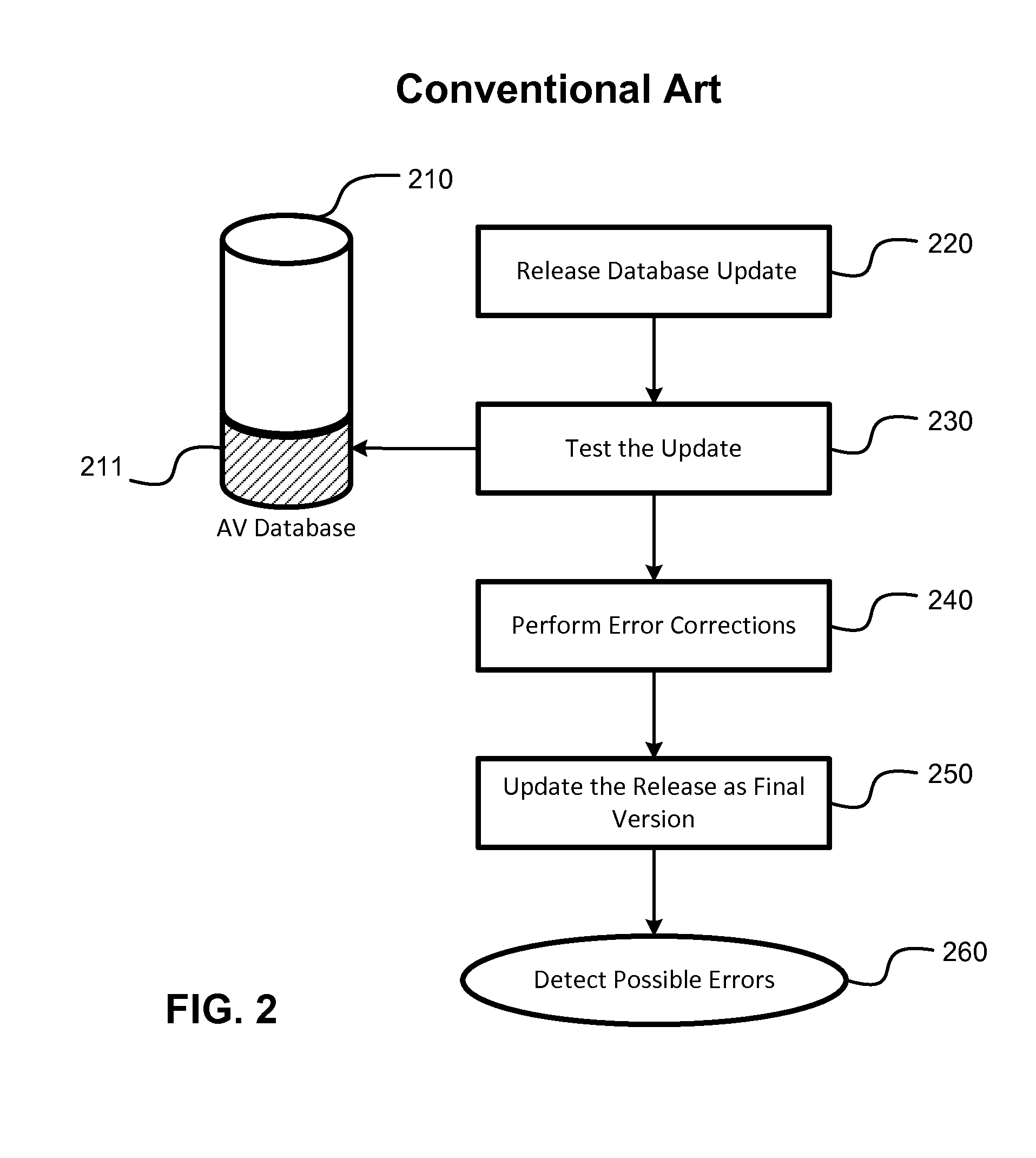

Silent-mode signature testing in Anti-malware processing

ActiveUS20110126286A1Effective signature testingShort response timeMemory loss protectionUnauthorized memory use protectionChecksumMalware

Method and computer program product for signature testing used in anti-malware processing. Silent signatures, after being tested, are not updated into a white list and are sent directly to users instead. If the silent signature coincides with malware signature, a user is not informed. A checksum (e.g., hash value) of a suspected file is sent to a server, where statistics are kept and analyzed. Based on collected false positive statistics of the silent-signature, the silent-signature is either valid or invalid. Use of the silent signatures provides for effective signature testing and reduces response time to new malware-related threats. The silent signature method is used for turning off a signature upon first false positive occurrence. Use of silent signatures allows improving heuristic algorithms for detection of unknown malware.

Owner:KASPERSKY LAB ZAO

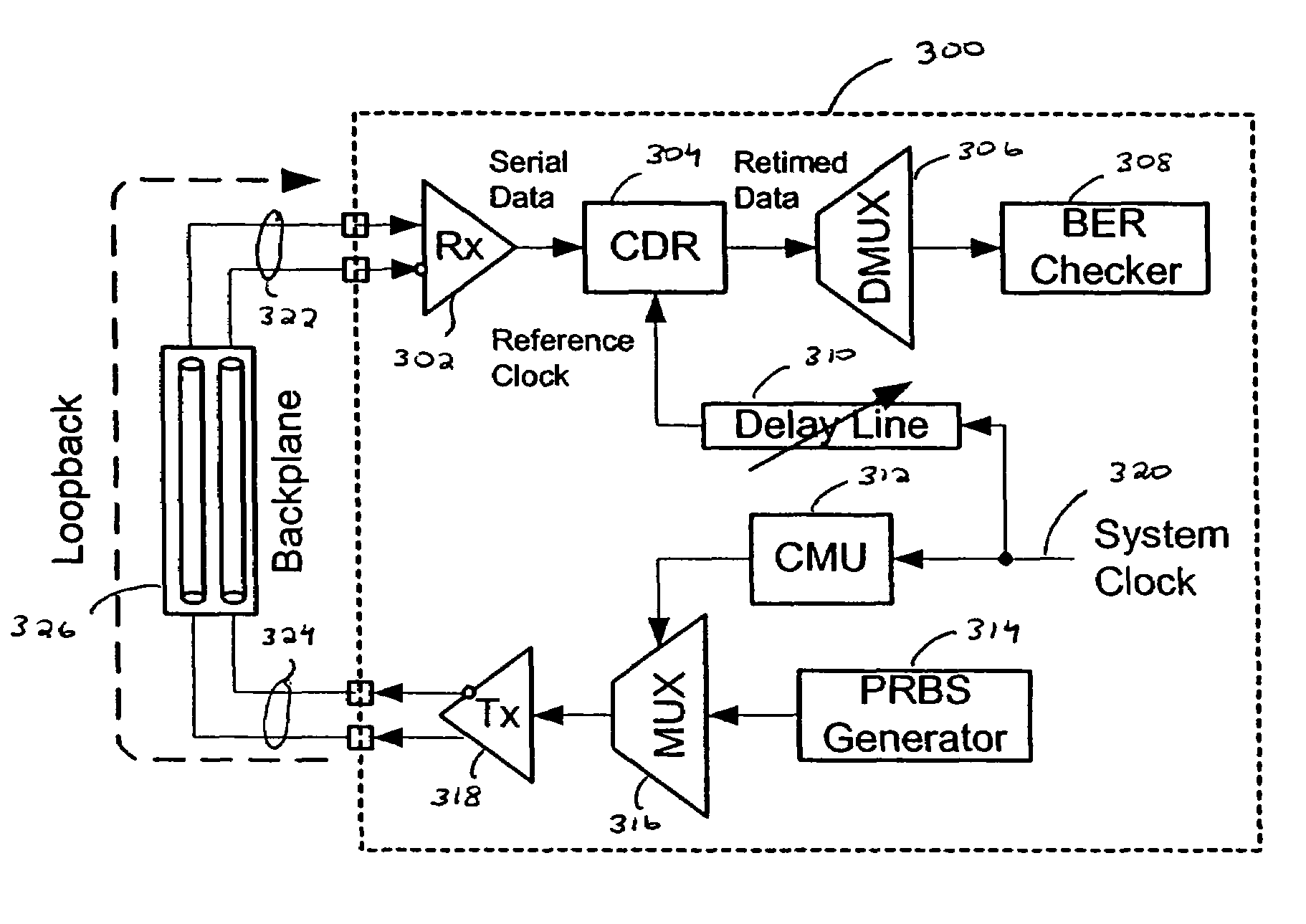

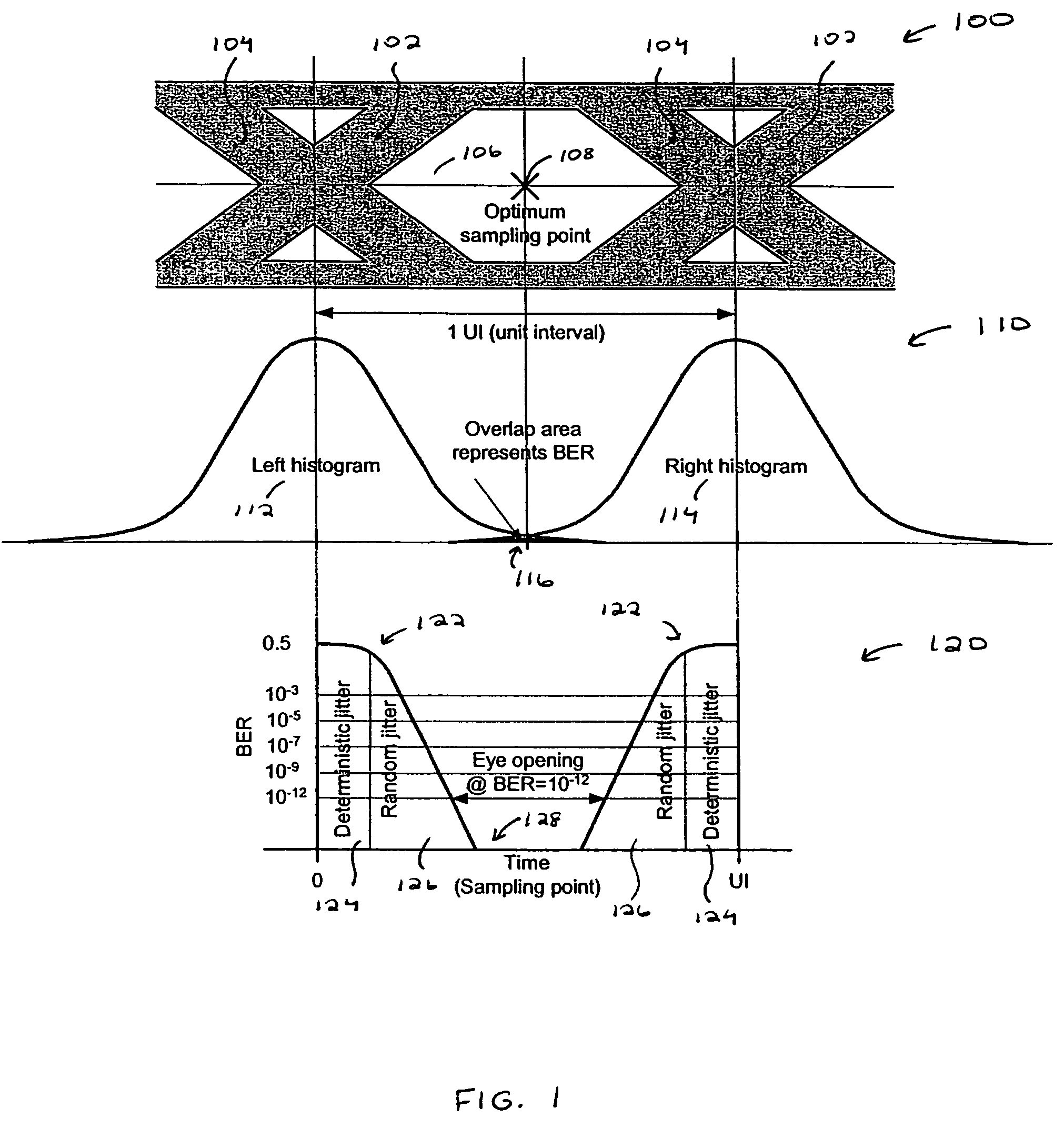

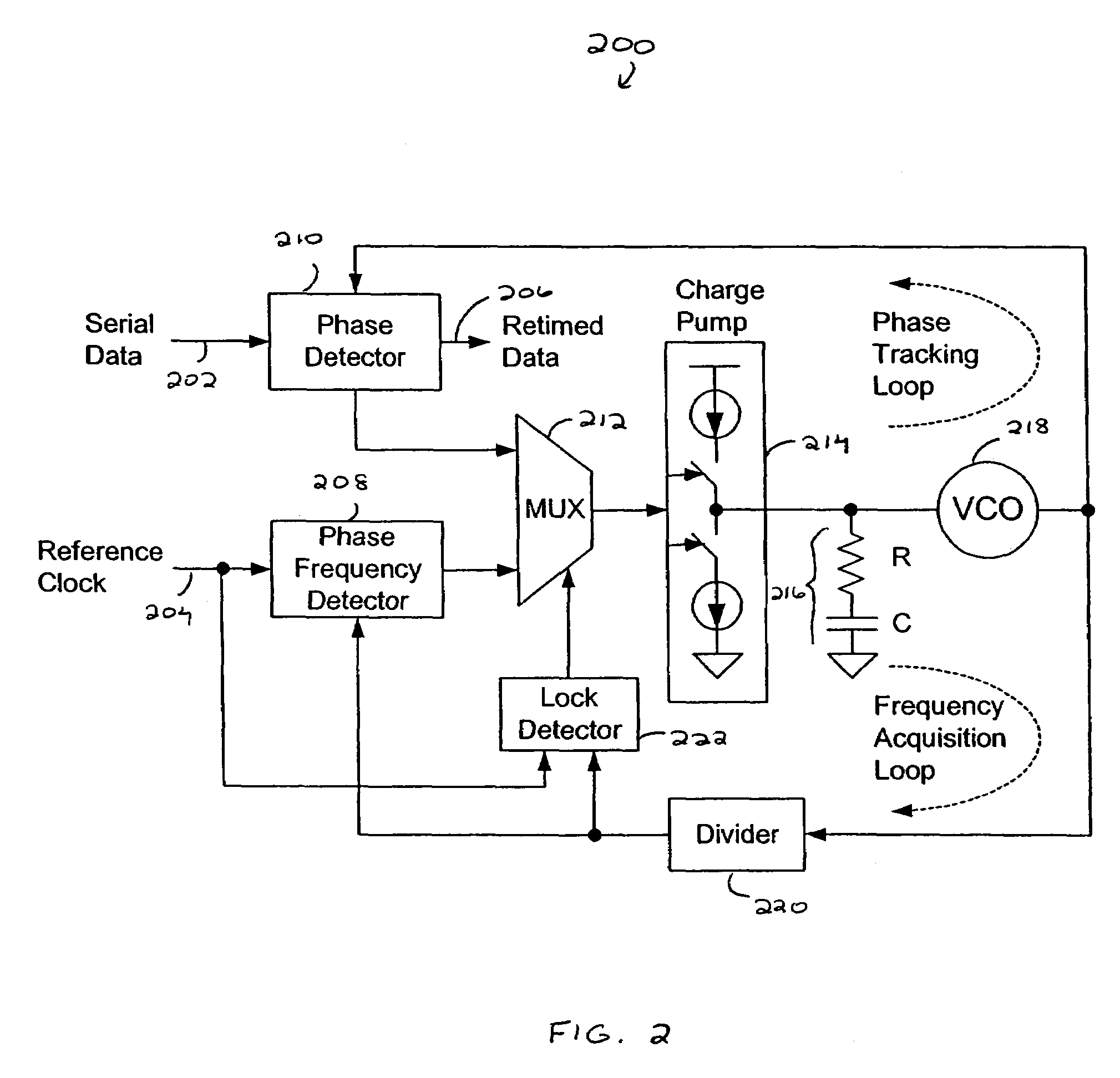

Built-in at-speed bit error ratio tester

InactiveUS7743288B1Low-cost solutionEfficient testingError preventionTransmission systemsEqualizationBuilt-in self-test

A built-in, at-speed BERT is provided that may be part of high-speed serial interface circuitry implemented on an integrated circuit. The built-in, at-speed BERT takes advantage of an existing clock data recovery (CDR) dual-loop architecture and built-in self test (BIST) circuitry. The built-in, at-speed BERT provides a low-cost solution for production testing of high-speed serial links, facilitating jitter analysis and evaluation of pre-emphasis and equalization performance. This further allows adaptation of pre-emphasis and equalization.

Owner:ALTERA CORP

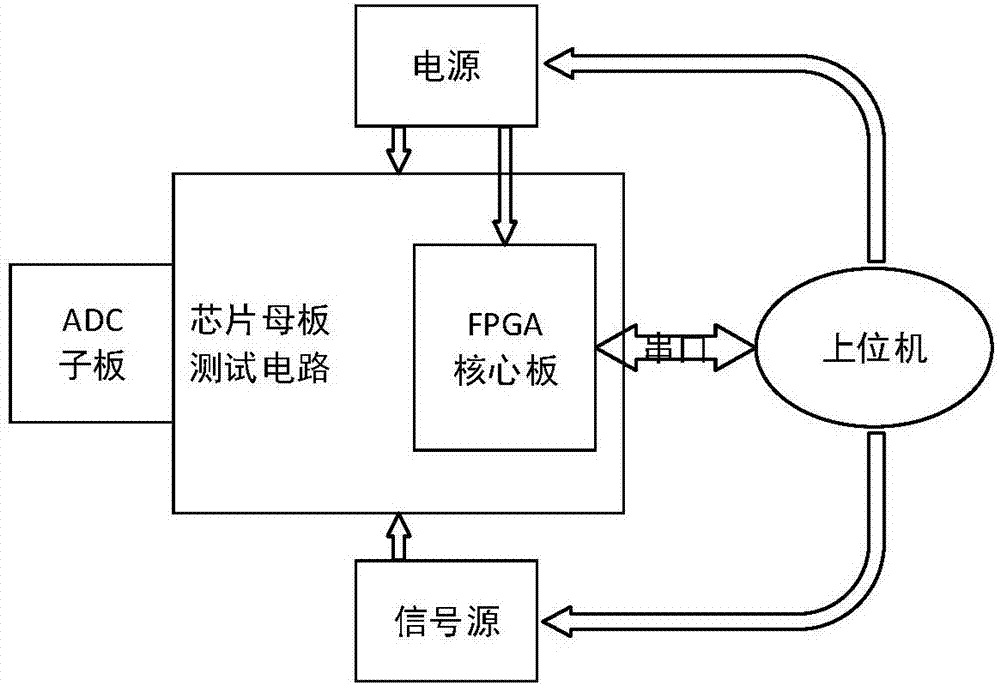

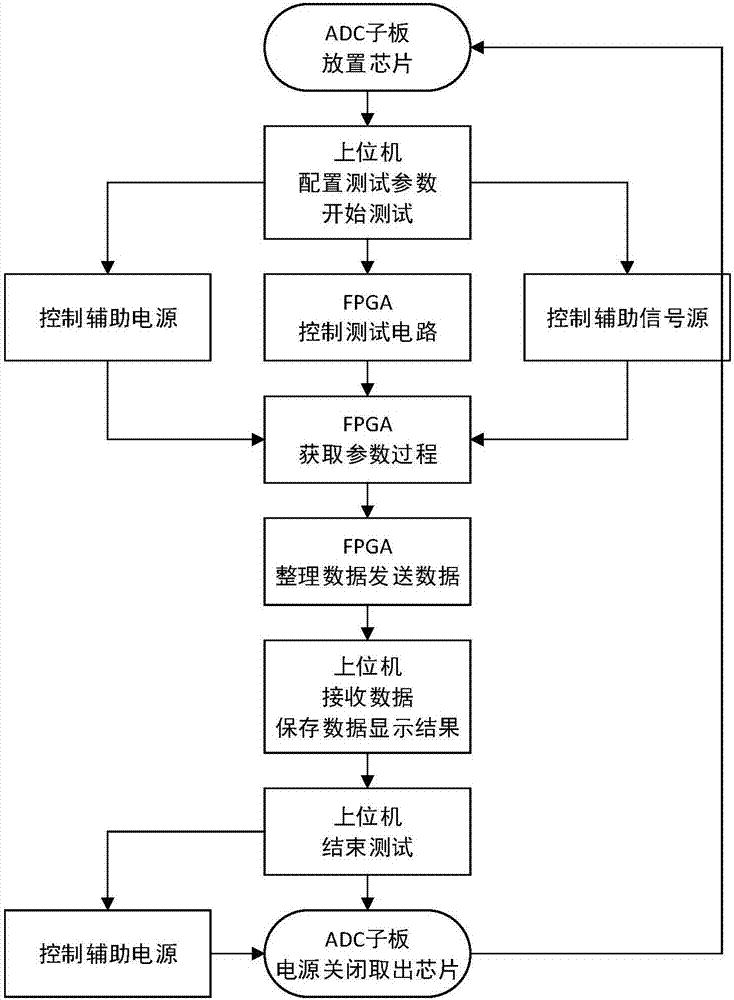

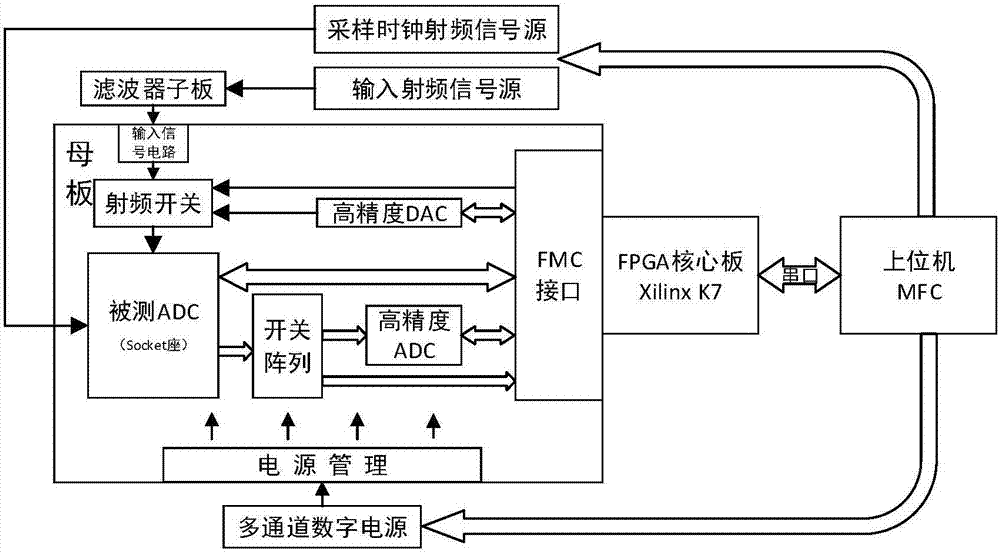

Automatic test platform of high-speed ADC chip and software framework design method thereof

ActiveCN107390109AIncrease test rateReliable high-speed data signal transmissionElectronic circuit testingTest platformAlgorithm design

The invention discloses an automatic test platform of a high-speed ADC chip and a software framework design method thereof. The design method comprises the steps of step 1, FPGA underlying logic drive design: the FPGA underlying logic part completes construction of the hardware foundation, including realizing underlying logic control, foundation computation and soft core hardware configuration of the hardware module; and synchronous drive algorithm design including the tested high-speed ADC, calibration algorithm design, hardware drive design of the onboard high-precision ADC / DAC and register array and hardware FFT operation; step 2, test parameter acquisition: the FPGA soft core receives an upper computer command to control the test process and transmits the command to the FPGA hardware program to drive an external circuit to acquire data so as to obtain the test parameter value by applying the processing algorithm, wherein the test parameters are mainly divided into static parameters and dynamic parameters; and step 3, upper computer program design. The high-precision level characteristic and the high-speed data characteristic of the chip can be simultaneously measured, and "one-key acquisition" can be realized through programming control.

Owner:苏州迅芯微电子有限公司

Method for testing semiconductor devices and an apparatus therefor

InactiveUS20060066293A1Good flexibilityEfficient loadingSemiconductor/solid-state device testing/measurementElectronic circuit testingElectricityEngineering

A method for testing integrated circuit devices and loading such devices into a test board for further testing and an apparatus therefor is disclosed. The method allows for selection between two modes of operation. In a first mode, the integrated circuit devices are subjected to an electrical test before being placed into the test board for further testing. In a second mode, the integrated circuit devices are tested after being placed in the test board. The apparatus allows for the selection between the first mode and the second mode. In either mode, information about the tested devices and the sockets in the test board is used to load the test boards intelligently. Intelligent loading means that devices under test (DUTs) are not placed in bad sockets and devices that do test bad are removed from the test board, with an option of replacing the failed DUT with another DUT before subsequent environmental testing of the DUTs in the test board is carried out.

Owner:KES SYST

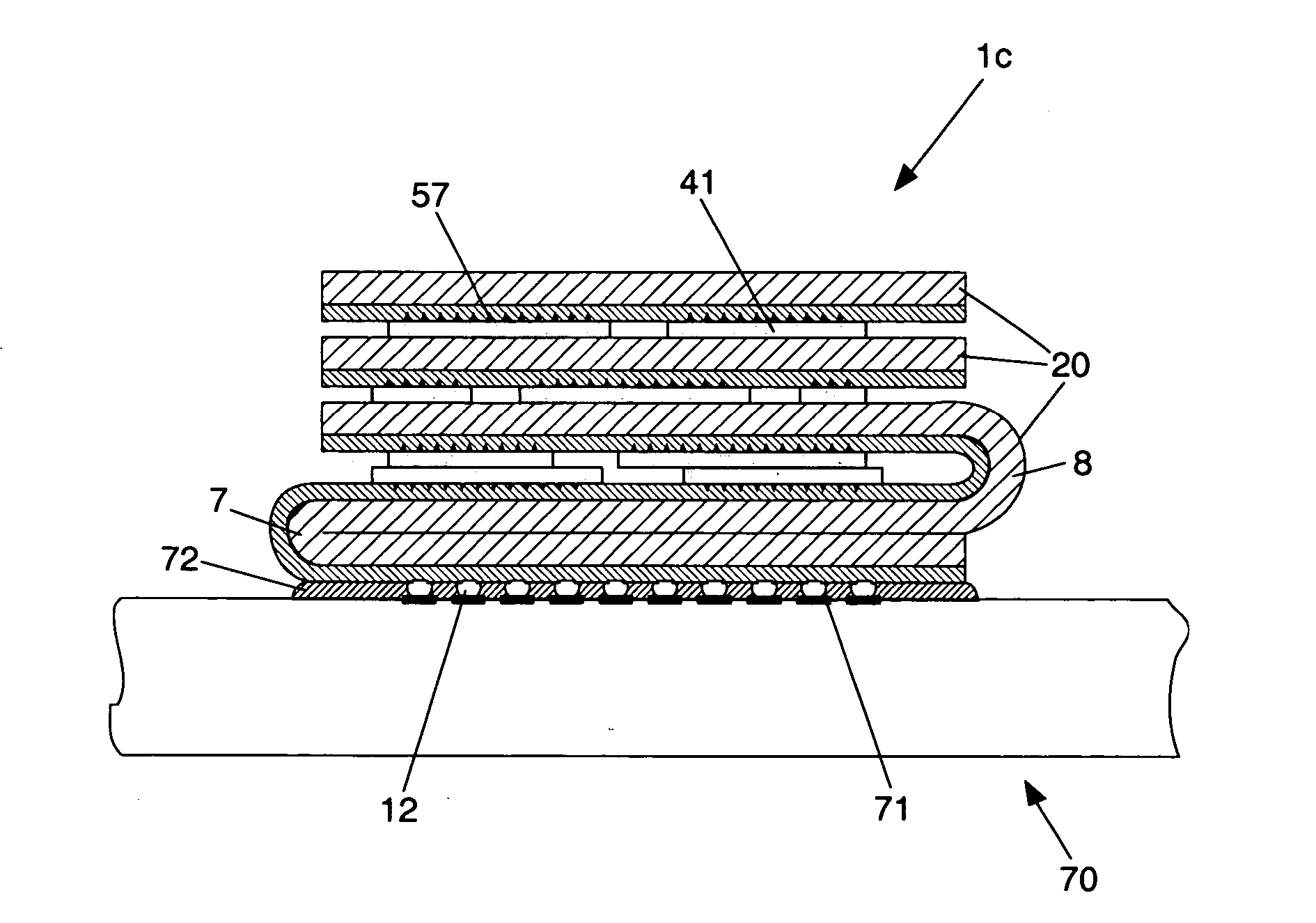

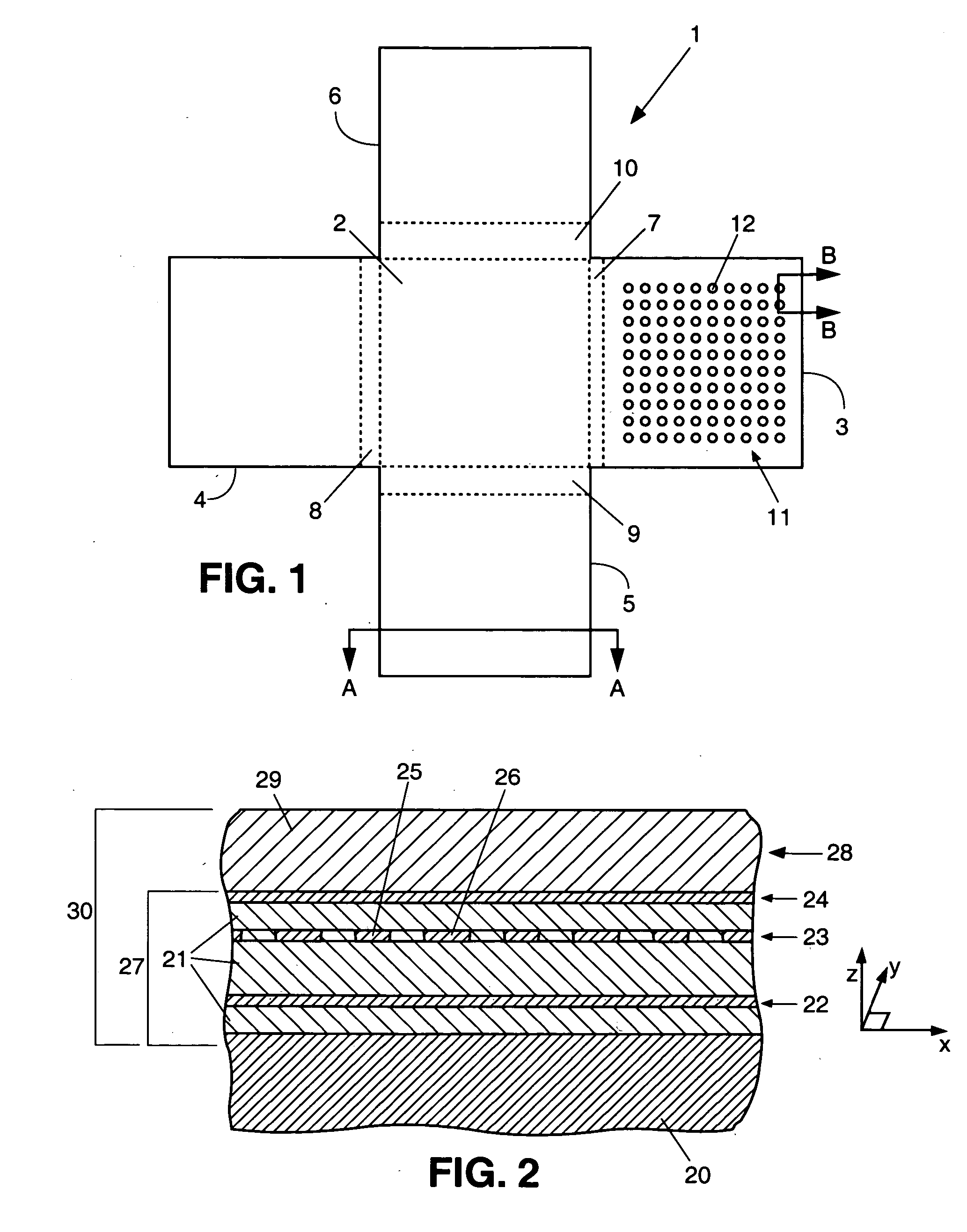

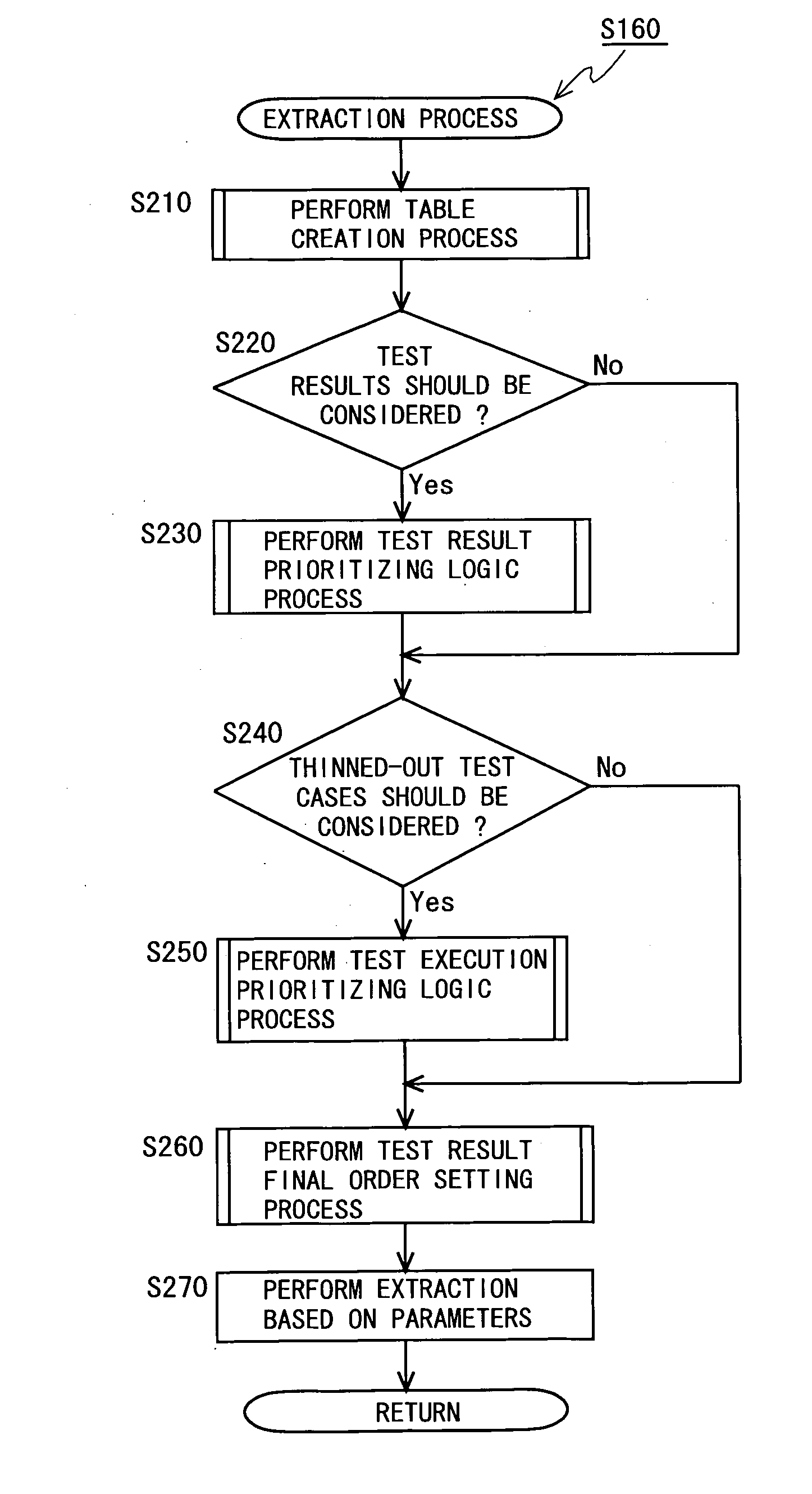

System in package

InactiveUS20050184376A1Improve cooling effectIncrease speedSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCopper conductorBand shape

A system in package (SIP) is fabricated on a sheet of copper foil. An interconnection circuit is fabricated on the foil using copper conductors and a dual damascene structure for each conductive layer. The preferred dielectric material is an amorphous fluorinated polymer called Cytop. Input / output traces of the interconnection circuit terminate in wells filled with solder. Chips are bumped and direct attached by inserting the bumps into the wells. The preferred bumps are gold stud bumps, and the preferred wells contain solder paste to a depth of approximately 15 microns. Imprinting is the preferred method for patterning; it enables 6-micron wide traces, 6-micron diameter vias, and a cost per well of around 0.02 cents. Stripline structures are described for a 4-layer stackup that can support operating frequencies of at least 10 GHz. New methods are proposed for testing the completed assembly and for rework of any chips that prove defective. After the assembly is fully tested and reworked in sheet form the copper foil is folded to form a stacked die package or system in package. 5-high and 9-high stacks are illustrated. The copper foil provides a low impedance thermal path for cooling every chip in the SIP.

Owner:SALMON TECH

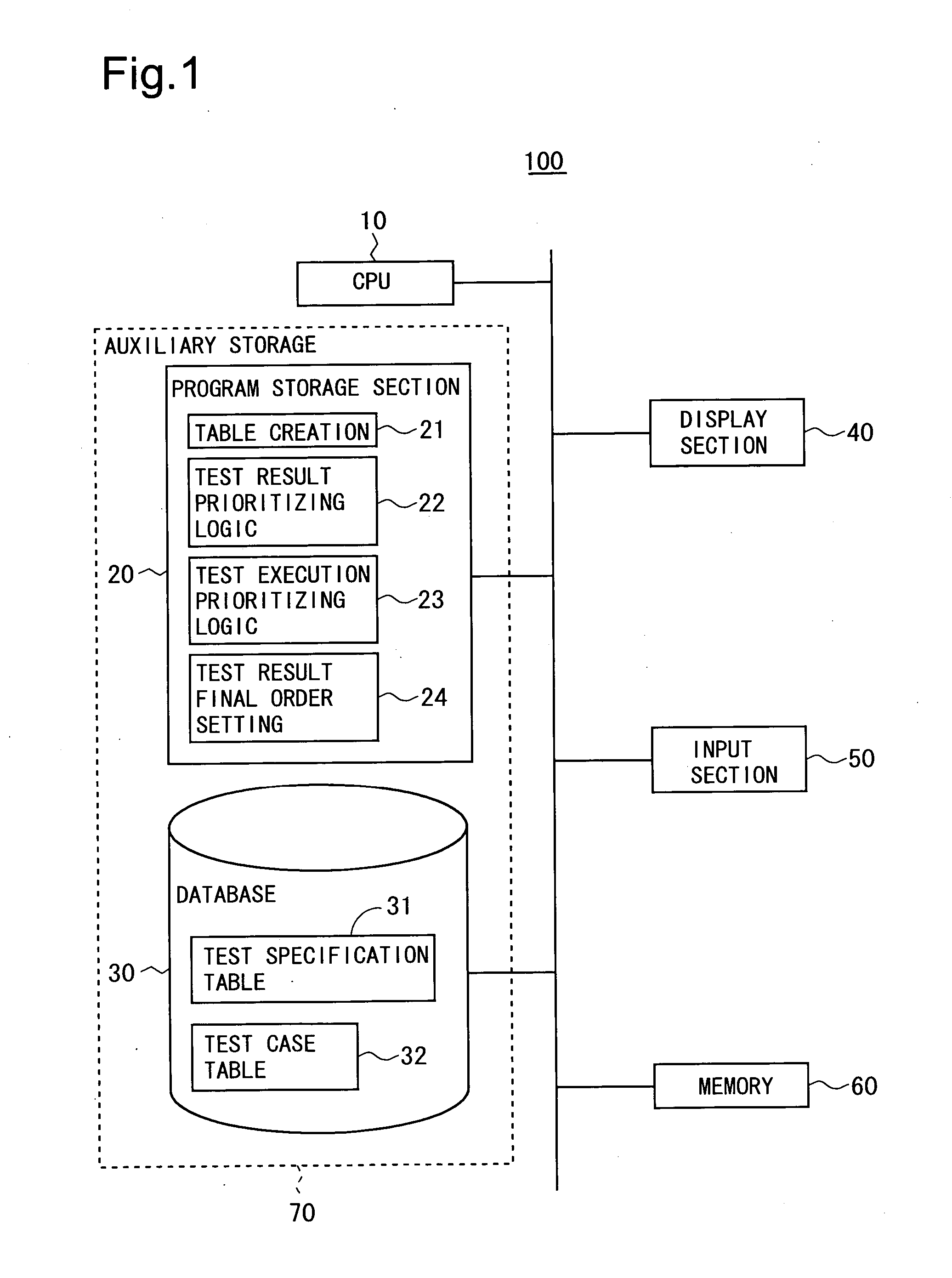

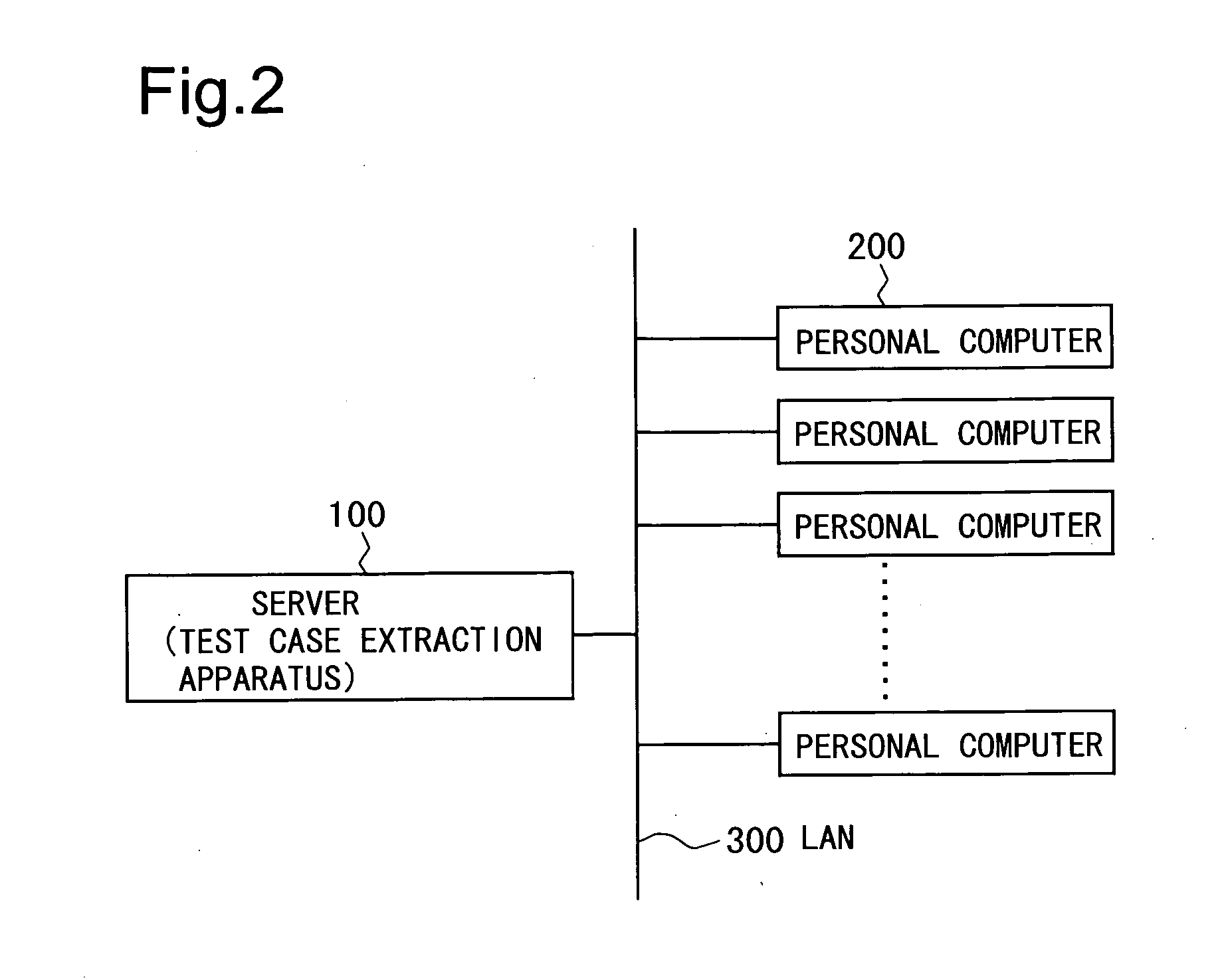

Test case extraction apparatus, program and method for software system

InactiveUS20070094189A1Efficient extractionEasy extractionError detection/correctionSpecial data processing applicationsSoftware systemThinning

A test case table stores created test cases and round-by-round test results for each test case. The operator uses a test case extraction dialogue to set test case thinning factors, and also uses a thinning parameter setting dialogue to set a priority order among logics applied for test case extraction. When a test case extraction process is executed, each test case is assigned a priority level for extraction based on the round-by-round test results for each test case in accordance with the set priority order among the logics. High-priority test cases are extracted based on the set thinning factors.

Owner:DAINIPPON SCREEN MTG CO LTD

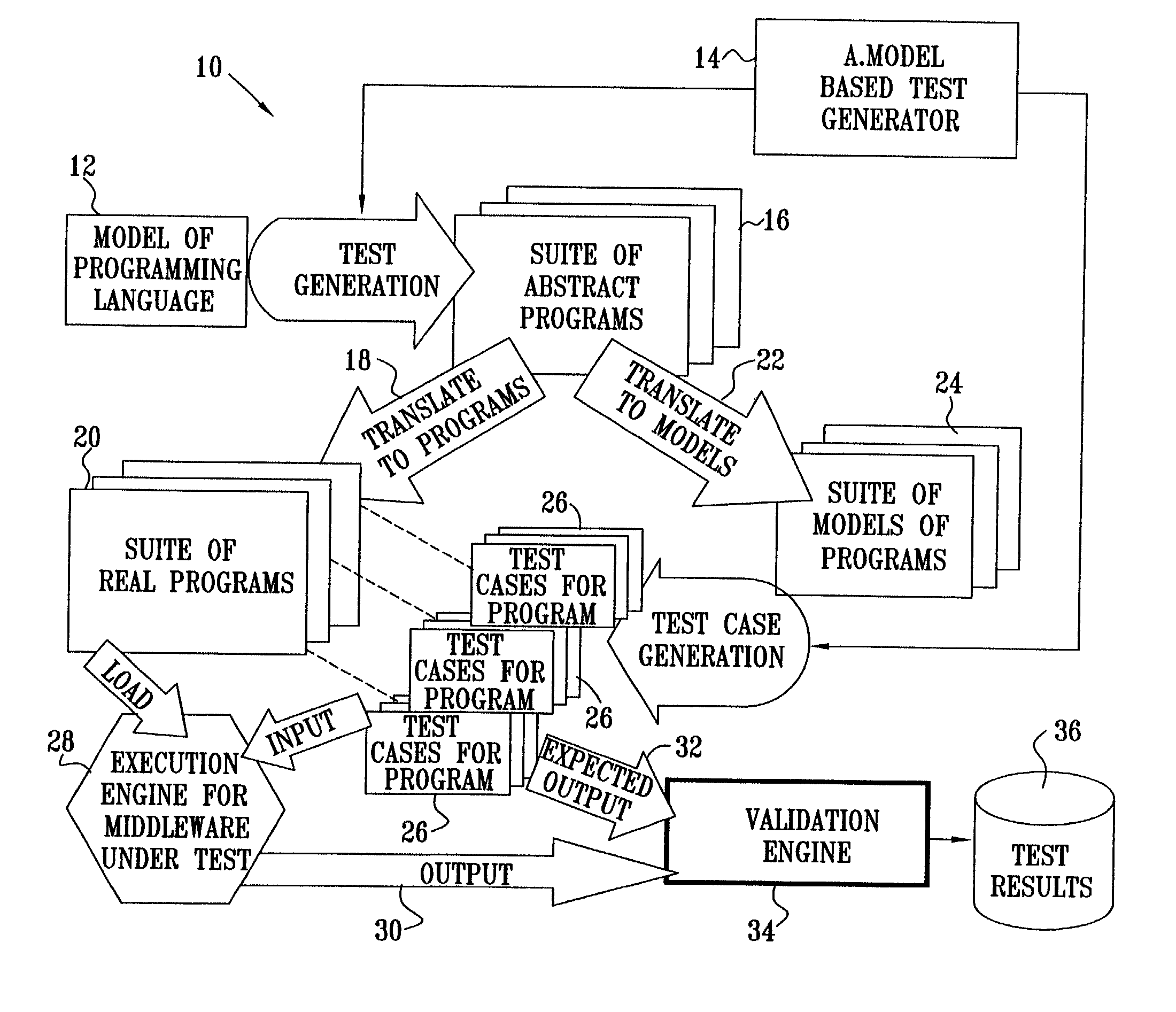

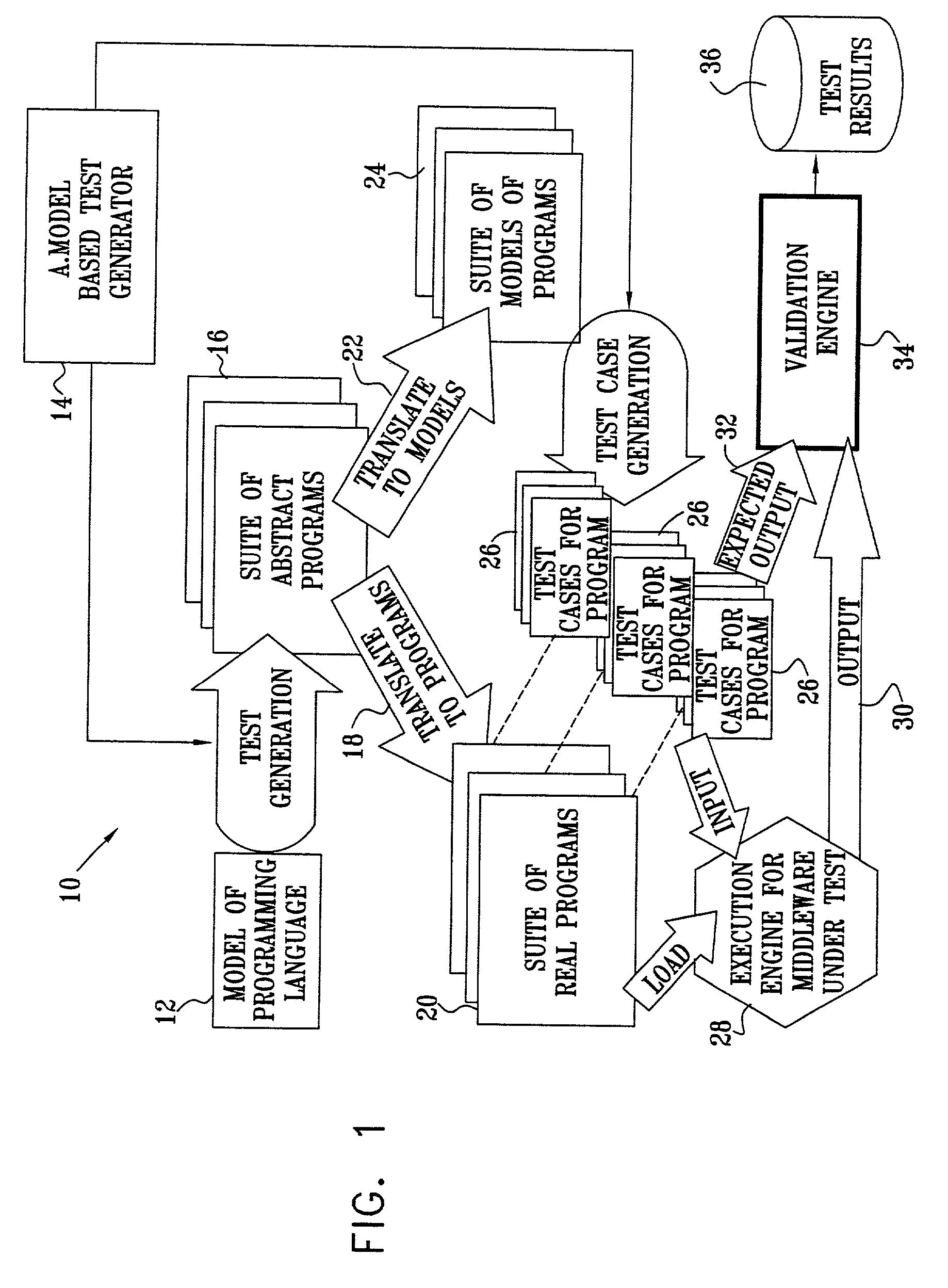

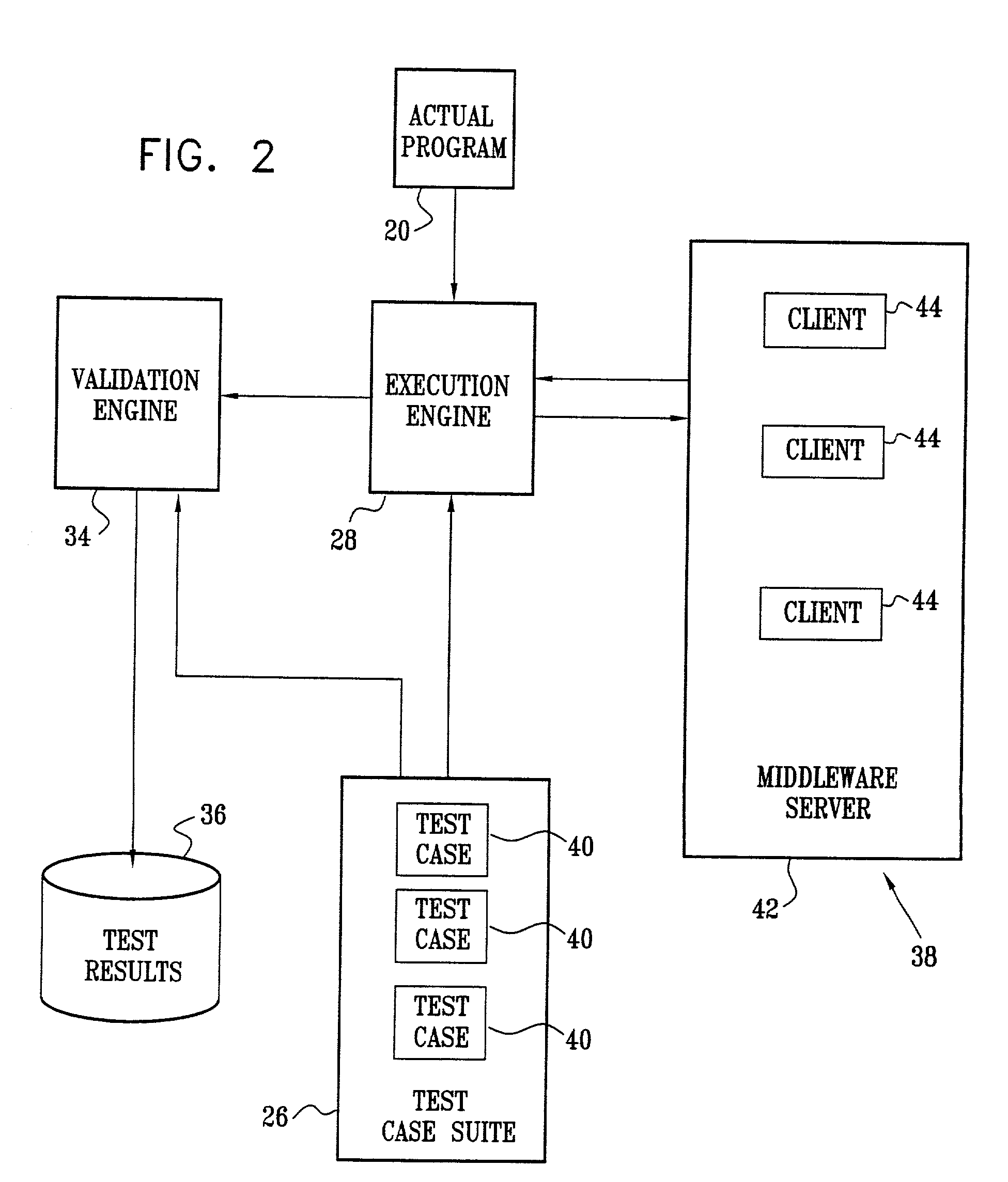

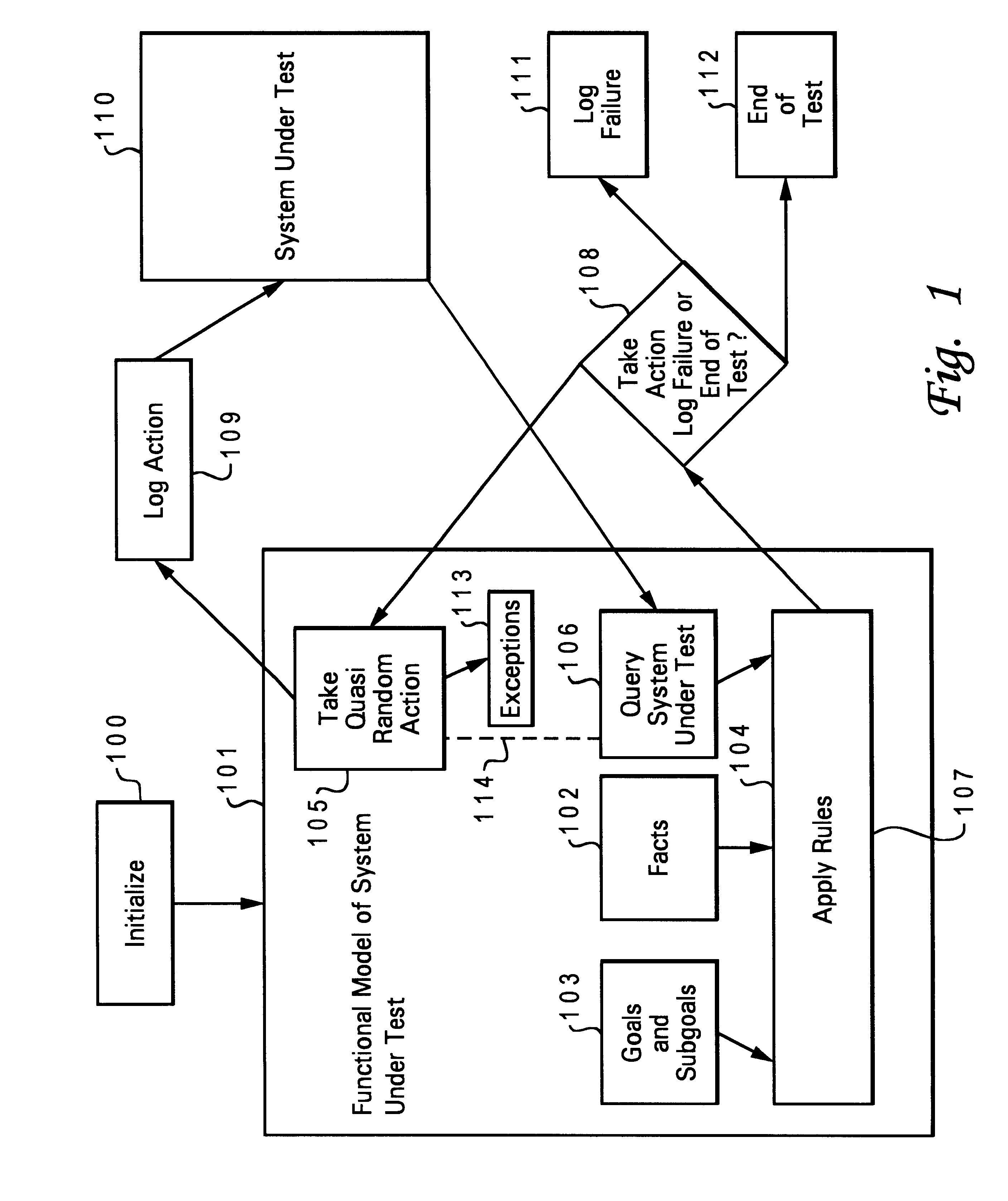

Recursive use of model based test generation for middleware validation

InactiveUS7117484B2Efficient testingSoftware testing/debuggingSpecific program execution arrangementsHigh level modelAbstract program

Owner:LINKEDIN

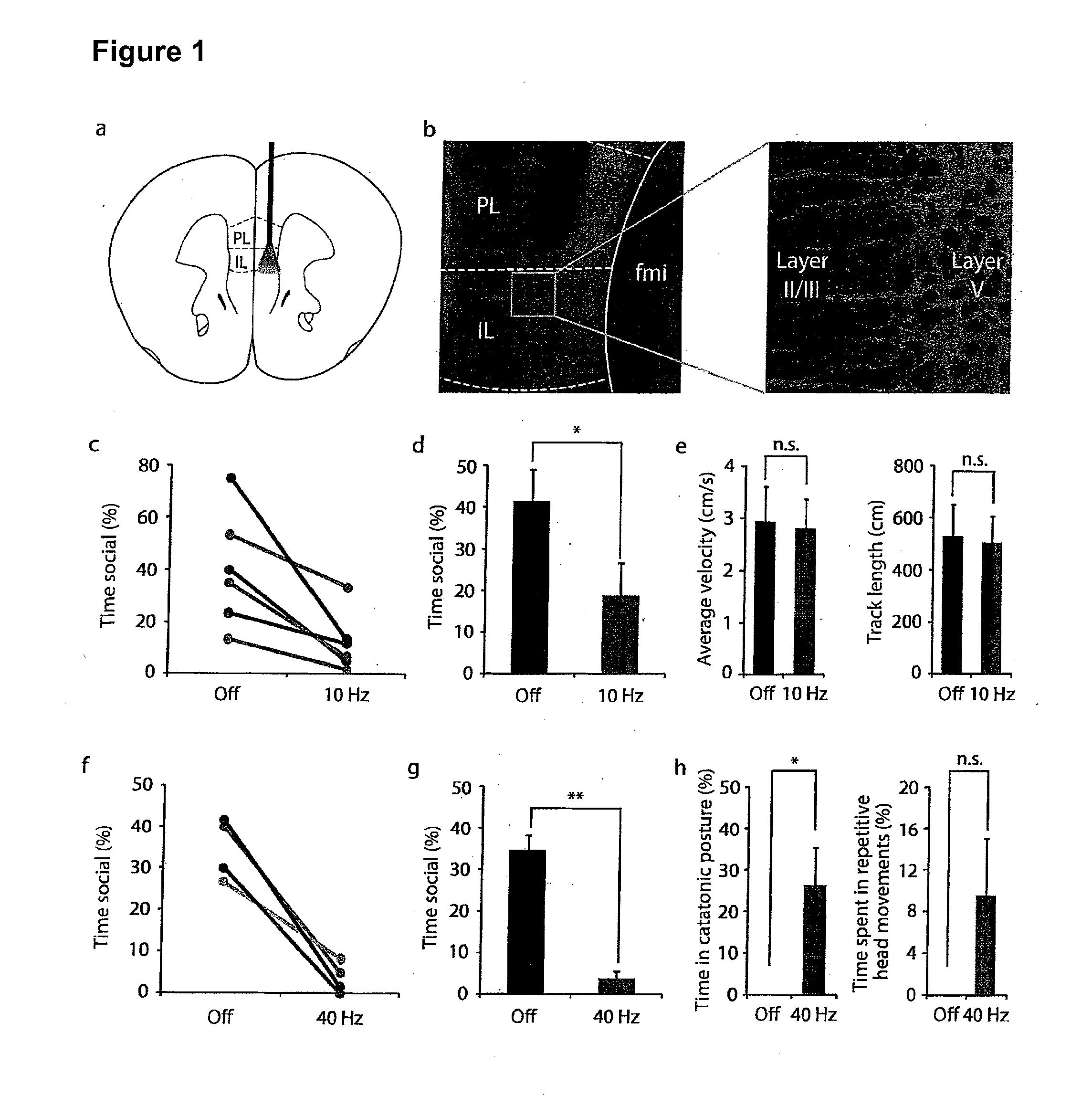

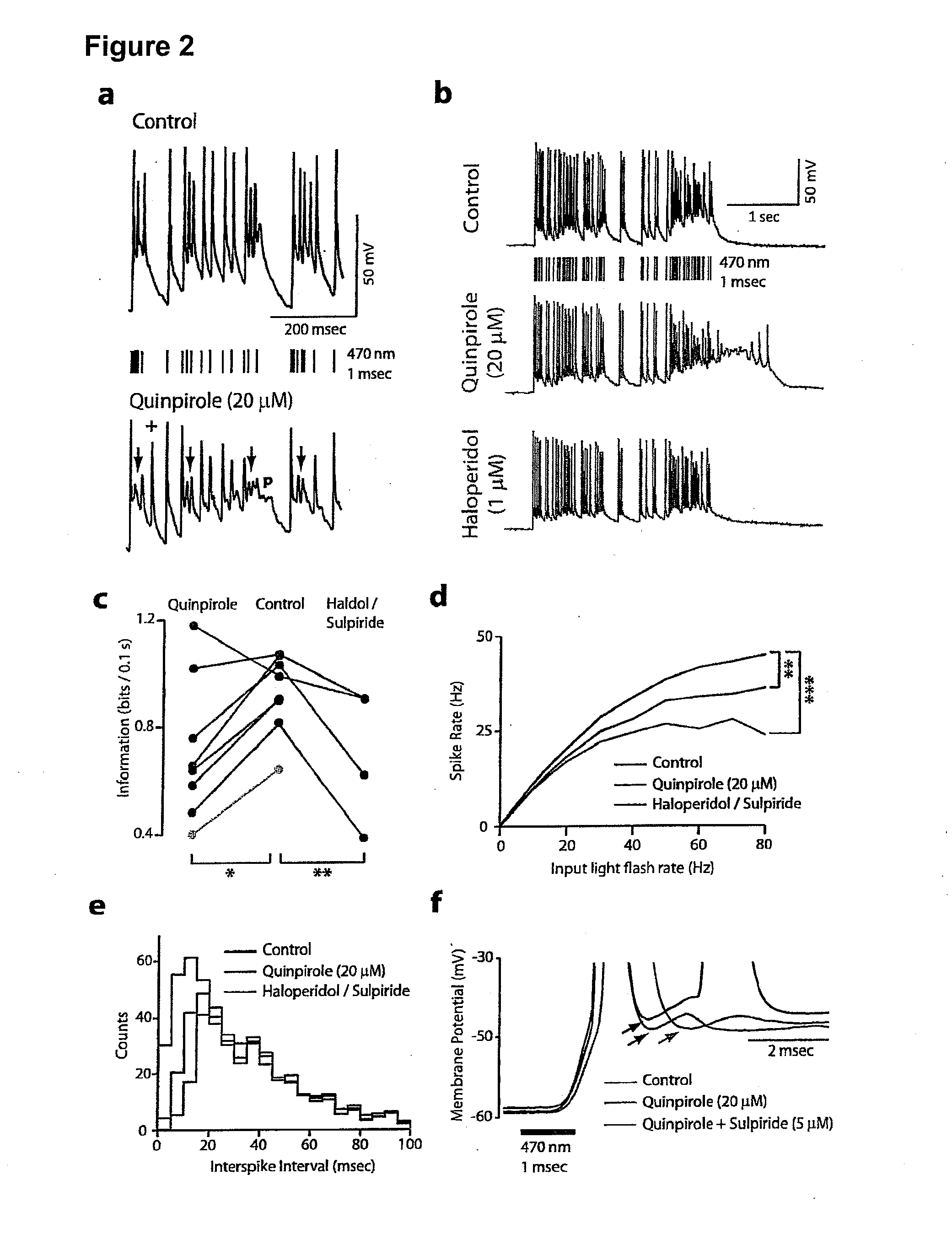

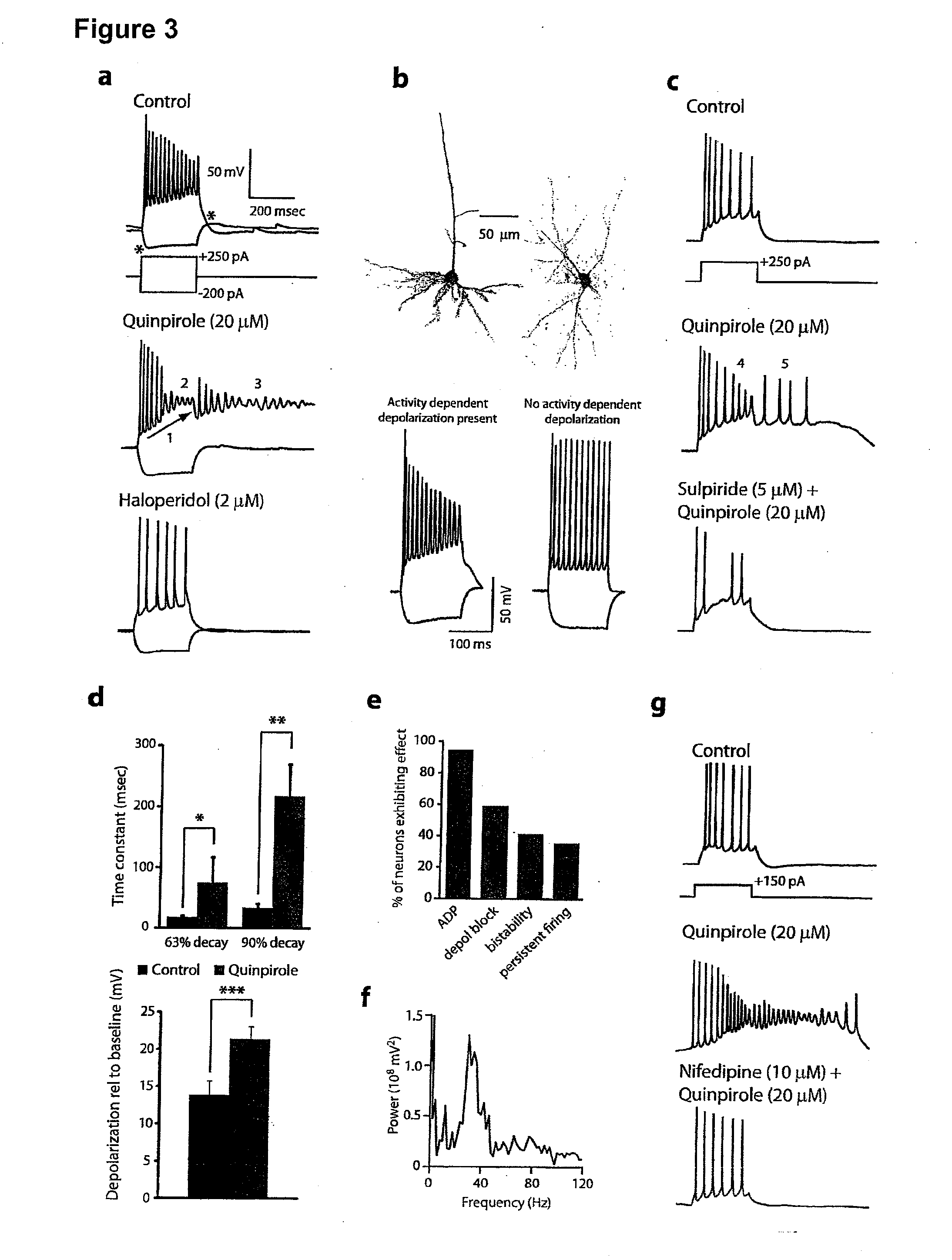

Control and Characterization of Psychotic States

InactiveUS20140082758A1Efficient testingCompounds screening/testingNervous disorderPsychotic stateOpsin

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

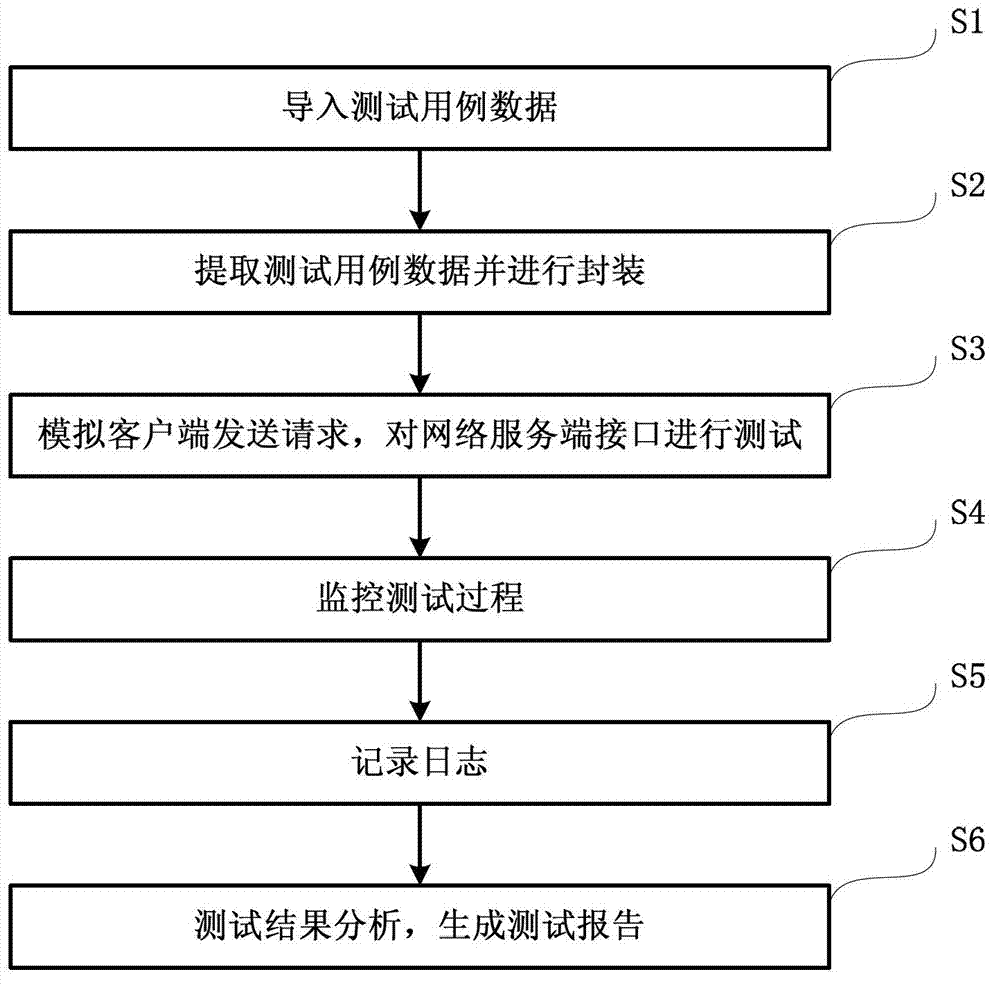

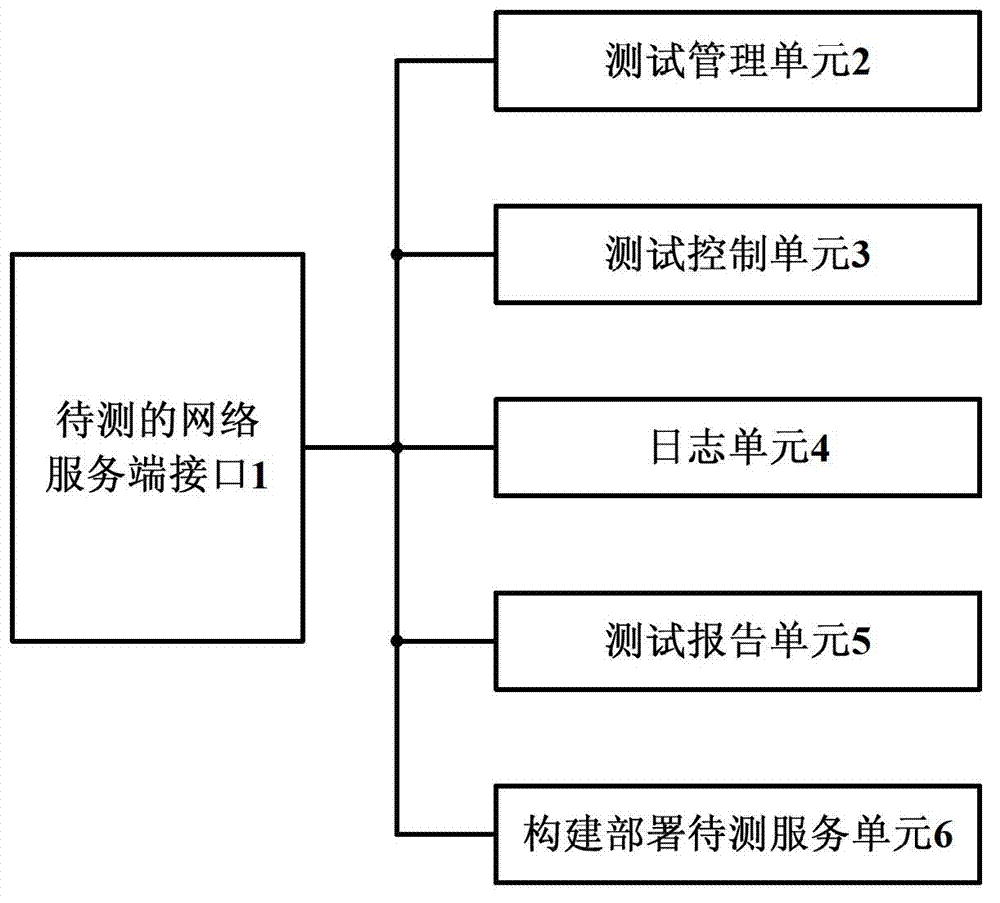

Automatic test method and test platform of network server-side interface

ActiveCN102932205AEfficient testingLow costData switching networksAutomatic test equipmentTest management

The invention discloses an automatic test method and a test platform of a network server-side interface. The method comprises the following steps: leading test case data; extracting and encapsulating the test case data; simulating a client to transmit a request, and testing the network server-side interface; monitoring a test process, and recording a log; analyzing the test result and generating a test report. The test platform comprises a test management unit, a test control unit, a log unit and a test report unit, wherein the test management unit is used for leading and managing the test case data; the test control unit is used for encapsulating the test case data, simulating the request of the client, testing the network server-side interface and monitoring the test process; the log unit is used for generating a log according to the data fed back by the test control unit, and recording an alarm, an error parameter value and position information; and the test report unit is used for carrying out cumulative statistics analysis based on anticipation of the test management unit according to an execution state of the test case data fed back by the test control unit, and automatically generating a test report.

Owner:SHENZHEN ARTEL TECH

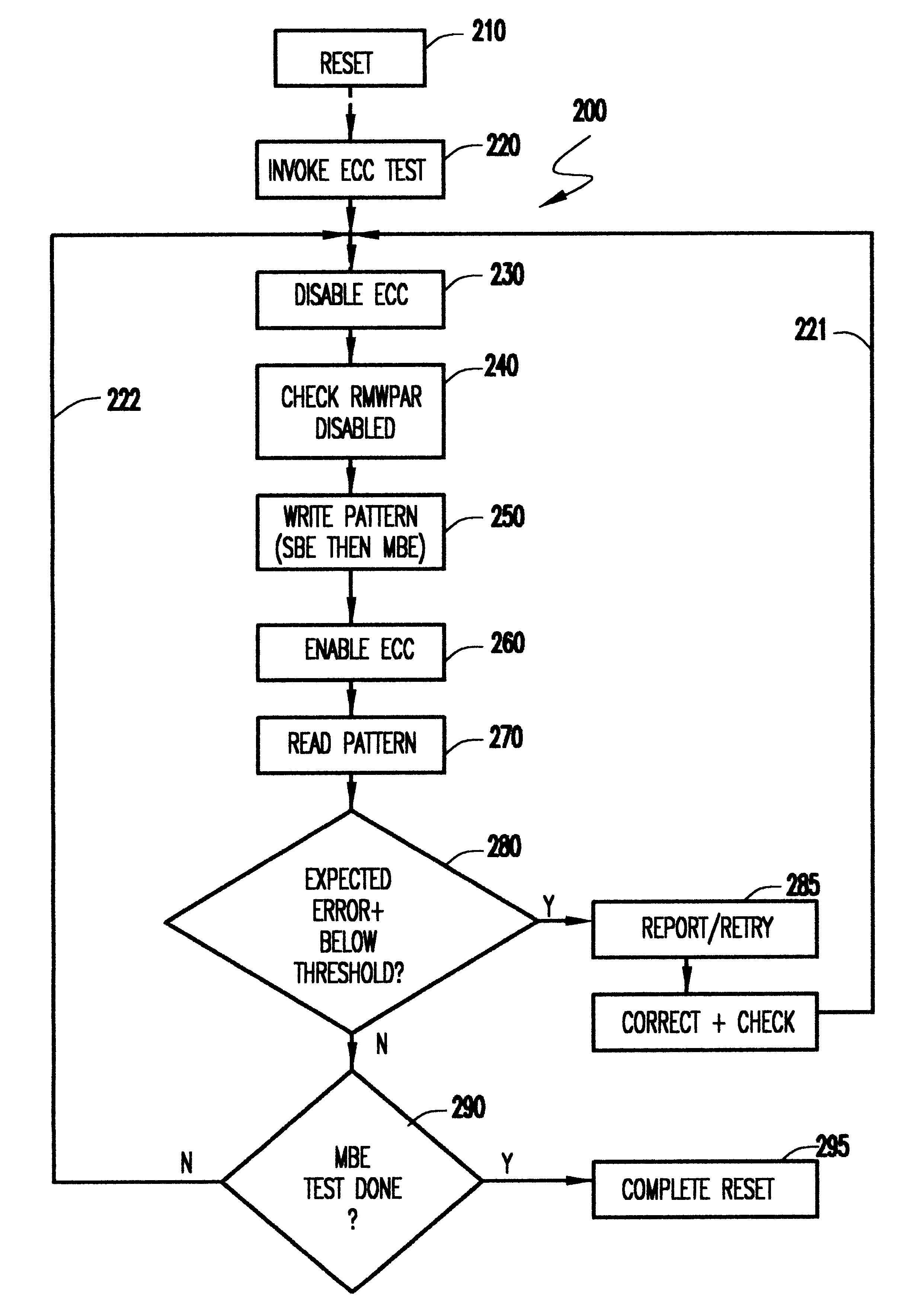

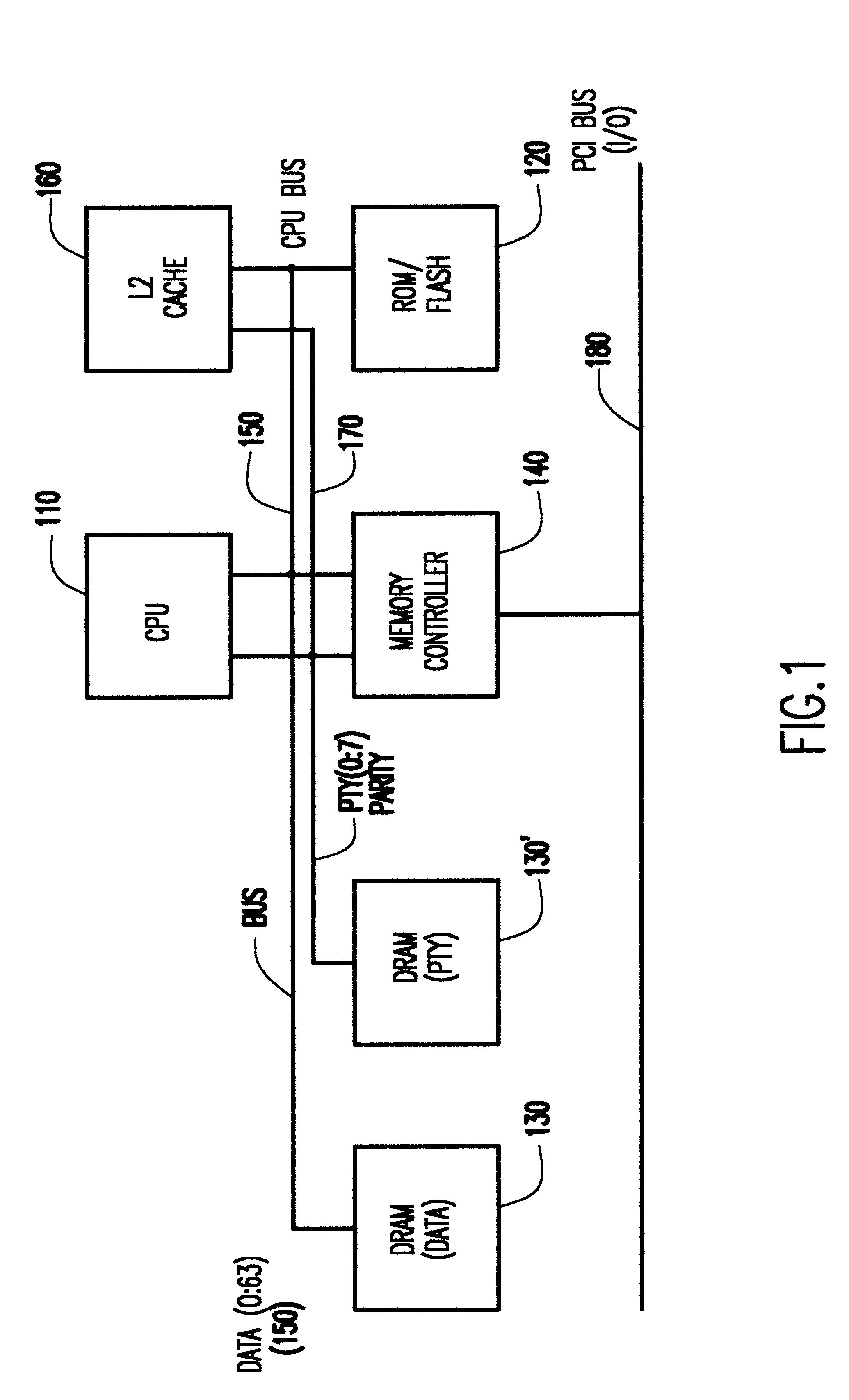

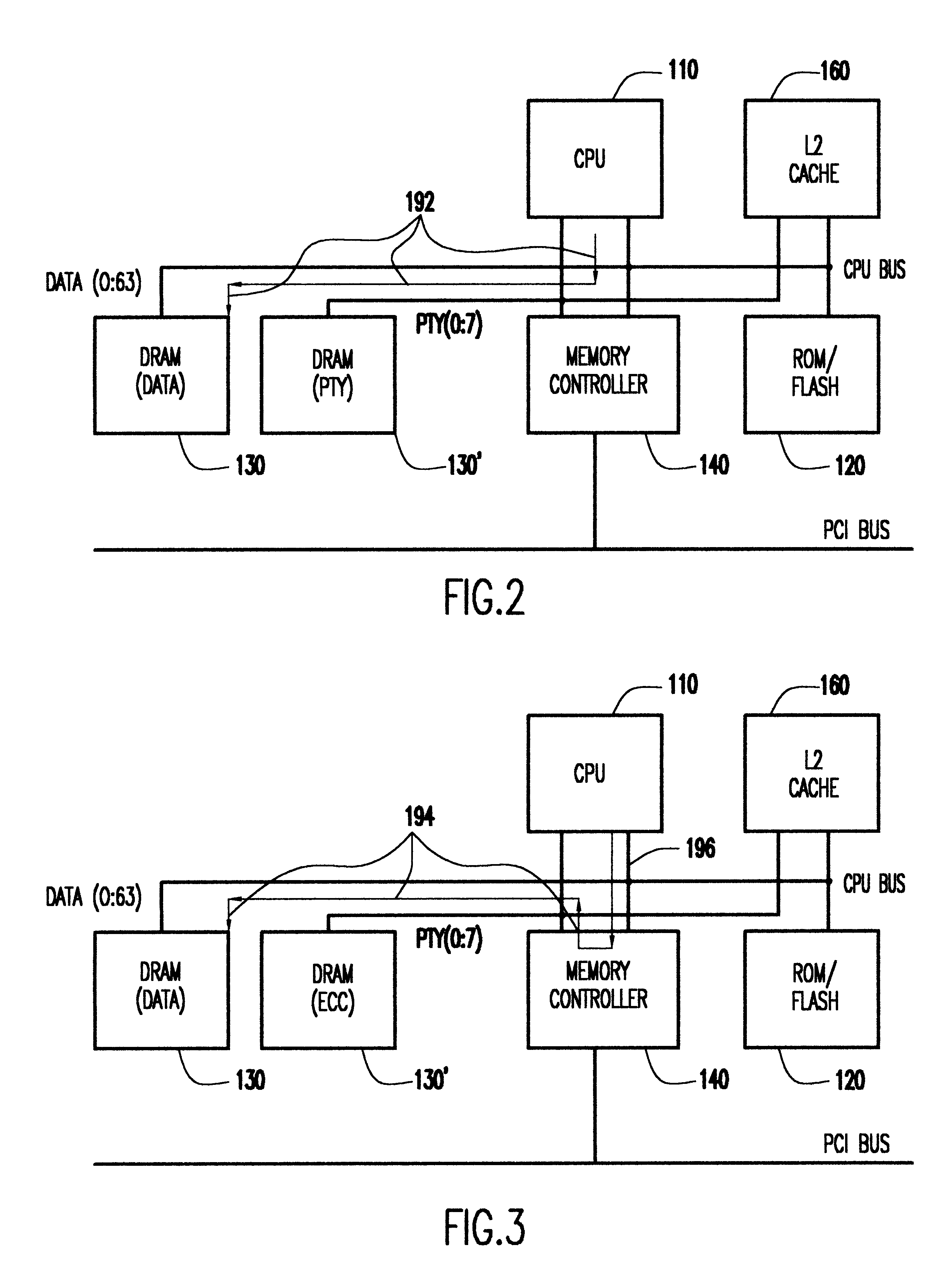

Testing error correcting code feature in computers that do not have direct hardware features for causing single bit and multi-bit errors

InactiveUS6237116B1Fast executionGuaranteed uptimeCode conversionCoding detailsMemory controllerError correcting

Built-in tests included in reset functions of single board computers can be rapidly performed to confirm adequate functionality without additional hardware support by disabling an error correcting code function in a memory controller, writing a pattern of predictable parity to a location in memory and reading and correcting the pattern with the error correcting code function of the memory controller re-enabled. Thus, resets caused by, for example, momentary soft errors or power interruptions can be executed within rigid time constraints and thus negligibly short interruptions of processor function.

Owner:LOCKHEED MARTIN CORP

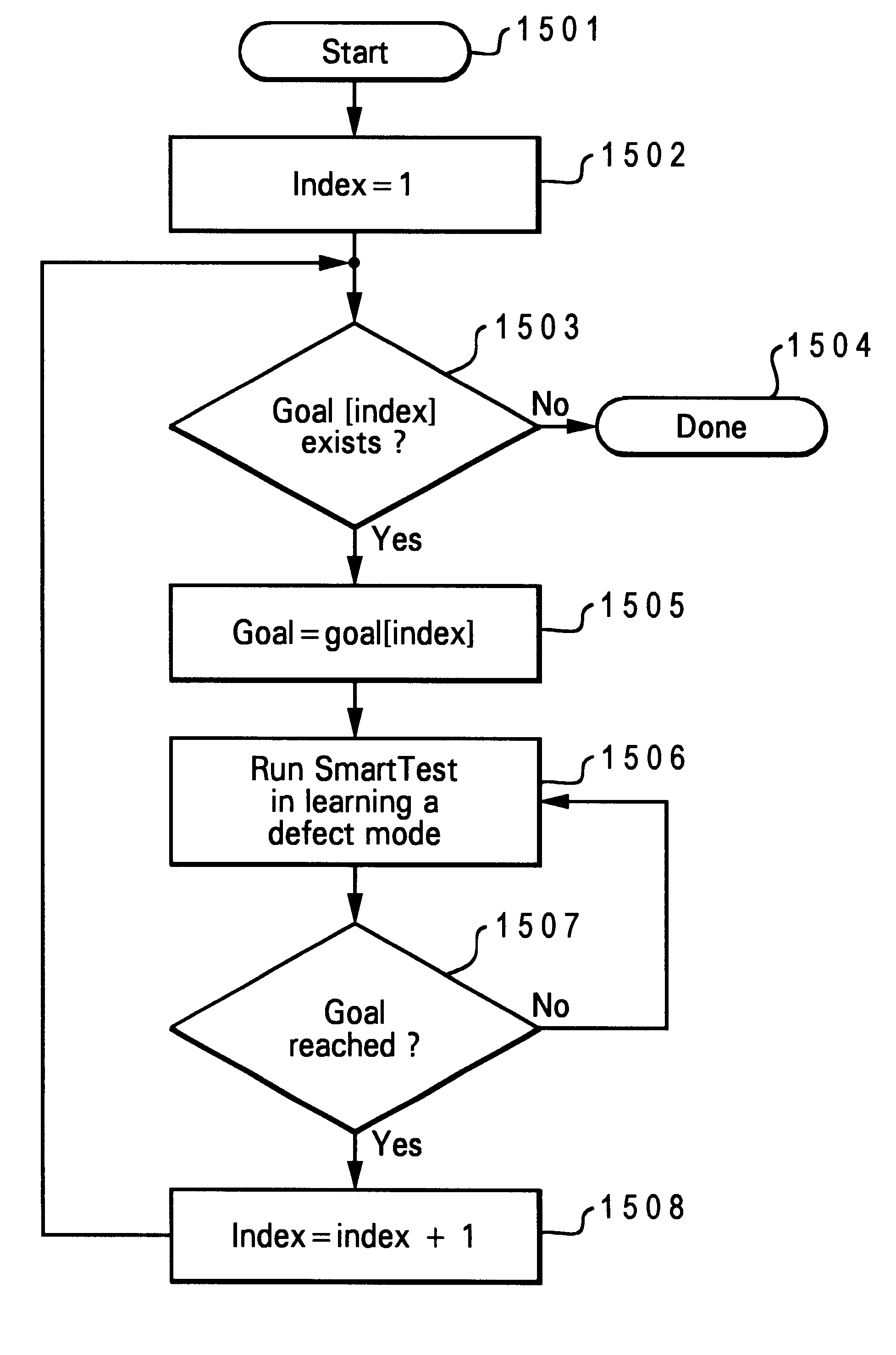

Method and apparatus for training an automated software test

InactiveUS6349393B1Efficient testingSoftware testing/debuggingSpecific program execution arrangementsSystem under testFeature model

An automated software test is provided which includes a functional model of a system to be tested. The automated software test is utilized to operate a system under test in accordance with specified facts, goals and rules. Quasi-random actions are taken within the system in accordance with specified rules and facts until a defined goal has been accomplished. Training the automated software test is accomplished by specifying a particular goal, i.e. identifying a particularly known defect, and thereafter running the test in a quasi-random fashion until the particular goal has been achieved. The number and nature of actions required to achieve that goal are logged and the process is then repeated until the shortest path required to achieve that goal has been determined. The log of actions which eventually reach a particularly defect may also be utilized a probable cause tree structure for future analysis.

Owner:IBM CORP

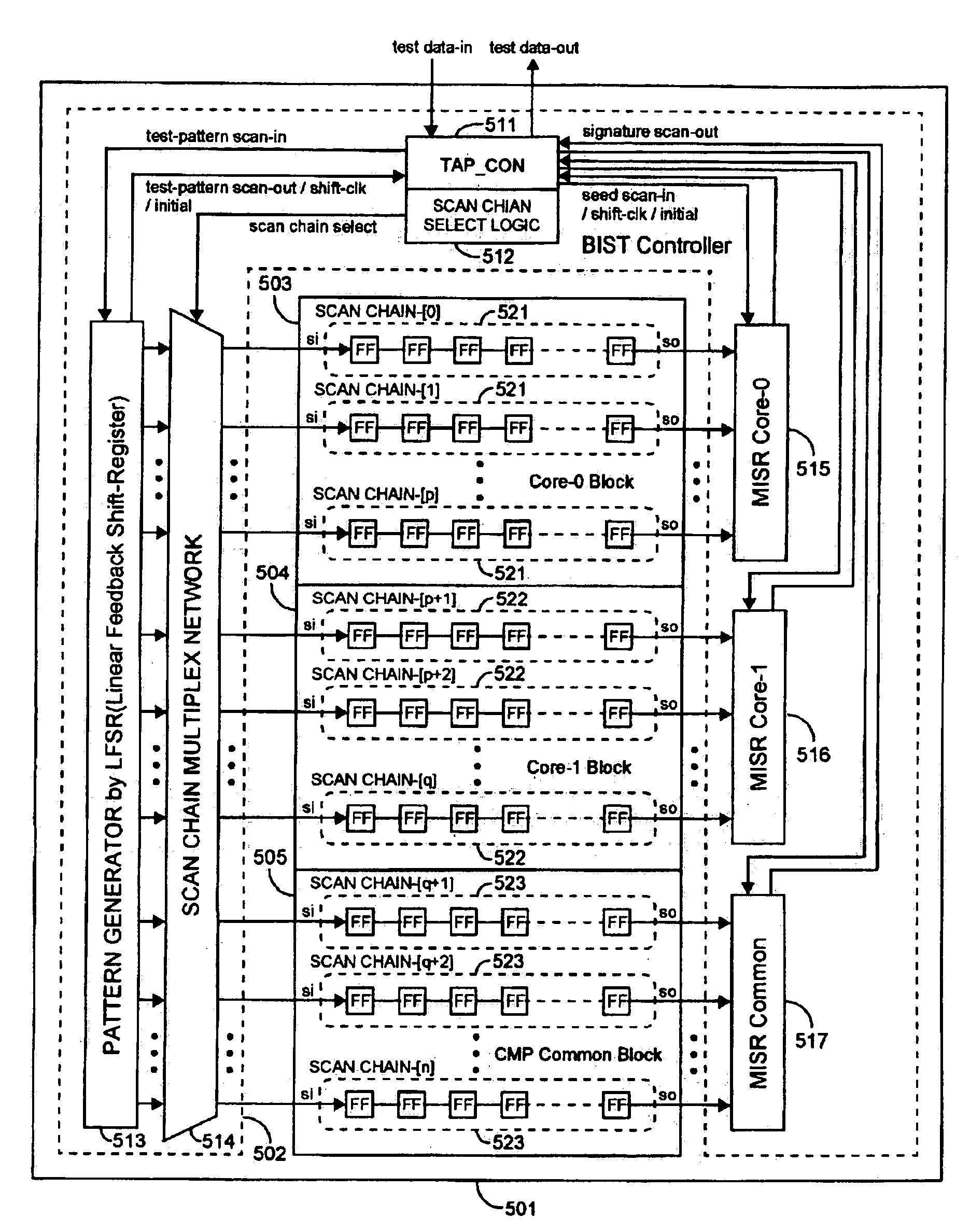

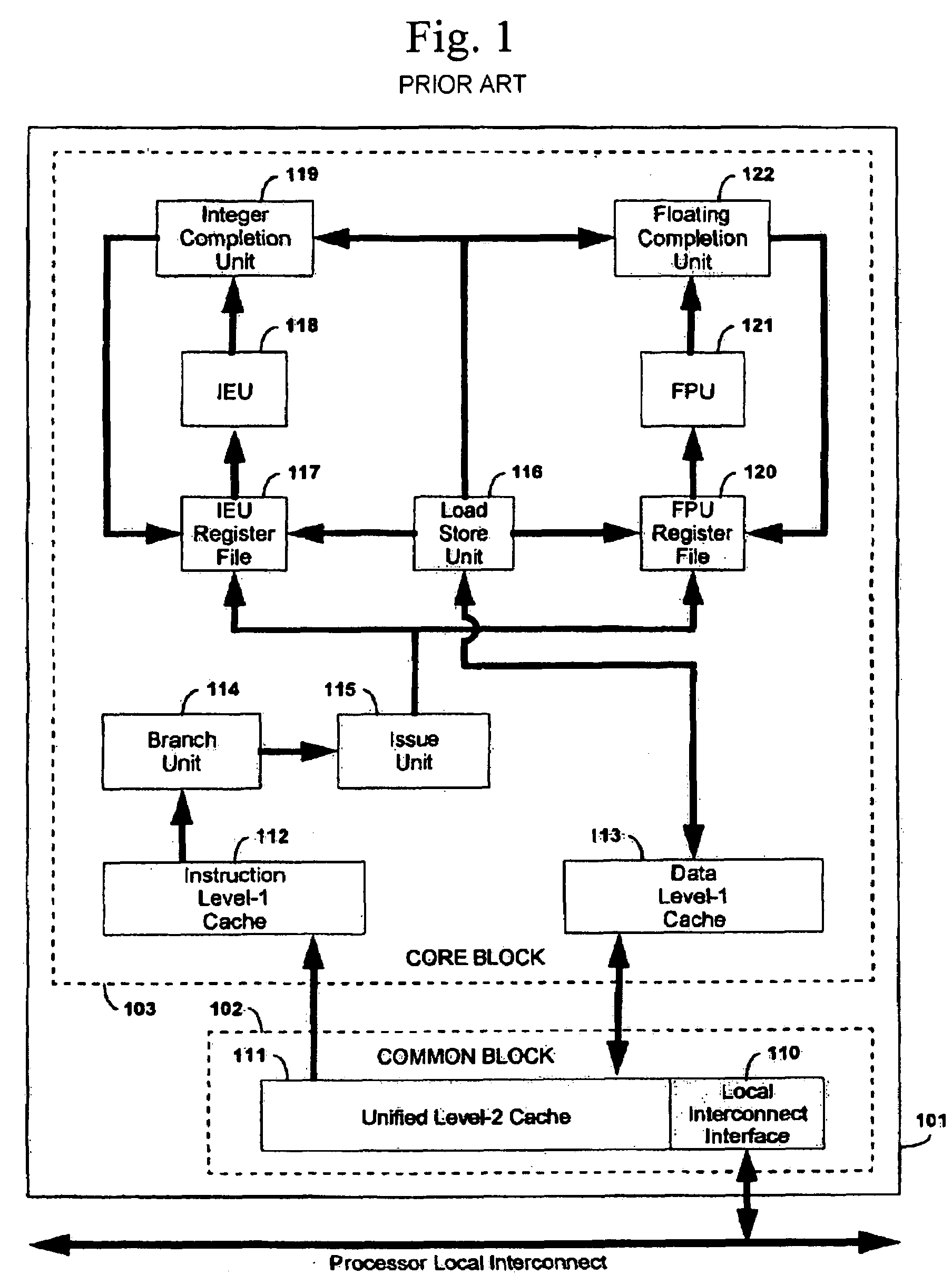

Multicore processor test method

ActiveUS7353440B2Easy to identifyIncrease productionElectronic circuit testingMemory loss protectionComputer hardwareComputer science

In processors having multiple cores, such as CMPs, an independent MISR test pattern compression circuit is provided for each logic block, which makes it possible to perform LSI tests more efficiently. A processor includes a plurality of logic block circuits, which include at least a first processor core circuit and a second processor core circuit, each processor core circuit having a scan chain circuit and being operable independently, and a common block circuit having a scan chain circuit and a cache circuit that is shared by the first processor core circuits and the second processor core circuits. The processor further includes, for each logic block, a test pattern generating circuit operable to generate a test pattern and input the test pattern to the scan chain of each logic block circuit, and a test pattern compression circuit operable to accept as input and compress the test pattern output by the scan chain of each logic block circuit.

Owner:FUJITSU LTD

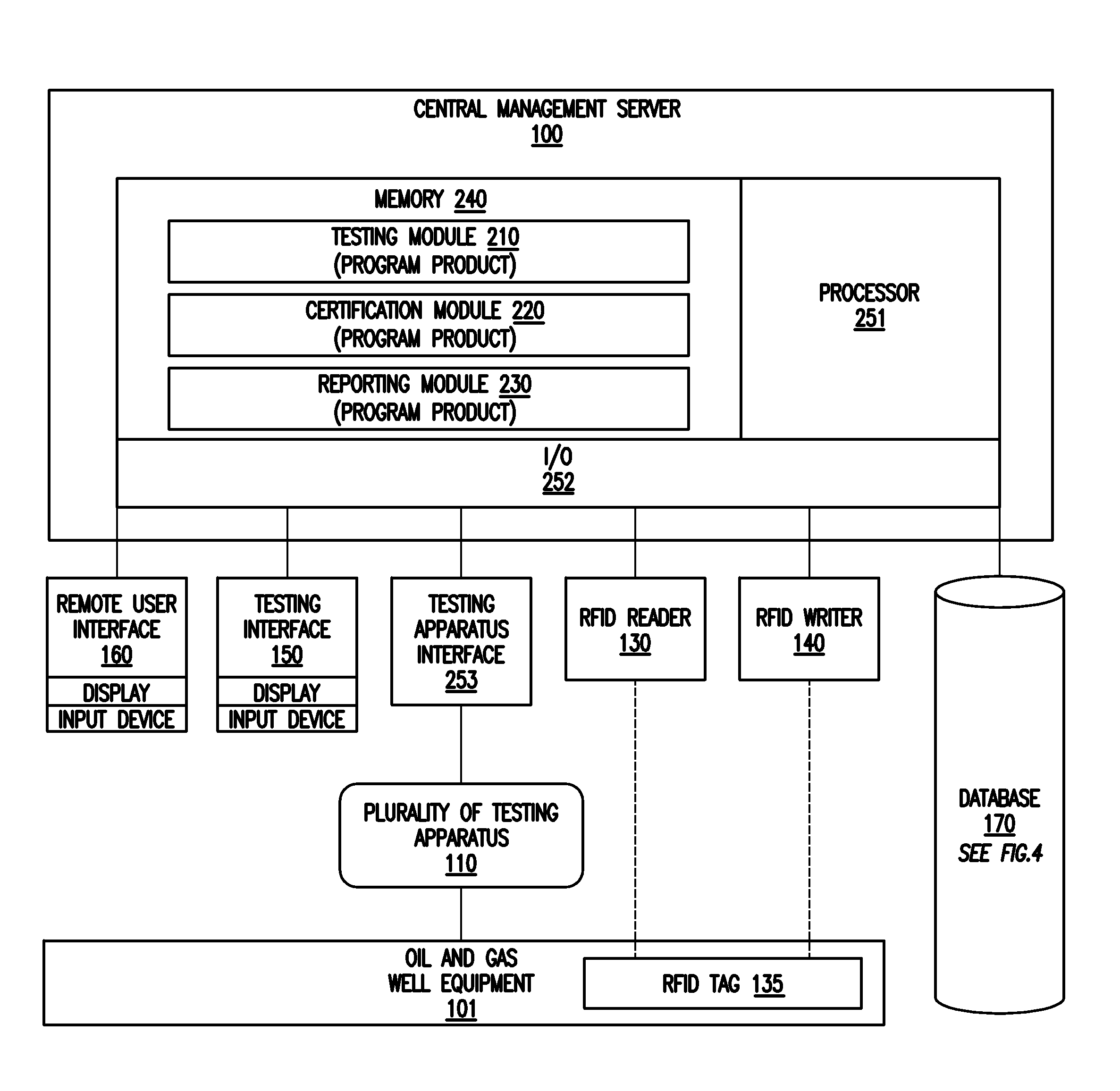

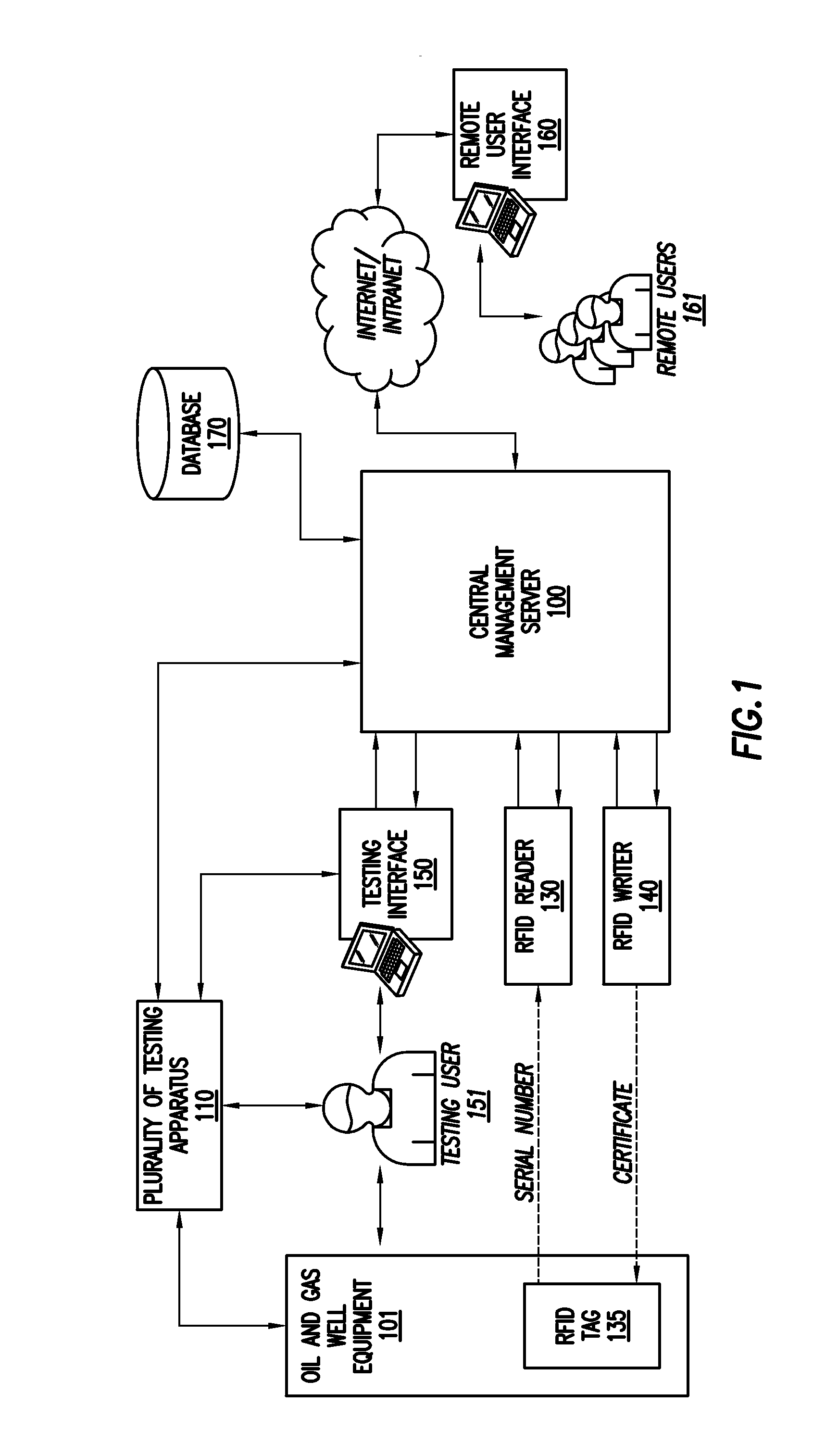

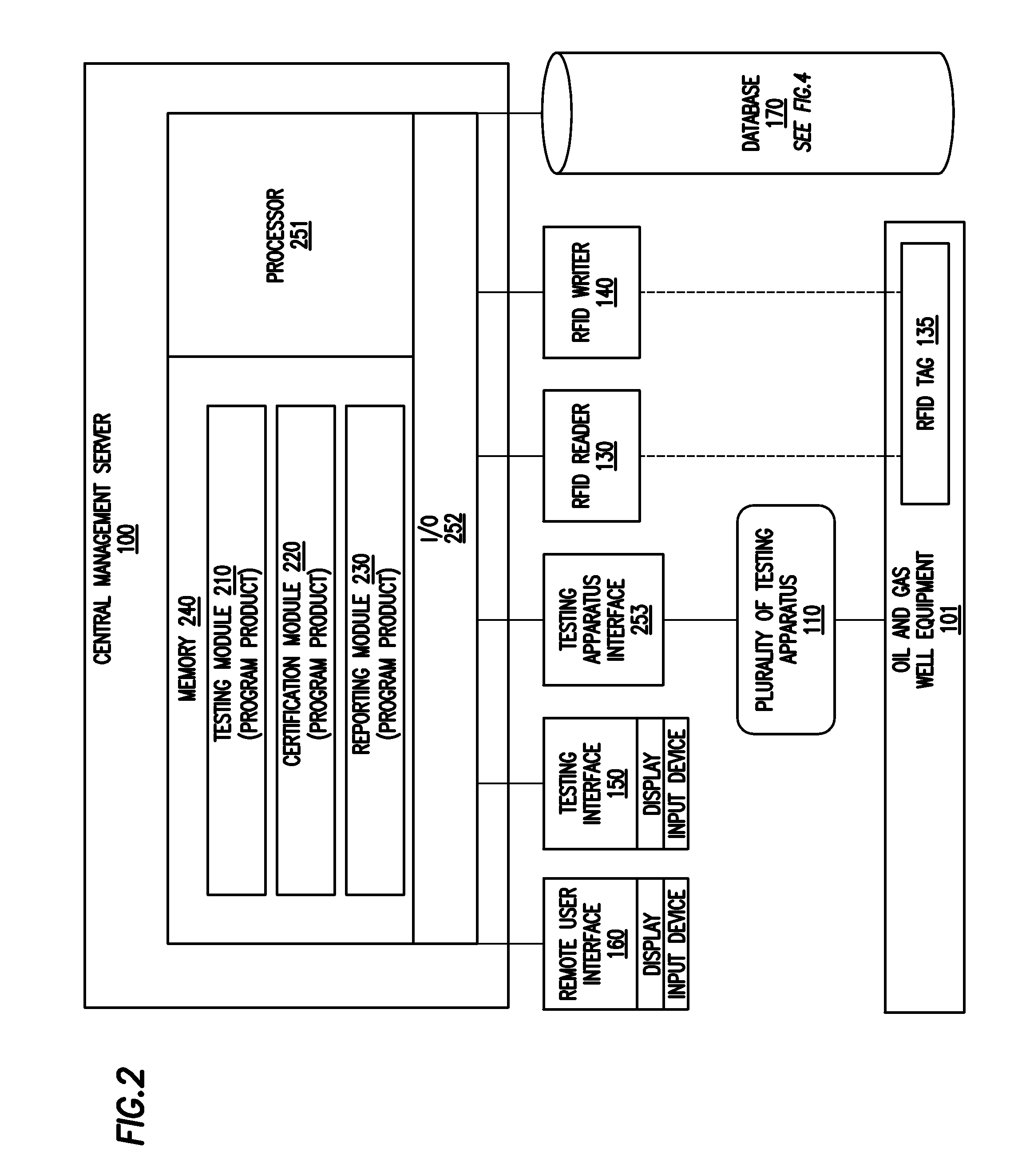

Machines, systems, computer-implemented methods, and computer program products to test and certify oil and gas equipment

InactiveUS20110270525A1Enhance testing managementEnhance management certificationElectric/magnetic detection for well-loggingSurveyTest specificationTest sequence

Embodiments of machines, systems, computer-implemented methods, and computer program products certify oil and gas well equipment. Embodiments identify a selected well equipment device, a device test specification, and testing sequences to be performed by a corresponding testing apparatus. Embodiments select a testing sequence responsive to the selected device. Embodiments control the testing apparatus for the selected testing sequence so that the corresponding testing apparatus performs the sequence responsive to the device test specification. Embodiments generate testing data for the selected testing sequence and link the testing data for the selected testing sequence to the device identifier for the device so that a certificate can be generated. Embodiments generate a certificate for the selected device responsive to the testing sequences having been performed upon the selected device and link the certificate for the selected device to the device identifier so that the certificate can be readily recalled.

Owner:S P M FLOW CONTROL

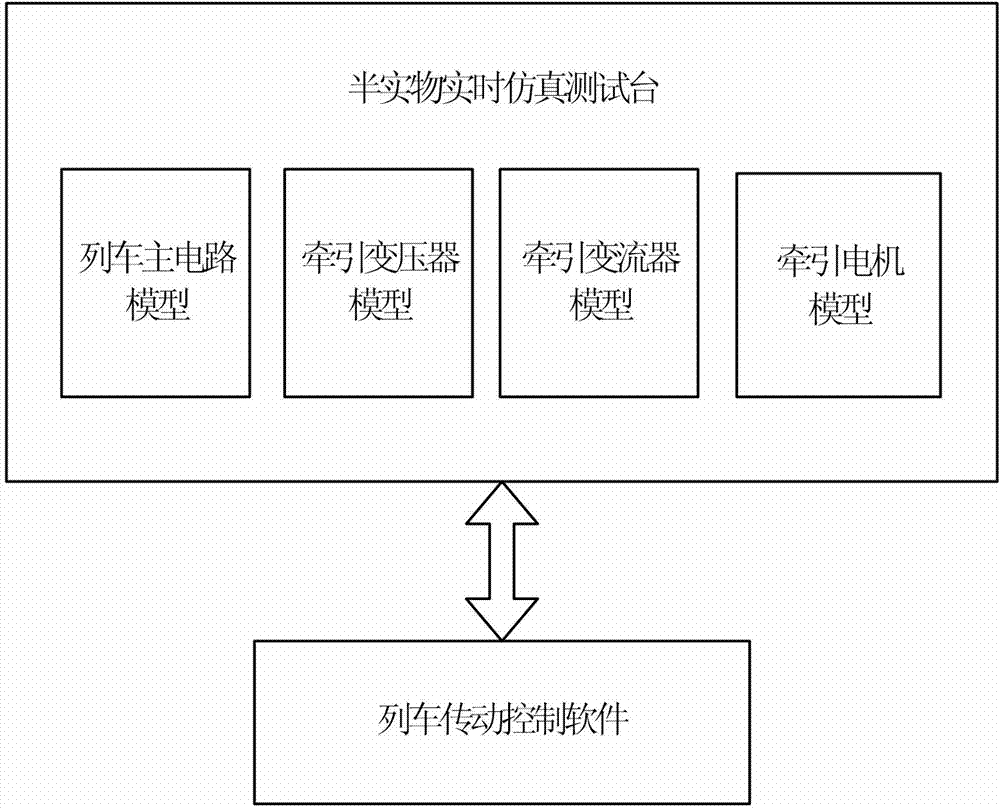

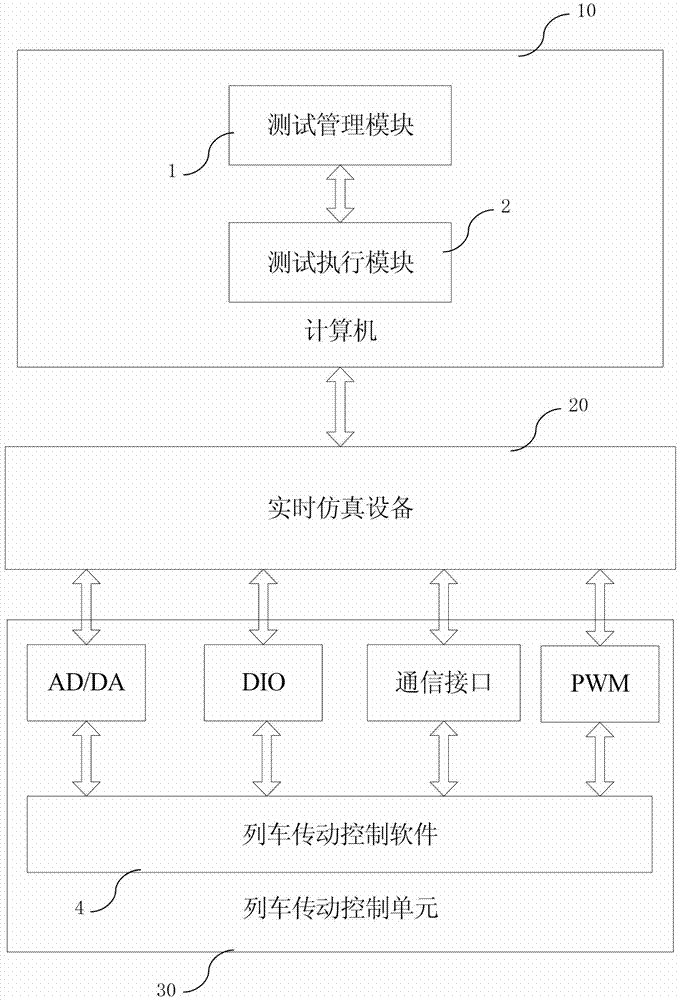

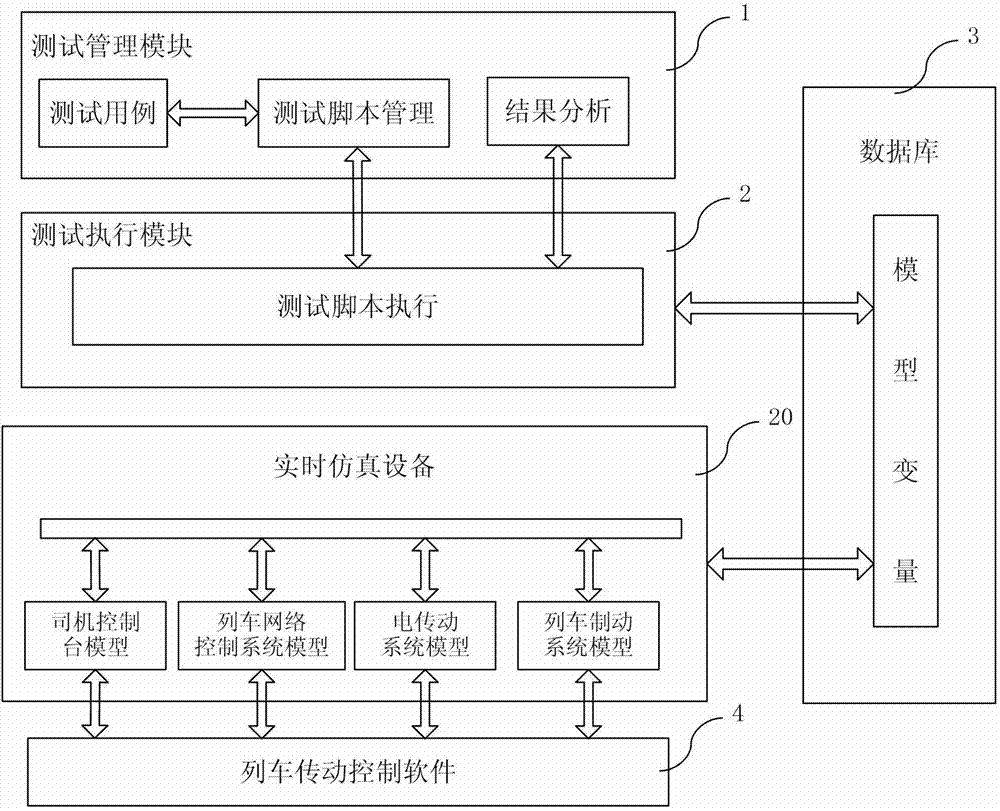

Automated train drive control software testing system and method

The invention discloses an automated train drive control software testing system and method. The system comprises train drive control software for conducting centralized control and real-time drive on a hardware IO interface unit in a train drive control unit and achieving real-time data acquisition and output control, a real-time simulation device for simulating an external device associated with the train drive control software, achieving dynamic simulation of the external device through software modeling and performing real-time data interaction with the train drive control unit, a computer including a testing management module and a testing execution module, wherein the testing management module manages a test case, a testing script and test result data, the testing execution module develops a testing script corresponding to a certain test case and automatically executes the corresponding testing script. The automated train drive control software testing system and method can achieve more convenient, quick and efficient testing, the problems and defects at a software design stage are decreased, and reproduction and analysis of field faults and problems can be performed so as to shorten a product development period and improve product quality.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

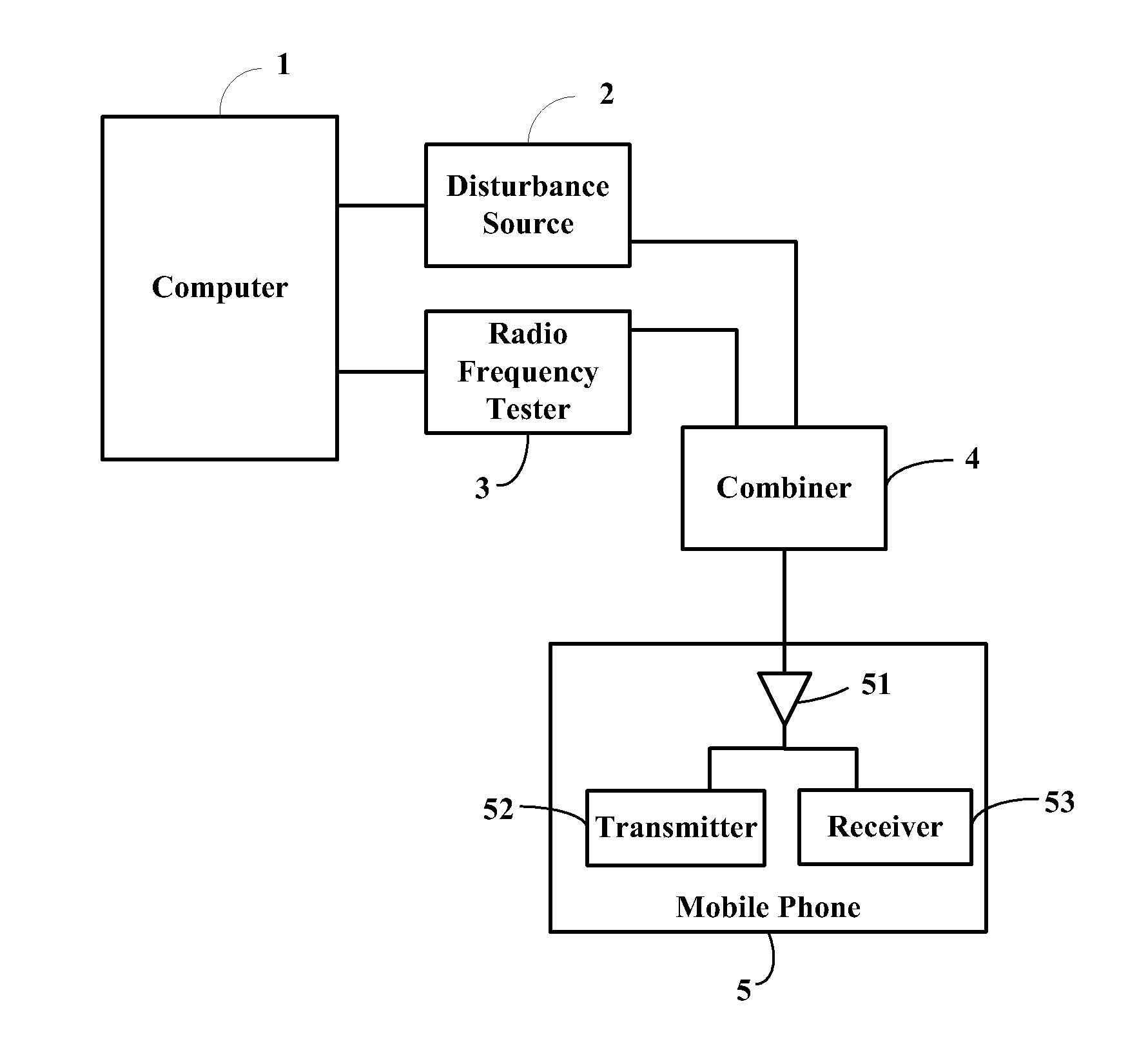

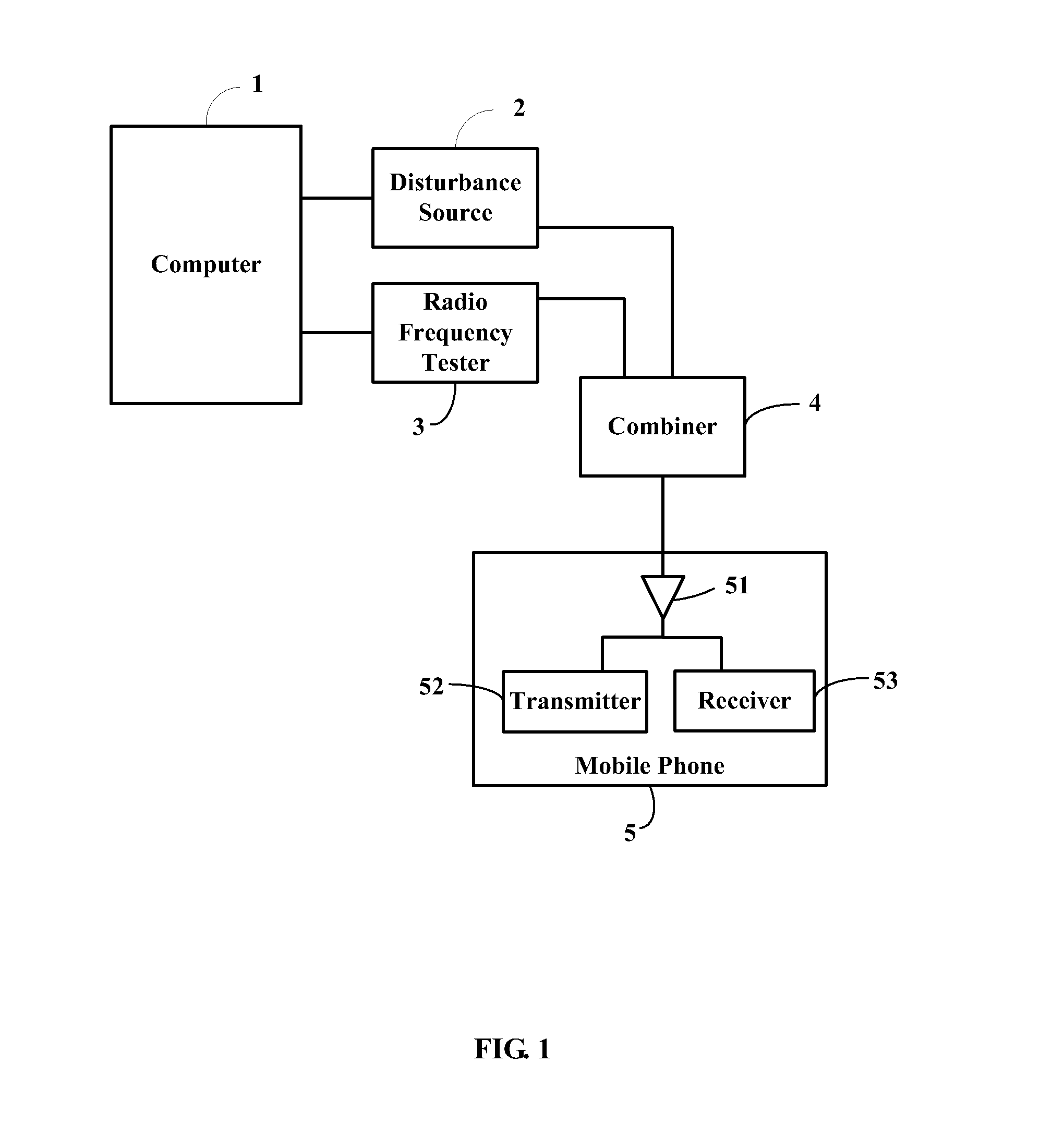

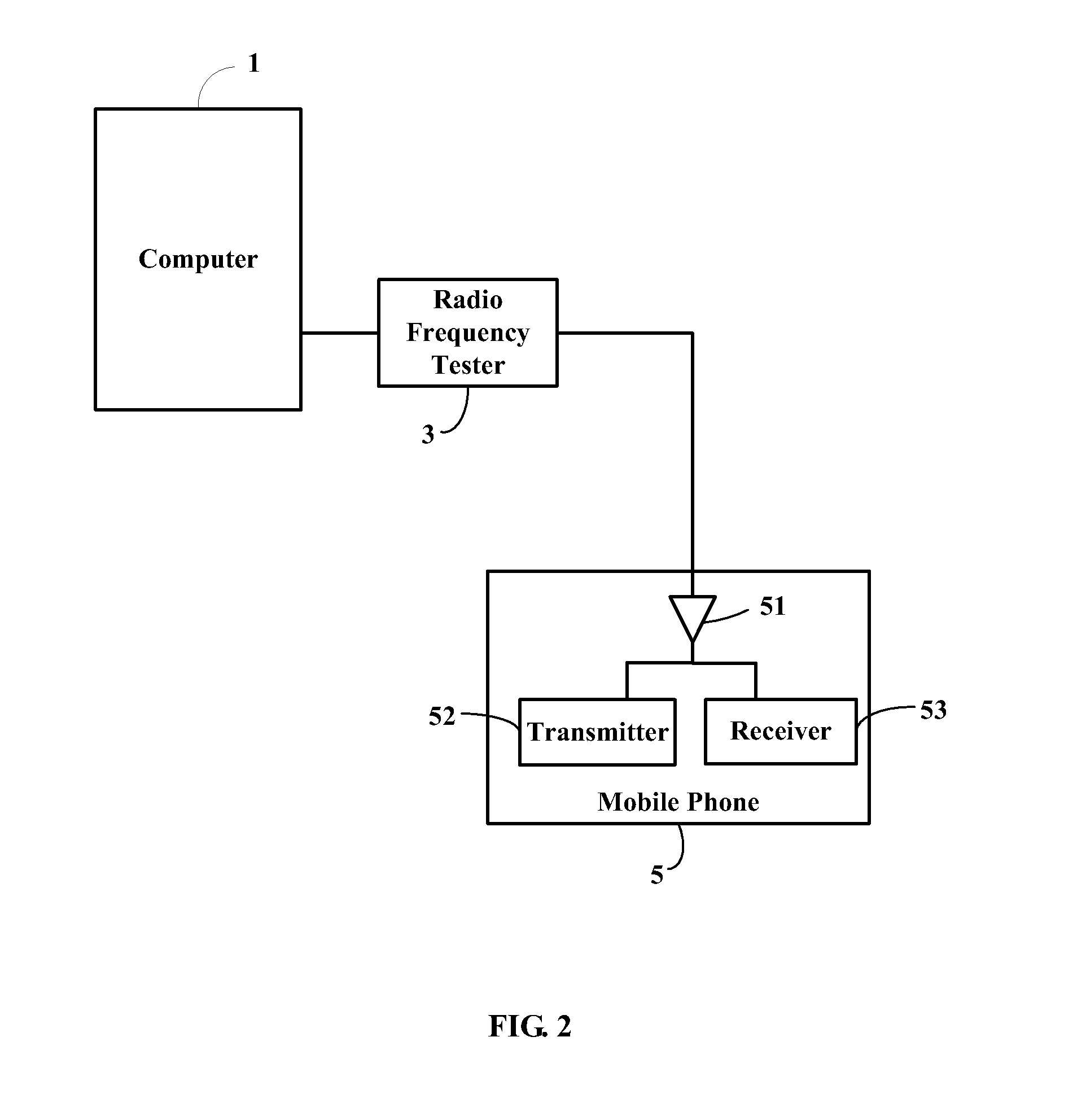

Method for performing a radio frequency test on a mobile phone

InactiveUS20090098868A1Efficient testingTests the performance of the radio frequency automatically and efficientlyTransmitters monitoringReceivers monitoringEngineeringRadio frequency

A method for performing an radio frequency test of a mobile phone (5) includes: setting standard parameters of a transmitter (52); controlling an RF tester (3) to send RF signals to a receiver (53); processing the RF signals and transmitting the processed RF signals to the transmitter, reprocessing the processed RF signals and transmitting the reprocessed signals to the RF tester; obtaining resulting parameters of the RF performance of the transmitter; determining whether the RF performance of the transmitter is acceptable; setting standard parameters of the receiver; controlling the RF tester to send RF signals to a combiner (4), and controlling a disturbance source (2) to send channel noise to the combiner; generating combined signals by combining the RF signals and the channel noise, and transmitting to the receiver; obtaining resulting parameters of the RF performance of the receiver; and determining whether the RF performance of the receiver is acceptable.

Owner:CHI MEI COMM SYST INC

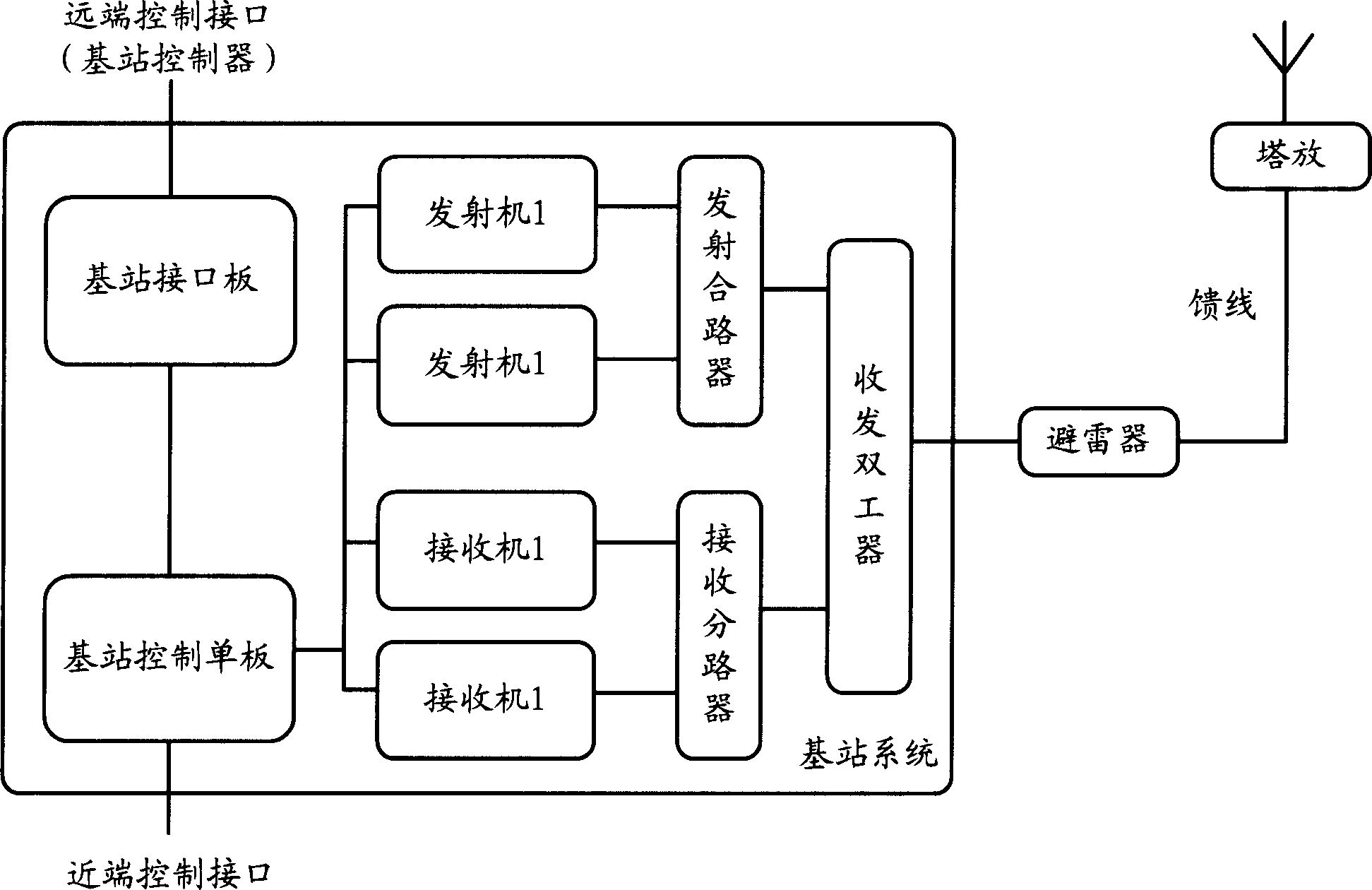

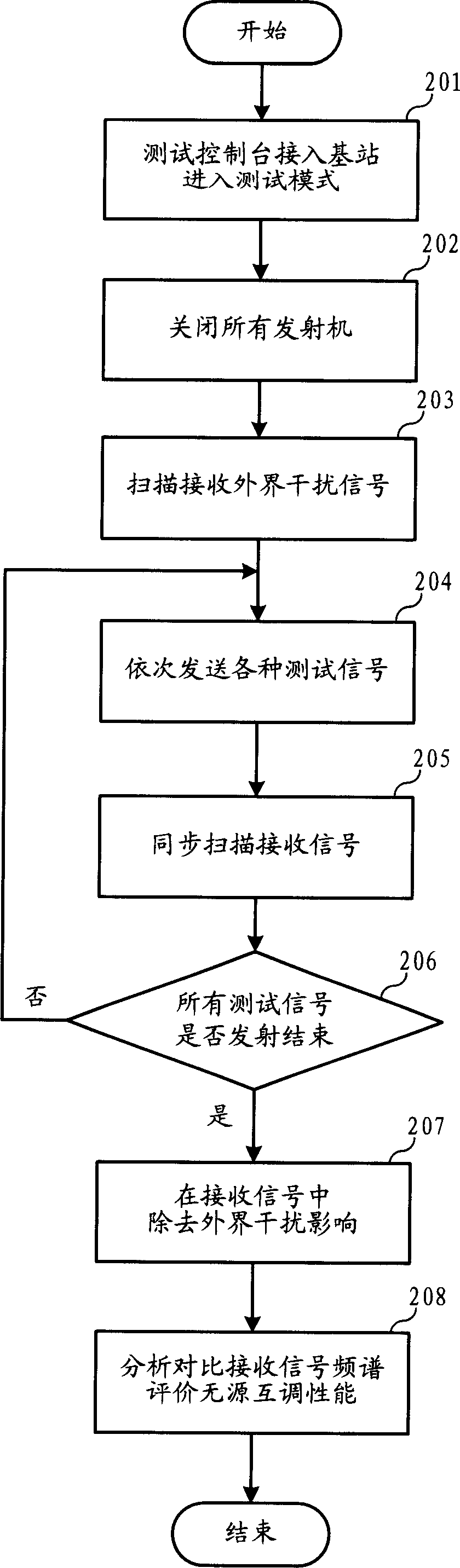

Passive intermodulation testing method of mobile communication base station system

ActiveCN1870473AImprove reception qualityEasy to testTransmitters monitoringRadio/inductive link selection arrangementsCommunications systemEngineering

This invention relates to test to the passive intermodulation performance of the communication system, which controls an emitter to emit test signals according to a preset mode, controls a receiver to scan and receive the signals in the test bands and analyze spectrums of the received signals to evaluate the entire passive intermodulation performance of the base station, in which, the original outside interference signals are received at the shut-off state of the emitter to eliminate its influence and measure the performance accurately and the received test bands are computed accurately by the known carrier frequency sphere, intermodulation stages and the received frequency sphere parameters and the test signal receiving quality is increased by scanning the emitted and received continuous waves.

Owner:HUAWEI TECH CO LTD