Patents

Literature

860 results about "Production testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Testing in Production (TiP) means to perform various tests in a production state or live environment. It helps you to focus on few areas of the functionalities used in the application that usually remains unscripted.

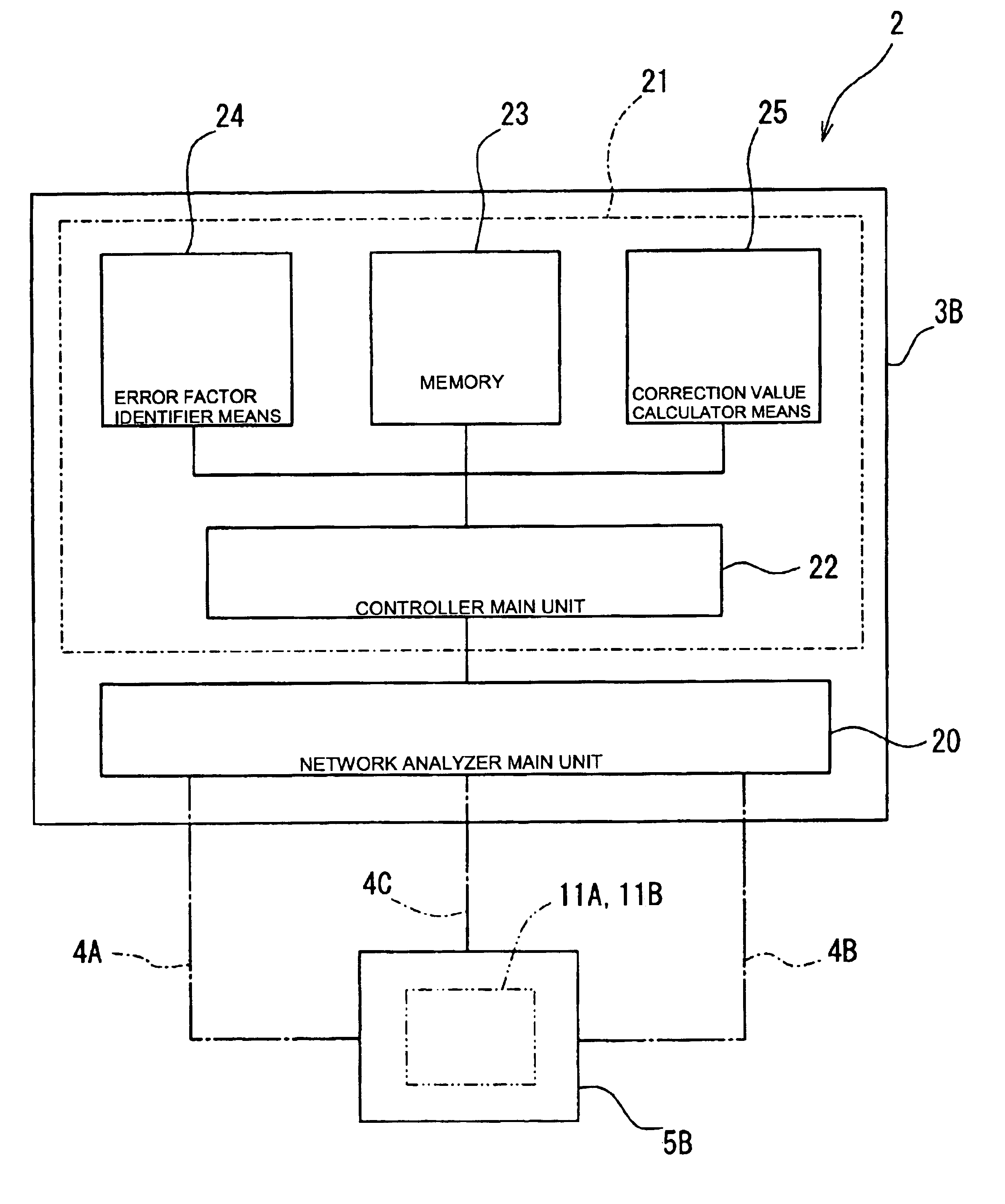

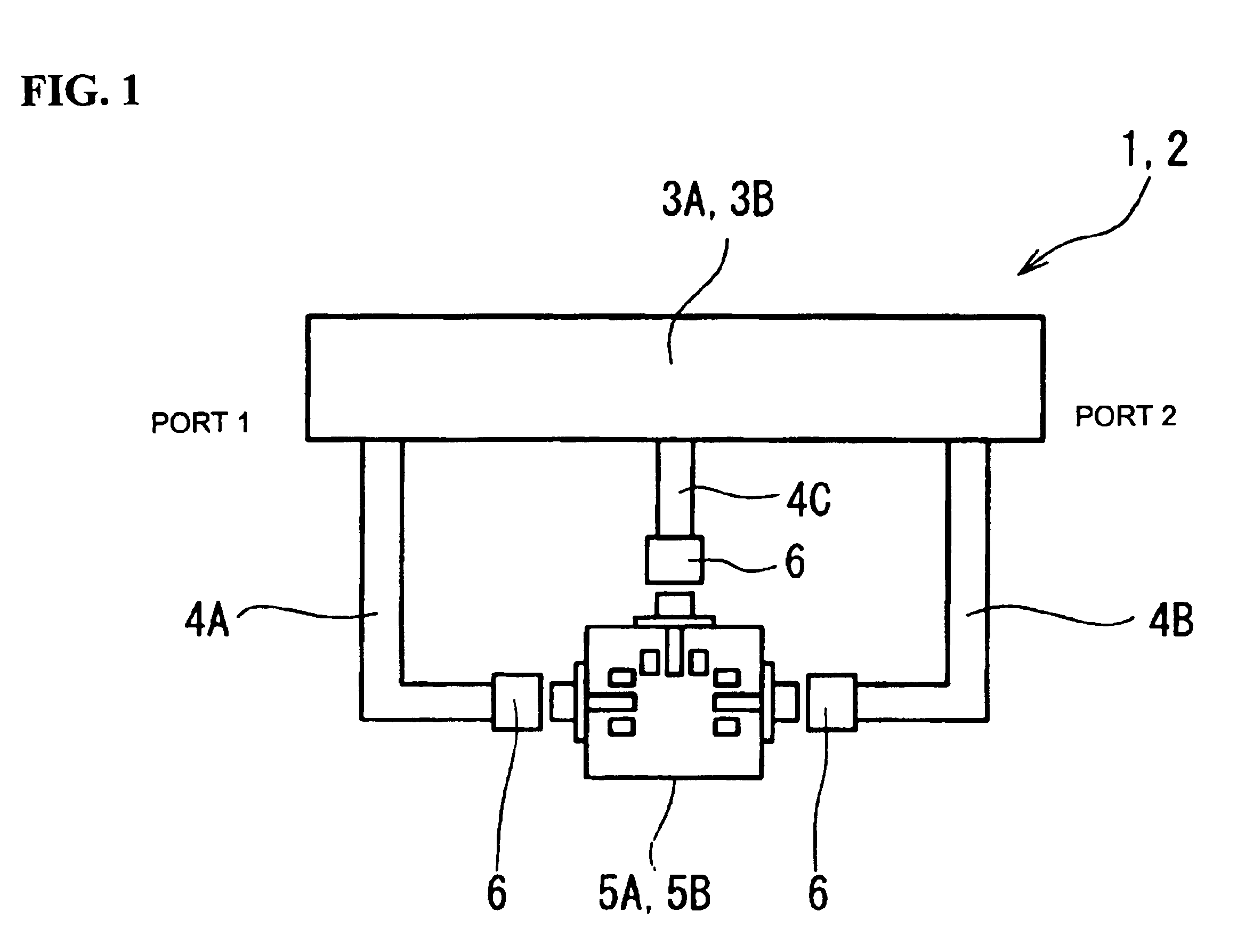

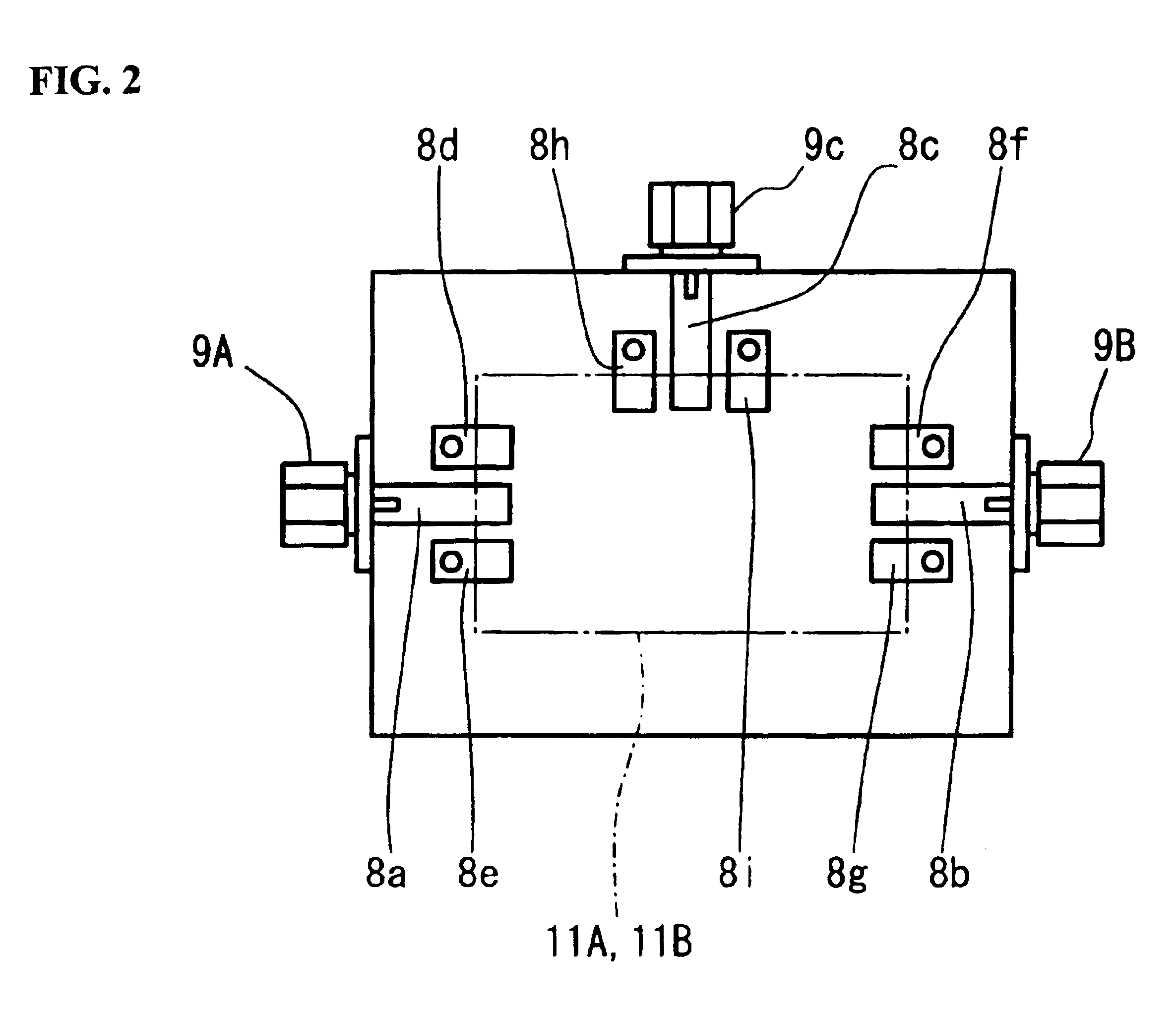

Method of correcting measurement error and electronic component characteristic measurement apparatus

ActiveUS6838885B2Easily and automatically expressedSuppress mutationResistance/reactance/impedenceElectrical testingObservational errorMeasurement device

A high-precision, multi-port compatible, relative correction method and apparatus for correcting measurement errors covering an increase in the number of ports of a non-coaxial electronic component, in which a relative correction adapter 31 is provided that is formed of a two-port network connected to each port of a production test fixture 5B adjacent to a measurement apparatus. The relative correction adapter has a characteristic that modifies the electrical characteristics generated by the production test fixture 5B having an electronic component under test mounted thereon into electrical characteristics generated by a standard test fixture 5A having the electronic component under test mounted thereon. An error factor of the relative correction adapter 31 is identified from a standard test fixture measurement value and a production test fixture measurement value of a correction data acquisition specimen 11B. A production test fixture measurement value of the electronic component under test 11A is corrected with the error factor of the relative correction adapter 31 to thereby obtain the standard test fixture measurement value of the electronic component under test 11A which is assumed to be obtained when the electronic component under test 11A.

Owner:MURATA MFG CO LTD

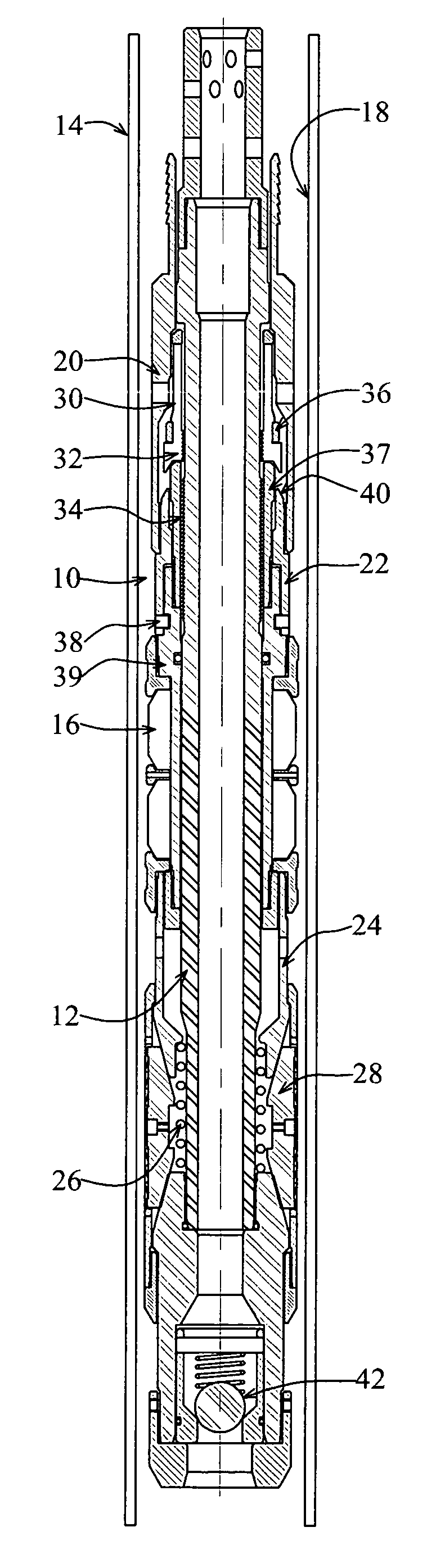

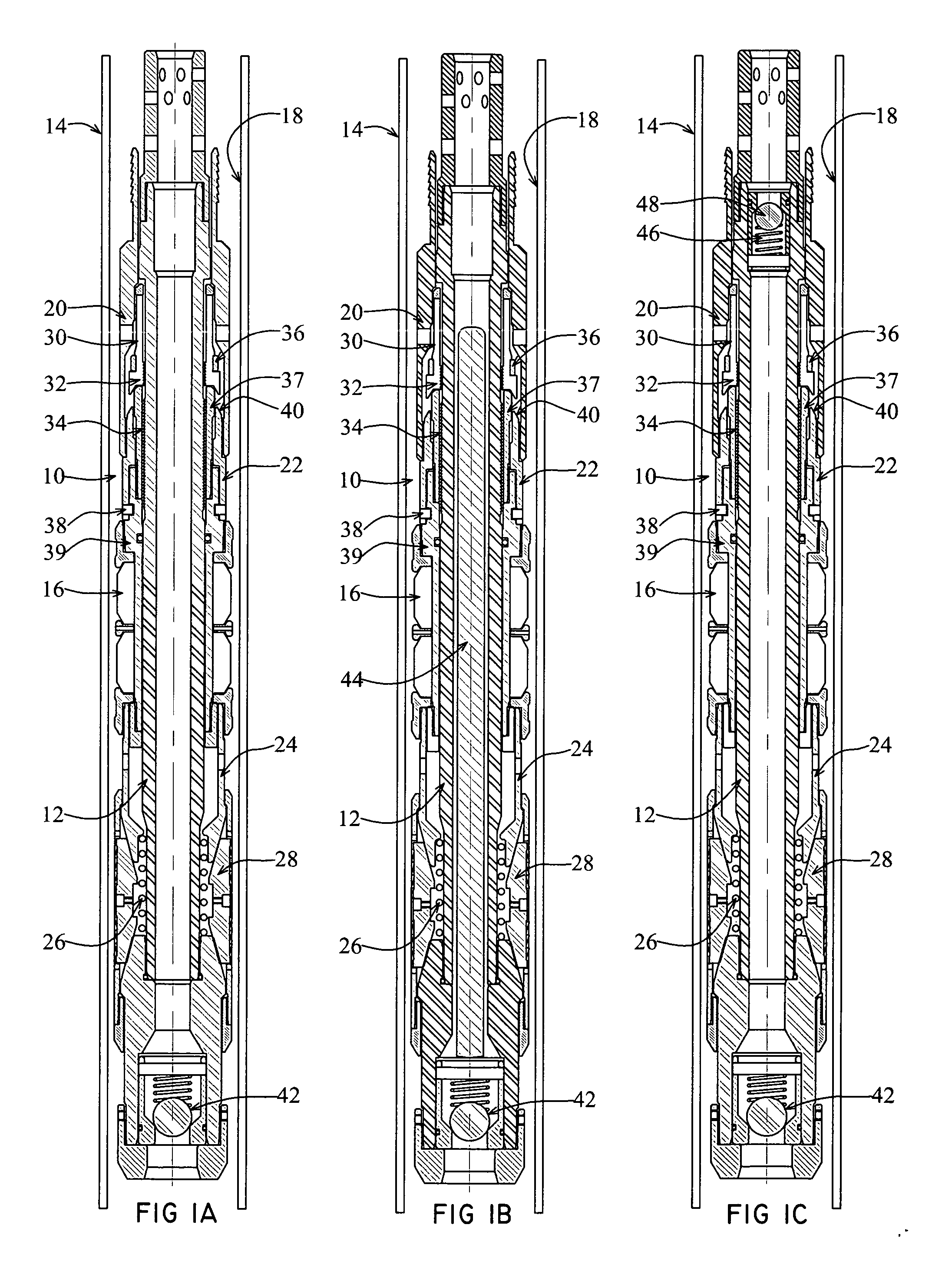

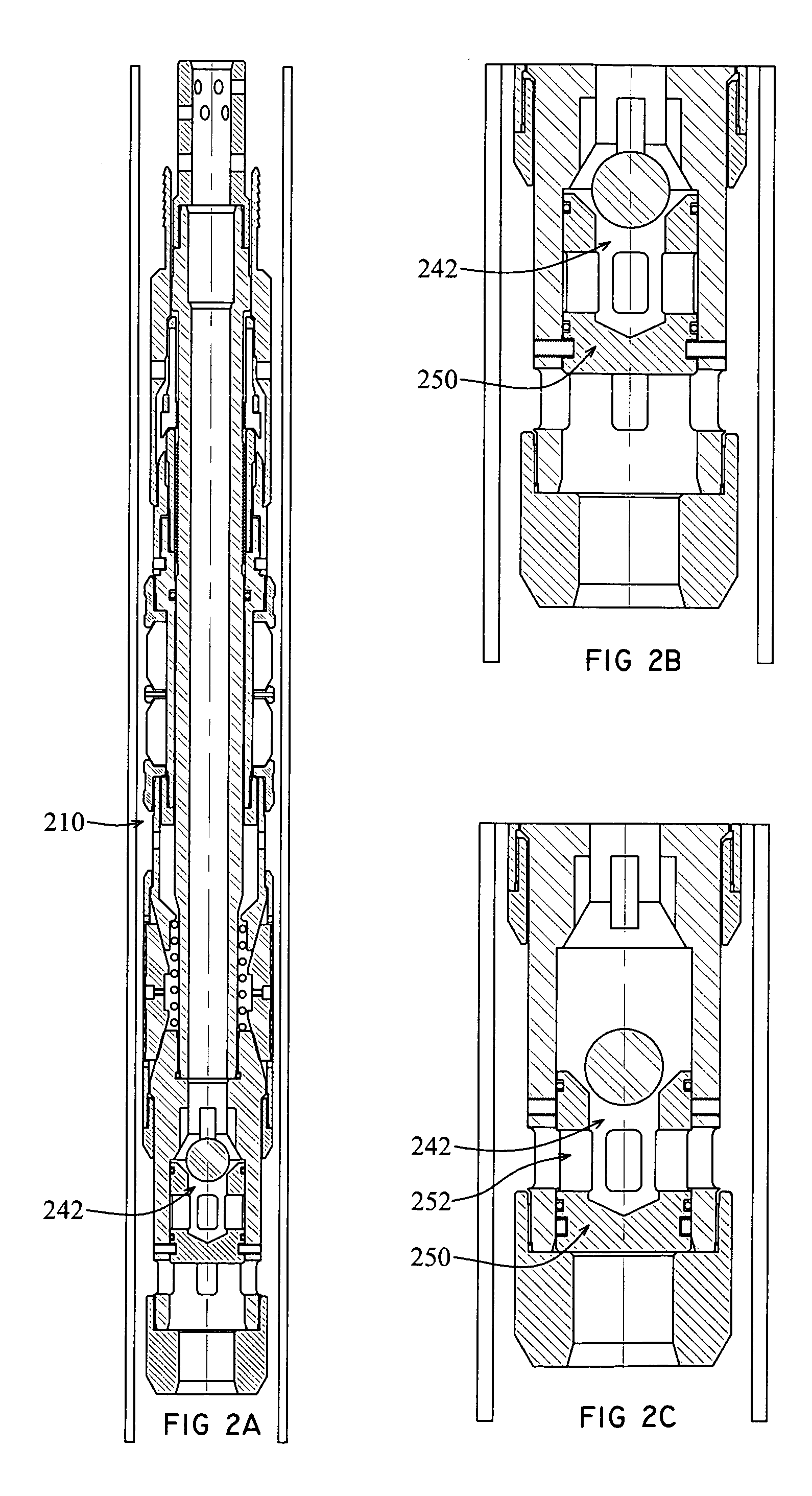

Retrievable frac packer

InactiveUS20070051521A1Reduce in quantityIncrease sealing forceFluid removalSealing/packingManufacturing engineeringProduction testing

A retrievable frac packer is provided which allows frac operations to be conducted with a single, retrievable tool, with the capability of providing positive zone production indications during production testing.

Owner:EAGLE DOWNHOLE SOLUTIONS

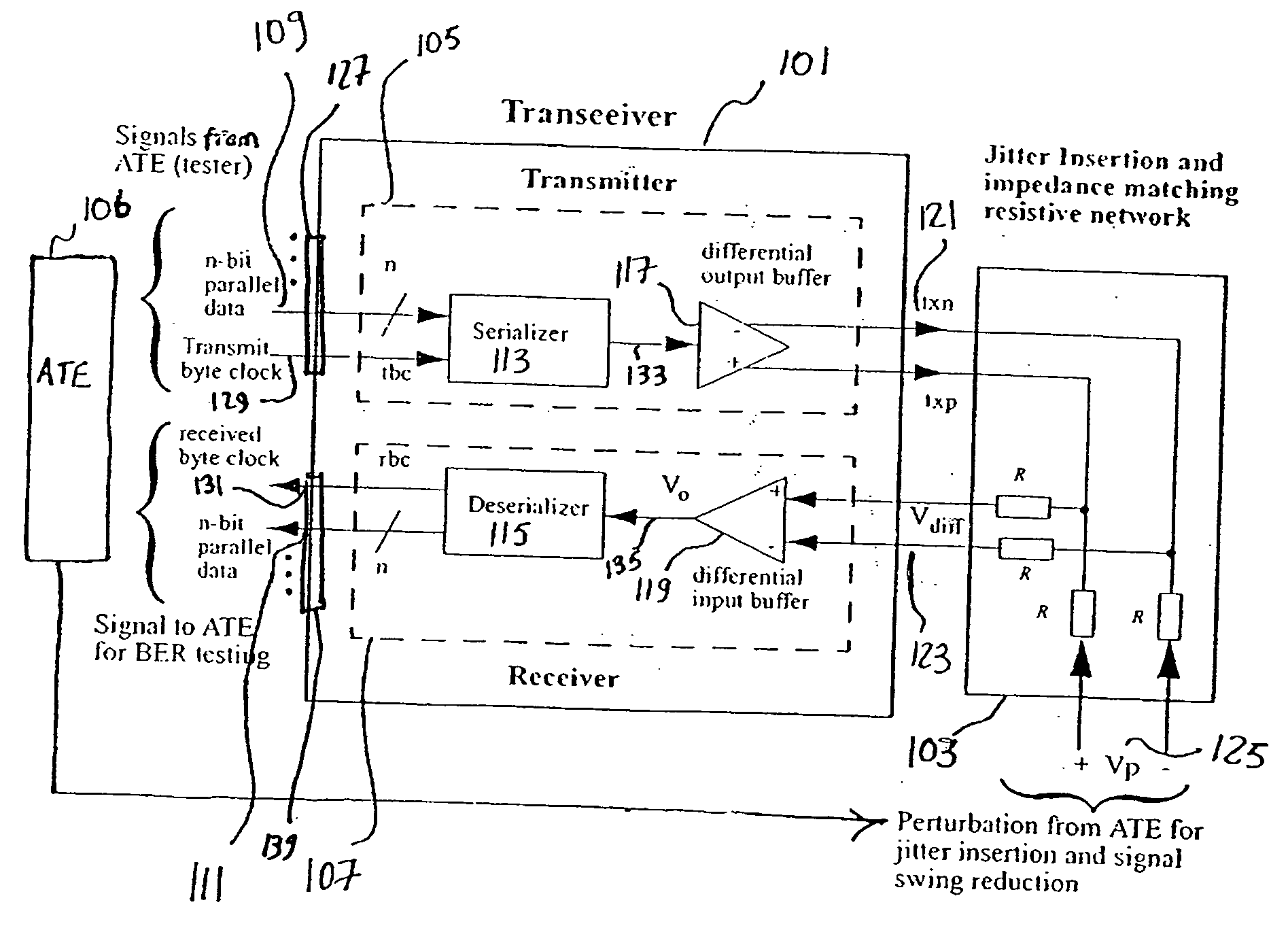

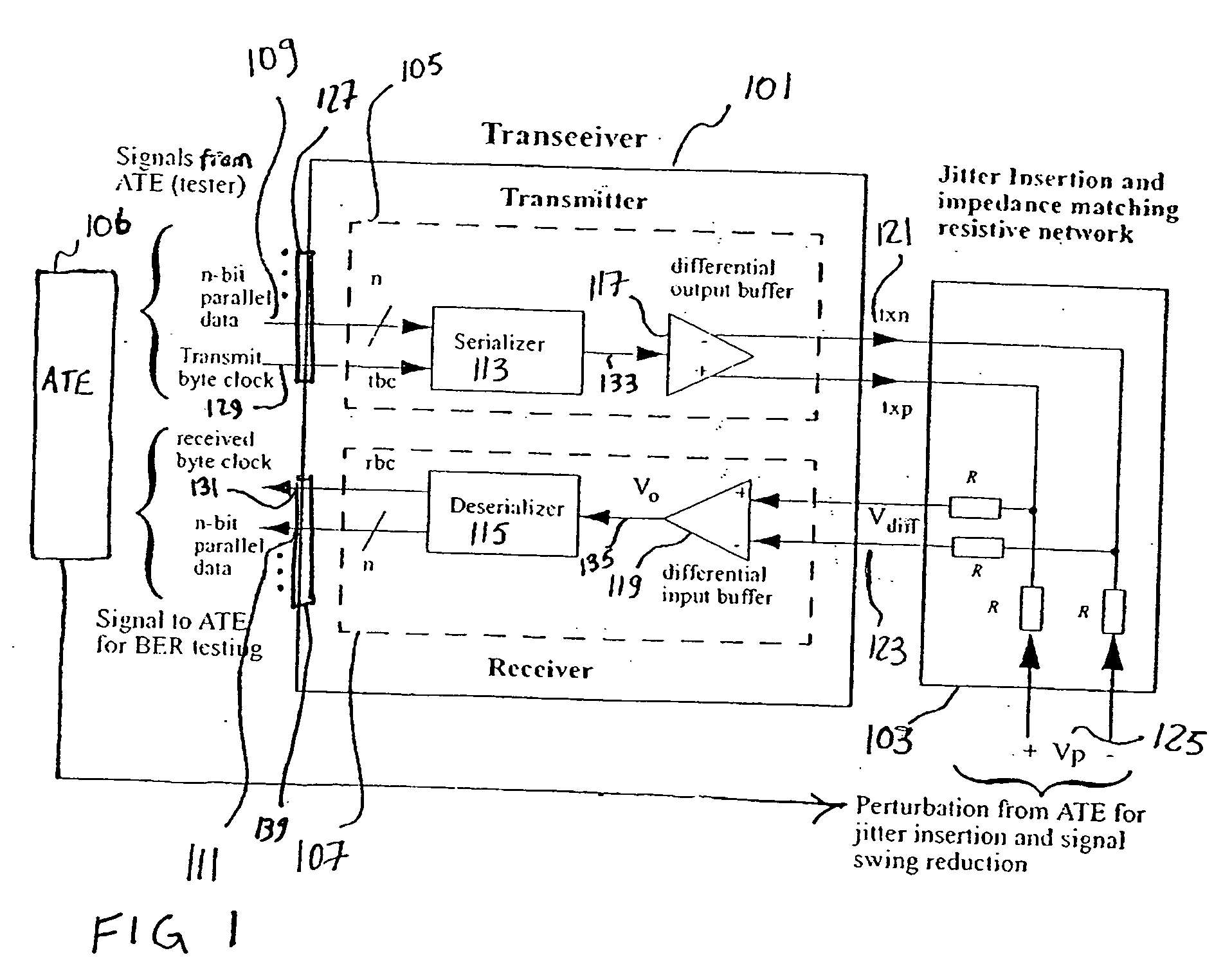

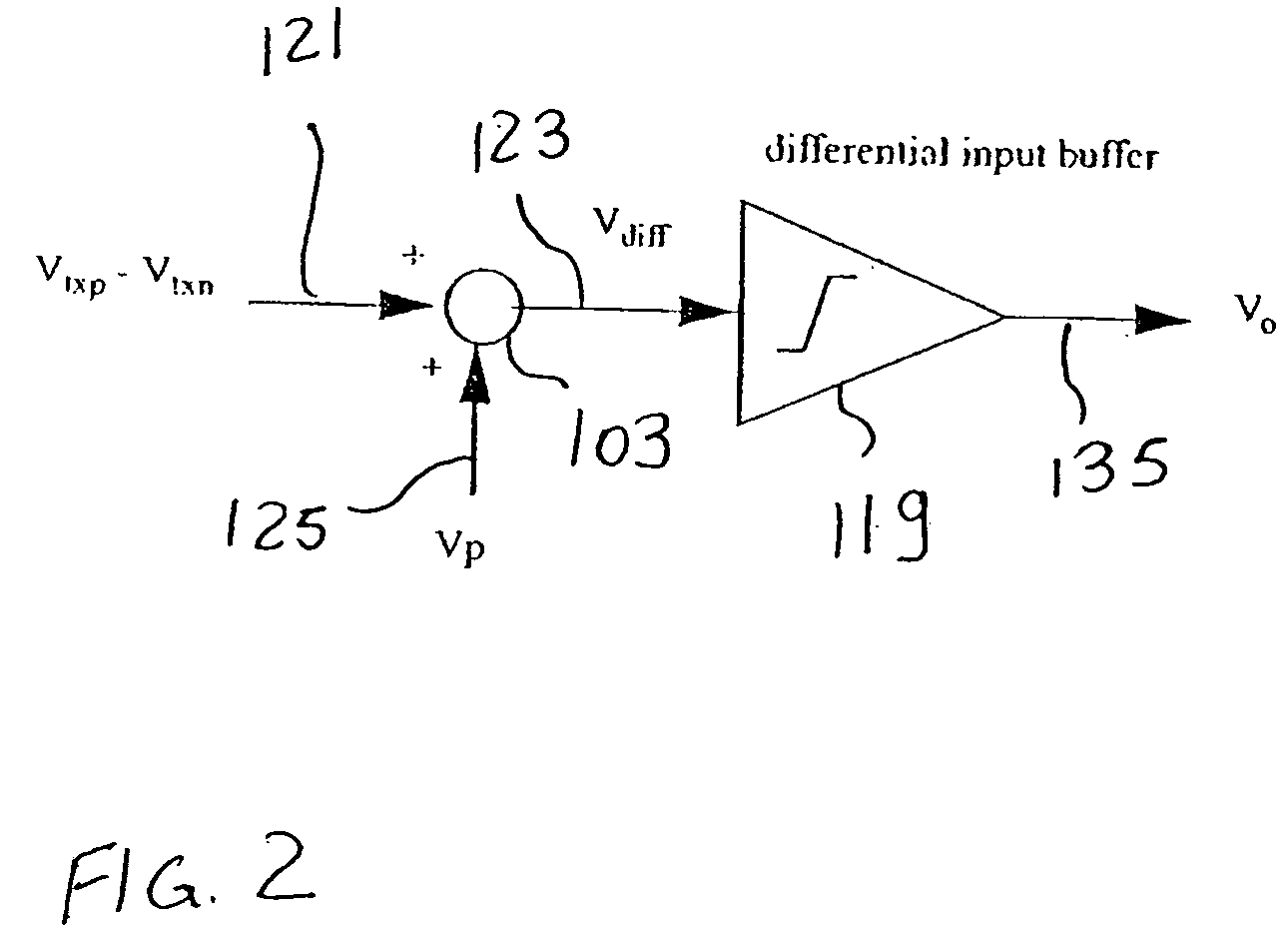

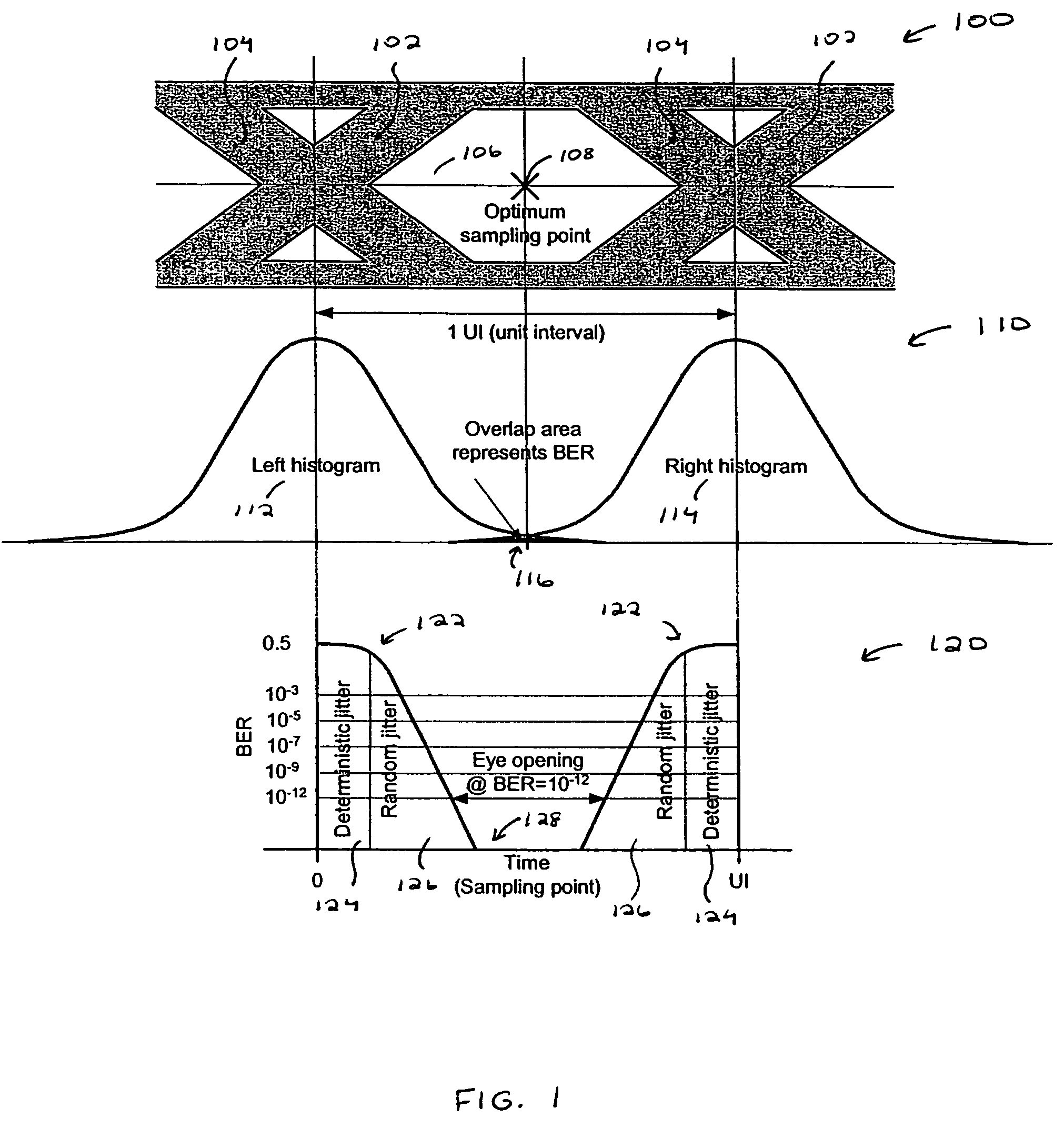

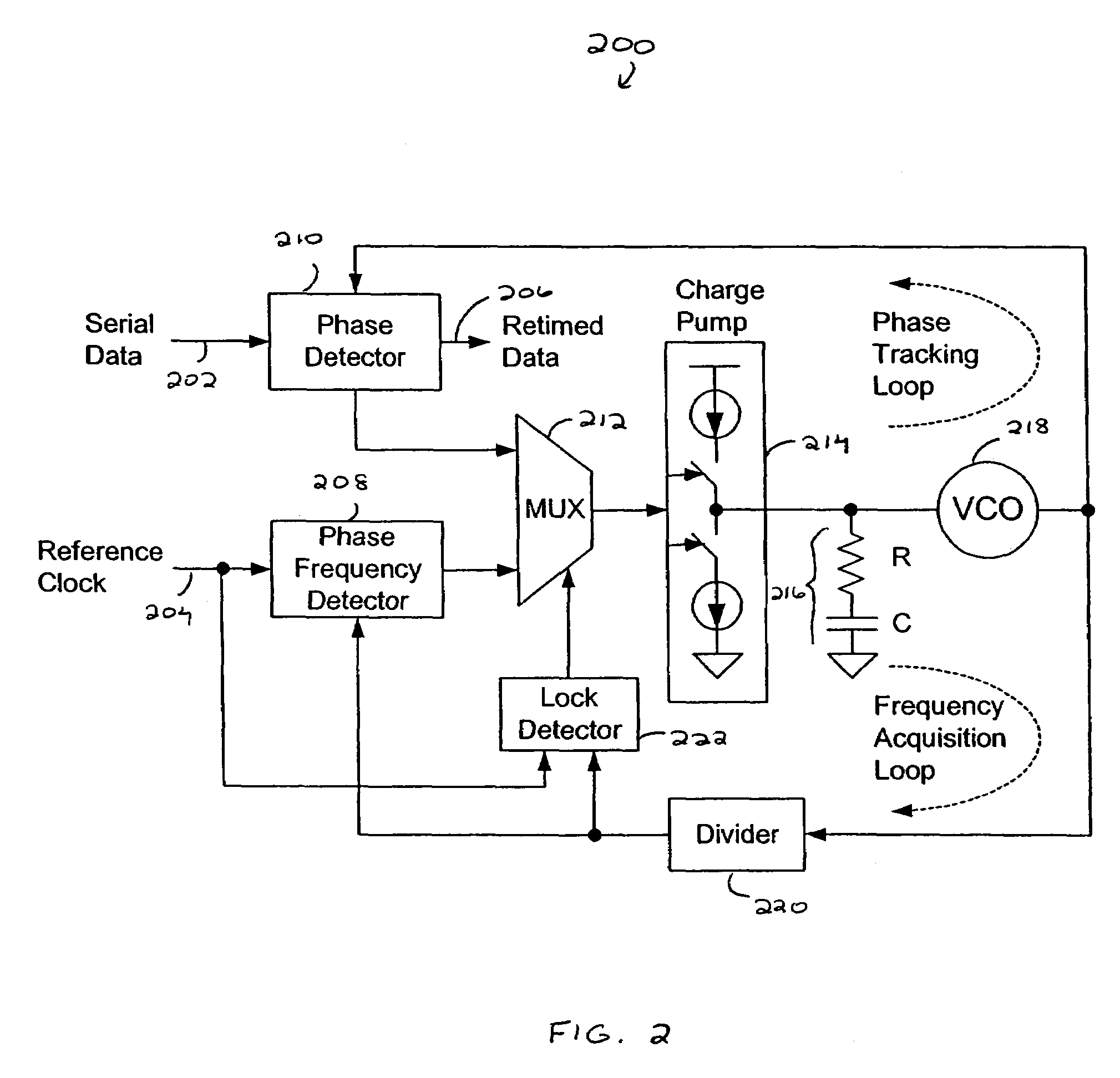

System and method for production testing of high speed communications receivers

InactiveUS20050172181A1Digital circuit testingElectrical measurement instrument detailsTransceiverLow voltage

A method for testing a semiconductor device with a multi-gigabit communications receiver includes combining a data output from a high-speed communications transmitter with a perturbation signal generated by automatic test equipment. The combined signal data signal including jitter and low voltage swings is input to the communications receiver port under test. The automatic test equipment determines the bit error rate of the parallel data output from the receiver port under test. This test method is appropriate for semiconductor devices with multiple transceiver ports.

Owner:MELLANOX TECHNOLOGIES LTD

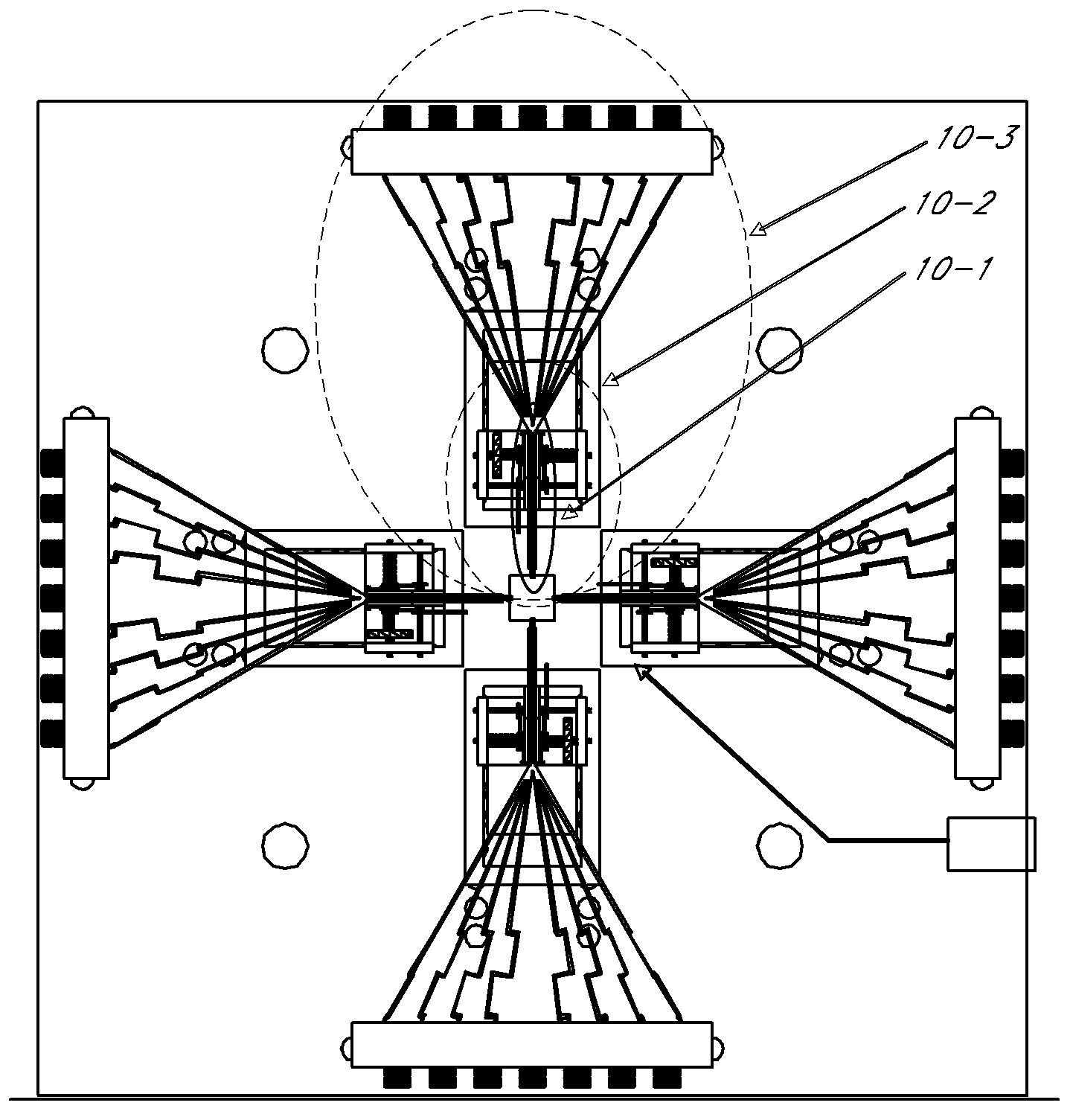

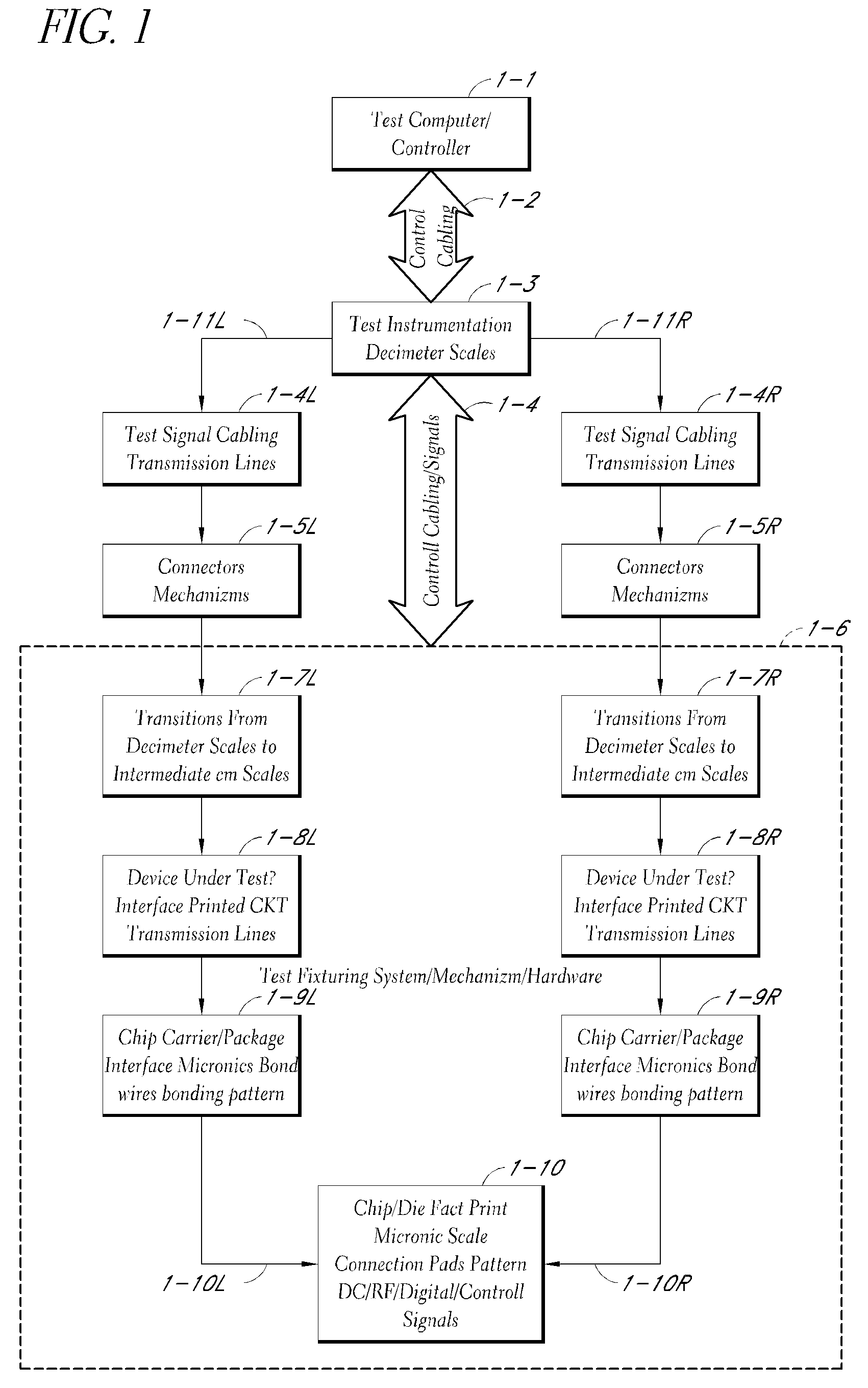

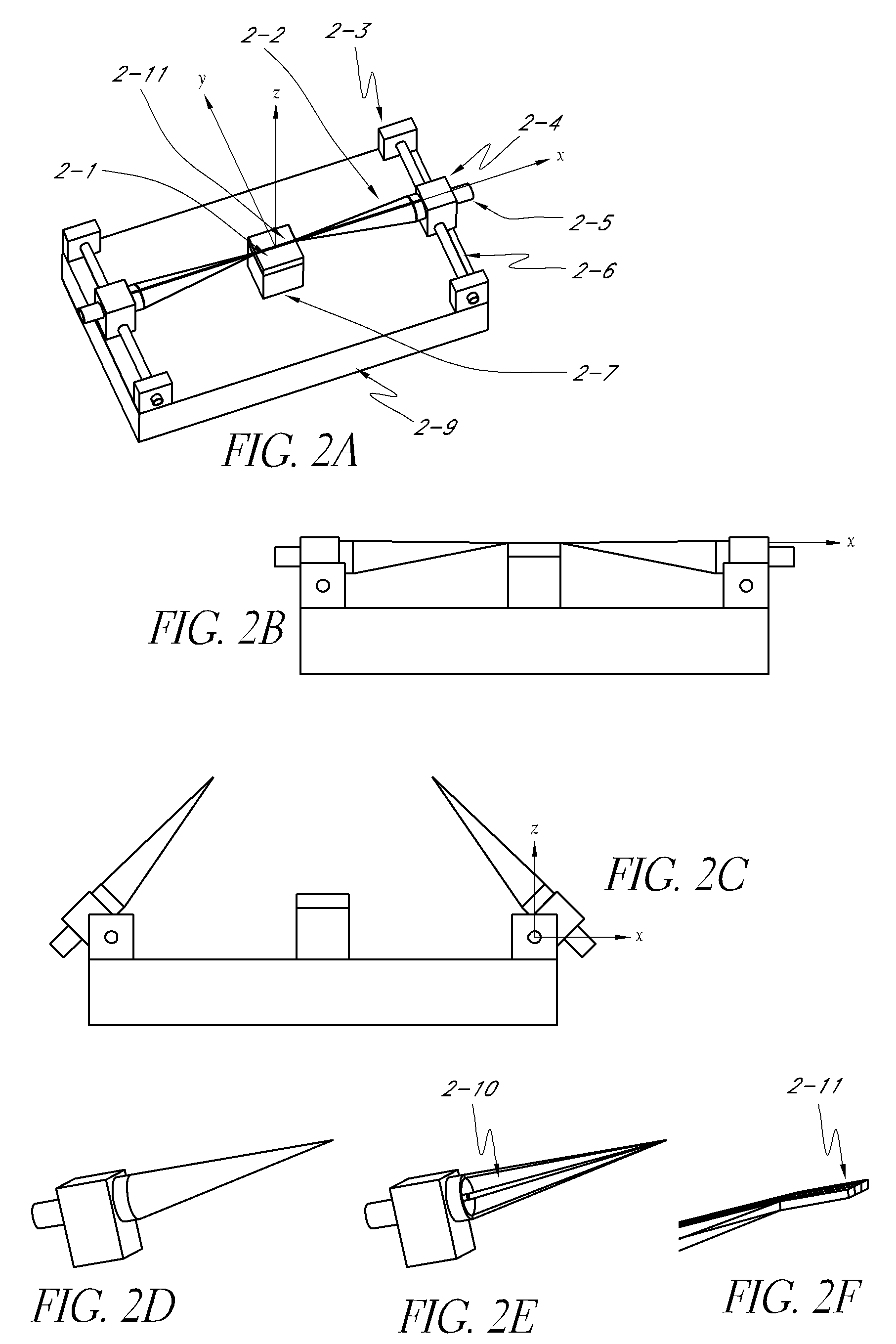

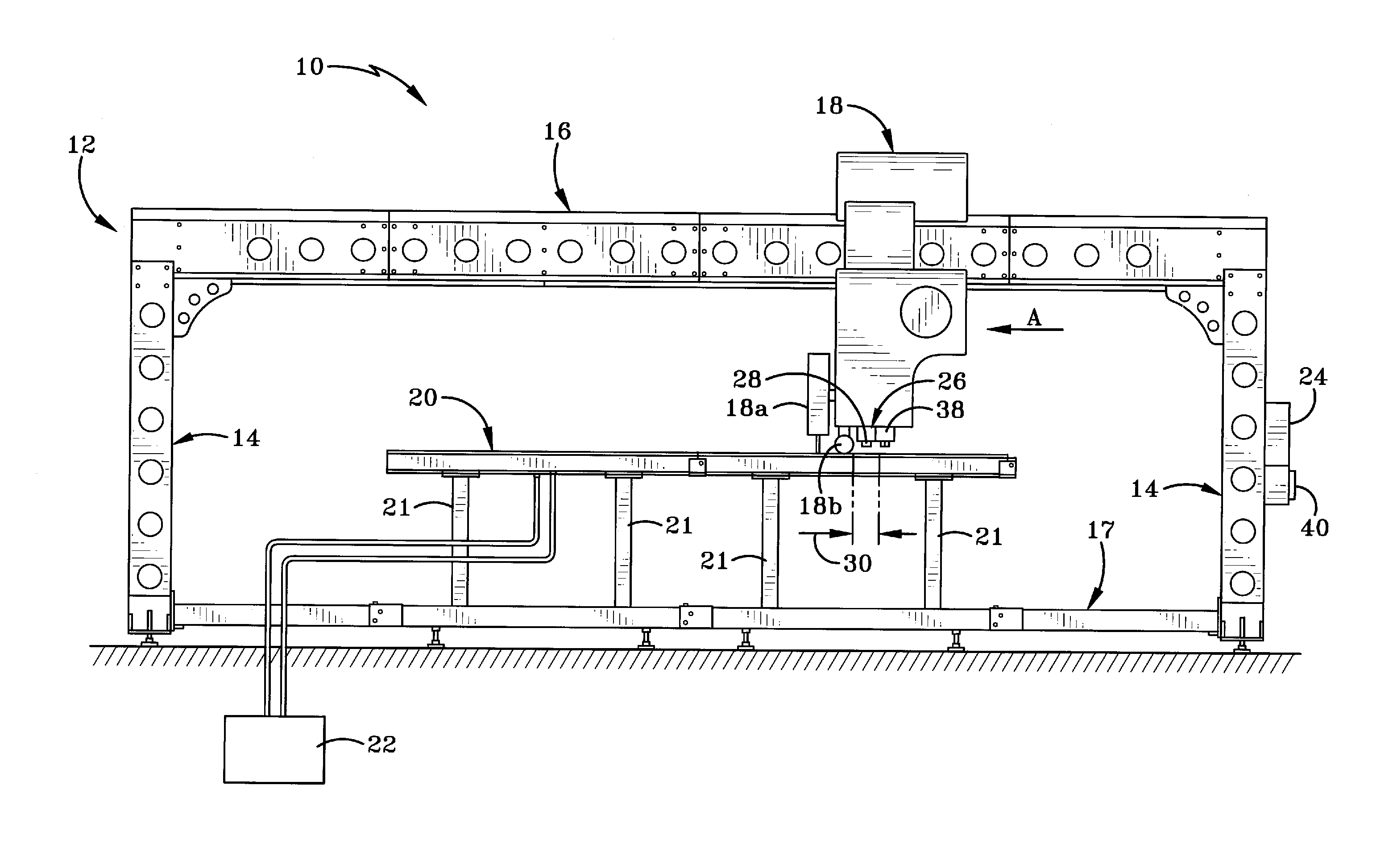

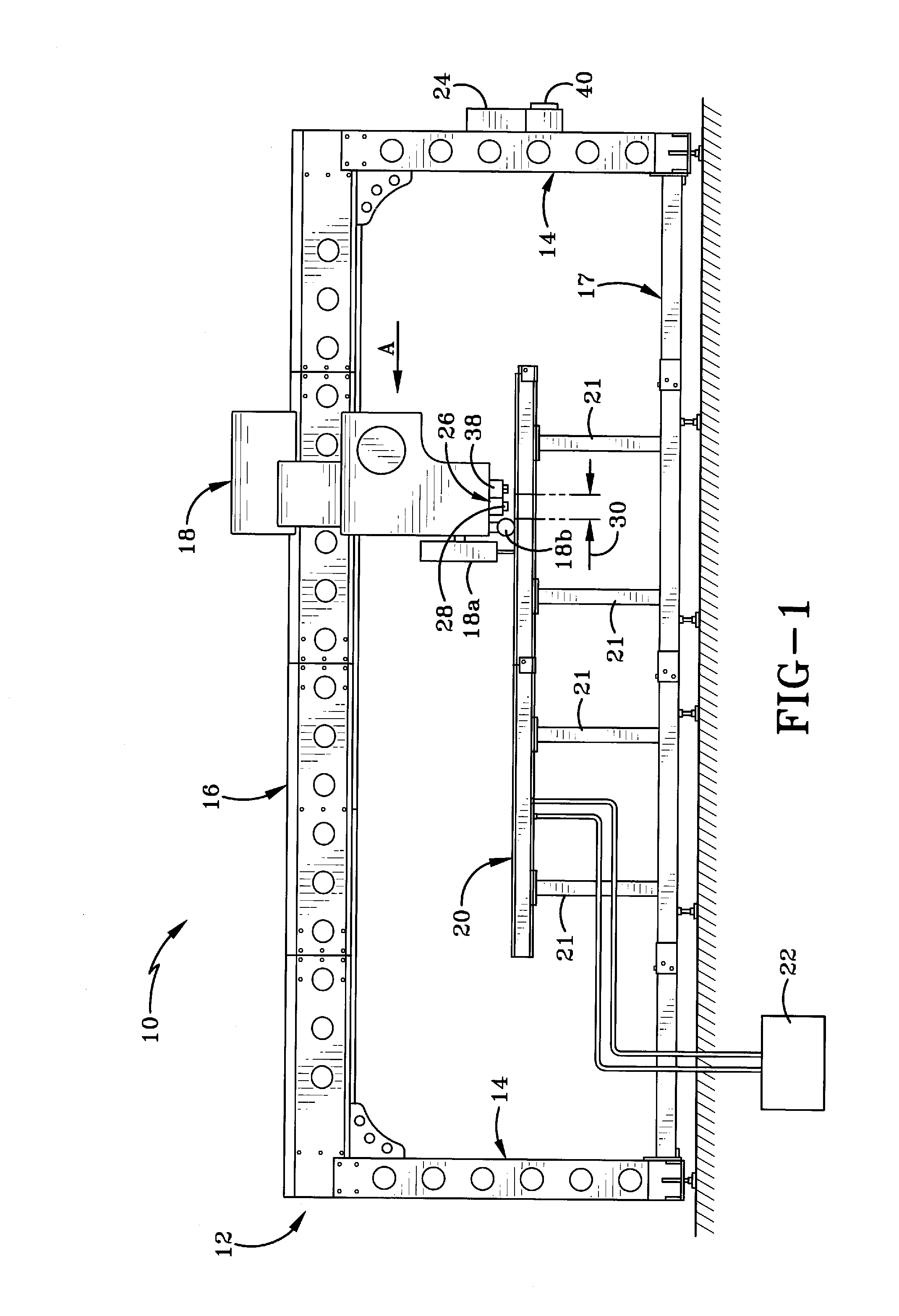

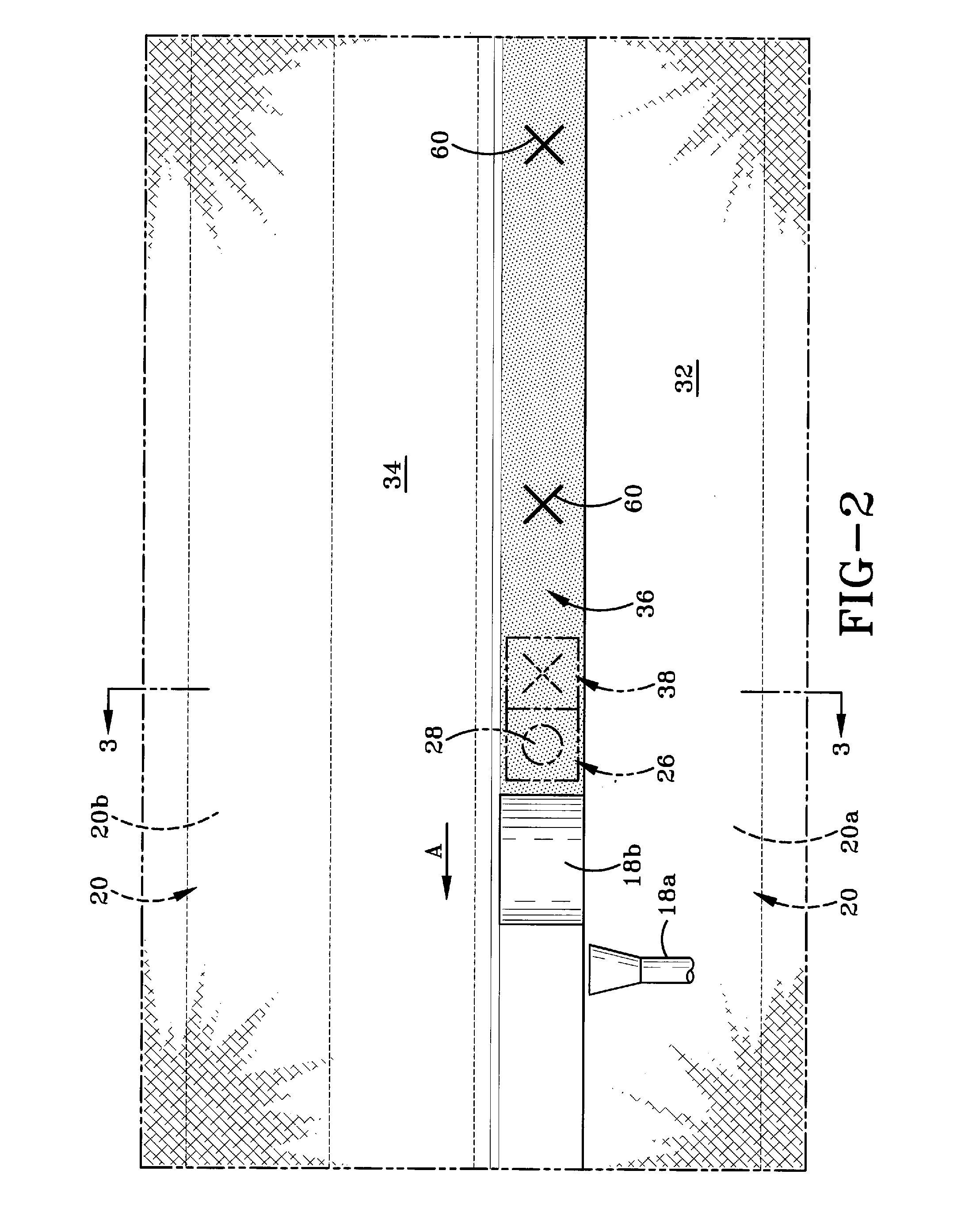

Scalable wideband probes, fixtures, and sockets for high speed IC testing and interconnects

ActiveUS20080265919A1Reducing cross talk and prasiticsIncrease speedElectrical measurement instrument detailsSolid-state devicesRadiation lossPicosecond

We introduce a new Periodic micro coaxial transmission line (PMTL) that is capable of sustaining a TEM propagation mode up to THz band. The PMTL can be manufactured using the current photolithographic processes. This transmission line can be embedded in microscopic layers that allow many new applications. We use the PMTL to develop a wideband highly scalable connector that is then used in a Probe that can be used for connecting to microscopic scale Integrated Circuits with picoseconds High Speed Digital and near THz Analogue performance in various stages of development from R&D to production testing. These probes, in one embodiment, provide a thin pen-like vertical probe tip that matches the die pad pattern precisely that can be as agile as a high speed plotter pen, connecting on the fly to any die pattern on a wafer. This approach allows the most valuable part of the test, namely the wafer to remain stationary and safe, and the least costly part of the test, namely the probe to take most of the wear and tear. We further use the embedded PMTL to develop a modular, scaleable and fully automated Universal Test Fixture for testing chips in various stages of development mainly for digital IC chips that can be utilized in production lines with pick and place of chips on tape to test every chip before insertion into circuits. One embodiment includes a low profile wideband Signal Launcher and an alligator type RF Clip that can be used at the edge of PCB's directly for validation broads. The Signal Launcher is used to develop a new versatile Flush Top Test Fixtures for individual device testing in various stages of development from die, to packaged, to Module, to Circuit Boards. The PMTL can also provide Confined Field Interconnects (CFI) between various elements on semiconductor wafers to reduce parasitic and radiation losses and practically eliminating cross talk, thus, increasing the speed of digital IC's. The PMTL is also used to develop a Universal Test Socket, and a Hand Probe with performance up to 220 GHz.

Owner:WAYMO LLC

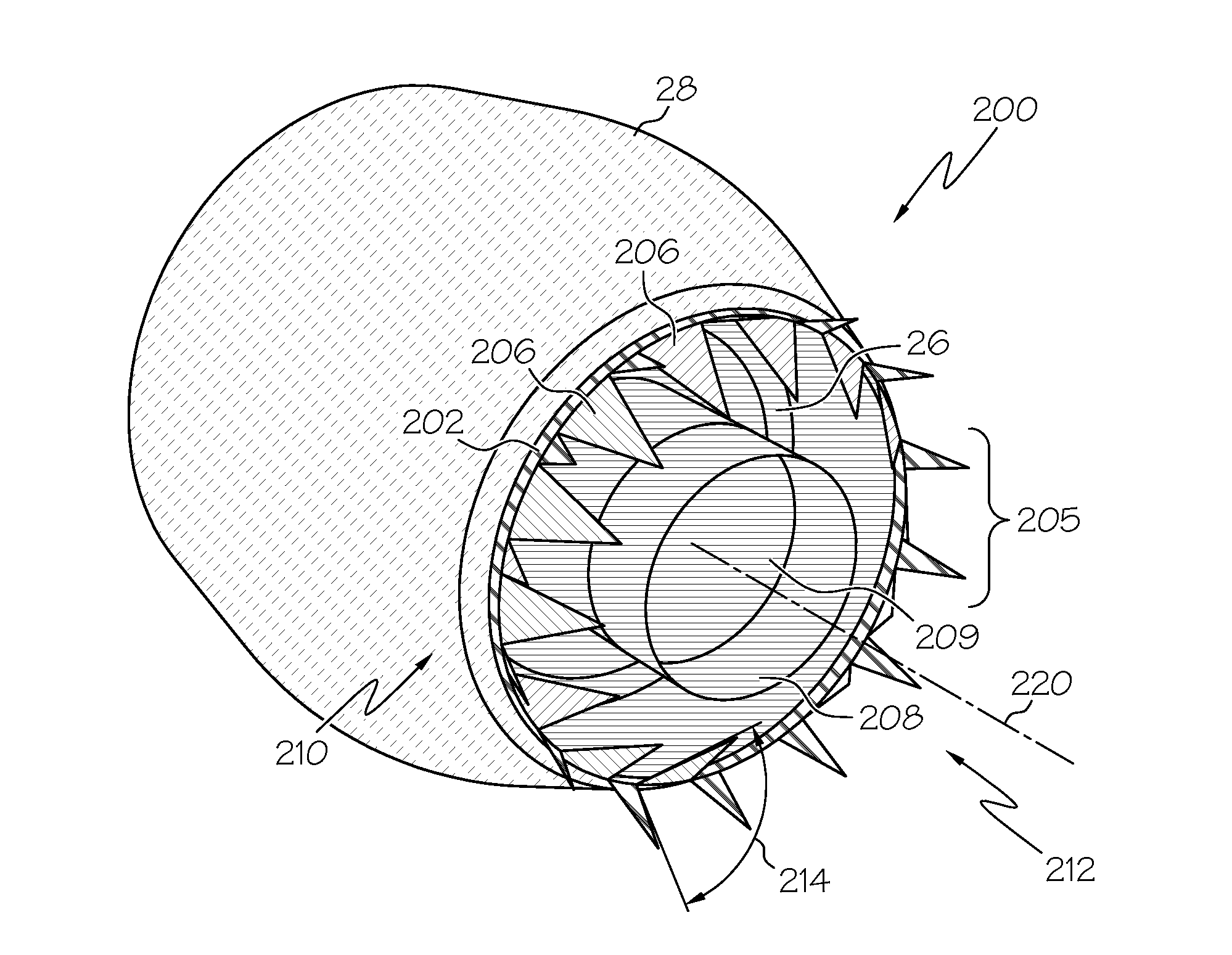

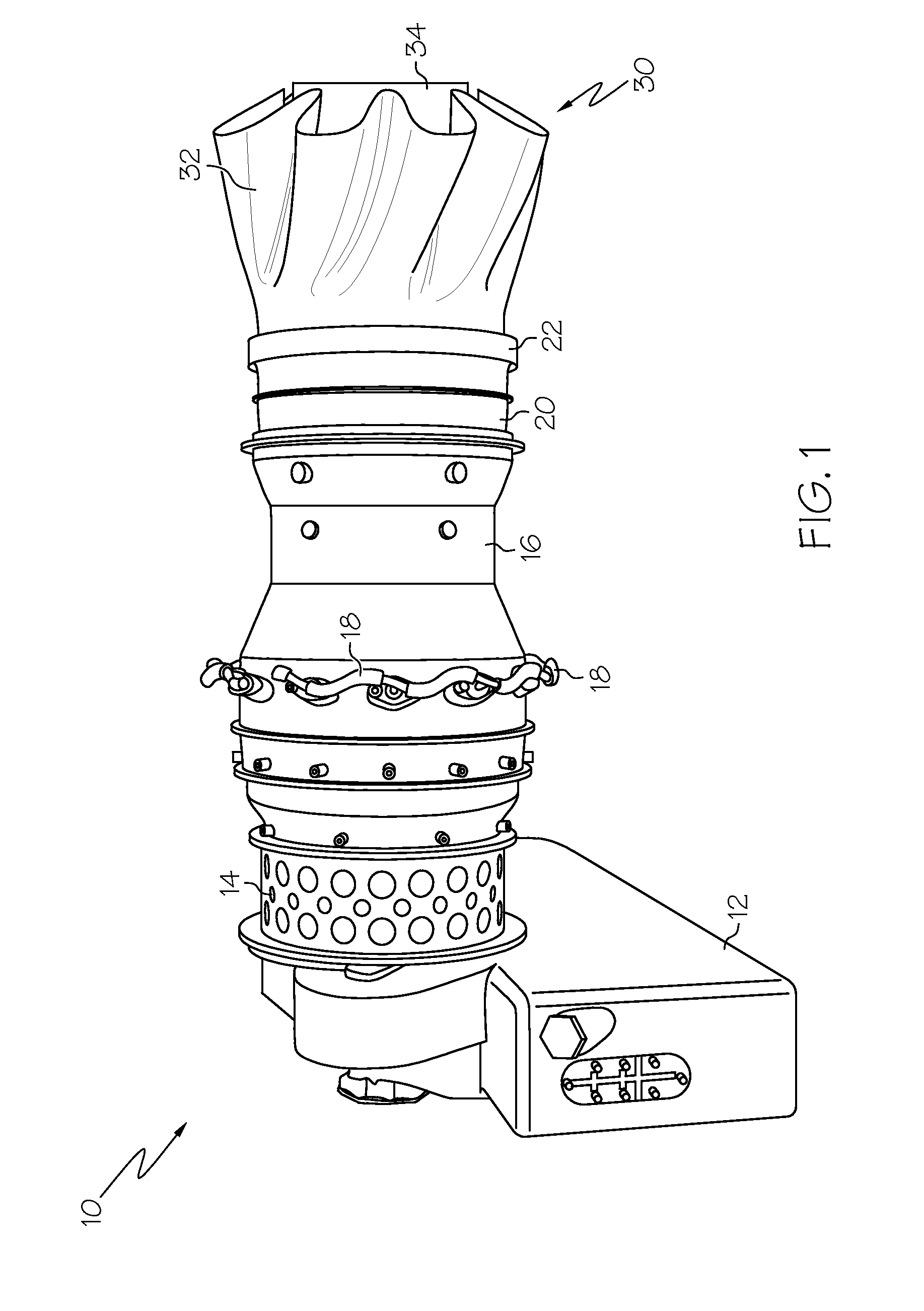

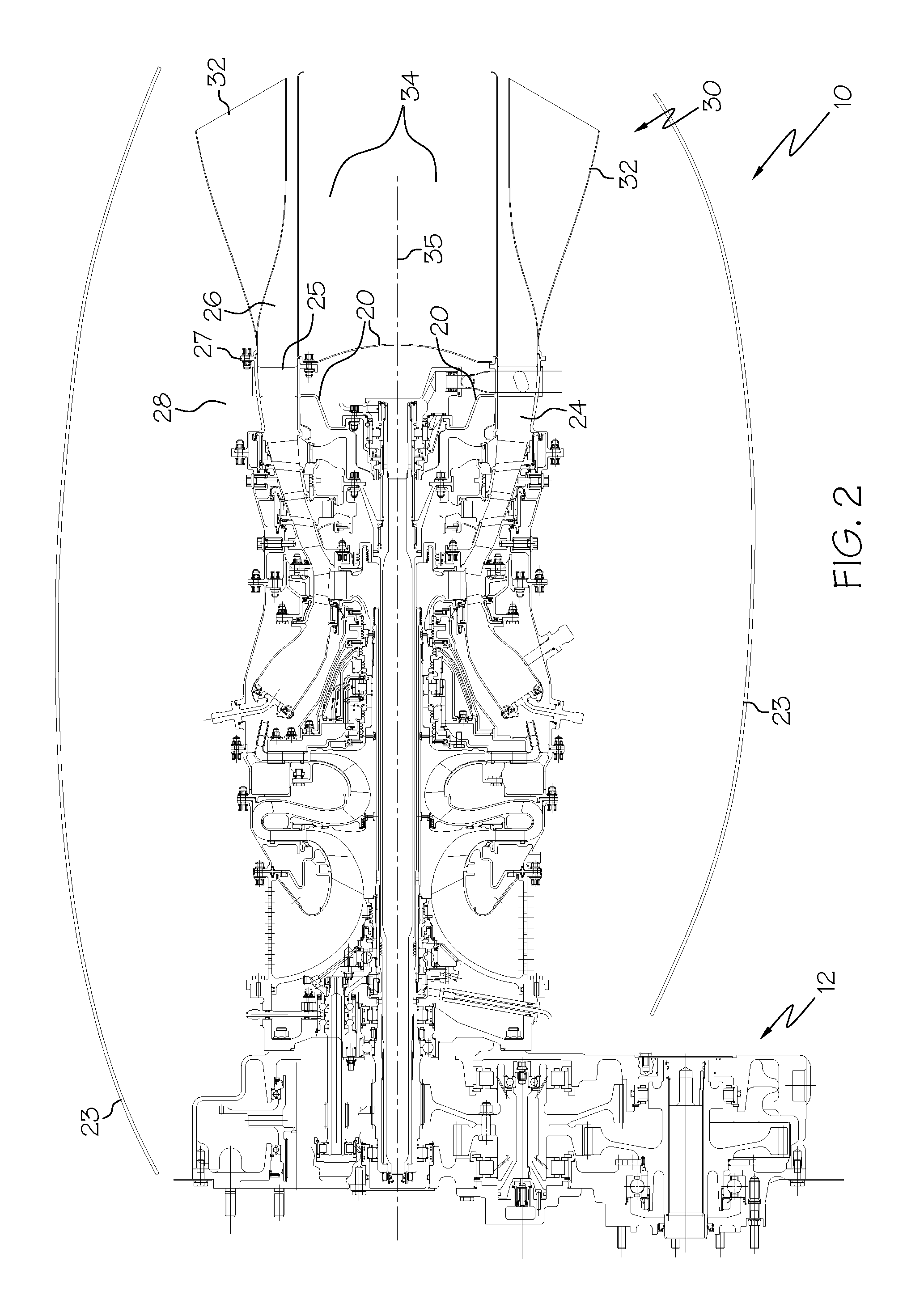

Compact mixer with trimmable open centerbody

ActiveUS7506501B2Power plant exhaust arrangementsEngine manufactureEngineeringMechanical engineering

Compact exhaust mixer assemblies comprising a compact mixer and a trimmable open centerbody are provided. The trimmable center body allows for adjustments of the open centerbody after manufacturing and during production testing. The trimmable open centerbody may be used to compensate for production tolerances making it possible to obtain the desired core effective area for proper engine operation. The compact mixer may be either lobed or serrated. The compact exhaust mixer assemblies have a length of about half that of conventional exhaust mixer assemblies.

Owner:HONEYWELL INT INC

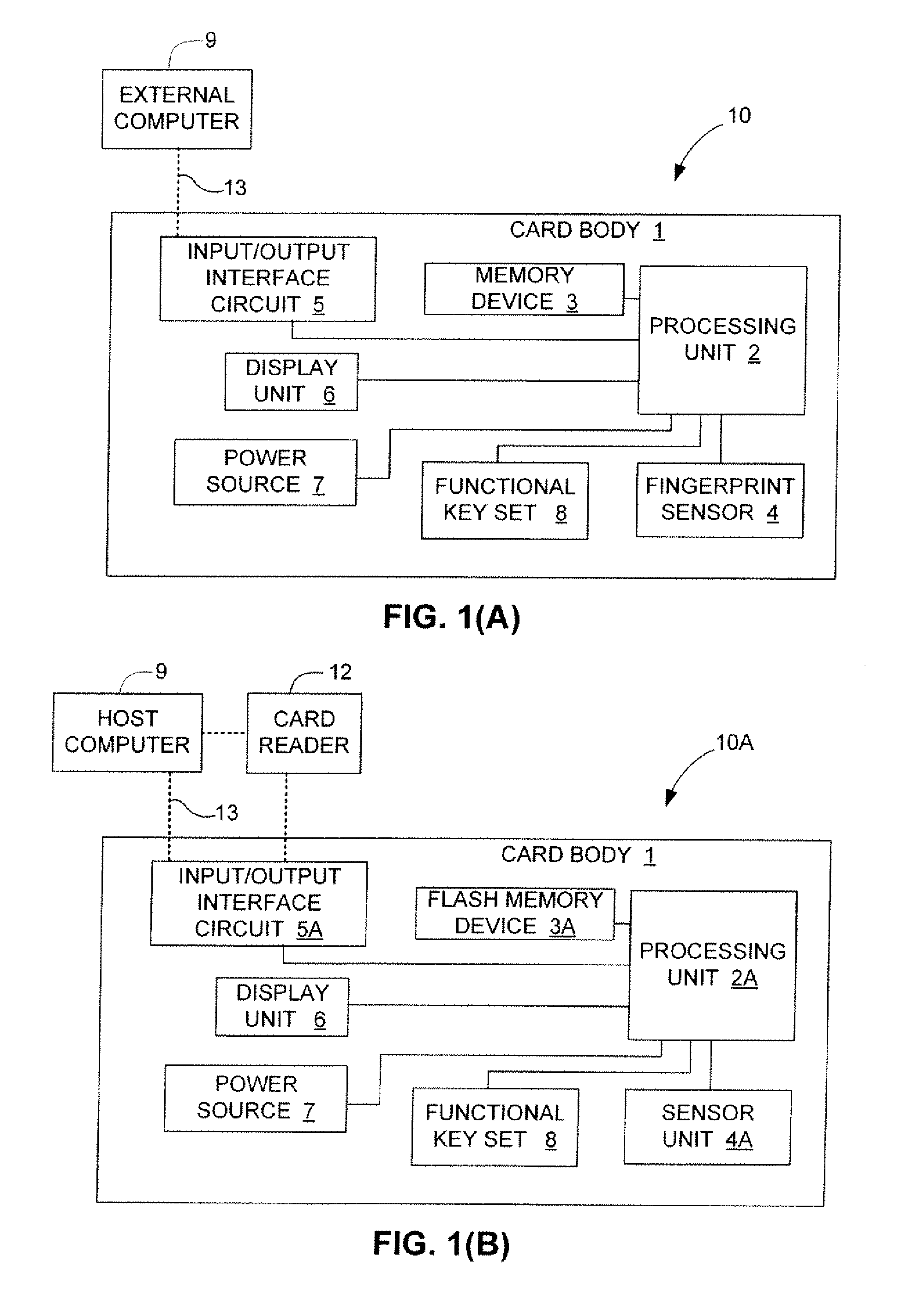

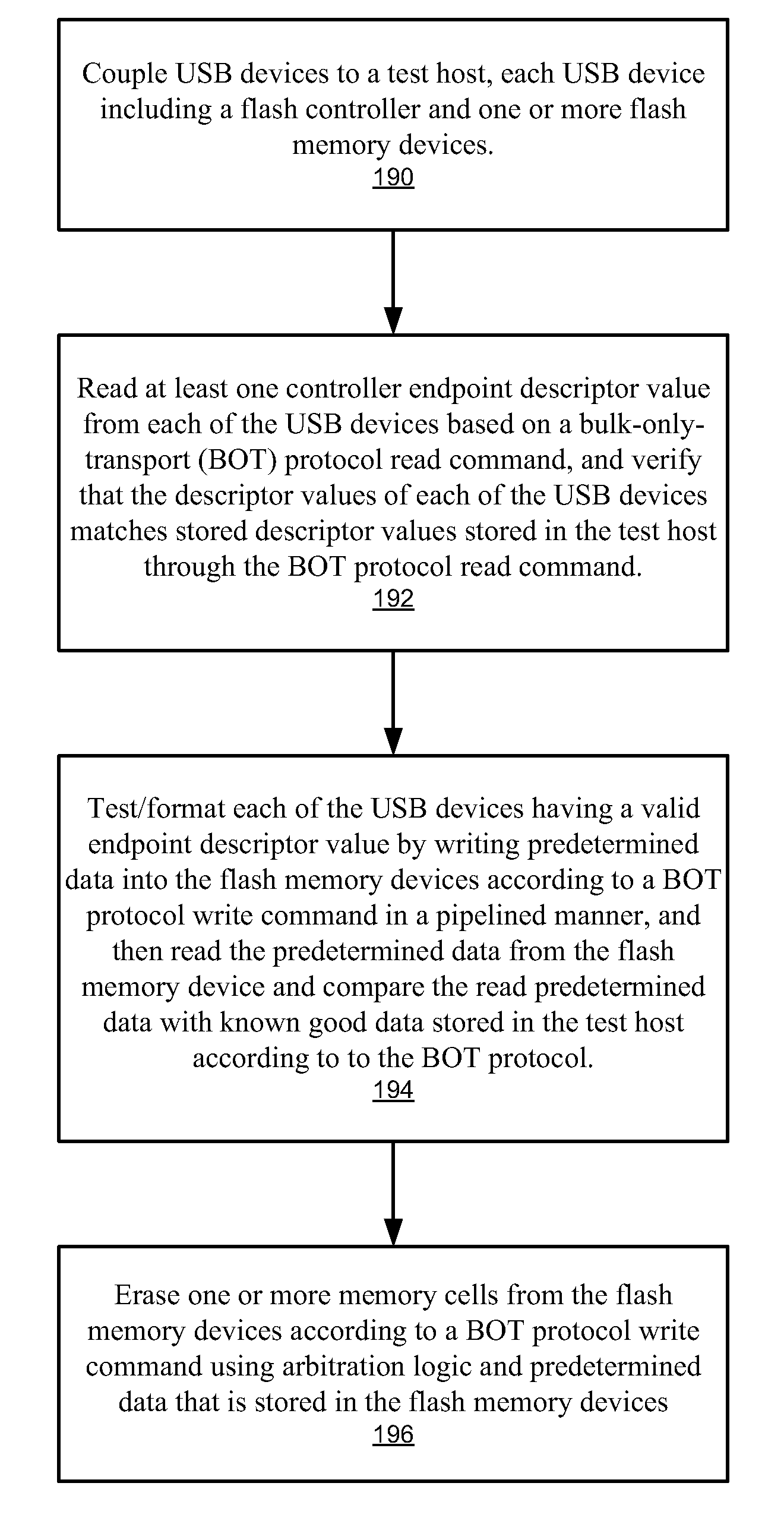

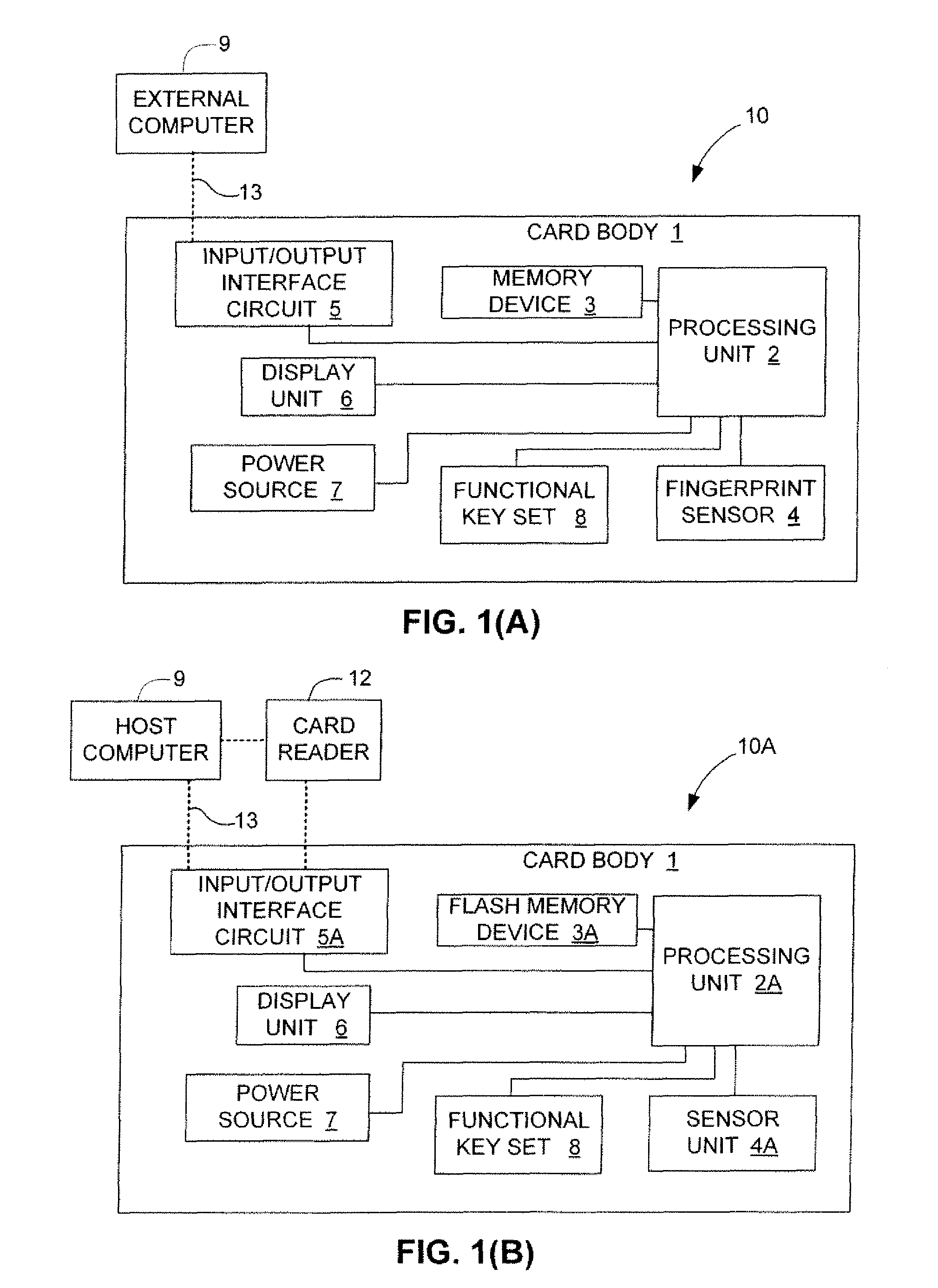

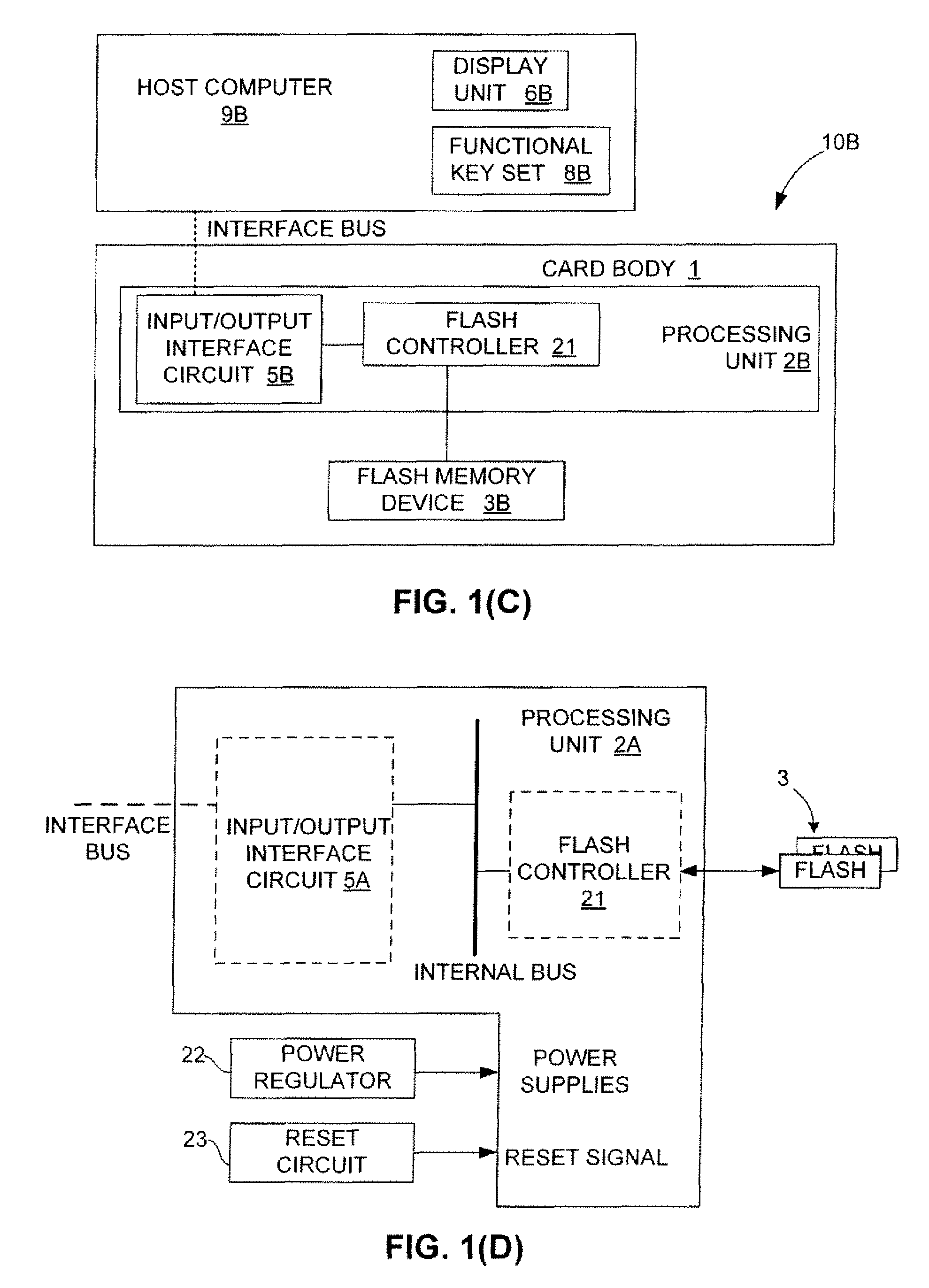

Mass production testing of USB flash cards with various flash memory cells

InactiveUS20080177922A1Improve efficiencyFacilitates high volume testing/formattingElectronic circuit testingError detection/correctionCard readerUSB

A high volume testing / formatting process is provided for Universal Serial Bus-based (USB-based) electronic data flash cards (USB devices) that meets the increasing demand for USB electronic data flash cards (USB devices). A test host is simultaneously coupled to the multiple USB devices (e.g., using a multi-port card reader or a probe fixture), a controller endpoint value is read from each of the USB devices and verified with a known good value, and then testing / formatting is performed on each of the USB devices by writing predetermined data into each USB device in a pipelined manner, then reading out and testing the predetermined data. In one embodiment, the test host implements a special USB driver that blocks standard USB registration procedures upon detecting the plurality of USB devices. Control and / or boot code data are written onto the flash memory device (i.e., instead of being provided on a controller ROM).

Owner:SUPER TALENT TECH CORP

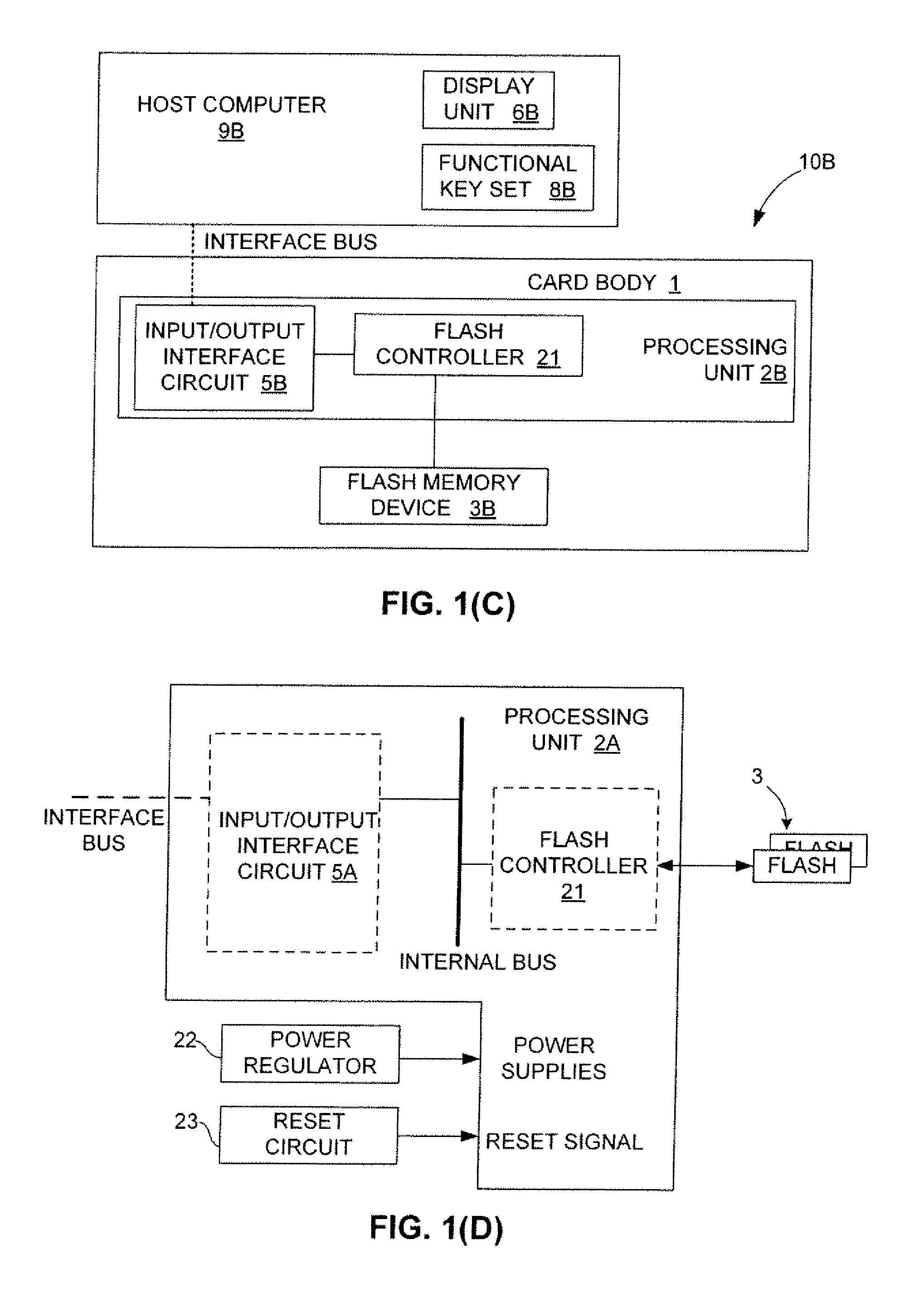

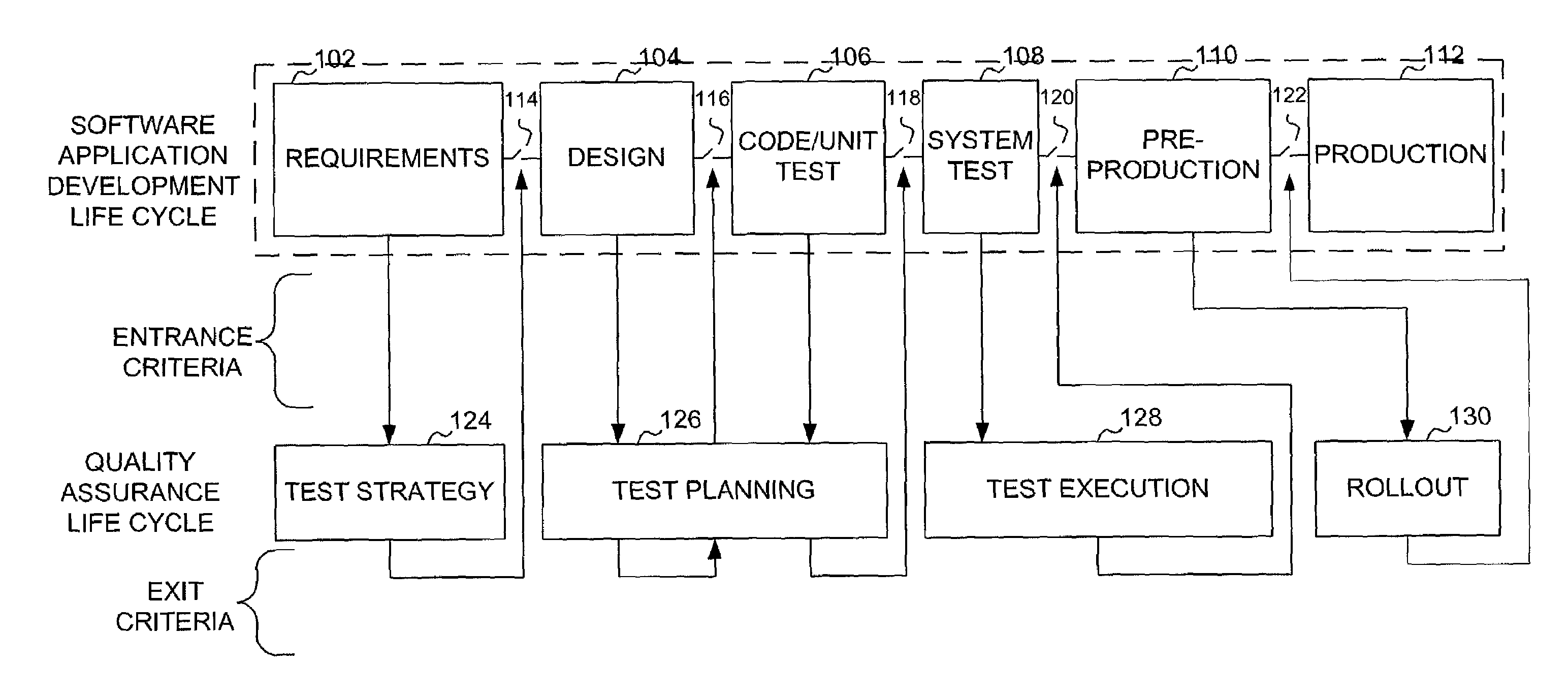

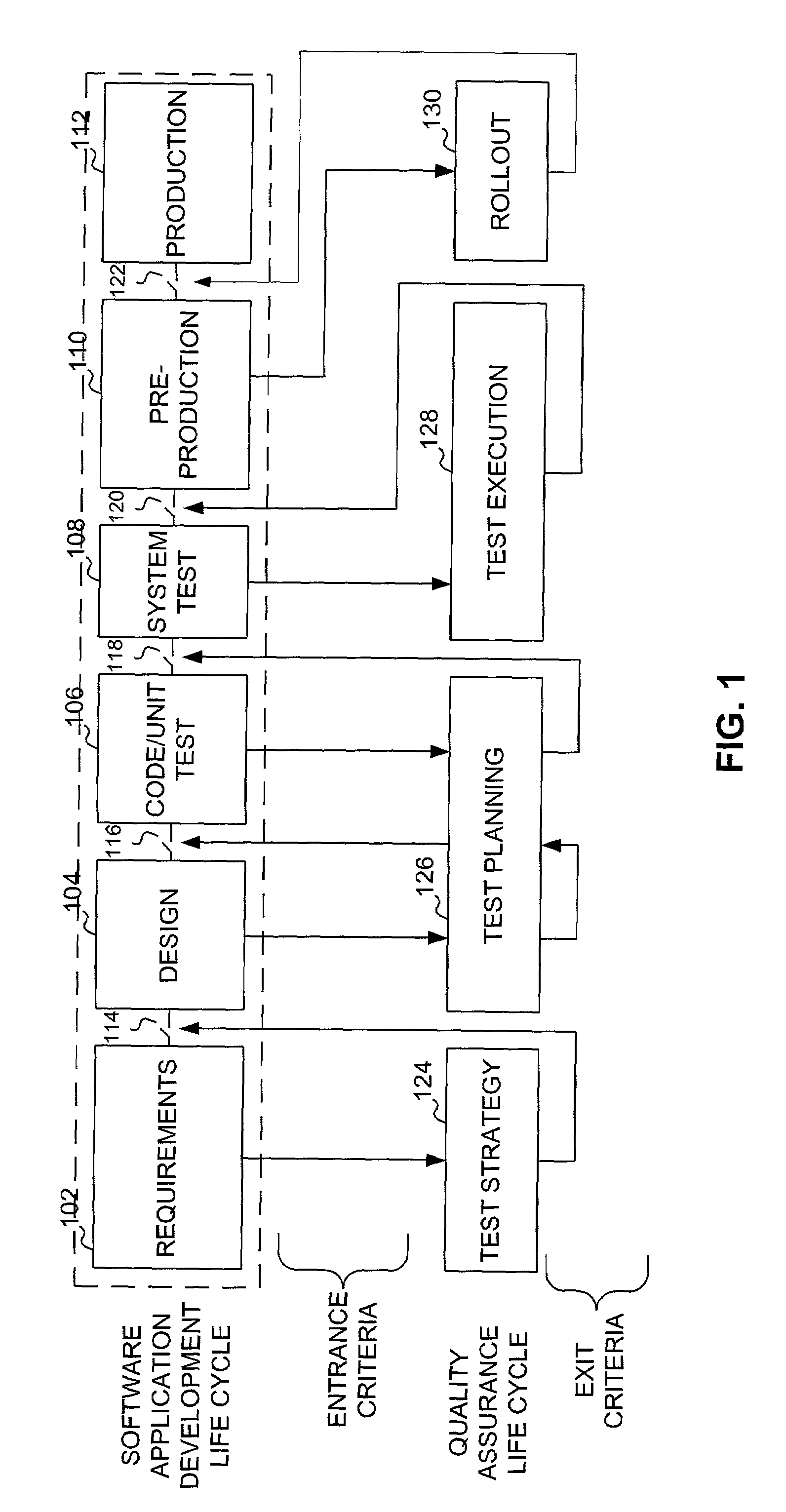

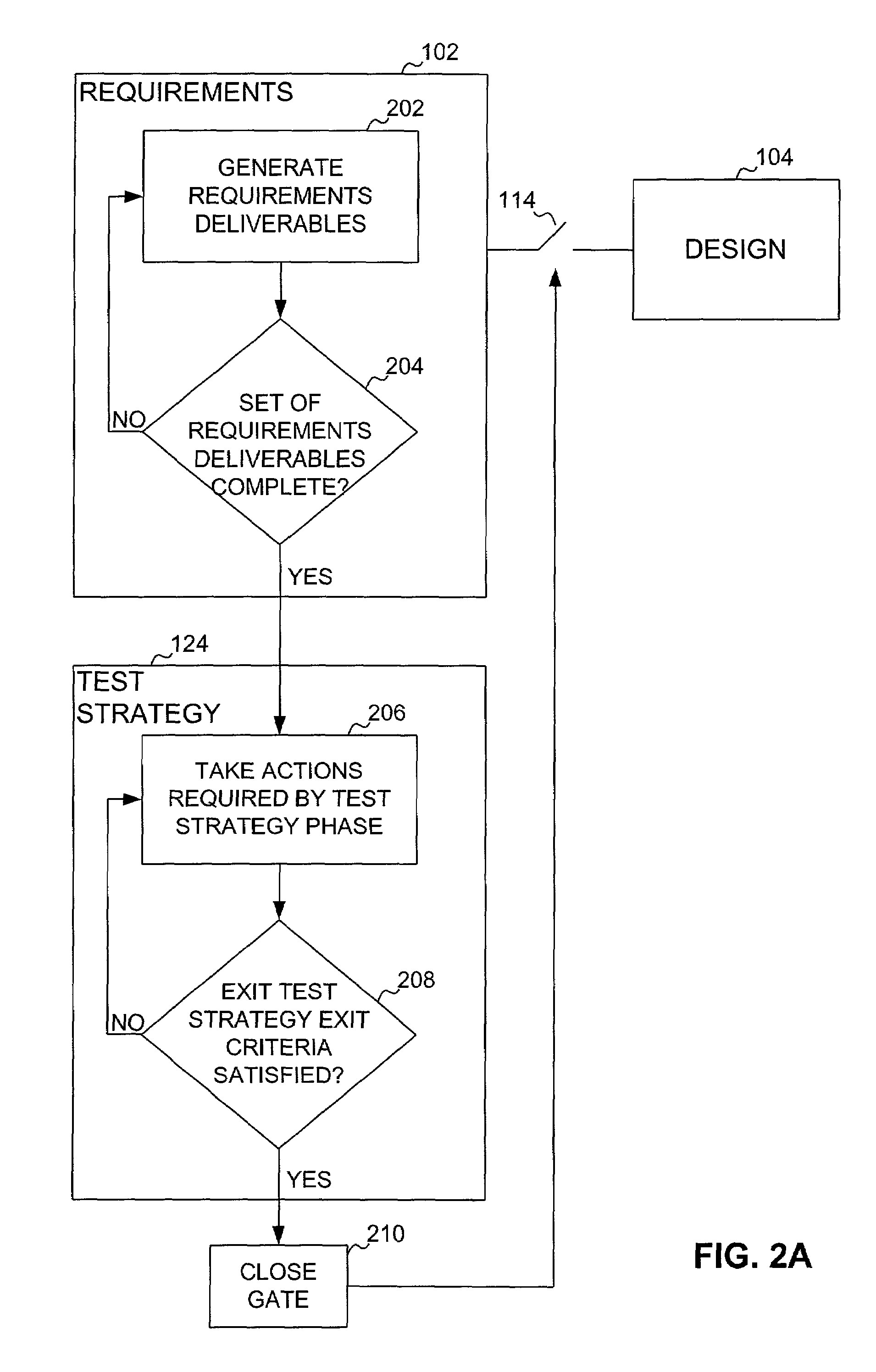

System and method for performing rapid application life cycle quality assurance

InactiveUS7080351B1Rapid life-cycle quality assuranceAvoid couplingResourcesSpecific program execution arrangementsDesign phaseQuality assurance

Performance of quality assurance for a computer application development proceeds in a series of phases. Each of the phases in the QA life cycle corresponds to one or more phases in a computer application development life cycle. For example, in one embodiment, the quality assurance life cycle includes four phases—a test strategy phase, a test planning phase, a test execution phase and a rollout phase. Each phase of the QA life cycle has entrance and exit criteria. The phase can be entered when the entrance criteria have been met. When the exit criteria are met, the phase causes a gate to be closed to allow the software development life cycle to proceed to the next phase. In one embodiment, the software life cycle includes six phases—a requirements phase, a design phase, a code / unit test phase, a system test phase, a pre-production test phase and a production test phase.

Owner:BELLSOUTH INTPROP COR

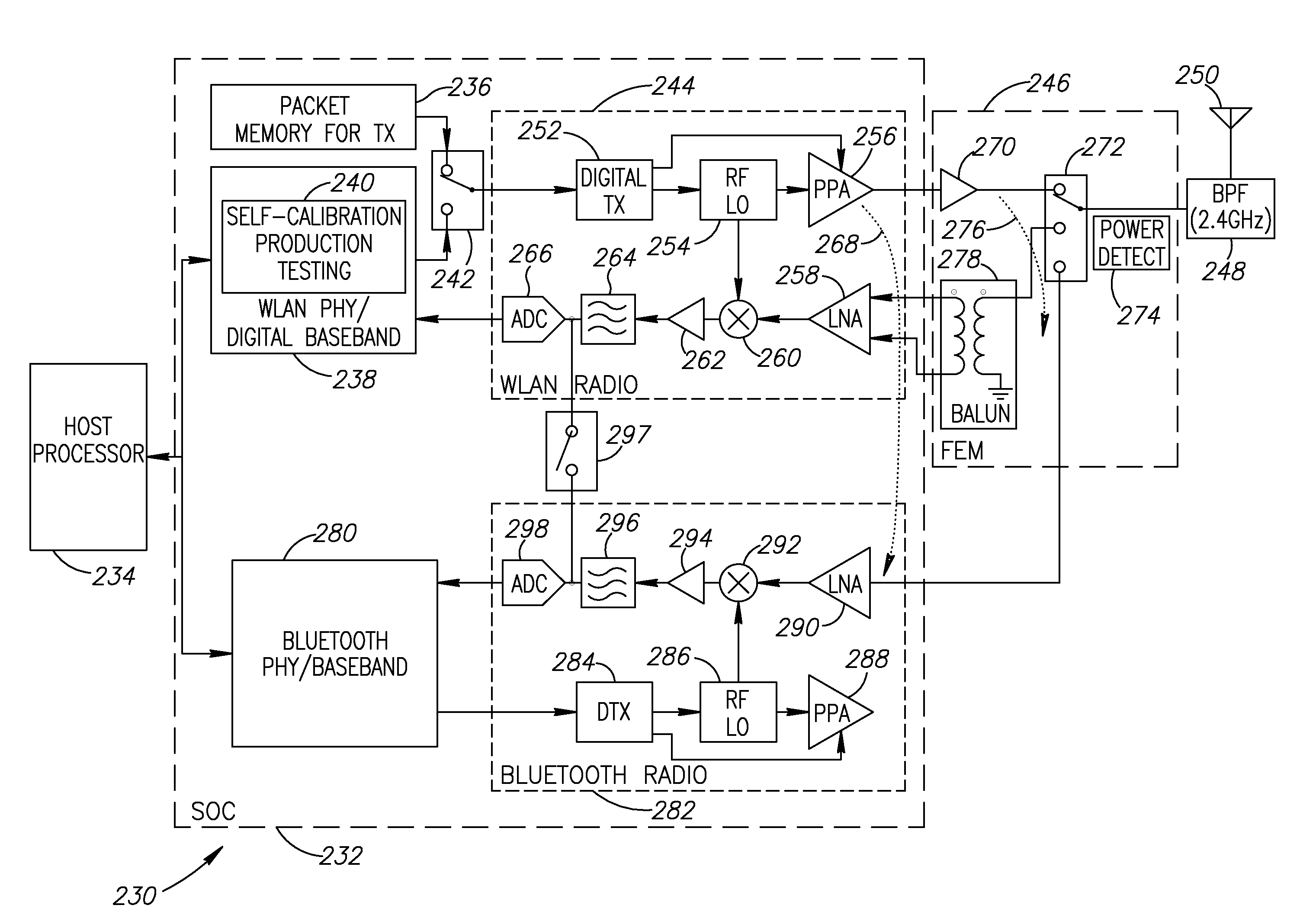

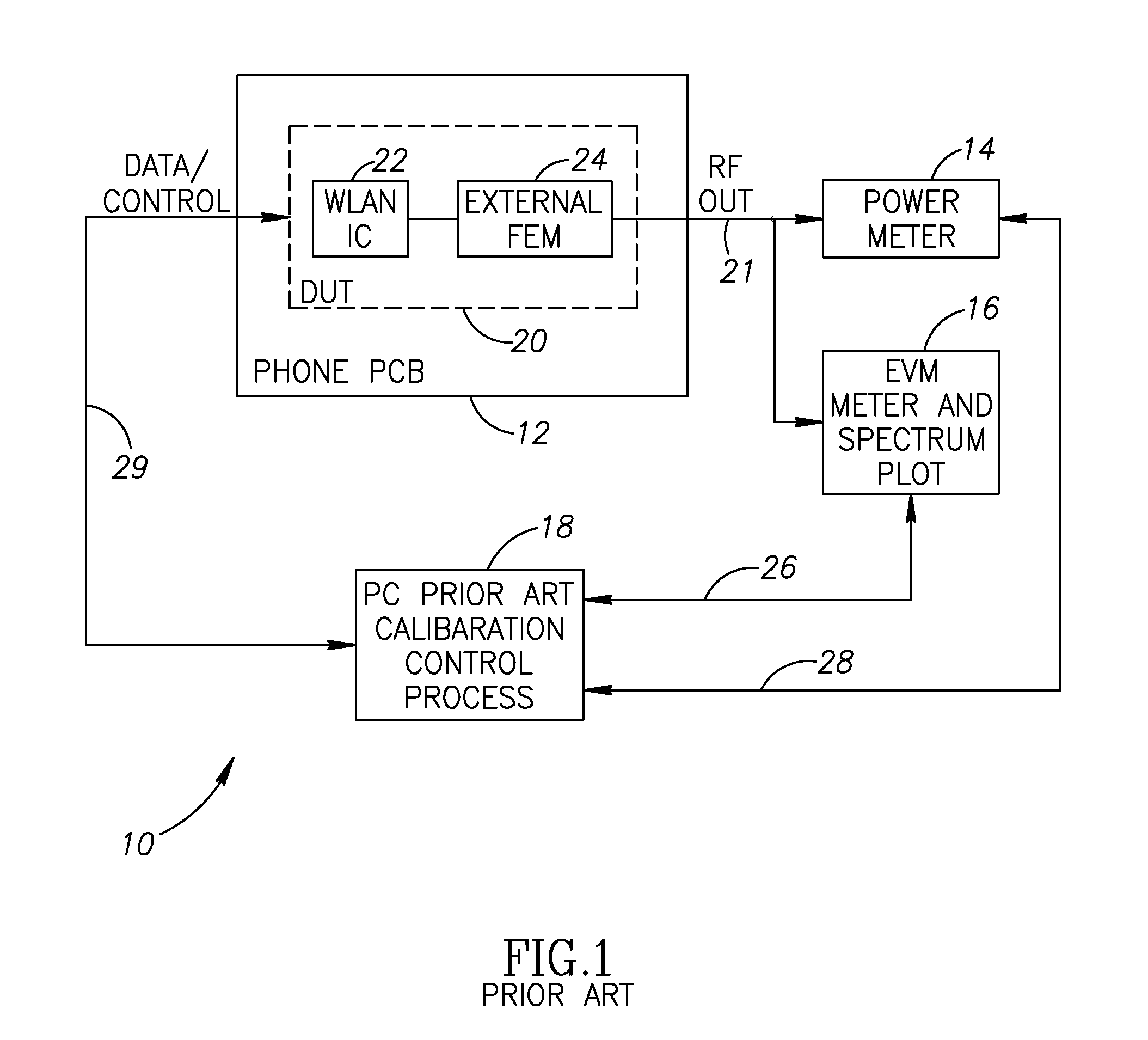

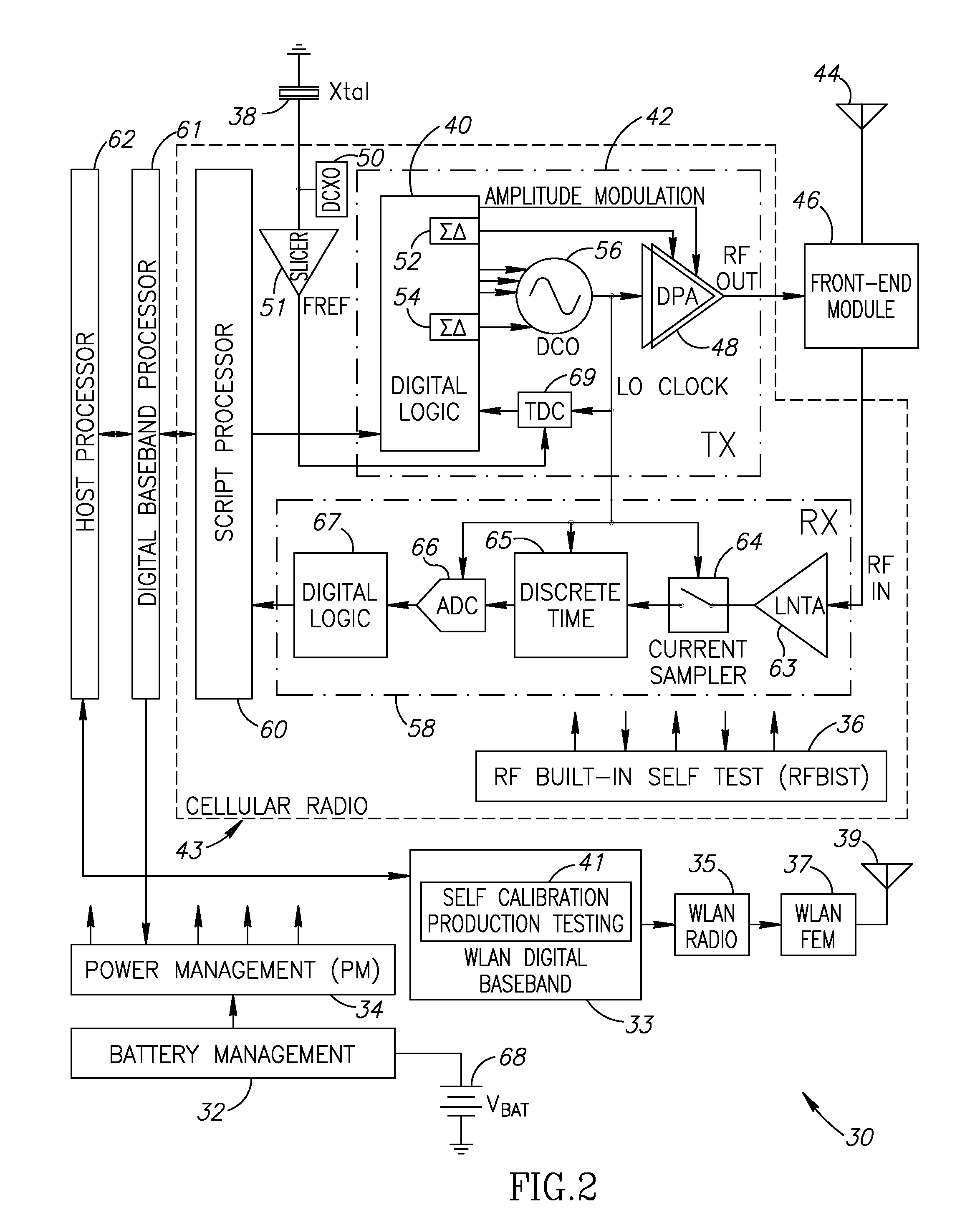

Transmitter built-in production line testing utilizing digital gain calibration

ActiveUS20080144707A1Easy to implementSuitable for useTransmitters monitoringResonant long antennasProduction lineAudio power amplifier

A novel and useful self-calibration based production line testing mechanism utilizing built-in closed loop measurements in the radio to calibrate the output power of an external power amplifier coupled to a SoC radio. The mechanism is applicable during production line testing and calibration which is performed on each SoC and associated external power amplifier after assembly at the target PCB of the final product. The mechanism calibrates the TX output power in three phases based on loopback EVM measurements. In a first phase, the PPA in the radio (SoC) is calibrated and gain versus output power is stored in a gain table in on-chip NVS. In a second phase, the maximum PPA TX power is determined using closed loop EVM measurements. The external PA is calibrated in a third phase and the maximum PA power is determined. During this third phase, the maximum power of the device is calculated, compared to the requirements of the particular standard and a pass / fail determination is thereby made.

Owner:TEXAS INSTR INC

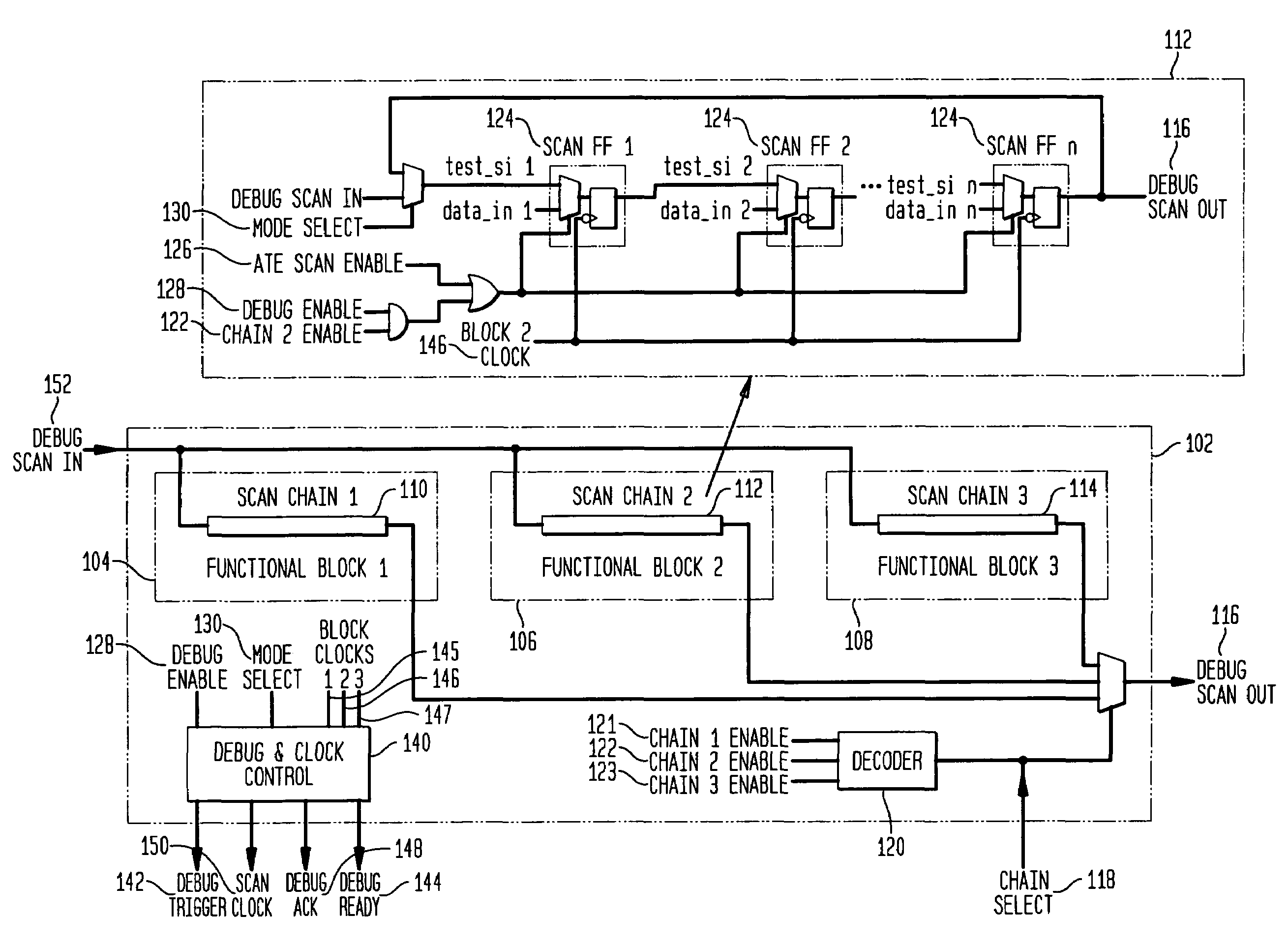

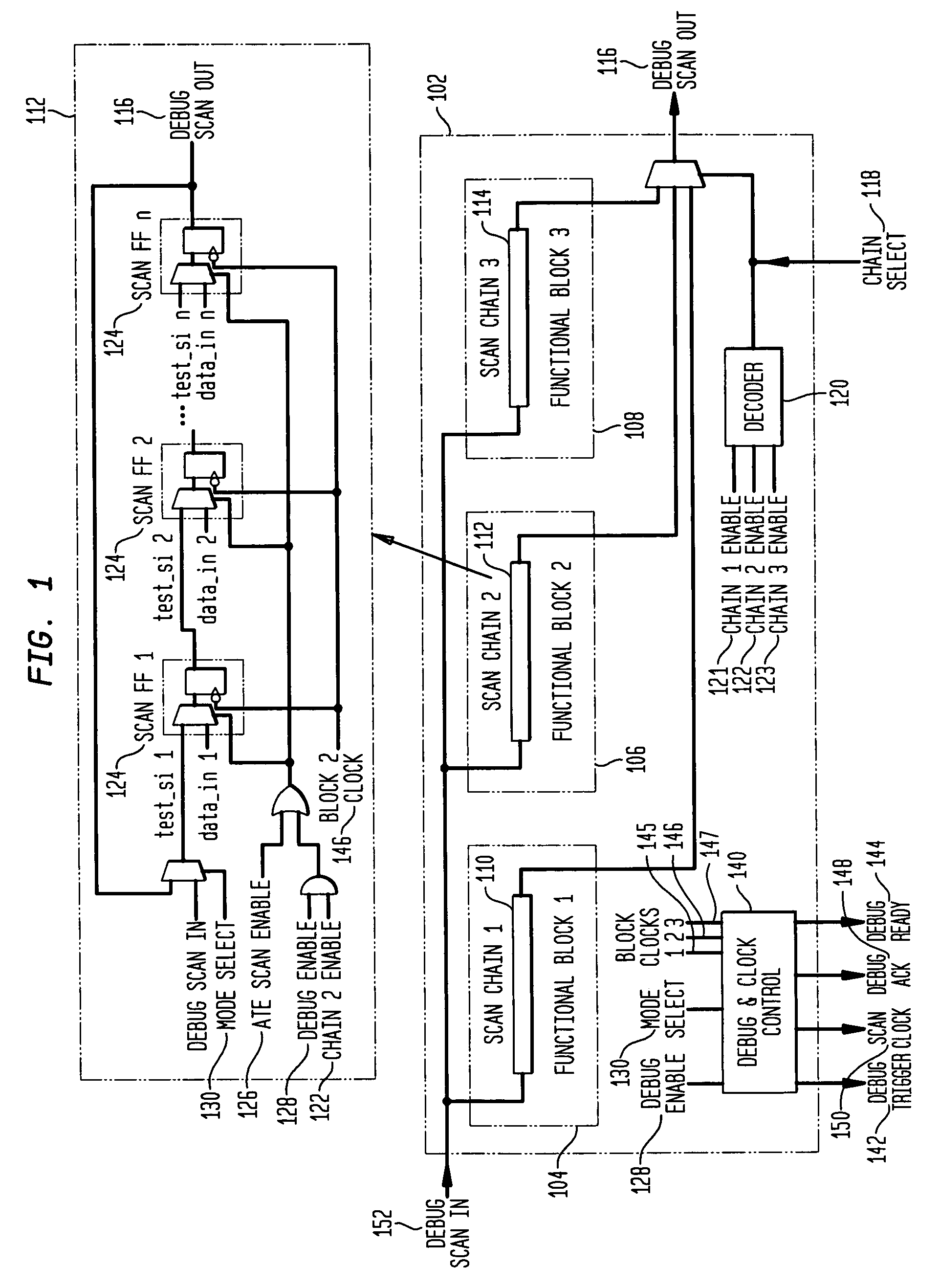

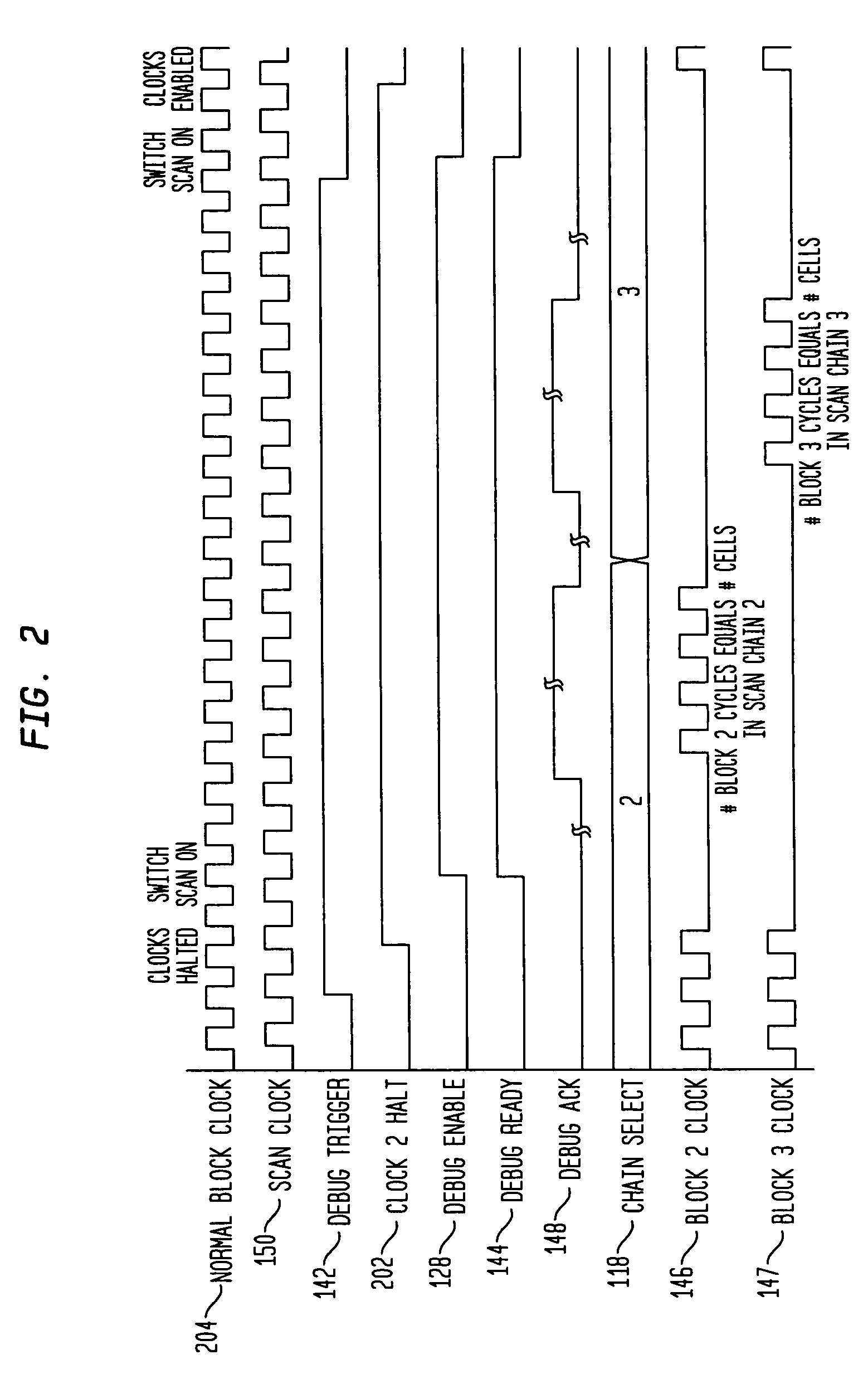

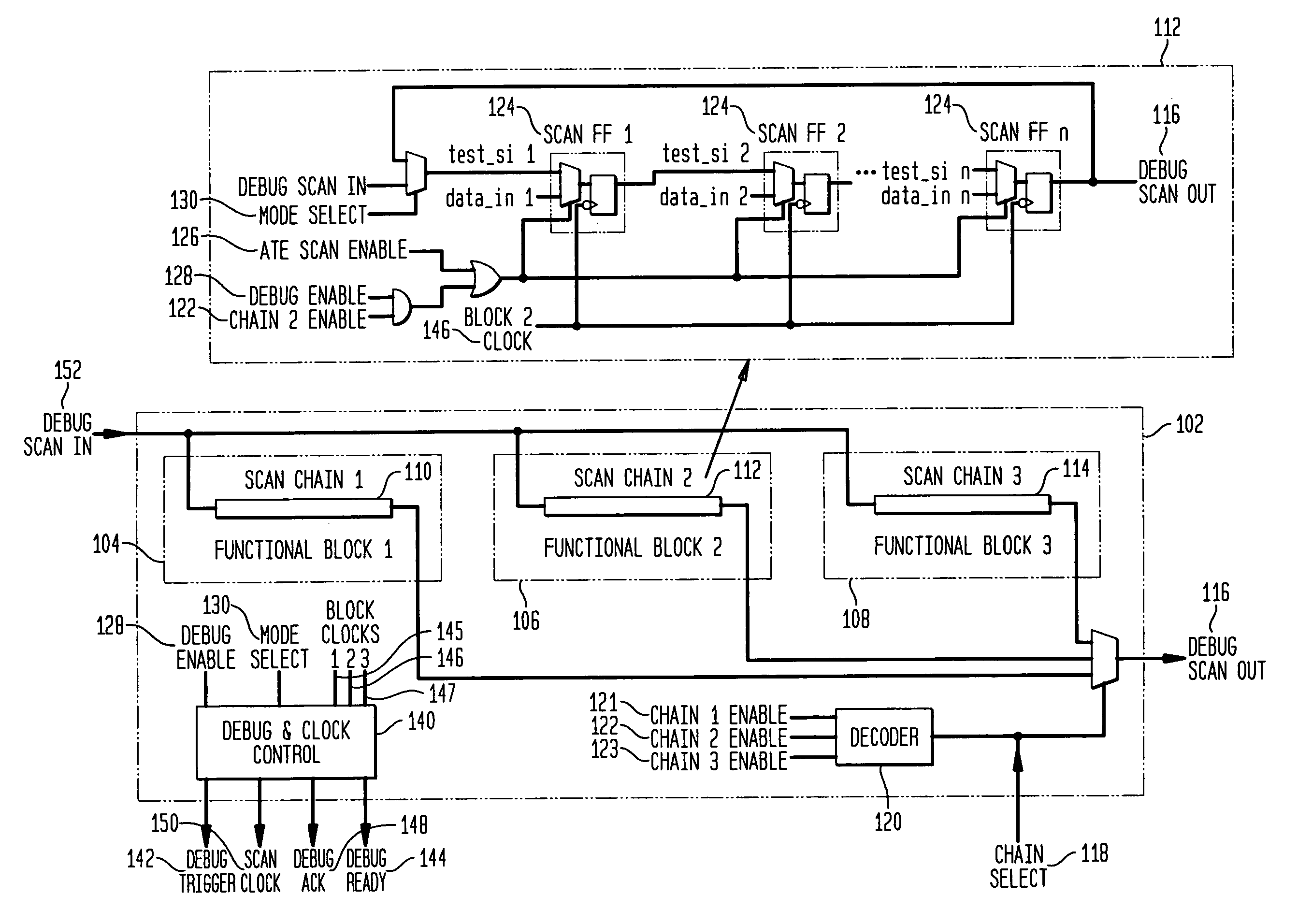

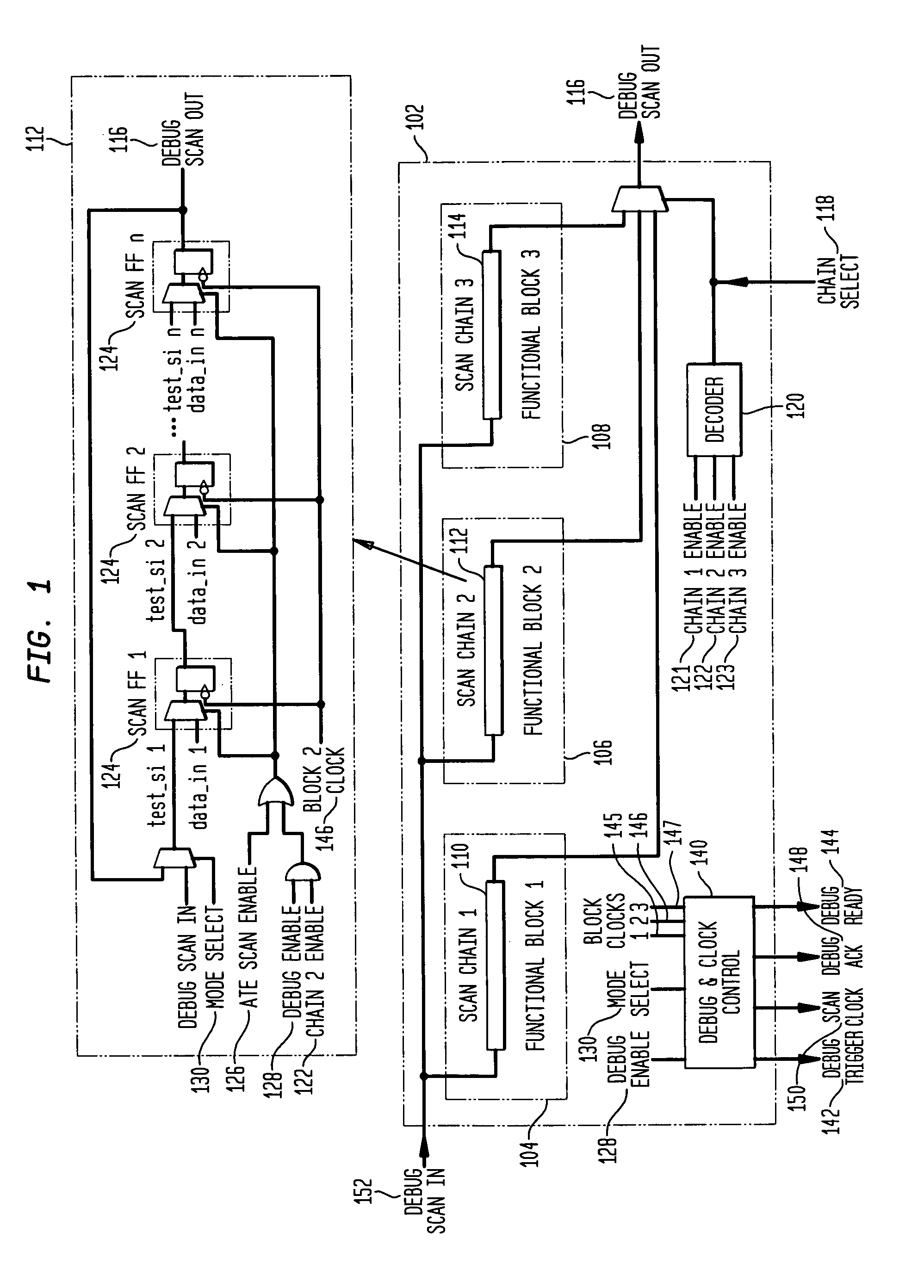

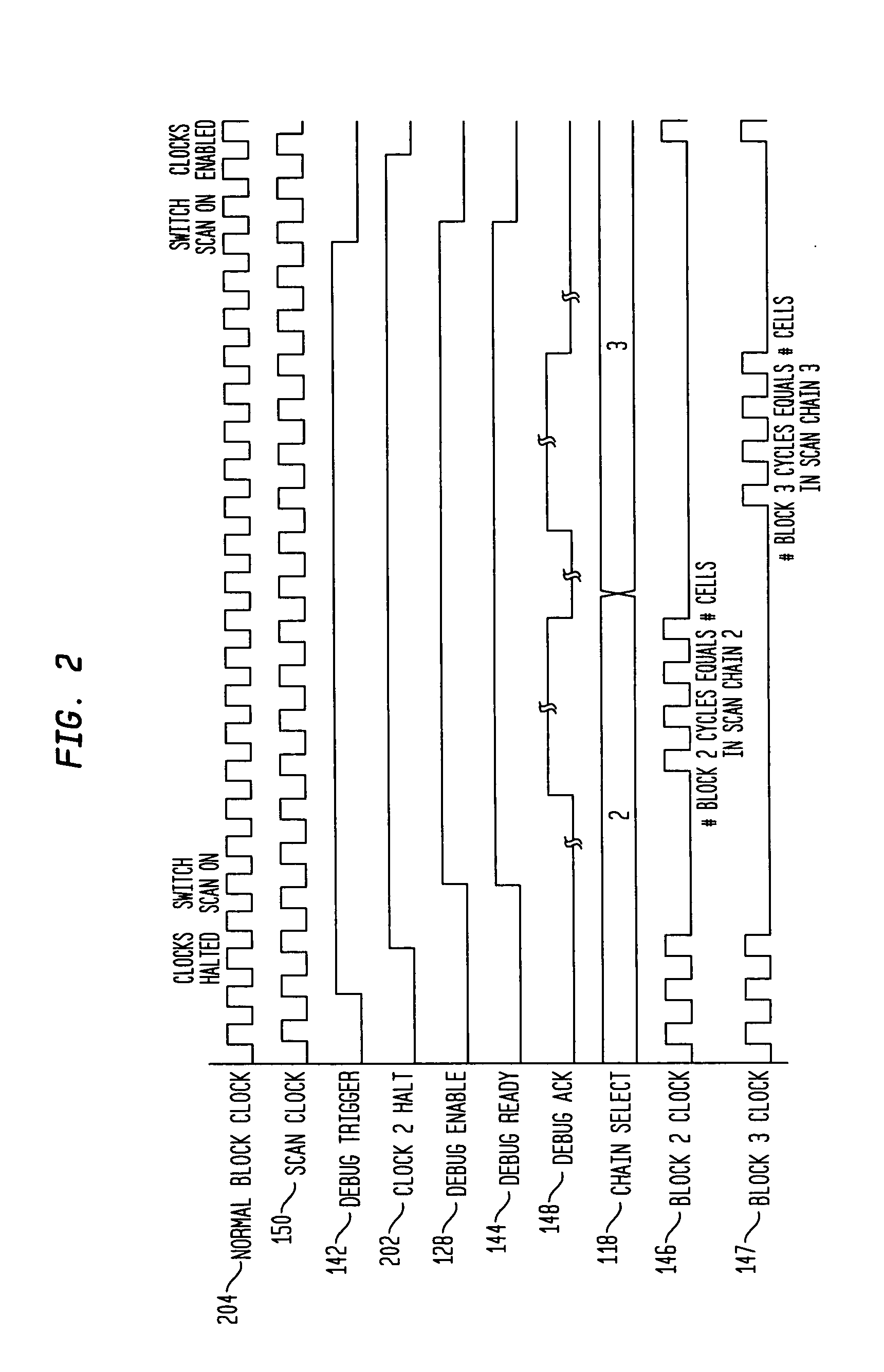

System and method for debugging system-on-chips

InactiveUS7219265B2Electronic circuit testingError detection/correctionComputer hardwareProcessor register

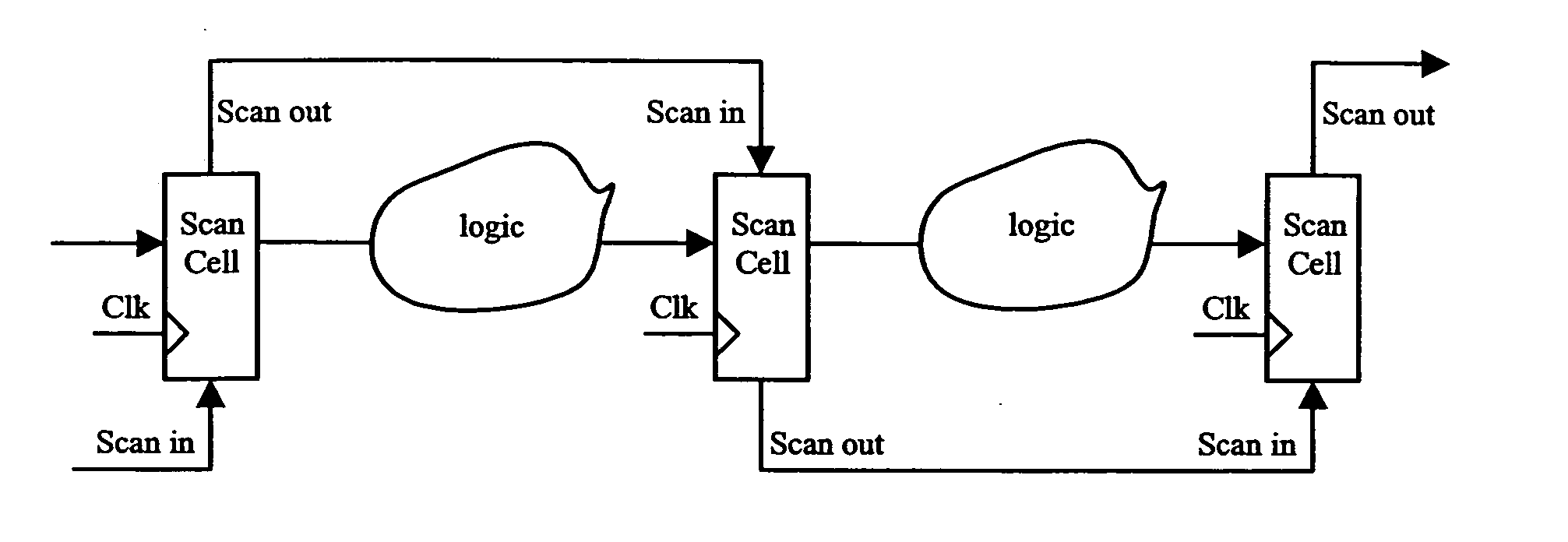

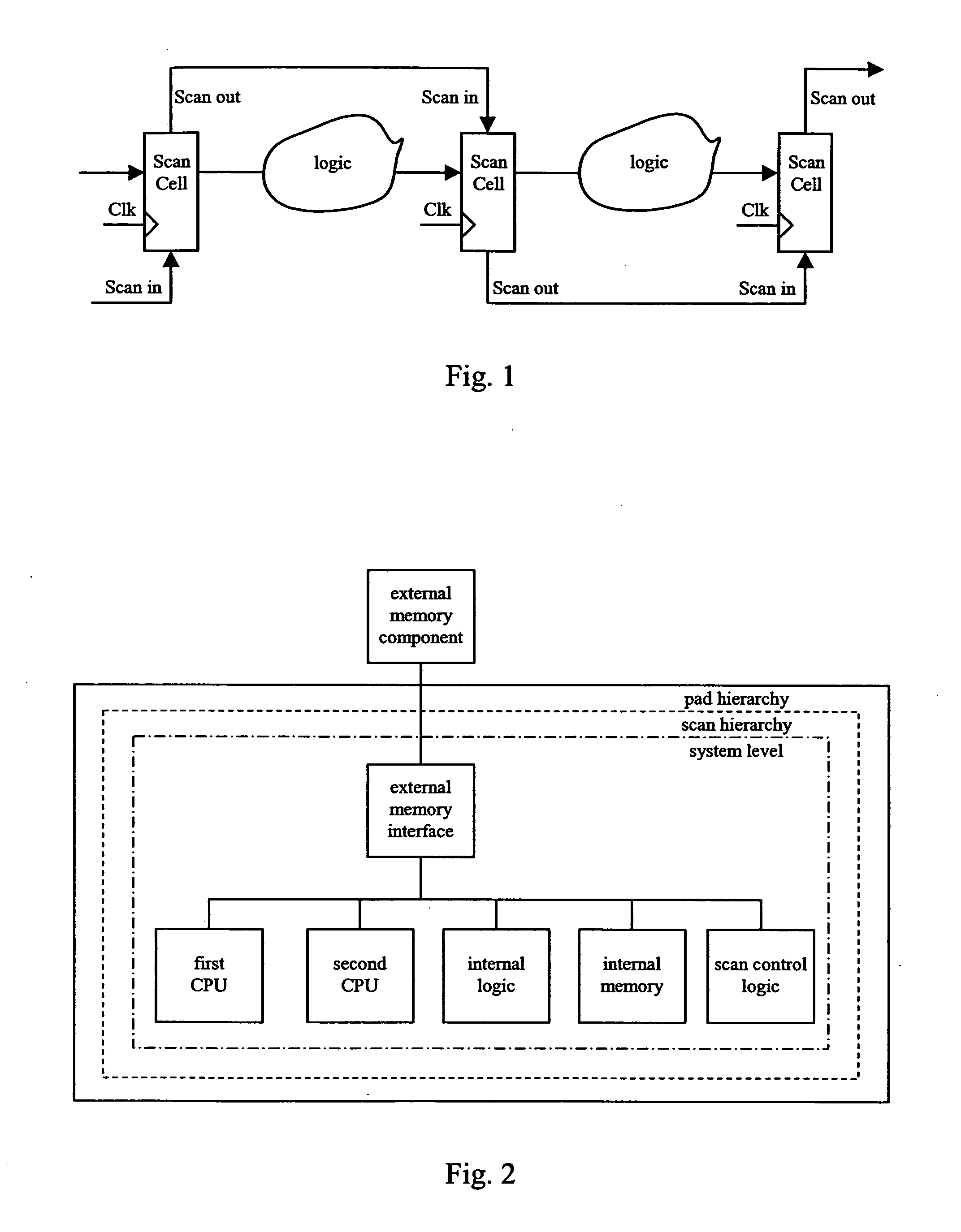

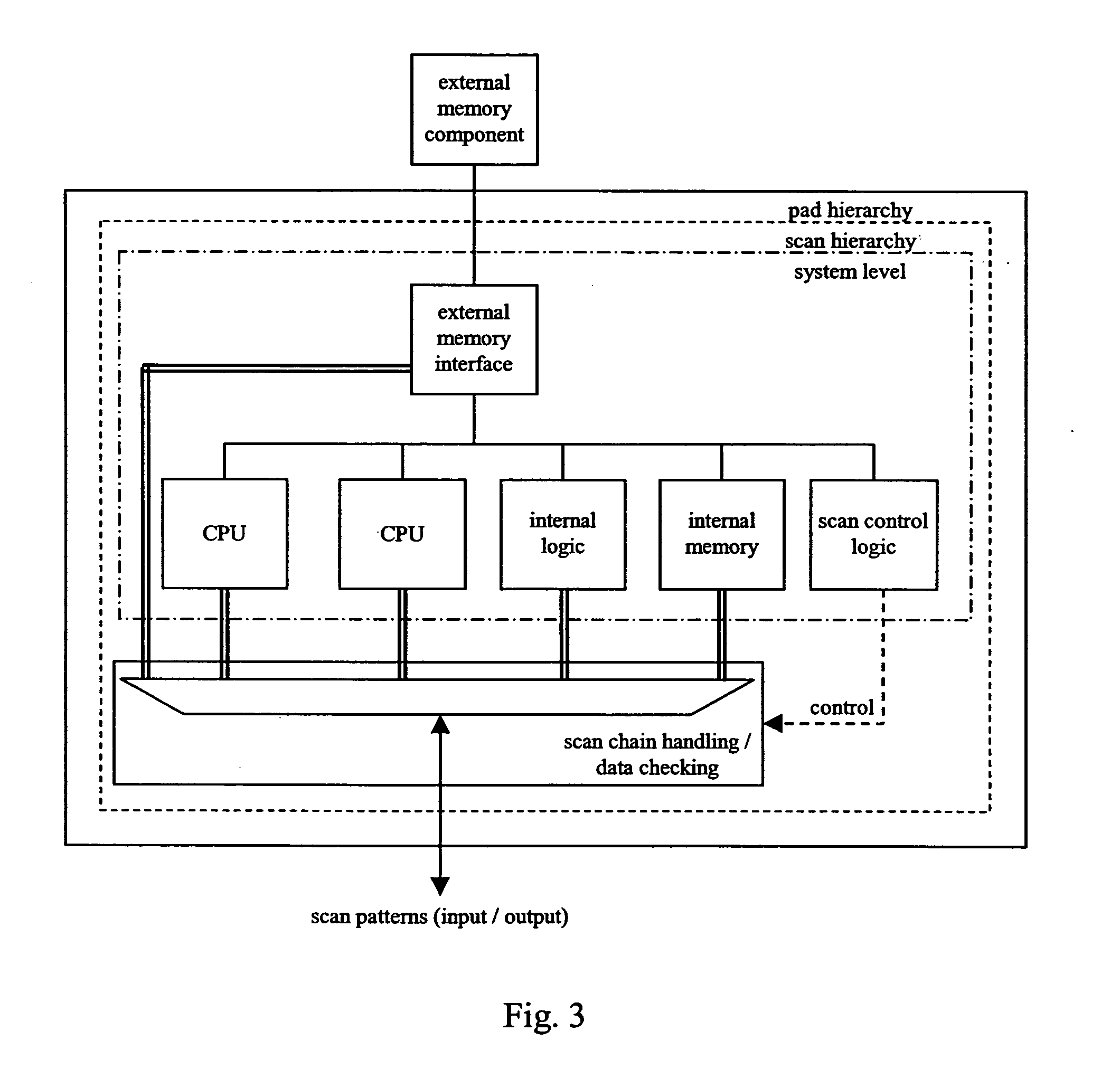

Large, complex SoCs comprise interconnections of various functional blocks. Such functional blocks contain scan chains that are used for their individual production testing. The present invention utilizes these scan chains as a tool in the debugging of these SoCs by providing the internal contents of registers and memories contained on the SoC device. Accordingly, both hardware and software designers are provided a means to observe the effect of their designs on the internal operation of the SoC device. The invention is compatible with current integrated circuit design methodology and requires minimal area on the SoC for support circuitry.

Owner:AVAGO TECH INT SALES PTE LTD

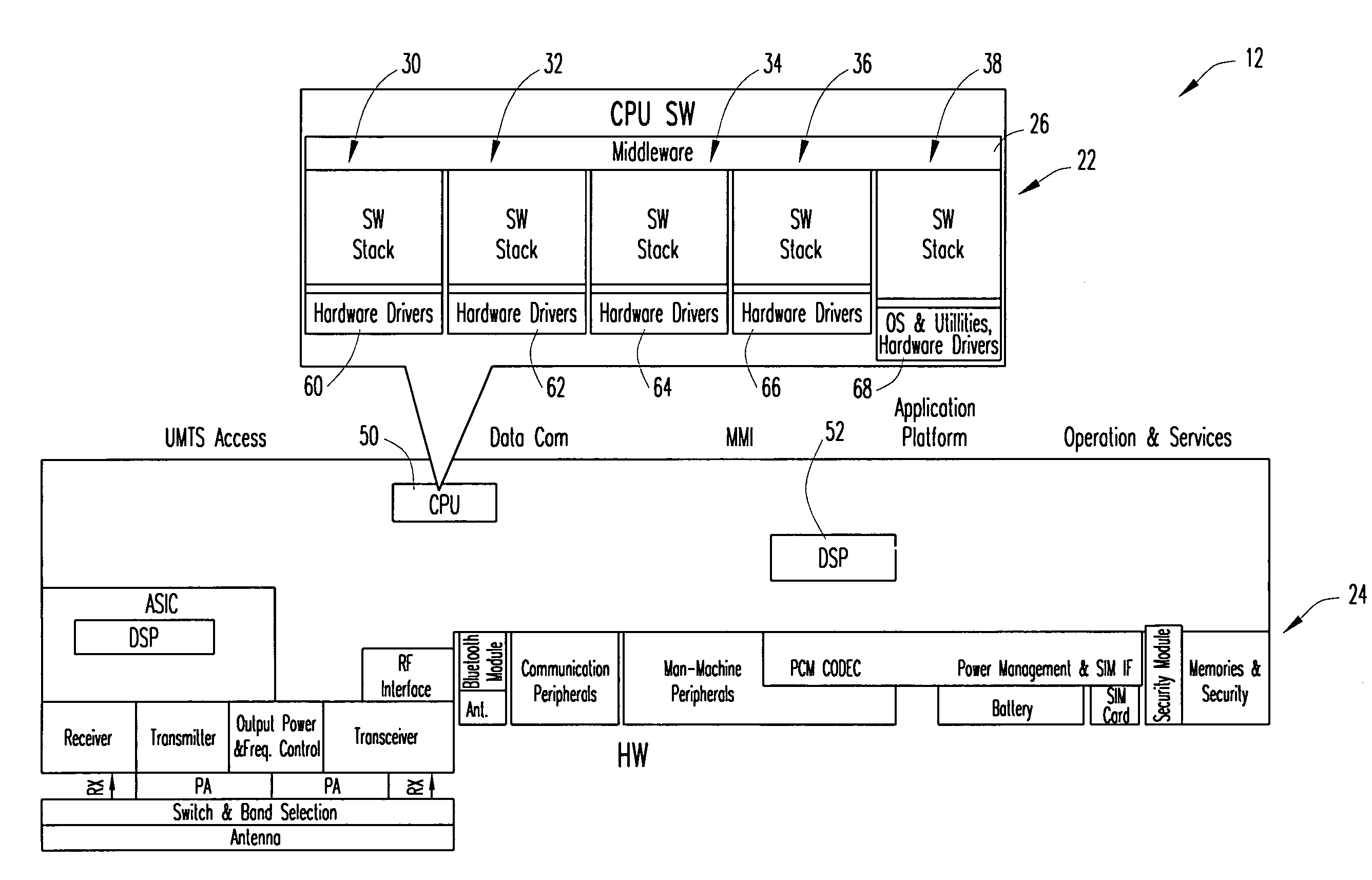

Method of and system for testing equipment during manufacturing

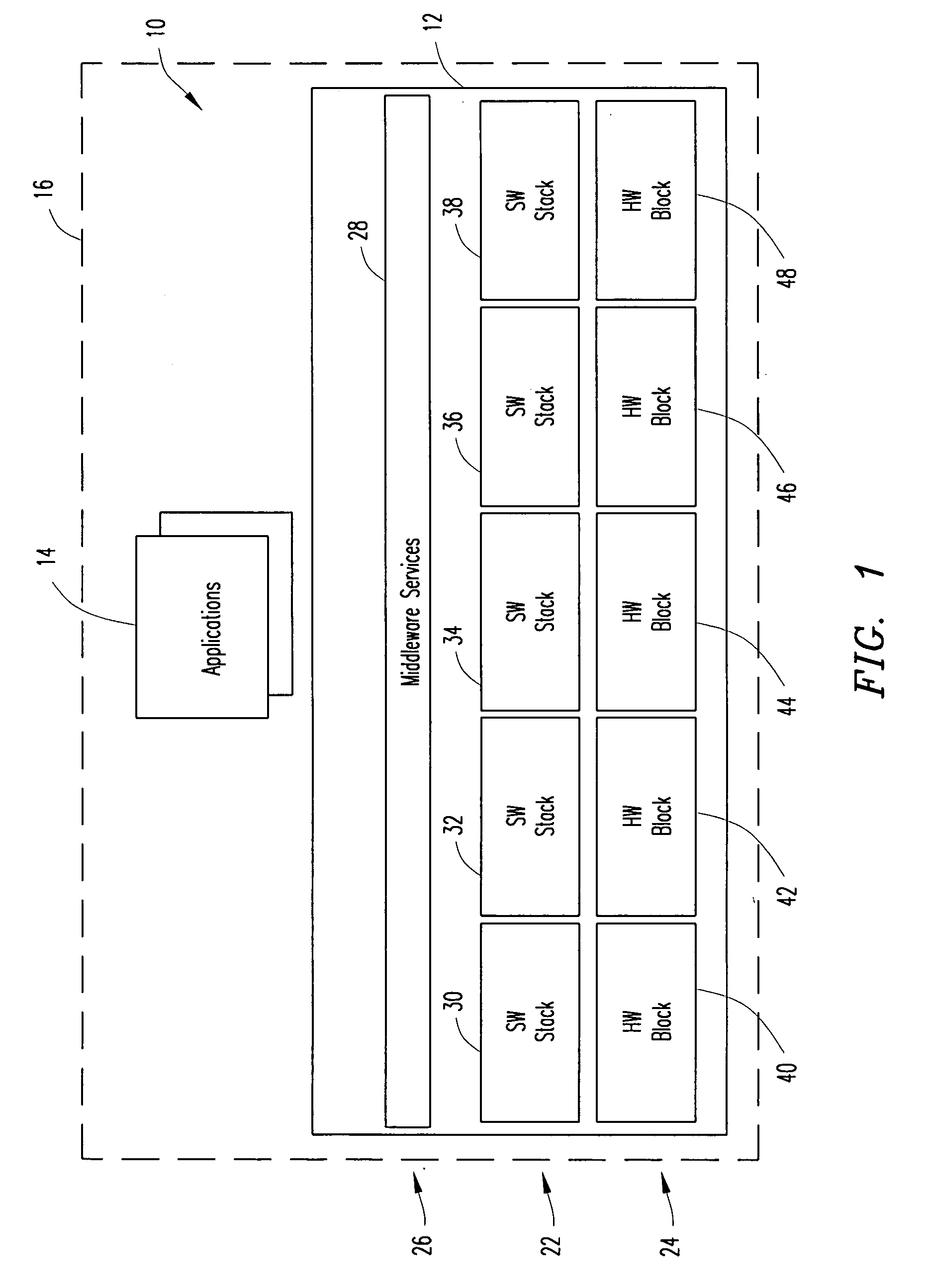

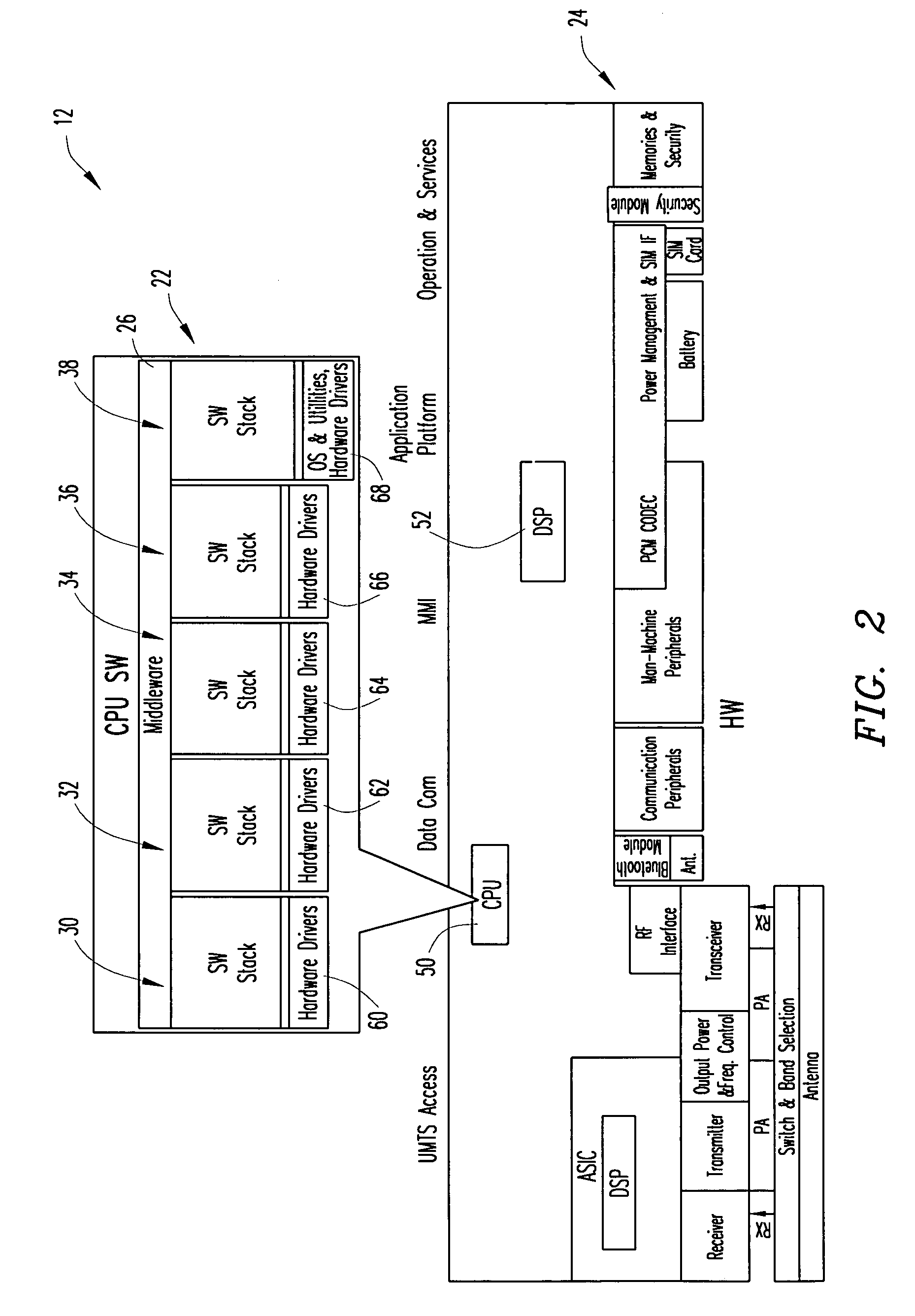

InactiveUS20040102187A1Radio/inductive link selection arrangementsAutomatic exchangesComputer hardwareCode space

A platform system for a mobile terminal for a wireless telecommunications system includes a mobile-terminal platform assembly. The mobile-terminal platform assembly includes a software services component having at least one functional software unit, a hardware component having at least one hardware unit associated with and controlled by the at least one functional software unit, and an interface component having at least one interface for providing access to the mobile-terminal platform assembly. The platform system also includes test application software loaded, installed, and run on the mobile-terminal platform assembly via the interface component. The test application software tests both software and hardware of the mobile terminal during both production testing and testing performed during a lifecycle of the mobile terminal. The test application software may be located in an unprotected code space of the mobile terminal in order to allow the test application software to be overwritten as needed to make space for other applications.

Owner:UNWIRED PLANET

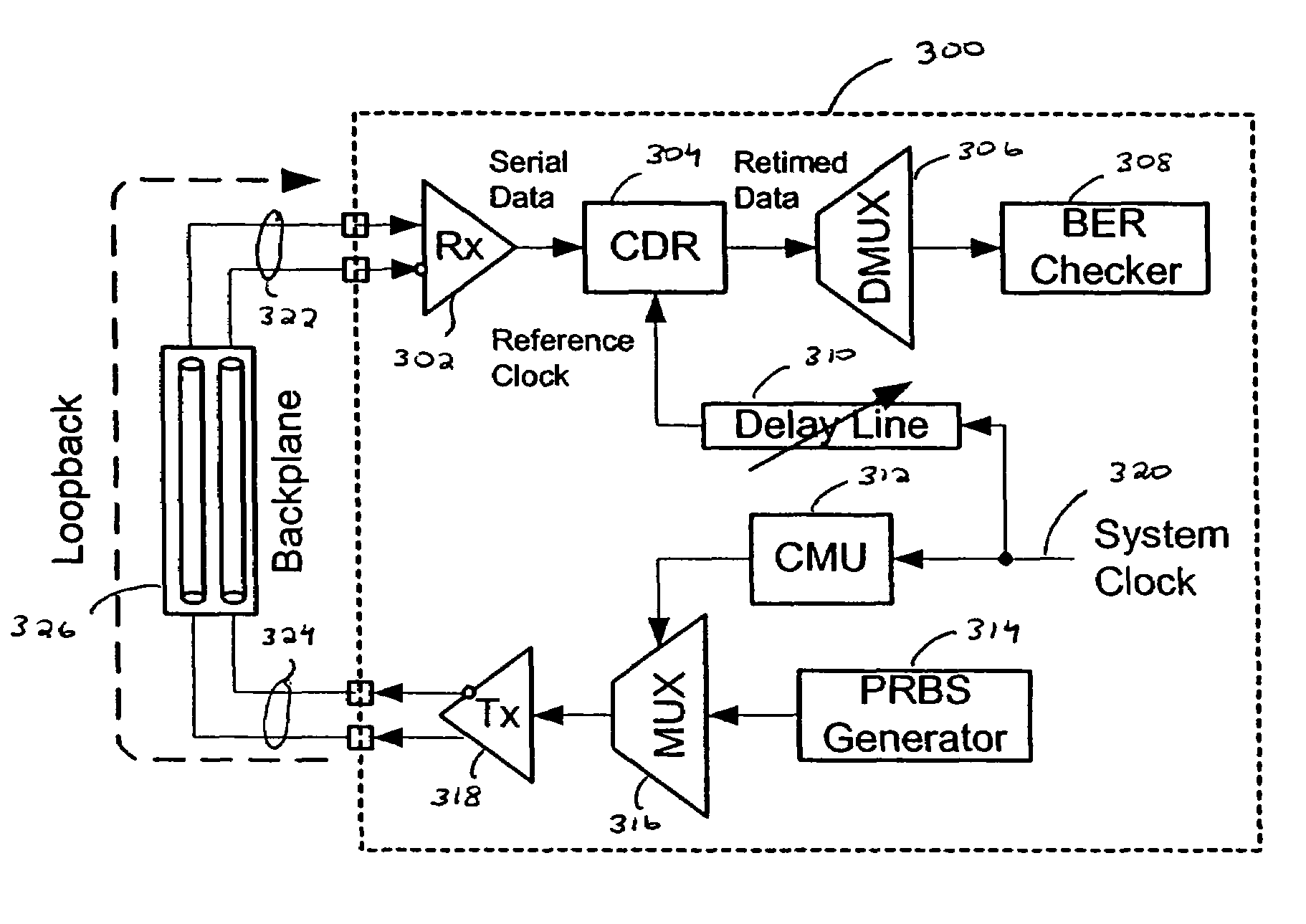

Built-in at-speed bit error ratio tester

InactiveUS7743288B1Low-cost solutionEfficient testingError preventionTransmission systemsEqualizationBuilt-in self-test

A built-in, at-speed BERT is provided that may be part of high-speed serial interface circuitry implemented on an integrated circuit. The built-in, at-speed BERT takes advantage of an existing clock data recovery (CDR) dual-loop architecture and built-in self test (BIST) circuitry. The built-in, at-speed BERT provides a low-cost solution for production testing of high-speed serial links, facilitating jitter analysis and evaluation of pre-emphasis and equalization performance. This further allows adaptation of pre-emphasis and equalization.

Owner:ALTERA CORP

Mass production testing of USB flash cards with various flash memory cells

InactiveUS7788553B2Facilitates efficient and high volume testing/formattingFacilitates high volume formatting/testingElectronic circuit testingError detection/correctionCard readerUSB

A high volume testing / formatting process is provided for Universal Serial Bus-based (USB-based) electronic data flash cards (USB devices) that meets the increasing demand for USB electronic data flash cards (USB devices). A test host is simultaneously coupled to the multiple USB devices (e.g., using a multi-port card reader or a probe fixture), a controller endpoint value is read from each of the USB devices and verified with a known good value, and then testing / formatting is performed on each of the USB devices by writing predetermined data into each USB device in a pipelined manner, then reading out and testing the predetermined data. In one embodiment, the test host implements a special USB driver that blocks standard USB registration procedures upon detecting the plurality of USB devices. Control and / or boot code data are written onto the flash memory device (i.e., instead of being provided on a controller ROM).

Owner:SUPER TALENT TECH CORP

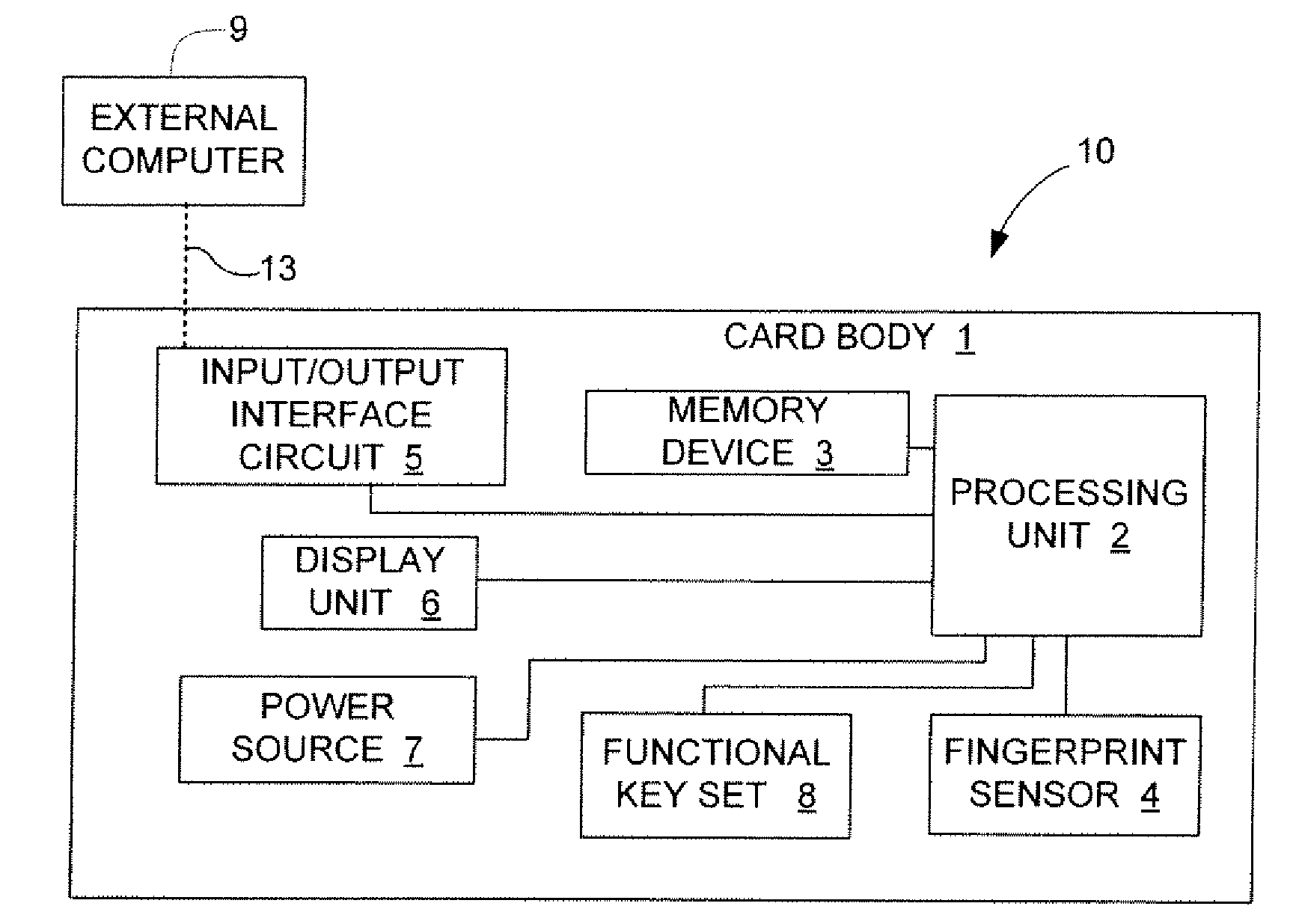

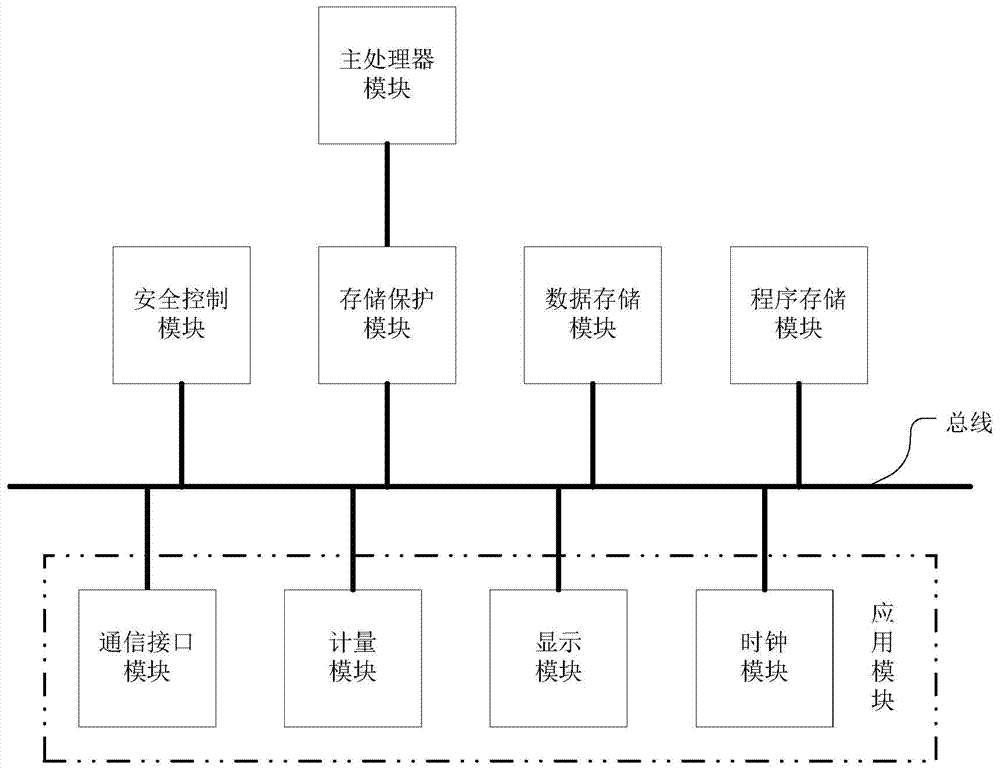

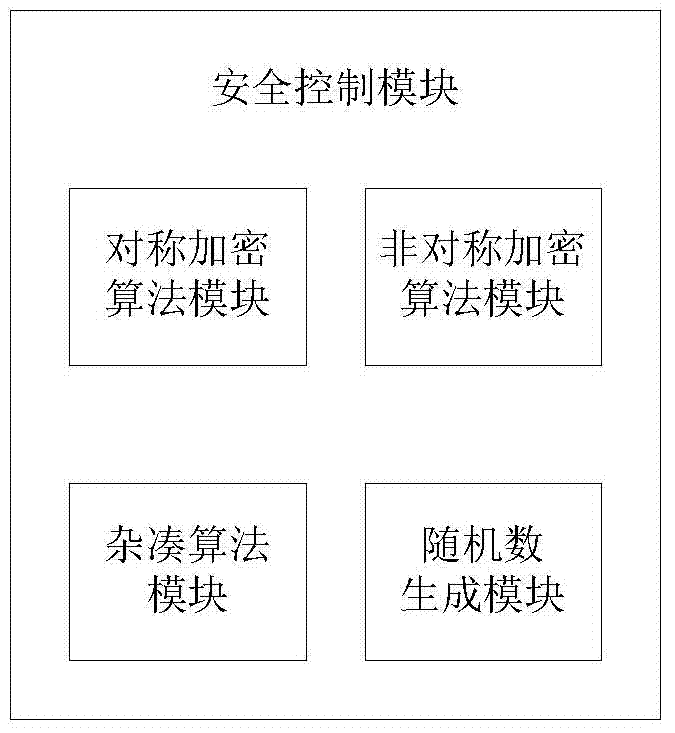

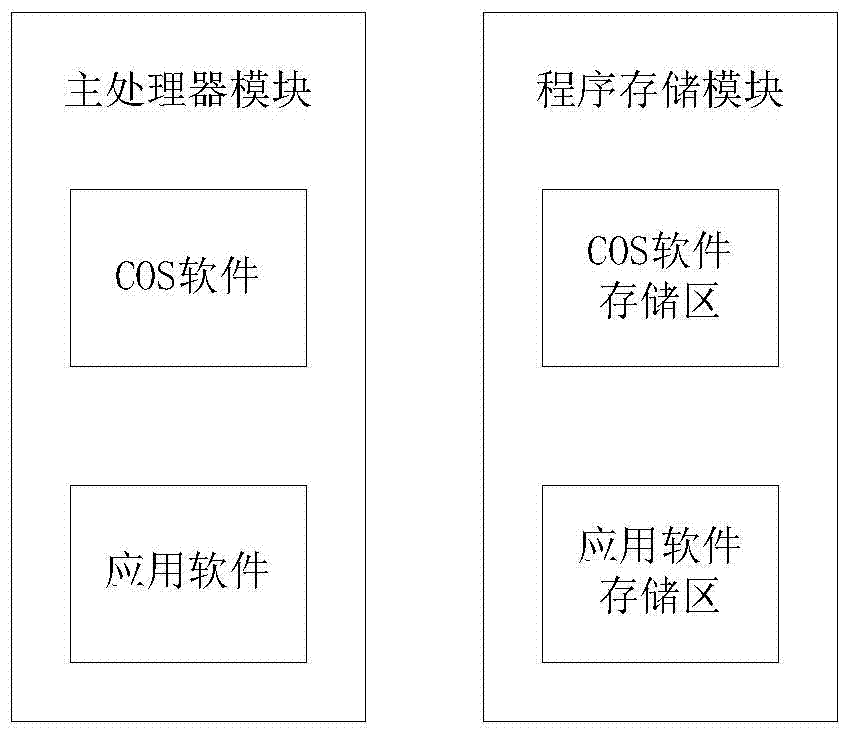

Intelligent electric meter main control chip and security encryption method

ActiveCN103679062AAvoid security breachesImprove securityInternal/peripheral component protectionDigital data authenticationElectric power systemApplication software

The invention provides an intelligent electric meter main control chip. The intelligent electric meter main control chip comprises an internal bus, a main processor module, a data storage module and at least one application module, wherein the main processor module, the data storage module and the application module are connected to the internal bus, and the application module comprises a metering module. A security control module is further integrated inside the chip, is connected to the internal bus and has a security encryption function. The chip further comprises a storage protecting module, wherein the storage protecting module is connected between the main processor module and the internal bus and is configured for shielding illegal memory access instructions. Due to the fact that the security control module is arranged inside the main control chip and connected with a center processing module through the internal bus, security holes of a security control chip of an application software bypass of an intelligent electric meter terminal can be effectively avoided, and meanwhile production and testing cost is reduced. The invention further provides a security encryption method based on the intelligent electric meter main control chip and a certificate authorization center, and security of an electric system is guaranteed further.

Owner:SHANGHAI BEILING

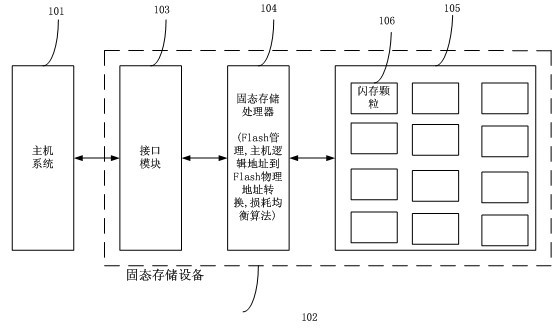

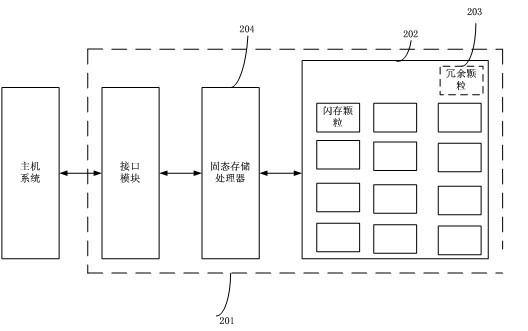

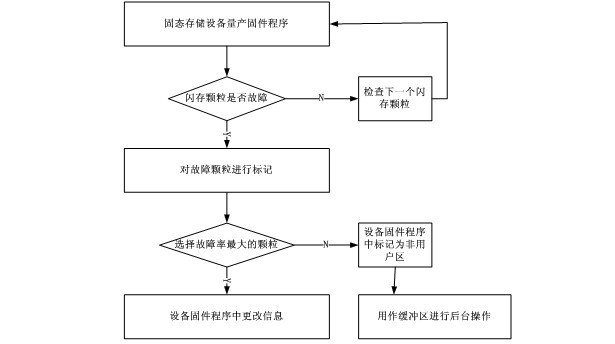

Fault tolerance design method for solid-state memory device

ActiveCN102043689AWill not affect the excellent rateExtended service lifeRedundant hardware error correctionSolid-state storageError-tolerant design

The invention discloses a fault tolerance design method for a solid-state memory device, in which standby redundant memory particles are additionally added in design of a circuit board of a memory device, when the device has flash memory fault in production back-end test or usage, the failed particles are substituted by the redundant memory particles, thereby ensuring that excellent rate of production of the memory device cannot be influenced even encapsulation test is not performed on the particles; simultaneously, service life of the device is effectively prolonged by adding the redundant memory particles in the method, when the flash memory particles in the device reach certain service life, the flash memory particles are substituted by the redundant particles or idle particles, so that the service life of the device is effectively prolonged through the continuous substitution. The method can be implemented in process of device production test and / or usage.

Owner:WUHAN SOLIC CZECHOSIOVAKIA DATA SCI & TECH +1

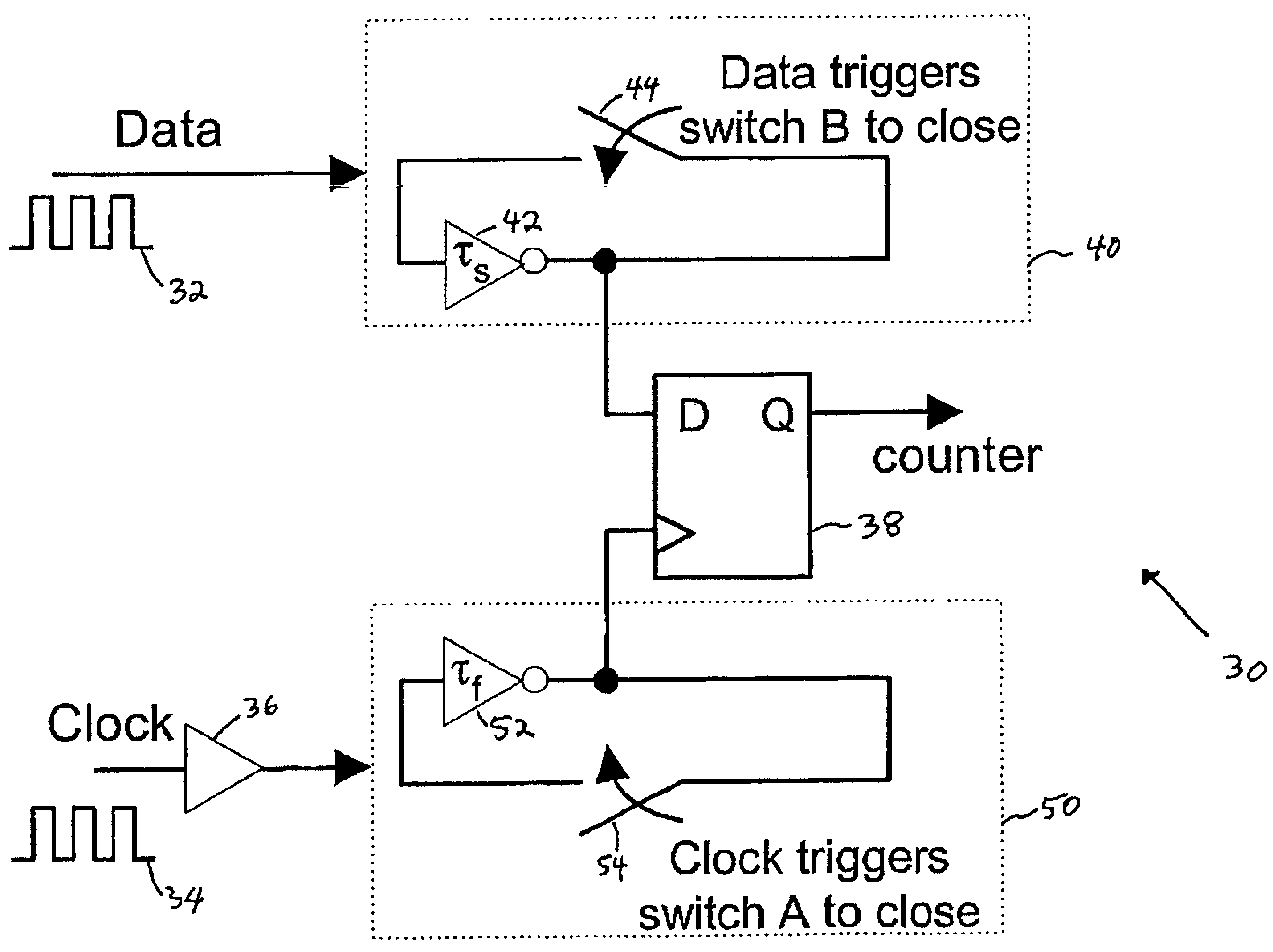

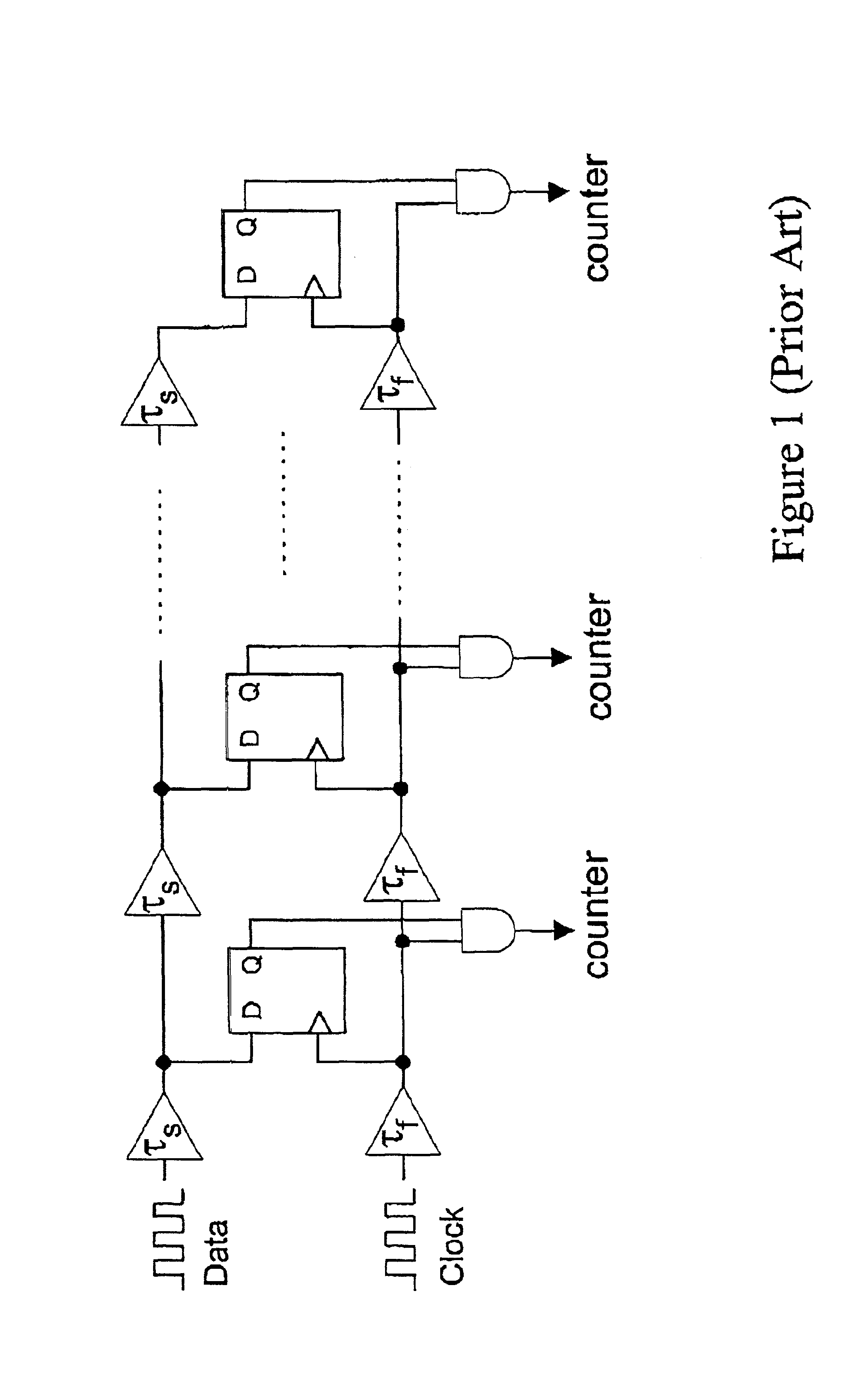

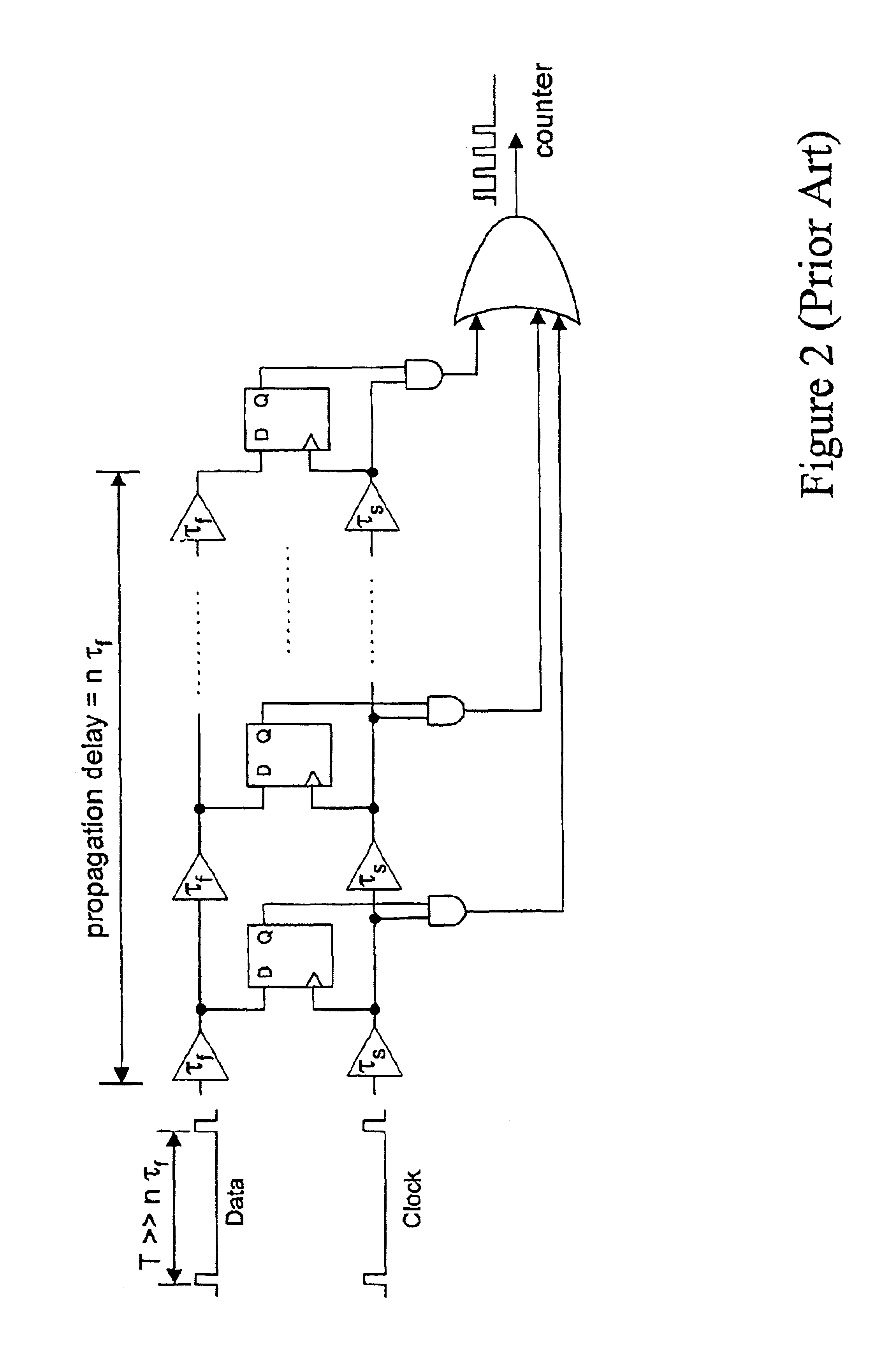

Timing measurement device using a component-invariant vernier delay line

InactiveUS6850051B2Reduced measurement timeAvoid matching problemsPulse characteristics measurementsFrequency to phase shift conversionSingle stageMeasurement device

In recent years, much effort has been placed on improving the performance of timing and jitter measurement devices using Delay Locked Loop (DLL) and Vernier Delay Line (VDL) techniques. However, these approaches require highly matched elements in order to reduce differential non-linearity timing errors. In an attempt to reduce the requirement on element matching, a component-invariant VDL technique is disclosed that enables the measurement device to be synthesized from an RTL description. The present invention is based on a single-stage VDL structure, which is used to mimic the behavior of a complete VDL. Furthermore, as test time is an important consideration during a production test, a method and system is provided that reduces test time at the expense of additional hardware.

Owner:MCGILL UNIV

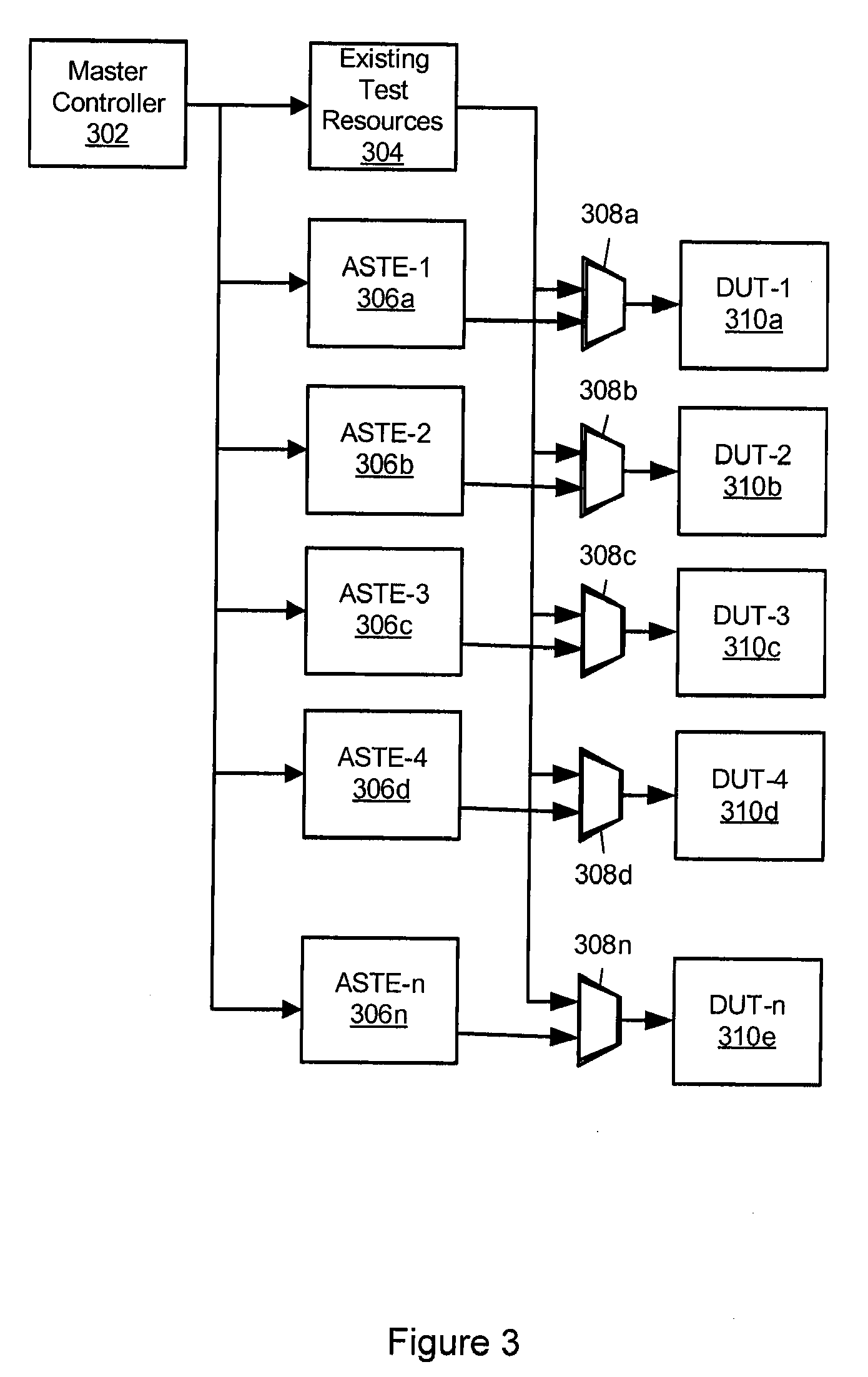

Application Specific Distributed Test Engine Architecture System And Method

InactiveUS20070245199A1Improve test throughputImprove overall utilizationElectronic circuit testingError detection/correctionDistributed testingTest requirements

An Application Specific Distributed Test Engine (ASDTE) that provides an optimized set of test resources for a given application. The test engine resources, configuration, functionality, and even the number of test engines can be changed as different devices are tested, or as different test methodologies are used with the system. This can be done by including the test engine configuration as a part of the application files that are loaded during the system set-up. This approach differs from conventional testing systems which limit testing to a fixed, limited, or standard stimulus / response engine configuration intended to test a variety of devices. Some of the benefits of the Application Specific Distributed Test Engine Architecture include: (1) a very high test throughput, (2) the ability to adapt system functionality and capabilities to meet different and new, unforeseen device test requirements on a lot-by-lot basis on a production test floor, and (3) the ability to change the number of test engines to optimize tester channels and system utilization.

Owner:POCHOWSKI ROBERT

Integrated circuit with leakage control and method for leakage control

InactiveUS20050149799A1Improved leakage power controlReduce leakage powerPower reduction by control/clock signalDigital circuit testingPower modeState variable

The present invention relates to integrated circuit with reduced leakage power and in particular to a methodology for retaining an operational state of at least a part of the integrated circuit while the part is in standby / low power mode. In detail, the inventive methodology is based on the use of scan chains being implemented in the integrated circuit for production testing purposes. Via the scan chains circuit-internal state-variable memory element content is read out and / or written in such that the operational state of for instance a specific part (power domain) of the integrated circuit may be captured on the basis of the circuit internal contents, retained in an adequately provided data storage and afterwards scanned into the specific part of the integrated circuit to restore the operational state thereof.

Owner:NOKIA CORP

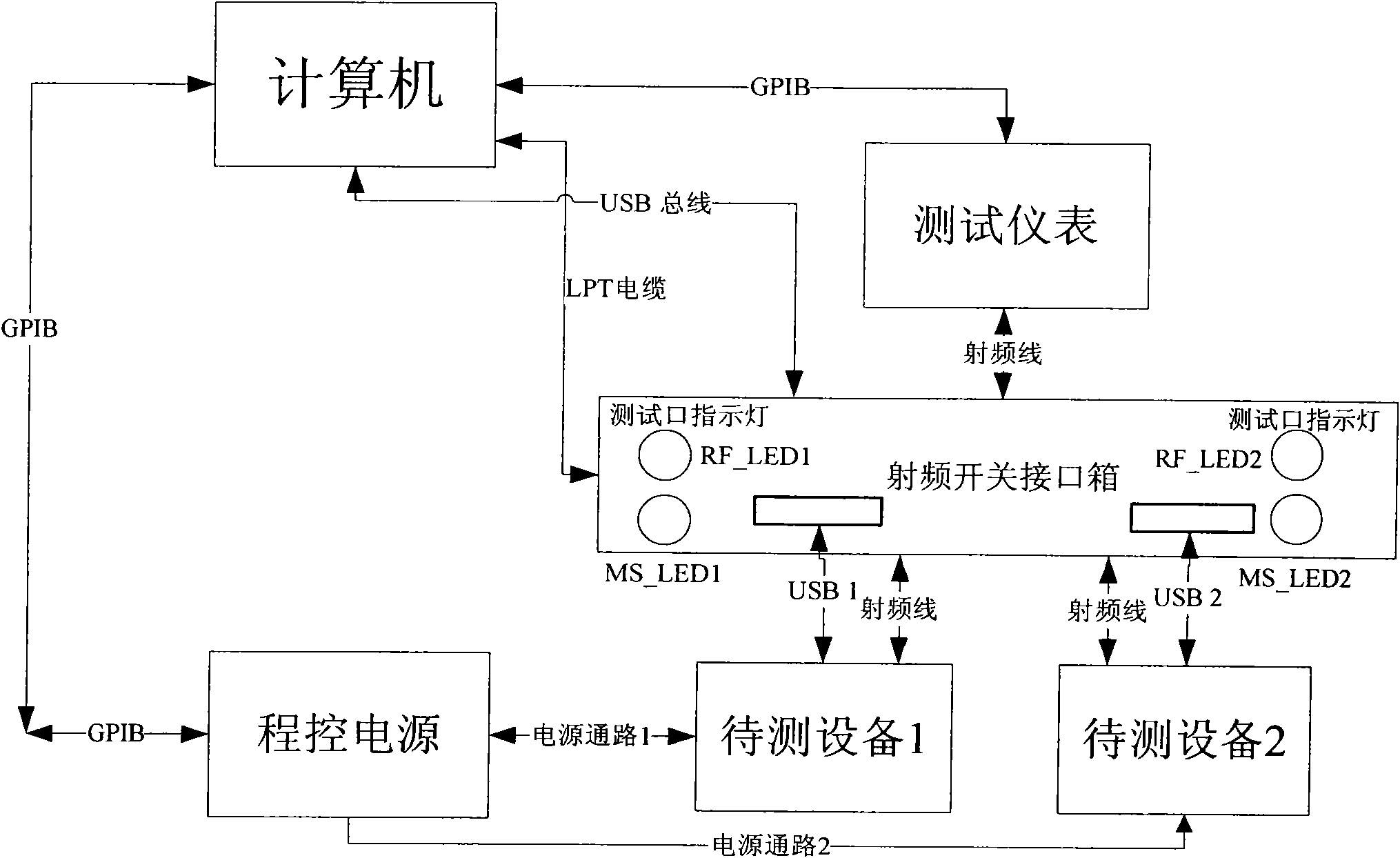

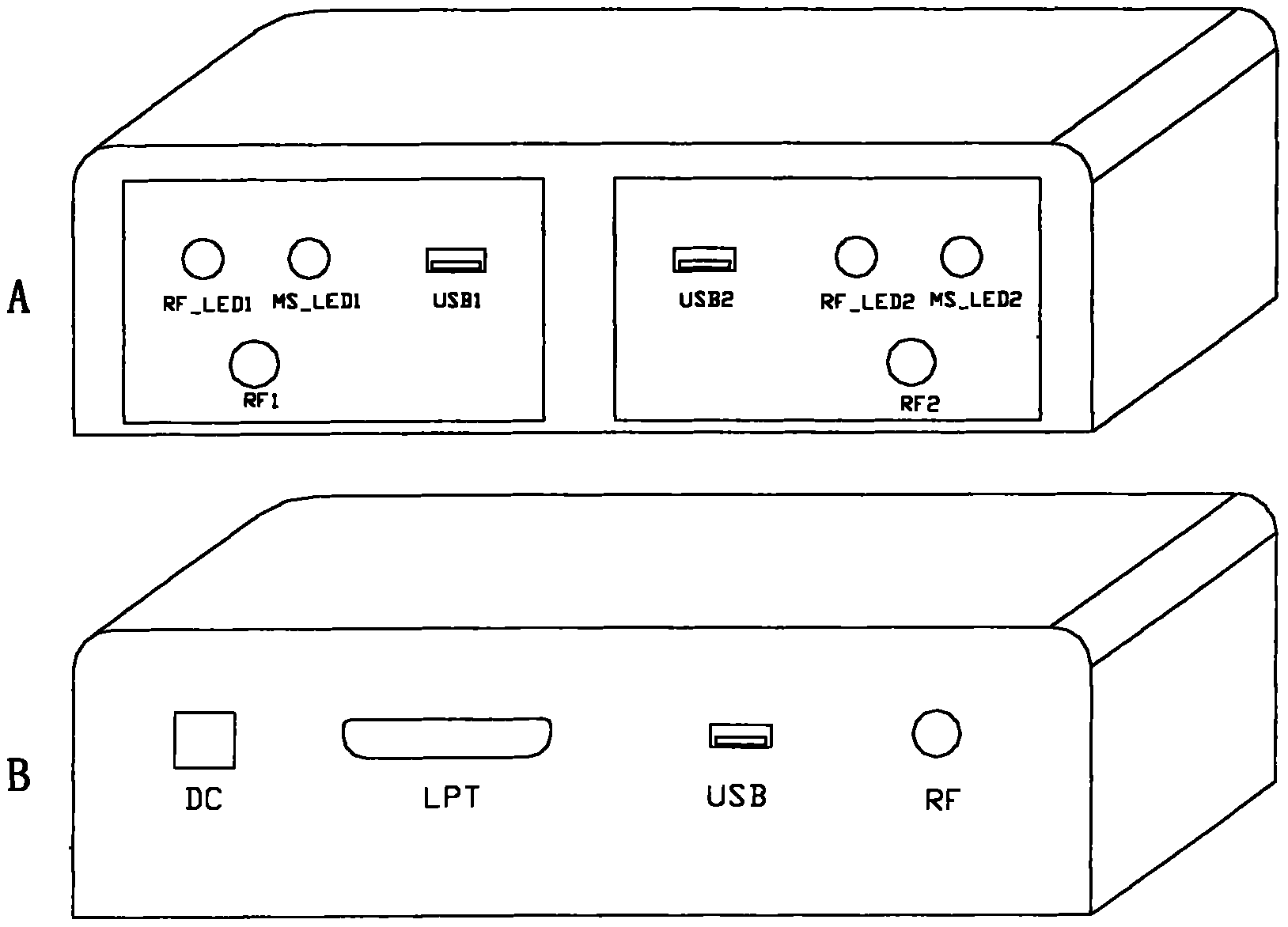

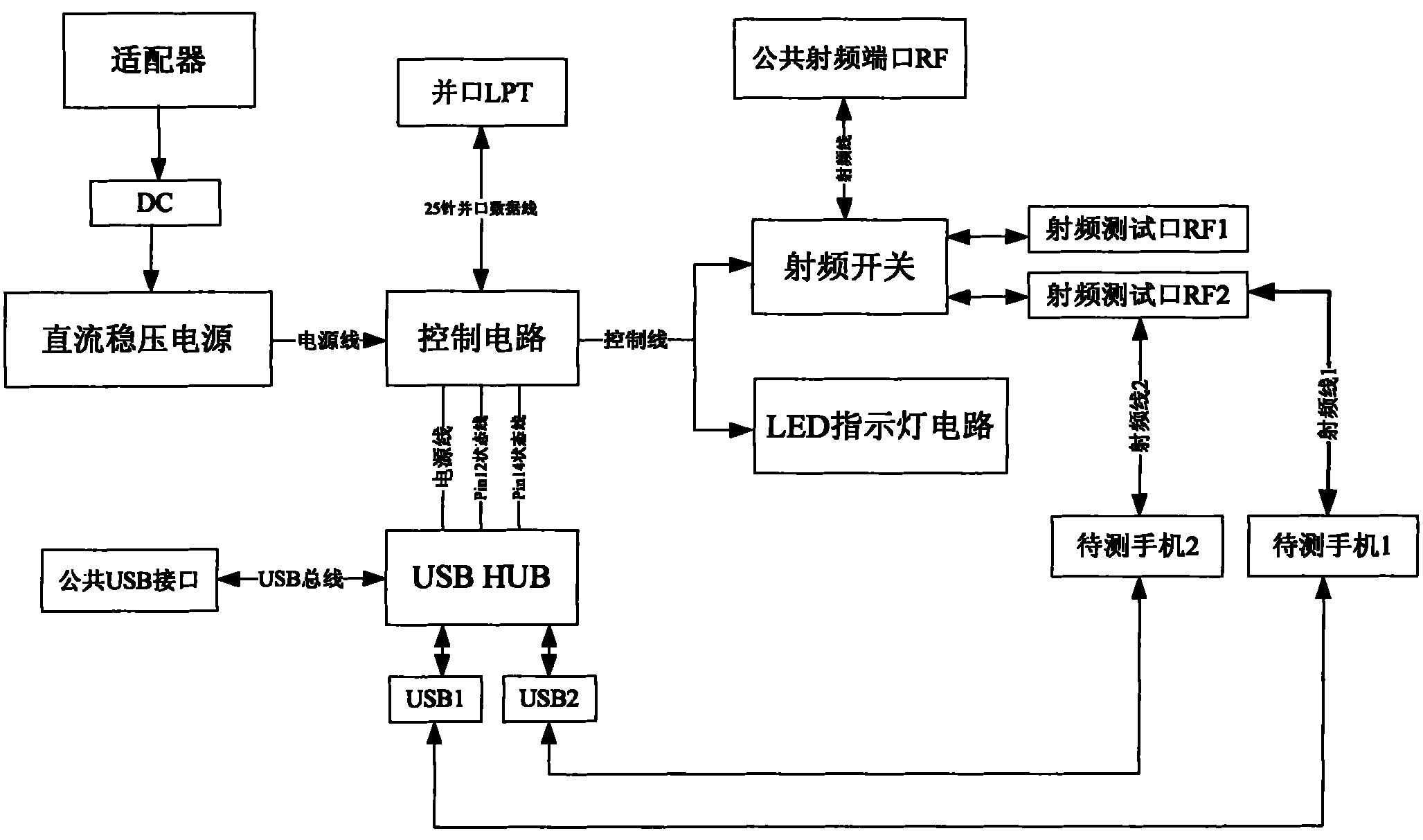

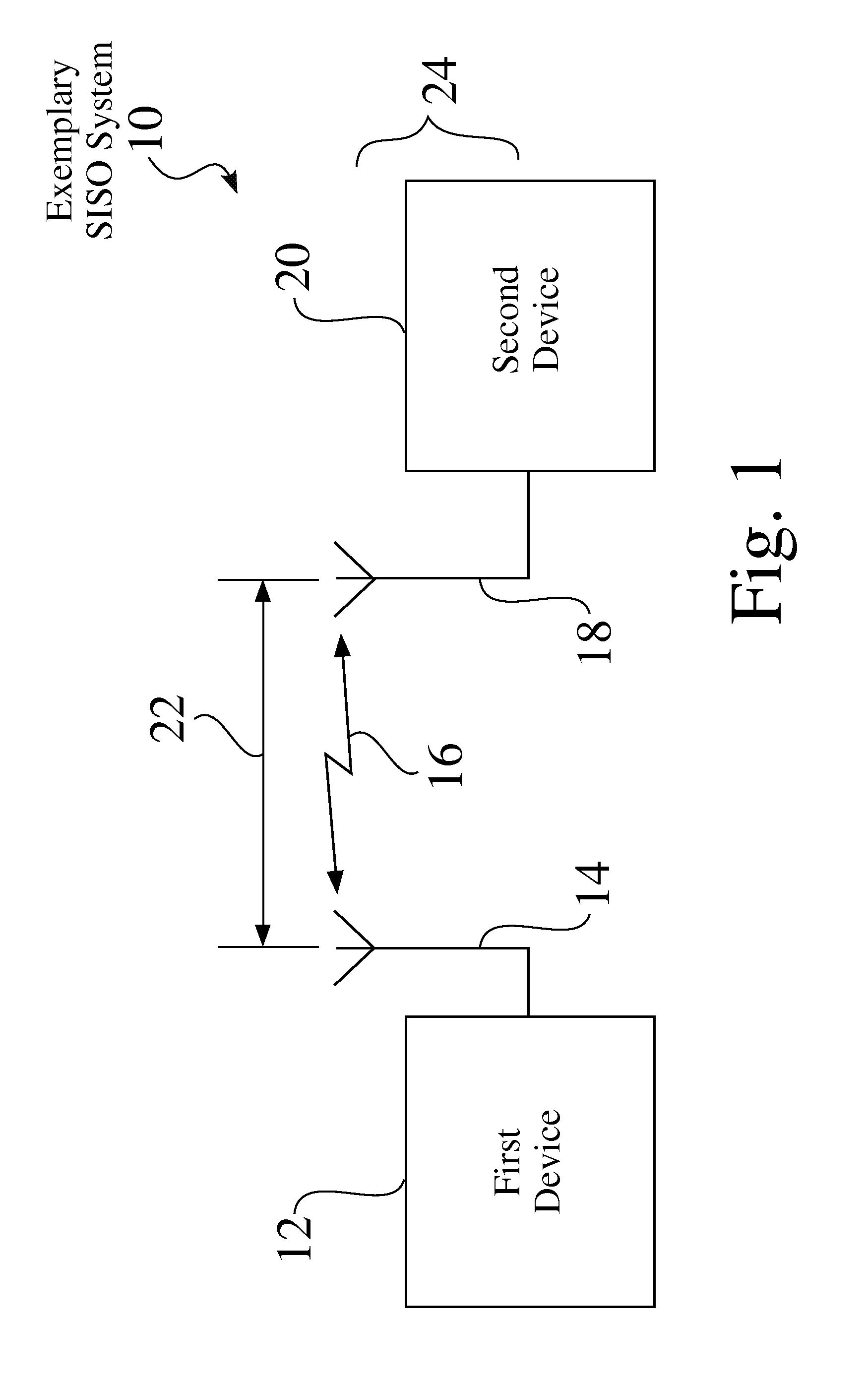

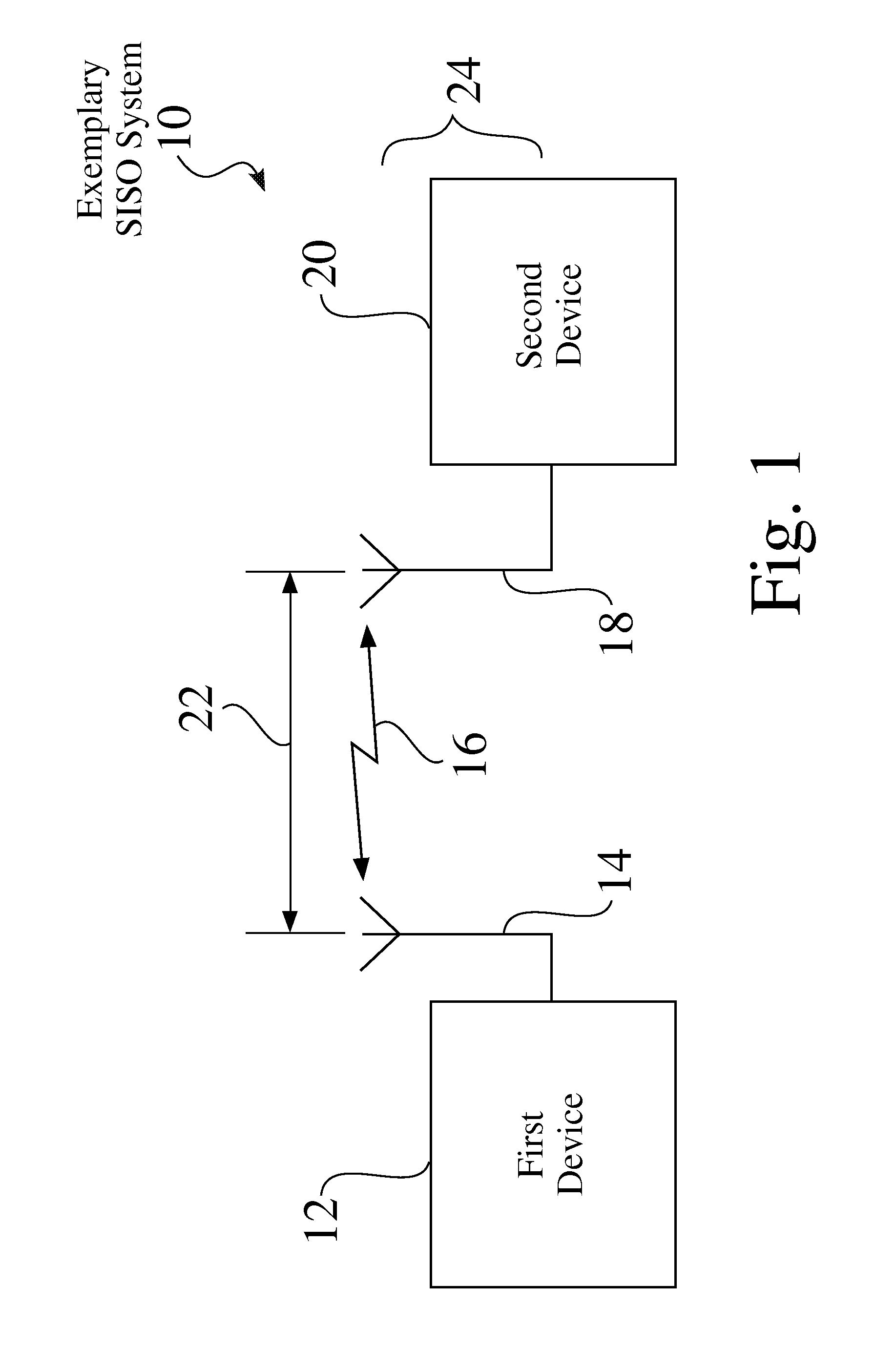

Radio frequency test system and method

ActiveCN101848043AAchieve zero waitEasy to operateTransmission monitoringTest channelComputer monitor

The invention discloses a radio frequency test system and a radio frequency test method. While the first equipment to be tested is tested by a testing instrument, the wiring and starting operation of the second equipment to be tested is performed; and after the test of the first equipment to be tested is finished, a test channel of the testing instrument is switched to the second equipment to be tested to test the second equipment to be tested. Zero wait of the testing instrument is realized by combining a radio frequency switching device with a parallel test program, so that the utilization ratio of the testing instrument reaches 100 percent, and the production testing capacity is improved under the condition that the resources of the testing instrument are limited. Meanwhile, an indicator lamp is arranged on the radio frequency switching device and is used for indicating current test conditions. Therefore, on the premise of unnecessarily opening a computer monitor, the test progressand test result can be clearly known through the luminous state of the indicator lamp, and the test operation of the technician is convenient.

Owner:QINGDAO HISENSE MOBILE COMM TECH CO LTD

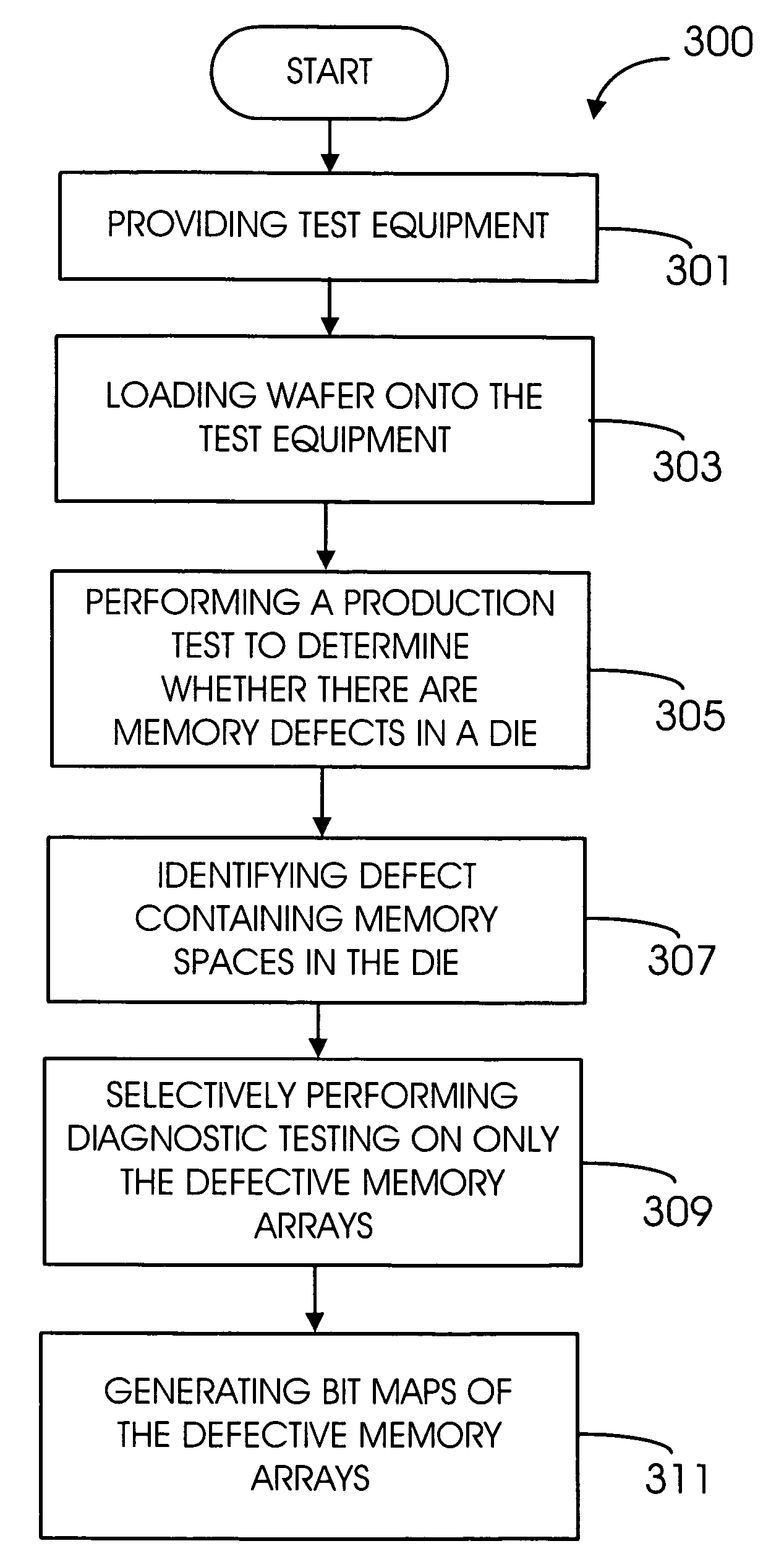

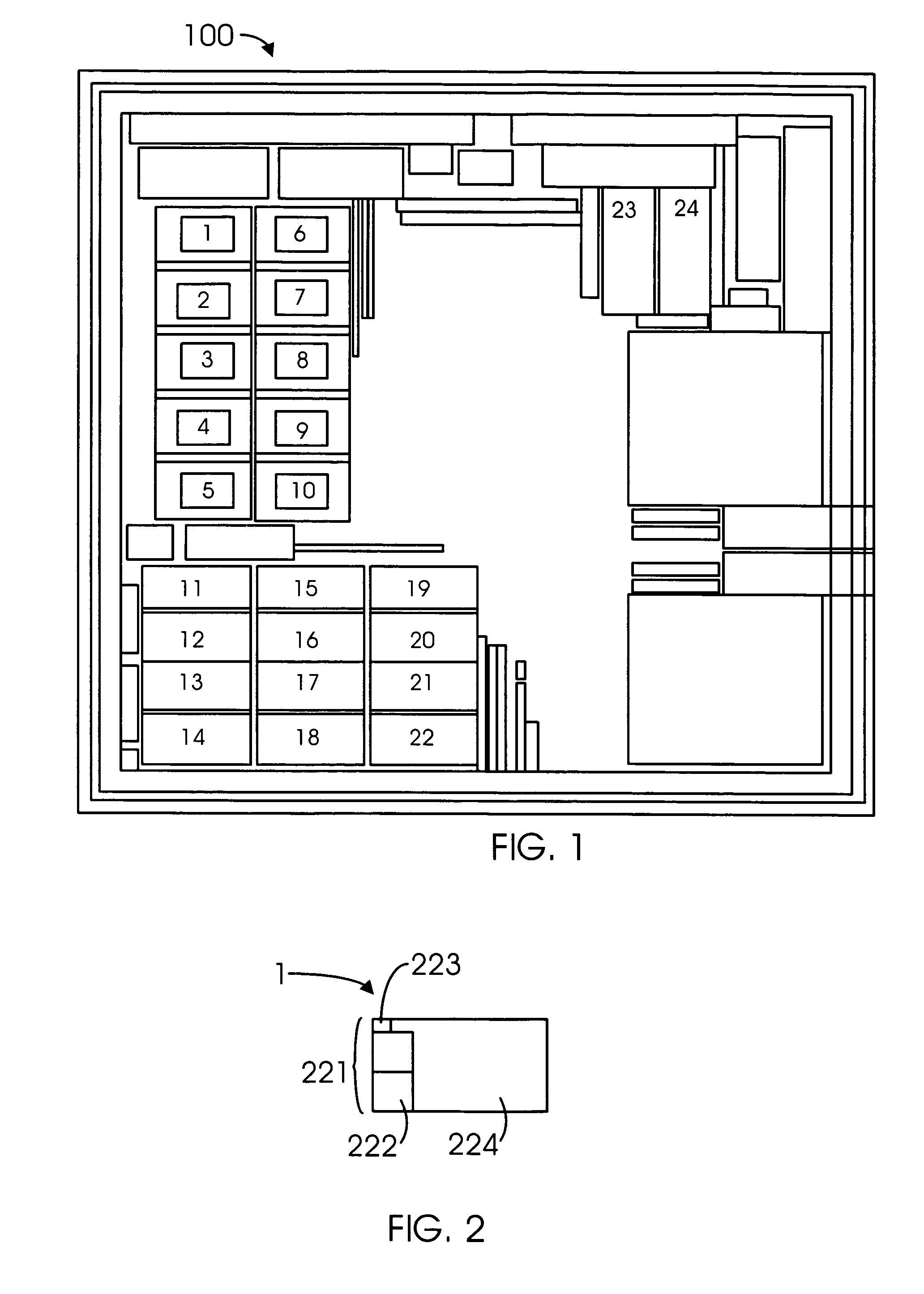

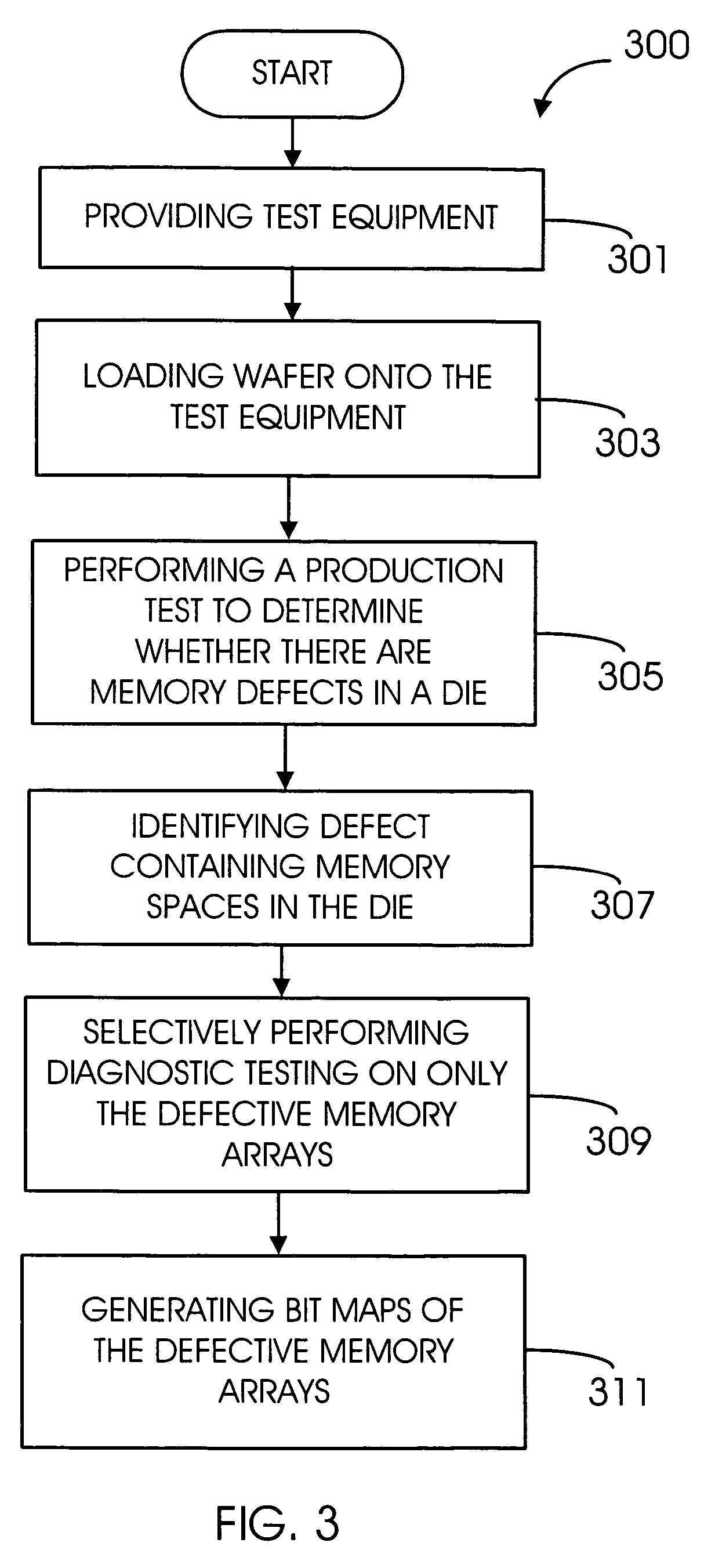

Process for conducting high-speed bitmapping of memory cells during production

The present invention is directed to a method of fast bitmapping defective memory arrays in semiconductor integrated circuit dice formed on a wafer. The method involves loading a wafer onto automated test equipment. Initial production testing is then performed on each die of the wafer to determine whether the memory arrays of each die are functioning properly. Where a die is found to have at least one defective memory array, the particular memory arrays of the die that contain defect are specifically identified using BIST circuitry forming part of the die. Then selectively performed diagnostic testing is performed on only the failed memory arrays of each defective die to generate memory array defect data. The memory array defect data is used to generate bit maps of the failed memory arrays using the memory array data.

Owner:LSI CORPORATION

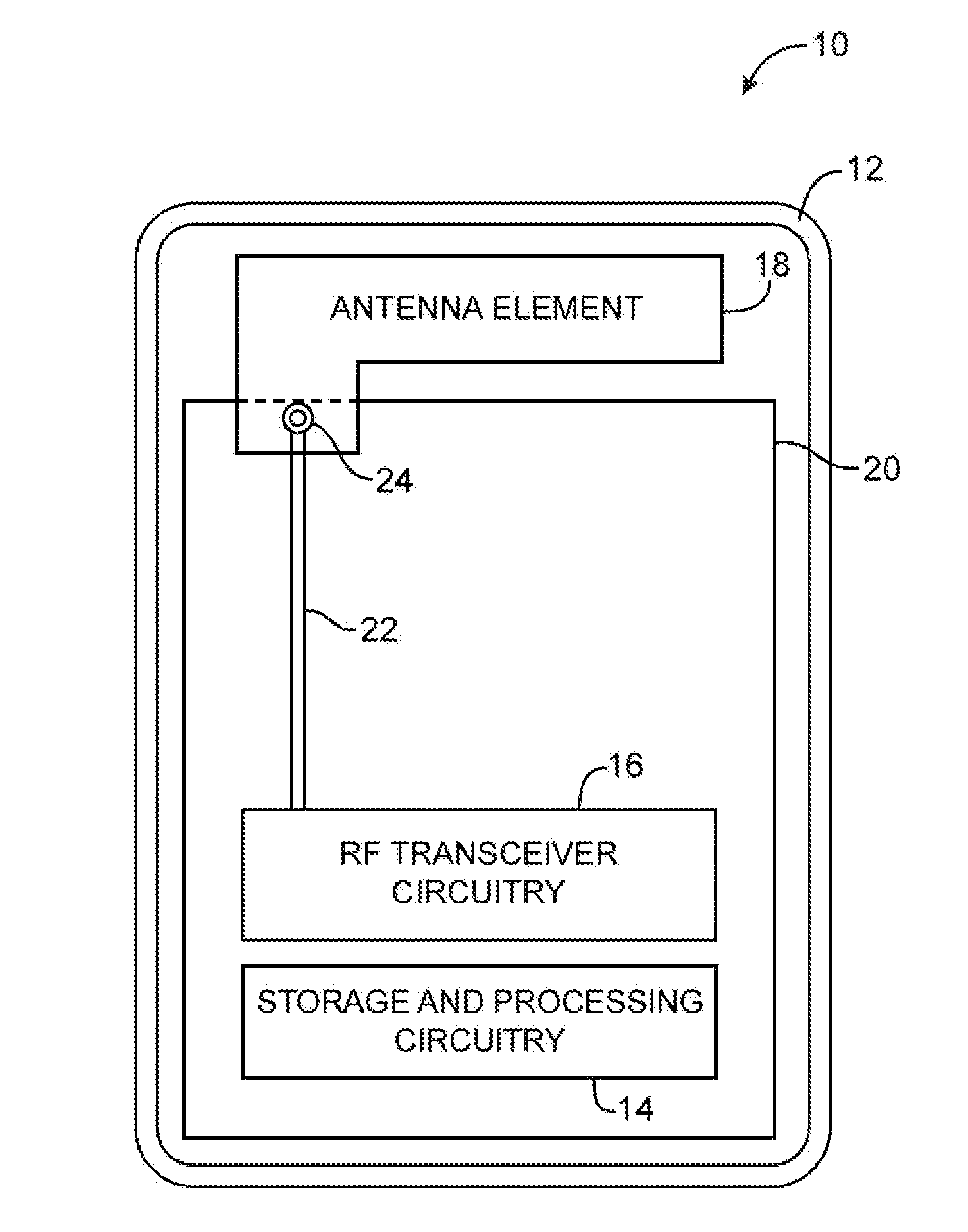

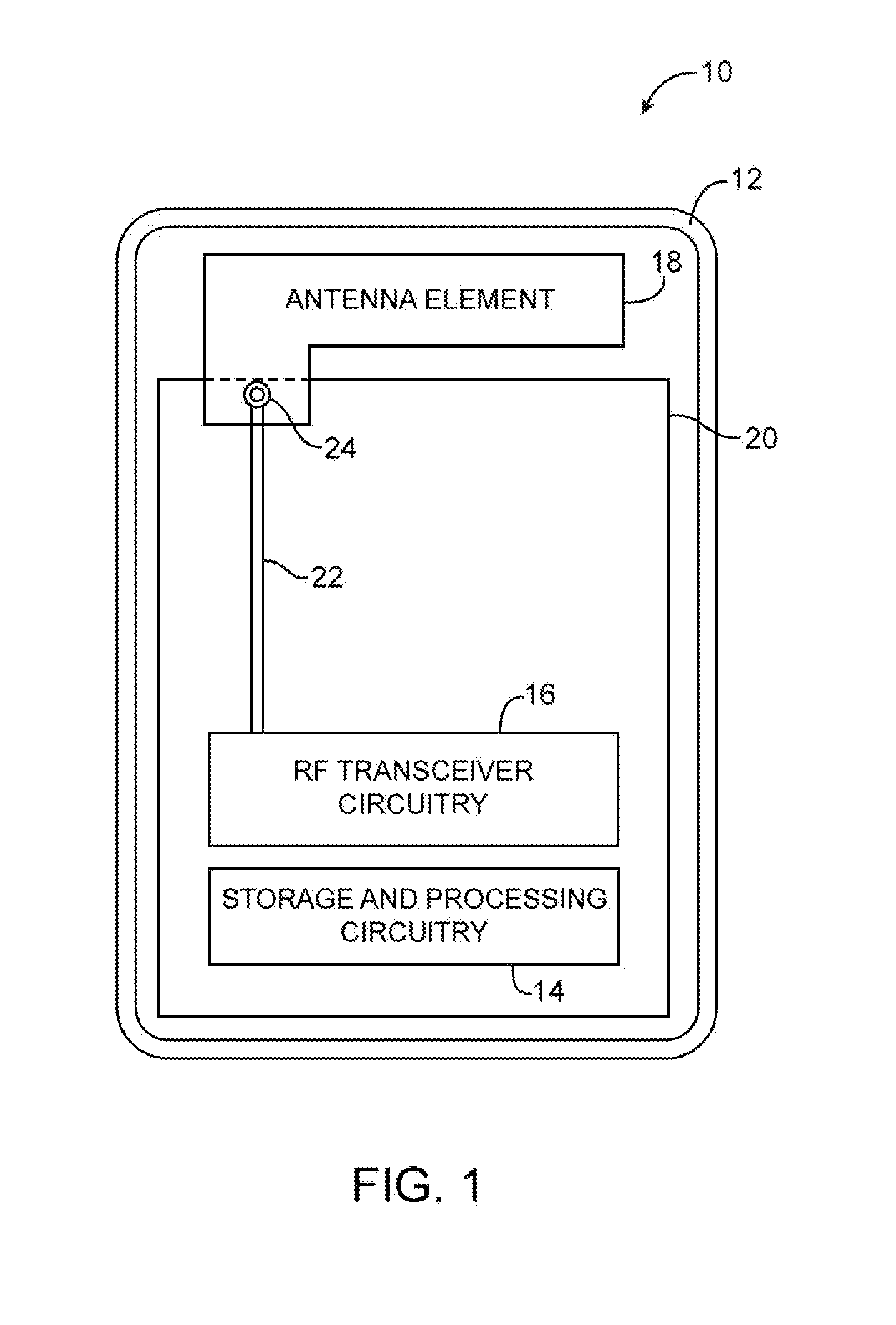

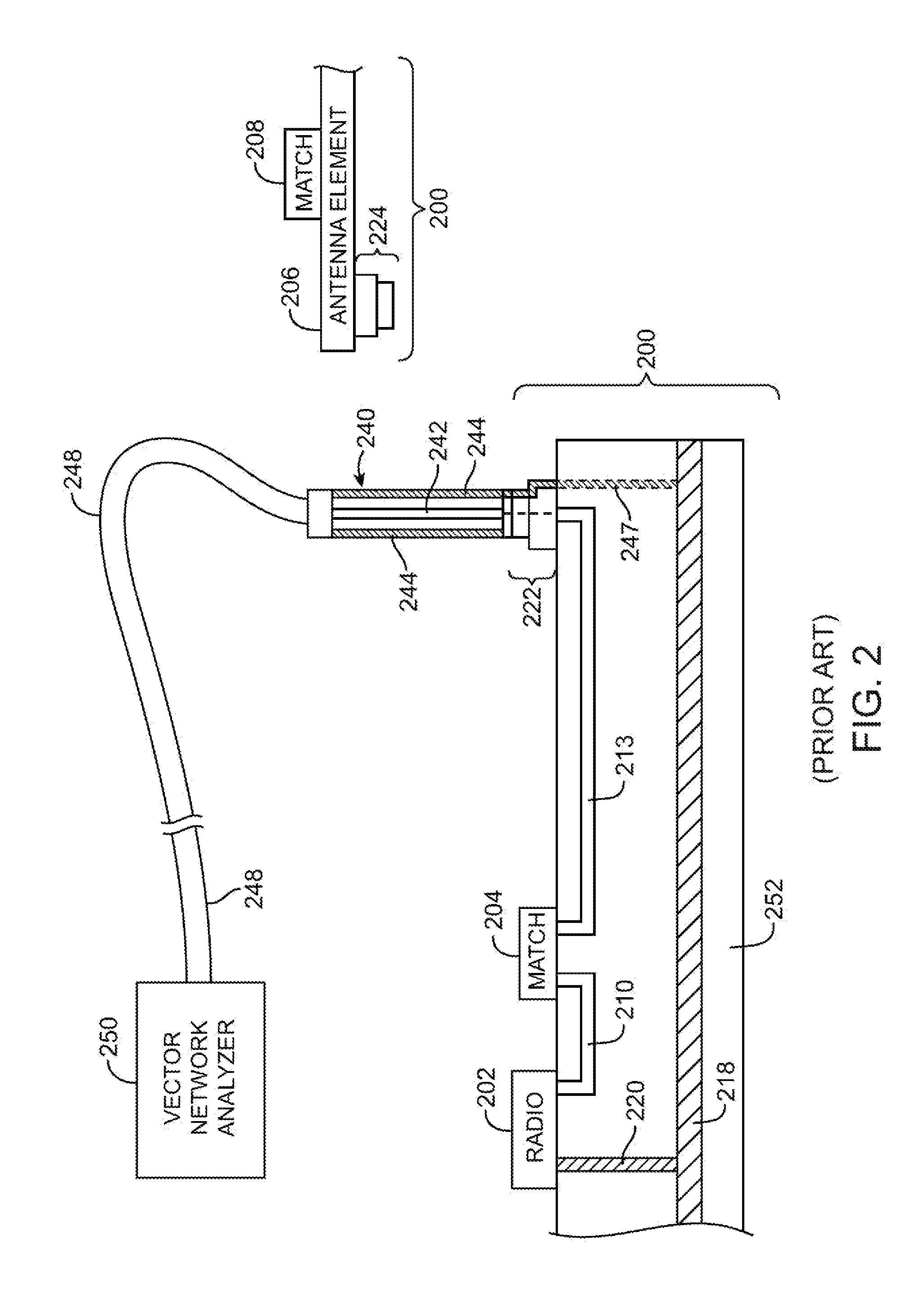

Radio-frequency test probes with integrated matching circuitry

ActiveUS20120262188A1Exact matchReceivers monitoringResistance/reactance/impedenceTransceiverEngineering

Wireless electronic devices include wireless communications circuitry such as transceiver circuitry coupled to an antenna resonating element. The transceiver circuitry and the antenna element may be formed on first and second substrates, respectively. In compact wireless devices, transceiver and antenna matching circuits may be formed on the first substrate. During production testing, a radio-frequency test probe with integrated matching circuitry may be used to mate with a corresponding contact point on the first substrate. The integrated matching circuitry may include resistors, capacitors, and inductors soldered in desired series-parallel configurations within the test probe. When the test probe is mated to the contact point on the first substrate, a test unit connected to the test probe may be used to perform radio-frequency measurements to determine whether the transceiver circuitry satisfies design criteria.

Owner:APPLE INC

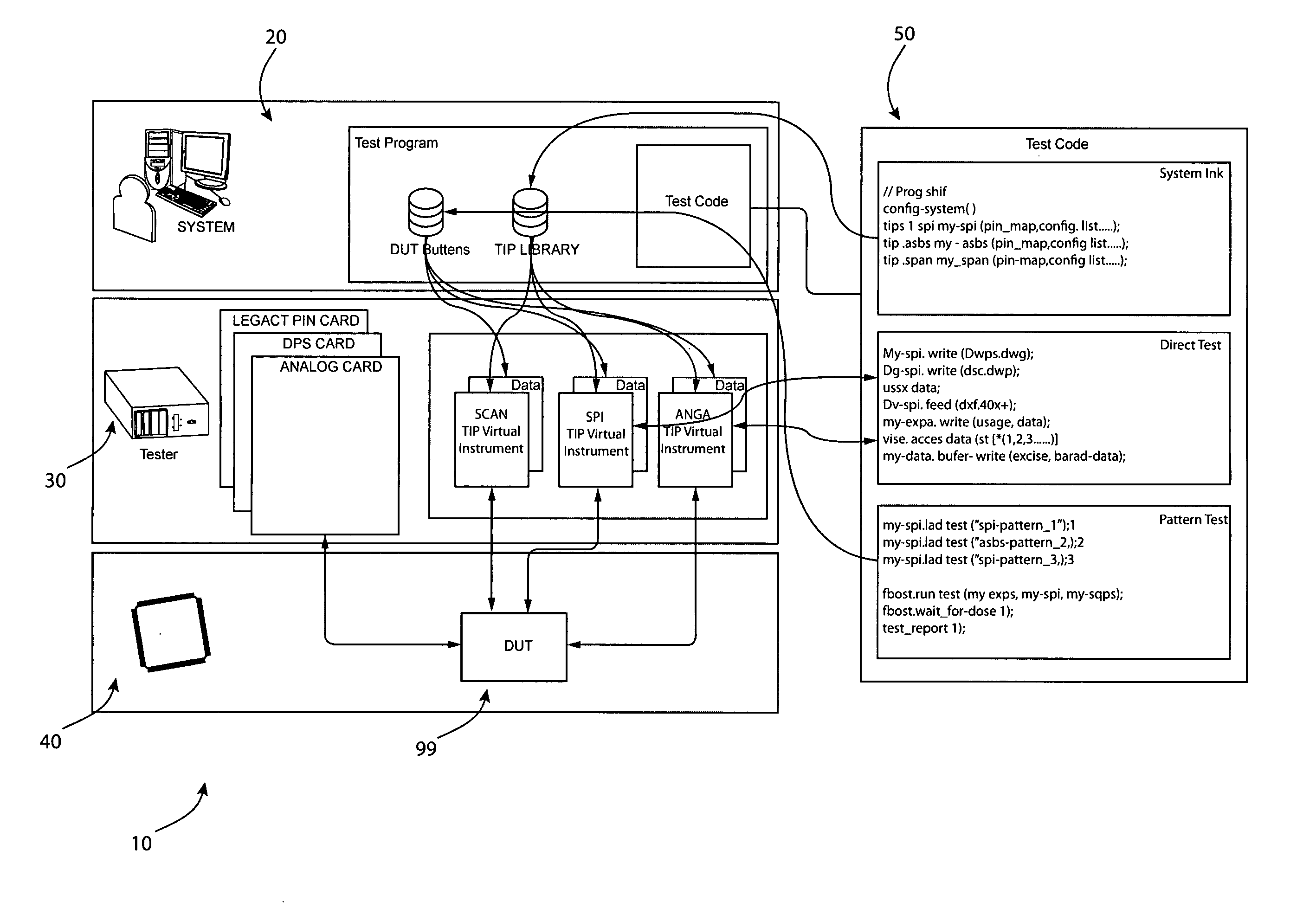

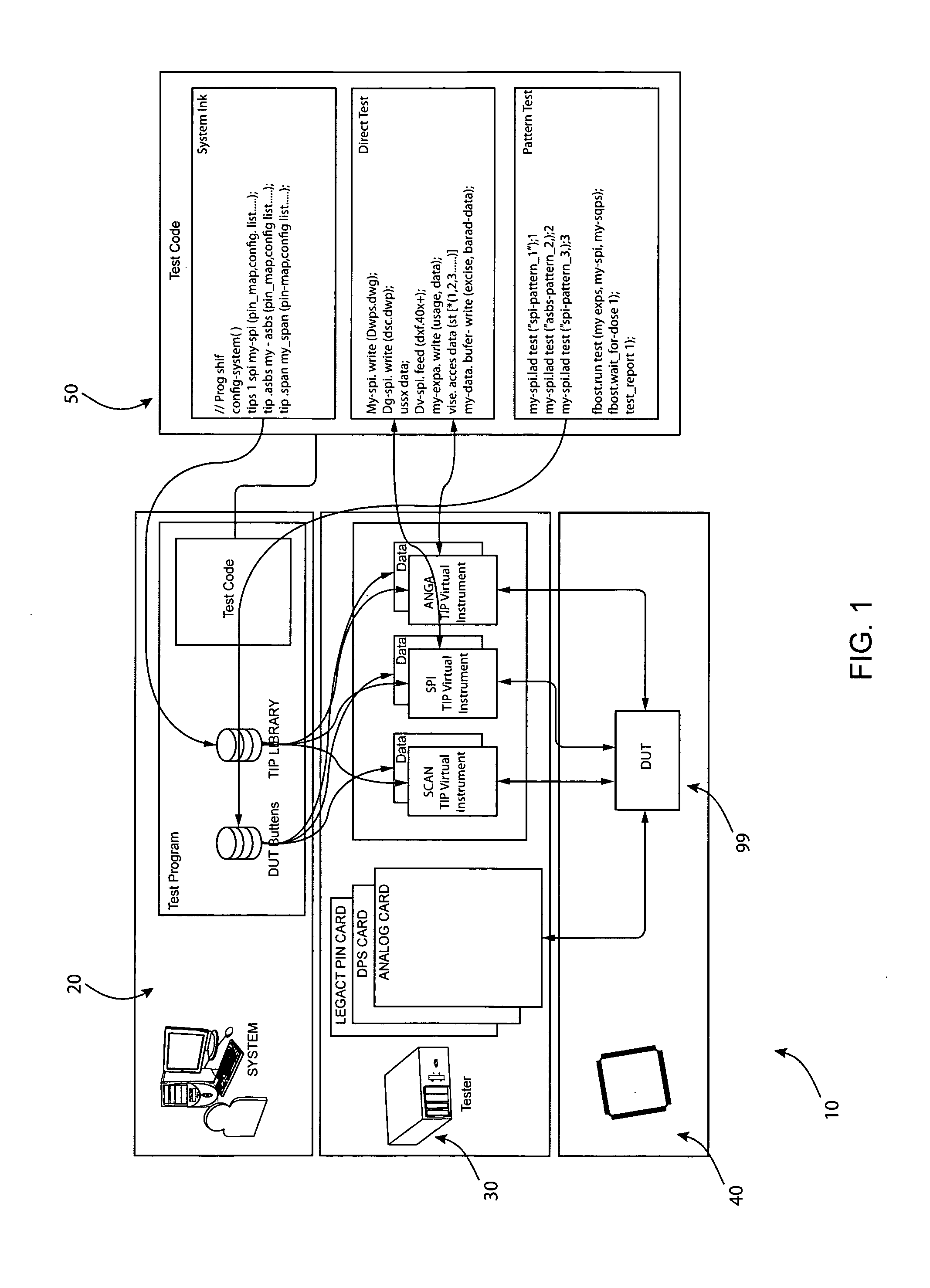

Test IP-Based A.T.E. Instrument Architecture

InactiveUS20130227367A1Implement extensionsError detection/correctionAutomated test systemsTest phaseUser interface

A test system based on multiple instances of reconfigurable instrument IP specifically matched to the device under test may be used in integrating automated testing of semiconductor devices between pre-silicon simulation, post-silicon validation, and production test phases, in one embodiment of software and hardware across all three phases, for different devices. The reconfigurable test system comprises: a tester instrument, instances of instrument IP instantiated in the tester instruments, a computer system, and a test program. The tester instrument connects to a device under test (DUT), and includes FPGAs reconfigurable for the three testing phases. The computer system has a user interface, and a controller connected to the reconfigurable tester instrument via a data bus. The test program stored on the controller, and the controller, instantiates interfaces and protocols, and certain process transactions to support the protocols, into FPGAs, to match device interfaces for each DUT, to execute test sequences.

Owner:CZAMARA ALLEN J +2

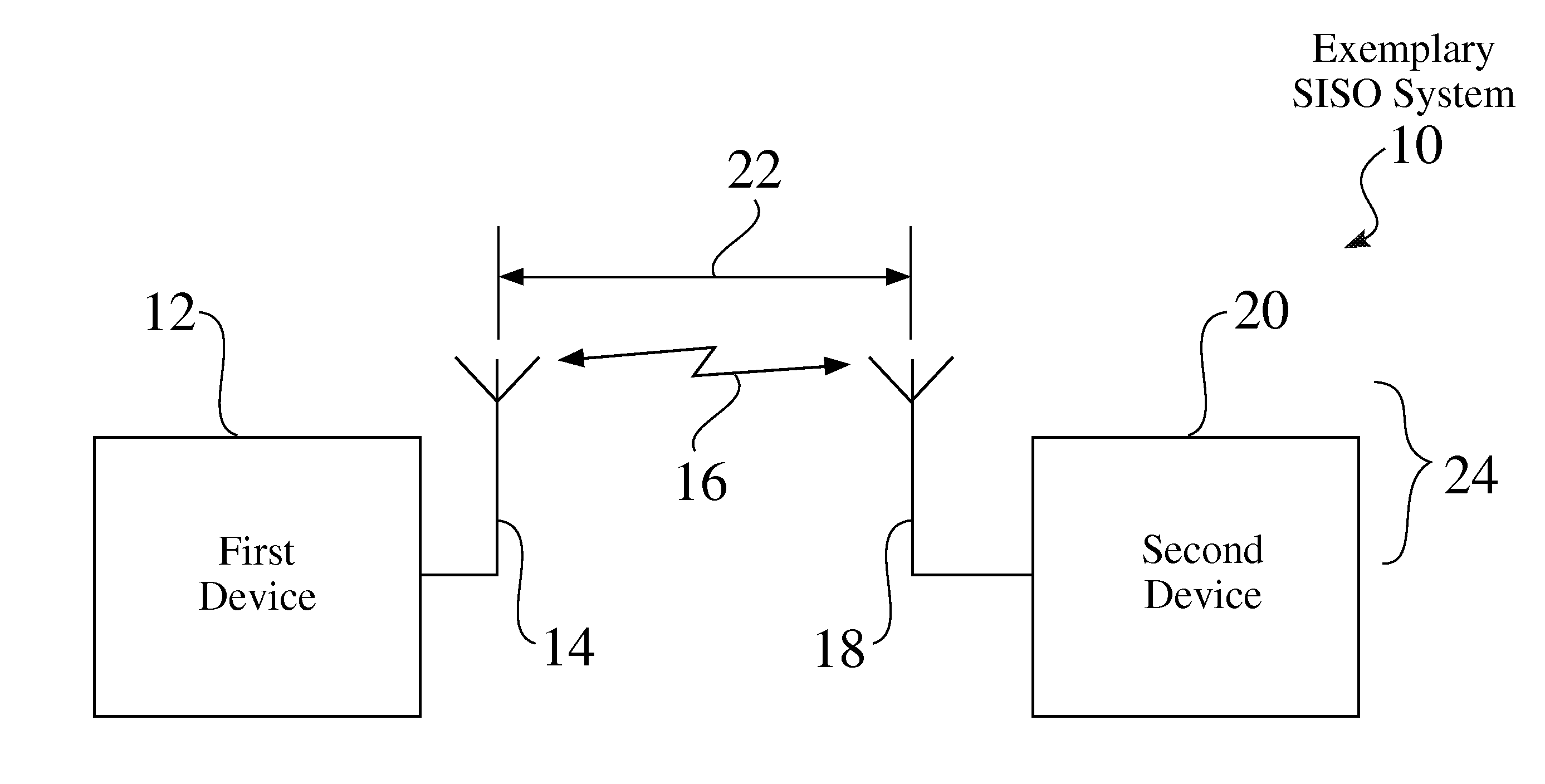

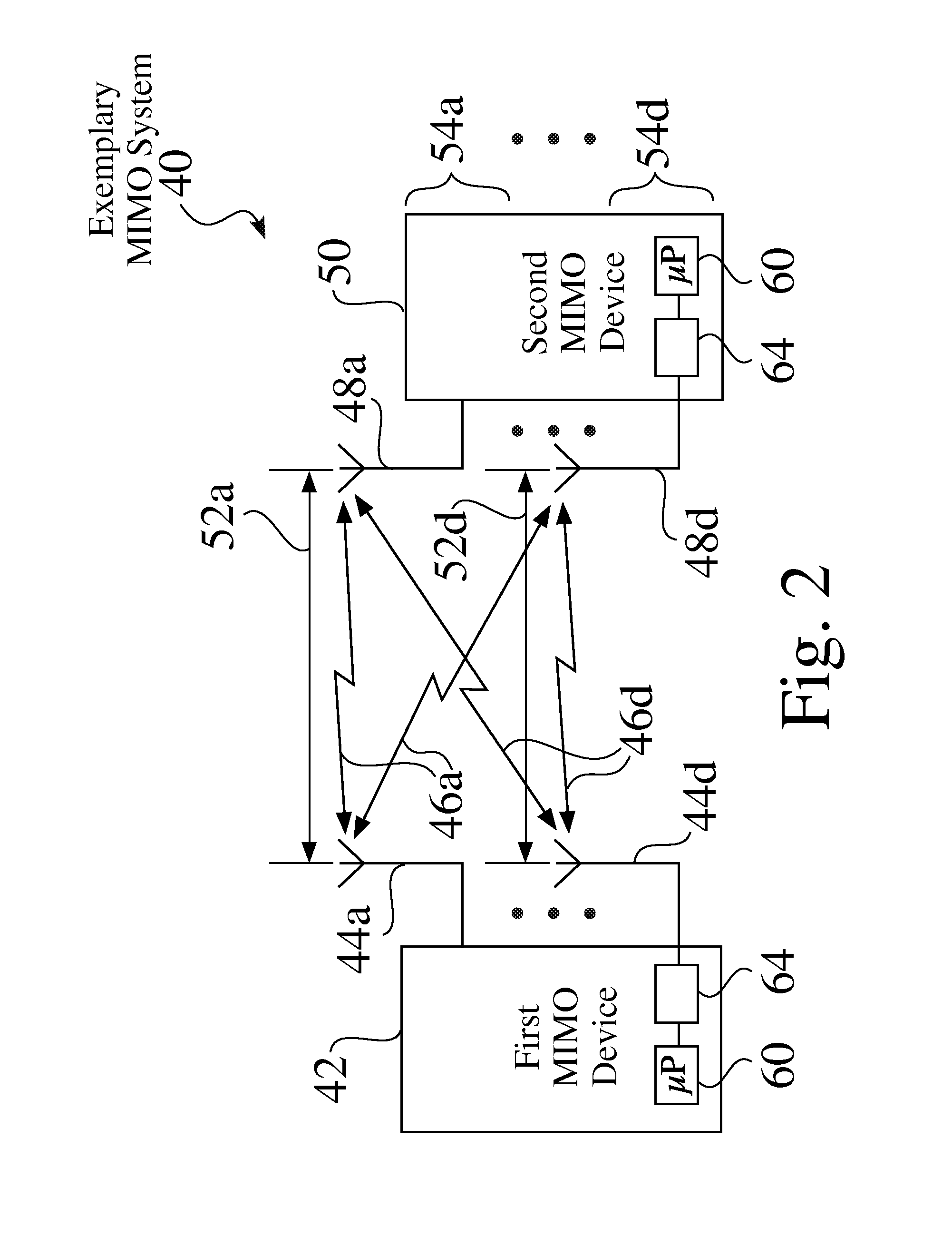

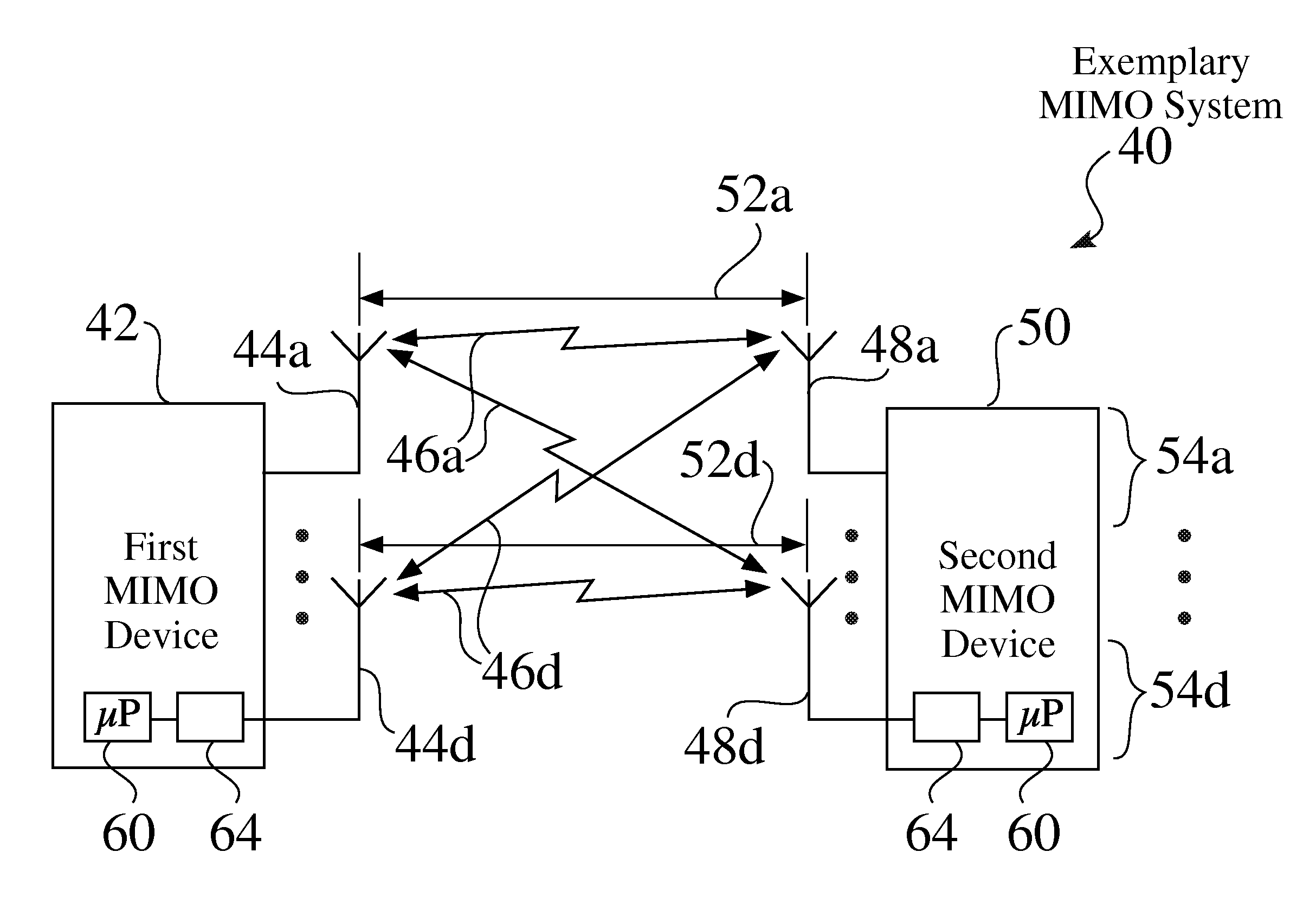

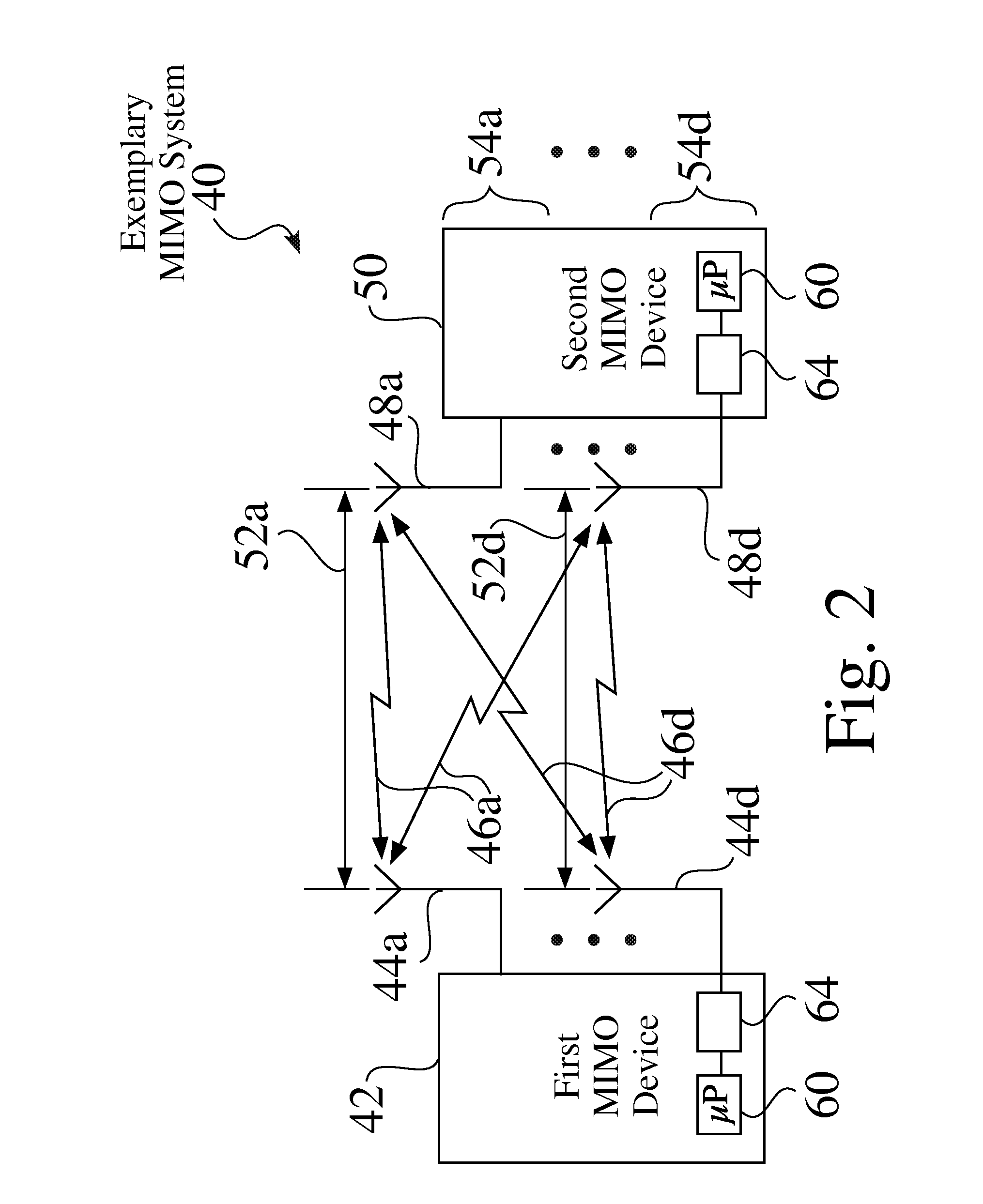

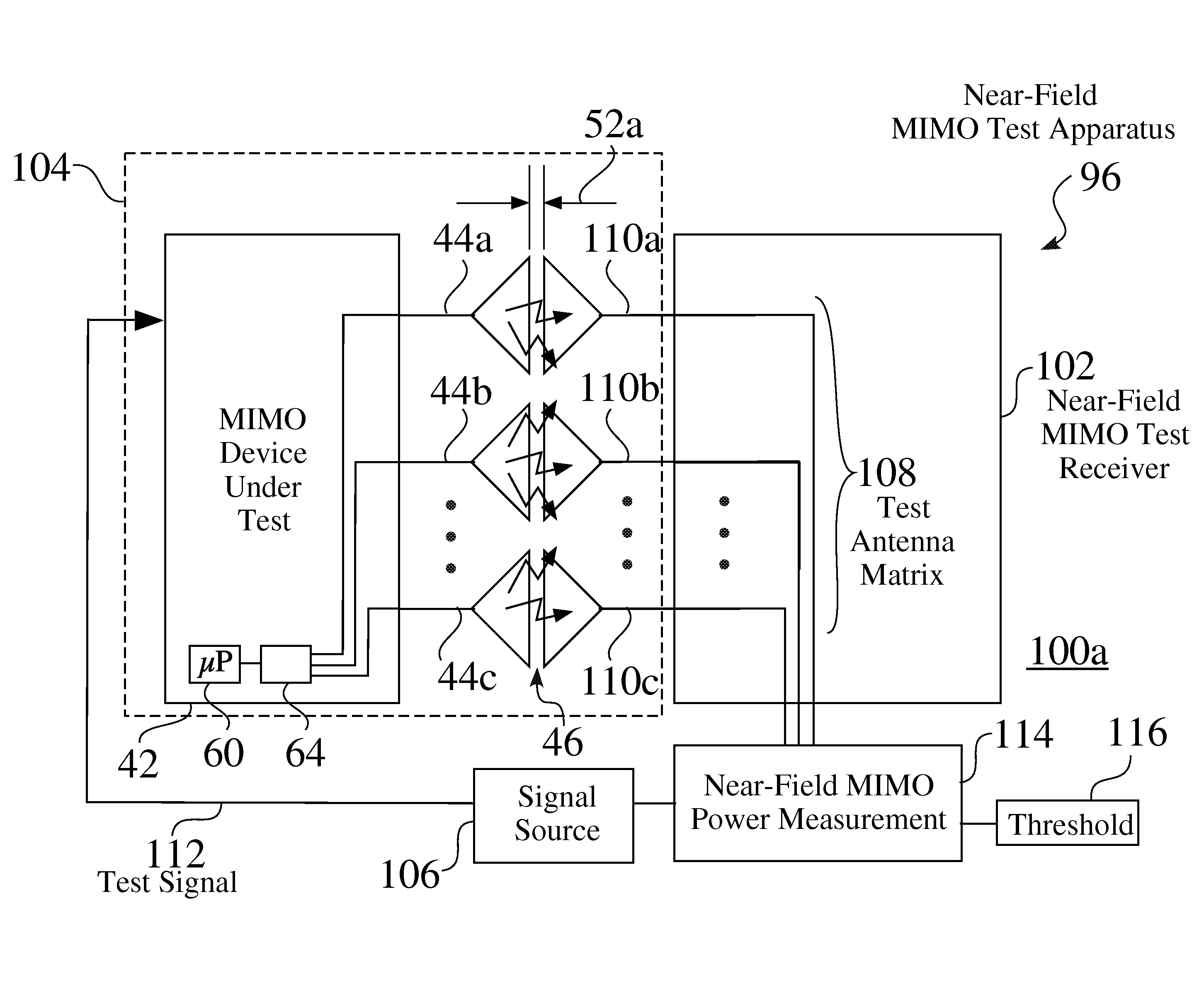

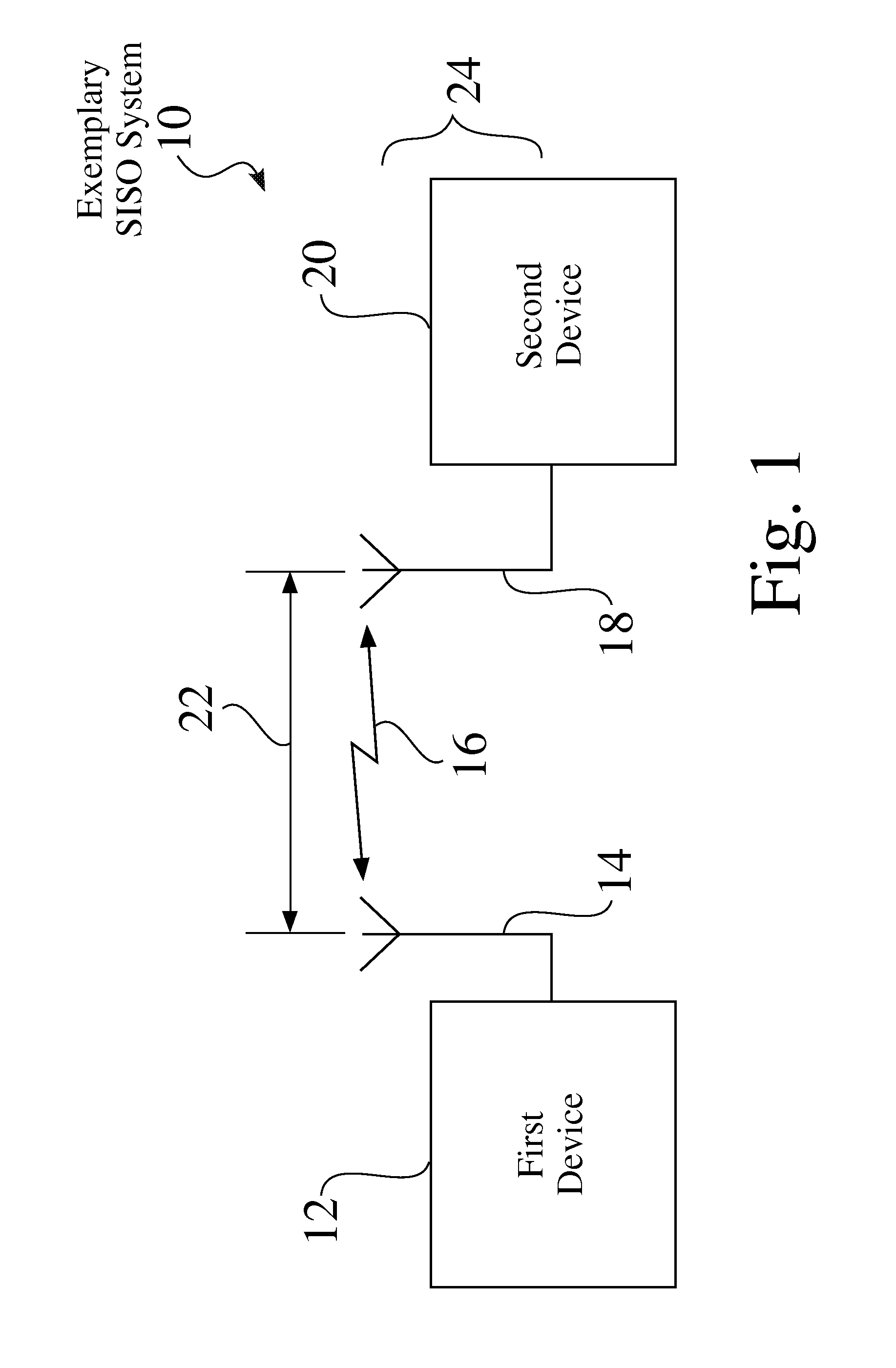

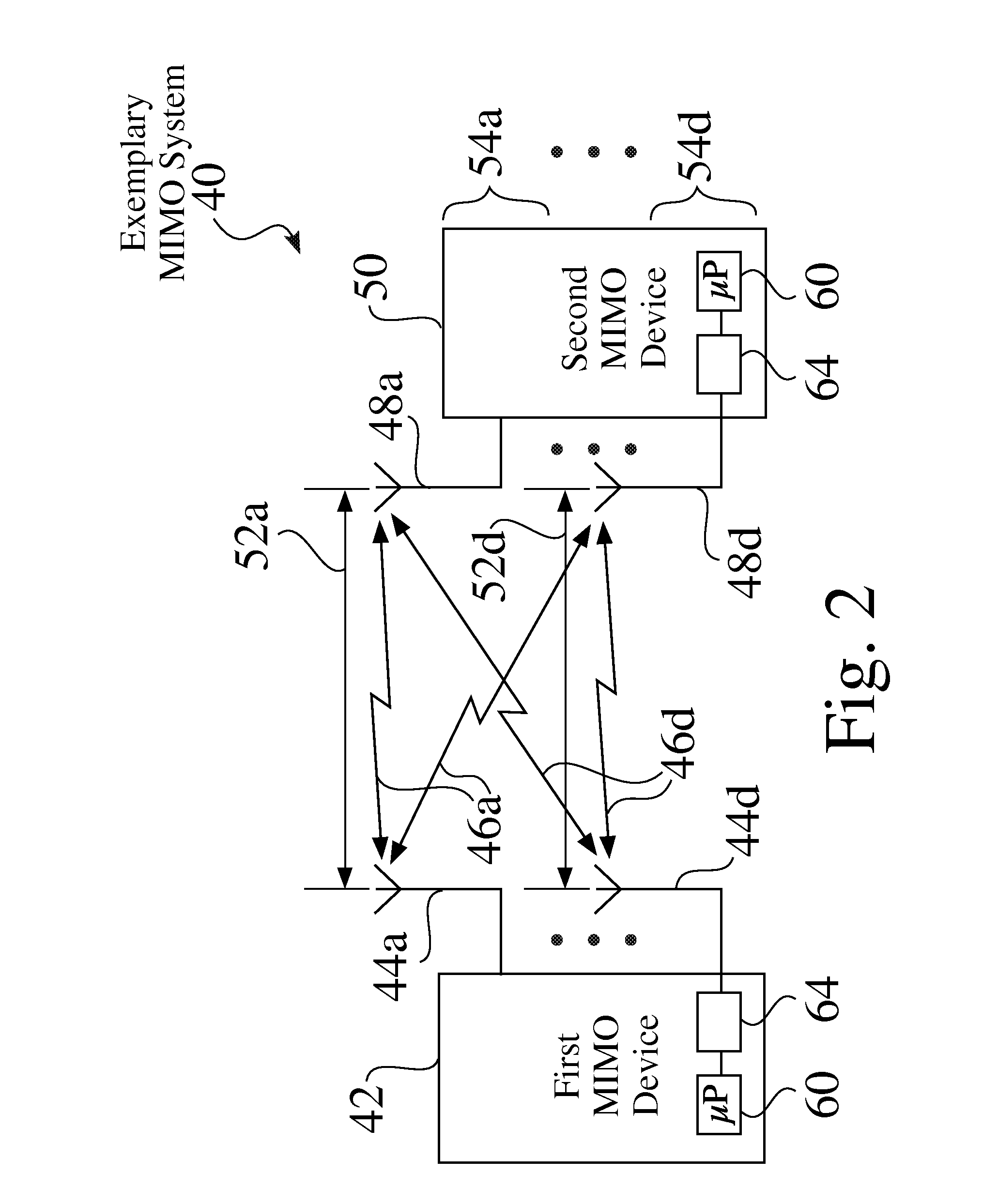

Near-field MIMO wireless test systems, structures, and processes

ActiveUS20140098846A1Easy to testTransmitters monitoringNear-field transmissionProcess systemsStructure of Management Information

Systems, processes, and structures allow enhanced near-field testing of the uplink and / or downlink performance of MIMO wireless devices (DUT), such as for any of product development, product verification, and / or production testing. Signal channels may preferably be emulated to test the performance of a device under test (DUT) over a range of simulated distances, within a near-field test environment. An enhanced process provides automated testing of a DUT over a wireless network, e.g. such as but not limited to a WLAN. The enhanced MIMO channel emulator may preferably be operated over a high dynamic range.

Owner:NETGEAR INC

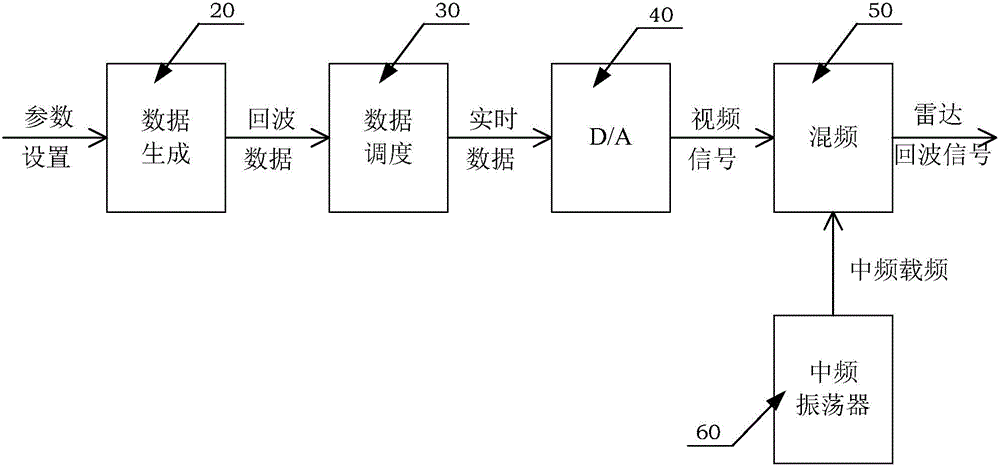

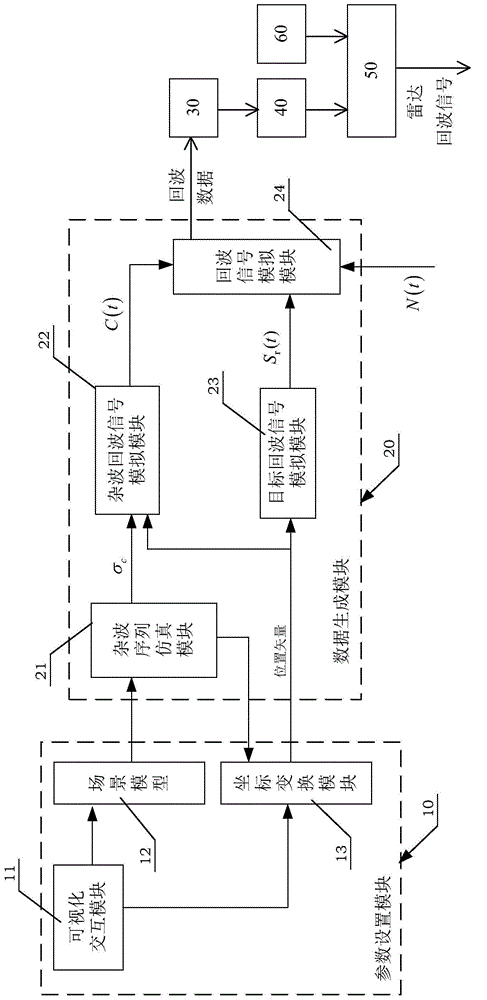

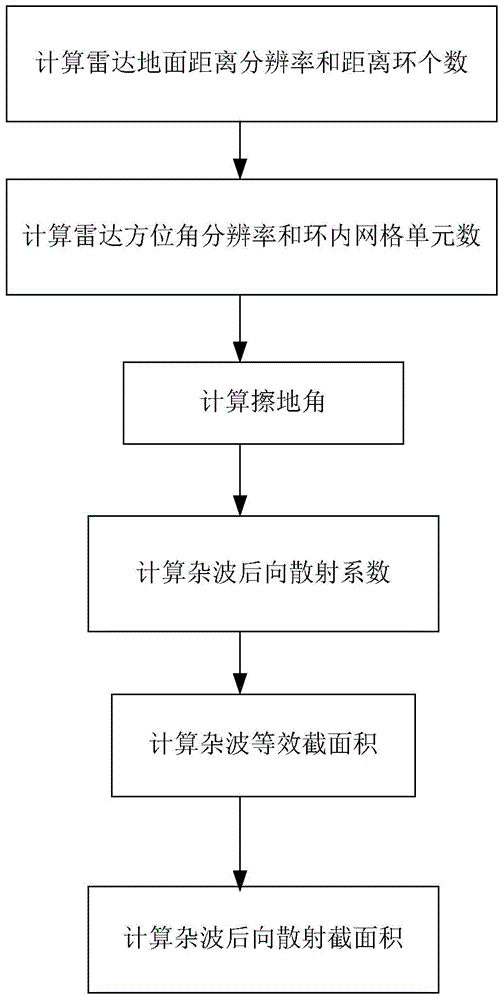

Radar echo signal simulator suitable for onboard radar system

ActiveCN104614713ACalculation time is shortImprove realismWave based measurement systemsRadar systemsTarget signal

The invention discloses a radar echo signal simulator suitable for an onboard radar system. The radar echo signal simulator suitable for the onboard radar system comprises a parameter setting module (10), a data generation module (20), a data scheduling module (30), a digital to analogue (D / A) conversion module (40), a frequency mixing module (50) and an intermediate frequency oscillator (60). The radar echo signal simulator suitable for the onboard radar system combines an application scene model with radar parameters and antenna parameters, uses a clutter statistics distributing model and a power spectrum model to simulate a clutter series corresponding to a needed background topography, uses a mesh generation method to generate a clutter echo signal, and then uses position information of a needed sensitive area to generate a related target echo wave, and finally fuses the clutter signal with a target signal so as to generate a radar echo wave which conforms to test requirements and send the radar echo wave back to a test radar. The radar echo signal simulator suitable for the onboard radar system can be used in multiple links of research and development, production testing, performance detection and the like of a radar device on an airship, reduces frequency of outfield experiments to the utmost, saves experiment cost, and shortens a research period.

Owner:BEIHANG UNIV

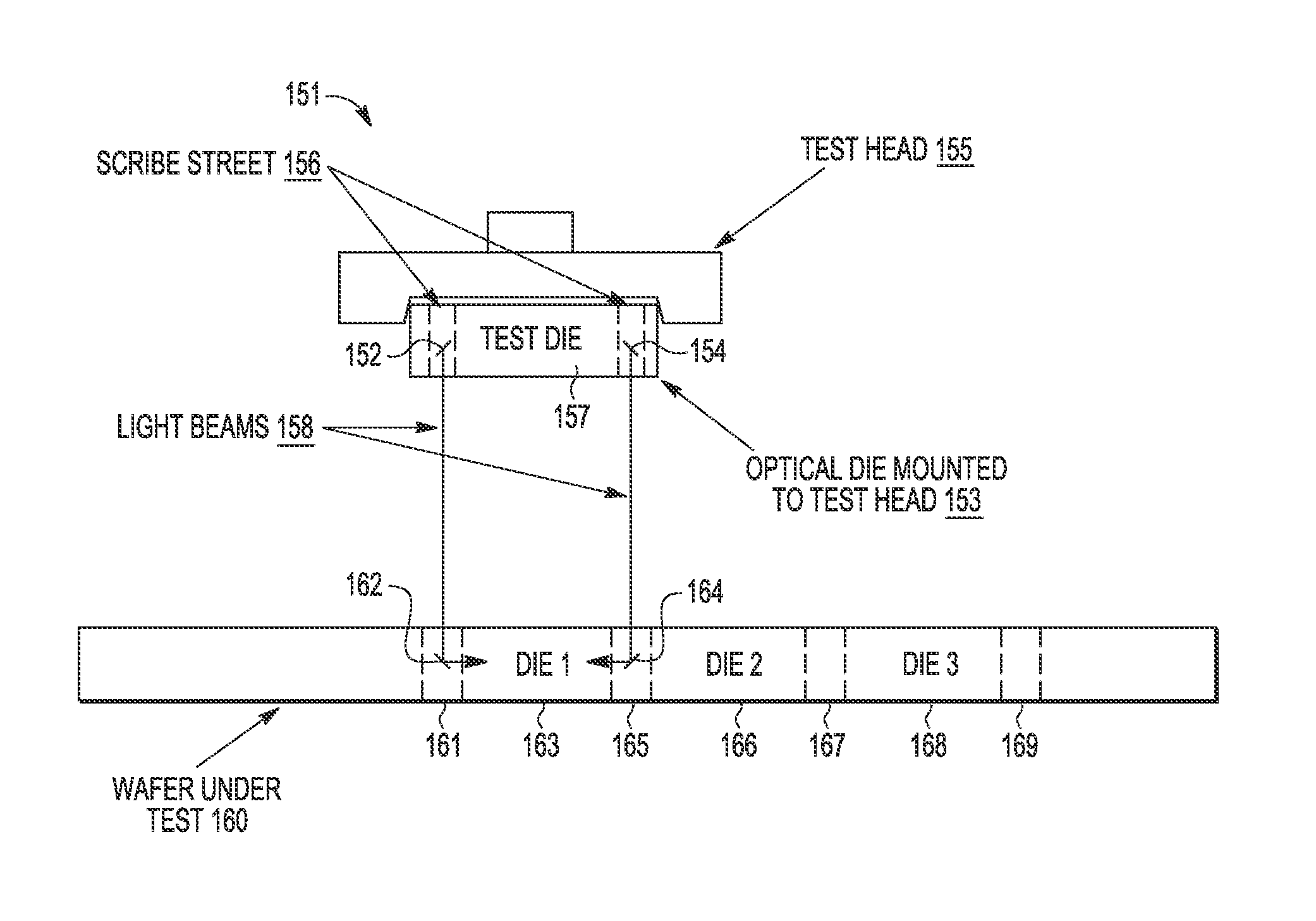

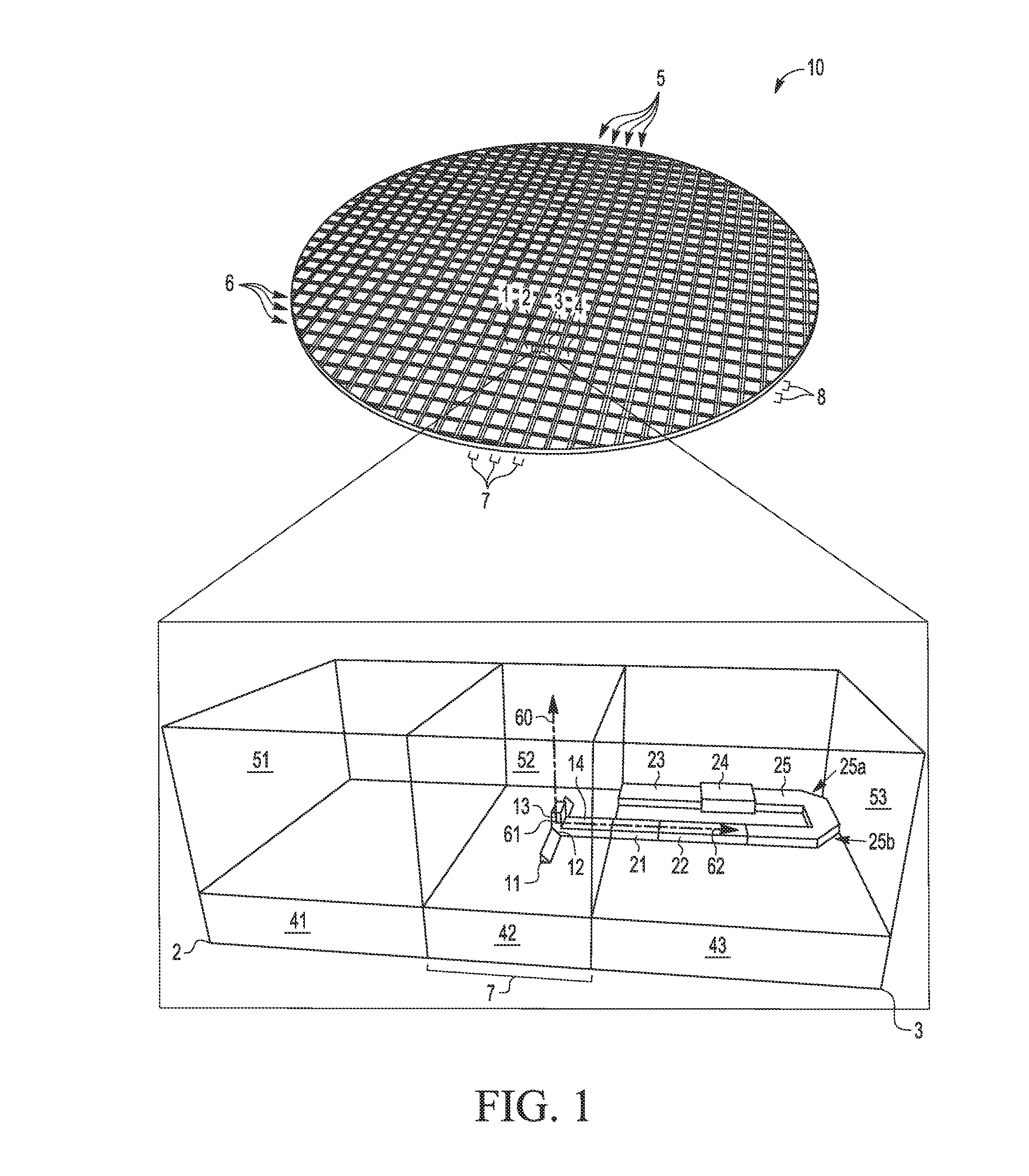

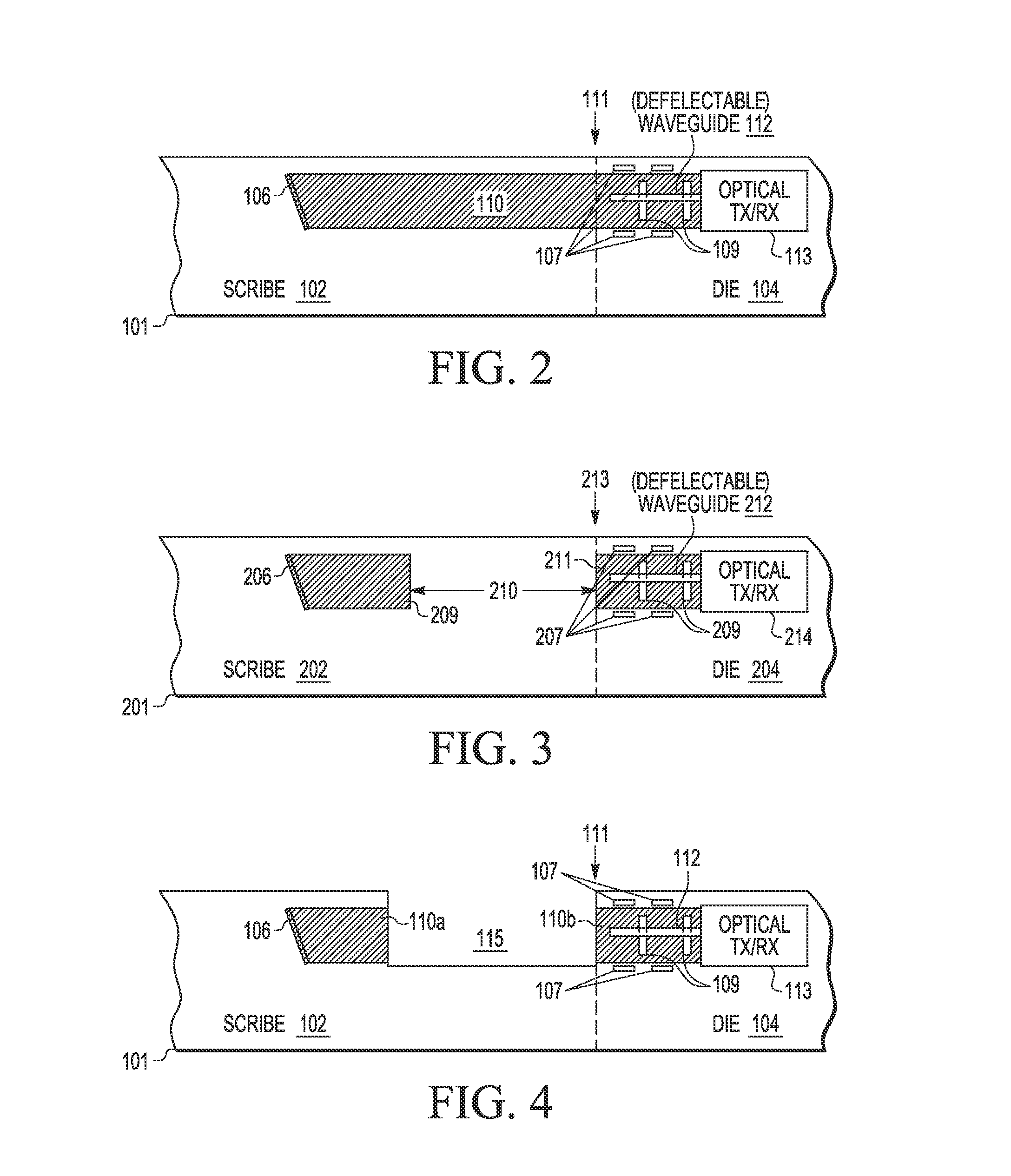

Optical Wafer and Die Probe Testing

InactiveUS20140363905A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingOptical testEngineering

An optical die probe wafer testing circuit arrangement and associated testing methodology are described for mounting a production test die (157) and surrounding scribe grid (156) to a test head (155) which is positioned over a wafer (160) in alignment with a die under test (163) and surrounding scribe grid (161, 165), such that one or more optical deflection mirrors (152, 154) in the test head scribe grid (156) are aligned with one or more optical deflection mirrors (162, 164) in the scribe grid (161, 165) for the die under test (163) to enable optical die probe testing on the die under test (163) by directing a first optical test signal (158) from the production test die (157), through the first and second optical deflection mirrors (e.g., 152, 162) and to the first die.

Owner:NXP USA INC

Method and apparatus for controlling welding of flexible fabrics

InactiveUS20140124125A1Improve integrityMechanical working/deformationControlling laminationEngineeringWeld seam

A machine and method for welding first and second fabric panels together. The machine includes a welding head which travels along a frame, applying heat and pressure to an overlapped region of the panels. An infrared camera is positioned to monitor the seam temperature after formation. The camera takes a thermal image across the width of the seam and transmits the data to a central processing unit (CPU). Programming in the CPU compares the thermal image data with a pre-programmed ideal temperature profile. Based on the comparison, the CPU makes adjustments to one or more of the speed of travel of the welding head, and the heat and pressure applied by the welding head, if necessary. The CPU activates an alarm to alert the machine operator if the adjustments aren't successful. The machine further includes a marking assembly for identifying regions on the welded seam which may require post-production testing.

Owner:MILLER WELDMASTER CORP

Near-field MIMO wireless transmit power measurement test systems, structures, and processes

ActiveUS20140161164A1Quickly and efficiently determineTransmitters monitoringNear-field transmissionProcess systemsMeasurement test

Systems, processes, and structures provide near-field transmit power measurement for MIMO wireless devices (DUT), such as for any of product development, product verification, and / or production testing. A test signal, such as comprising a pulse train signal, is provided to a MIMO device under test (DUT), wherein portions of the test signal controllably steered and sequentially transmitted from each of the device antennas, to one or more test antennas that are positioned in close proximity to the MIMO DUT. The near-field power of the received test signals is measured, to quickly and efficiently determine if one or more data streams of the MIMO DUT has a problem.

Owner:NETGEAR INC

System and method for debugging system-on-chips

InactiveUS20050193254A1Electronic circuit testingError detection/correctionComputer hardwareSoftware design

Large, complex SoCs comprise interconnections of various functional blocks. Such functional blocks contain scan chains that are used for their individual production testing. The present invention utilizes these scan chains as a tool in the debugging of these SoCs by providing the internal contents of registers and memories contained on the SoC device. Accordingly, both hardware and software designers are provided a means to observe the effect of their designs on the internal operation of the SoC device. The invention is compatible with current integrated circuit design methodology and requires minimal area on the SoC for support circuitry.

Owner:AVAGO TECH INT SALES PTE LTD

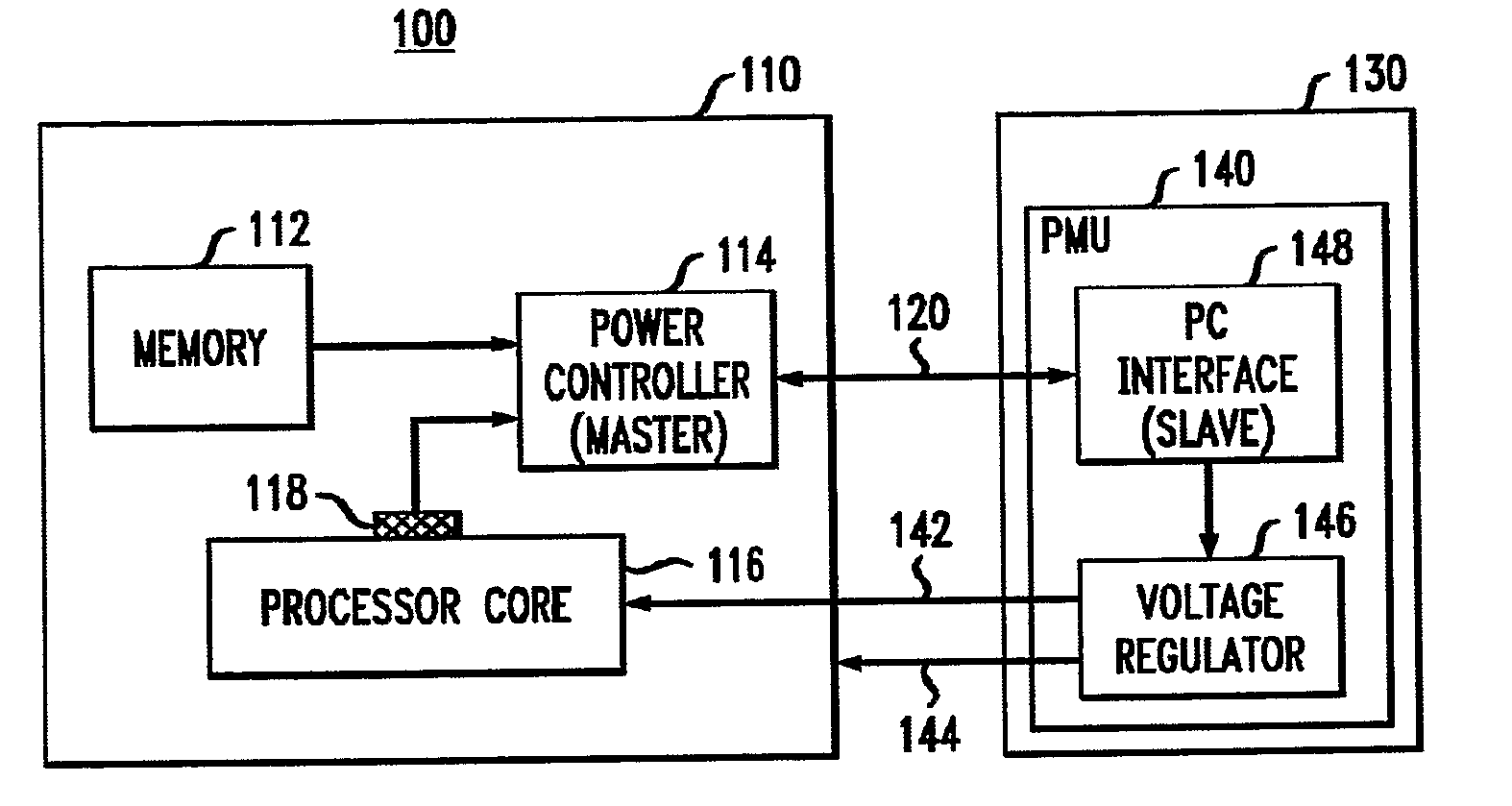

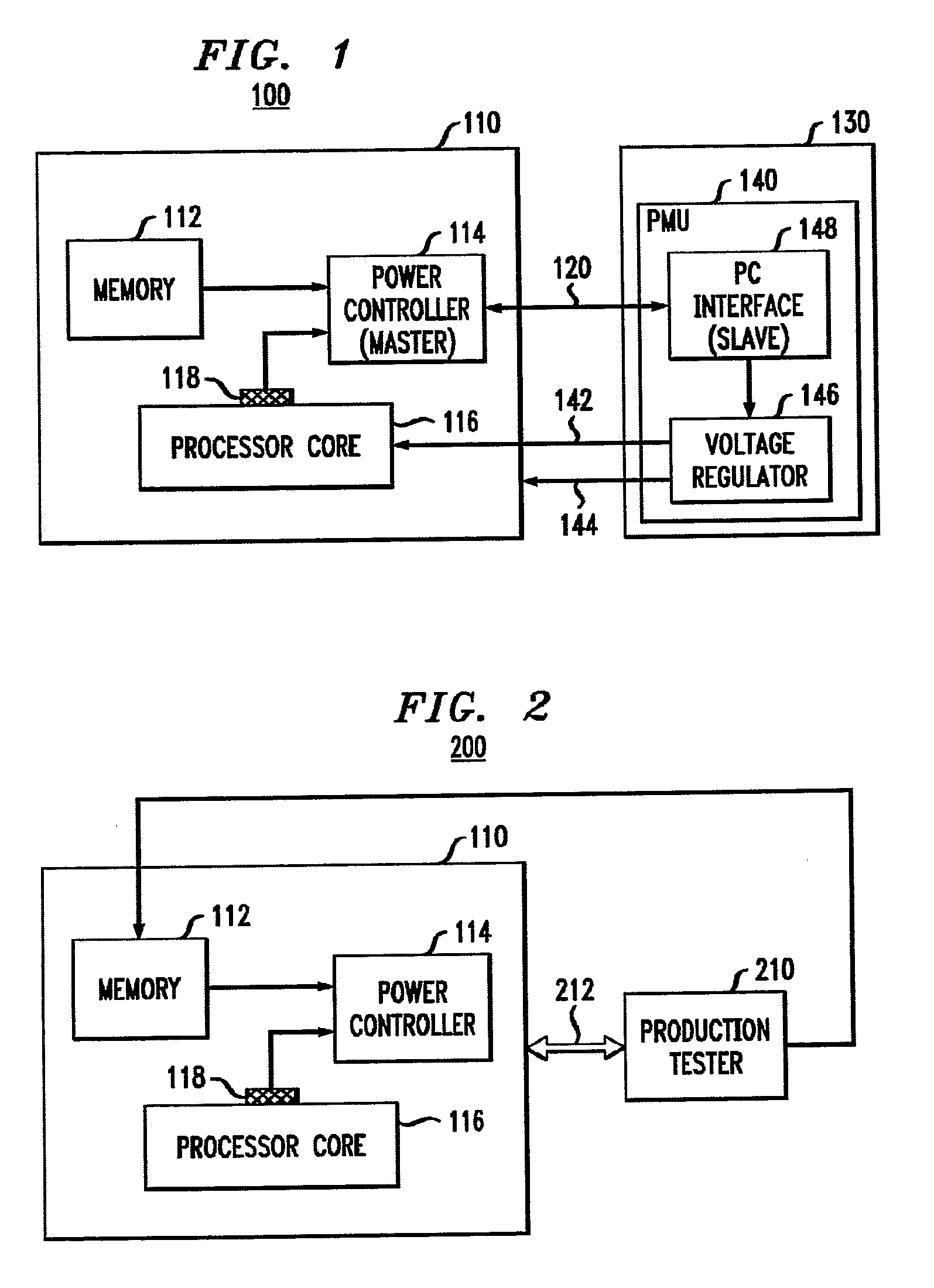

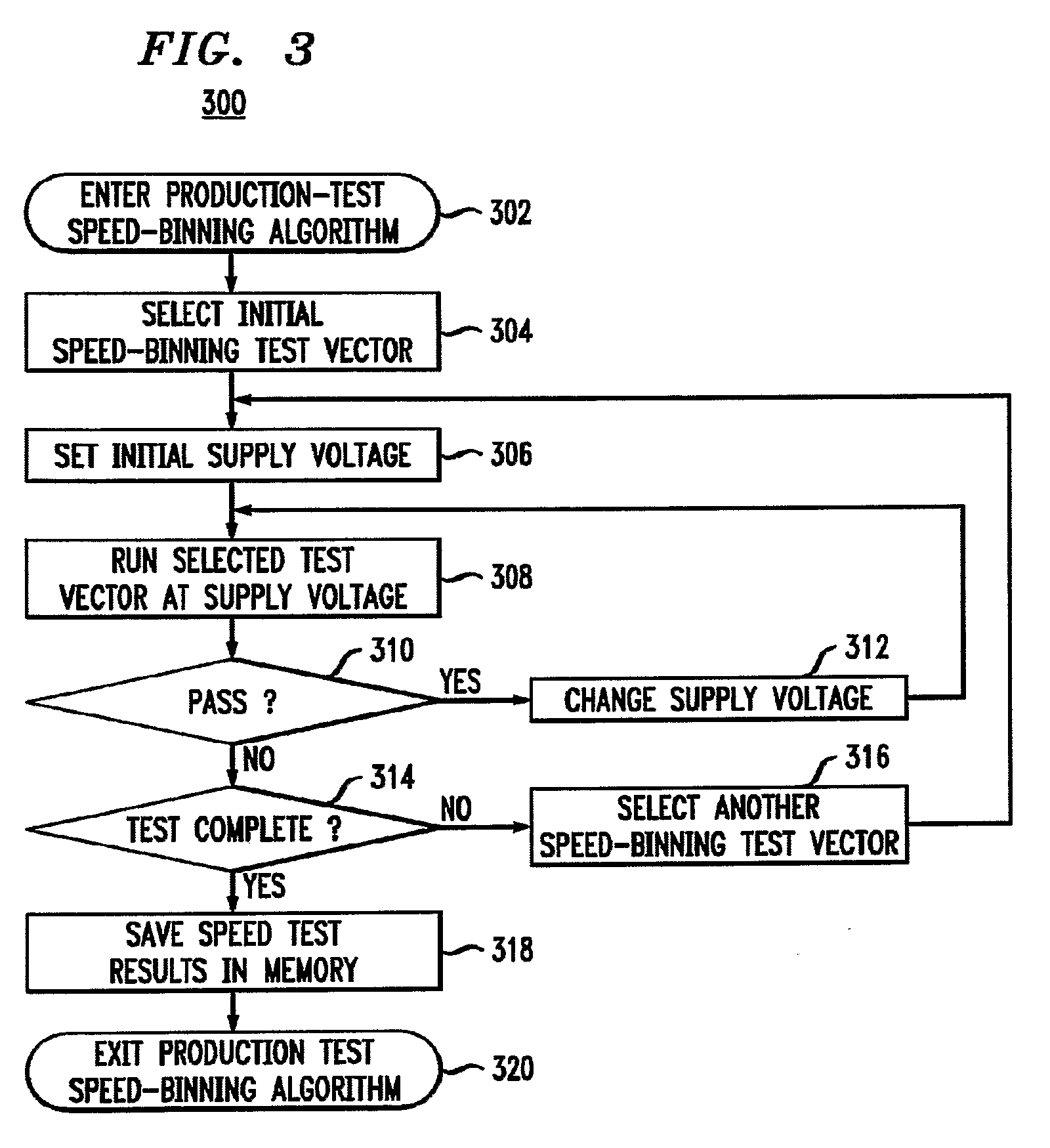

Speed binning for dynamic and adaptive power control

ActiveUS20100017042A1Increase power consumptionGreat customizationMechanical power/torque controlLevel controlPower controllerEngineering

A representative digital circuit of the invention has an on-chip, non-volatile memory, to which chip-specific speed-binning data that characterize performance of the digital circuit are written during production testing. During normal operation, the power controller that controls power-supply signals applied to the digital circuit reads the speed-binning data from the on-chip memory for use as input parameters for dynamic supply-voltage scaling, dynamic clock scaling, and / or adaptive power control that optimize (e.g., minimize) power consumption in the digital circuit. Advantageously over the prior art, the accuracy and efficiency of dynamic and / or adaptive power control arc improved because the chip-specific speed-binning data enable the power controller to better customize the power-management algorithm for the given digital circuit.

Owner:AVAGO TECH INT SALES PTE LTD

Near-field MIMO wireless transmit power measurement test systems, structures, and processes

ActiveUS8824588B2Quickly and efficiently determineTransmitters monitoringNear-field transmissionProcess systemsMeasurement test

Systems, processes, and structures provide near-field transmit power measurement for MIMO wireless devices (DUT), such as for any of product development, product verification, and / or production testing. A test signal, such as comprising a pulse train signal, is provided to a MIMO device under test (DUT), wherein portions of the test signal controllably steered and sequentially transmitted from each of the device antennas, to one or more test antennas that are positioned in close proximity to the MIMO DUT. The near-field power of the received test signals is measured, to quickly and efficiently determine if one or more data streams of the MIMO DUT has a problem.

Owner:NETGEAR INC

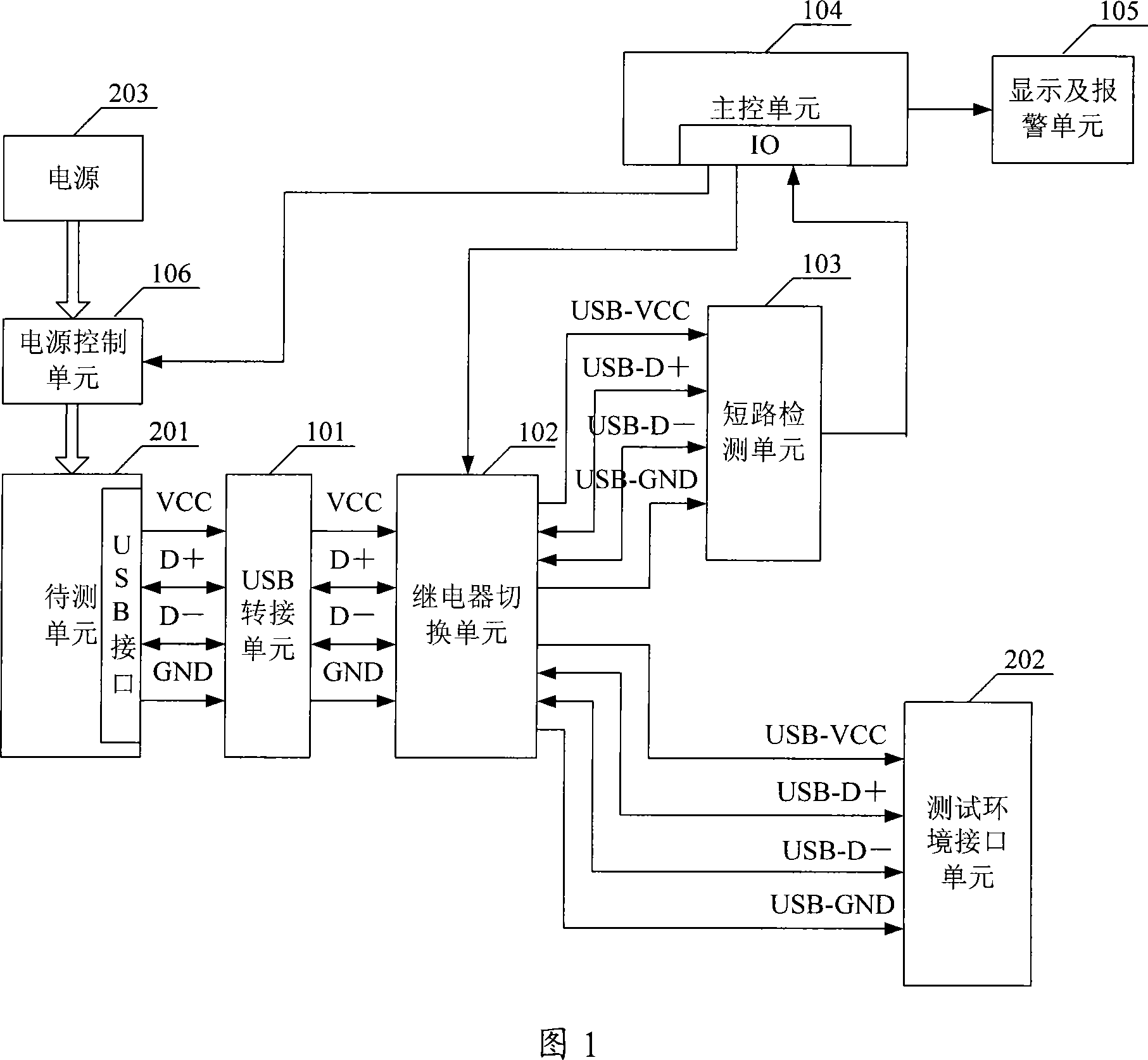

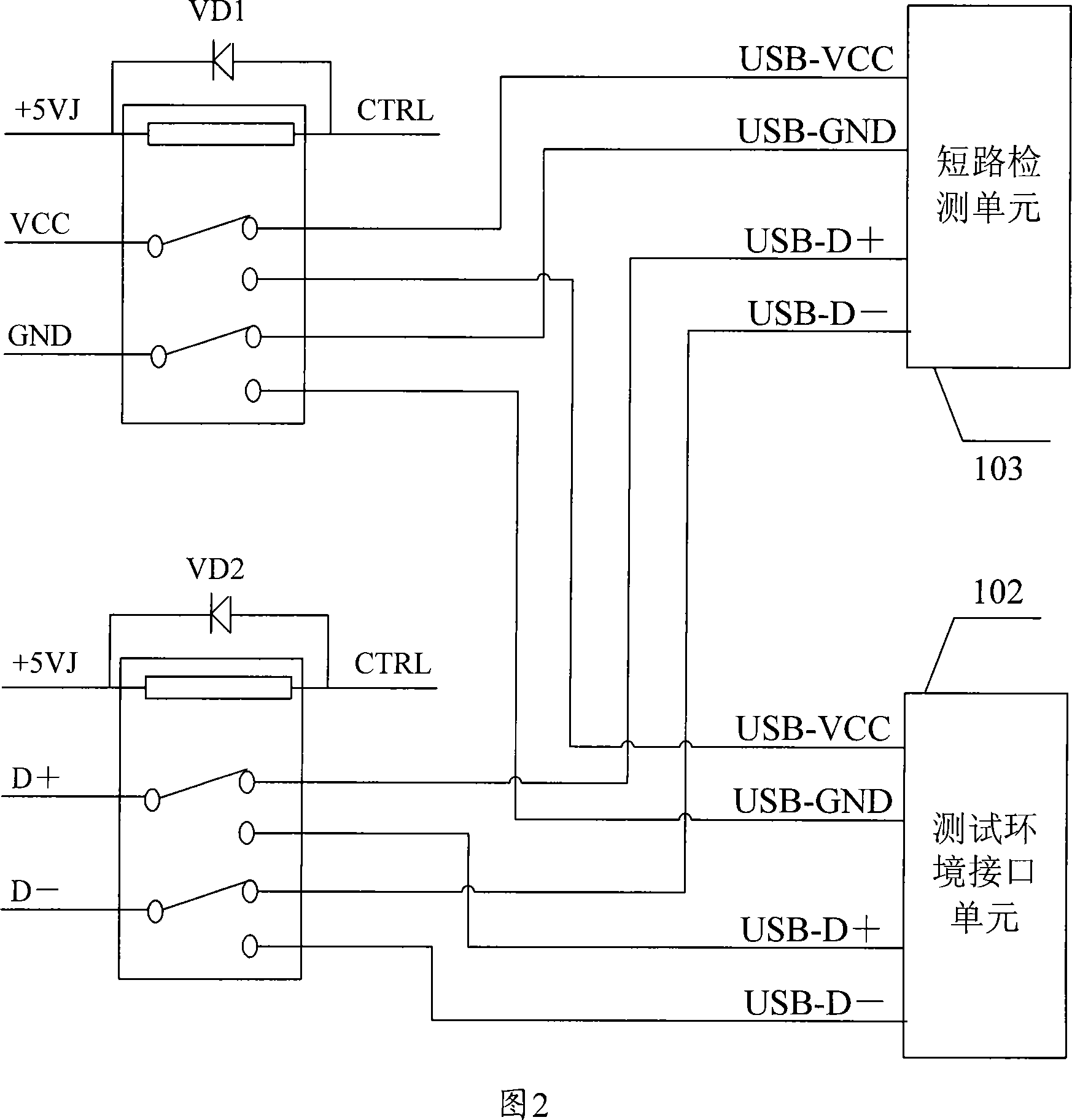

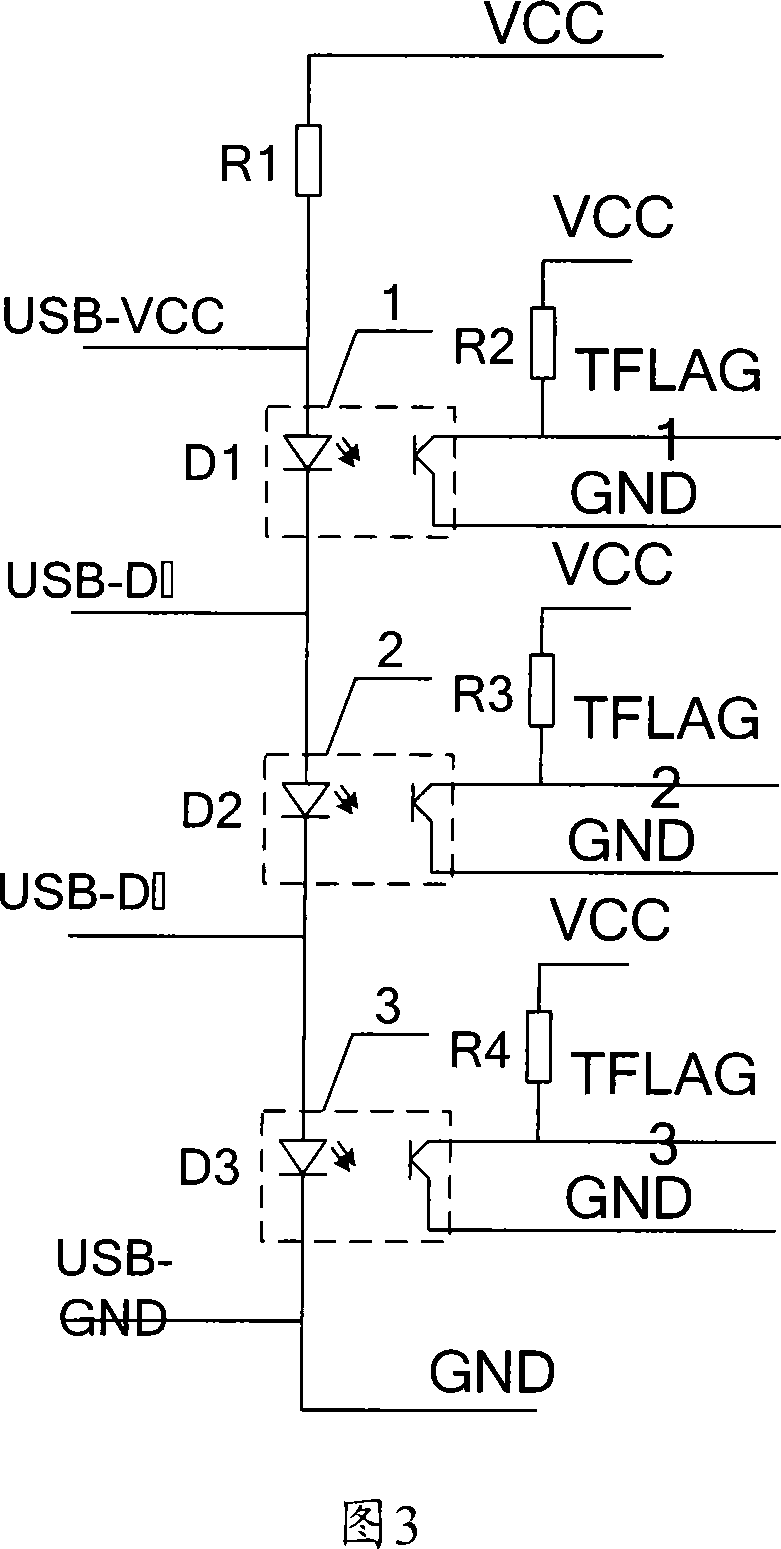

USB bus interface checking device and checking method

A USB bus interface detection device comprises a USB transfer unit, a displaying and alarming unit and a short-circuit detection unit used to detect whether the USB interface is in short circuit; wherein, the USB transfer unit is provided with an input terminal and an output terminal corresponding to the terminals of the detected USB interface; the short-circuit detection unit comprises a plurality of input terminals and at least one output terminal; the input terminals of the short-circuit detection unit are connected with the corresponding terminals of the detected USB interface through the USB transfer unit, and the output terminal of the short-circuit detection unit outputs the signal of the short-circuit detection result; the displaying and alarming unit is used to display the detection result and to make alarming caution for the short circuit. The present invention has the advantages that the design of the software and the hardware is simple, the speed is fast and the cost is low, before the detected unit is powered, the short-circuit detection of the USB bus interface is performed at first, thereby effectively guaranteeing the security of the detected unit and the detection environment; the device can also be used as a part of the USB bus interface test circuit in the production testing environment.

Owner:ZTE CORP