Patents

Literature

975results about "Automated test systems" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

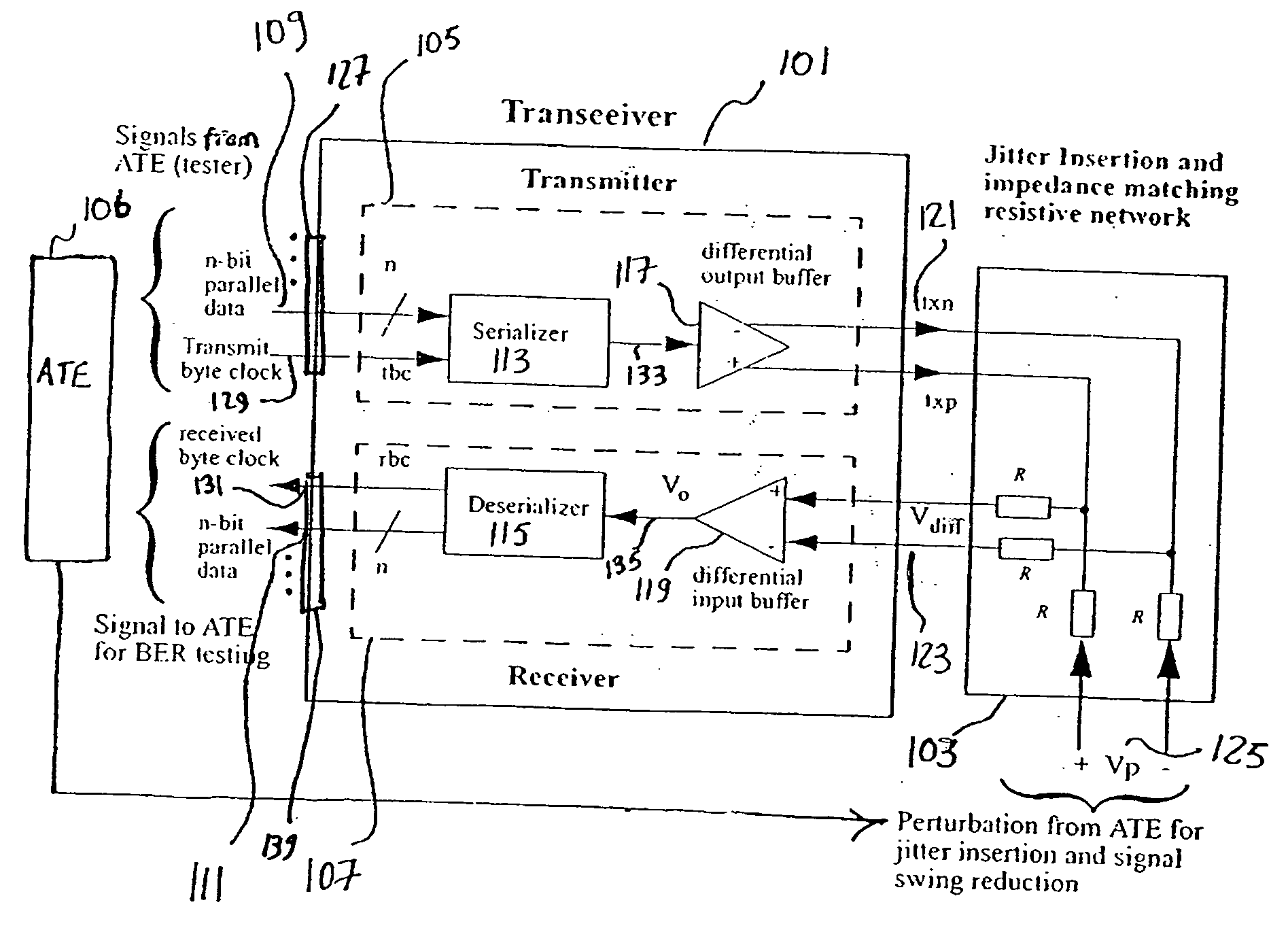

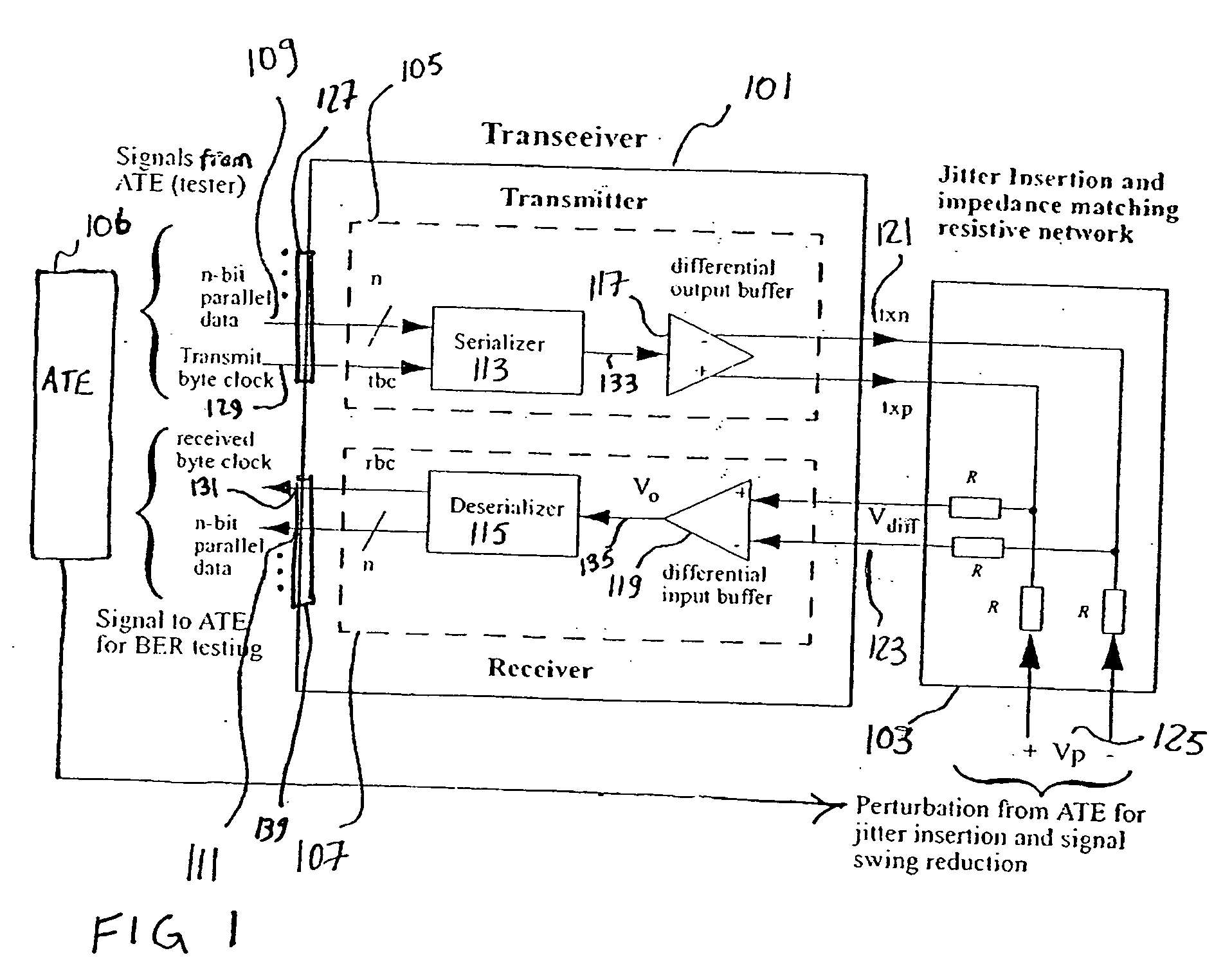

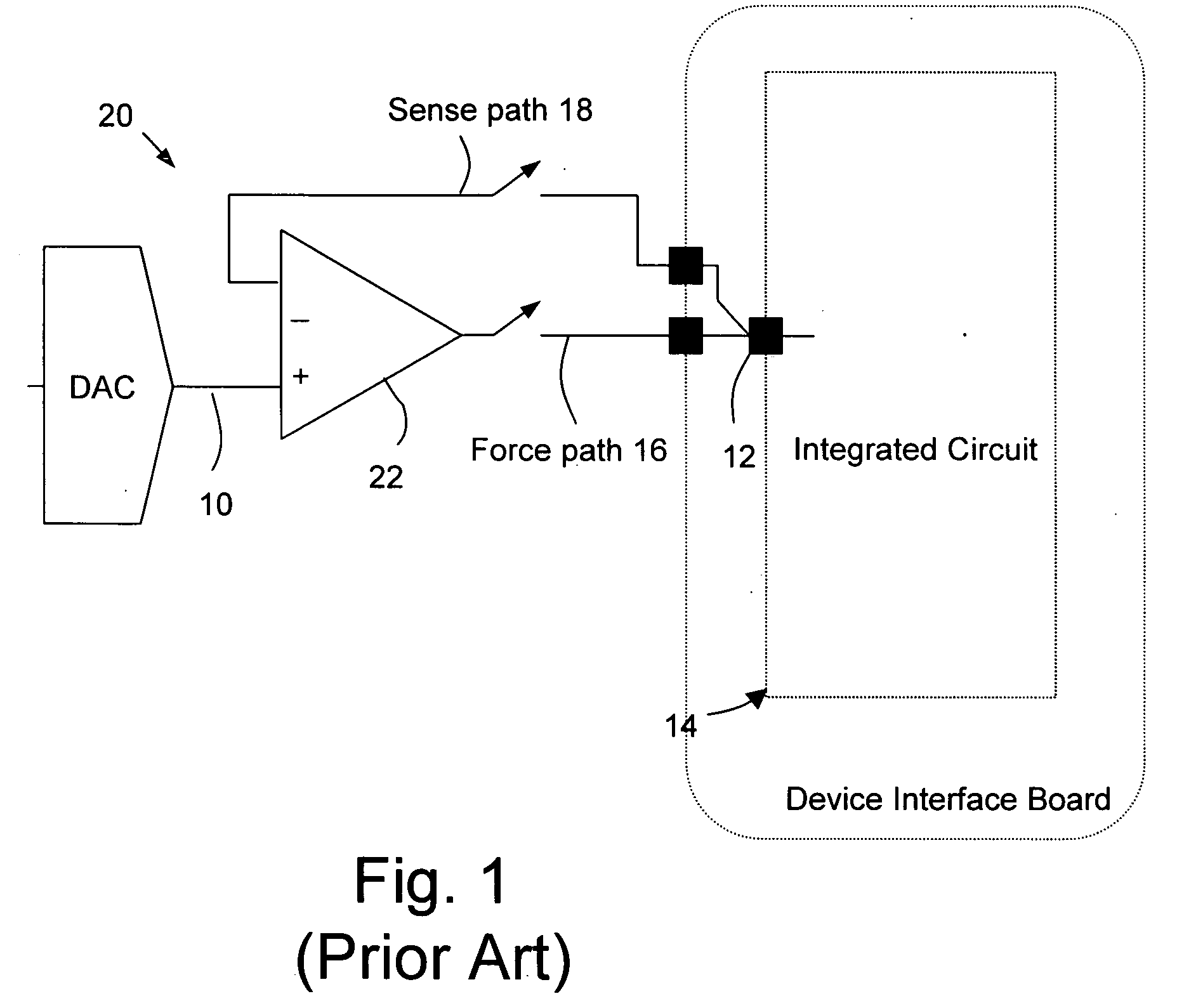

System and method for production testing of high speed communications receivers

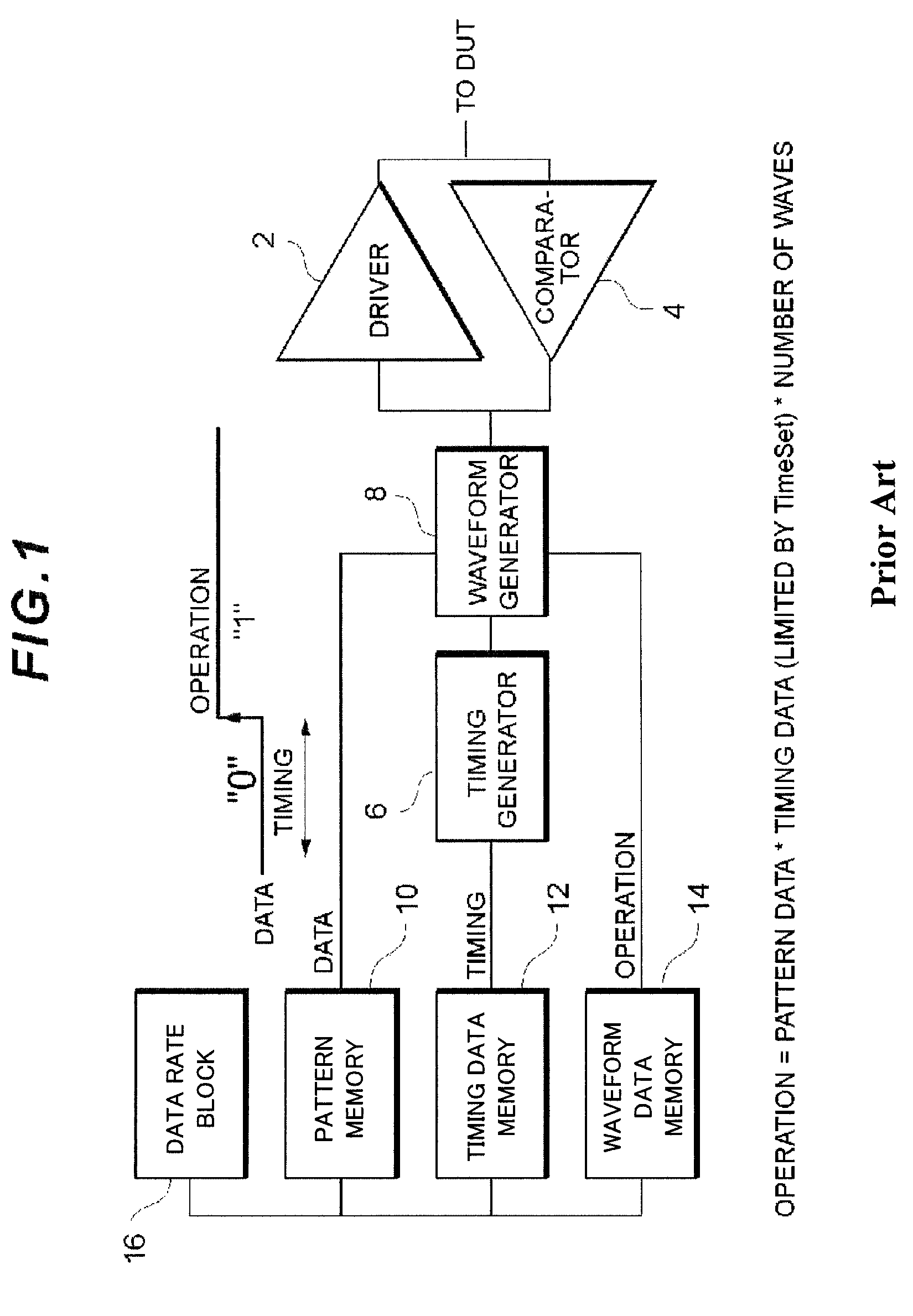

InactiveUS20050172181A1Digital circuit testingElectrical measurement instrument detailsTransceiverLow voltage

A method for testing a semiconductor device with a multi-gigabit communications receiver includes combining a data output from a high-speed communications transmitter with a perturbation signal generated by automatic test equipment. The combined signal data signal including jitter and low voltage swings is input to the communications receiver port under test. The automatic test equipment determines the bit error rate of the parallel data output from the receiver port under test. This test method is appropriate for semiconductor devices with multiple transceiver ports.

Owner:MELLANOX TECHNOLOGIES LTD

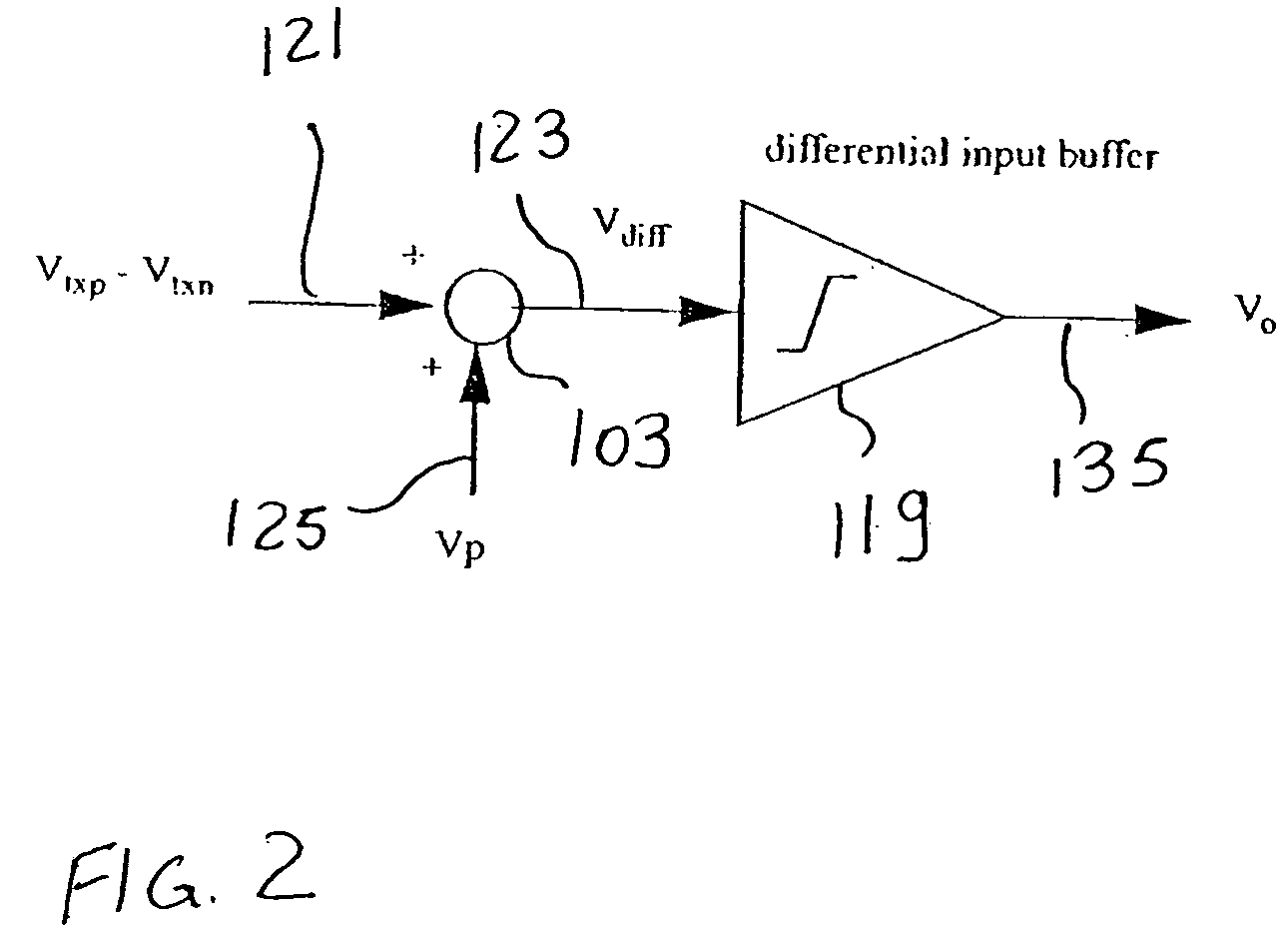

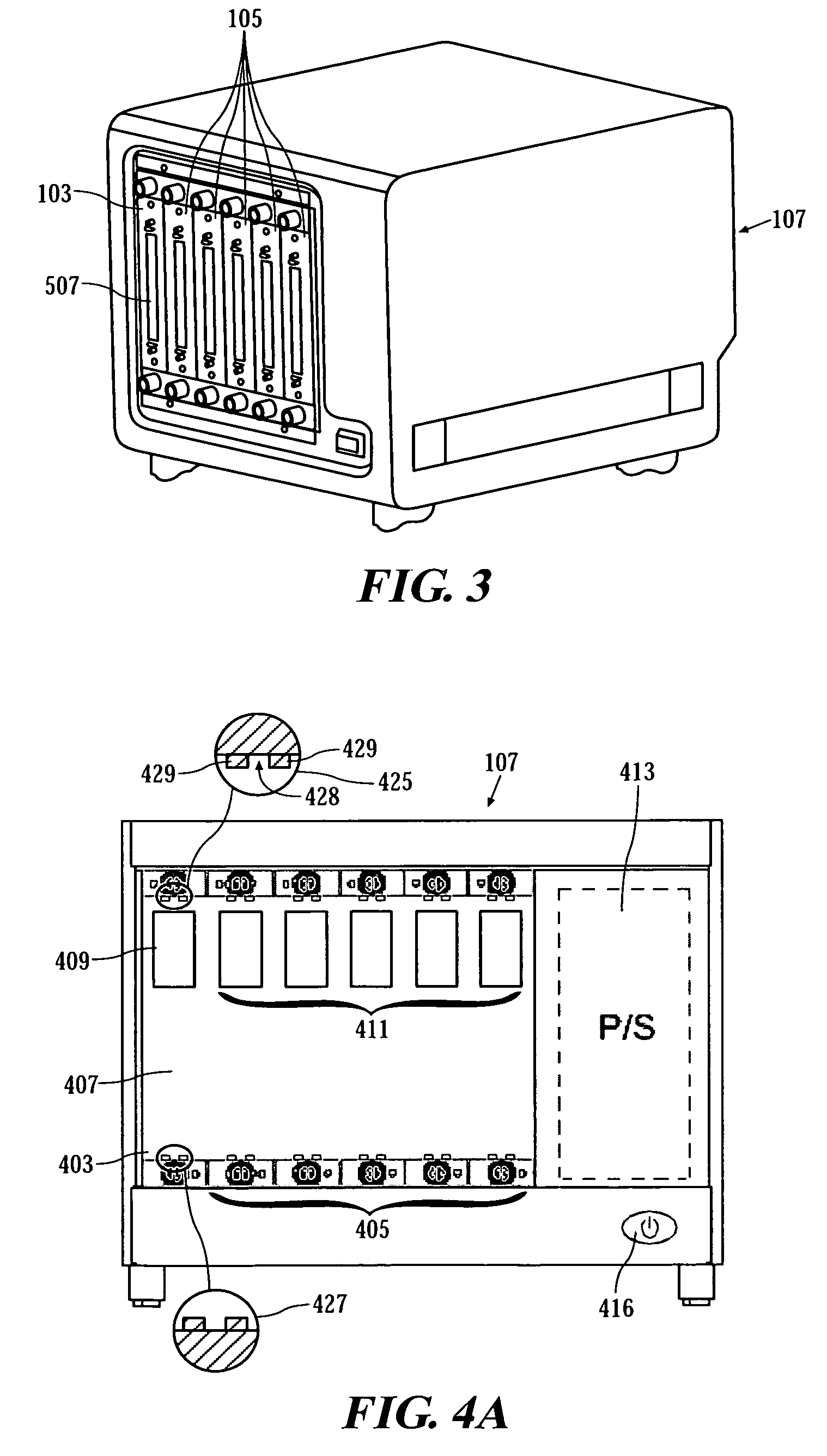

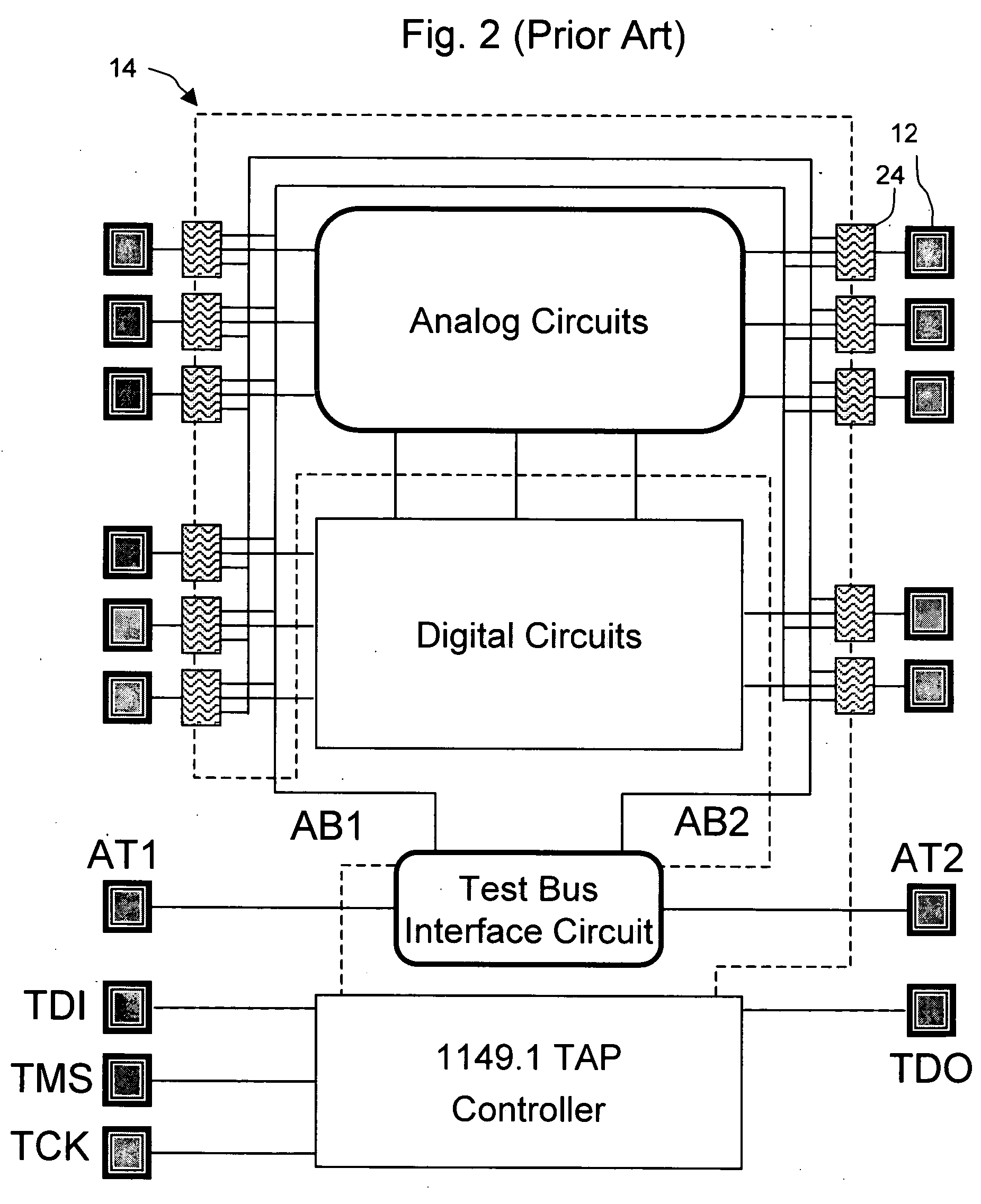

Electronic instrument system with multiple-configuration instrument modules

InactiveUS7242590B1Magnetic/electric field screeningRack/frame constructionElectricityElectronic instrument

An electronic instrument system uses a “DualPlay” concept comprising first and second mutually-exclusive modes of operation. The system includes an instrument module having first and second communications channels, each for linking the instrument module to one or more processors. The first communications channel comprises a first connector attached to the instrument module for mating to a backplane connector electrically connected to traces. The system operates in the first mode when the instrument module communicates through the first communications channel. Additionally, the system operates in the second mode when the instrument module communicates through the second communications channel, the first connector is disengaged from the backplane connector and the electronic instrument is not communicating through the first communications channel.

Owner:AGILENT TECH INC

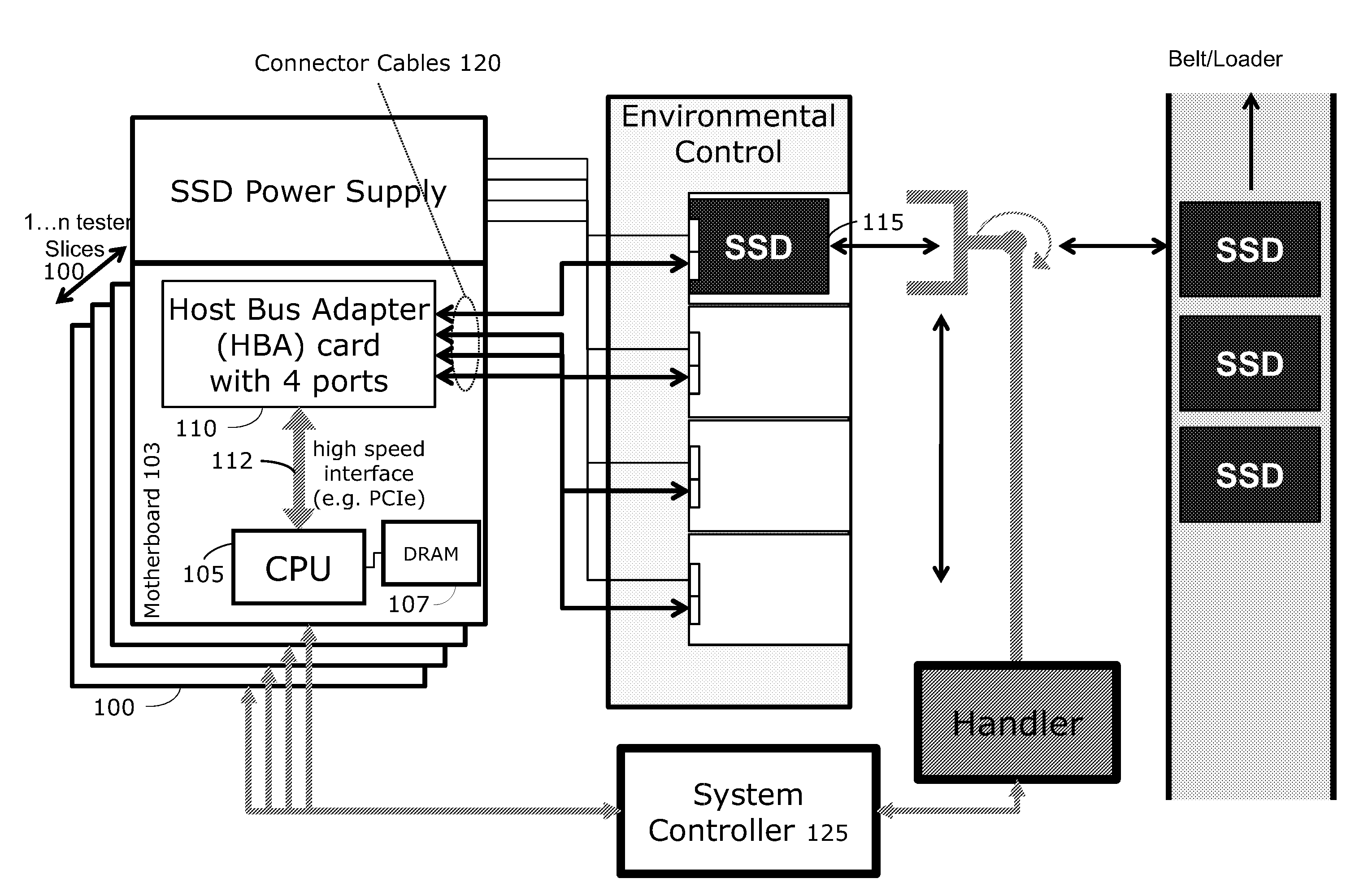

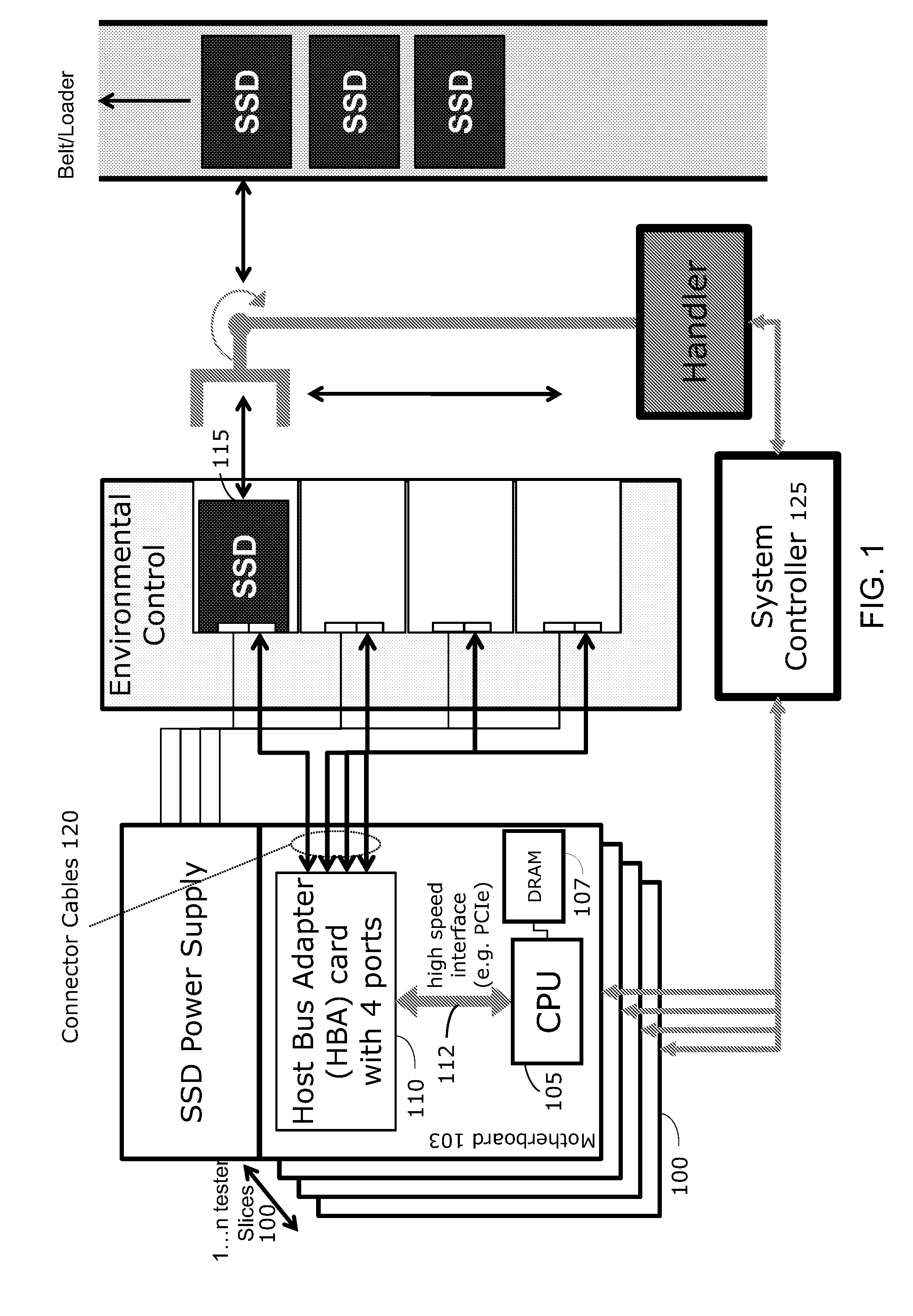

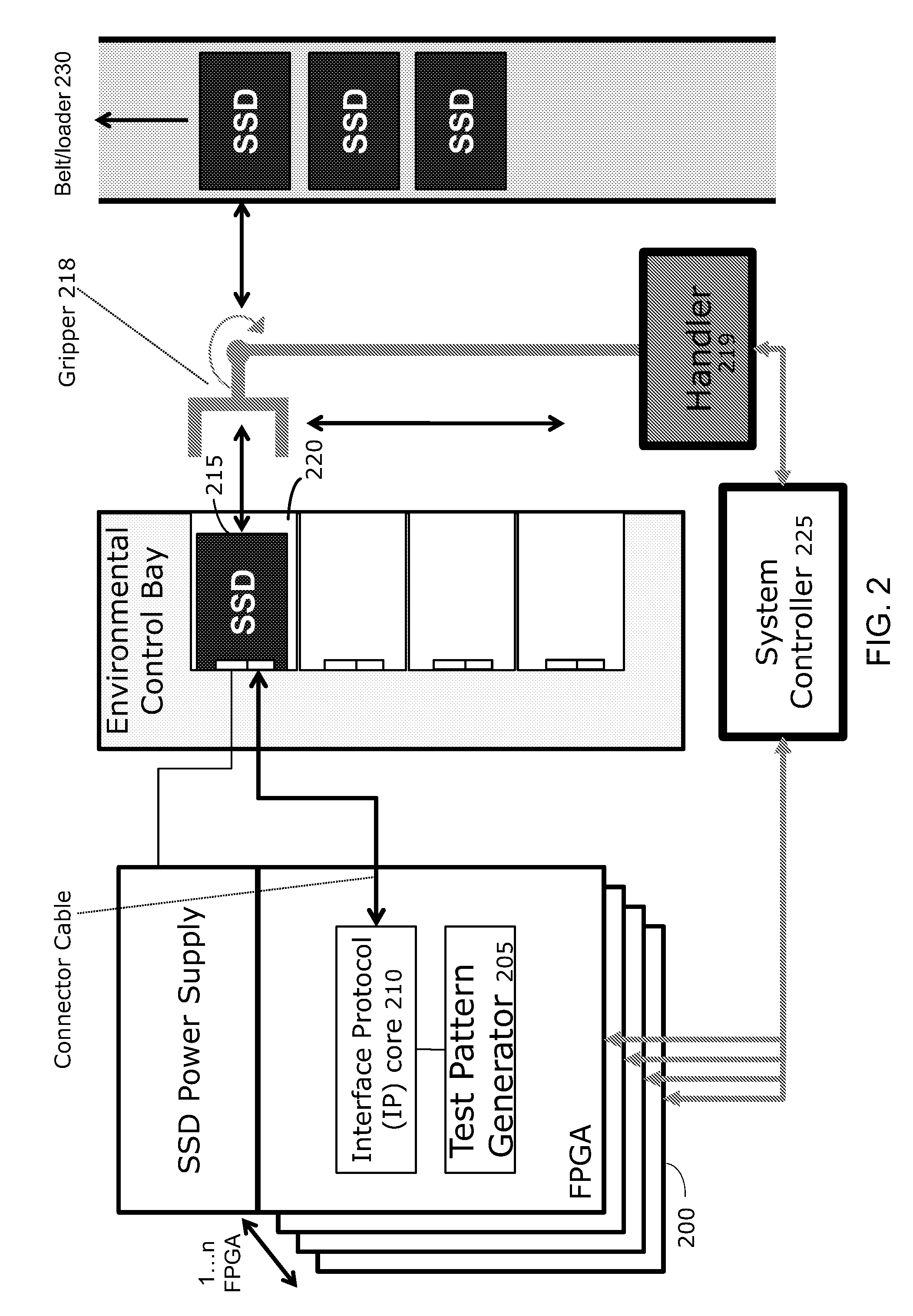

Flexible storage interface tester with variable parallelism and firmware upgradeability

ActiveUS20120191402A1Resistance/reactance/impedenceError detection/correctionTester deviceAutomatic testing

A system for use in automated test equipment. In one embodiment, the system includes a configurable integrated circuit (IC) programmable to provide test patterns for use in automated test equipment. The configurable IC includes a configurable interface core that is programmable to provide functionality of one or more protocol based interfaces for a device under test (DUT) and is programmable to interface with the DUT. The system also includes a connection configurable to couple the configurable IC to the DUT.

Owner:ADVANTEST CORP

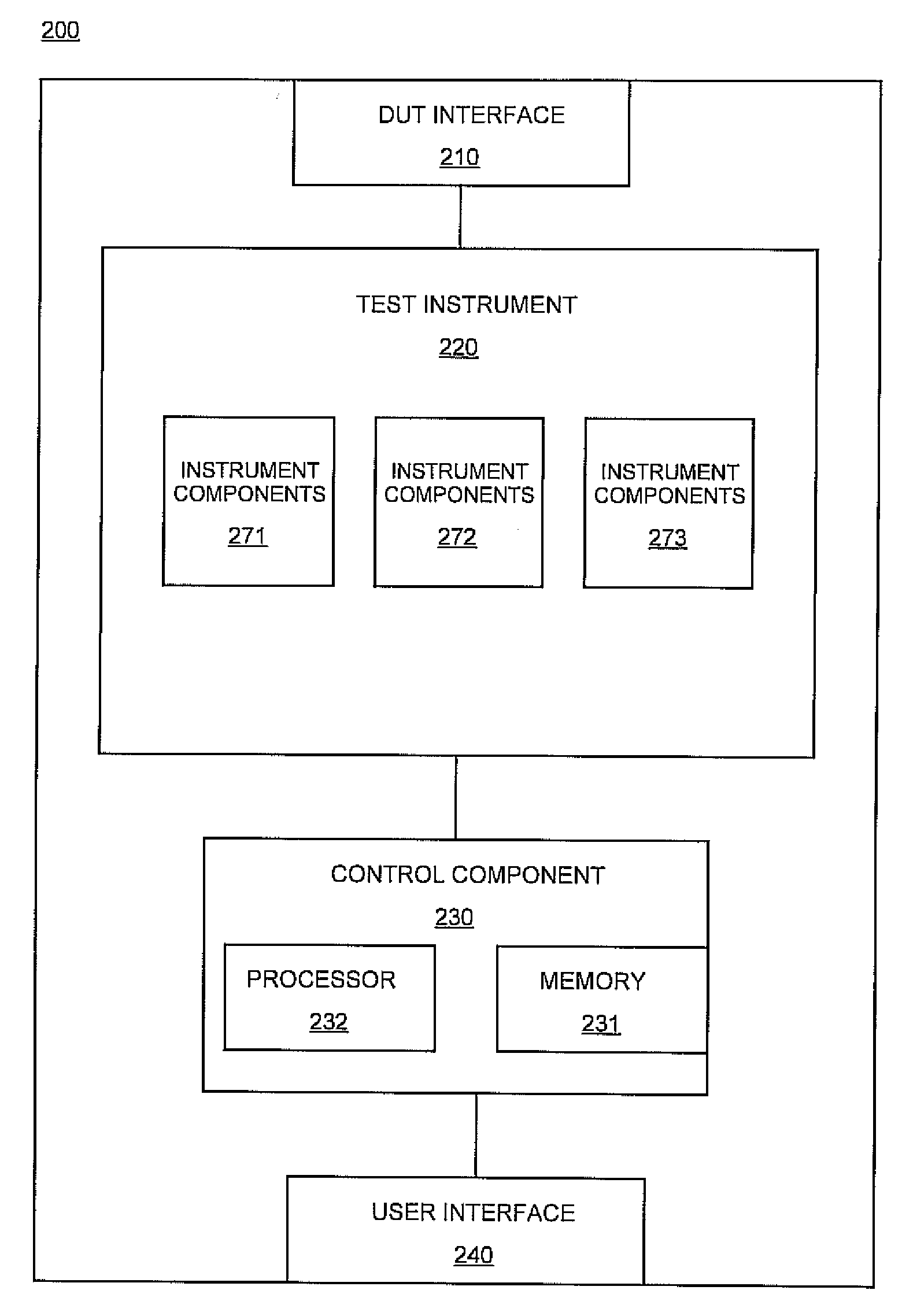

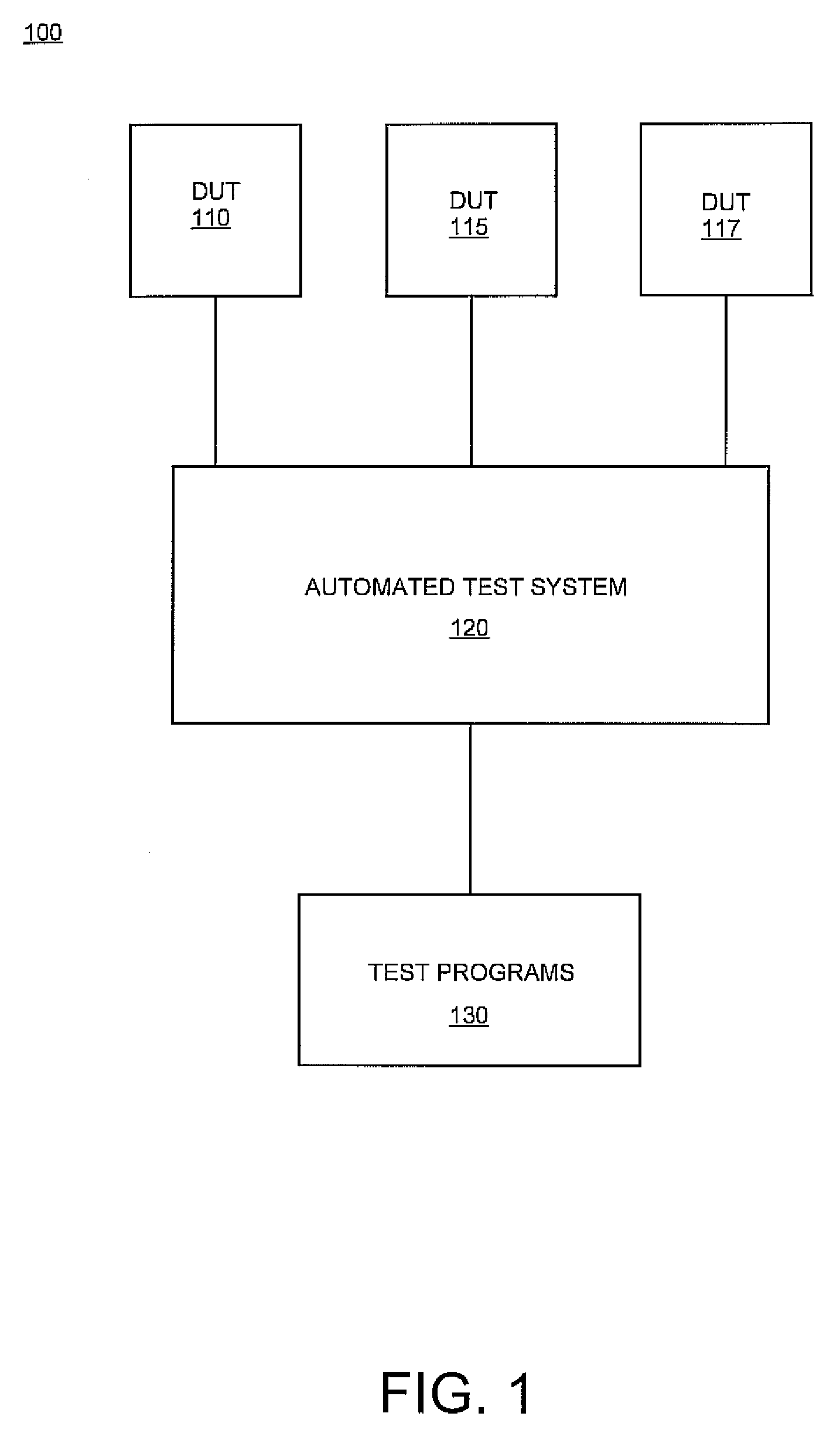

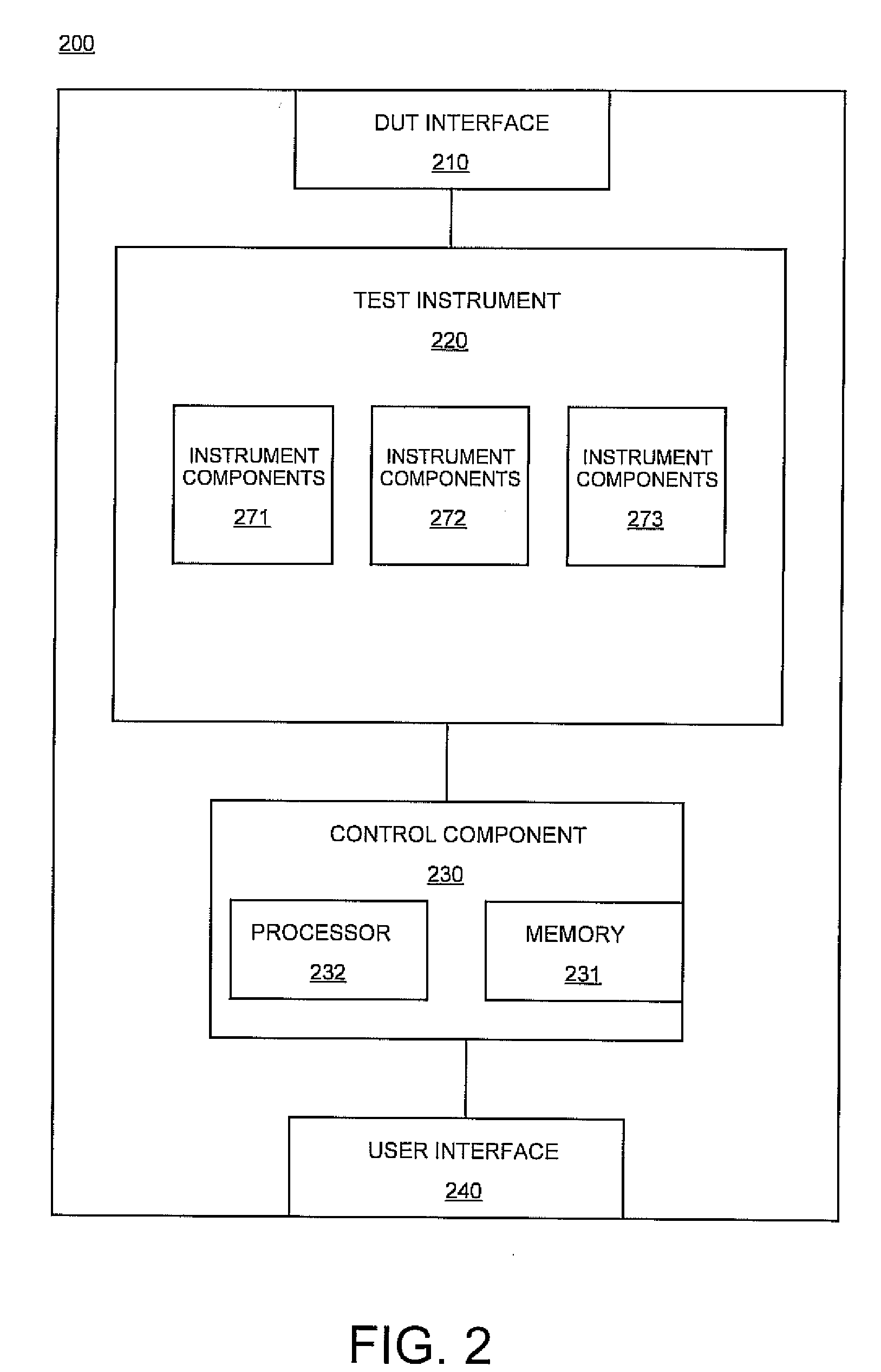

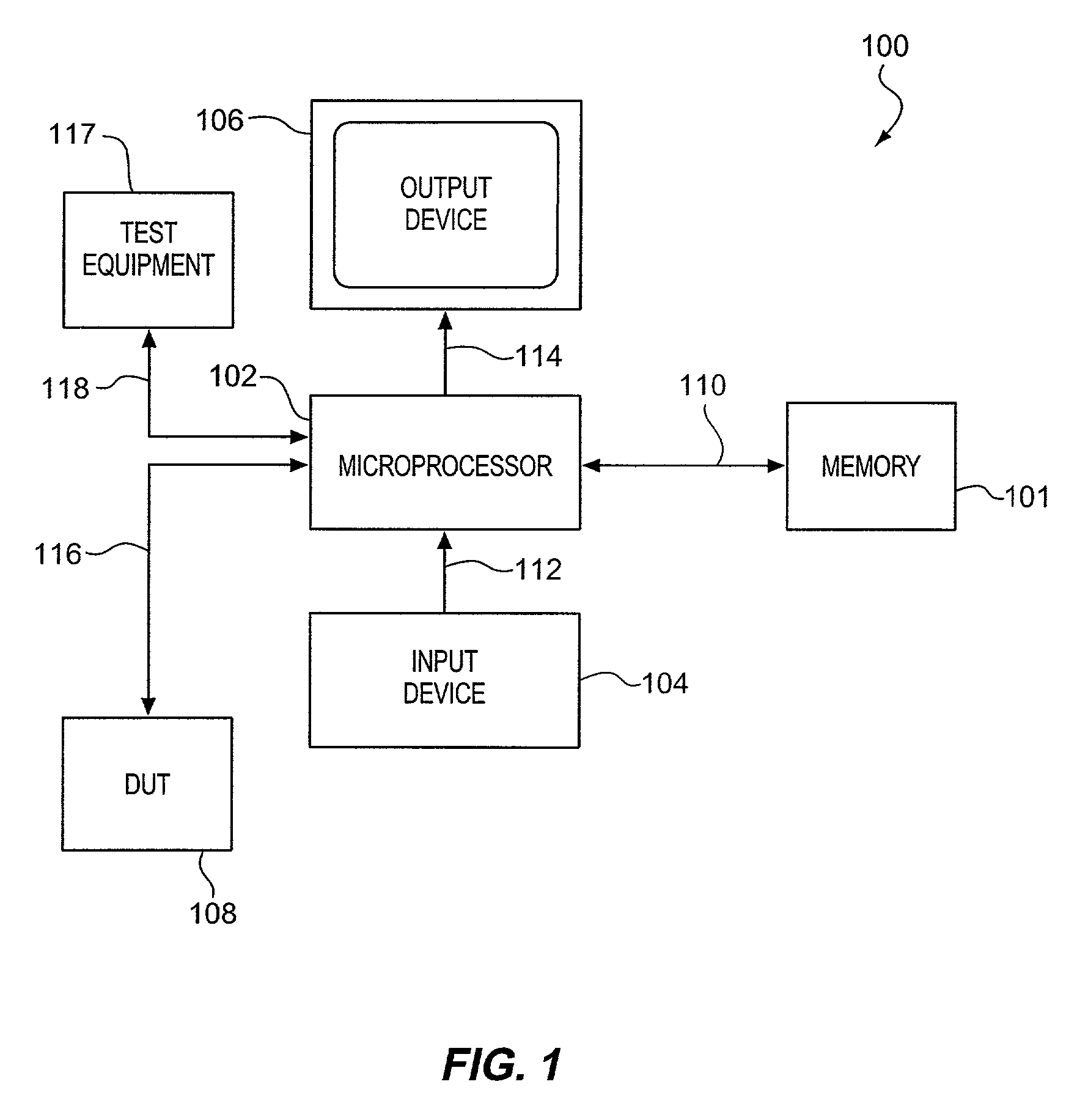

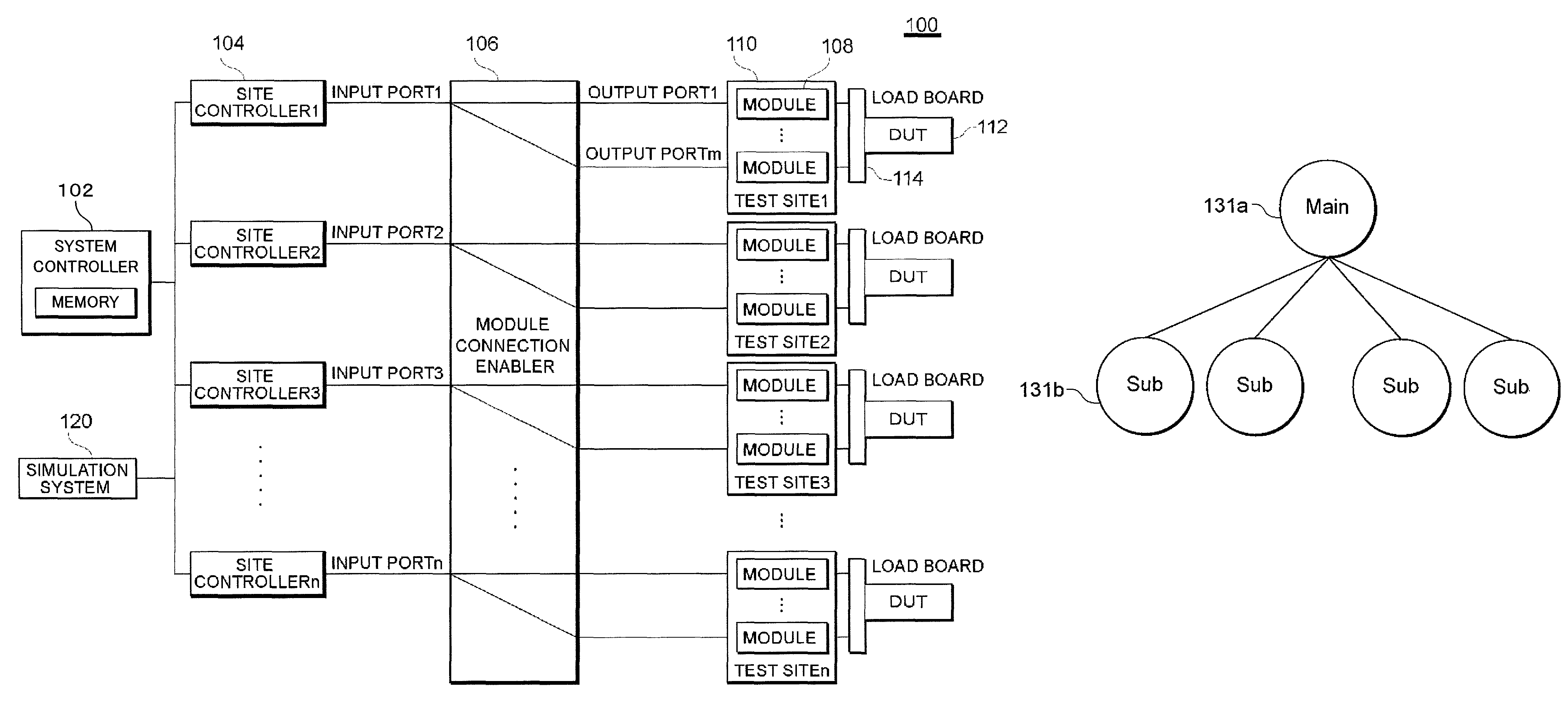

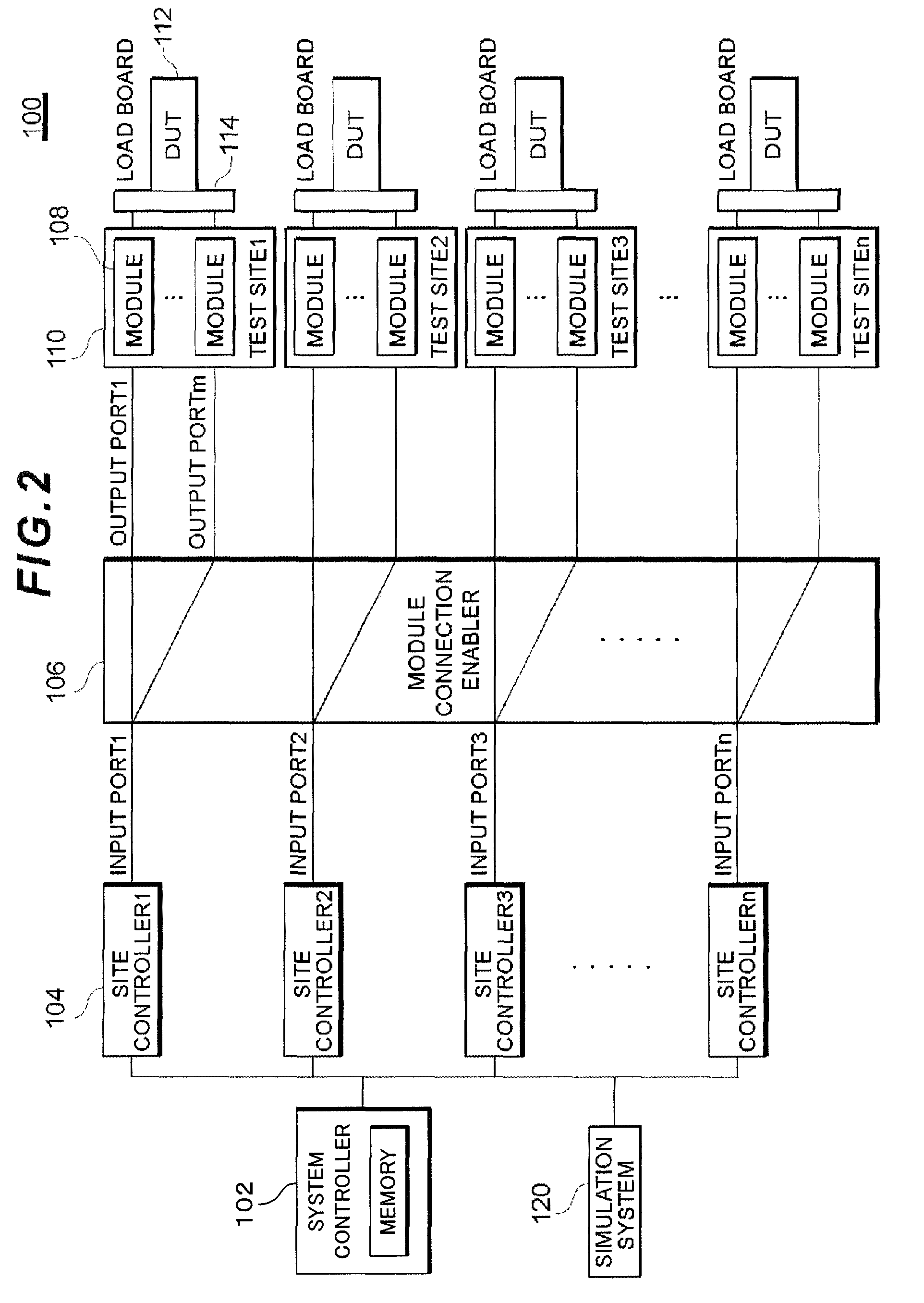

Automated test system and method

InactiveUS20100023294A1Special data processing applicationsAutomated test systemsComputer hardwareEquipment under test

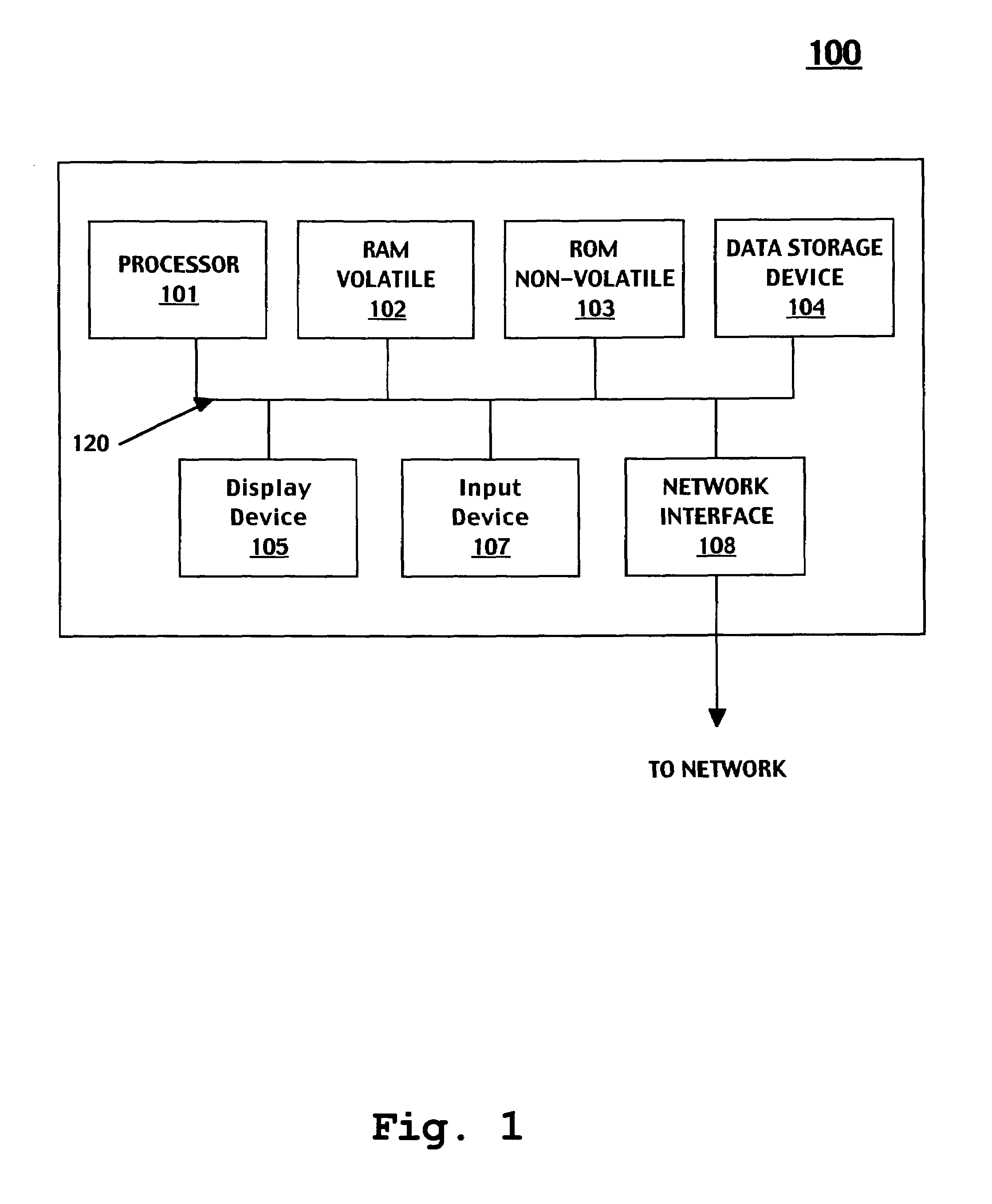

An efficient automated testing system and method are presented. In one embodiment, an automated testing system includes a control component and an automated test instrument for testing a device or a plurality of devices (e.g., packages or wafers containing multiple independent different devices) under test. The automated test instrument component performs testing operation on the device or devices under test (DUT). The control component manages testing activities of a test instrument testing the device under test, including managing implementation of a plurality of test programs loaded as a group. In one exemplary implementation, the automated test system also includes a DUT interface and a user interface. The device under test interface interfaces with a device or devices under test.

Owner:CREDENCE SYSTEMS

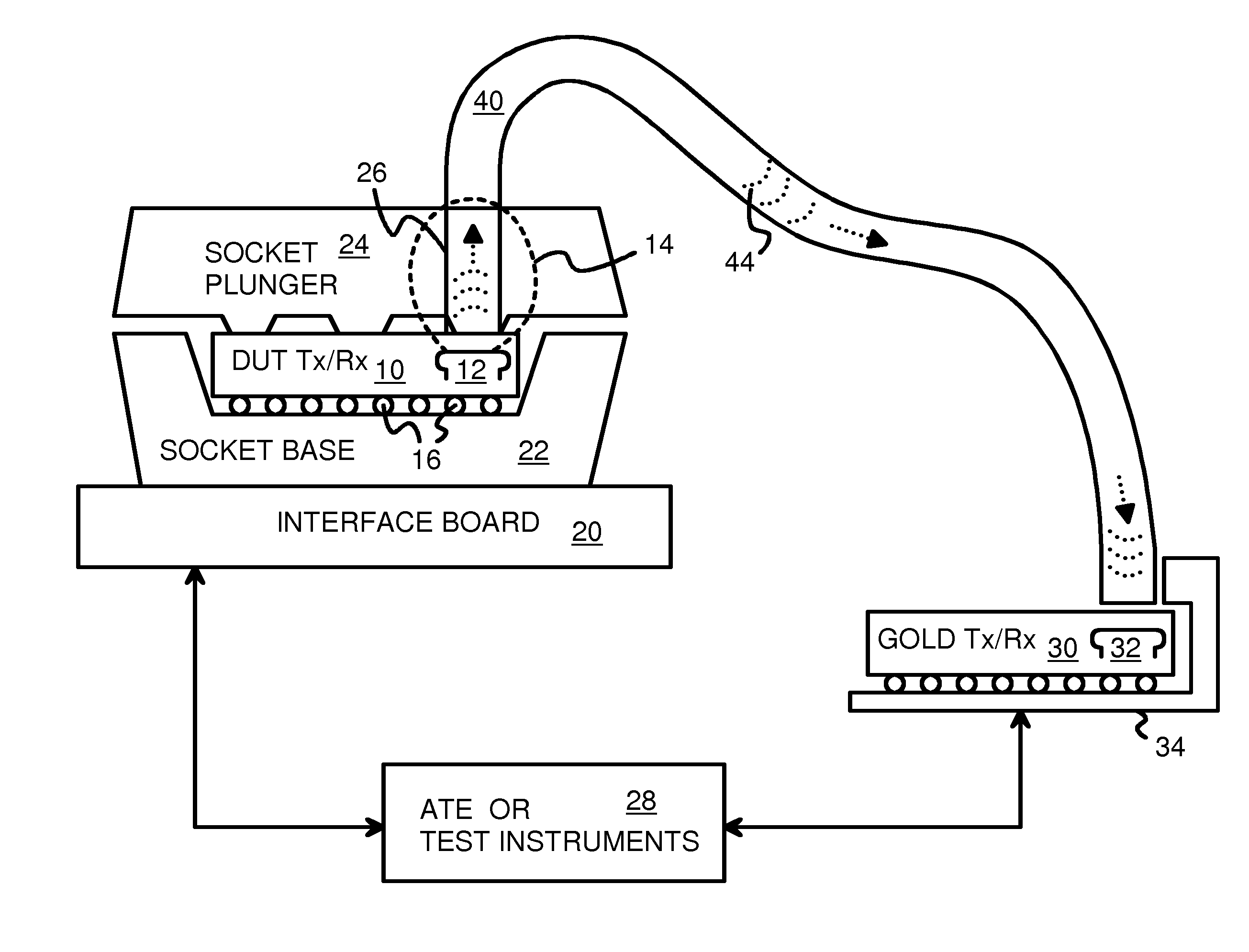

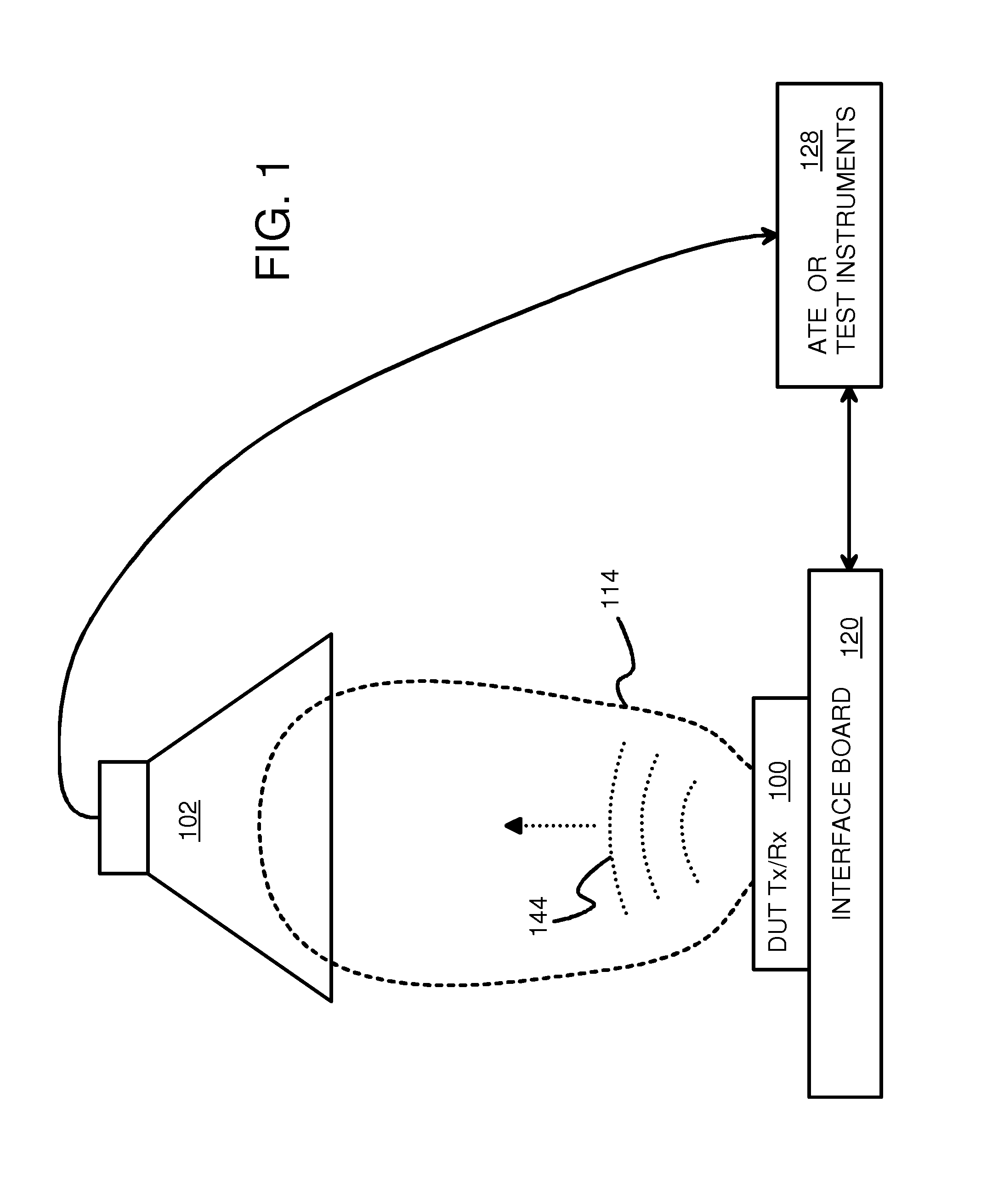

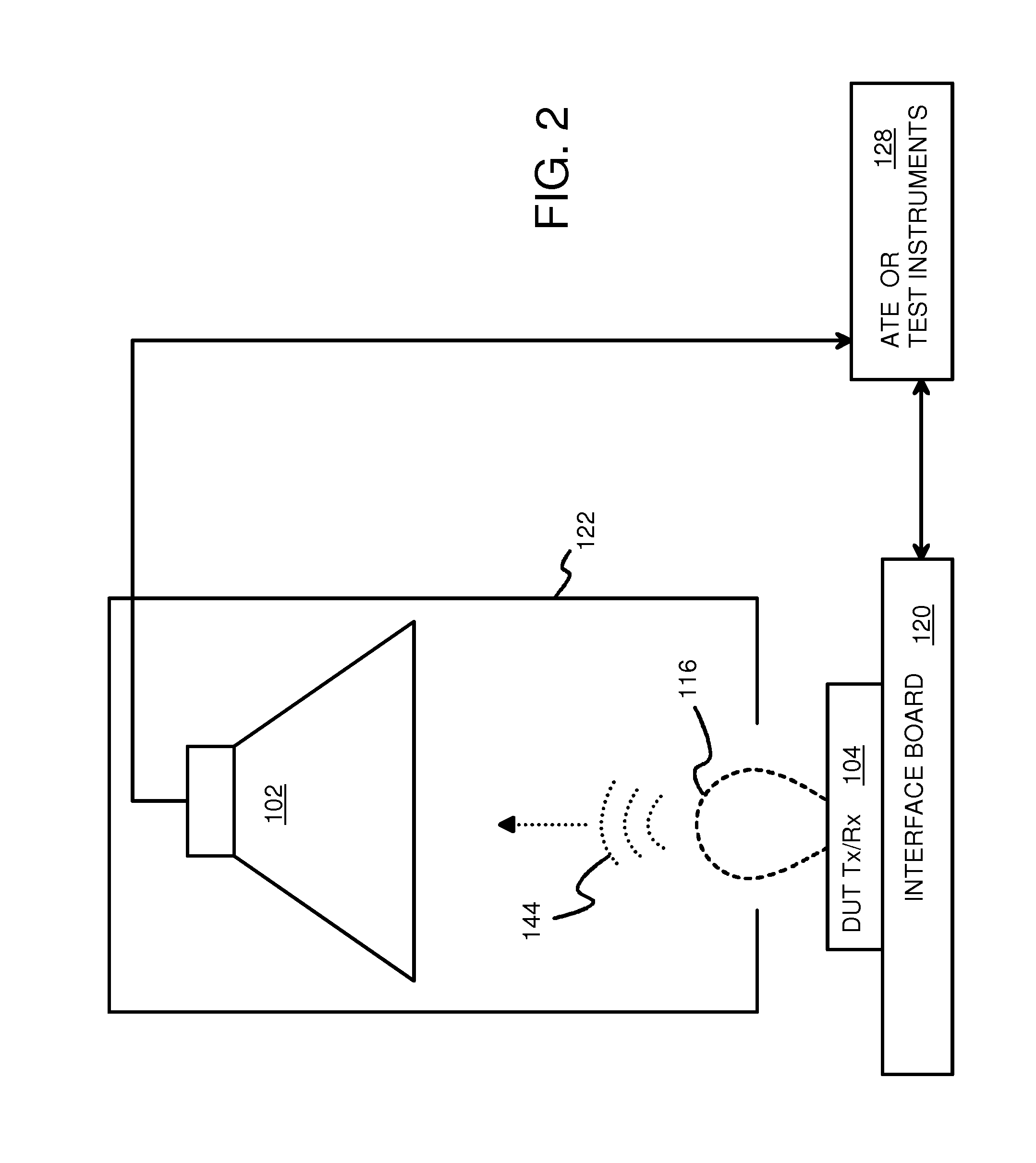

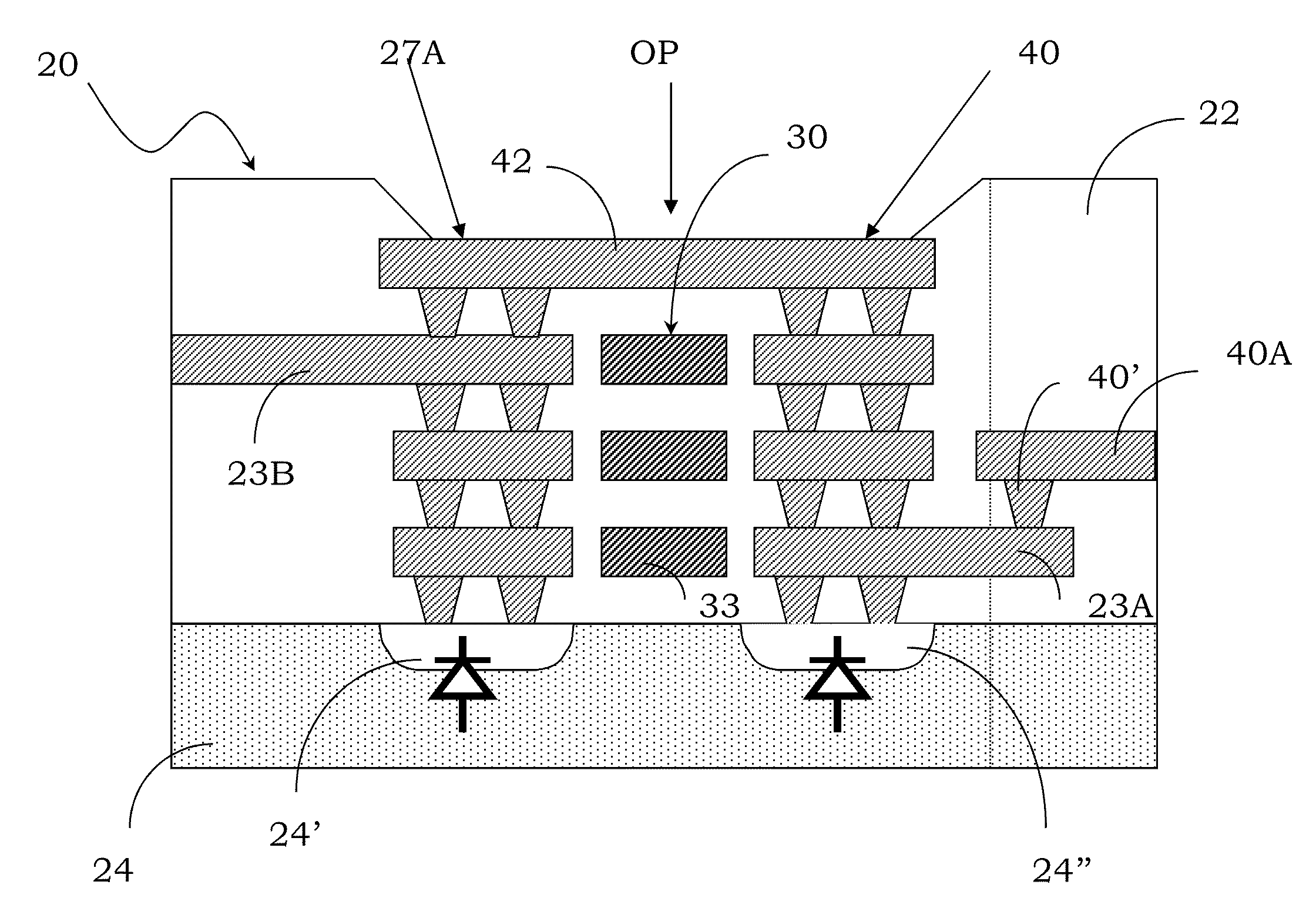

Waveguides for Capturing Close-Proximity Electromagnetic Radiation Transmitted by Wireless Chips During Testing on Automated Test Equipment (ATE)

A test fixture has a flexible plastic cable that acts as a waveguide. The Device-Under-Test (DUT) is a small transceiver and antenna that operate in the Extremely High-Frequency (EHF) band of 30-300 GHz. The size of the DUT transceiver is very small, limiting the power of emitted electromagnetic radiation so that close-proximity communication is used. The envelope for reception may only extend for about a centimeter from the DUT transceiver, about the same size as the test socket. A slot is formed in the test socket very near to the antenna. The slot receives one end of the plastic waveguide. The slot extends into the envelope by the DUT transceiver so that close-proximity radiation is captured by the plastic waveguide. The waveguide has a high relative permittivity and reflective metalized walls so that the radiation may be carried to a receiver that is outside the envelope.

Owner:MOLEX INC

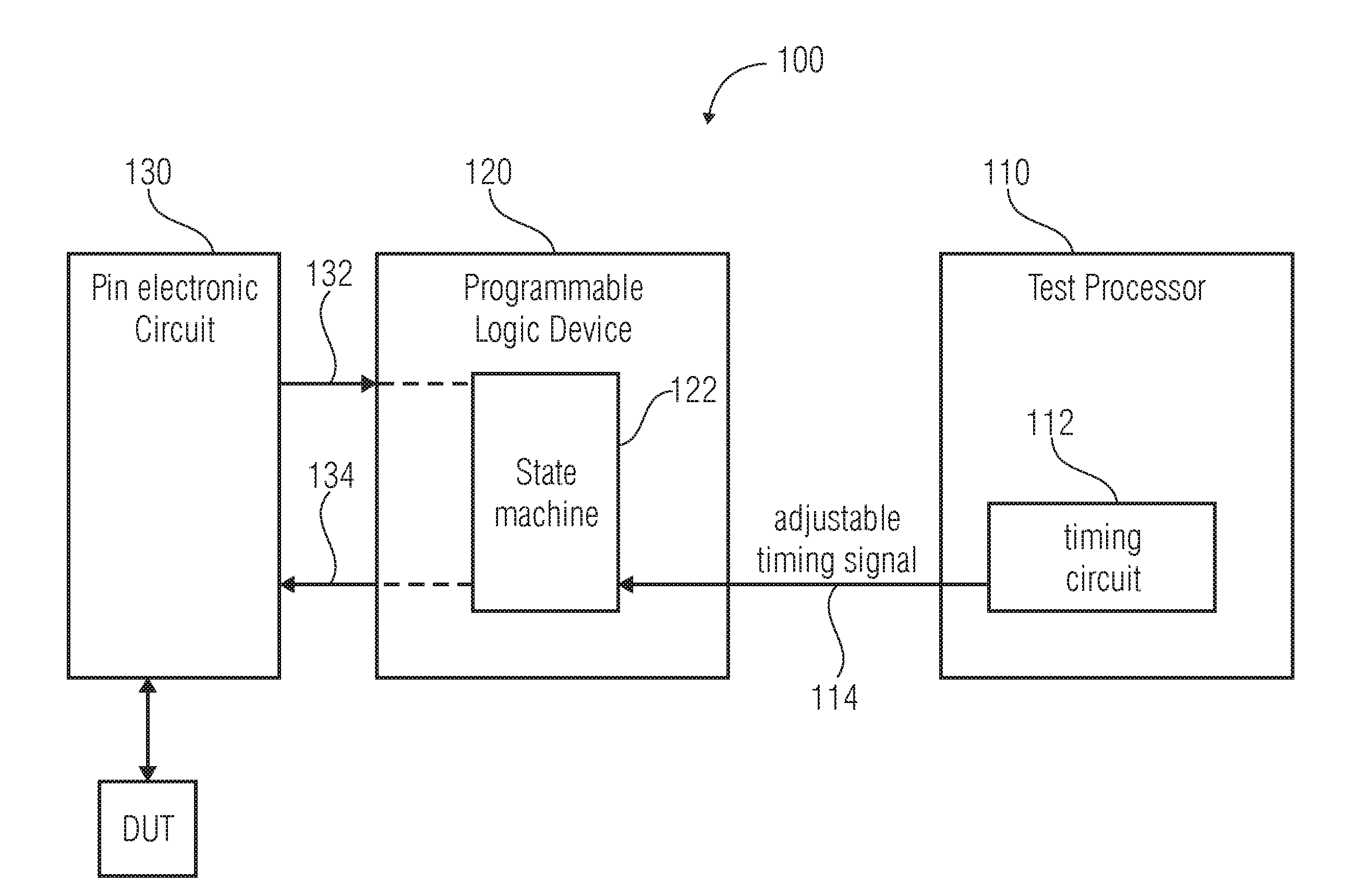

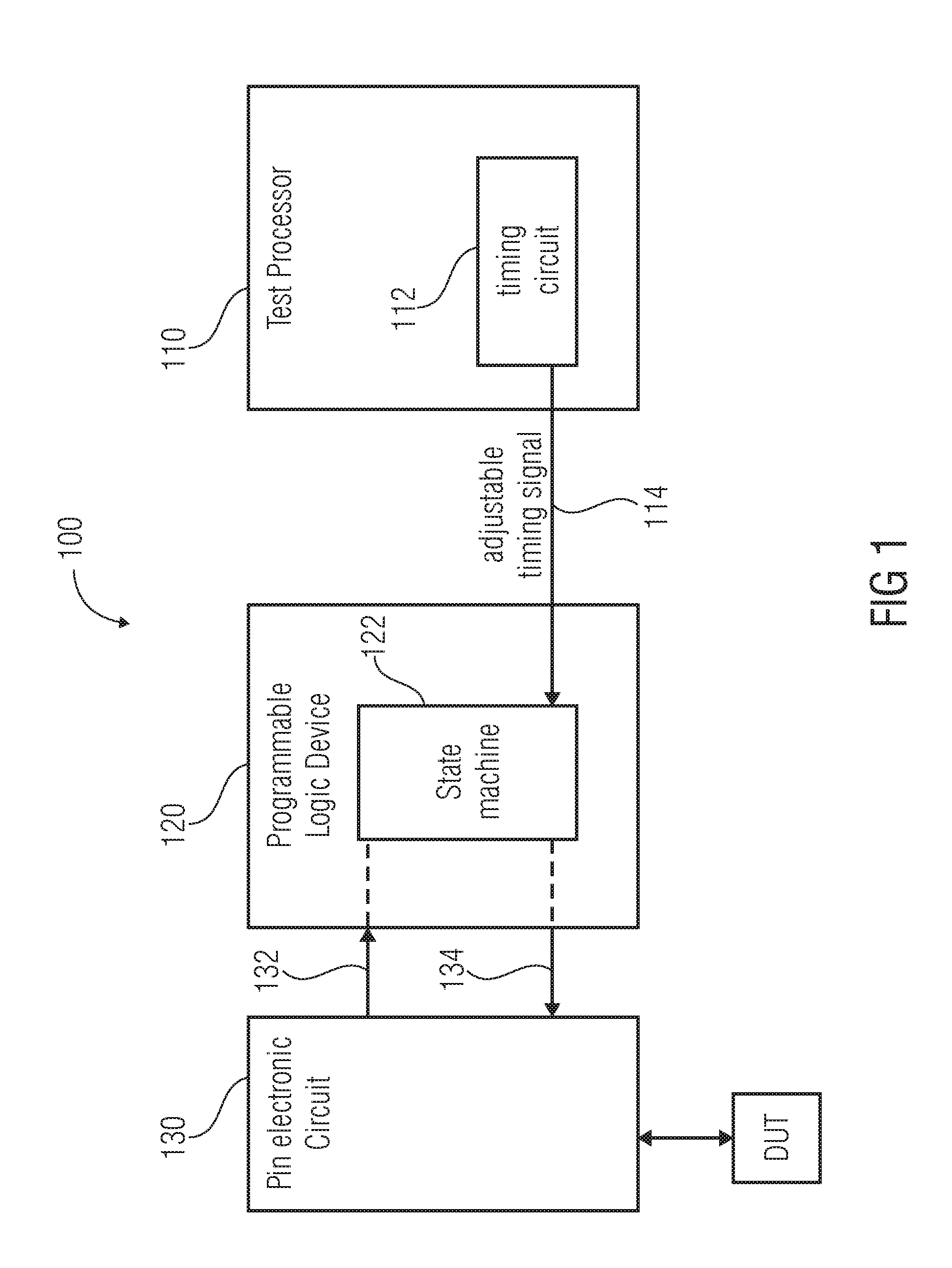

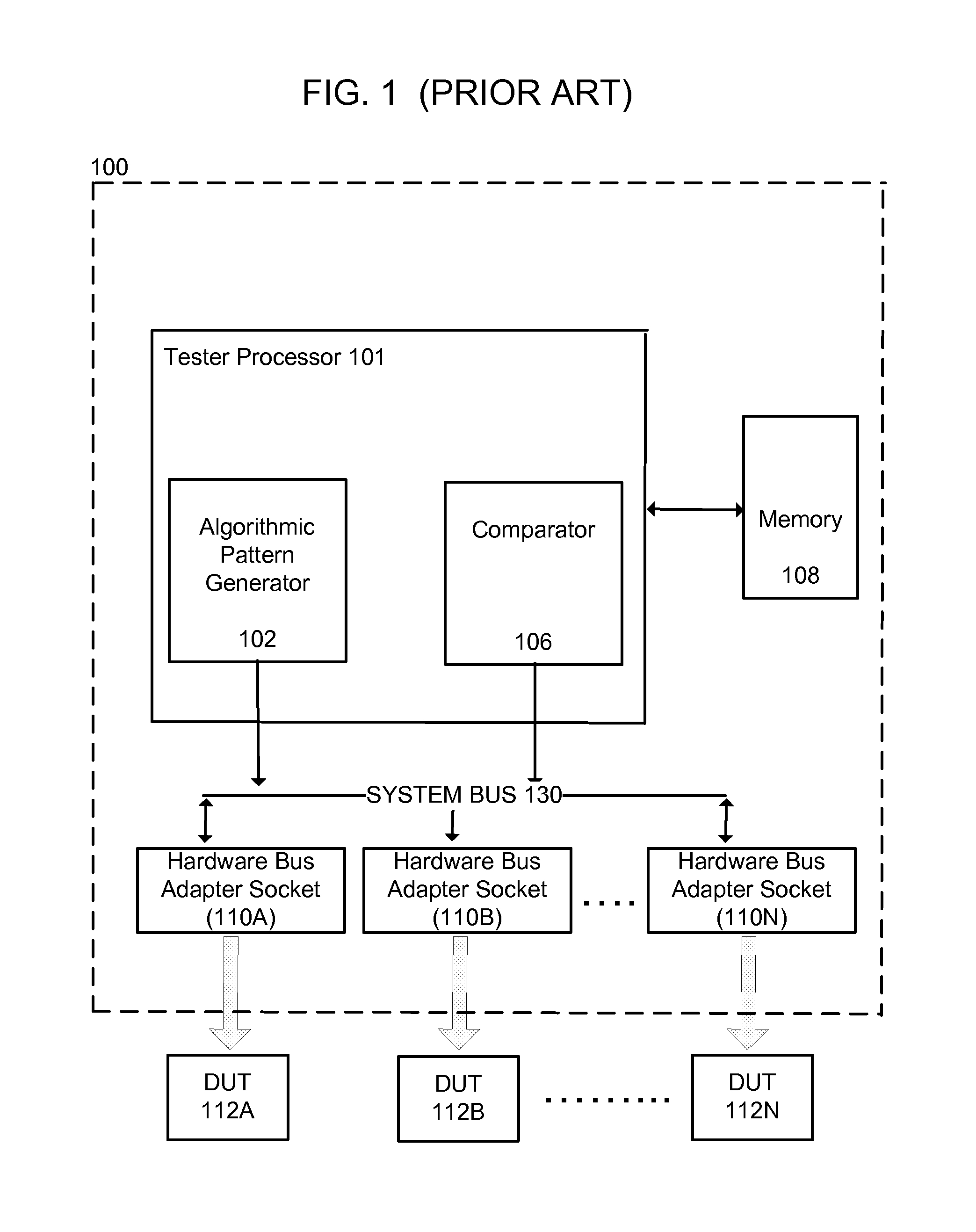

Re-configurable test circuit, method for operating an automated test equipment, apparatus, method and computer program for setting up an automated test equipment

ActiveUS20110276302A1Resistance/reactance/impedenceAutomated test systemsAutomatic test equipmentProgrammable logic device

A re-configurable test circuit for use in an automated test equipment includes a test circuit, a test processor and a programmable logic device. The pin electronics circuit is configured to interface the re-configurable test circuit with a DUT. The test processor includes a timing circuit configured to provide one or more adjustable-timing signals having adjustable timing. The programmable logic device is configured to implement a state machine, a state sequence of which depends on one or more input signals received from the pin electronics circuit, to provide an output signal, which depends on a current or previous state of the state machine, to the pin electronics circuit in response to the signal(s) received from the pin electronics circuit. The test processor is coupled to the programmable logic device to provide at least one of the adjustable-timing signal(s) to the programmable logic device to define timing of the programmable logic device.

Owner:ADVANTEST CORP

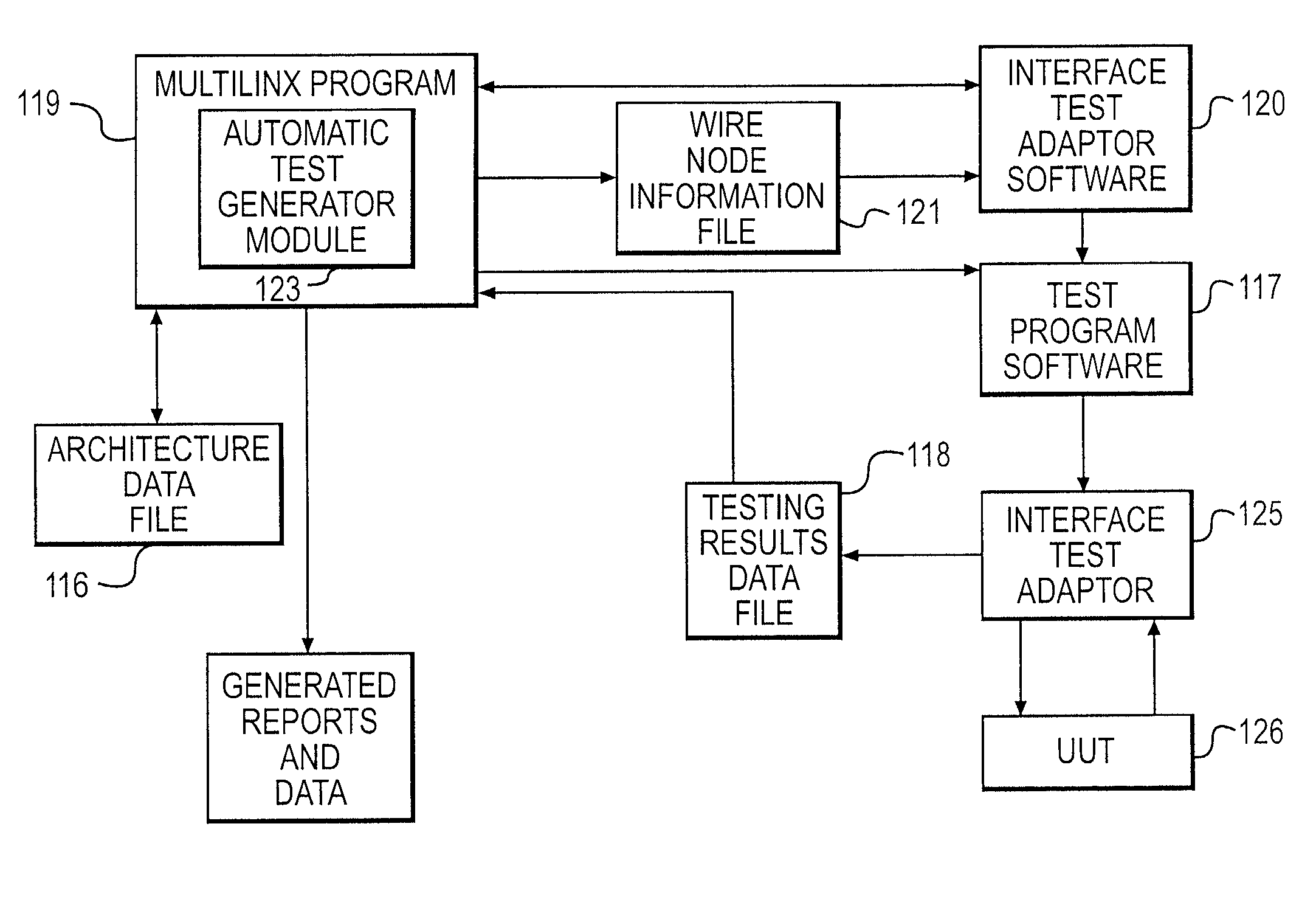

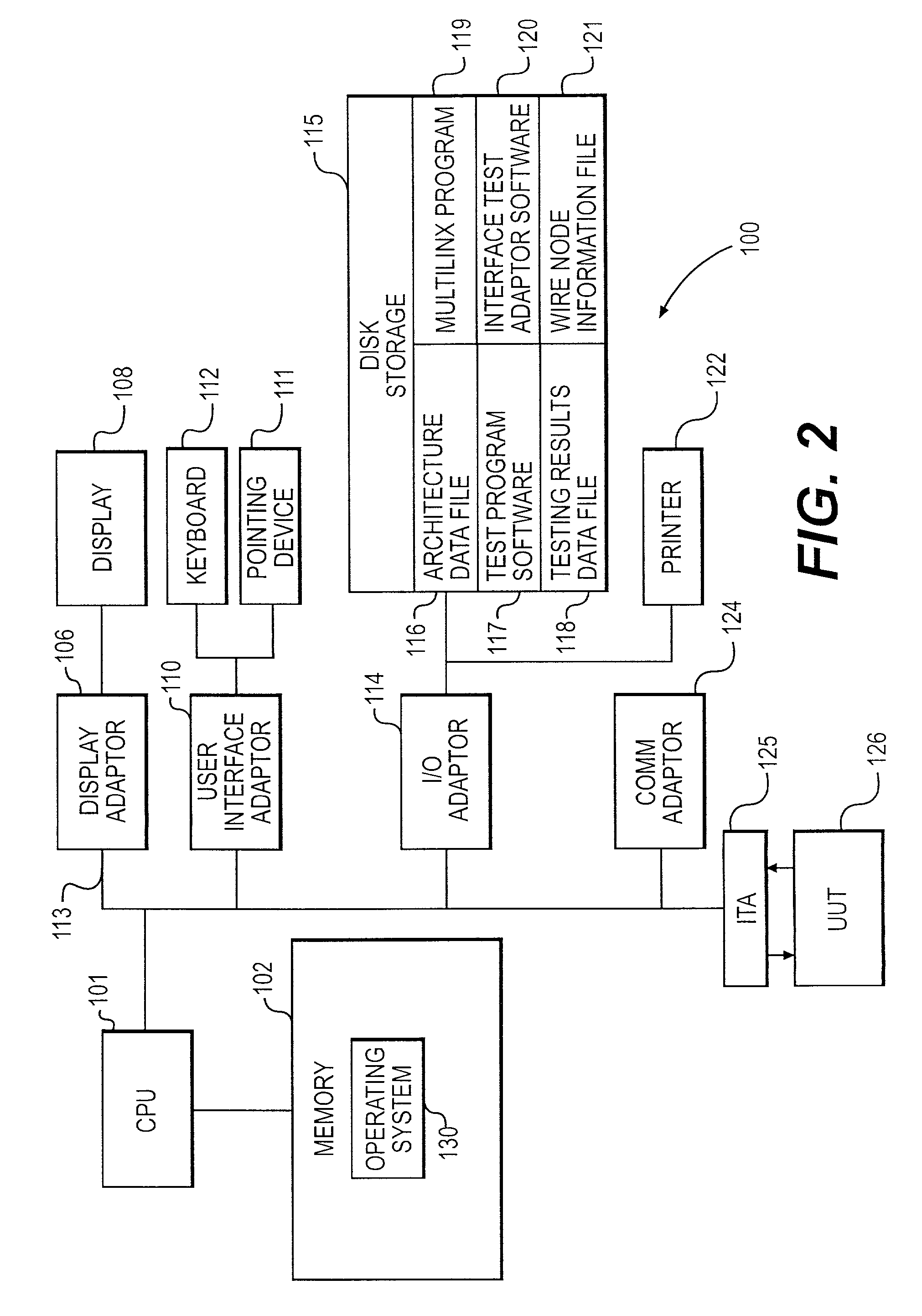

System and method for intelligent wire testing

InactiveUS20020147561A1Resistance/reactance/impedenceTesting circuitsAutomatic test equipmentRelational database

A system and method for providing an intelligent wire testing capability for complex hardware systems. The system is comprised of a software application with a relational database interfacing with an automatic test equipment module. The relational database contains all of a system's architecture information plus all of the text and parametric information associated with the design. During a system test, the subject invention uses the wiring / system architecture as disclosed in the relational database together with an automatically generated test program to identify faults in a unit under test. Using the architecture knowledge, the subject invention is capable of automatically generating a wire harness schematic for printout or display on a CRT. The architecture knowledge also allows a technician to quickly distinguish between a broken wire and an unused pin in a connector. After the test, the observed values are stored in a testing results file for later review and trend analysis. Data from the trend analysis provides the technician with the data necessary to assess the state of the wiring in the UUT. At the completion of testing, the testing results file stays with the UUT thereby ensuring access to a complete testing history of the UUT at any time.

Owner:GRC INT INC

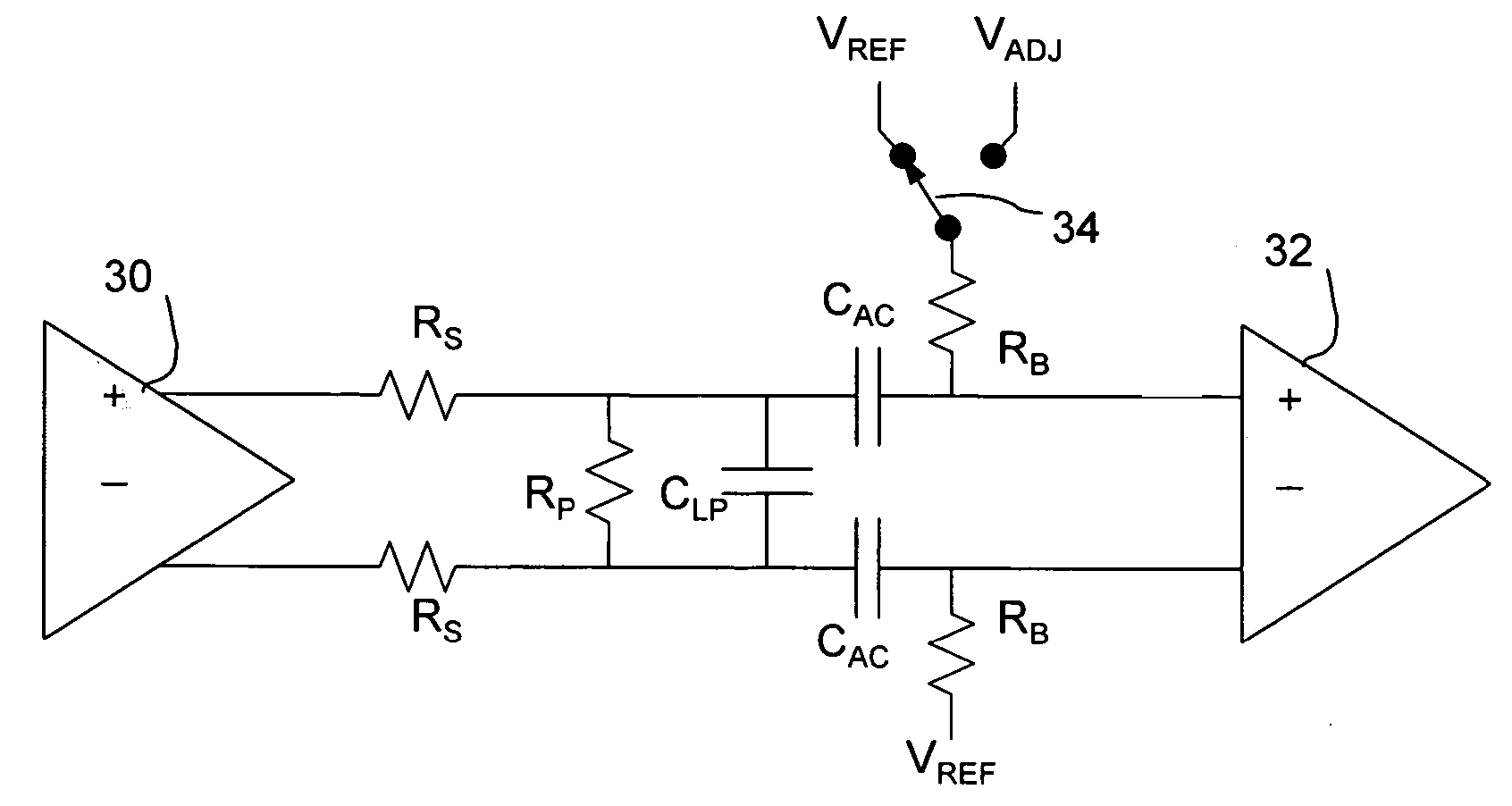

Circuit and method for testing high speed data circuits

InactiveUS20040123197A1Digital circuit testingError detection/correctionCapacitanceDigital transition

A circuit and method are described in which a DC voltage or current is connected to a high frequency, AC-coupled signal path between a transmitter and a receiver, and the bit error rate of the data transmission is tested while applying an altered bias voltage to the received signal. The bias voltage can be connected via a resistor, inductor or transistors. The transmitted signal is attenuated resistively, and a load capacitance is applied whose value causes digital transition times to exceed one unit interval. An intended application is testing of an integrated circuit, serializer / deserializer (serdes) operating above 1 GHz.

Owner:MENTOR GRAPHICS CORP

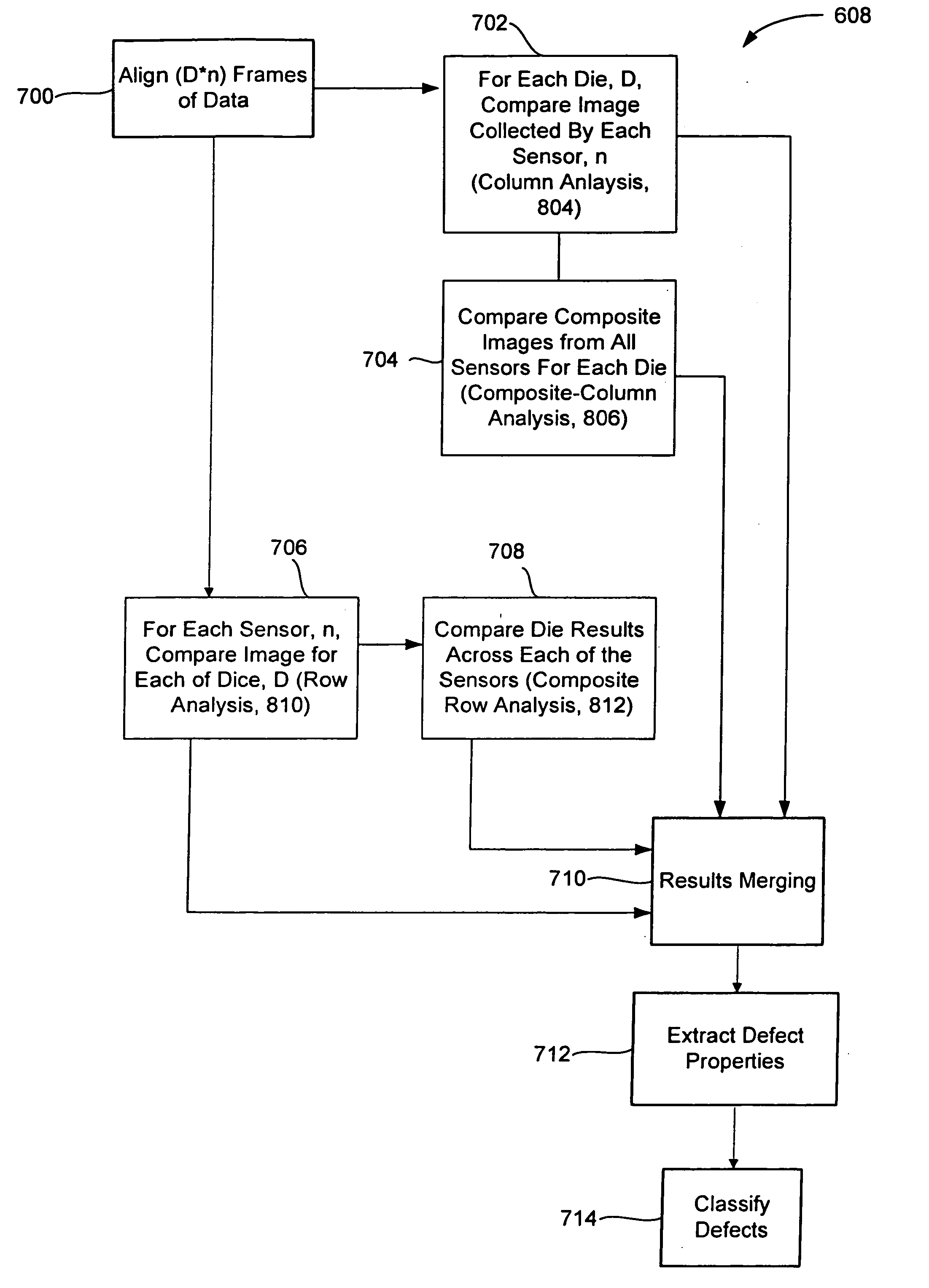

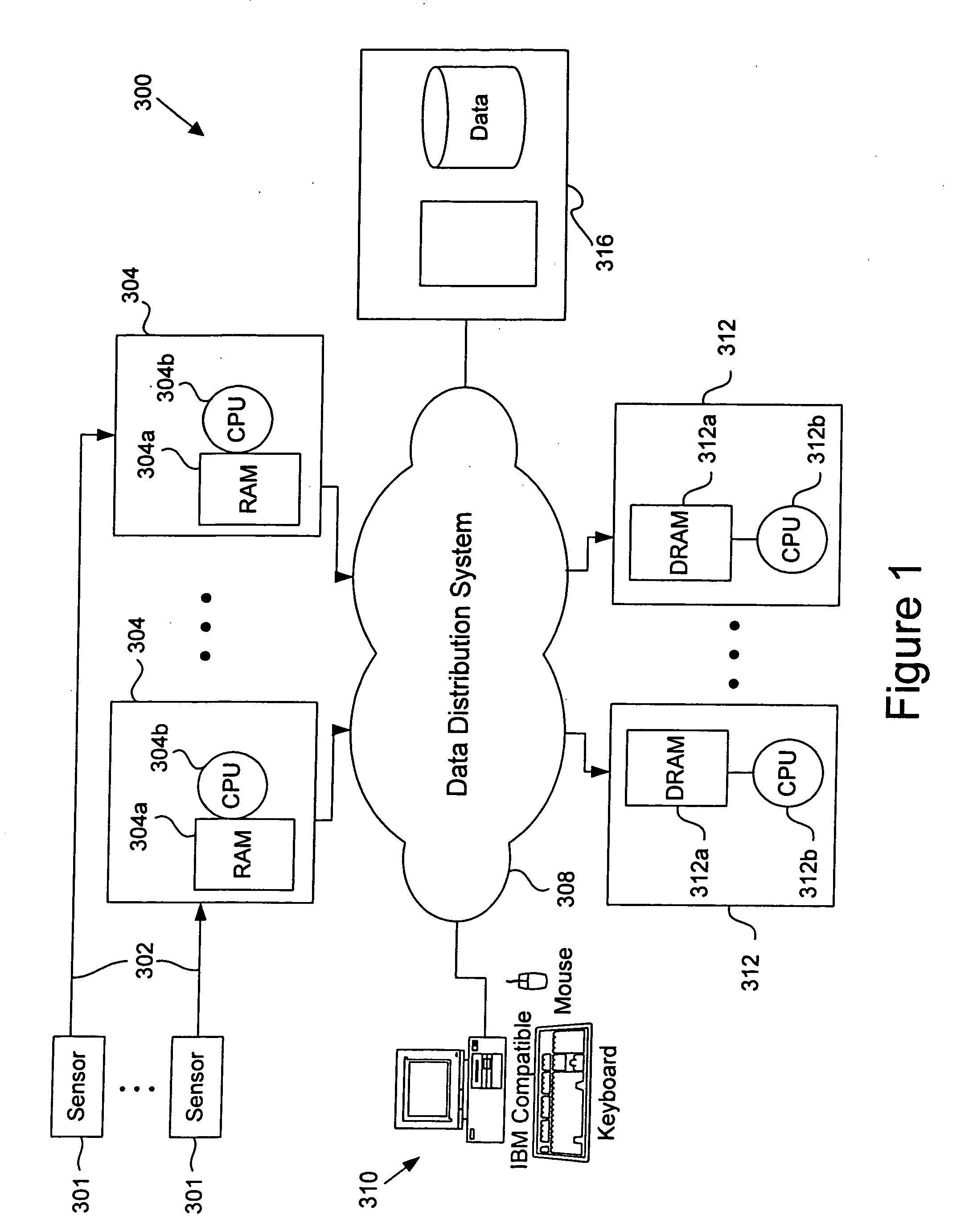

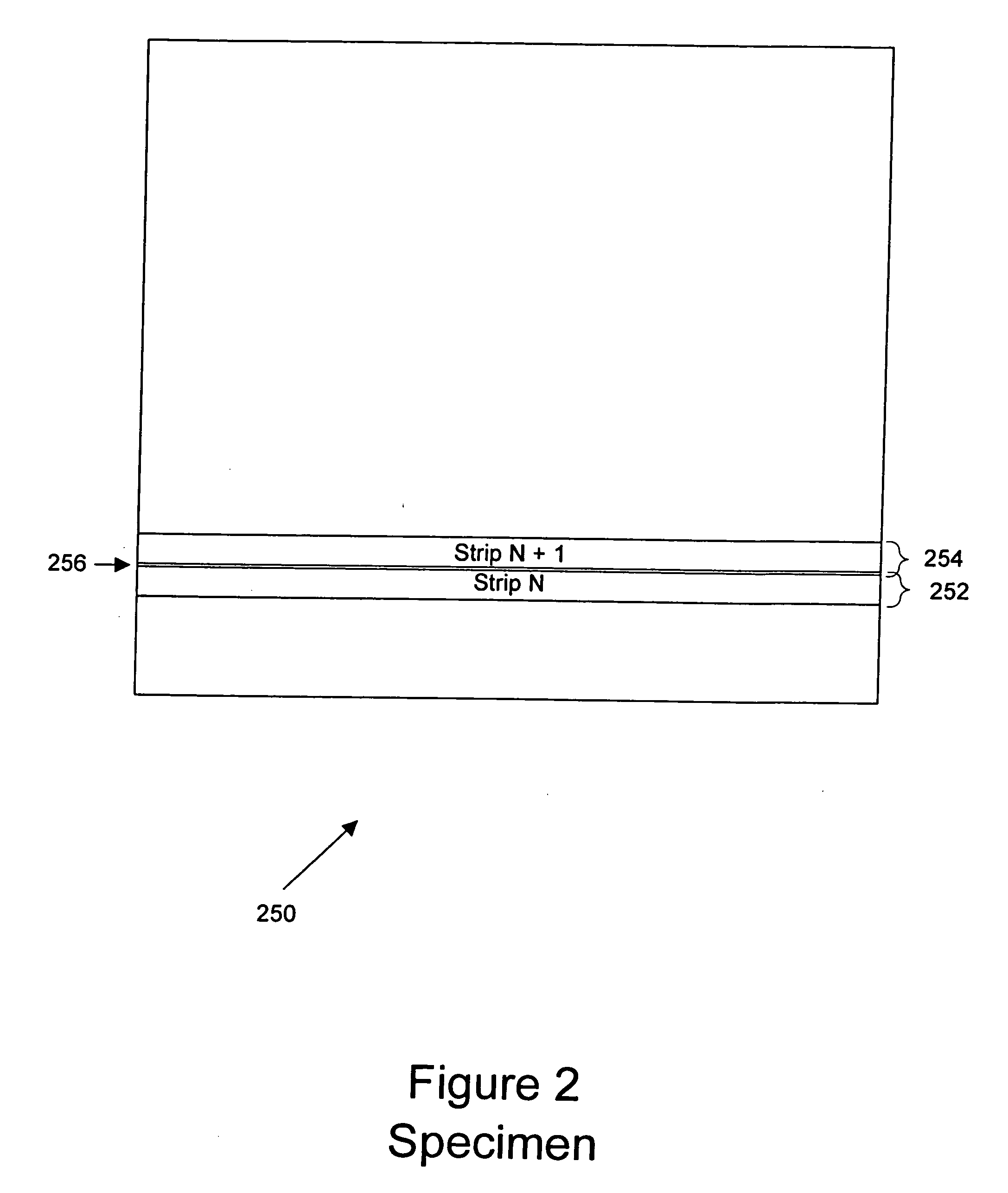

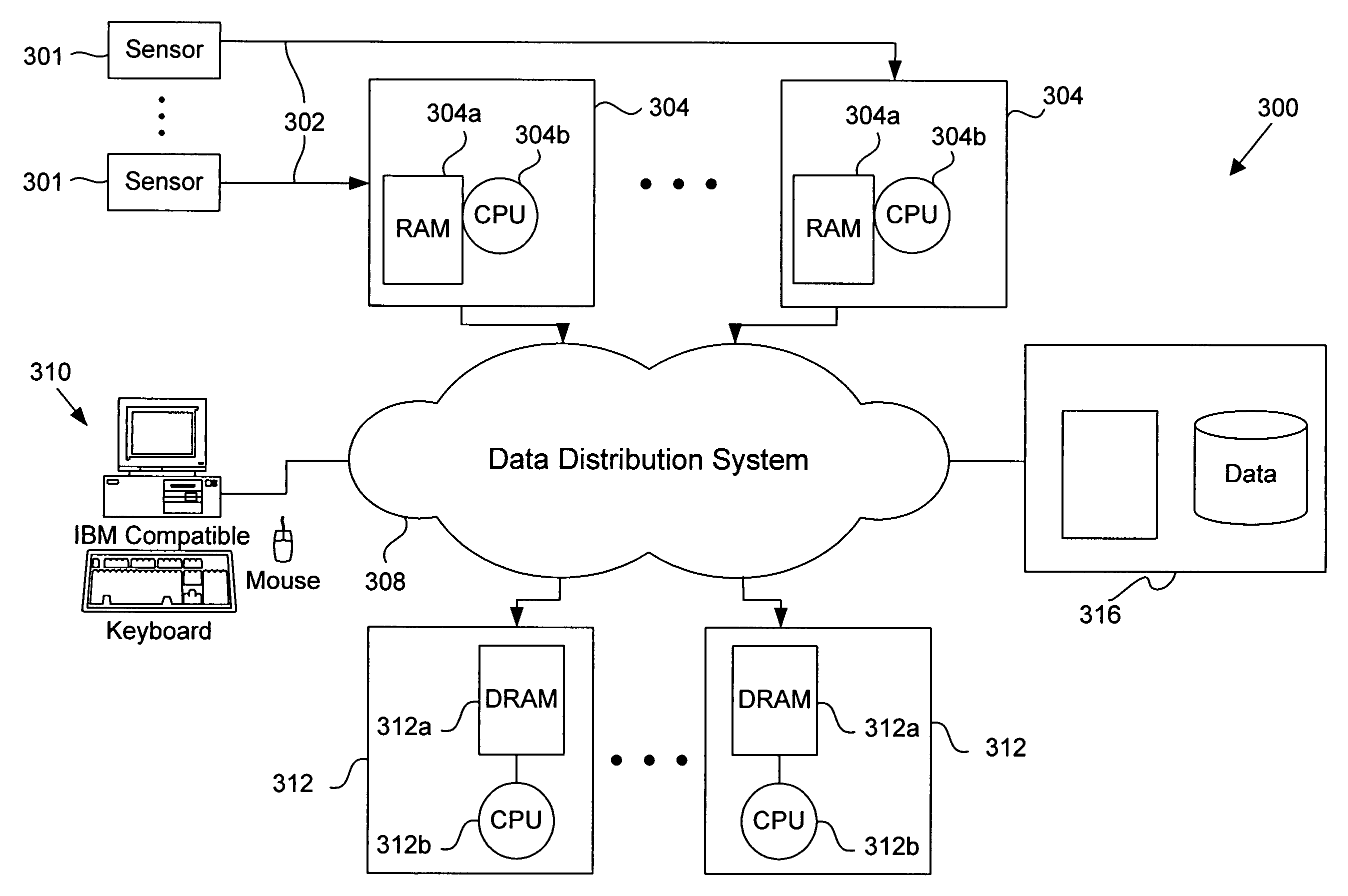

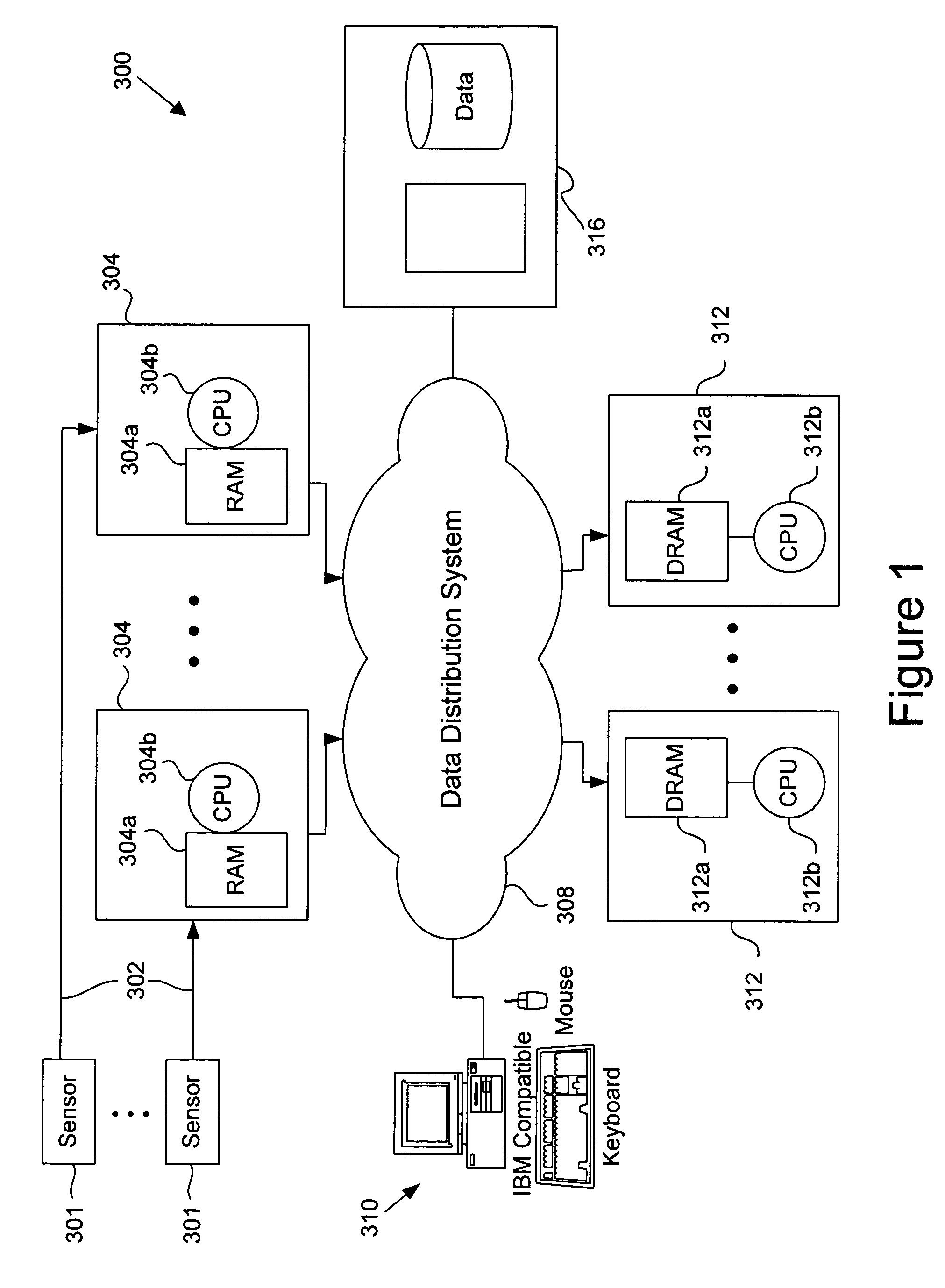

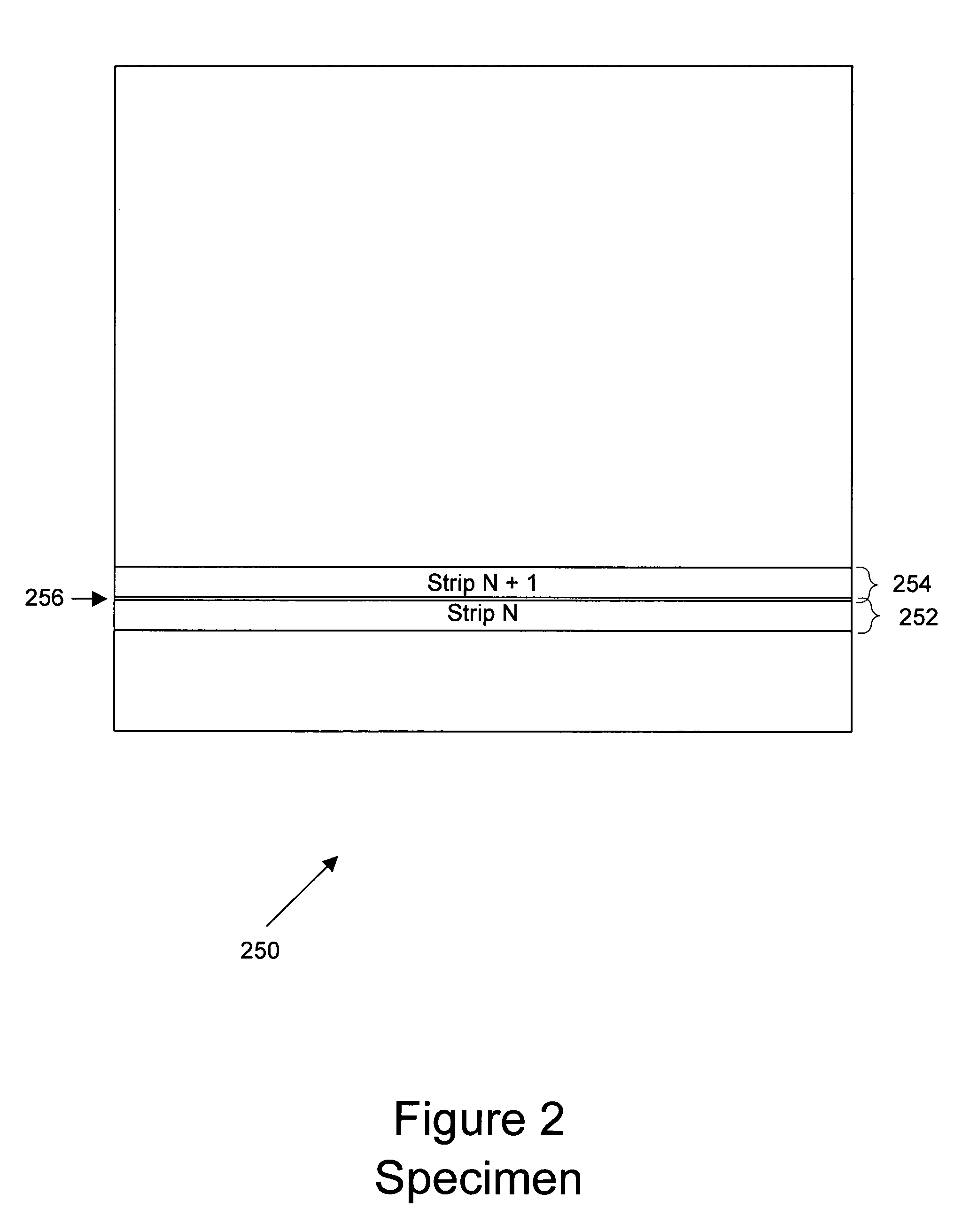

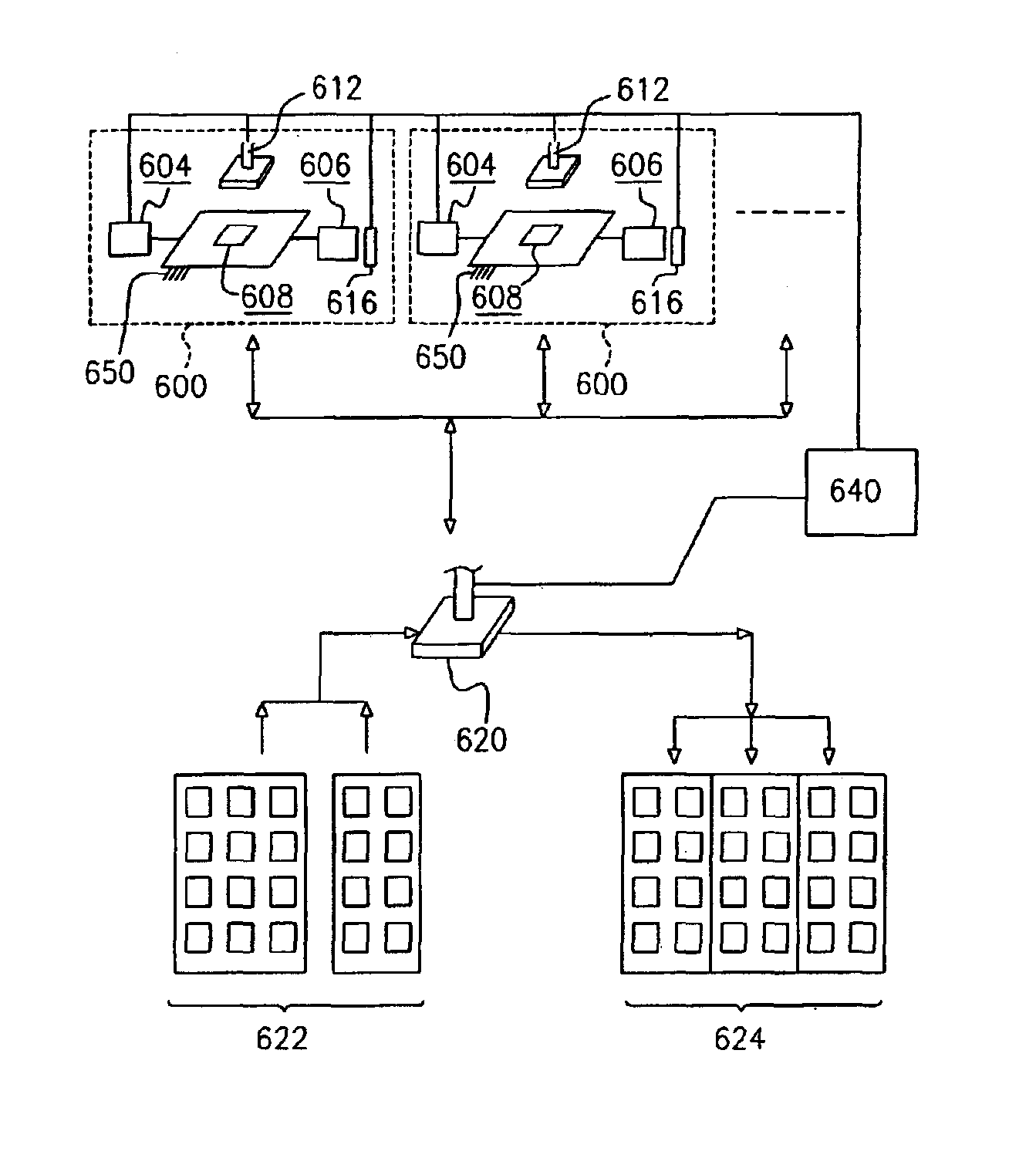

Defect detection using multiple sensors and parallel processing

Techniques for detecting defects on semiconductor wafers are described. The techniques involve a parallel processing system wherein a data distribution system contains data distribution nodes that are interconnected by multiple data transfer paths. This configuration allows data collected by any of the detectors to be routed to any one of a plurality of processing nodes. This in turn allows a variety of defect analysis algorithms to be implemented.

Owner:KLA TENCOR TECH CORP

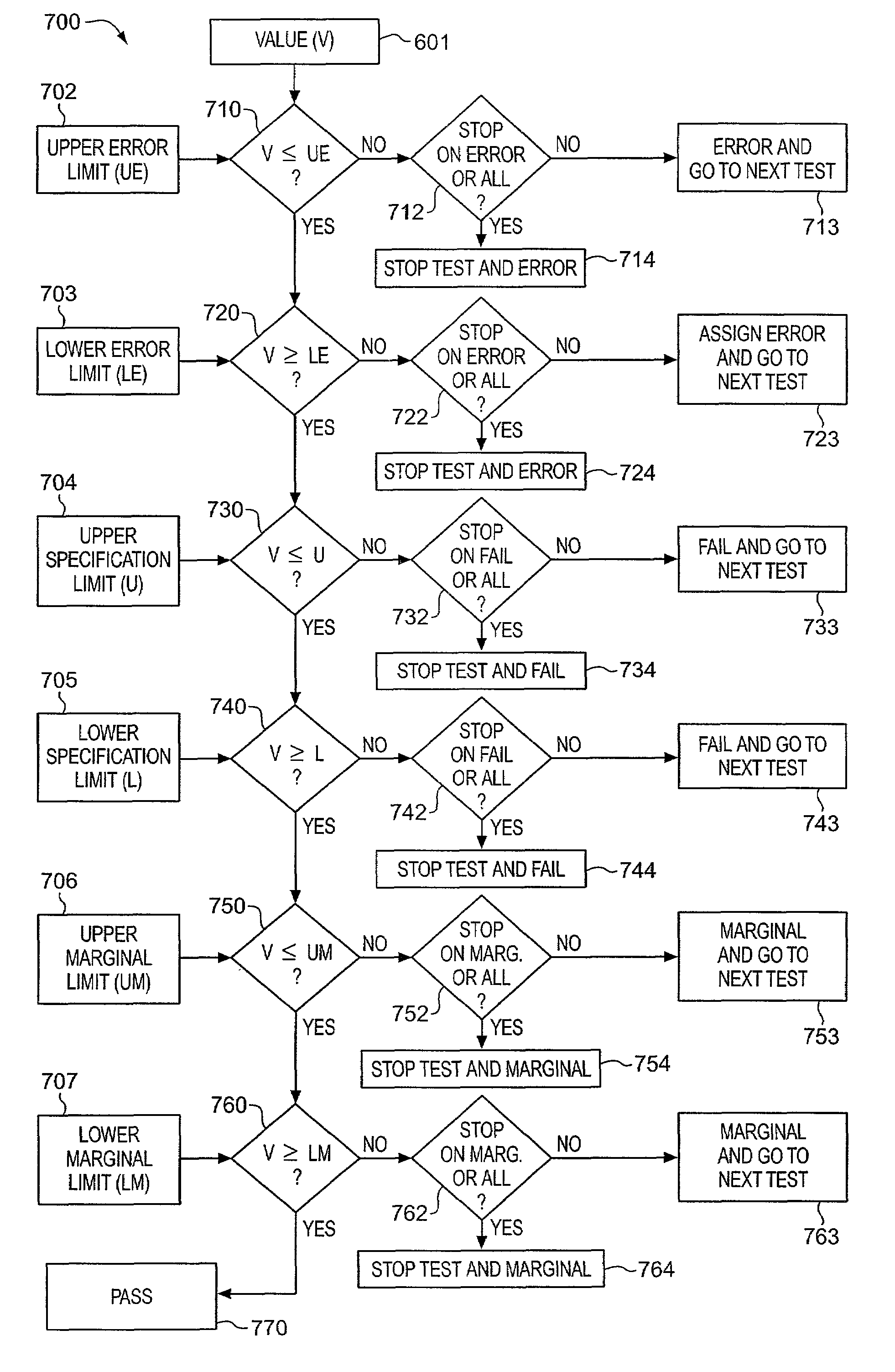

Electronic test program that can distinguish results

InactiveUS7047442B2Easy to doEasy to identifyError detection/correctionMultiple digital computer combinationsGraphicsGraphical user interface

An electronic test system that distinguishes erroneous and marginal results. The test system includes a memory and an electronic processor for controlling the execution of the test, obtaining test results and generating test results. The test results include a determination of whether the condition of the test datapoints is pass, fail, error or marginal, where pass indicates that the DUT has met a specification, fail indicates that the DUT has not met the specification, error indicates that the test system or interface to the DUT has failed, and marginal indicates that the system is marginally within specification. The test results are displayed on a graphical user interface. The test system provides the ability to control the progress of the test system based on the results. For example, the system can be programmed to stop on erroneous results, marginal results, failed results, combinations of the forgoing, or stop after each measurement. When the system stops, a drop-down window appears explaining the reason for the stoppage.

Owner:AGILENT TECH INC

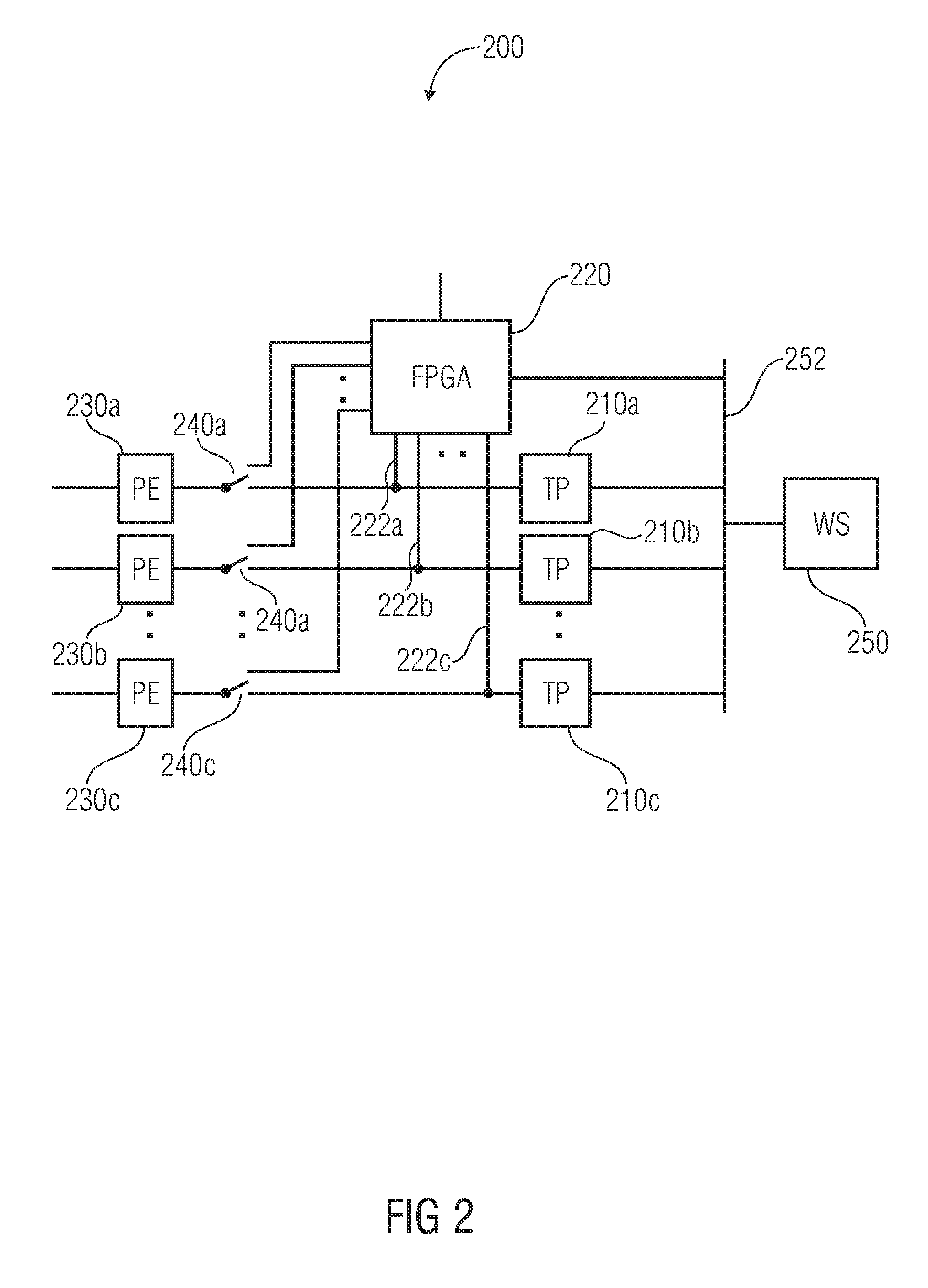

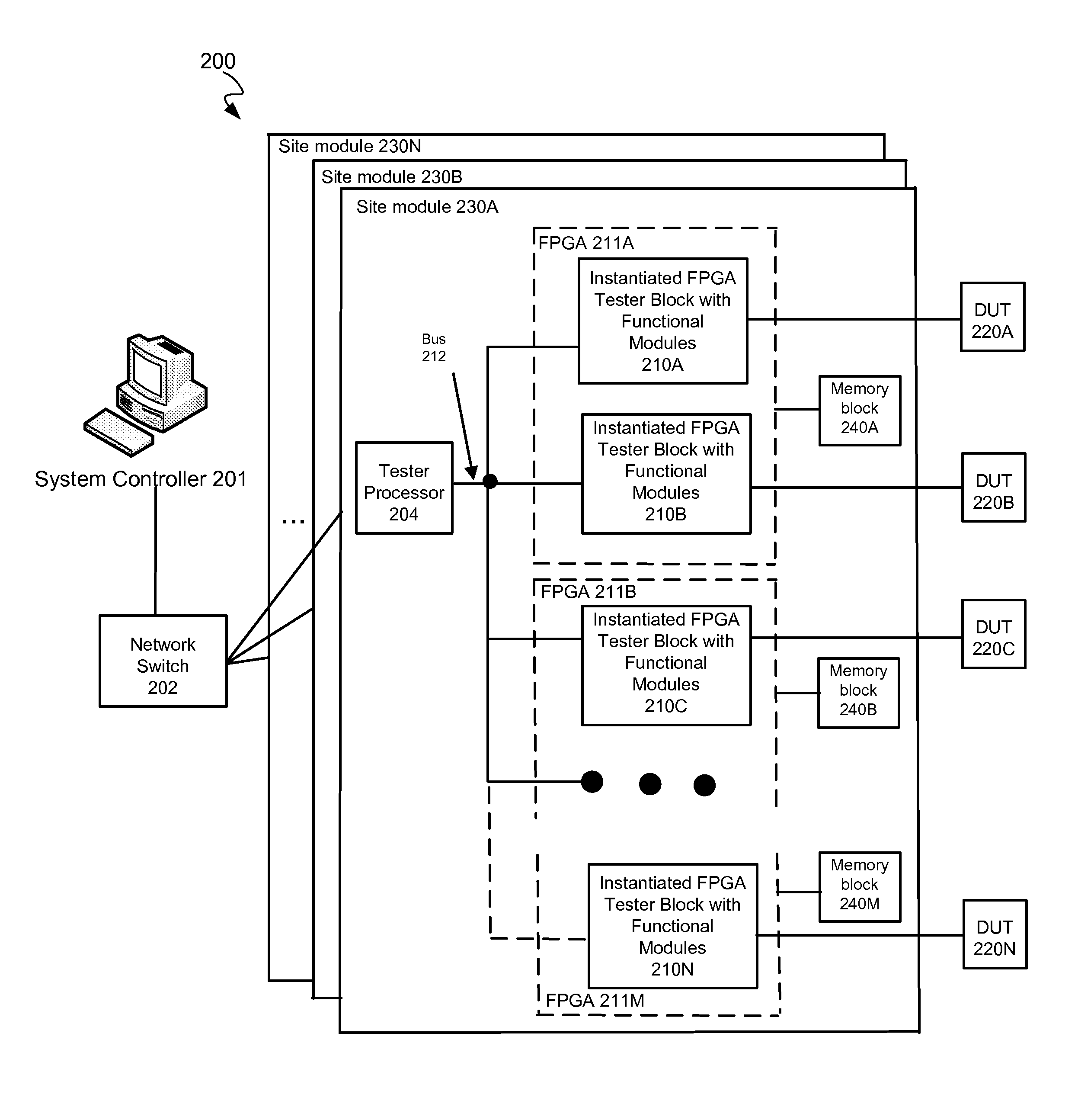

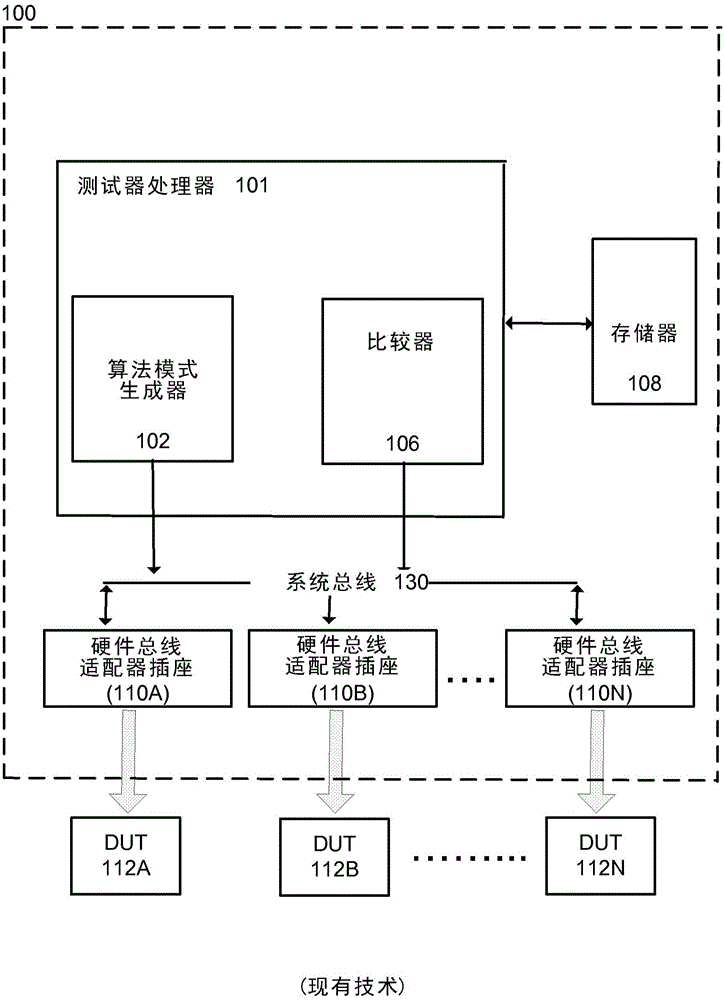

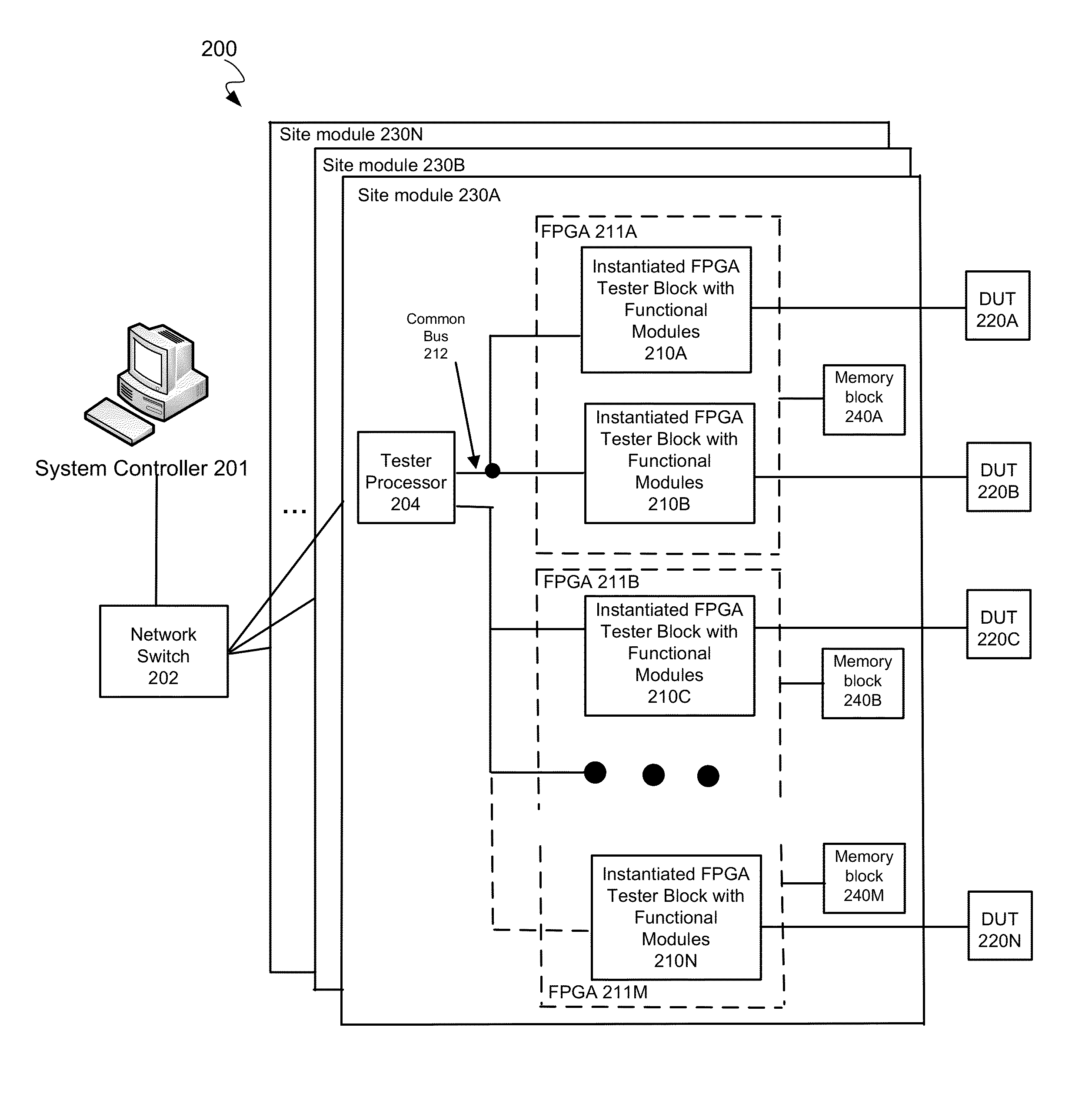

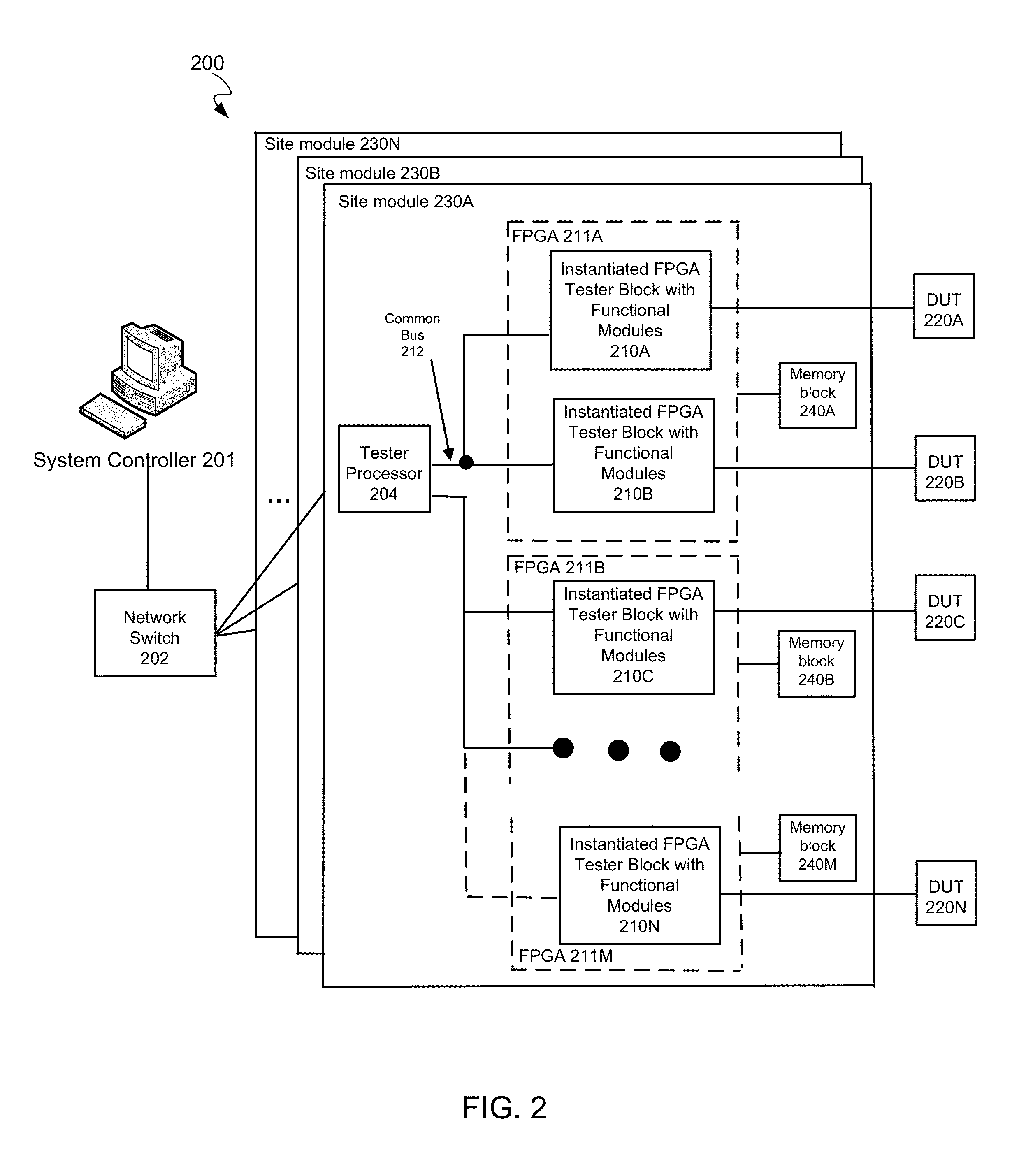

Tester with mixed protocol engine in a FPGA block

ActiveUS20140236526A1Bandwidth requirement can be keptMinimal processing loadResistance/reactance/impedenceAutomated test systemsHybrid protocolSpeed test

Automated test equipment capable of performing a high-speed test of semiconductor devices is presented. The automated test equipment comprises a system controller for controlling a test program, wherein the system controller is coupled to a bus. The tester system further comprises a plurality of modules also coupled to the bus, where each module is operable to test a plurality of DUTs. Each of the modules comprises a tester processor coupled to the bus and a plurality of configurable blocks communicatively coupled to the tester processor. Each of the configurable blocks is operable to communicate with an associated DUT and further operable to be programmed with a communication protocol for communicating test data to and from said associated device under test.

Owner:ADVANTEST CORP

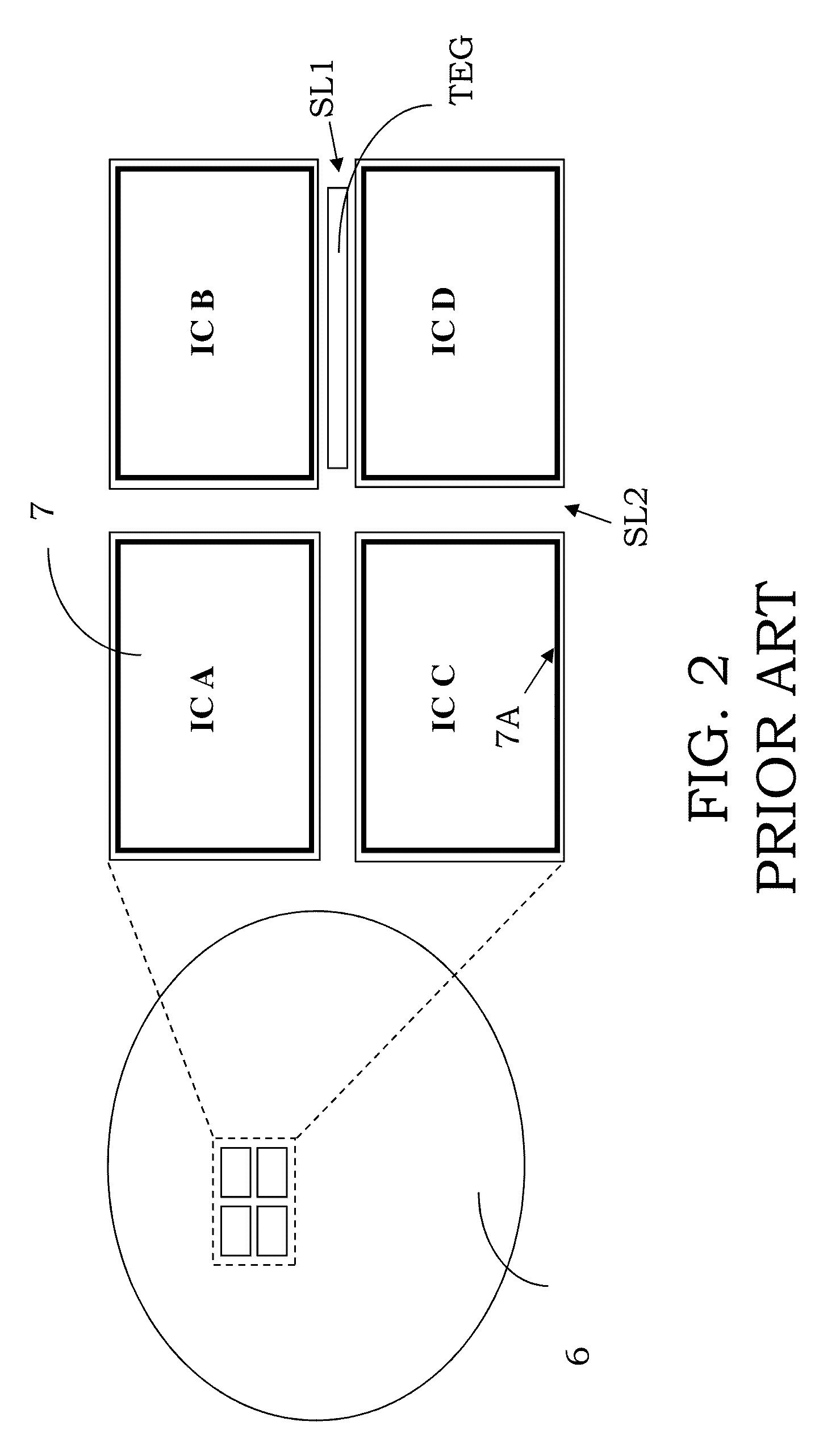

Integrated circuit comprising at least an integrated antenna

ActiveUS20130027073A1Accurate operationSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsIntegrated antennaEngineering

An integrated circuit on a substrate including at least one peripheral portion that surrounds an active area and is realized close to at least one scribe line providing separation with other integrated circuits realized on a same wafer. The integrated circuit includes at least one conductive structure that extends in its peripheral portion on different planes starting from the substrate and realizes an integrated antenna for the circuit.

Owner:STMICROELECTRONICS SRL

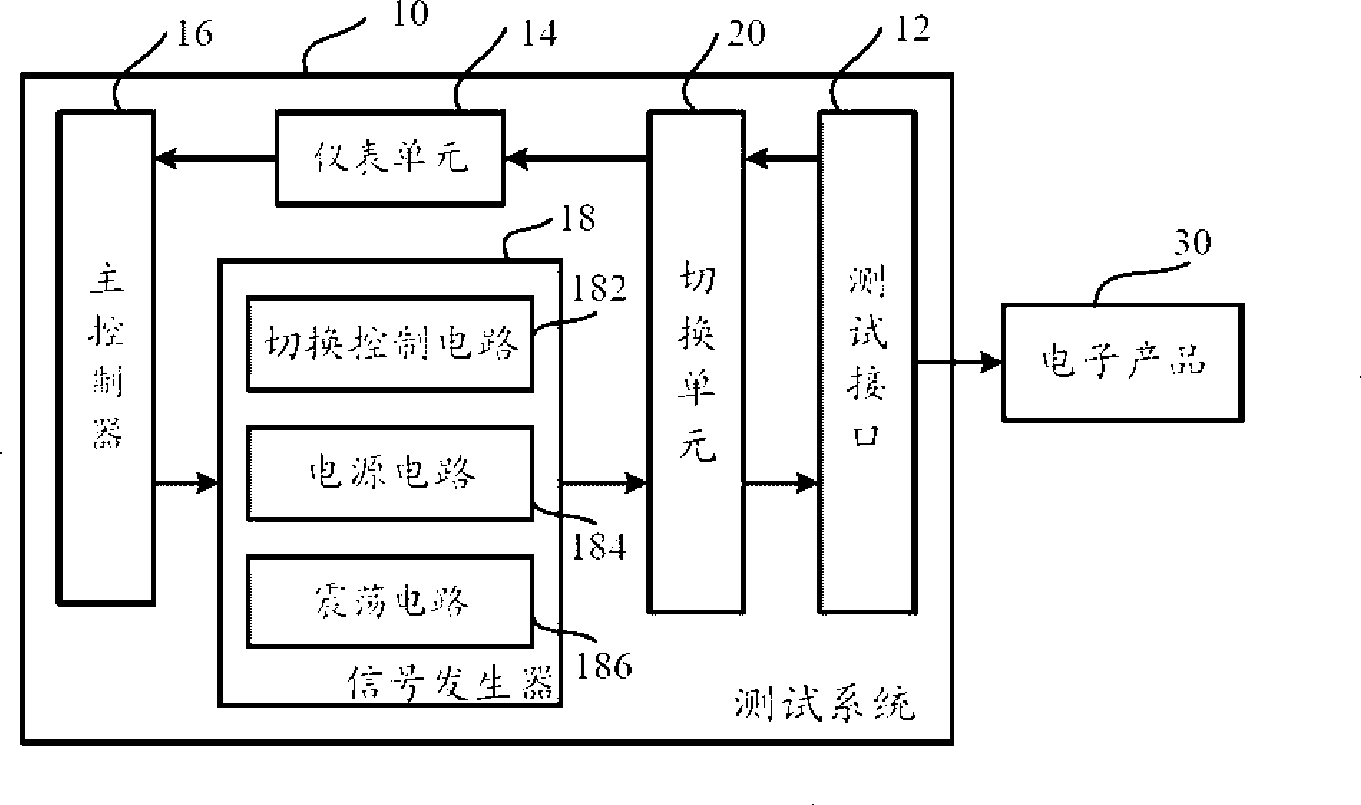

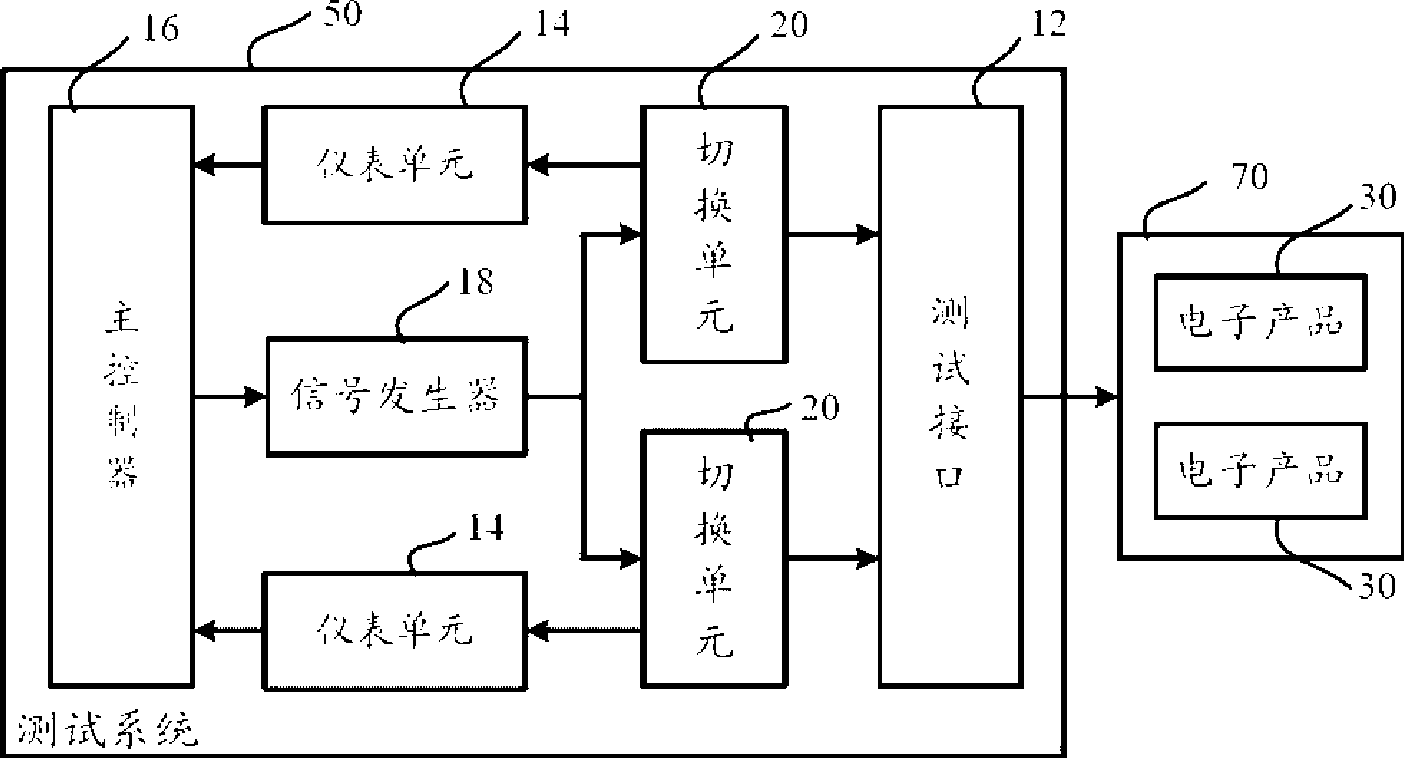

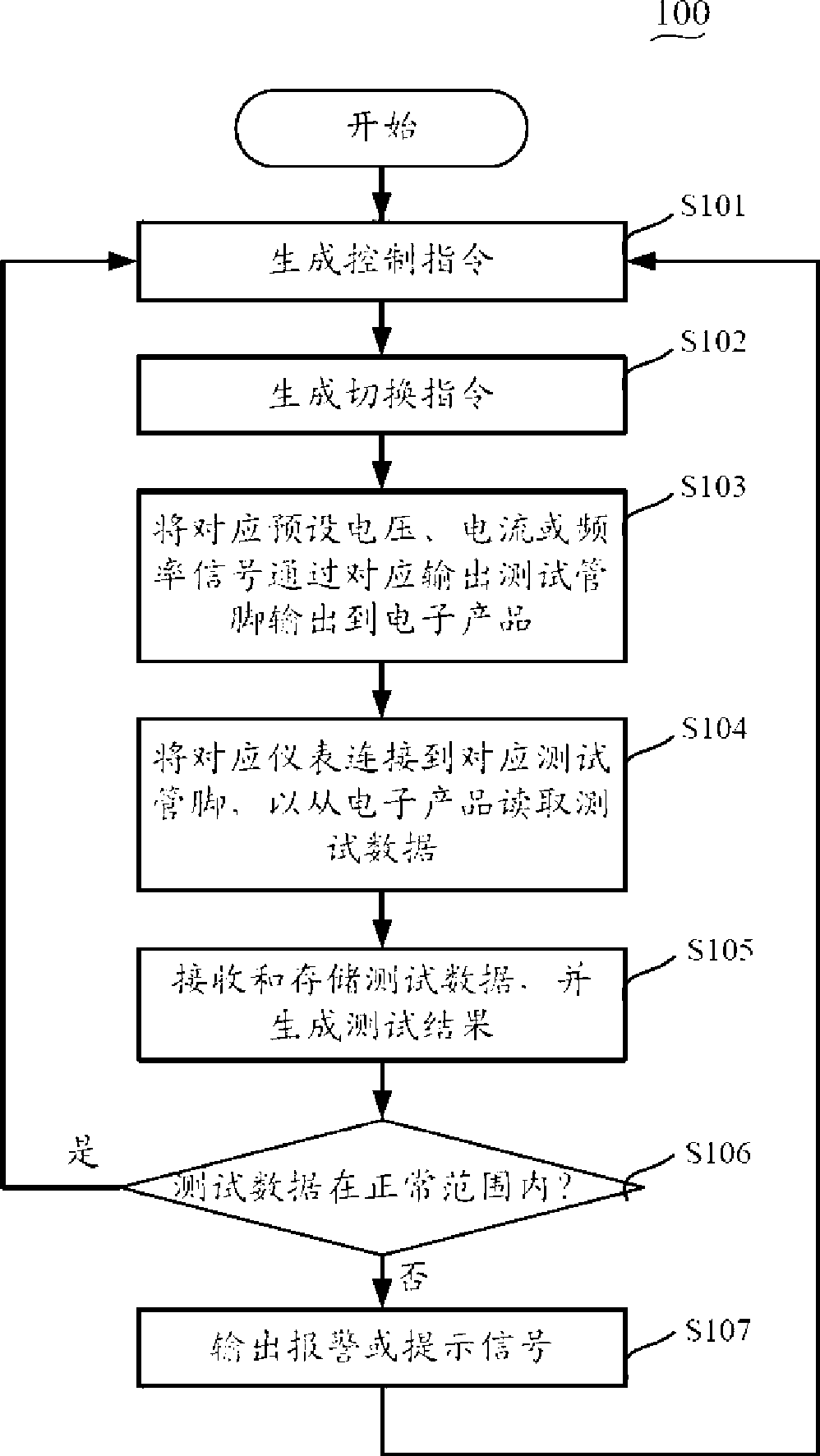

Test system and method

InactiveCN101435841AThe testing process is simpleEasy to operateDetecting faulty computer hardwareAutomated test systemsTest efficiencyTest flow

The invention provides a test system. The test system comprises a test interface, a main controller, a signal generator and an instrument unit, wherein the test interface comprises a plurality of test pins connected with test points of an electric product to be tested; the main controller is used to output control commands; the signal generator is used to output preset signals according to the control commands to the electric product through the test interface; the instrument unit comprises a plurality of instruments for reading test data from corresponding test pins and outputting the test data to the main controller; and the main controller is also used to judge and record whether the test data is in the normal range. The invention also provides a test method. The method has the advantages that the test flow is simple, the operation is easy, a worker can independently operate the test system without training, and the test system can automatically complete all test items without needing to move the testing electric product, thereby saving human and labor resources, lowering cost of the whole test and improving product test efficiency and correct rate of test results.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

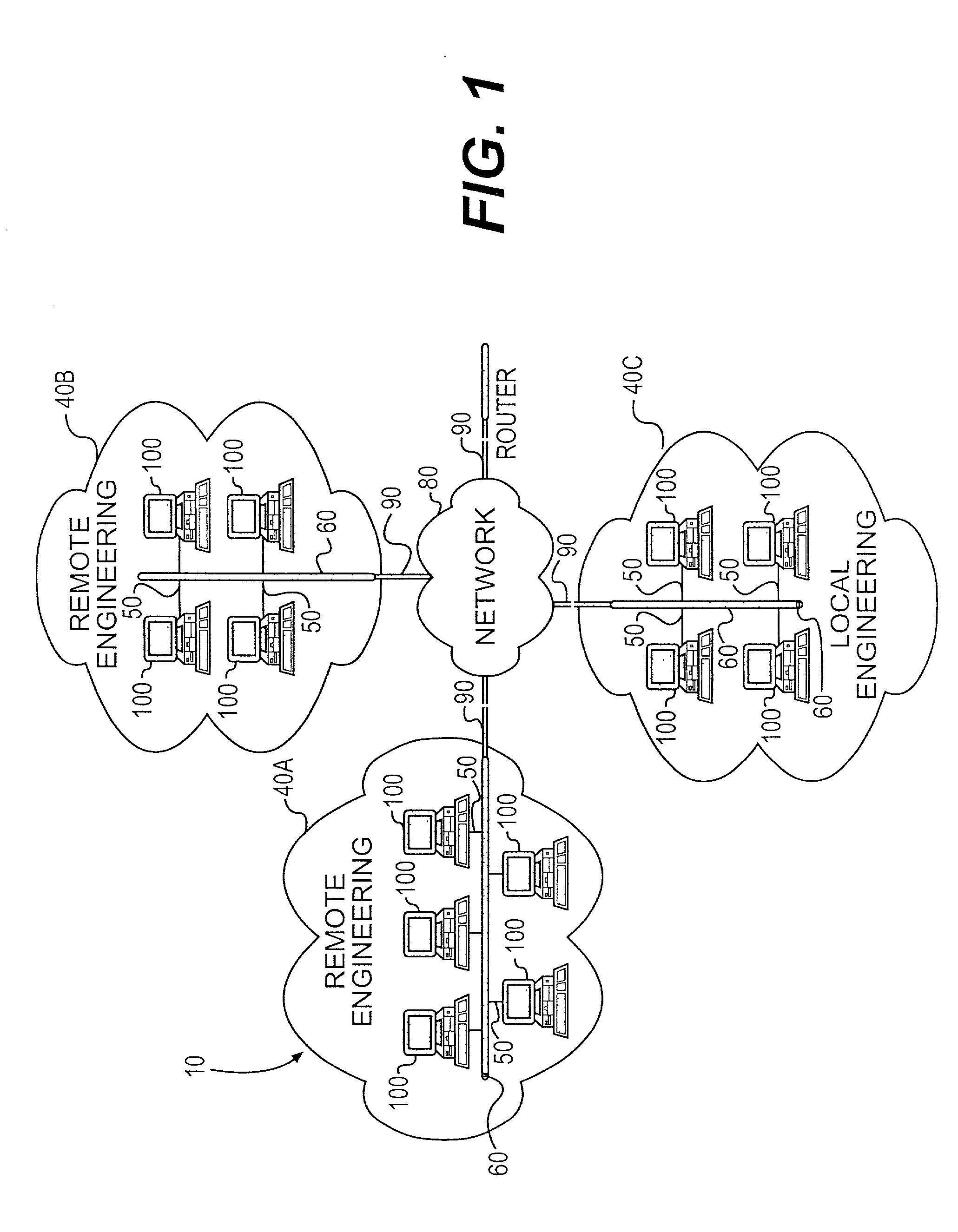

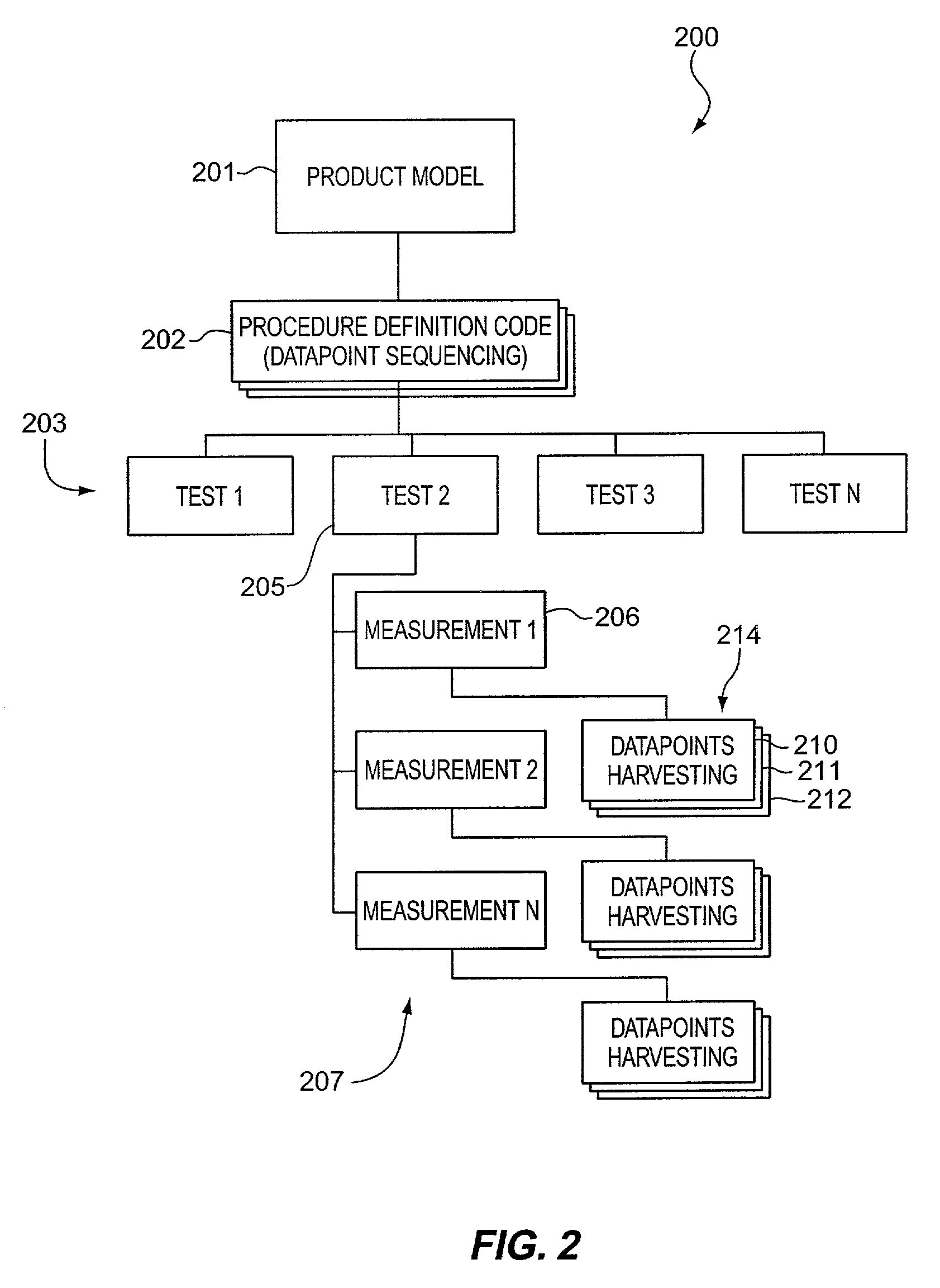

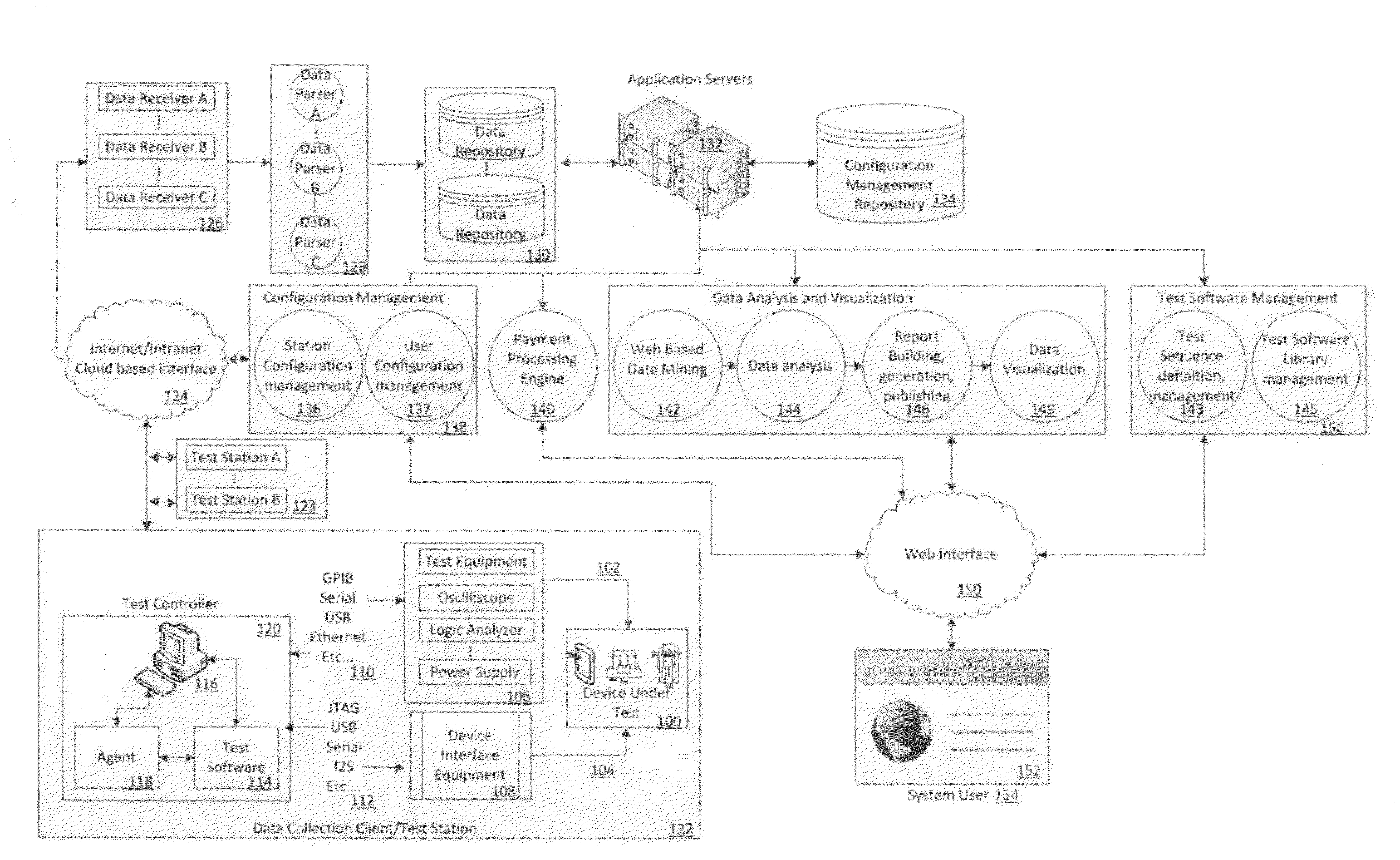

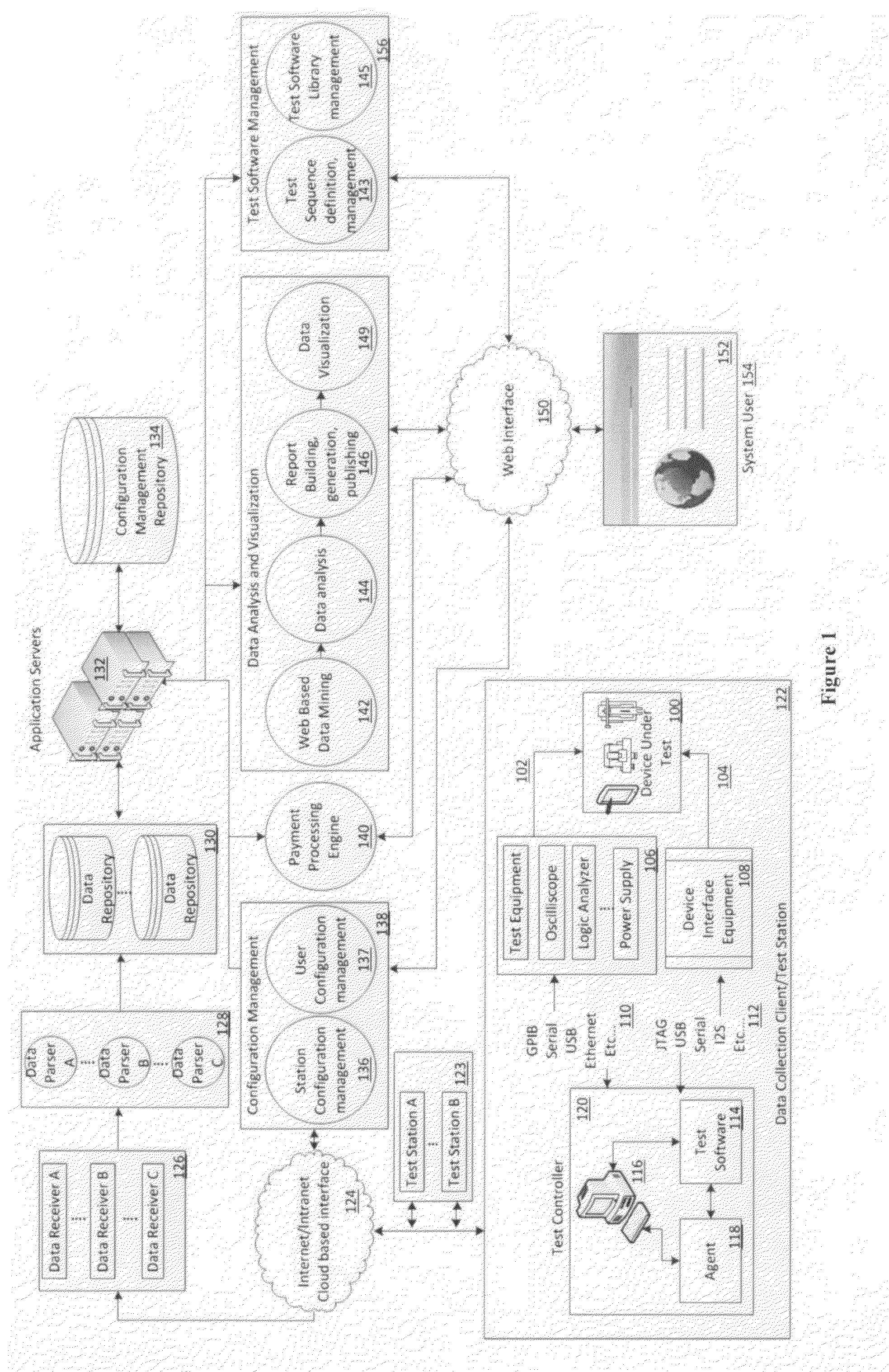

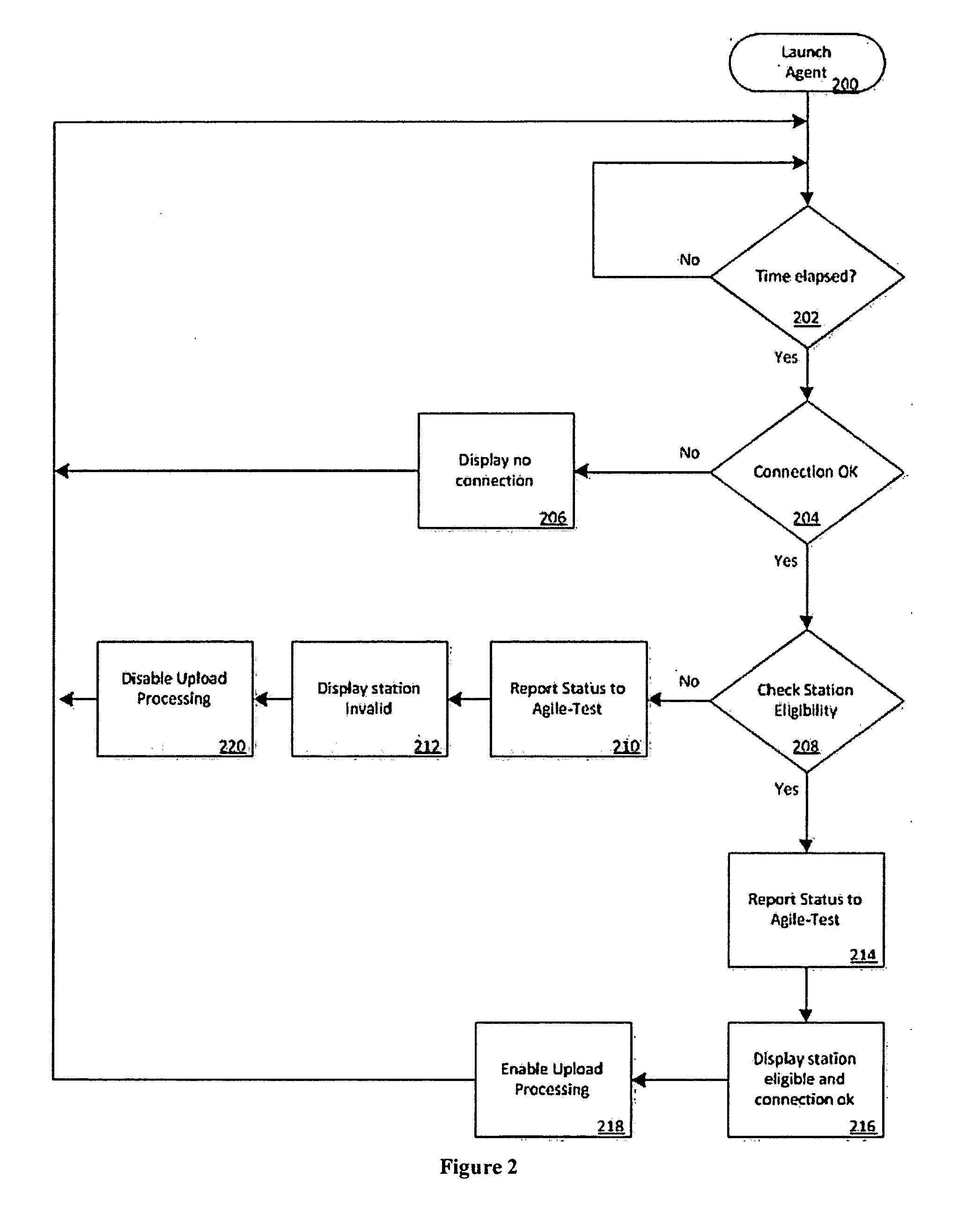

Enterprise Test System Platform and Associated Method for Interoperable Test Data Management, Test Development, Test Libraries and Test Workflow Management and Automation

InactiveUS20140032637A1Functional testingMultiple digital computer combinationsTest executionDevelopment testing

This Invention provides a system-level framework for an enterprise-level test environment. The environment provides test development, automation, and execution processes for product validation and verification, and allows the interoperability of test cases, data, equipment information, and results across various enterprise platforms. The system, with its processes and methods, provides various mechanisms for managing test configurations, developing test plans, managing test data, and developing test reports from one or more test-stations and / or from one or more test equipment(s) for one or more Device(s) Under Test (DUT). These mechanisms include, but are not limited to, functions such as data management and sharing, test library reusability, test station management, test configuration management, test execution, test report development, and data mapping / plotting. The system can be customized to support scalable enterprise requirements. The development of the standardized data handling and communication processes and methods allows inter-system communication and interoperability of test information across various platforms.

Owner:WEIR MICHAEL

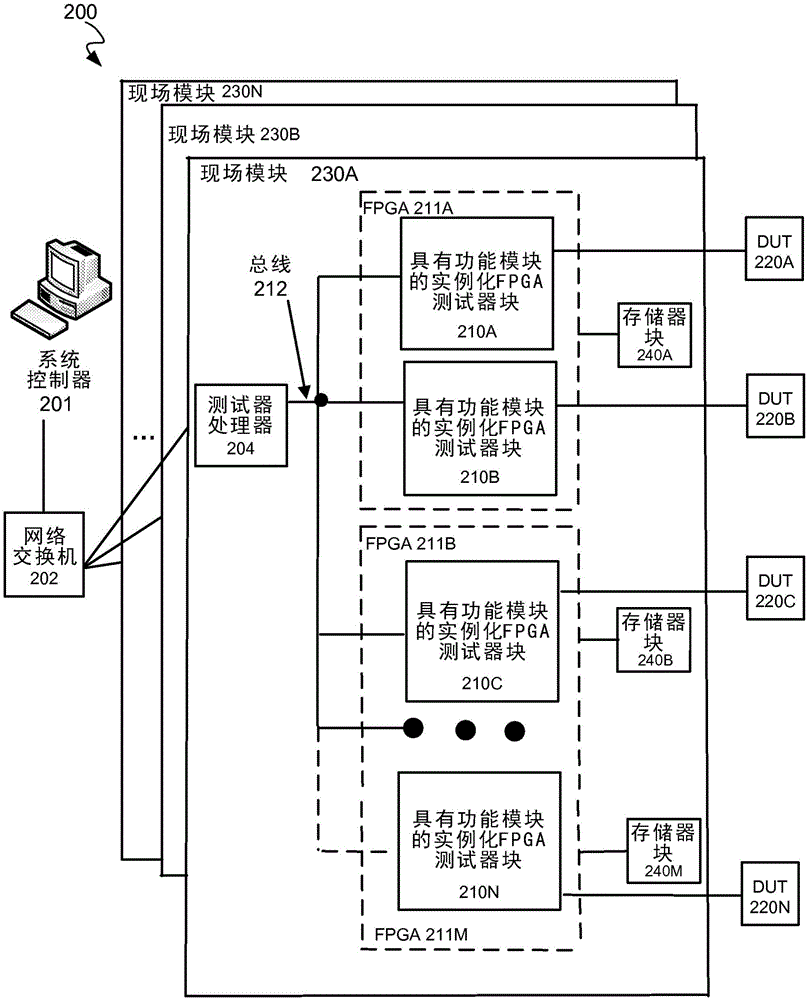

A tester with mixed protocol engine in a FPGA block

Automated test equipment capable of performing a high-speed test of semiconductor devices is presented. The automated test equipment comprises a system controller for controlling a test program, wherein the system controller is coupled to a bus. The tester system further comprises a plurality of modules also coupled to the bus, where each module is operable to test a plurality of DUTs. Each of the modules comprises a tester processor coupled to the bus and a plurality of configurable blocks communicatively coupled to the tester processor. Each of the configurable blocks is operable to communicate with an associated DUT and further operable to be programmed with a communication protocol for communicating test data to and from said associated device under test.

Owner:ADVANTEST CORP

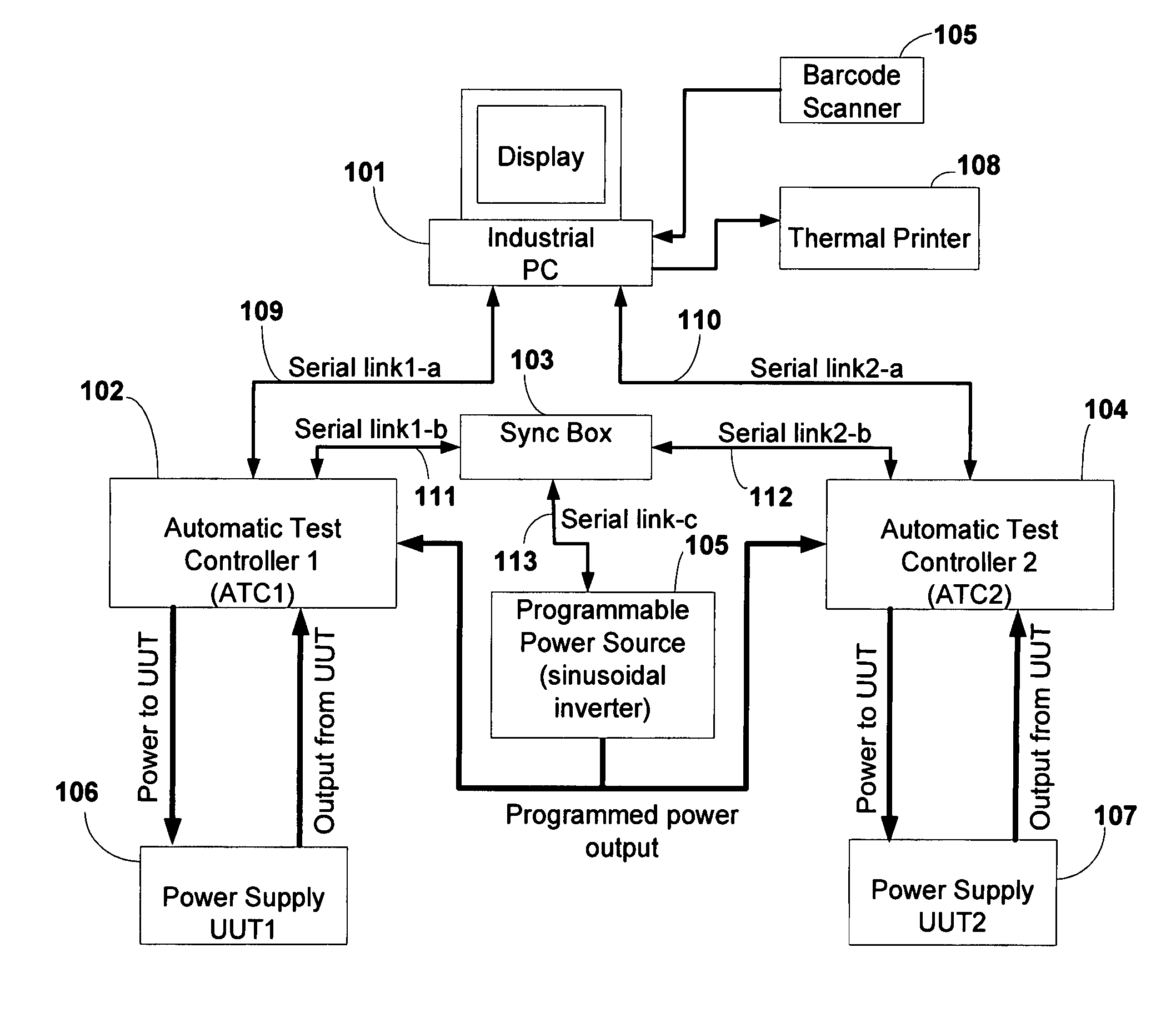

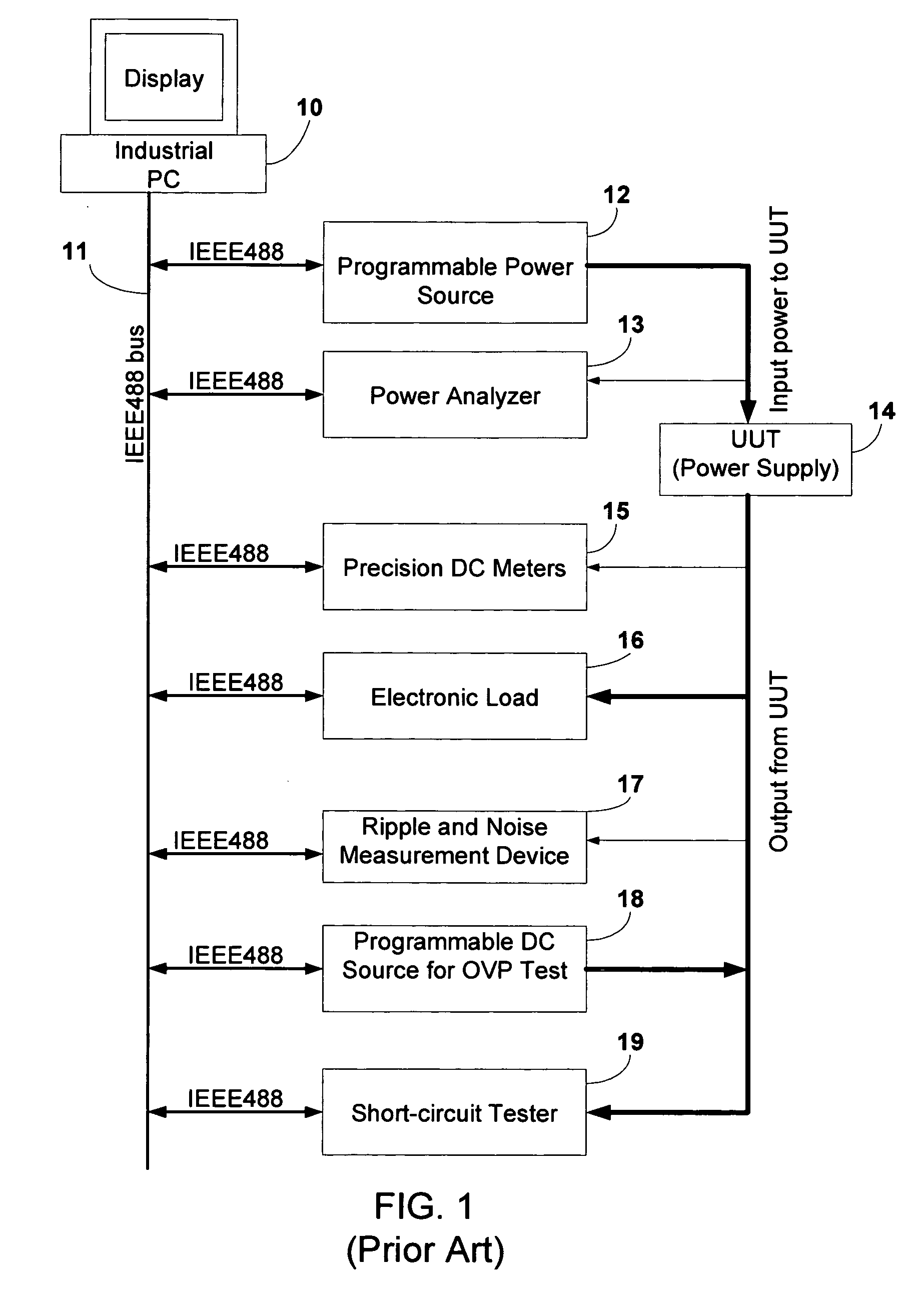

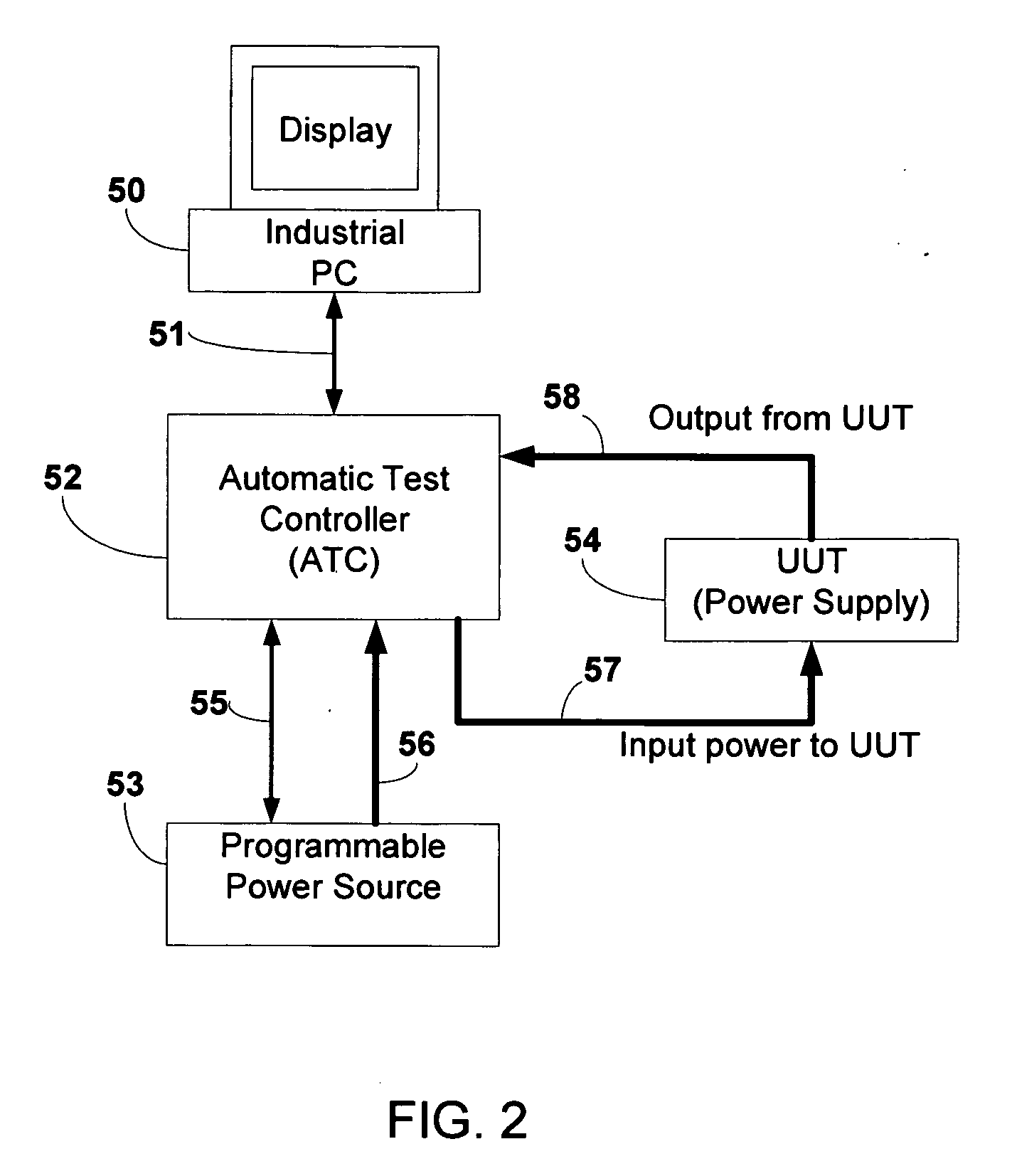

System architecture and apparatus for programmable automatic power supply testing

InactiveUS20100225466A1Low costReduce equipment costsElectric devicesResistance/reactance/impedenceAutomatic test equipmentSystem testing

A cost-effective system architecture and apparatus for programmable automatic power supply testing. The system utilizes board level interface between various system testing modules and an Automatic Test Controller (ATC). The ATC receives coded test requests from the software on an industrial PC and control the various testing modules inside ATC to execute the tests. Test results were sent back to the PC and saved in a result file. A single industrial PC can control two or more ATC's and test two or more power supply units simultaneously. The ATC based test system is lower cost than the conventional Automatic Test Equipment which uses device level interface and standardized test devices.

Owner:SYNERGISTIC TECH SOLUTIONS

Test equipment, method for loading test plan and program product

InactiveUS7809520B2Resistance/reactance/impedenceTesting circuitsEquipment under testSystem controller

Test equipment includes a memory to which a test plan that includes a plurality of sub-test plans is loaded and a system controller that, when the test equipment actually examines a device-under-test (DUT), loads the test plan to the memory by the unit of the sub-test plan and supplies a test signal to the DUT by interpreting the loaded test plan.

Owner:ADVANTEST CORP

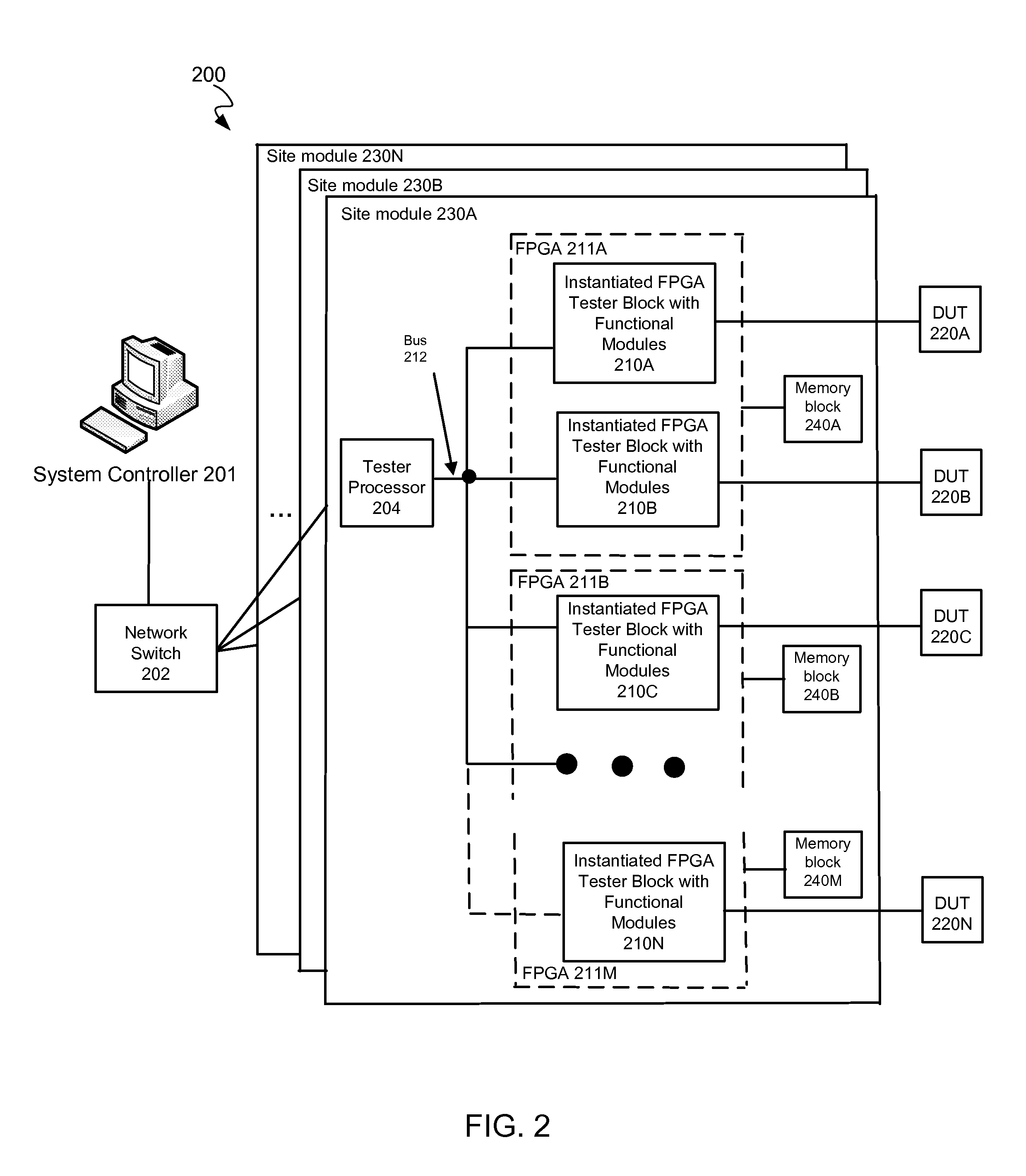

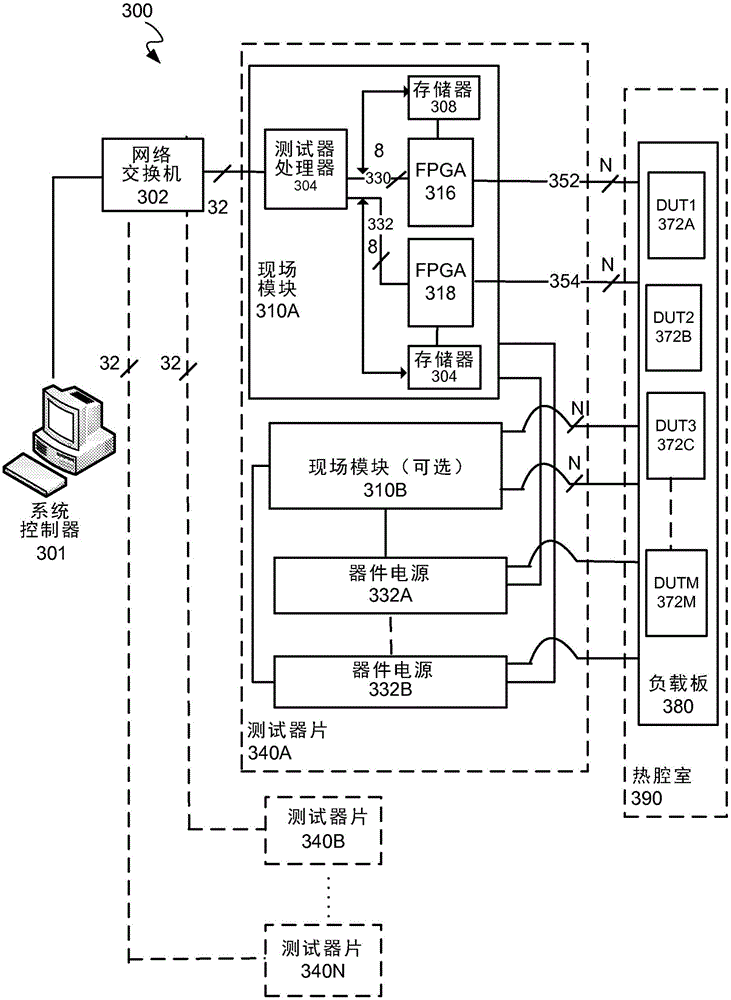

Tester with acceleration on memory and acceleration for automatic pattern generation within a FPGA block

ActiveUS20140236524A1Bandwidth requirement can be keptMinimal processing loadTesting/calibration of speed/acceleration/shock measurement devicesSpecial data processing applicationsAutomatic test pattern generationHardware acceleration

Automated test equipment capable of performing a high-speed test of semiconductor devices is presented. The automated test equipment apparatus comprises a computer system comprising a tester processor, wherein the tester processor is communicatively coupled to a plurality of FPGA components. Each of the plurality of FPGA components is coupled to a memory module and comprises: an upstream port operable to receive commands and data from the tester processor; a downstream port operable to communicate with a respective DUT from a plurality of DUTs; and a plurality of hardware accelerator circuits, wherein each of the accelerator circuits is configured to communicate with one of the plurality of DUTs. Each of the plurality of hardware accelerator circuits comprises a pattern generator circuit configurable to automatically generate test pattern data to be written to the one of the plurality of DUTs and a comparator circuit configured to compare data read from the one of the plurality of DUTs with test pattern data written to the one of the plurality of DUTs

Owner:ADVANTEST CORP

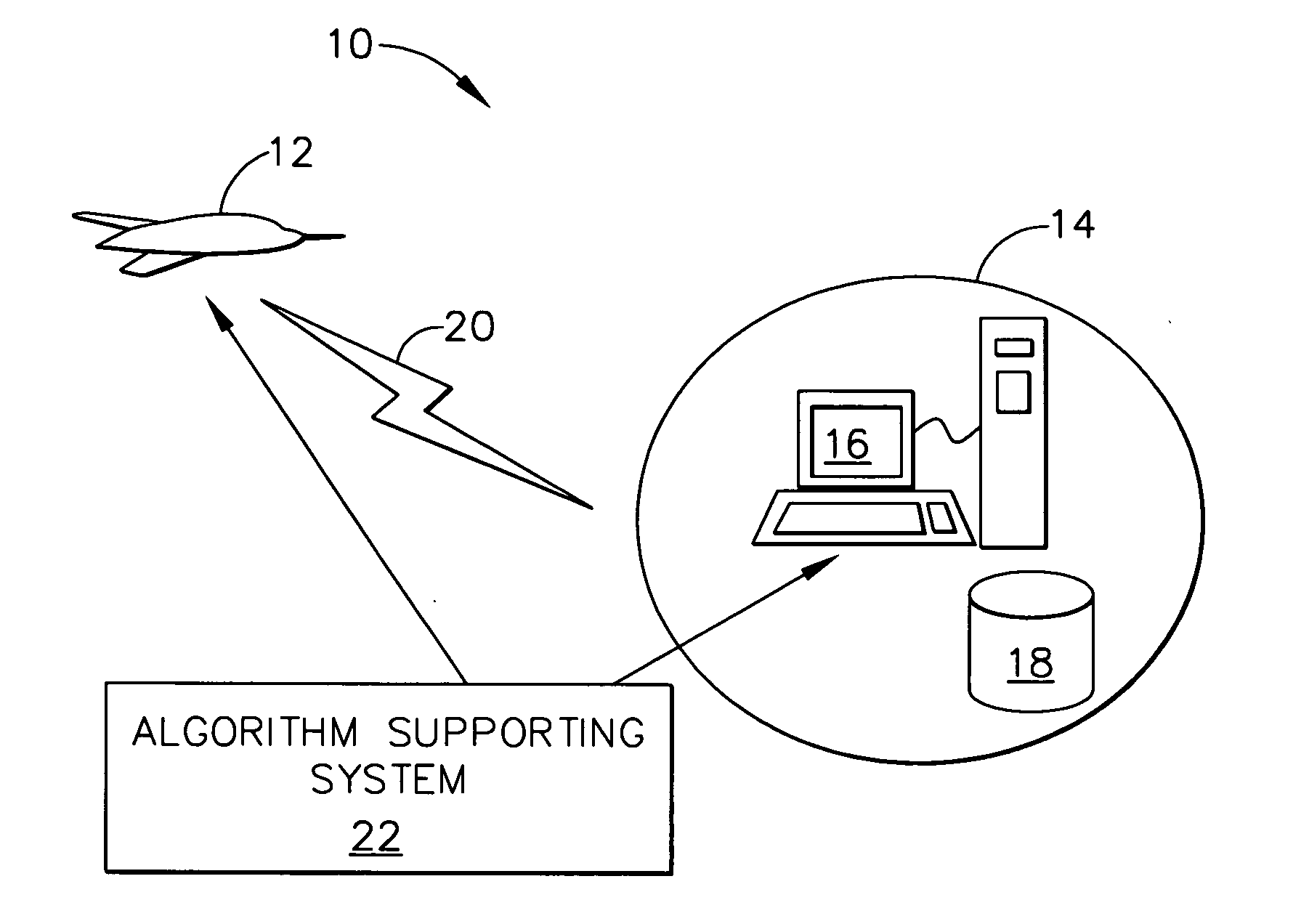

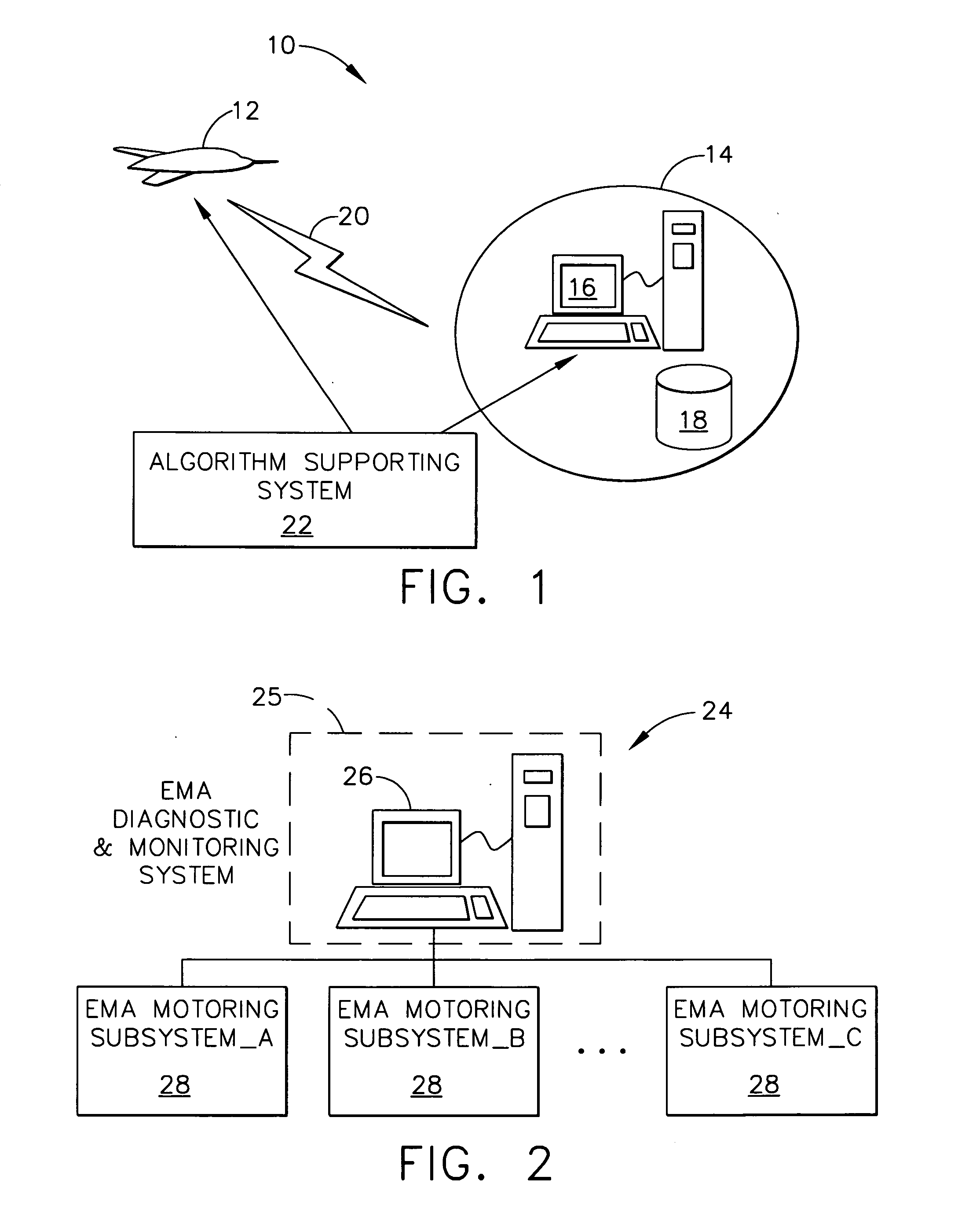

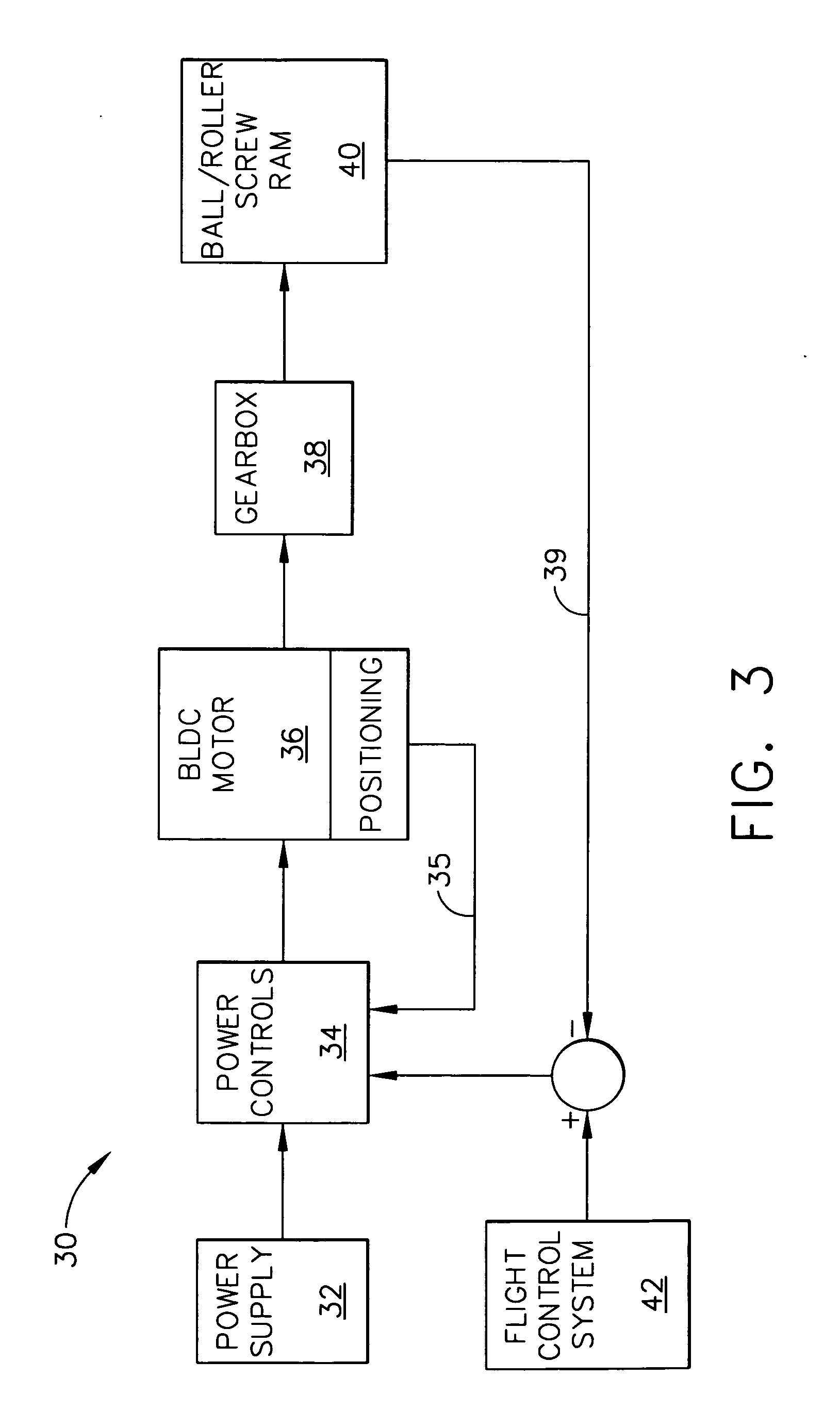

Variable-structure diagnostics approach achieving optimized low-frequency data sampling for EMA motoring subsystem

ActiveUS20050212523A1ConfidenceData processing applicationsActuated automaticallyPower controllerElectronic systems

The present invention provides a diagnostics methodology and embedded electronic system that allows optimized low-frequency data sampling for EMA motoring subsystems in an operating vehicle. Each of the EMA motoring subsystems includes: an EMA; at least one motor for driving the EMA; and power controls for operating the motor, wherein the power controls includes a DSP controller for sampling and processing data at low-frequency sampling rates. The diagnostic methodology includes a method that has the steps of: determining an operational mode of the EMA motoring subsystem; selecting a sampling rate optimized for the determined operational mode; acquiring and processing data at the selected sampling rate; and analyzing the processed data to identify and classify a fault of the EMA motoring subsystem.

Owner:THE BOEING CO

Defect detection using multiple sensors and parallel processing

Techniques for detecting defects on semiconductor wafers are described. The techniques involve a parallel processing system wherein a data distribution system contains data distribution nodes that are interconnected by multiple data transfer paths. This configuration allows data collected by any of the detectors to be routed to any one of a plurality of processing nodes. This in turn allows a variety of defect analysis algorithms to be implemented.

Owner:KLA TENCOR TECH CORP

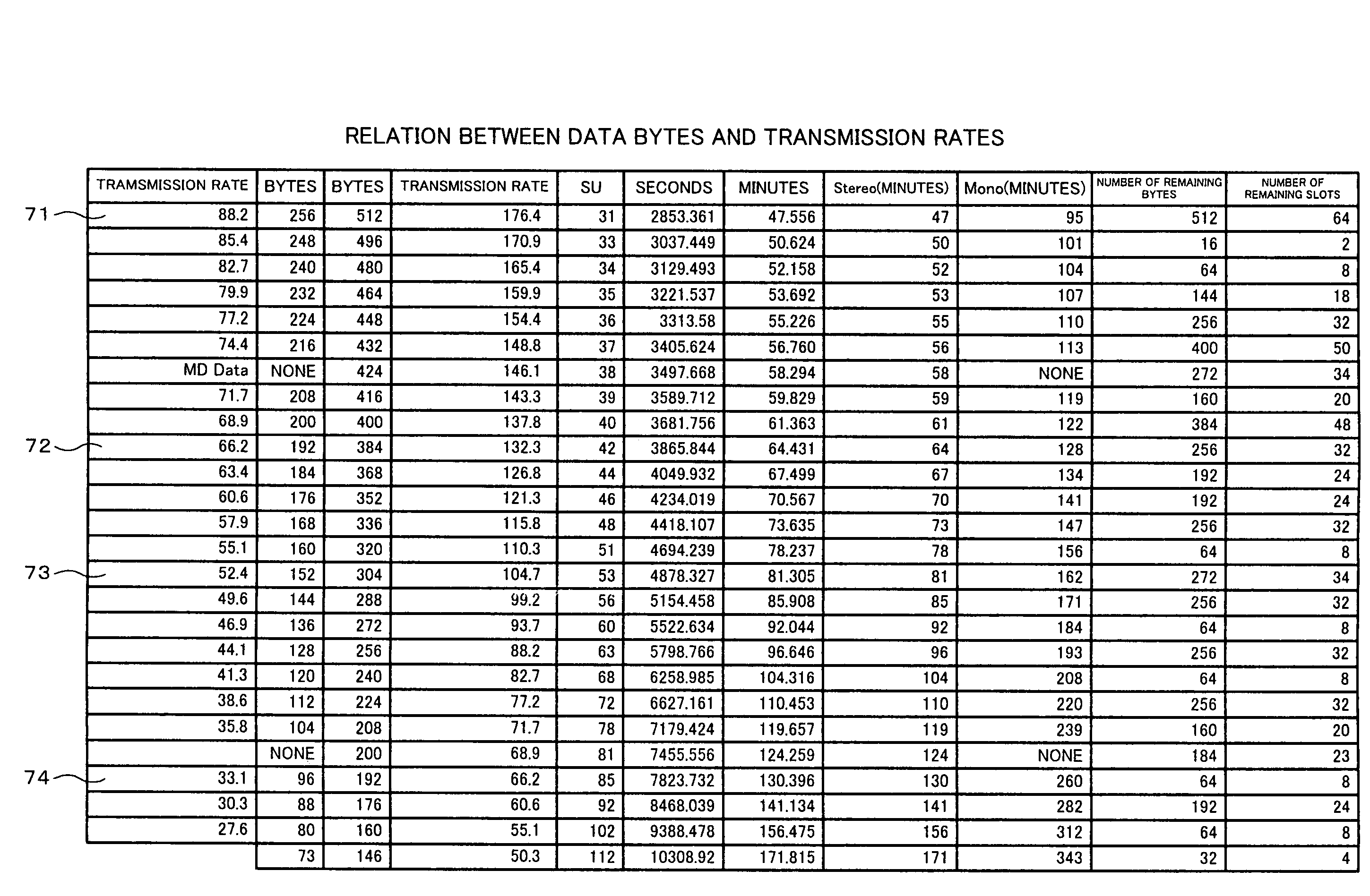

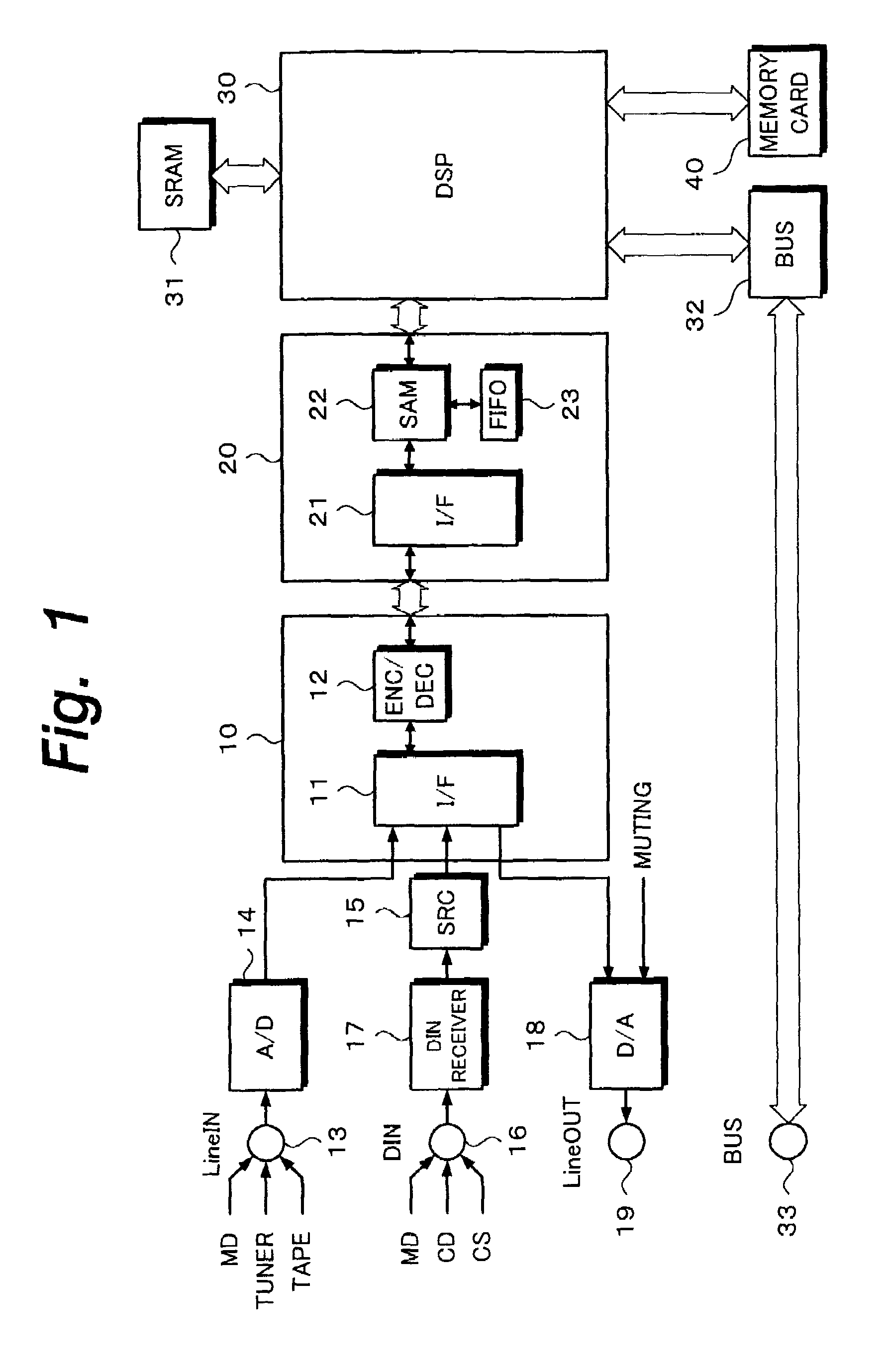

Non-volatile record medium, recording method, and recording apparatus

InactiveUS6985584B1Efficient executionRead-only memoriesSemiconductor/solid-state device manufacturingComputer hardwareRecording duration

A non-volatile recording medium for recording a digital audio signal that has been compressed at a compression rate selectable in a predetermined range and block-segmented in a predetermined data length is disclosed, wherein the predetermined data length of which the digital audio data is block-segmented is decided in consideration of the maximum recordable time and the data length of which the digital audio signal is encrypted.

Owner:SONY CORP

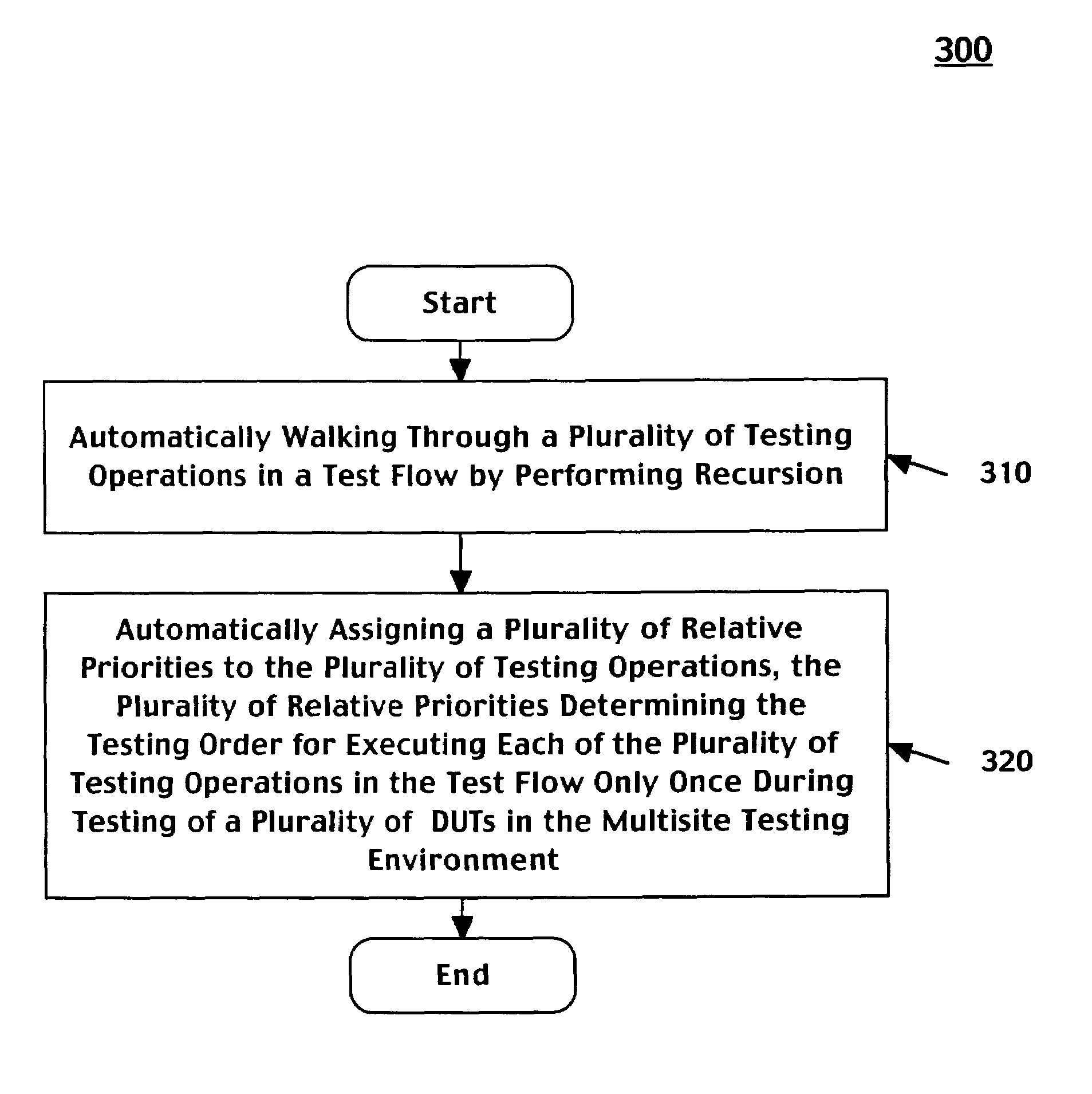

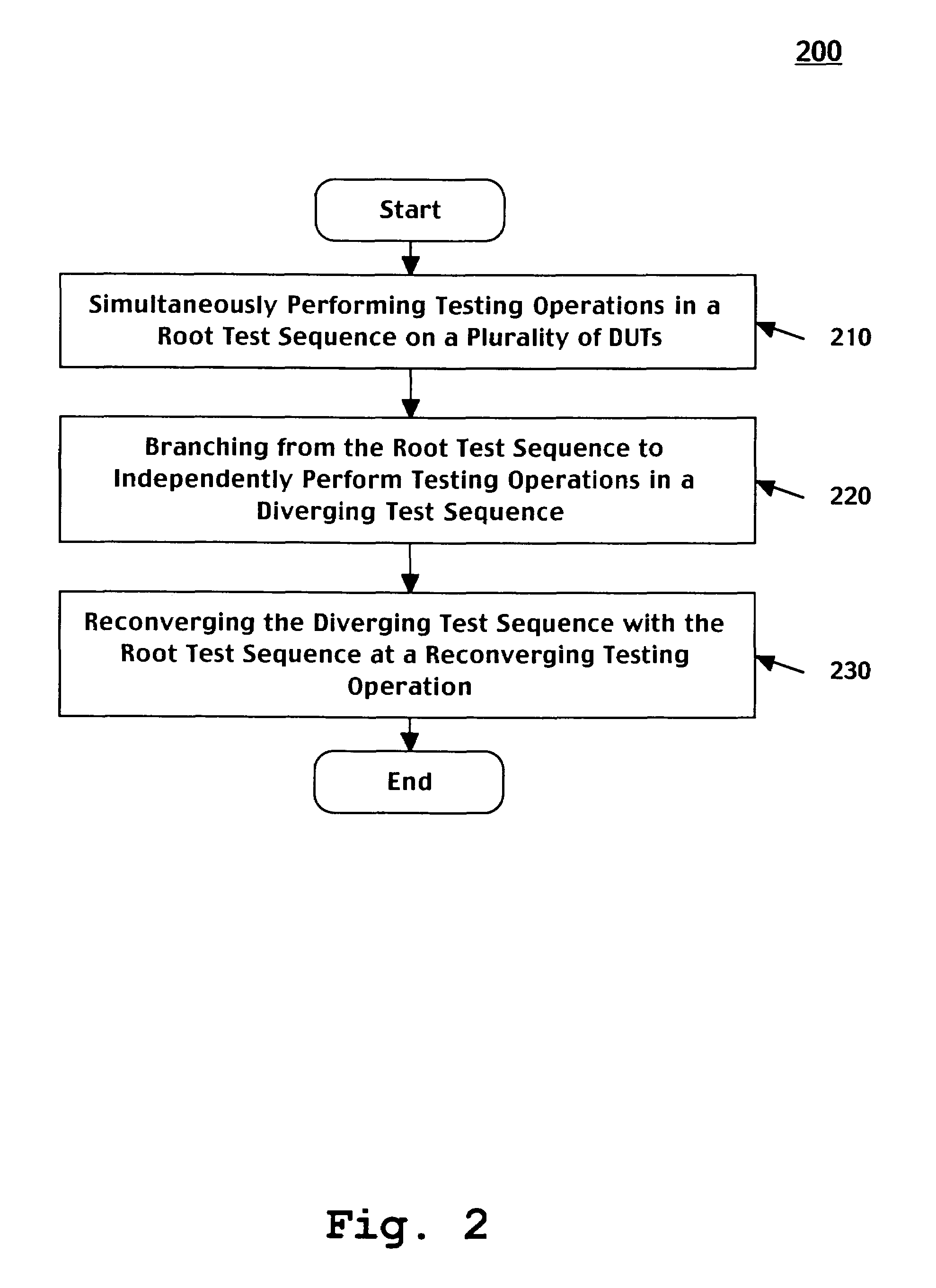

Method and system for automatically determining a testing order when executing a test flow

A method and system for automated multisite testing. Specifically, in one embodiment, a method is disclosed for determining a testing order of plurality of testing operations of a test flow in a multisite testing environment. The method begins by automatically walking through the test flow by performing recursion on the plurality of testing operations. Next, the method automatically assigns a plurality of relative priorities to the plurality of testing operations. The plurality of relative priorities determine the testing order used when executing each of the plurality of testing operations in said test flow. Each of the plurality of testing operations is executed only once when testing a plurality of devices under test (DUTs) in the multisite testing environment.

Owner:ADVANTEST CORP

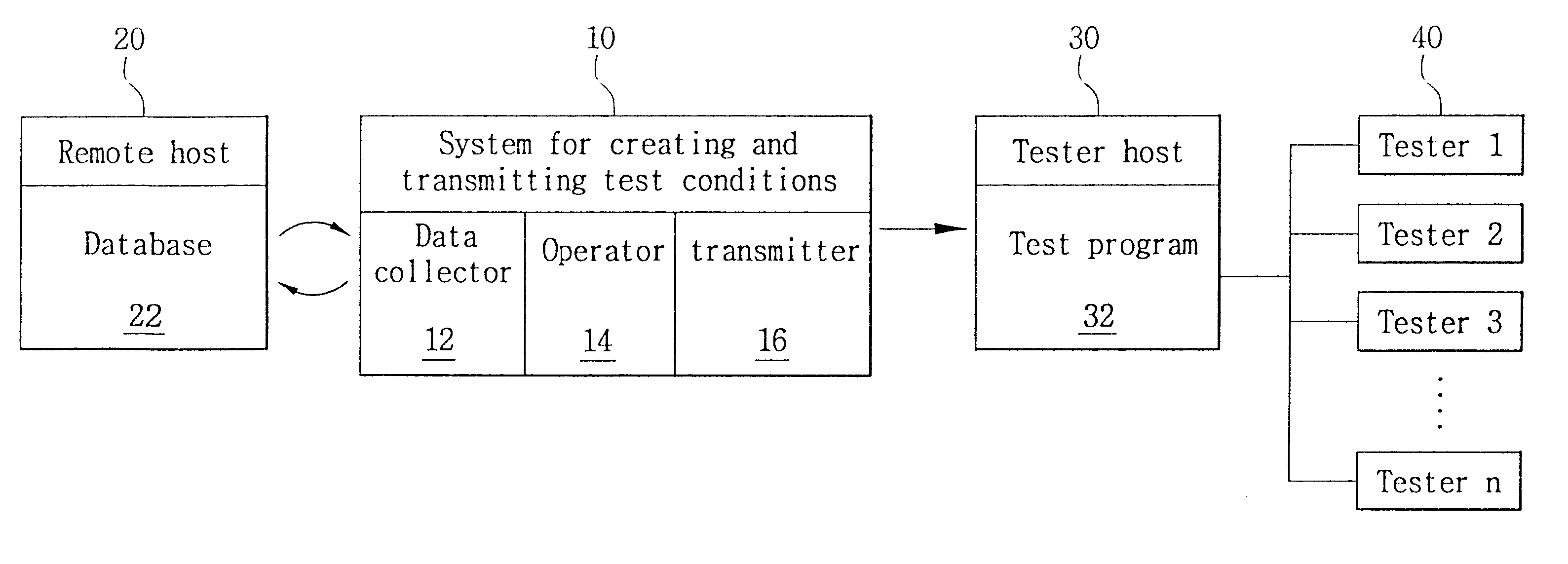

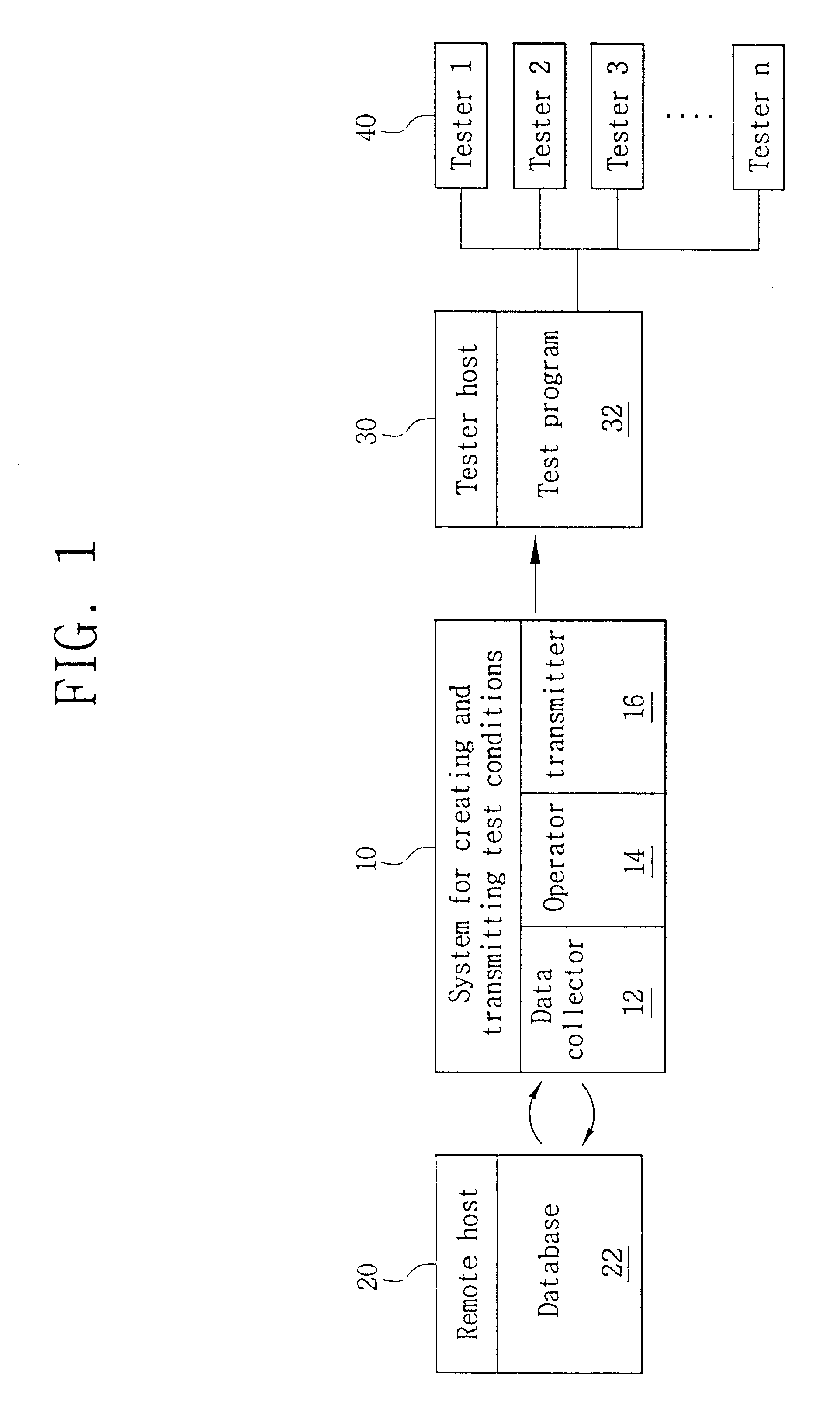

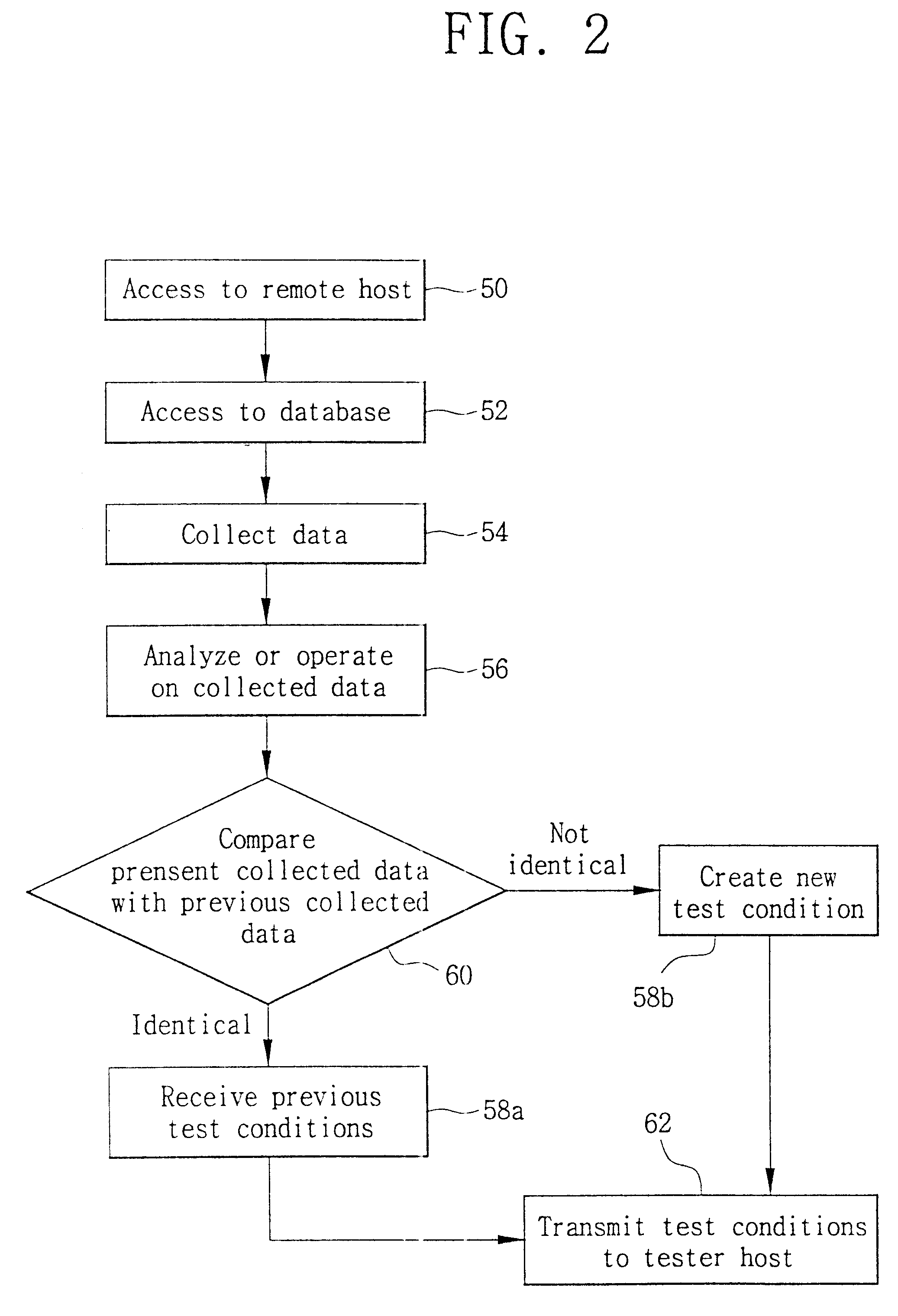

System and method for automatically creating and transmitting test conditions of integrated circuit devices

InactiveUS6236952B1Semiconductor/solid-state device testing/measurementResistance/reactance/impedenceTest engineerApplication-specific integrated circuit

Production information for ASIC (Application Specific Integrated Circuit) devices is stored in a database of a remote host system, and data necessary for a test program which controls testers for testing the IC devices are automatically created and transmitted to a tester host. This automatic system collects the data necessary for the test condition from the remote host database; creates the test condition by comparing the collected data with a predetermined handling condition; transmits the test condition to a tester host which controls a plurality of testers using corresponding test programs; and loads the test condition into the corresponding test program. This system avoids human errors which often result when test engineers write test conditions manually, and also allows quick response to a situation when new specific IC devices are required by a customer.

Owner:SAMSUNG ELECTRONICS CO LTD

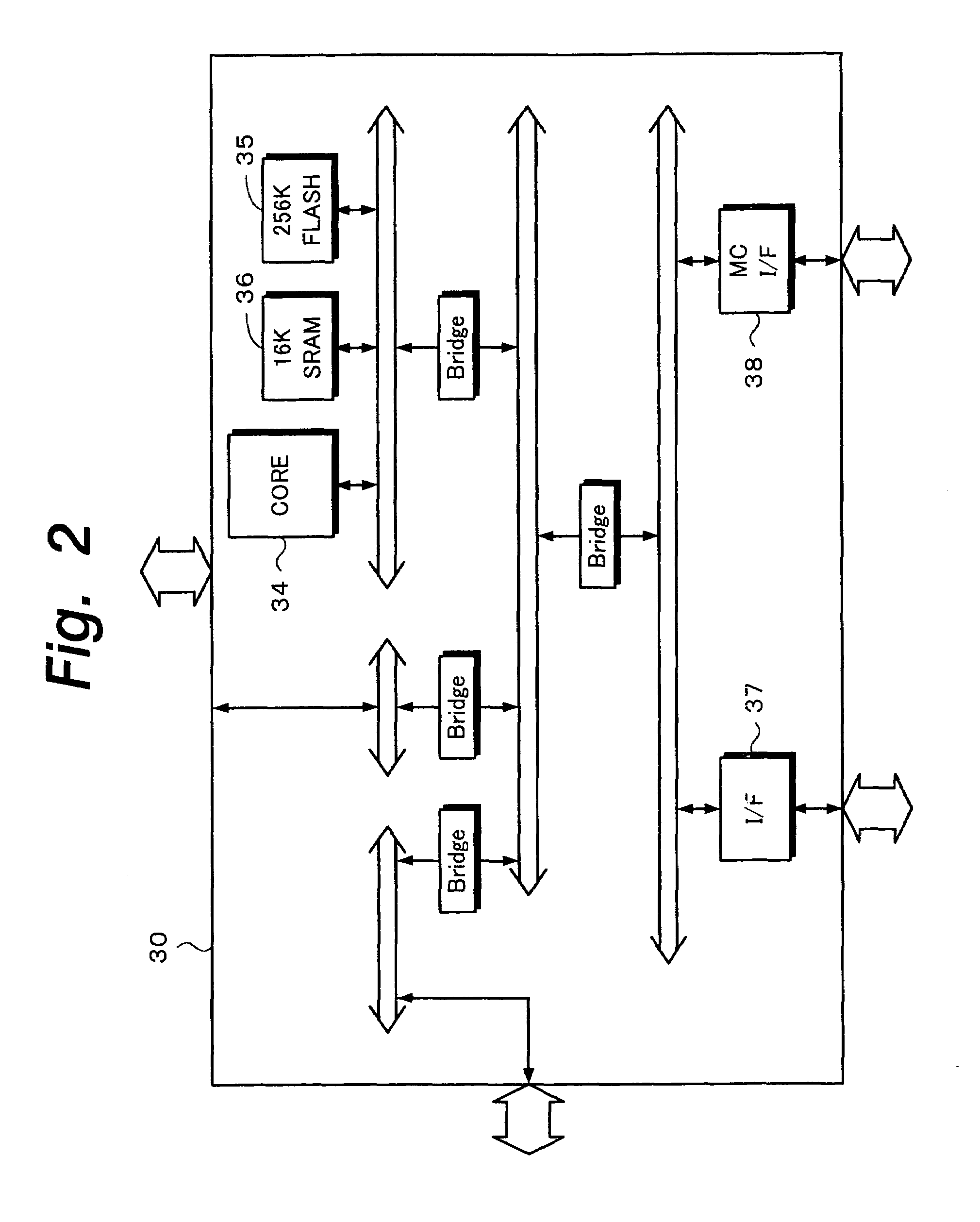

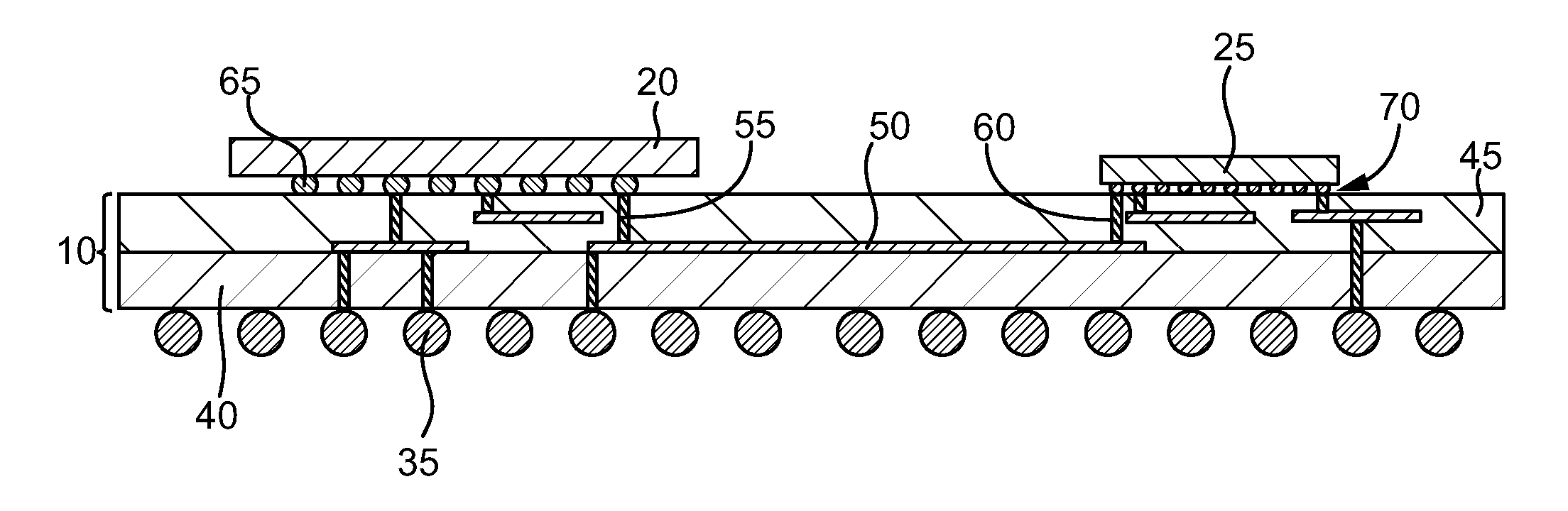

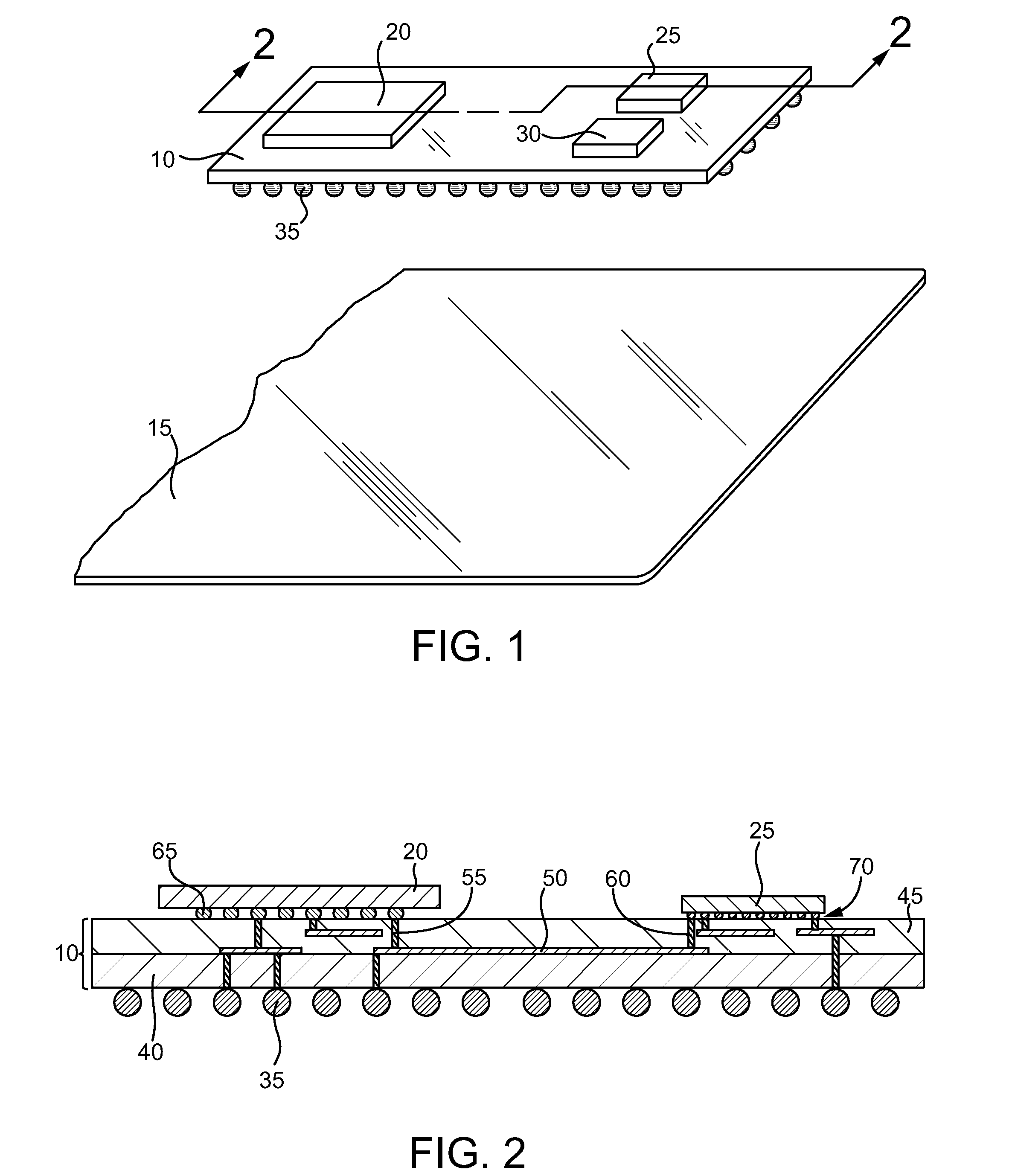

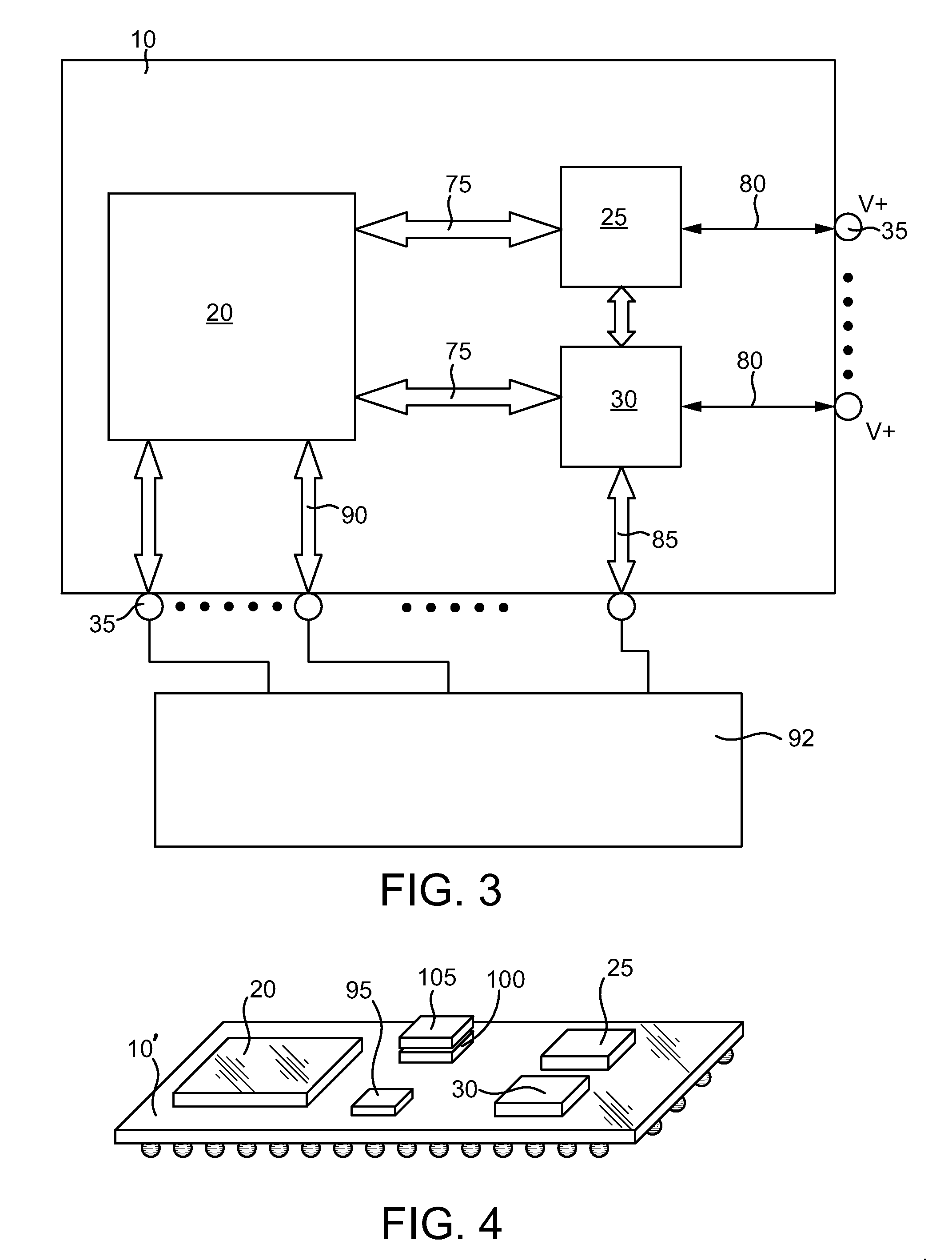

Semiconductor chip with offloaded logic

PendingUS20160329312A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsInterposerSemiconductor chip

Various semiconductor chip and interposer devices are disclosed. In one aspect, an apparatus is provided that includes an interposer, a first semiconductor chip mounted on the interposer and a second semiconductor chip mounted on and electrically connected to the first semiconductor chip by the interposer. The second semiconductor chip includes offloaded logic of the first semiconductor chip.

Owner:ADVANCED MICRO DEVICES INC

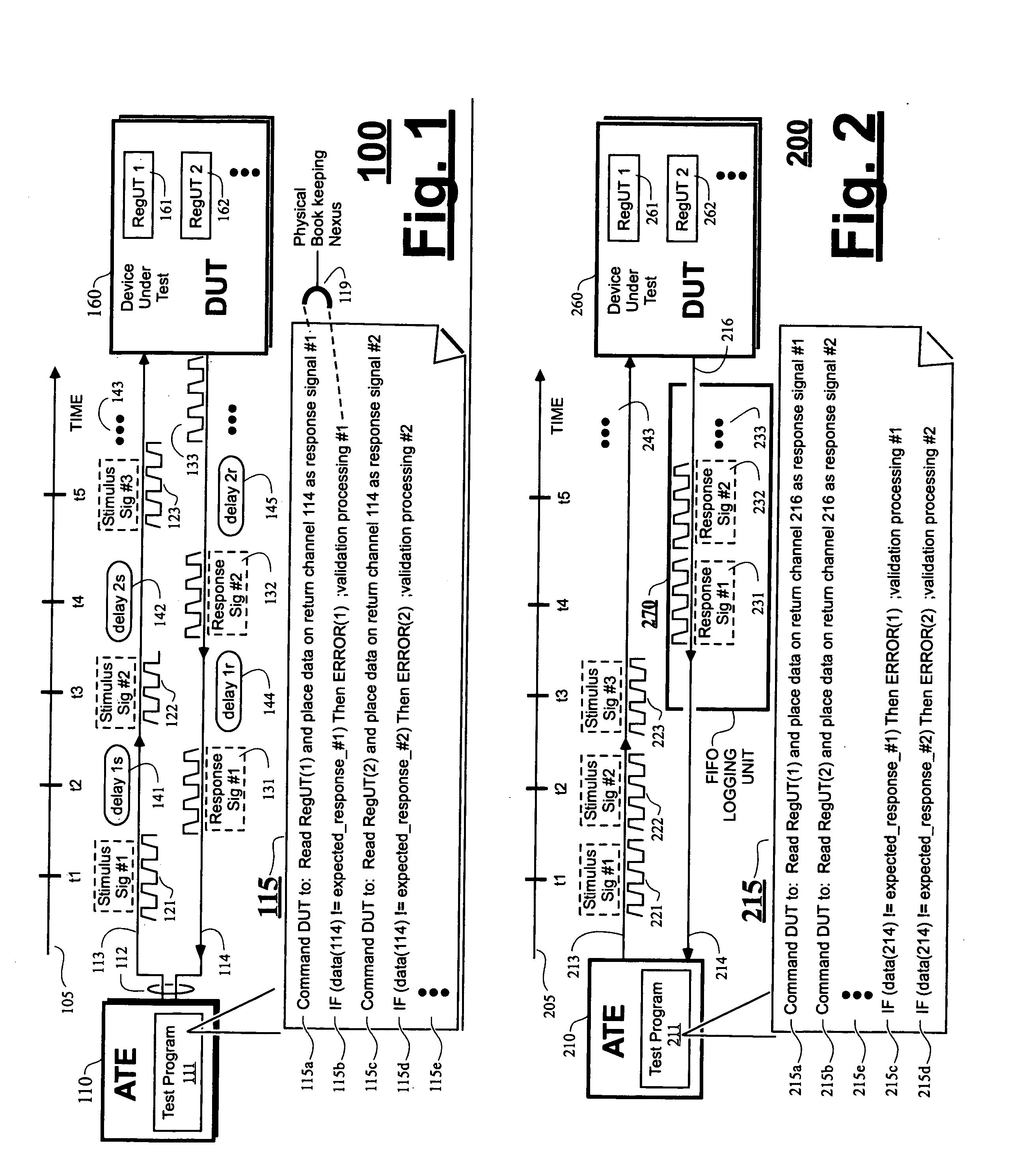

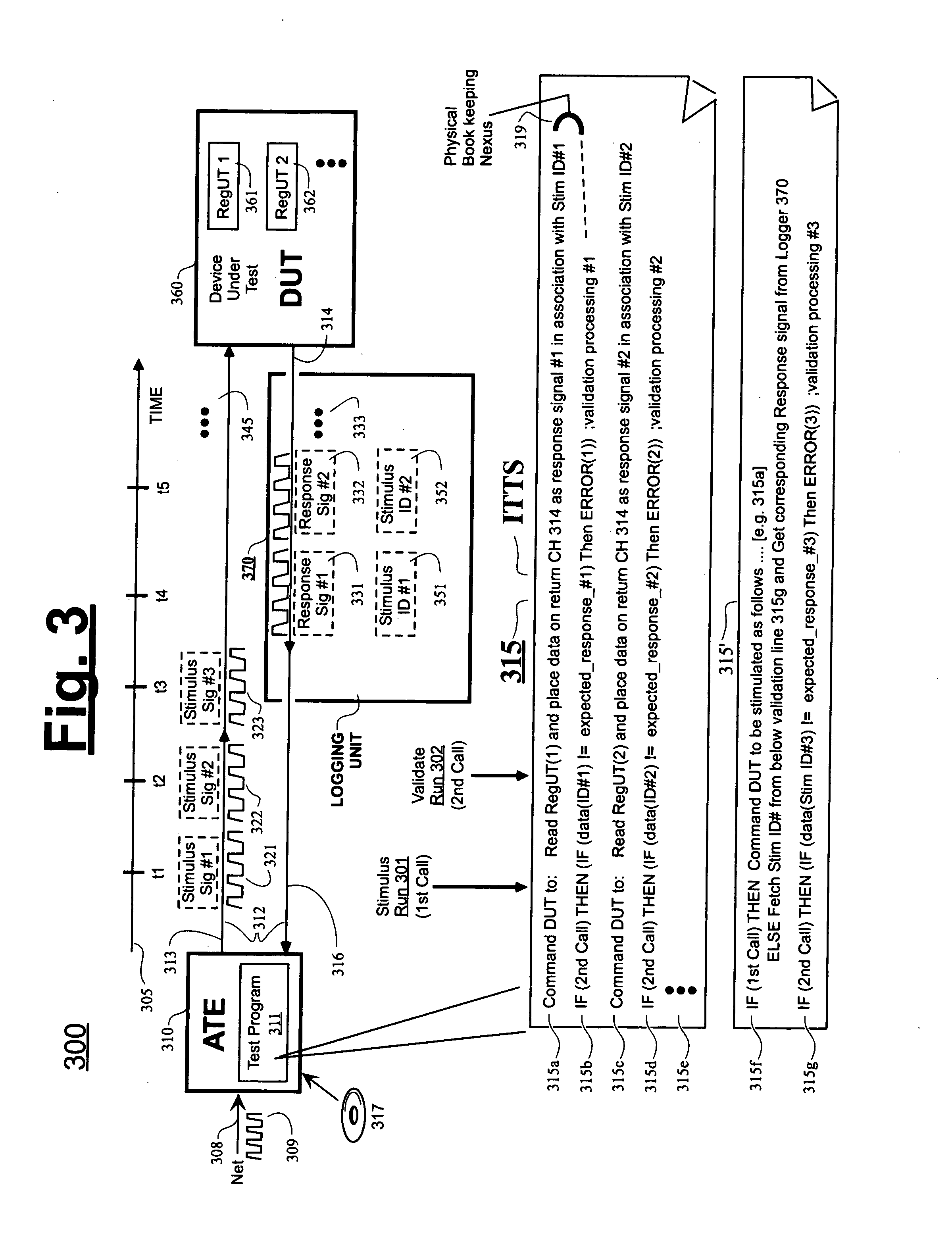

Automated device testing using intertwined stimulus-generation and response validation specifications for managing DUT's that generate out-of-order responses

InactiveUS20070101215A1Error detection/correctionAutomated test systemsAutomatic test equipmentTest specification

Owner:MICROSEMI STORAGE SOLUTIONS US INC

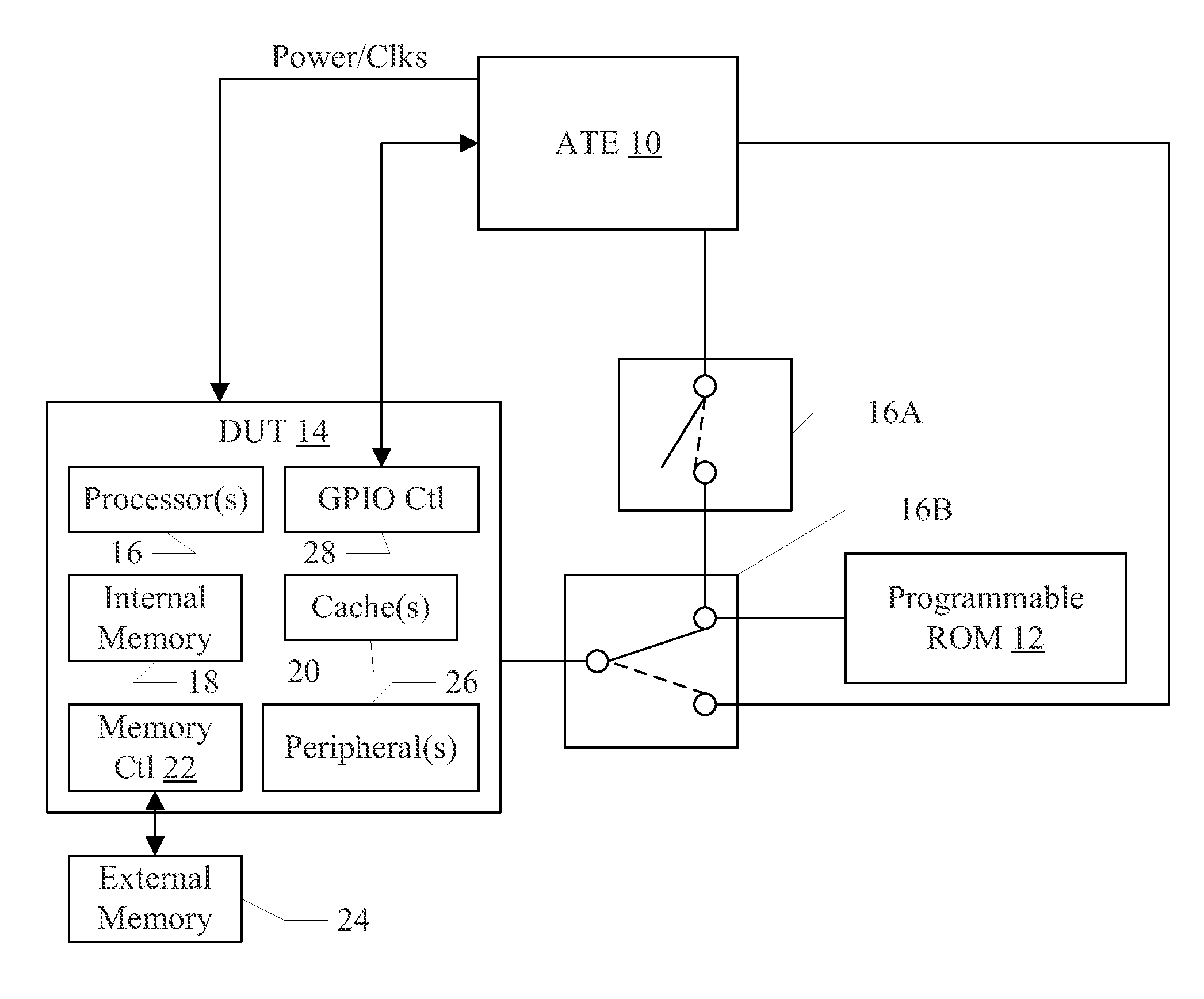

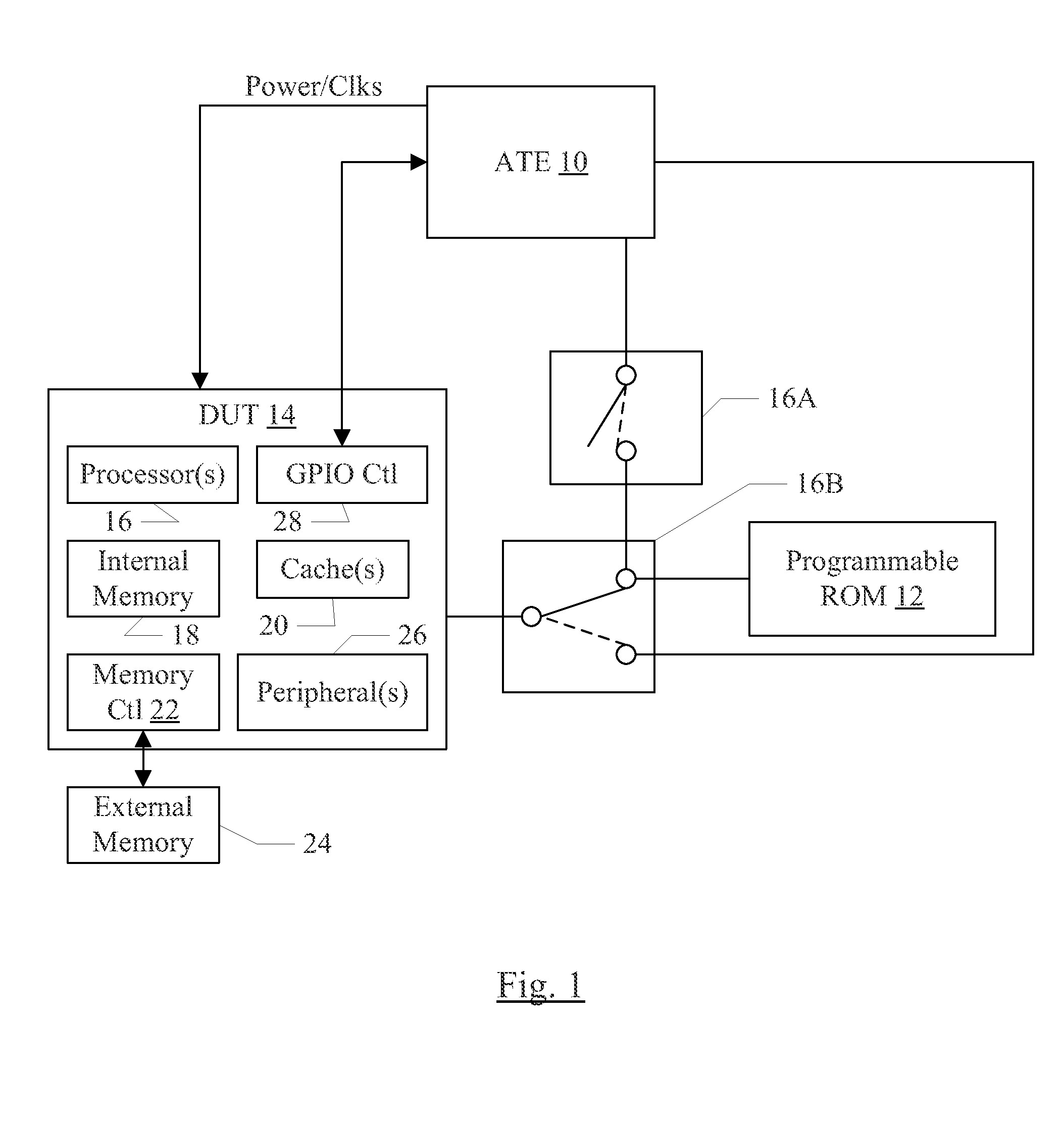

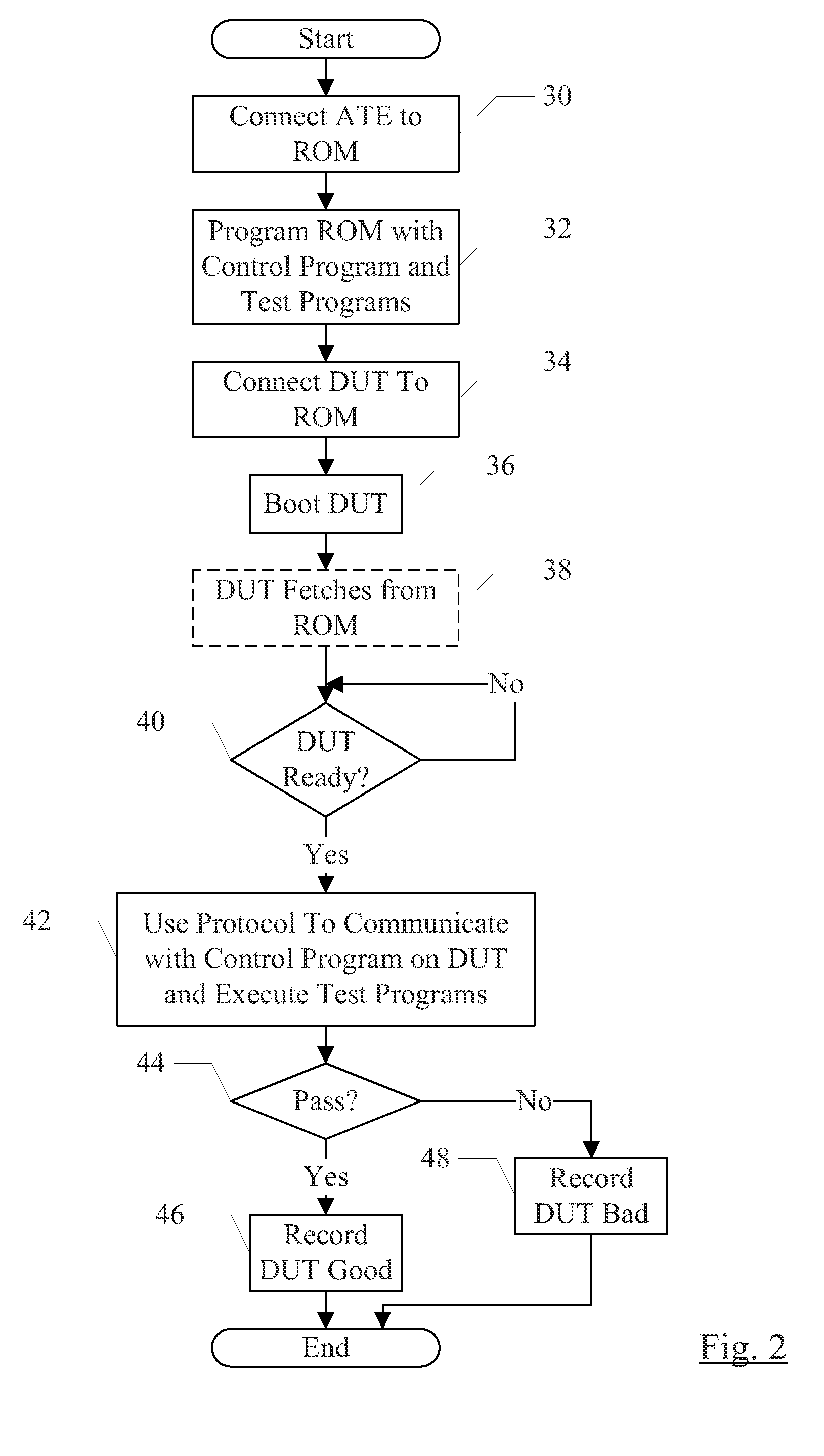

Test Method Using Memory Programmed with Tests and Protocol To Communicate between Device Under Test and Tester

InactiveUS20100312517A1Test accurateEfficient testingResistance/reactance/impedenceSpecial data processing applicationsEquipment under testTest vector

In an embodiment, a test method is implemented to test an integrated circuit that includes at least one processor. The method may include programming a memory to which the integrated circuit is coupled during testing with one or more test programs. The integrated circuit may be booted, and the processor may execute the test programs from the memory. In one embodiment, the memory may also store a control program that may manage the execution of the tests. In an embodiment, the control program may also implement a protocol to communicate with the ATE to perform the testing. The protocol may be implemented over a set of general purpose input / output (I / O) pins, for example. Using the protocol and test vectors on the ATE, the tests may be selected and executed, and test results may be reported.

Owner:APPLE INC

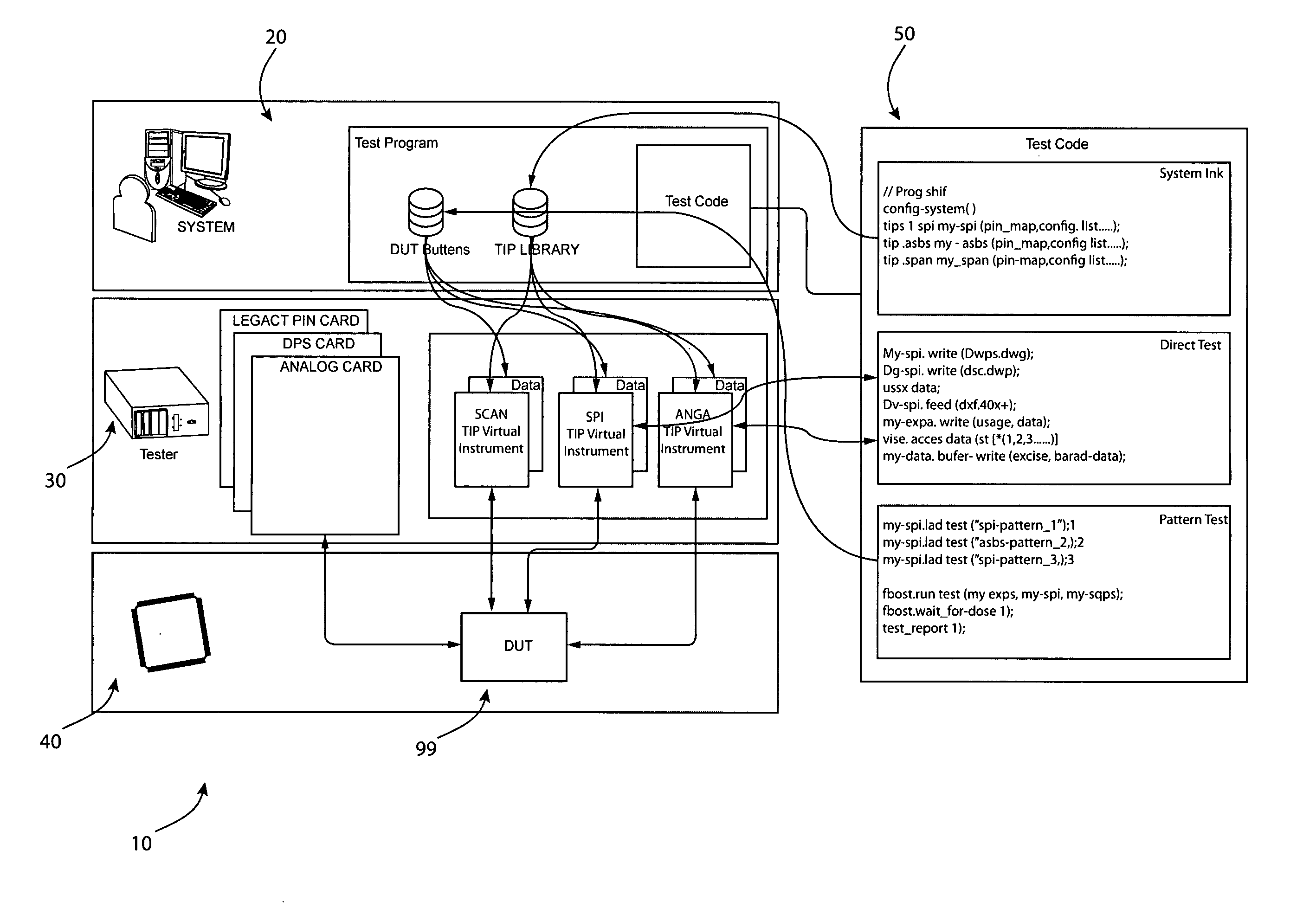

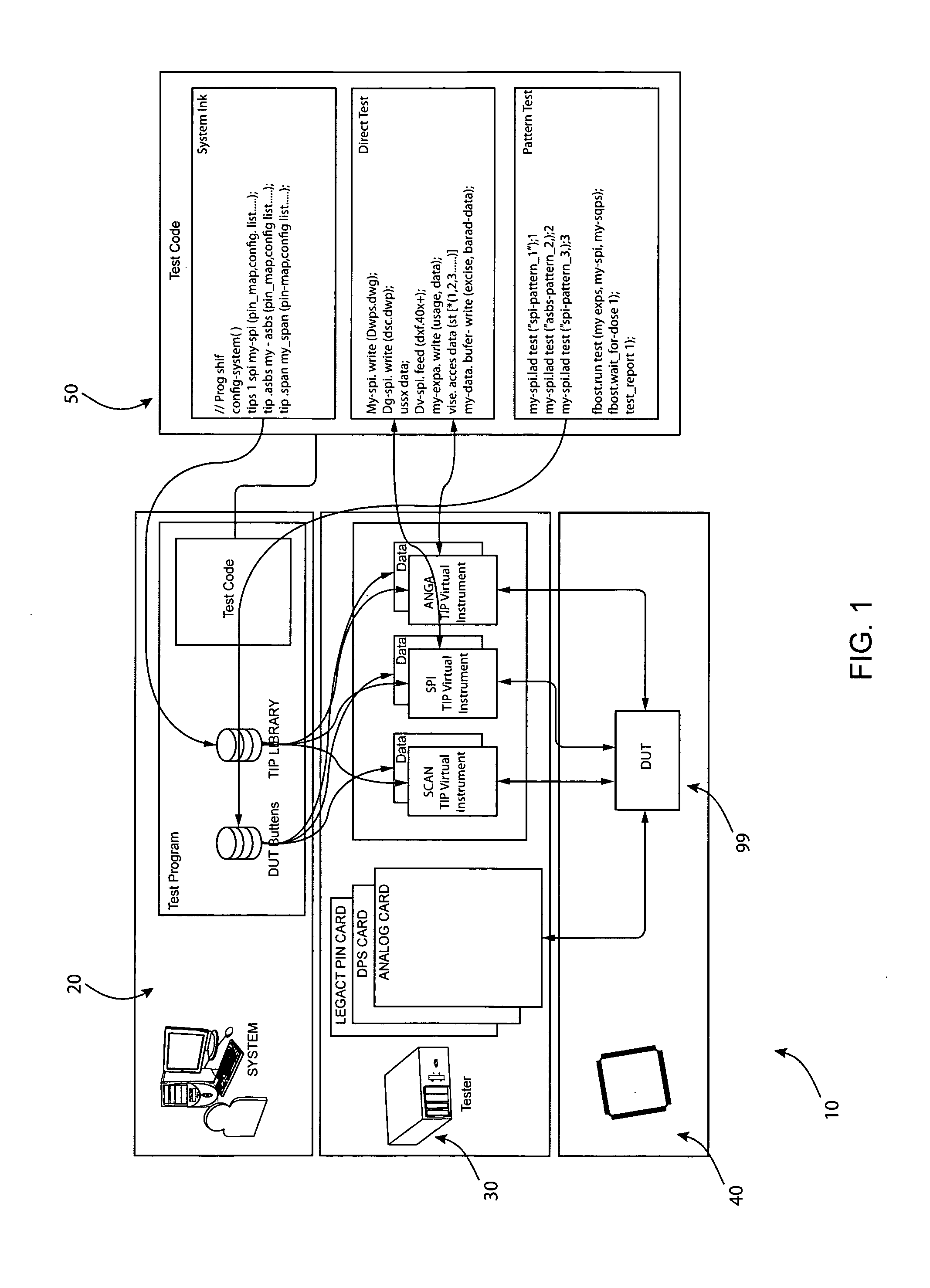

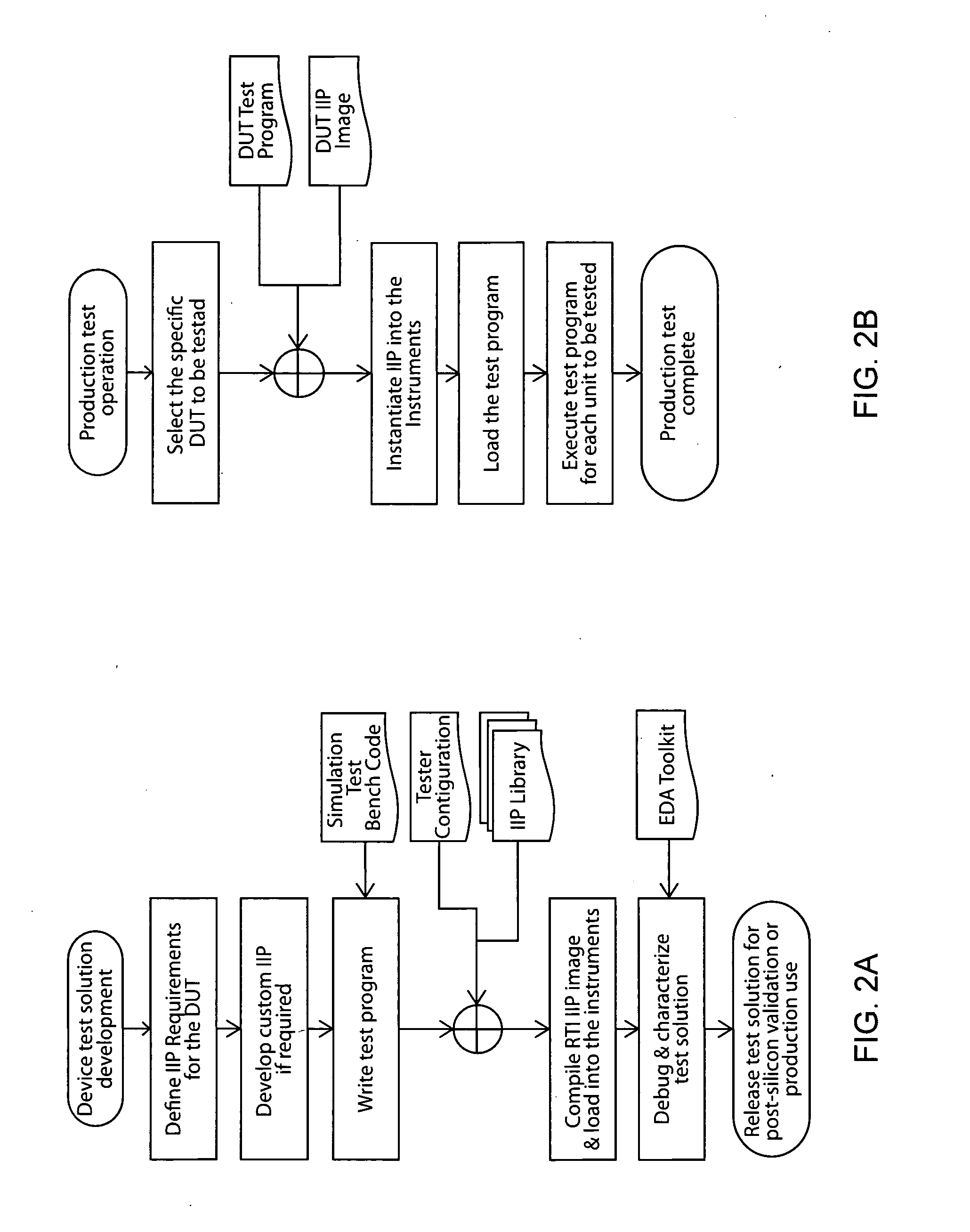

Test IP-Based A.T.E. Instrument Architecture

InactiveUS20130227367A1Implement extensionsError detection/correctionAutomated test systemsTest phaseUser interface

A test system based on multiple instances of reconfigurable instrument IP specifically matched to the device under test may be used in integrating automated testing of semiconductor devices between pre-silicon simulation, post-silicon validation, and production test phases, in one embodiment of software and hardware across all three phases, for different devices. The reconfigurable test system comprises: a tester instrument, instances of instrument IP instantiated in the tester instruments, a computer system, and a test program. The tester instrument connects to a device under test (DUT), and includes FPGAs reconfigurable for the three testing phases. The computer system has a user interface, and a controller connected to the reconfigurable tester instrument via a data bus. The test program stored on the controller, and the controller, instantiates interfaces and protocols, and certain process transactions to support the protocols, into FPGAs, to match device interfaces for each DUT, to execute test sequences.

Owner:CZAMARA ALLEN J +2

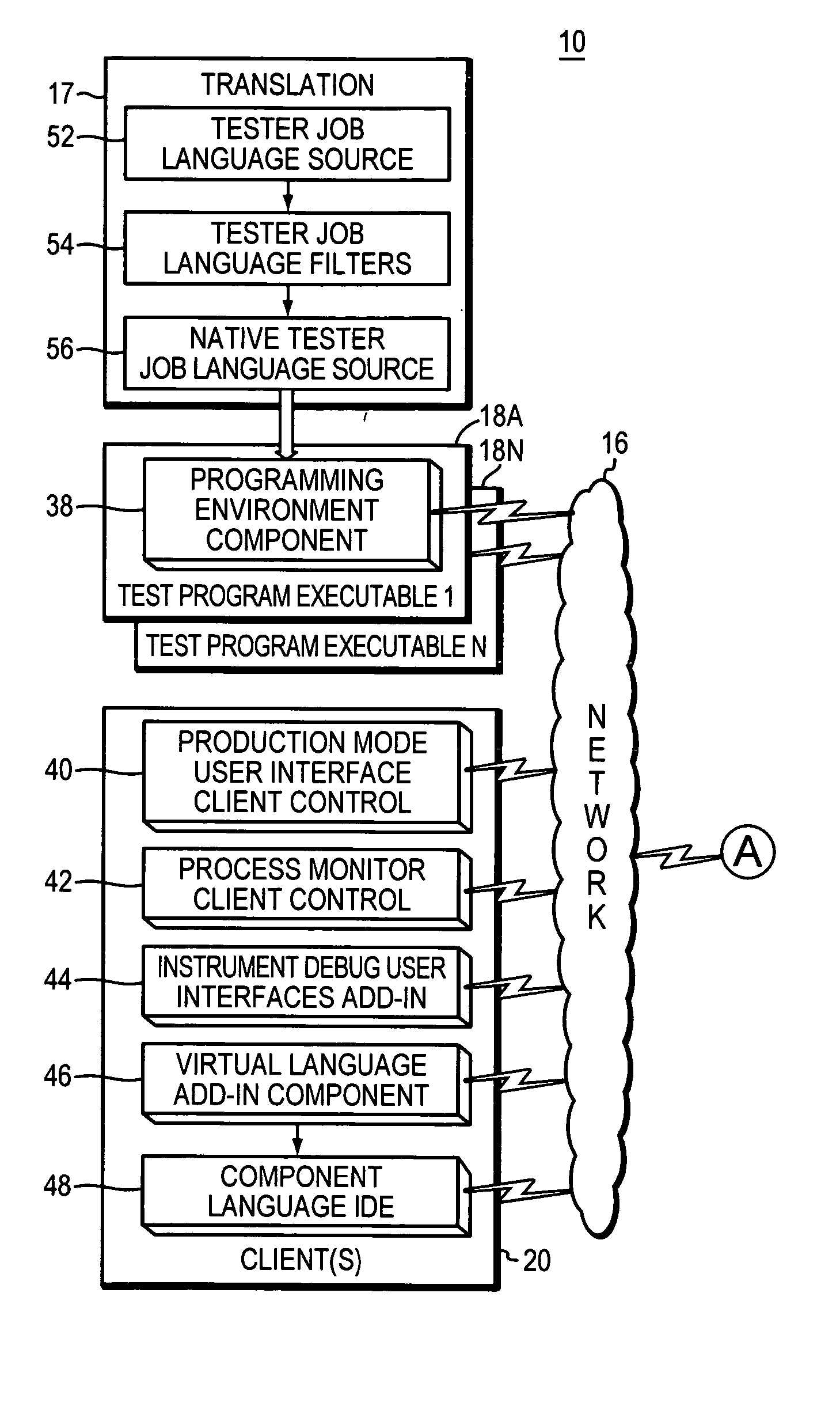

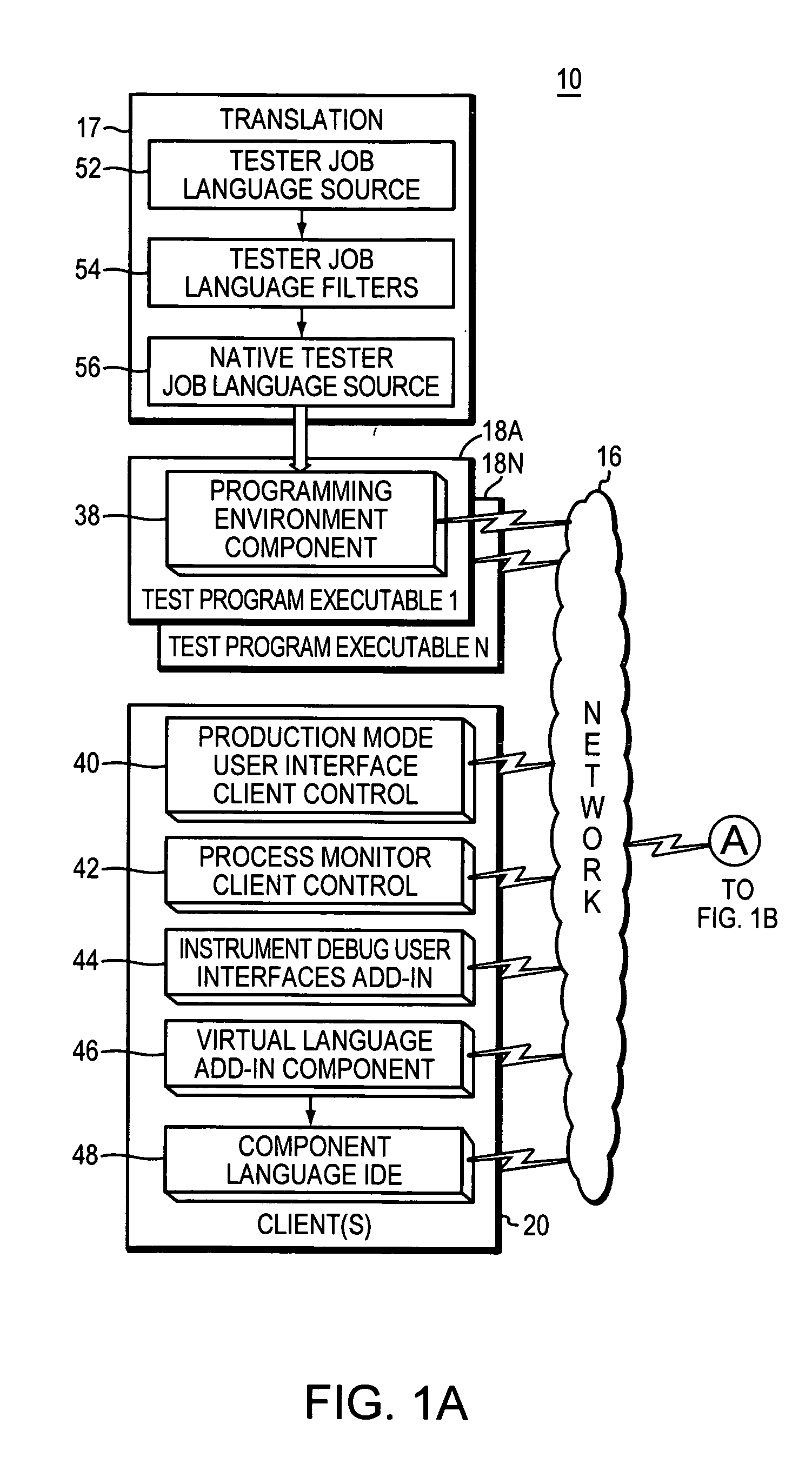

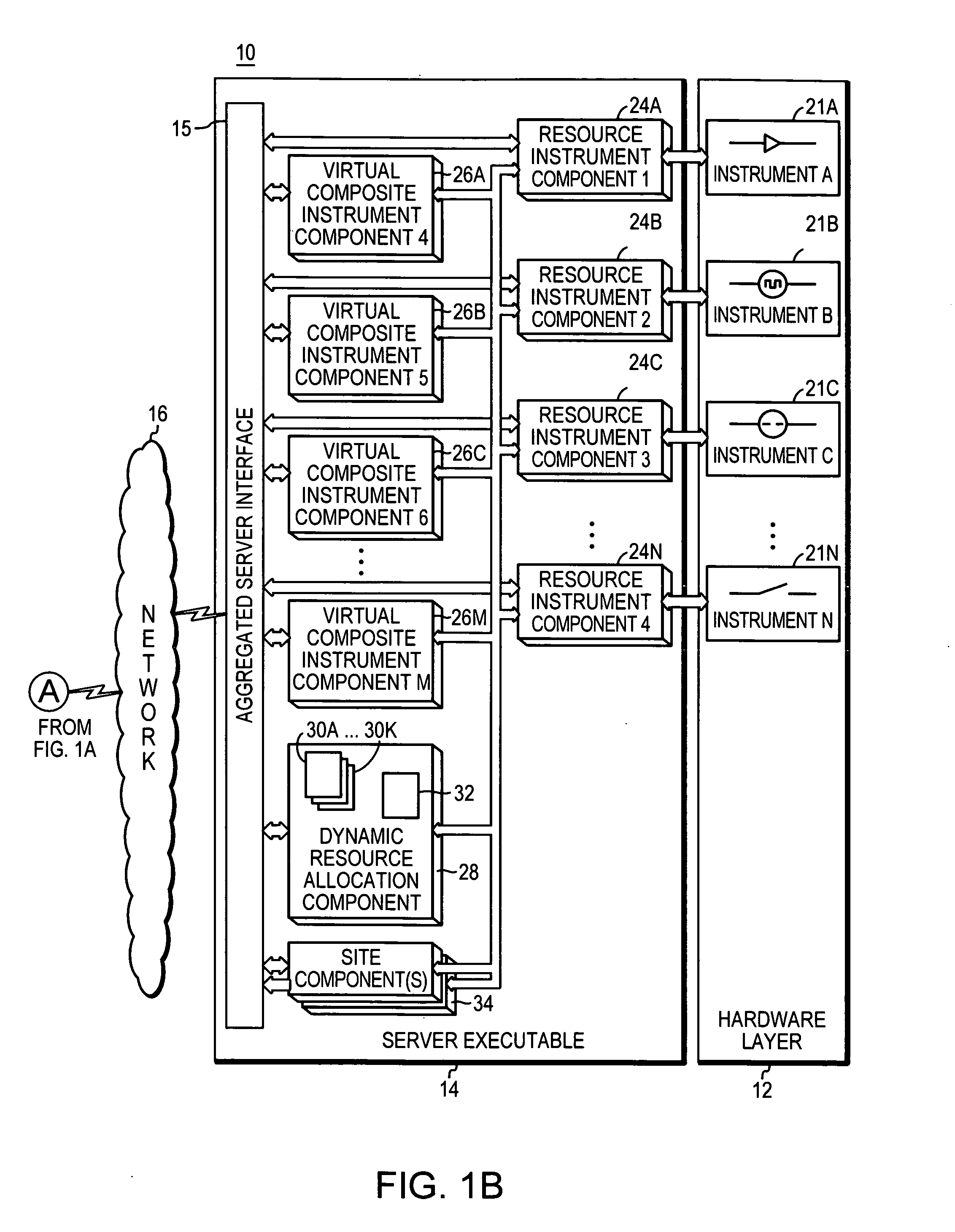

Polymorphic automatic test systems and methods

InactiveUS20050193306A1Increase resourcesImprove productivityError preventionTransmission systemsAutomatic test equipmentSoftware architecture

An Analog / mixed signal automatic test system includes a software architecture that creates a virtual composite instruments through novel software dynamic allocation of low level resources. These virtual composite instruments provide backwards and forwards compatibility to a variety of automatic test equipment, known or available on the market. The virtual composite instruments are free from the normal constraints imposed by hardware implementations. Creation of the virtual composite instruments allows a single piece of automatic test equipment system to emulate many implementations of automatic test equipment, providing higher utilization, and therefore a lower cost test solution for device manufacturers. The test instruments are preferably object controls and are preferably instantiated and controlled by the test system server. This allows multiple users to control the tester simultaneously across, for example, the Internet.

Owner:PRACTICAL ENG

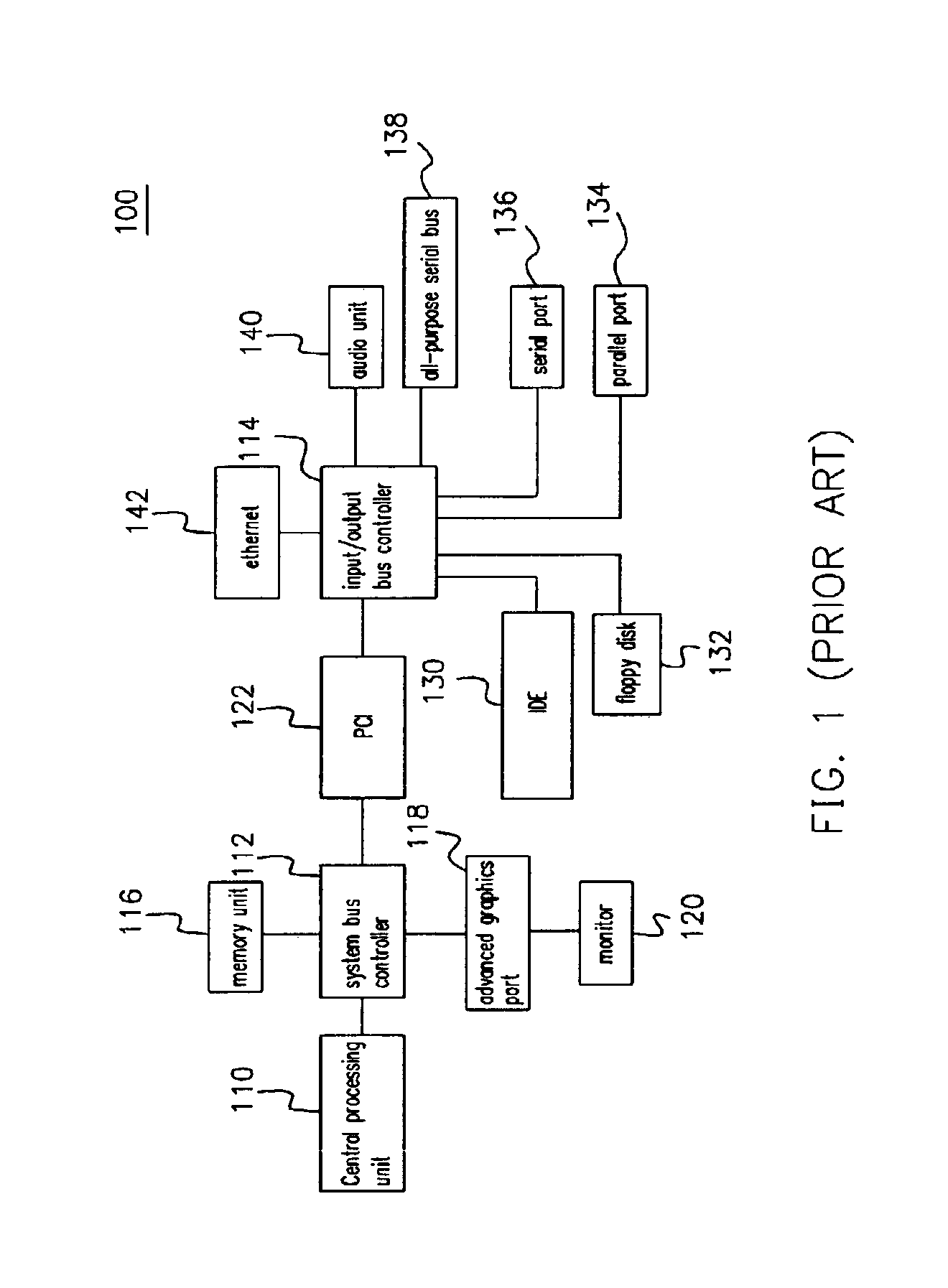

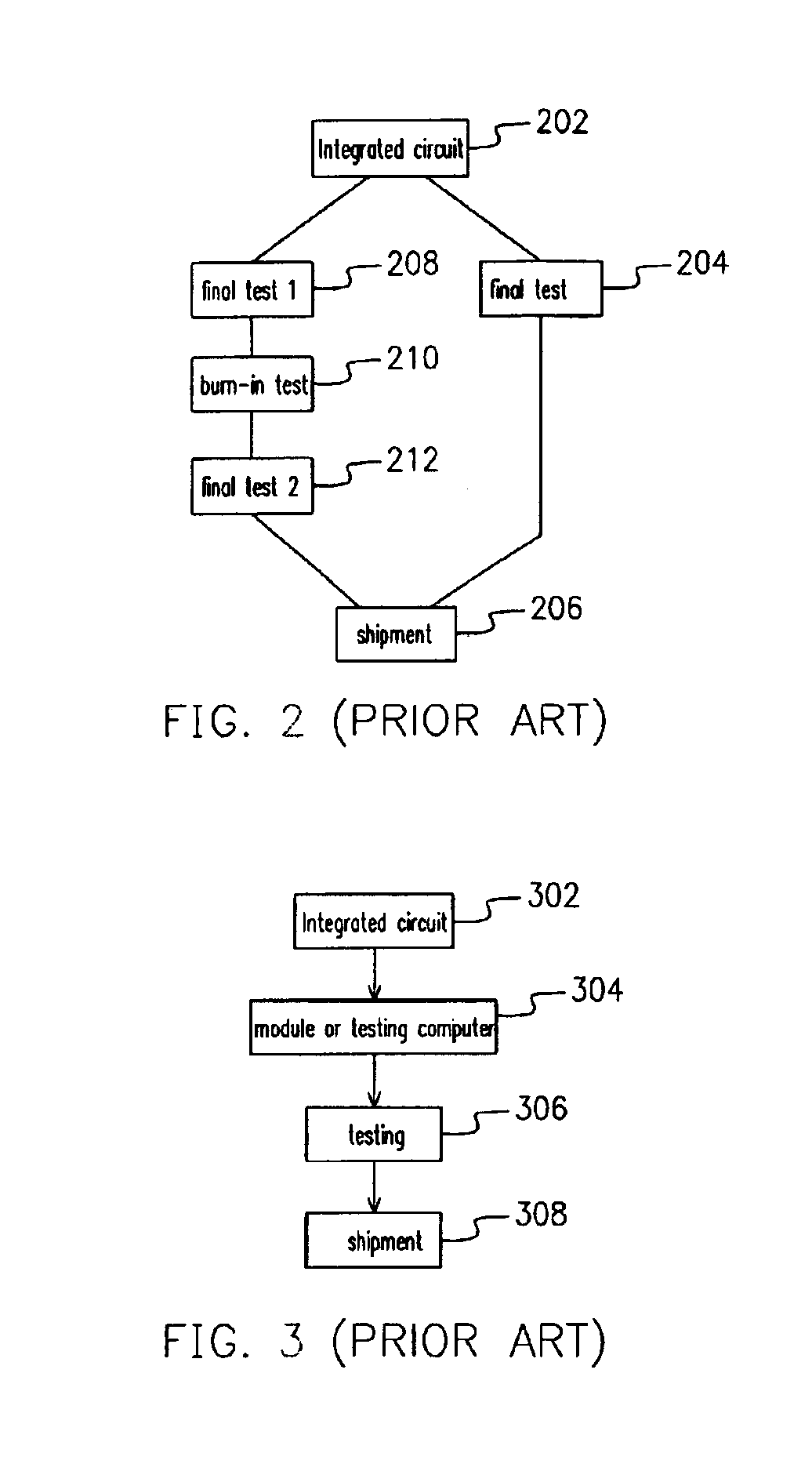

Automatic integrated circuit testing system and device using an integrative computer and method for the same

InactiveUS6914424B2Ensure qualityEnsure reliabilitySpecial data processing applicationsAutomated test systemsElectricityCombined test

An automatic integrated circuit testing system, device and method using an integrative computer. The system includes a machine frame having at least one testing computer for holding and testing the integrated circuit. The machine frame also has at least one automatic plugging / unplugging machine for engaging the integrated circuits with the computer system and removing the integrated circuits after testing has been completed. The machine frame further includes at least one controller device electrically connected to the testing computer and the automatic plugging / unplugging machine for controlling the movements of the automatic plugging / unplugging machine and the testing computer. The testing computer and the integrated circuit together form an integrative computer system capable of executing various general application programs and special testing programs for integrative testing and analysis.

Owner:VIA TECH INC

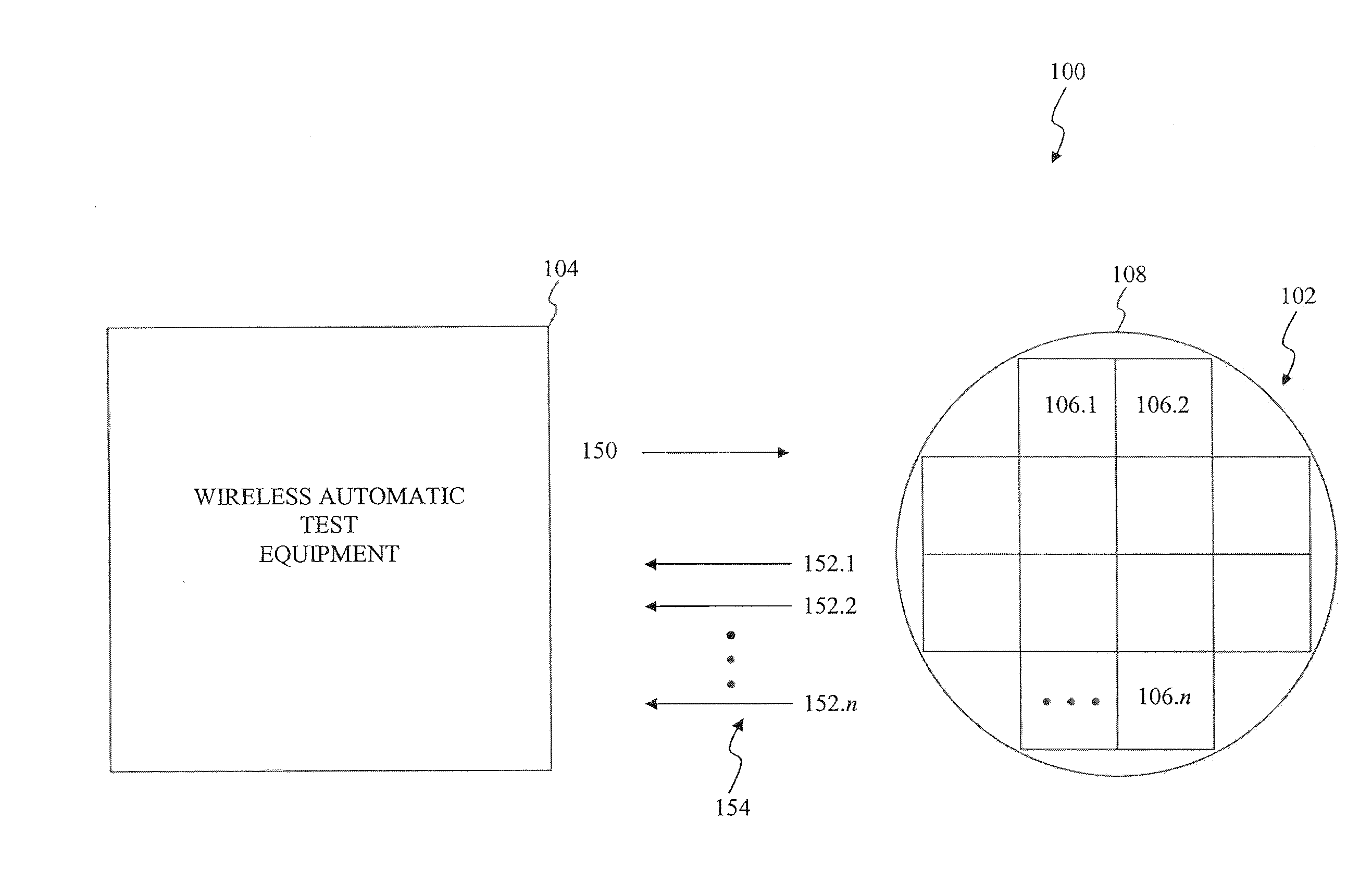

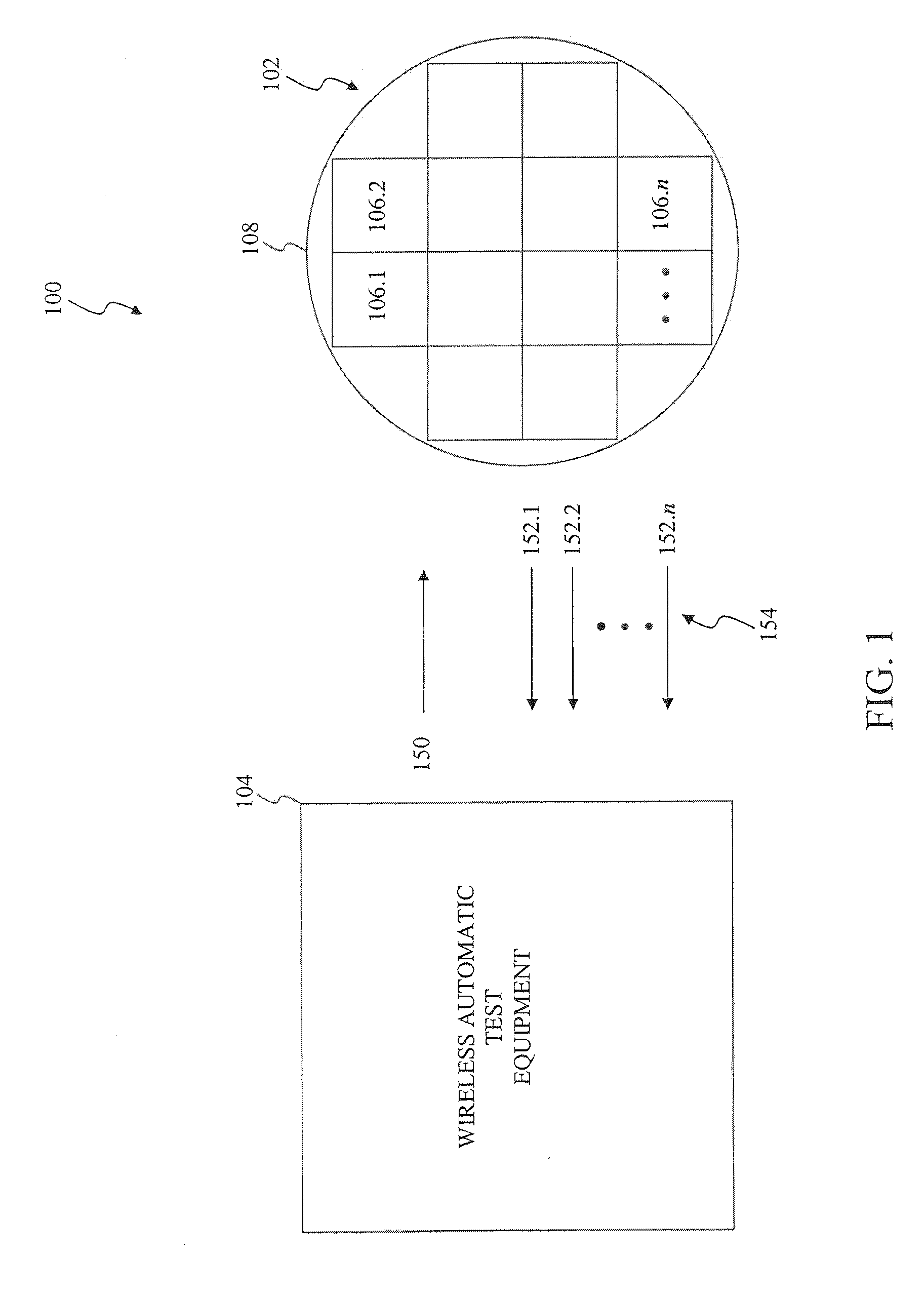

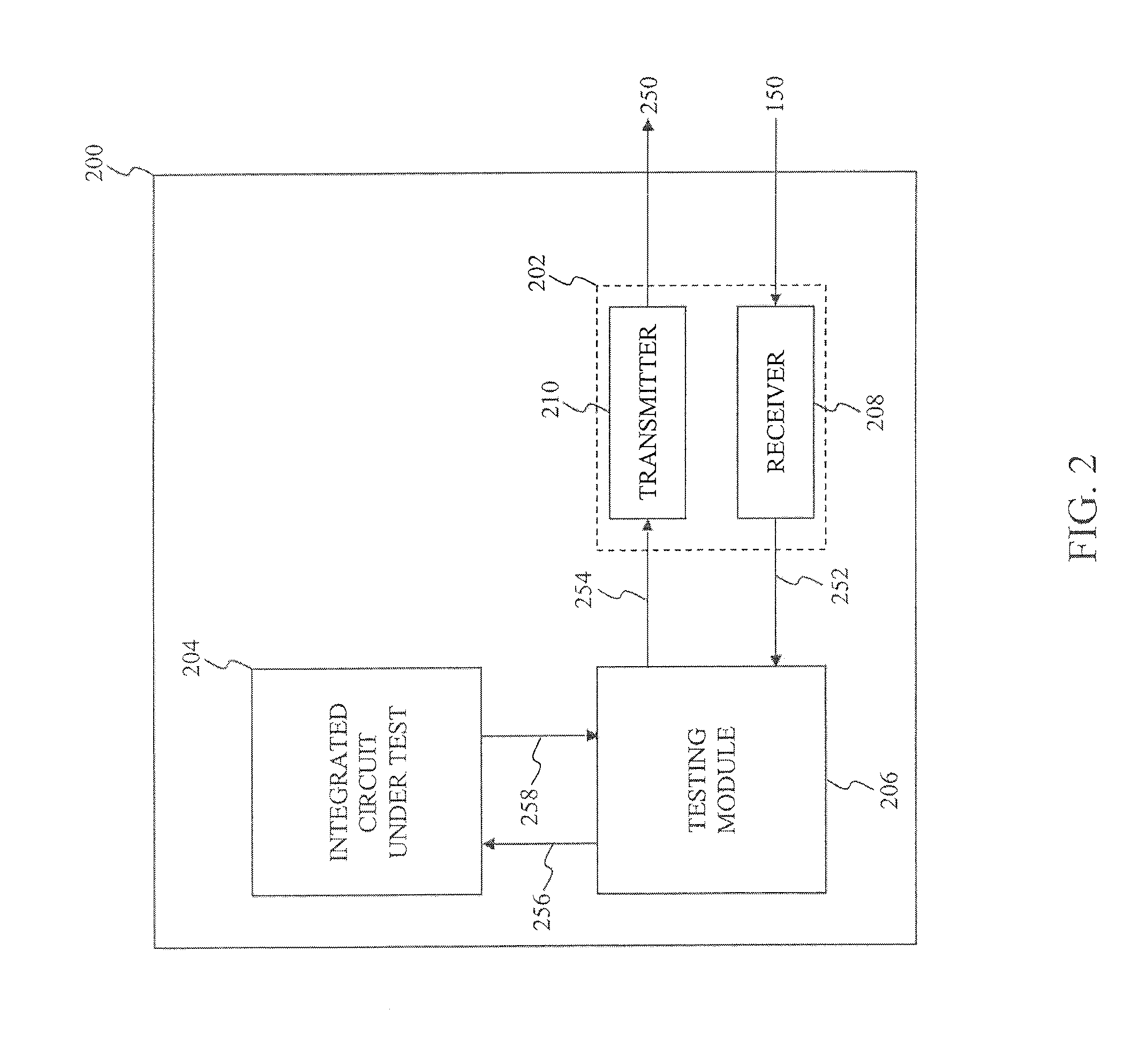

Simultaneous Testing of Semiconductor Components on a Wafer

InactiveUS20110313710A1Resistance/reactance/impedenceSpecial data processing applicationsAutomatic test equipmentThree-dimensional space

Methods and apparatus are disclosed to simultaneously, wirelessly test semiconductor components formed on a semiconductor wafer. The semiconductor components transmit respective outcomes of a self-contained testing operation to wireless automatic test equipment via a common communication channel. Multiple receiving antennas observe the outcomes from multiple directions in three dimensional space. The wireless automatic test equipment determines whether one or more of the semiconductor components operate as expected and, optionally, may use properties of the three dimensional space to determine a location of one or more of the semiconductor components. The wireless testing equipment may additionally determine performance of the semiconductor components by detecting infrared energy emitted, transmitted, and / or reflected by the semiconductor wafer before, during, and / or after a self-contained testing operation.

Owner:AVAGO TECH INT SALES PTE LTD