Patents

Literature

1978 results about "Hardware implementations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

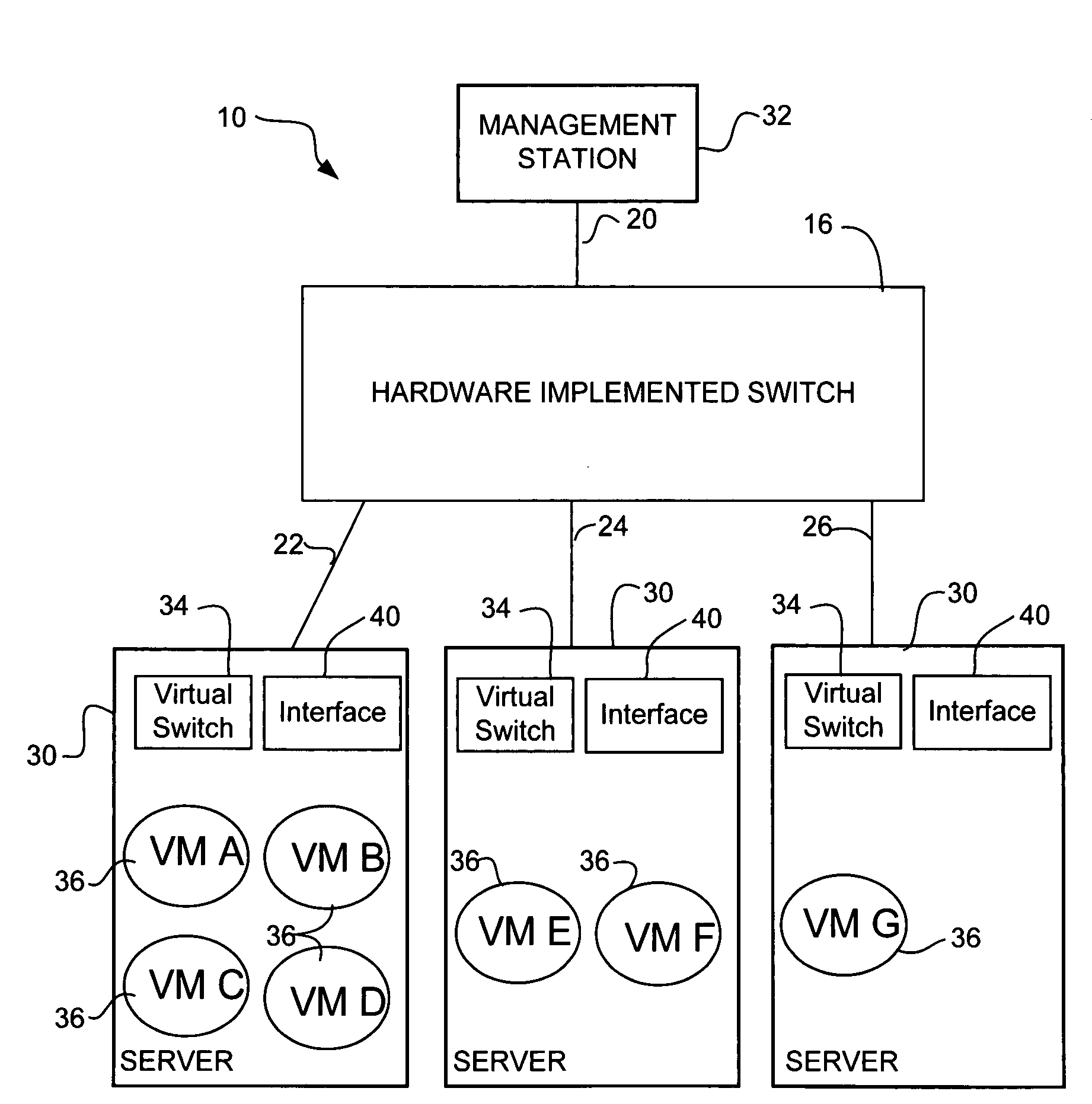

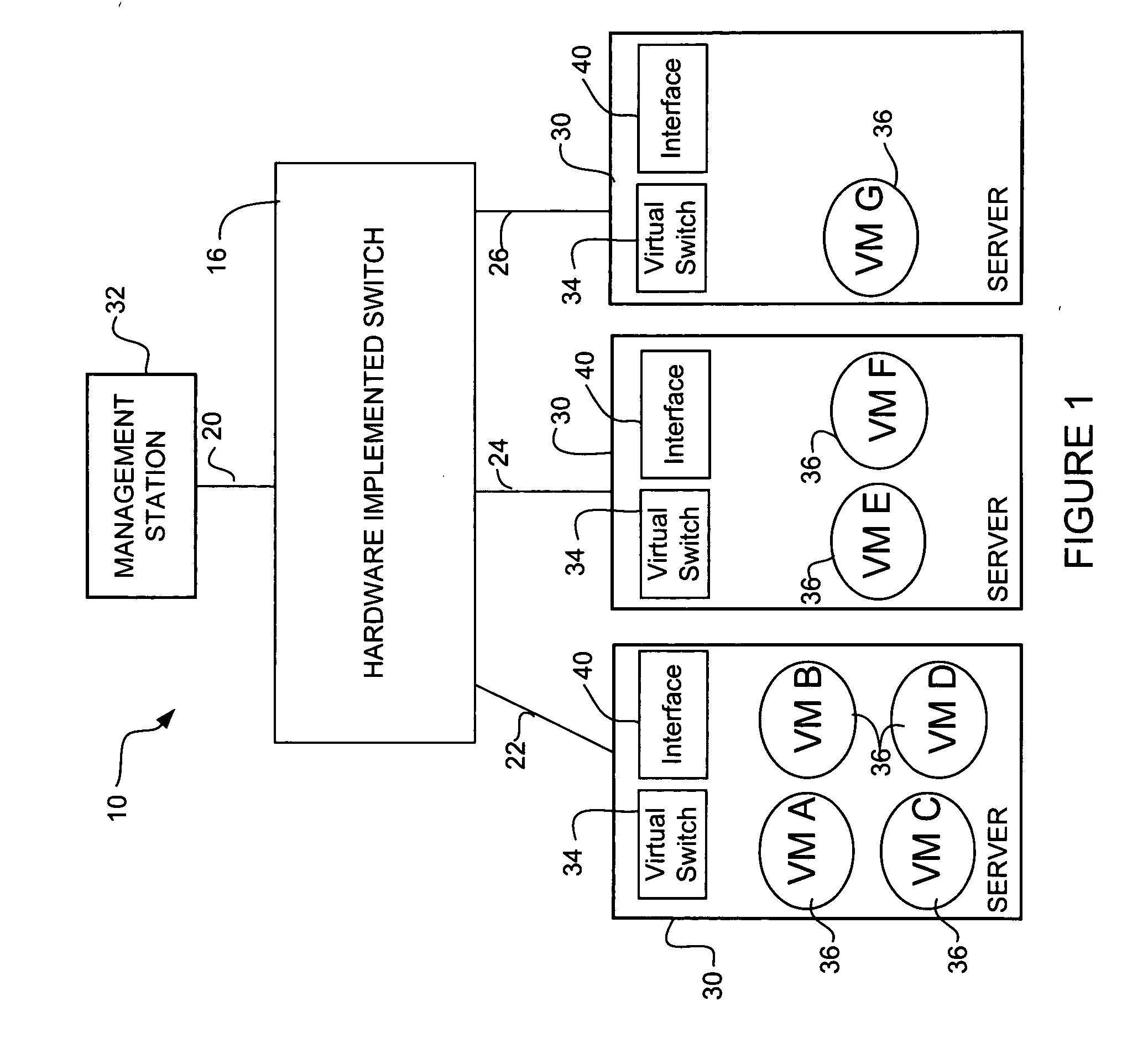

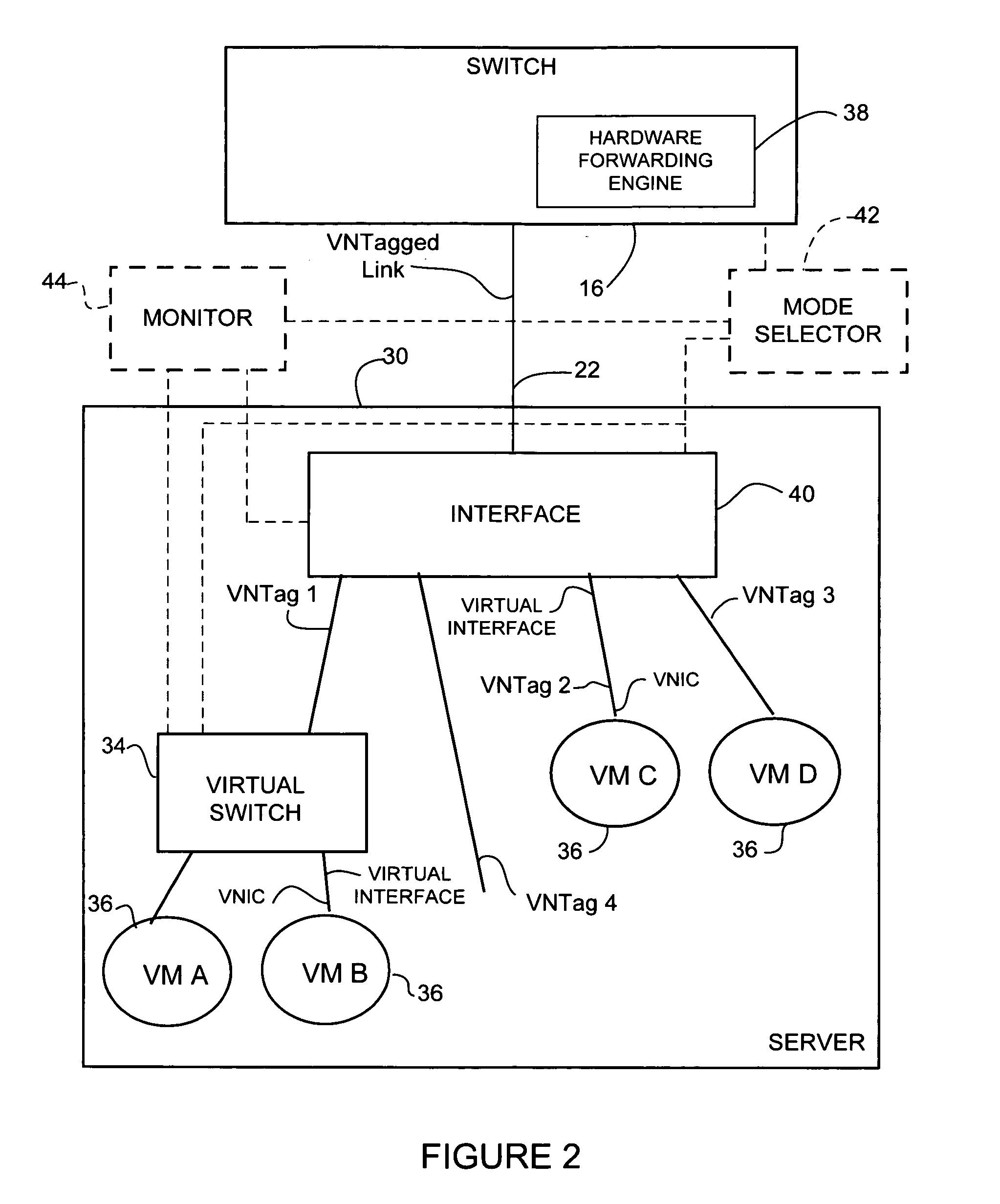

Traffic forwarding for virtual machines

ActiveUS20100275199A1Multiprogramming arrangementsTransmissionVirtual switchHardware implementations

In one embodiment, an apparatus configured for communication with a plurality of virtual machines includes a virtual switch in communication with one or more of the virtual machines, an interface in communication with one or more of the virtual machines and configured for communication with a hardware implemented switch, and a mode selector for assigning to each of the virtual machines, a mode of operation for forwarding data from the virtual machine and switching the assigned mode of operation at one or more of the virtual machines. The mode of operation is selected from a first mode wherein the data is forwarded by the hardware implemented switch and a second mode wherein the data is forwarded by the virtual switch.

Owner:CISCO TECH INC

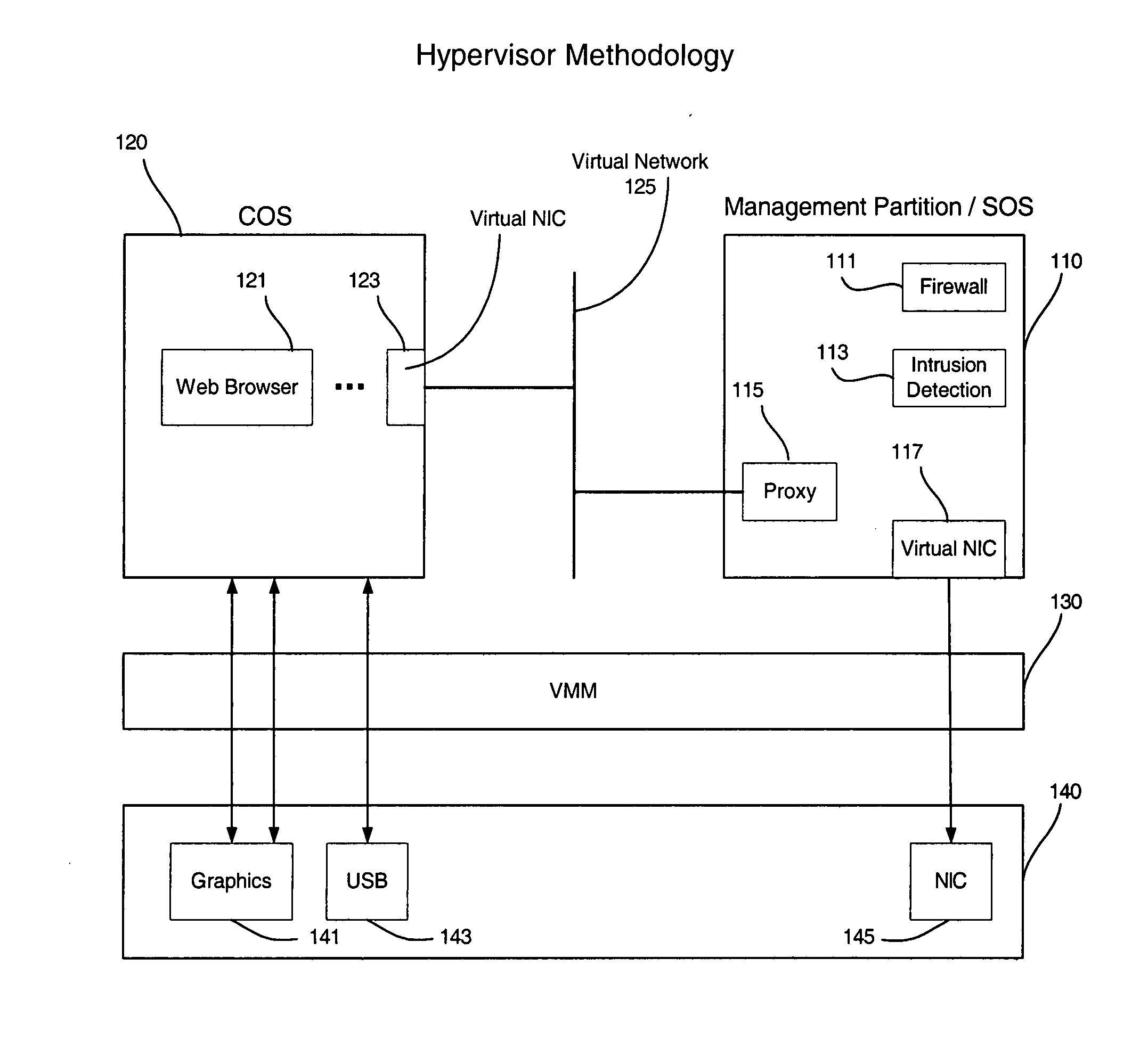

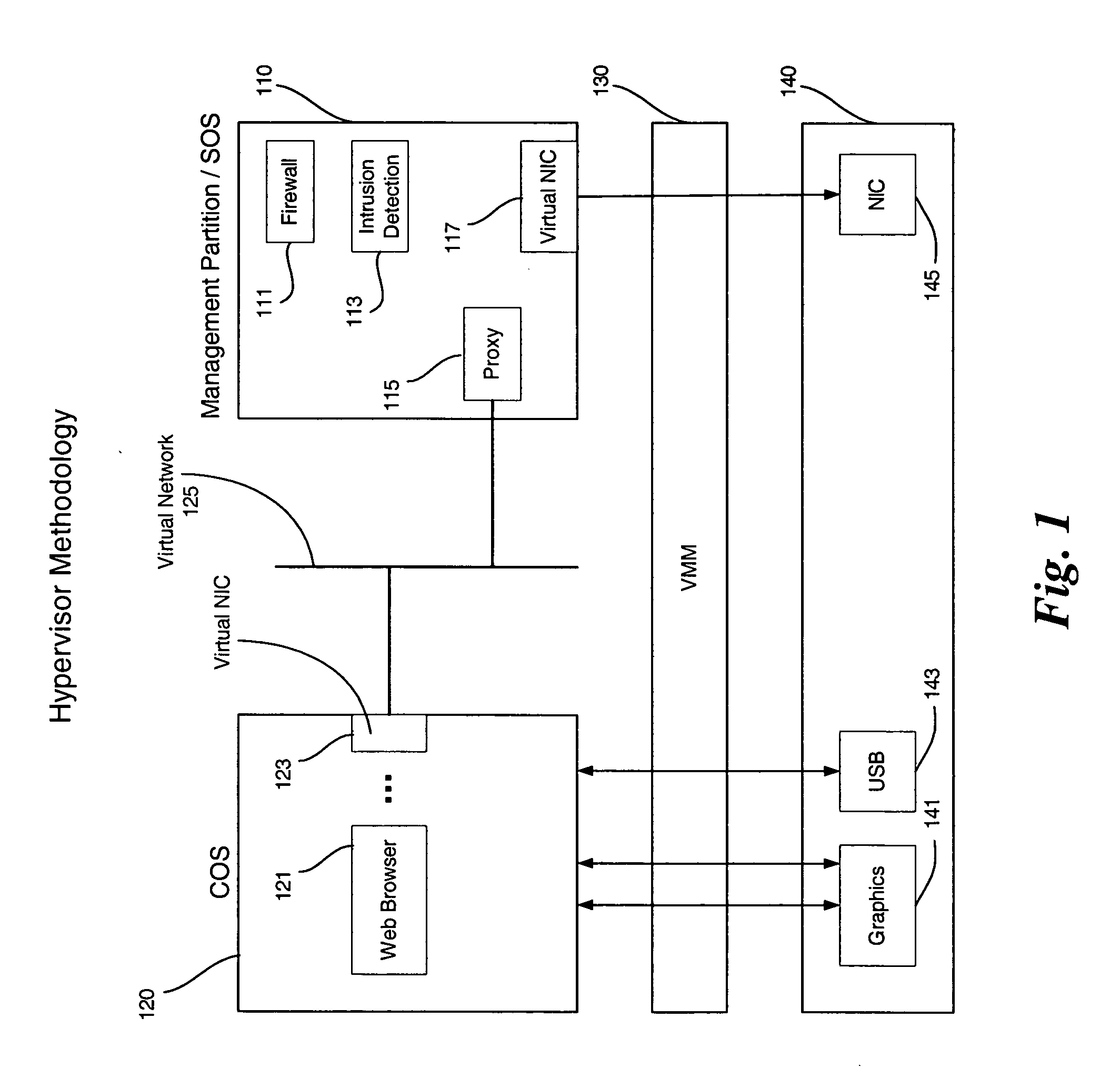

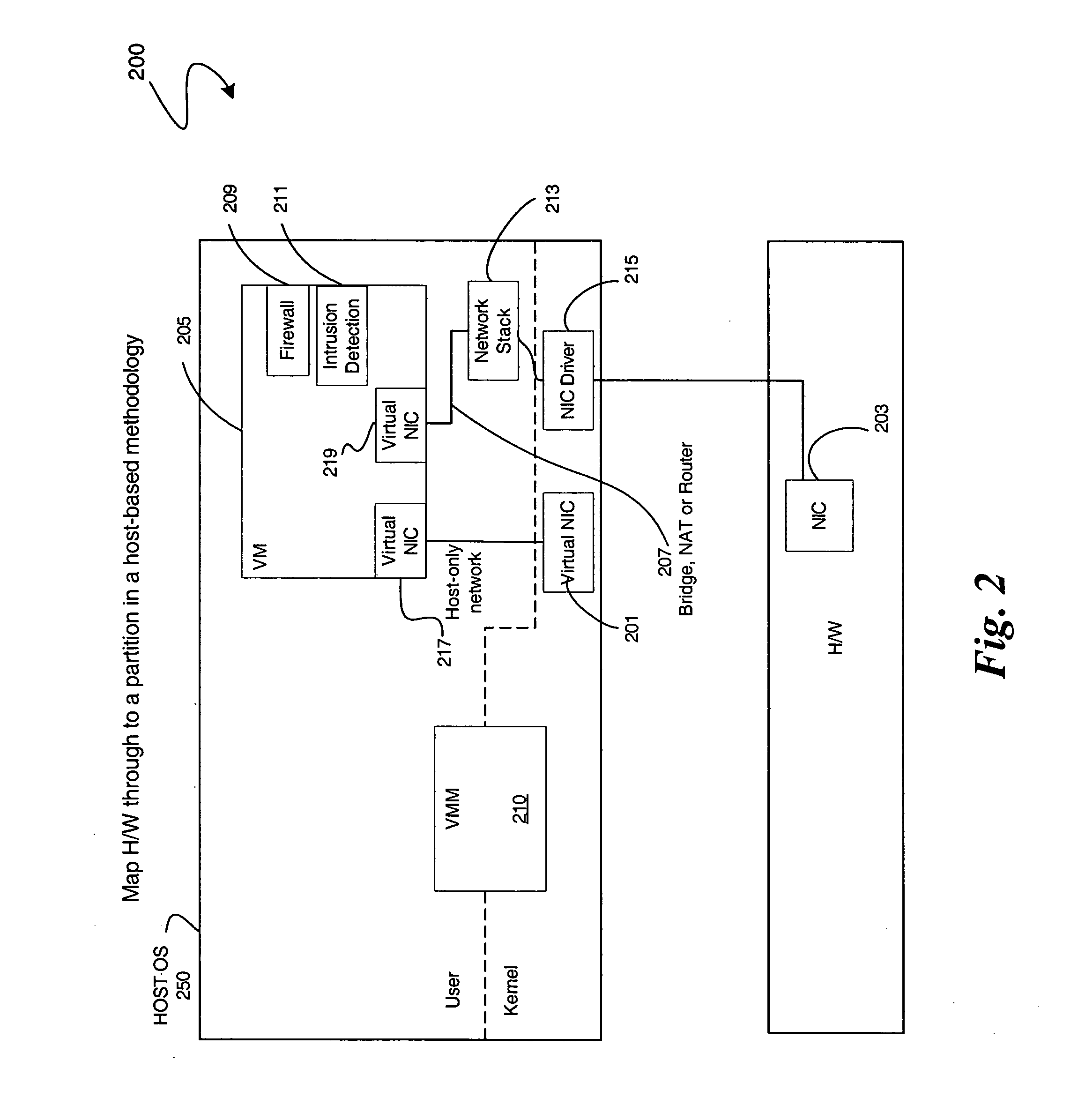

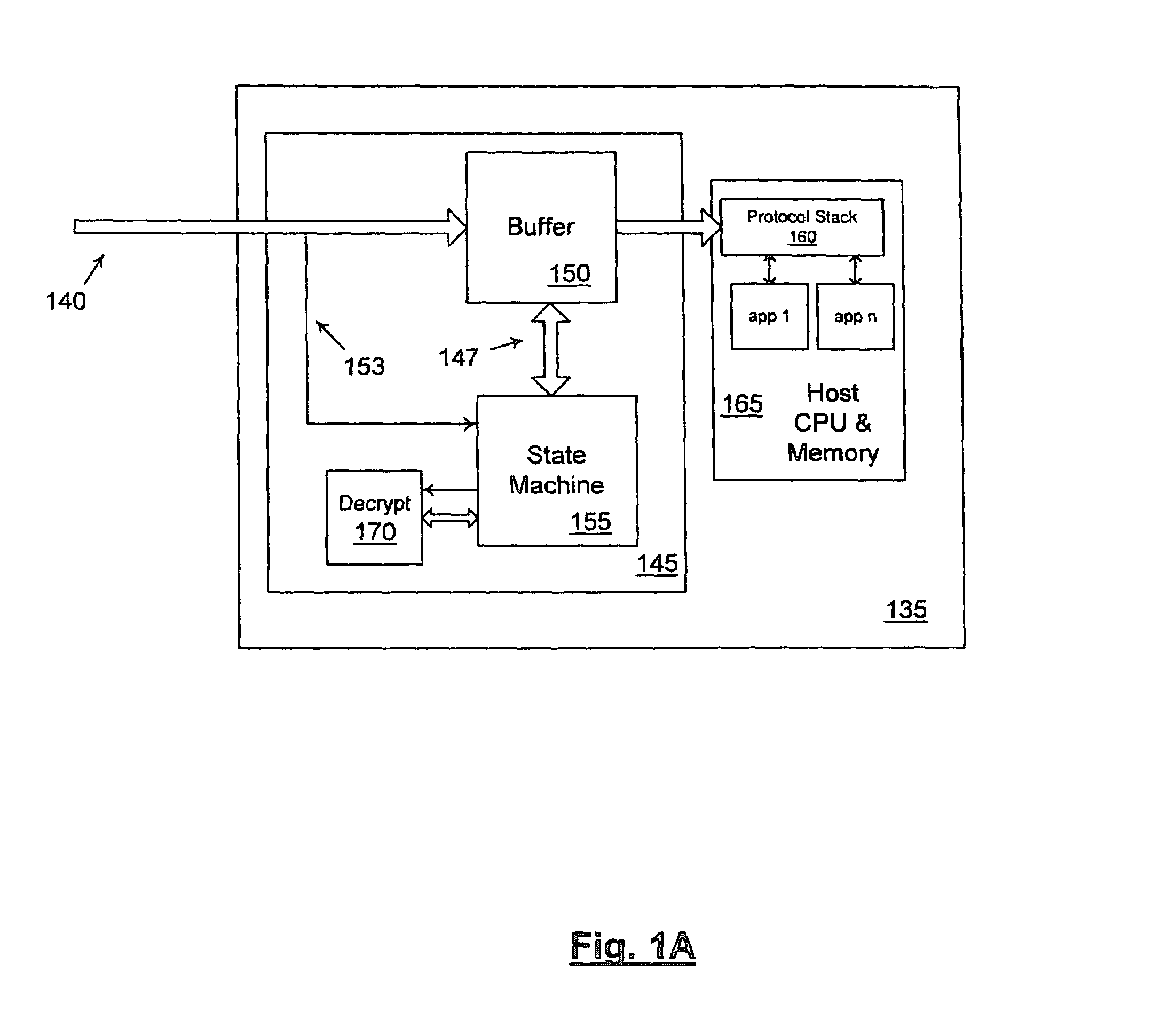

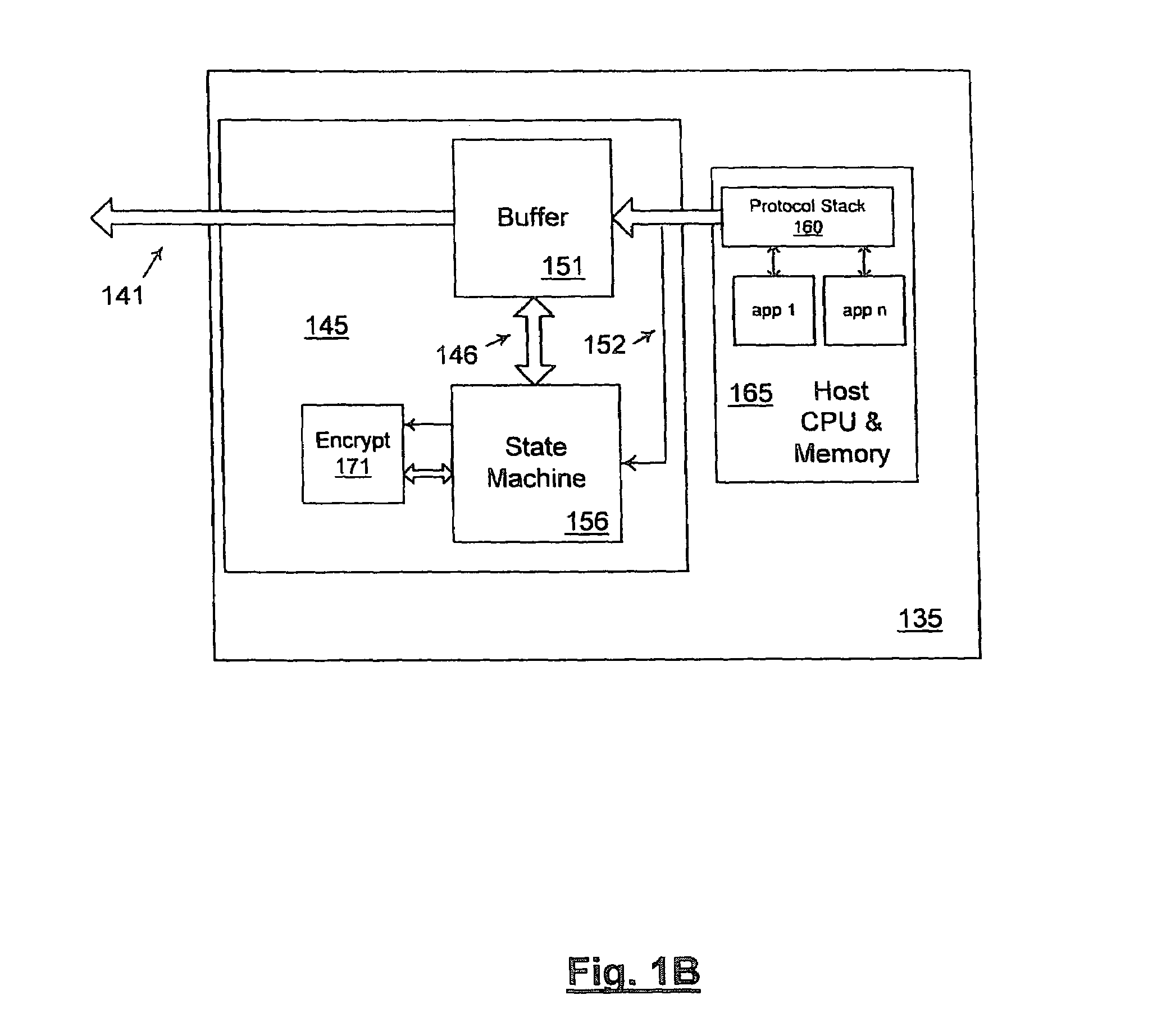

Enabling platform network stack control in a virtualization platform

InactiveUS20060070066A1TransmissionSoftware simulation/interpretation/emulationVirtualizationData pack

In some embodiments, the invention involves protecting network communications in a virtualized platform. An embodiment of the present invention is a system and method relating to protecting network communication flow using packet encoding / certification and the network stack. One embodiment uses a specialized engine or driver in the network stack to encode packets before being sent to physical network controller. The network controller may use a specialized driver to decode the packets, or have a hardware implementation of a decoder. If the decoded packet is certified, the packet is transmitted. Otherwise, the packet is dropped. An embodiment of the present invention utilizes virtualization architecture to implement the network communication paths. Other embodiments are described and claimed.

Owner:INTEL CORP

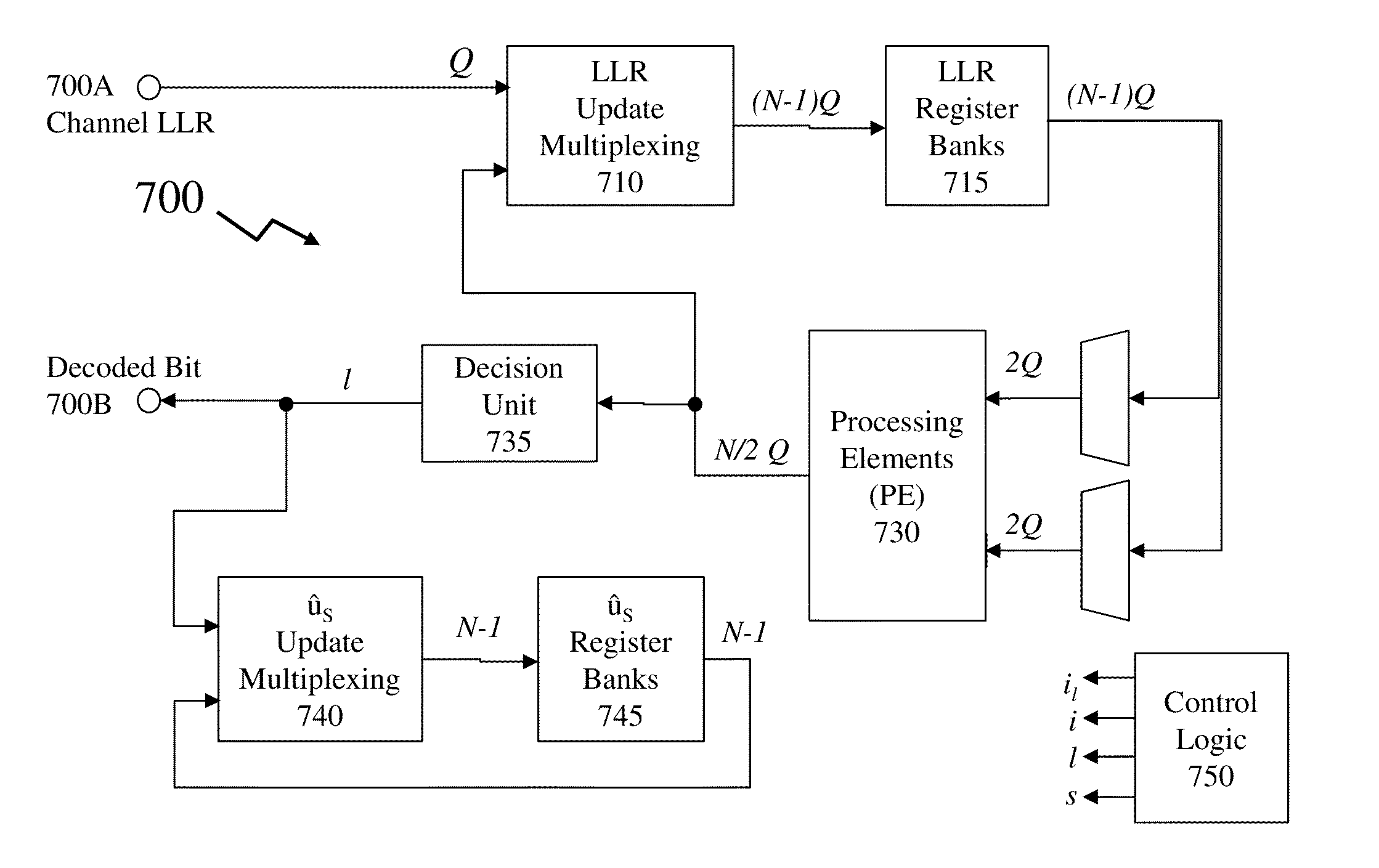

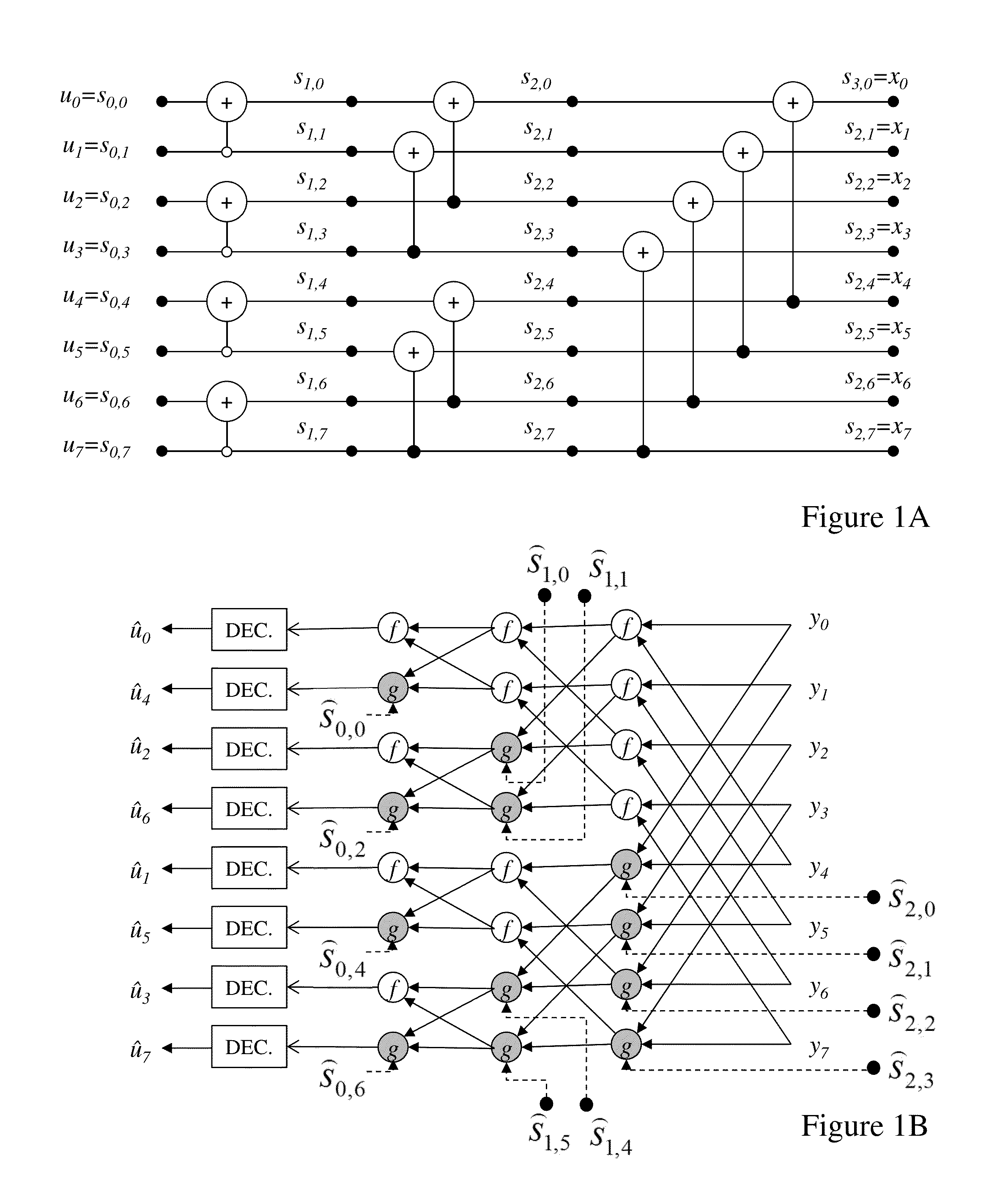

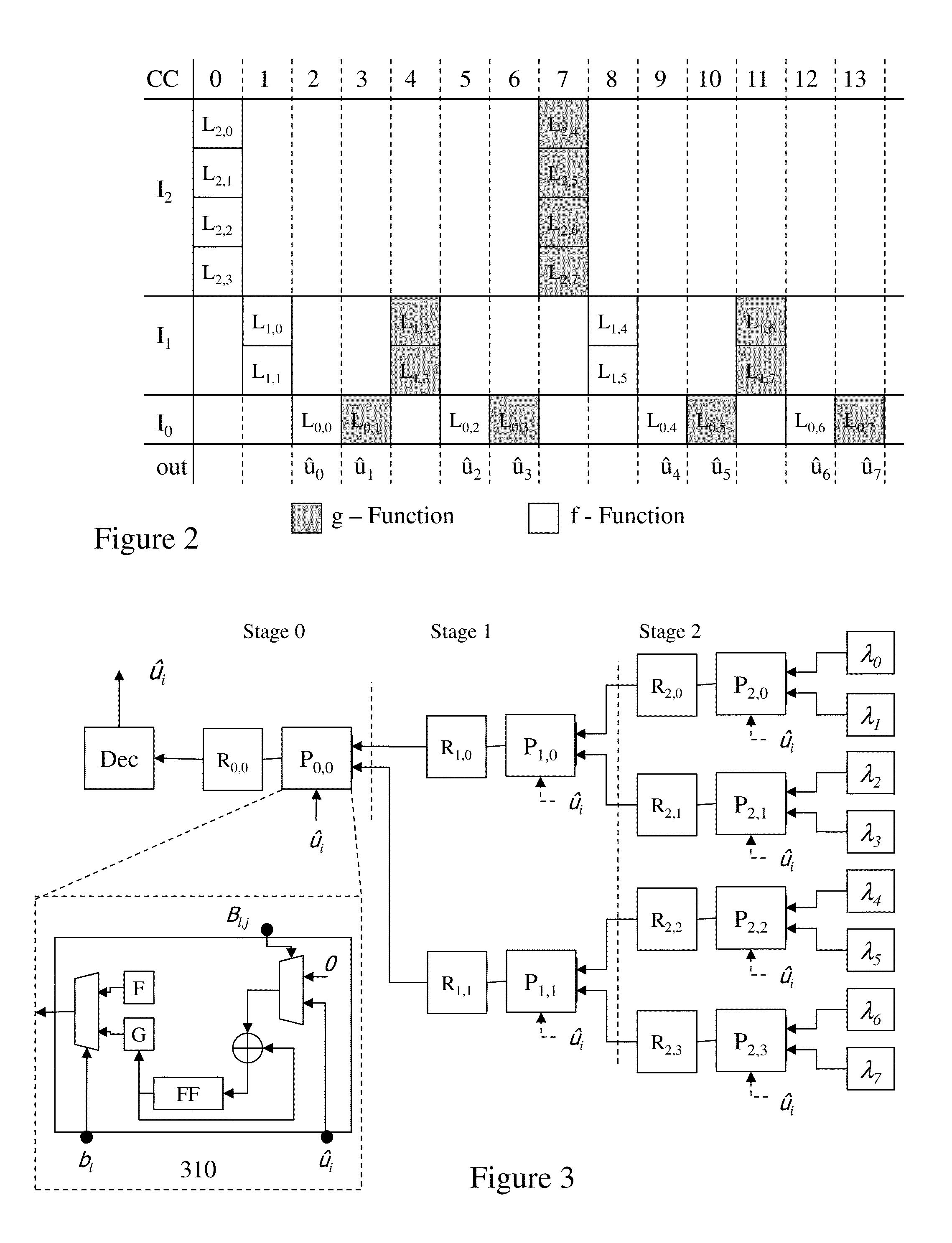

Methods and Systems for Decoding Polar Codes

ActiveUS20130117344A1Improve performanceMitigate such drawbackCode conversionError correction/detection using linear codesProcessing elementHardware implementations

Coding within noisy communications channels is essential but a theoretical maximum rate defines the rate at which information can be reliably transmitted on this noisy channel. Capacity-achieving codes with an explicit construction eluded researchers until polar codes were proposed. However, whilst asymptotically reaching channel capacity these require increasing code lengths, and hence increasingly complex hardware implementations. It would be beneficial to address architectures and decoding processes to reduce polar code decoder complexity both in terms of the number of processing elements required, but also the number of memory elements and the number of steps required to decode a codeword. Beneficially architectures and design methodologies established by the inventors address such issues whilst reducing overall complexity as well as providing methodologies for adjusting decoder design based upon requirements including, but not limited to, cost (e.g. through die area) and speed (e.g. through latency, number of cycles, number of elements etc).

Owner:THE ROYAL INSTITUTION FOR THE ADVANCEMENT OF TECH MCGILL UNIV +1

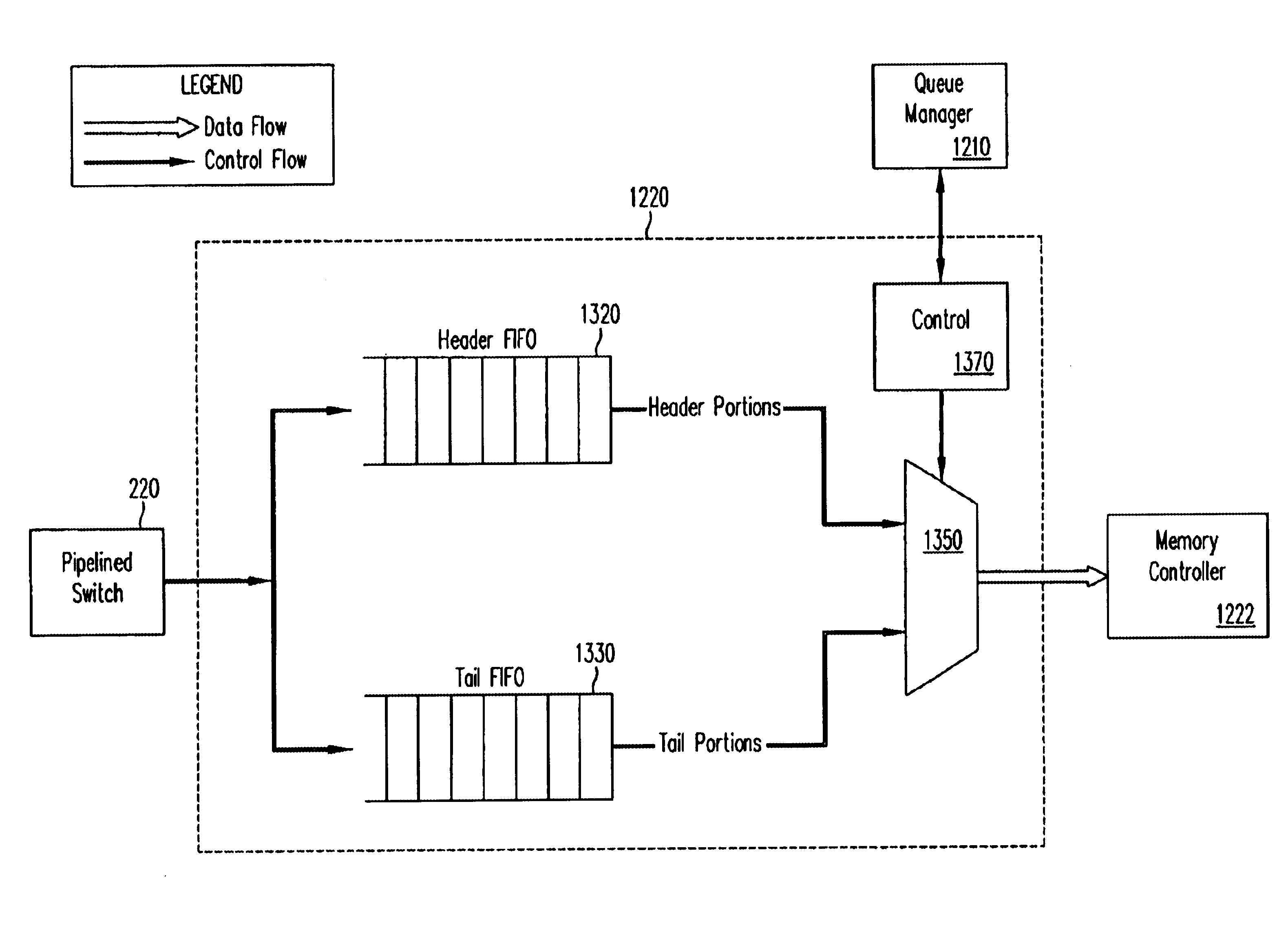

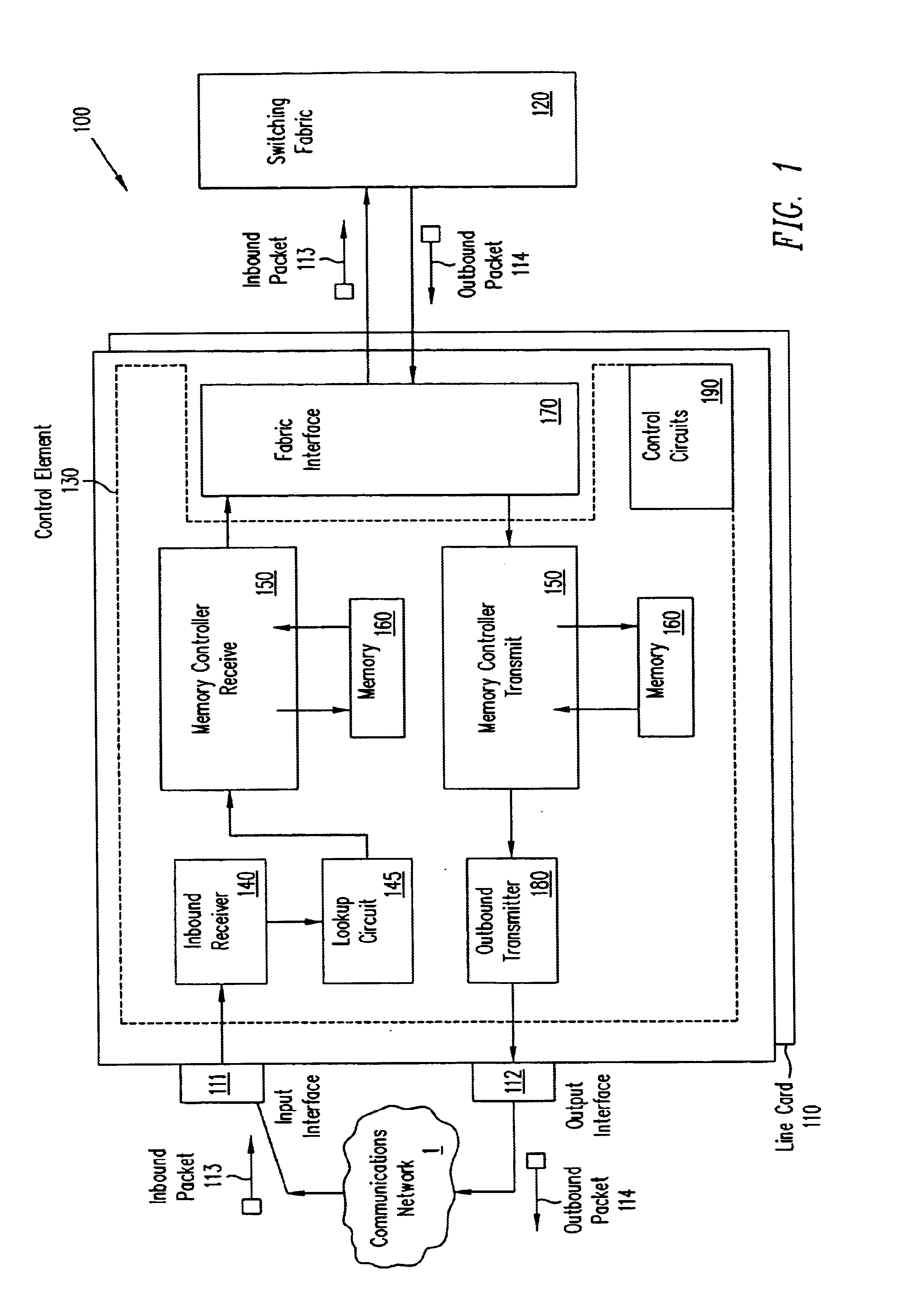

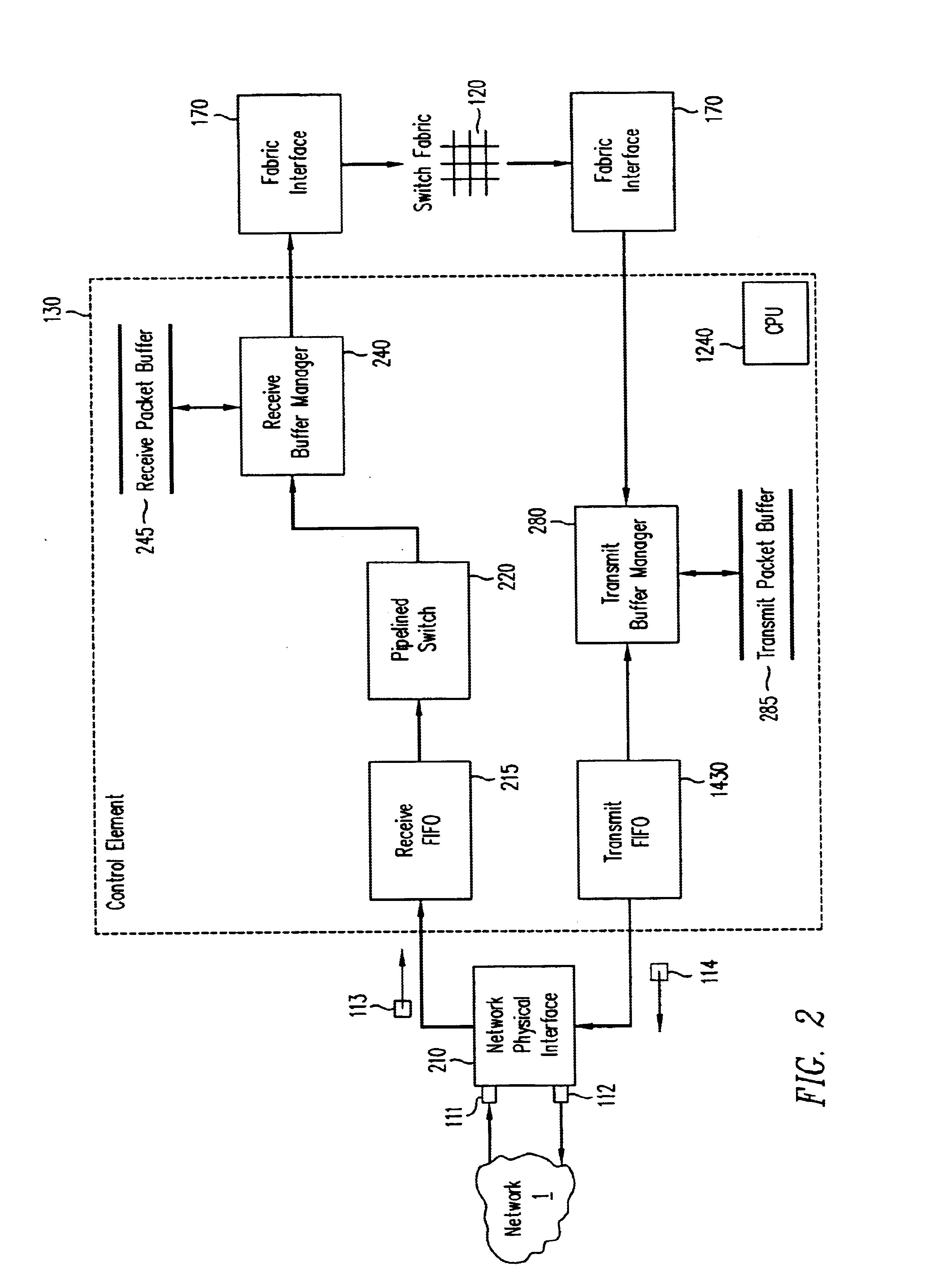

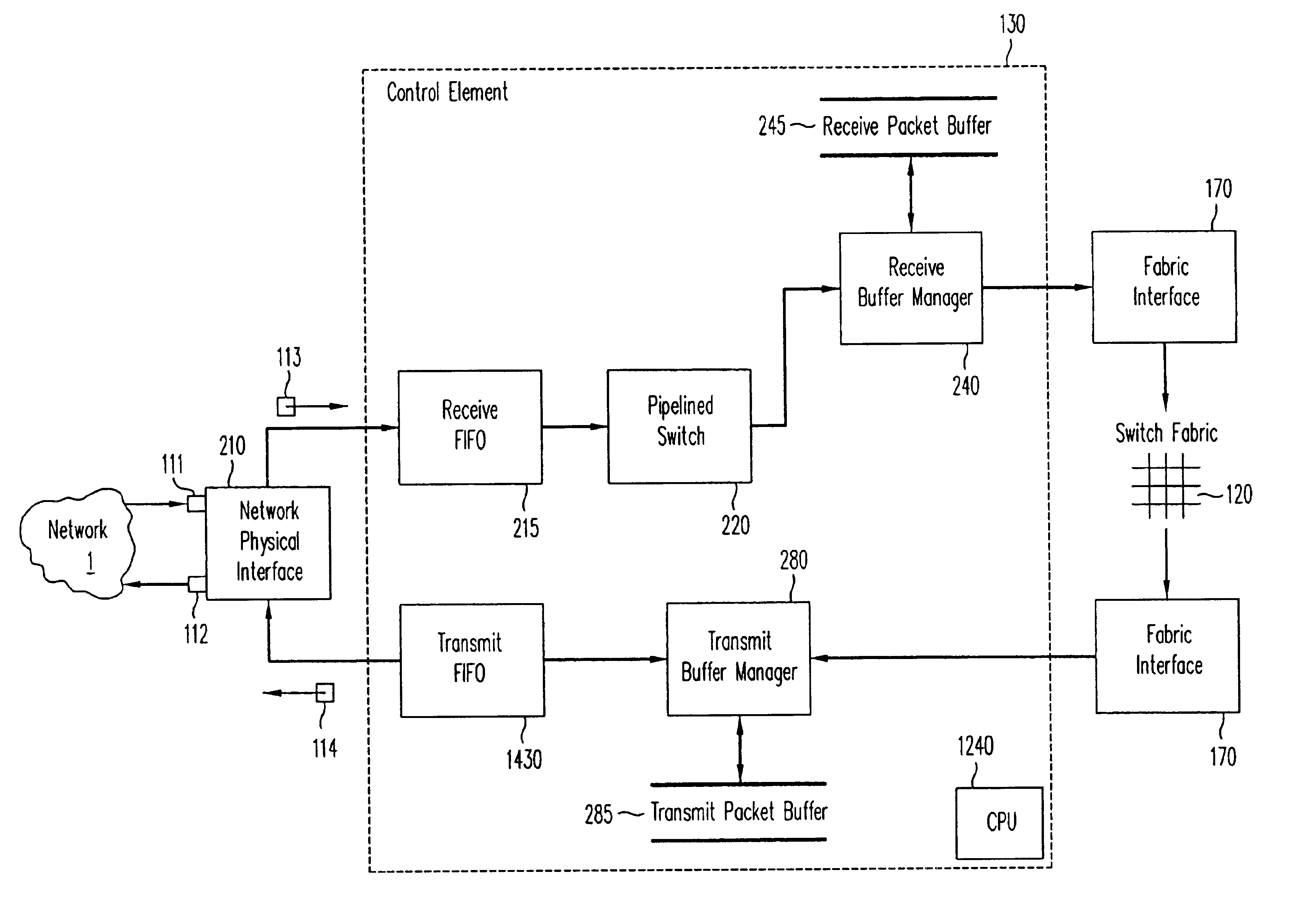

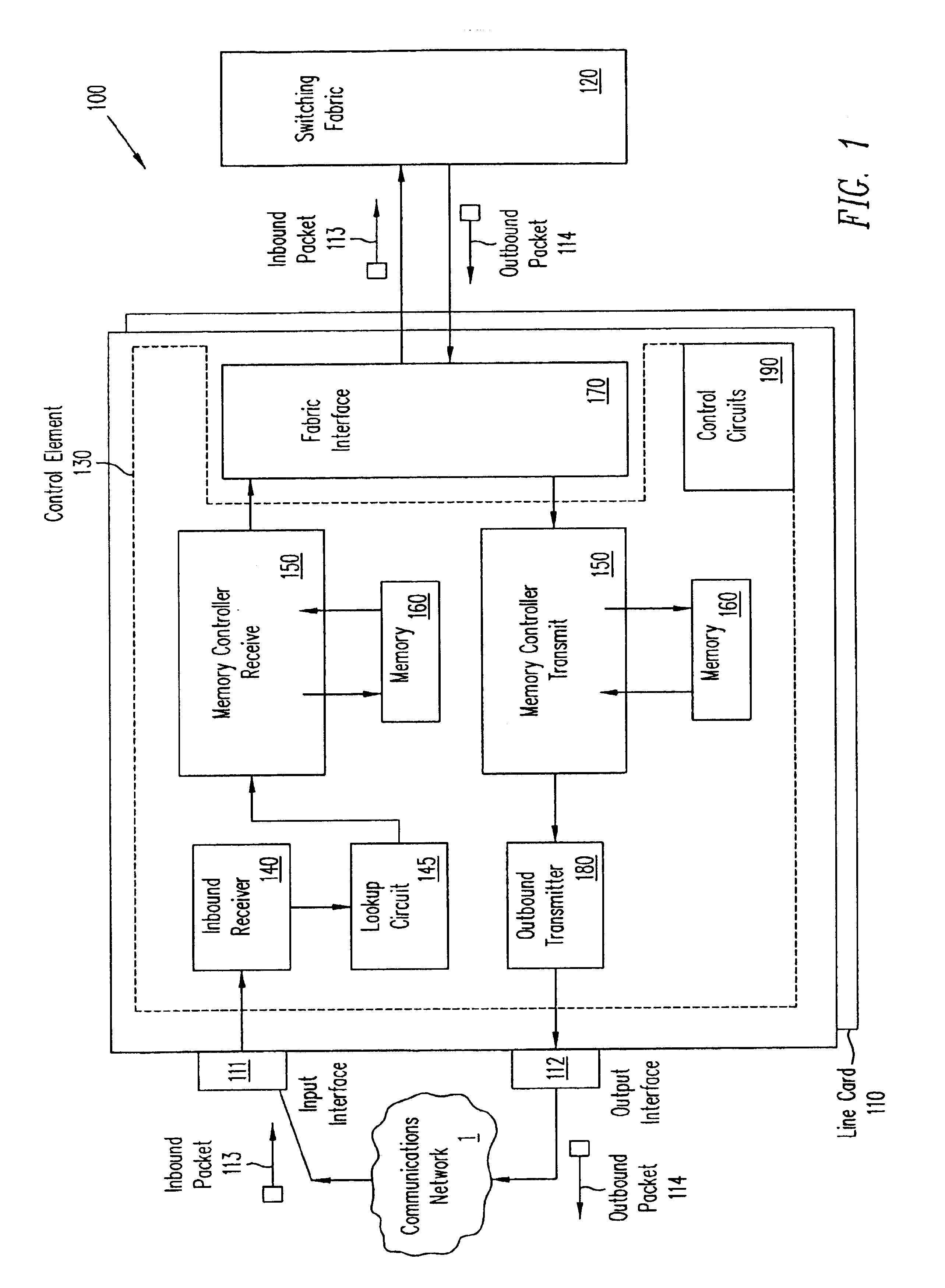

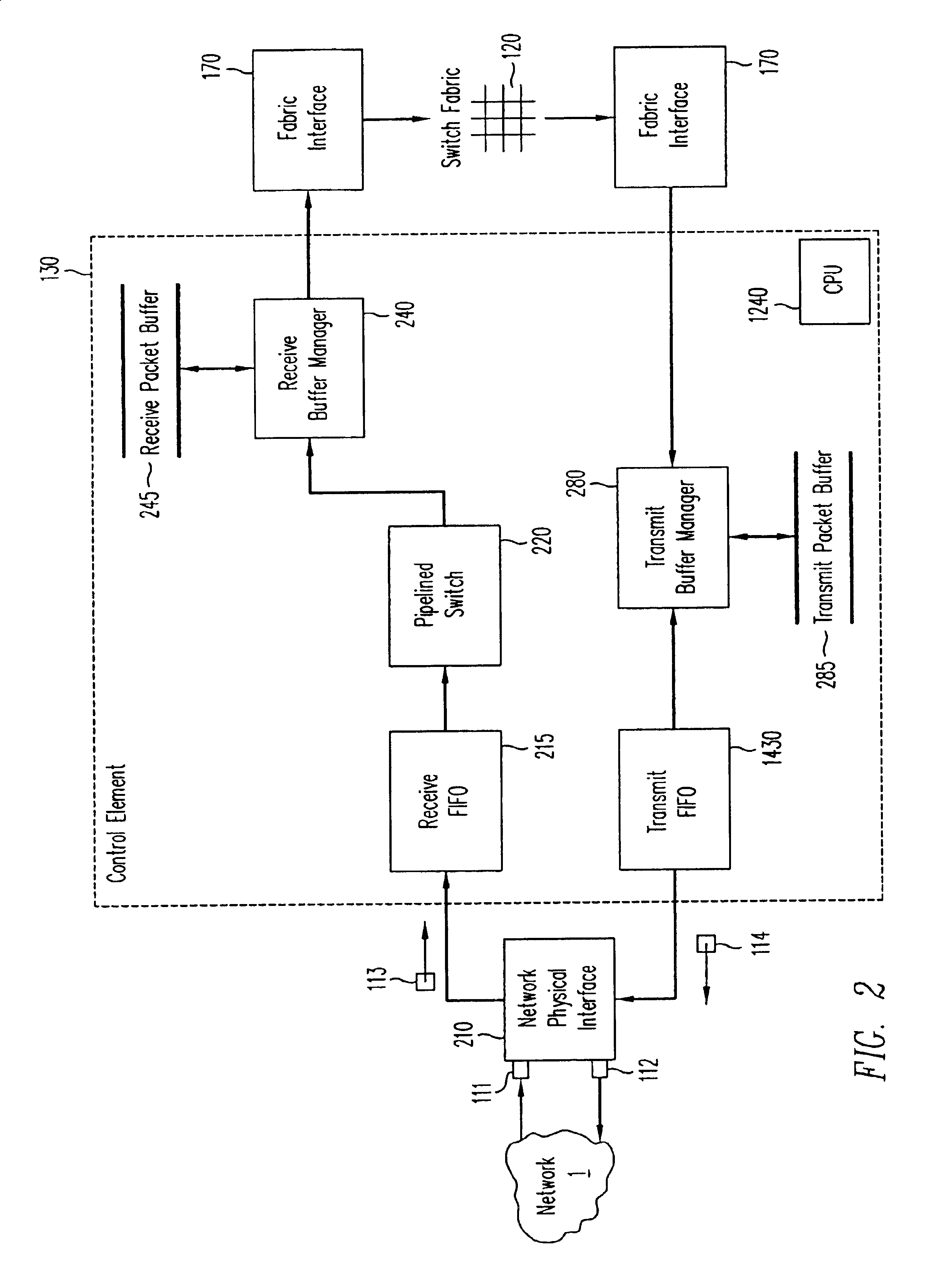

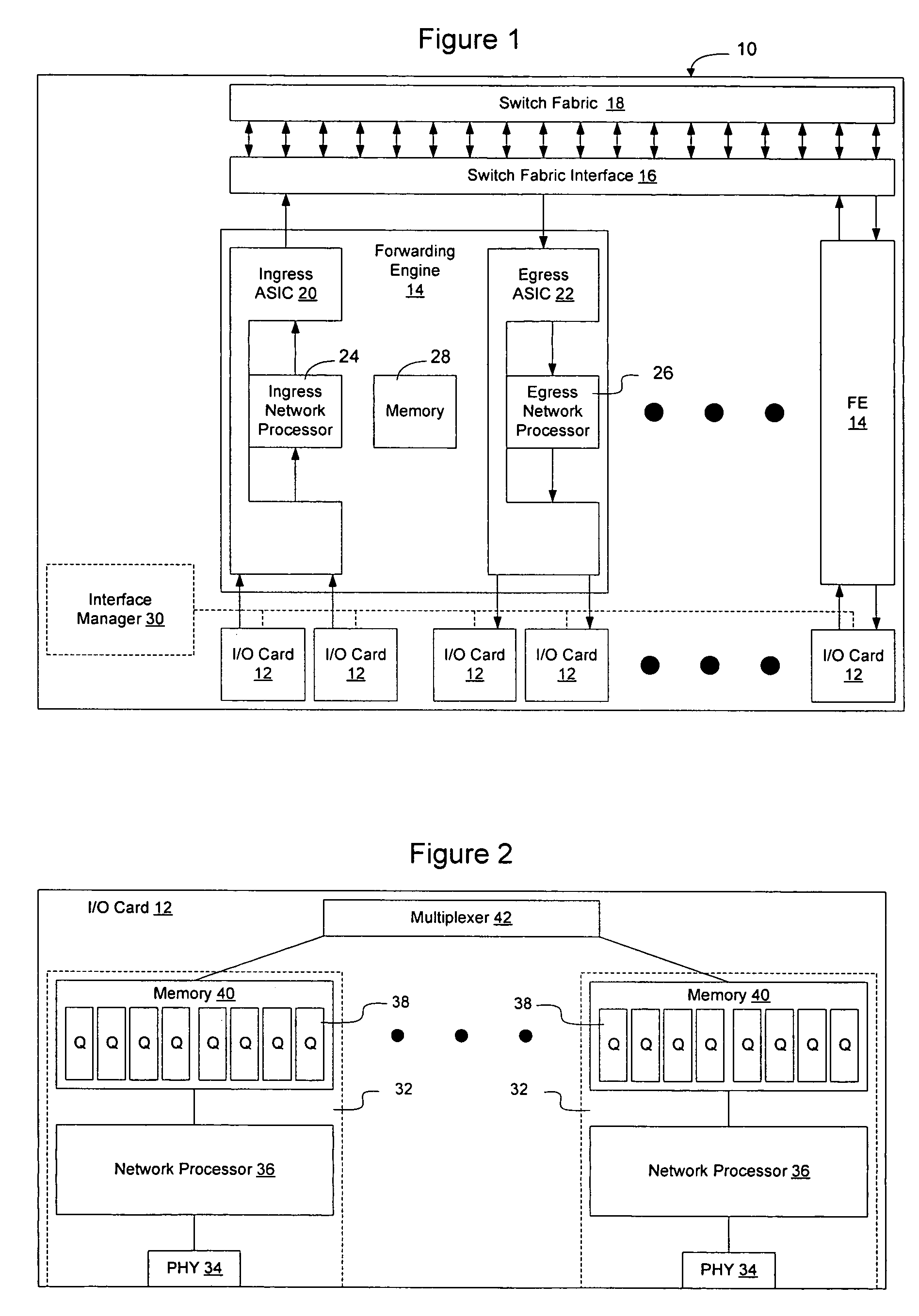

High-speed hardware implementation of MDRR algorithm over a large number of queues

InactiveUS6778546B1Data switching by path configurationStore-and-forward switching systemsHardware implementationsComputer science

A pipelined linecard architecture for receiving, modifying, switching, buffering, queuing and dequeuing packets for transmission in a communications network. The linecard has two paths: the receive path, which carries packets into the switch device from the network, and the transmit path, which carries packets from the switch to the network. In the receive path, received packets are processed and switched in an asynchronous, multi-stage pipeline utilizing programmable data structures for fast table lookup and linked list traversal. The pipelined switch operates on several packets in parallel while determining each packet's routing destination. Once that determination is made, each packet is modified to contain new routing information as well as additional header data to help speed it through the switch. Each packet is then buffered and enqueued for transmission over the switching fabric to the linecard attached to the proper destination port. The destination linecard may be the same physical linecard as that receiving the inbound packet or a different physical linecard. The transmit path consists of a buffer / queuing circuit similar to that used in the receive path. Both enqueuing and dequeuing of packets is accomplished using CoS-based decision making apparatus and congestion avoidance and dequeue management hardware. The architecture of the present invention has the advantages of high throughput and the ability to rapidly implement new features and capabilities.

Owner:CISCO TECH INC

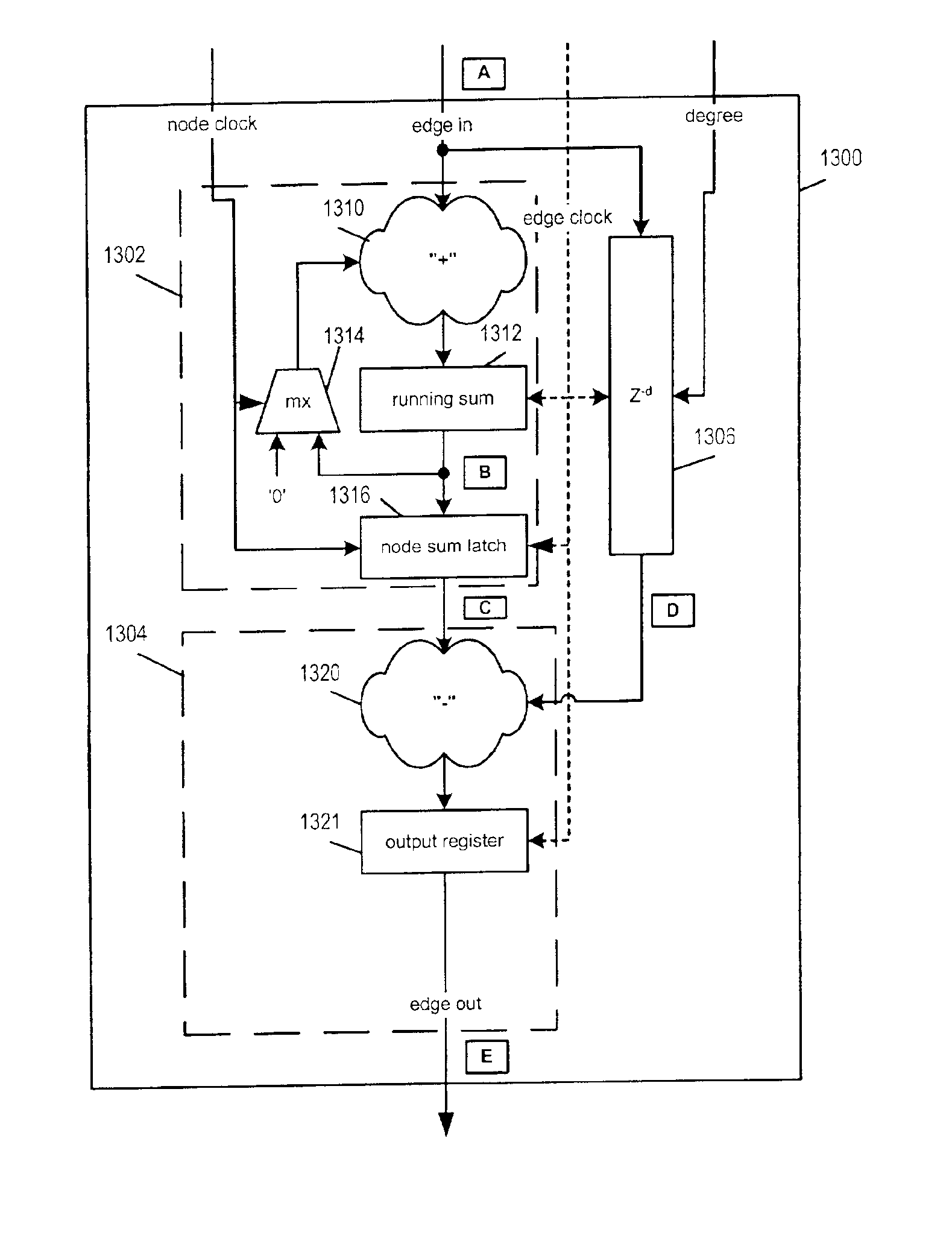

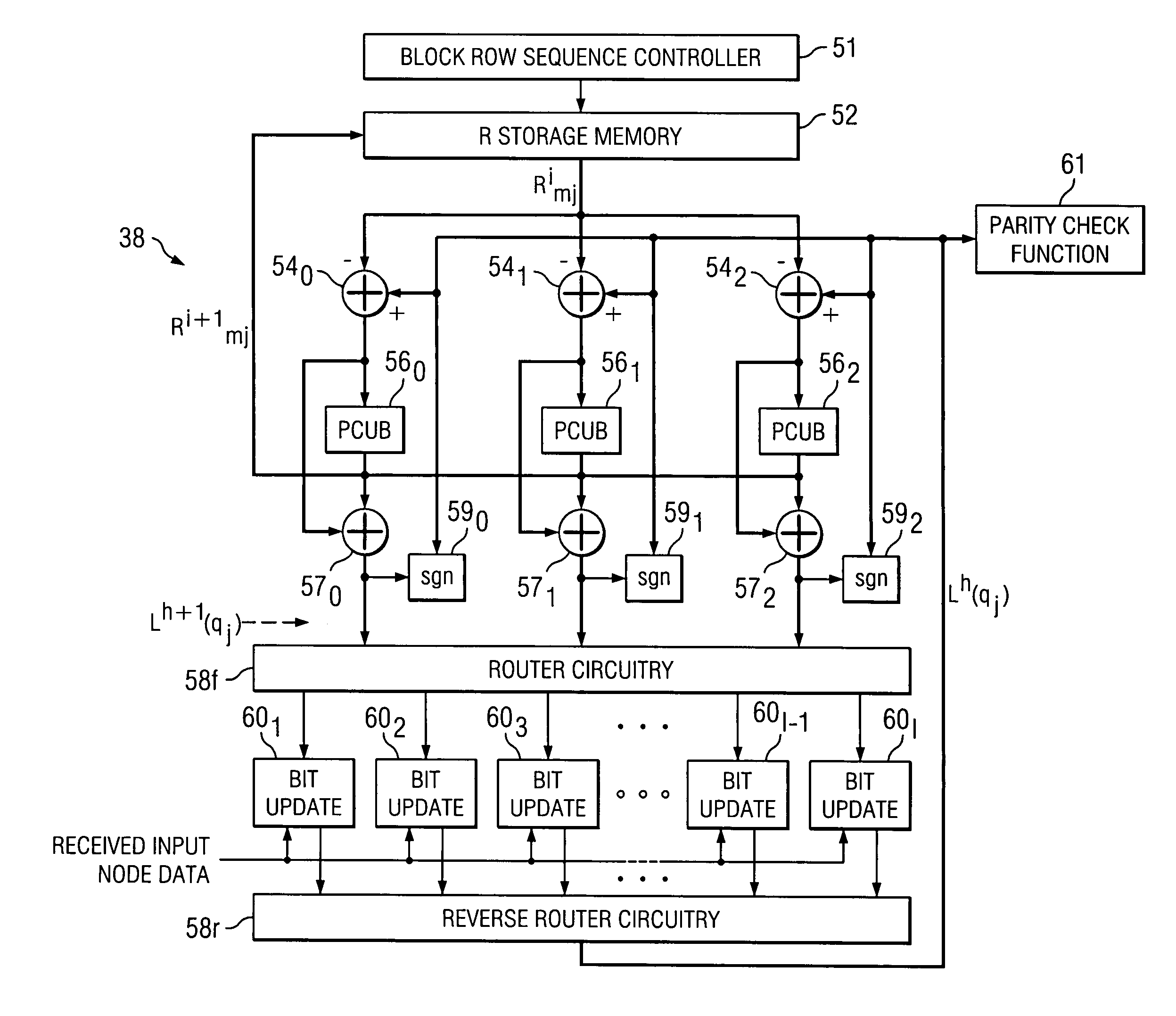

Node processors for use in parity check decoders

InactiveUS6938196B2Big errorCompensating for such errorError prevention/detection by using return channelOther decoding techniquesComputer moduleMessage processing

Techniques for implementing message passing decoders, e.g., LDPC decoders, are described. To facilitate hardware implementation messages are quantized to integer multiples of ½ ln2. Messages are transformed between more compact variable and less compact constraint node message representation formats. The variable node message format allows variable node message operations to be performed through simple additions and subtractions while the constraint node representation allows constraint node message processing to be performed through simple additions and subtractions. Variable and constraint nodes are implemented using an accumulator module, subtractor module and delay pipeline. The accumulator module generates an accumulated message sum. The accumulated message sum for a node is stored and then delayed input messages from the delay pipeline are subtracted there from to generate output messages. The delay pipeline includes a variable delay element making it possible to sequentially perform processing operations corresponding to nodes of different degrees.

Owner:QUALCOMM INC

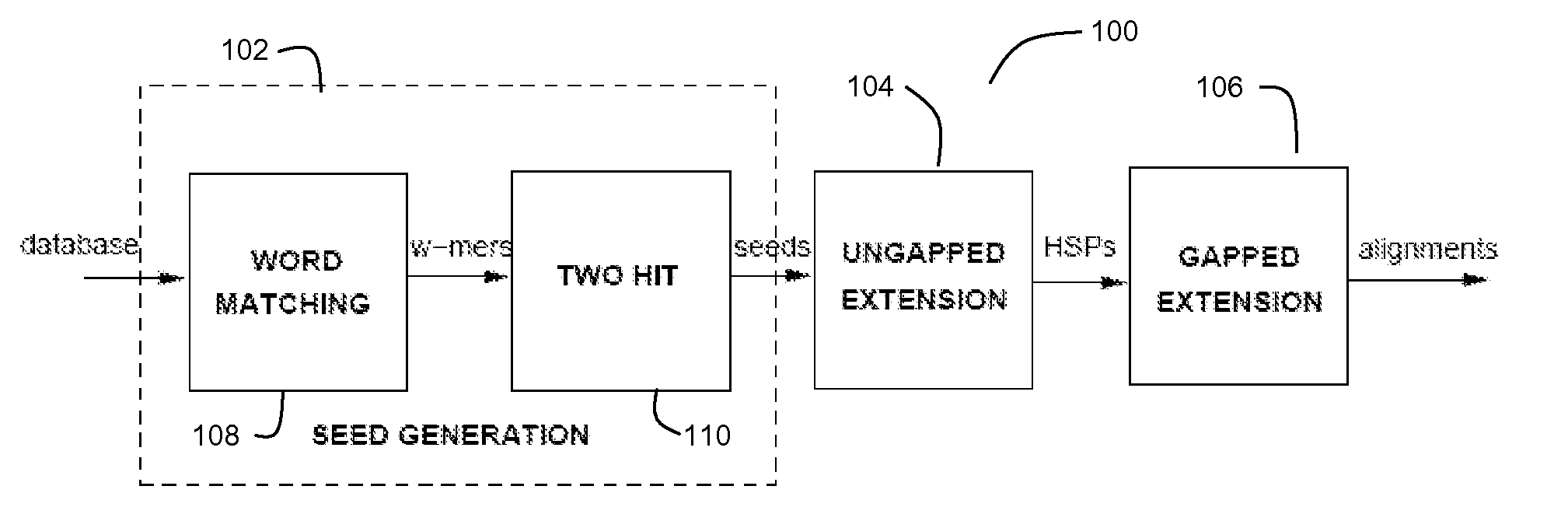

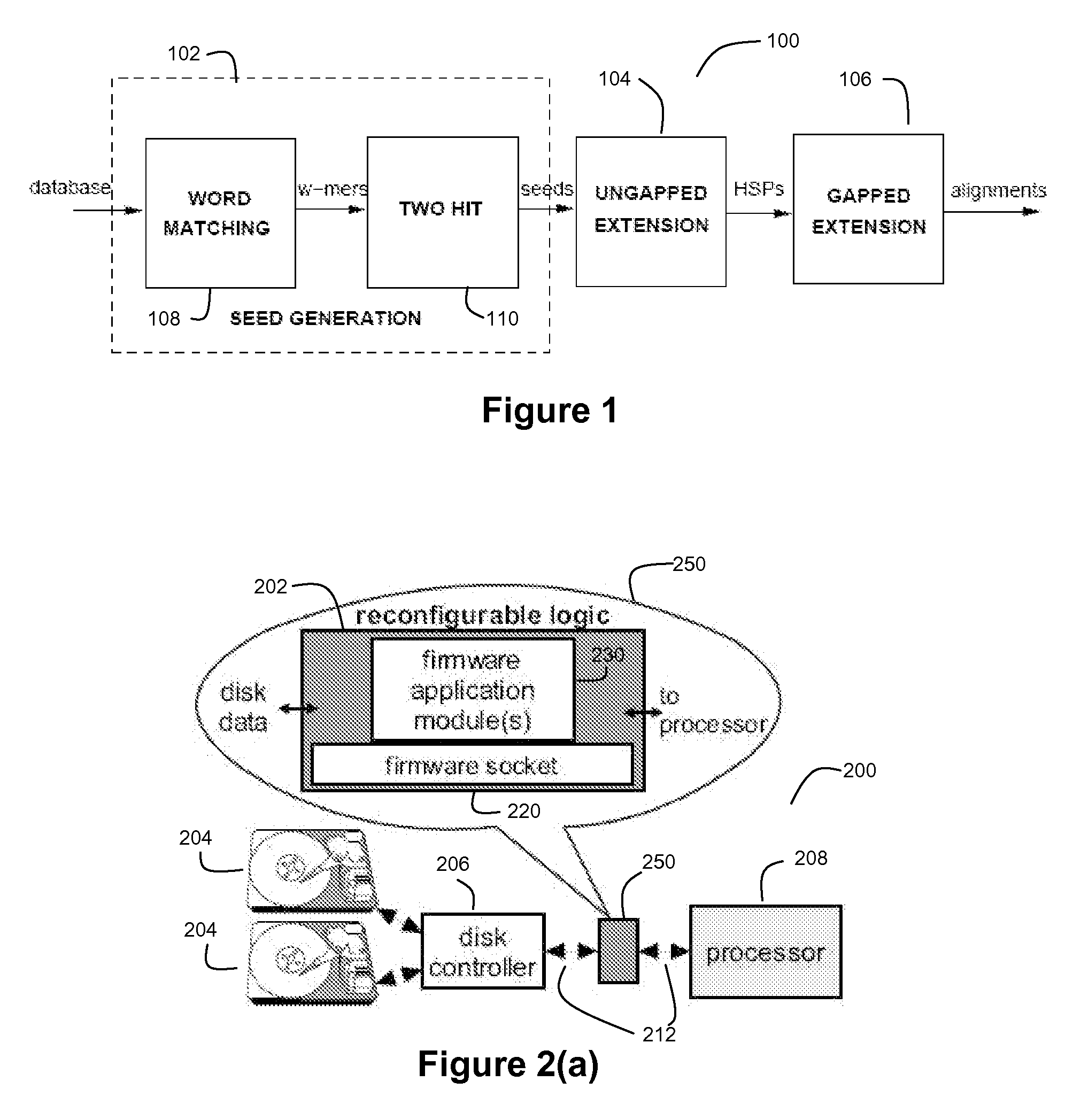

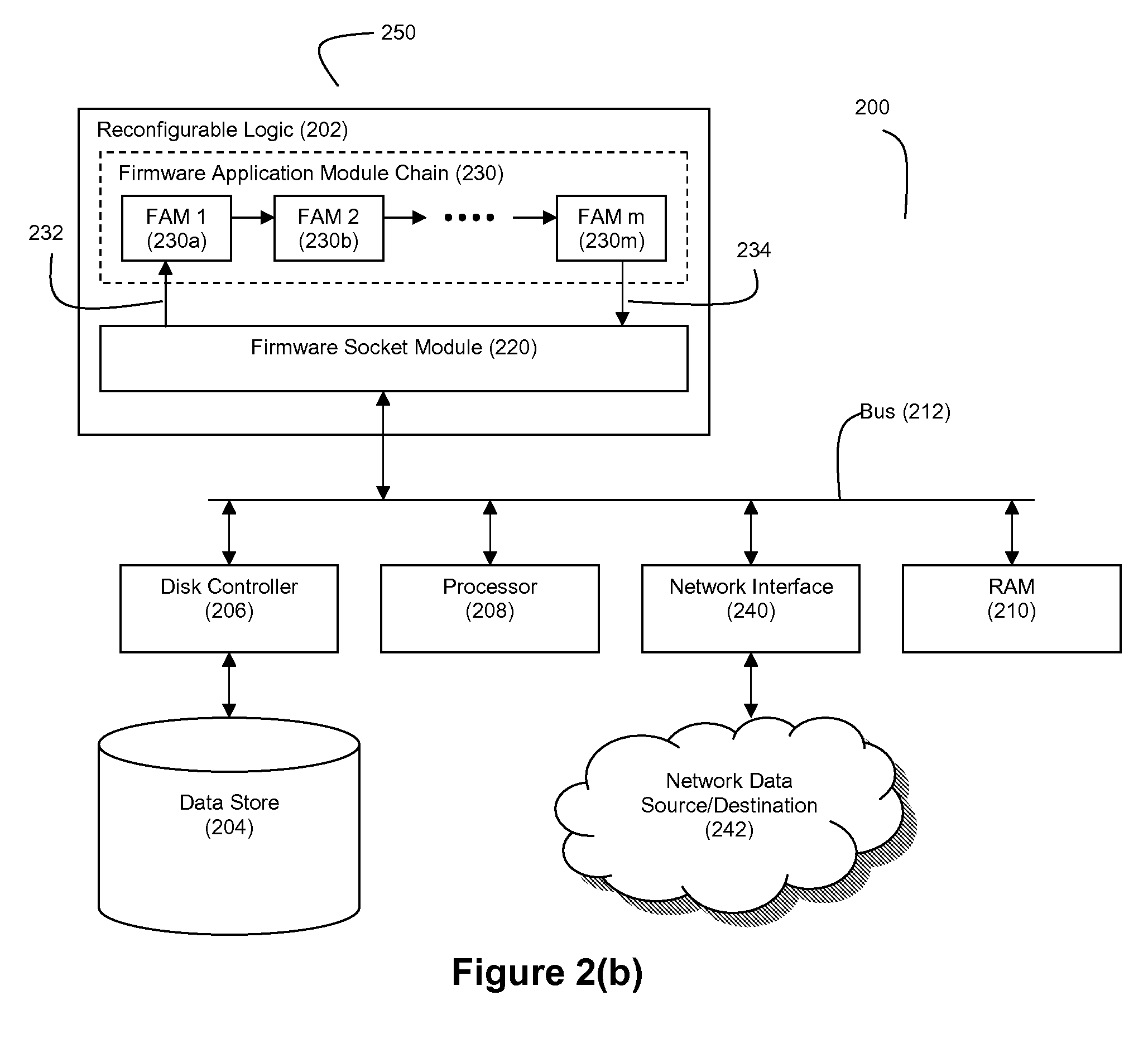

Method and Apparatus for Protein Sequence Alignment Using FPGA Devices

InactiveUS20080086274A1Quick understandingImprove throughputBiological testingSequence analysisAdemetionineHardware implementations

Disclosed herein is a hardware implementation for performing sequence alignment that preferably deploys a seed generation stage, an ungapped extension stage, and at least a portion of a gapped extension stage as a data processing pipeline on at least one hardware logic device. Hardware circuits for the seed generation stage, the ungapped extension stage, and the gapped extension stage are individually disclosed. In a preferred embodiment, the pipeline is arranged for performing BLASTP sequence alignment searching. Also, in a preferred embodiment, the at least one hardware logic device comprises at least one reconfigurable logic device such as an FPGA.

Owner:CHAMBERLAIN ROGER +4

High-speed hardware implementation of red congestion control algorithm

InactiveUS6813243B1Error preventionFrequency-division multiplex detailsParallel processingHardware implementations

A pipelined linecard architecture for receiving, modifying, switching, buffering, queuing and dequeuing packets for transmission in a communications network. The linecard has two paths: the receive path, which carries packets into the switch device from the network, and the transmit path, which carries packets from the switch to the network. In the receive path, received packets are processed and switched in an asynchronous, multi-stage pipeline utilizing programmable data structures for fast table lookup and linked list traversal. The pipelined switch operates on several packets in parallel while determining each packet's routing destination. Once that determination is made, each packet is modified to contain new routing information as well as additional header data to help speed it through the switch. Each packet is then buffered and enqueued for transmission over the switching fabric to the linecard attached to the proper destination port. The destination linecard may be the same physical linecard as that receiving the inbound packet or a different physical linecard. The transmit path consists of a buffer / queuing circuit similar to that used in the receive path. Both enqueuing and dequeuing of packets is accomplished using CoS-based decision making apparatus and congestion avoidance and dequeue management hardware. The architecture of the present invention has the advantages of high throughput and the ability to rapidly implement new features and capabilities.

Owner:CISCO TECH INC

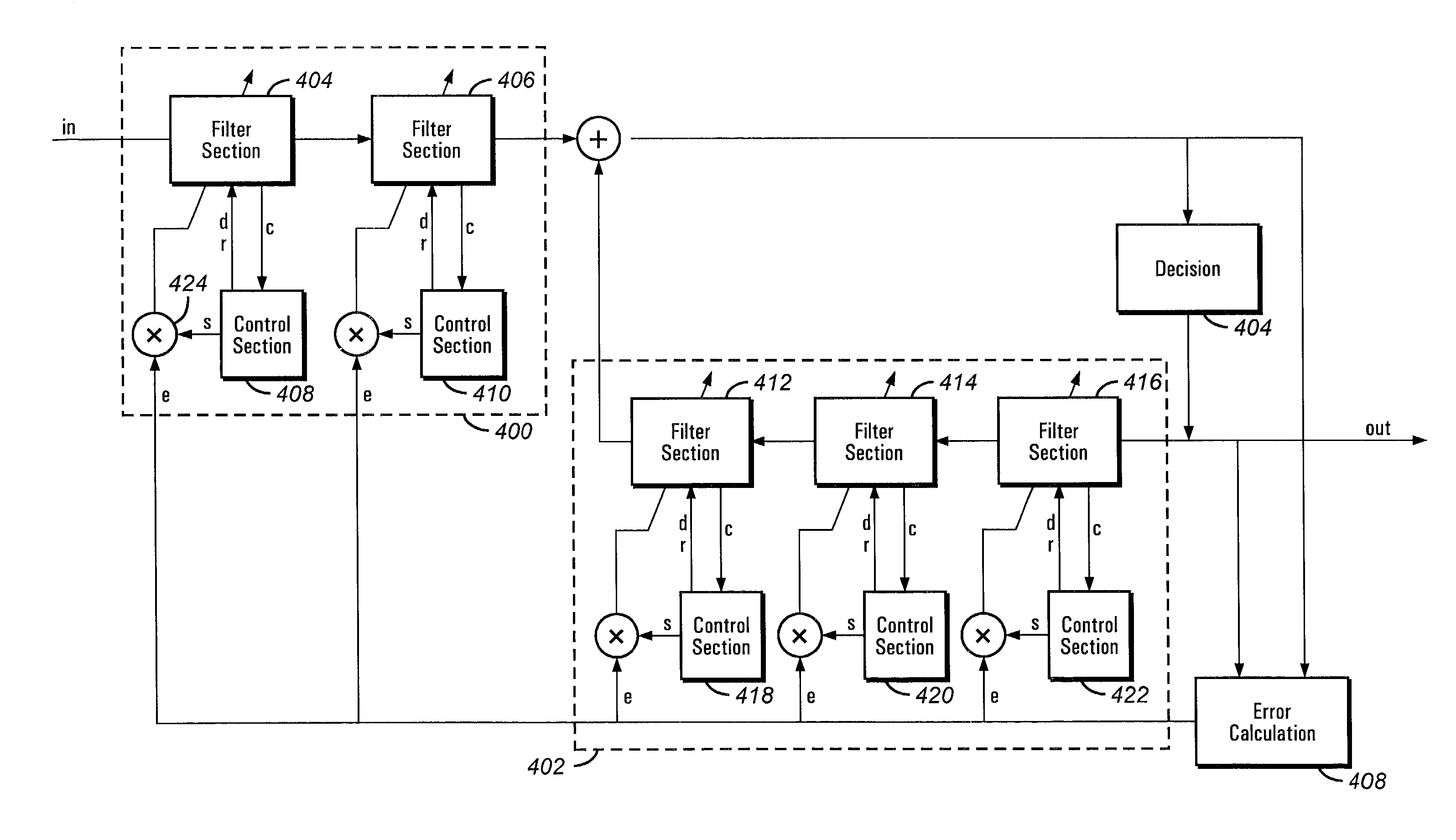

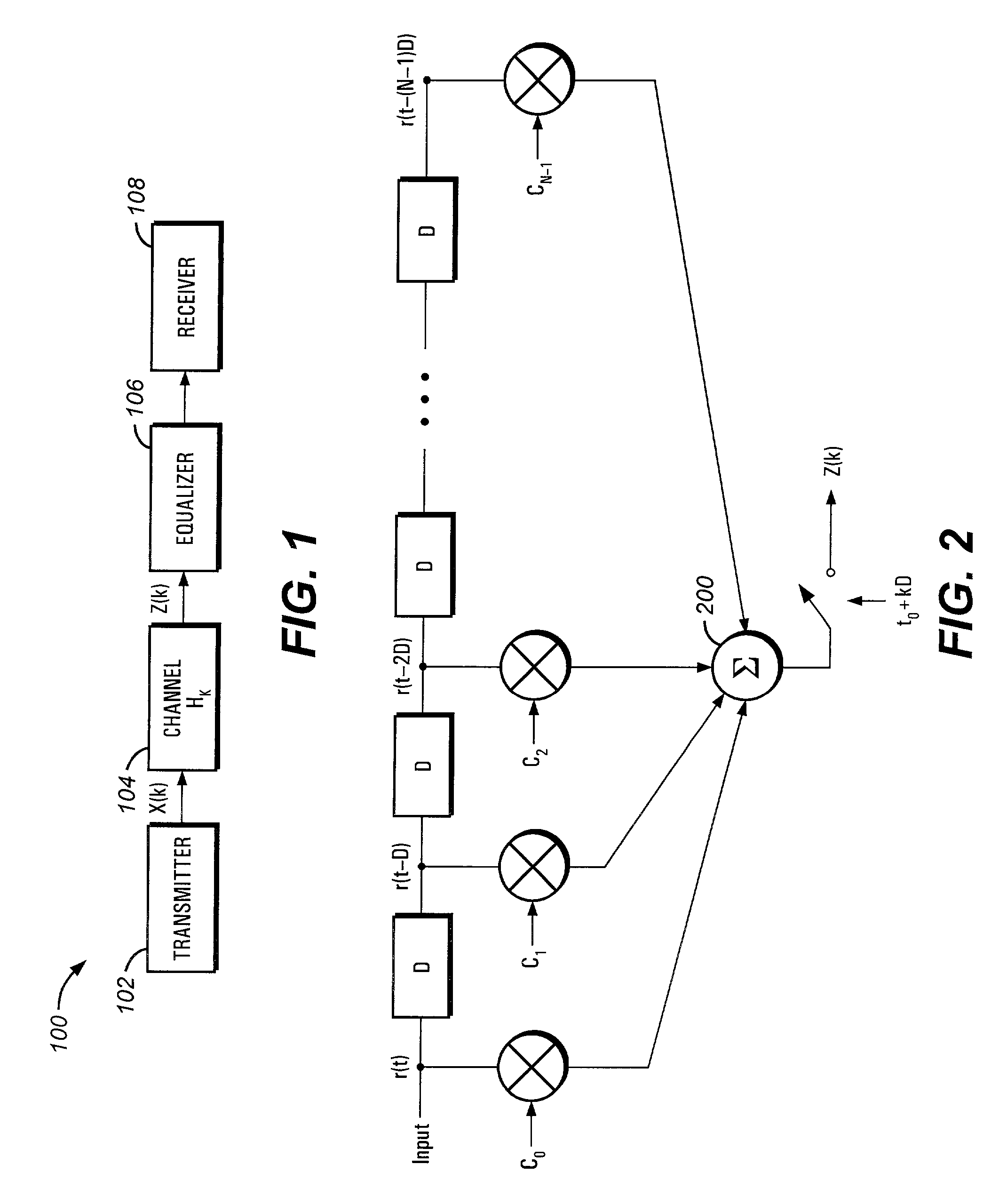

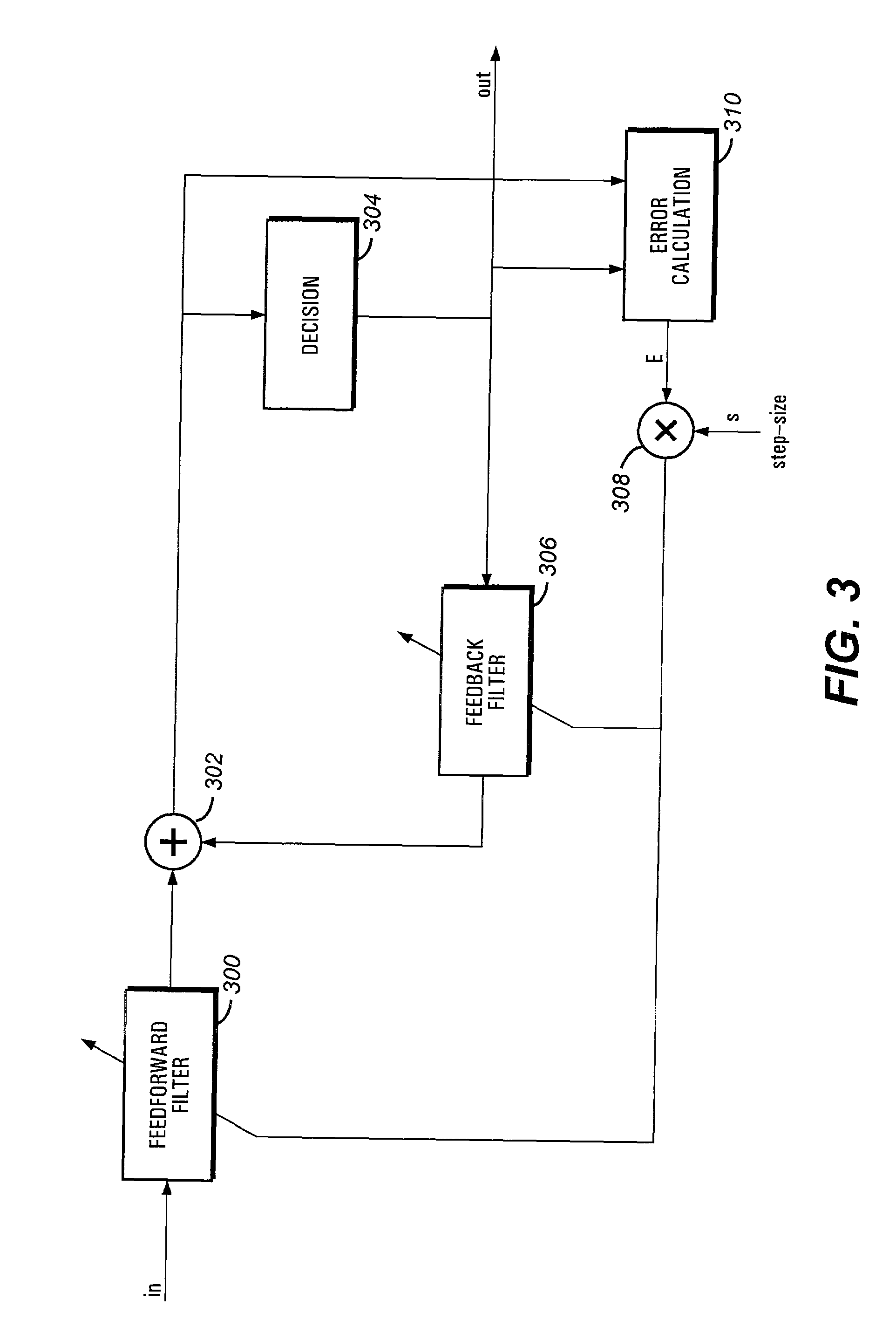

Convergence speed, lowering the excess noise and power consumption of equalizers

An equalizer for equalizing channel multi-path distortion includes digital filters. To improve the convergence speed and tracking ability of the equalizer while lowering noise and power consumption, the digital filters are divided into sections. Various parameters of the sections, such as step-size, shutdown and update rates can be controlled. Control of the various parameters can be realized either in software on an embedded or external processor or by dedicated hardware.

Owner:CONEXANT SYST INC

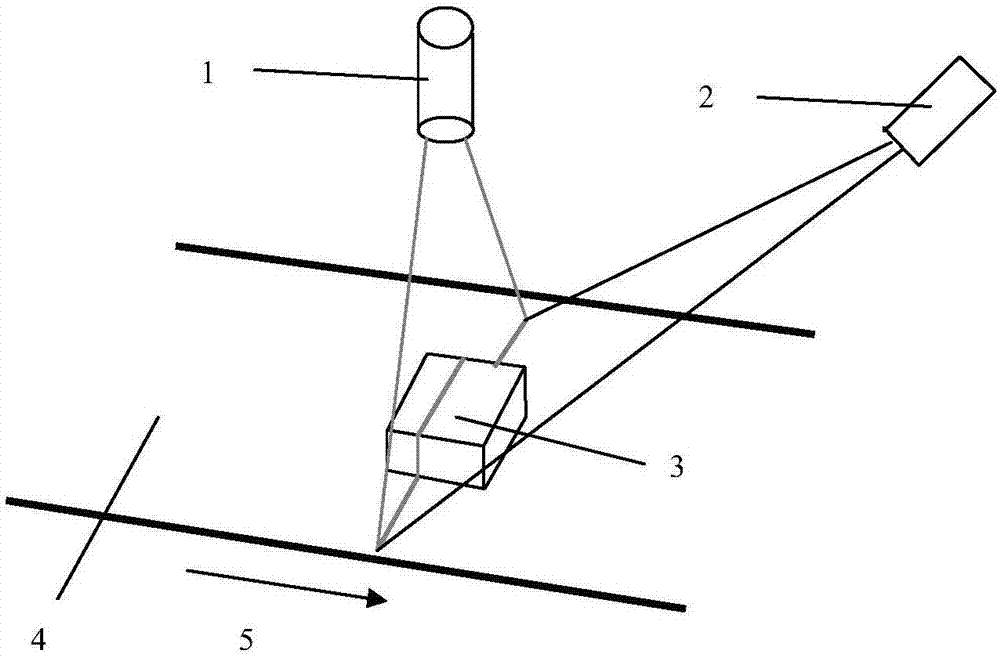

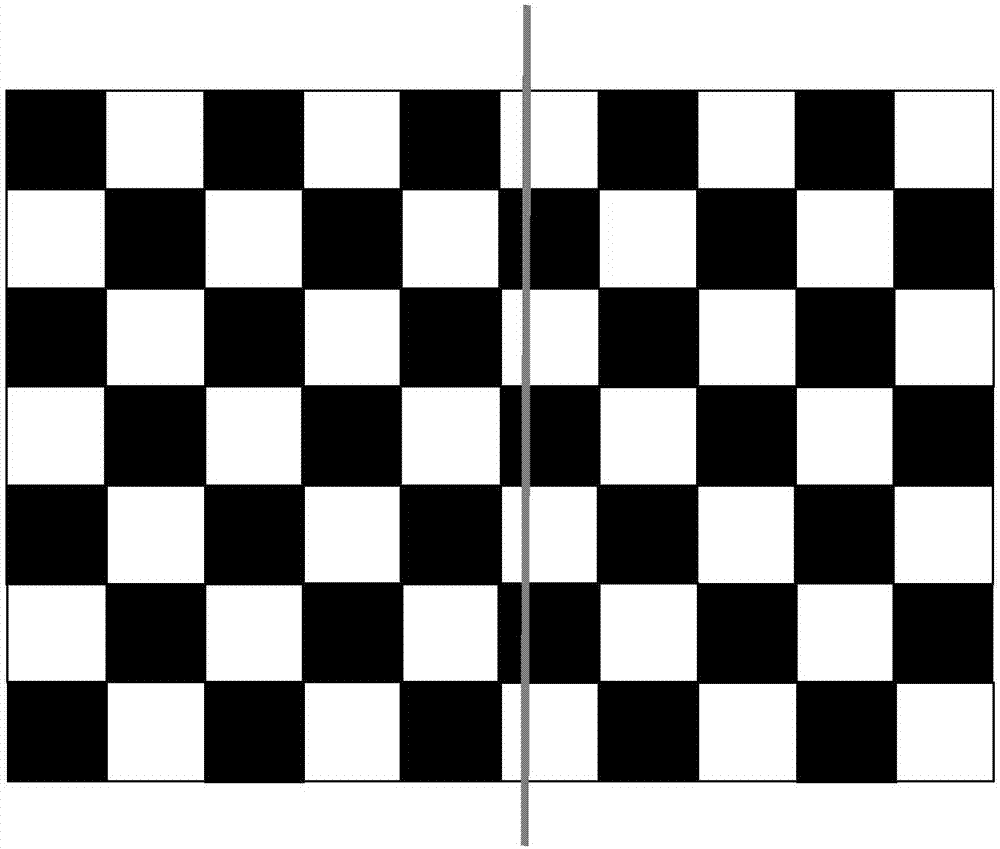

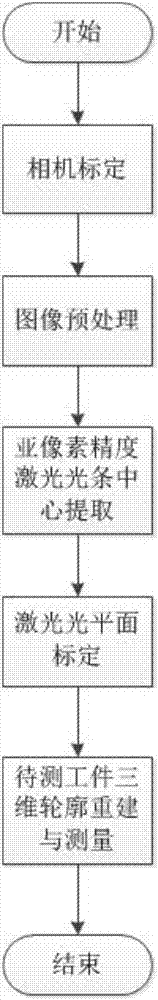

A method of 3D contour measurement of a workpiece on a conveyor belt based on line laser scanning

ActiveCN107578464AHigh measurement accuracyAccurate measurementImage analysisUsing optical meansMobile laser scanningLaser light

The invention discloses a method of 3D contour measurement of a workpiece on a conveyor belt based on line laser scanning. The method comprises the following steps of obtaining camera internal and external parameters through camera calibration, carrying out filtering and laser light strip center position initial extraction through an image preprocessing step, carrying out sub-pixel precision refinement on the center coordinates of a light bar, obtaining a light plane equation through the laser light plane calibration and finally carrying out reconstruction and measurement of the three-dimensional contour information of a workpiece to be measured. The workpiece 3D contour measurement brought forward by the invention has the following advantages: a high measurement precision which means thethree-dimensional contour information of the workpiece to be measured can be accurately obtained through the laser light bar extraction with sub-pixel precision and 3D reconstruction; a fast measurement speed which means real-time measurement of 3D contour information of the workpiece to be tested can be realized to improve the efficiency of industrial production site operations; and low hardwarecosts which is realized in a hardware implementation mode in which laser is combined with a monocular camera. Accordingly, the technical method of the application has advantages such as being in a non-contact mode, high in measurement precision, fast in speed and low in cost, and can be applied to an industrial automation production process to realize accurate measurement of the 3D contour information of the workpiece on the conveyor belt.

Owner:CHANGSHA XIANGJI HAIDUN TECH CO LTD

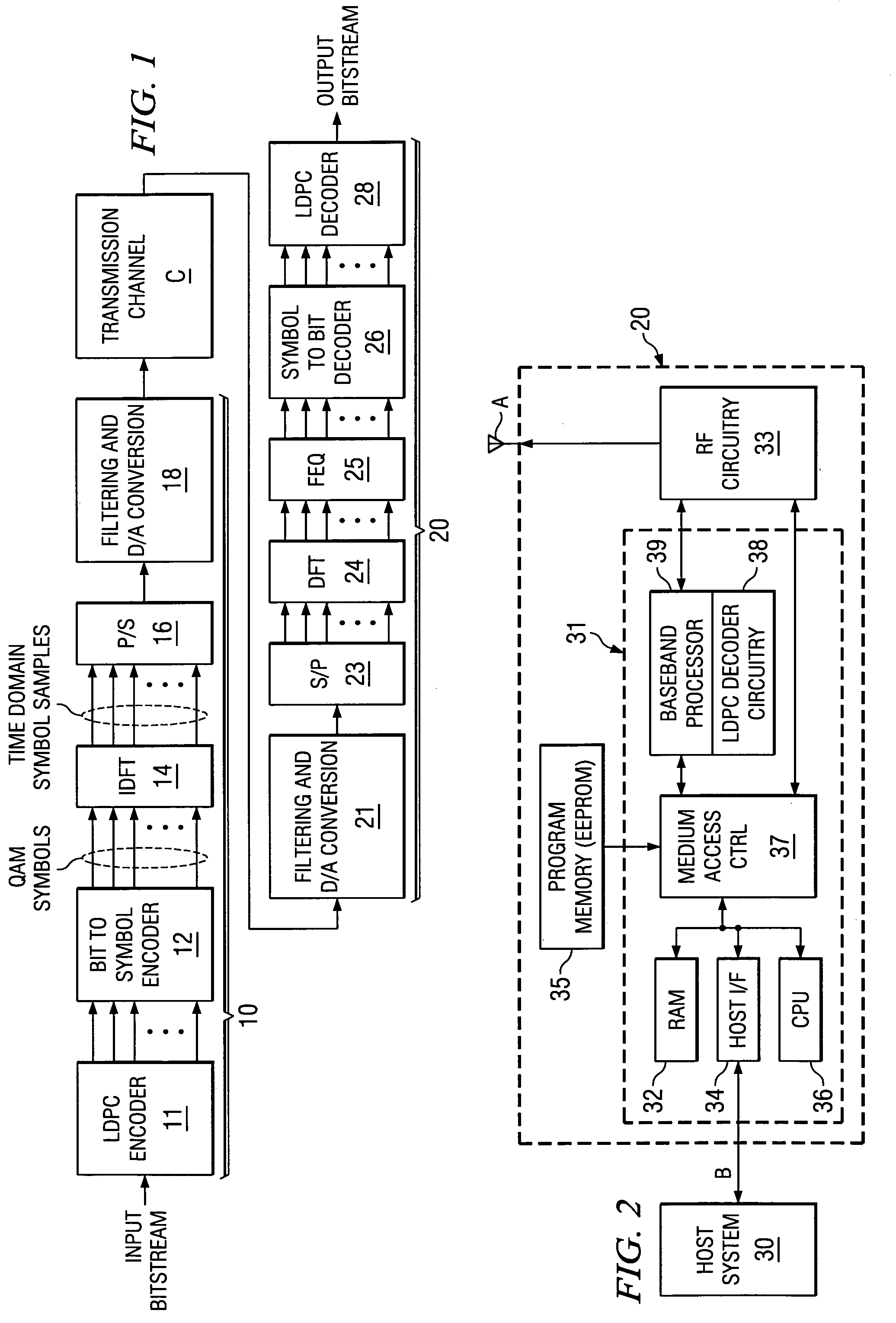

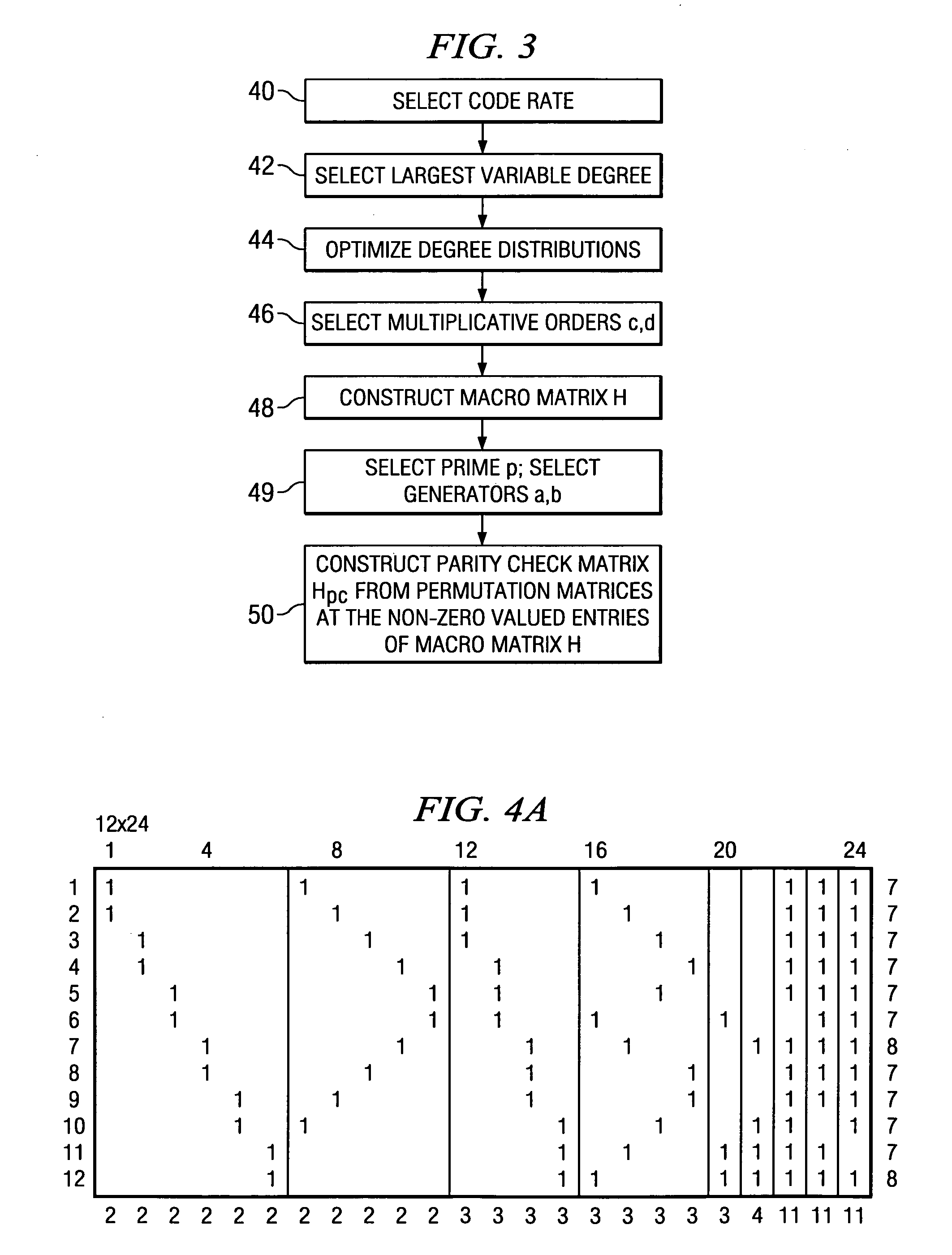

Hardware-efficient low density parity check code for digital communications

ActiveUS7178080B2Efficient implementationEfficient constructionError correction/detection using multiple parity bitsCode conversionMatrix groupParity-check matrix

Owner:TEXAS INSTR INC

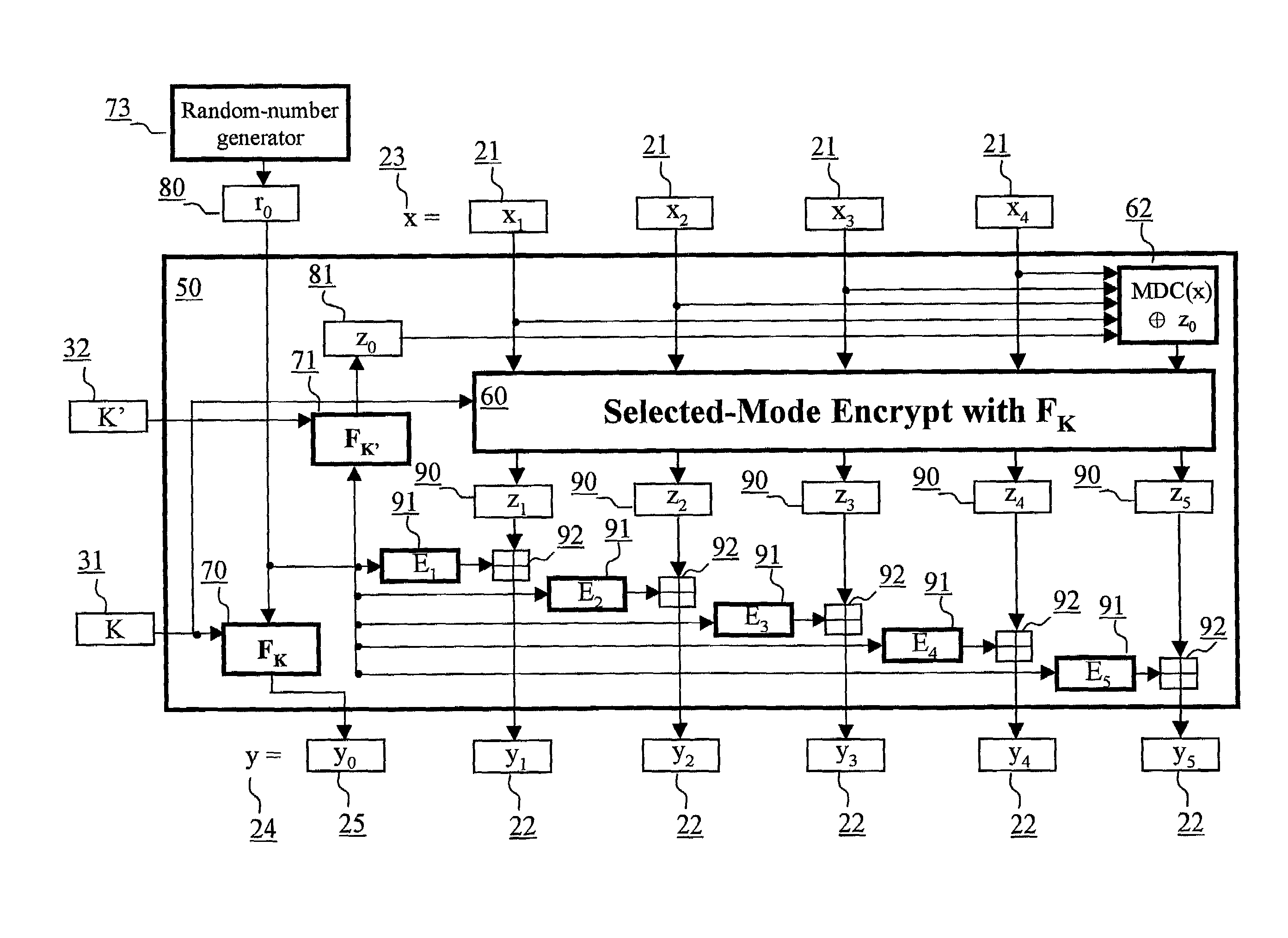

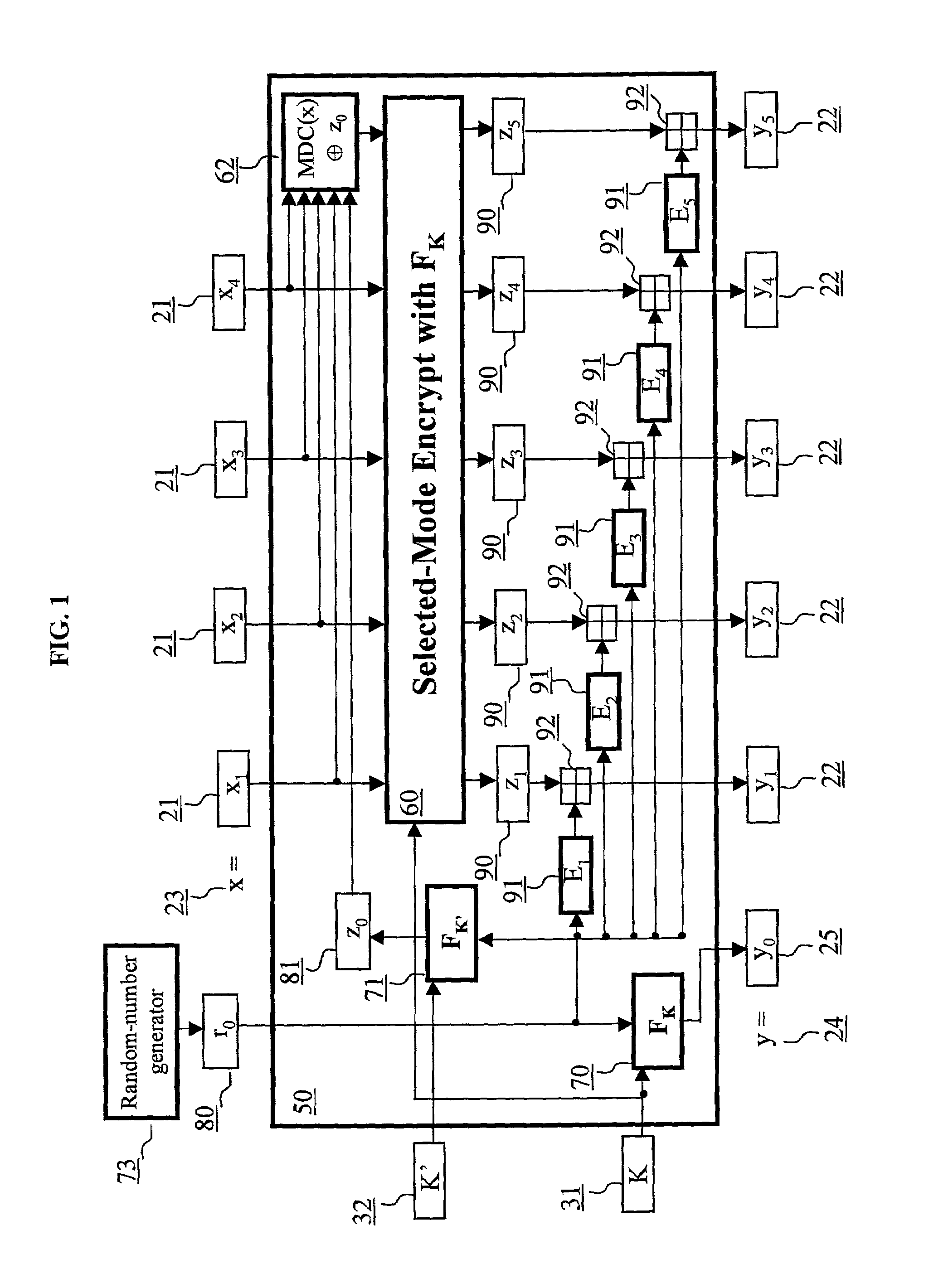

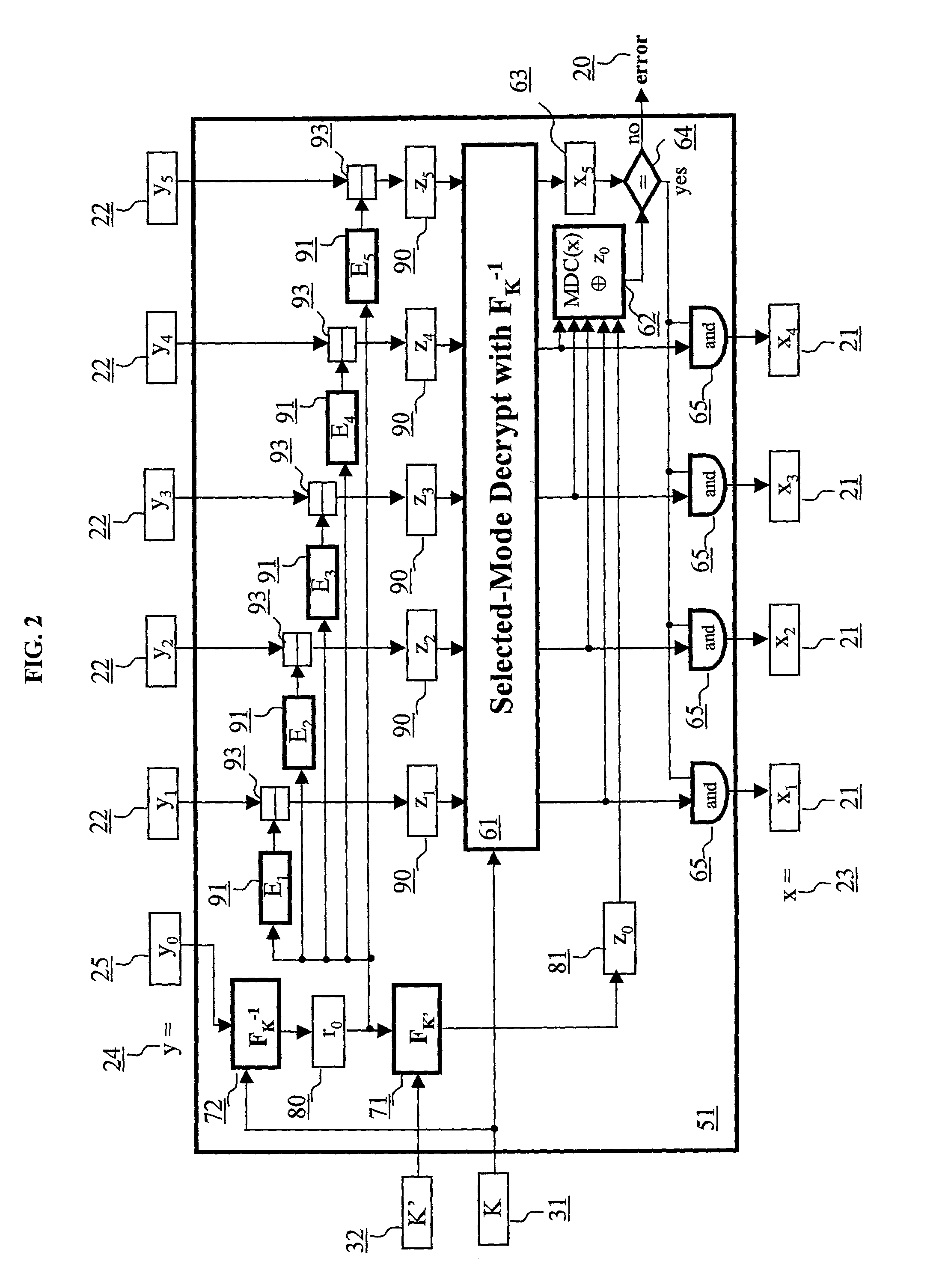

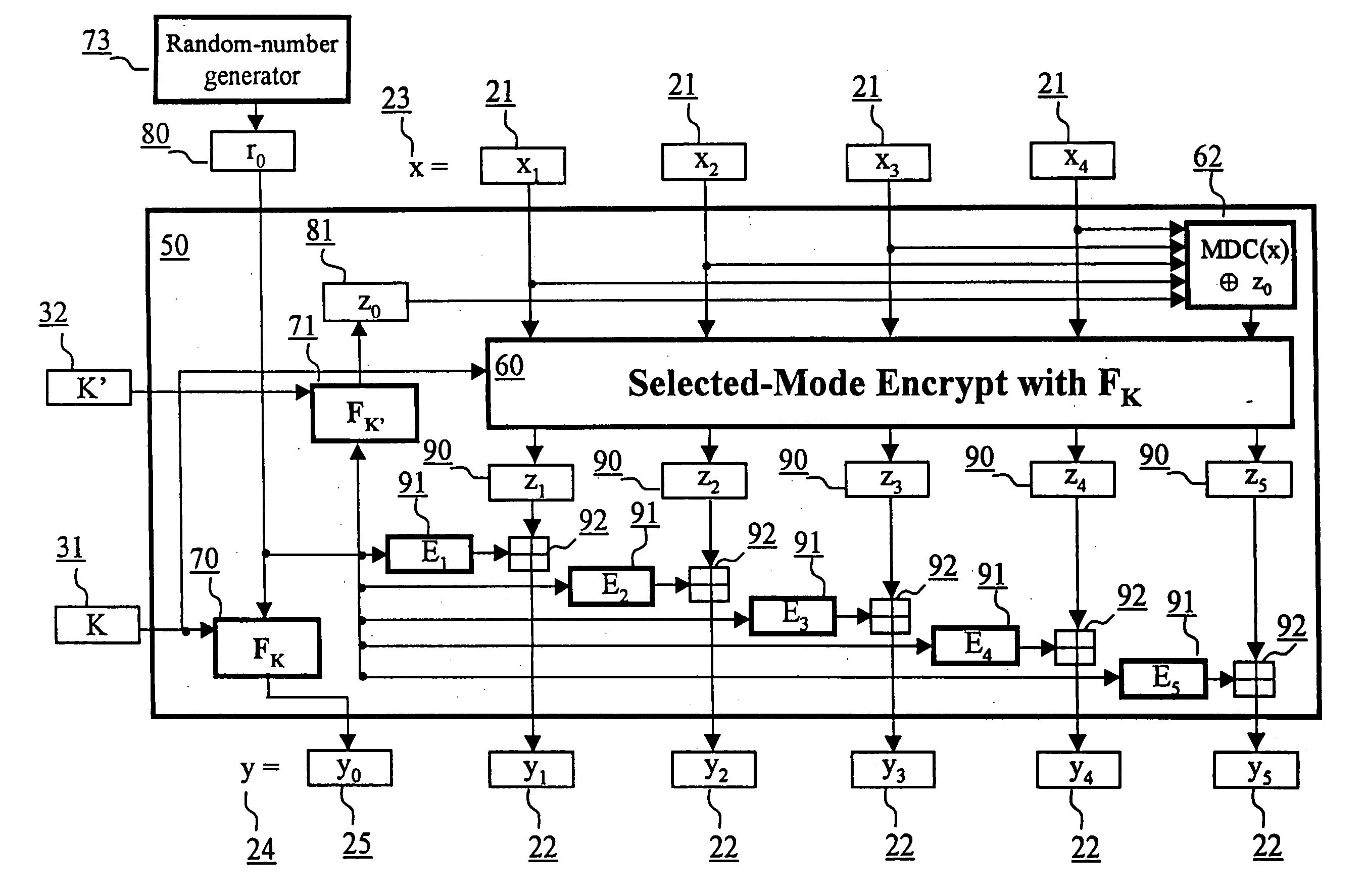

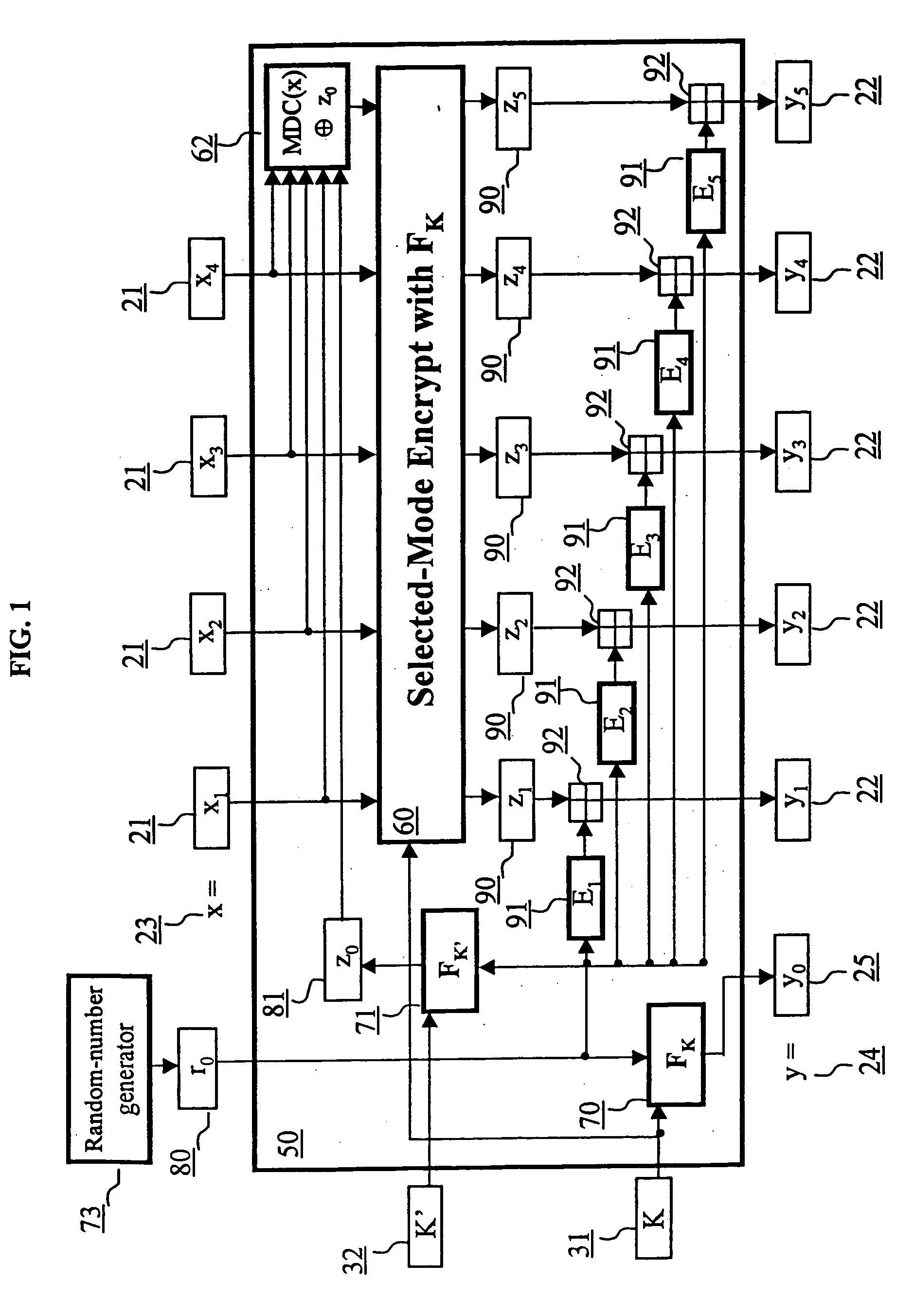

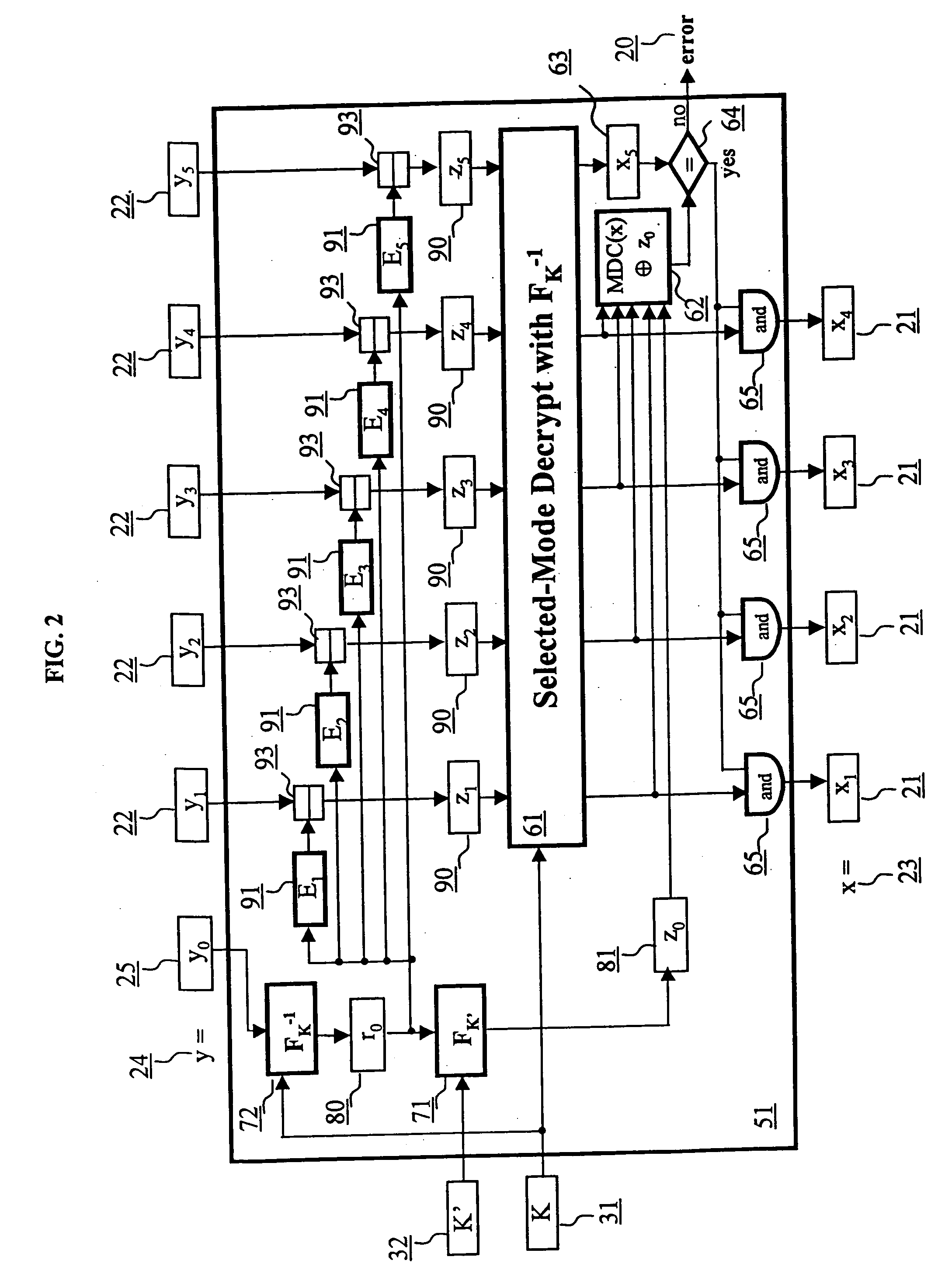

Block encryption method and schemes for data confidentiality and integrity protection

ActiveUS6973187B2Encryption apparatus with shift registers/memoriesUser identity/authority verificationPower applicationComputer hardware

A block encryption method and schemes (modes of operation) that provide both data confidentiality and integrity with a single cryptographic primitive and a single processing pass over the input plaintext string by using a non-cryptographic Manipulation Detection Code function for secure data communication over insecure channels and for secure data storage on insecure media. The present invention allows, in a further aspect, software and hardware implementations, and use in high-performance and low-power applications, and low-power, low-cost hardware devices. The block encryption method and schemes of this invention allow, in yet a further aspect, encryption and decryption in parallel or pipelined manners in addition to sequential operation. In a yet further aspect, the block encryption method and schemes of this invention are suitable for real-time applications.

Owner:VDG

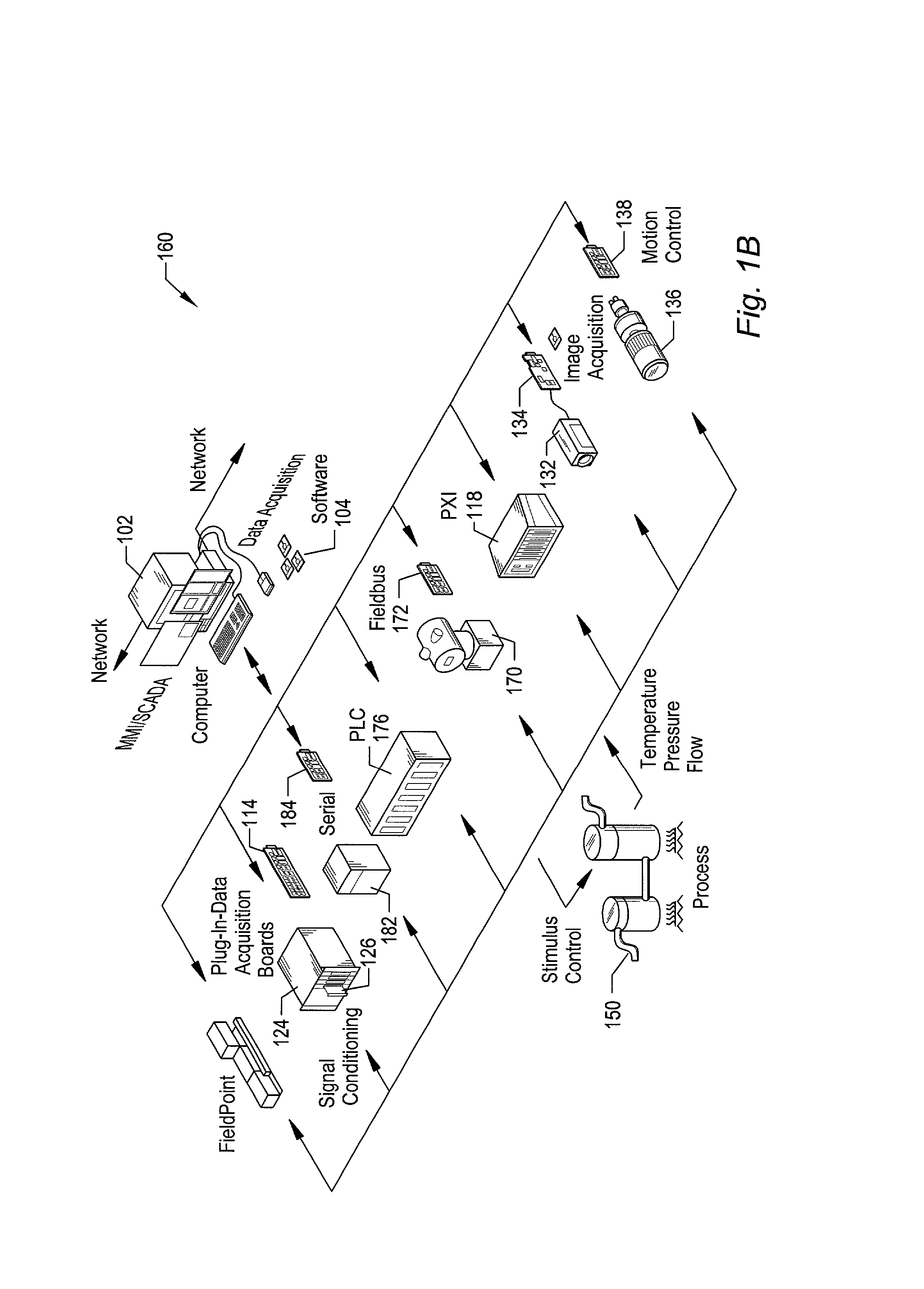

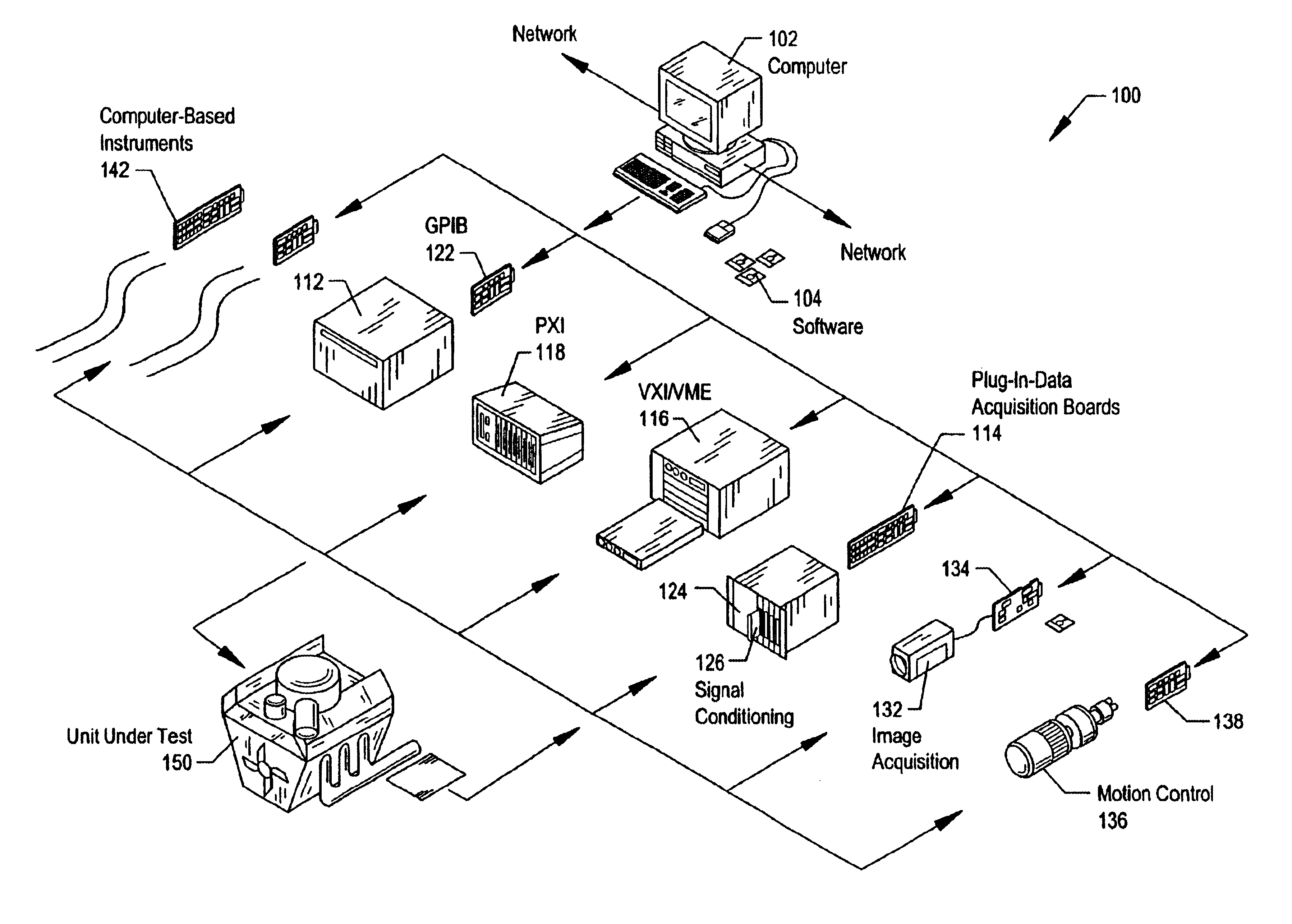

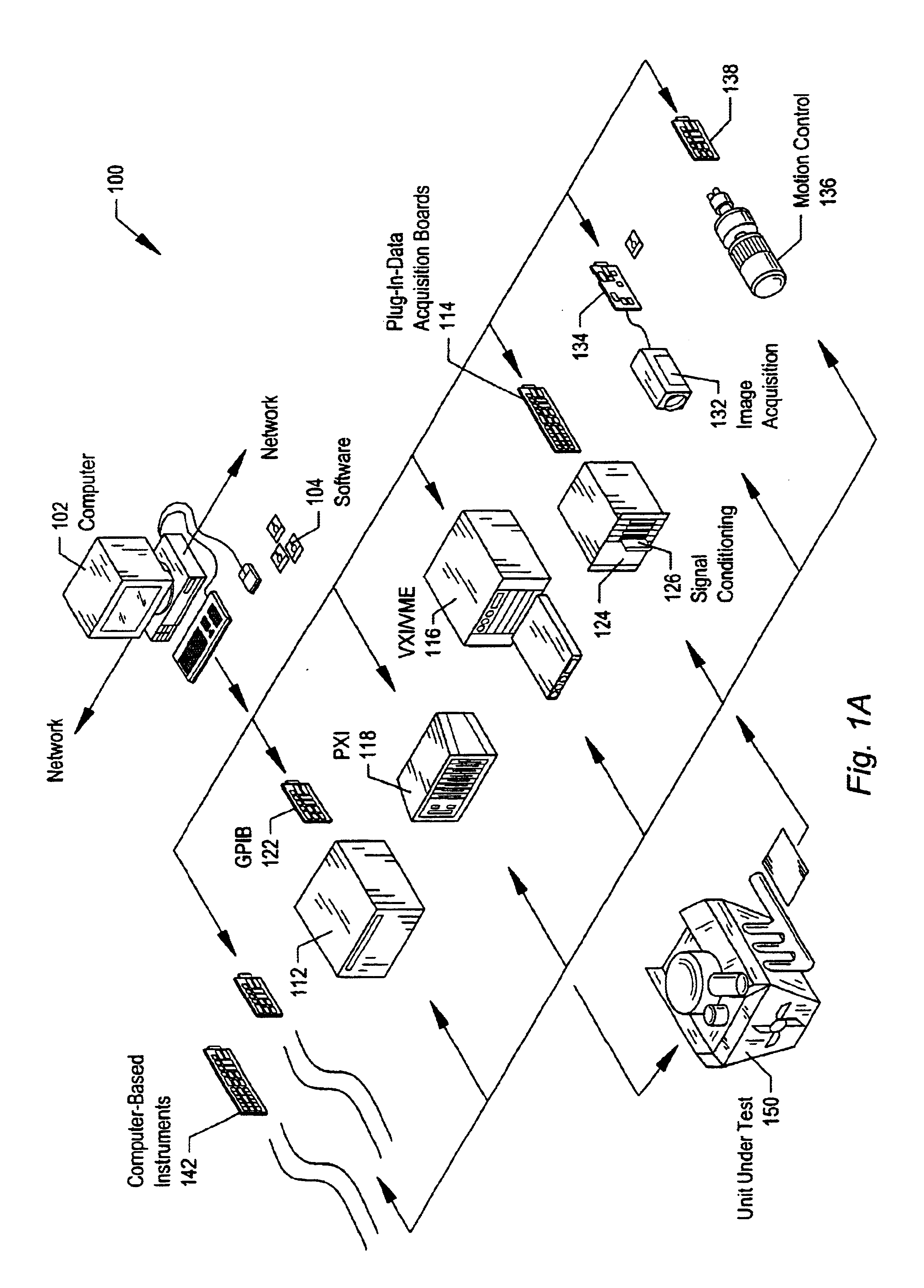

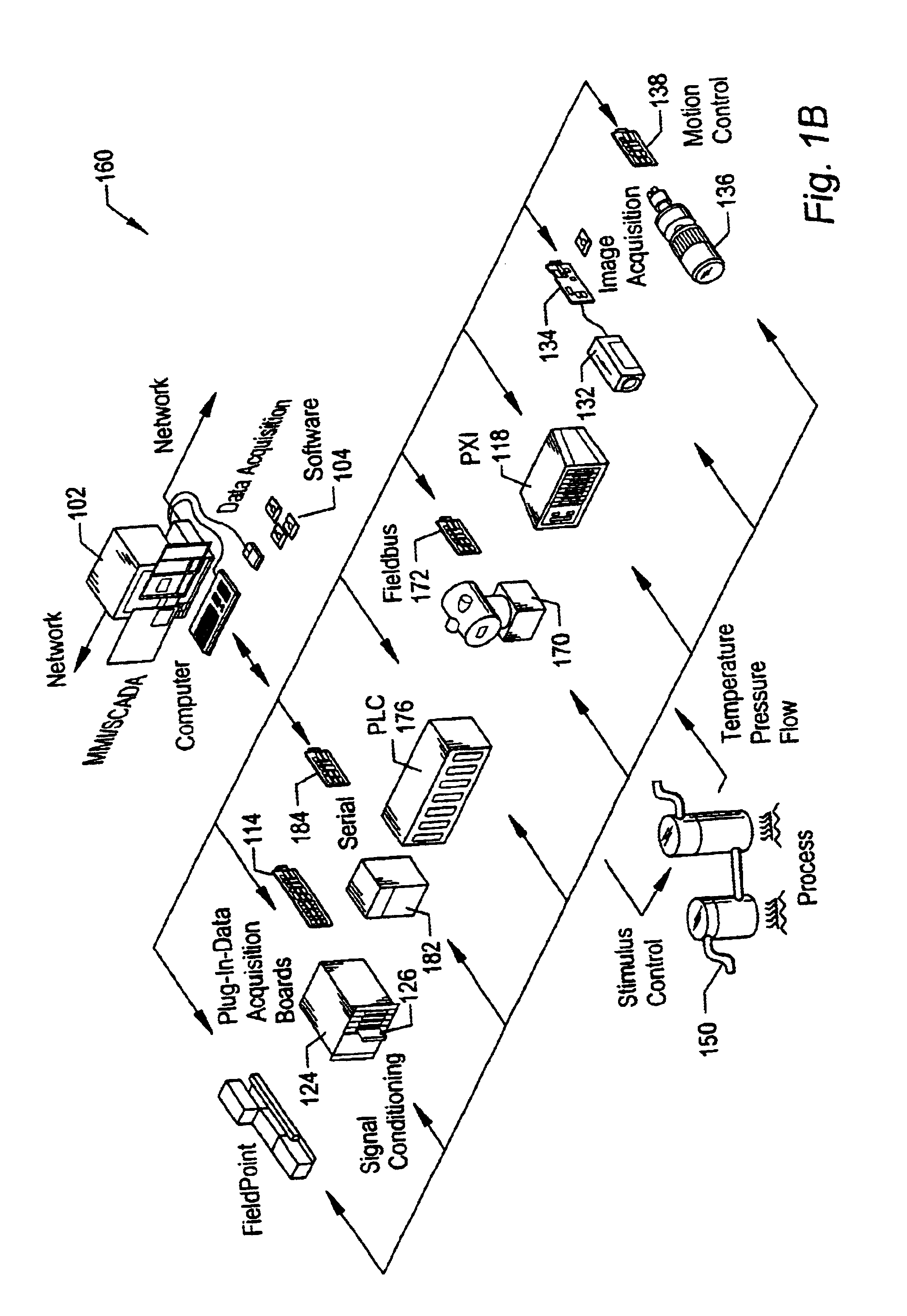

System and method for configuring an instrument to perform measurement functions utilizing conversion of graphical programs into hardware implementations

InactiveUS20020080174A1Detecting faulty hardware by remote testCathode-ray tube indicatorsGraphicsComputer hardware

A computer-implemented system and method for generating a hardware implementation of graphical code. The method may operate to configure an instrument to perform measurement functions, wherein the instrument includes a programmable hardware element. The method comprises first creating a graphical program, wherein the graphical program may implement a measurement function. A portion of the graphical program may be converted into a hardware implementation on a programmable hardware element, and a portion may optionally be compiled into machine code for execution by a CPU. The programmable hardware element is thus configured utilizing a hardware description and implements a hardware implementation of at least a portion of the graphical program.

Owner:NATIONAL INSTRUMENTS

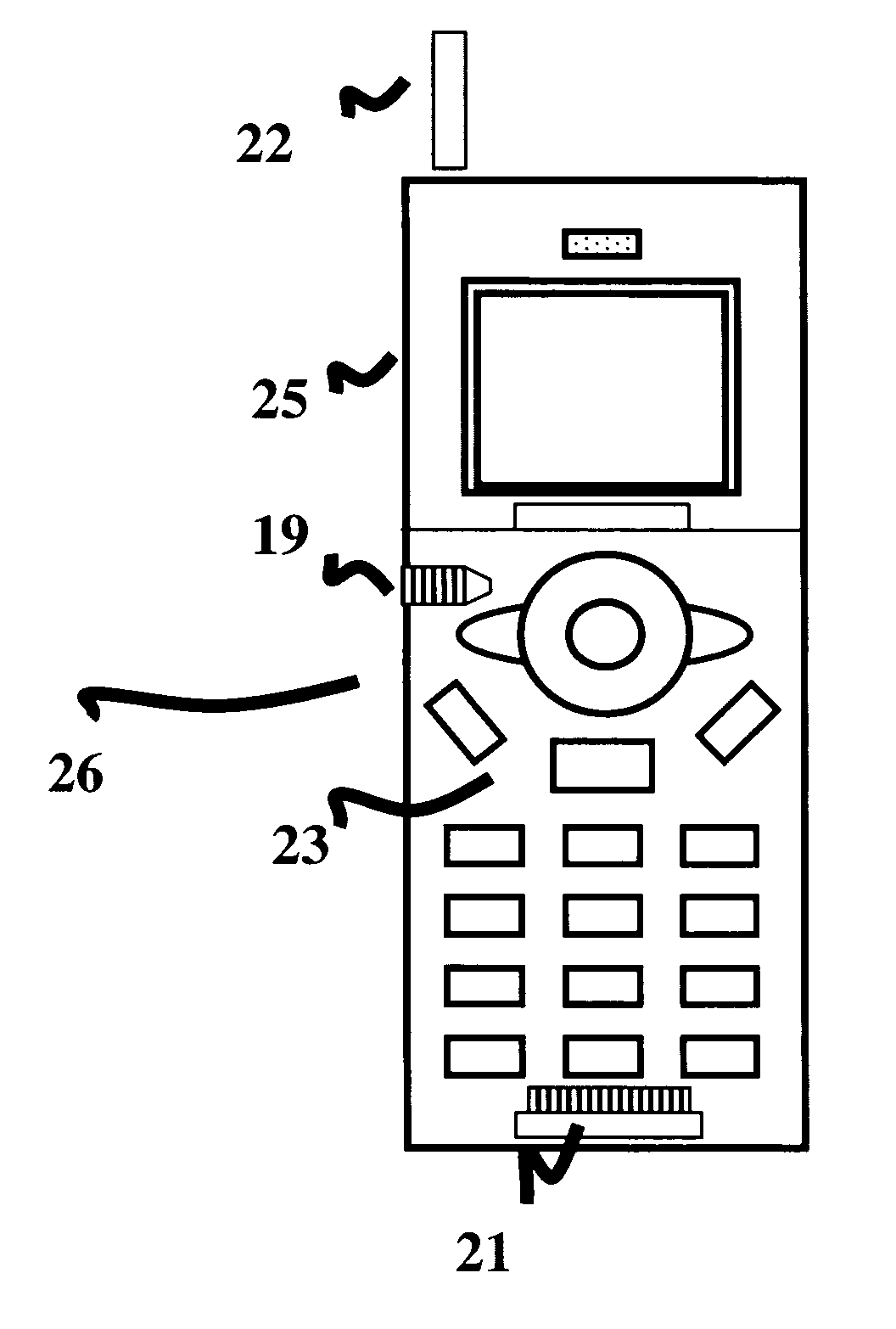

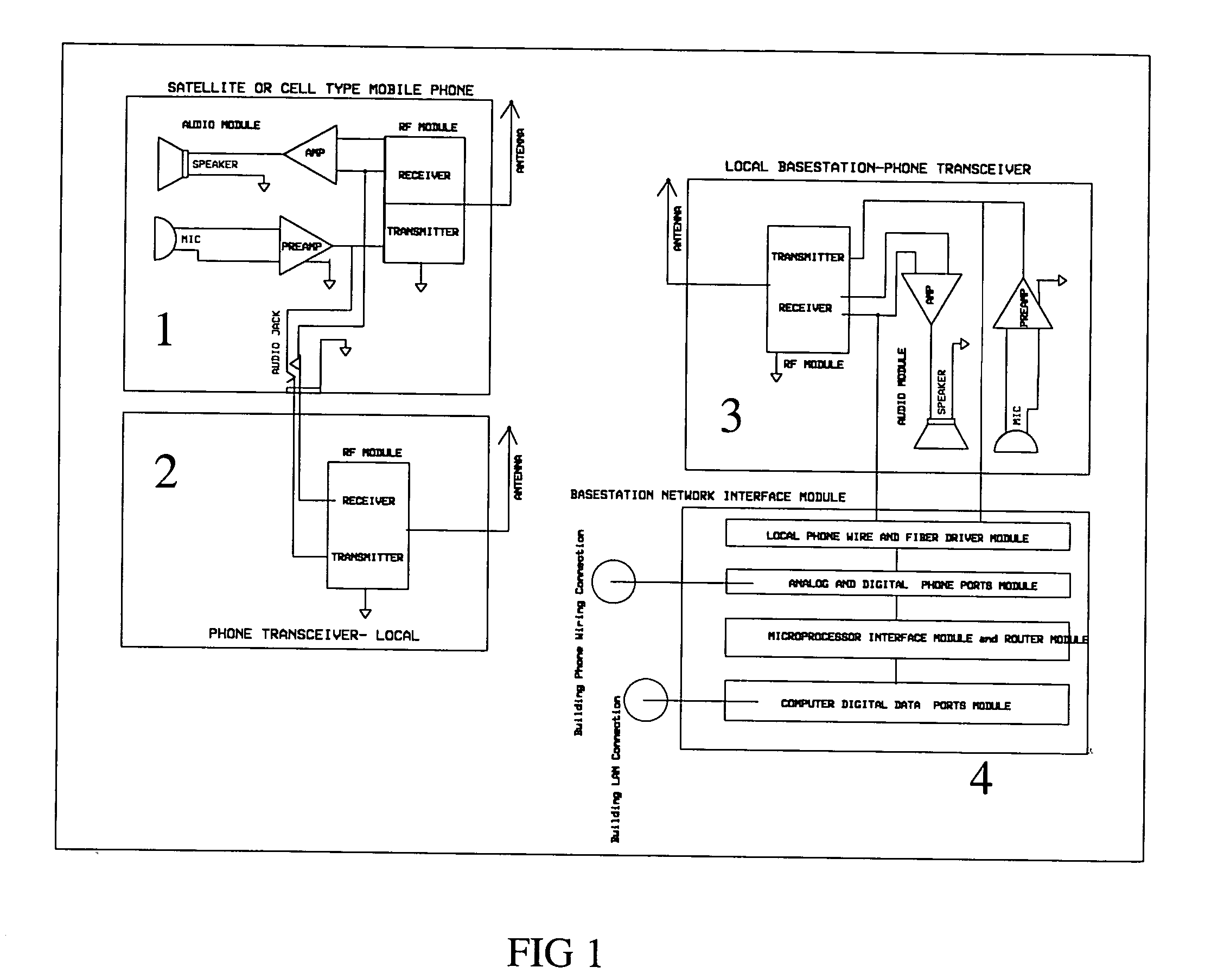

Mobile phone extension and data interface via an audio headset connection

A method and apparatus is present for achieving simple and inexpensive communications from wired phones to mobile or cell phones called a mobile phone extension. It is inexpensive because of flexible system architecture and simple hardware implementation. It allows phone calls to be made from wired phones over a cell phone. It is simple because audio signals from a microphone and speaker of a wired handset are connected to the mobile phone via a simple plug connection to the headset audio port. Alternatively, the system works with wireless connections between headsets and mobile phones. When the connection is made with a base station, it can be a wired or cordless phone or device acting as the base station. The disclosed system allows electronic apparatus to use a common mobile phone to link its communication instead of having an embedded phone separate from the user's personal phone. Other uses provide a means to communicate with a wireless headset while connecting audio from other devices such as audio devices such as players and records, and data devices. Even if the later is only speaker audio only, but it can contain microphone audio too. Thus useful apparatus and methods are claimed to connect mobile phones and wireless headsets with wired phone handset audio or other audio or video, and digital devices. One such audio player is the “I-Pod” known as a trademark of Apple Corporation. These devices can thus be connected with the disclosed interface, even when not using a wired phone, so audio from a cell phone and other devices can be received on the same headset. Use of gesture technology and particular command sets are also claimed for controlling devices using

Owner:CEHELNIK THOMAS G

Block encryption method and schemes for data confidentiality and integrity protection

InactiveUS20060056623A1Encryption apparatus with shift registers/memoriesUser identity/authority verificationPower applicationComputer hardware

Owner:VDG

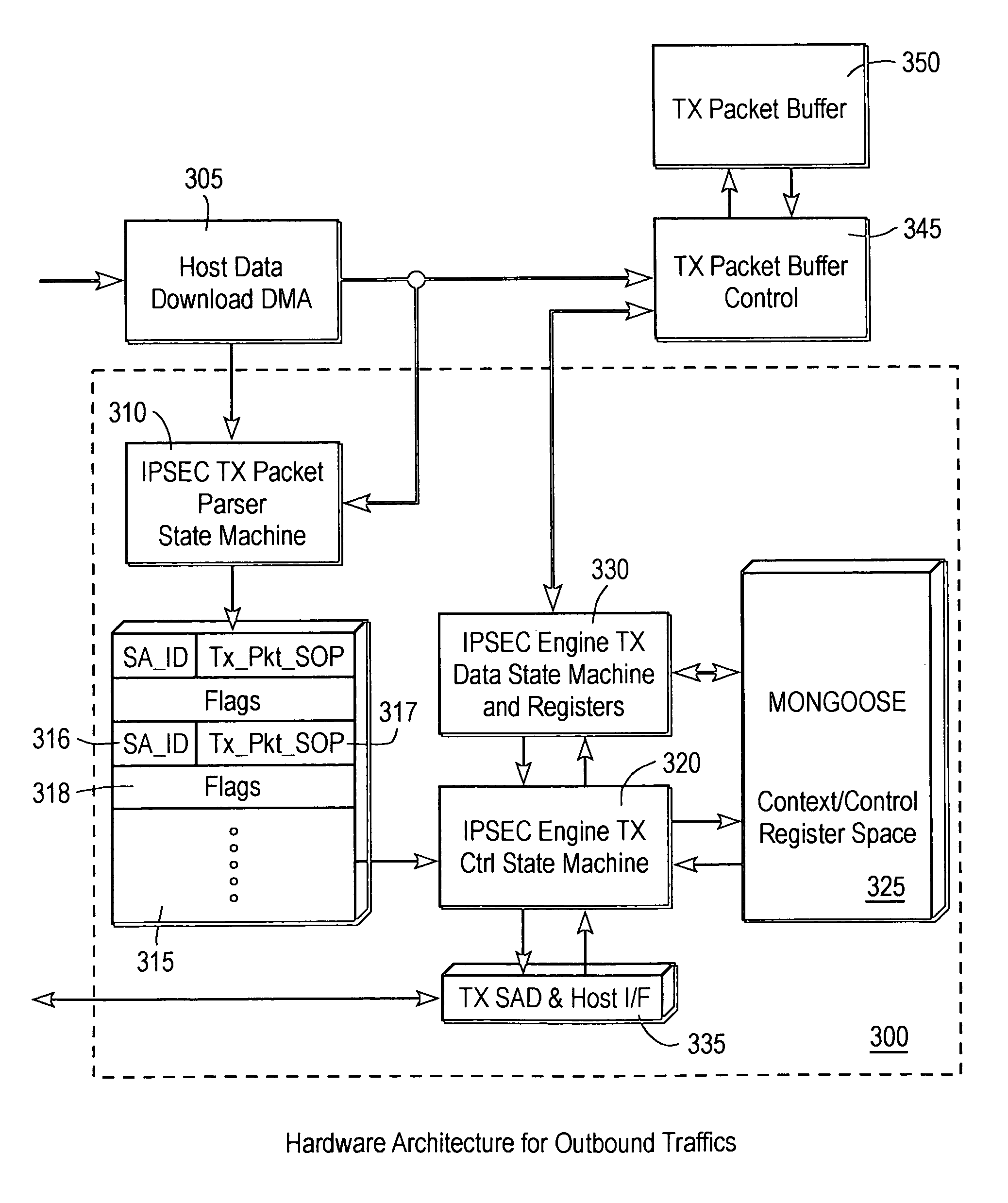

High performance IPSEC hardware accelerator for packet classification

InactiveUS7003118B1Increase the burdenDeterioration in throughputData switching by path configurationMultiple digital computer combinationsIPsecHardware implementations

An architecture for a high performance IPSEC accelerator. The architecture includes components for scanning fields of packets, programming an IPSEC services device according to the scanned fields, and modifying the scanned packet with an output from the IPSEC security services device. Preferably, the architecture is implemented in hardware, and attached to a host machine. Hardware devices, fast in comparison to software processing and network speeds, allows the computationally intensive IPSEC processes to be completed in real-time and reduce or eliminate bottlenecks in the path of a packet being sent or received to / from a network.

Owner:HEWLETT PACKARD DEV CO LP

System and method for configuring an instrument to perform measurement functions utilizing conversion of graphical programs into hardware implementations

InactiveUS6784903B2Detecting faulty hardware by remote testCathode-ray tube indicatorsGraphicsComputer hardware

A computer-implemented system and method for generating a hardware implementation of graphical code. The method may operate to configure an instrument to perform measurement functions, wherein the instrument includes a programmable hardware element. The method comprises first creating a graphical program, wherein the graphical program may implement a measurement function. A portion of the graphical program may be converted into a hardware implementation on a programmable hardware element, and a portion may optionally be compiled into machine code for execution by a CPU. The programmable hardware element is thus configured utilizing a hardware description and implements a hardware implementation of at least a portion of the graphical program.

Owner:NATIONAL INSTRUMENTS

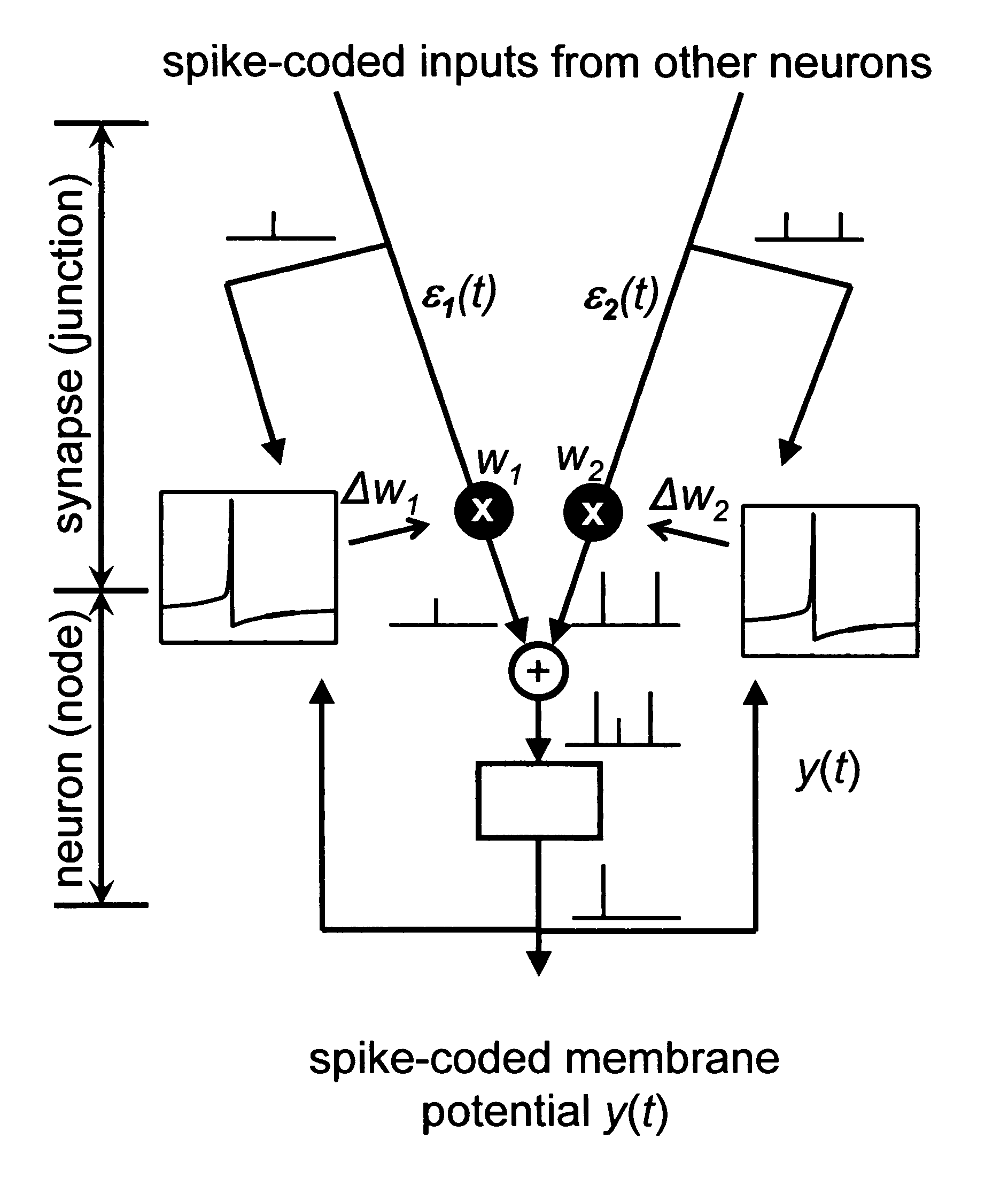

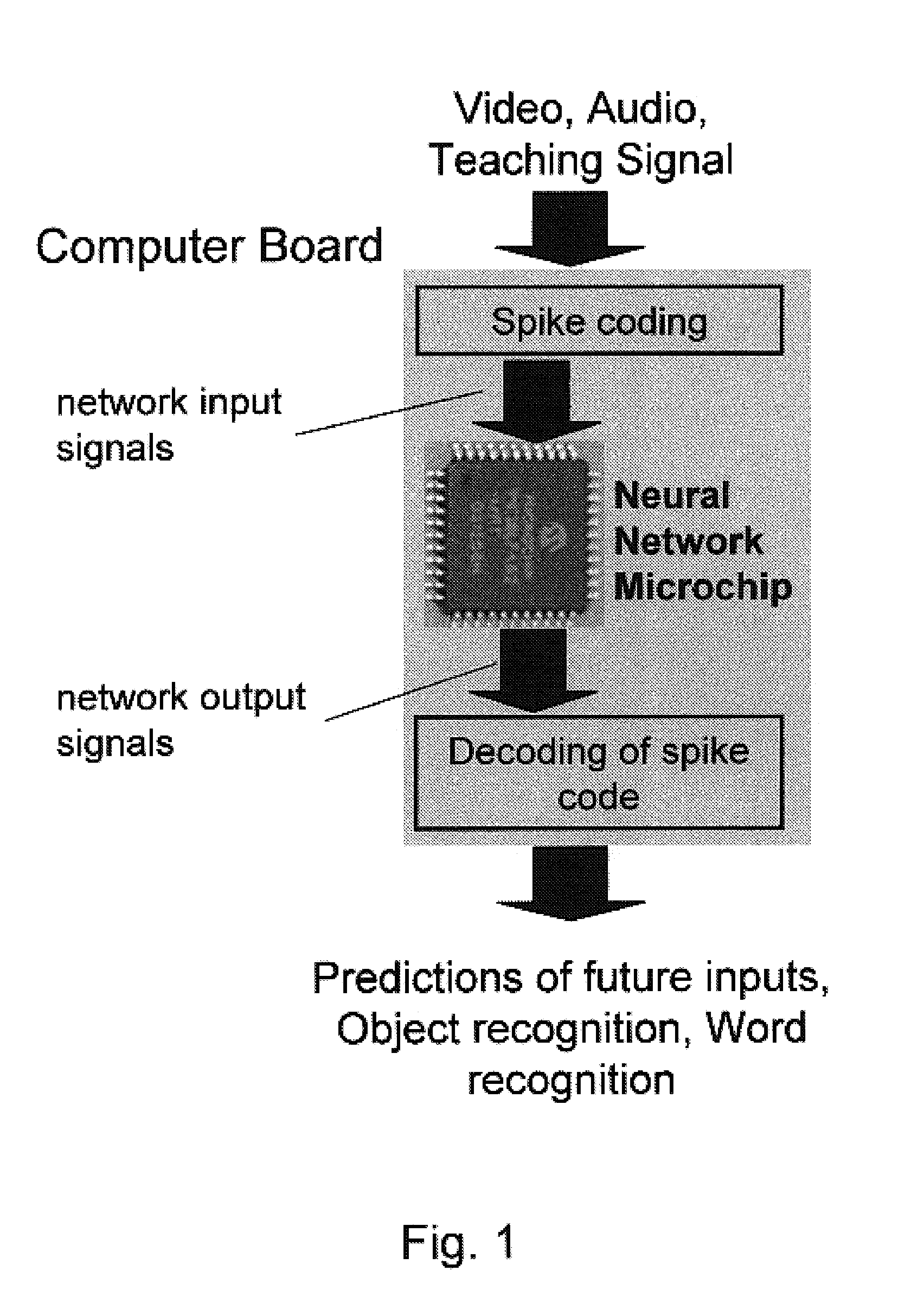

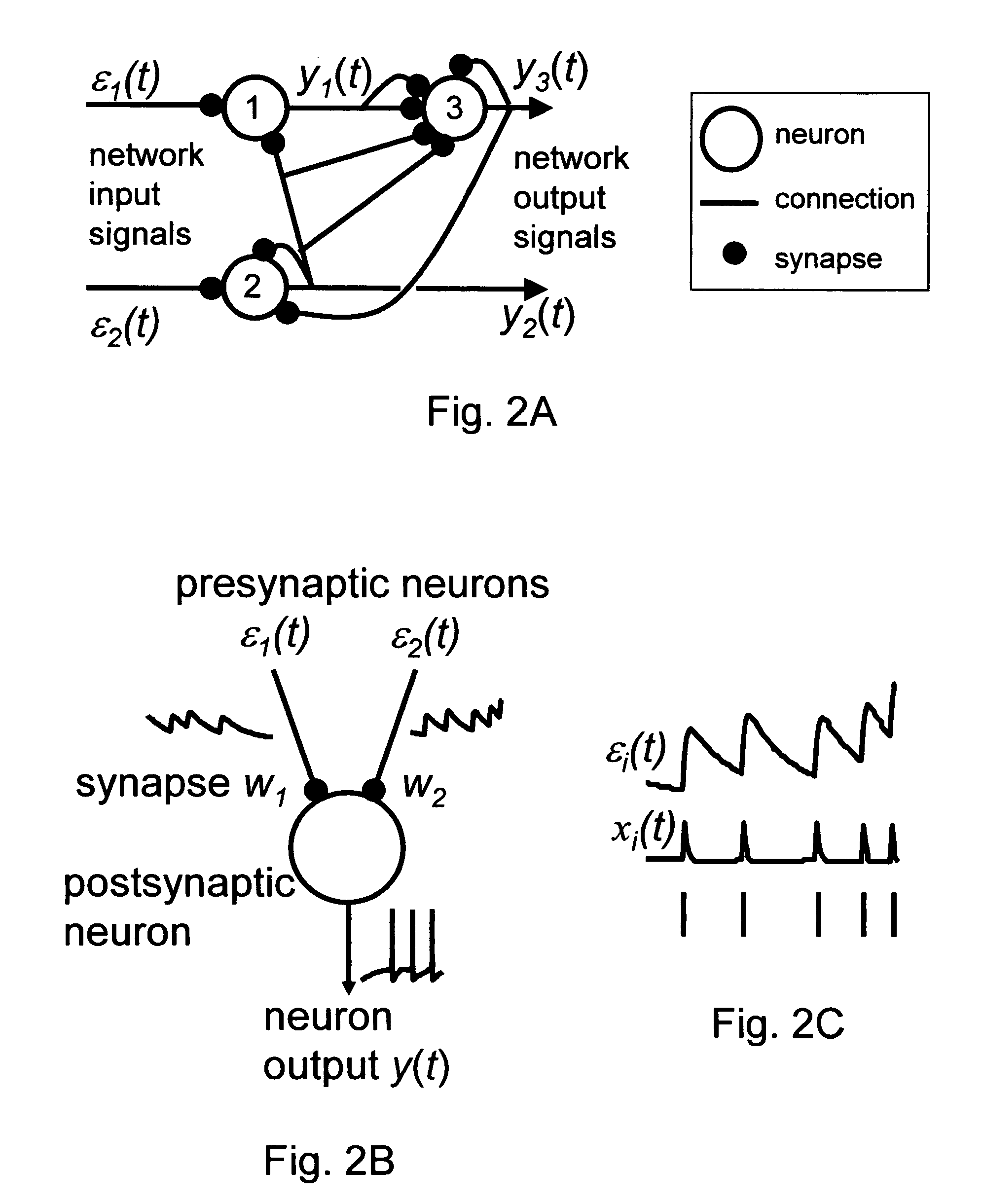

Applications of an algorithm that mimics cortical processing

An information processing system having neuron-like signal processors that are interconnected by synapse-like processing junctions that simulates and extends capabilities of biological neural networks. The information processing systems uses integrate-and-fire neurons and Temporally Asymmetric Hebbian learning (spike timing-dependent learning) to adapt the synaptic strengths. The synaptic strengths of each neuron are guaranteed to become optimal during the course of learning either for estimating the parameters of a dynamic system (system identification) or for computing the first principal component. This neural network is well-suited for hardware implementations, since the learning rule for the synaptic strengths only requires computing either spike-time differences or correlations. Such hardware implementation may be used for predicting and recognizing audiovisual information or for improving cortical processing by a prosthetic device.

Owner:SURI ROLAND ERWIN

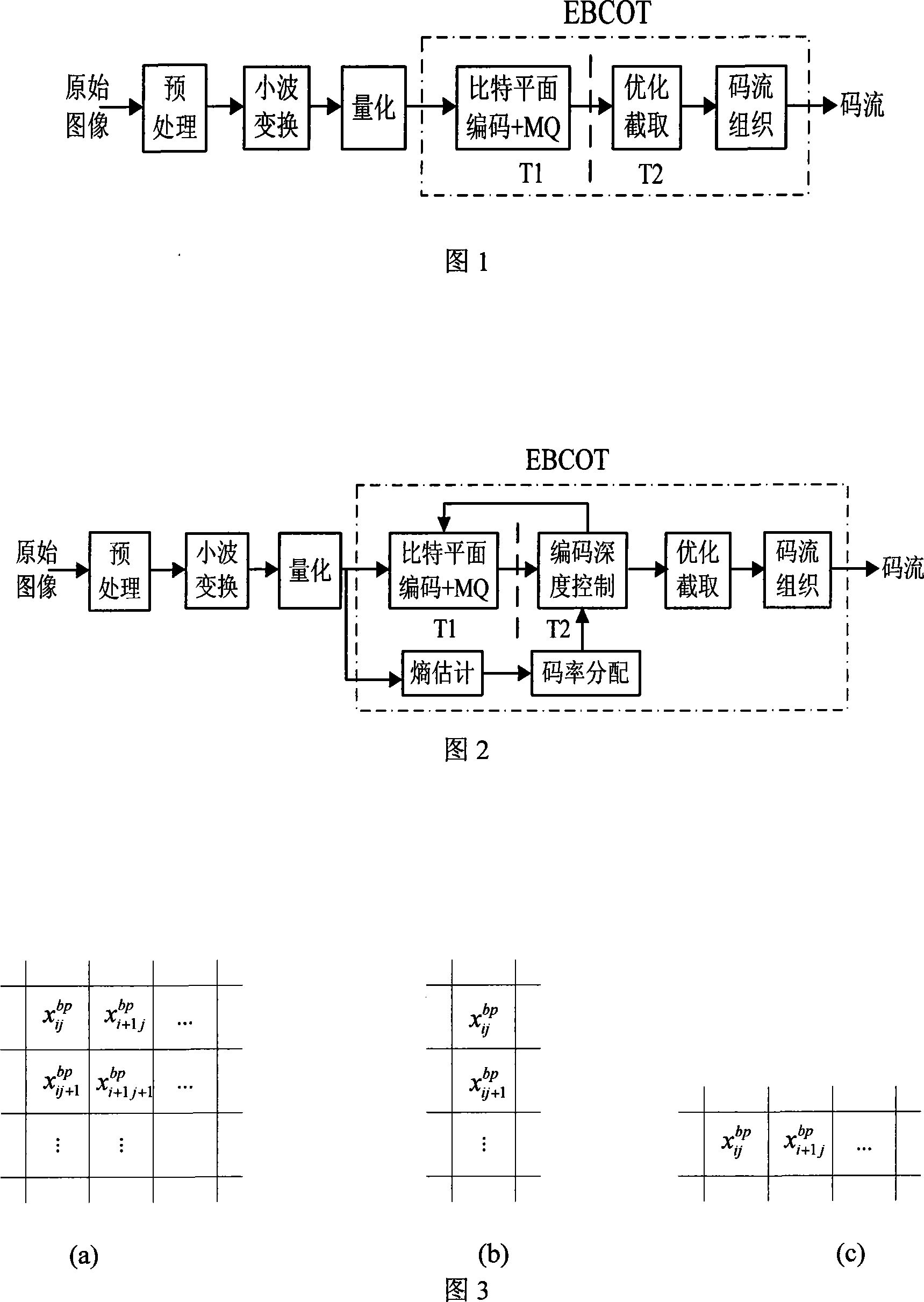

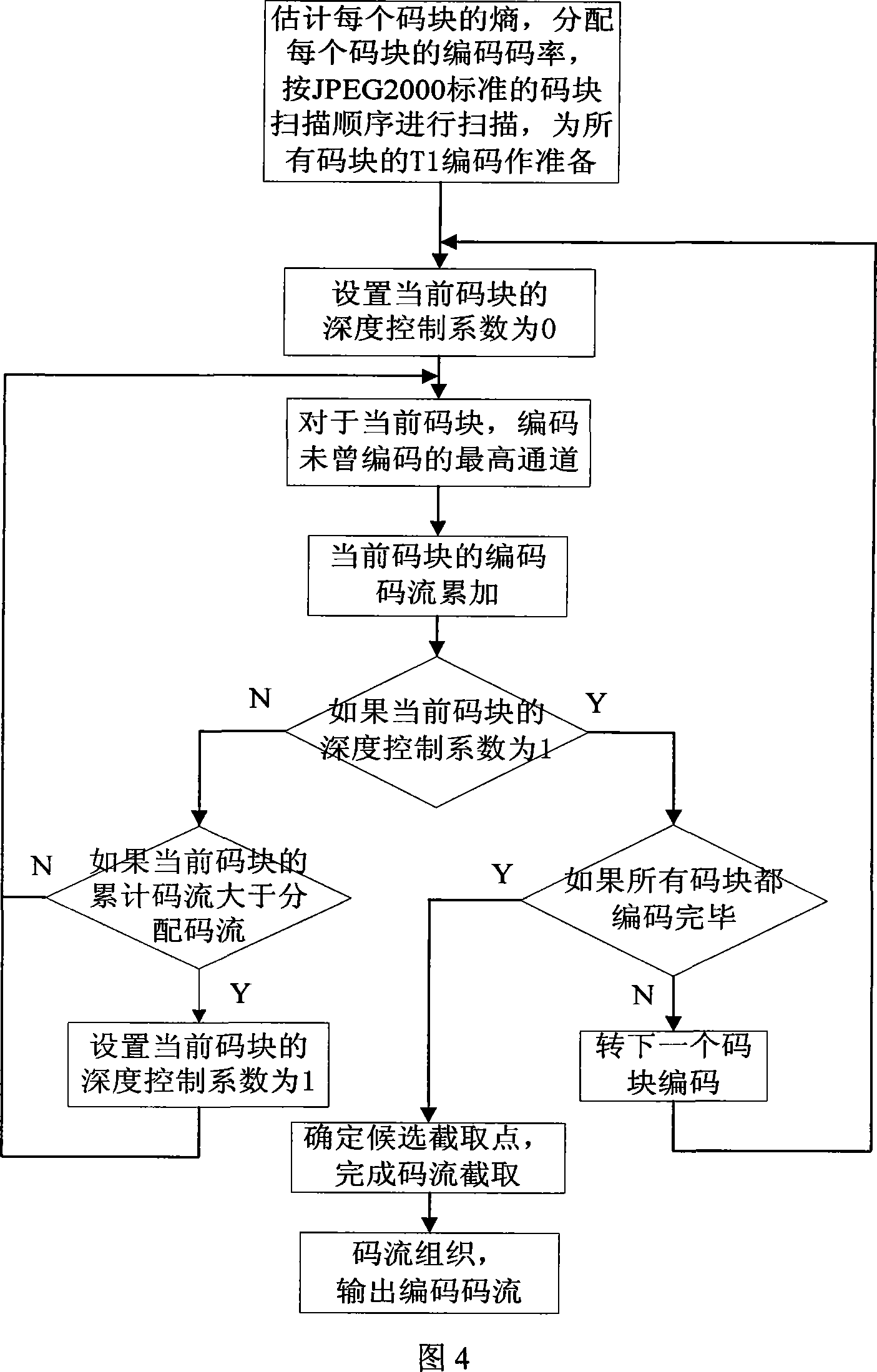

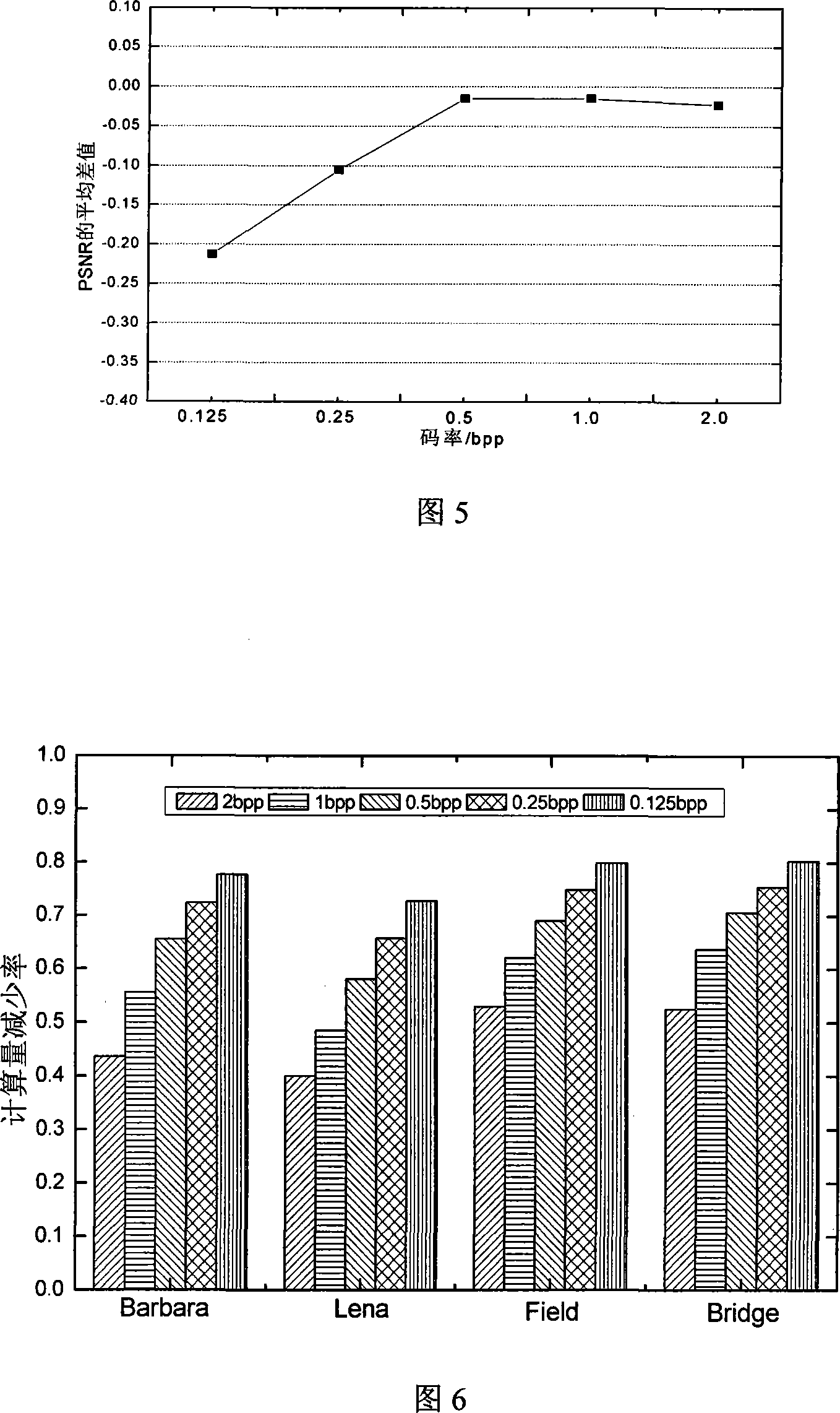

JPEG2000 self-adapted rate control system and method based on pre-allocated code rate

InactiveCN101106711AAccurate code rate pre-allocationPre-allocated precisionTelevision systemsDigital video signal modificationCoding blockControl system

The invention discloses a JPEG2000 self-adapting rate control system and a method based on pre-assignment of code rate, mainly solving the problem of large calculation amount and large memory size of JPEG2000 encoding method. The code block of the original image after pretreatment, wavelet transformation and quantification is output by two lines, one line directly enters the bit plane and MQ coder; for the other line, the entropy of each code block is estimated by the entropy estimate module, sent to the code rate assignment module to assign code rate, and the code rate of each code block is feed back to the bit plane and MQ coder through the encoding depth control module, after the code blocks are encoded by the bit plane, further feed back to the encoding depth control module to determine the output code stream of each encoded code block, and the output code stream is under optimal interception and code stream organization to output the ultimate code stream. At the same time, the invention can change the threshold value of the encoding depth control coefficient as required, to flexibly control the encoding depth in order to improve the image compression quality. The invention has the advantages of low complexity and easiness for hardware implementation, and is suitable for various JPEG2000 image real-time compression systems.

Owner:SHANDONG HUAYU AEROSPACE TECH CO LTD

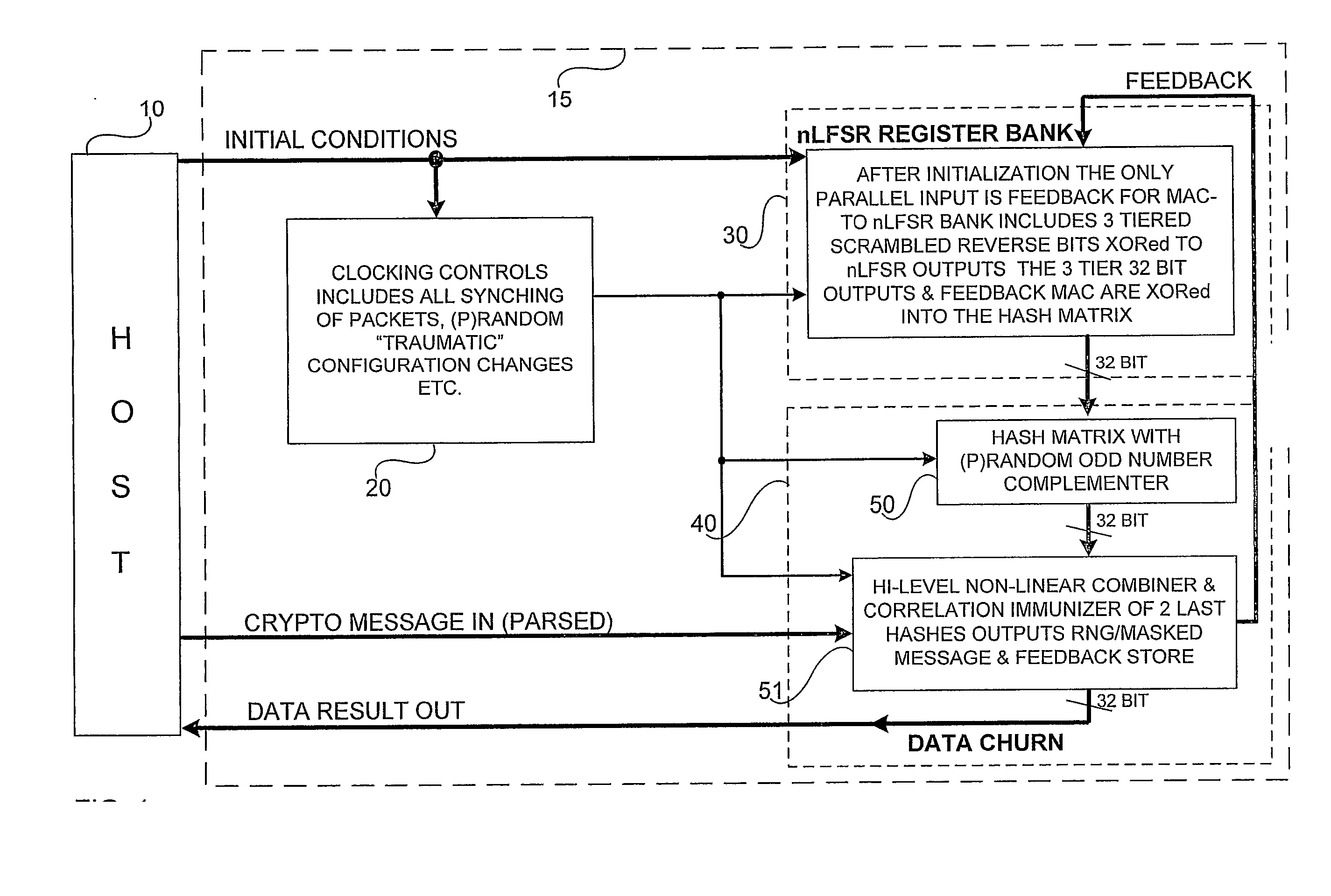

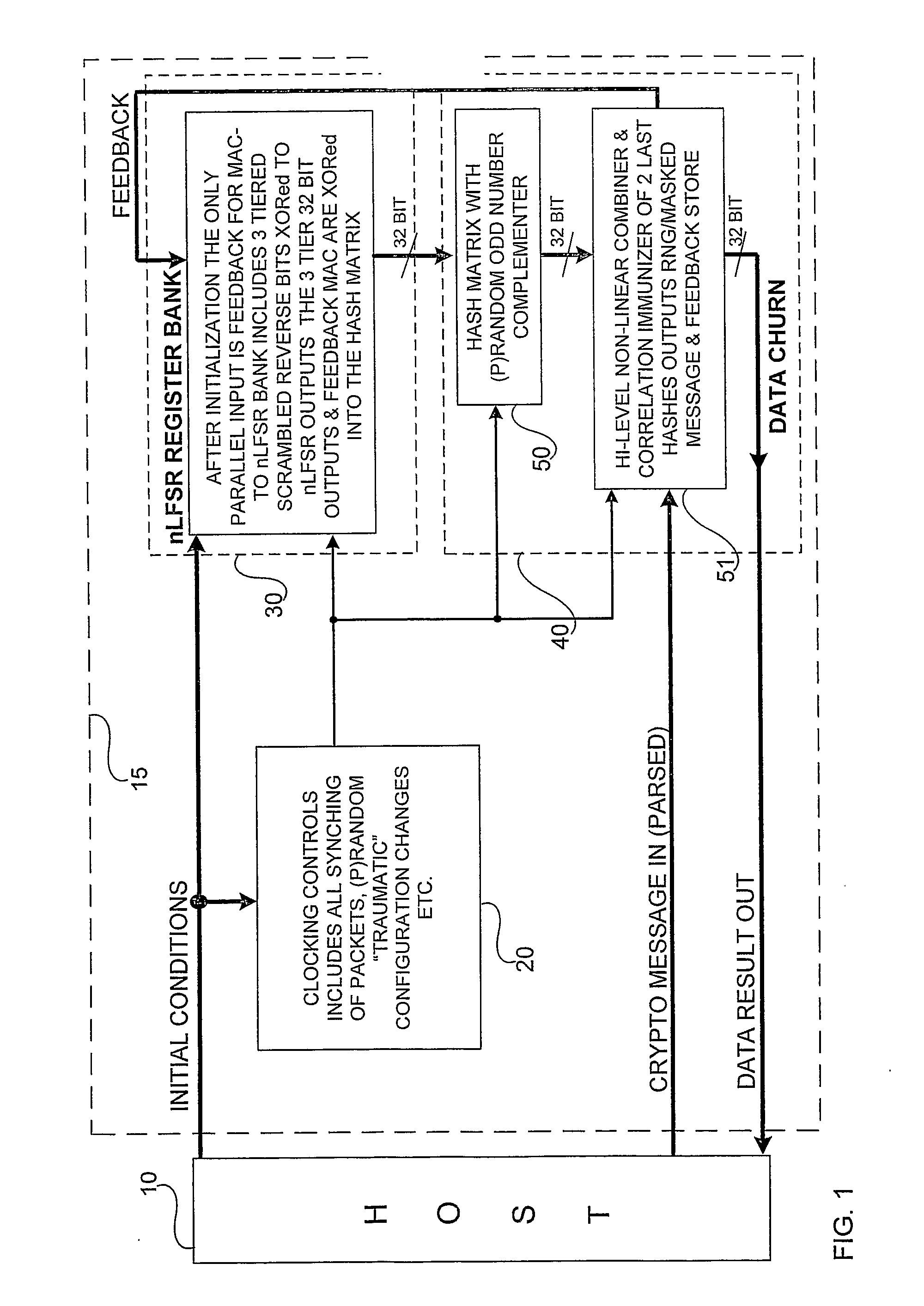

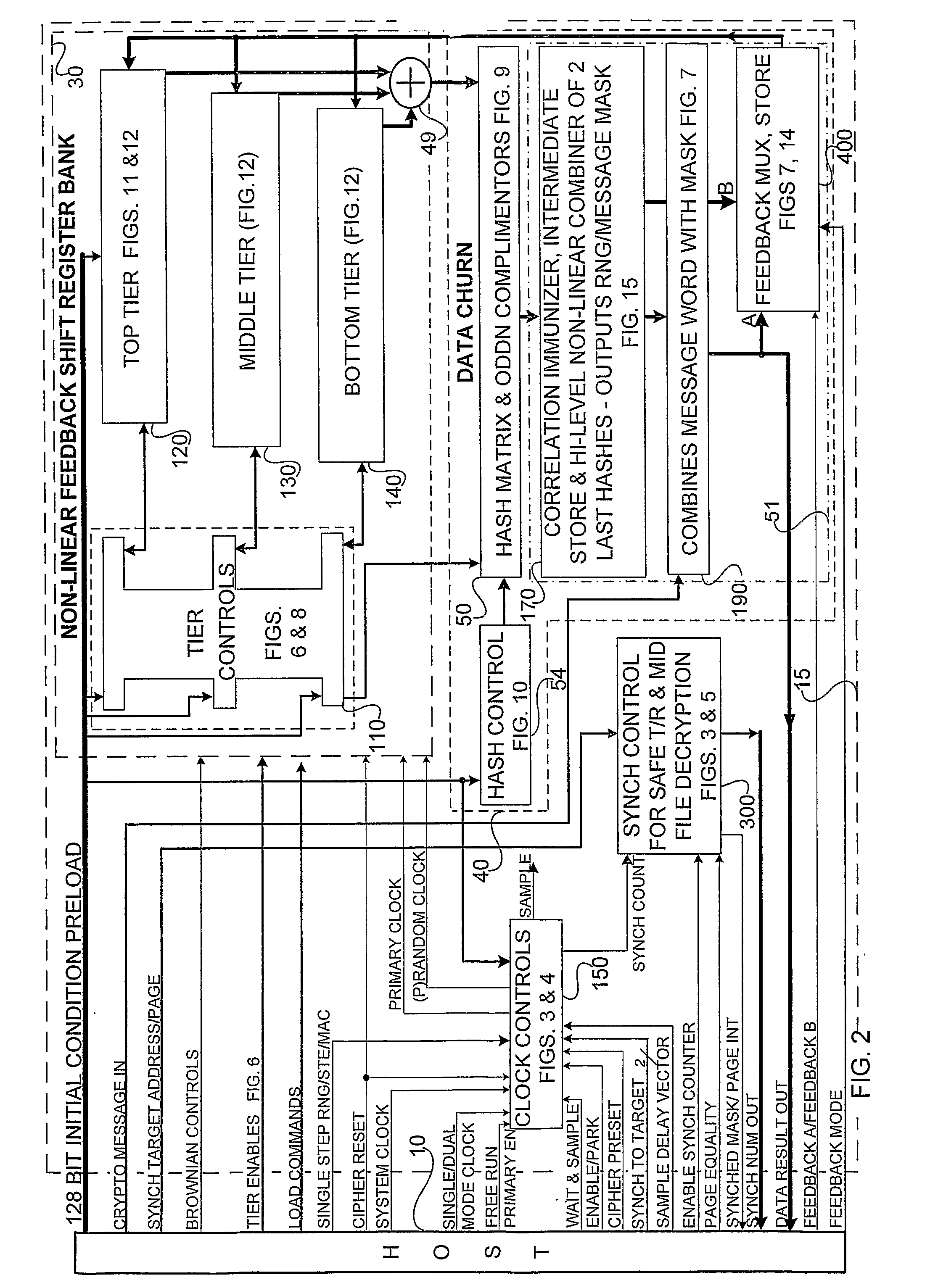

Accelerated Throughtput Synchronized Word Stream Cipher, Message Authenticator and Zero-Knowledge Output Random Number Generator

ActiveUS20070244951A1Small loss of entropyNecessary numberSynchronising transmission/receiving encryption devicesRandom number generatorsComputer hardwareFrame sequence

Systems and methods are disclosed, especially designed for very compact hardware implementations, to generate random number strings with a high level of entropy at maximum speed. For immediate deployment of software implementations, certain permutations have been introduced to maintain the same level of unpredictability which is more amenable to hi-level software programming, with a small time loss on hardware execution; typically when hardware devices communicate with software implementations. Particular attention has been paid to maintain maximum correlation immunity, and to maximize non-linearity of the output sequence. Good stream ciphers are based on random generators which have a large number of secured internal binary variables, which lead to the page synchronized stream ciphering. The method for parsed page synchronization which is presented is especially valuable for Internet applications, where occasionally frame sequences are often mixed. The large number of internal variables with fast diffusion of individual bits wherein the masked message is fed back into the machine variables is potentially ideal for message authentication procedures.

Owner:FORTRESS GB

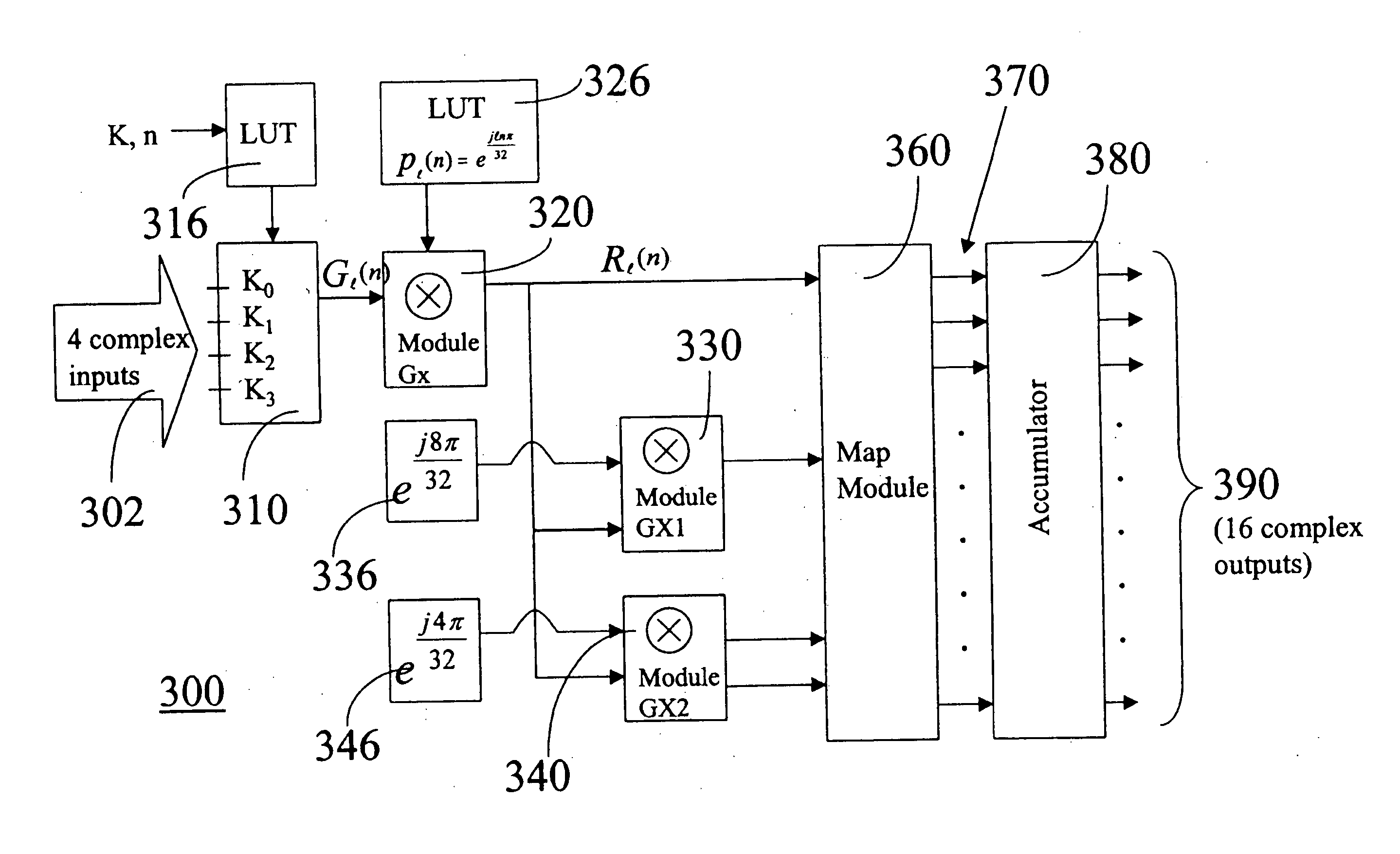

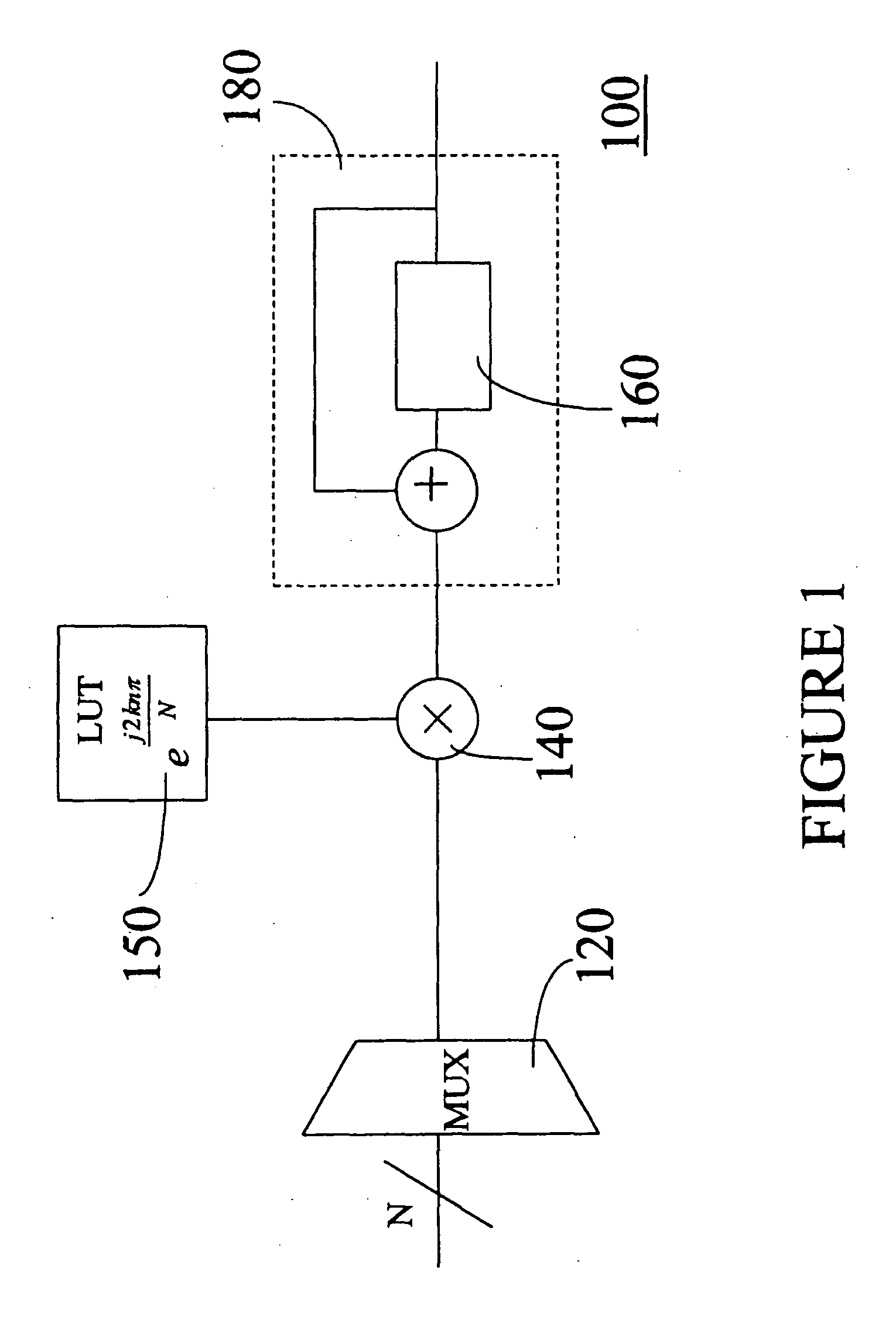

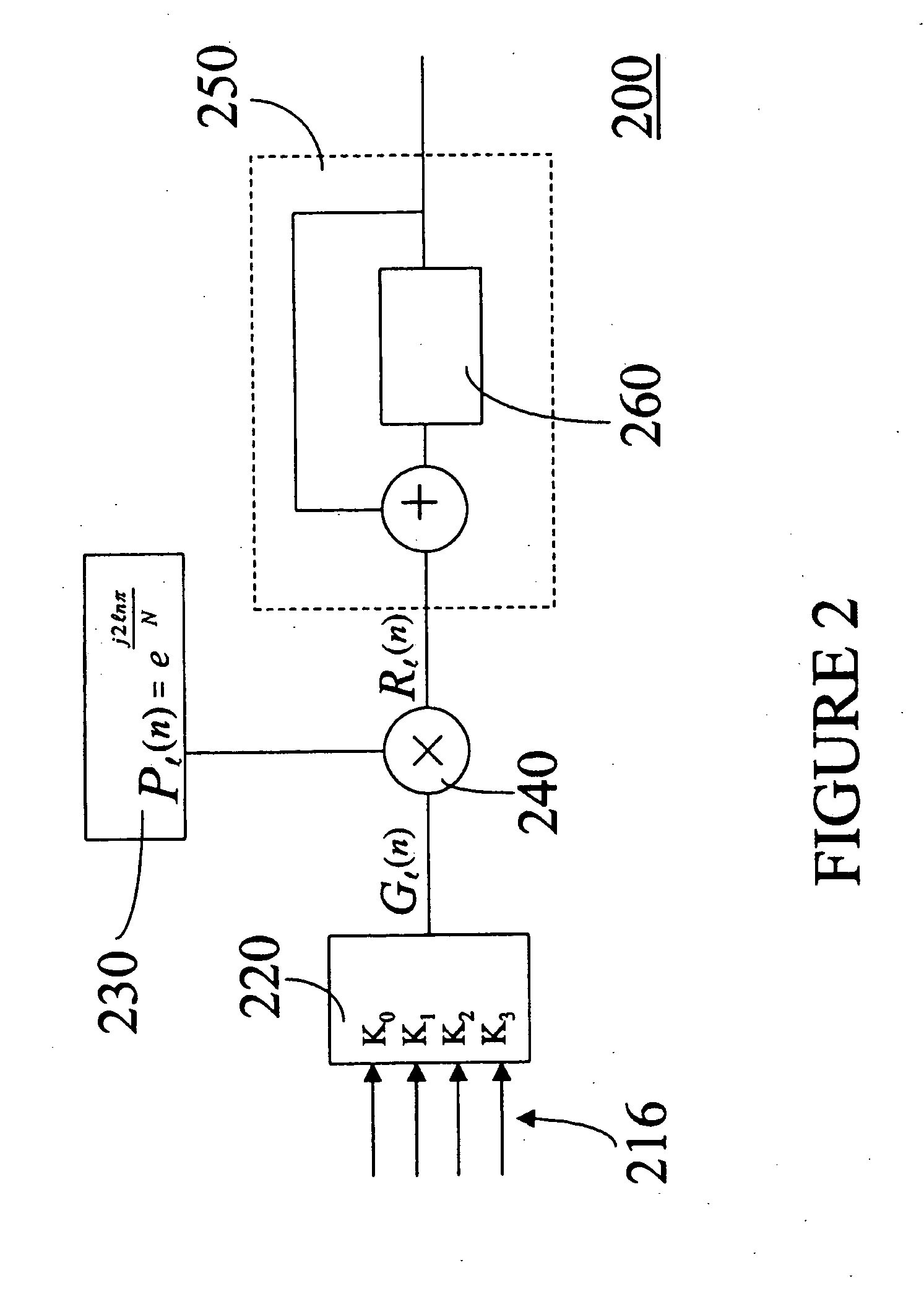

Optimized FFT/IFFT module

ActiveUS20050058059A1Ease of hardware implementationMinimize the numberAmplitude-modulated carrier systemsRadio transmissionTheoretical computer scienceComputer module

The present invention discloses an optimal hardware implementation of the FFT / IFFT operation that minimizes the number of clock cycles required to compute the FFT / IFFT while at the same time minimizing the number of complex multipliers needed. For performing an N-point FFT / IFFT operation in N clock cycles, the optimal hardware implementation consists of several modules. An input module receives a plurality of inputs in parallel and combines the inputs after applying a multiplication factor to each of the inputs. At least one multiplicand generator is used to provide multiplicands to the system. At least two complex multiplier modules for performing complex multiplications are required with at least one of the complex multiplier modules receiving an output from the input module. Each of the complex multiplier modules receives multiplicands from the at least one multiplicand generator. Furthermore, at least one of the complex multiplier modules receives an output of another complex multiplier module. A map module is provided for receiving outputs of the at least two complex multiplier modules, the map module selecting and applying a multiplication factor to each of the outputs received to generate multiple outputs. Finally, an accumulation module receives and performs an accumulation task on each of the multiple outputs of the map module thereby generating a corresponding number of multiple outputs. In a preferred embodiment, the N-point FFT / IFFT operation is performed in N clock cycles using (N32+1)complex multipliers. In a specific implementation, a system comprising 3 complex multipliers is used to compute a 64-point FFT / IFFT operation in 64 clock cycles. Advantageously, the total number of clock cycles required to complete the FFT / IFFT operation is minimized while at the same time minimizing the number of complex multipliers needed.

Owner:ZARBANA DIGITAL FUND

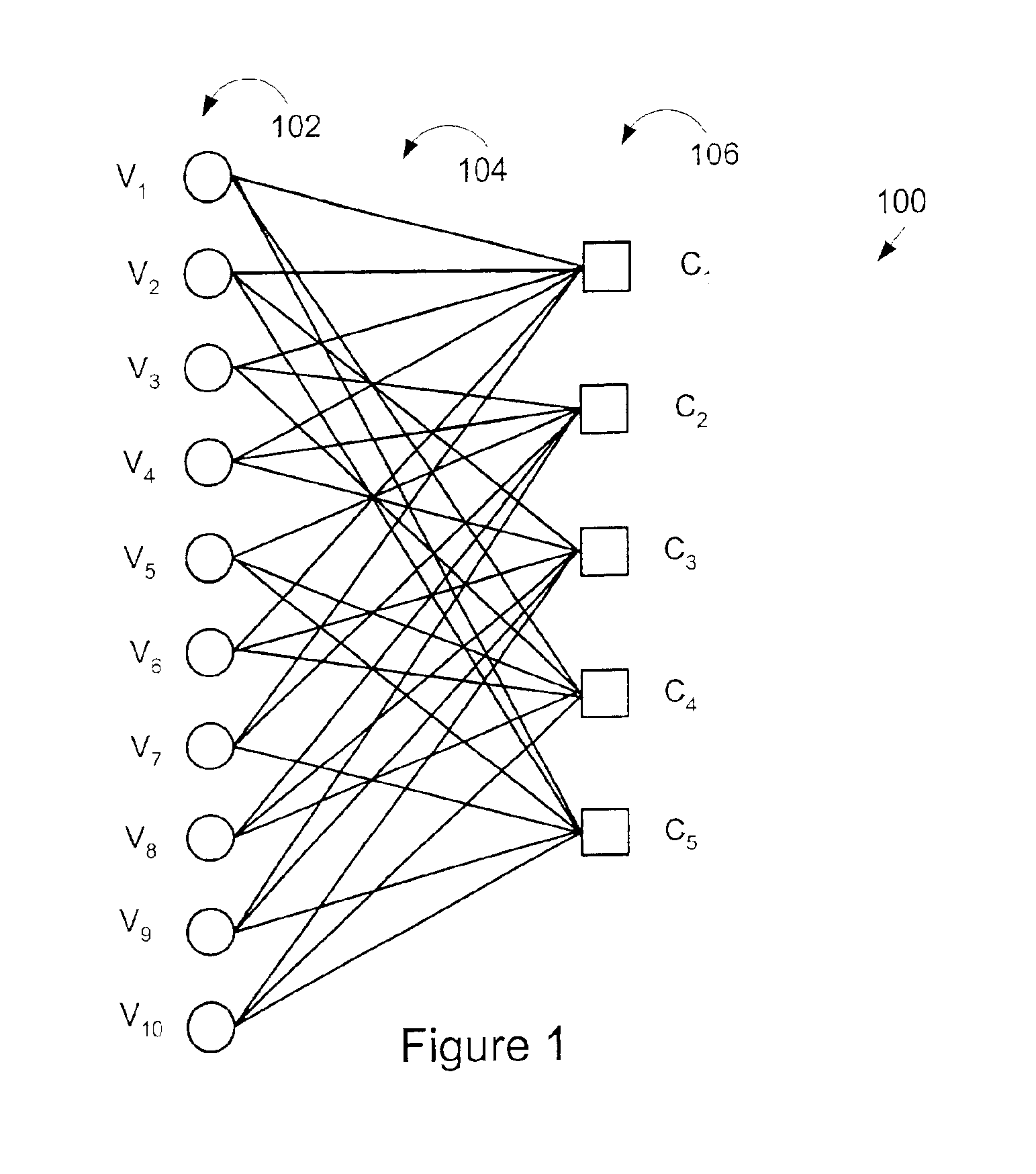

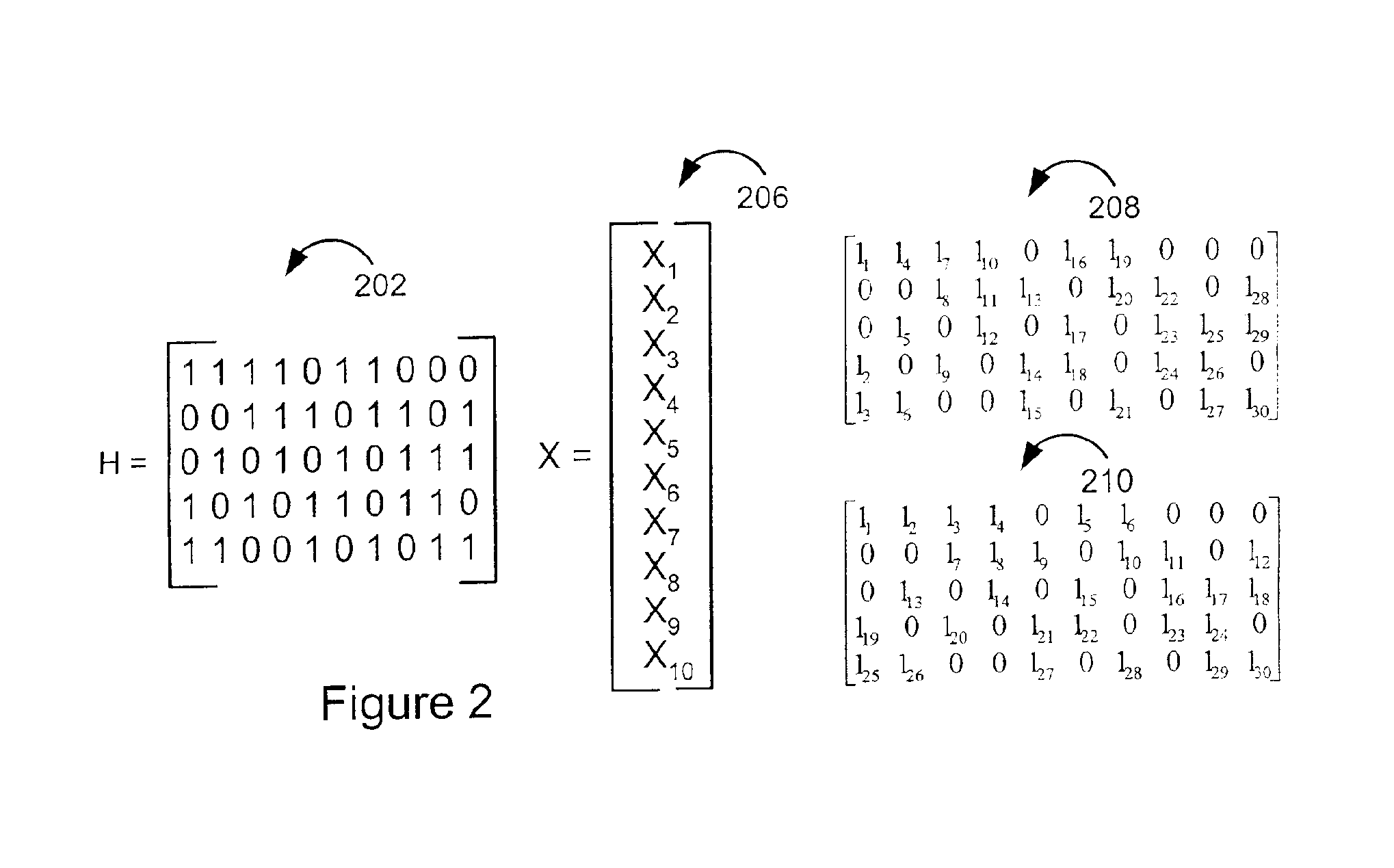

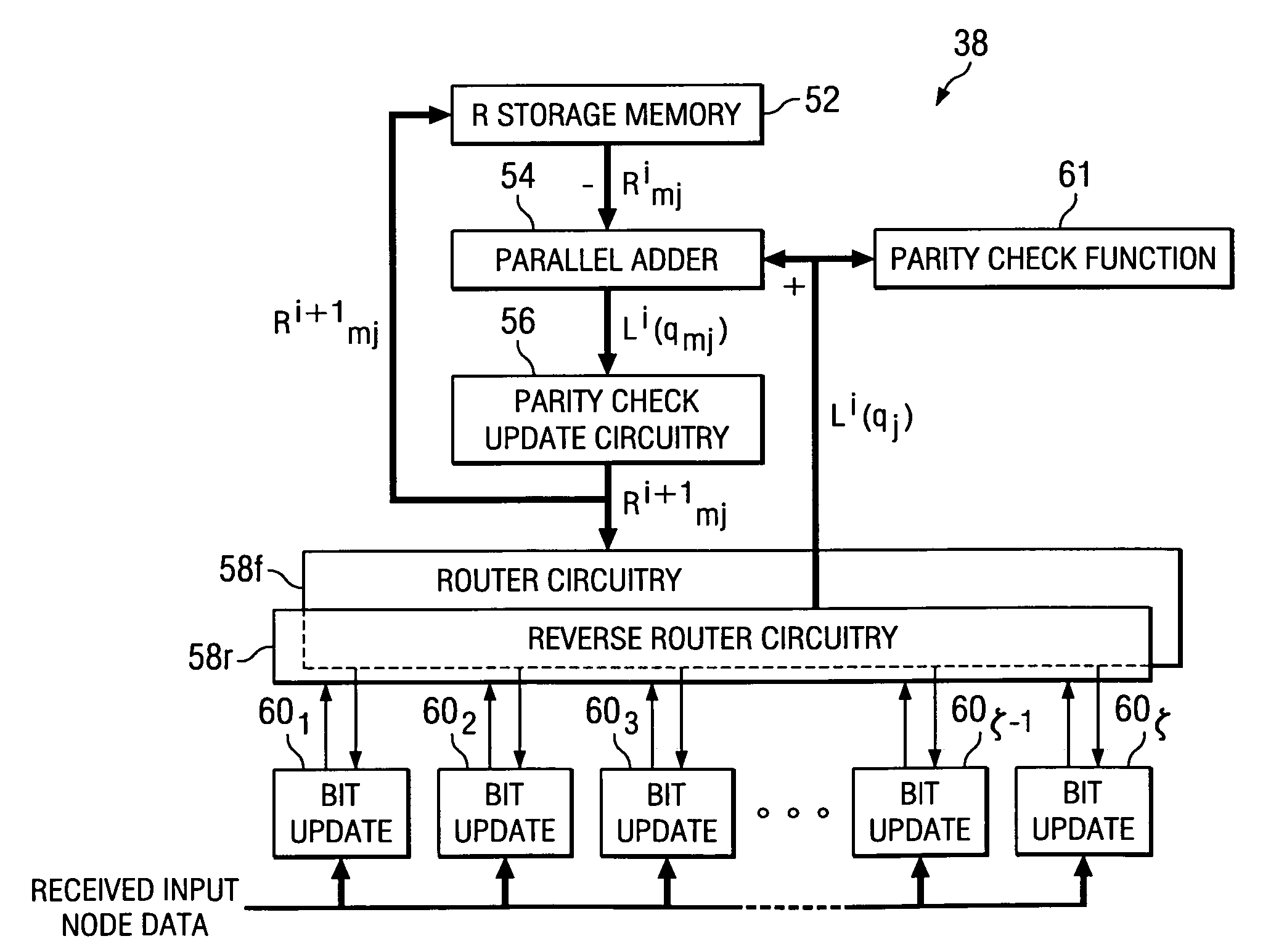

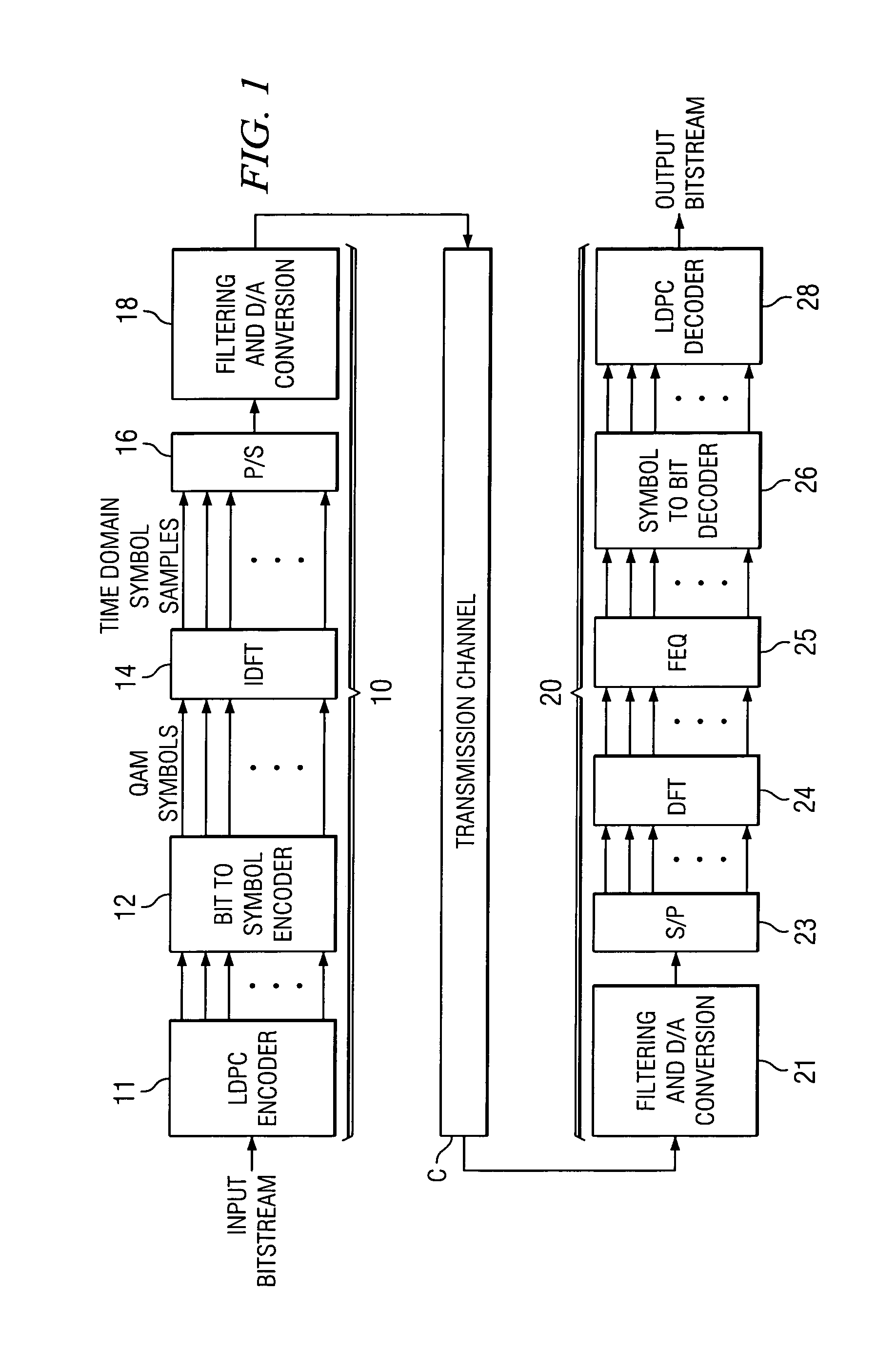

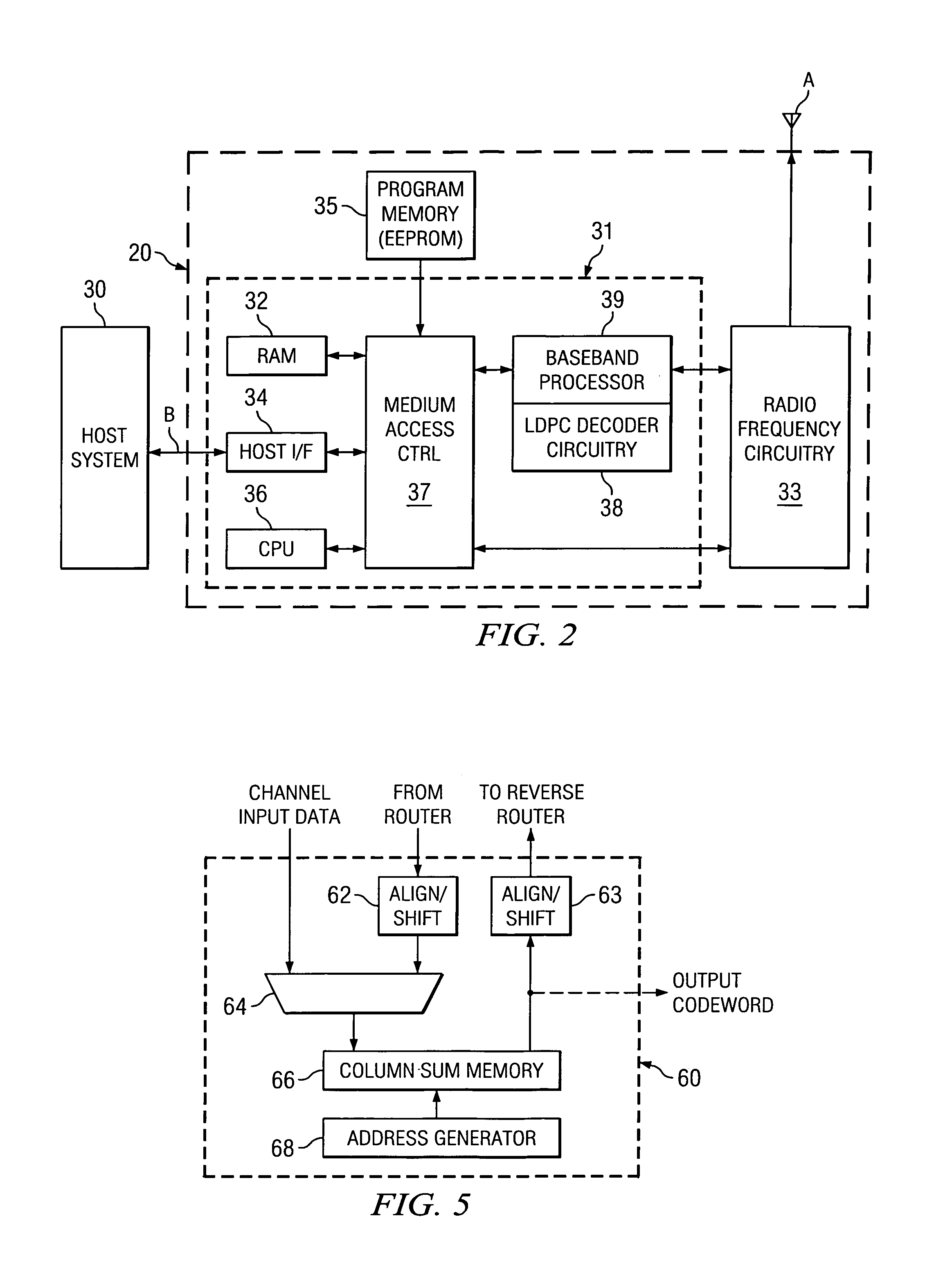

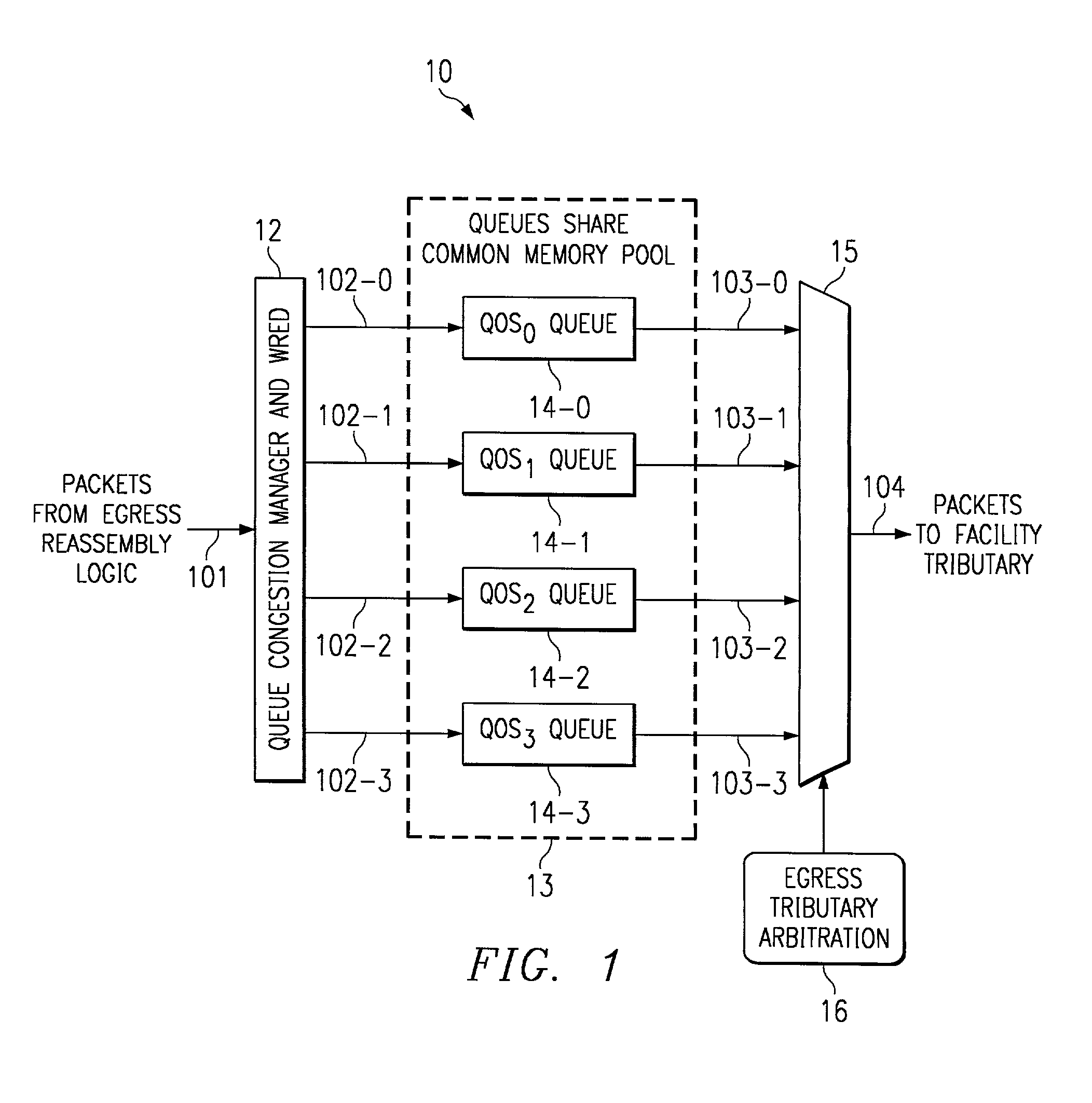

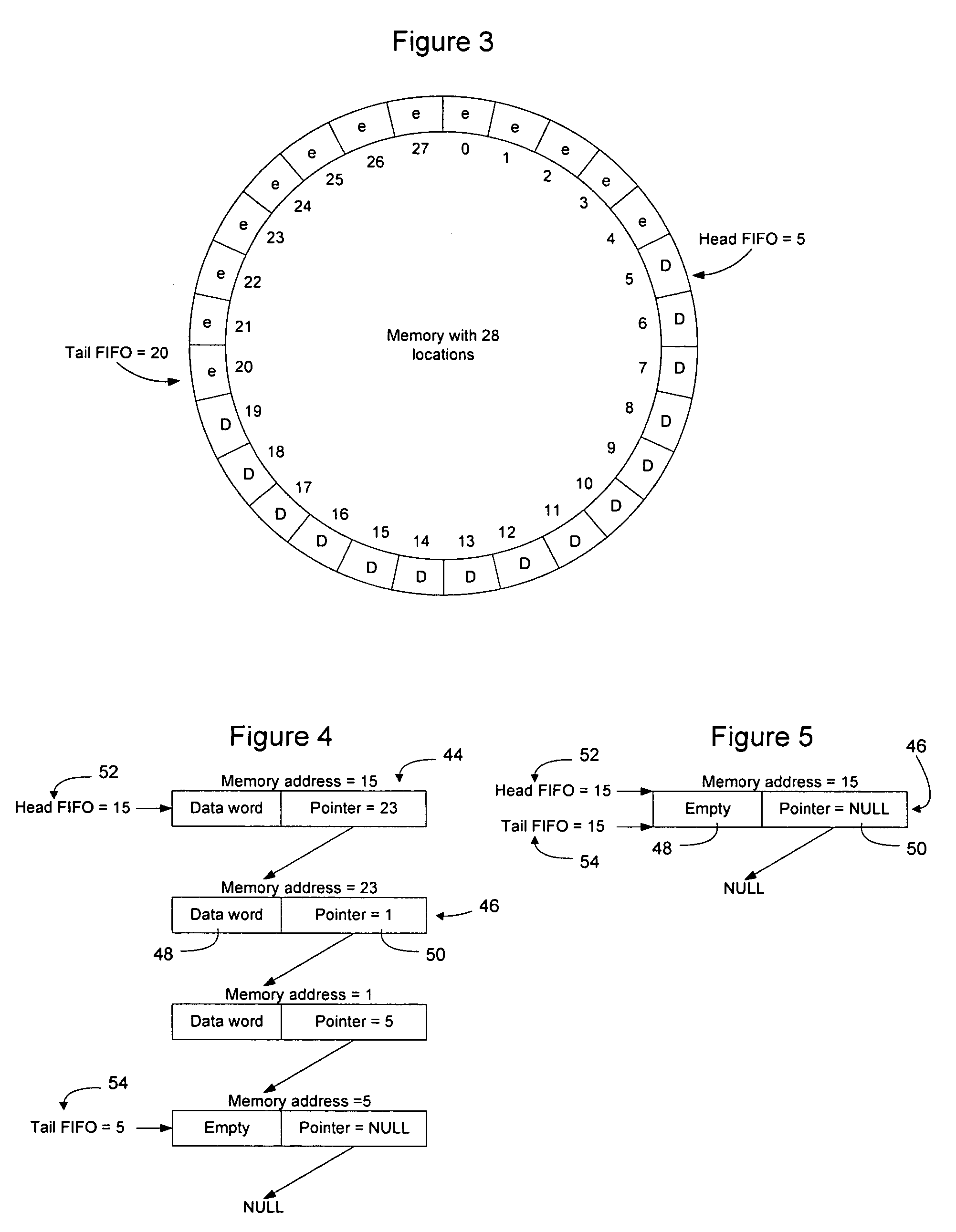

Layered low density parity check decoding for digital communications

ActiveUS7139959B2Efficient implementationMost efficientError preventionError detection/correctionParity-check matrixTheoretical computer science

A low density parity check (LDPC) code that is particularly well adapted for hardware implementation of a belief propagation decoder circuit (38) is disclosed. The LDPC code is arranged as a parity check matrix (H) whose rows and columns represent check sums and input nodes, respectively. The parity check matrix is grouped into subsets of check sum rows, in which the column weight is a maximum of one. The decoder circuitry includes a parity check value estimate memory (52). Adders (54) generate extrinsic estimates, from immediately updated input node probability estimates, and the extrinsic estimates are applied to parity check update circuitry (56) for generating new parity check sum value estimates. These parity check sum value estimates are stored back into the memory (52), and after addition with the extrinsic estimates, are stored in a column sum memory (66) of a corresponding bit update circuit (60) as updated probability values for the input nodes.

Owner:TEXAS INSTR INC

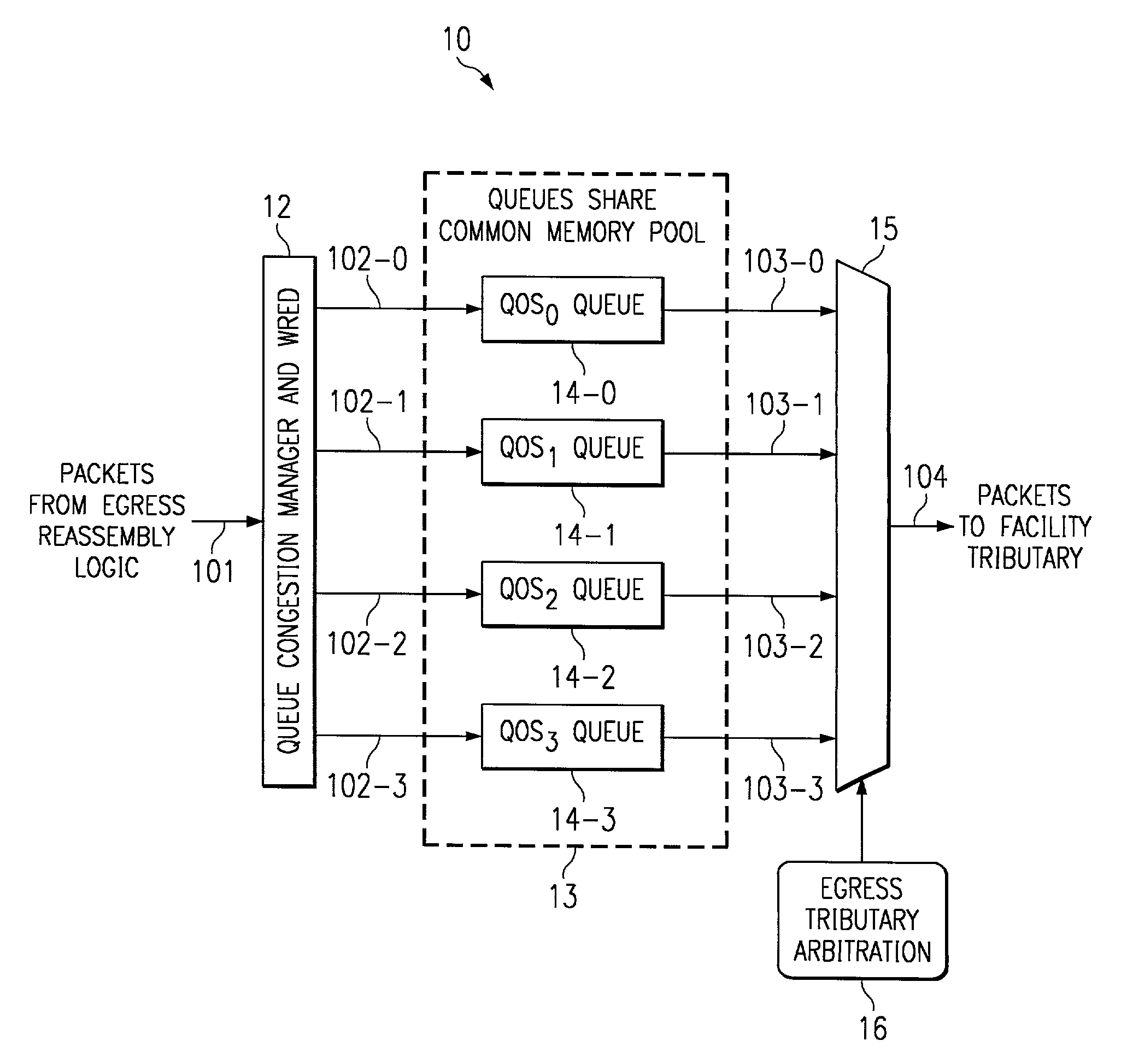

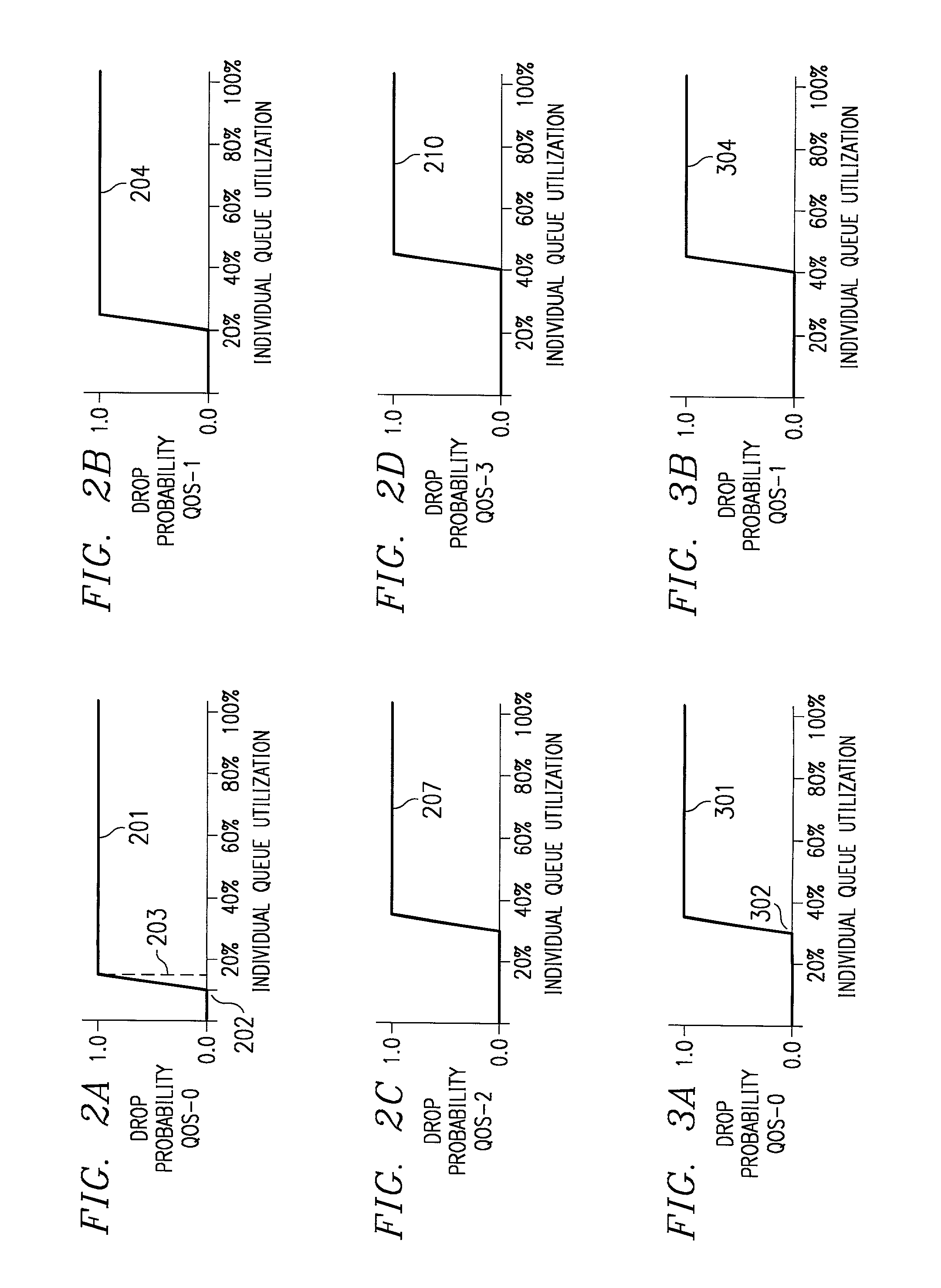

System and method for router queue and congestion management

In a multi-QOS level queuing structure, packet payload pointers are stored in multiple queues and packet payloads in a common memory pool. Algorithms control the drop probability of packets entering the queuing structure. Instantaneous drop probabilities are obtained by comparing measured instantaneous queue size with calculated minimum and maximum queue sizes. Non-utilized common memory space is allocated simultaneously to all queues. Time averaged drop probabilities follow a traditional Weighted Random Early Discard mechanism. Algorithms are adapted to a multi-level QOS structure, floating point format, and hardware implementation. Packet flow from a router egress queuing structure into a single egress port tributary is controlled by an arbitration algorithm using a rate metering mechanism. The queuing structure is replicated for each egress tributary in the router system.

Owner:AVAGO TECH INT SALES PTE LTD

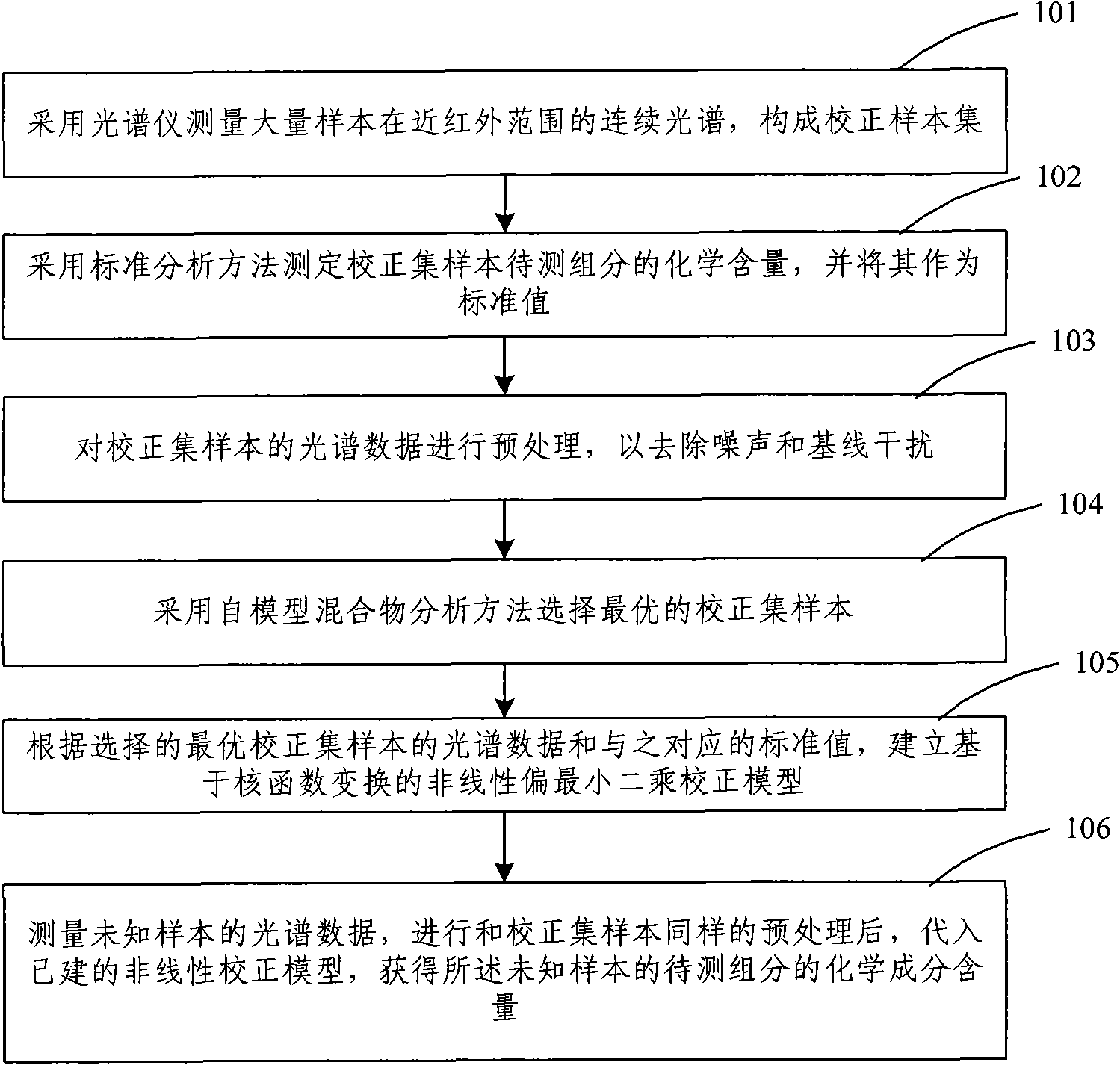

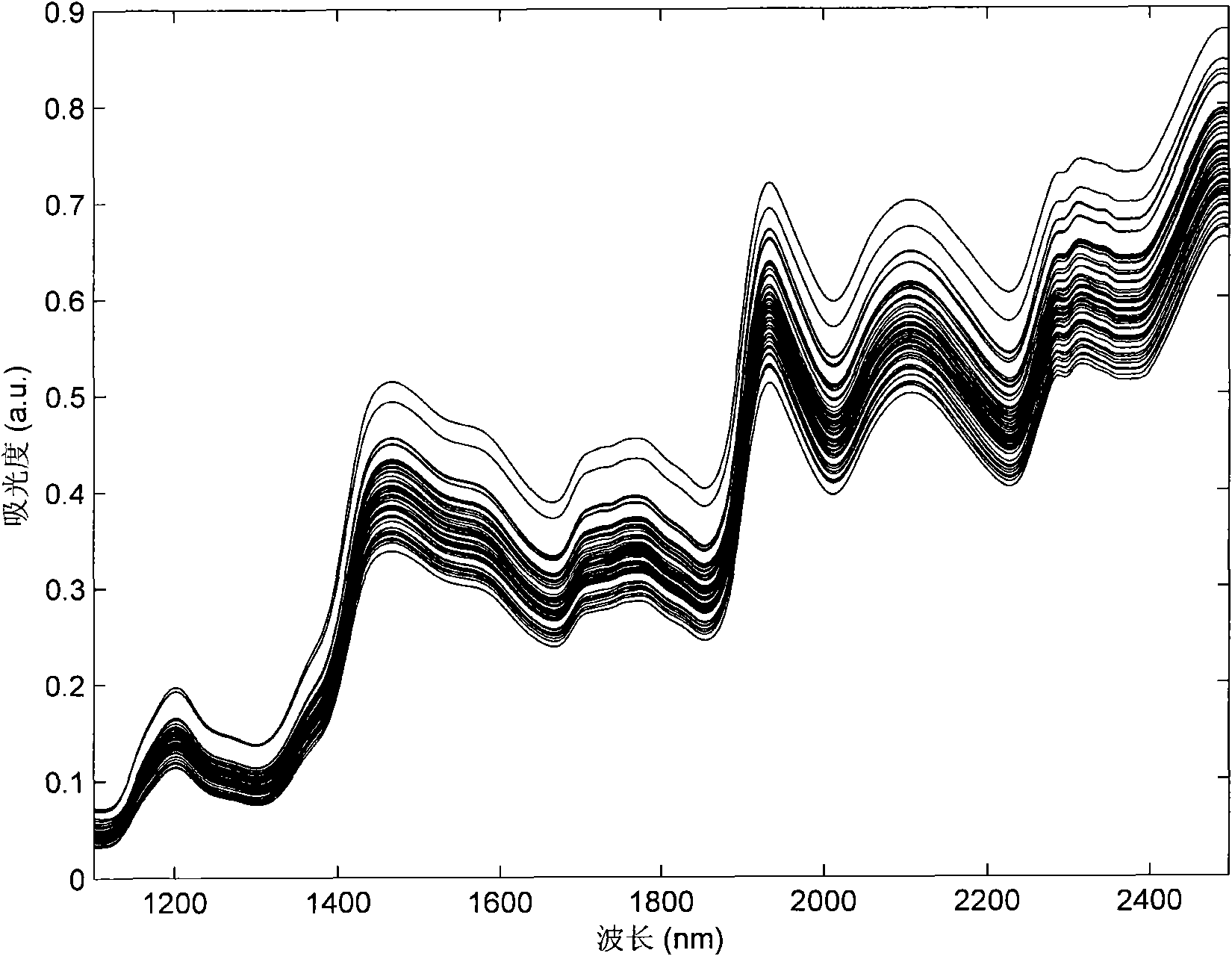

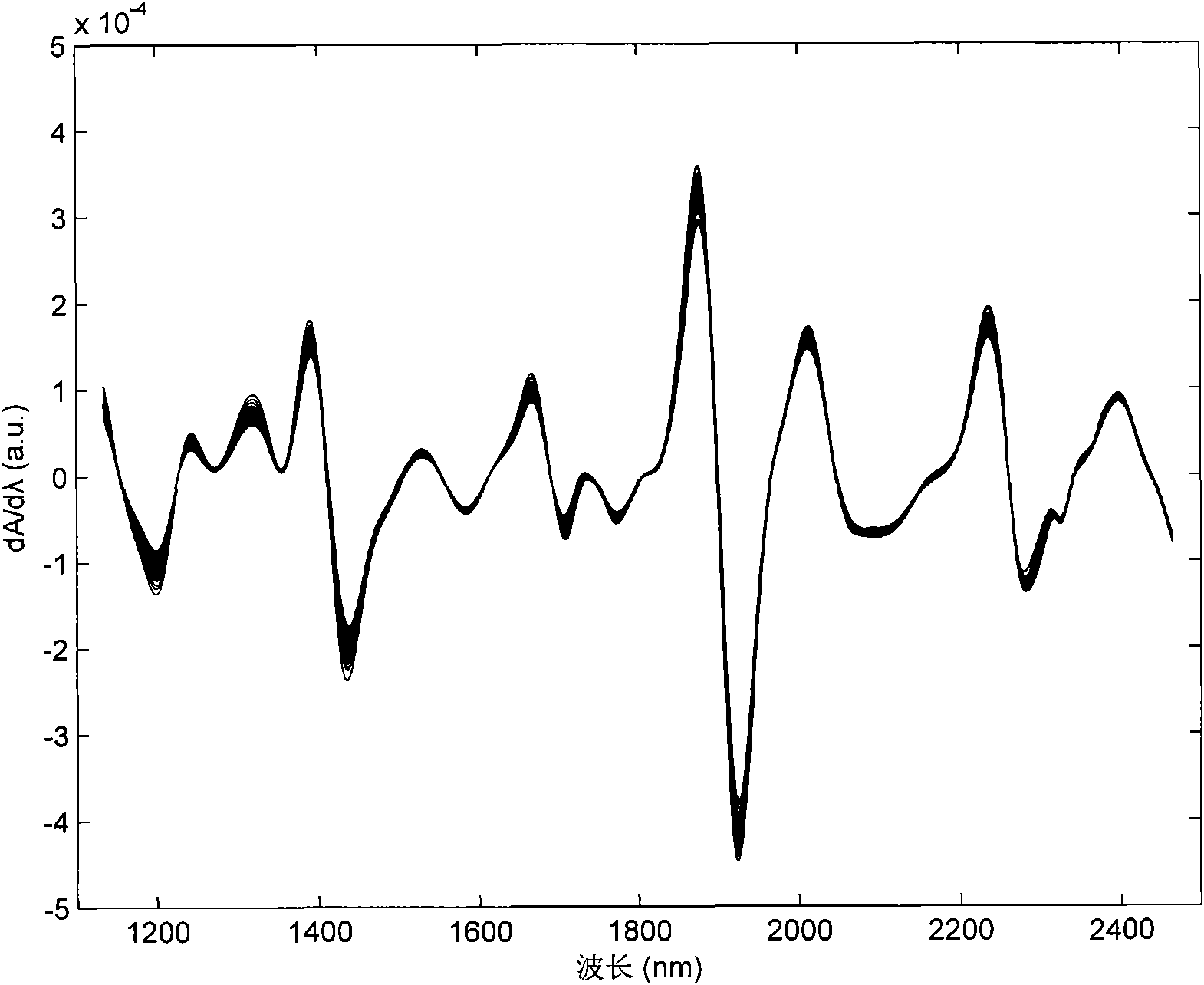

Near infrared spectrum nondestructive testing method and device for material component content

InactiveCN101915744AReduce complexityImprove modeling efficiencyColor/spectral properties measurementsInfraredNonlinear calibration

The invention discloses a near infrared spectrum nondestructive testing method and a near infrared spectrum nondestructive testing device for material component content. The method comprises the following steps of: collecting calibration set samples by using a spectrometer, pretreating a spectrum, selecting an optimal calibration sample set through sample optimization and establishing a nonlinear calibration model by using the optimal calibration sample set, collecting spectrum samples with unknown component content by using the spectrometer, pretreating the spectrum in a mode which is the same as that of pretreating the calibration set samples, and detecting the component content of the unknown sample through the established nonlinear calibration model. The method and the device can effectively solve the problems of complex calibration model, slow training speed and difficult hardware implementation in the conventional near infrared nondestructive testing method for the material component content and obviously improve the accuracy and stability of a nondestructive testing result of the material component content.

Owner:BEIHANG UNIV

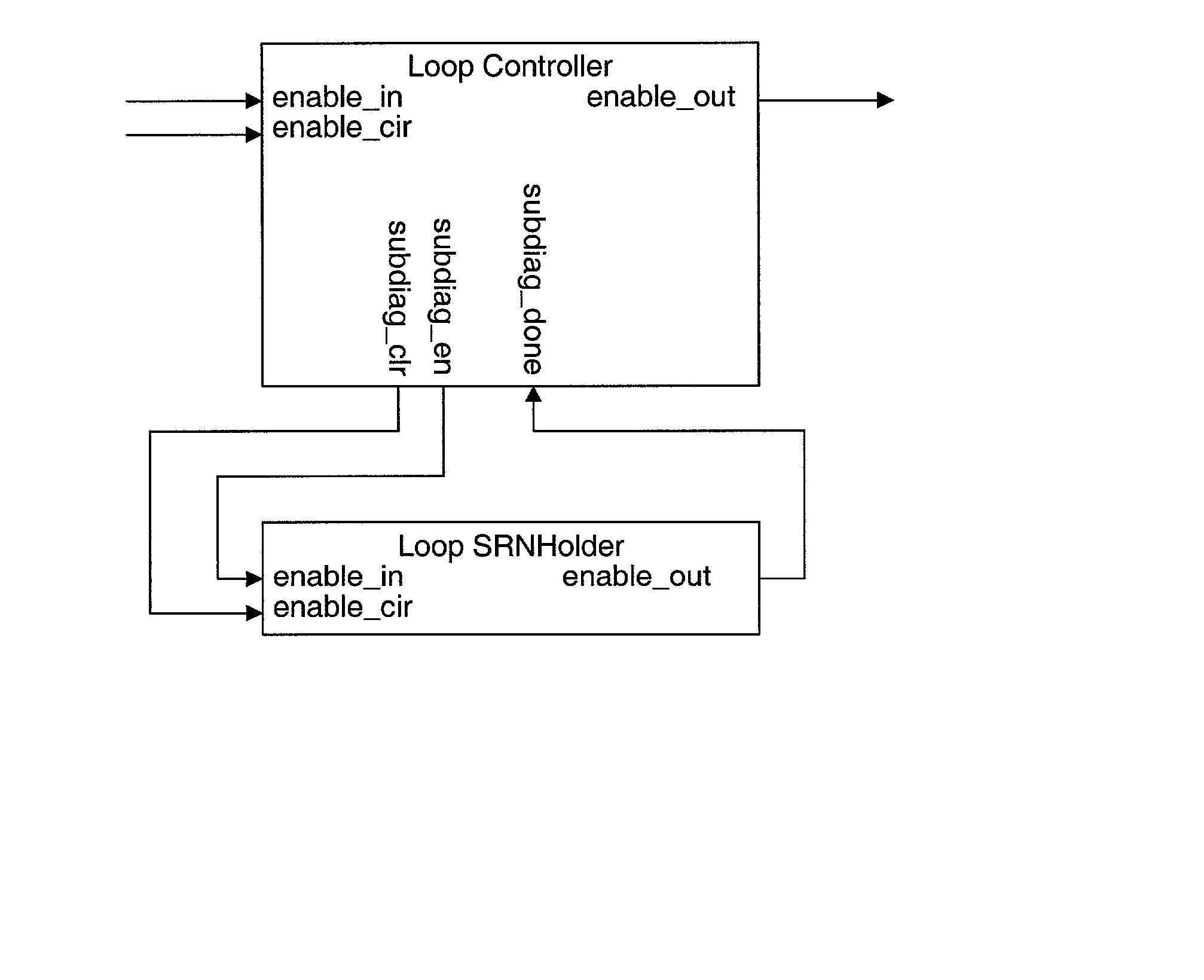

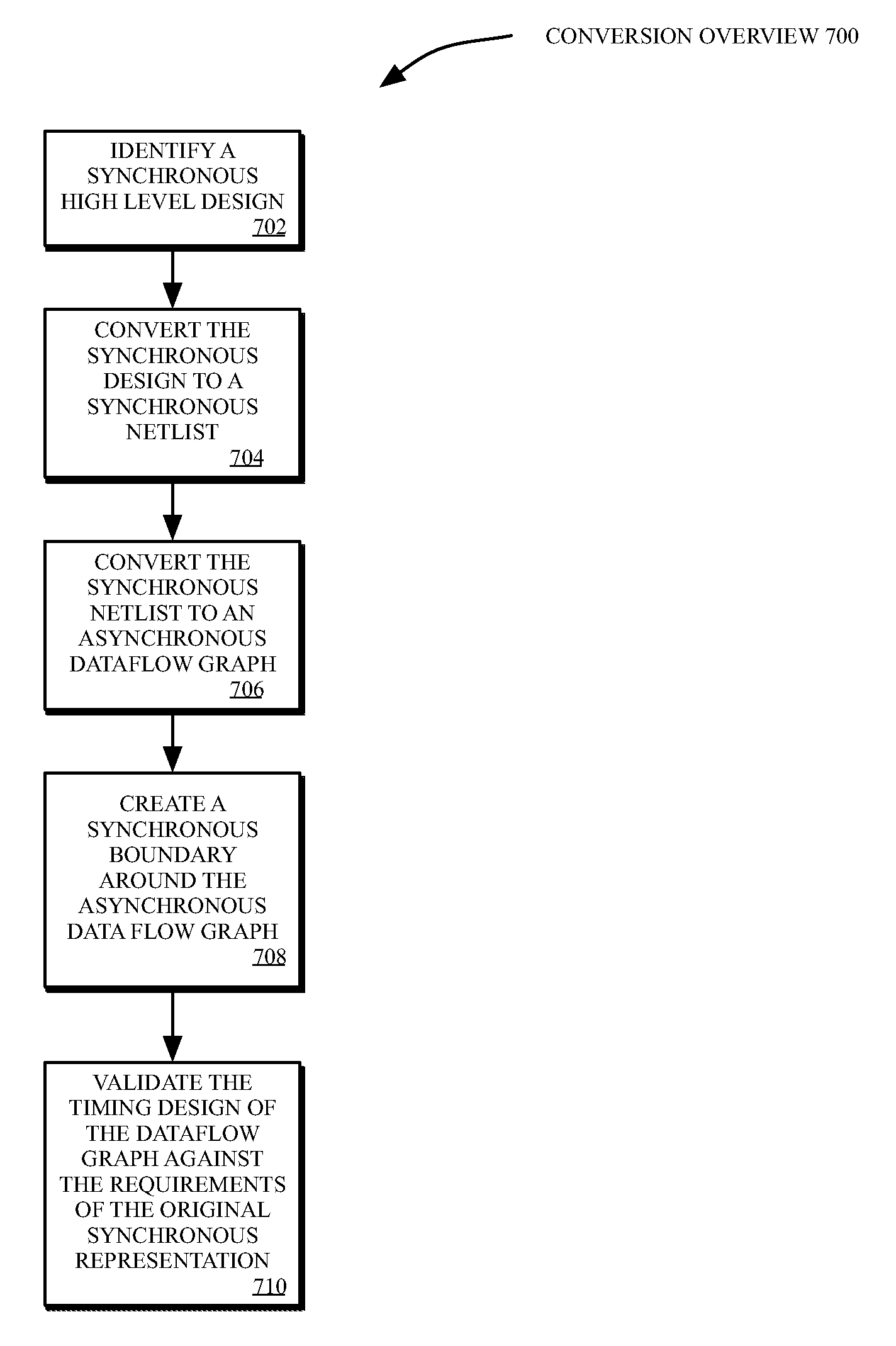

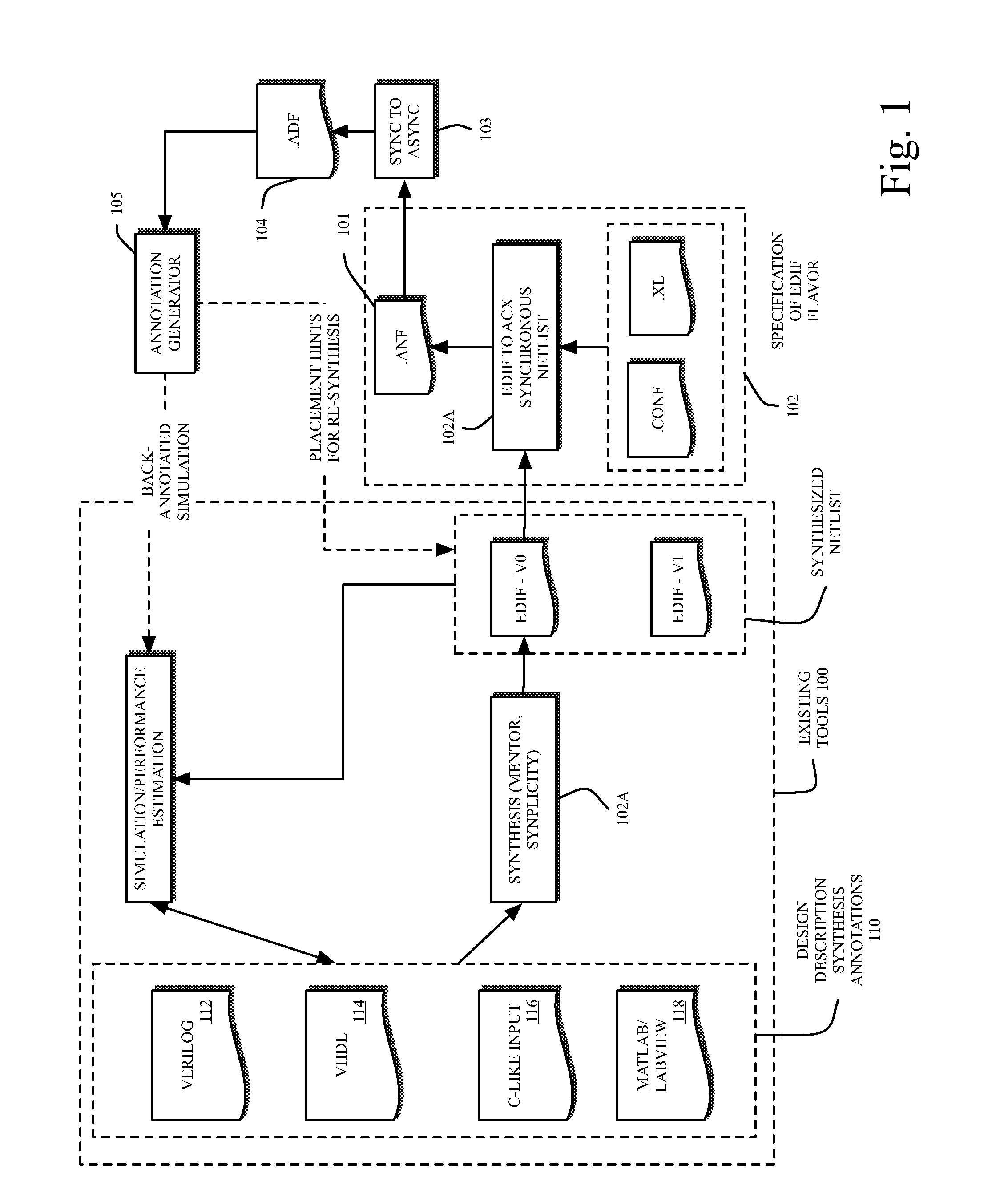

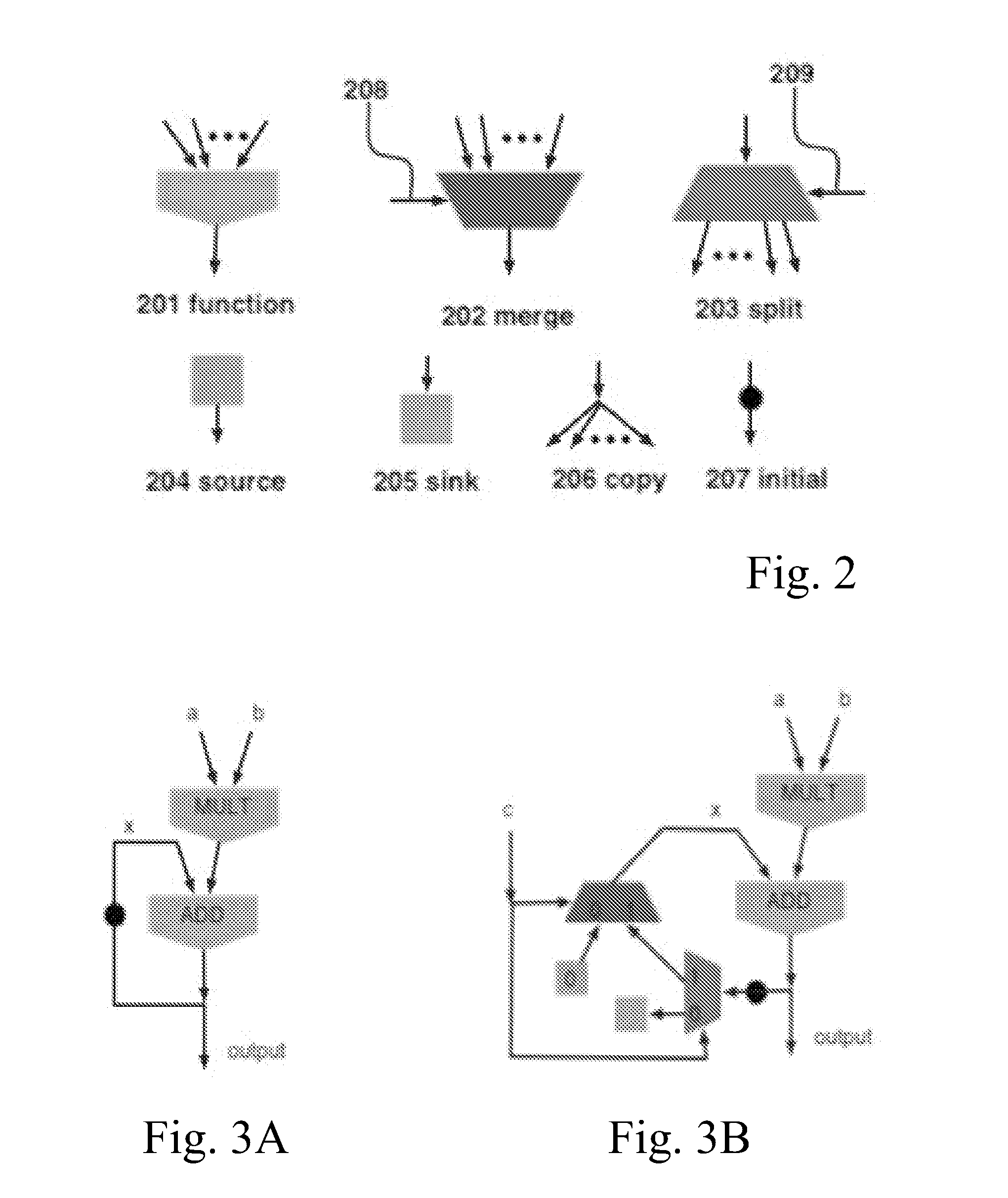

Systems and methods for performing automated conversion of representations of synchronous circuit designs to and from representations of asynchronous circuit designs

ActiveUS20070256038A1Easy to FeedbackCAD circuit designSoftware simulation/interpretation/emulationComputer architectureAsynchronous circuit design

Methods and systems automate an approach to provide a way to convert a circuit design from a synchronous representation to an asynchronous representation without any designer or user interaction or redesign of the synchronous circuit. An optimized, automated, non-Interactive conversion of representations of synchronous circuit designs to and from representations of asynchronous circuit designs, facilitating traditional electronic design automation (EDA) tools to process and manipulate asynchronous designs while allowing synchronous designs to be implemented using asynchronous hardware solutions. The invention also facilitates feedback to synchronous design tools in synchronous representation for optimization and iteration of the design process by engineers, eliminating the need for engineers to be aware of the underlying asynchronous architecture of the underlying hardware implementation.

Owner:ACHRONIX SEMICON CORP

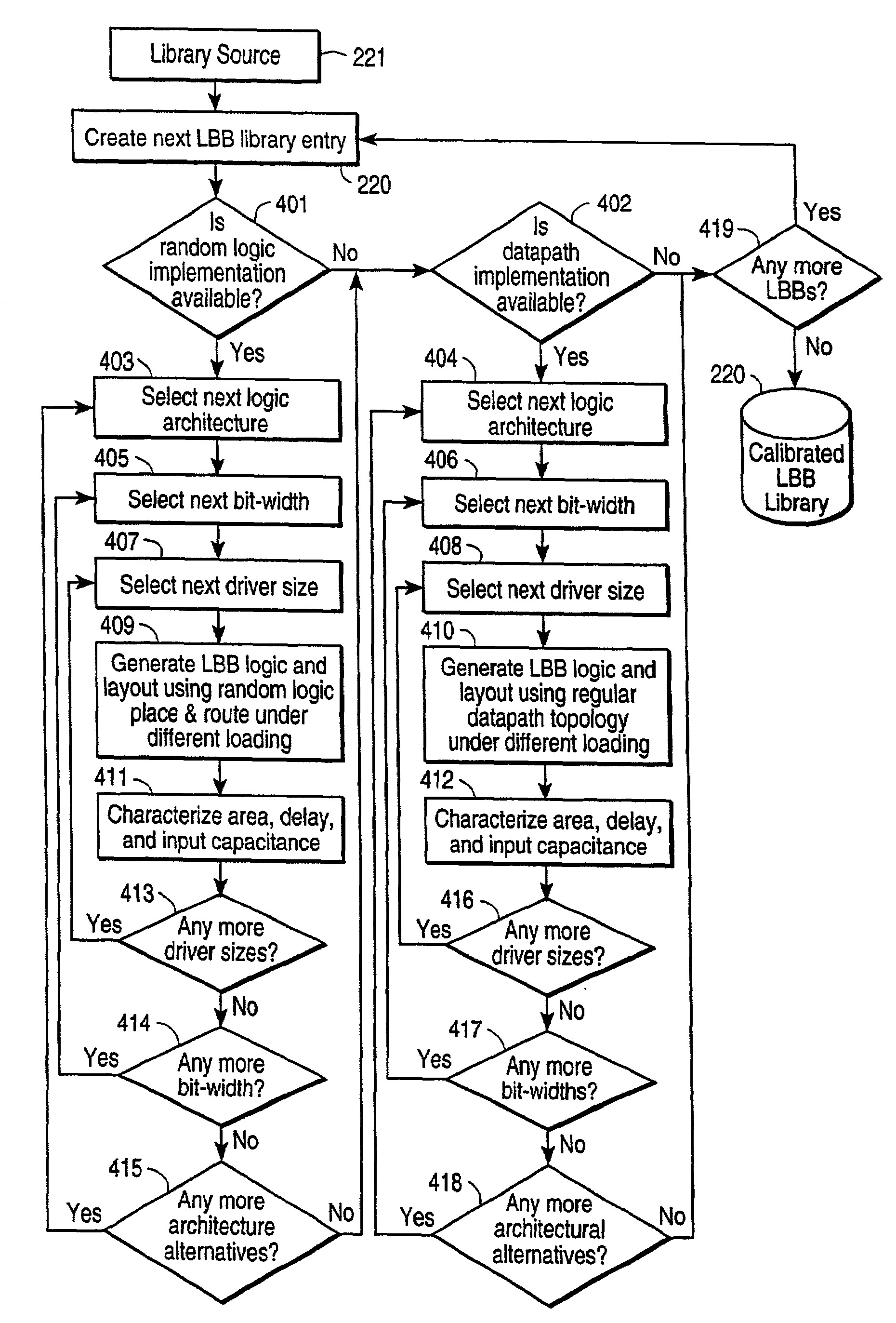

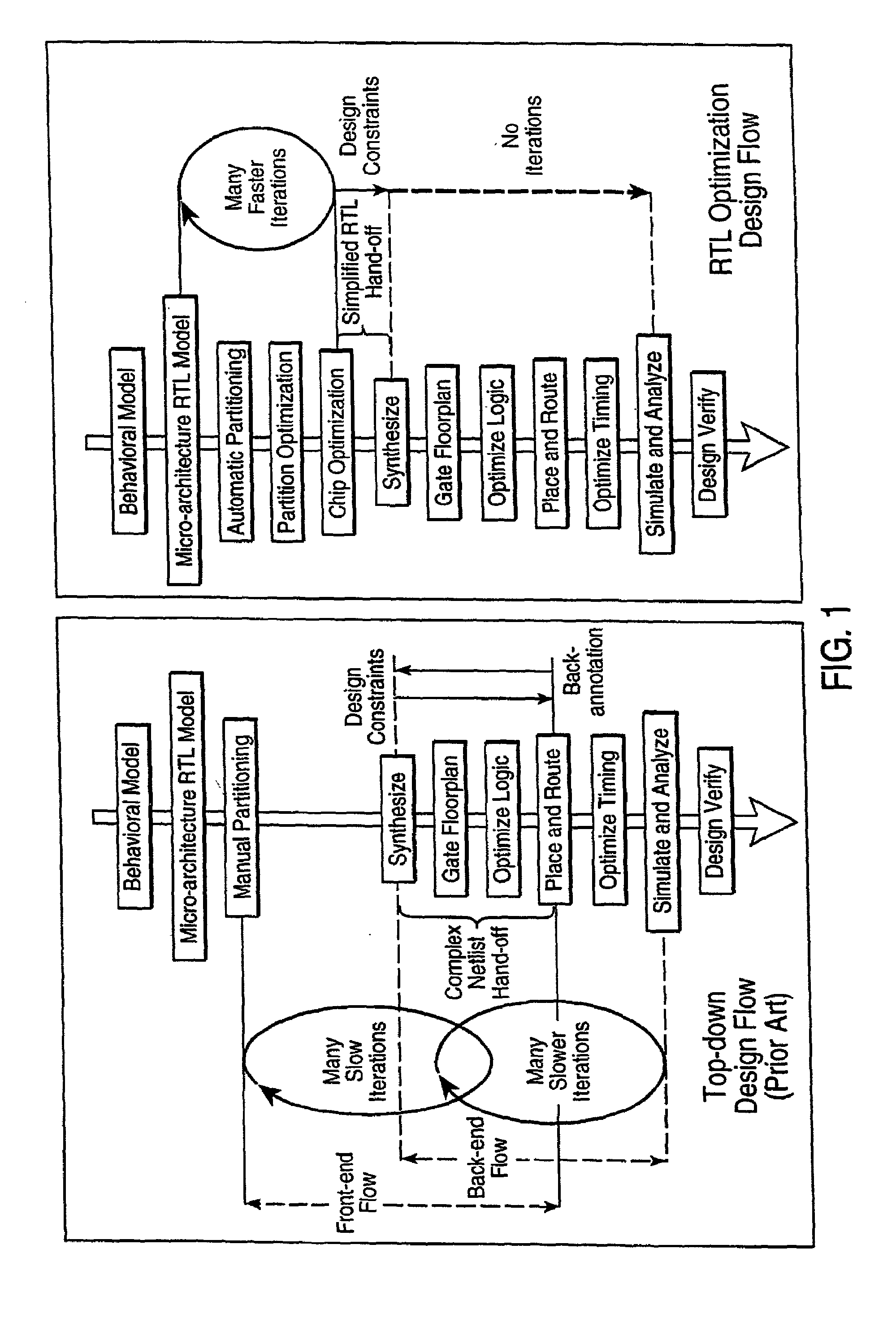

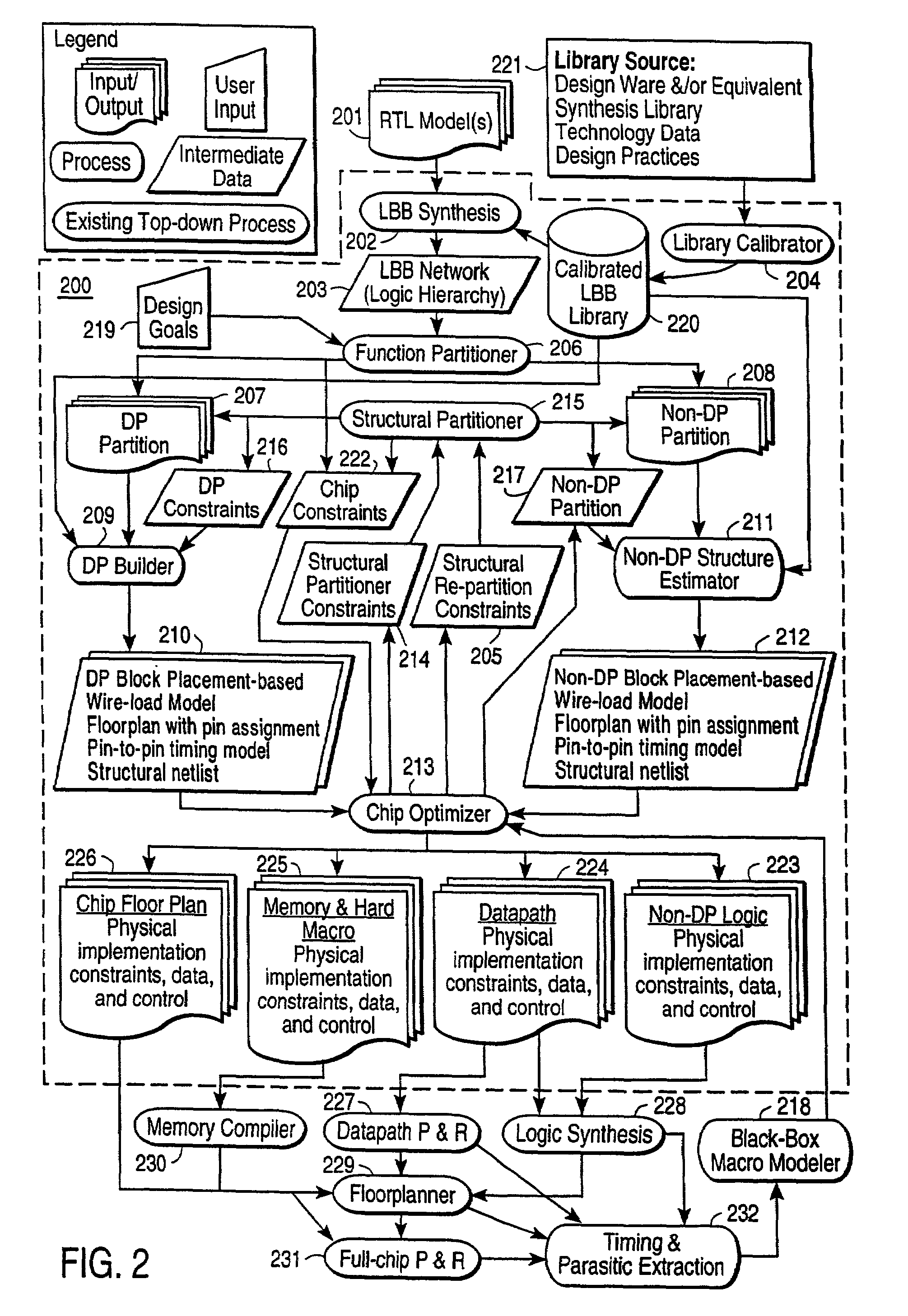

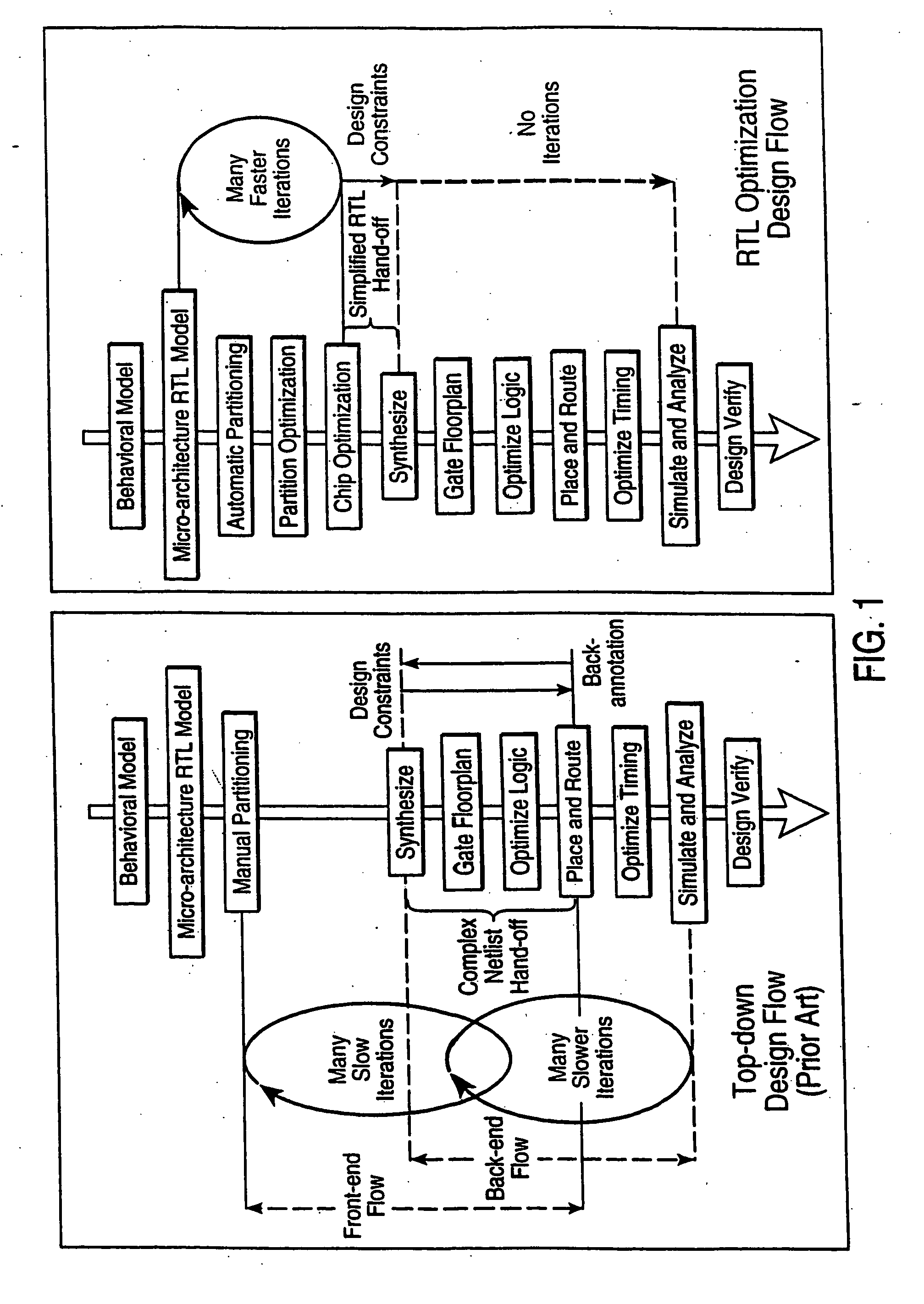

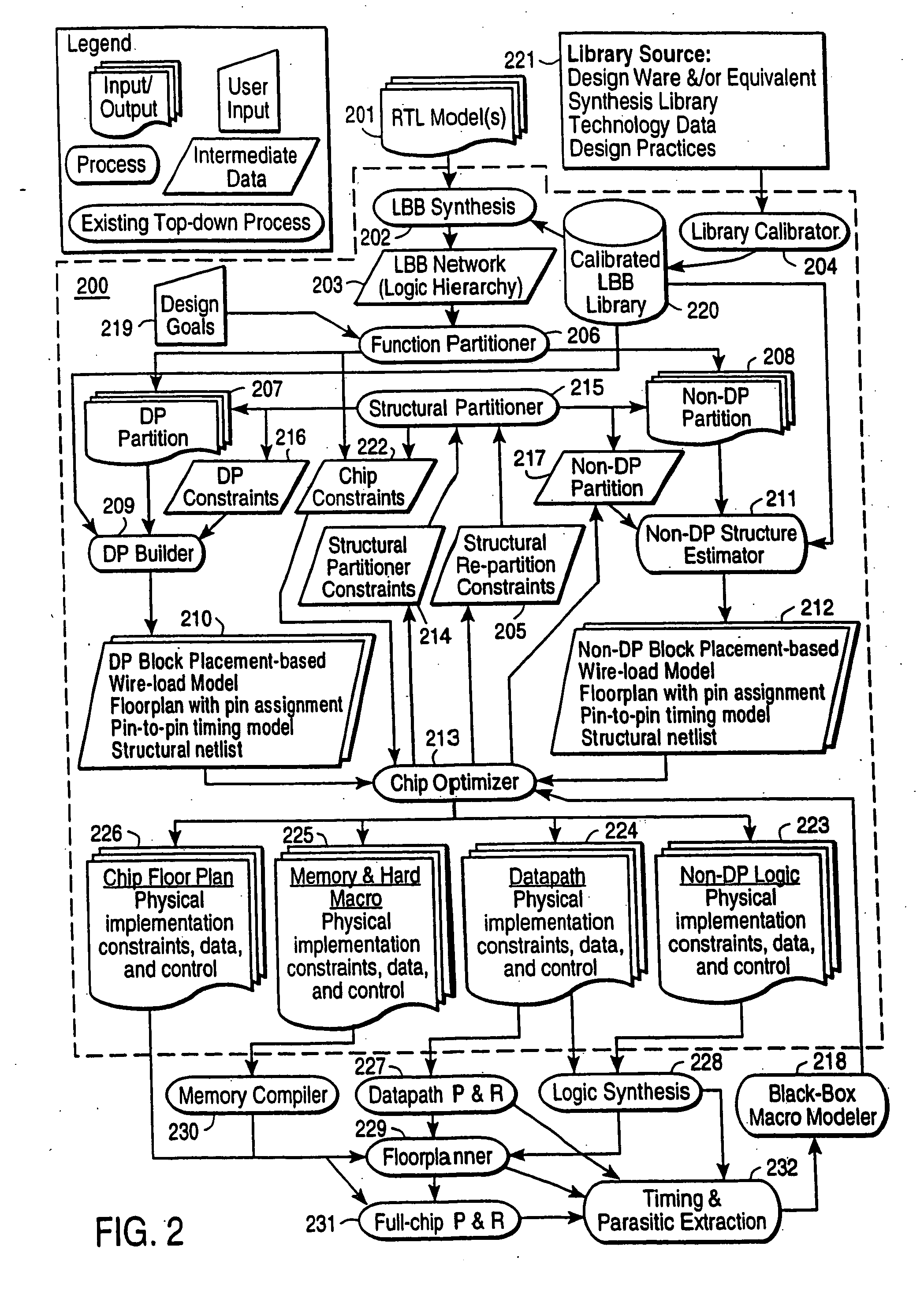

Creating optimized physical implementations from high-level descriptions of electronic design using placement-based information

InactiveUS7143367B2Enhances existing top-down EDA systemsHigh densityDetecting faulty computer hardwareCAD circuit designComputer architectureLoad model

Owner:SYNOPSYS INC

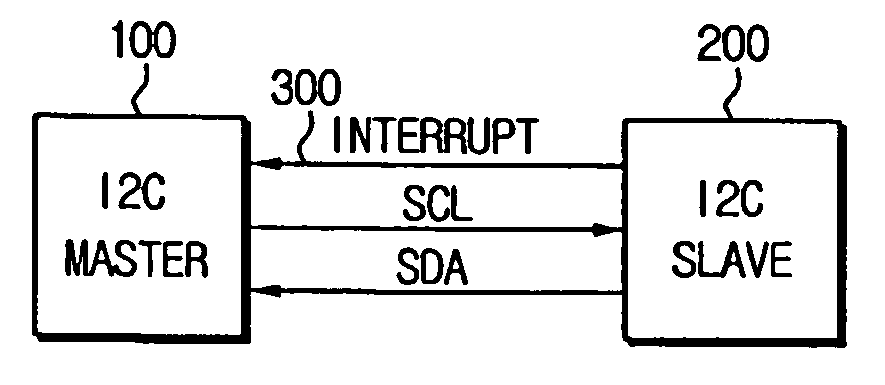

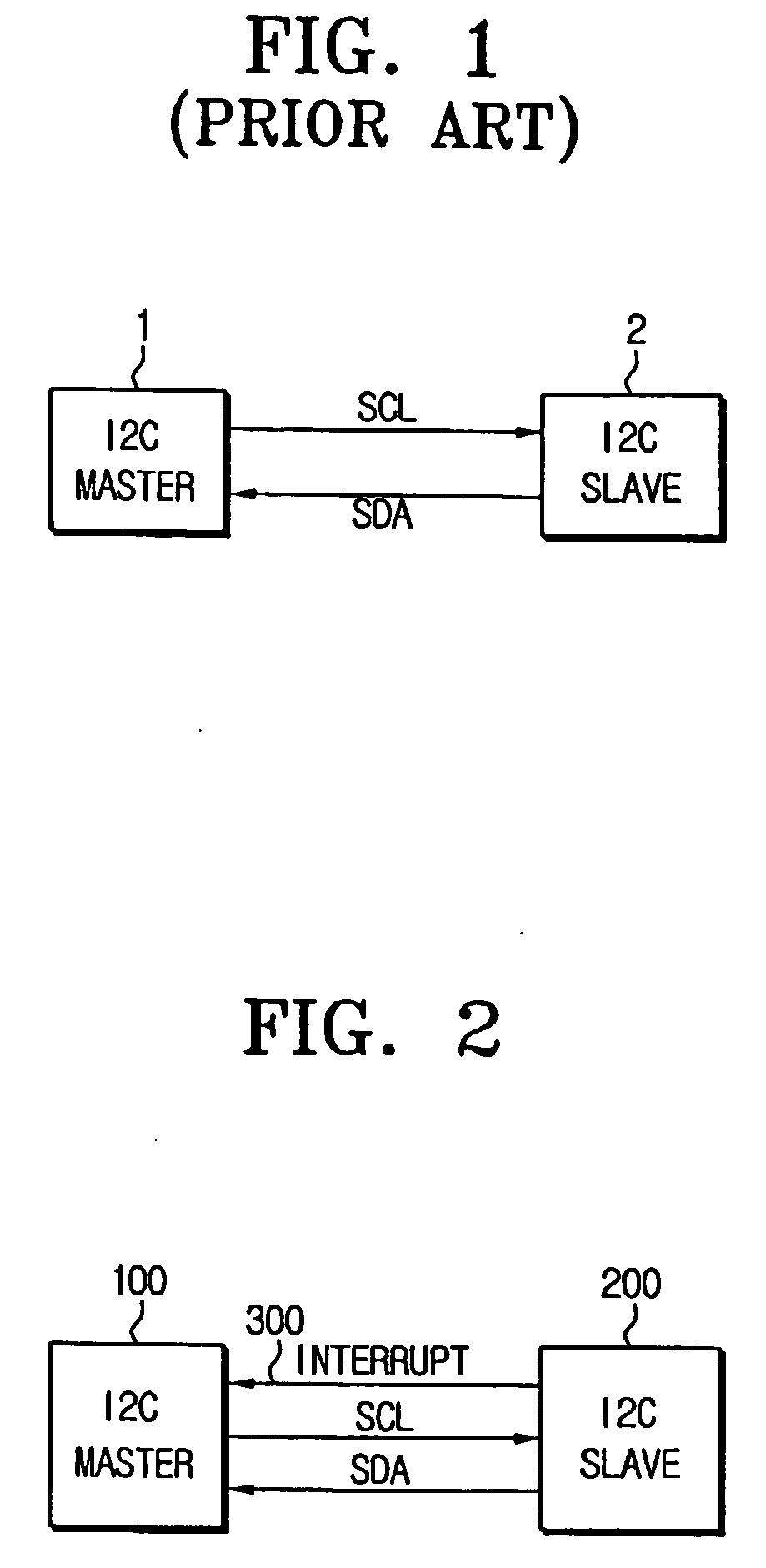

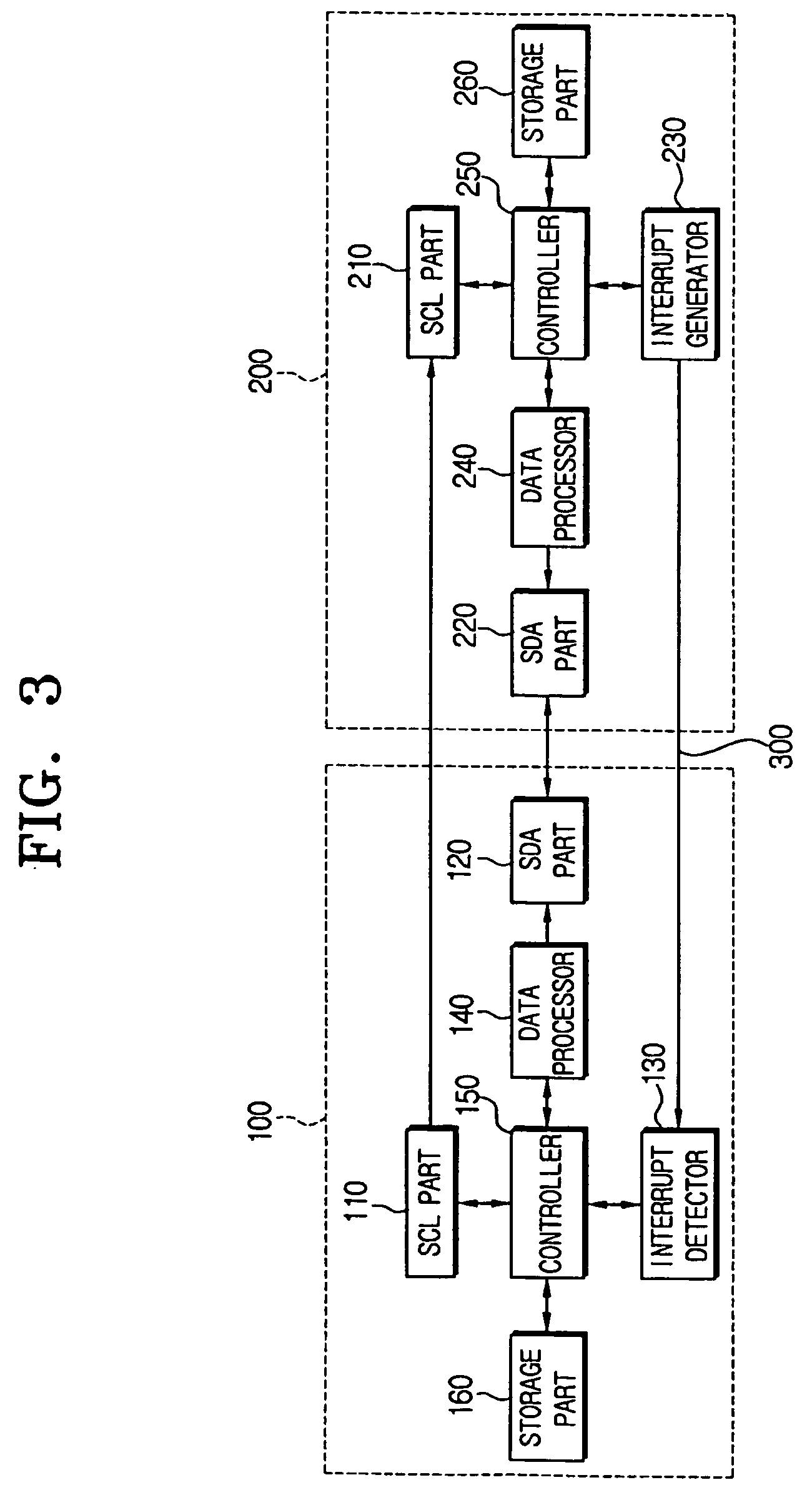

I2C communication system and method enabling bi-directional communications

A communication system and method enabling bi-directional I2C communications is disclosed. In the communication system having a master and at least one slave that communicate with each other through an I2C bus comprising a Serial Clock line (SCL) and a Serial Data line (SDA), the master and slave are directly connected on an interrupt line, and, if the slave sends to the master an interrupt requesting communications, the master performs communications with the slave through the SCL and the SDA. Therefore, the communication system and method enables slaves to generate an interrupt to request communications to the master, so bi-directional communications between microprocessors can be achieved in a simple hardware implementation.

Owner:SAMSUNG ELECTRONICS CO LTD

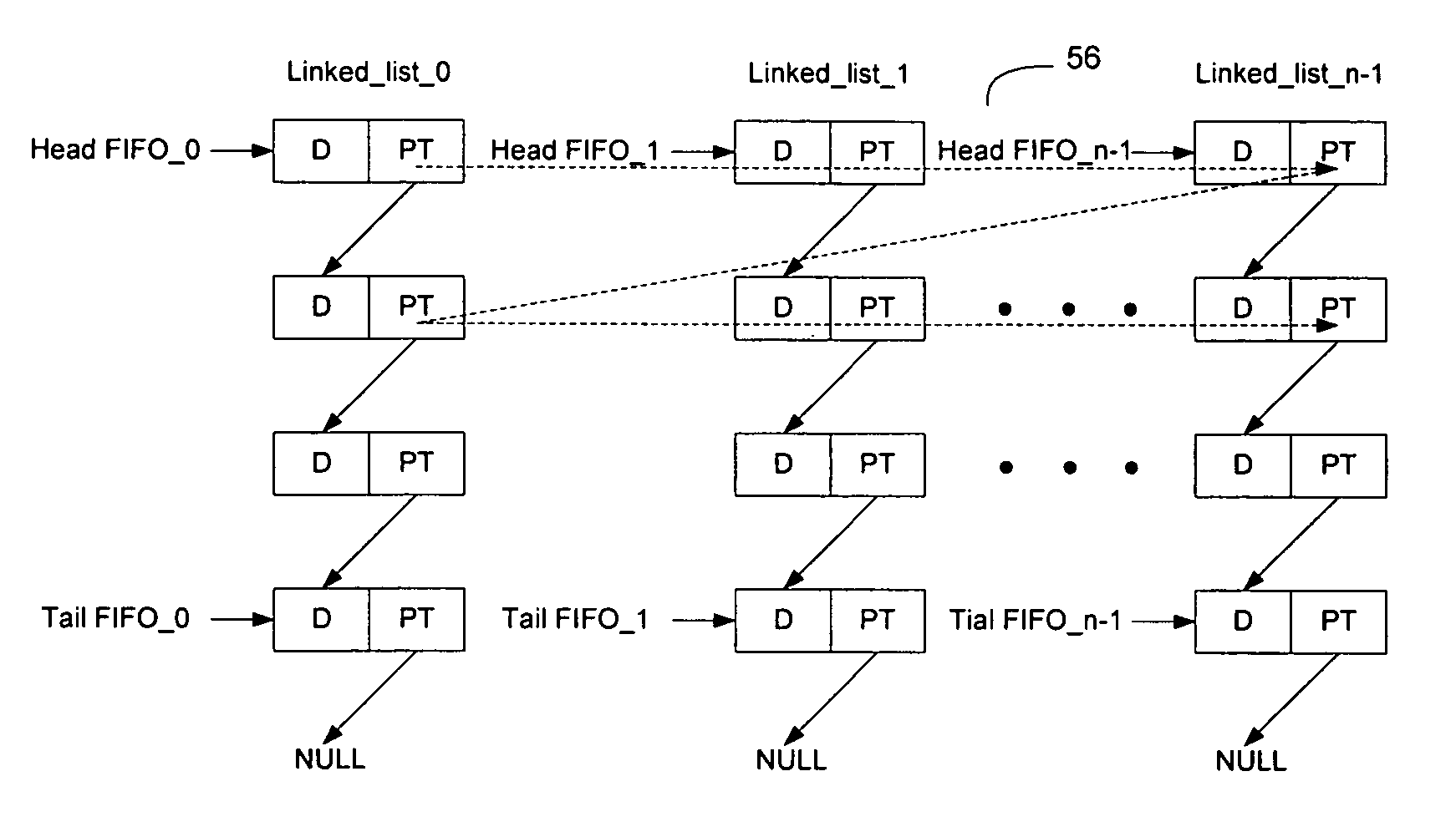

Implementing FIFOs in shared memory using linked lists and interleaved linked lists

InactiveUS20060031643A1Easy to readOvercomes drawbackMemory systemsInput/output processes for data processingData fieldTerm memory

Owner:AVAYA INC

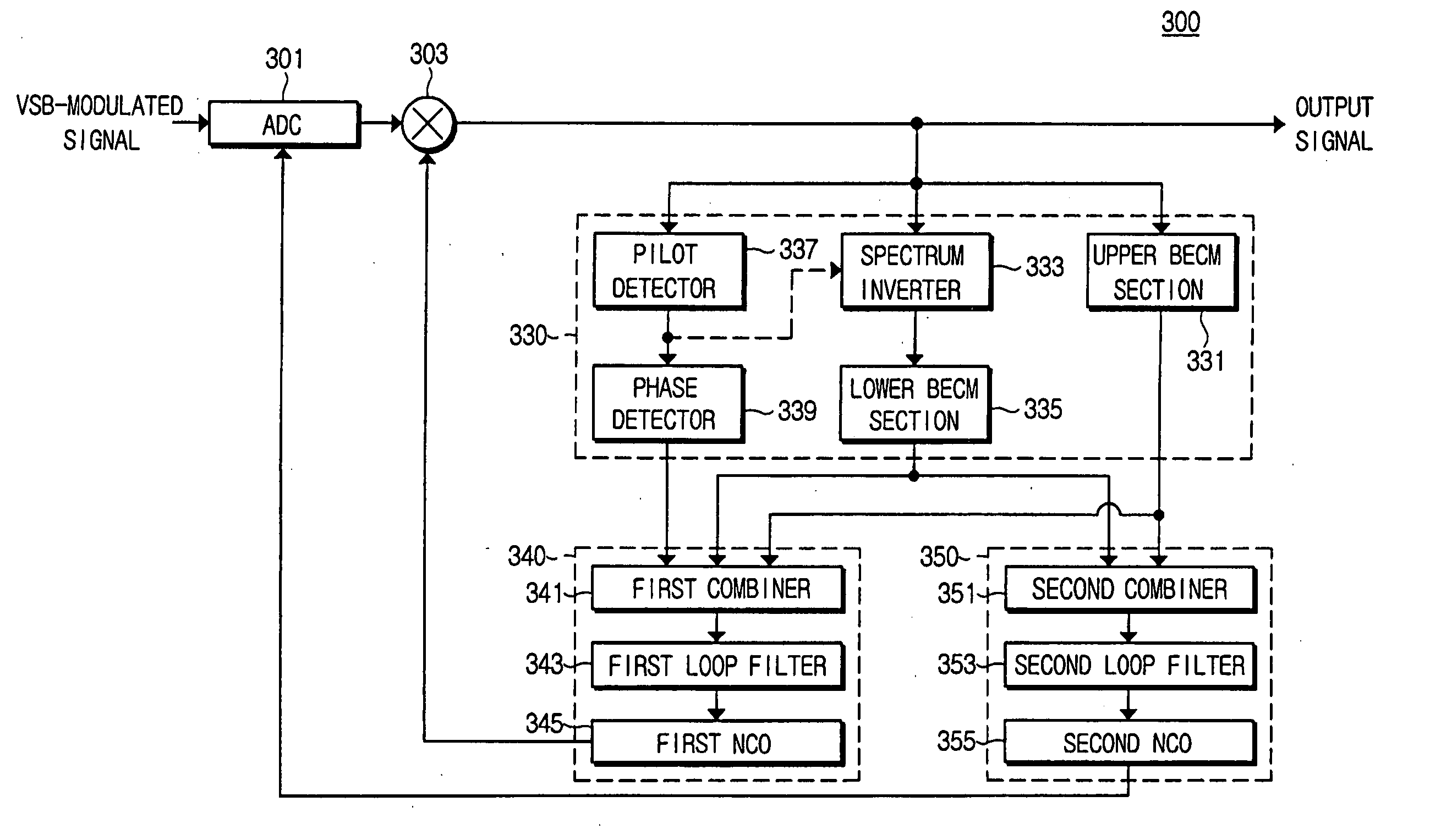

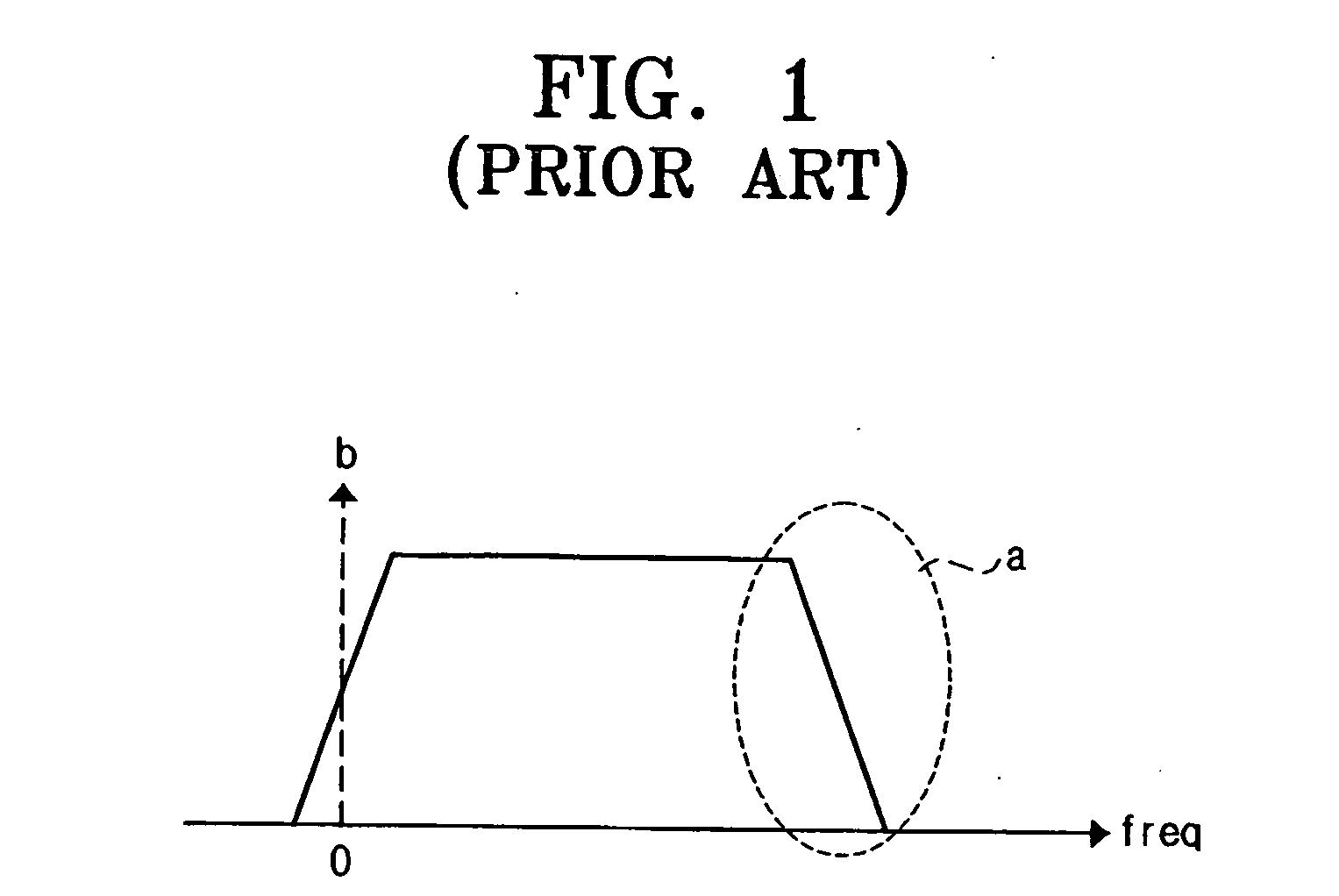

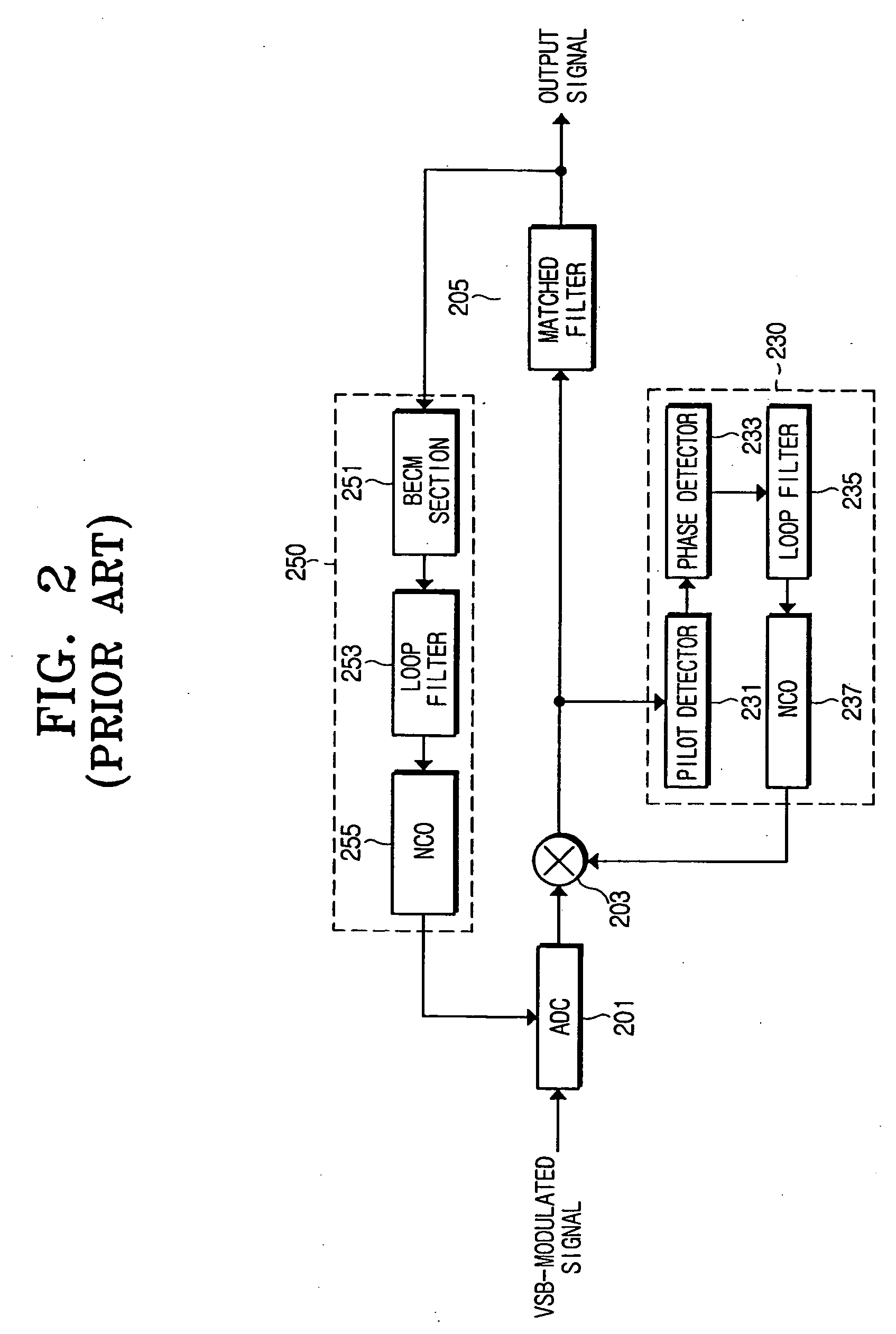

Carrier and symbol timing recovery apparatus usable with a vestigial side band receiver and recovery method thereof

InactiveUS20060078071A1Amplitude demodulation by homodyne/synchrodyne circuitsModulation with suppressed carrierRecovery methodEngineering

A carrier and symbol timing recovery apparatus usable in a VSB (Vestigial Side Band) receiver, and a method thereof. For a carrier and symbol timing recovery, error information is detected using a pilot signal, an upper sideband and a lower sideband of a received signal. Each of the detected error information is multiplied by a predetermined weight, respectively, and the results of the respective multiplications are added / combined. Therefore, even though the pilot signal may be corrupted, the carrier recovery can nevertheless be accurately performed. Additionally, even though the upper sideband of a received VSB-modulated signal may be corrupted, the lower sideband can be utilized to perform the symbol timing recovery. As a result, performance of a receiving system can be improved even under unfavorable channel characteristics. Moreover, since the carrier recovery and the symbol timing recovery are executed through a single apparatus, it becomes possible to simplify a hardware implementation thereof.

Owner:SAMSUNG ELECTRONICS CO LTD

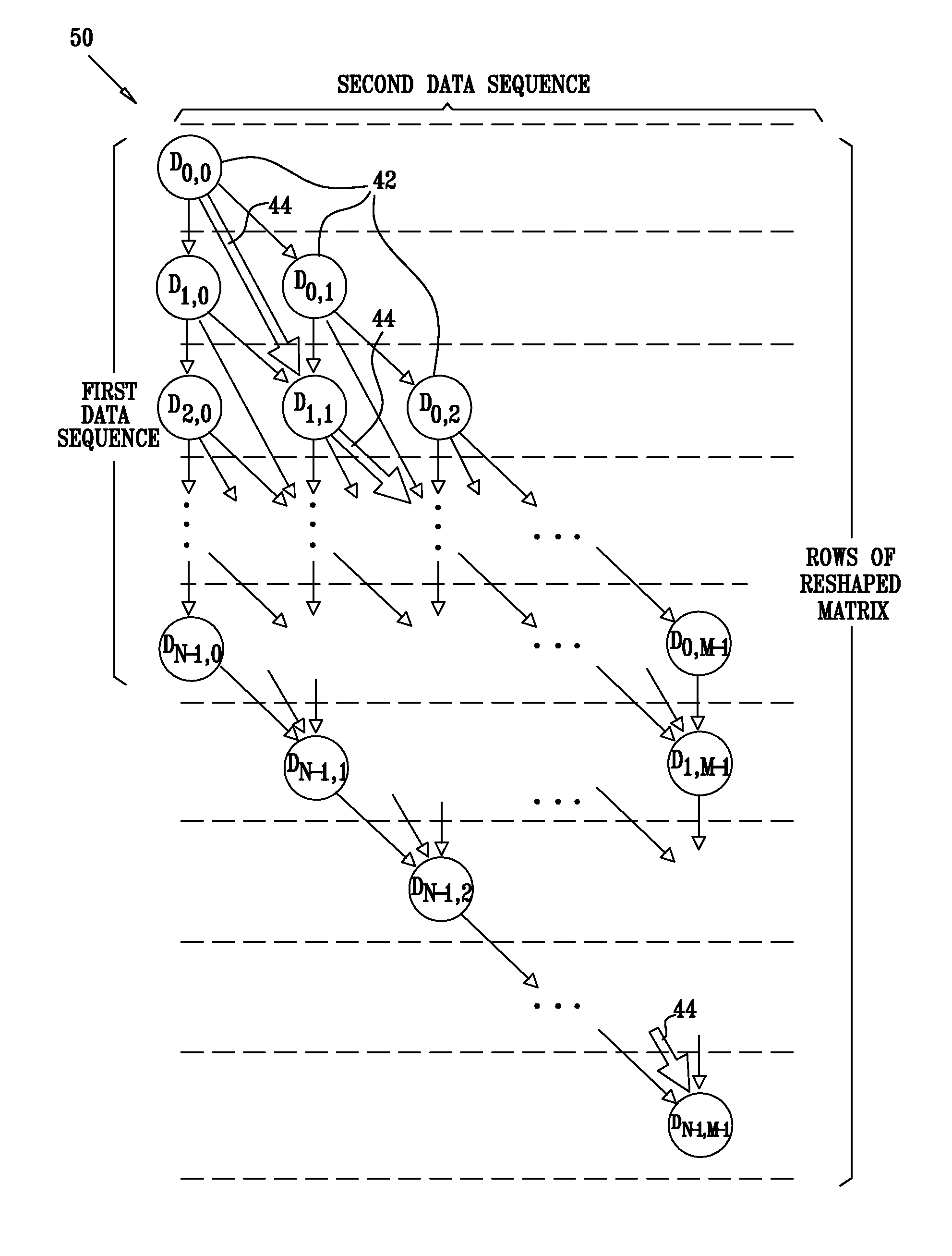

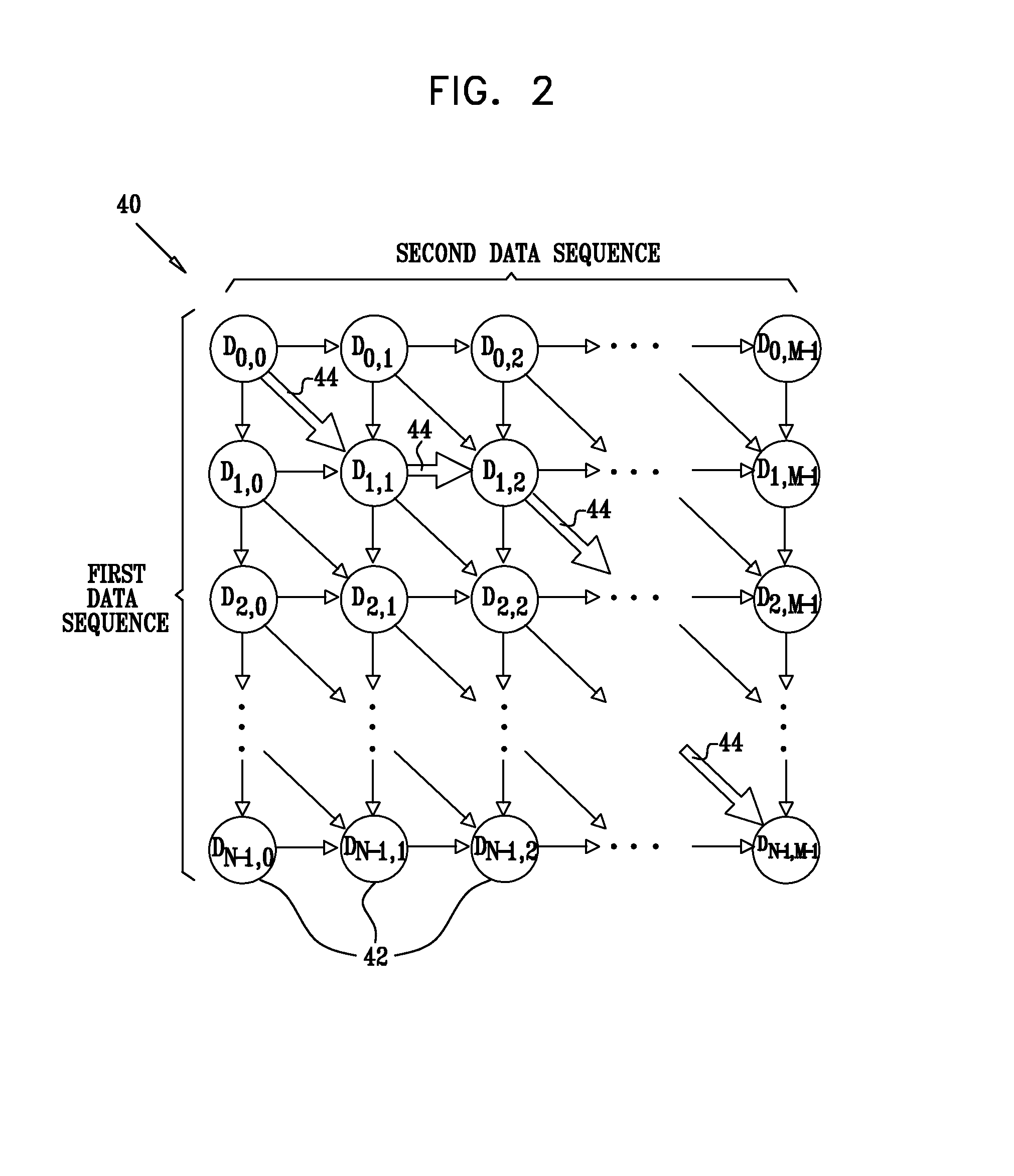

Vectorization of dynamic-time-warping computation using data reshaping

InactiveUS20090150313A1Removing data dependencyGenetic modelsDigital computer detailsDistance matrixAlgorithm

A method for comparing data sequences includes accepting first and second data sequences of data elements. A distance matrix is computed. The matrix includes rows and columns of matrix elements, describing distances between the data elements of the first sequence and the data elements of the second data sequence. The distance matrix is reshaped by applying successive, incremental shifts to the rows or columns so as to produce a reshaped matrix. A best-score path through the reshaped matrix is calculated using vector operations, so as to quantify a similarity between the first and second data sequences. Due to vectorization, a significant increase in computation speed is achieved in both software and hardware implementations.

Owner:IBM CORP

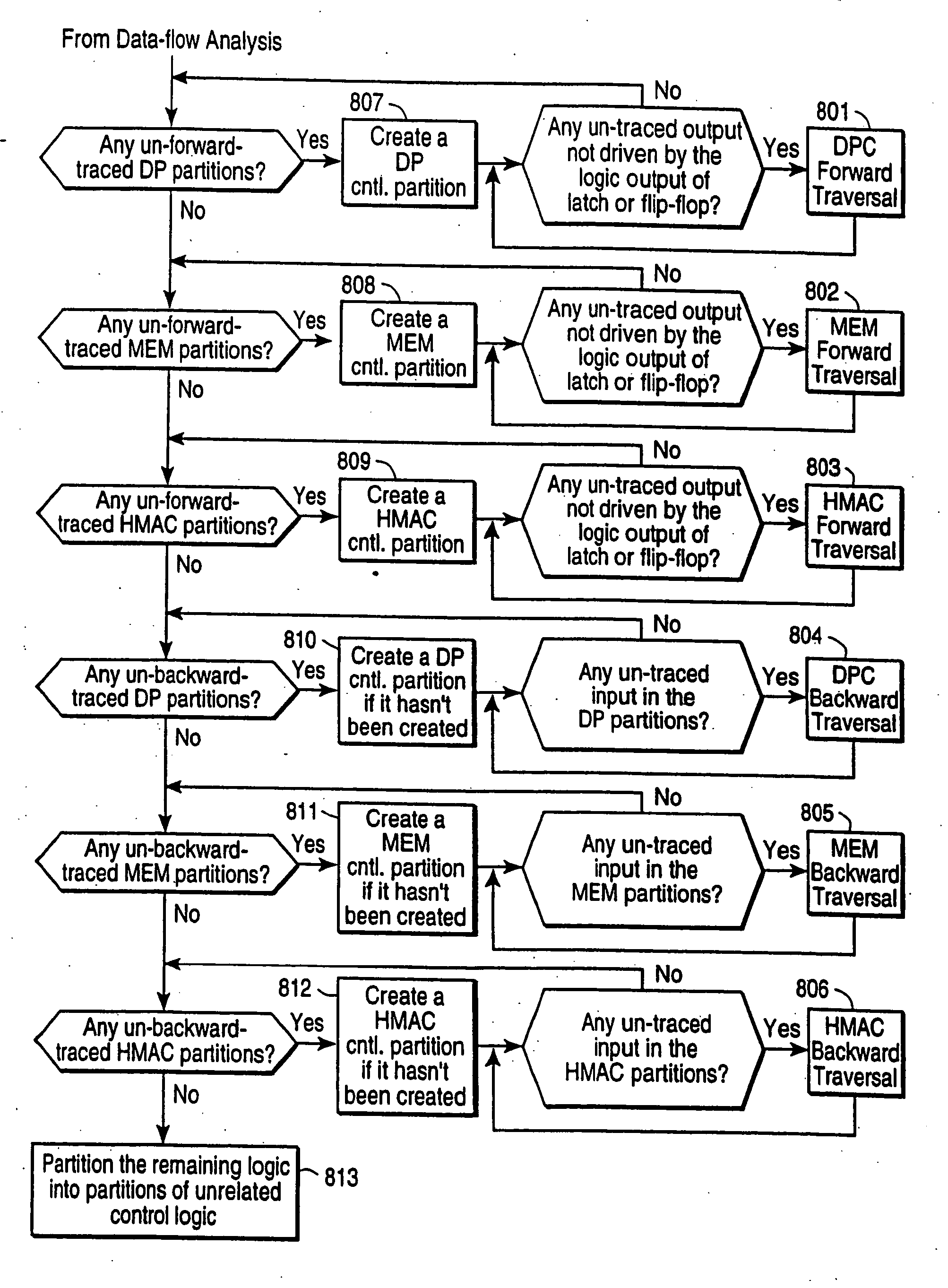

Creating optimized physical implementations from high-level descriptions of electronic design using placement-based information

InactiveUS20060053396A1Improve performanceHigh densityCAD circuit designSoftware simulation/interpretation/emulationComputer architectureData file

An electronic design automation system provides optimization of RTL models of electronic designs, to produce detailed constraints and data precisely defining the requirements for the back-end flows leading to design fabrication. The system takes a RTL model of an electronic design and maps it into an efficient, high level hierarchical representation of the hardware implementation of the design. Automatic partitioning partitions the hardware representation into functional partitions, and creates a fully characterized performance envelope for a range of feasible implementations for each of the partitions, using accurate placement based wire load models. Chip-level optimization selects and refines physical implementations of the partitions to produce compacted, globally routed floorplans. Chip-level optimization iteratively invokes re-partitioning passes to refine the partitions and to recompute the feasible implementations. In this fashion, a multiple-pass process converges on an optimal selection of physical implementations for all partitions for the entire chip that meet minimum timing requirements and other design goals. The system outputs specific control and data files which thoroughly define the implementation details of the design through the entire back-end flow process, thereby guaranteeing that the fabricated design meets all design goals without costly and time consuming design iterations.

Owner:MAGMA DESIGN AUTOMATION