Patents

Literature

216 results about "Asynchronous circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

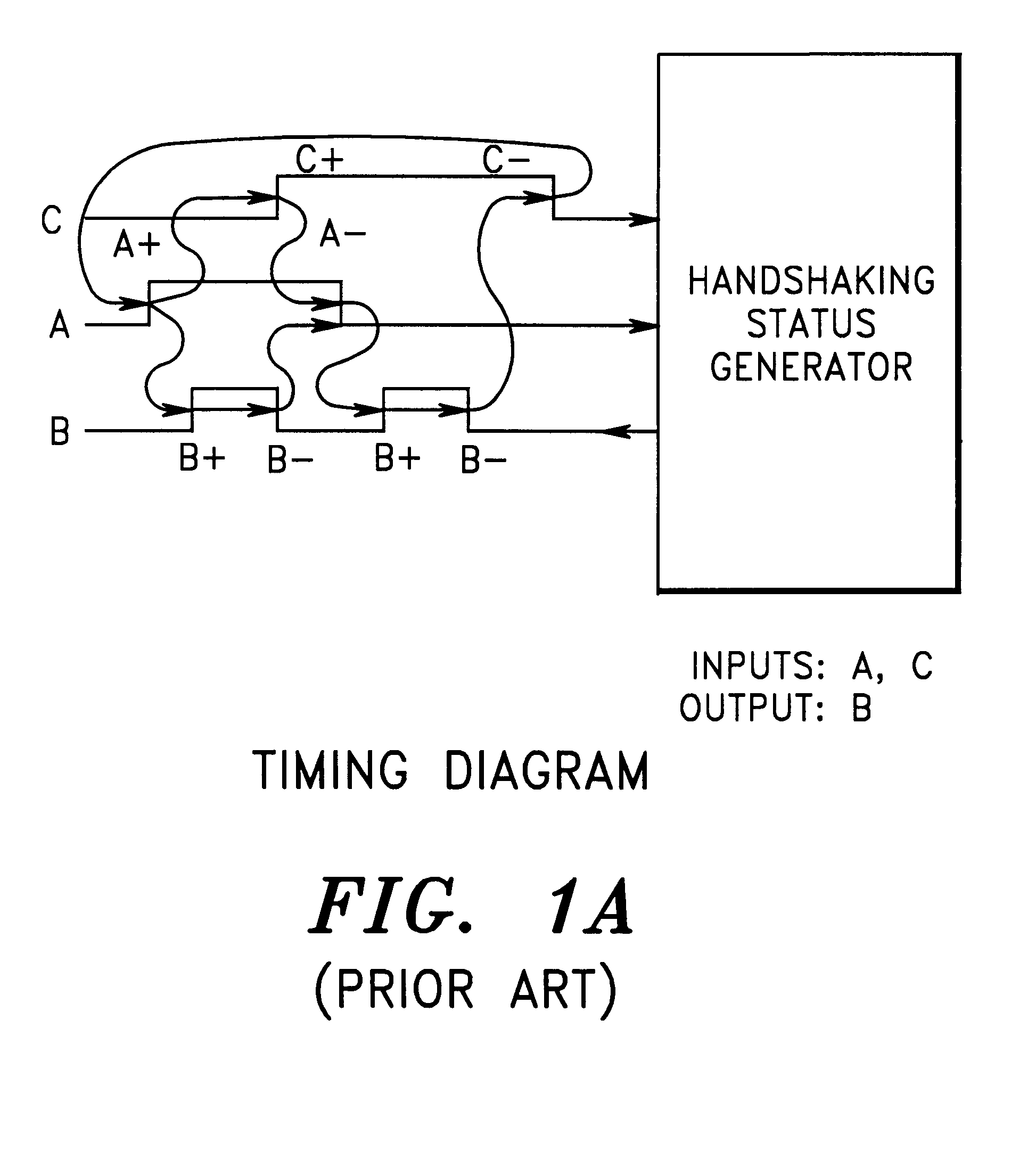

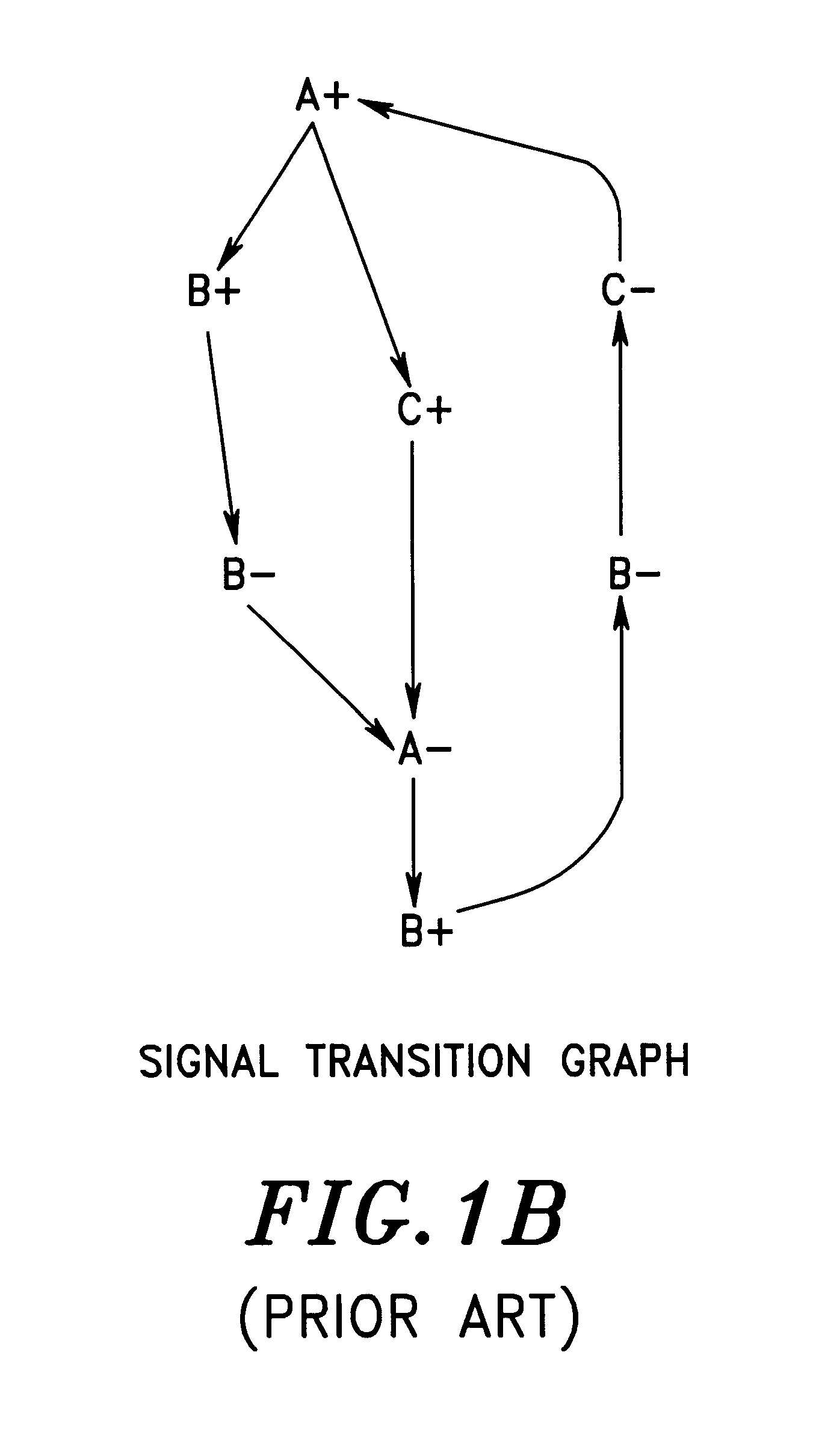

An asynchronous circuit, or self-timed circuit, is a sequential digital logic circuit which is not governed by a clock circuit or global clock signal. Instead it often uses signals that indicate completion of instructions and operations, specified by simple data transfer protocols. This type of circuit is contrasted with synchronous circuits, in which changes to the signal values in the circuit are triggered by repetitive pulses called a clock signal. Most digital devices today use synchronous circuits. However asynchronous circuits have the potential to be faster, and may also have advantages in lower power consumption, lower electromagnetic interference, and better modularity in large systems. Asynchronous circuits are an active area of research in digital logic design.

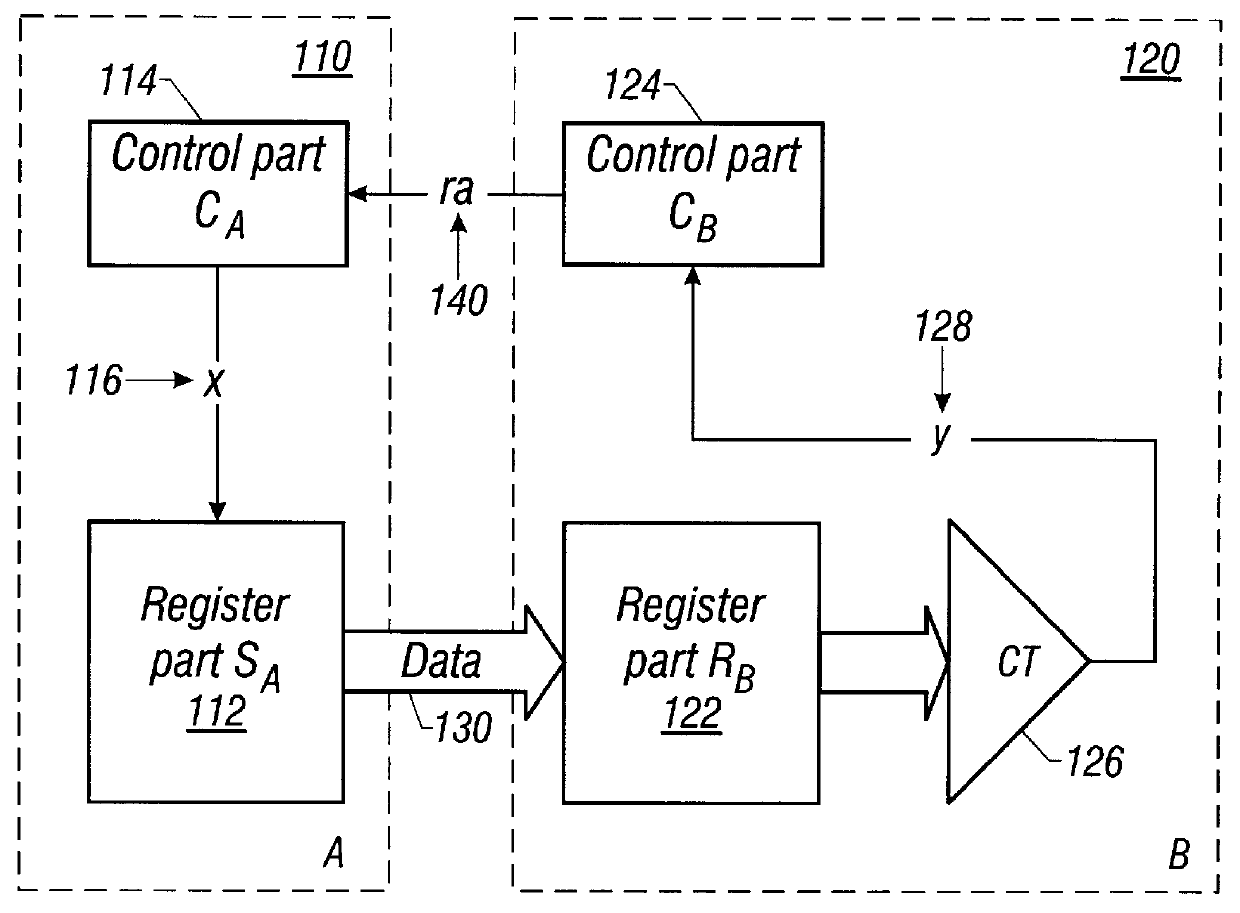

Pipelined completion for asynchronous communication

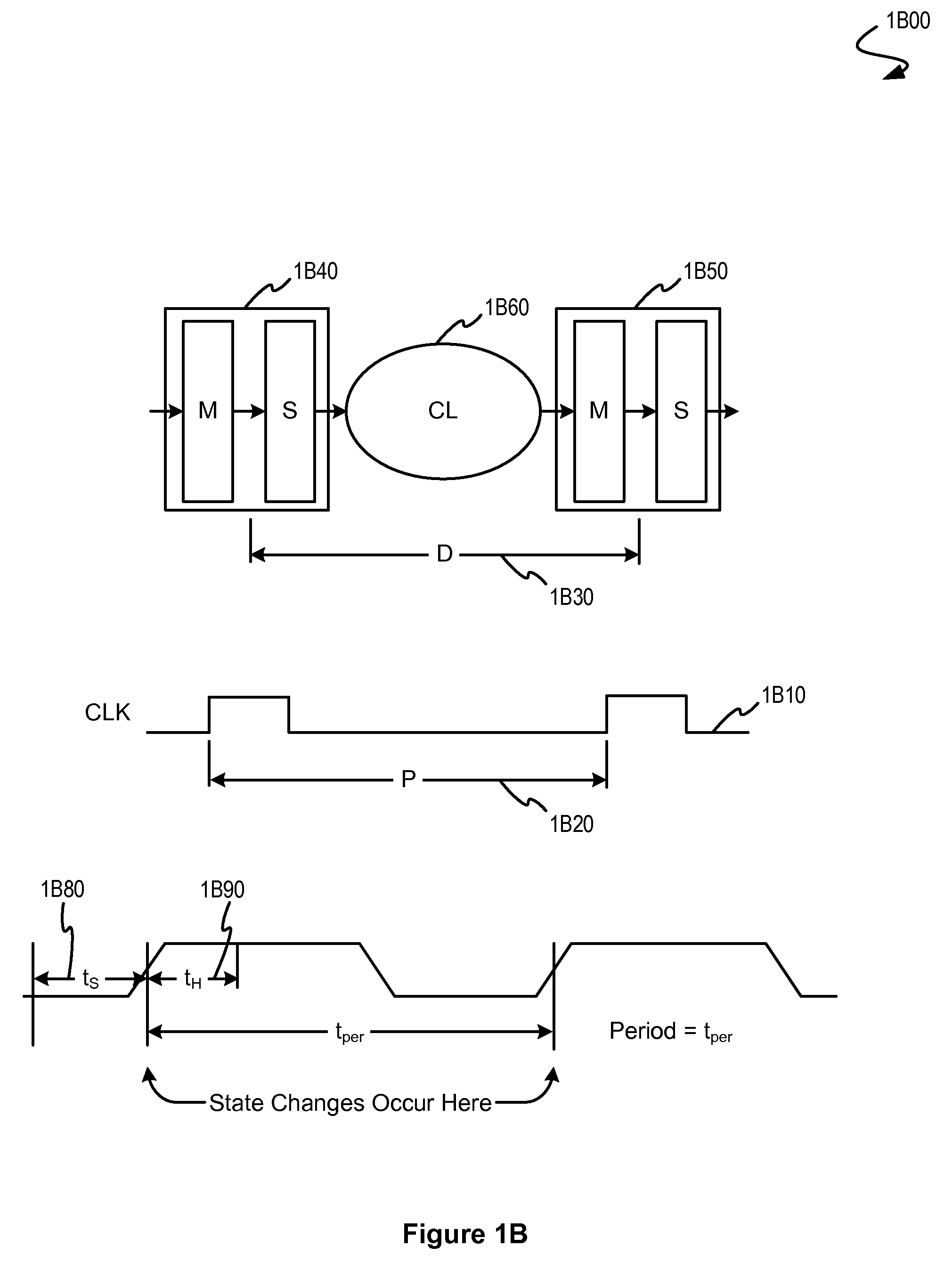

InactiveUS6038656AImprove throughputLower latencyArchitecture with single central processing unitMemory systemsAsynchronous circuitAsynchronous communication

Owner:CALIFORNIA INST OF TECH

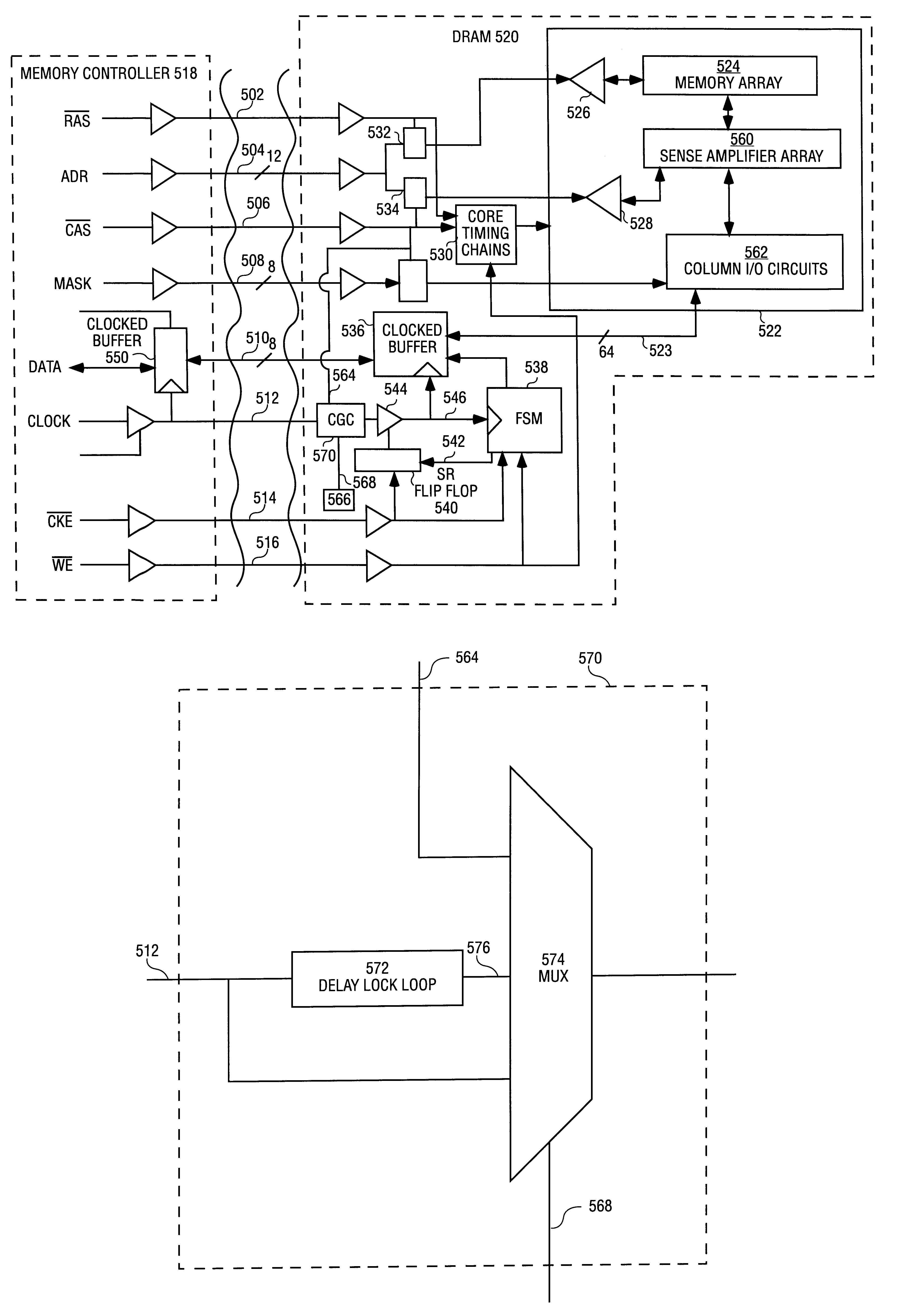

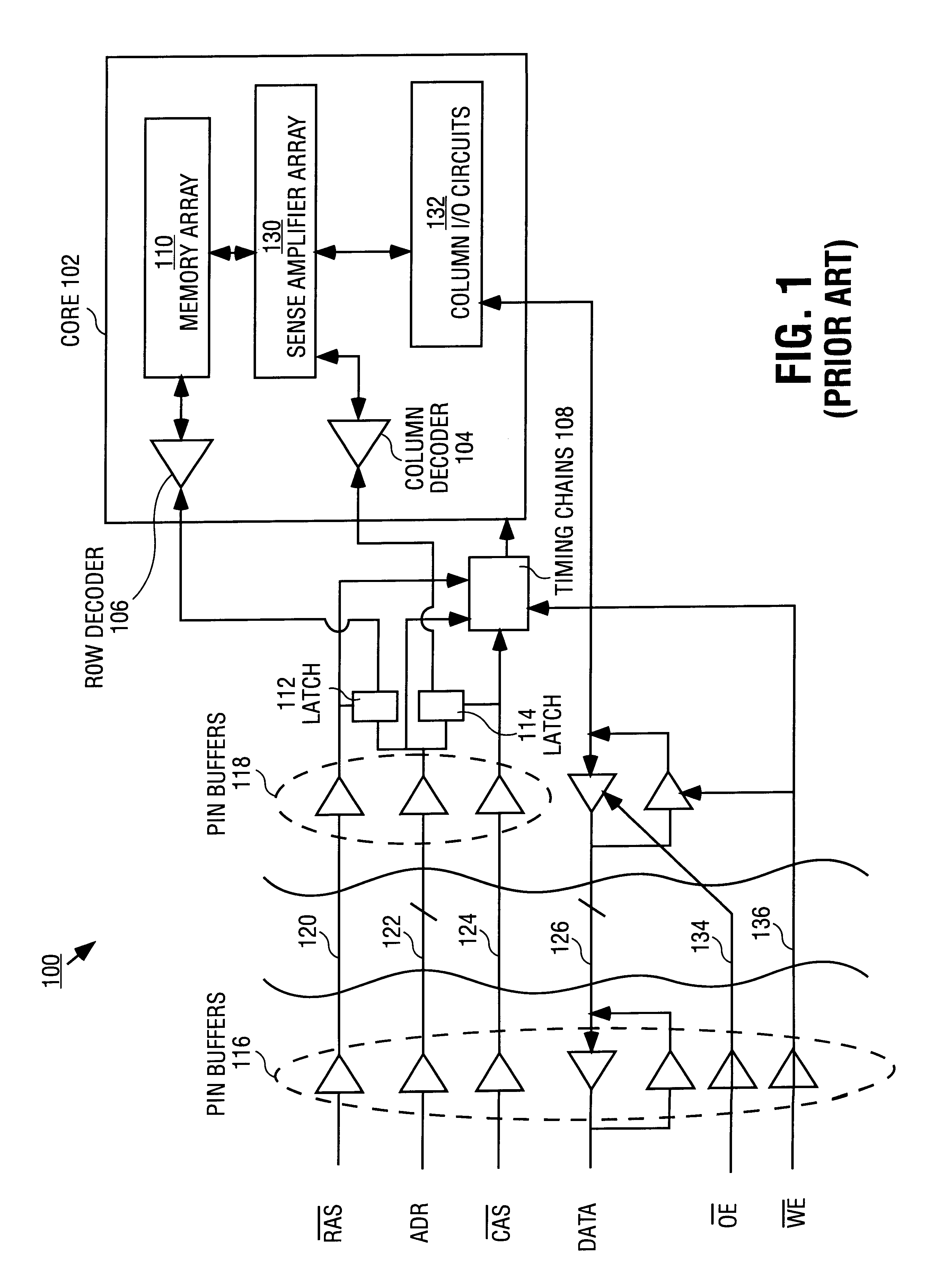

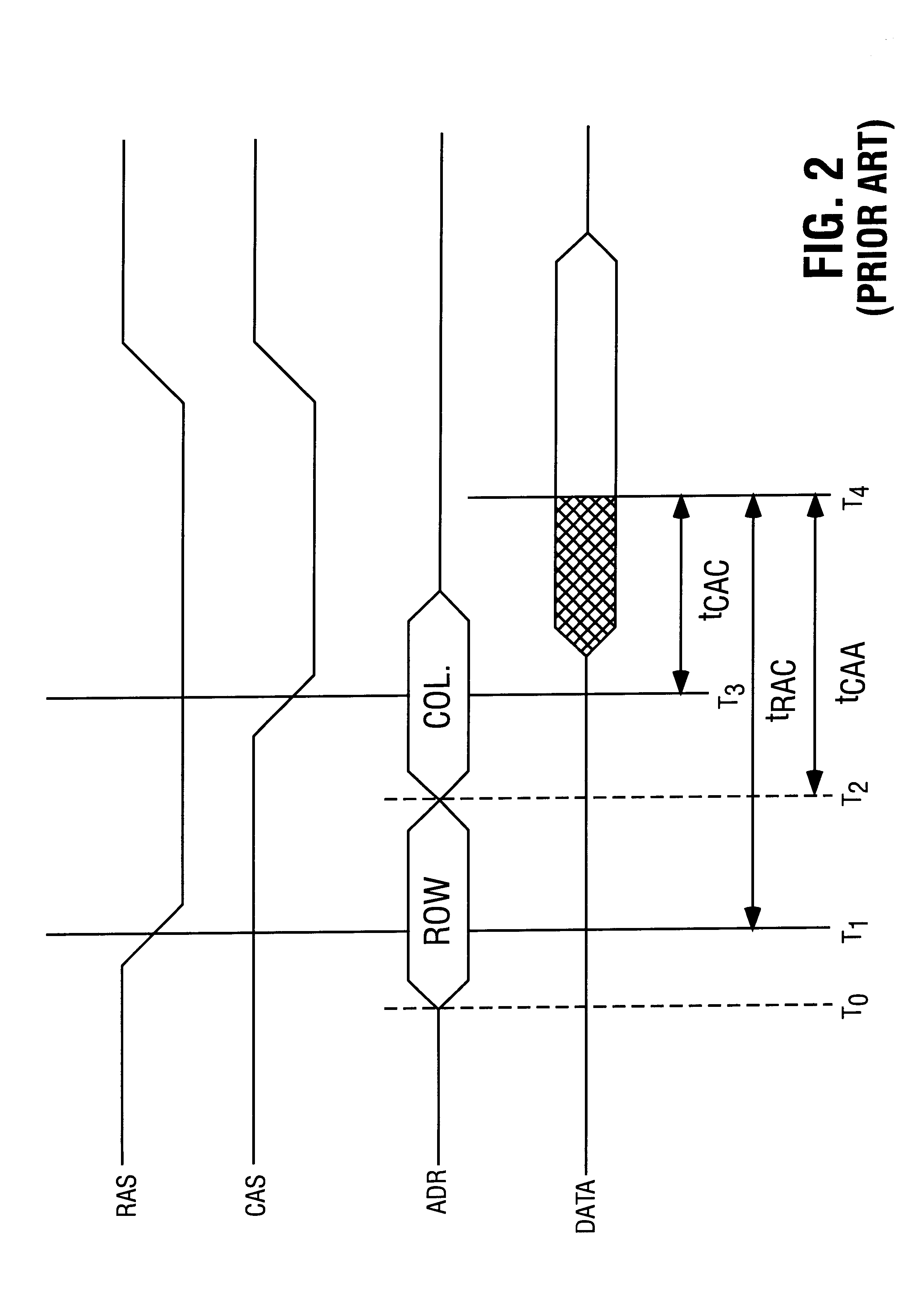

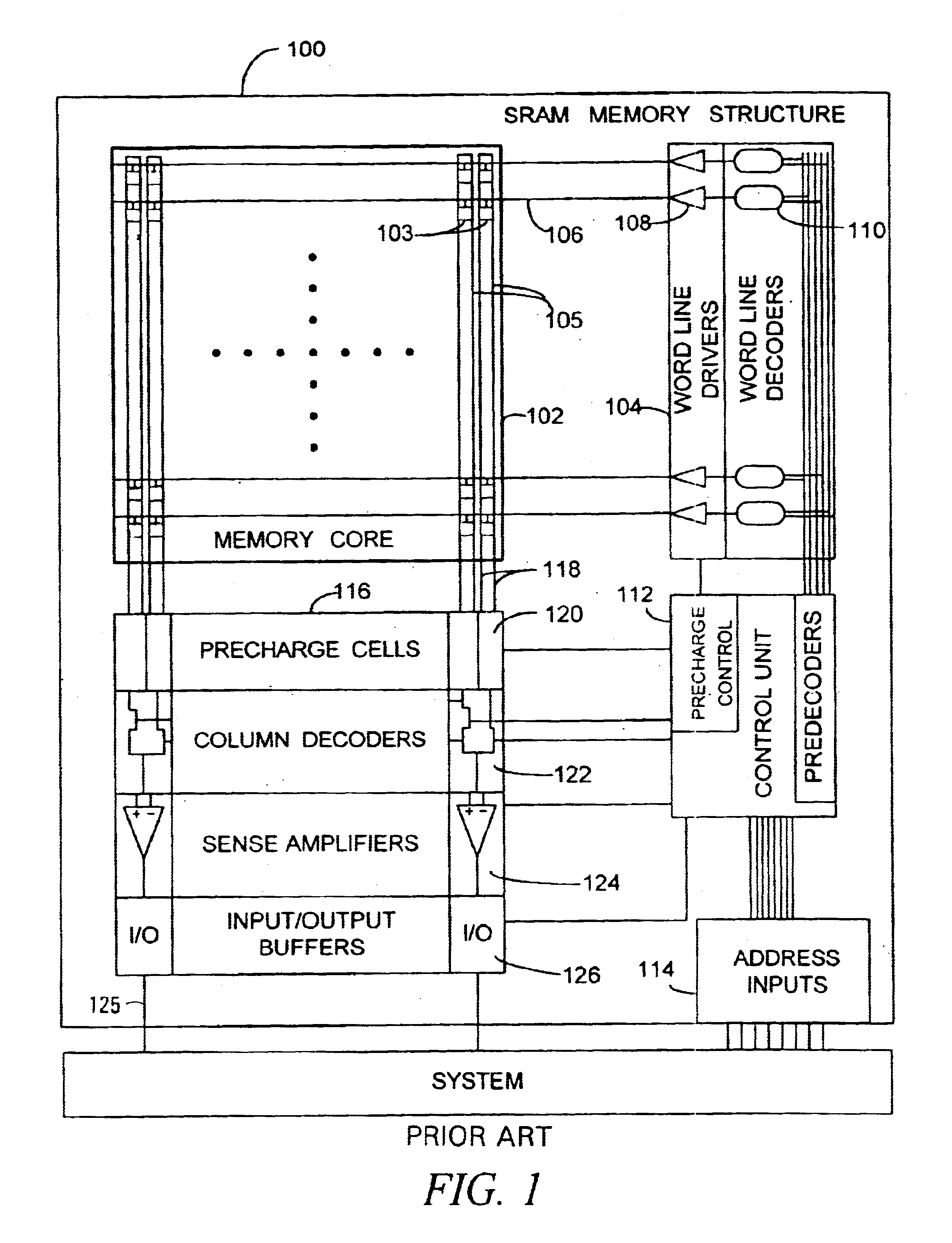

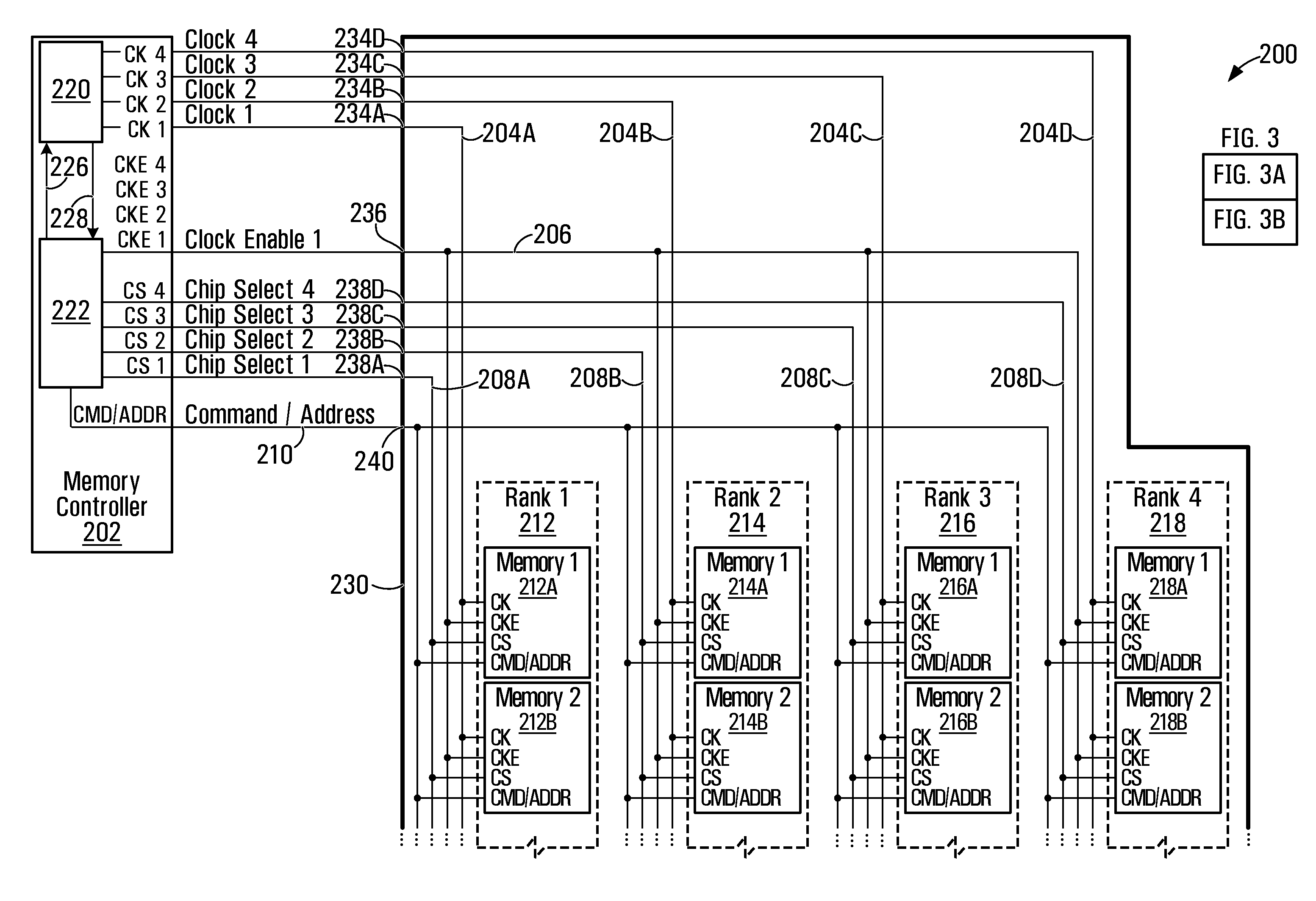

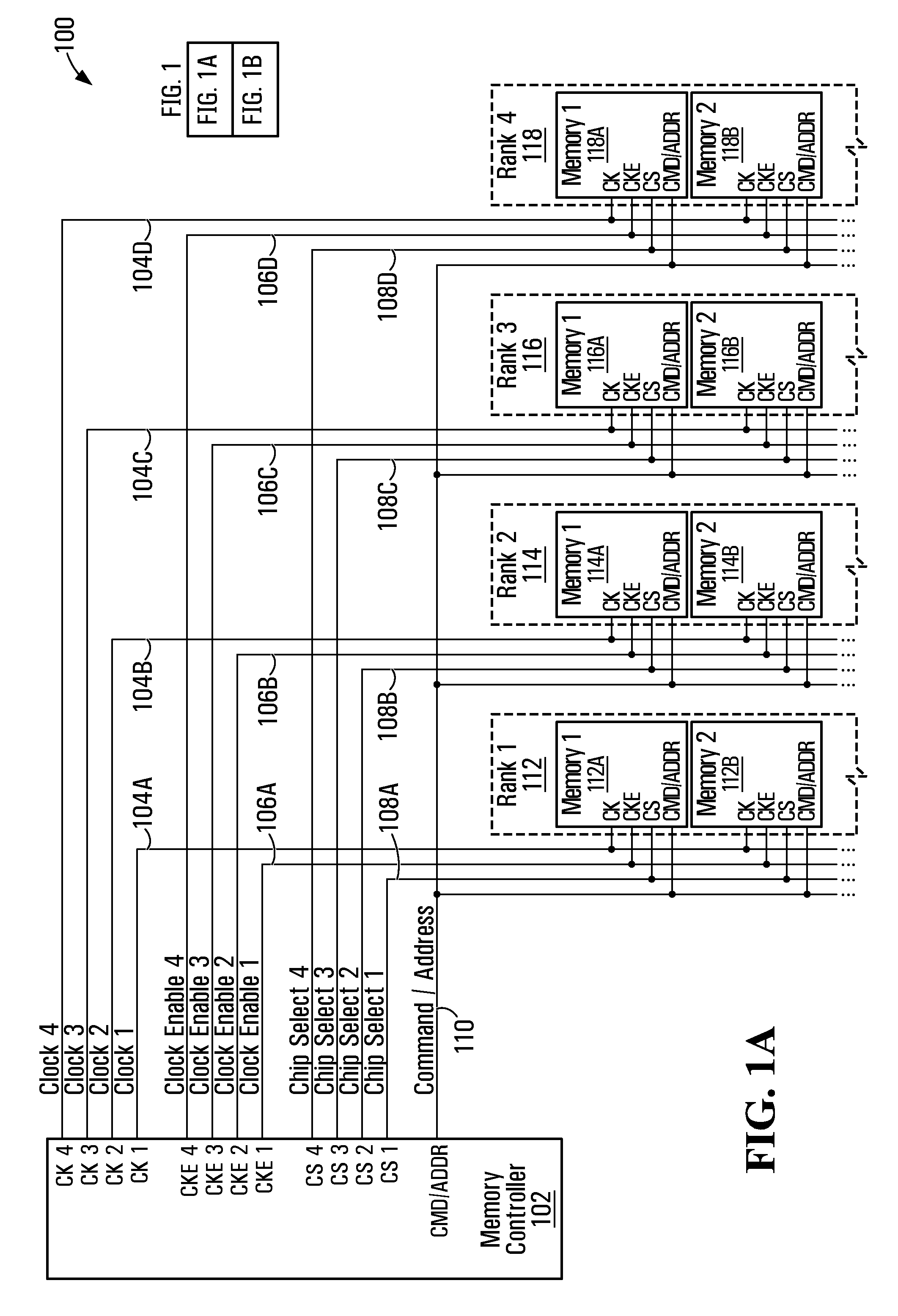

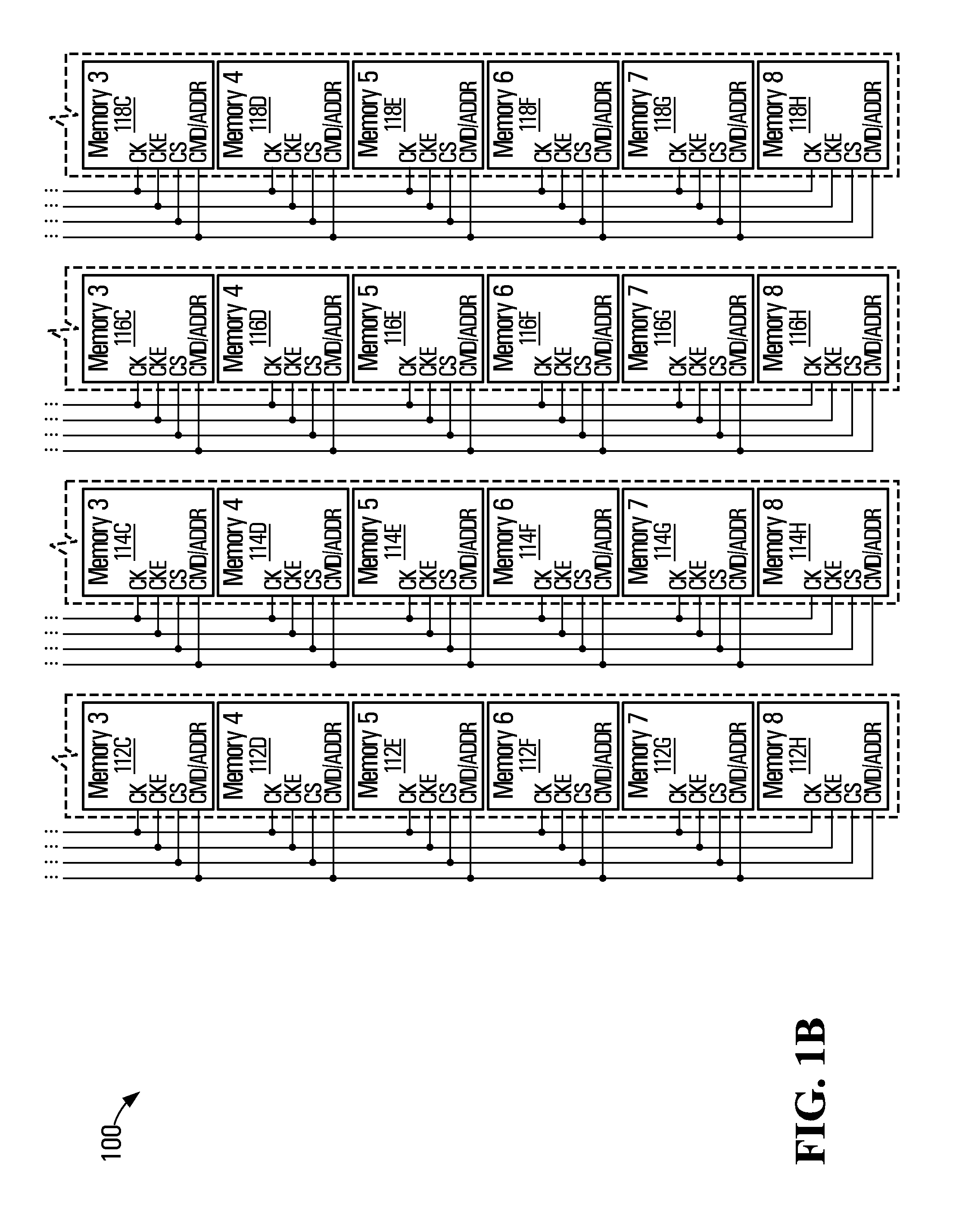

Asynchronous request/synchronous data dynamic random access memory

InactiveUS6209071B1Improve balanceReducing latency and power requirementEnergy efficient ICTDigital storagePower modeAsynchronous circuit

A method and system for transferring information within a computer system is provided. The system includes a memory device that has a lower power mode in which data transfer circuitry is not driven by a clock signal, and a higher power mode in which data transfer circuitry is driven by a clock signal. The system further includes a memory controller that sends control signals to the memory device to initiate a data transfer transaction. The memory device receives the control signals asynchronously, and assumes the second mode in response to one of the control signals. While the memory device is in the second mode, the memory controller sends a control signal to identify a particular clock cycle. The memory device synchronously transfers the data. The memory device determines when to begin the data transfer based on the identified clock cycle and the type of data transfer that has been specified.

Owner:RAMBUS INC

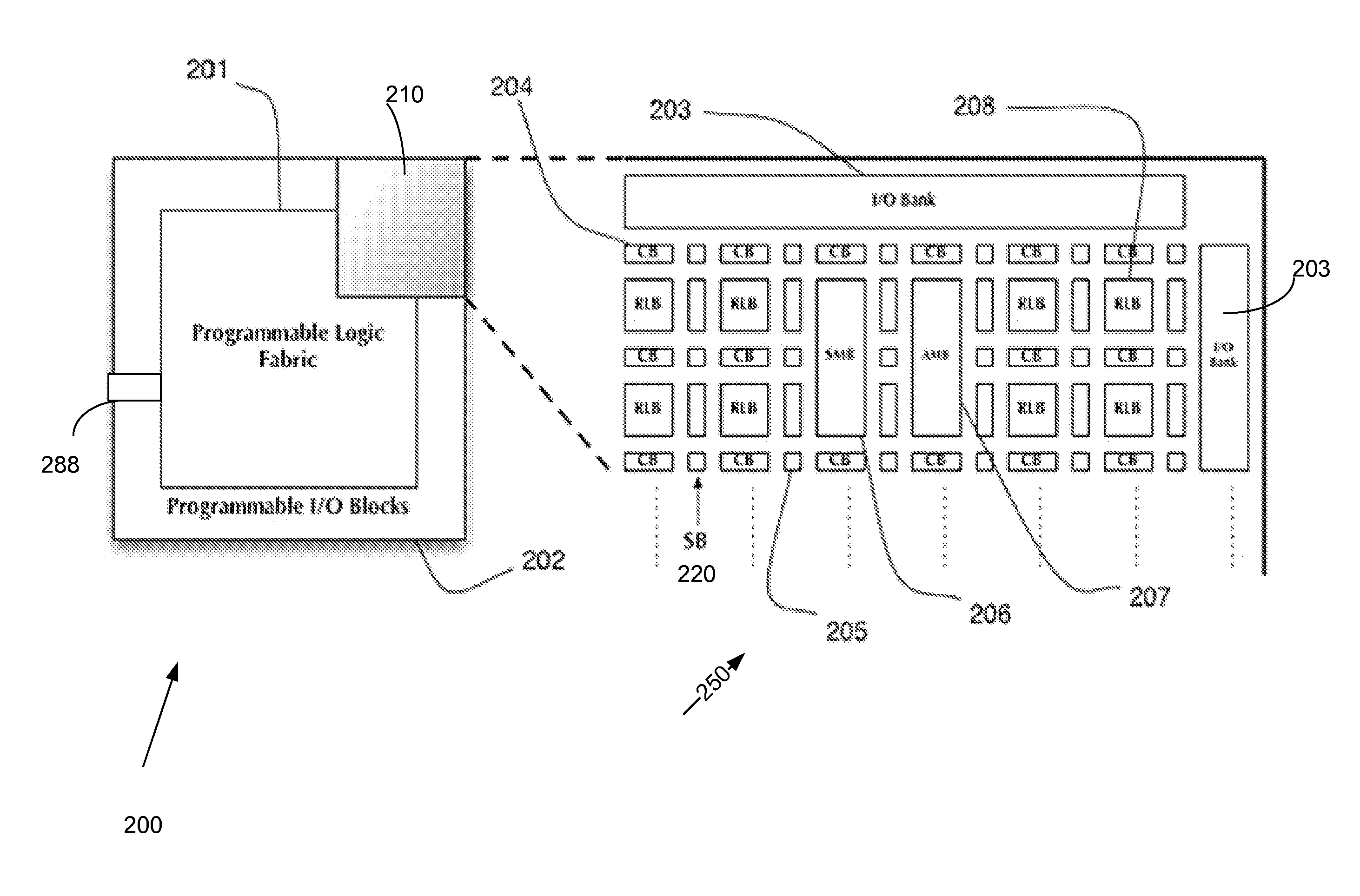

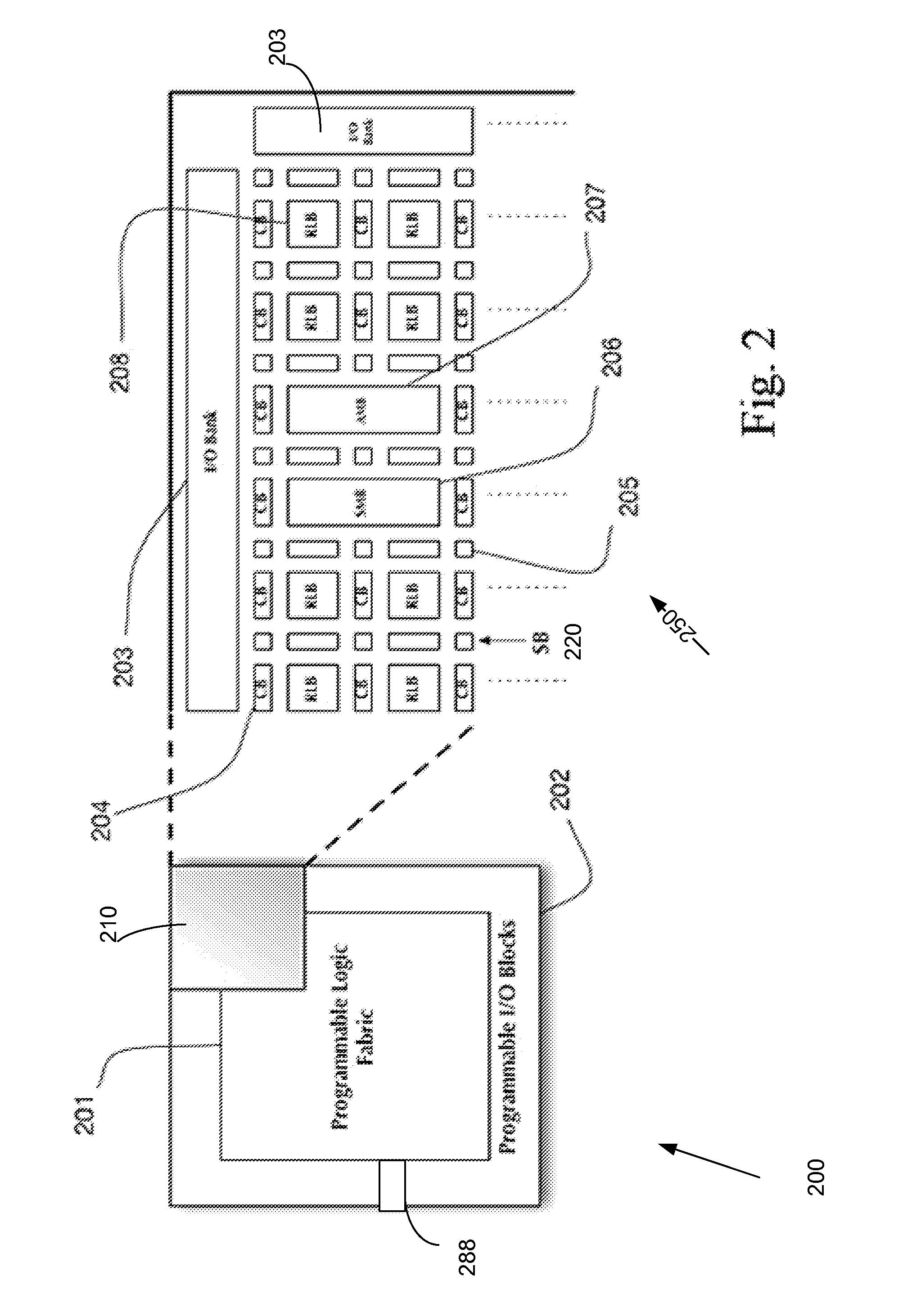

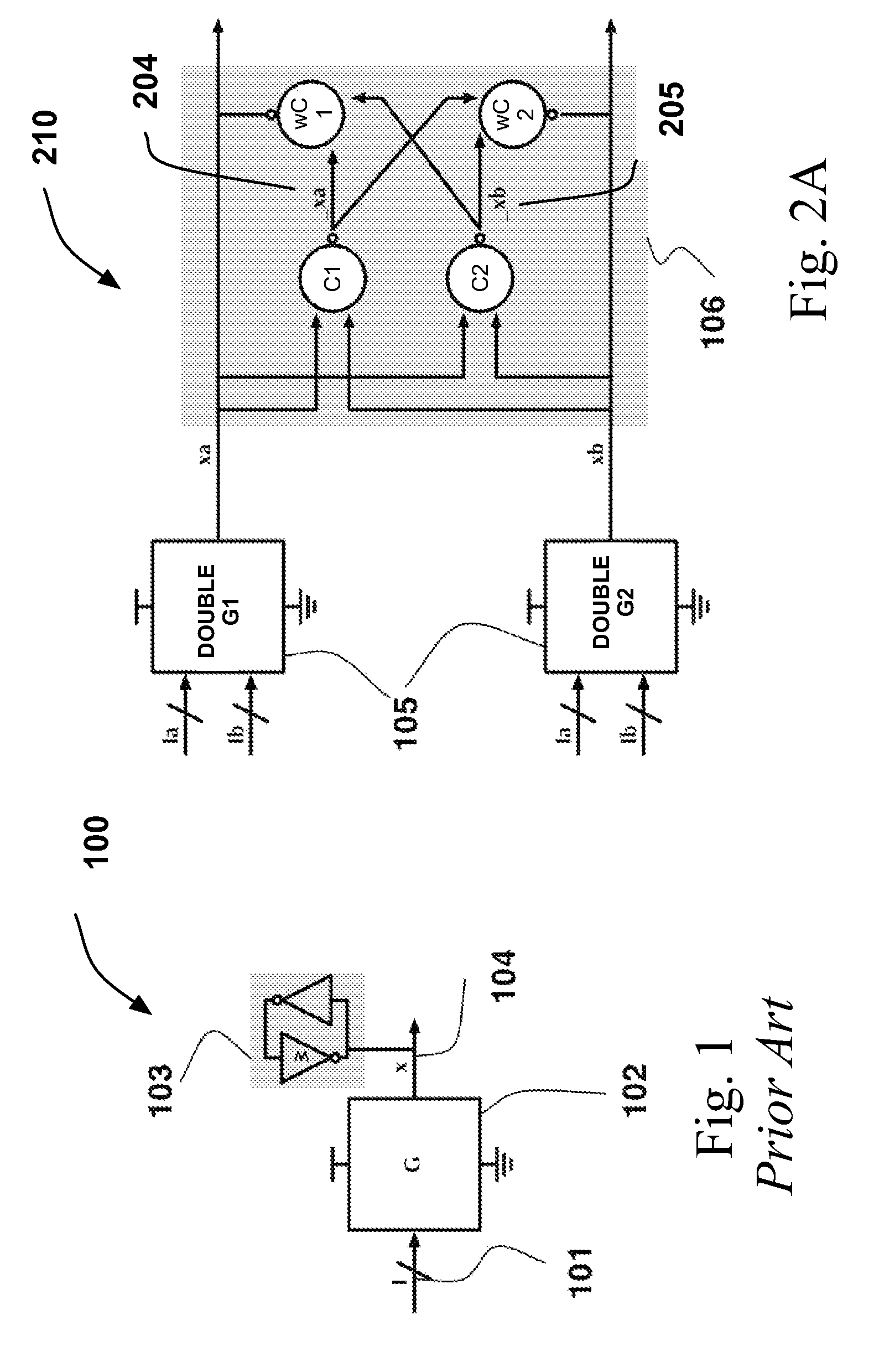

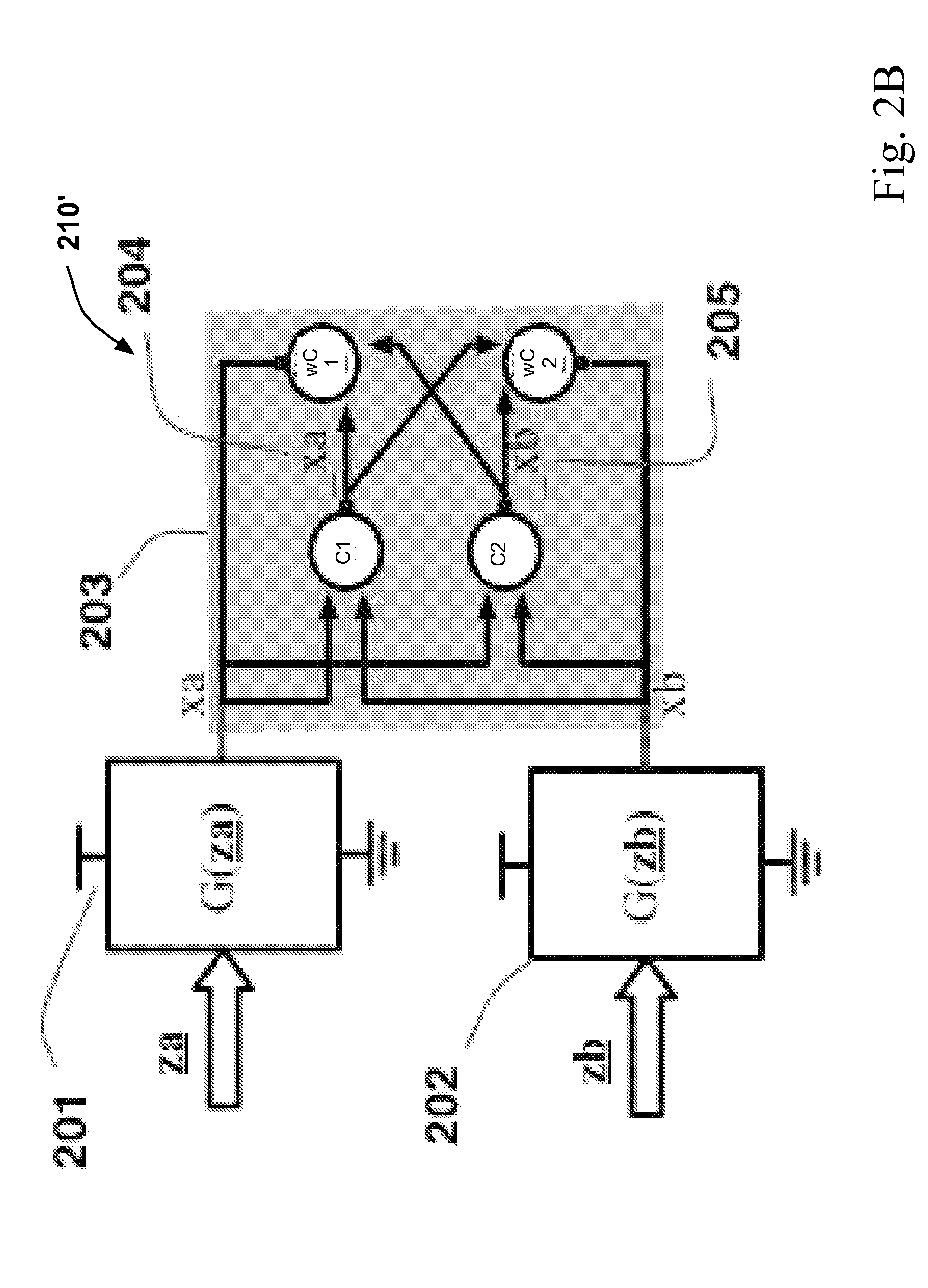

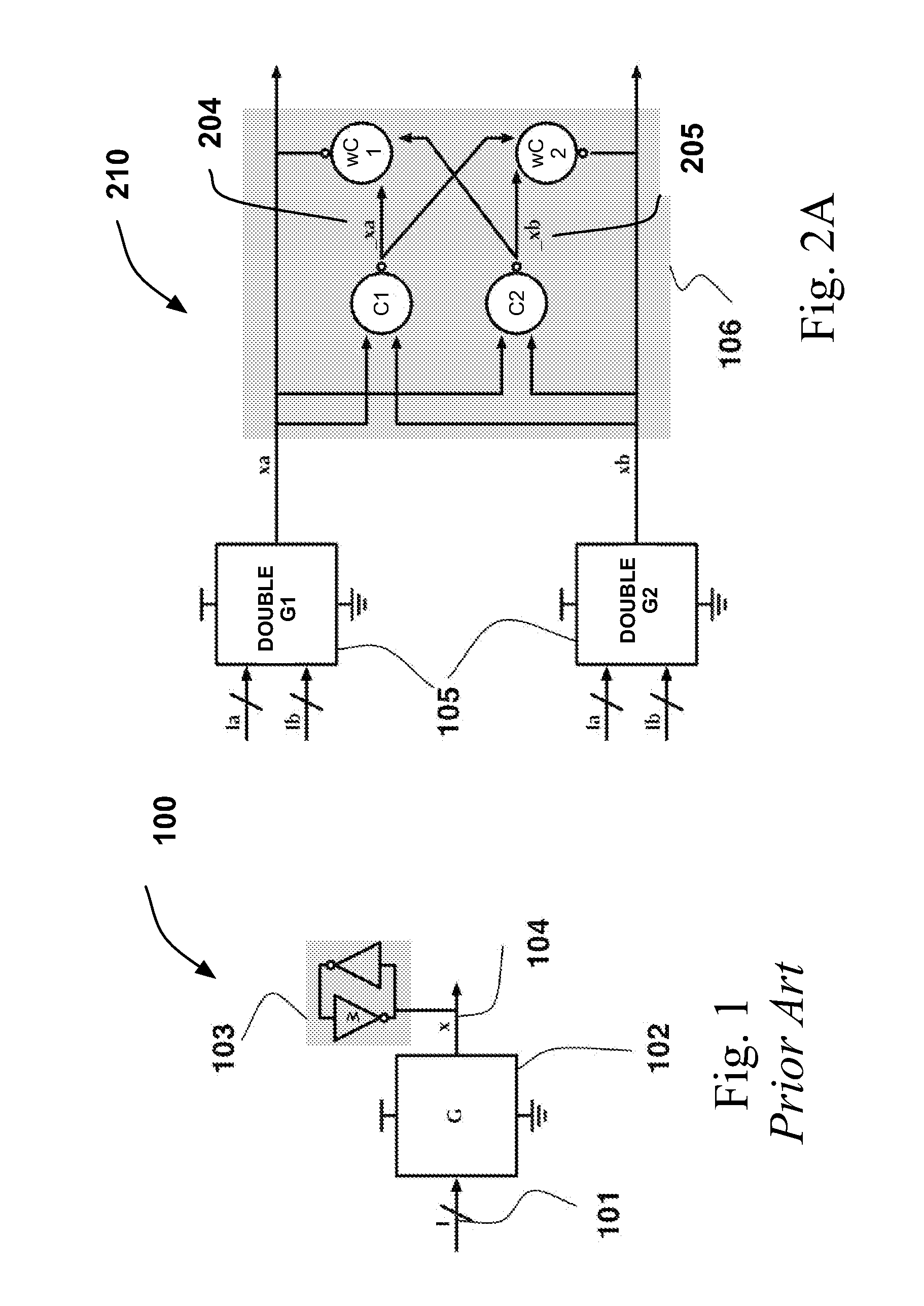

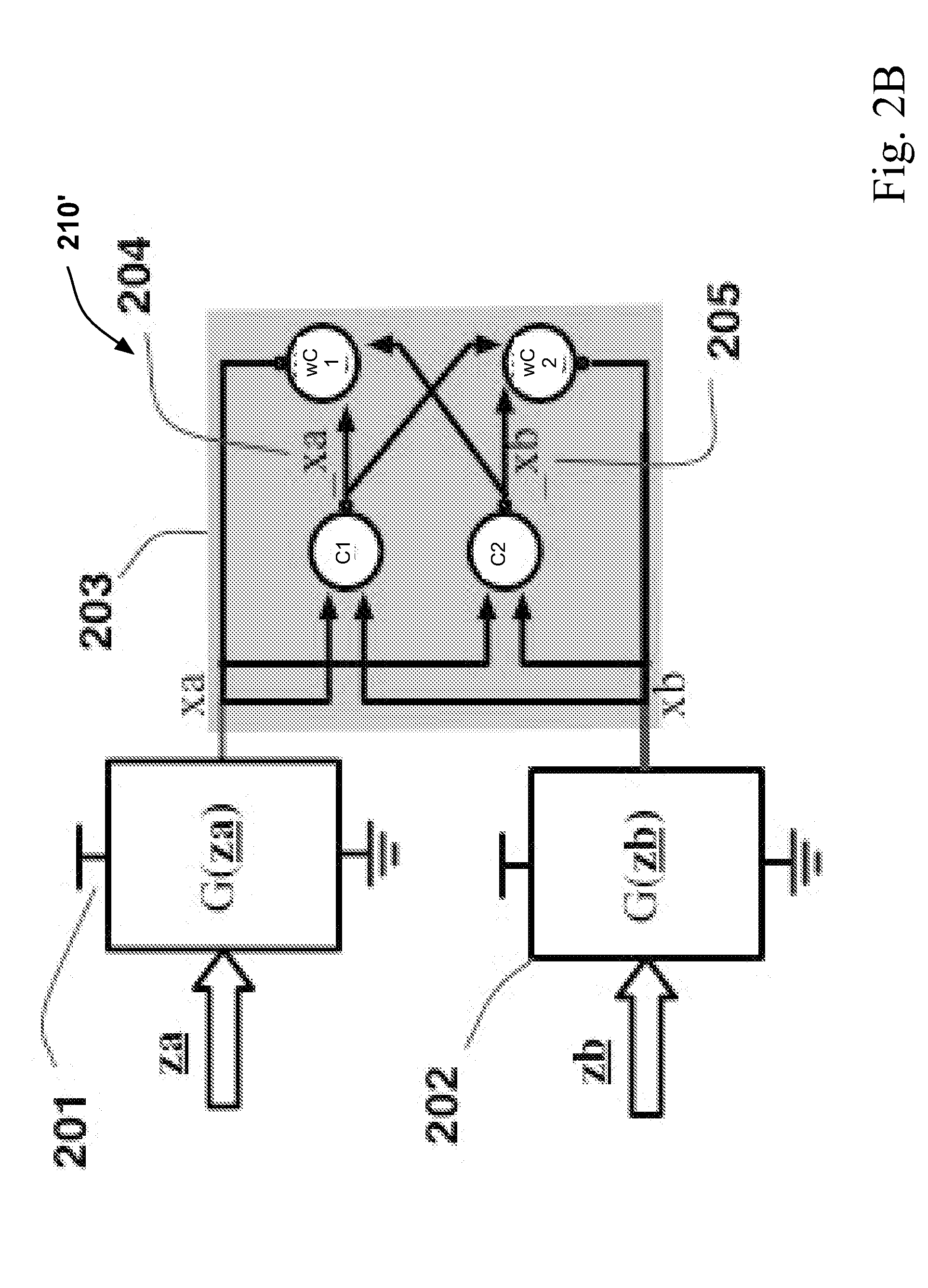

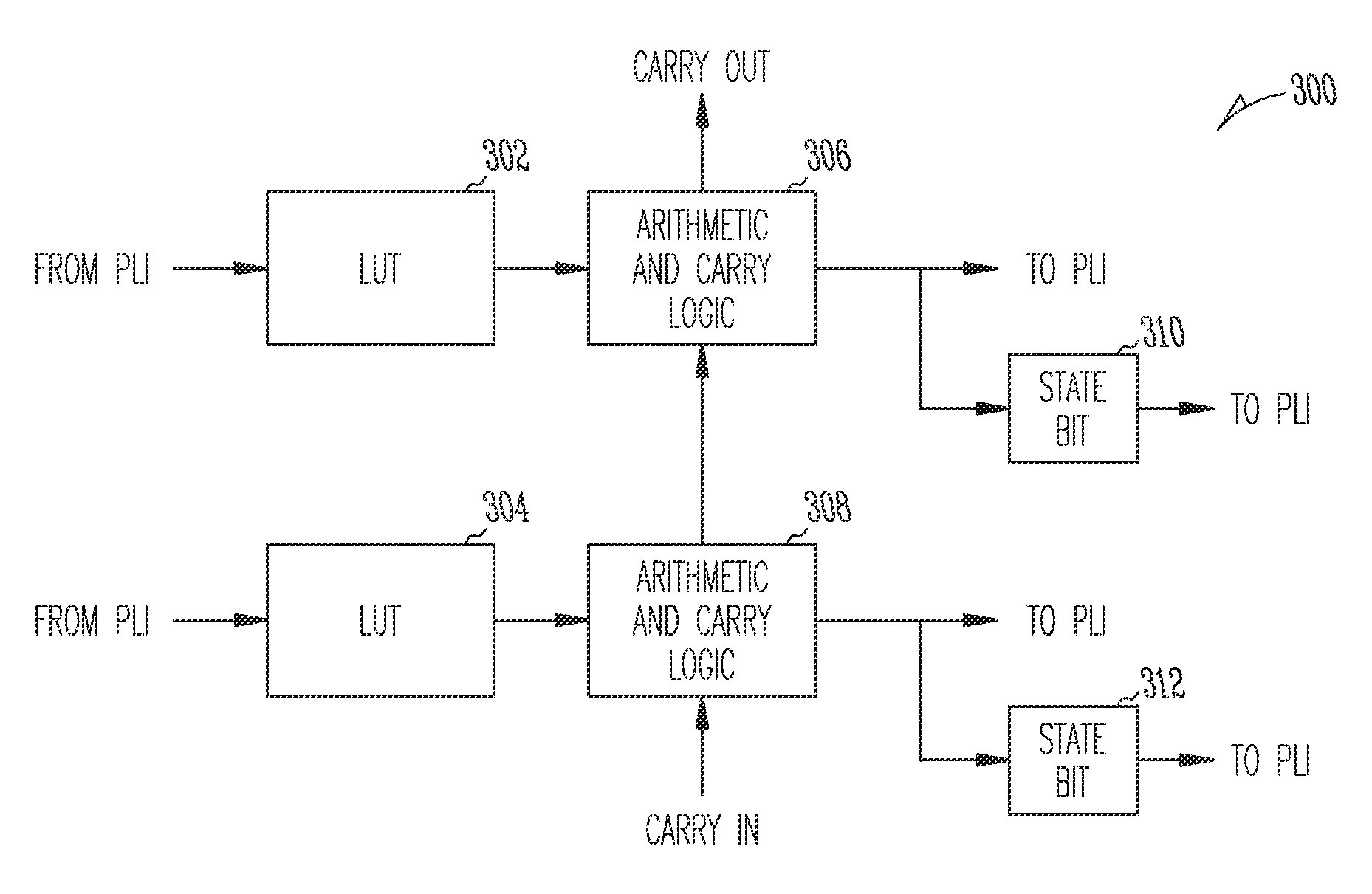

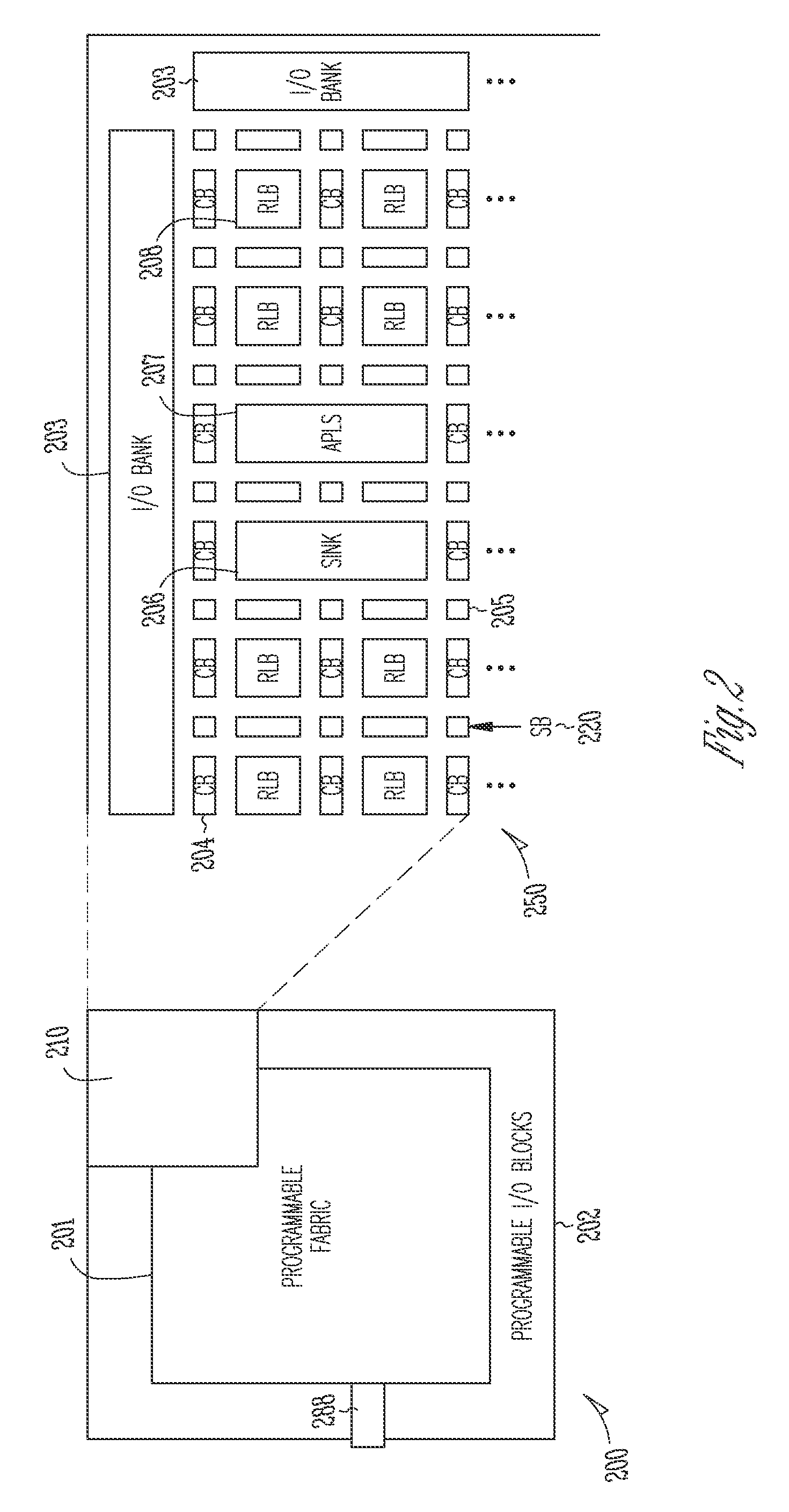

Reconfigurable logic fabrics for integrated circuits and systems and methods for configuring reconfigurable logic fabrics

Owner:ACHRONIX SEMICON CORP

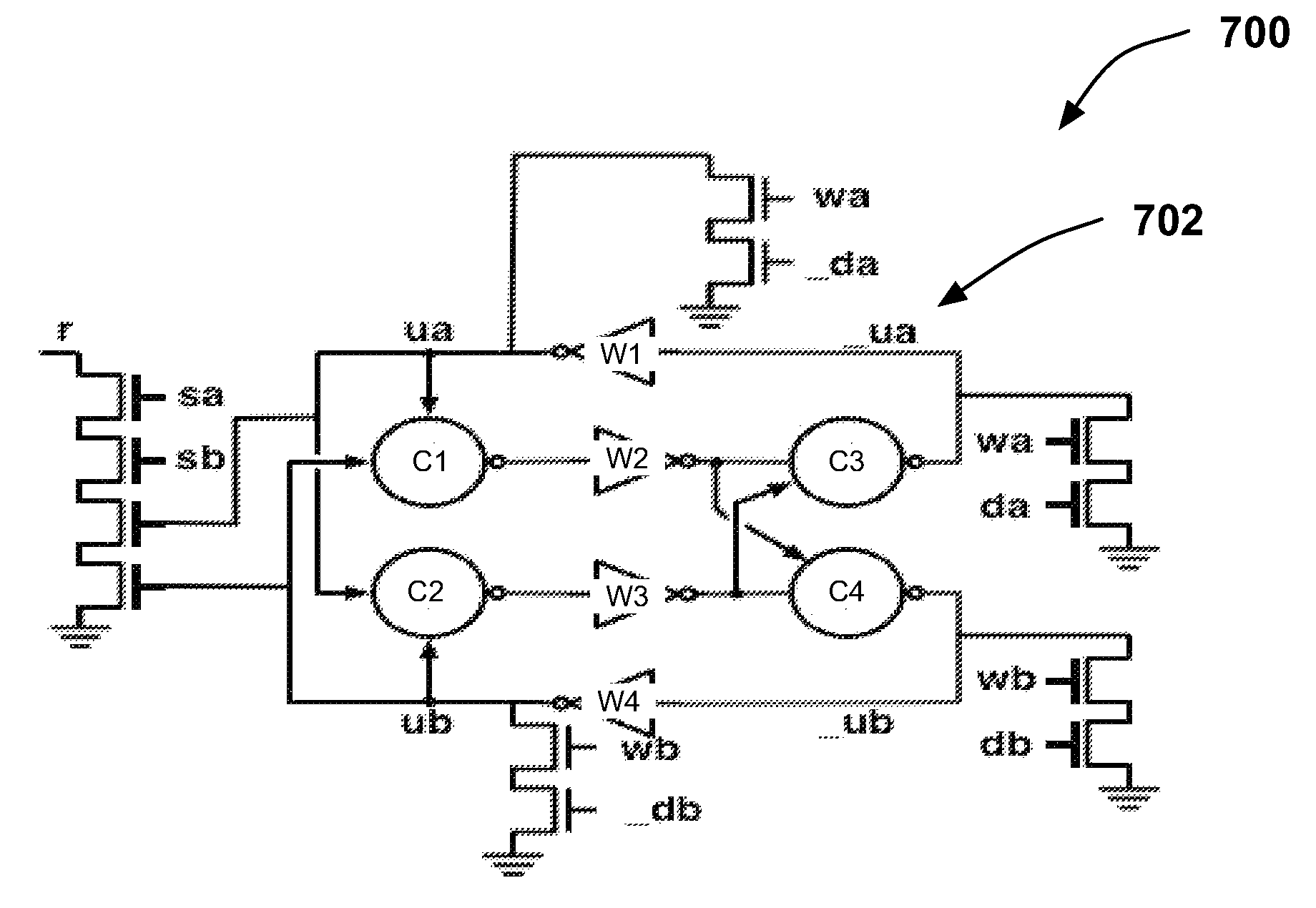

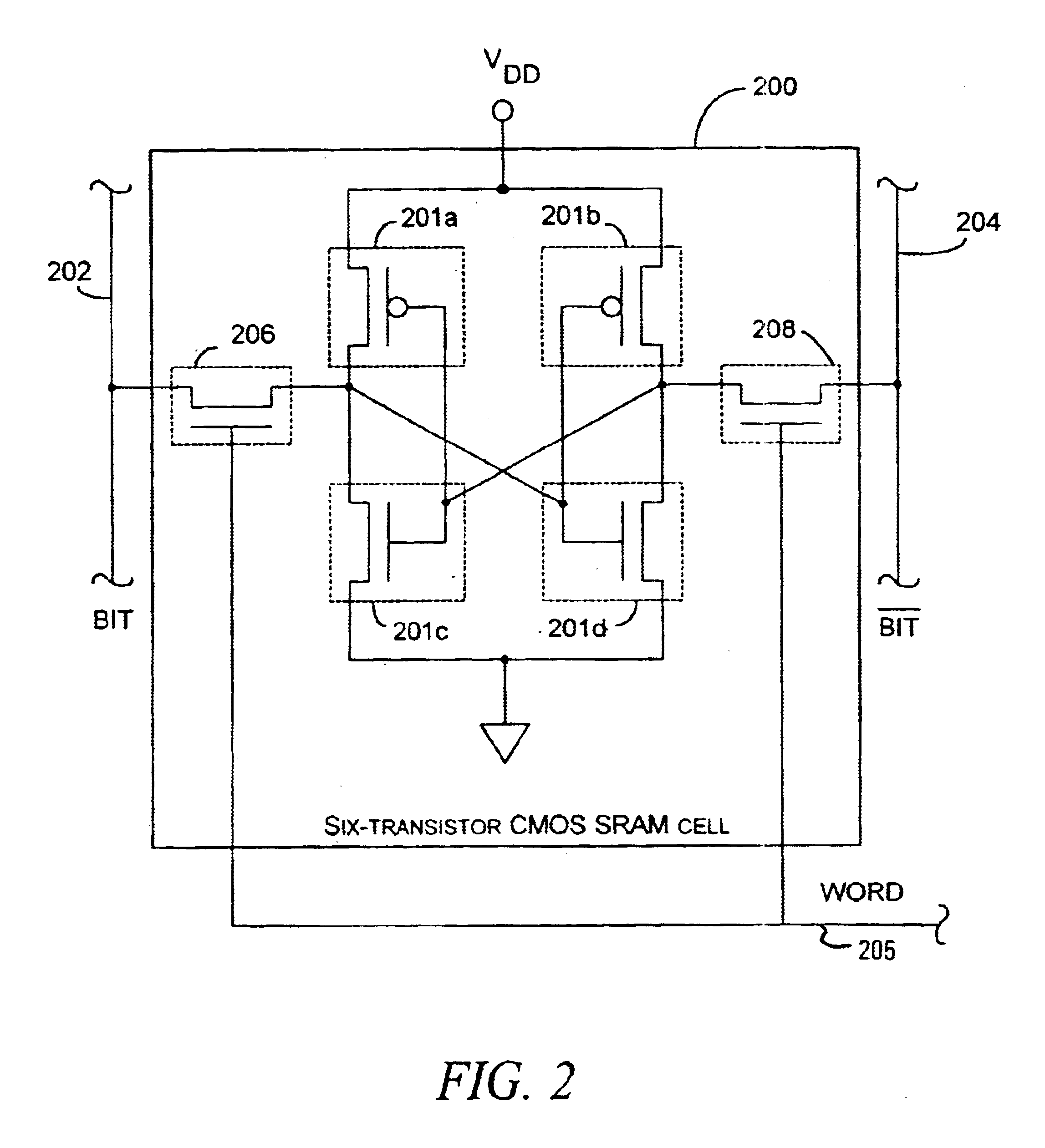

Fault tolerant asynchronous circuits

ActiveUS7505304B2Reliability increasing modificationsDigital storageAsynchronous circuitMemory circuits

Owner:ACHRONIX SEMICON CORP

Fault tolerant asynchronous circuits

ActiveUS20070262786A1Reliability increasing modificationsFail-safe circuitsAsynchronous circuitMemory circuits

New and improved methods and circuit designs for asynchronous circuits that are tolerant to transient faults, for example of the type introduced through radiation or, more broadly, single—event effects. SEE-tolerant configurations are shown and described for combinational logic circuits, state-holding logic circuits and SRAM memory circuits.

Owner:ACHRONIX SEMICON CORP

Fault tolerant asynchronous circuits

ActiveUS20070253240A1Reliability increasing modificationsDigital storageAsynchronous circuitHemt circuits

New and improved methods and circuit designs for asynchronous circuits that are tolerant to transient faults, for example of the type introduced through radiation or, more broadly, single-event effects. SEE-tolerant configurations are shown and described for combinational logic circuits, state-holding logic circuits and SRAM memory circuits.

Owner:ACHRONIX SEMICON CORP

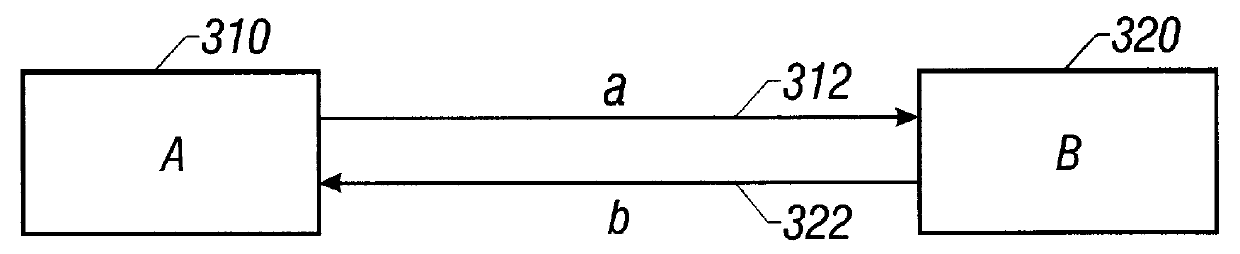

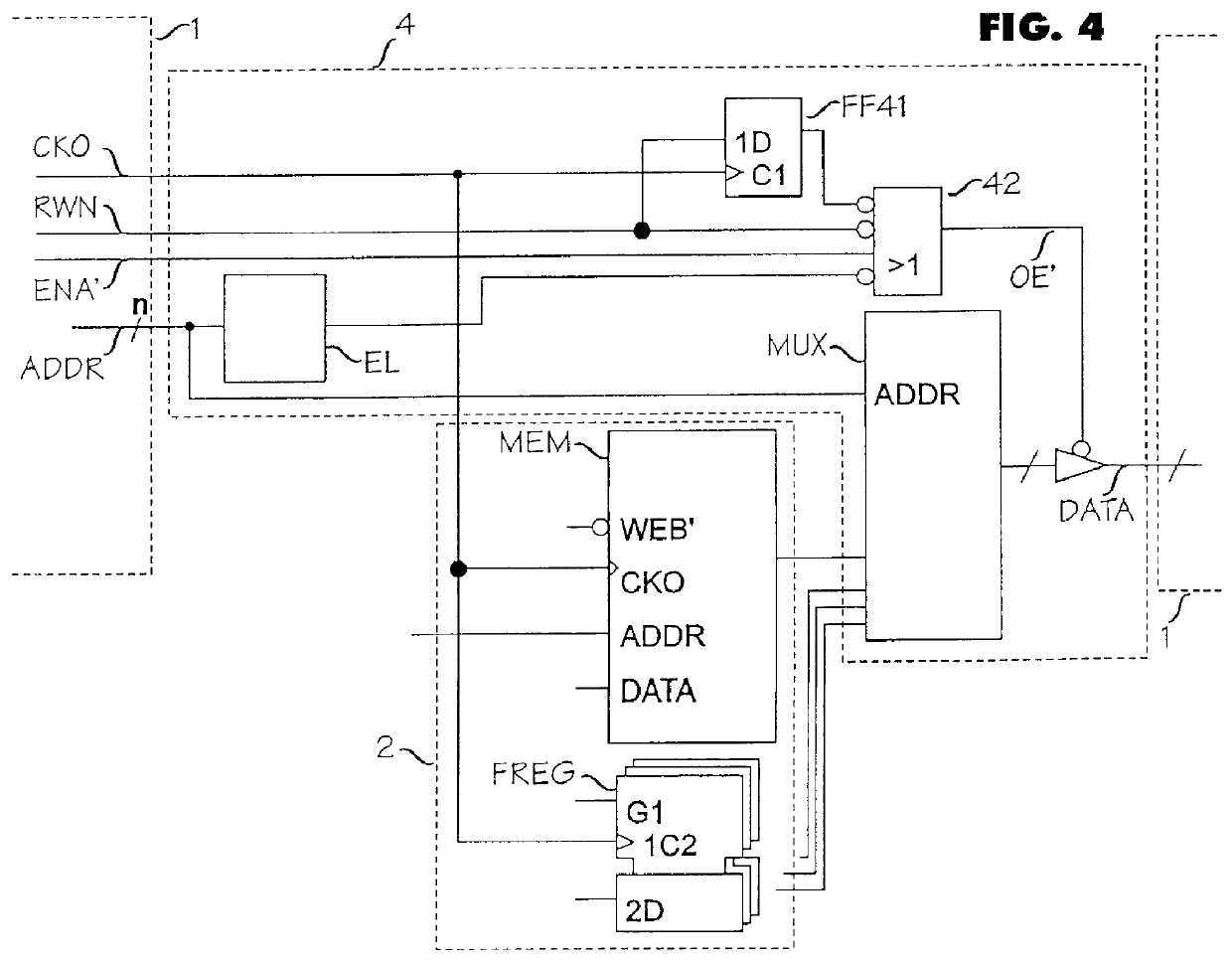

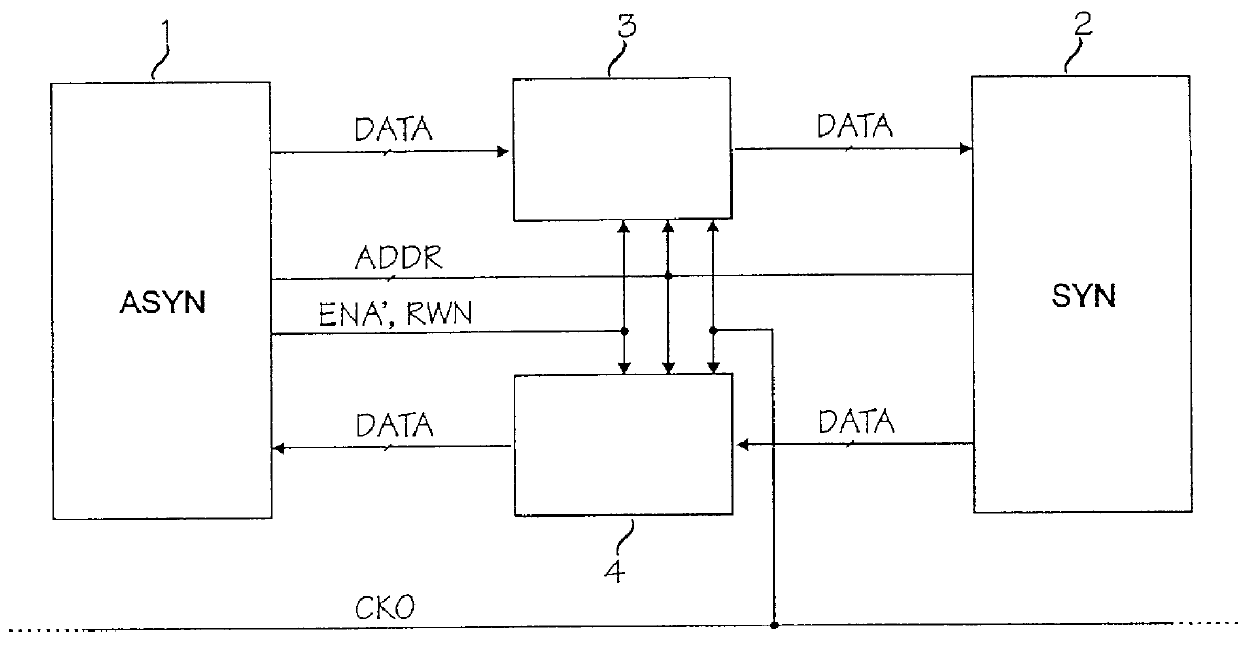

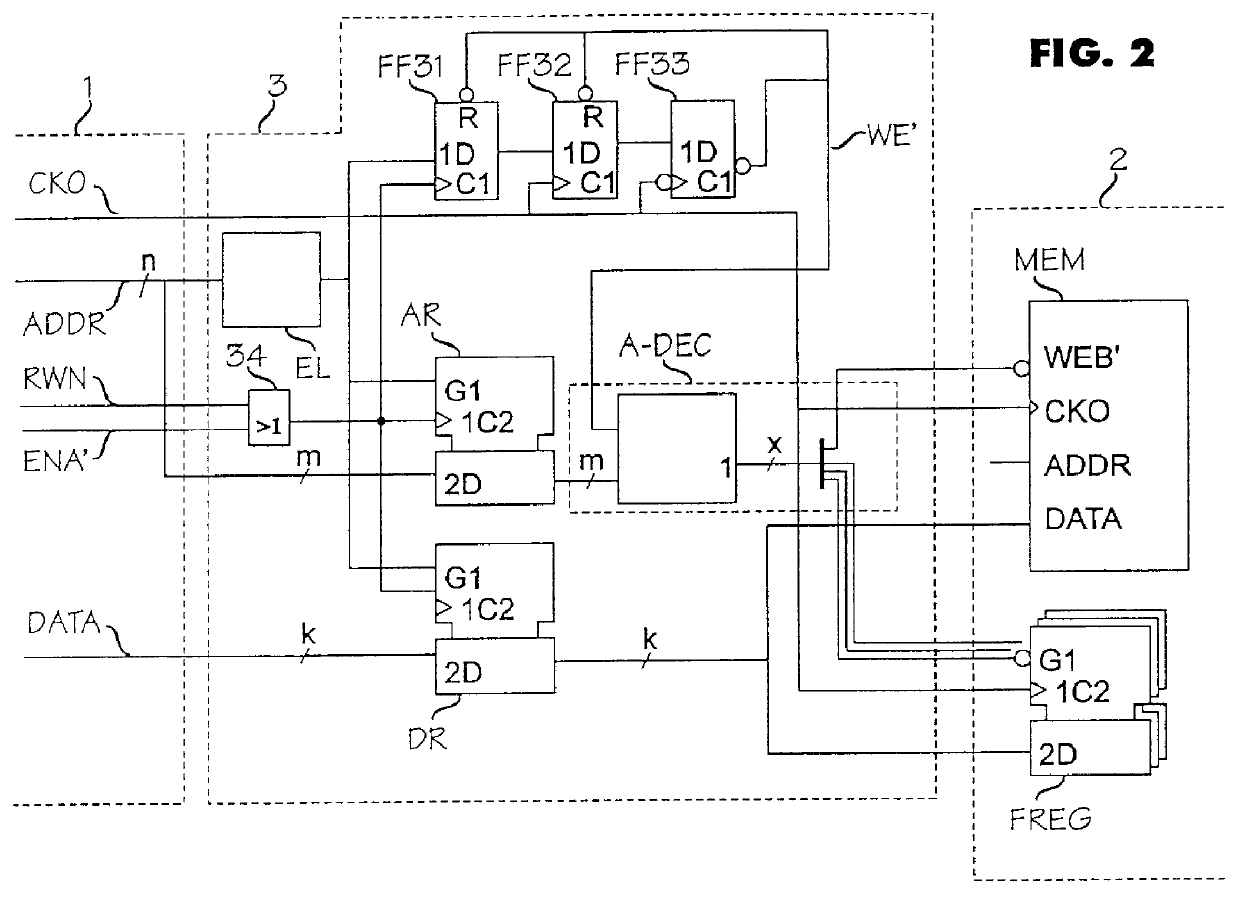

Method and apparatus for adapting an asynchronous bus to a synchronous circuit

InactiveUS6075830ALess sensitiveGenerating/distributing signalsSynchronising arrangementAsynchronous circuitProcessor register

PCT No. PCT / FI96 / 00285 Sec. 371 Date Nov. 28, 1997 Sec. 102(e) Date Nov. 28, 1997 PCT Filed May 23, 1996 PCT Pub. No. WO96 / 38793 PCT Pub. Date Dec. 5, 1996Many digital processors have an asynchronous bus controlled by two control signals. To interface a synchronous memory to an asynchronous bus, interface logic is required. In an interface for transferring data from an asynchronous circuit to a synchronous circuit, data to be written are written in an intermediate register while timing control signals are being synchronized to a system clock by means of flip-flops. Correspondingly, in an interface for transferring data from the synchronous circuit to the asynchronous circuit, a signal indicating a read transaction from the synchronous circuit is synchronized to the system clock by means of a flip-flop circuit.

Owner:NOKIA TECHNOLOGLES OY

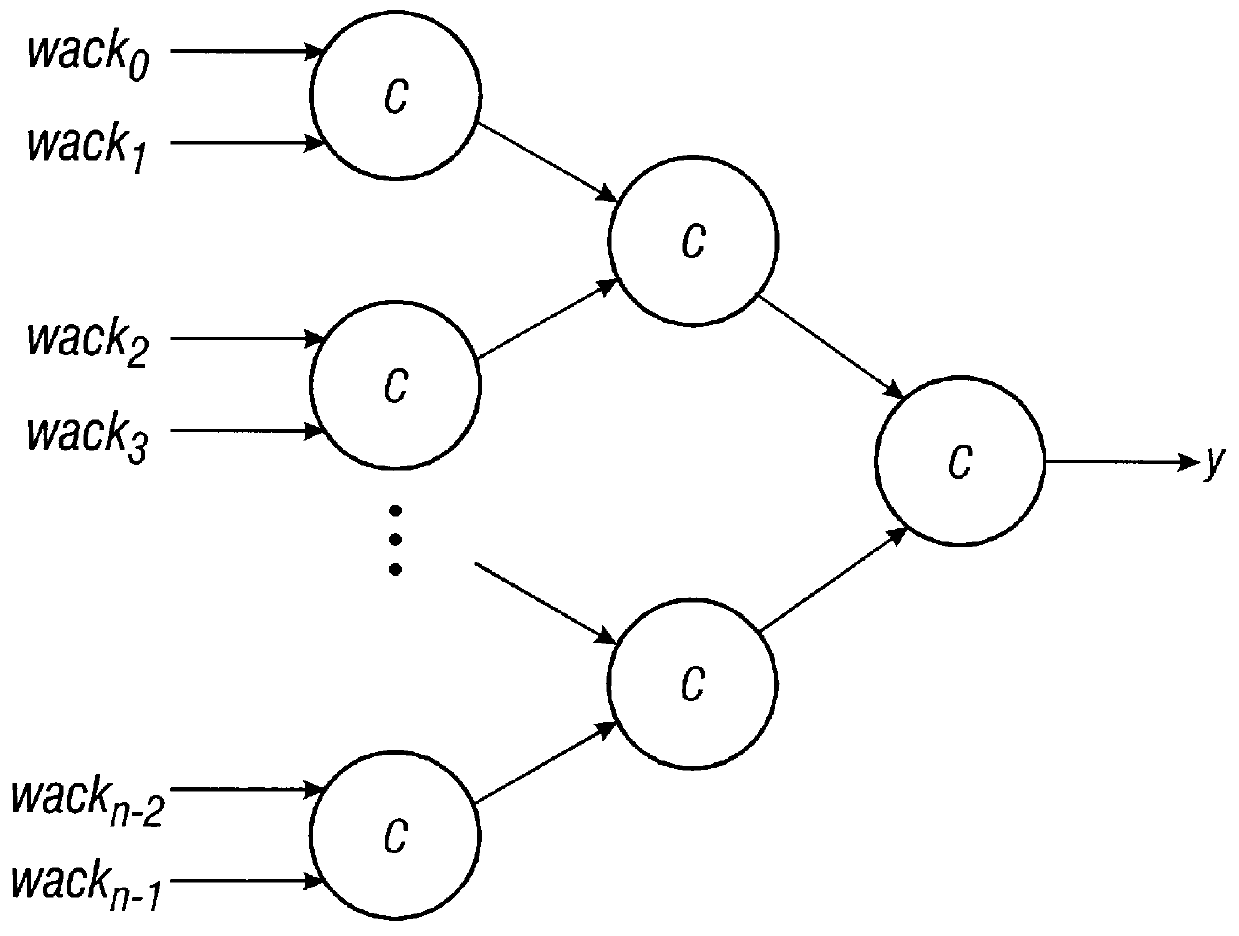

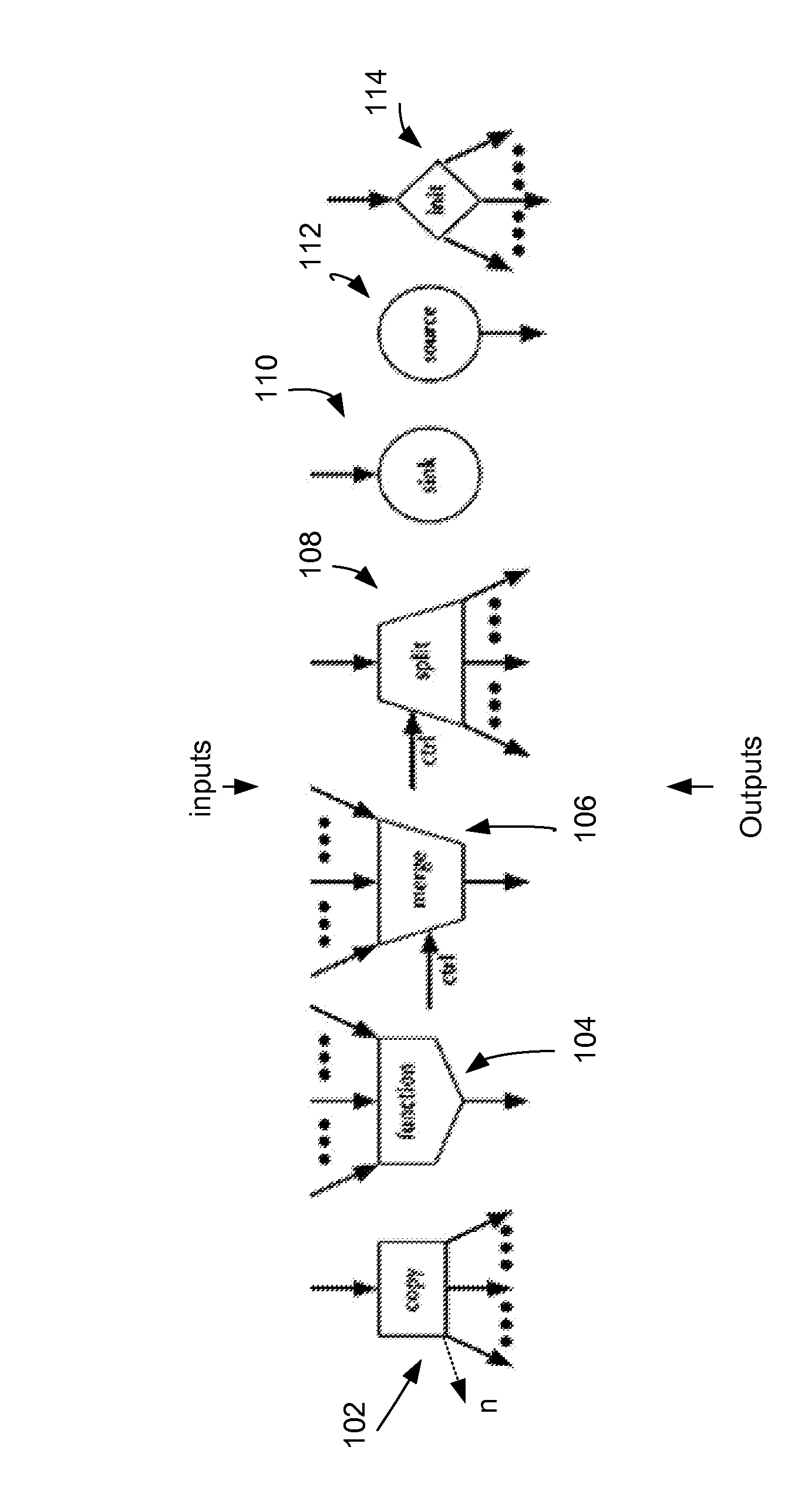

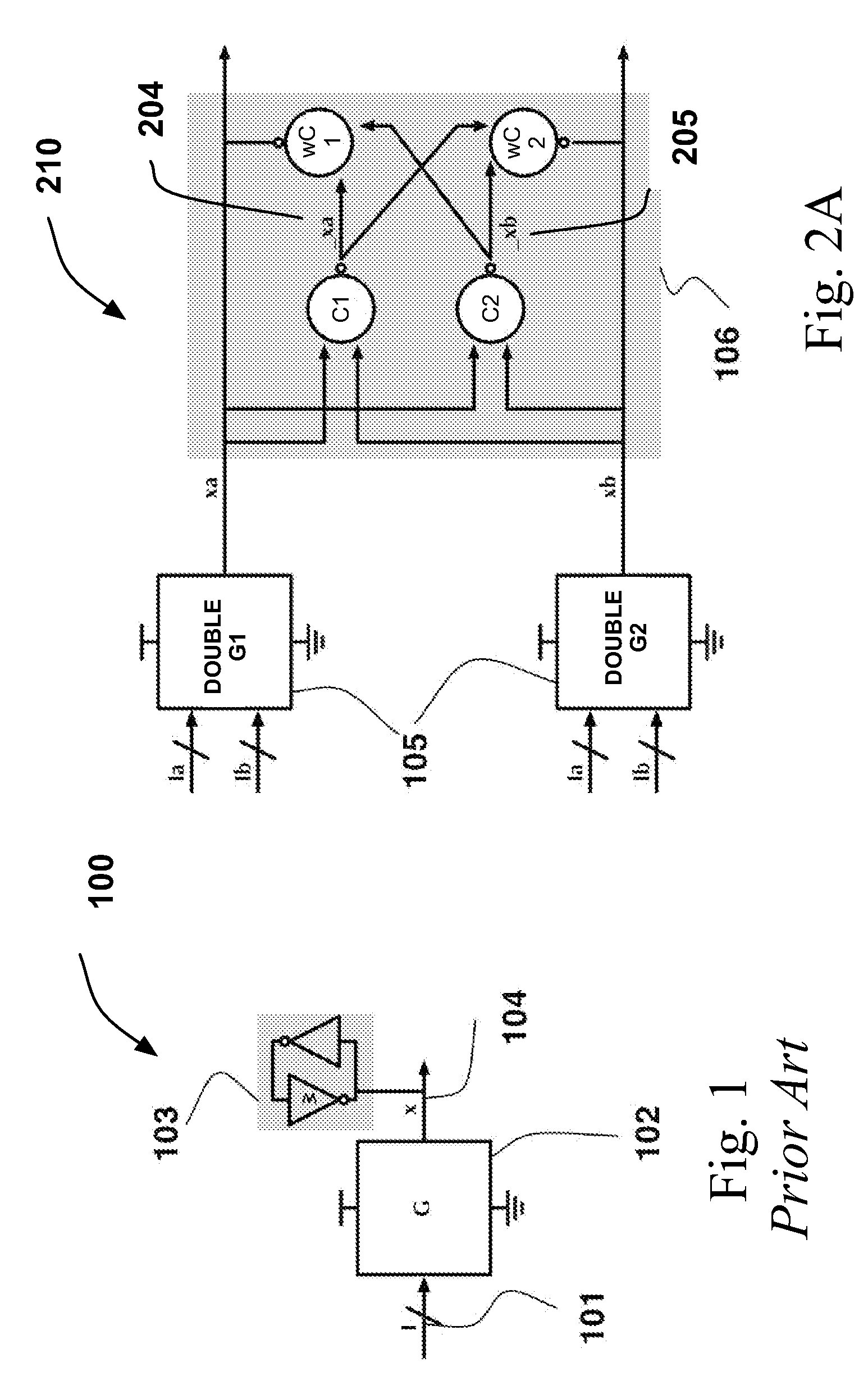

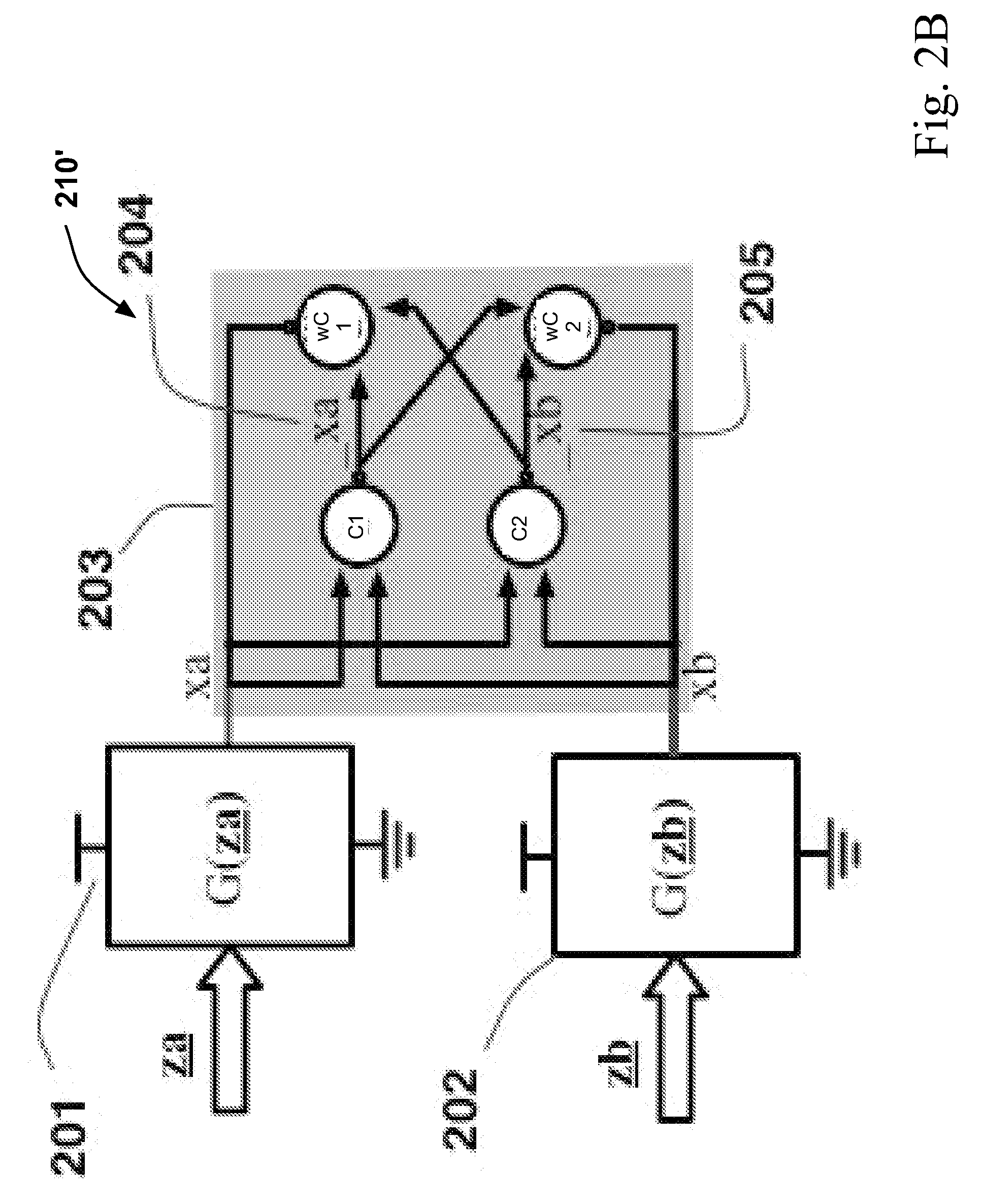

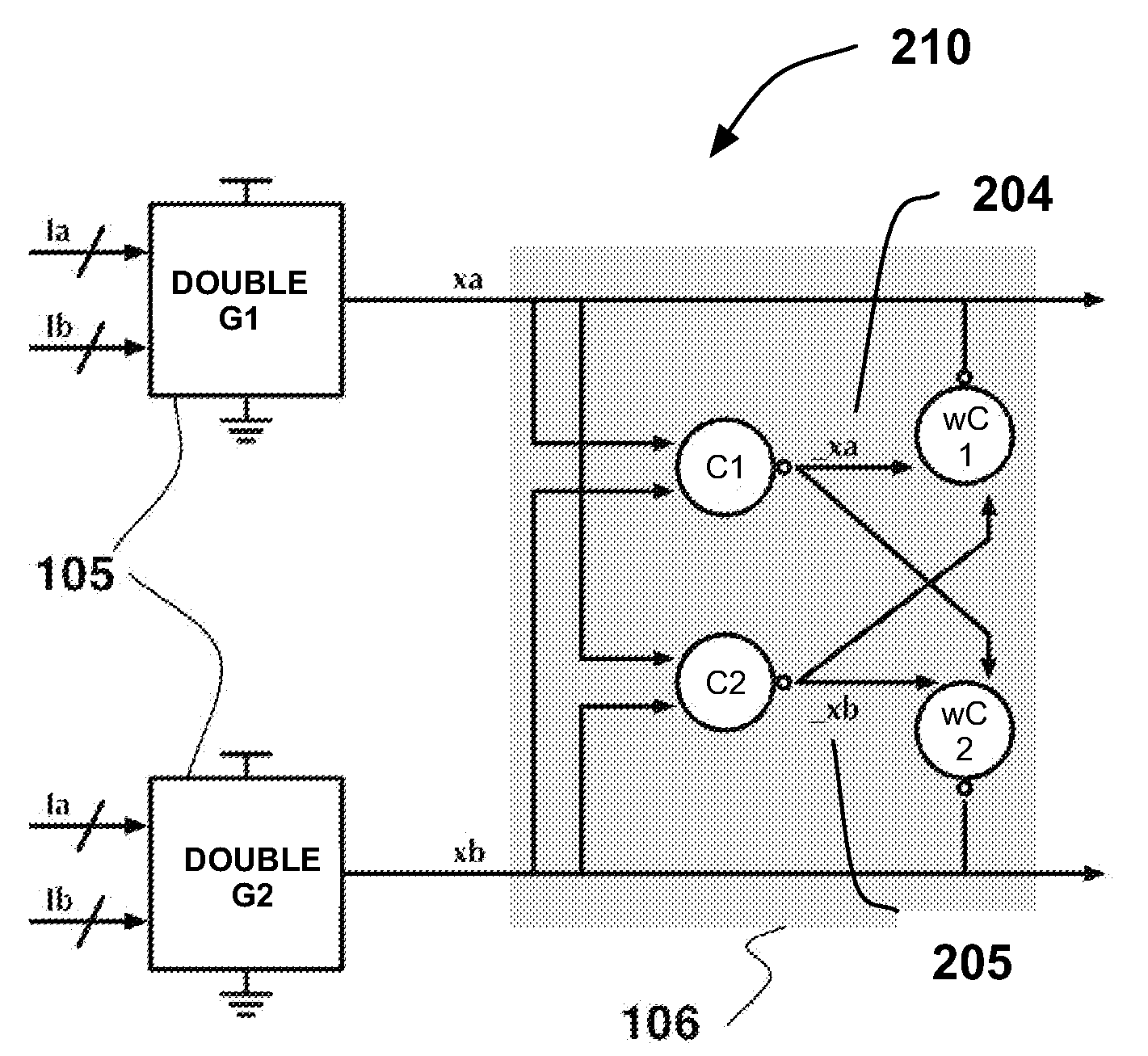

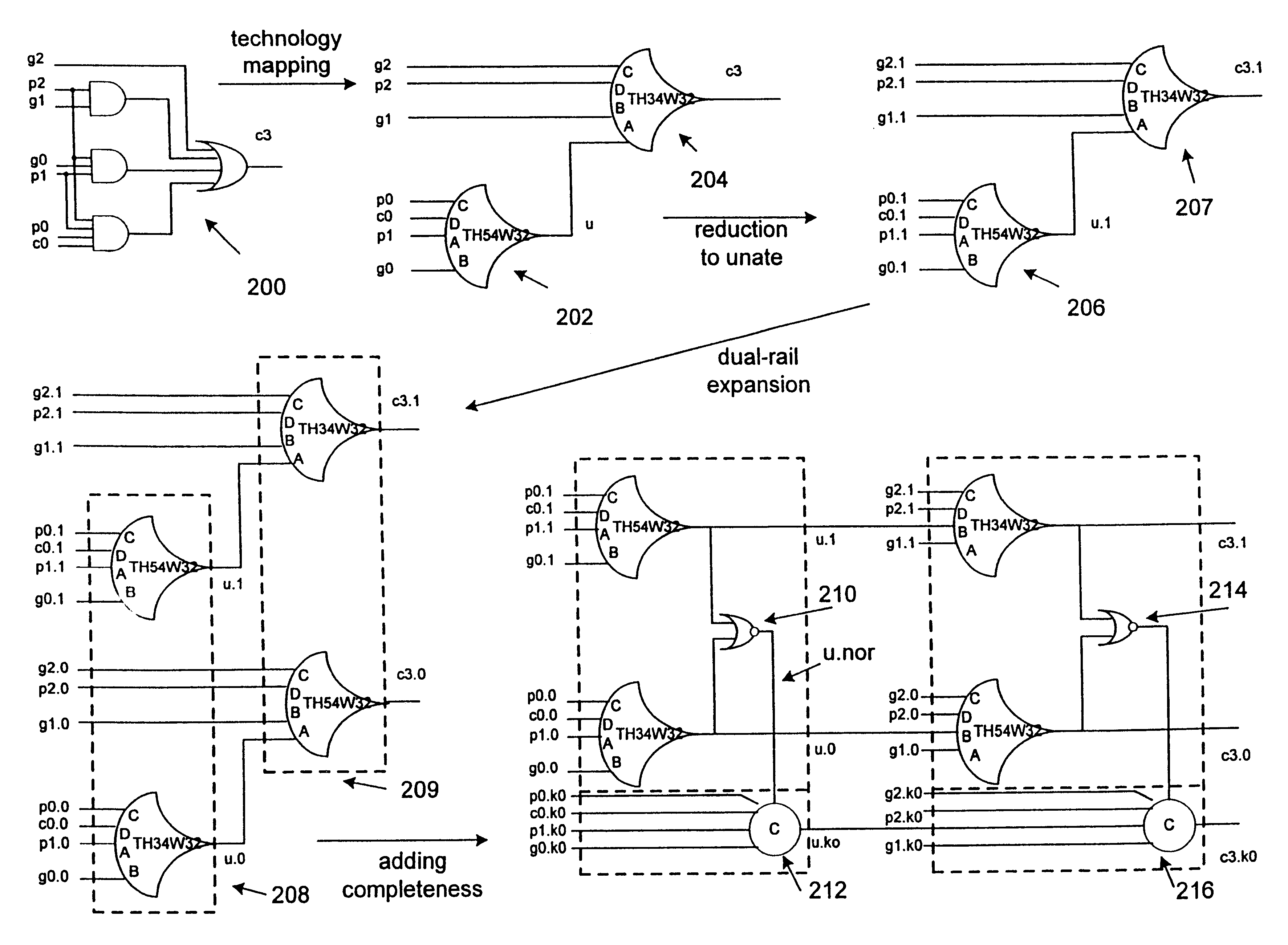

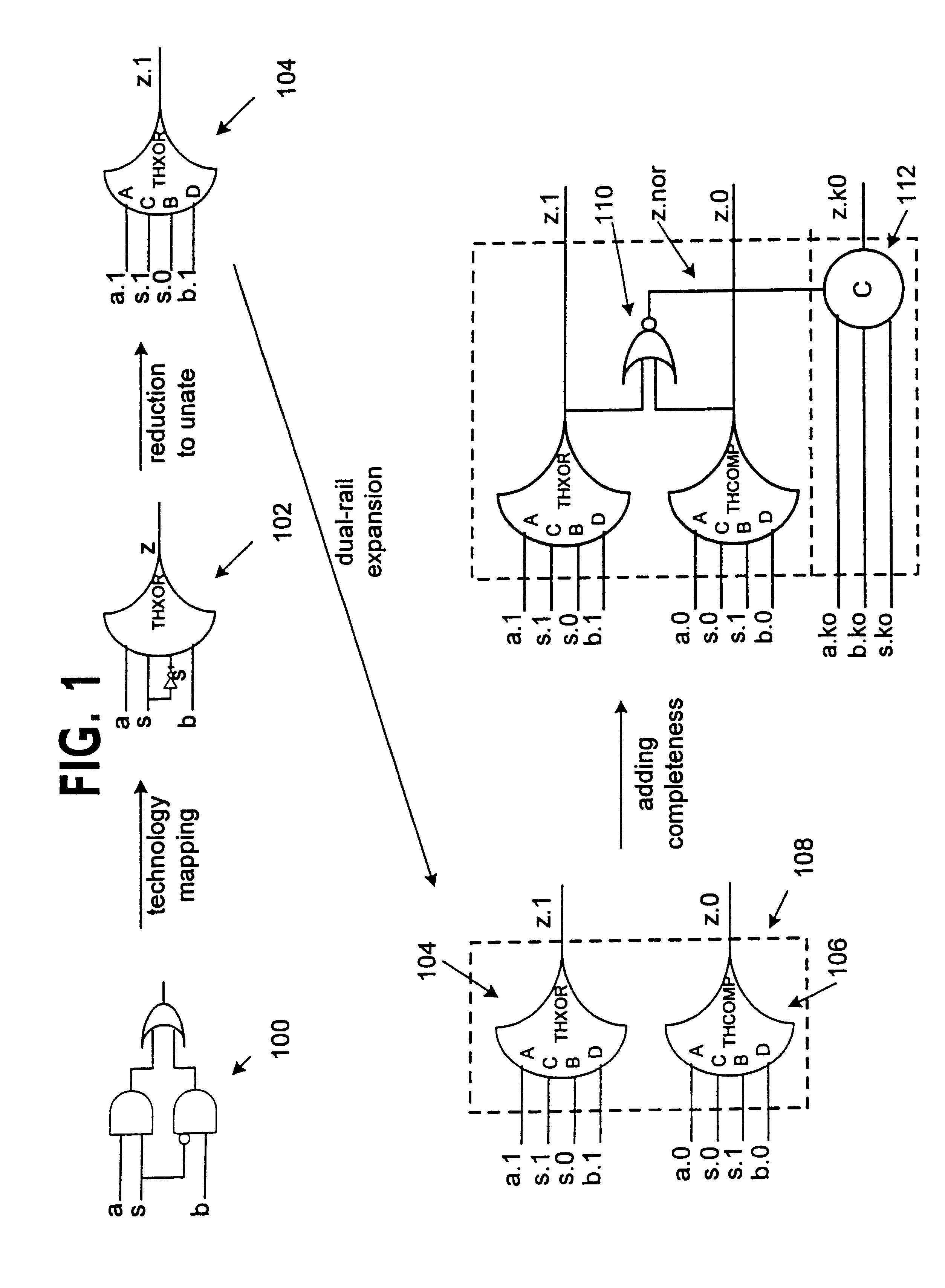

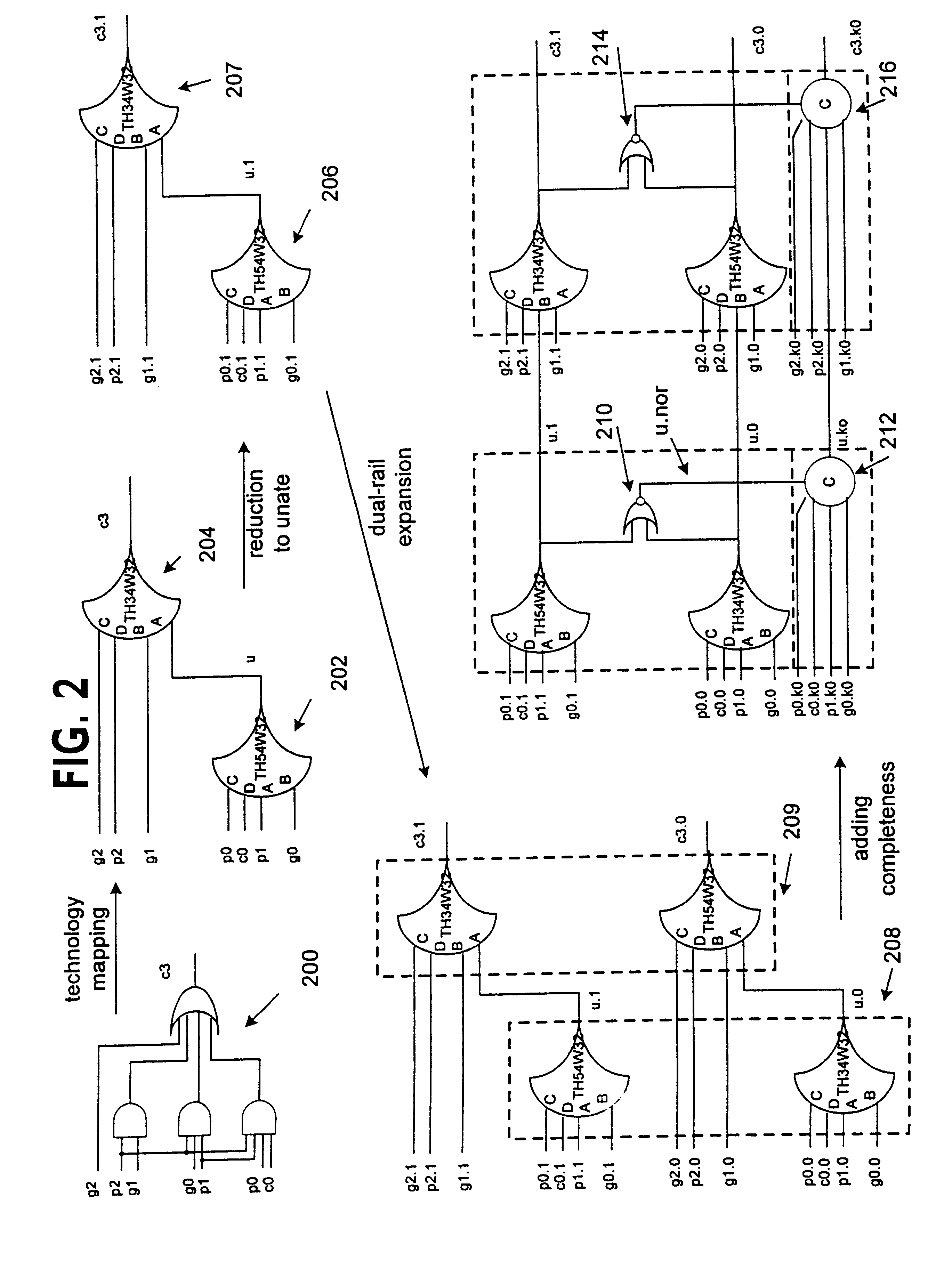

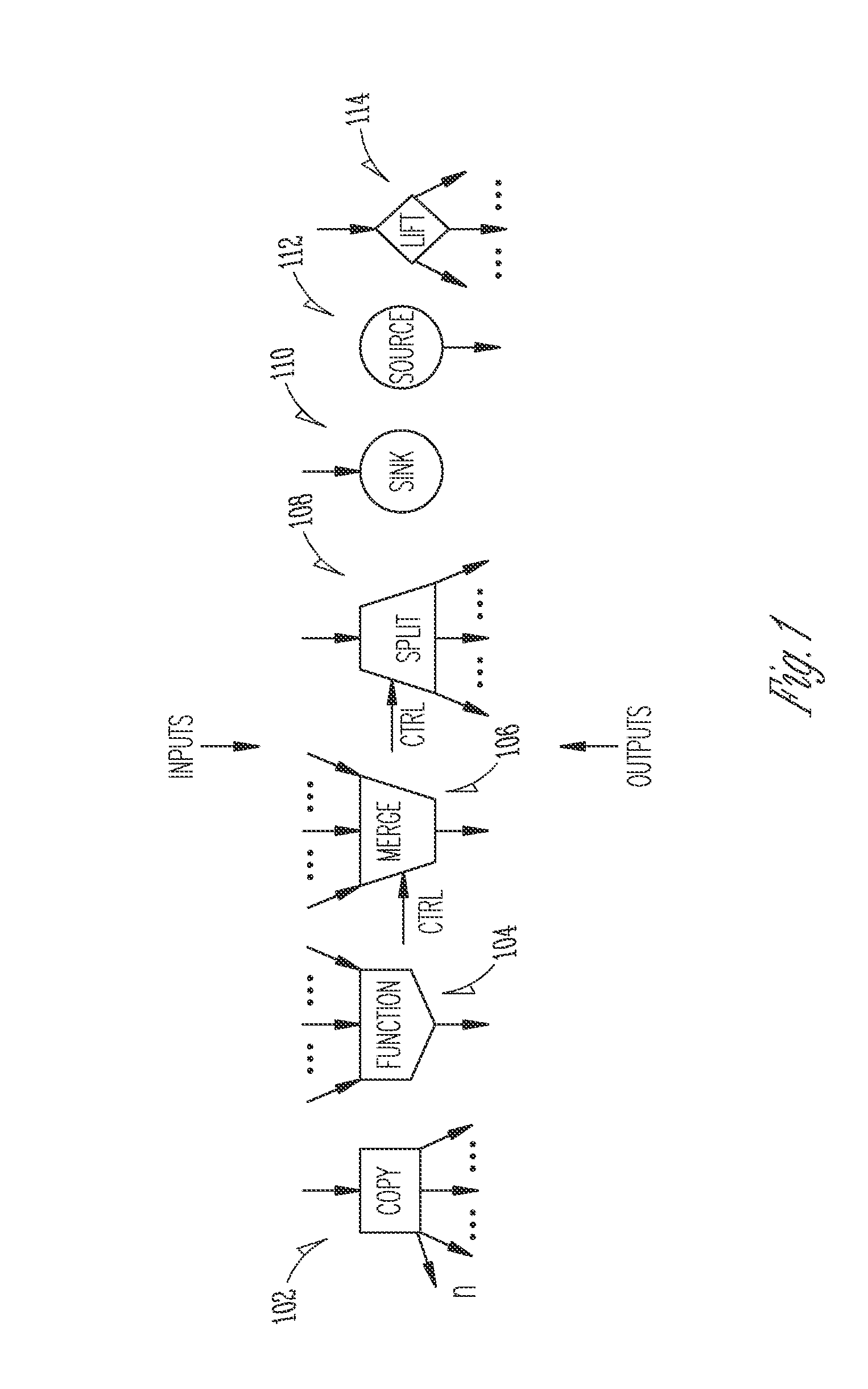

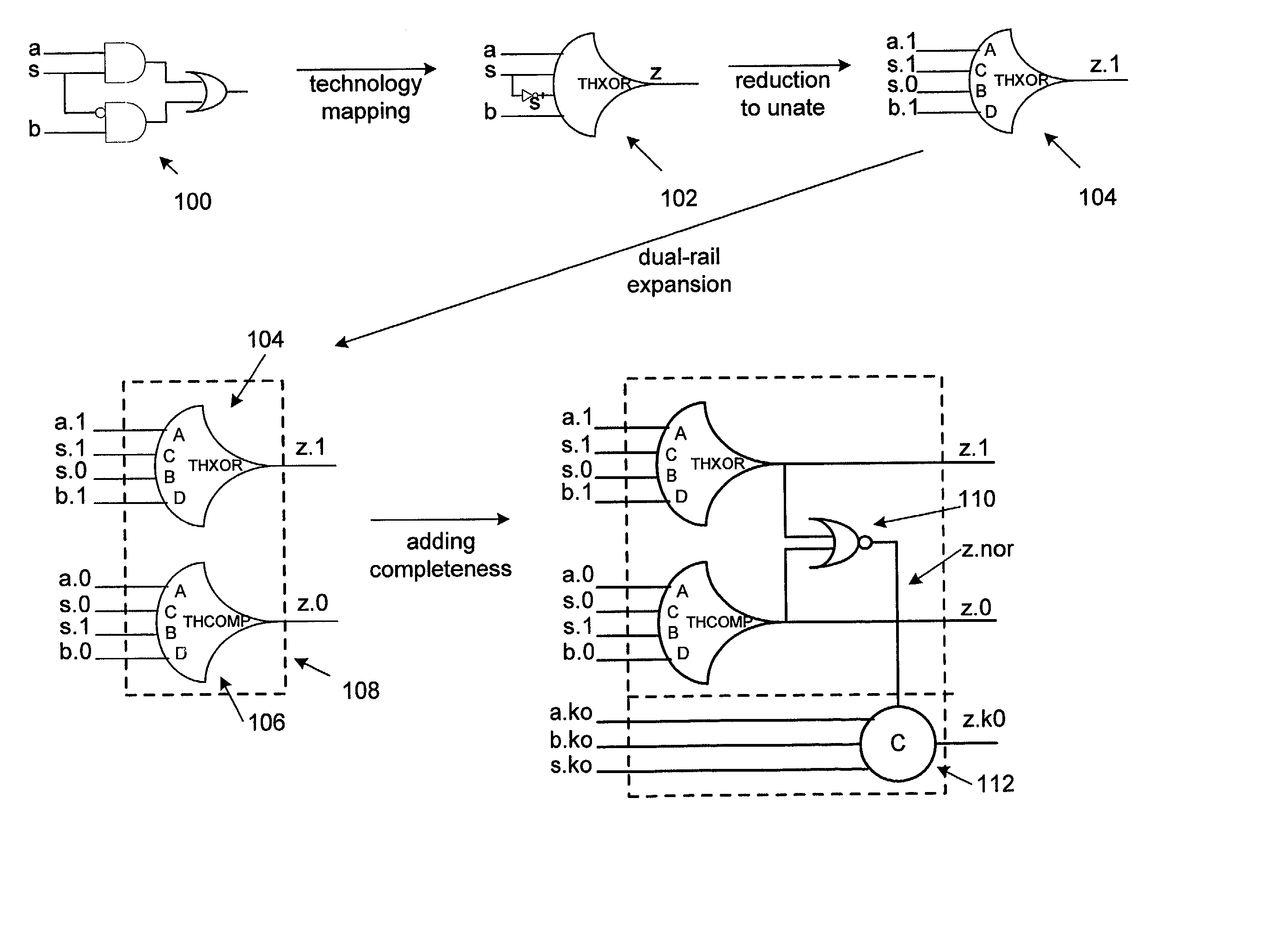

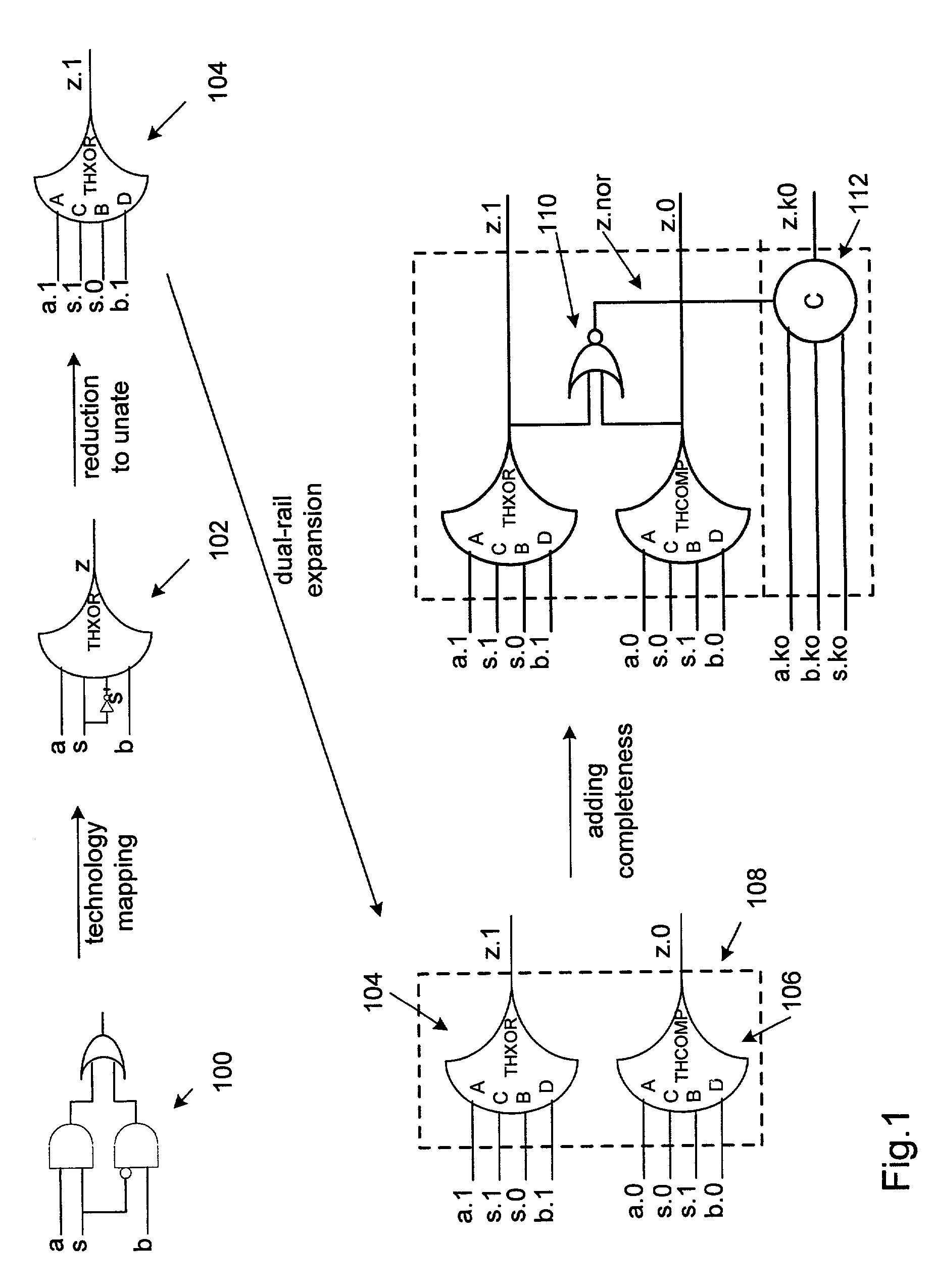

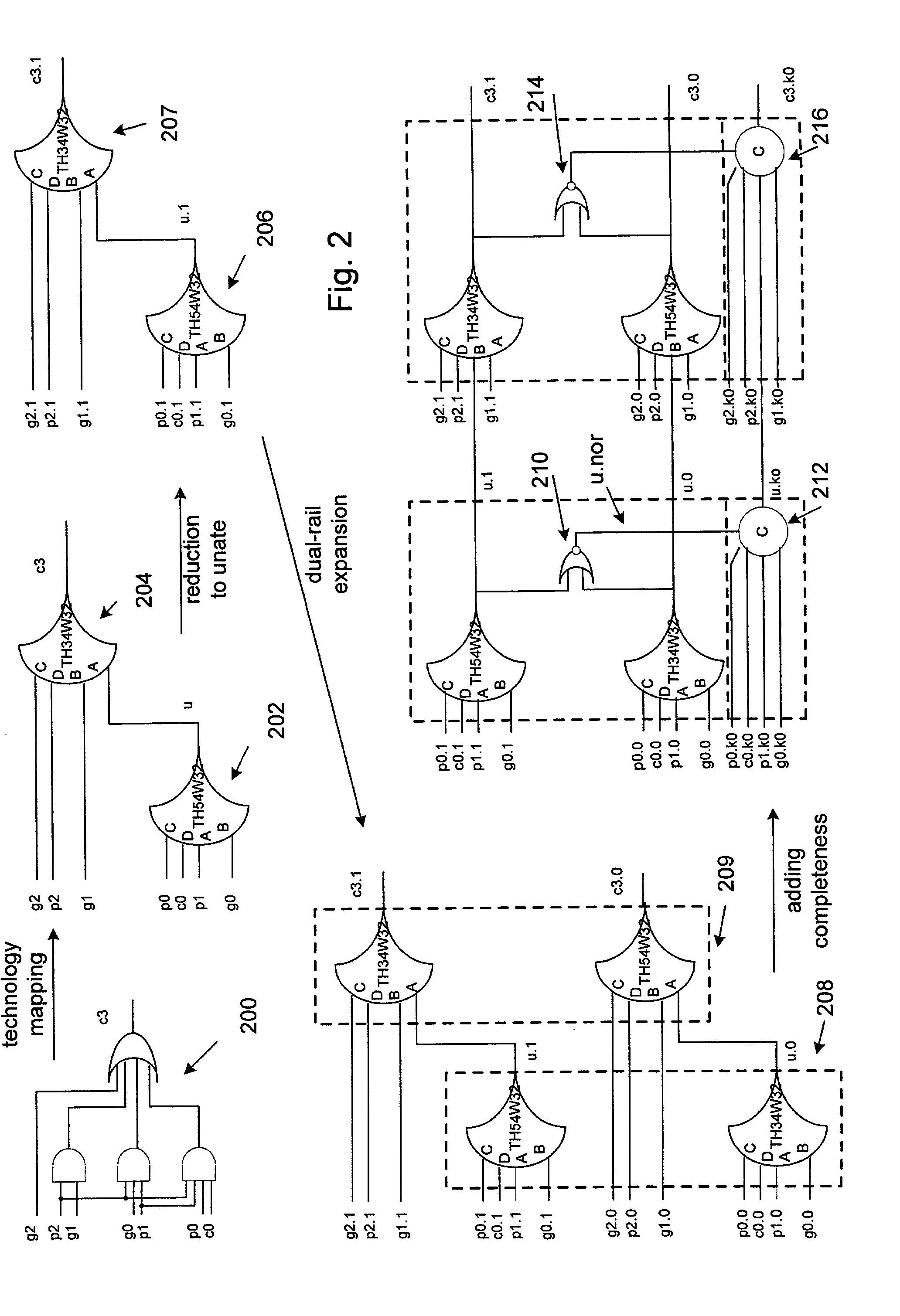

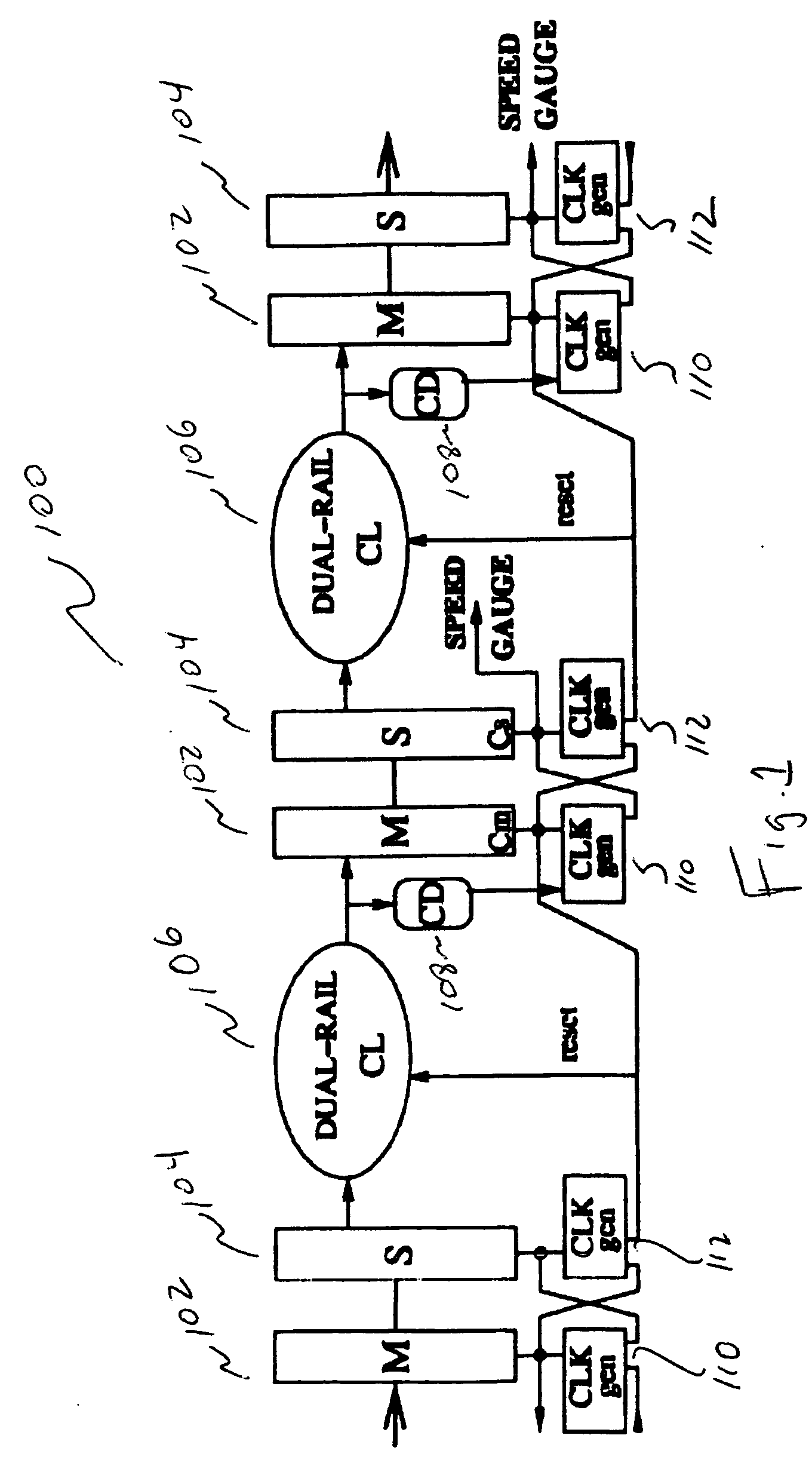

Multi-rail asynchronous flow with completion detection and system and method for designing the same

A method for designing a multi-rail asynchronous circuit is provided. The method includes providing a circuit having n circuit paths, defining a plurality of nodes, each node having an n-rail signal output and at least one n-rail signal input, each rail of the n-rail signal input being connected to a different one of the plurality of circuit paths, and adding completeness detection to each of the plurality of nodes, completion detection for a downstream one of the plurality of nodes being at least partially based on completion detection from an upstream one of the plurality of nodes. Signals propagate along the plurality of data paths independent of the completeness detection.

Owner:WAVE COMPUTING INC

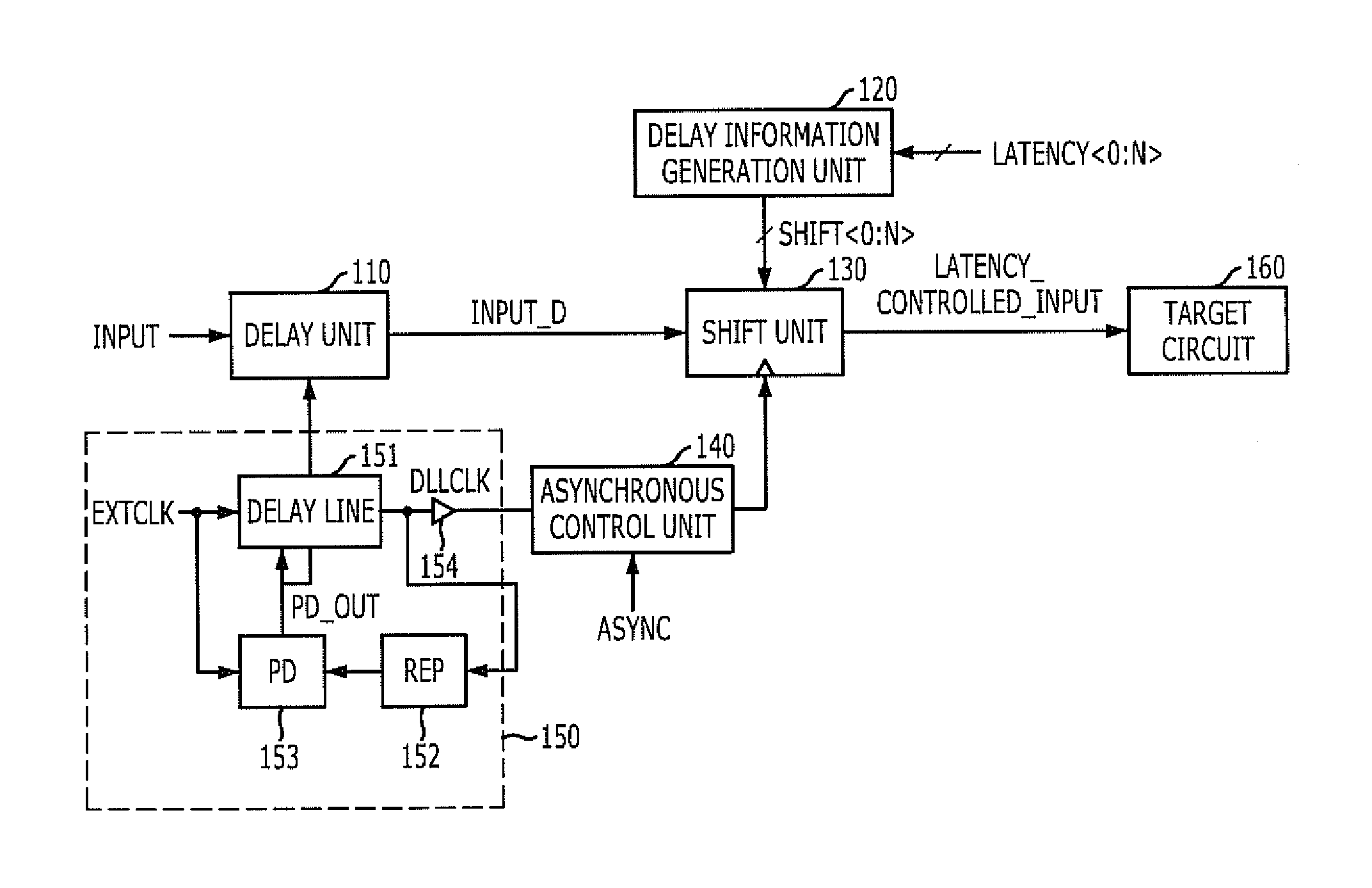

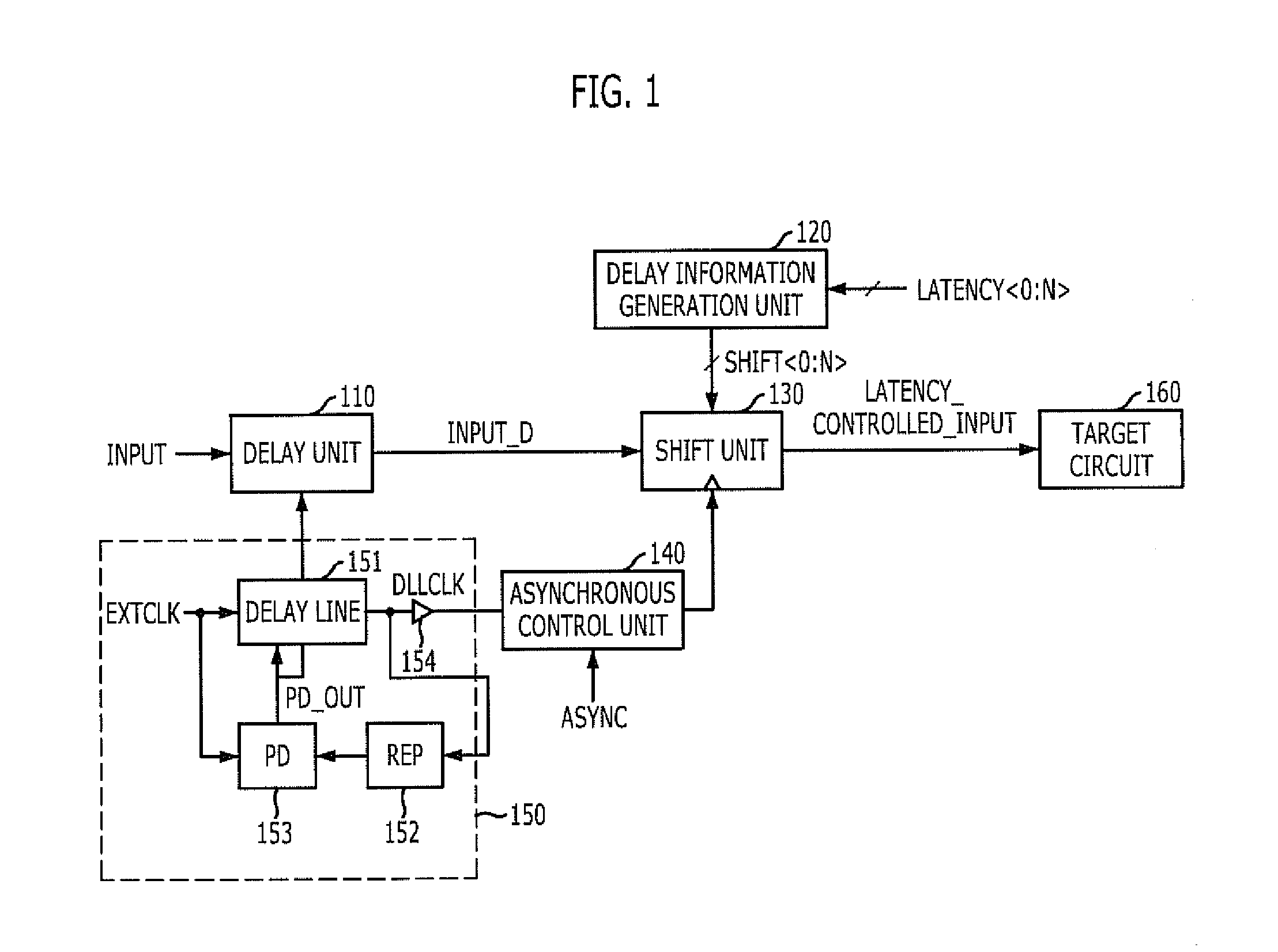

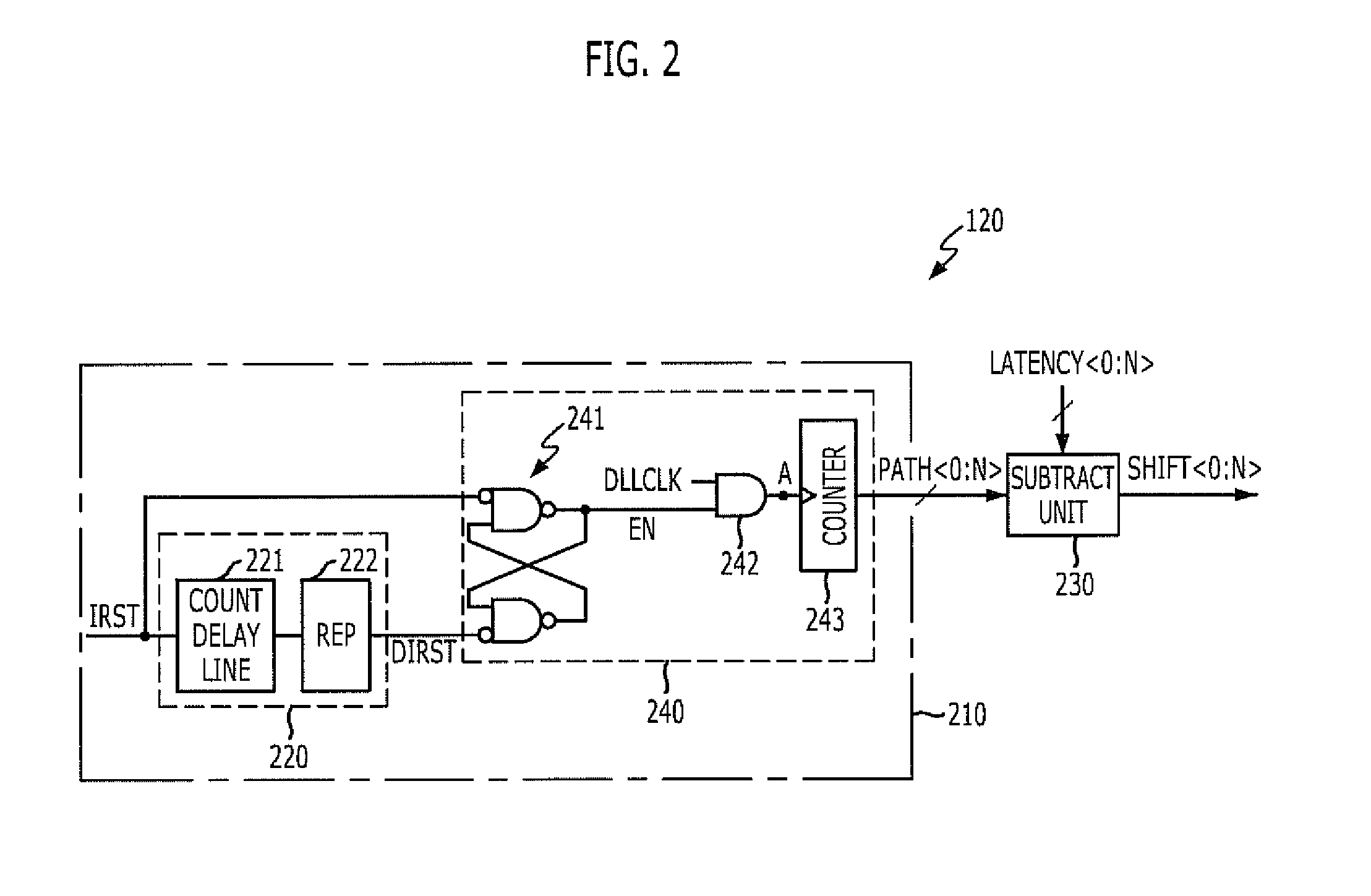

Latency control circuit and semiconductor memory device including the same

A latency control circuit includes a delay unit configured to delay an input signal for a delay corresponding to a phase difference between an external clock and an internal clock and generate a delayed input signal, a delay information generation unit configured to generate a delay information based on a latency information and a delay amount of the input signal caused by a chip including the latency control circuit, a shift unit configured to shift the delayed input signal for a time period corresponding to the delay information in synchronism with the internal clock and an asynchronous control unit configured to selectively control the shift unit to output the delayed input signal without performing a shift operation.

Owner:SK HYNIX INC

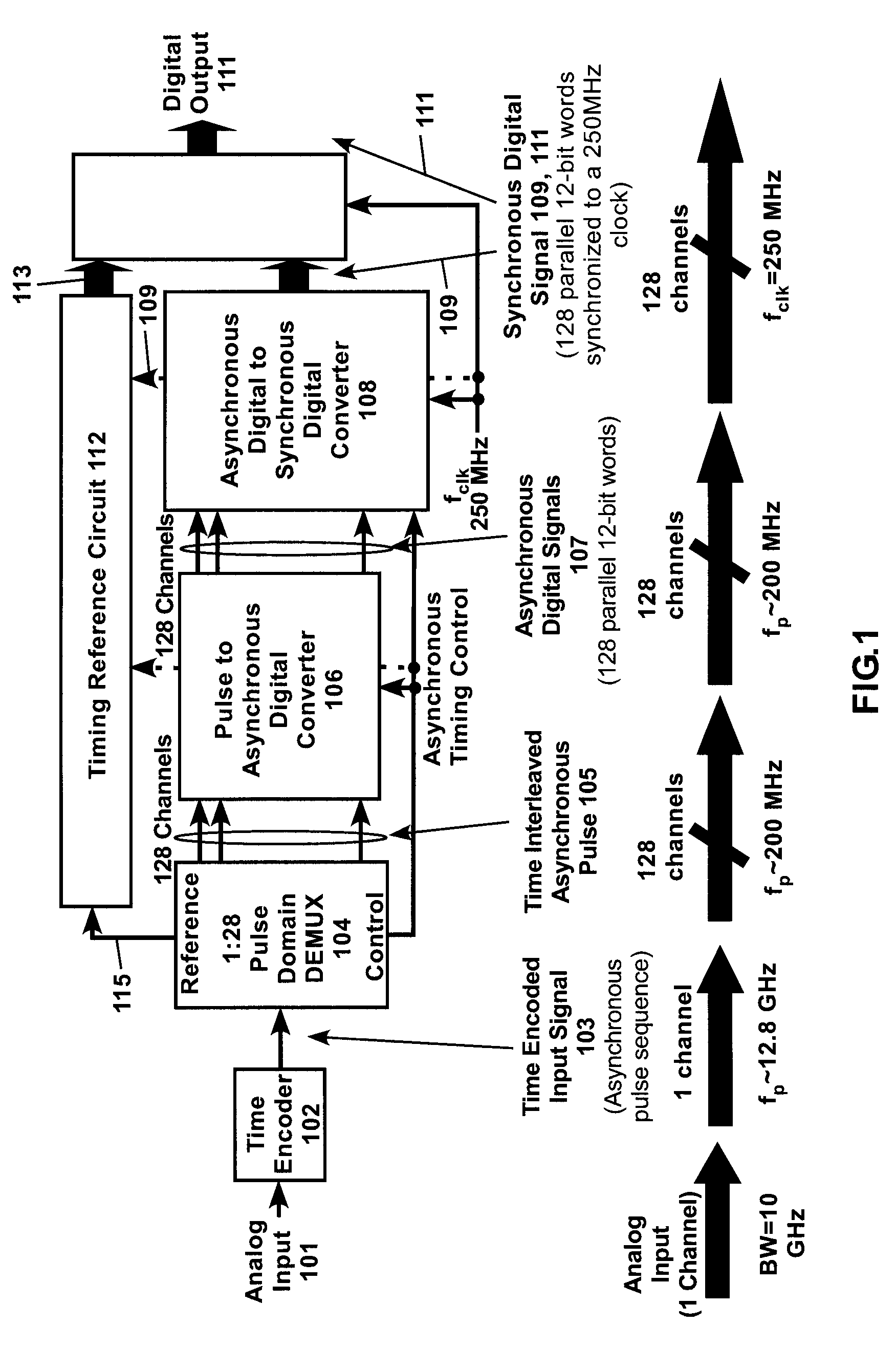

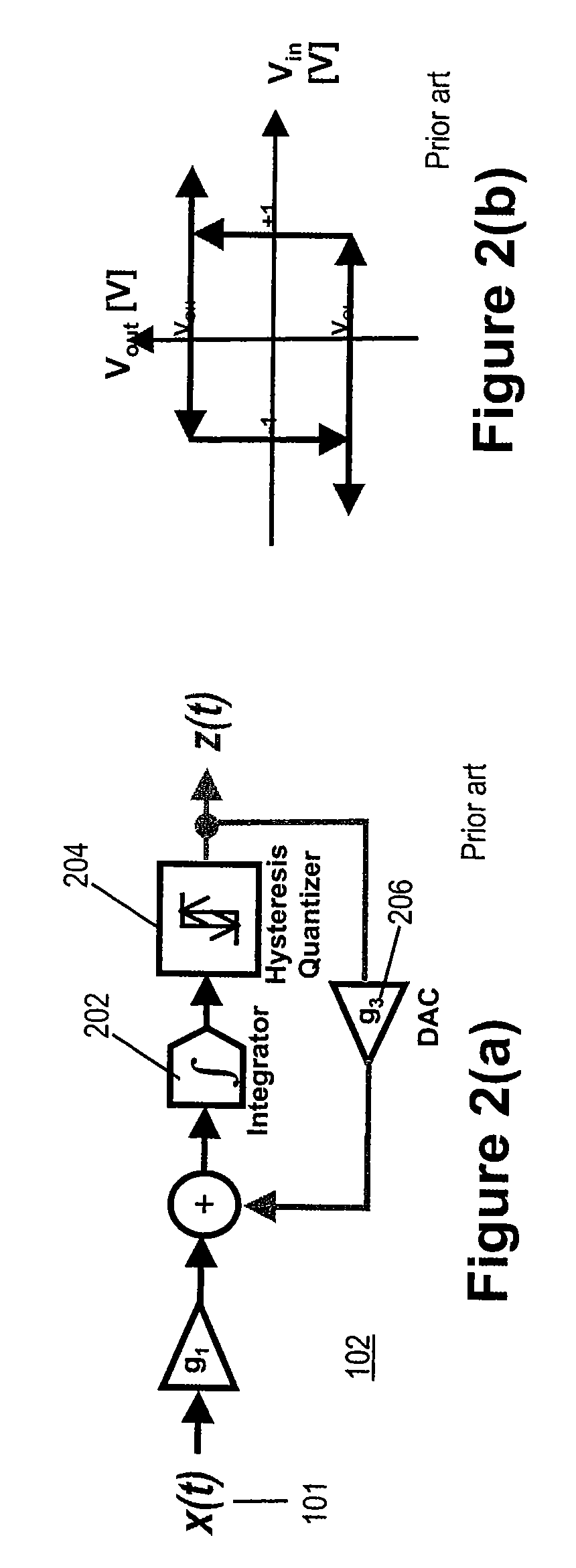

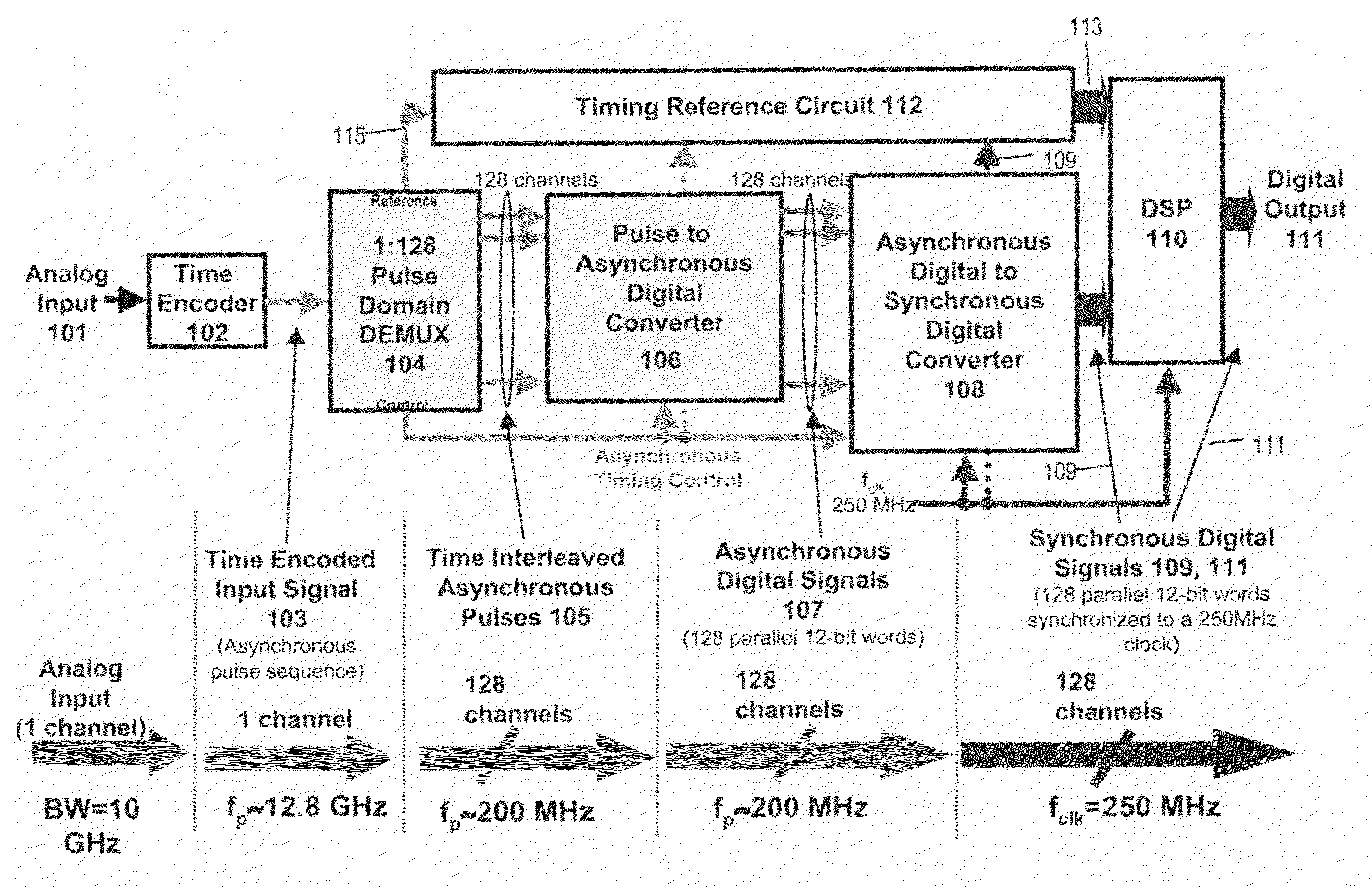

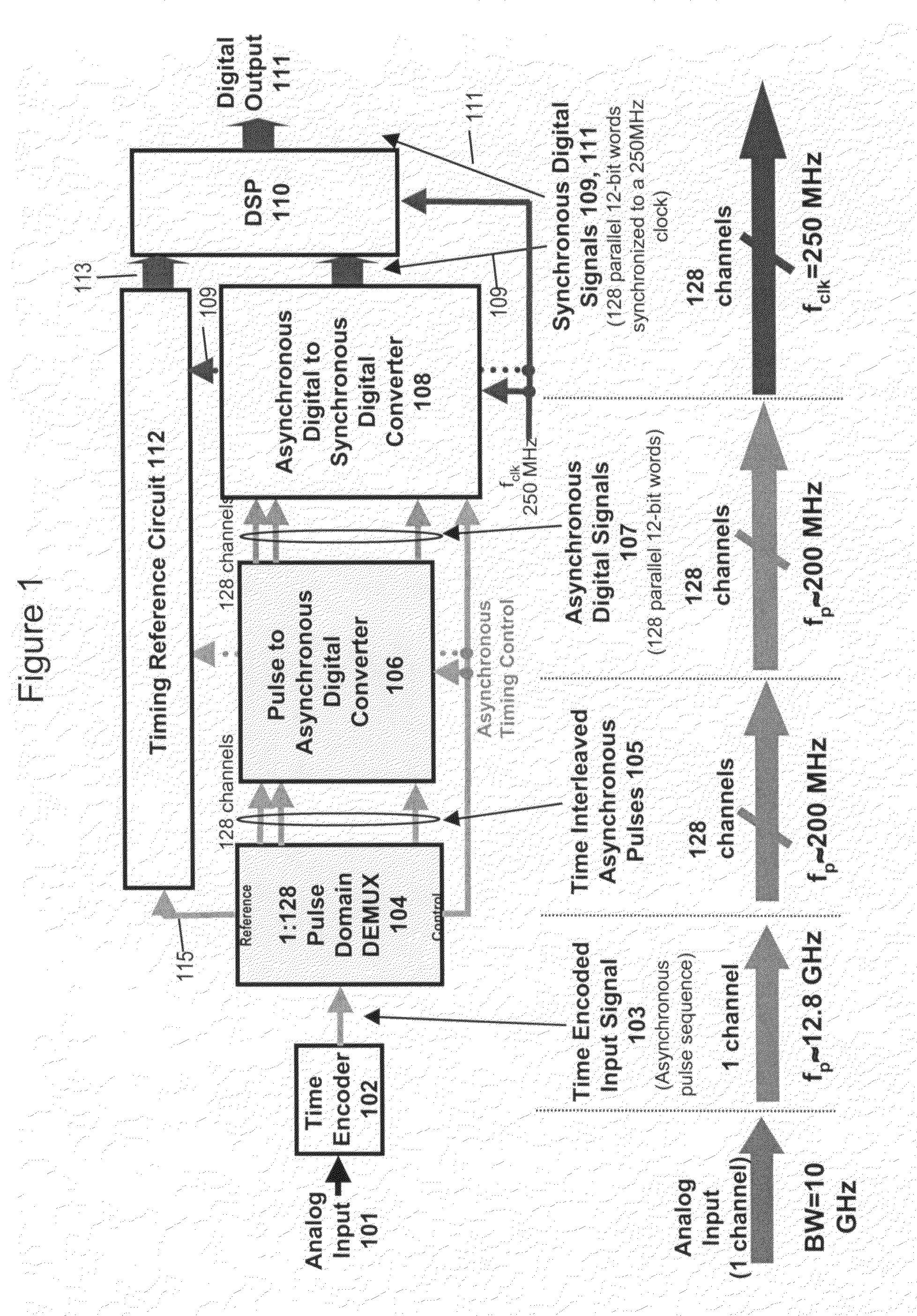

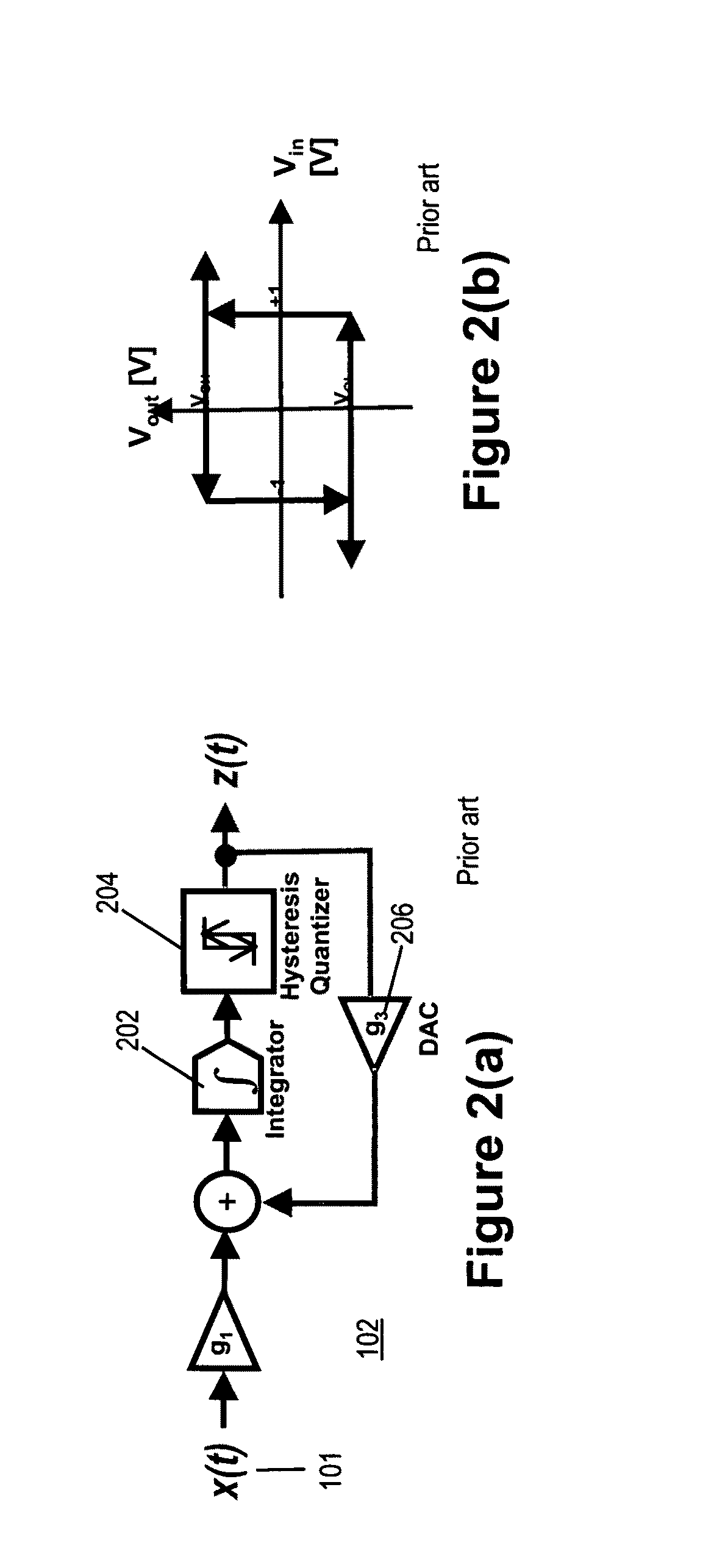

Analog to digital converter using asynchronous pulse technology

InactiveUS7750835B1Analogue/digital conversionElectric signal transmission systemsLow speedDigital down converter

A digital to analog converter includes a time encoder that converts an analog input signal into a asynchronous pulse sequence, a pulse asynchronous DeMUX circuit that converts the asynchronous pulse sequence into a parallel stream of pulse sequences at a relatively lower speed, a parallel pulse to asynchronous digital converter, an asynchronous digital to synchronous digital converter, a timing reference circuit to generate absolute time references, and a Digital Signal Processor. This architecture provides for analog to digital conversion based on pulse encoding with a parallel digitization scheme of the pulse encoded signal.

Owner:HRL LAB

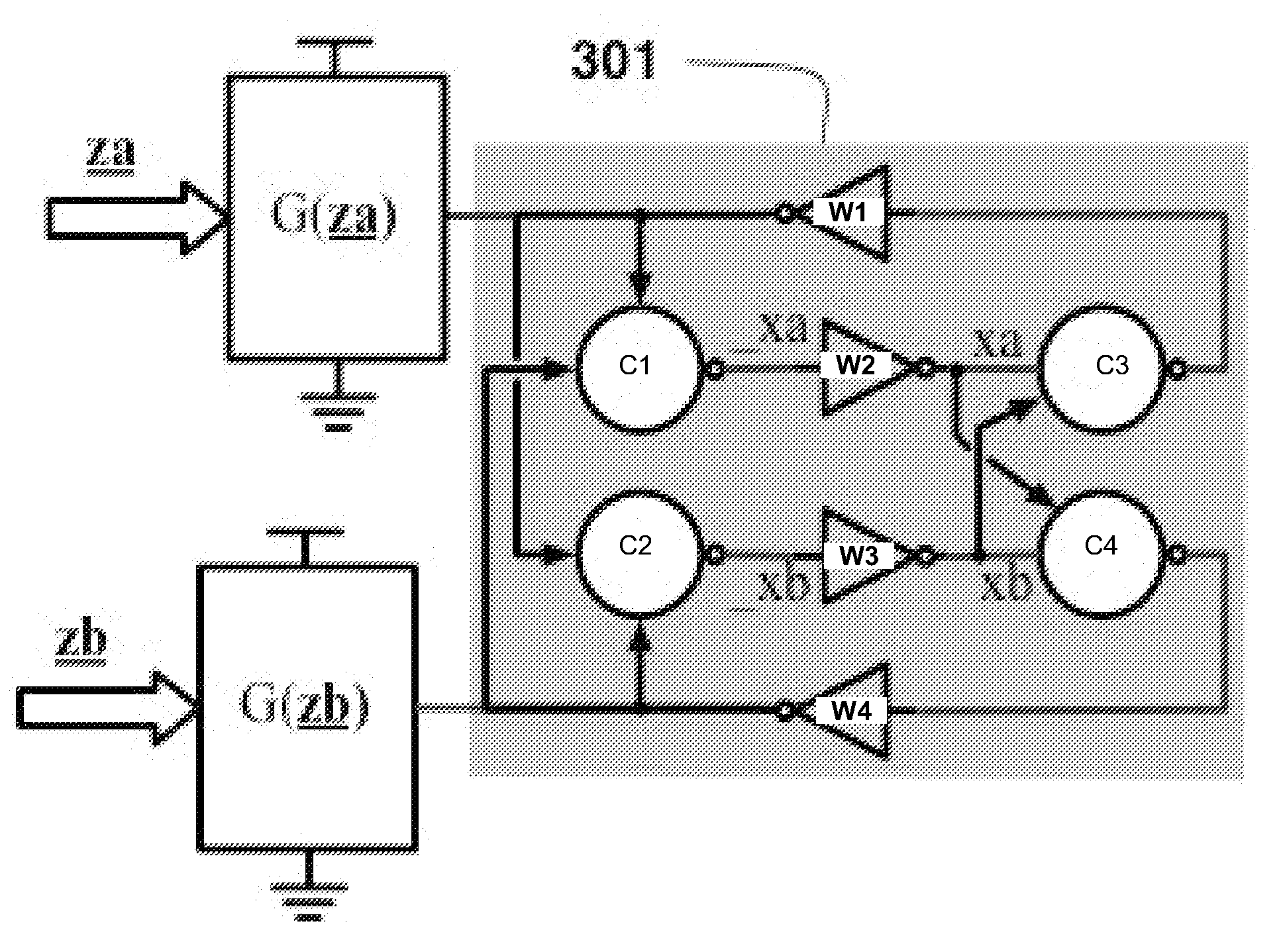

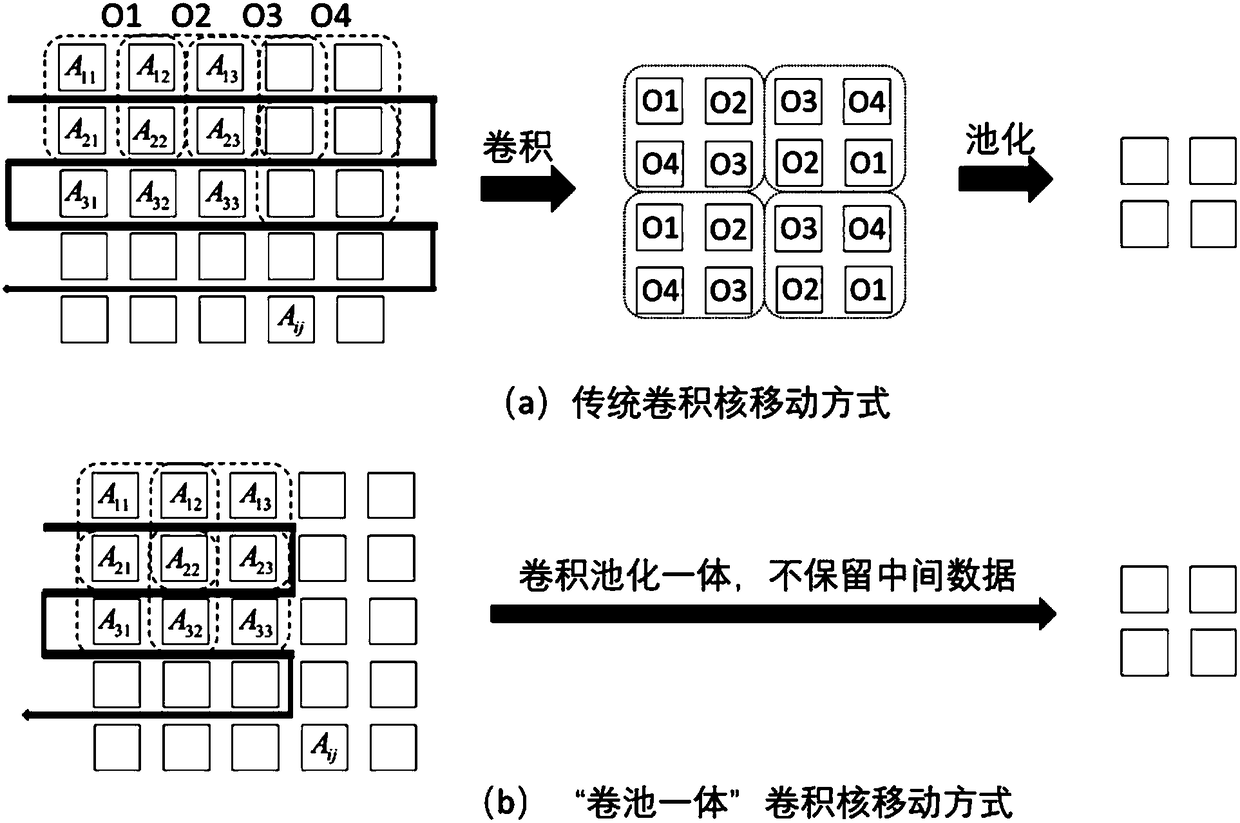

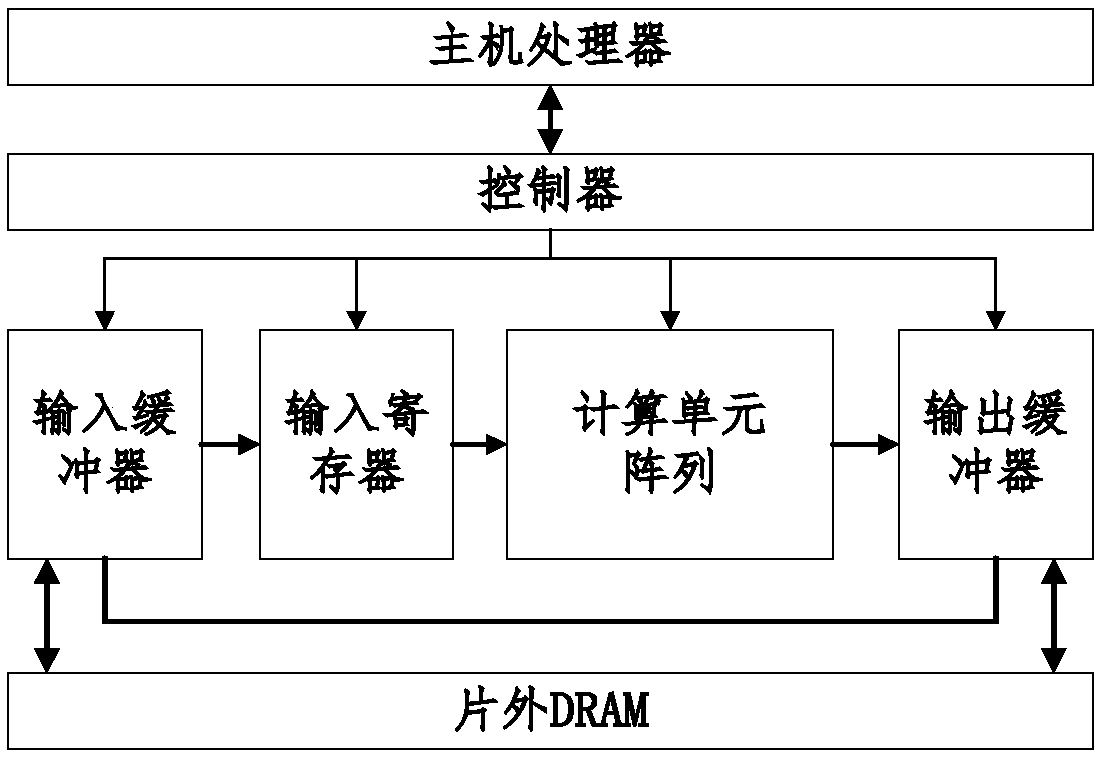

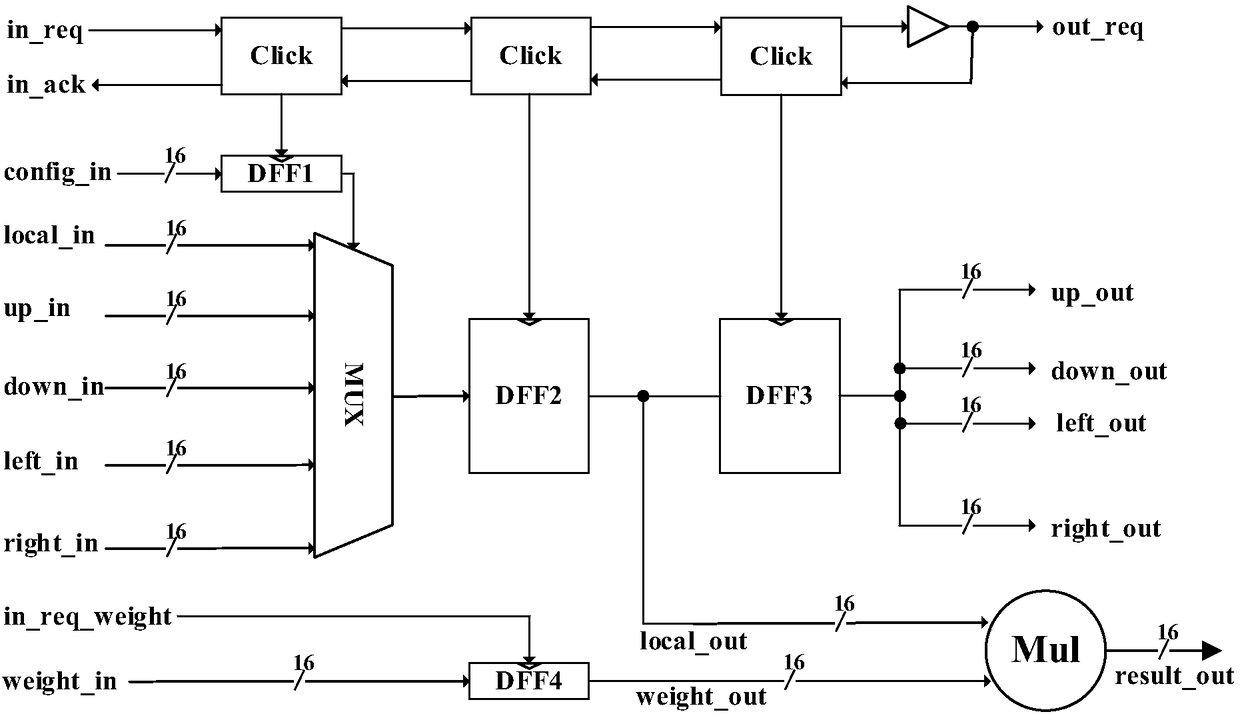

Reconfigurable convolutional neural network acceleration circuit based on asynchronous logic

InactiveCN108537331ARealize communicationImprove parallelismPhysical realisationAsynchronous circuitParallel computing

The present invention provides a reconfigurable convolutional neural network acceleration circuit based on asynchronous logic. The circuit comprises three portions consisting of basic processing elements (PE), a processing array formed by the PEs and a configurable pooling unit. The circuit employs the basic configuration of a reconfigurable circuit to perform reconfiguration of the pressing arrayfor different convolutional neural network models; the circuit is integrally based on the asynchronous logic to employ a lock clock generated by Click units in an asynchronous circuit to replace a global clock in a synchronous circuit and employ an asynchronous pipeline architecture formed by cascading the Click units; and finally, the circuit employs the asynchronous communicating Mesh network to achieve data reuse to reduce power dissipation through reduction of the number of times of accessing the memory. The circuit provided by the invention is flexible and high in degree of parallelism and data reuse rate, and has a power consumption advantage compared to an acceleration circuit implemented through synchronous logic so as to greatly improve the processing speed of the convolutional neural network in the low power consumption.

Owner:TSINGHUA UNIV

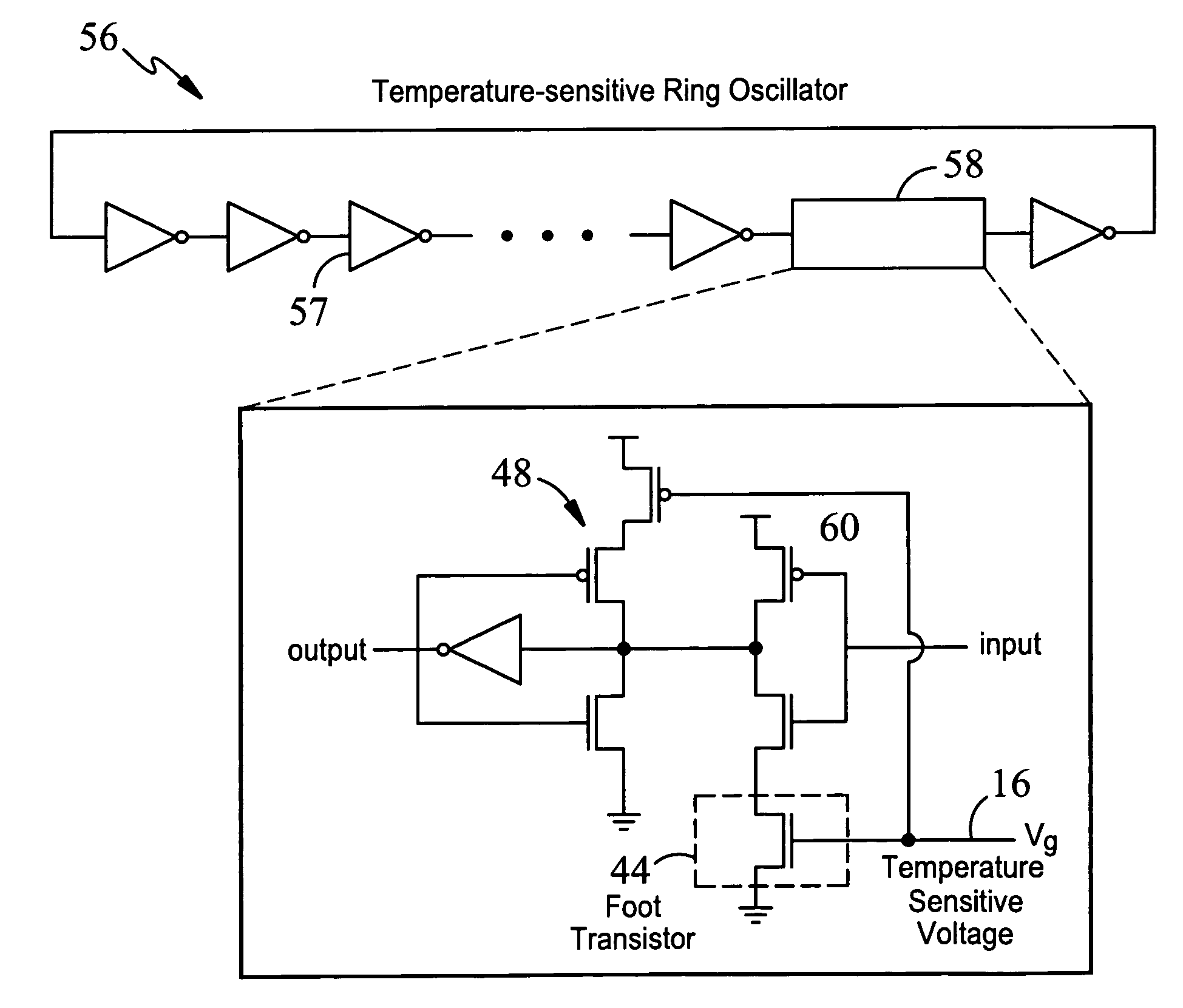

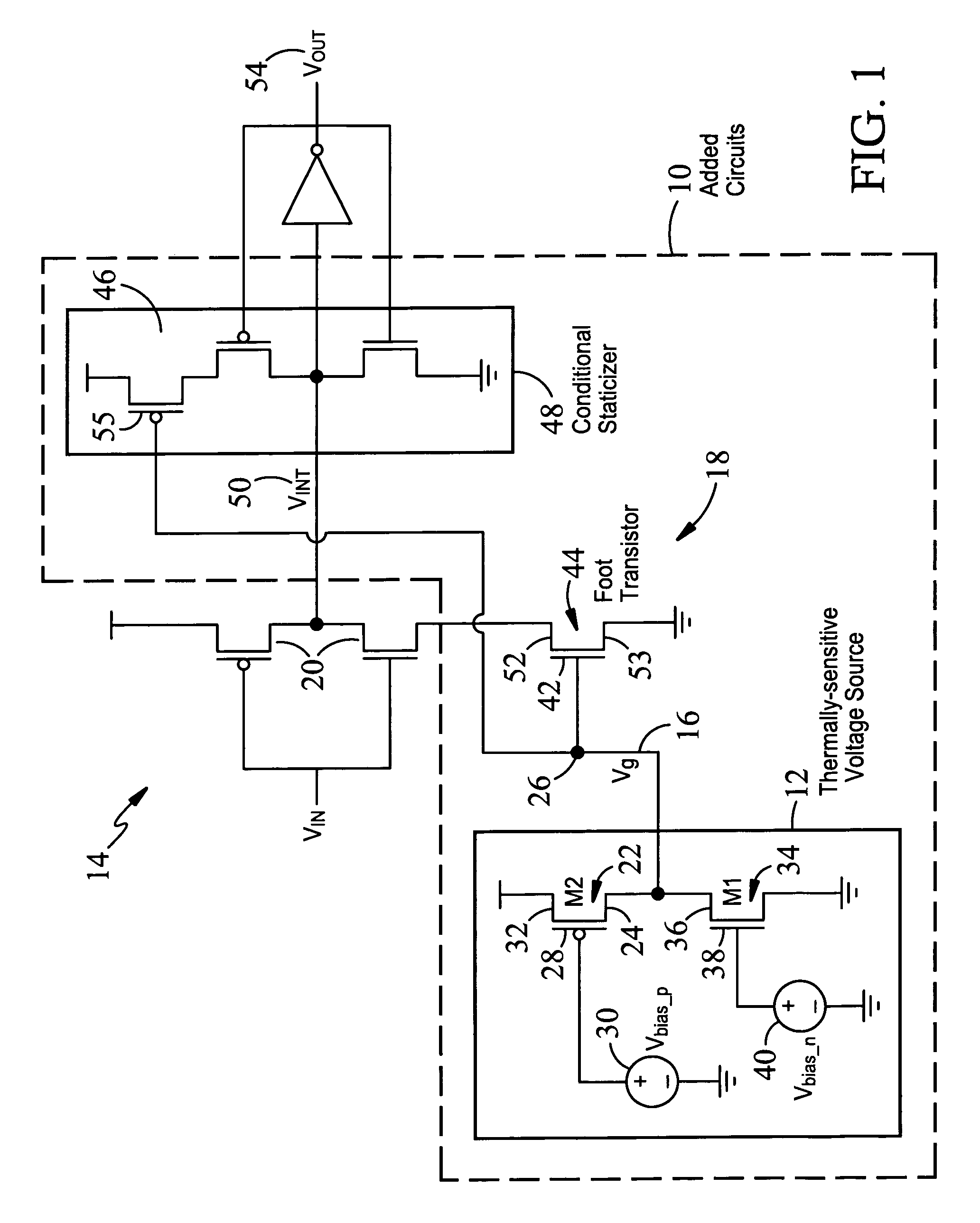

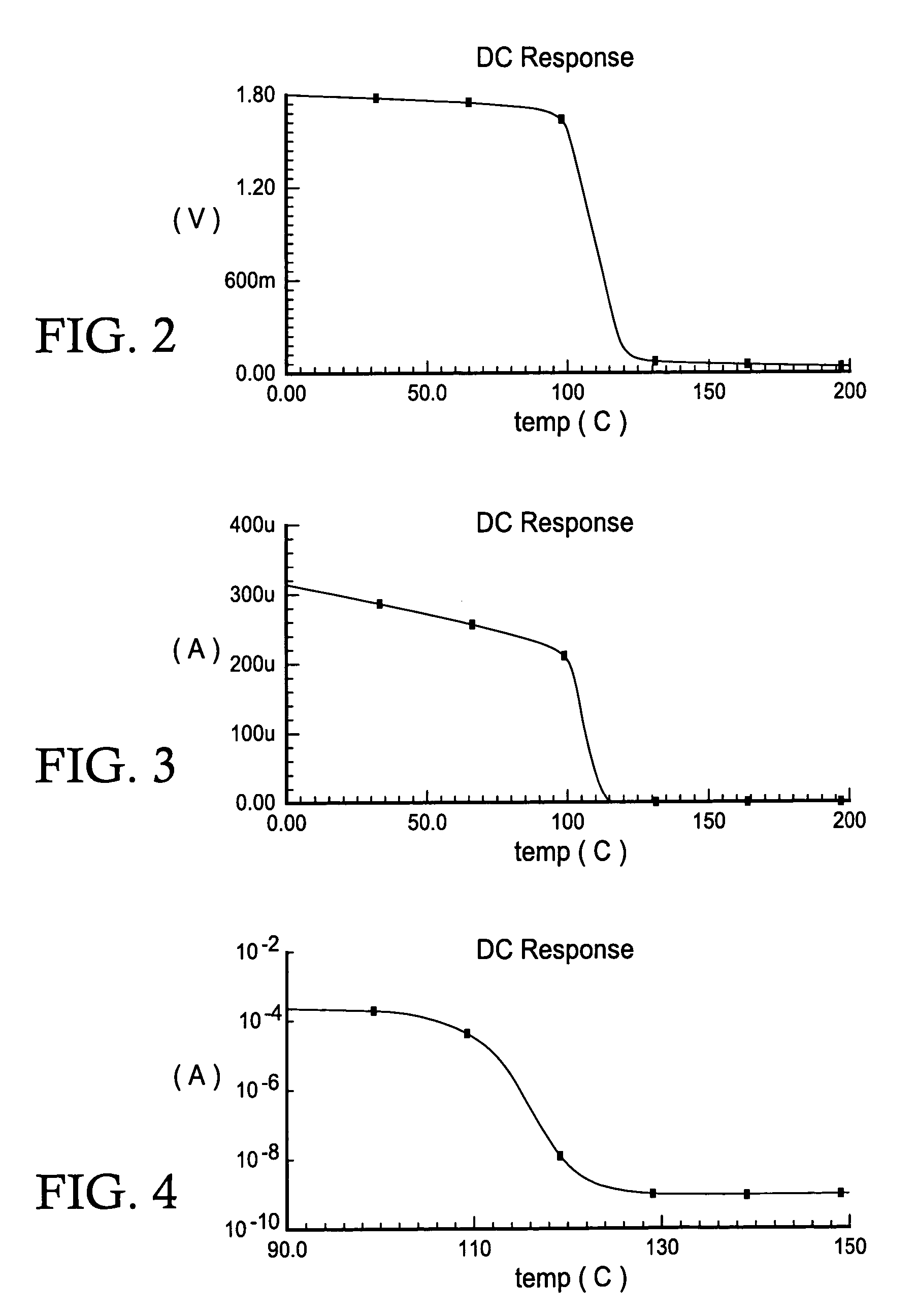

Self-timed thermally-aware circuits and methods of use thereof

InactiveUS7411436B2Without imposing significant implementation overheadStall-free performance-throttlingElectronic switchingNetwork modifications to reduce temperatureAsynchronous circuitEngineering

Apparatus and methods for regulating gate delays of synchronous and asynchronous digital circuits. Thermally-sensitive circuits include, generally, temperature sensitive voltage sources outputting a voltage signal indicative of the temperature of the digital circuit, where the voltage signal reflects non-linear temperature sensitivity above a predetermined threshold temperature, and delay mechanisms receiving said temperature sensitive voltage signal(s) as input and being configured to automatically continuously modulate the speed of signal propagation through the circuit in response to said voltage signal, thereby causing circuit elements within the circuits to switch less frequently and consequently causing the circuit elements to generate less heat with increasing circuit temperature.

Owner:CORNELL RES FOUNDATION INC

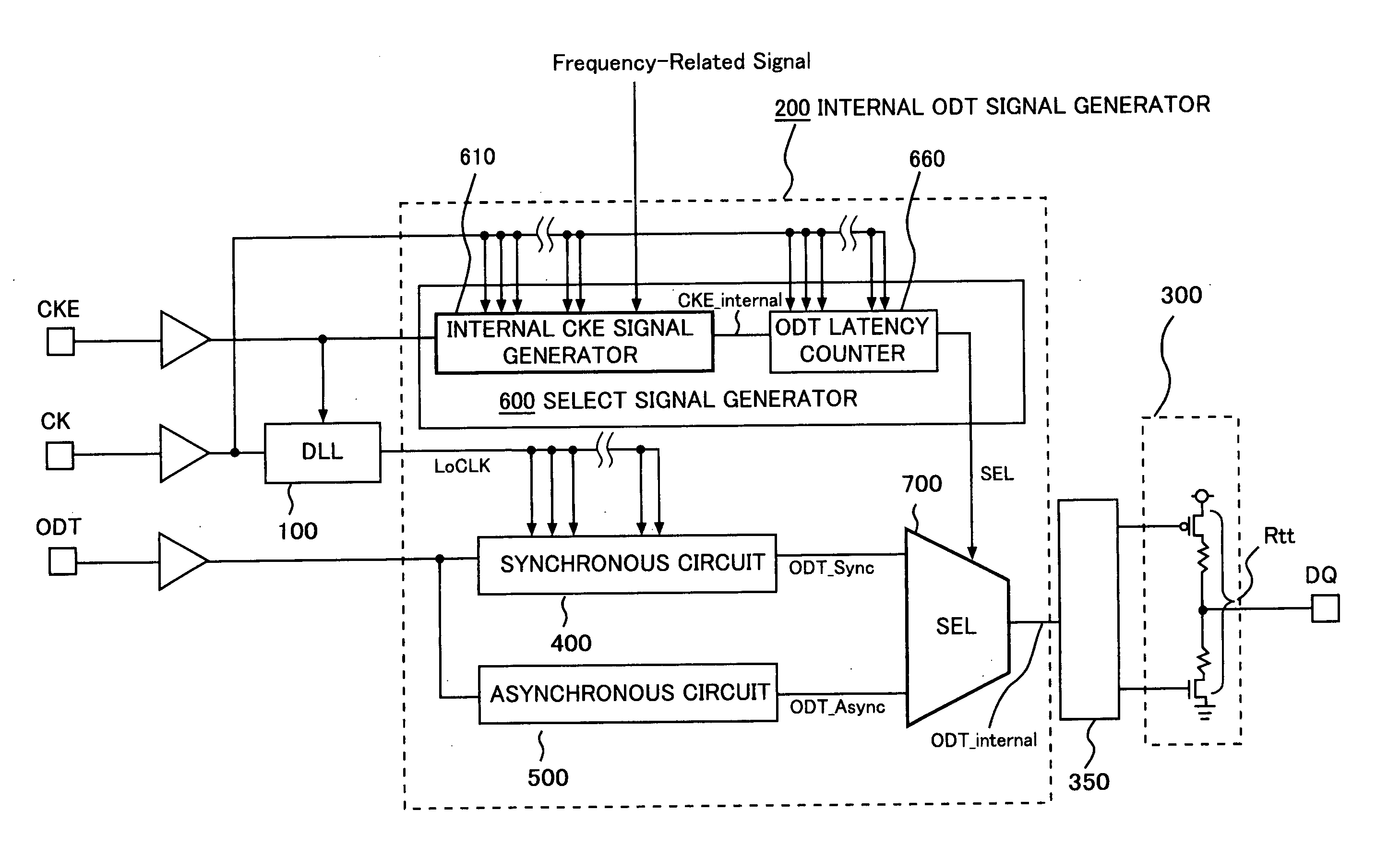

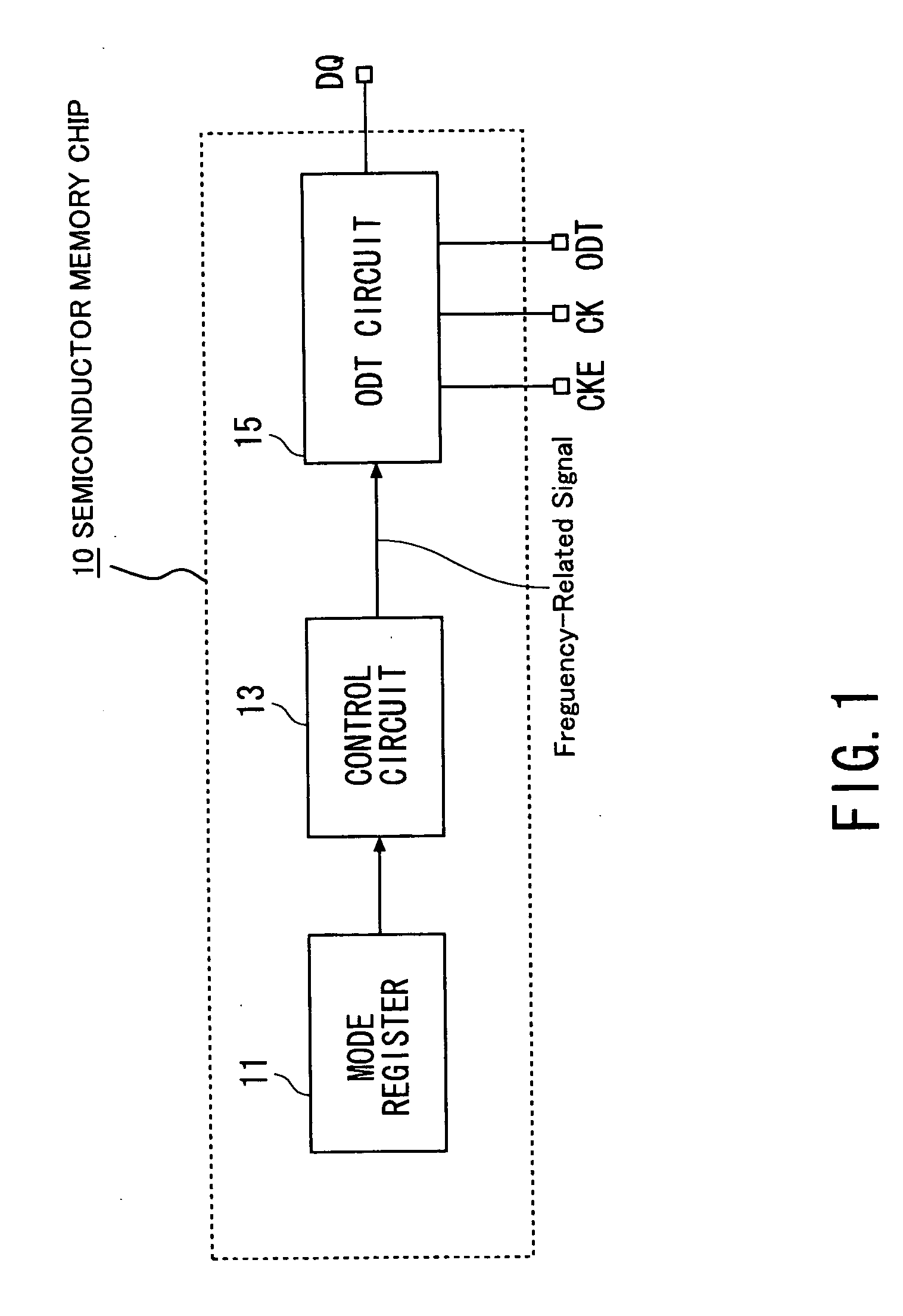

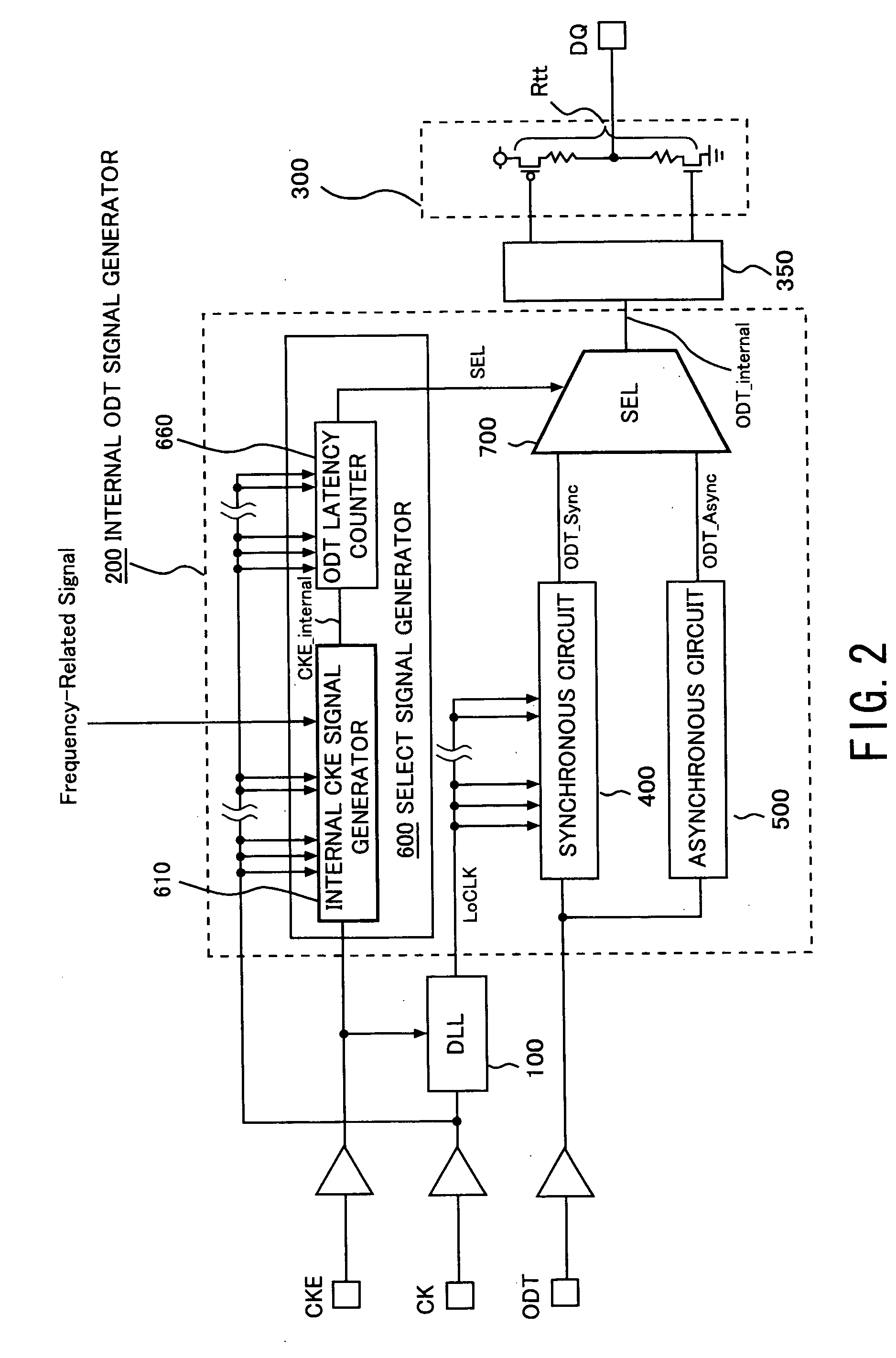

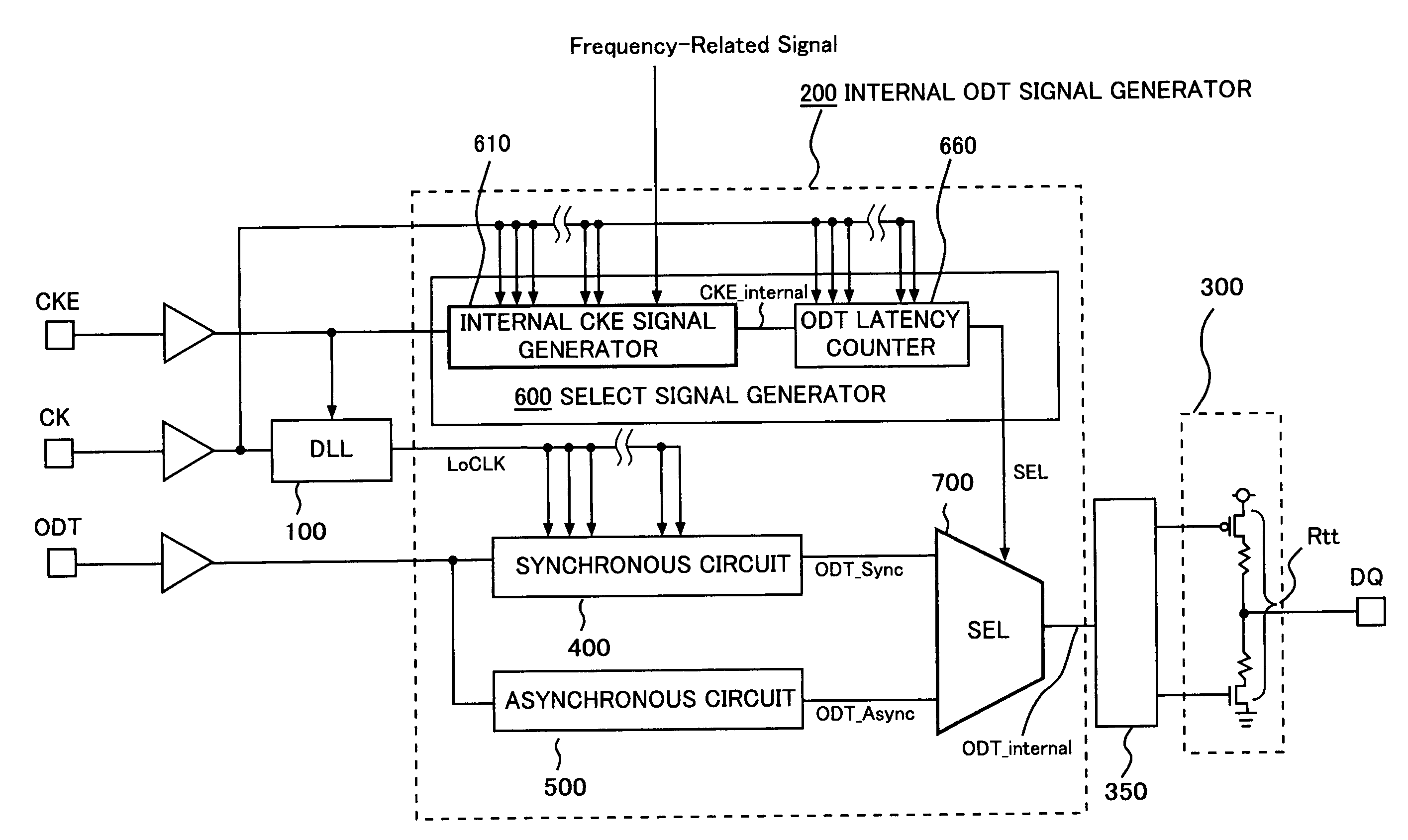

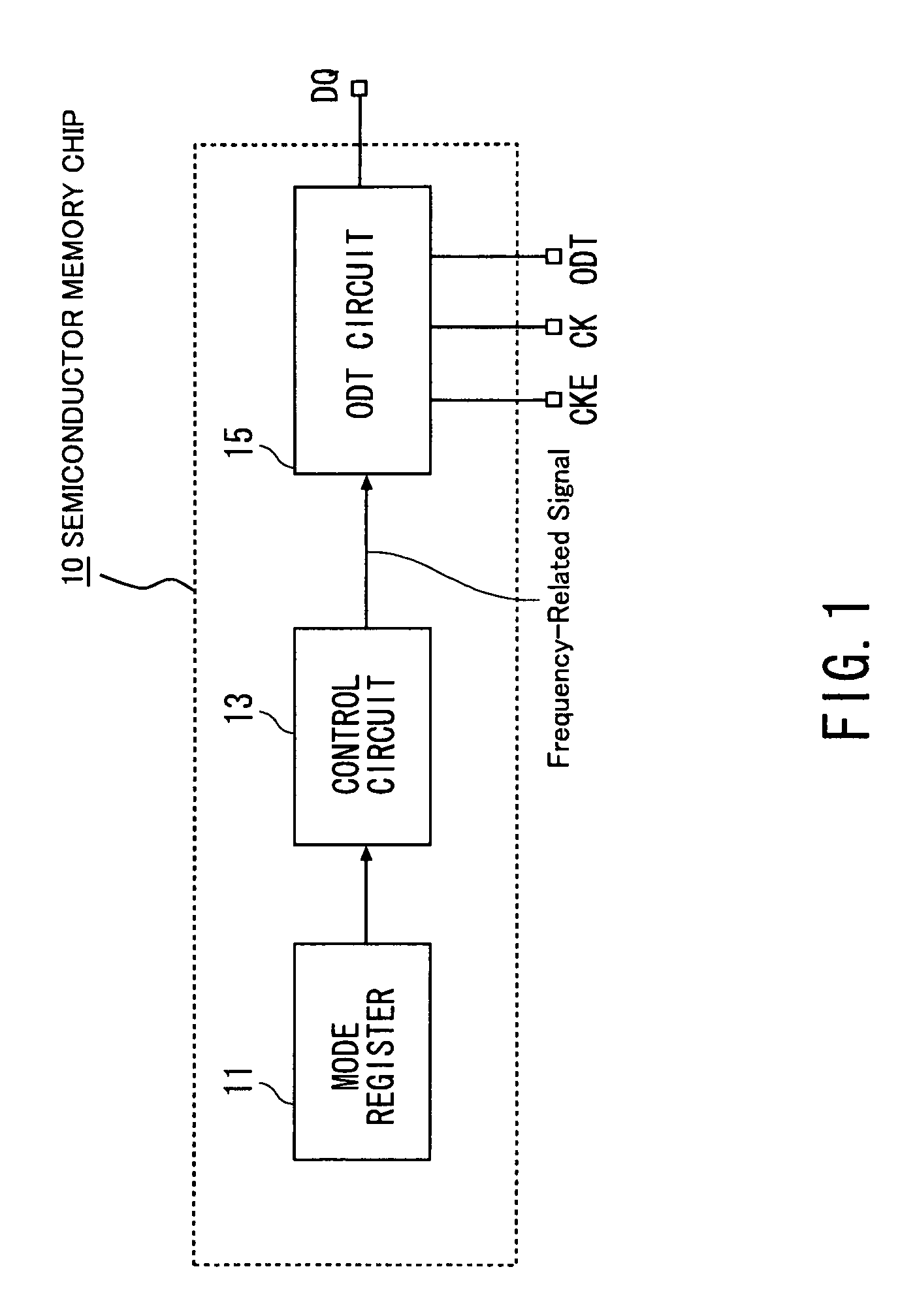

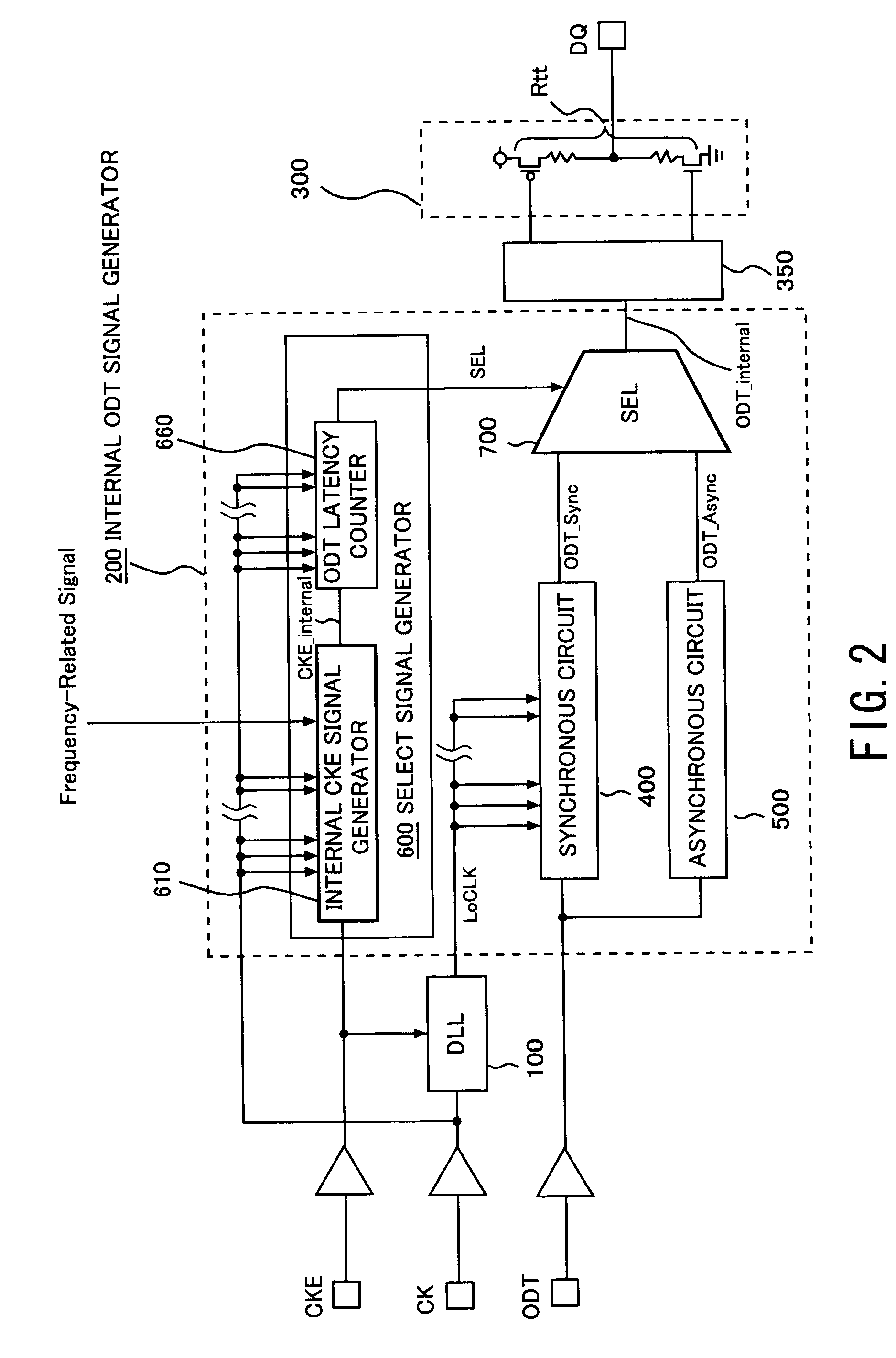

Semiconductor memory chip with on-die termination function

ActiveUS20070103188A1Reliability increasing modificationsPulse automatic controlAsynchronous circuitDelay-locked loop

A semiconductor memory chip with an On-Die Termination (ODT) function is disclosed, which comprises a delay locked loop (DLL) circuit, a synchronous circuit, an asynchronous circuit, a select signal generator, and a selector. The DLL circuit is configured to produce a local clock signal in response to a clock signal when a clock enable (CKE) signal is asserted. The DLL circuit has a predetermined boost time. The select signal generator is configured to assert a select signal in consideration of the predetermined boost time. The selector is configured to select an output of the asynchronous circuit until the select signal is asserted but to select another output of the synchronous circuit after the select signal is asserted.

Owner:LONGITUDE LICENSING LTD

Analog to digital converter using asynchronous pulse technology

A digital to analog converter includes a time encoder that converts an analog input signal into a asynchronous pulse sequence, a pulse asynchronous DeMUX circuit that converts the asynchronous pulse sequence into a parallel stream of pulse sequences at a relatively lower speed, a parallel pulse to asynchronous digital converter, an asynchronous digital to synchronous digital converter, a timing reference circuit to generate absolute time references, and a Digital Signal Processor. This architecture provides for analog to digital conversion based on pulse encoding with a parallel digitization scheme of the pulse encoded signal.

Owner:HRL LAB

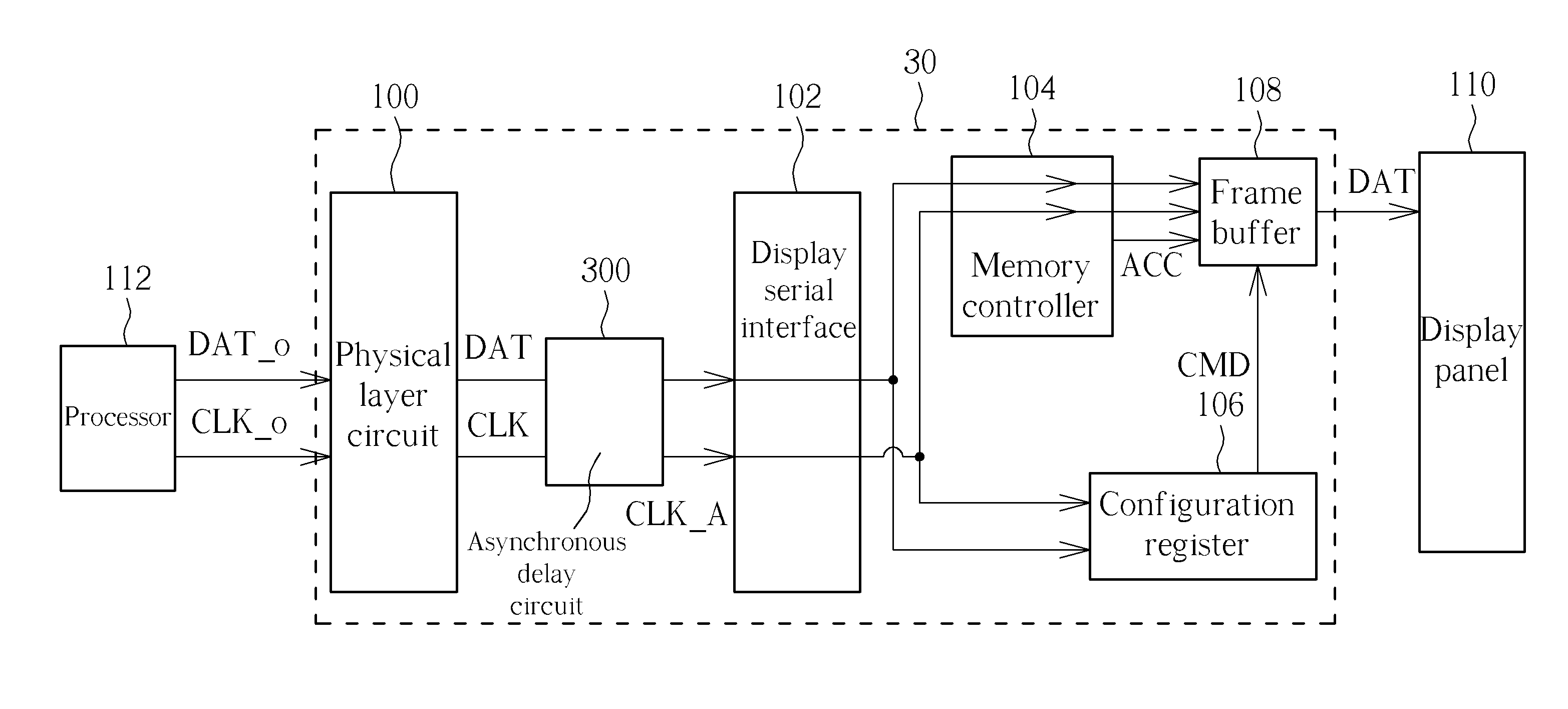

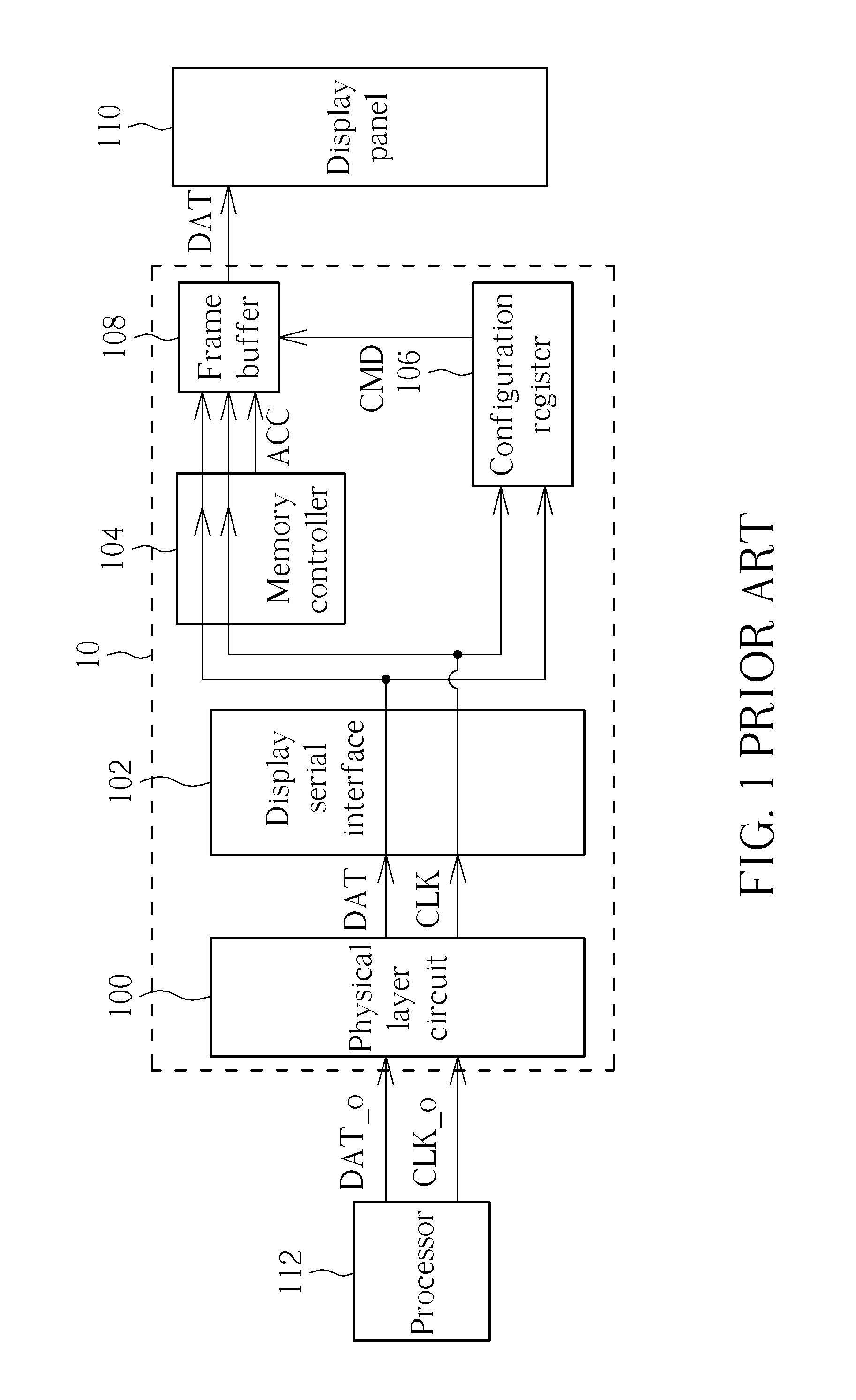

Display Interface Circuit

InactiveUS20120287140A1Static indicating devicesElectric digital data processingAsynchronous circuitProcessor register

A display interface circuit includes a physical layer circuit for receiving and modulating an original data signal and an original clock signal, a frame buffer for storing and outputting the data signal according to the clock signal and a command signal, a display serial interface for transmitting the data signal and the clock signal through packetization, a configuration register for generating the command signal according to an asynchronous clock signal and the data signal, and an asynchronous delay circuit for adjusting a clock latency that the clock signal takes to be sent to the configuration register to generate the asynchronous clock signal.

Owner:NOVATEK MICROELECTRONICS CORP

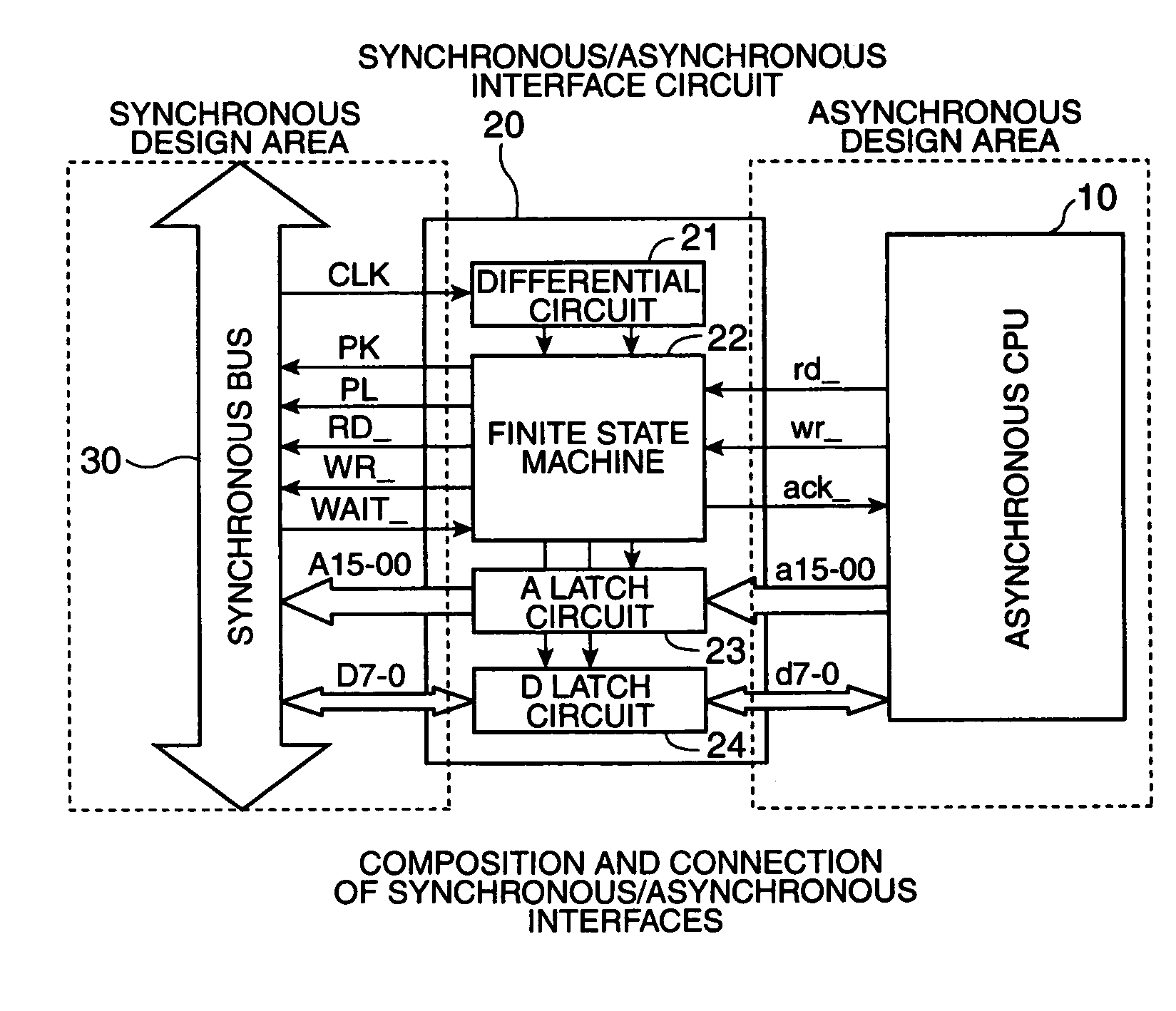

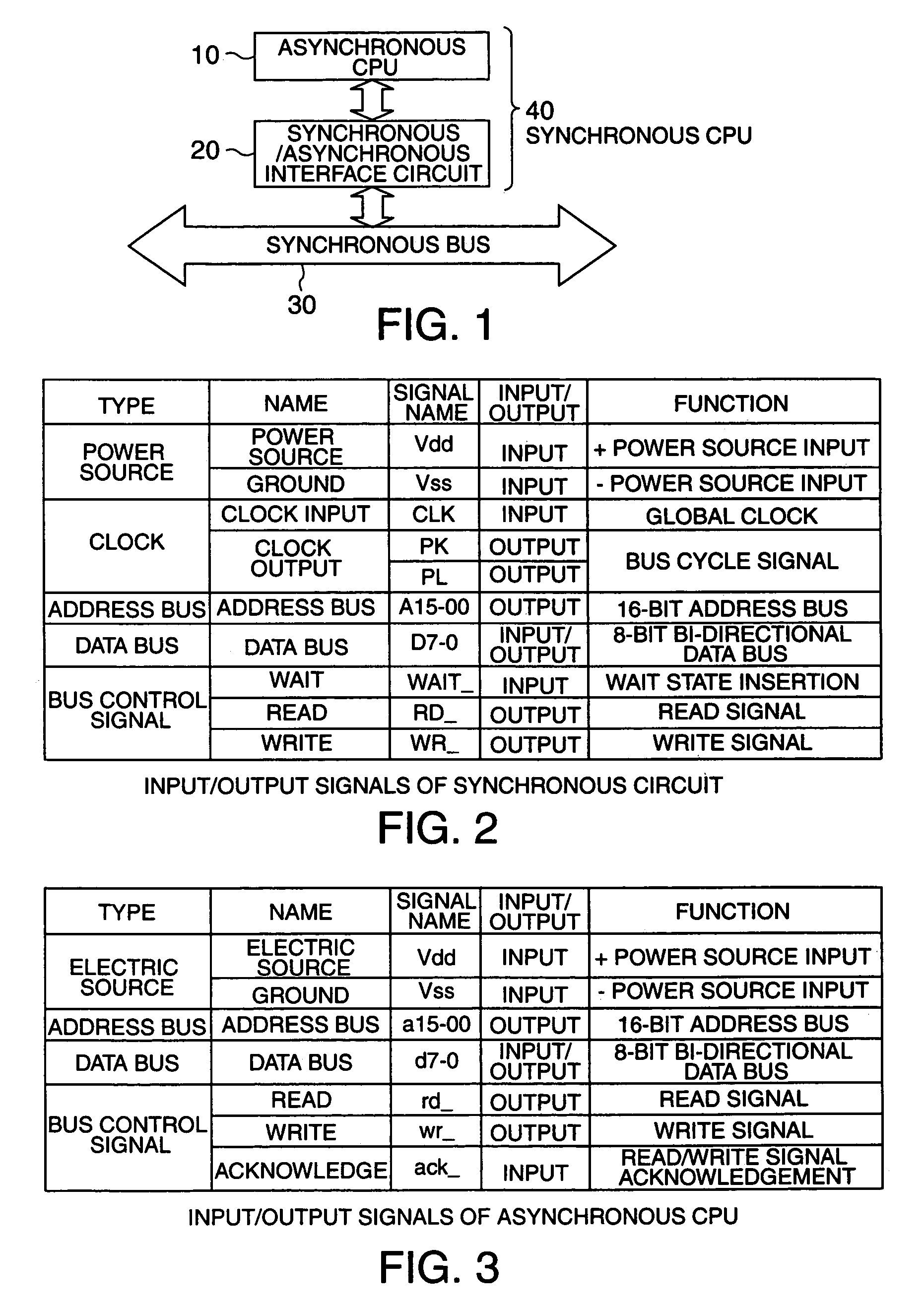

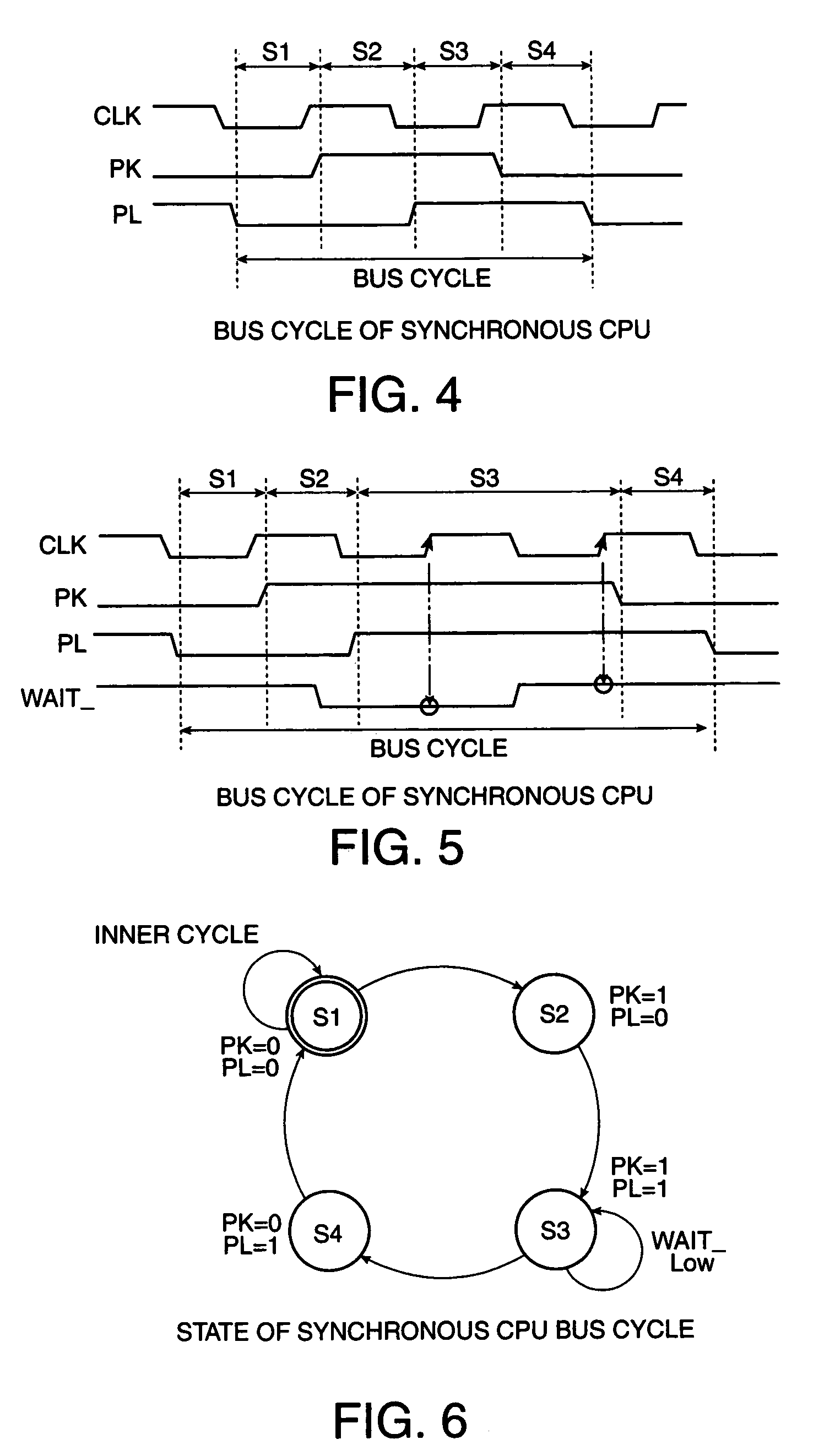

Synchronous/asynchronous interface circuit and electronic device

InactiveUS7395450B2Generating/distributing signalsTransmission path multiple useAsynchronous circuitFinite-state machine

An exemplary embodiment provides a synchronous / asynchronous interface circuit and an electronic device for coupling an asynchronous circuit block onto a globally synchronous circuit system. A synchronous / asynchronous interface circuit according to an exemplary embodiment of the present invention includes a finite state machine that controls access cycles between a synchronous bus and an asynchronous CPU in an event-driven fashion and a detection circuit that detects beginnings of the access cycles. In interfacing with the asynchronous CPU, the finite state machine controls the access cycles by transiting in states handshaking with the asynchronous CPU. Meanwhile, in interfacing with the synchronous bus, the finite state machine controls the access cycle by transiting in states synchronizing with a global clock supplied from the synchronous bus.

Owner:SEIKO EPSON CORP

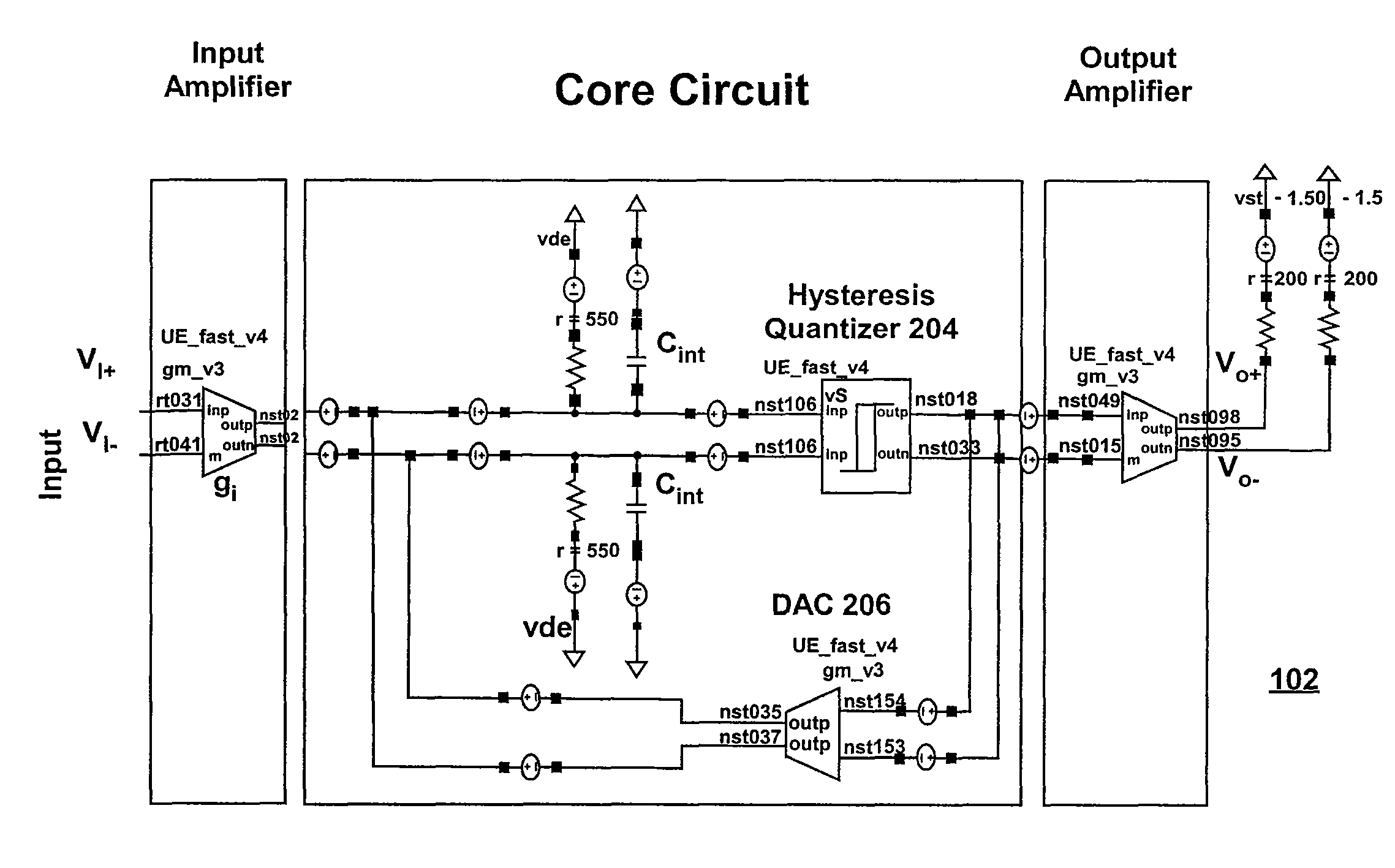

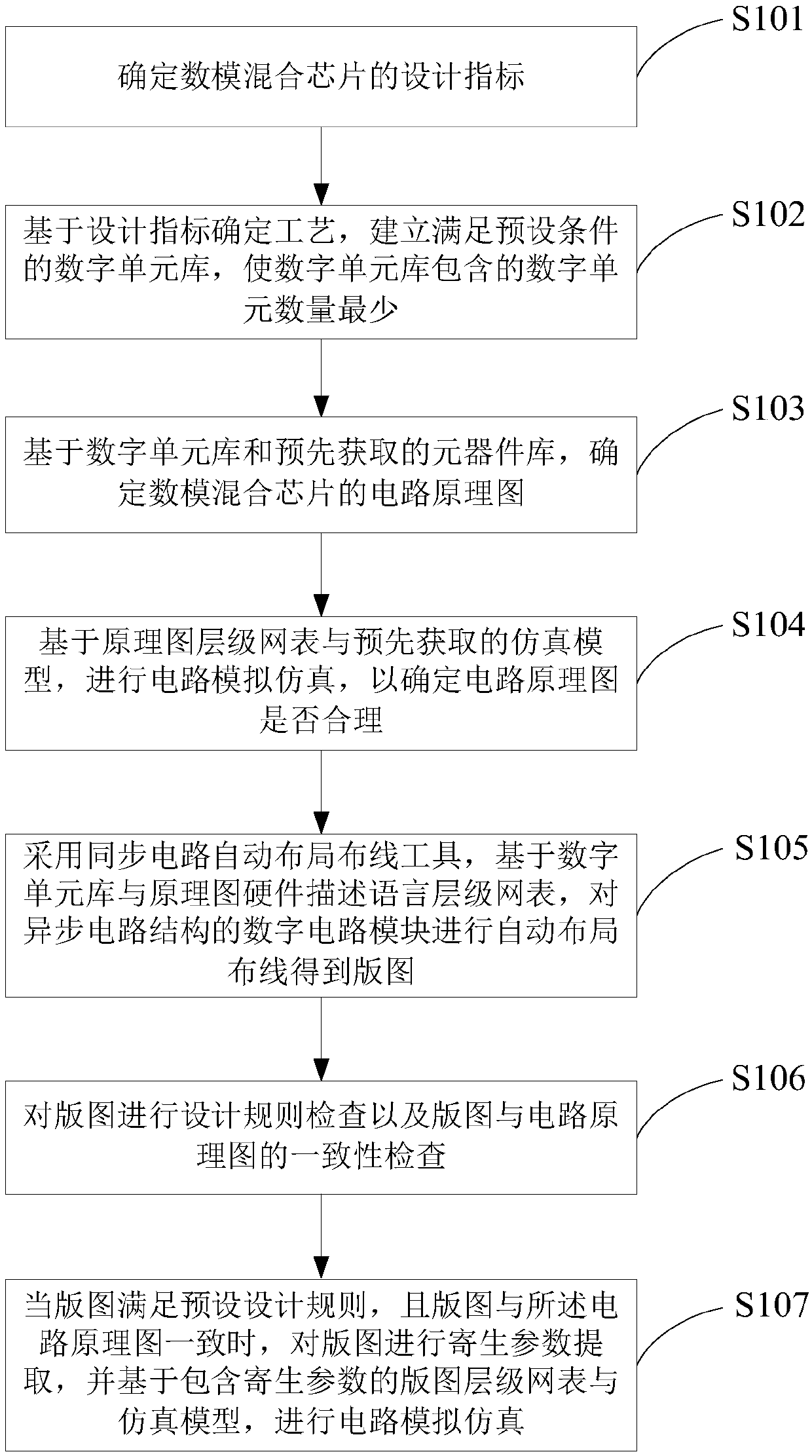

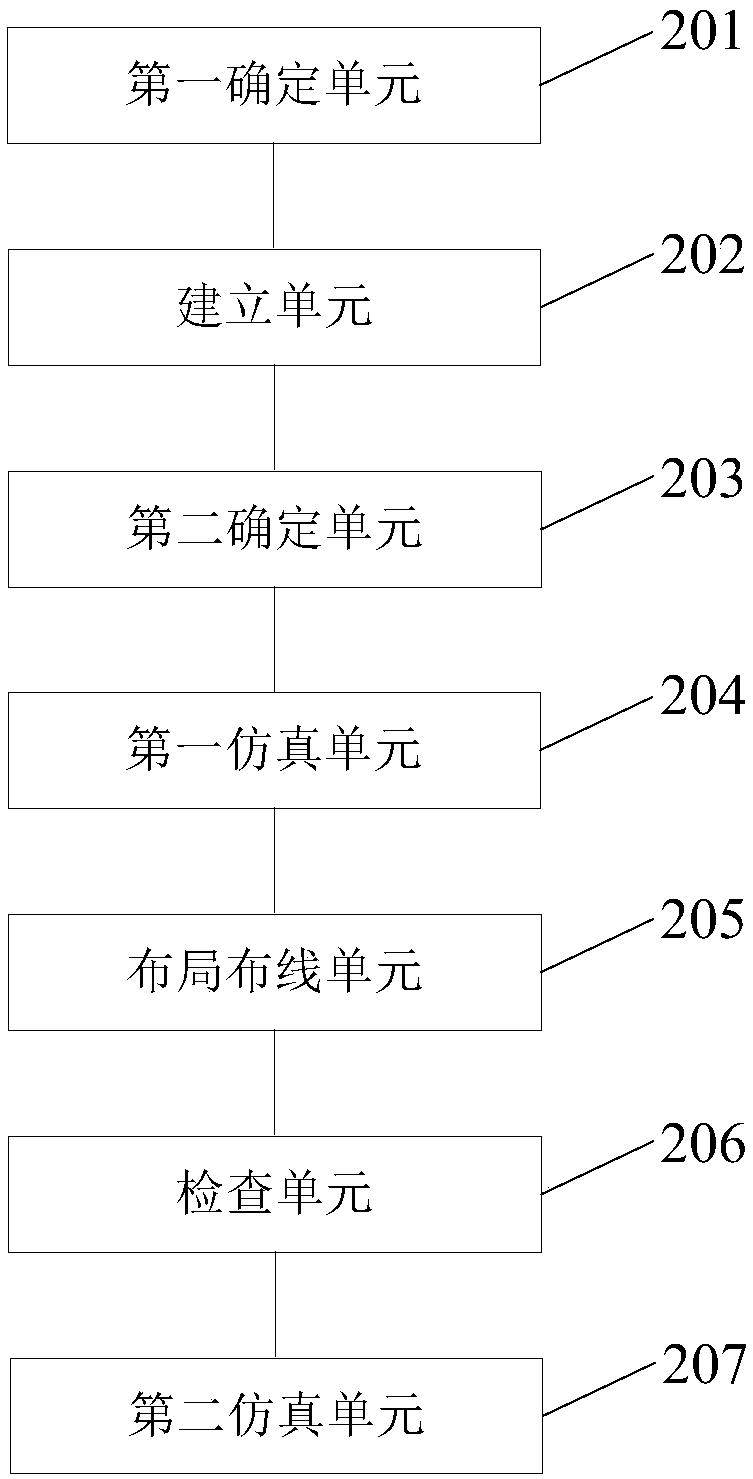

A full customization method and system for a digital-analog hybrid chip asynchronous circuit

ActiveCN109684755AReduce in quantityShorten the design cycleCAD circuit designEnergy efficient computingAsynchronous circuitDesign cycle

The invention discloses a full customization method and system for a digital-analog hybrid chip asynchronous circuit. the method includes: based on a process for determining design indexes based on adigital-analog hybrid chip, establishing a digital unit library meeting a preset condition, wherein the number of the digital units contained in the digital unit library is minimum; designing a circuit schematic diagram of the digital-analog hybrid chip based on a digital unit library and a component library; and performing automatic layout and wiring on the digital circuit module of the asynchronous circuit structure by adopting a synchronous circuit automatic layout and wiring tool to obtain a layout, and performing circuit analog simulation on the layout hierarchical netlist containing parasitic parameters and the simulation model after determining that the layout meets a design rule and the layout is consistent with a circuit schematic diagram. According to the invention, the design cycle and workload of establishing the digital unit library are reduced by establishing the digital unit library with the least number of digital units; Based on a digital cell library, a synchronous circuit automatic layout and wiring tool is adopted to perform automatic layout and wiring on the digital circuit module of the asynchronous circuit structure so as to improve the wiring efficiency.

Owner:佛山中科芯蔚科技有限公司

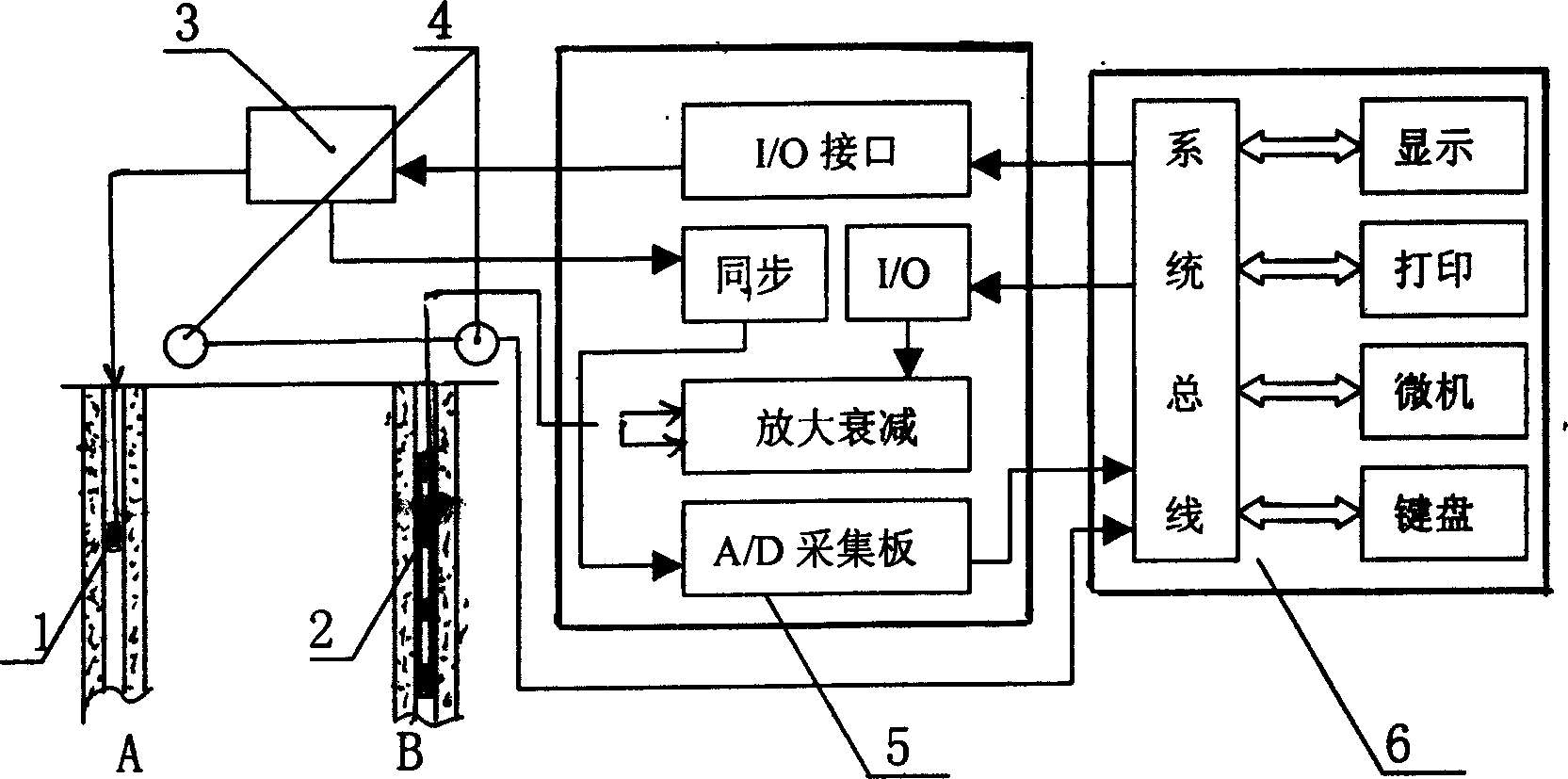

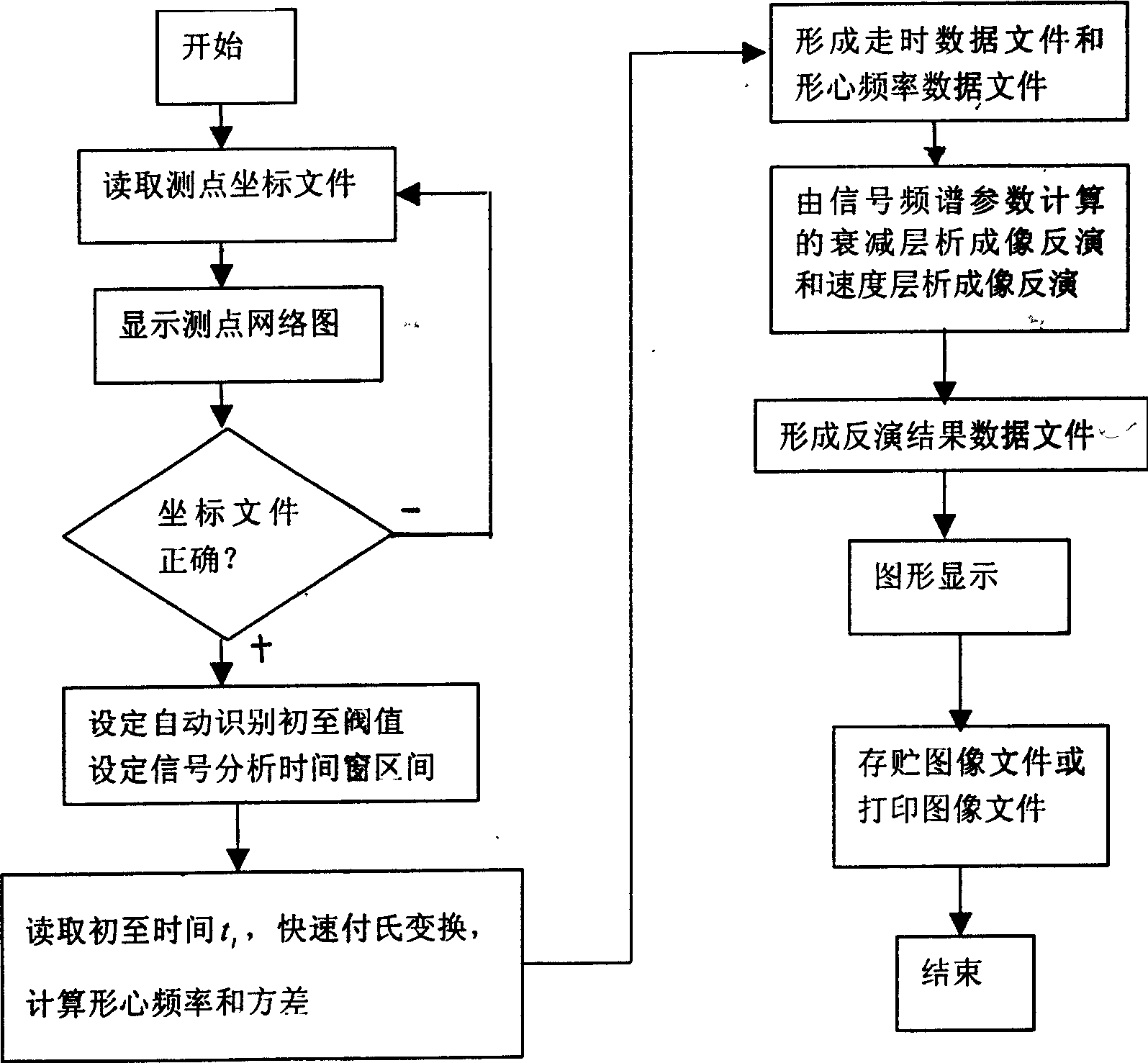

System for testing quality of cast in place concrete pile

InactiveCN1696686AImprove measurement efficiencyImprove quality detection accuracyAnalysing solids using sonic/ultrasonic/infrasonic wavesReflected wavesData acquisition

A quality detection system of concrete pile comprises ultrasonic wave emitting device, data processing unit, ultrasonic wave receiving device, data collector and depth counting coder, The ultrasonic wave receiving device is composed of receiving transverter formed by multiple ultrasonic wave transverters; the data collector is composed of I / O interface circuit, synchronous circuit, amplification - attenuation circuit and multichannel A / D collection plate; the depth counting coder is used to control position of transverter in guide tube for ensuring measurement accuracy.

Owner:SHANDONG UNIV OF SCI & TECH

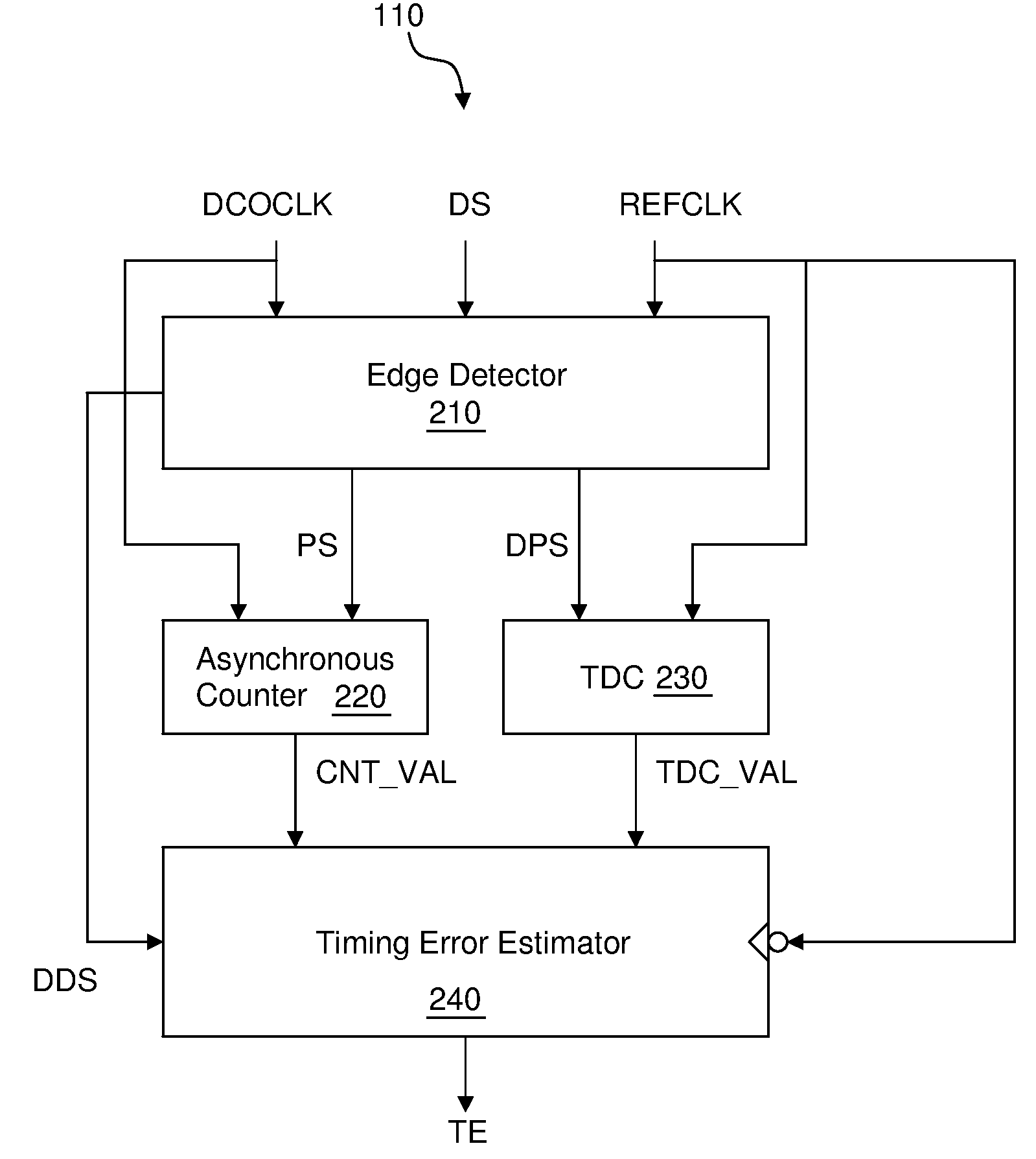

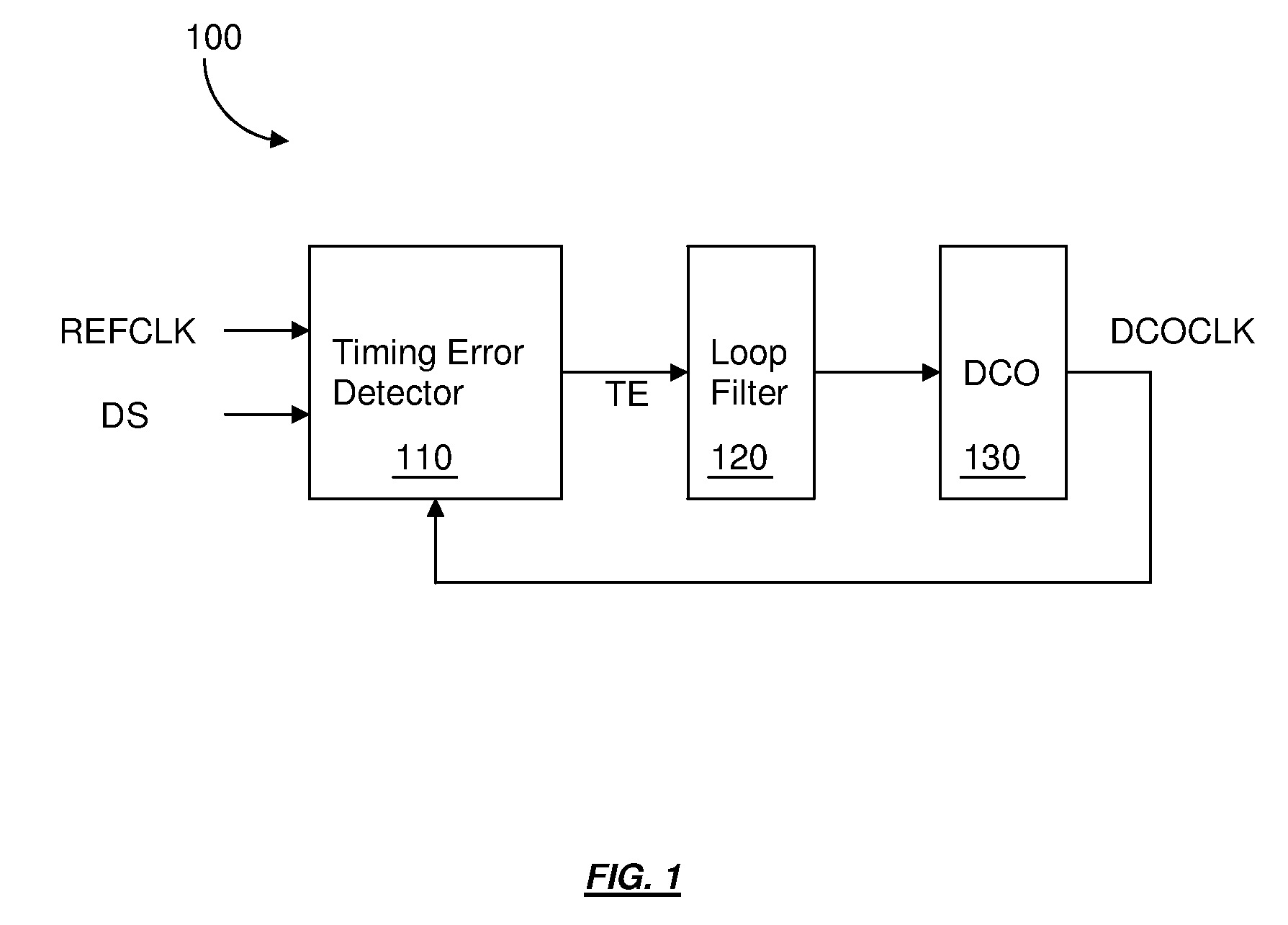

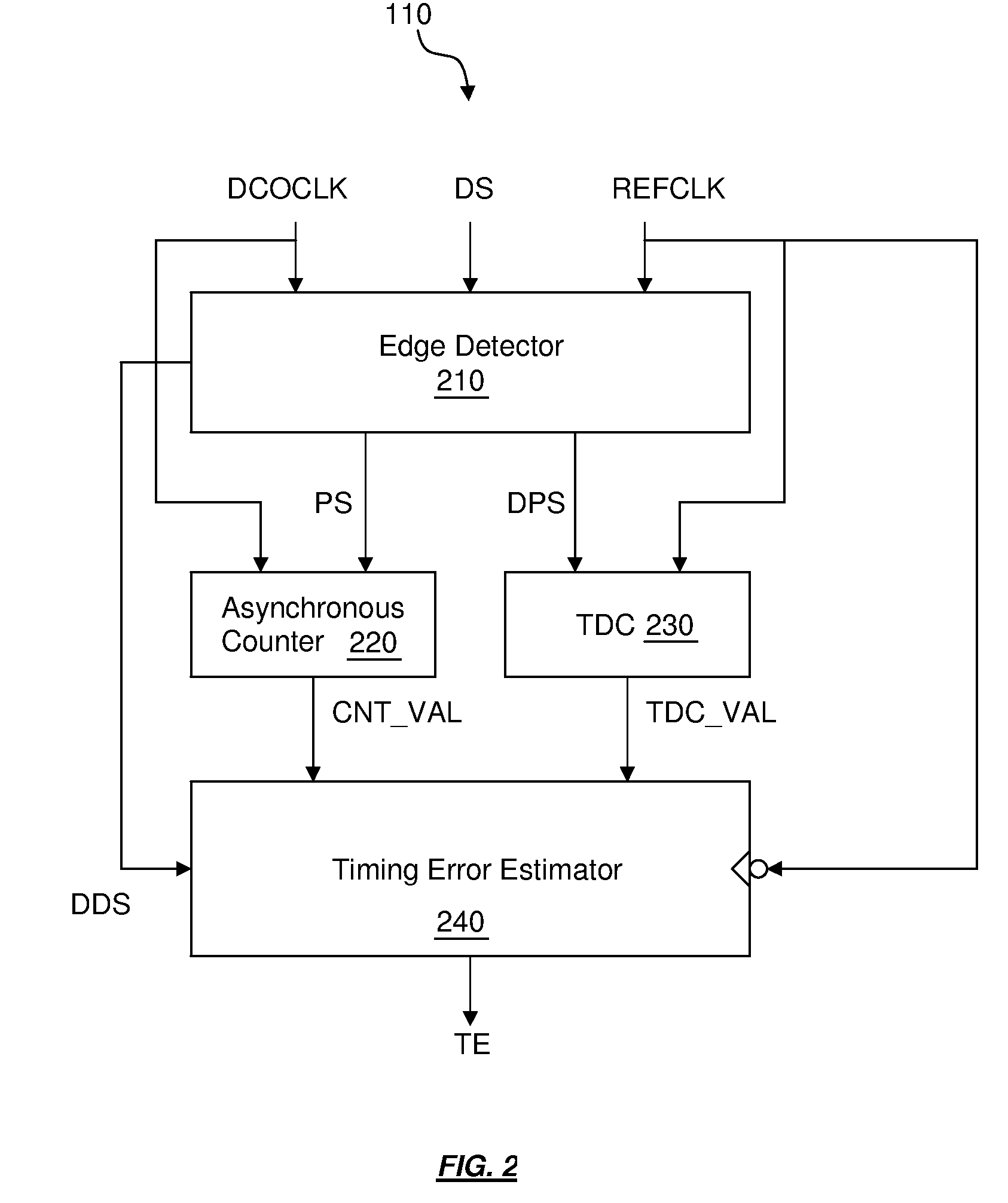

Asynchronous counter based timing error detection

ActiveUS20090307518A1Pulse automatic controlCounting chain asynchronous pulse countersAsynchronous circuitDigital converter

A method for estimating a timing difference between a first clock signal and a second clock signal is disclosed. The estimating method comprising: generating an edge signal by detecting an edge of the second clock signal by sampling the second clock signal using the first clock signal; generating a delayed edge signal by a further sampling of the second clock signal using the first clock signal; generating a first intermediate code by counting a number of clock edges of the first clock signal within a duration defined by the edge signal using an asynchronous counter; generating a second intermediate code to represent a timing difference between the second clock signal and the delayed edge signal using a time-to-digital converter; and generating an output code using a weighted sum of the first intermediate code and the second intermediate code.

Owner:REALTEK SEMICON CORP

Reconfigurable logic fabrics for integrated circuits and systems and methods for configuring reconfigurable logic fabrics

Owner:ACHRONIX SEMICON CORP

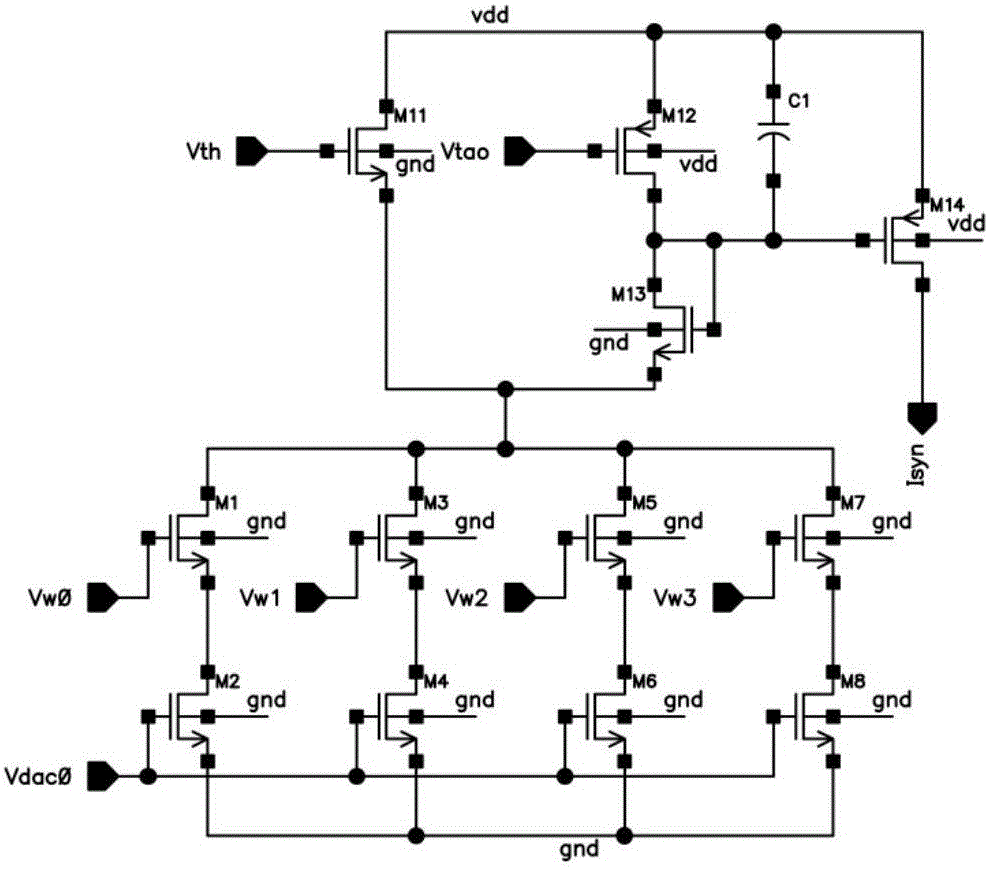

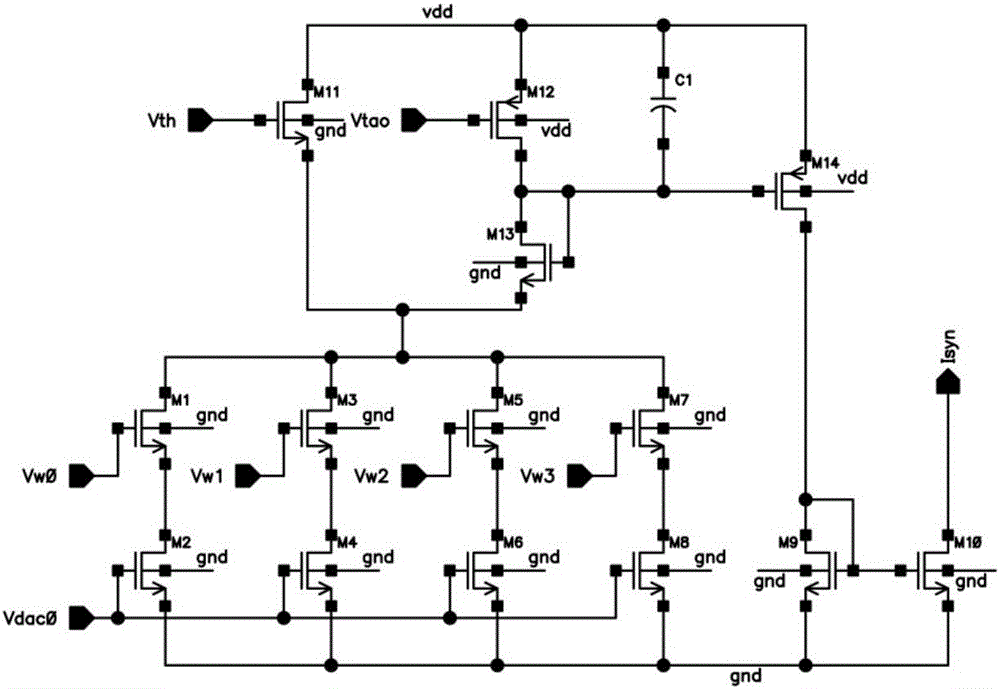

Digital-analog hybrid neural network chip architecture

The invention discloses a digital-analog hybrid neural network chip architecture. The architecture comprises a two-dimensional SRAM module, an analog synaptic circuit, a nerve cell circuit, an AER communication module, and a master control digital unit. The two-dimensional SRAM module is taken as a storage unit of neural network connection relation and a synaptic weight value. The analog synaptic circuit and the nerve cell circuit respectively consist of an MOSFET circuit working in a subthreshold section. The AER communication module serves as the input and output interfaces of a chip, and employs an AER protocol for communication. All control circuits in the architecture are synchronous digital circuits. The architecture is low in power consumption, is high in degree of parallelism, and can achieve a neural network algorithm in a reasonable chip area, wherein the neural network algorithm is more complex in nerve cell functions, is larger in network scale, and is more flexible in connection.

Owner:ZHEJIANG UNIV

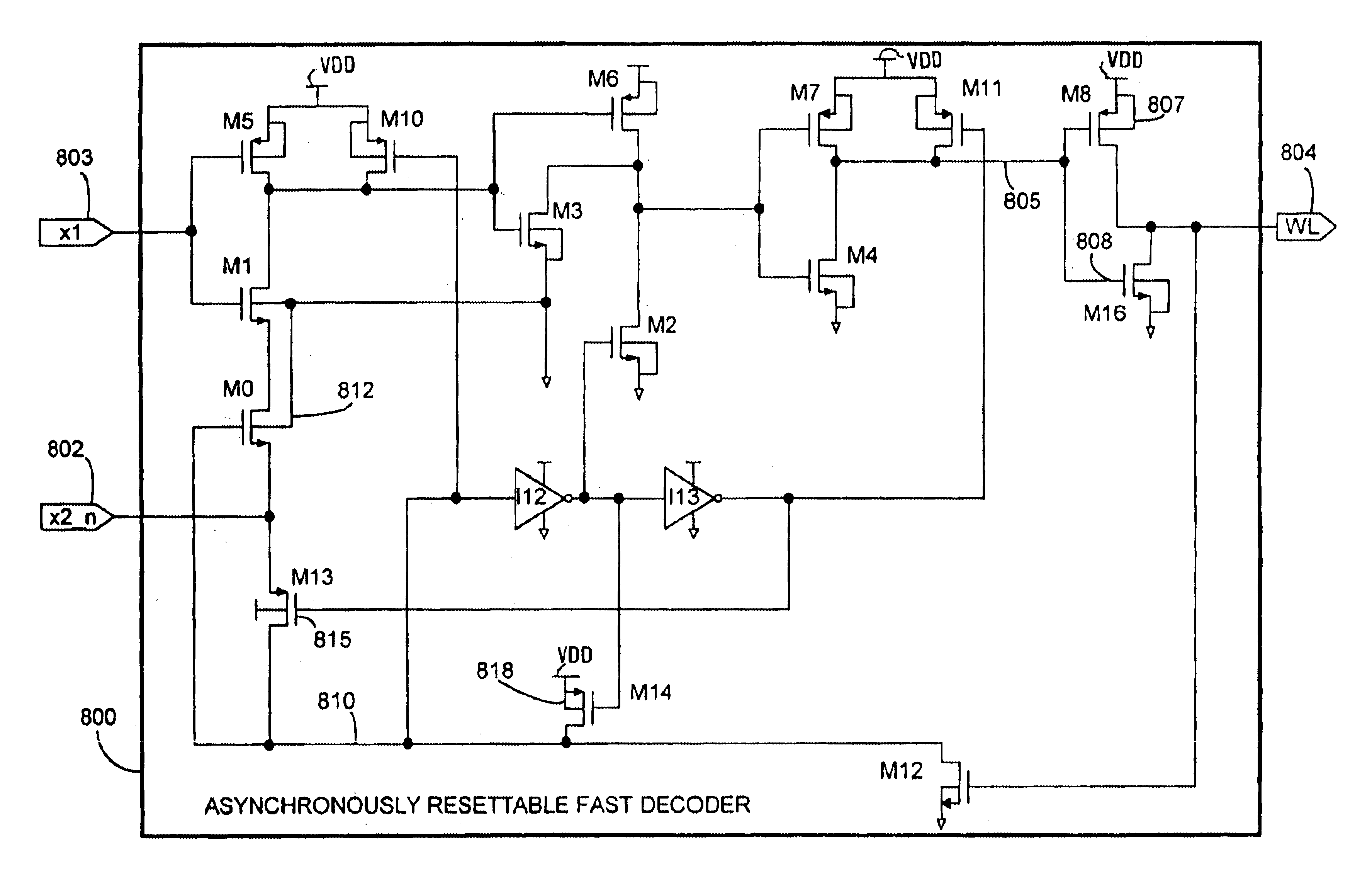

Asynchronously-resettable decoder with redundancy

Owner:AVAGO TECH INT SALES PTE LTD

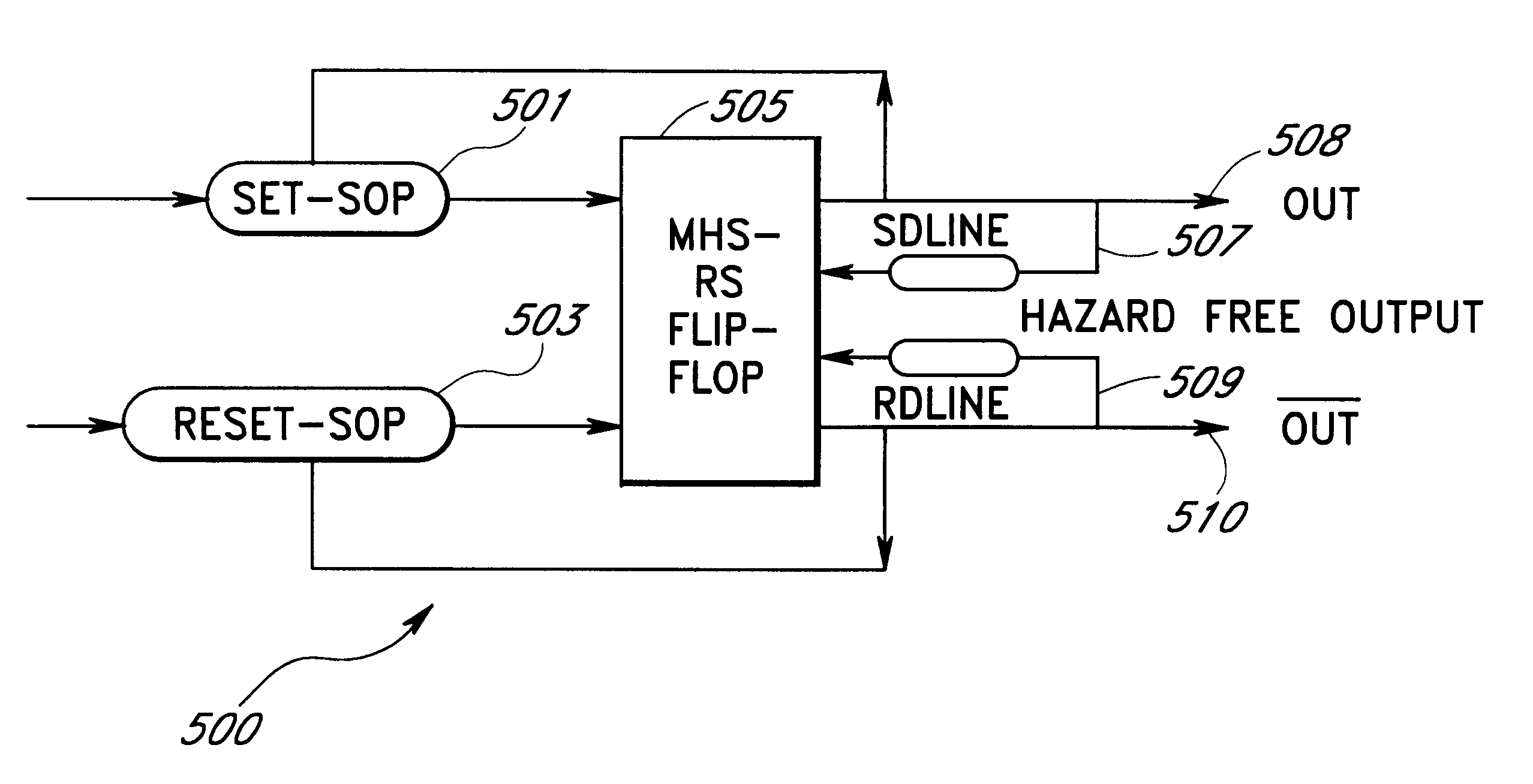

System and method for generating a hazard-free asynchronous circuit

InactiveUS6226774B1Digital data processing detailsCAD circuit designGeneral purposeAsynchronous circuit

A flip-flop-based circuit architecture generates a hazard-free asynchronous signal given the SET and RESET sum-of-product (SOP) solutions to an asynchronous process. The flip-flop SET and RESET SOP solutions can be hazardous. Thus, general purpose synchronous optimization tools (which are indifferent to hazards) can be used to derive the optimal SOP solutions. A fixed layer built around the SOP cores eliminates all hazards in the circuit. In one embodiment, the architecture is optimized by eliminating an RS latch and delay lines in the SOP cores. The architecture of the present invention is guaranteed to admit any semi-modular race-free state graph representation of an asynchronous process that satisfies the n-shot requirement. The state graph representations can be examined to determine if alternate, solution-specific, simplified architectures can be employed that further decrease the final area by the elimination of flip-flops or the elimination of a timing delay.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Clock generation for synchronous circuits with slow settling control signals

ActiveUS20080059829A1Reduce power consumptionDigital storageGenerating/distributing signalsAsynchronous circuitControl signal

A circuit includes a clock generator for providing a clock signal to a synchronously operated digital circuit and a control signal generator for providing a control signal to the synchronously operated digital circuit. The control signal generator is interconnected to the clock generator to suppress the clock signal for a defined duration as a control signal is provided. The defined duration allows the control signal to settle to allow said synchronously operated digital circuit to unambiguously sample said control signal. The control signal generator may place the synchronous digital circuit in a lower power consumption state.

Owner:ATI TECH INC

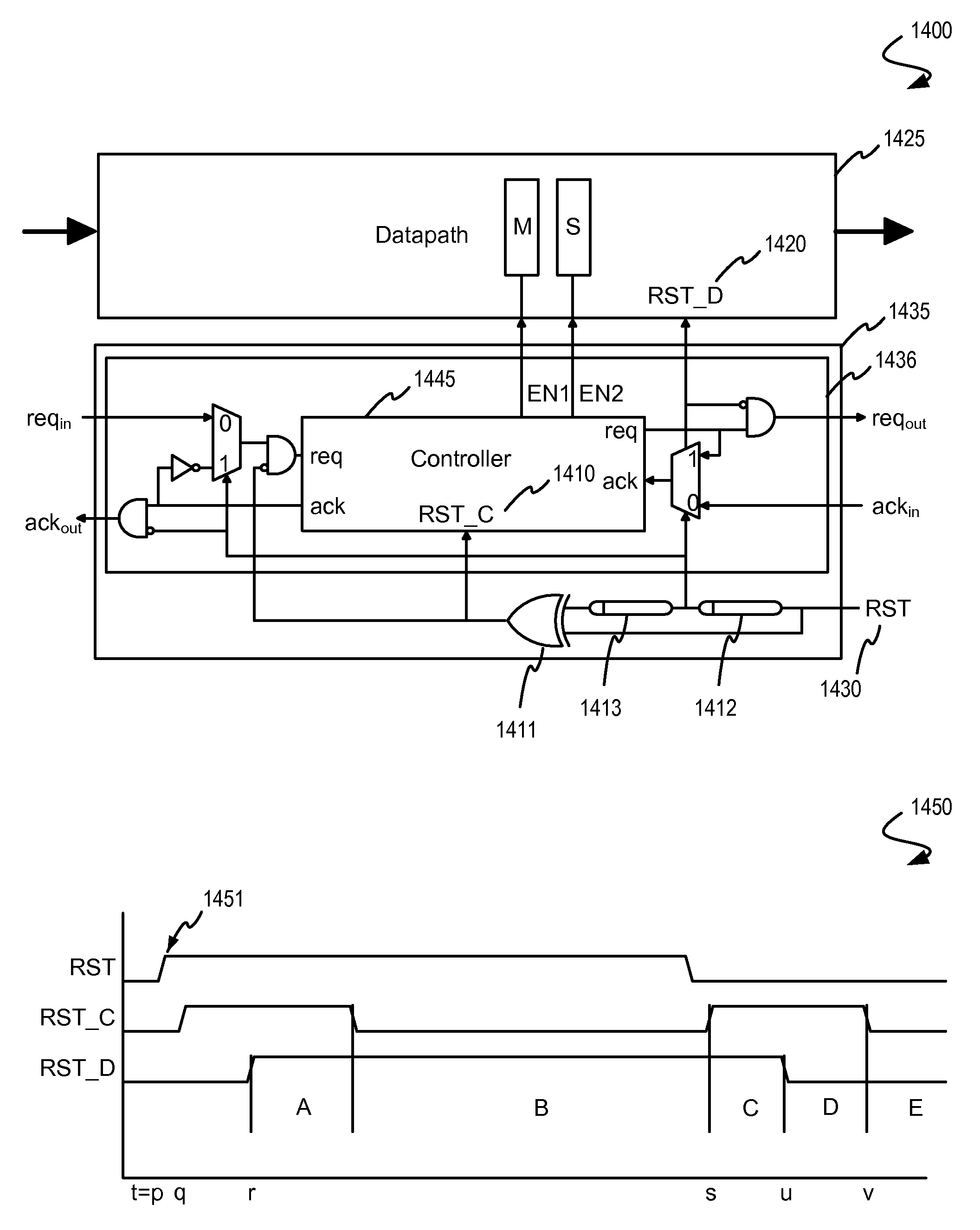

Variability-aware scheme for asynchronous circuit initialization

InactiveUS7701255B2Logic circuits characterised by logic functionPulse automatic controlAsynchronous circuitMathematical model

Owner:INPHI +1

Multi-rail asynchronous flow with completion detection and system and method for designing the same

InactiveUS20020188912A1Digital data processing detailsCAD circuit designAsynchronous circuitEngineering

A method for designing a multi-rail asynchronous circuit is provided. The method includes providing a circuit having n circuit paths, defining a plurality of nodes, each node having an n-rail signal output and at least one n-rail signal input, each rail of the n-rail signal input being connected to a different one of the plurality of circuit paths, and adding completeness detection to each of the plurality of nodes, completion detection for a downstream one of the plurality of nodes being at least partially based on completion detection from an upstream one of the plurality of nodes. Signals propagate along the plurality of data paths independent of the completeness detection.

Owner:WAVE COMPUTING INC

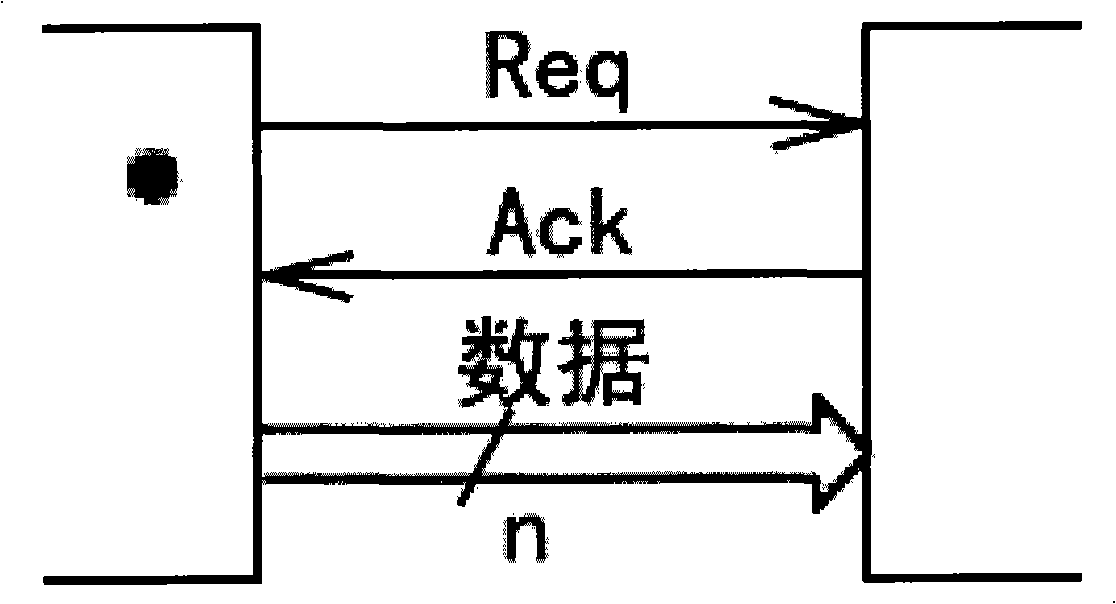

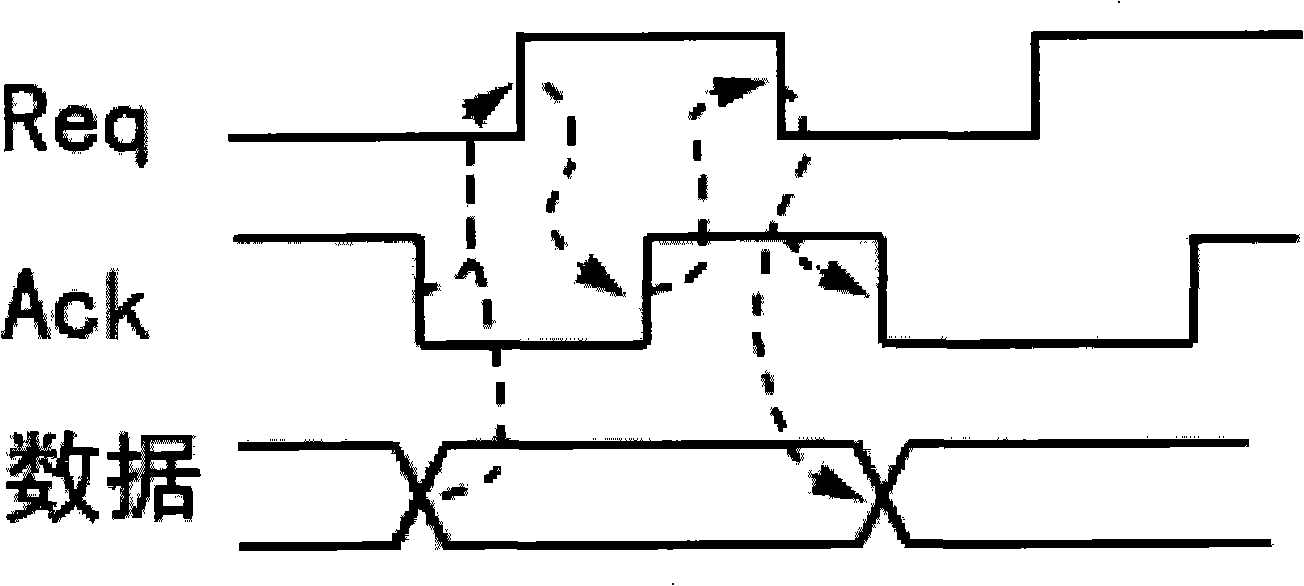

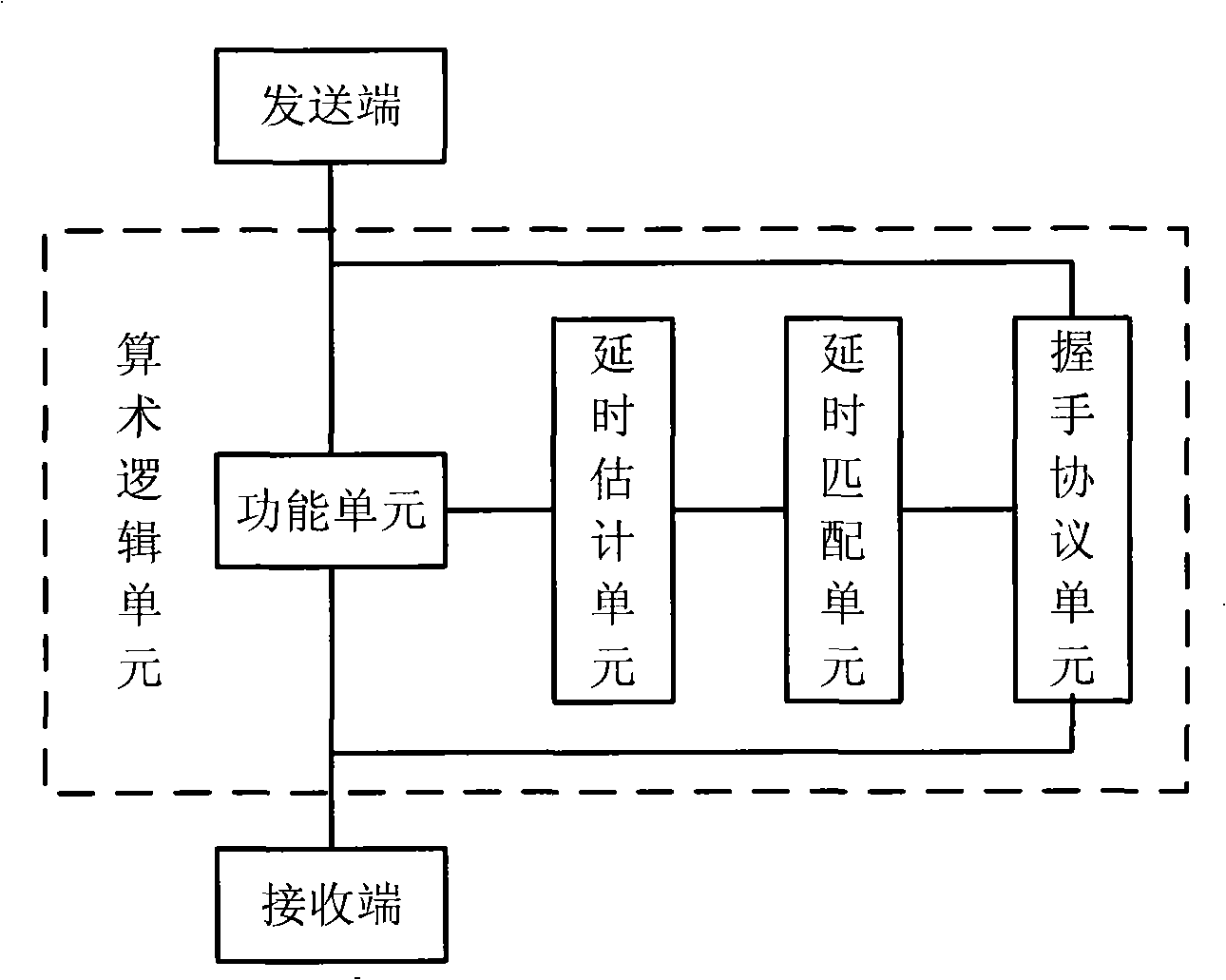

Arithmetic logic unit using asynchronous circuit to implement

InactiveCN101303643AAvoid performance lossImprove performanceProgram controlMemory systemsArithmetic logic unitAsynchronous circuit

The invention relates to an arithmetic logic unit which is realized by adopting an asynchronous circuit. The arithmetic logic unit includes a functional unit which receives the calculation control command and input data of a transmitting end and implements the arithmetic logic calculation of the input data; a timelag evaluation unit which carries out timelag evaluation according to the type of the calculation control command and the detail input data received by the functional unit; a timelag matching unit which selects a calculation timelag matched with the functional unit; a handshake protocol unit which controls the transmitting end to generate a request signal simultaneously when the transmitting end transmits the input data to lead the input to be synchronous. The handshake protocol unit informs a receiving end to take out the output data of the functional unit after the calculation timelag and controls the receiving end to generate a reply signal to lead the output to be synchronous. The arithmetic logic unit of the invention has the characteristic of high property, overcomes the property loss of a synchronous circuit which can only realize the timelag of the worst situation; has the characteristic of low power consumption and saves the circuit area.

Owner:RESEARCH INSTITUTE OF TSINGHUA UNIVERSITY IN SHENZHEN

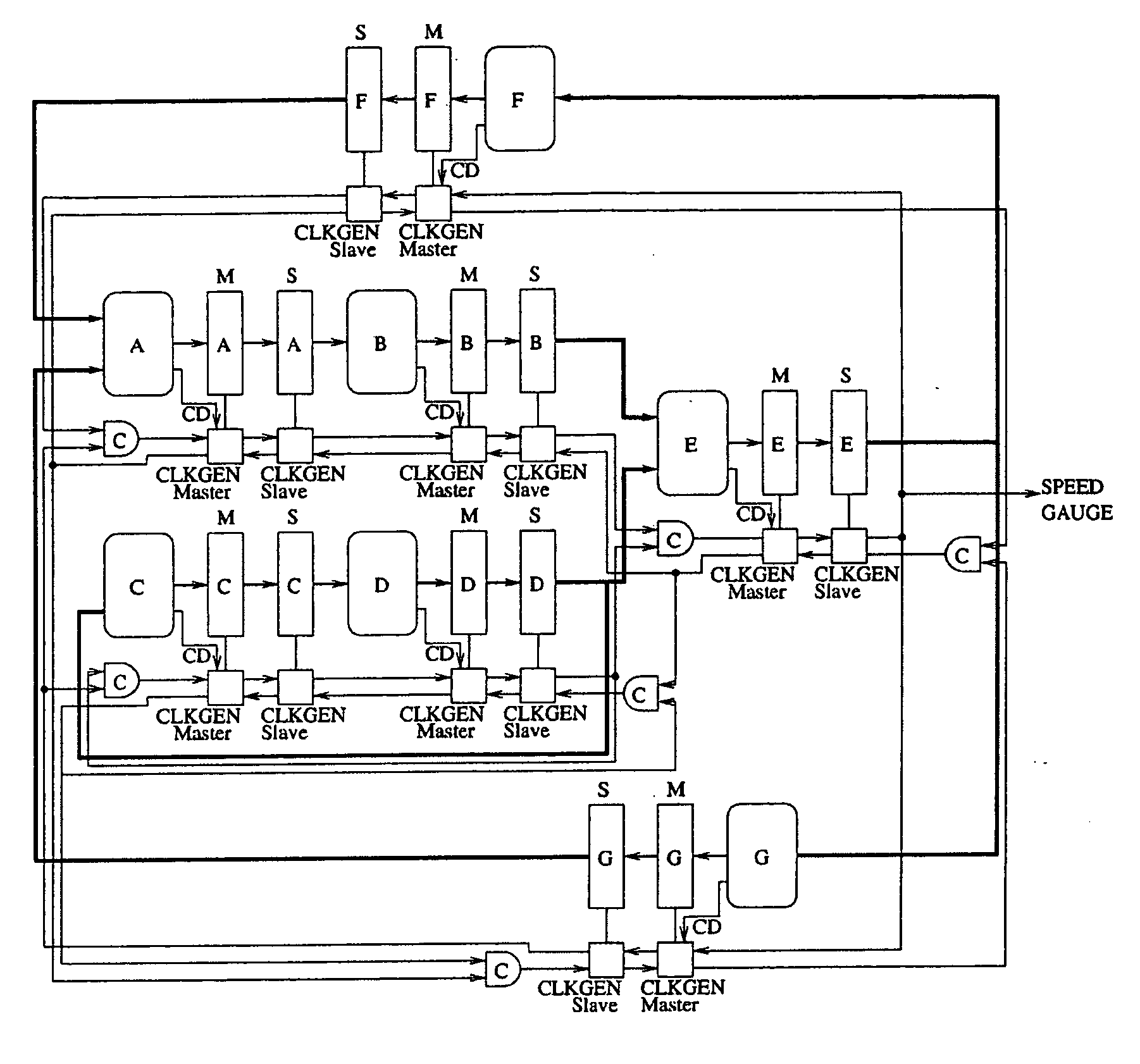

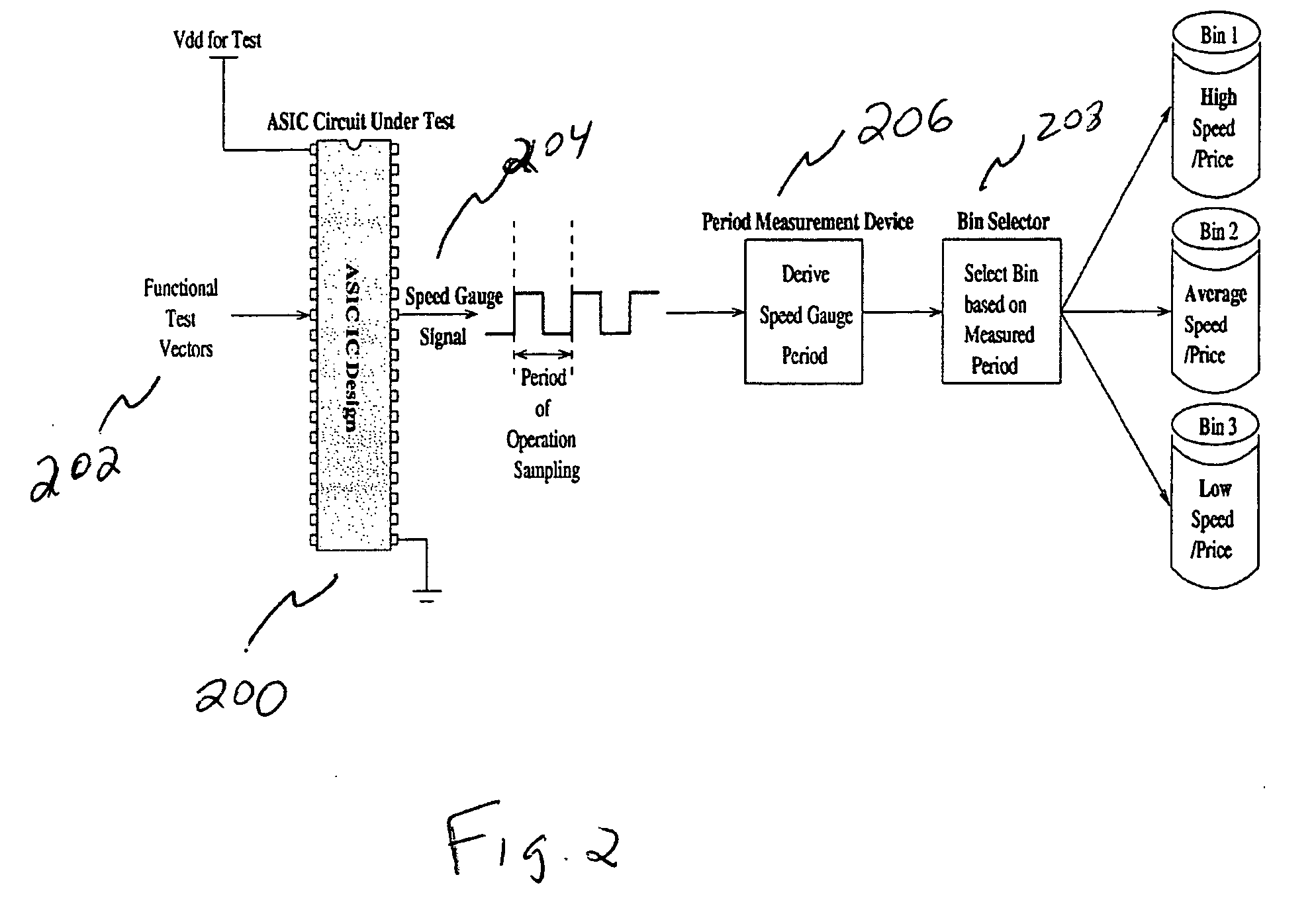

System and method of determining the speed of digital application specific integrated circuits

InactiveUS20060156050A1Good delaySignificant processing timeElectrical testingStructural/machines measurementAsynchronous circuitEngineering

According to one embodiment of the present invention, a system for identifying a running speed of an integrated circuit is provided. An asynchronous multi-rail circuit is configured to receive input data and transmit output data. A completion detection circuit is configured to generate a completion detection signal for the asynchronous multi-rail circuit. A variable clock generator configured to be driven by at least the completion detection signal. A synchronous circuit element configured to receive at least a portion of the output data and configured to be clock driven by a clock signal from the variable clock generator. A period of the clock signal represents a running speed of the asynchronous circuit.

Owner:INST OF COMP SCI FOUND FOR RES TECH - HELLAS ICS

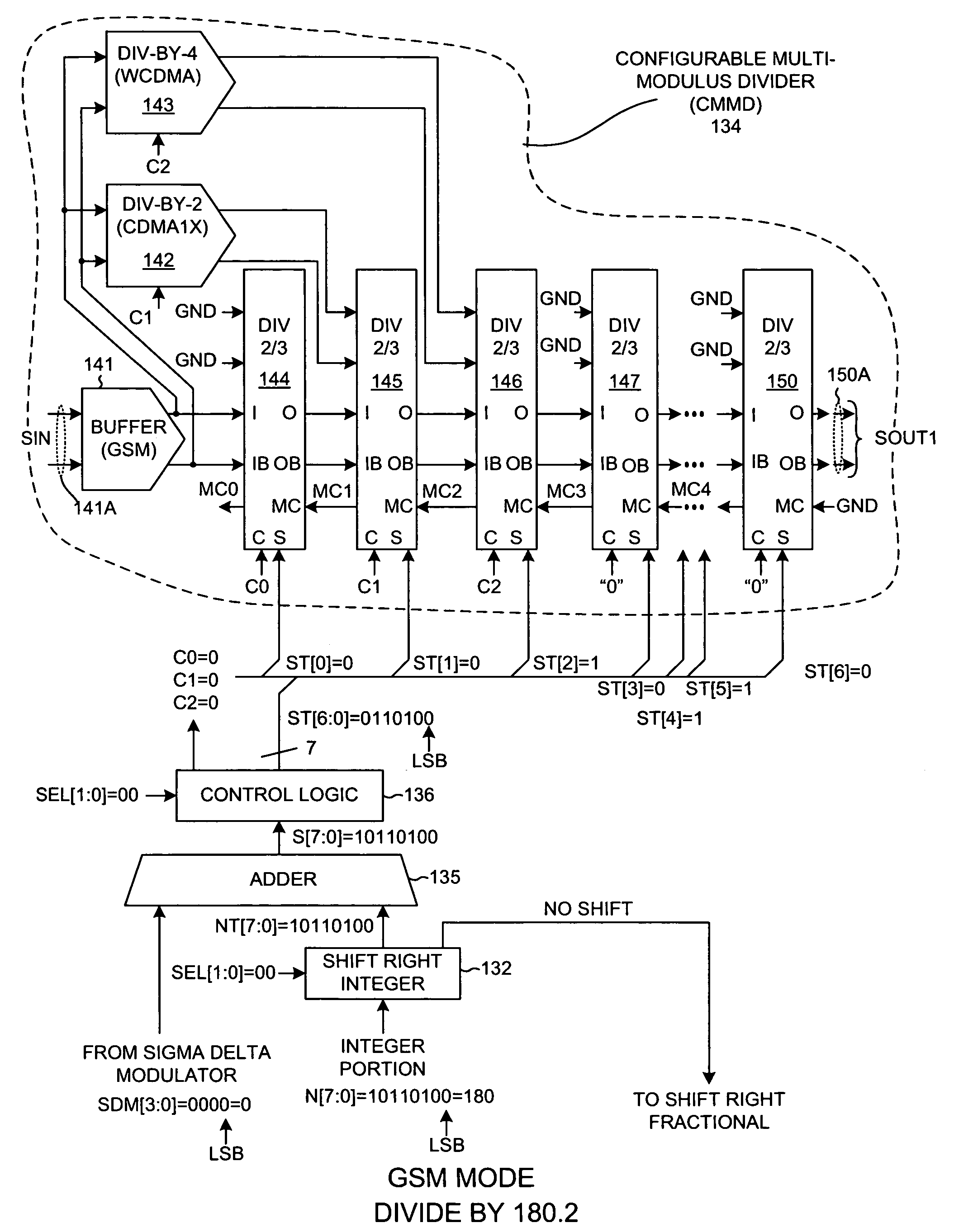

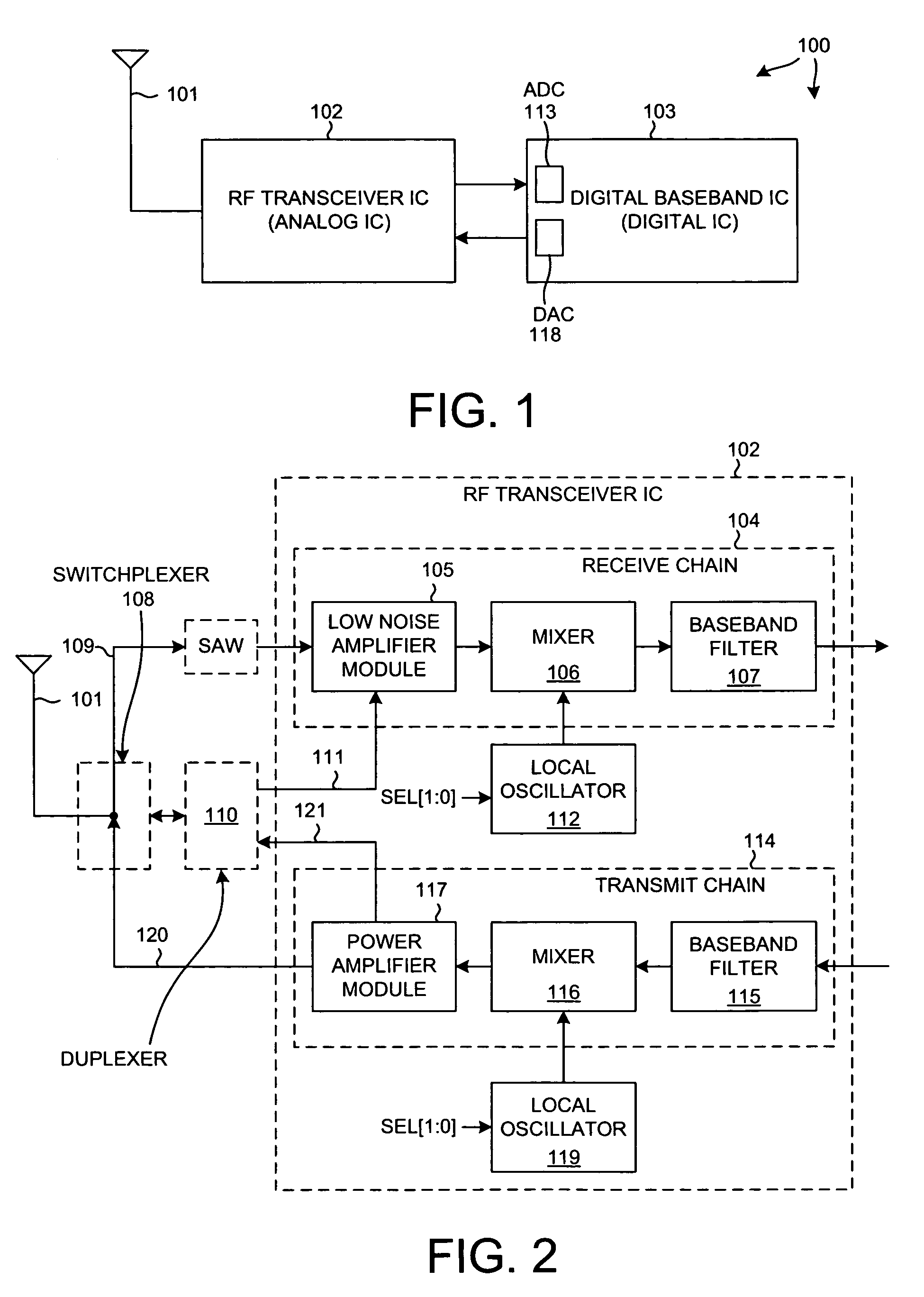

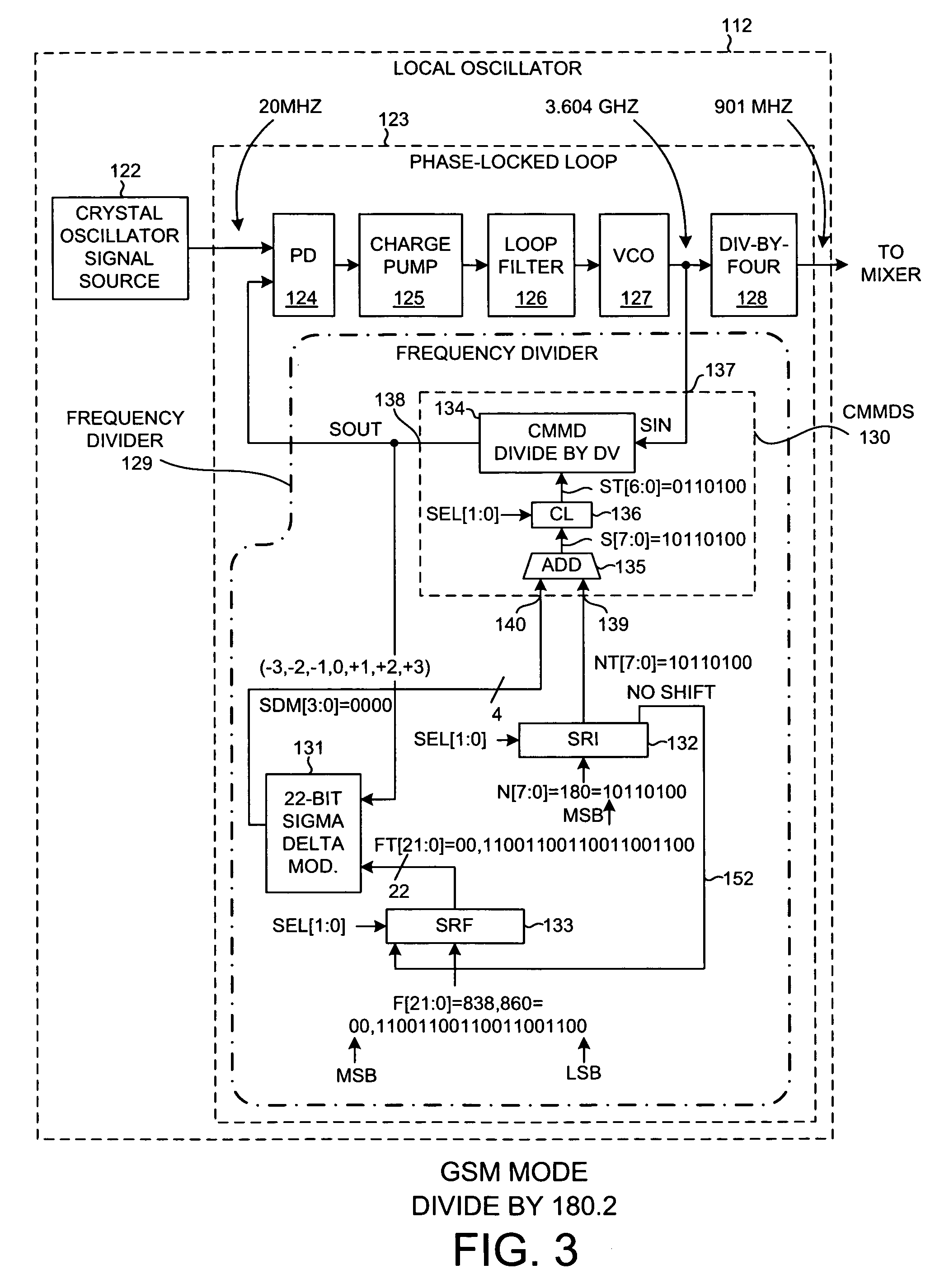

Configurable multi-modulus frequency divider for multi-mode mobile communication devices

ActiveUS7379522B2Reduce noiseConsume some amount of powerEnergy efficient ICTPulse automatic controlAsynchronous circuitLocal oscillator

Within a mobile communication device (for example, a cellular telephone), there is a local oscillator. The local oscillator includes a novel frequency divider that includes a novel configurable multi-modulus divider (CMMD). The frequency divider is configurable into a selectable one of multiple configurations involving different mixes of synchronous and asynchronous circuitry. In each configuration, the frequency divider produces an amount of noise and consumes an amount of power. Power consumption is loosely inversely related to noise produced in that the modes with the highest power consumption produce the least amount of noise, and vice versa. The mobile communication device is operable in one of multiple different communication standards (for example, GSM, CDMA1X and WCDMA). The different communication standards impose different noise requirements on the frequency divider. By using the lowest power configuration that satisfies the noise requirements of the standard being used, power consumption of the cellular telephone is reduced.

Owner:QUALCOMM INC

Semiconductor memory chip with on-die termination function

ActiveUS7688671B2Reliability increasing modificationsPulse automatic controlAsynchronous circuitDelay-locked loop

A semiconductor memory chip with an On-Die Termination (ODT) function is disclosed, which comprises a delay locked loop (DLL) circuit, a synchronous circuit, an asynchronous circuit, a select signal generator, and a selector. The DLL circuit is configured to produce a local clock signal in response to a clock signal when a clock enable (CKE) signal is asserted. The DLL circuit has a predetermined boost time. The select signal generator is configured to assert a select signal in consideration of the predetermined boost time. The selector is configured to select an output of the asynchronous circuit until the select signal is asserted but to select another output of the synchronous circuit after the select signal is asserted.

Owner:LONGITUDE LICENSING LTD