A full customization method and system for a digital-analog hybrid chip asynchronous circuit

A digital-analog hybrid and asynchronous circuit technology, applied in the electronic field, can solve the problems of small quantity, high authorization fee, design cost, trial and error cost, error correction cost, and expensive test cost, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

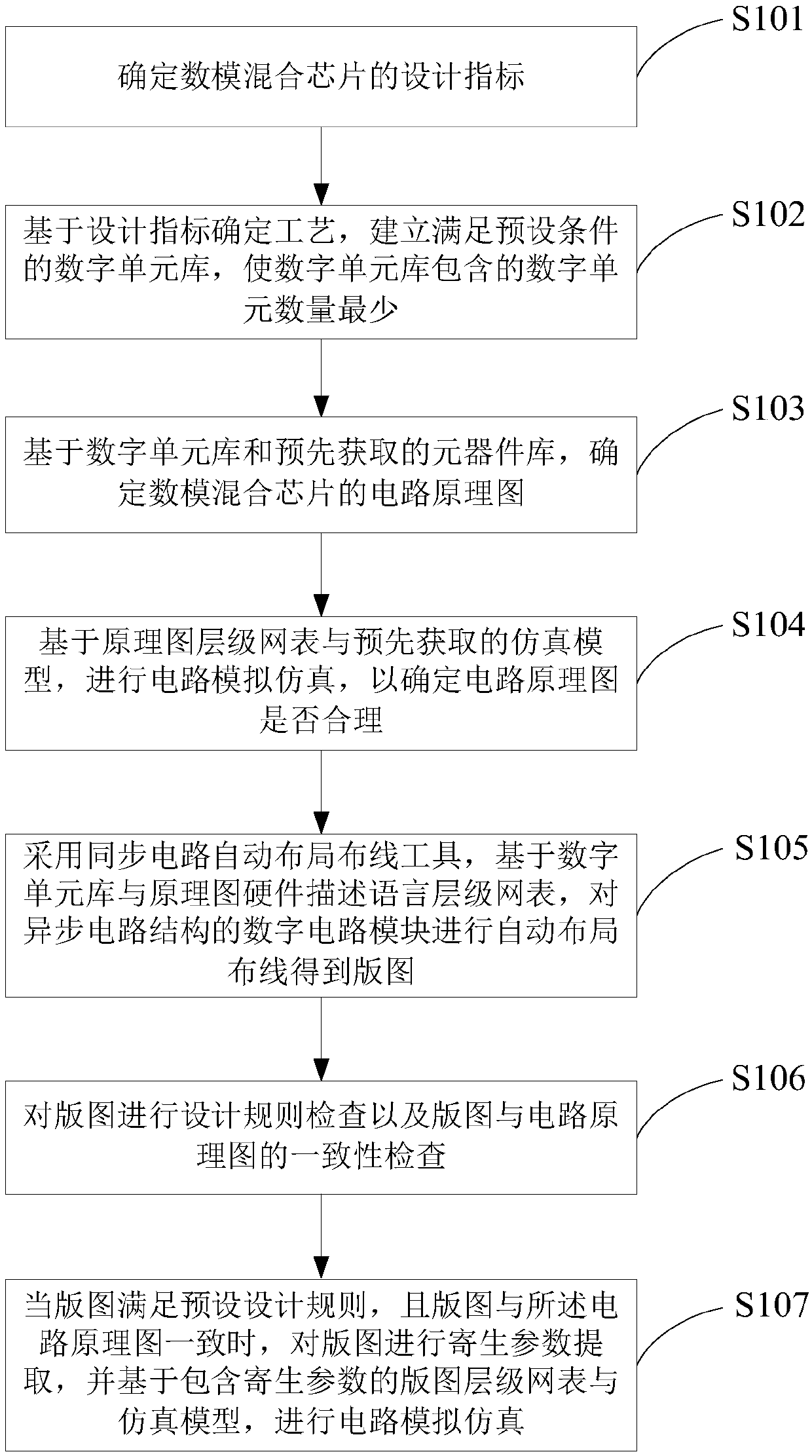

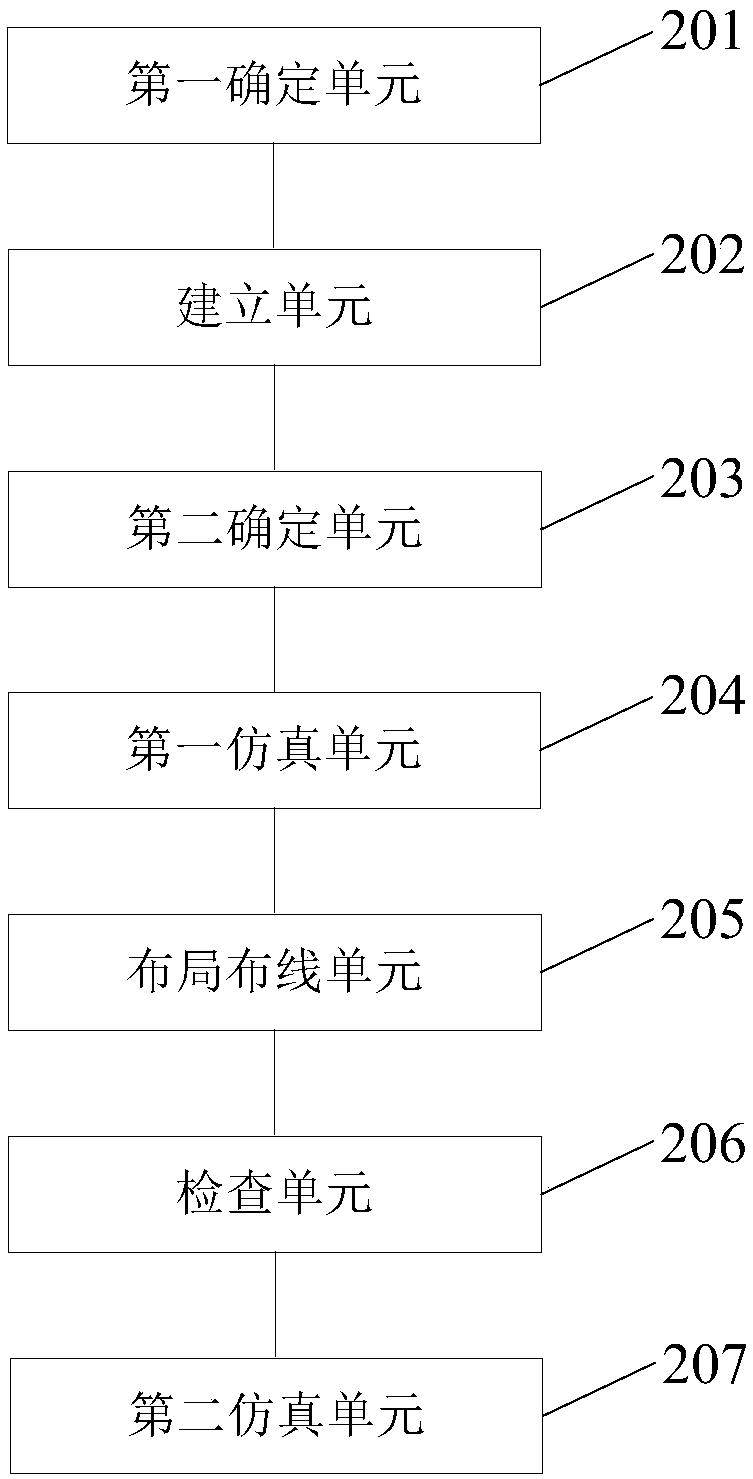

Method used

Image

Examples

Embodiment Construction

[0077] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0078] It should be noted that the semi-custom design method in this application is a design method relative to the full-custom design method. For the convenience of understanding, some concepts involved in this application are explained as follows:

[0079] Synchronous circuit: The clock input terminals of all flip-flops are connected to the same clock pulse source, so the state changes of all flip-flops are synchronized with the input clock pulse signal.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More