Patents

Literature

12990results about How to "Improve portability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Vacuum assisted wound dressing

ActiveUS8715256B2Small and lightImprove portabilityPlastersAdhesive dressingsTopical Negative-Pressure TherapyVacuum assisted

Owner:SMITH & NEPHEW PLC

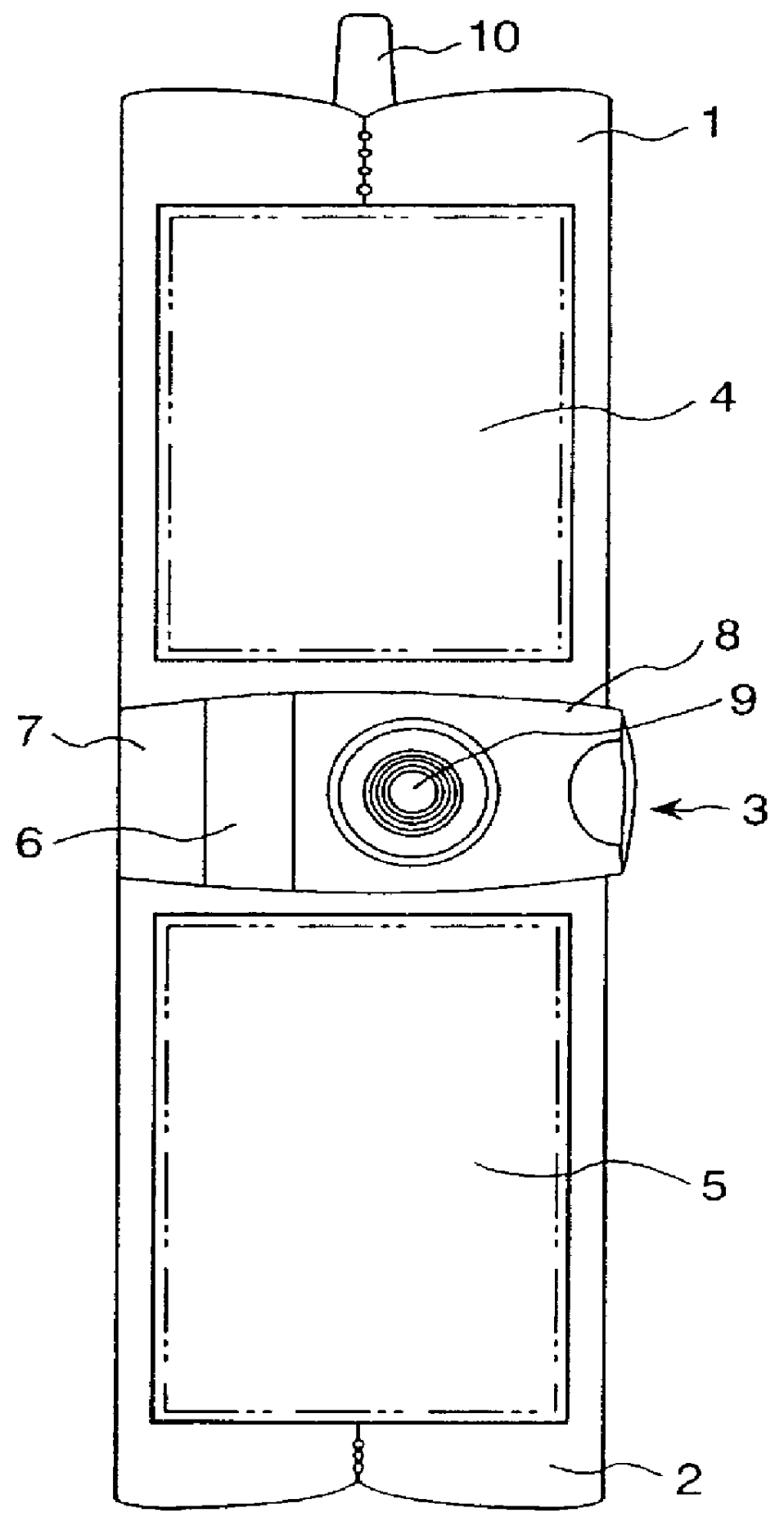

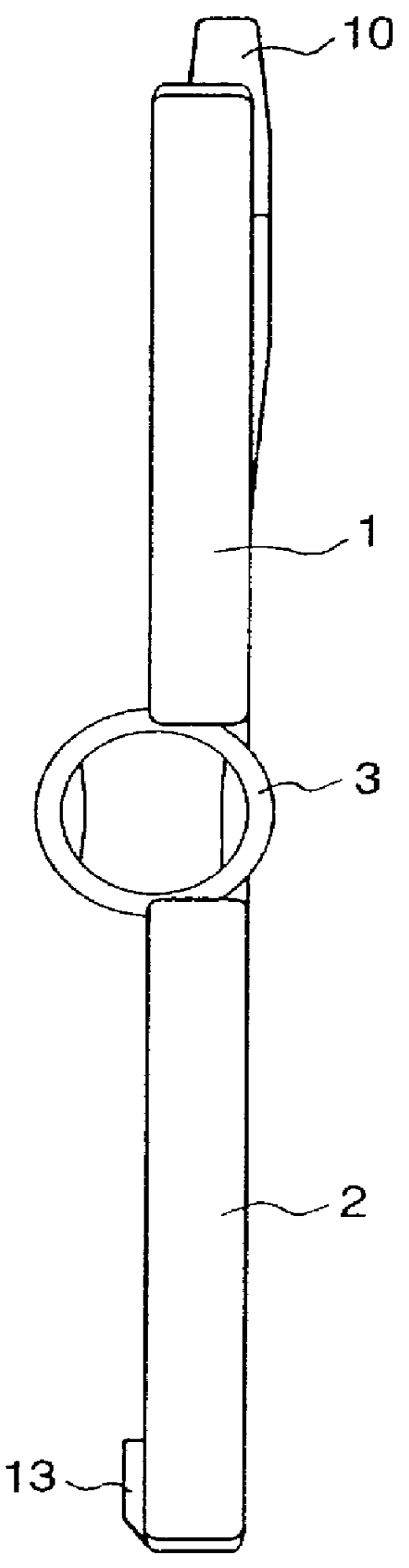

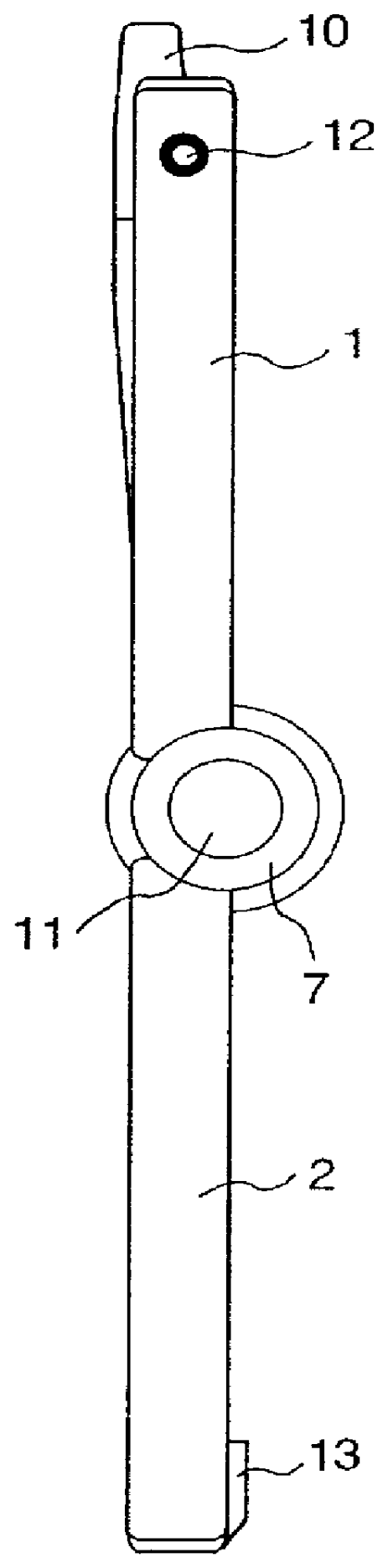

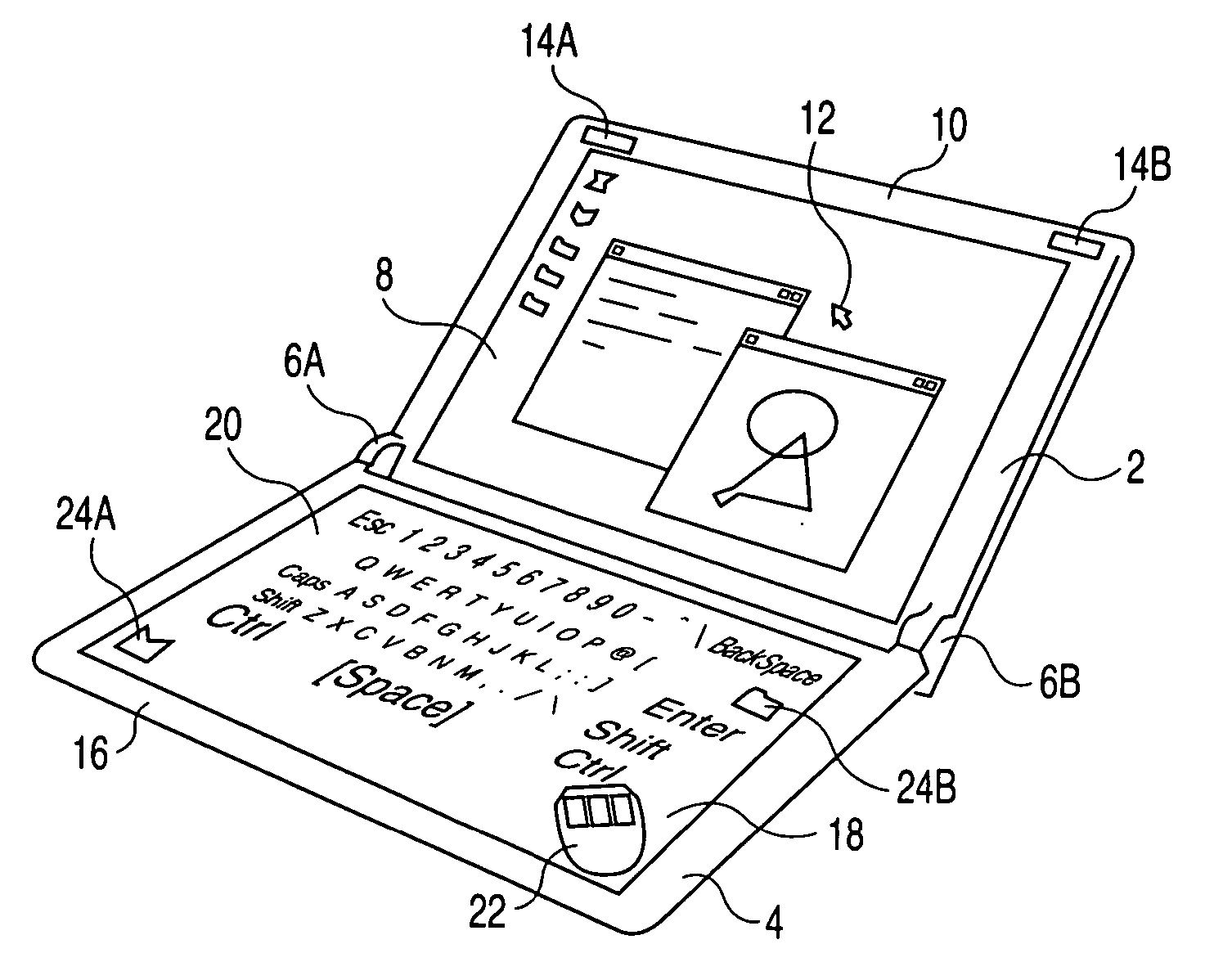

Information communication terminal device

InactiveUS6069648AImprove portabilitySolve the real problemCordless telephonesTelevision system detailsCamera lensCamera image

An upper case and a lower case are rotatably connected in a connection part. The connection part is constructed by a rotary shaft supporting part integrated in the lower case, a rotary shaft which is integrated in the upper case and a part of which is rotatably fit into the rotary shaft supporting part, and a housing member having a part rotatably fit into the rotary shaft supporting part. A video camera and a camera lens are housed in the housing member. A display / operation part is provided almost in the whole upper case and a display / operation part is provided almost in the whole lower case. In the display / operation parts and, in addition to camera images of the video camera, a reception image, and various data, touch-type operation buttons are displayed. The display / operation parts and have the functions as the operation part as well as the display part. "Recording" mode, "transmission / reception" mode, and "information acquisition" mode can be selectively set and the device can be used according to the mode.

Owner:MAXELL HLDG LTD

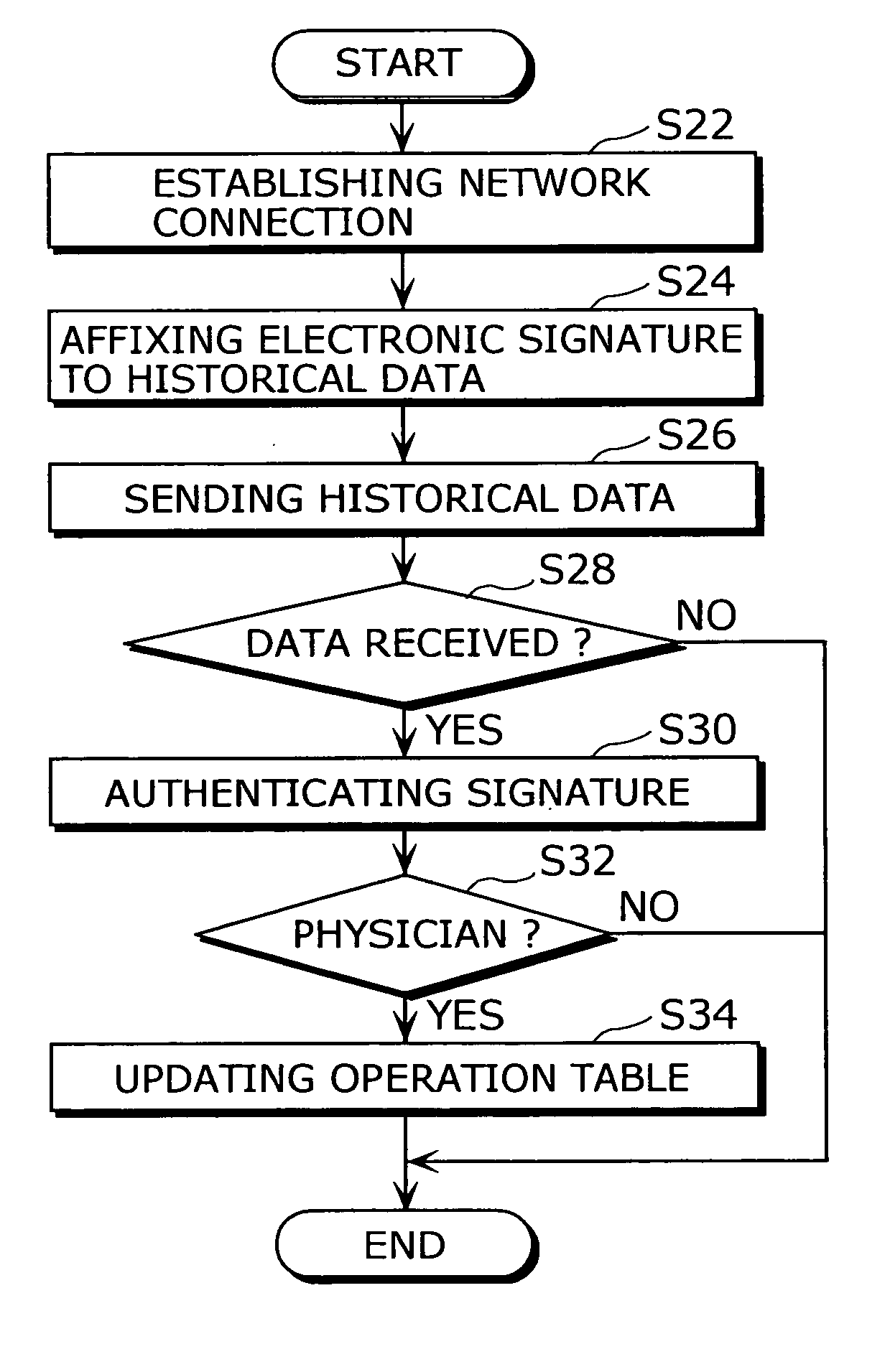

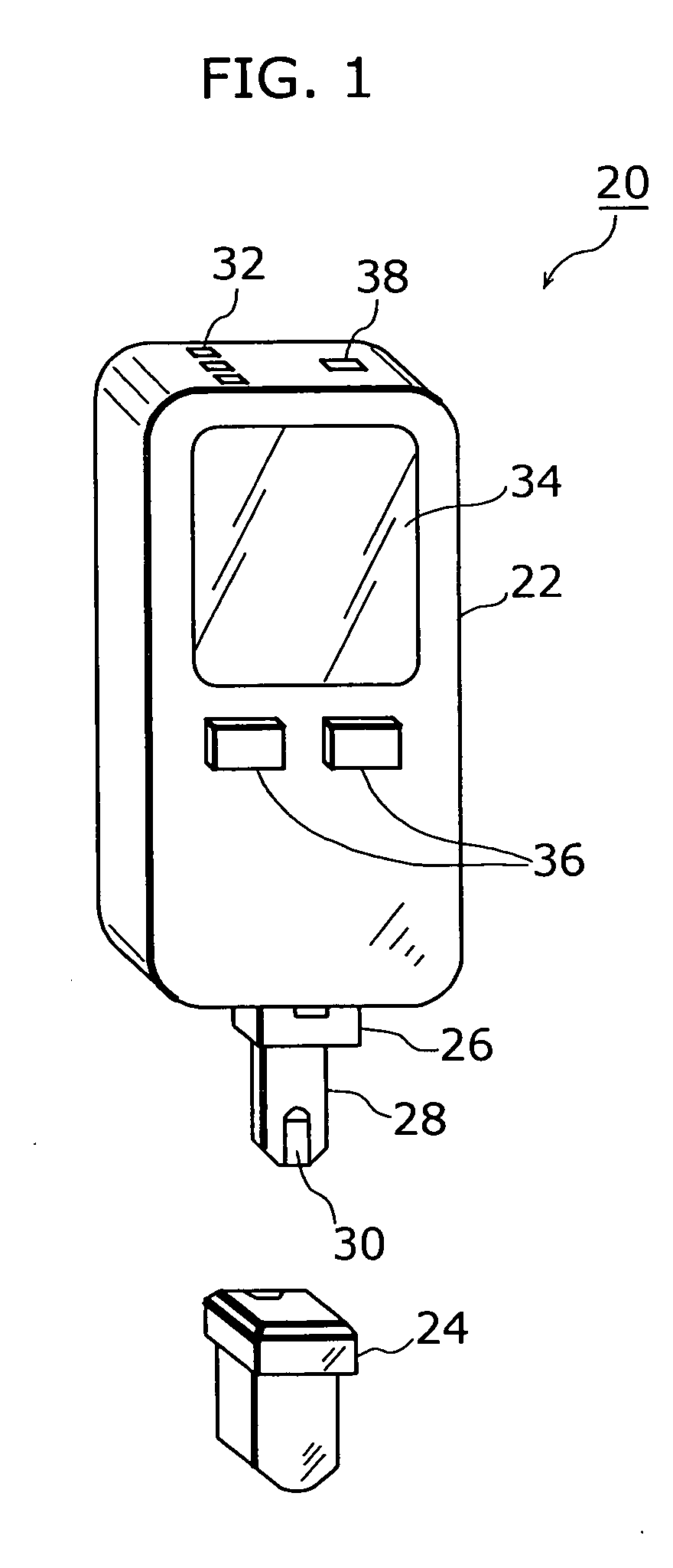

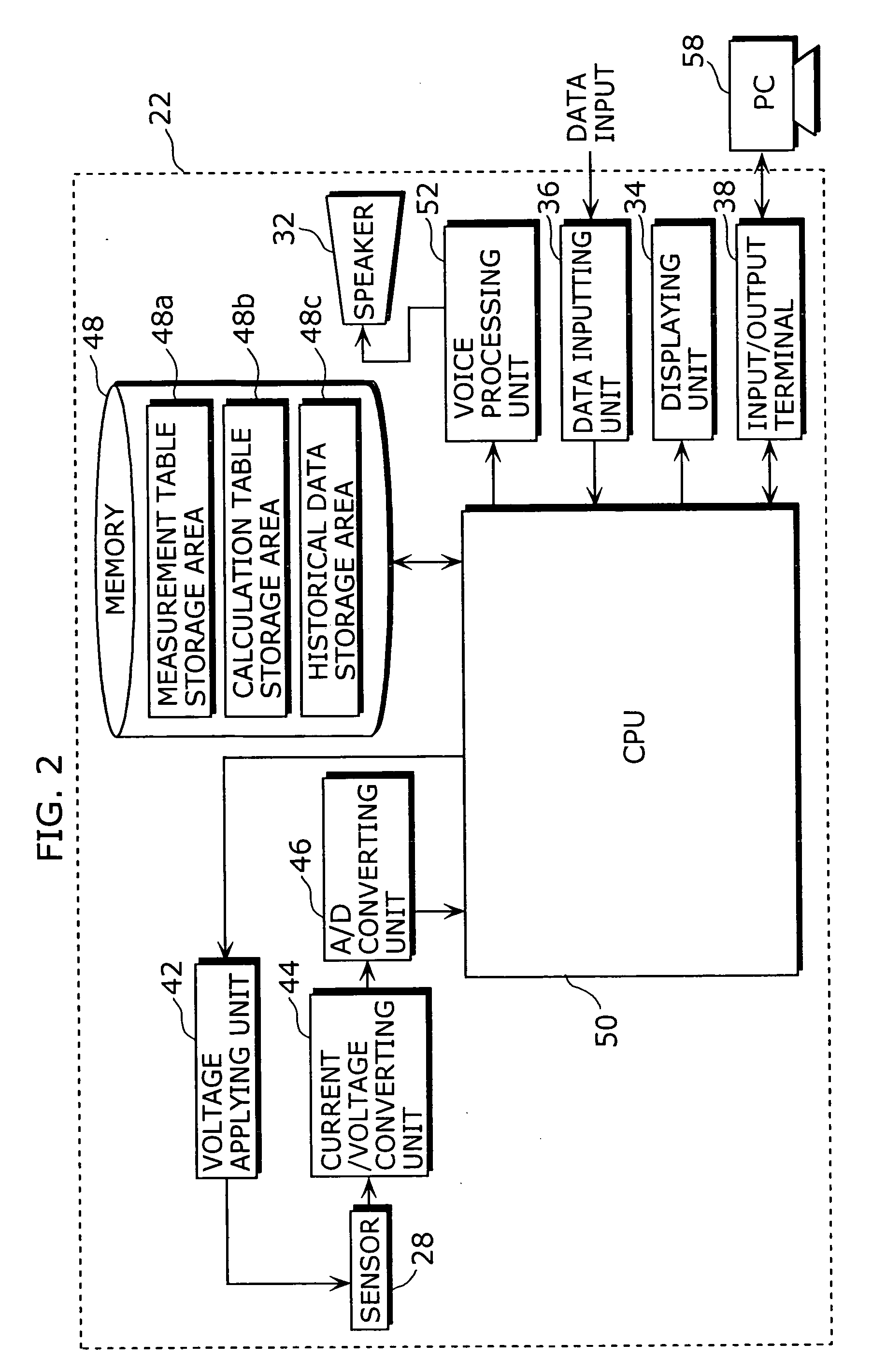

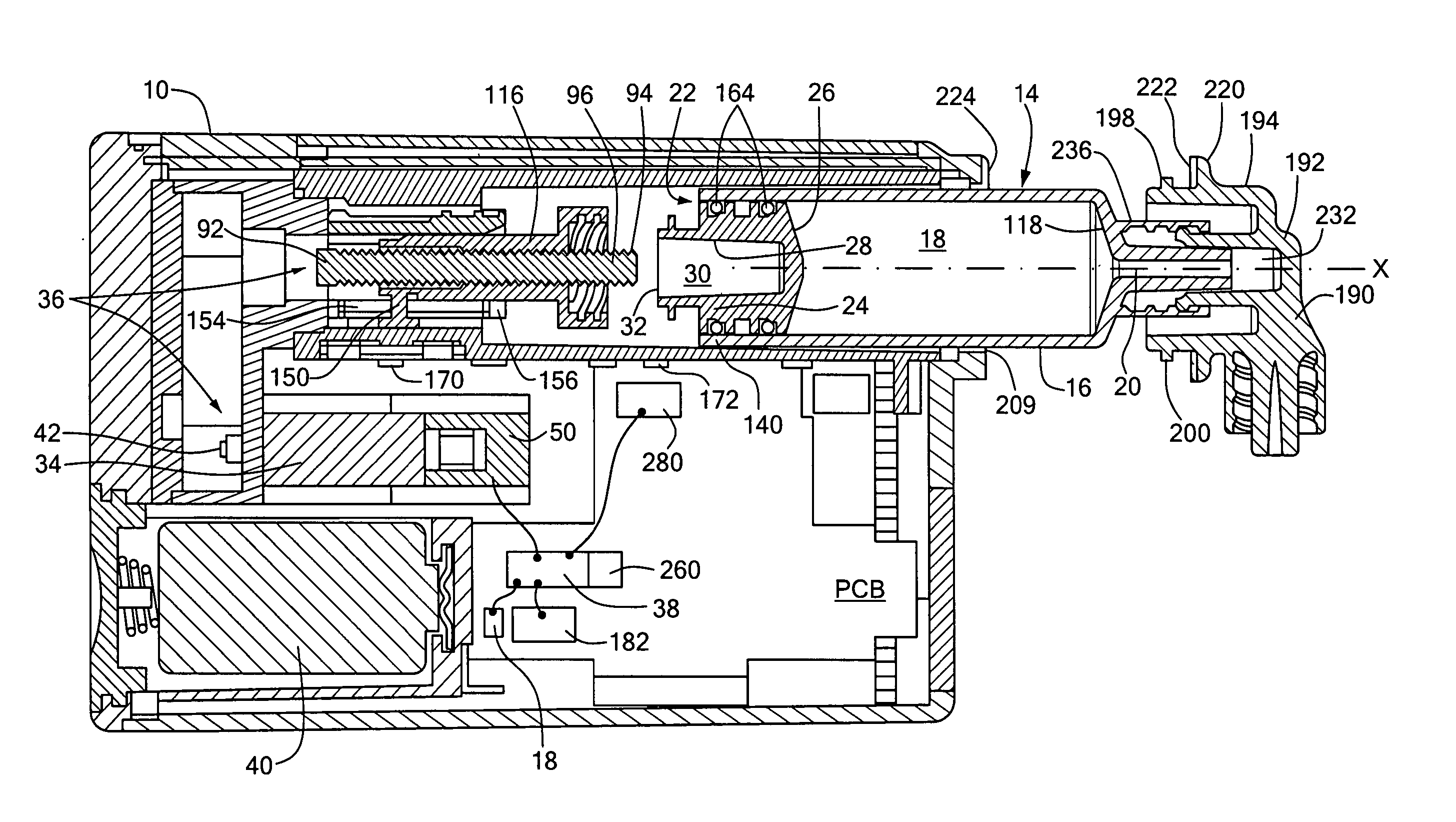

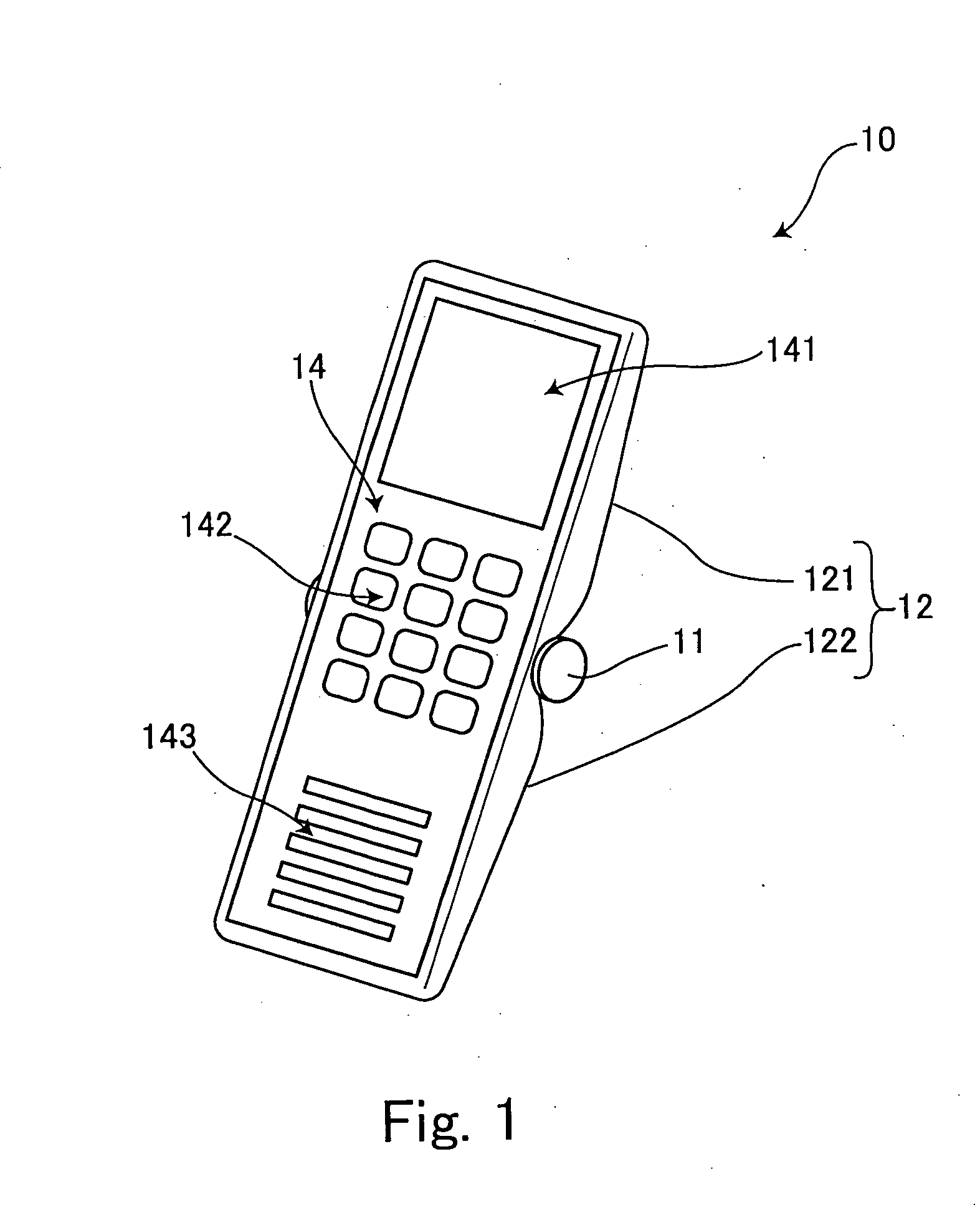

Dosage determination supporting device, injector, and health management supporting system

InactiveUS20050177398A1Improve reliabilityImprove portabilityData processing applicationsInfusion syringesSupporting systemMedicine

A dosage determination supporting apparatus, which is able to precisely determine a dosage in accordance with the health condition of a user, is provided with: a sensor (28) for measuring the blood sugar level obtained from the blood of the user; a memory (48) for storing an operation table showing a correspondence between the blood sugar level and the amount of insulin; a CPU (50) for calculating the amount of insulin corresponding to the blood sugar level, with reference to the operation table stored in the memory (48); a displaying unit (34) for displaying the amount of insulin; and a voice processing unit (52) for performing the voice processing on the amount of insulin and outputting the voice through a speaker (32).

Owner:PANASONIC CORP

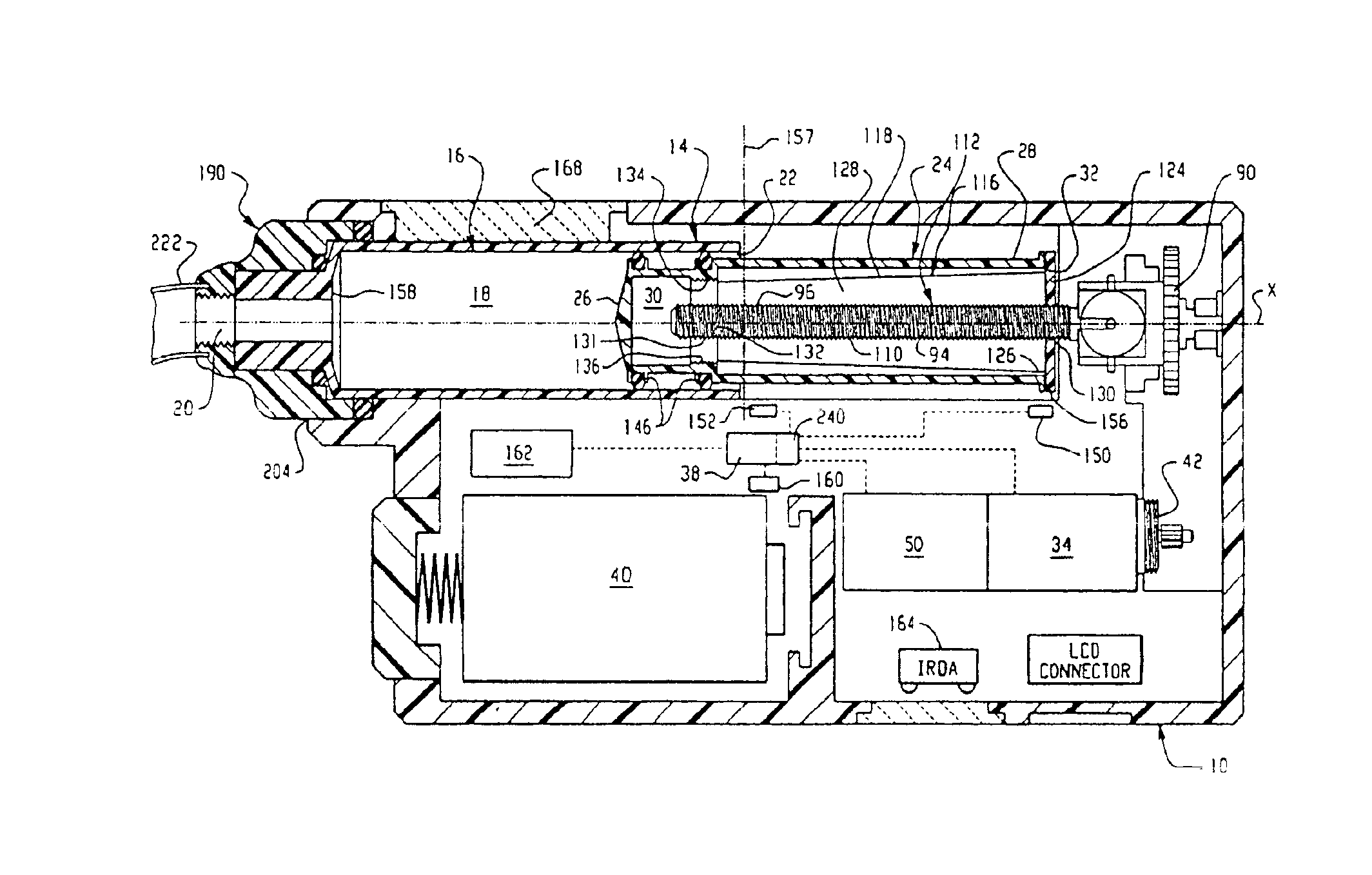

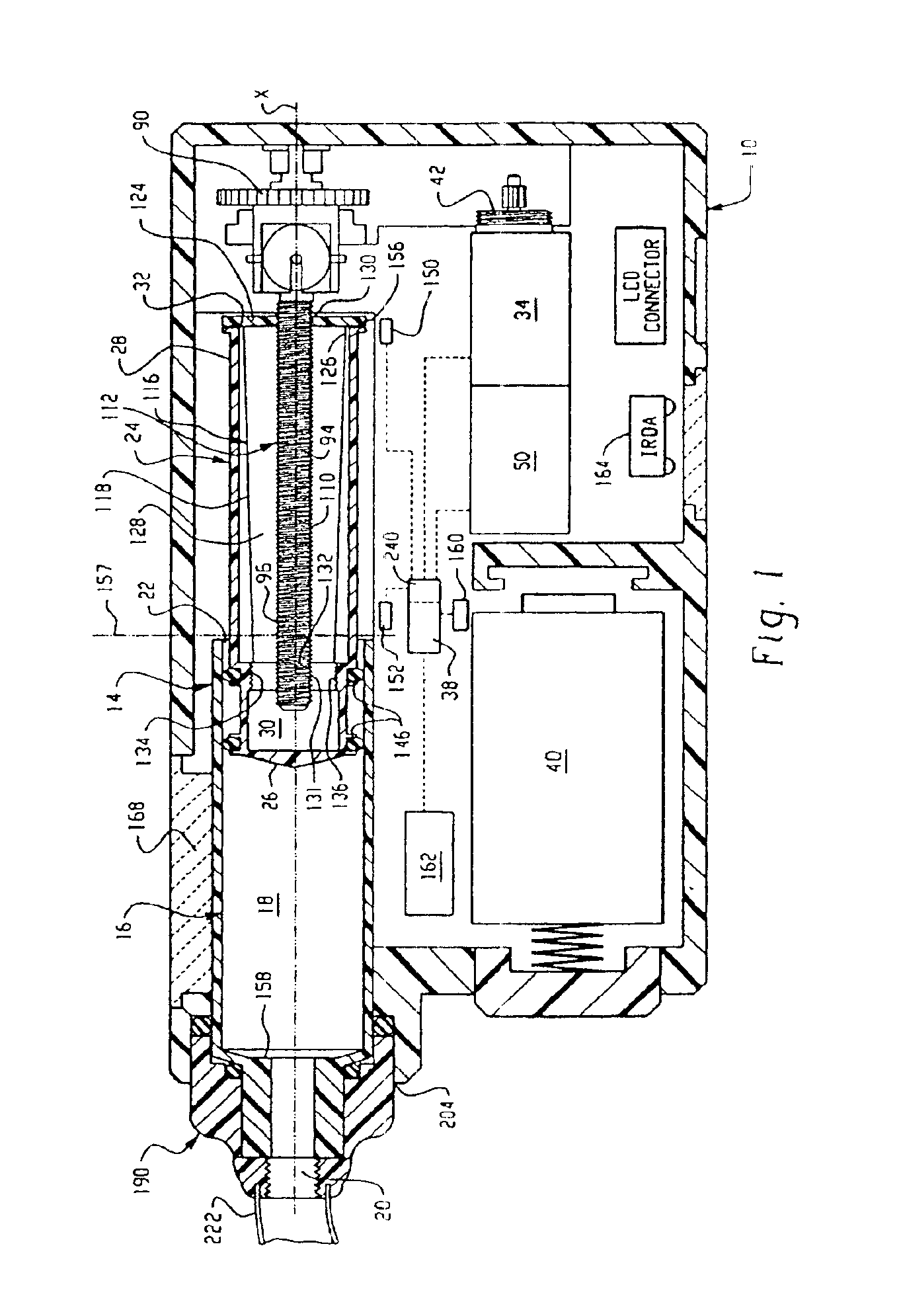

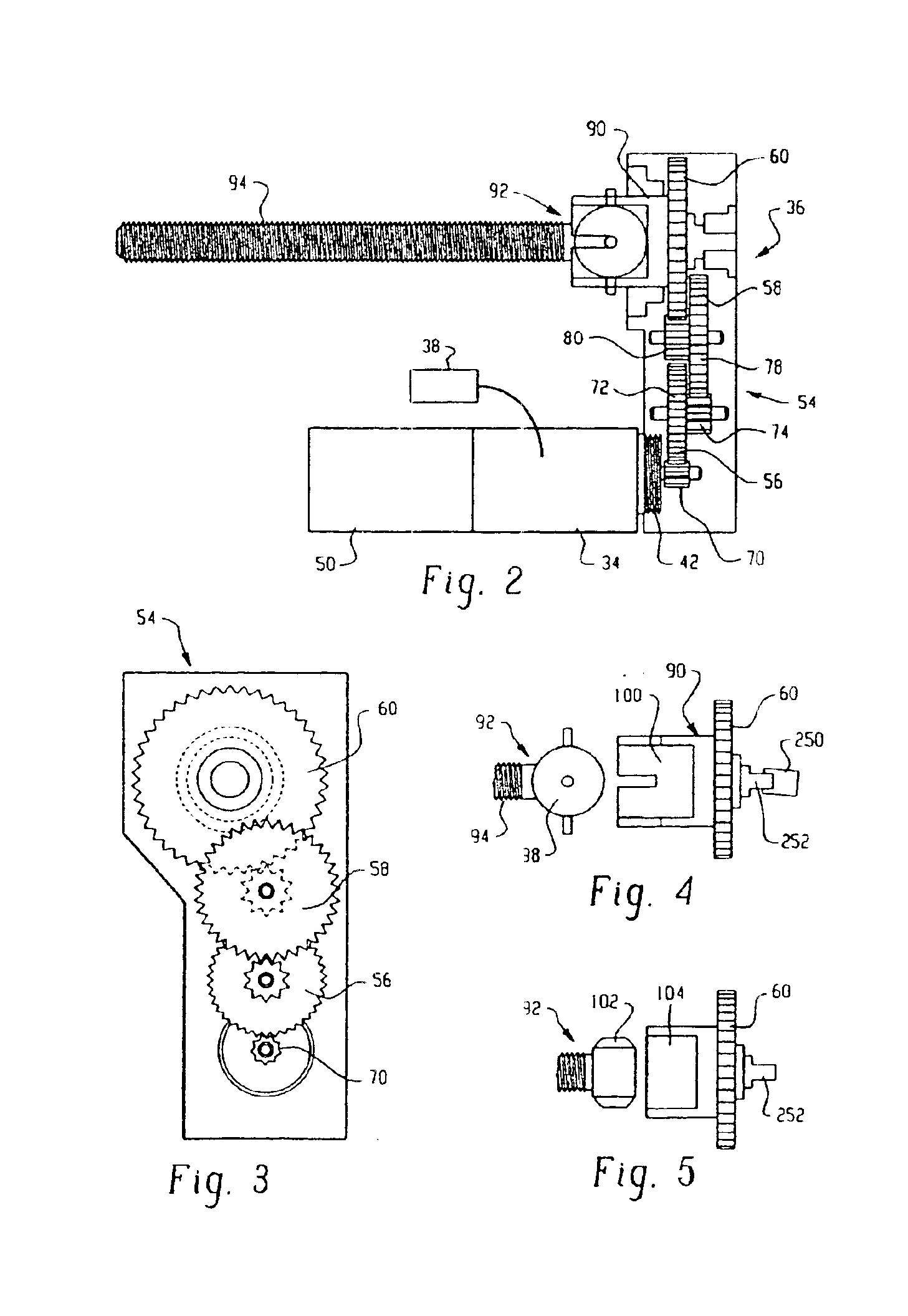

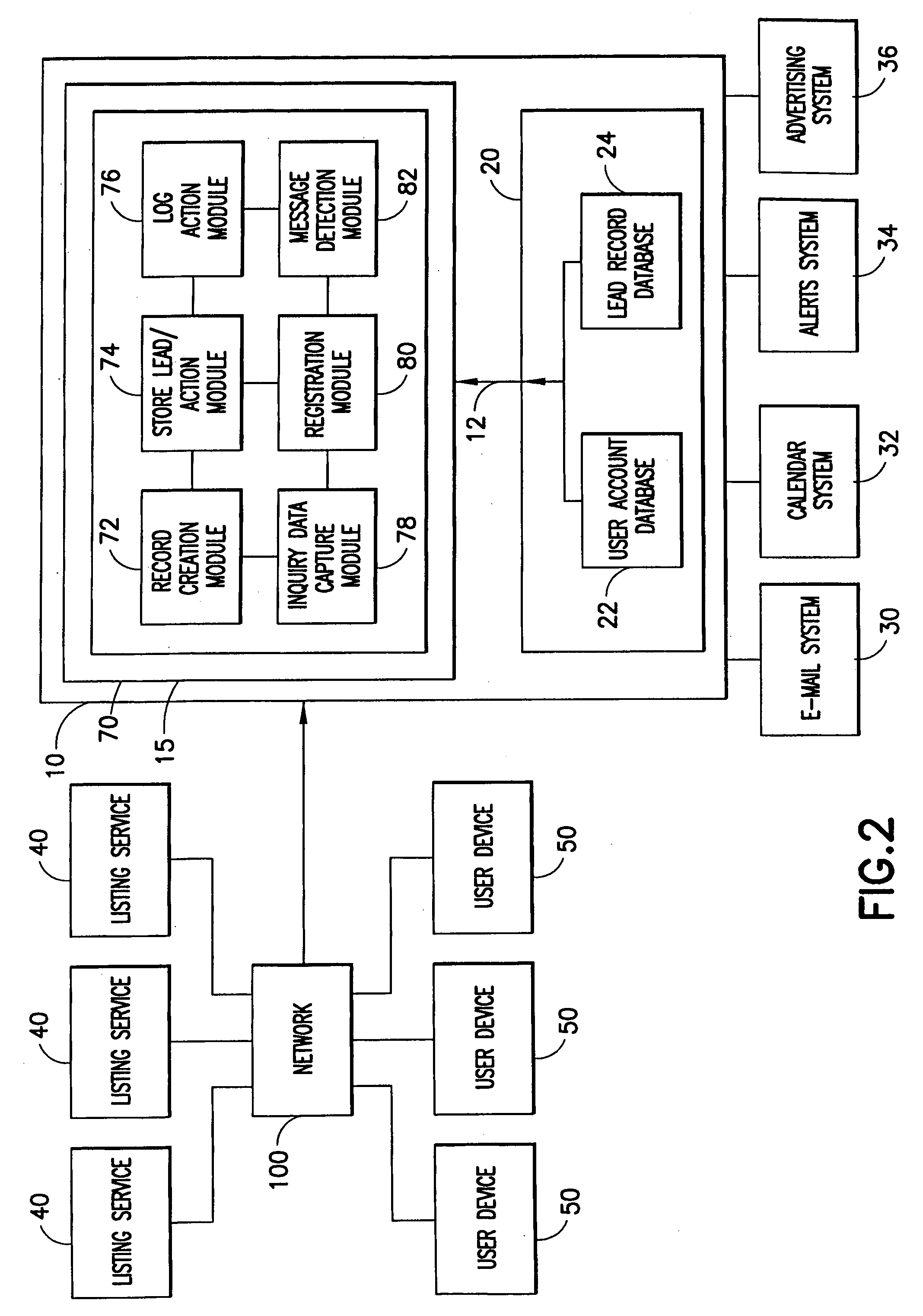

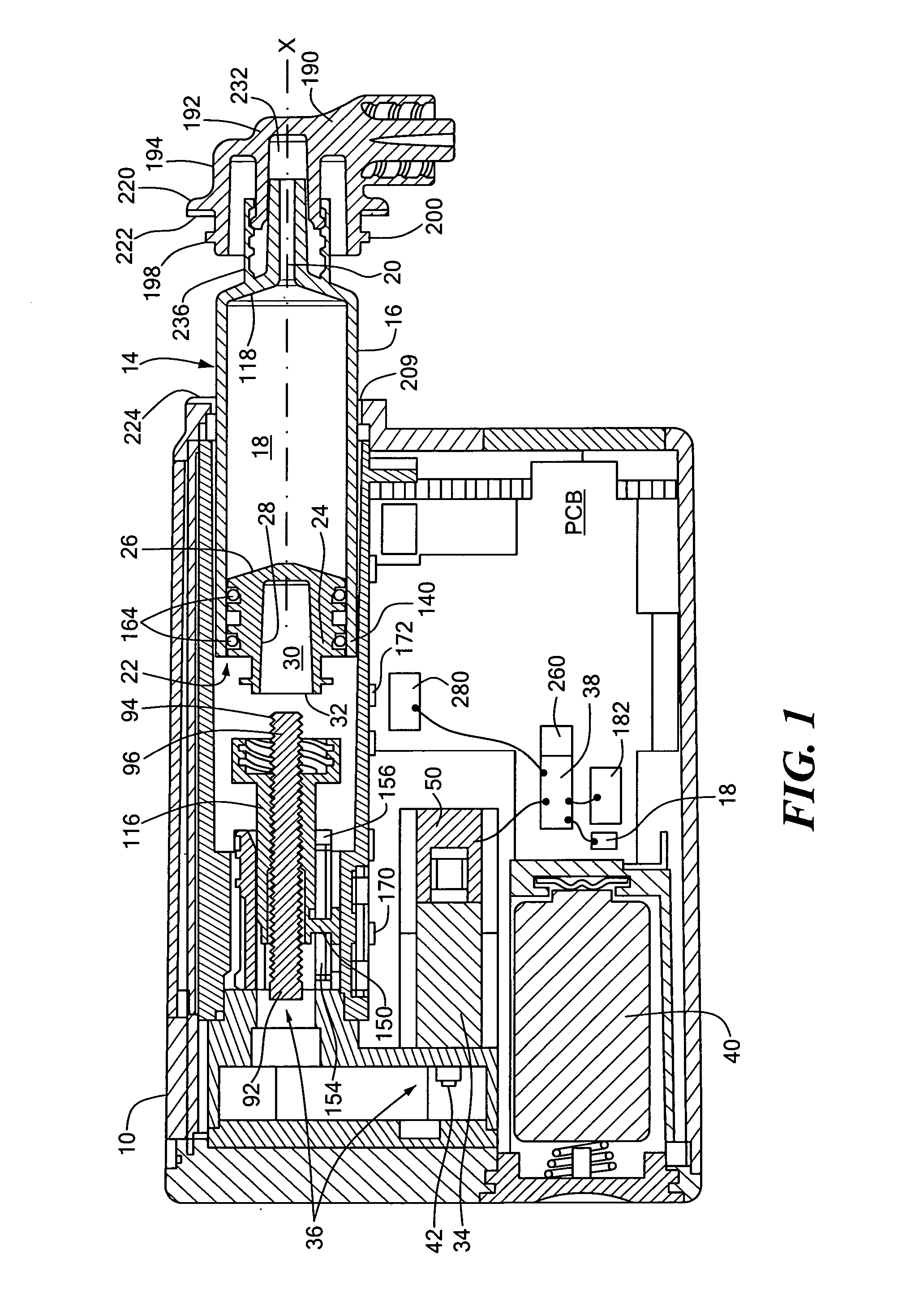

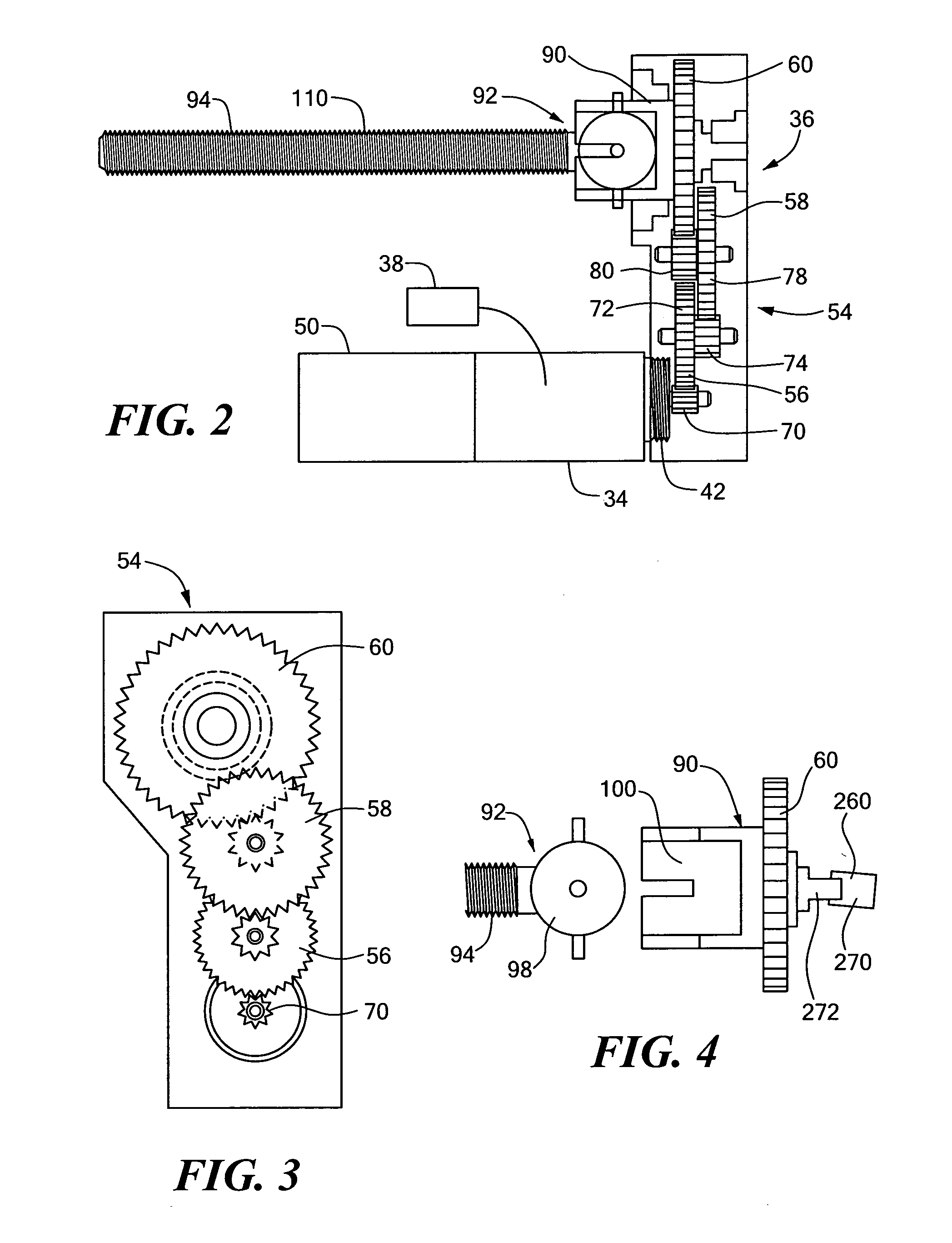

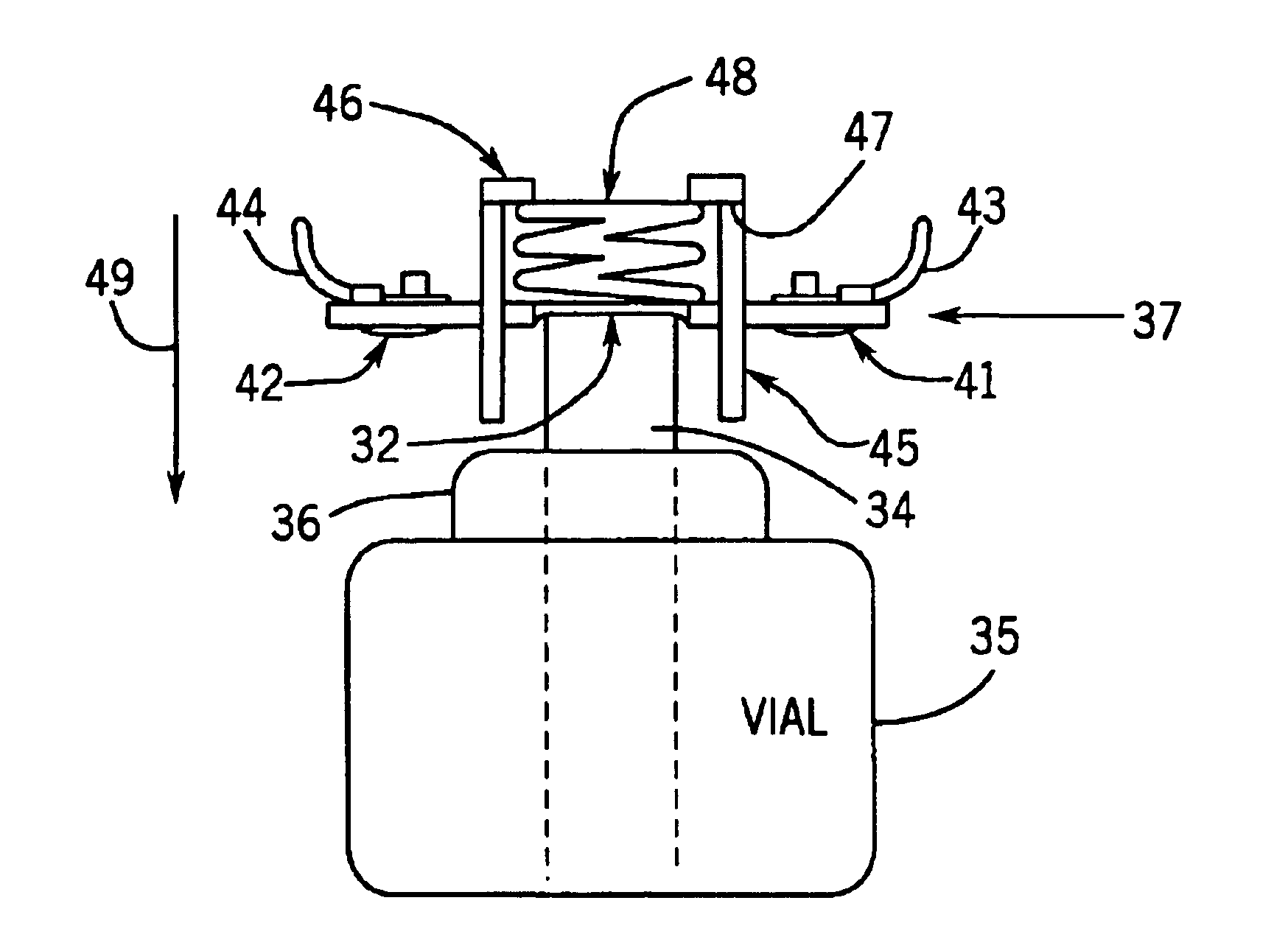

Drive system for an infusion pump

InactiveUS6854620B2Small sizeImprove portabilityClosure using stoppersLarge containersLinear motionProximity sensor

A pump system for an infusion system includes a linear drive (36, 36′) which minimizes the space occupied by the pump components in a portable housing (10, 10′). A motor (34) and a motor drive shaft (42) are arranged in parallel with, and adjacent to a syringe (14, 14′) and lead screw (94, 94′). A gear box (54) connects the drive shaft and lead screw to transfer rotational movements between them. A piston driving member, such as a cone (116) or drive nut (116′) converts the rotational movement of the lead screw into linear motion of a syringe piston (24). Sensors (150, 152) detect when the piston or cone is in a “home” position and in an “end” position, respectively. Optionally, a proximity sensor (170) is used to ensure that the cone and the piston (24) are abutting during dispensing. Alternatively, a clamping member (350) selectively clamps the lead screw (94′) against linear motion in at least a dispensing direction.

Owner:TRIVIDIA HEALTHCARE SYST LLC

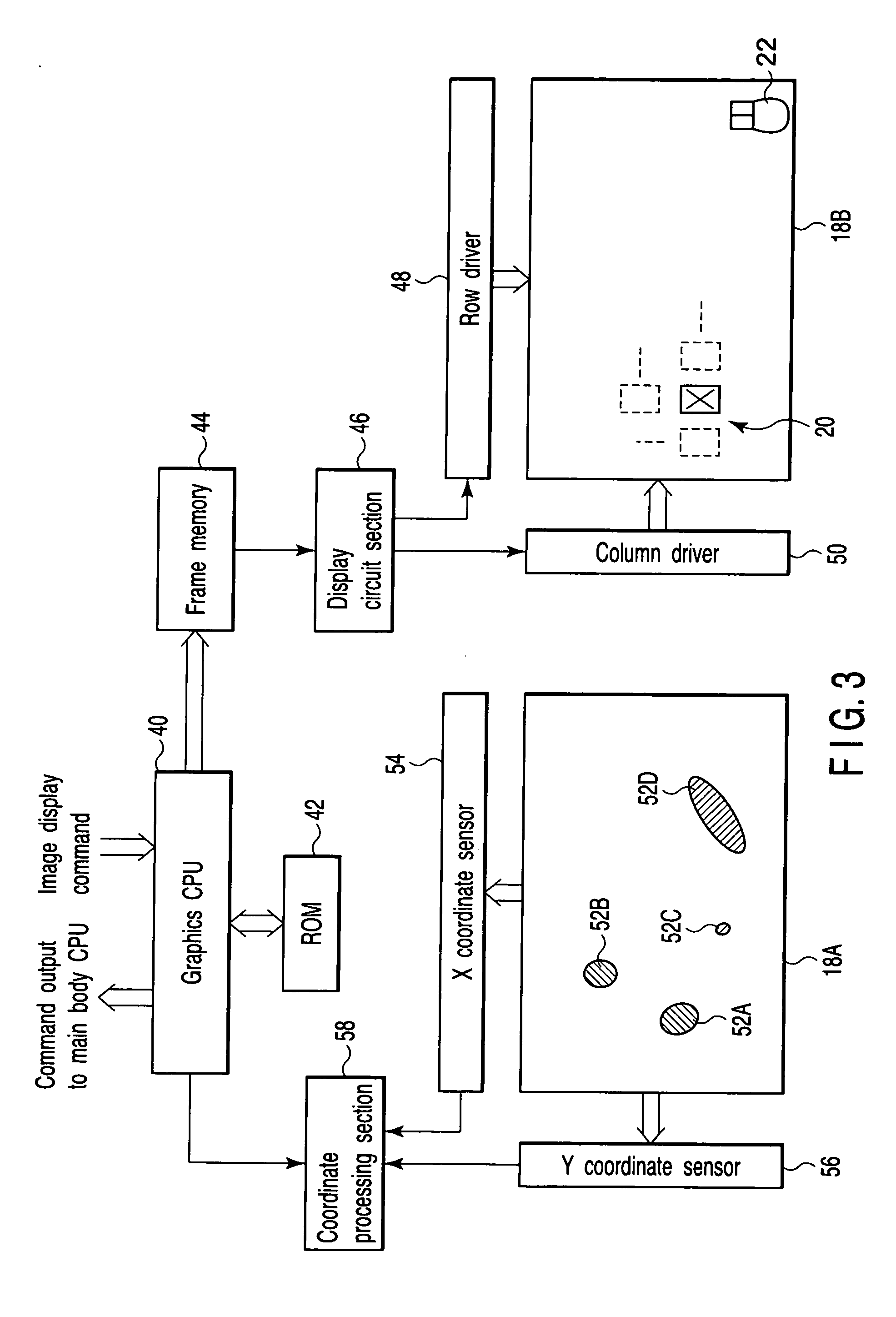

Electronic apparatus having universal human interface

InactiveUS20060034042A1Improve portabilityEasy to operateDetails for portable computersVisual presentationHuman–machine interfaceDisplay device

An electronic apparatus includes first and second display devices having first and second display screens held in first and second housings, respectively. The second display screen is provided with a sensor which generates an output signal determining an input area in response to an external predetermined input to the second display screen. The first and second housings are connected together by a connecting mechanism so that an opening angle between the first and second housings can be adjusted. A first interface image is displayed on the second display screen. An instruction input to the interface image is determined on the basis of a sensor output signal. In response to the instruction input, a second display image is displayed in place of the first display image. In response to the instruction input, a second interface image is displayed in place of the first interface image.

Owner:KK TOSHIBA

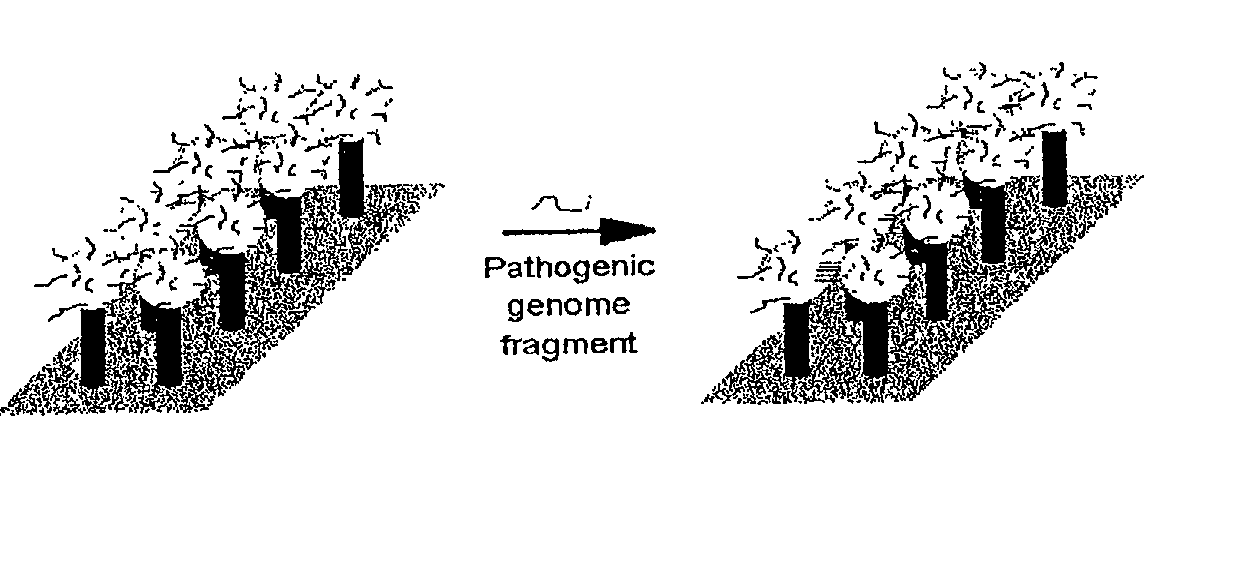

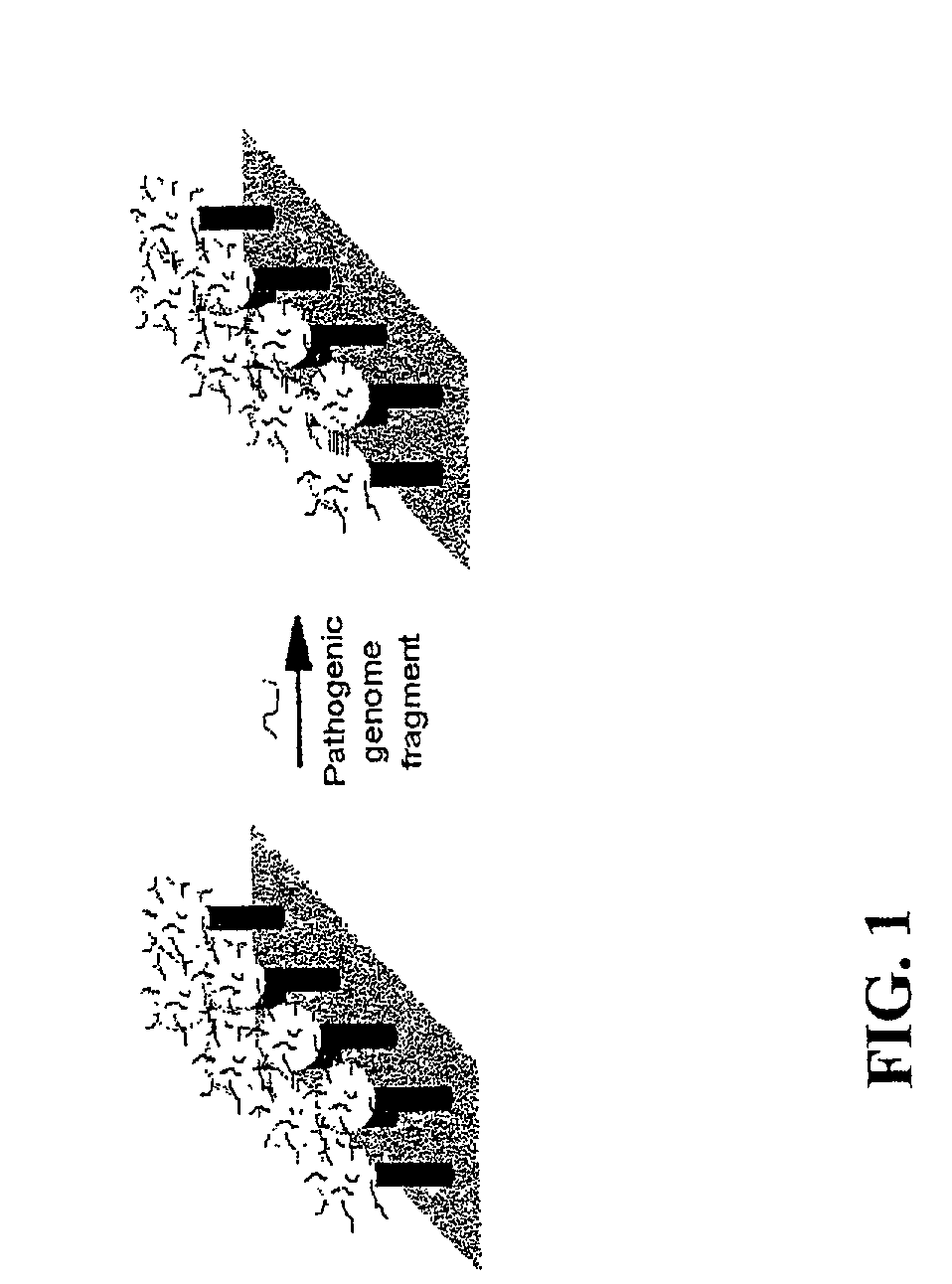

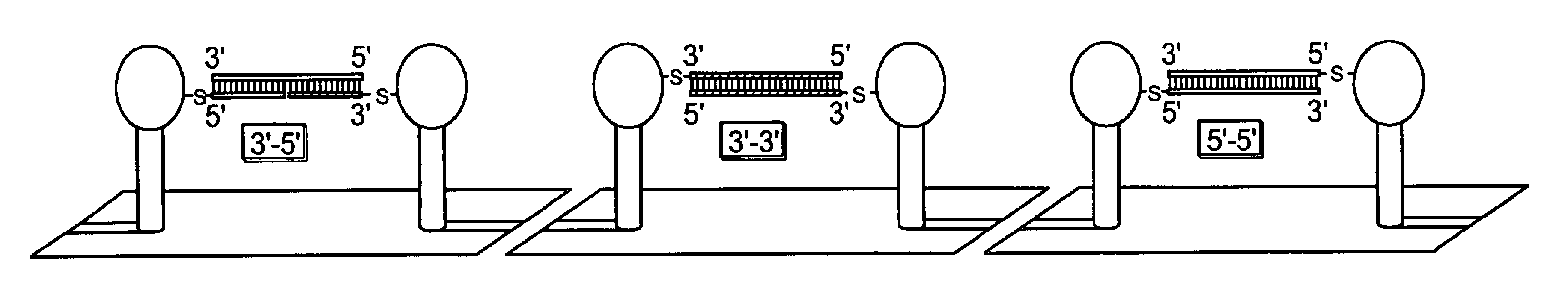

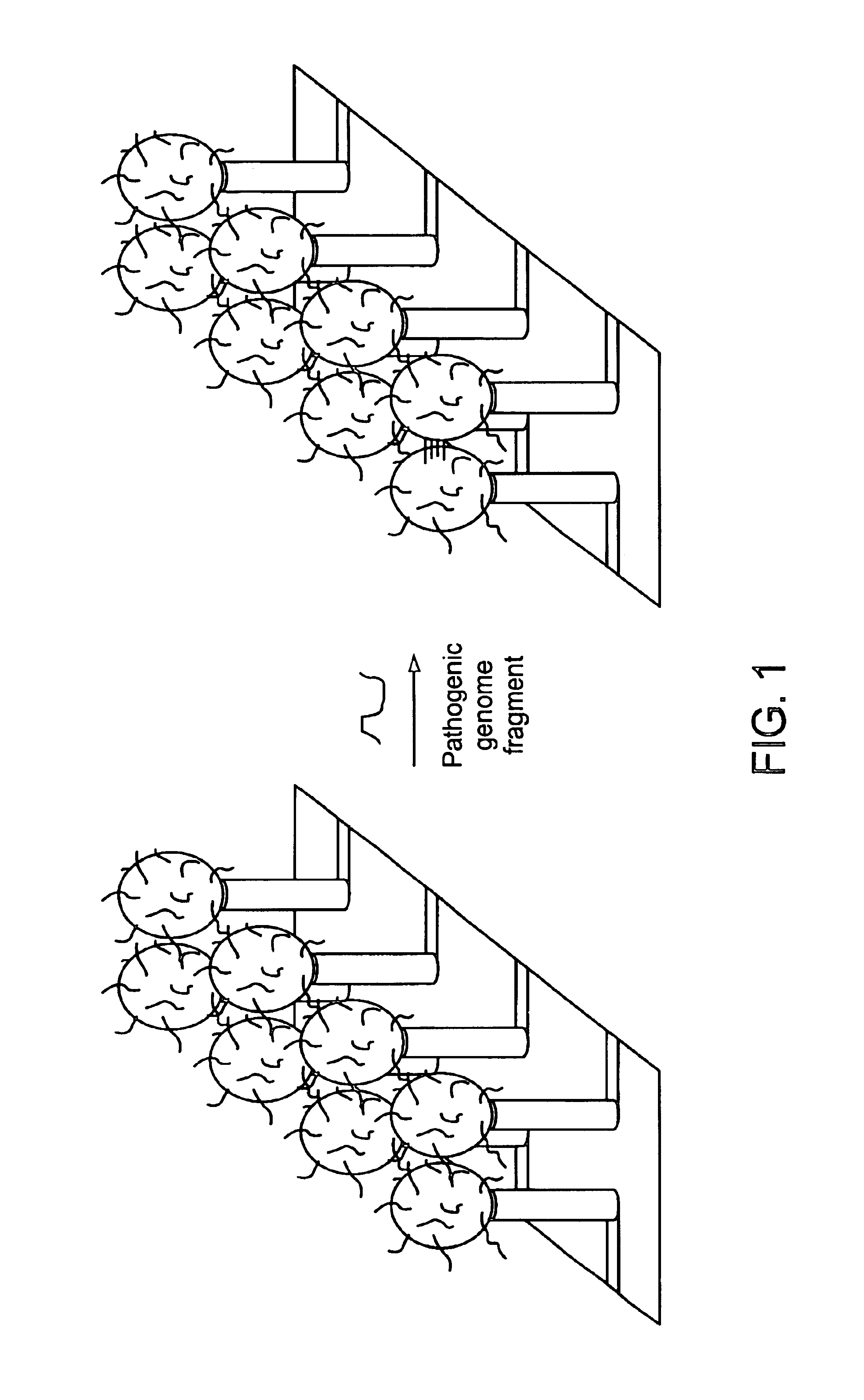

DNA-bridged carbon nanotube arrays

InactiveUS20020172963A1High precisionHigh sensitivityBioreactor/fermenter combinationsMaterial nanotechnologyChemical ligationElectron transfer reactions

A class of biological sensing devices that include a substrate comprising an array of carbon nanotubes (CNTs) to which are chemically attached biological molecules is disclosed. The attached biological molecules are capable of electrical conductivity that is responsive to chemical changes occurring as a result of their interaction with target species. A means for means for using DNA as a material of potential in molecular electronic sensor devices, being primarily based on molecular electron-transfer reaction processes between DNA-binding donors and acceptors is also disclosed, including composition, method of manufacture and their use are described.

Owner:TRUSTEES OF BOSTON COLLEGE THE

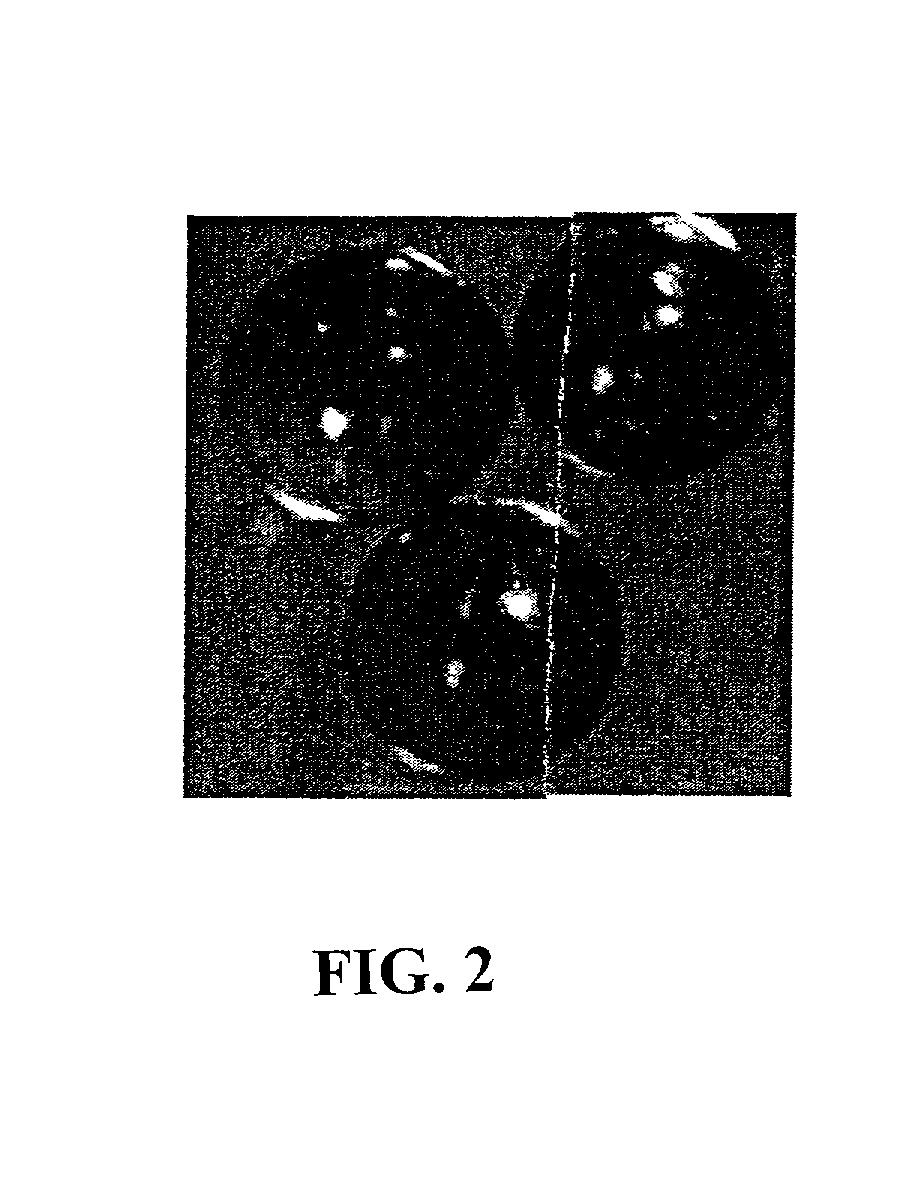

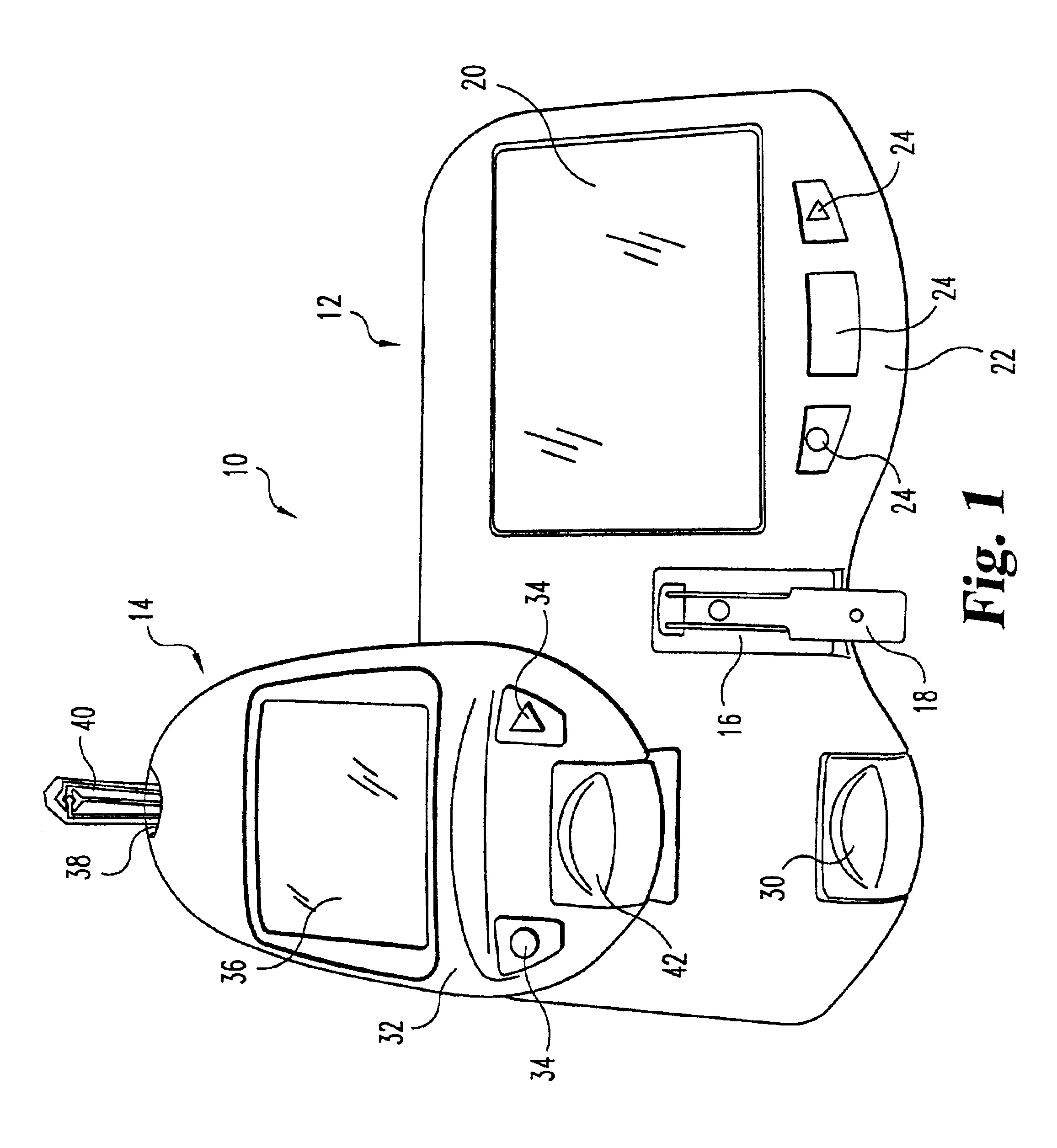

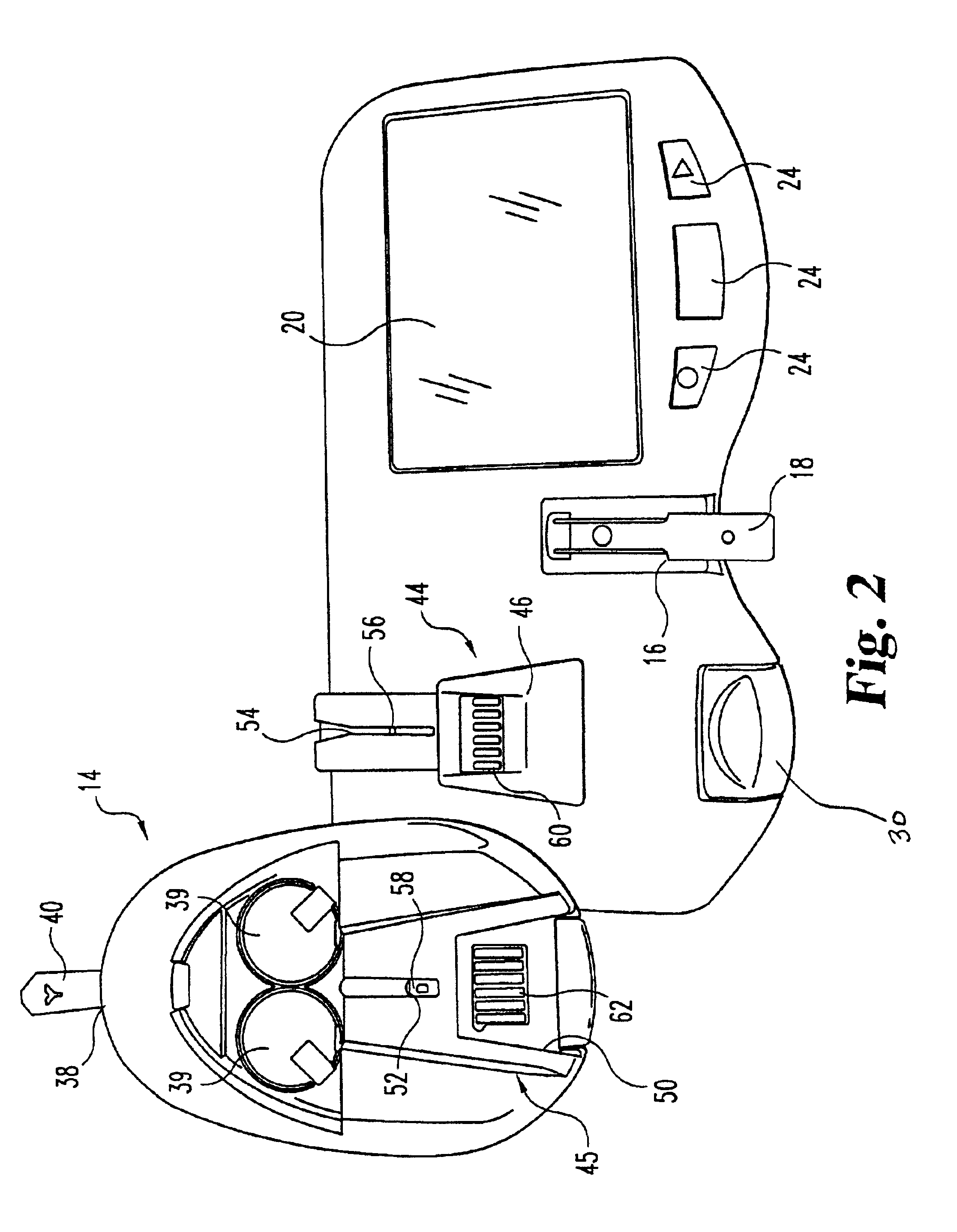

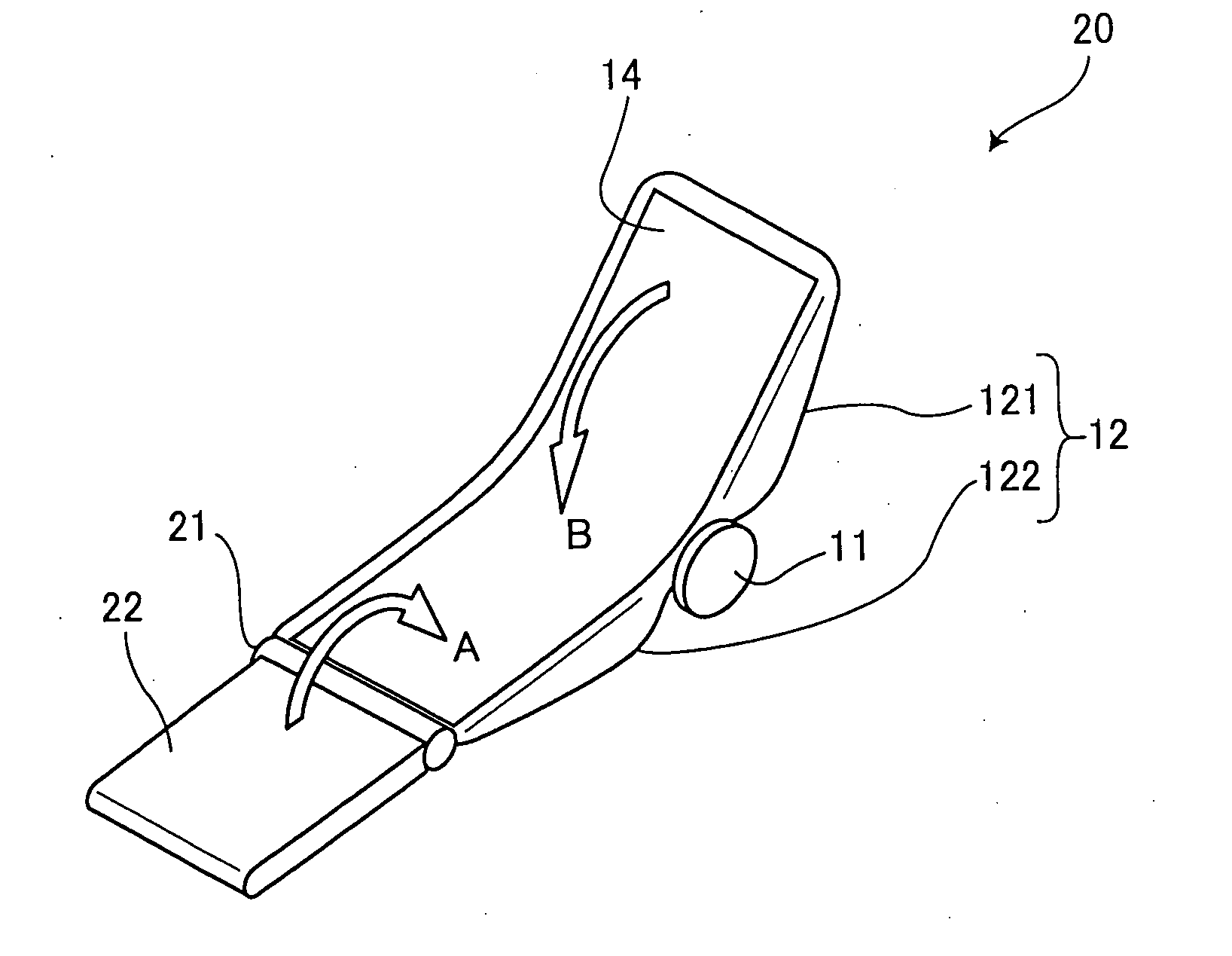

Body fluid test apparatus with detachably mounted portable tester

InactiveUS6849237B2Sacrificing abilityMonitor glucose levelImmobilised enzymesBioreactor/fermenter combinationsGlucose meter deviceHand held

A test apparatus having a base which performs a plurality of tests for different analytes in body fluids. A portable tester, such as a glucose meter, is detachably mounted to the base and provides a convenient and ergonomic hand-held instrument which a diabetic may carry to frequently monitor blood glucose levels. When mounted or docked to the base, the portable tester is data linked to the base. The invention provides a communications network among the base, the portable tester and another device such as a PC. The portable tester can therefore be kept small and inexpensive since advanced computing and data storage capabilities are provided in the base or a PC.

Owner:POLYMER TECH SYST

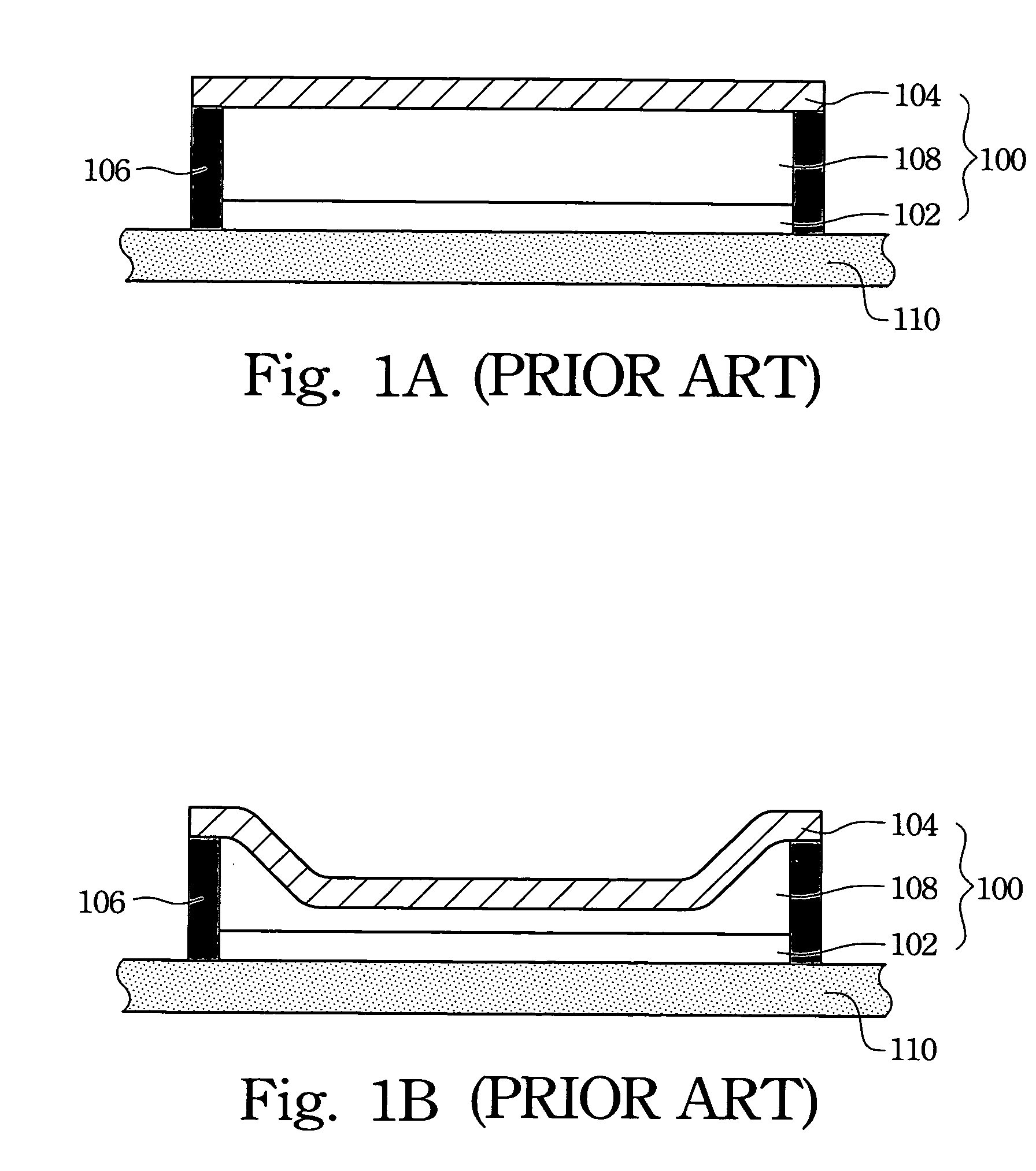

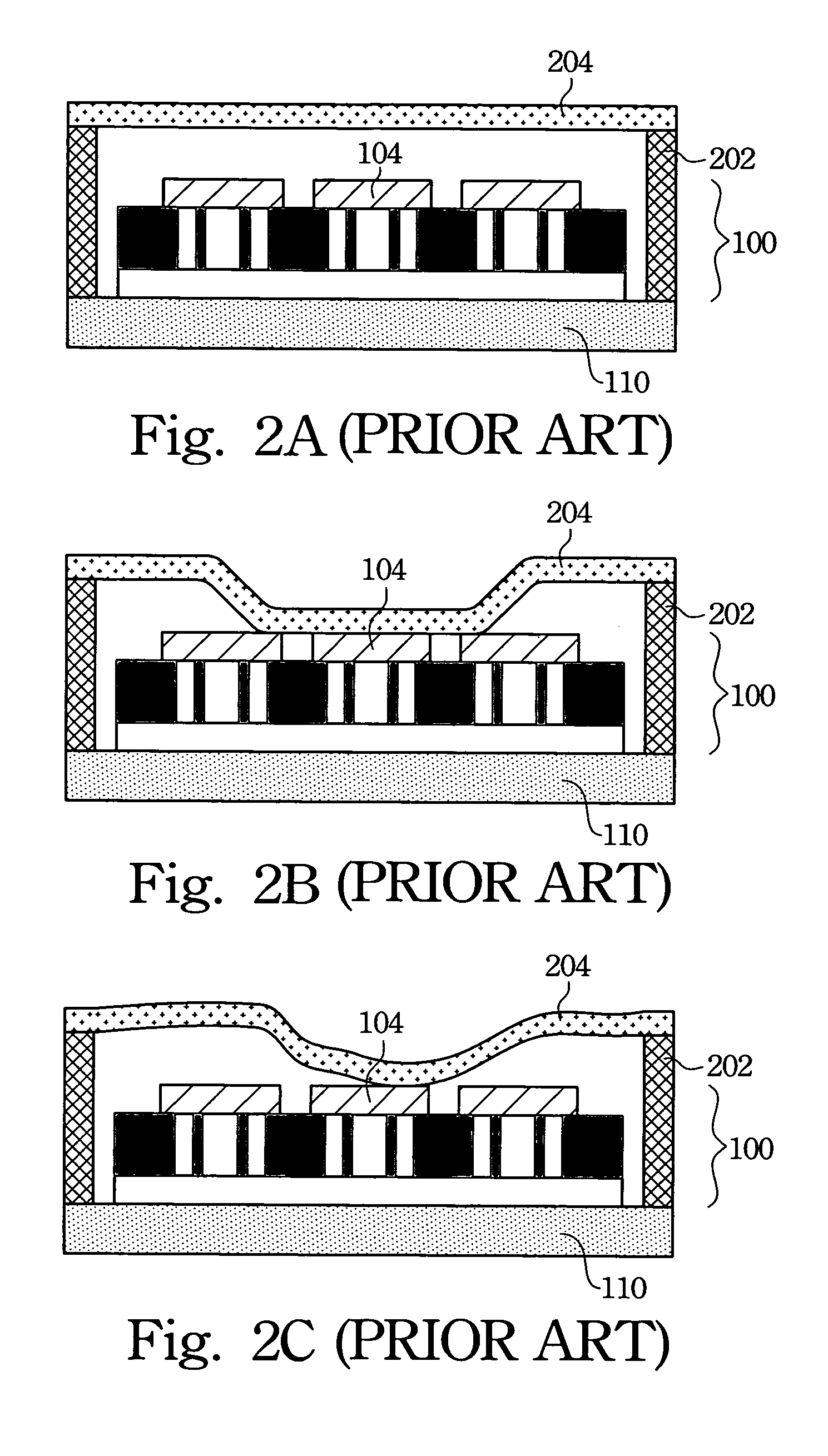

Interference display plate and manufacturing method thereof

InactiveUS20050195462A1Reduce distortionHigh selectivityNon-linear opticsIdentification meansDisplay boardEngineering

Owner:SNAPTRACK

Portable wireless charging pad

ActiveUS20150015195A1Mobility and portability be enhanceIncrease mobilityBatteries circuit arrangementsElectric powerInductive chargingReceiver

Owner:ENERGOUS CORPORATION

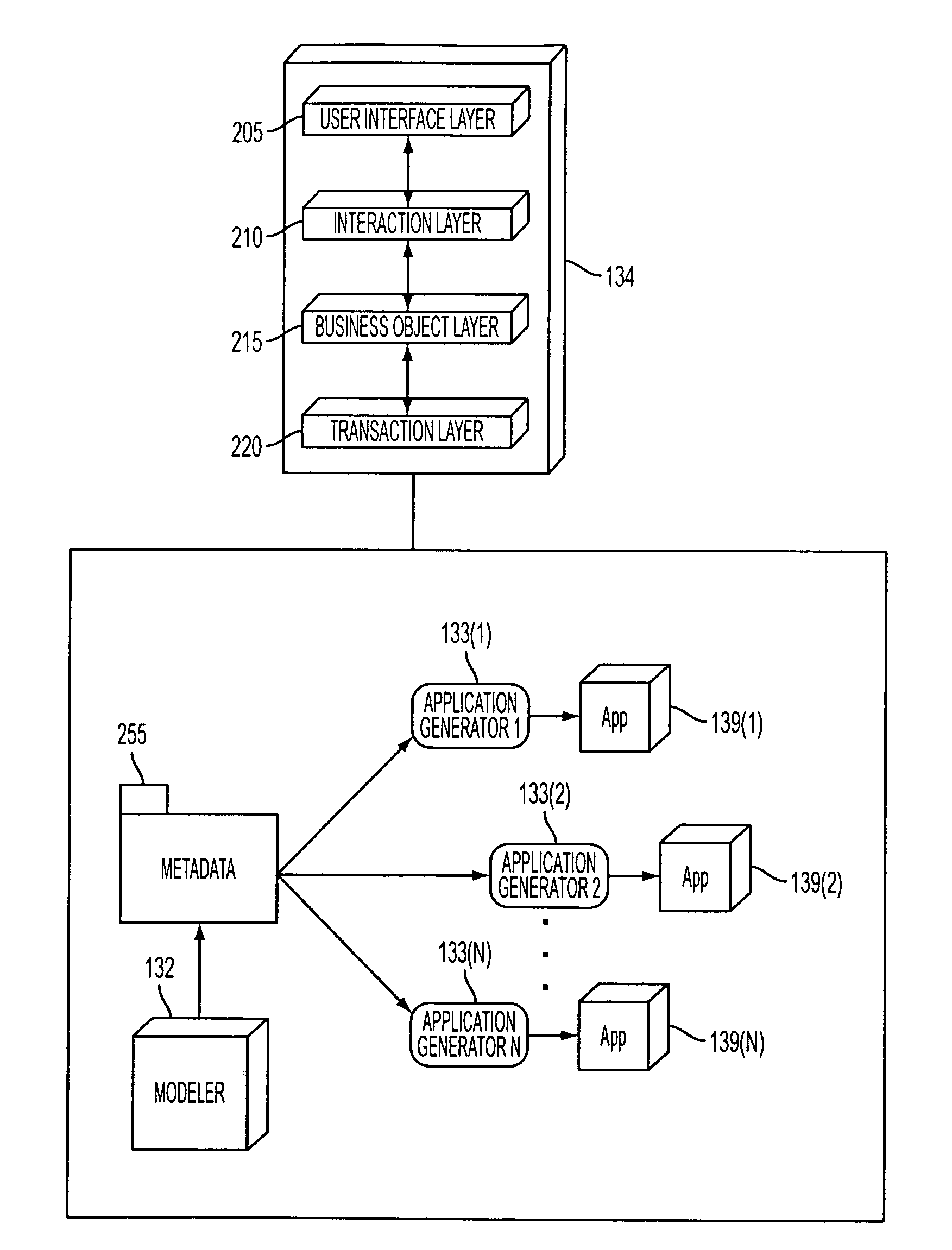

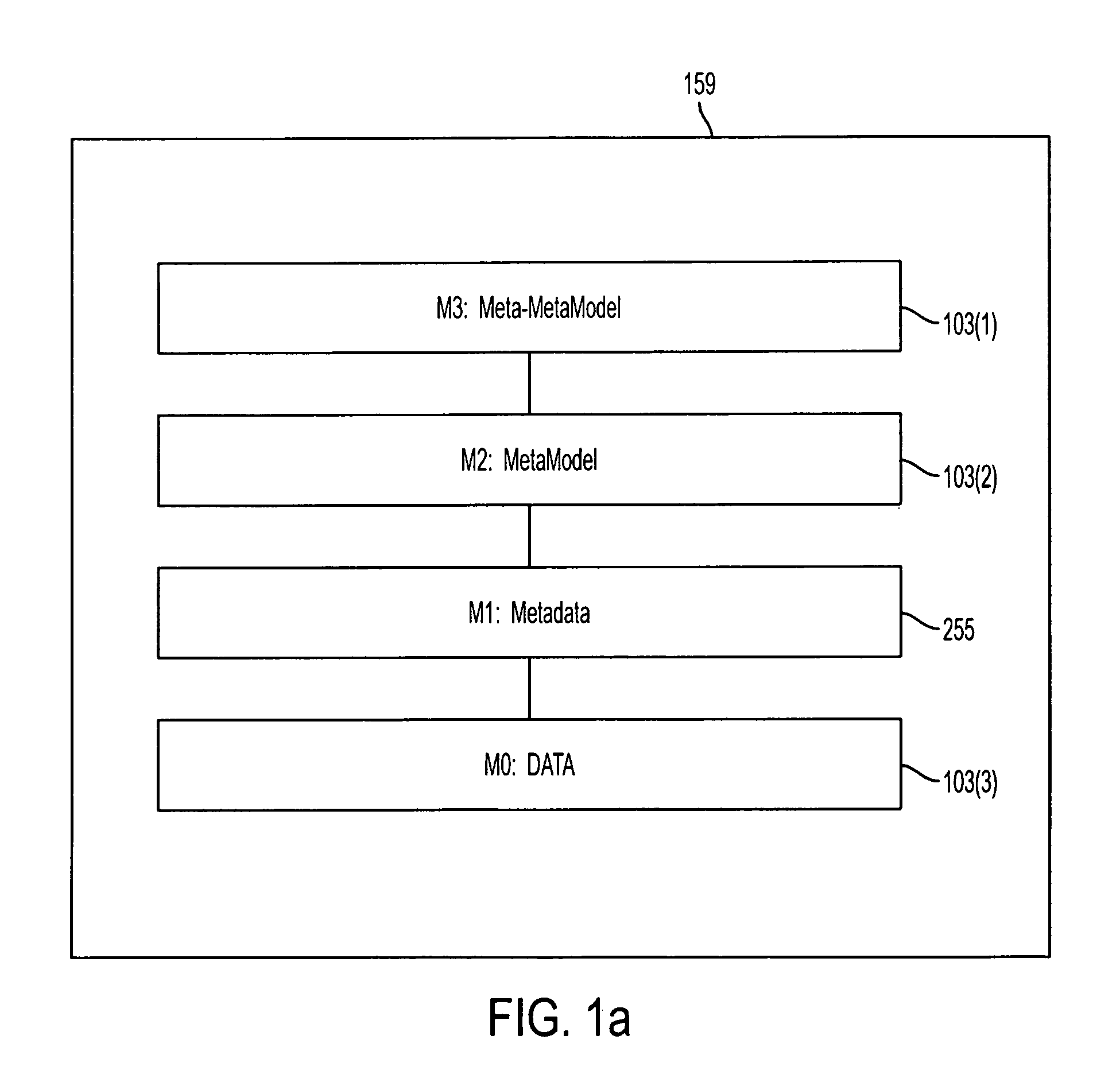

Cross-platform development for devices with heterogeneous capabilities

ActiveUS7240327B2Good serviceFunction increaseMultiple digital computer combinationsSpecific program execution arrangementsSoftware engineeringOutput device

A system for generating software applications for a plurality of heterogeneous computing devices. Each computing device has different capabilities. The system outputs device-specific versions of a software application each tailored to the capabilities of the associated computing device in response to receiving device-independent modeling information characterizing the software application. The system includes a framework, a plurality of object types, a modeling tool, and a plurality of device-specific code generators. The framework defines common services on the computing devices. Each object type has a functional relationship to the common services provided by the framework. The modeling tool defines instances of the plurality of object types based on modeling information received as input, outputting a metadata structure describing the behavior and functionality of a software application. From the metadata, the code generators generate device-specific application code tailored to the capabilities of the associated devices.

Owner:SAP AG

DNA-bridged carbon nanotube arrays

InactiveUS6958216B2High sensitivityImprove portabilityImmobilised enzymesBioreactor/fermenter combinationsChemical ligationElectron transfer reactions

A class of biological sensing devices that include a substrate comprising an array of carbon nanotubes (CNTs) to which are chemically attached biological molecules is disclosed. The attached biological molecules are capable of electrical conductivity that is responsive to chemical changes occurring as a result of their interaction with target species. A means for means for using DNA as a material of potential in molecular electronic sensor devices, being primarily based on molecular electron-transfer reaction processes between DNA-binding donors and acceptors is also disclosed, including composition, method of manufacture and their use are described.

Owner:TRUSTEES OF BOSTON COLLEGE THE

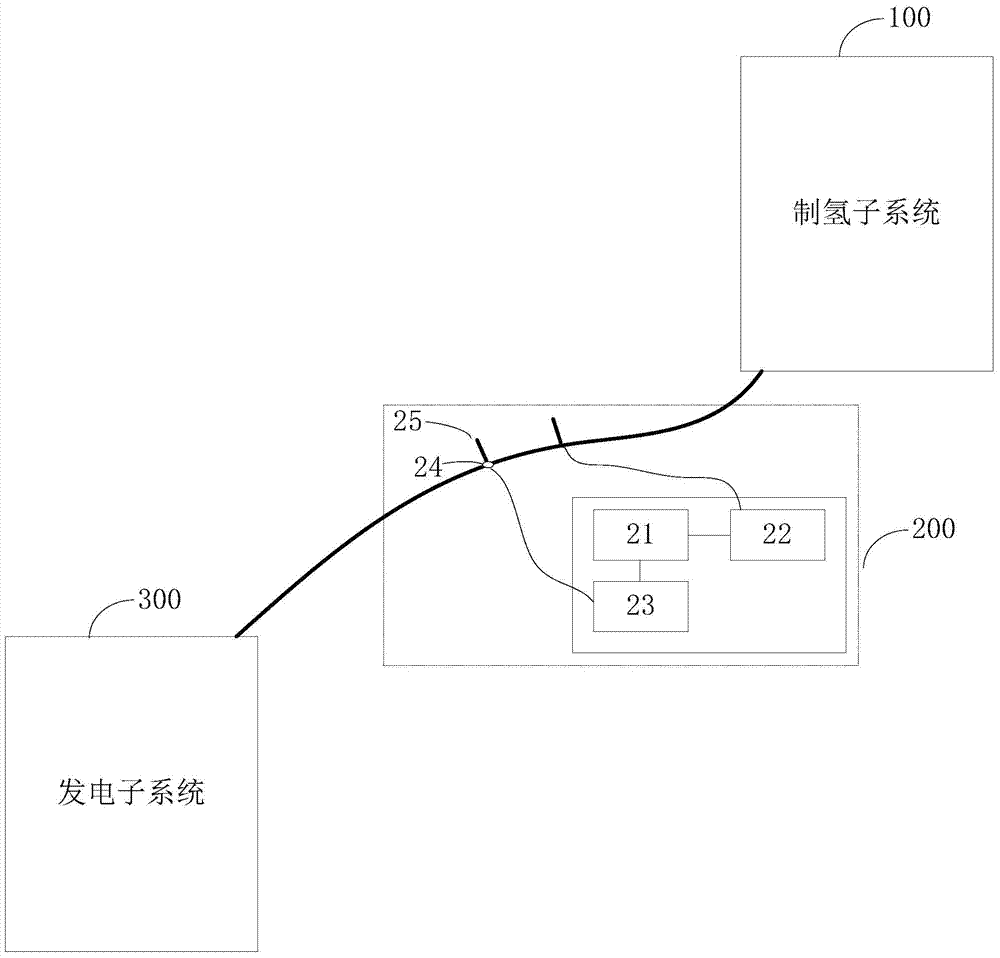

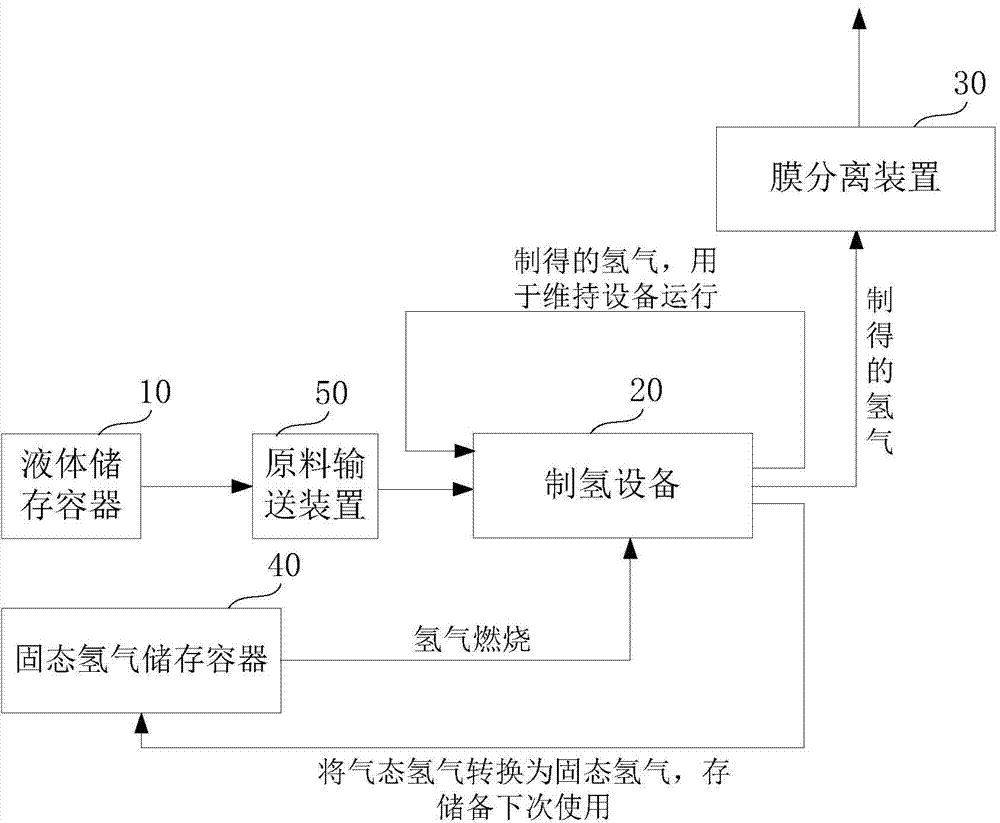

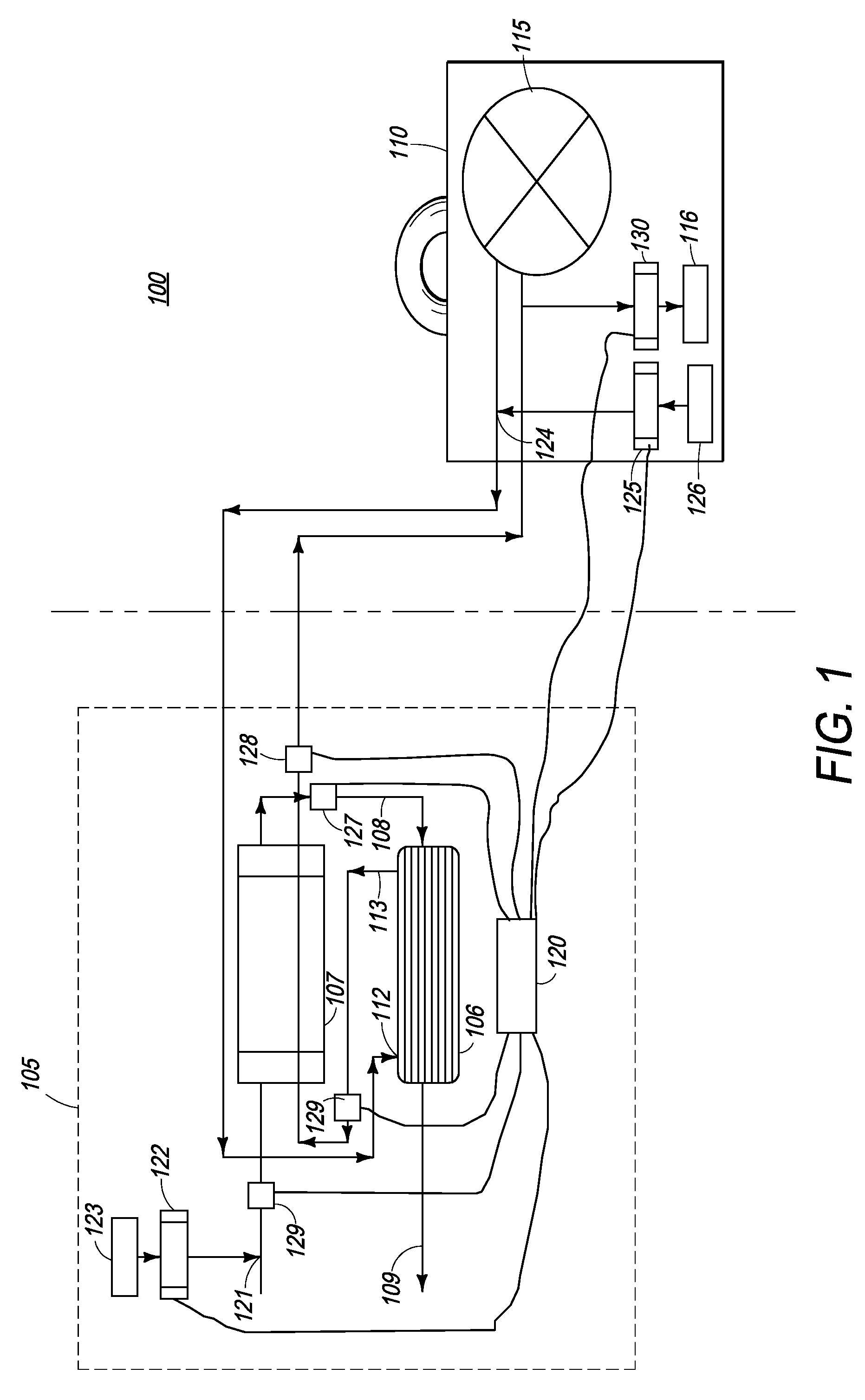

System and method for instant hydrogen production and power generation

The invention discloses a system and a method for instant hydrogen production and power generation. The system comprises a hydrogen production subsystem, an air pressure adjusting subsystem and a power generation subsystem, wherein the hydrogen production subsystem is used for preparing hydrogen from methanol water and transmitting the prepared hydrogen to the power generation subsystem in real time through a transmission pipeline; the transmission pipeline is provided with the air pressure adjusting subsystem for adjusting air pressure inside the transmission pipeline; the power generation subsystem is used for generating power by virtue of hydrogen prepared by the hydrogen production subsystem; the air pressure adjusting subsystem comprises a microprocessor, an air pressure sensor, a valve controller and an air outlet valve; the air pressure sensor is arranged in the transmission pipeline, and is used for sensing data of the air pressure inside the transmission pipeline and sending the data of the air pressure to the microprocessor; the microprocessor is used for controlling the on and off of the air outlet valve according to the data of the air pressure sensed by the air pressure sensor. Power can be generated by instantly prepared hydrogen, a hydrogen buffer tank is not required, and thus the portability and mobility of the hydrogen production and power generation system can be improved.

Owner:SHANGHAI HYDROGEN MOBILE REFRMER INSTR

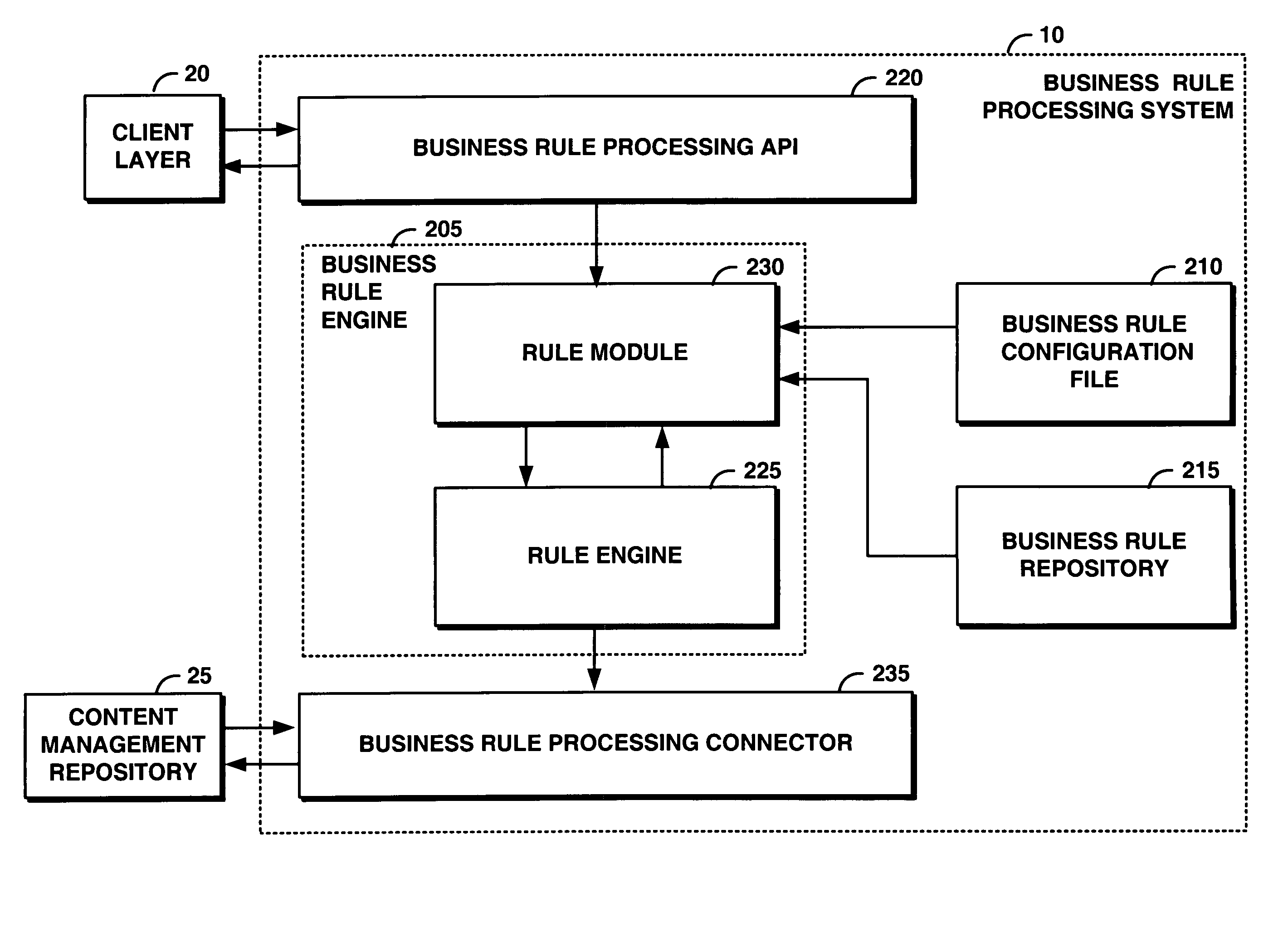

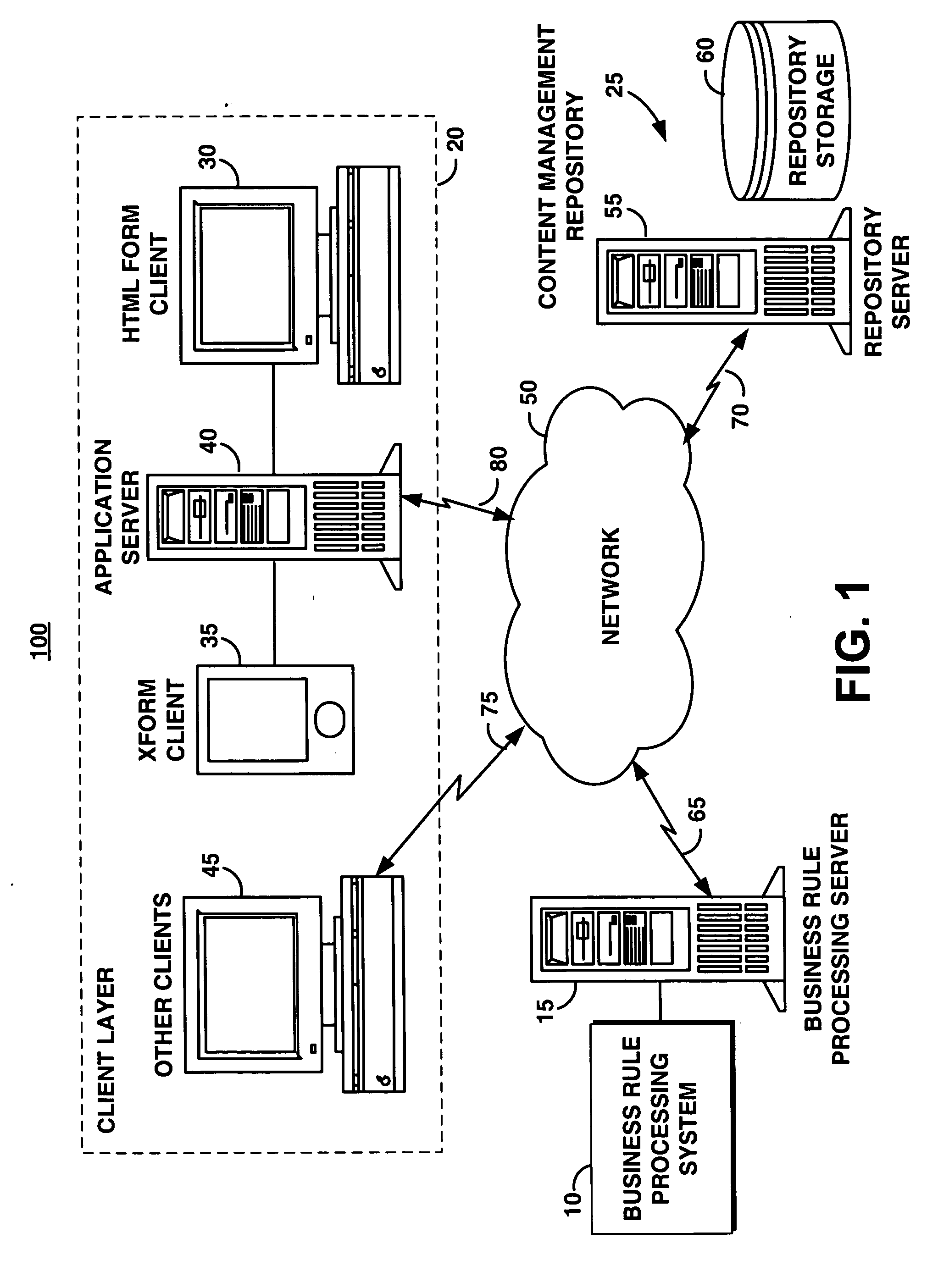

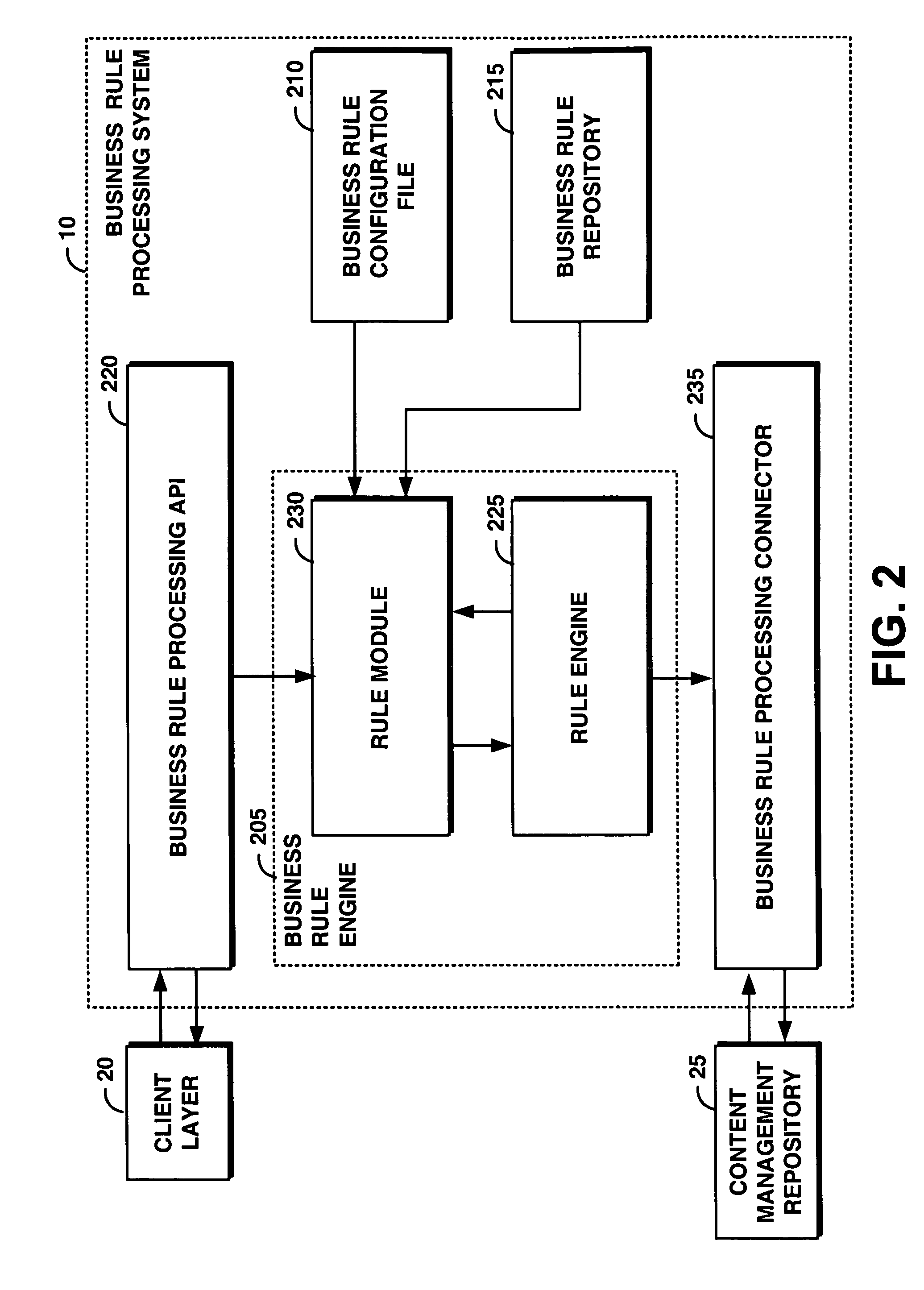

System and method for automatically processing dynamic business rules in a content management system

ActiveUS20070094199A1Development and maintenance cost is substantially reducedAccelerates business rule update cycleOffice automationKnowledge representationBusiness ruleBusiness logic

A business rule processing system automatically processes dynamic business rules in a content management system, allowing frequent updates to the business rules. The updates can be automatically adapted by the system without restarting the content management system. The system utilizes a stand-alone rule engine. Business logic is encoded as business rule definition files using a platform-independent language; the business rule definition files are stored in a central business rule repository. The business rules are managed and executed by the rules engine; the rules engine provides business rule processing services to other parts of the content management system. The system reduces development and maintenance cost, accelerates the business rule update cycle, and simplifies administration efforts.

Owner:SERVICENOW INC

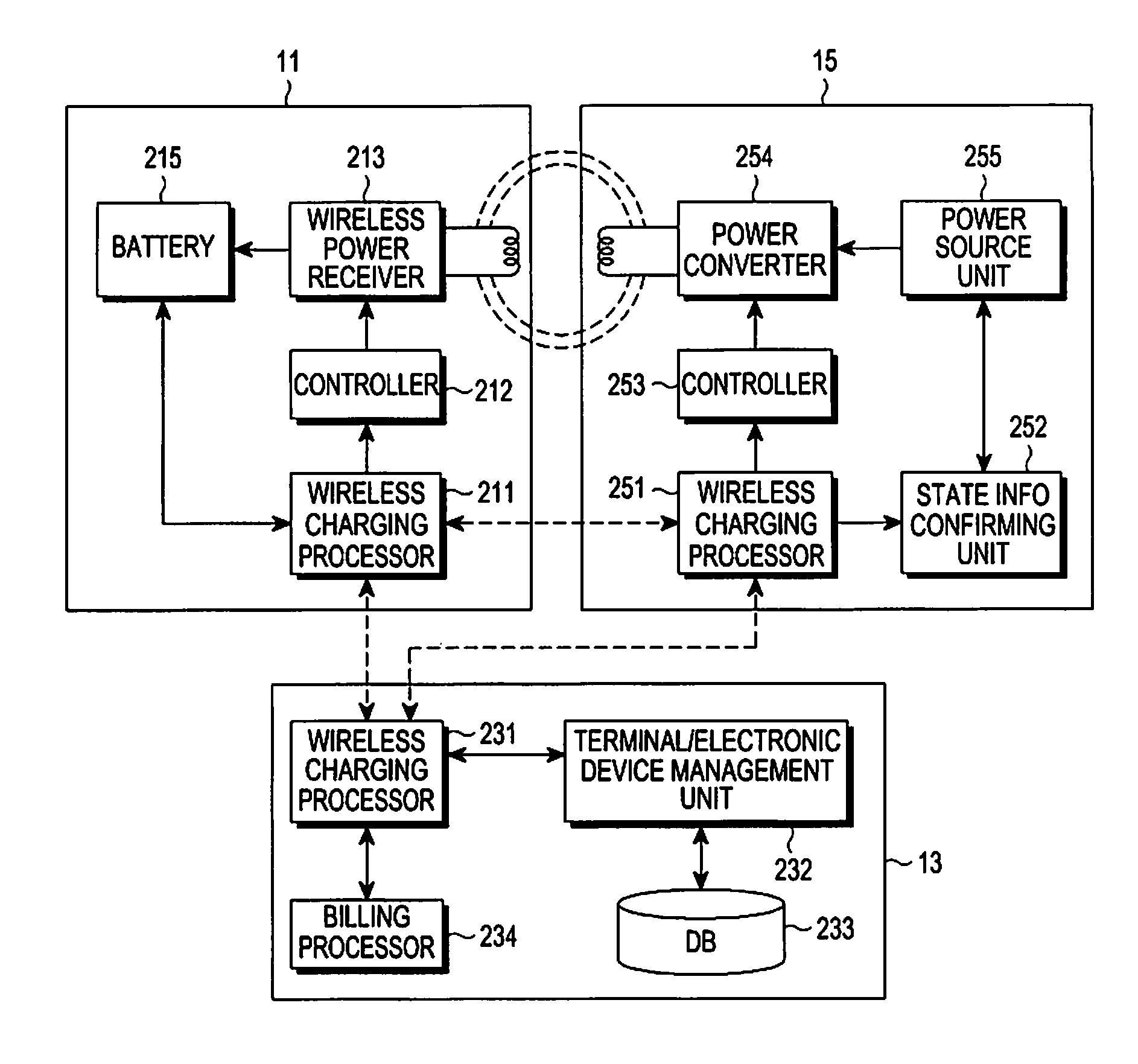

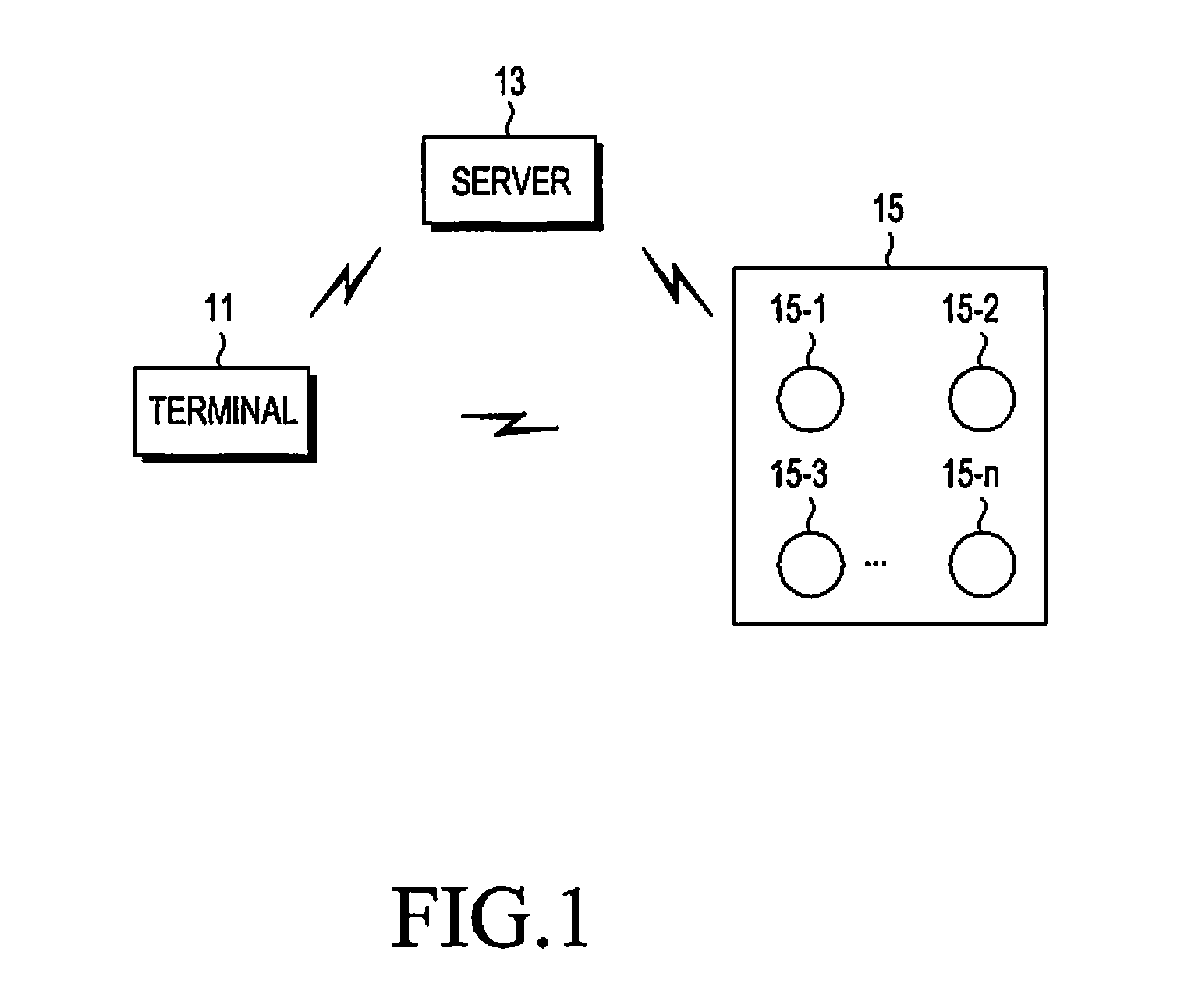

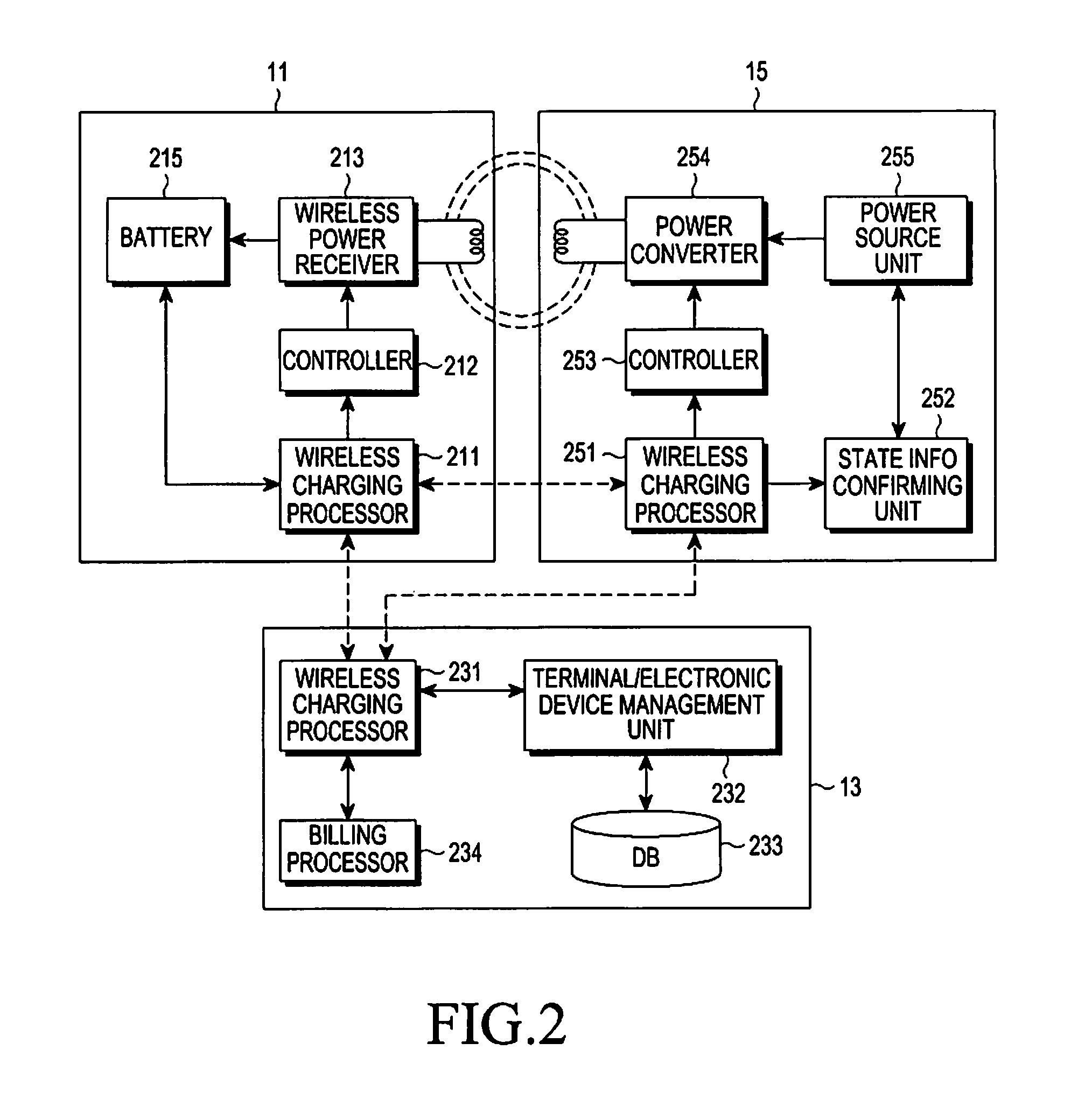

Method for wireless charging using communication network

ActiveUS20110221391A1Improve efficiencyImprove portabilityNear-field transmissionCircuit monitoring/indicationInductive chargingSwitched communication network

Owner:SAMSUNG ELECTRONICS CO LTD

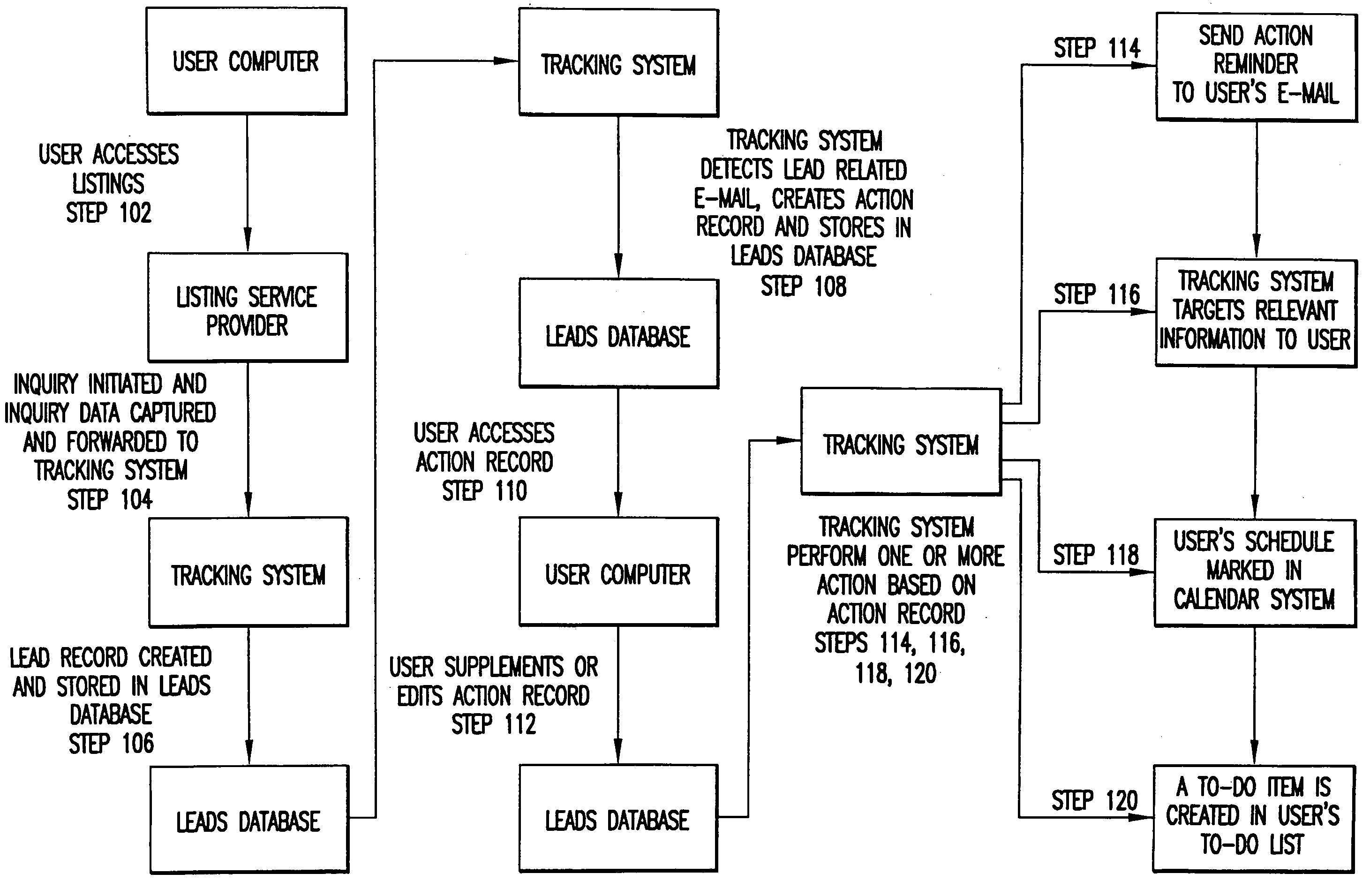

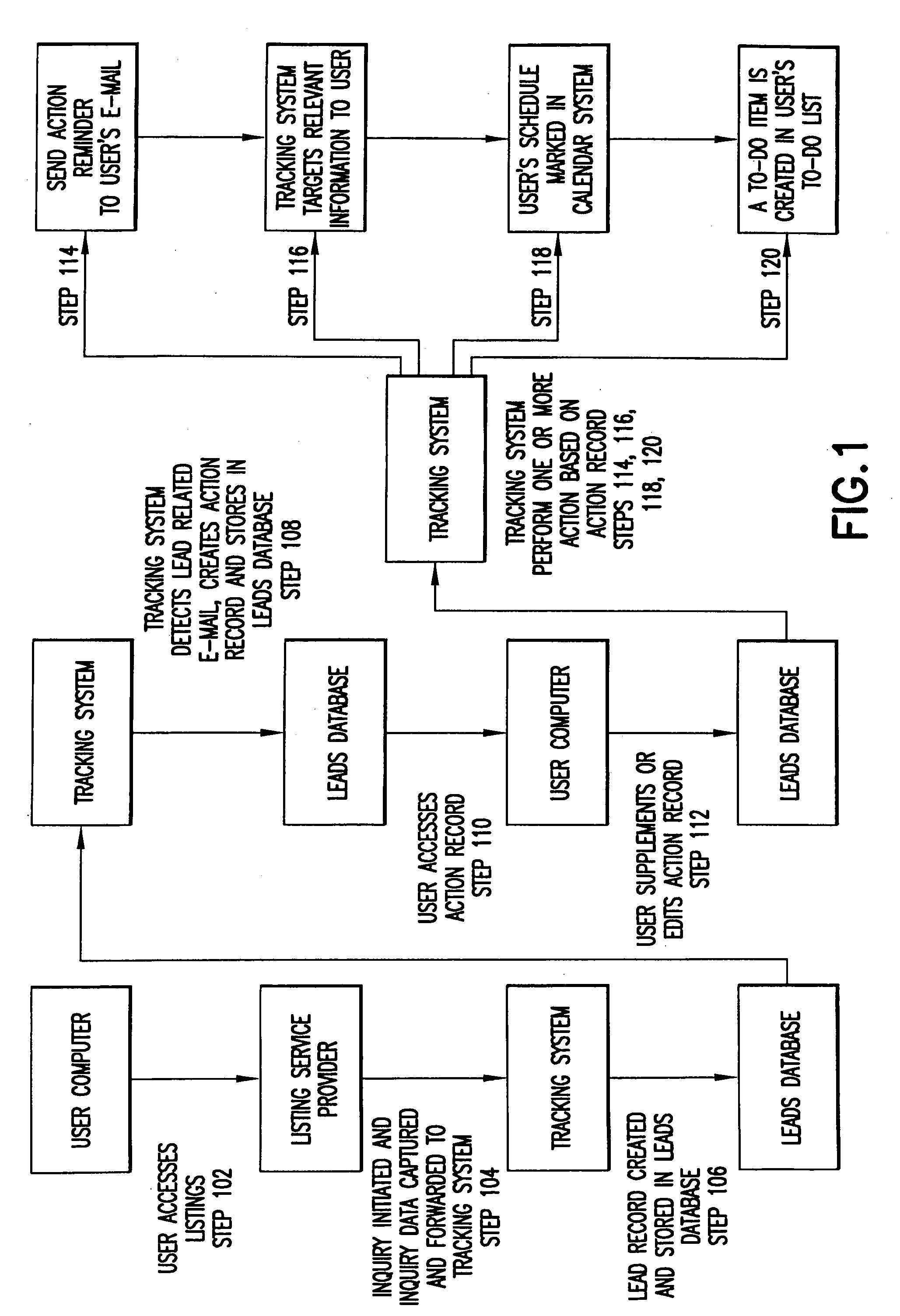

Listing service tracking system and method for tracking a user's interaction with a listing service

InactiveUS20050125408A1Improve portabilityReceive quicklyDigital data processing detailsMultiple digital computer combinationsAncillary serviceWorld Wide Web

A listing service tracking system and method for tracking a user's interaction with a listing service operates on a core tracking platform that utilizes a “lead” based concept to allow a user to efficiently and concurrently manage a large number of different leads initiated on one or more listing services. In an exemplary embodiment, the core listing service tracking platform is a software application that can be adapted to track a user's interaction with various types of listing services and to communicate with and integrate various types of ancillary services, such as e-mail, calendar systems, alerts systems, and the like.

Owner:OATH INC

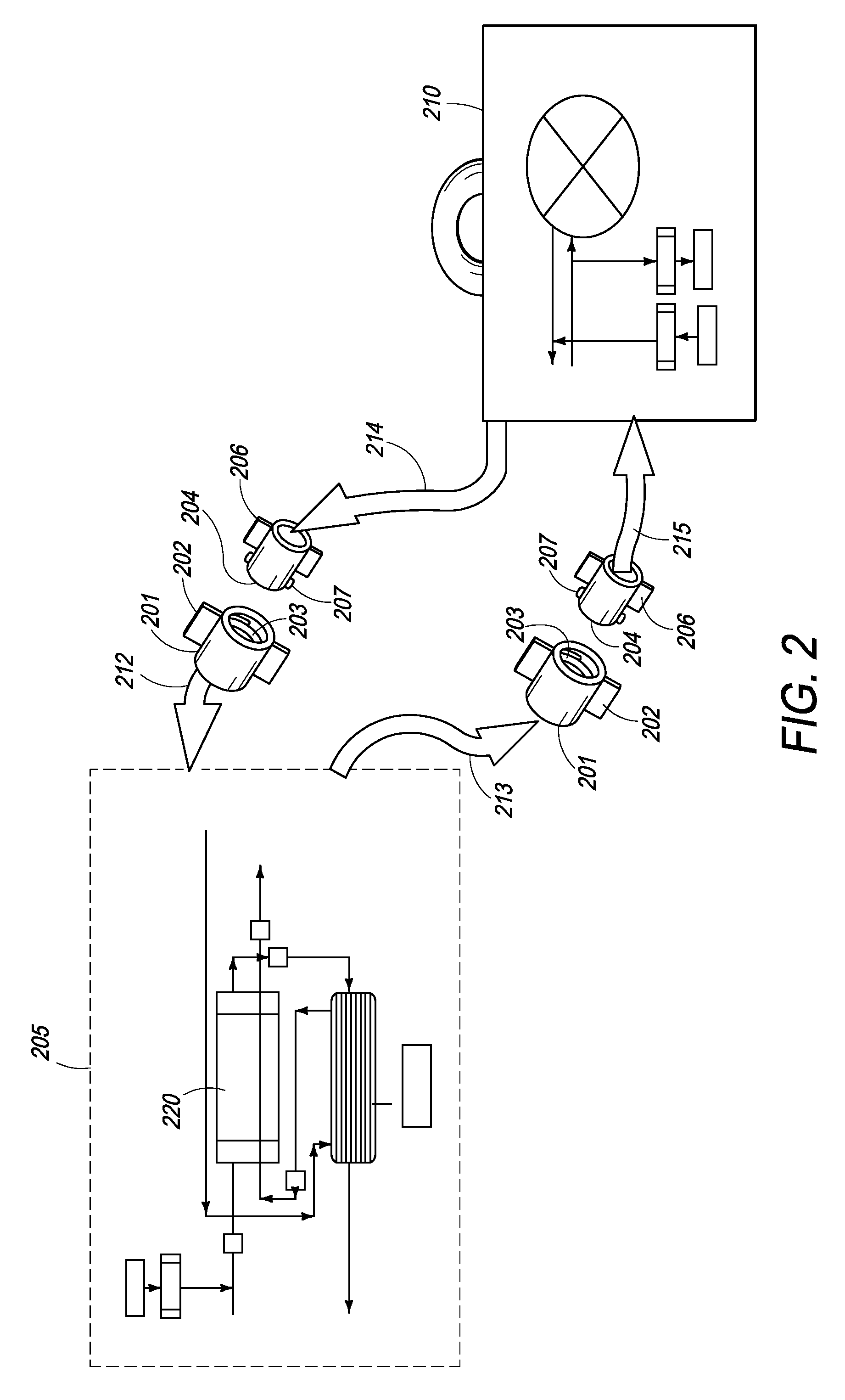

Coupling system for an infusion pump

InactiveUS20050020980A1Small sizeImprove portabilityMedical devicesPressure infusionLinear motionMotor drive

A pump system for an infusion system includes a linear drive (36, 36′) which minimizes the space occupied by the pump components in a portable housing (10, 10′). A motor (34) and a motor drive shaft (42) are arranged in parallel with, and adjacent to a syringe (14, 14′) and lead screw (94, 94′). A gear box (54) connects the drive shaft and lead screw to transfer rotational movements between them. A piston driving member, such as a drive nut (116) converts the rotational movement of the lead screw into linear motion of a syringe piston (24). A cap (190, 190′) couples the syringe (14, 14′) to the housing and provides an outlet for the liquid to be dispensed. In one embodiment, the cap (190′) is configured to rotate relative to the housing in one direction only, during locking. Rotational movement is also used for locking the piston (24) to the drive nut (116) against relative axial movement. In another embodiment, the cap (190′) carries a rotatable hub (330) which is connected at a first end (336) with an infusion line (191) and at a second end defines a needle (338) for piercing a closure (340) on the syringe.

Owner:INOUE YOSHIO +4

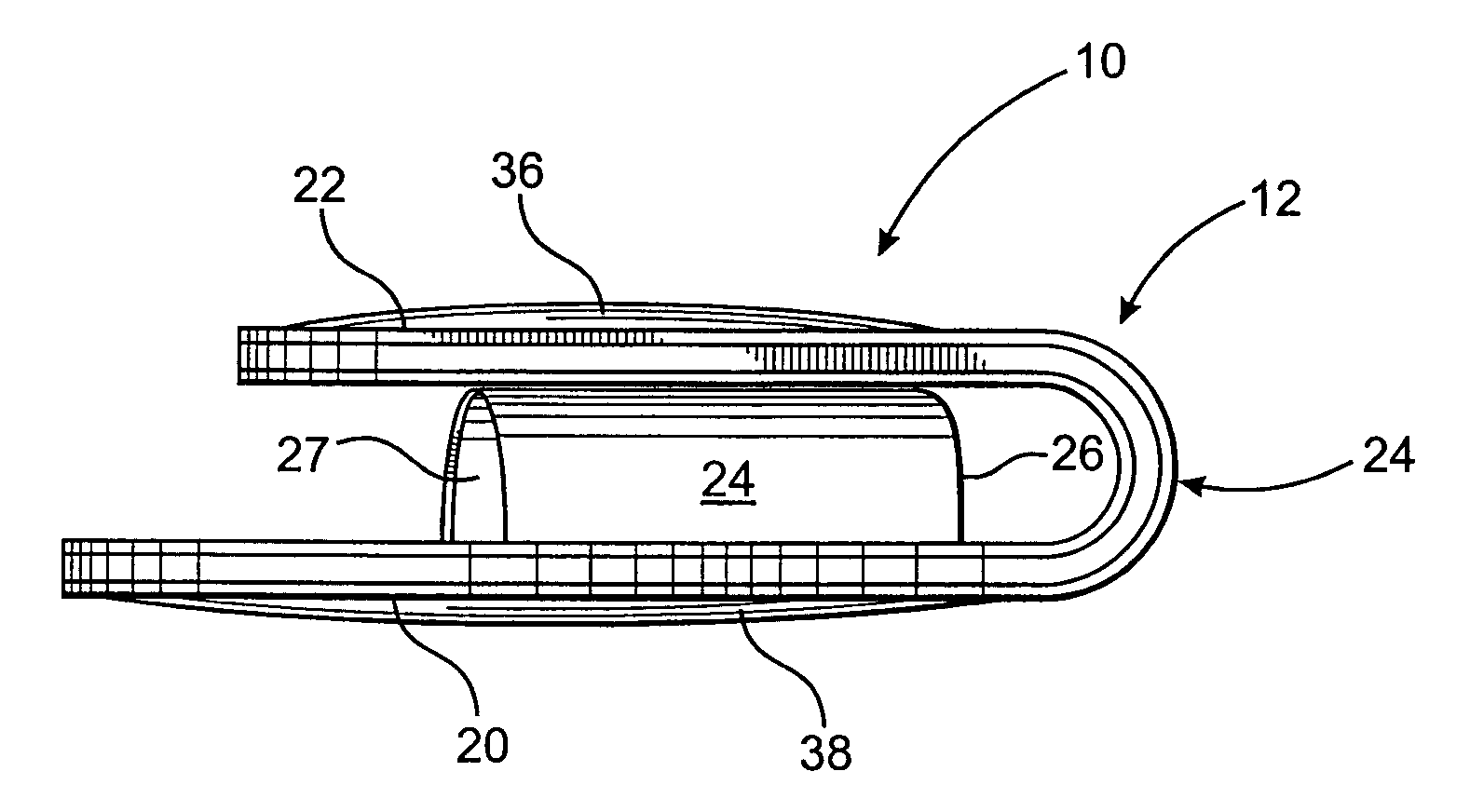

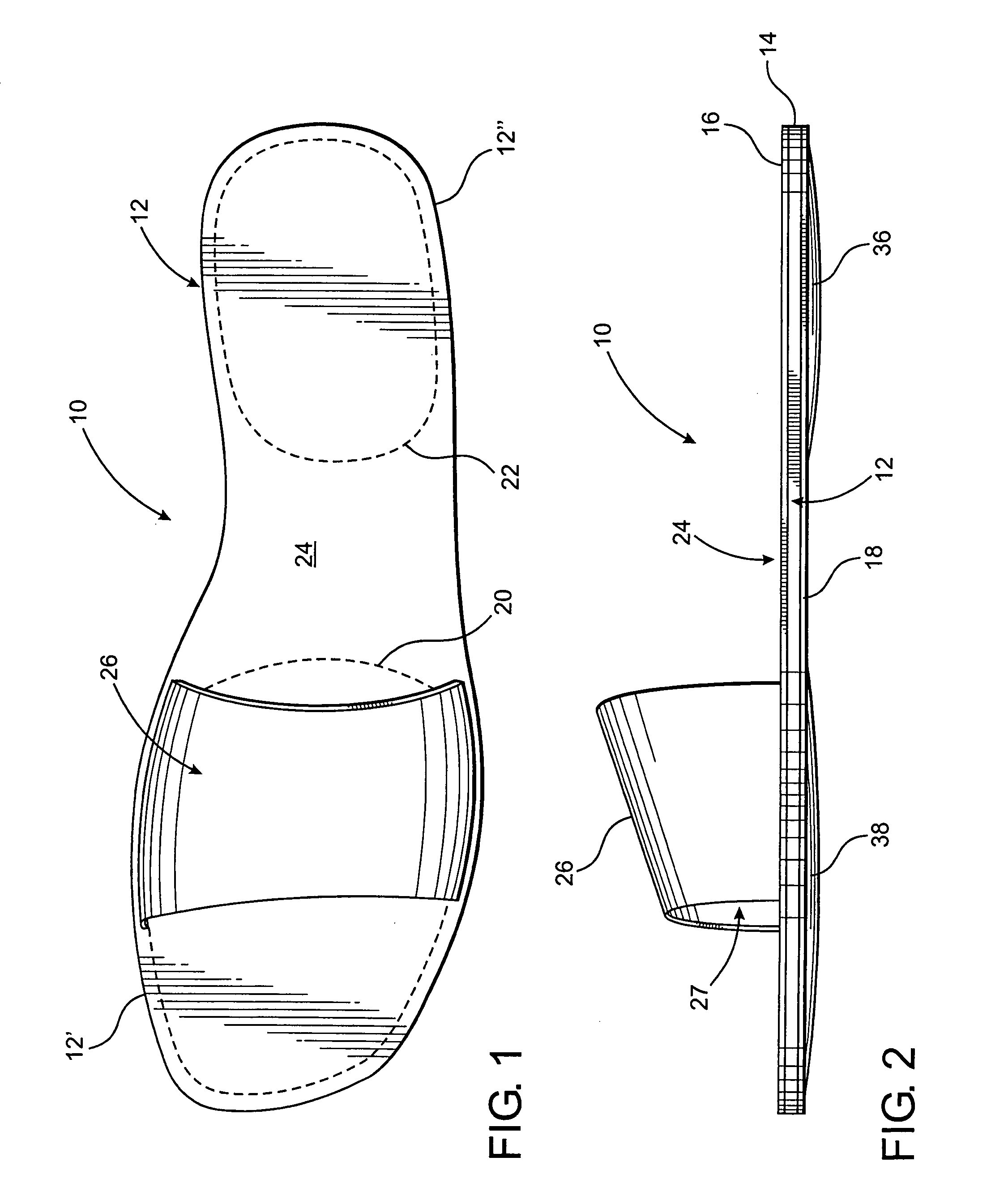

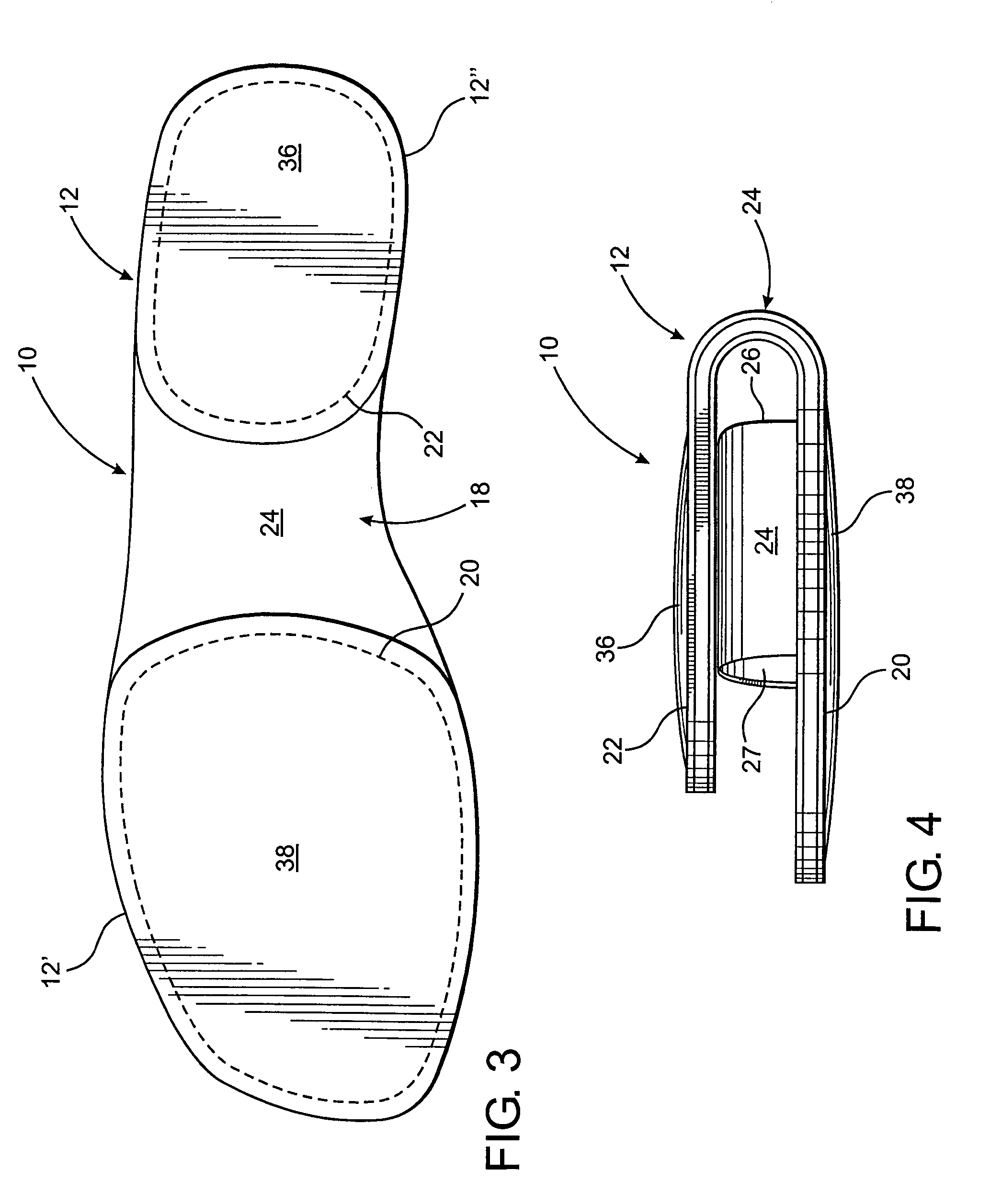

Collapsible footwear

A footwear assembly structured to be collapsible comprising a sole including a front portion and a rear portion movably interconnected by an intermediate segment. An upper extends along at least a portion of the length of the sole, depending upon the style of the footwear, wherein the upper and the sole are preferably structured to define the sandal configuration which may vary in style. The intermediate portion includes sufficient flexibility to significantly reduce the size of the sandal by folding the sole into a stored orientation defined by the front and rear portions disposed in at least partially overlying relation to one another. A pouch-like container is dimensioned and configured to receive and maintain at least a pair of the sandals on the interior thereof, when in the stored orientation.

Owner:LOLA STYLE

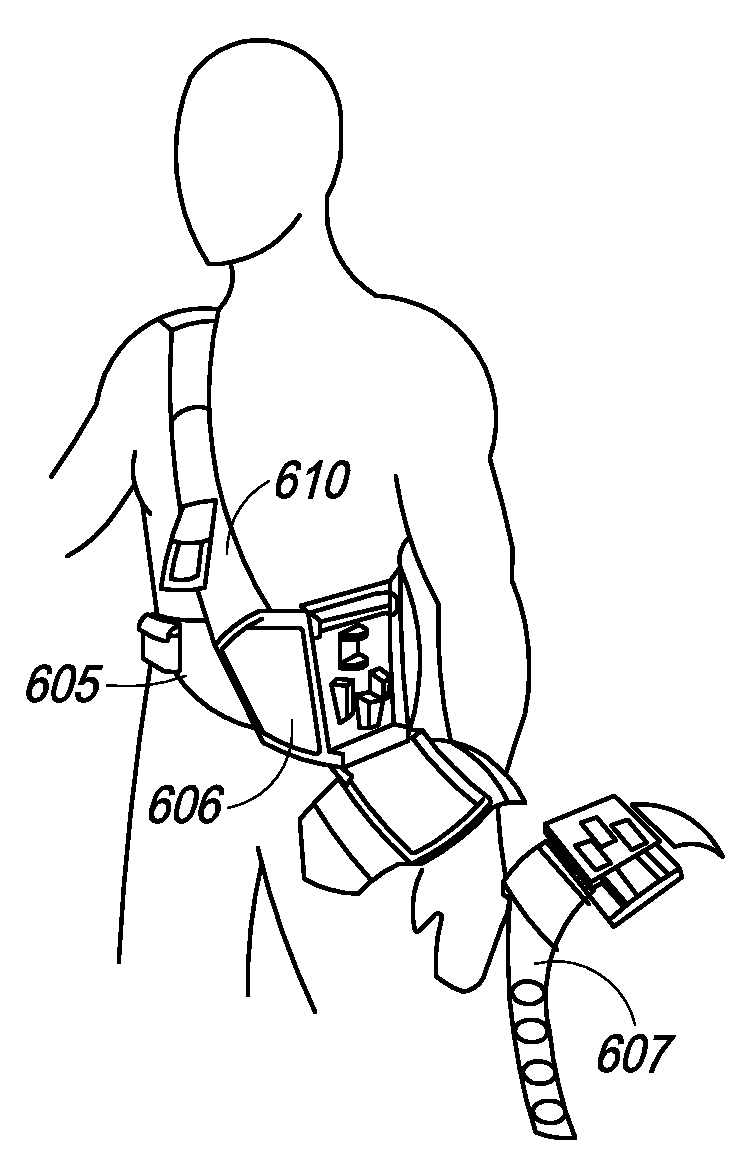

Wearable dialysis methods and devices

InactiveUS20090120864A1Optimal flexibilityHighly portableOther chemical processesDialysis systemsDialysis fluidDialysis method

The present invention provides a portable continuous dialysis system configured as a wearable belt in fluid communication with a separate portable unit in the form of an easy to carry bag-pack or case, or a fanny pack wearable around the shoulder. In one embodiment, the wearable belt unit comprises a dialyzer and a pump, such as a dual pulsatile pump, while the portable unit comprises a dialysate regeneration system and a waste collection bag. In another embodiment, the wearable belt unit comprises a manifold for blood circuit, while the portable unit comprises a manifold for dialysate circuit. The placement of components can be varied between the portable unit and the wearable belt unit, depending upon factors such as comparative weight and size of the belt and portable units, the ease of operation of the dialysis system by the patient, the overall length of the tubing system and the safety of operation of the overall system.

Owner:FRESENIUS USA INC

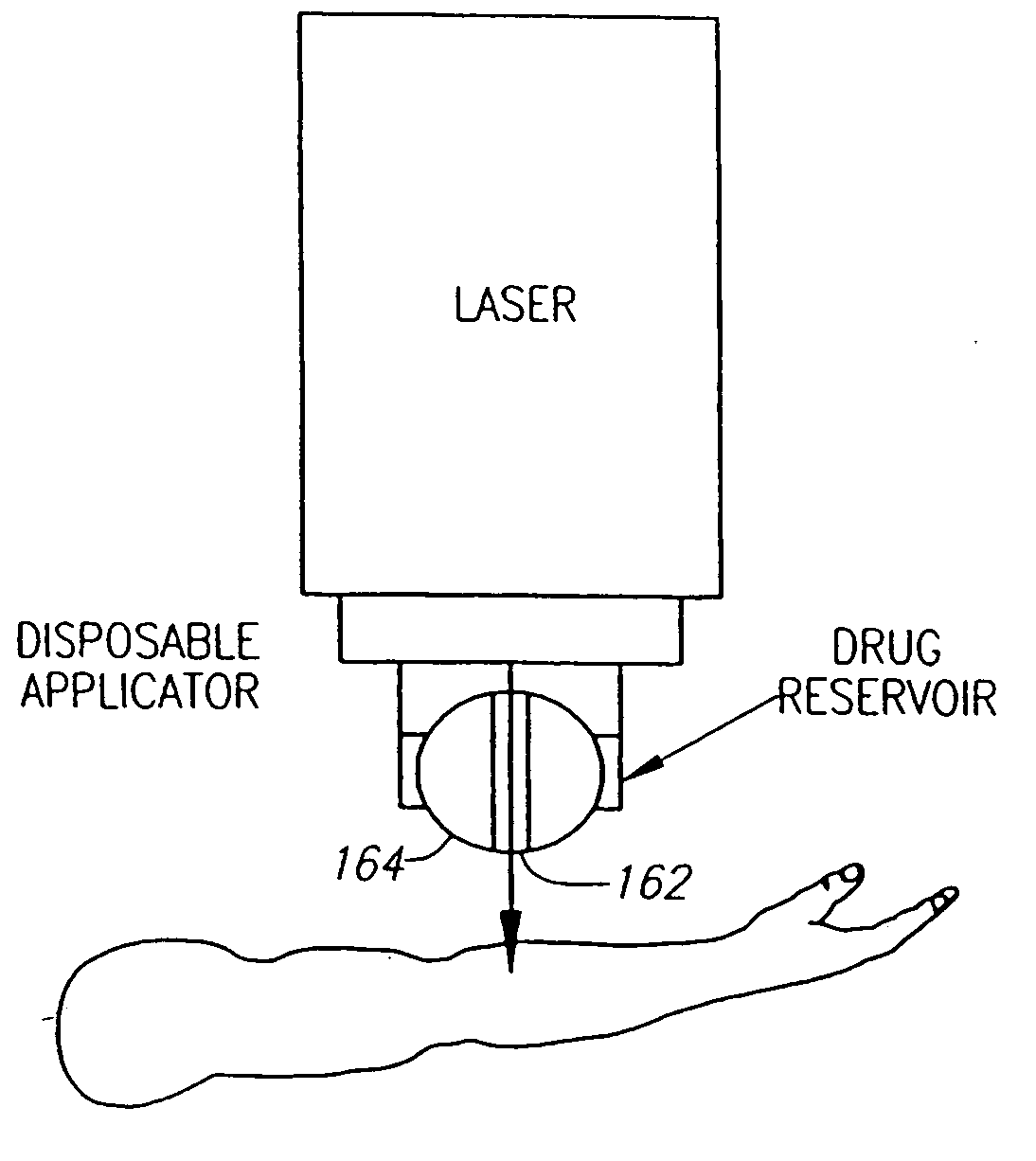

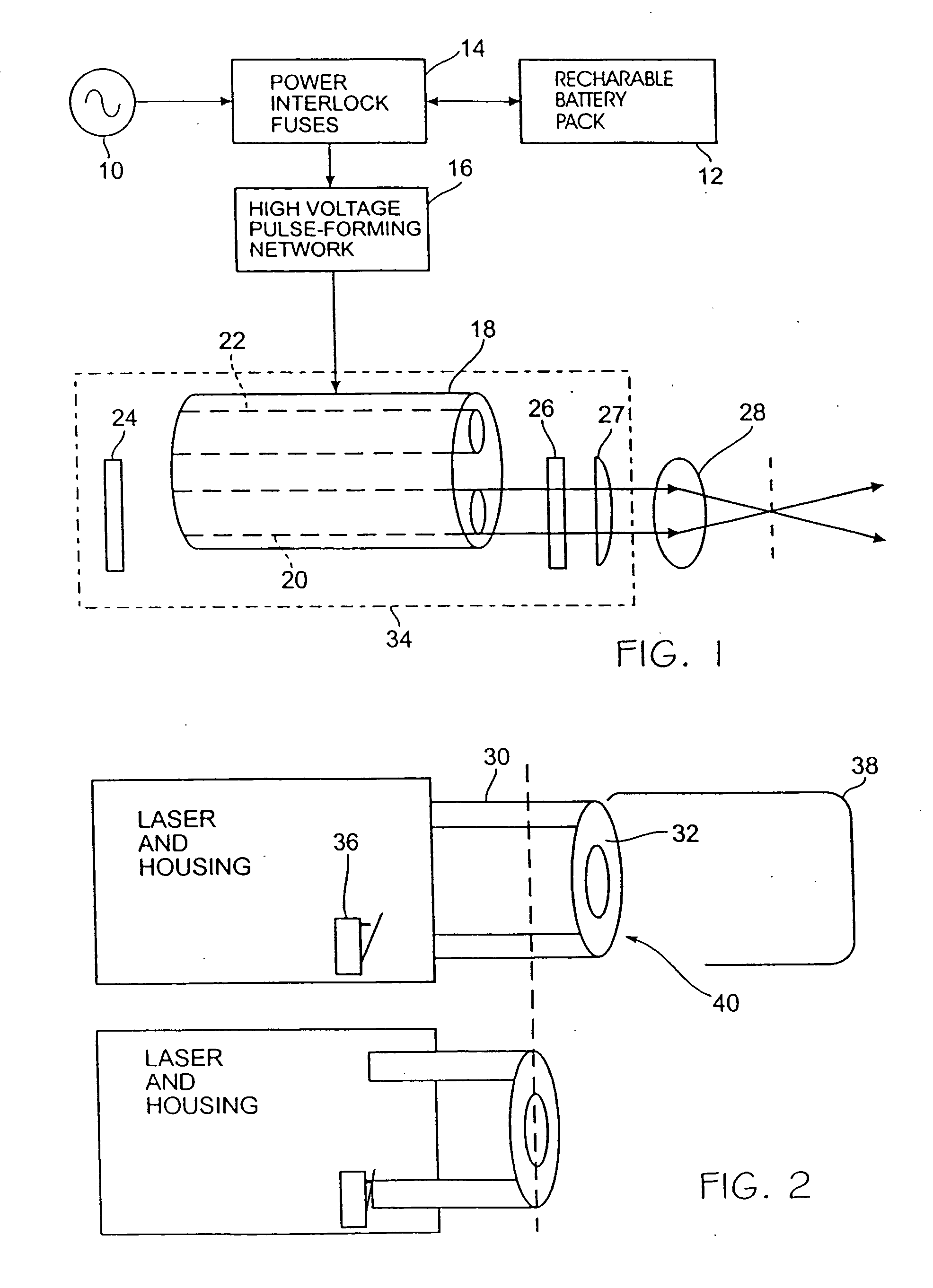

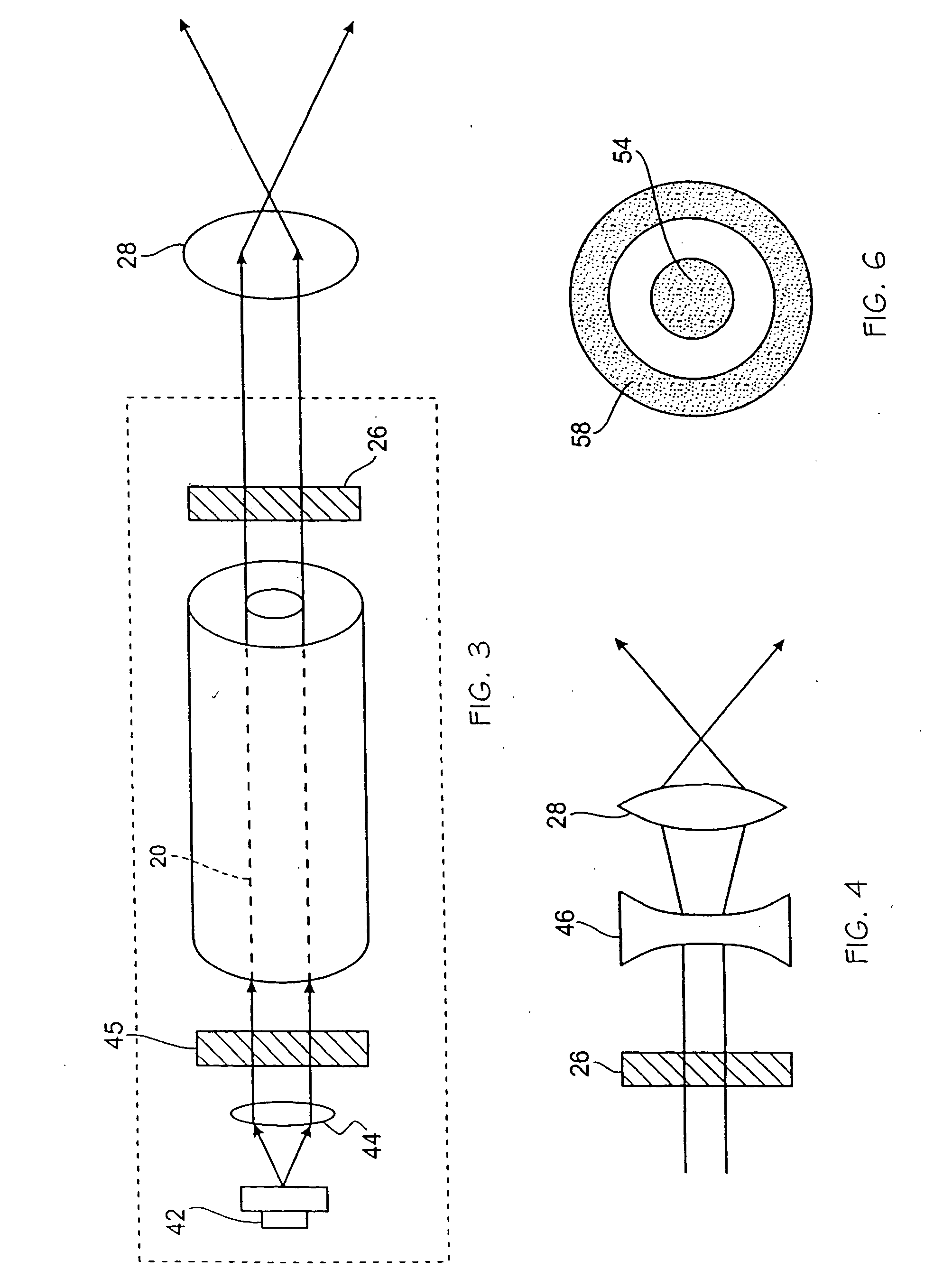

Removable tip for laser device with transparent lens

InactiveUS20050010198A1Eliminate undesired damageEliminate unnecessary damageElectric tinnitus maskersSurgical needlesStratum corneumStress gradient

The present invention provides an improved method of removing fluids, gases or other biomolecules, or delivering a pharmaceutical composition, through the skin of a patient without the use of a sharp or needle. The method includes the step of irradiating the stratum corneum, an applied pharmaceutical or an absorbing material, using a laser. By selection of parameters, the laser irradiates the selected material or tissue to create pressure gradients, plasma, cavitation bubbles, or other forms of tissue ablation or alteration. These methods increase the diffusion of pharmaceuticals into, or fluids, gases or other biomolecules out of, the body. For this invention, a pharmaceutical composition can be applied to the skin before or after laser irradiation.

Owner:TRANSMEDICA INT

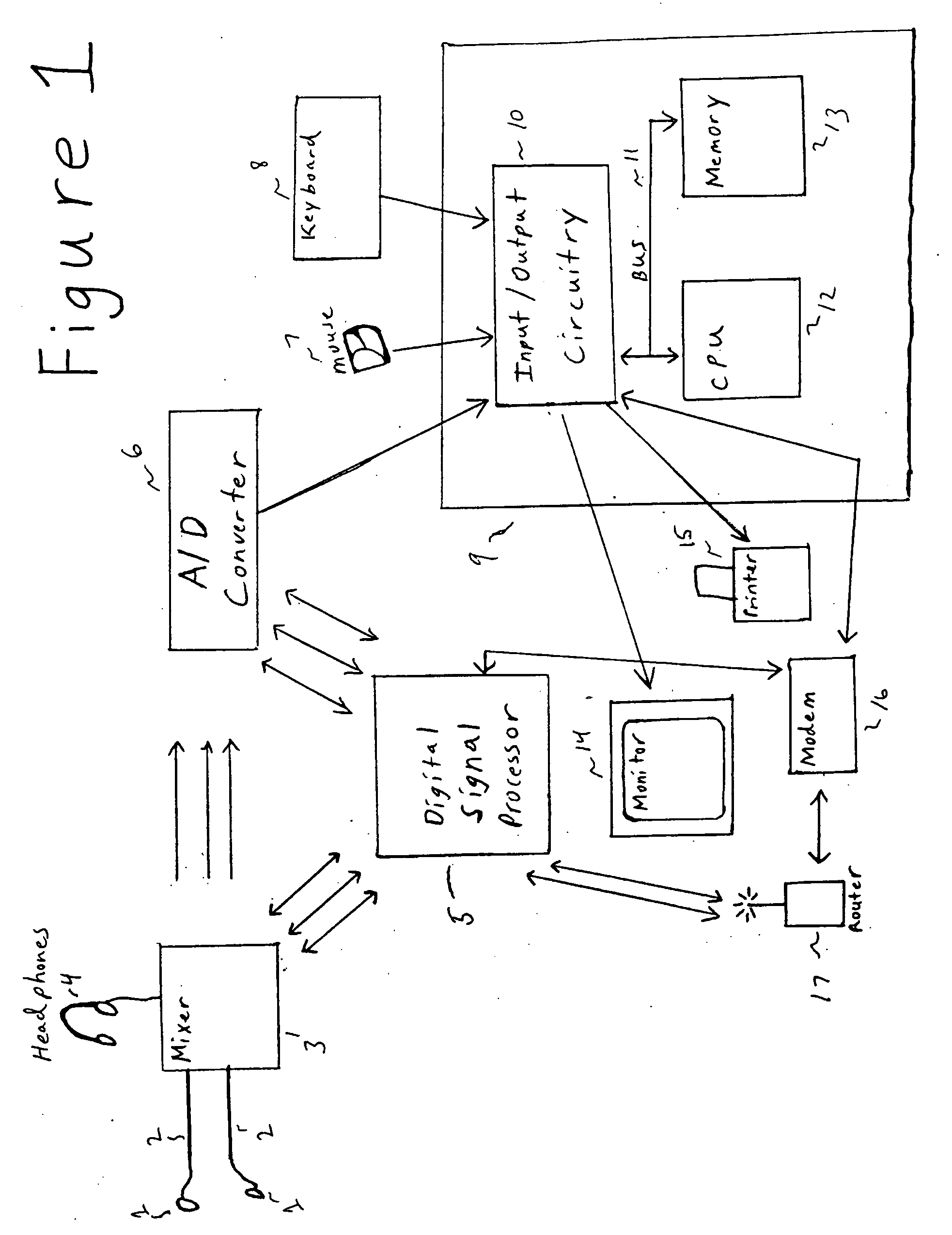

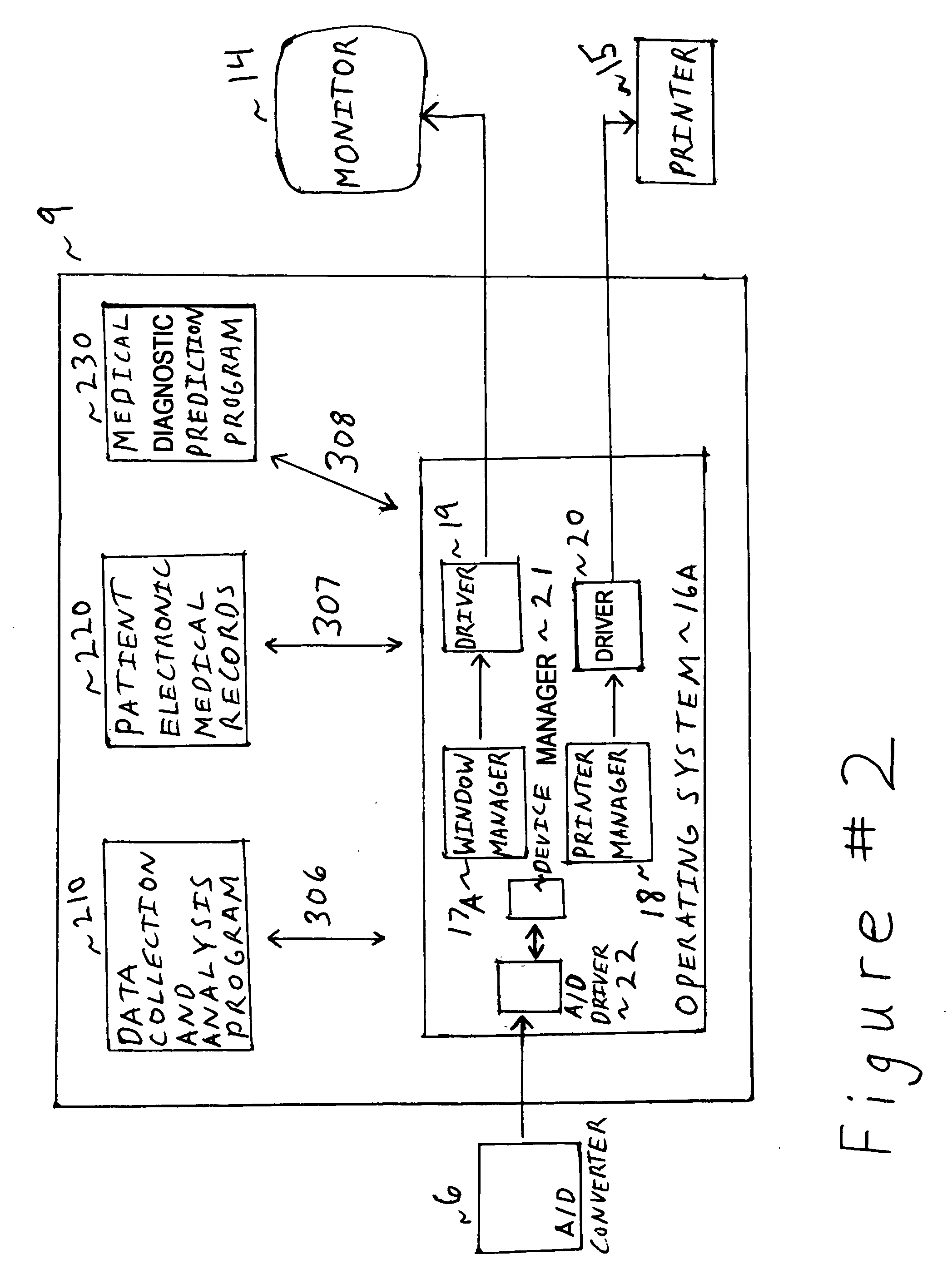

System and method for acquisition and analysis of physiological auditory signals

ActiveUS20070282174A1Improve clinical efficiencyImprove clinical outcomesStethoscopeDiagnostic recording/measuringGraphicsDigital signal processing

A diagnostic system for collecting, processing, recording and analyzing sounds associated with the physiologic activities of various human organs. The system includes a plurality of transducers placed on the body surface at the operator's discretion. The microphones are coupled to analogue / digital signal processing circuitry for enhancement of the desired signal and exclusion of ambient noise. An A / D converter digitizes the incoming data and transmits data, which is divided into a multitude of discrete blocks, received over very finite intervals of time, to a computer workstation and moved through an analysis program sequentially. The program is displayed as a series of icons which depict operations that the program performs and which allow the operator to reprogram the system at any time. The data is finally displayed in graphical format and stored in memory as the program processes each block sequentially.

Owner:AUDIO EVOLUTION DIAGNOSTICS INC

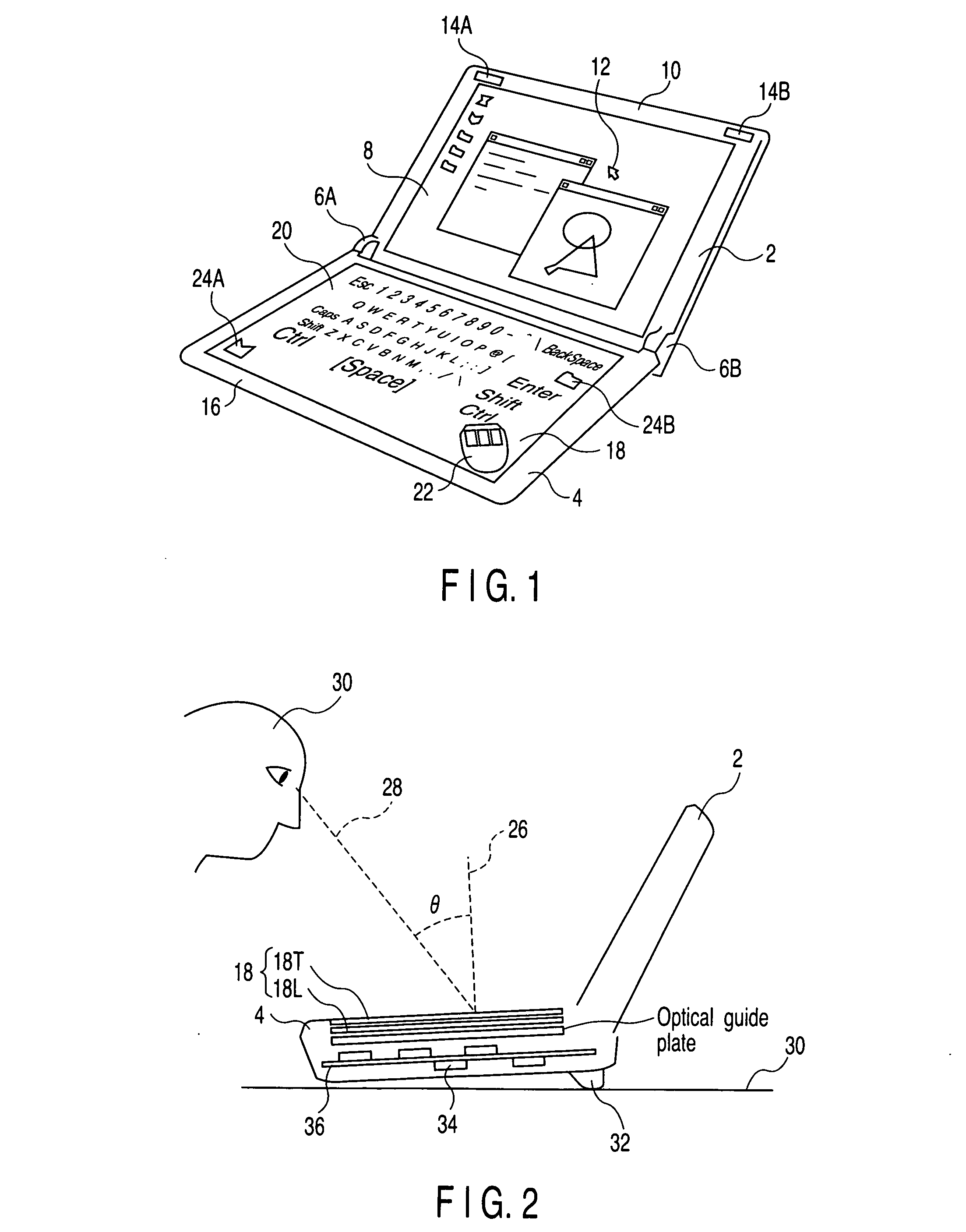

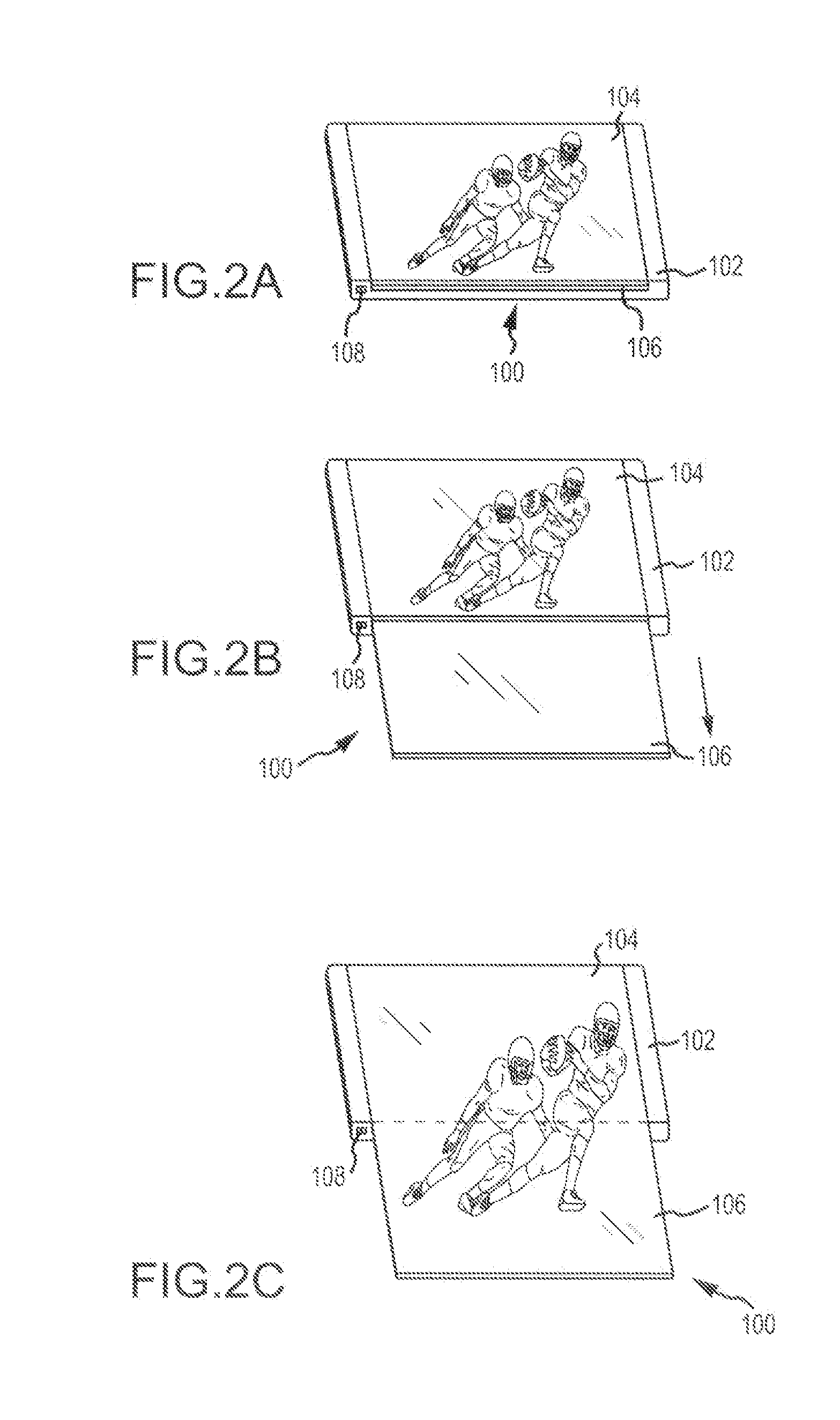

Image display apparatus

InactiveUS20060050169A1High level of portabilityEnlarged display screenTelevision system detailsColor television detailsComputer graphics (images)Image display

An image display apparatus have two frames, a flexible image display screen and a unit. The two frames mutually closable and openable are linked through a pivot. When the two frames are closed, the flexible image display screen is arranged inside the two frames, being folded into two with its part being curved. The image display screen is opened when the two frames are opened. The unit is supported by one of the two frames so as to pivot freely between a housed position and a position in the use of the display screen. The housed position is where the unit is placed on the display screen. When the display screen is in use, the unit is moved outside the display screen. By turning the unit to the housed position and closing the two frames, the unit is further housed in the position sandwiched by the folded display screen.

Owner:FUJIFILM CORP

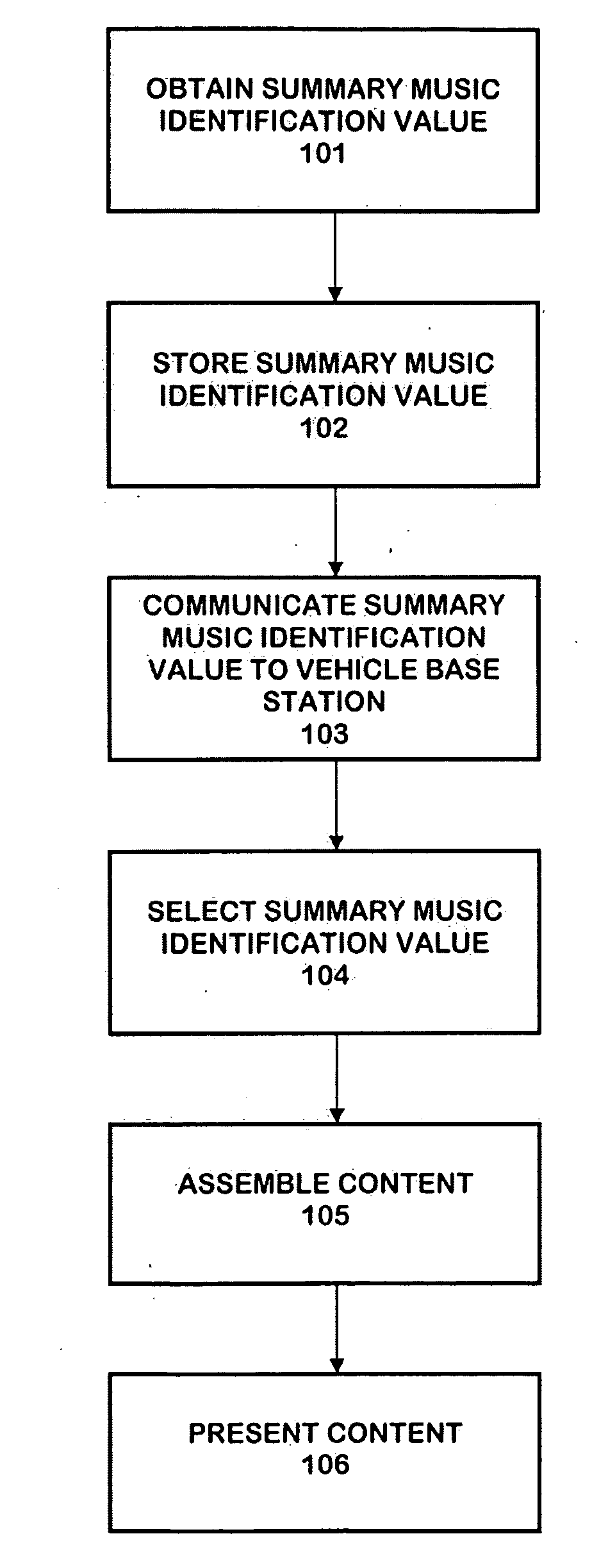

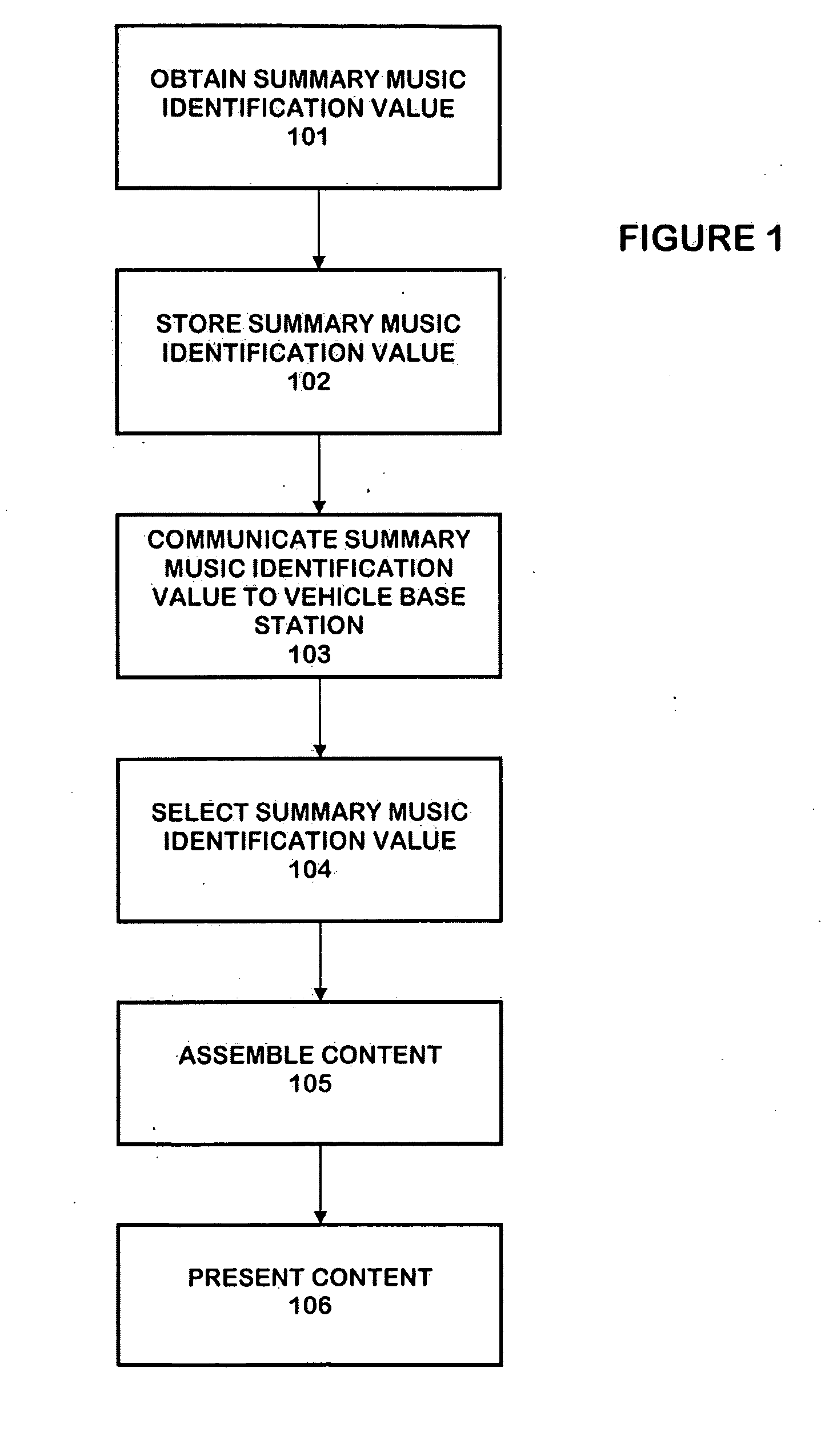

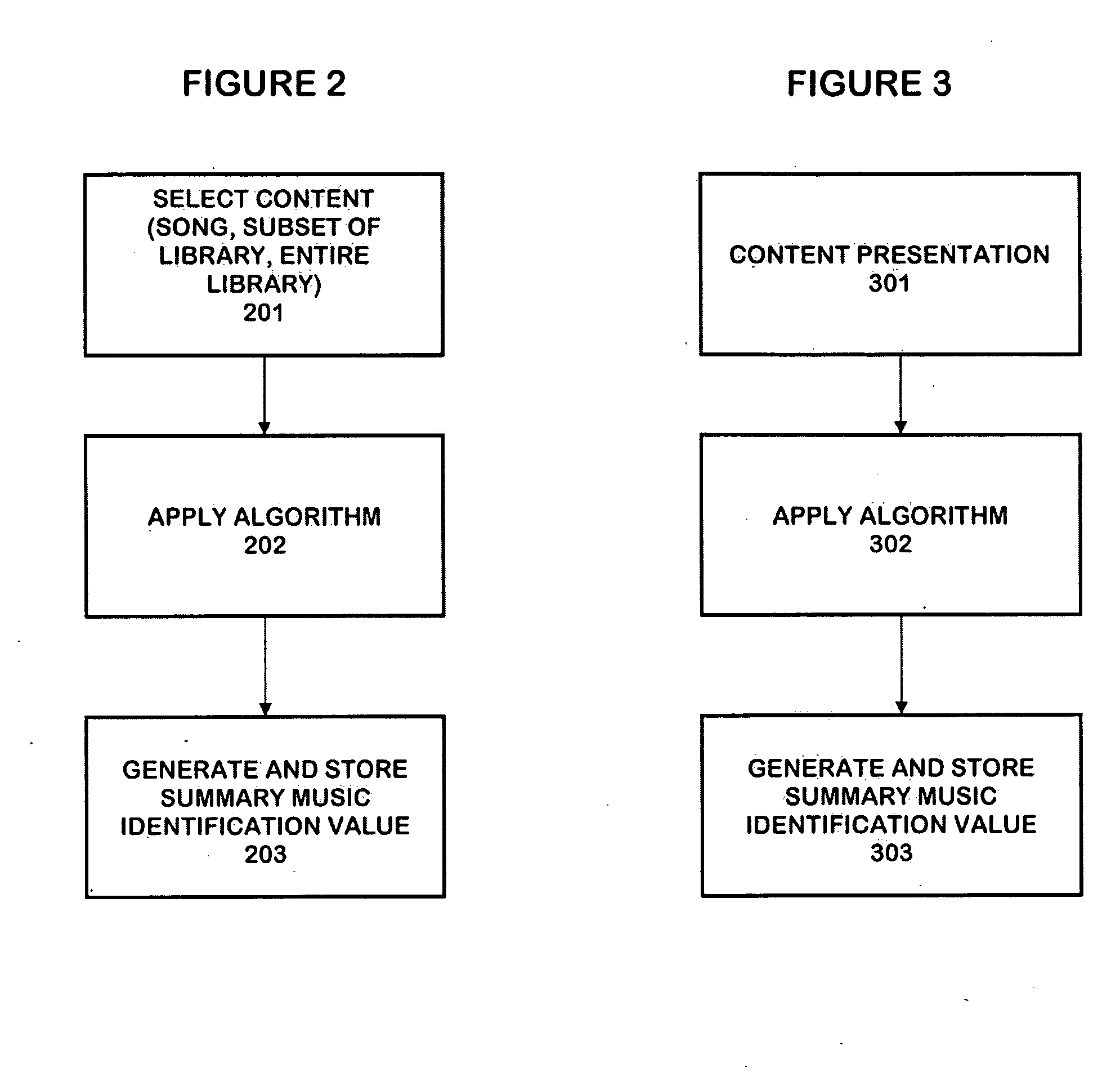

Vehicle infotainment system with virtual personalization settings

InactiveUS20090164473A1Reduce distractionsScalable functionalityElectrophonic musical instrumentsElectronic editing digitised analogue information signalsPersonalizationDistraction

The personalized content system of the system combines a summary music identification value creation and identification algorithm that represents a mathematical summary music identification of a song, an audio file, or other relational music criteria and data (e.g. title, artist, genre, style, beats per minute, etc.) or any combination thereof. The derived value represents the musical taste or style attributes of a song or style. The analysis and generation of the summary music identification value is intended to take place while outside the vehicle where attention can be paid and vehicle distraction and safety is not an issue. A user can generate a single summary music identification value or can generate multiple summary music identification values for different criteria. In other cases, summary music identification values can be defined for genre, but with a much more personal touch possible than with fixed playlist radio stations. In another embodiment, a user can obtain and use someone else's summary music identification value (e.g. a celebrity, artist, friend, etc.) and use it with the system.

Owner:HARMAN INT IND INC +1

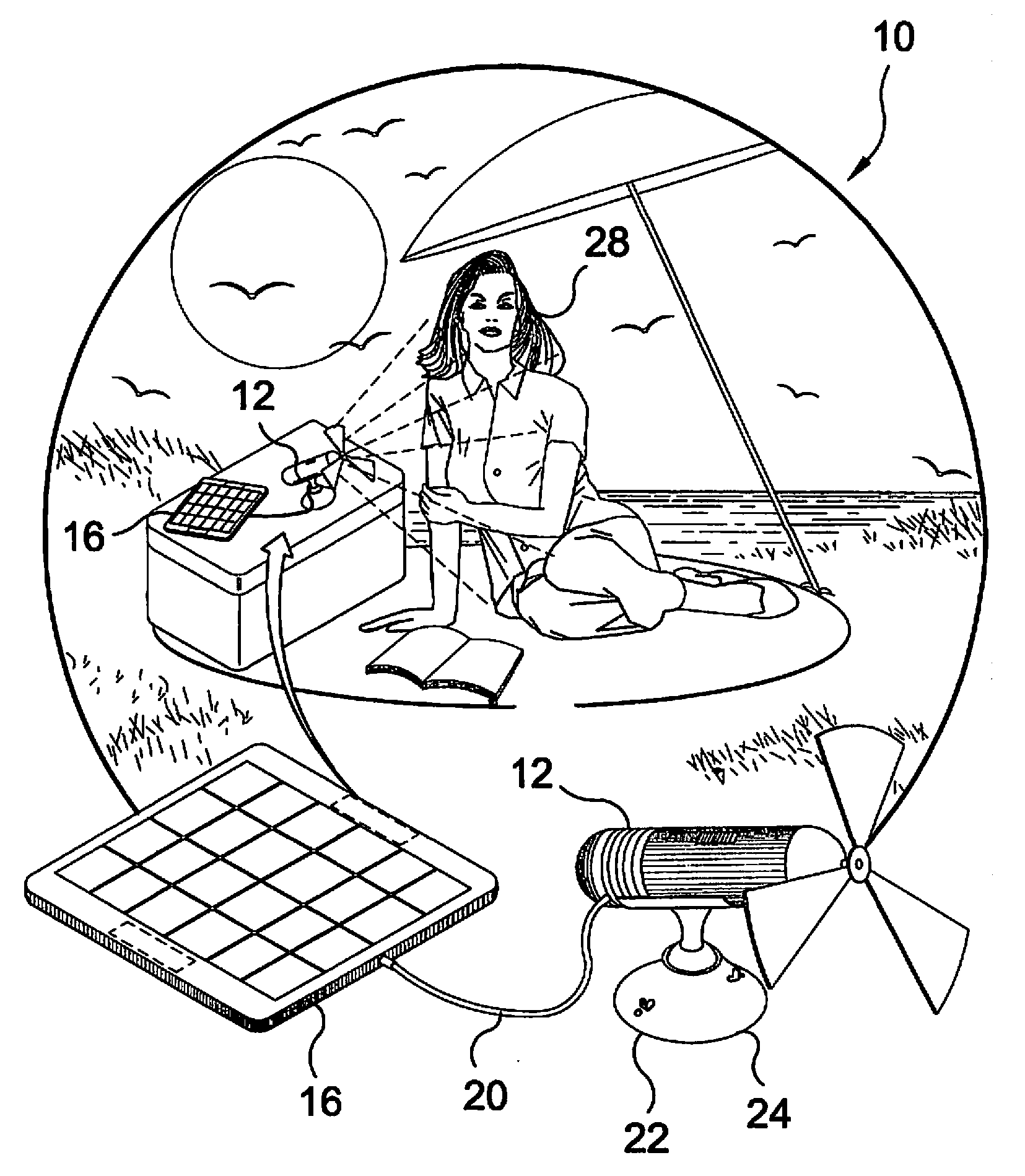

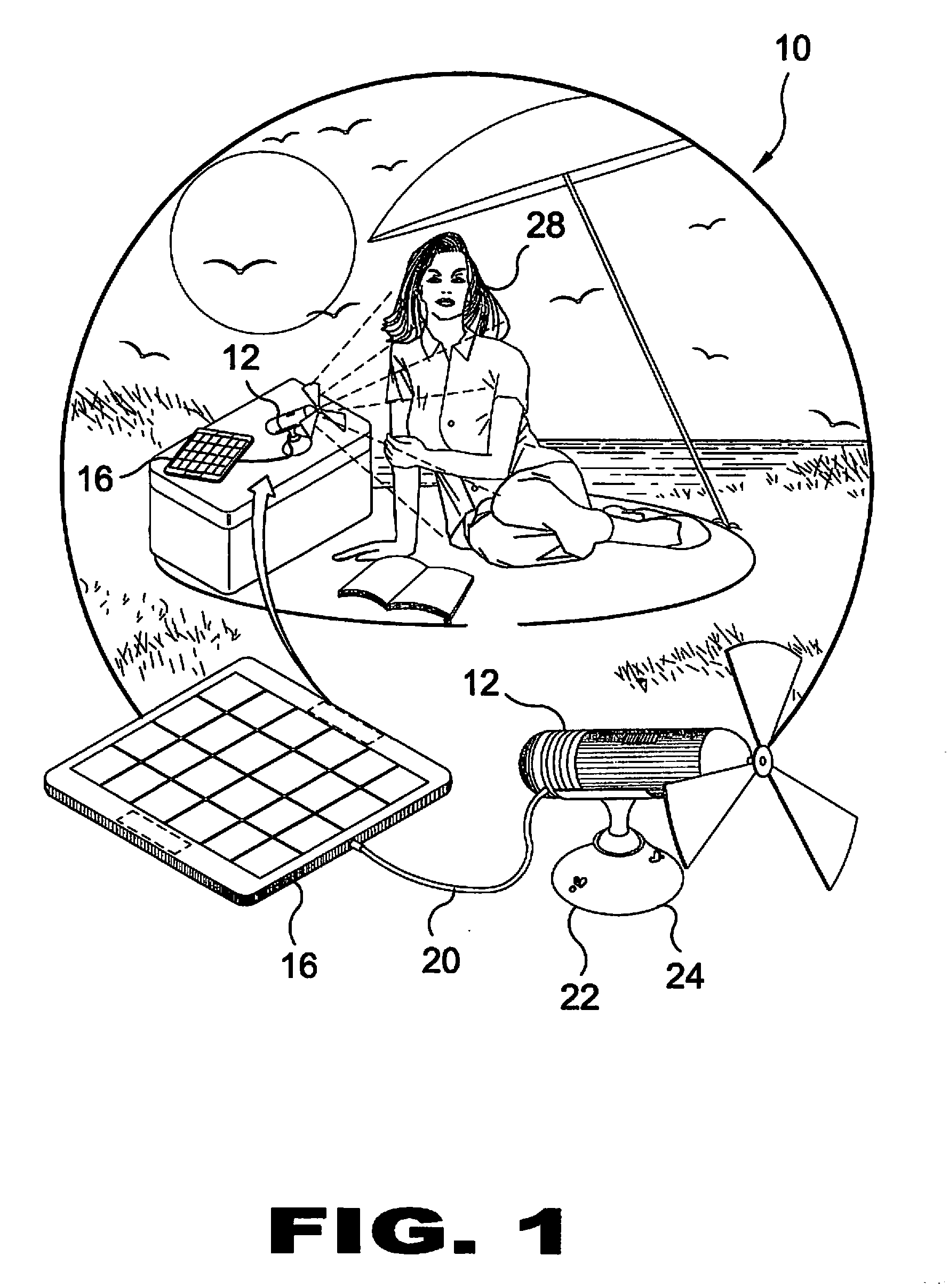

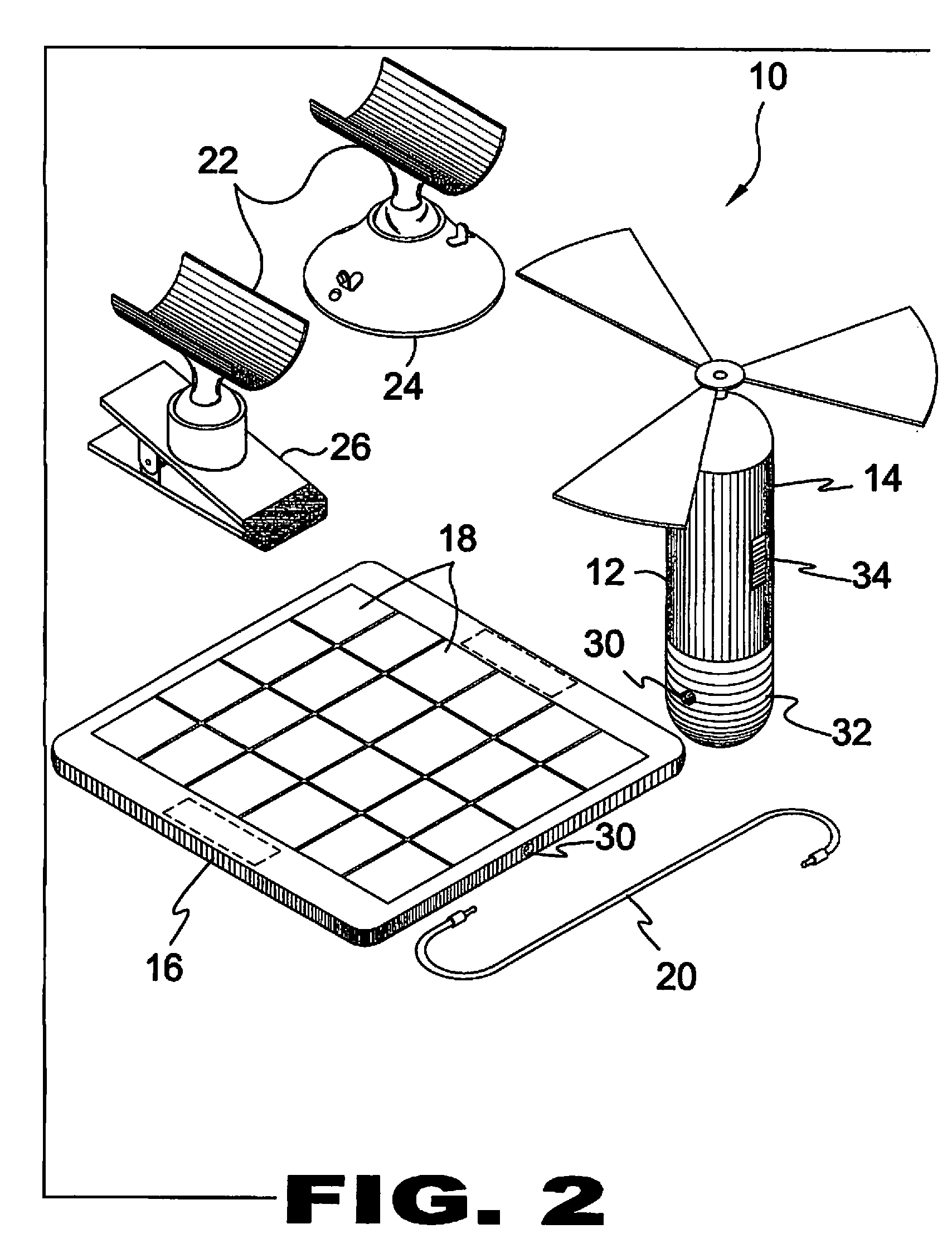

Solar Powered Fan

InactiveUS20080152482A1Improve portabilityLighting and heating apparatusAxial flow pumpsRechargeable battery packBroad spectrum

A solar powered personal fan with a much broader spectrum of both portable and fixed operating applications whereas prior art is application specific. This device also provides a plurality of fixed and portable power supplies. A solar panel, rechargeable battery pack or home charger can all be used as a power supply to operate the present invention.

Owner:PATEL AMISH

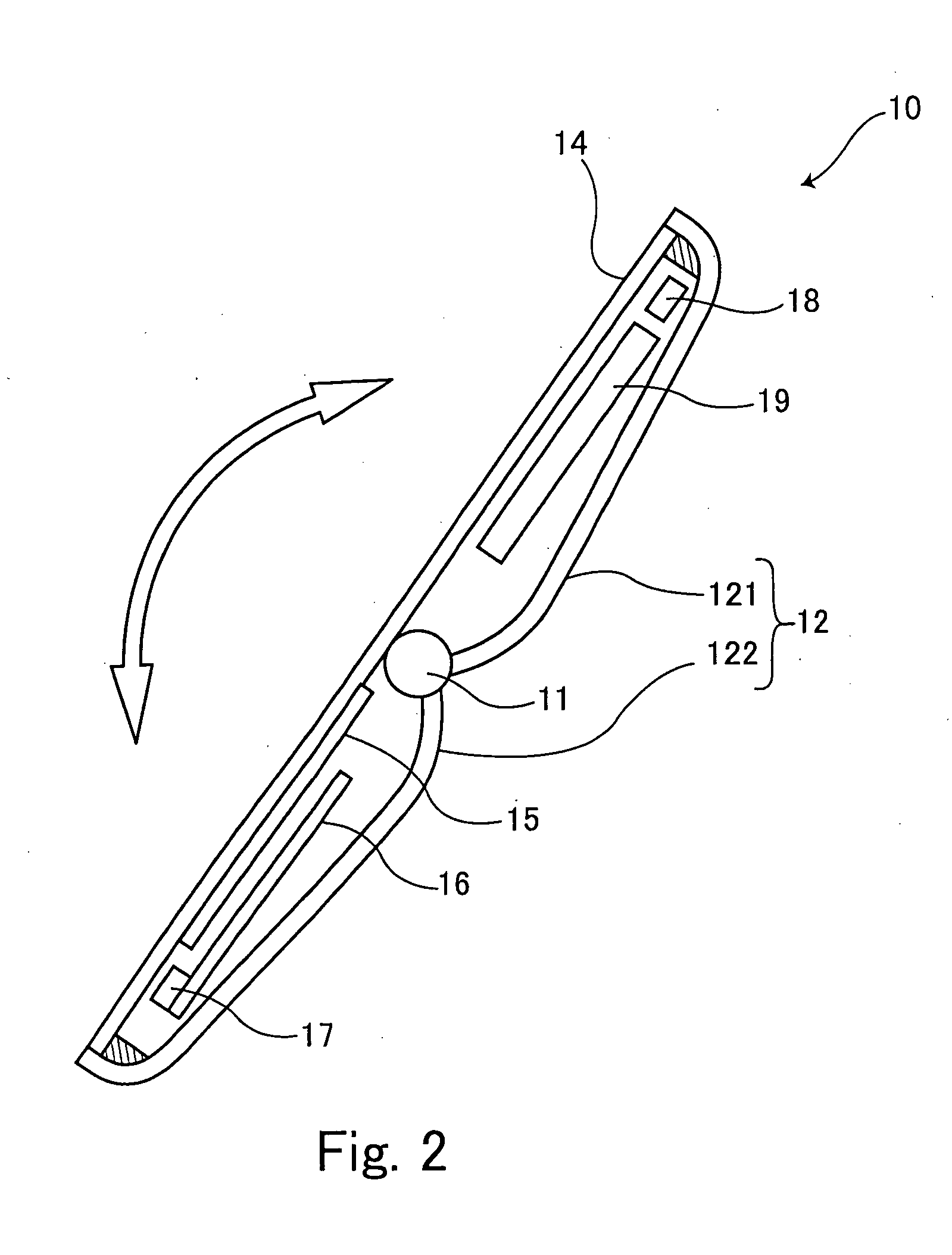

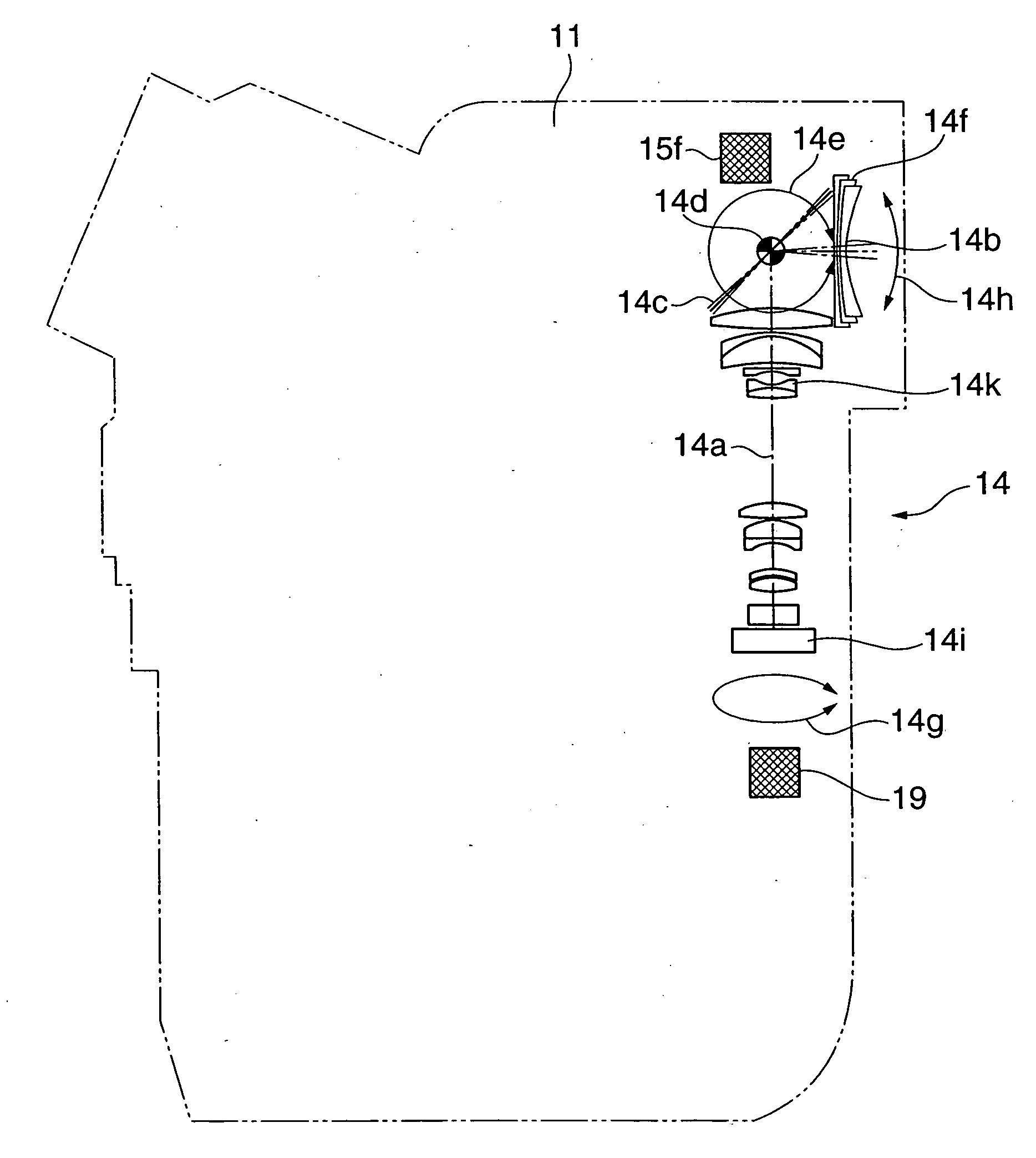

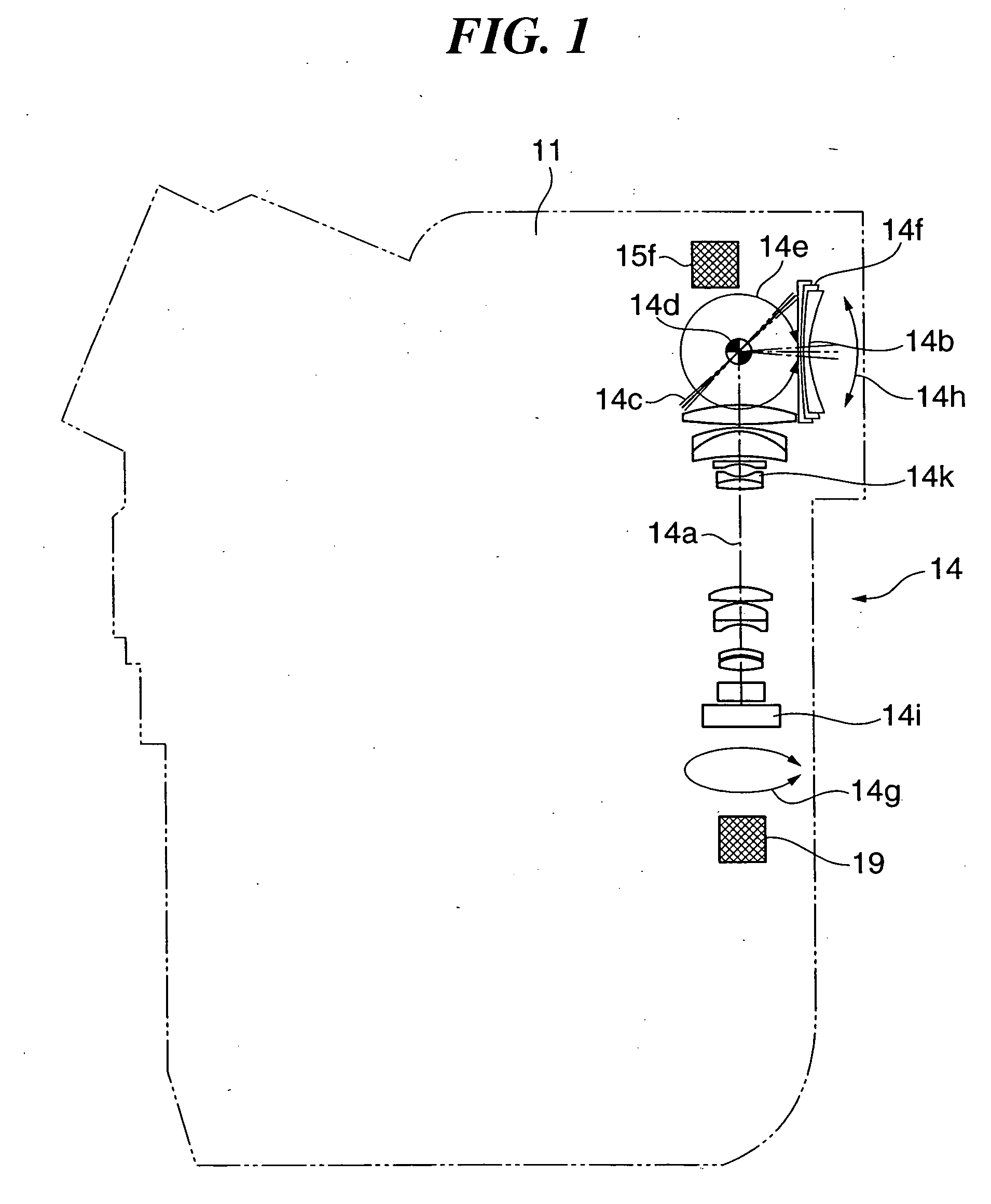

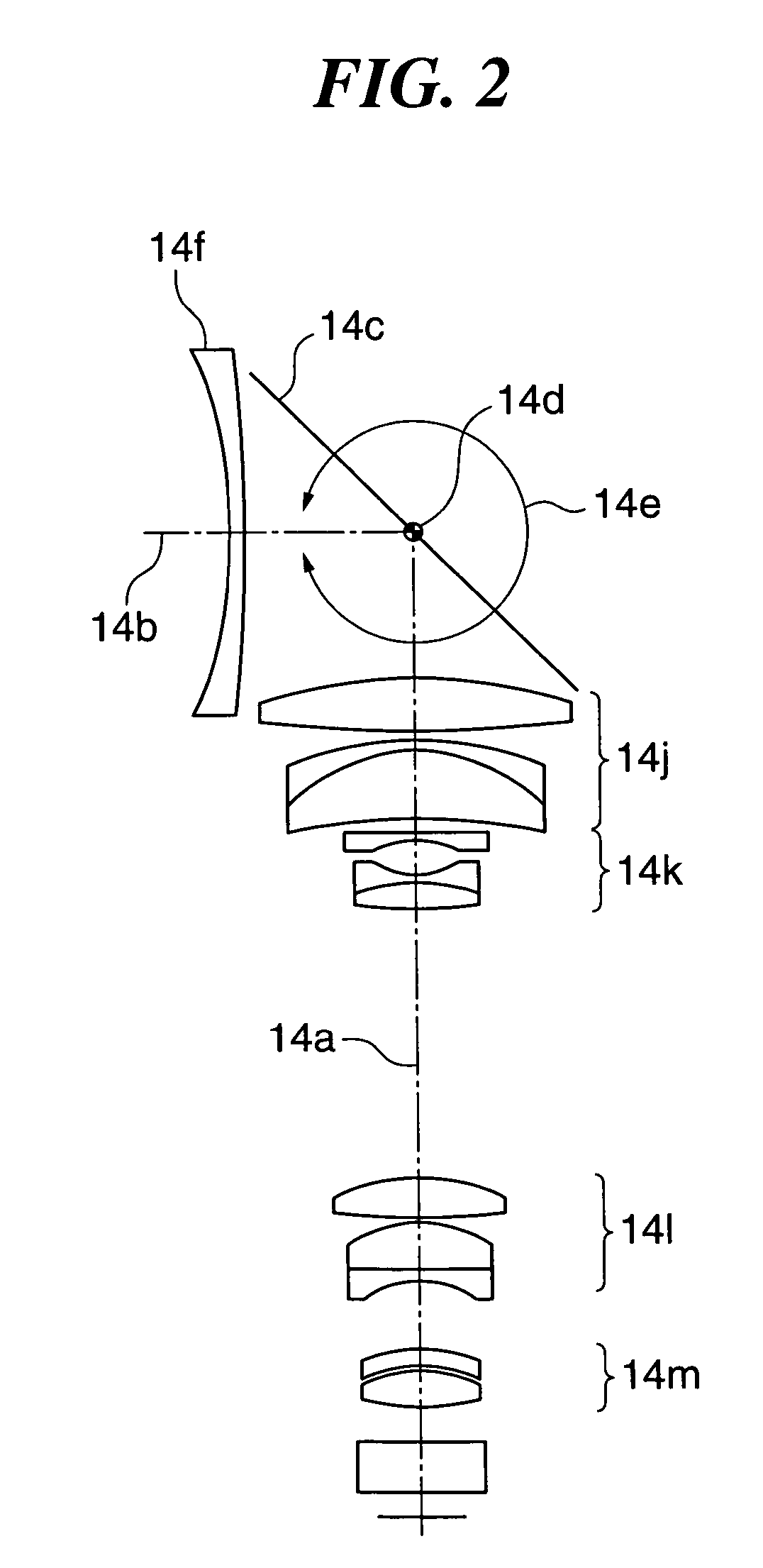

Photographing apparatus and control method therefor

InactiveUS20060067672A1Small sizeEasy to handleTelevision system detailsMirrorsActuatorElectric signal

A photographing apparatus which realizes a taking lens barrel whose shape is not largely changed during panning or tilting shot, thereby being compact in size and easy to handle. In the photographing apparatus, an image pickup device (14i) outputs an electric signal from object light. A bending optical system (14) has a front lens (14f) and lens groups (14j, 14k, 14l, and 14m) and a mirror (14c) disposed between the front lens and the laminated lens 14j, to guide the object light to the image pickup device. A panning actuator (19) and a tilt actuator (15f) cause the mirror and the front lens or the lens groups to be pivotally moved in unison about respective different axes to thereby change a shooting direction.

Owner:CANON KK

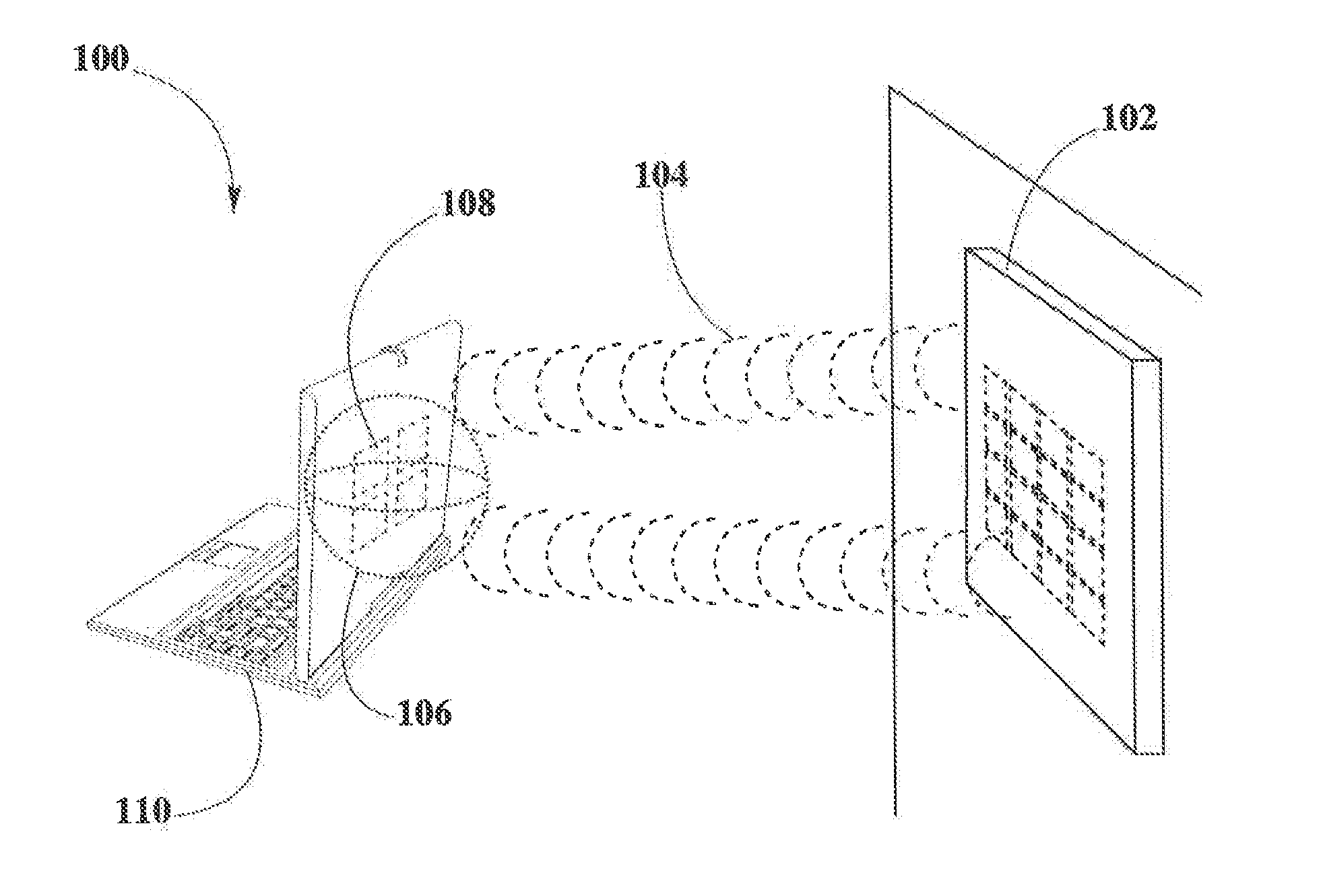

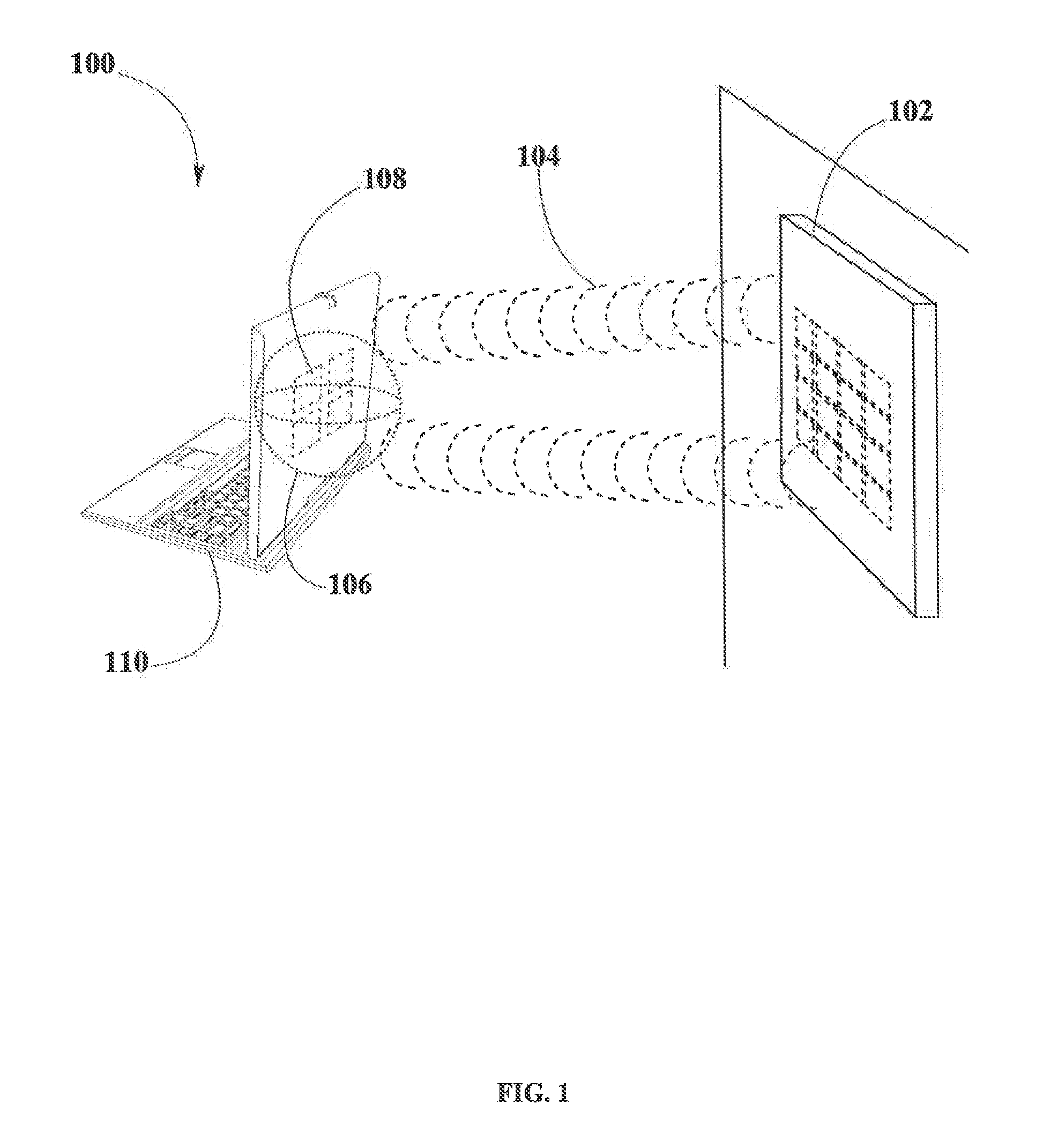

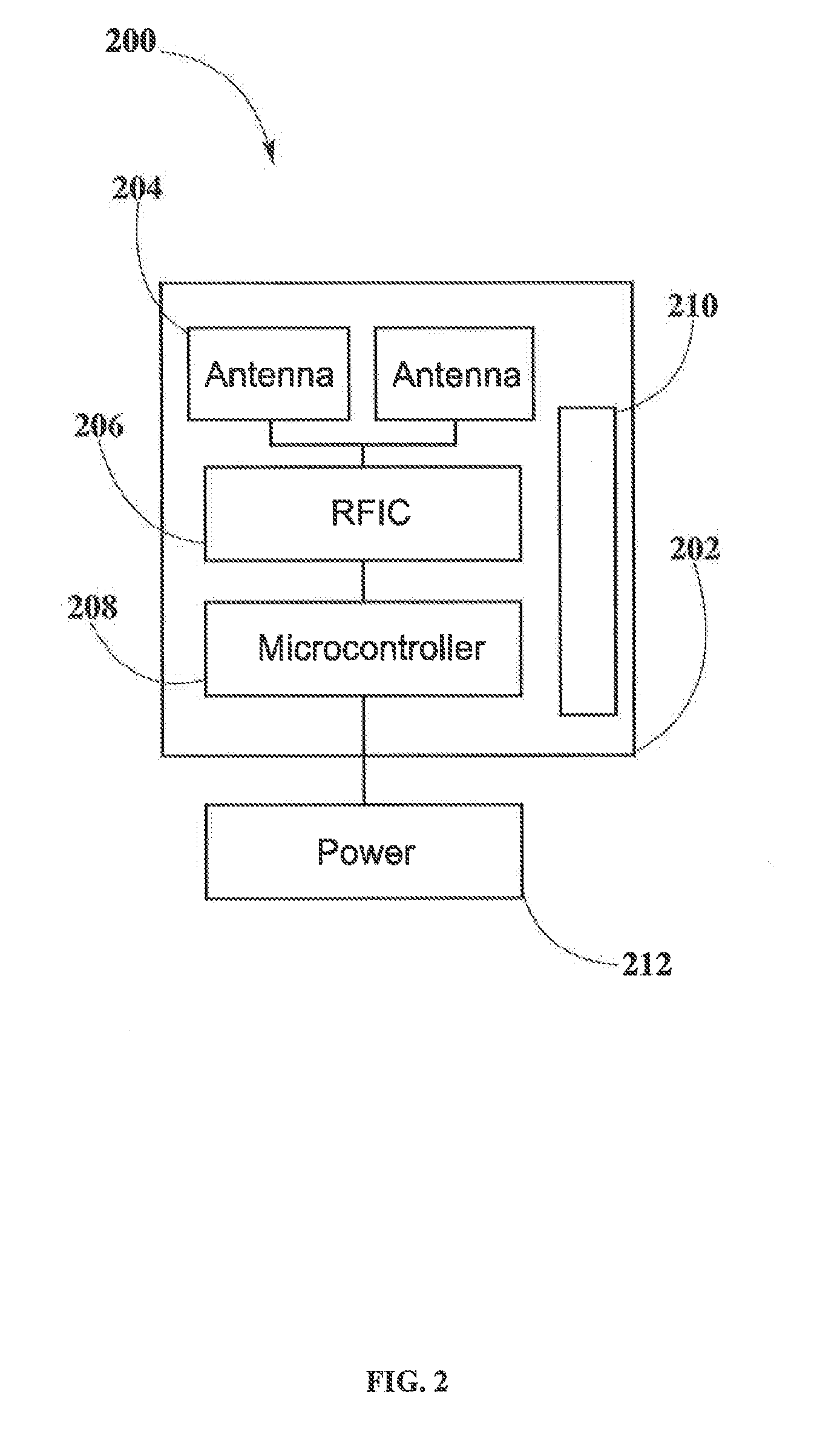

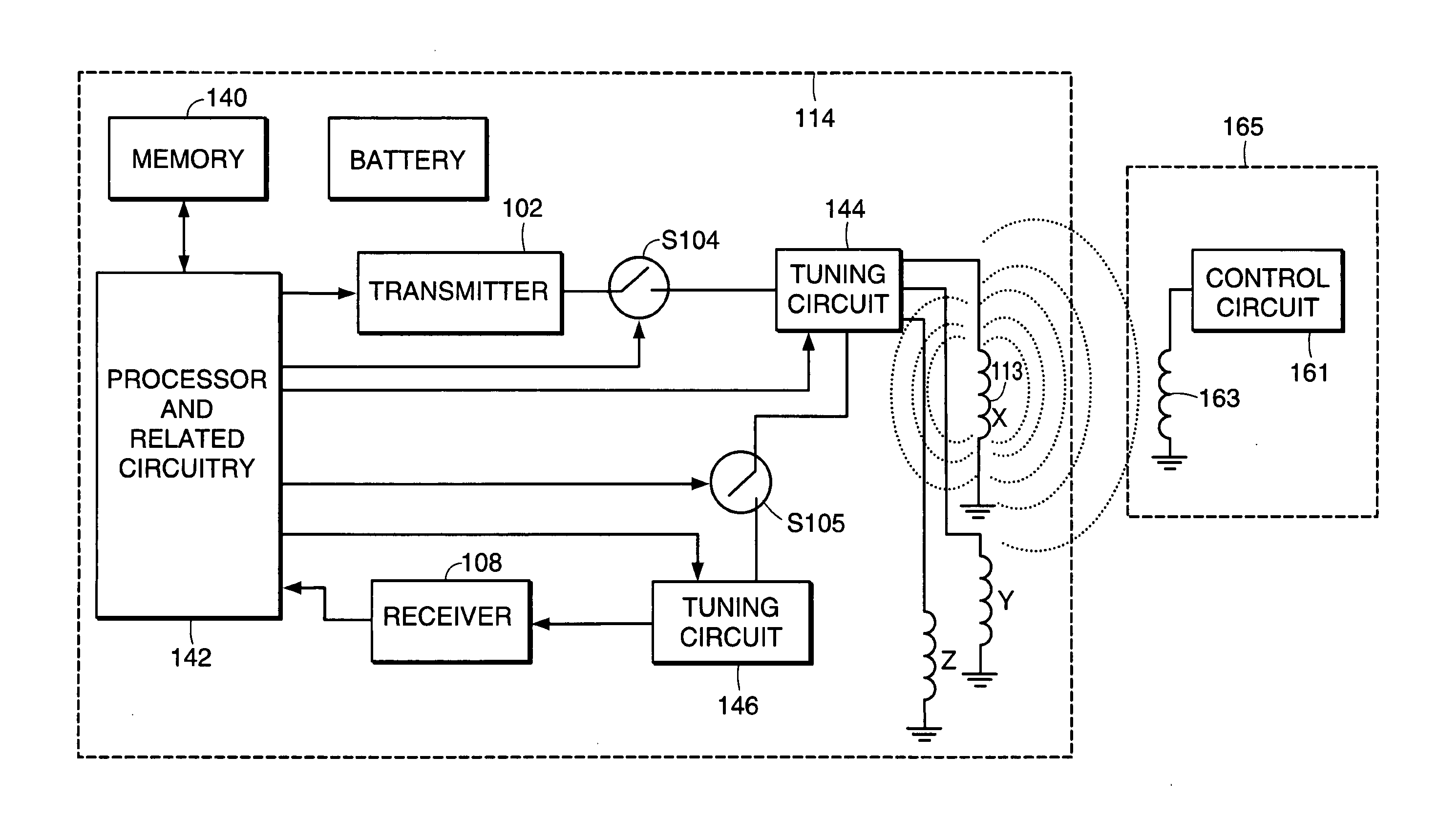

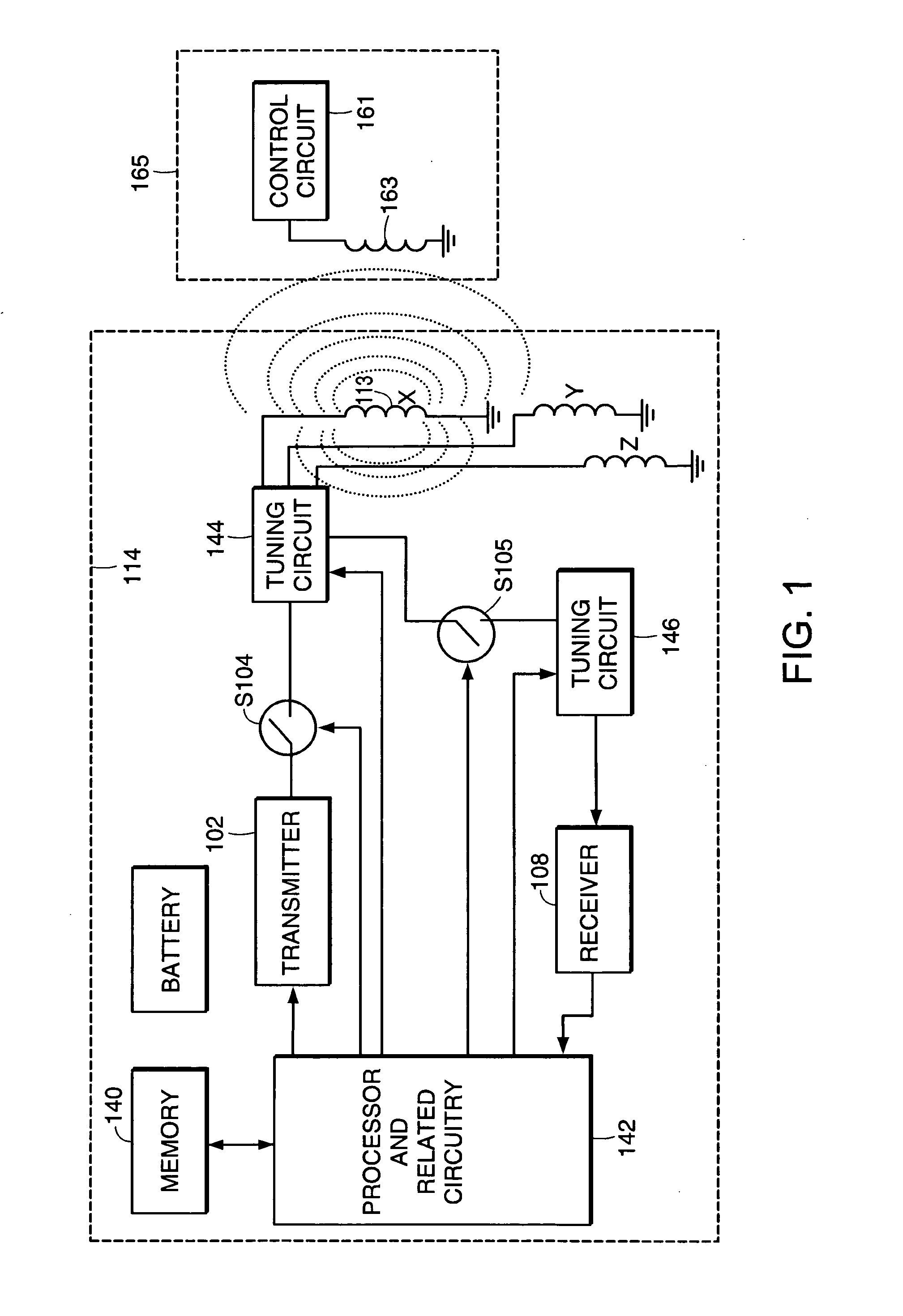

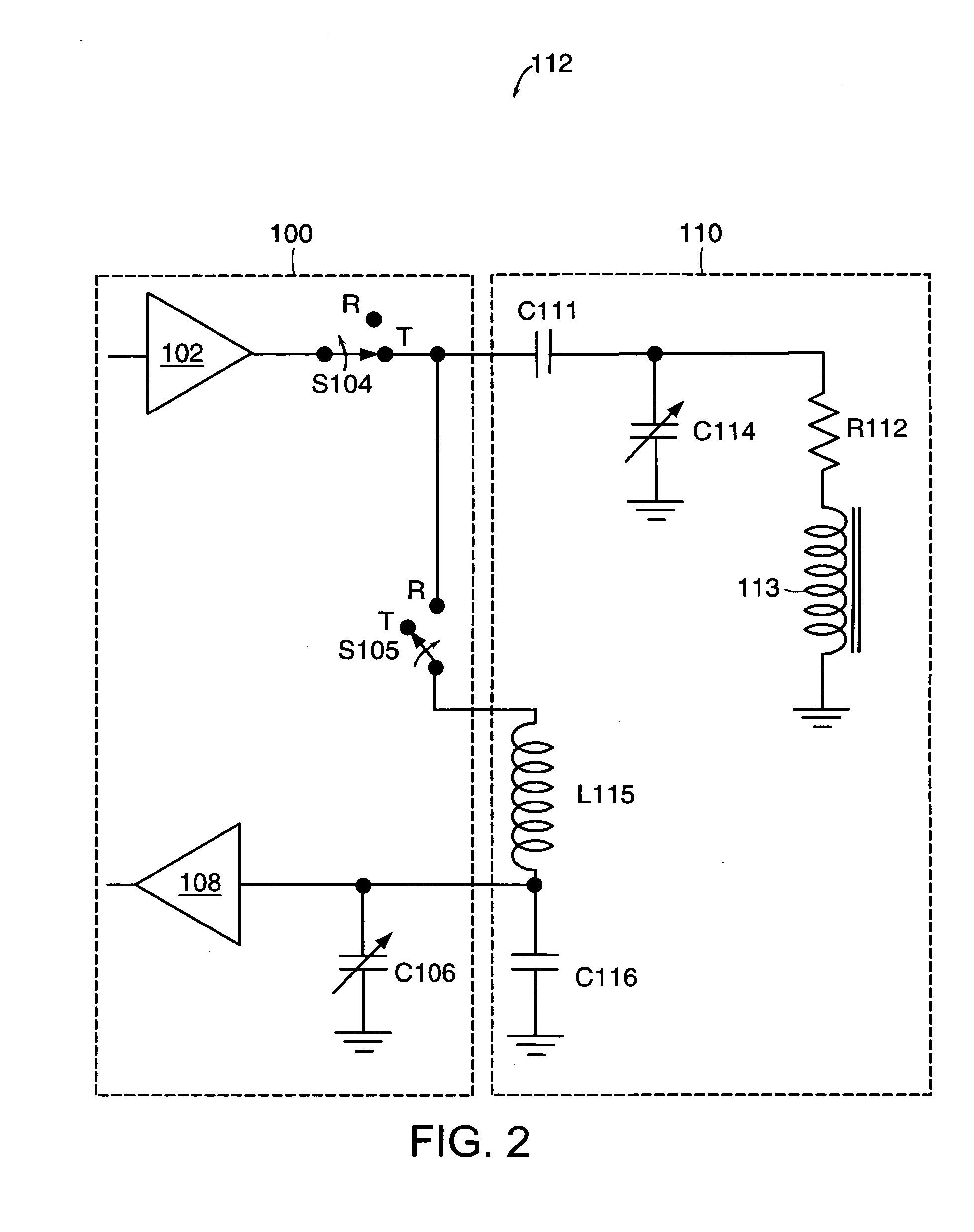

Wireless communication over a transducer device

InactiveUS20070082611A1Small sizeReduce weightCordless telephonesSubstation speech amplifiersElectricityTransducer

One aspect of the present invention is generally directed towards a system and method of tuning a transducer for transmitting and receiving a wireless signal. In an illustrative embodiment, a single transducer is coupled to a first or second circuit for either transmitting or receiving, respectively. Generally, electrical characteristics of the first circuit are adjusted to increase a magnetic field generated by the transducer. Conversely, electrical characteristics of the second circuit are adjusted to increase a signal generated by the transducer for receiving a magnetic field. Accordingly, a single transducer device can be tuned for either transmitting or receiving a corresponding wireless signal.

Owner:FREELINC HLDG LLC

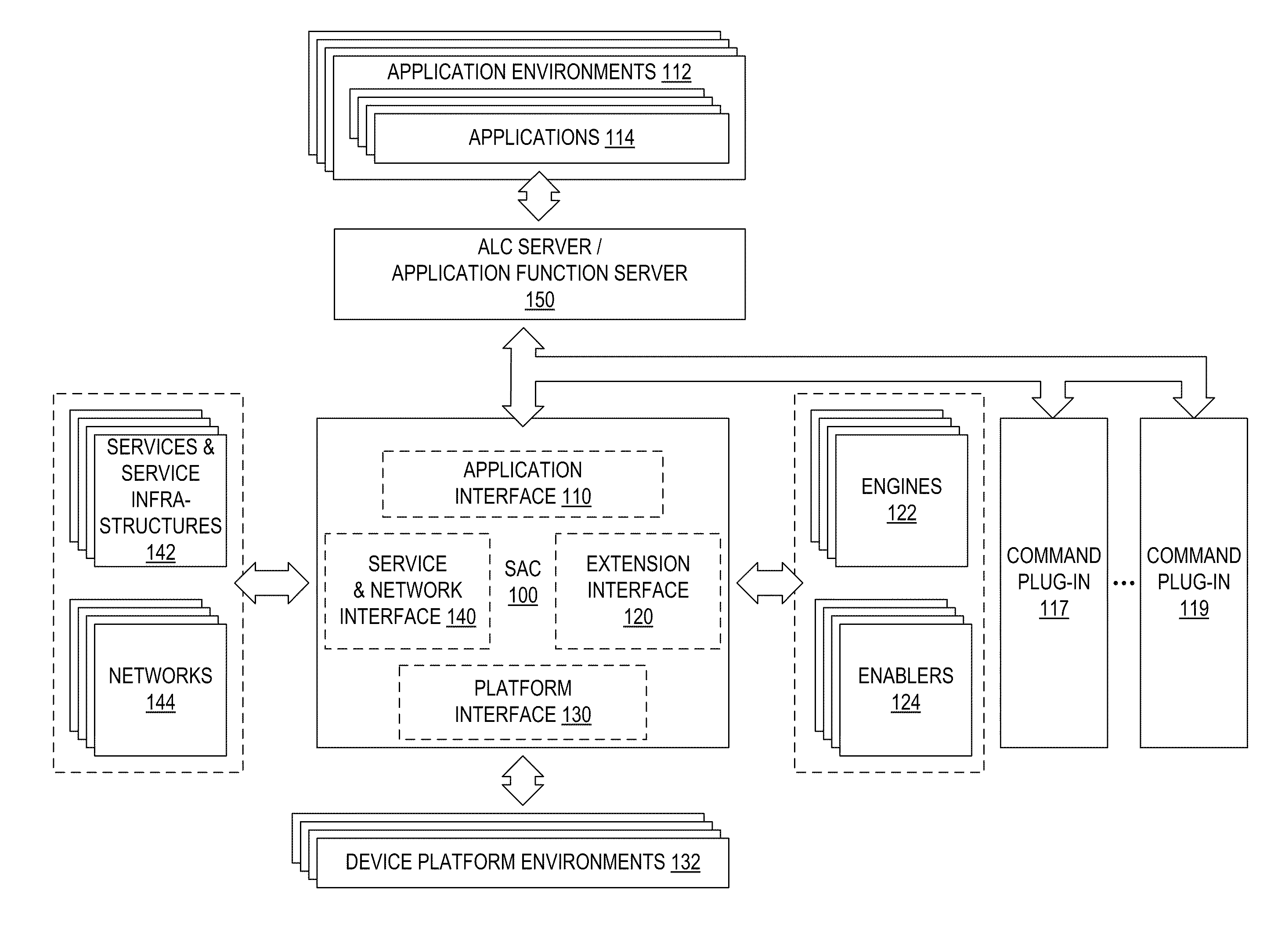

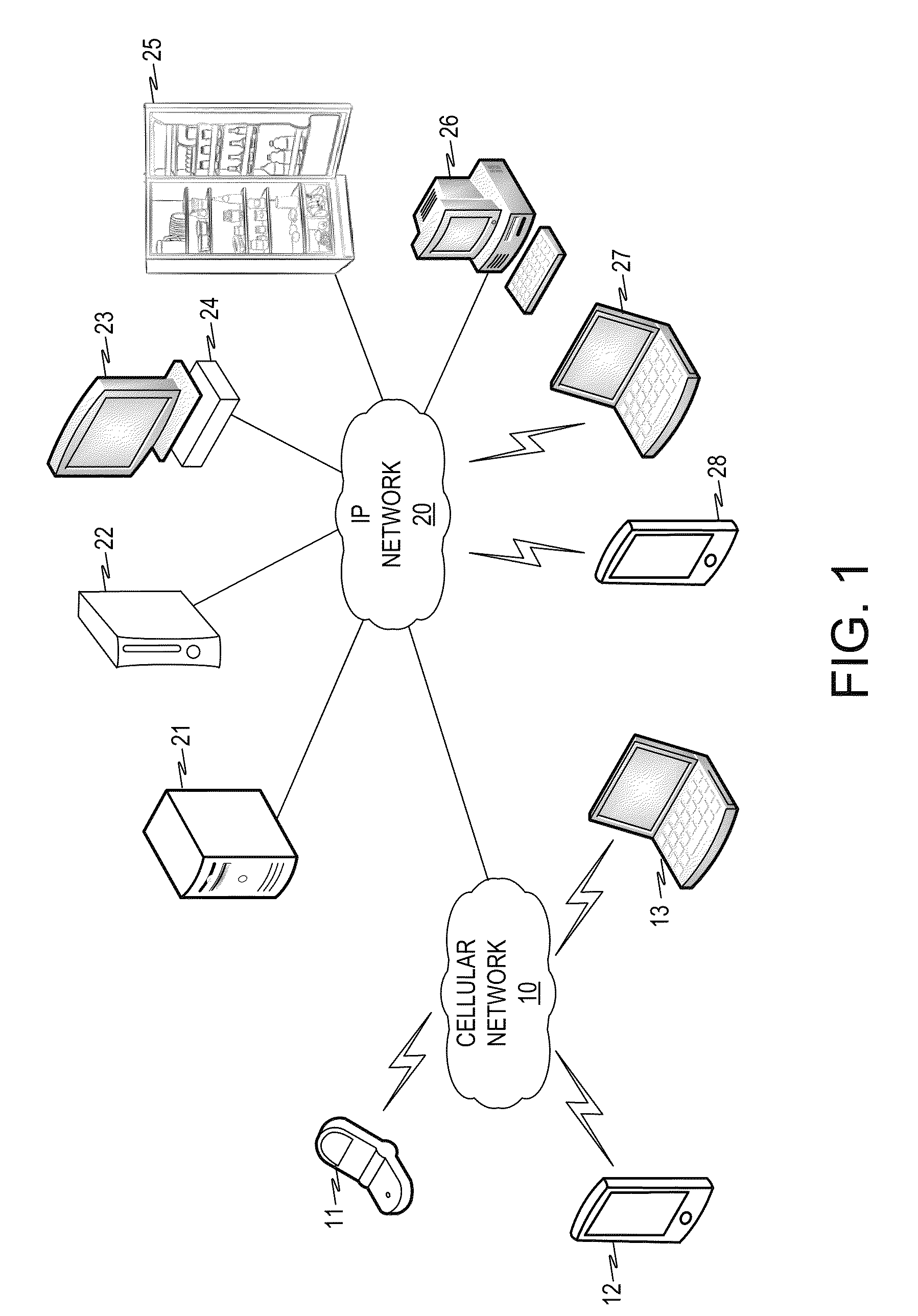

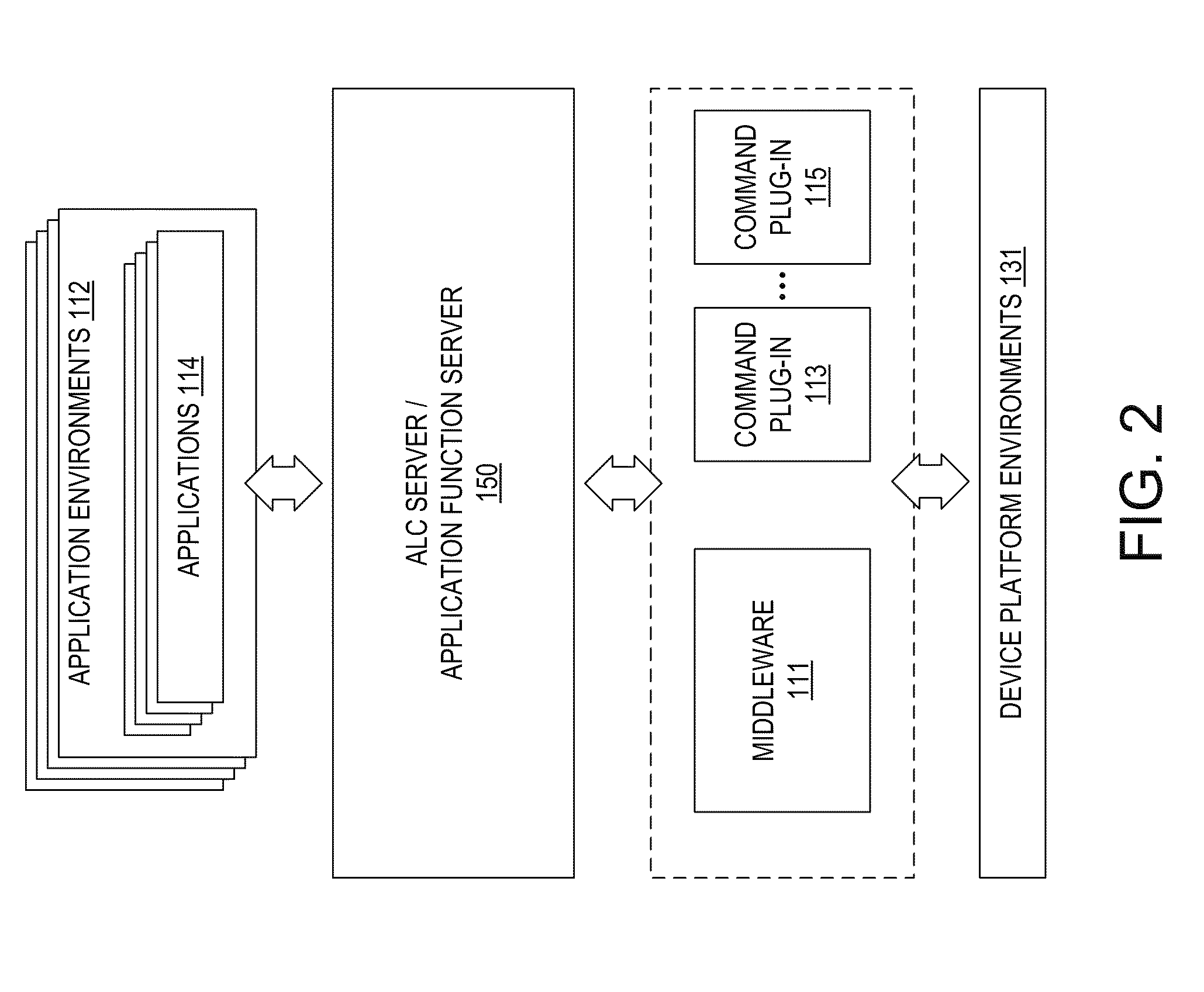

System, method and apparatus for providing functions to applications on a digital electronic device

InactiveUS20100257539A1Enabling and simplifying application developmentShorten development timeService provisioningInterprogram communicationDiscrete functionsApplication software

To greatly simplify the developer's task, an application function server or application logic controller (“ALC”) server runs on a digital electronic device with a common set of tools and methods to deliver high-value capabilities to applications developed in different application languages and running in various different application environments. The applications and the application function server have a local client-server relationship. The functions themselves are provided by various plug-ins. The interface of a plug-in illustratively is a discrete set of functions, common to the command plug-ins. The ALC Server accepts simplified commands directly from the applications, applies the appropriate policy, and interacts with the plug-ins to perform the requested functions on behalf of the applications. The result is that applications can use various capabilities without dealing with the complex methods, standards, and system interoperability required to make the technologies work, and technology additions and upgrades can be performed independently from the applications that use them.

Owner:ECRIO

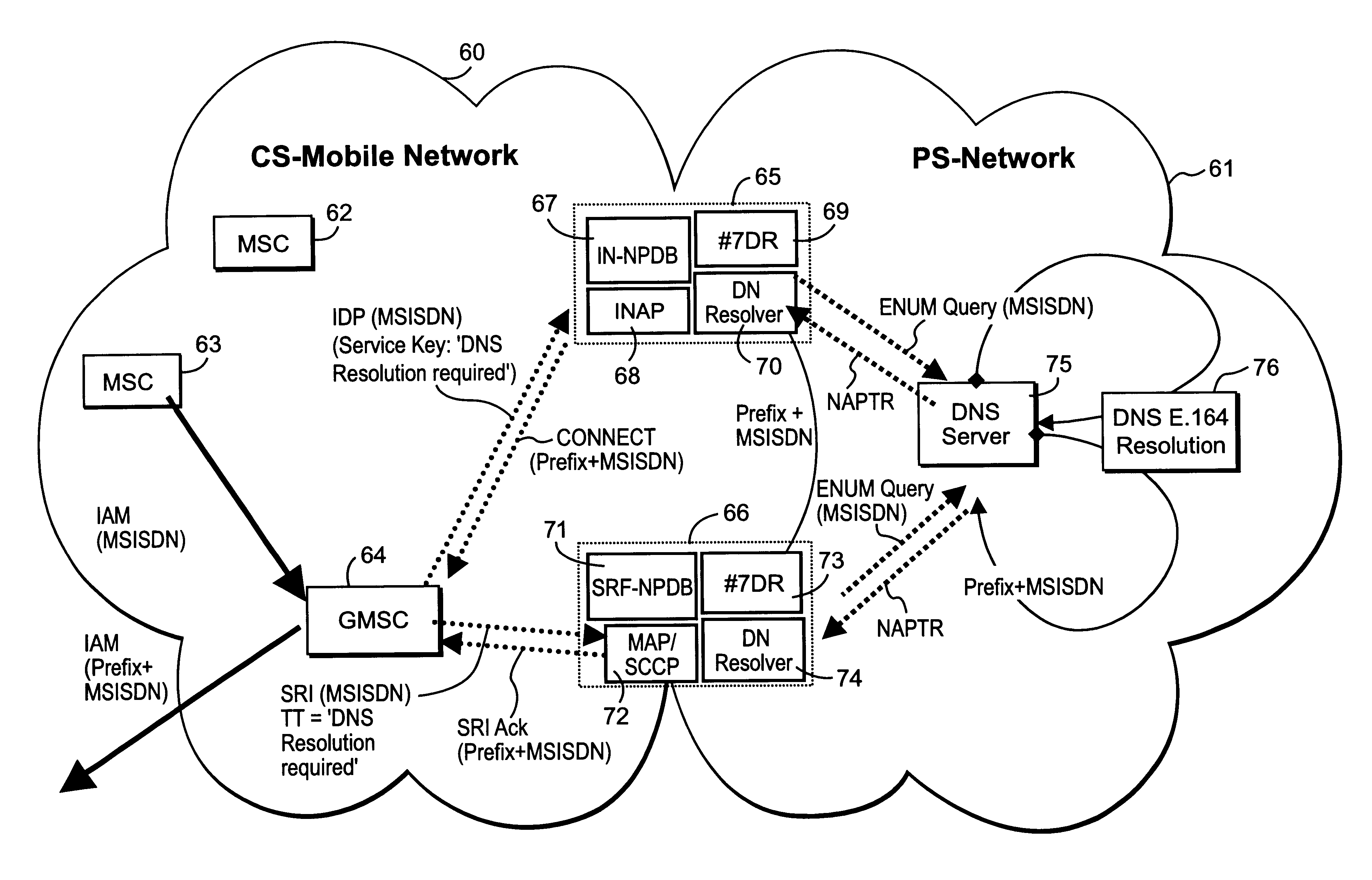

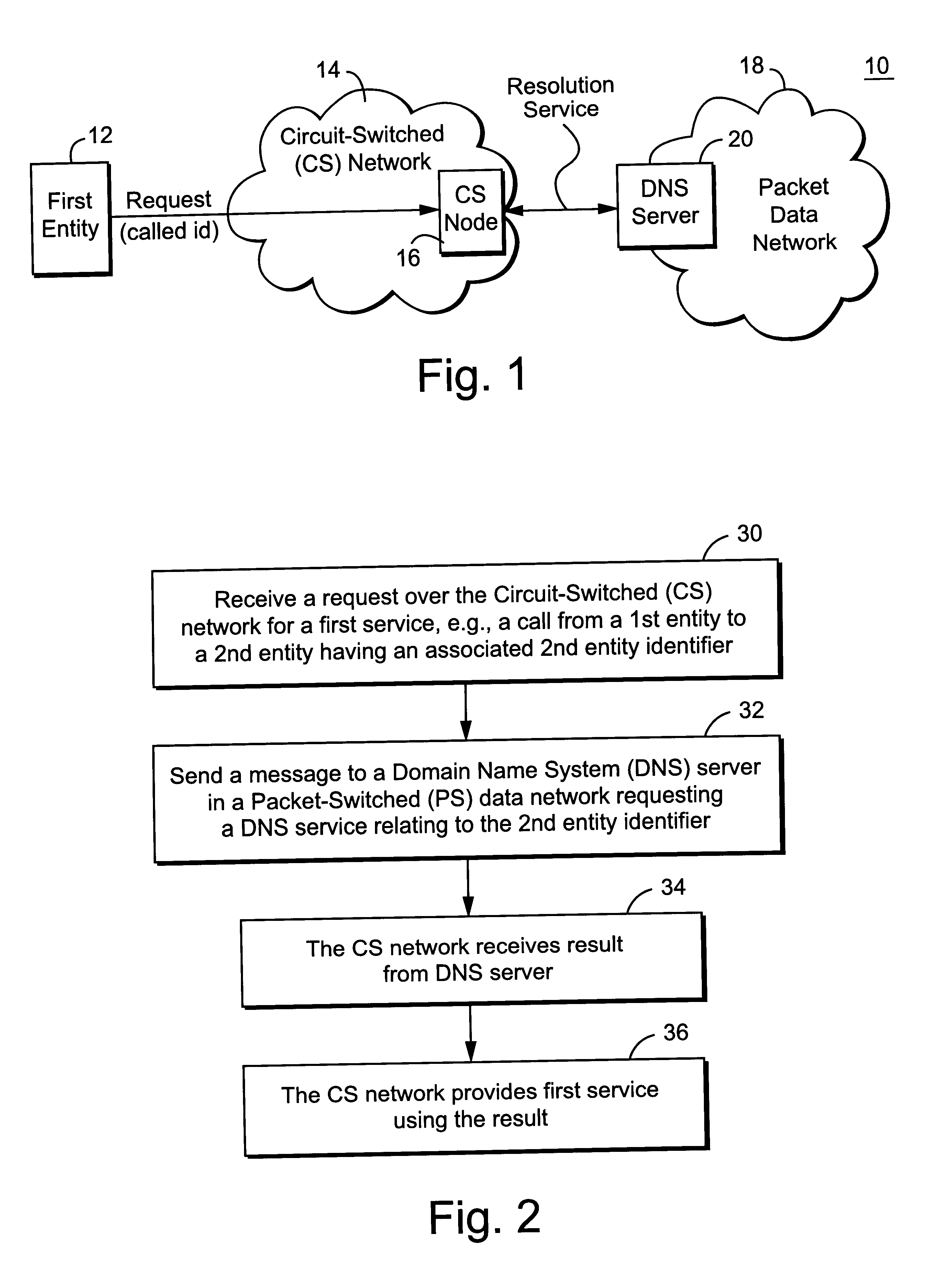

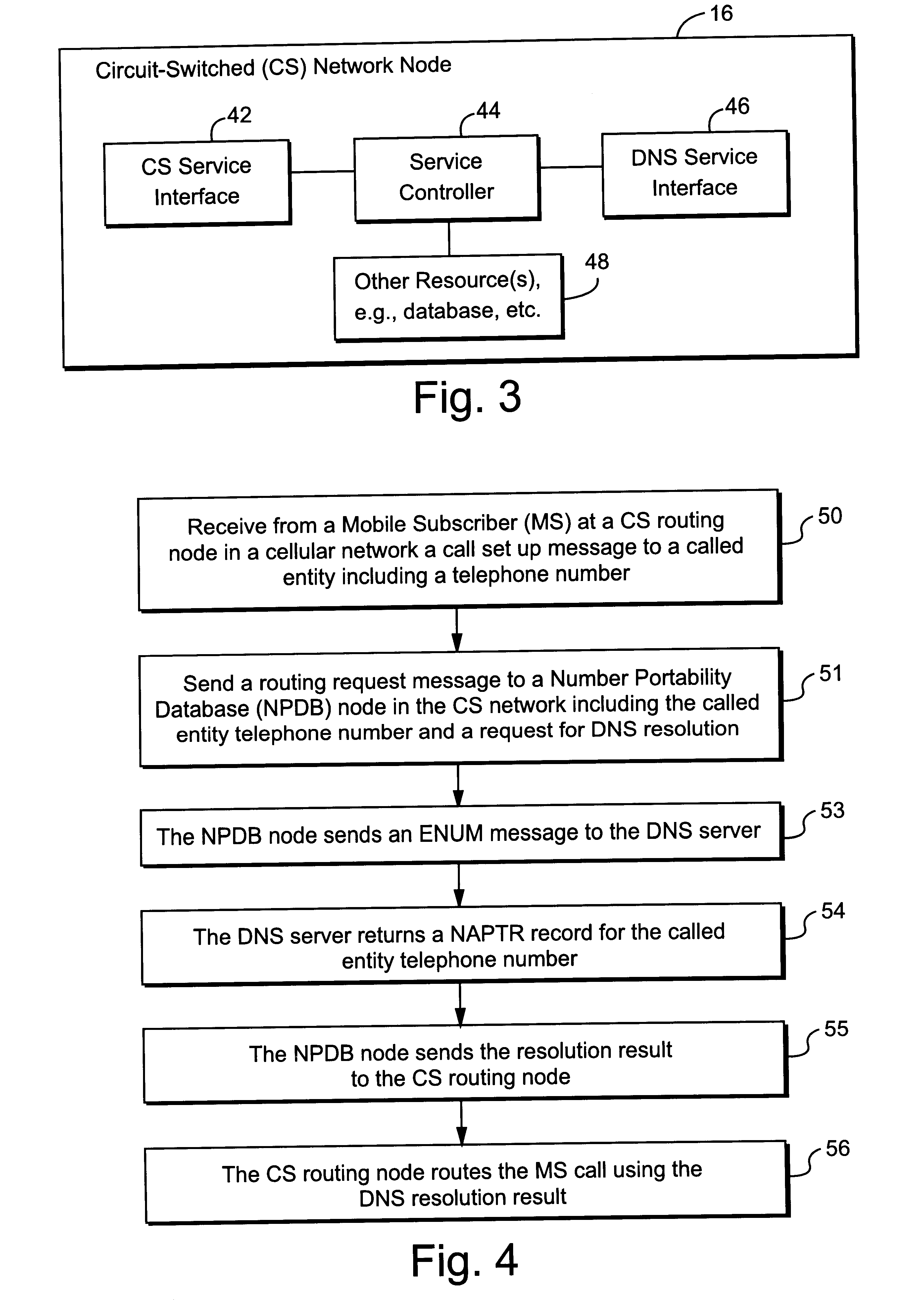

Method and apparatus to carry out resolution of entity identifier in circuit-switched networks by using a domain name system

InactiveUS6839421B2Without configurationWithout expenseSpecial service provision for substationMultiplex system selection arrangementsDomain nameEntity identifier

An efficient interface for service exchange is provided between a circuit-switched communications network and a domain naming system (DNS) in a packet-switched communications network. A node in the circuit-switched communications network receives from a first entity a request for a first service involving a second entity associated with a second entity identifier. A message is sent from the circuit-switched network node to a DNS server in the packet-switched network requesting a second service related to the second entity identifier. The result of the second service from the DNS server is used in providing the first service.

Owner:TELEFON AB LM ERICSSON (PUBL)

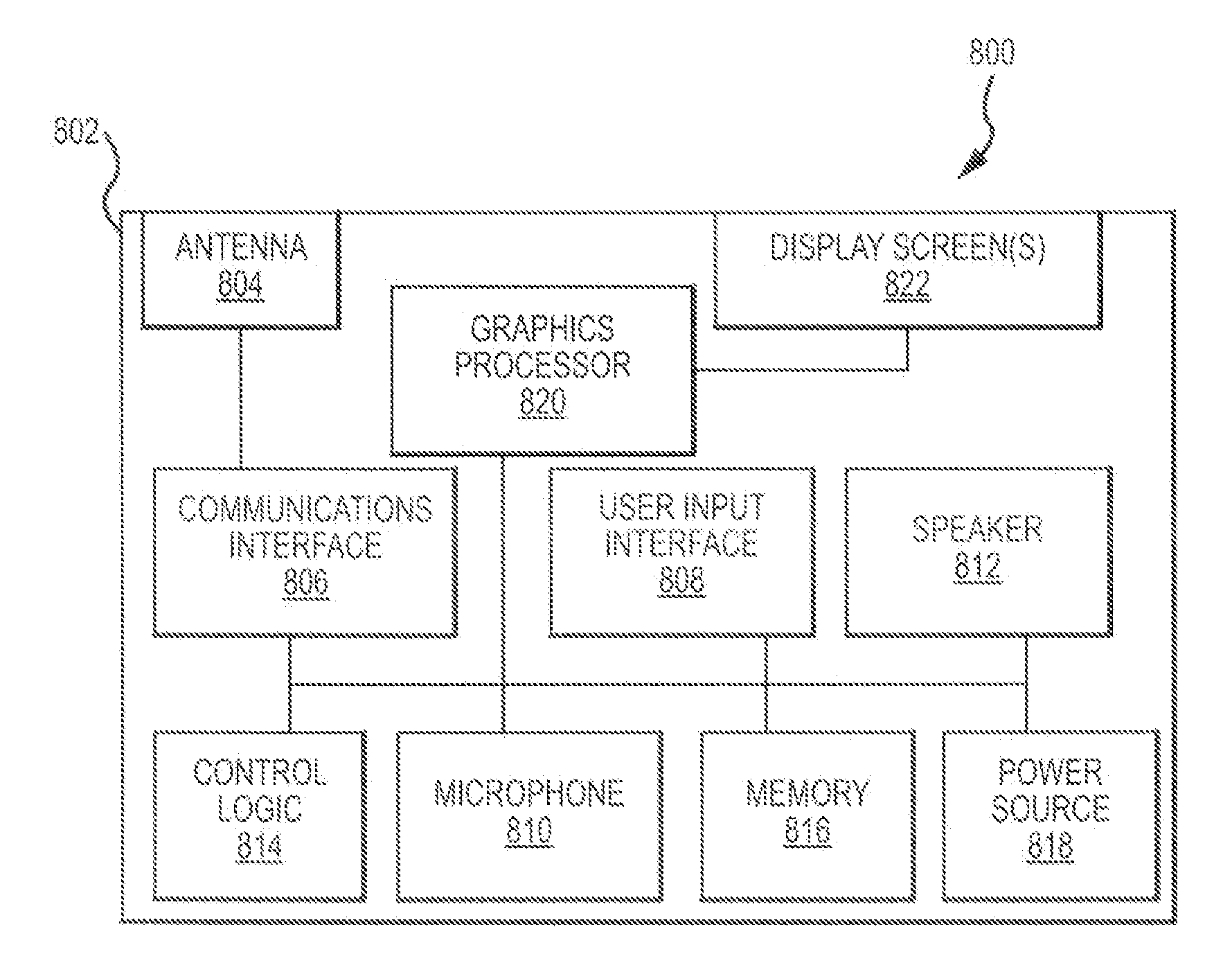

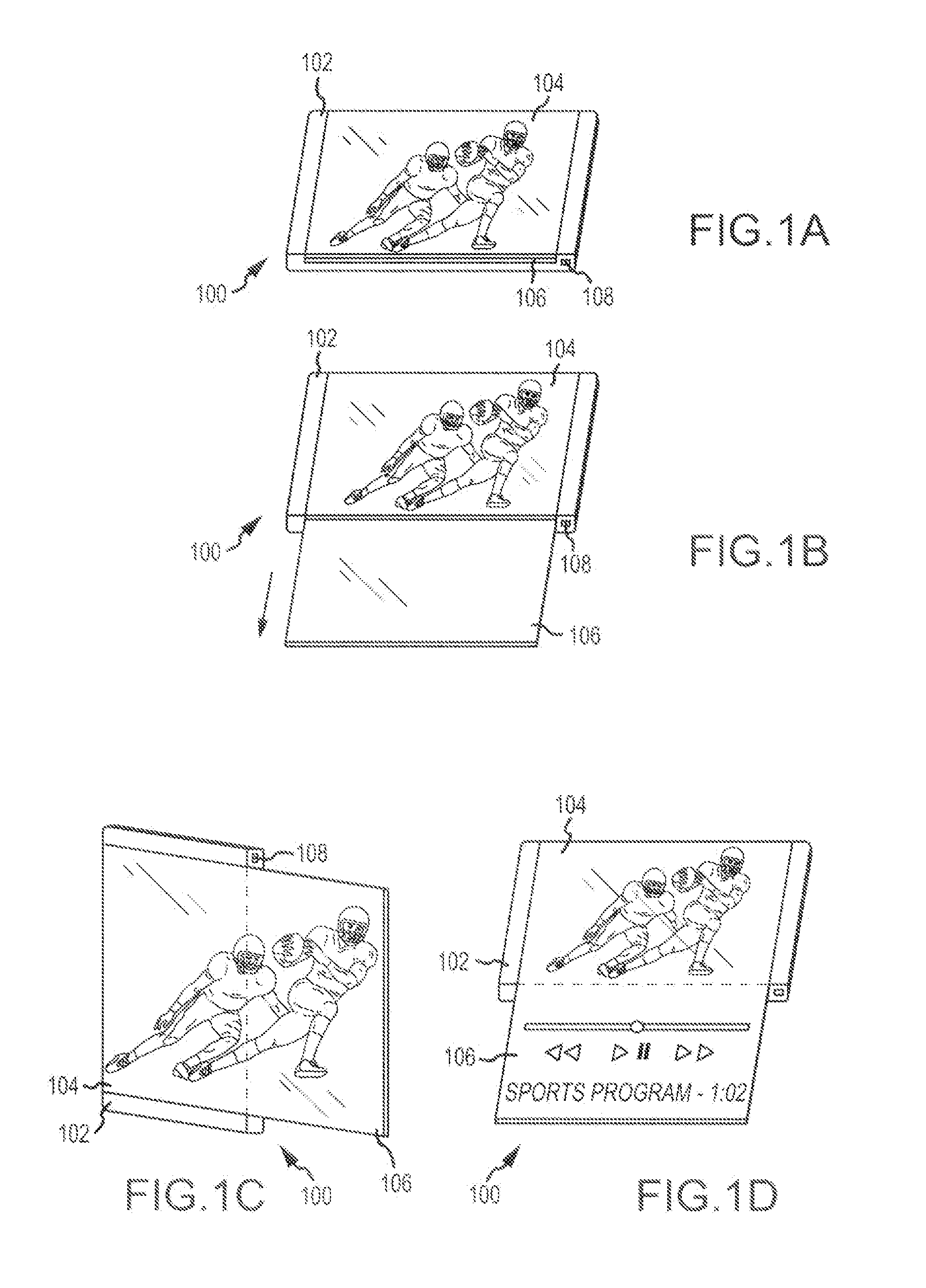

Communications device with extendable screen

ActiveUS20120280924A1Thinner and lighter displayHigh resolution displayDevices with multiple display unitsStatic indicating devicesGraphical displayImage resolution

Described herein are apparatuses and mechanisms for providing an extendable screen in a portable communications device. A portable communications device may be provided with a multi-part screen, a portion of which may be extended to provide an expanded viewing display surface or may be retracted to provide a reduced viewing mode and increased portability. In a reduced viewing mode, a graphical display may be provided on a first, visible portion of a multi-part display screen, where one or more other screen portions are retracted and / or obscured from view in order to provide a portable mode for the communications device. In an extended viewing mode, the one or more other screen portions may be extended and / or brought into the same plane as a first portion of the multi-part display in order to provide increased display size and resolution.

Owner:DISH TECH L L C

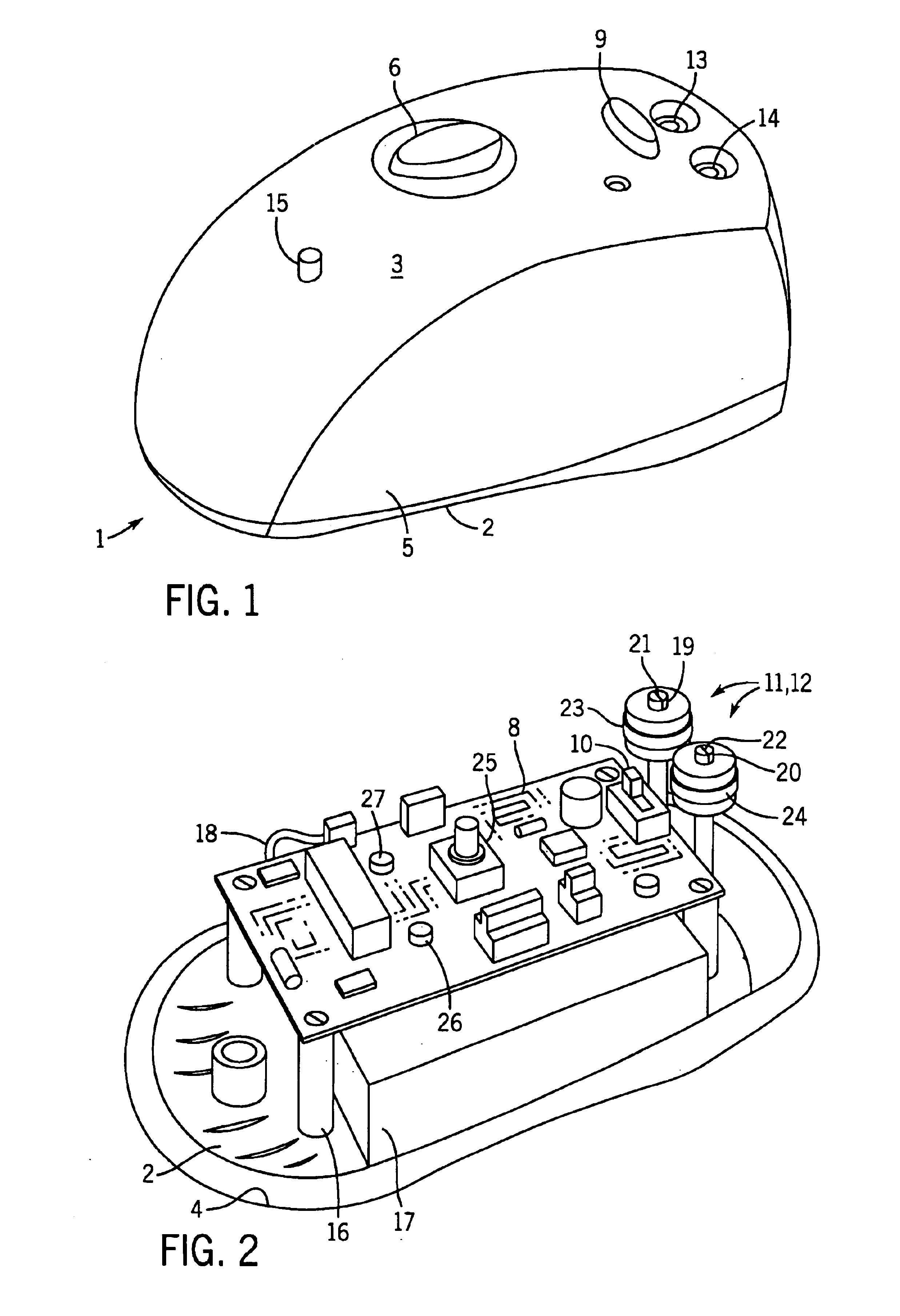

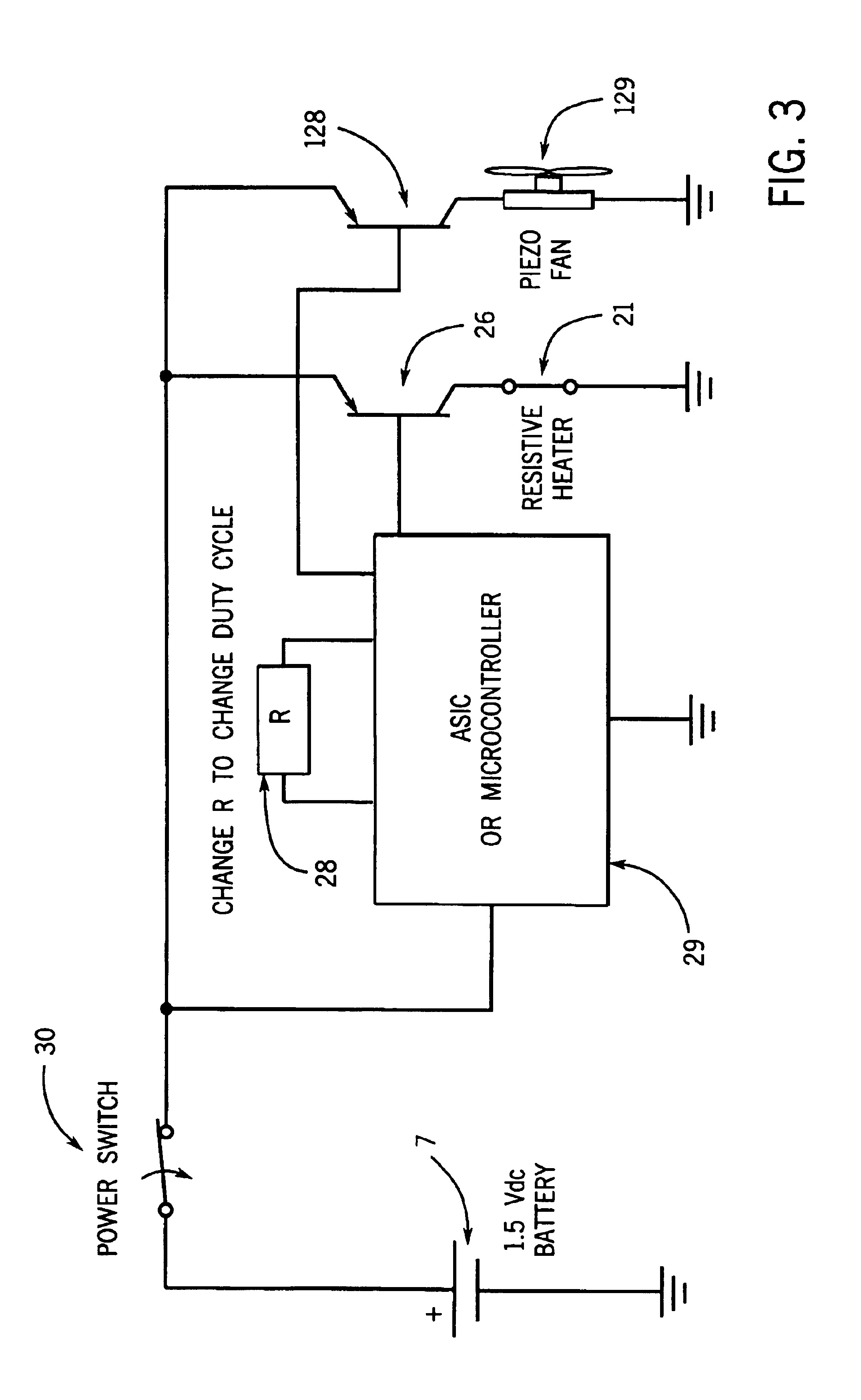

Localized surface volatilization

InactiveUS6909840B2Improved vaporizationIncrease vapor pressureDomestic stoves or rangesLiquid heating fuelElectrical resistance and conductanceProduct gas

The present invention relates to an apparatus and method for rapid flash-like volatilization of high and low vapor pressure components from liquid or solid emanators which is in contact with a point or localized heat source. Vaporization is promoted by a geometrically small electrically resistive heating element with variable activation for pulsed or cyclic heating of an emanating surface containing the volatile components. The apparatus is primarily directed towards the treatment of residential air for fragrancing, odor elimination, treatment of insects or pests, air sanitization, air and surface antibacterial or antimicrobial treatment, or other ambient air or surface modification by way of gas or vapor distribution.

Owner:SC JOHNSON & SON INC

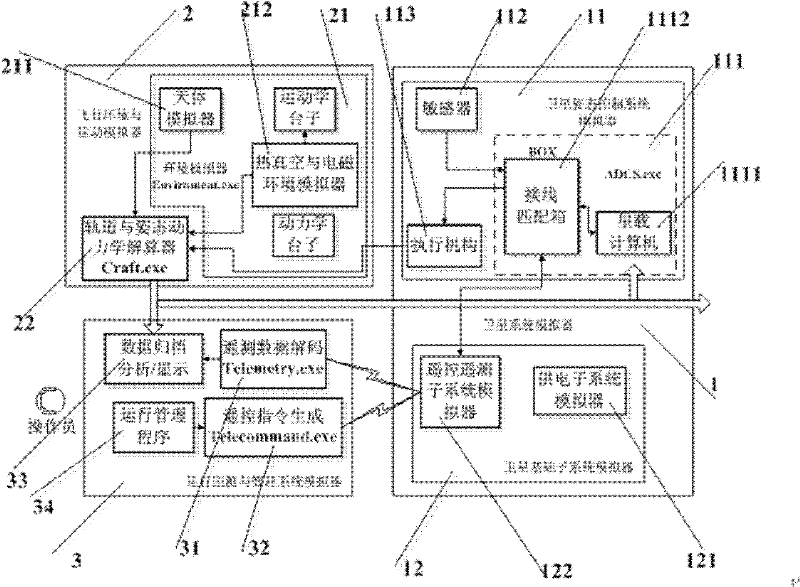

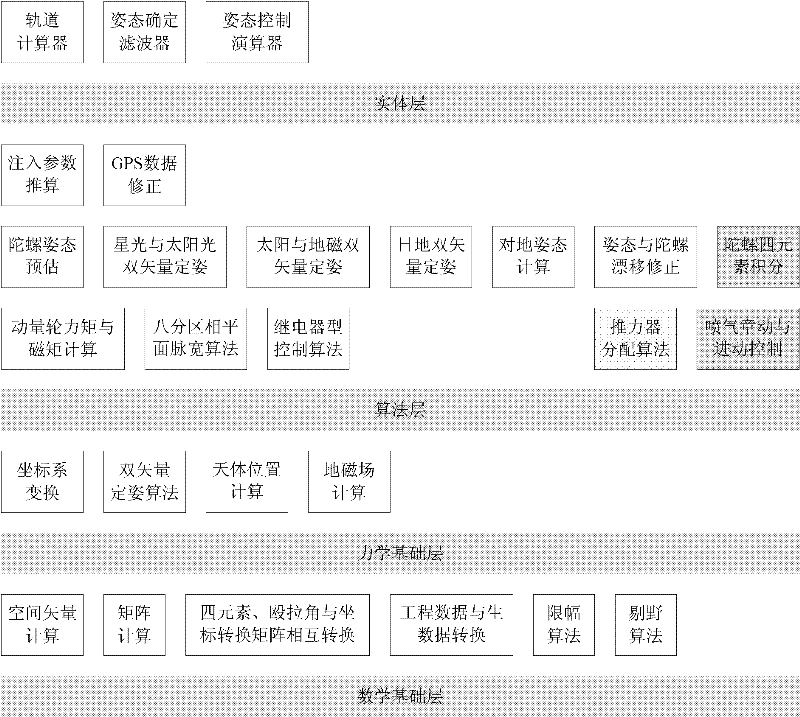

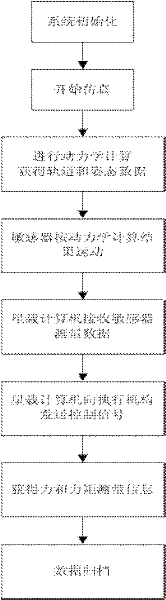

Cross-platform extendible satellite dynamic simulation test system

InactiveCN102354123AReduce complexityImprove general performanceSimulator controlExtensibilityElectromagnetic environment

The invention discloses a cross-platform extendible satellite dynamic simulation test system, which comprises a satellite attitude control system simulator, a flight environment and motion simulator, a satellite basic subsystem simulator and an operation monitoring and management system simulator. The satellite attitude control system simulator comprises a sensor simulator, a controller simulatorand an actuating mechanism simulator; the flight environment and motion simulator comprises an orbit and attitude dynamics resolver, a celestial body simulator, a kinematics and dynamics turntable, akinematics and dynamics translation platform, a hot vacuum and electromagnetic environment simulator and the like; and the satellite basic subsystem simulator comprises a power supply subsystem simulator and a remote measuring and remote control subsystem simulator. The operation monitoring and management system simulates functions of a satellite ground measurement and control center, such as remote measuring data decoding, remote control command generating, data archiving and analyzing and operation managing. The cross-platform extendible satellite dynamic simulation test system has strong extendibility, can be conveniently transplanted on a development and debugging platform, a distributed real-time simulation platform and an embedded semi-physical real-time simulation platform.

Owner:BEIHANG UNIV