Patents

Literature

599 results about "Logic structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

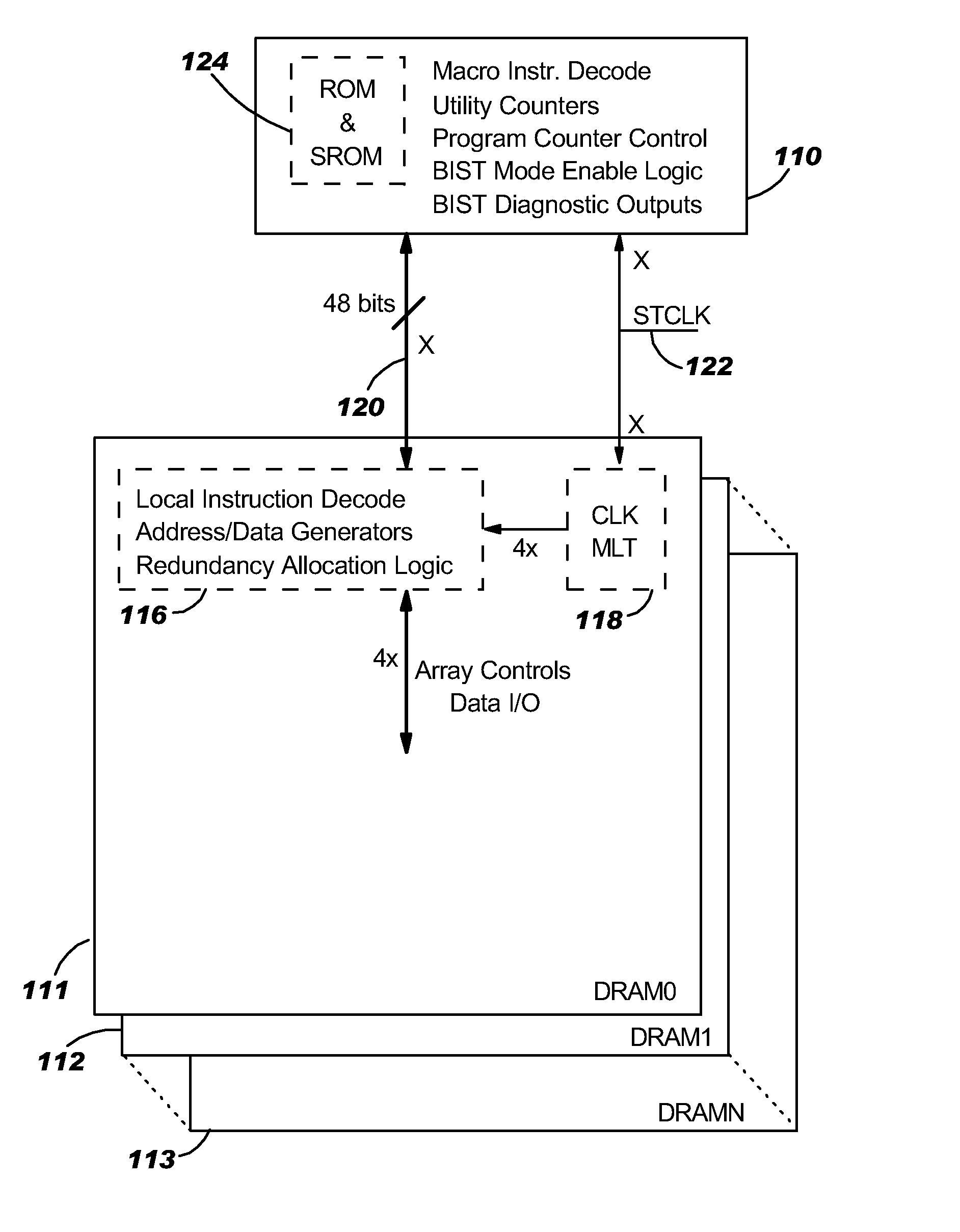

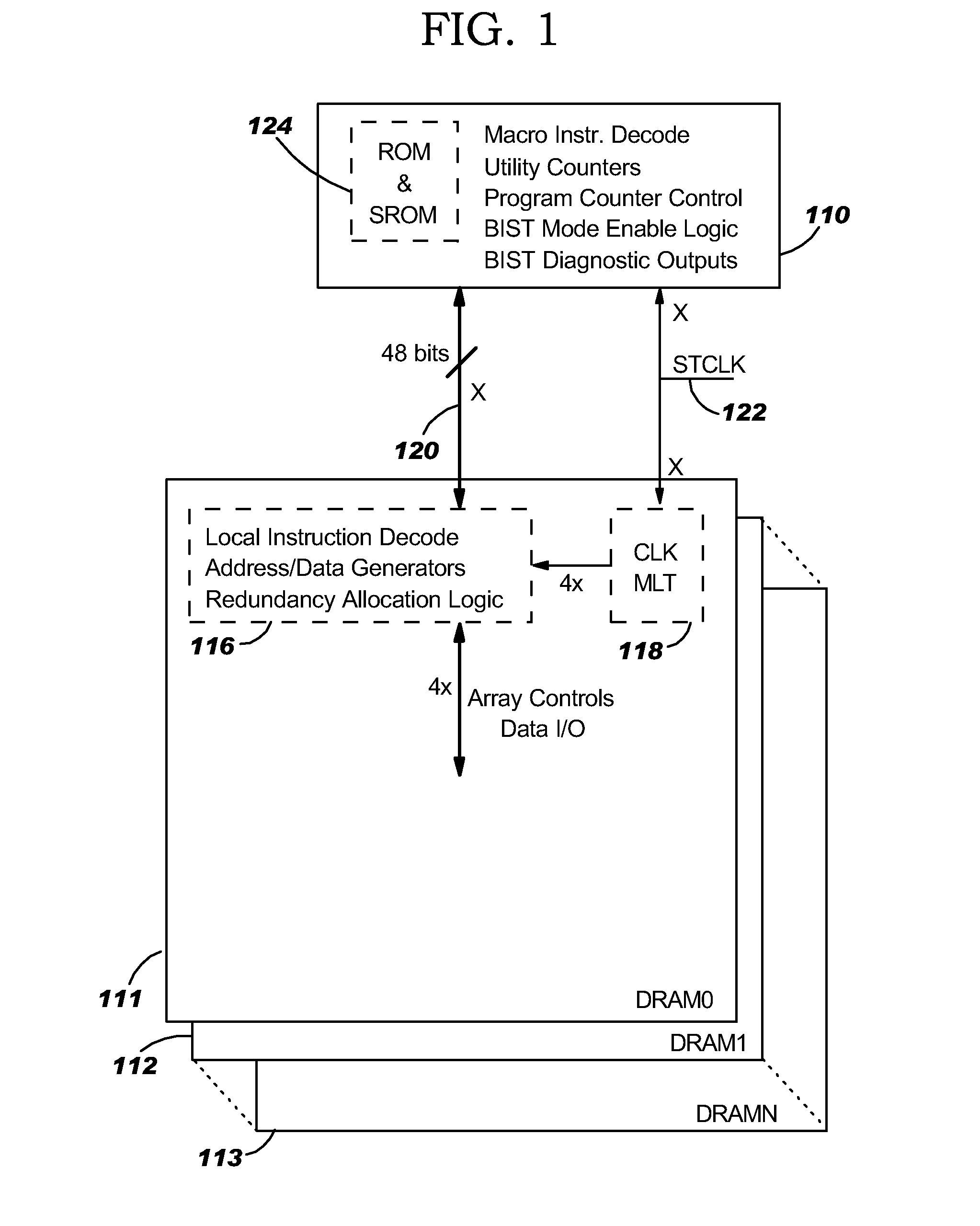

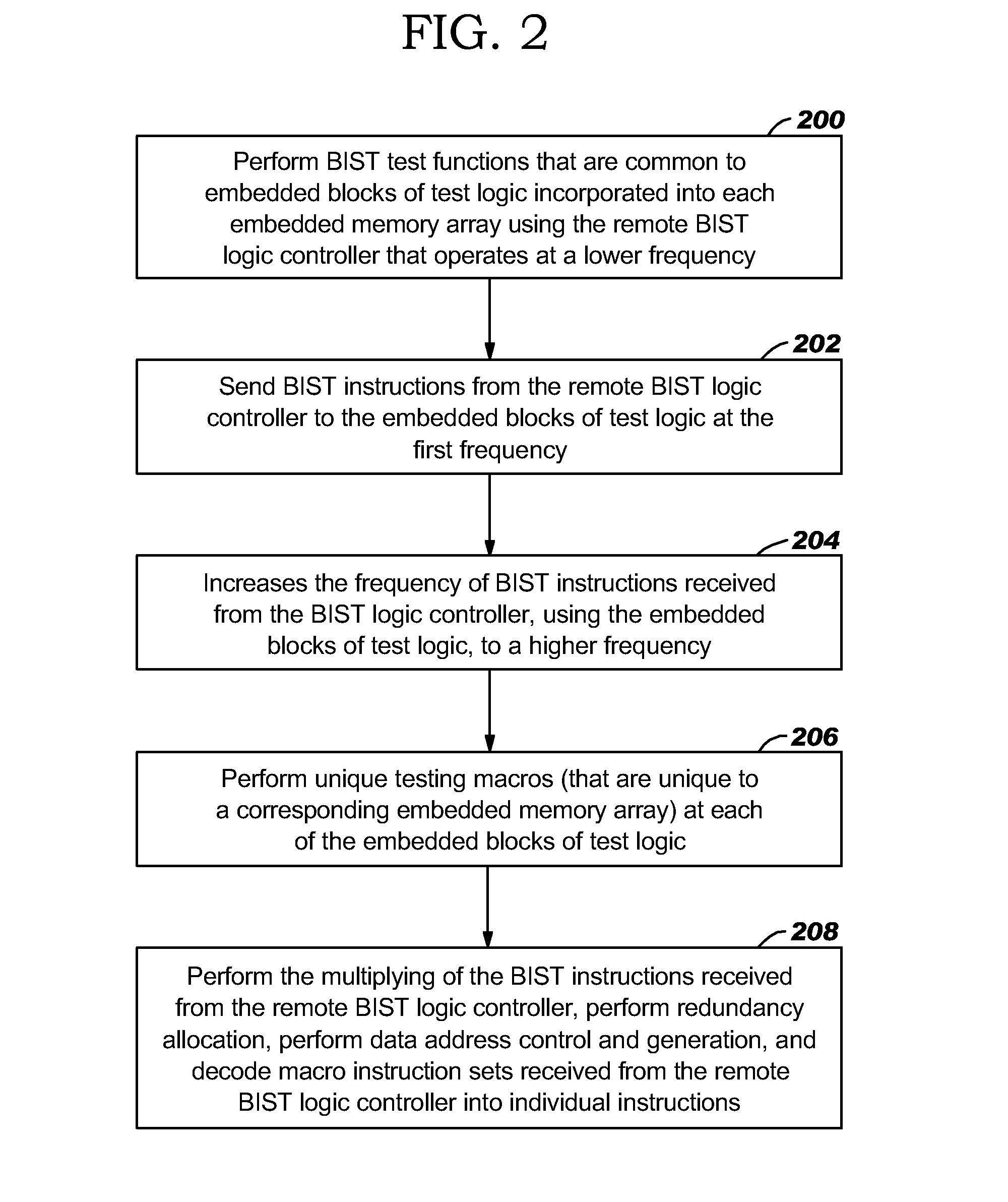

Remote bist for high speed test and redundancy calculation

InactiveUS20080215937A1Reduce frequencyIncrease processing frequencyDigital circuit testingFunctional testingLow speedSpeed test

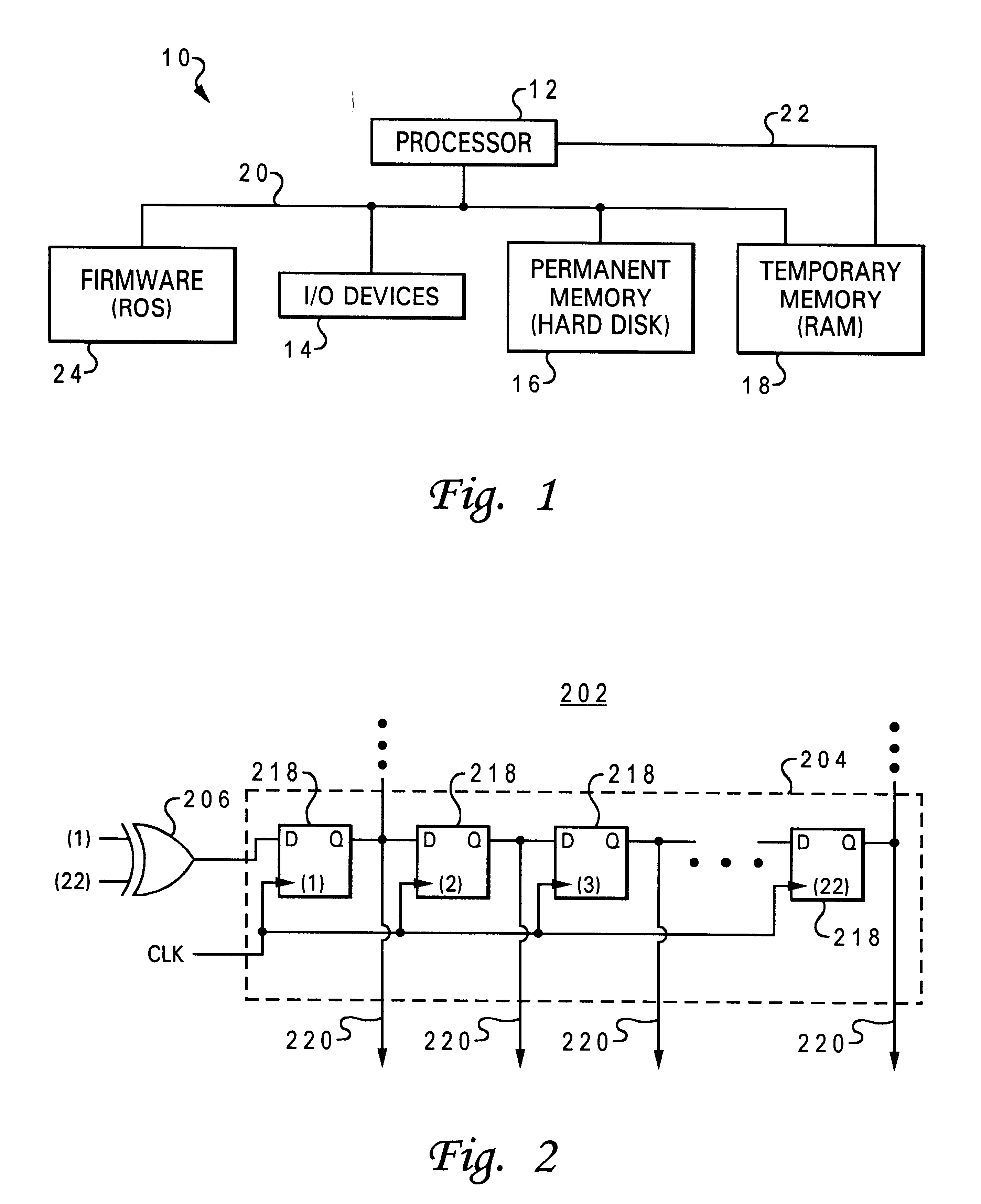

Disclosed in a hybrid built-in self test (BIST) architecture for embedded memory arrays that segments BIST functionality into remote lower-speed executable instructions and local higher-speed executable instructions. A standalone BIST logic controller operates at a lower frequency and communicates with a plurality of embedded memory arrays using a BIST instruction set. A block of higher-speed test logic is incorporated into each embedded memory array under test and locally processes BIST instructions received from the standalone BIST logic controller at a higher frequency. The higher-speed test logic includes a multiplier for increasing the frequency of the BIST instructions from the lower frequency to the higher frequency. The standalone BIST logic controller enables a plurality of higher-speed test logic structures in a plurality of embedded memory arrays.

Owner:META PLATFORMS INC

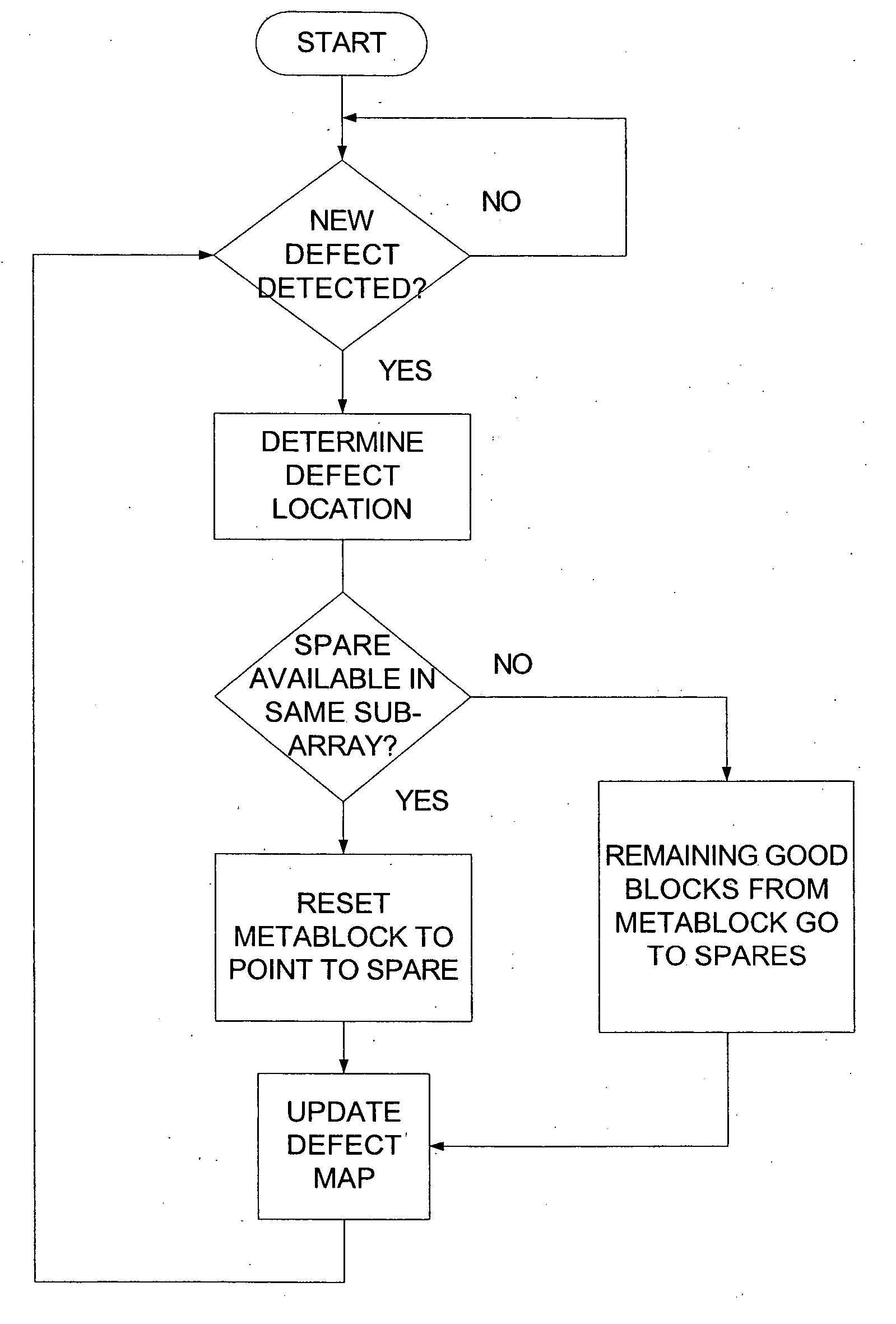

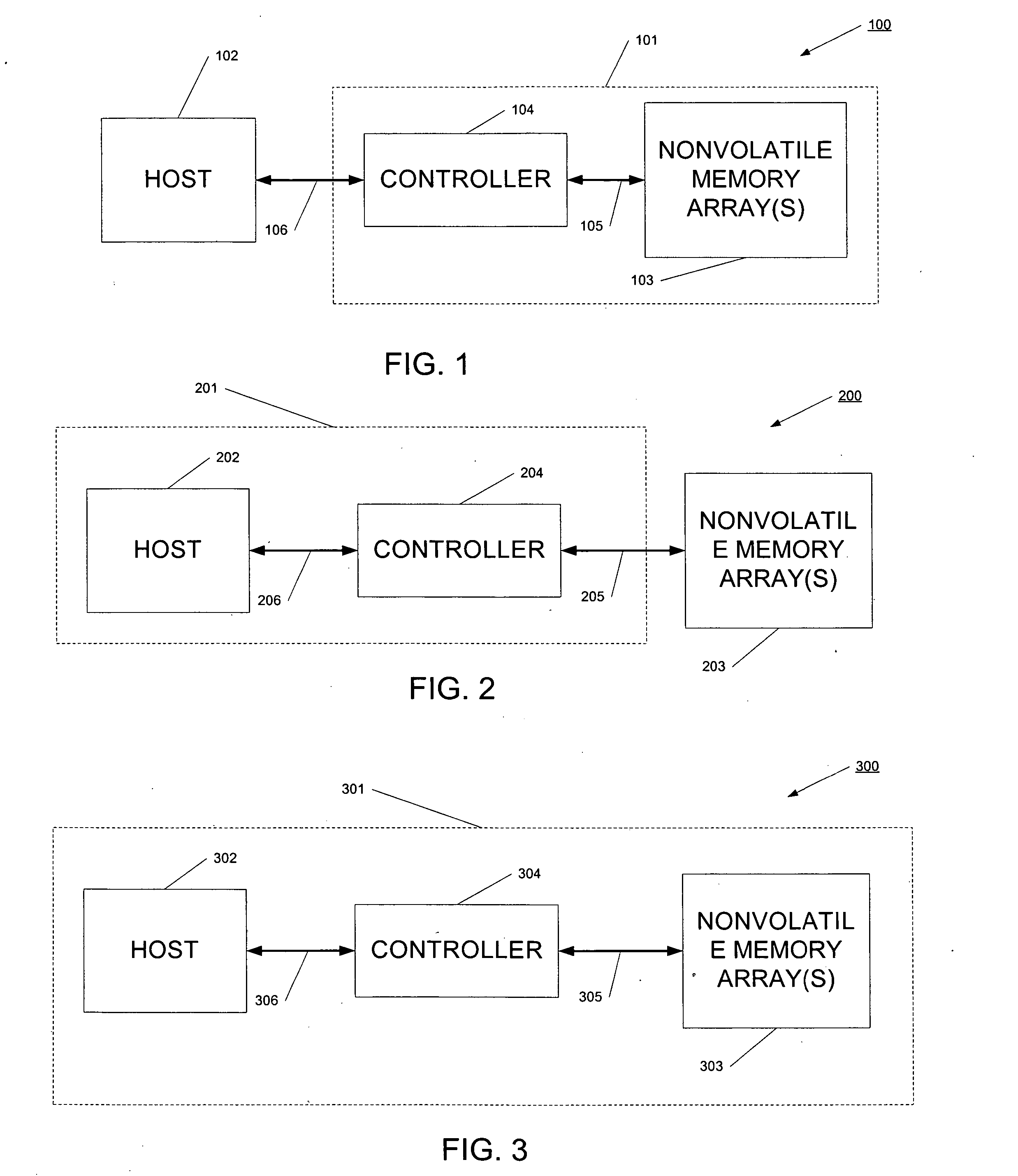

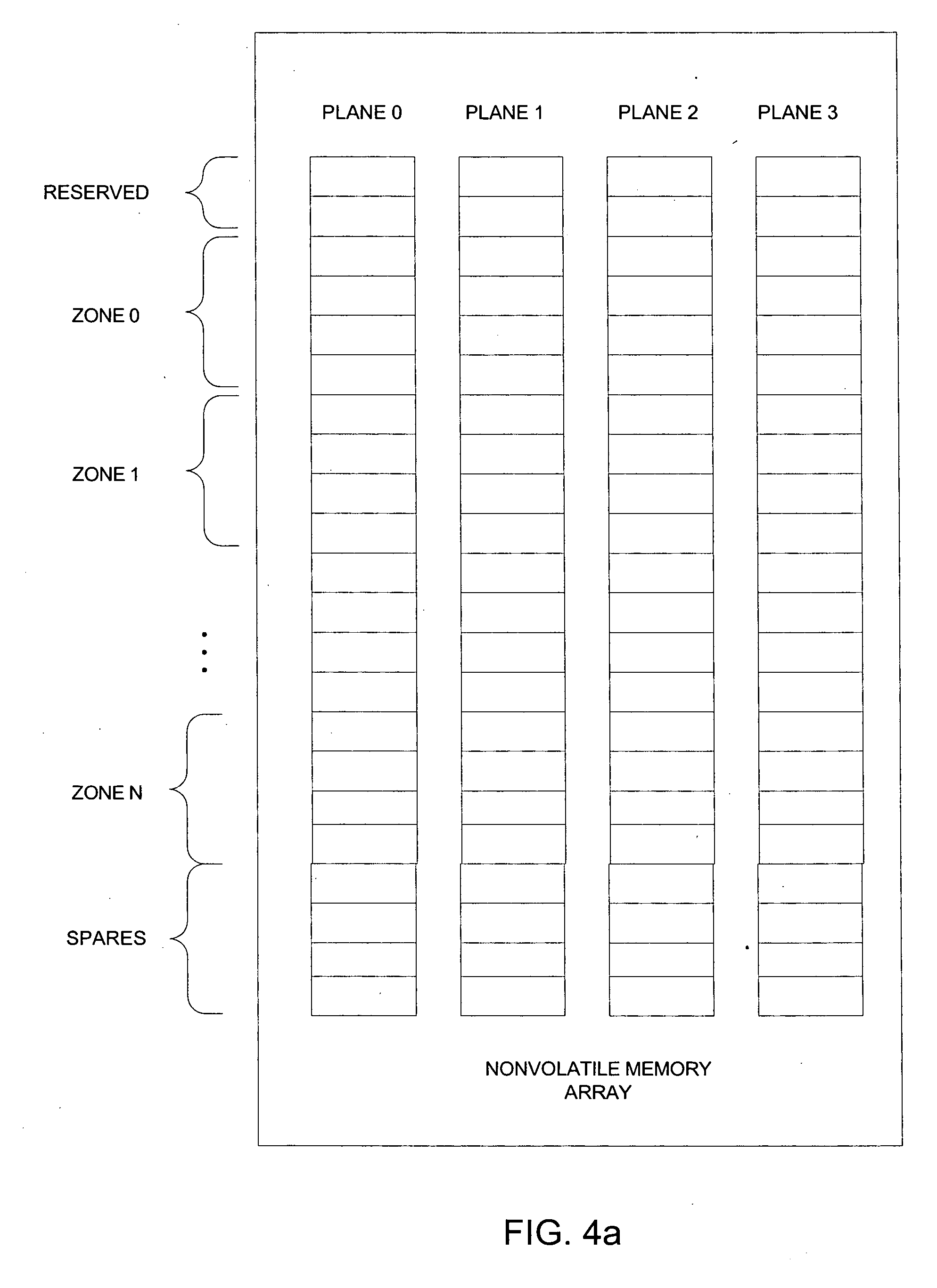

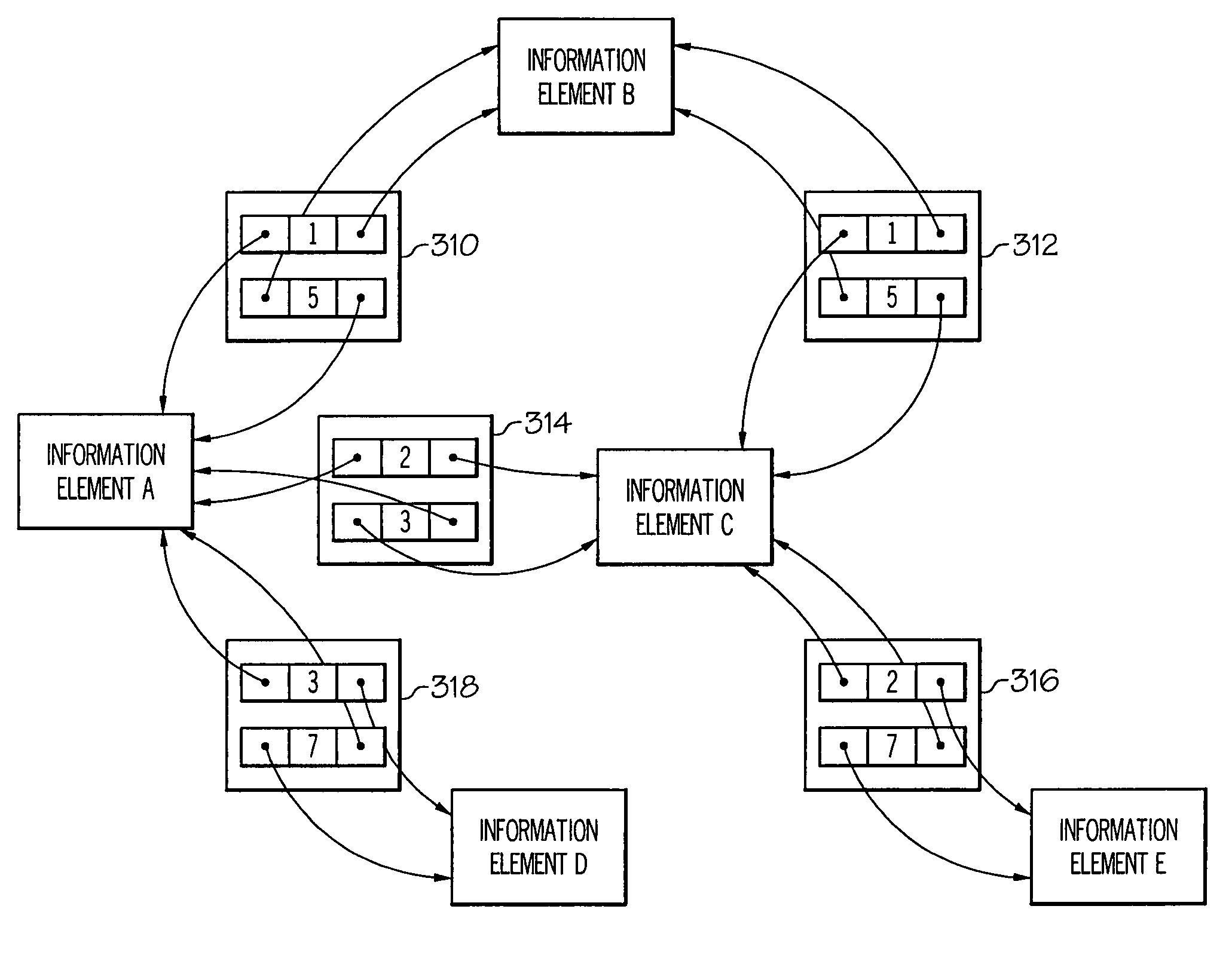

Adaptive deterministic grouping of blocks into multi-block units

InactiveUS20050144516A1Overcome limitationsMemory architecture accessing/allocationInput/output to record carriersSelf adaptiveLogic structure

The present invention presents techniques for the linking of physical blocks of a non-volatile memory into composite logical structures or “metablocks”. After determining an initial linking of good physical blocks into metablocks, a record of the linking is maintained in the non-volatile memory where it can be readily accessed when needed. In one set of embodiments, the initially linking is deterministically formed according to an algorithm and can be optimized according to the pattern of any bad blocks in the memory. As additional bad blocks arise, the linking is updated using by replacing the bad blocks in a linking with good blocks, preferably in the same sub-array of the memory as the block that they are replacing.

Owner:SANDISK TECH LLC

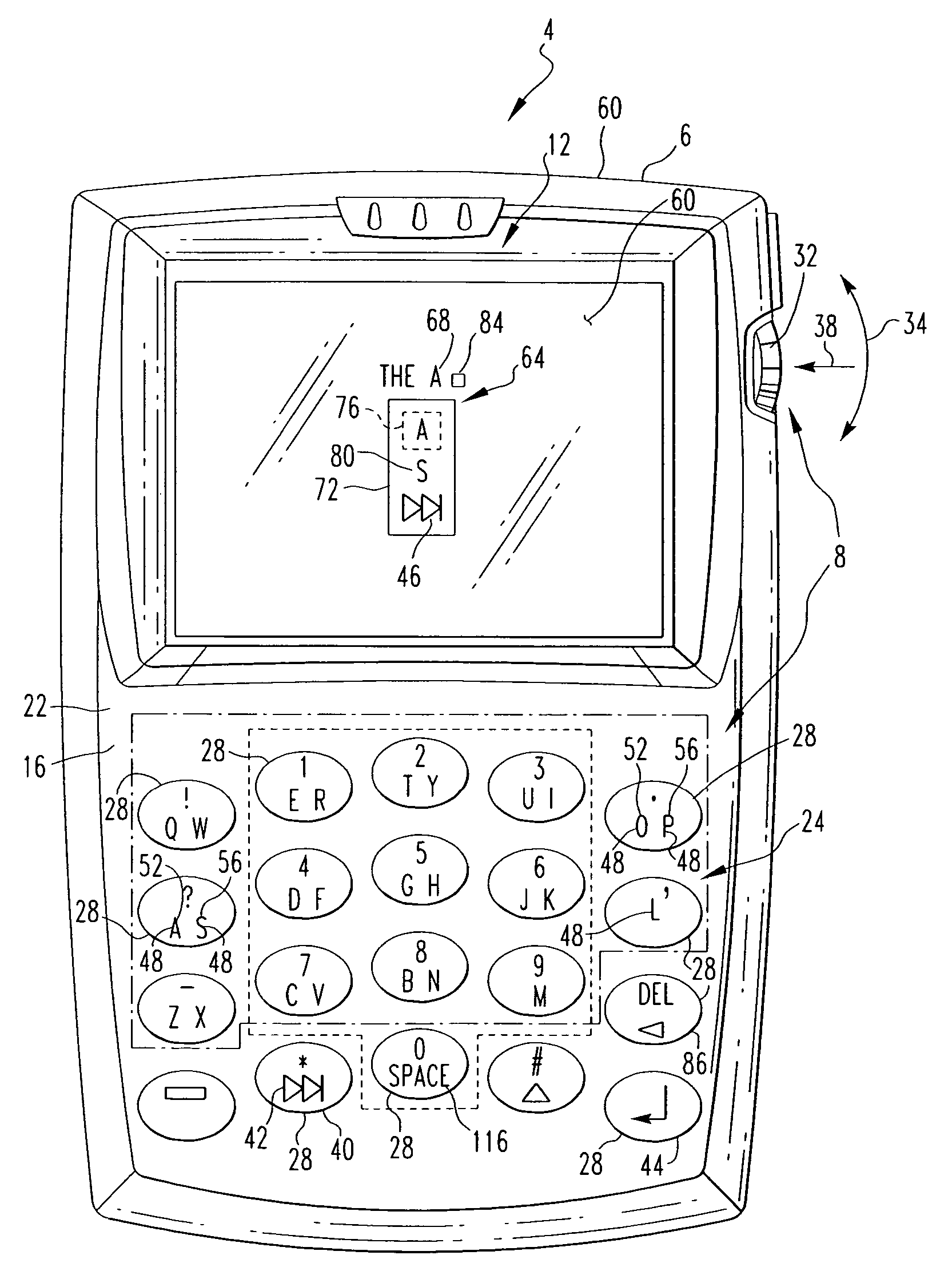

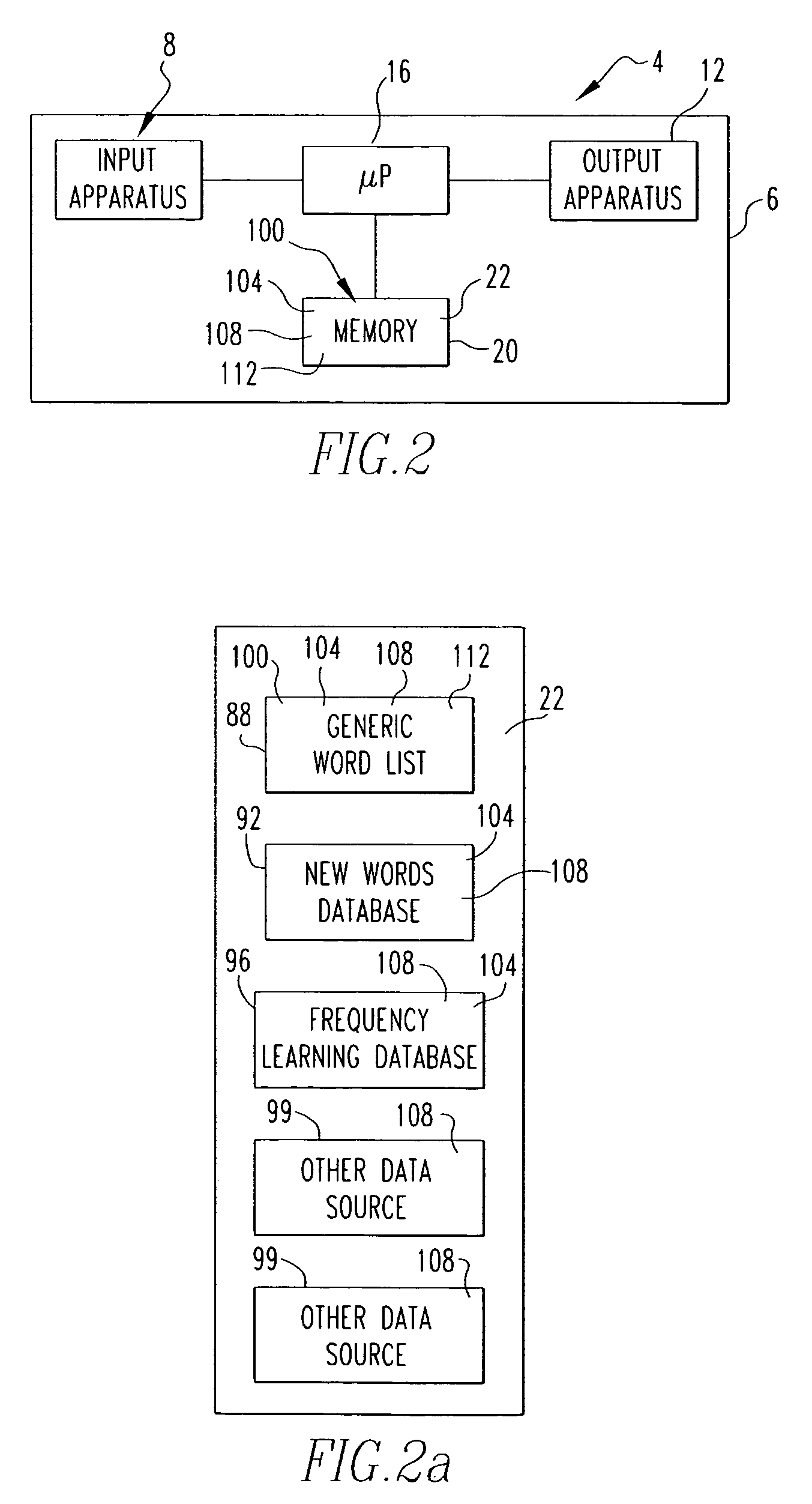

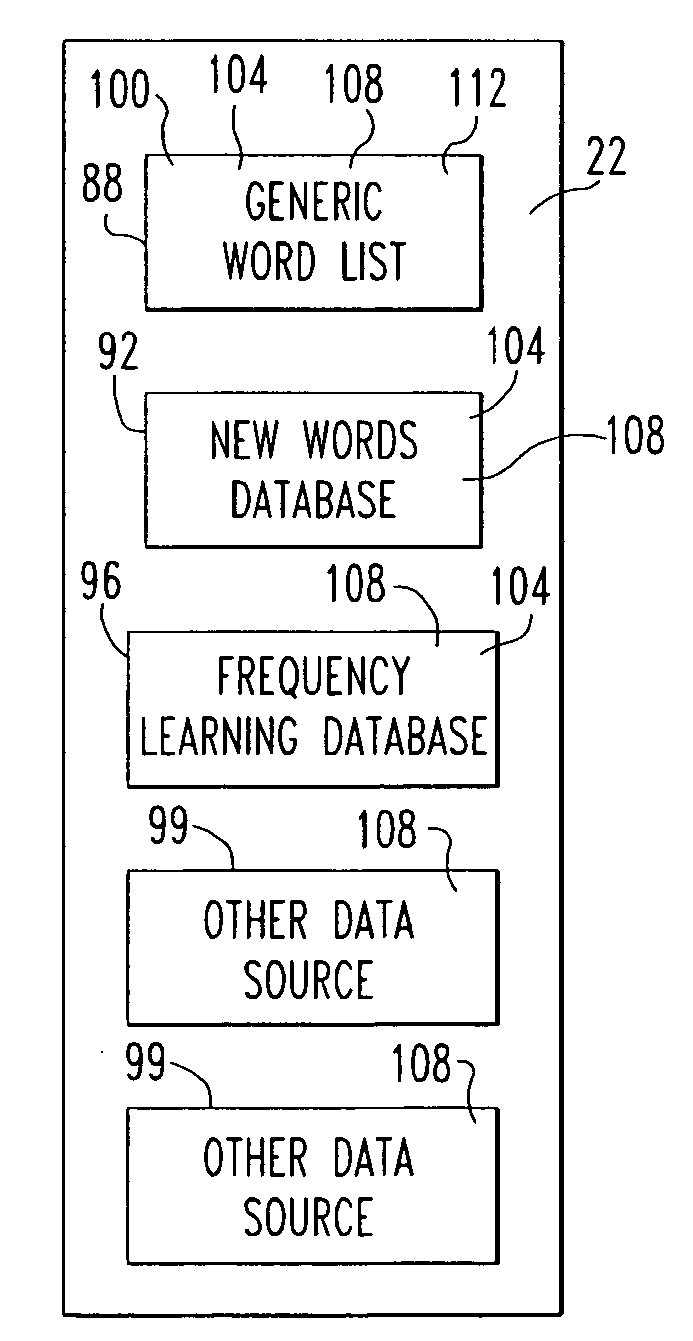

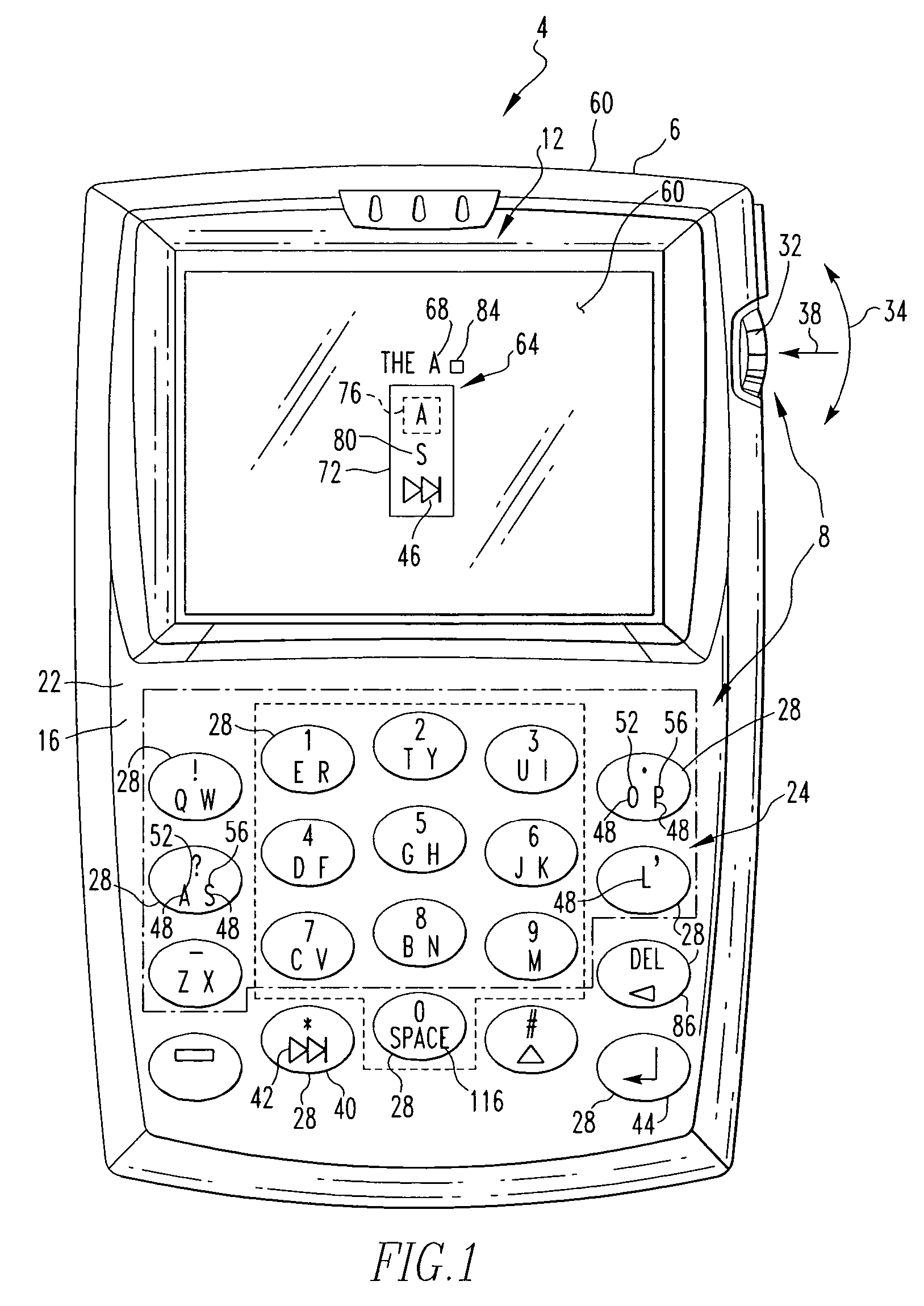

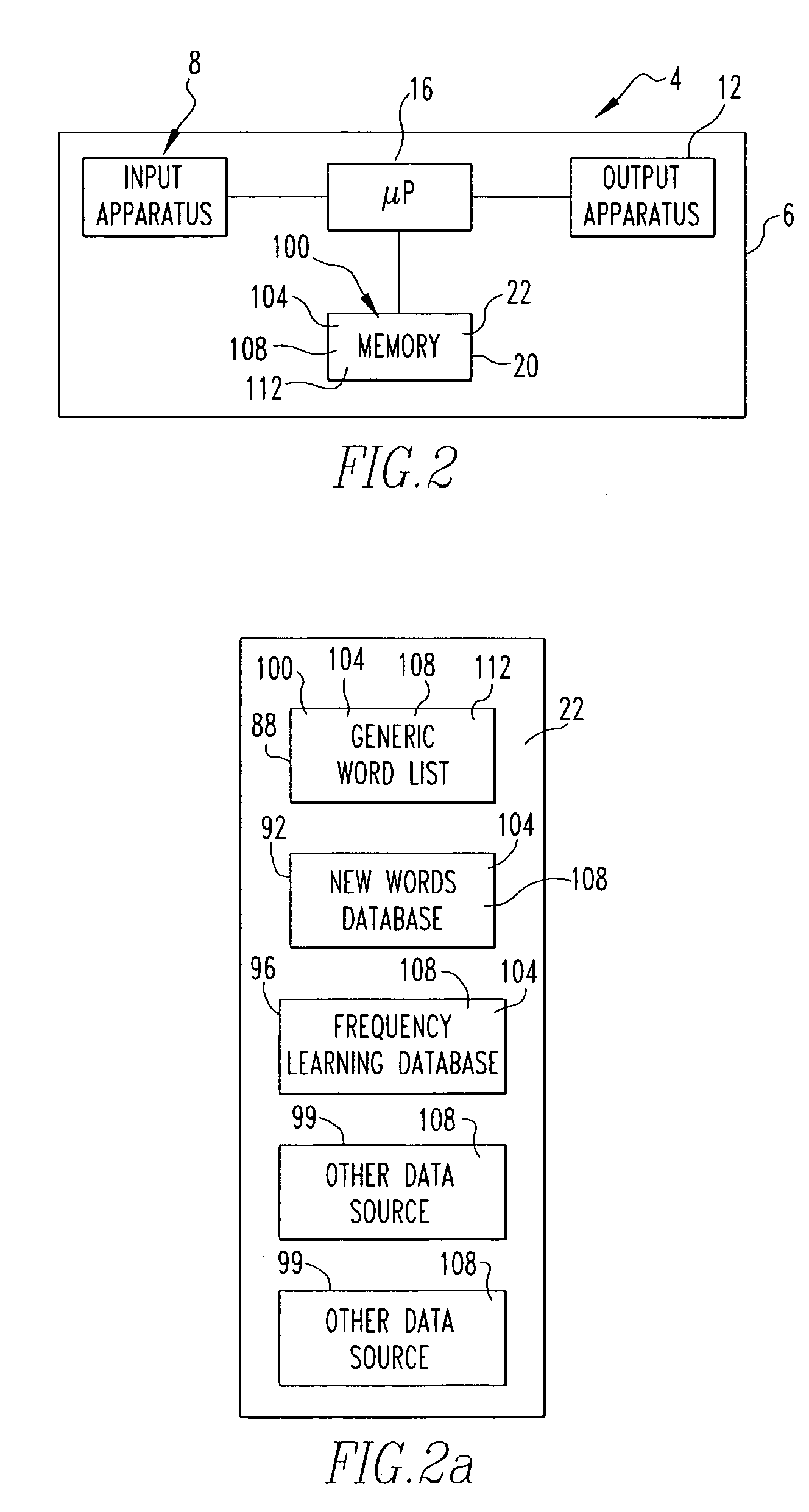

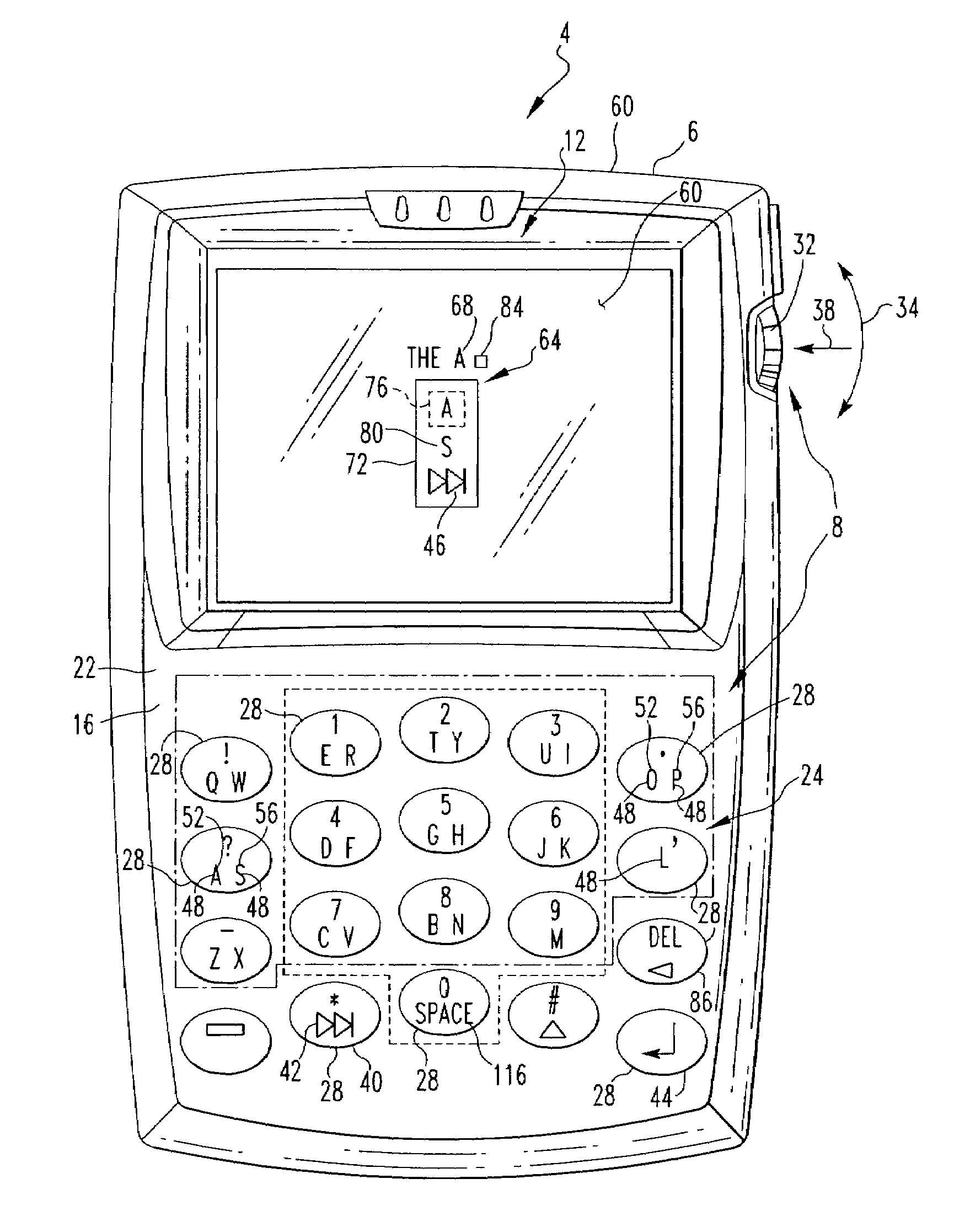

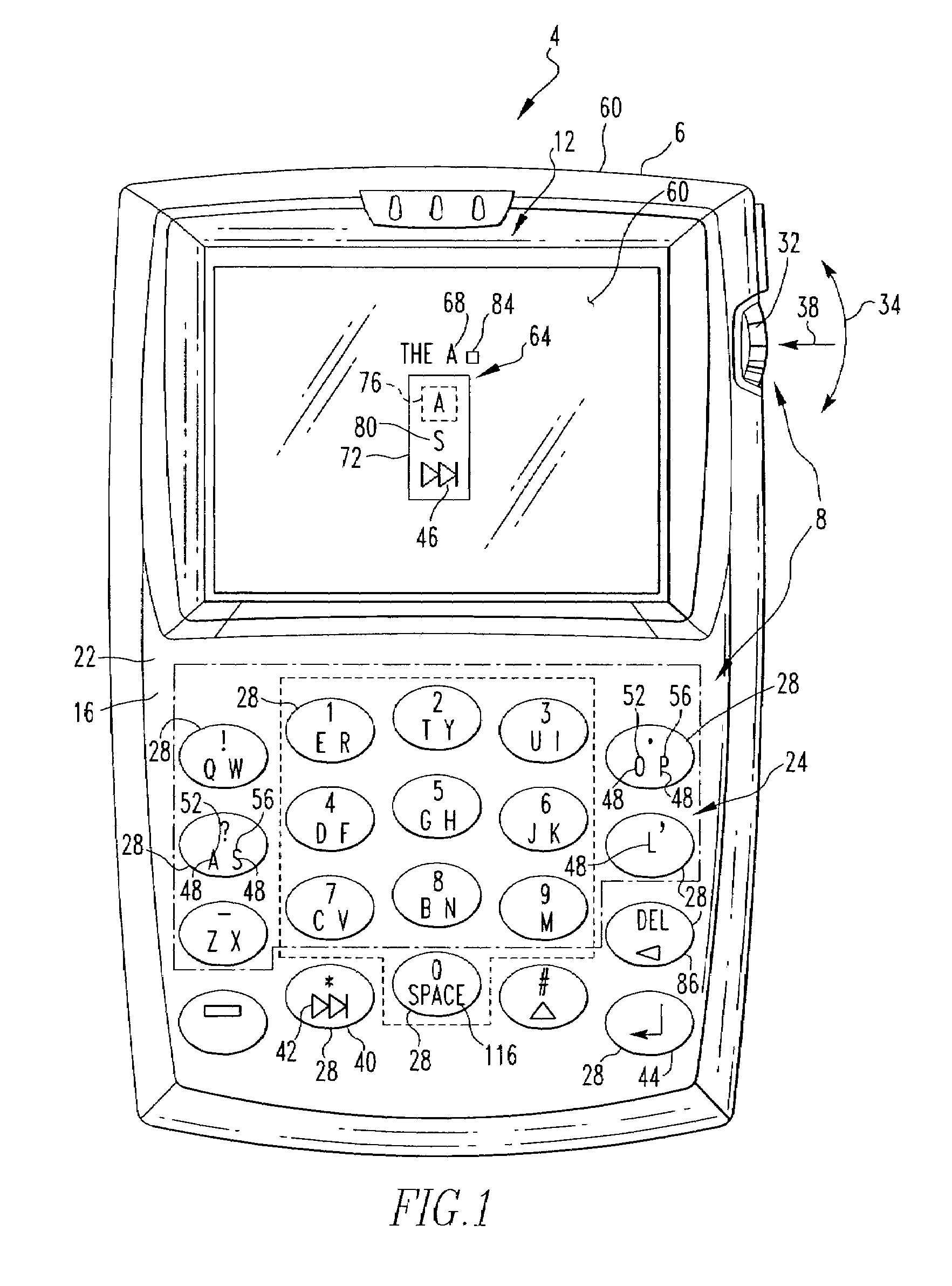

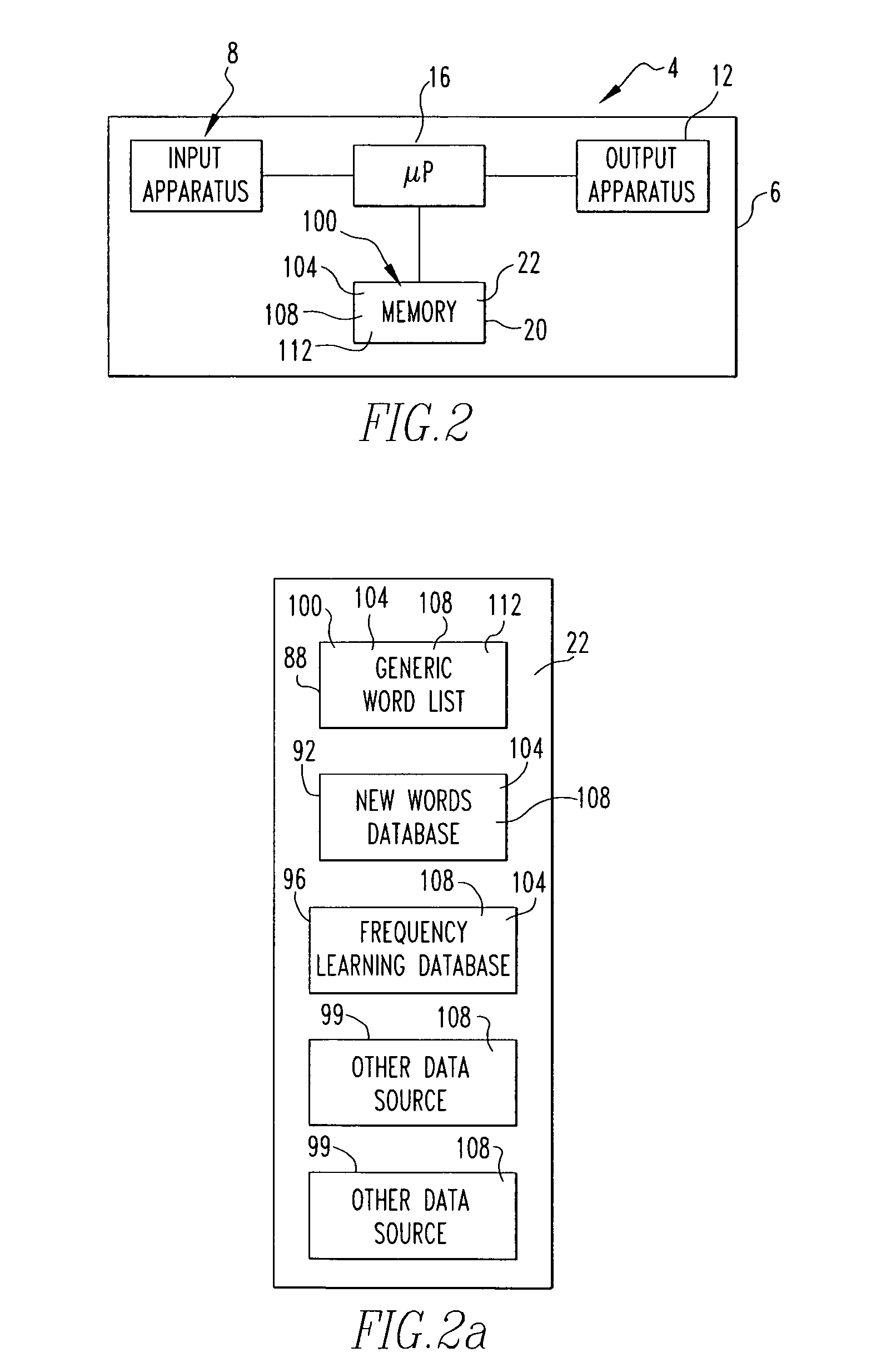

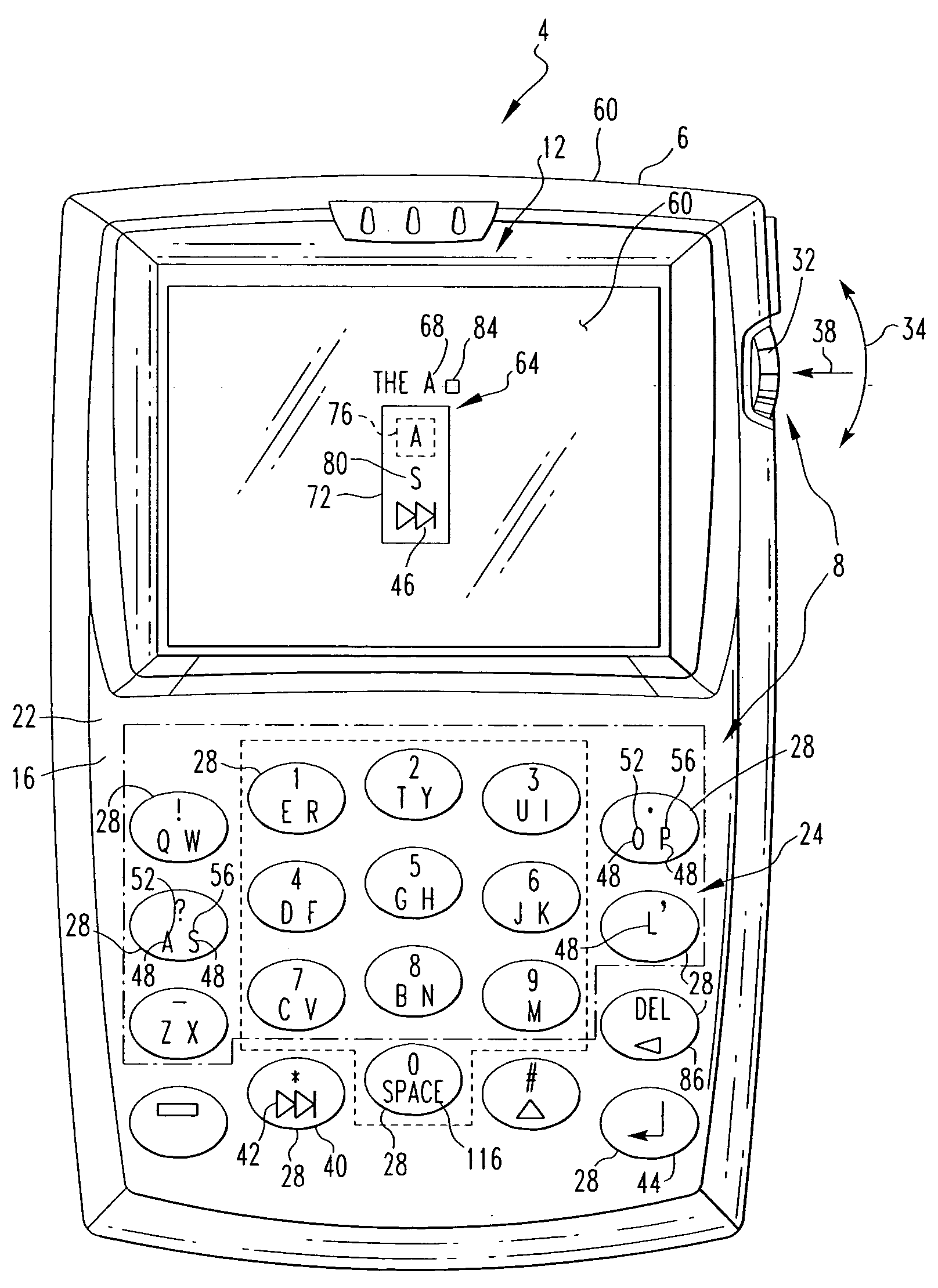

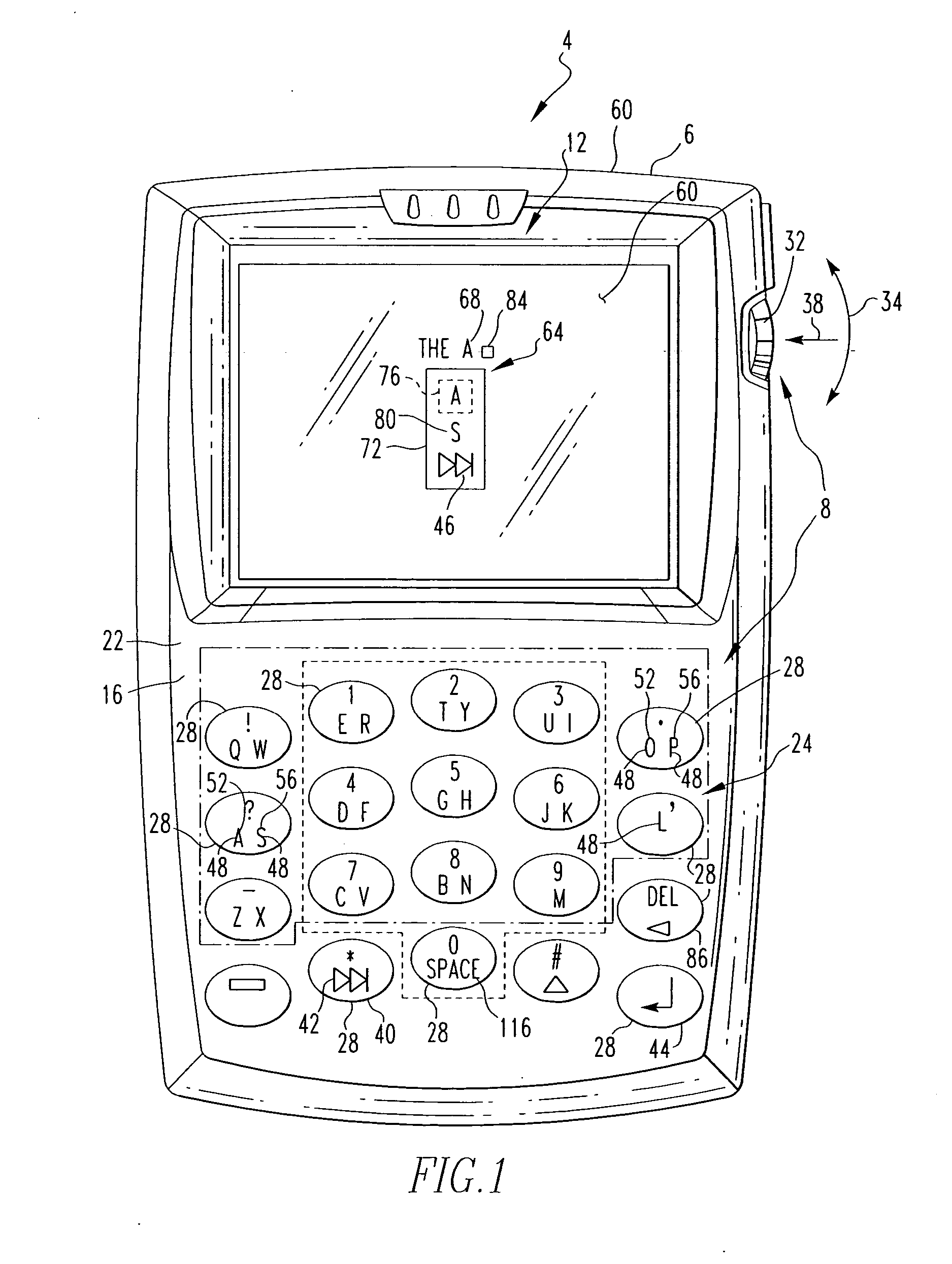

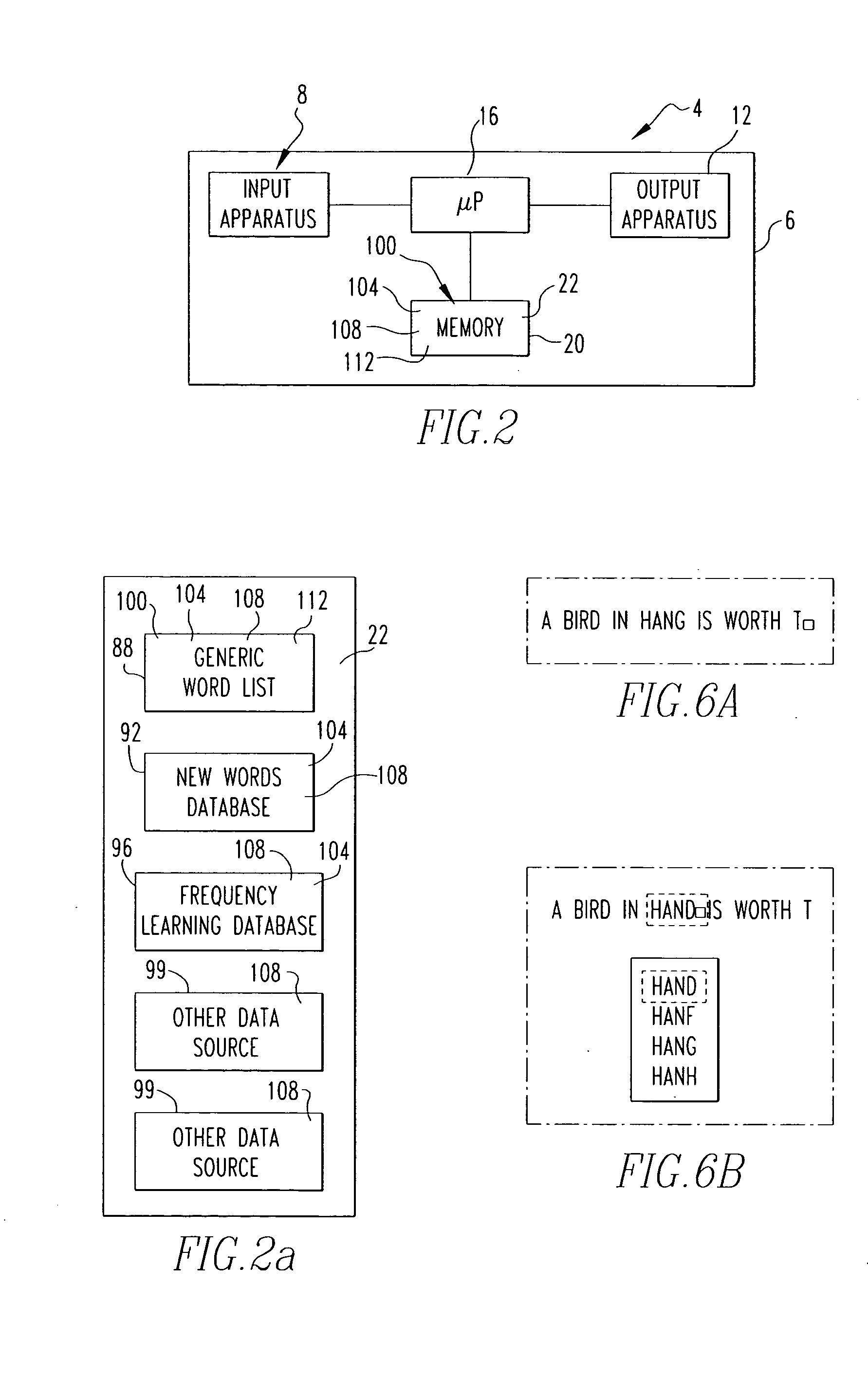

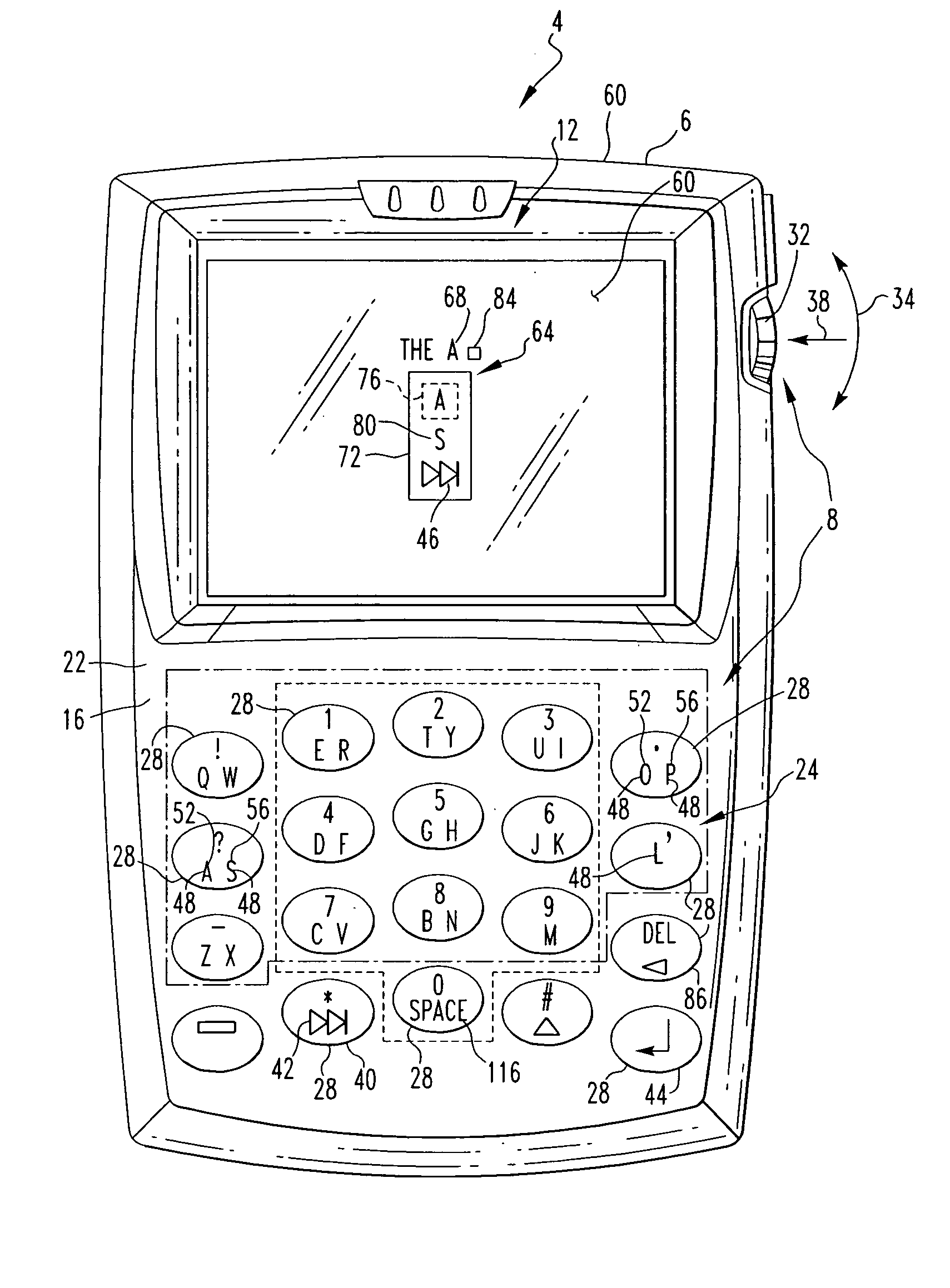

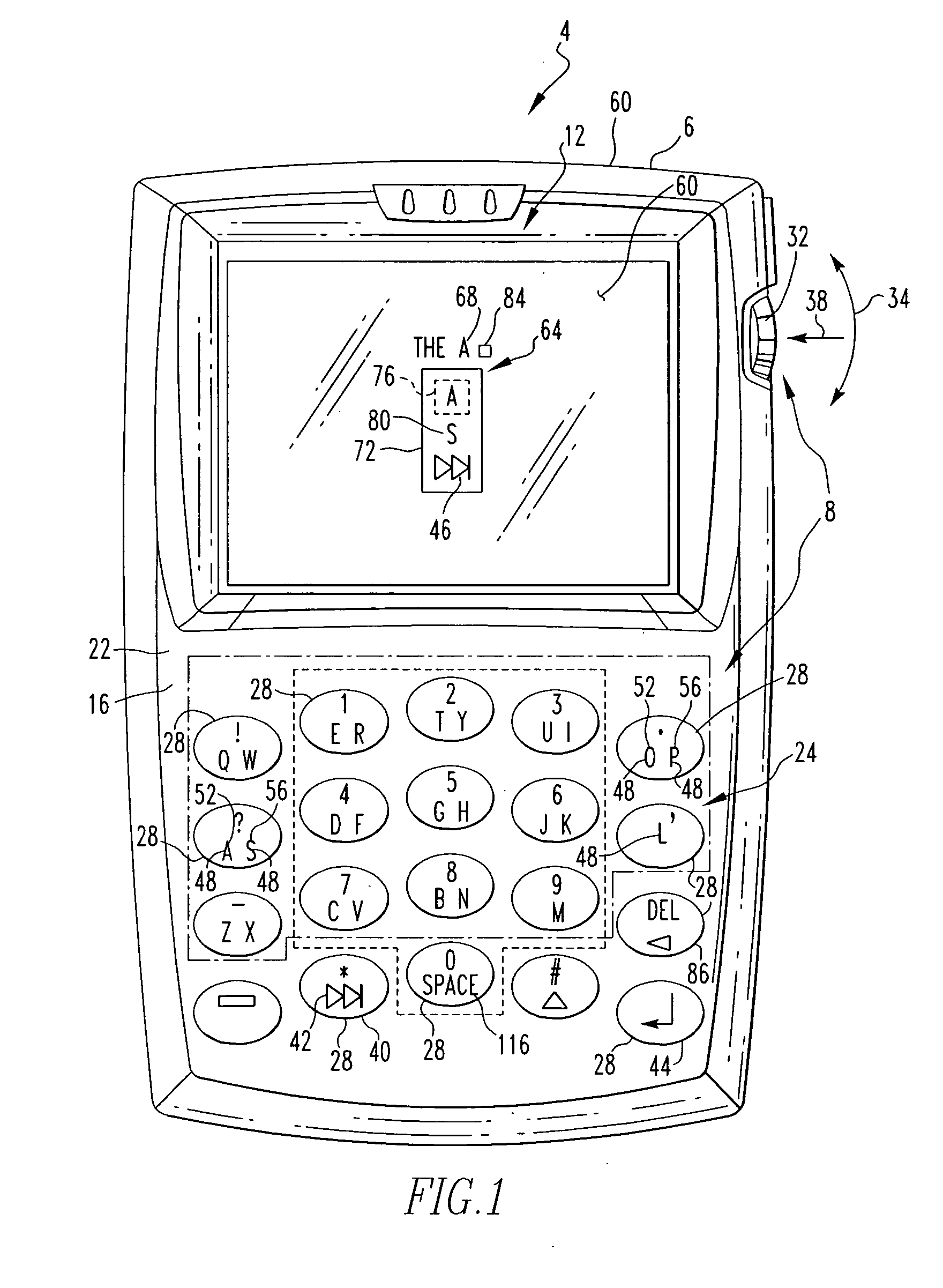

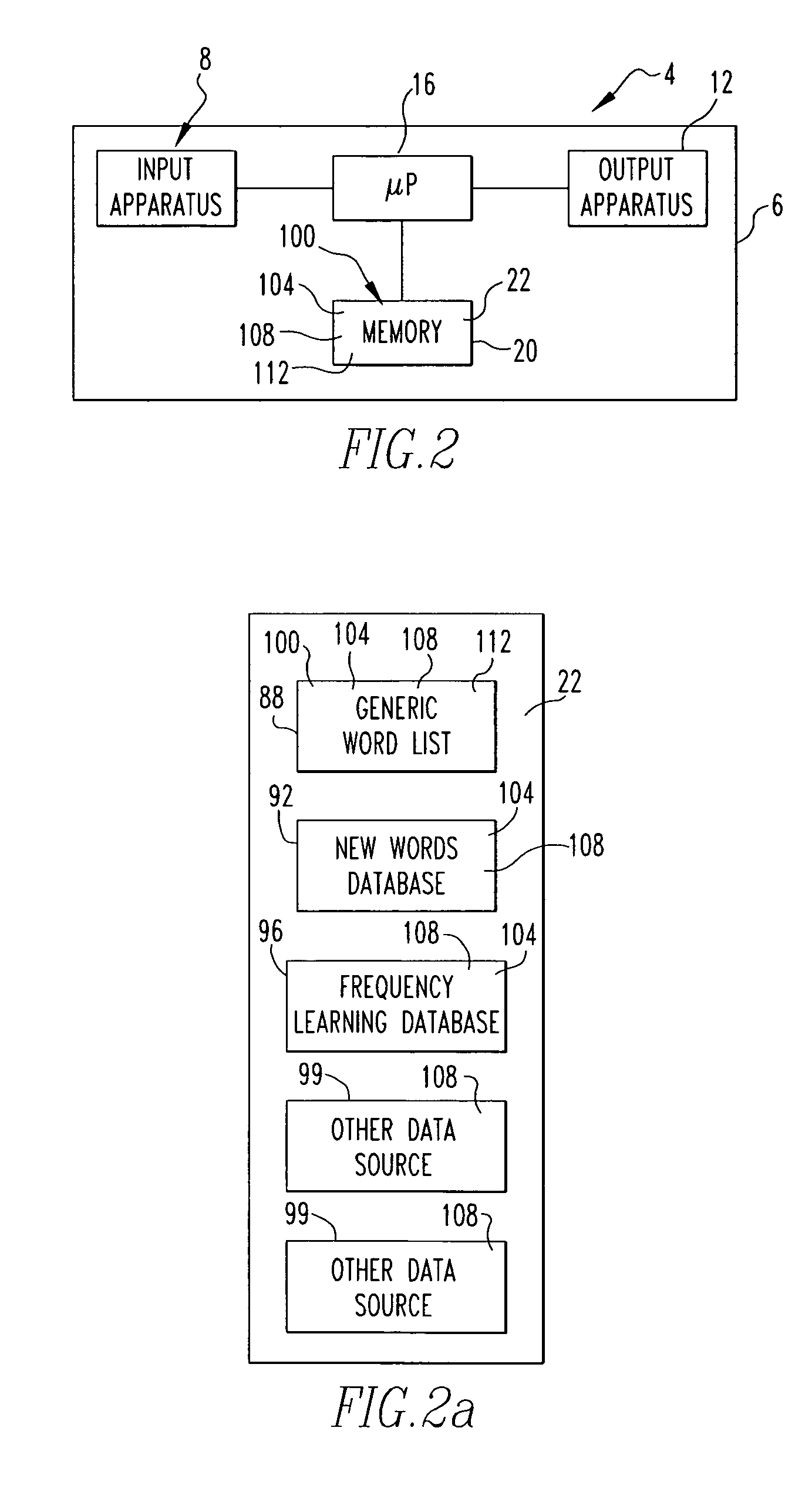

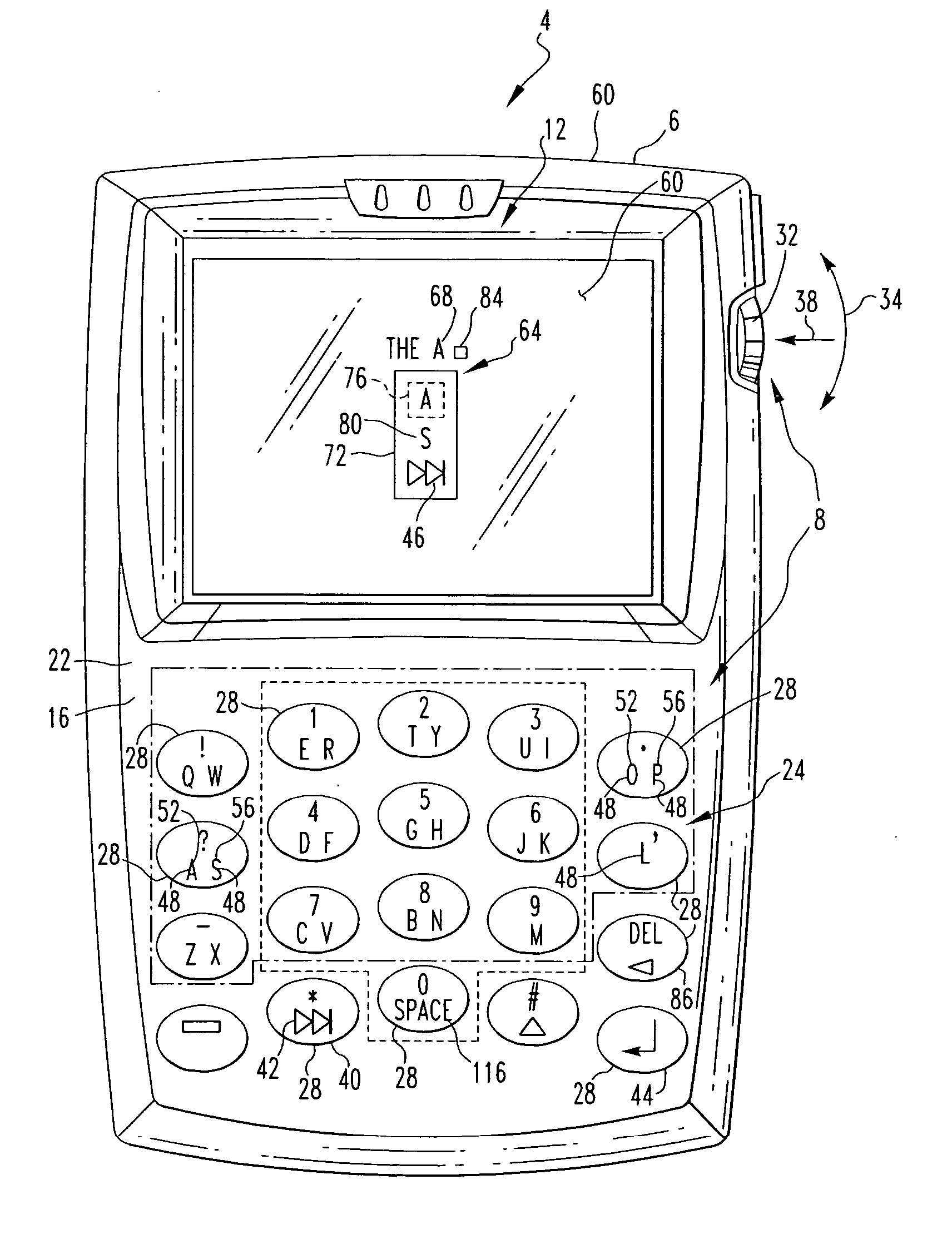

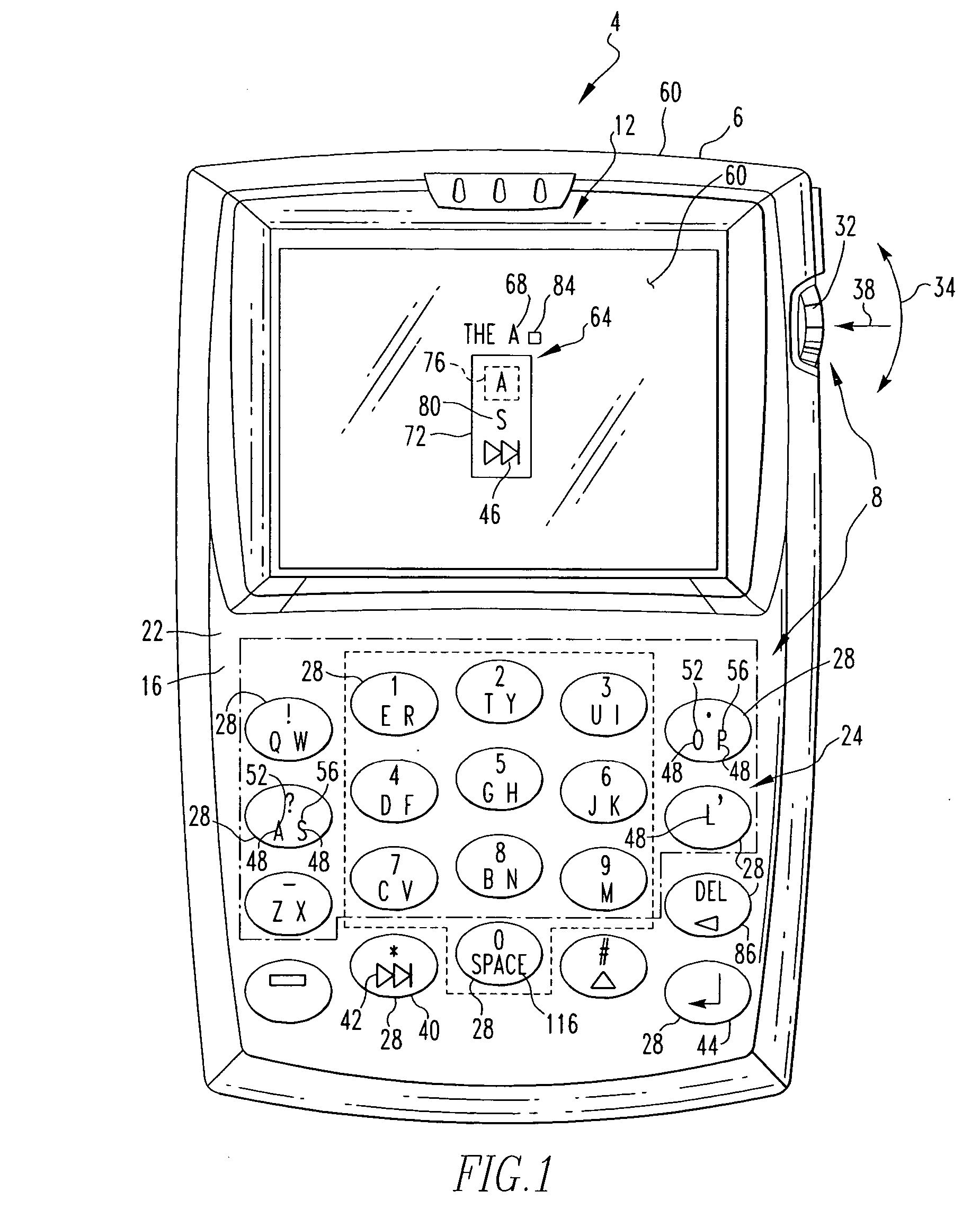

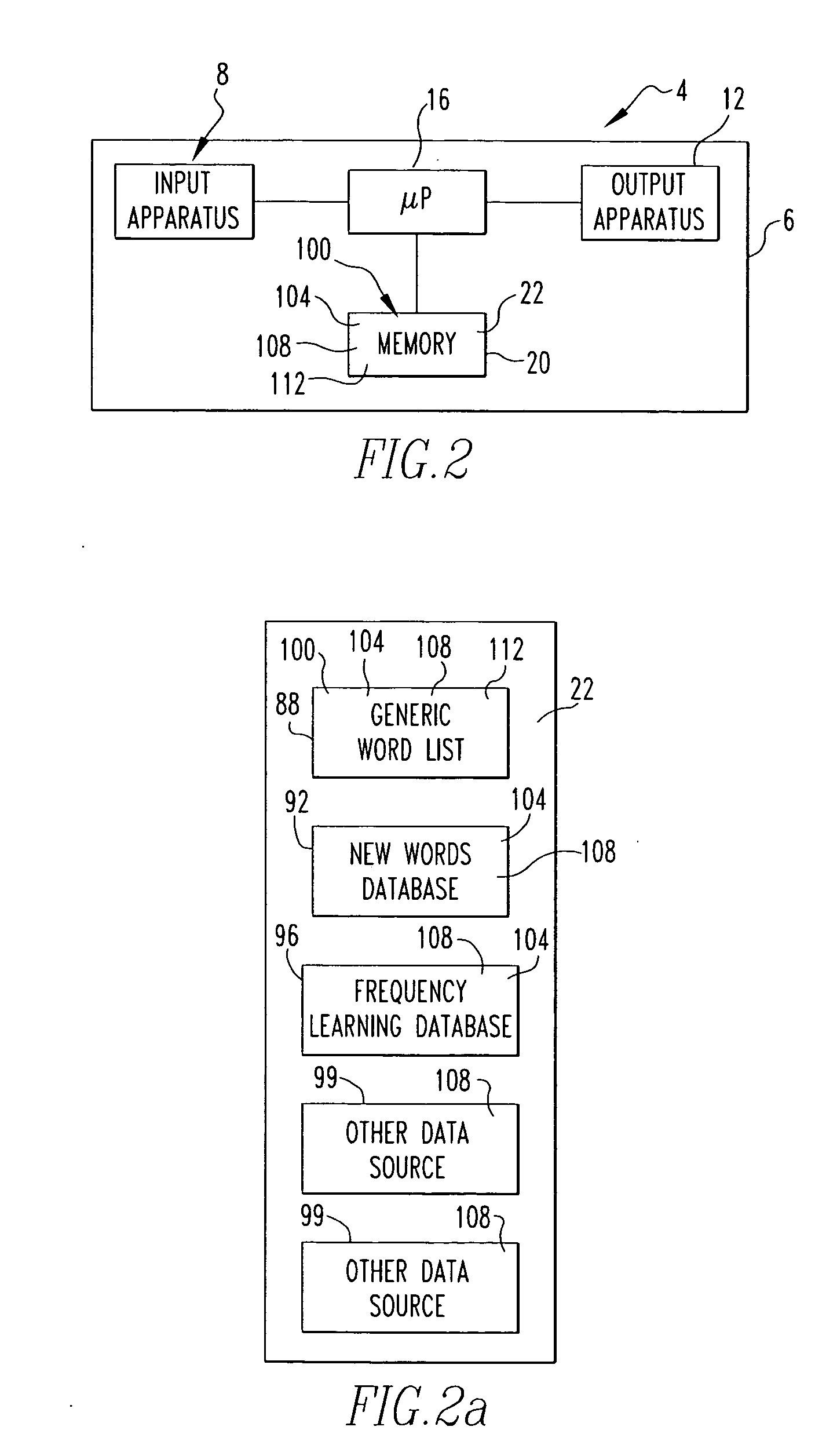

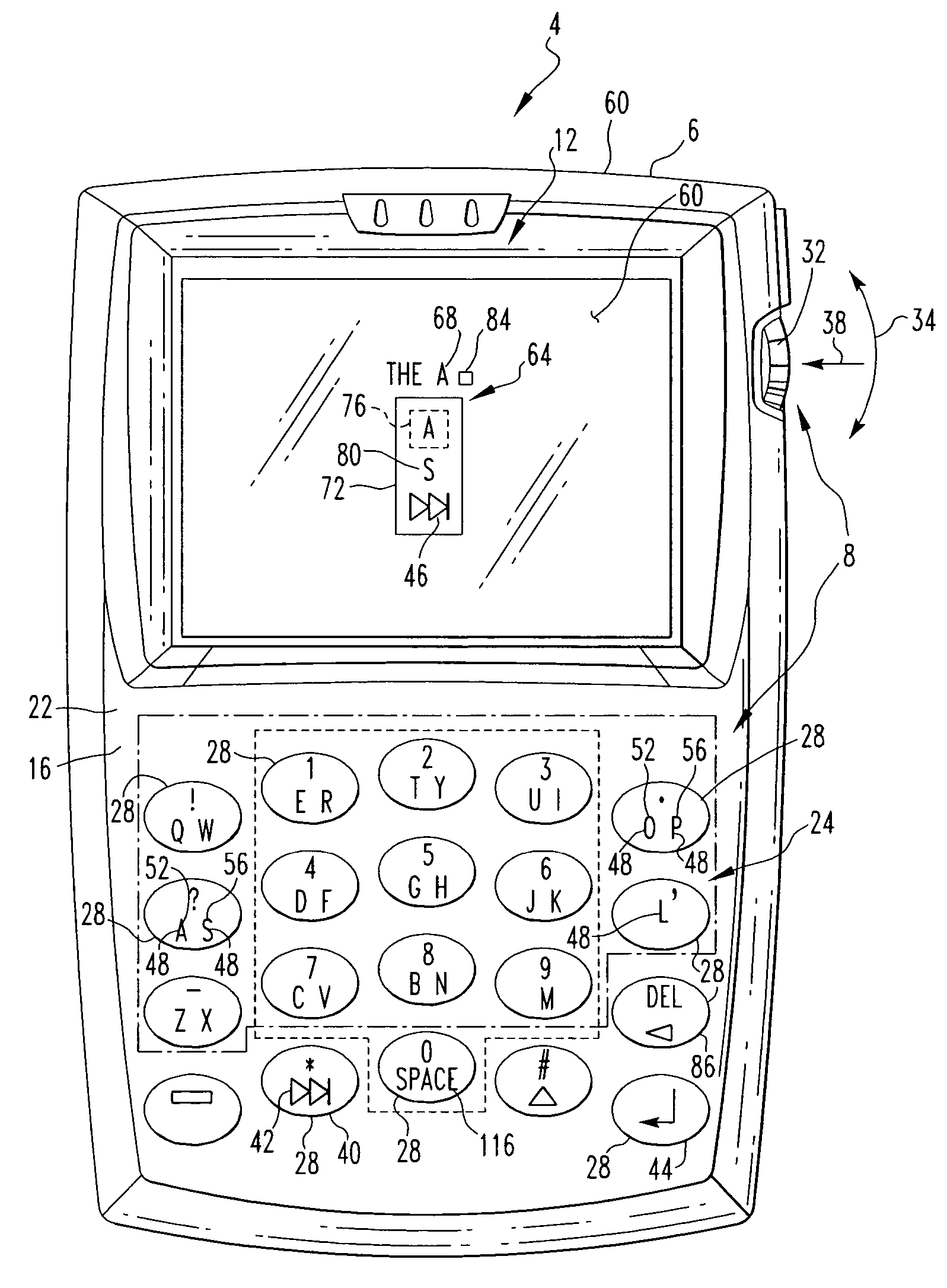

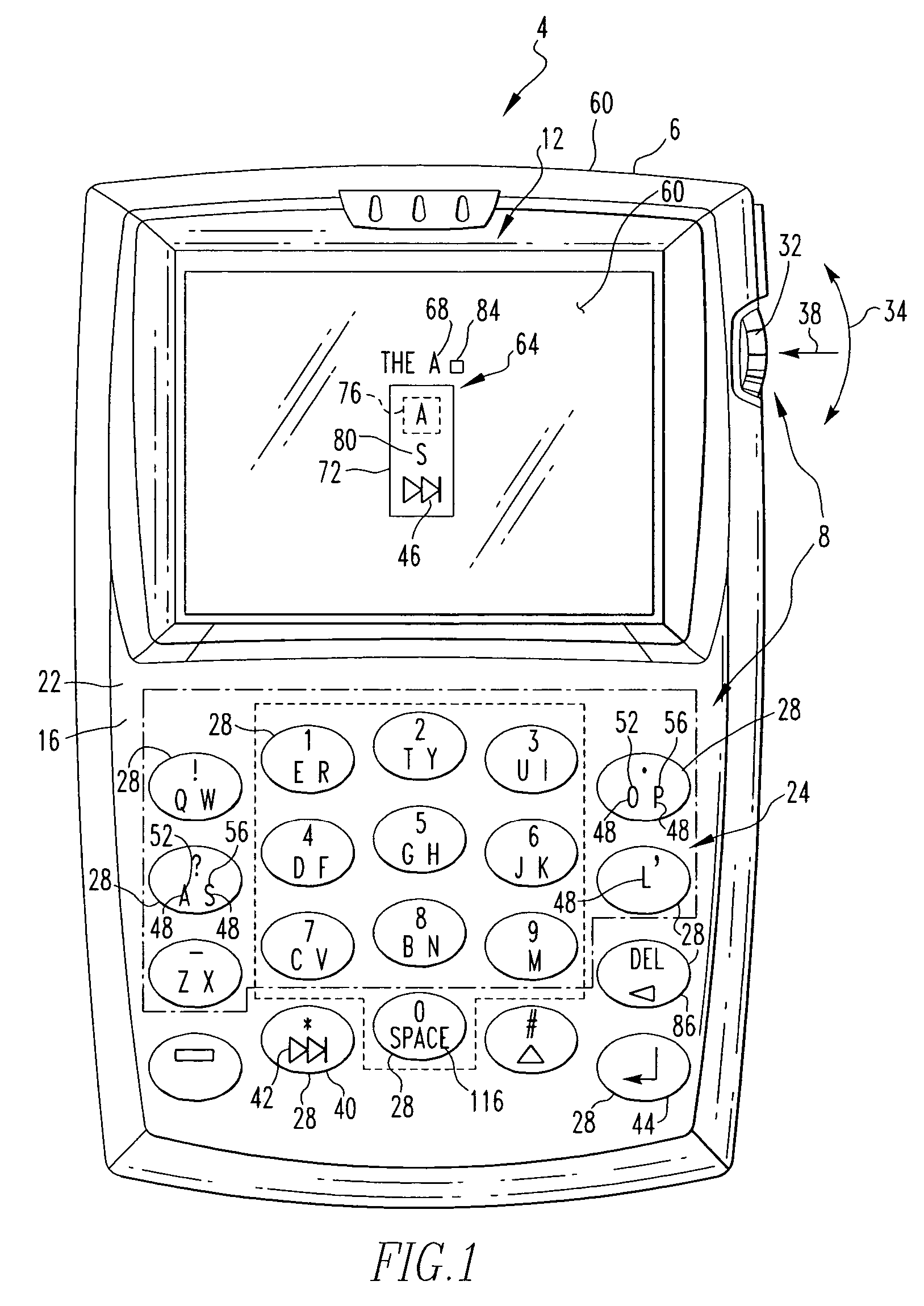

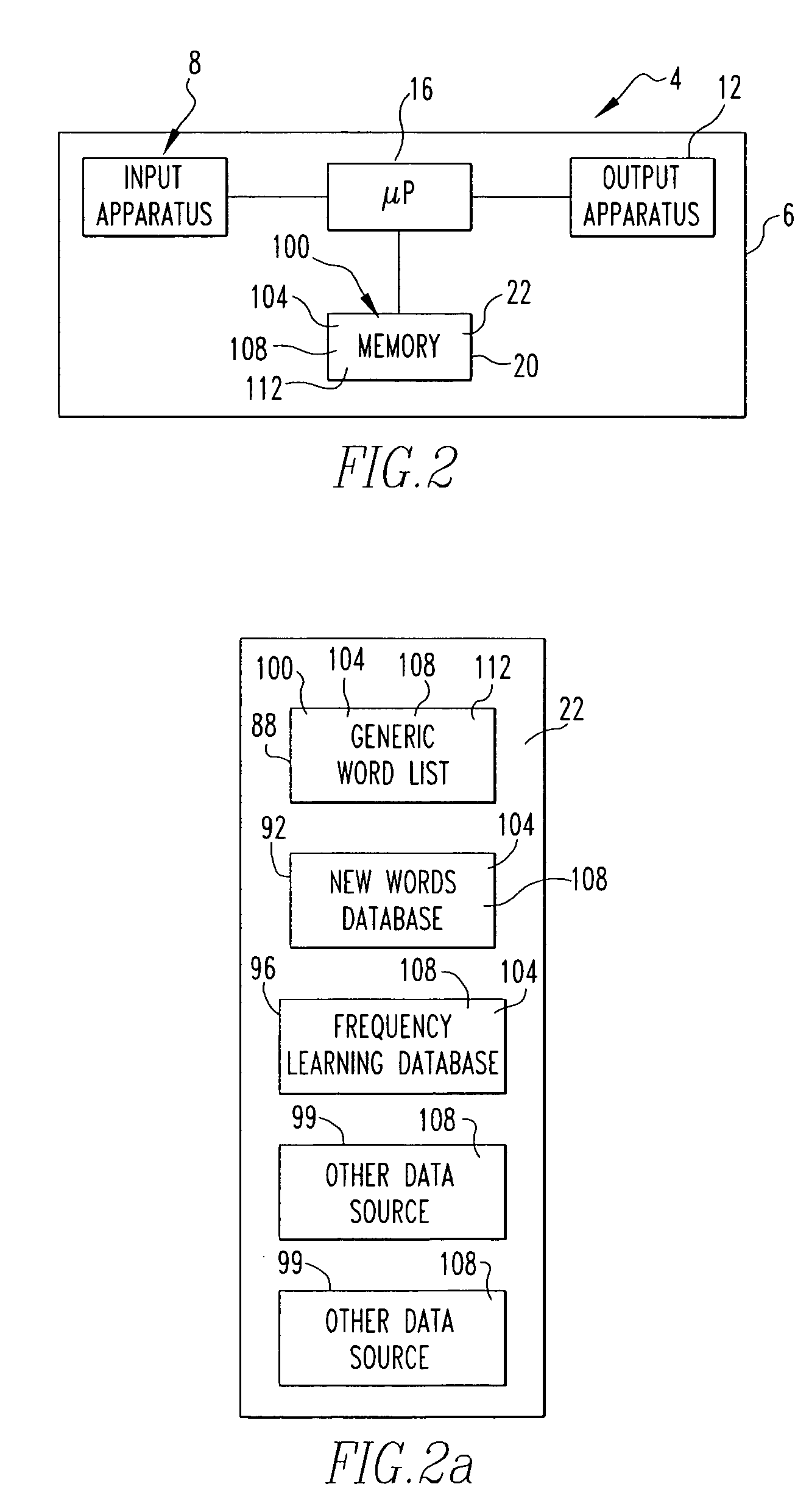

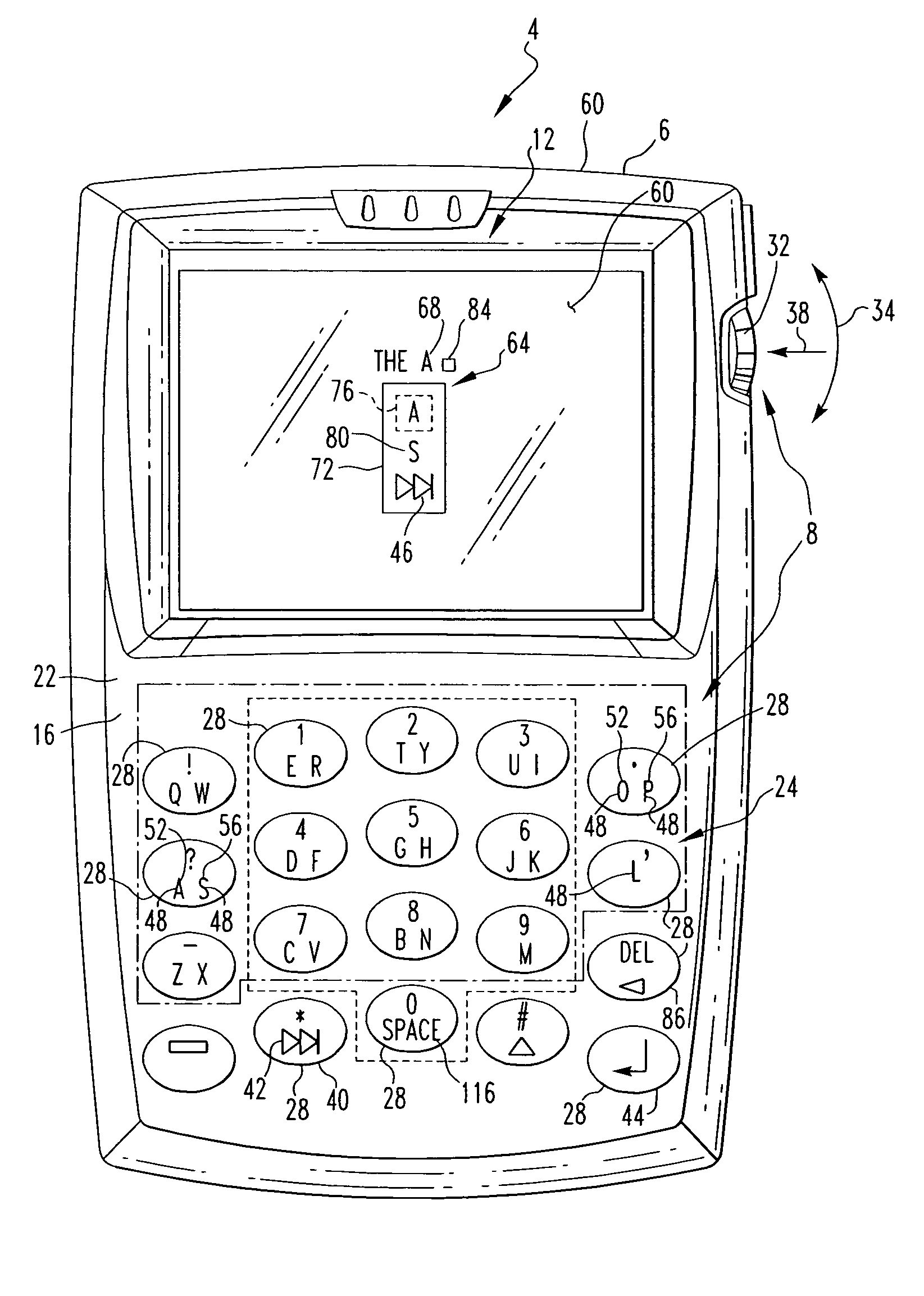

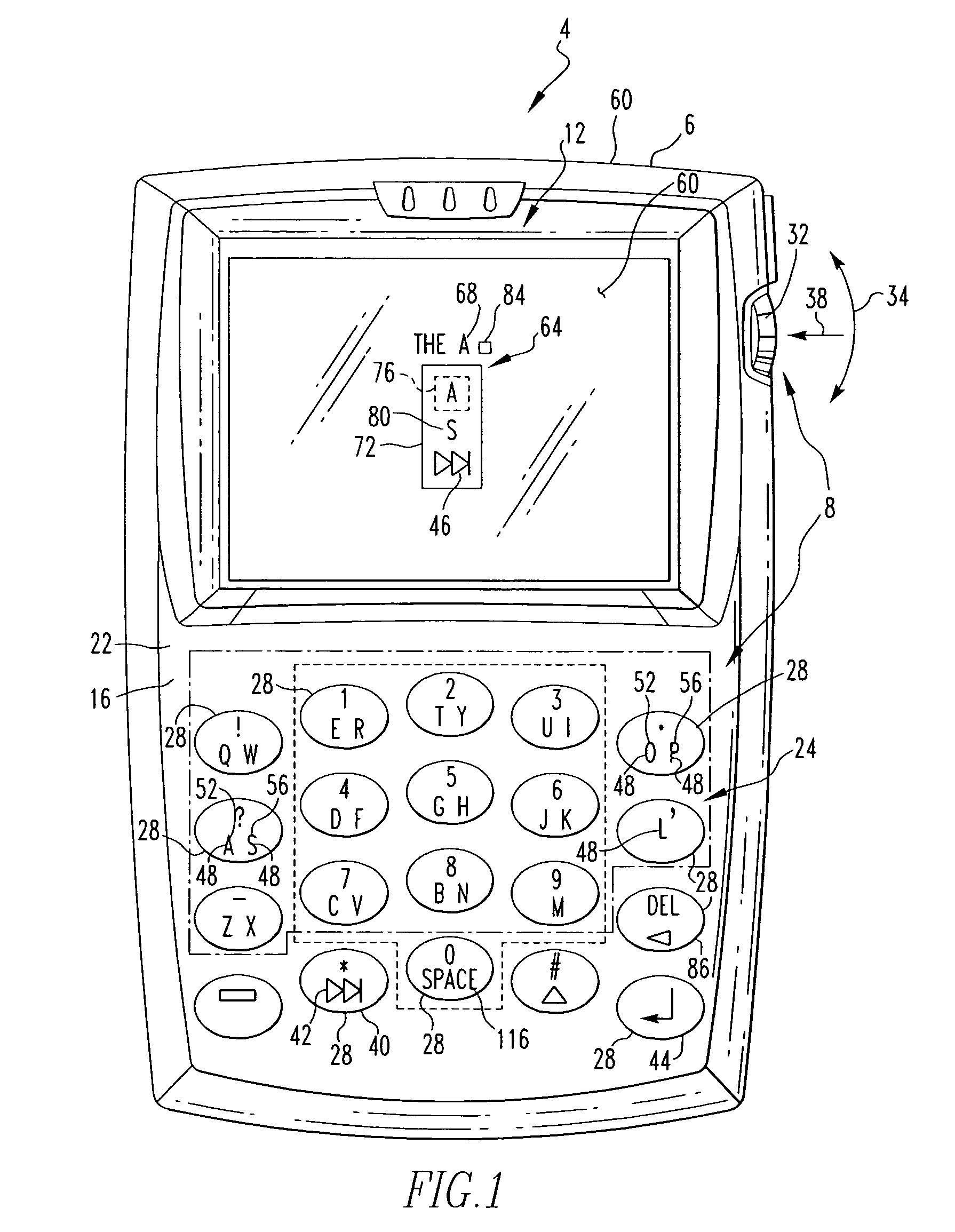

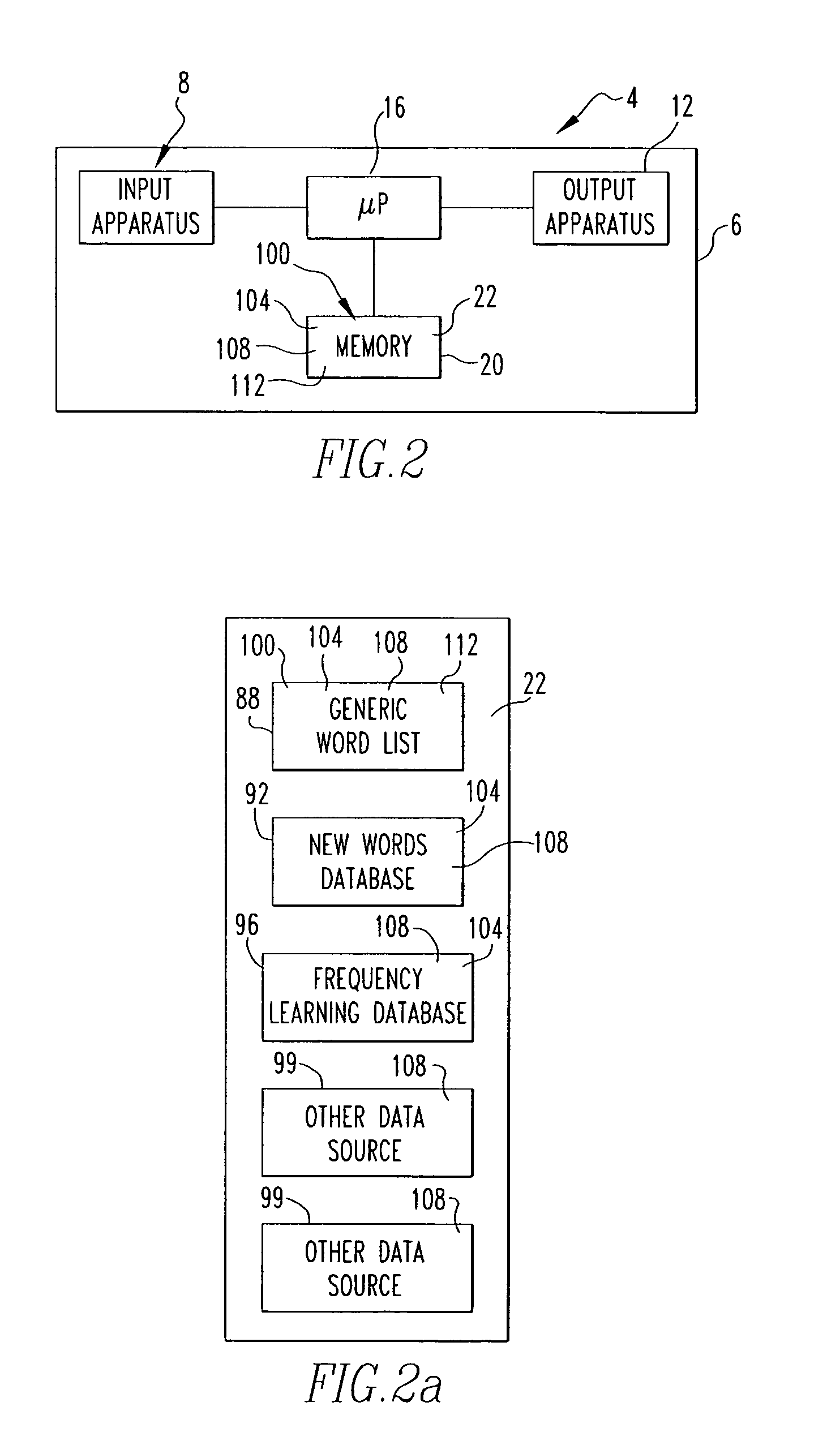

Handheld electronic device with text disambiguation

ActiveUS7477238B2Good choiceReduced QWERTYInput/output for user-computer interactionElectronic switchingGraphicsText entry

A handheld electronic device includes a reduced QWERTY keyboard and is enabled with disambiguation software. The device provides output in the form of a default output and a number of variants. The output is based largely upon the frequency, i.e., the likelihood that a user intended a particular output, but various features of the device provide additional variants that are not based solely on frequency and rather are provided by various logic structures resident on the device. The device enables editing during text entry and also provides a learning function that allows the disambiguation function to adapt to provide a customized experience for the user. The disambiguation function can be selectively disabled and an alternate keystroke interpretation system provided. Additionally, the device can facilitate the selection of variants by displaying a graphic of a special <NEXT> key of the keypad that enables a user to progressively select variants generally without changing the position of the user's hands on the device. If a field into which text is being entered is determined to be a special input field, a disambiguated result can be sought first from a predetermined data source prior to seeking results from other data sources on the device.

Owner:MALIKIE INNOVATIONS LTD

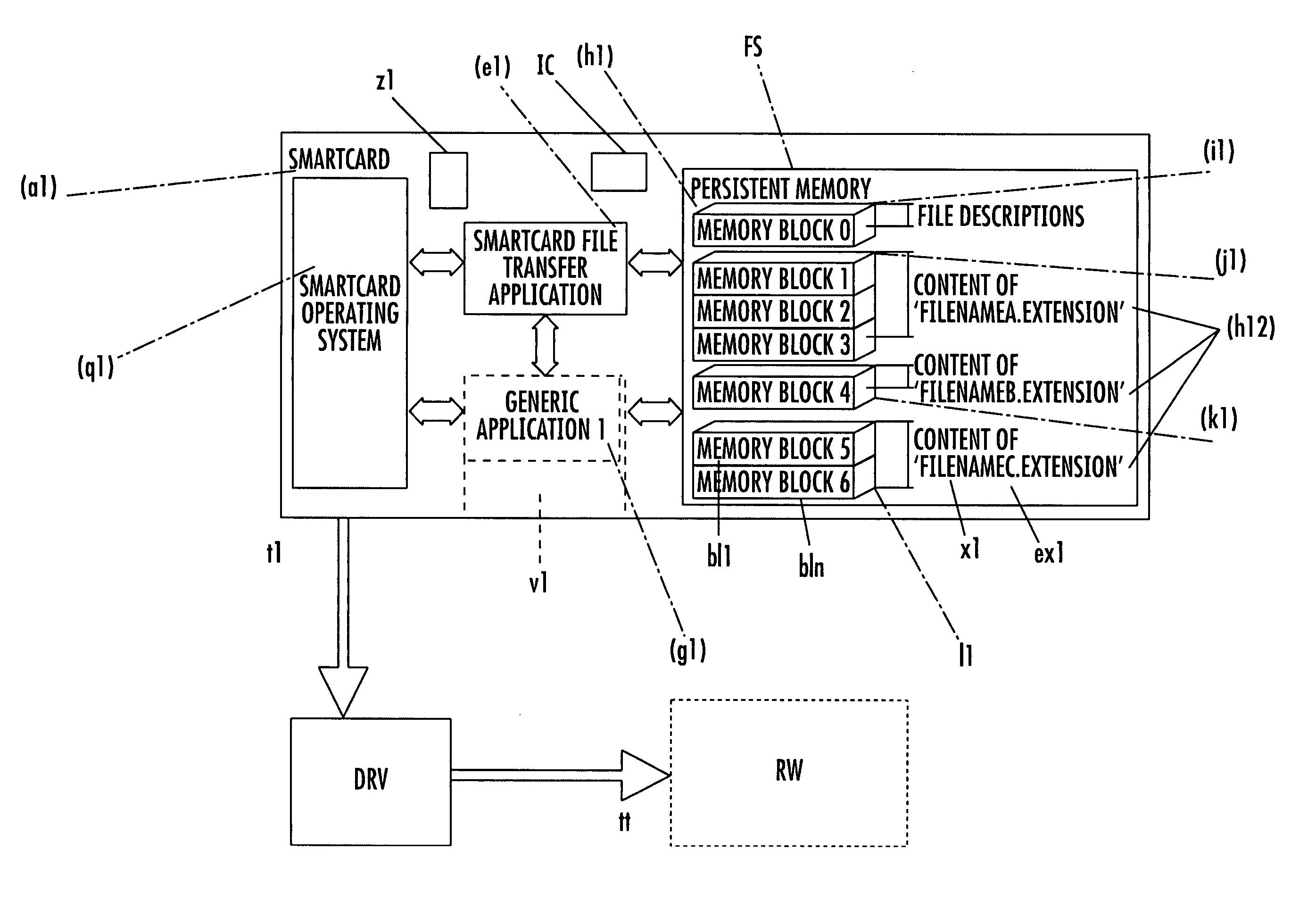

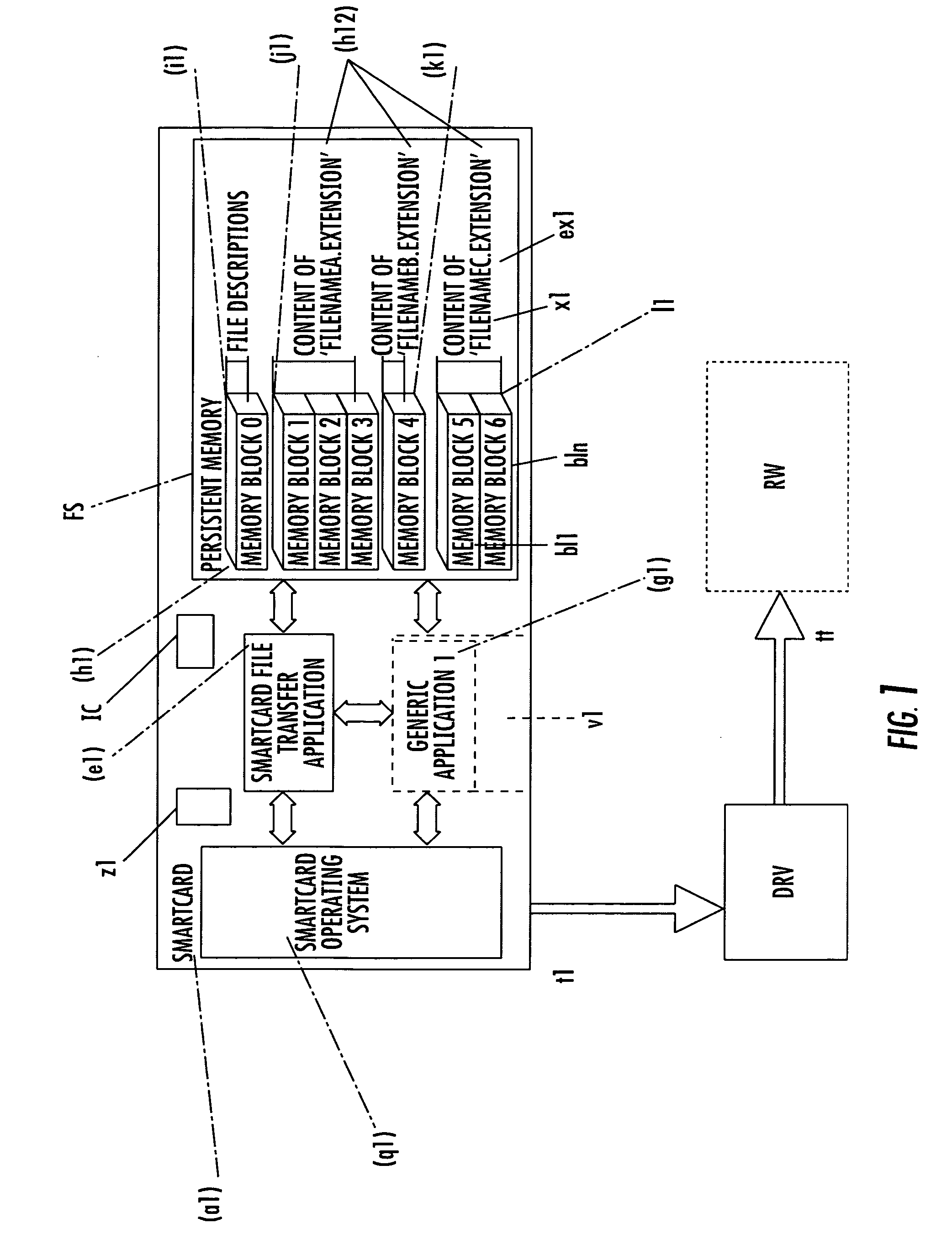

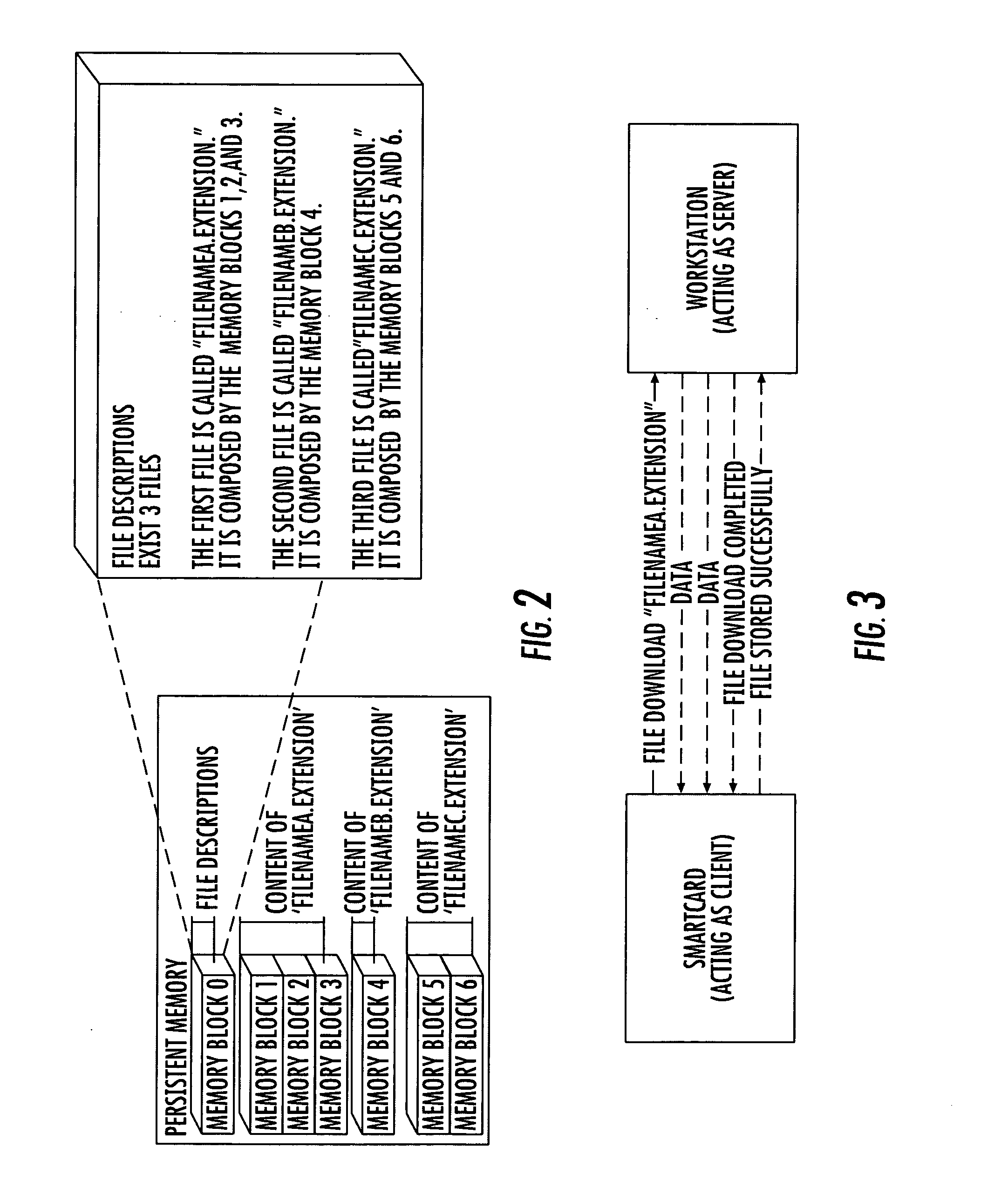

IC card file system

InactiveUS20070152070A1AccessibilityAcutation objectsDigital data information retrievalIntel HEXApplication software

File system for IC CARD comprising an integrated circuit IC, non volatile memories ROM and / or E2PROM and at least a volatile memory RAM, for organizing files storage inside the non volatile memories and defining, through a logical structure, their accessibility by an IC Card application, stored inside one of said non volatile memories or IC or loaded in the volatile memory and in communication with an external read-write device; an interchange application, stored inside one of said non volatile memories, drives the organization of files in an additional tag-length logic structures of arbitrary length, allowing the identification of files through alphanumeric identifiers of arbitrary length and extension, and their accessibility by an external read-write device, eventually non IC card purpose, like a workstation a personal computer or a PDA interconnected to the IC Card by means of standard communication interface. The file system organizes said tag-length logic structure as individually memory blocks, each identified by an hexadecimal identification number and a block size and one of these memory blocks, more particularly one per non volatile memory, describes the content of the non volatile memory, comprising the number of files stored, their file name and extension and, for each file, the location of memory blocks composing its content.

Owner:STMICROELECTRONICS INT NV

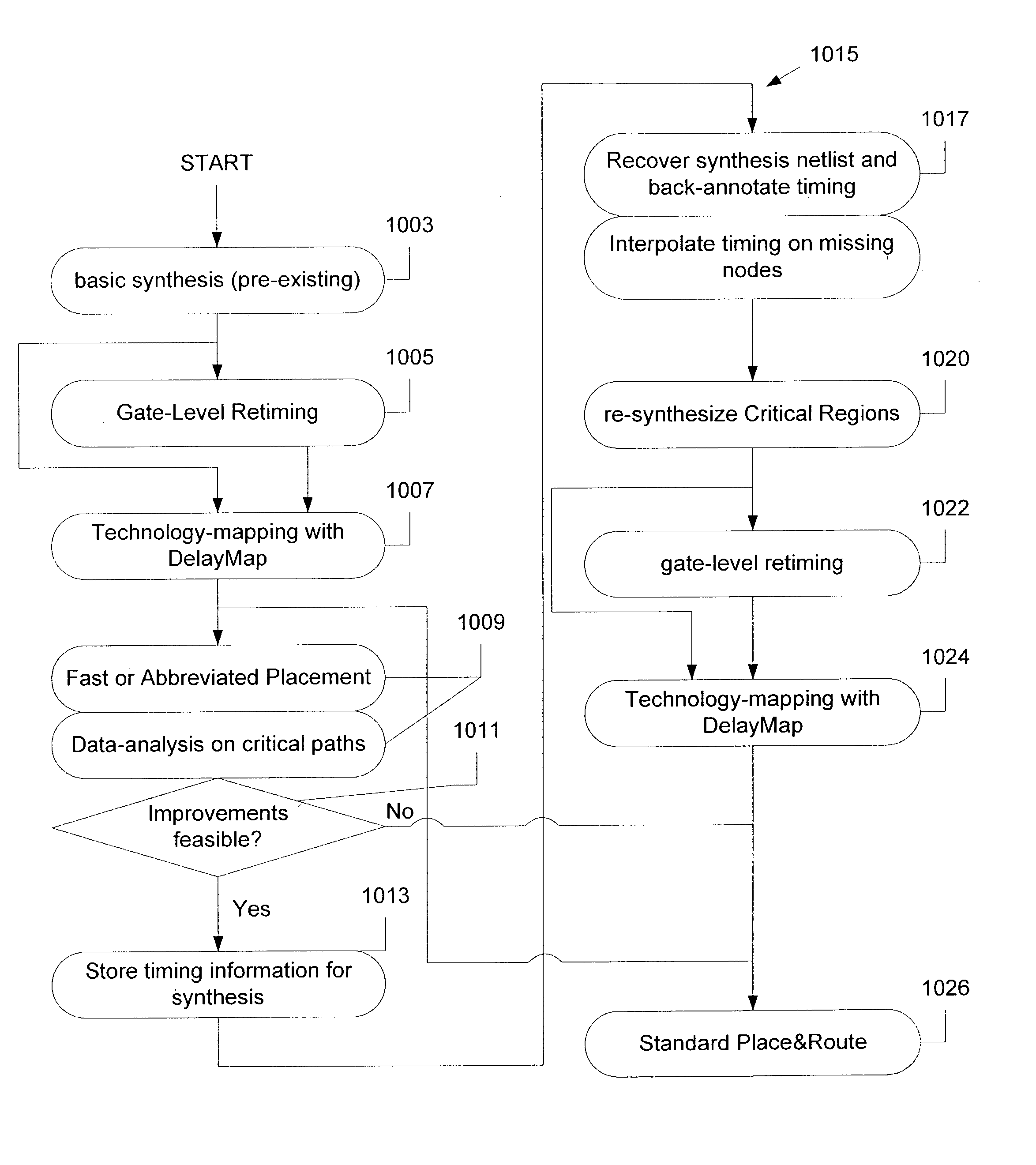

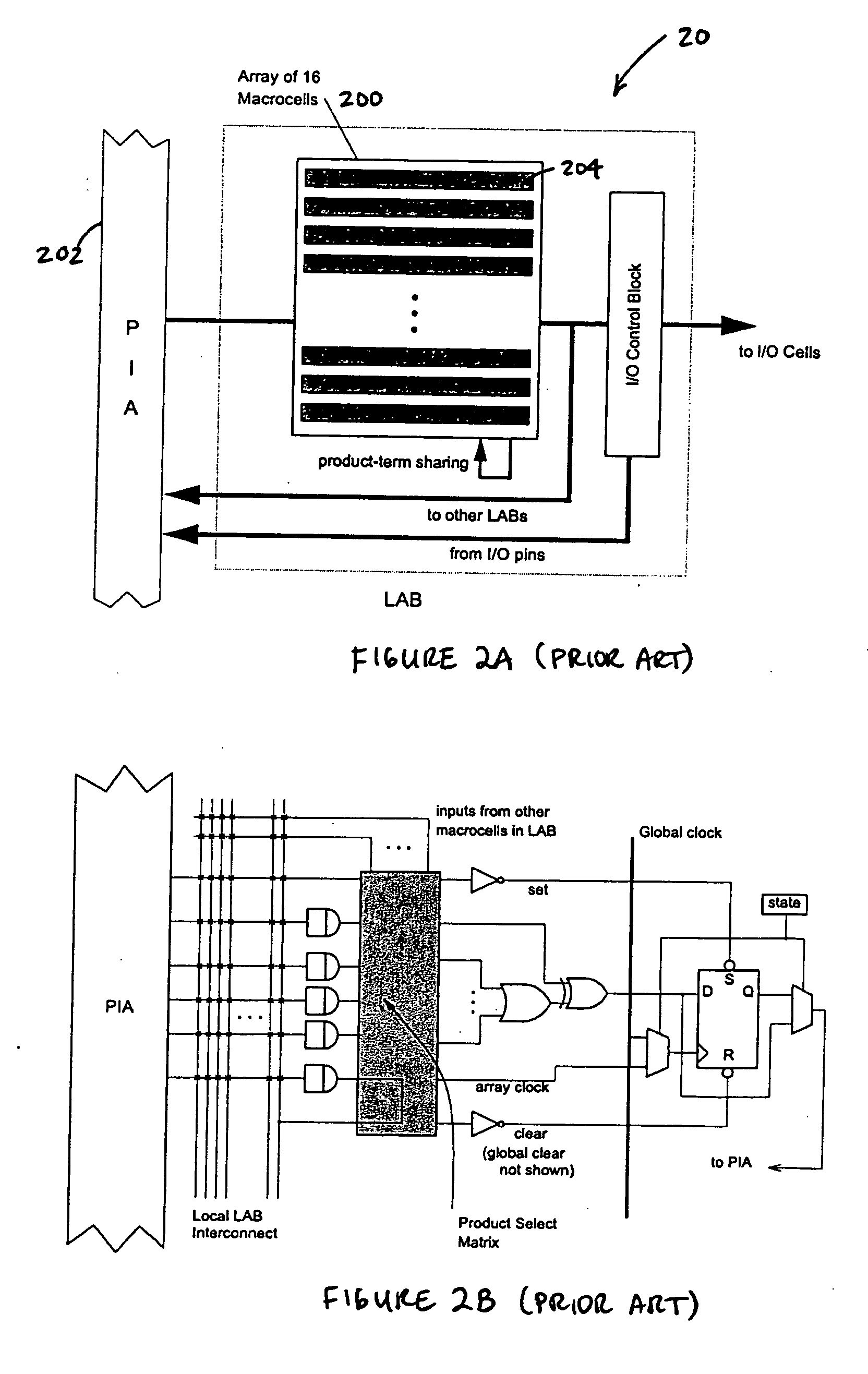

Physical resynthesis of a logic design

InactiveUS7337100B1Simple designMinimize time delayElectronic circuit testingAnalogue computers for electric apparatusThird partyVisibility

A multiple-pass synthesis technique improves the performance of a design. In a specific embodiment, synthesis is performed in two or more passes. In a first pass, a first synthesis is performed, and in a second or subsequent pass, a second synthesis or resynthesis is performed. During the first synthesis, the logic will be mapped to for example, the logic structures (e.g., logic elements, LUTs, synthesis gates) of the target technology such as a programmable logic device. Alternatively a netlist may be provided from a third party. Before the second synthesis, a fast or abbreviated fit may be performed of the netlist to a specific device (e.g., specific programmable logic device product). Before the second synthesis, the netlist obtained from the first synthesis (or provided by a third party) is unmapped and then the second synthesis is performed. Since a partial fit is performed, the second synthesis has more visibility and optimize the logic better than by using a single synthesis pass. After the second synthesis pass, a more detailed fit is performed.

Owner:ALTERA CORP

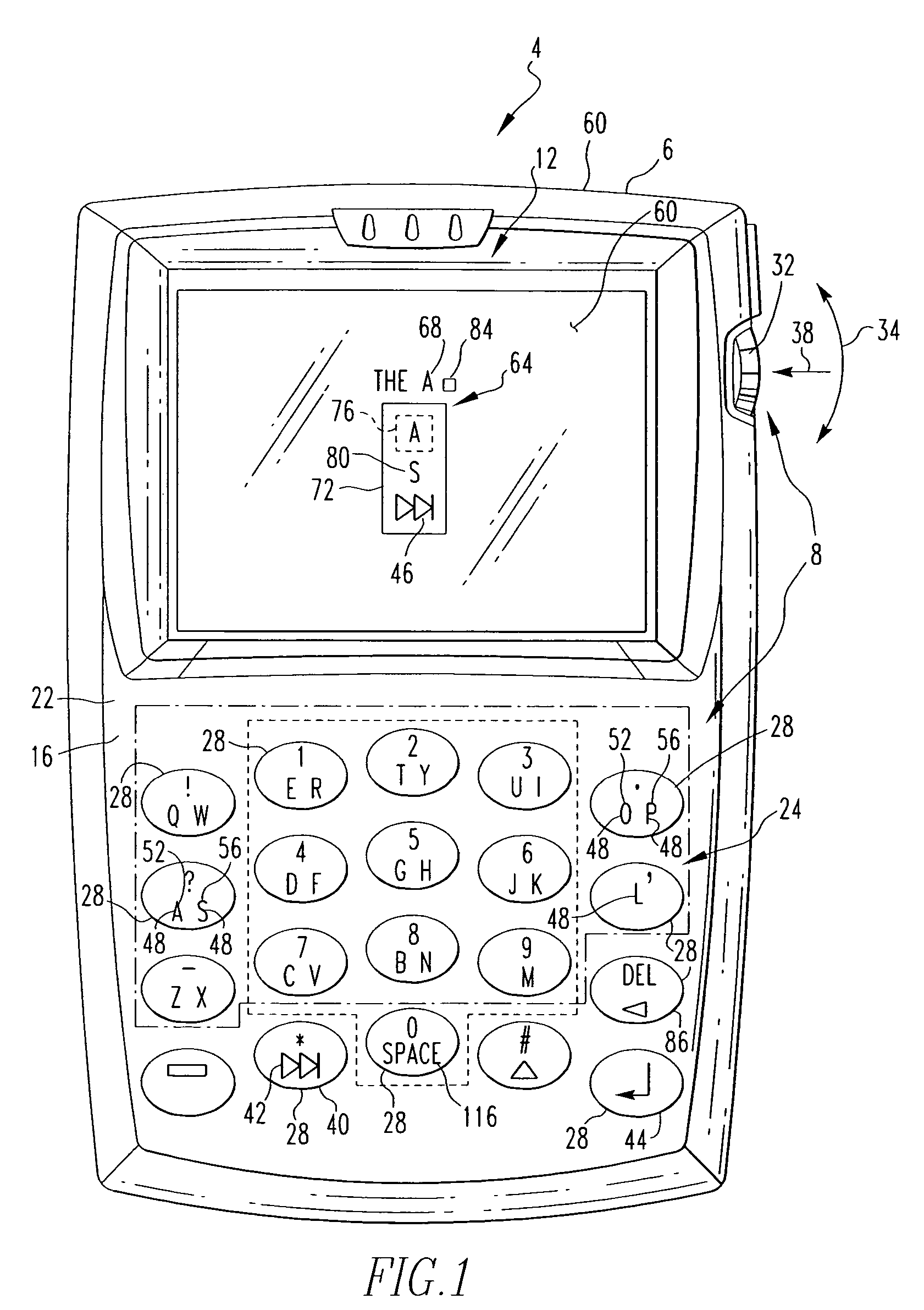

Handheld electronic device with text disambiguation

ActiveUS20050273332A1Good choiceReduced QWERTYElectronic switchingCathode-ray tube indicatorsGraphicsText entry

A handheld electronic device includes a reduced QWERTY keyboard and is enabled with disambiguation software. The device provides output in the form of a default output and a number of variants. The output is based largely upon the frequency, i.e., the likelihood that a user intended a particular output, but various features of the device provide additional variants that are not based solely on frequency and rather are provided by various logic structures resident on the device. The device enables editing during text entry and also provides a learning function that allows the disambiguation function to adapt to provide a customized experience for the user. The disambiguation function can be selectively disabled and an alternate keystroke interpretation system provided. Additionally, the device can facilitate the selection of variants by displaying a graphic of a special <NEXT> key of the keypad that enables a user to progressively select variants generally without changing the position of the user's hands on the device.

Owner:MALIKIE INNOVATIONS LTD

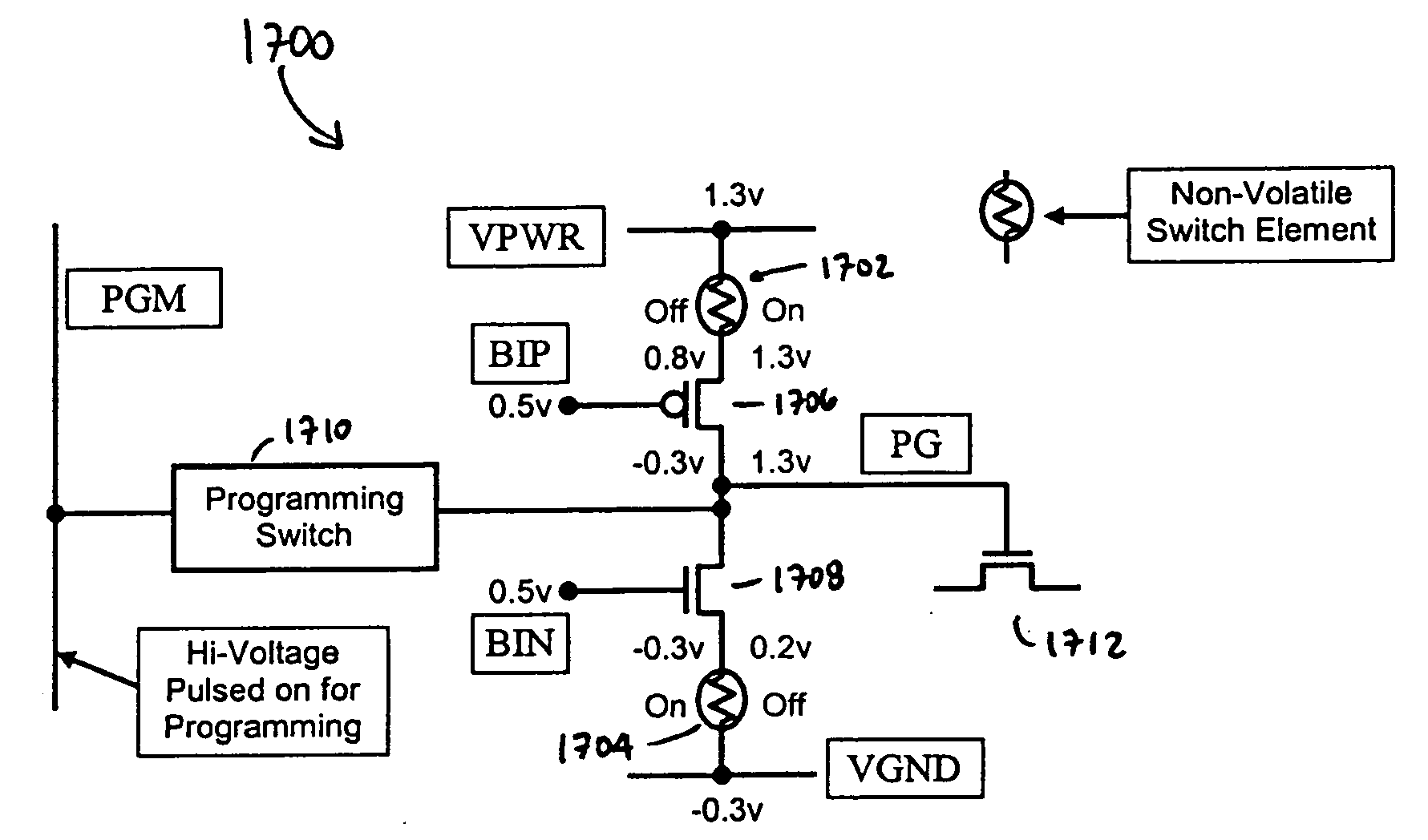

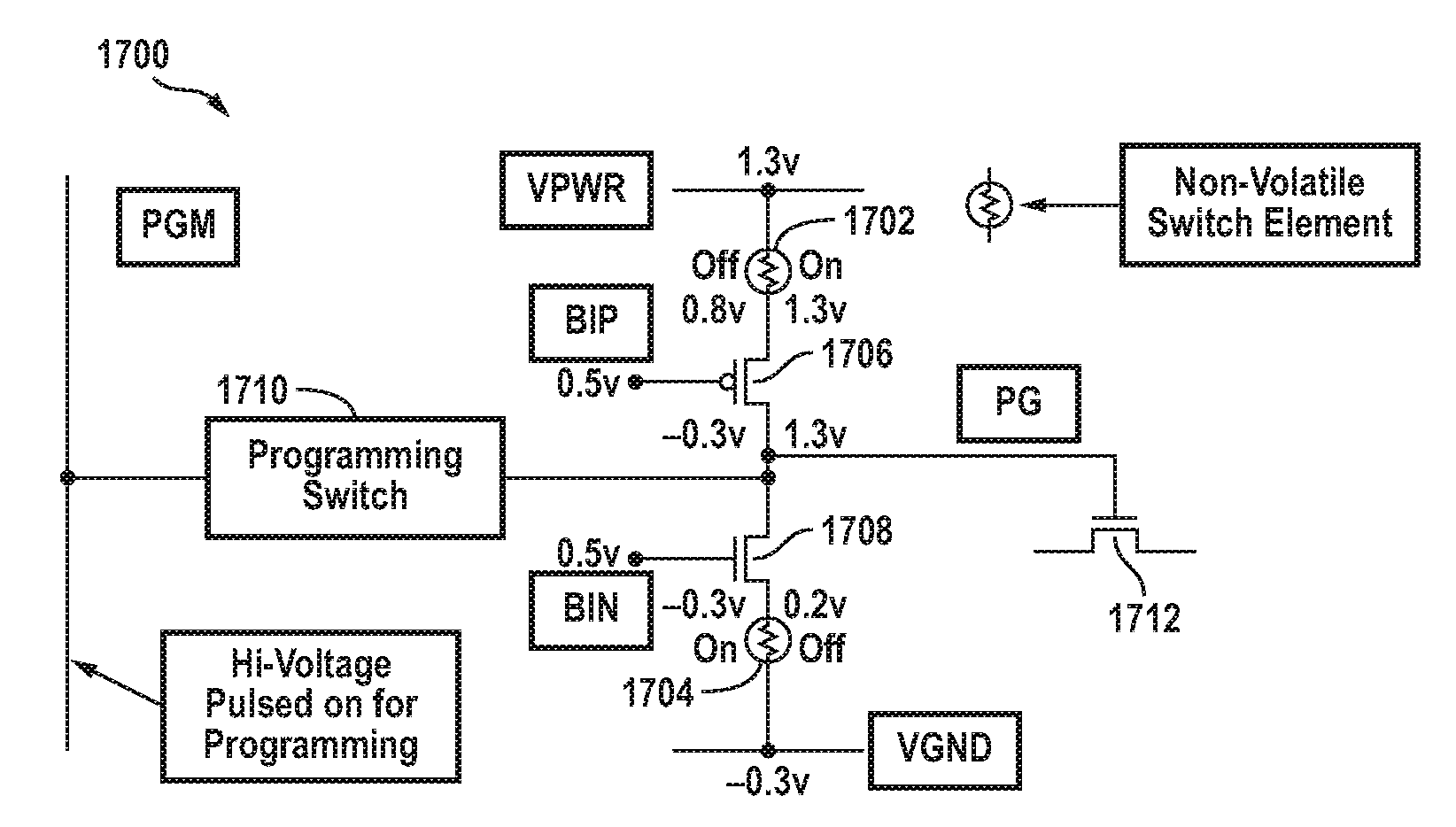

Reconfigurable logic structures

InactiveUS20070146012A1Logic circuits characterised by logic functionNanoinformaticsElectronic structurePhase-change memory

Reconfigurable electronic structures and circuits using programmable, non-volatile memory elements. The programmable, non-volatile memory elements may perform the functions of storage and / or a switch to produce components such as crossbars, multiplexers, look-up tables (LUTs) and other logic circuits used in programmable logic structures (e.g., (FPGAs)). The programmable, non-volatile memory elements comprise one or more structures based on Phase Change Memory, Programmable Metallization, Carbon Nano-Electromechanical (CNT-NEM), or Metal Nano-Electromechanical device technologies.

Owner:CSWITCH

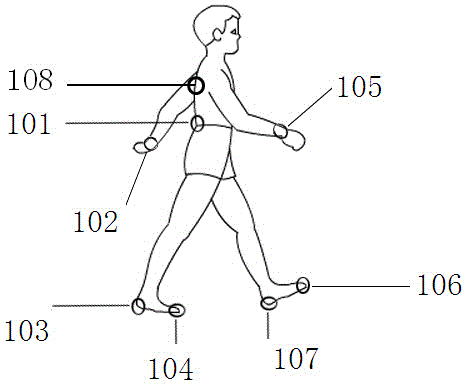

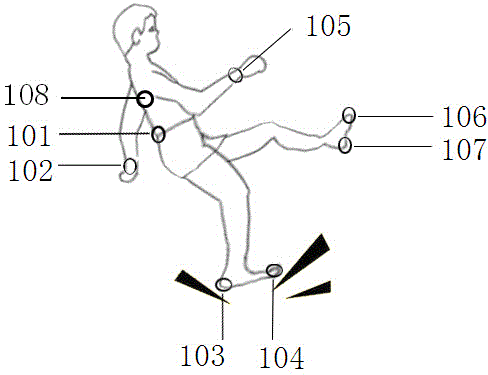

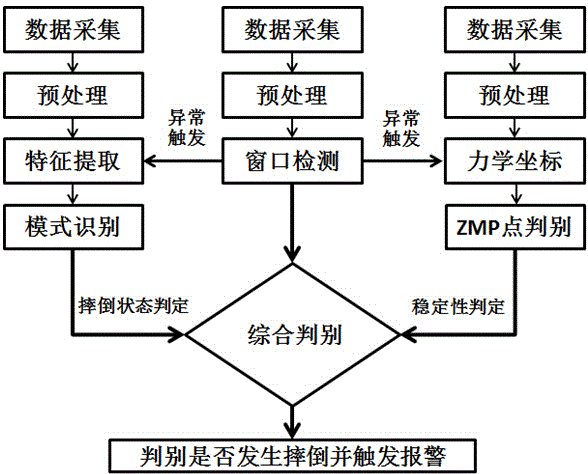

Wearing type dynamic real-time fall detection method and device

ActiveCN103976739AAchieve protectionHigh precisionCharacter and pattern recognitionDiagnostic recording/measuringHuman bodyHardware structure

The invention discloses a wearing type dynamic real-time fall detection method and device. The wearing type detection device comprises a specific hardware structure consisting of a foot part, a waist part, a wrist part and a back part. According to the dynamic real-time fall detection method, real-time judgment of the fall of human body in any state can be finished. The core algorithm of the detection device comprises a threshold opening logic structure caused by sudden change of gait acceleration, a human body posture dynamic stability judgment algorithm based on zero moment point (ZMP), and a fall mode identification algorithm based on a human body motion database. A complete dynamic real-time detection system is constructed, and the aims of wide application field, low dependence on the application environment and real-time detection are fulfilled. Moreover, the detection method and the detection device are high in accuracy, and have the advantages of low system cost, small system size and good convenience in wearing.

Owner:BEWIS TECH

Handheld electronic device with text disambiguation

ActiveUS7091885B2Good choiceReduced QWERTYInput/output for user-computer interactionElectronic switchingGraphicsText entry

A handheld electronic device includes a reduced QWERTY keyboard and is enabled with disambiguation software. The device provides output in the form of a default output and a number of variants. The output is based largely upon the frequency, i.e., the likelihood that a user intended a particular output, but various features of the device provide additional variants that are not based solely on frequency and rather are provided by various logic structures resident on the device. The device enables editing during text entry and also provides a learning function that allows the disambiguation function to adapt to provide a customized experience for the user. The disambiguation function can be selectively disabled and an alternate keystroke interpretation system provided. Additionally, the device can facilitate the selection of variants by displaying a graphic of a special <NEXT> key of the keypad that enables a user to progressively select variants generally without changing the position of the user's hands on the device.

Owner:MALIKIE INNOVATIONS LTD

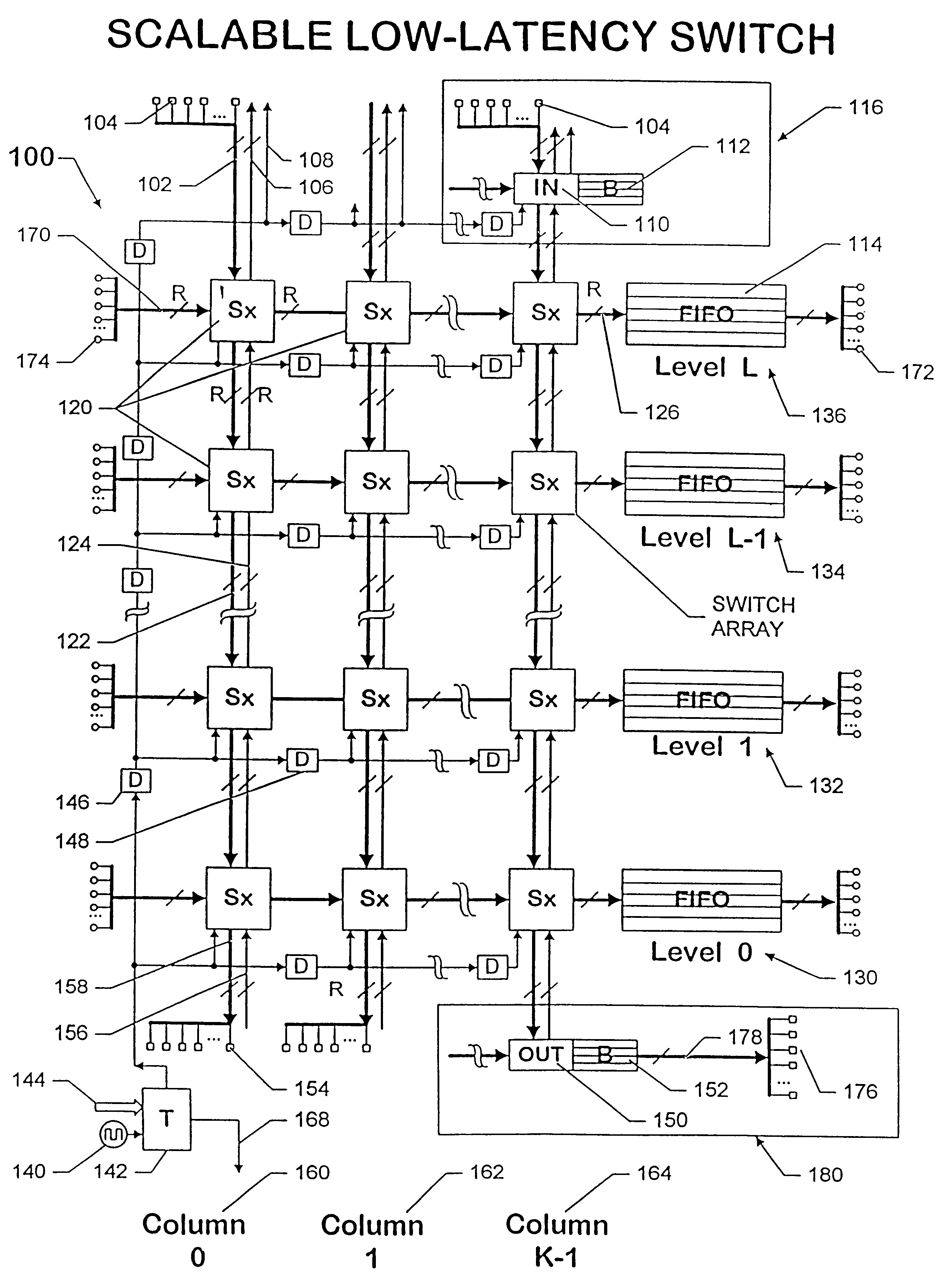

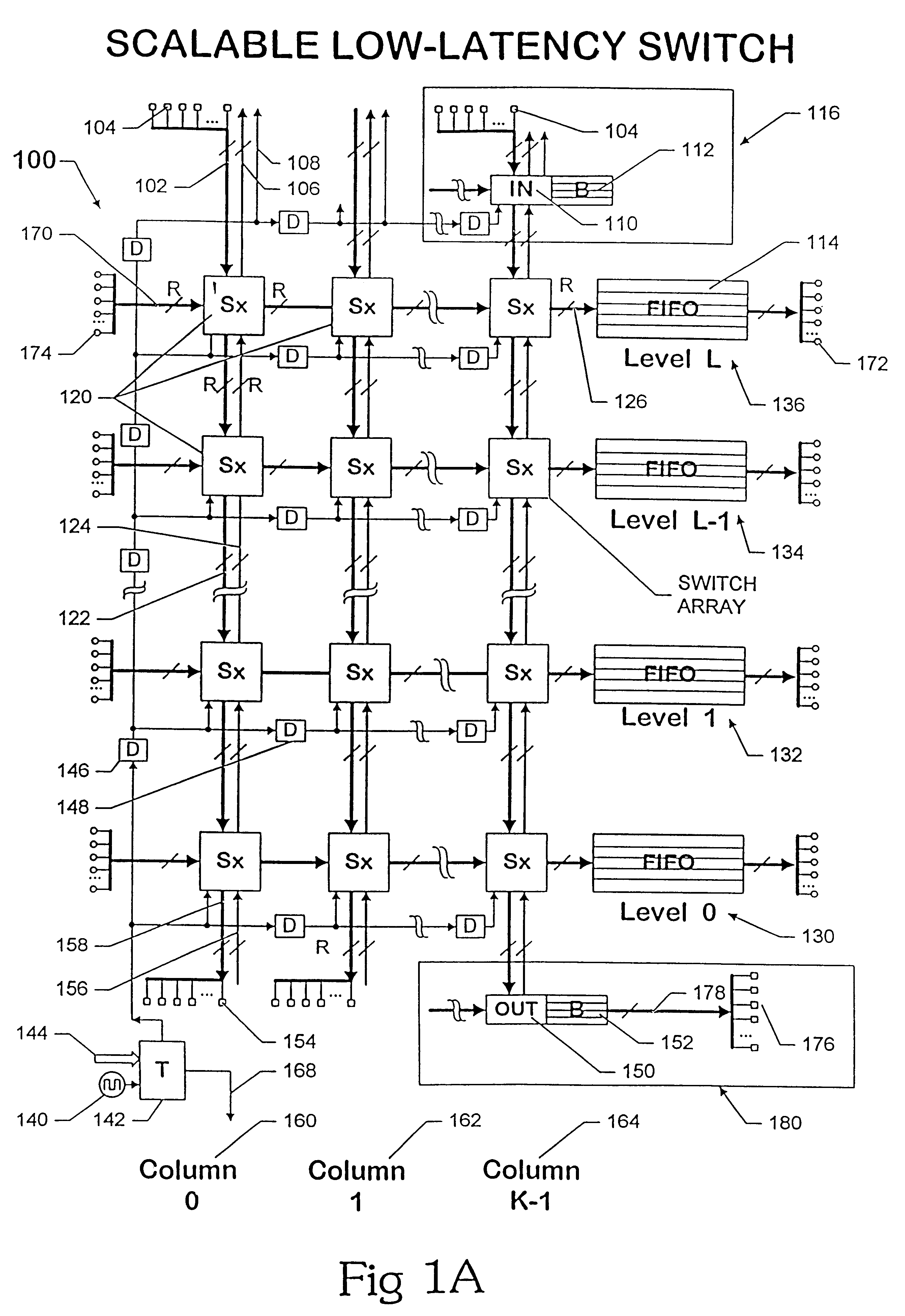

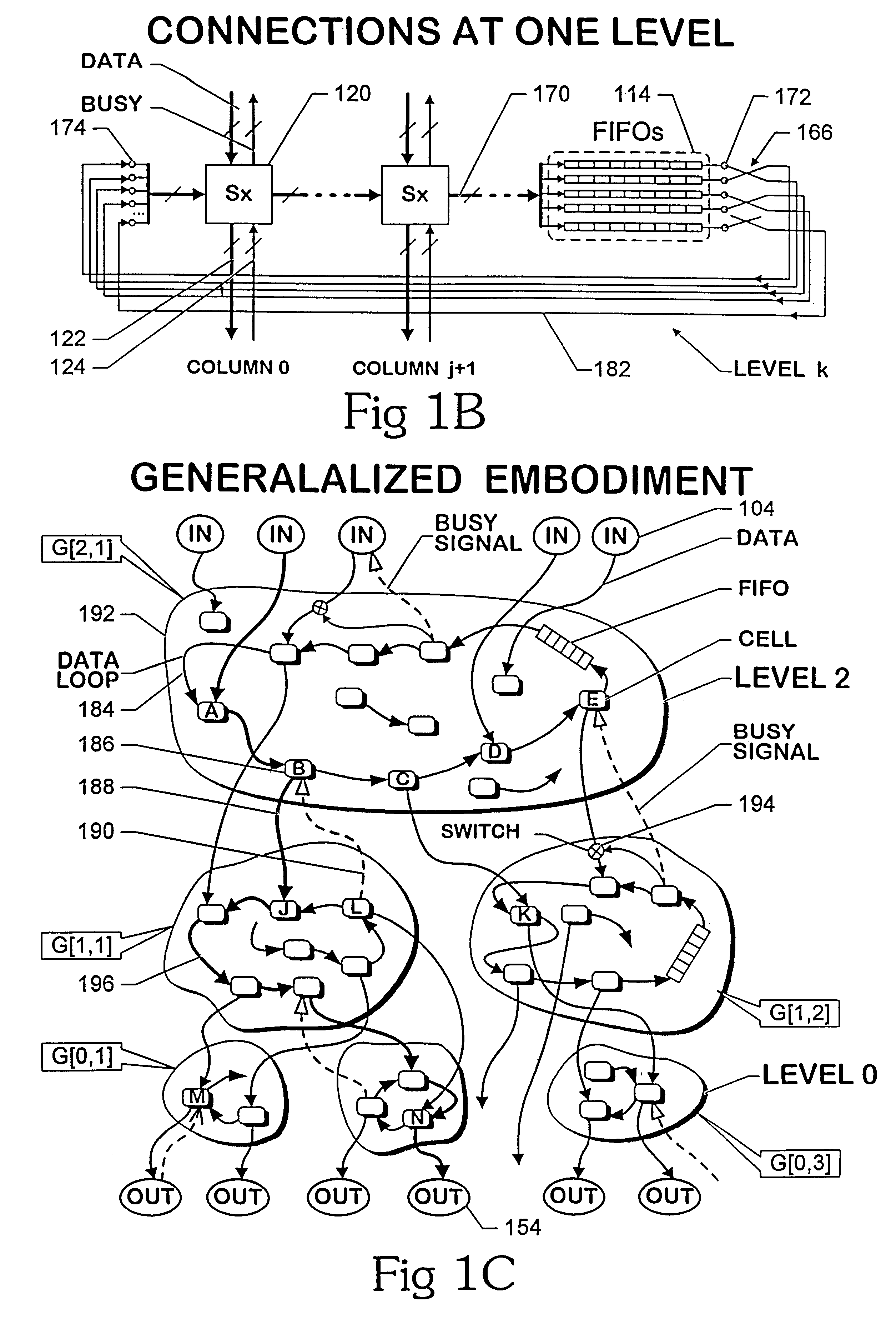

Scaleable low-latency switch for usage in an interconnect structure

InactiveUS6289021B1High bandwidthLower latencyData switching by path configurationCommunications systemLatency (engineering)

A scalable low-latency switch extends the functionality of a multiple level minimum logic interconnect structure for usage in computers of all types, networks and communication systems. The multiple level minimum logic interconnect structure employs a data flow technique based on timing and positioning of messages moving through the structure. The scalable low-latency switch is distributed throughout multiple nodes in the structure so that a supervisory controller providing a global control function and complex logic structures are avoided while the interconnect structure operates as a "deflection" or "hot potato" system in which processing and storage overhead at each node is reduced. The interconnect structure using the scalable low-latency switch employs a method of achieving wormhole routing through an integrated circuit chip by a novel procedure for inserting messages into the chip. Rather than simultaneously inserting a message into each unblocked node on the outer cylinder at every angle, messages are inserted simultaneously into two columns A and B only if an entire message fits between A and B. Messages are inserted into column 0 at time 0. Messages are inserted into column 1 at time t0+tC, where time tCis the time for a first bit of a message to move from column 0 to column 1 on the top level. Messages are inserted into column 2 at time t0+2tC, and so forth. The strategy prevents the first bit of one message from colliding with an interior bit of another message already in the switch. Contention between entire messages is addressed by resolving the contention between the first bit only so that messages wormhole through many cells.

Owner:HEWLETT PACKARD CO +1

Handheld electronic device with text disambiguation

ActiveUS20060058995A1Good choiceReduced QWERTYNatural language data processingSpecial data processing applicationsGraphicsText entry

In view of the foregoing, an improved handheld electronic device includes a keypad in the form of a reduced QWERTY keyboard and is enabled with disambiguation software. As a user enters keystrokes, the device provides output in the form of a default output and a number of variants from which a user can choose. The output is based largely upon the frequency, i.e., the likelihood that a user intended a particular output, but various features of the device provide additional variants that are not based solely on frequency and rather are provided by various logic structures resident on the device. The device enables editing during text entry, and when initiating an activity session on a word such as during editing, the display outputs variants of the entire word being edited, rather than providing as variants only those parts of a word that are being edited. The device also provides a learning function that allows the disambiguation function to adapt to provide a customized experience for the user. In certain predefined circumstances, the disambiguation function can be selectively disabled and an alternate keystroke interpretation system provided. Additionally, the device can facilitate the selection of variants by displaying a graphic of a special <NEXT> key of the keypad that enables a user to progressively select variants generally without changing the position of the user's hands on the device.

Owner:MALIKIE INNOVATIONS LTD

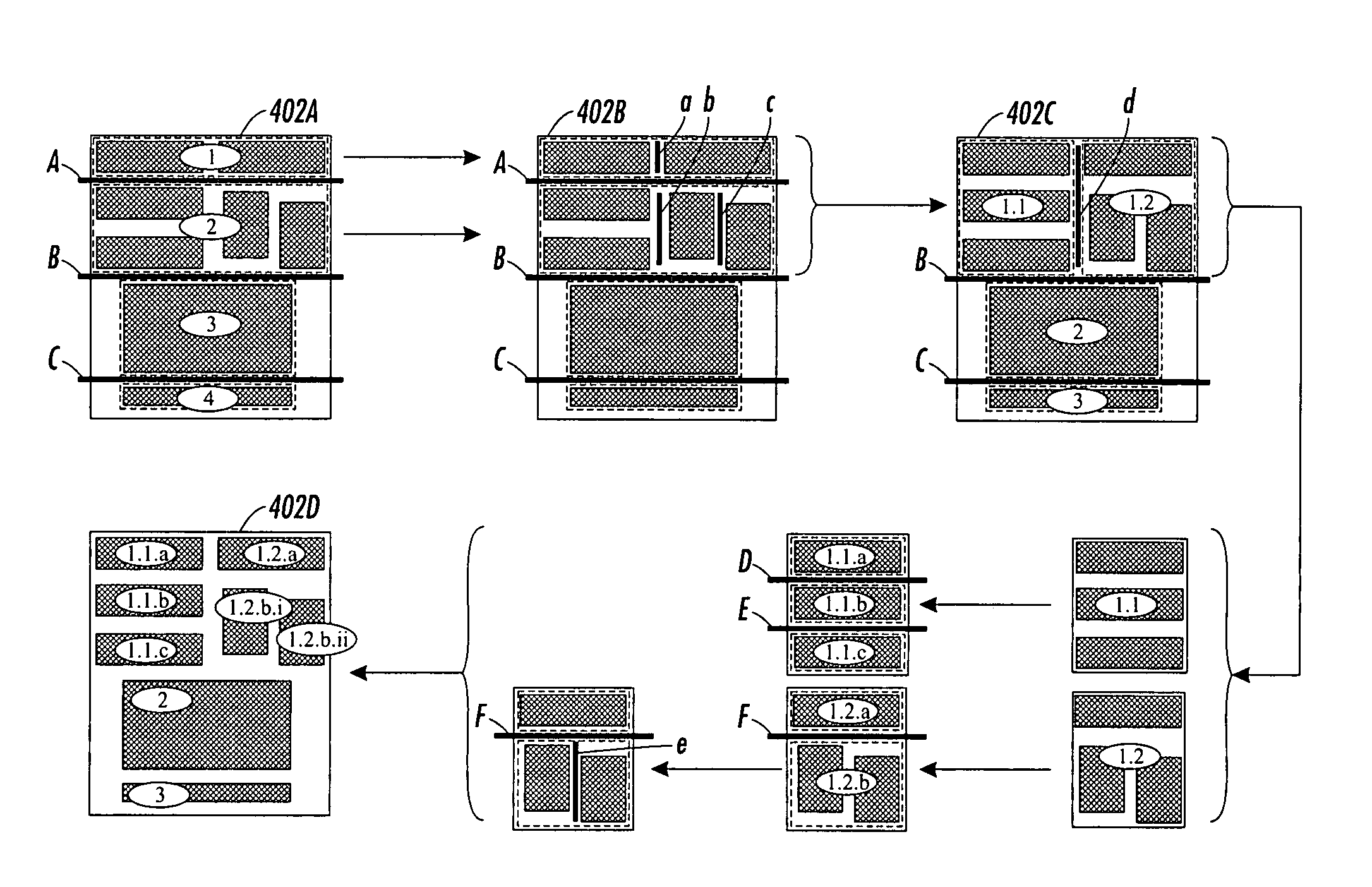

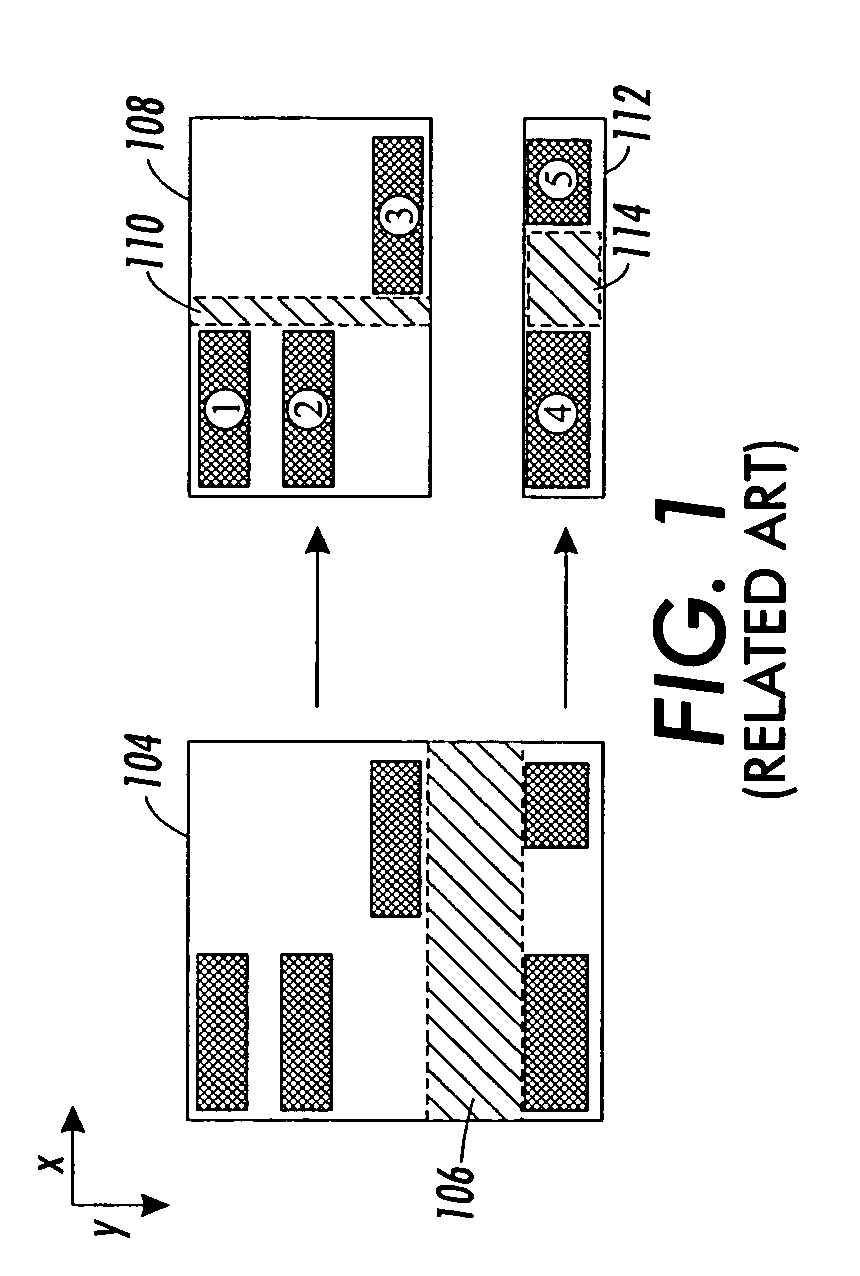

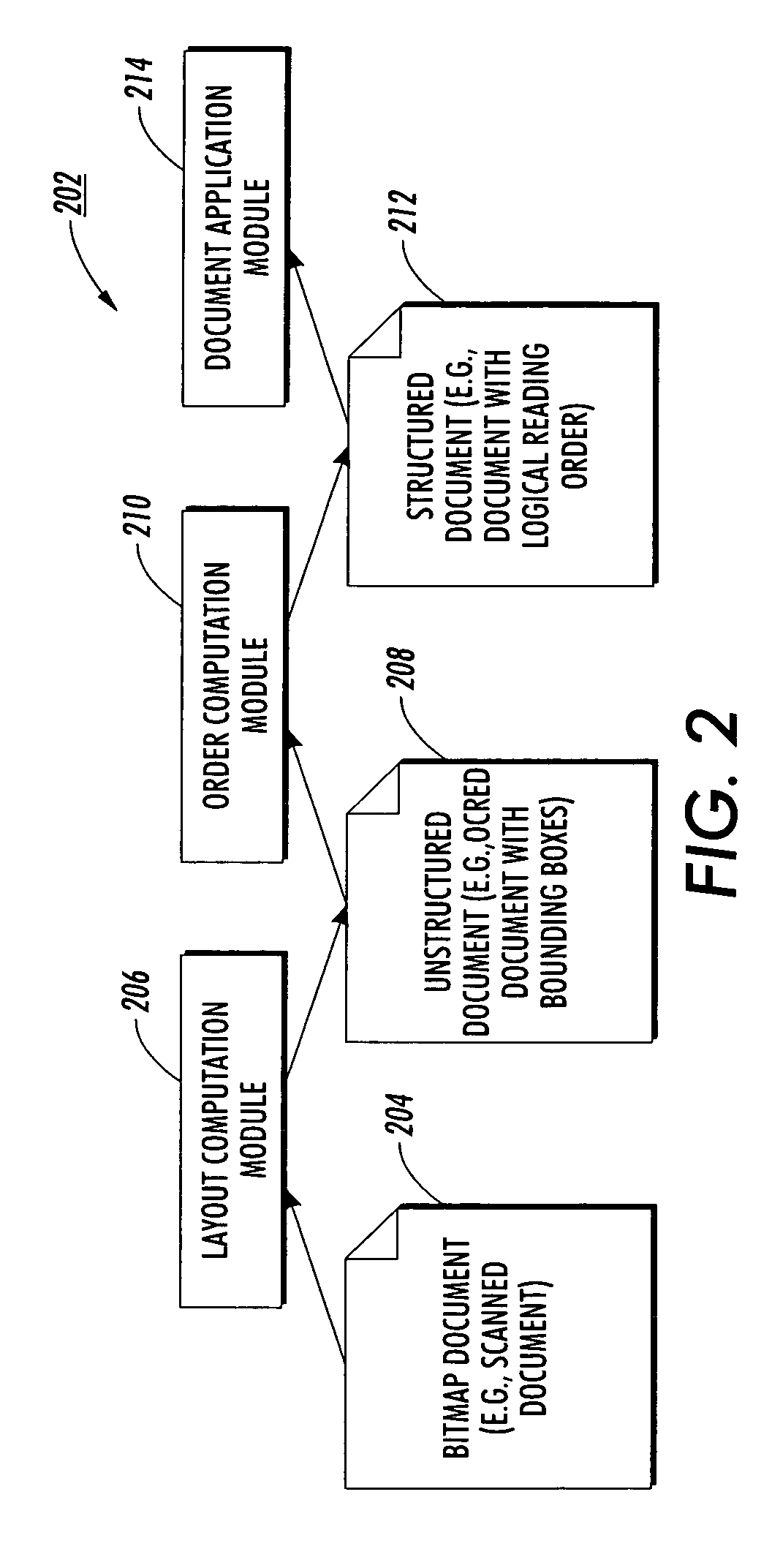

Method and apparatus for determining logical document structure

Owner:XEROX CORP

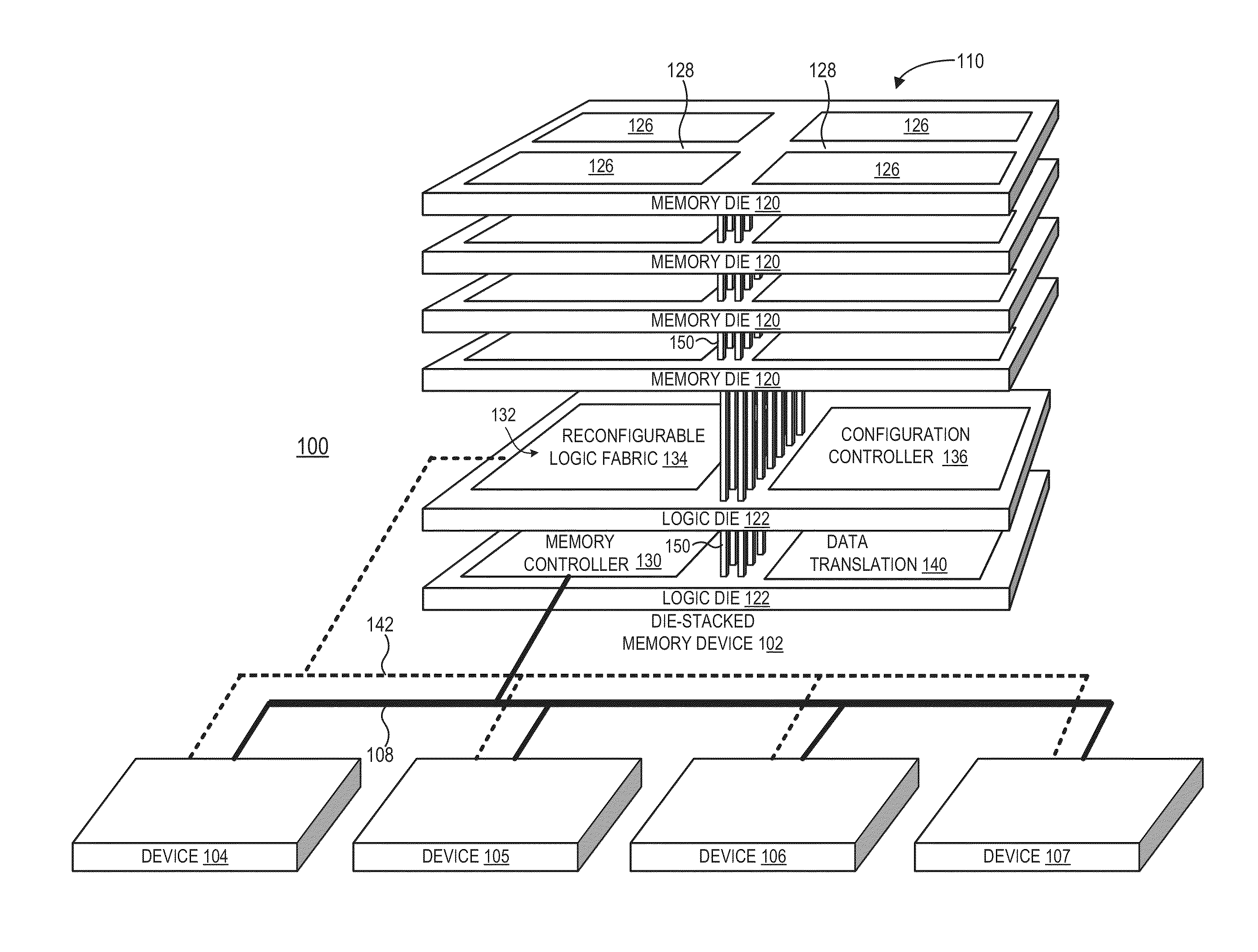

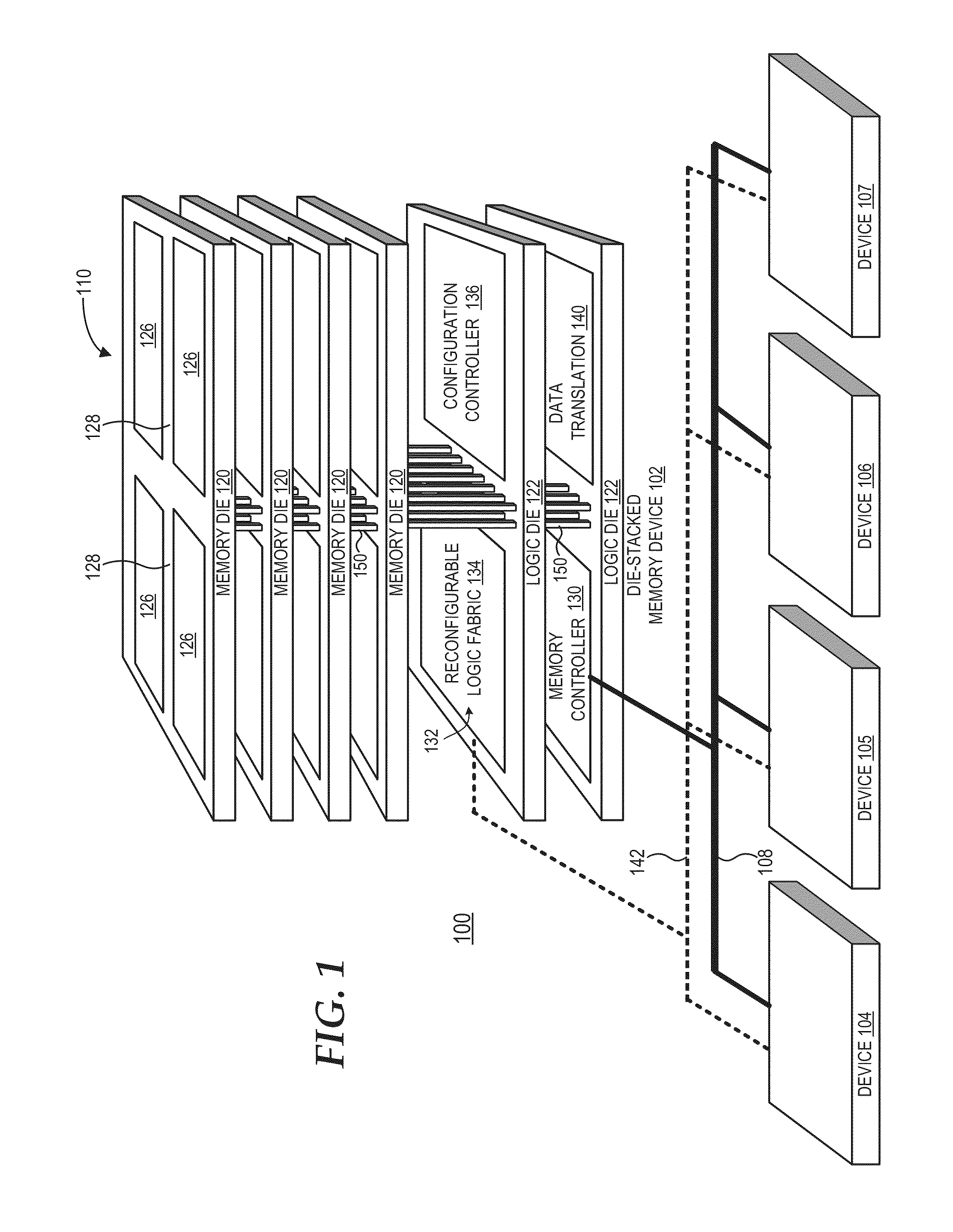

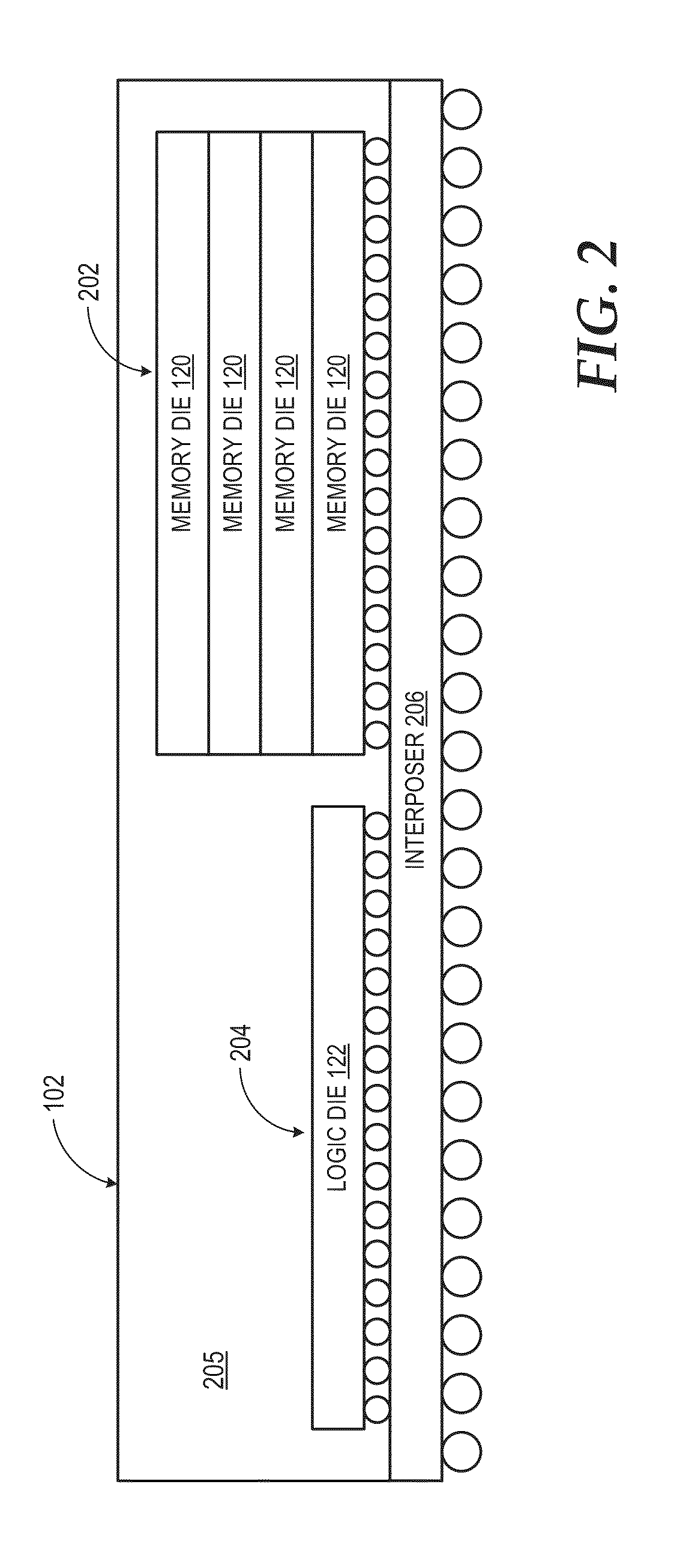

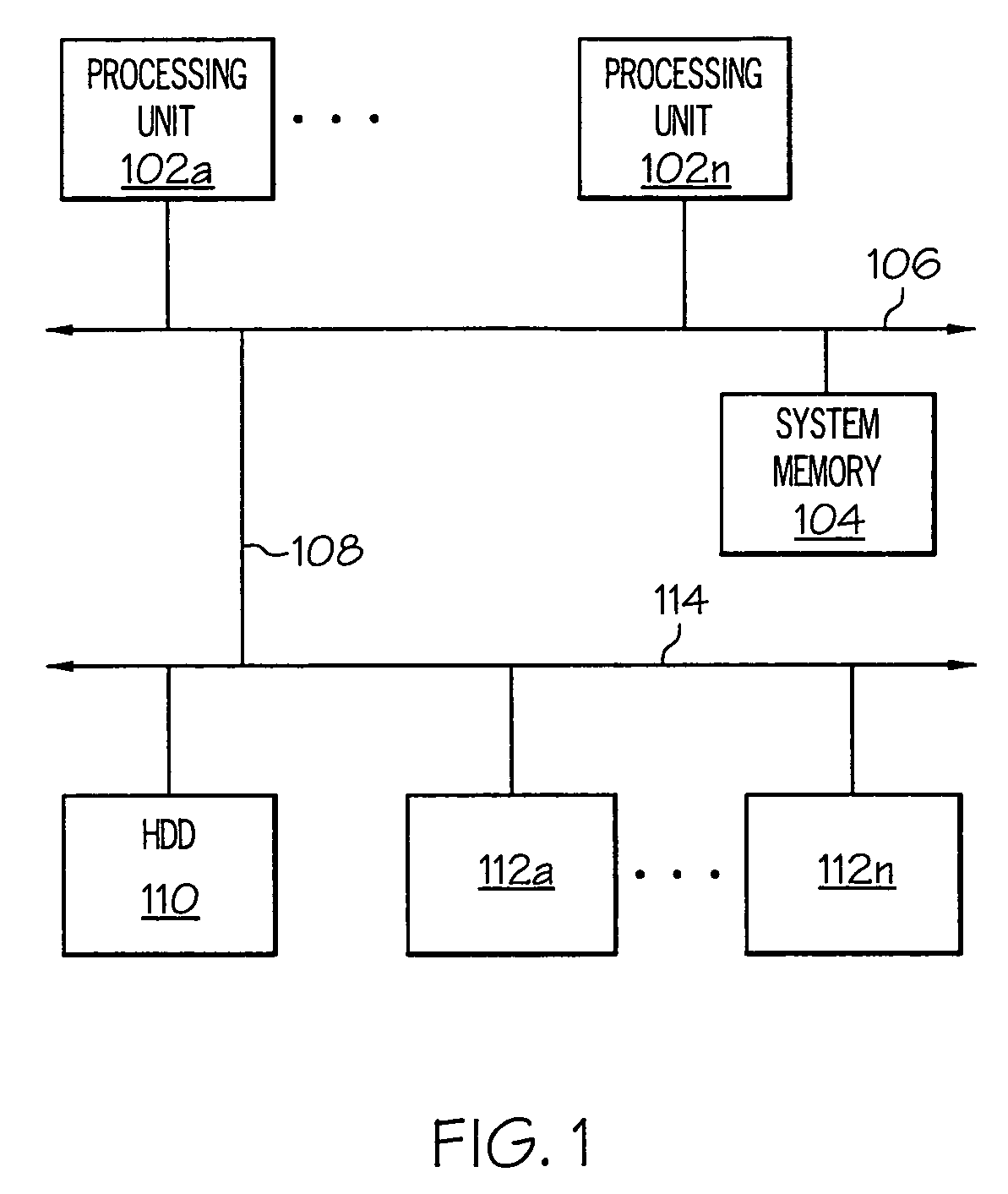

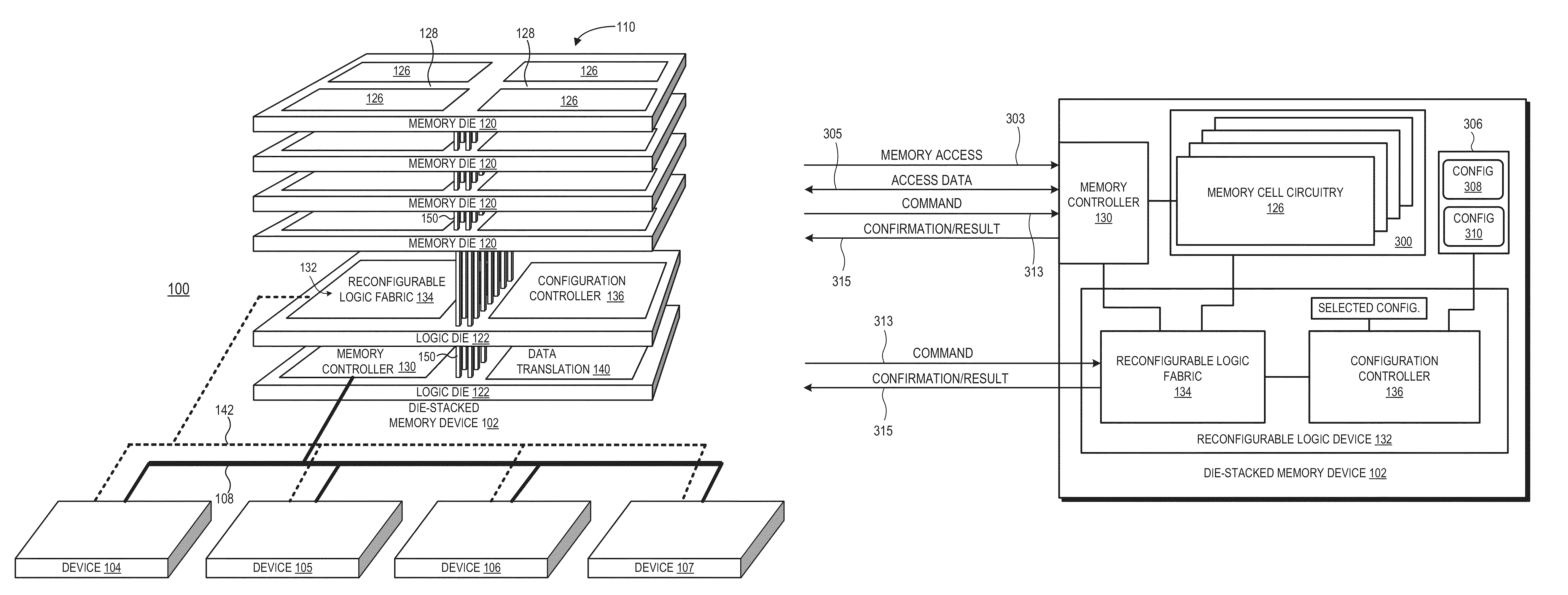

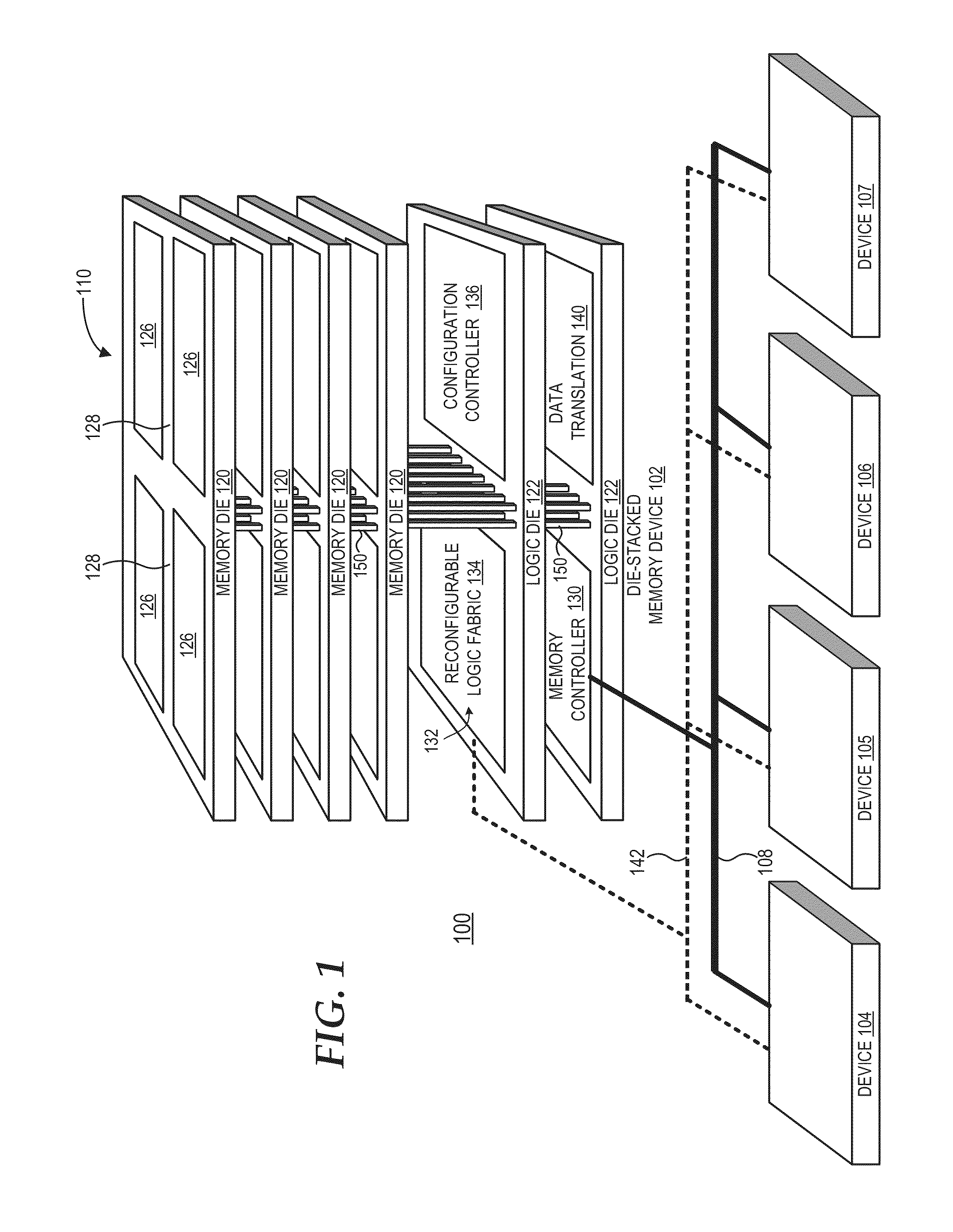

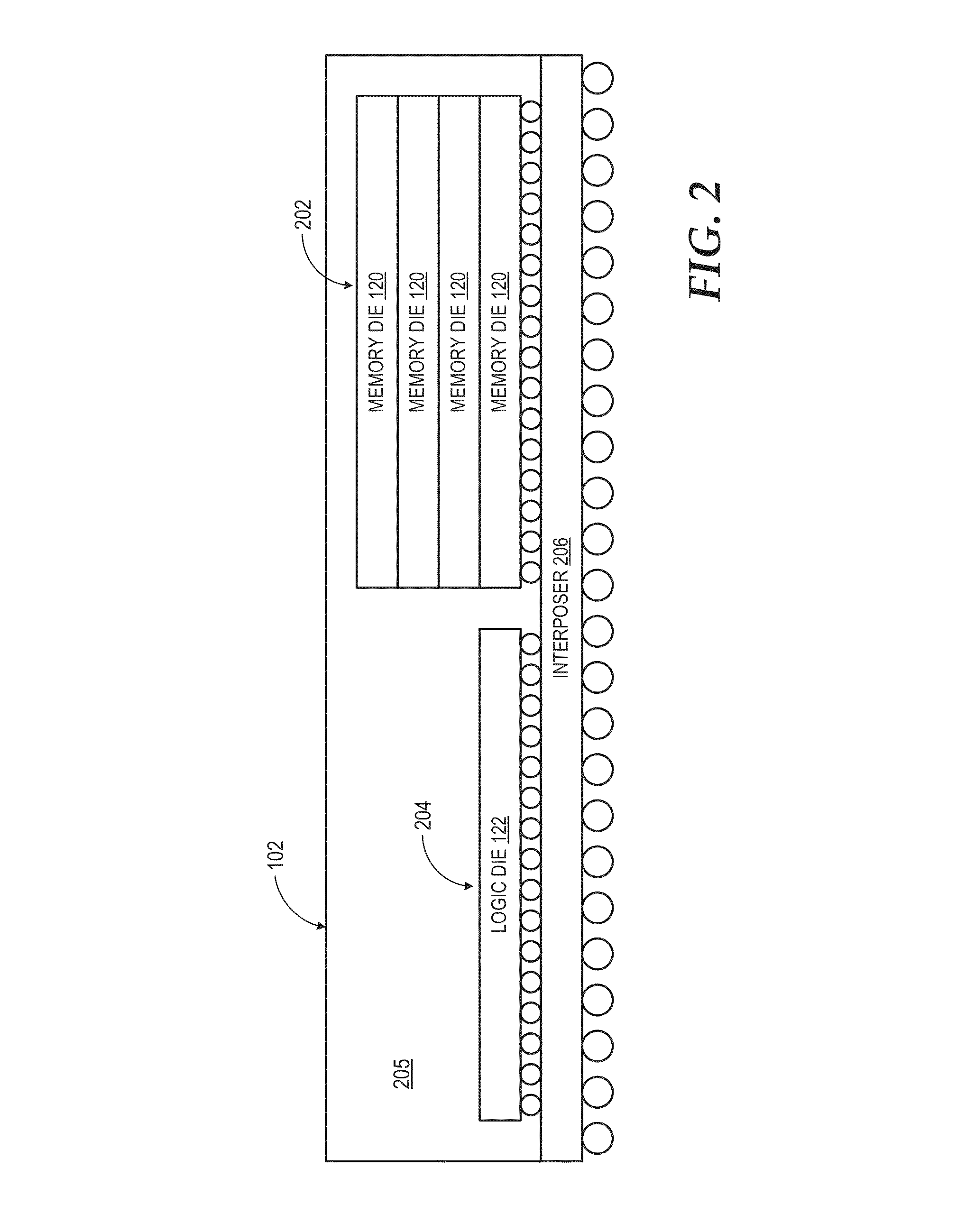

Die-stacked memory device with reconfigurable logic

ActiveUS20140176187A1Error detection/correctionSolid-state devicesHigh bandwidthLatency (engineering)

A die-stacked memory device incorporates a reconfigurable logic device to provide implementation flexibility in performing various data manipulation operations and other memory operations that use data stored in the die-stacked memory device or that result in data that is to be stored in the die-stacked memory device. One or more configuration files representing corresponding logic configurations for the reconfigurable logic device can be stored in a configuration store at the die-stacked memory device, and a configuration controller can program a reconfigurable logic fabric of the reconfigurable logic device using a selected one of the configuration files. Due to the integration of the logic dies and the memory dies, the reconfigurable logic device can perform various data manipulation operations with higher bandwidth and lower latency and power consumption compared to devices external to the die-stacked memory device.

Owner:ADVANCED MICRO DEVICES INC

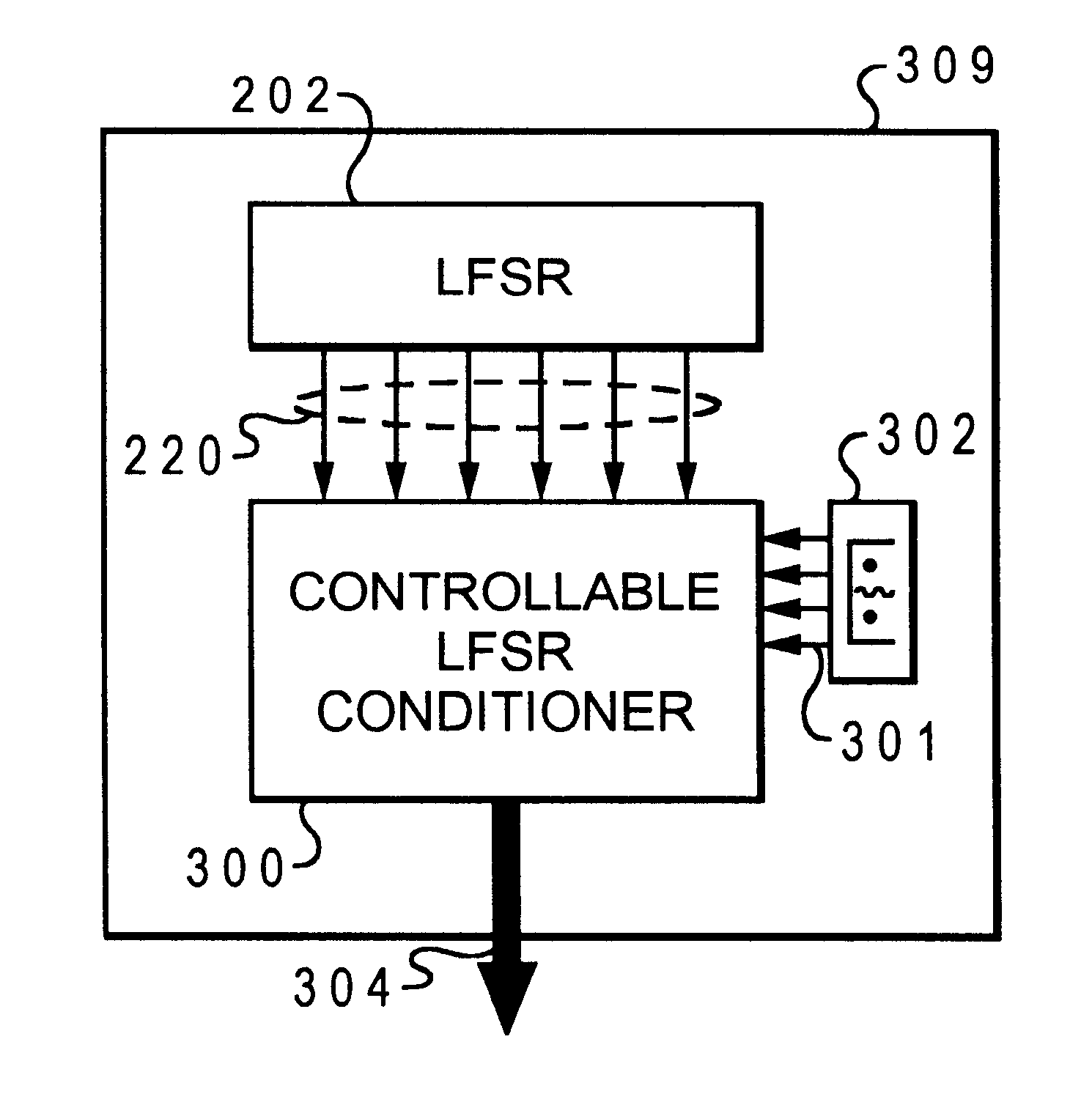

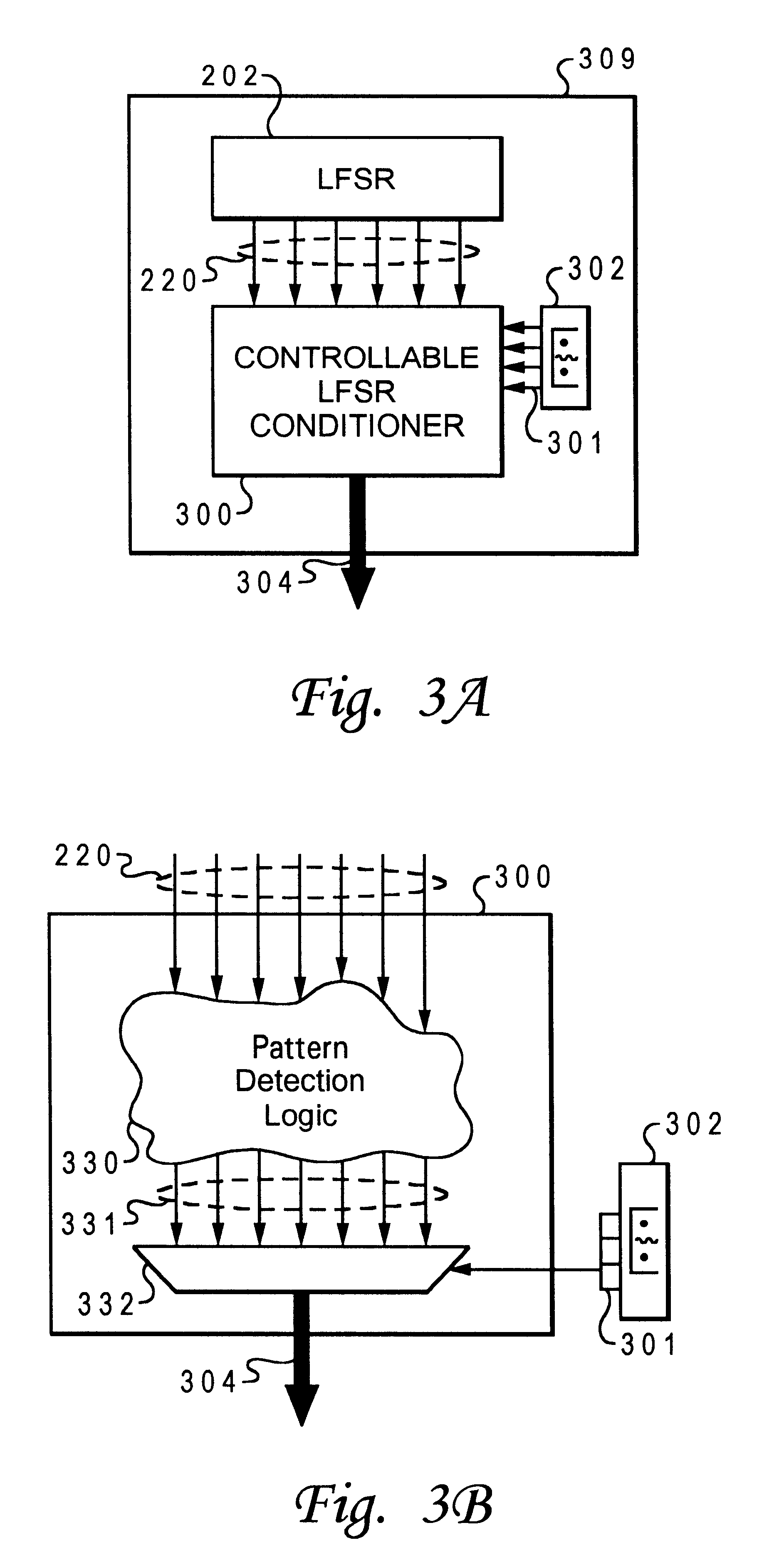

Method and system for run-time logic verification of operations in digital systems

InactiveUS6590929B1Random number generatorsError detection/correctionRuntime verificationRunning time

A system for controllable run-time verification of operations in a logic structure of a digital system. The system comprises a controllable bit stream generator which produces a controlled bit stream output. The controlled bit stream output corresponds to a bit sequence which instantiates a verification of operations within the logic structure. The system also comprises means for coupling the controlled bit stream output to the logic structure to verify the operations of the logic structure.

Owner:IBM CORP

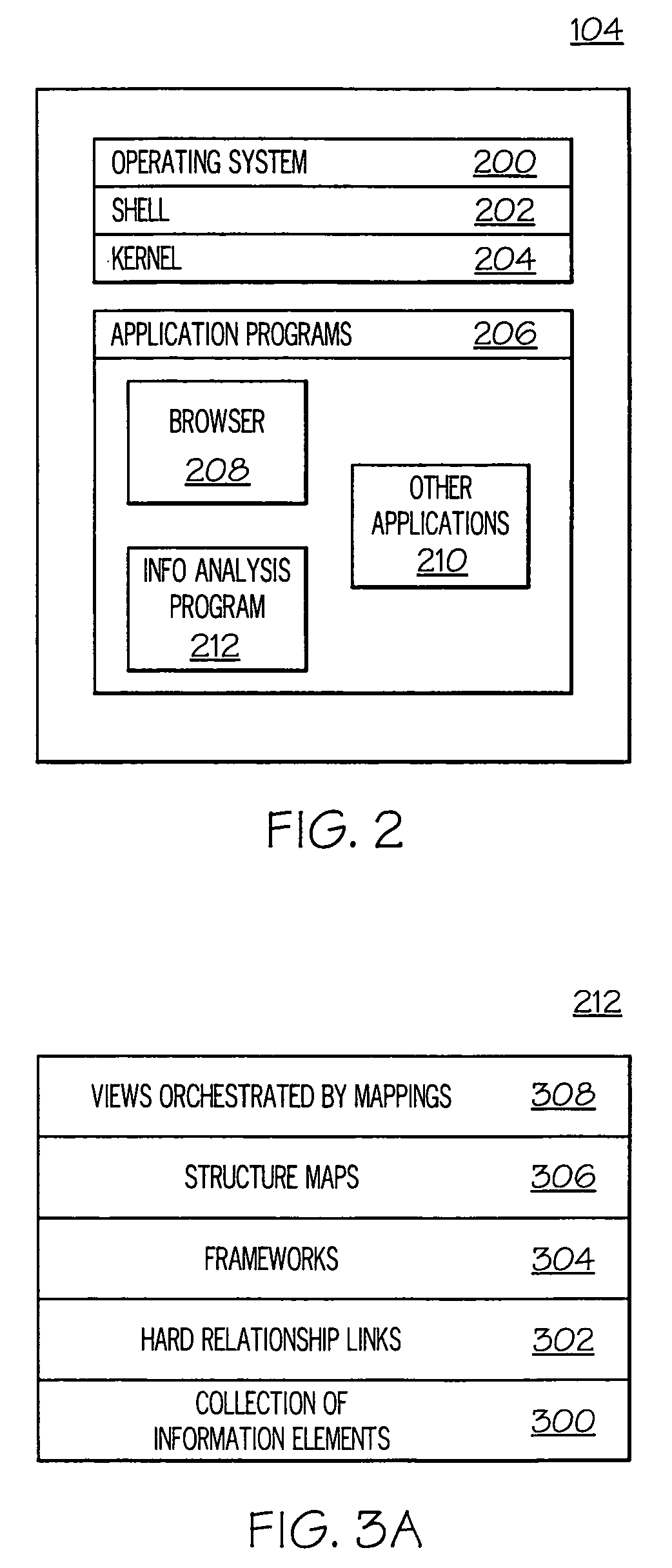

System and method of unstructured analysis through the application of multiple structure maps

InactiveUS7848260B2Error preventionFrequency-division multiplex detailsInformation analysisStructure of Management Information

Owner:LINKEDIN

Handheld electronic device with text disambiguation

ActiveUS20050283540A1Good choiceReduced QWERTYInput/output for user-computer interactionNatural language translationGraphicsText entry

A handheld electronic device includes a reduced QWERTY keyboard and is enabled with disambiguation software. The device provides output in the form of a default output and a number of variants. The output is based largely upon the frequency, i.e., the likelihood that a user intended a particular output, but various features of the device provide additional variants that are not based solely on frequency and rather are provided by various logic structures resident on the device. The device enables editing during text entry and also provides a learning function that allows the disambiguation function to adapt to provide a customized experience for the user. The disambiguation function can be selectively disabled and an alternate keystroke interpretation system provided. Additionally, the device can facilitate the selection of variants by displaying a graphic of a special <NEXT> key of the keypad that enables a user to progressively select variants generally without changing the position of the user's hands on the device.

Owner:MALIKIE INNOVATIONS LTD

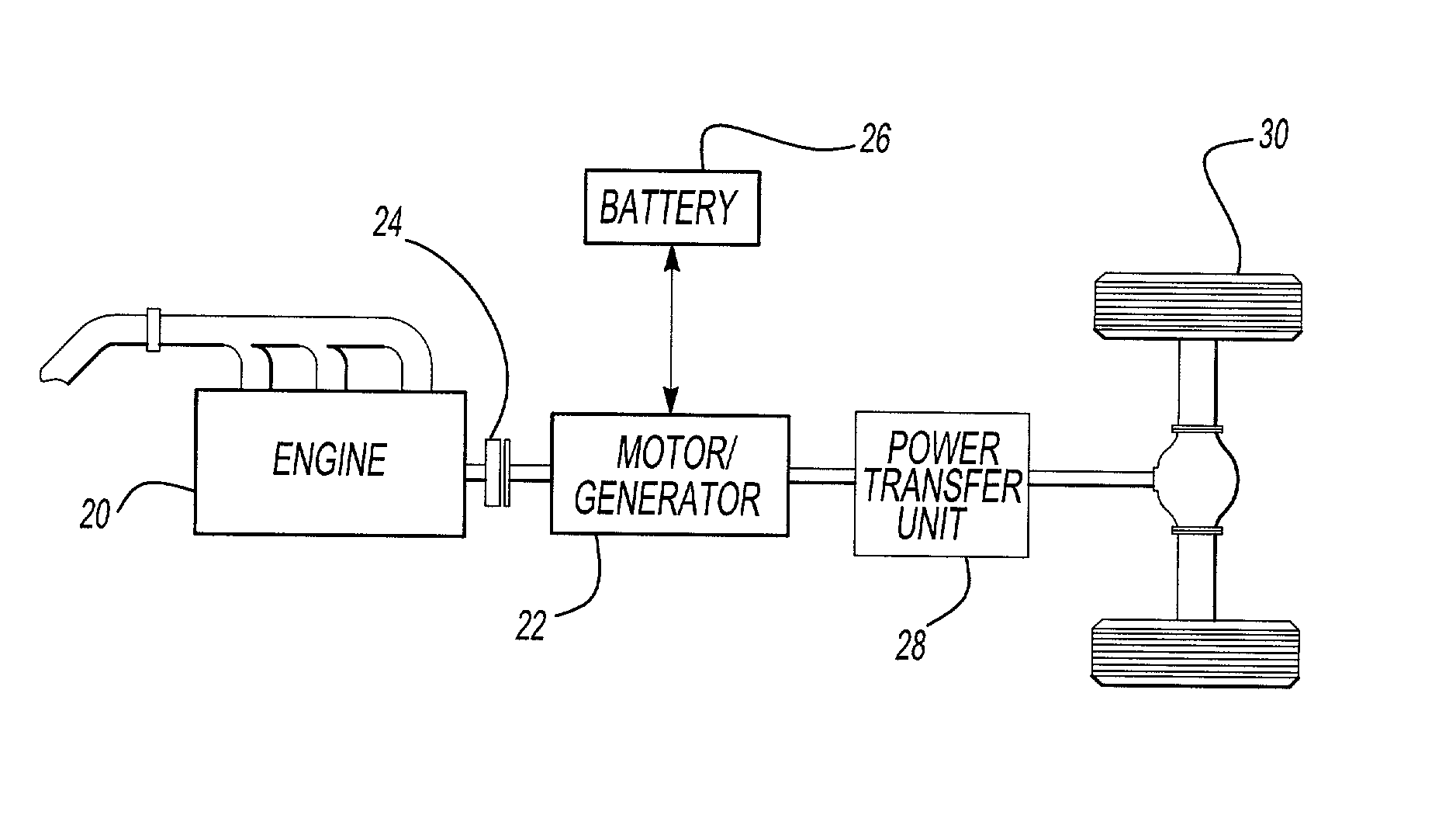

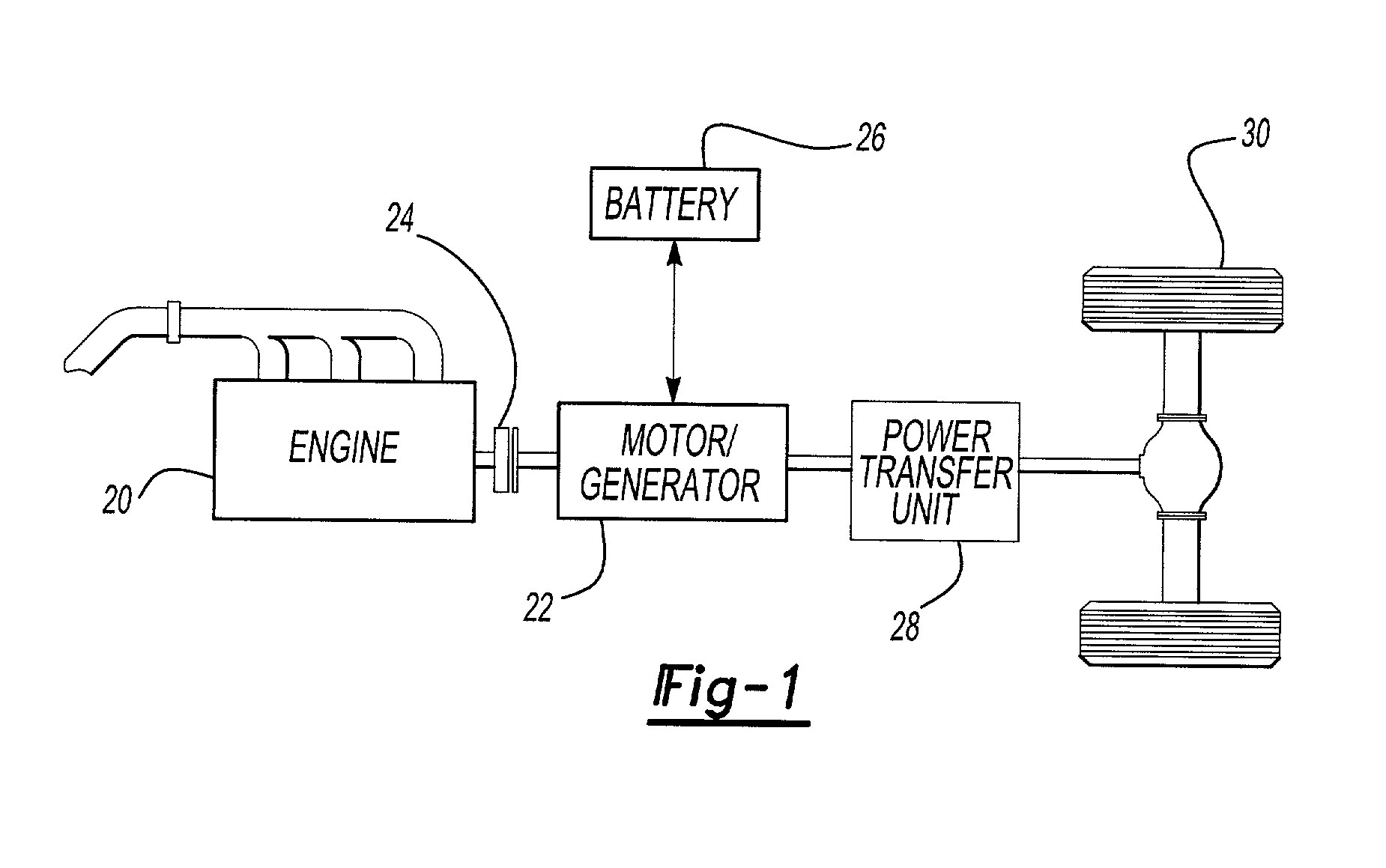

Control system and method for a parallel hybrid electric vehicle

InactiveUS20030098187A1Auxillary drivesElectrical controlControl systemStructure of Management Information

The present invention provides a control strategy for a parallel hybrid electric vehicle (HEV) configuration where power from the engine and the motor can each independently provide torque to the vehicle powertrain. The invention has a logical structure defining main system operating modes (states) and the transition between the different states. In addition to the predefined states, the present invention provides a set of rules defining logical relationships between each of the plurality of predefined states and a set of commands unique to each state. These commands are supplied to subsystem controllers to achieve desired vehicle functionality. The predefined states can be prioritized according to operator demands, energy management requirements, and system fault occurrences. The present invention can also be configured to have at least one of a plurality of transition flags. Each transition flag represents a logical relationship associated with efficient management of energy, operator demand, or system faults.

Owner:FORD GLOBAL TECH LLC

Handheld electronic device with text disambiguation

ActiveUS20060007121A1Good choiceReduced QWERTYInput/output for user-computer interactionElectronic switchingGraphicsText entry

A handheld electronic device includes a reduced QWERTY keyboard and is enabled with disambiguation software. The device provides output in the form of a default output and a number of variants. The output is based largely upon the frequency, i.e., the likelihood that a user intended a particular output, but various features of the device provide additional variants that are not based solely on frequency and rather are provided by various logic structures resident on the device. The device enables editing during text entry and also provides a learning function that allows the disambiguation function to adapt to provide a customized experience for the user. The disambiguation function can be selectively disabled and an alternate keystroke interpretation system provided. Additionally, the device can facilitate the selection of variants by displaying a graphic of a special <NEXT> key of the keypad that enables a user to progressively select variants generally without changing the position of the user's hands on the device.

Owner:MALIKIE INNOVATIONS LTD

Reconfigurable logic structures

InactiveUS7511532B2Logic circuits characterised by logic functionNanoinformaticsElectronic structurePhase-change memory

Reconfigurable electronic structures and circuits using programmable, non-volatile memory elements. The programmable, non-volatile memory elements may perform the functions of storage and / or a switch to produce components such as crossbars, multiplexers, look-up tables (LUTs) and other logic circuits used in programmable logic structures (e.g., (FPGAs)). The programmable, non-volatile memory elements comprise one or more structures based on Phase Change Memory, Programmable Metallization, Carbon Nano-Electromechanical (CNT-NEM), or Metal Nano-Electromechanical device technologies.

Owner:CSWITCH

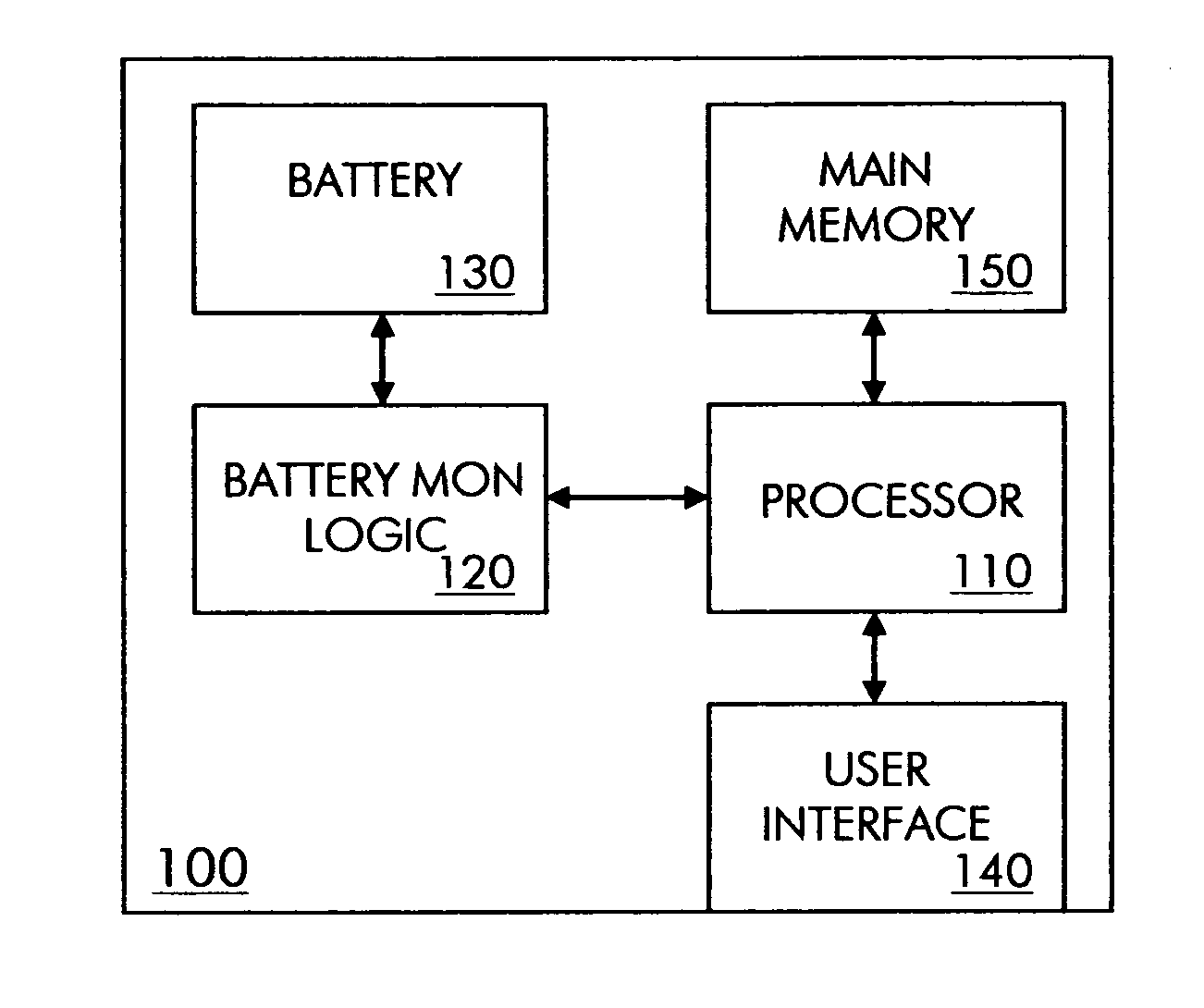

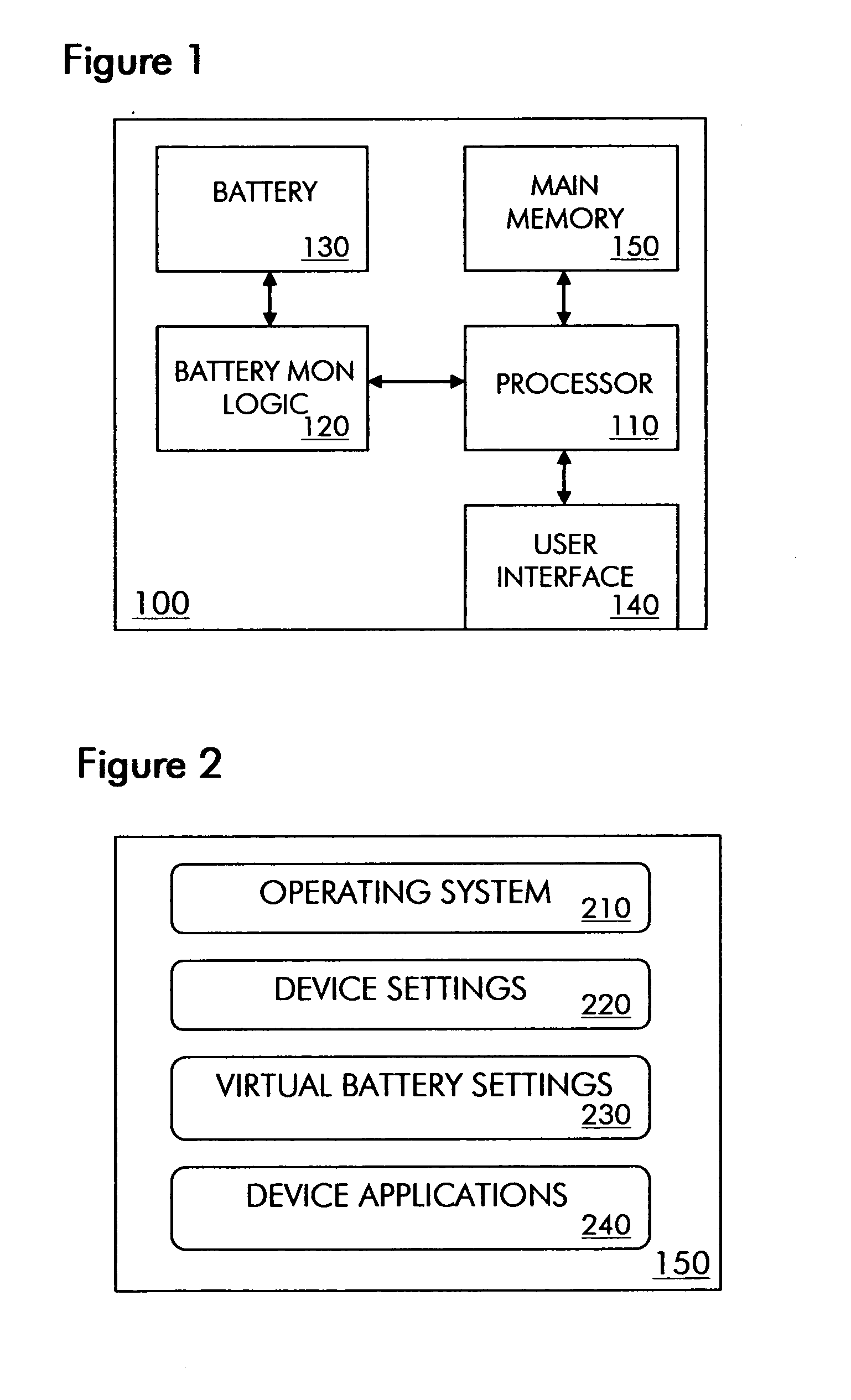

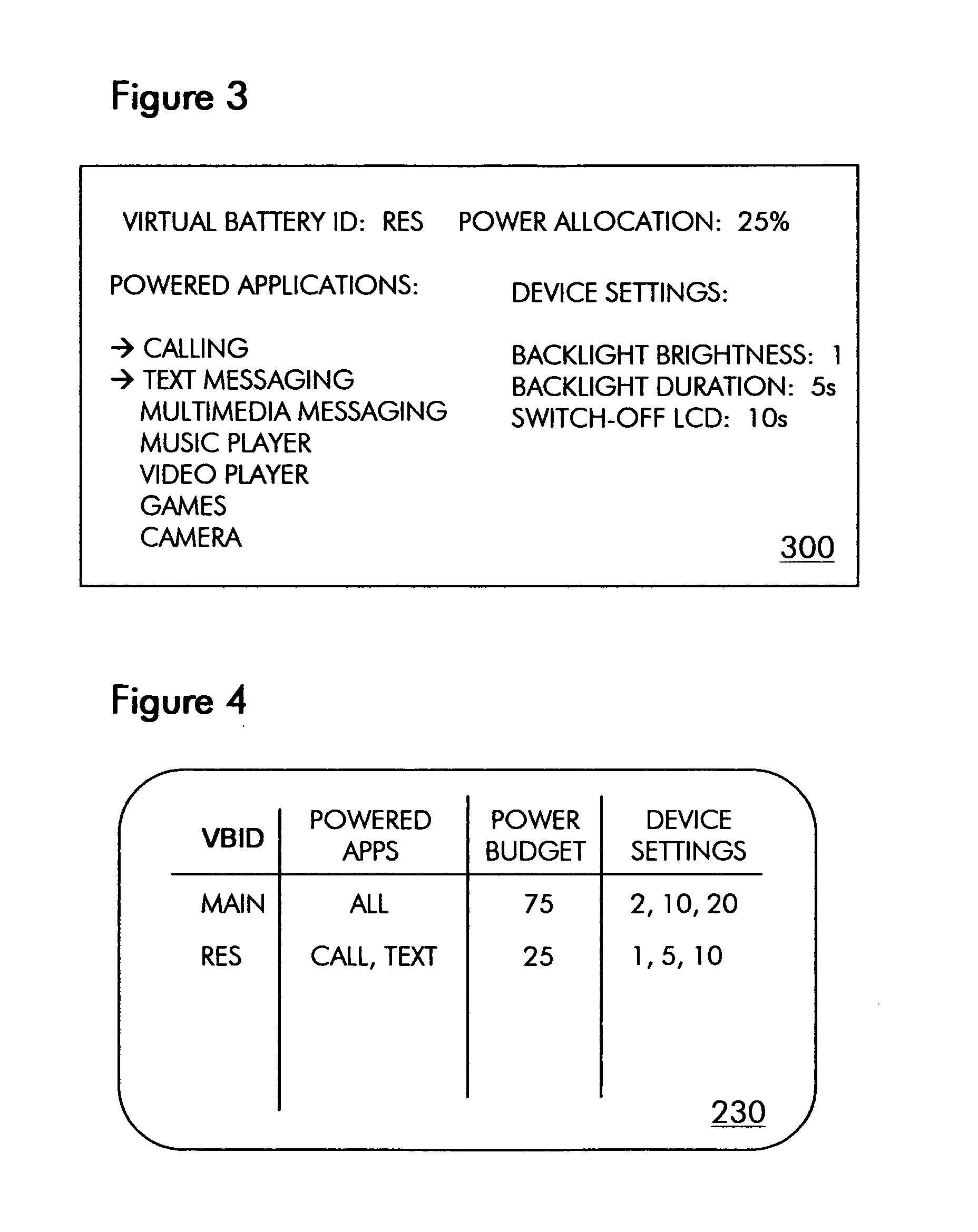

Virtual batteries for wireless communication device

ActiveUS20070243852A1Efficiently allocate powerReduce usageEnergy efficient ICTPower managementTelecommunicationsPower budget

The present invention provides virtual batteries for a wireless communication device. Generally speaking, a virtual battery is a logical construct on a wireless communication device that powers a defined set of wireless communication device applications and has a defined power budget from one or more physical batteries on the device. Through judicious assignment of wireless communication device applications and power budgets to virtual batteries, a user of a wireless communication device can efficiently allocate power among competing wireless communication device applications.

Owner:SHARP KK

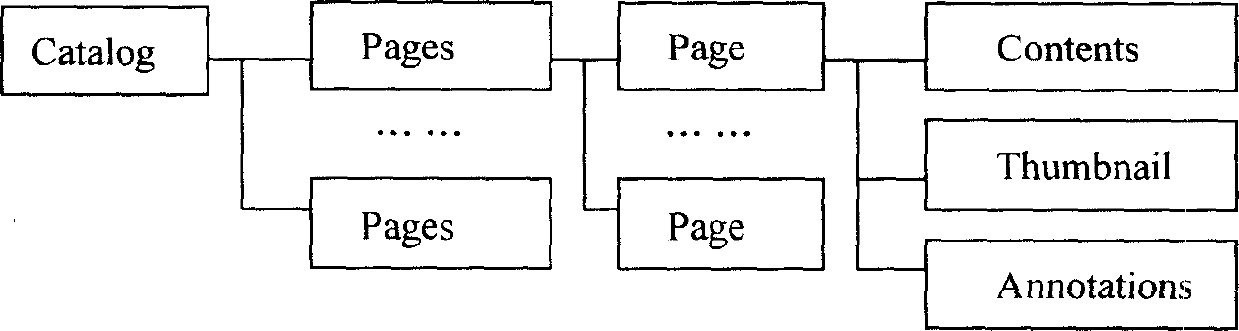

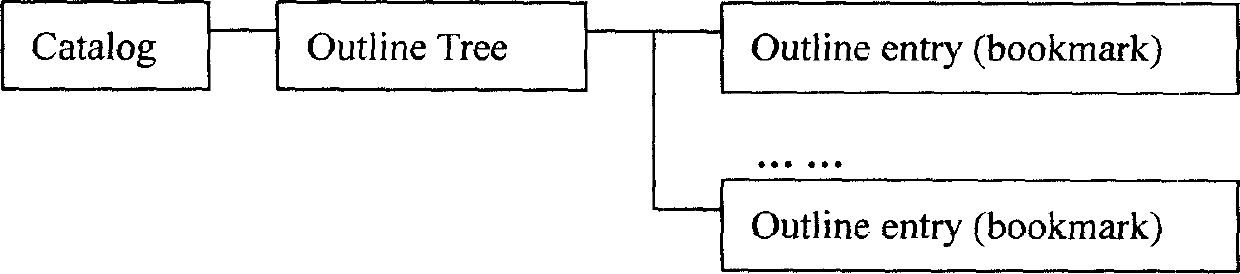

Method of PDF file information extraction system based on XML

InactiveCN1687926AImprove automatic classificationImprove retrieval efficiencySpecial data processing applicationsDocumentationXML

The invention discloses a method for XML-based PDF document information drawing system, an information converting method, belonging to the class of information technique and including the steps: (1) designing DTD, i.e. firstly analyzing and selecting external information cell data and internal information cell data; (2) drawing the semantic information of the PDF document, i.e. firstly drawing the content flow of each page stored in the PDF document for decoding, and then converting the physical structure of the PDF document to a logic structure, and finally drawing the external information cell data and internal information cell data; (3) generating a XML document. The invention can further process the XML document, thus raising the efficiencies of automatically classifying documents and searching user information.

Owner:FUZHOU UNIV

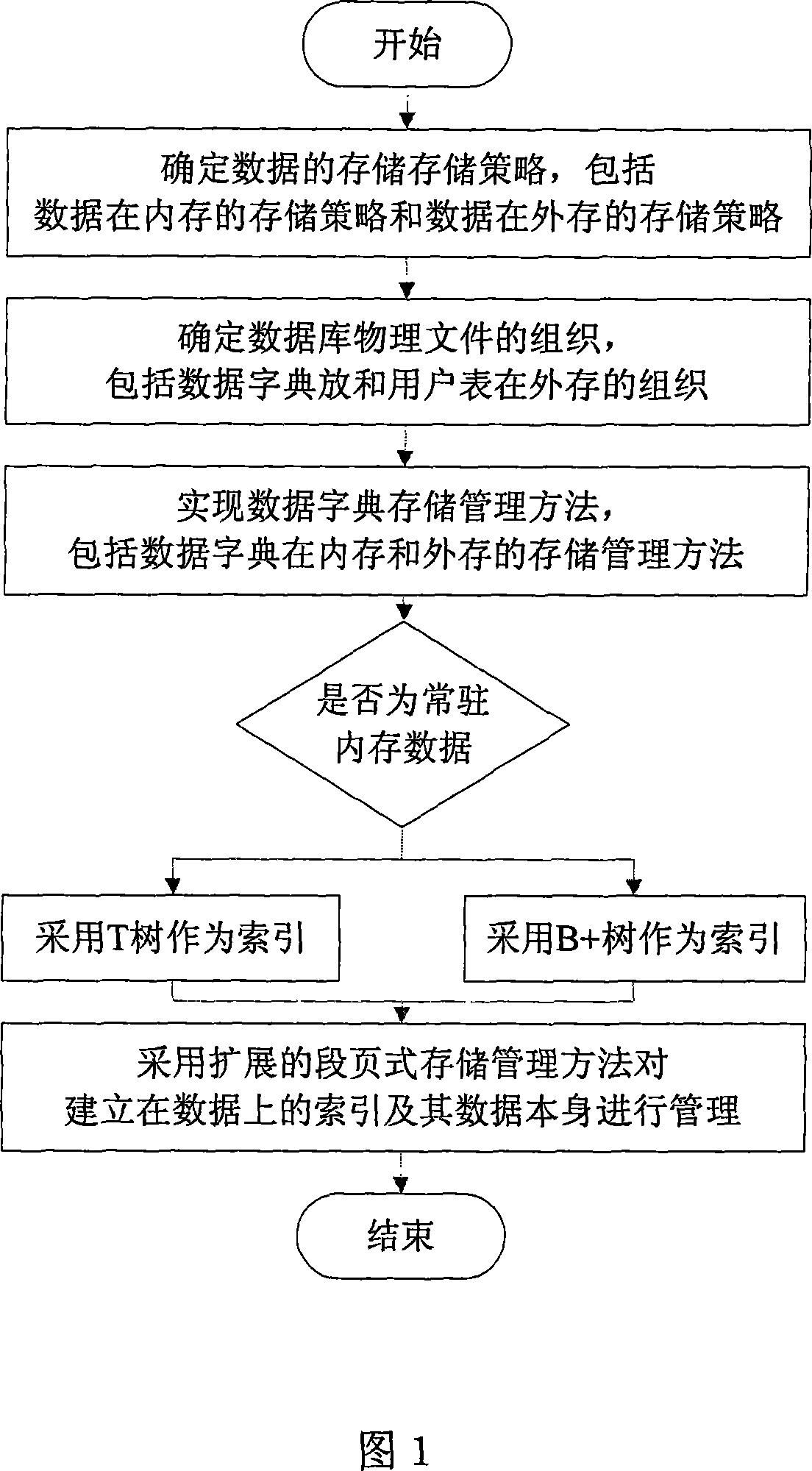

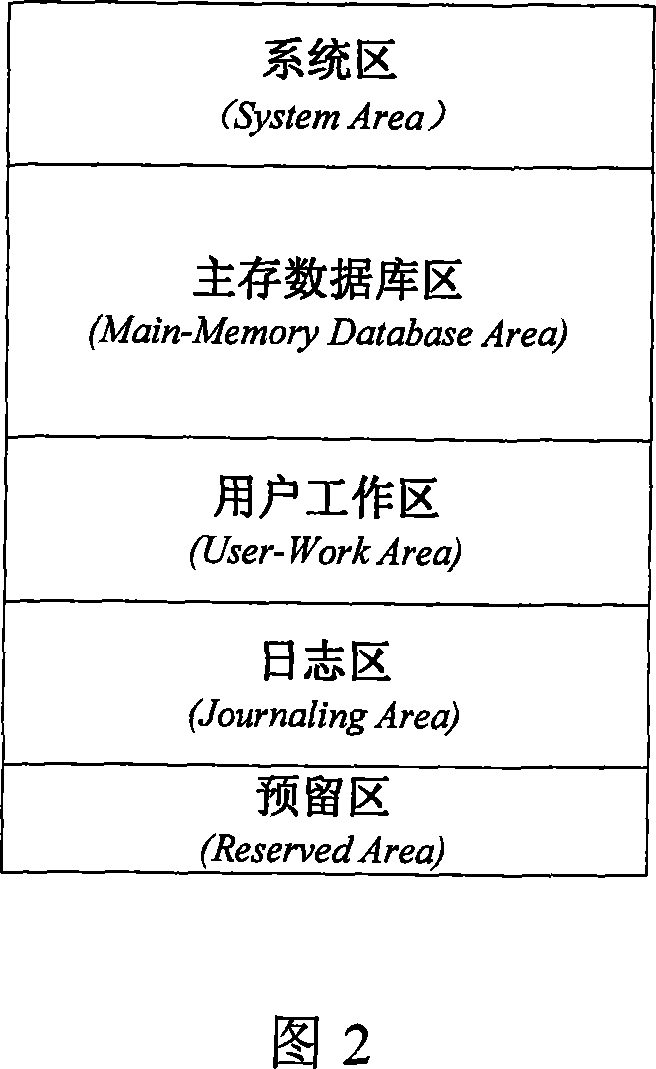

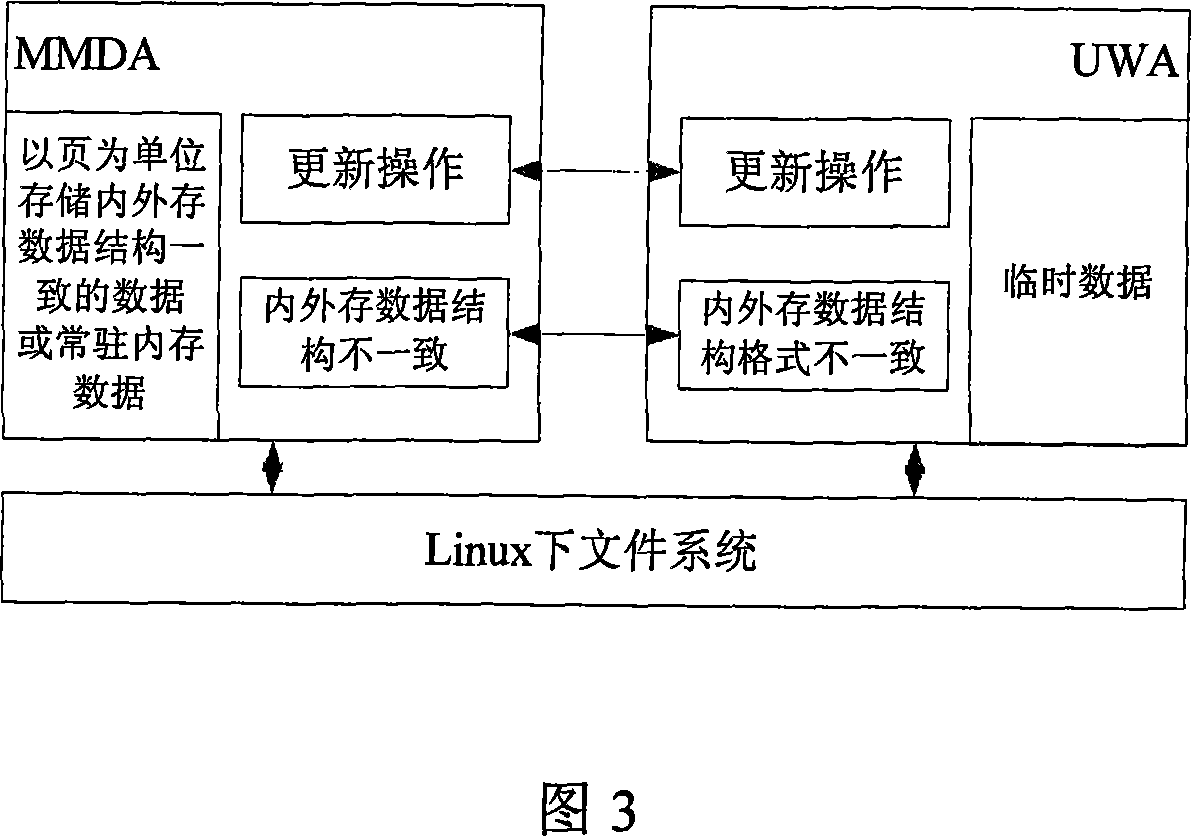

Embedded database storage management method

InactiveCN101055589AGuaranteed compactnessImprove loading speedSpecial data processing applicationsEmbedded databaseData access

A storage mamagement method of embedded database,includes that: (1) the storage strategy of data in the memory is that: if logic structure accords with physical structure, the structure is into a divided system area, a main storage database area, a user working area, a log area and a preformed area; the storage strategy of data in the external memory is that: logic structure is divided into a database table, a segment and a database block; physical structure includes a physical file and a physical block; (2) the physical file organization of database is that: a data dictionary is placed at the heading, a user table since then; (3) the memory management of data dictionaryin the external memory is that: the described information of physical file is stored in the file header, denotative definition kind and attribute definition kind adopt a three section type storage form; data dictionary adopt a page type memory management method in the memory; (4) a permanent memory data is stored using T tree and a a permanent external memory data is stored using B+ tree; data and its index are managed using a extended segment memory management method. The invention improves the utilization rate of memory space, and accelerate the speed of data to access.

Owner:BEIHANG UNIV

Handheld electronic device with text disambiguation

ActiveUS7283065B2Good choiceReduced QWERTYElectronic switchingCathode-ray tube indicatorsGraphicsText entry

A handheld electronic device includes a reduced QWERTY keyboard and is enabled with disambiguation software. The device provides output in the form of a default output and a number of variants. The output is based largely upon the frequency, i.e., the likelihood that a user intended a particular output, but various features of the device provide additional variants that are not based solely on frequency and rather are provided by various logic structures resident on the device. The device enables editing during text entry and also provides a learning function that allows the disambiguation function to adapt to provide a customized experience for the user. The disambiguation function can be selectively disabled and an alternate keystroke interpretation system provided. Additionally, the device can facilitate the selection of variants by displaying a graphic of a special <NEXT> key of the keypad that enables a user to progressively select variants generally without changing the position of the user's hands on the device.

Owner:MALIKIE INNOVATIONS LTD

Handheld electronic device with text disambiguation

ActiveUS7324083B2Good choiceReduced QWERTYInput/output for user-computer interactionCathode-ray tube indicatorsText entryLogic structure

A handheld electronic device includes a reduced QWERTY keyboard and is enabled with disambiguation software. The device provides output in the form of a default output and a number of variants. The output is based largely upon the frequency, i.e., the likelihood that a user intended a particular output, but various features of the device provide additional variants that are not based solely on frequency and rather are provided by various logic structures resident on the device. The device enables editing during text entry and also provides a learning function that allows the disambiguation function to adapt to provide a customized experience for the user. The disambiguation function can be selectively disabled and an alternate keystroke interpretation system provided.

Owner:MALIKIE INNOVATIONS LTD

Die-stacked memory device with reconfigurable logic

ActiveUS8922243B2Error detection/correctionSolid-state devicesHigh bandwidthProgrammable logic device

A die-stacked memory device incorporates a reconfigurable logic device to provide implementation flexibility in performing various data manipulation operations and other memory operations that use data stored in the die-stacked memory device or that result in data that is to be stored in the die-stacked memory device. One or more configuration files representing corresponding logic configurations for the reconfigurable logic device can be stored in a configuration store at the die-stacked memory device, and a configuration controller can program a reconfigurable logic fabric of the reconfigurable logic device using a selected one of the configuration files. Due to the integration of the logic dies and the memory dies, the reconfigurable logic device can perform various data manipulation operations with higher bandwidth and lower latency and power consumption compared to devices external to the die-stacked memory device.

Owner:ADVANCED MICRO DEVICES INC

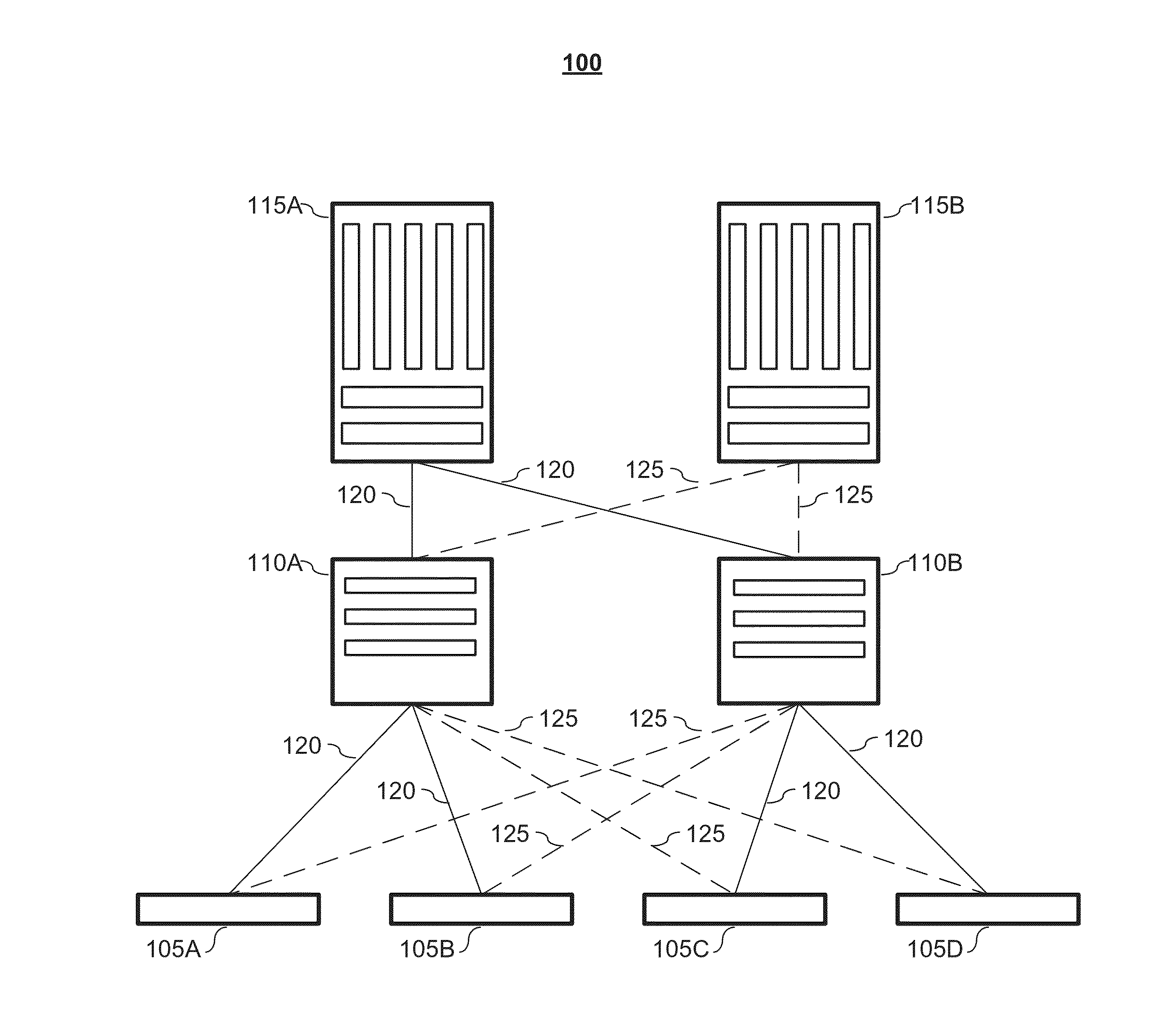

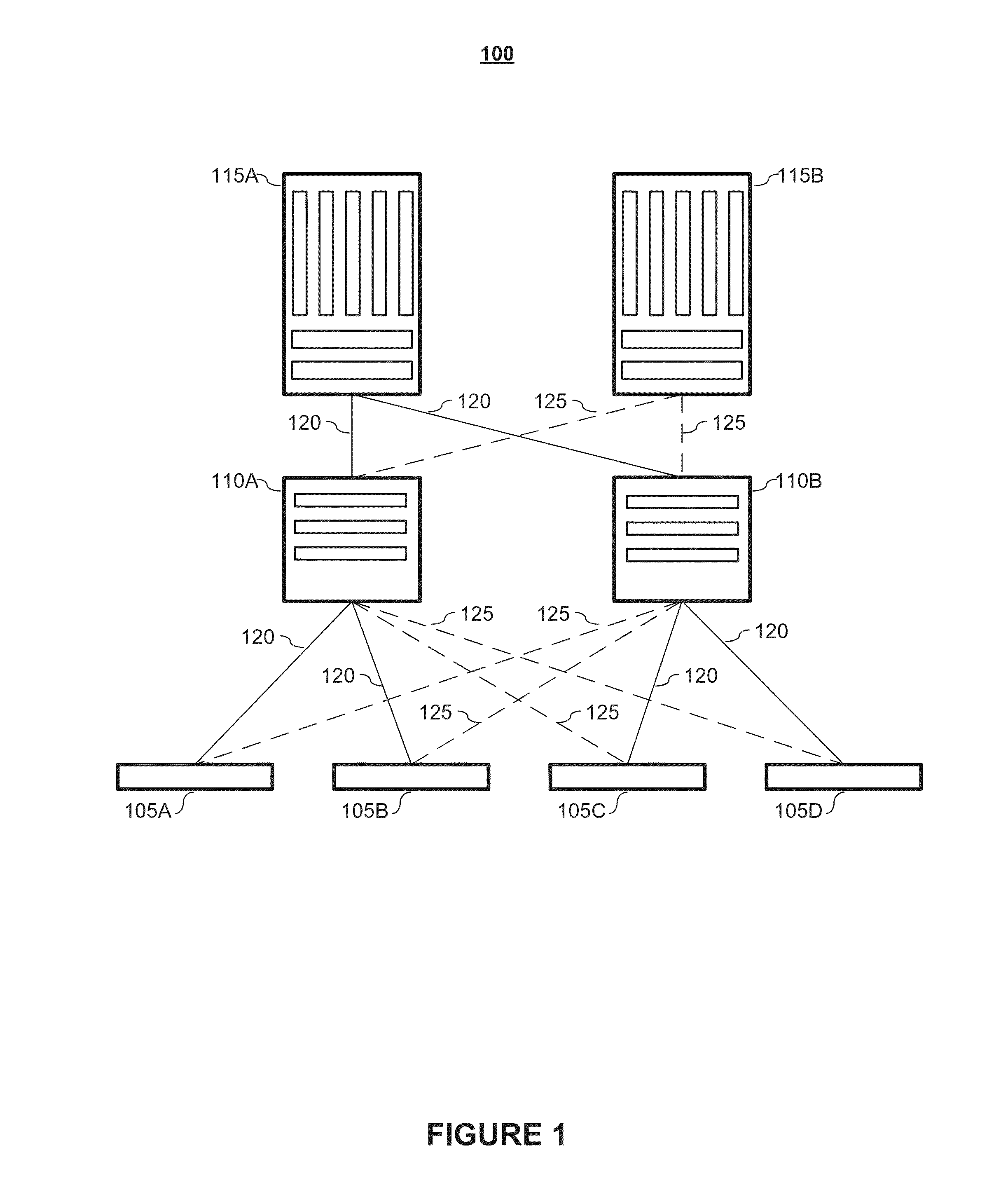

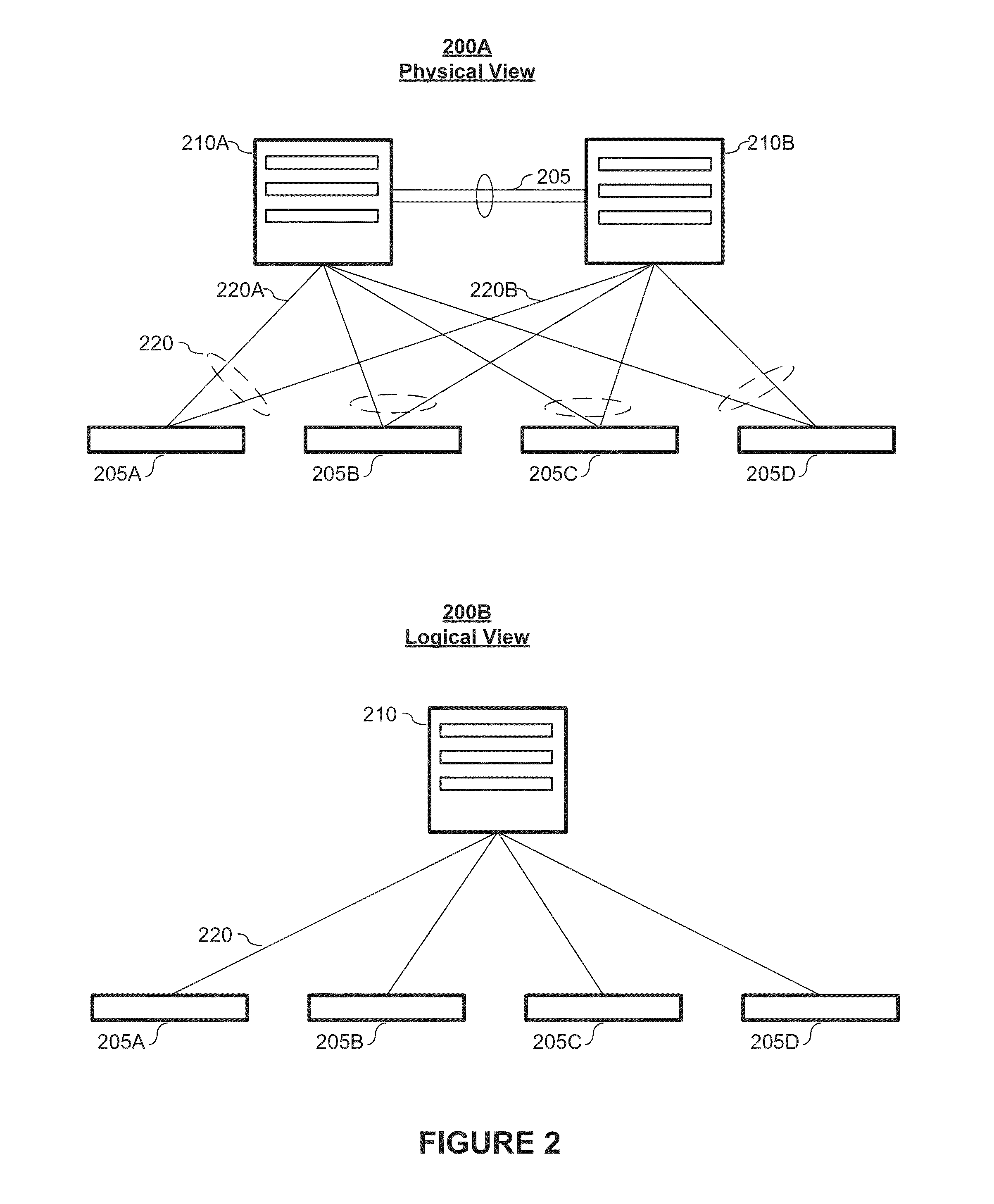

N-Node Virtual Link Trunking (VLT) Supporting Arbitrary Topologies

ActiveUS20150256405A1Data switching by path configurationHybrid transportVirtual Link TrunkingAccess network

Aspects of the present invention include an arbitrary N-Node virtual link trunking (VLT) system comprising a set of N nodes collectively provide a logical fabric-level view that is consistent across the set of N nodes. Embodiments of the arbitrary N-Node VLT system comprise a control plane mechanism to provide Layer 2 multipathing between access network devices (switches or servers) and the core network. The N-Node VLT system provides a loop-free topology with active-active load-sharing of uplinks from access to the core. Accordingly, the N-Node VLT system eliminates the disadvantage of Spanning Tree Protocol (STP) (active-standby links) by allowing link aggregation group (LAG) terminations on multiple separate distribution or core switches and also supporting a loop-free topology. Additional benefits of an N-Node VLT system include, but are not limited to, higher resiliency, improved link utilization, and improved manageability of the network.

Owner:DELL PROD LP

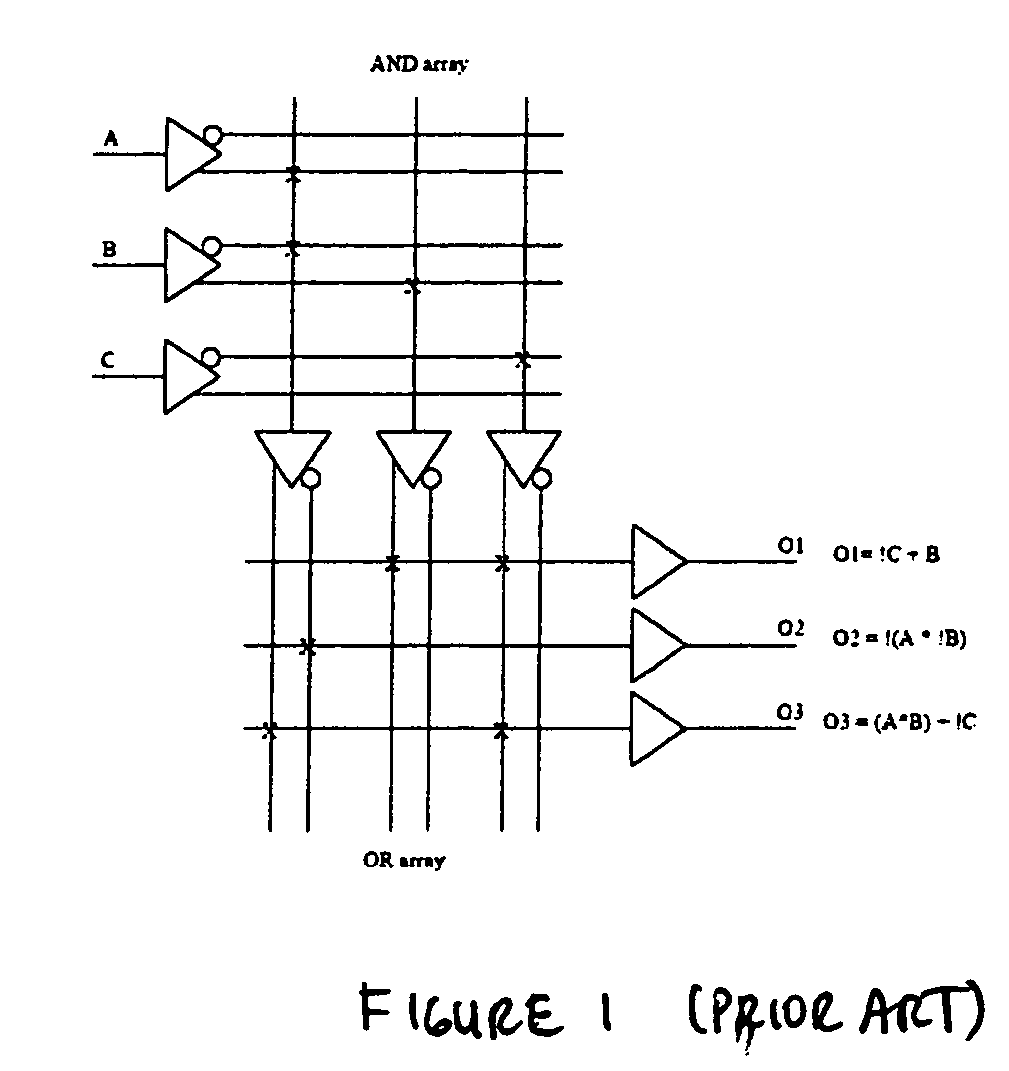

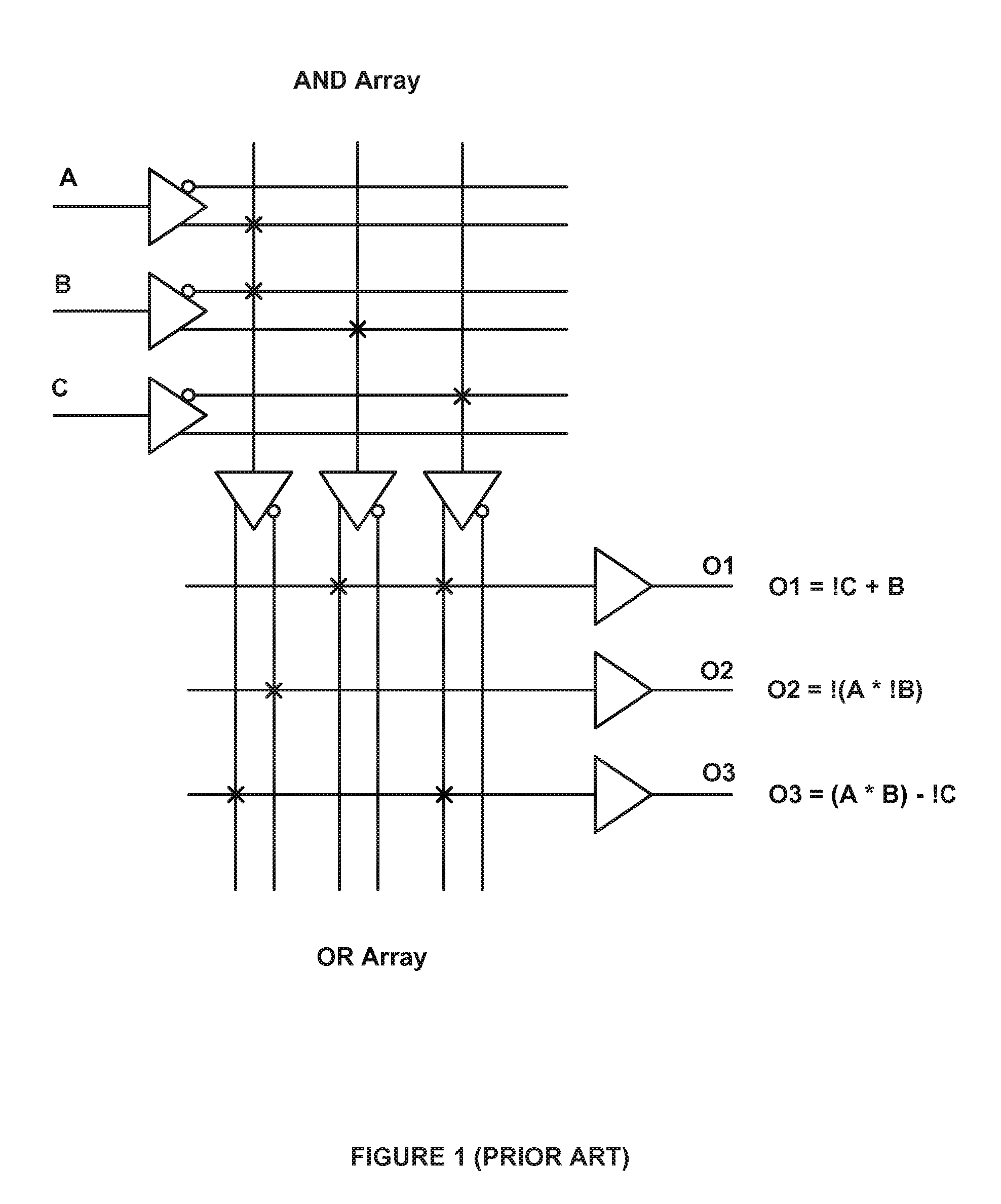

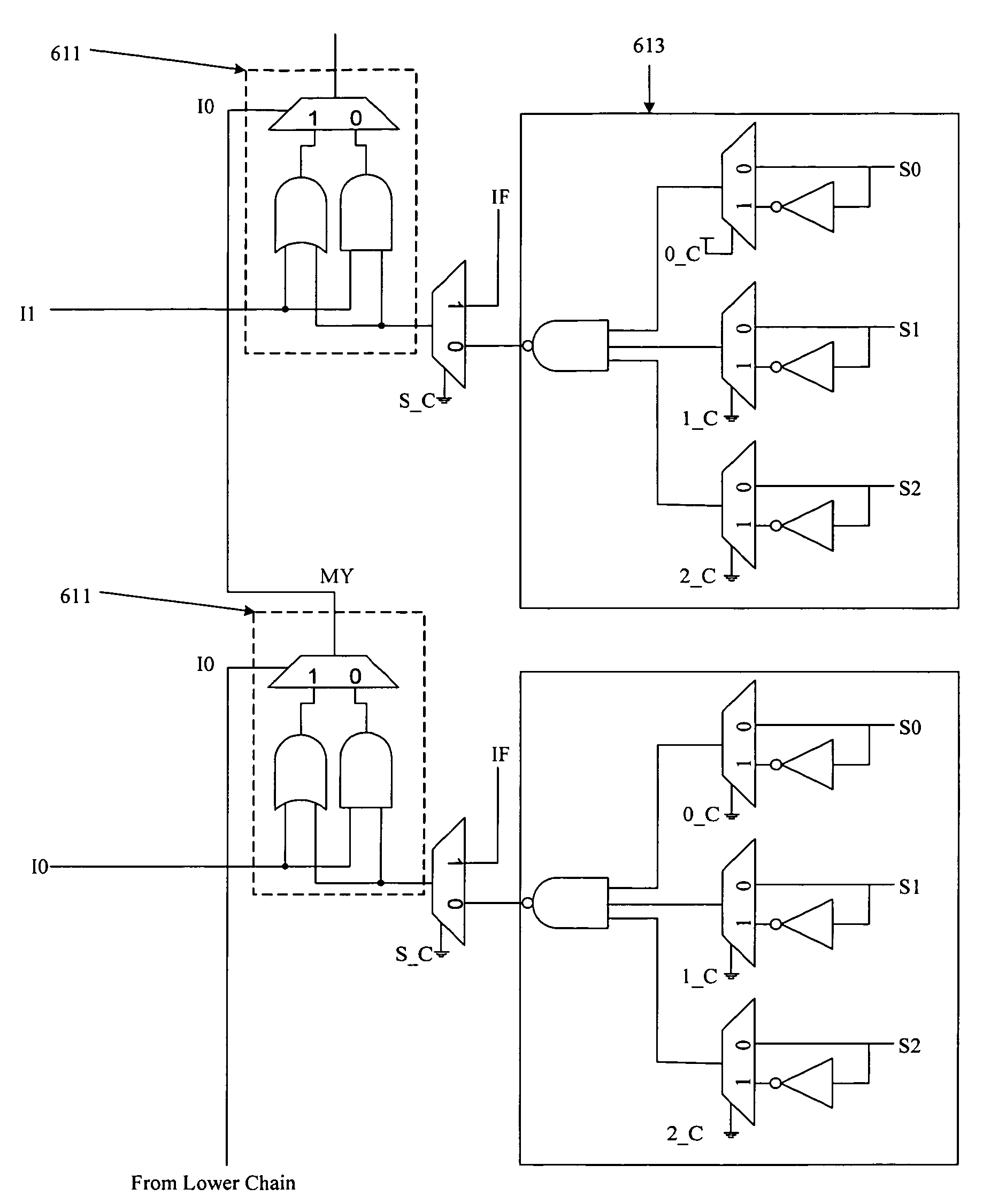

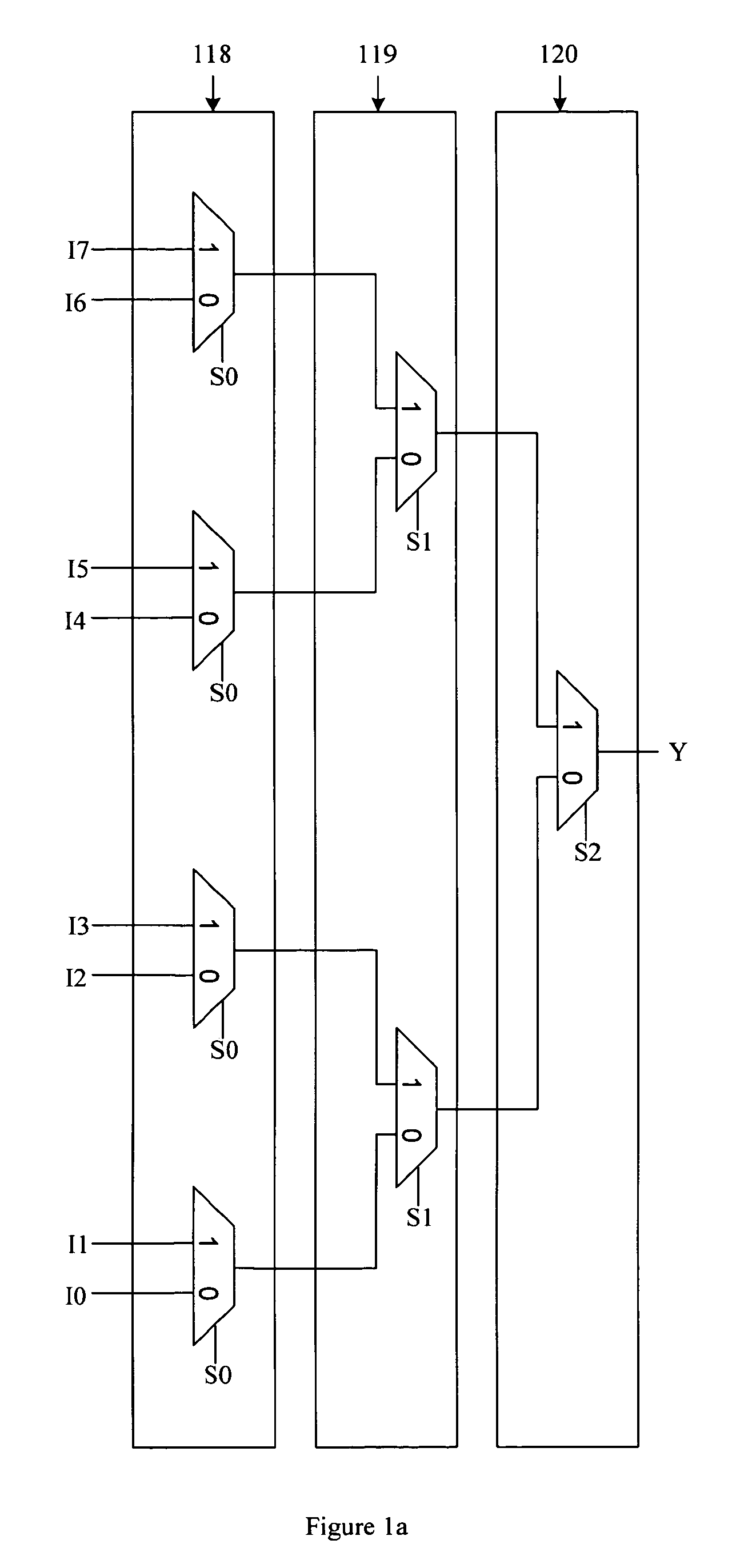

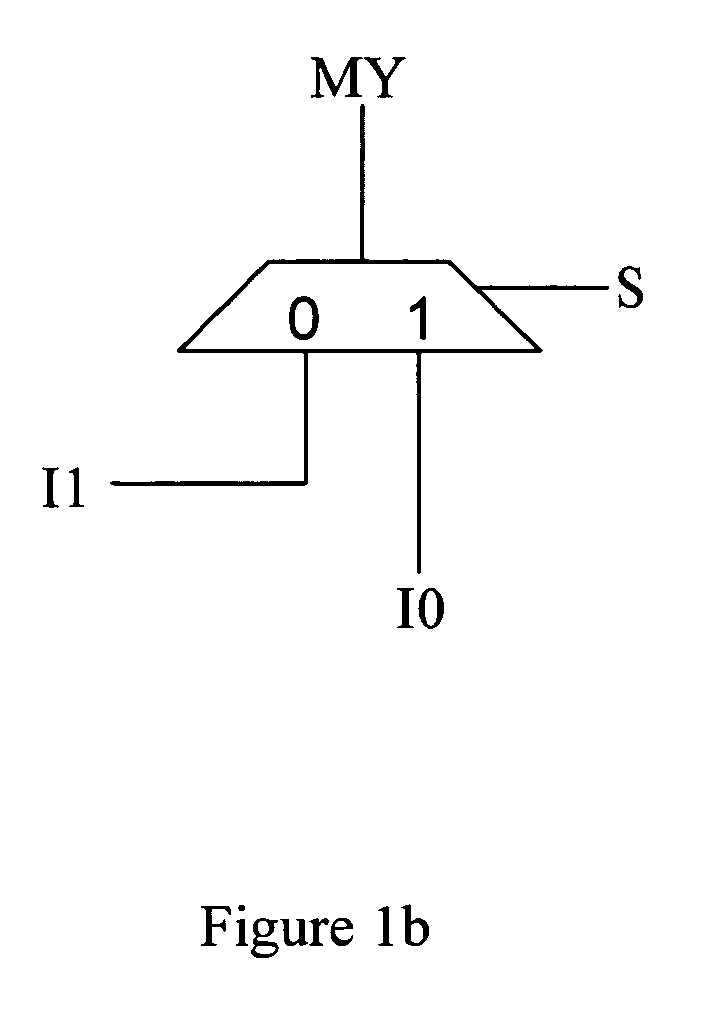

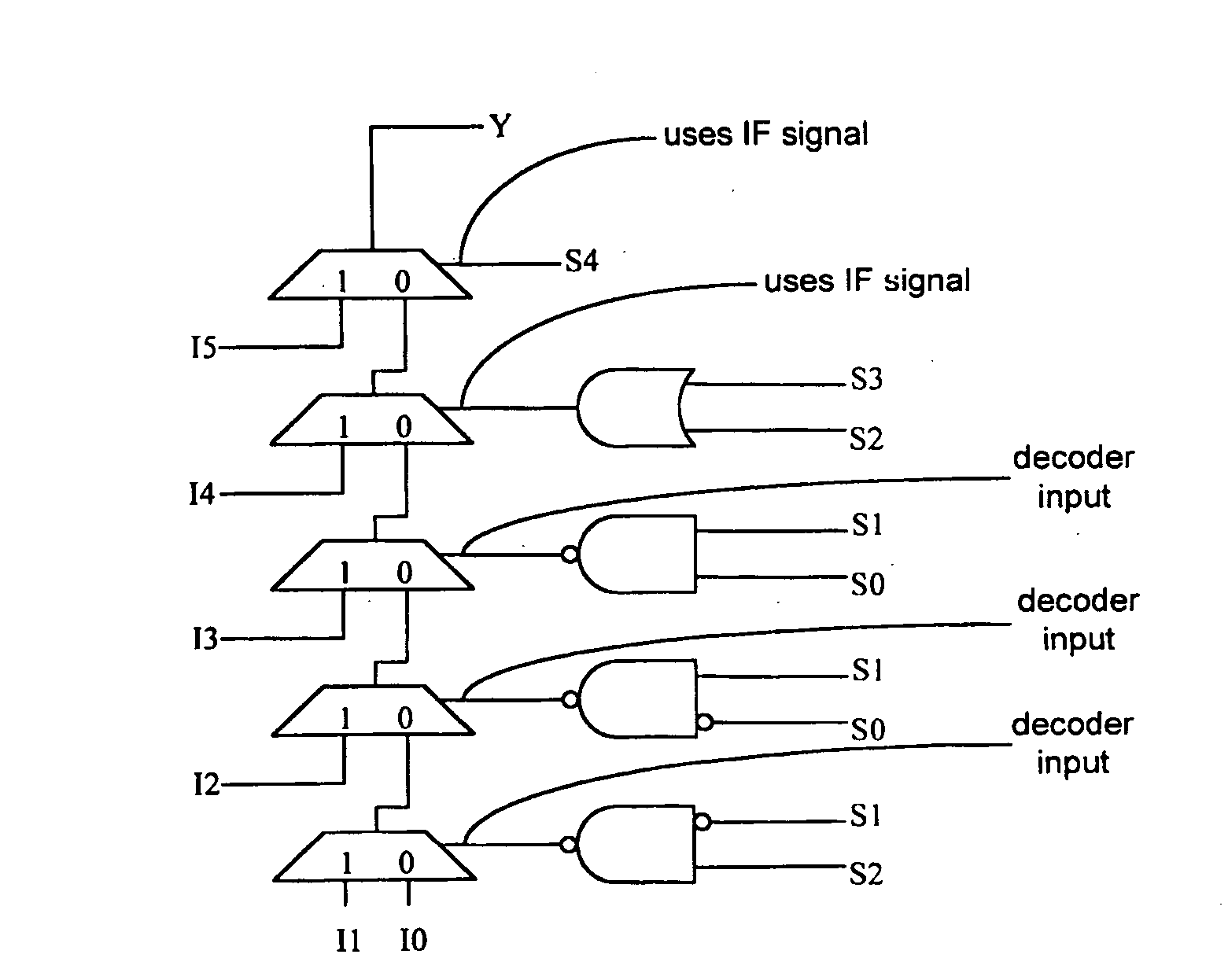

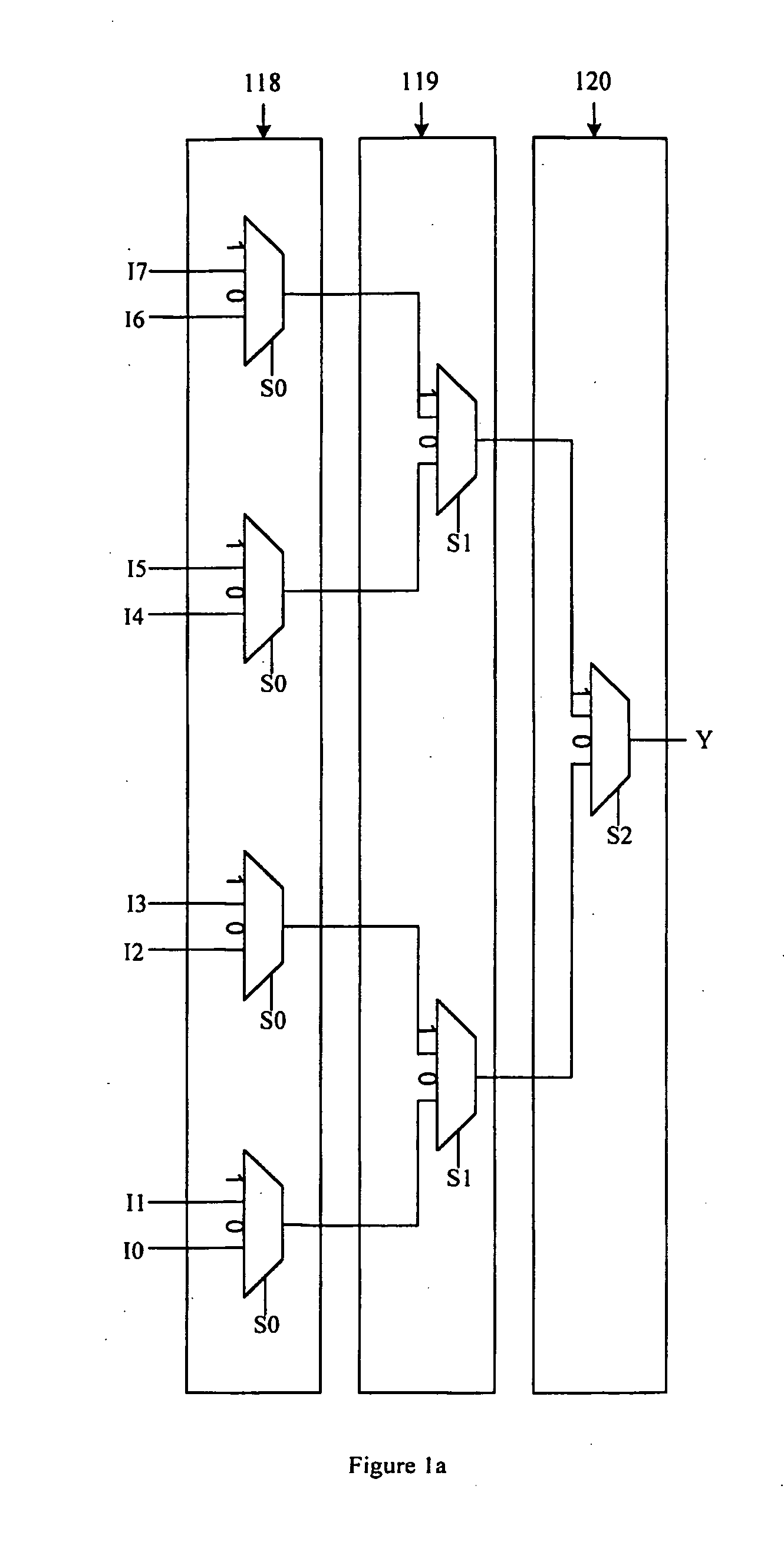

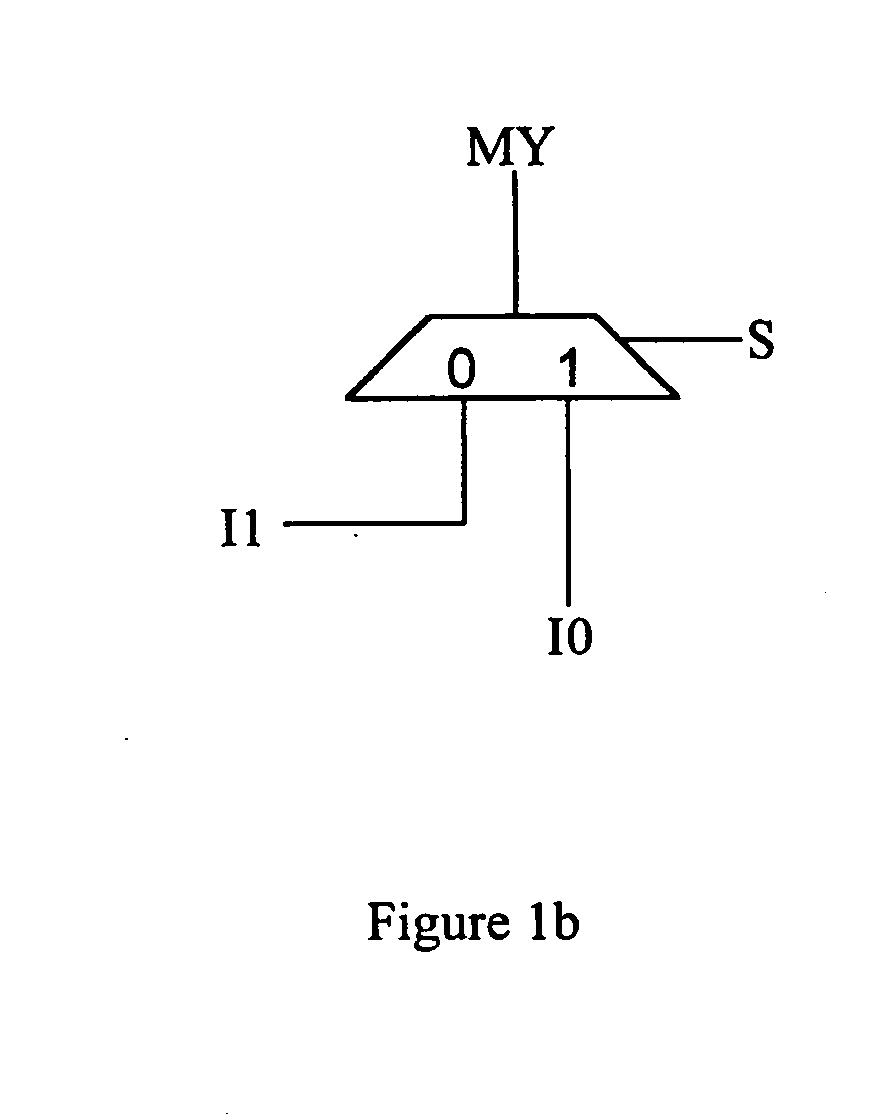

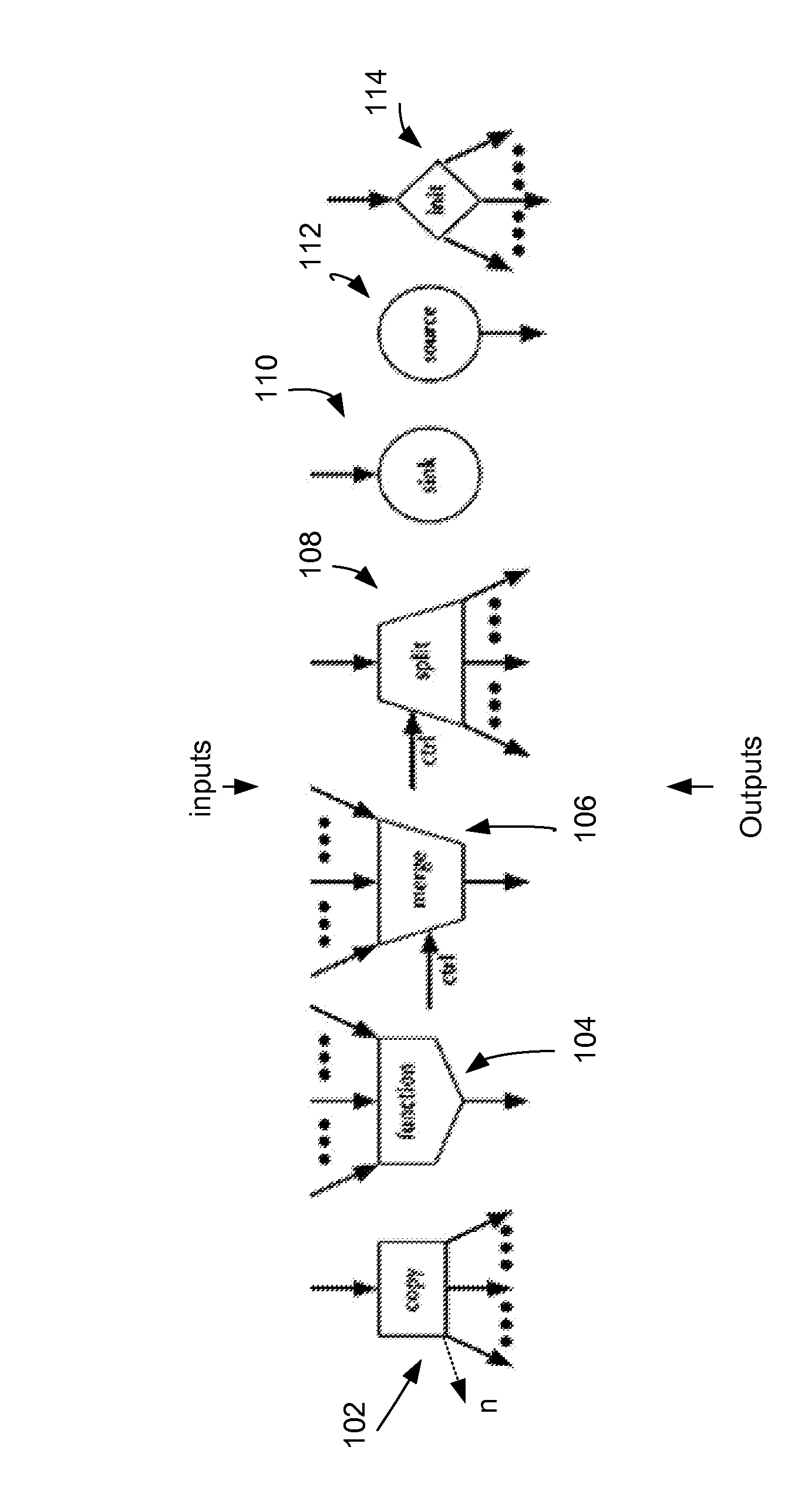

Versatile multiplexer-structures in programmable logic using serial chaining and novel selection schemes

InactiveUS7358761B1Logic circuits using elementary logic circuit componentsComputation using denominational number representationProgrammable logic deviceMultiplexer

Logic design apparatus and method provides serial multiplexer chains in a programmable logic fabric, each element in the chain either selects output of block, or passes output from earlier element of the chain. Select line is a decoder structure or output from configurable function generator that is configured at power-on to create correct selection. Using such structure, larger multiplexer, including priority multiplexers, tristate buses or larger look-up tables (LUTs) can be created. These novel structures can implement priority, non-priority or tristate multiplexers.

Owner:VENTURE LENDING & LEASING IV V +1

Versatile multiplexer-structures in programmable logic using serial chaining and novel selection schemes

Owner:AGATE LOGIC BEIJING

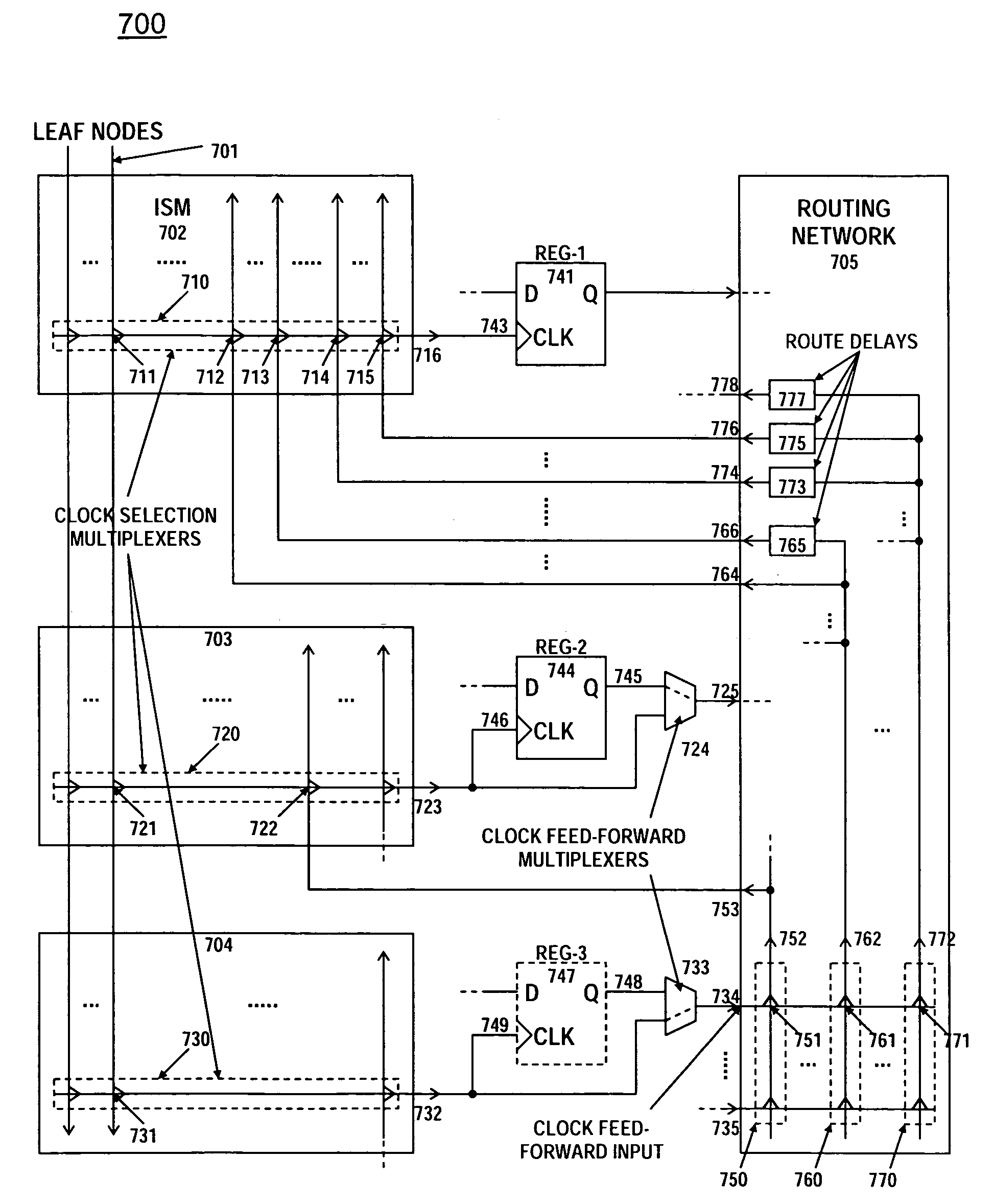

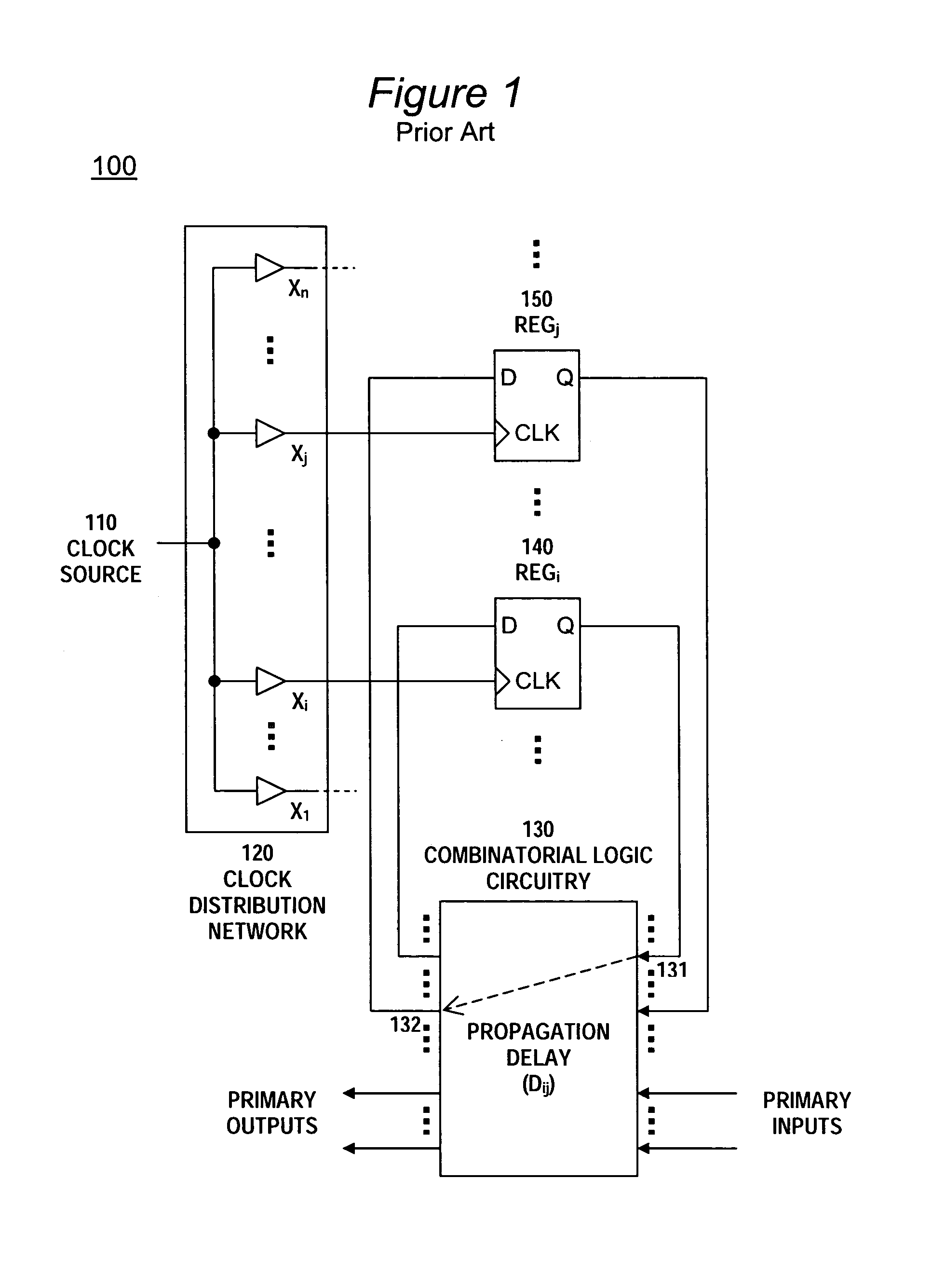

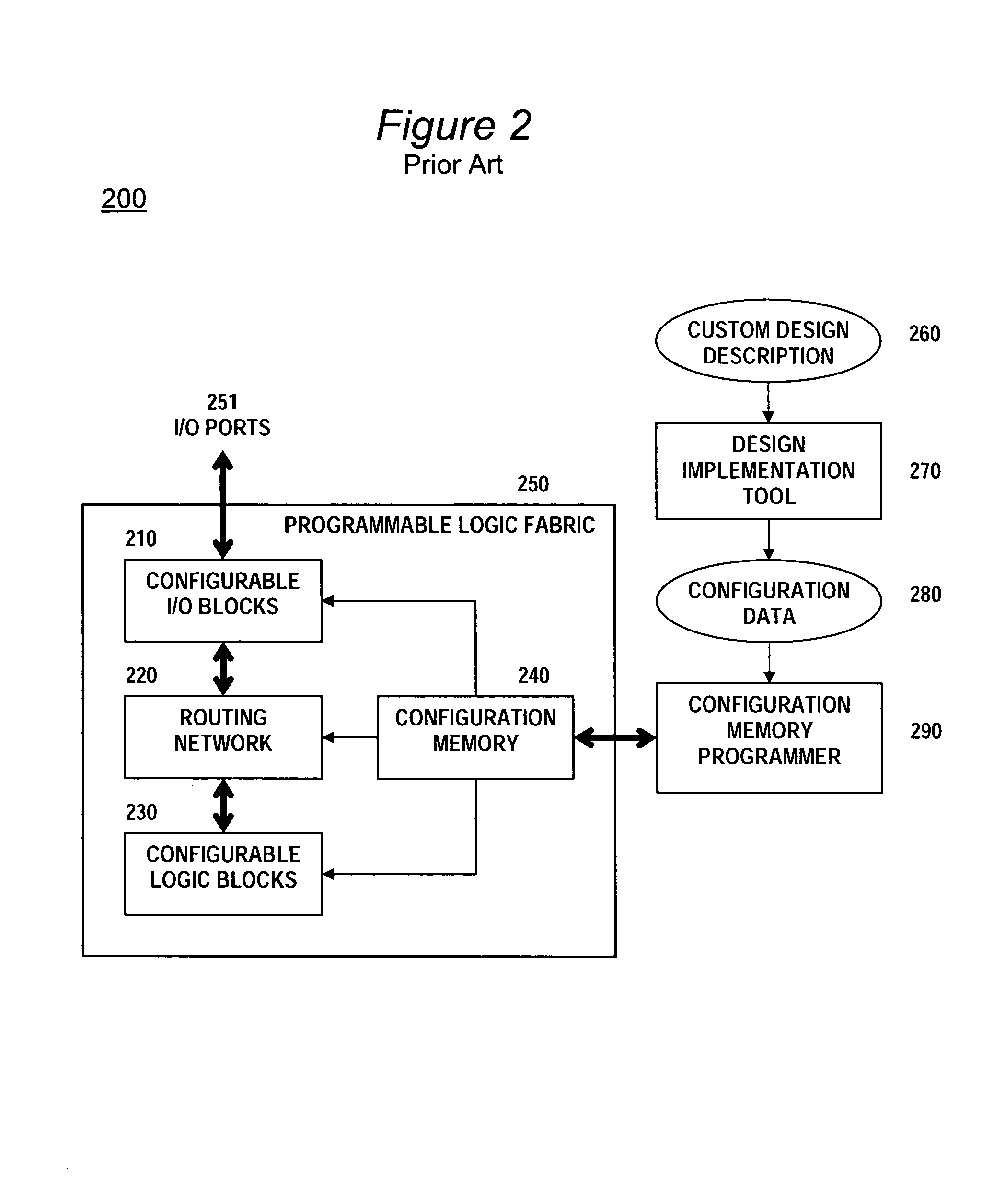

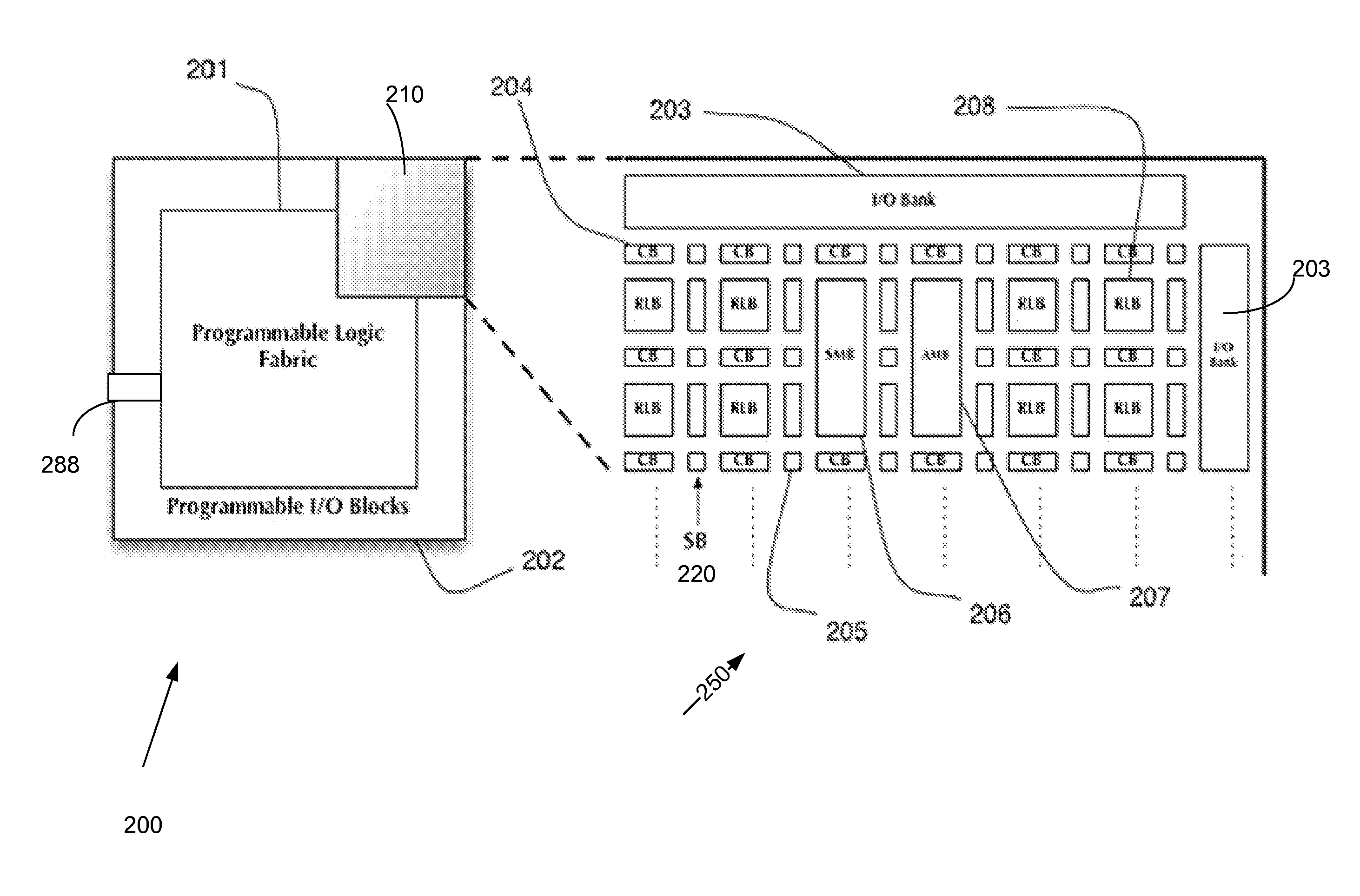

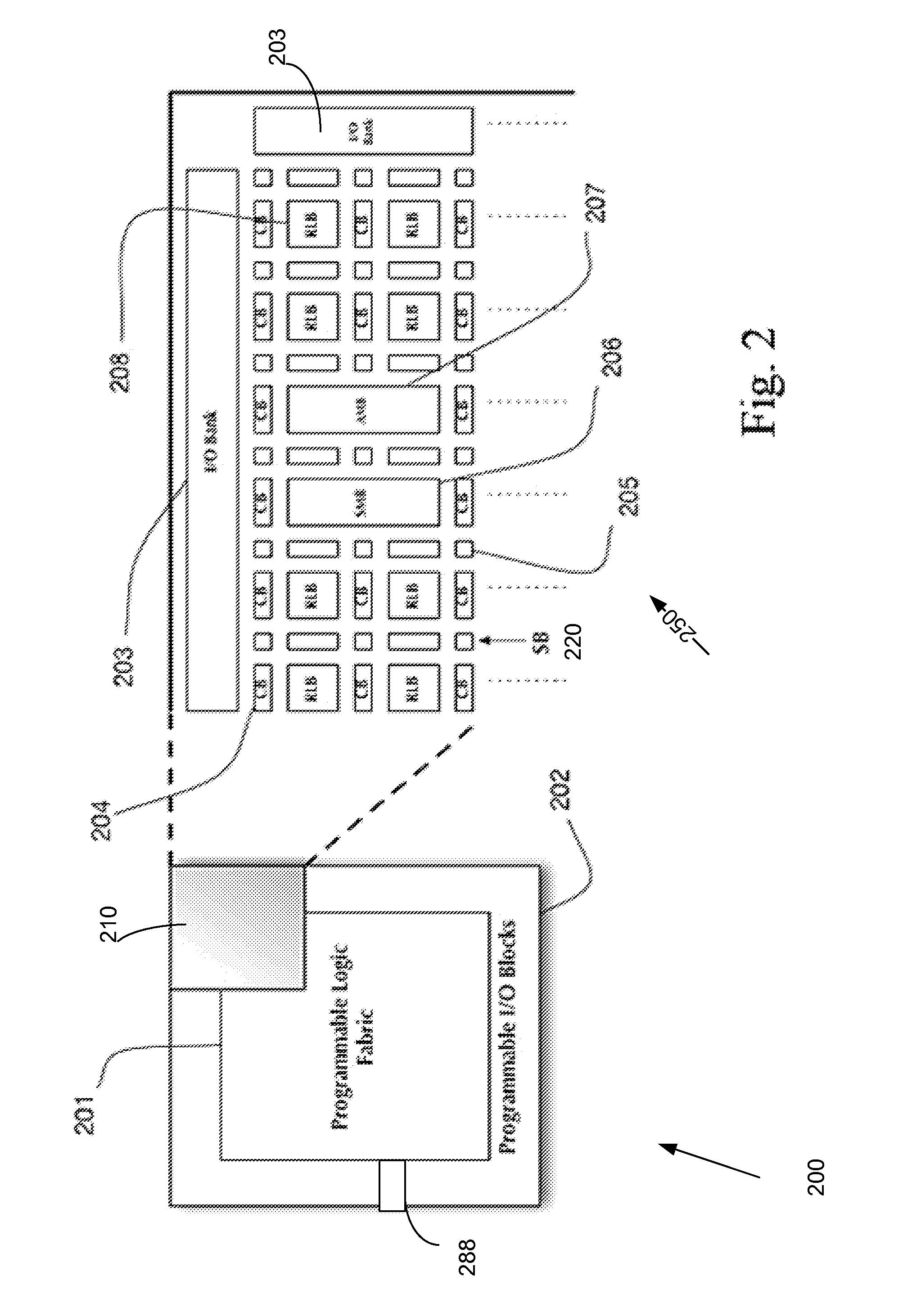

Apparatus and method for clock skew adjustment in a programmable logic fabric

InactiveUS7362135B1Minimize operating periodMinimize clock periodSolid-state devicesCAD circuit designProcessor registerProgrammable logic device

A programmable logic fabric includes configurable logic block (CLB) containing registers and combinatorial logic elements. An input switch matrix distributes incoming signals to CLB inputs or inputs of embedded logic elements including a register clock. A routing network allows a variety of routing paths with distinct delays to be selected to route the CLB outputs to the input switch matrices. Presented clock delay insertion architectures allow a leaf node of dedicated clock network and a register clock input can be alternatively routed through the routing network, thereby allowing for the generation of a variable amount of clock delay. Required clock delay for each register minimizing the clock period is computed by clock skew optimization program. A set of alternative clock routes is generated for each register clock where each route delay is close to the corresponding required delay while satisfying the monotone increasing conditions. Optimal clock route for each register clock can be efficiently selected from the alternative clock routes by an integer monotonic program to reduce the clock period of a custom design implemented in the fabric.

Owner:CHANG HYUN TAEK