Patents

Literature

1031 results about "Electronic structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In quantum chemistry, electronic structure is the state of motion of electrons in an electrostatic field created by stationary nuclei. The term encompass both the wave functions of the electrons and the energies associated with them. Electronic structure is obtained by solving quantum mechanical equations for the aforementioned clamped-nuclei problem.

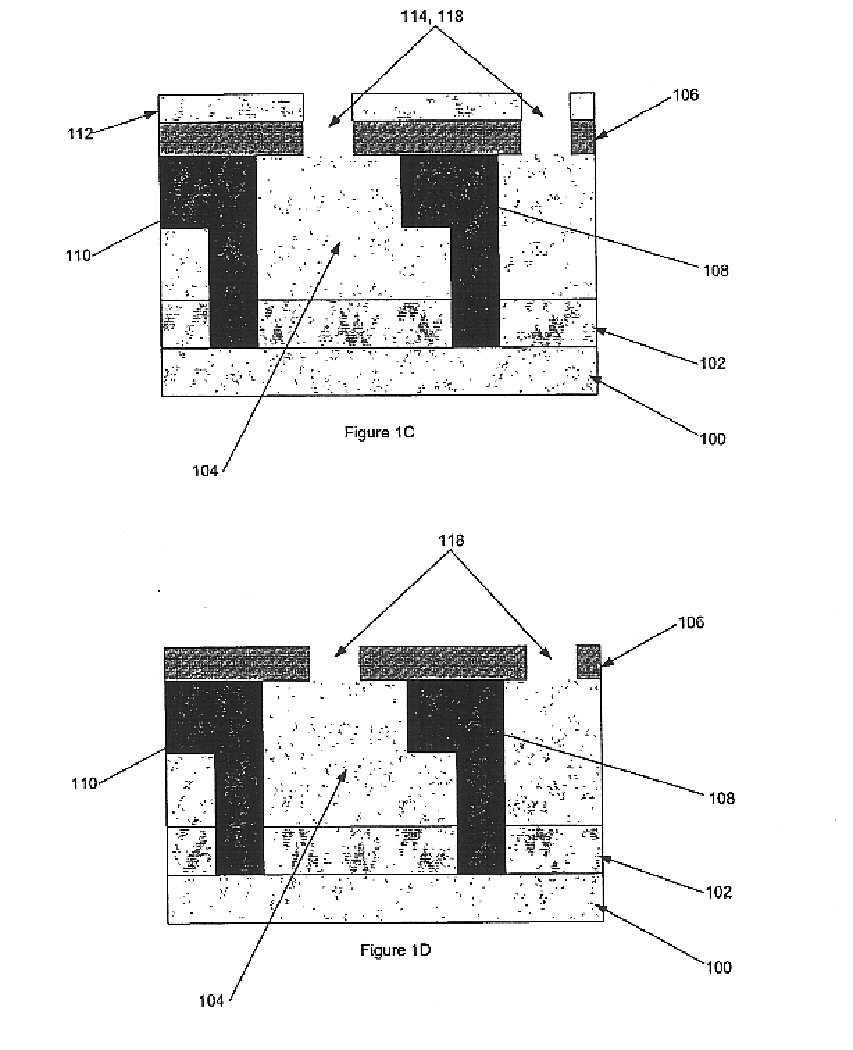

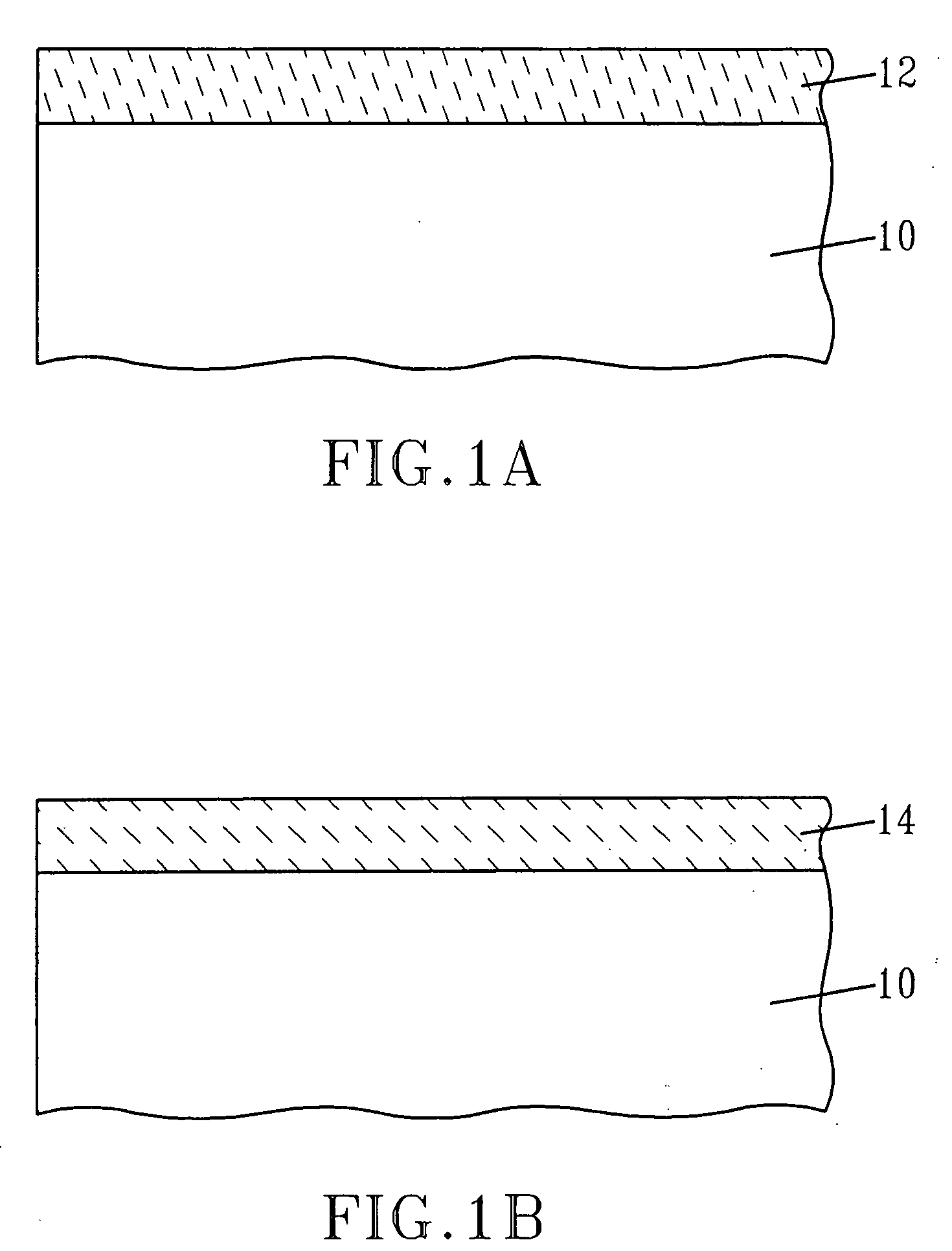

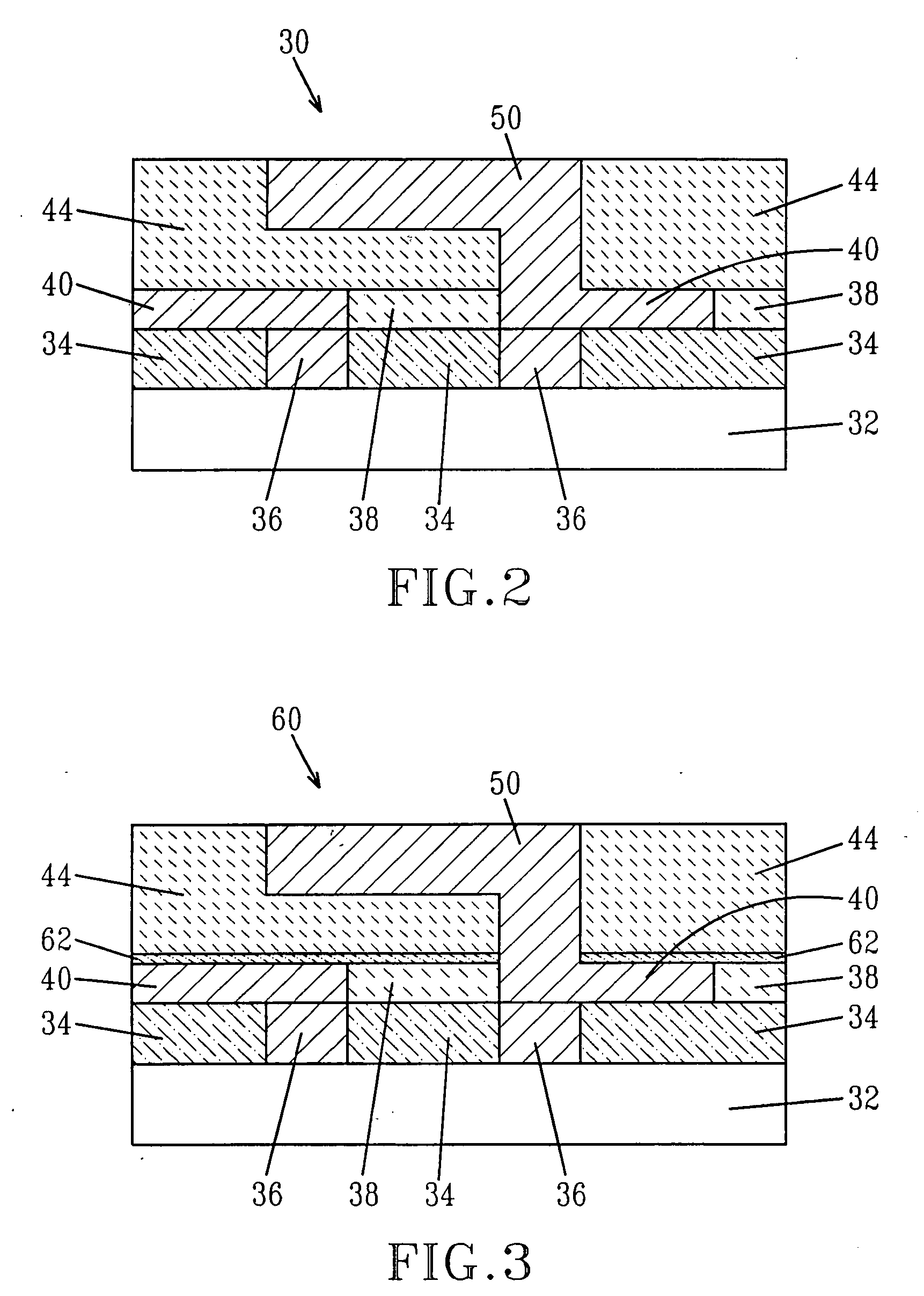

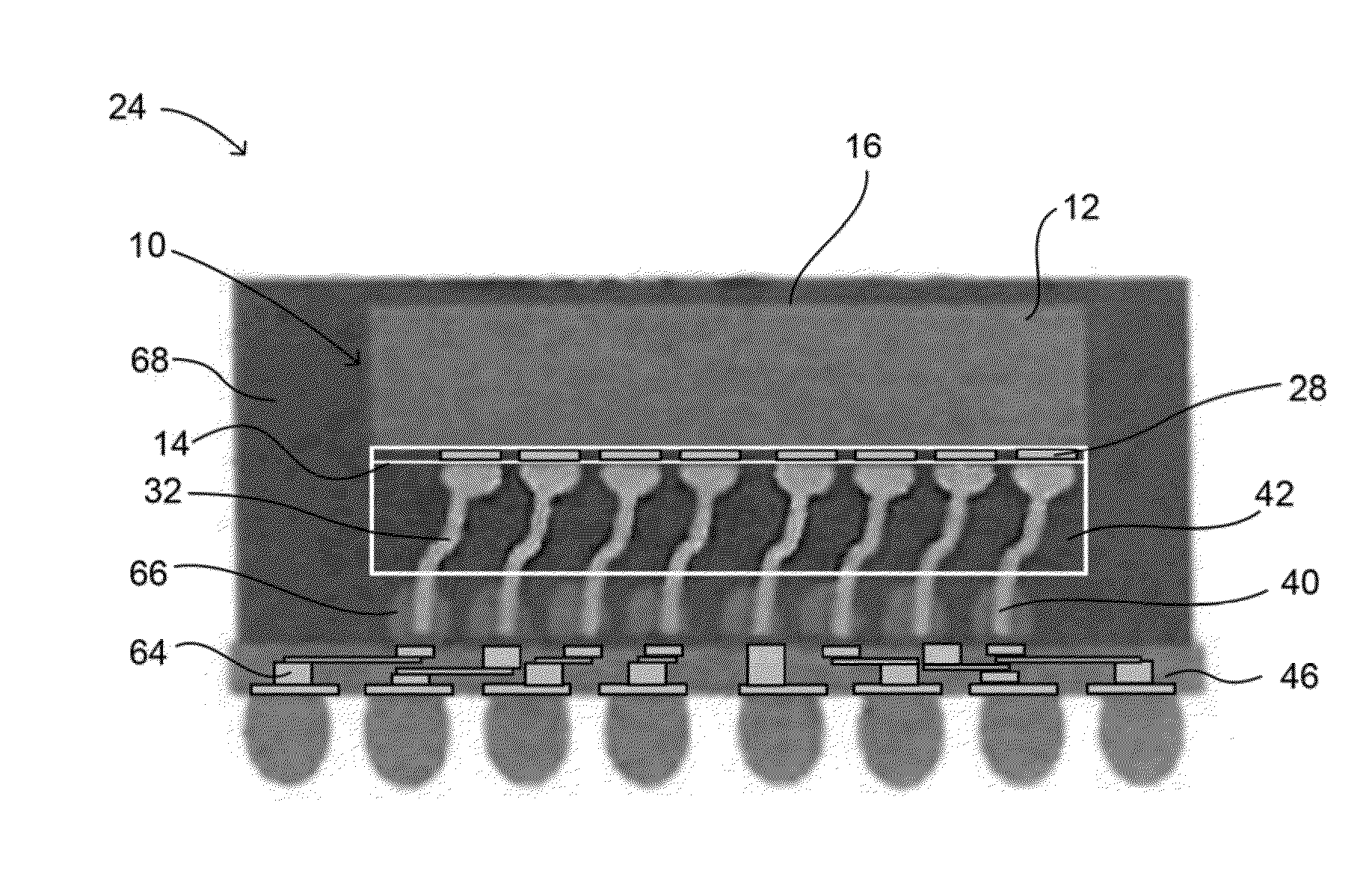

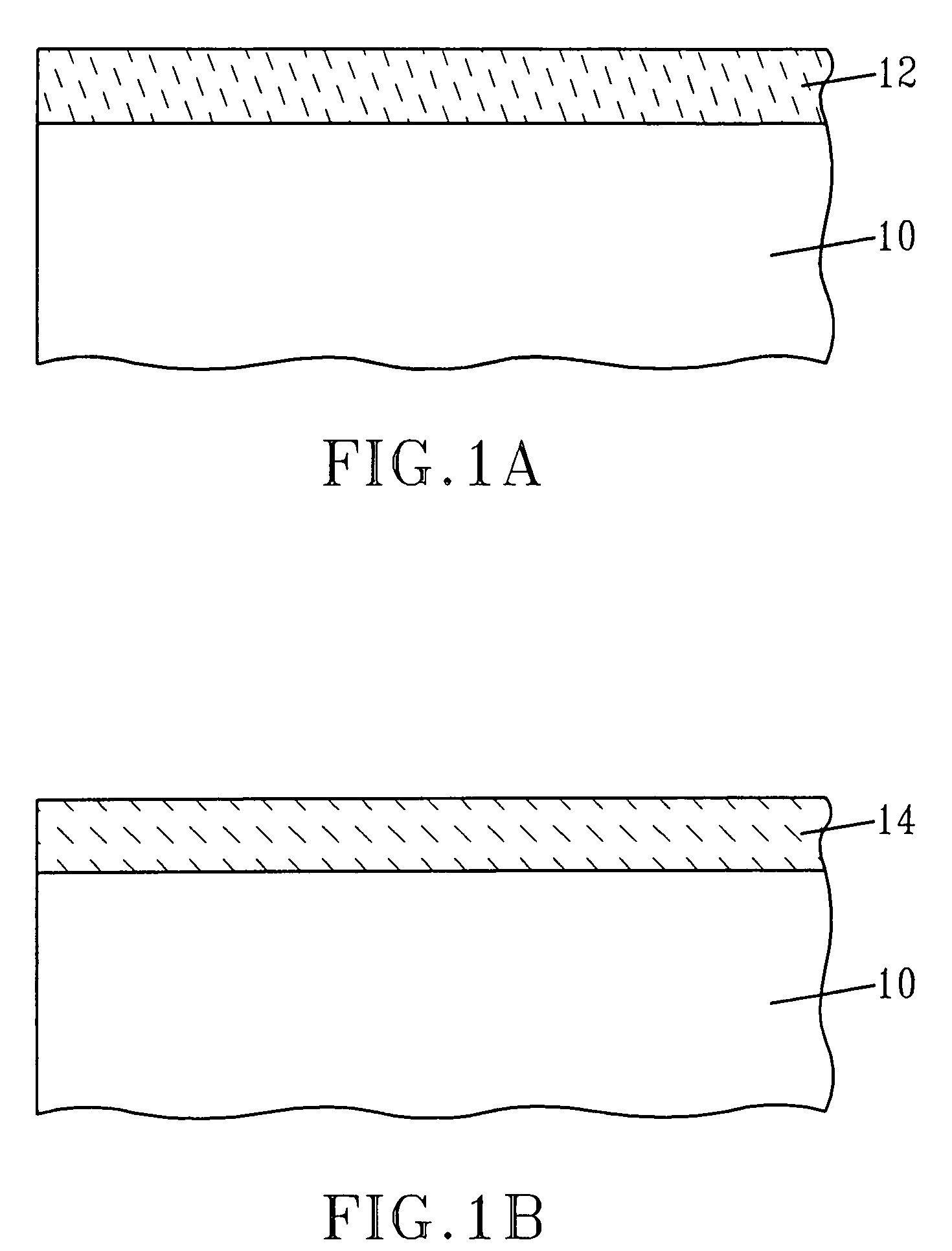

Opto-electronic package structure having silicon-substrate and method of forming the same

InactiveUS20090273005A1Simplify component complexityIncrease heatSolid-state devicesSemiconductor/solid-state device manufacturingElectronic structureOpto electronic

Owner:TOUCH MICRO SYST TECH

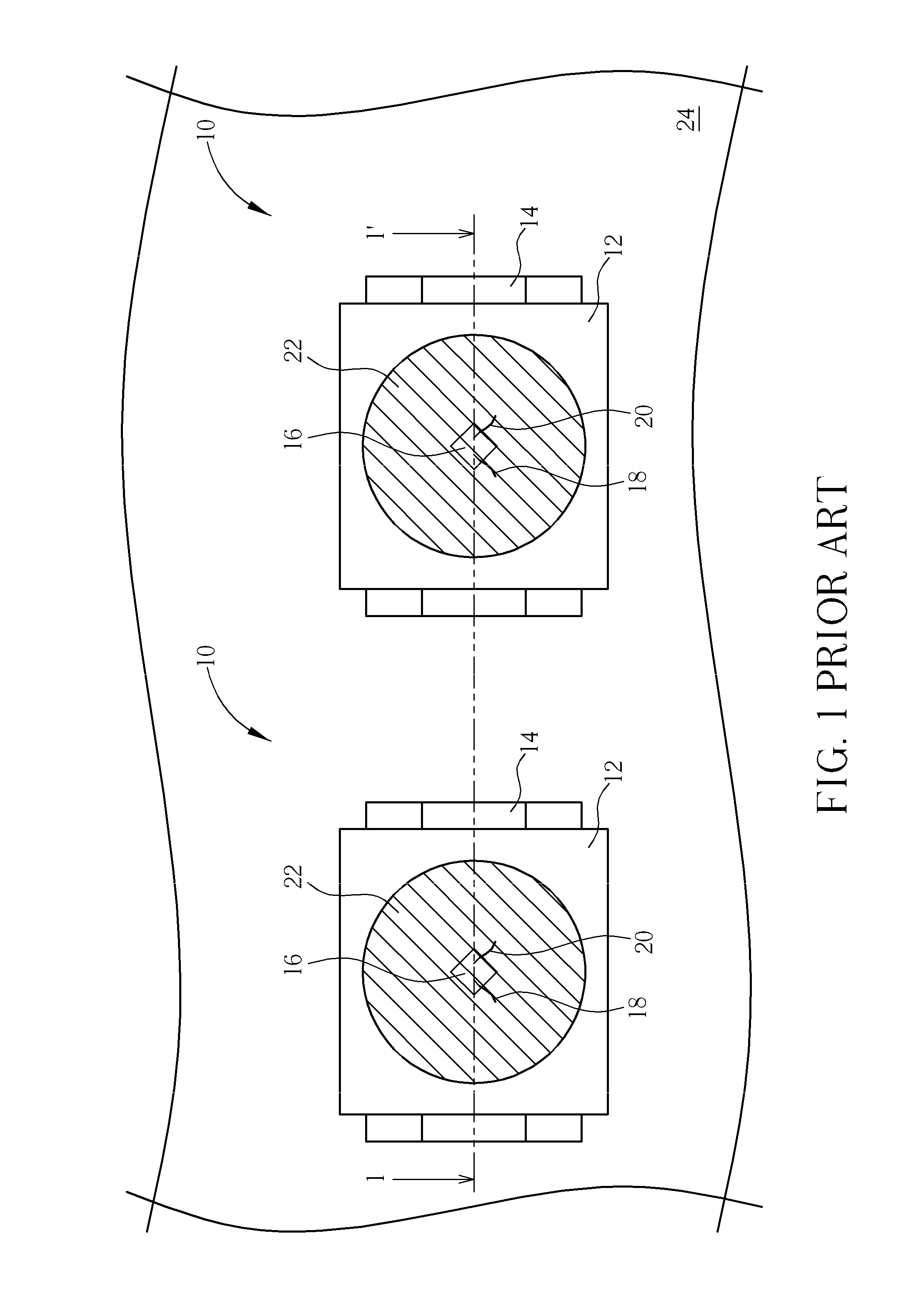

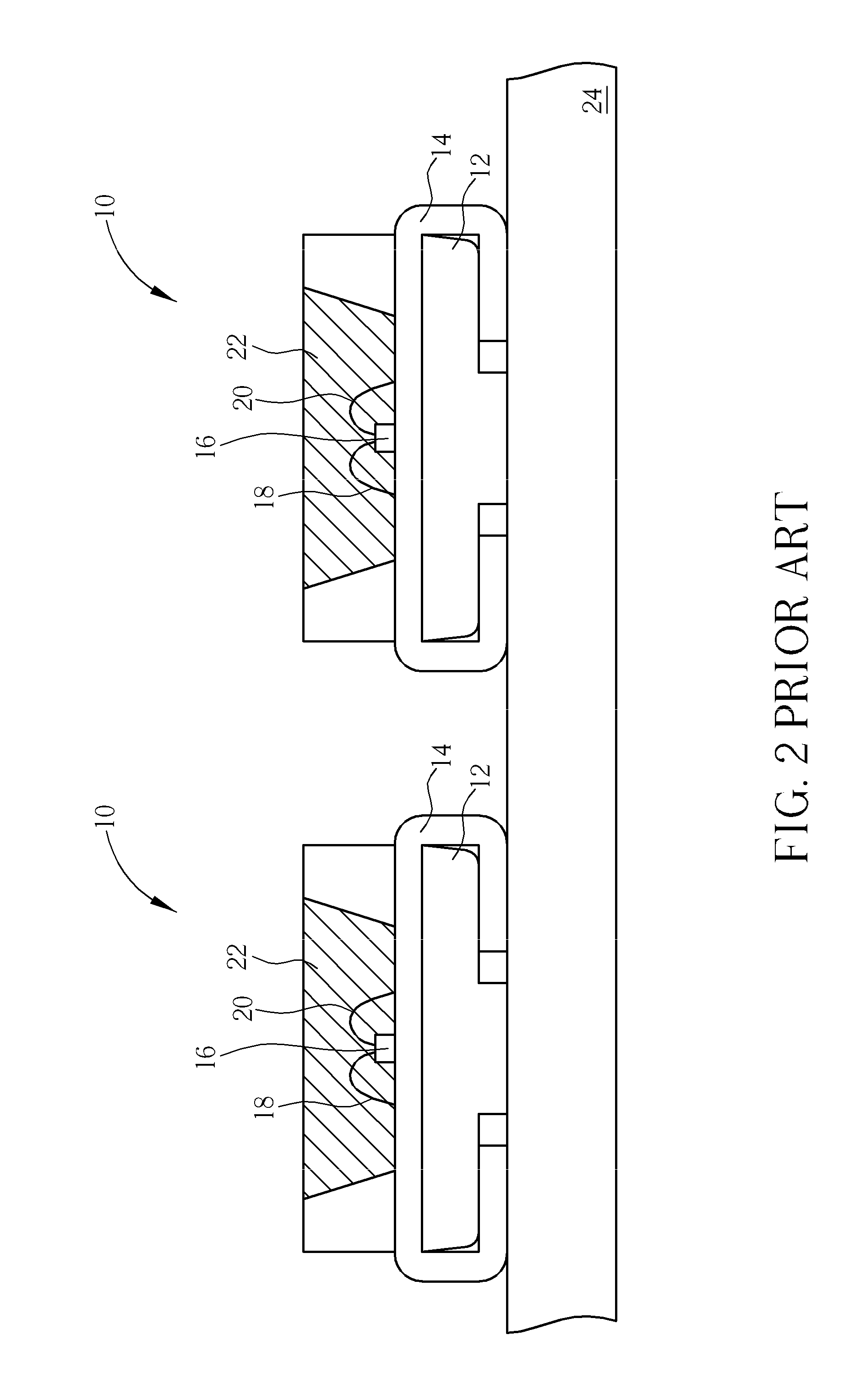

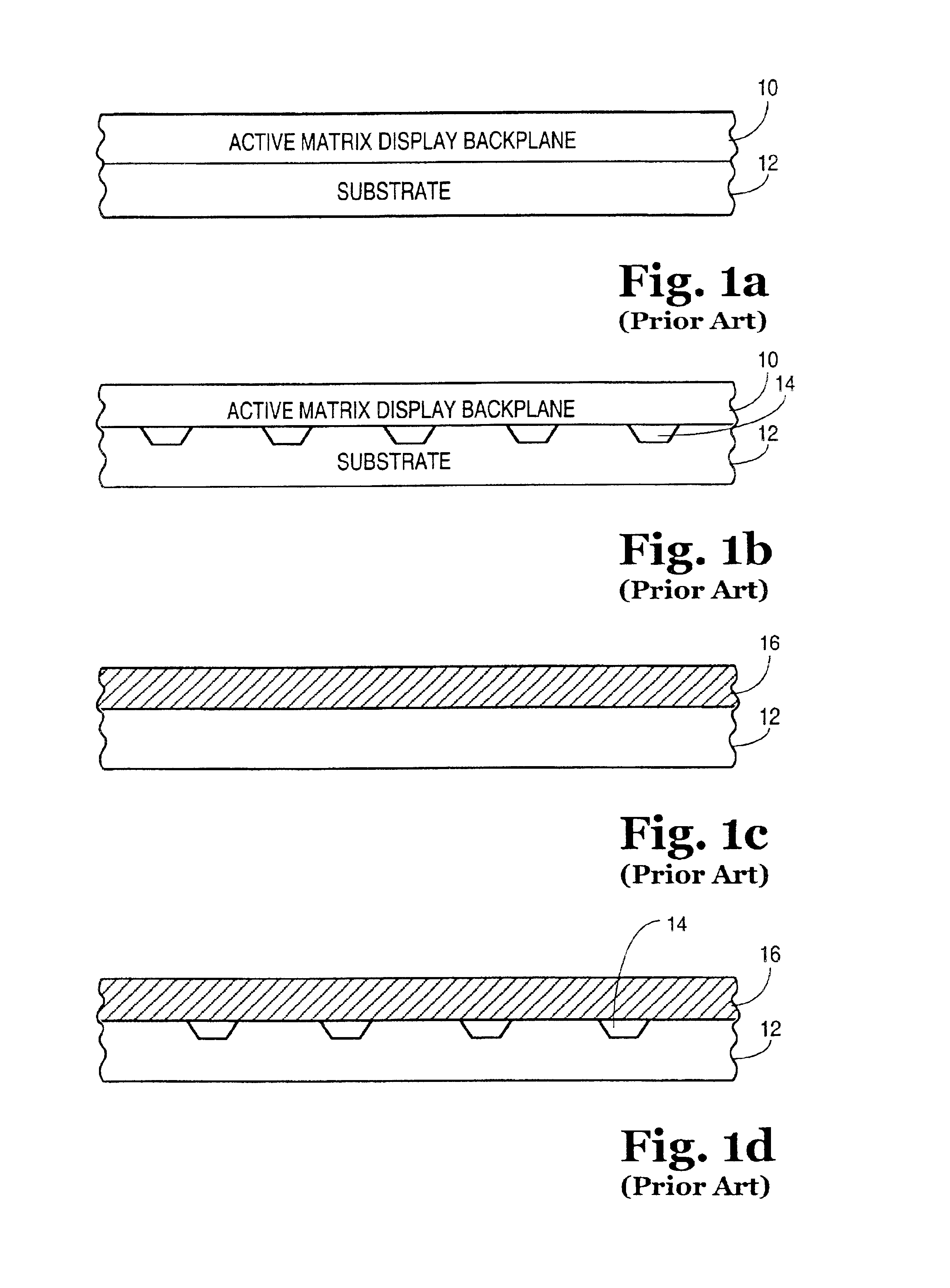

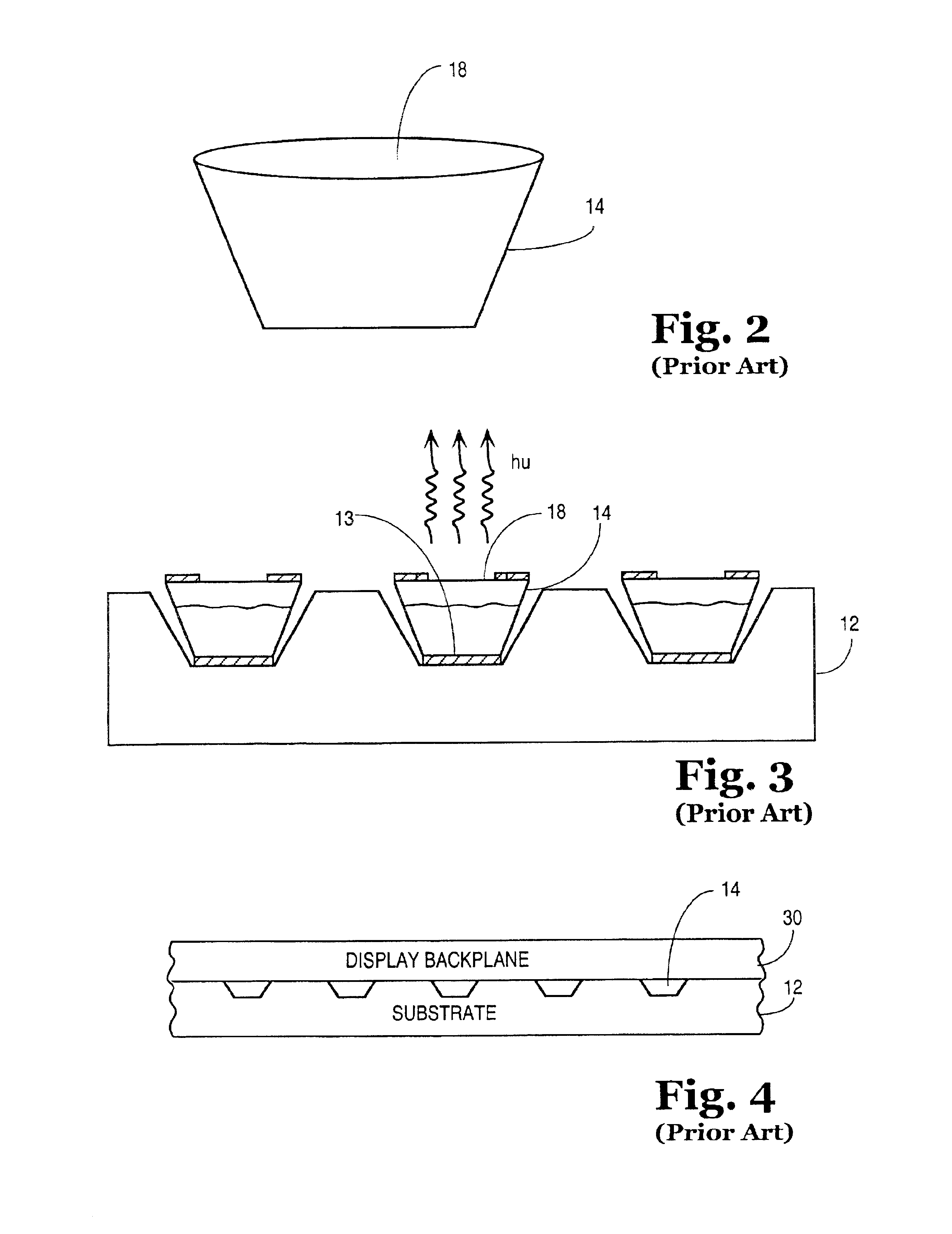

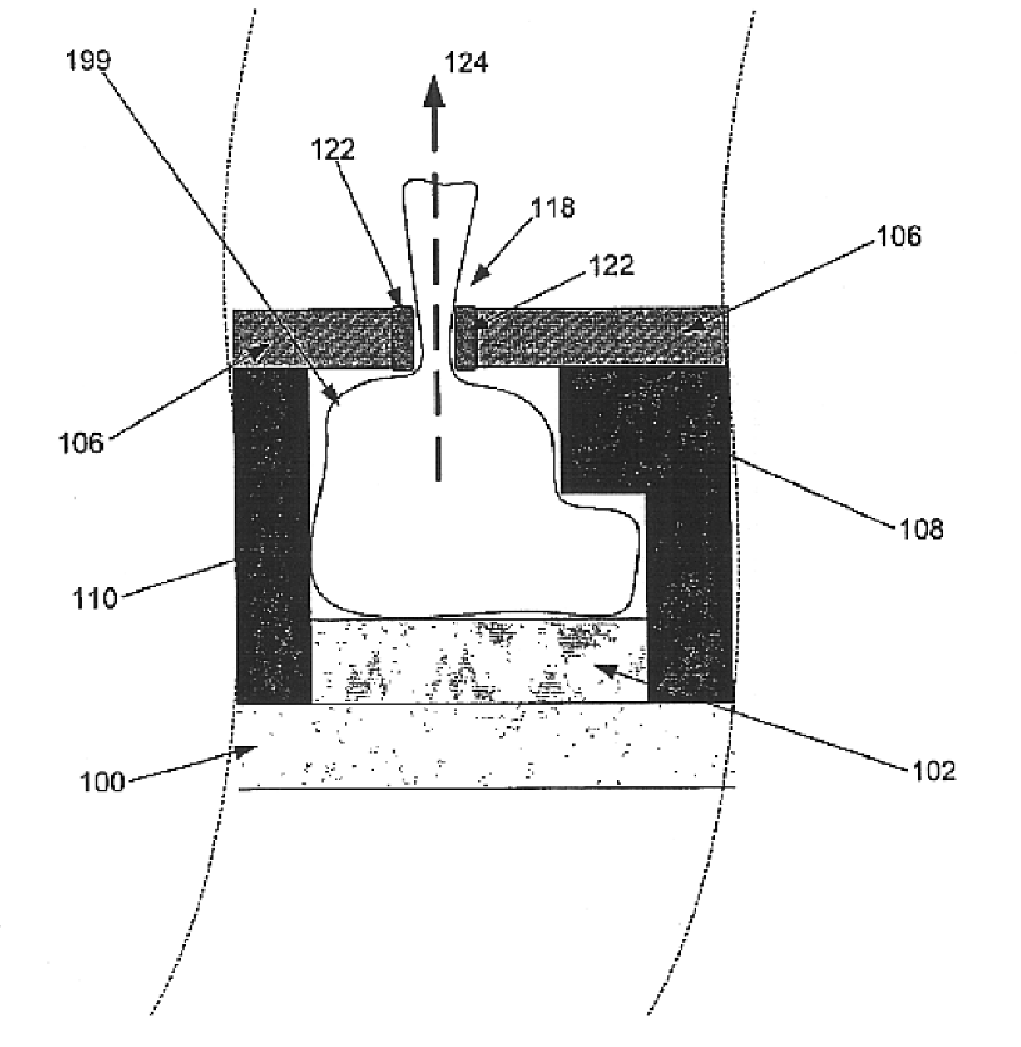

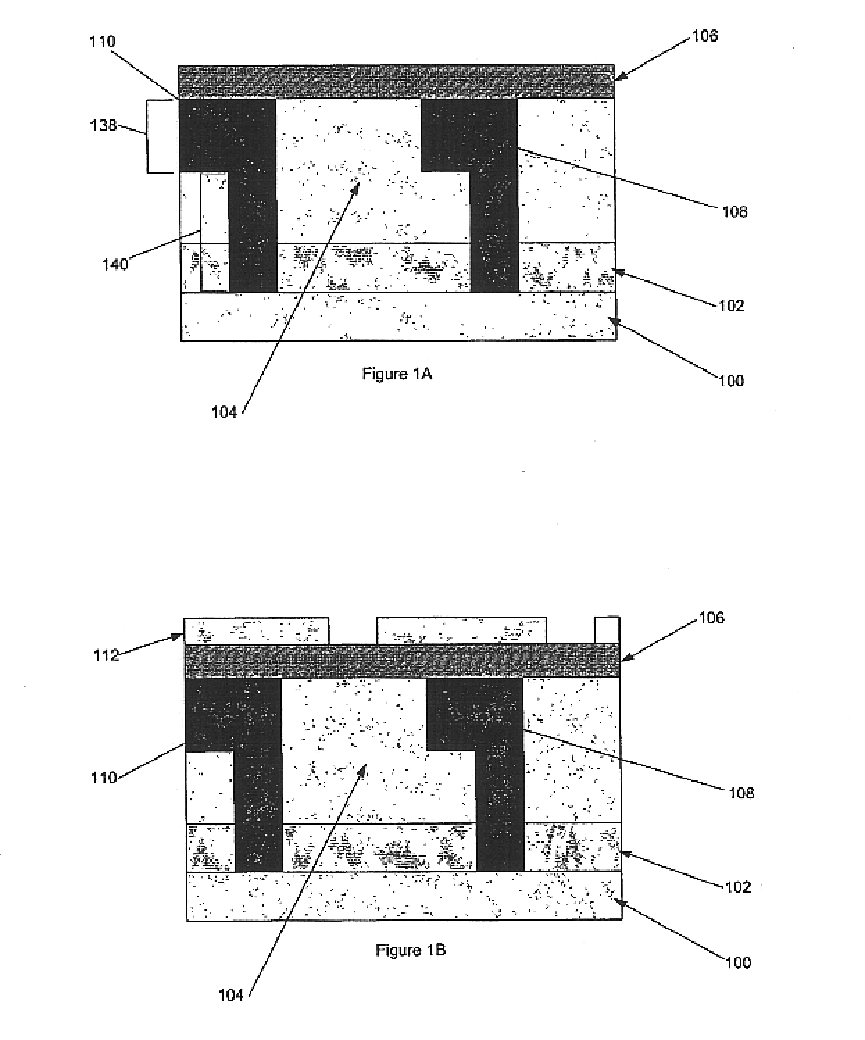

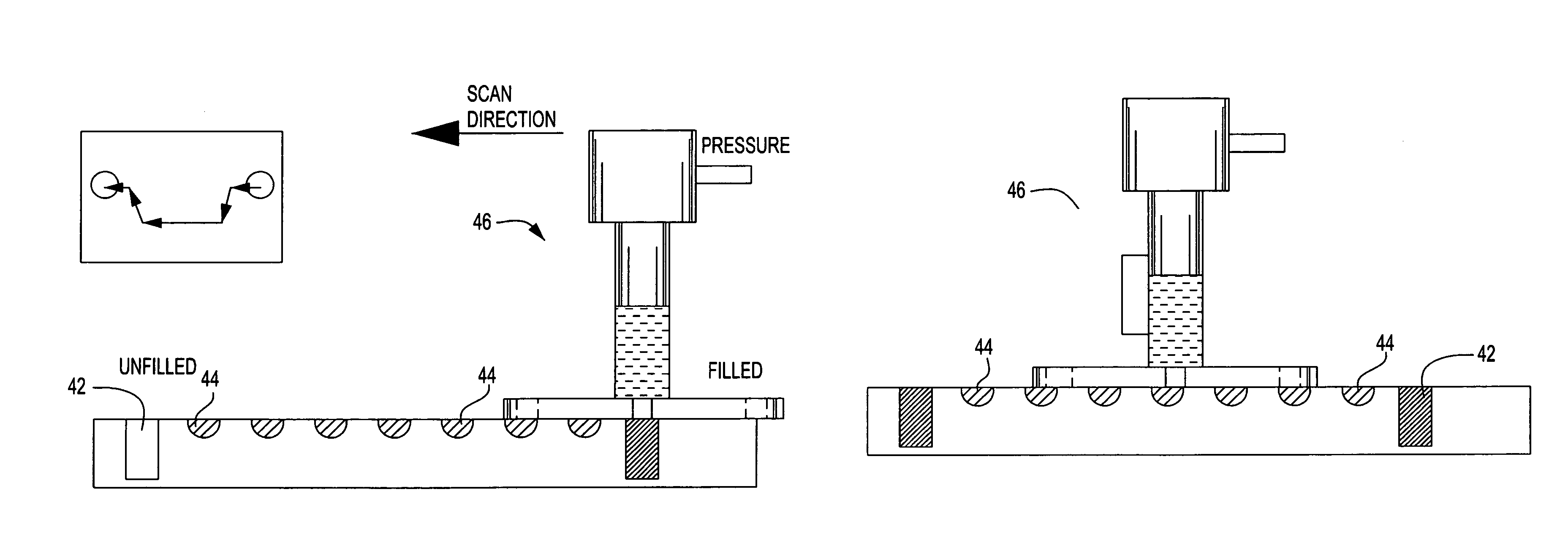

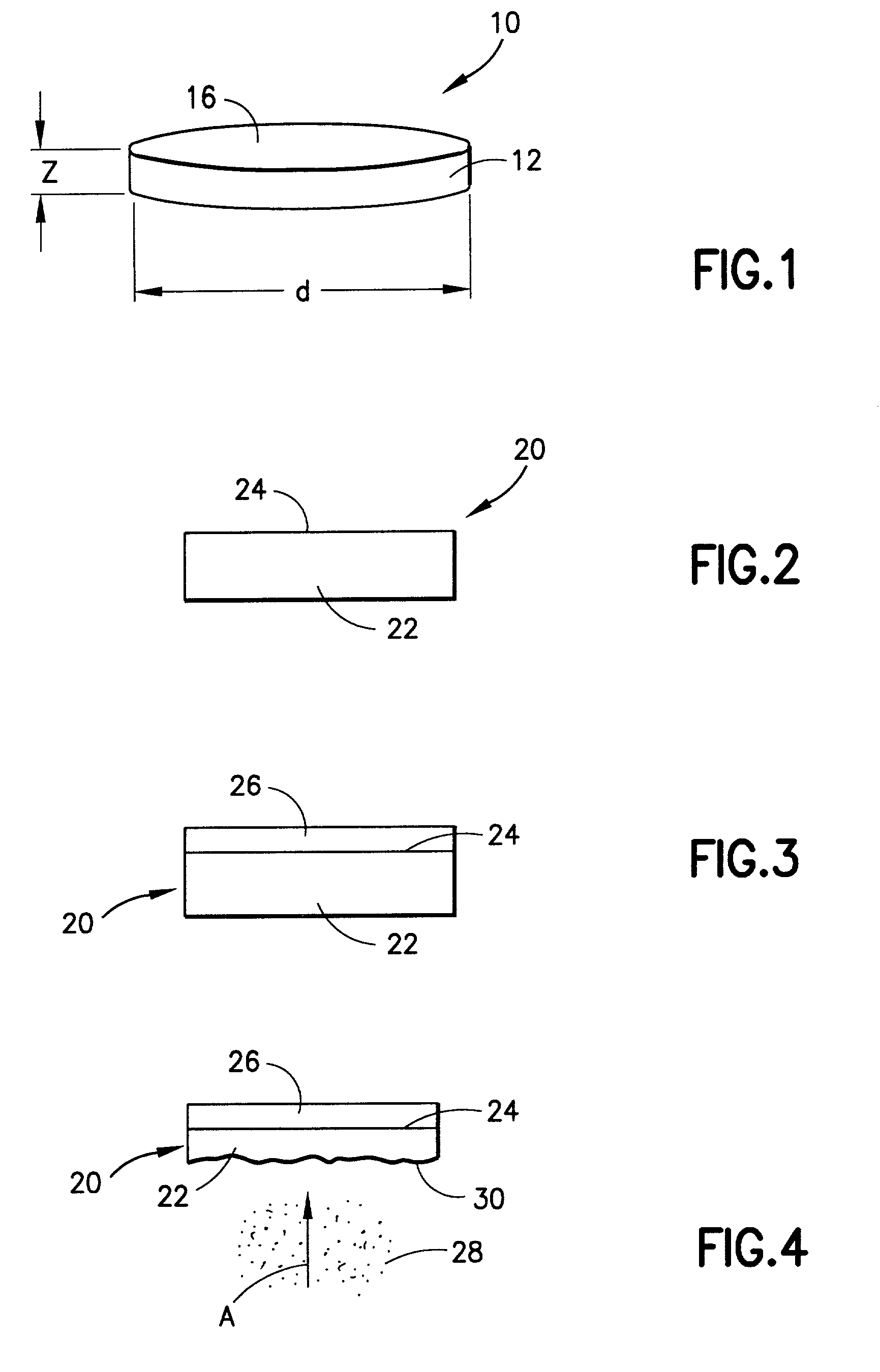

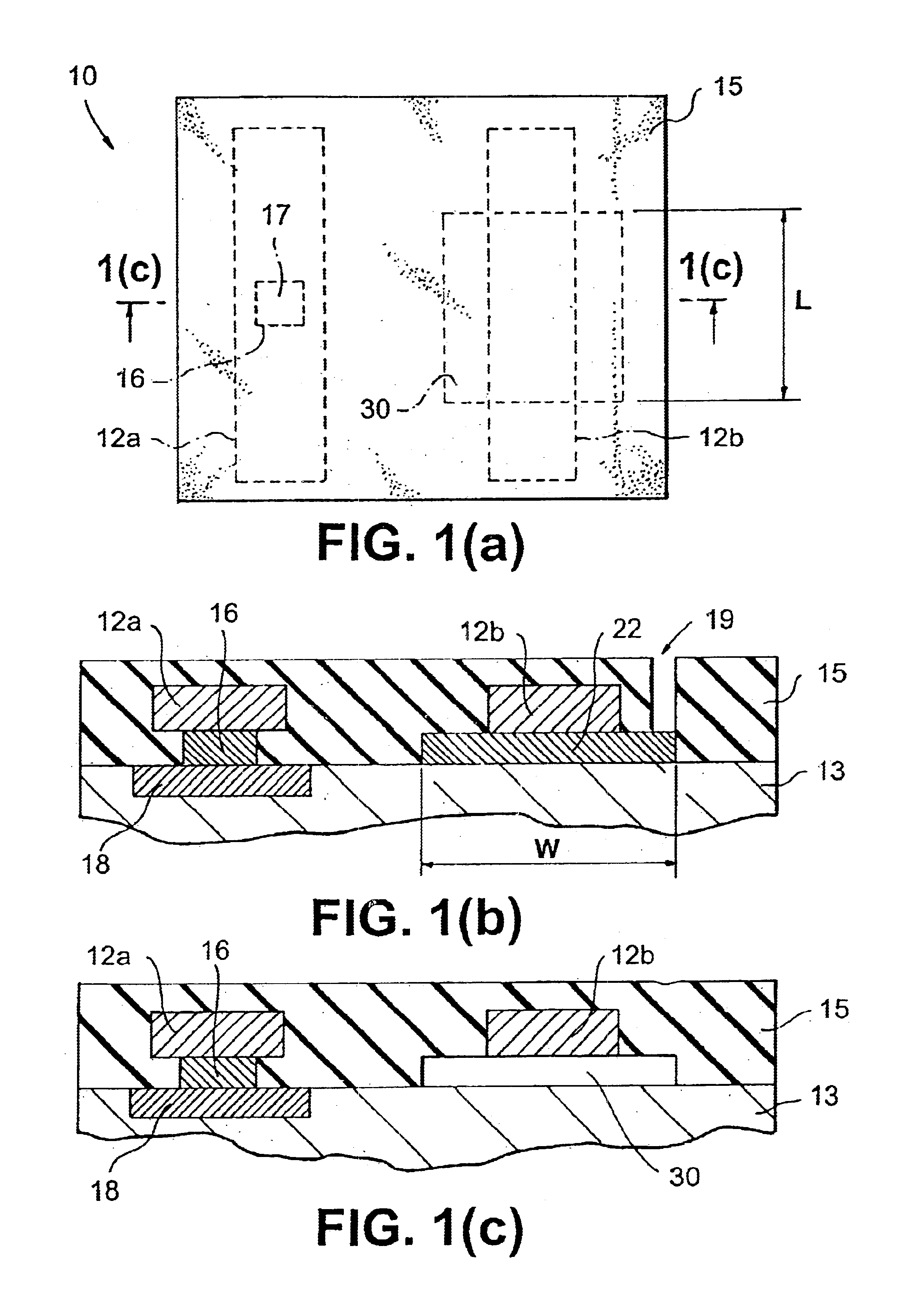

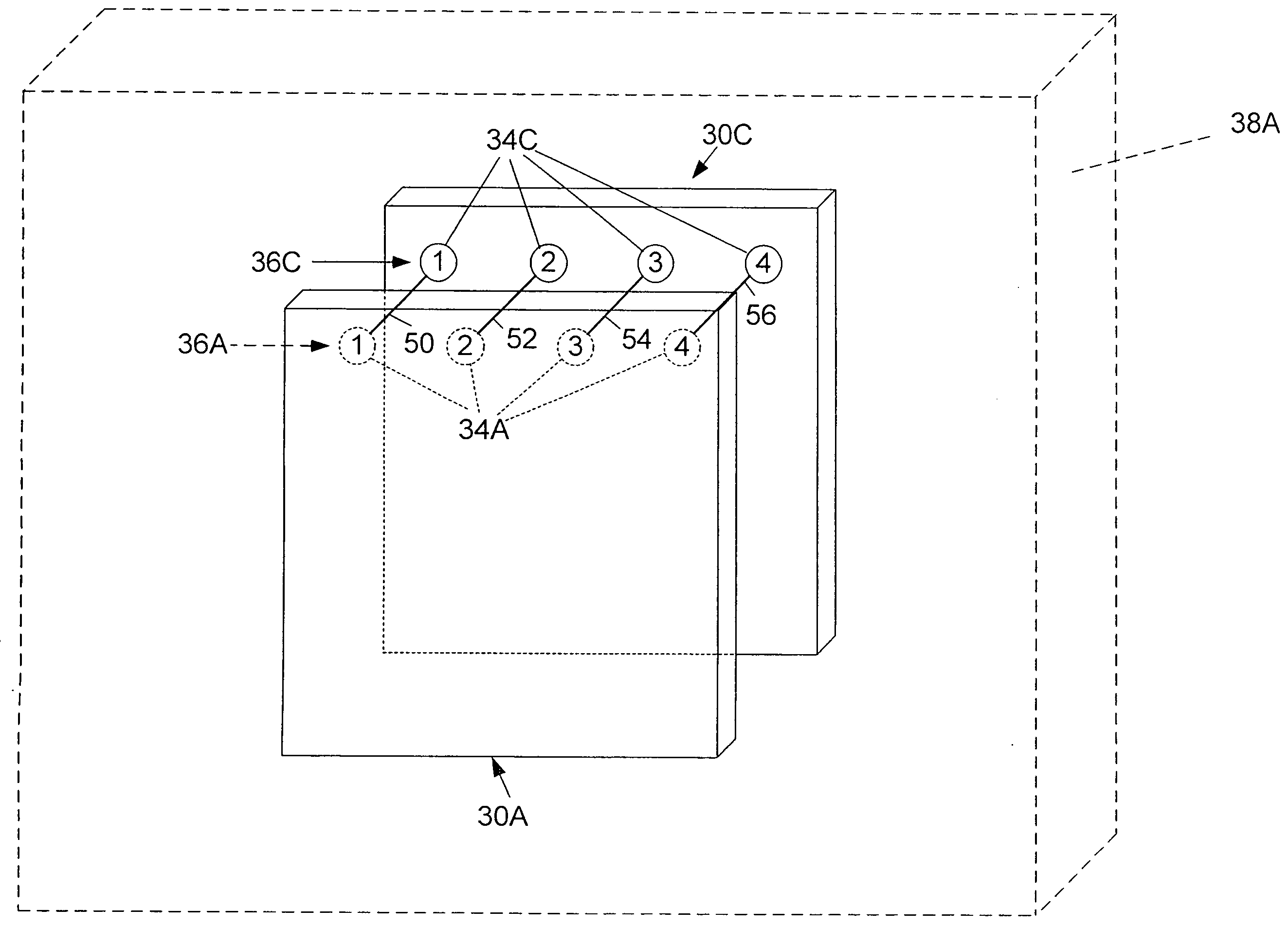

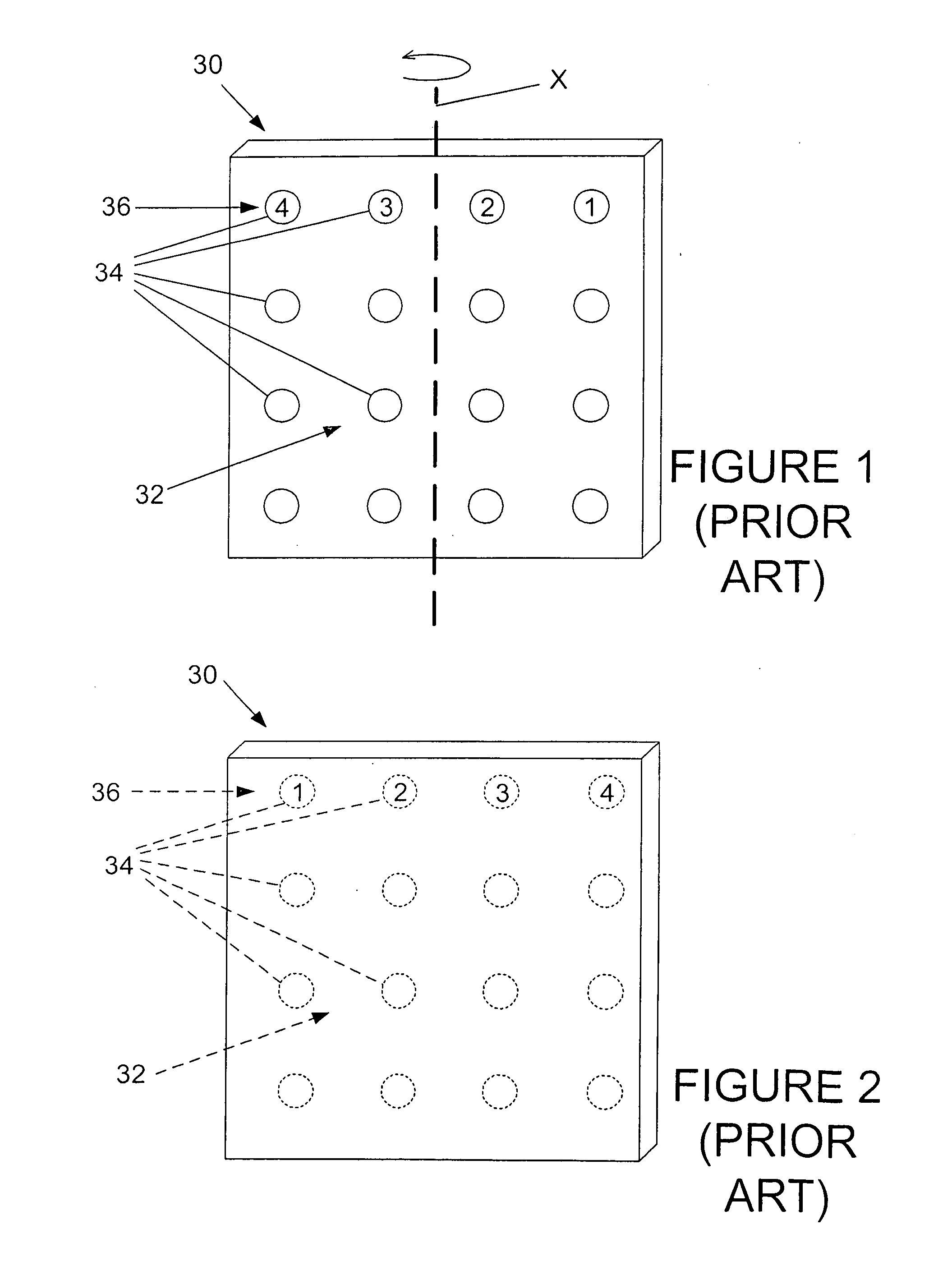

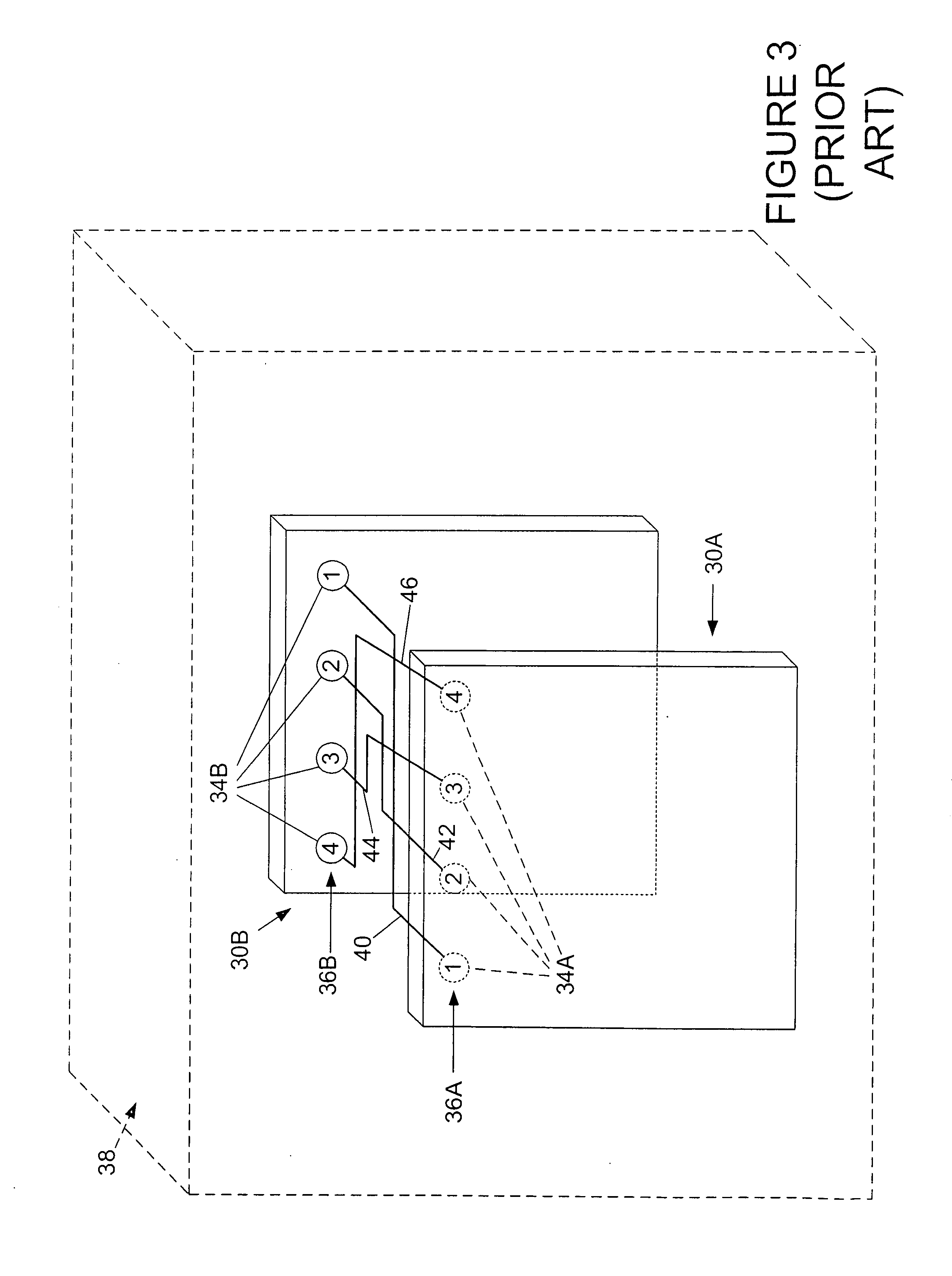

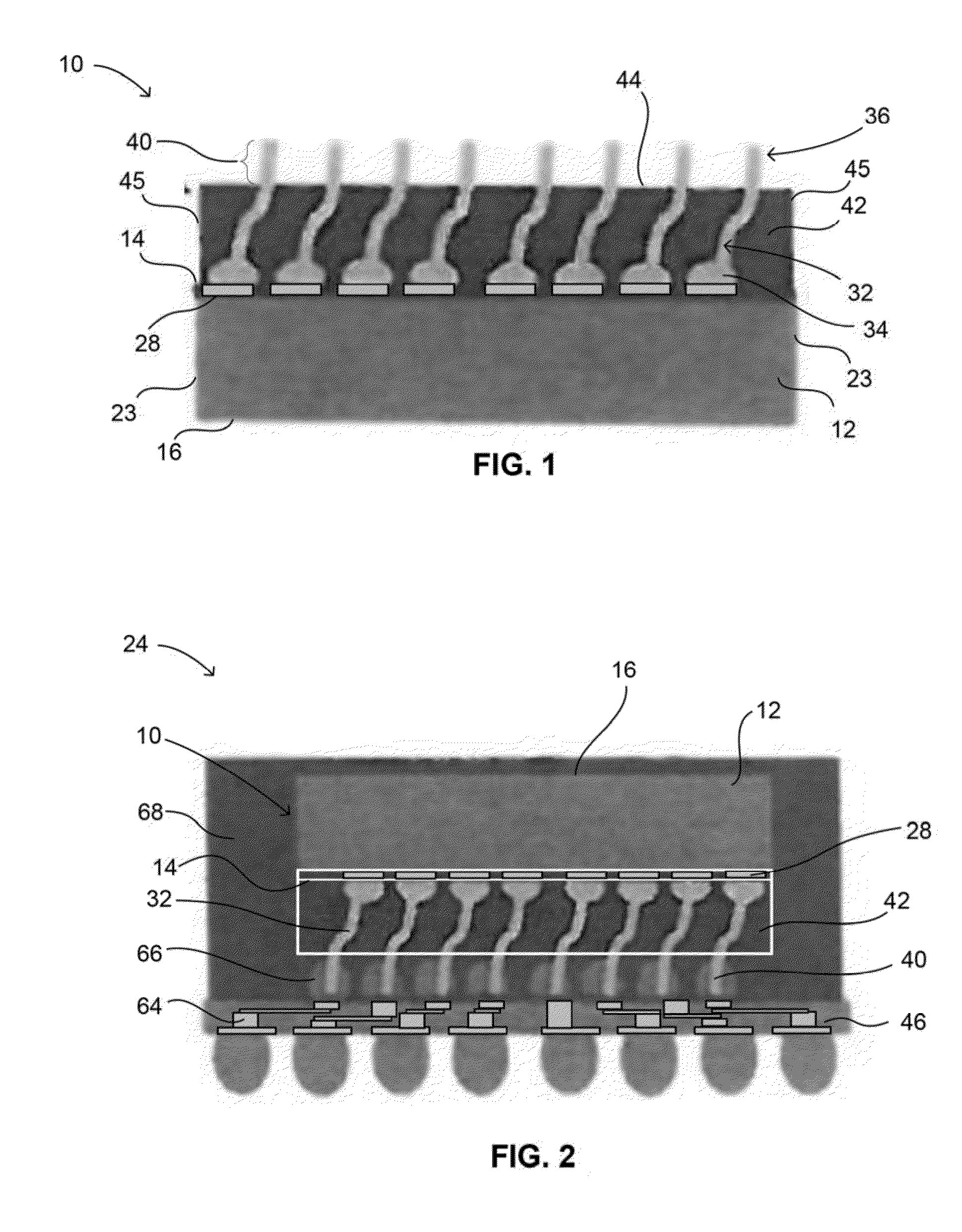

Apparatuses and methods for forming electronic assemblies

InactiveUS6863219B1Minimizing chanceInformation retrieval from punched cardsSolid-state devicesElectronic structureDisplay device

Apparatuses and methods for forming displays are claimed. One embodiment of the invention includes a contact smart card wherein fluidic self assembly is used to build the microelectronic structures on the display such that a contact smart data is transmitted unidirectionally. A contact smart card is inserted directly into a device that transfers data to a display coupled to the smart card. Another embodiment of the invention relates to a contactless smart card in which fluidic self assembly is also used here to build the display. Data is transmitted to an antenna that is embedded in the contactless card in which a plurality of blocks were deposited thereon.

Owner:RUIZHANG TECH LTD CO

Air gap interconnect method

InactiveUS6861332B2Semiconductor/solid-state device detailsSolid-state devicesElectronic structureEngineering

A low-k dielectric sacrificial material is formed within a microelectronic structure covered with a layer defining an exhaust vent. At an appropriate time, the underlying sacrificial material is decomposed and exhausted away through the exhaust vent. Residue from the exhausted sacrificial material accumulates at the vent location during exhaustion until the vent is substantially occluded. As a result, an air gap is created having desirable characteristics as a dielectric.

Owner:INTEL CORP

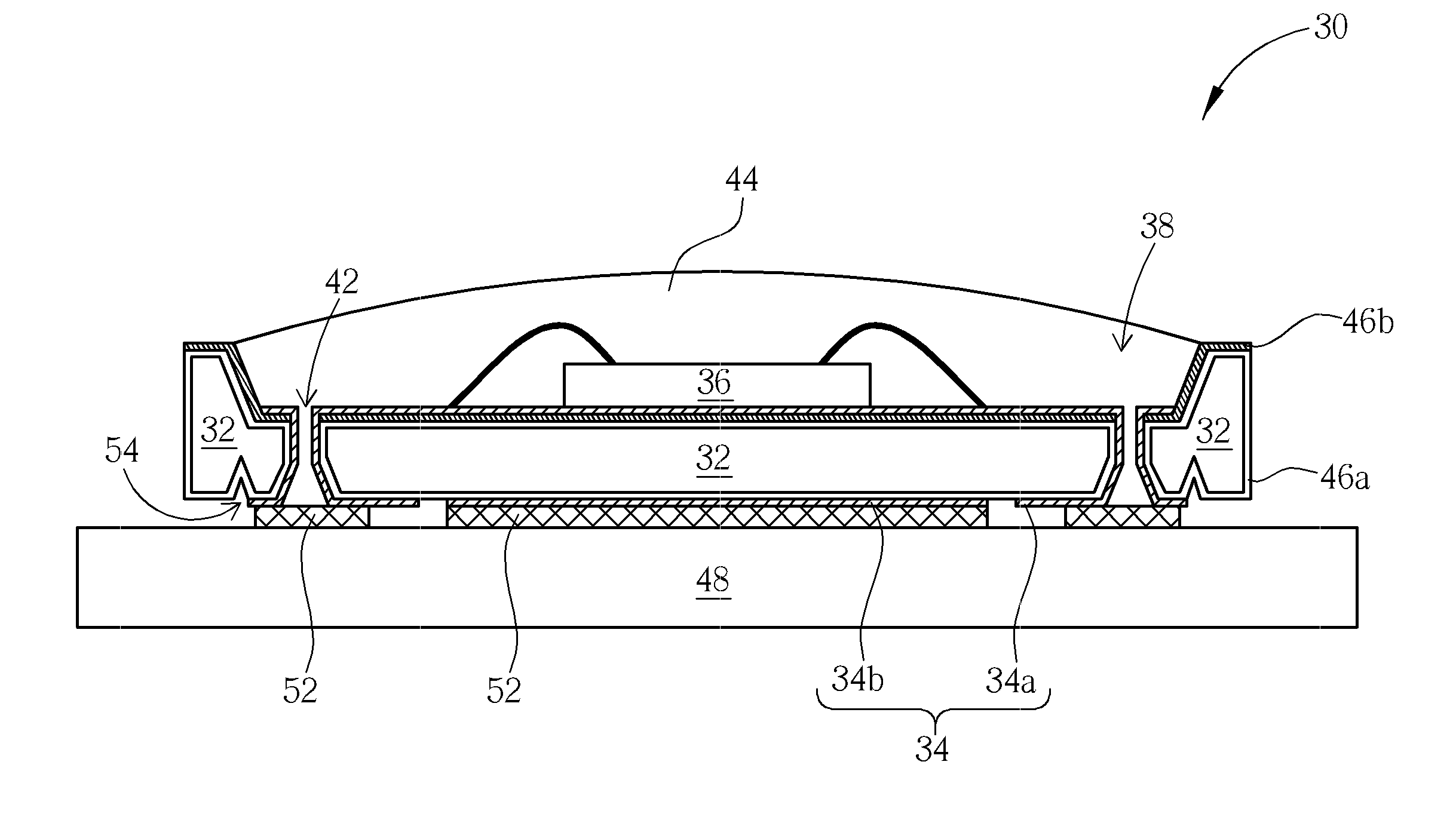

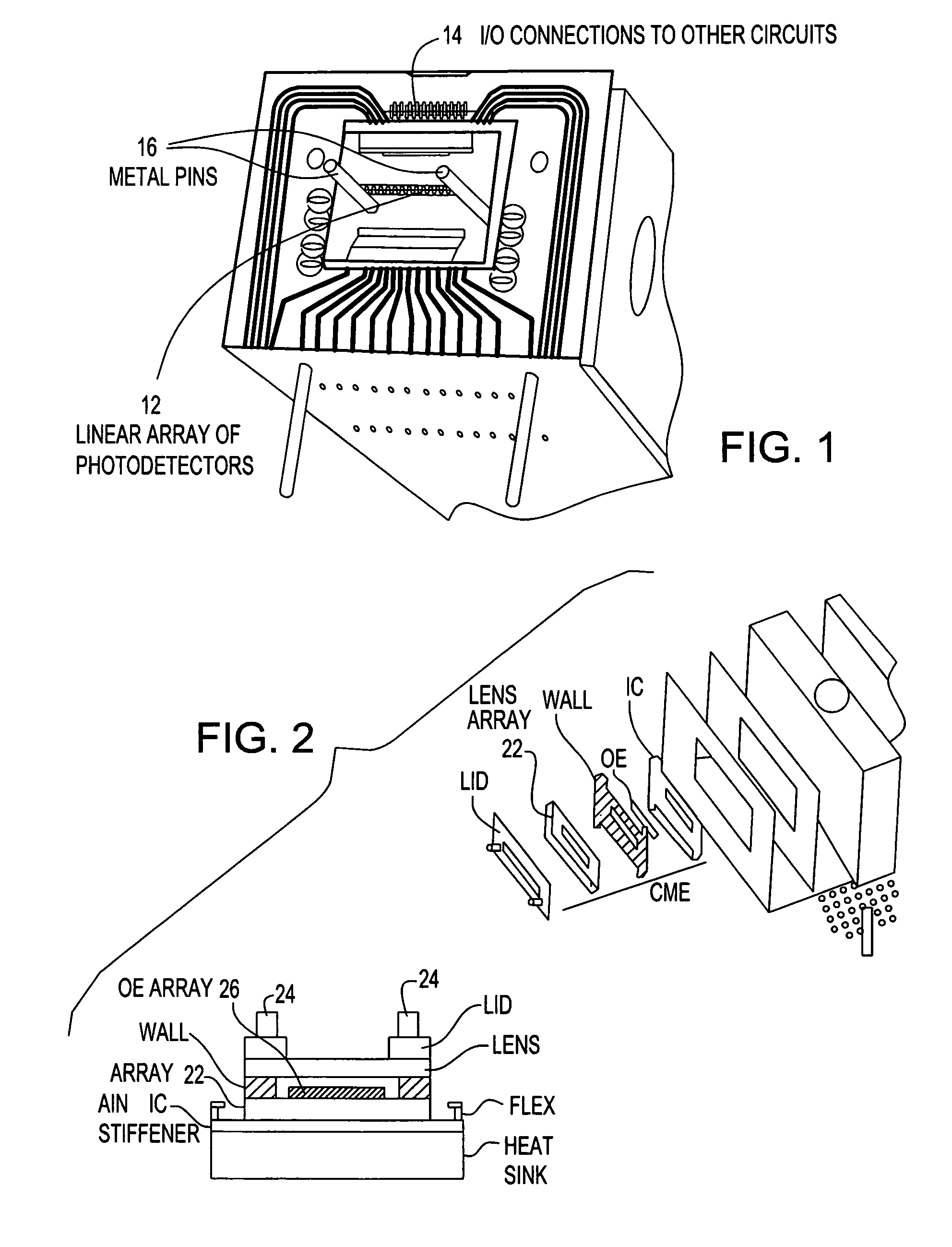

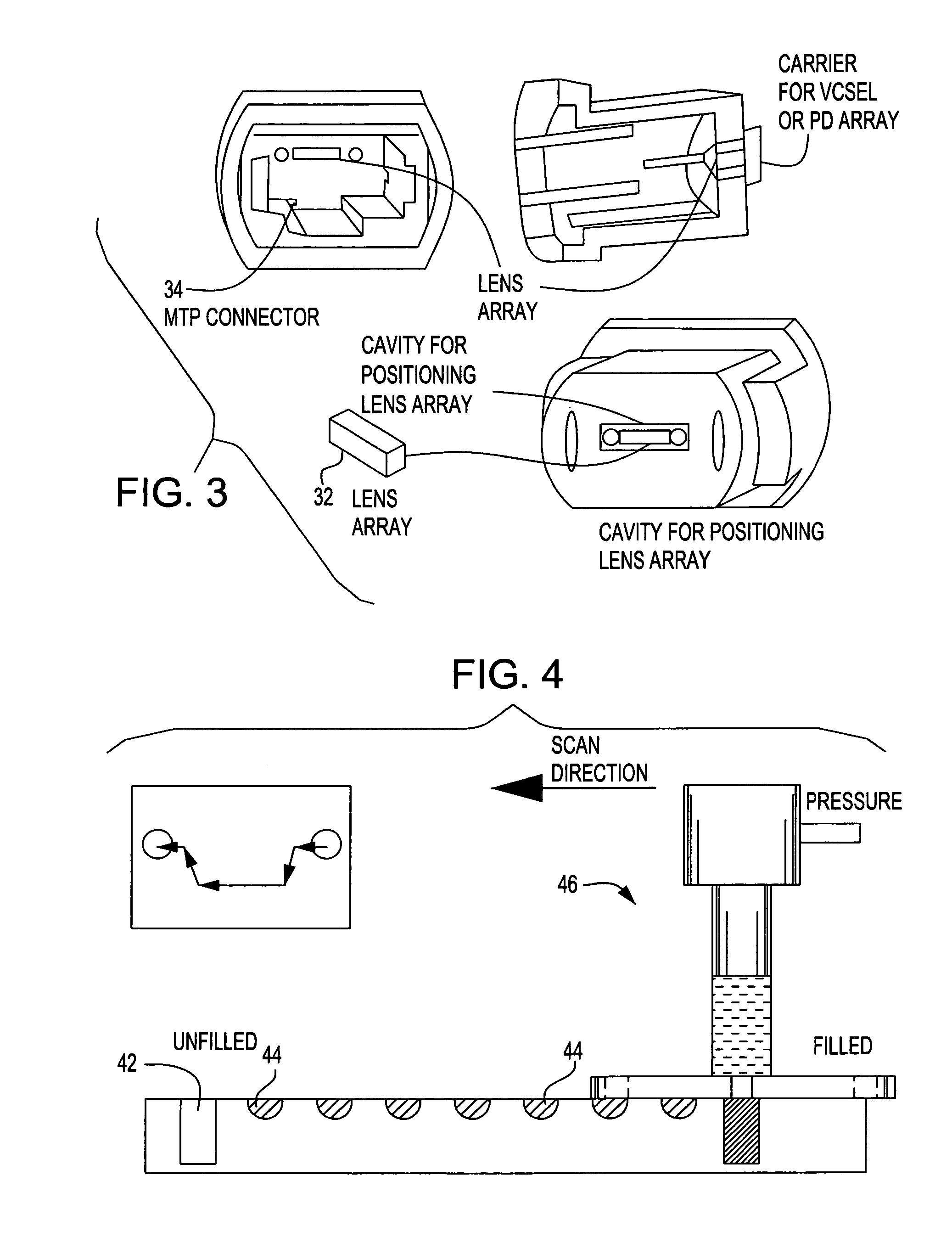

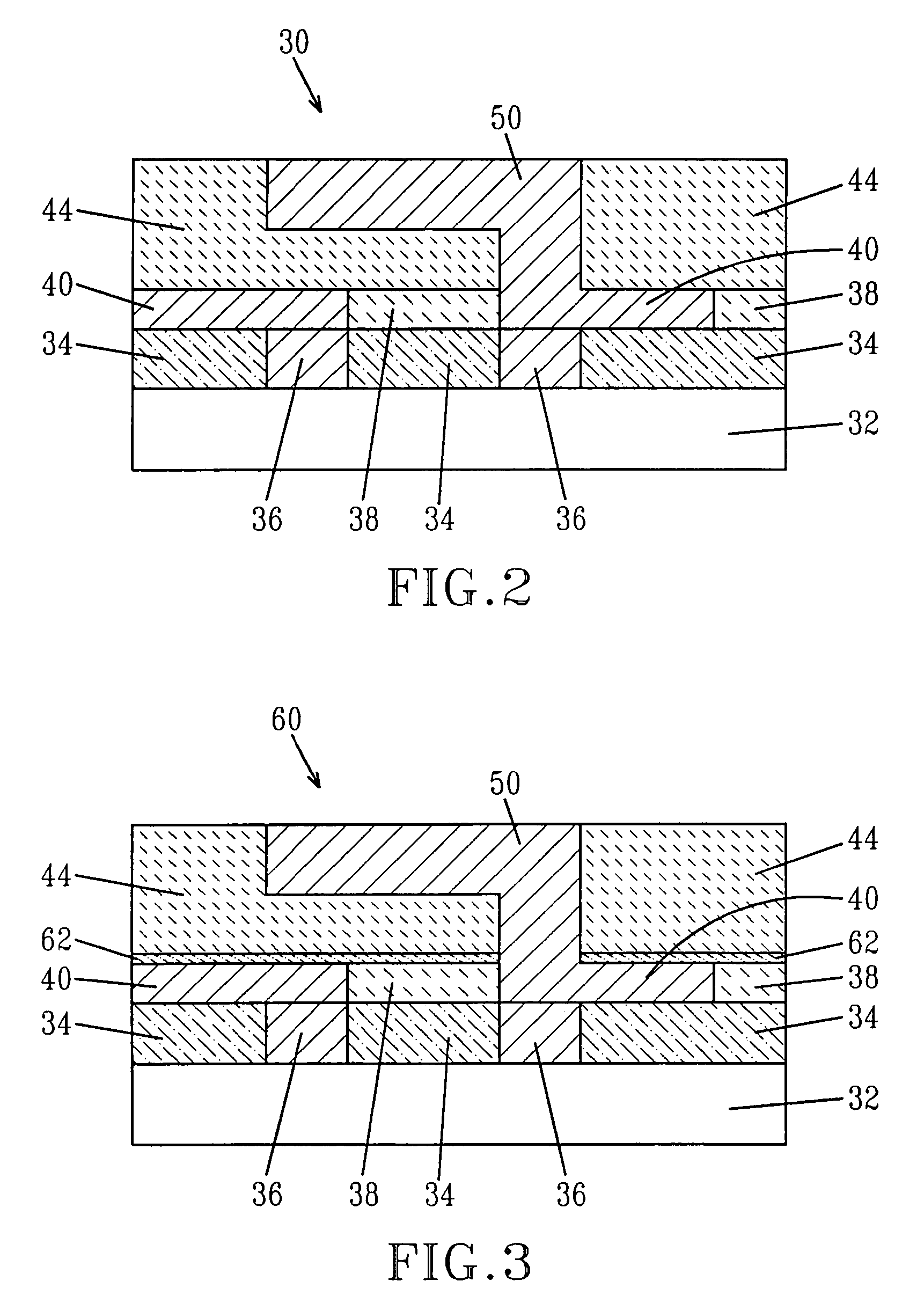

Hybrid optical/electronic structures fabricated by a common molding process

InactiveUS7391572B2Improve thermal performanceEasy alignmentOptical articlesGlass shaping apparatusElectricityElectronic structure

Owner:INT BUSINESS MASCH CORP

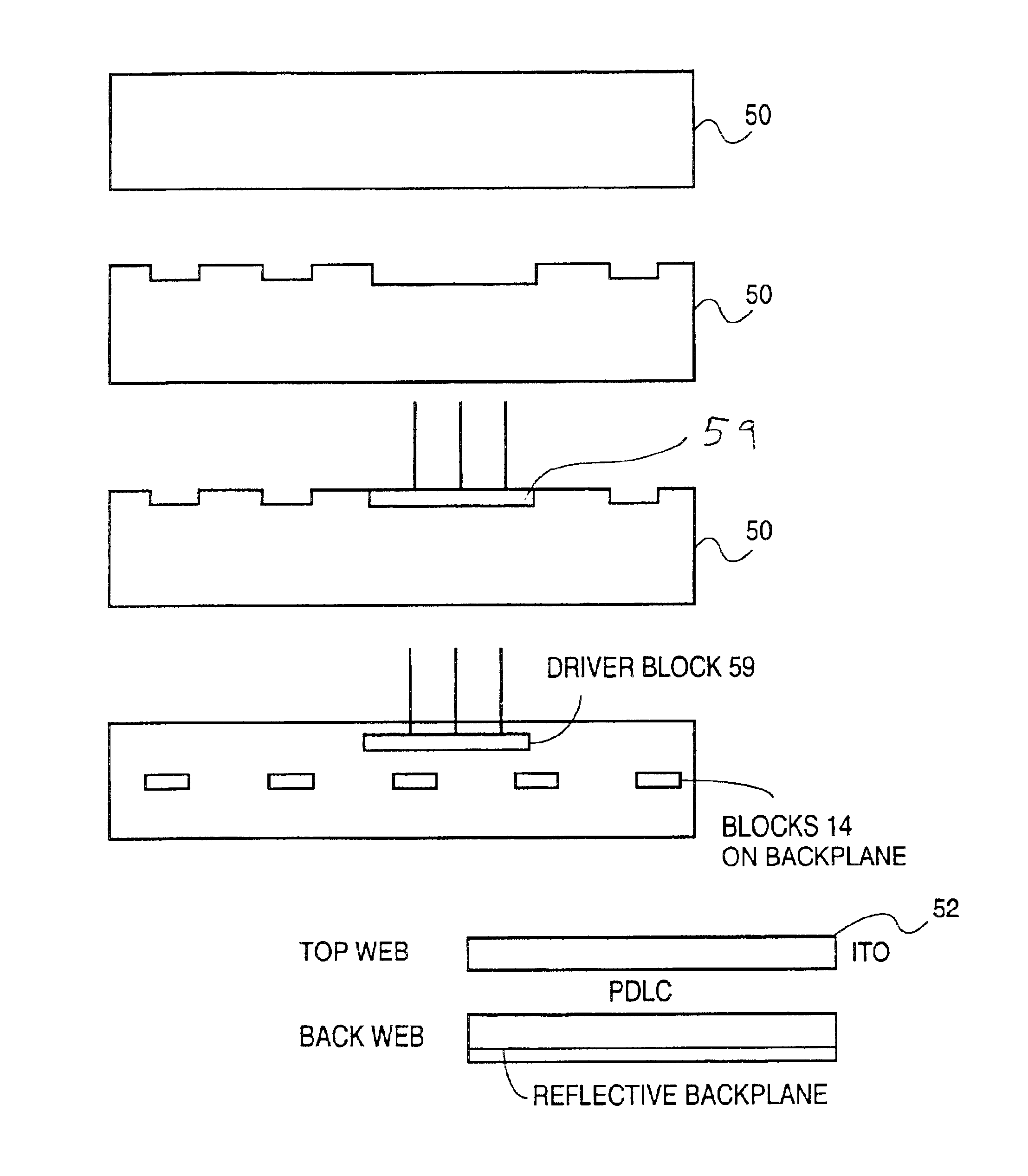

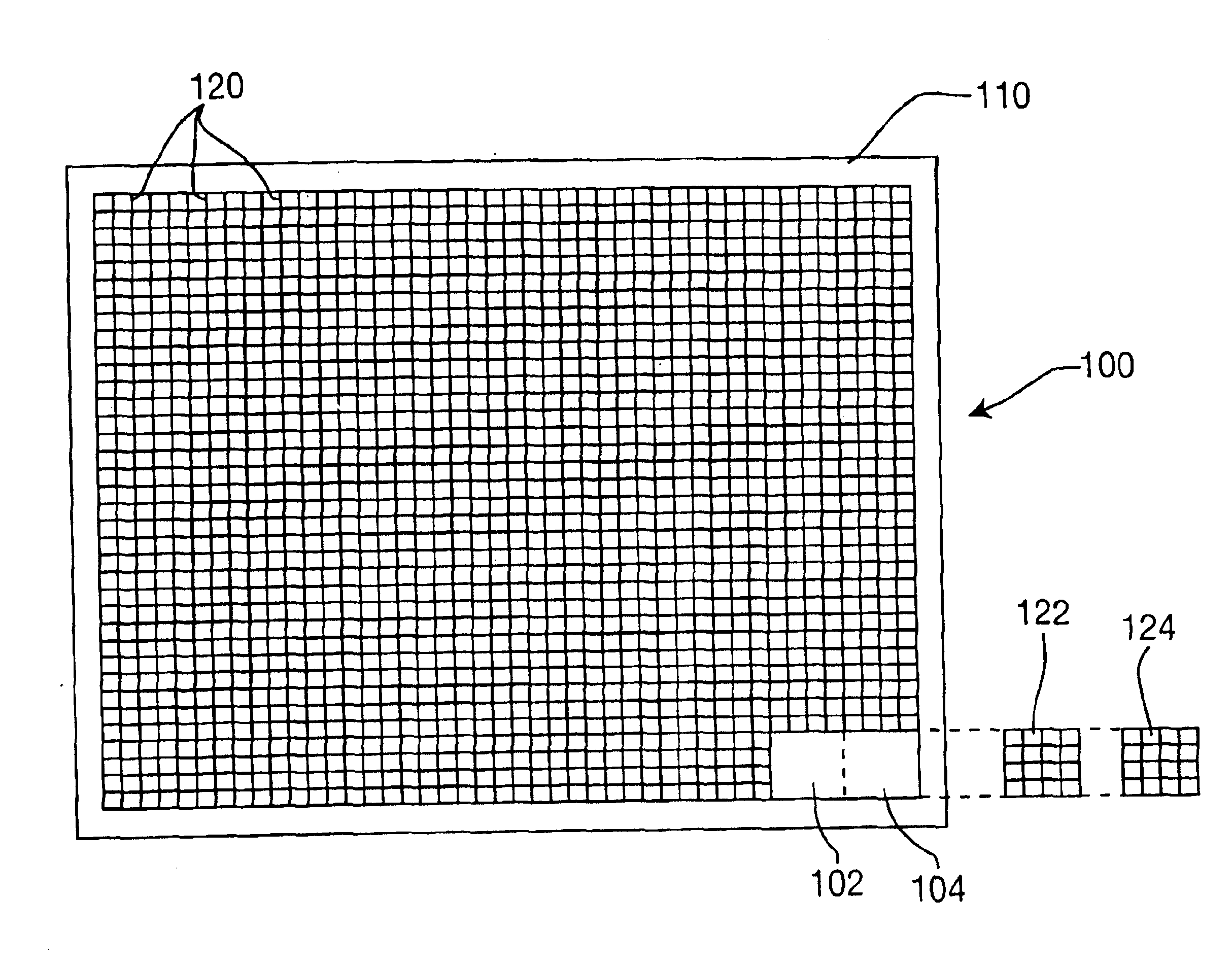

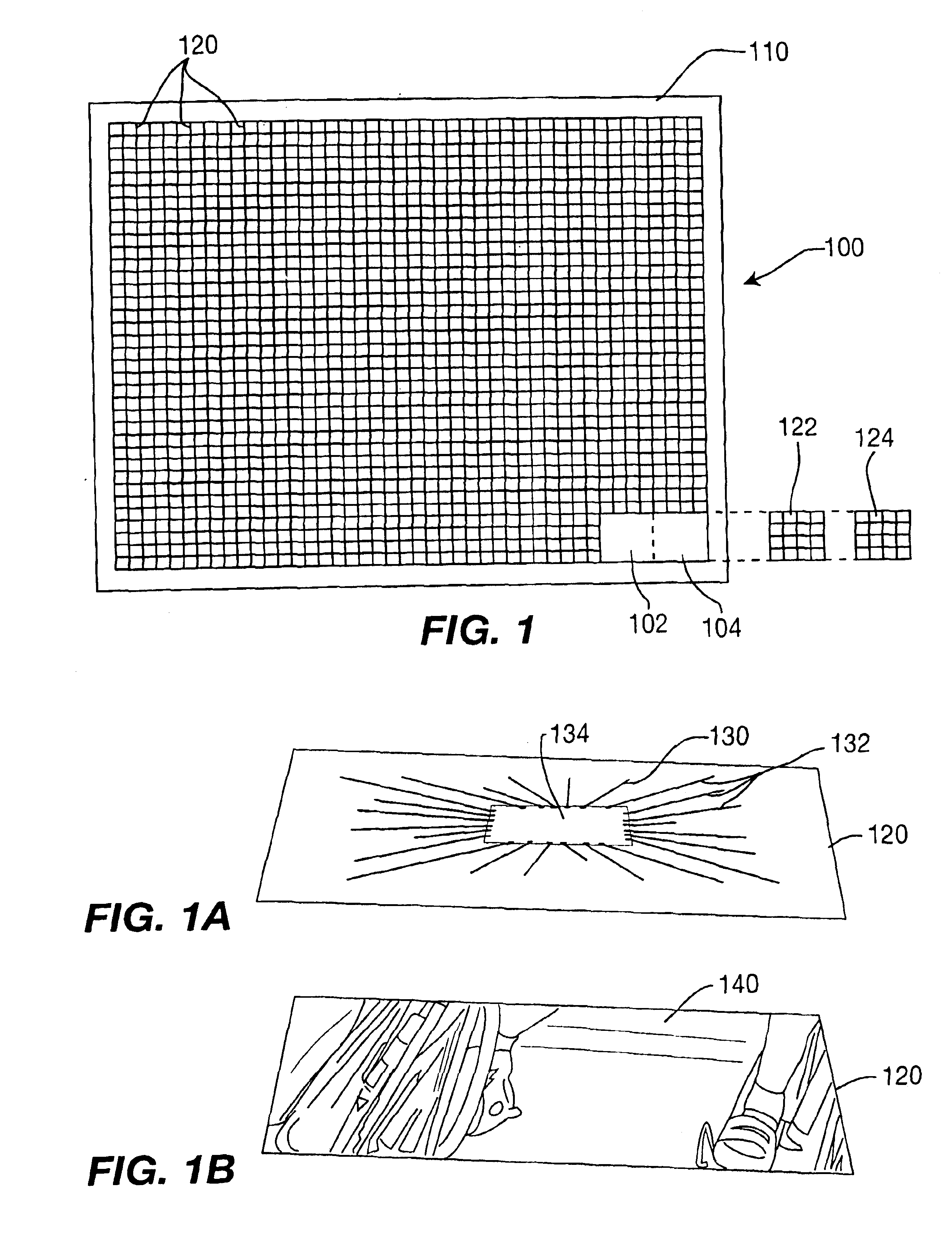

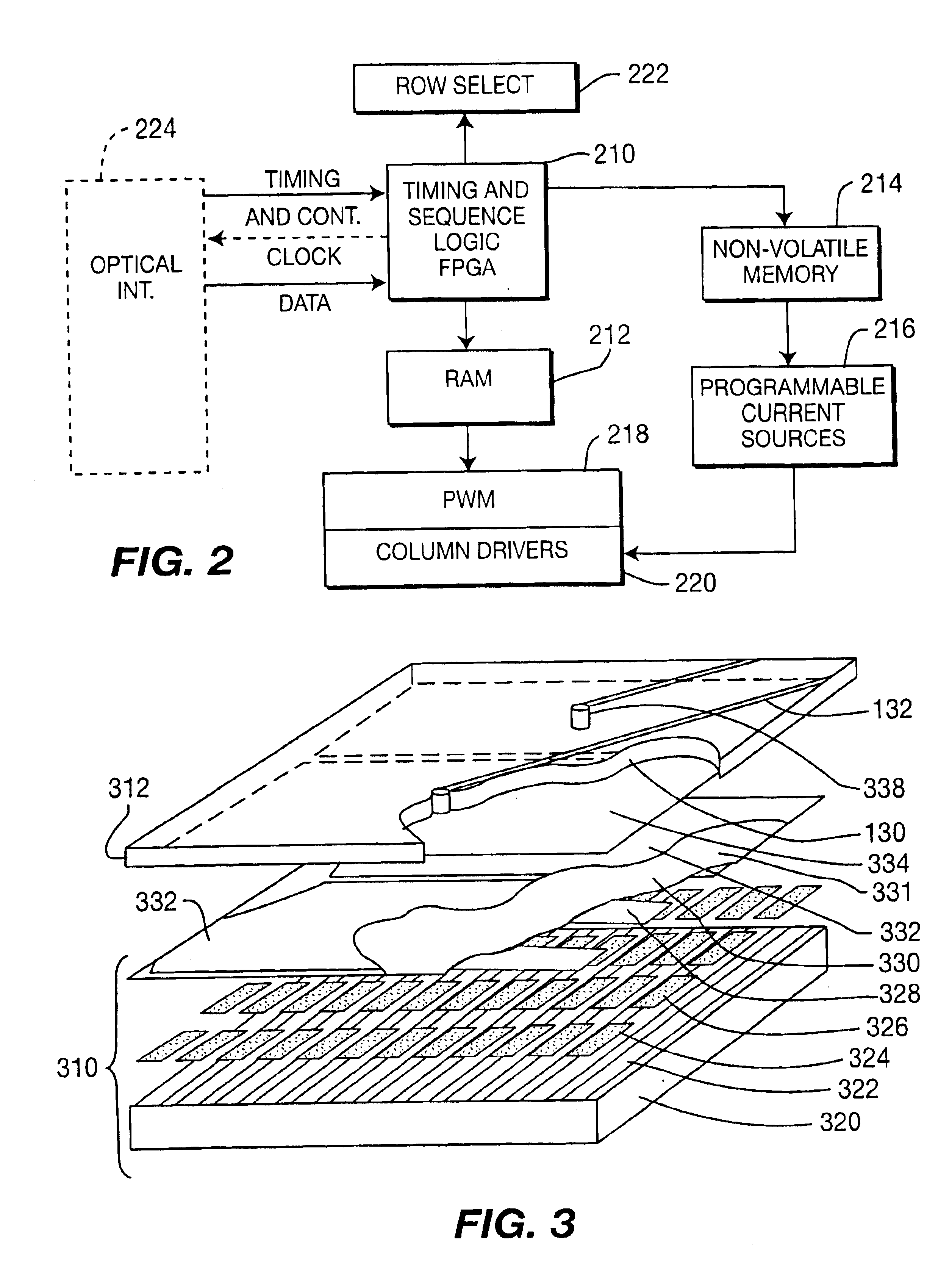

Tiled electronic display structure

InactiveUS6897855B1Television system detailsElectroluminescent light sourcesDisplay deviceElectrical connection

Owner:MEC MANAGEMENT LLC +1

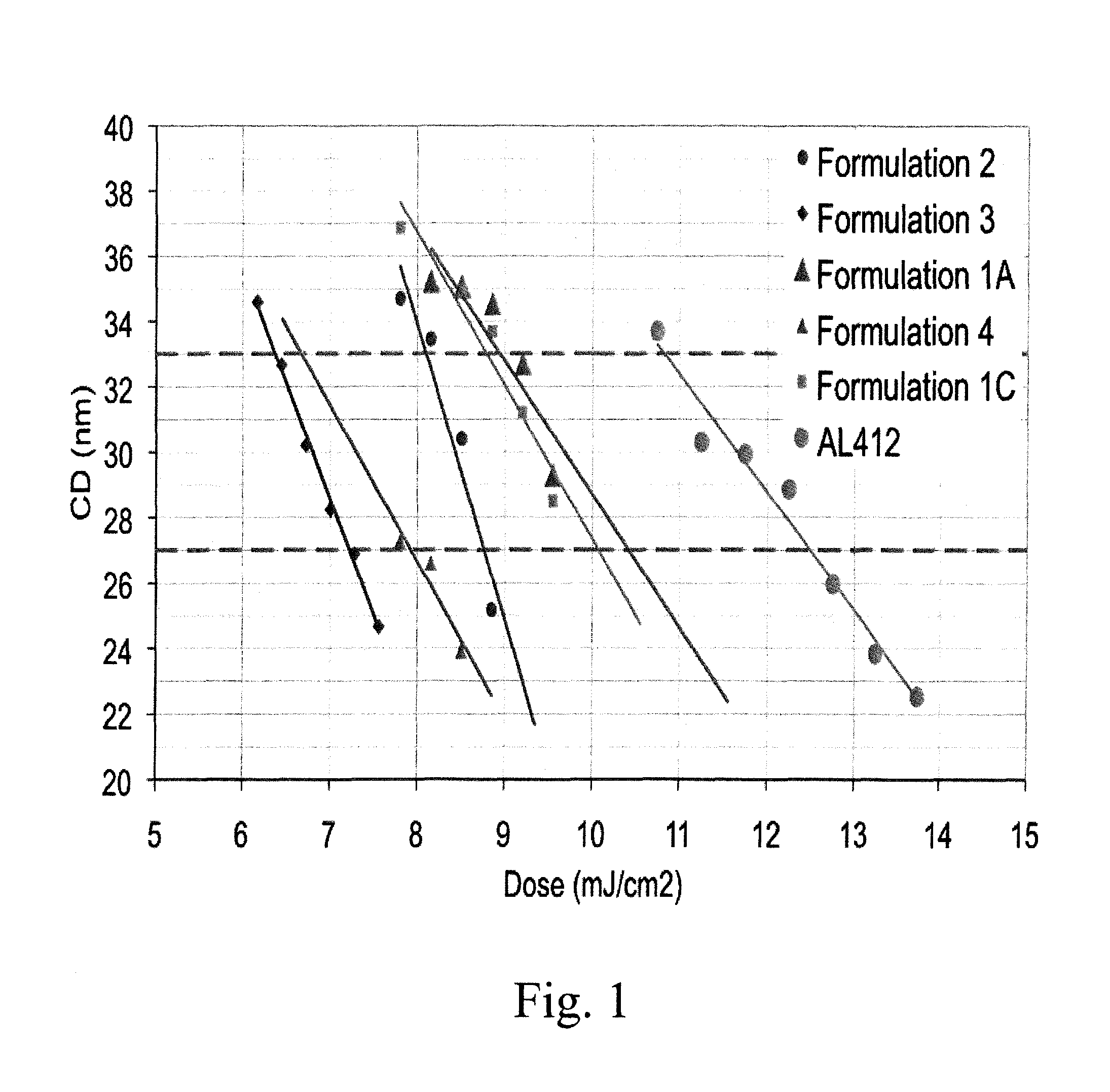

Assist layers for EUV lithography

ActiveUS8968989B2Reduce negative impactMaterial nanotechnologyPhotosensitive materialsElectronic structureLithographic artist

The present invention provides novel methods of fabricating microelectronics structures, and the resulting structures formed thereby, using EUV lithographic processes. The method involves utilizing an assist layer immediately below the photoresist layer. The assist layer can either be directly applied to the substrate, or it can be applied to any intermediate layer(s) that may be applied to the substrate. The preferred assist layers are formed from spin-coatable, polymeric compositions. The inventive method allows reduced critical dimensions to be achieved with improved dose-to-size ratios, while improving adhesion and reducing or eliminating pattern collapse issues.

Owner:BREWER SCI

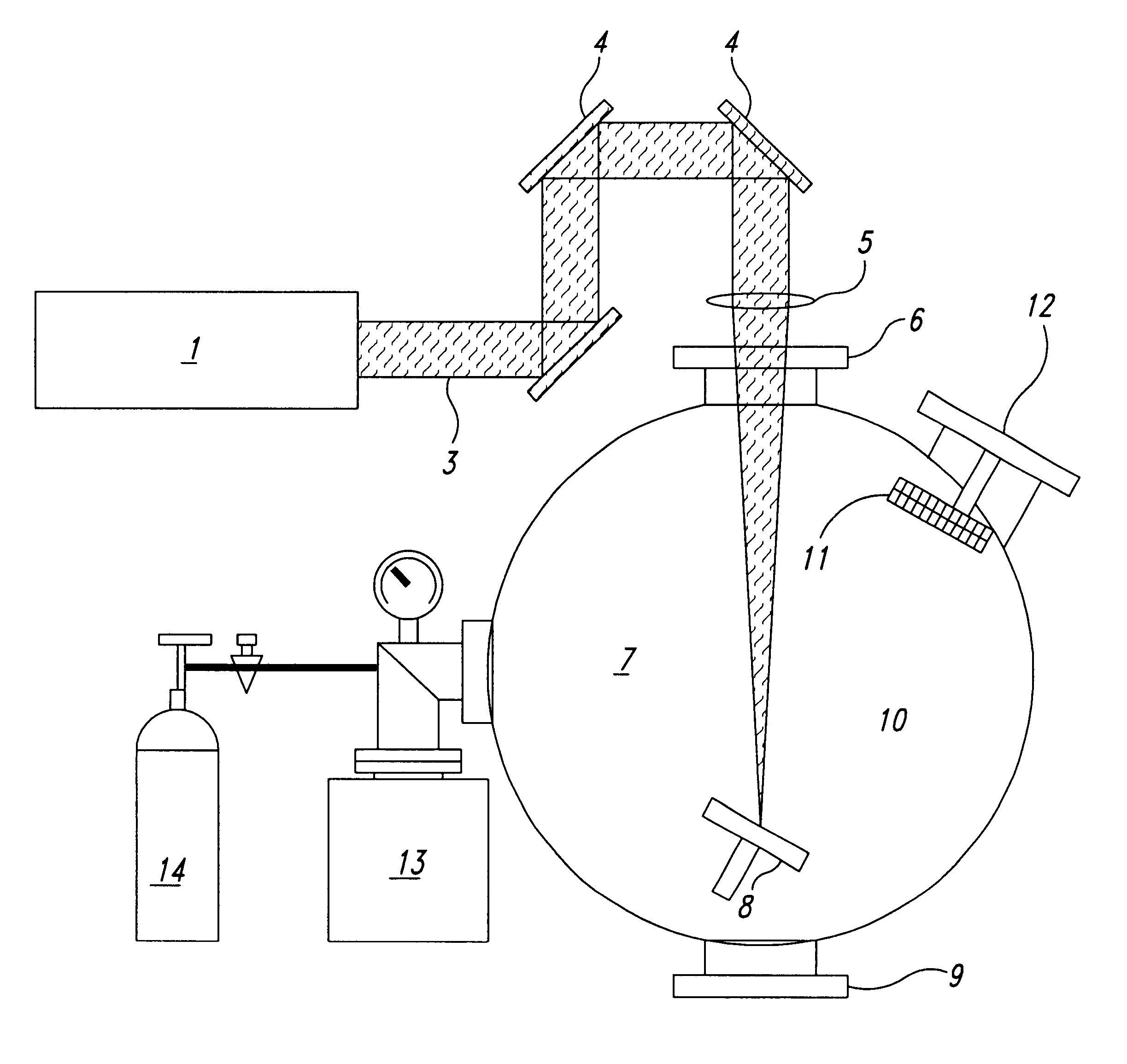

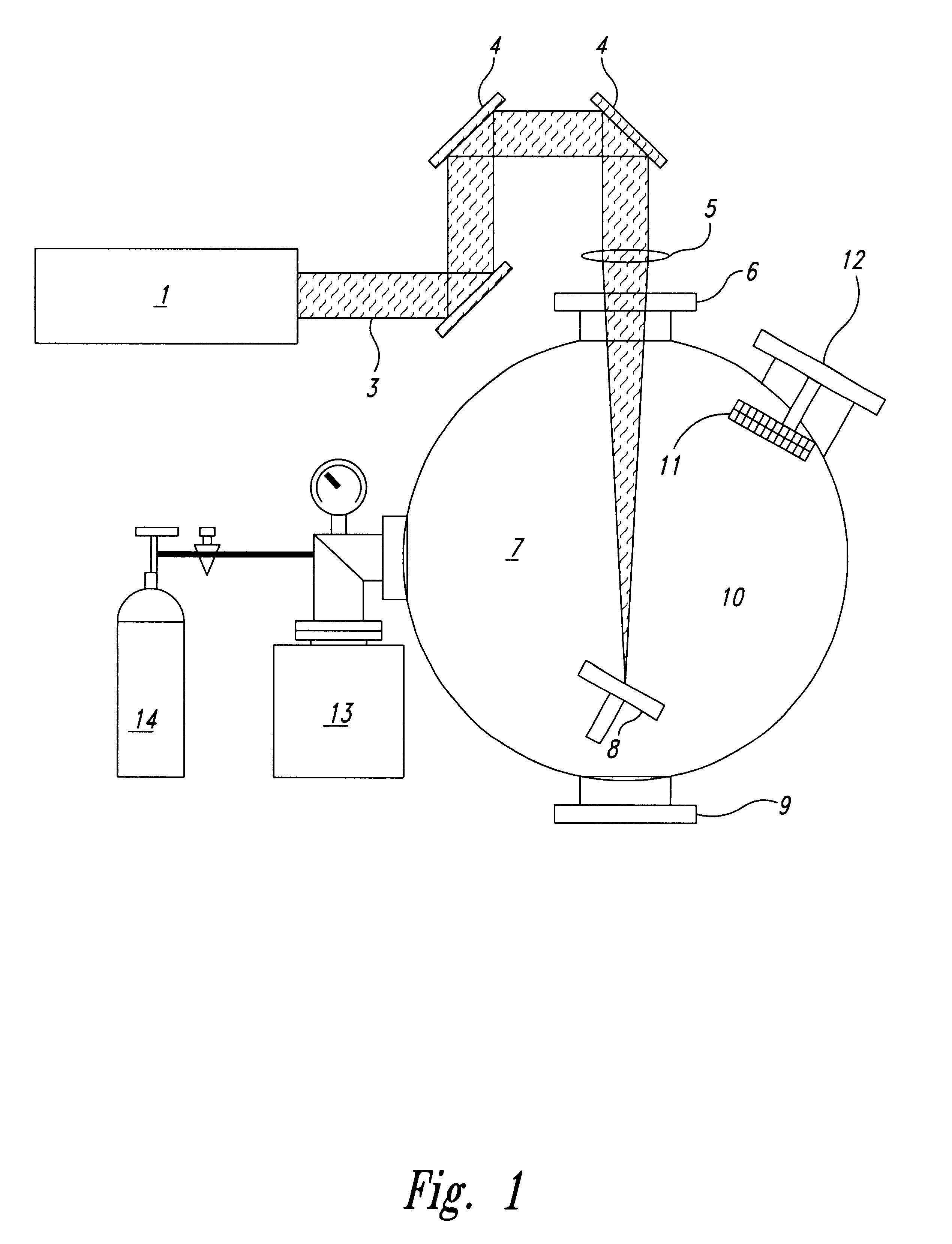

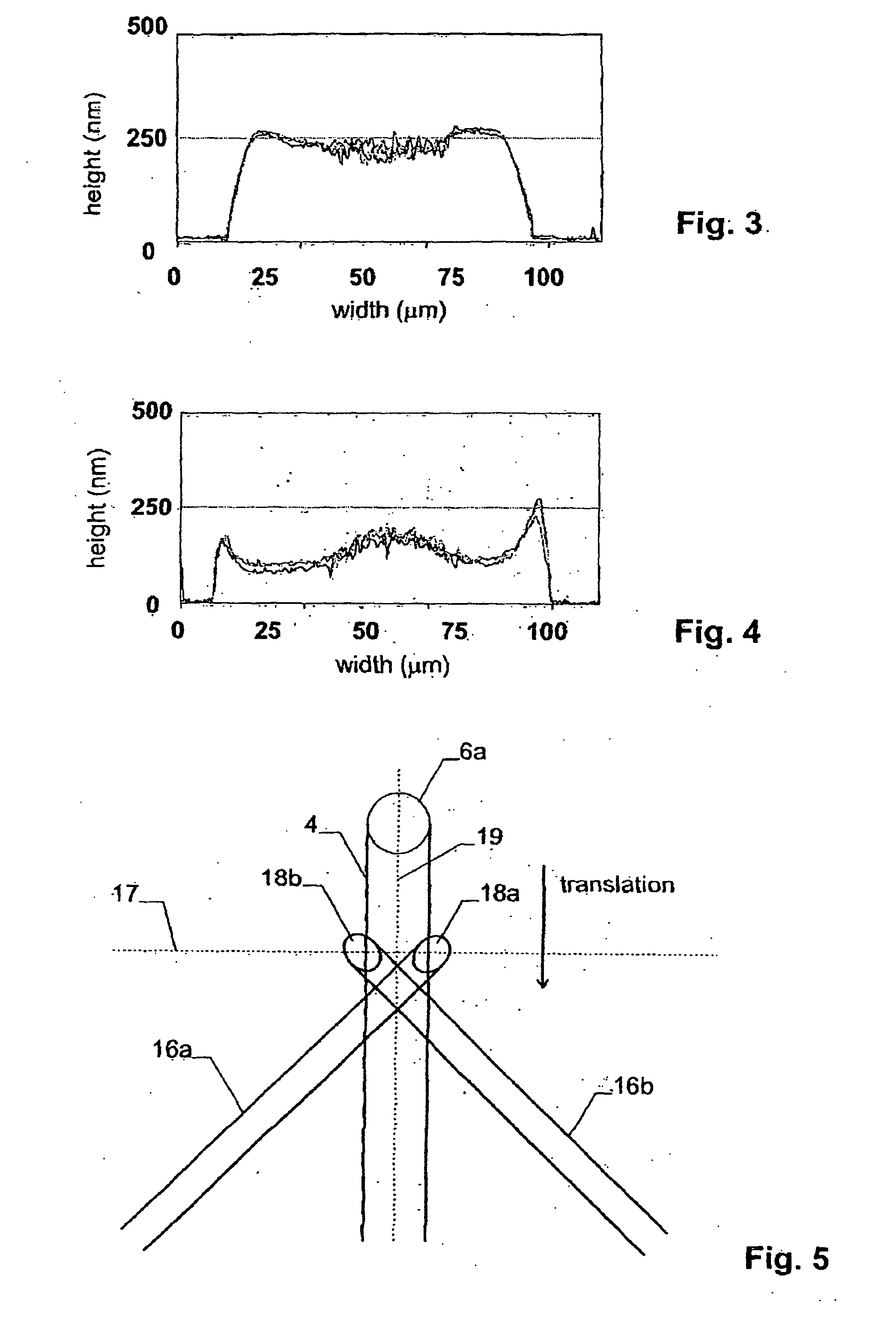

Method of deposition of thin films of amorphous and crystalline microstructures based on ultrafast pulsed laser deposition

InactiveUS6312768B1Improve surface qualityImprove efficiencyMaterial nanotechnologyElectric discharge heatingMacroscopic scaleCarbon nanotube

Powerful nanosecond-range lasers using low repetition rate pulsed laser deposition produce numerous macroscopic size particles and droplets, which embed in thin film coatings. This problem has been addressed by lowering the pulse energy, keeping the laser intensity optional for evaporation, so that significant numbers of the macroscopic particles and droplets are no longer present in the evaporated plume. The result is deposition of evaporated plume on a substrate to form thin film of very high surface quality. Preferably, the laser pulses have a repetition rate to produce a continuous flow of evaporated material at the substrate. Pulse-range is typically picosecond and femtosecond and repetition rate kilohertz to hundreds of megahertz. The process may be carried out in the presence of a buffer gas, which may be inert or reactive, and the increased vapour density and therefore the collision frequency between evaporated atoms leads to the formation of nanostructured materials of increasing interest, because of their peculiar structural, electronic and mechanical properties. One of these is carbon nanotubes, which is a new form of carbon belonging to the fullerene (C60) family. Carbon nanotubes are seamless, single or multishell co-axial cylindrical tubules with or without dome caps at the extremities. Typically diameters range from 1 nm to 50 nm with a length >1 mum. The electronic structure may be either metallic or semiconducting without any change in the chemical bonding or adding of dopant. In addition, the materials have application to a wide range of established thin film applications.

Owner:AUSTRALIEN NAT UNIV

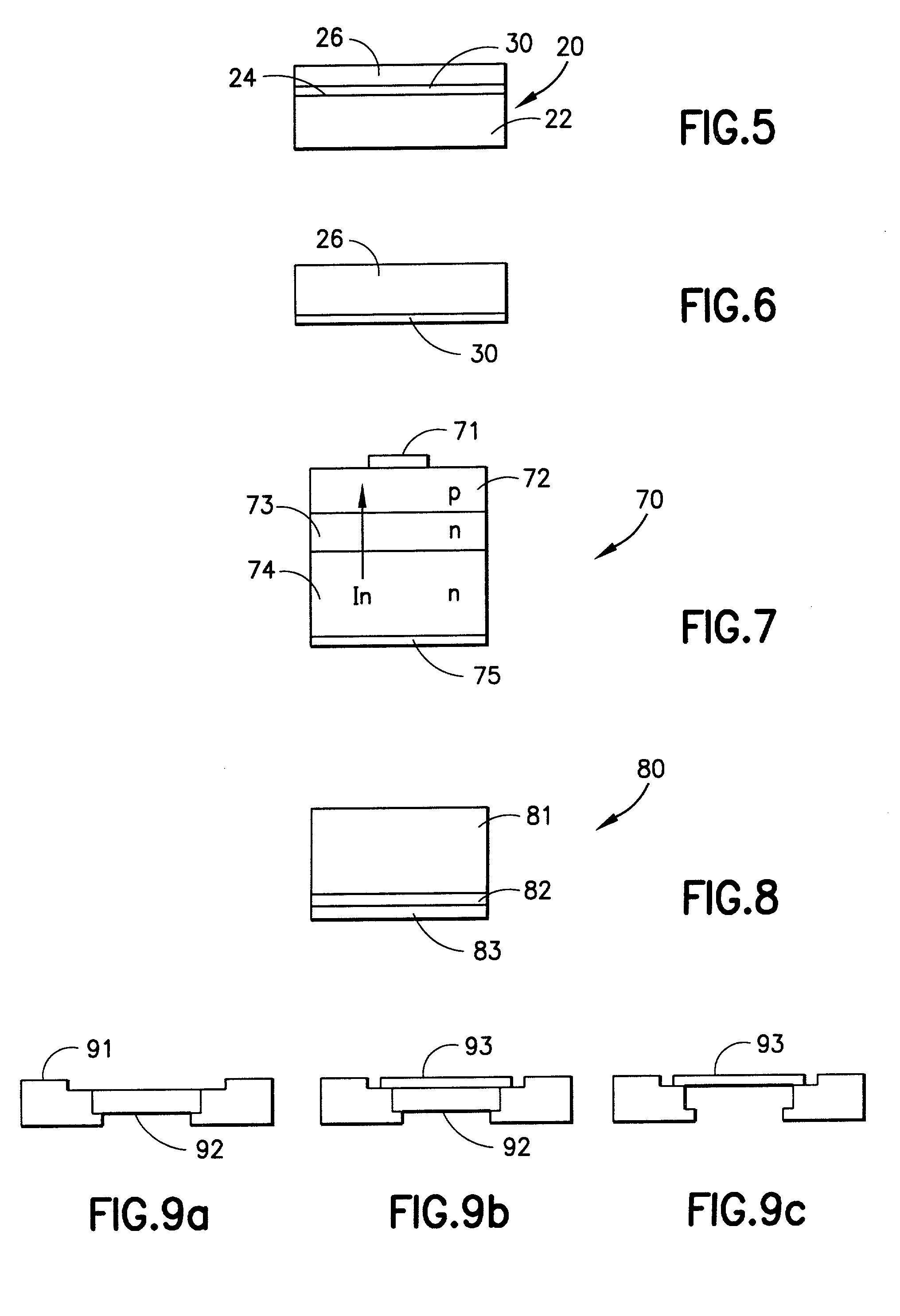

Bulk single crystal gallium nitride and method of making same

InactiveUS20010008656A1Enhance crystallinity and other characteristicAvoid etchingEnvelopes/bags making machineryLayered productsElectronic structureSingle crystal

A single crystal M*N article, which may be made by a process including the steps of: providing a substrate of material having a crystalline surface which is epitaxially compatible with M*N; depositing a layer of single crystal M*N over the surface of the substrate; and removing the substrate from the layer of single crystal M*N, e.g., with an etching agent which is applied to the substrate to remove same, to yield the layer of single crystal M*N as said single crystal M*N article. The bulk single crystal M*N article is suitable for use as a substrate for the fabrication of microelectronic structures thereon, to produce microelectronic devices comprising bulk single crystal M*N substrates, or precursor structures thereof.

Owner:ADVANCED TECH MATERIALS INC

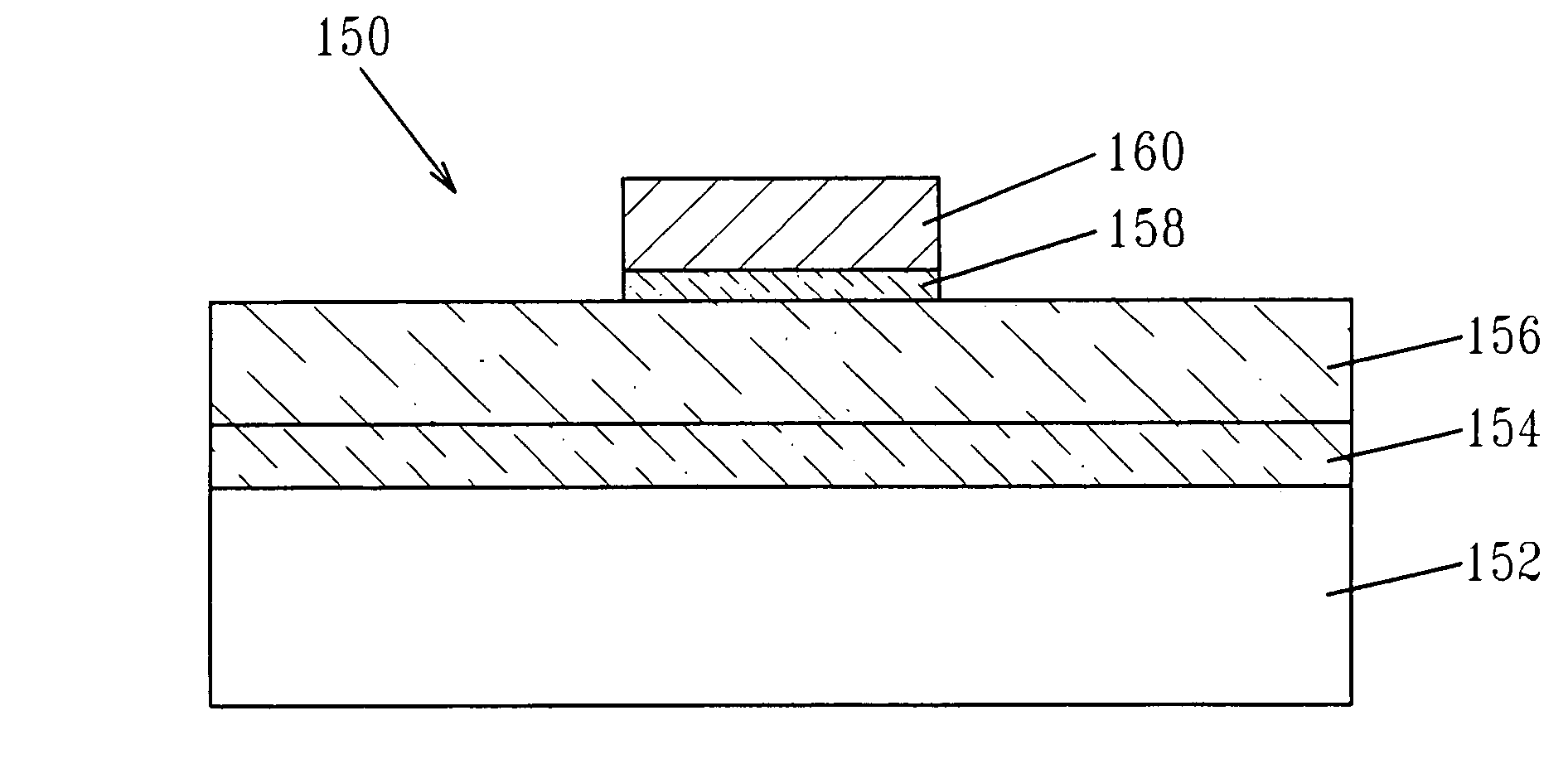

Deposition of hafnium oxide and/or zirconium oxide and fabrication of passivated electronic structures

InactiveUS6982230B2Stable to reducing condition necessaryImprove electrical performanceSolid-state devicesSemiconductor/solid-state device manufacturingElectronic structureHydrogen

A method of fabricating hafnium oxide and / or zirconium oxide films is provided. The methods include providing a mixture of Hf and / or Zr alkoxide dissolved, emulsified or suspended in a liquid; vaporizing at least the alkoxide and depositing the vaporized component at a temperature of greater than 400° C. The resultant film is dense, microcrystalline and is capable of self-passivation when treated in a hydrogen plasma or forming gas anneal.

Owner:GLOBALFOUNDRIES INC

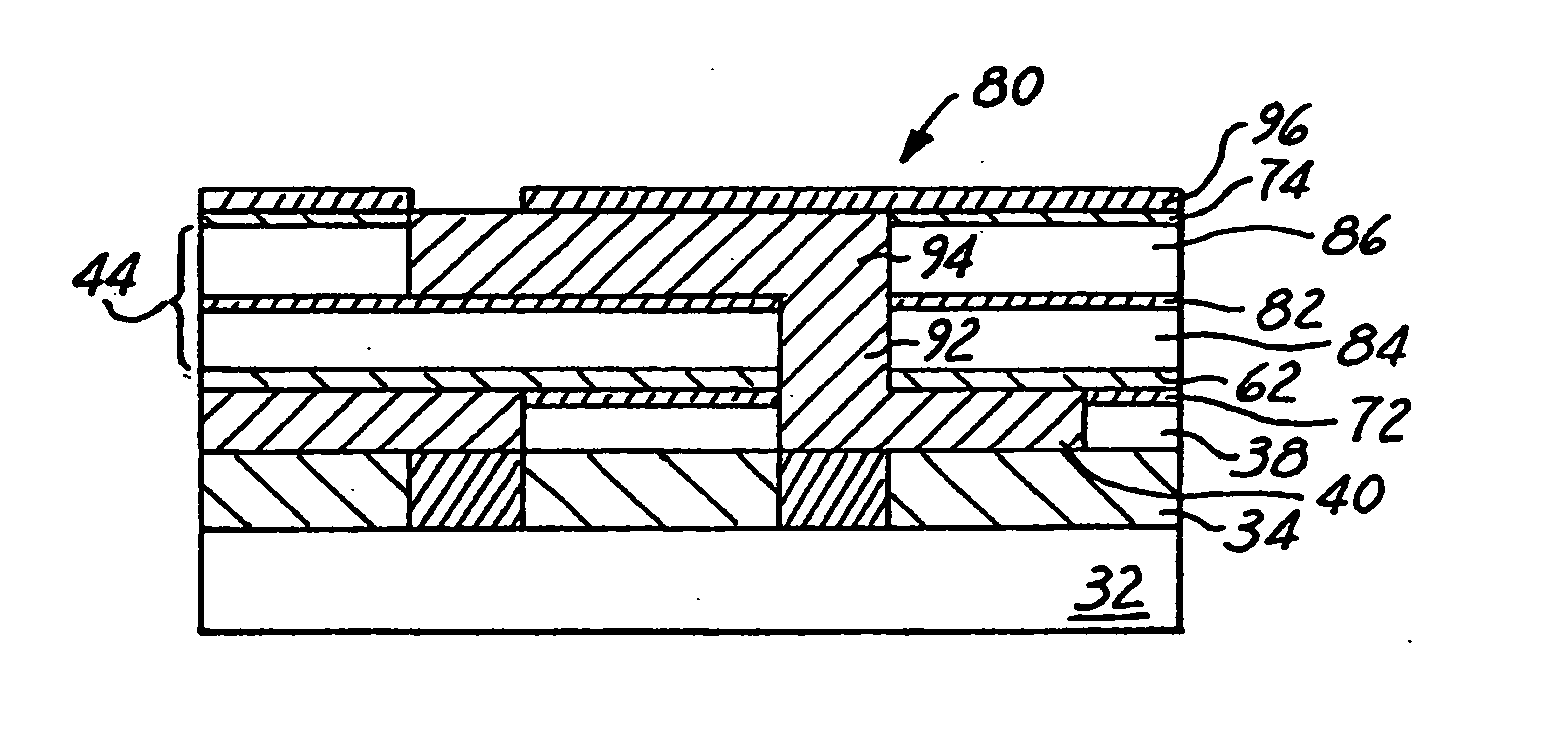

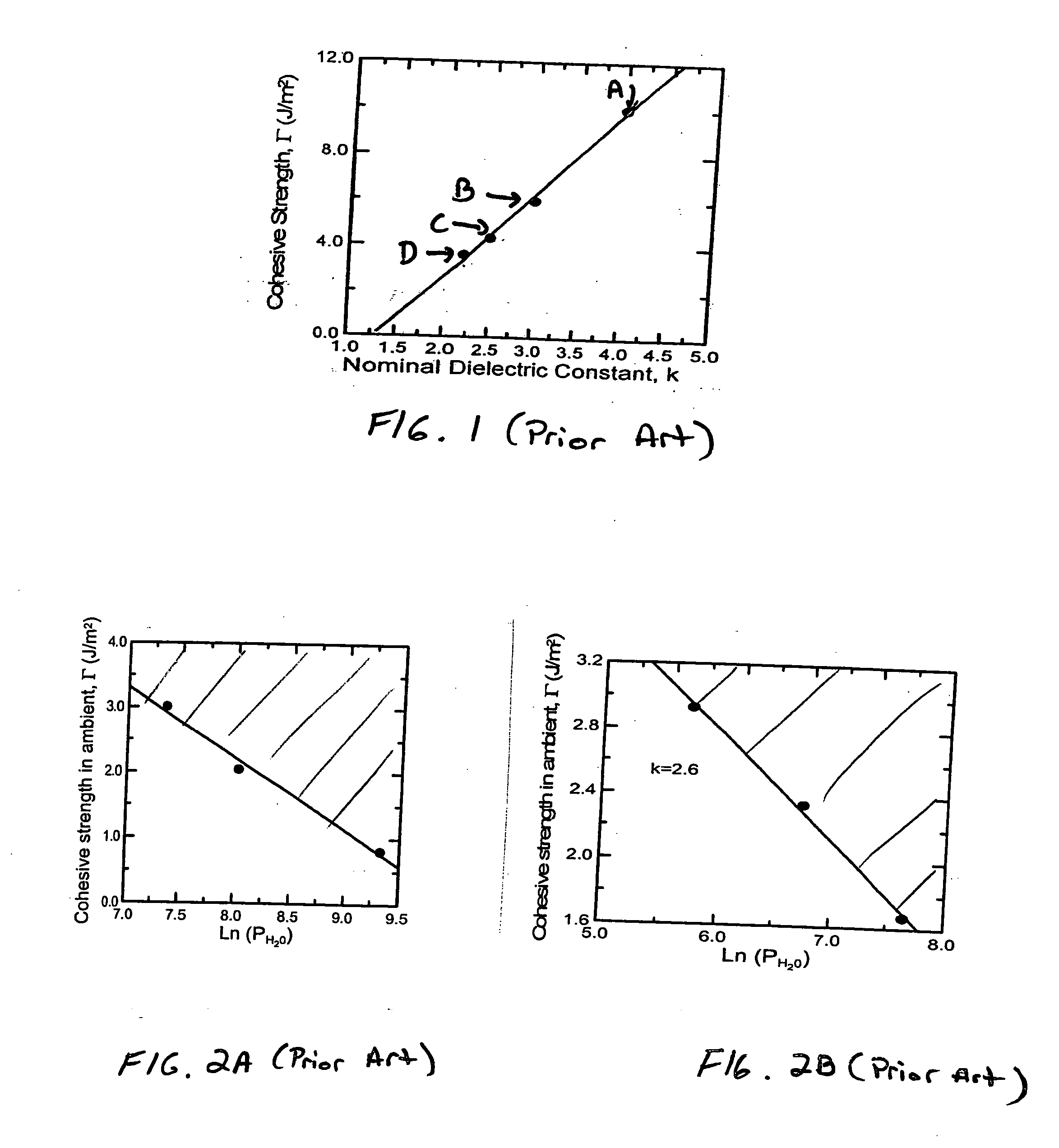

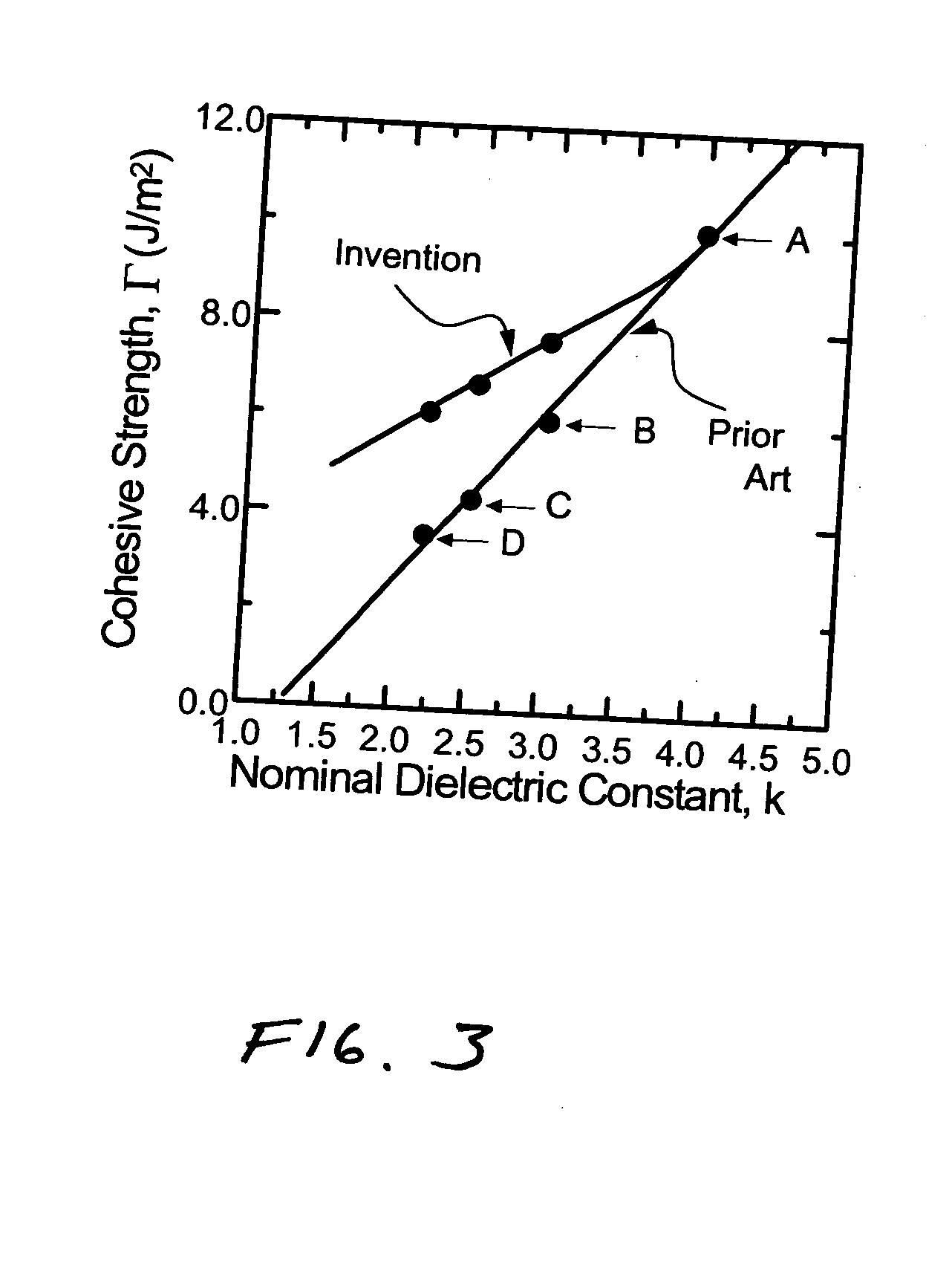

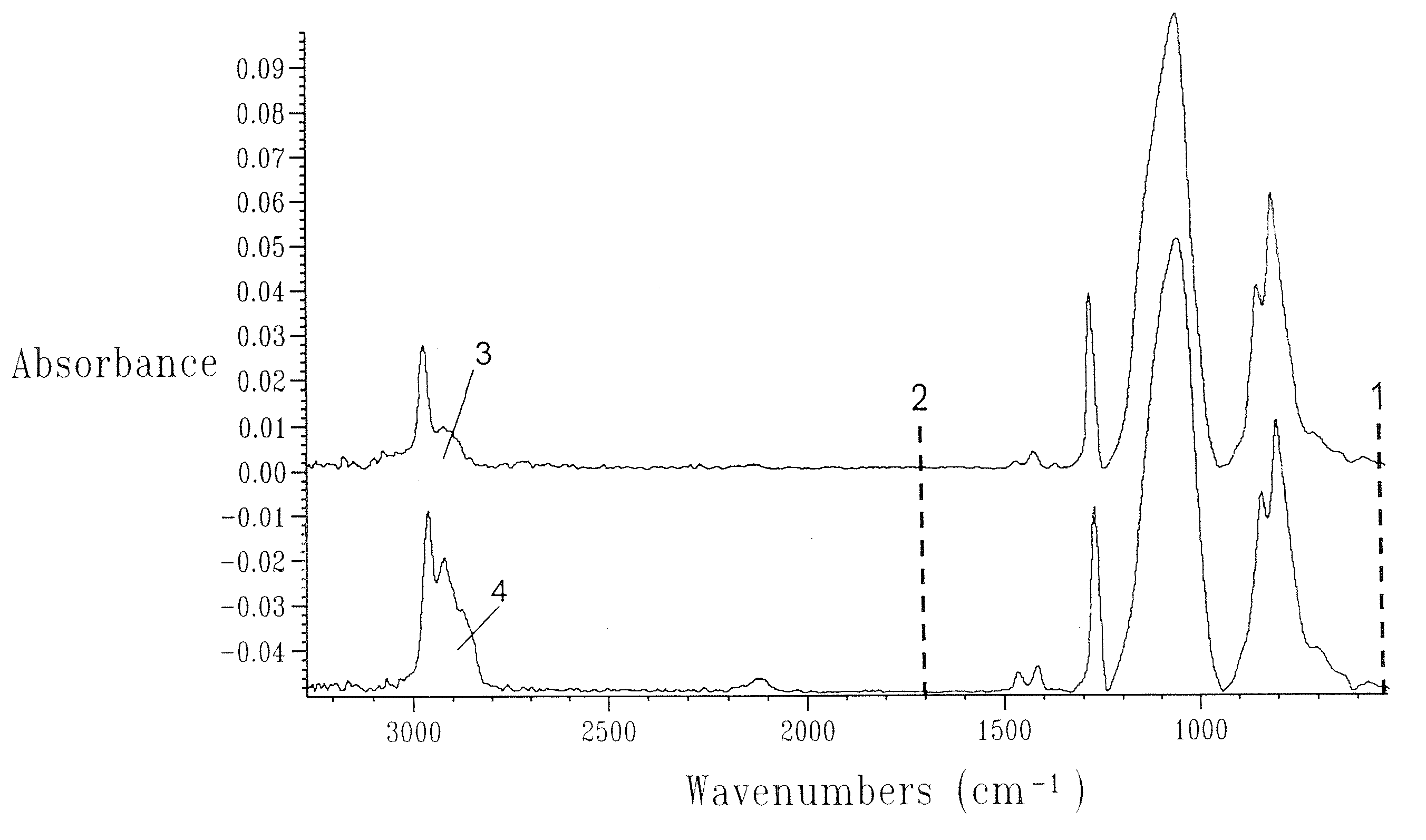

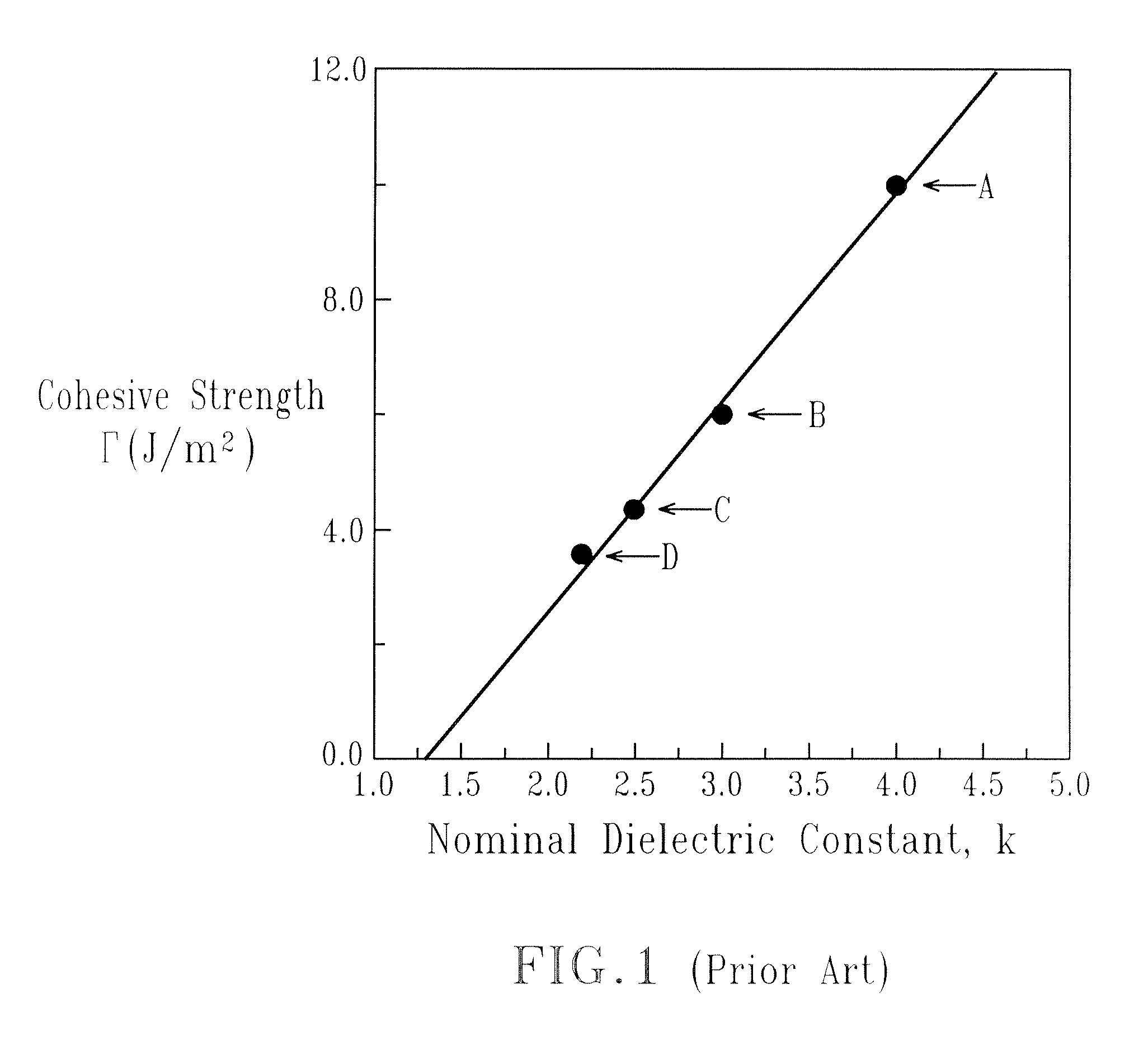

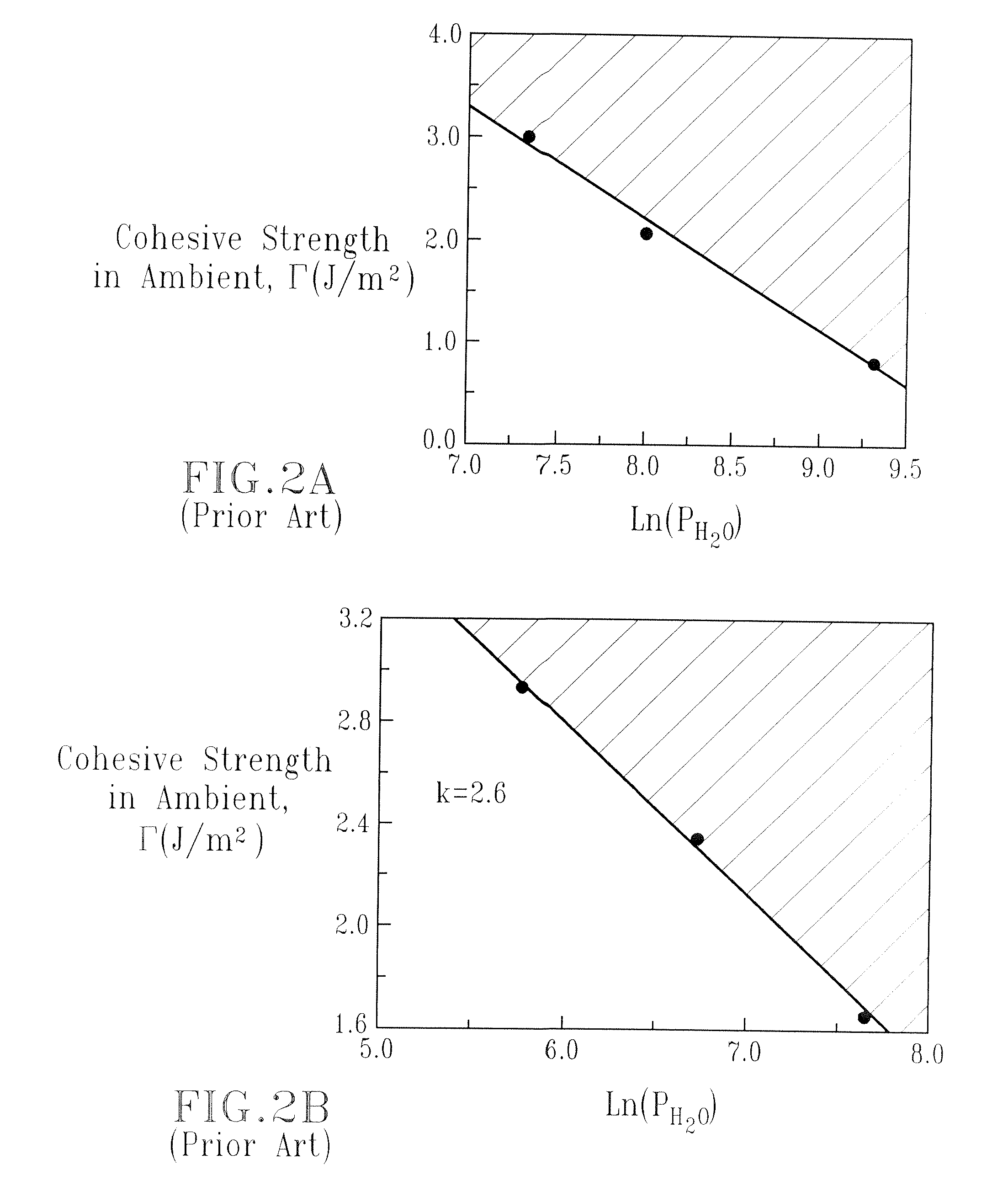

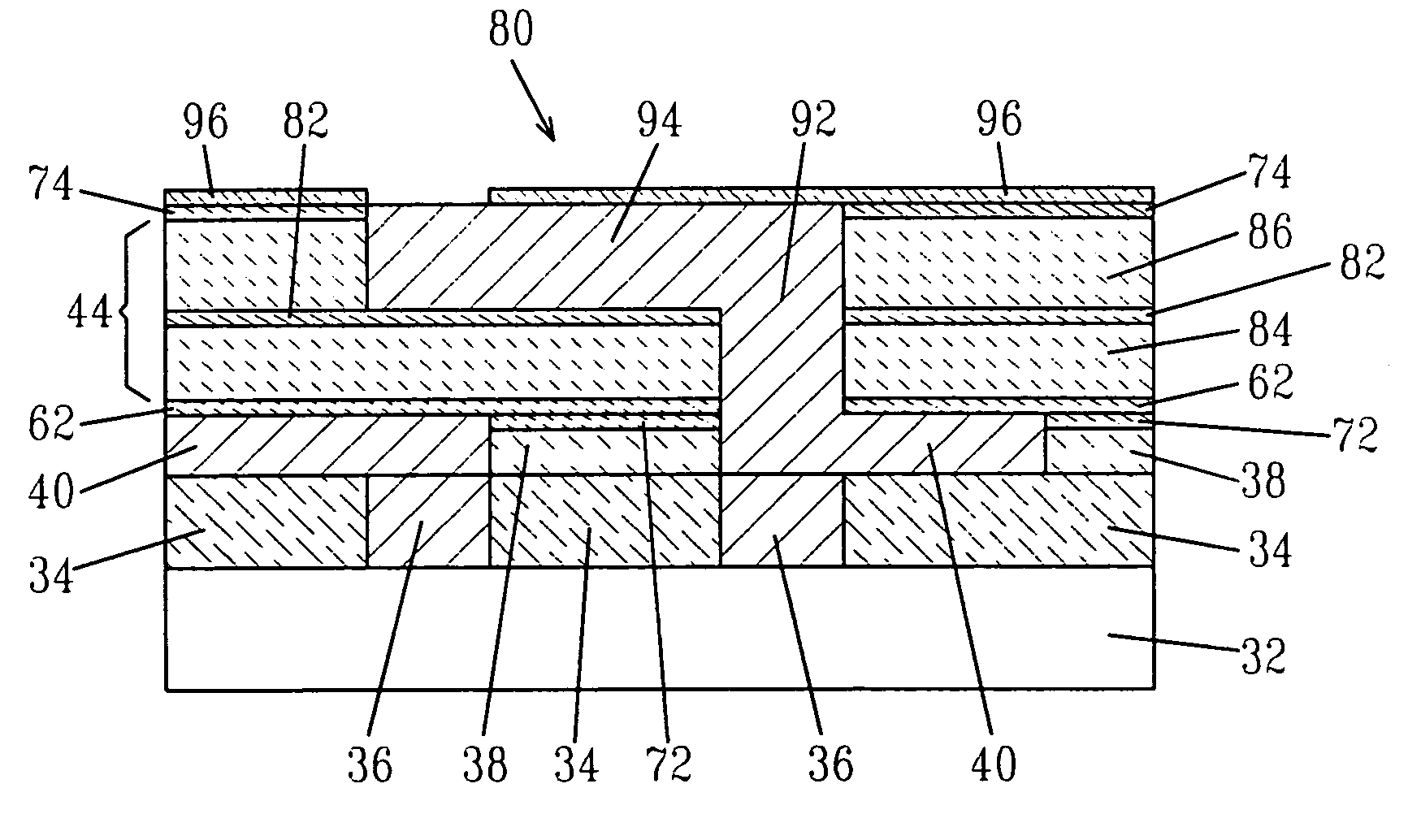

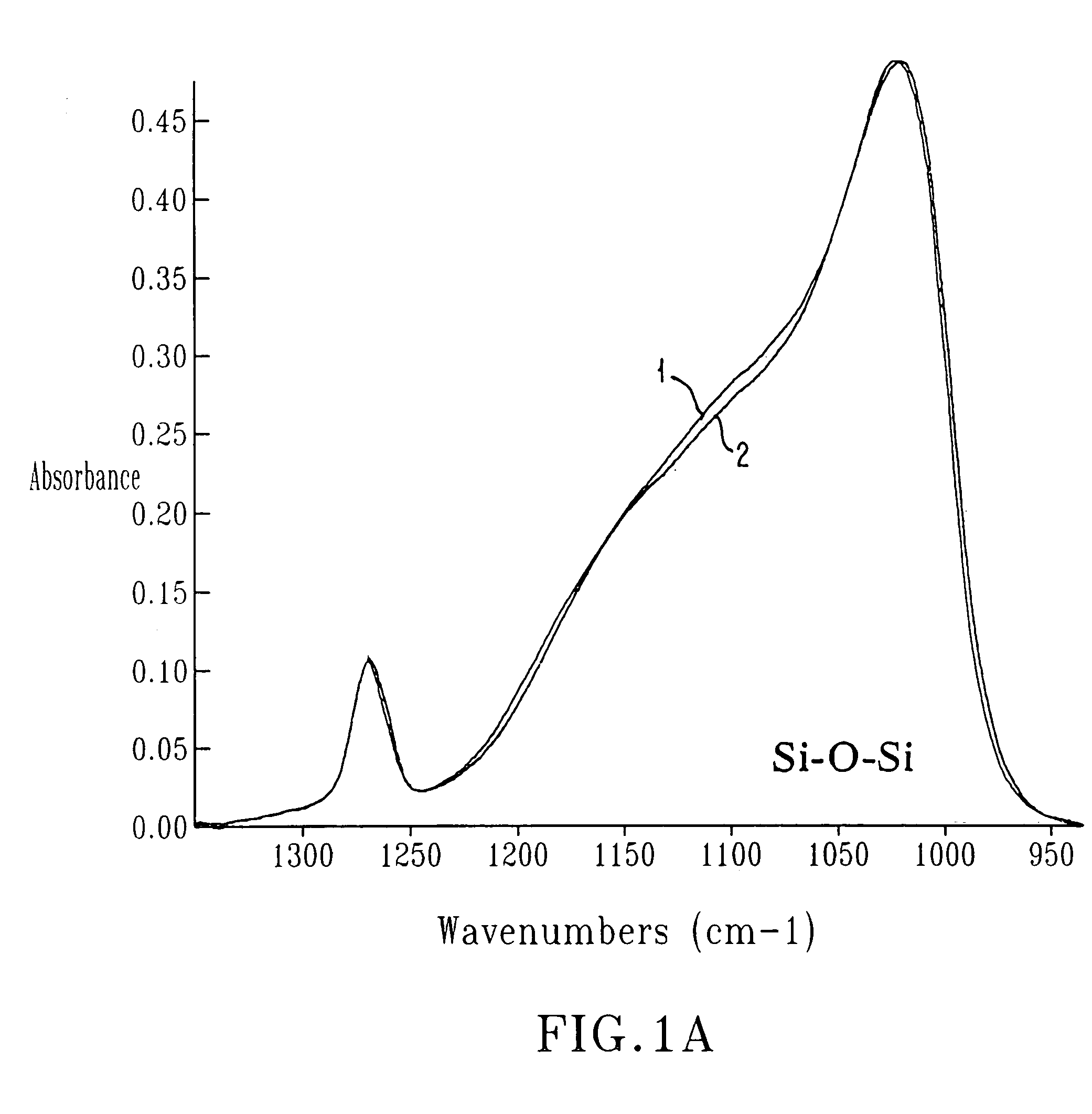

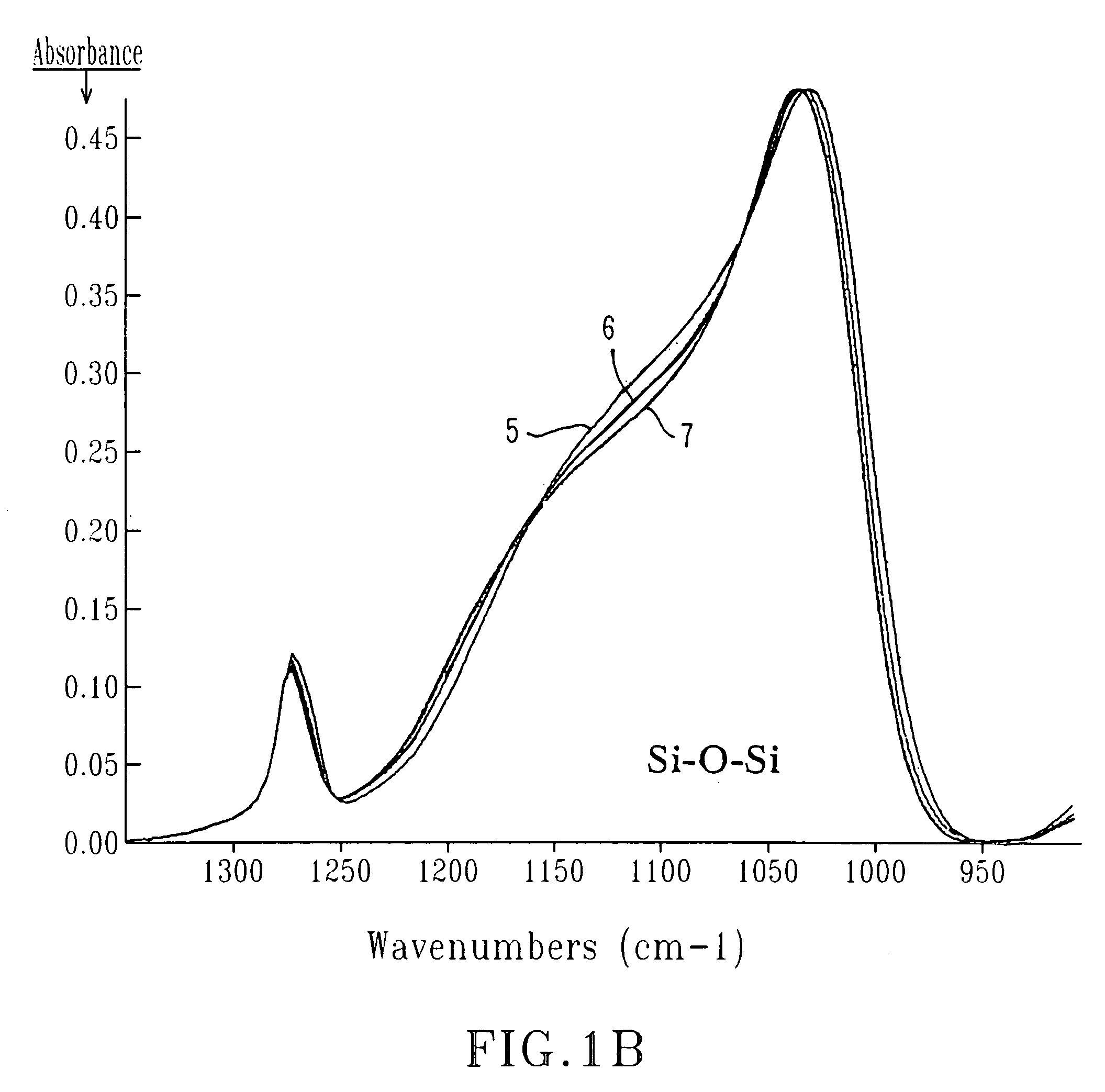

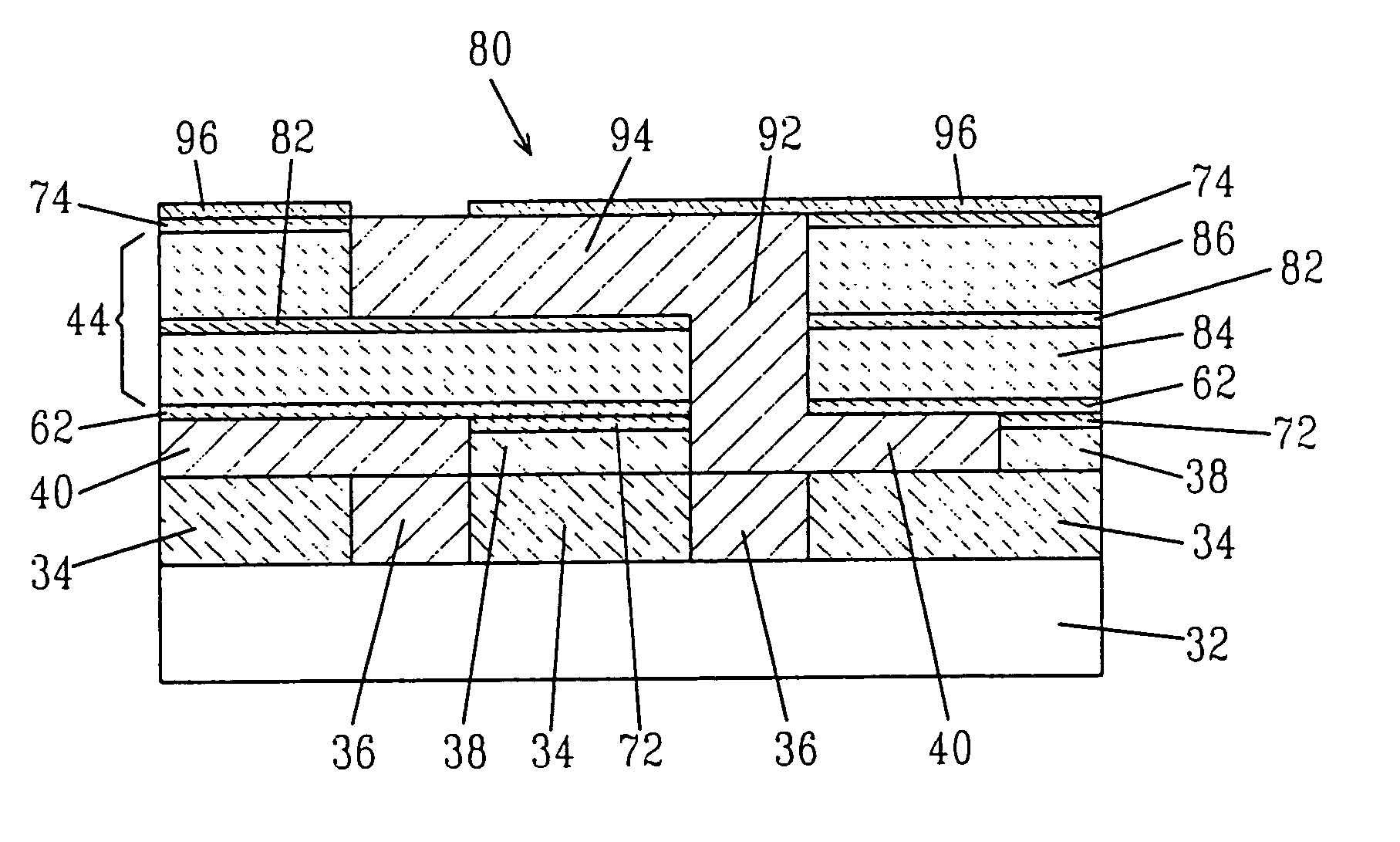

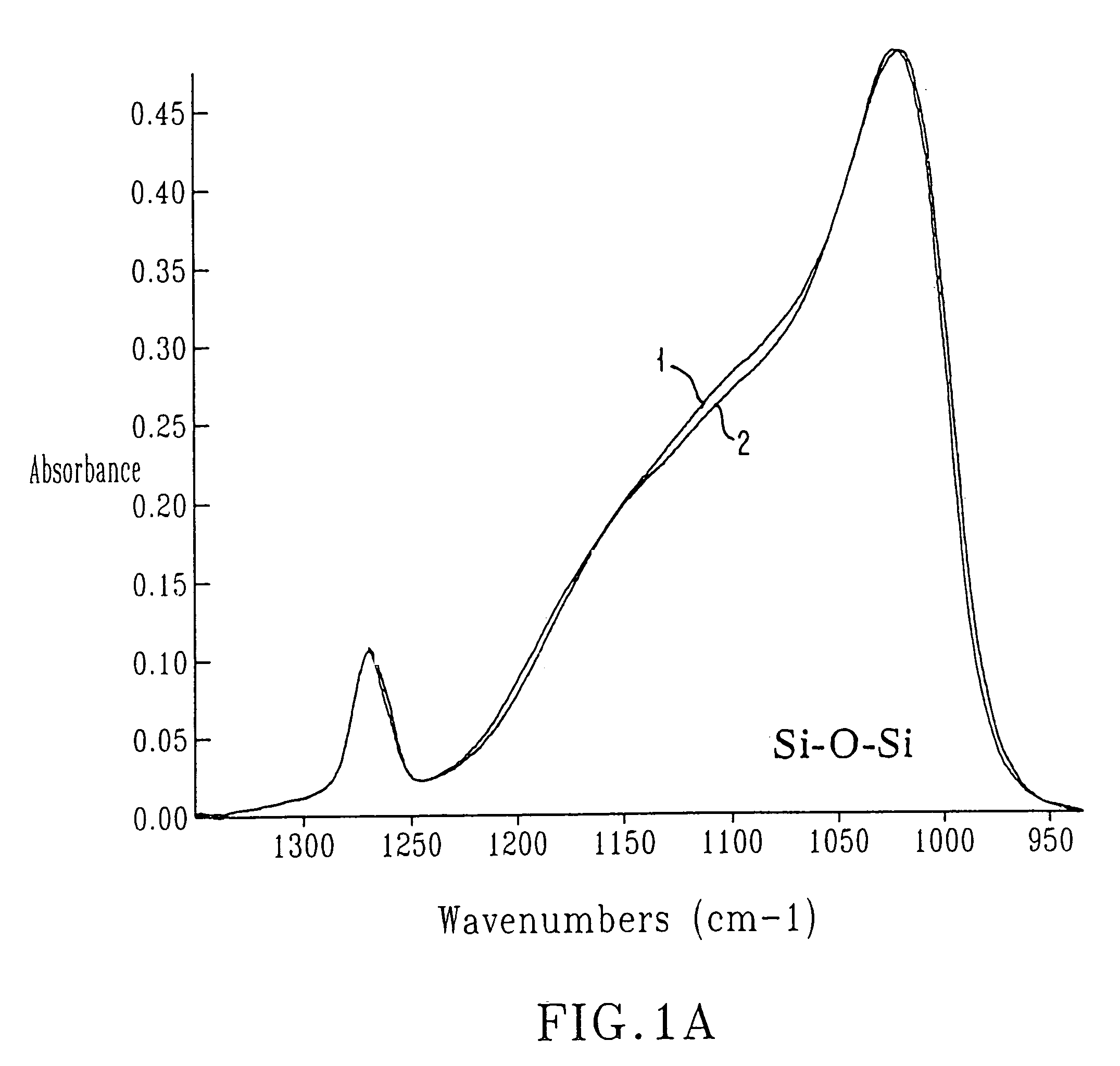

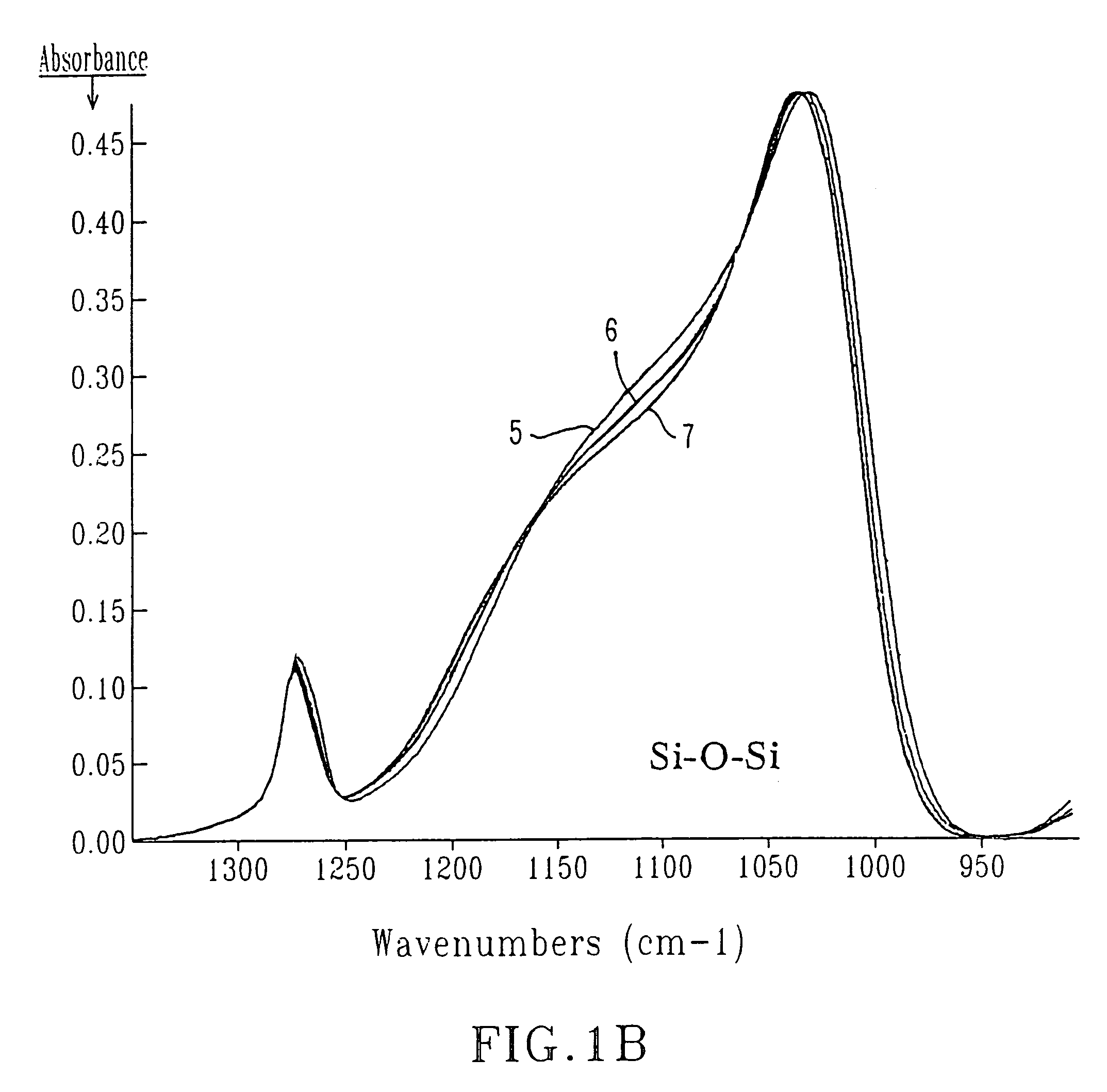

SiCOH dielectric material with improved toughness and improved Si-C bonding, semiconductor device containing the same, and method to make the same

InactiveUS20050194619A1Small slopeDelayed slopeSolid-state devicesSemiconductor/solid-state device manufacturingElectronic structureDevice material

A low-k dielectric material with increased cohesive strength for use in electronic structures including interconnect and sensing structures is provided that includes atoms of Si, C, O, and H in which a fraction of the C atoms are bonded as Si—CH3 functional groups, and another fraction of the C atoms are bonded as Si—R—Si, wherein R is phenyl, —[CH2]n— where n is greater than or equal to 1, HC═CH, C═CH2, C═C or a [S]n linkage, where n is a defined above.

Owner:INTEL CORP

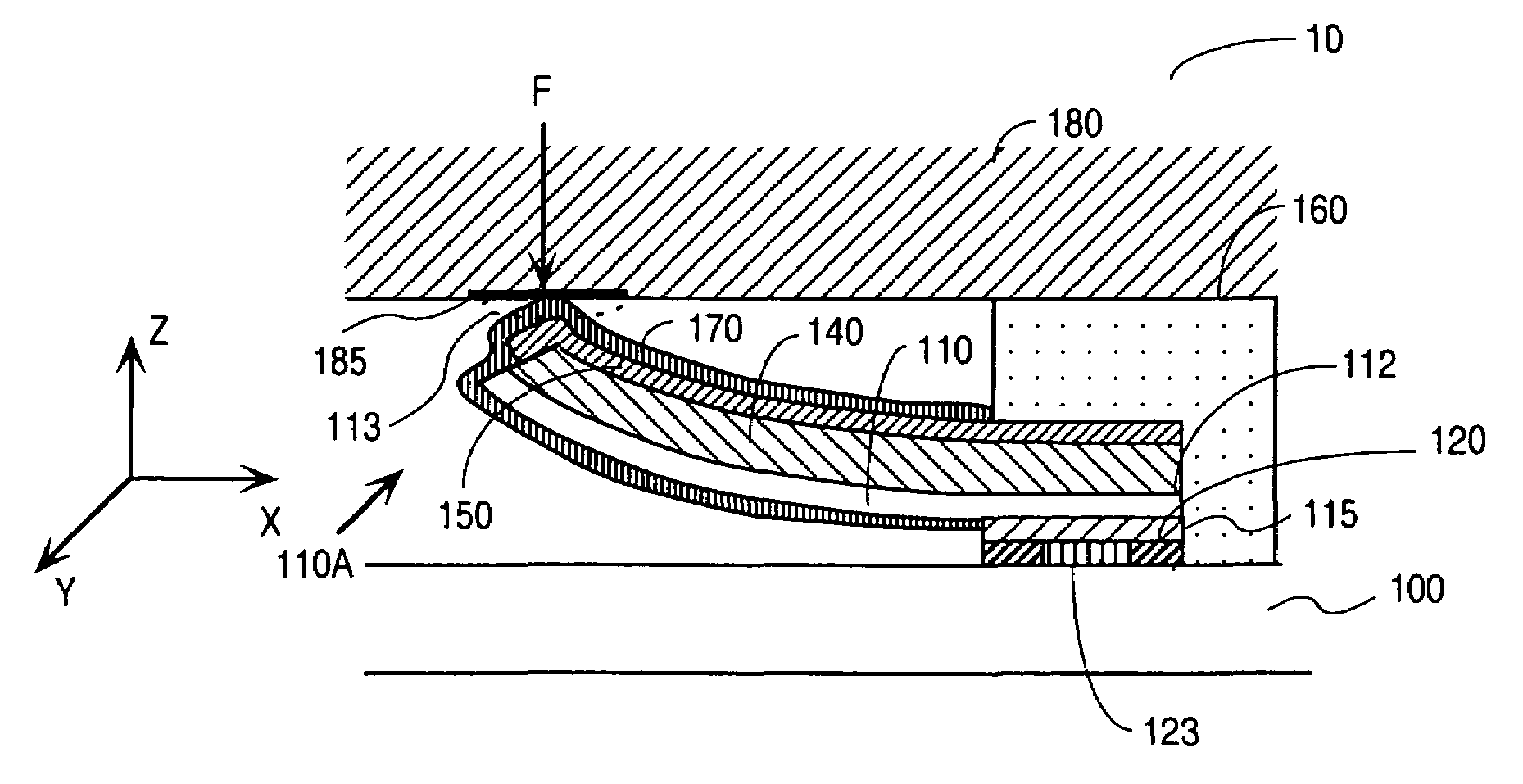

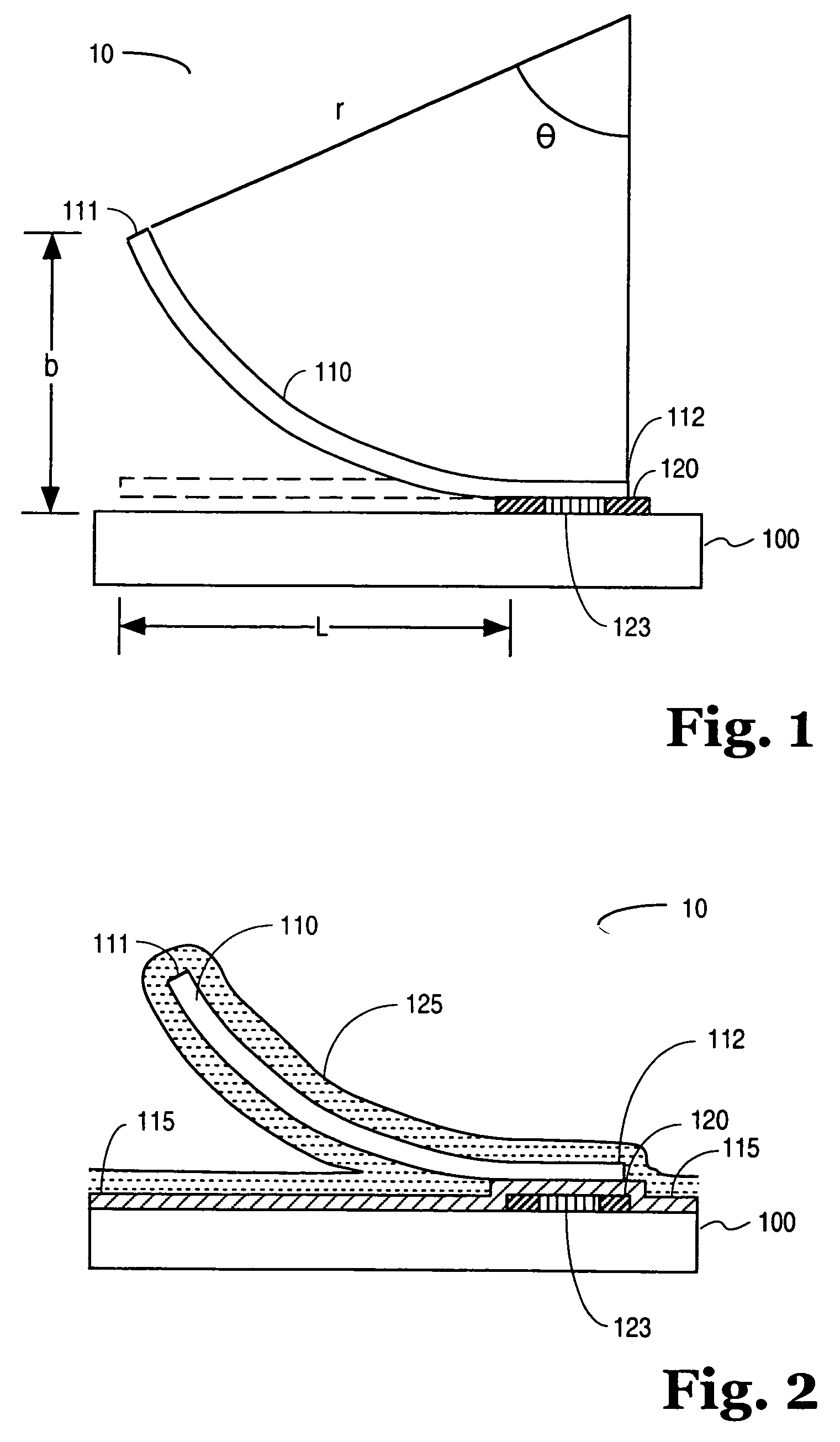

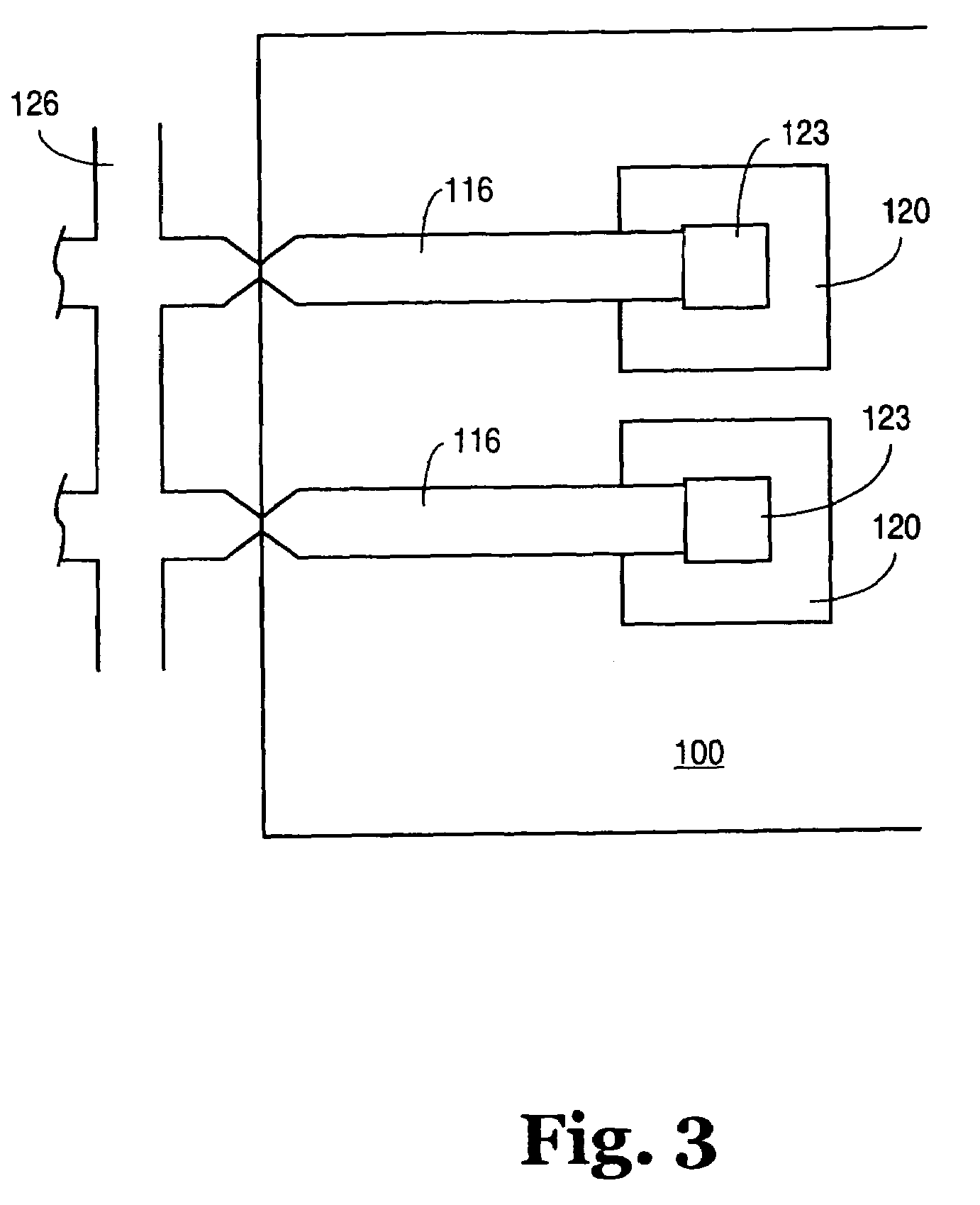

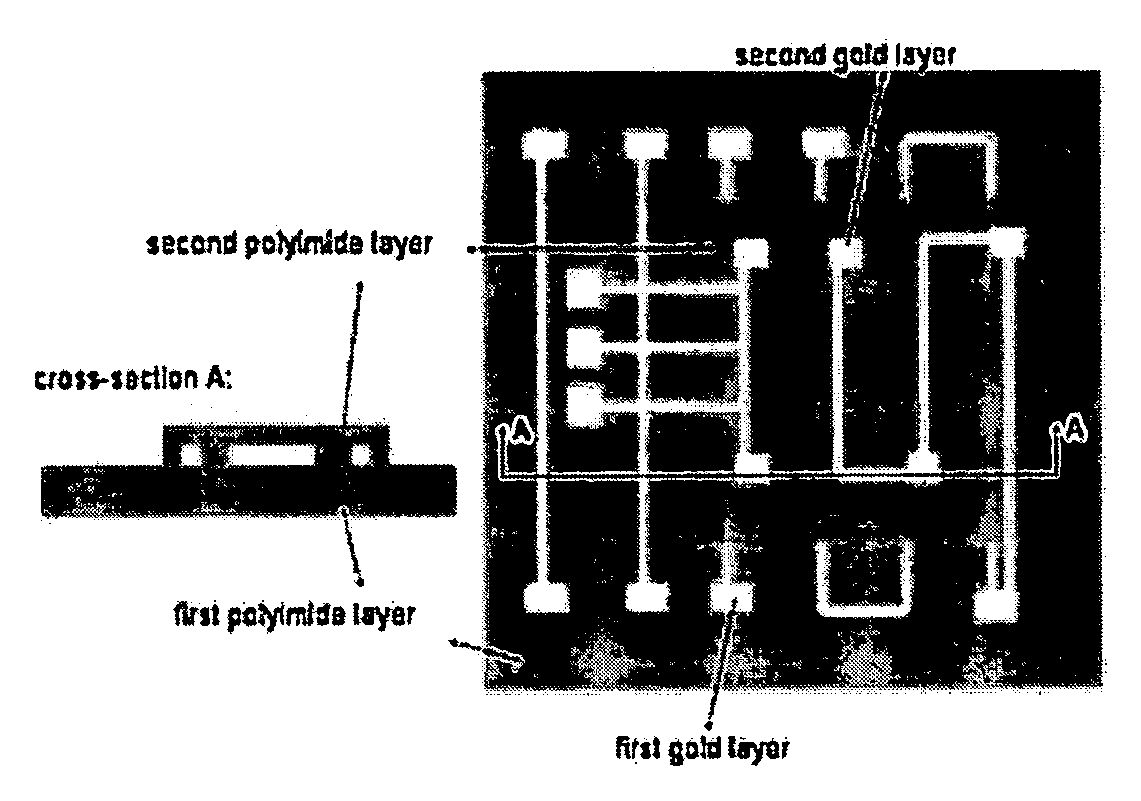

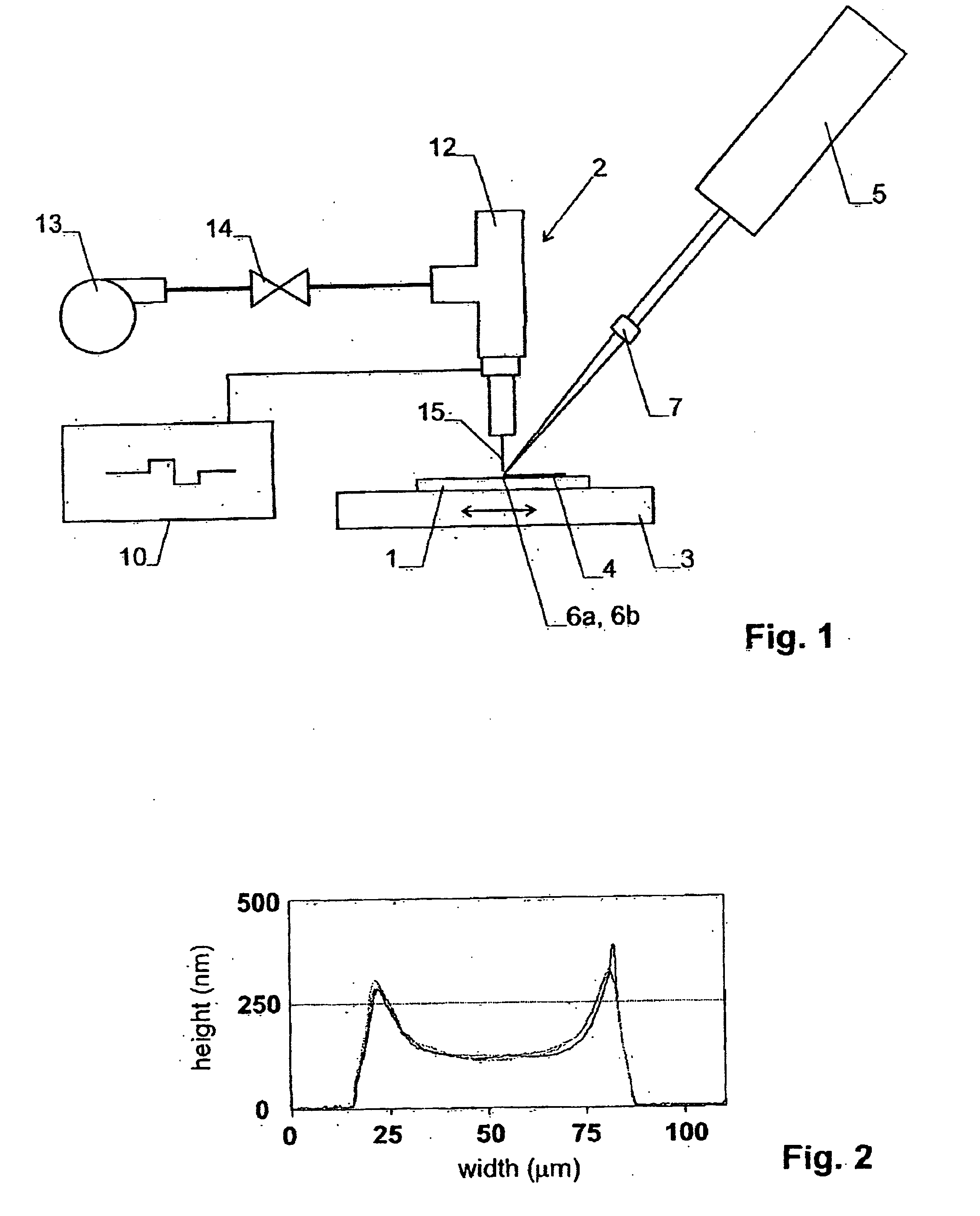

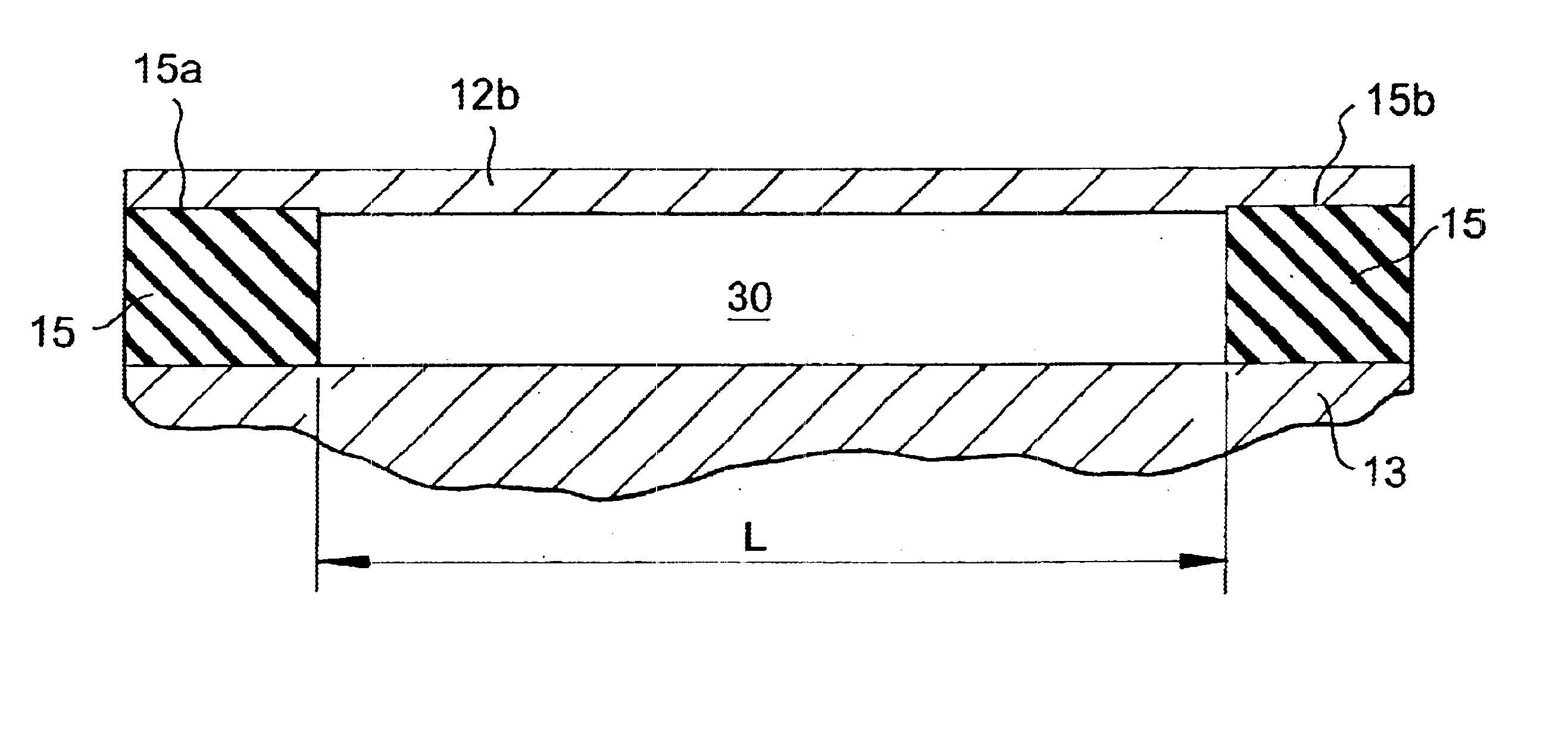

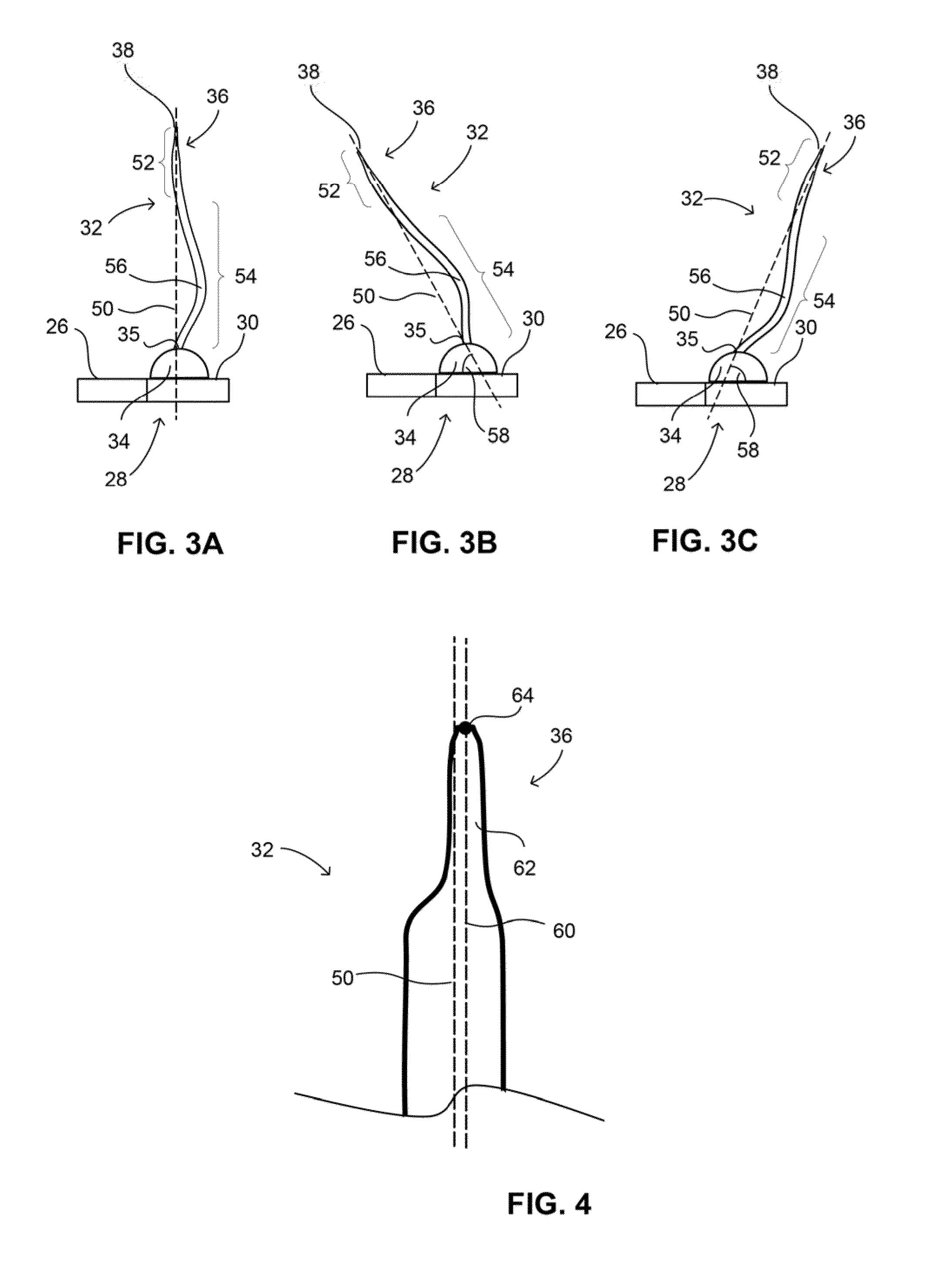

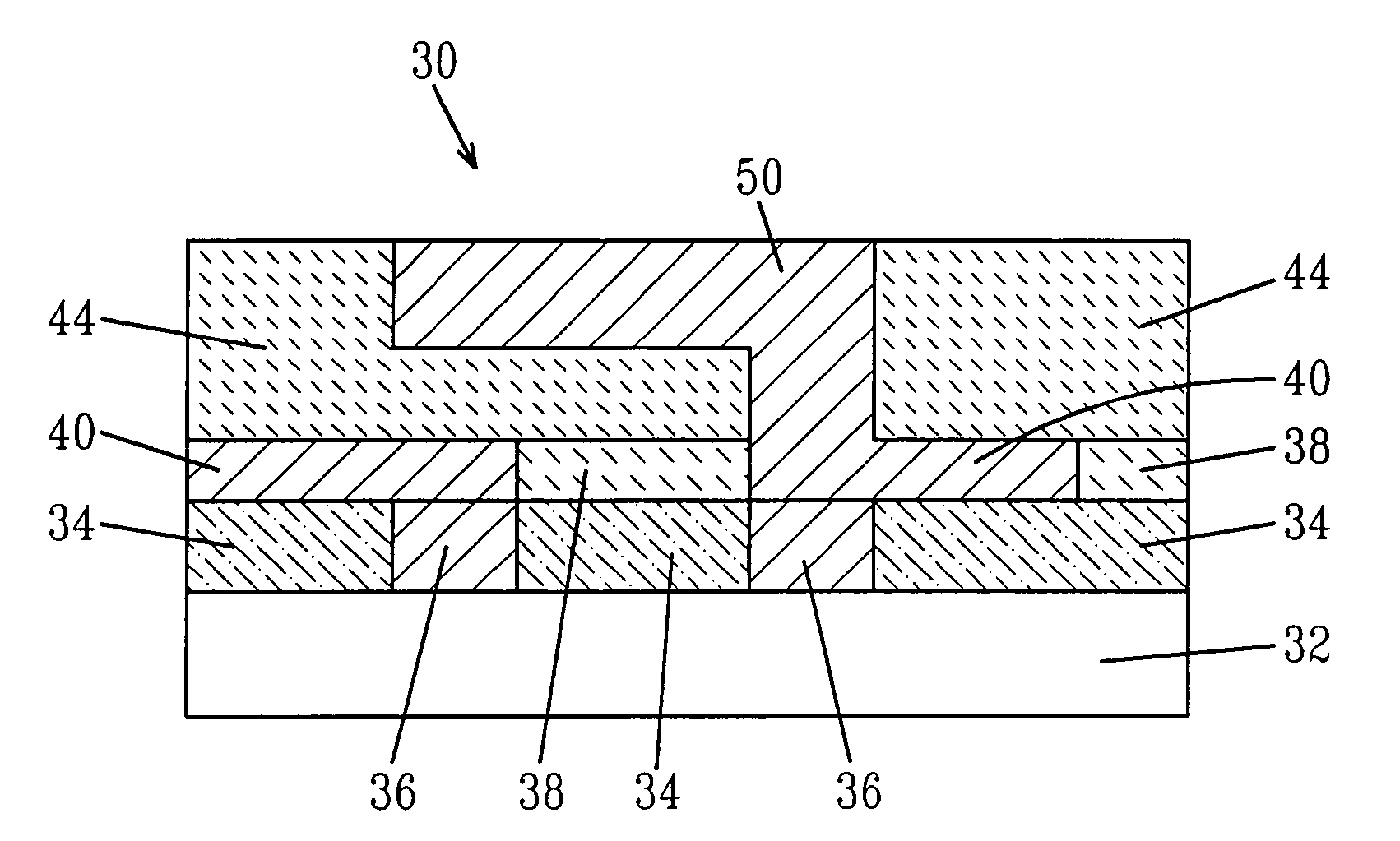

Interconnect for microelectronic structures with enhanced spring characteristics

InactiveUS7048548B2Measurable amount of resiliencyIncrease elasticityElectrical measurement instrument detailsSemiconductor/solid-state device detailsElectronic structureEngineering

An interconnection element and a method of forming an interconnection element. In one embodiment, the interconnection element includes a first structure and a second structure coupled to the first structure. The second structure coupled with the first material has a spring constant greater than the spring constant of the first structure alone. In one embodiment, the interconnection element is adapted to be coupled to an electronic component tracked as a conductive path from the electronic component. In one embodiment, the method includes forming a first (interconnection) structure coupled to a substrate to define a shape suitable as an interconnection in an integrated circuit environment and then coupling, such as by coating, a second (interconnection) structure to the first (interconnection) structure to form an interconnection element. Collectively, the first (interconnection) structure and the second (interconnection) structure have a spring constant greater than a spring constant of the first (interconnection) structure.

Owner:FORMFACTOR INC

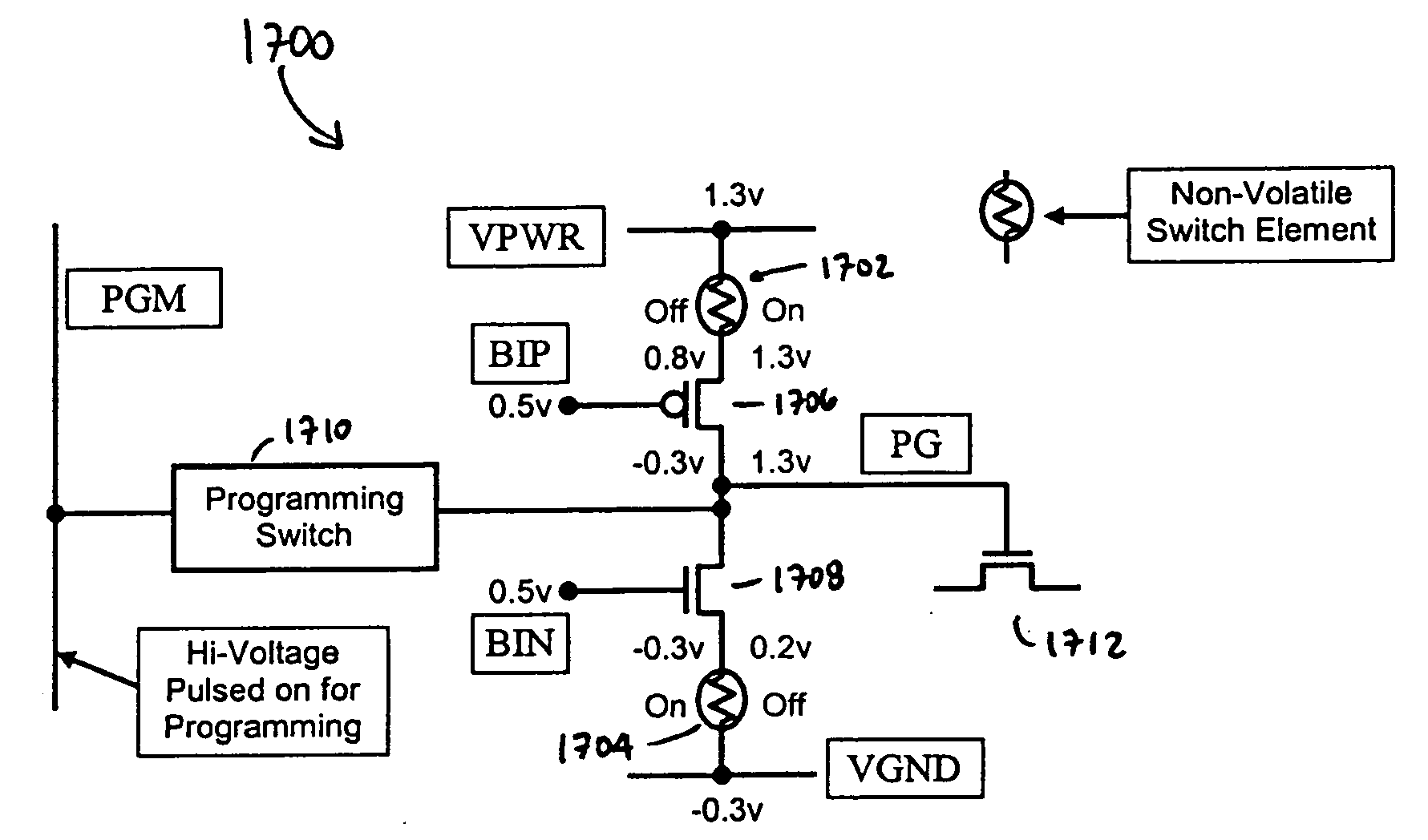

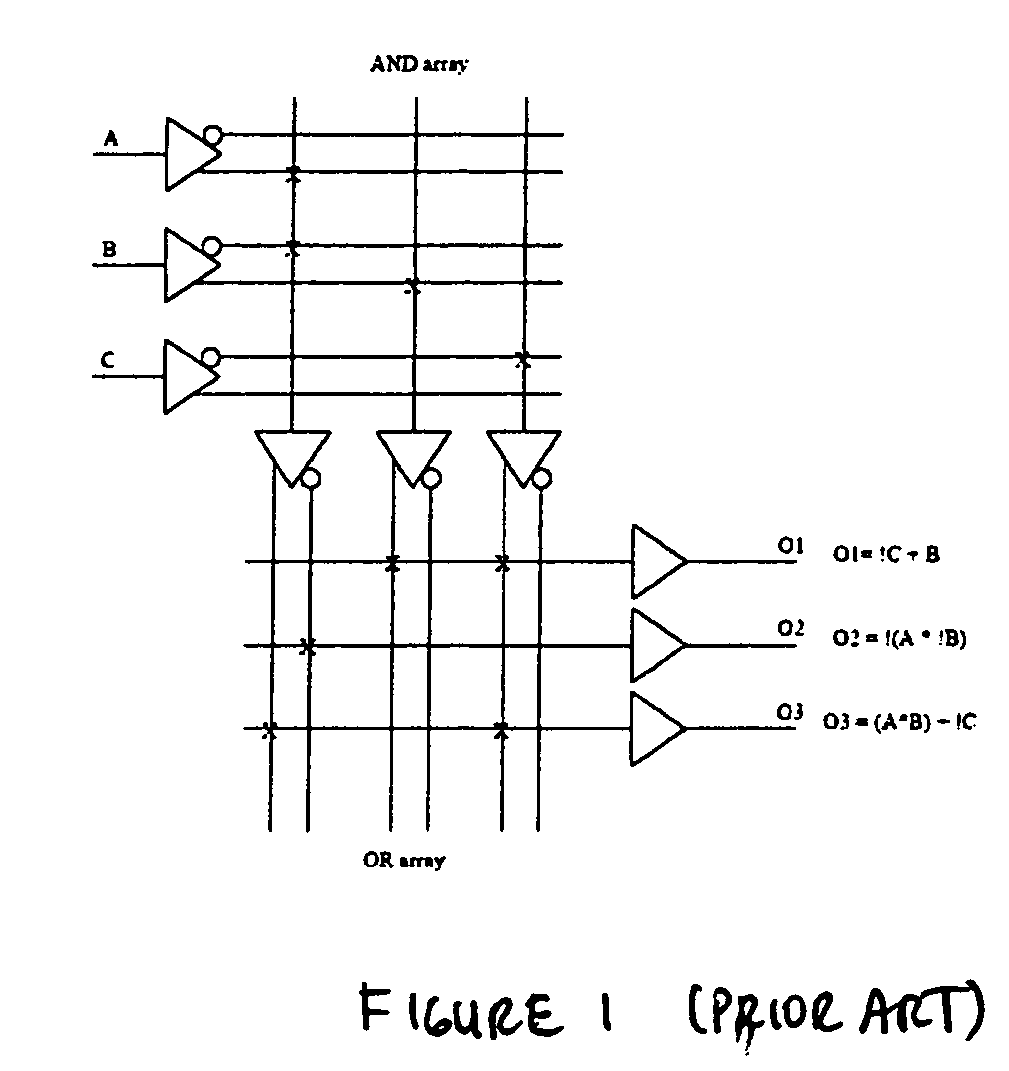

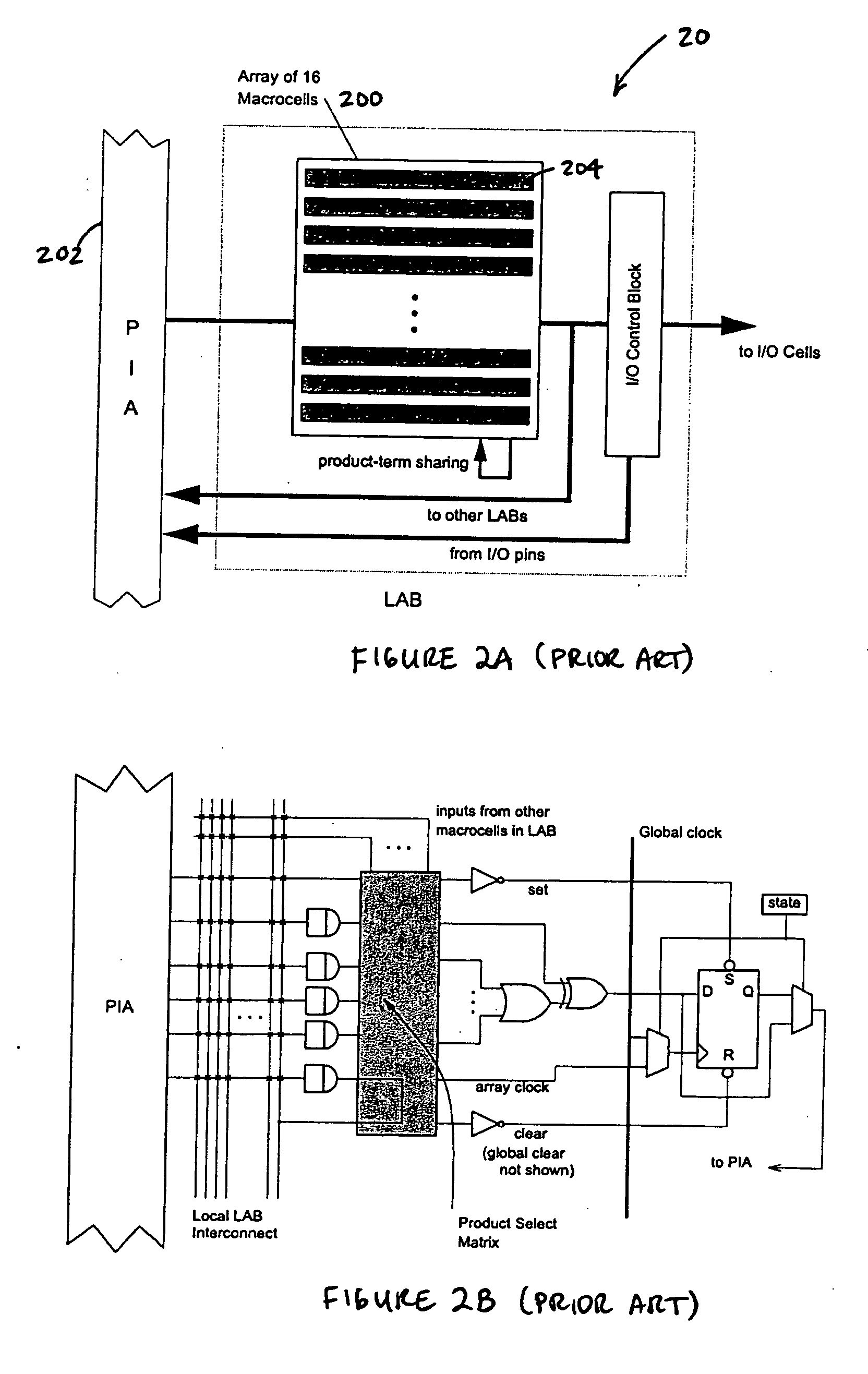

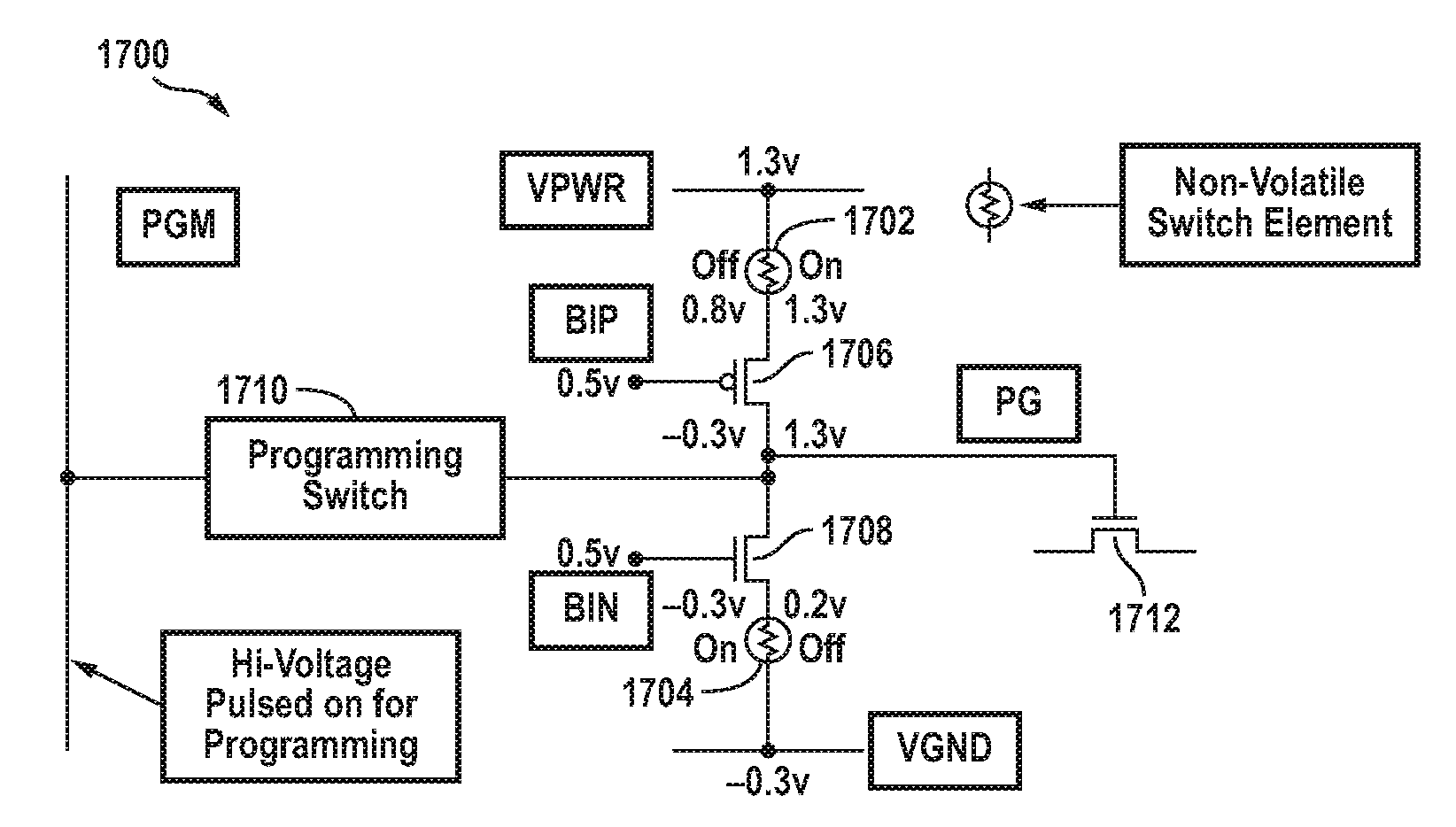

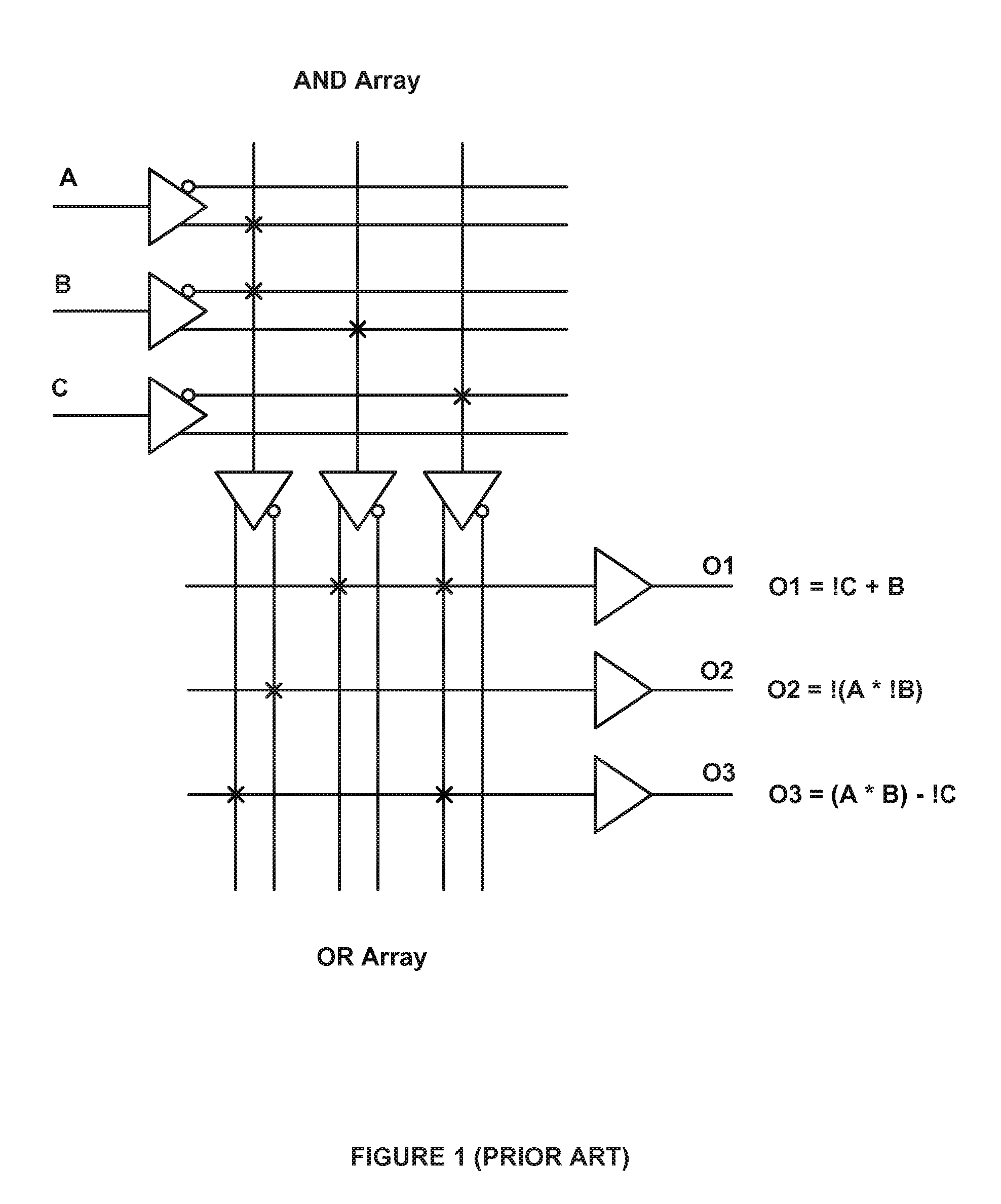

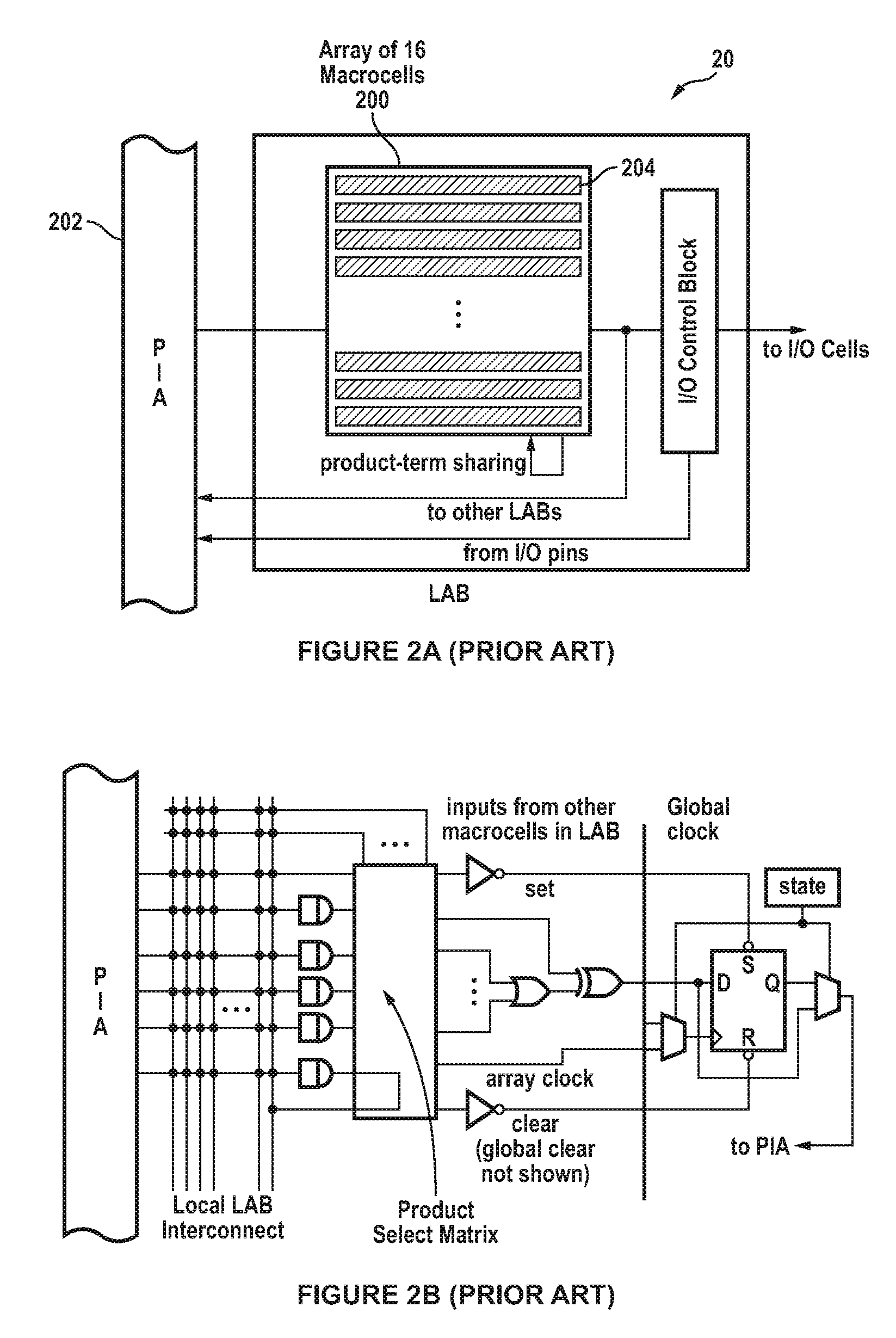

Reconfigurable logic structures

InactiveUS20070146012A1Logic circuits characterised by logic functionNanoinformaticsElectronic structurePhase-change memory

Reconfigurable electronic structures and circuits using programmable, non-volatile memory elements. The programmable, non-volatile memory elements may perform the functions of storage and / or a switch to produce components such as crossbars, multiplexers, look-up tables (LUTs) and other logic circuits used in programmable logic structures (e.g., (FPGAs)). The programmable, non-volatile memory elements comprise one or more structures based on Phase Change Memory, Programmable Metallization, Carbon Nano-Electromechanical (CNT-NEM), or Metal Nano-Electromechanical device technologies.

Owner:CSWITCH

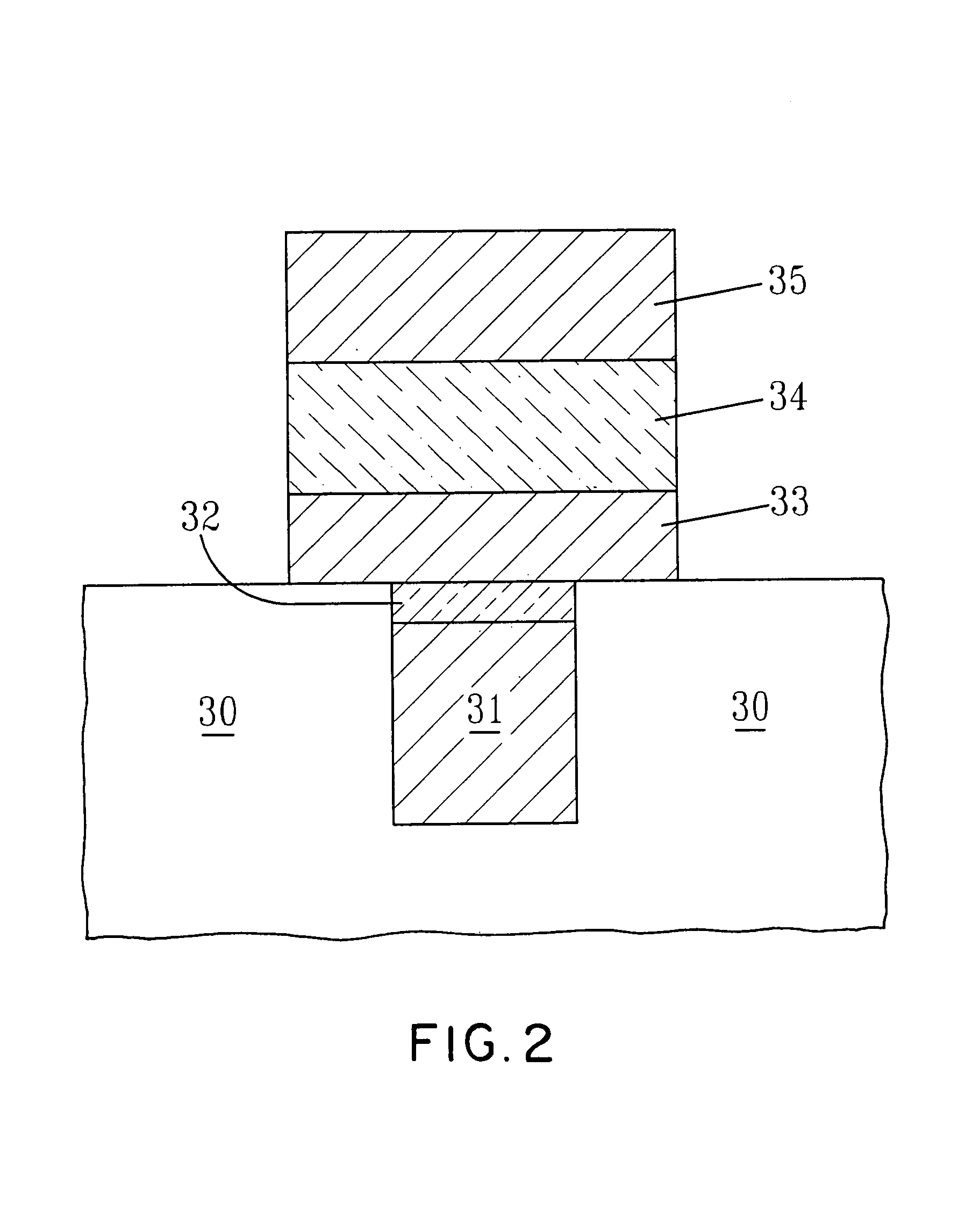

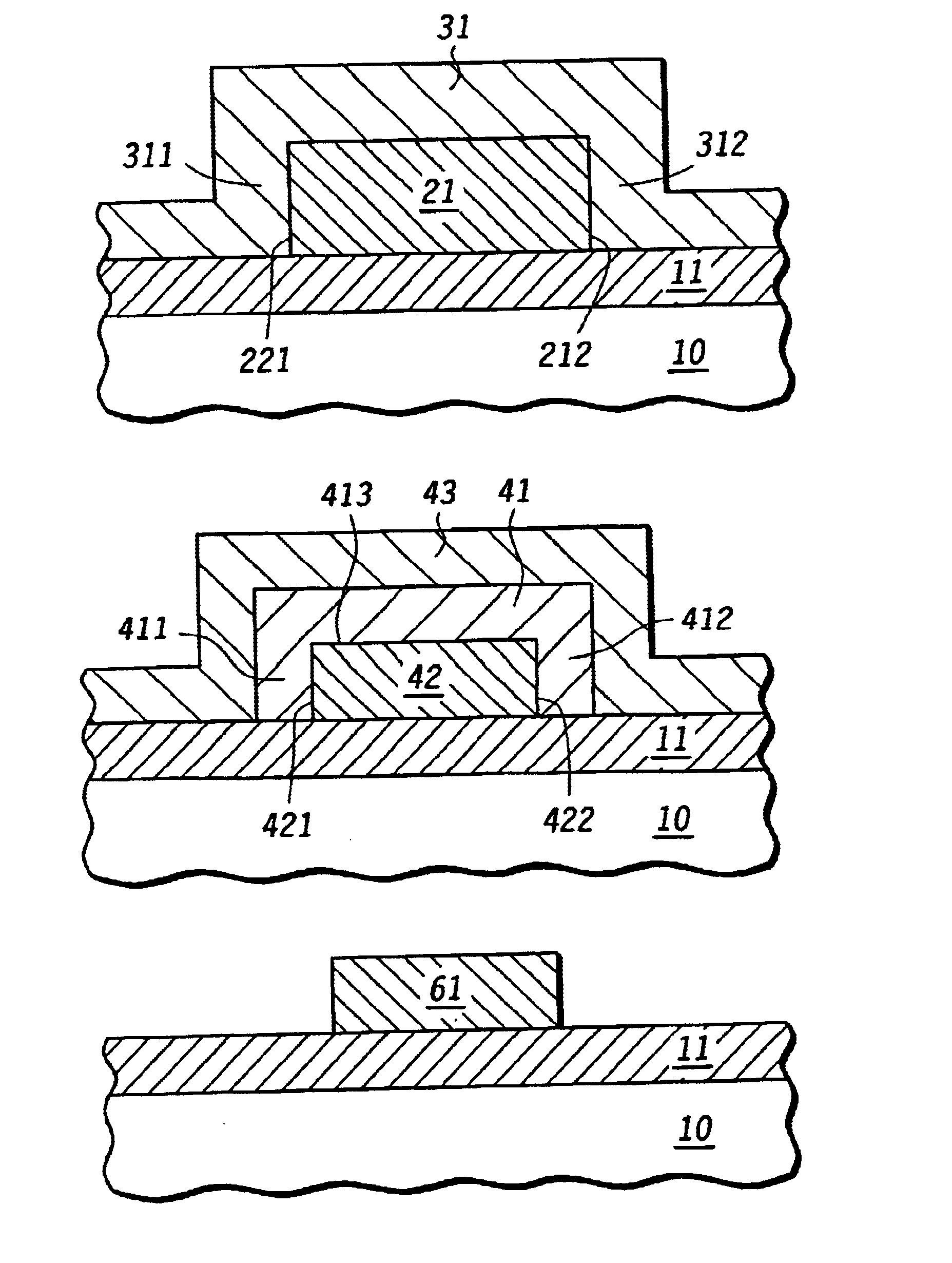

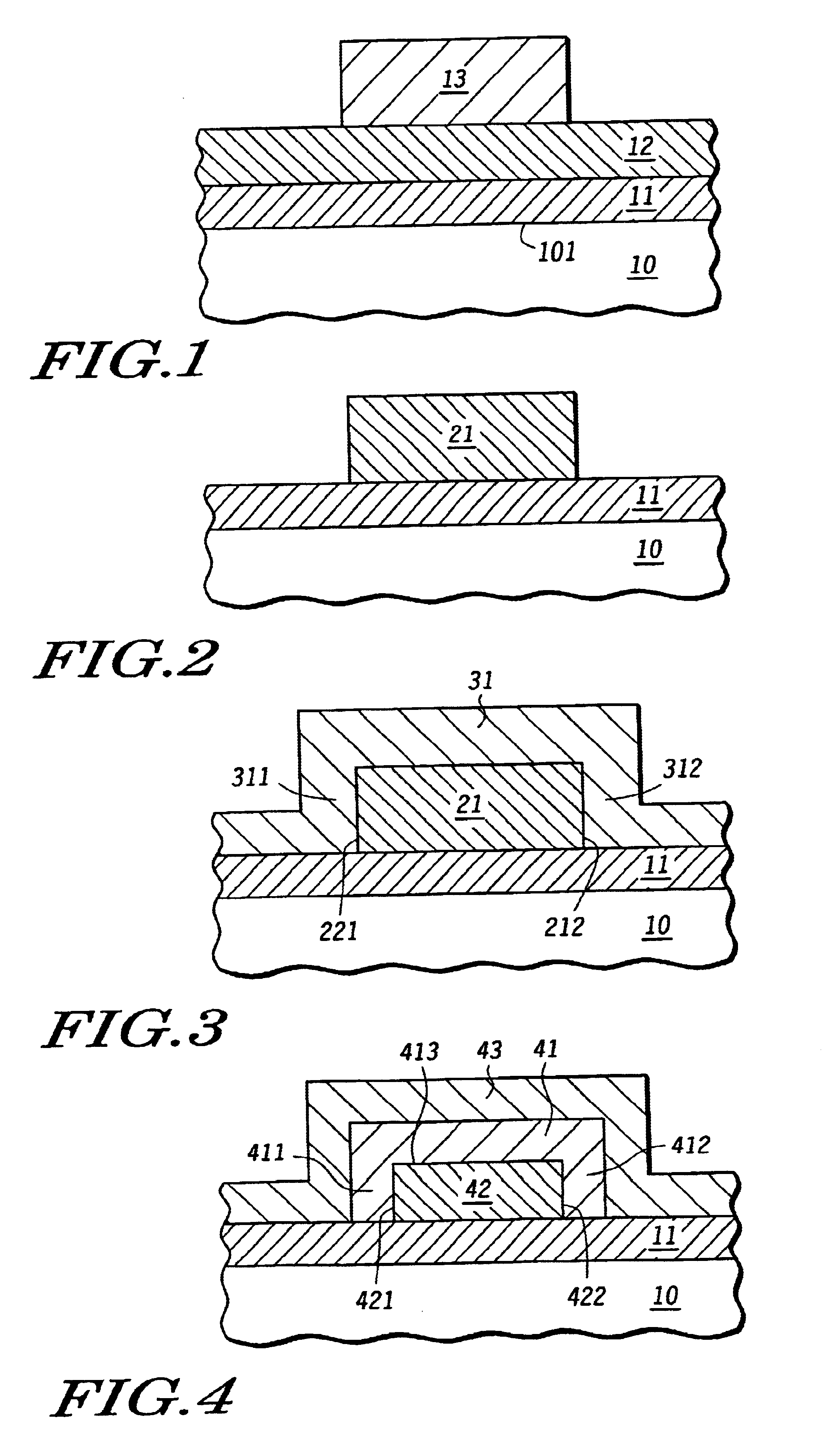

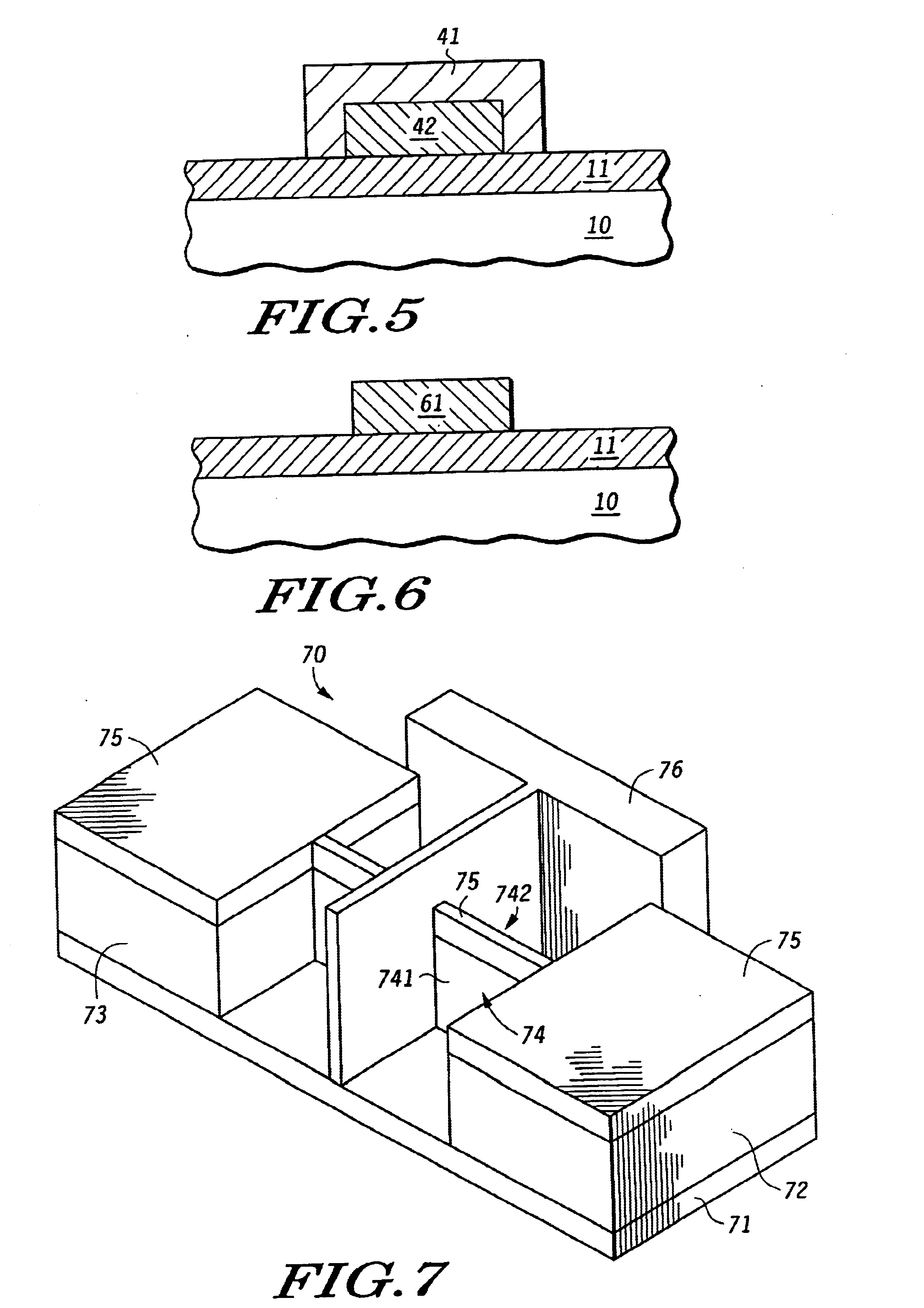

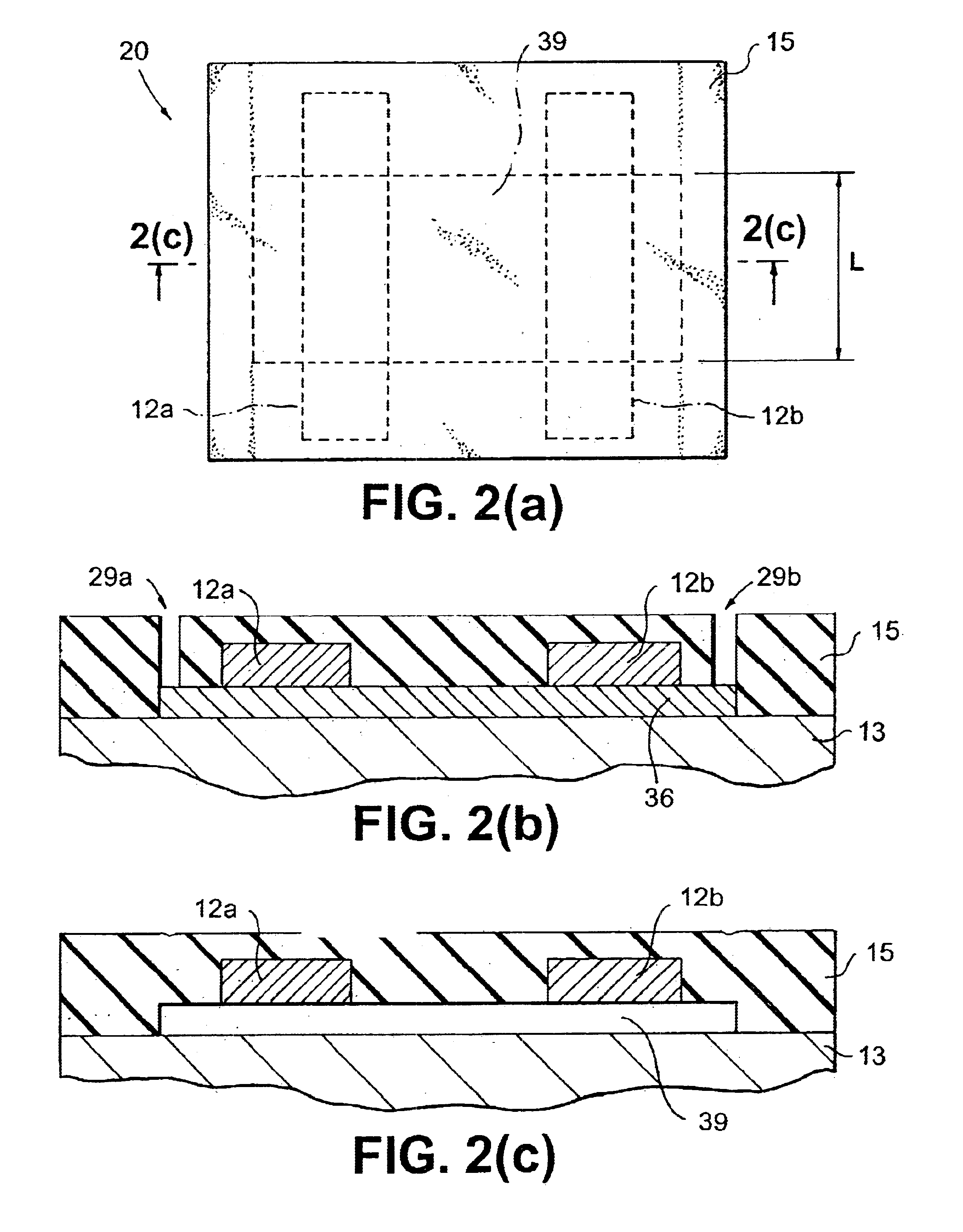

Method for forming an electronic structure using etch

A method of forming a conductive structure having a length that is less than the length define by photolithographic patterning. A silicon layer (12) is formed in a MeOx dielectric layer (11) is photolithographically patterned to a predetermined first length. A metal layer (31) is formed conformally to at least the sidewalls of the silicon layer and then is reacted with the silicon to form a metal silicide (41). In particular, metal silicide abutments (411,412) are formed contiguous to sidewalls (421,422) of a reduced conductor (42). The remaining metal layer and the metal silicide are etched away, resulting in a conductor having predetermined second length that is less than the predetermined first length.

Owner:NORTH STAR INNOVATIONS

Methods to form SiCOH or SiCNH dielectrics and structures including the same

InactiveUS20080009141A1Low costSimple methodSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricElectronic structure

Methods of forming dielectric films comprising Si, C, O and H atoms (SiCOH) or Si, C, N and H atoms (SiCHN) that have improved cohesive strength (or equivalently, improved fracture toughness or reduced brittleness), and increased resistance to water degradation of properties such as stress-corrosion cracking, Cu ingress, and other critical properties are provided. Electronic structures including the above materials are also included herein.

Owner:GLOBALFOUNDRIES INC

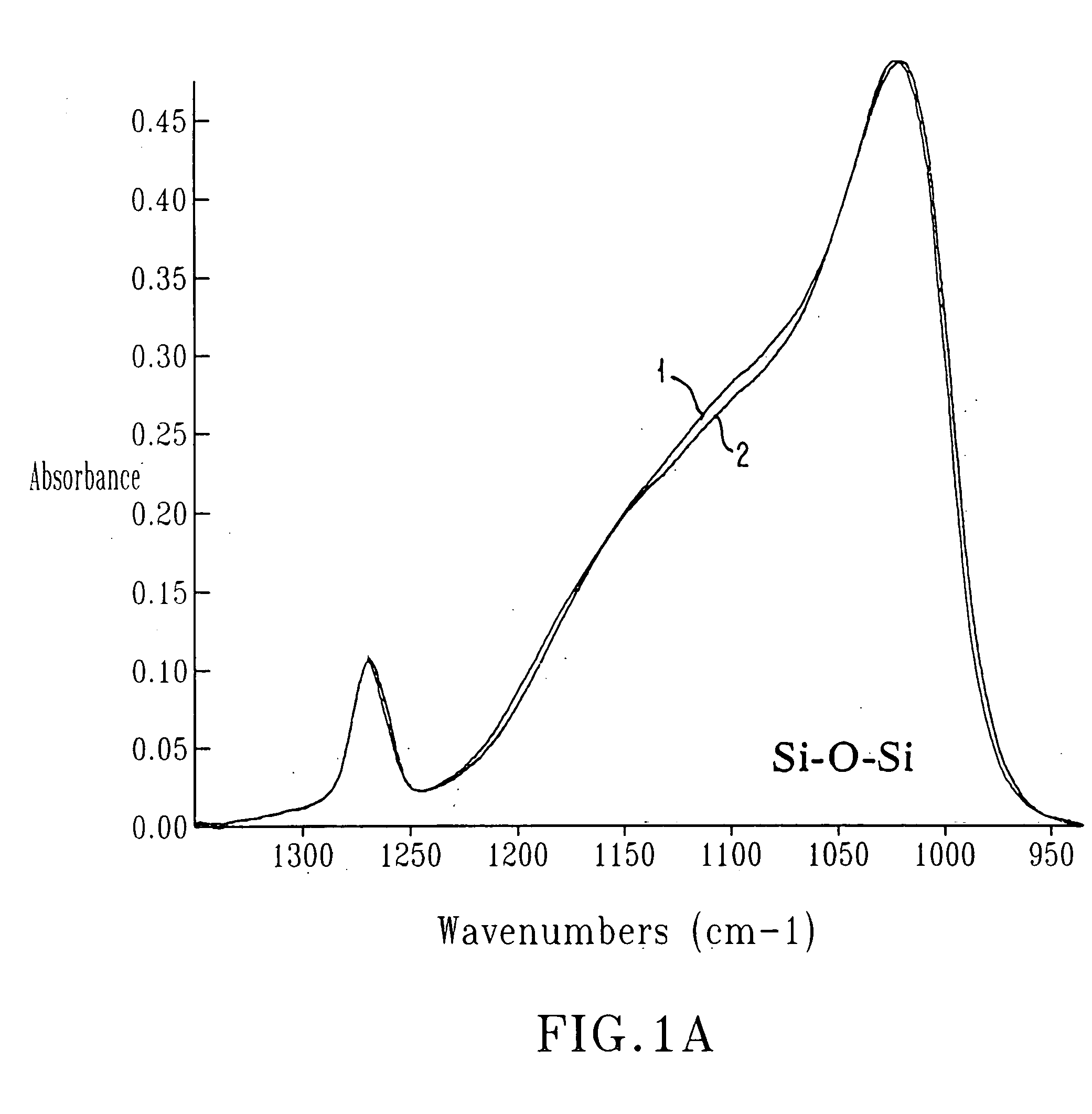

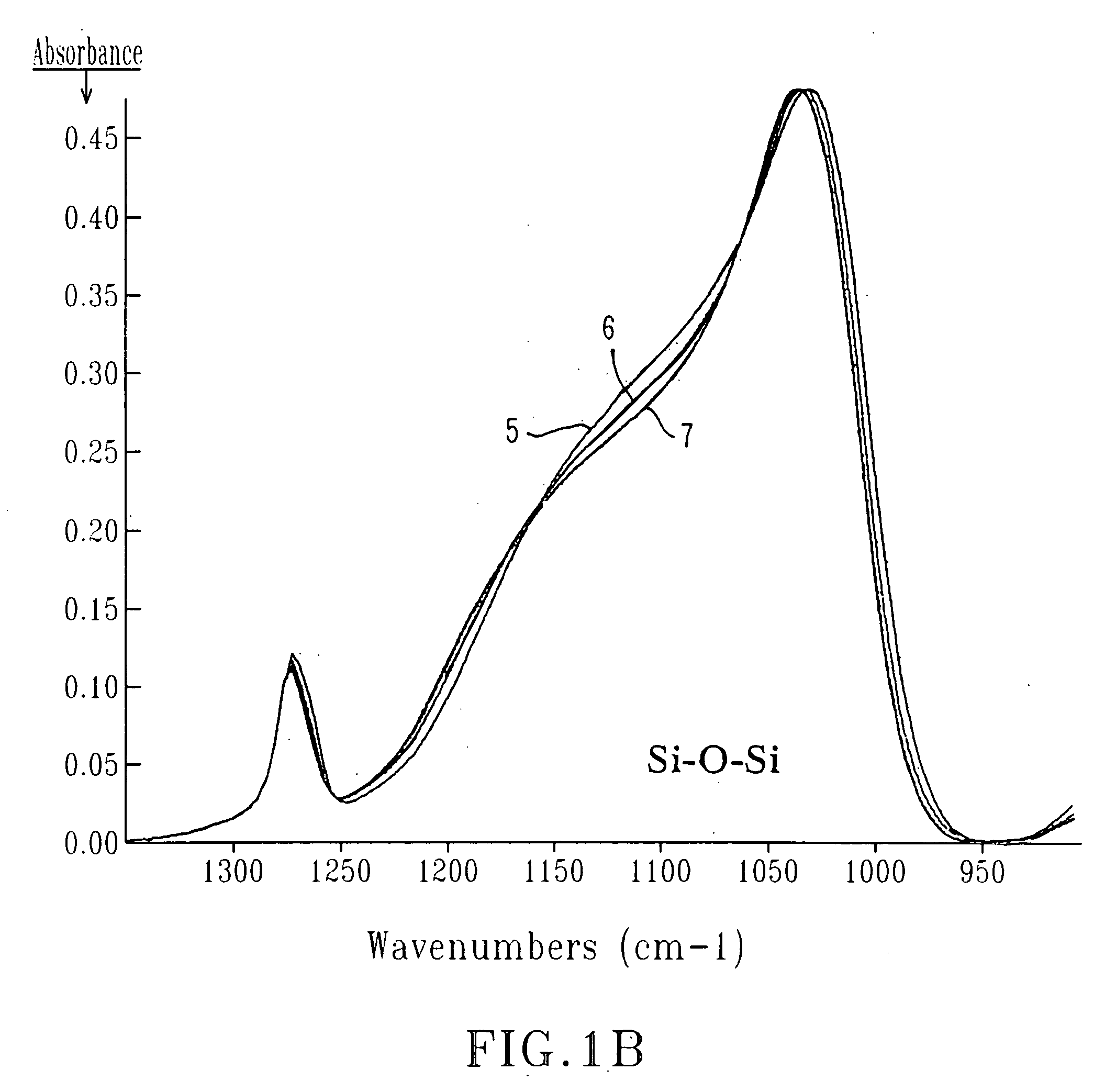

Low k and ultra low k SiCOH dielectric films and methods to form the same

ActiveUS20050156285A1Resistance to crack formationSemiconductor/solid-state device detailsSolid-state devicesDielectricElectronic structure

Dielectric materials including elements of Si, C, O and H having specific values of mechanical properties (tensile stress, elastic modulus, hardness cohesive strength, crack velocity in water) that result in a stable ultra low k film which is not degraded by water vapor or integration processing are provided. The dielectric materials have a dielectric constant of about 2.8 or less, a tensile stress of less than 45 MPa, an elastic modulus from about 2 to about 15 GPa, and a hardness from about 0.2 to about 2 GPa. Electronic structures including the dielectric materials of the present invention as well as various methods of fabricating the dielectric materials are also provided.

Owner:GLOBALFOUNDRIES US INC

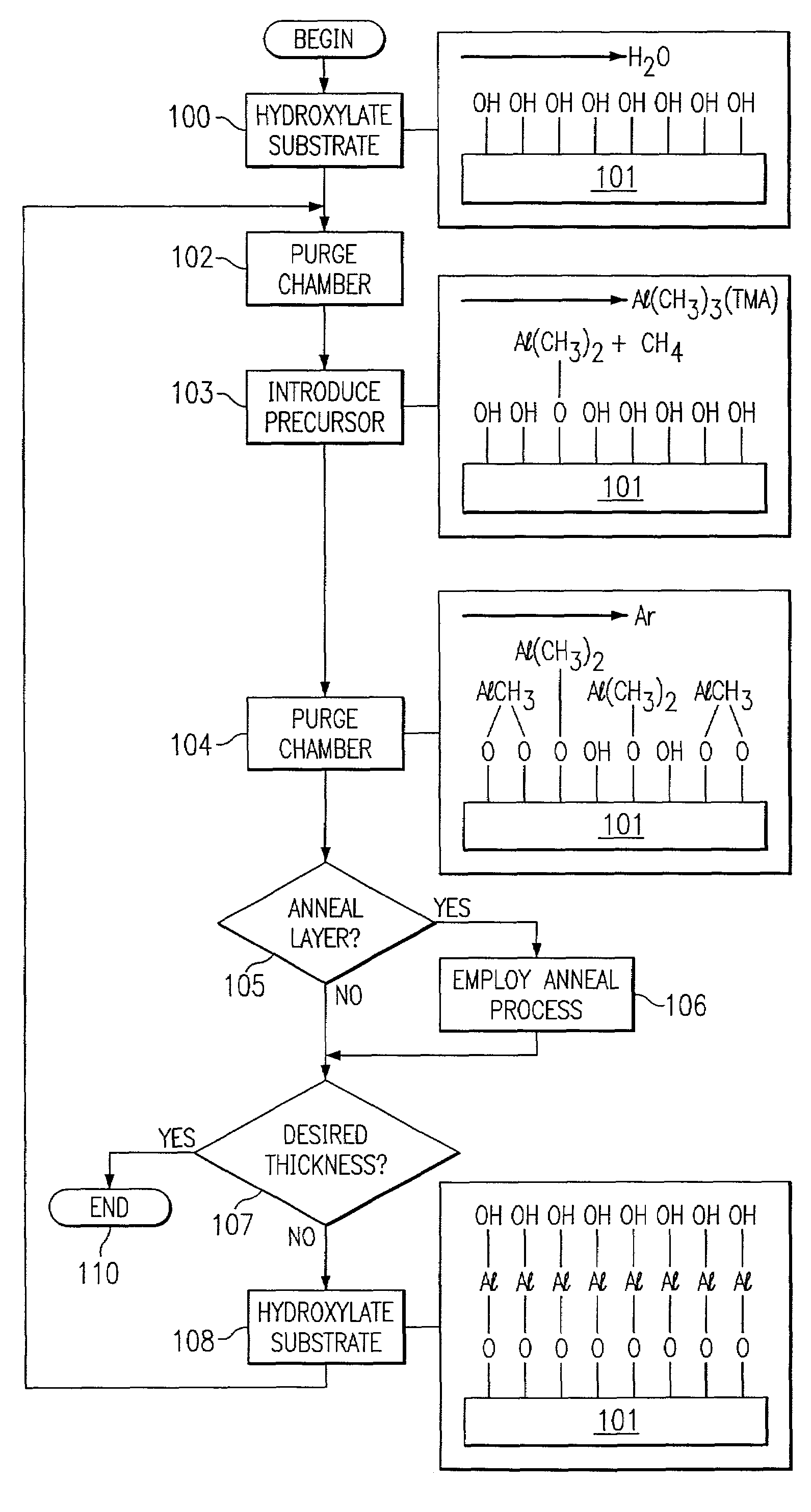

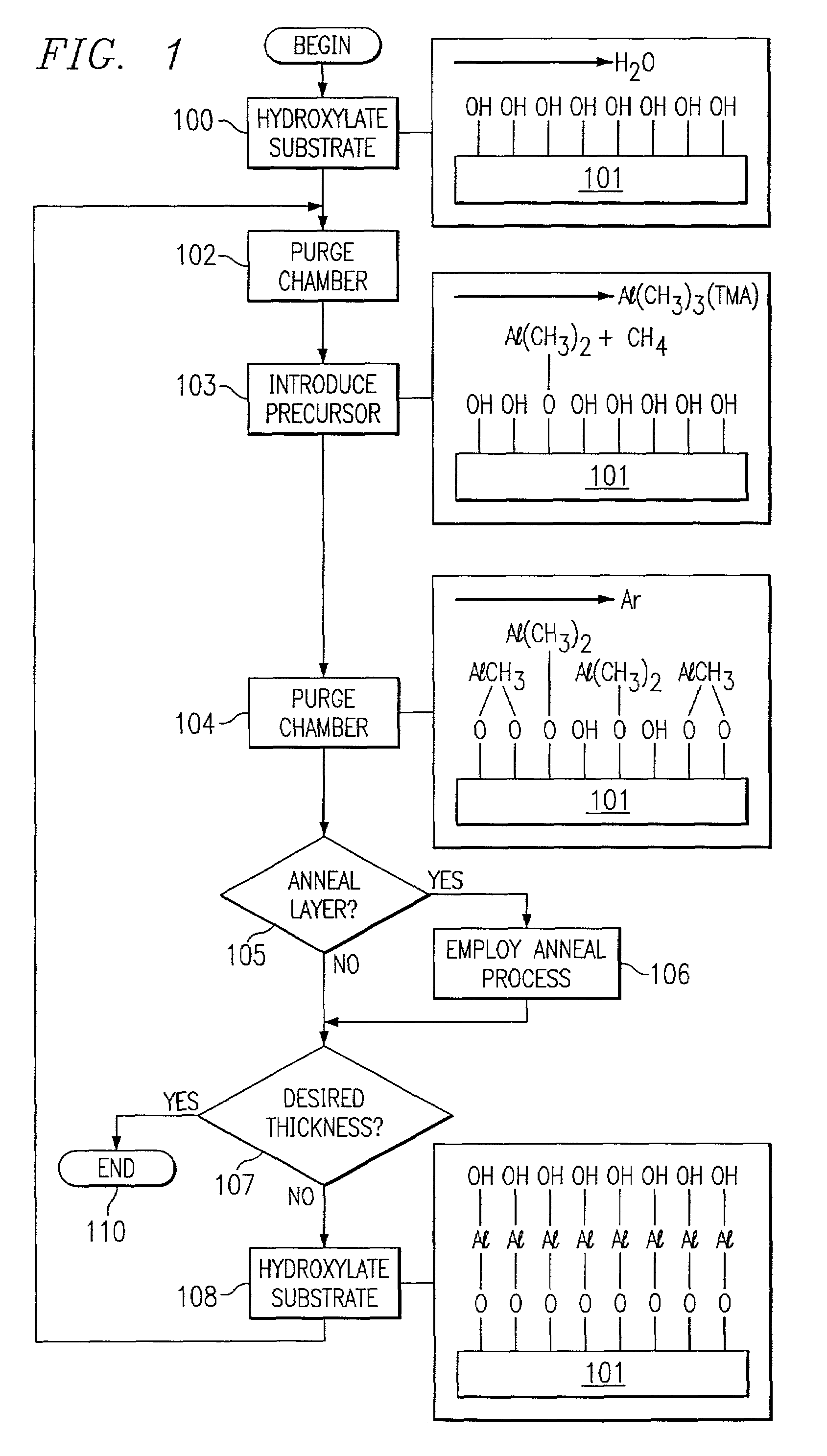

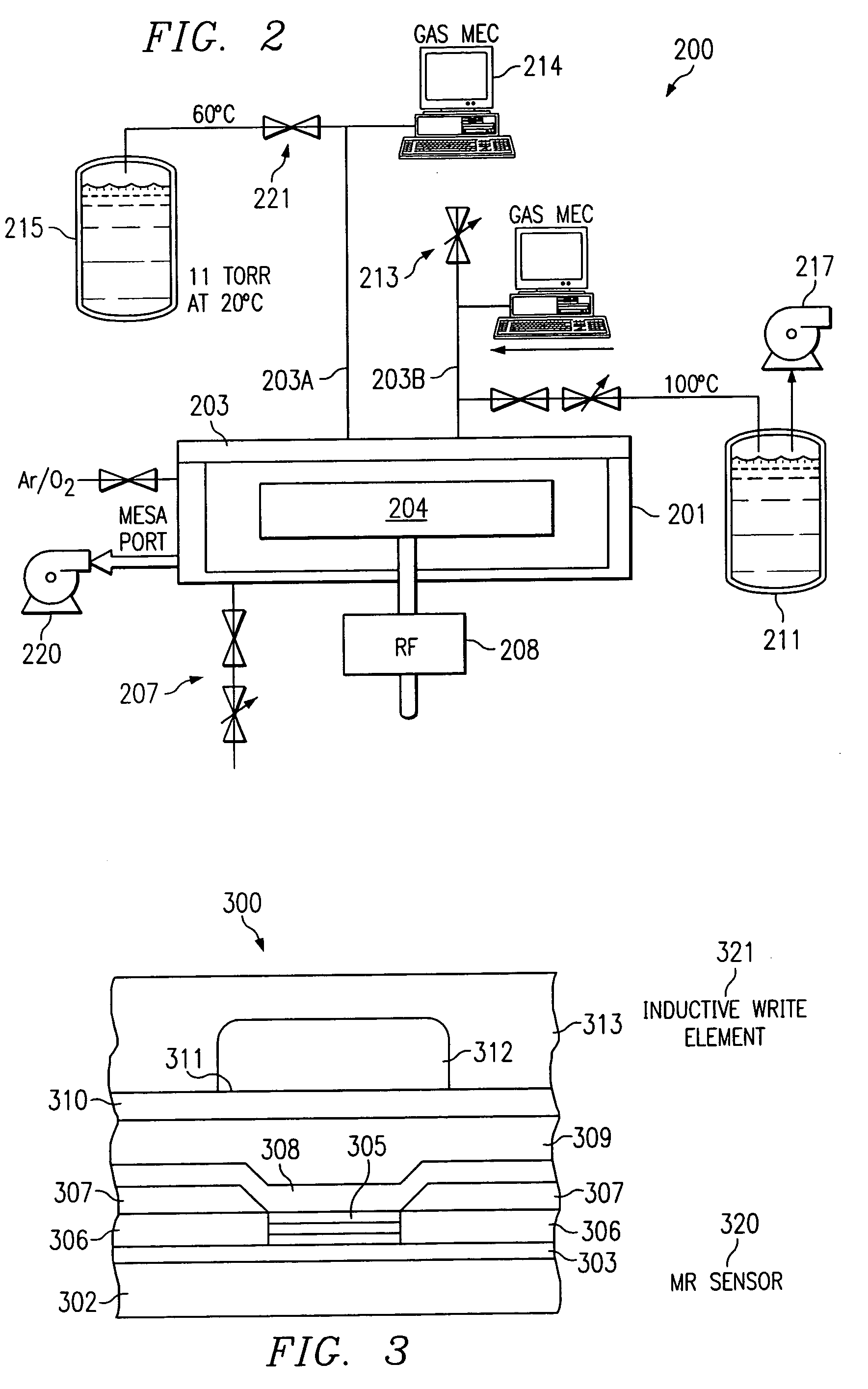

Atomic layer deposition for fabricating thin films

InactiveUS7037574B2High breakdown strengthImprove breakdown voltageNanostructure applicationLiquid surface applicatorsElectronic structureBreakdown strength

An atomic layer deposition (ALD) process deposits thin films for microelectronic structures, such as advanced gap and tunnel junction applications, by plasma annealing at varying film thicknesses to obtain desired intrinsic film stress and breakdown film strength. The primary advantage of the ALD process is the near 100% step coverage with properties that are uniform along sidewalls. The process provides smooth (Ra˜2 Å), pure (impurities<1 at. %), AlOx films with improved breakdown strength (9–10 MV / cm) with a commercially feasible throughput.

Owner:CVC PRODS

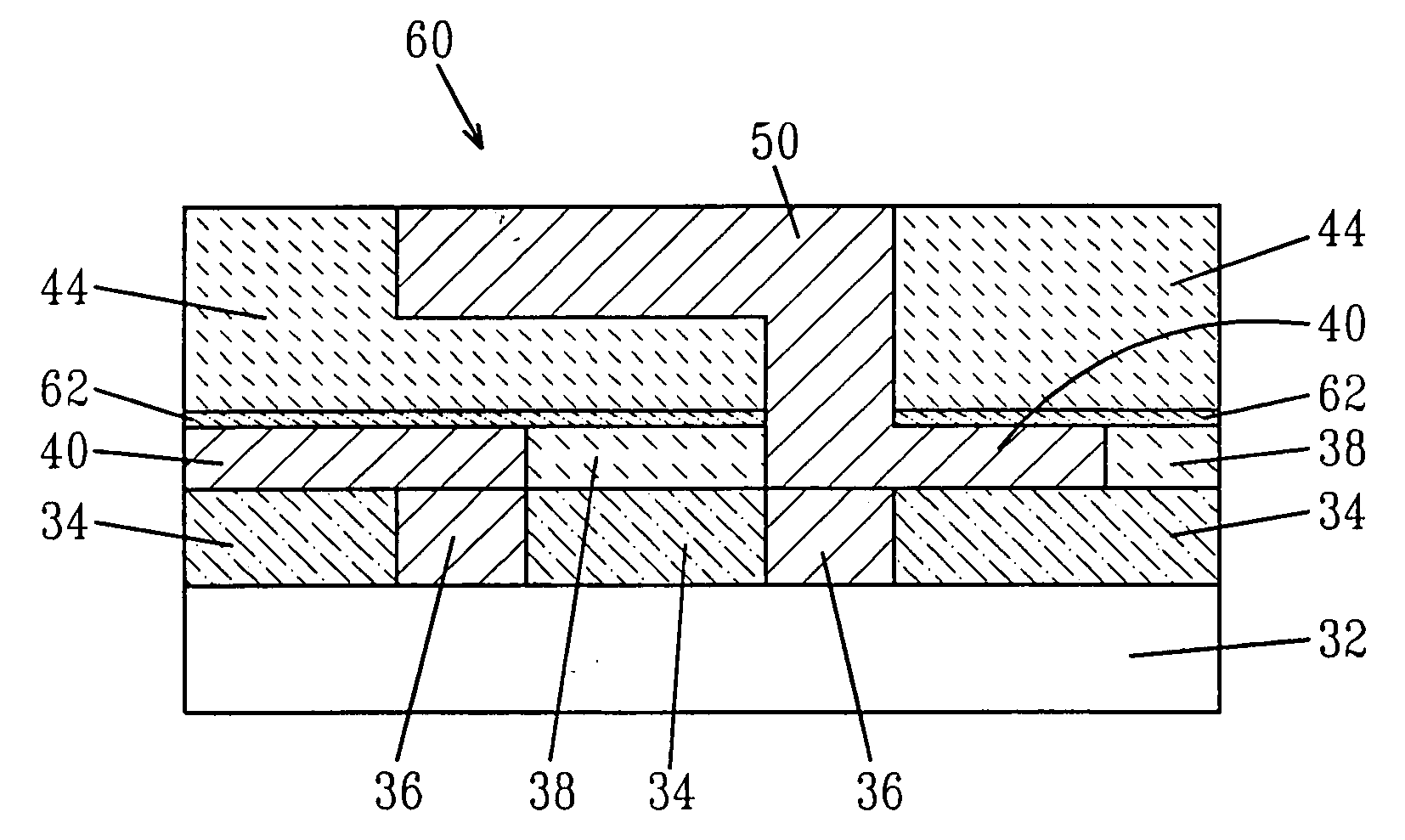

Maskless nanofabrication of electronic components

InactiveUS20100035375A1Reduce the amount requiredEfficient methodRadiation applicationsSolid-state devicesElectronic structureNanoparticle

The present invention relates to systems, materials and methods for the formation of conducting, semiconducting, and dielectric layers, structures and devices from suspensions of nanoparticles. Drop-on-demand systems are used in some embodiments to fabricate various electronic structures including conductors, capacitors, FETs. Selective laser ablation is used in some embodiments to pattern more precisely the circuit elements and to form small channel devices.

Owner:RGT UNIV OF CALIFORNIA +1

Ultra low k plasma enhanced chemical vapor deposition processes using a single bifunctional precursor containing both a SiCOH matrix functionality and organic porogen functionality

InactiveUS20060079099A1Easy to controlImprove film thickness uniformitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingDisiloxaneEpoxy

A method for fabricating a SiCOH dielectric material comprising Si, C, O and H atoms from a single organosilicon precursor with a built-in organic porogen is provided. The single organosilicon precursor with a built-in organic porogen is selected from silane (SiH4) derivatives having the molecular formula SiRR1R2R3, disiloxane derivatives having the molecular formula R4R5R6—Si—O—Si—R7R8R9, and trisiloxane derivatives having the molecular formula R10R11R12—Si—O—Si—R13R14—O—Si—R15R16R17 where R and R1-17 may or may not be identical and are selected from H, alkyl, alkoxy, epoxy, phenyl, vinyl, allyl, alkenyl or alkynyl groups that may be linear, branched, cyclic, polycyclic and may be functionalized with oxygen, nitrogen or fluorine containing substituents. In addition to the method, the present application also provides SiCOH dielectrics made from the inventive method as well as electronic structures that contain the same.

Owner:GLOBALFOUNDRIES INC

Low k and ultra low k SiCOH dielectric films and methods to form the same

Dielectric materials including elements of Si, C, O and H having specific values of mechanical properties (tensile stress, elastic modulus, hardness cohesive strength, crack velocity in water) that result in a stable ultra low k film which is not degraded by water vapor or integration processing are provided. The dielectric materials have a dielectric constant of about 2.8 or less, a tensile stress of less than 45 MPa, an elastic modulus from about 2 to about 15 GPa, and a hardness from about 0.2 to about 2 GPa. Electronic structures including the dielectric materials of the present invention as well as various methods of fabricating the dielectric materials are also provided.

Owner:GLOBALFOUNDRIES U S INC

Low K and ultra low K SiCOH dielectric films and methods to form the same

ActiveUS20060055004A1Resistance to crack formationSemiconductor/solid-state device detailsSolid-state devicesDielectricElectronic structure

Dielectric materials including elements of Si, C, O and H having specific values of mechanical properties (tensile stress, elastic modulus, hardness cohesive strength, crack velocity in water) that result in a stable ultra low k film which is not degraded by water vapor or integration processing are provided. The dielectric materials have a dielectric constant of about 2.8 or less, a tensile stress of less than 45 MPa, an elastic modulus from about 2 to about 15 GPa, and a hardness from about 0.2 to about 2 GPa. Electronic structures including the dielectric materials of the present invention as well as various methods of fabricating the dielectric materials are also provided.

Owner:GLOBALFOUNDRIES U S INC

Electronic fuse structure and method of manufacturing

InactiveUS6633055B2Load minimizationMinimum of process stepThyristorSemiconductor/solid-state device detailsCapacitanceElectrical conductor

A gap conductor structure for an integrated electronic circuit that may function as an electronic fuse device or as a low capacitance inter level signal line is integrated as part of the semi-conductor chip wiring. The gap conducting structure includes one or more air gap regions of predefined volume that fully or partially exposes a length of interlevel conductor layer in an IC. Alternately, the air gap region may wholly located within the dielectric region below a corresponding conductor and separated by insulator. When functioning as a fuse, the gap region acts to reduce thermal conductivity away from the exposed portion of the conductor enabling generation of higher heat currents in the conducting line with lower applied voltages sufficient to melt a part of the conducting line. The presence of gaps, and hence, the fuses, are scalable and may be tailored to the capacity of currents they must carry with the characteristics of the fuses defined by a circuit designer. Furthermore, conducting structures completely or partially exposed in the air gap may function as low capacitance minimum delay transmission lines.< / PTEXT>

Owner:GOOGLE LLC

Connections for electronic devices on double-sided circuit board

ActiveUS20090250255A1Final product manufacturePrinted electric component incorporationElectronic structureEngineering

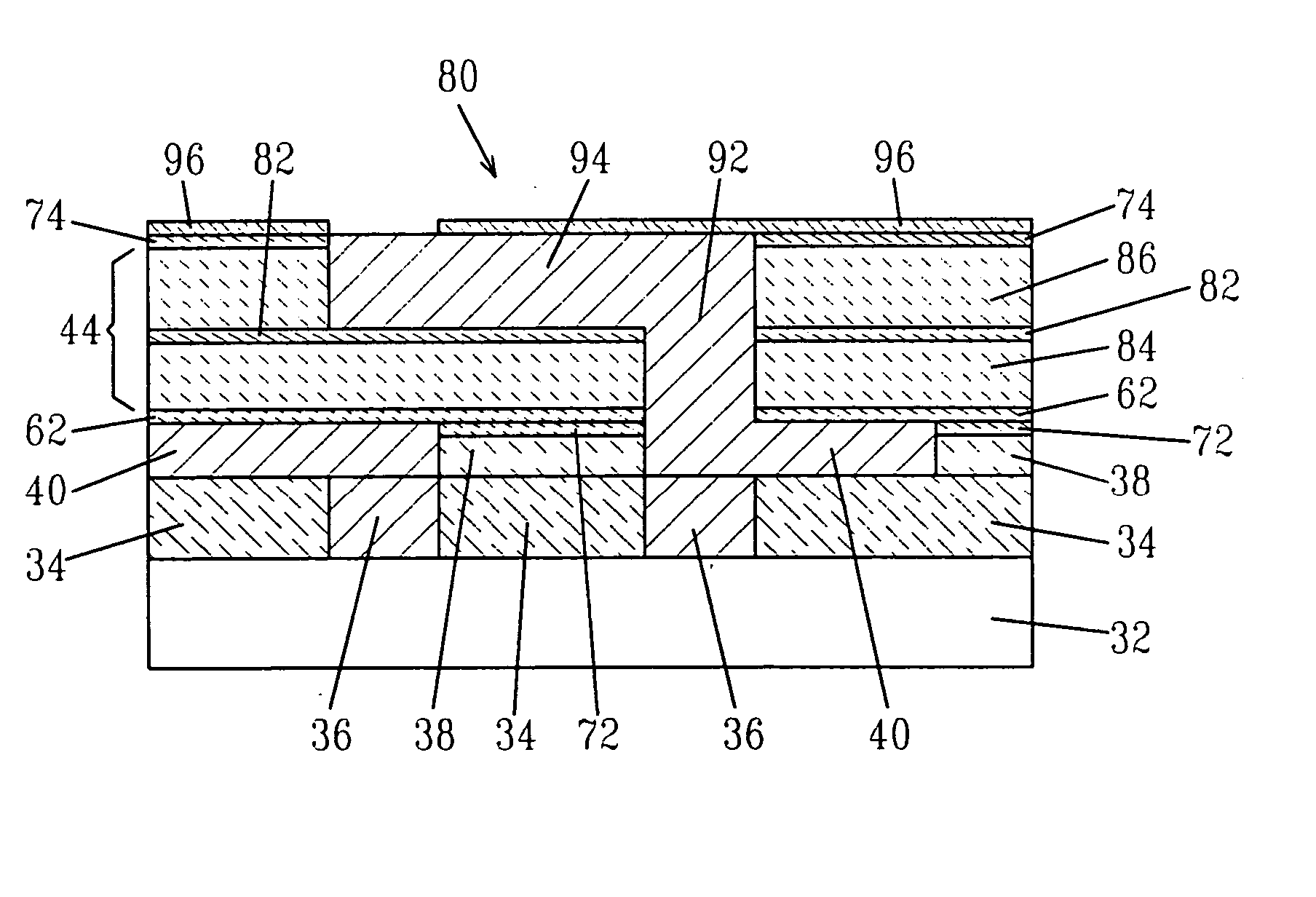

In the present electronic structure, a substrate is provided in the form of a circuit board. First and second electronic devices are positioned on opposite sides of the circuit board, each having a plurality of contacts connected to the circuit board. Each of the contacts of the first device is connected to a contact of the second device by a connector though the circuit board. At least one of the contacts of the first device is connected to the contact of the second device which is most adjacent to that contact of the first device across the circuit board.

Owner:CYPRESS SEMICON CORP

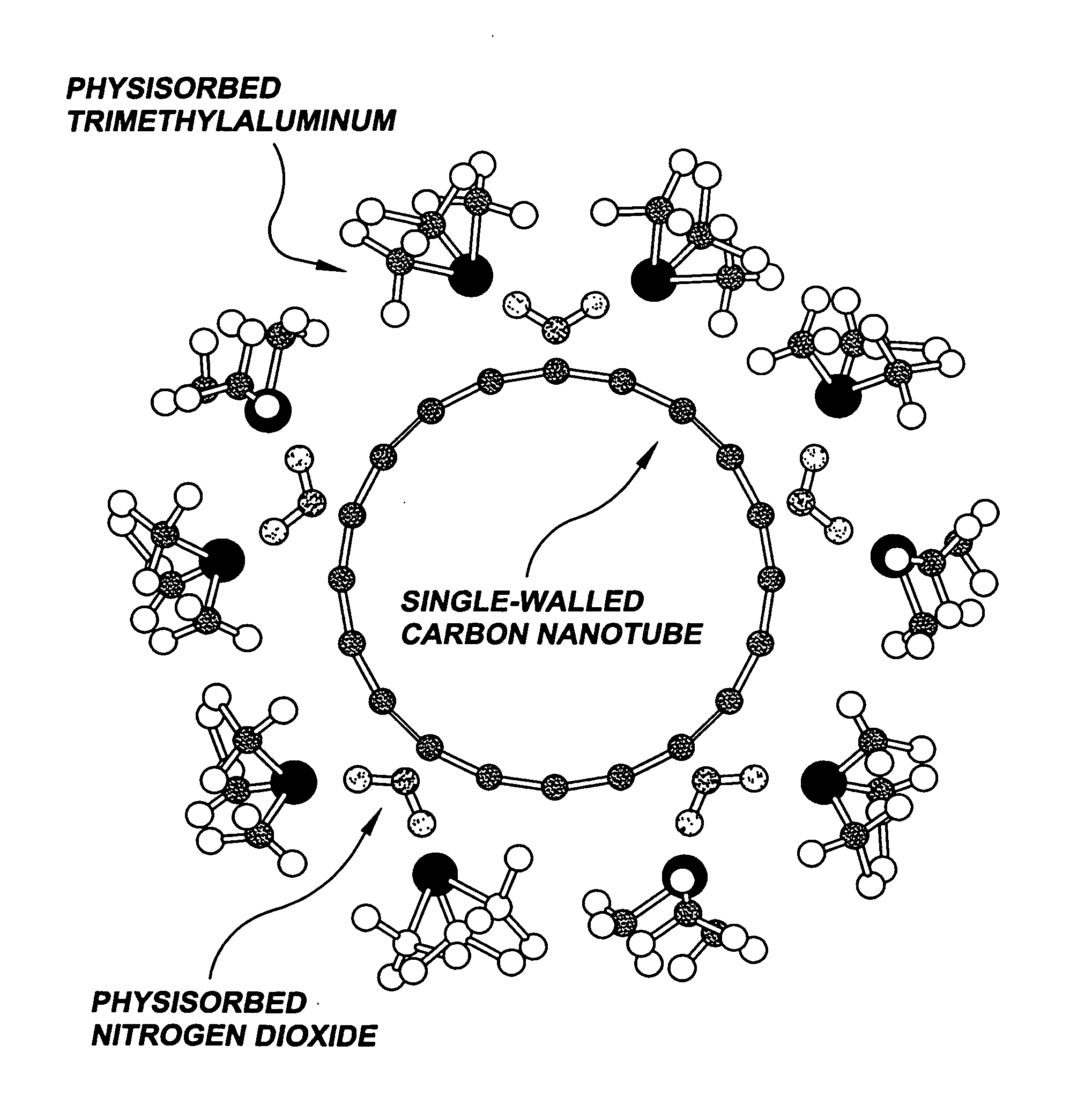

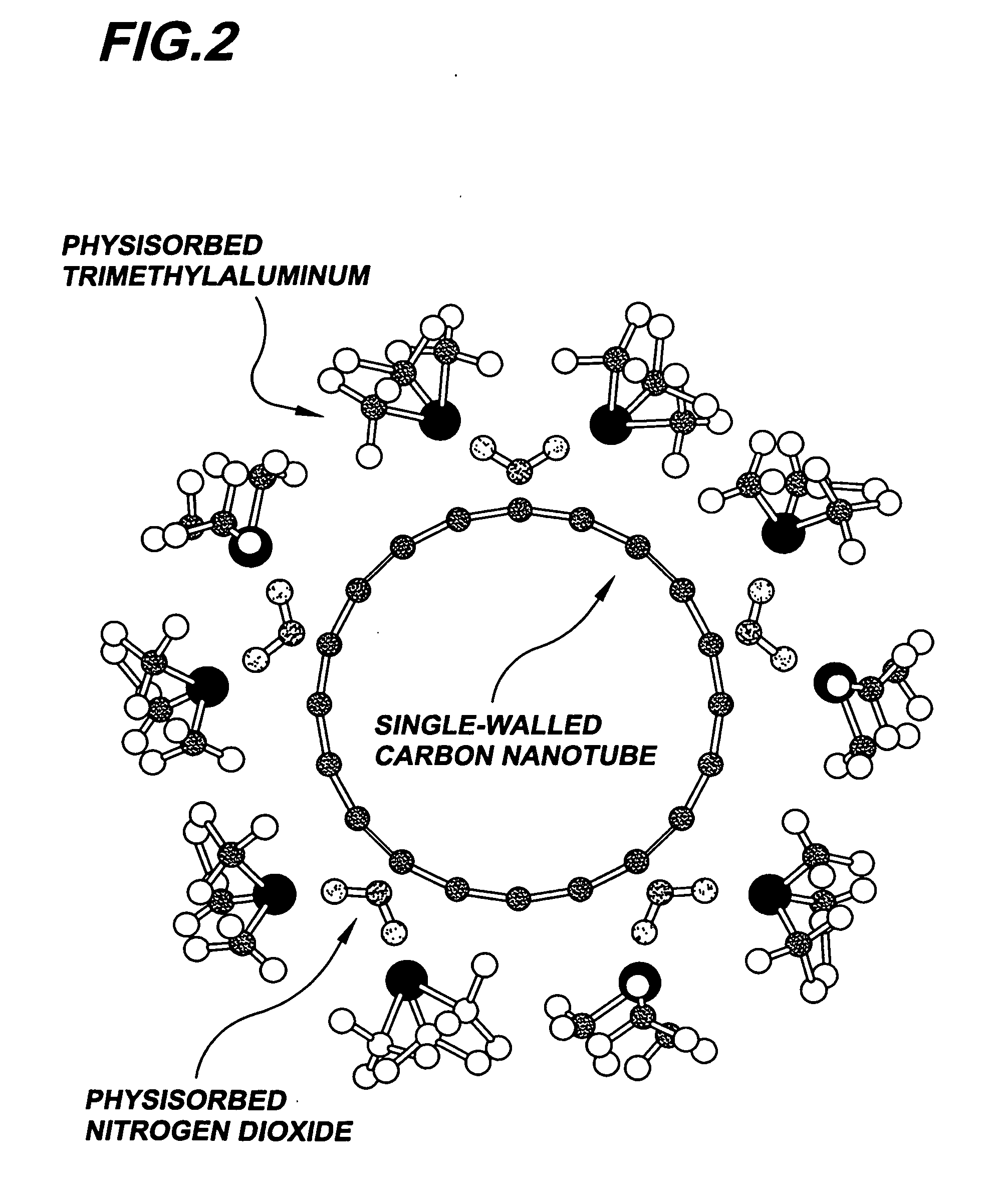

Gas-phase functionalization of surfaces including carbon-based surfaces

The invention provides methods functionalizing a planar surface of a graphene layer, a graphite surface, or microelectronic structure. The graphene layer, graphite surface, or planar microelectronic structure surface is exposed to at least one vapor including at least one functionalization species that non-covalently bonds to the graphene layer, a graphite surface, or planar microelectronic surface while providing a functionalization layer of chemically functional groups, to produce a functionalized graphene layer, graphite surface, or planar microelectronic surface.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

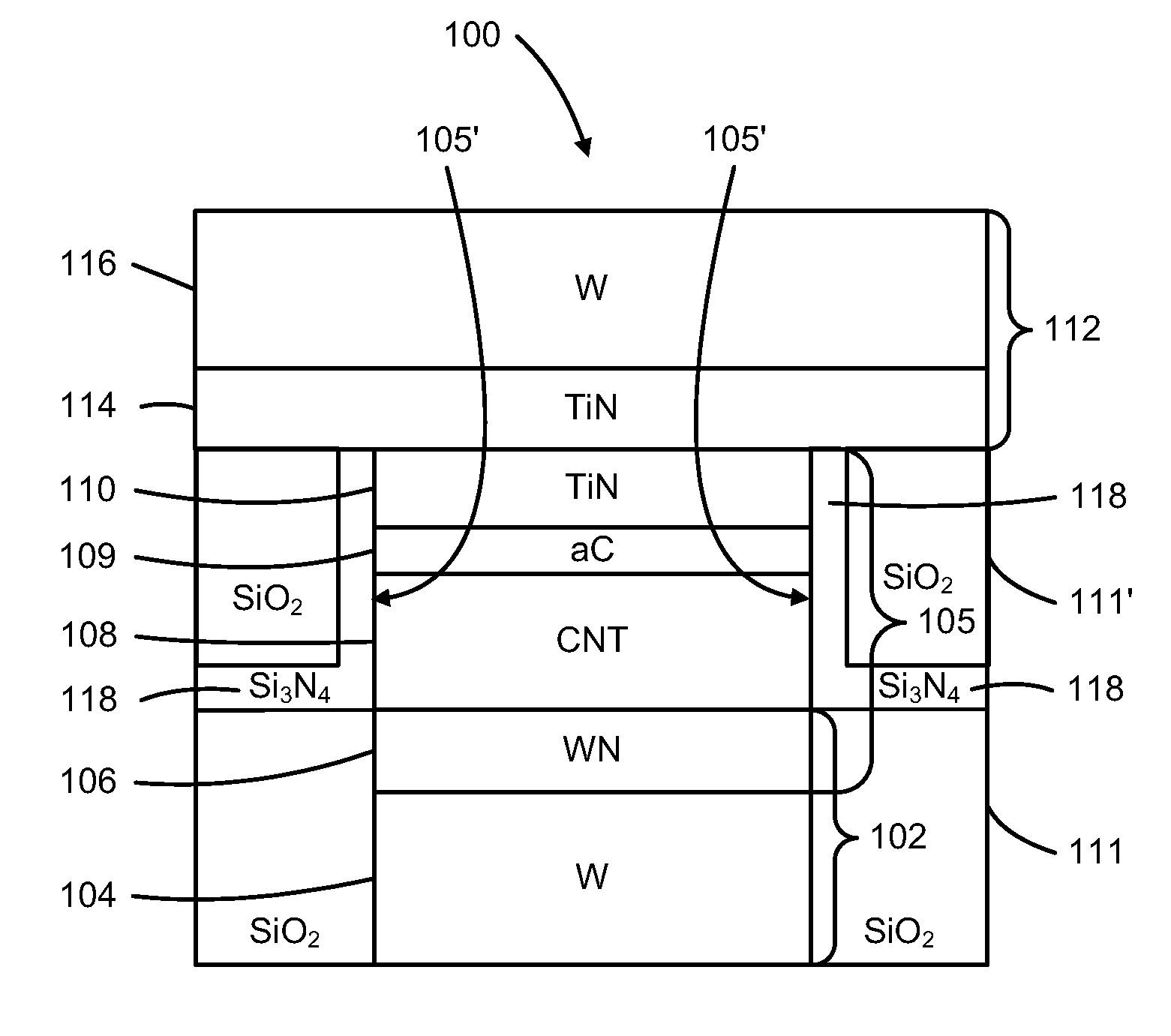

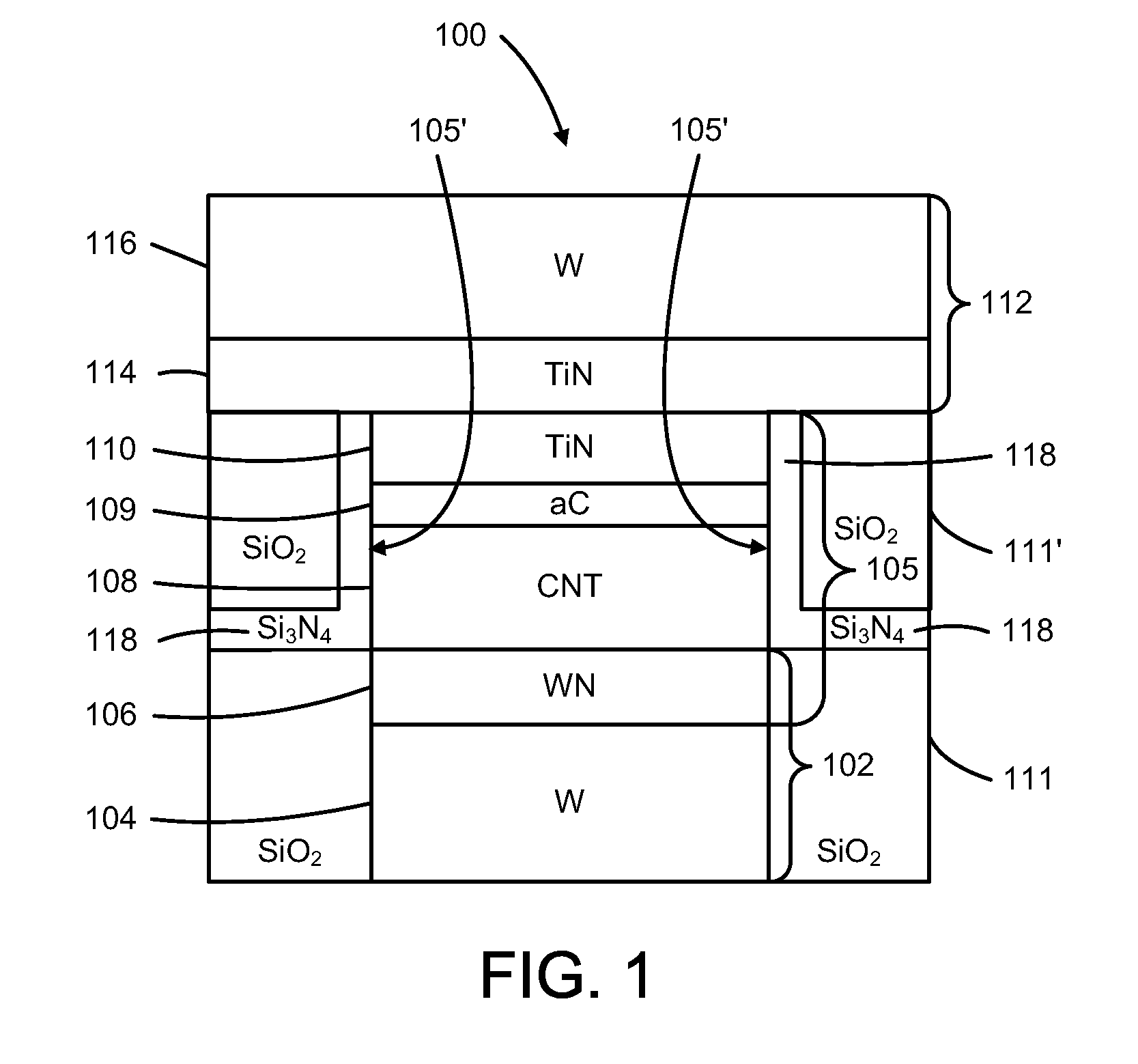

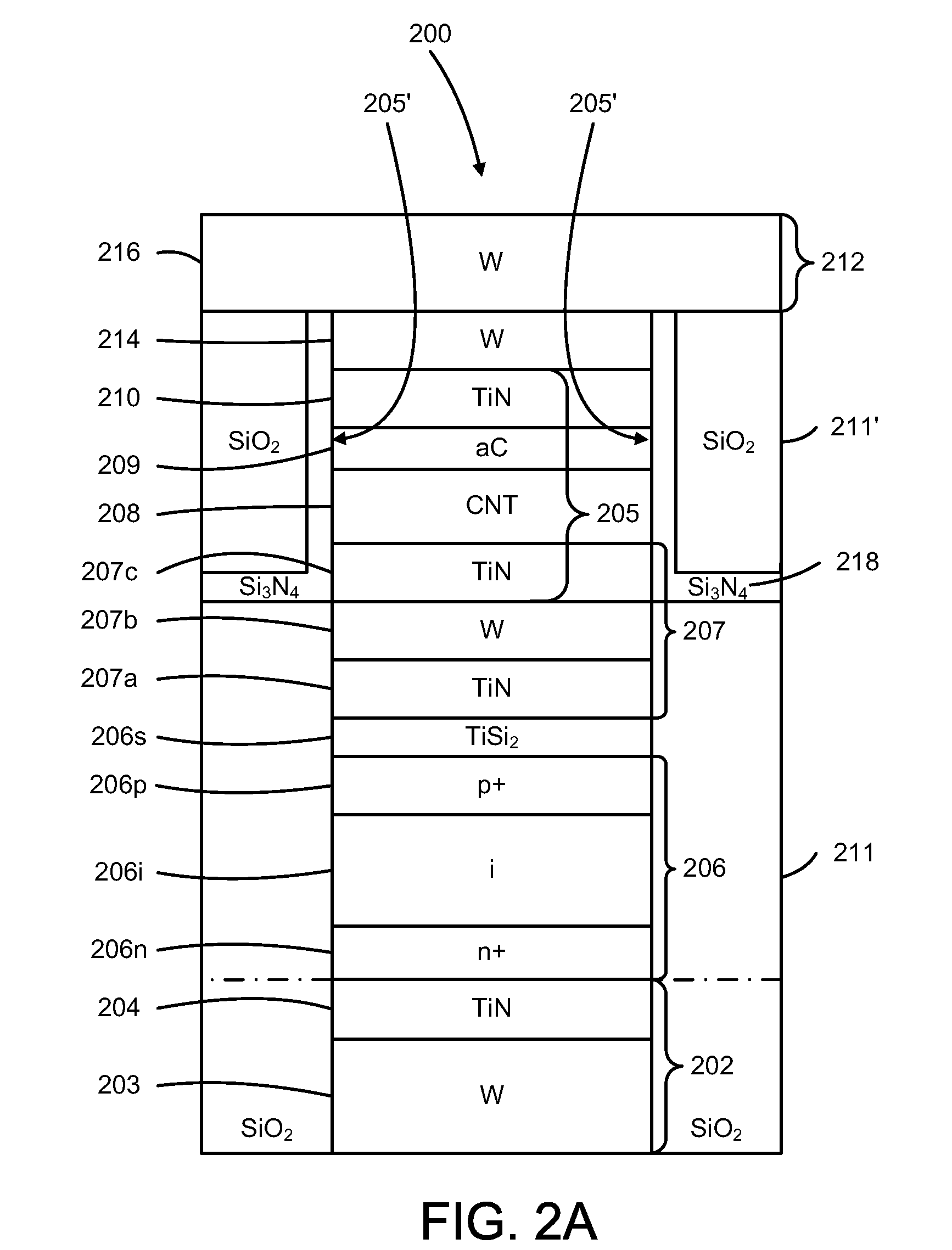

Electronic devices including carbon-based films having sidewall liners, and methods of forming such devices

ActiveUS20100012912A1Solid-state devicesSemiconductor/solid-state device manufacturingElectronic structureOxygen

Methods in accordance with aspects of this invention form microelectronic structures in accordance with other aspects of this invention, such as non-volatile memories, that include (1) a layerstack having a pattern including sidewalls, the layerstack comprising a resistivity-switchable layer disposed above and in contact with a bottom electrode, and a top electrode disposed above and in contact with the resistivity-switchable layer; and (2) a dielectric sidewall liner in contact with the sidewalls of the layerstack; wherein the resistivity-switchable layer includes a carbon-based material, and the dielectric sidewall liner includes an oxygen-poor dielectric material. Numerous additional aspects are provided.

Owner:SANDISK TECH LLC

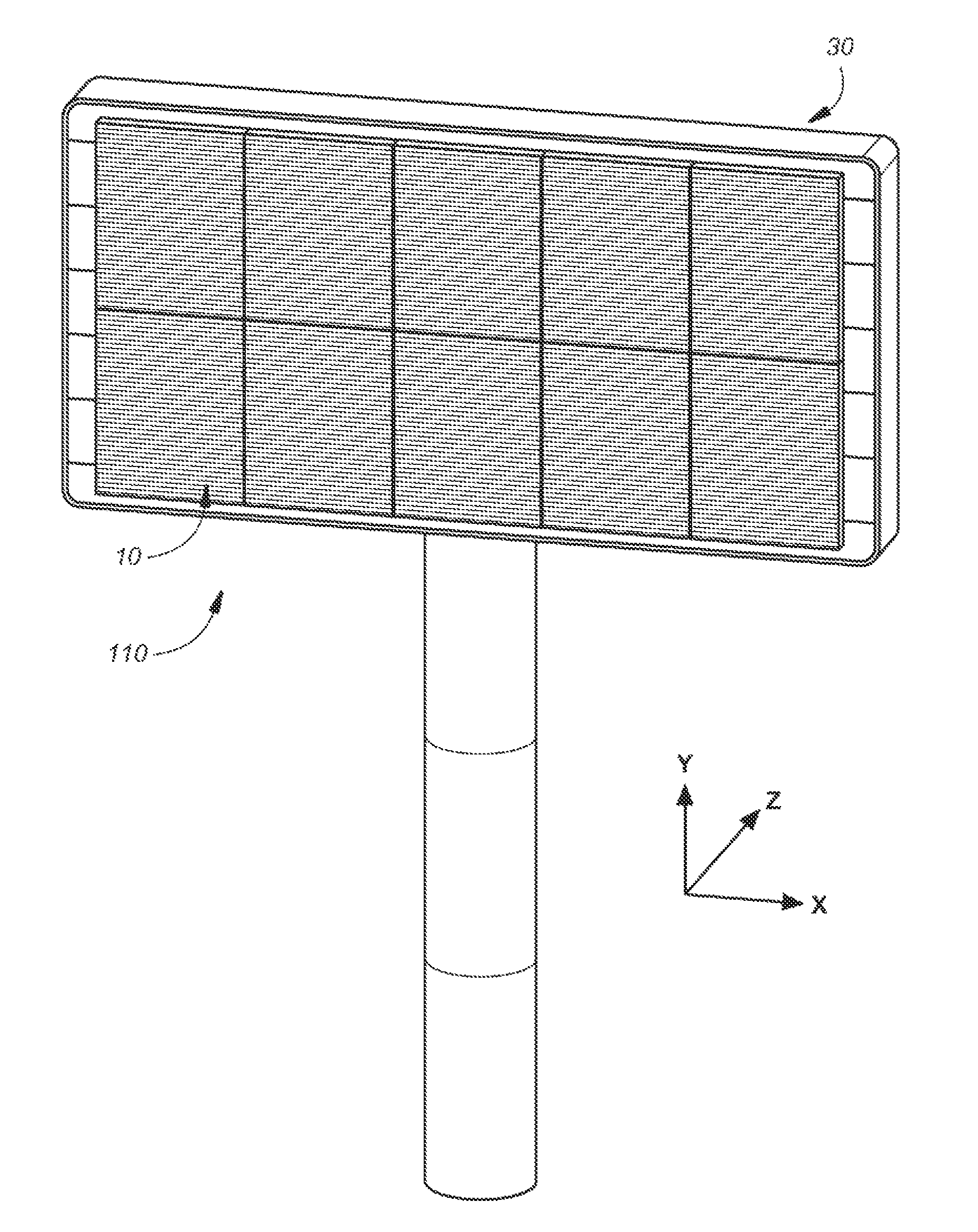

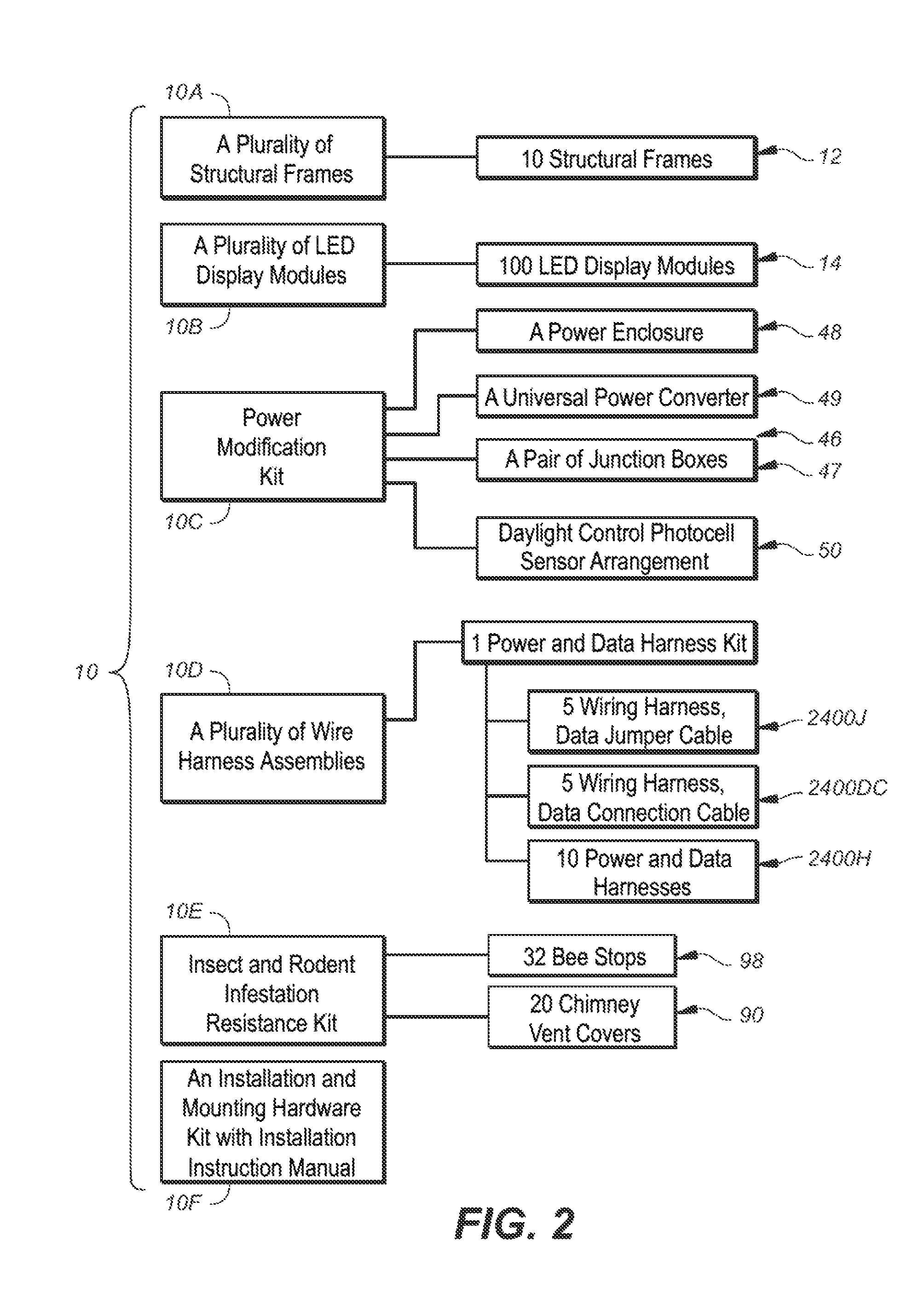

Modular installation and conversion kit for electronic sign structure and method of using same

InactiveUS8824125B1Facilitate dataImprove powerBus-bar/wiring layoutsSubstation/switching arrangement casingsElectronic structureModularity

An out of the box signage kit facilitates in field conversion of a static billboard having an anchored planar mounting structure into a large format billboard type electronic sign that includes a plurality of interchangeable weatherized display modules; a plurality of hand mountable interchangeable structural frames for supporting the plurality of weatherized display modules, each structural frame having a back portion for mounting to a frontside of the anchored planar mounting structure and a front portion defining a plurality of bay members for receiving corresponding ones of said plurality of weatherized display modules; and a plurality of interchangeable wire harnesses, each individual wire harness including a first end for coupling to a power source mounted on a backside of the anchored planar mounting structure, each individual wire harness having a plurality of power extensions for coupling the power source to at least one of the display modules.

Owner:ADTI MEDIA

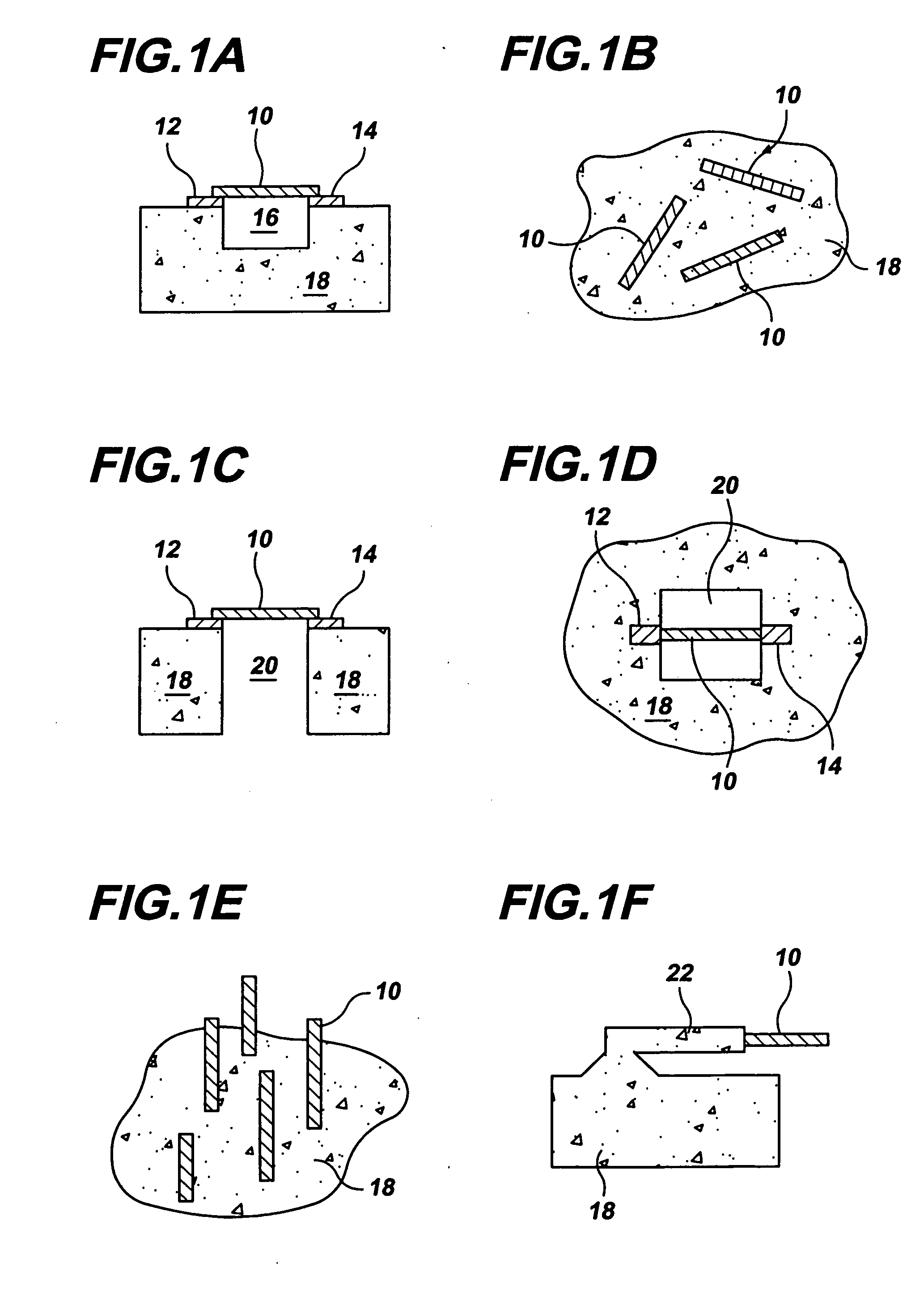

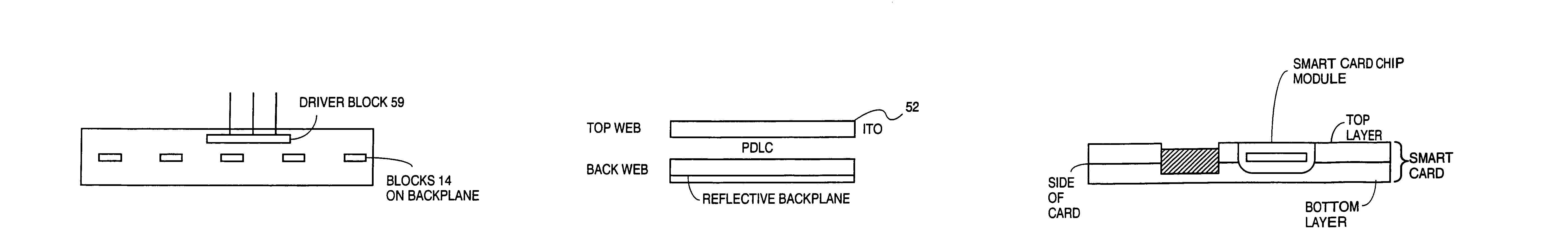

Apparatuses and methods for forming electronic assemblies

InactiveUS7417306B1Minimizing chanceSemiconductor/solid-state device detailsSolid-state devicesElectronic structureEngineering

Apparatuses and methods for forming microelectronic assemblies are claimed. One embodiment of the invention includes a contact smart card wherein fluidic self assembly is used to build the microelectronic structures on the microelectronic assembly such that a contact smart data is transmitted unidirectionally. A contact smart card is inserted directly into a device that transfers data to a microelectronic assembly coupled to the smart card. Another embodiment of the invention relates to a contactless smart card in which fluidic self assembly is also used here to build the microelectronic assembly. Data is transmitted to an antenna that is embedded in the contactless card in which a plurality of blocks were deposited thereon.

Owner:RUIZHANG TECH LTD CO

Reconfigurable logic structures

InactiveUS7511532B2Logic circuits characterised by logic functionNanoinformaticsElectronic structurePhase-change memory

Reconfigurable electronic structures and circuits using programmable, non-volatile memory elements. The programmable, non-volatile memory elements may perform the functions of storage and / or a switch to produce components such as crossbars, multiplexers, look-up tables (LUTs) and other logic circuits used in programmable logic structures (e.g., (FPGAs)). The programmable, non-volatile memory elements comprise one or more structures based on Phase Change Memory, Programmable Metallization, Carbon Nano-Electromechanical (CNT-NEM), or Metal Nano-Electromechanical device technologies.

Owner:CSWITCH

Microelectronic element with bond elements to encapsulation surface

InactiveUS20150076714A1Semiconductor/solid-state device detailsSolid-state devicesElectronic structureEdge surface

A microelectronic structure includes a semiconductor having conductive elements at a first surface. Wire bonds have bases joined to the conductive elements and free ends remote from the bases, the free ends being remote from the substrate and the bases and including end surfaces. The wire bonds define edge surfaces between the bases and end surfaces thereof. A compliant material layer extends along the edge surfaces within first portions of the wire bonds at least adjacent the bases thereof and fills spaces between the first portions of the wire bonds such that the first portions of the wire bonds are separated from one another by the compliant material layer. Second portions of the wire bonds are defined by the end surfaces and portions of the edge surfaces adjacent the end surfaces that are extend from a third surface of the compliant later.

Owner:INVENSAS LLC

Ultra low k plasma enhanced chemical vapor deposition processes using a single bifunctional precursor containing both a SiCOH matrix functionality and organic porogen functionality

InactiveUS7491658B2Improve film propertiesEasy to controlSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricEpoxy

A method for fabricating a SiCOH dielectric material comprising Si, C, O and H atoms from a single organosilicon precursor with a built-in organic porogen is provided. The single organosilicon precursor with a built-in organic porogen is selected from silane (SiH4) derivatives having the molecular formula SiRR1R2R3, disiloxane derivatives having the molecular formula R4R5R6—Si—O—Si—R7R8R9, and trisiloxane derivatives having the molecular formula R10R11R12—Si—O—Si—R13R14—O—Si—R15R16R17 where R and R1-17 may or may not be identical and are selected from H, alkyl, alkoxy, epoxy, phenyl, vinyl, allyl, alkenyl or alkynyl groups that may be linear, branched, cyclic, polycyclic and may be functionalized with oxygen, nitrogen or fluorine containing substituents. In addition to the method, the present application also provides SiCOH dielectrics made from the inventive method as well as electronic structures that contain the same.

Owner:GLOBALFOUNDRIES INC

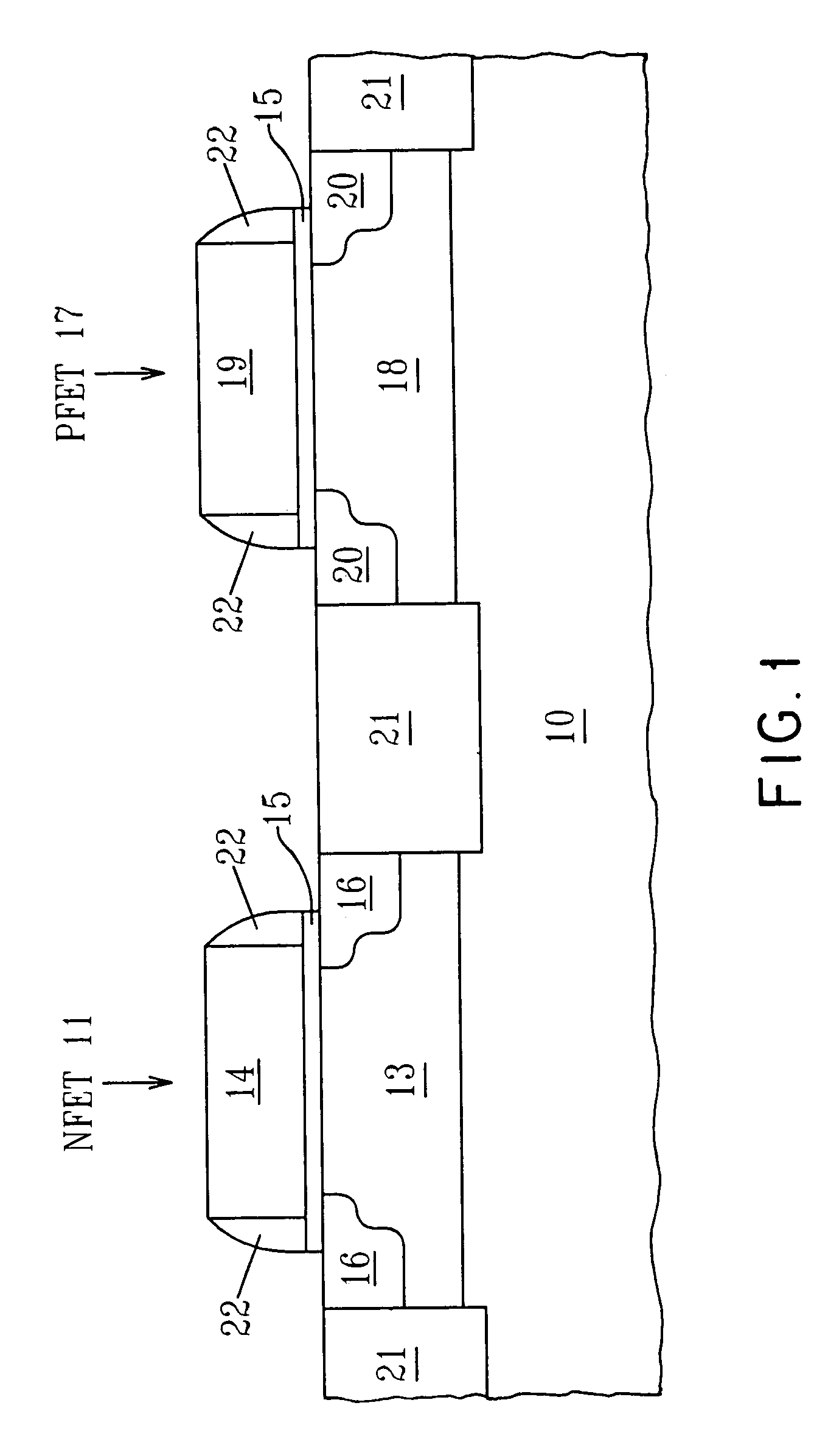

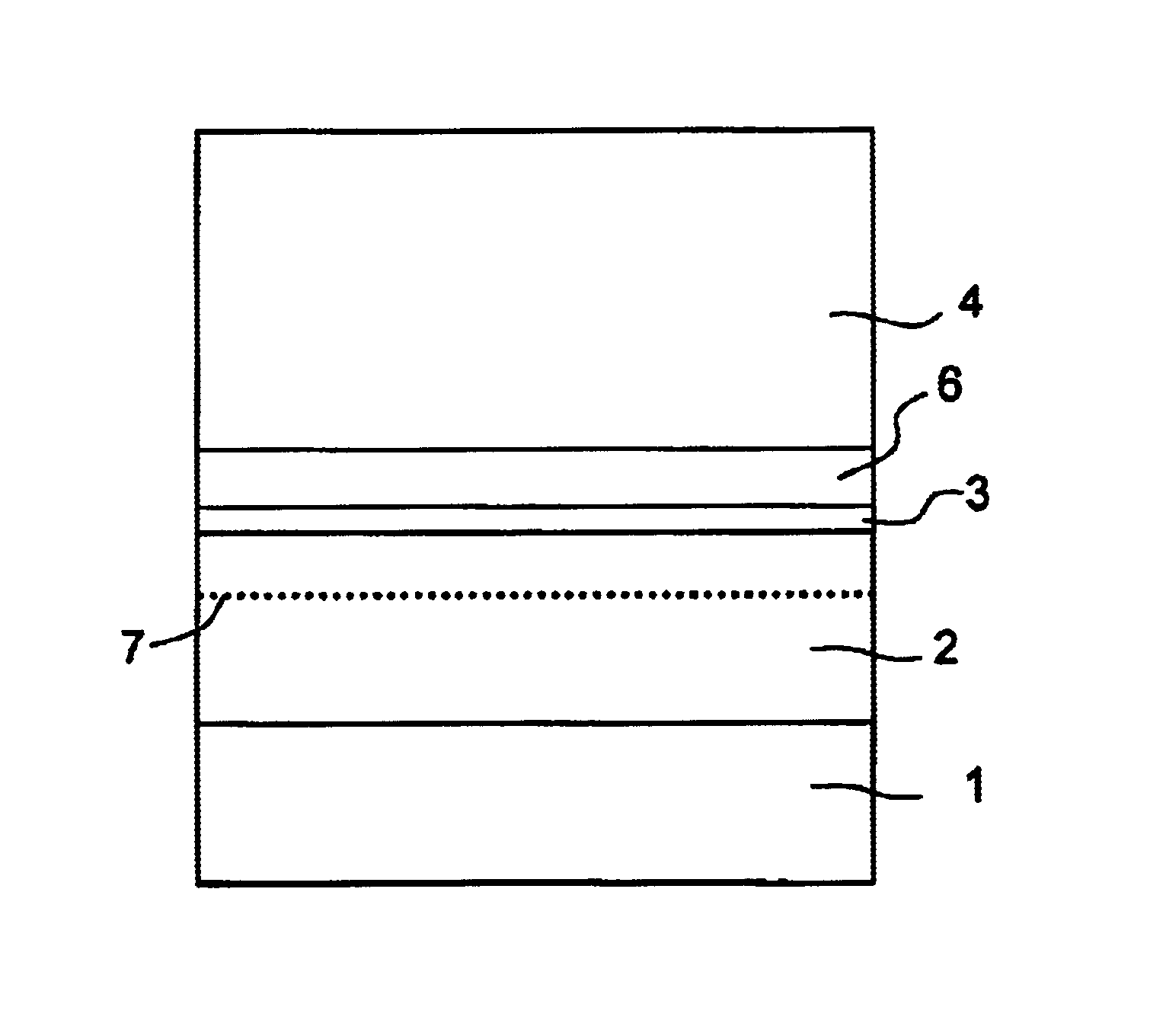

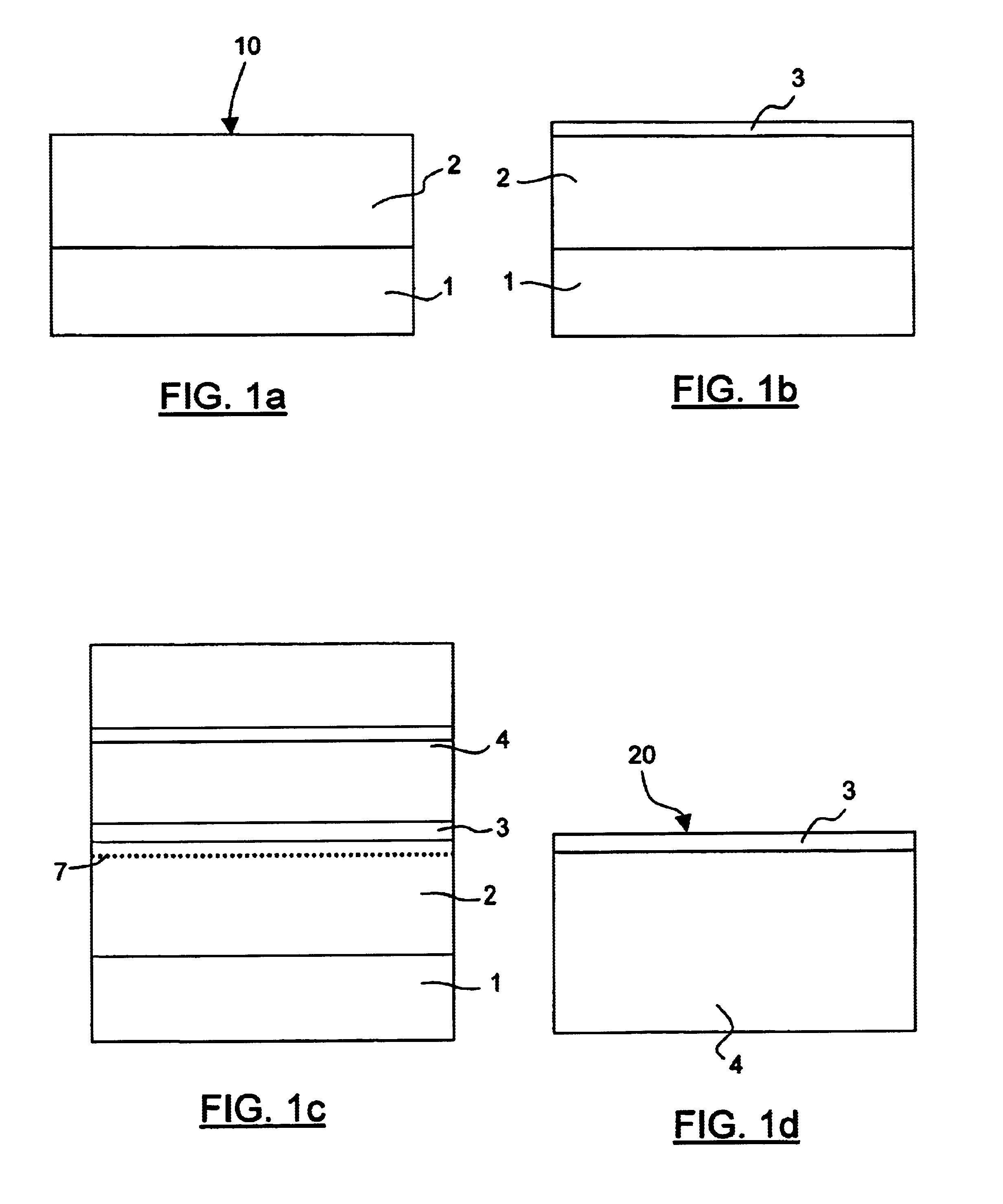

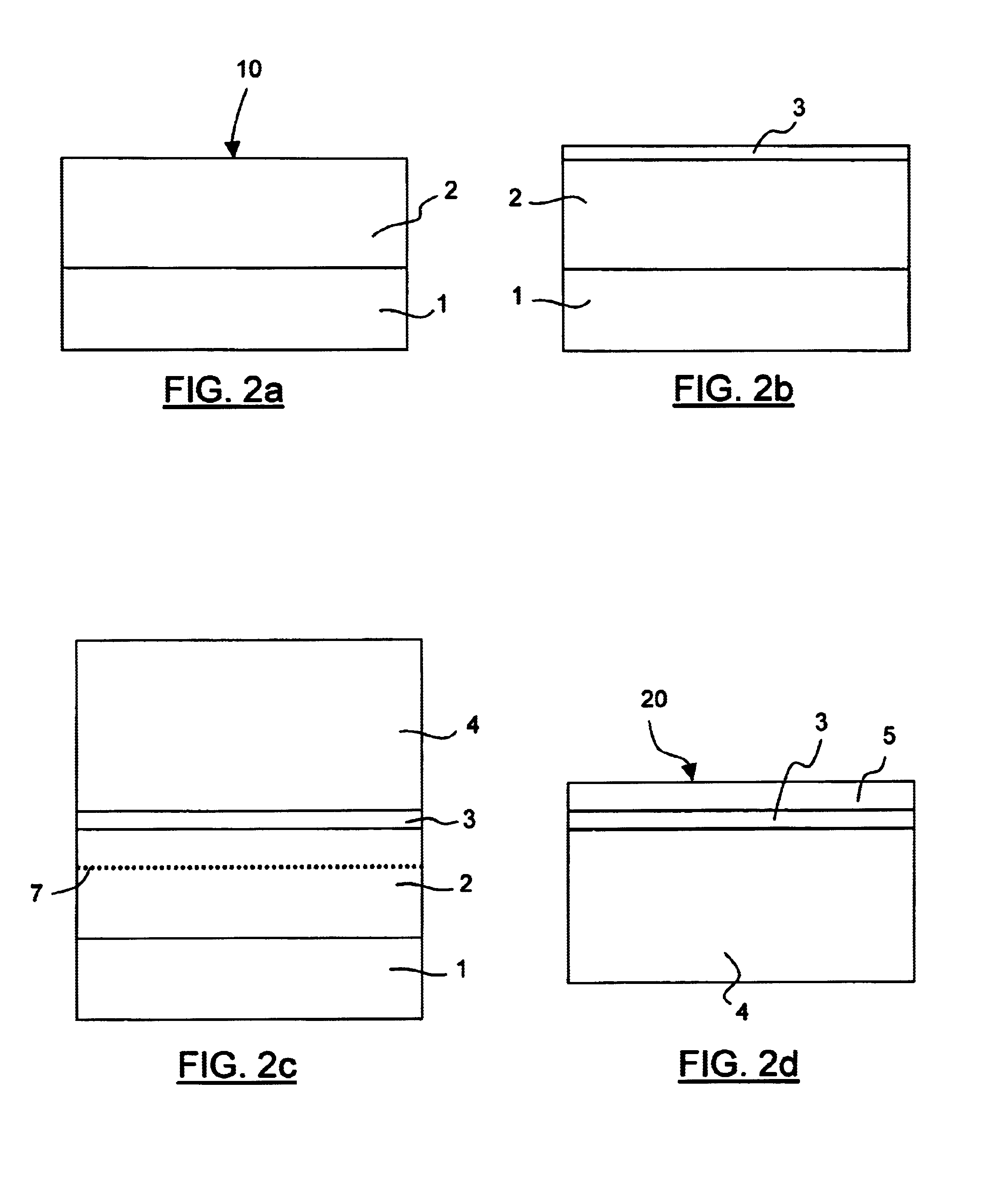

Process for transferring a layer of strained semiconductor material

InactiveUS6953736B2Improve electrical performancePrevent substantial relaxation of strainSemiconductor/solid-state device manufacturingSemiconductor devicesElectronic structureSemiconductor materials

The invention relates to a process for producing an electronic structure that includes a thin layer of strained semiconductor material from a donor wafer. The donor wafer has a lattice parameter matching layer that includes an upper layer of a semiconductor material having a first lattice parameter and a film of semiconductor material having a second, nominal, lattice parameter that is substantially different from the first lattice parameter and that is strained by the matching layer. This process includes transfer of the film to a receiving substrate. The invention also relates to the semiconductor structures that can be produced by the process.

Owner:SOITEC SA