Microelectronic element with bond elements to encapsulation surface

a microelectronic element and bonding technology, applied in the field of microelectronic elements, can solve the problems of affecting the reliability and performance of the device, affecting the reliability of the device, and stressing the solder mass (or other structure)

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

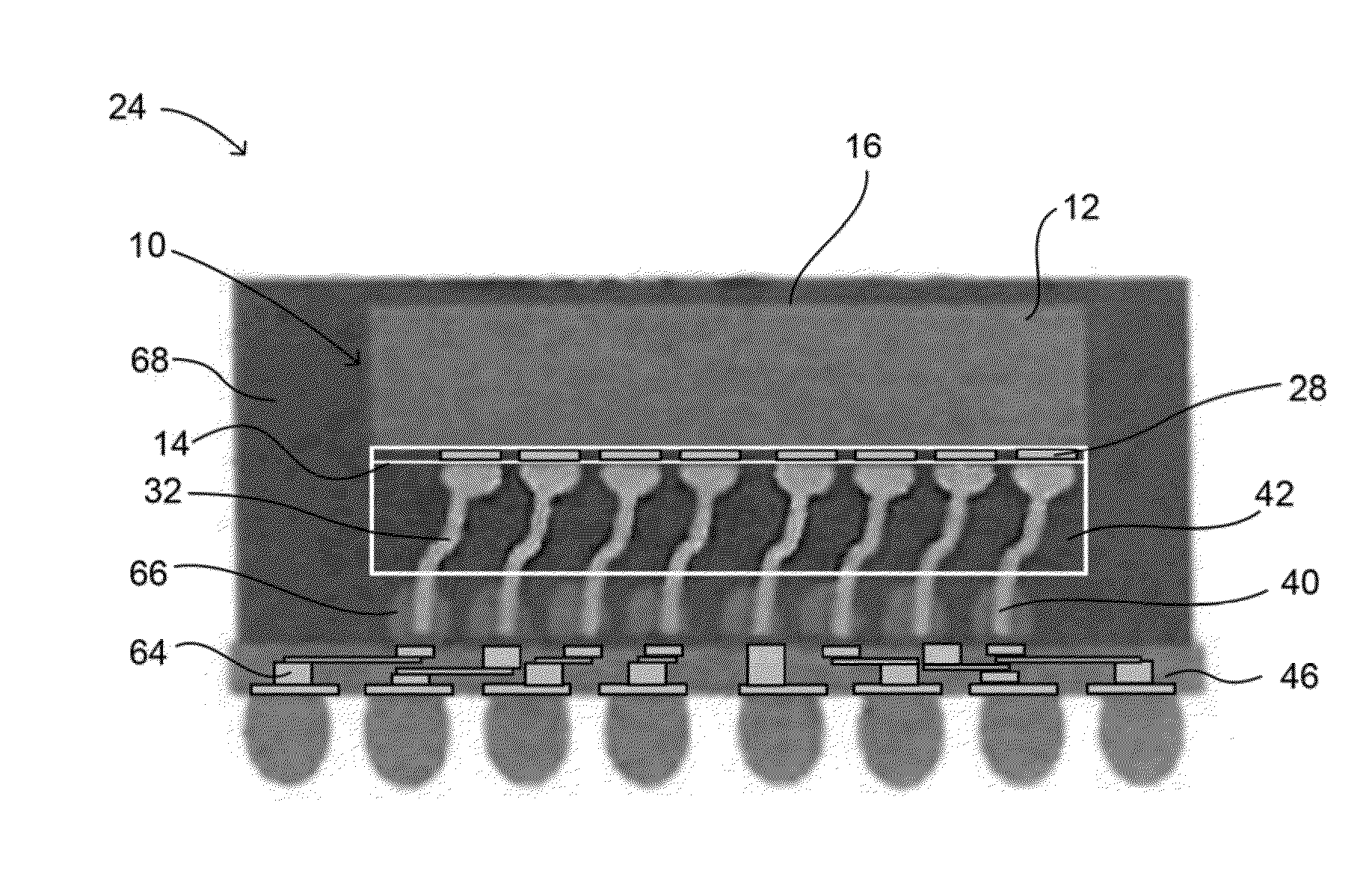

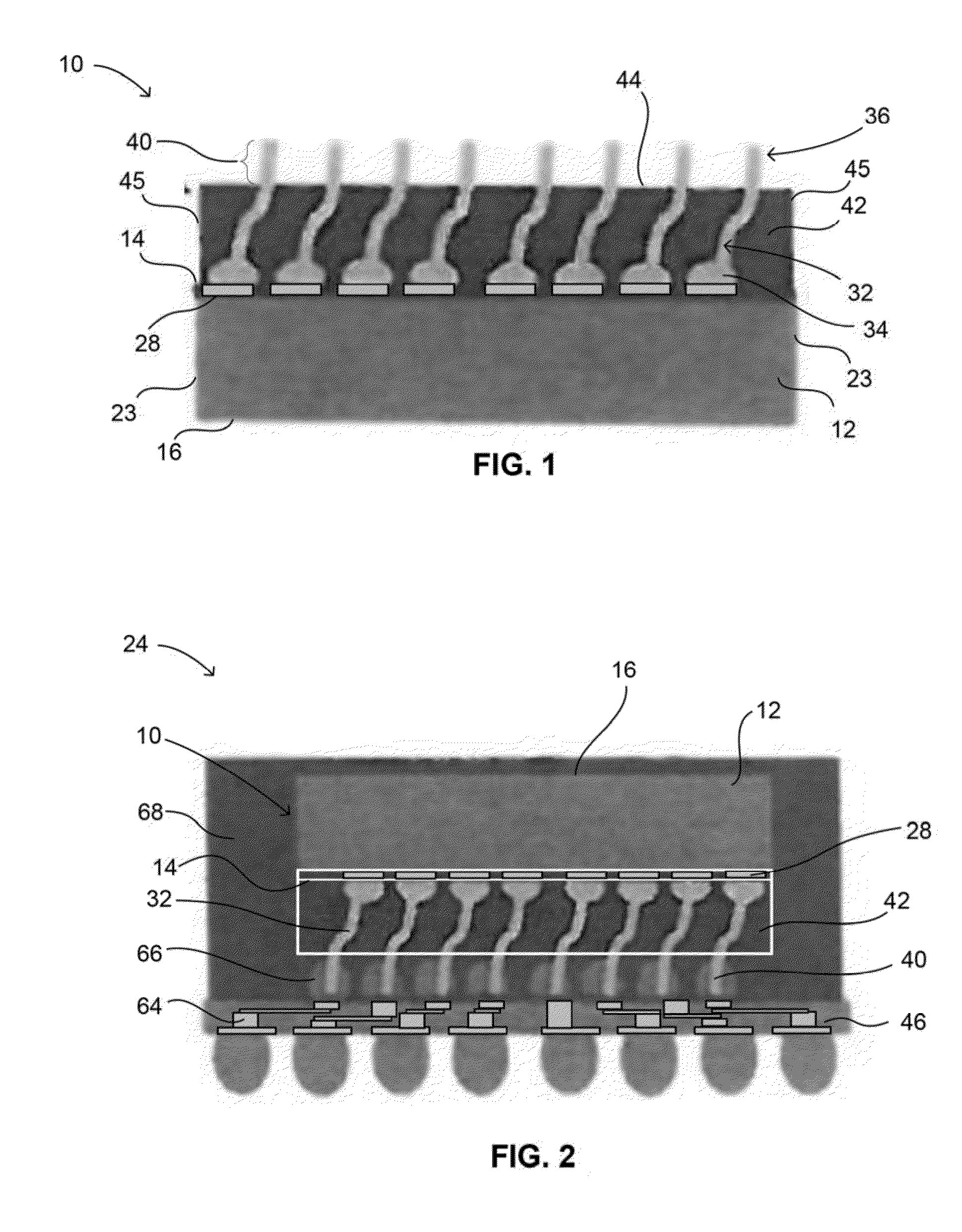

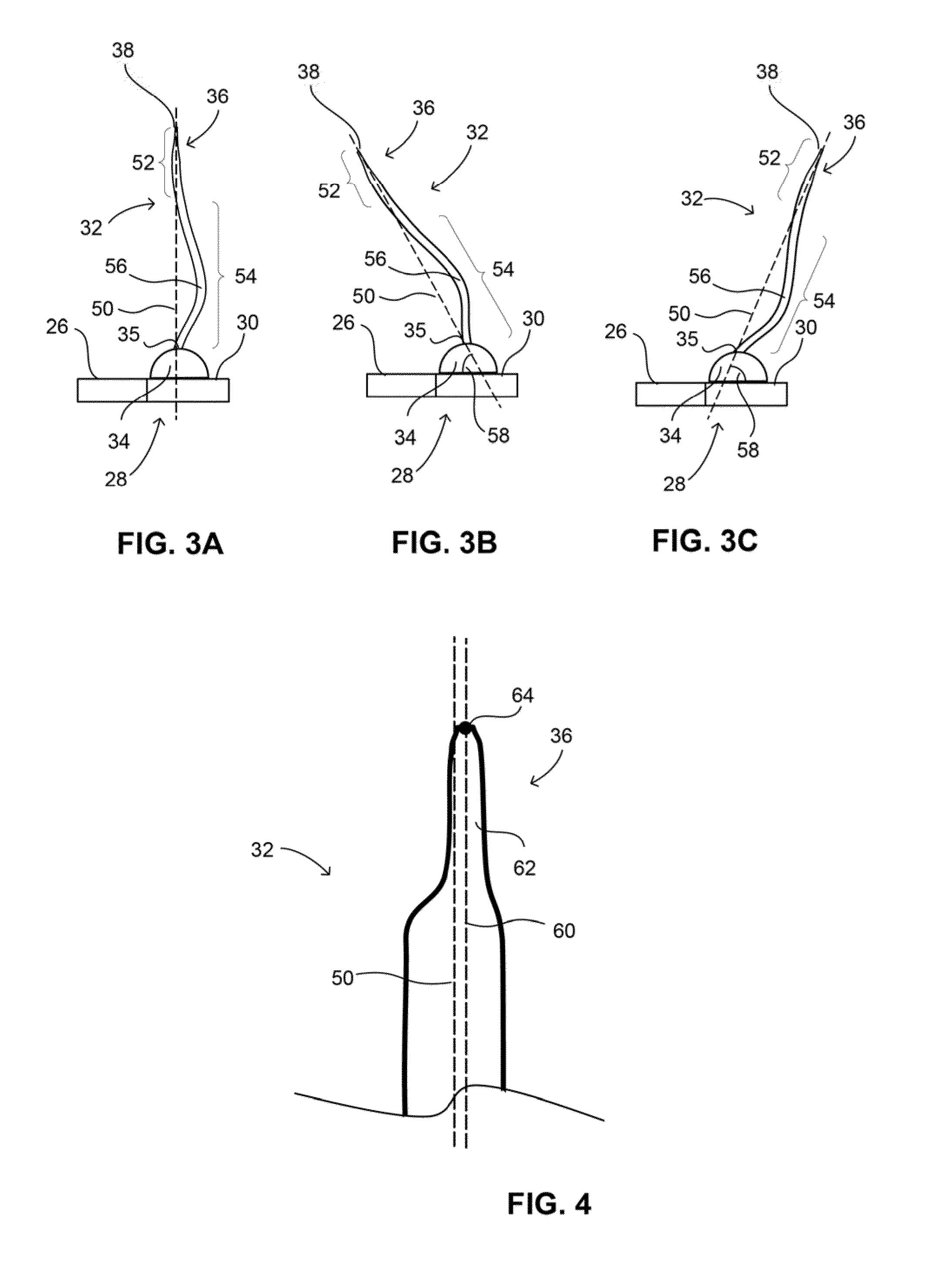

[0031]Turning now to the figures, where similar numeric references are used to indicate similar features, there is shown in FIG. 1 a microelectronic structure 10 that can be in the form of a microelectronic element according to an embodiment of the present invention. The embodiment of FIG. 1 is a microelectronic element in the form of a semiconductor die 12 (also referred to as a semiconductor chip) having a plurality of wire bonds 32 extending from contacts 28 thereof to extending portions 40 thereof that extend above a compliant material layer 42 that covers and separates remaining portions of the wire bonds 32 from each other, including portions thereof adjacent semiconductor die 12. The structure 10 can then used in computer or other electronic applications either alone or in an assembly with further components.

[0032]The microelectronic element 10 of FIG. 1 includes semiconductor die 12 having a first surface 14 and a second surface 16. For purposes of this discussion, the first...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More