Adaptive deterministic grouping of blocks into multi-block units

a technology of adaptive deterministic grouping and blocks, applied in the direction of memory adressing/allocation/relocation, input/output to record carriers, instruments, etc., can solve the problems of cell no longer usable, floating gate eventually wears out and breaks down, and the number of limitations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

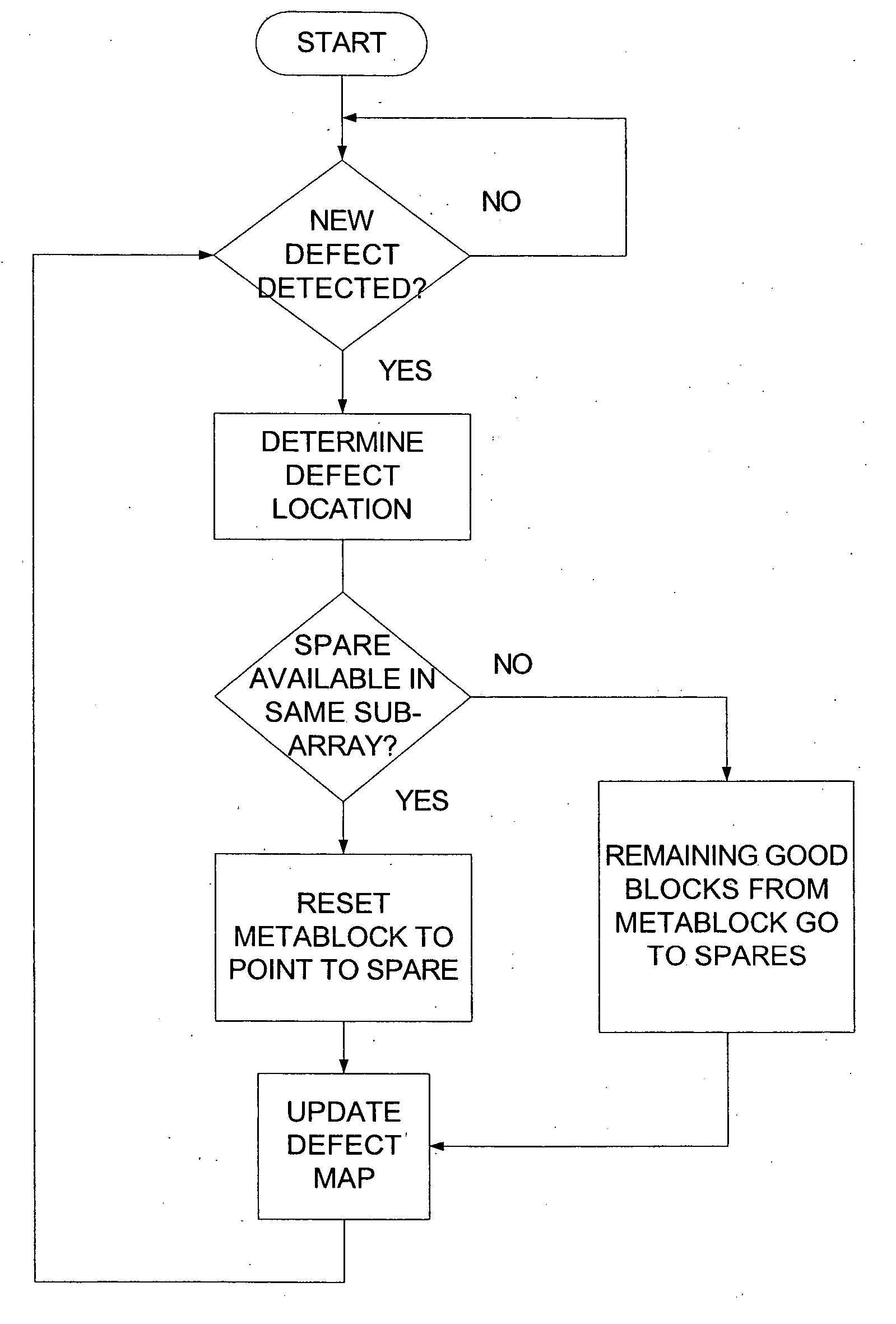

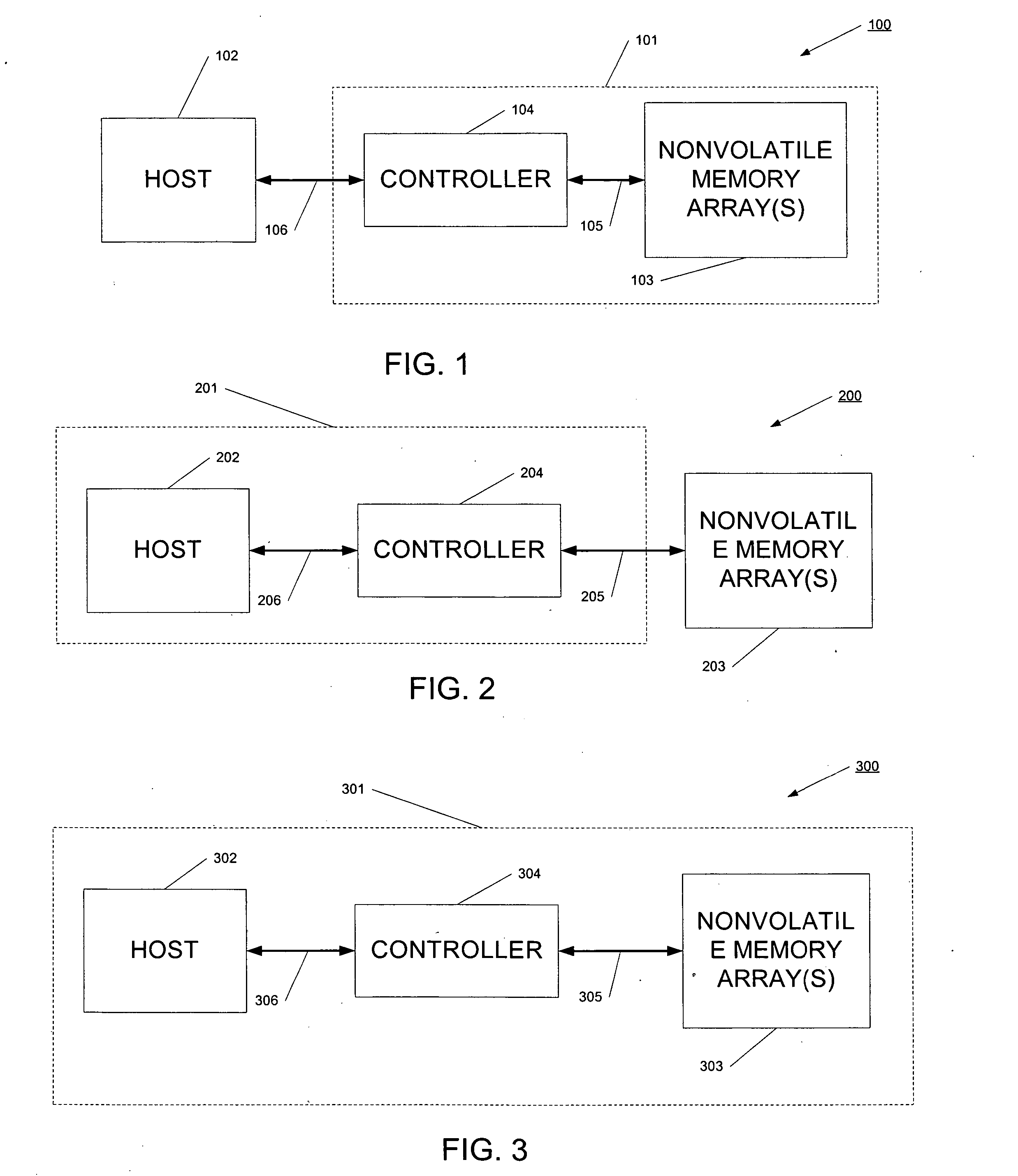

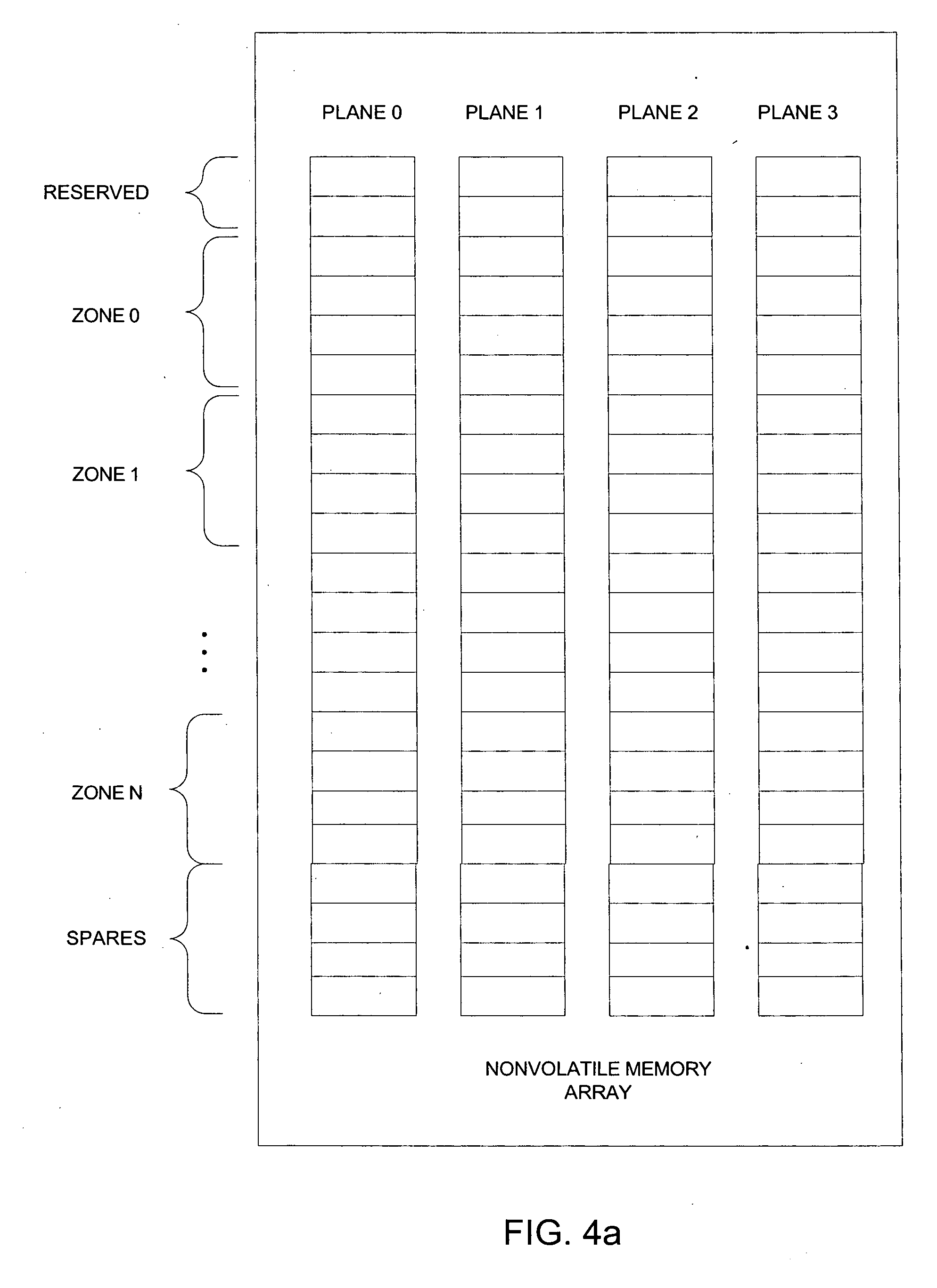

[0027] Generally, the memory system of the present invention maintains in its main non-volatile memory a record of the linking of blocks into multi-block metablock structures. This record contains a defect map of factory and grown defects in a map table that can be read into non-volatile memory on demand. This map is updated as grown defects are encountered and blocks are assigned to new locations. Metablocks are preferable formed by one block in each of several subarrays, or planes, and in this case, the grouping is done preferably with same-numbered blocks in each plane, with the exception of blocks that are marked bad and placed in the map. In one embodiment, the blocks are directly mapped to alternate blocks. Metablocks that would contain the defective block are then reformed with the alternate block in the corresponding plane. Rather than maintain a complete record of the linking of blocks into metablocks within the non-volatile memory, a “standard” linking can be based on an a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More