Patents

Literature

589 results about "Speed test" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

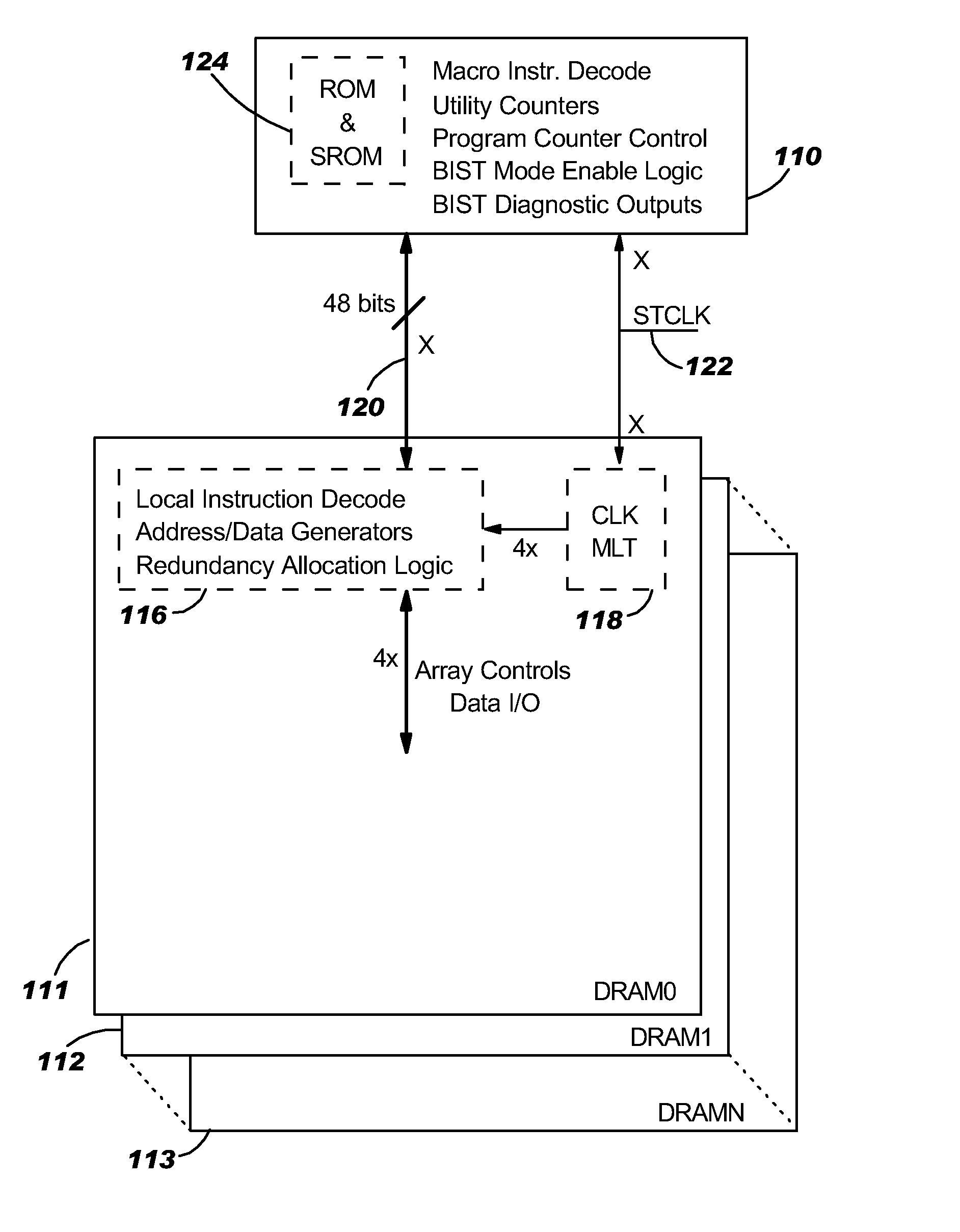

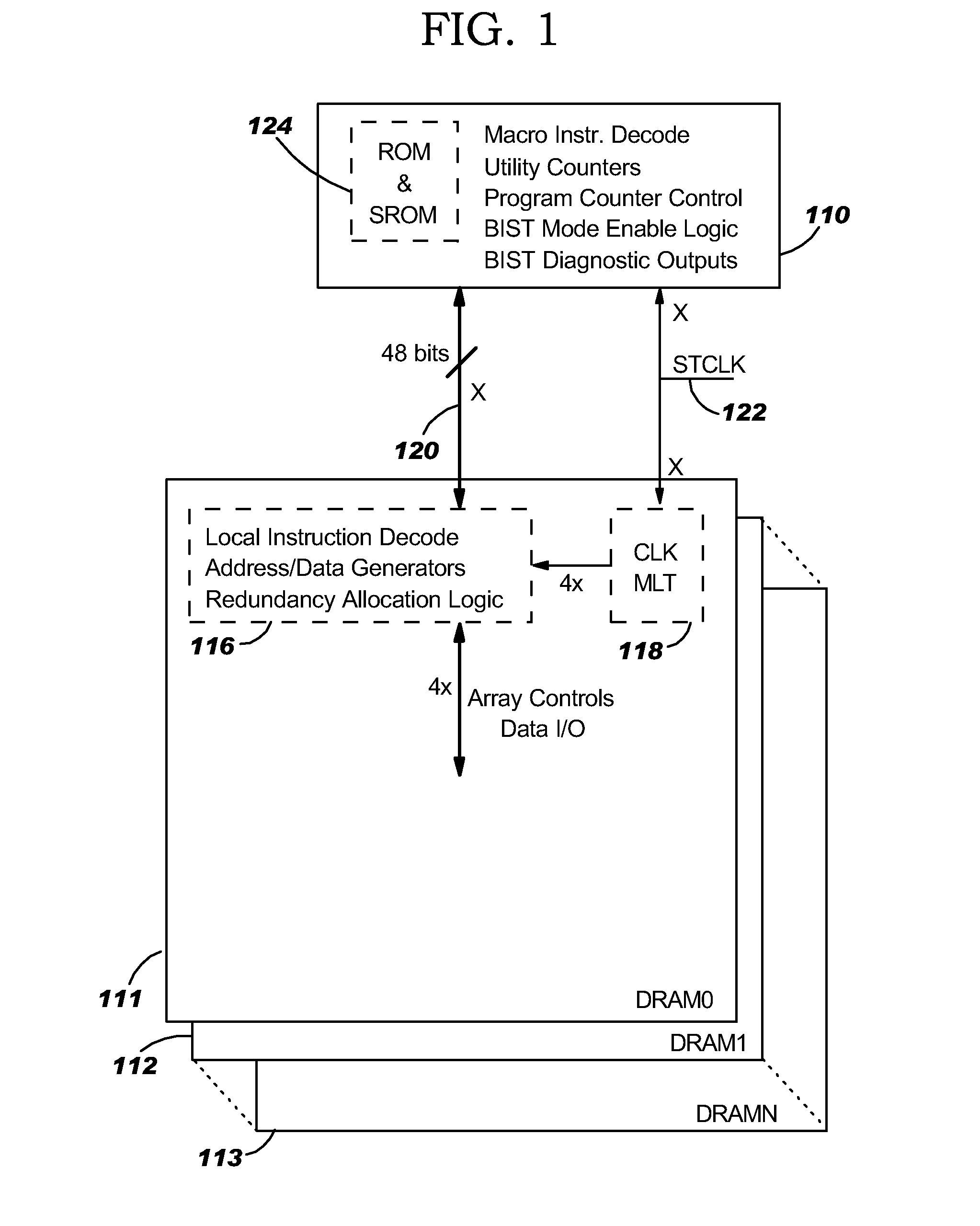

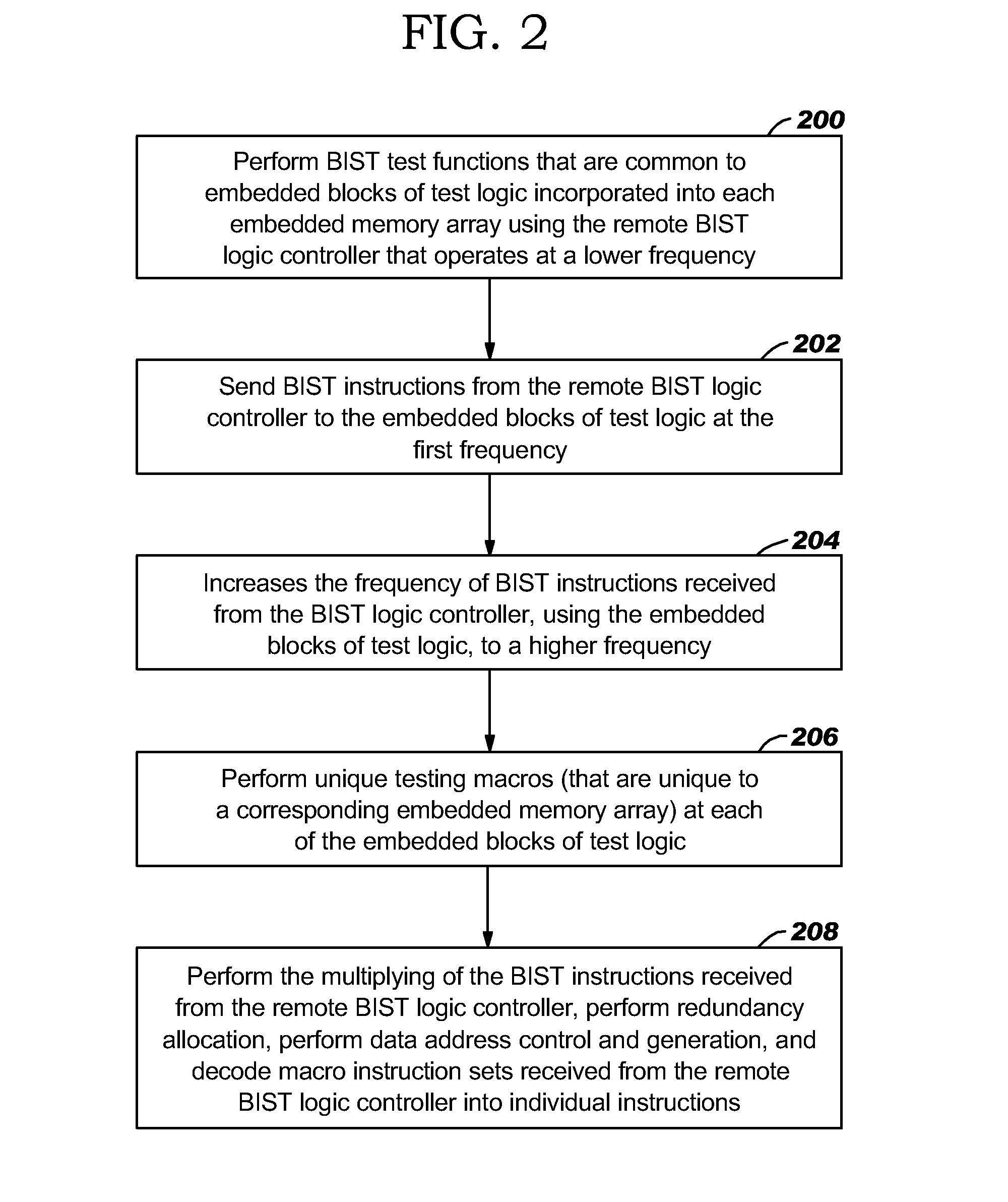

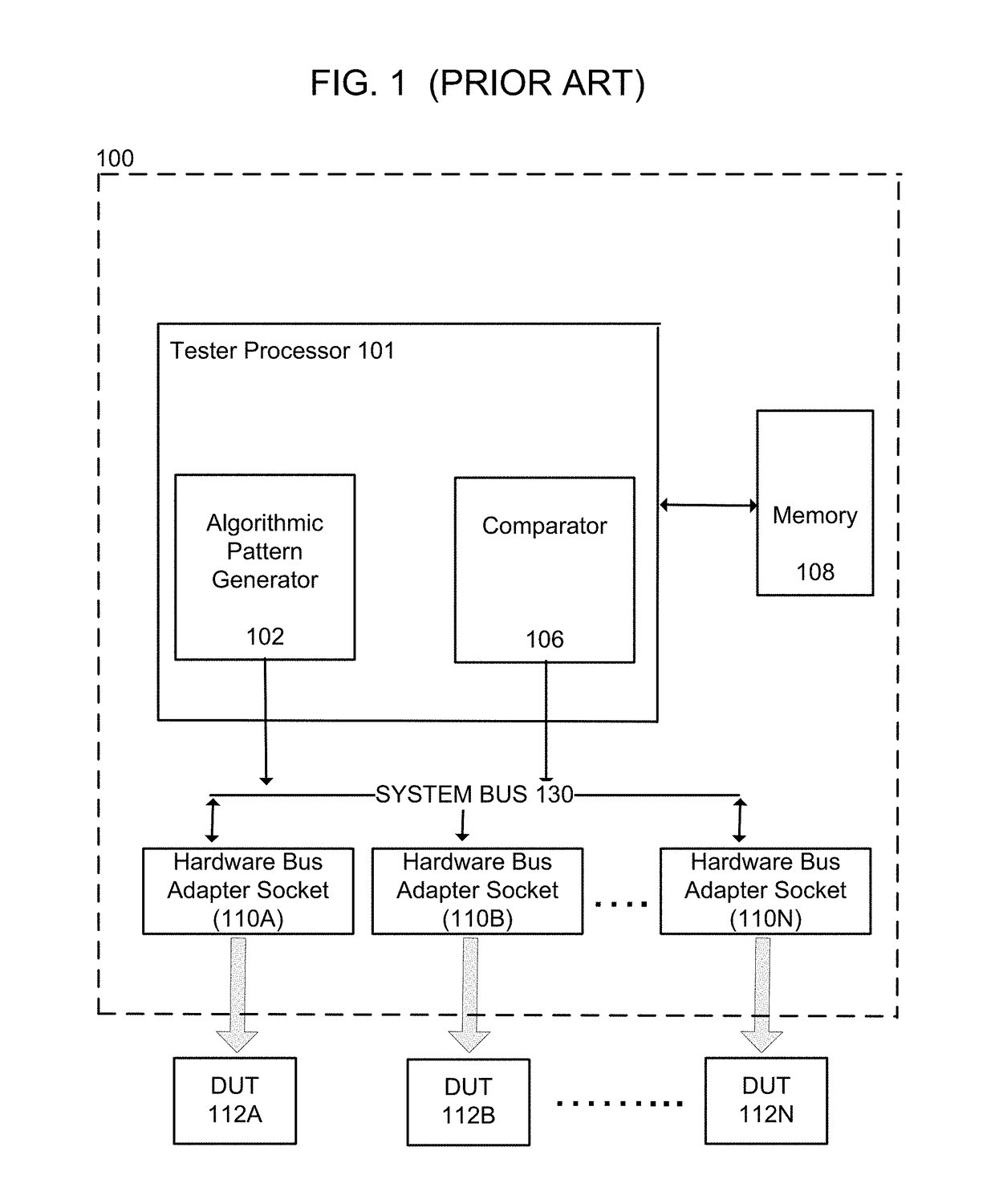

Remote bist for high speed test and redundancy calculation

InactiveUS20080215937A1Reduce frequencyIncrease processing frequencyDigital circuit testingFunctional testingLow speedSpeed test

Disclosed in a hybrid built-in self test (BIST) architecture for embedded memory arrays that segments BIST functionality into remote lower-speed executable instructions and local higher-speed executable instructions. A standalone BIST logic controller operates at a lower frequency and communicates with a plurality of embedded memory arrays using a BIST instruction set. A block of higher-speed test logic is incorporated into each embedded memory array under test and locally processes BIST instructions received from the standalone BIST logic controller at a higher frequency. The higher-speed test logic includes a multiplier for increasing the frequency of the BIST instructions from the lower frequency to the higher frequency. The standalone BIST logic controller enables a plurality of higher-speed test logic structures in a plurality of embedded memory arrays.

Owner:META PLATFORMS INC

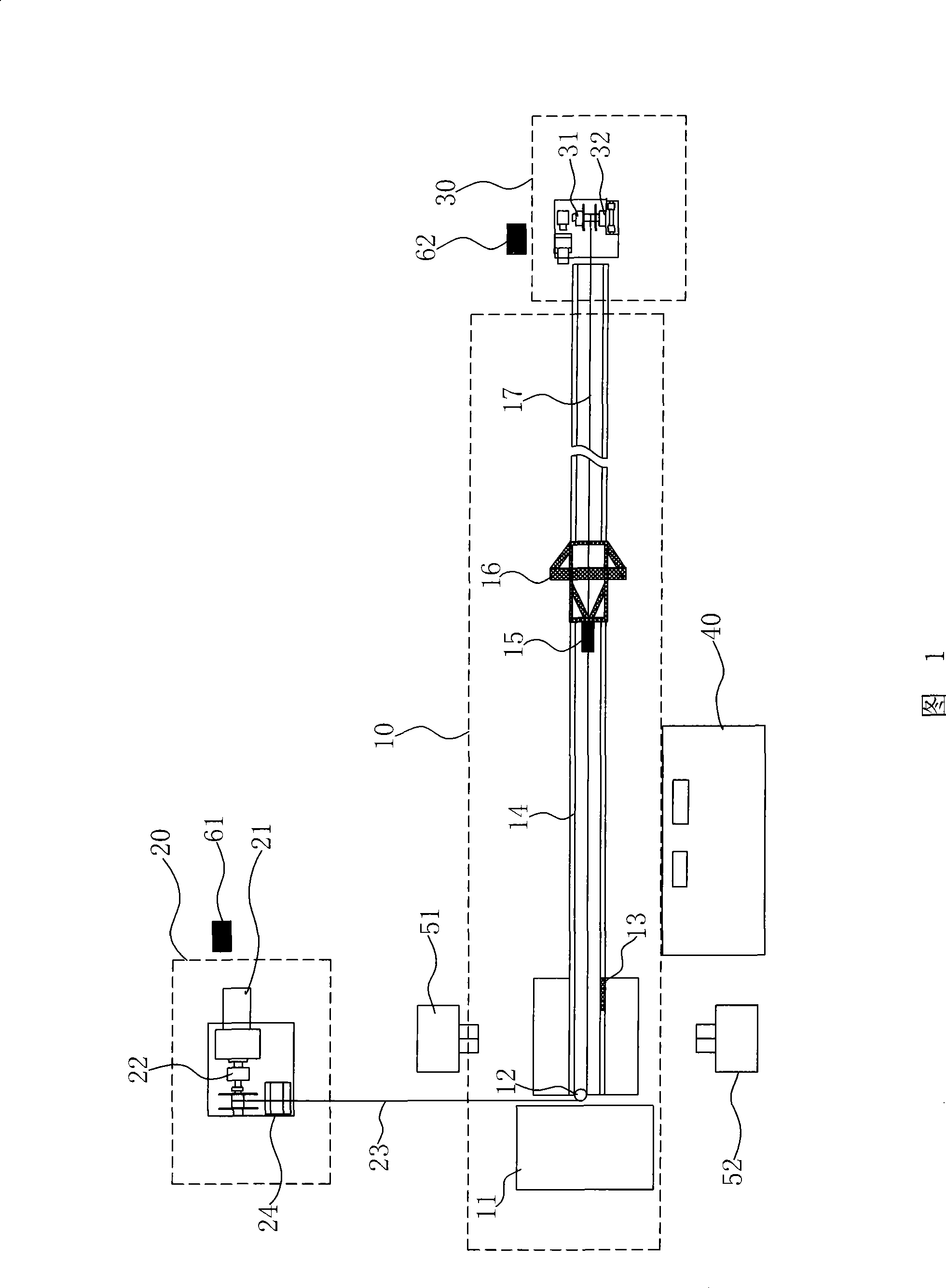

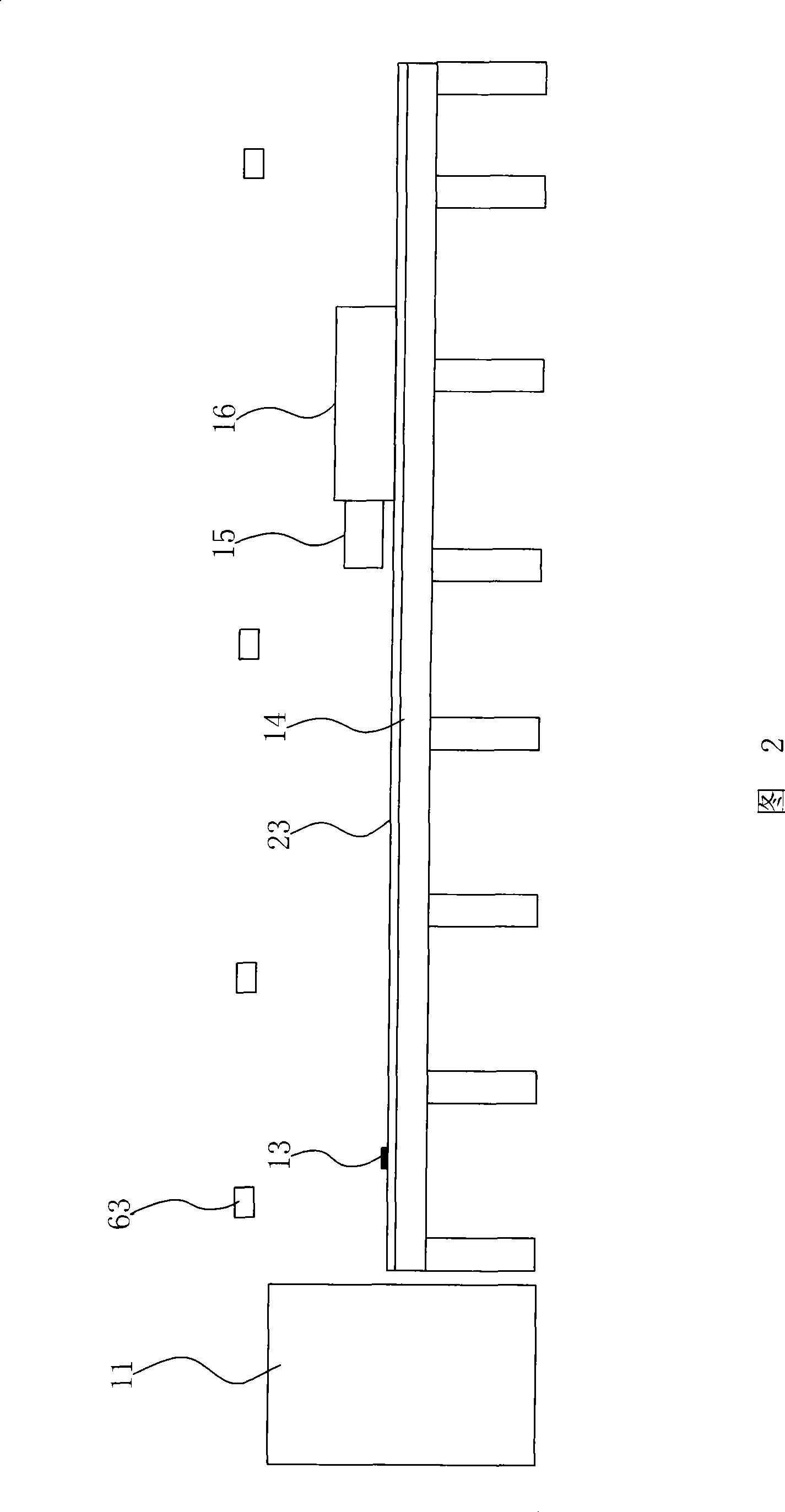

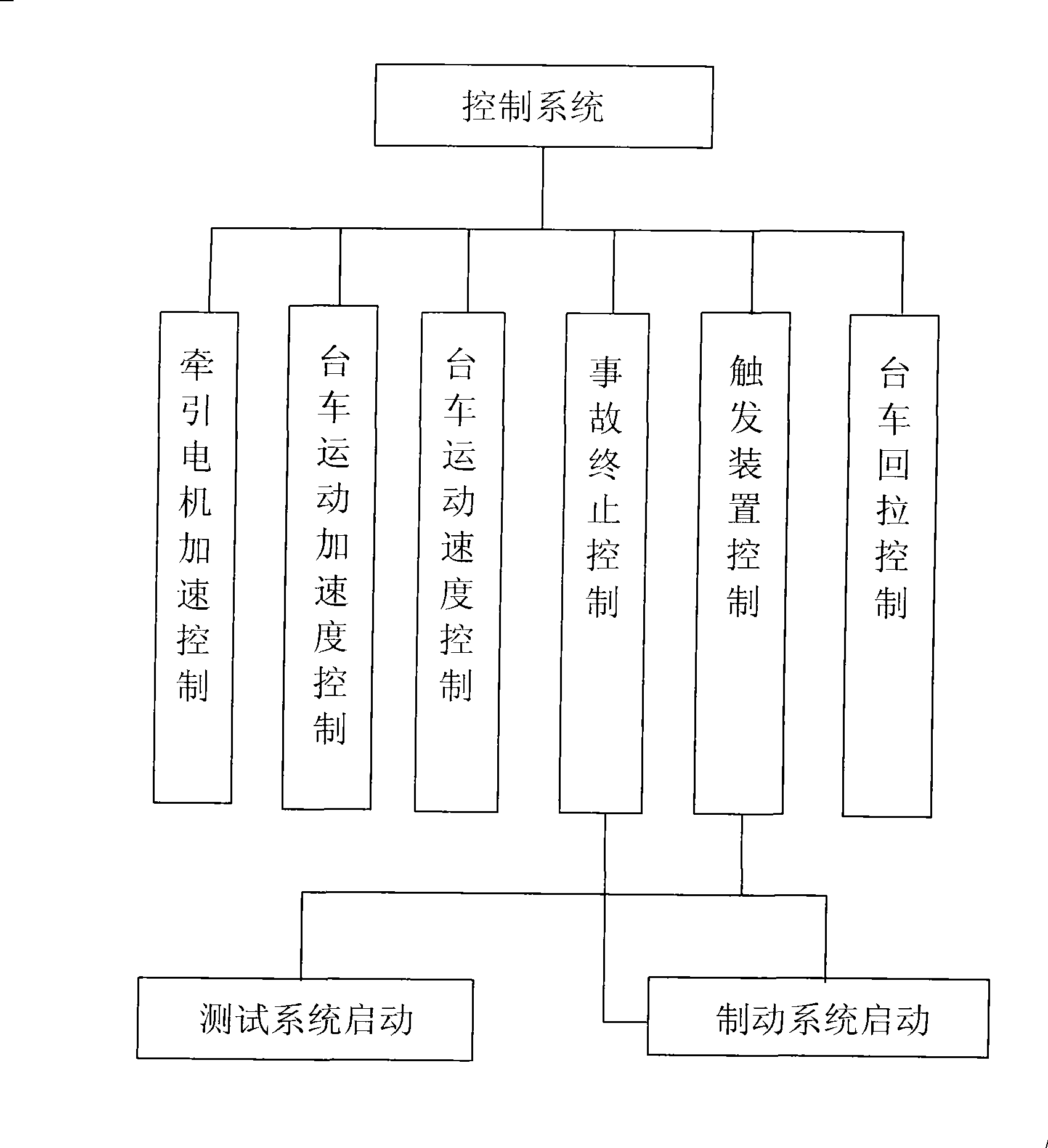

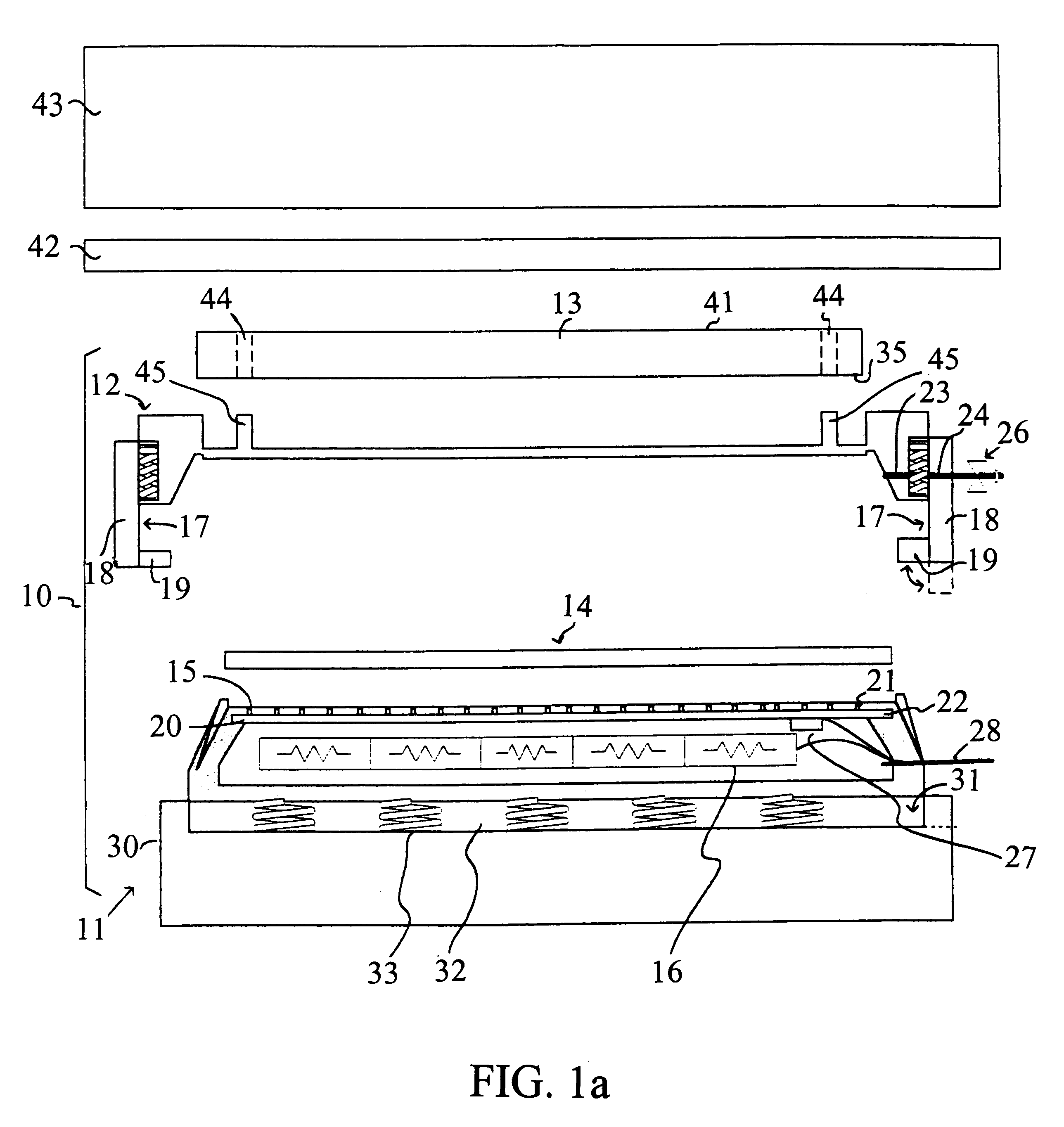

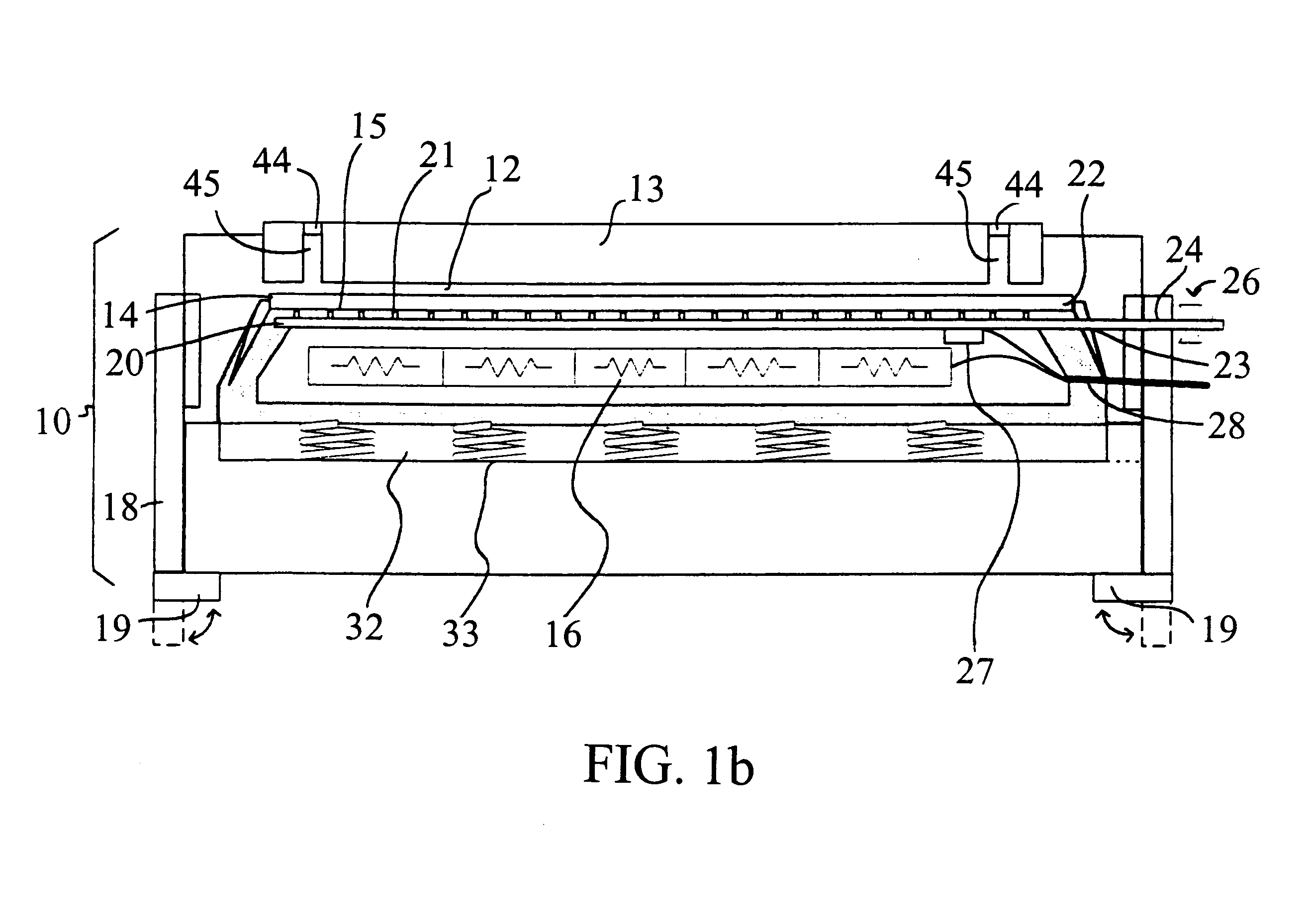

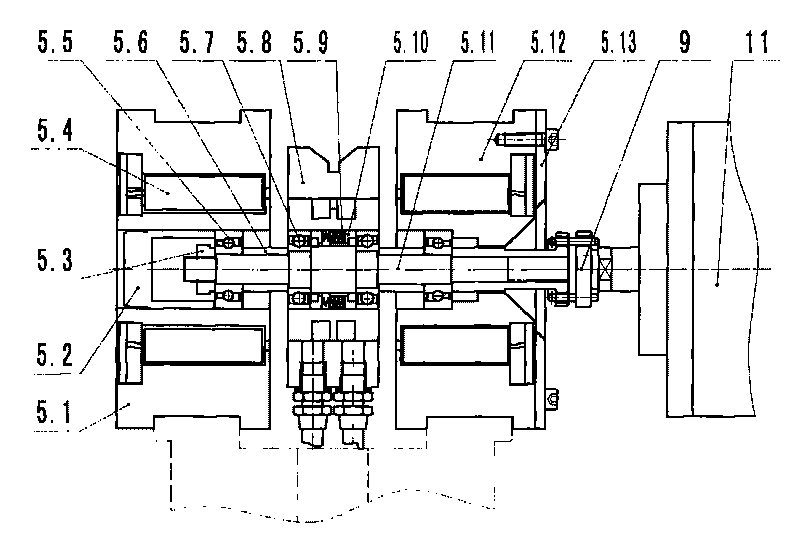

Vehicle component real object collision test method and tester

ActiveCN101430251ADetermination of impact forceDetermination of transient accelerationRailway vehicle testingShock testingComplete dataSpeed test

The invention discloses a test method for real object crash of vehicle components and a test device thereof. The test method comprises the following steps: the vehicle components are fixed on a carrying trolley which can move on a track, the speed of the trolley is increased to a test value by traction with a drive system before preparing for crash an impact wall; when the carrying trolley moves to a set position before the impact wall, a trigger device is started to detach the drive system from the carrying trolley, a test component and the carrying trolley are caused to crash the impact wall without drive power; a vehicle-borne acceleration test system is arranged on the carrying trolley so as to complete data acquisition in real time; and the trigger device triggers a speed test system, an impact force test system and a high-speed camera system at the same time. The test method of the real object crash of the vehicle components and the test device can help measure objective data in real time such as the impact force, a transient acceleration, component deformation and speed output at the moment of crash, and further can record deformation sequence images of the components during the whole crash course so as to get scientific and exact analysis results.

Owner:CENT SOUTH UNIV

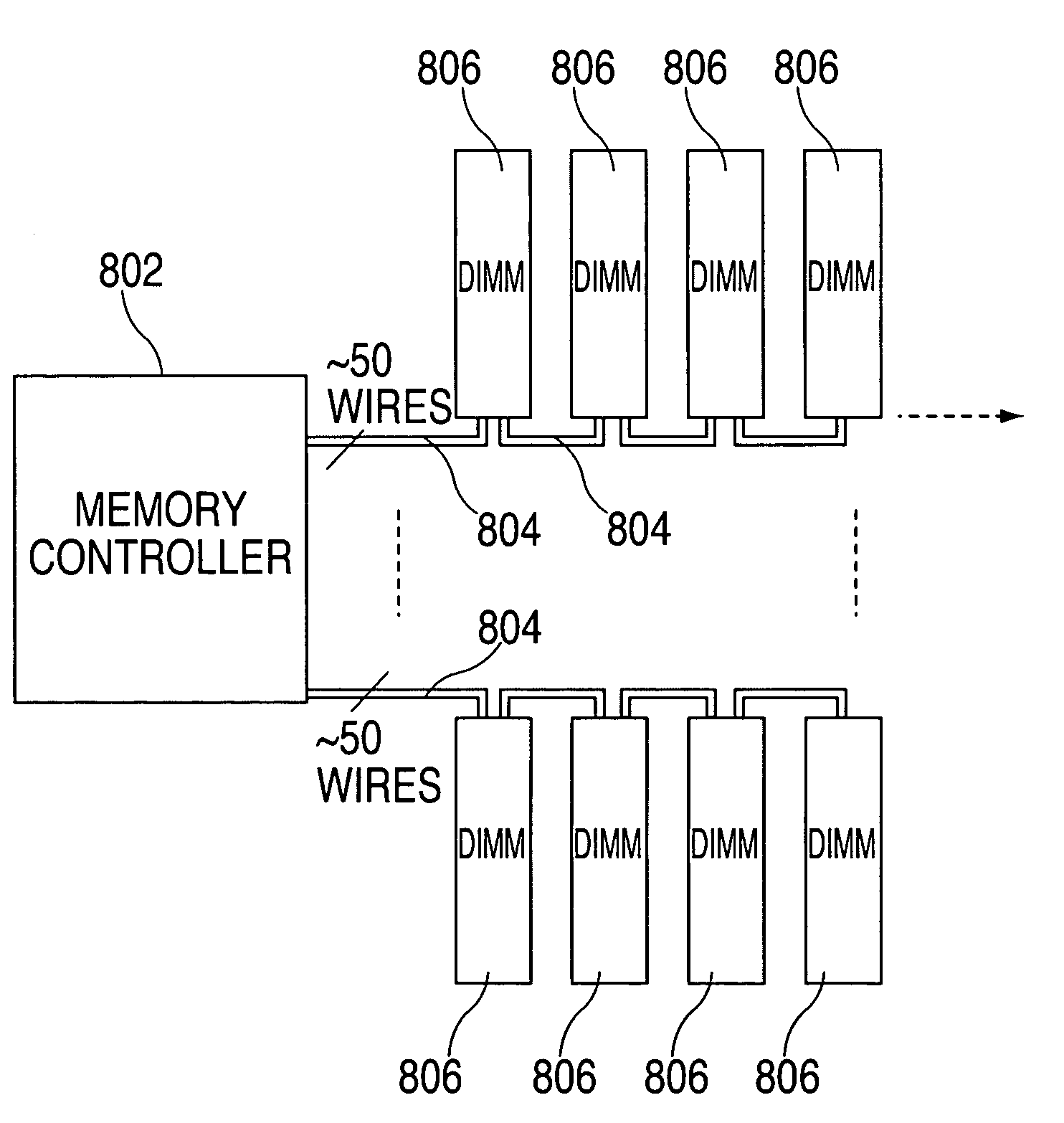

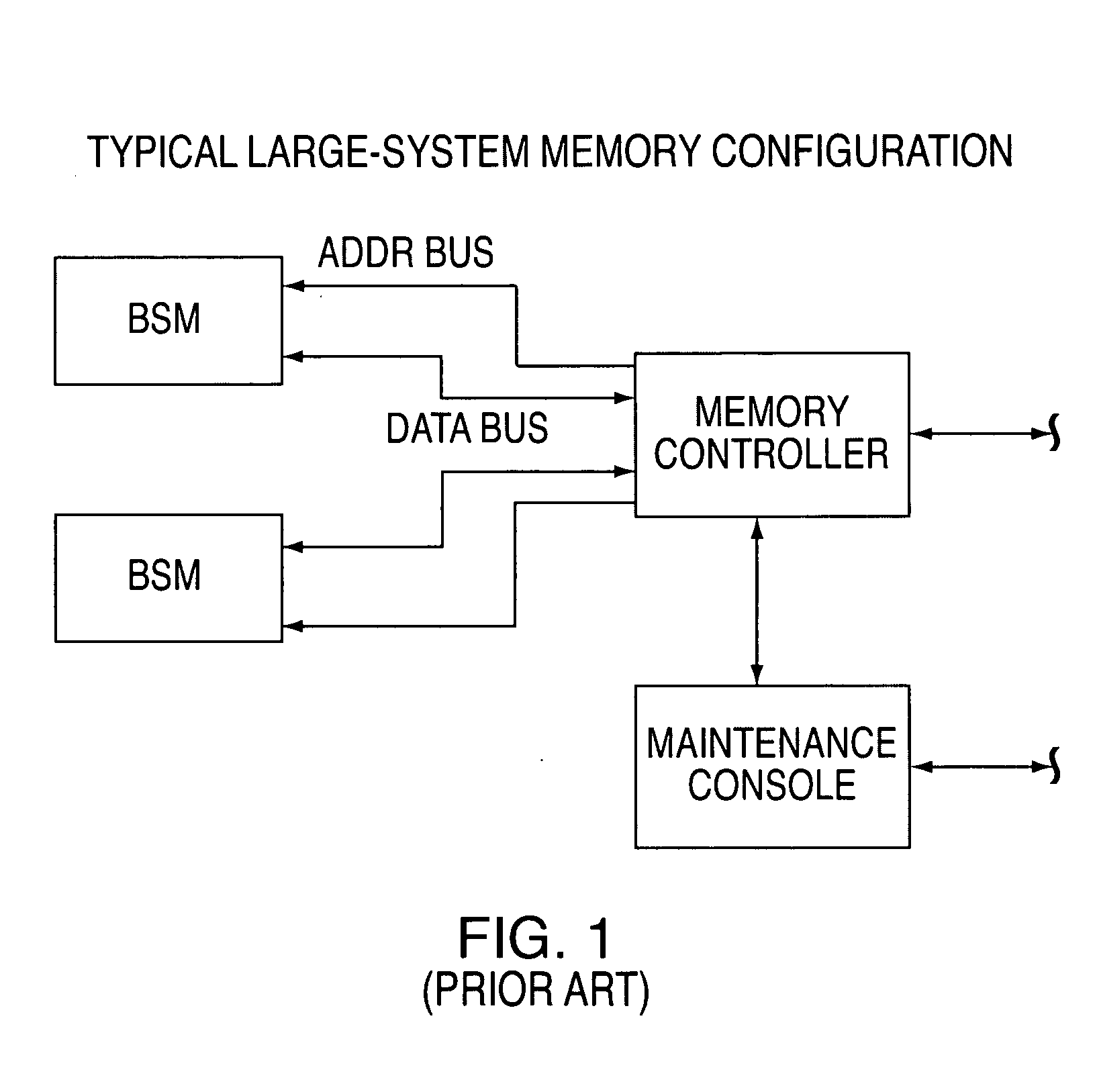

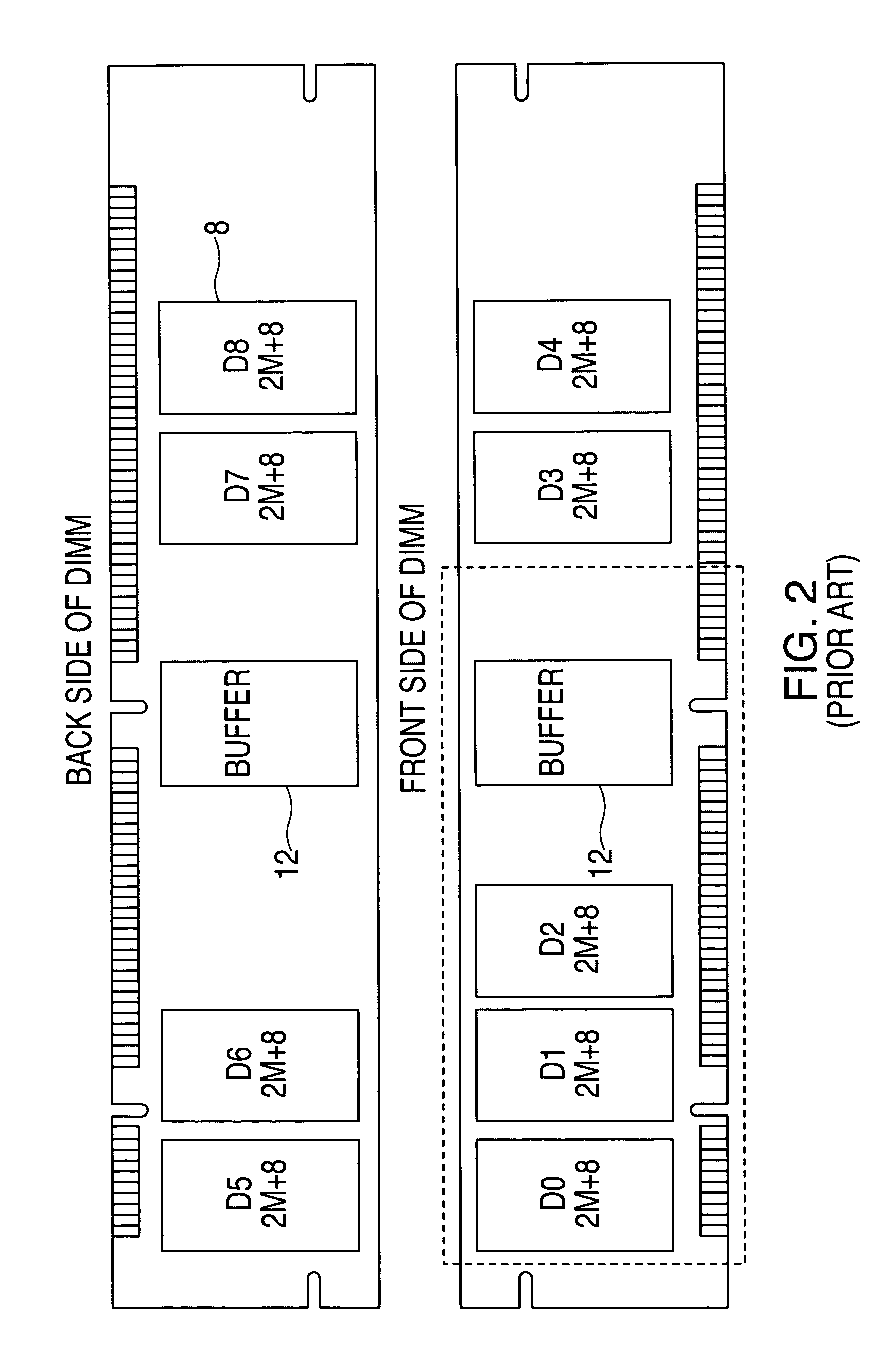

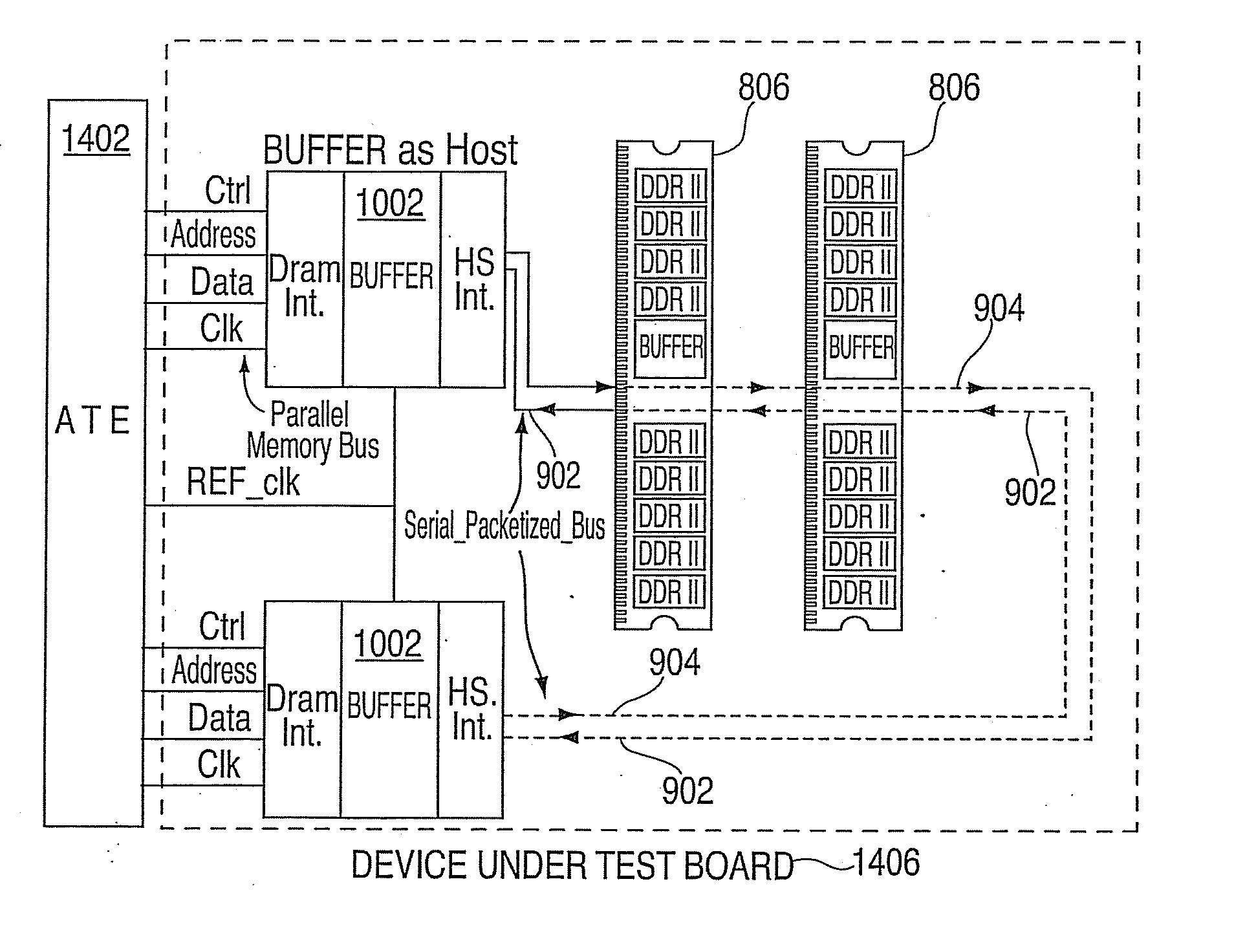

System, method and storage medium for providing a high speed test interface to a memory subsystem

ActiveUS20060107186A1Increase speedElectronic circuit testingCode conversionSpeed testOperation mode

A buffer device for testing a memory subsystem. The buffer device includes a parallel bus port adapted for connection to a slow speed bus and a serial bus port adapted for connection to a high speed bus. The high speed bus operates at a faster speed than the slow speed bus. The buffer device also includes a bus converter having a standard operating mode for converting serial packetized input data received via the serial bus port into parallel bus output data for output via the parallel bus port. The buffer device also includes an alternate operating mode for converting parallel bus input data received via the parallel bus port into serial packetized output data for output via the serial bus port. The serial packetized input data is consistent in function and timing to the serial packetized output data.

Owner:META PLATFORMS INC

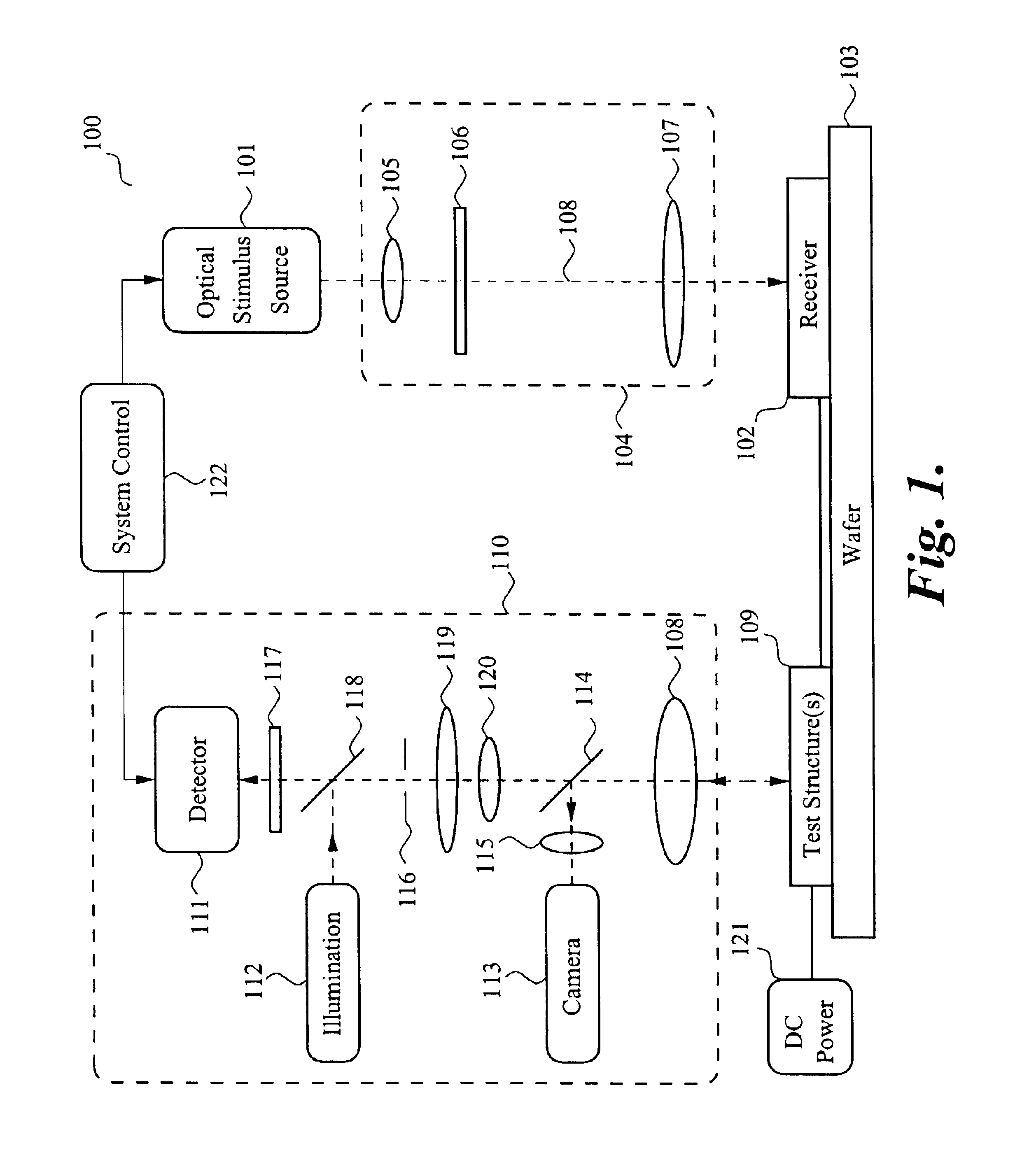

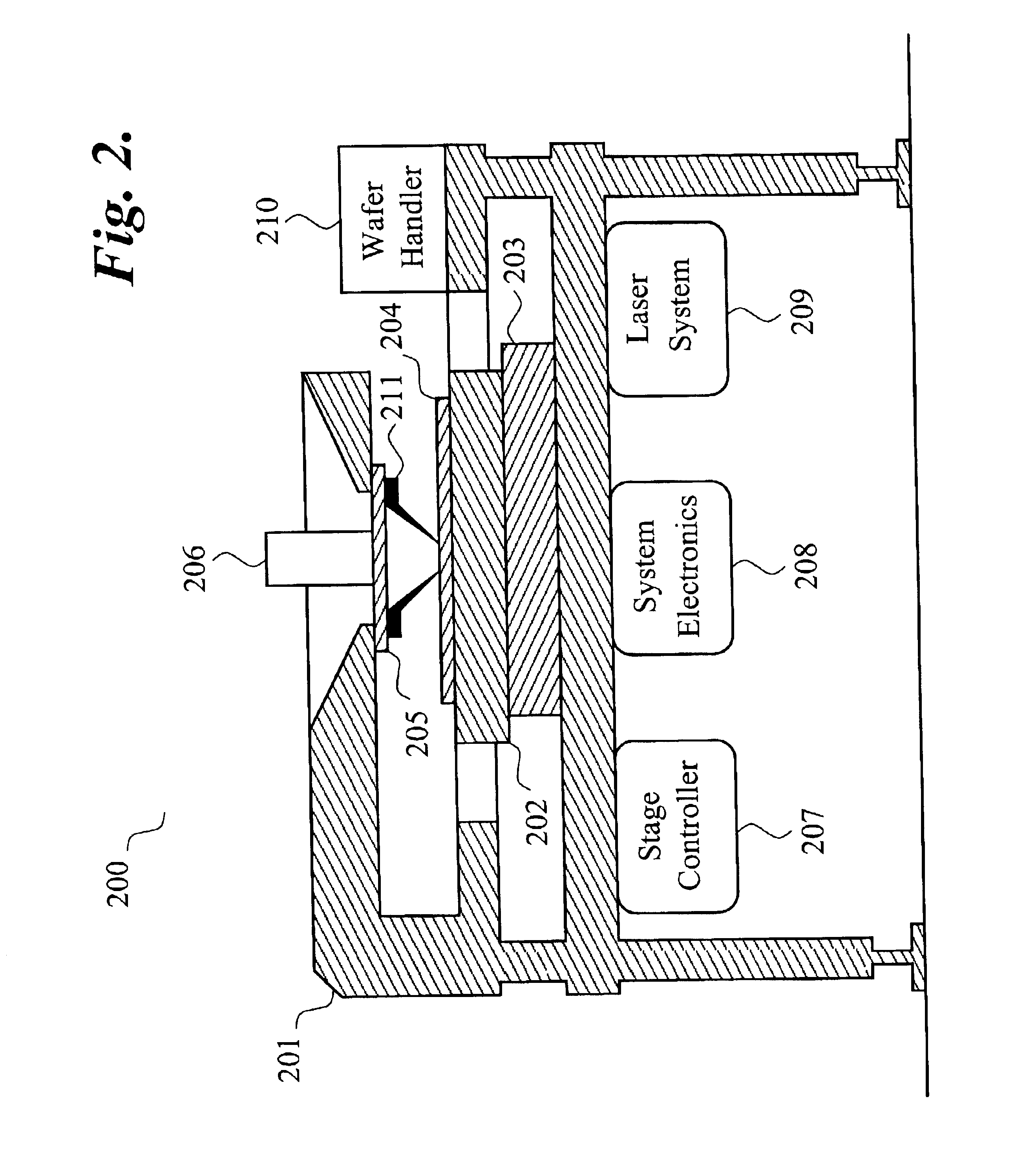

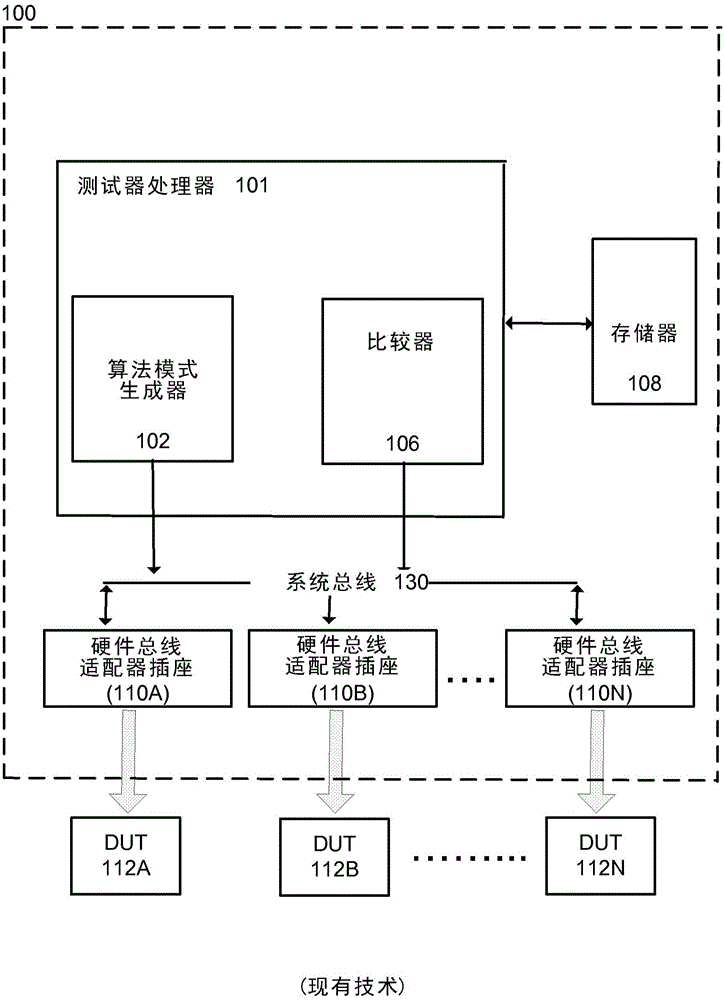

Apparatus and method for dynamic diagnostic testing of integrated circuits

InactiveUS6859031B2Semiconductor/solid-state device testing/measurementMagnetic property measurementsPhoton counting detectorElectricity

Owner:CREDENCE SYSTEMS

System, method and storage medium for providing a high speed test interface to a memory subsystem

A buffer device for testing a memory subsystem. The buffer device includes a parallel bus port adapted for connection to a slow speed bus and a serial bus port adapted for connection to a high speed bus. The high speed bus operates at a faster speed than the slow speed bus. The buffer device also includes a bus converter having a standard operating mode for converting serial packetized input data received via the serial bus port into parallel bus output data for output via the parallel bus port. The buffer device also includes an alternate operating mode for converting parallel bus input data received via the parallel bus port into serial packetized output data for output via the serial bus port. The serial packetized input data is consistent in function and timing to the serial packetized output data.

Owner:META PLATFORMS INC

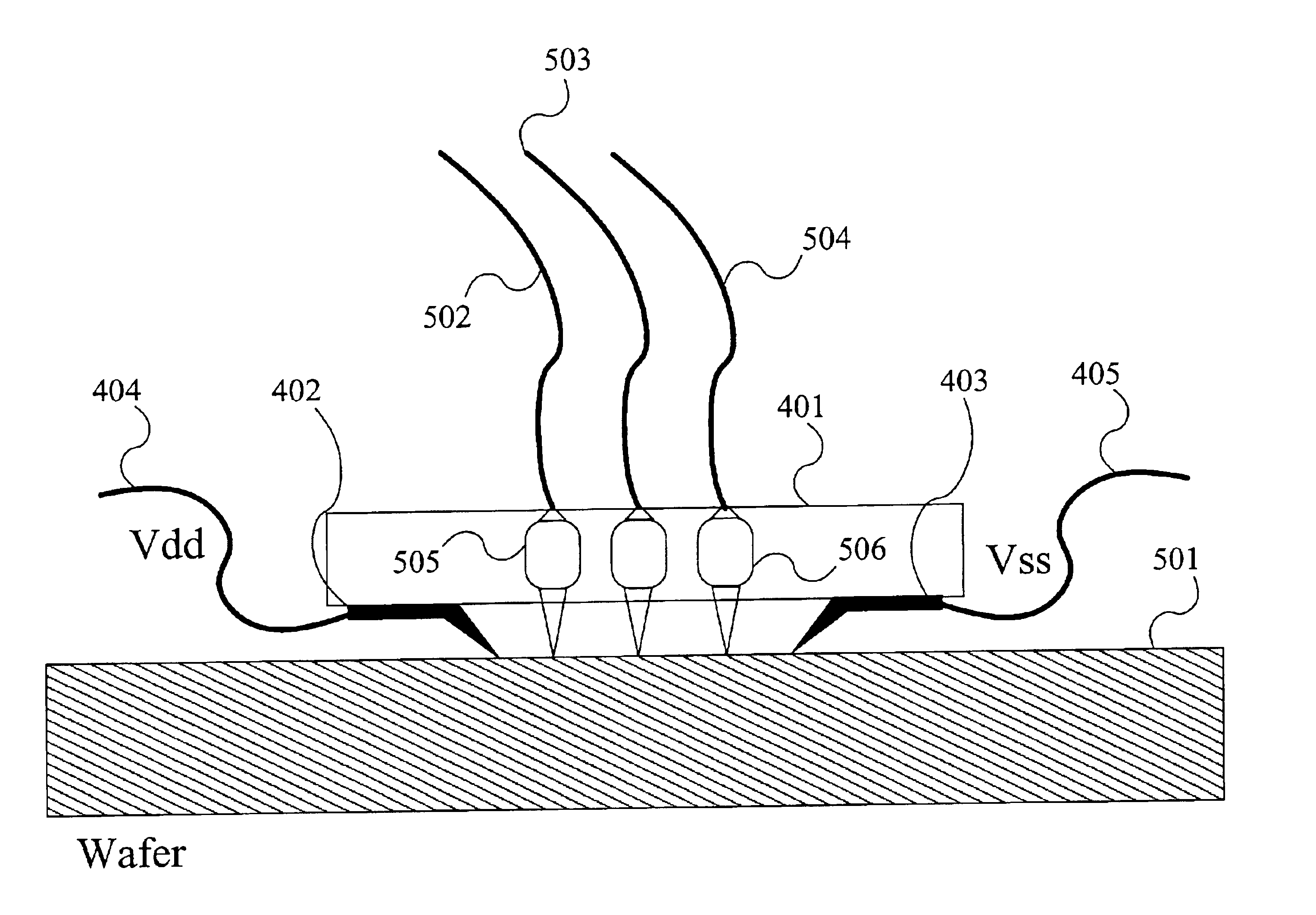

Wafer probe card

InactiveUS6265888B1Electrical measurement instrument detailsFault location by increasing destruction at faultProbe cardSpeed test

An apparatus to heat and test a semiconductor wafer includes a probe card and tests a plurality of die simultaneously at the wafer level. In the present invention, the apparatus heats the wafer to sufficient temperatures to perform burn-in and a speed test. A method of testing the semiconductor allows certain die to be repaired that would otherwise be scrapped in a conventional process where bun-in and other tests are performed on packaged die. The method also eliminates steps associated with handling individually packaged parts, reduces burn-in space and consolidates certain test steps.

Owner:SCS HIGHTECH +1

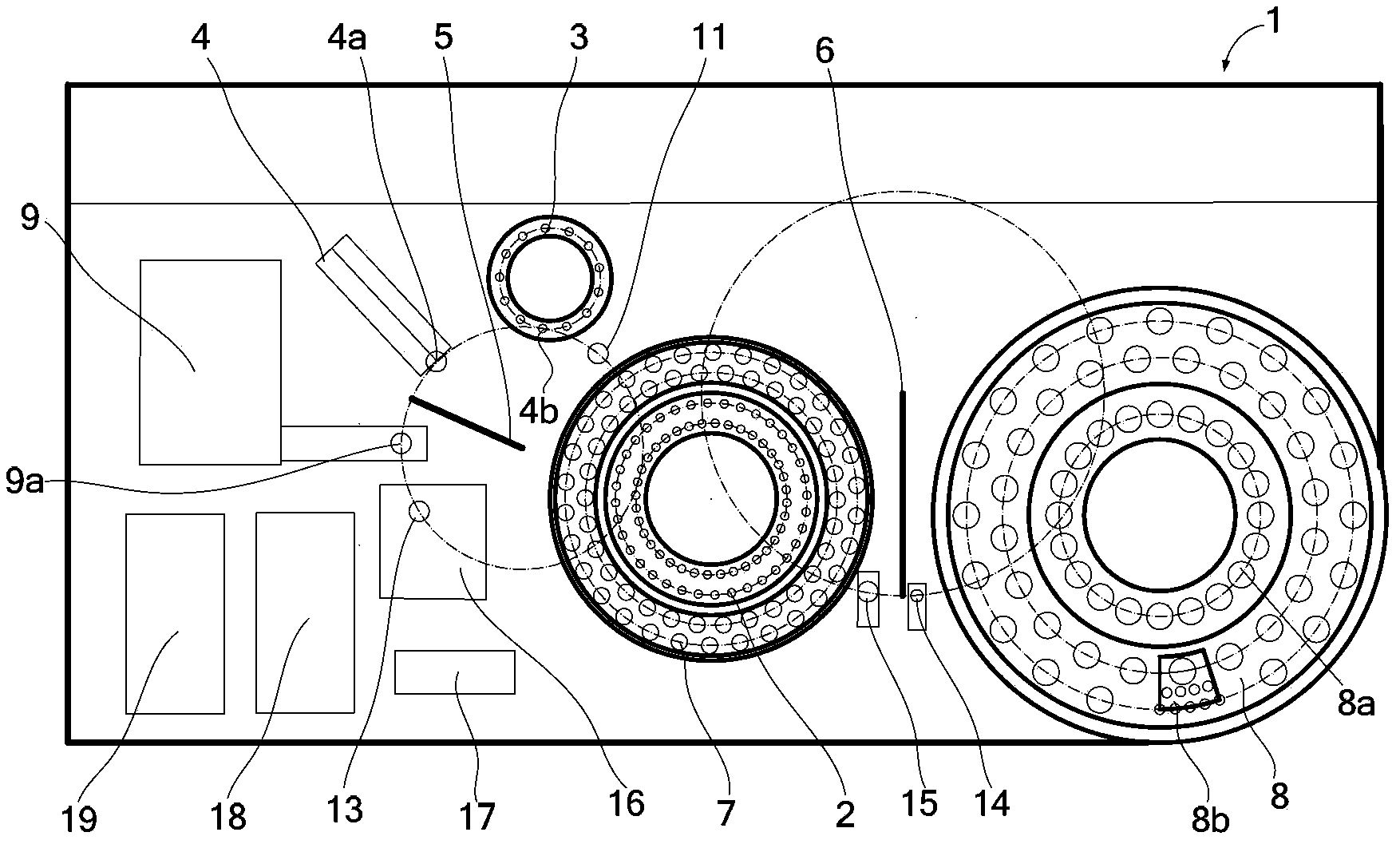

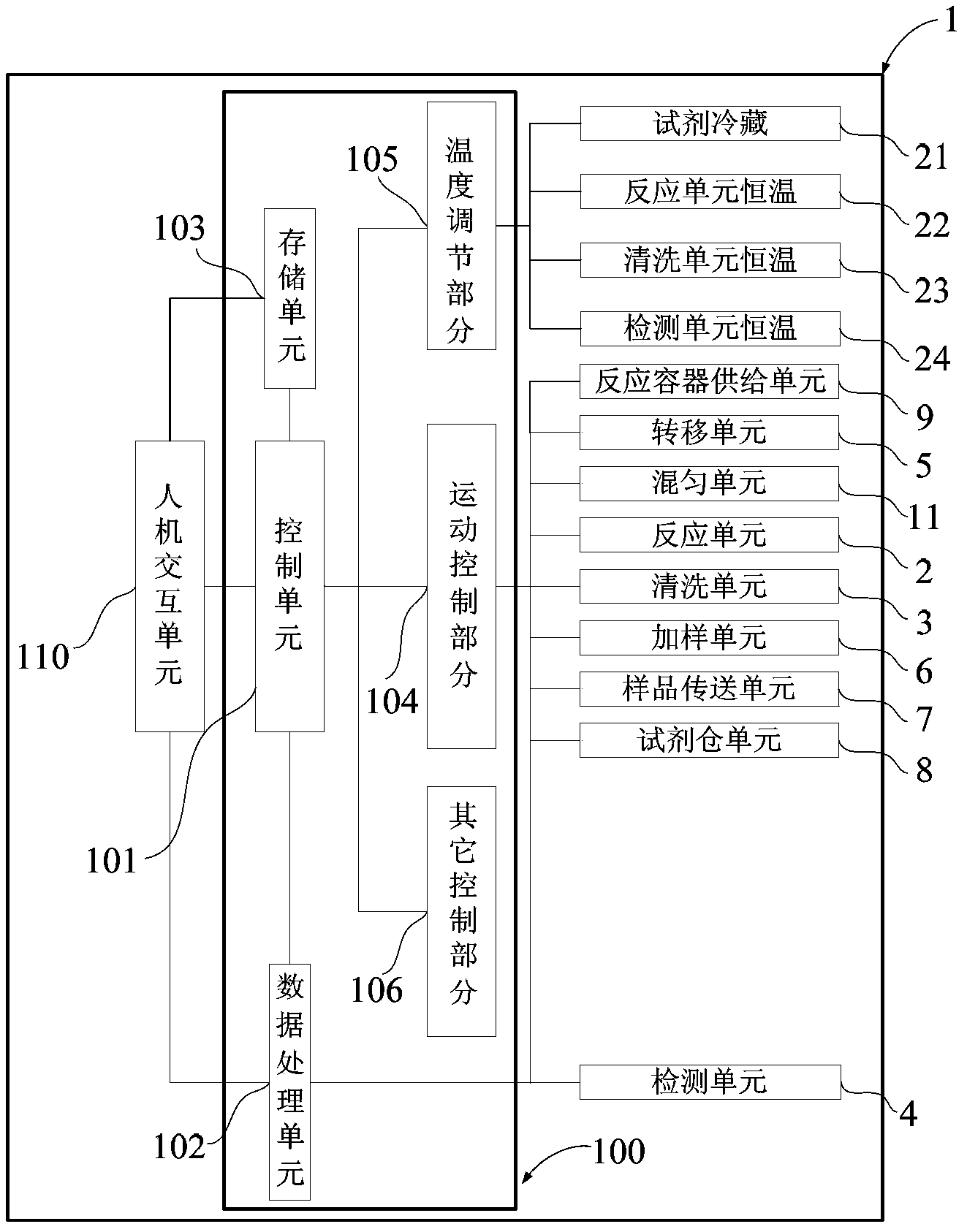

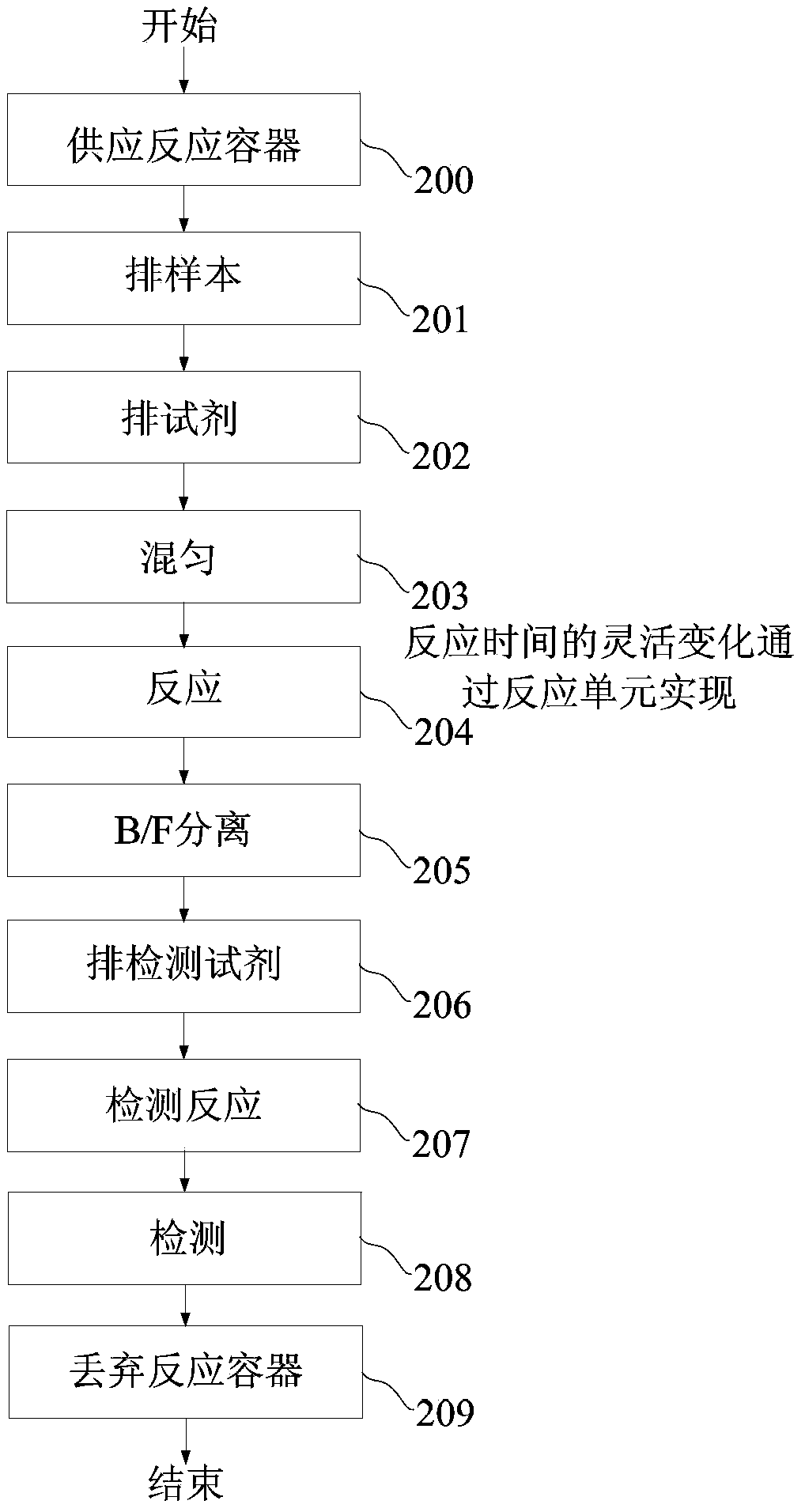

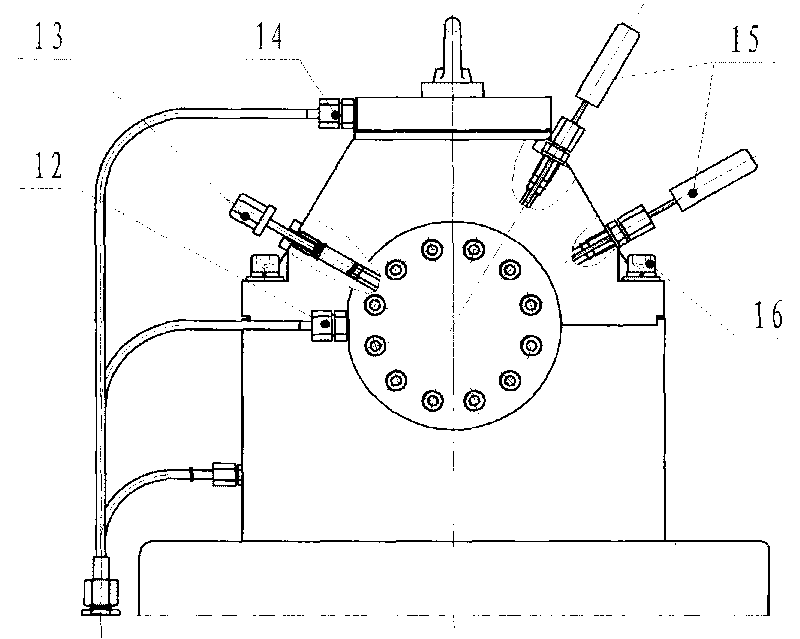

Automatic analysis apparatus and automatic analysis method

The invention relates to an automatic analysis apparatus. The apparatus includes a reaction container supply unit, a reagent warehouse receipt, a sample transfer unit, a reaction incubation unit, a cleaning and separating unit, a detection unit, a sample adding unit, a transfer unit and a control system. An automatic analysis method using the automatic analysis apparatus includes the following steps: (1) supplying a reaction container; (2) adding an analysis sample and an analysis reagent; (3) reacting; (4) cleaning, and separating; (5) adding a detection reagent; (6) reacting; and (7) detecting. The automatic analysis apparatus and the automatic analysis method can flexibly realize a variety of test modes and reaction times, reduce the size of a whole machine, reduce the cost, and make the whole machine have a compact structure; and the automatic analysis apparatus has scalability, can easily realize high speed test, and is suitable for analysis under different test modes and reaction times.

Owner:SUZHOU HAOOUBO BIOPHARML

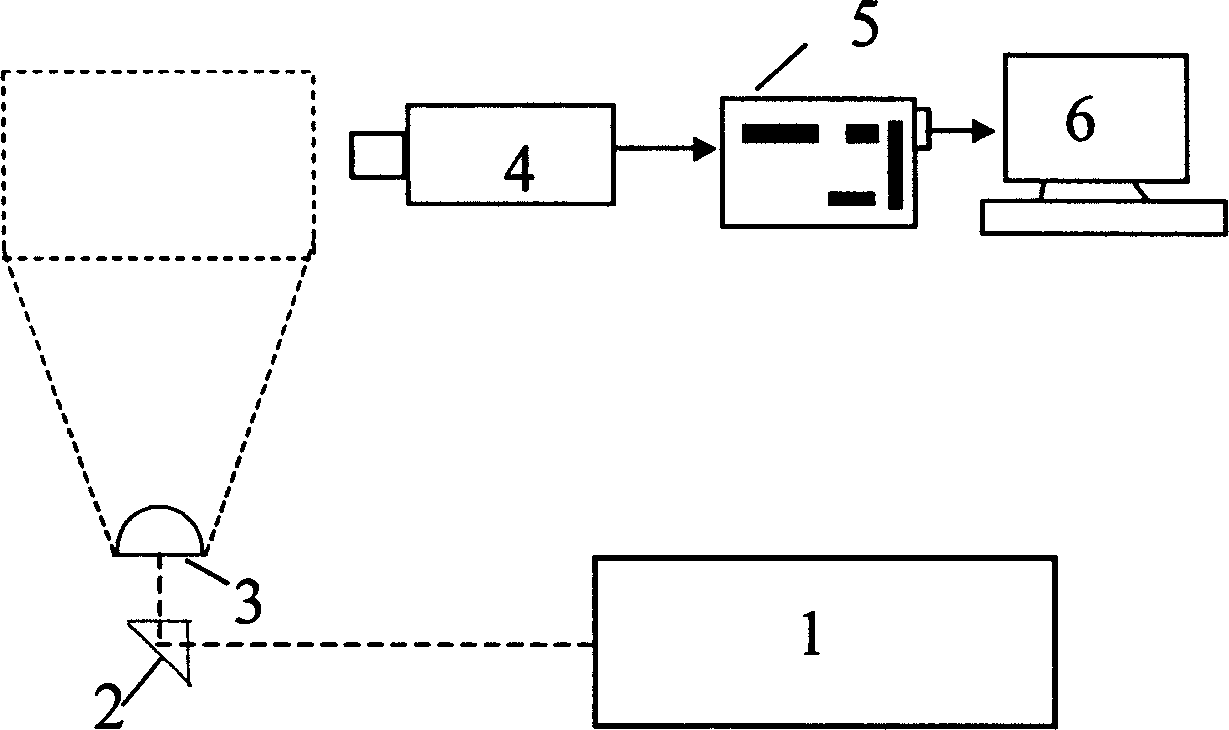

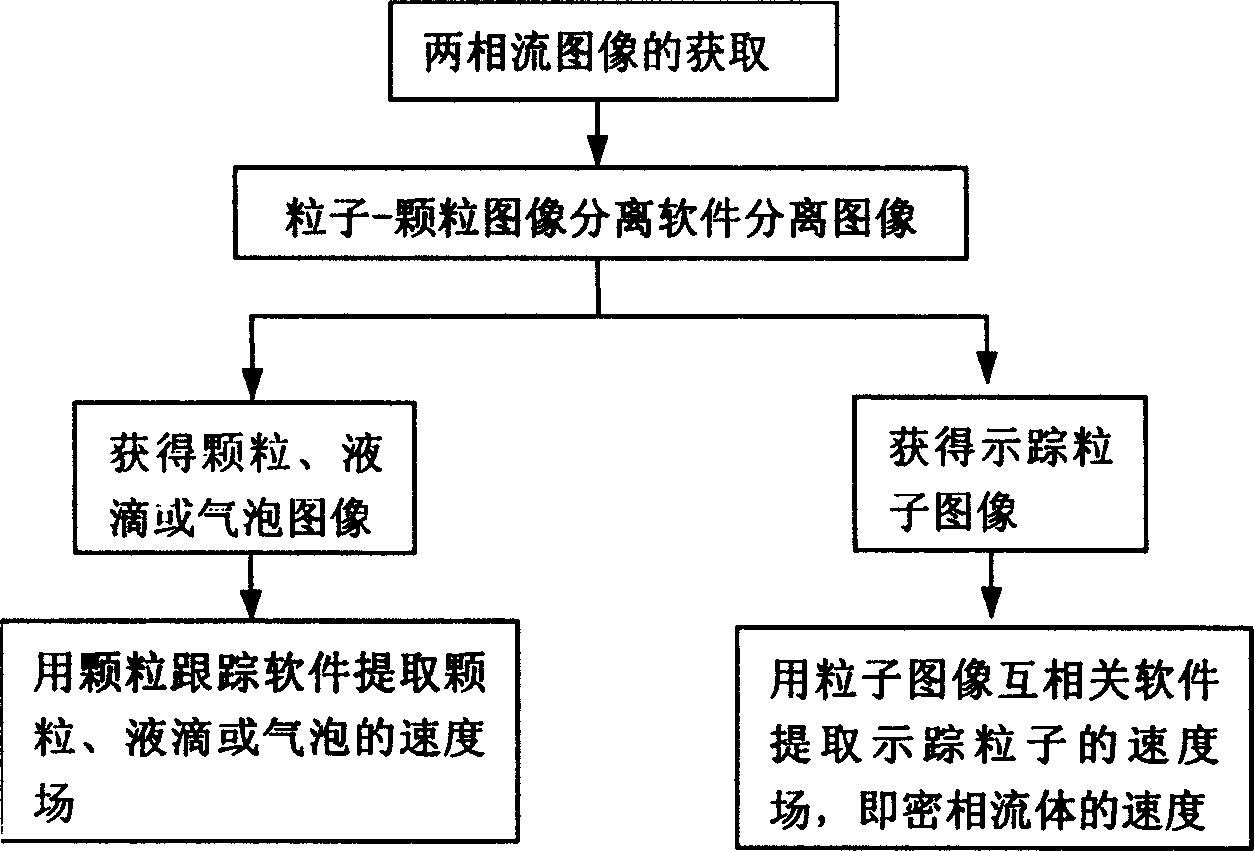

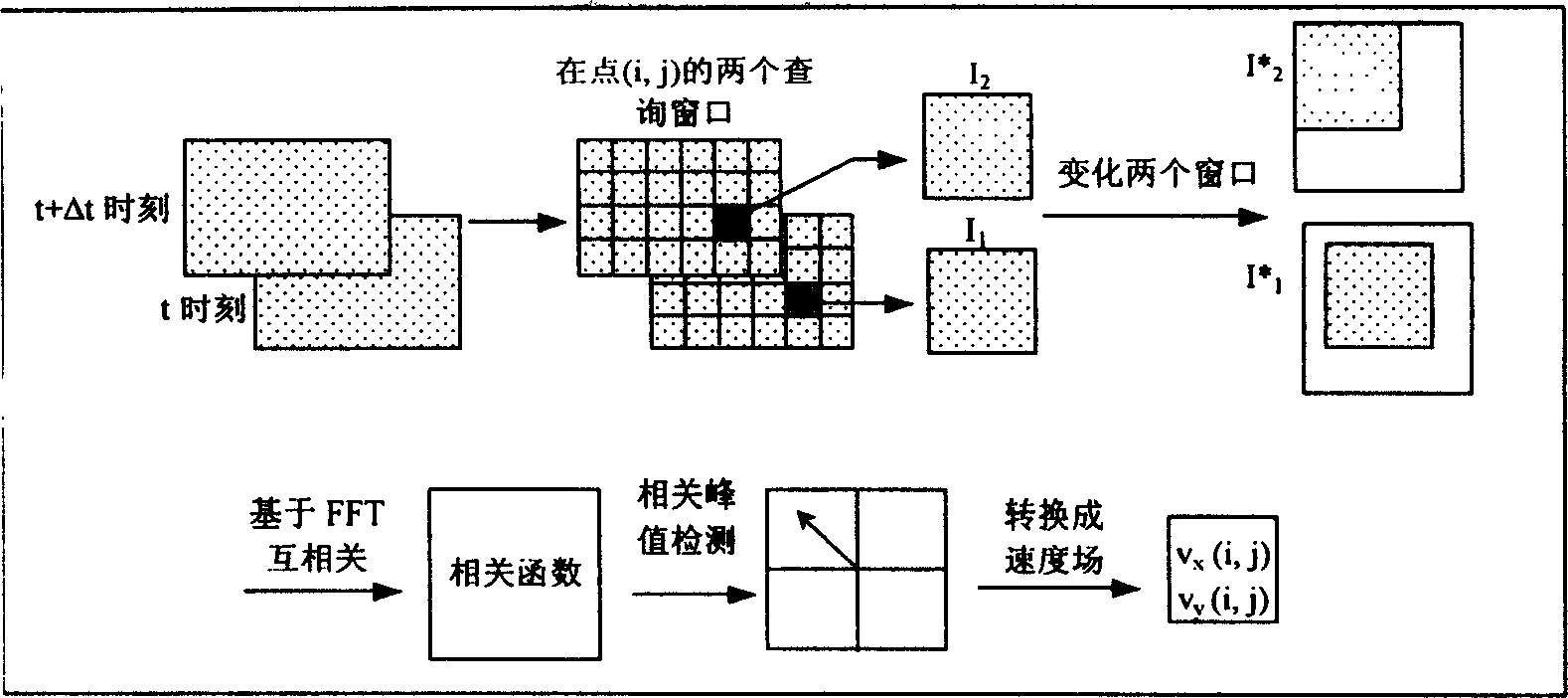

Two-phase flow digital particle image speed measurement method and device

InactiveCN1654962AGood monochromaticityHas a Gaussian distributionDevices using time traversedFluid speed measurementMeasurement deviceSpeed test

This invention discloses a two-phase flow digital particle image speed test method and its device, which uses suitable particles to trace flow of fluids and uses high speed CCD camera to register motion images for tracing particles, liquid drops or gas bubbles, applies an image process method to separate the images of scattered phase particles drops or bubbles from original images and extracts velocities of them from their images and applies an improved cross correlation technology based on quick Fourier transformation to extract the velocity field of the tracing particles to realize the synchronous measurement to the two phase flows with different phase velocity fields. The device includes a HeNe laser, a triple prism and a cylinder lens, a high speed CCD camera, an image collecting card and a control and image process computer.

Owner:ZHEJIANG UNIV

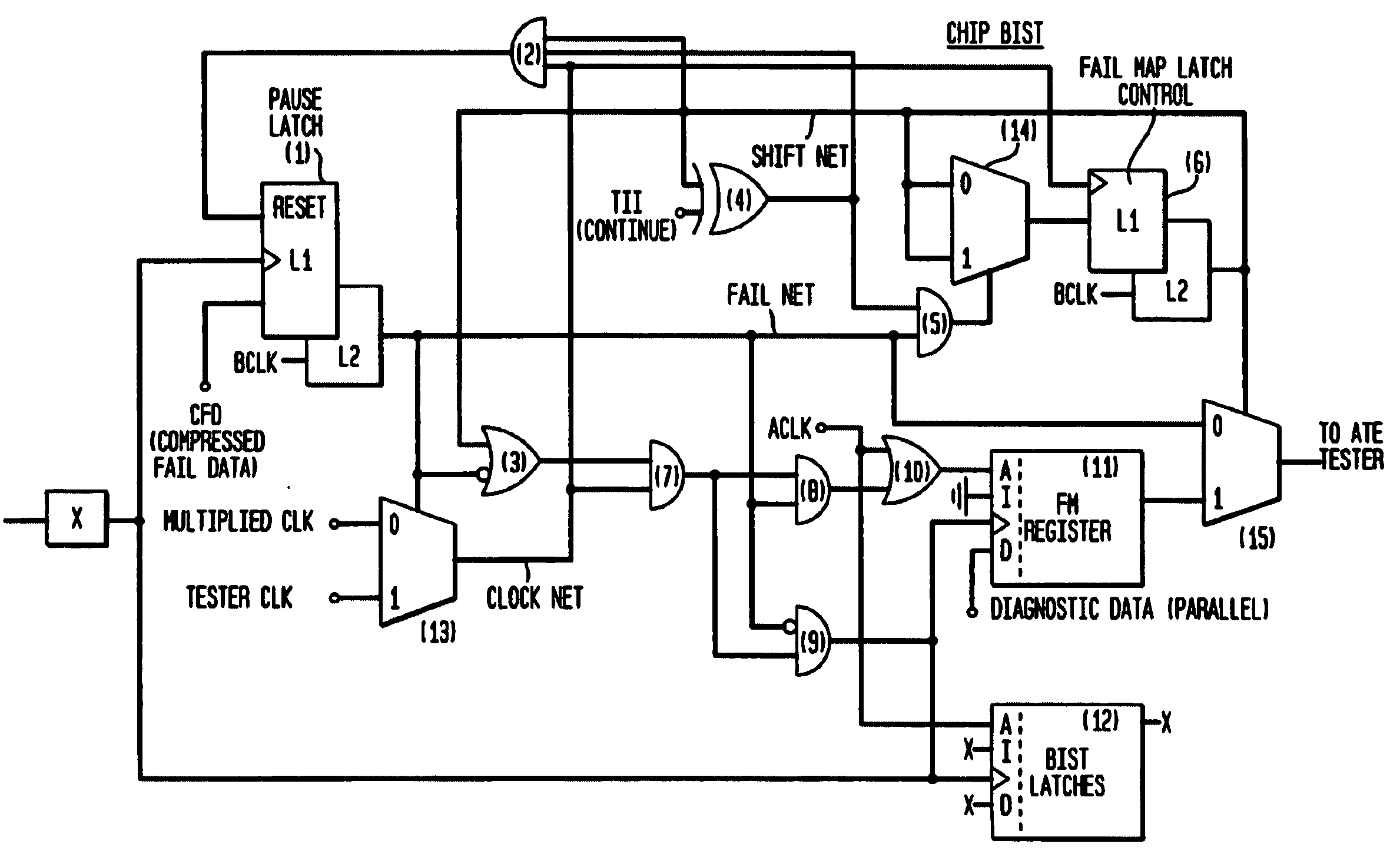

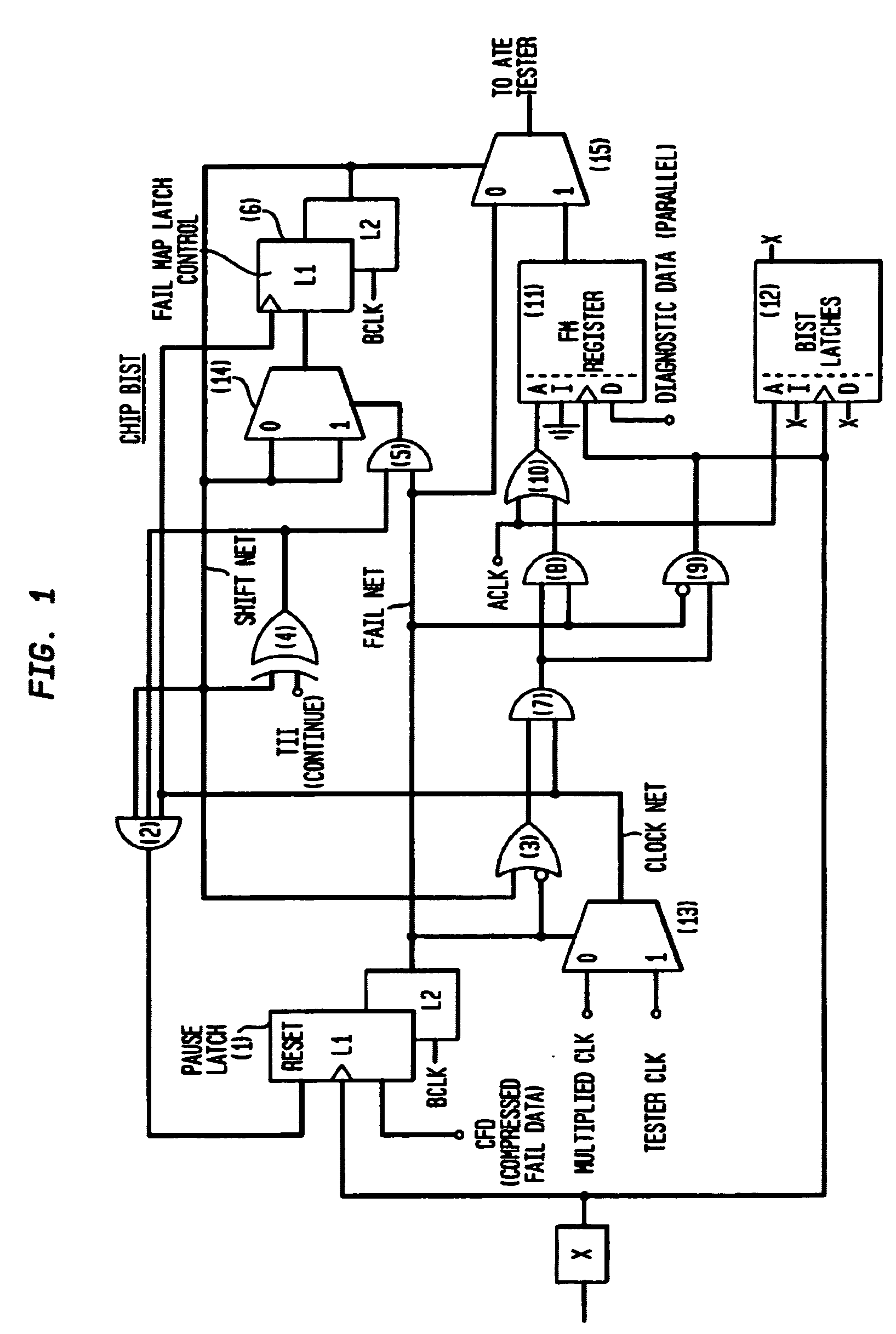

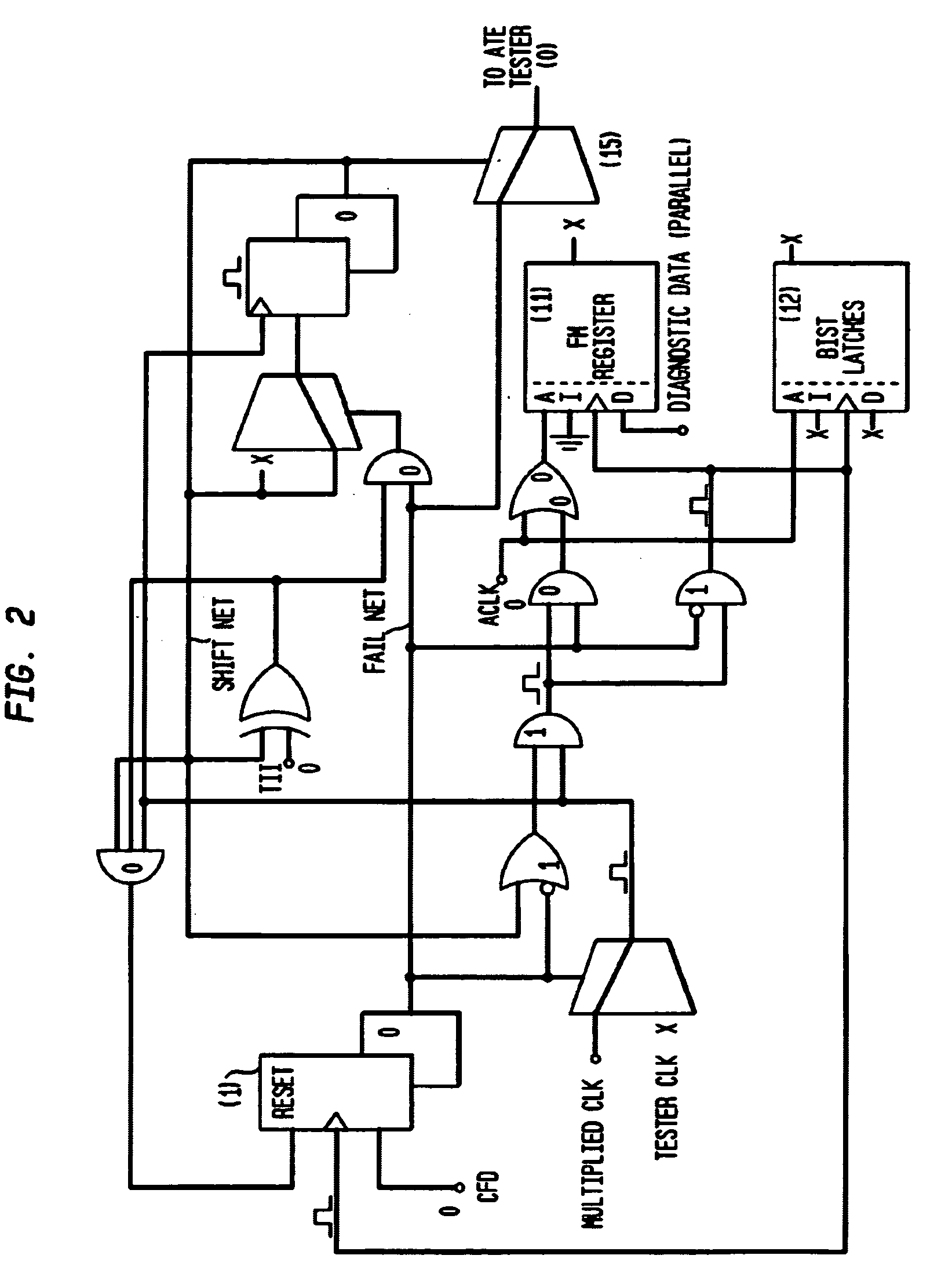

Automatic bit fail mapping for embedded memories with clock multipliers

A bit fail map circuit accurately generates a bit fail map of an embedded memory such as a DRAM by utilizing a high speed multiplied clock generated from a low-speed Automated Test Equipment (ATE) tester. The circuit communicates between the ATE tester, the embedded memory under test, Built-In Self-Test (BIST) and Built-In Redundancy Analysis (BIRA). An accurate bit fail map of an embedded DRAM memory is provided by pausing the BIST test circuitry at a point when a fail is encountered, namely a mismatch between BIST expected data and the actual data read from the array, and then shifting the bit fail data off the chip using the low-speed ATE tester clock. Thereafter, the high-speed test is resumed from point of fail by again running the BIST using the high-speed internal clock, to provide at-speed bit Fail Maps.

Owner:IBM CORP

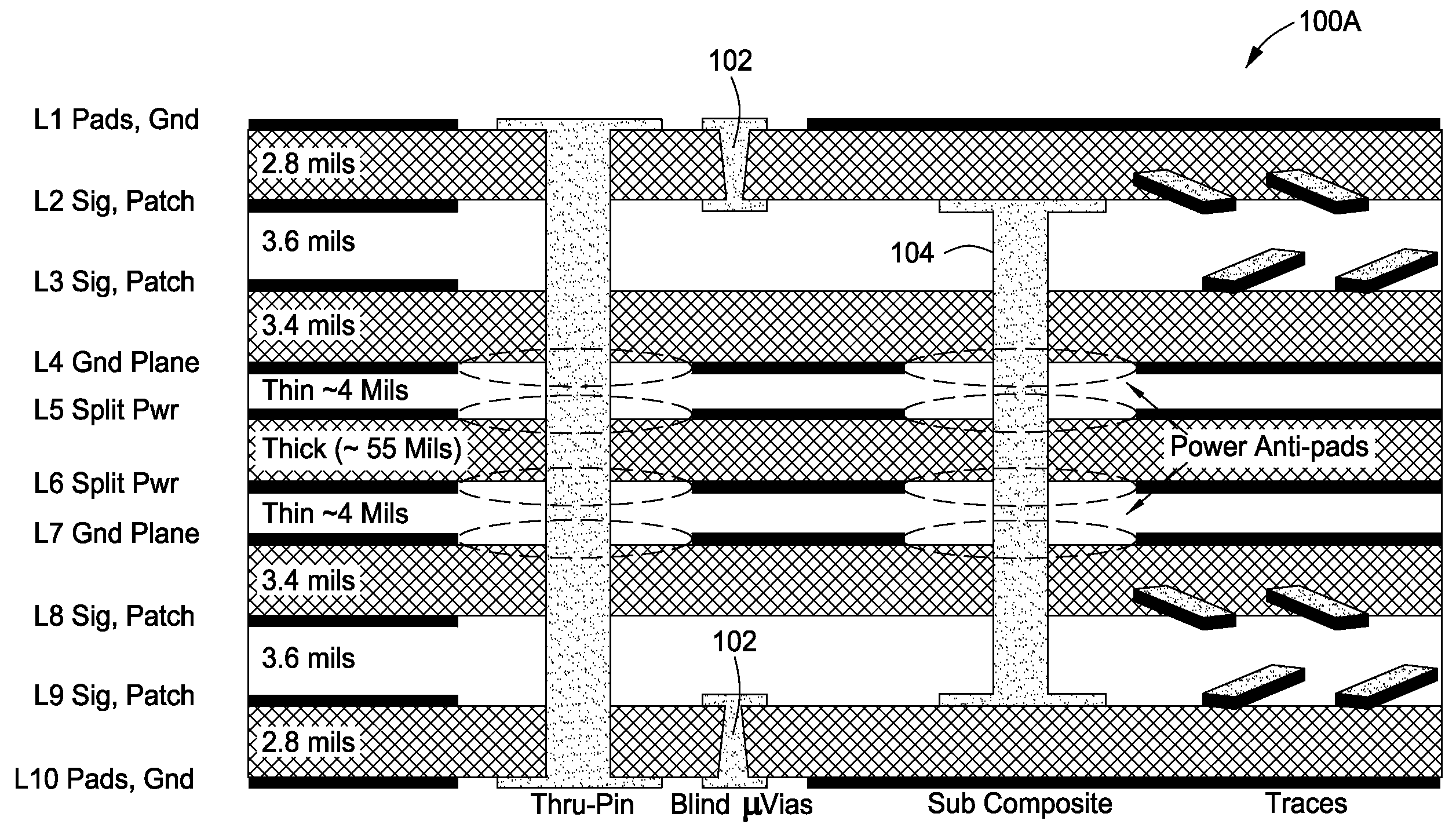

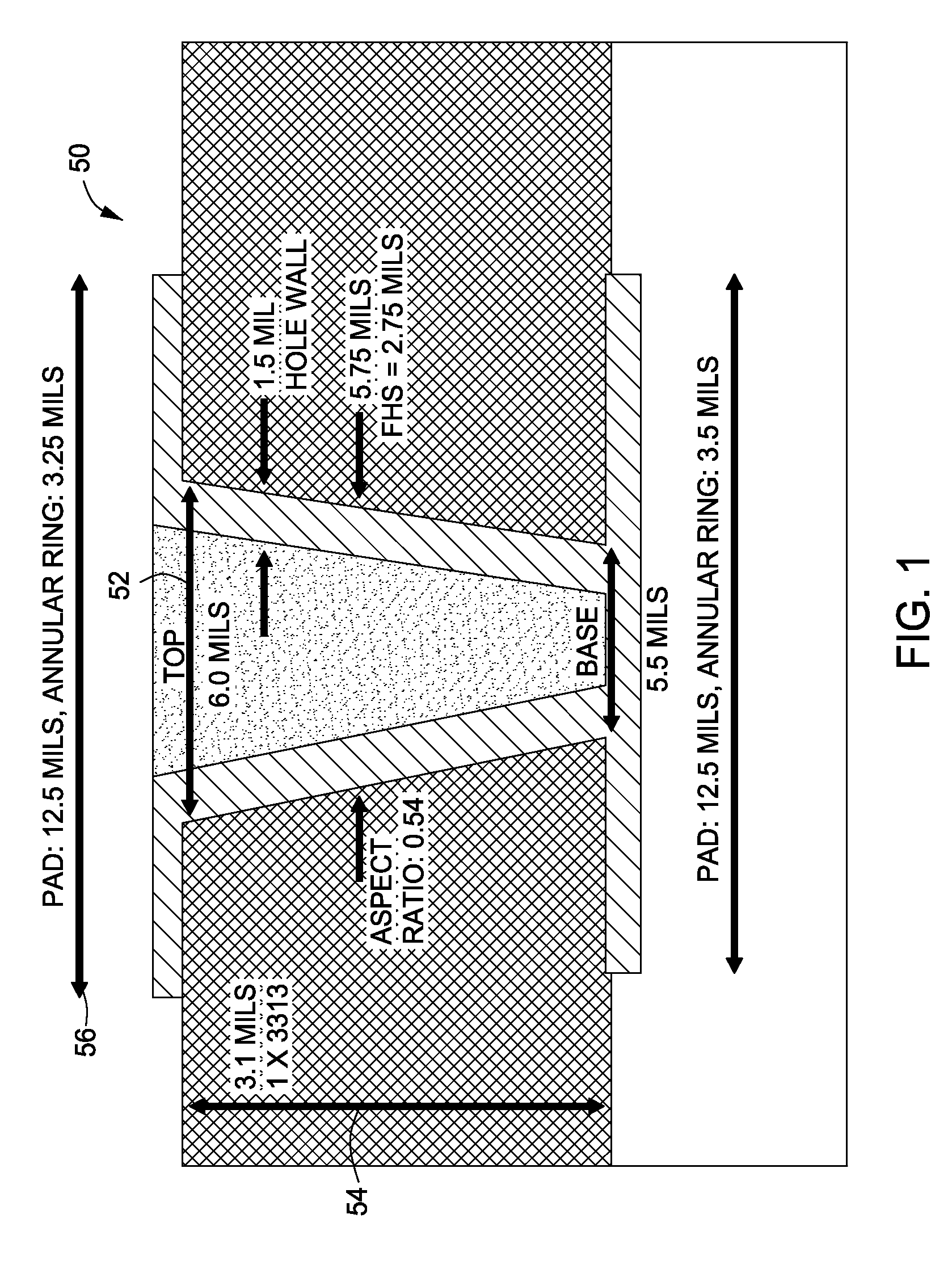

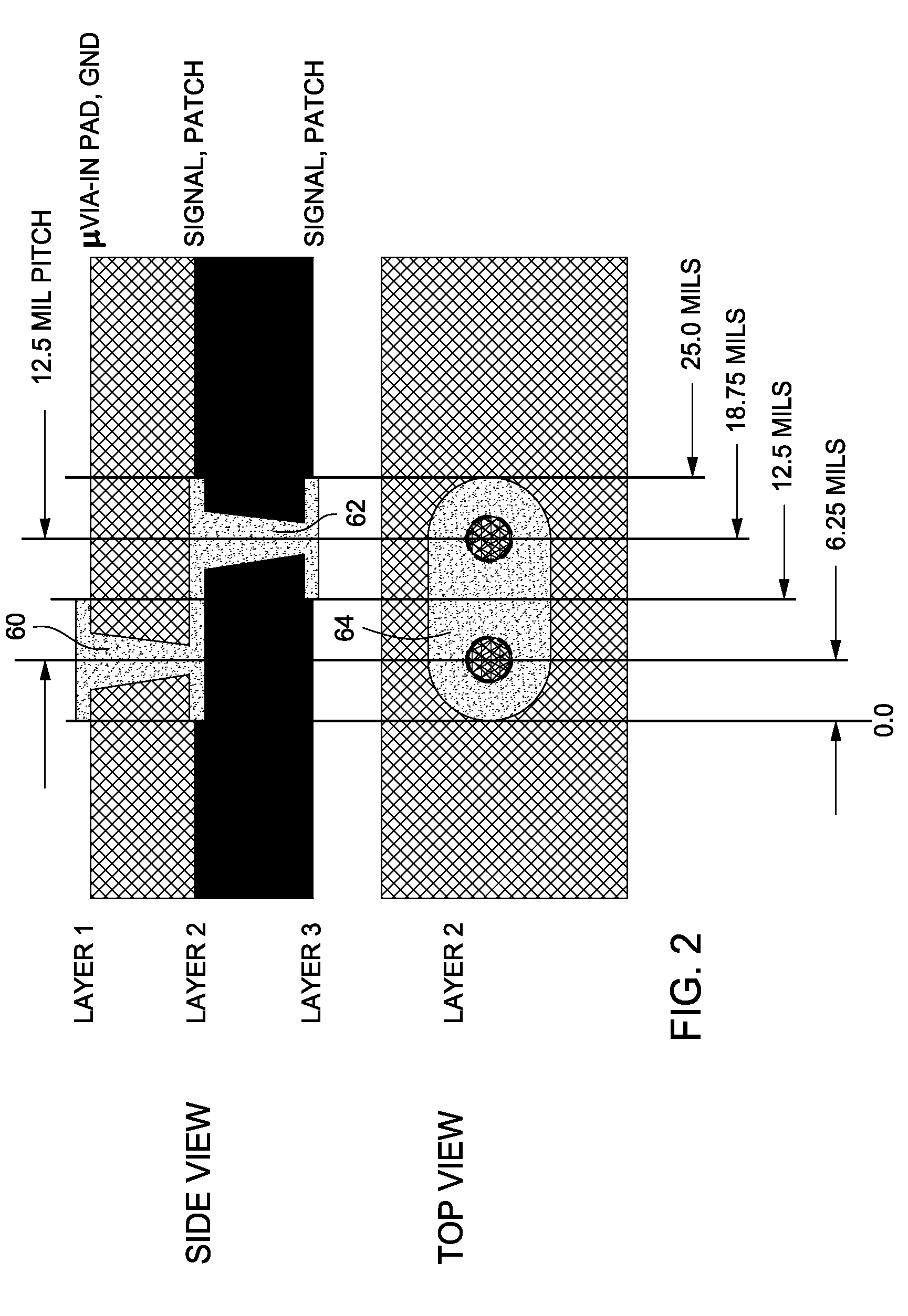

Conductive dome probes for measuring system level multi-ghz signals

ActiveUS20080250377A1Final product manufactureCross-talk/noise/interference reductionHigh densityReflection loss

Methods and apparatus for accessing a high speed signal routed on a conductive trace on an internal layer of a printed circuit board (PCB) using high density interconnect (HDI technology) are provided. The conductive trace may be coupled to a microvia (μVia) having a conductive dome disposed above the outer layer pad of the μVia. In-circuit test (ICT) fixtures or high speed test probes may interface with the conductive dome to test the high speed signal with decreased reflection loss and other parasitic effects when compared to conventional test points utilizing plated through-hole (PTH) technology.

Owner:CISCO TECH INC

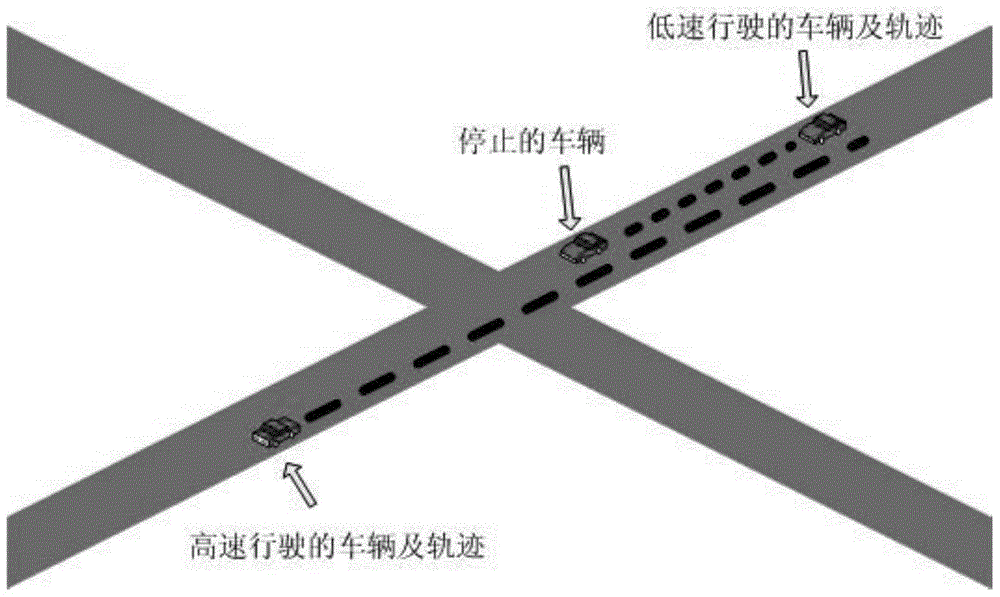

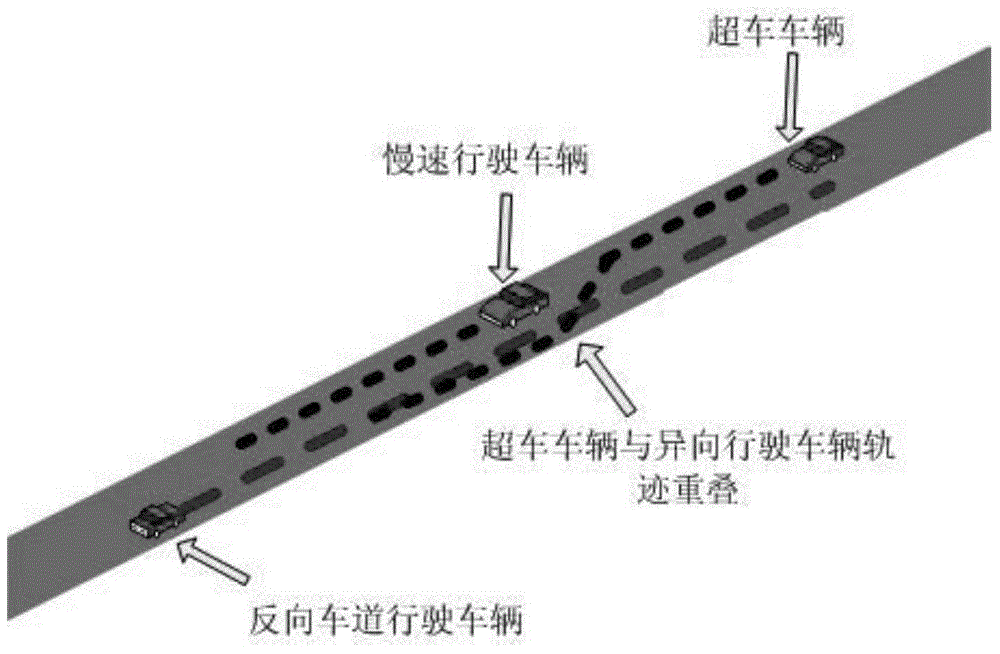

Anti-collision method and system under different vehicle conditions

ActiveCN104537889ATimely anti-collision alarmSmall amount of calculationAnti-collision systemsRisk levelInformation transmission

The invention discloses an anti-collision method and system under different vehicle conditions, and belongs to the technical field of vehicle safety. The method includes the steps that the vehicle conditions are judged according to the vehicle speed and the corresponding safety distance, and the trajectory calculation quantity, the trajectory computing cycle, and the information sending cycle are determined according to the different vehicle conditions, vehicle trajectories are calculated according to the trajectory calculation quantity, the trajectory computing cycle and vehicle running states, the vehicle trajectories are periodically broadcast, anti-collision detection is conducted through the comparison between the vehicle trajectory of one vehicle and the vehicle trajectories of other vehicles, and if it is detected that a collision possible occurs, an early warning signal is output. The anti-collision method and system under the different vehicle conditions can achieve distinguishing of different risk levels of the vehicles through a vehicle condition determination strategy, targeted anti-collision warming for dangerous vehicles can be conducted, information transmission amount can be reduced through scattering the trajectory calculation to each vehicle, the decision making early warning speed test is improved, the occurrence of the vehicle collision is effectively prevented, and traffic accidents are reduced.

Owner:四川九洲投资控股集团有限公司

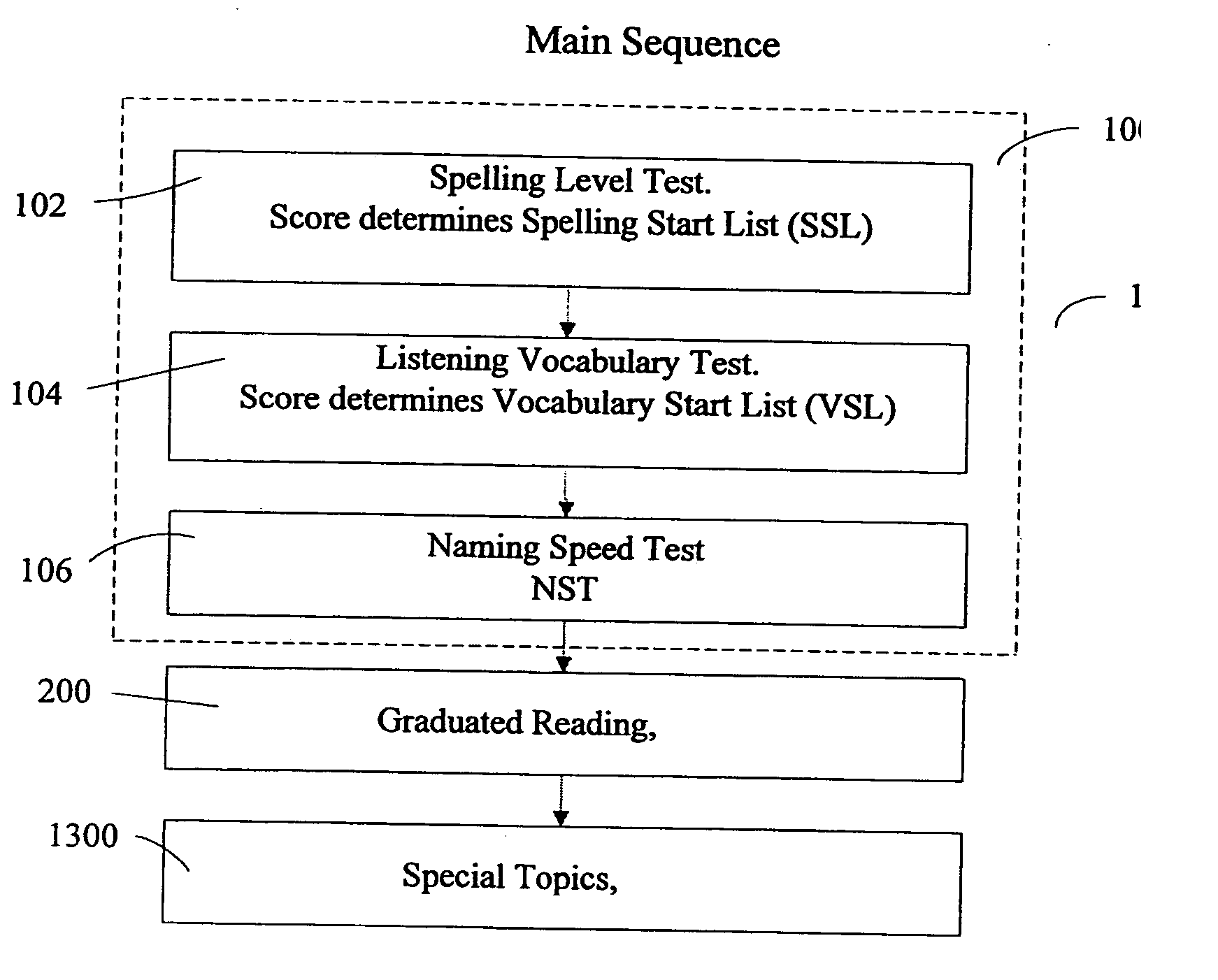

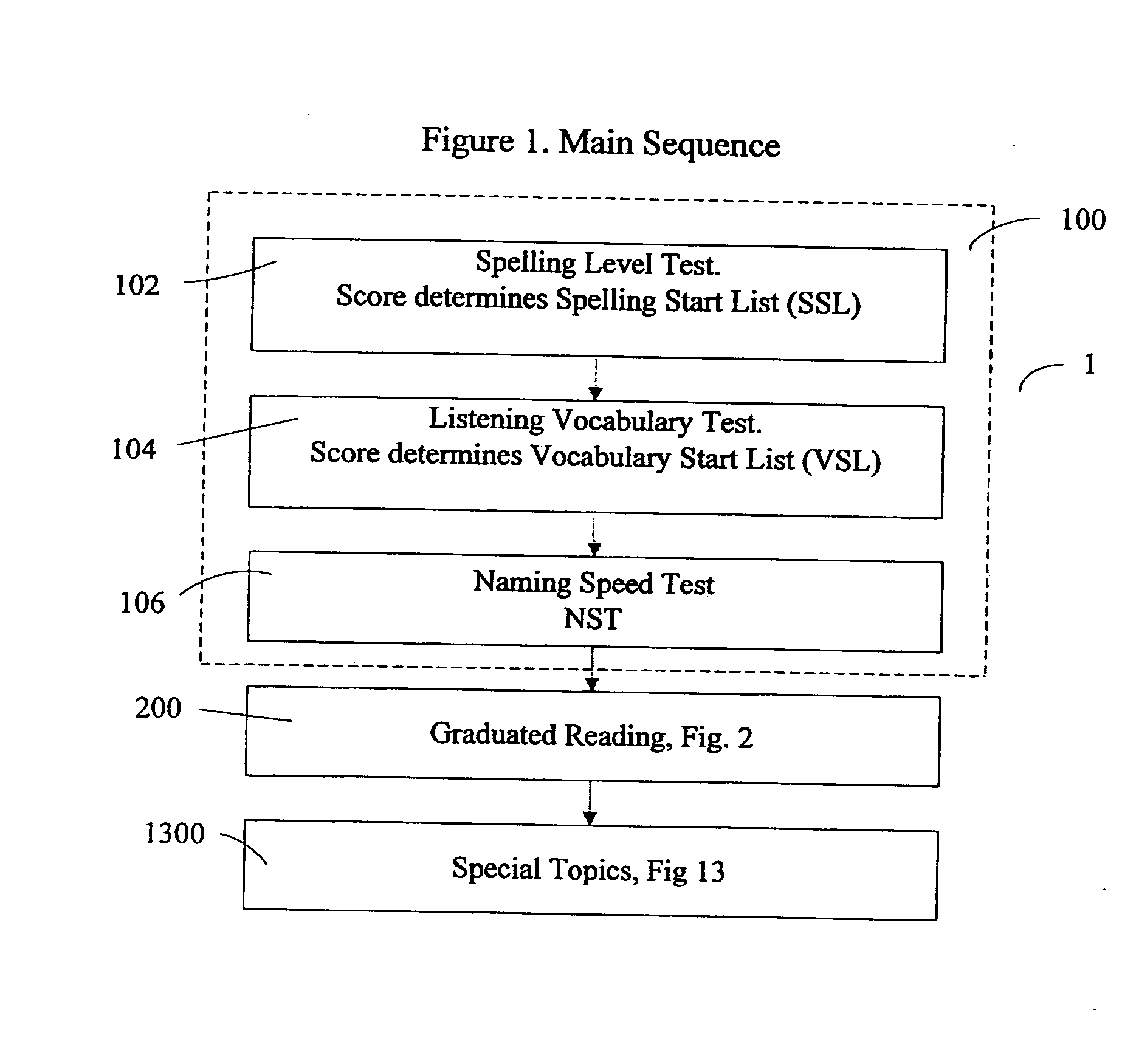

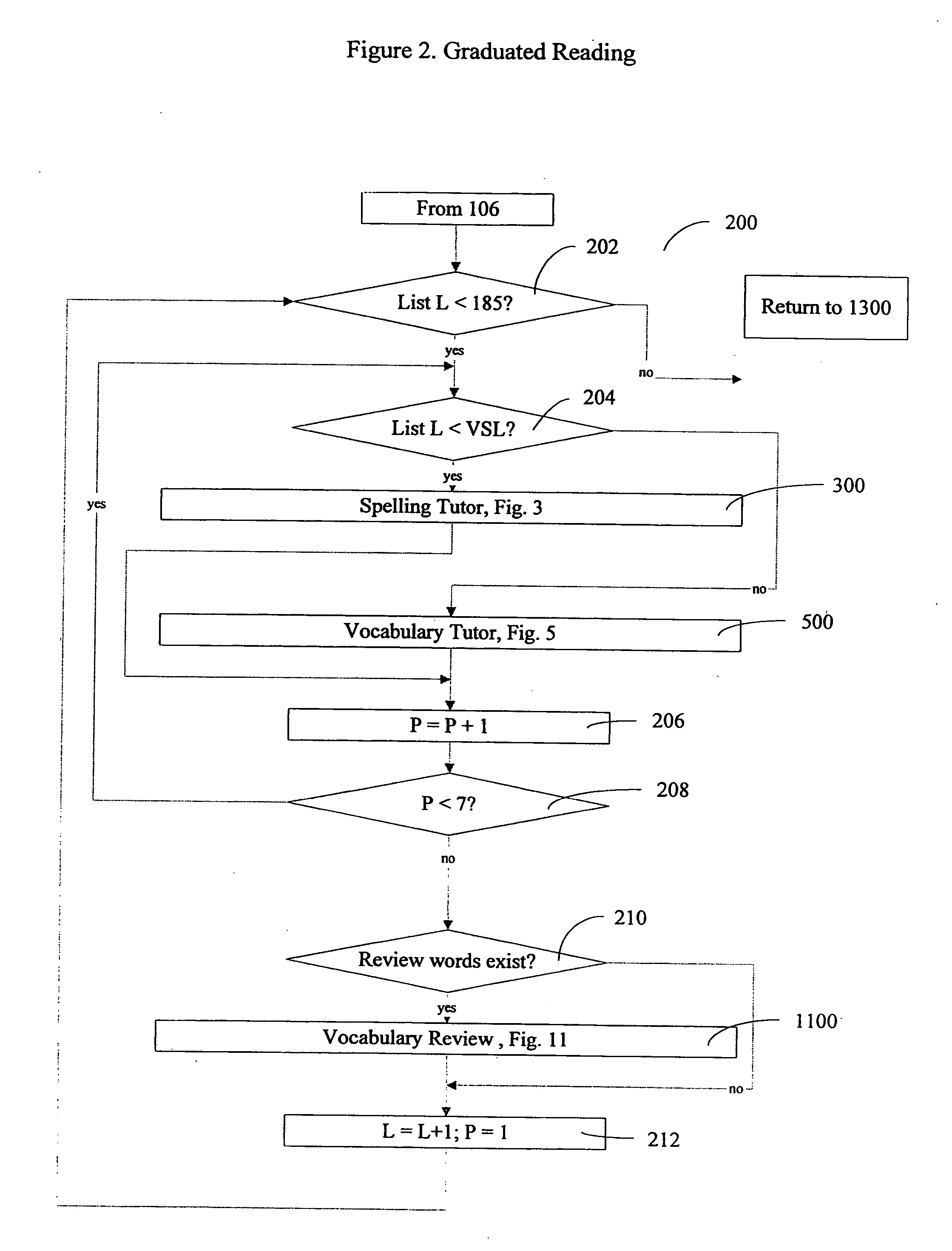

Computer assisted reading tutor apparatus and method

A method and apparatus for teaching readers including providing a placement spelling, placement listening vocabulary and speed test through a computer. A speed coefficient based on results from the placement tests is computed. A starting word list is determined based on the results of the tests. A listening vocabulary skill score is compared to a spelling skill score to determine a teaching program to present through the computer. The method includes a vocabulary loop, a spelling loop and a speed test applied to the word list and wherein the speed test results determine the value of the coefficient applied to a next word list.

Owner:CARVER RONALD P +2

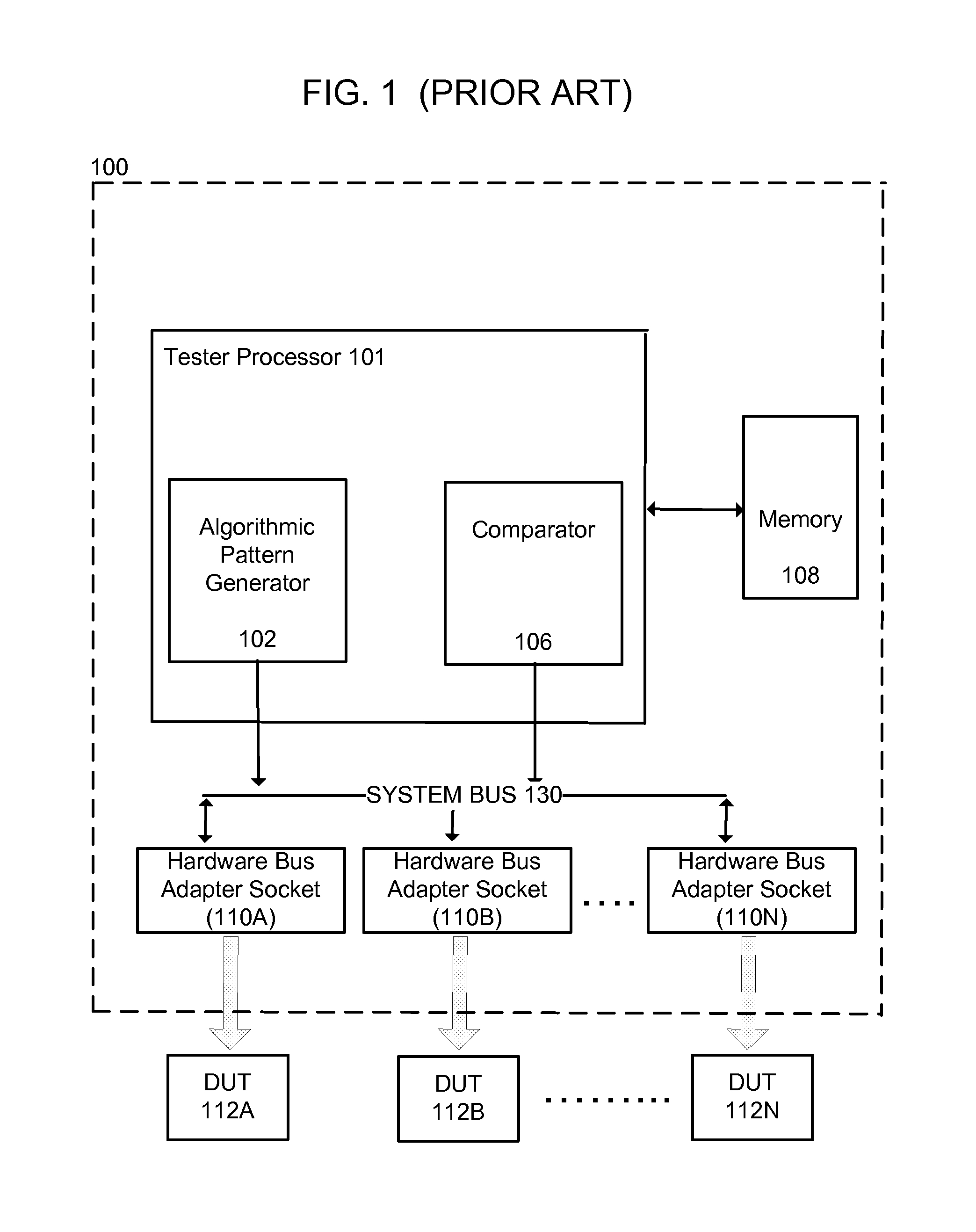

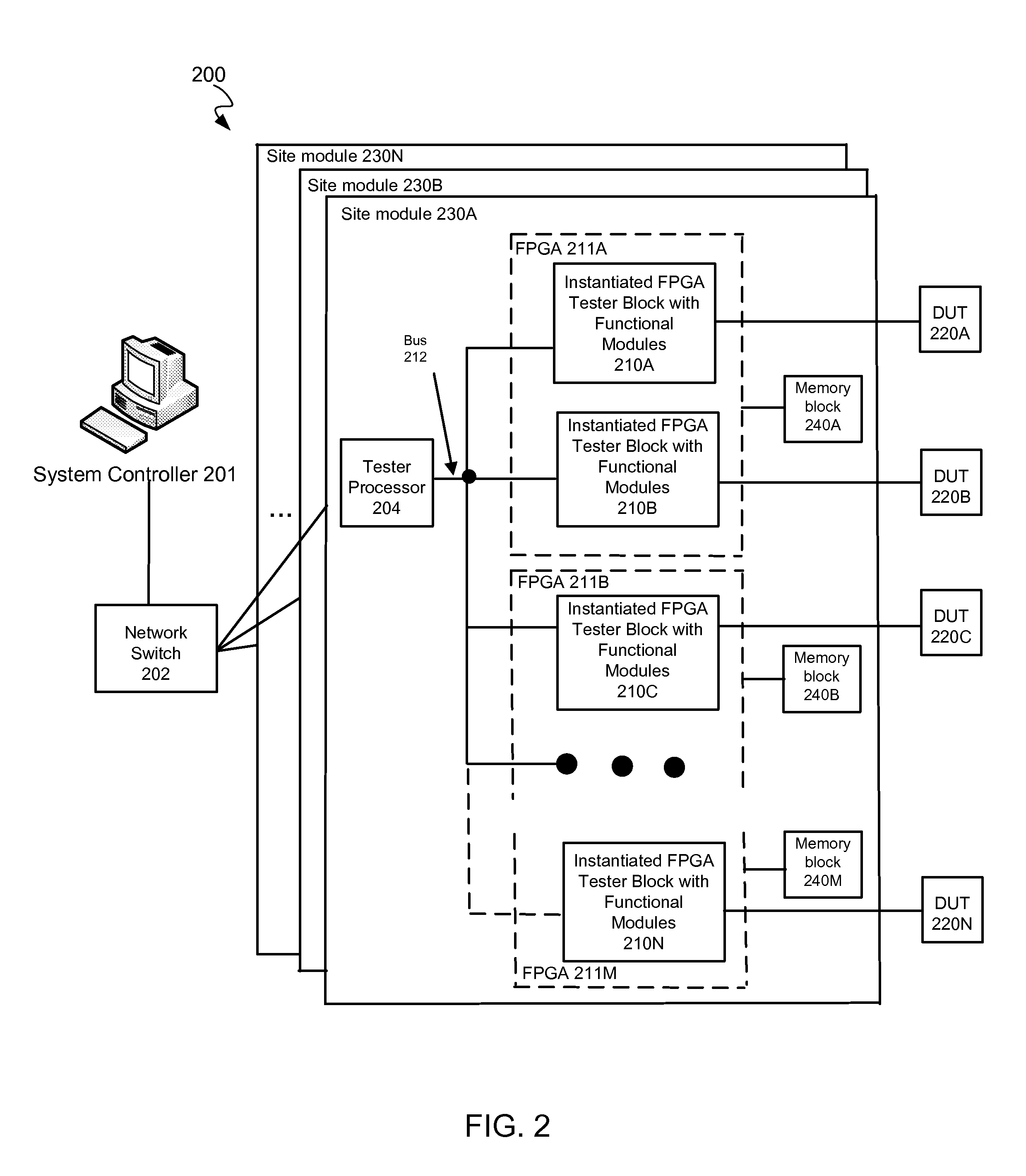

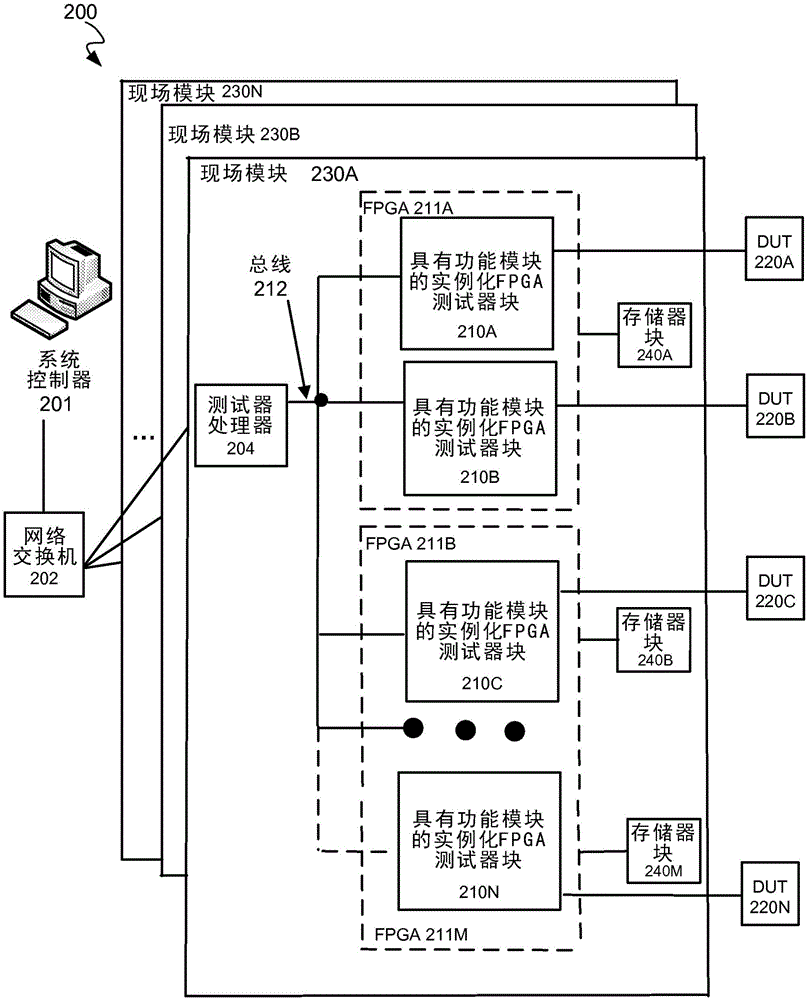

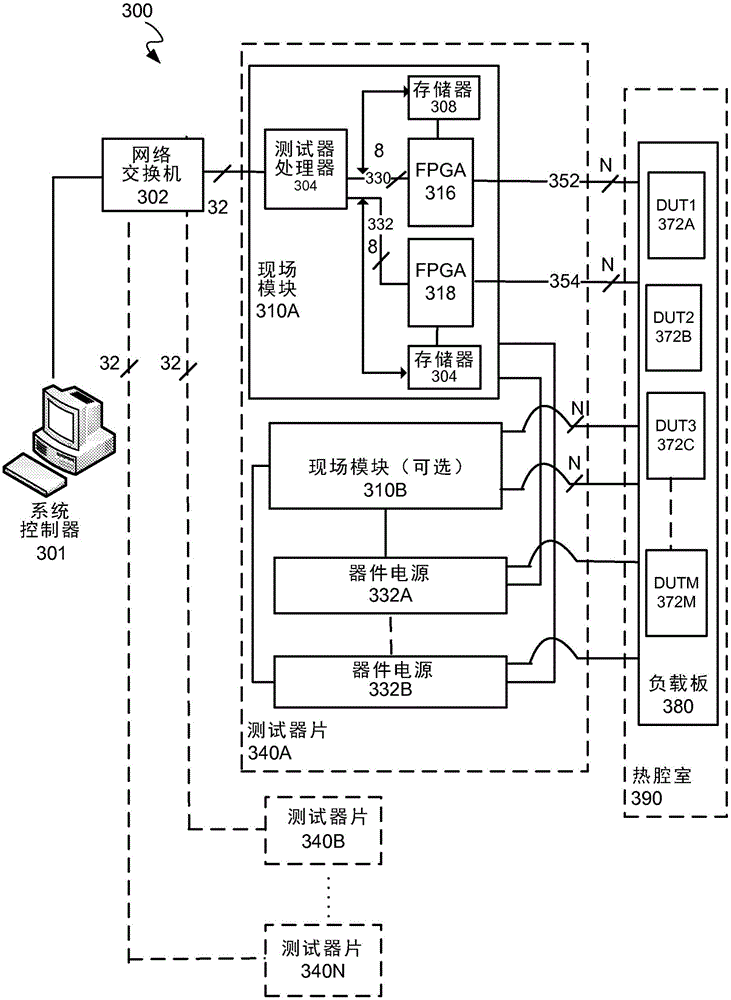

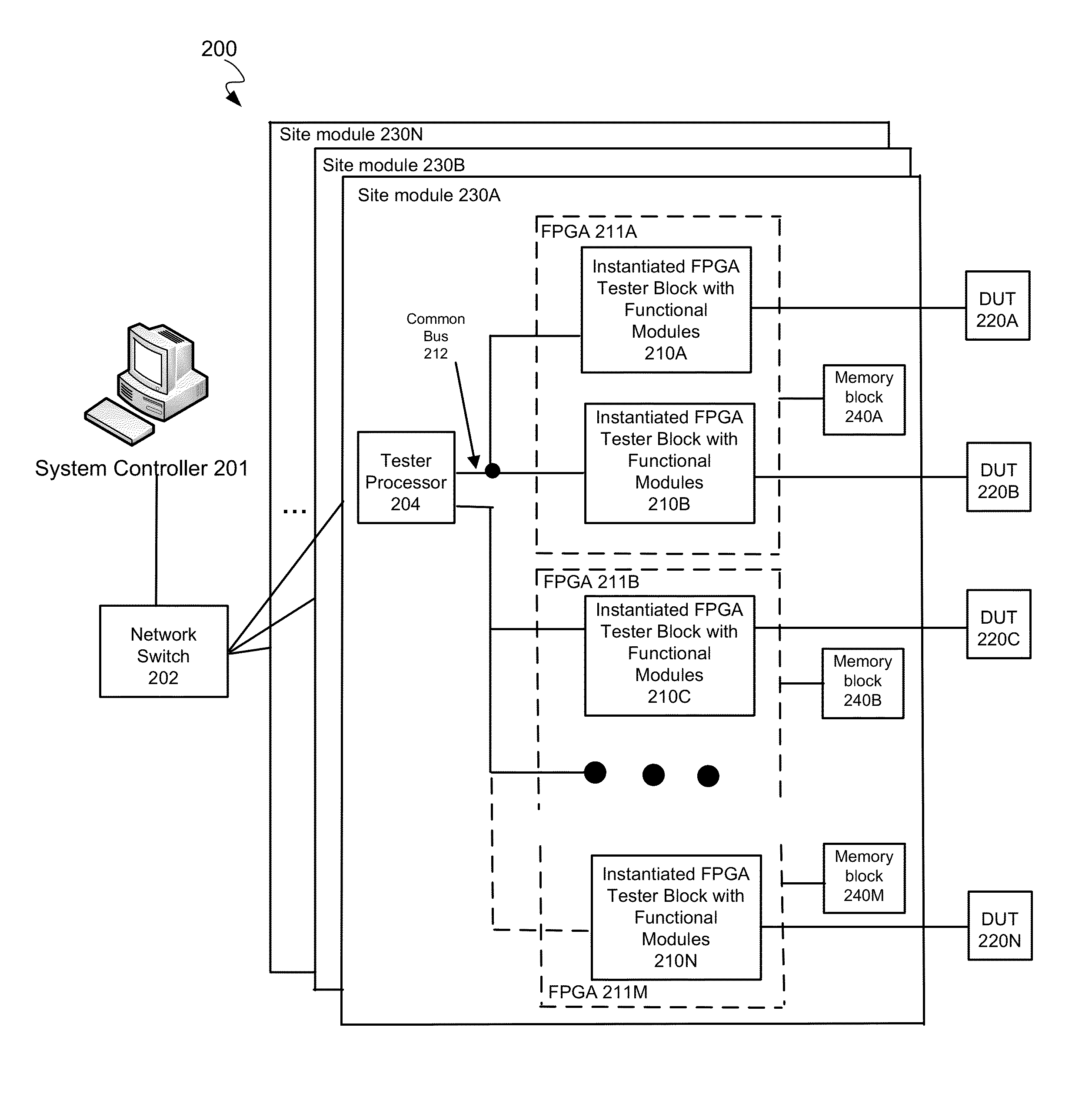

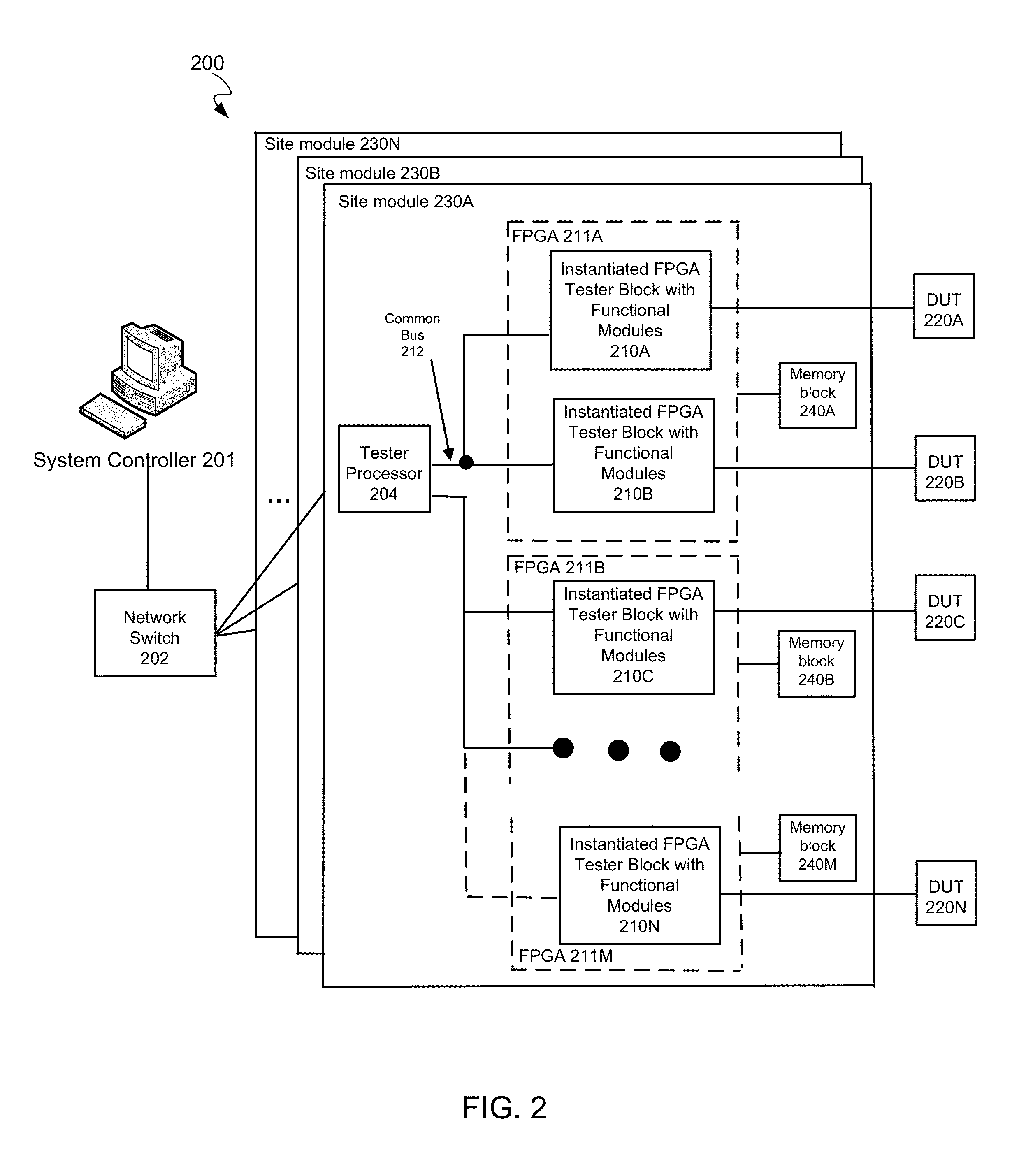

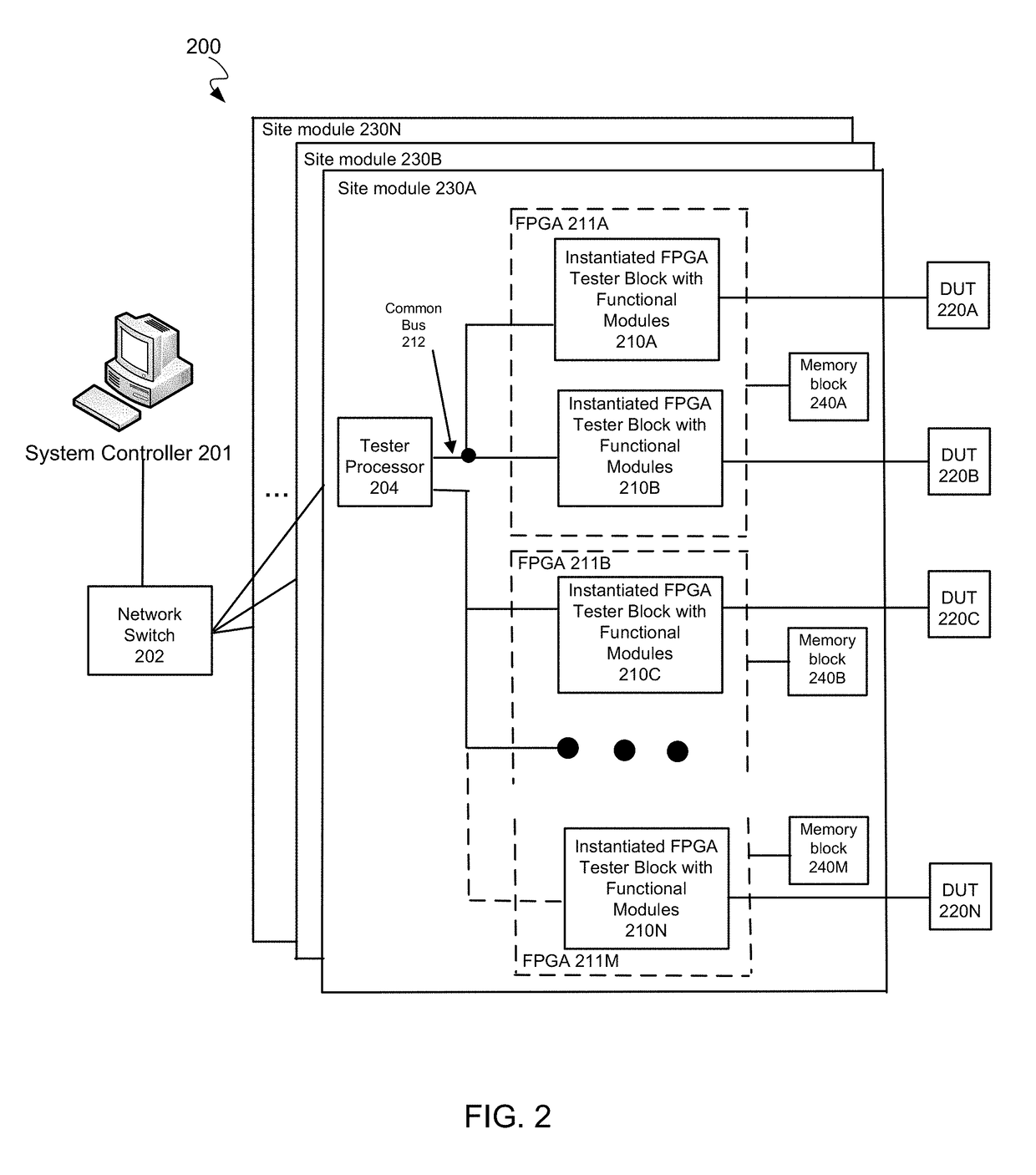

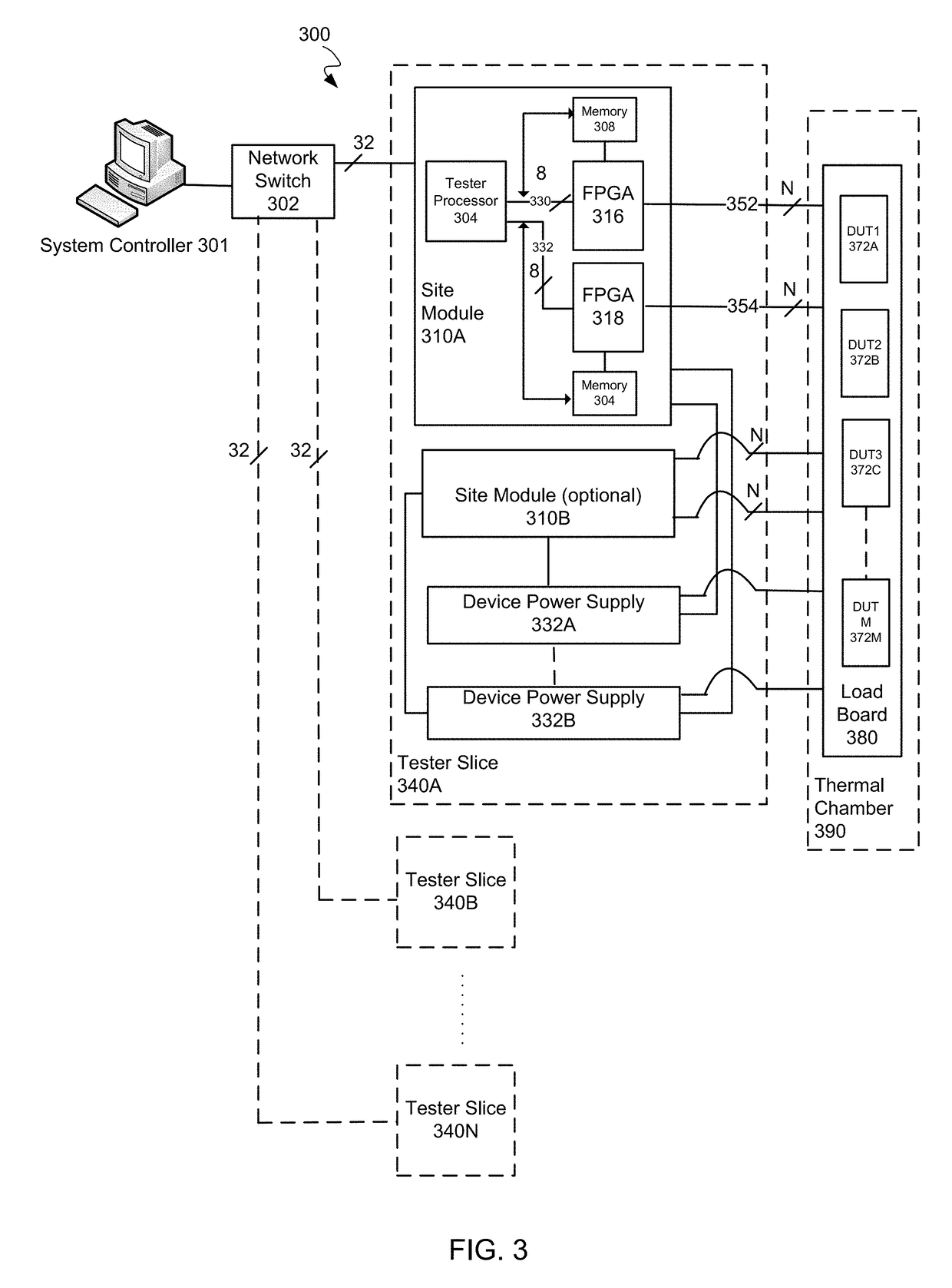

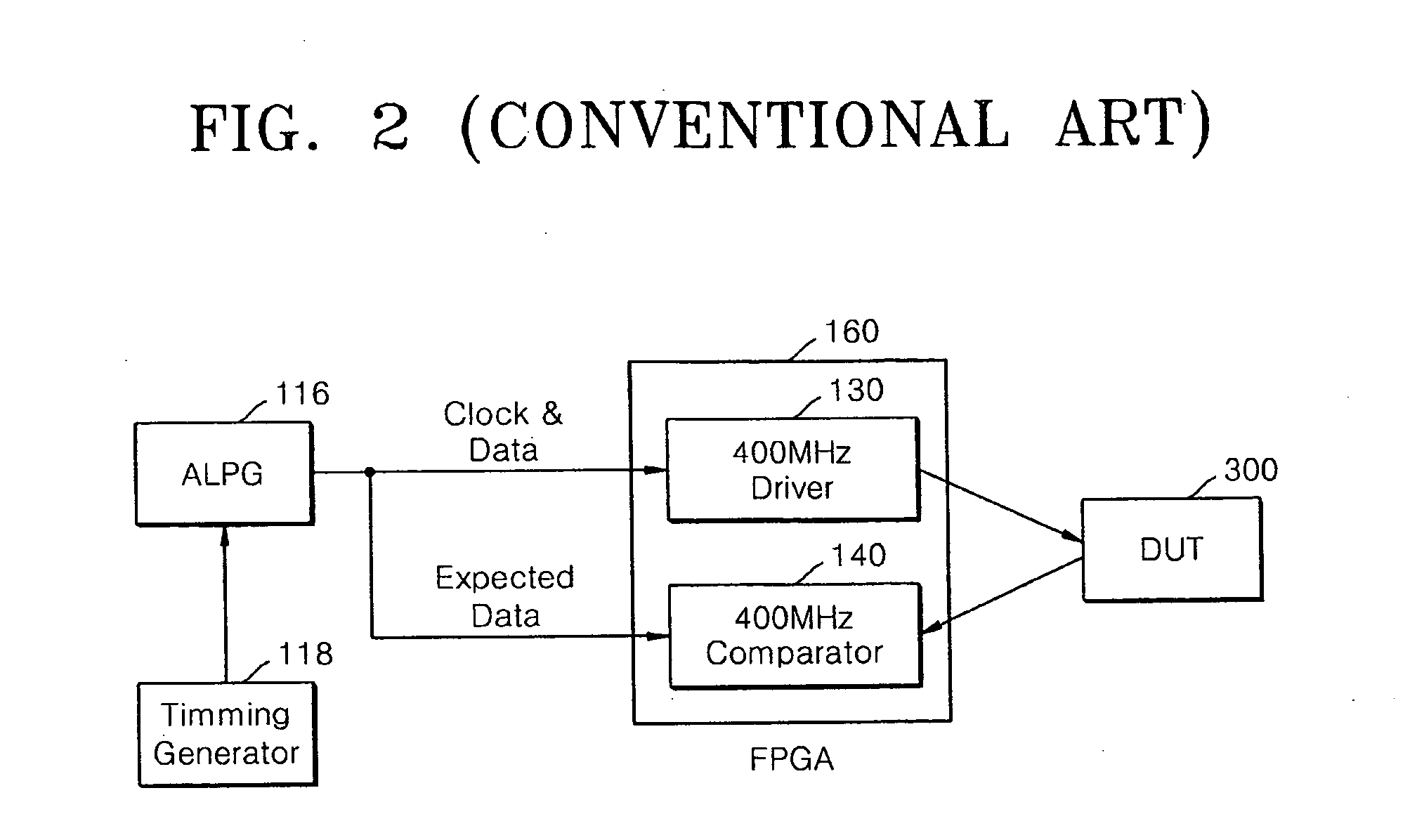

Tester with mixed protocol engine in a FPGA block

ActiveUS20140236526A1Bandwidth requirement can be keptMinimal processing loadResistance/reactance/impedenceAutomated test systemsHybrid protocolSpeed test

Automated test equipment capable of performing a high-speed test of semiconductor devices is presented. The automated test equipment comprises a system controller for controlling a test program, wherein the system controller is coupled to a bus. The tester system further comprises a plurality of modules also coupled to the bus, where each module is operable to test a plurality of DUTs. Each of the modules comprises a tester processor coupled to the bus and a plurality of configurable blocks communicatively coupled to the tester processor. Each of the configurable blocks is operable to communicate with an associated DUT and further operable to be programmed with a communication protocol for communicating test data to and from said associated device under test.

Owner:ADVANTEST CORP

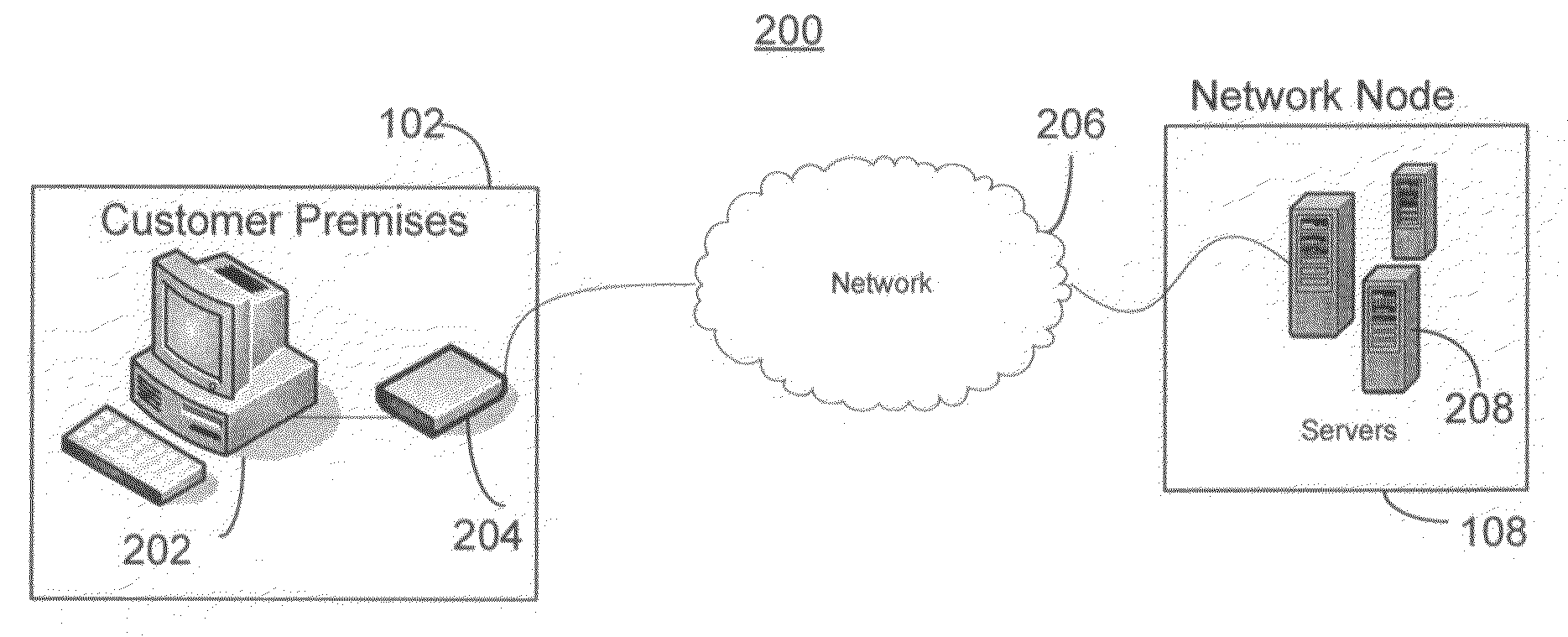

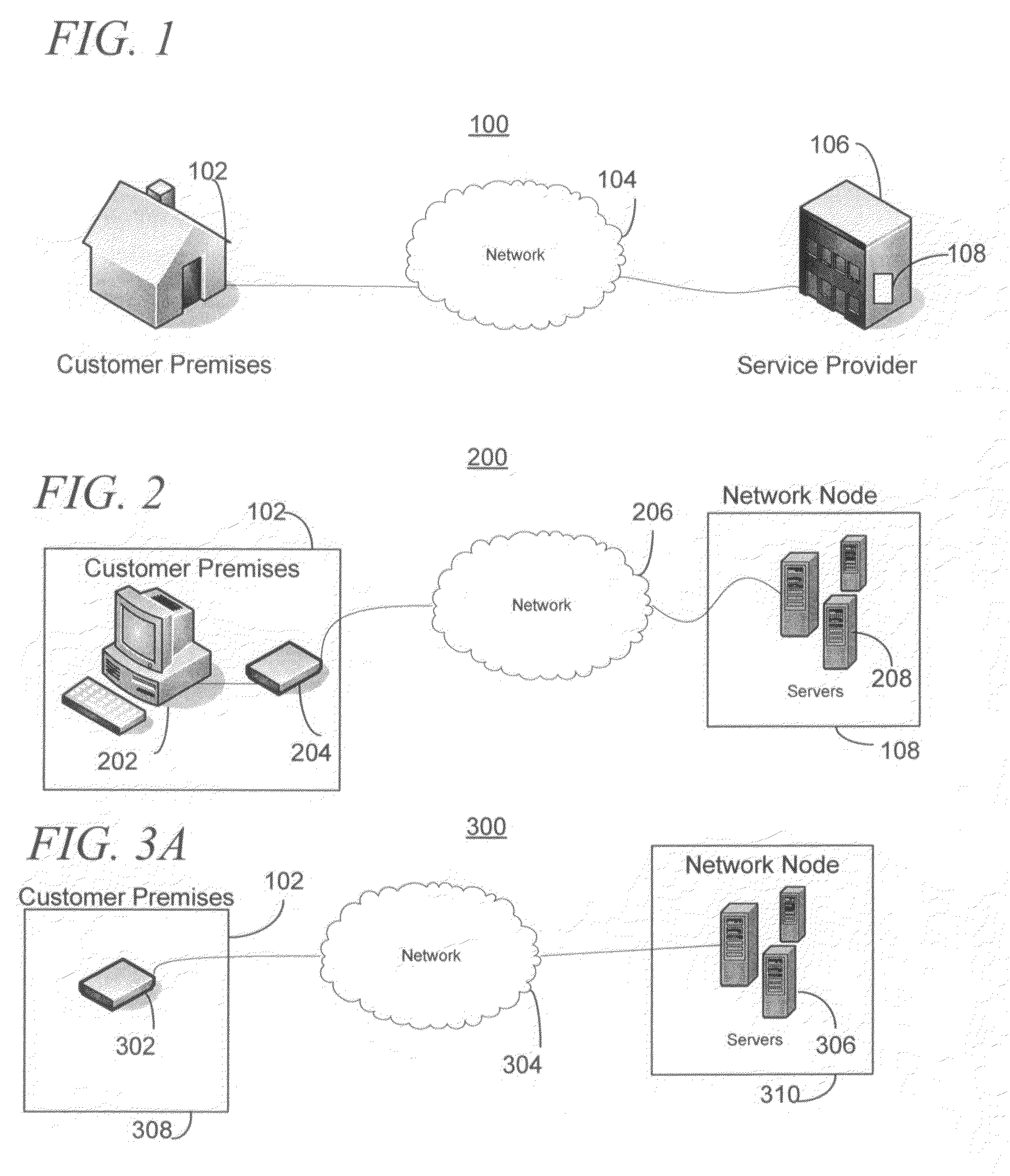

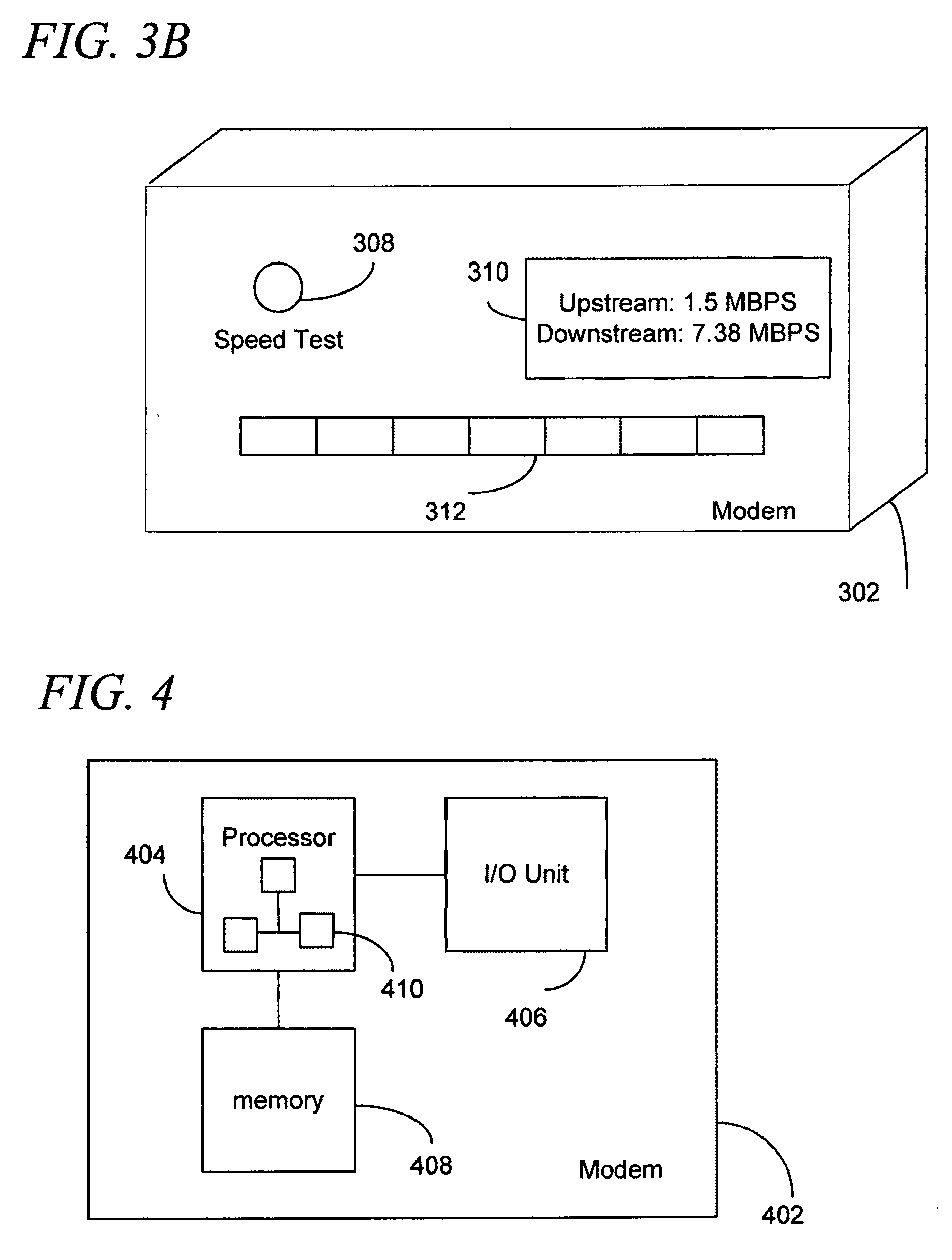

System and method for an integrated DSL/cable modem performance test

ActiveUS20090113045A1Overcome inaccuraciesOvercome limitationsDigital computer detailsData switching networksModem deviceSpeed test

A modem, method, and system is presented for performing a data communications speed test or line speed test between a network node and a customer premises. The modem may be configured to perform calculations for determining the data communications speed without interference of network elements or overhead modules that cause data communications to be inaccurate or otherwise affected.

Owner:CENTURYLINK INTPROP

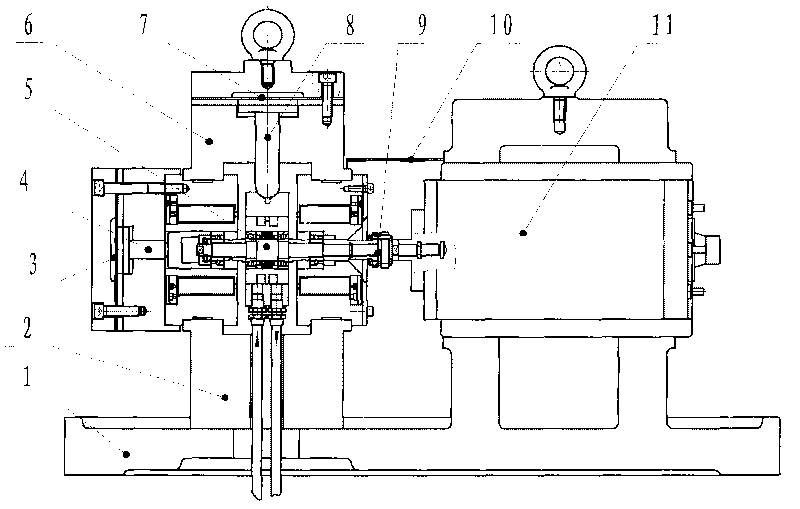

High-temperature high-speed test method for sealed bearing

InactiveCN101718625AImprove the state of stressEasy to achieve high speedMachine bearings testingElectricityComputer control system

The invention relates to a high-temperature high-speed test method for a sealed bearing, which comprises the following steps of: firstly designing a testing device, installing two sets of testing accompanying bearings on a testing main shaft, and pretightening through a set of spring and a pressure ring; installing the two sets of testing bearings at the left end and the right end of the testing main shaft, connecting an electric main shaft through a shaft coupling and additionally covering a shield; starting cooling circulating water, adding cooling water into a loading sleeve, starting a hydraulic station, an electric main shaft variable-frequency driving system and a computer control system, applying 20-30 percent of the maximum axial test load and 20-30 percent of the maximum radial test load to the testing bearings, starting the electric main shaft to reach 15-20 percent of the highest rotational speed and running for 15-25 minutes after the heating temperature reaches a set value, and then sequentially adding axial loads and radial loads and increasing the rotational speed of the electric main shaft so as to reach the highest rotational speed when the power consumption current of the electric main shaft tends to be steady; and carrying out computer data processing for the data and images in different time periods of the whole testing process and working out a test conclusion.

Owner:LUOYANG BEARING SCI & TECH CO LTD

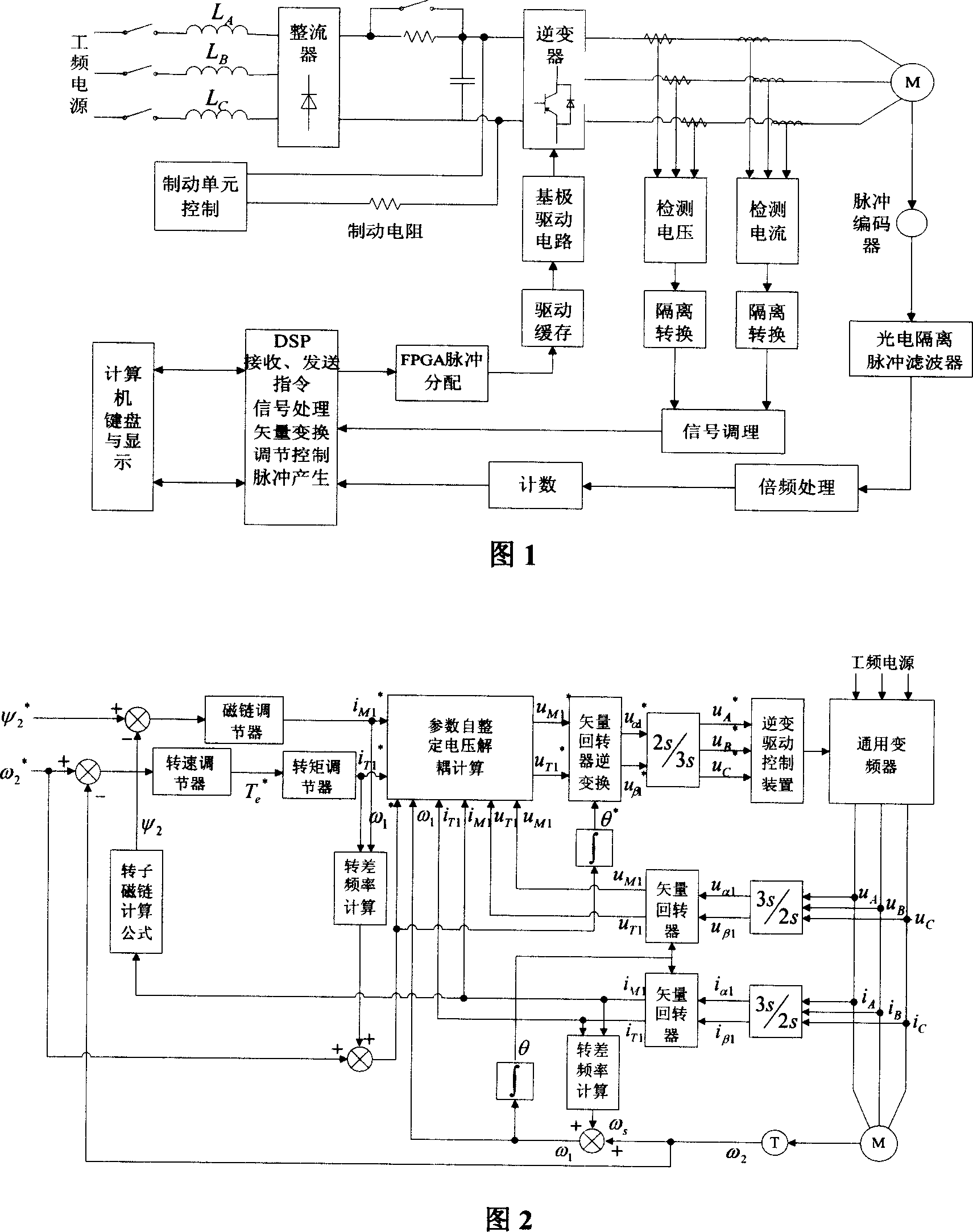

Voltage decoupling variable-frequency control vector controlling method with parameter self-regulating function

InactiveCN101013876AImprove controlThe output value is independentElectronic commutation motor controlAC motor controlFrequency changerVoltage control

The invention relates to one voltage decoupling transducer gear vector control method with parameters self-integrating functions, which tests transducer displacement motor stator end voltage, current and rotor speed through outlet voltage test unit, current test unit and speed test unit; according the vector converting the three-phase voltage, current into two-phase rotation coordinates value; for control given value exerting negative feedback adjust and for computation; through decoupling to get control value through inverse vector conversion computation to get three-phase voltage control value for recycle execution.

Owner:SHANGHAI JIAO TONG UNIV

A tester with mixed protocol engine in a FPGA block

Automated test equipment capable of performing a high-speed test of semiconductor devices is presented. The automated test equipment comprises a system controller for controlling a test program, wherein the system controller is coupled to a bus. The tester system further comprises a plurality of modules also coupled to the bus, where each module is operable to test a plurality of DUTs. Each of the modules comprises a tester processor coupled to the bus and a plurality of configurable blocks communicatively coupled to the tester processor. Each of the configurable blocks is operable to communicate with an associated DUT and further operable to be programmed with a communication protocol for communicating test data to and from said associated device under test.

Owner:ADVANTEST CORP

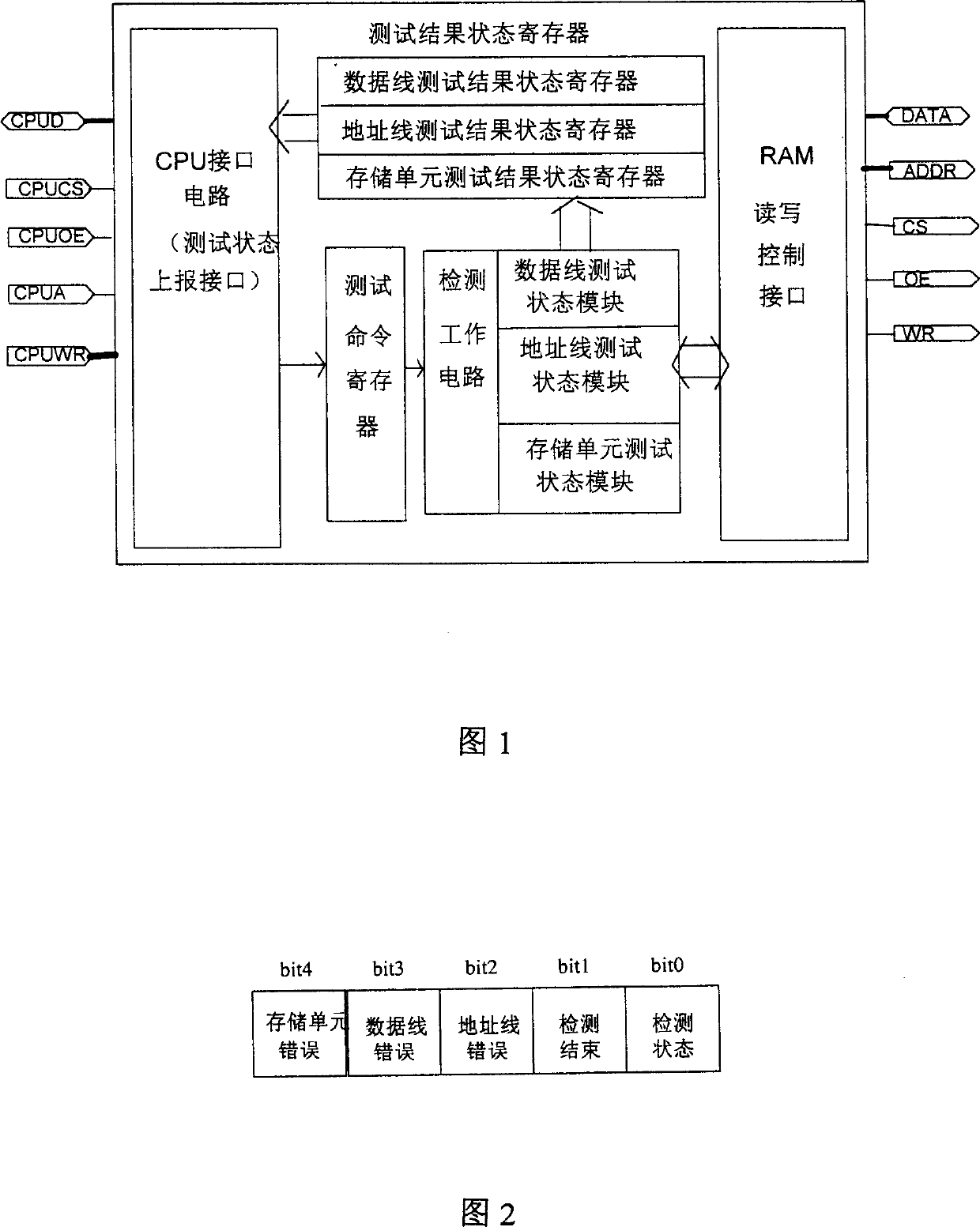

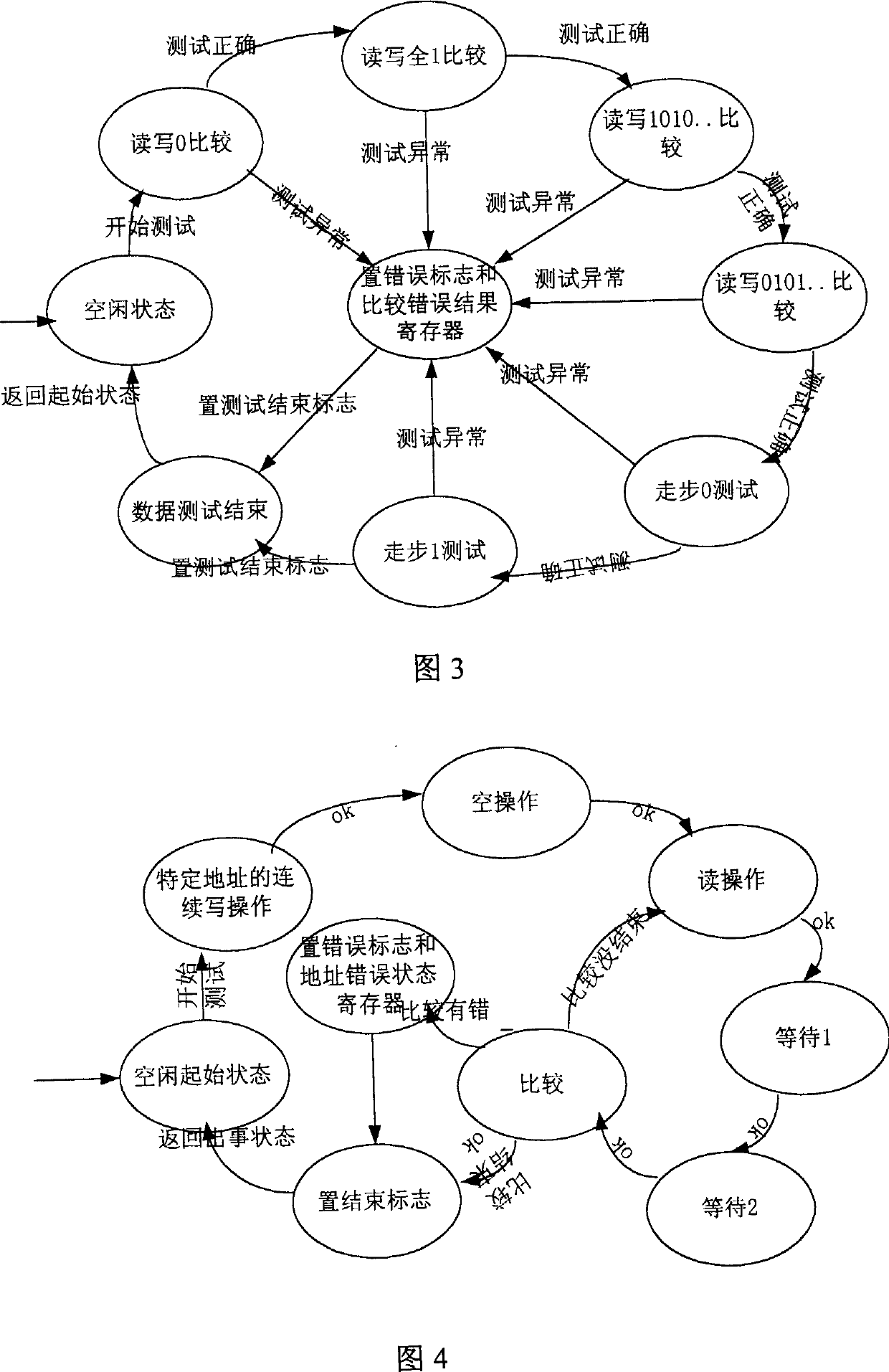

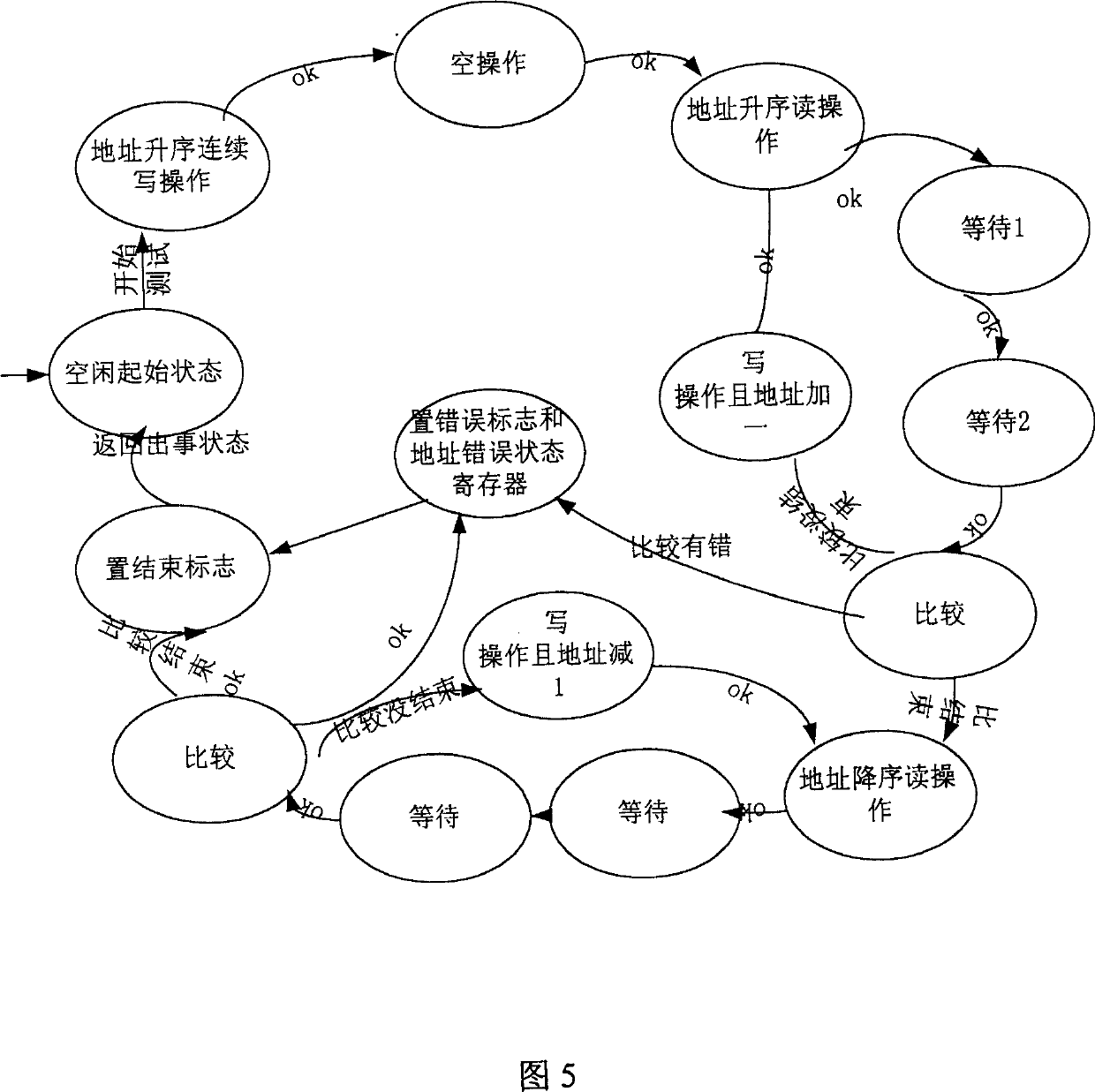

RAM high speed test control circuit and its testing method

InactiveCN1427420AEfficient detectionComprehensive testSemiconductor/solid-state device testing/measurementElectronic circuit testingTest typesStep test

A control circuit for high-speed test of RAM is disclosed, which is based on hardware logic for correct location of failure and high test efficiency. Its test method includes such steps as setting up the state of test command register, choosing test type, strobing test register, testing data lines by comparison, testing address lines by comparison, step test of memory units, and analyzing error type by reading state registers.

Owner:HUAWEI TECH CO LTD

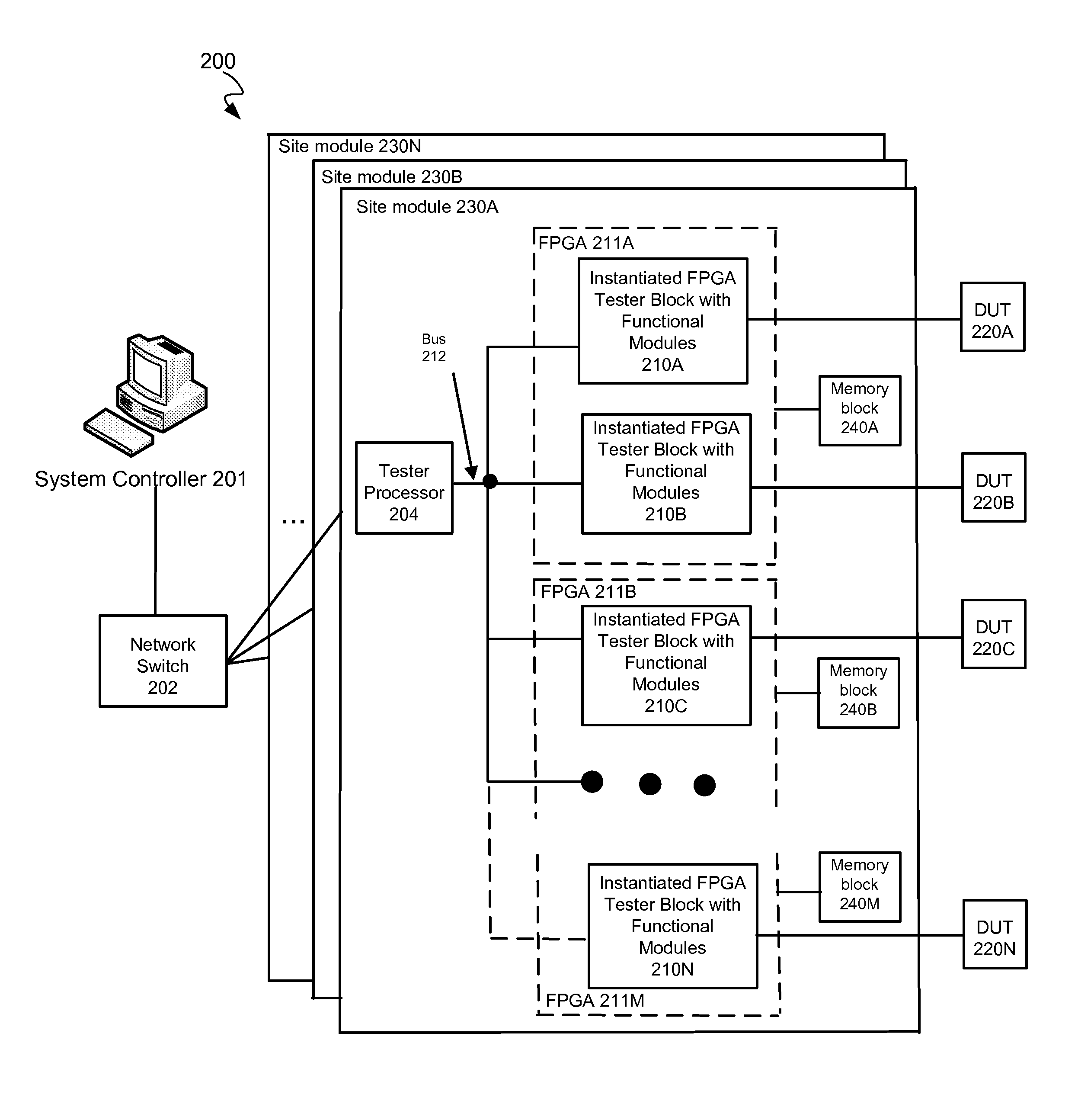

Tester with acceleration on memory and acceleration for automatic pattern generation within a FPGA block

ActiveUS20140236524A1Bandwidth requirement can be keptMinimal processing loadTesting/calibration of speed/acceleration/shock measurement devicesSpecial data processing applicationsAutomatic test pattern generationHardware acceleration

Automated test equipment capable of performing a high-speed test of semiconductor devices is presented. The automated test equipment apparatus comprises a computer system comprising a tester processor, wherein the tester processor is communicatively coupled to a plurality of FPGA components. Each of the plurality of FPGA components is coupled to a memory module and comprises: an upstream port operable to receive commands and data from the tester processor; a downstream port operable to communicate with a respective DUT from a plurality of DUTs; and a plurality of hardware accelerator circuits, wherein each of the accelerator circuits is configured to communicate with one of the plurality of DUTs. Each of the plurality of hardware accelerator circuits comprises a pattern generator circuit configurable to automatically generate test pattern data to be written to the one of the plurality of DUTs and a comparator circuit configured to compare data read from the one of the plurality of DUTs with test pattern data written to the one of the plurality of DUTs

Owner:ADVANTEST CORP

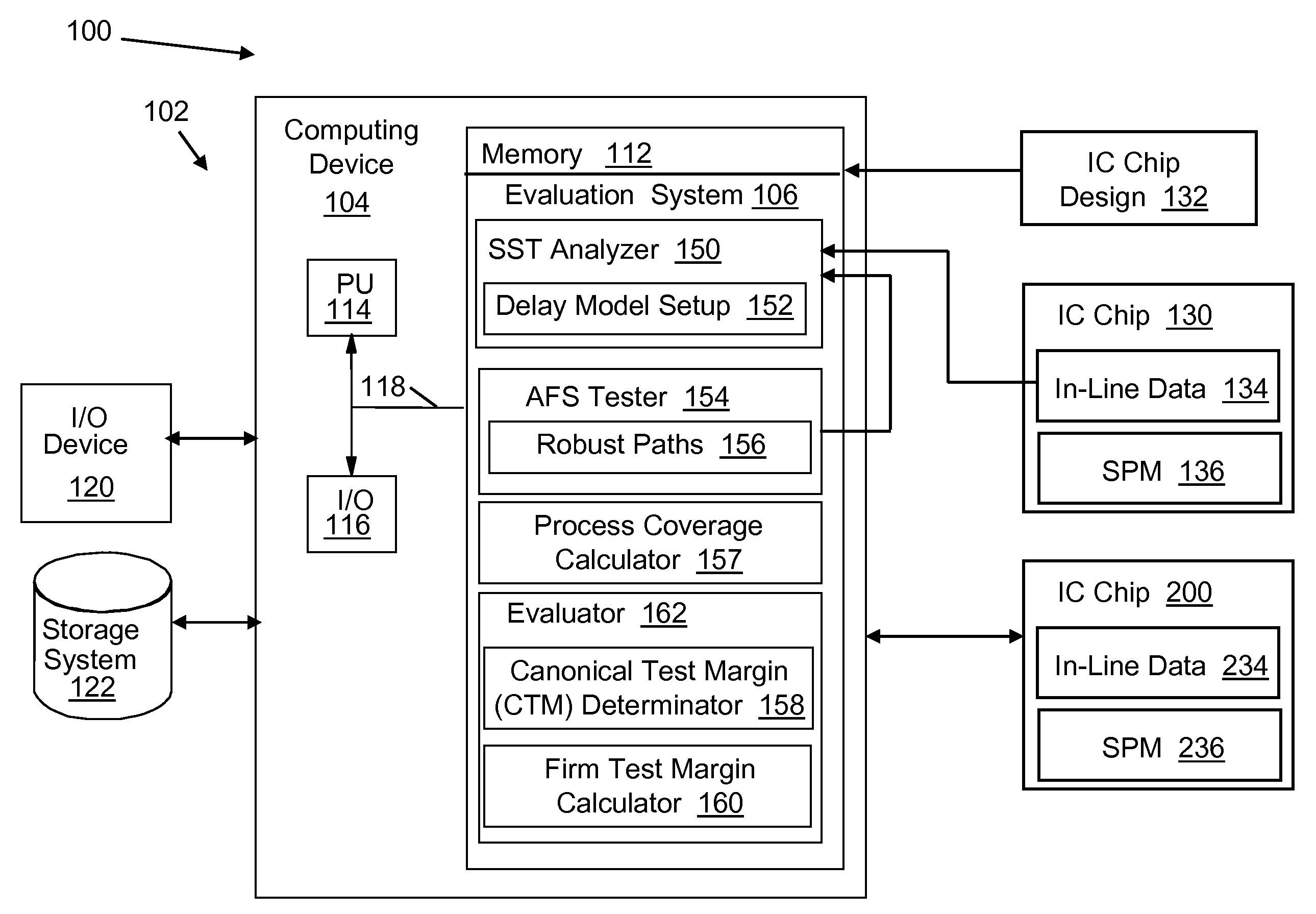

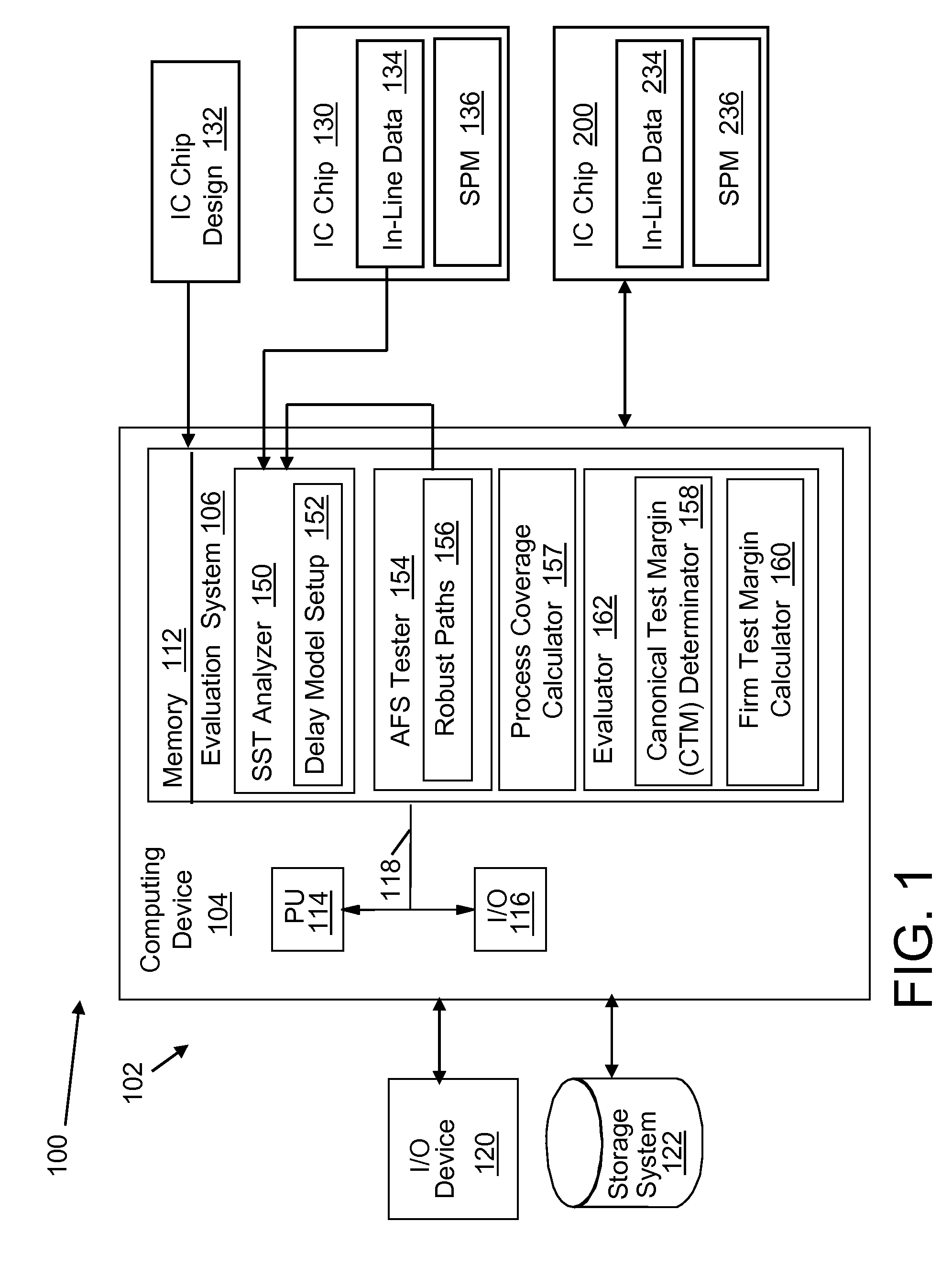

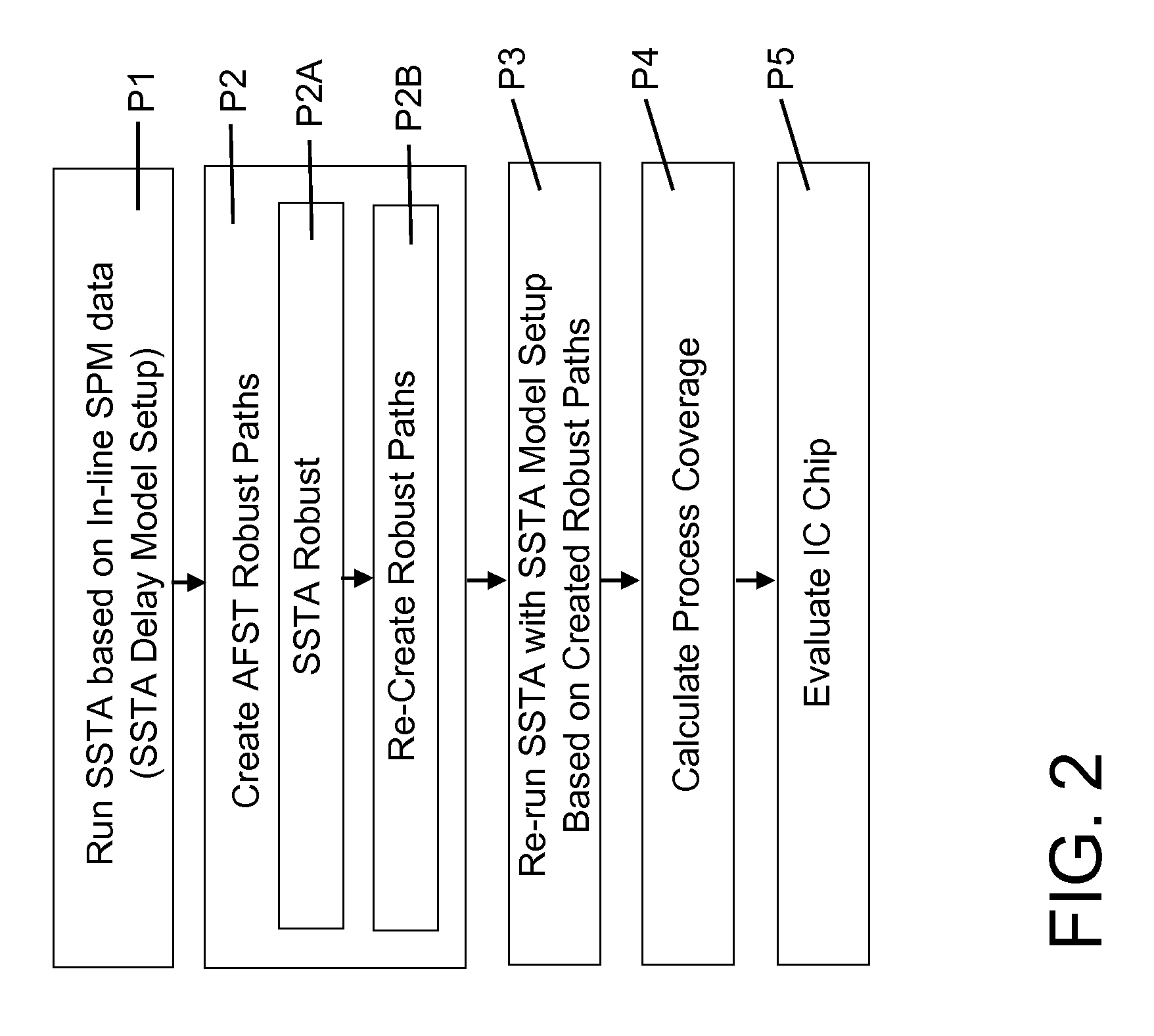

IC chip at-functional-speed testing with process coverage evaluation

ActiveUS7620921B2Semiconductor/solid-state device testing/measurementProbabilistic CADSpeed testComputation process

Methods, systems and program products for evaluating an IC chip are disclosed. In one embodiment, the method includes running a statistical static timing analysis (SSTA) of a full IC chip design; creating at-functional-speed test (AFST) robust paths for an IC chip, the created robust paths representing a non-comprehensive list of AFST robust paths for the IC chip; and re-running the SSTA with the SSTA delay model setup based on the created robust paths. A process coverage is calculated for evaluation from the SSTA runnings; and a particular IC chip is evaluated based on the process coverage.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

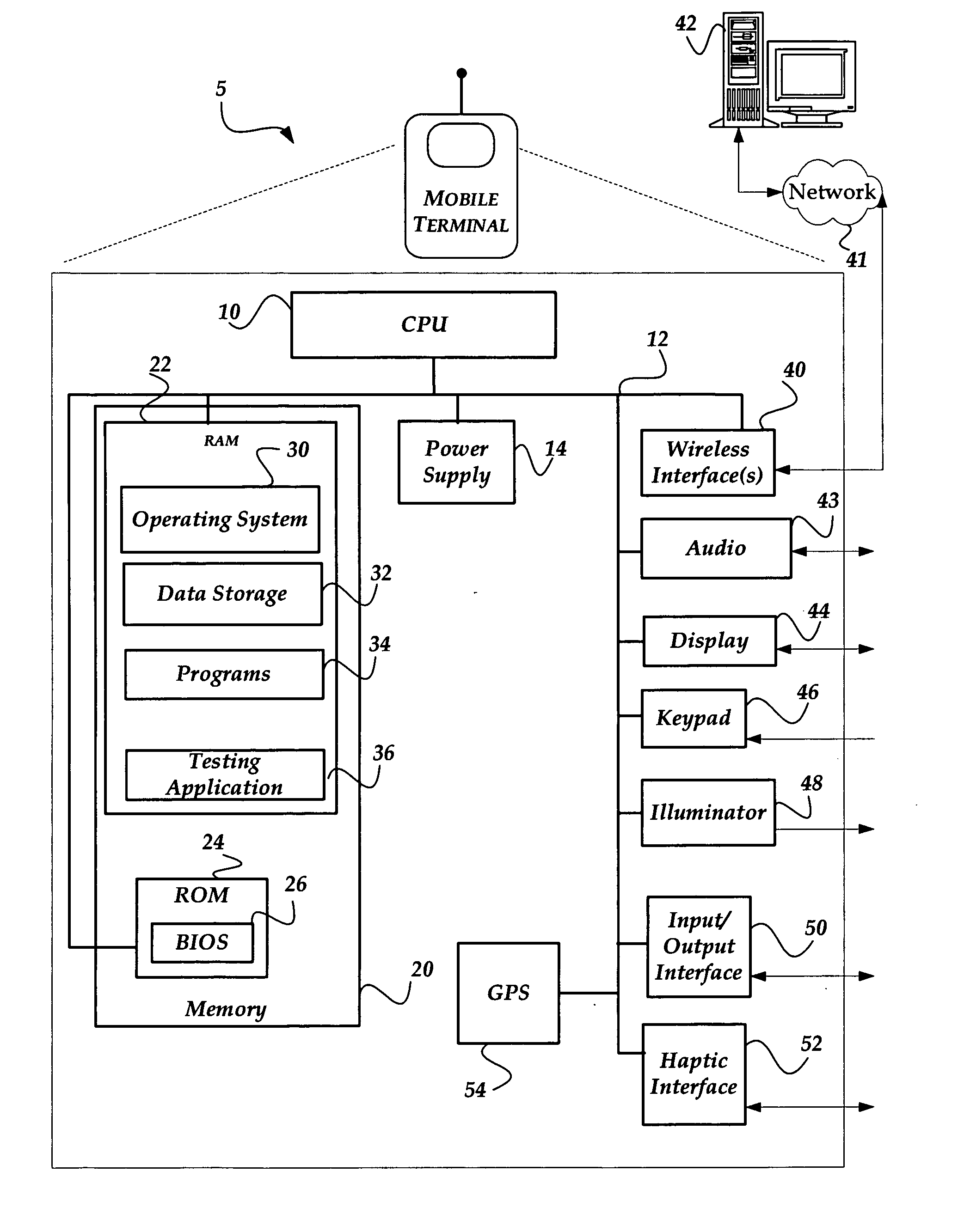

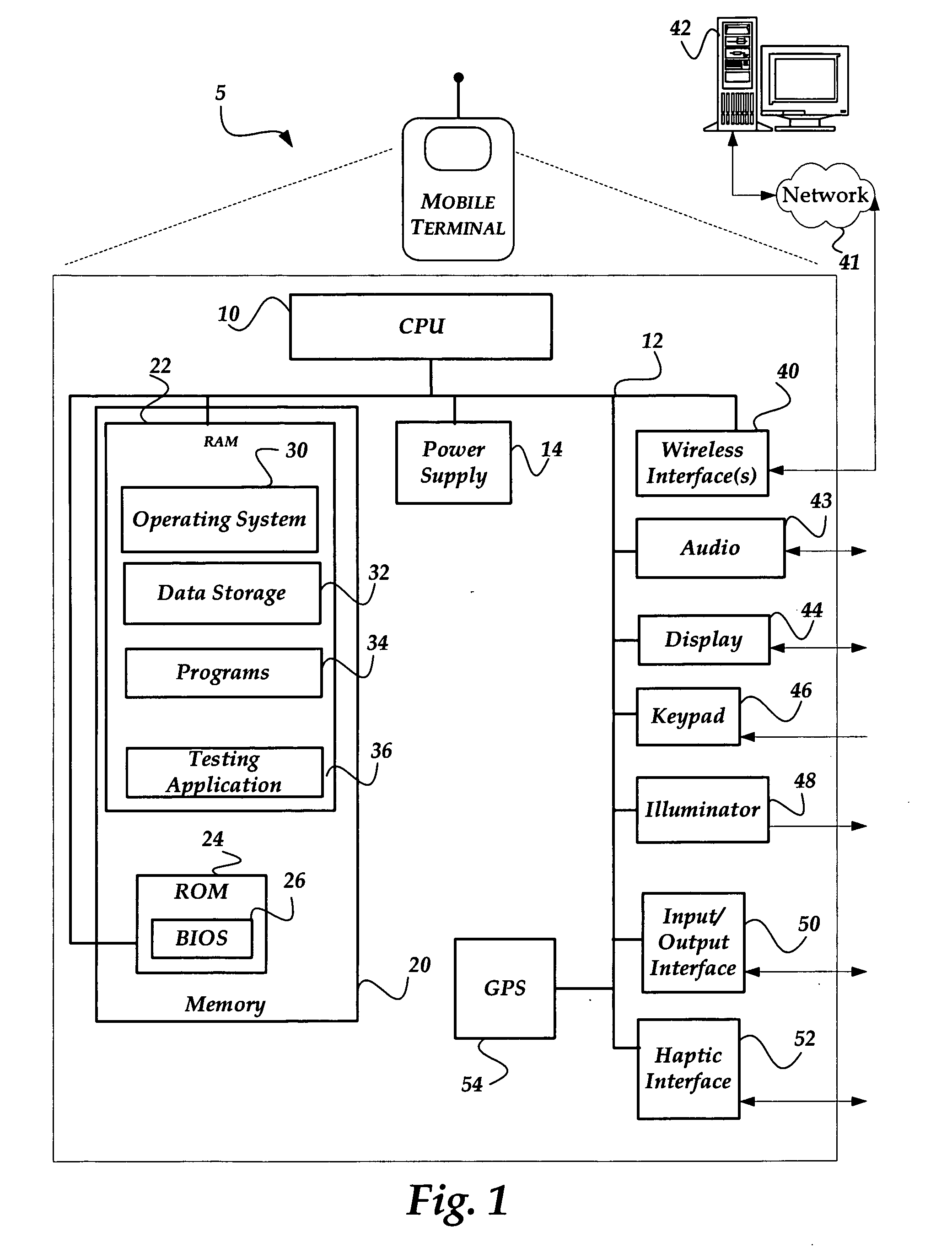

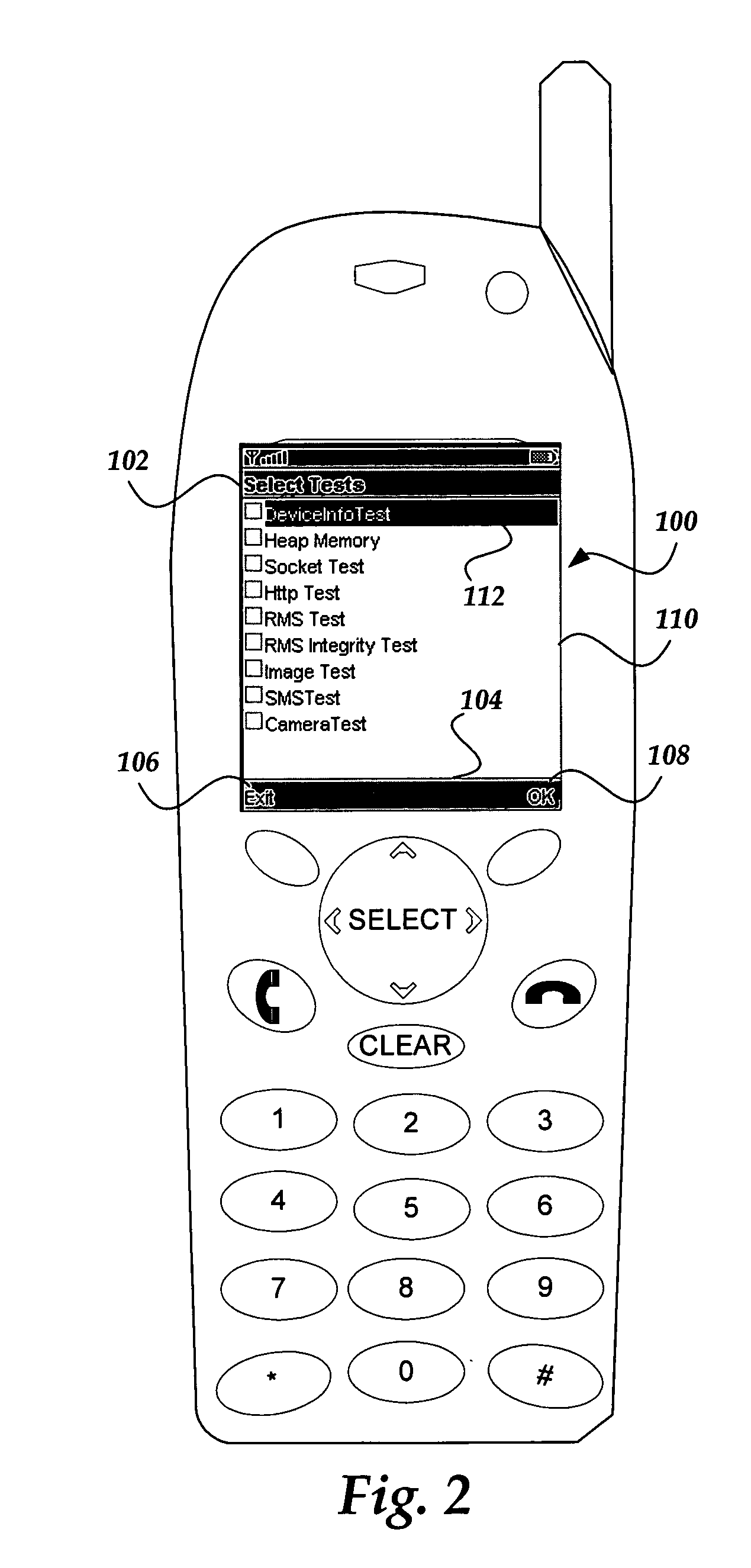

Tester for determining the validity of a feature in a remote device

ActiveUS20060205397A1Substation equipmentRadio/inductive link selection arrangementsComputer hardwareSpeed test

One or more test classes implement an object oriented interface that specifies an execution method and a results method called from a user interface running on the mobile terminal or an emulator. The user interface enables a user to select one or more tests to run, view results, and upload results to a server. For each test, the user interface calls the execution method to initiate the test and obtain a success or failure indication. The user interface also calls the results method to obtain data on a capability and / or to obtain validation that the capability is complete and reliable. Tests that require specific hardware are activated or deactivated, depending on whether the mobile terminal includes the required hardware. Test include a memory size test, a memory integrity test, a socket connection test, an HTTP test, a camera test, an image rendering speed test, a message test, and the like.

Owner:R2 SOLUTIONS

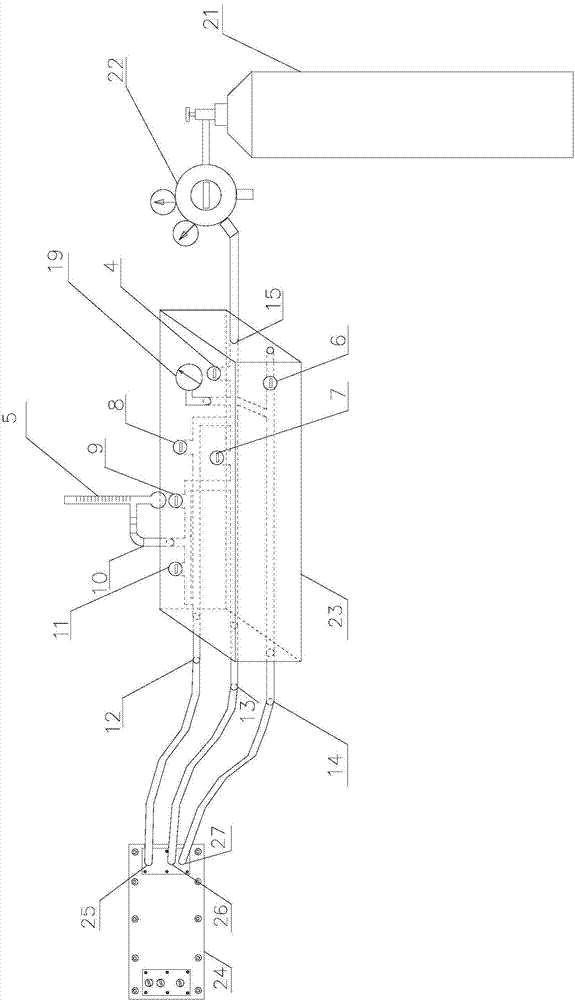

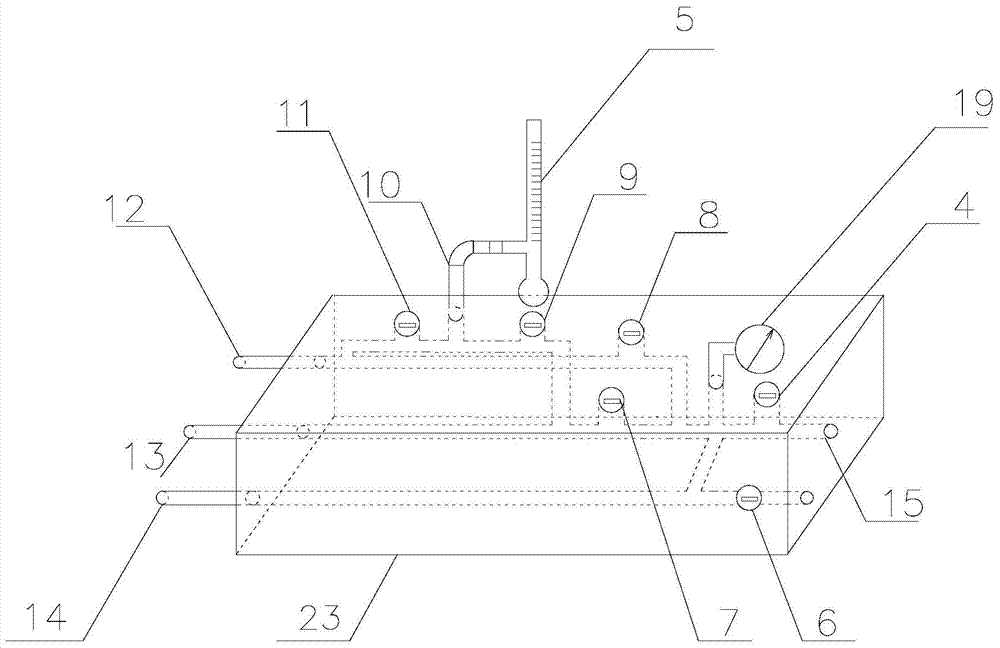

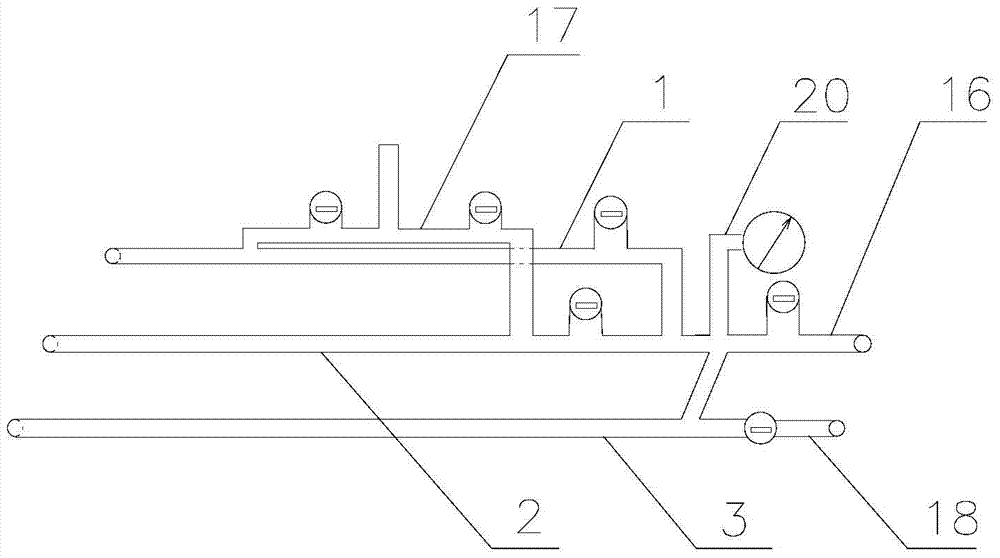

Online gas tightness detection device and method for fuel cell stack

ActiveCN103900773AAvoid timeImprove work efficiencyMeasurement of fluid loss/gain rateFuel cellsSpeed test

The invention discloses an online gas tightness detection device and method for a fuel cell stack. The online gas tightness detection device for the fuel cell stack comprises a pressure gauge, a gas tightness portable test box and a gas leakage speed test meter, wherein a pipe is arranged in the gas tightness portable test box, a required control valve is arranged on the pipe, and the pipe and the control valve can be matched to perform gas tightness detection on the fuel cell stack by testing gas. The online gas tightness detection device for the fuel cell stack is reasonable in structure and easy to operate. By means of the online gas tightness detection method for the fuel cell stack, work efficiency and economic benefit can be increased effectively, gas tightness detection operation is simplified greatly, and efficient and reasonable detection on the fuel cell stack can be achieved.

Owner:SUNRISE POWER CO LTD +1

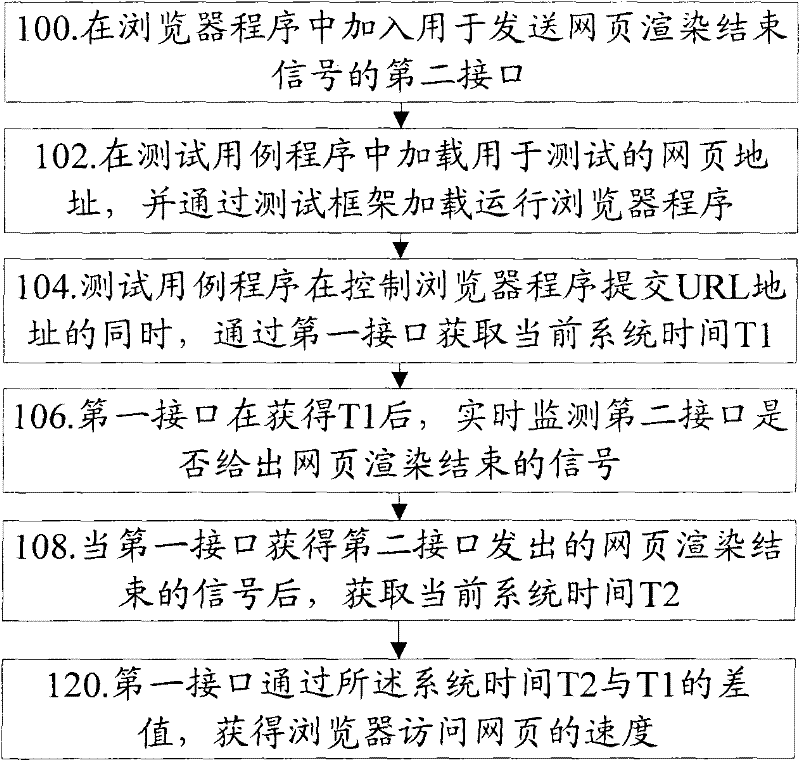

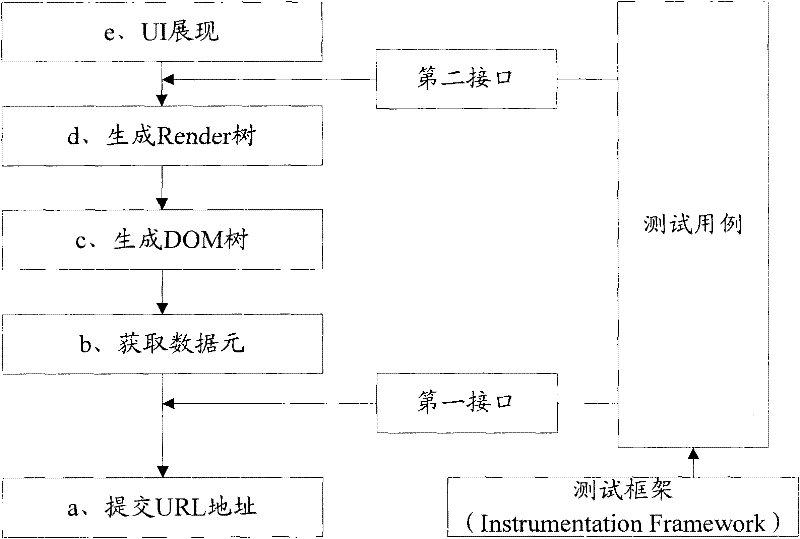

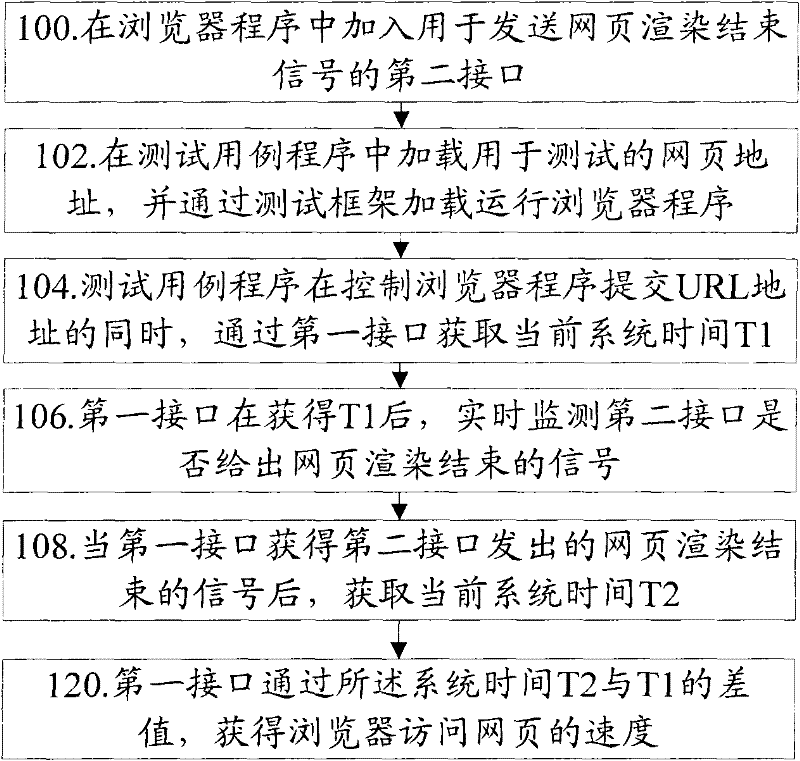

Testing method and device of webpage access speed

ActiveCN102479151AImplement speed measurementSoftware testing/debuggingSpecial data processing applicationsSpeed testSystem time

The invention discloses a testing method and device of webpage access speed, which can be used to solve the technical problems that the webpage access speed cannot be tested automatically, rapidly and accurately during the webpage access speed test based on a handheld device. According to the invention, first system time can be acquired through a first interface when a URL (uniform resource locator) address is submitted, and then a second interface can indicate the first interface to acquire second system time after the webpage rendering is finished and before the UI (user interface) is showed, and finally the total time of the webpage access can be obtained by calculating the difference value between the first system time and the second system time. By using the method and device provided by the invention, the webpage speed of the browser can be tested automatically and accurately.

Owner:TENCENT TECH (SHENZHEN) CO LTD

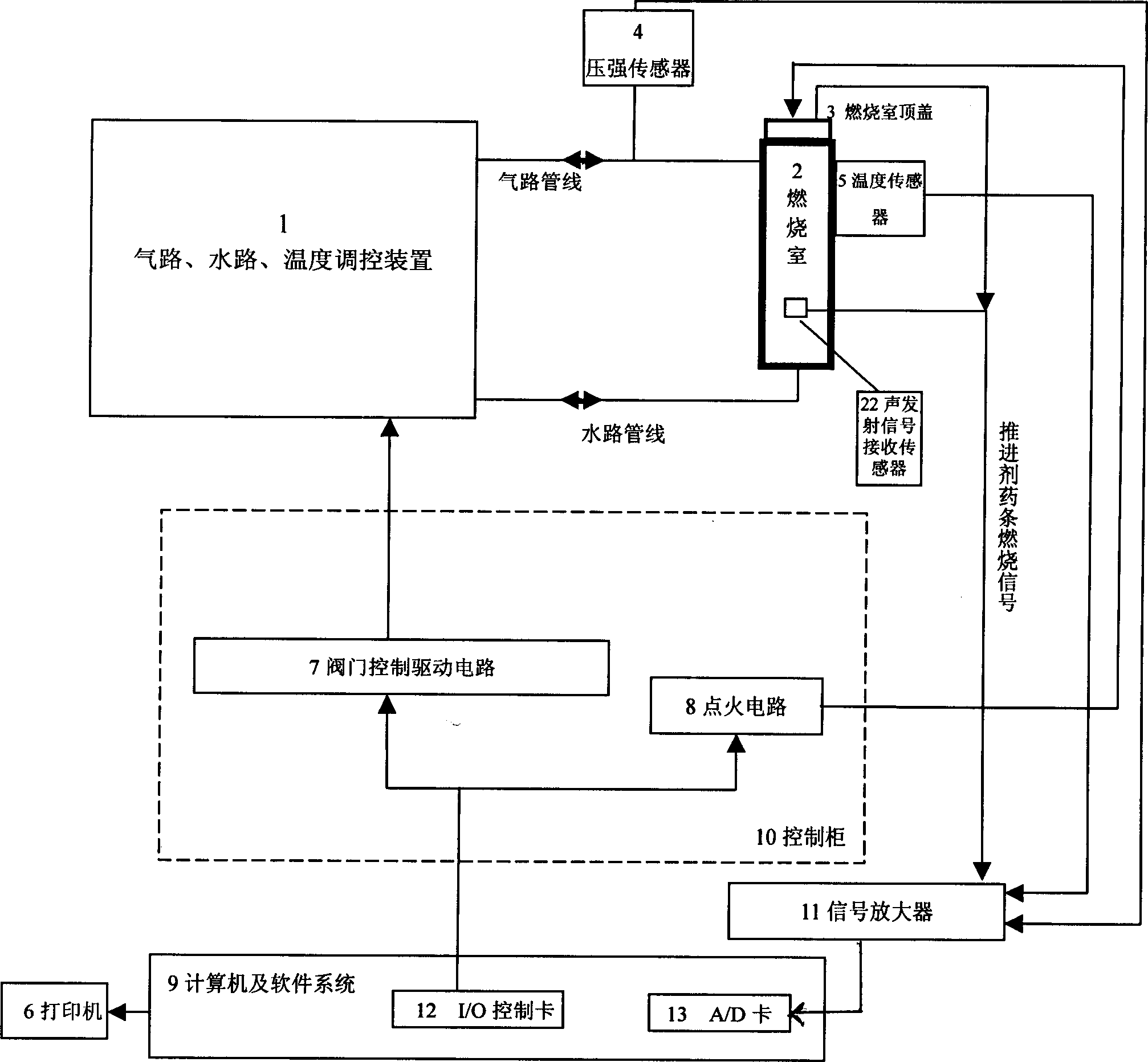

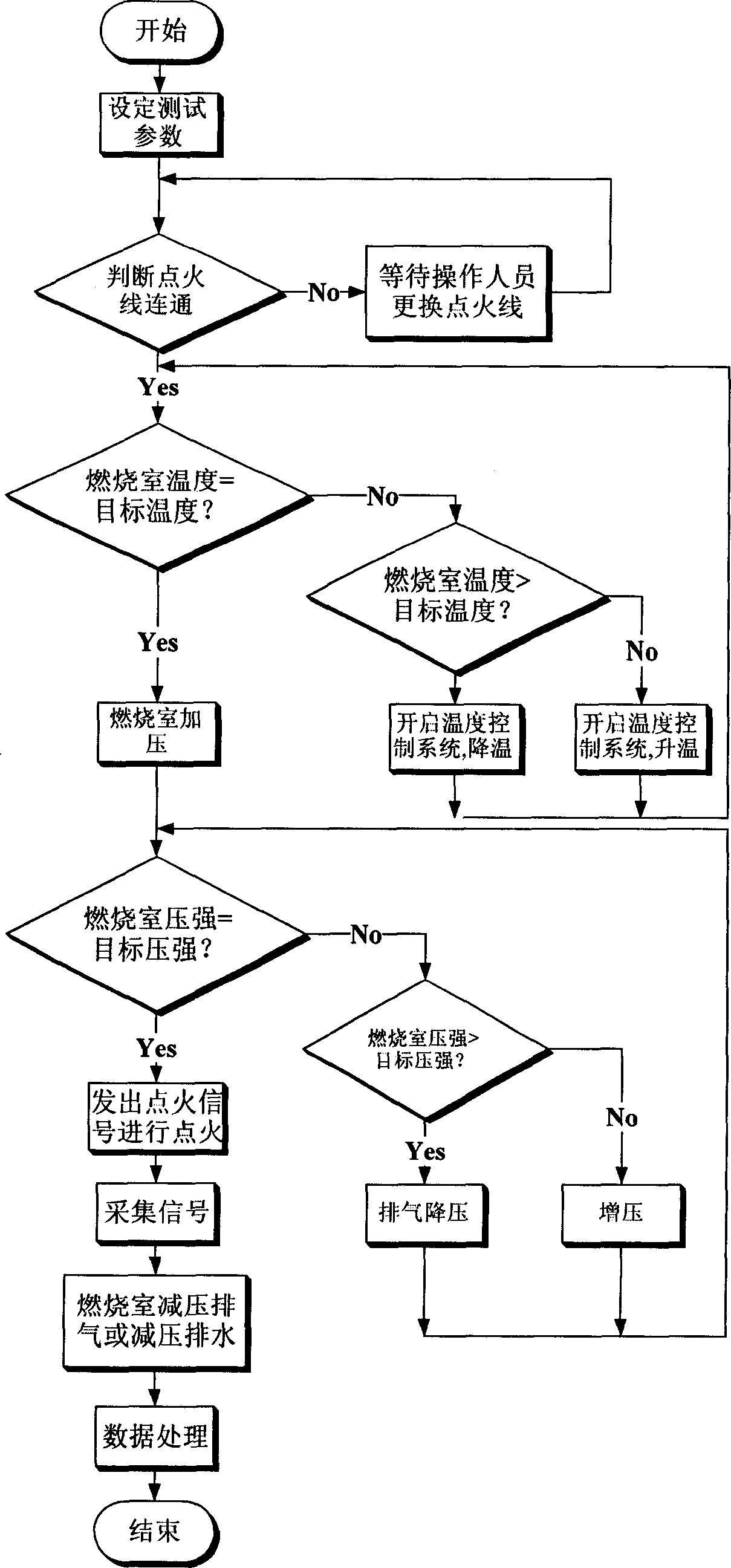

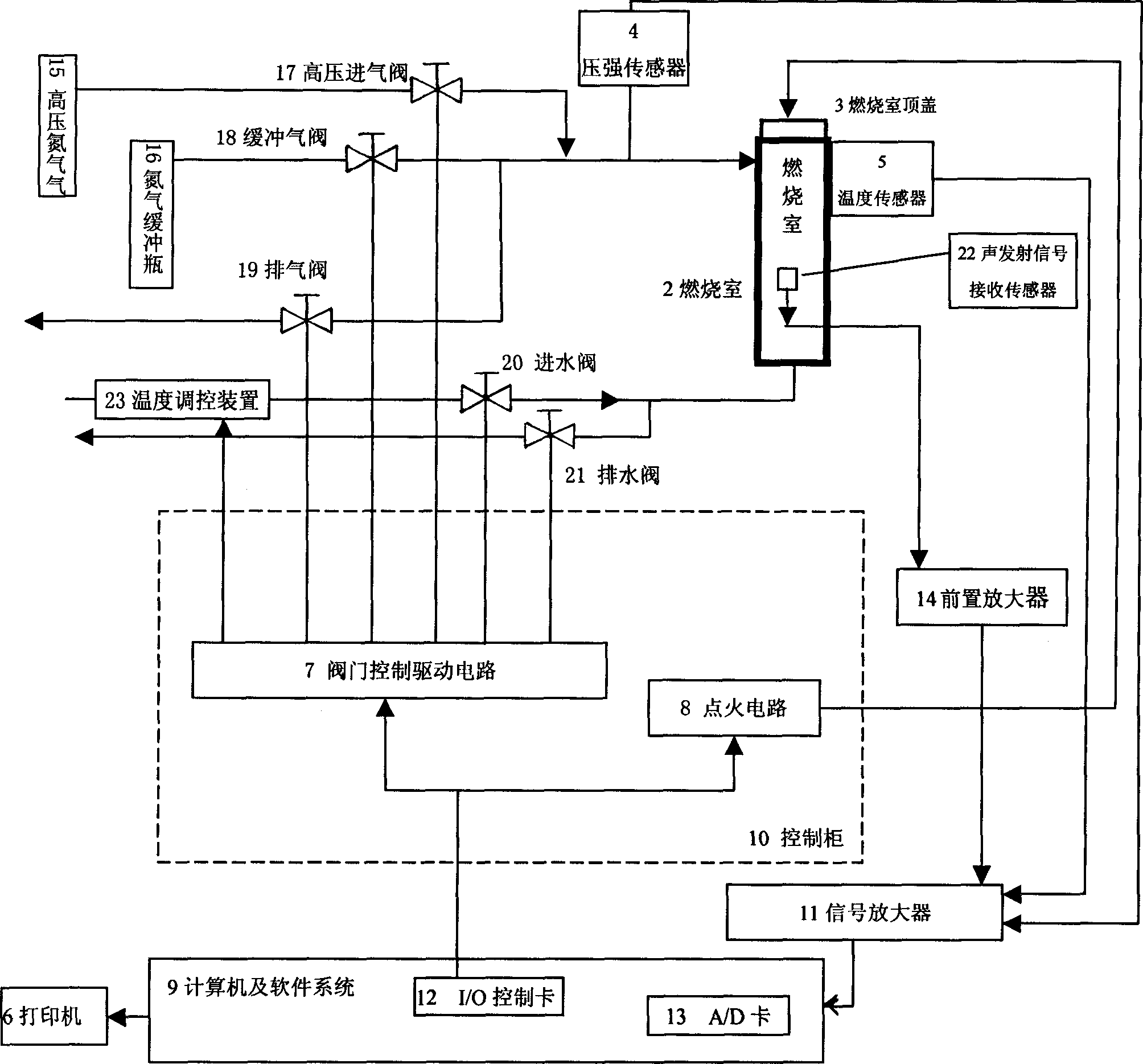

Rocket solid propellant burning velocity testing system

InactiveCN1888897AAvoiding Band Mismatch ProblemsLarge measuring rangeFuel testingCombustion chamberControl signal

A rocket solid propellant combustion speed test system relates to test equipment technology field. It enhances the test precision and test efficiency of the solid propellant combustion speed, achieves the management of the test date and data self-disposal to complete the automatization of the test process. It adopts the computer technology based on the existing technology. The system relates to firebox, signal collection equipment, gas way, waterway, temperature adjust equipment and designed system control equipment. The system control equipment relates to computer, control soft and control box made up of valve control drive circuit and ignition circuit. Signal collection equipment gets test signal from the firebox and magnifies it to carry to system control equipment. The computer deals with the data and sends control signal to the valve controlled by the valve control drive circuit and ignition circuit to switch on, interdict or ignite the solid propellant drug bar. It is mainly used for the rocket solid propellant combustion speed test.

Owner:XIDIAN UNIV

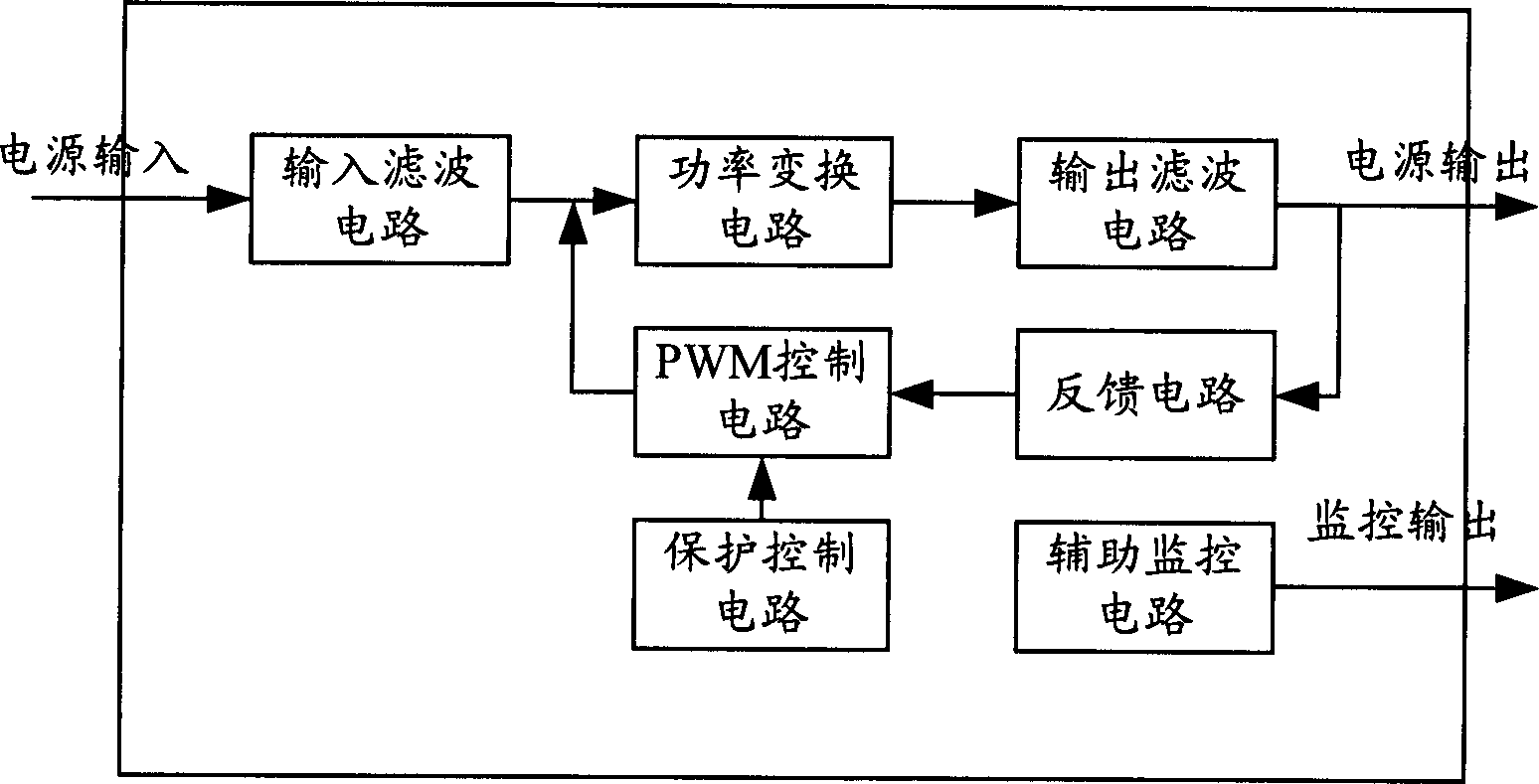

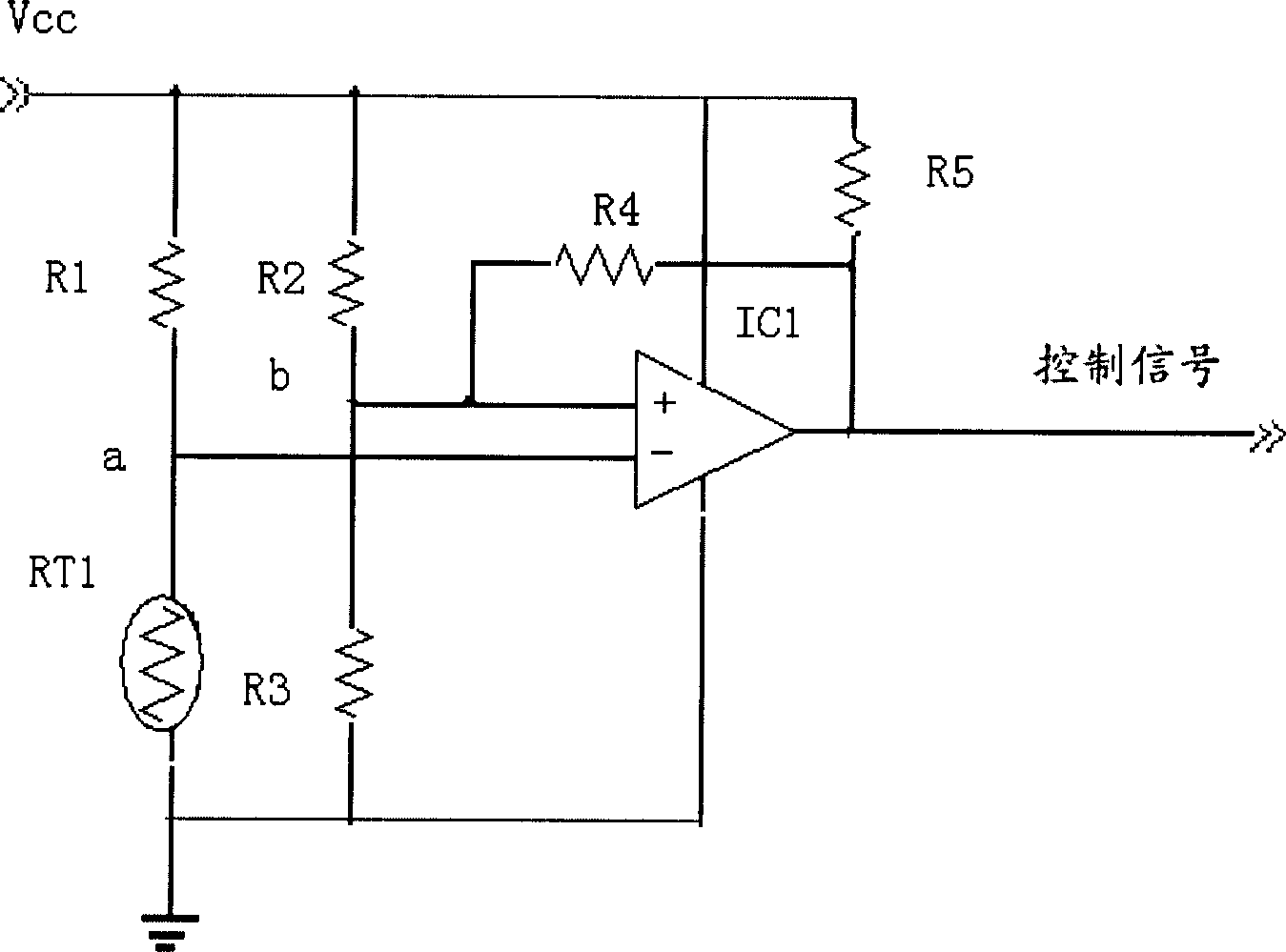

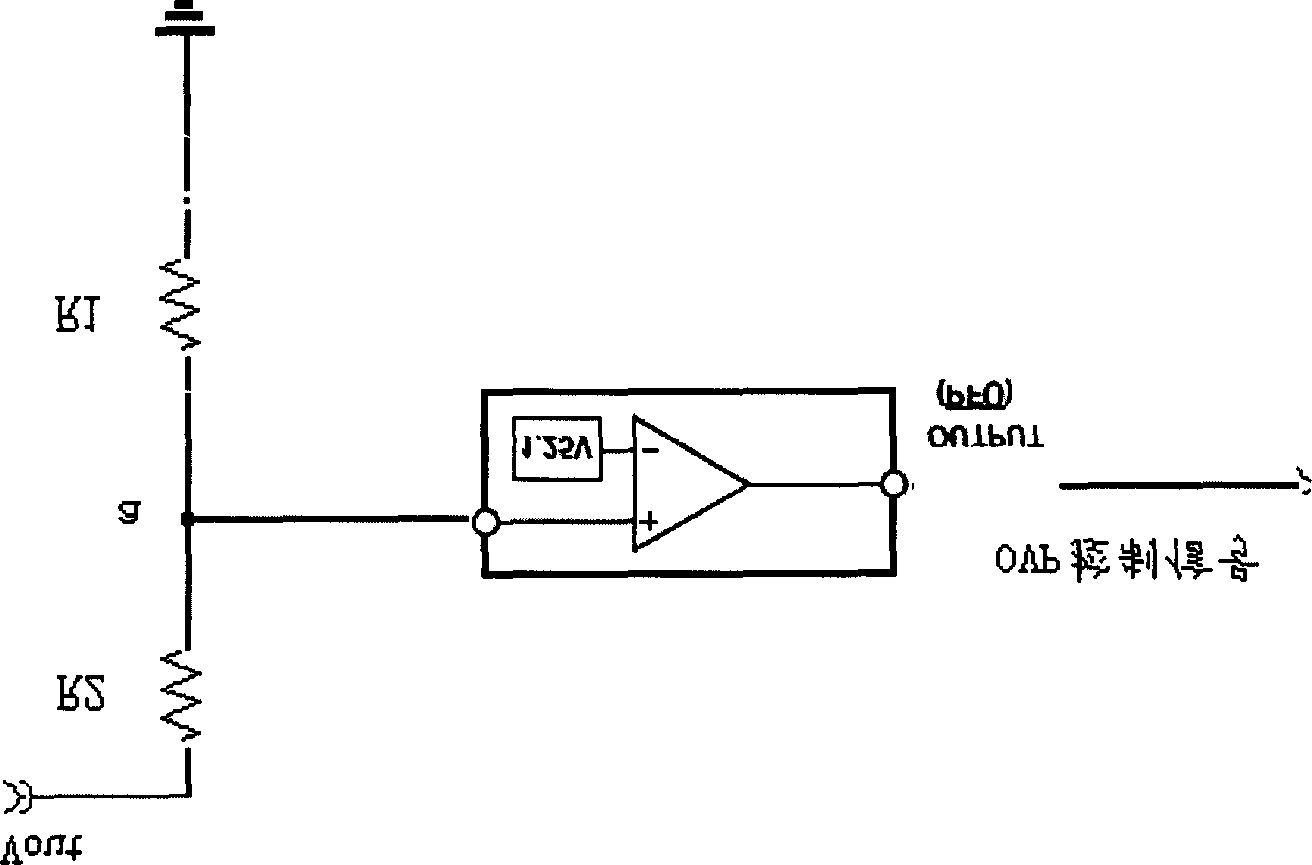

Apparatus and method for protecting electric source

ActiveCN1787314ASo as not to damageLow costEmergency protective circuit arrangementsSpeed testEngineering

This invention discloses a supply protection device including at least a protection circuit and its corresponding protection control circuit used in controlling said protection circuit to start or stop the supply protection function. This invention also discloses a supply protection method, which designs a protection circuit corresponding to the protected parameter, when the applied device works normally, said protection circuit protects the supply module, when the device carries out high speed test or high speed stress selection, the hardware or the software forbids the protection circuits to protect the supply module.

Owner:NEW H3C TECH CO LTD

Tester with acceleration on memory and acceleration for automatic pattern generation within a FPGA block

ActiveUS10161993B2Bandwidth requirement can be keptMinimal processing loadDigital circuit testingError detection/correctionAutomatic test pattern generationHardware acceleration

Automated test equipment capable of performing a high-speed test of semiconductor devices is presented. The automated test equipment apparatus comprises a computer system comprising a tester processor, wherein the tester processor is communicatively coupled to a plurality of FPGA components. Each of the plurality of FPGA components is coupled to a memory module and comprises: an upstream port operable to receive commands and data from the tester processor; a downstream port operable to communicate with a respective DUT from a plurality of DUTs; and a plurality of hardware accelerator circuits, wherein each of the accelerator circuits is configured to communicate with one of the plurality of DUTs. Each of the plurality of hardware accelerator circuits comprises a pattern generator circuit configurable to automatically generate test pattern data and a comparator circuit configured to compare data.

Owner:ADVANTEST CORP

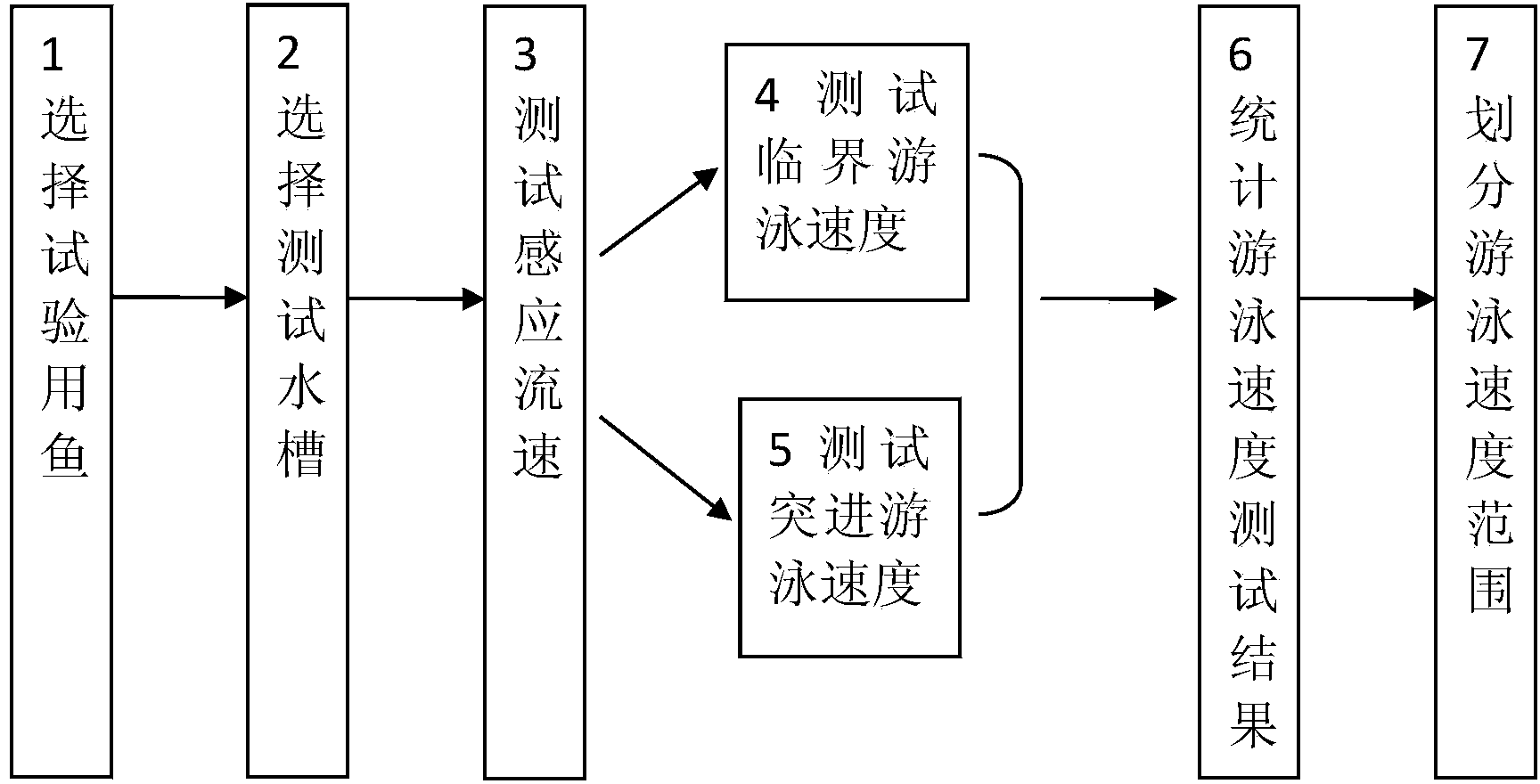

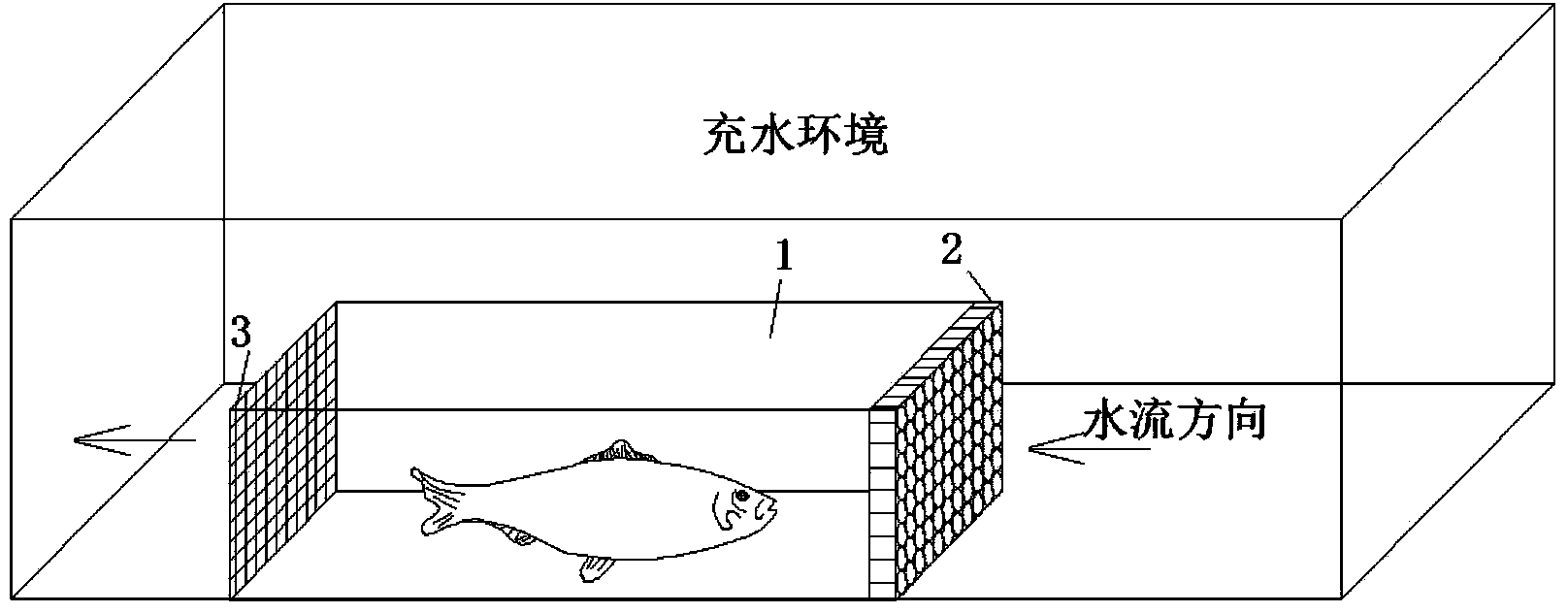

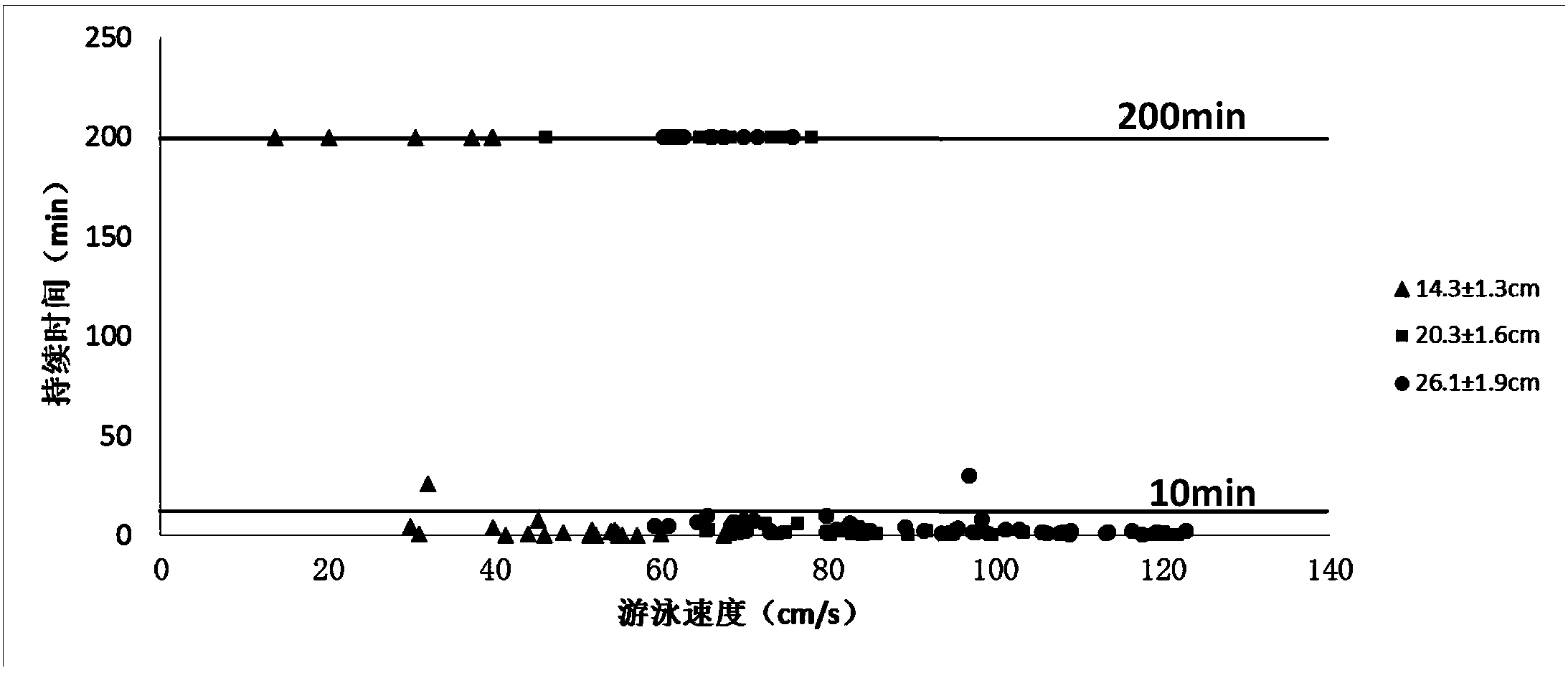

Method for evaluating swimming ability of fishes and application

The invention discloses a method for evaluating the swimming ability of fishes and application of the method in the fish passage facility design. The method comprises the steps that (1) fishes are selected as a target; (2) a test water channel is selected; (3) the sensing flow velocities of the fishes are tested, wherein the total length index, the body length index and the weight index of each fish are recorded, and temporary rearing continues; (4) the critical swimming speeds of the fishes are tested; (5) the onrush swimming speeds of the fishes are tested, wherein the total length index, the body length index and the weight index of each fish are recorded, and the onrush swimming speeds of the fishes are calculated; (6) repeated testing is carried out; (7) statistics is carried out on swimming speed test results, wherein the median of the sensing flow velocities, obtained through repeated testing, of the target fishes, the median of the critical swimming speeds, obtained through repeated testing, of the target fishes, and the median of the onrush swimming speeds, obtained through repeated testing, of the target fishes are calculated; (8) the range of the continuing swimming speeds, the range of durable swimming speeds and the range of the outburst swimming speeds are obtained in a short time, comprehensive evaluation is carried out on the swimming speeds of the fishes, and the maximum flow velocity of a main body structure, the fish luring flow velocity of an inlet, and the range of the flow velocities of an outlet in the fish passage facility design are determined.

Owner:WATER ENG ECOLOGICAL INST CHINESE ACAD OF SCI

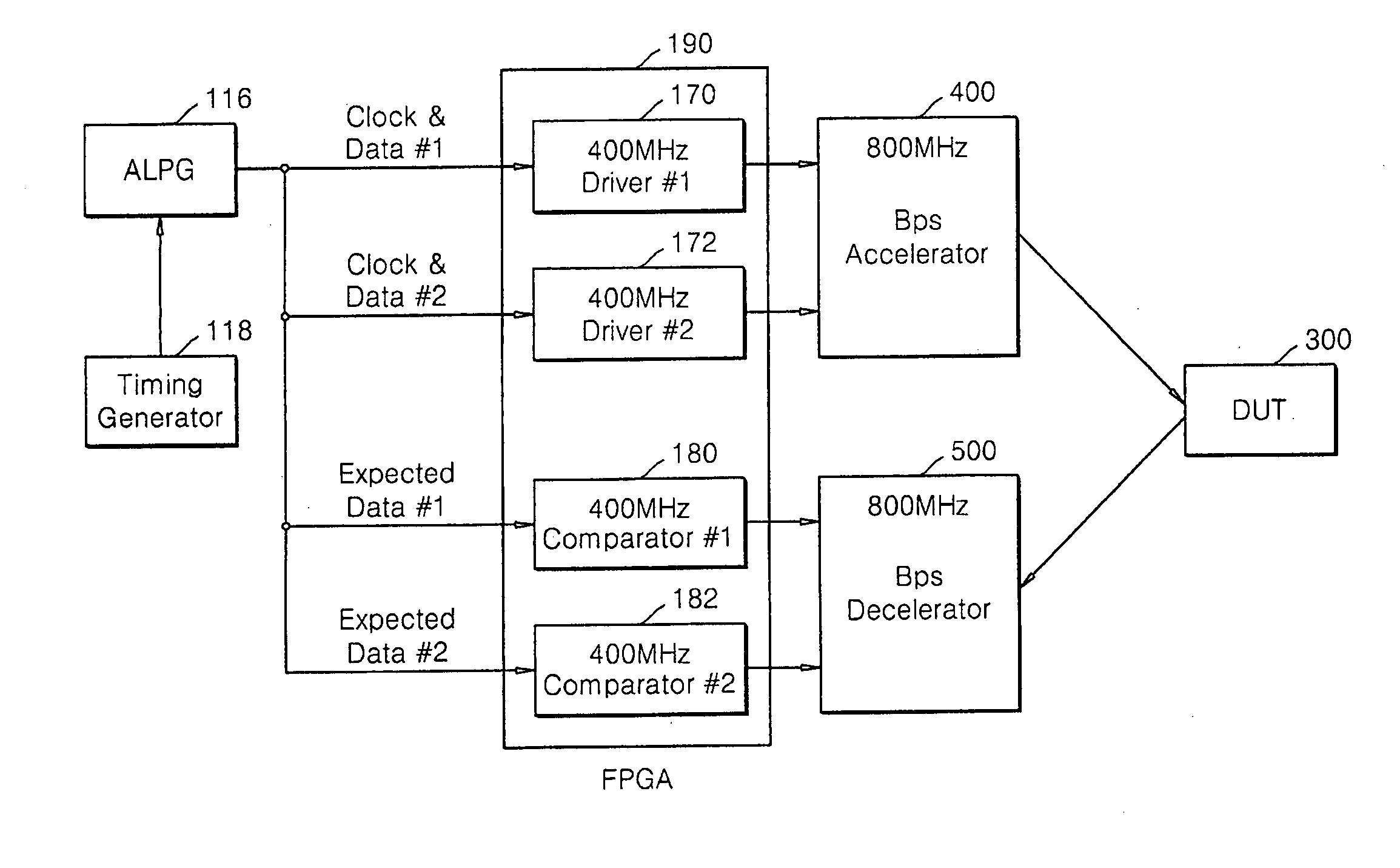

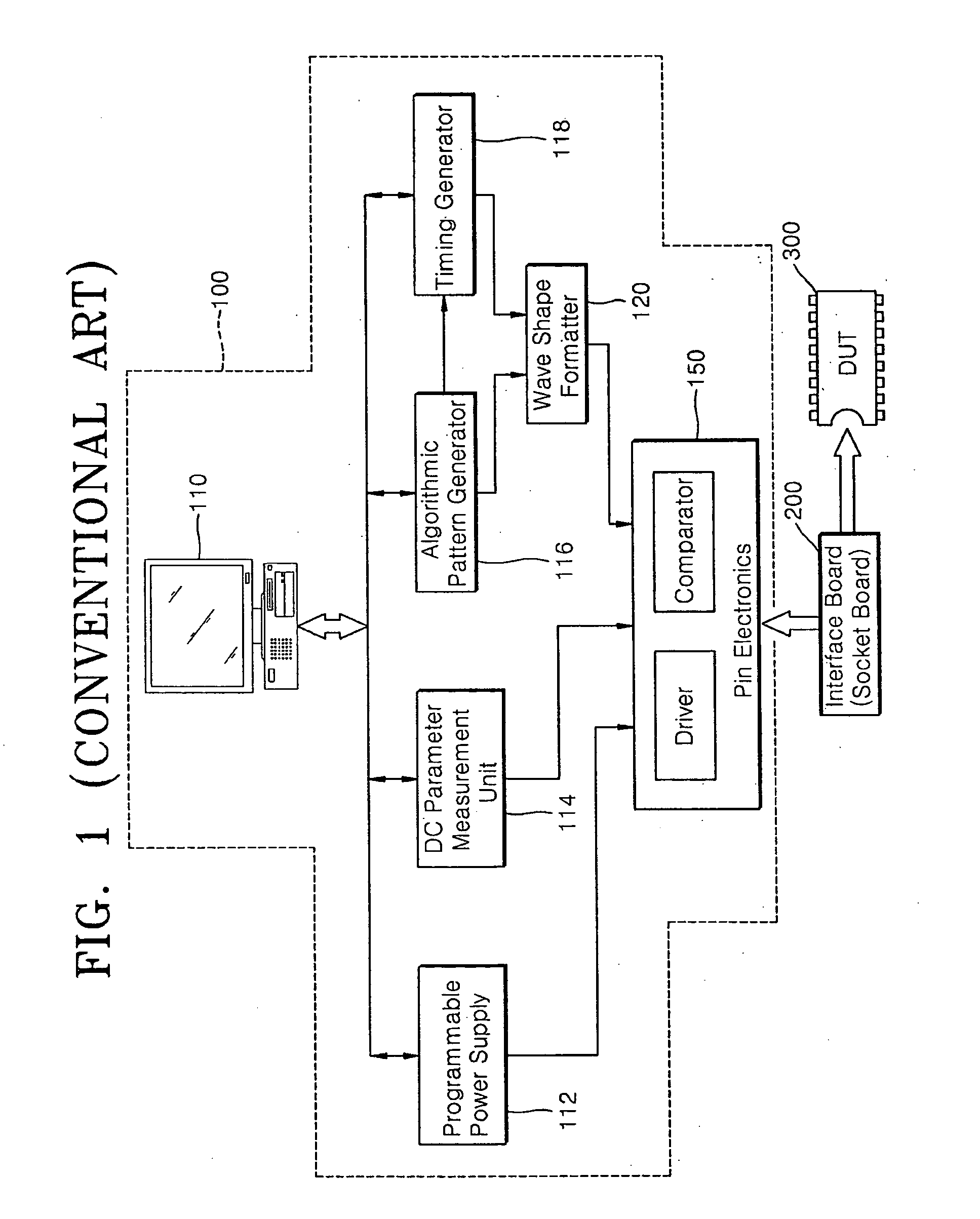

Automatic test equipment capable of high speed test

ActiveUS20080204066A1Increase the maximum operating frequencyVoltage/current isolationStatic storageElectricityAutomatic test equipment

Automatic test equipment is capable of performing a high-speed test of semiconductor devices, with a low cost and high efficiency. The automatic test equipment (ATE) comprises: an ATE body configured to electrically test semiconductor devices; a field programmable gate array (FPGA) controlling drivers and comparators on the ATE; an accelerator connected to an output terminal of the FPGA and that doubles an operating frequency of the FPGA; and a decelerator connected to an output terminal of the FPGA and that converts an operating frequency of data transferred from the semiconductor device to the operating frequency of the FPGA.

Owner:SAMSUNG ELECTRONICS CO LTD

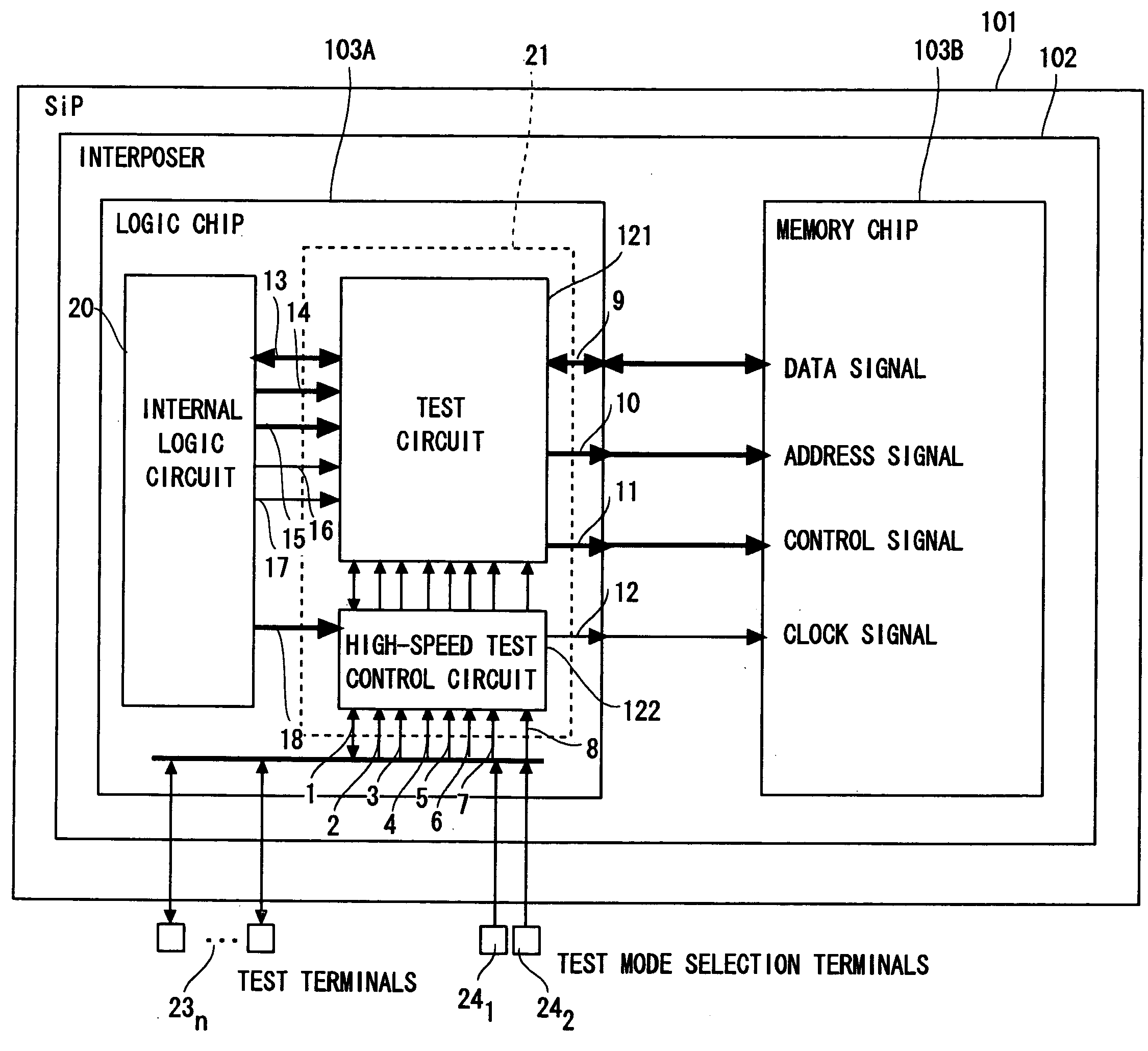

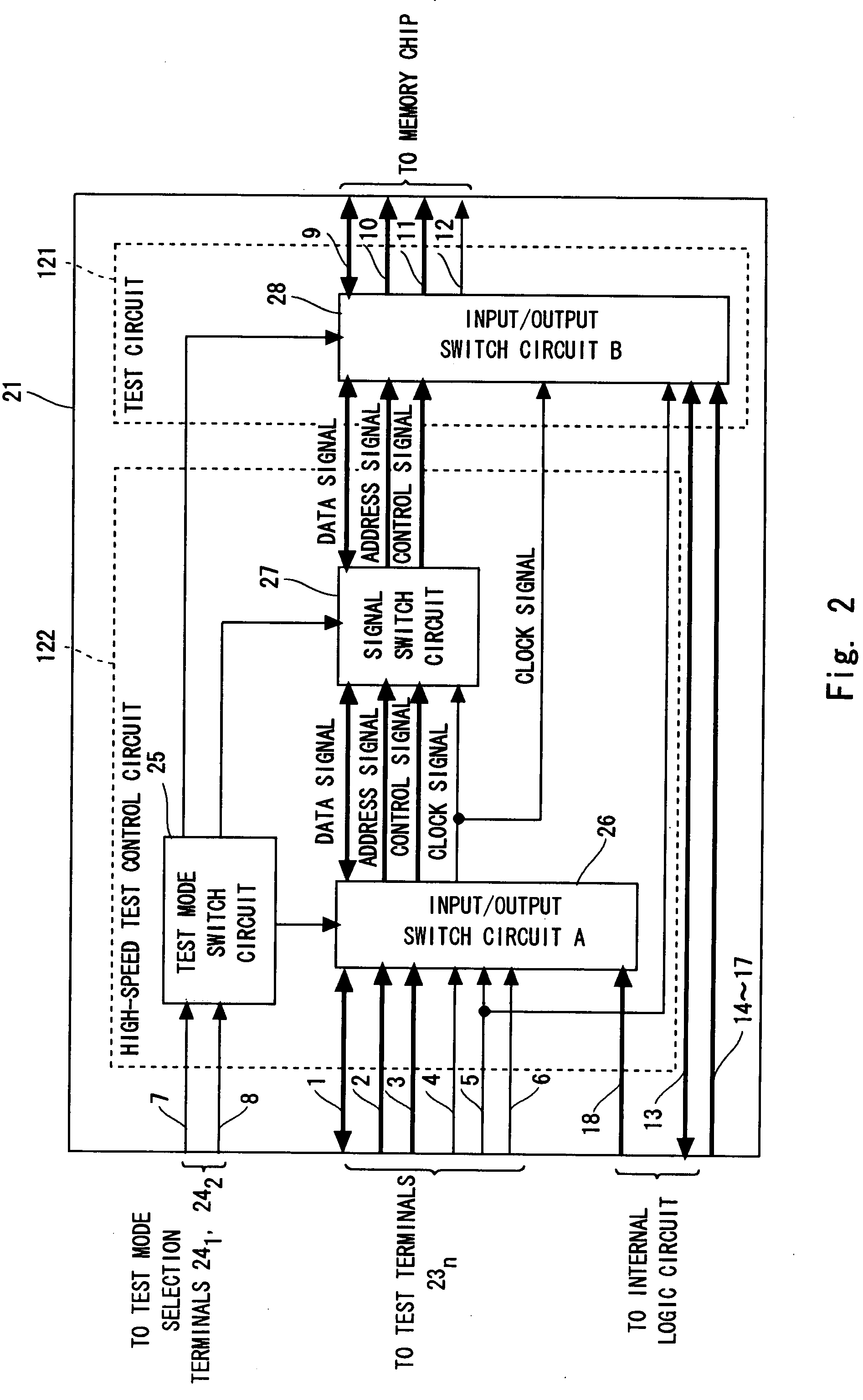

Semiconductor apparatus and test method therefor

InactiveUS20070245200A1Increase speedElectronic circuit testingError detection/correctionElectricityMemory chip

A SiP includes a logic chip and a memory chip. The memory chip includes a memory circuit to be tested, and the logic chip includes an internal logic circuit and a test processor electrically connected therewith. The test processor is connected with an access terminal of the memory circuit and supplies a test signal input from an external terminal to the access terminal to thereby test the memory circuit. The test processor includes a high-speed test control circuit to adjust signal delay and supplies a test signal from the external terminal to the access terminal through the high-speed test control circuit when performing high-speed test at an actual operation speed.

Owner:RENESAS ELECTRONICS CORP

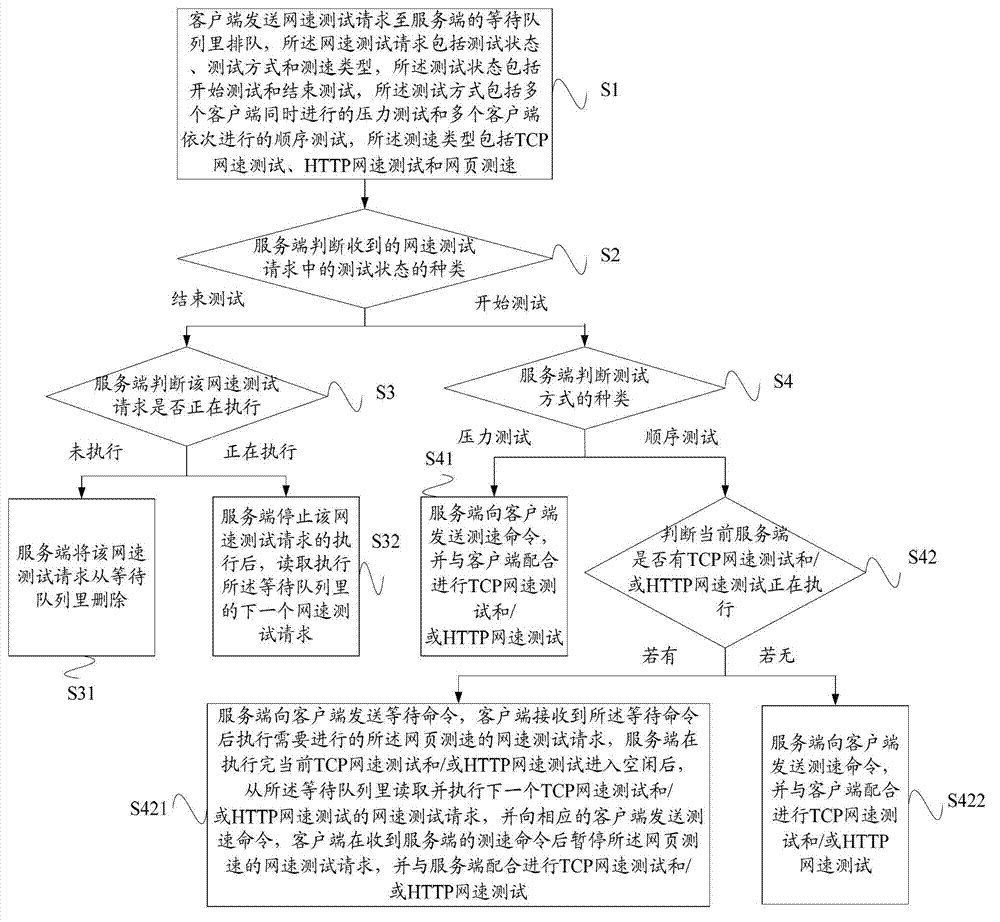

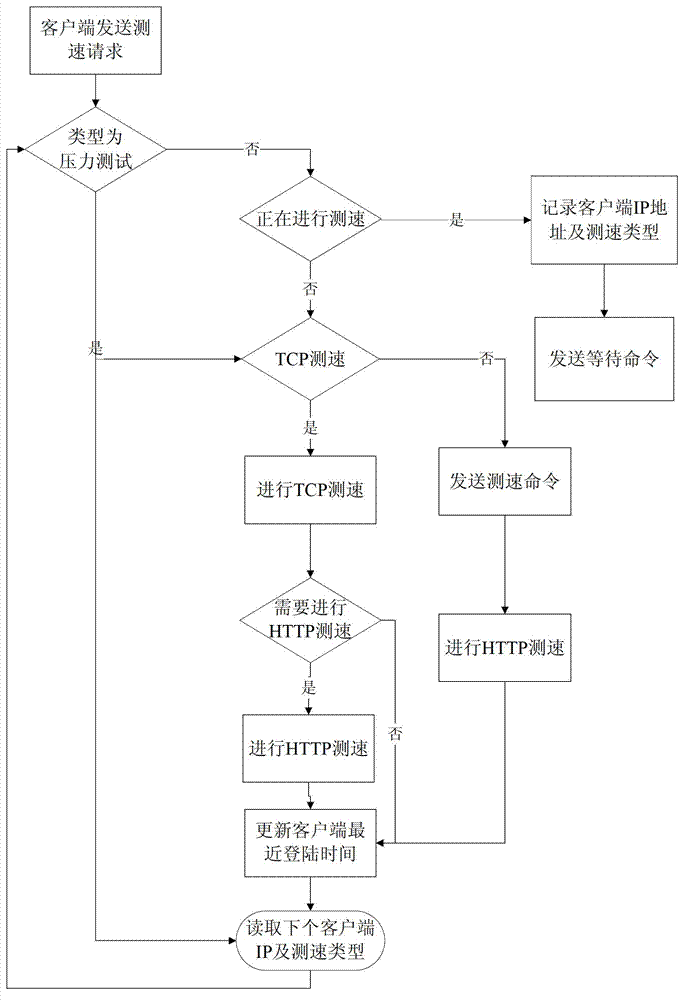

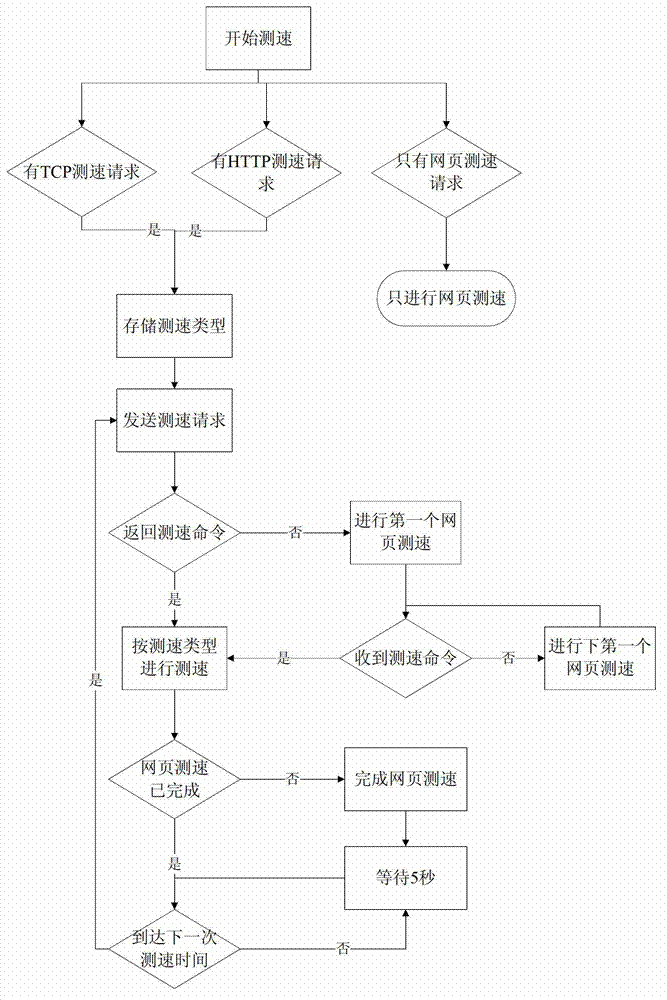

Network speed test method and network speed test system

ActiveCN103051498AIntuitive and objective detectionAccurate Bandwidth DataData switching networksSpeed testClient-side

The invention relates to a network speed test method and a network speed test system. The method includes the following steps: a network speed test request is sent into a waiting queue of a server by a client to be queued; if the judgment result of the server is test starting, then the server judges the variety of a test mode; if the test mode is pressure test, then the server sends a speed-testing command to the client, and cooperates with the client to carry out a TCP (transfer control protocol) network speed test and / or an HTTP (hypertext transfer protocol) network speed test; if the test mode is sequence test, whether the TCP network speed test and / or the HTTP network speed test are / is executed by the current server is judged, if so, then a waiting command is sent to the client, and if not, then the server cooperates with the client to carry out the TCP network speed test and / or the HTTP network speed test. The invention can visually and objectively test the speed of all broadband networks to provide reliable technical support for users to obtain accurate bandwidth data of operators.

Owner:上海泰峰检测认证有限公司