Patents

Literature

58results about How to "Increase the maximum operating frequency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

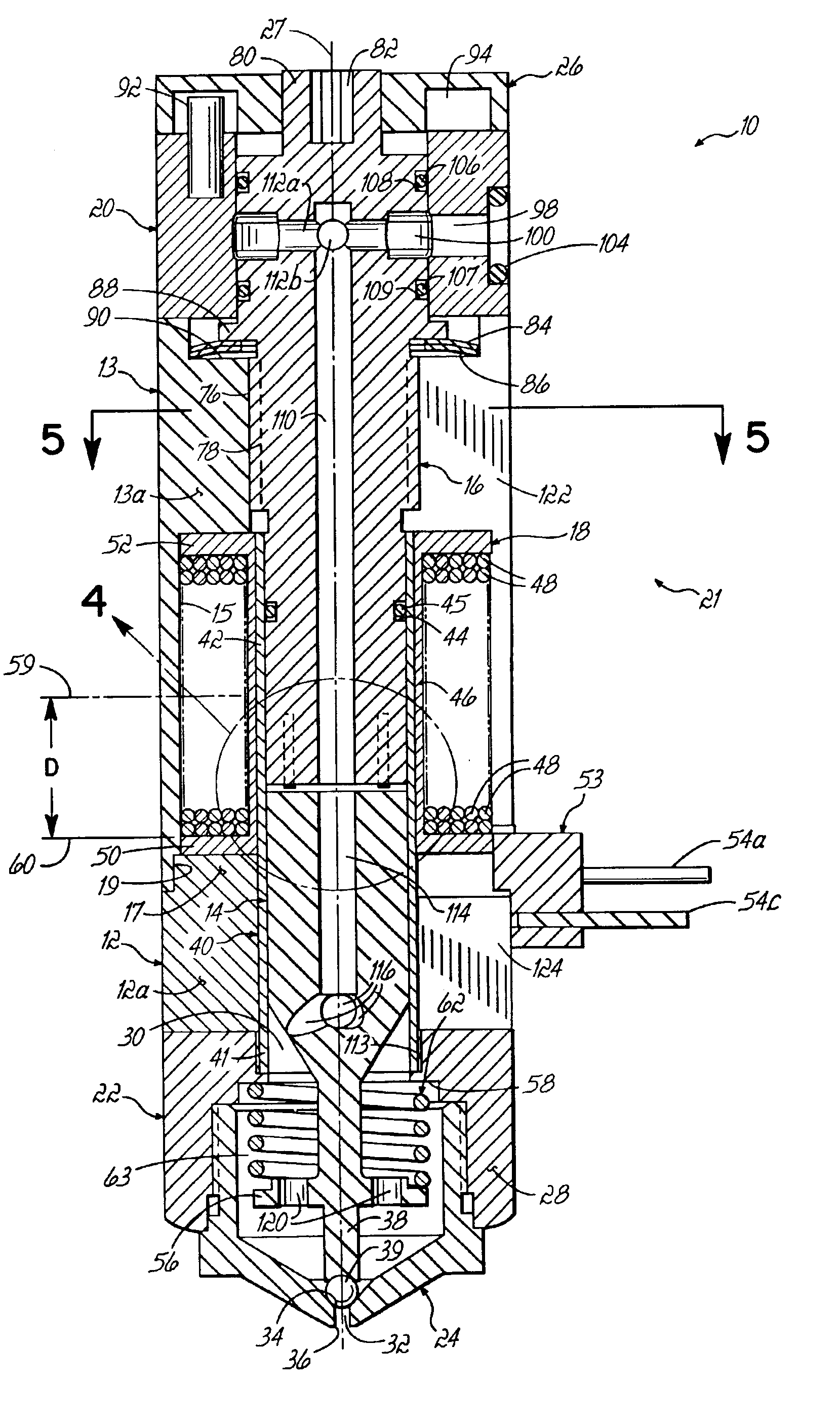

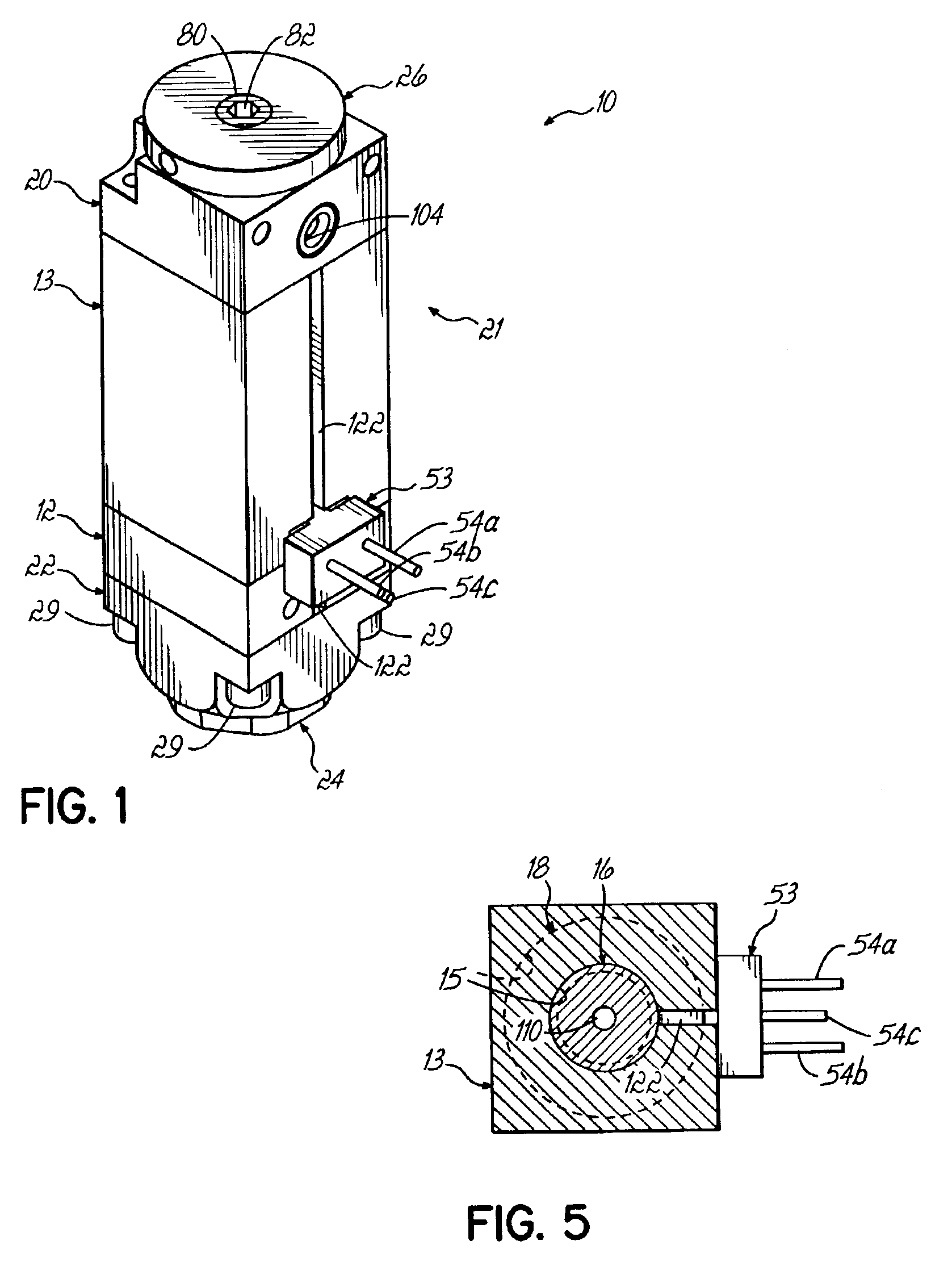

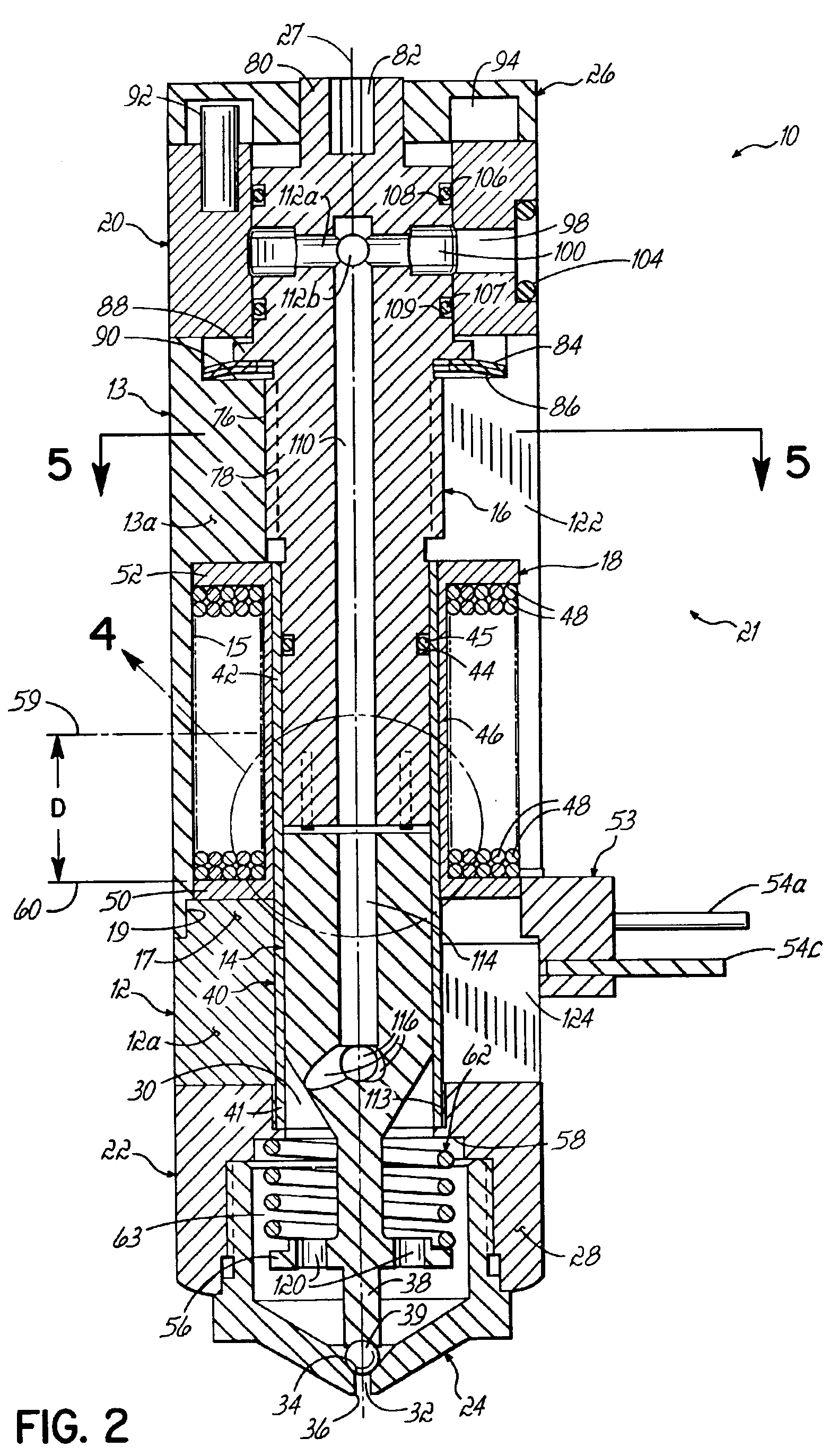

Electrically-operated dispensing module

InactiveUS6994234B2Reduce generationSmall volumeLiquid surface applicatorsPower operated devicesViscous liquidComputer module

Electrically-operated dispensing modules capable of dispensing small volumes of a viscous liquid at high operating frequencies and reproducibly among successive dispensed volumes of viscous liquid without the occurrence of stringing. The dispensing module may include a flux element having a portion effective for interrupting circumferential electrical current paths. In another aspect, an end face of a pole piece of the dispensing module may include one or more non-magnetic spacer elements that prevent contact between the pole piece and armature when the dispensing module is opened.

Owner:NORDSON CORP

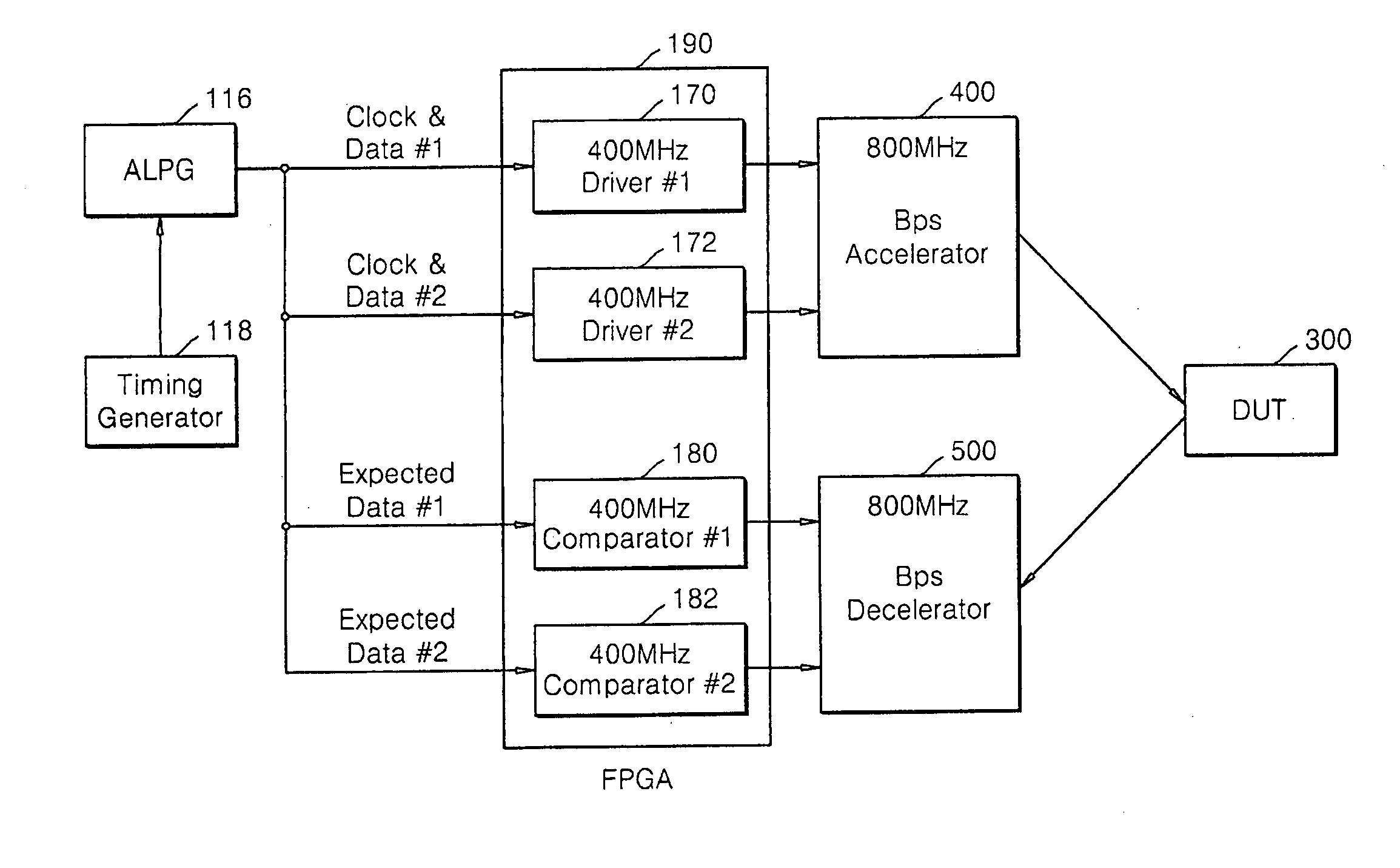

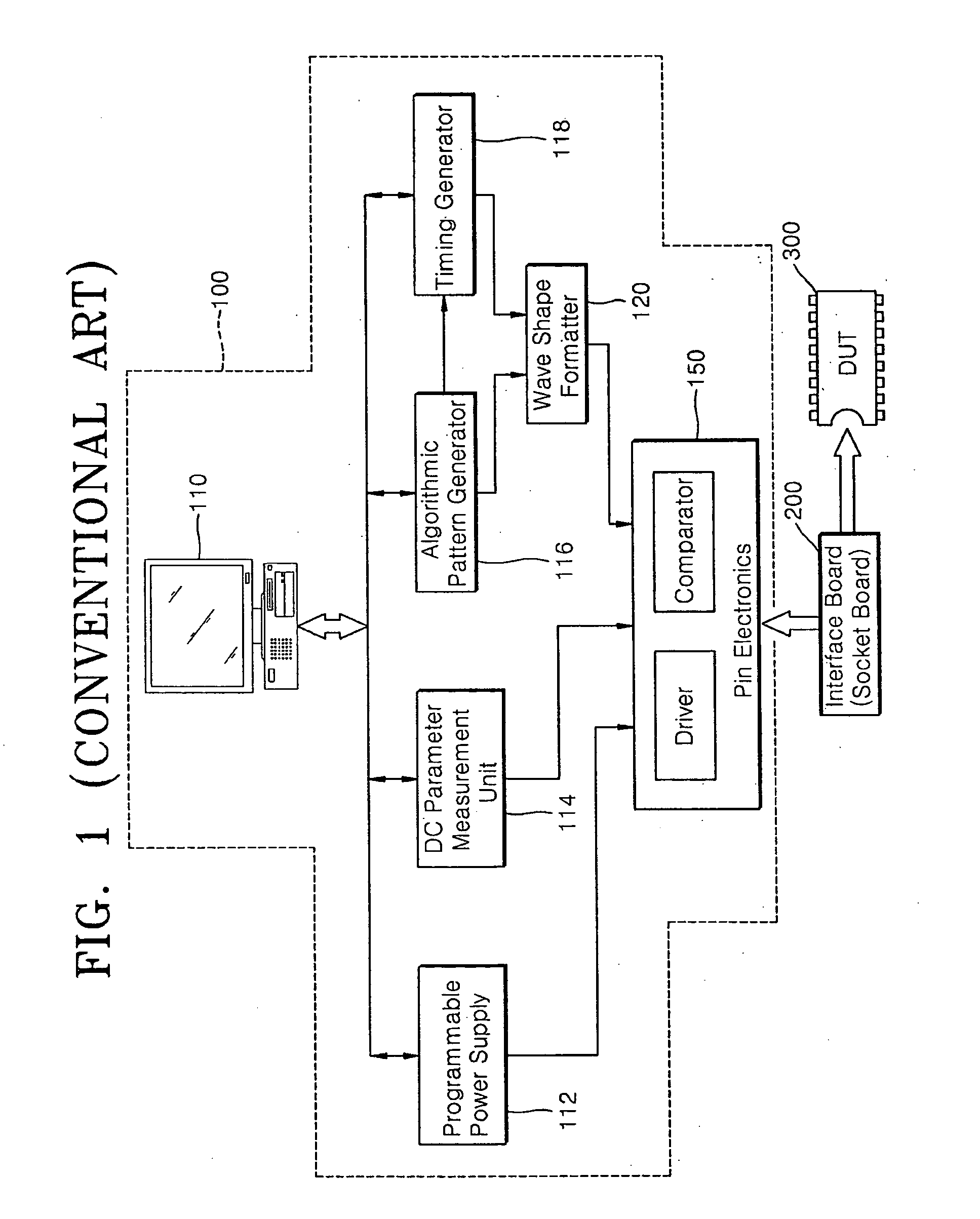

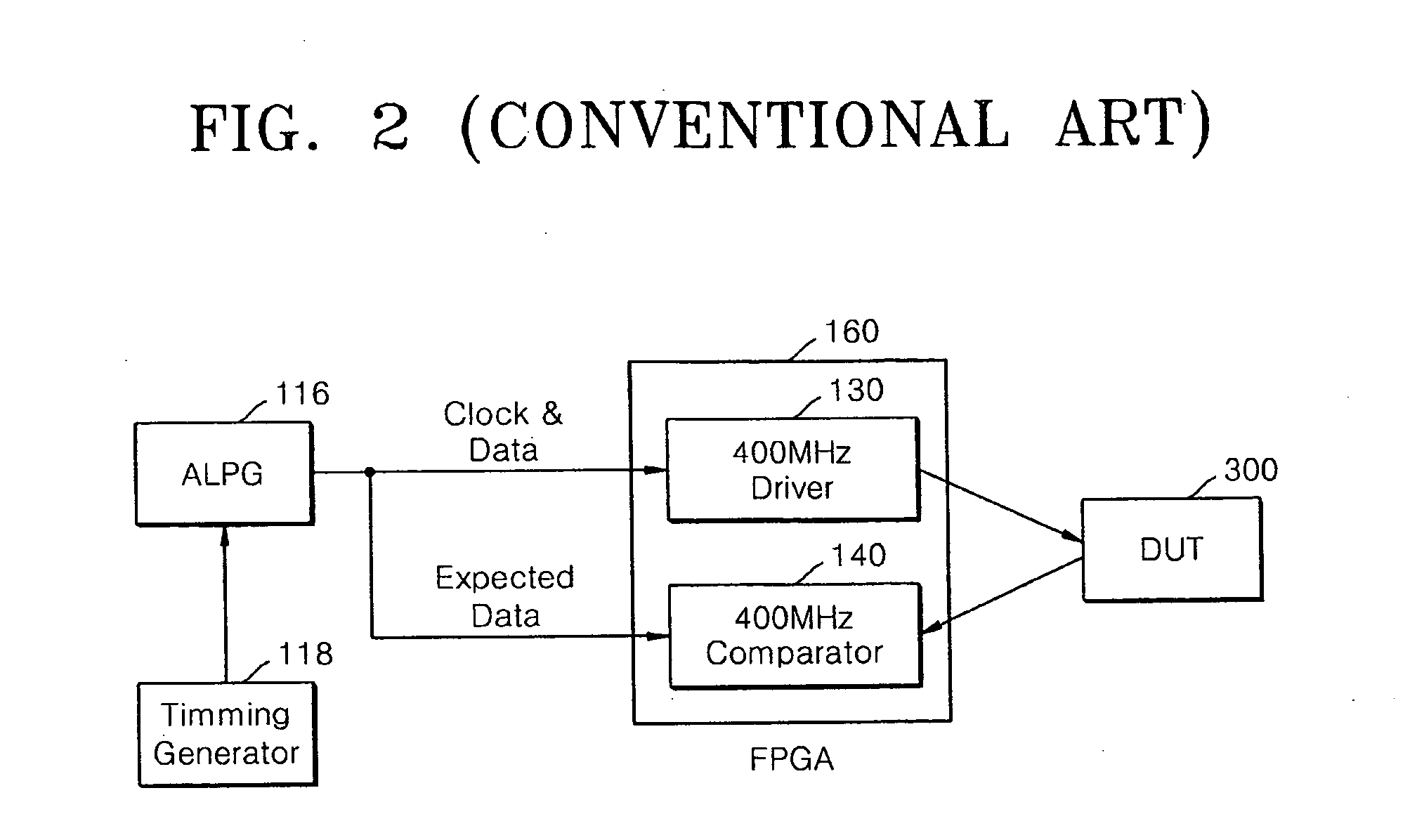

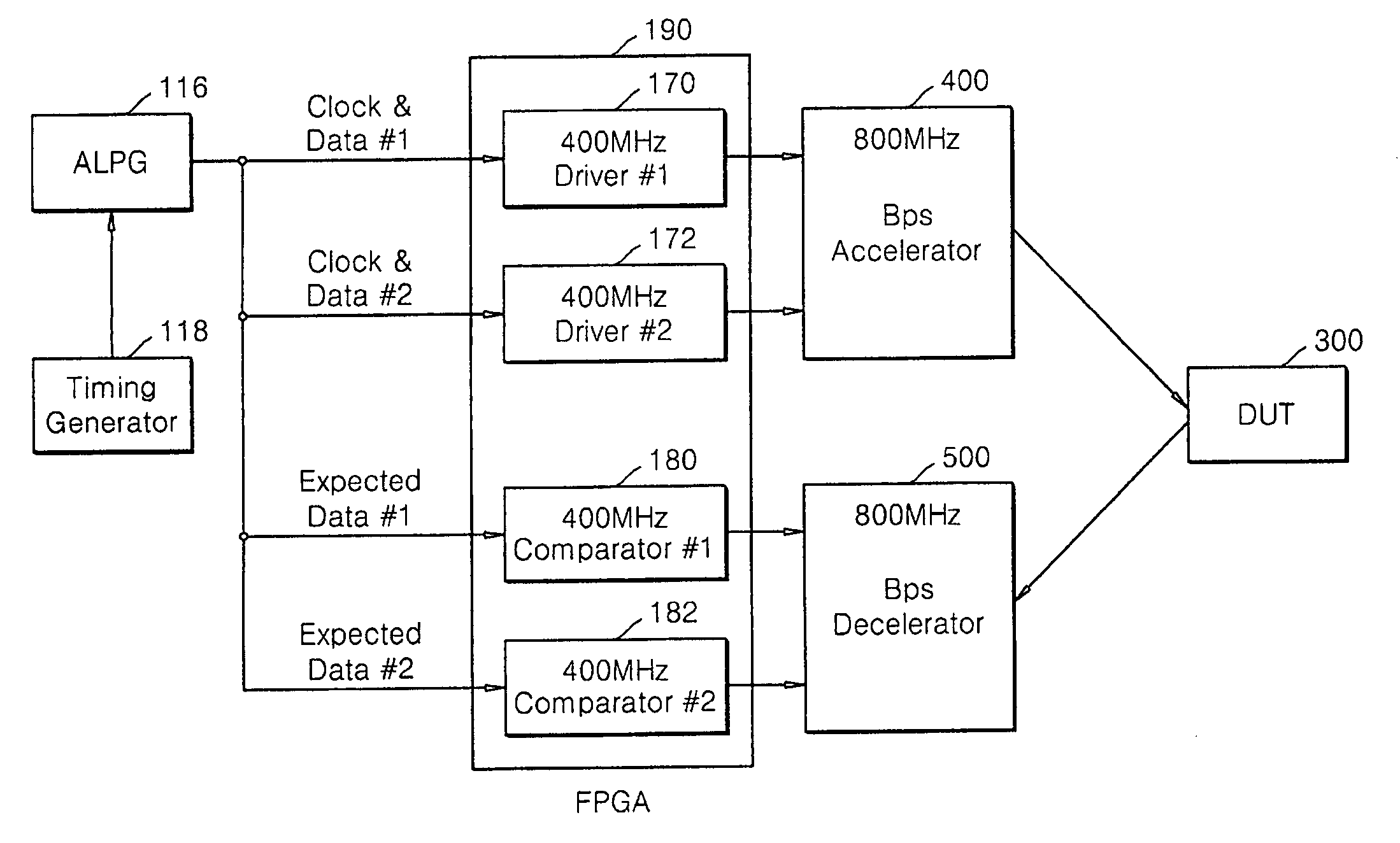

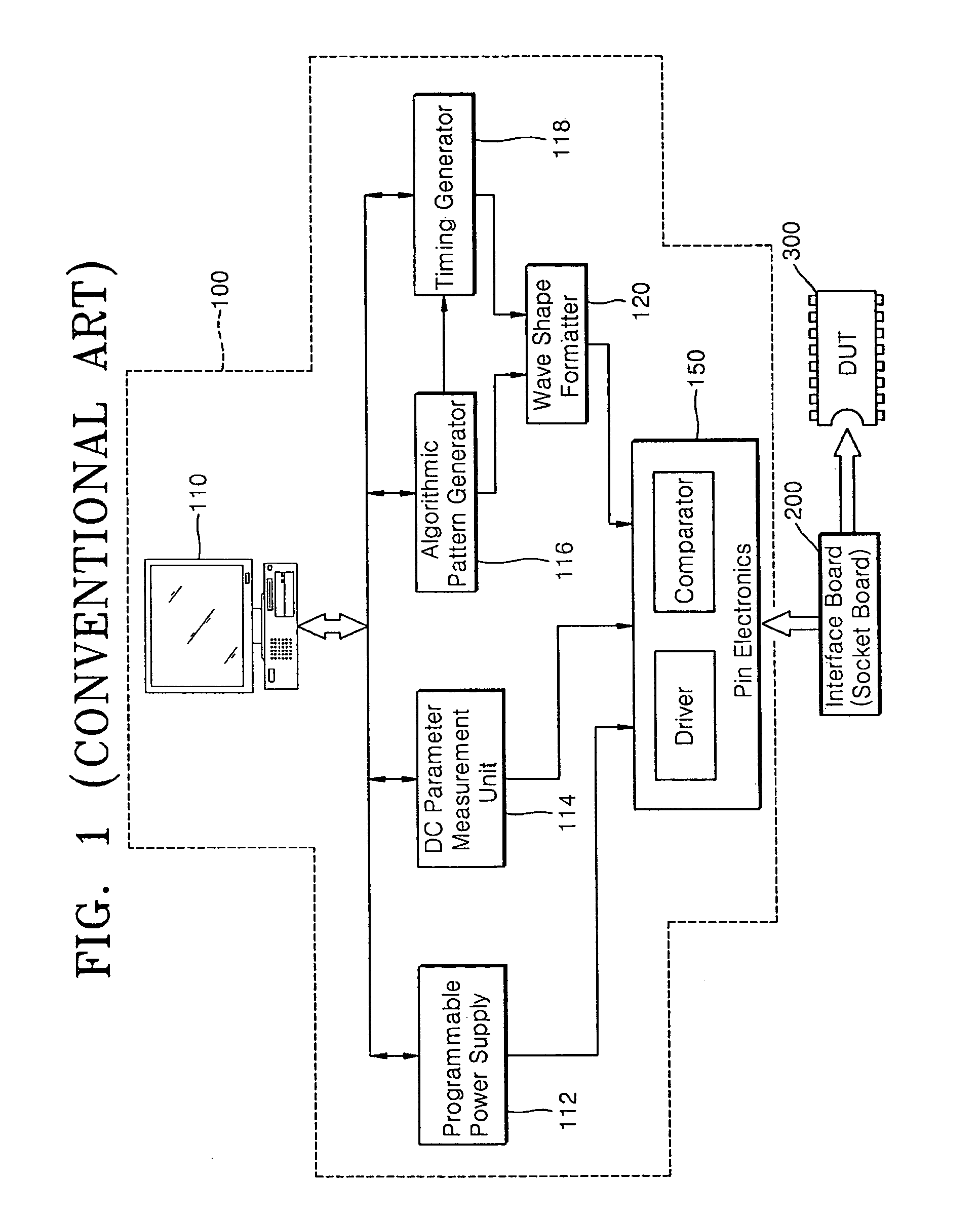

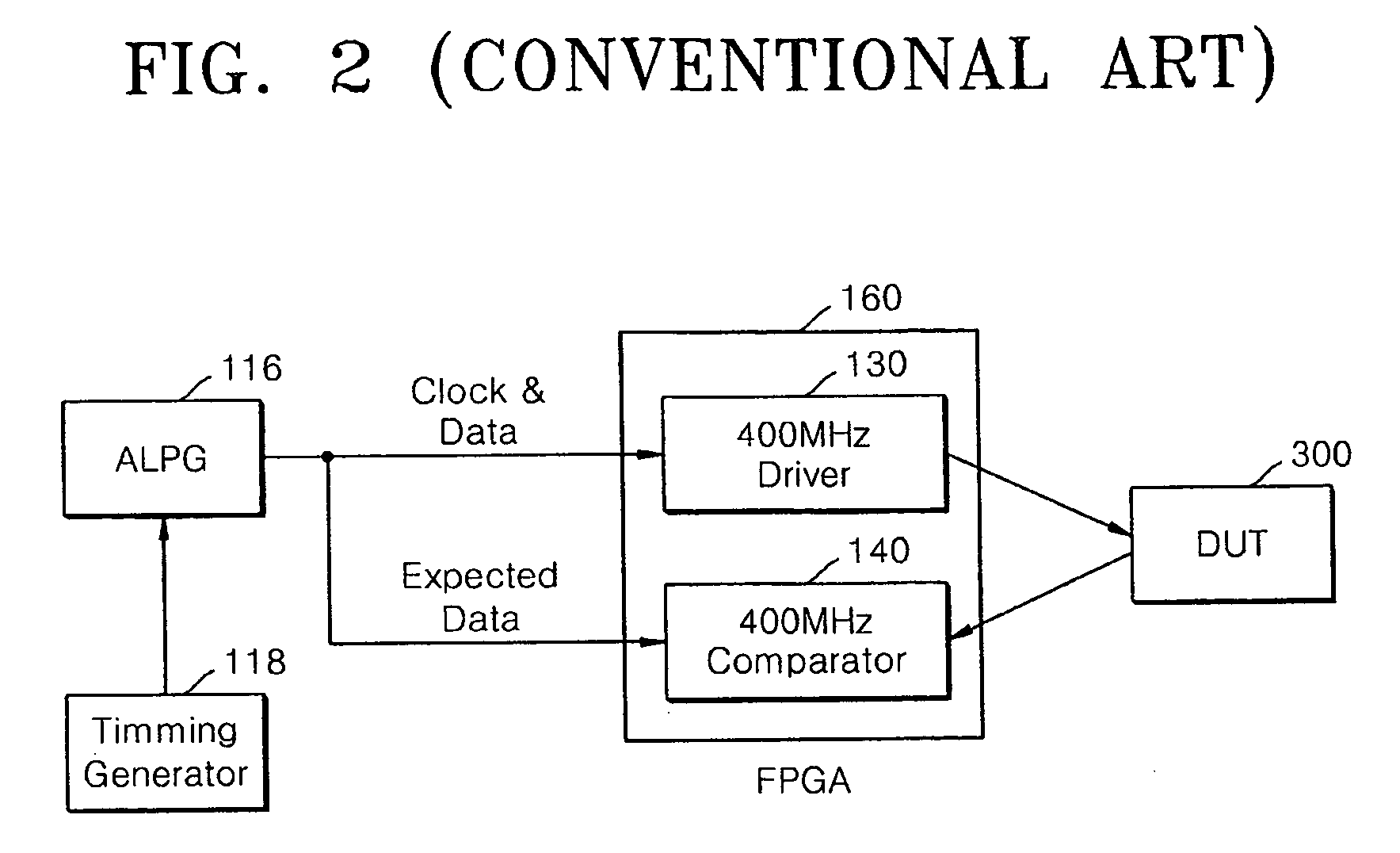

Automatic test equipment capable of high speed test

ActiveUS20080204066A1Increase the maximum operating frequencyVoltage/current isolationStatic storageElectricityAutomatic test equipment

Automatic test equipment is capable of performing a high-speed test of semiconductor devices, with a low cost and high efficiency. The automatic test equipment (ATE) comprises: an ATE body configured to electrically test semiconductor devices; a field programmable gate array (FPGA) controlling drivers and comparators on the ATE; an accelerator connected to an output terminal of the FPGA and that doubles an operating frequency of the FPGA; and a decelerator connected to an output terminal of the FPGA and that converts an operating frequency of data transferred from the semiconductor device to the operating frequency of the FPGA.

Owner:SAMSUNG ELECTRONICS CO LTD

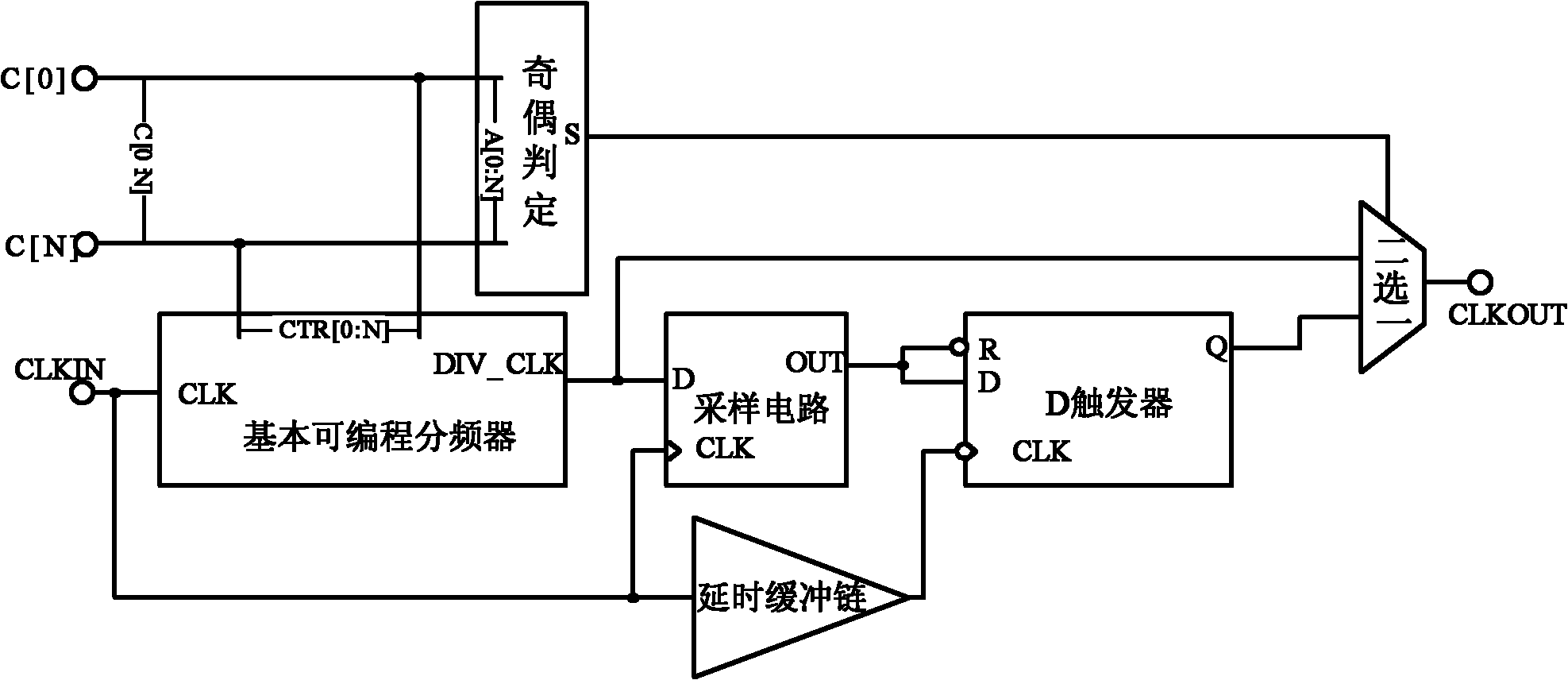

Programmable 50%-duty cycle frequency divider

ActiveCN102035540AIncrease the maximum operating frequencyClock Duty Cycle ImprovementCounting chain synchronous pulse countersDecision circuitEngineering

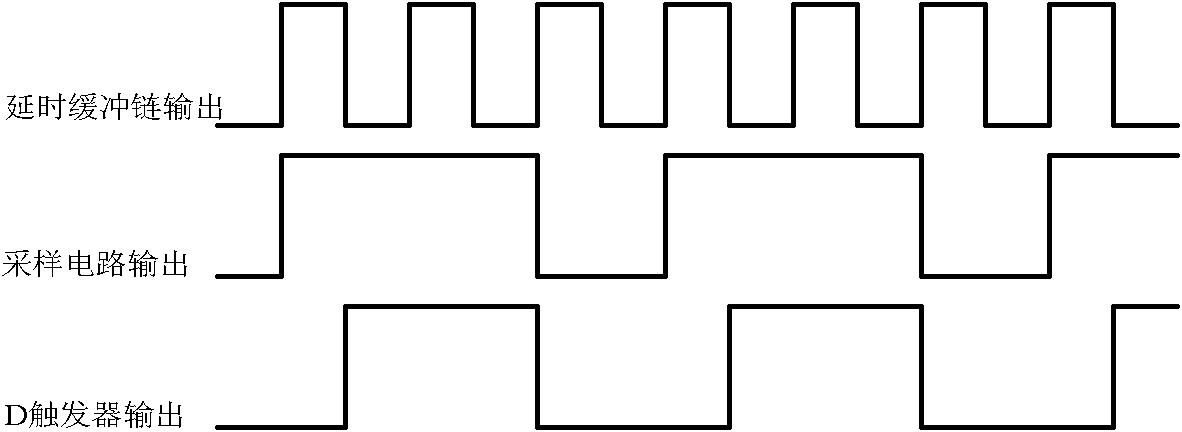

The invention discloses a programmable 50%-duty cycle frequency divider which comprises a basic programmable frequency divider, a sampling circuit, a D (DICE (Dual Interlocked Cell)) trigger, a delay buffer chain, an odd-even decision circuit and an alternative multi-path selector. Aiming at the duty cycle problem of clock output of a programmable frequency divider during the odd frequency division of the programmable frequency divider, the basic programmable frequency divider is adopted to perform frequency division for an original clock; a clock with 50% duty cycle is output during even frequency division; a clock, the difference of a high level and a low level of which is one original clock period, is output during odd frequency division; and then, a half original clock period is respectively added to and subtracted from a high level and a lower level of the odd frequency division clock to generate an odd frequency division clock with 50% duty cycle; and thus, the programmable frequency divider can output an 50%-duty cycle clock in any frequency division ratio.

Owner:CHANGSHA JINGJIA MICROELECTRONICS

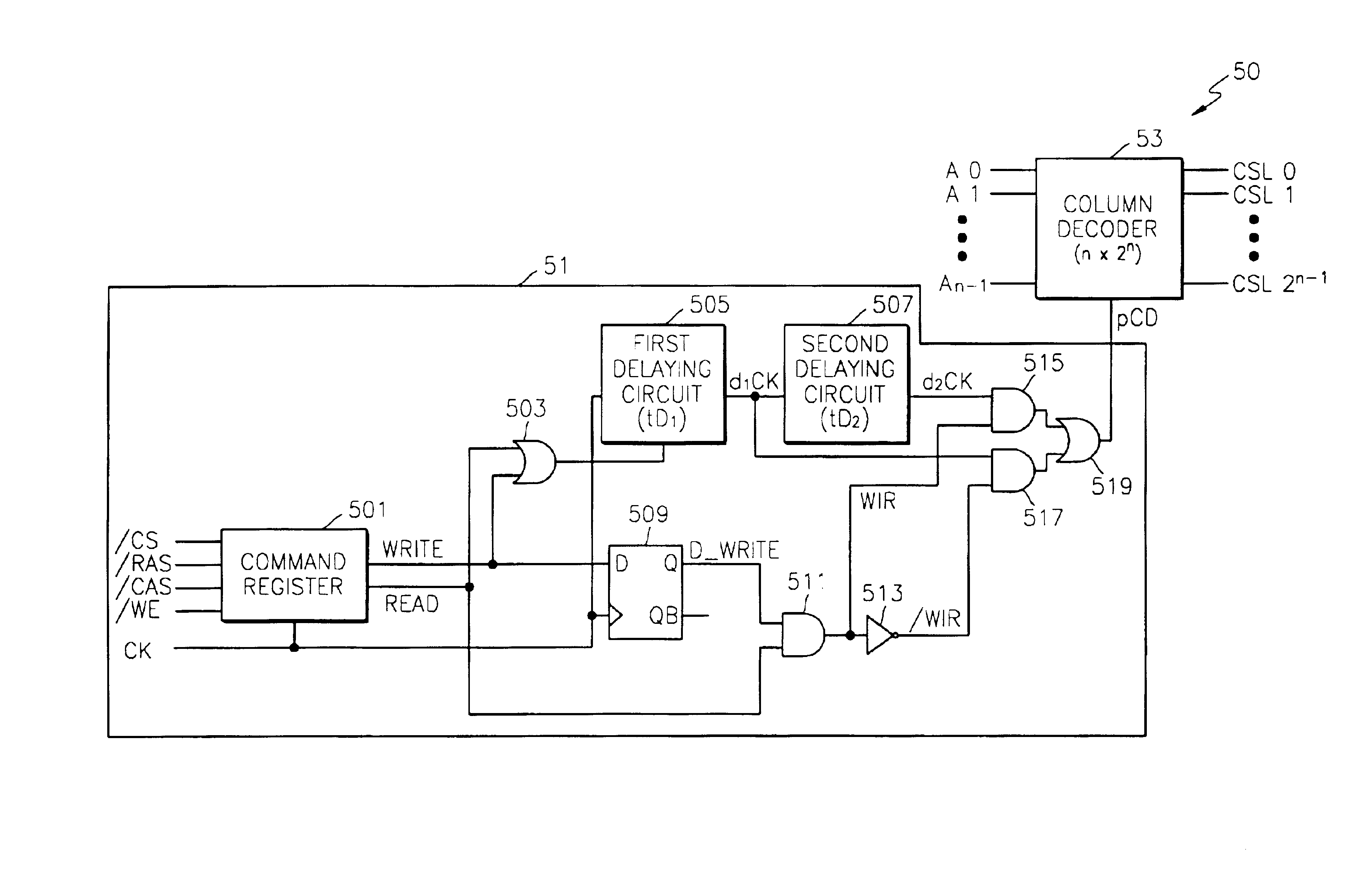

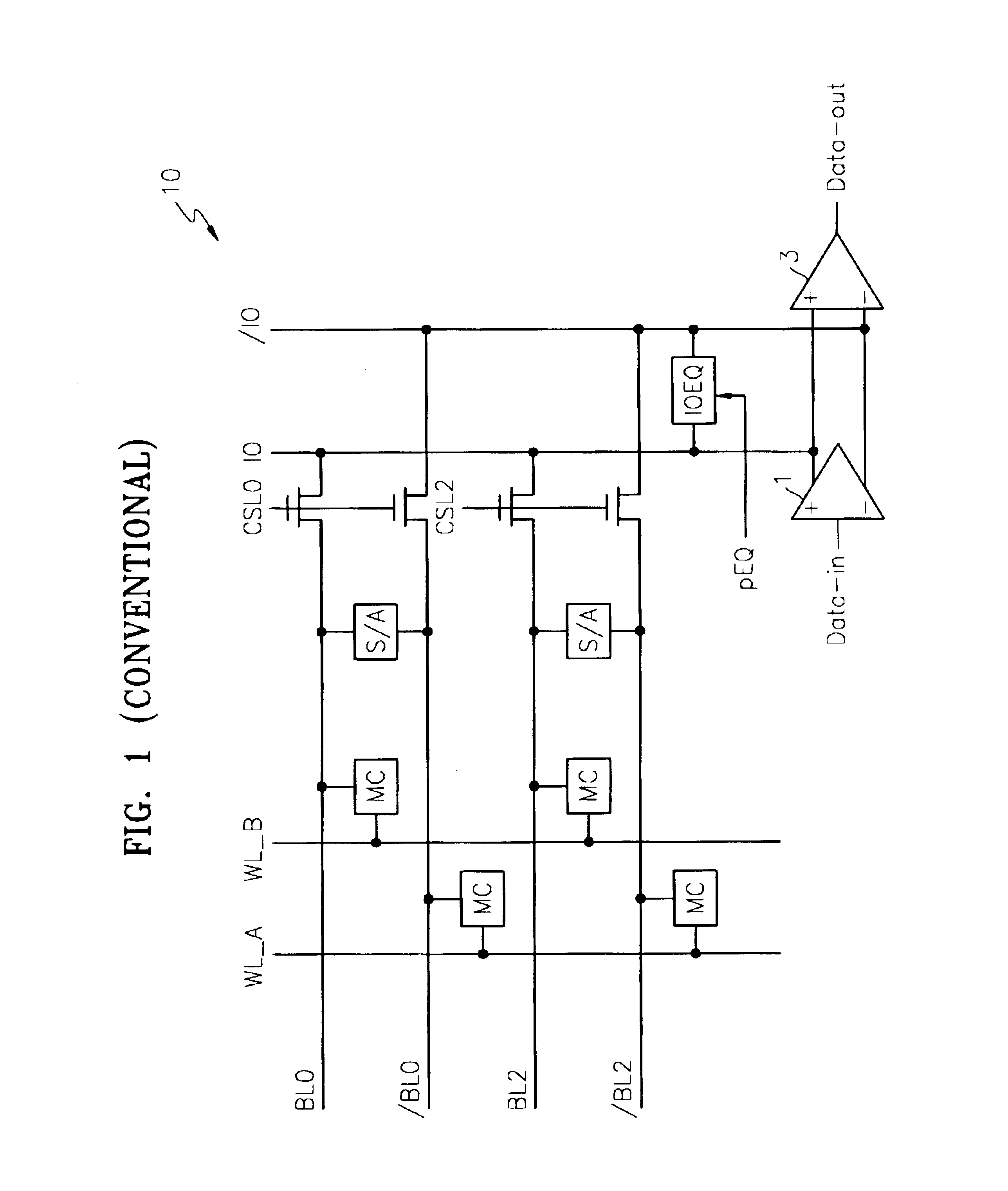

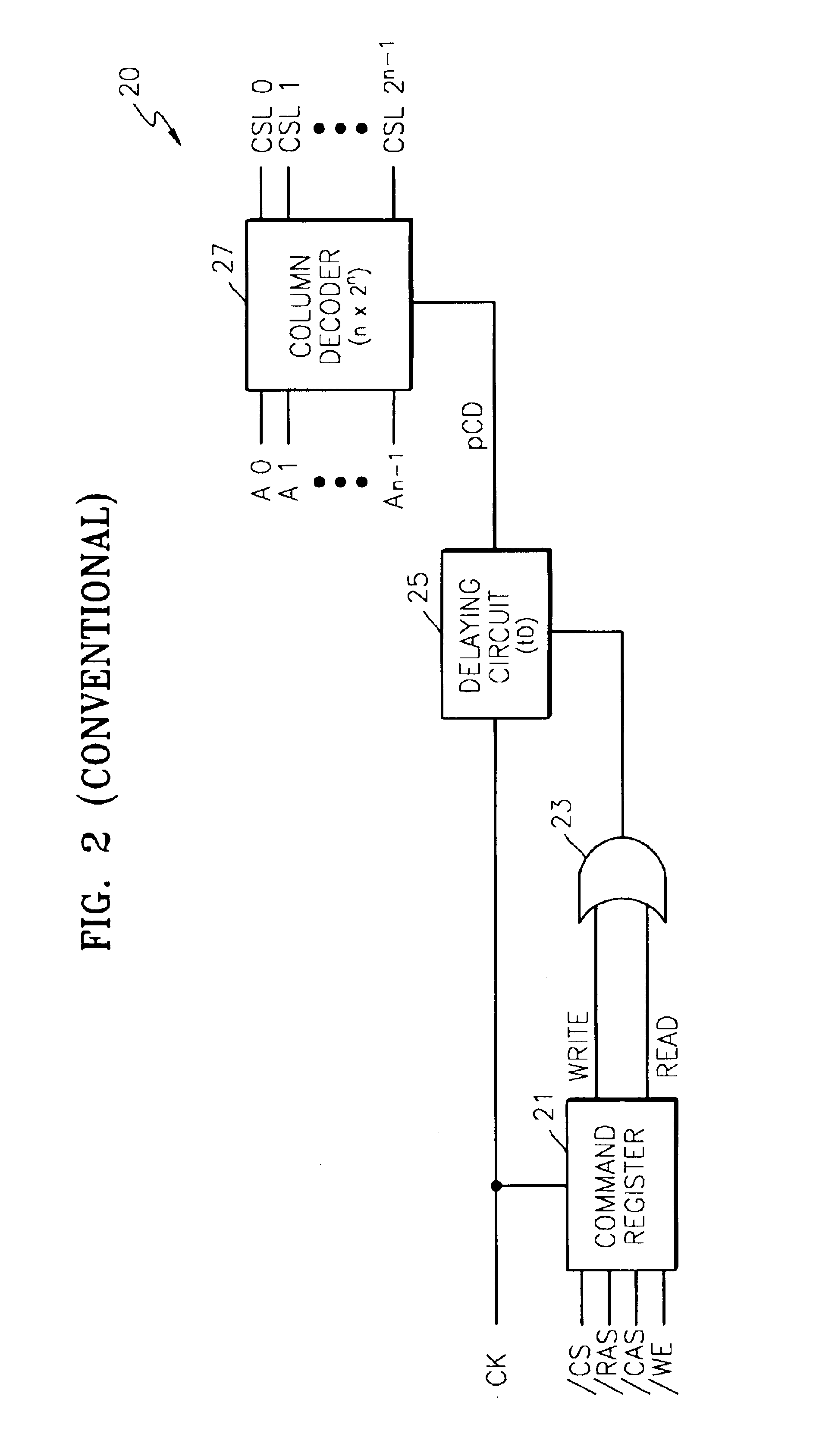

Method for controlling column decoder enable timing in synchronous semiconductor device and apparatus thereof

InactiveUS6839291B2Increase the maximum operating frequencyDigital storageControl signalDevice material

A method for controlling column decoder enable timing including determining if there is a gap between a data write command and a data read command which occur consecutively; generating a timing control signal for delaying received clock signal for an amount of time which depends on the determination result; and activating a column decoder in response to the timing control signal. Generating a timing control signal includes generating a timing control signal having a first delay time if there is a gap and generating a timing control signal having a second delay time if there is no gap, when the first delay time is shorter than the second delay time. An effect is an increase in the maximum operating frequency of a system for outputting data.

Owner:SAMSUNG ELECTRONICS CO LTD

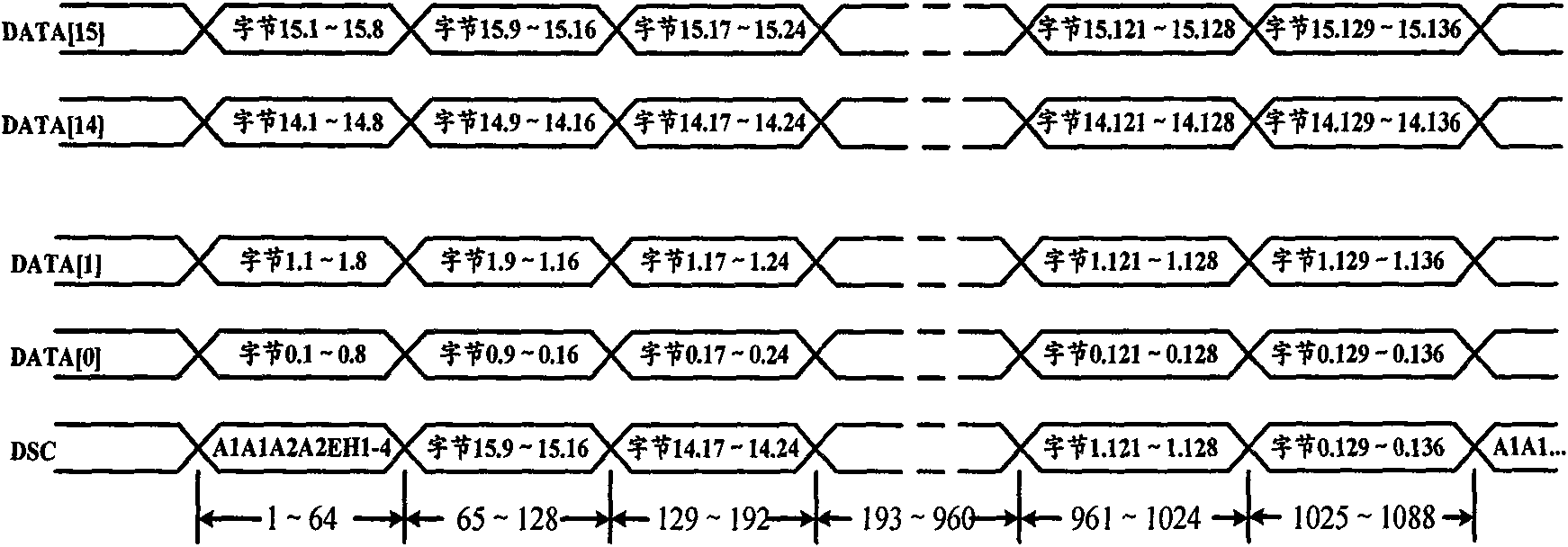

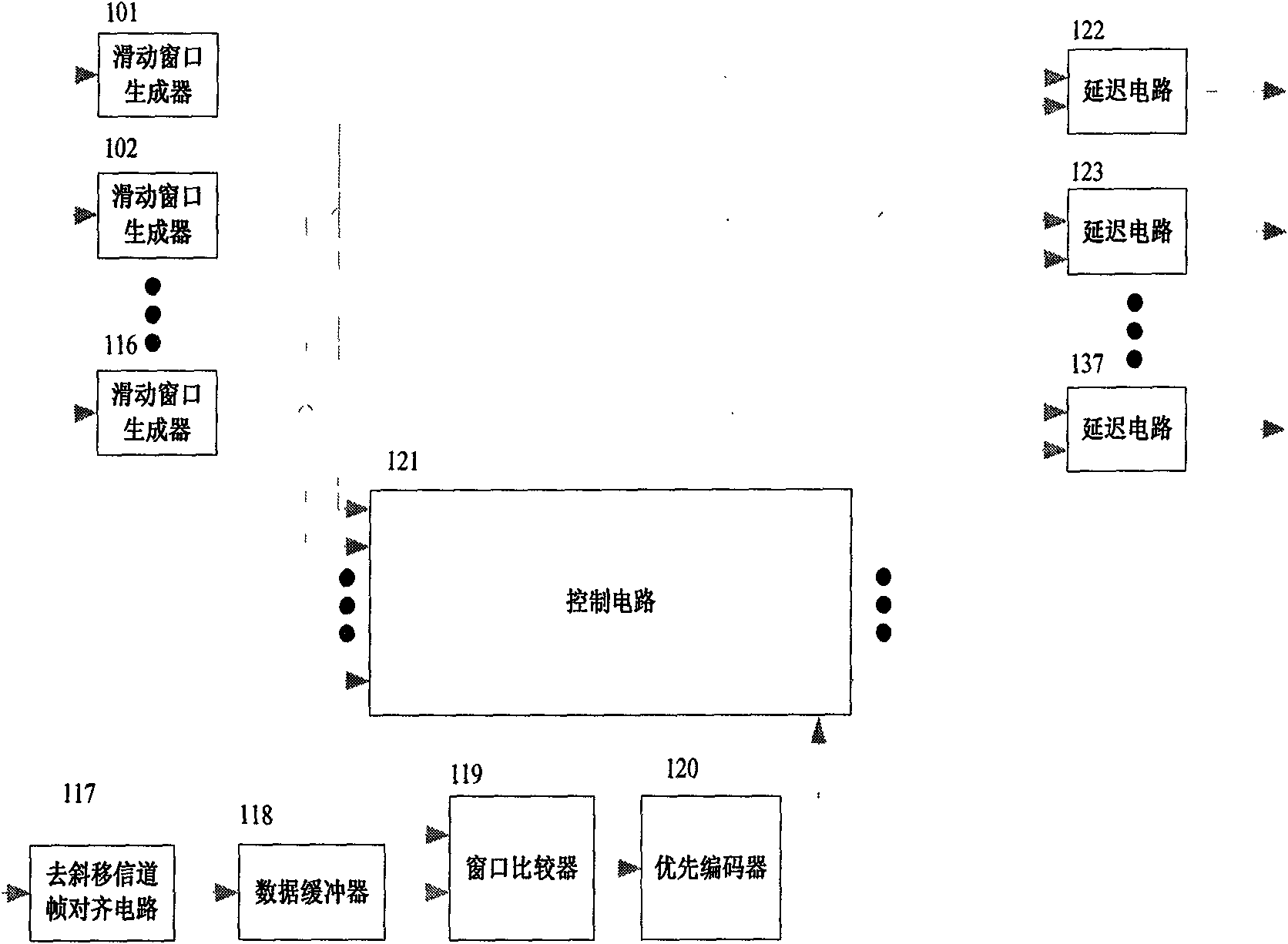

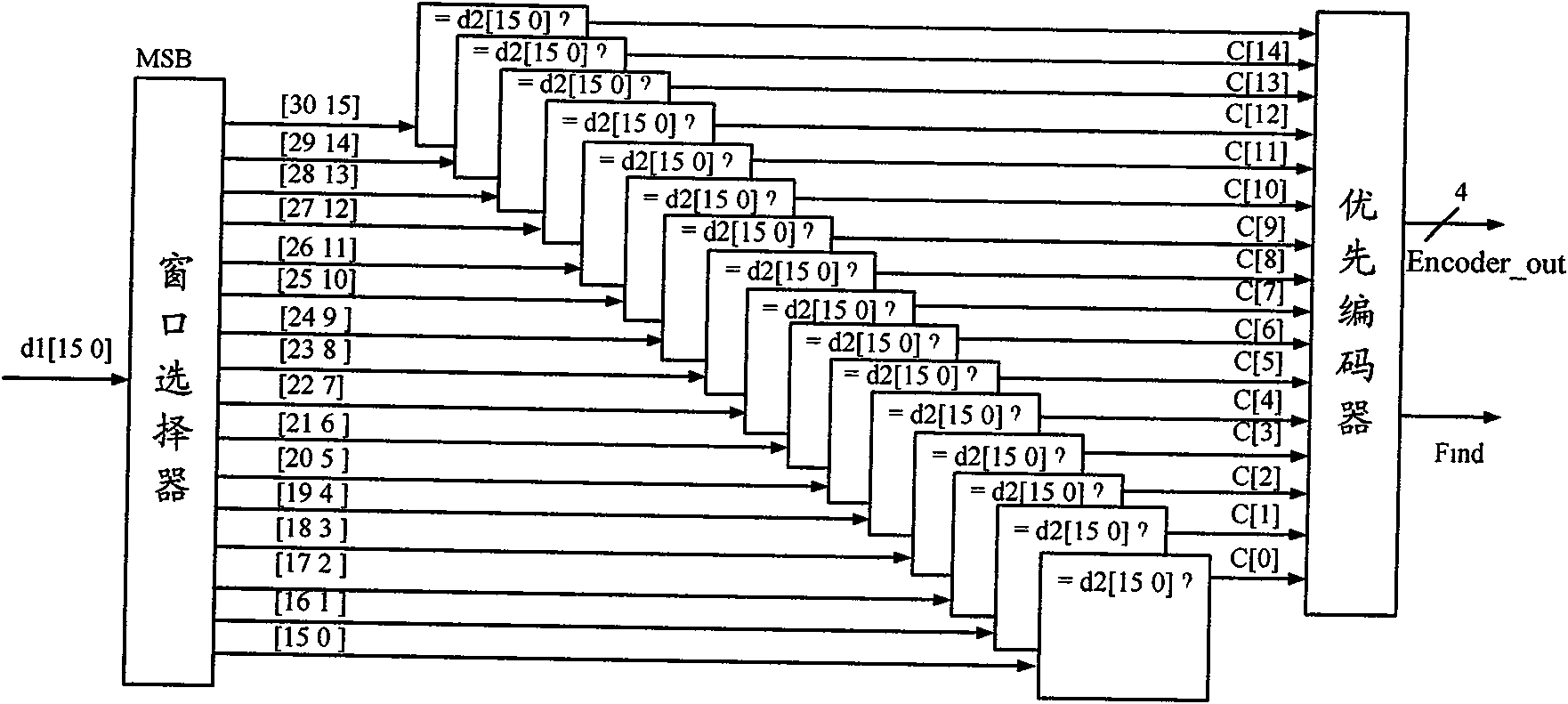

Deskew device and method applied to high-speed parallel optical interconnection system

InactiveCN101552766AIncrease the maximum operating frequencyReduced fan-outTransmissionLogic circuit coupling/interface arrangementsHome positionSlide window

The invention relates to a deskew device and method applied to a high-speed parallel optical interconnection system, which can be applied to a 40 Gbps very short distance optical transmission system. The frame alignment circuit of a deskew channel adopts a window comparator and a priority encoder, and determines the frame original position according to the search of frame delimiters, so as to realize the frame alignment. The data of each data channel is compared with the copy information of each data channel borne in the deskew channel after frame alignment so as to obtain the skewing amount of each data channel, and each data channel is aligned with the deskew channel, thereby achieving the alignment of 16 data channels. The fan-out of the circuit can be effectively reduced, the operating speed can be improved, and the device resource can be saved; moreover, a sliding window generator designed based on a shift register is matched with the window comparator to work, thereby being capable of adjusting the skewing amount among channels in wider range and improving the design flexibility and practicability.

Owner:SOUTHEAST UNIV

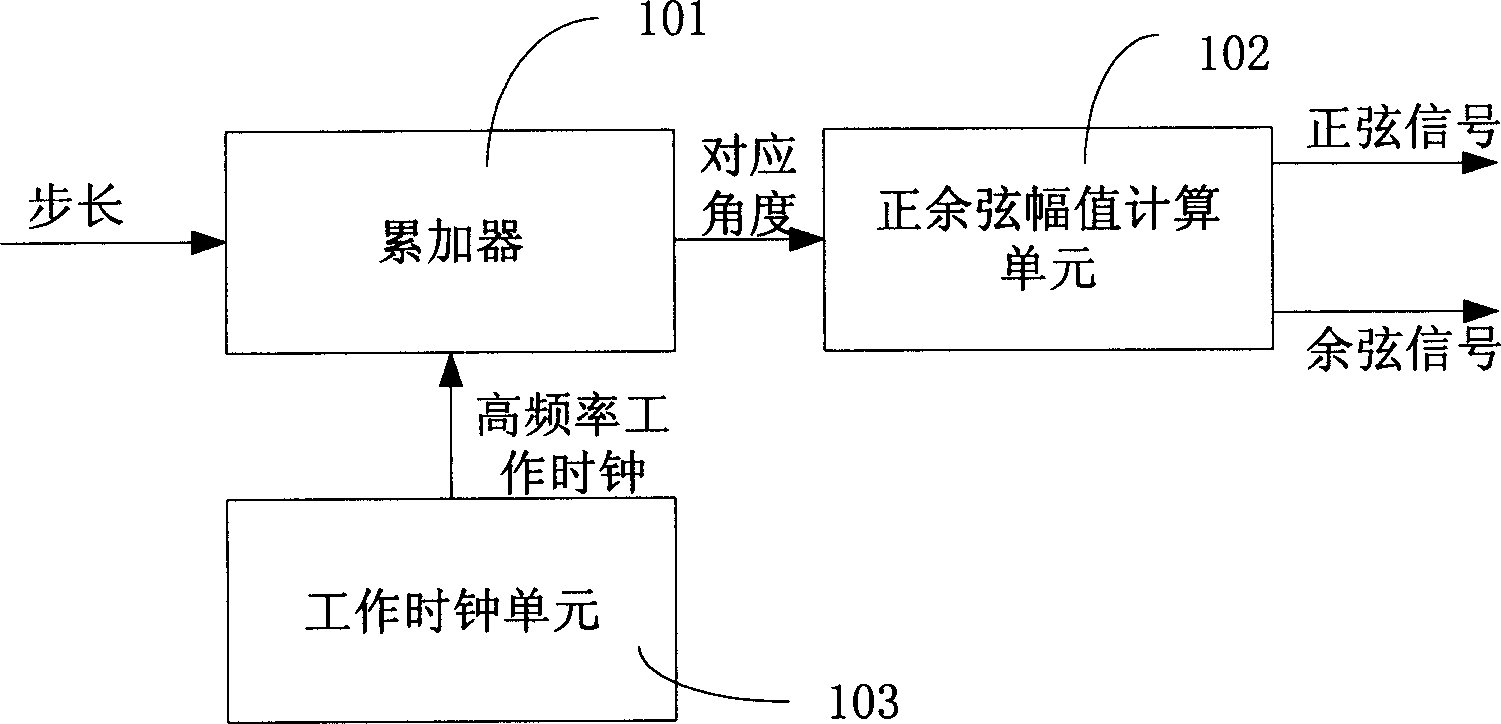

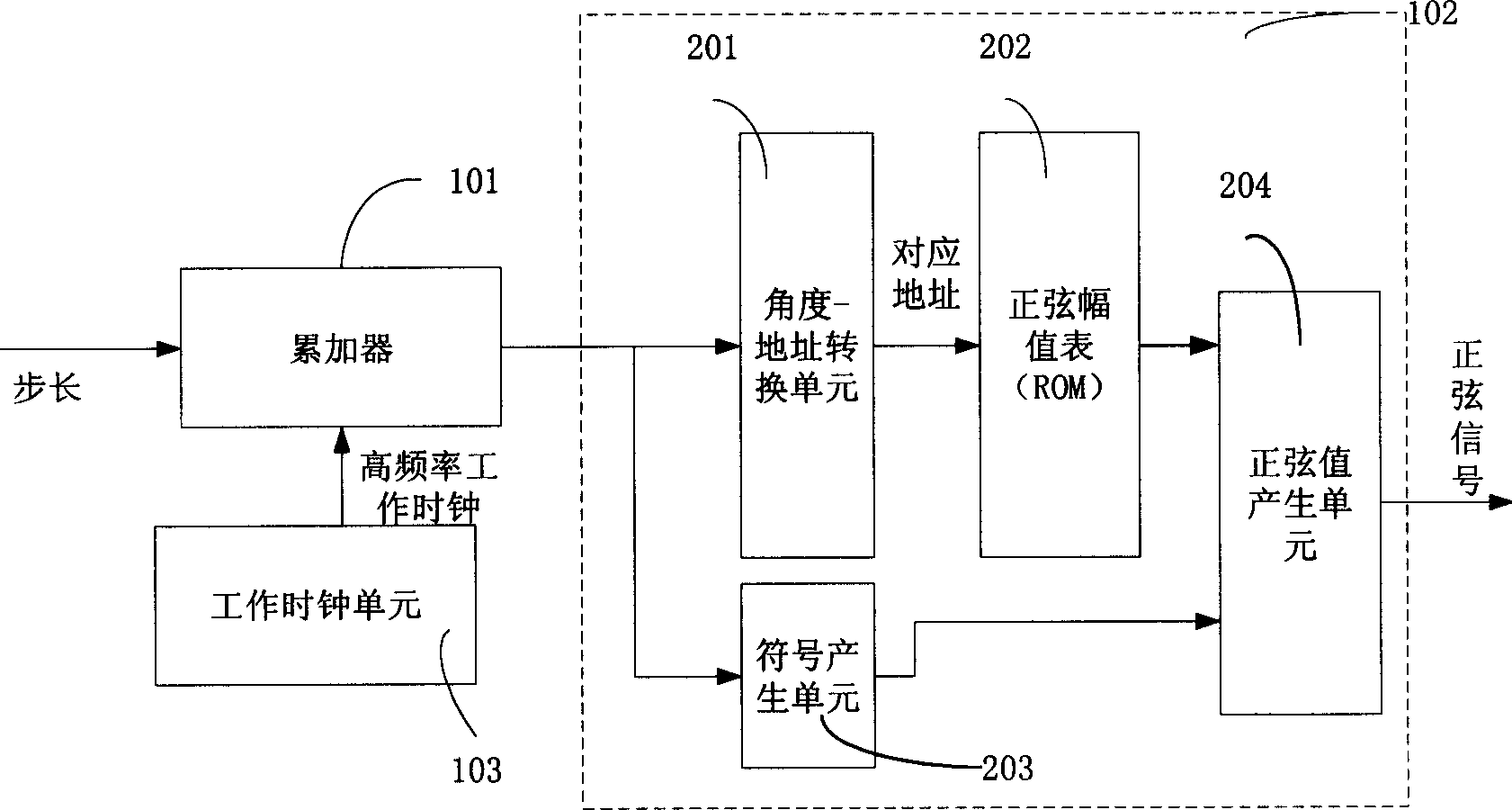

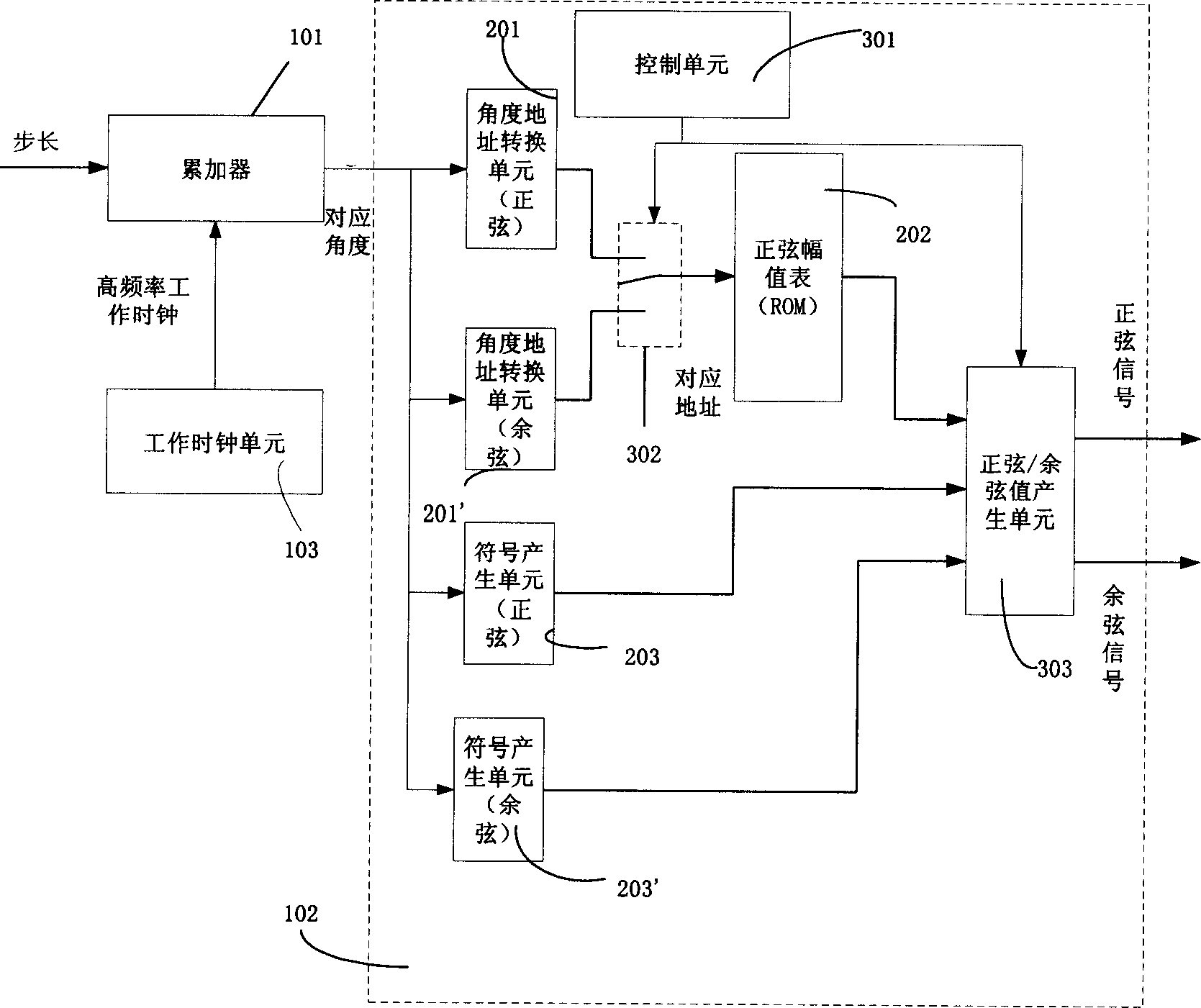

Numerically controlled vibrator and its sinusoidal and cosine signal generating method

InactiveCN1437316AIncrease the maximum operating frequencyIncrease working frequencyPulse automatic controlNumerically controlled oscillatorComputer science

The present invention is one numerically controlled vibrator and its sinusoidal and cosine signal generating method. Based on that within the first eighth period, both the sinusoidal function and thecosine function have their absolute values appearing once in the united image, one united amplitude table of sinusoidal function and cosine function in the first eighth period is constituted. Throughtable lookup to determine the sign and corresponding data of current function values, both the sinusoidal function and the consin function signal output is obtained. By means of increasing the width of the data in the table and decreasing looked-up address range in the table, the present invention can raise the vibration frequency of the digit controlled oscillator while maintaining the lower hardware cost of the digital controlled oscillator.

Owner:刘建 +3

Automatic test equipment capable of high speed test

ActiveUS7772828B2Increase the maximum operating frequencyVoltage/current isolationStatic storageElectricityAutomatic test equipment

Owner:SAMSUNG ELECTRONICS CO LTD

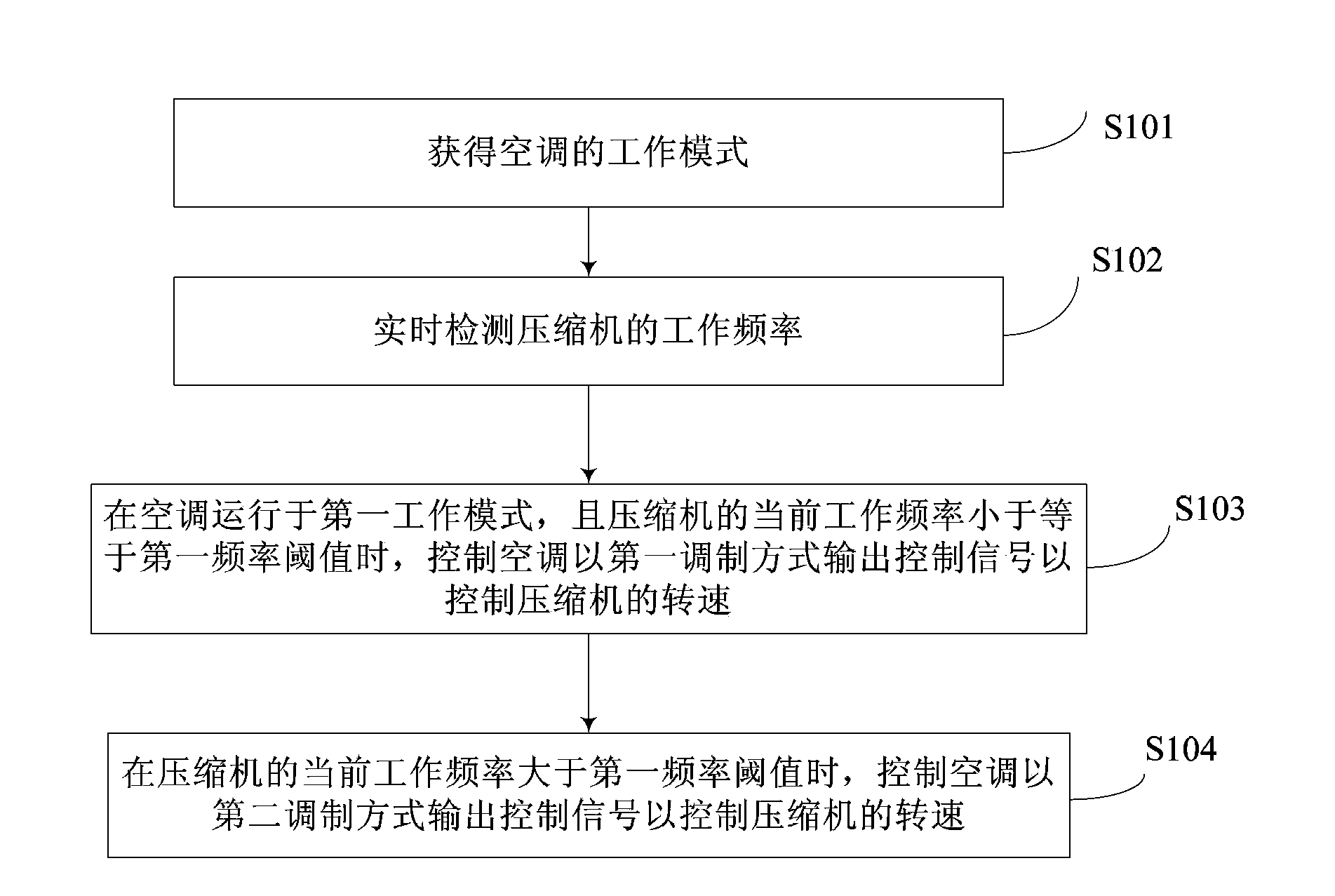

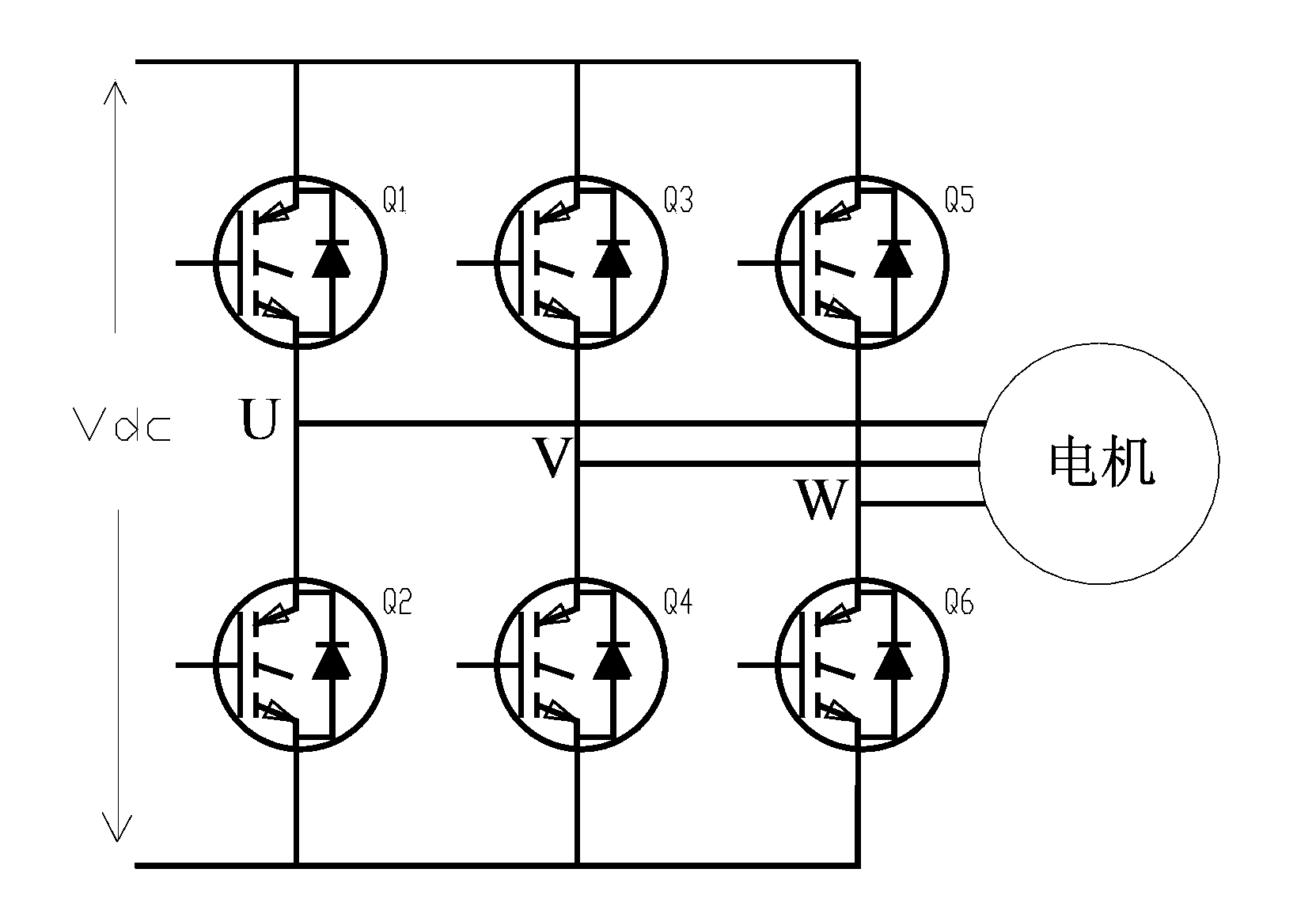

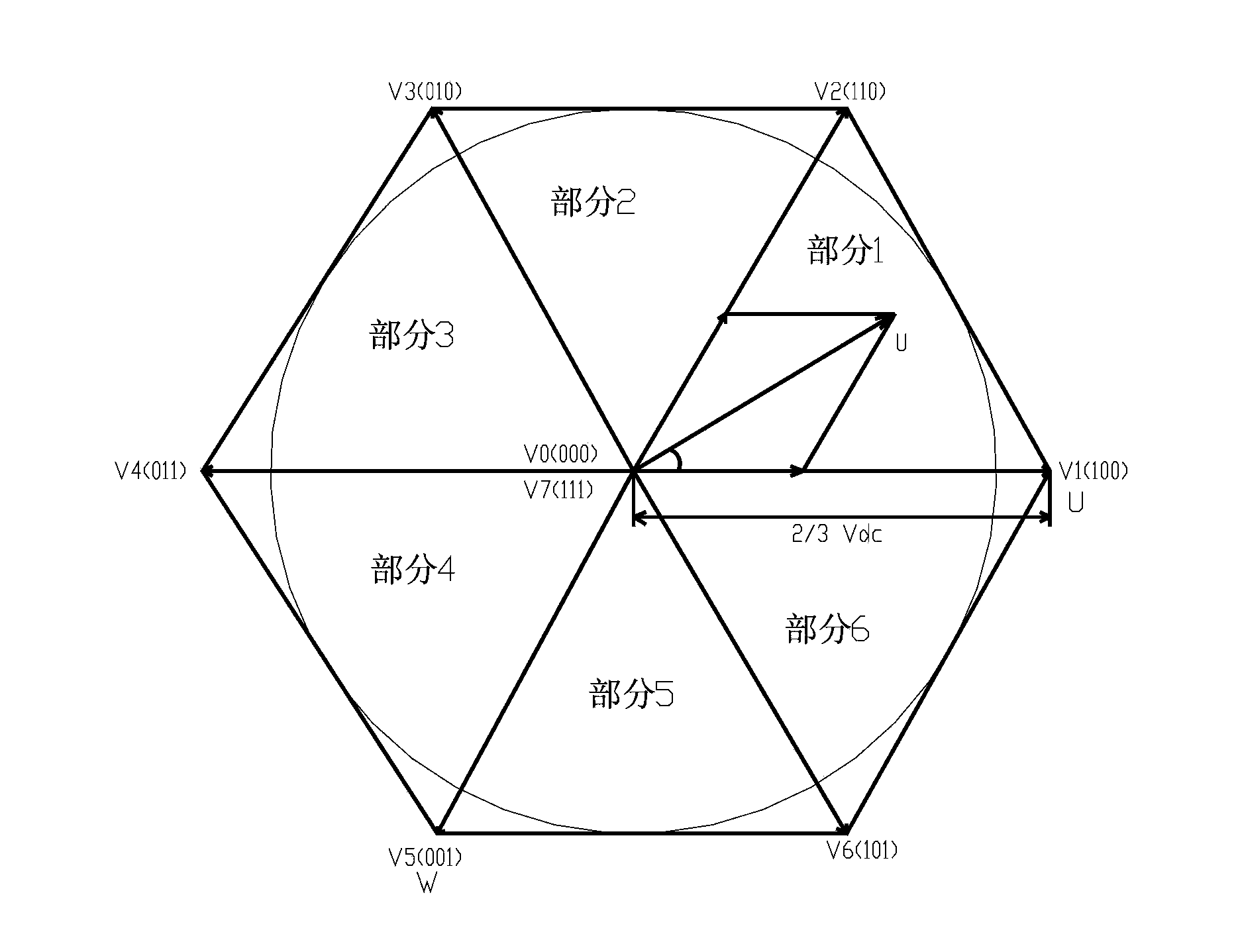

Control method and control device of air conditioner compressor

ActiveCN104121173AReduce operating frequencyIncrease the maximum operating frequencyPump controlPositive-displacement liquid enginesPower conditionerControl signal

The invention provides a control method and control device of an air conditioner compressor. The control method of the air conditioner compressor includes the following steps that work modes of an air conditioner are obtained, wherein the work modes include the first work mode and the second work mode; work frequency of the compressor is detected in real time; when the air conditioner operates in the first work mode and the current work frequency of the compressor is smaller than or equal to a first frequency threshold, the air conditioner is controlled to output a control signal in a first modulation mode to control rotation speed of the compressor; when the current work frequency of the compressor is larger than the first frequency threshold, the air conditioner is controlled to output a control signal in a second modulation mode to control rotation speed of the compressor. By means of the control method and control device of the air conditioner compressor, stability of the air conditioner operating at low frequency can be improved, operation frequency of the air conditioner compressor can be lowered to the largest extent, energy consumption is lowered, the largest operation frequency of the air conditioner compressor can be improved, and meanwhile temperature of a power device is controlled to the in a preset range.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD +1

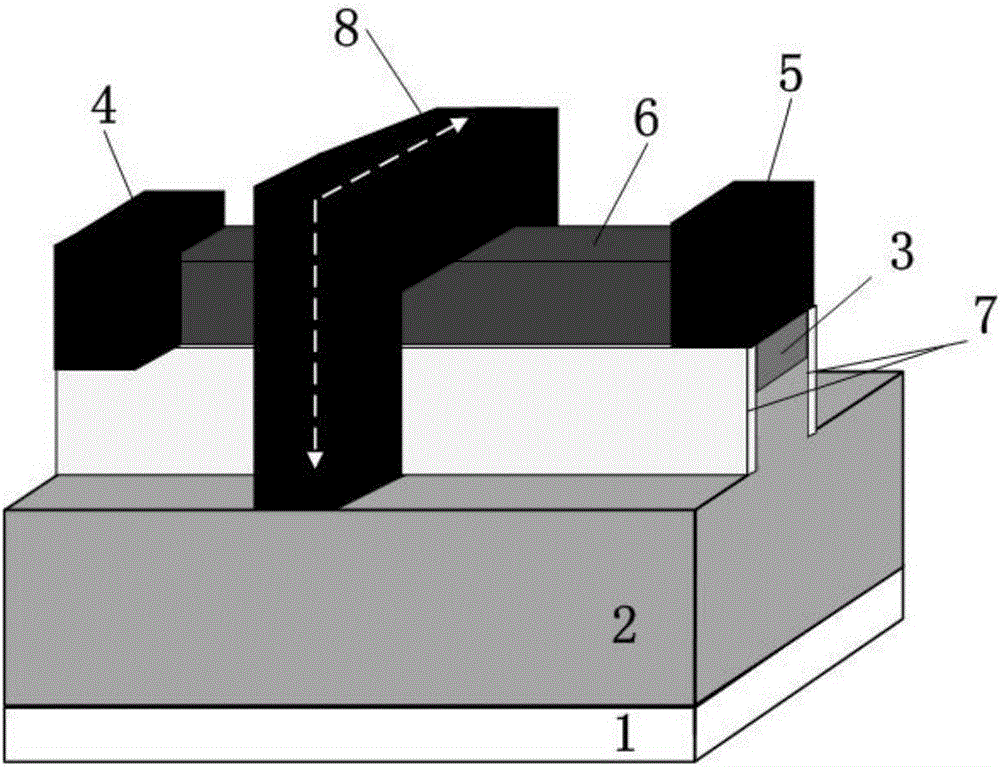

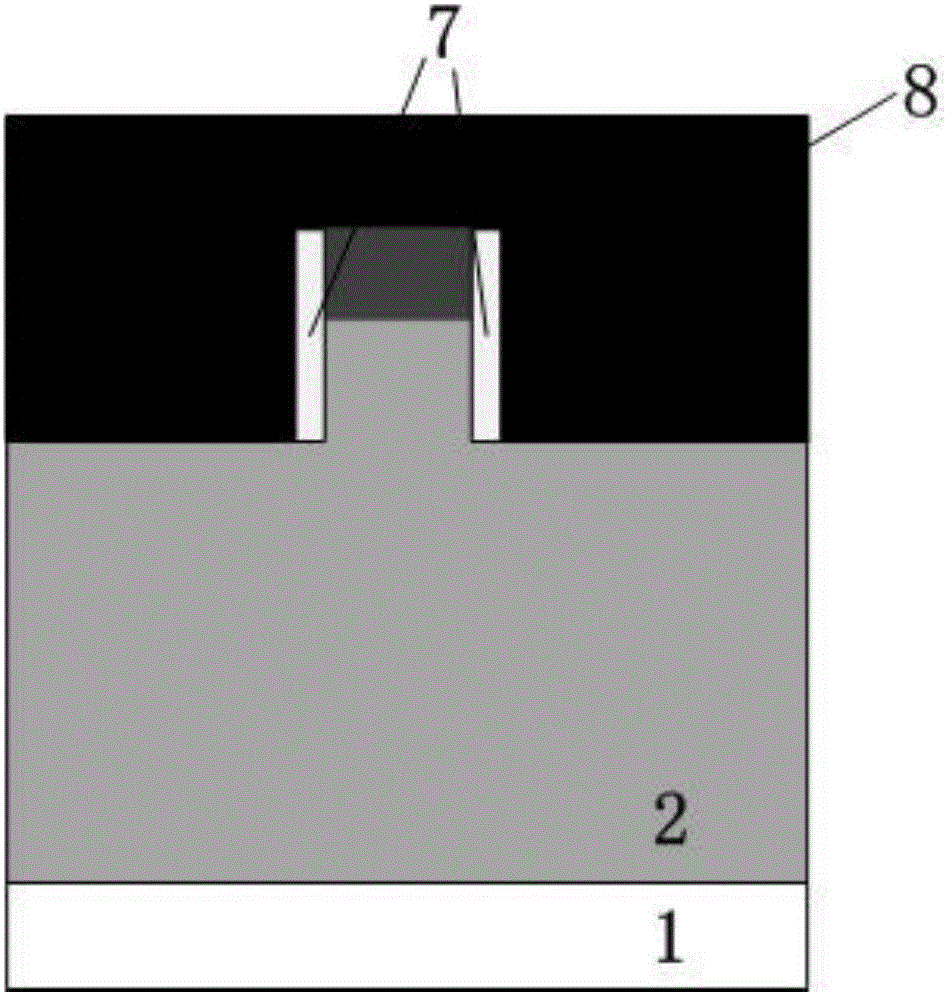

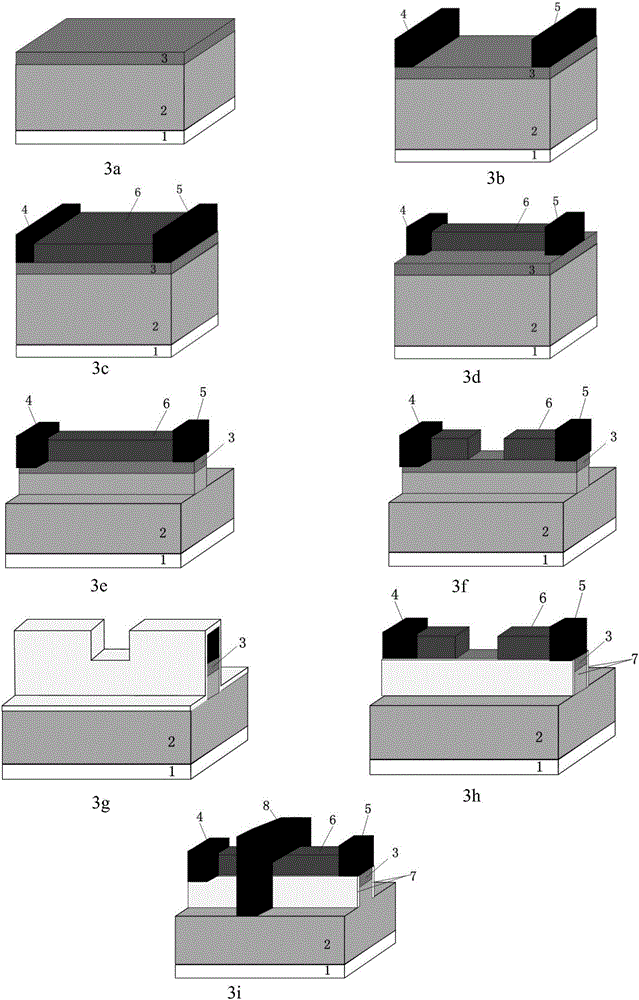

GaN side wall insulated gate fin-type high-electron mobility transistor and manufacturing method thereof

InactiveCN106684151ASuppress leakageReduce parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesMicrowave powerEngineering

The invention relates to a GaN side wall insulated gate fin-type high-electron mobility transistor and manufacturing method thereof. A transistor structure of the invention orderly comprises a substrate, a buffer layer, a barrier layer and a passivation layer from bottom to top; a source electrode is arranged at one end above the barrier layer, and a drain electrode is arranged at another end above the barrier layer; the passivation layer is arranged above the barrier layer between the source electrode and the drain electrode; and a groove is formed in the passivation layer; the high-electron mobility transistor is characterized by further comprising a GaN based three-dimensional fin and a gate electrode, and an insulating medium is arranged on a side wall of the GaN based three-dimensional fin; a part of the gate electrode is covered on the barrier layer in the groove to form the Schottky contact; another part of the gate electrode is covered on the insulating medium on the side wall of the GaN based three-dimensional fin to form an insulated gate structure. The GaN based three-dimensional fin type device has the advantages of being small in gate electric leakage, high in output current, good in gate-control capacity and high in frequency characteristics, and can be used for a large-power microwave power device.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

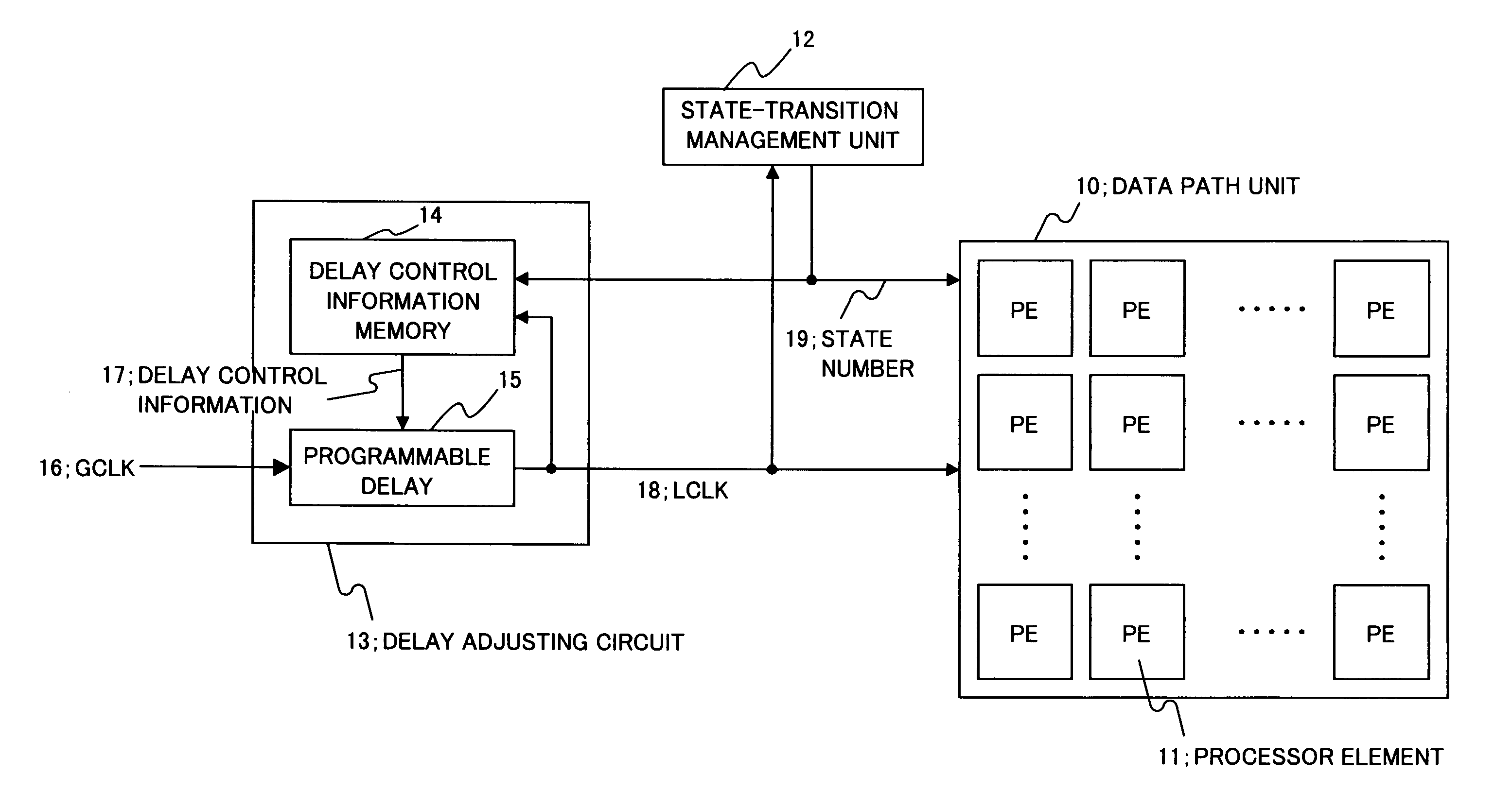

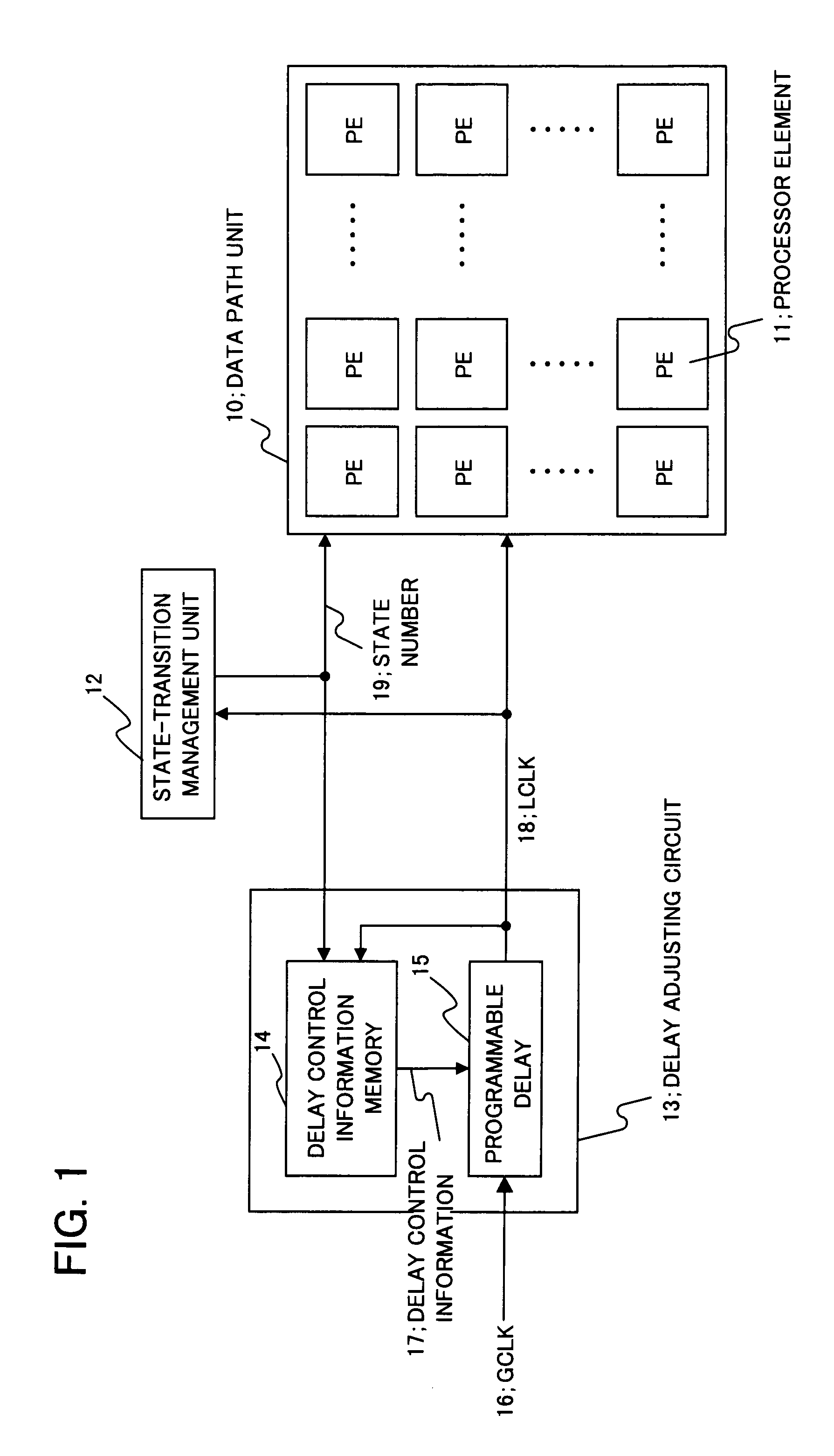

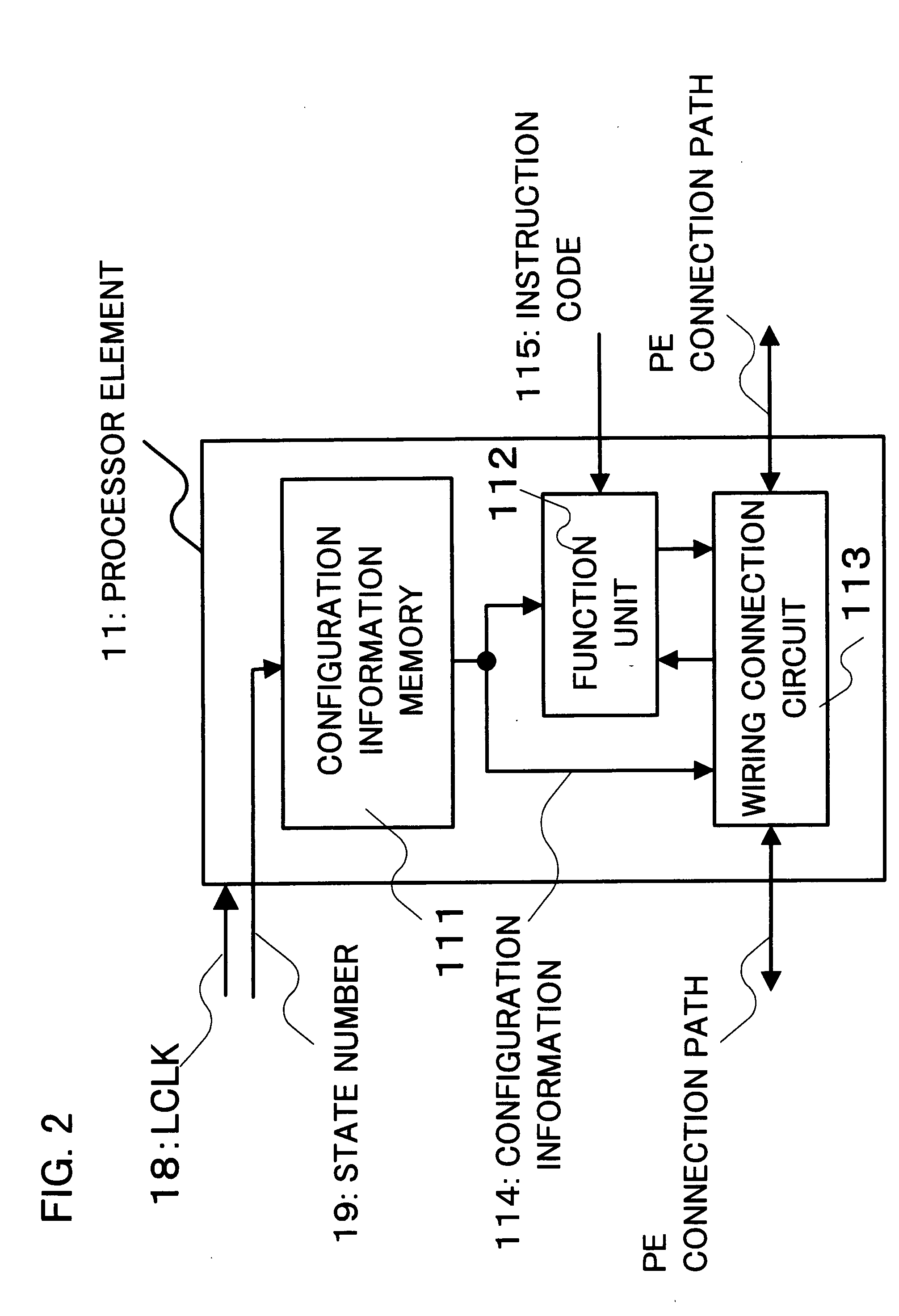

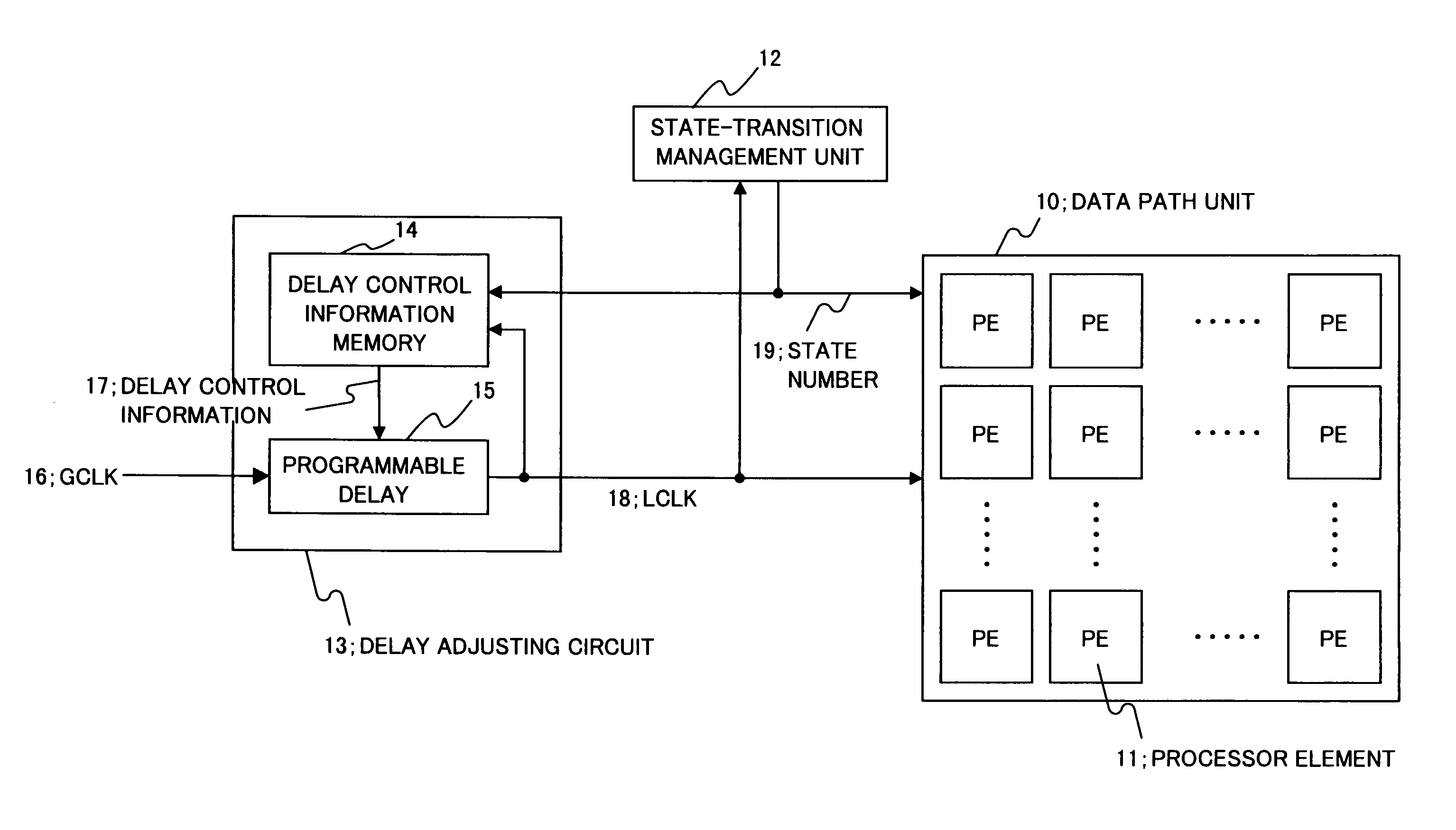

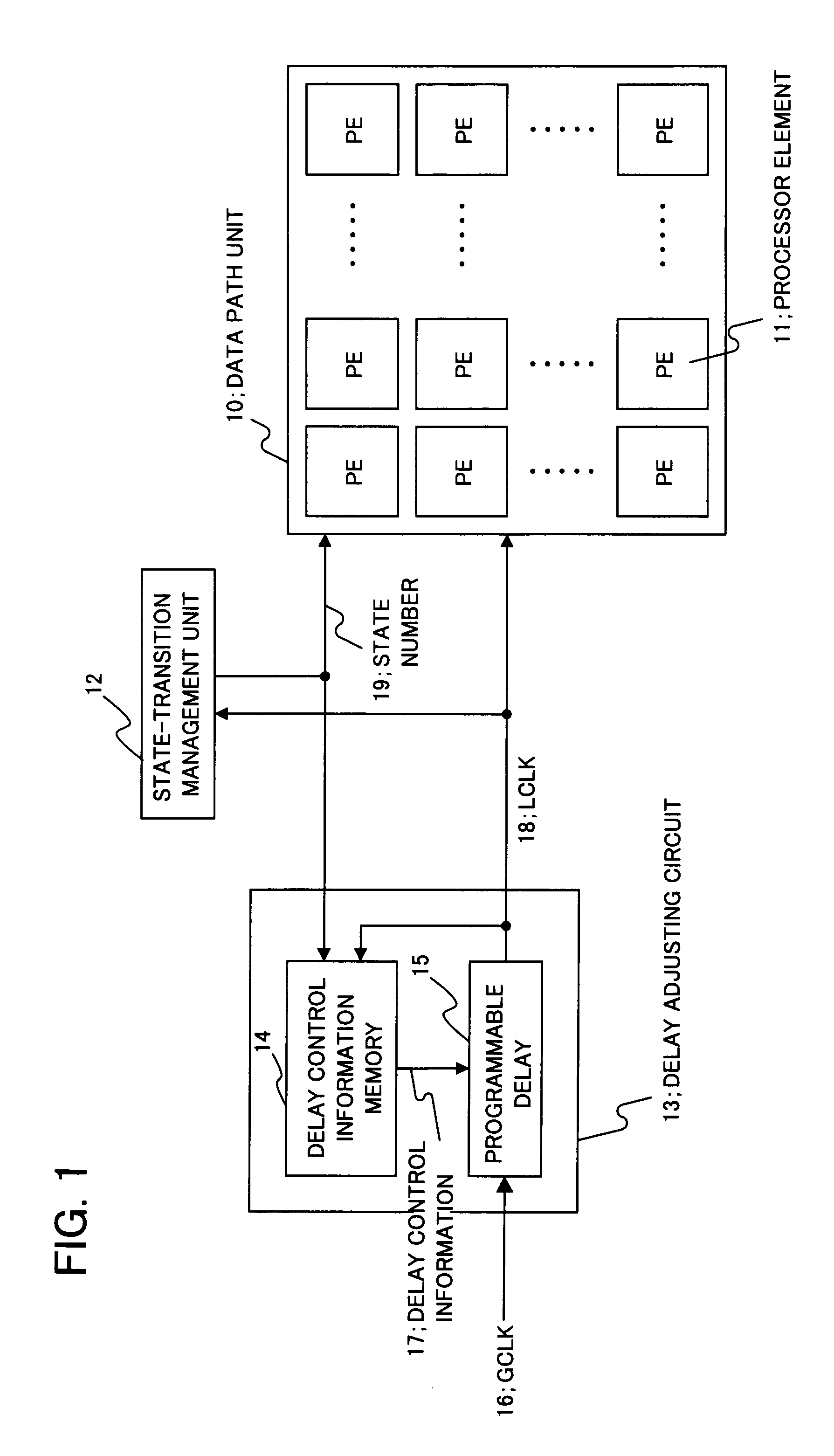

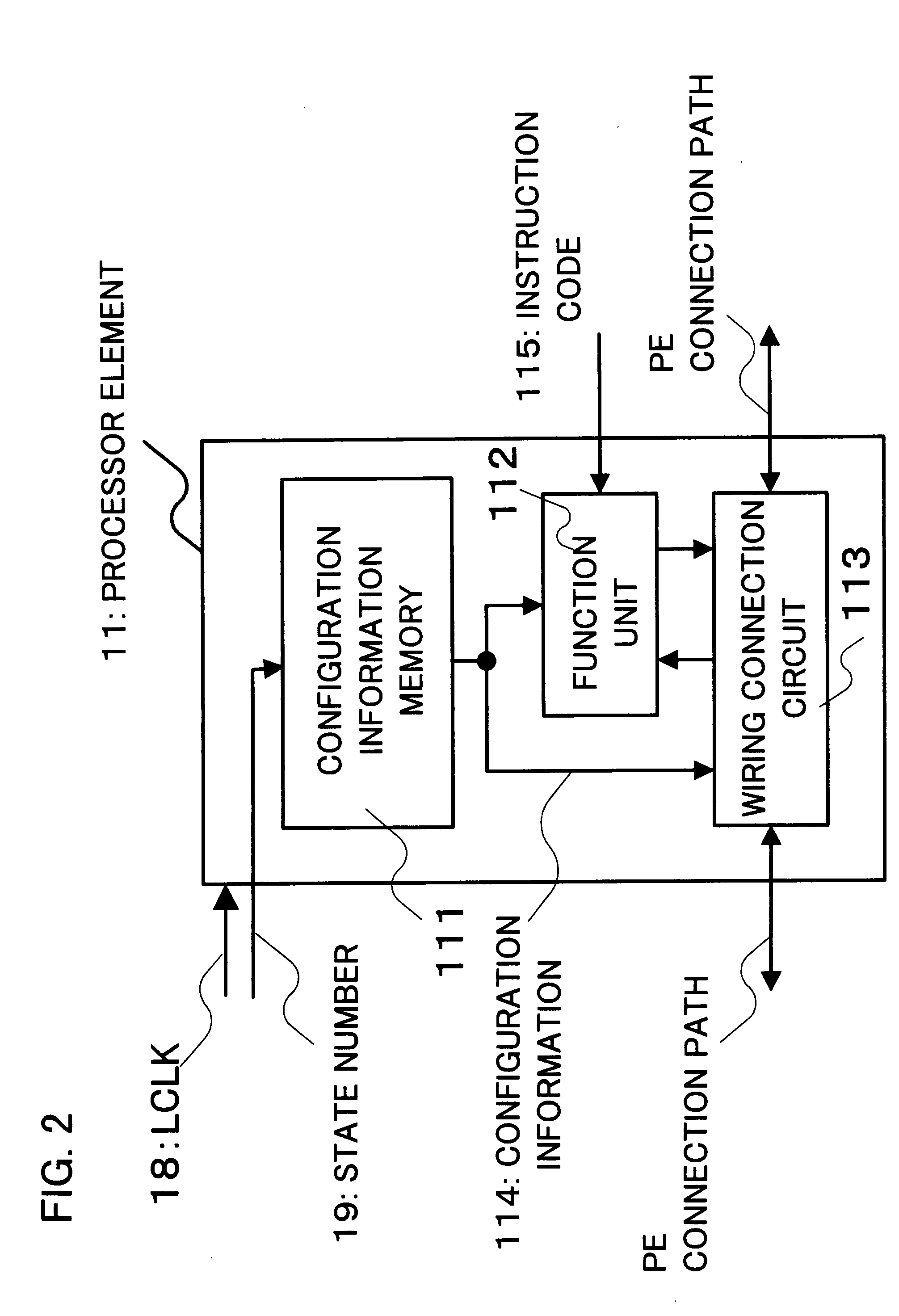

Array-type processor having delay adjusting circuit

ActiveUS20080201526A1Operation efficiency can be improvedDifficult to adjustDigital computer detailsGenerating/distributing signalsProcessor elementManagement unit

Disclosed is an array-type processor including a data path unit in which a plurality of processor elements are arranged in an array; a state-transition management unit that stores information for controlling changeover of data paths; and a delay adjusting circuit that adjusts delay of the input clock signal based upon information output from the state-transition management unit, and provides the delay-adjusted clock signal to the data path unit. The delay adjusting circuit has a delay control information memory and a programmable delay. The delay control information memory stores a plurality of items of delay control information, delay control information is read out using a configuration number supplied from the state-transition management unit as an address, and the delay control information is applied to the programmable array. The programmable delay delays the input clock signal by a delay time specified by the delay control information and provides the delayed clock signal to the data path unit.

Owner:RENESAS ELECTRONICS CORP

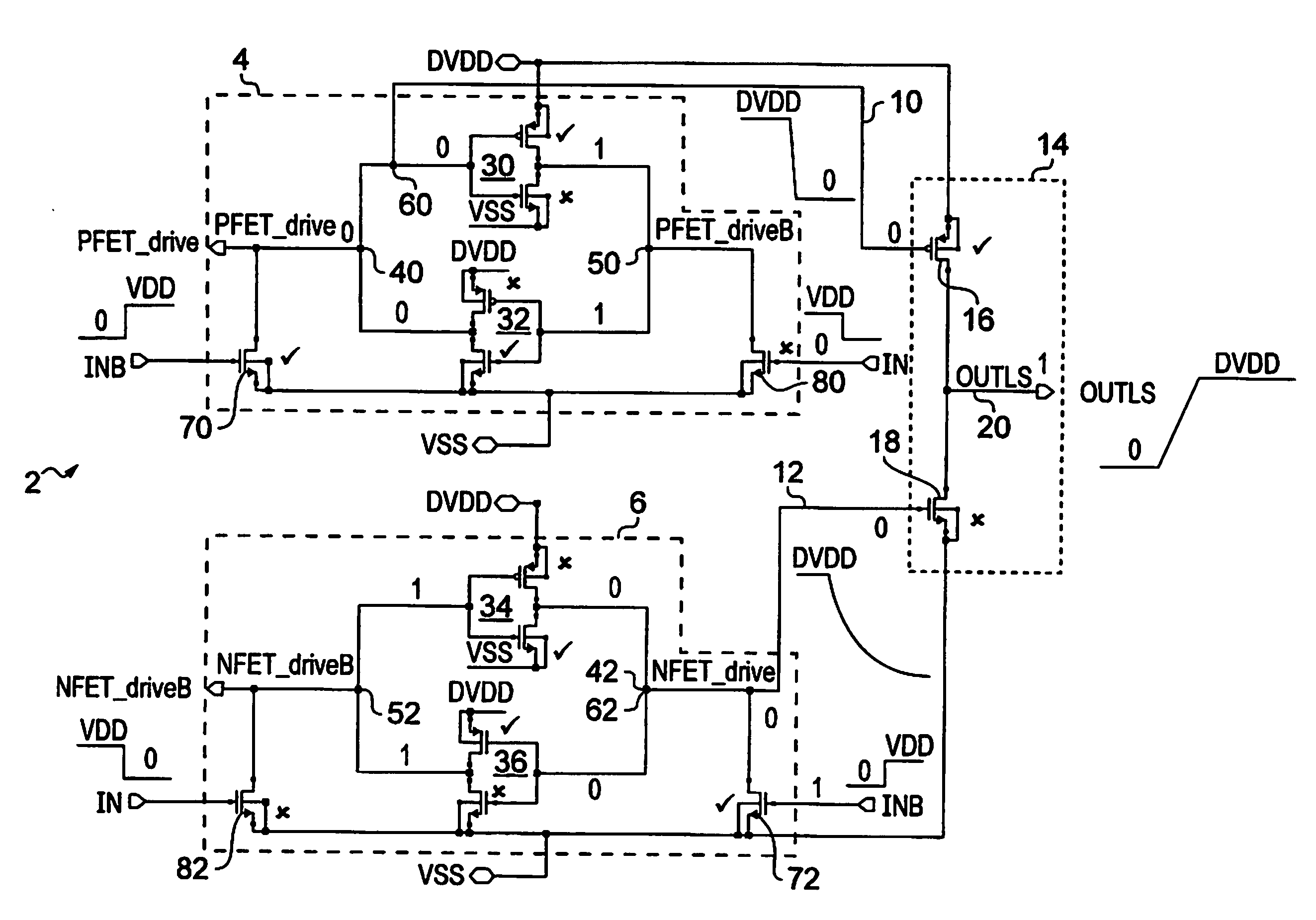

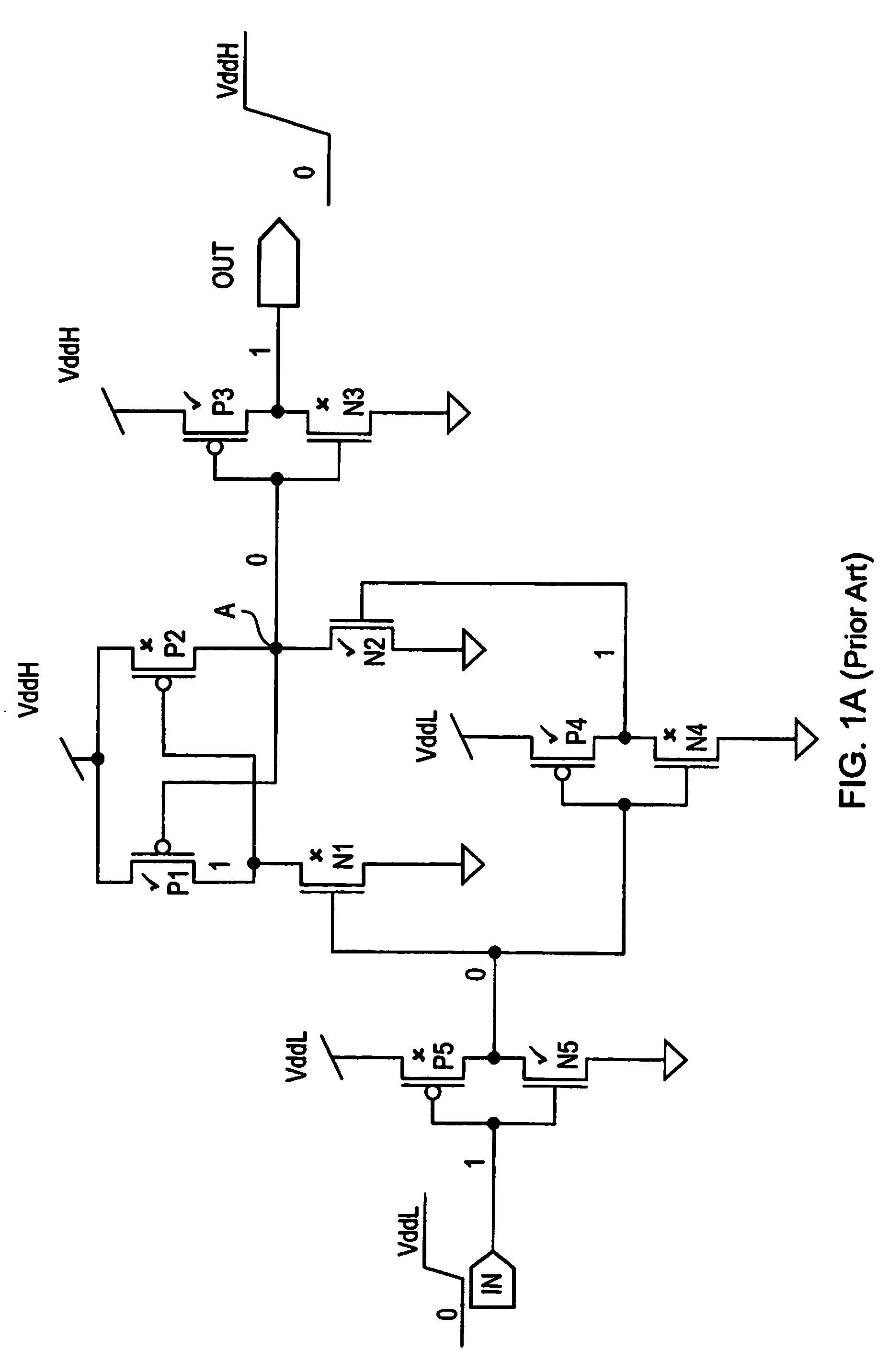

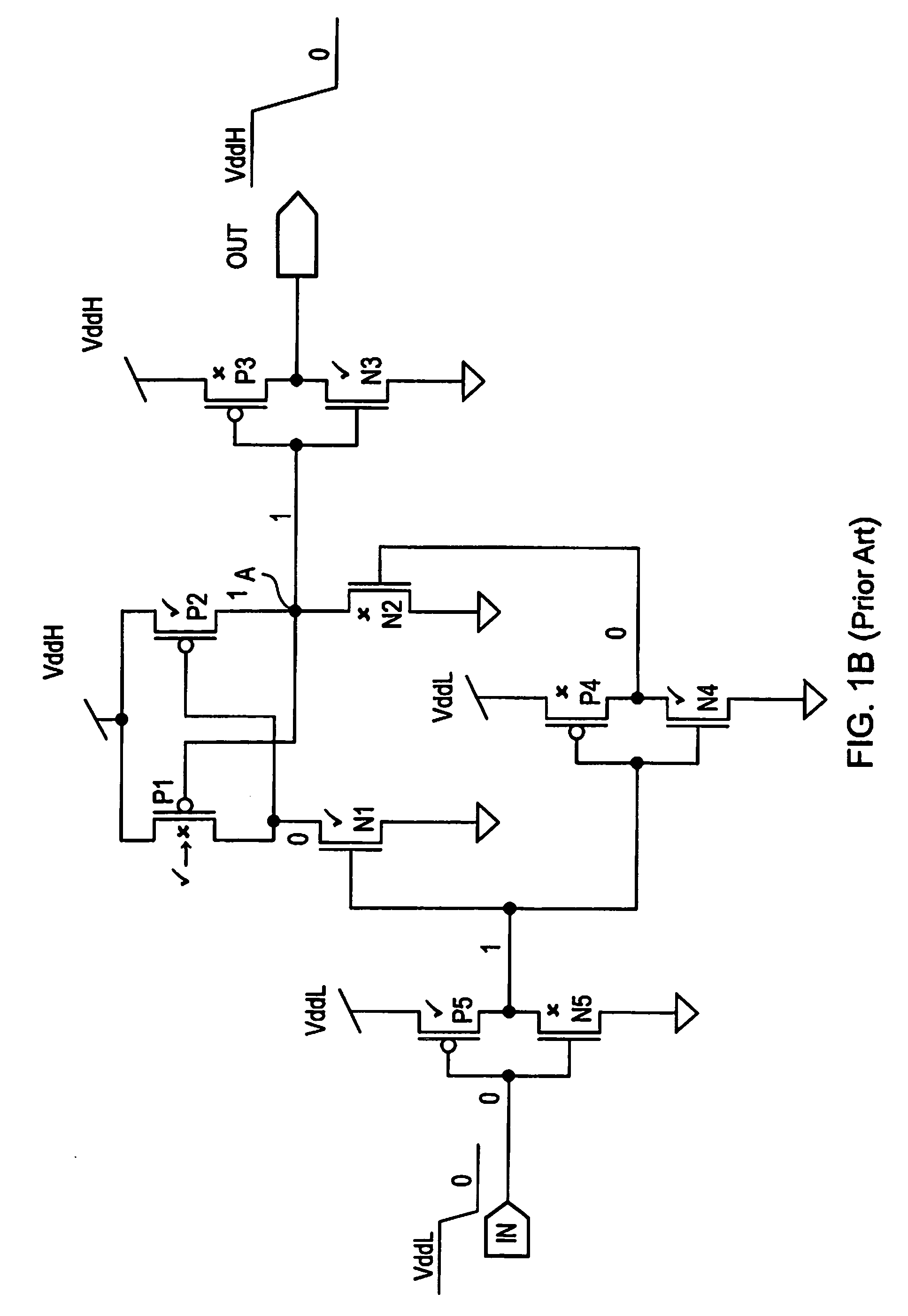

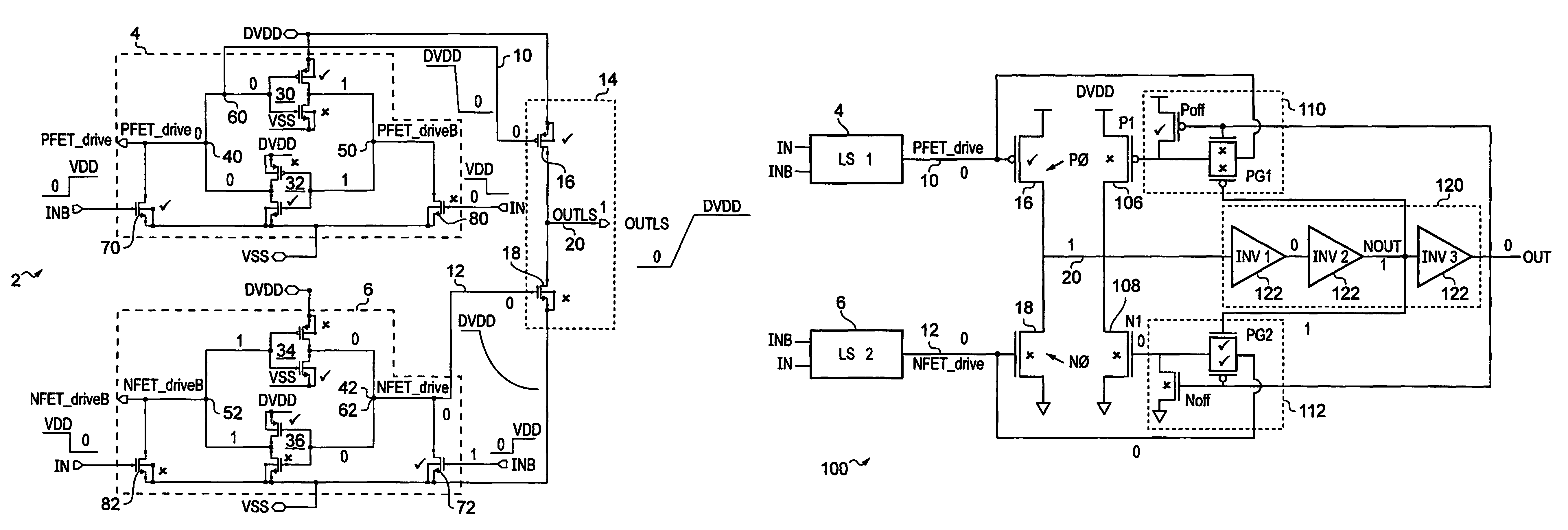

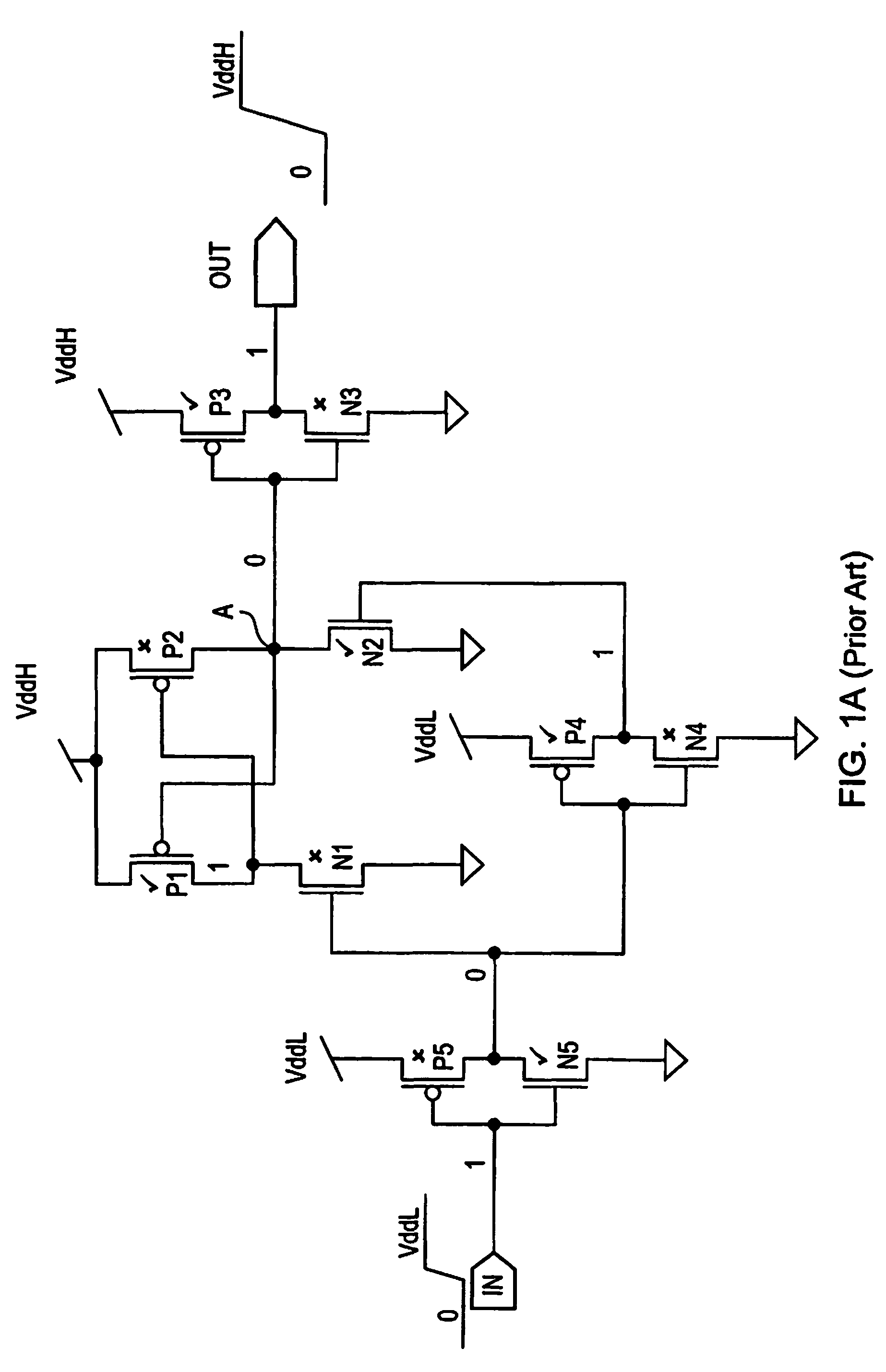

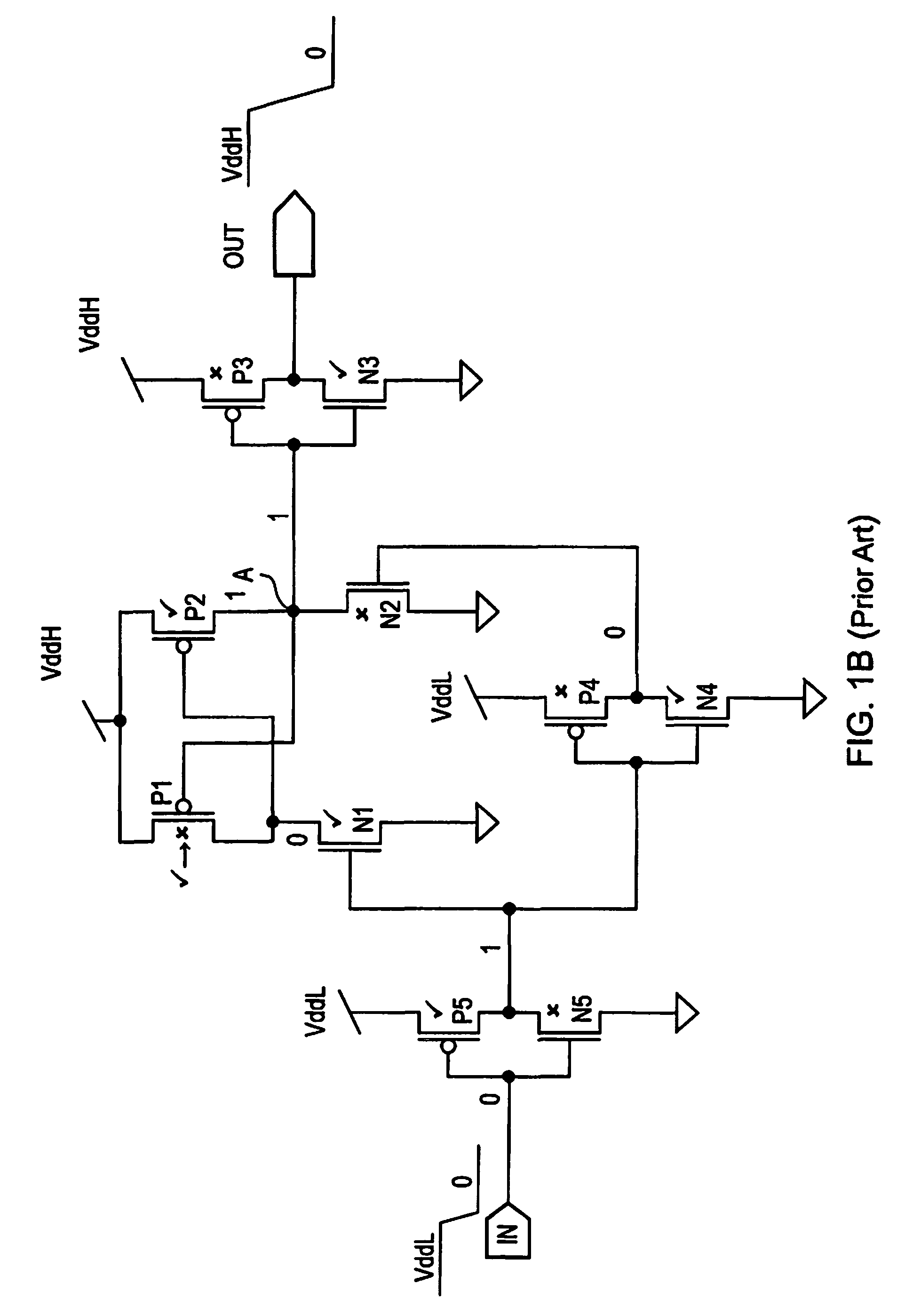

Level shifting circuitry

ActiveUS20120299631A1High frequencyQuick transitionPulse automatic controlElectric pulse generatorLevel shiftingLow voltage

Level shifting circuitry comprises a first level shifter and a second level shifter. In response to a falling edge transition of an input signal, the first level shifter generates a primary transition of a first intermediate signal faster than the second level shifter generates a secondary transition of a second intermediate signal. In response to a rising edge of the input signal, the second level shifter generates a primary transition of the second intermediate signal faster than the first level shifter generates a secondary transition of the first intermediate signal. Output switching circuitry is provided to switch an output signal between an output high voltage level and an output low voltage level in response to the primary transition of the first intermediate signal and the primary transition of the second intermediate signal.

Owner:ARM LTD

Switching system for electrical impedance tomography

ActiveCN102707695AOvercoming crosstalkOvercoming distortionDiagnostic recording/measuringSensorsElectrical resistance and conductanceData acquisition

The invention discloses a switching system for electrical impedance tomography (EIT). The switching system comprises a flexible flat cable pin-shaped socket, a D-SUB connector, four shape memory alloy (SMA) connectors, four groups of decoding circuits, four groups of electric control switch circuits and a shielding driving circuit, wherein the shielding driving circuit is connected with the D-SUB connector through a shielding signal connecting wire; the input ends of the four groups of electric control switch circuits are connected with the D-SUB connector through an internal connecting bus respectively; the input end of each group of decoding circuit is connected with the output end of a group of electric control switch circuit respectively; the output ends of the four groups of decoding circuits are connected to the same flexible flat cable pin-shaped socket; and each SMA connector is connected to a group of electric control switch circuit. The switching system is ingenious in concept; the switching system of the conventional EIT system forms a subsystem independent from a data acquisition system, so that an electrode distribution parameter is reduced; and due to the adoption of novel switches and a shielding driving technology, the whole EIT system has the advantages of high imaging accuracy, high imaging speed, long service life, wide working frequency range and the like.

Owner:SEALAND TECH CHENGDU

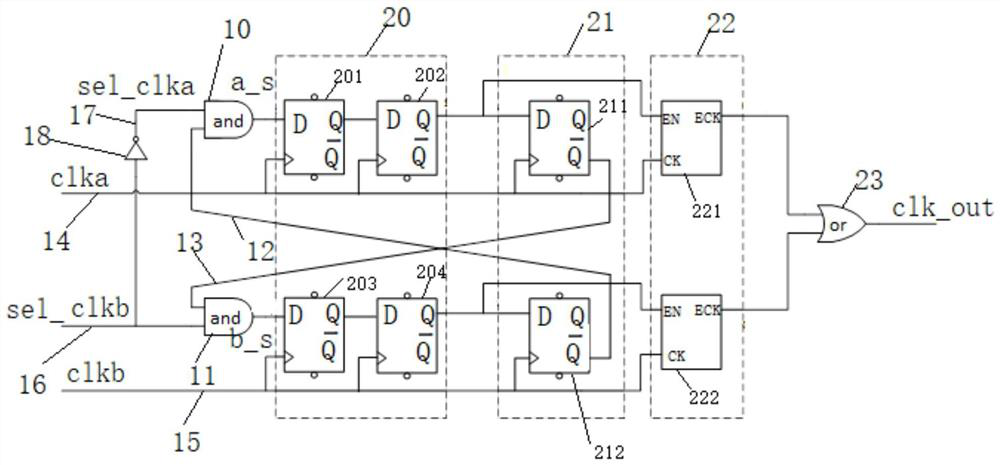

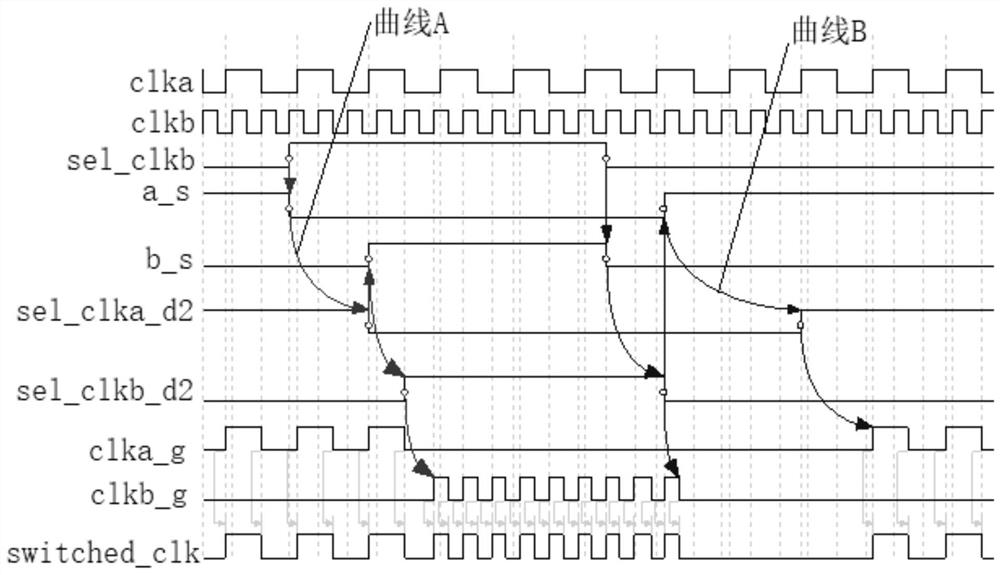

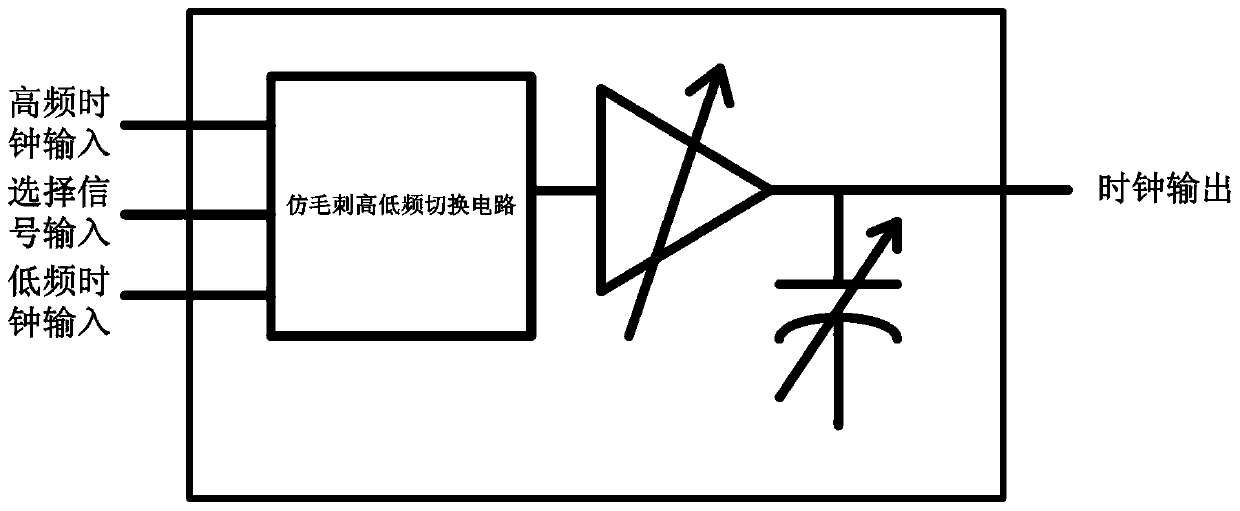

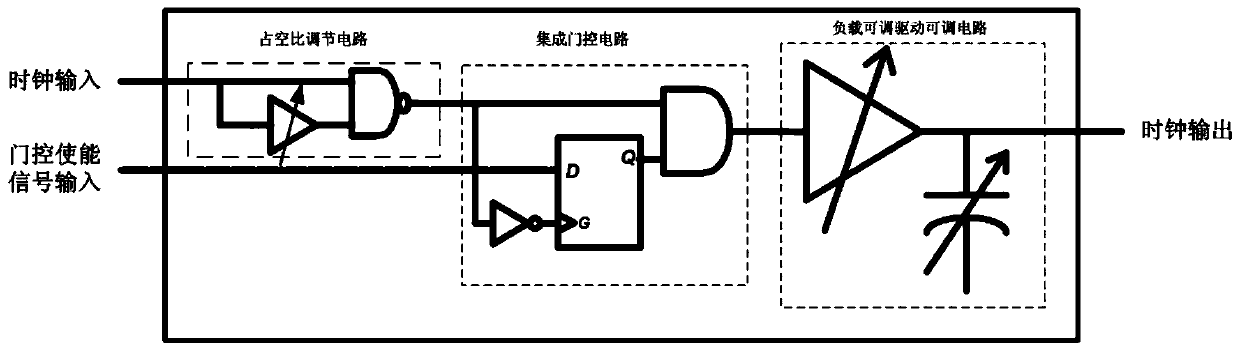

Clock dynamic switching circuit

PendingCN112130617AIncrease the maximum operating frequencyGenerating/distributing signalsPulse manipulationComputer architectureHemt circuits

The invention relates to the technical field of circuit design, in particular to a clock dynamic switching circuit. The circuit comprises a first AND gate, a second AND gate, a first clock enable signal line, a second clock enable signal line, a first feedback signal line, a second feedback signal line, a first clock signal line, a second clock signal line, a level synchronization circuit, a clockgating circuit and an OR gate circuit. The level synchronization circuit is used for synchronizing the first clock enable signal line and a first clock signal and synchronizing the second clock enable signal line and a second clock signal, and the clock gating circuit is used for controlling on-off of the clock signals. According to the circuit, the positive edge of the clock is used for triggering all devices in the circuit, a half-cycle path does not exist any more, the highest operation frequency of the circuit is improved, clock glitch is avoided through a feedback mechanism, and signalsoutput by the circuit are free of burrs.

Owner:深圳市鹏芯数据技术有限公司

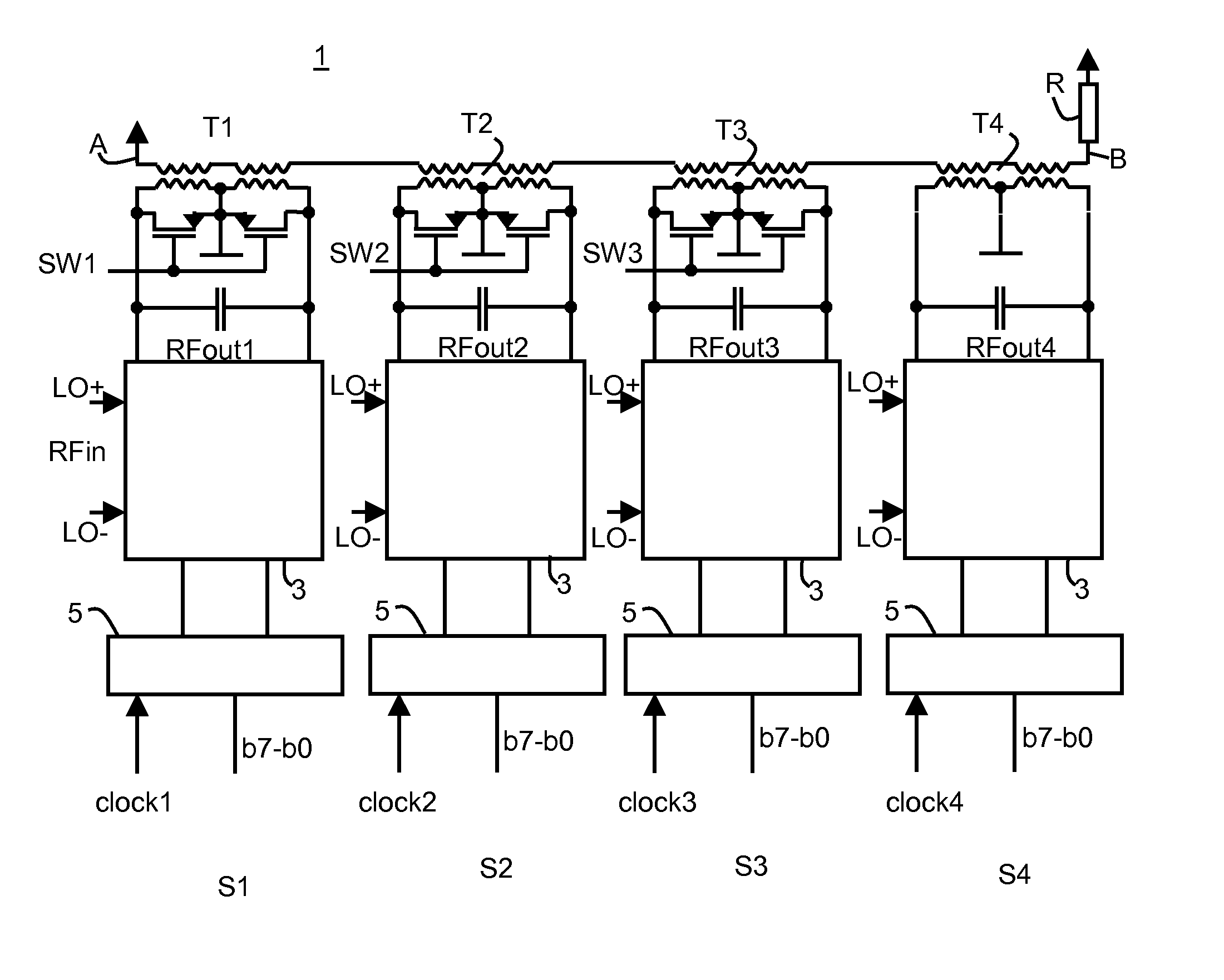

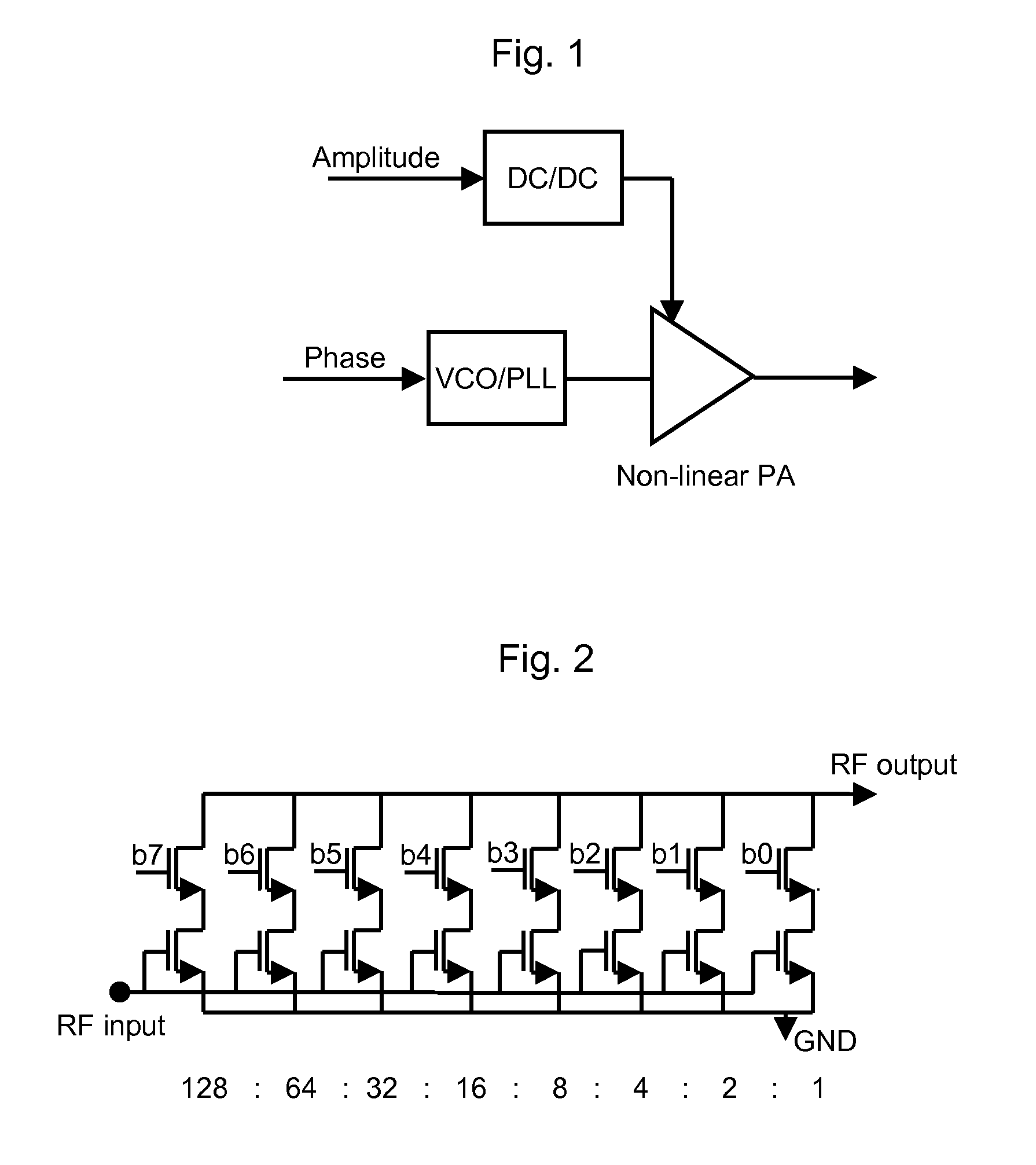

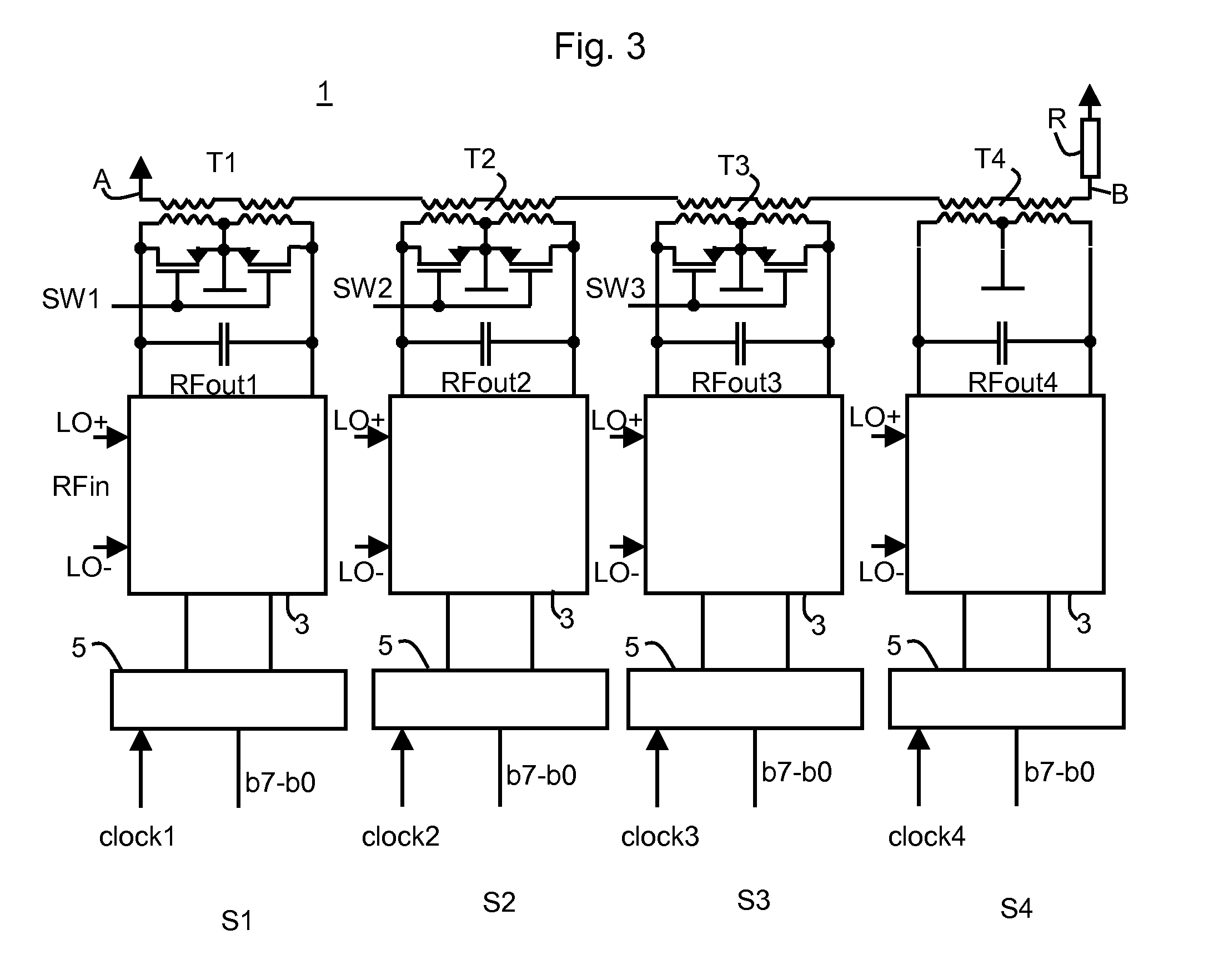

Output stage for a digital RF transmitter, method for providing an RF output signal in a digital RF transmitter, and digital RF transmitter

InactiveUS8237503B2Small sizeIncrease the maximum operating frequencyPush-pull amplifiersPhase-splittersTransformerEngineering

An output stage (1) for a digital RF transmitter is provided. The output stage comprises: an input adapted to receive an input signal (RFin, b7-b0) to be transmitted; a plurality N of power amplification sections (S1, S2, S3, S4); and an output (A, B) providing an output voltage signal. Each of the N power amplification sections (S1, S2, S3, S4) is arranged to receive the input signal (RFin, b7-b0) and comprises a transformer (T1, T2, T3, T4) adapted to provide a respective output signal. Each transformer comprises a primary stage and a secondary stage; the secondary stages of the transformers (T1, T2, T3, T4) of the N power amplification sections (S1, S2, S3, S4) are combined such that a combined output voltage signal of the output stage is provided. The N power amplification sections (S1, S2, S3, S4) are adapted such that the input signal (RFin, b7-b0) is latched by clock signals (clock1, clock2, clock3, clock4) comprising different phases.

Owner:AMPLEON NETHERLANDS

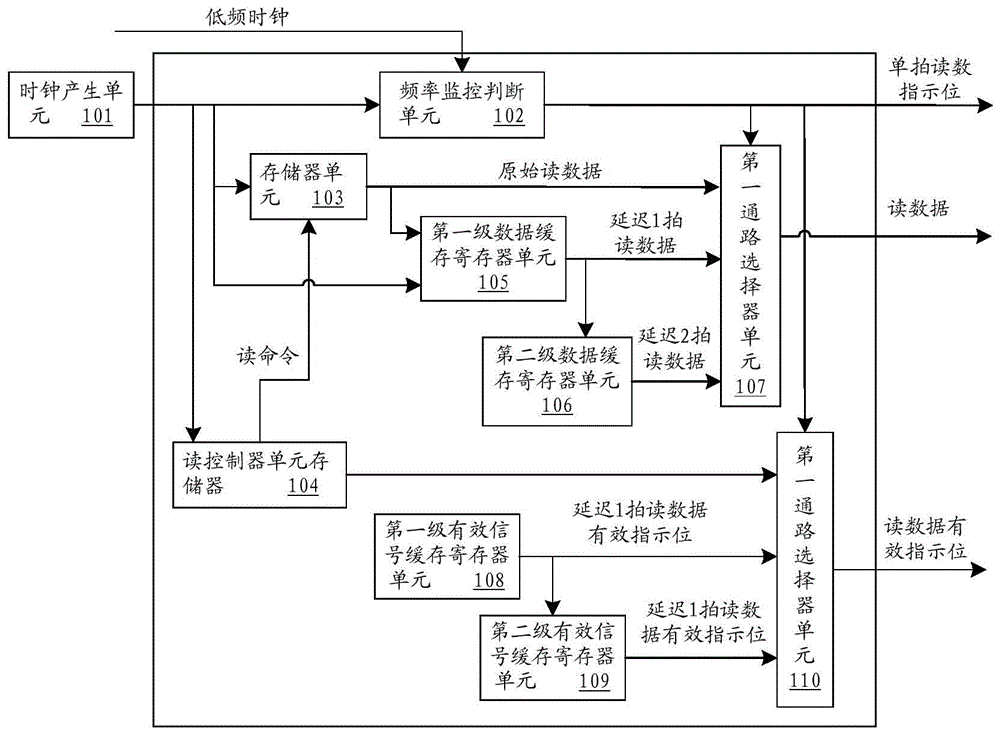

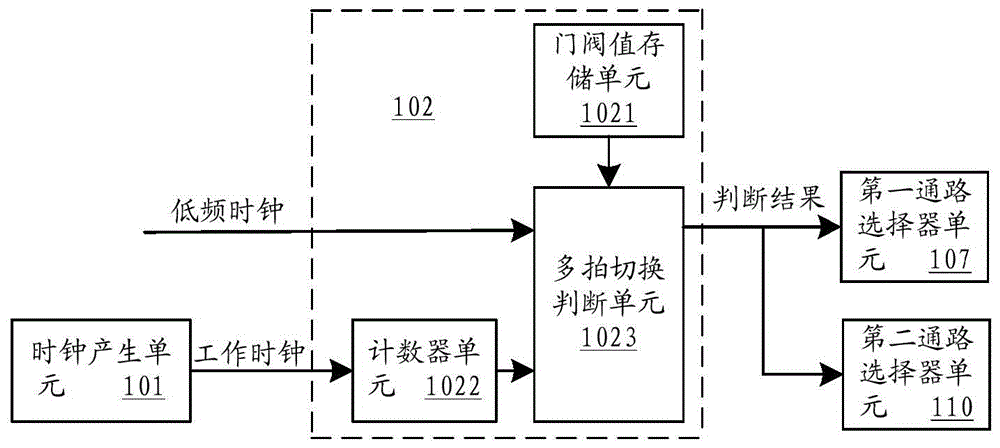

Method and device for chip to adaptively regulate reading time sequence path

ActiveCN105701041ATiming path shorteningIncrease the maximum operating frequencyElectric digital data processingClock rateSelf adaptive

The invention provides a method and a device for a chip to adaptively regulate a reading time sequence path. A read control unit memory outputs a read command to a memory unit to carry out a read operation, and meanwhile, the effective indication bit of the original read data is set to be effective after one period of the read command; according to the received read command and a work clock, the memory unit outputs the original read data; the original read data are individually delayed for one period and two periods; according to a judgment result of the frequency of the work clock, an access selection operation is carried out, one path of three inputs, including the original read data, the read data which is delayed for one period and the read data which is delayed for two periods, is selected as output read data; the effective indication bit of the original read data is individually delayed for one period and two periods; and according to the judgment result of the frequency of the work clock, the access selection operation is carried out, one path of three inputs, including the effective indication bit of the original read data and the effective indication bits of the two delayed read data, is selected as the effective indication bit of the output read data.

Owner:FUZHOU ROCKCHIP SEMICON

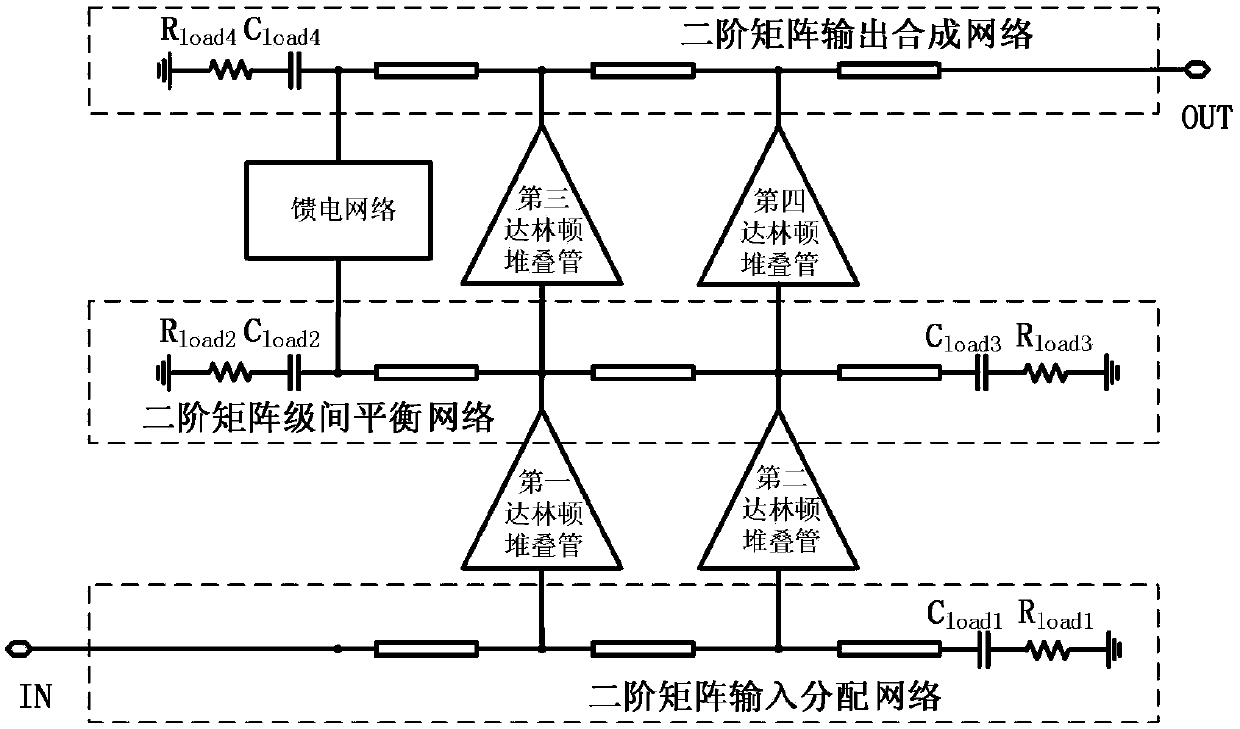

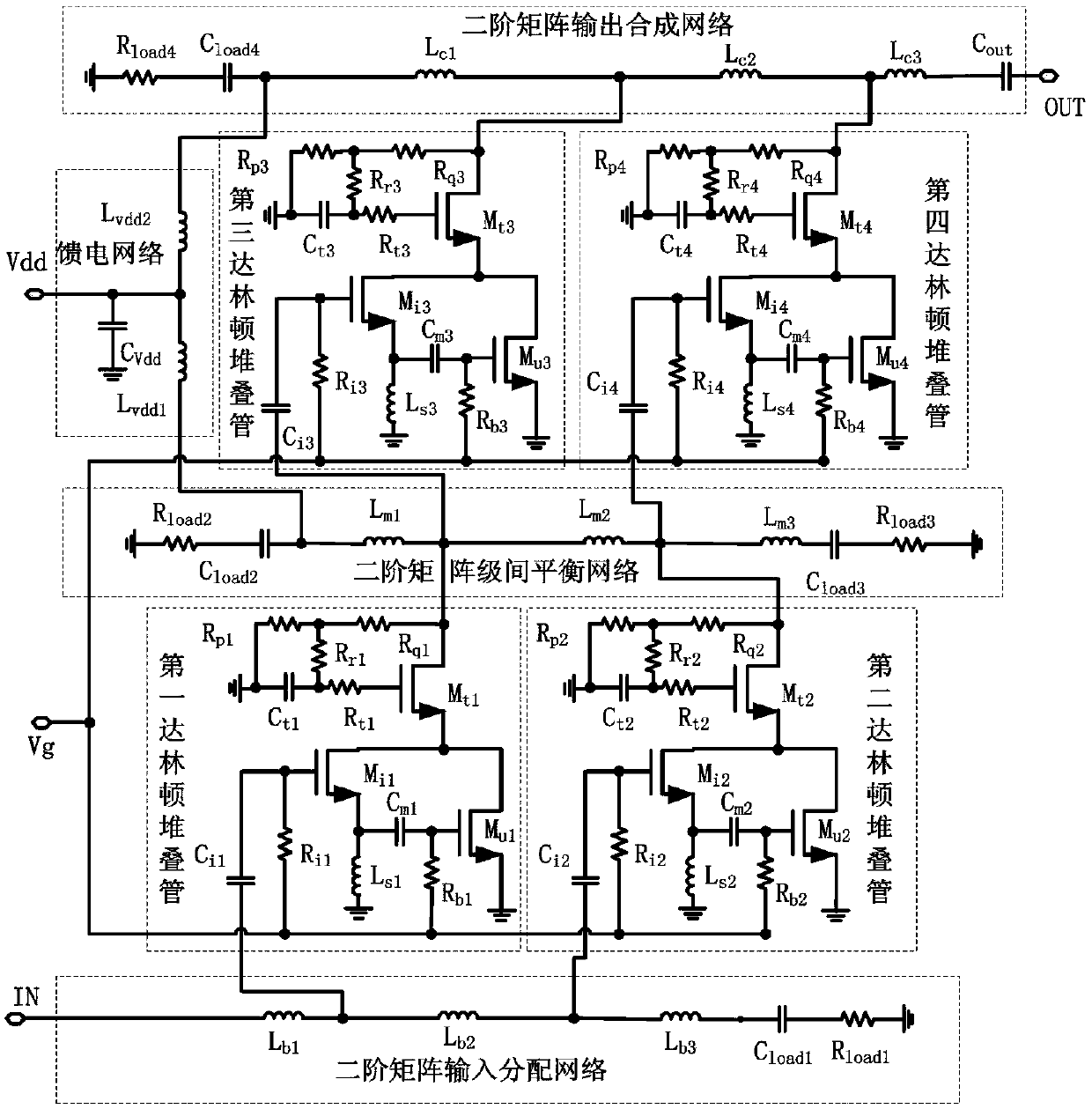

Ultra-wideband amplifier based on Darlington stacked tubes

PendingCN109687831AImprove stabilityImprove efficiencyRF amplifierDifferential amplifiersBalancing networkUltra-wideband

The invention discloses an ultra-wideband amplifier based on Darlington stacked tubes. The ultra-wideband amplifier comprises a second-order matrix input distribution network, a second-order matrix interstage balance network, a second-order matrix output synthesis network, a first Darlington stacked tube, a second Darlington stacked tube, a third Darlington stacked tube, a fourth Darlington stacked tube and a feed network connected with the second-order matrix interstage balance network and the second-order matrix output synthesis network. A core framework adopts a matrix amplification networkconsisting of the first to fourth Darlington stacked tubes, and the influence of the Darlington stacked tubes on artificial transmission lines in the matrix amplification network is considered, so that the accuracy of circuit design is greatly improved, the later debugging difficulty of the circuit is reduced, and the whole power amplifier has a good broadband high-gain and high-power output capability.

Owner:QINGHAI UNIV FOR NATITIES

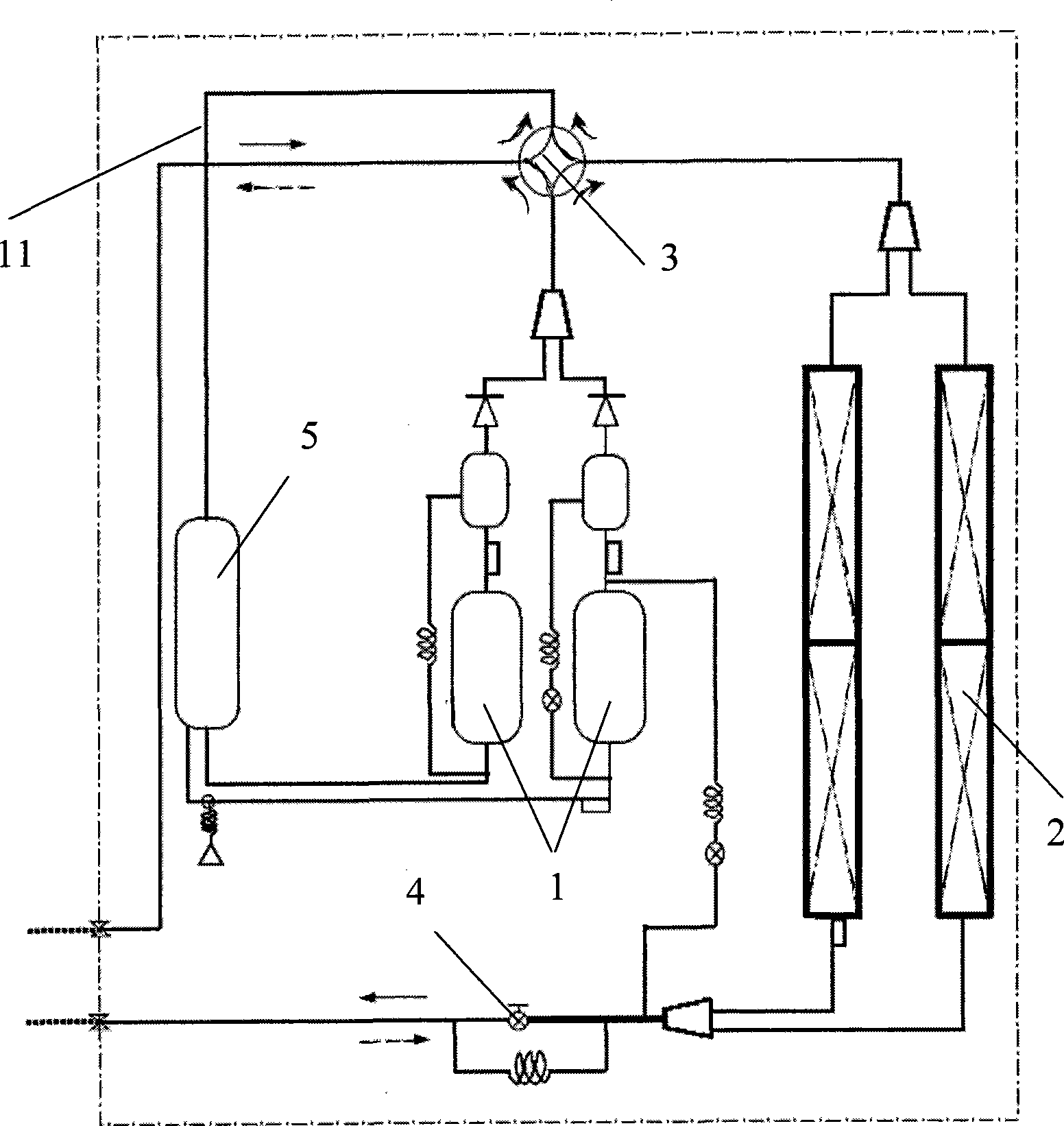

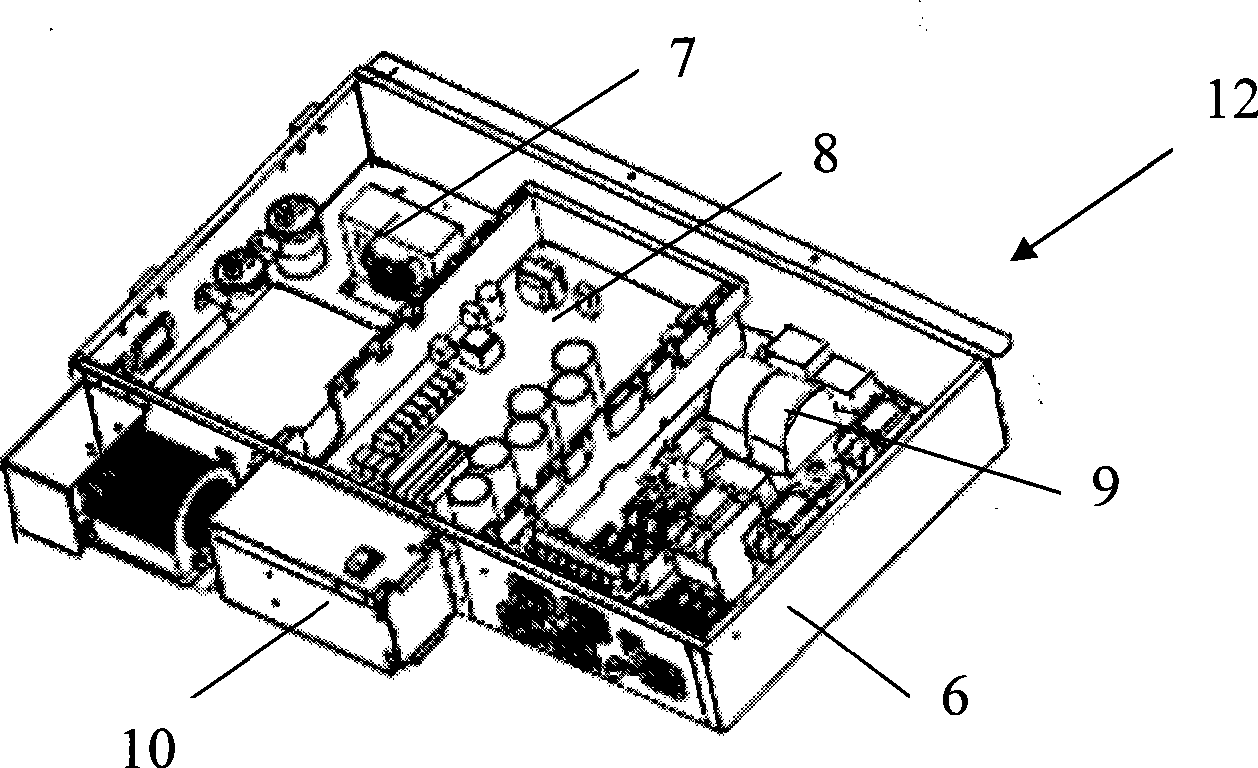

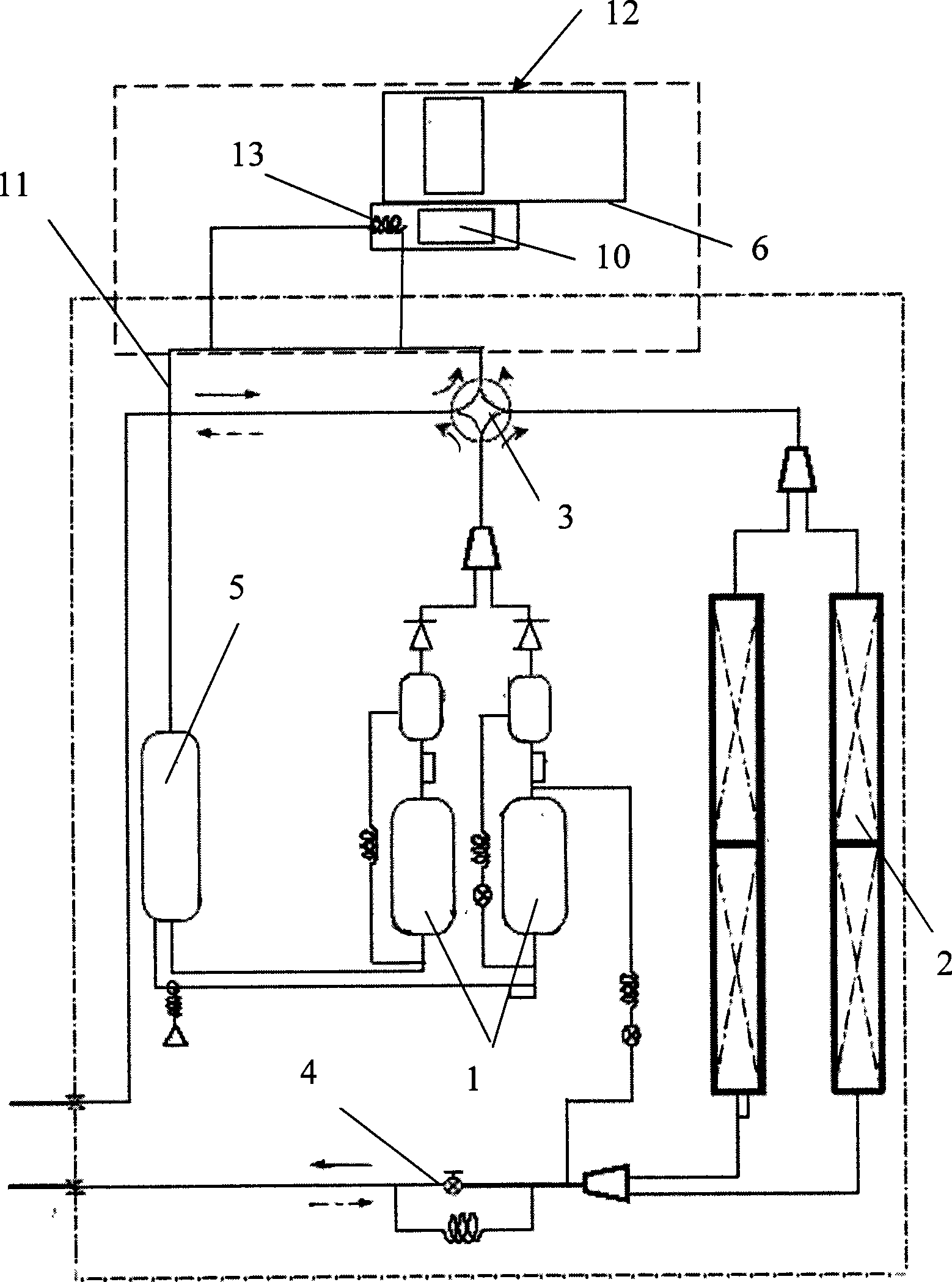

Frequency-changing air conditioner outdoor machine

InactiveCN101377322AReduce the temperatureIncrease the maximum operating frequencyLighting and heating apparatusAir conditioning systemsVariable frequency controlEngineering

The invention discloses a variable frequency air conditioner outdoor unit, which comprises a shell, a chassis, a constant speed compressor and an inverter compressor, an outdoor heat exchanger, an expansion valve, a fan assembly, a baffle and a controller; wherein, the controller consists of a box body, an electronic component arranged in the box body, a fan and a hood; a tubule adjacent to the fan is connected with in parallel the coolant pipe which is arranged among the indoor heat exchanger, the constant speed compressor and the inverter compressor. The tubule is connected with in parallel the coolant pipe between the indoor heat exchanger and the compressor, and the tubule is arranged at the exhaust inlet of the fan of the control box, therefore, the low-temperature coolant which flows through the tubule can be used to cool the outdoor air near the exhaust inlet, thus reducing the temperature of the air into the control box provided by the fan, and effectively reducing the temperature of the variable frequency controller; thereby the maximum operating frequency of the inverter compressor can be improved to meet the requirement for output capacity.

Owner:LG ELECTRONICS (TIANJIN) APPLIANCES CO LTD

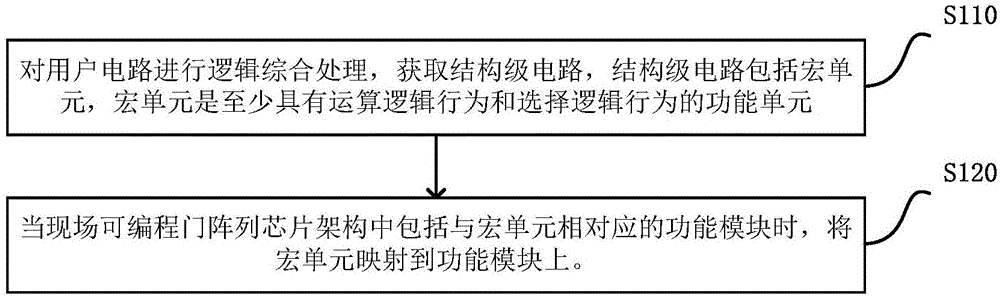

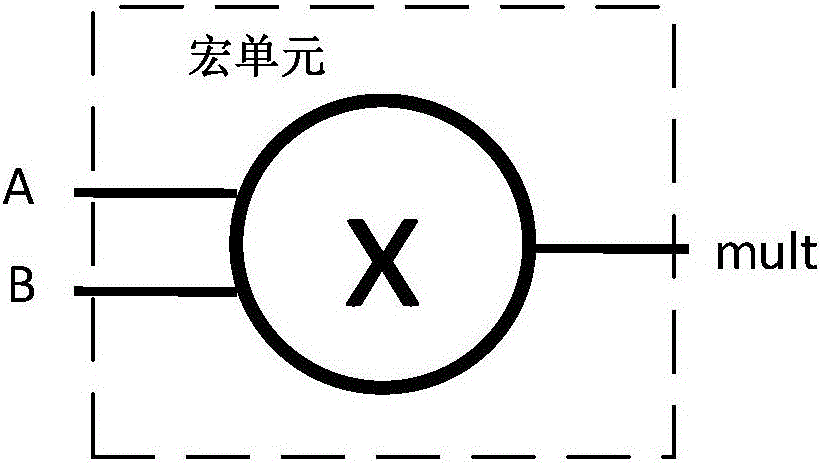

Field-programmable gate array chip-based process mapping method

InactiveCN106407535AIncrease working frequencyAvoid time costCAD circuit designSpecial data processing applicationsMapping algorithmTime cost

The embodiment of the invention provides a field-programmable gate array chip-based process mapping method. According to the method, a structure level circuit can be obtained through logic synthesis processing on a user circuit; the structure level circuit comprises a macroelement; and the macroelement is a function unit which at least comprises an operating logic behavior and a selecting logic behavior. When a field-programmable gate array chip architecture comprises a function module corresponding to the macroelement, the macroelement is mapped to the function module. According to the method, the universality of a process mapping algorithm can be reserved to the maximal extent; and different characteristics of multiple novel FPGA chip architectures can also be quickly supported, so that the time cost and the space (a software memory) cost are reduced; and the maximum work frequency fmax of an overall FPGA chip is improved.

Owner:HERCULES MICROELECTRONICS CO LTD

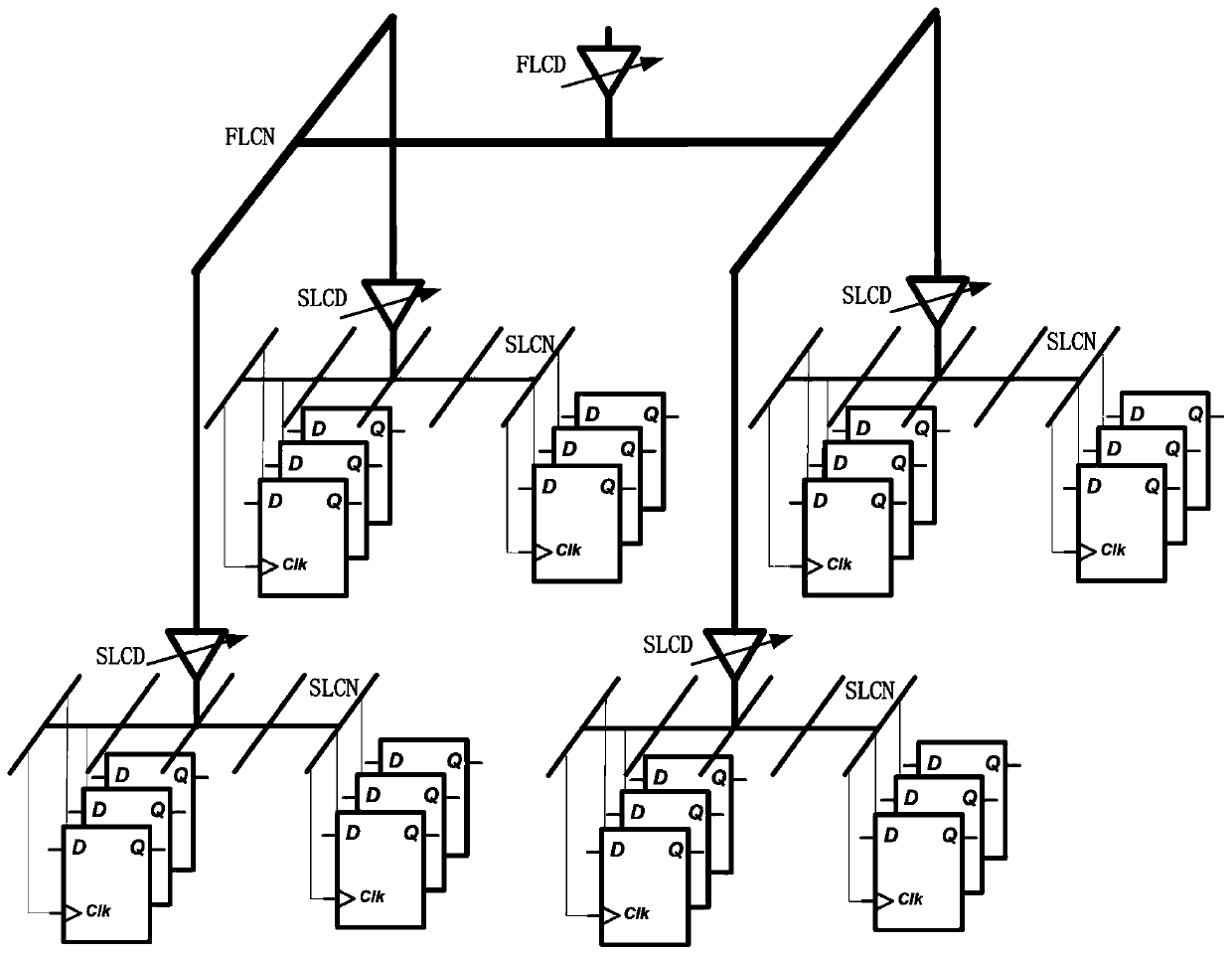

Clock distribution network rapid design method

ActiveCN110688723AReduce loadLower latencyGeometric CADCharacter and pattern recognitionComputer hardwareCluster algorithm

The invention relates to a clock distribution network rapid design method. A clock network is divided into a first-stage clock network and a second-stage clock network, the first-stage clock network is driven by a first-stage clock network driving unit, the second-stage clock network is driven by a second-stage clock network driving unit, and the method comprises the following steps: adopting a time sequence priority layout, and obtaining the position of a trigger; dividing the trigger into a plurality of local areas by adopting a clustering algorithm according to the layout parameters, and establishing a second-stage clock network; dividing the second-stage clock network driving unit into a plurality of areas with uniform loads by adopting a clustering algorithm according to the layout parameters, and establishing a first-stage clock network; and winding the first-stage clock network and the second-stage clock network. The clock network delay can be reduced, and the clock network loadis reduced.

Owner:上海高性能集成电路设计中心

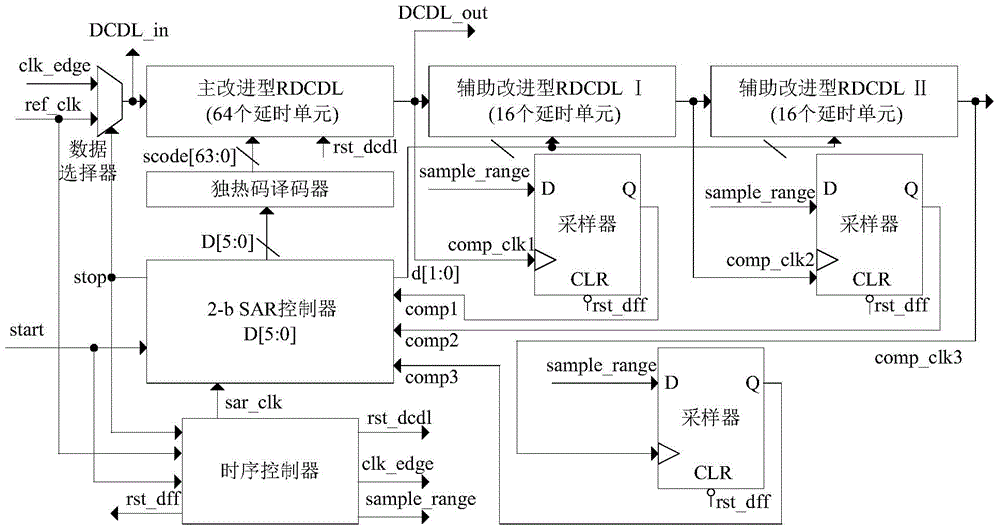

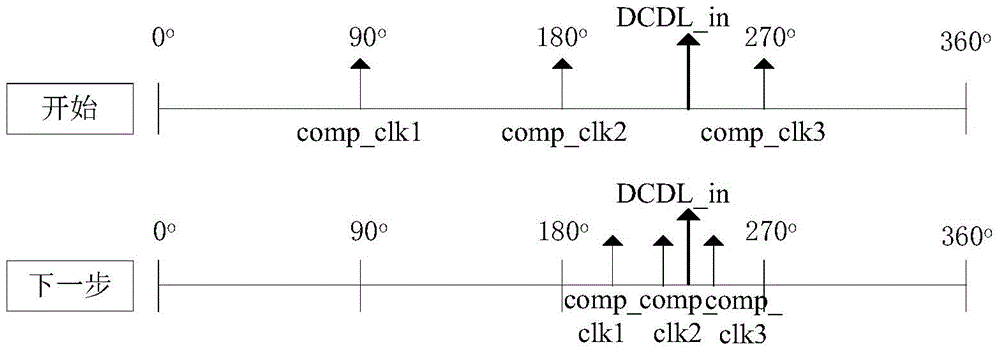

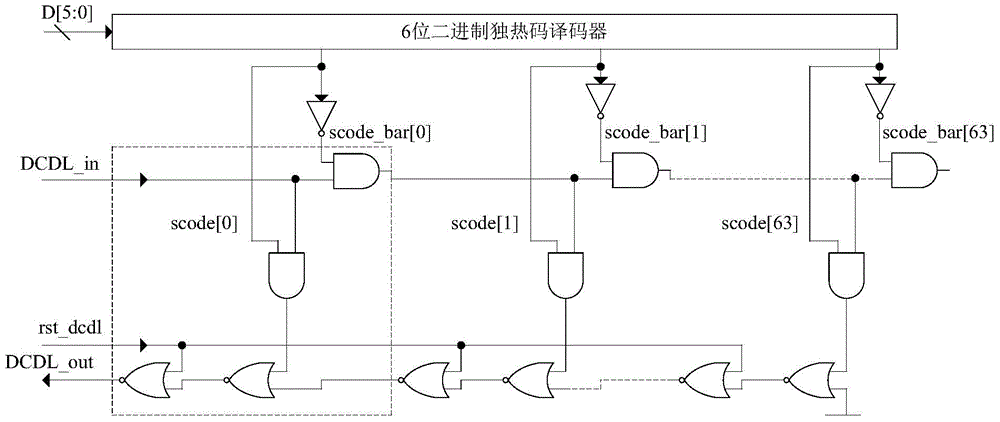

Improved full-digital successive approximation register delay lock loop (SARDLL) system

The invention discloses an improved full digital successive approximation register delay lock loop (SARDLL) system. The SARDLL system comprises a 2-b SAR controller, a time sequence controller, three samplers, a one-hot coding encoder, a main RDCDL and two auxiliary RDCDLs. The SAR controller adopts the 2-b SAR algorithm to increase the lock speed of the SARDLL system. The main RDCDL is an improved RDCDL with 64 delay units. Each auxiliary RDCDL is an improved RDCDL with 16 delay units. Each delay unit in the improved RDCDL comprises two AND gates and two NOR gates. The SARDLL system increases the lock speed, meanwhile expands the working frequency range of the system, increases the maximum working frequency of the system, reduces chip area, reduces system power consumption and further improves the performance.

Owner:HEFEI UNIV

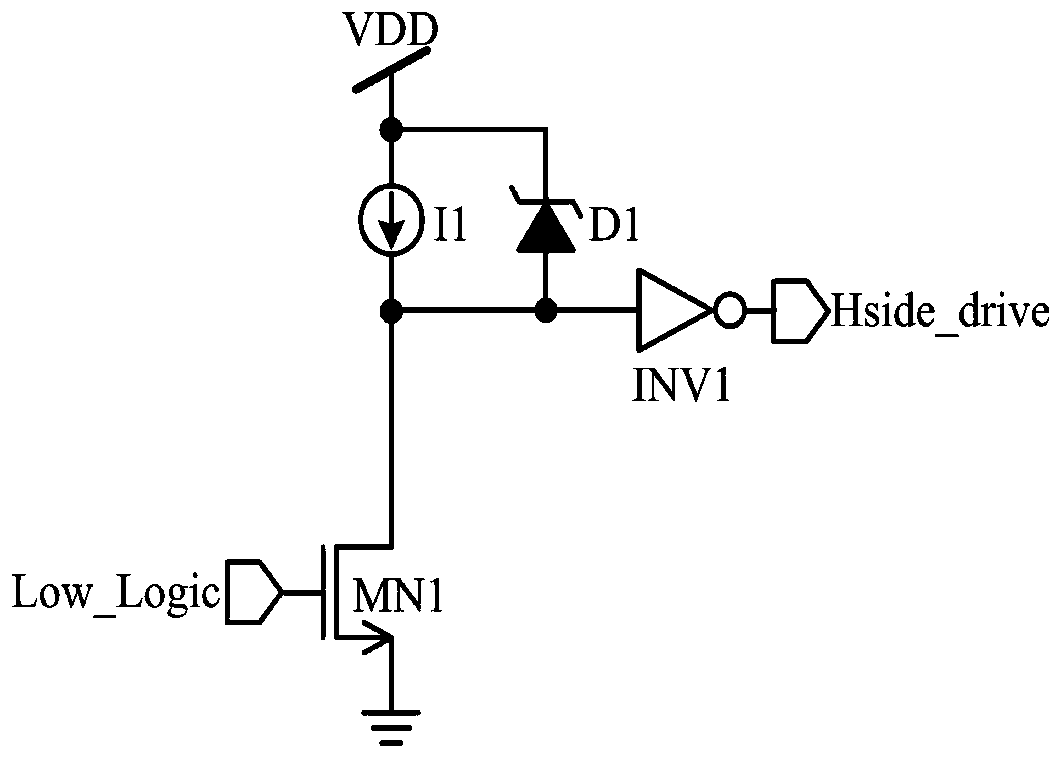

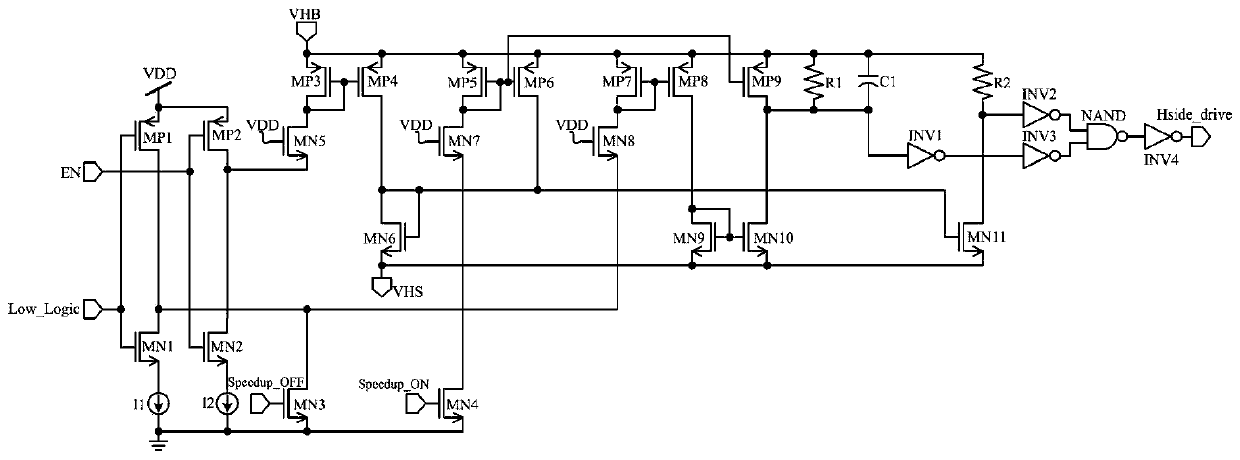

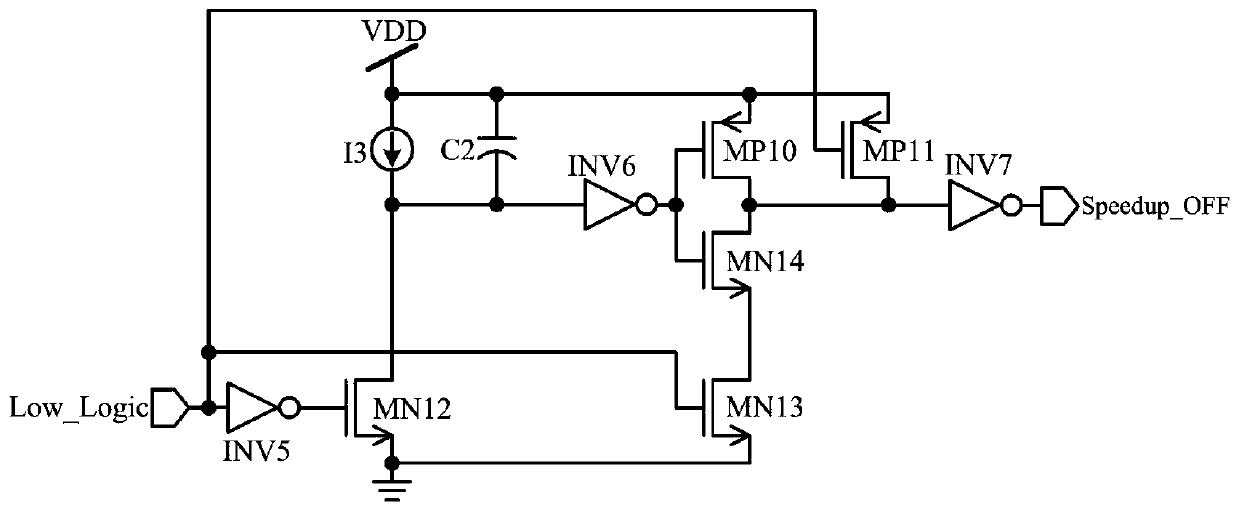

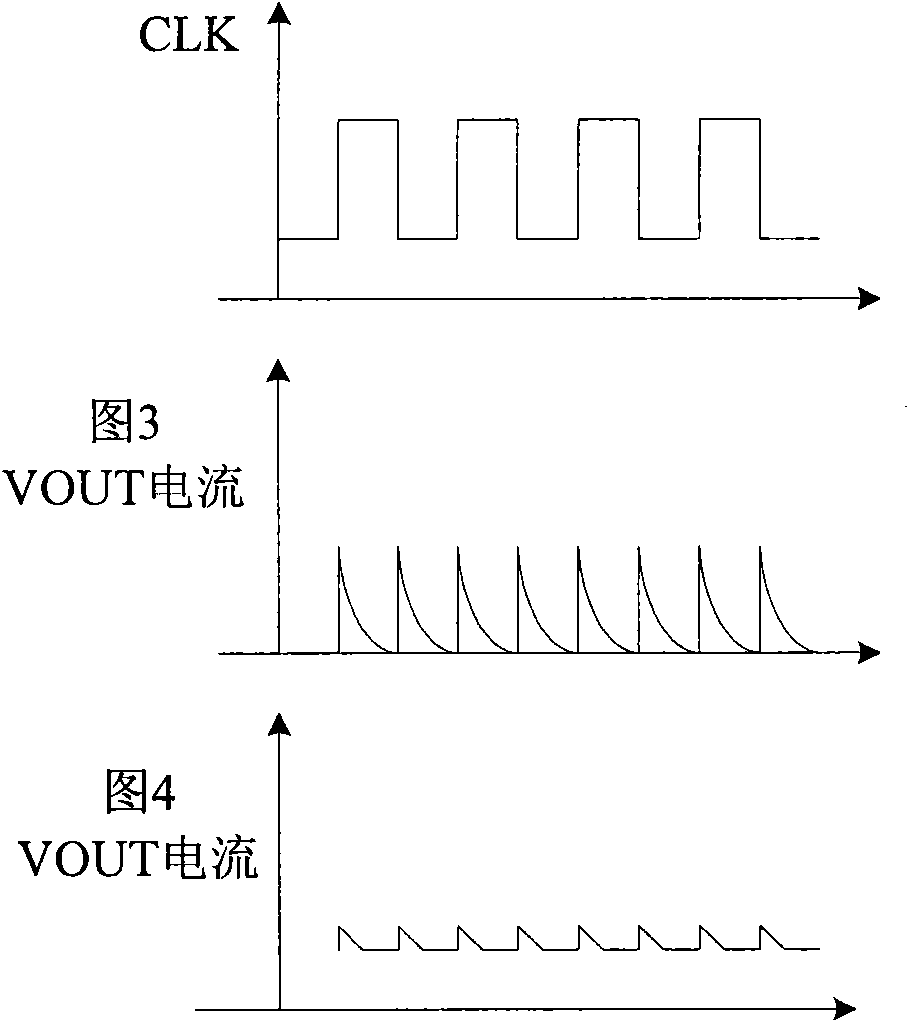

A high-speed low-power-consumption level shift circuit

ActiveCN109921769AAccelerate closingShorten closing timeLogic circuits coupling/interface using field-effect transistorsElectronic switchingEngineeringTurn on time

The invention discloses a high-speed low-power-consumption level shift circuit, and belongs to the technical field of integrated circuits. The high-speed low-power-consumption level shift circuit is characterized in that Speedup _ OFF and Speedup _ ON signals are added; when Low _ Logistic becomes high, a Speedup _ OFF narrow pulse is generated to achieve closing acceleration of the high-end driving power tube, and when Low _ Logistic becomes low, a Speedup _ ON narrow pulse is generated to achieve opening acceleration of the high-end driving power tube. The turn-off and turn-on time of the high-end driving power tube is reduced, the maximum working frequency of the chip is improved, and the application range of the chip is expanded; when the chip is in a steady state, the Speedup _ OFF and the Speedup _ ON are constantly 0, additional current cannot be introduced into the level shift circuit, and the power consumption of the chip is reduced.

Owner:58TH RES INST OF CETC

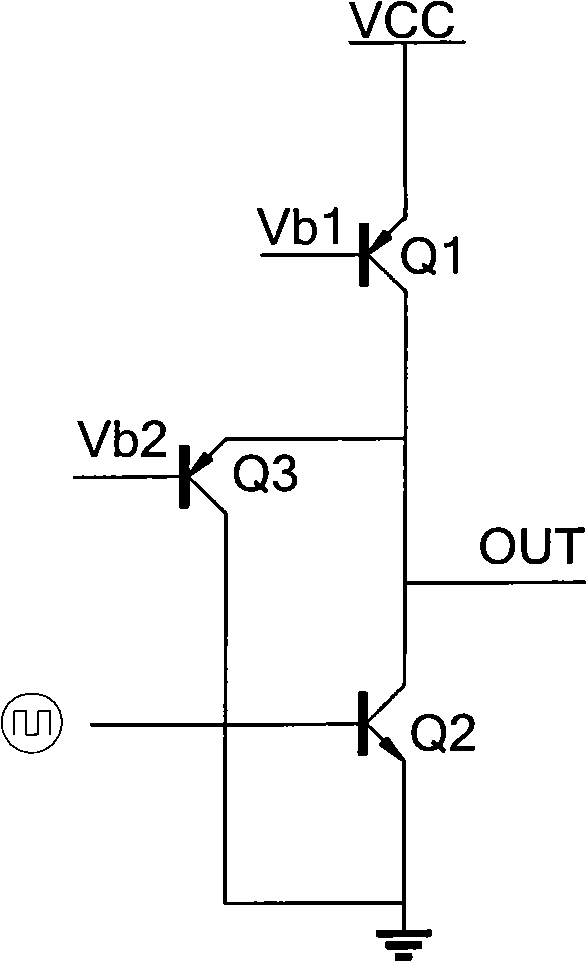

Charge pump, charge pump booster circuit and operating method thereof

InactiveCN101908821AAvoid the problem that the switching speed is limited by the PNP tubeIncrease the maximum operating frequencyApparatus without intermediate ac conversionEngineeringOperating frequency

The invention provides a charge pump comprising a power supply VCC, a first PNP pipe Q1, a second PNP pipe Q3 and an NPN pipe Q2, wherein the emitting electrode of the first PNP pipe Q1 is connected with the power supply VCC; the base electrode of the first PNP pipe Q1 is connected with a first electric potential Vb1; the base electrode of the second PNP pipe Q3 is connected with a second electric potential Vb2; the base electrode of the NPN pipe Q2 is connected with a clock signal CLK; the collector electrode of the second PNP pipe Q3 and the emitting electrode of the NPN pipe Q2 are grounded; and the collector electrode of the first PNP pipe Q1, the emitting electrode of the second PNP pipe Q3 and the collector electrode of the NPN pipe Q2 are connected to be as the output end OUT of the charge pump. The invention simultaneously provides a charge pump booster circuit realized by utilizing the charge pump and an operating method thereof. Because the charging and discharging speed of the charge pump booster circuit does not depend on the PNP pipe but the switching speed of the NPN pipe in the charge pump, the switching speed of the charge pump is avoided being limited by the PNP pipe, the maximum operating frequency of the charge pump is increased, and the loading capacity of the charge pump booster circuit is improved.

Owner:HANGZHOU SILAN MICROELECTRONICS

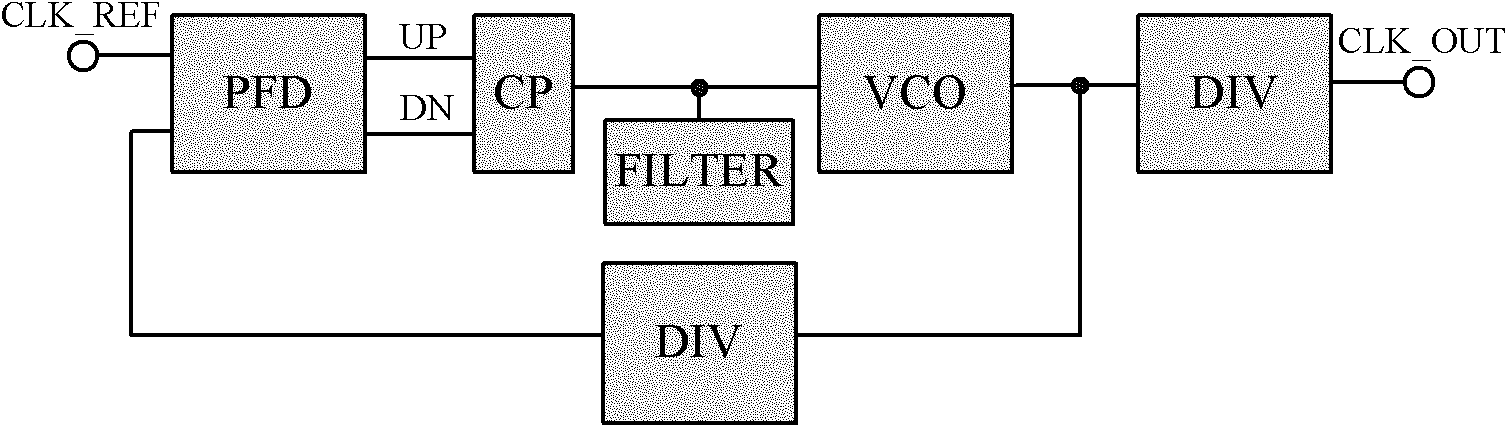

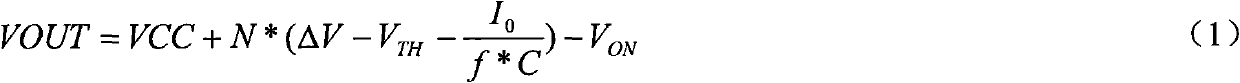

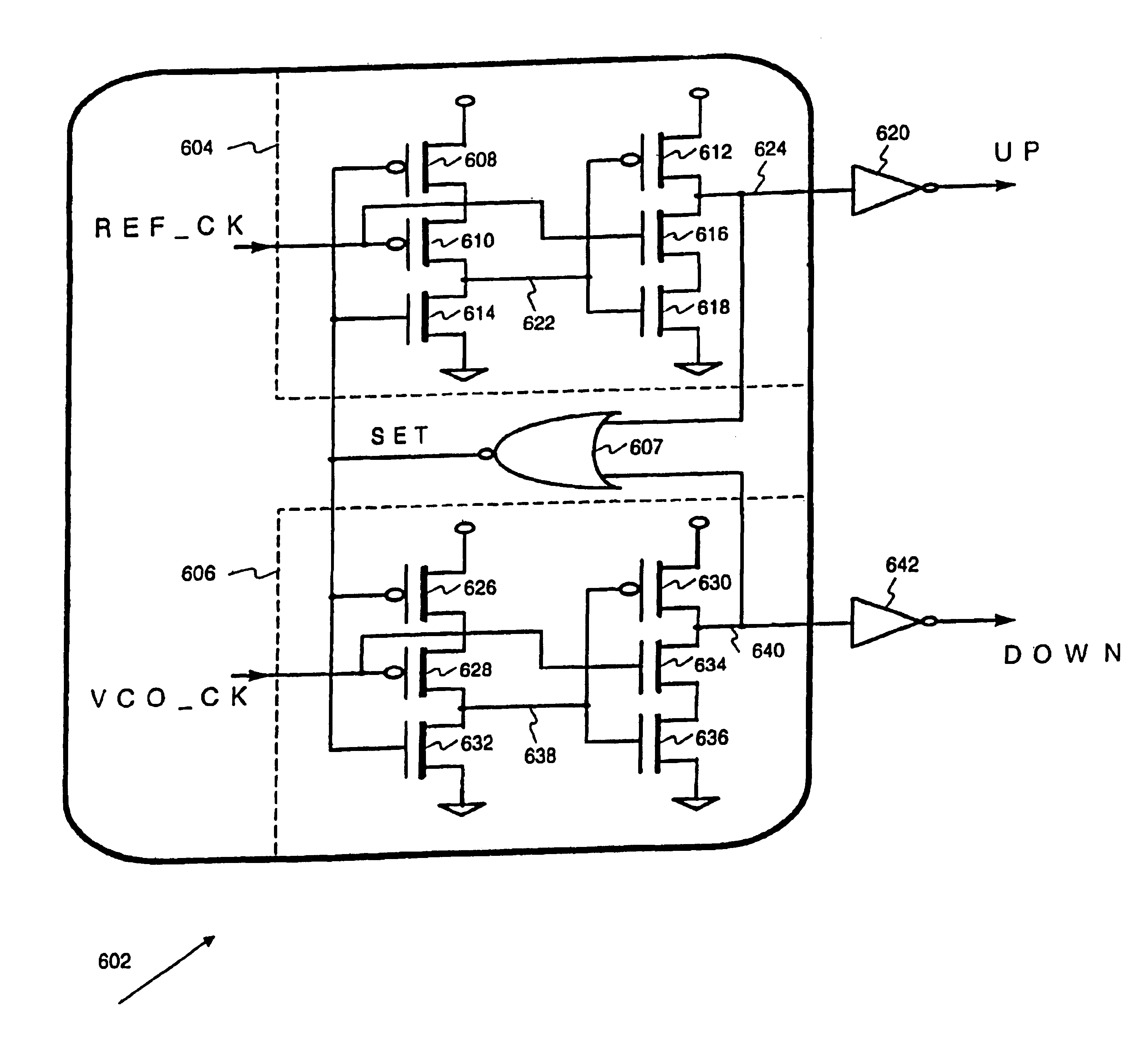

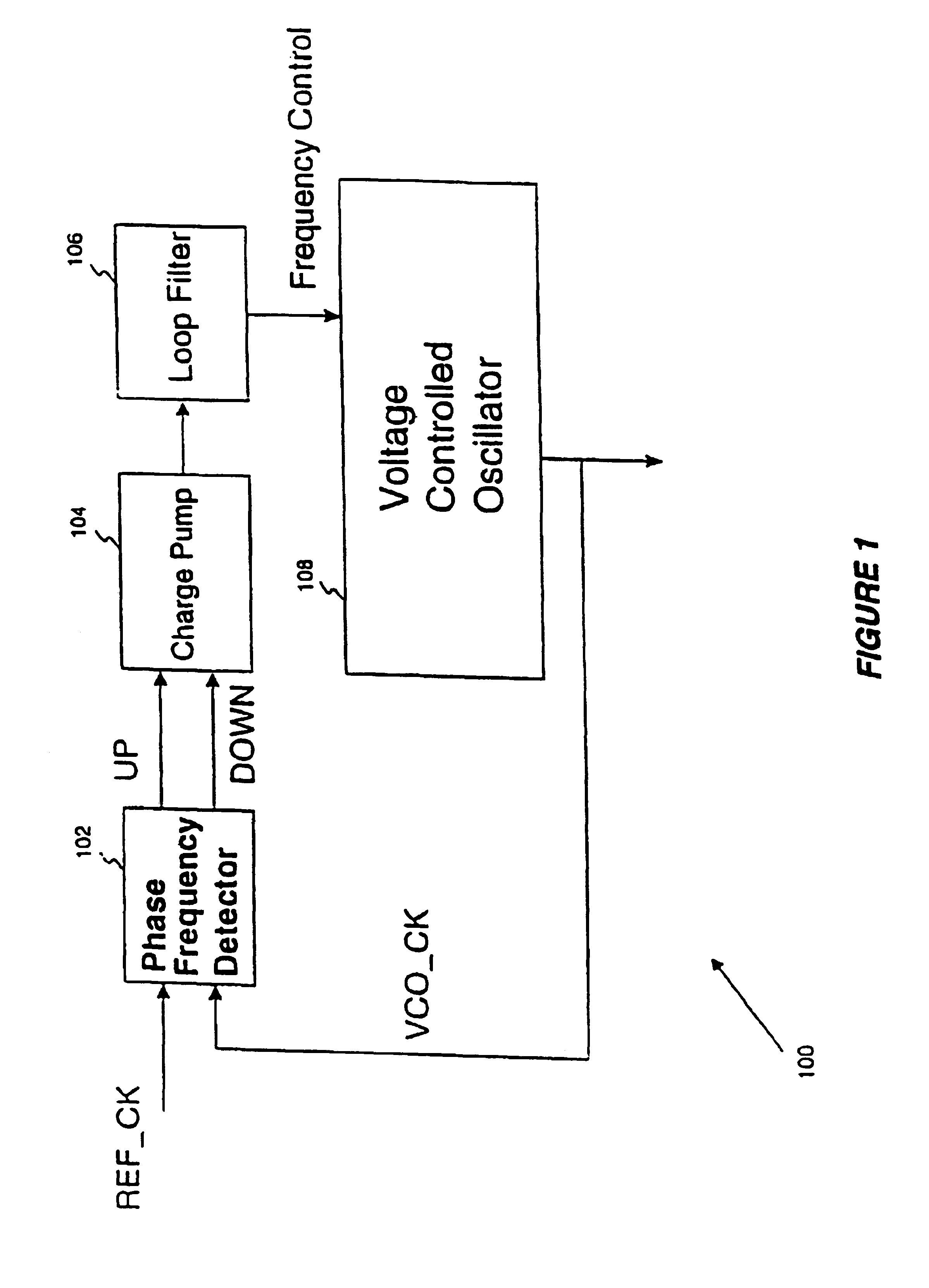

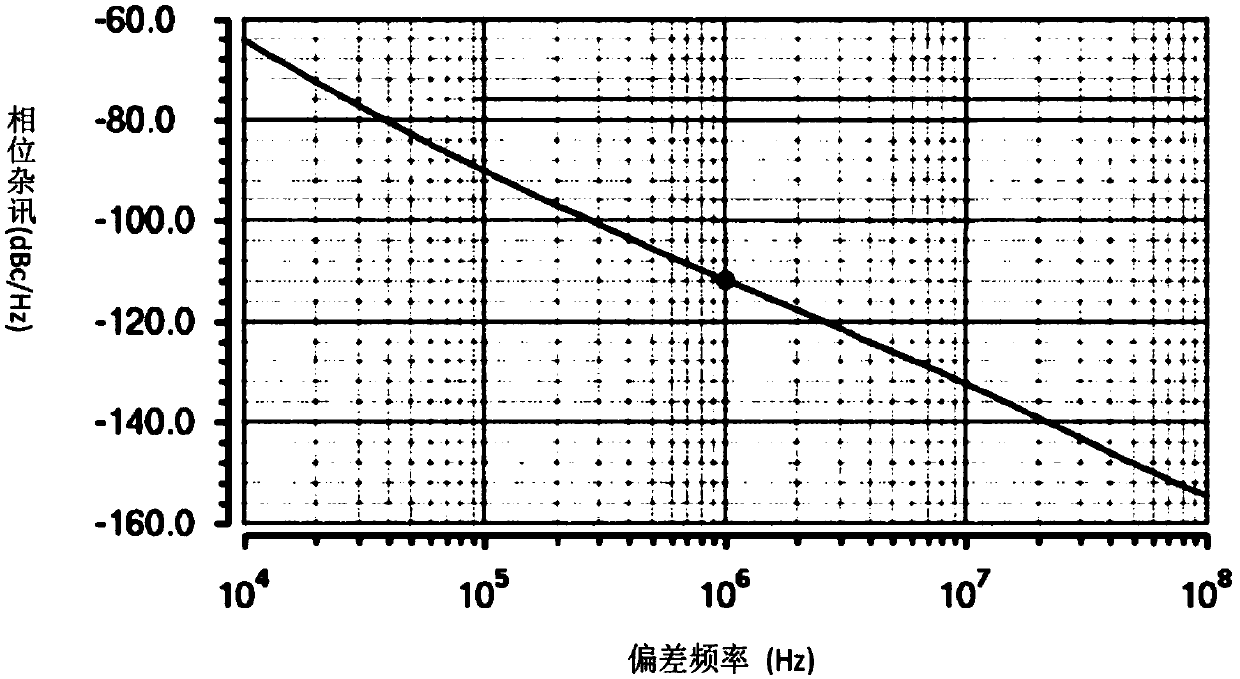

High-speed and high-precision phase locked loop

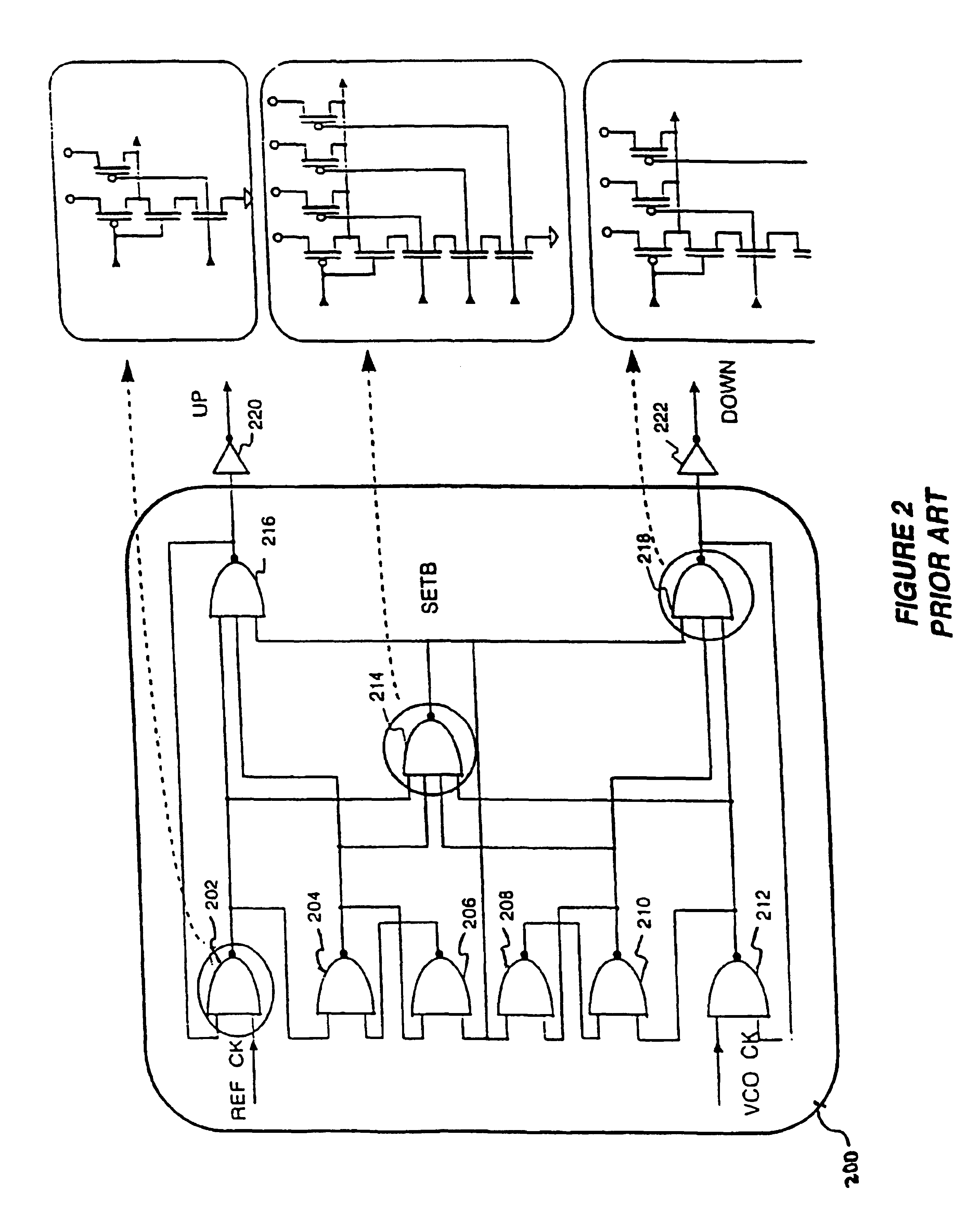

InactiveUS6930560B2Reduce Propagation DelayImprove accuracyMultiple input and output pulse circuitsPulse automatic controlPhase differencePhase frequency detector

A phase lock loop includes a charge pump, a voltage controlled oscillator (VCO), and a phase frequency detector. The phase frequency detector has a dynamic logic structure. The phase frequency detector generates up and down signals for directing the charge pump to provide a voltage signal to the VCO to vary the frequency of the VCO clock. The difference between the up and down signals is indicative of the phase difference between the reference clock signal and the VCO clock. The phase frequency detector includes up and down signal generators for generating the up and down signals, respectively.

Owner:SUPER INTERCONNECT TECH

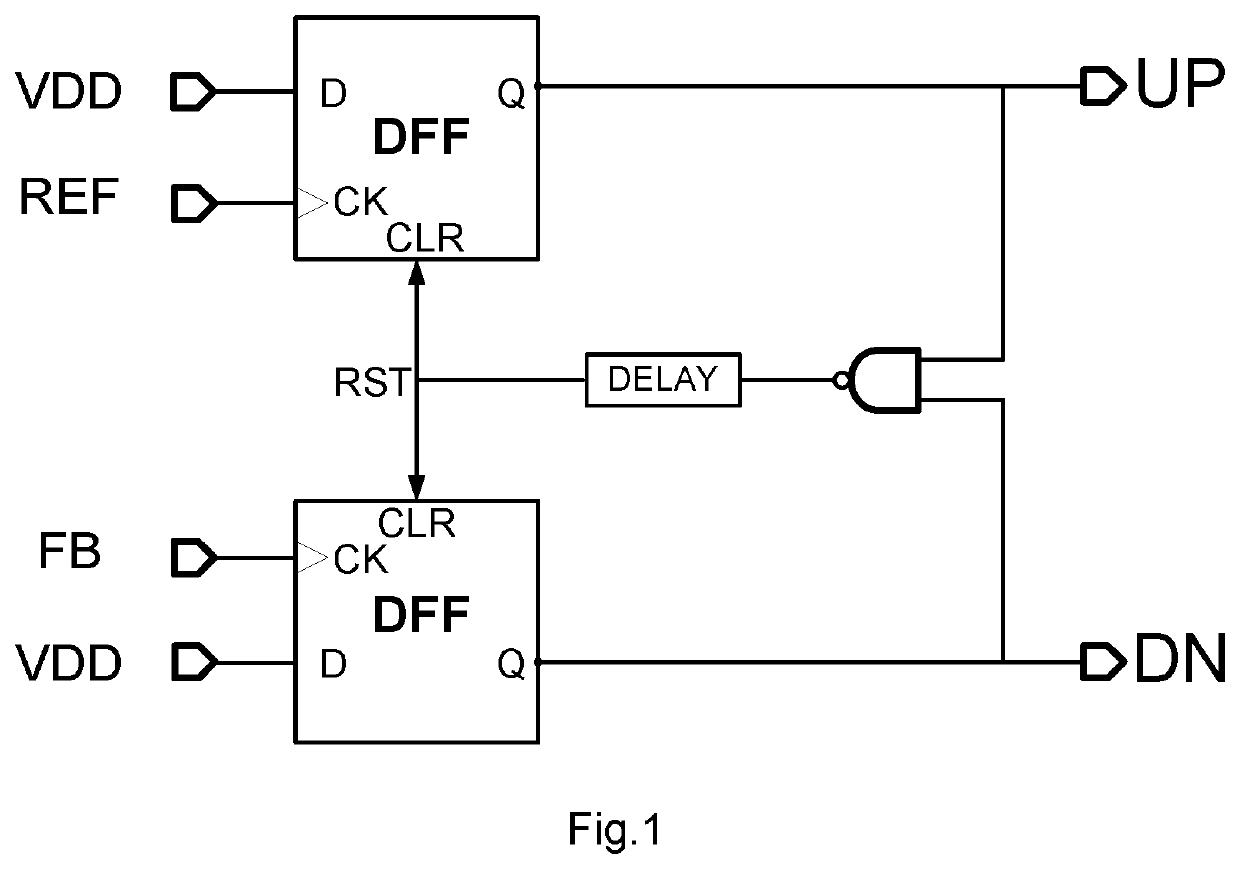

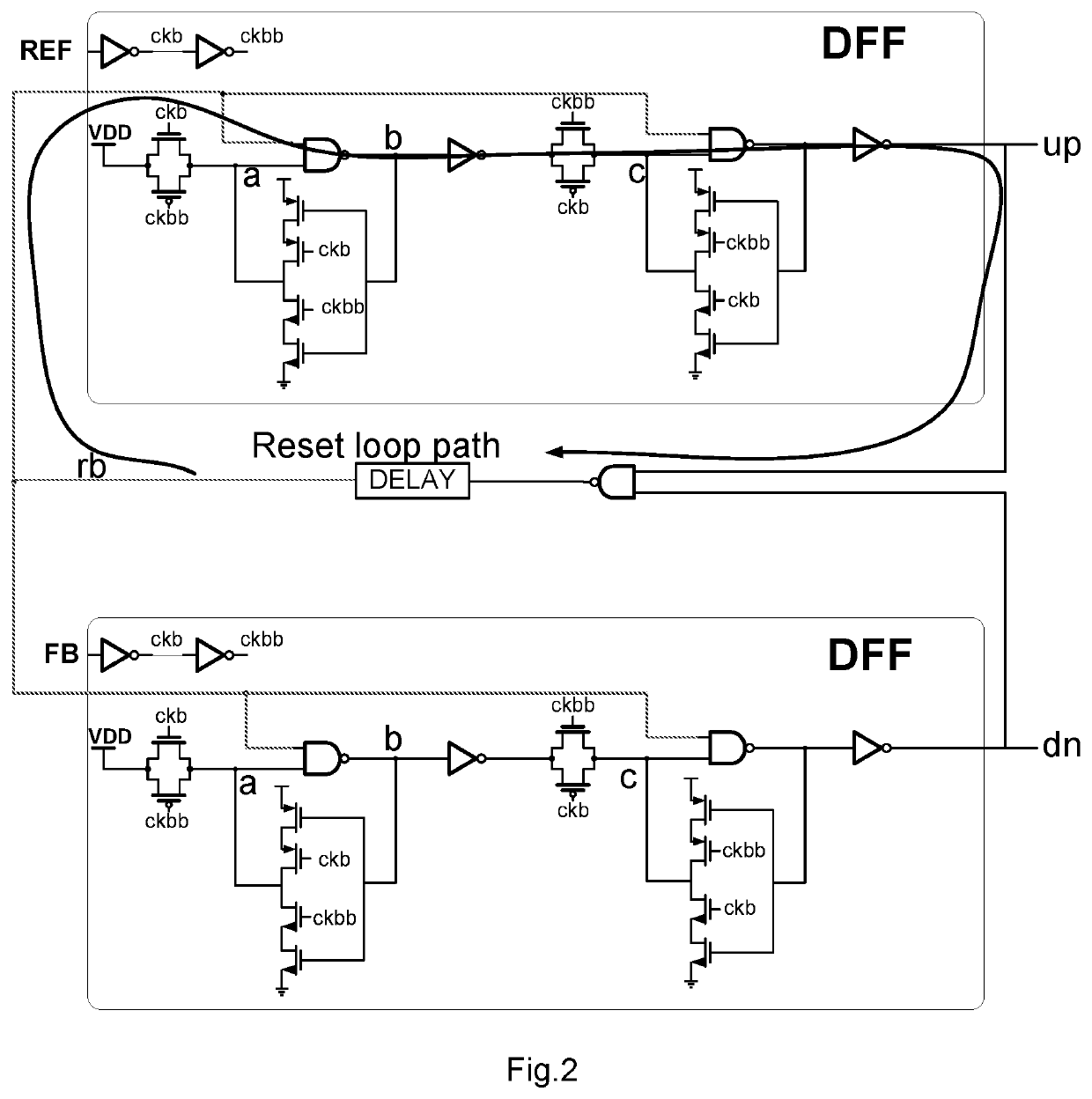

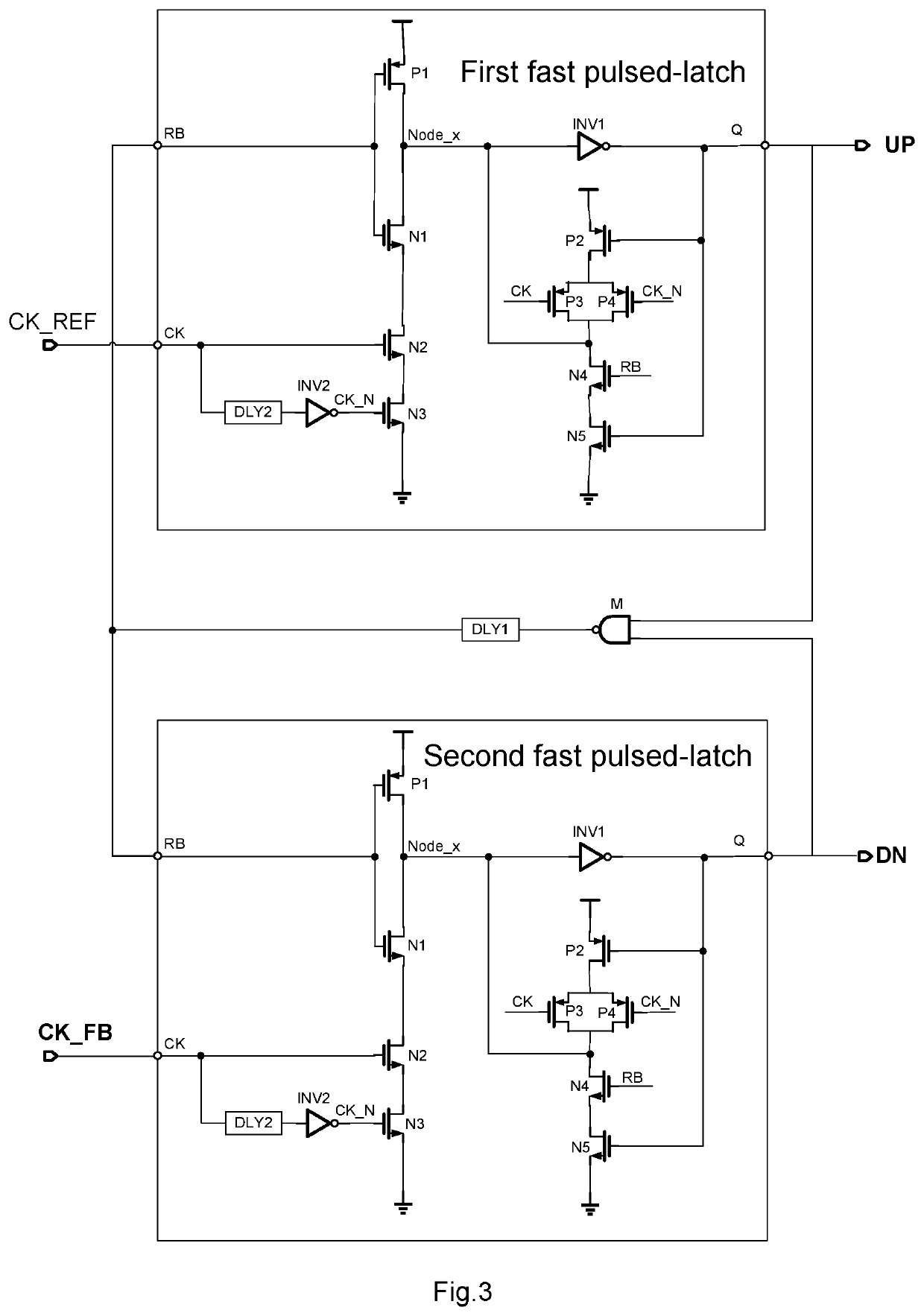

Fast phase frequency detector

ActiveUS20200295766A1Loop delay is reducedIncrease maximum operating frequencyPulse automatic controlOscillations comparator circuitsFast pulsePhase detector

Disclosed a fast phase frequency detector, comprising: two fast pulsed-latches, a NAND gate and an adjustable delay circuit. The fast pulsed-latches comprises: a pulse generating circuit, a reset circuit, and an output latch circuit; the pulse generating circuit is configured to generate a power supply pulse signal when a rising edge of the clock signal arrives, the power supply pulse signal causing the input of the output latch circuit to be a low level; the output latch circuit is configured to maintain its current output state when the clock signal or the reset signal is invalid; the reset circuit is configured to set the input of the output latch circuit to be a high level. By using fast pulsed-latches with clock and reset control, the fast phase frequency detector of the present application shortens the reset loop delay and increases the maximum operating frequency of the phase frequency detector.

Owner:MONTAGE TECHNOLOGY CO LTD

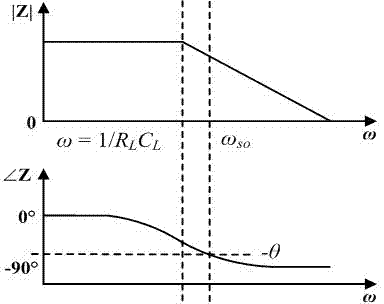

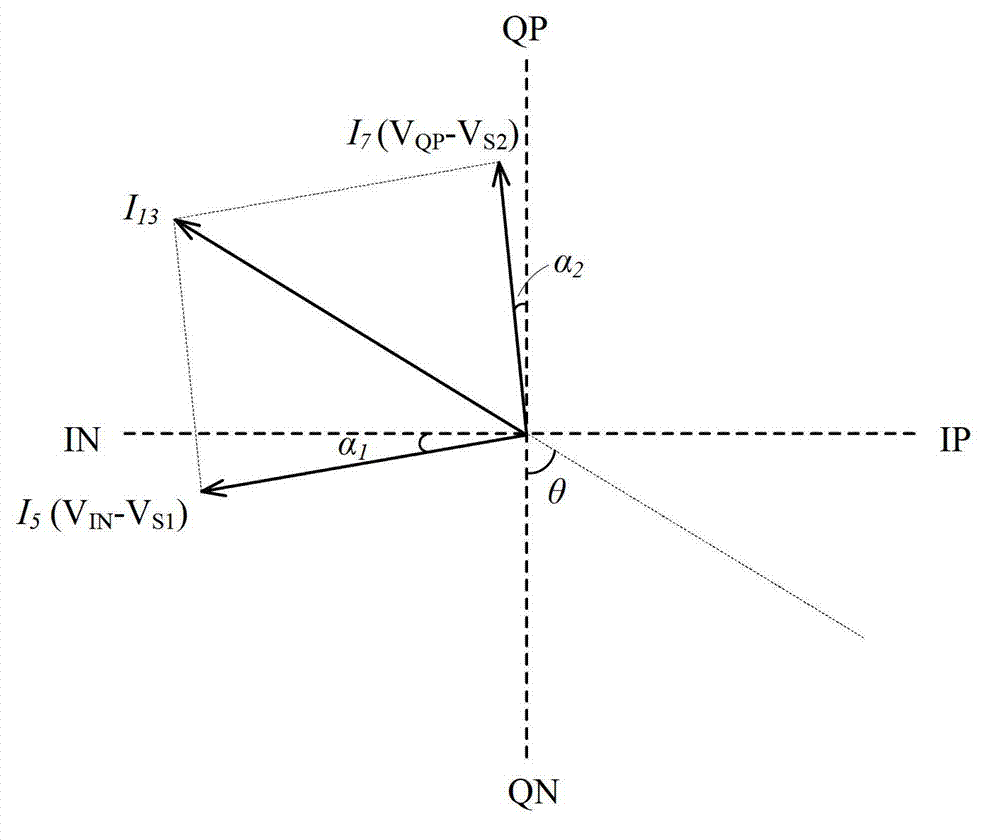

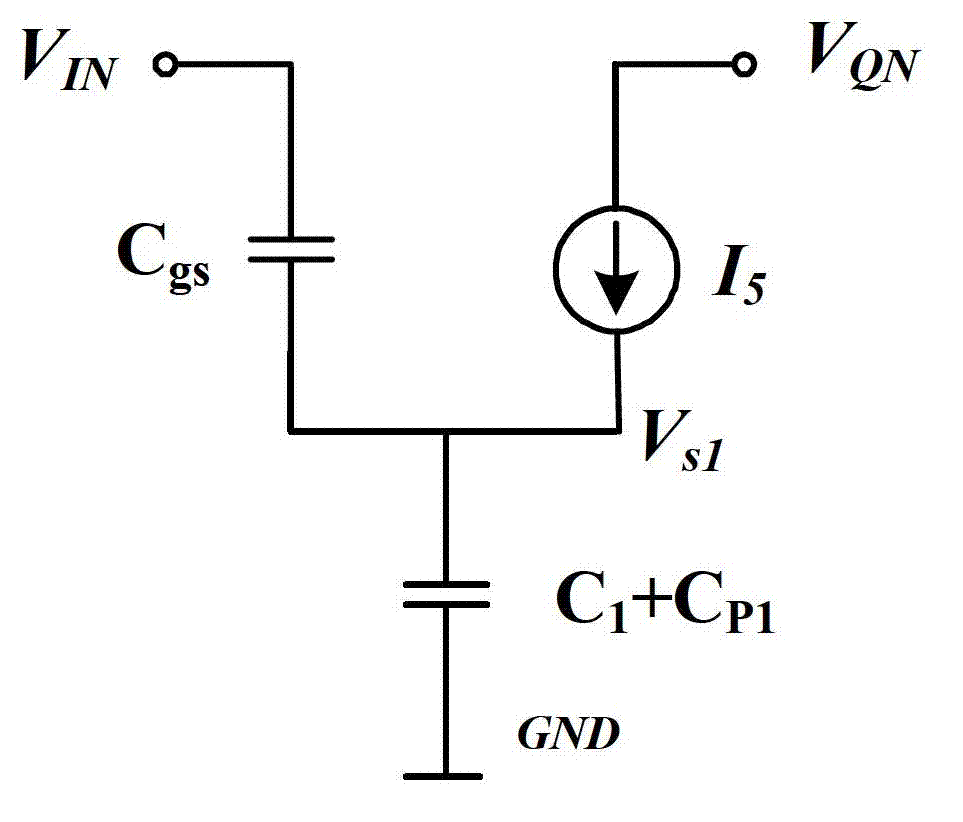

New type high speed prescale circuit

ActiveCN103208990AHigh self-oscillating frequencyWide crossover rangeCounting chain synchronous pulse countersLogic circuitsOxide semiconductorPhase shifted

The invention discloses a new type high speed prescale circuit which comprises two current mode logic latches (D-Latch) and two MIM (Metal Injection Molding) capacitors or two MOS (Metal Oxide Semiconductor) pipe capacitors which achieve a current shaping function. An MOS sampling tube source common mold point of each of the two D-Latches is respectively connected with an amplitude phase current shaping unit to change amplitudes and phases of sampling tube current ID under a large signal operation state and enlarge phase shift theta which needs to be compensated through a load RC (Remote Control) network and accordingly a higher self-oscillation frequency is obtained and the high speed pre-frequency dividing circuit is provided with a higher working efficiency and a wider frequency-dividing range. The new type high speed prescale circuit is capable of being widely applied to a phase-locked loop module or a related module of a frequency synthesizer in the radio frequency identification field.

Owner:杭州中科微电子有限公司

Level shifting circuitry

ActiveUS8638157B2High frequencyQuick transitionPulse automatic controlElectric pulse generatorLevel shiftingLow voltage

Level shifting circuitry comprises a first level shifter and a second level shifter. In response to a falling edge transition of an input signal, the first level shifter generates a primary transition of a first intermediate signal faster than the second level shifter generates a secondary transition of a second intermediate signal. In response to a rising edge of the input signal, the second level shifter generates a primary transition of the second intermediate signal faster than the first level shifter generates a secondary transition of the first intermediate signal. Output switching circuitry is provided to switch an output signal between an output high voltage level and an output low voltage level in response to the primary transition of the first intermediate signal and the primary transition of the second intermediate signal.

Owner:ARM LTD

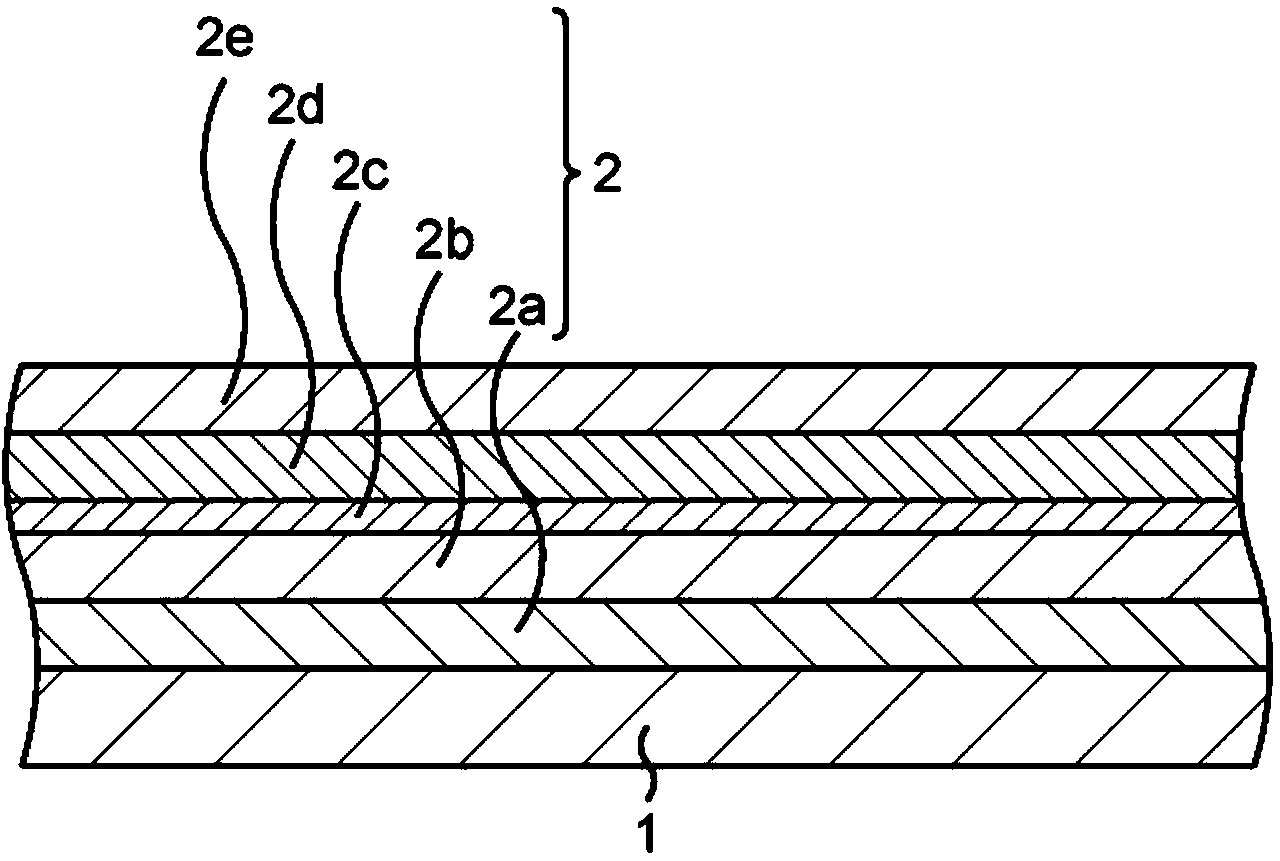

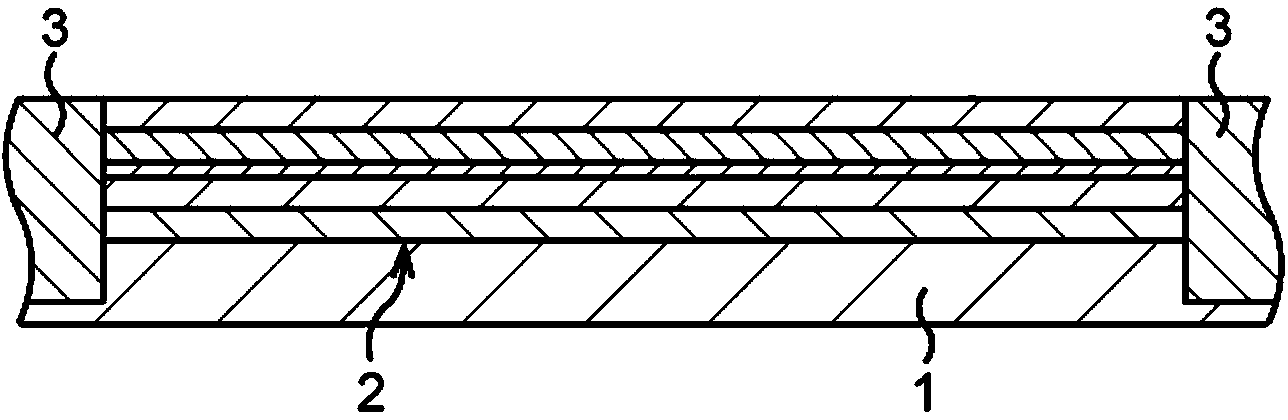

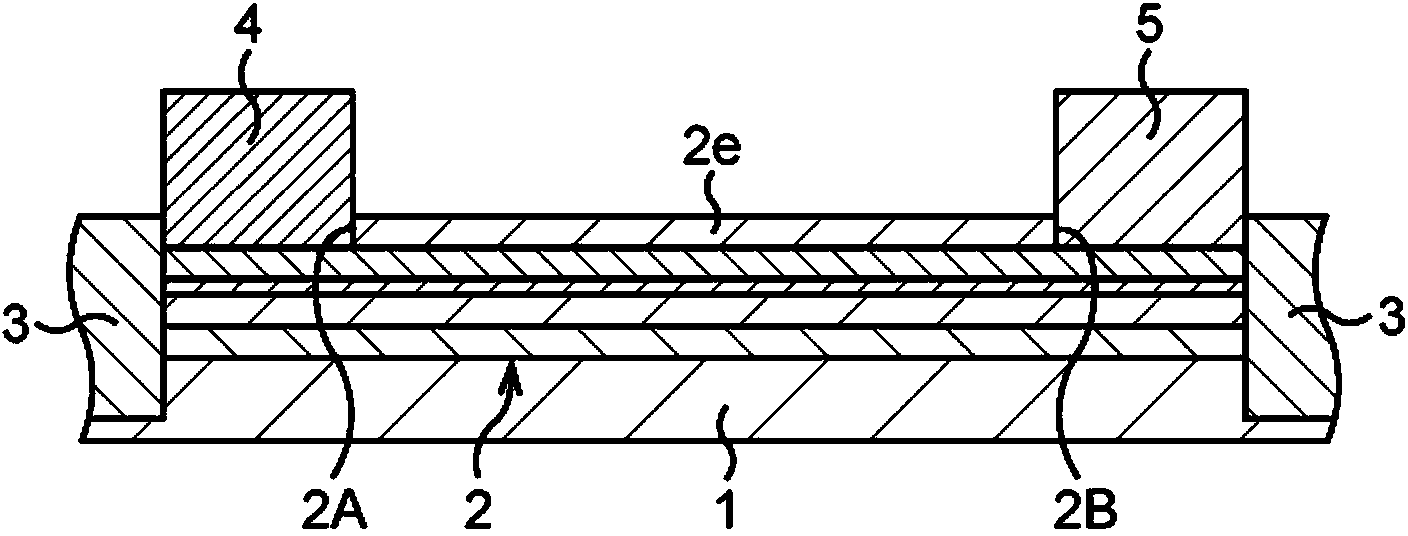

Semiconductor Device And Method Of Manufacturing The Same

ActiveCN104112672AIncrease the maximum operating frequencyImprove reliabilityHigh frequency amplifiersSemiconductor/solid-state device detailsEngineeringSemiconductor

A semiconductor device includes: a first electrode (4); a second electrode (5); an interlayer insulating film (9) made of a porous insulating material and formed above the first electrode and the second electrode; and connection parts (11a, 11b) electrically connected to the first electrode and the second electrode respectively, wherein a cavity (13) is formed between the interlayer insulating film and the first electrode, the second electrode, and parts of the connection parts.

Owner:FUJITSU LTD

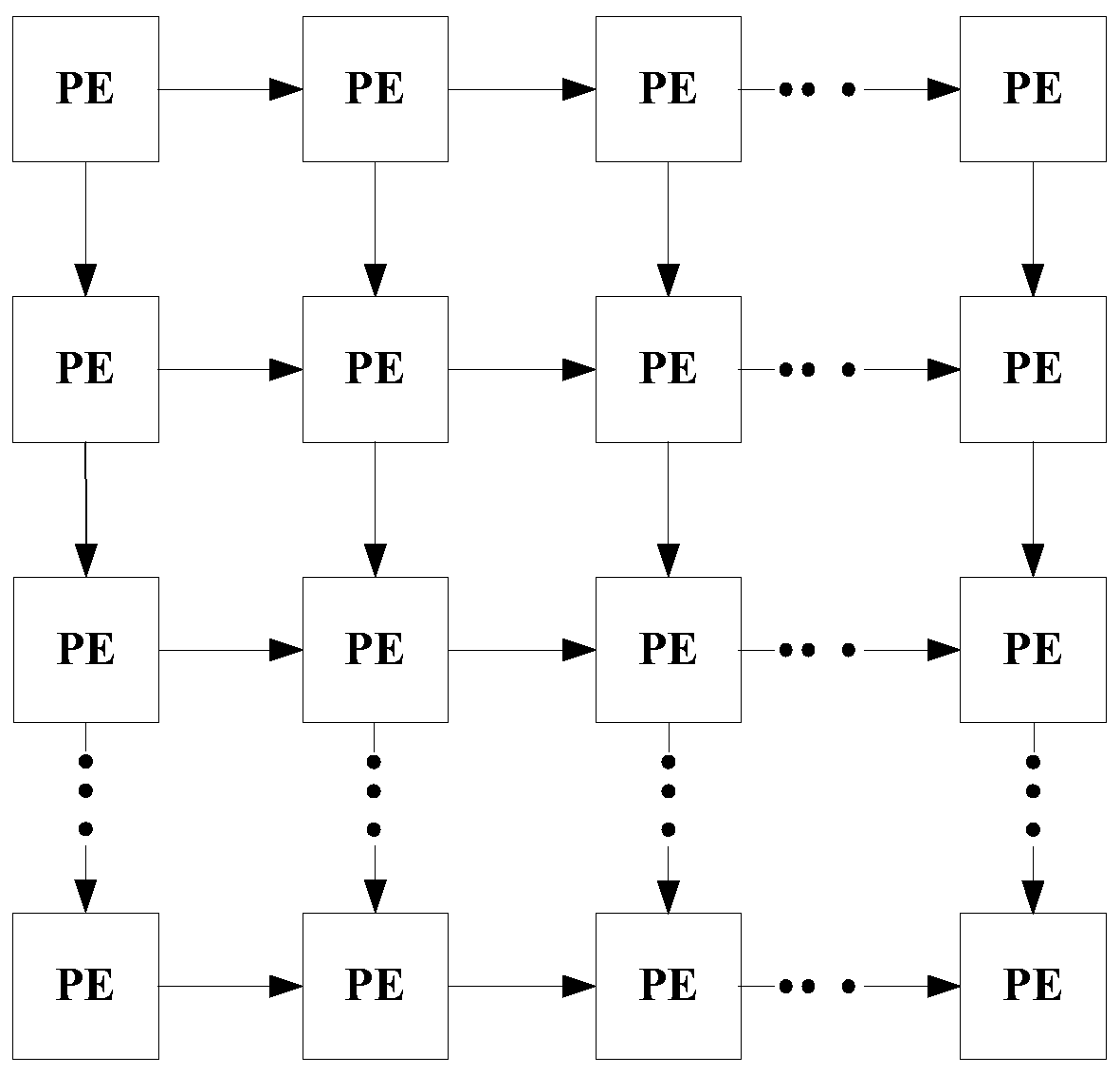

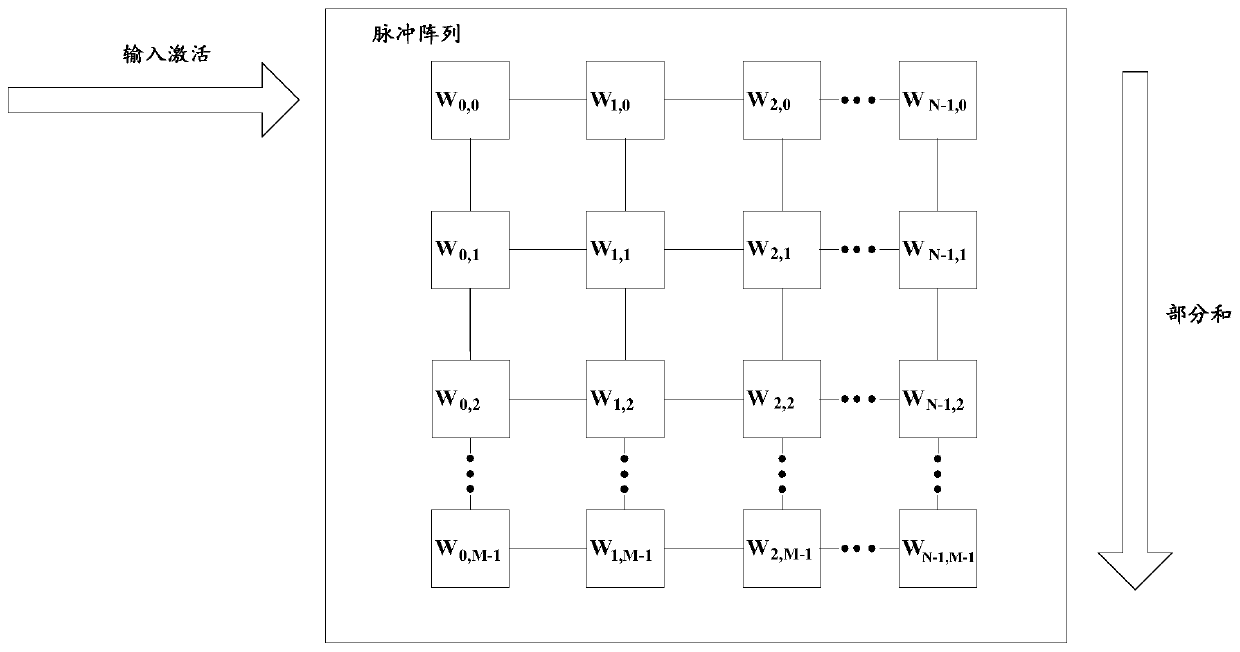

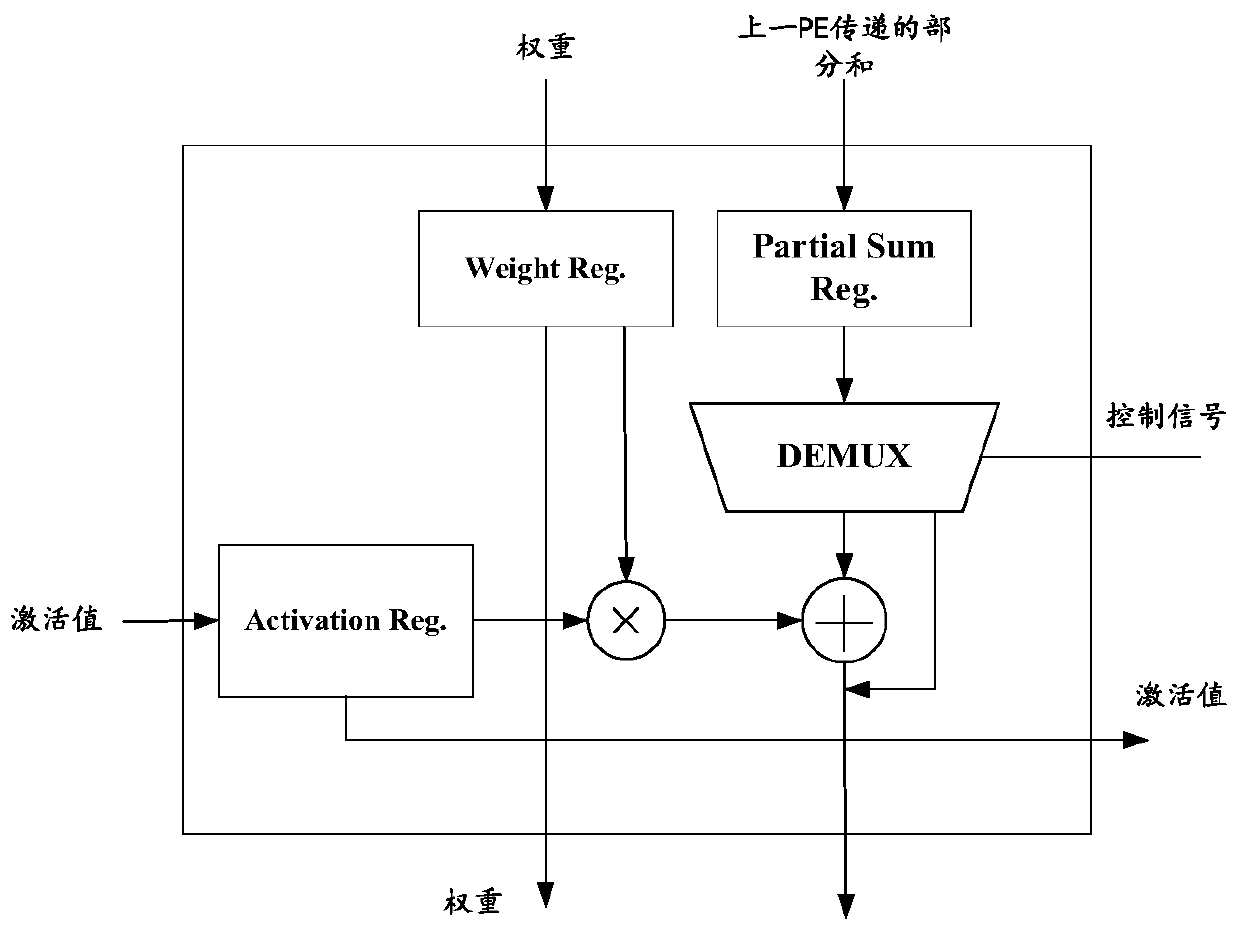

Convolutional neural network optimization method and device based on pulse array

ActiveCN110852422ALow maximum operating frequencyIncrease the maximum operating frequencyNeural architecturesPhysical realisationAlgorithmProcessing element

The invention provides a convolutional neural network optimization method and device based on a pulse array, so as to improve the lowest highest operation frequency in all PEs participating in calculation. The convolutional neural network comprises at least one convolutional layer. The convolution layer comprises at least one group of filters. The convolution operation executed by any convolutionlayer comprises the following steps: scanning on an input activation matrix by using a filter; wherein the pulse array is used for executing convolution calculation related to each convolution layer and comprises N rows and M columns of processing units PE; wherein the register of any PE participating in convolution calculation is used for storing the weight value of the corresponding filter. Themethod comprises the steps of determining an initial PE operation array for processing convolution operation of a convolution layer of the current layer; wherein the initial PE operation array comprises a row number n and a column number m; wherein n is smaller than or equal to N, and m is smaller than or equal to M; and replacing the PE with the lowest highest operation frequency in the initial PE operation array to obtain an optimized PE operation array.

Owner:JILIN UNIV

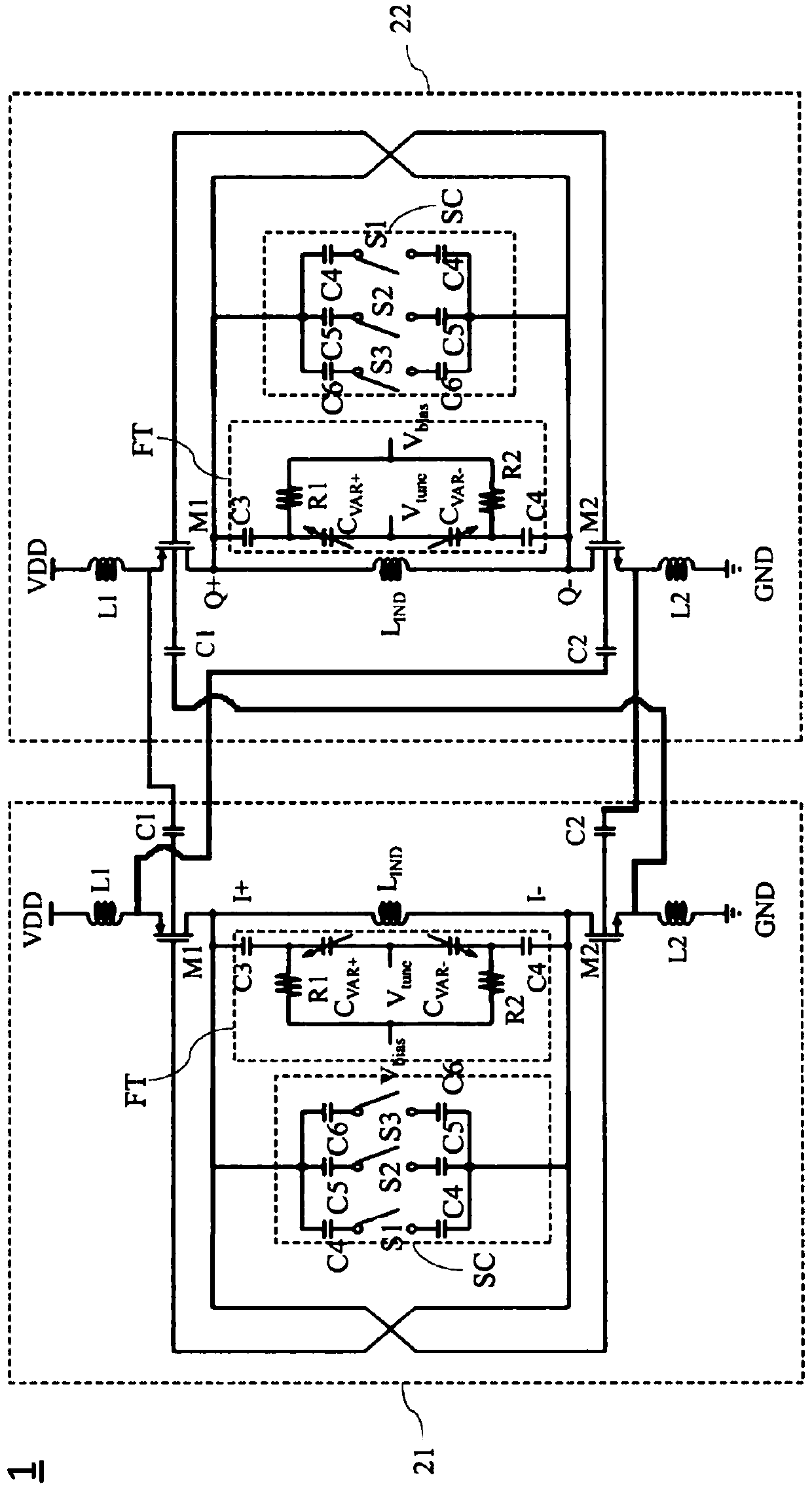

Transformer feed-back quadrature voltage controlled oscillator and communication apparatus using same

InactiveCN109842378AReduce output loadIncrease the maximum operating frequencyModulation transferencePulse automatic controlCapacitanceTransformer

A transformer feed-back quadrature voltage controlled oscillator (QVCO) is provided, and the QVCO comprises a first half circuit and a second half circuit, and the first half circuit and the second half circuit respectively comprise a first coupling capacitor, a second coupling capacitor, an induction inductor, a PMOS transistor, an NMOS transistor and a frequency modulation circuit. Base electrodes of the PMOS transistor and the NMOS transistor are respectively connected to a first end of the first coupling capacitor and a first end of the second coupling capacitor. The drain electrode of thePMOS transistor is connected with the first end of the induction inductor, the grid electrode of the NMOS transistor is connected to the drain electrode of the PMOS transistor, and the drain electrode of the NMOS transistor is connected to the grid electrode of the PMOS transistor and the second end of the induction inductor. The frequency modulation circuit is connected to the drain electrode ofthe PMOS transistor and the drain electrode of the NMOS transistor.

Owner:徐克铭

Array-type processor having delay adjusting circuit for adjusting a clock cycle in accordance with a critical path delay of the data path

ActiveUS8402298B2Increase the maximum operating frequencyImprove processing efficiencyDigital computer detailsGenerating/distributing signalsDatapathState switching

Disclosed is an array-type processor including a data path unit in which a plurality of processor elements are arranged in an array; a state-transition management unit that stores information for controlling changeover of data paths; and a delay adjusting circuit that adjusts delay of the input clock signal based upon information output from the state-transition management unit, and provides the delay-adjusted clock signal to the data path unit. The delay adjusting circuit has a delay control information memory and a programmable delay. The delay control information memory stores a plurality of items of delay control information, delay control information is read out using a configuration number supplied from the state-transition management unit as an address, and the delay control information is applied to the programmable array. The programmable delay delays the input clock signal by a delay time specified by the delay control information and provides the delayed clock signal to the data path unit.

Owner:RENESAS ELECTRONICS CORP