Clock distribution network rapid design method

A clock distribution network, clock network technology, applied in computer-aided design, computing, computer parts and other directions, can solve the problems of high-quality winding resources affecting design performance, increasing clock network power consumption, and clock grid line occupation, etc. The effect of increasing the maximum operating frequency, reducing the clock network load, and reducing the impact of timing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Below in conjunction with specific embodiment, further illustrate the present invention. It should be understood that these examples are only used to illustrate the present invention and are not intended to limit the scope of the present invention. In addition, it should be understood that after reading the teachings of the present invention, those skilled in the art can make various changes or modifications to the present invention, and these equivalent forms also fall within the scope defined by the appended claims of the present application.

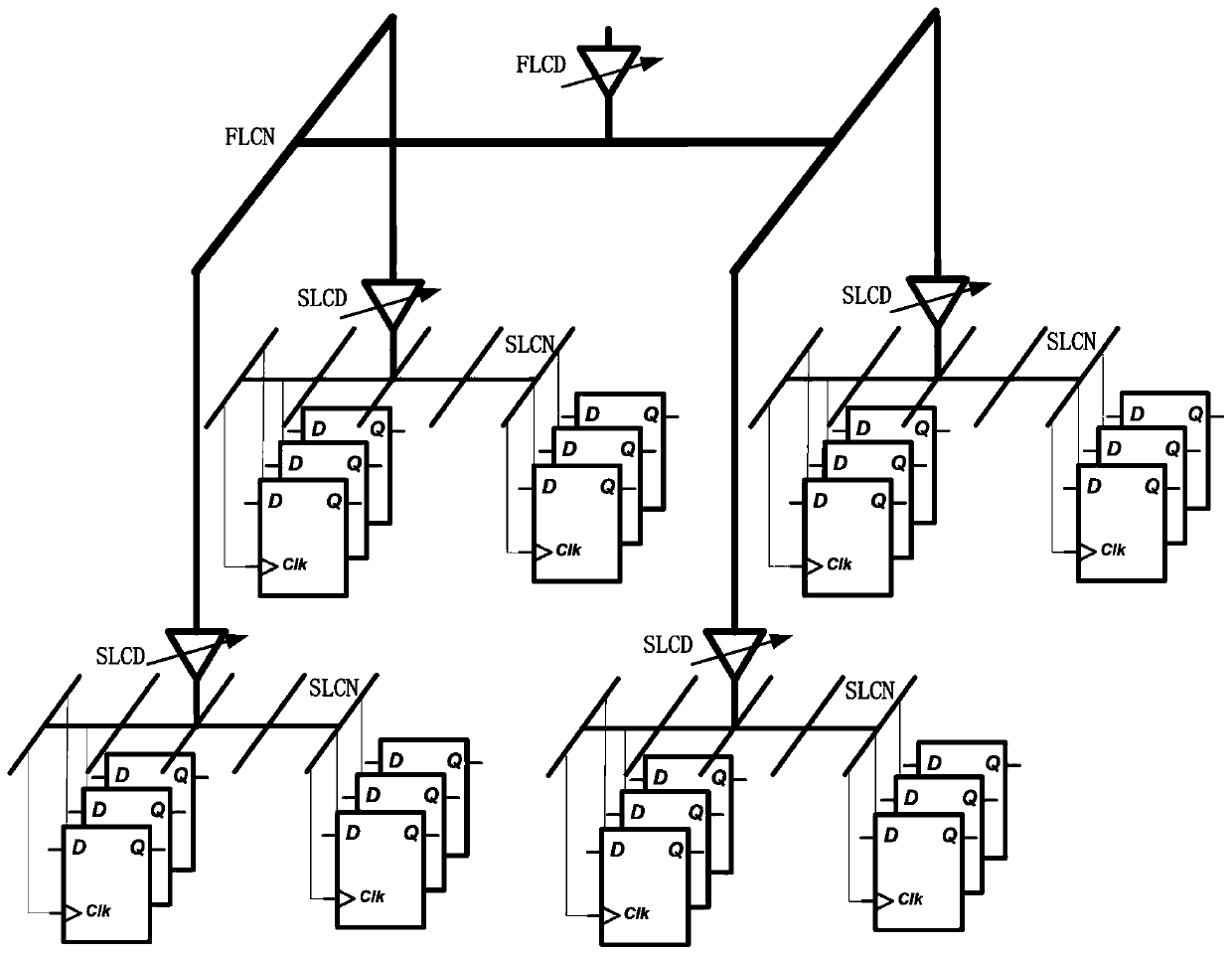

[0022] Embodiments of the present invention relate to a rapid design method of a clock distribution network, such as figure 1 As shown, the method divides the clock network into a first-level clock network (abbreviated as FLCN) and a second-level clock network (abbreviated as SLCN), wherein the first-level clock network is driven by a first-level clock network driver unit (abbreviated as FLCD) , the second-level clock network ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More