Patents

Literature

9476 results about "Circuit design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

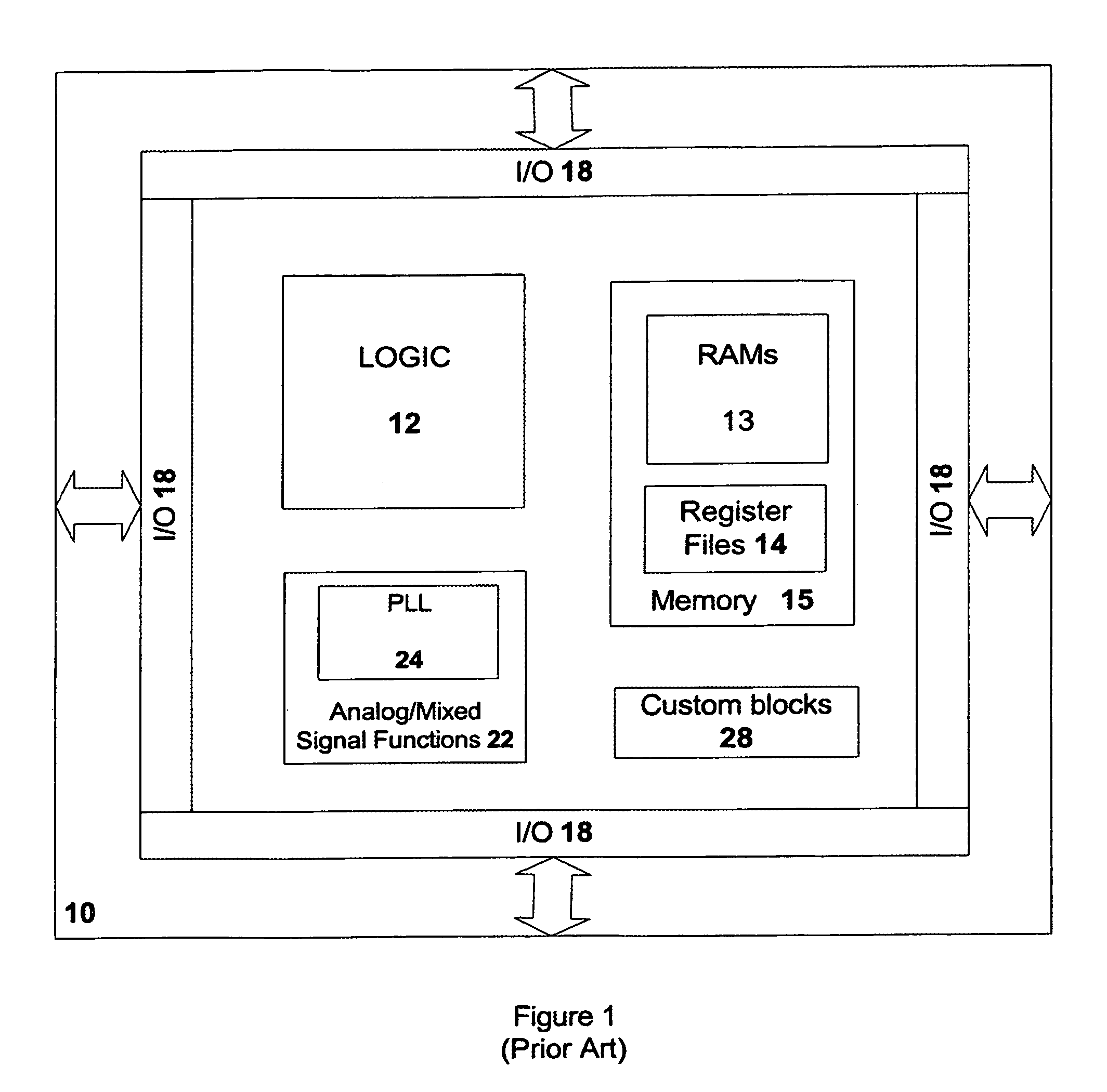

The process of circuit design can cover systems ranging from complex electronic systems all the way down to the individual transistors within an integrated circuit. For simple circuits the design process can often be done by one person without needing a planned or structured design process, but for more complex designs, teams of designers following a systematic approach with intelligently guided computer simulation are becoming increasingly common. In integrated circuit design automation, the term "circuit design" often refers to the step of the design cycle which outputs the schematics of the integrated circuit. Typically this is the step between logic design and physical design.

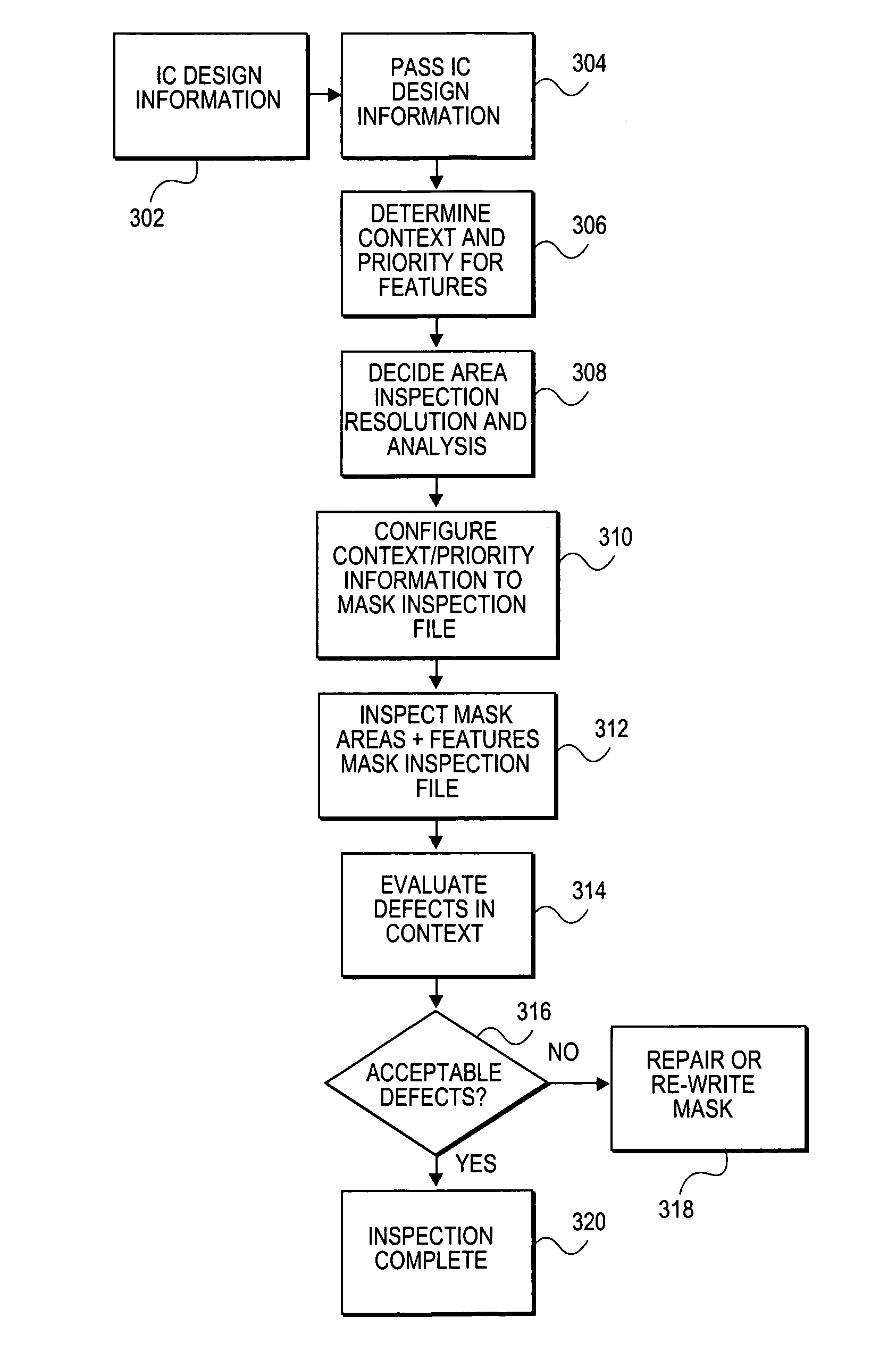

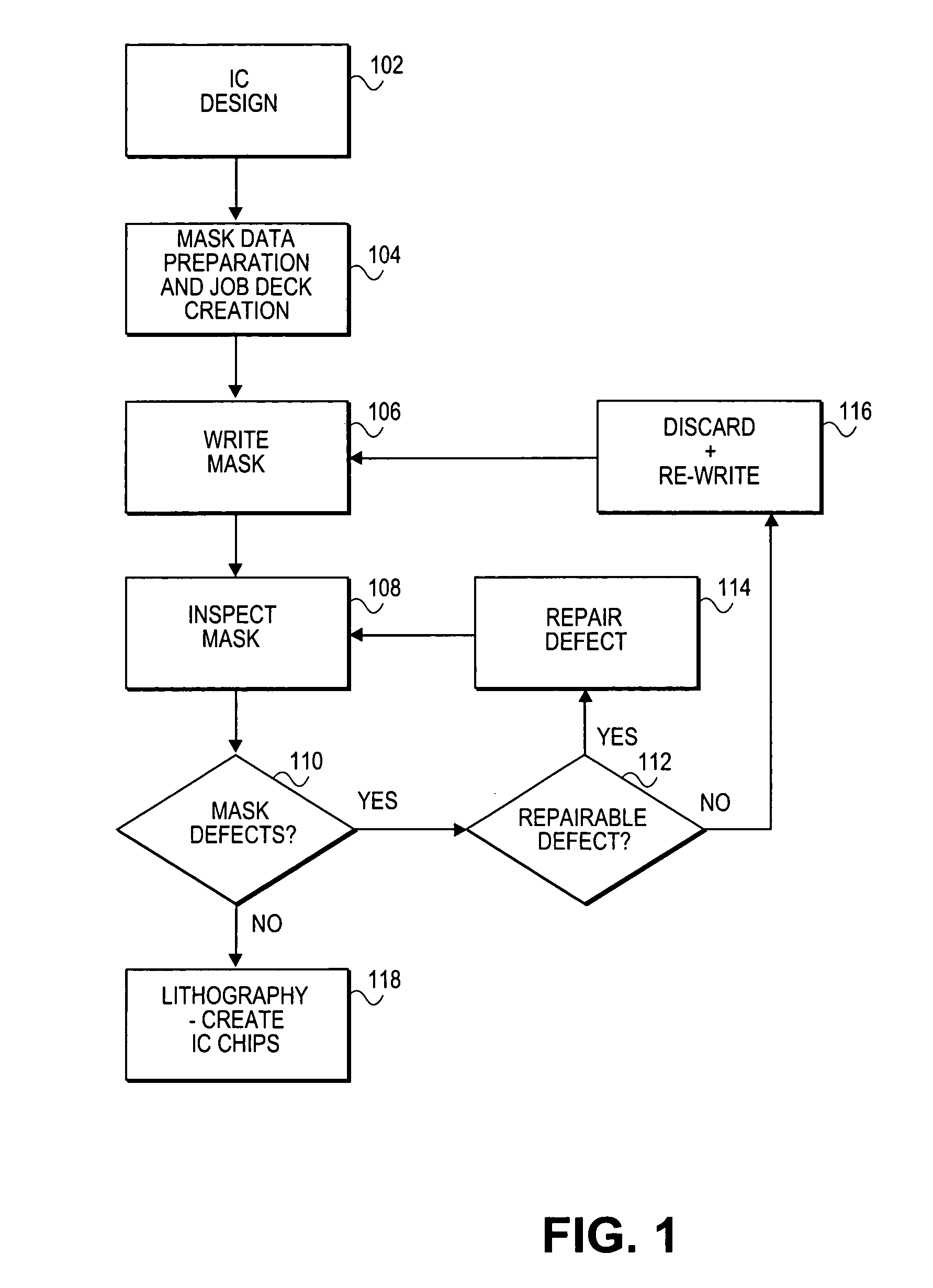

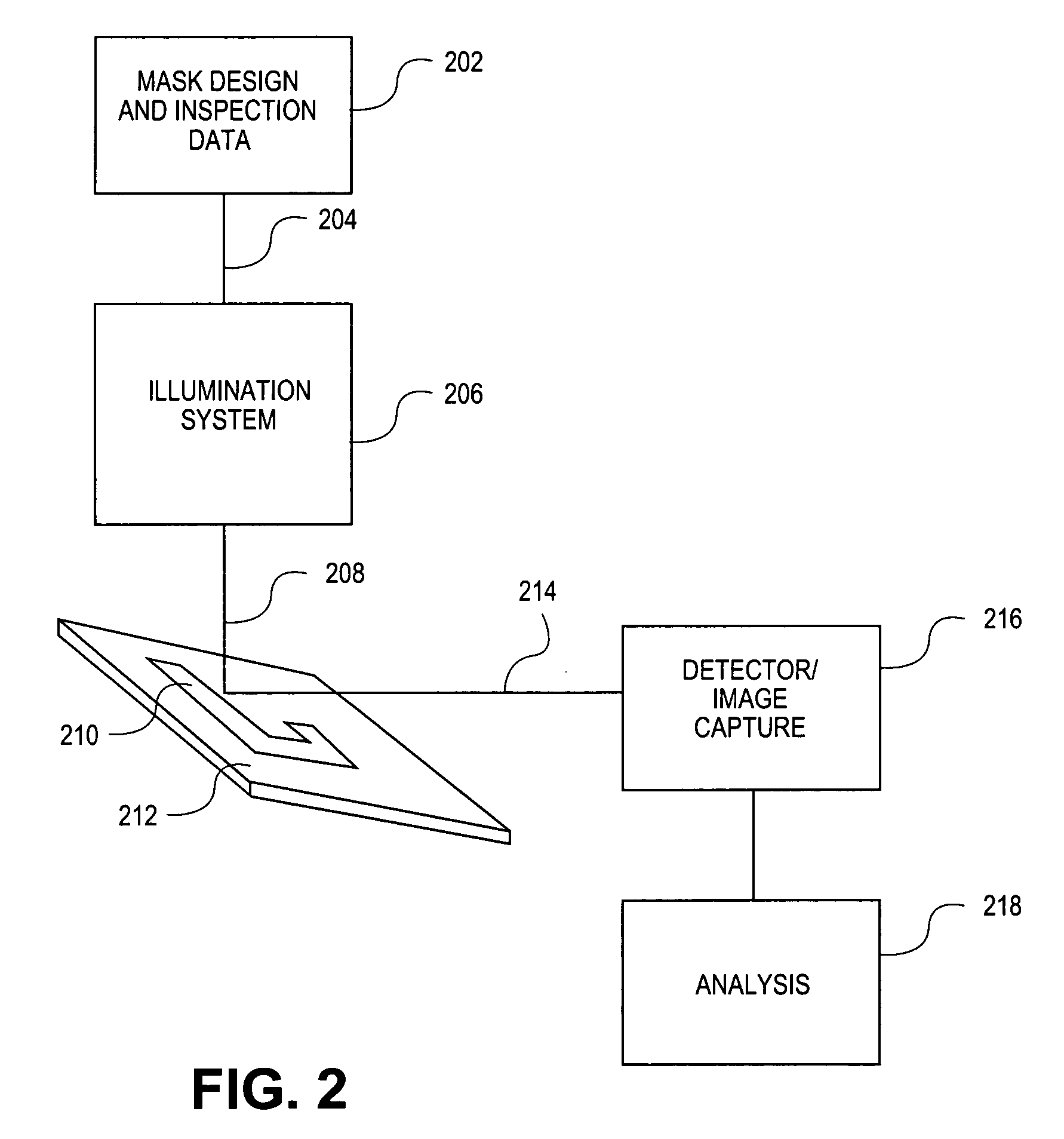

Method and system for context-specific mask inspection

InactiveUS7231628B2Electrical testingCharacter and pattern recognitionMask inspectionContext specific

A method for inspecting lithography masks includes generating integrated circuit design data and using context information from the integrated circuit design data to inspect a mask.

Owner:CADENCE DESIGN SYST INC

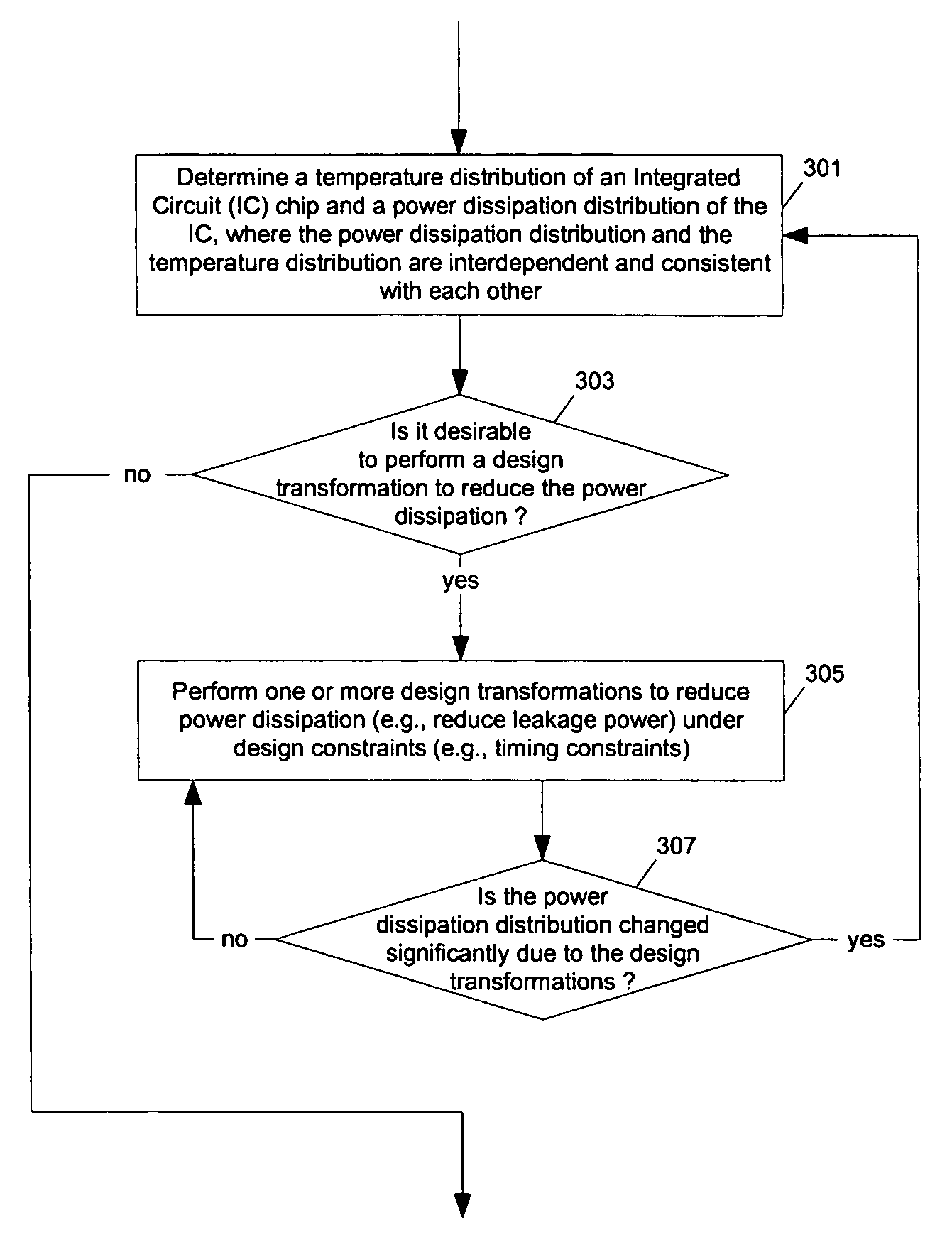

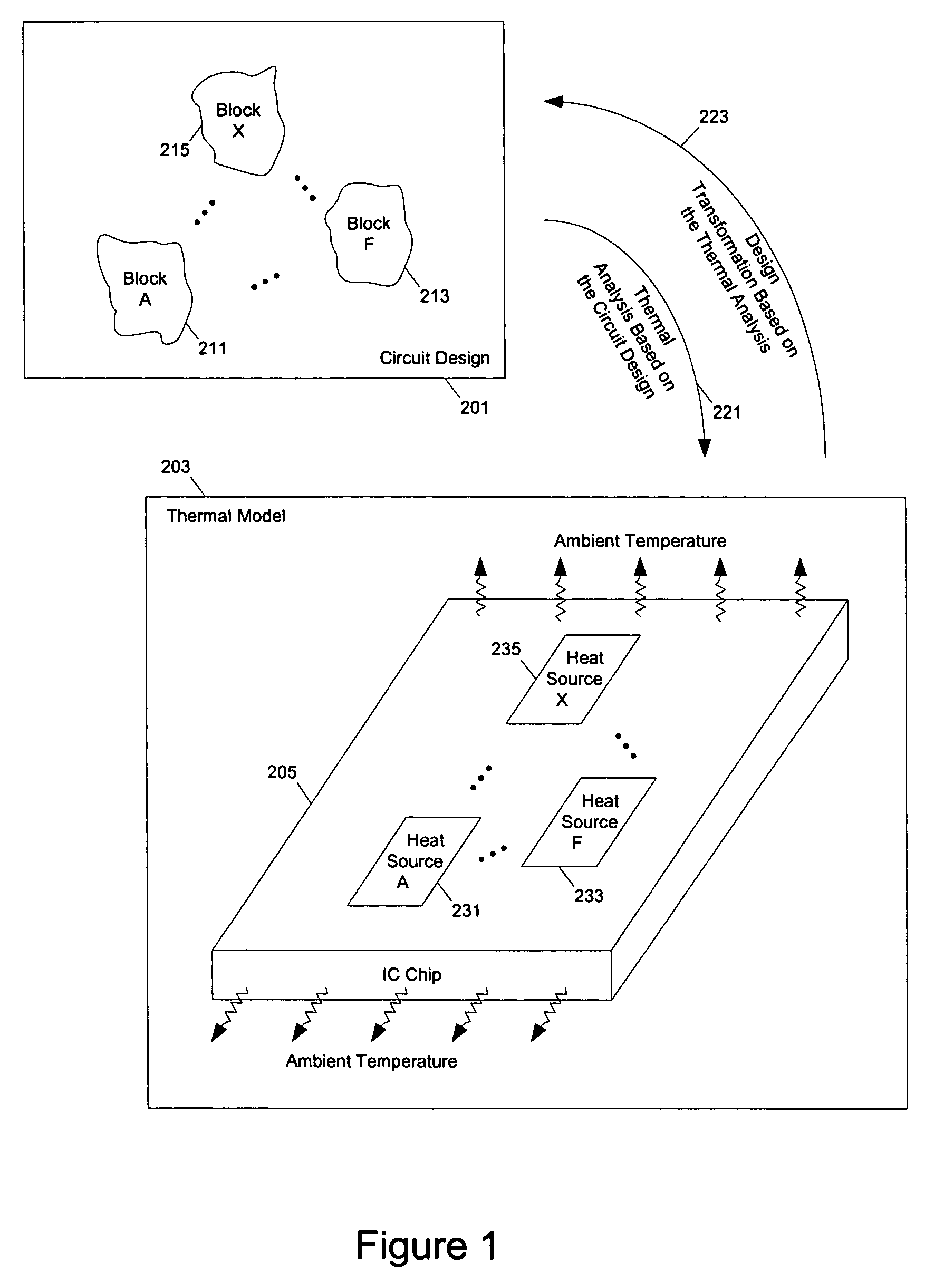

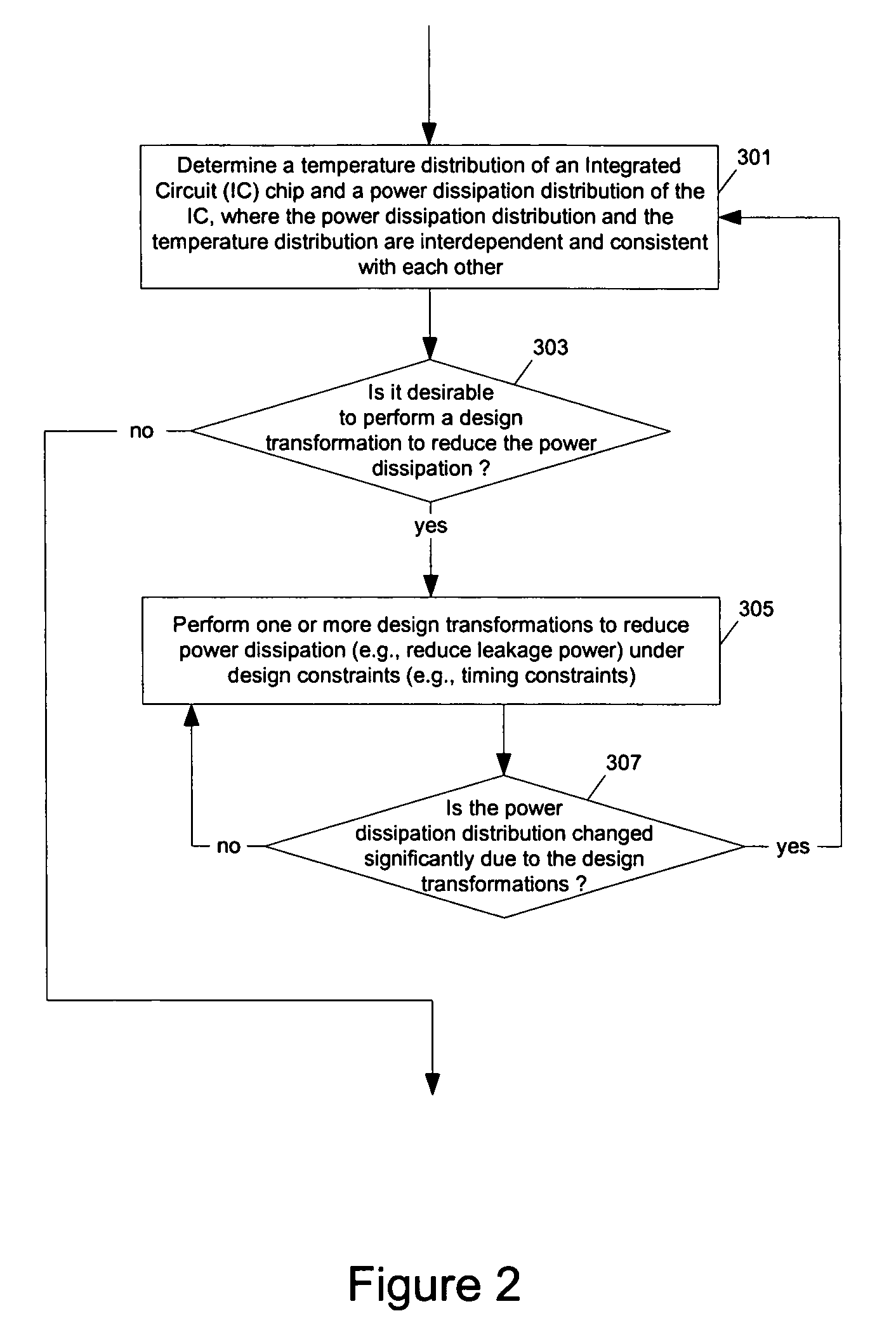

Methods and apparatuses for thermal analysis based circuit design

ActiveUS7366997B1Reduce power consumptionExtension of timeSoftware simulation/interpretation/emulationSpecial data processing applicationsPower usageTransition time

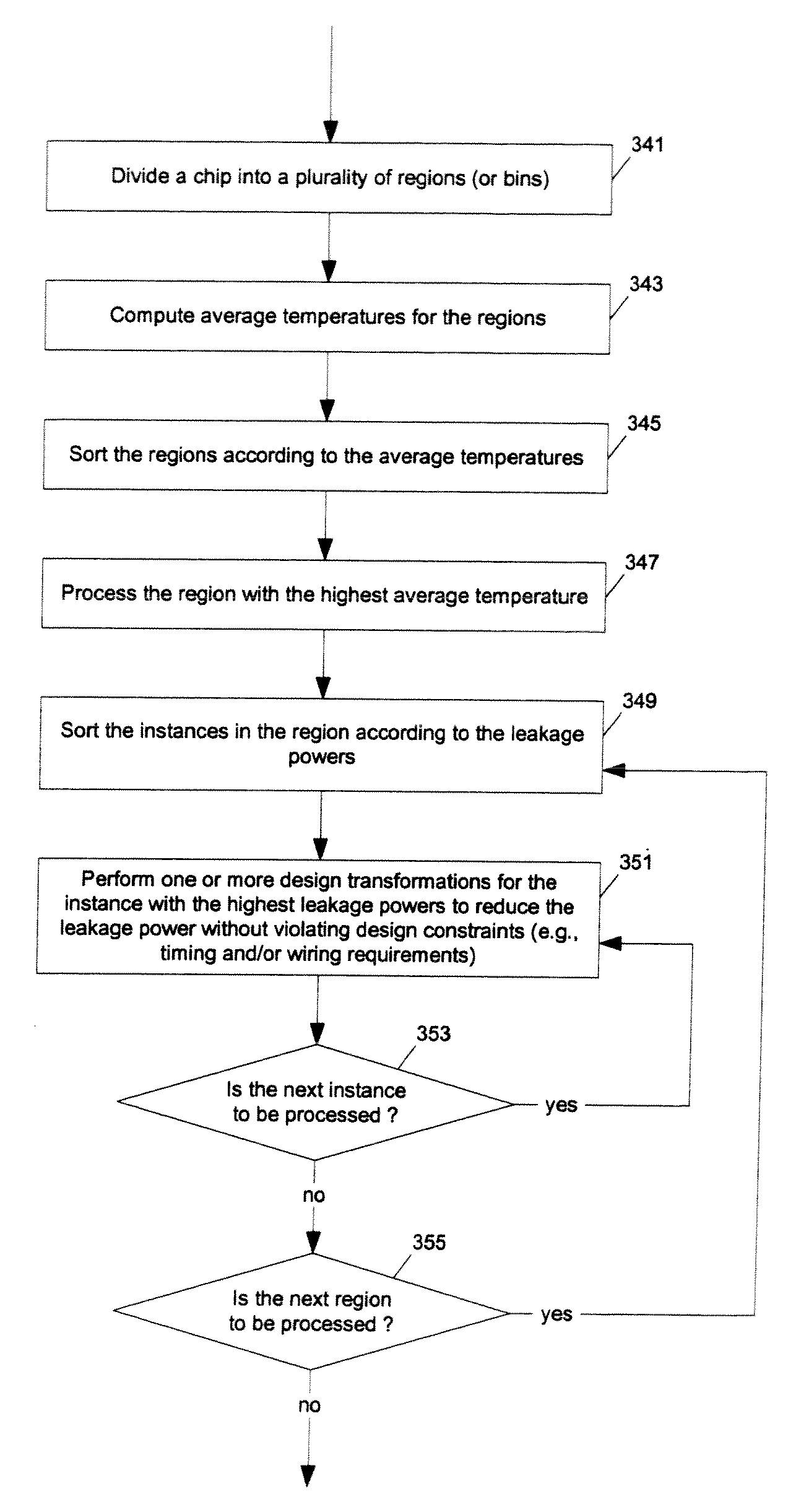

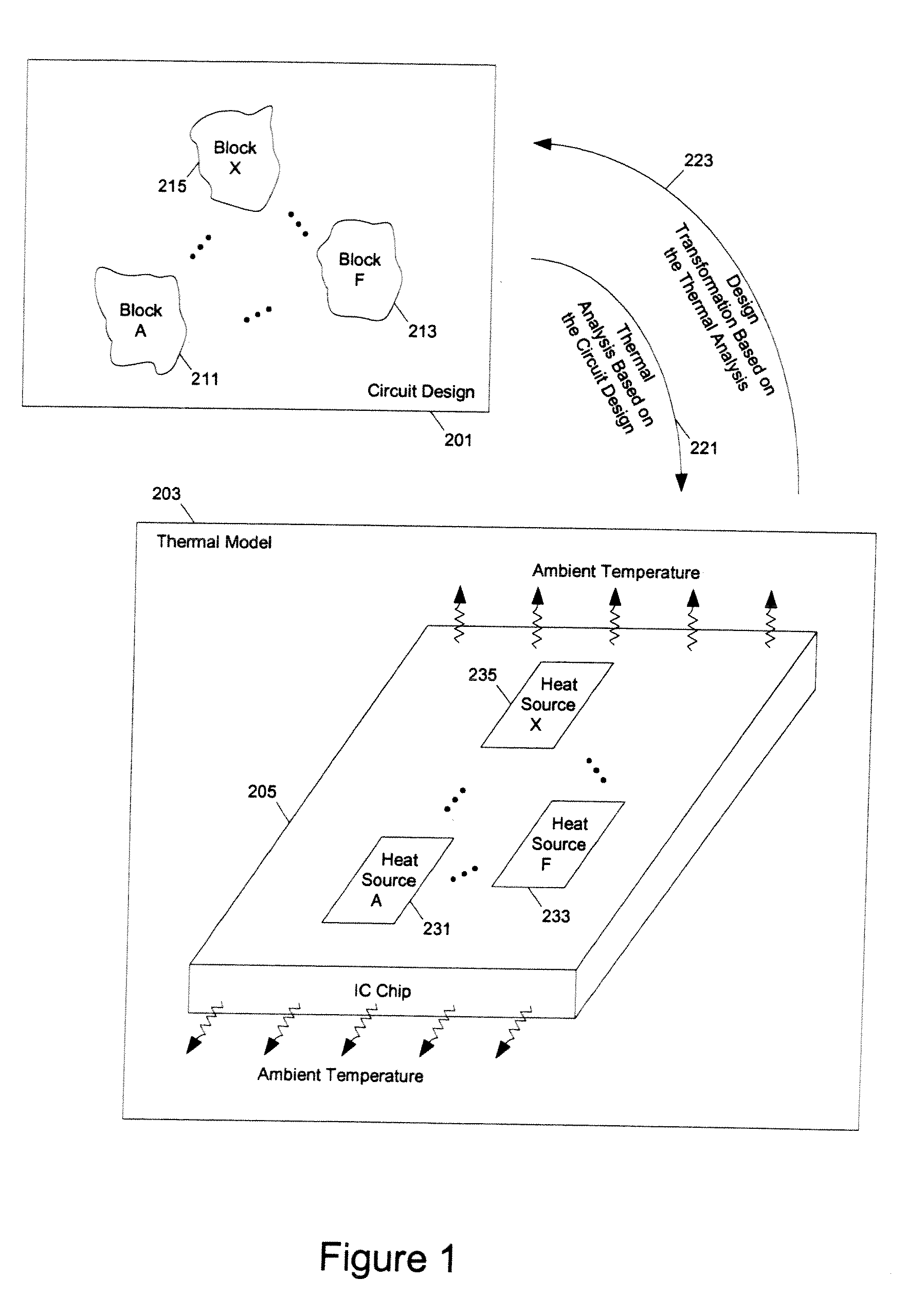

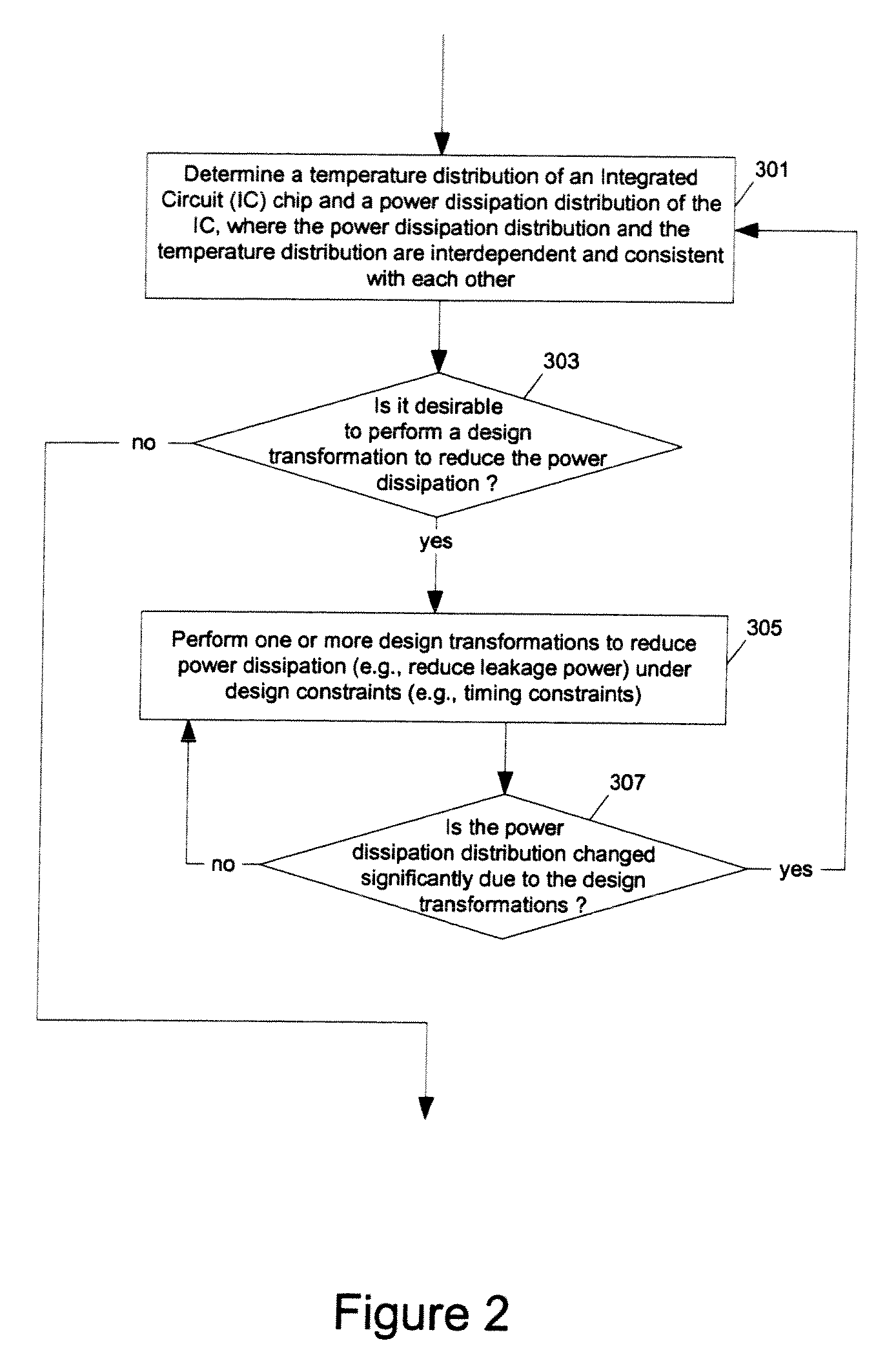

Methods and apparatuses for circuit design to reduce power usage, such as reducing temperature dependent power usage, and / or to improve timing, such as reducing temperature dependent delay or transition time. At least one embodiment of the present invention reduces the power dissipation and improves the timing of an integrated circuit to optimize the design. A thermal analysis is used to determine the temperature dependent power dissipation of a circuit and the temperature distribution of the circuit resulting from dissipating the heat created by the temperature dependent power dissipation. Then, the components of the design are selectively transformed to reduce the power dissipation and to improve timing based on the temperature solution. The transformation may include placement changes and netlist changes, such as the change of transistor threshold voltages for cells or for blocks of the circuit chip.

Owner:SYNOPSYS INC

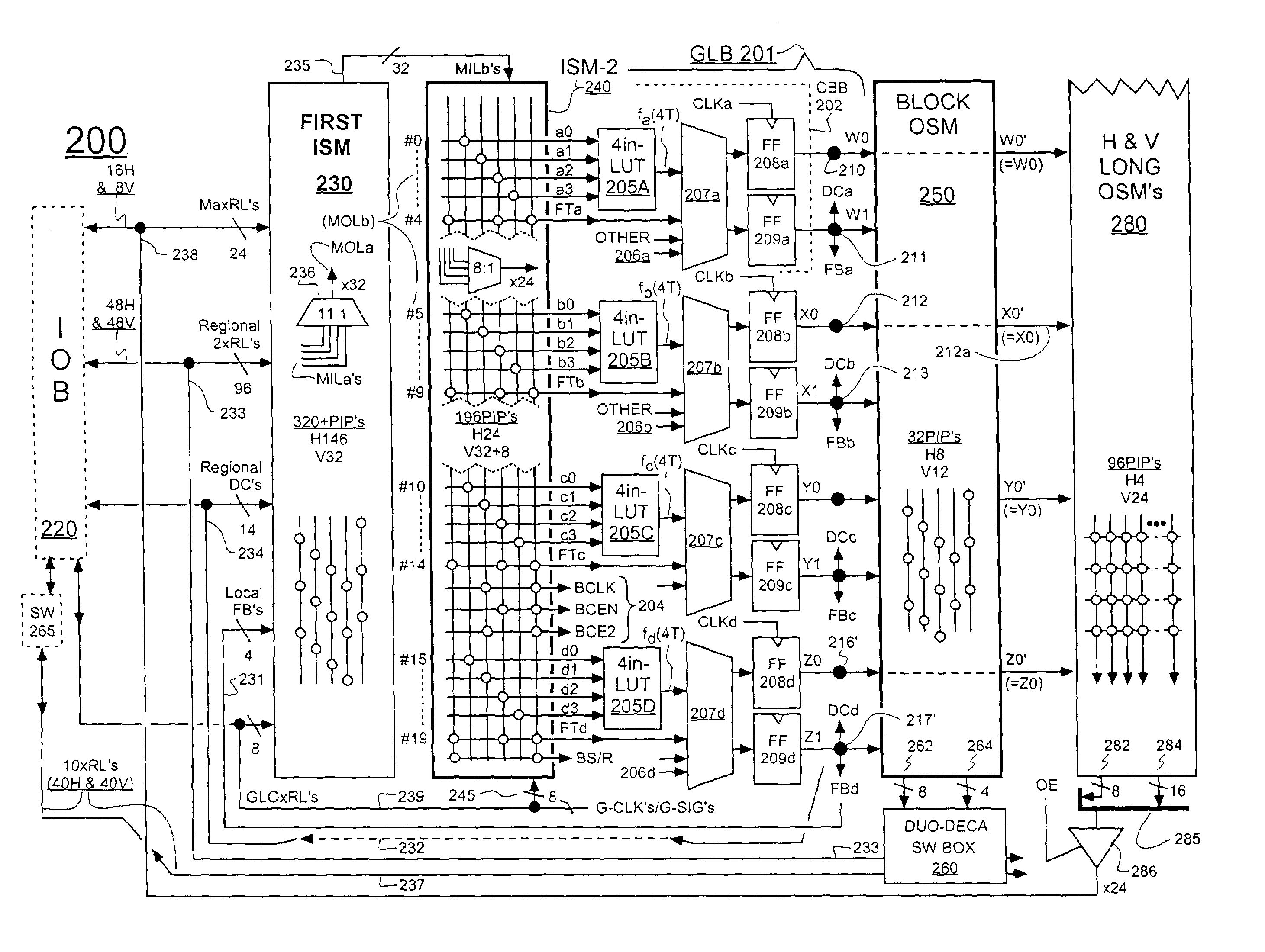

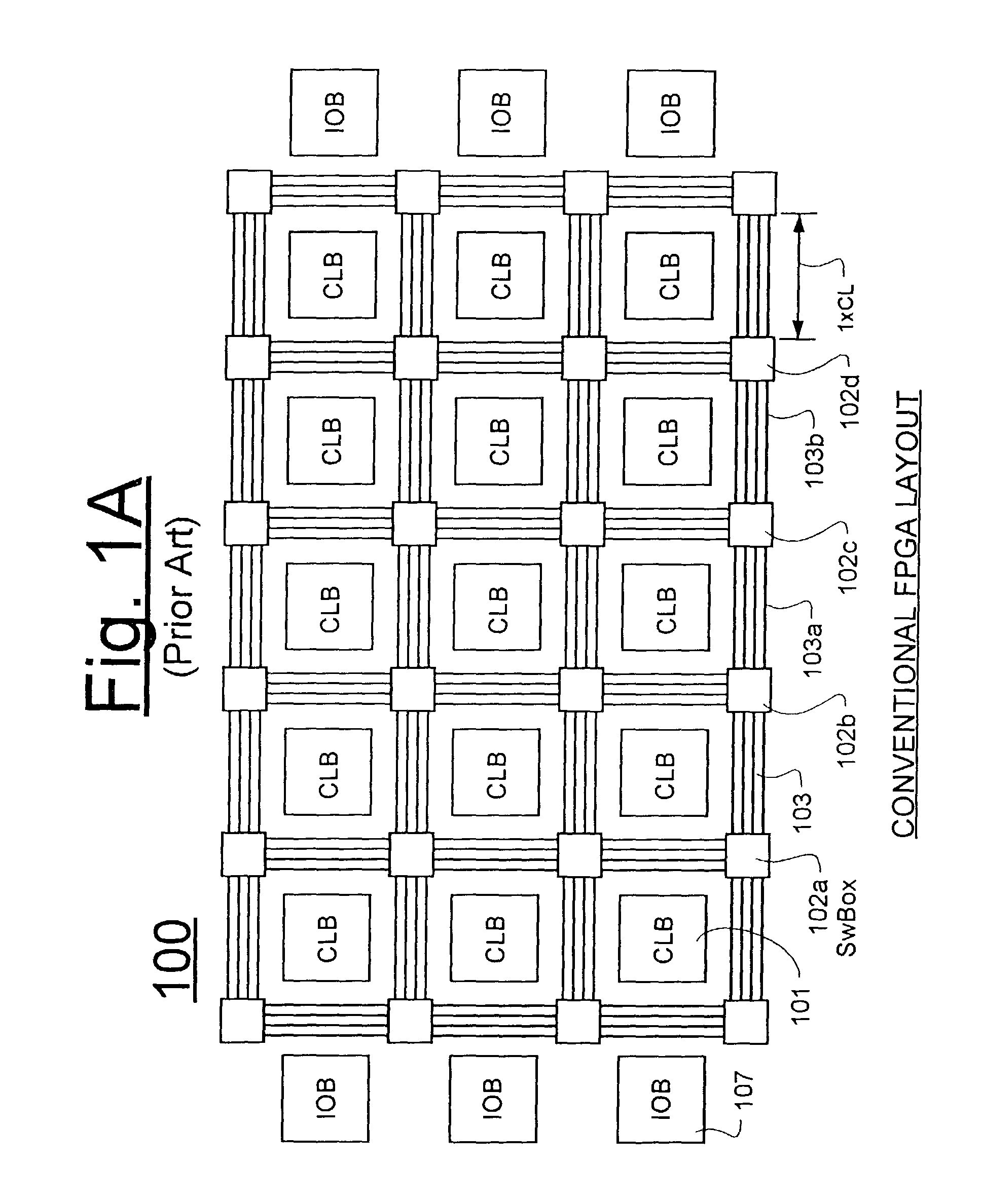

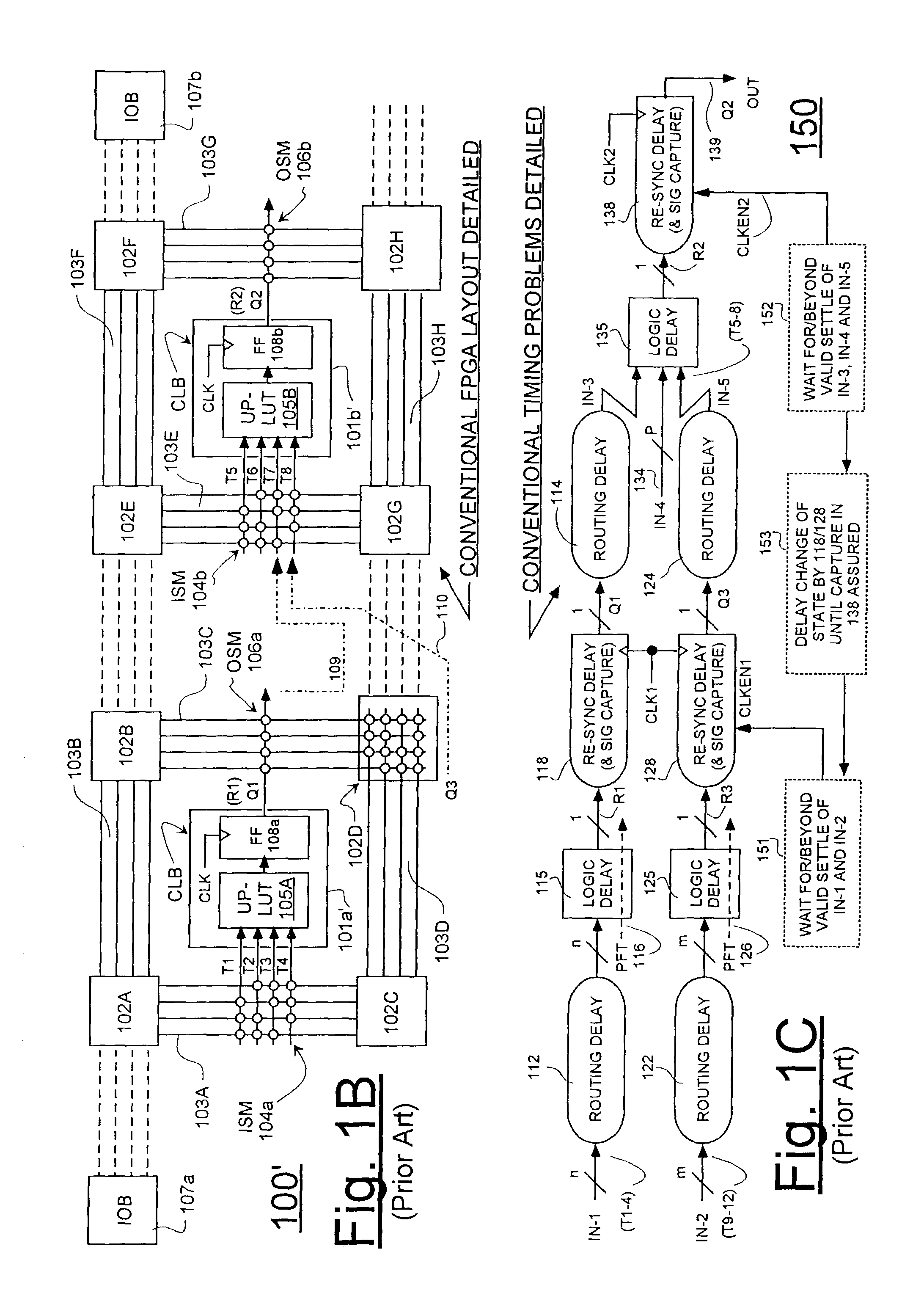

FPGA with register-intensive architecture

ActiveUS7028281B1Minimize resourceReduce consumptionSolid-state devicesCAD circuit designProcessor registerMultiplexer

Field programmable gate arrays (FPGA's) may be structured in accordance with the disclosure to have a register-intensive architecture that provides, for each of plural function-spawning LookUp Tables (e.g. a 4-input, base LUT's) within a logic block, a plurality of in-block accessible registers. A register-feeding multiplexer means may be provided for allowing each of the plural registers to equivalently capture and store a result signal output by the corresponding, base LUT of the plural registers. Registerable, primary and secondary feedthroughs may be provided for each base LUT so that locally-acquired input signals of the LUT may be fed-through to the corresponding, in-block registers for register-recovery purposes without fully consuming (wasting) the lookup resources of the associated, base LUT. A multi-stage, input switch matrix (ISM) may be further provided for acquiring and routing input signals from adjacent, block-interconnect lines (AIL's) and / or block-intra-connect lines (e.g., FB's) to the base LUT's and / or their respective, registerable feedthroughs. Techniques are disclosed for utilizing the many in-block registers and / or the registerable feedthroughs and / or the multi-stage ISM's for efficiently implementing various circuit designs by appropriately configuring such register-intensive FPGA's.

Owner:LATTICE SEMICON CORP

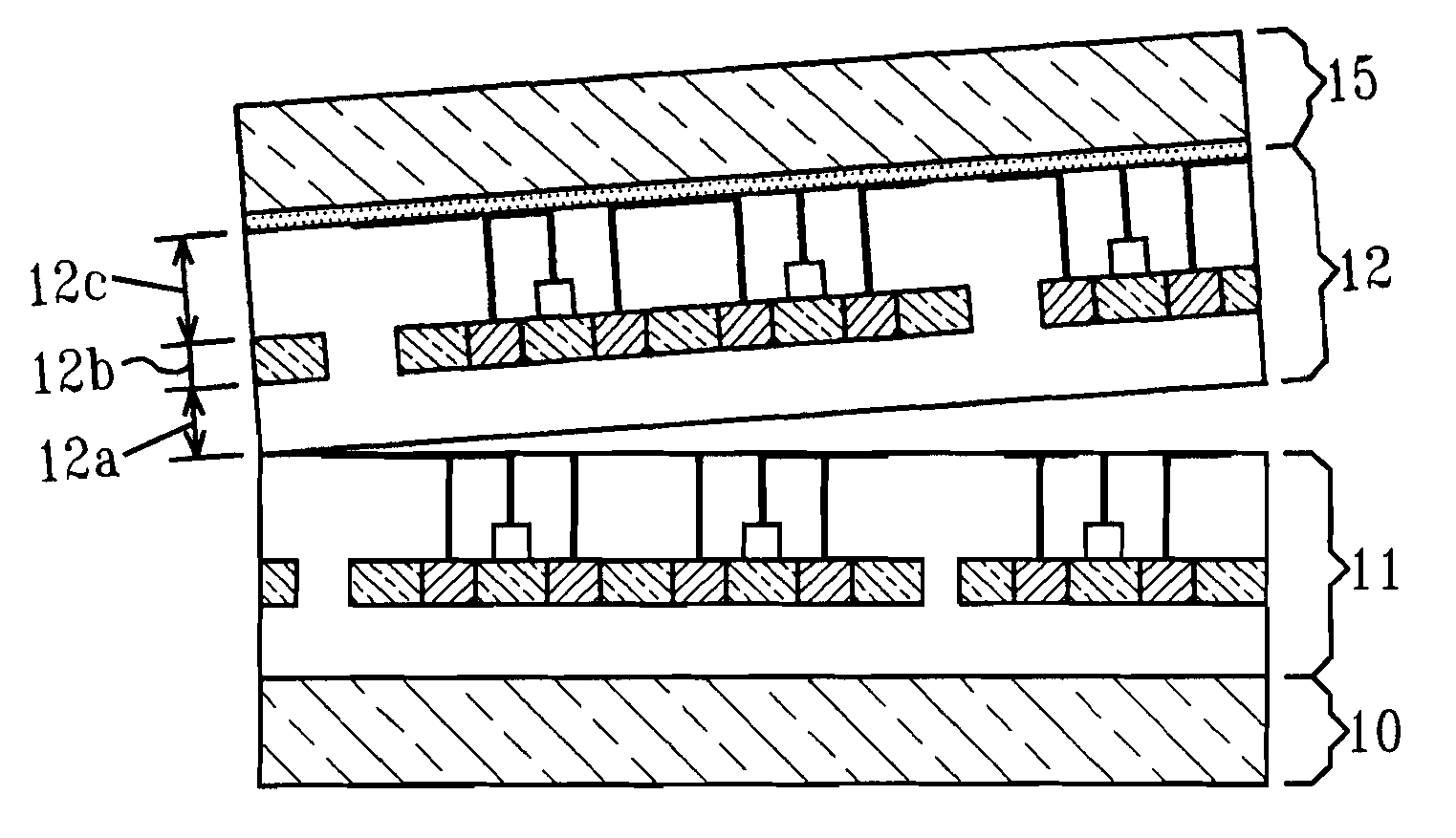

3-dimensional integrated circuit architecture, structure and method for fabrication thereof

ActiveUS20070228383A1Solid-state devicesSemiconductor/solid-state device manufacturingPerformance enhancementAudio power amplifier

An integrated circuit design, structure and method for fabrication thereof includes at least one logic device layer and at least two additional separate memory array layers. Each of the logic device layer and the at least two memory array layers is independently optimized for a particular type of logic device or memory device disposed therein. Preferably also disposed within the logic device layer are array sense amplifiers, memory array output drivers and like higher performance circuitry otherwise generally disposed within memory array layer substrates. All layers may be independently powered to provide additional performance enhancement.

Owner:IBM CORP

Methods and apparatuses for thermal analysis based circuit design

ActiveUS20080168406A1Reduce power consumptionExtension of timeSoftware simulation/interpretation/emulationSpecial data processing applicationsEngineeringPower usage

Methods and apparatuses for circuit design to reduce power usage, such as reducing temperature dependent power usage, and / or to improve timing, such as reducing temperature dependent delay or transition time. At least one embodiment of the present invention reduces the power dissipation and improves the timing of an integrated circuit to optimize the design. A thermal analysis is used to determine the temperature dependent power dissipation of a circuit and the temperature distribution of the circuit resulting from dissipating the heat created by the temperature dependent power dissipation. Then, the components of the design are selectively transformed to reduce the power dissipation and to improve timing based on the temperature solution. The transformation may include placement changes and netlist changes, such as the change of transistor threshold voltages for cells or for blocks of the circuit chip.

Owner:SYNOPSYS INC

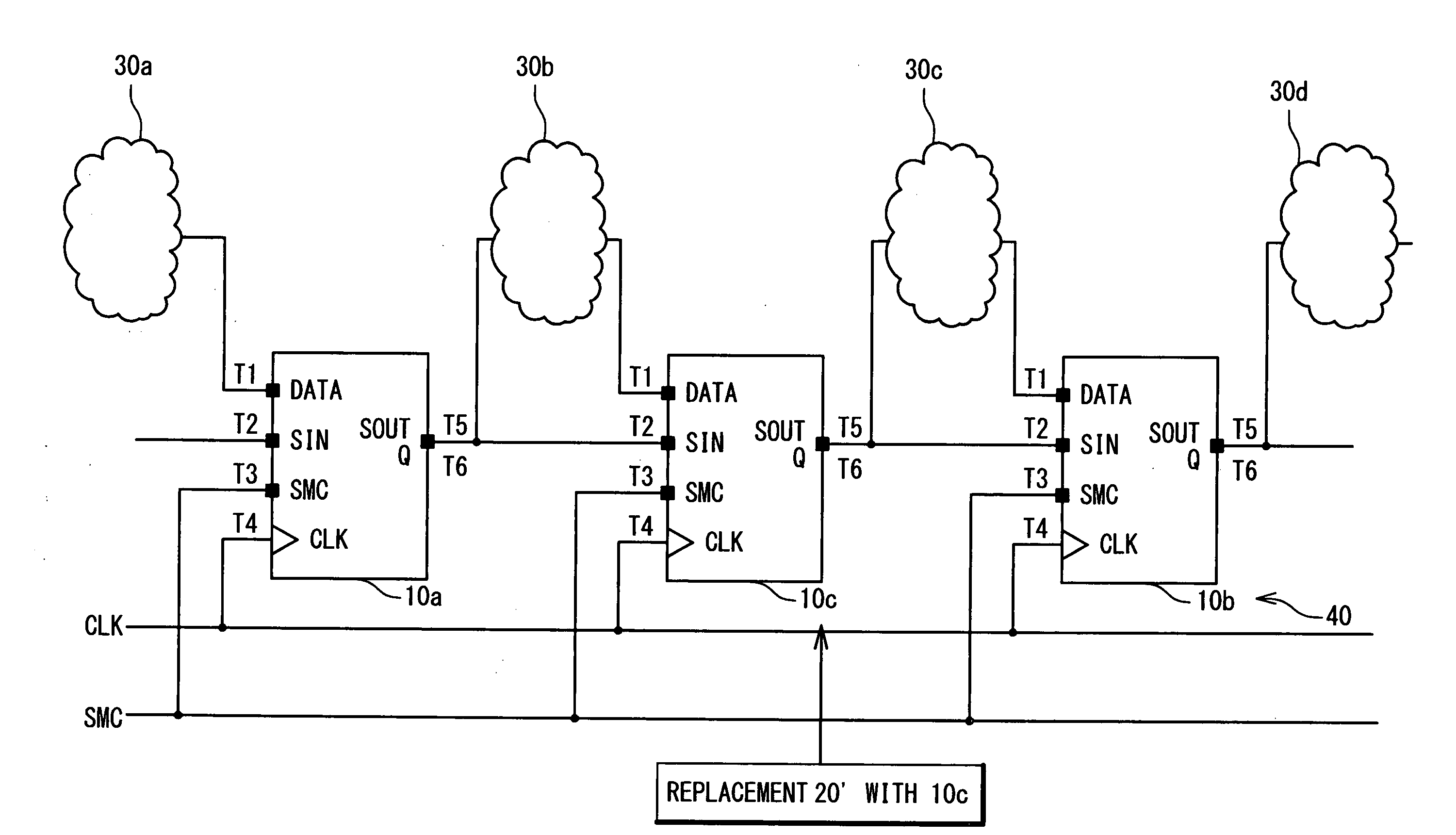

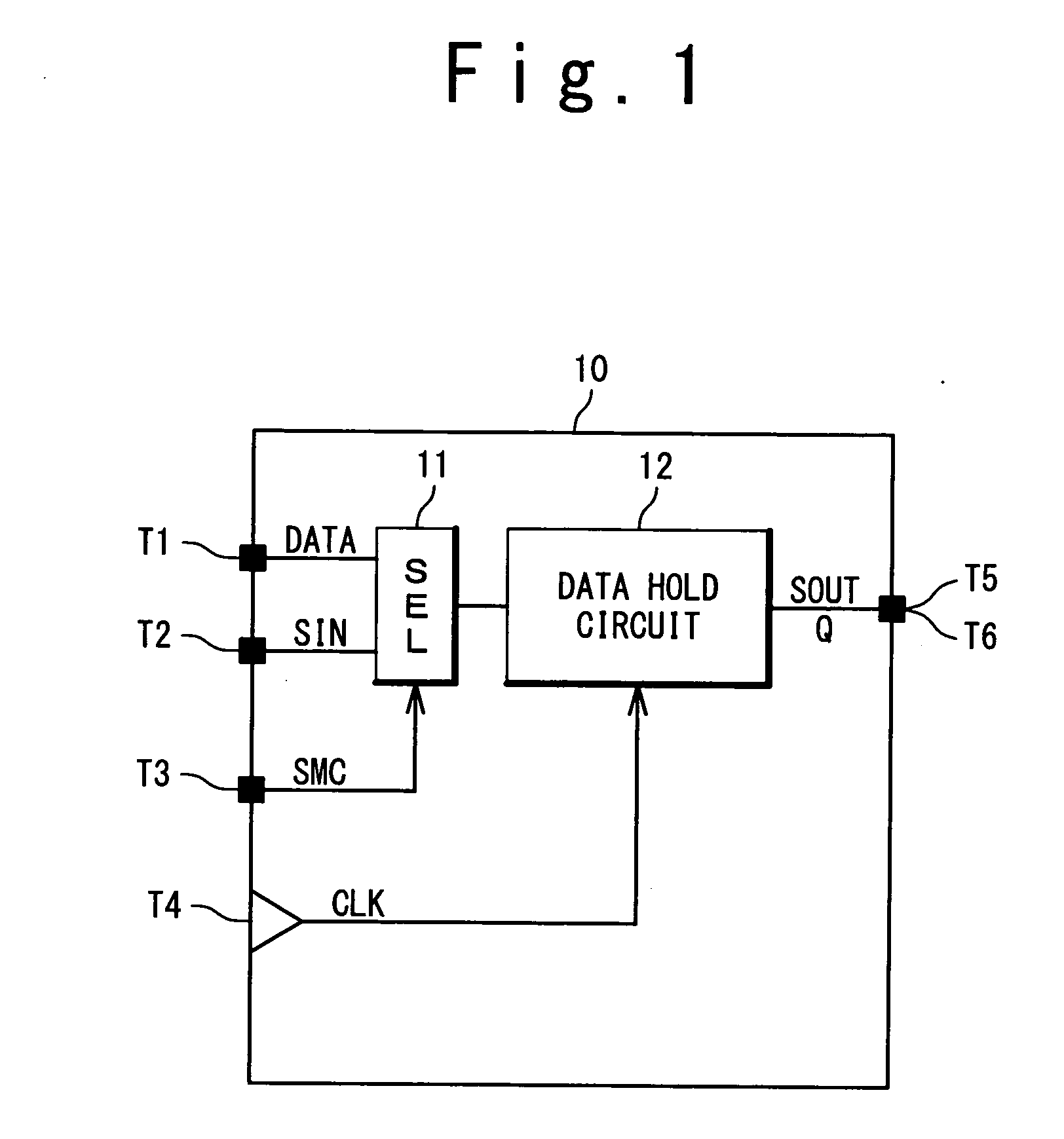

Integrated circuit design based on scan design technology

InactiveUS20090032899A1Effect of power consumption reduction is enhancedReduce power consumptionElectronic circuit testingSolid-state devicesEngineeringCircuit design

An integrated circuit is provided with a scan chain including a scan flip-flop and a dummy block. The dummy block has a clock terminal receiving a clock signal, a scan input terminal connected to a scan data line within the scan chain, and a scan output terminal connected to another scan data line within the scan chain. The dummy block is configured to output data on the scan output terminal in response to input data fed to the scan input terminal, not responsively to the clock signal.

Owner:RENESAS ELECTRONICS CORP

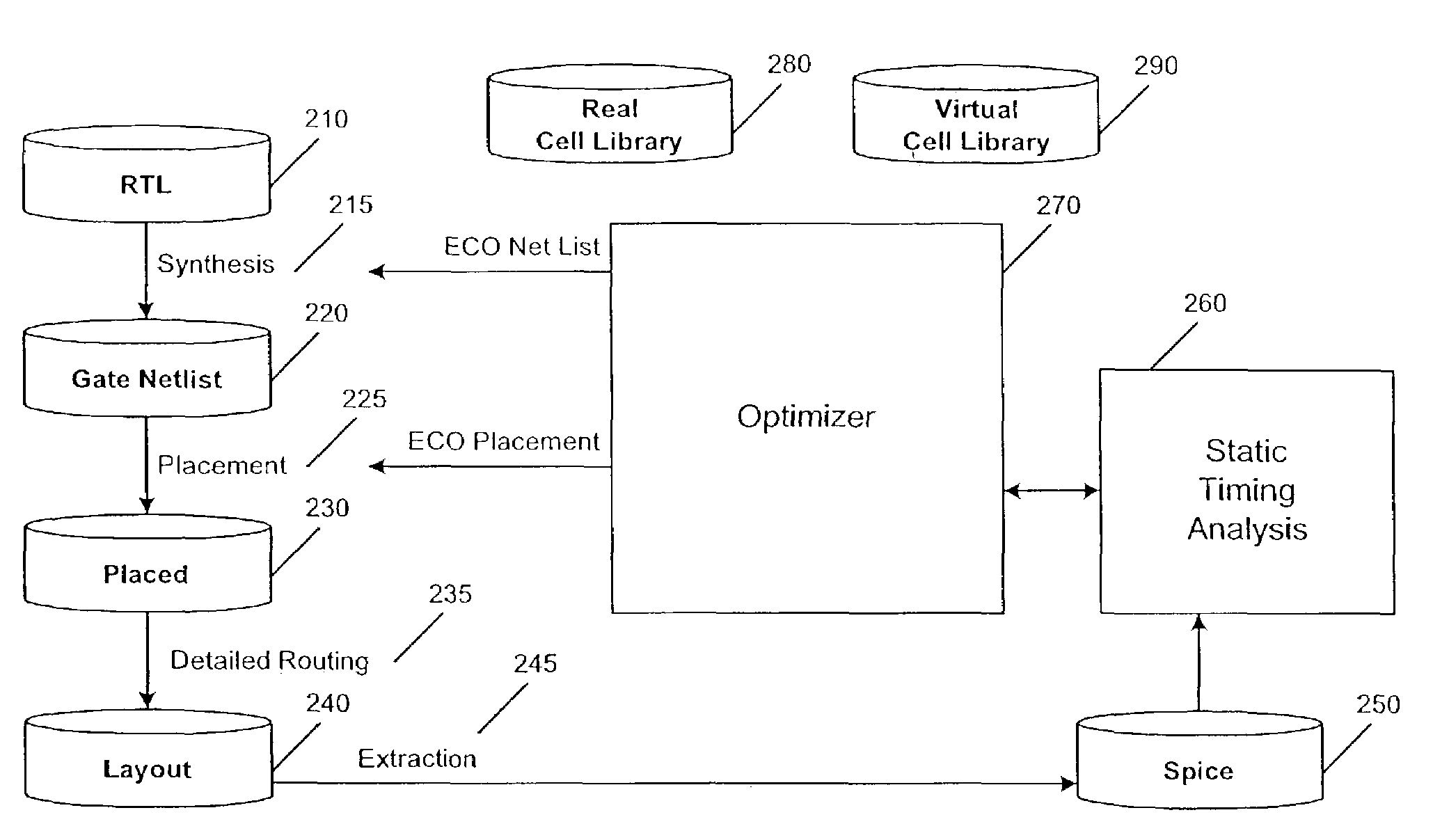

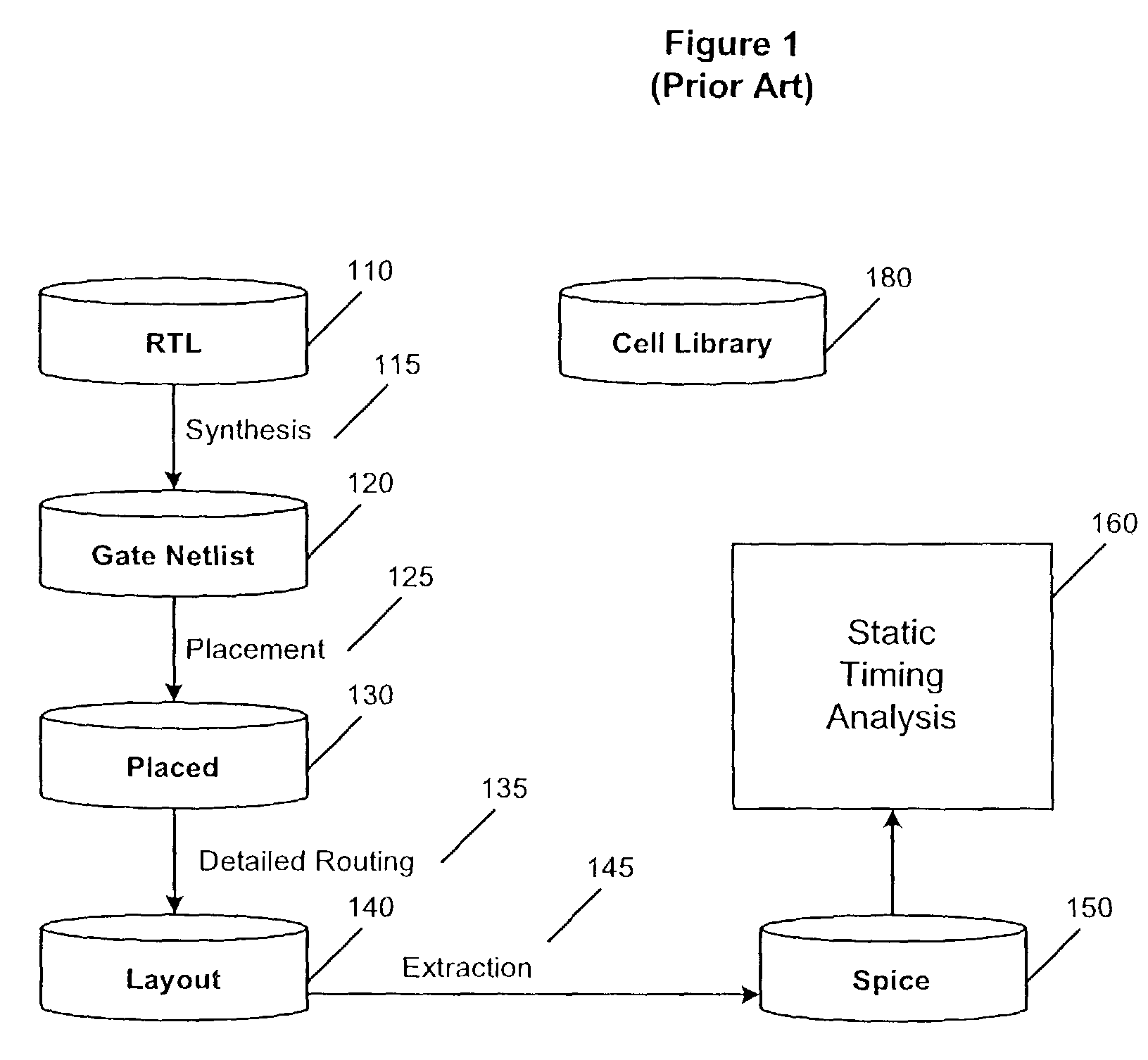

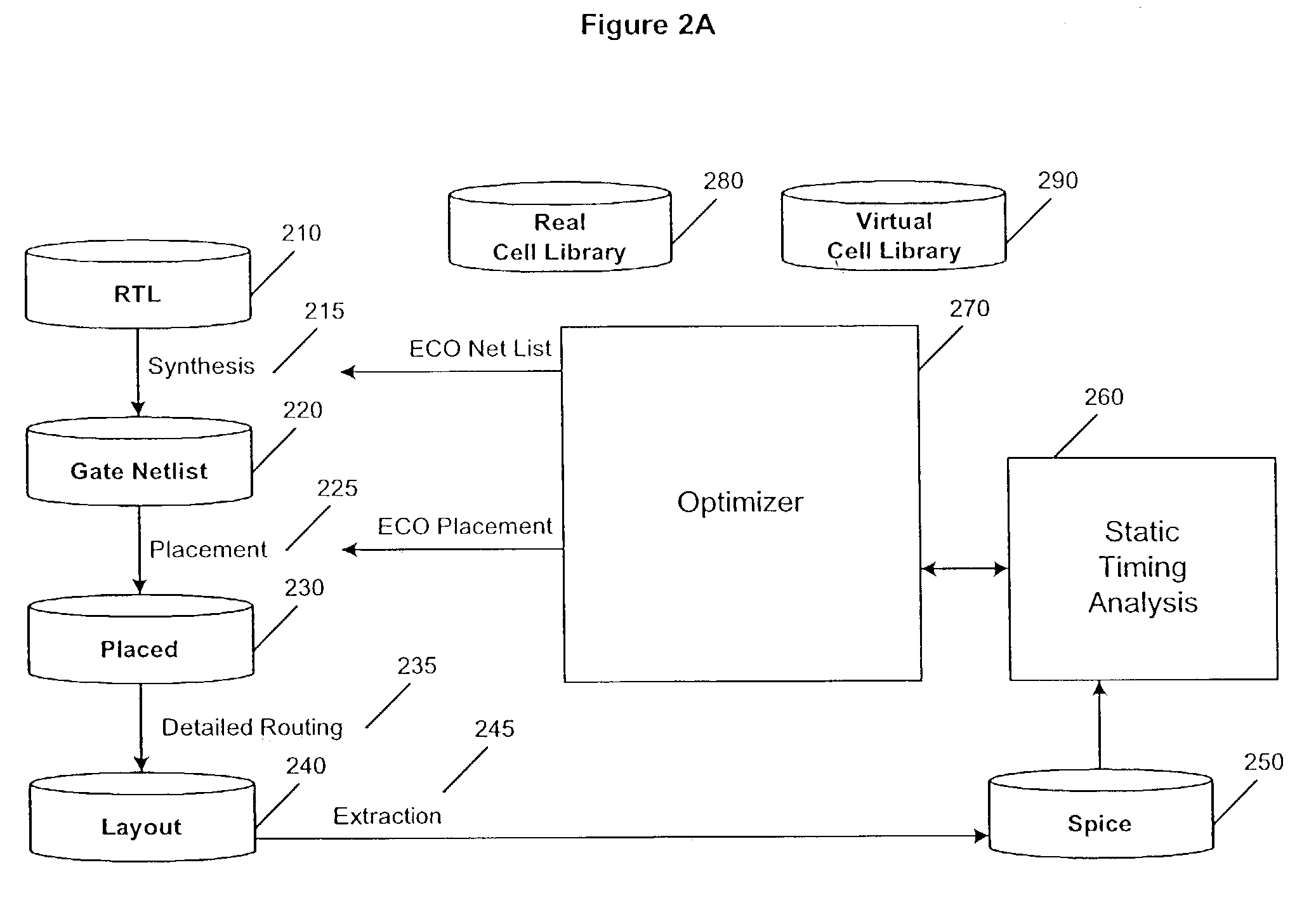

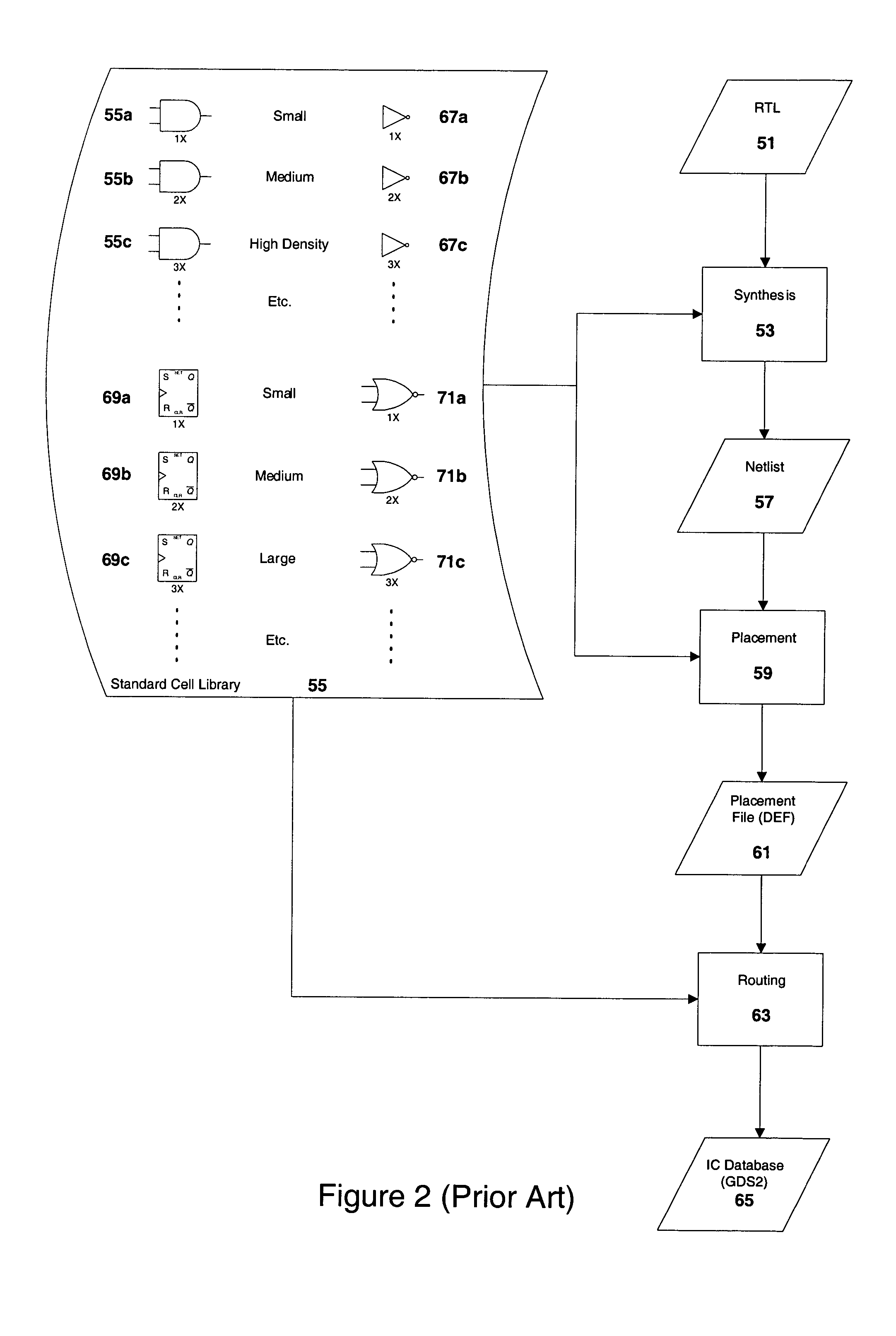

Optimization of circuit designs using a continuous spectrum of library cells

InactiveUS7107551B1Minimal impactSimple designMulti-objective optimisationSoftware simulation/interpretation/emulationVirtual cellSoftware engineering

A method and apparatus for optimizing a circuit design using a library of cells in which a continuous spectrum of cells are provided. A library containing real and virtual cells is used so that cells can be selected across a wide spectrum of a design parameter, such as drive strength. The cells are provided in discrete steps small enough that the effect of having a continuous spectrum of cells is achieved. After optimization, only the cells finally selected need be actually synthesized, and when these constitute a small percentage of the total number of cells, the impact to library size and final placement and routing is minimized. Thus the ability to optimize across a continuous spectrum is achieved while preserving a cell library based design flow.

Owner:ARM INC

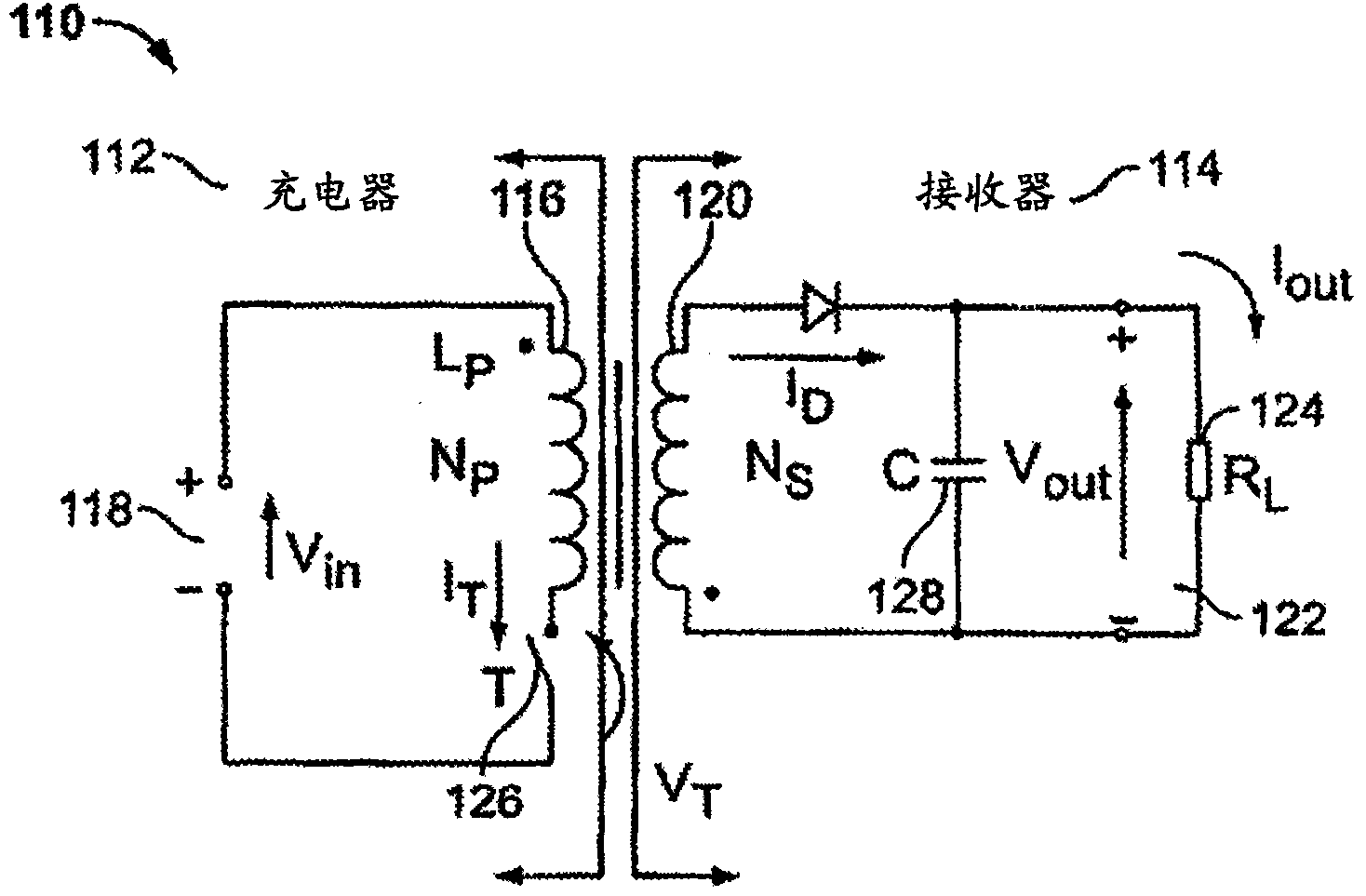

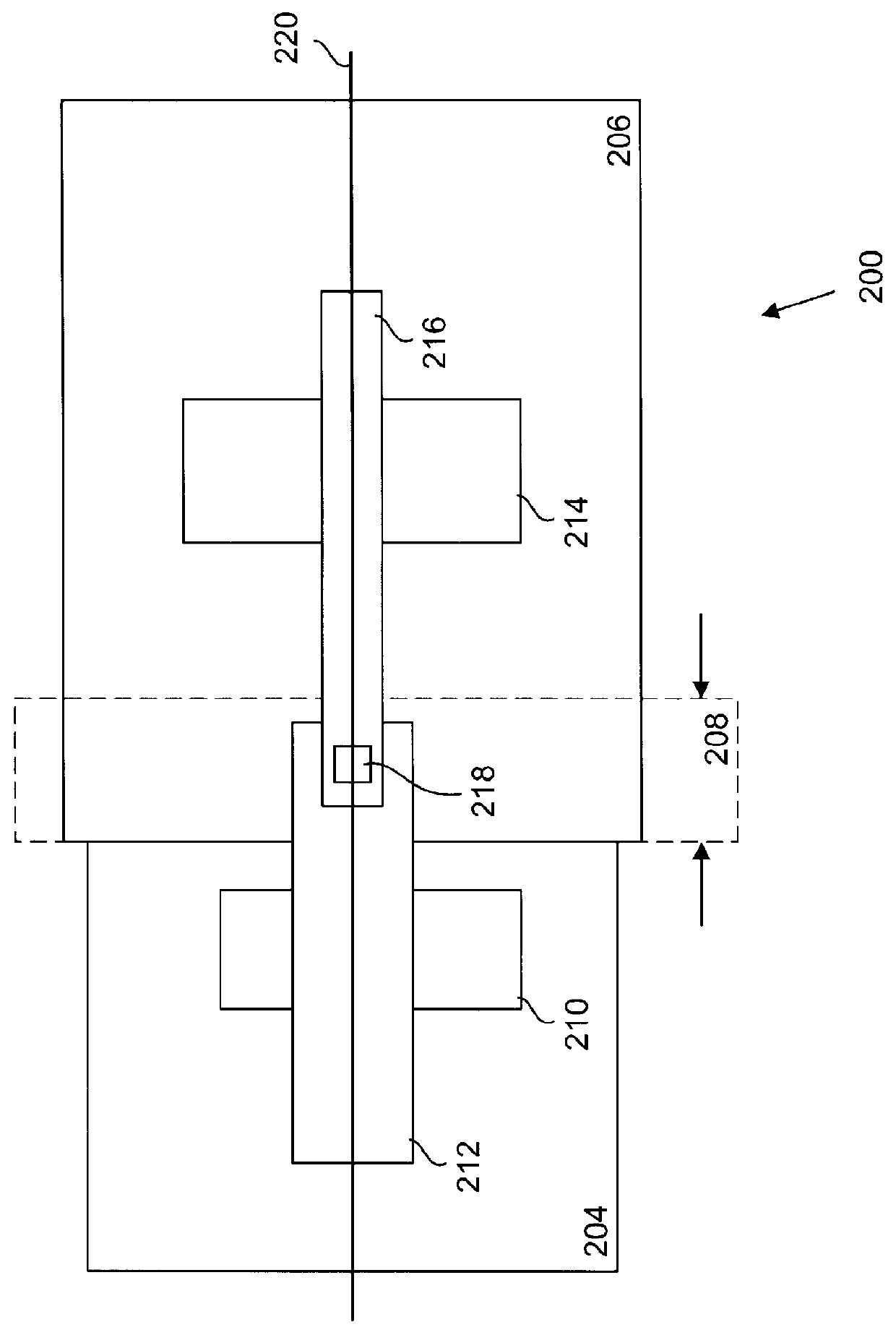

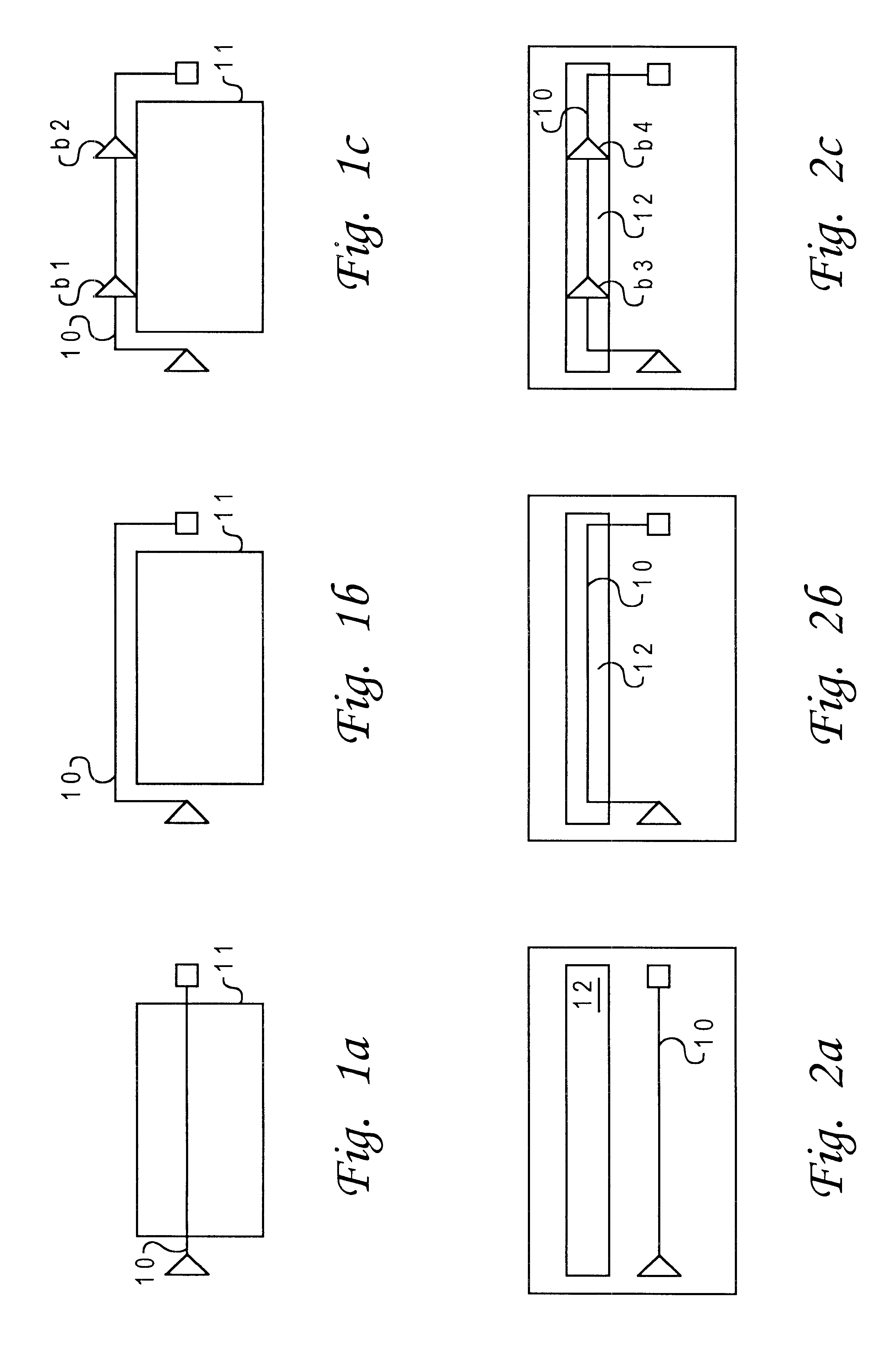

System and method for inductive charging of portable devices

ActiveCN101971453AImprove power transfer efficiencyEasy to changeTransformersMobile unit charging stationsEngineeringReceiver coil

A system and method for variable power transfer in an inductive charging or power system. In accordance with an embodiment the system comprises a pad or similar base unit that contains a primary, which creates an alternating magnetic field. A receiver comprises a means for receiving the energy from the alternating magnetic field from the pad and transferring it to a mobile device, battery, or other device. In accordance with various embodiments, additional features can be incorporated into the system to provide greater power transfer efficiency, and to allow the system to be easily modified for applications that have different power requirements. These include variations in the material used to manufacture the primary and / or the receiver coils; modified circuit designs to be used on the primary and / or receiver side; and additional circuits and components that perform specialized tasks, such as mobile device or battery identification, and automatic voltage or power-setting for different devices or batteries.

Owner:MOJO MOBILITY

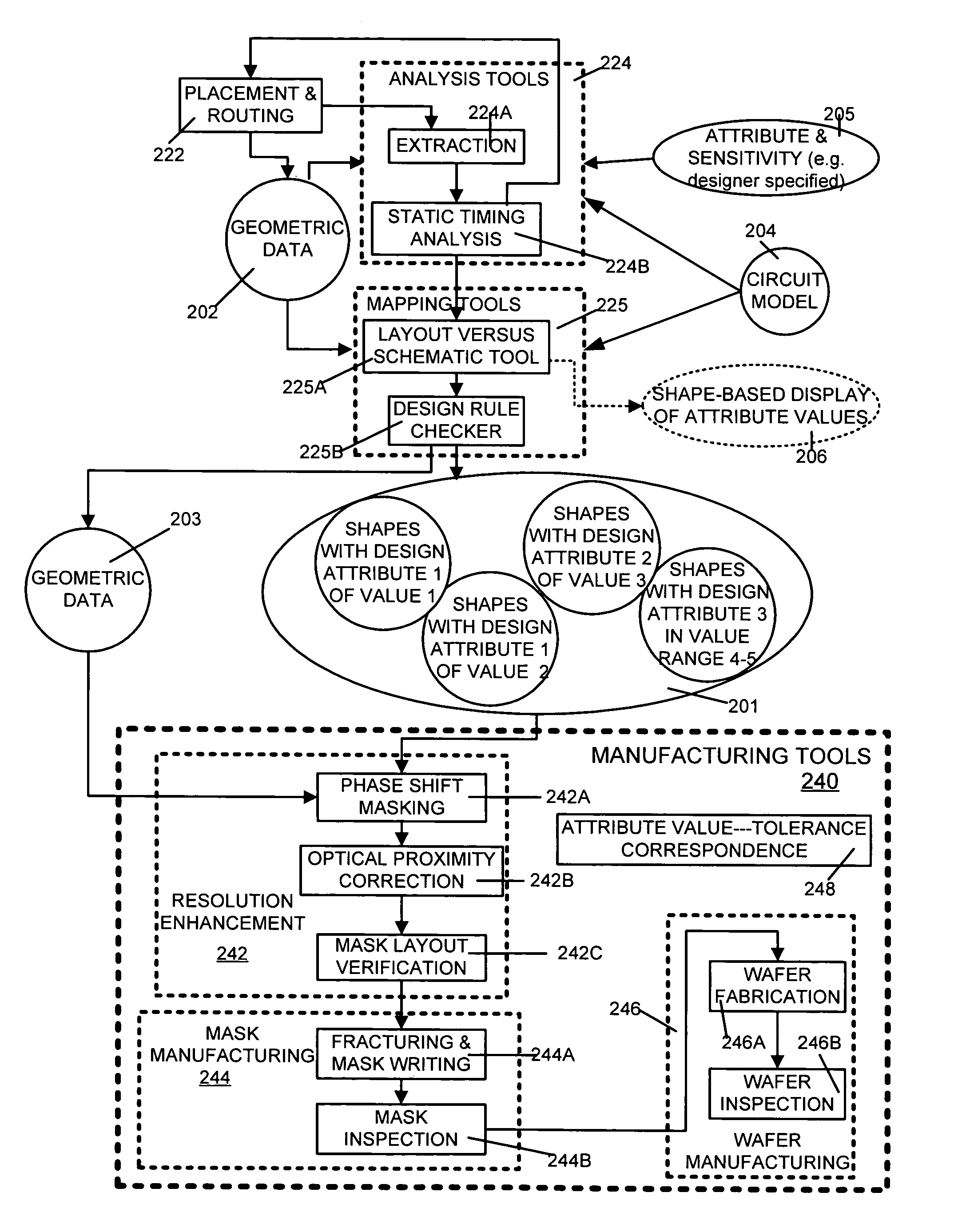

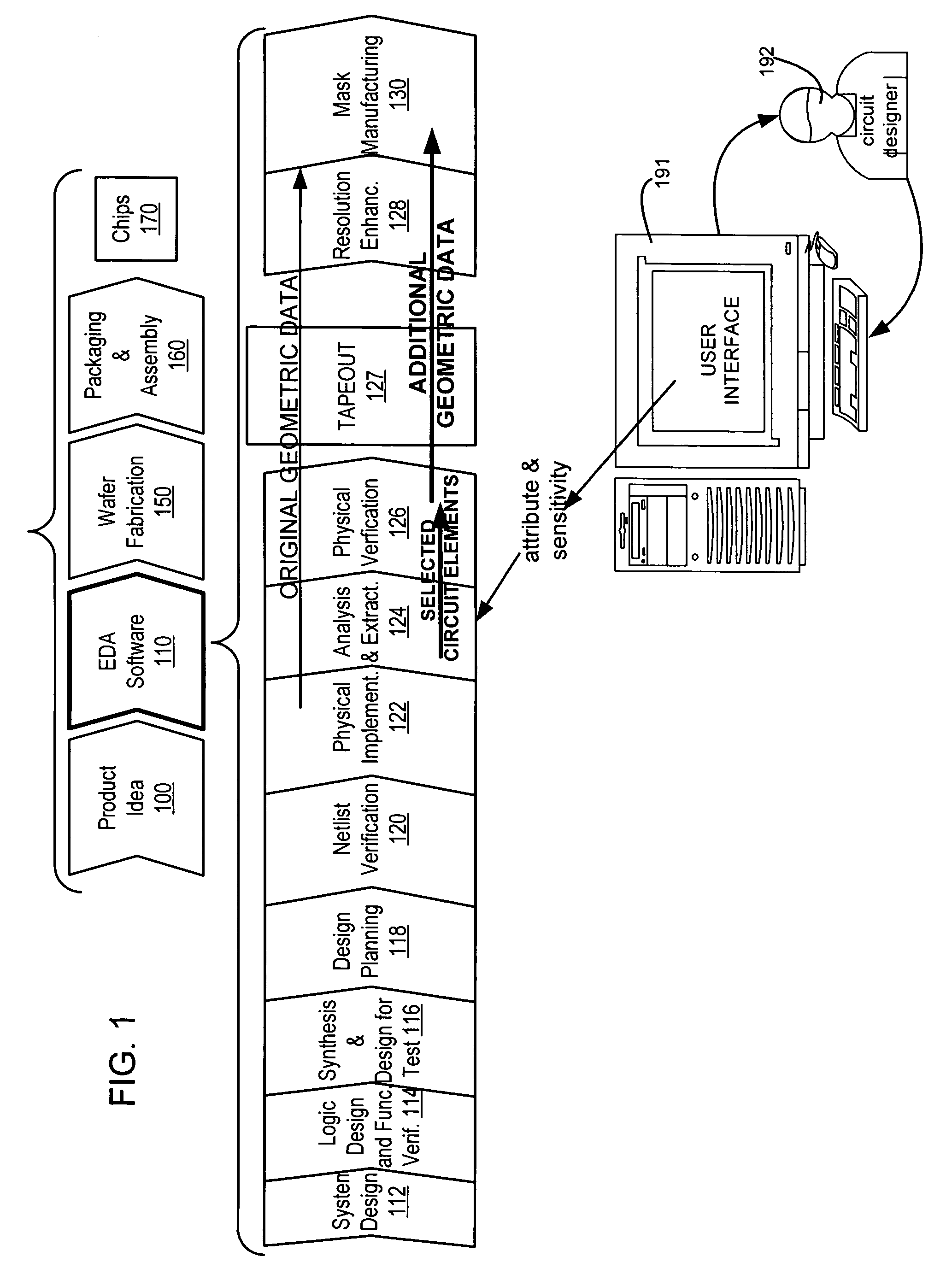

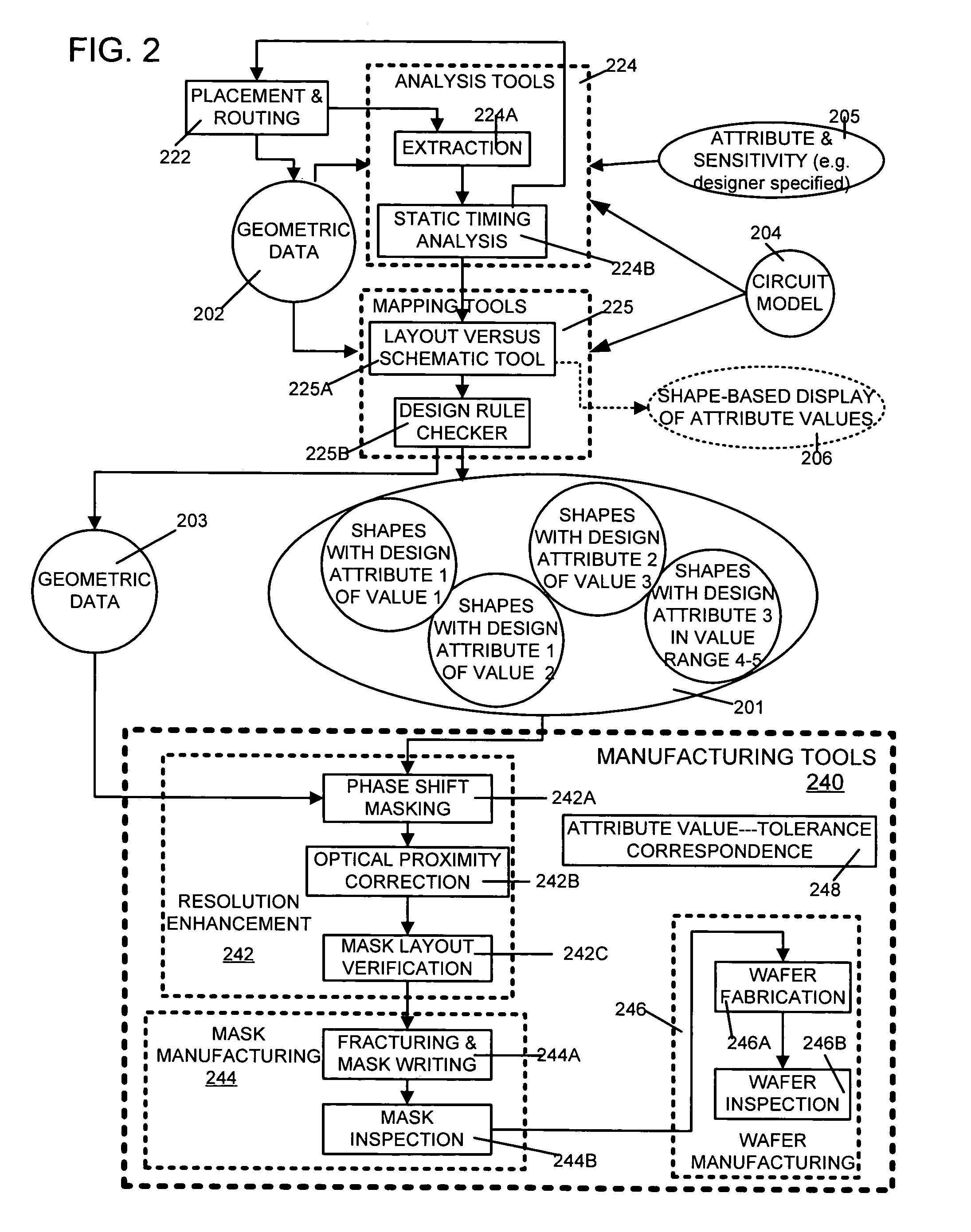

Silicon tolerance specification using shapes as design intent markers

ActiveUS7458045B2High yieldCAD circuit designSoftware simulation/interpretation/emulationEngineeringSilicon

Design-specific attributes of a circuit (such as timing, power, electro-migration, and signal integrity) are used to automatically identify one or more regions of one or more layers in a layout of the circuit. The automatically identified regions may be provided to a manufacturing tool in GDSII by use of overlapping shapes in, or alternatively by moving existing shapes to, a different layer / datatype pair. For example, information about the automatically identified regions may be stored using a conventional datatype (e.g. value 0) with a new layer, or alternatively using a conventional layer (e.g. metal 3) with a new datatype (e.g. value 1), depending on the embodiment. The automatically identified regions contain cells and / or features (e.g. groups of shapes and / or individual shapes) whose tolerance in silicon (to be fabricated) is automatically changed from default, based on the design-specific attribute(s) and sensitivity thereto, expressed as design intent by a circuit designer.

Owner:SYNOPSYS INC

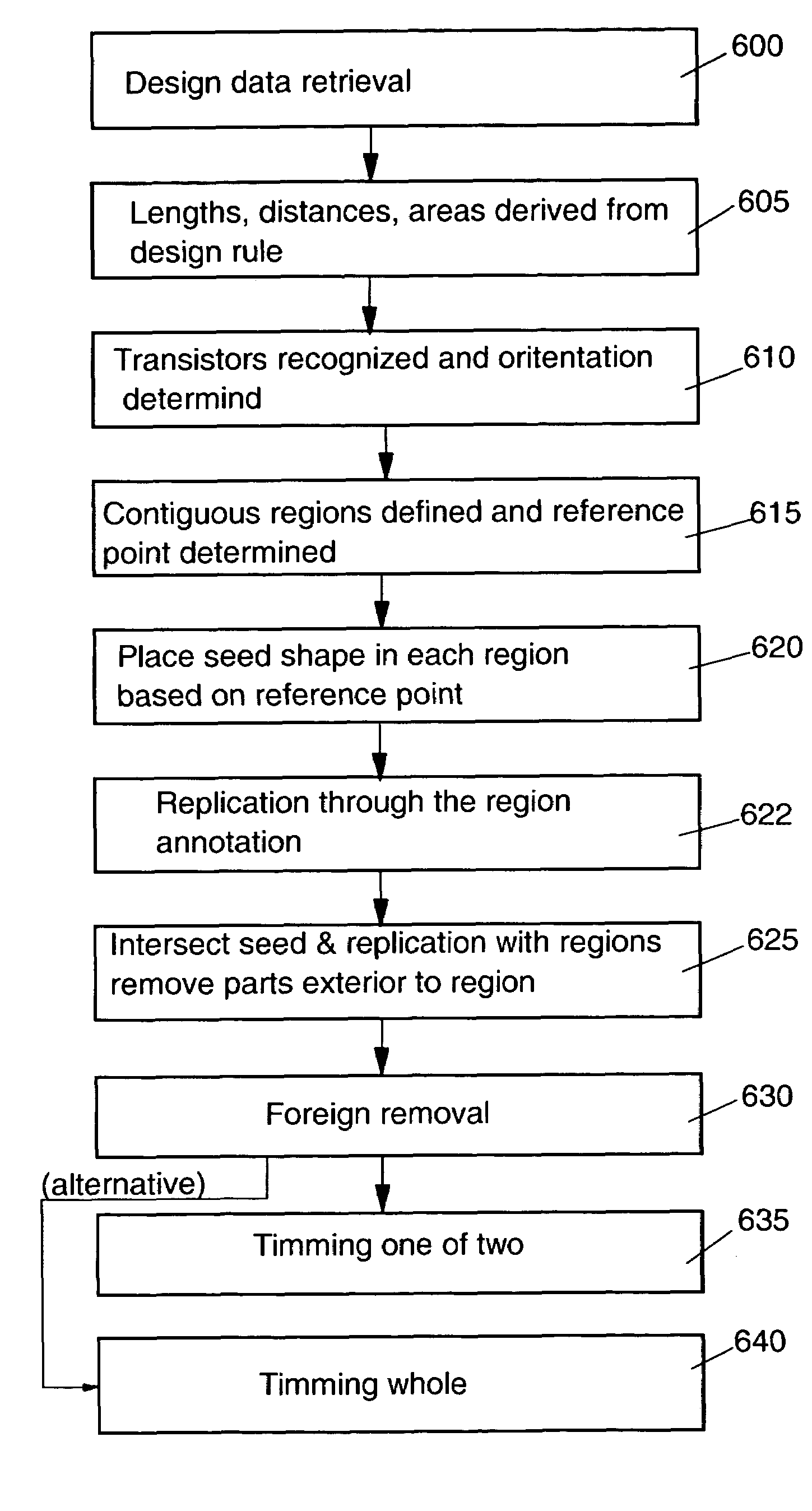

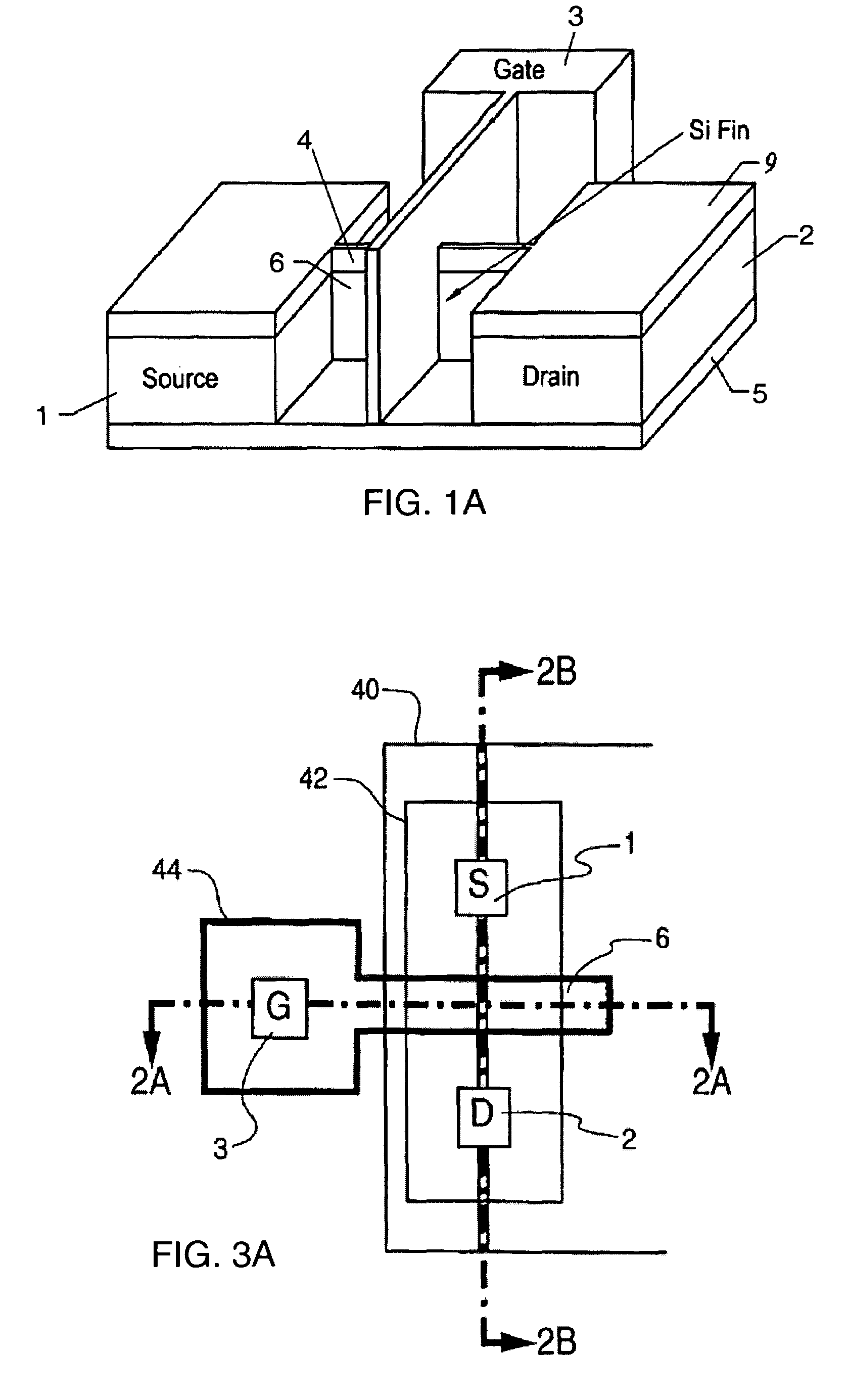

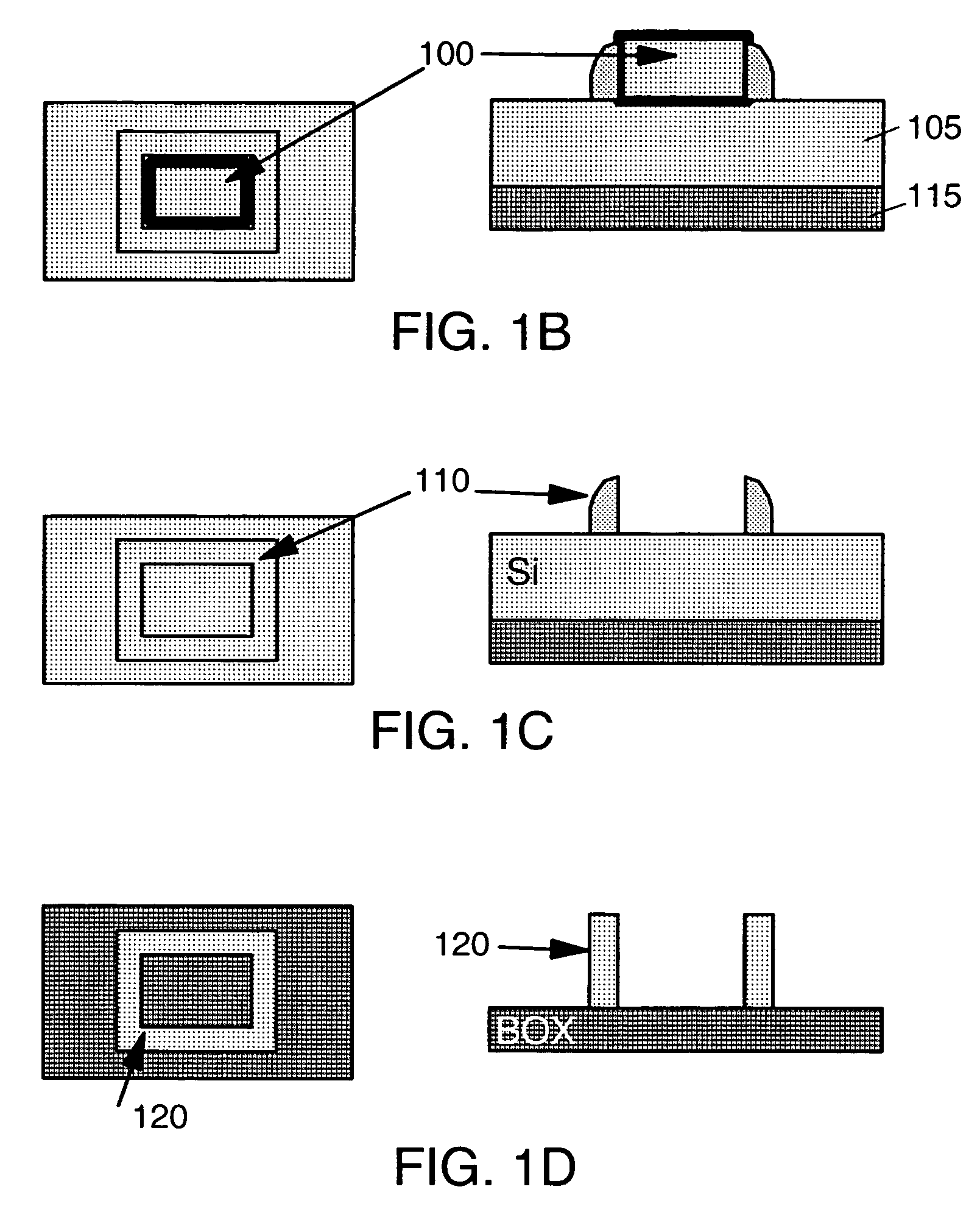

Method and device for automated layer generation for double-gate FinFET designs

InactiveUS7315994B2Reduce effortEnhance layeringTransistorSolid-state devicesEngineeringUnit structure

Owner:INT BUSINESS MASCH CORP

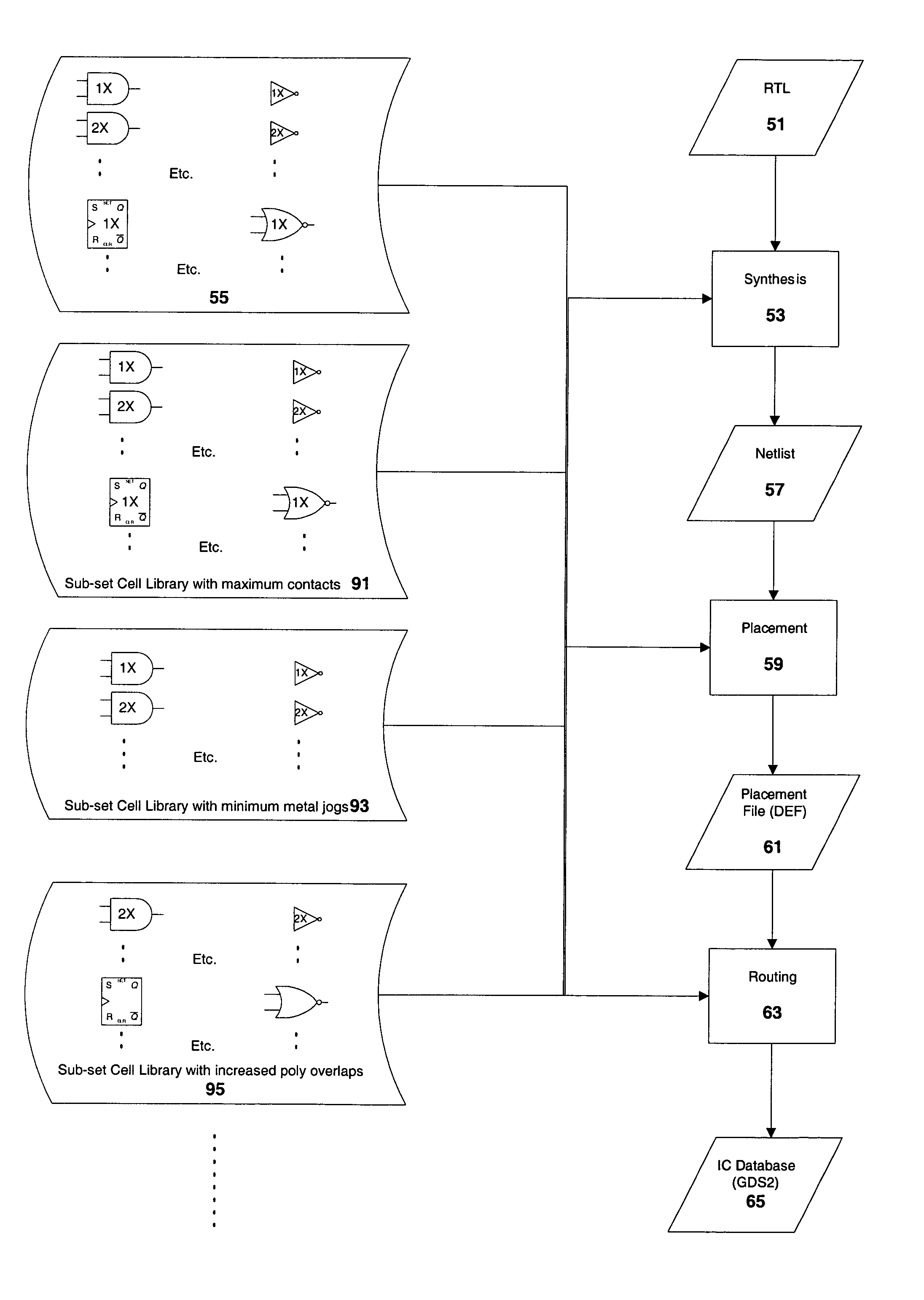

Yield maximization in the manufacture of integrated circuits

InactiveUS6957402B2Increase productionHigh yieldSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingComputer-aidedEngineering

A method and apparatus for improving the manufacturability of Integrated Circuits (ICs) formed on semiconductor dies is described. A plurality of different designs for some or all of the standard cells are made available to the circuit designer. Each different design may address a different problem associated with different manufacturing processes or a different design related yield limiter. Each of the design variants is characterized indicating its relative ease of manufacture, or it's yield sensitivity to certain IC design factors. The designer, typically with assistance from computer aided tools, can then select the standard cell variant for each of the cell used in the IC design that best addresses his or her design constraints. In other embodiments, variant versions of I / O cells and memory cells could also be created and made available to the designer in a similar fashion.

Owner:ARM INC

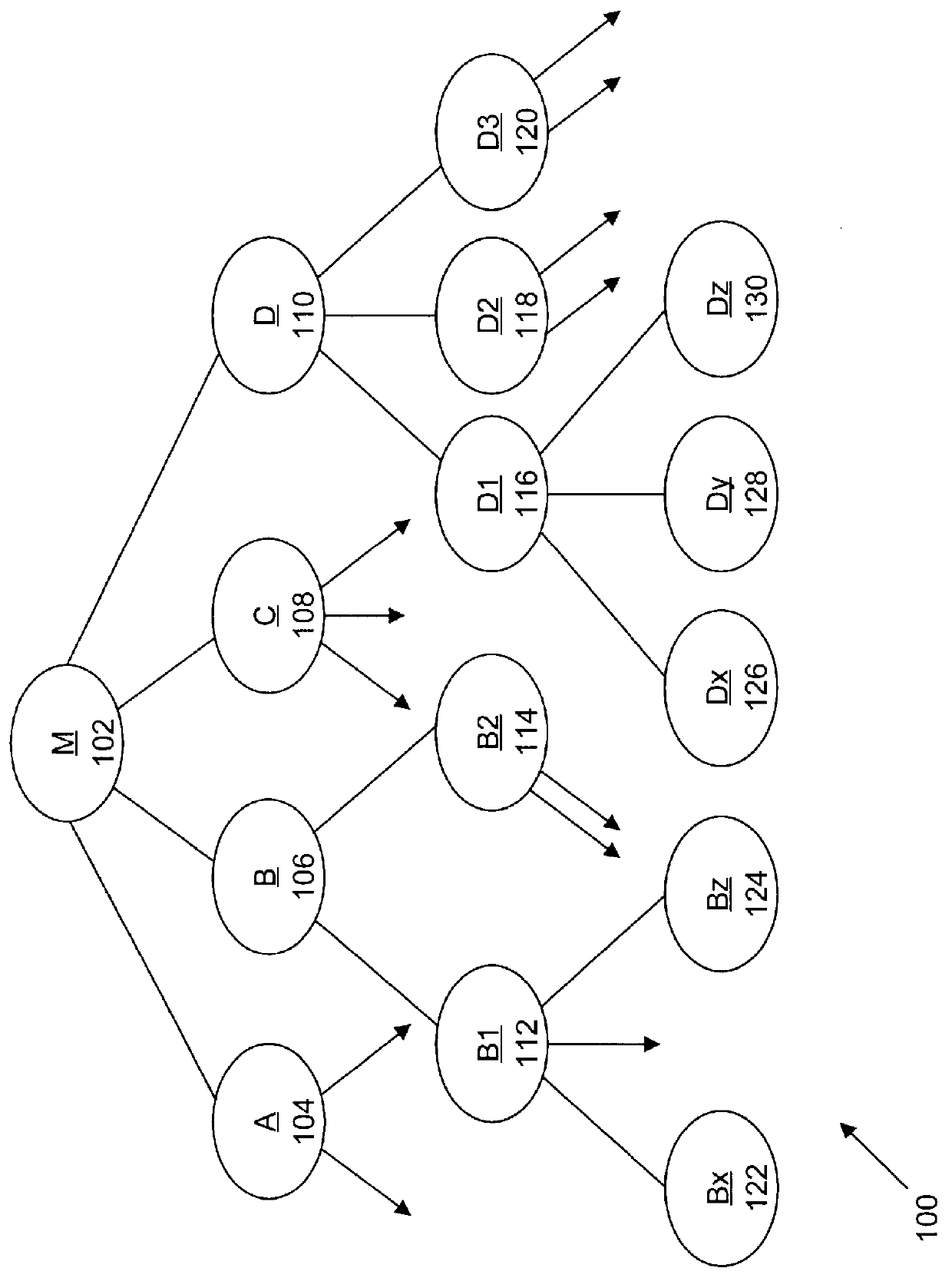

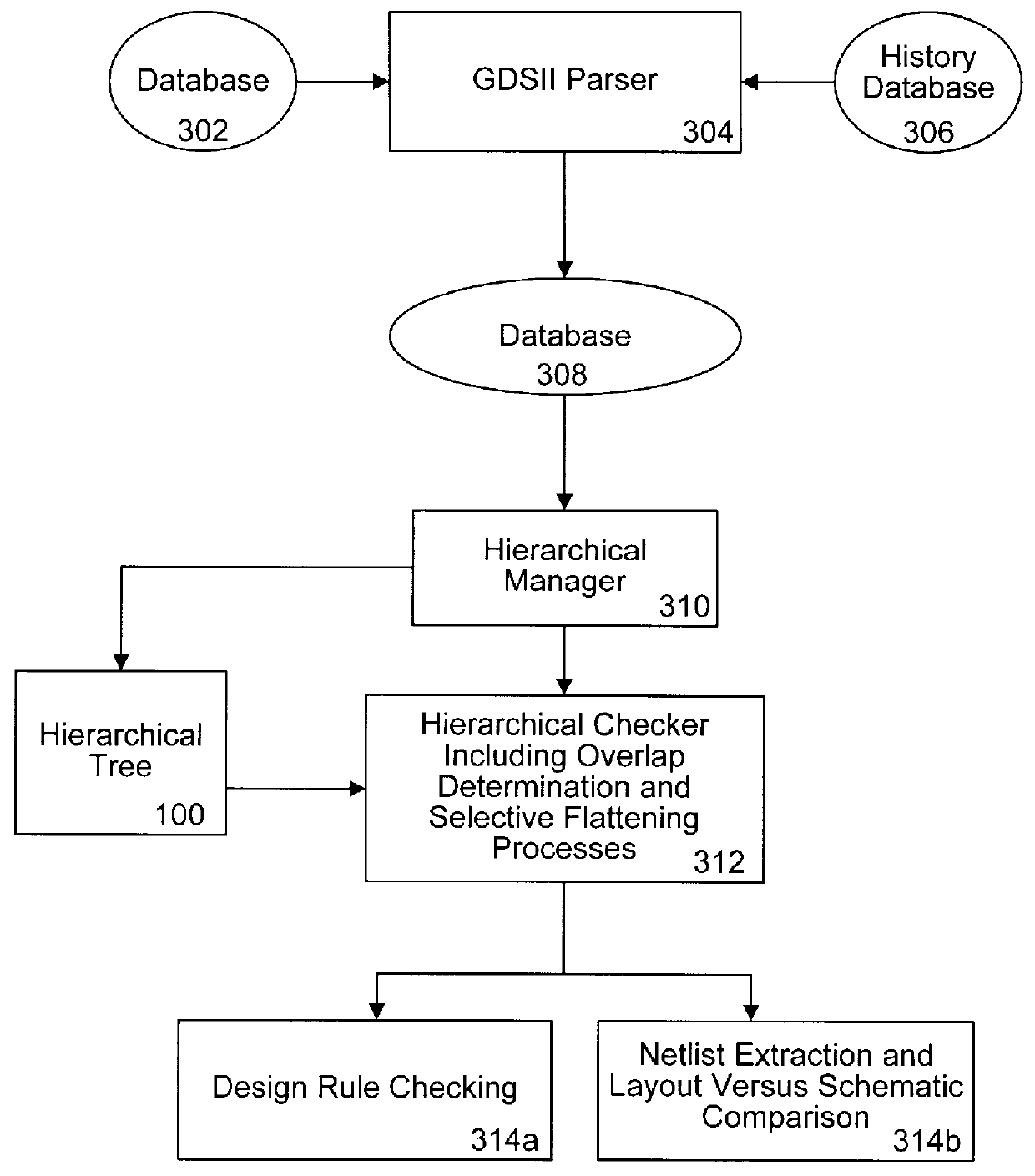

Layout overlap detection with selective flattening in computer implemented integrated circuit design

InactiveUS6011911AValid checkComputer aided designSoftware simulation/interpretation/emulationComputer architectureLayout Versus Schematic

The present invention relates to a method for efficiently performing hierarchical design rules checks (DRC) and layout versus schematic comparison (LVS) on layout areas of an integrated circuit where cells overlap or where a cell and local geometry overlap. With the present invention, a hierarchical tree describes the integrated circuit's layout data including cells having parent-child relationships and including local geometry. The present invention performs efficient layout verification by performing LVS and DRC checking on the new portions of an integrated circuit design and layout areas containing overlapping cells. When instances of cells overlap, the present invention determines the overlap area using predefined data structures that divide each cell into an array of spatial bins. Each bin of a parent is examined to determine if two or more cell instances reside therein or if a cell instance and local geometry reside therein. Once overlap is detected, the areas of the layout data corresponding to the overlap areas are selectively flattened prior to proceeding to DRC and LVS processing. During selective flattening of the overlap areas, the hierarchical tree is traversed from the top cell down through intermediate nodes to the leaf nodes. Each time geometry data is located during the traversal, it is pushes directly to the top cell without being stored in intermediate locations. This provides an effective mechanism for selective flattening.

Owner:SYNOPSYS INC

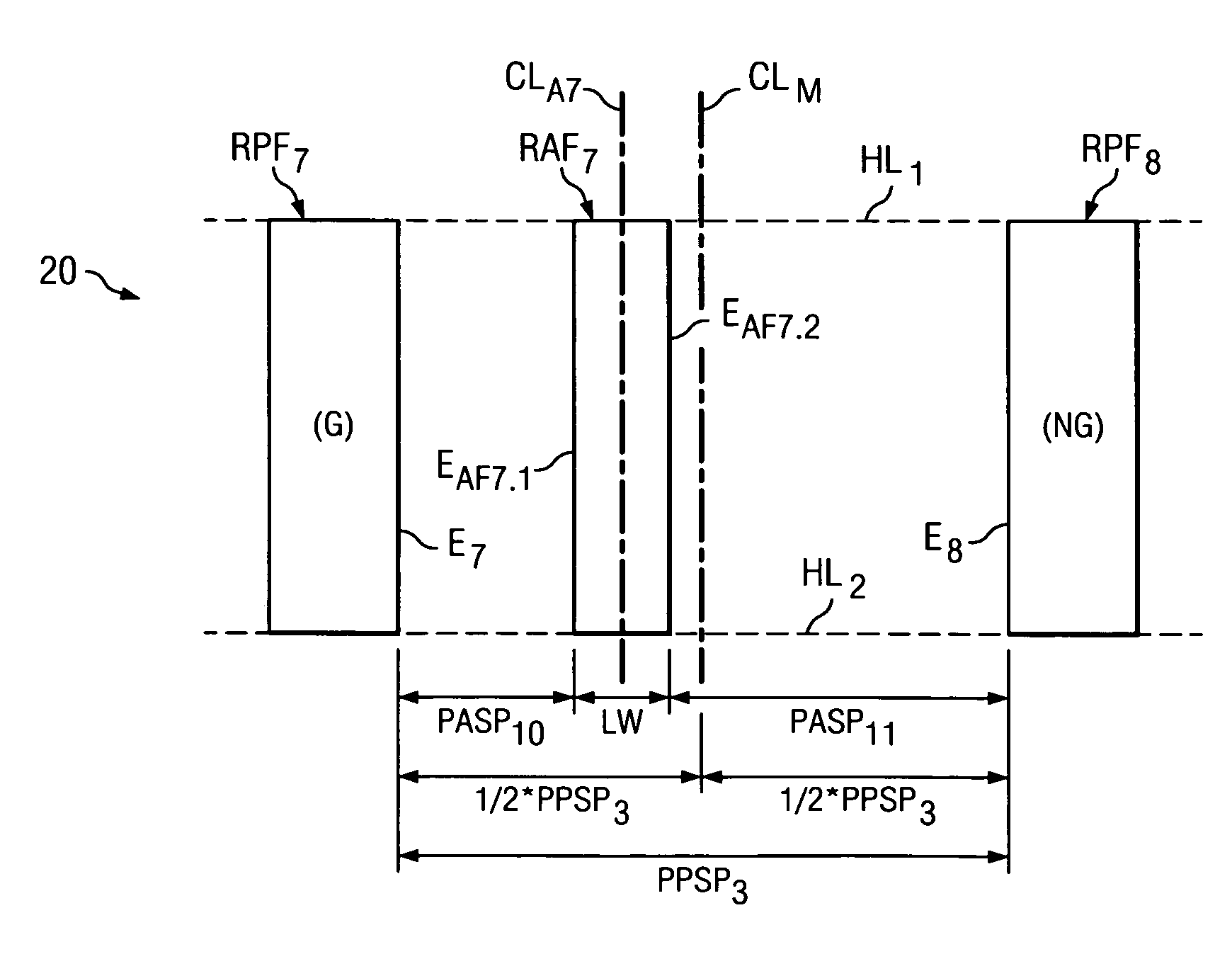

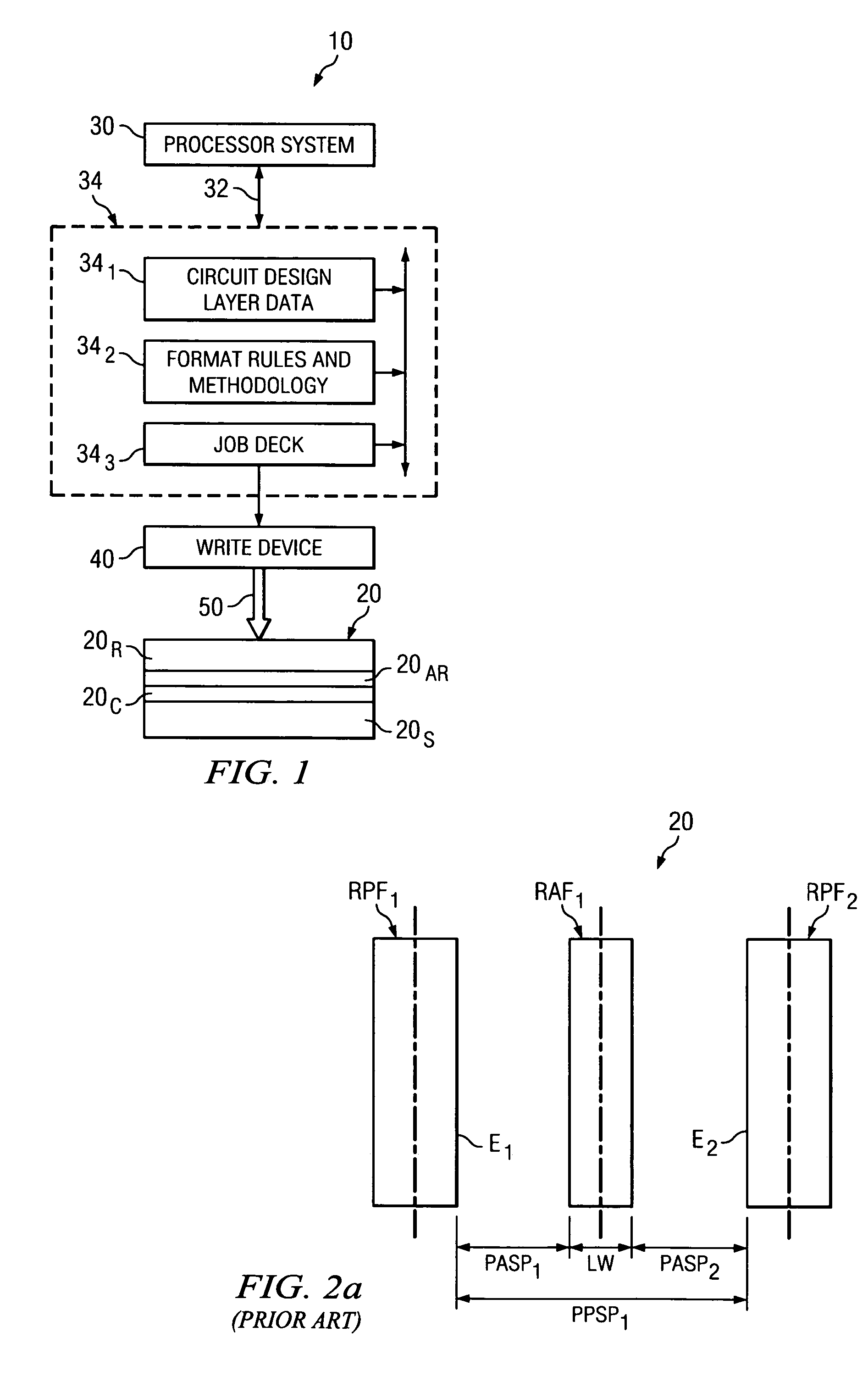

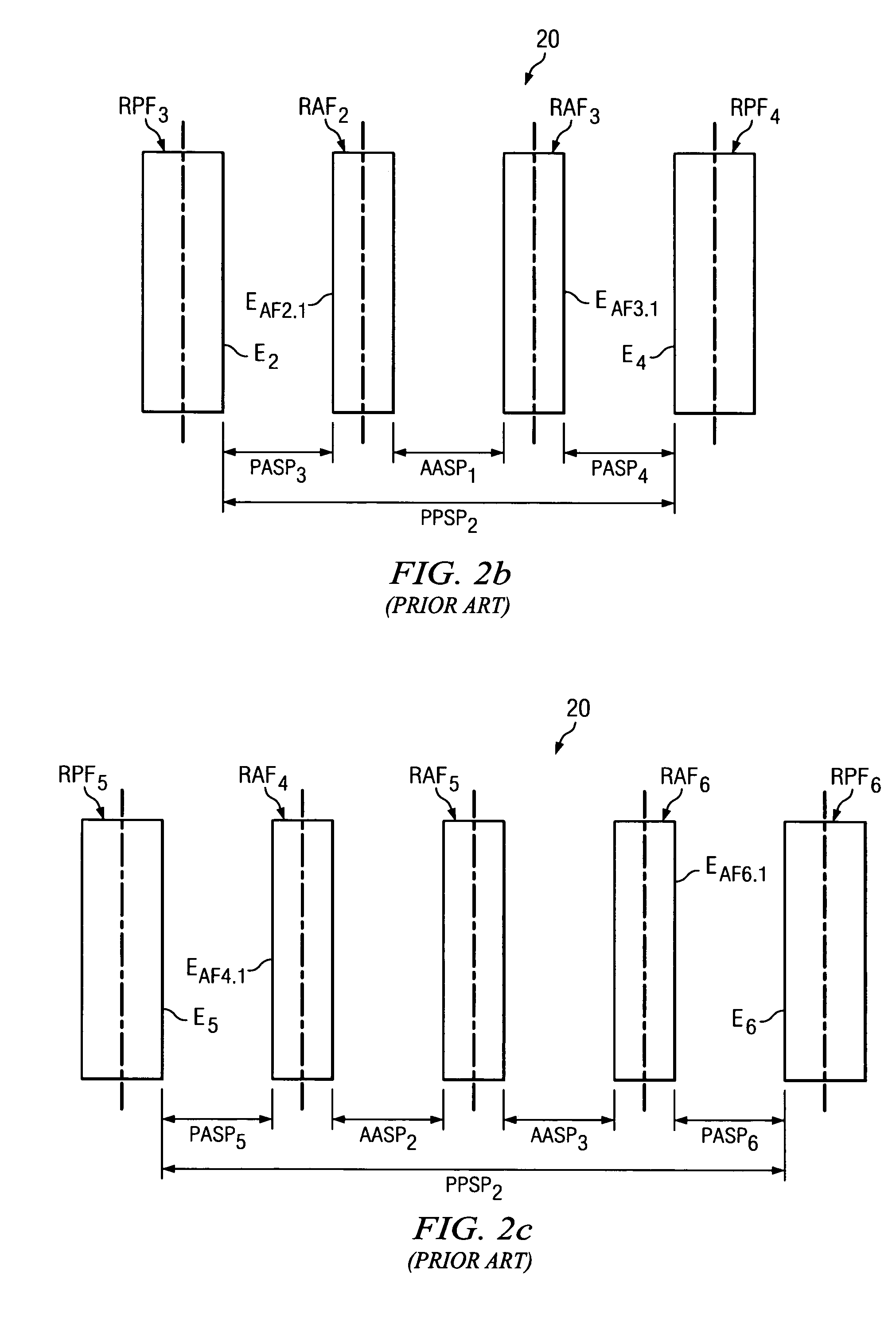

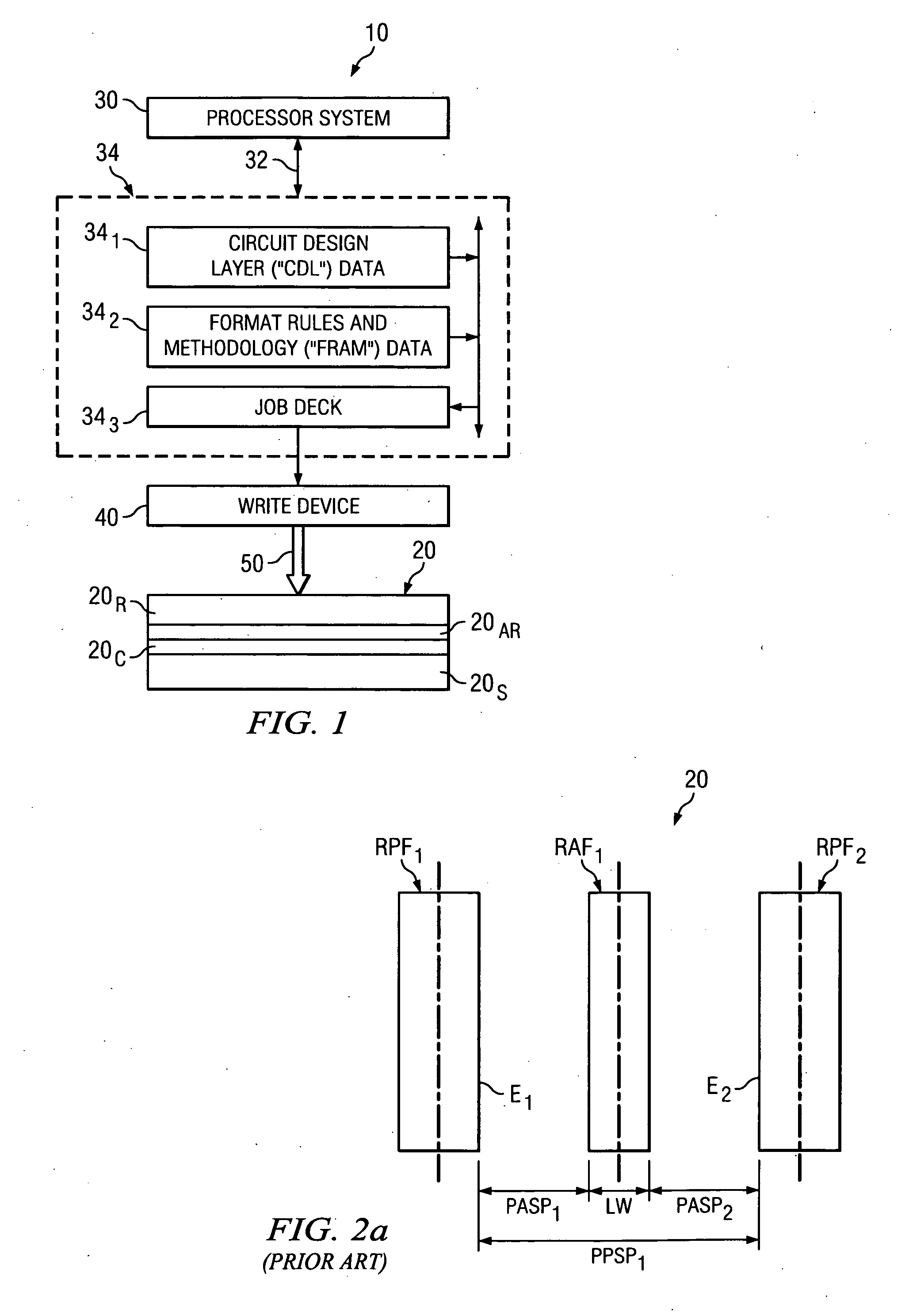

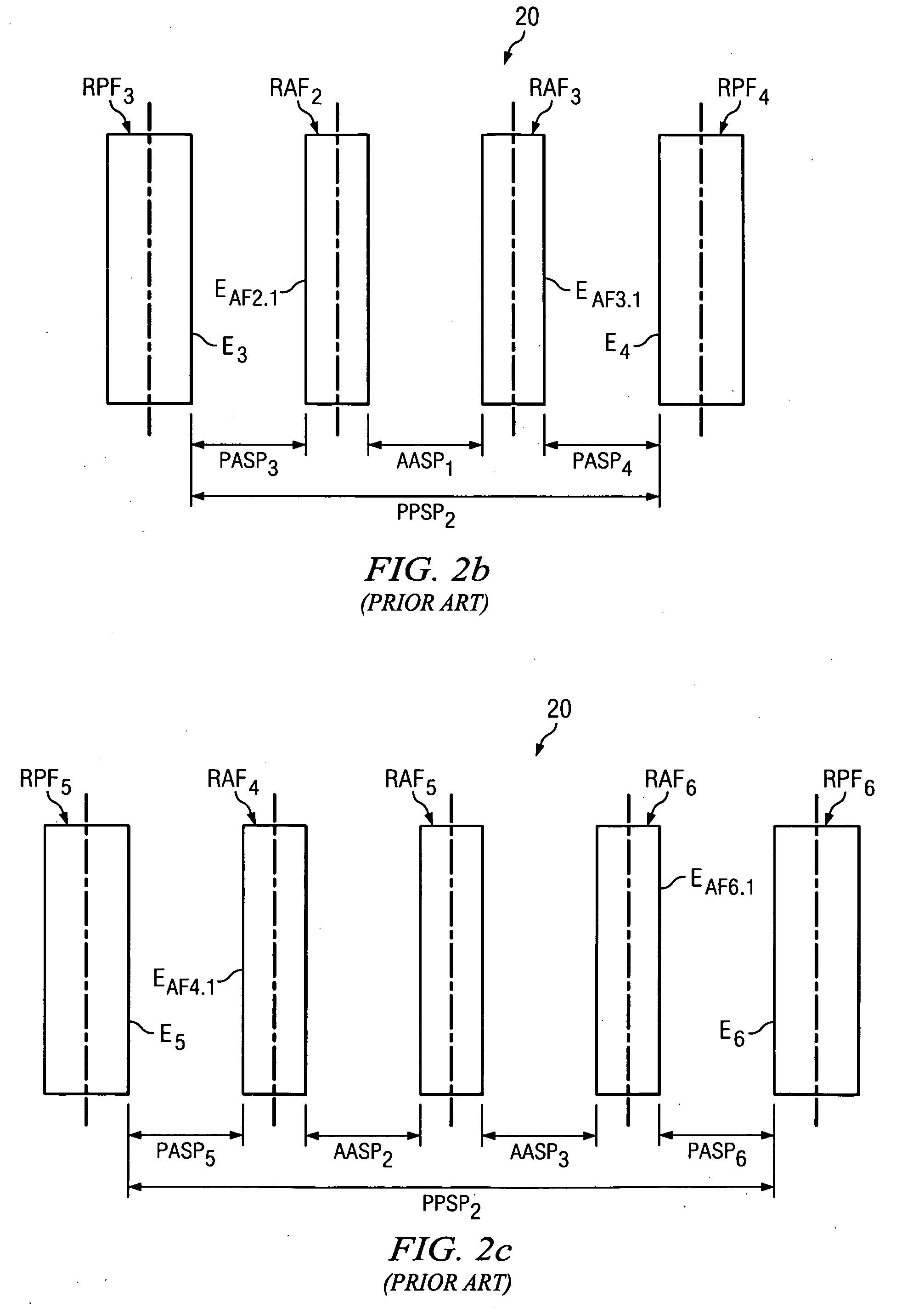

Method of locating sub-resolution assist feature(s)

ActiveUS7200835B2Originals for photomechanical treatmentSpecial data processing applicationsData fileComputing systems

A method of operating a computing system to determine reticle data. The reticle data is for completing a reticle for use in projecting an image to a semiconductor wafer. The method receives circuit design layer data comprising a desired circuit layer layout, and the layout comprises a plurality of lines. The method also identifies in the plurality of lines a first line portion for use as a first circuit function and a second line portion for use as a second circuit function that differs from the first circuit function. The first line portion is parallel and adjacent to the second line portion. The method also provides the reticle data in an output data file for use in forming features on the reticle. The method also indicates parameters for forming first and second primary features as well as at least one assist feature on the reticle having an area between the first primary feature and the second primary feature, wherein in use of the reticle for use in projecting the image to the semiconductor wafer the area will favor greater assistance to the first primary feature as compared to the second primary feature.

Owner:TEXAS INSTR INC

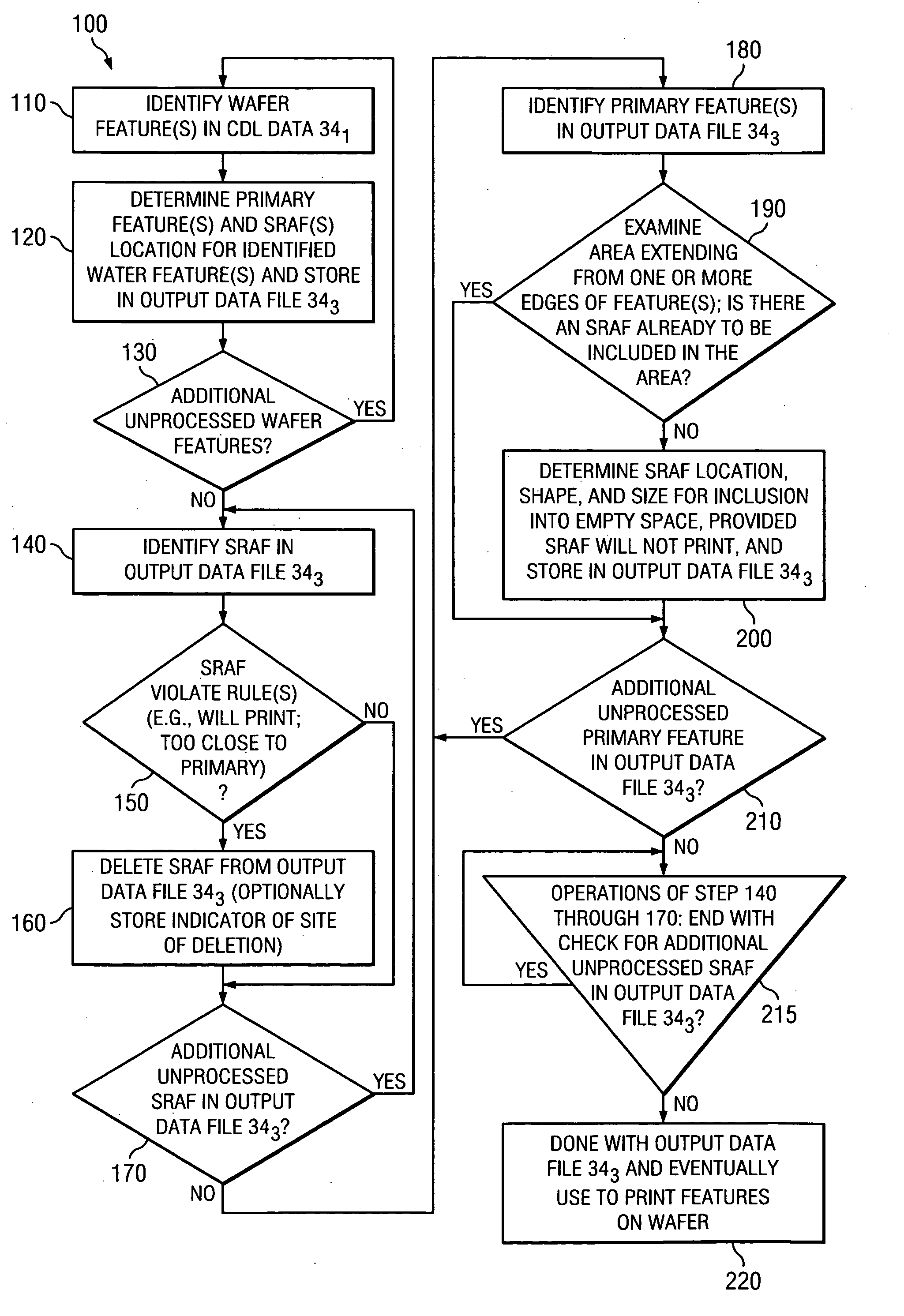

Method of inclusion of sub-resolution assist feature(s)

InactiveUS20080082952A1Originals for photomechanical treatmentSpecial data processing applicationsData fileComputer science

A method of operating a computing system to determine reticle data. The reticle data is for completing a reticle for use in projecting an image to a semiconductor wafer. The method comprises receiving circuit design layer data comprising a desired circuit layer layout, the layout comprising a plurality of circuit features. The method further comprises providing the reticle data for inclusion in an output data file for use in forming reticle features on the reticle. This providing step comprises a first iteration and a second iteration. In a first iteration, the method indicates parameters for forming a plurality of primary features and a first plurality of assist features on the reticle and it selectively removes the parameters of selected ones of the first plurality assist features. In a second iteration, the method indicates parameters for forming a second plurality of assist features on the reticle.

Owner:TEXAS INSTR INC

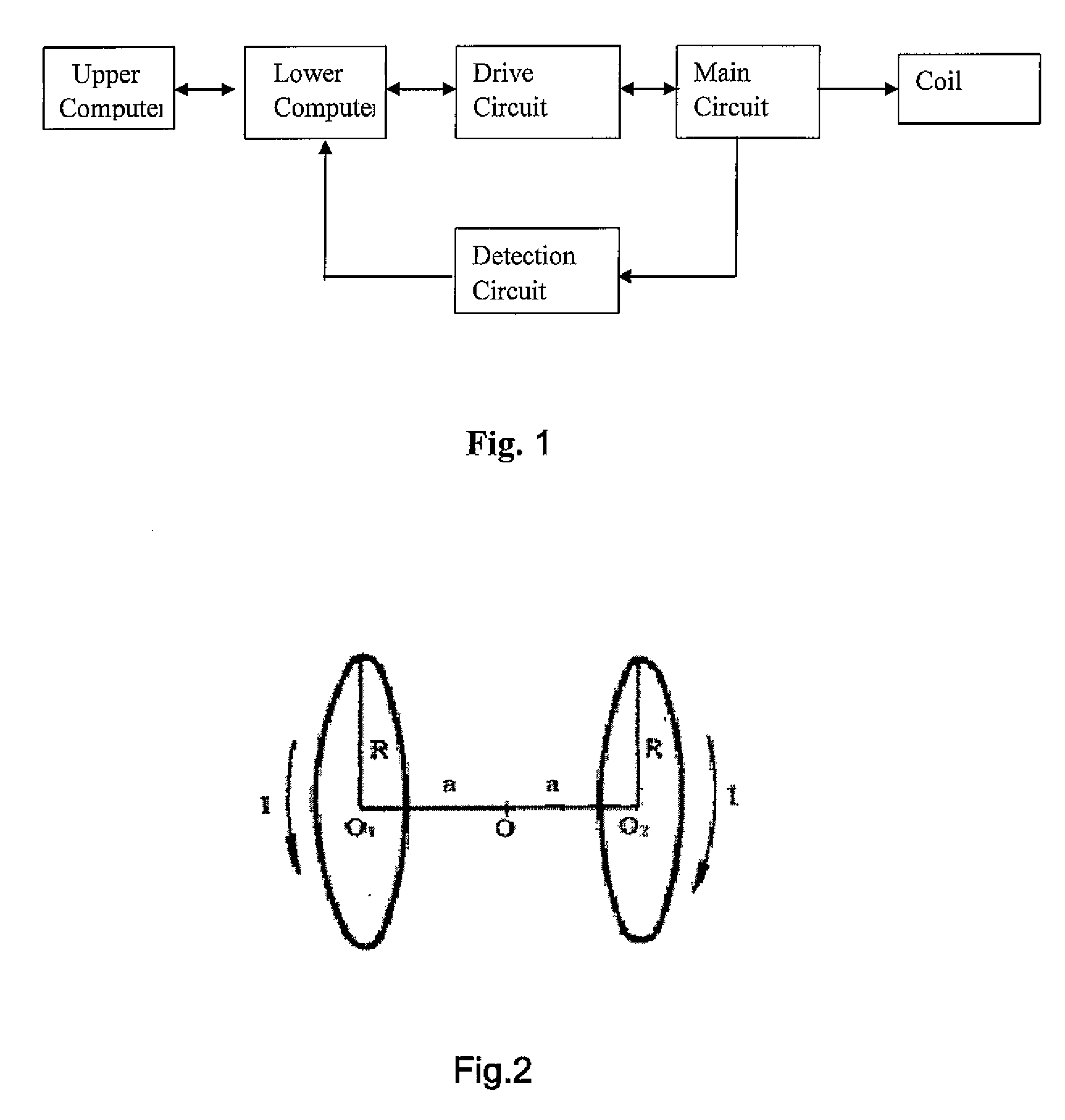

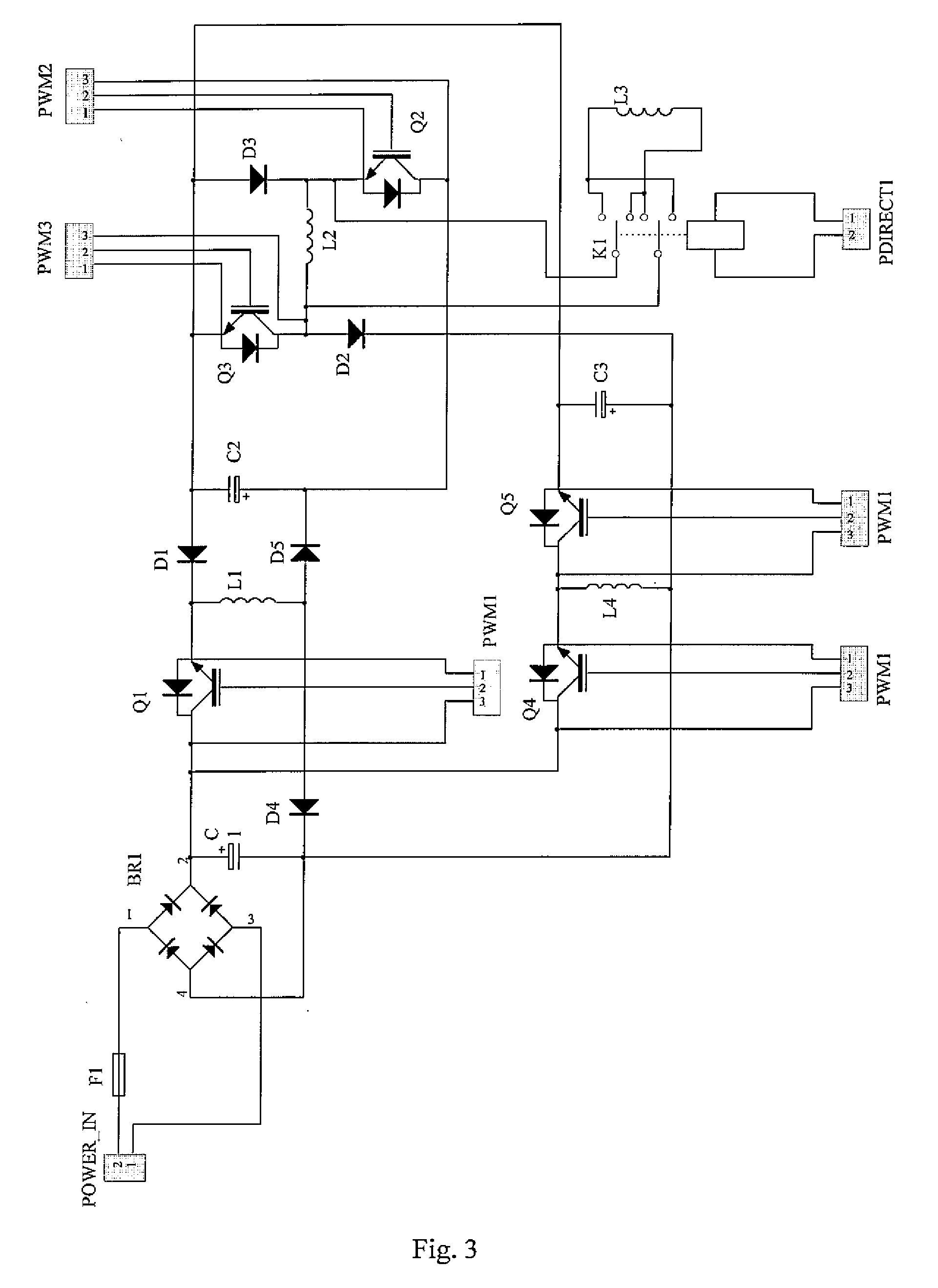

Magnetic Stimulating Circuit For Nervous Centralis System Apparatus, Purpose, and Method Thereof

ActiveUS20080200749A1High frequencyImprove brain functionElectrotherapyMagnetotherapy using coils/electromagnetsWide areaDisease

A magnetic stimulation apparatus for central nervous system and circuit thereof and use of the apparatus and method of using the apparatus are shown. Controlling circuit design and outputting wave form signal to a drive power supply circuit enables the drive power supply circuit to output current of corresponding wave form to coils, and by means of the design of the shape, number of turns, size, interval of the coils, generates within a certain region inside the coils a desired time-variant magnetic field which is then applied to the brain of an animal or a human being so that the central nervous system can receive a wide area synergy magnetic stimulation with a precise wave form, high frequency or a combination of a plurality of frequency components, thus achieving the treatment of nervous and psychiatric diseases or brain function improvement in combination with behavior guidance, thought guidance, or psychological guidance.

Owner:ZHENG YUNFENG

System and method for designing a common centroid layout for an integrated circuit

ActiveUS20070294652A1Computer programmed simultaneously with data introductionCAD circuit designEngineeringLinearity

An exemplary common centroid layout design system receives various inputs about an integrated circuit (IC) design. Based on such inputs, the system calculates a common centroid unit, which represents an array of segments of each device in the IC design. The number of segments for each device within the common centroid unit is selected based on the respective sizes of the devices. The common centroid unit is then tiled to automatically define the complete layout for the IC object. The system selects an algorithm for tiling the common centroid unit based on the size of such unit such that, upon completion of the tiling process, all of the devices have a common centroid. In other words, the system selects an algorithm for tiling such that a common centroid layout design is generated. Using the common centroid layout design, the IC object can be manufactured so that it is immune to linear process gradients and more resistant to non-linear gradients relative to ICs that do not have a common centroid layout design.

Owner:ADTRAN

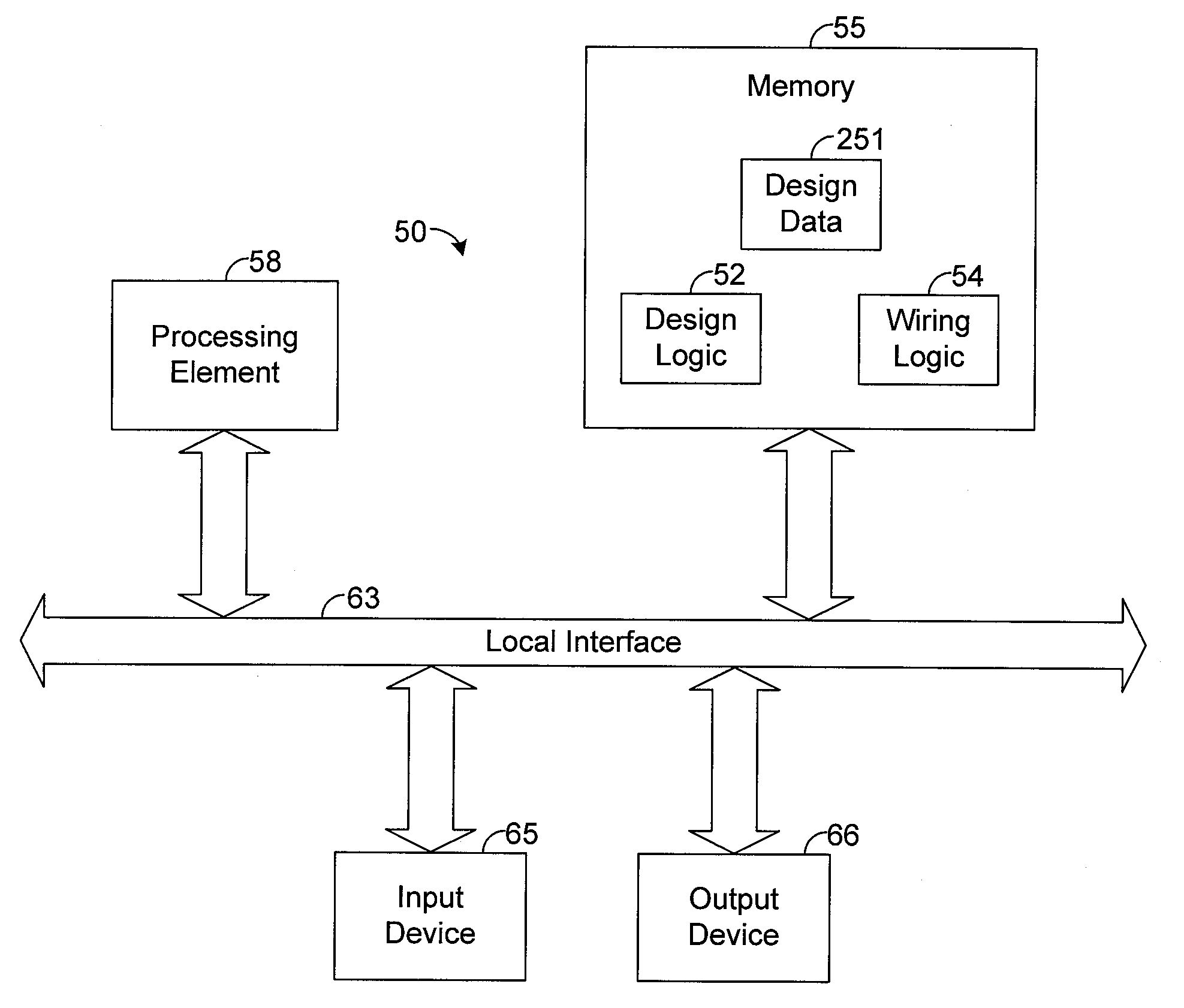

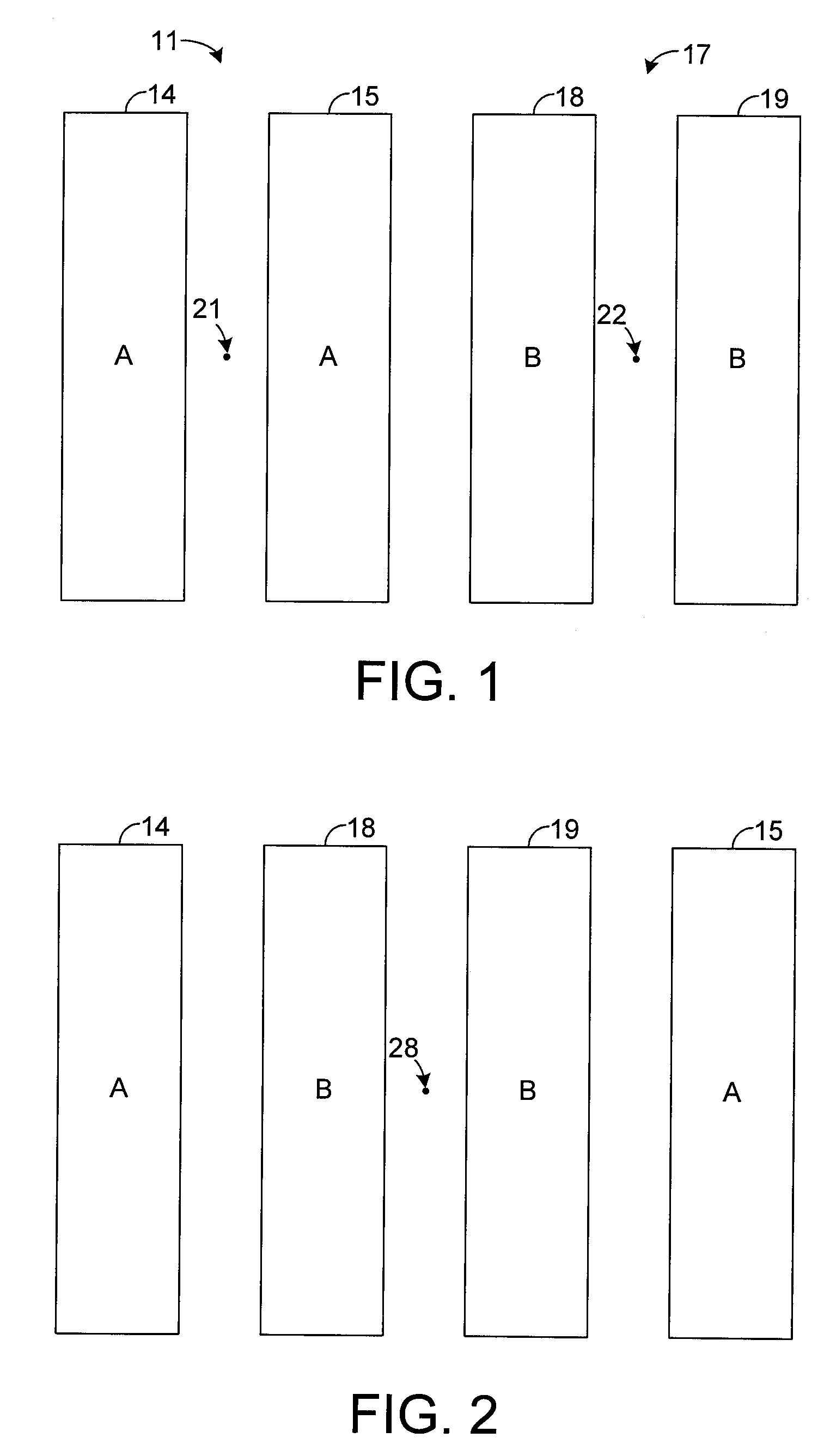

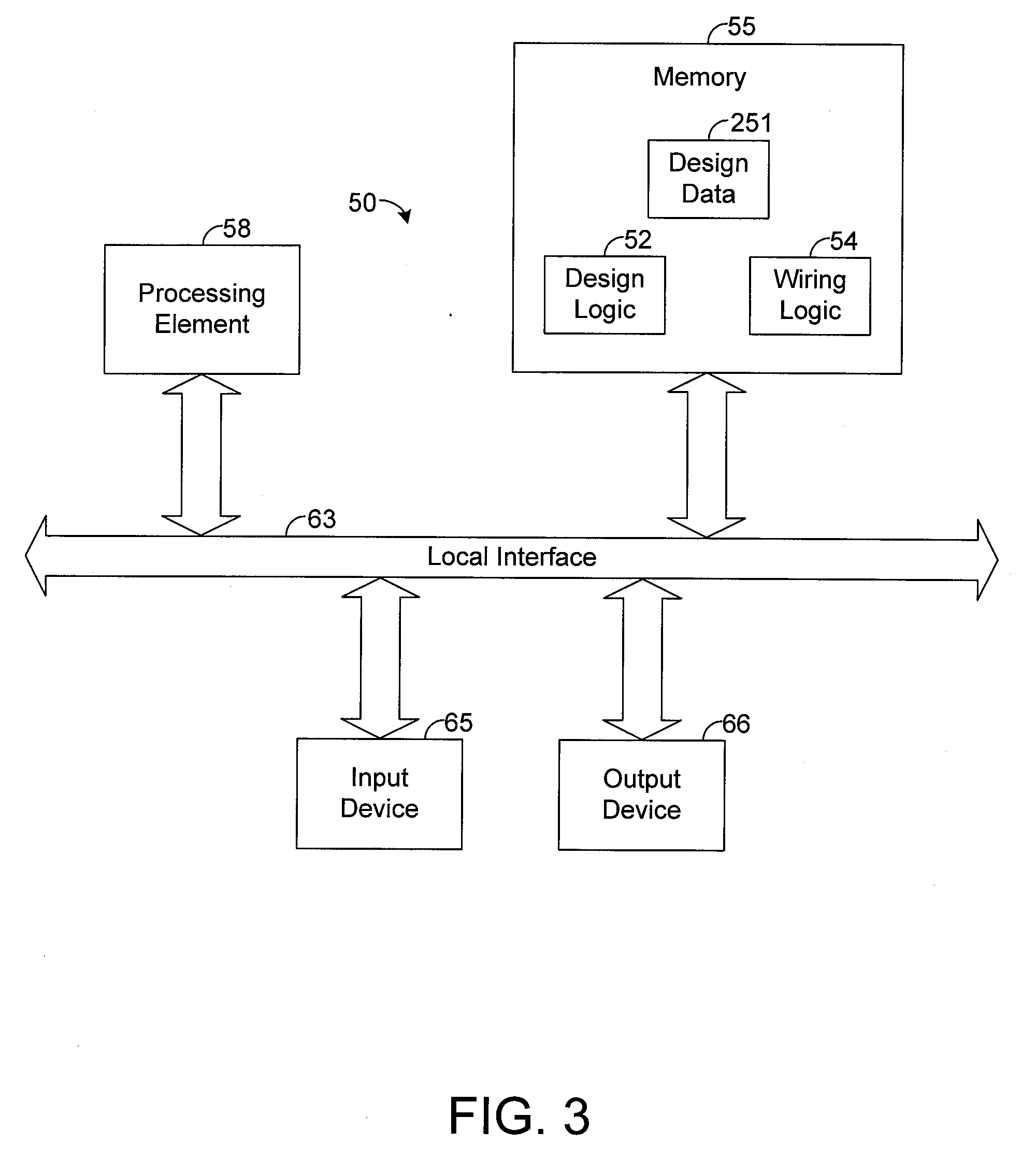

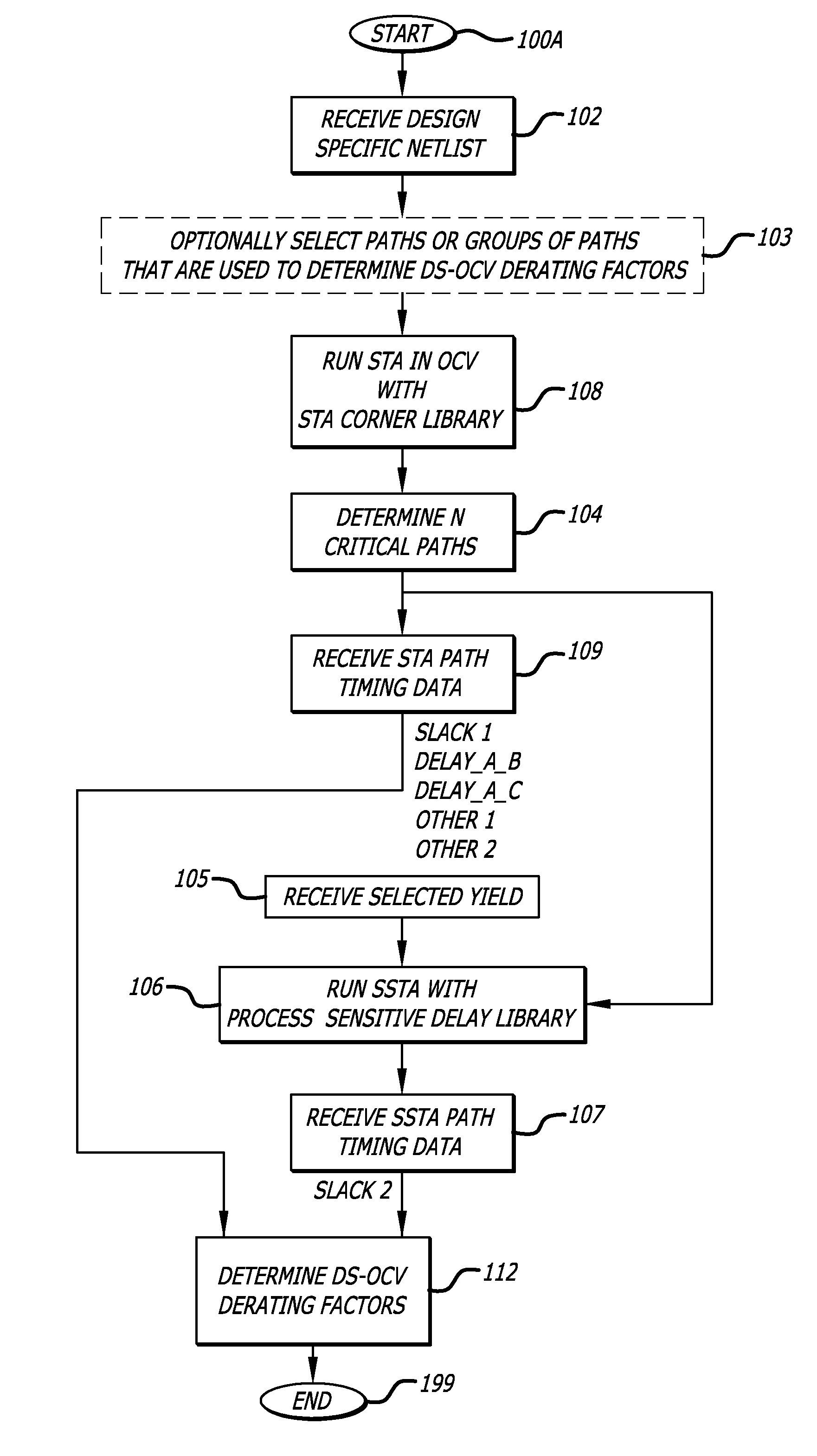

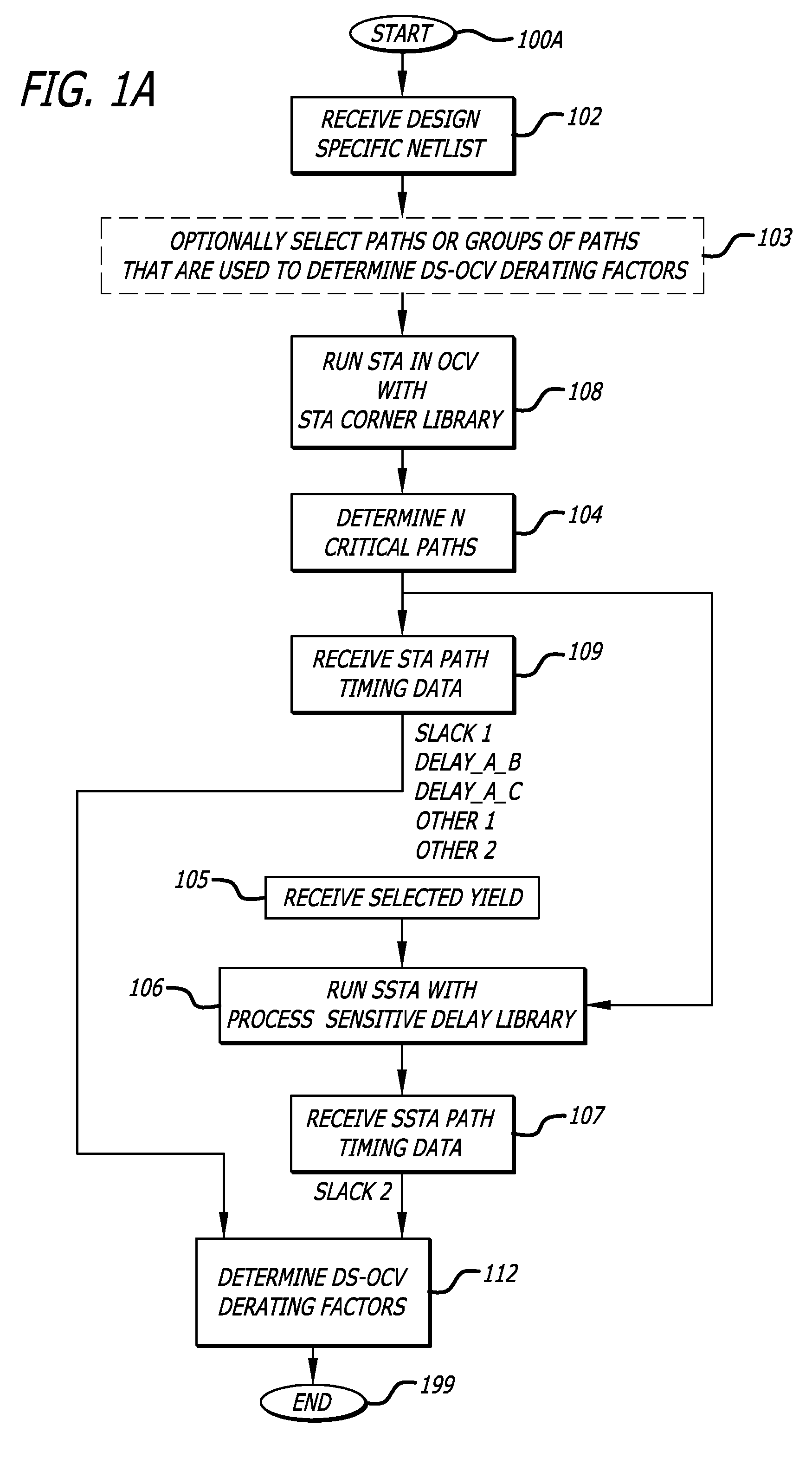

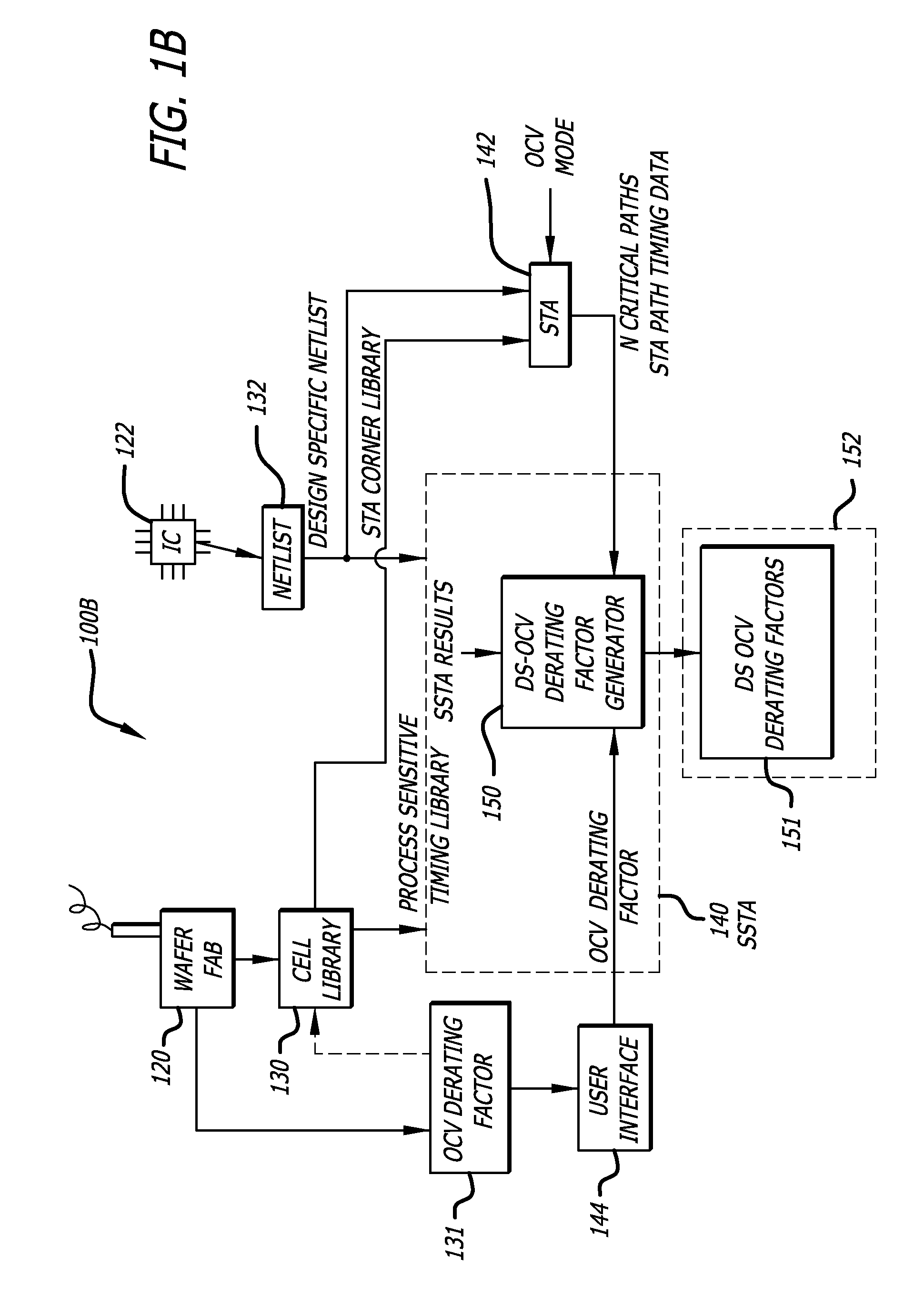

Design-specific on chip variation de-rating factors for static timing analysis of integrated circuits

InactiveUS8336010B1Reduce running timeDesign specificationComputer aided designSoftware simulation/interpretation/emulationTime informationDying processes

In one embodiment of the invention, a method of analysis of a circuit design with respect to within-die process variation is disclosed to generate a design-specific on chip variation (DS-OCV) de-rating factor. The method includes executing a static timing analysis (STA) in an on-chip variation mode using a process corner library. Collecting timing information of the top N critical timing paths. Executing a statistical static timing analysis (SSTA) on the N critical timing paths using timing models characterized for SSTA with sensitivities of delays to process variables. Compare the two timing results and deriving DS-OCV de-rating factors for the clock / data paths to be used in a STA OCV timing analysis to correctly account for the effects of process variations. A user may select to specify DS-OCV de-rating factors for paths or groups of paths and achieve an accurate timing analysis report in a reduced amount of run-time.

Owner:CADENCE DESIGN SYST INC

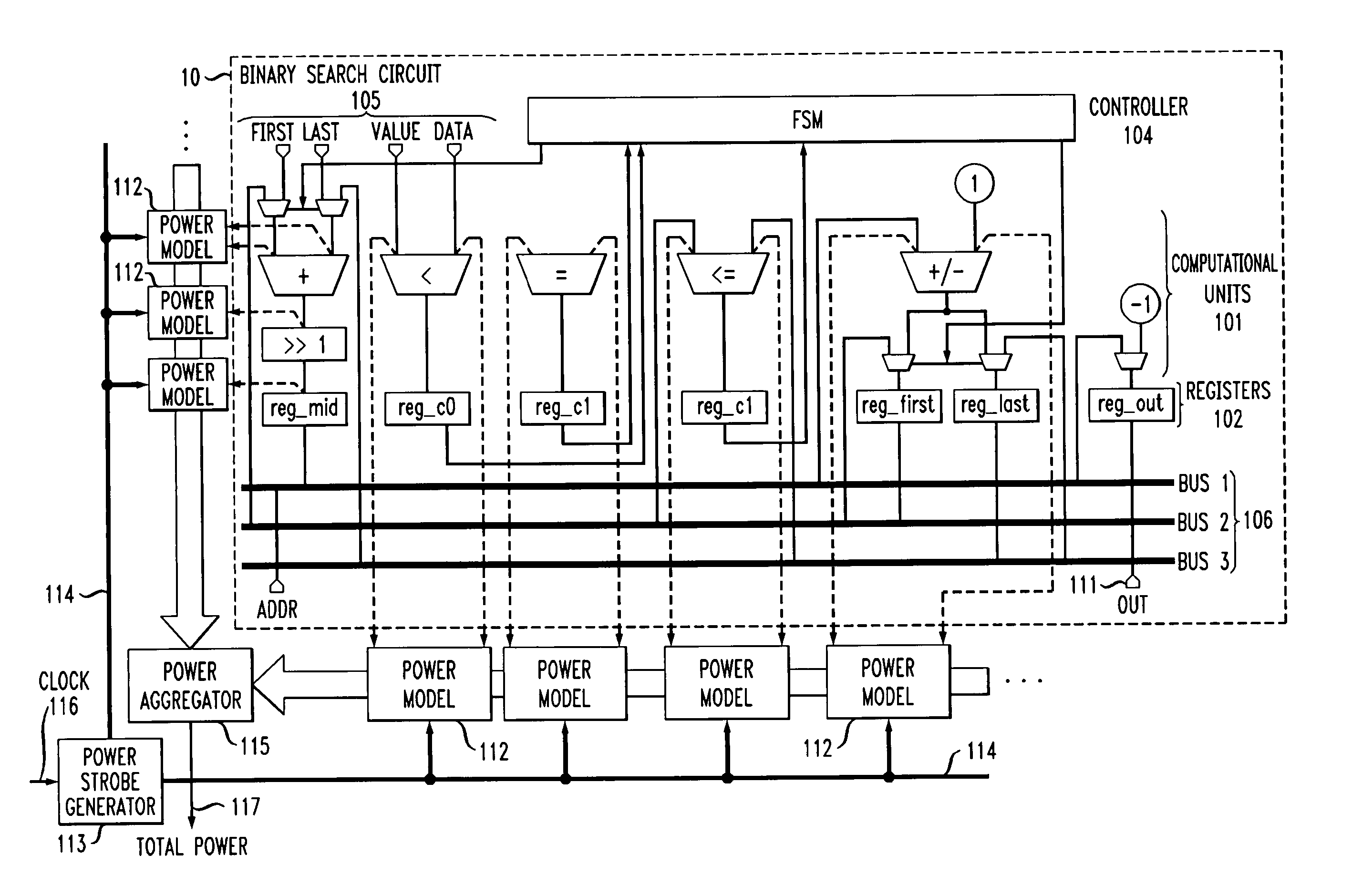

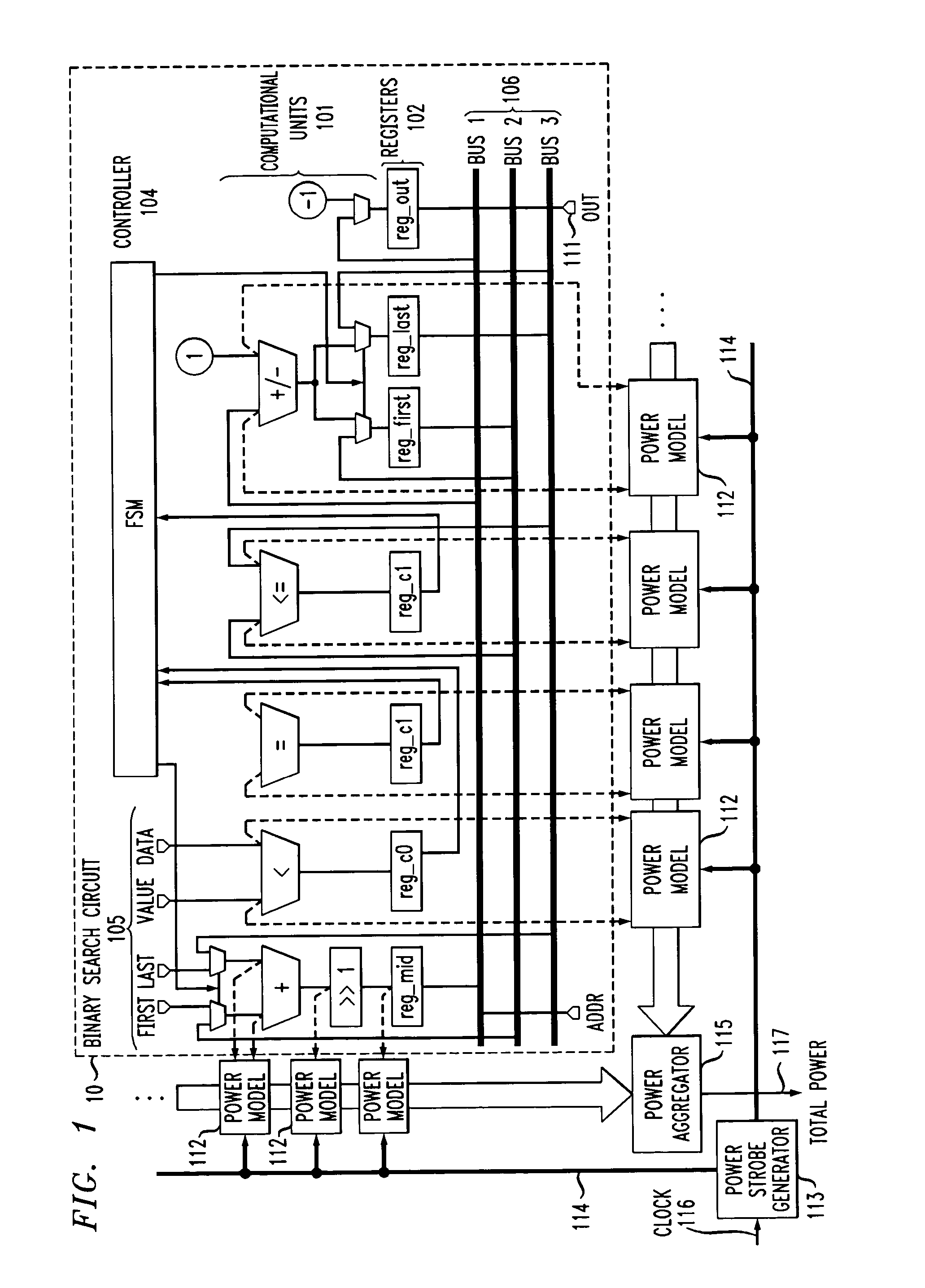

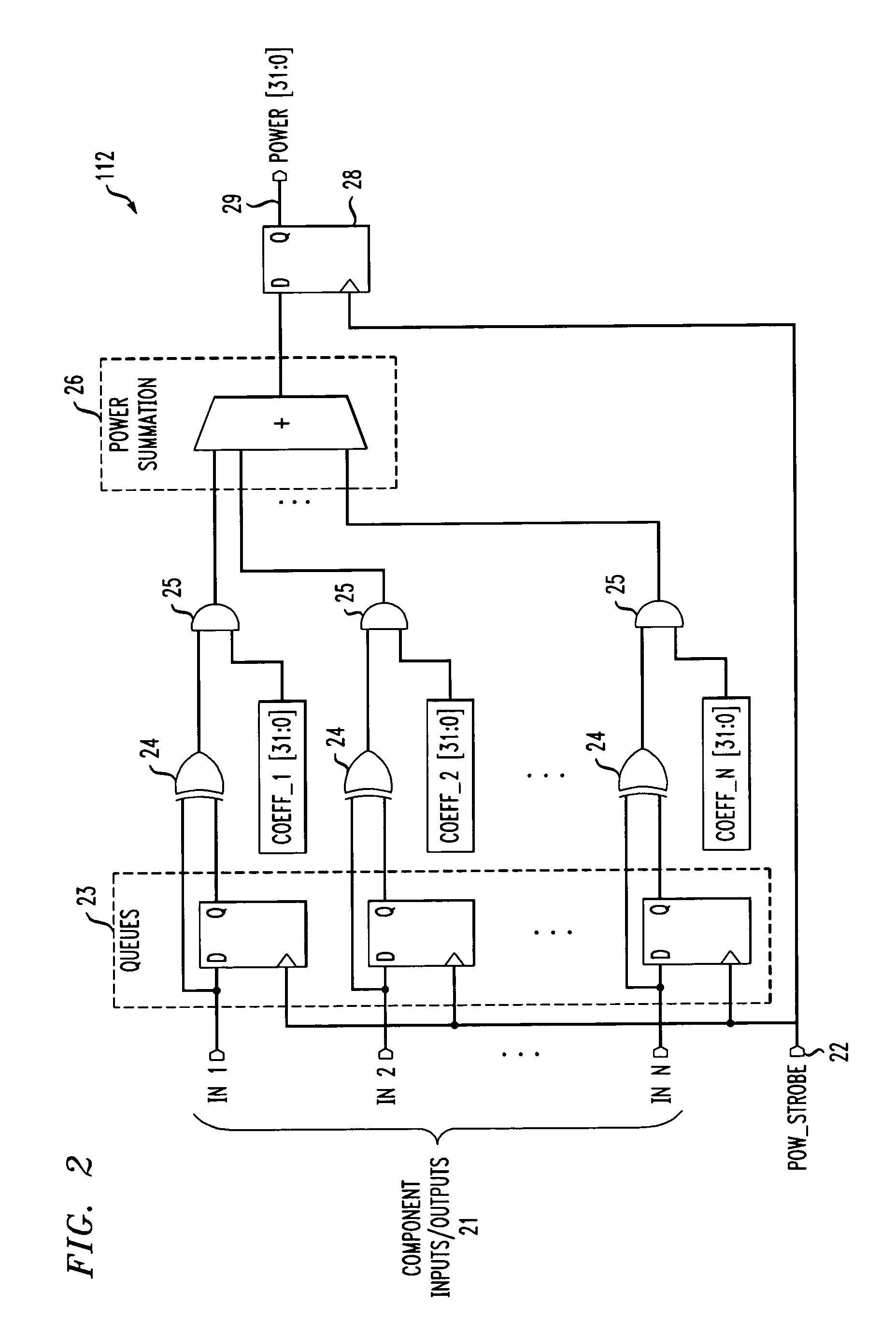

Power estimation through power emulation

InactiveUS20060058994A1Shorten the timeIncrease the areaCAD circuit designSoftware simulation/interpretation/emulationHardware emulationCircuit design

The time required to estimate the amount of power that will be consumed by a circuit under design is significantly speeded up. Specifically, the steps involved in power estimation (power model evaluation, aggregation) are implemented as power estimation circuitry that is added to the design of the functional circuit during circuit design. The resulting power-model-enhanced circuit is mapped onto a hardware emulation platform, one of whose outputs is a computation of the estimated power computed by the power estimation circuitry during the emulation. As compared to state-of-the-art commercial power estimation tools, speed-ups from around 10-fold to over 500-fold can be realized.

Owner:NEC LAB AMERICA

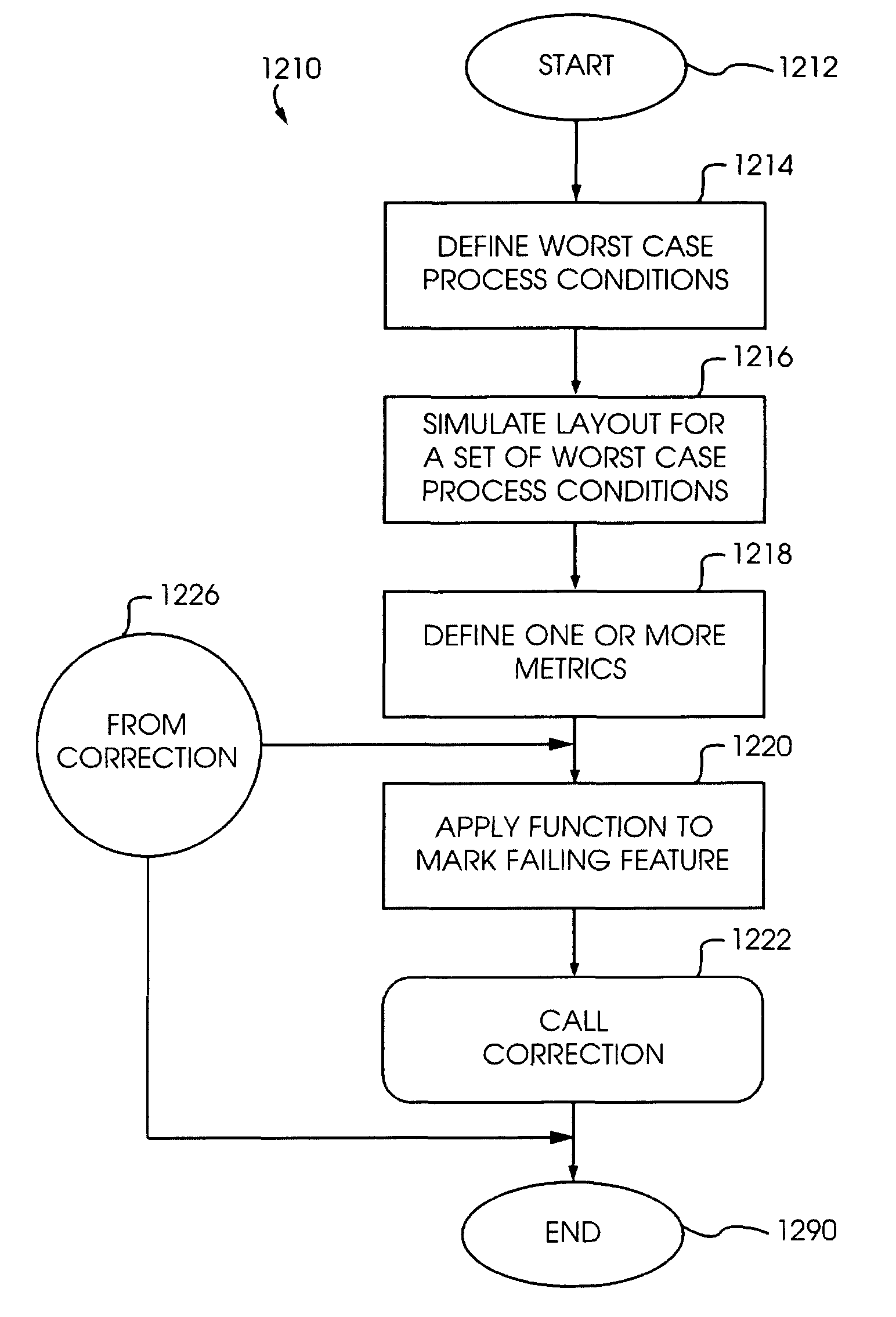

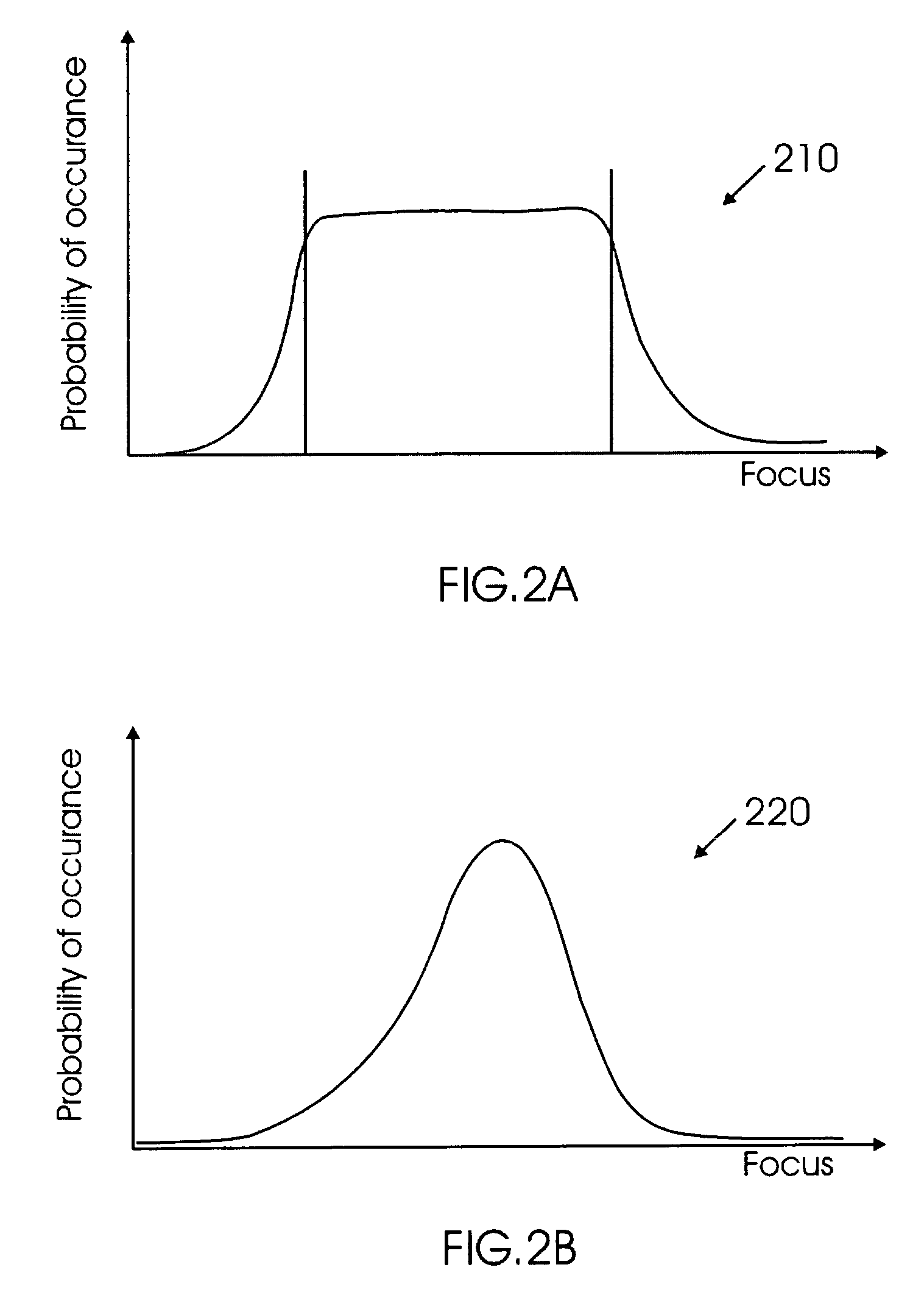

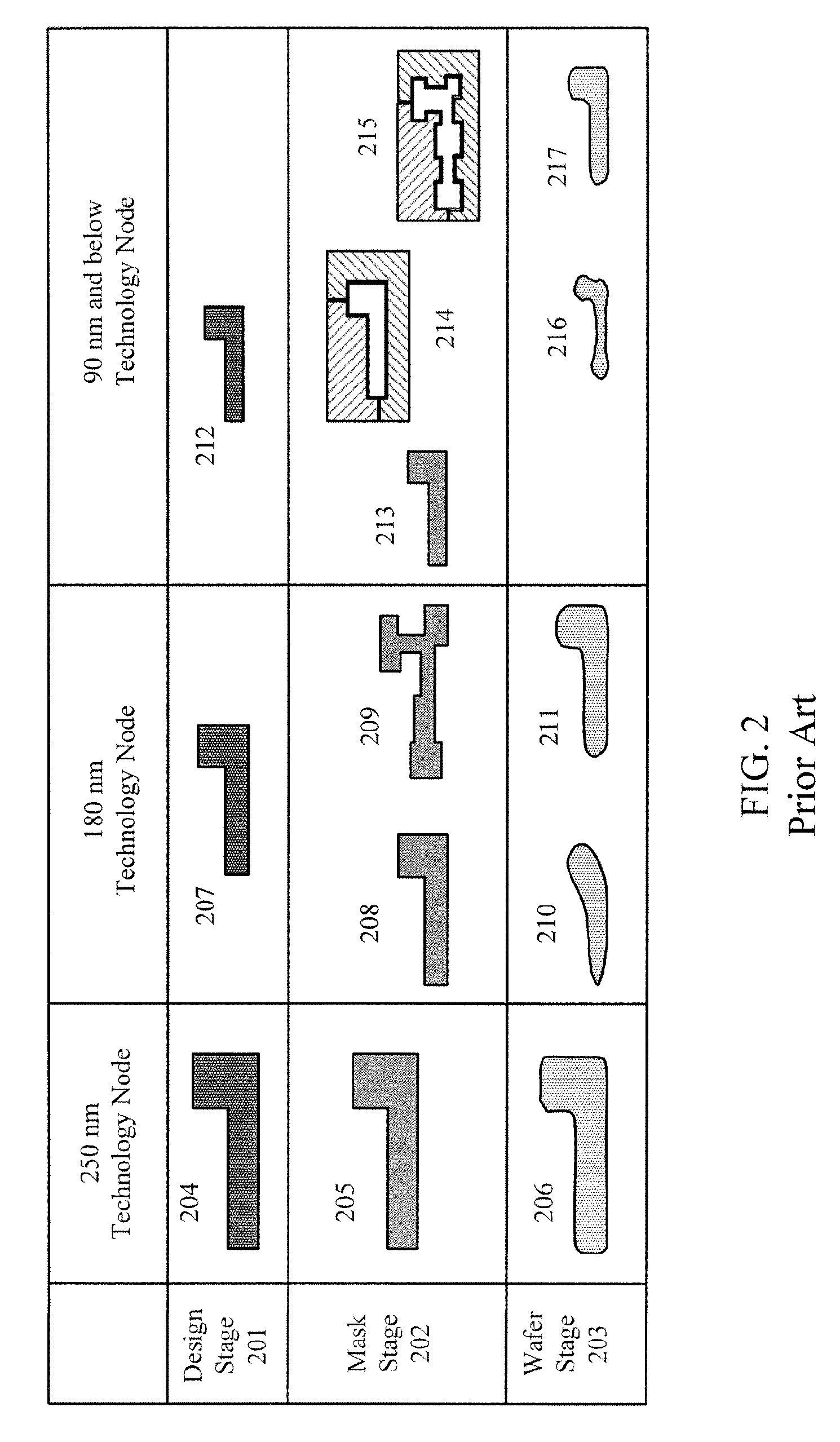

Optical lithography correction process

A apparatus and method for correcting a process critical layout includes characterizing the influence of individual ones of a set of worst case process variations on a simulated nano-circuit layout design and then correcting layout geometries in the simulated nano-circuit layout based on such characterizations.

Owner:CADENCE DESIGN SYST INC

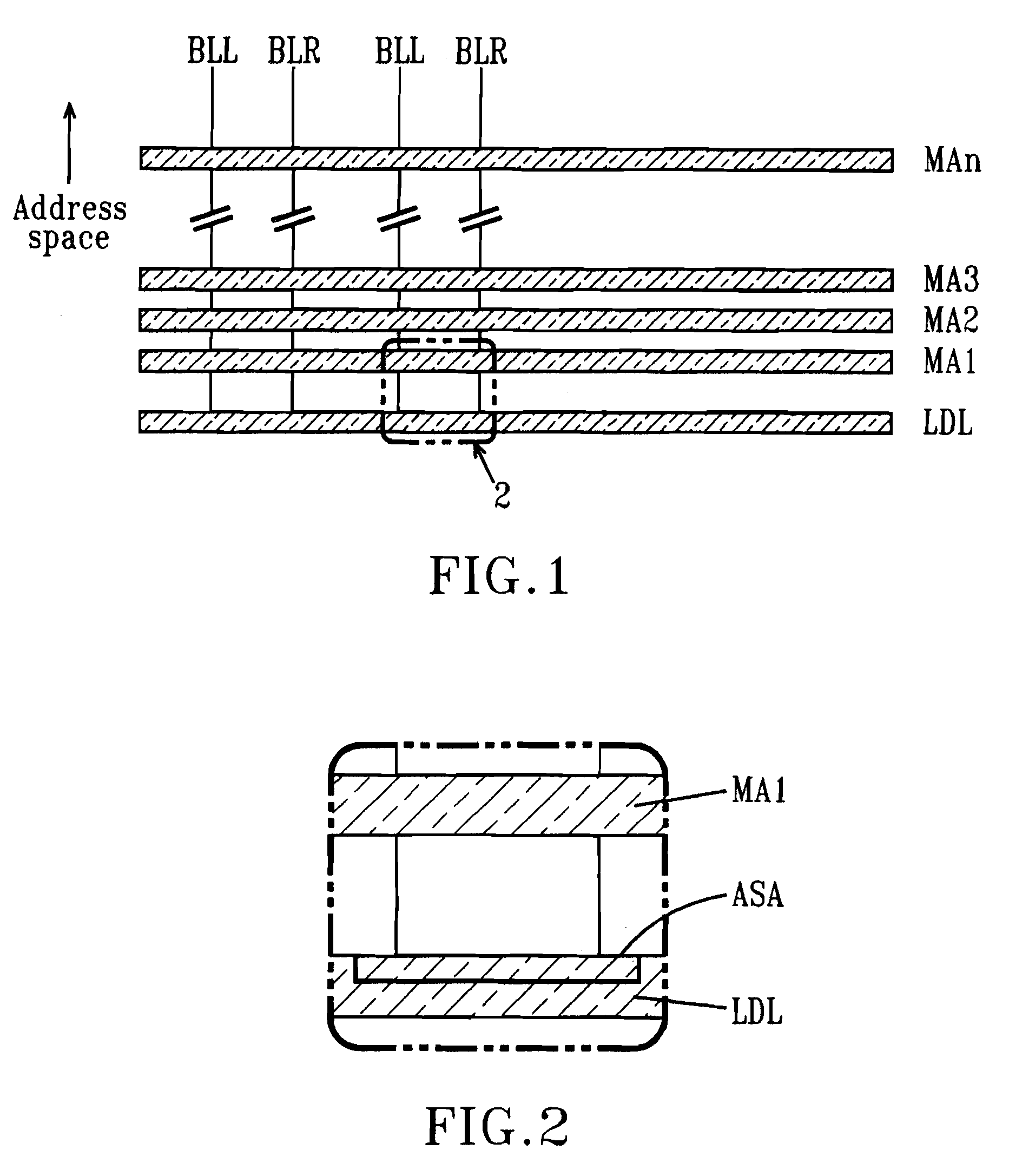

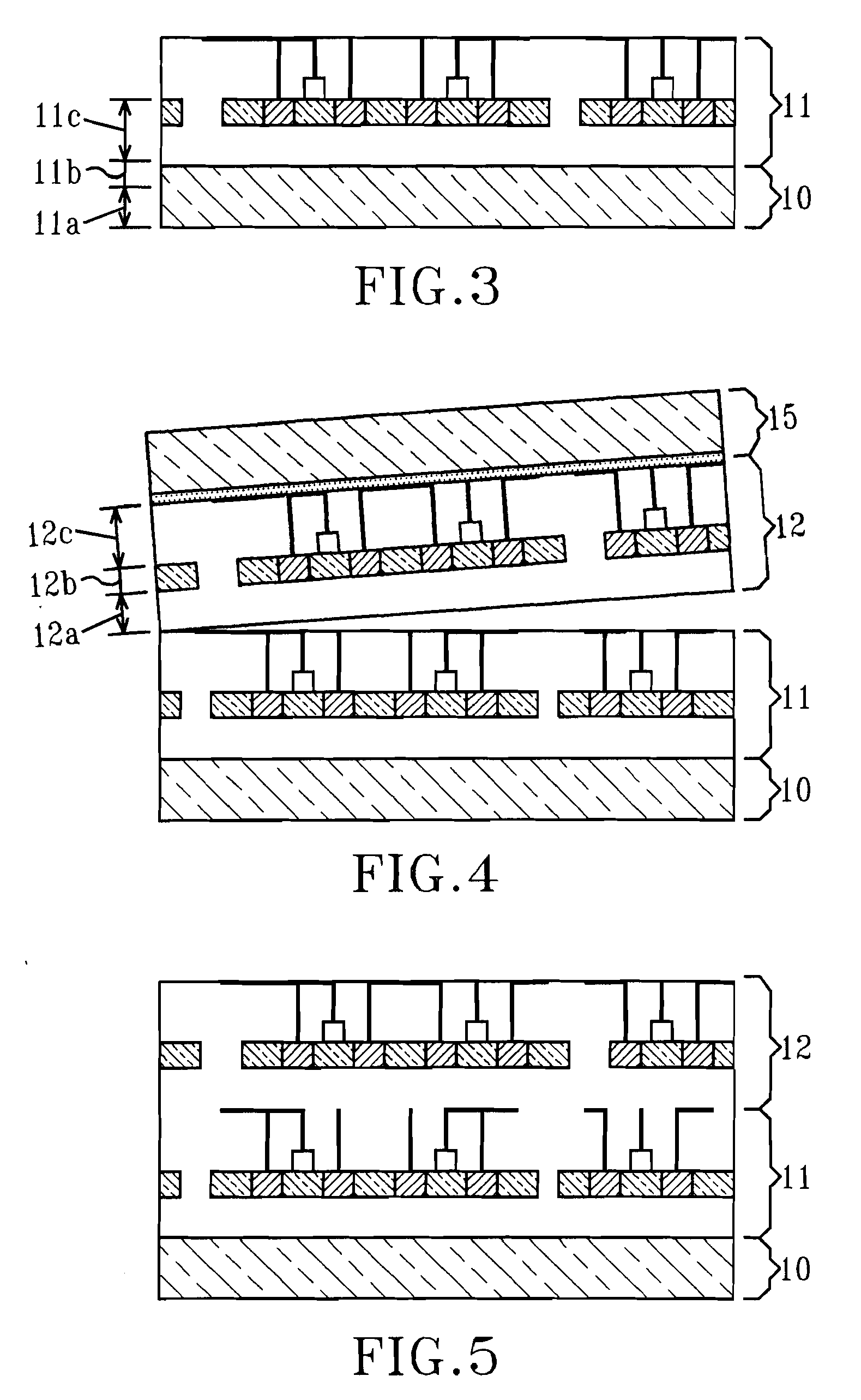

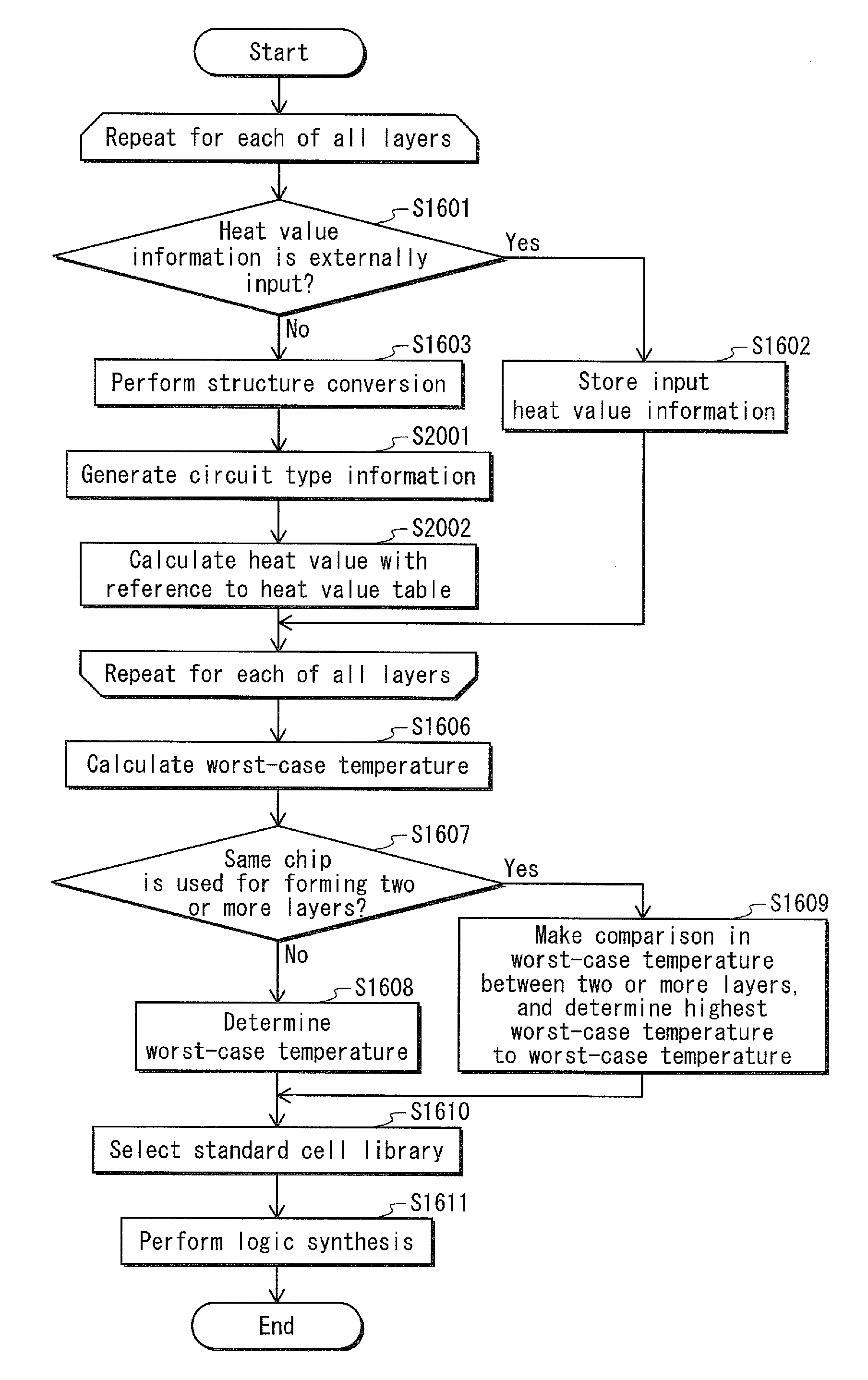

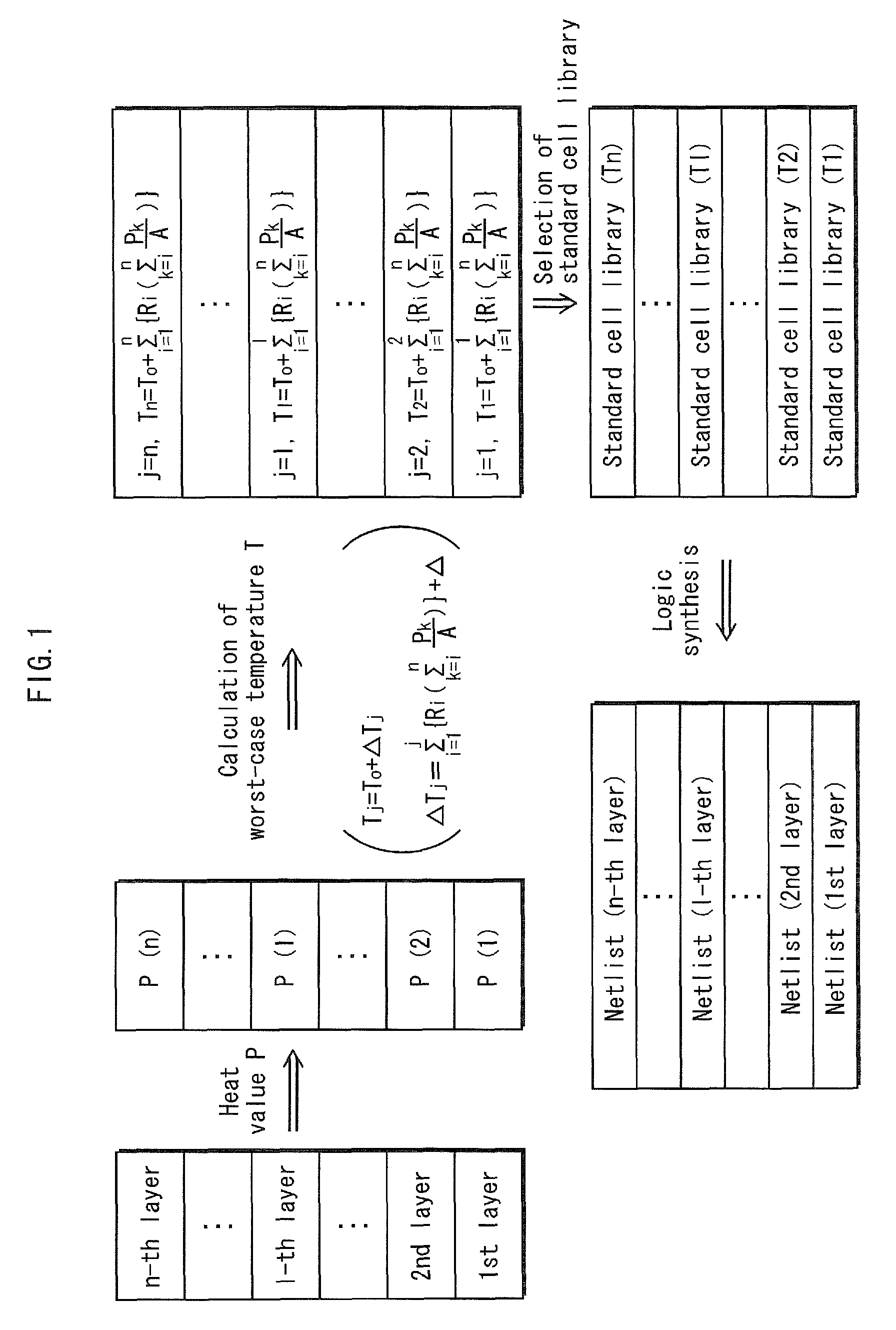

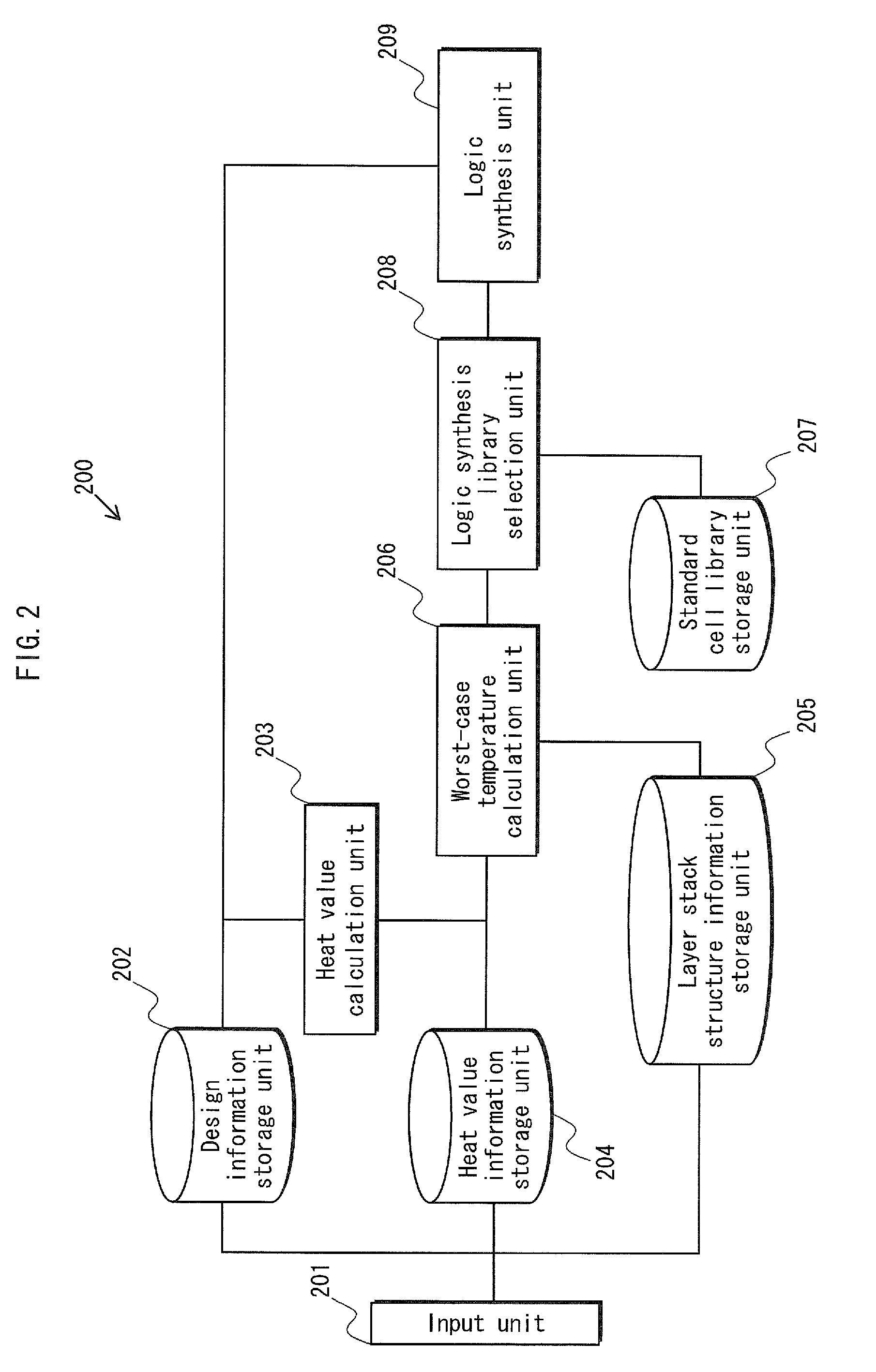

Three-dimensional integrated circuit design device, three-dimensional integrated circuit design, method, and program

InactiveUS8566762B2Increase the areaReduce power consumptionSolid-state devicesComputer aided designEngineeringThree-dimensional integrated circuit

A worst-case temperature calculation unit calculates, based on heat value information of each layer of a three-dimensional integrated circuit to be designed and stack structure information of the three-dimensional integrated circuit, a worst-case temperature of a layer during operation that is targeted for logic synthesis. A logic synthesis library selection unit selects a library appropriate for the calculated worst-case temperature. A logic synthesis unit performs logic synthesis on the targeted layer with use of the selected library.

Owner:PANASONIC CORP

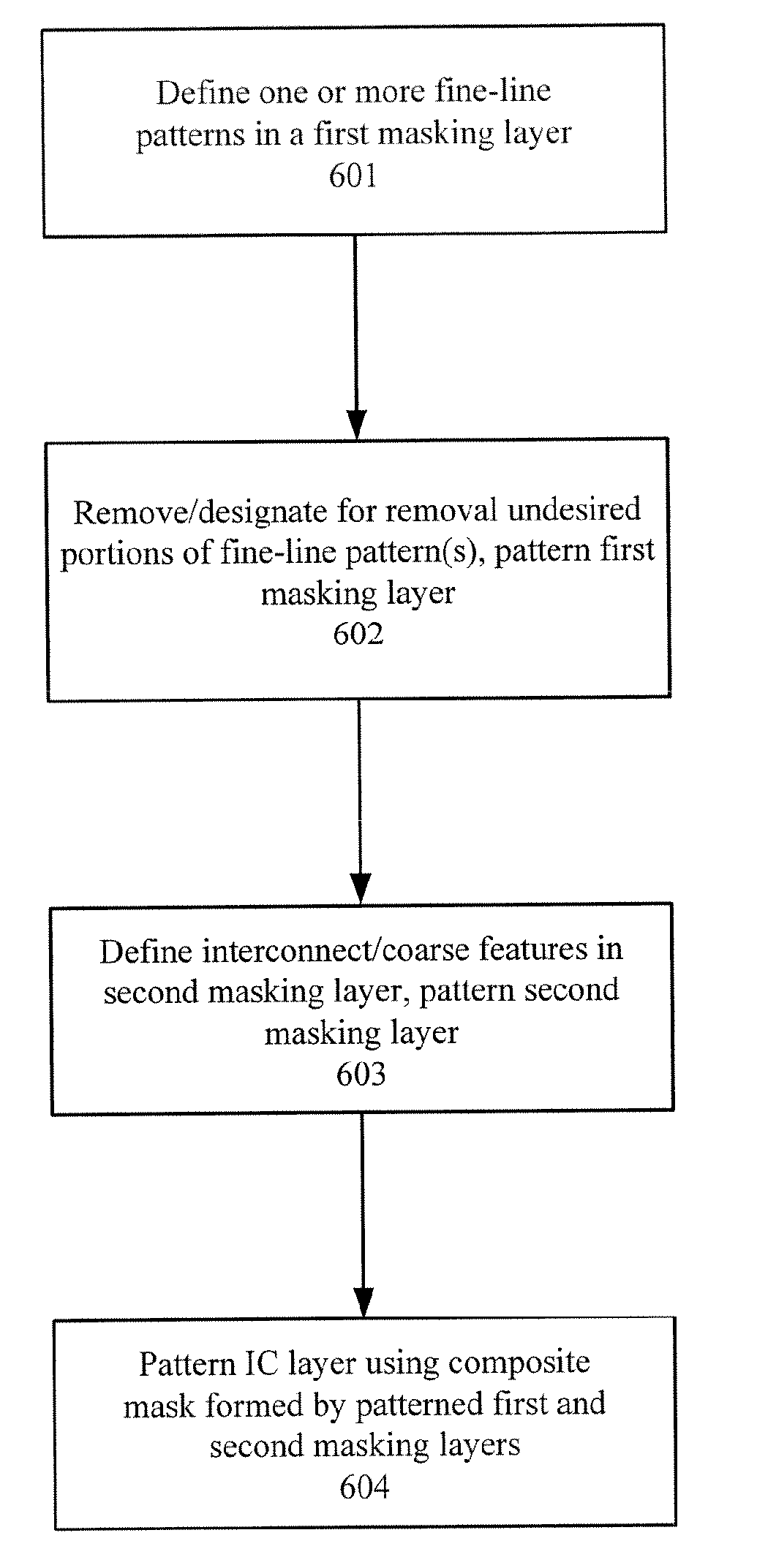

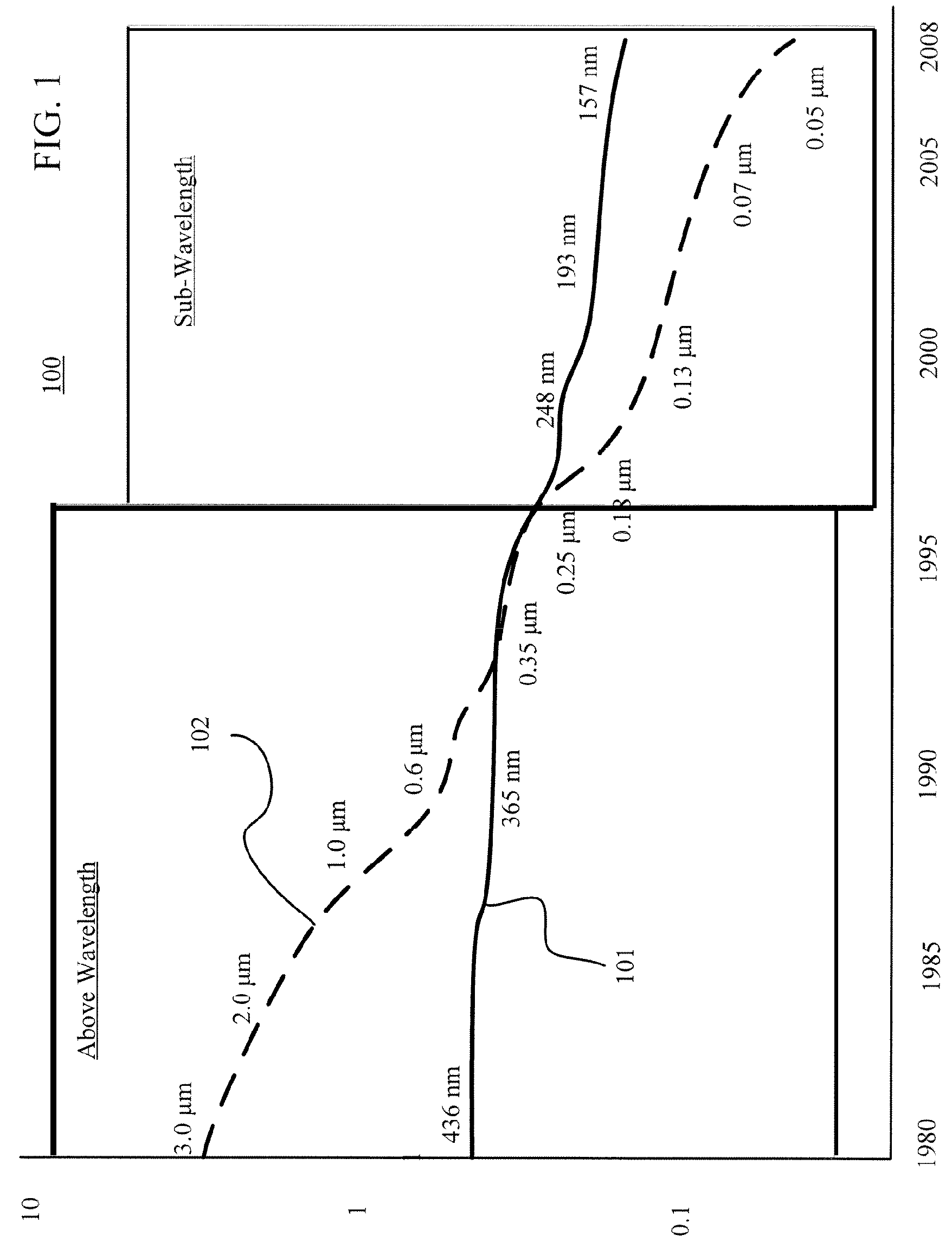

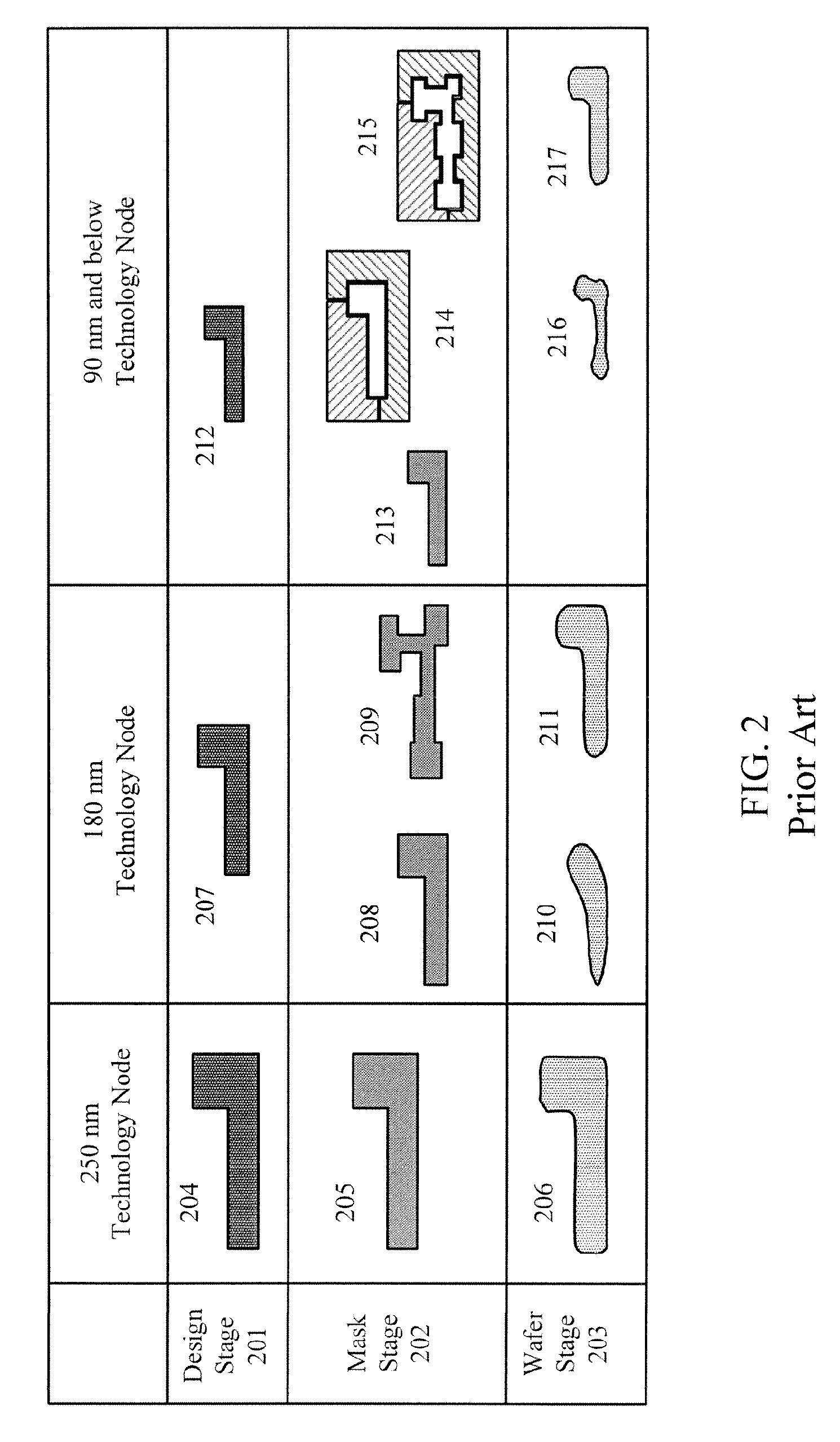

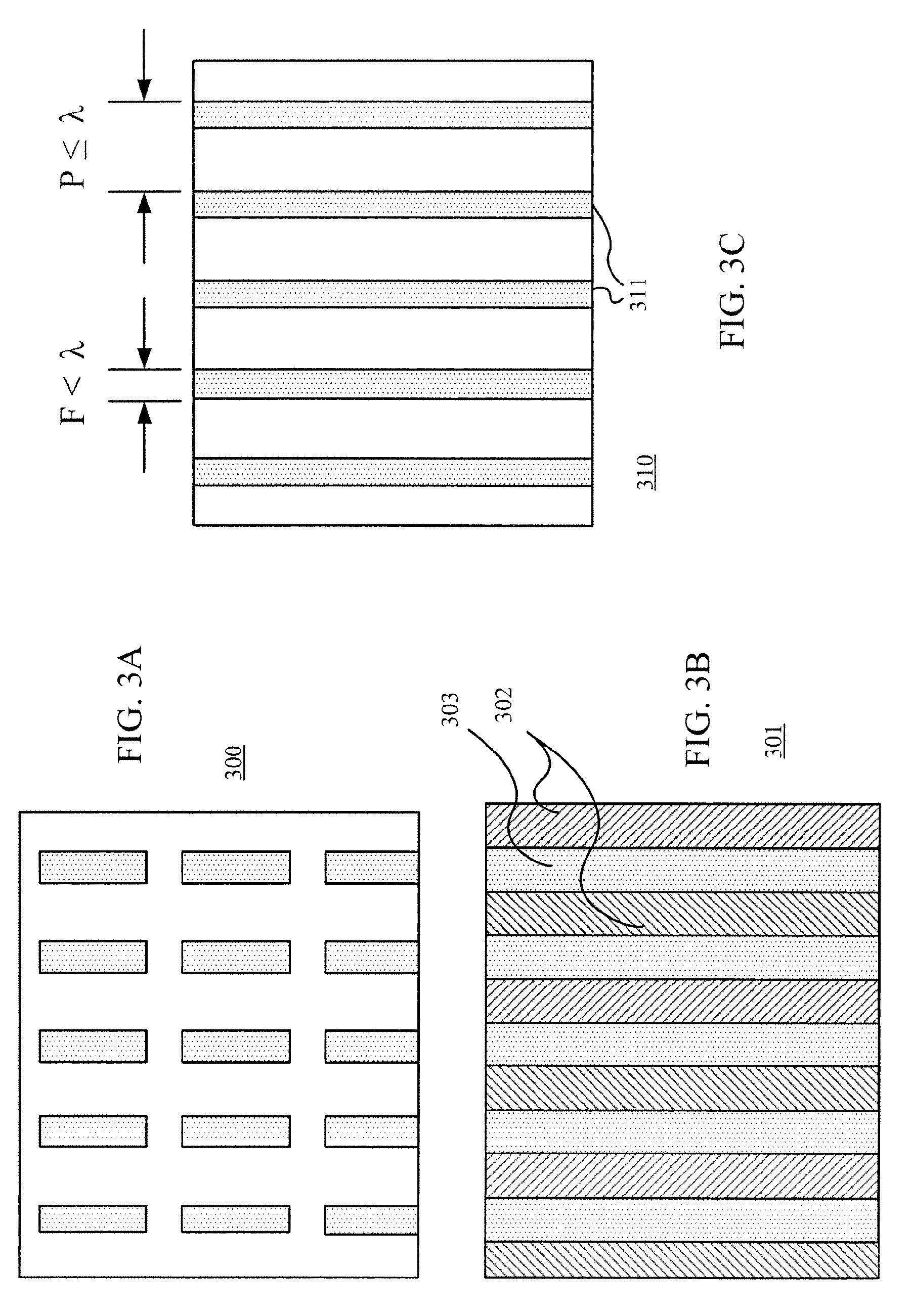

Patterning A Single Integrated Circuit Layer Using Multiple Masks And Multiple Masking Layers

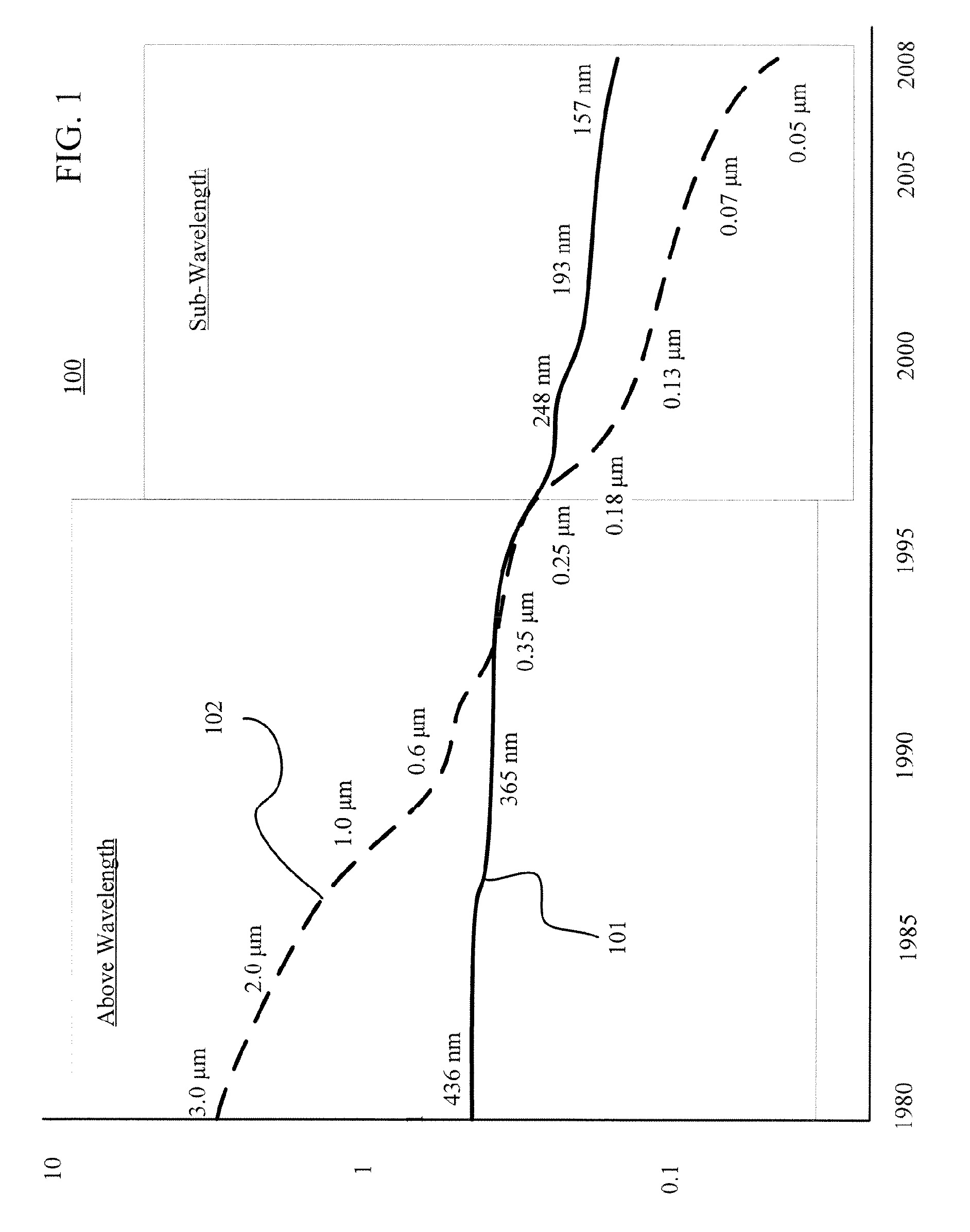

ActiveUS20070275309A1Increase productionEasy to useSemiconductor/solid-state device manufacturingPhotosensitive material processingResolution enhancement technologiesLength wave

A multiple mask and a multiple masking layer technique can be used to pattern a single IC layer. A resolution enhancement technique can be used to define one or more fine-line patterns in a first masking layer, wherein each fine-line feature is sub-wavelength. Moreover, the pitch of each fine-line pattern is less than or equal to that wavelength. The portions of the fine-line features not needed to implement the circuit design are then removed or designated for removal using a mask. After patterning of the first masking layer, another mask can then be used to define coarse features in a second masking layer formed over the patterned first masking layer. At least one coarse feature is defined to connect two fine-line features. The IC layer can be patterned using the composite mask formed by the patterned first and second masking layers.

Owner:SYNOPSYS INC

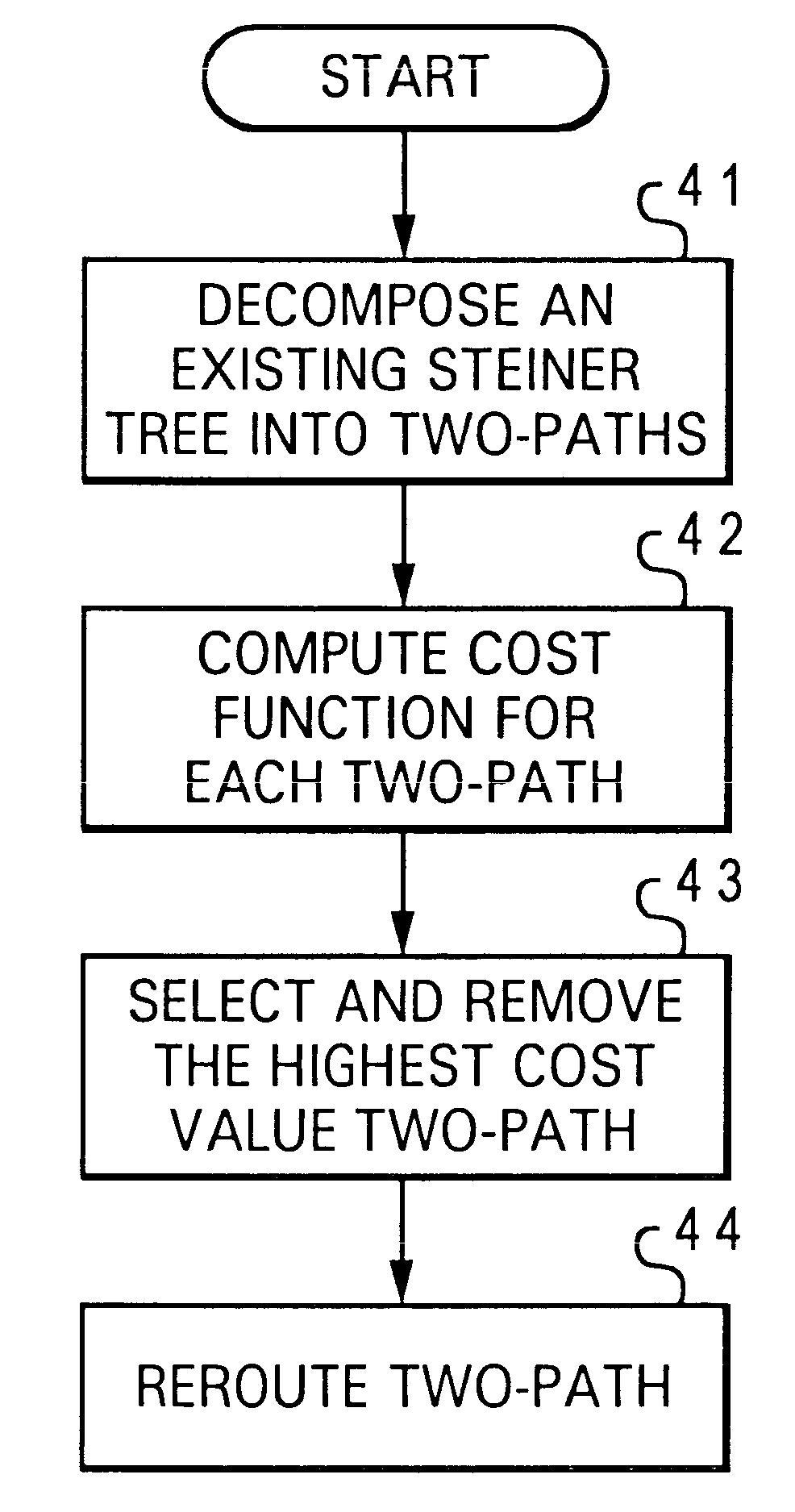

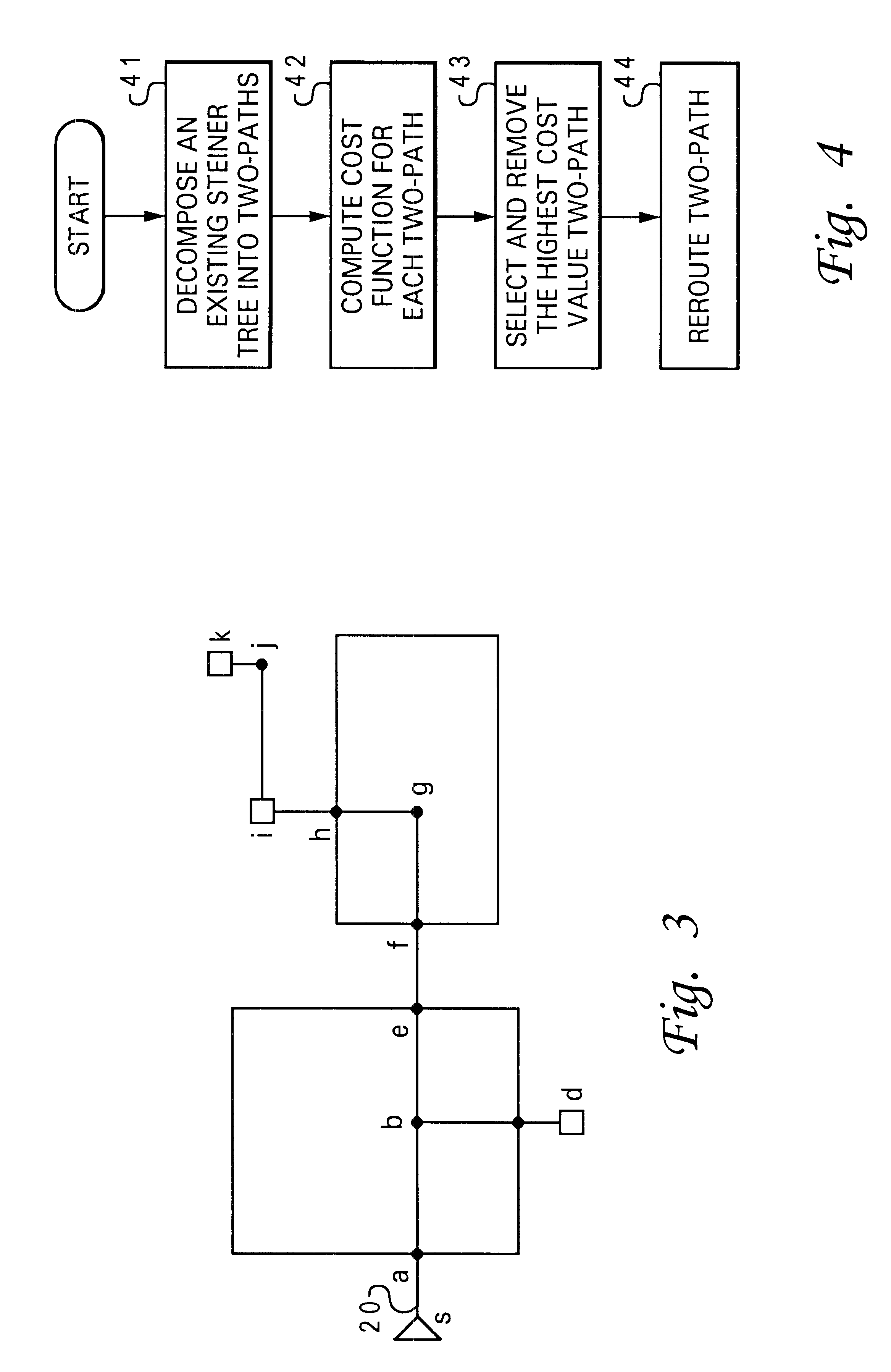

Method and system for re-routing interconnects within an integrated circuit design having blockages and bays

InactiveUS6401234B1Computer aided designSoftware simulation/interpretation/emulationRouting algorithmCircuit design

A method and system for re-routing interconnects within an integrated circuit design having blockages and bays is disclosed. A net within the integrated circuit design is initially decomposed into multiple two-paths. The net includes interconnects previously routed by utilizing a Steiner tree routing algorithm. Next, a cost associated with each of the two-paths is calculated. A two-path having a a high cost is subsequently selected and re-routed with a lower cost two-path.

Owner:IBM CORP

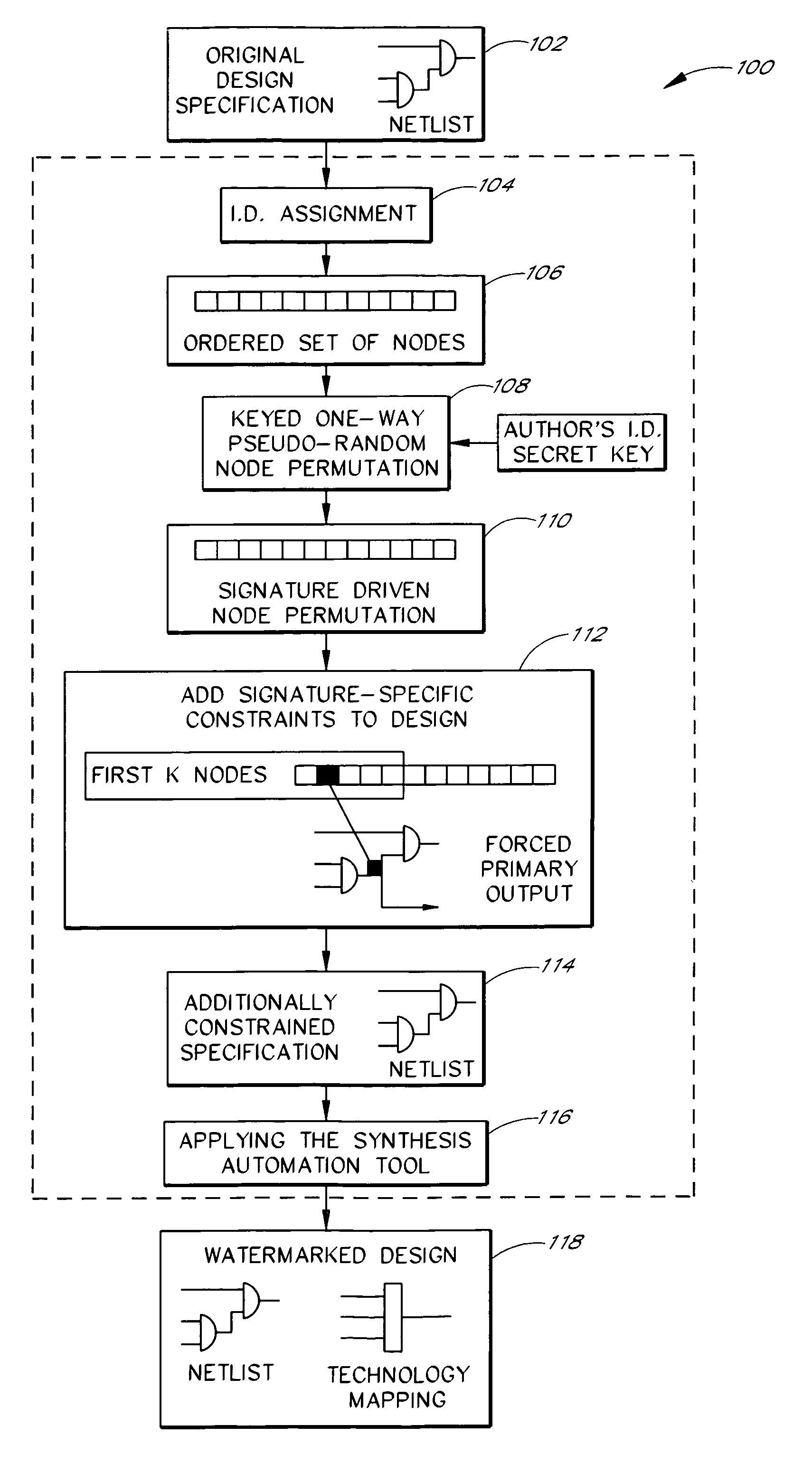

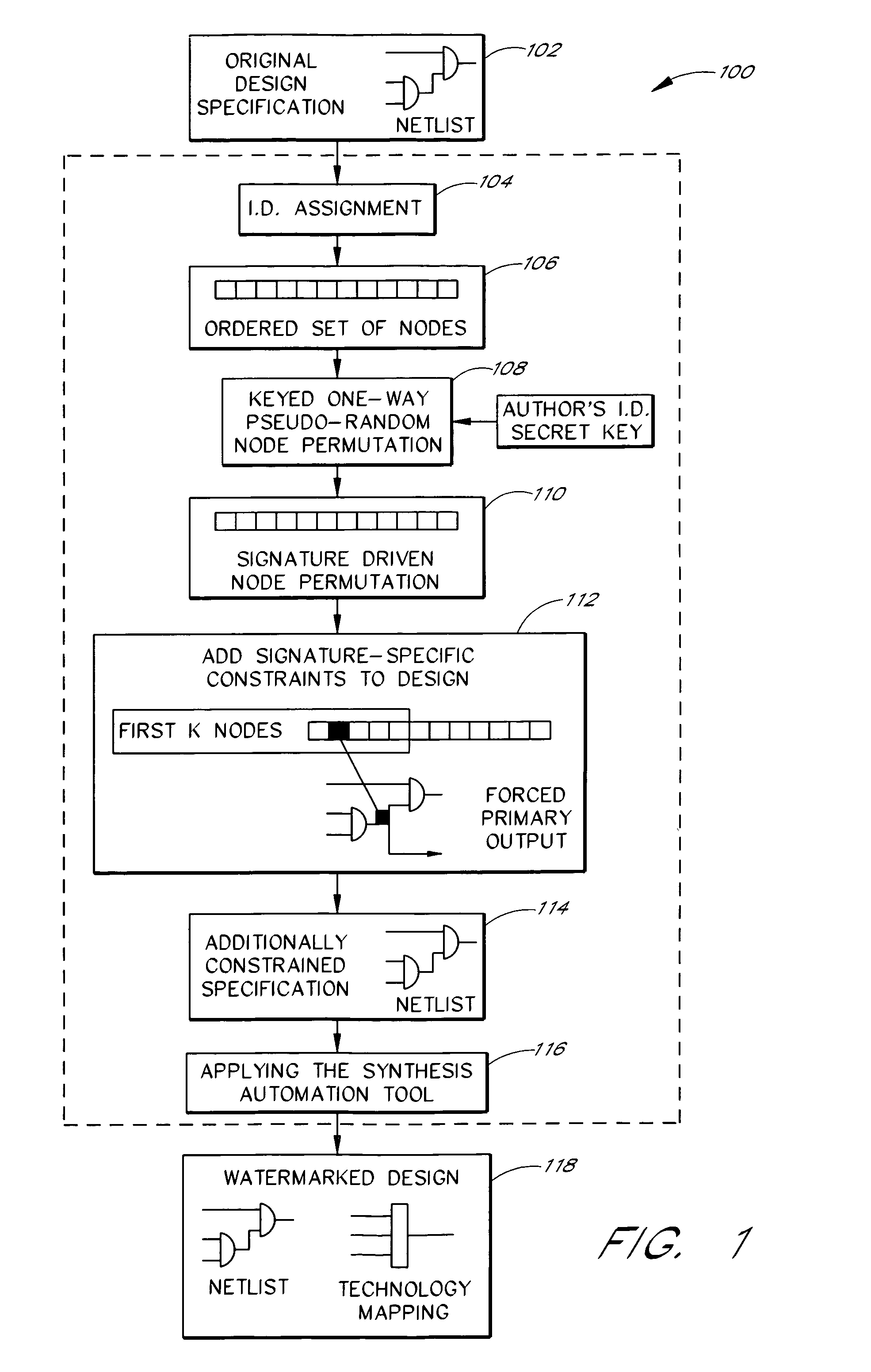

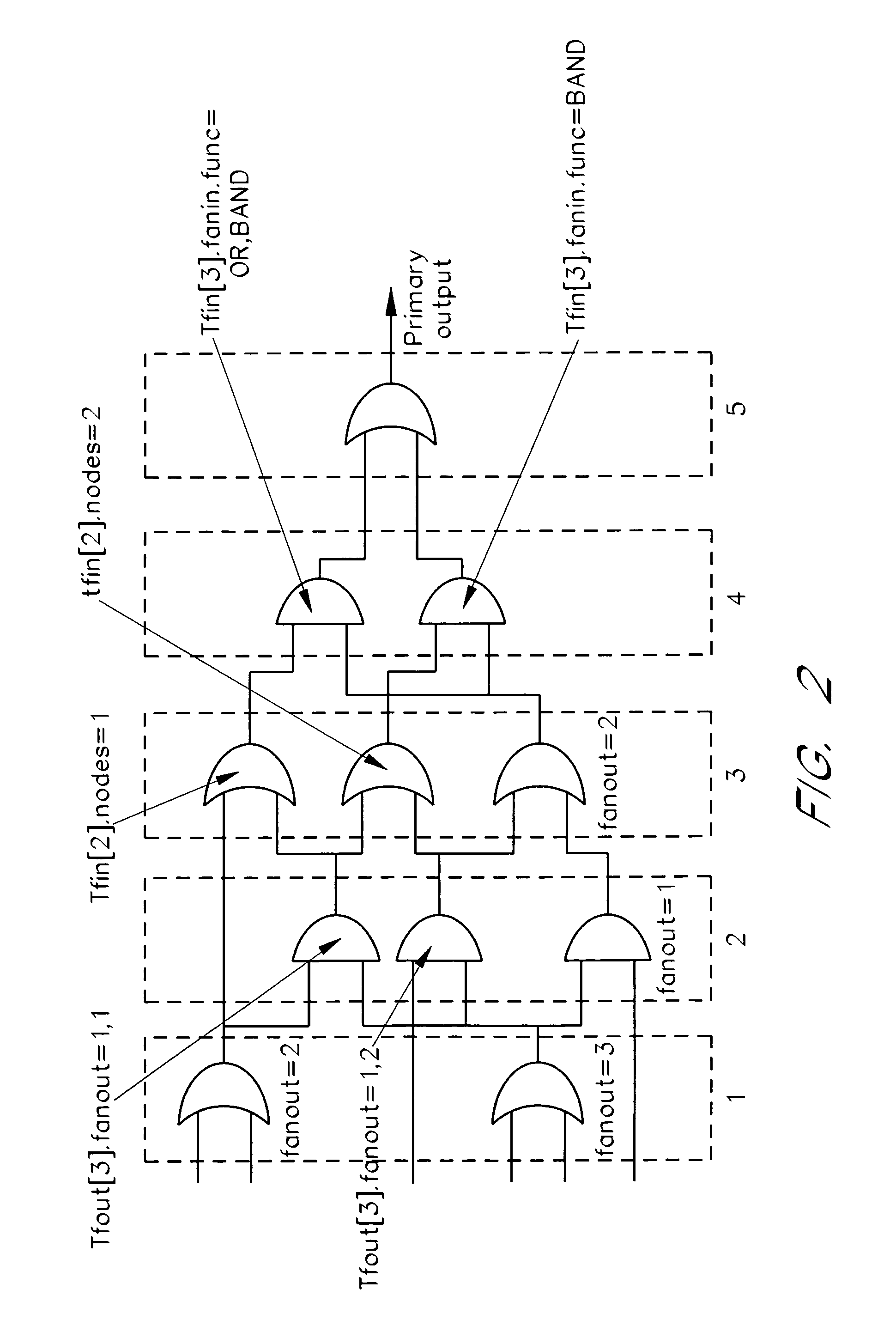

Methods and systems for the identification of circuits and circuit designs

InactiveUS7017043B1Generate efficientlyDigital data processing detailsUser identity/authority verificationTheoretical computer scienceCircuit design

The present invention is related to systems and methods for adding a signature to circuit design. In one embodiment, a first set of constraints used to specify a functional portion of the circuit design is received. A second set of constraints used to specify the signature is received as well. The circuit design is generated based on at least the first constraints and the second constraints, wherein the signature is embedded in the functional portion.

Owner:RGT UNIV OF CALIFORNIA

Patterning a single integrated circuit layer using multiple masks and multiple masking layers

ActiveUS7537866B2Low costEasy to controlSemiconductor/solid-state device manufacturingPhotosensitive material processingResolution enhancement technologiesWavelength

A multiple mask and a multiple masking layer technique can be used to pattern a single IC layer. A resolution enhancement technique can be used to define one or more fine-line patterns in a first masking layer, wherein each fine-line feature is sub-wavelength. Moreover, the pitch of each fine-line pattern is less than or equal to that wavelength. The portions of the fine-line features not needed to implement the circuit design are then removed or designated for removal using a mask. After patterning of the first masking layer, another mask can then be used to define coarse features in a second masking layer formed over the patterned first masking layer. At least one coarse feature is defined to connect two fine-line features. The IC layer can be patterned using the composite mask formed by the patterned first and second masking layers.

Owner:SYNOPSYS INC

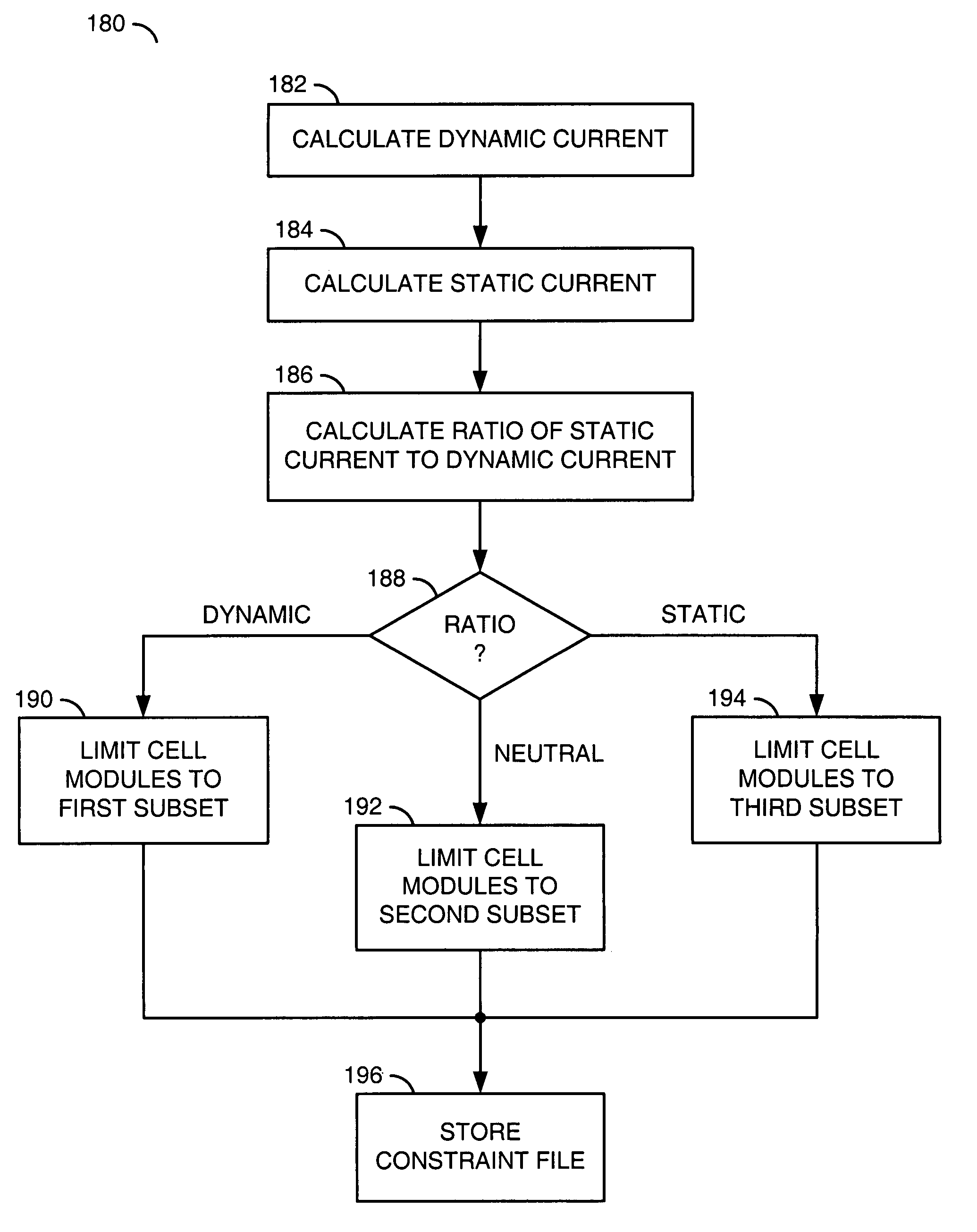

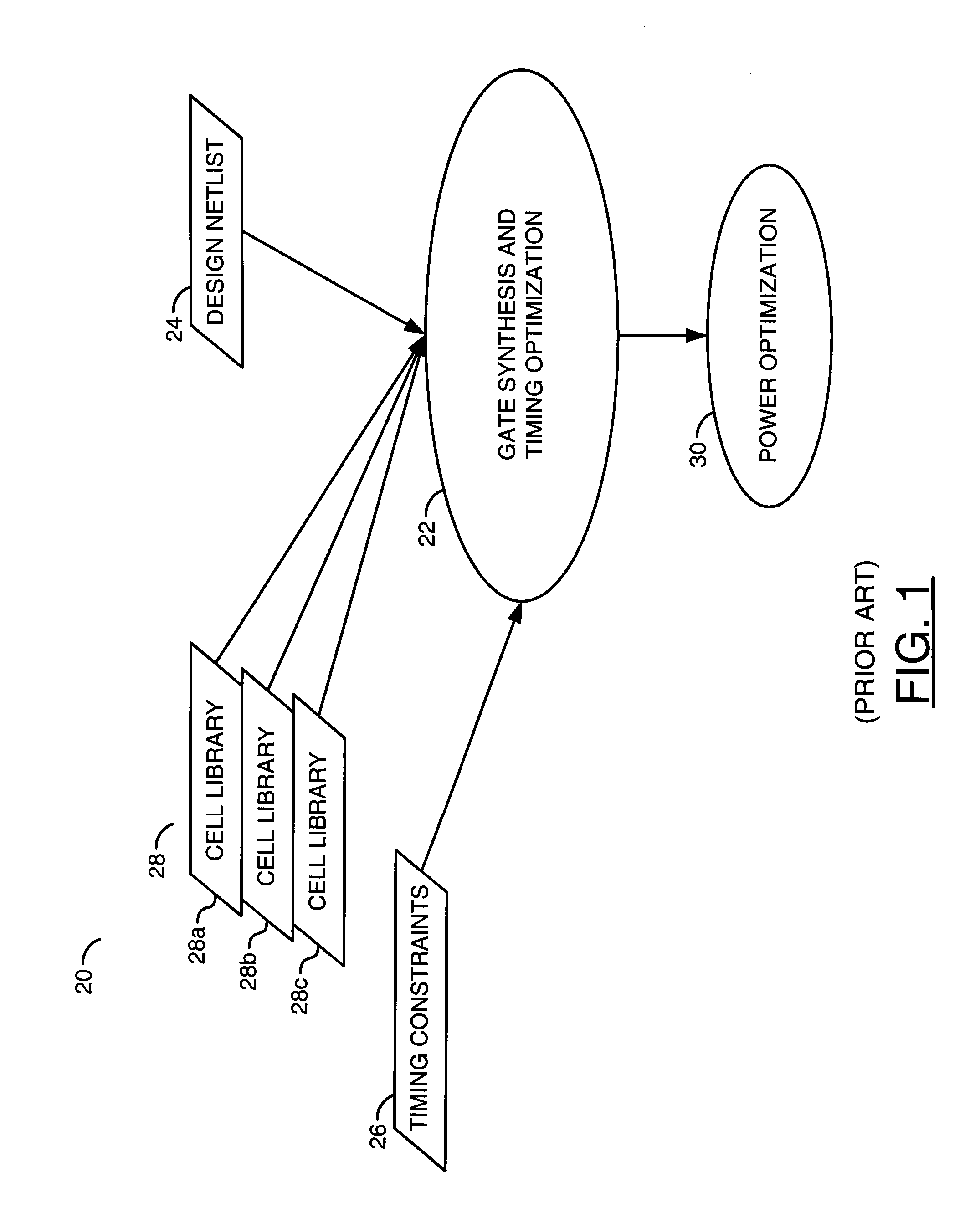

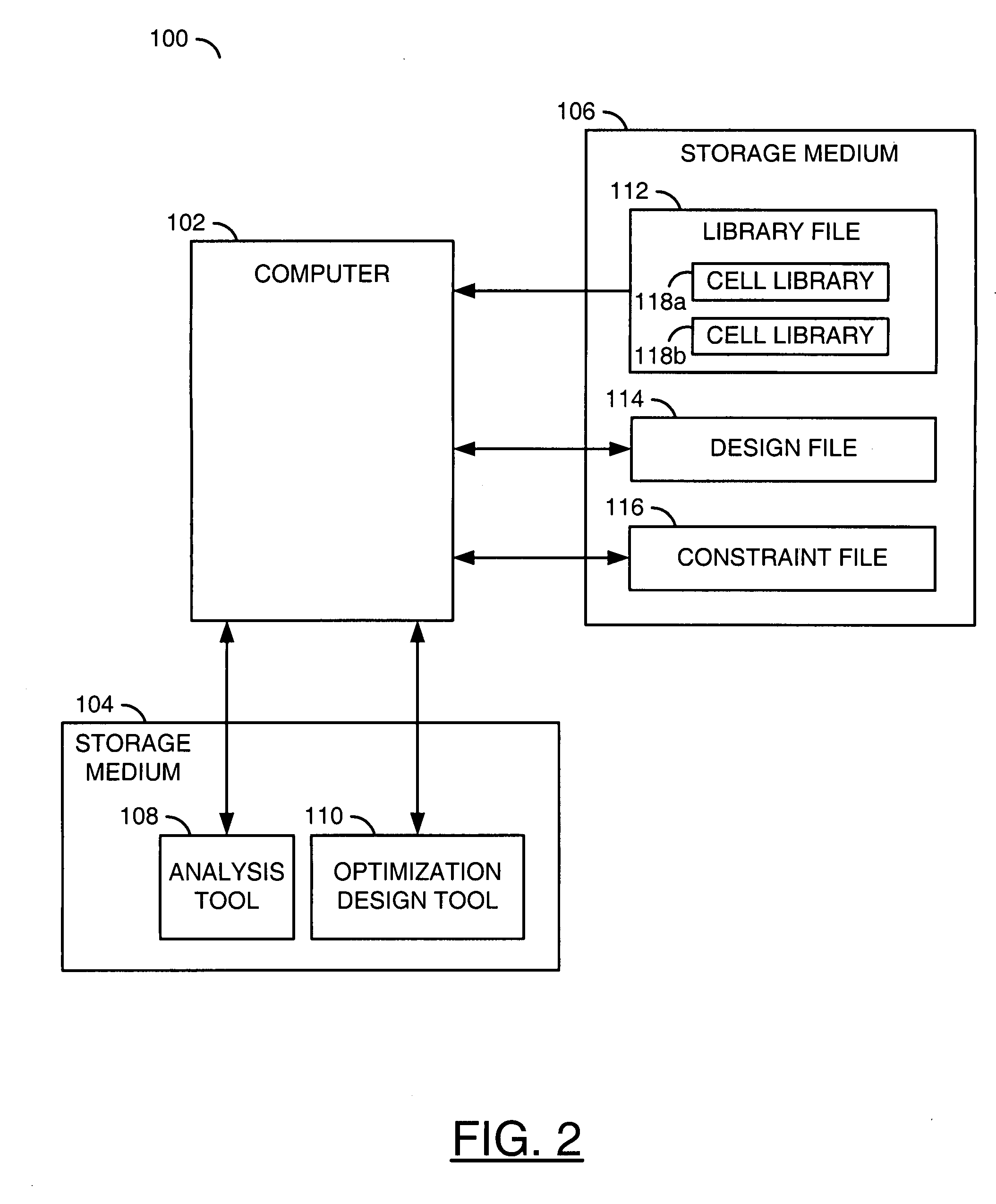

Cell library management for power optimization

InactiveUS7496867B2CAD circuit designSoftware simulation/interpretation/emulationPower optimizationOperating system

A method of managing a cell library regarding power optimization is disclosed. The method generally includes the steps of (A) reading a plurality of first modules within a first region of a circuit design stored in a design file, (B) calculating a first merit value indicating a relative sensitivity of the first region to a power consumption, the first merit value having a range from a static power dominated value to a dynamic power dominated value and (C) creating a constraint file configured to limit a design tool to a first subset of a plurality of replacement modules based on the first merit value such that the design tool automatically optimizes the power consumption of the first region by replacing at least one of the first modules with at least one of the replacement modules within the first subset, the replacement modules residing in a library file.

Owner:BELL SEMICON LLC

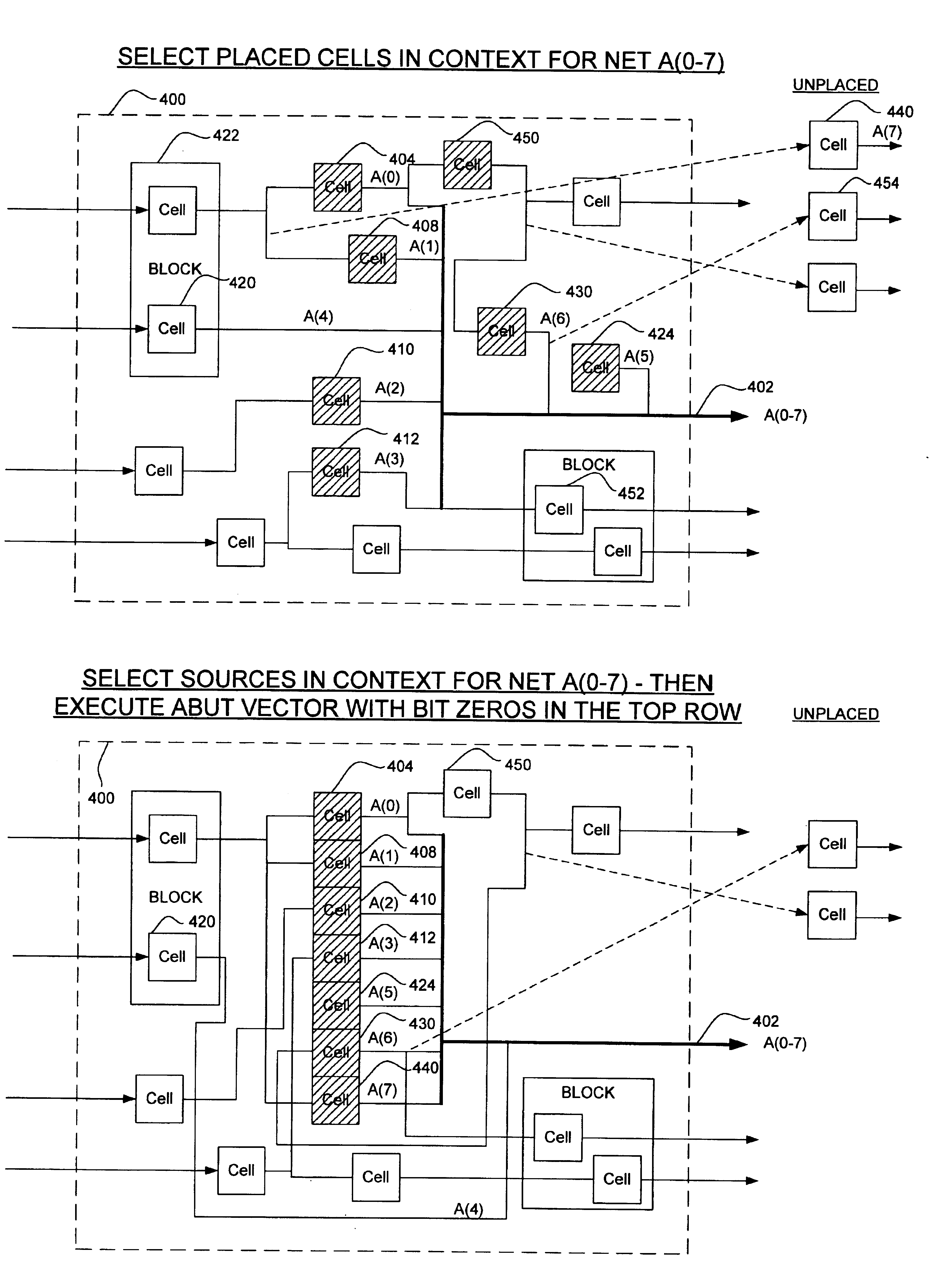

Method and apparatus for selecting and aligning cells using a placement tool

InactiveUS6889370B1Efficient identificationEfficient selectionComputer aided designSoftware simulation/interpretation/emulationEngineeringCircuit design

Methods and apparatus for efficiently identifying, selecting and aligning cells within a circuit design are disclosed. Preferably, a net or group-of nets is first identified by the circuit designer. Then, selected cells that are connected to the selected net or group of nets are identified by the placement tool. A qualification or filter may be provided for filtering which cells are selected. For example, the filter may allow only those cells that are source cells, destination cells, placed cells, unplaced cells, etc., or any combination thereof to be selected. The selected cells may be aligned in a direction of an alignment axis, if desired.

Owner:UNISYS CORP

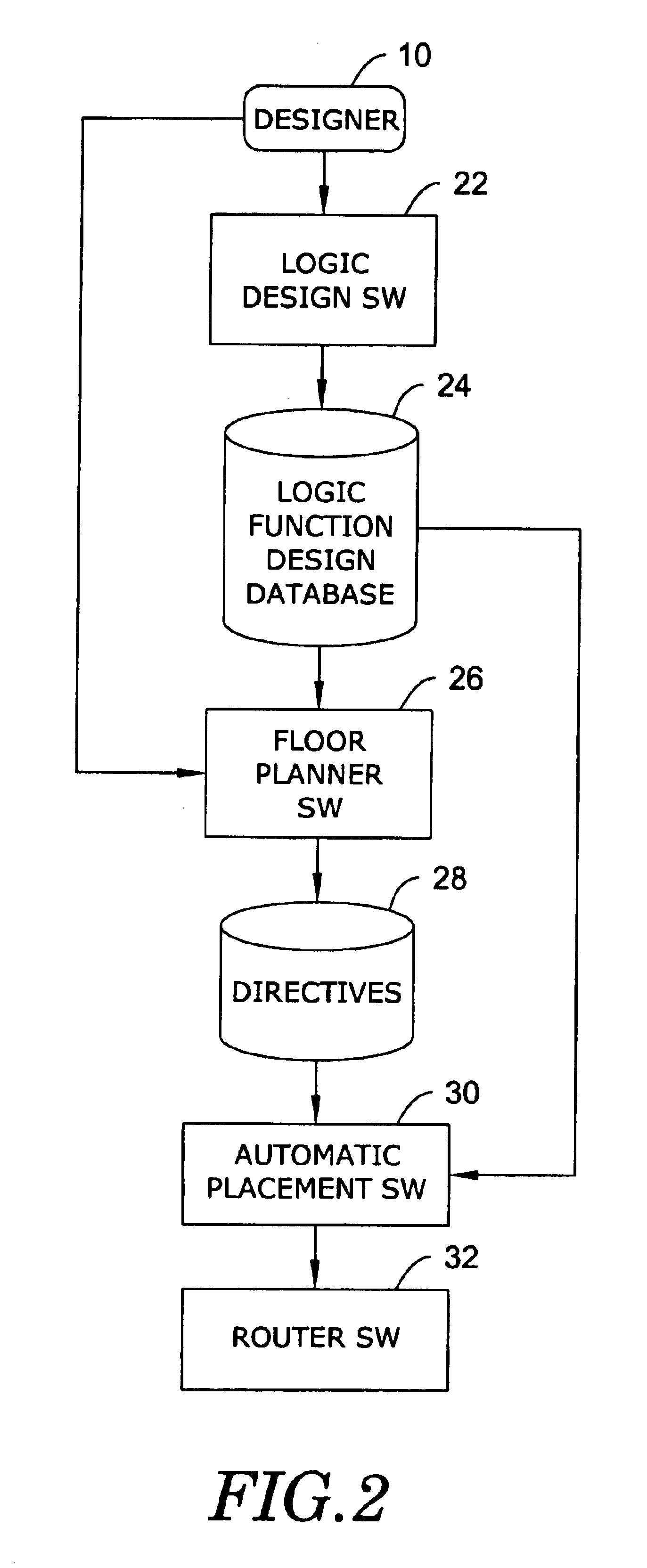

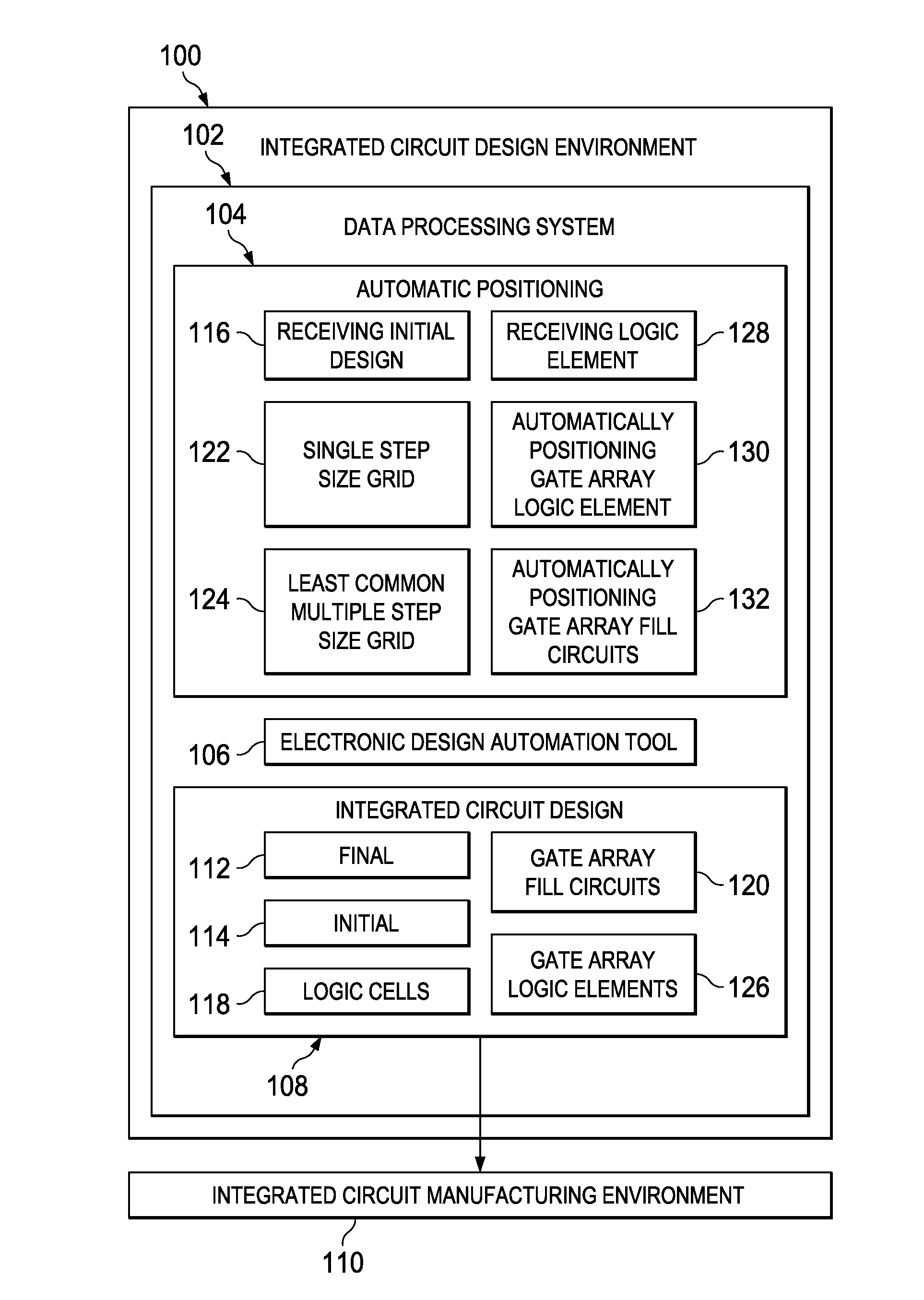

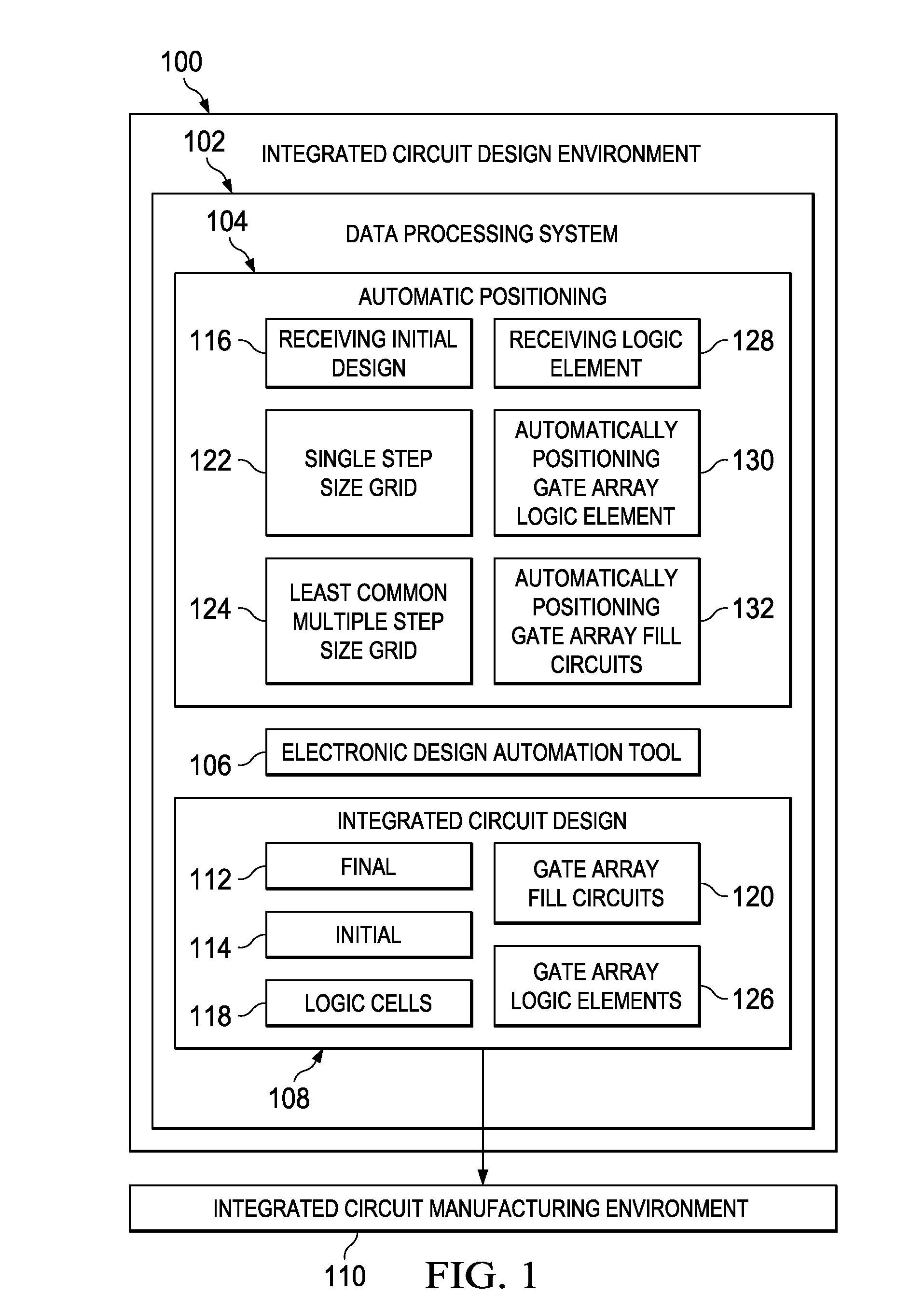

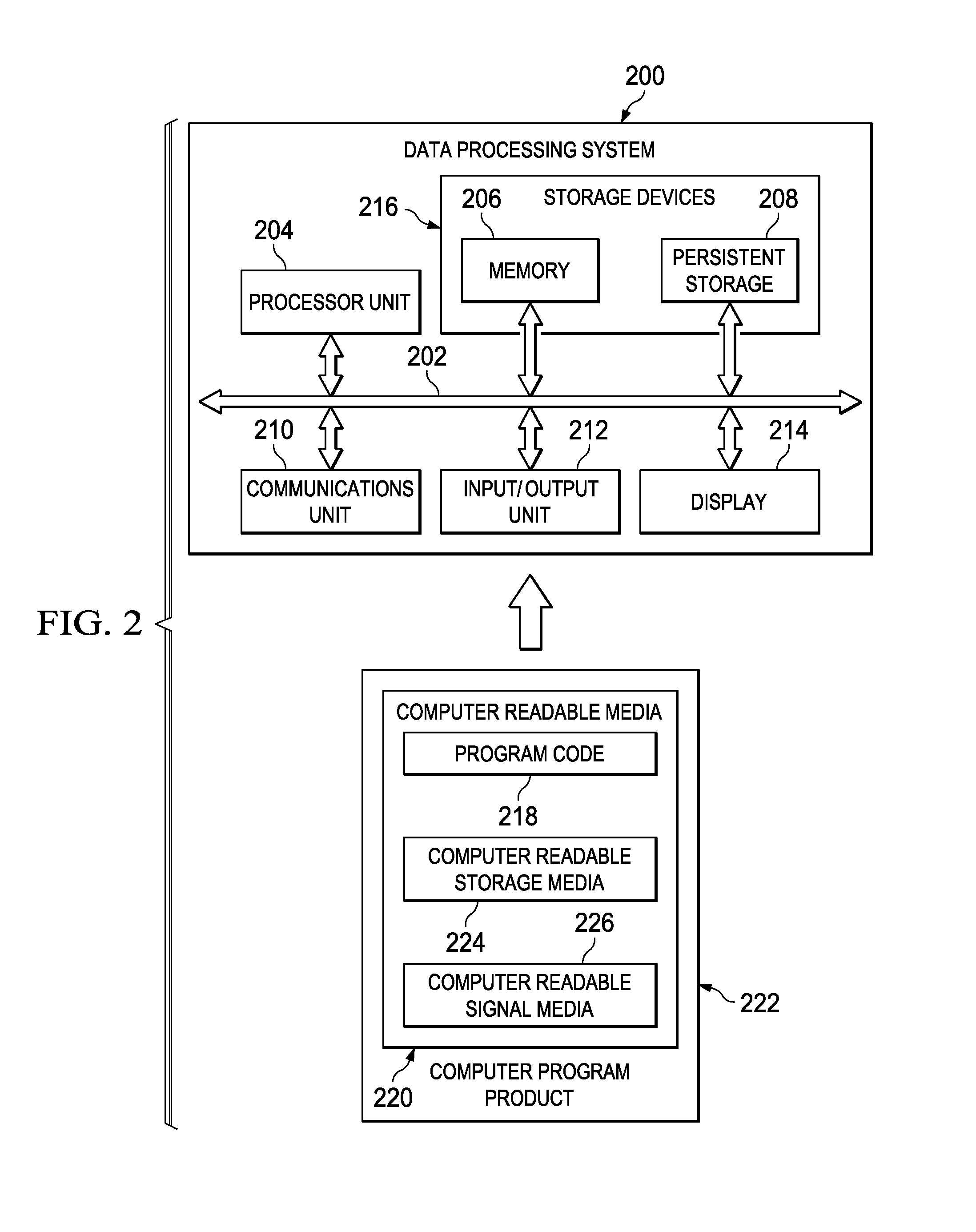

Automatic Positioning of Gate Array Circuits in an Integrated Circuit Design

ActiveUS20110072407A1Computer programmed simultaneously with data introductionComputer aided designLogic cellGate array

An automated method and apparatus for positioning gate array circuits in an integrated circuit design. An initial integrated circuit design includes logic cells and gate array fill circuits positioned thereon. The gate array fill circuits are positioned in available space between the adjacent logic cells so as to fill the available space with the maximum gate array fill circuits. A gate array logic element to be positioned in the integrated circuit design, such as may be required by an engineering change to the circuit design, is automatically positioned between adjacent logic cells so as to allow for full utilization of any space remaining between the adjacent logic cells by gate array fill circuits.

Owner:GLOBALFOUNDRIES US INC

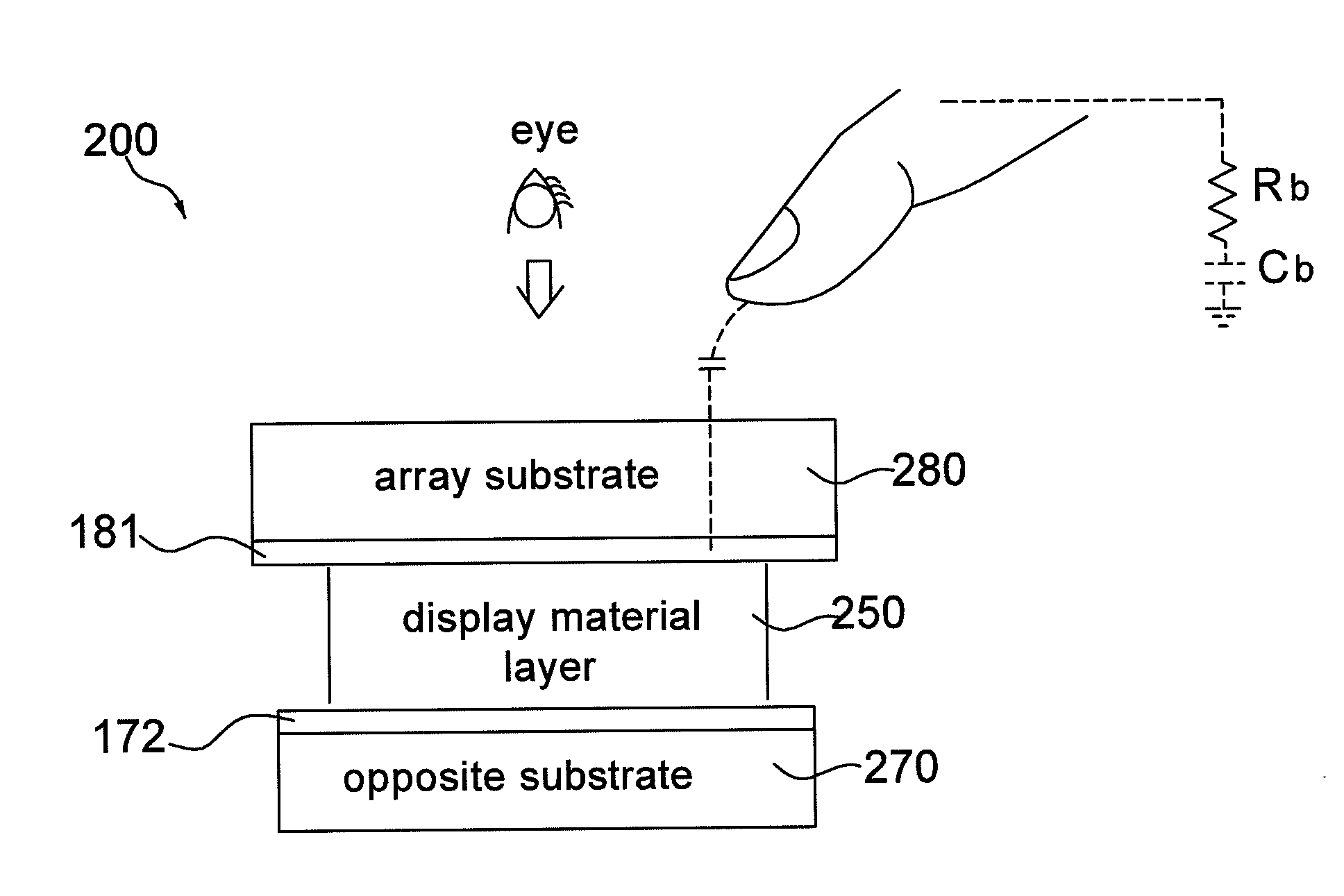

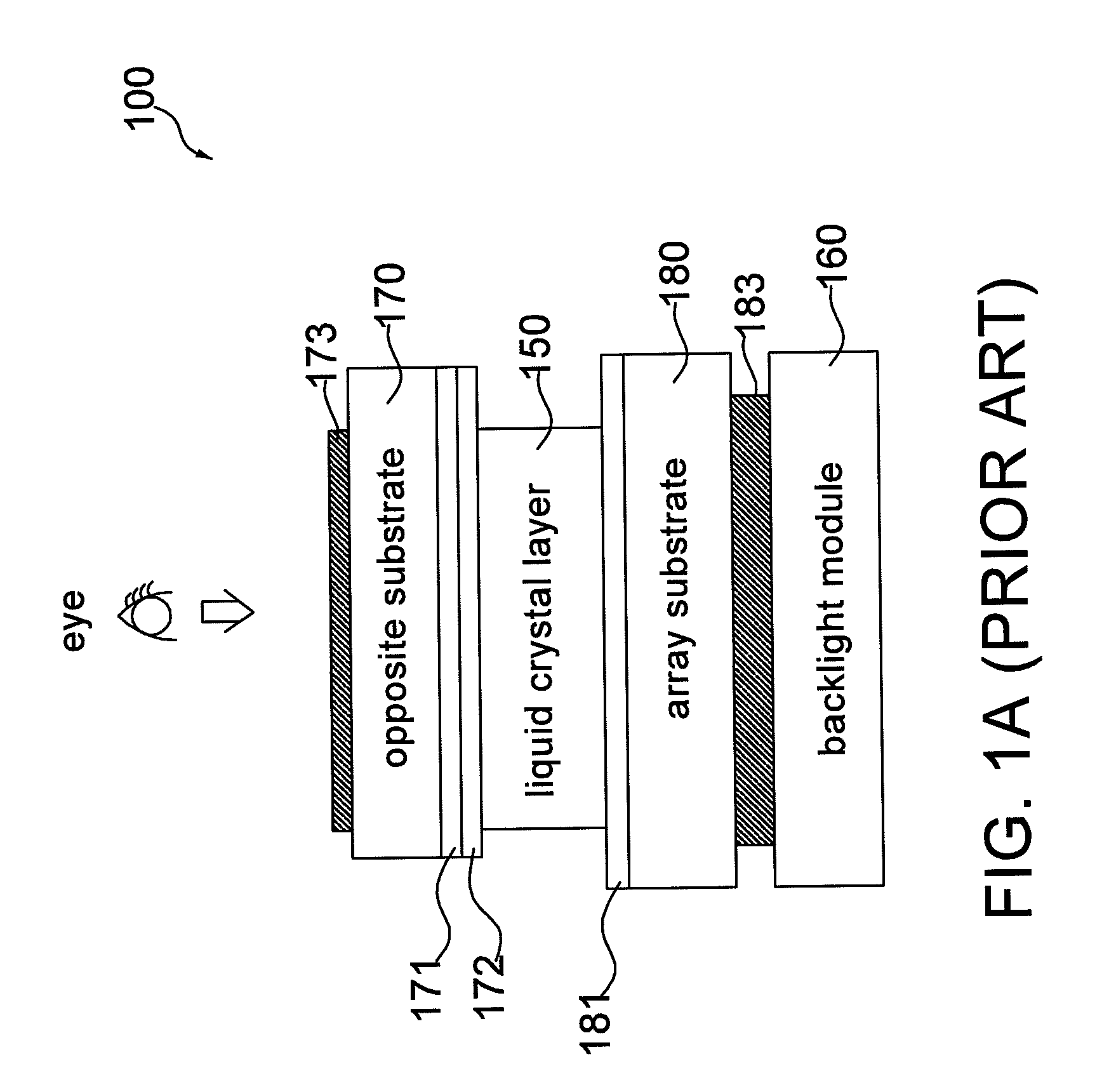

Touch display device

A touch display apparatus is disclosed. Without additional touch device, either the reversed AM structure or a conventional PM structure is provided to combine with the human body's conductive properties and the noise-immune sensing circuit design, thereby to achieve the purpose of displaying images and performing multi-touch detection simultaneously. Thus, the hardware cost and the power consumption are reduced.

Owner:SILICON INTEGRATED SYSTEMS

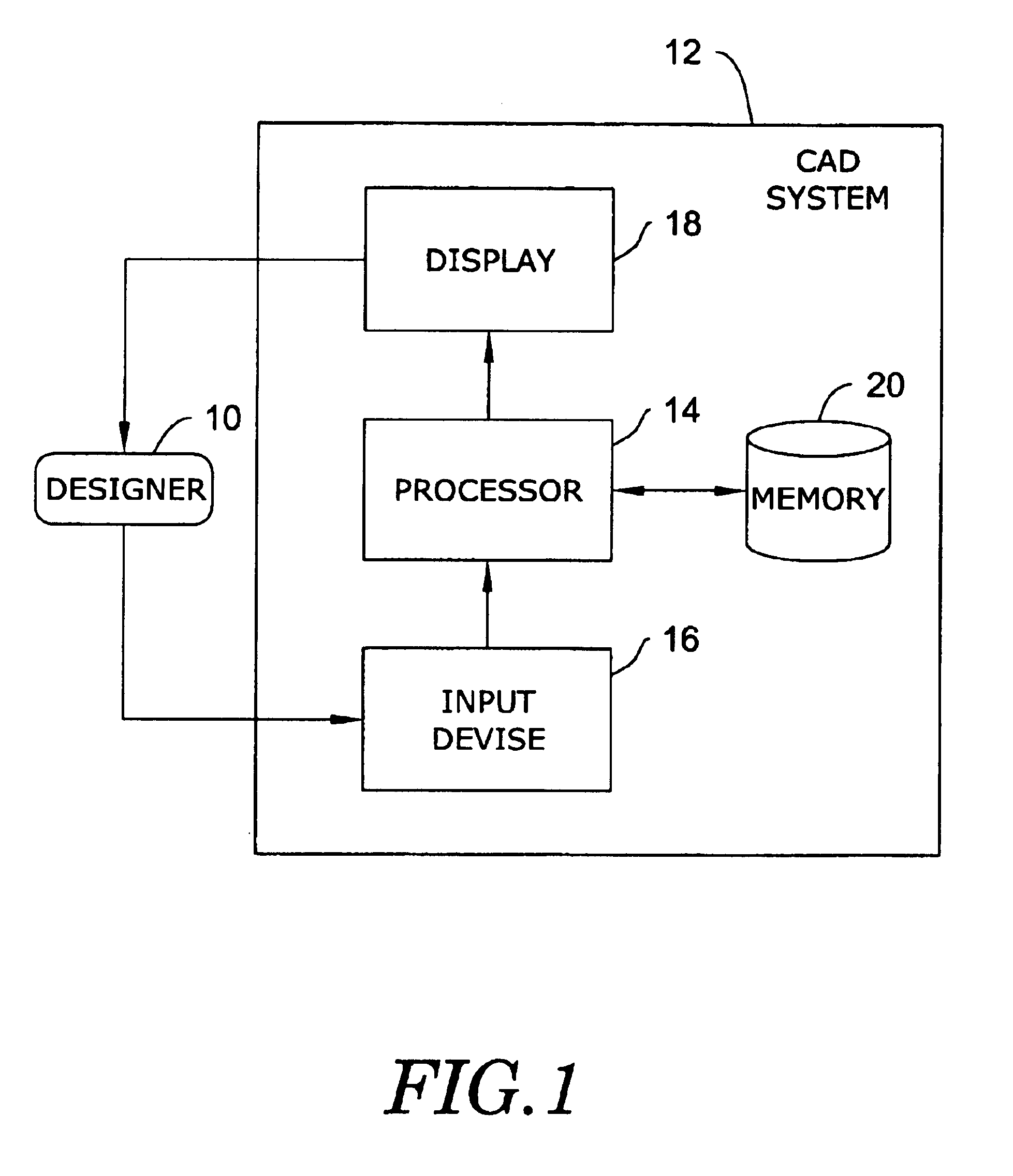

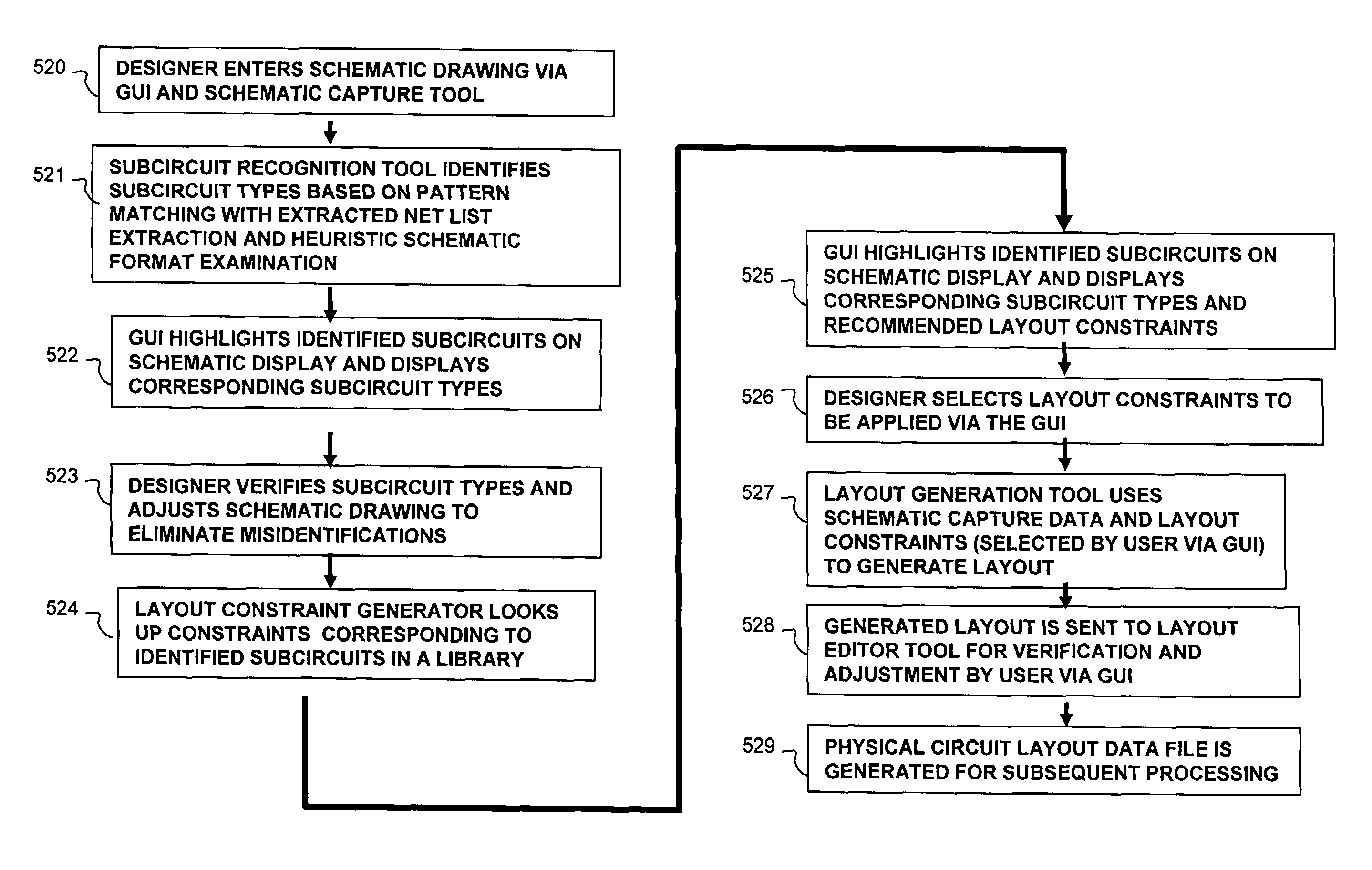

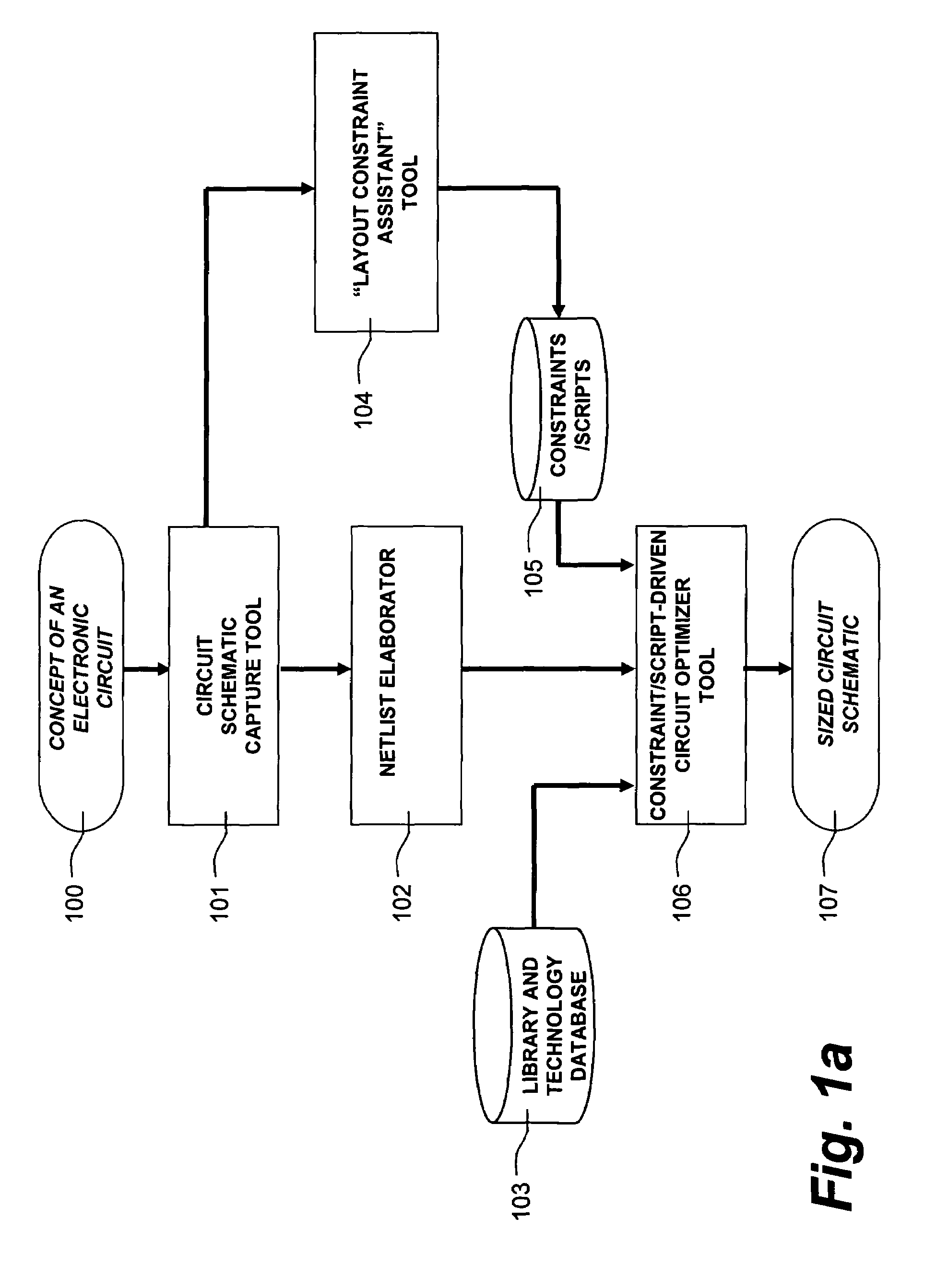

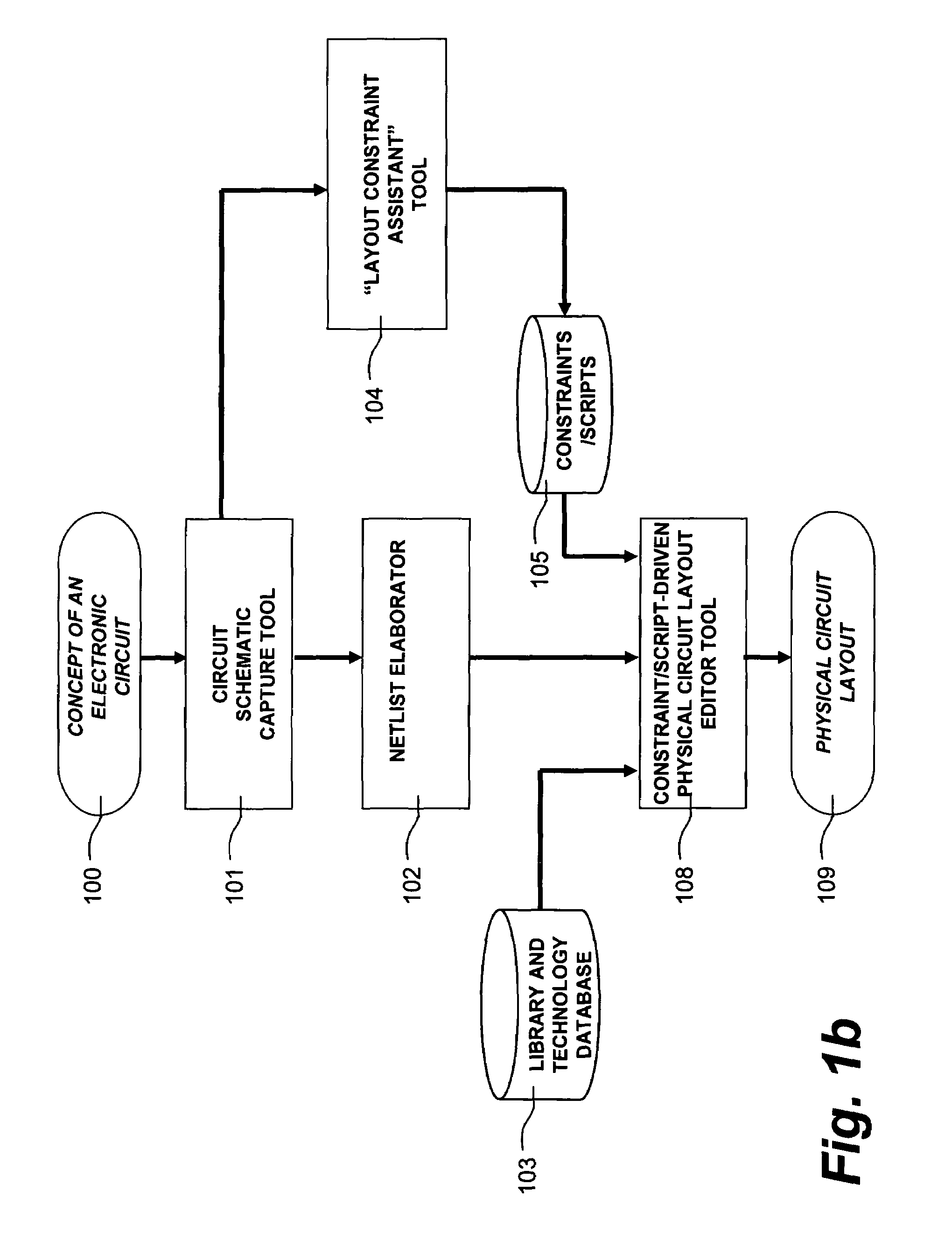

Constraint assistant for circuit design

InactiveUS7418683B1Less likelyAvoid wasting timeSpecial data processing applicationsSymbolic schematicsComputer Aided DesignEngineering

A computer aided design tool and method for designing IC layouts by recommending subcircuit layout constraints based upon an automated identification from a circuit schematic of subcircuit types requiring special IC layout constraints. Subcircuit types are identified on the basis of netlist examination, as well as cues from the layout of the circuit schematic.

Owner:CADENCE DESIGN SYST INC

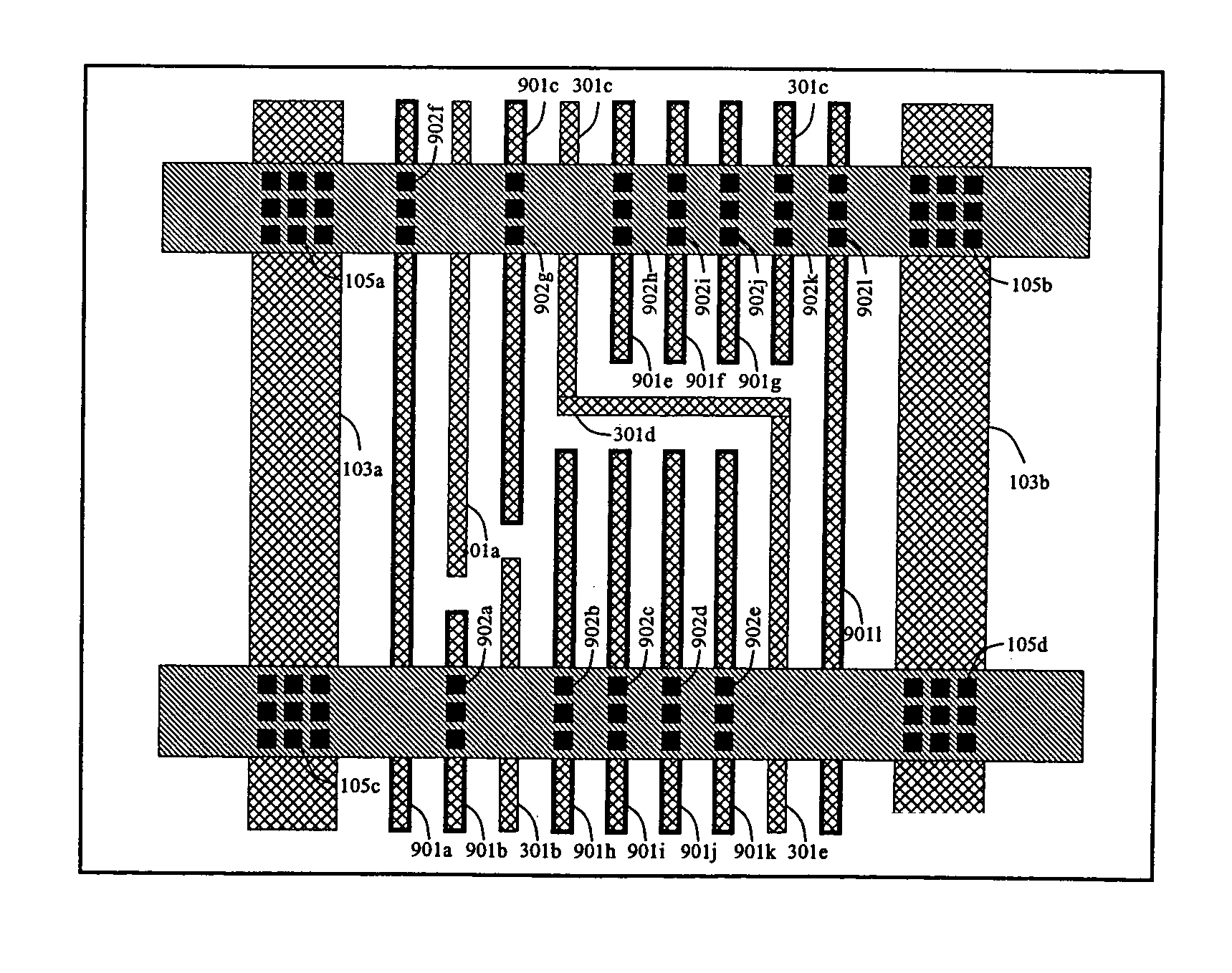

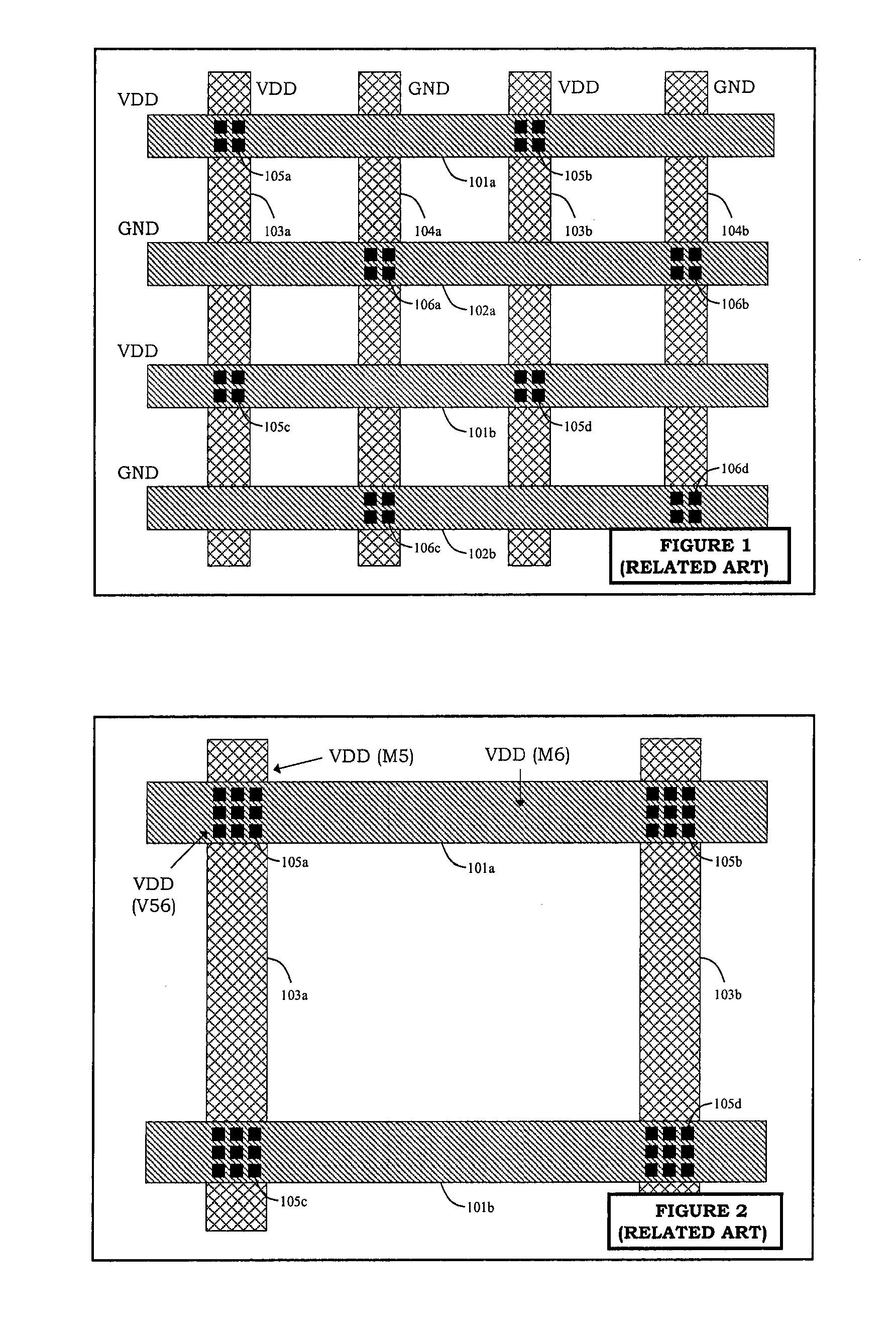

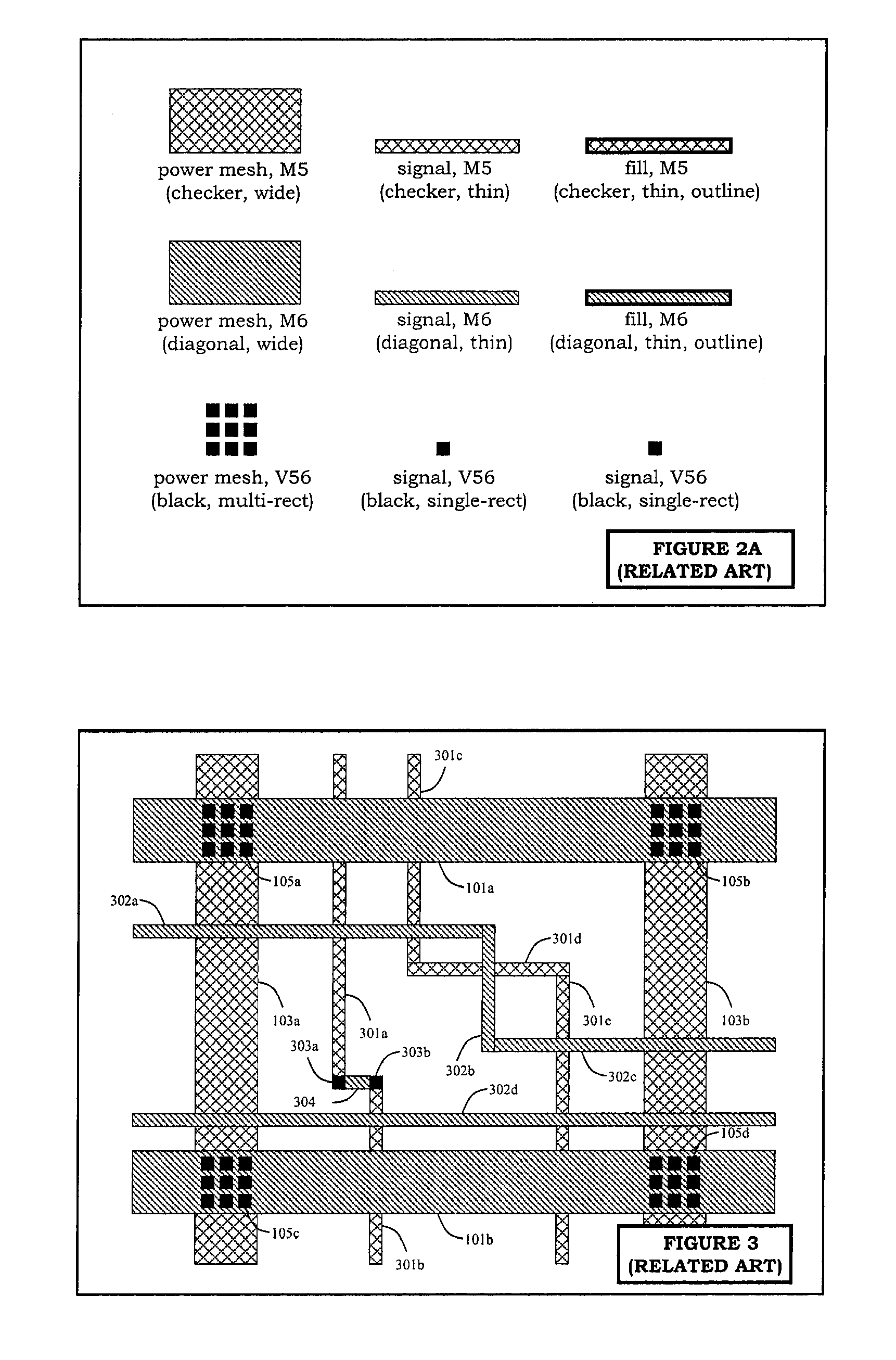

Redundantly tied metal fill for IR-drop and layout density optimization

ActiveUS7240314B1Reduce voltage dropAvoid volume increaseSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceVoltage drop

An integrated circuit and a method for using metal fill geometries to reduce the voltage drop in power meshes. Metal fill geometries are connected to the power mesh using vias or wires at multiple locations. Metal fill geometries are connected to other floating metal fill geometries using vias or wires at multiple locations. The circuit design introduces maximum redundancy between metal fill geometries and power mesh geometries, but partial redundancy between metal fill geometries and metal fill geometries. In particular, the redundancy in connectivity between metal fill geometries and metal fill geometries is kept minimal to reduce the number of geometries introduced. The high redundancy between metal fill geometries and power mesh geometries and the partial redundancy among metal fill geometries result in a smaller IR-drop by reducing the effective resistance on a power mesh. Hence, the invention use redundancy carefully and advantageously to achieve simultaneous metal density and IR-drop optimization without introducing excessive number of metal fill geometries.

Owner:SYNOPSYS INC