Patents

Literature

2725 results about "Unit structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Units in structure. A structure is a separate building that either has open spaces on all sides or is separated from other structures by dividing walls that extend from ground to roof.

Hexagonal architecture

InactiveUS6407434B1Reduce total wirelength interconnect congestionReduce the numberTransistorSemiconductor/solid-state device detailsCapacitanceElectrical conductor

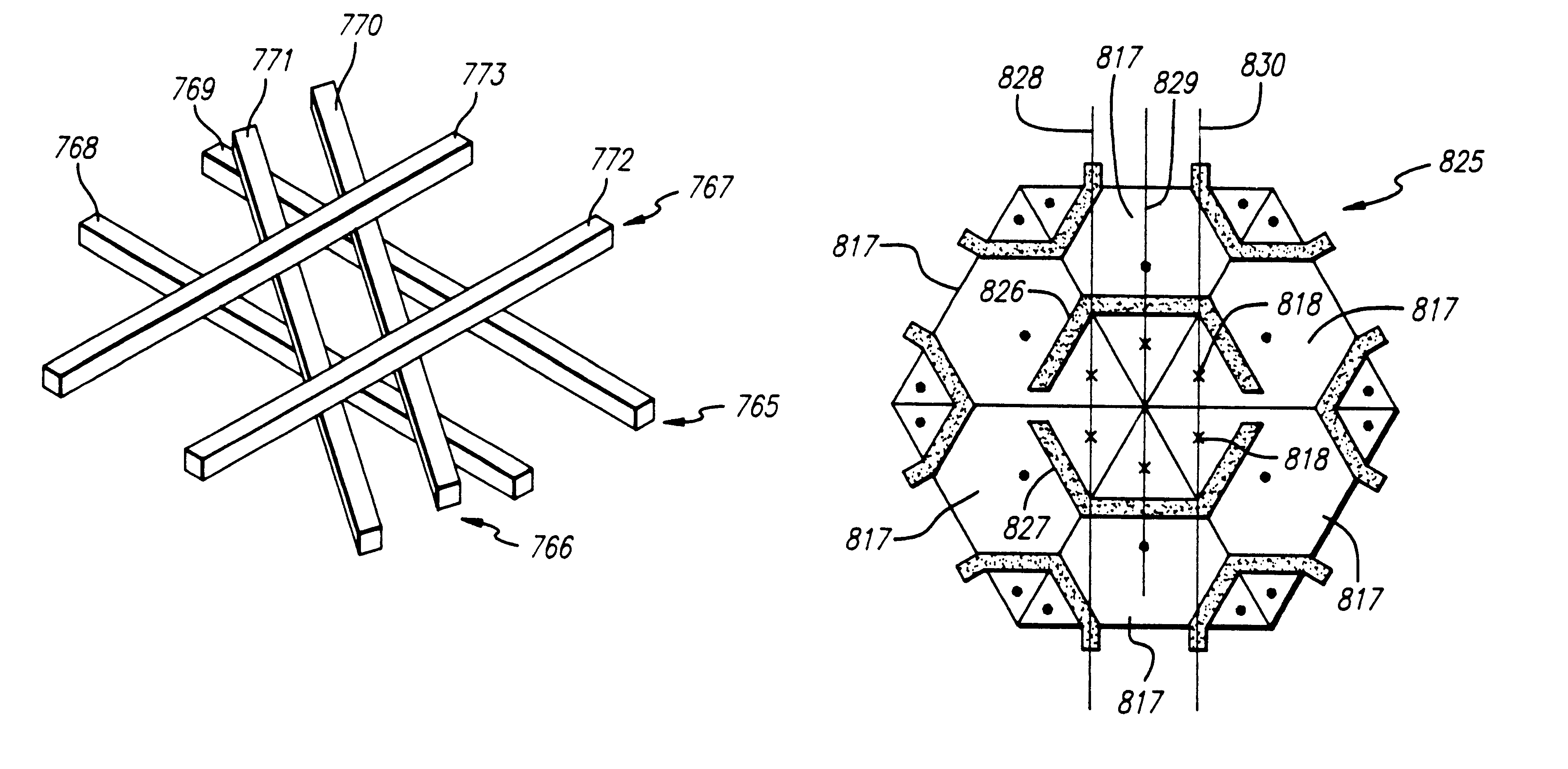

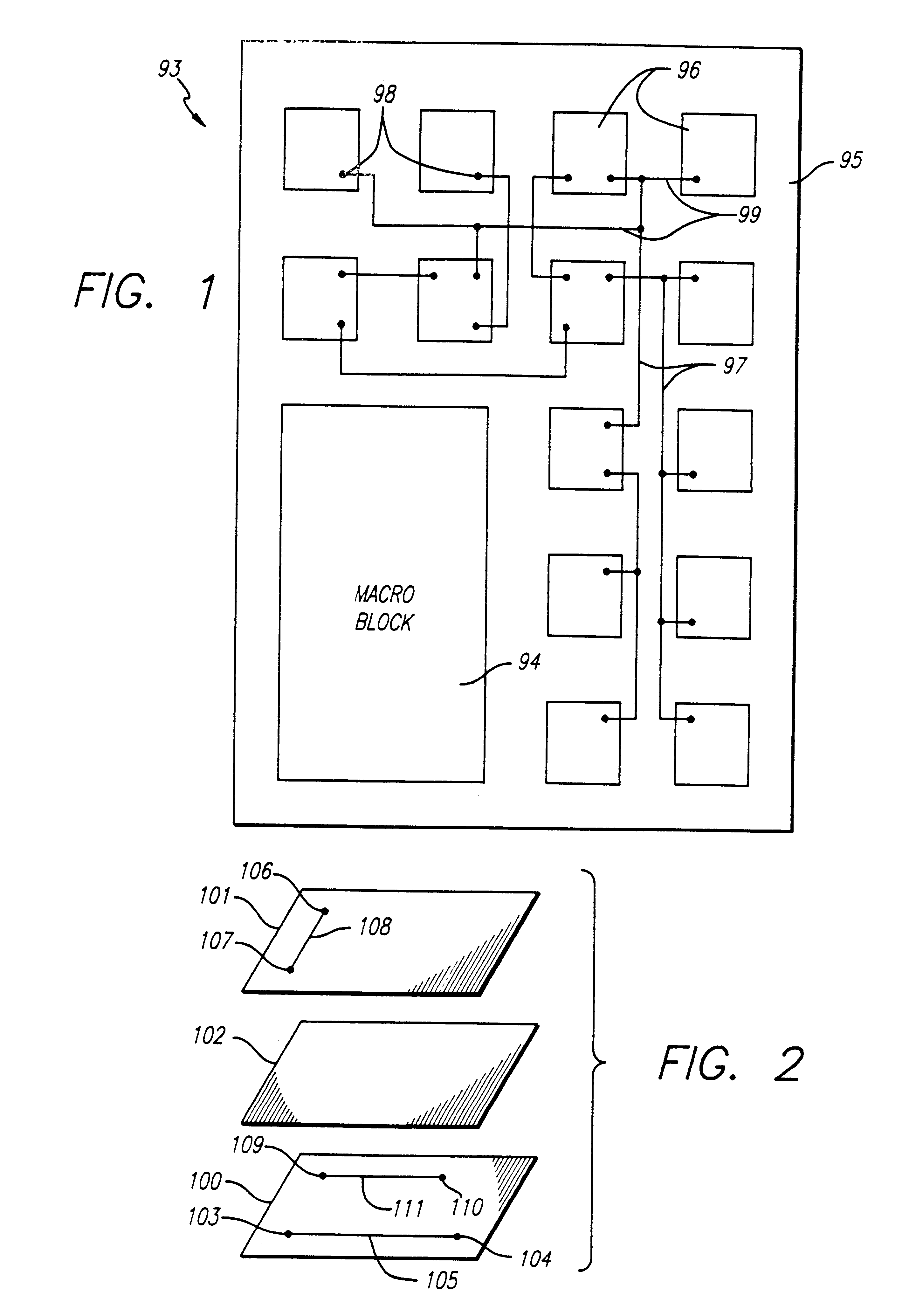

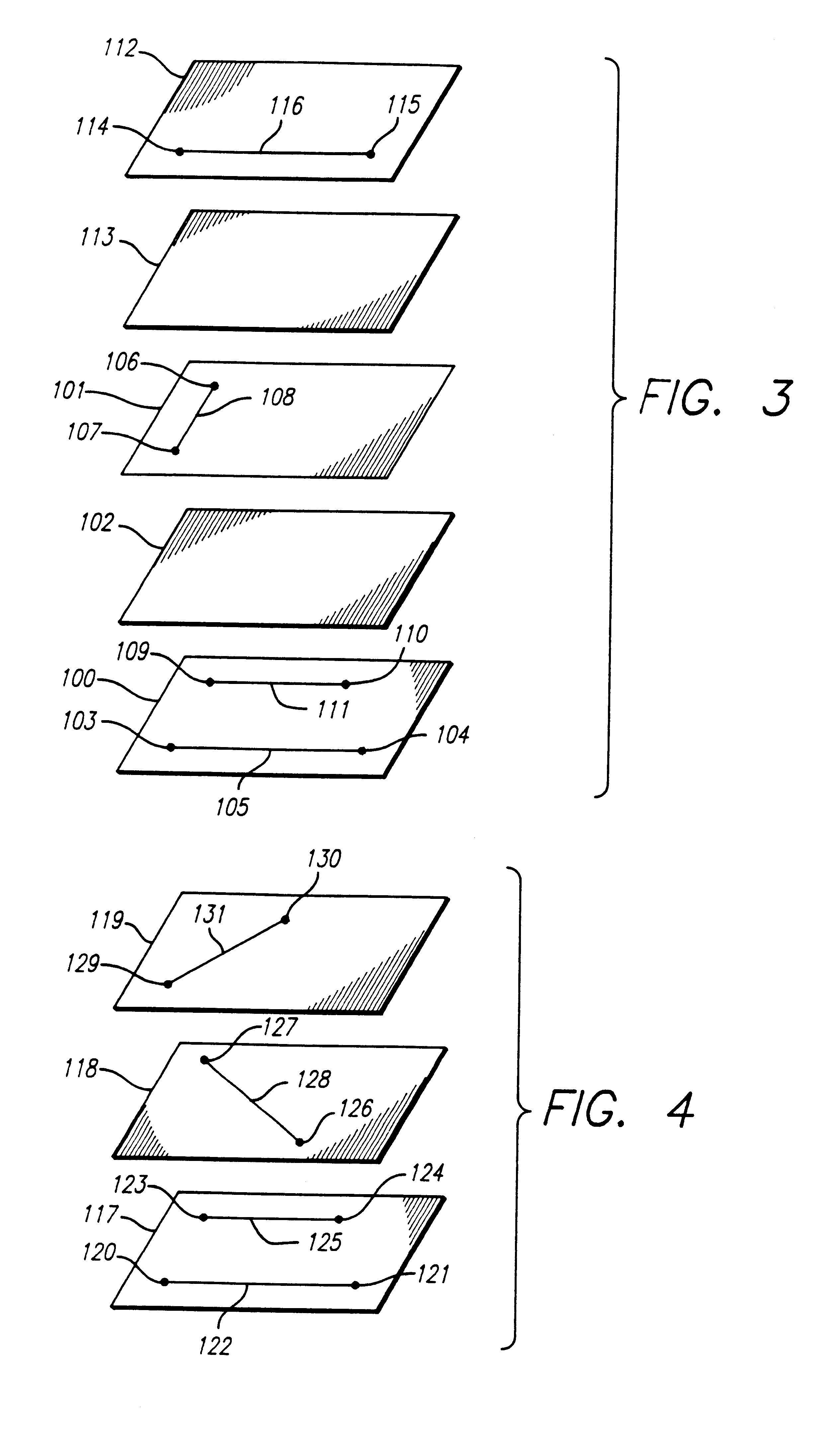

Several inventions are disclosed. A cell architecture using hexagonal shaped cells is disclosed. The architecture is not limited to hexagonal shaped cells. Cells may be defined by clusters of two or more hexagons, by triangles, by parallelograms, and by other polygons enabling a variety of cell shapes to be accommodated. Polydirectional non-orthogonal three layer metal routing is disclosed. The architecture may be combined with the tri-directional routing for a particularly advantageous design. In the tri-directional routing arraingement, electrical conductors for interconnecting terminals of microelectronic cells of an integrated circuit preferrably extend in three directions that are angularly displaced from each other by 60°. The conductors that extend in the three directions are preferrably formed in three different layers. A method of minimizing wire length in a semiconductor device is disclosed. A method of minimizing intermetal capacitance in a semiconductor device is disclosed. A novel device called a "tri-ister" is disclosed. Triangular devices are disclosed, including triangular NAND gates, triangular AND gates, and triangular OR gates. A triangular op amp and triode are disclosed. A triangular sense amplifier is disclosed. A DRAM memory array and an SRAM memory array, based upon triangular or parallelogram shaped cells, are disclosed, including a method of interconnecting such arrays. A programmable variable drive transistor is disclosed. CAD algorithms and methods are disclosed for designing and making semiconductor devices, which are particularly applicable to the disclosed architecture and tri-directional three metal layer routing.

Owner:BELL SEMICON LLC

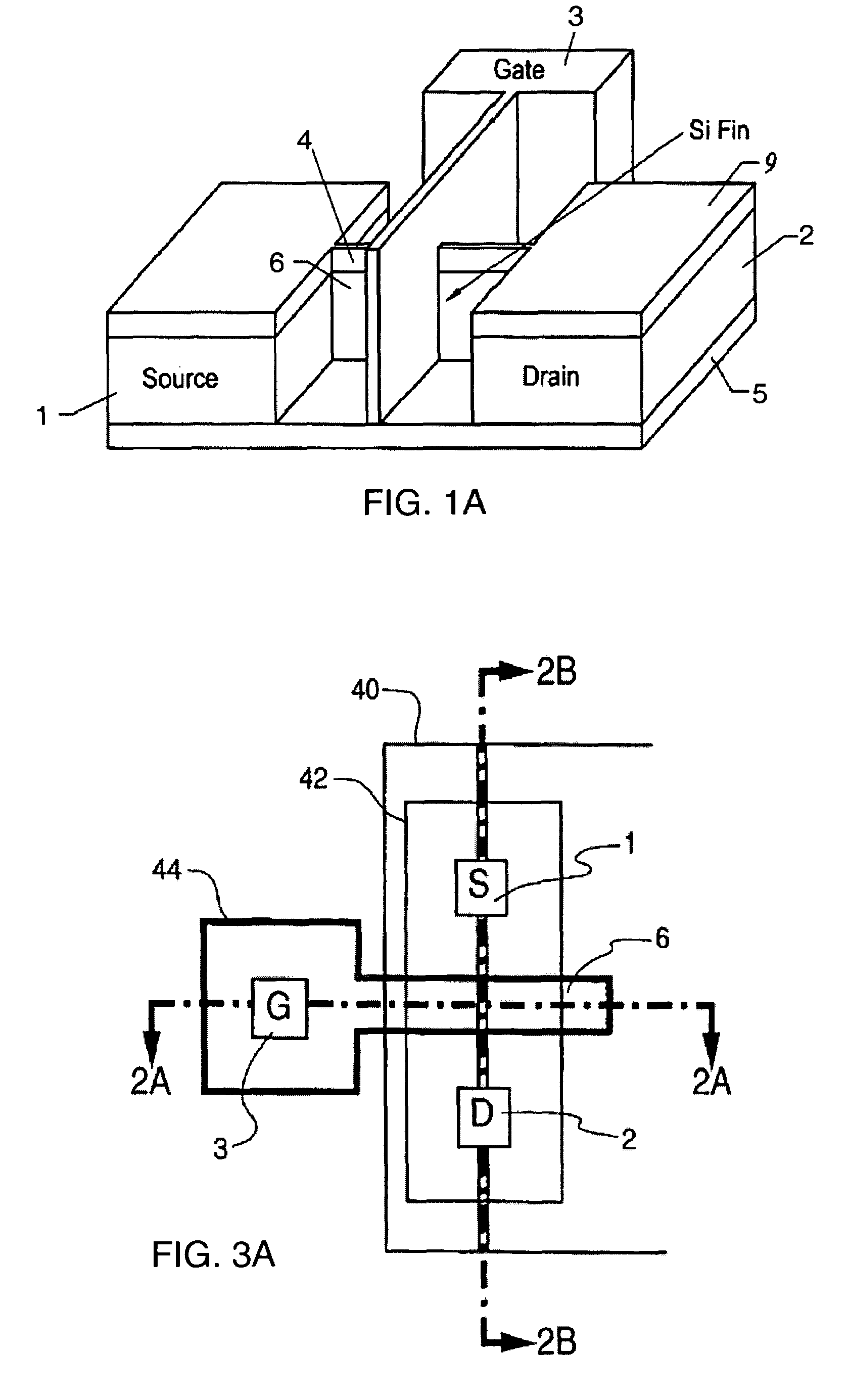

Method and device for automated layer generation for double-gate FinFET designs

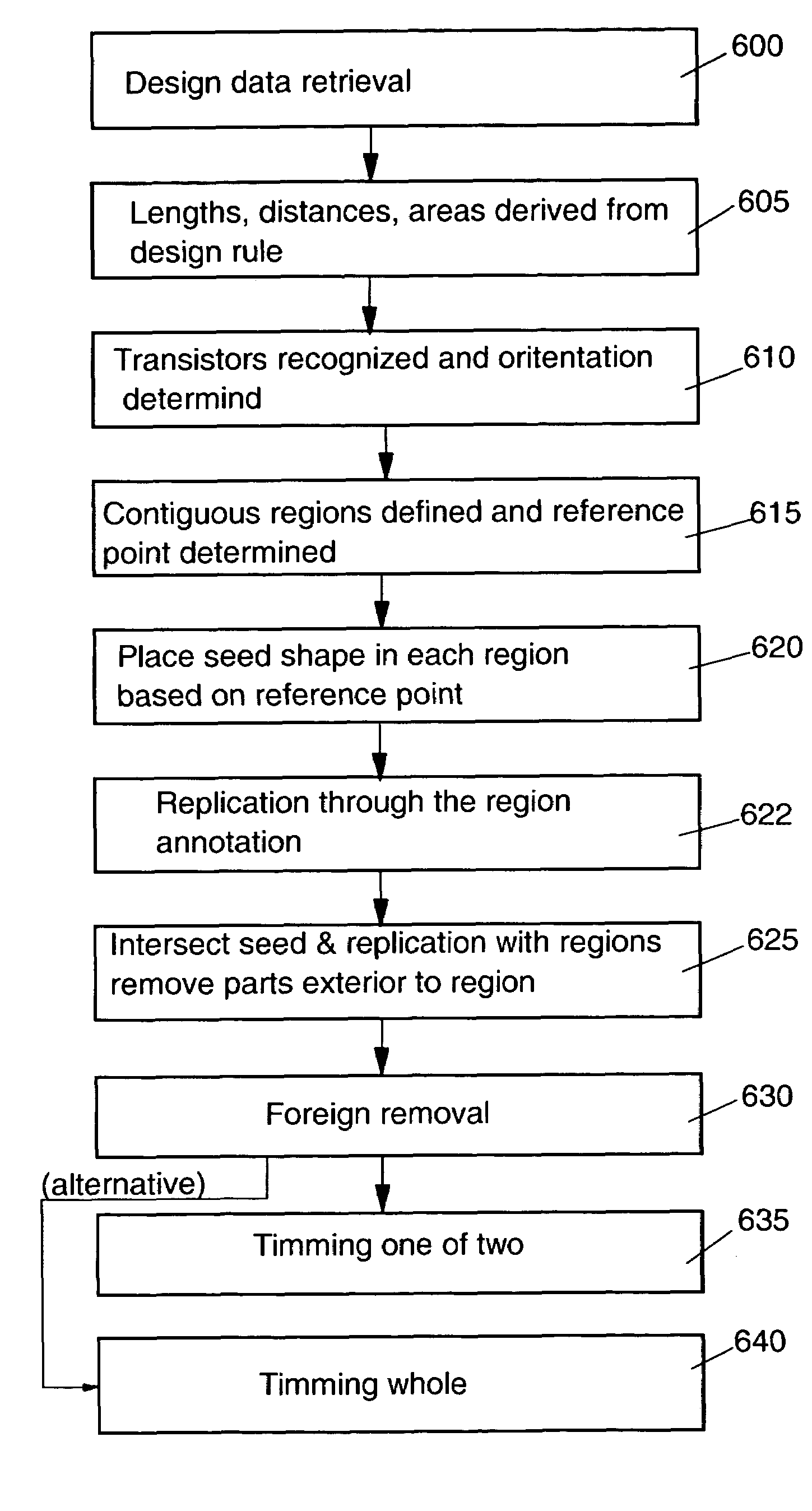

InactiveUS7315994B2Reduce effortEnhance layeringTransistorSolid-state devicesEngineeringUnit structure

Owner:INT BUSINESS MASCH CORP

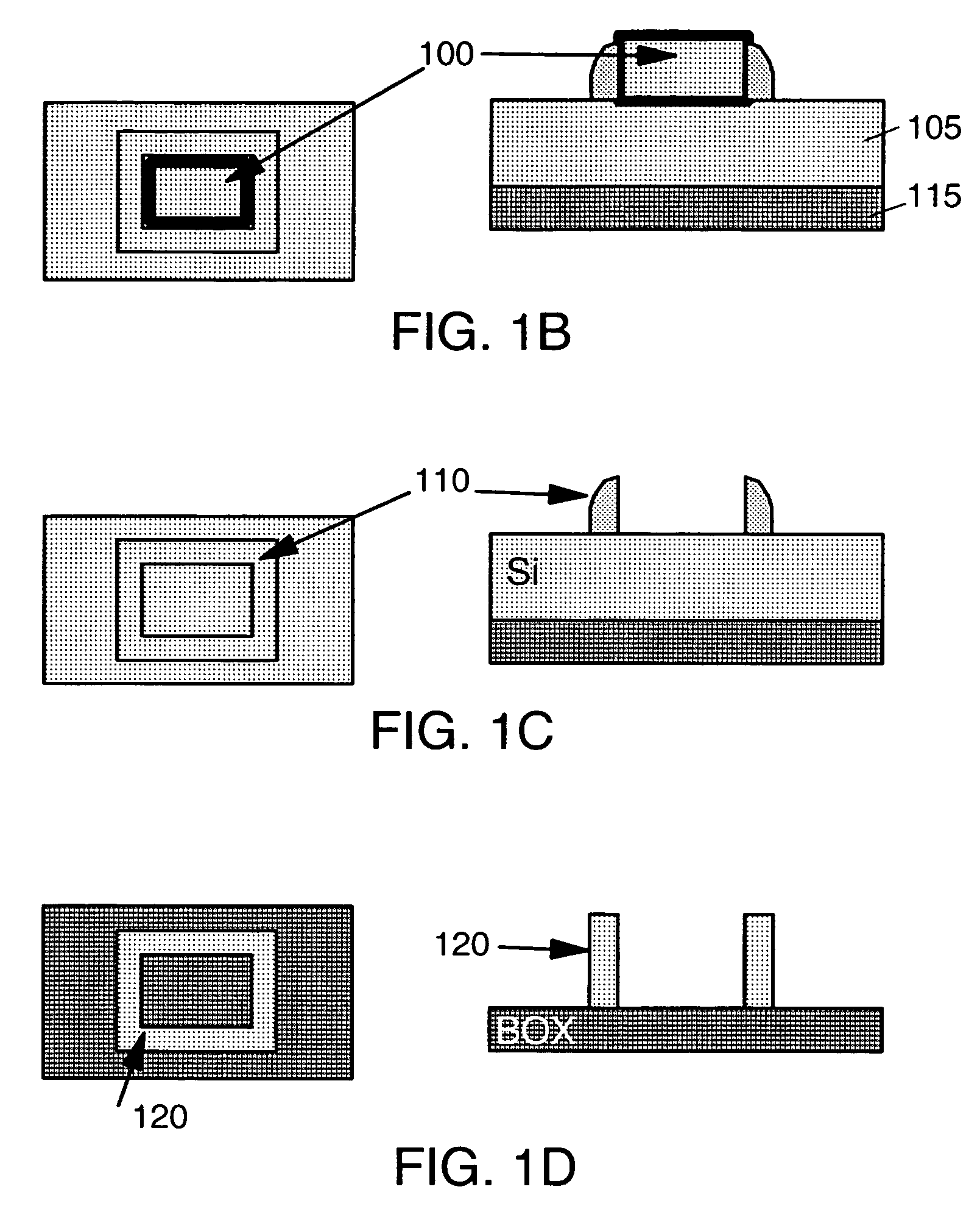

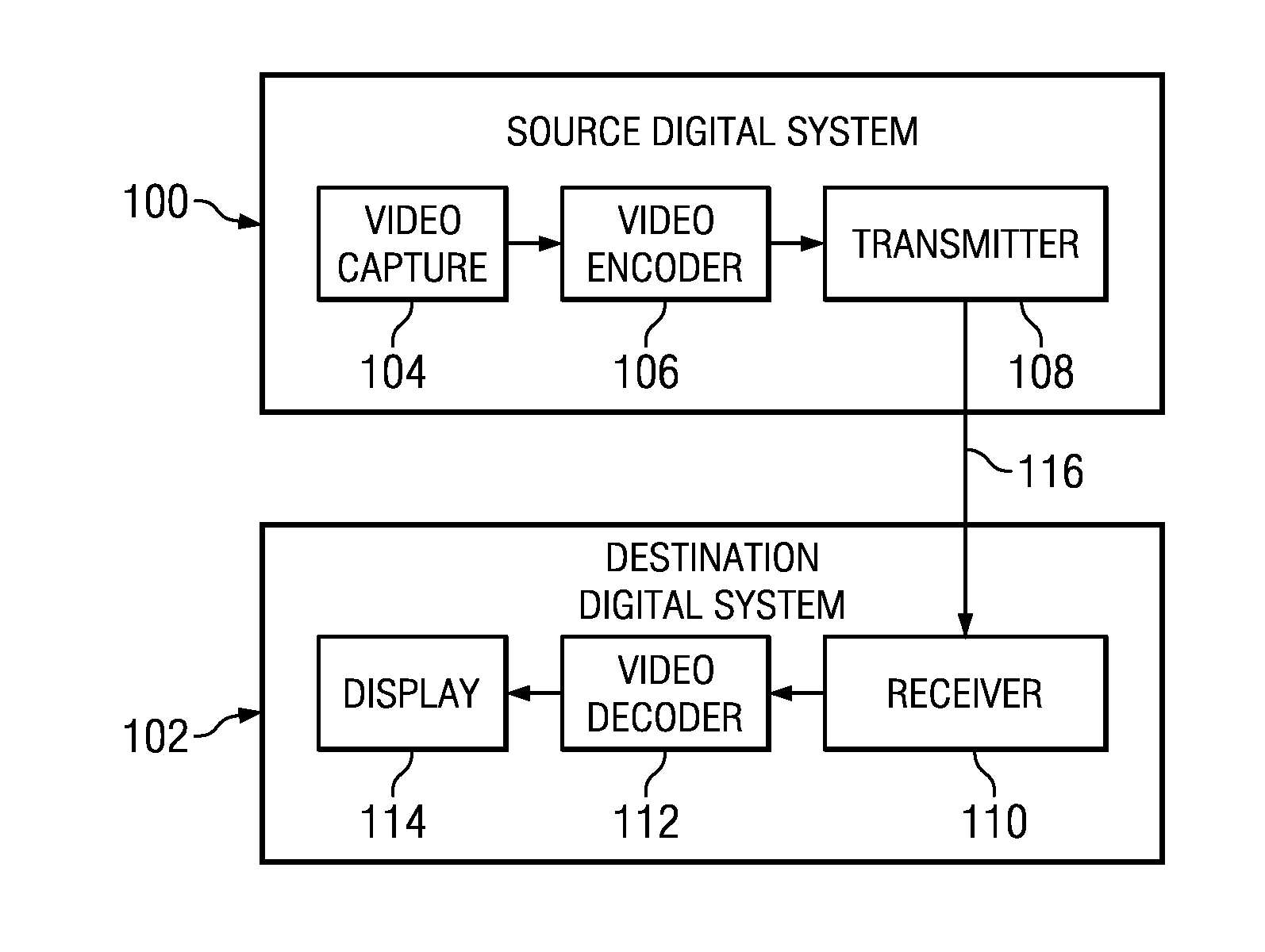

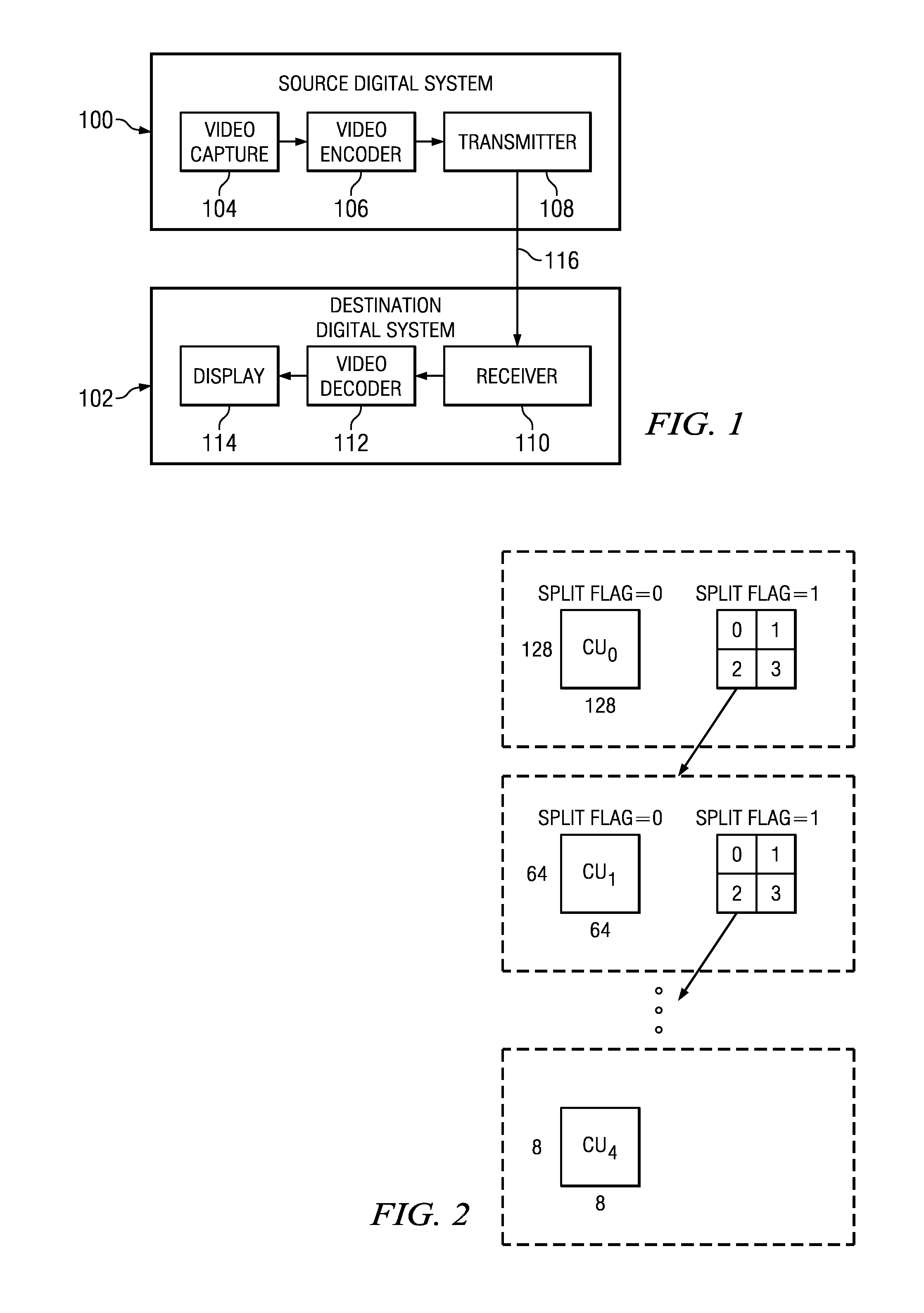

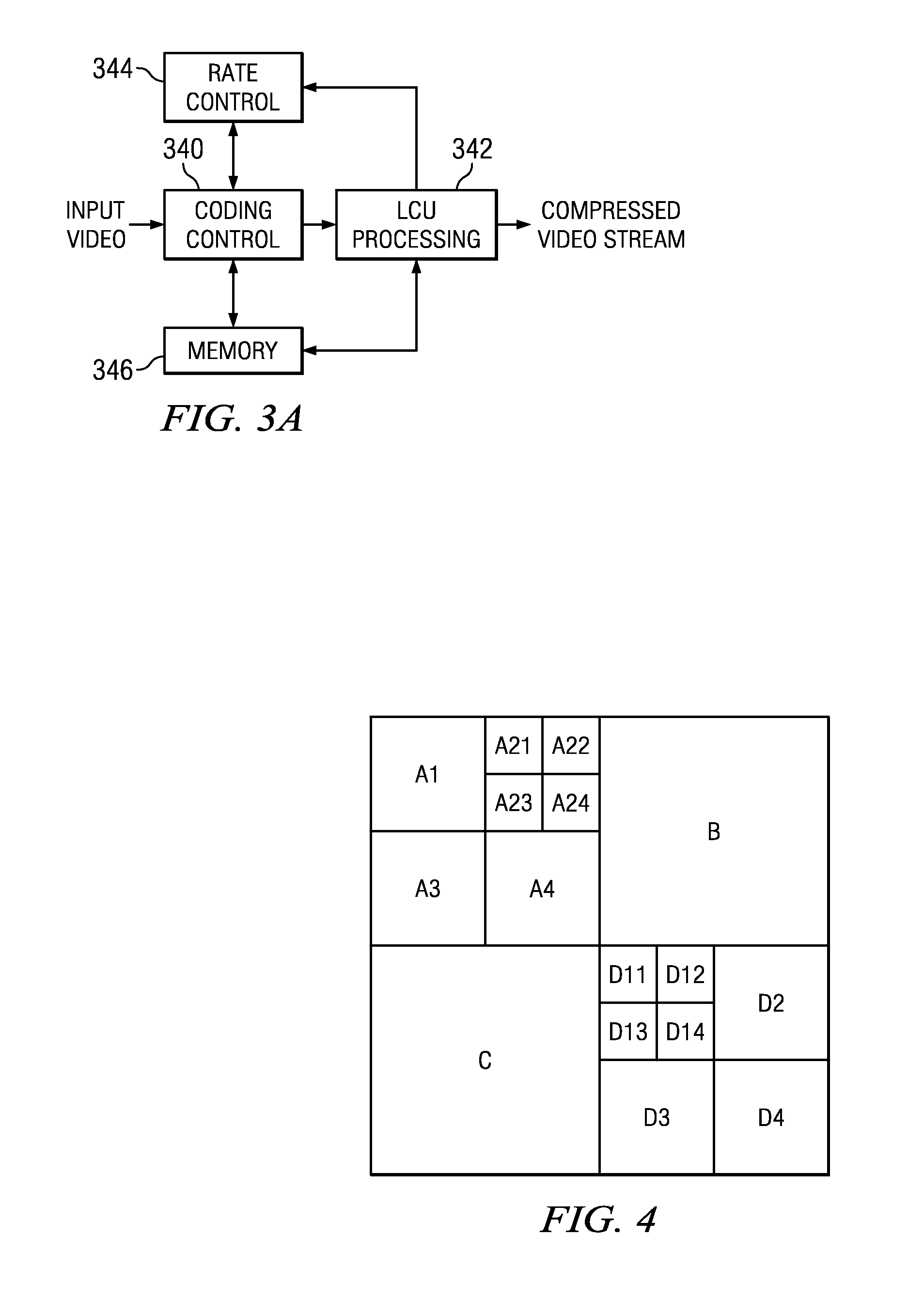

Coding Unit Quantization Parameters in Video Coding

InactiveUS20110274162A1Color television with pulse code modulationColor television with bandwidth reductionComputer architectureVideo encoding

A method is provided that includes receiving a coded largest coding unit in a video decoder, wherein the coded largest coding unit includes a coded coding unit structure and a plurality of coded quantization parameters, and decoding the coded largest coding unit based on the coded coding unit structure and the plurality of coded quantization parameters.

Owner:TEXAS INSTR INC

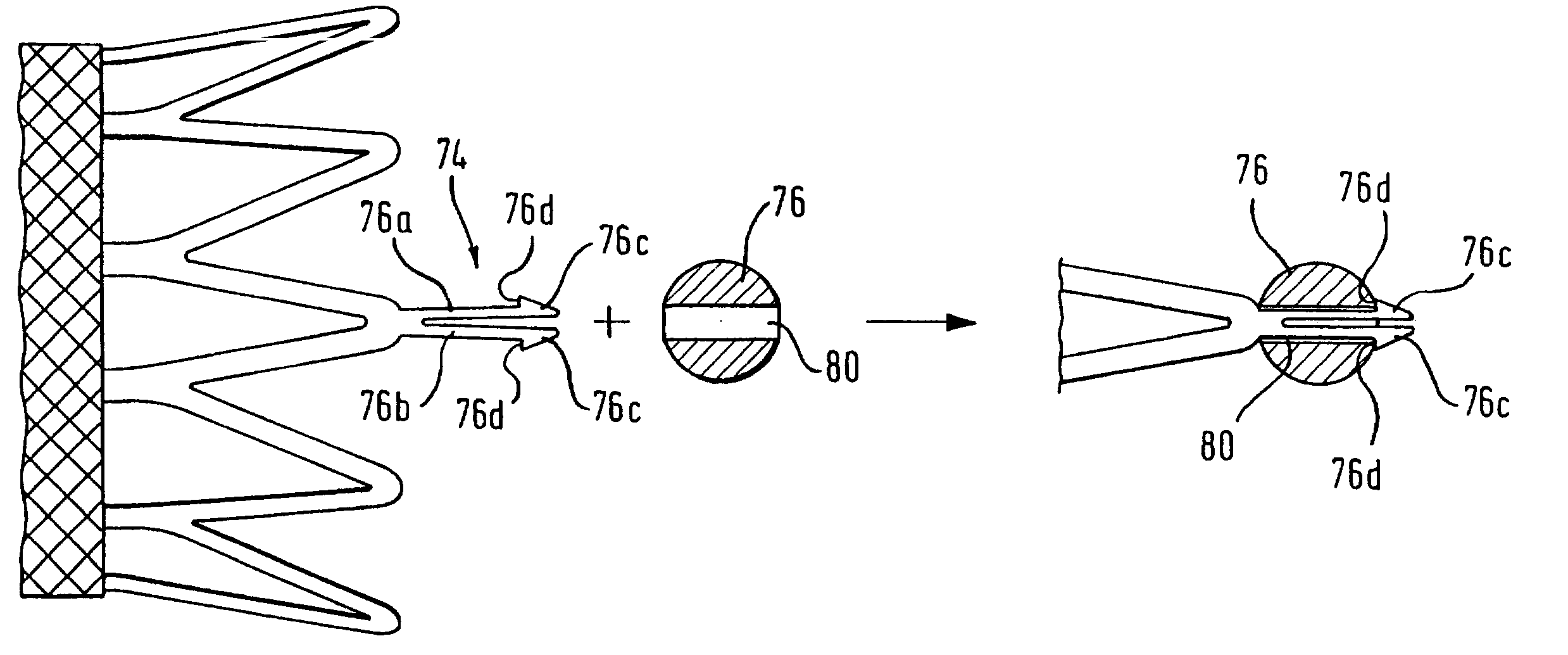

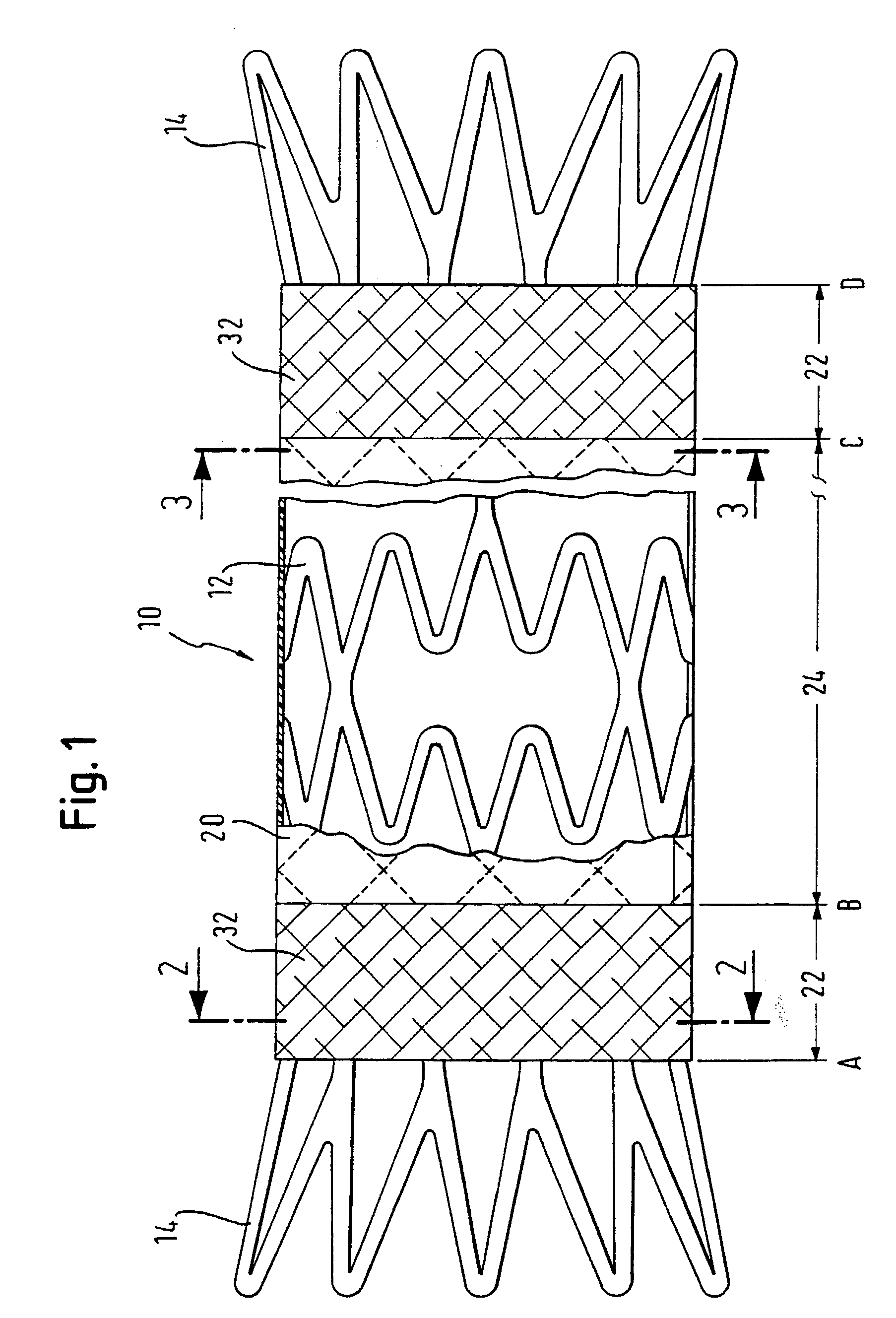

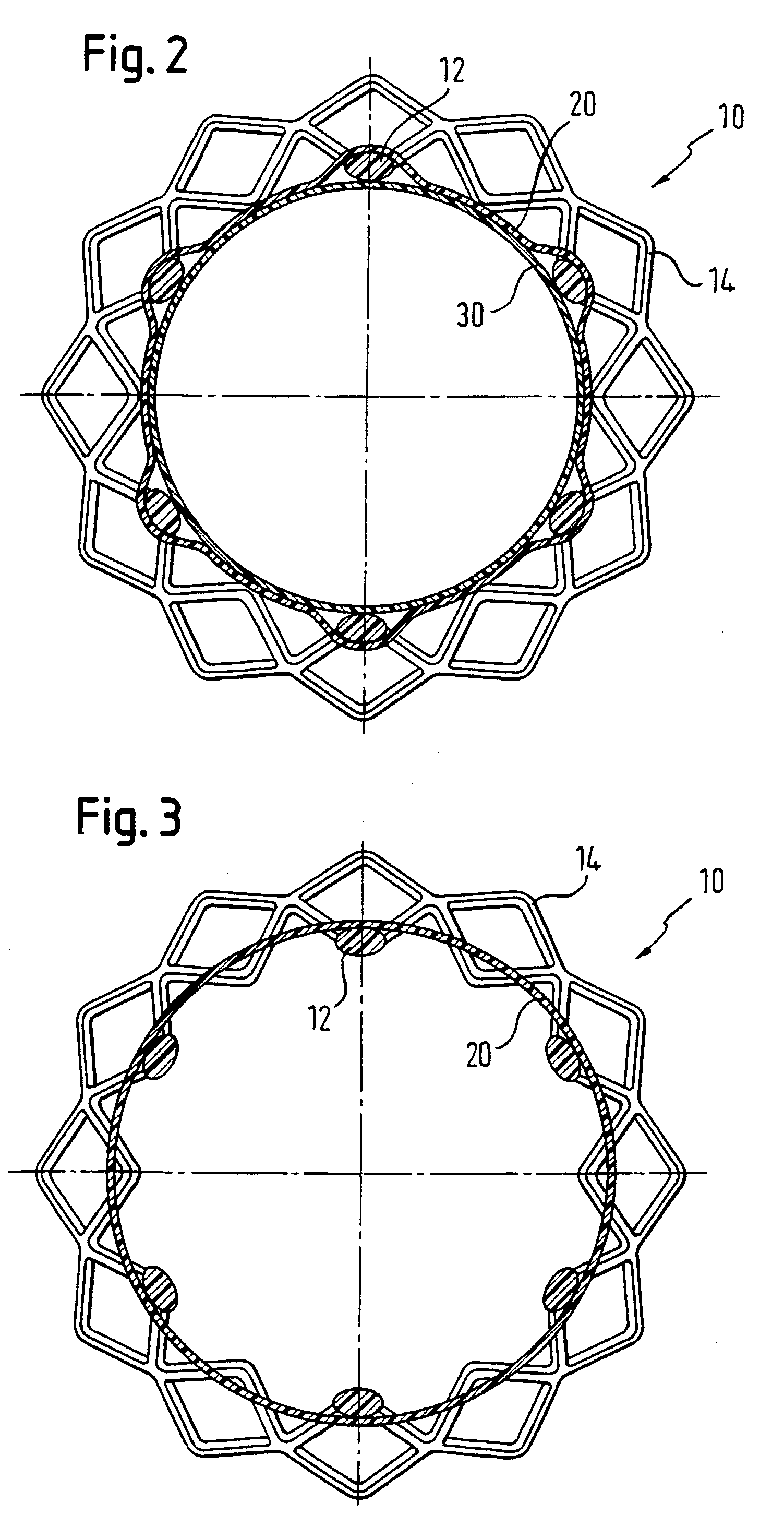

Stent matrix

InactiveUS20030144725A1Increase anchoring forceAmeliorate degree of traumaStentsSurgeryMedicineUnit structure

An object of this invention is to provide a radially expandable stent (1) that holds a passageway enlarged by placing the stent (1) into a lumen. The stent (1) comprises a cylindrical frame formed by a plurality of unit structures (11, 12, . . . 16, . . . ); said unit structures (11, 12, . . . 16, . . . ) formed into a closed zig-zag configuration including an endless series of straight sections (111) and joined by bends (112), and arranged face to face into a shape of multistage; connecting members (31, 33, 35, 37 . . . ), which connect said unit structures (11, 12, . . . 16, . . . ); and a mesh (91), which is wrapped around an outside of said frame.

Owner:ANGIOMED GMBH & CO MEDIZINTECHNIK KG

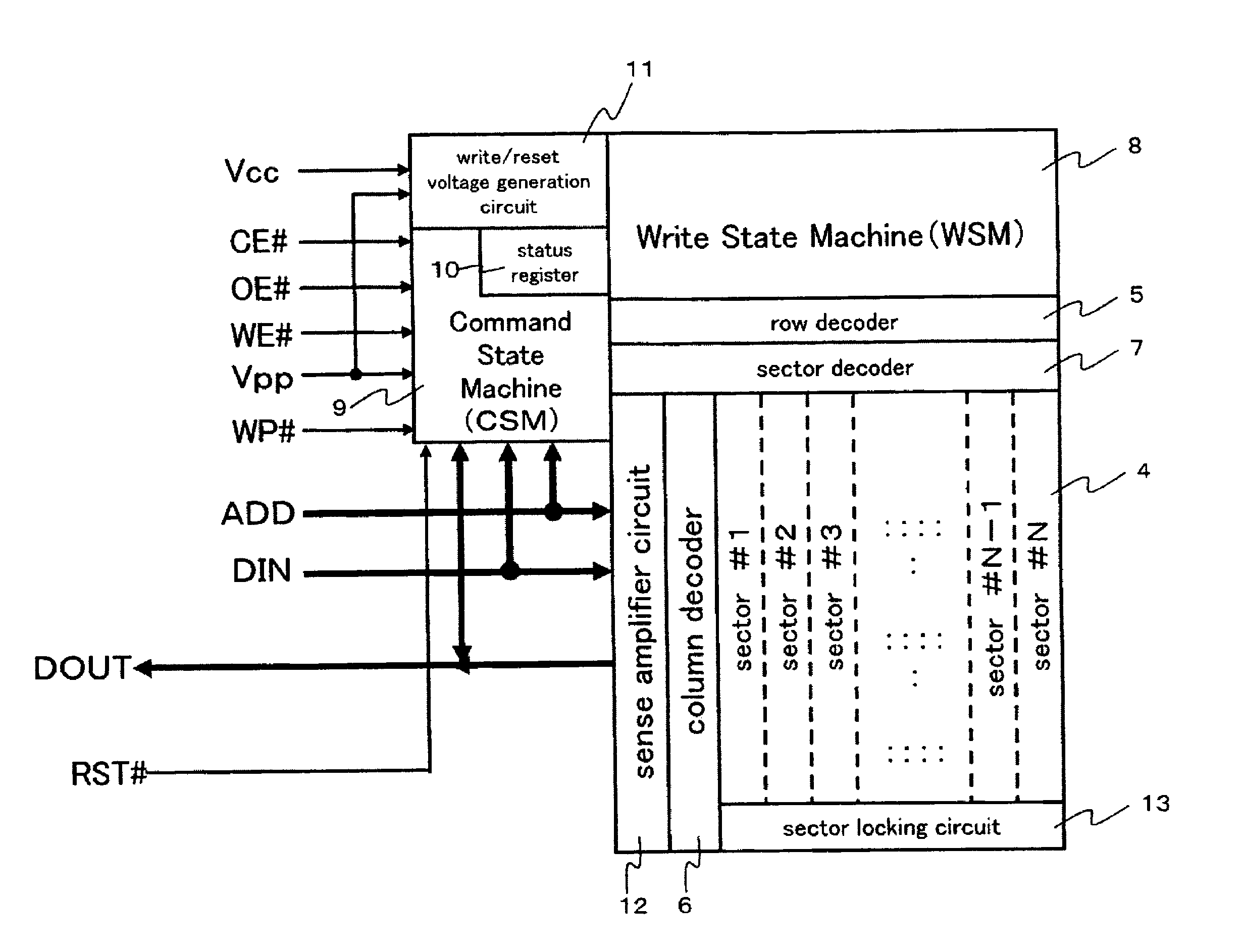

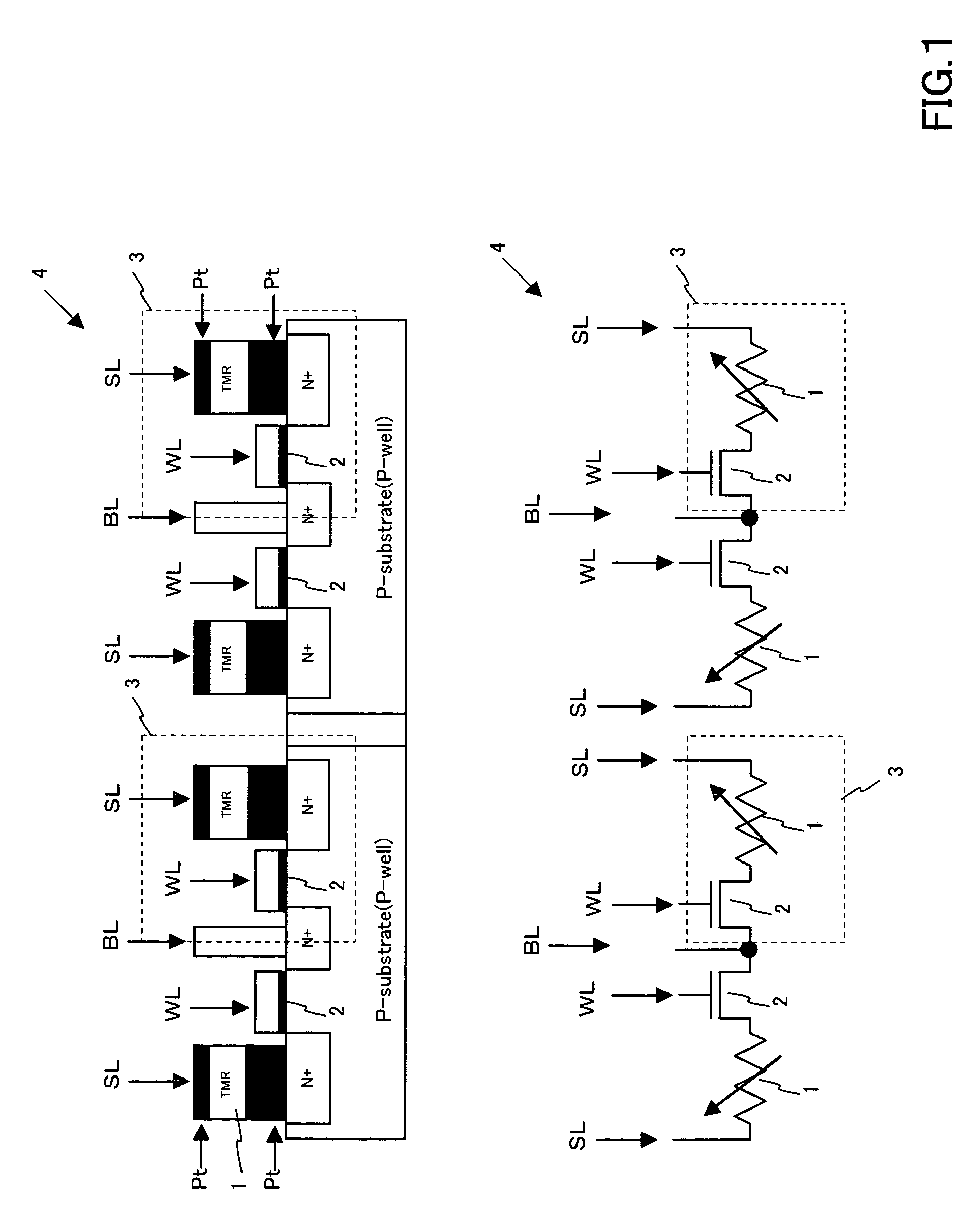

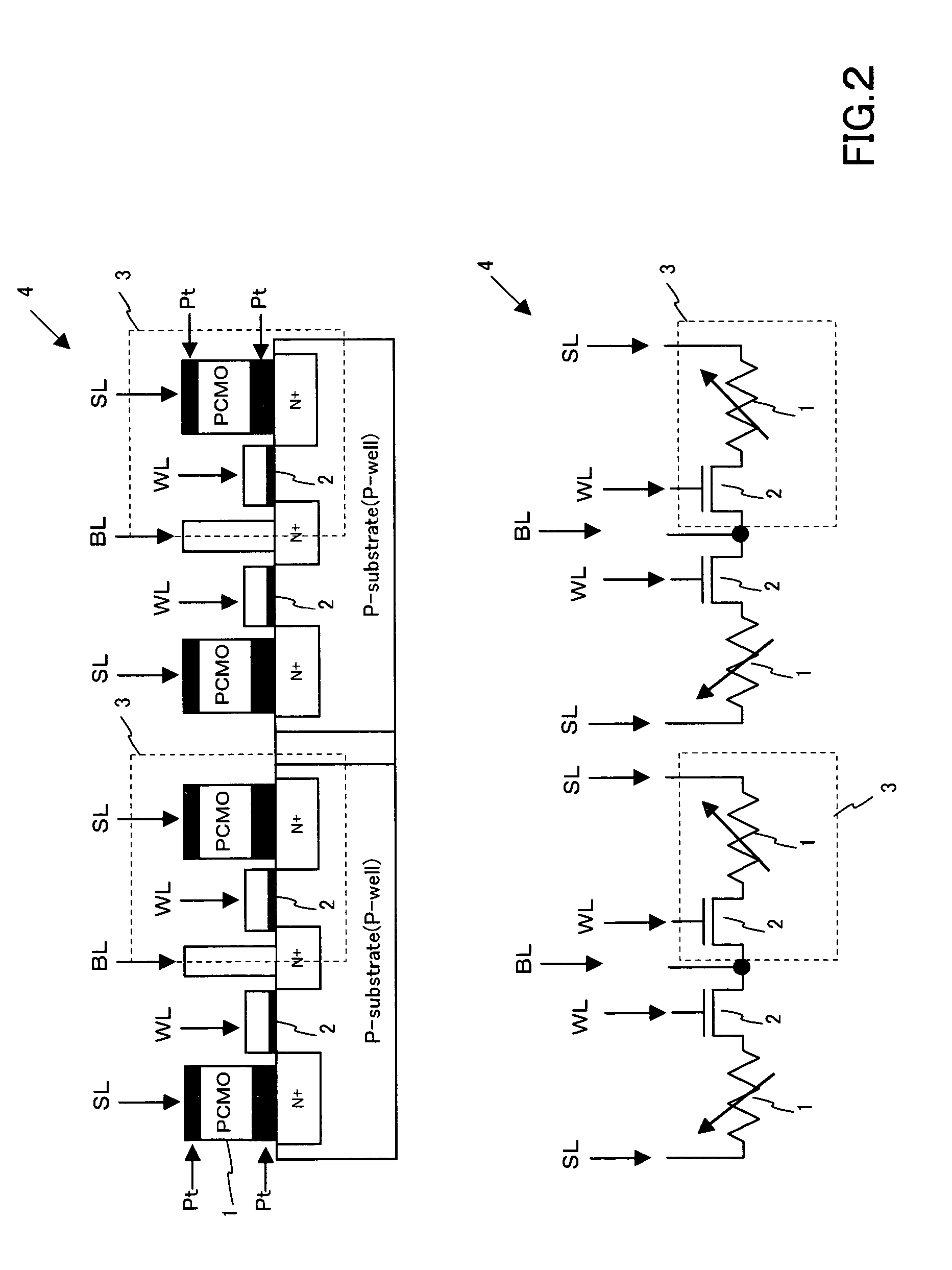

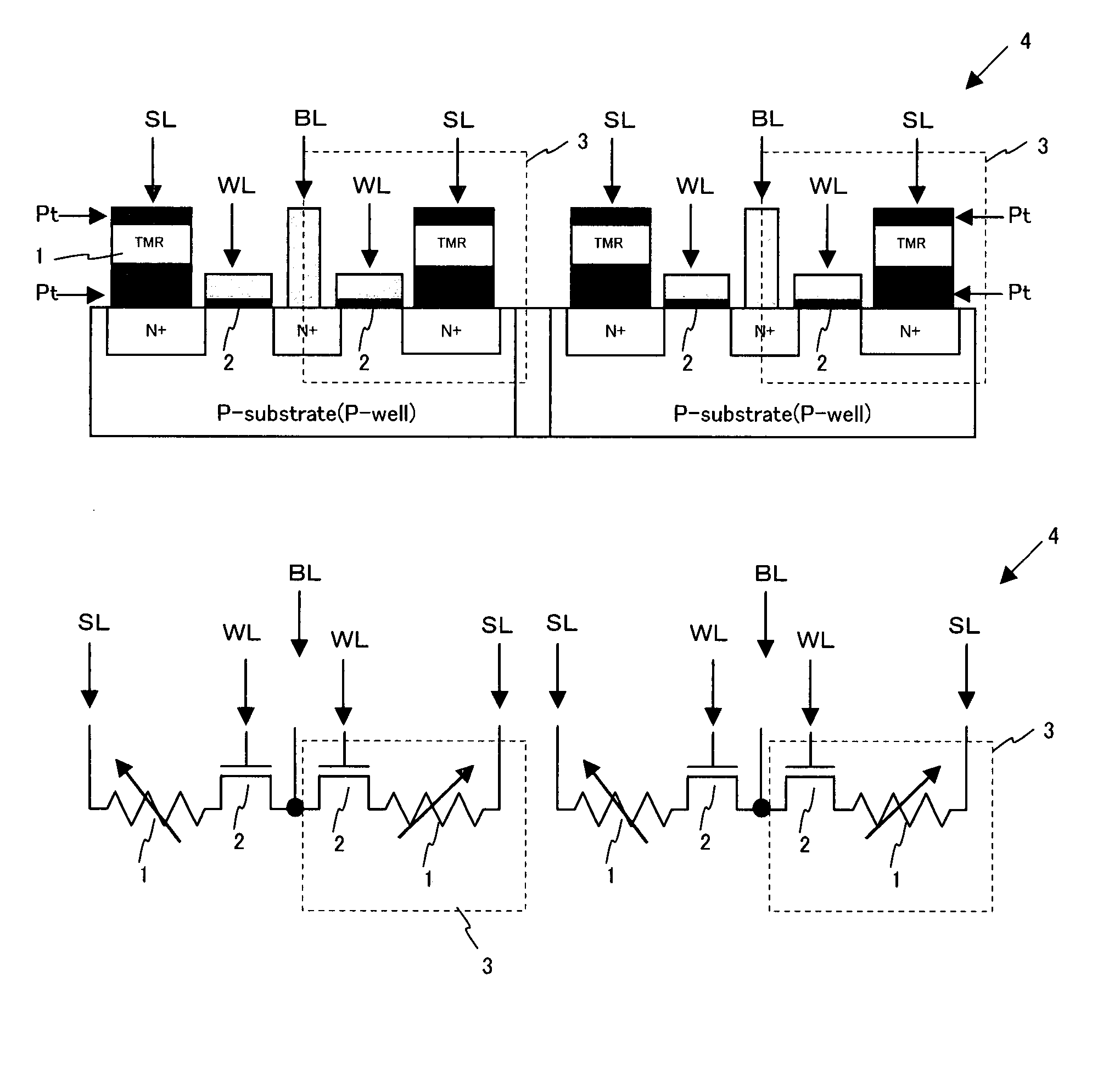

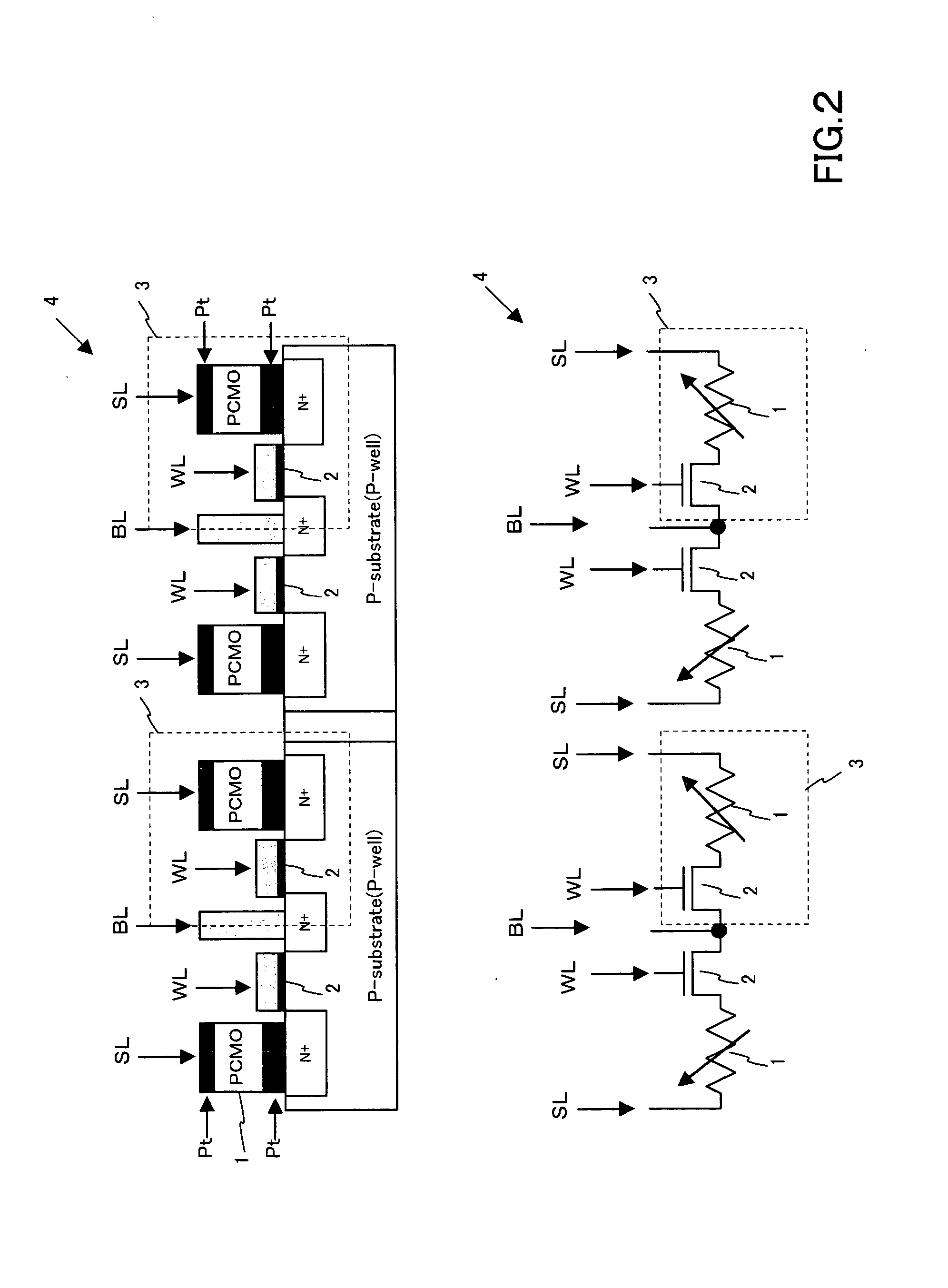

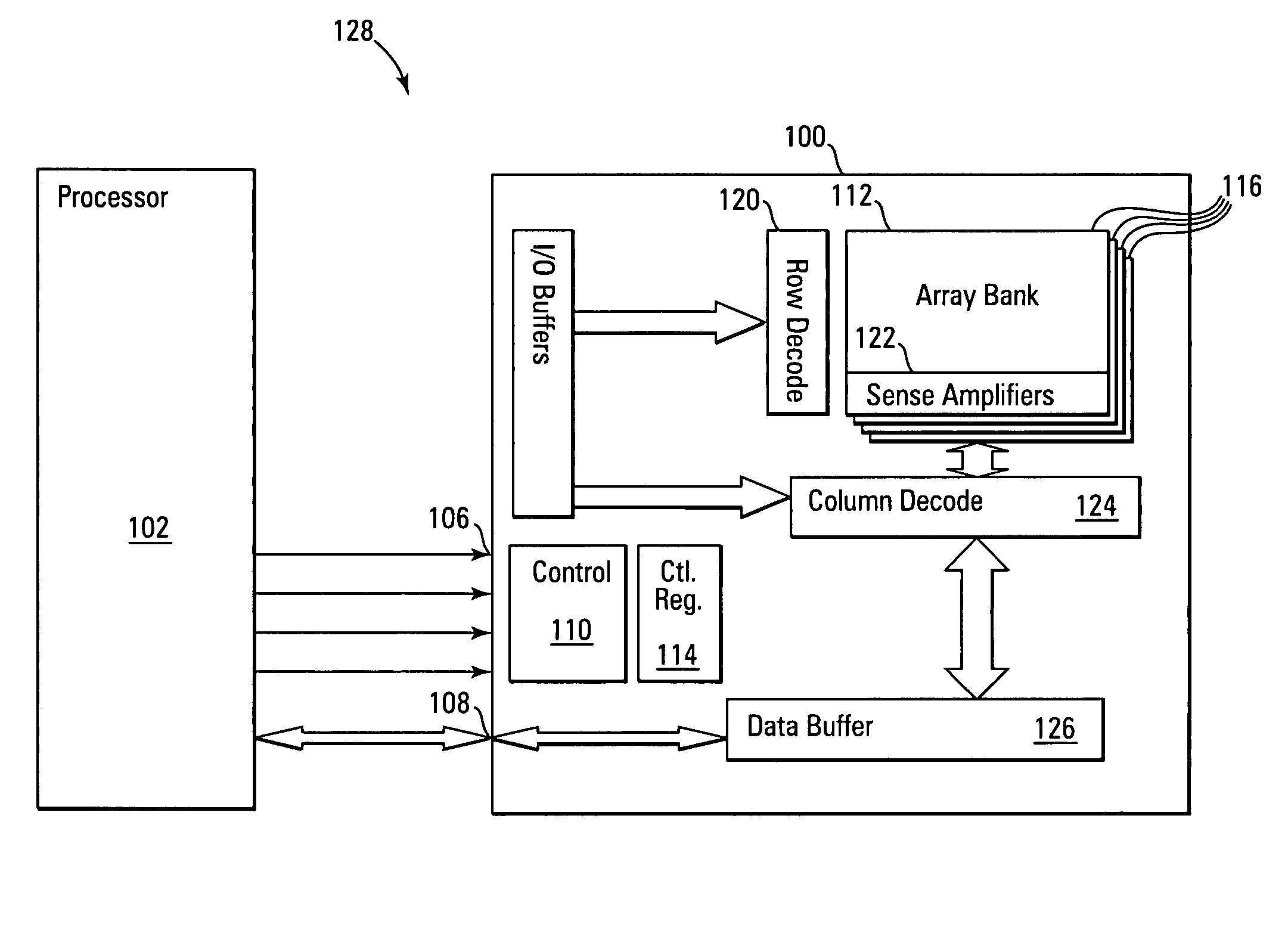

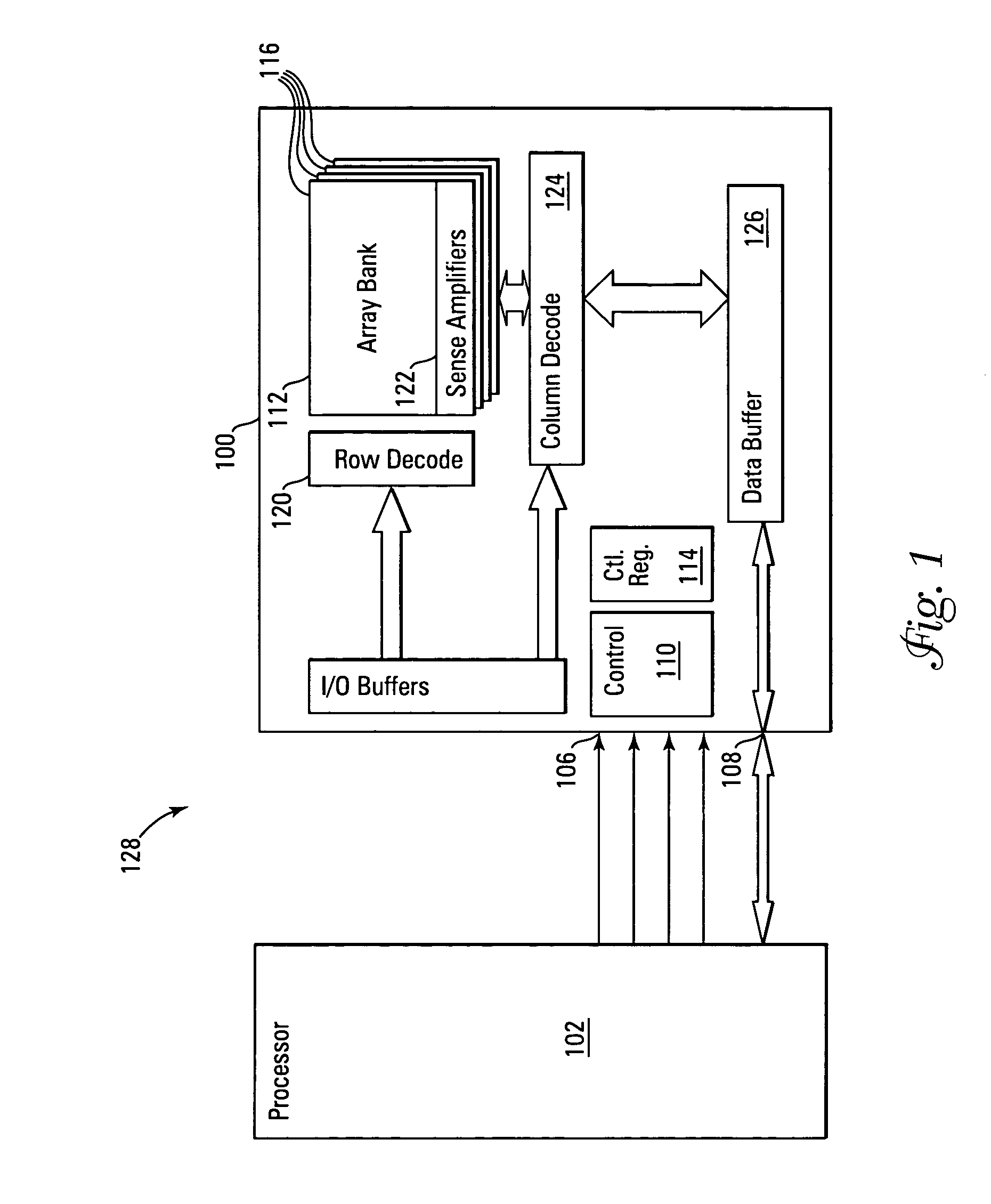

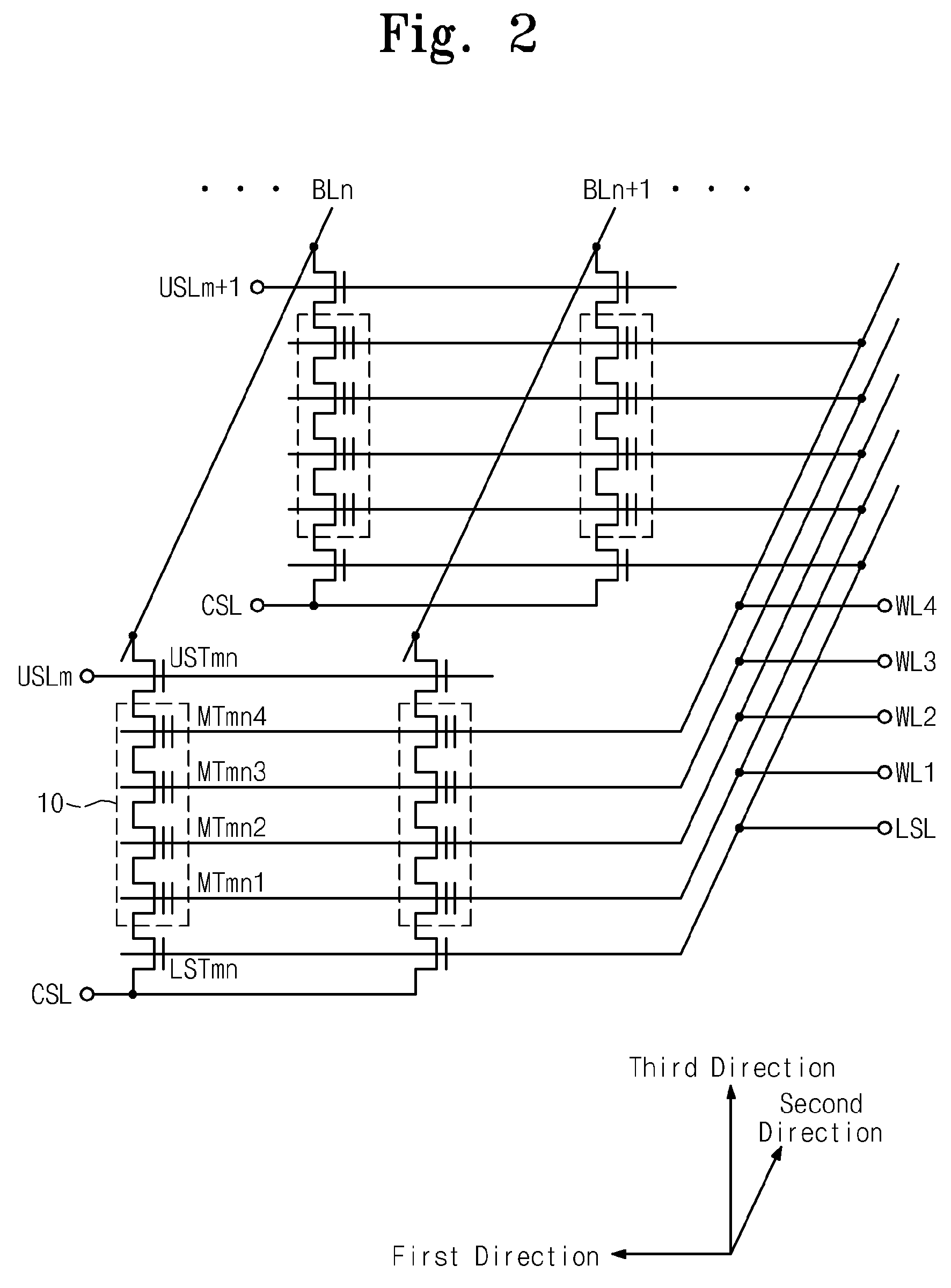

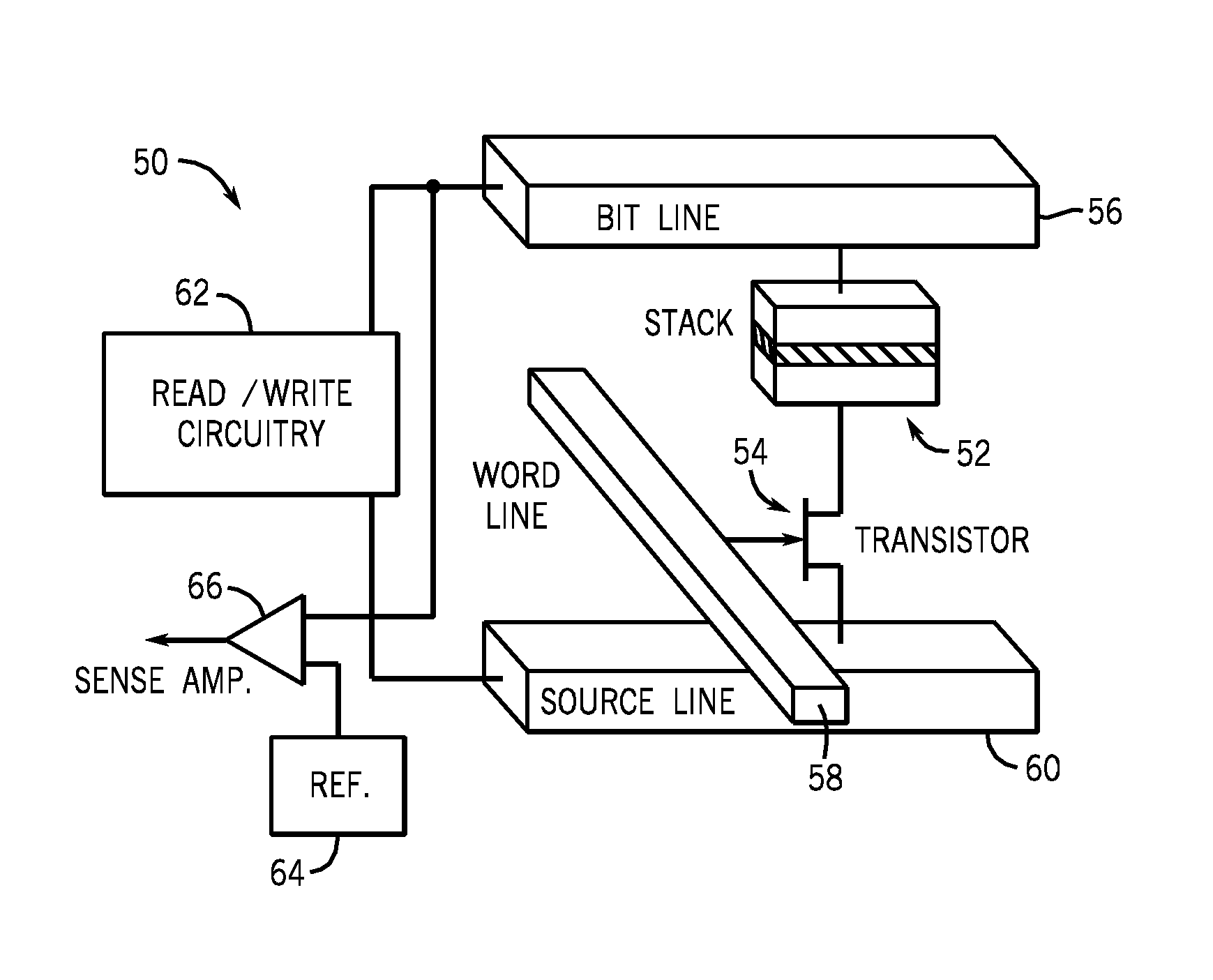

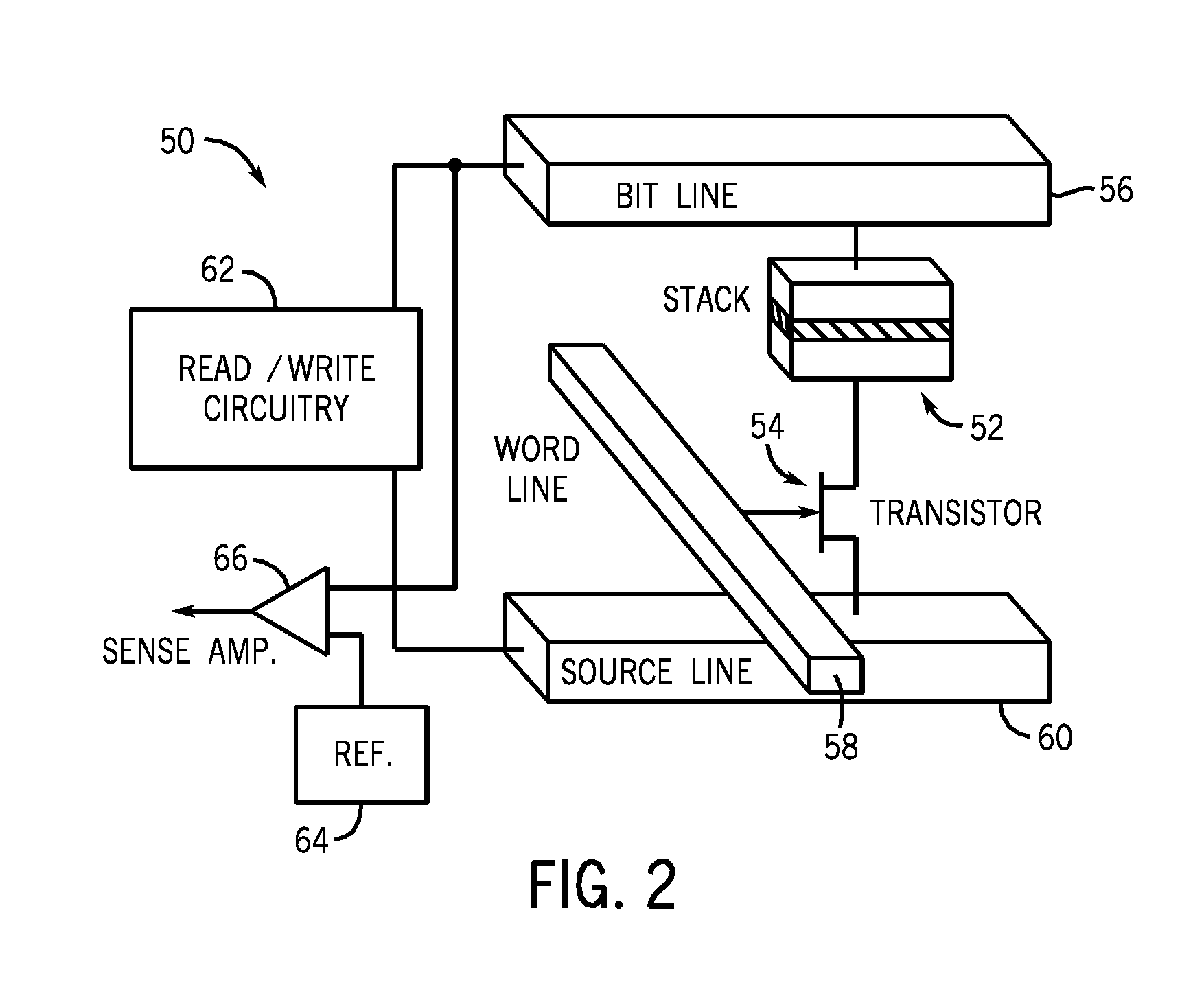

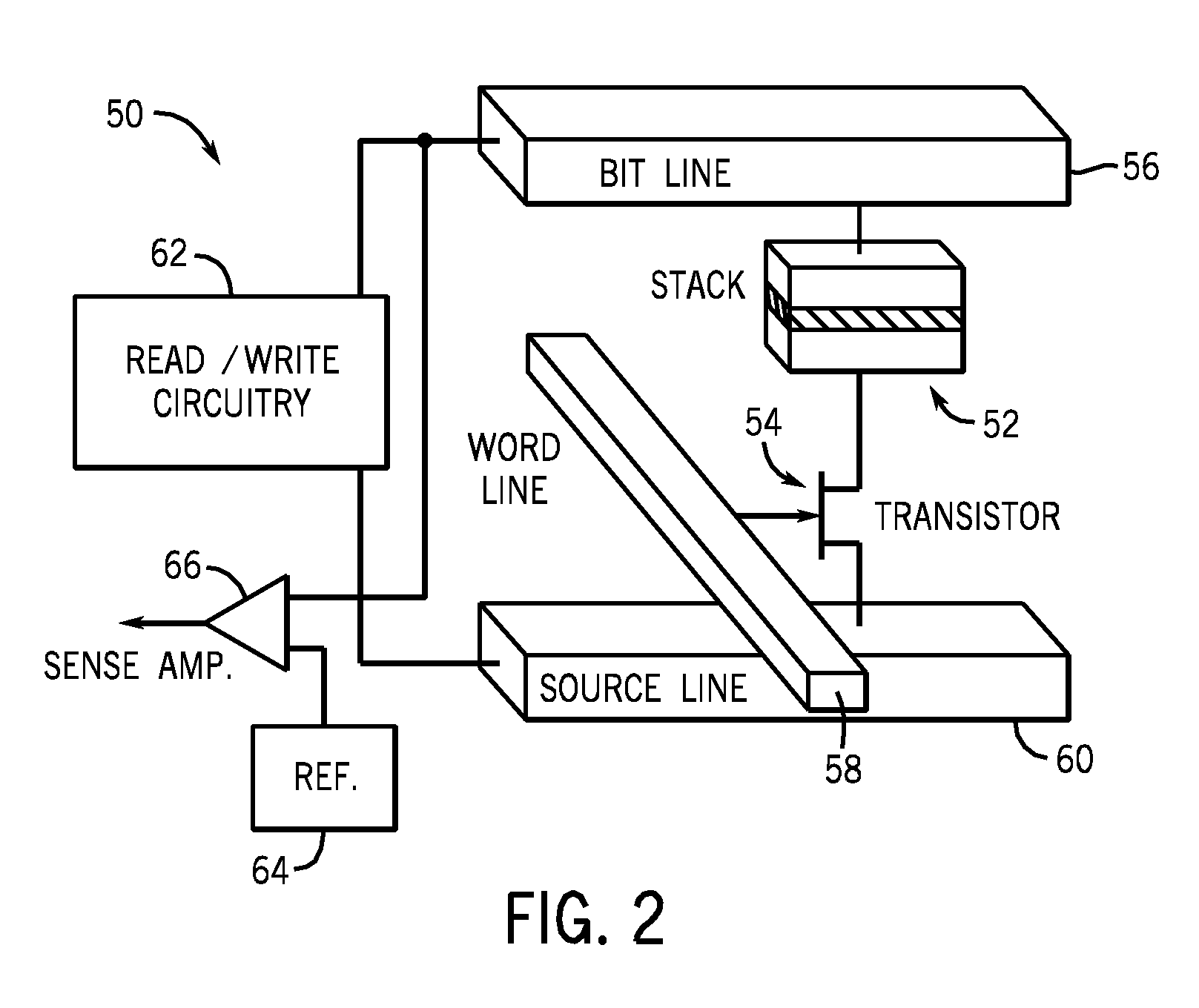

Nonvolatile semiconductor memory device

ActiveUS7057922B2Stress minimizationReliable dataNanoinformaticsSolid-state devicesBit lineEngineering

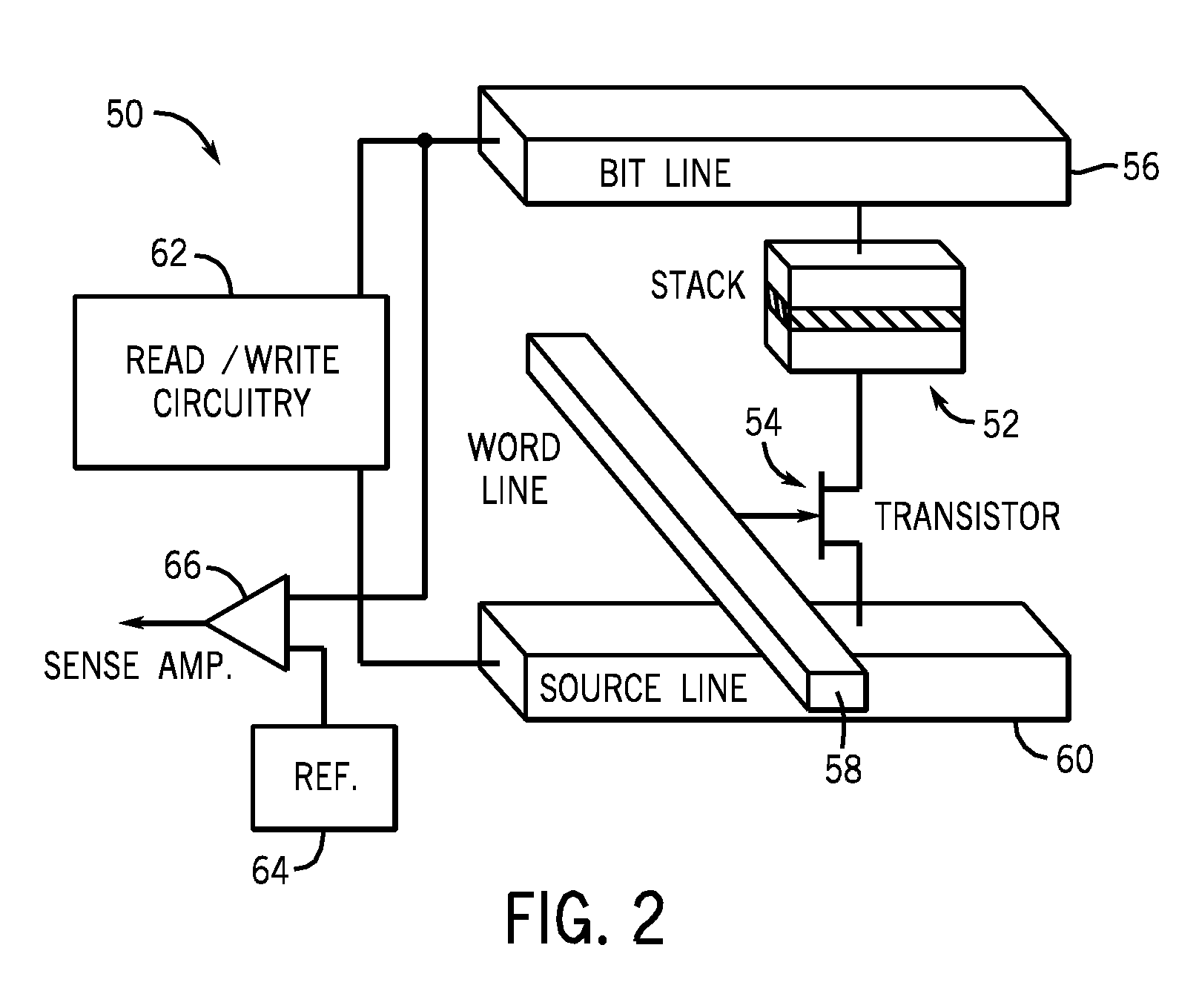

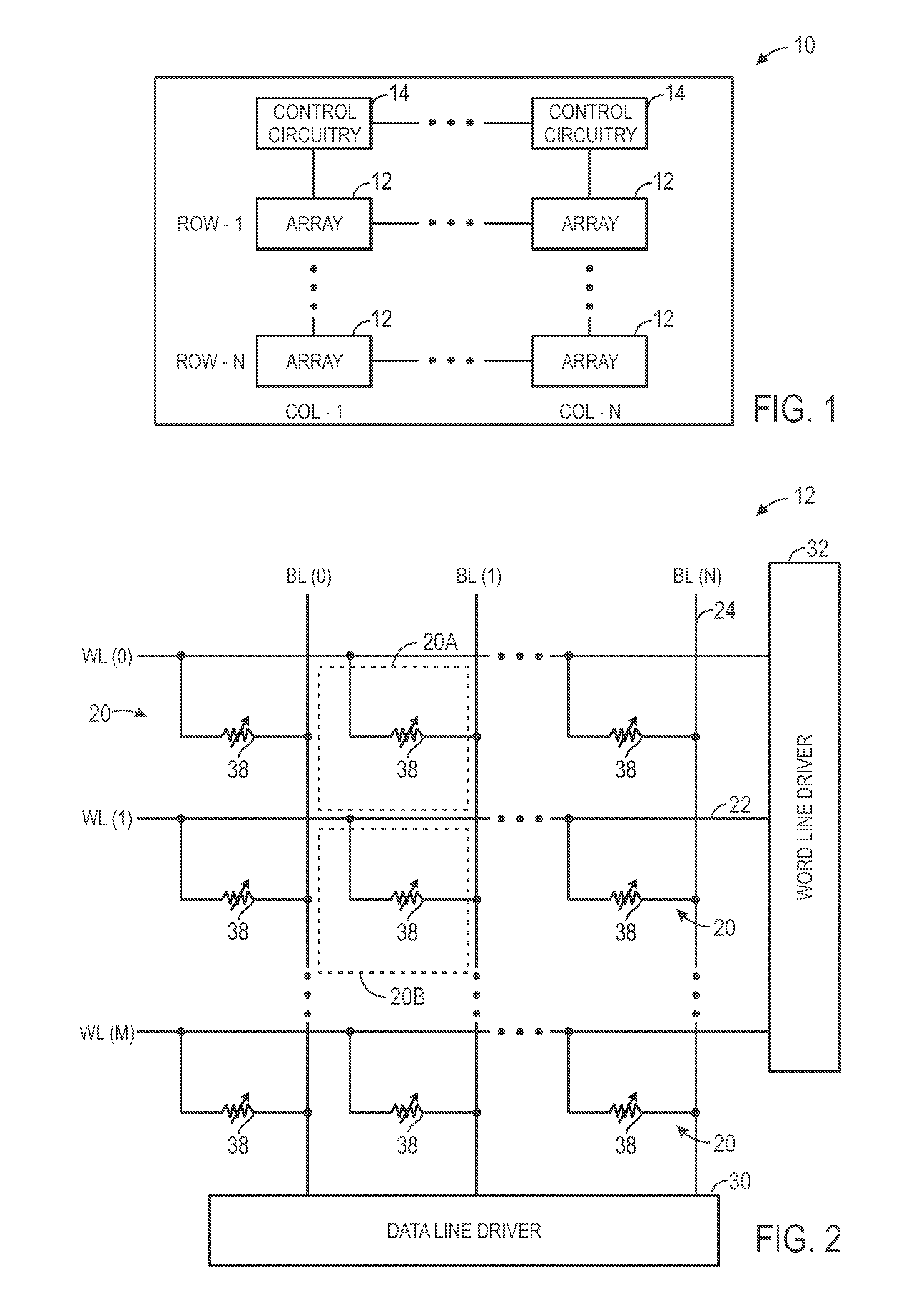

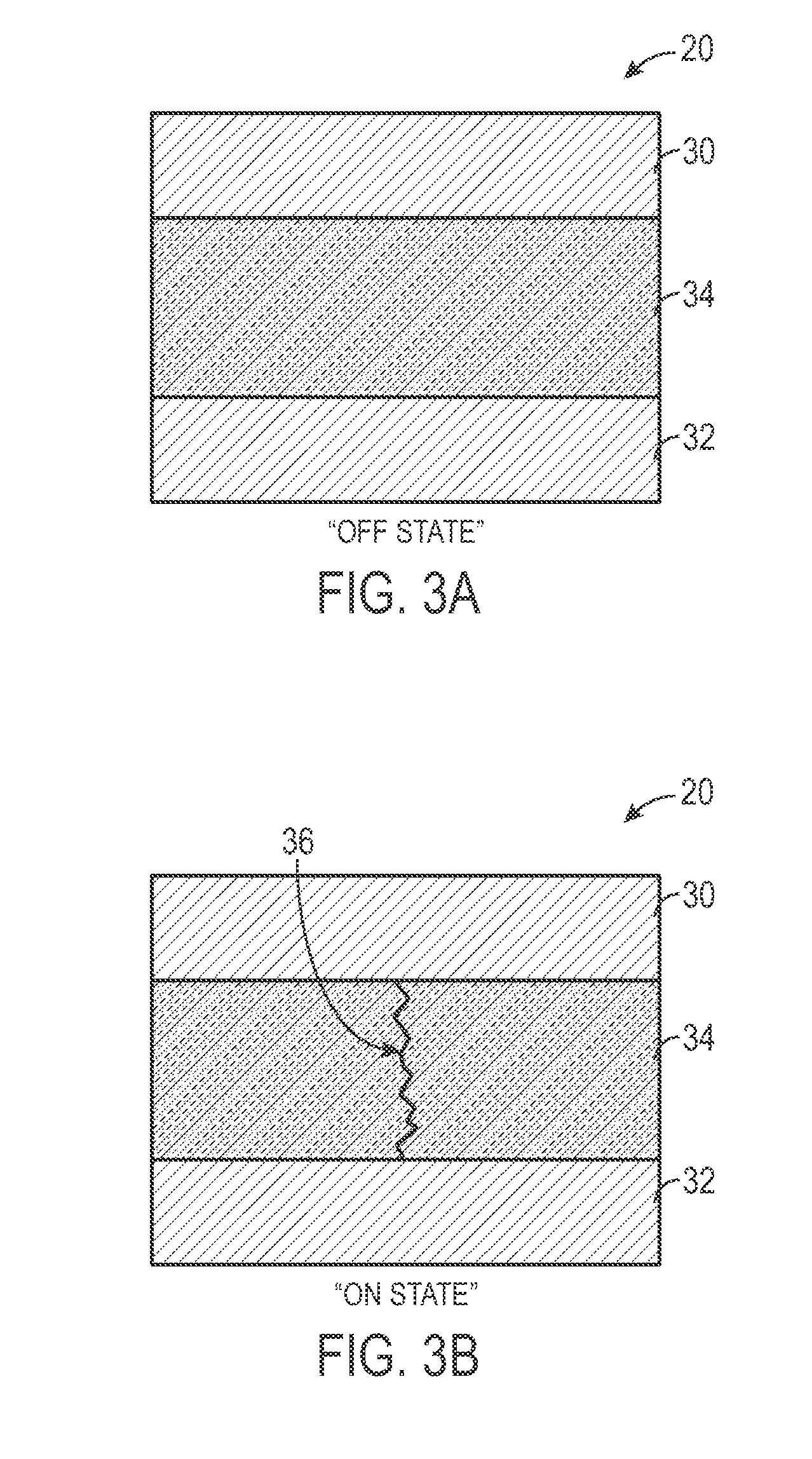

The present invention employs a memory cell structure in that one end of a variable resistance element (1) for storing information by change of electric resistance is connected to a source of a selection transistor (2) to form a memory cell (3) and, in a memory cell array (4), a drain of the selection transistor (2) is connected to a common bit line (BL) in a column direction, the other end of the variable resistance element (1) is connected to a source line (SL) and a gate of the selection transistor (2) is connected to a common word line (WL) in a row direction. In the memory cell structure, an operation of resetting data stored in the memory cell (3) is carried out for each of sectors including the plural memory cells (3) commonly connected to the source line (SL).

Owner:SAMSUNG ELECTRONICS CO LTD

Nonvolatile semiconductor memory device

ActiveUS20050122768A1Minimize of currentMinimize stress of voltageNanoinformaticsSolid-state devicesBit lineCommon word

The present invention employs a memory cell structure in that one end of a variable resistance element (1) for storing information by change of electric resistance is connected to a source of a selection transistor (2) to form a memory cell (3) and, in a memory cell array (4), a drain of the selection transistor (2) is connected to a common bit line (BL) in a column direction, the other end of the variable resistance element (1) is connected to a source line (SL) and a gate of the selection transistor (2) is connected to a common word line (WL) in a row direction. In the memory cell structure, an operation of resetting data stored in the memory cell (3) is carried out for each of sectors including the plural memory cells (3) commonly connected to the source line (SL).

Owner:SAMSUNG ELECTRONICS CO LTD

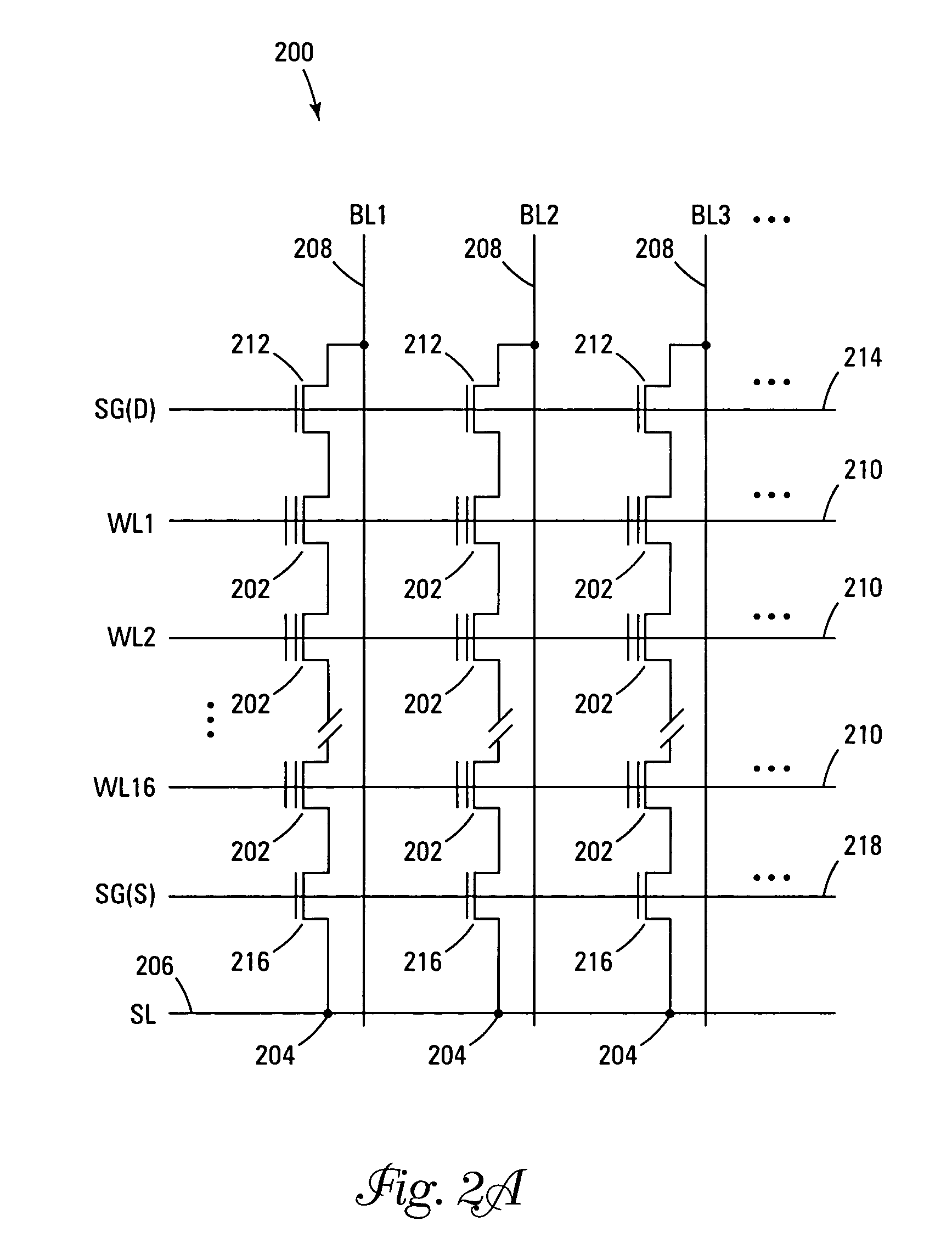

NAND flash depletion cell structure

InactiveUS20060044872A1Scale upIncrease supplyRead-only memoriesDigital storageCapacitanceRC time constant

NAND architecture Flash memory strings, memory arrays, and memory devices are described that utilize depletion mode floating gate memory cells. Depletion mode floating gate memory cells allow for increased cell current through lower channel rdS resistance and decreased “narrow width” effect, allowing for increased scaling of NAND memory cell strings. In addition, the required voltages for reading and programming operations are reduced, allowing the use of more efficient, lower voltage charge pumps and a reduction circuit element feature sizes and layouts. Cell inhibit of unselected cells is also increased, reducing the likelihood of cell disturb in the memory array. Operation speed is improved by increasing read current of the selected NAND string and by increasing the ability to overcome the RC time constants of circuit lines and capacitances through lowered voltage swings and increased current supplies.

Owner:MICRON TECH INC

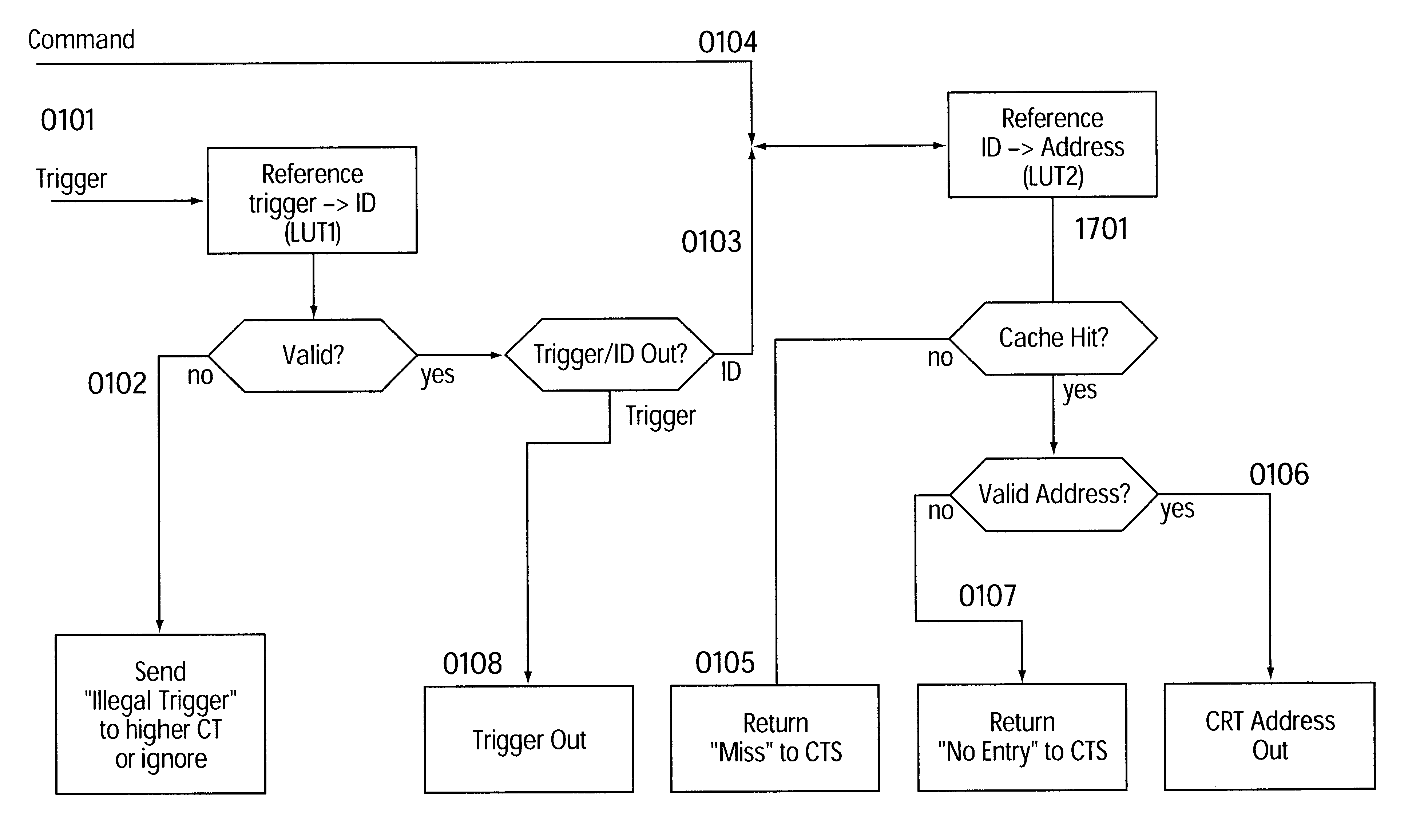

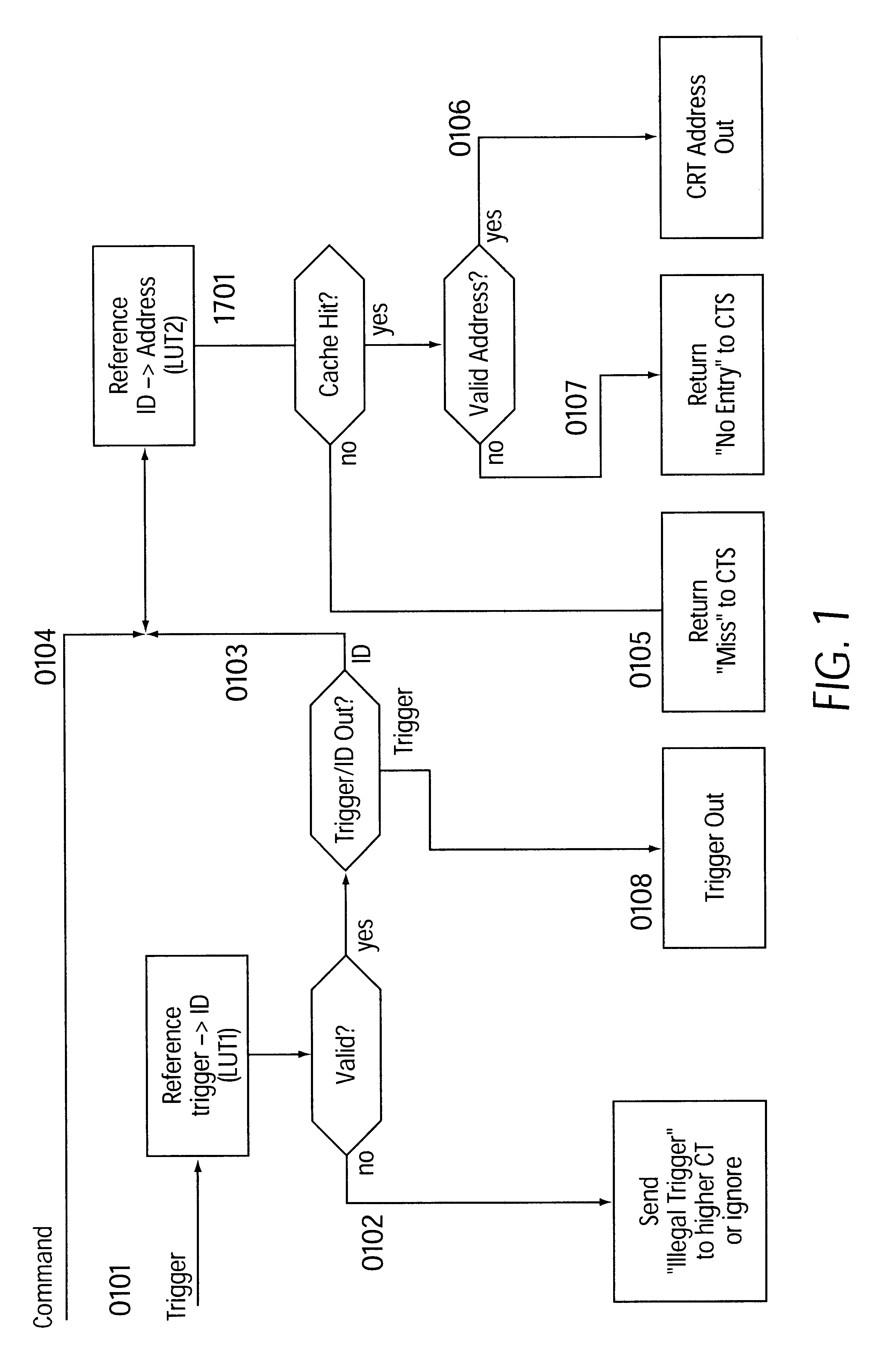

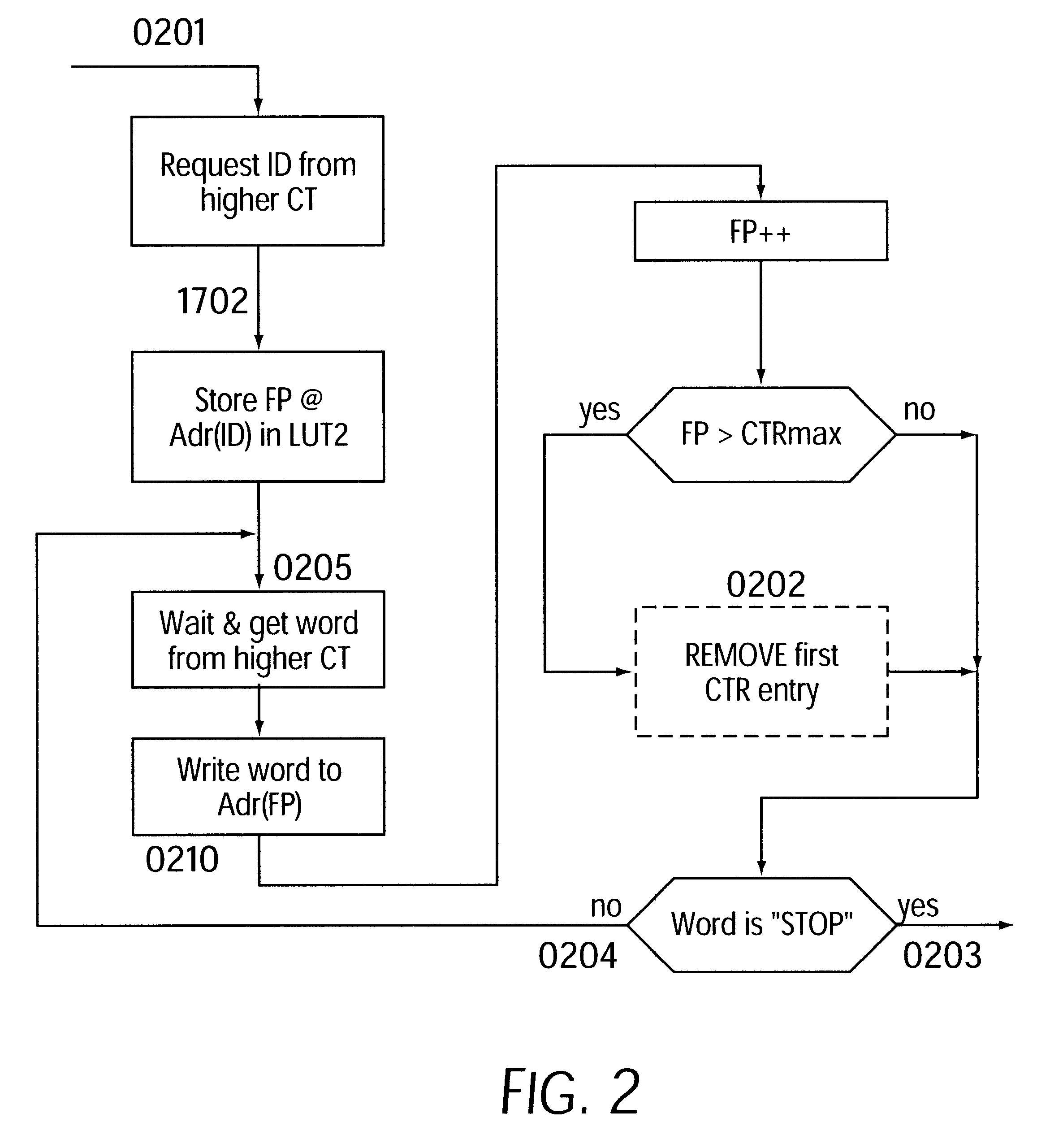

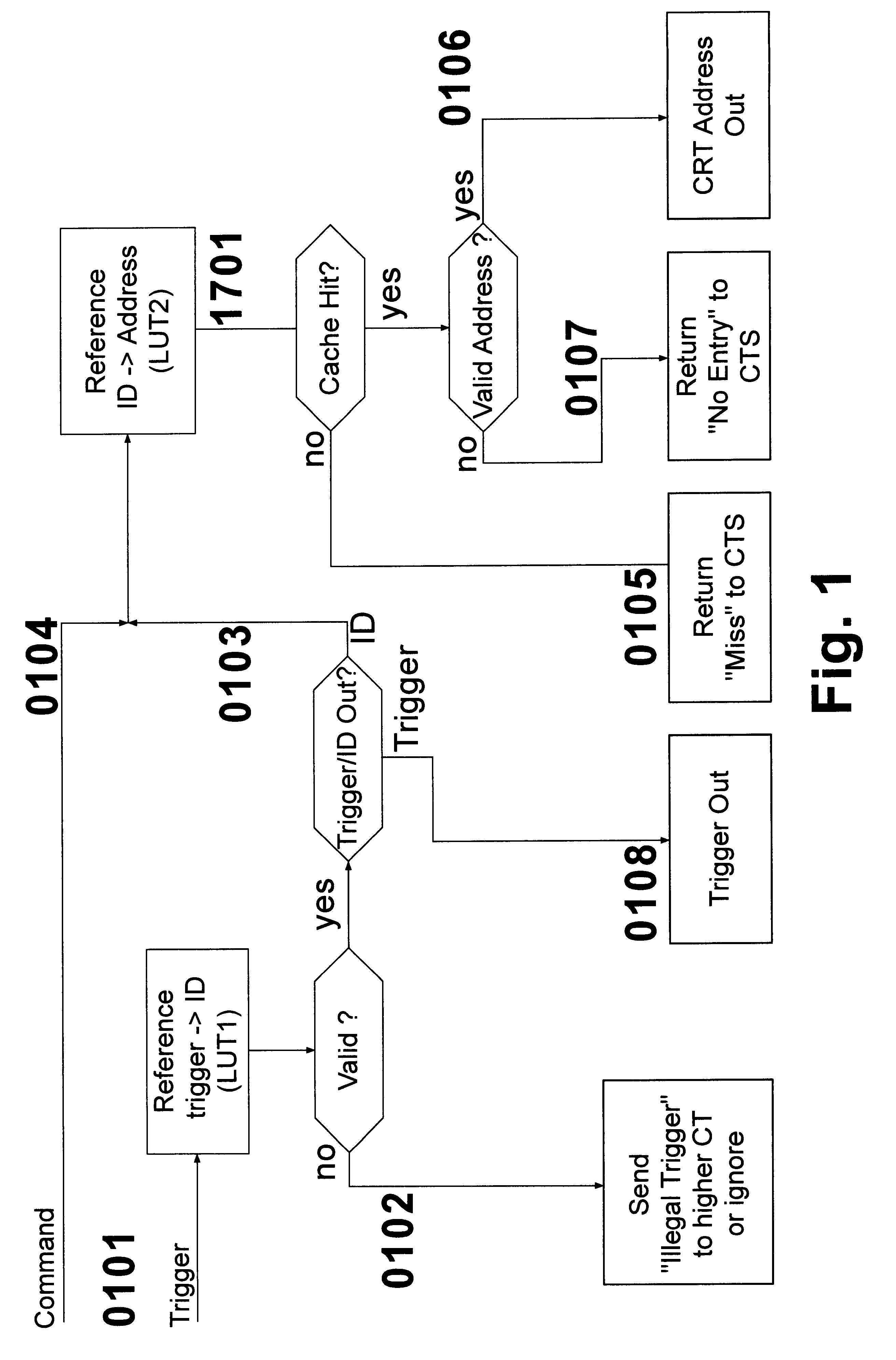

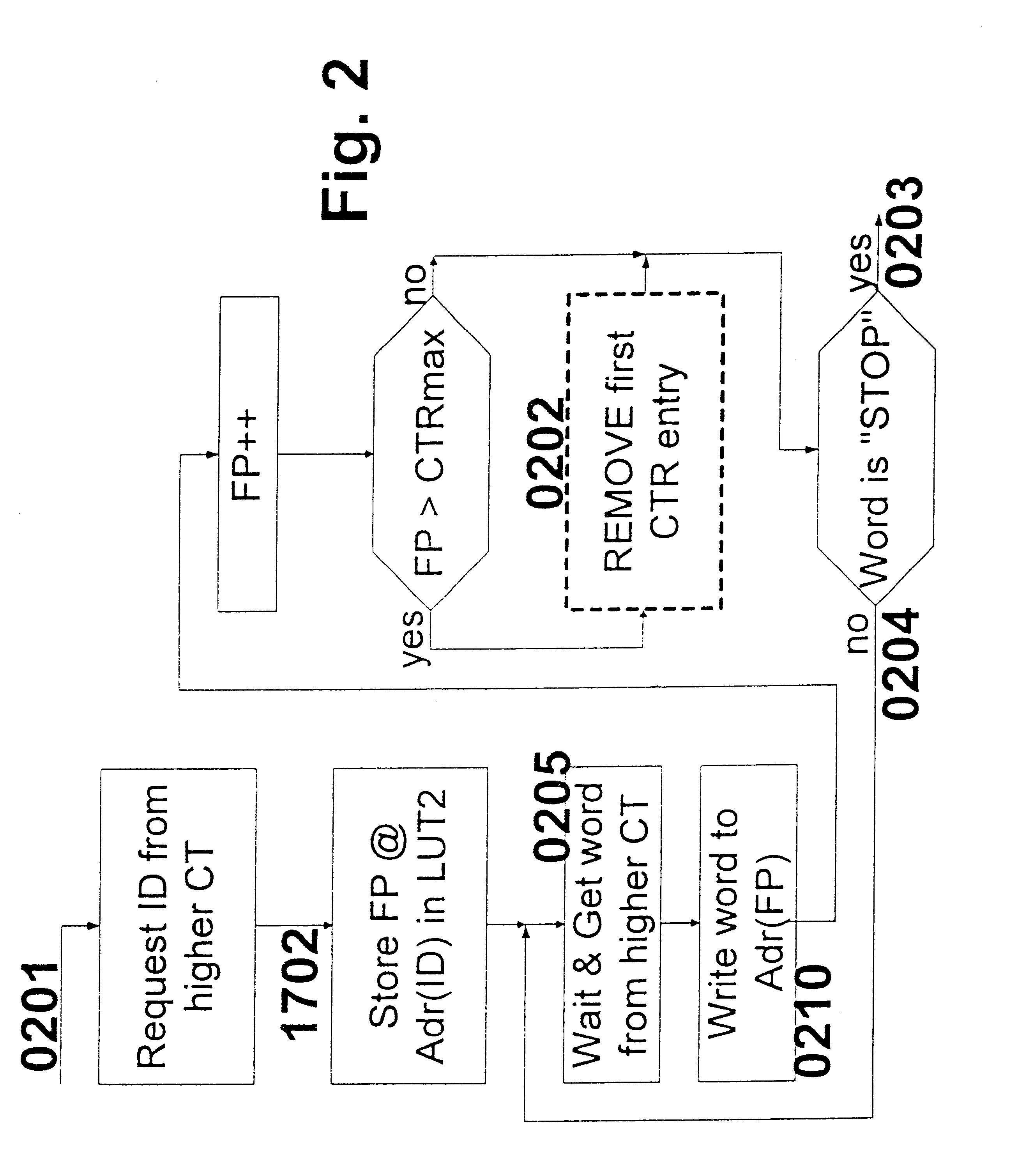

Method for hierarchical caching of configuration data having dataflow processors and modules having two-or multidimensional programmable cell structure (FPGAs, DPGAs, etc.)--

InactiveUS6480937B1Improve performanceEasy transferMemory adressing/allocation/relocationProgram controlData stream processingComputer module

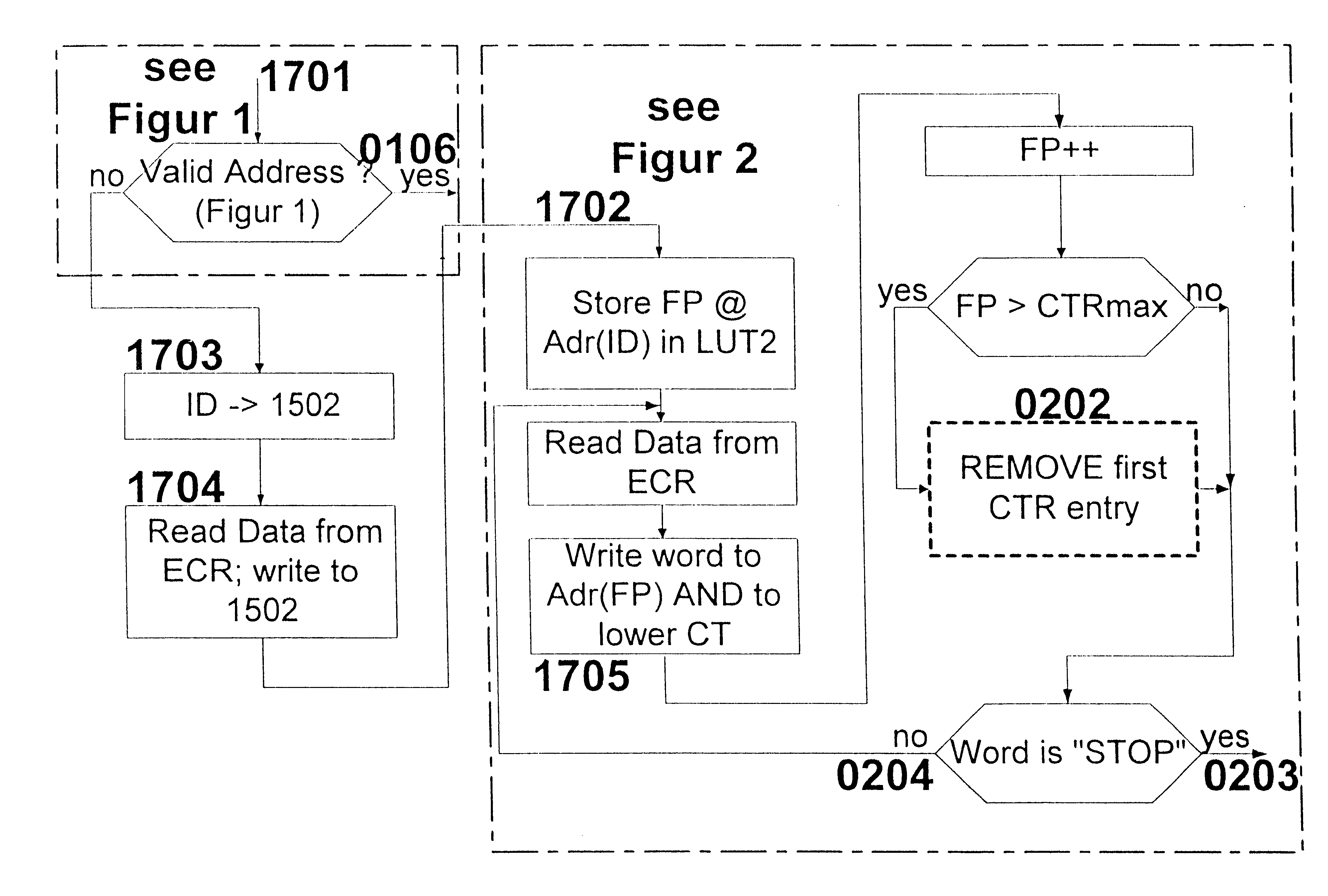

A method of caching commands in microprocessors having a plurality of arithmetic units and in modules having a two- or multidimensional cell arrangement is provided. The method includes combining a plurality of cells and arithmetic units to form a plurality of groups, assigning a cache unit to a group, and connecting the cache unit to a higher level unit via a tree structure. The cache unit may send requests for required commands to the higher level cache unit, which may return a command sequence including the required command, if the higher level cache unit holds the first command sequence including the required command in the higher level cache unit's local memory.

Owner:SCIENTIA SOL MENTIS AG +1

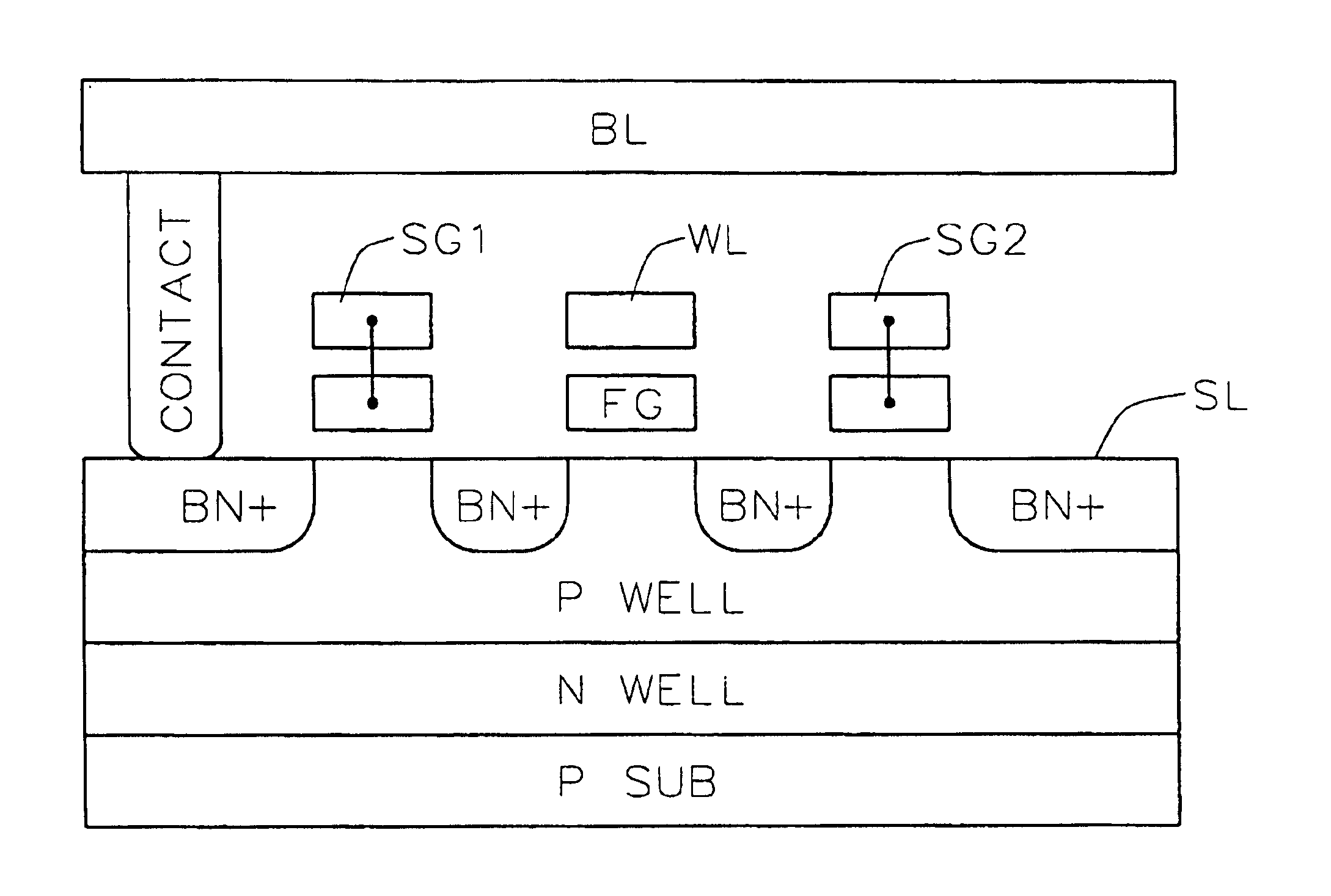

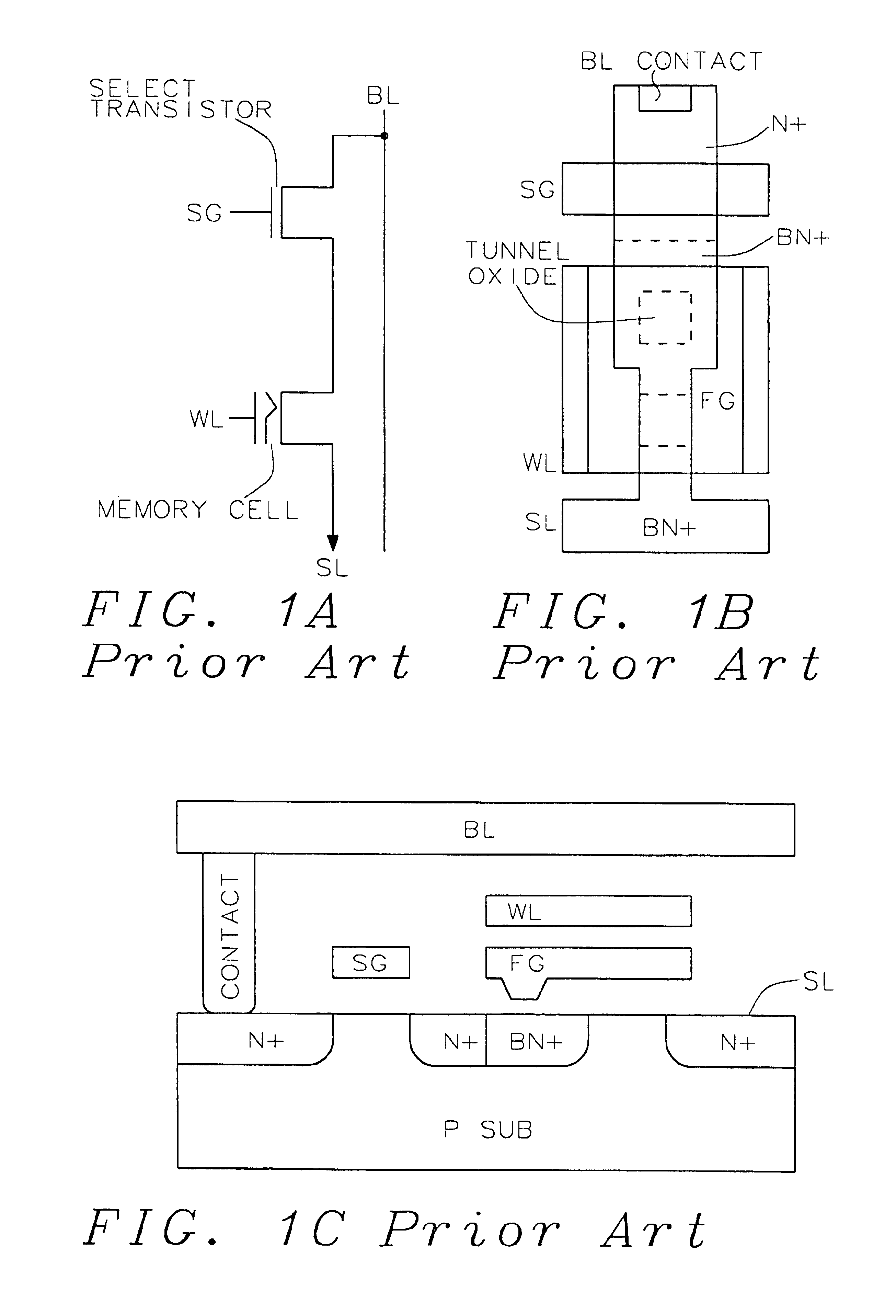

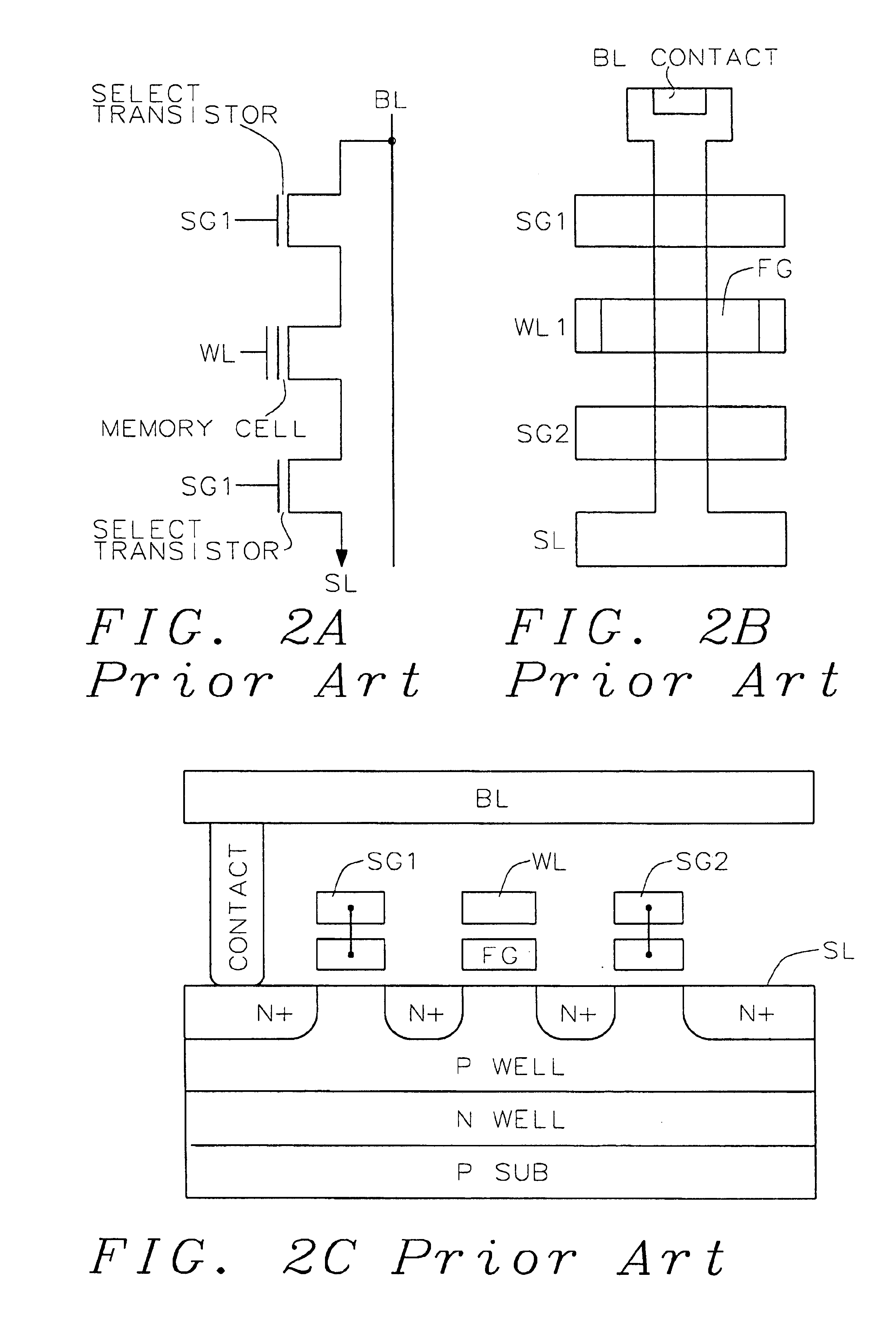

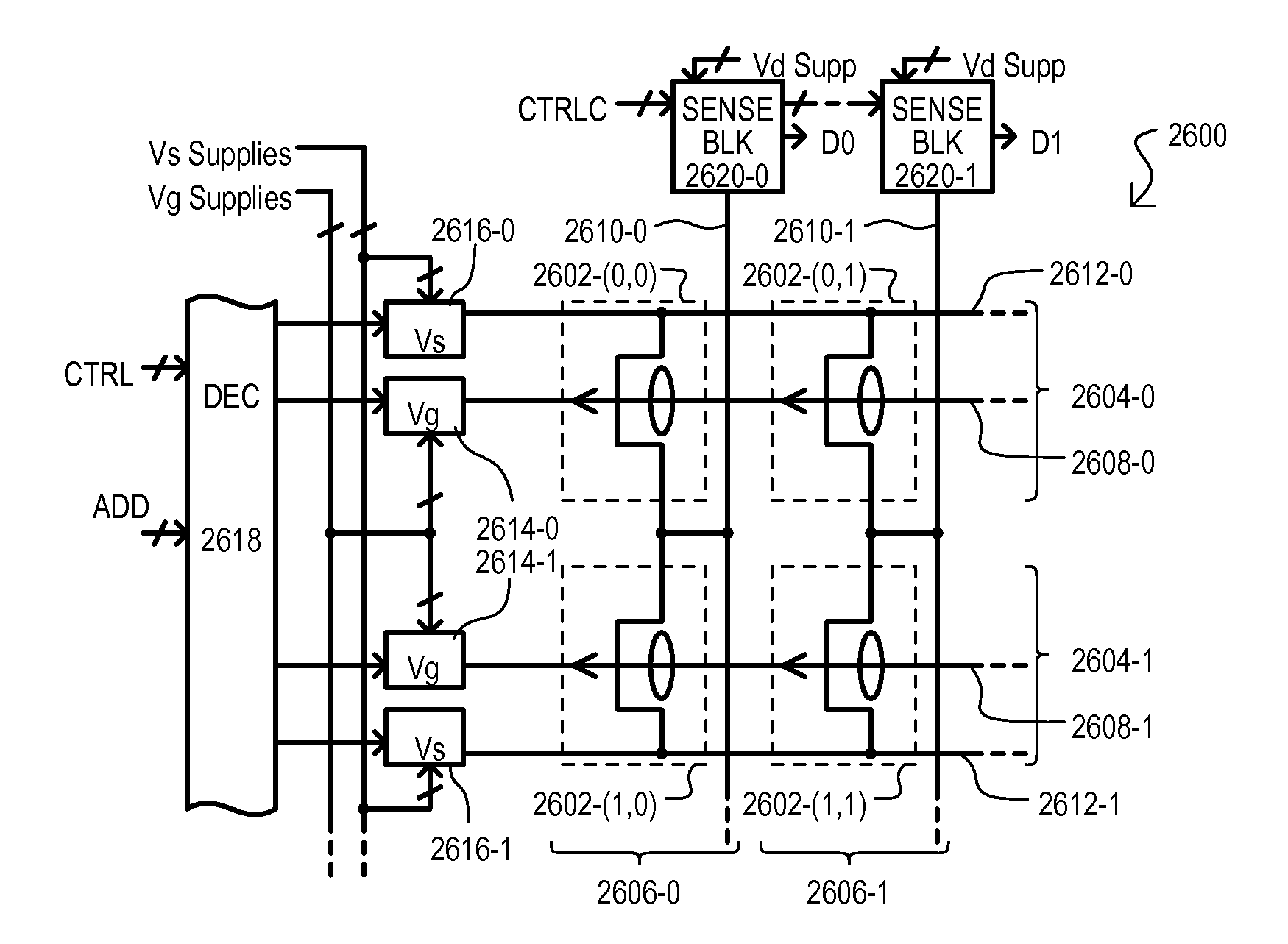

Monolithic, combo nonvolatile memory allowing byte, page and block write with no disturb and divided-well in the cell array using a unified cell structure and technology with a new scheme of decoder and layout

InactiveUS6862223B1Eliminate area-consuming divided triple-wellSuperior combo, monolithic, nonvolatile memorySolid-state devicesRead-only memoriesUnit structureByte

A novel FLASH-based EEPROM cell, decoder, and layout scheme are disclosed to eliminate the area-consuming divided triple-well in cell array and allows byte-erase and byte-program for high P / E cycles. Furthermore, the process-compatible FLASH cell for EEPROM part can be integrated with FLASH and ROM parts so that a superior combo, monolithic, nonvolatile memory is achieved. Unlike all previous arts, the novel combo nonvolatile memory of the present invention of ROM, EEPROM and FLASH or combination of any two is made of one unified, fully compatible, highly-scalable BN+cell and unified process. In addition, its cell operation schemes have zero array overhead and zero disturbance during P / E operations. The novel combo nonvolatile memory is designed to meet the need in those markets requiring flexible write size in units of bytes, pages and blocks at a lower cost.

Owner:CALLAHAN CELLULAR L L C

Method of self-synchronization of configurable elements of a programmable module

InactiveUS6542998B1Generating/distributing signalsTransmission path multiple useIndependent elementComputer architecture

A method which permits self-synchronization of elements to be synchronized. Synchronization is neither implemented nor managed by a central entity. By shifting synchronization into each element, more synchronization tasks can also be performed simultaneously, because independent elements no longer interfere with one another when accessing the central synchronization entity. In a module with a two- or multi-dimensionally arranged programmable cell structure, each configurable element can access the configuration and status register of other configurable elements over an interconnecting structure and thus can have an active influence on their function and operation. The configuration can thus be accomplished by a load logic from a processing array.

Owner:SCIENTIA SOL MENTIS AG

Cells of a customizable logic array device having independently accessible circuit elements

InactiveUS20080030228A1Easy to useReduce in quantitySolid-state devicesLogic circuits using elementary logic circuit componentsUnit structureElectrical and Electronics engineering

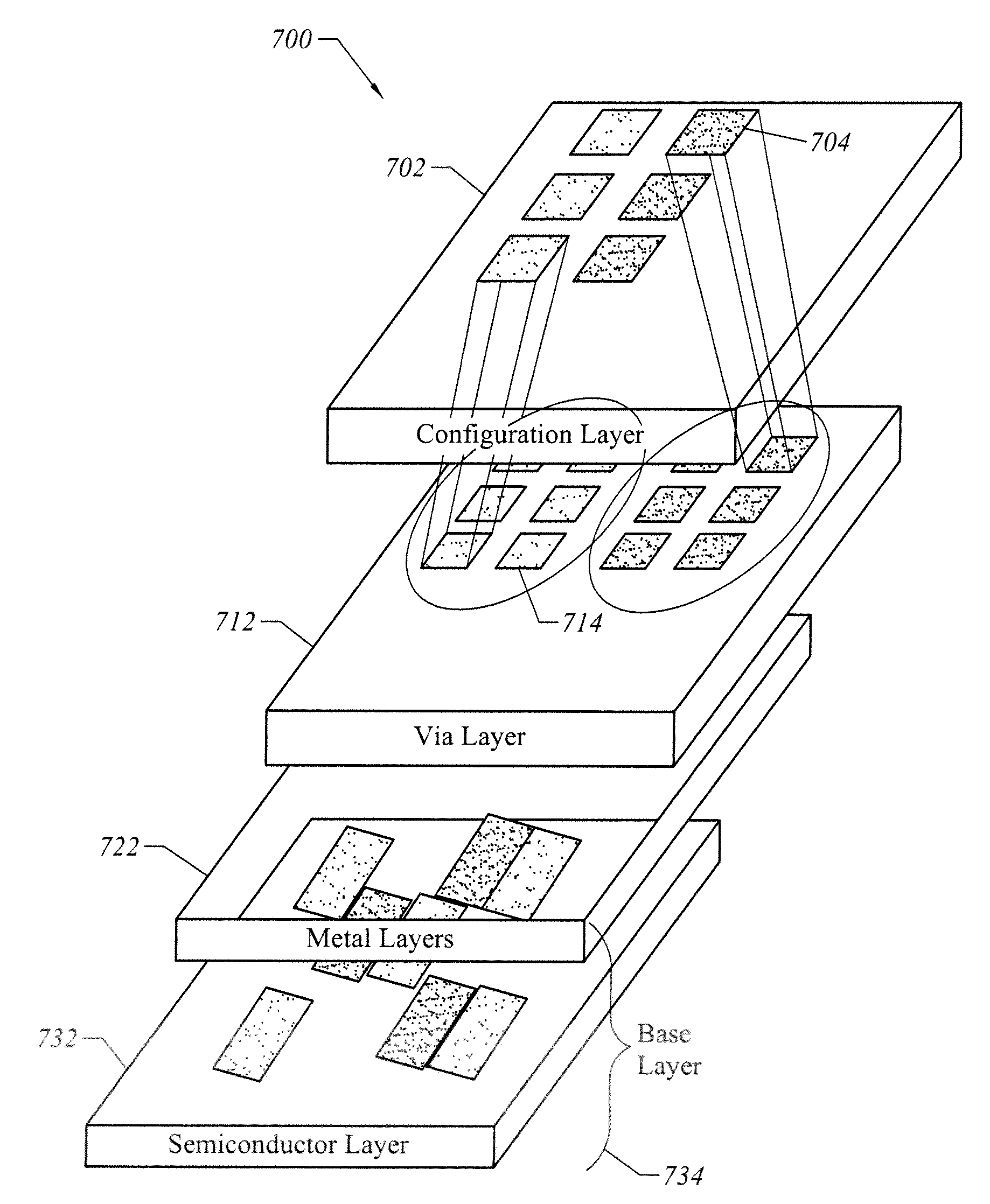

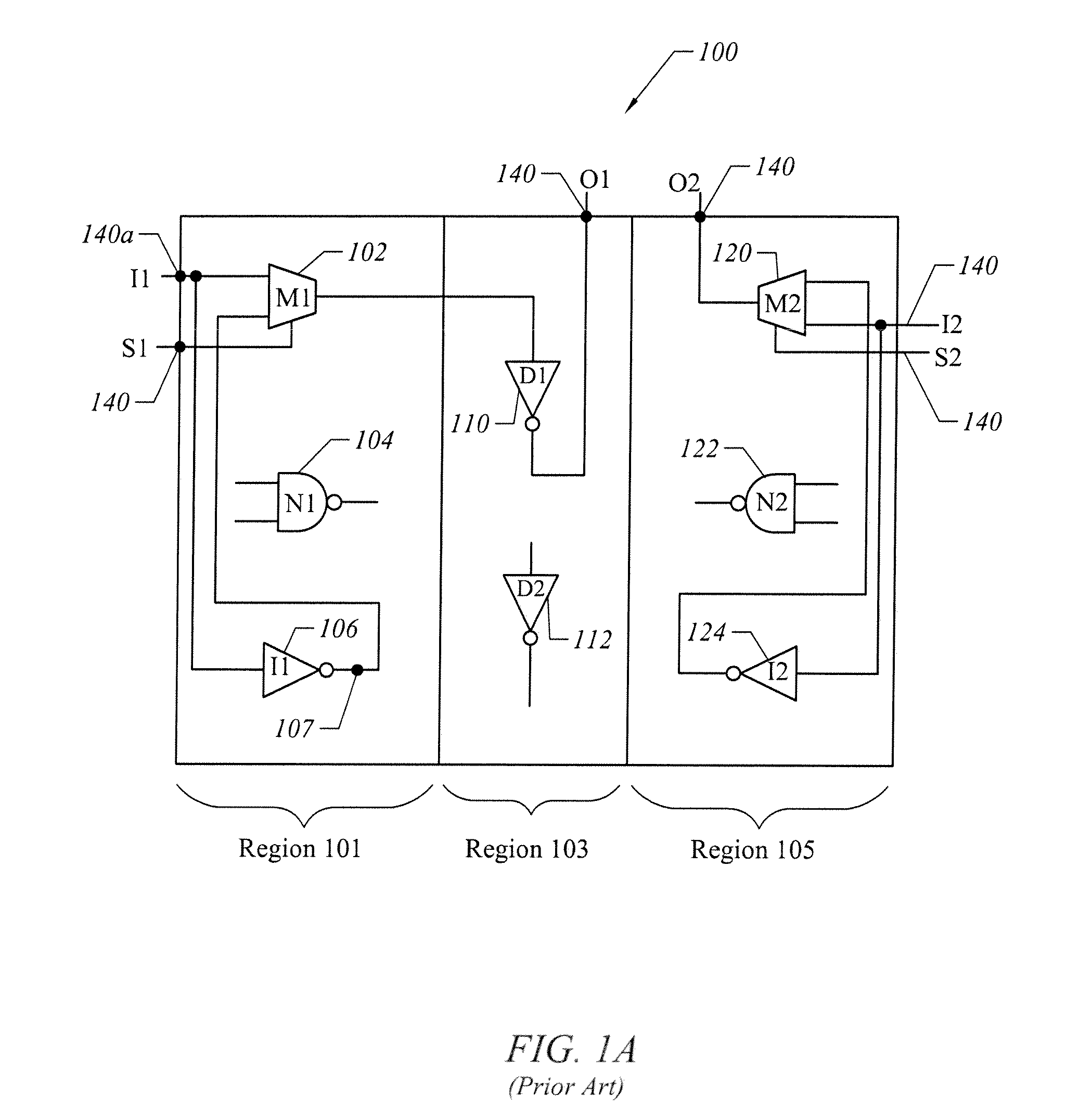

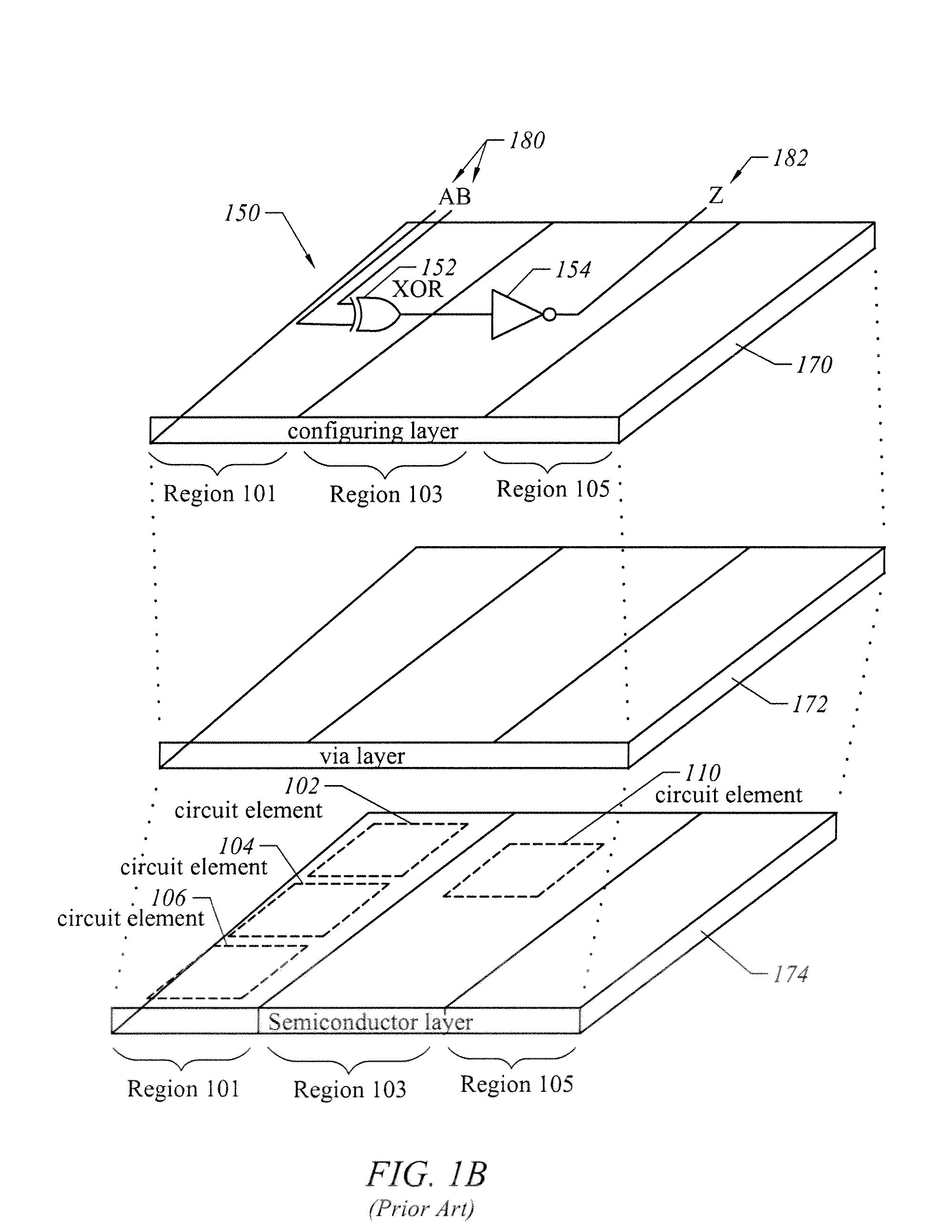

Various embodiments of the invention provide for cell structures having independently accessible circuit elements as a part of a customizable logic array device. In one embodiment, a cell forming a portion of a customizable logic array device includes a base layer, which, in turn, including circuit elements each having one or more inputs and one or more outputs. The cell also includes a configuration layer configured to form a logic device from one or more of the circuit elements. Further, the cell includes an interlayer connection layer configured to connect each of the inputs and the outputs to the configuration layer so as to enable each of the circuit elements to be independently accessible. Advantageously, the interlayer connection layer facilitates usage of each of the circuit elements to reduce the number of unused circuit elements in the cell.

Owner:SILICON VALLEY BANK

Method for deadlock-free configuration of dataflow processors and modules with a two- or multidimensional programmable cell structure (FPGAs, DPGAs, etc.)

InactiveUS6571381B1Memory adressing/allocation/relocationData resettingAuto-configurationData stream processing

A method of deadlock-free, automatic configuration and reconfiguration of modules having a two- or multidimensional cell arrangement, in which a unit for controlling the configuration and reconfiguration manages a set of associated configurable elements, the set being a subset or the total set of all configurable elements, and the management takes place as follows: reconfiguration requests from the associated configurable elements are sent to the unit; the unit processes the requests; the unit processes the configuration data of the command sequence; and after the configuration data has been fully processed, new requests are accepted again, the configuration data still to be loaded of the existing previous requests being loaded from a buffer memory (FILMO) into the configurable elements until a new request occurs.

Owner:SCIENTIA SOL MENTIS AG

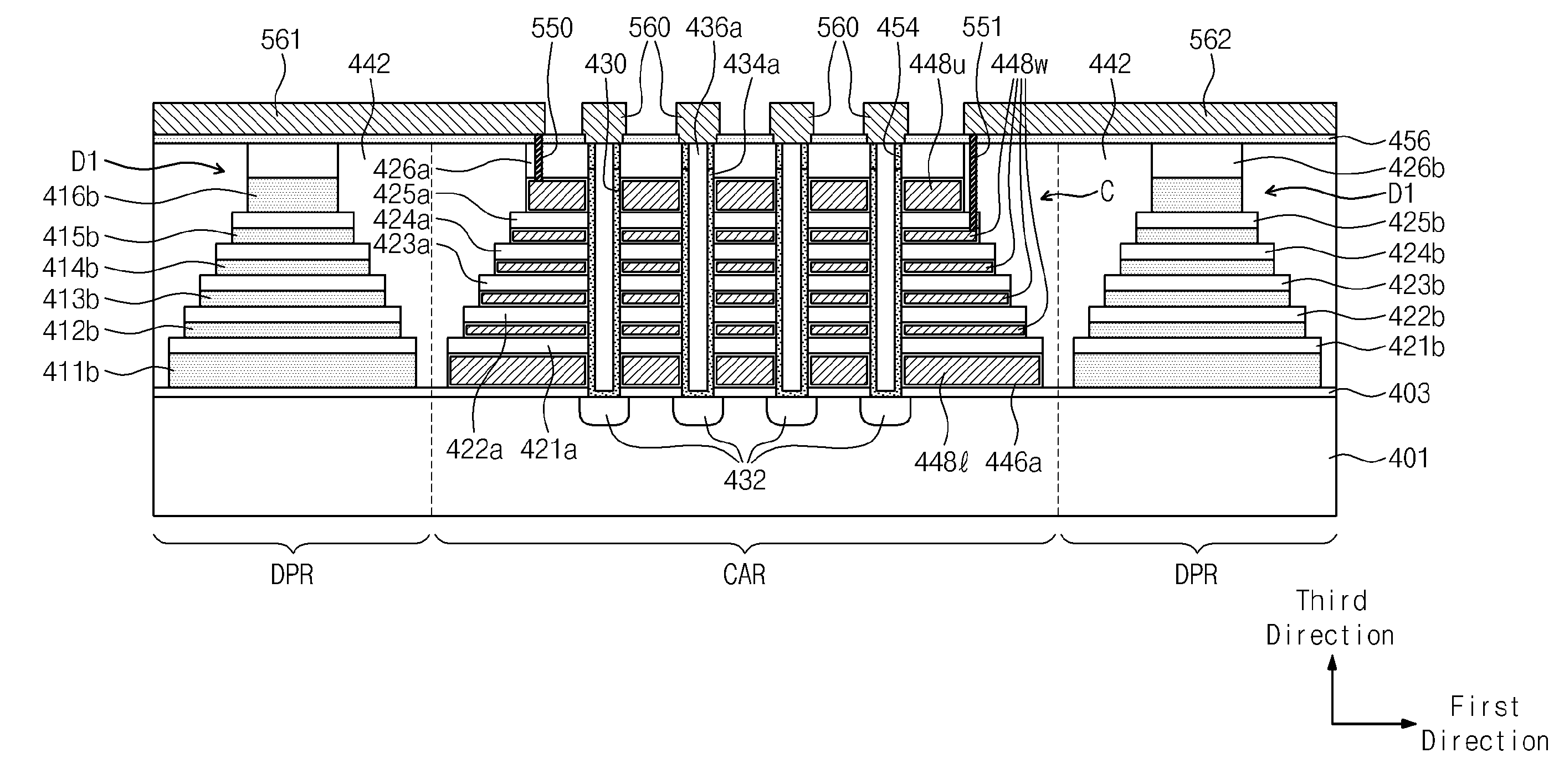

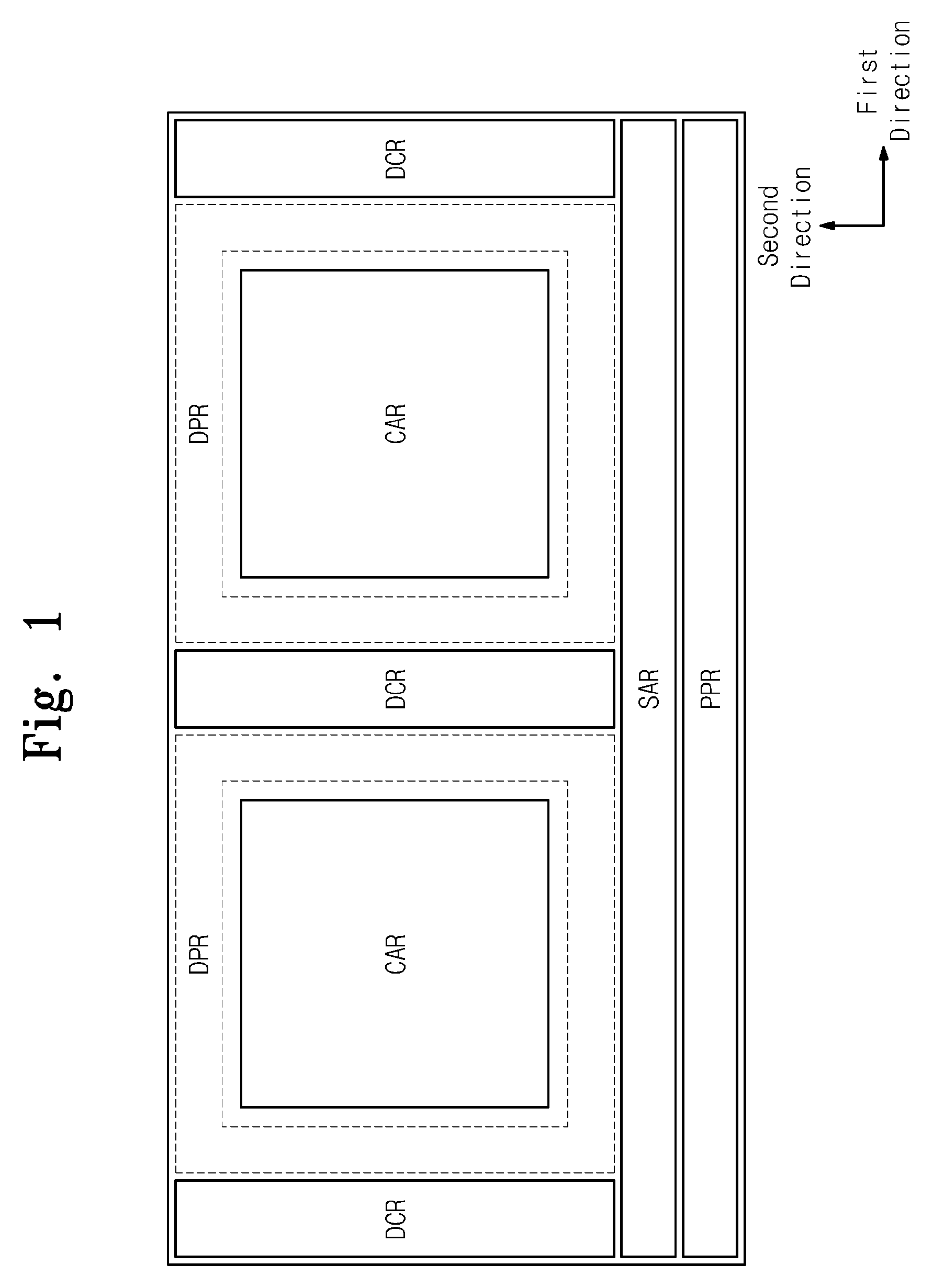

Semiconductor device and method of fabricating the same

A semiconductor device has a substrate that includes a cell array region and a dummy pattern region surrounding the cell array region. The cell array region includes a cell structure having a plurality of cell active pillars extending in a vertical direction from the cell array region of the substrate and includes cell gate patterns and cell gate interlayer insulating patterns alternately stacked on the substrate. The cell gate patterns and cell gate interlayer insulating patterns have sides facing the cell active pillars. The dummy pattern region includes a damp-proof structure.

Owner:SAMSUNG ELECTRONICS CO LTD

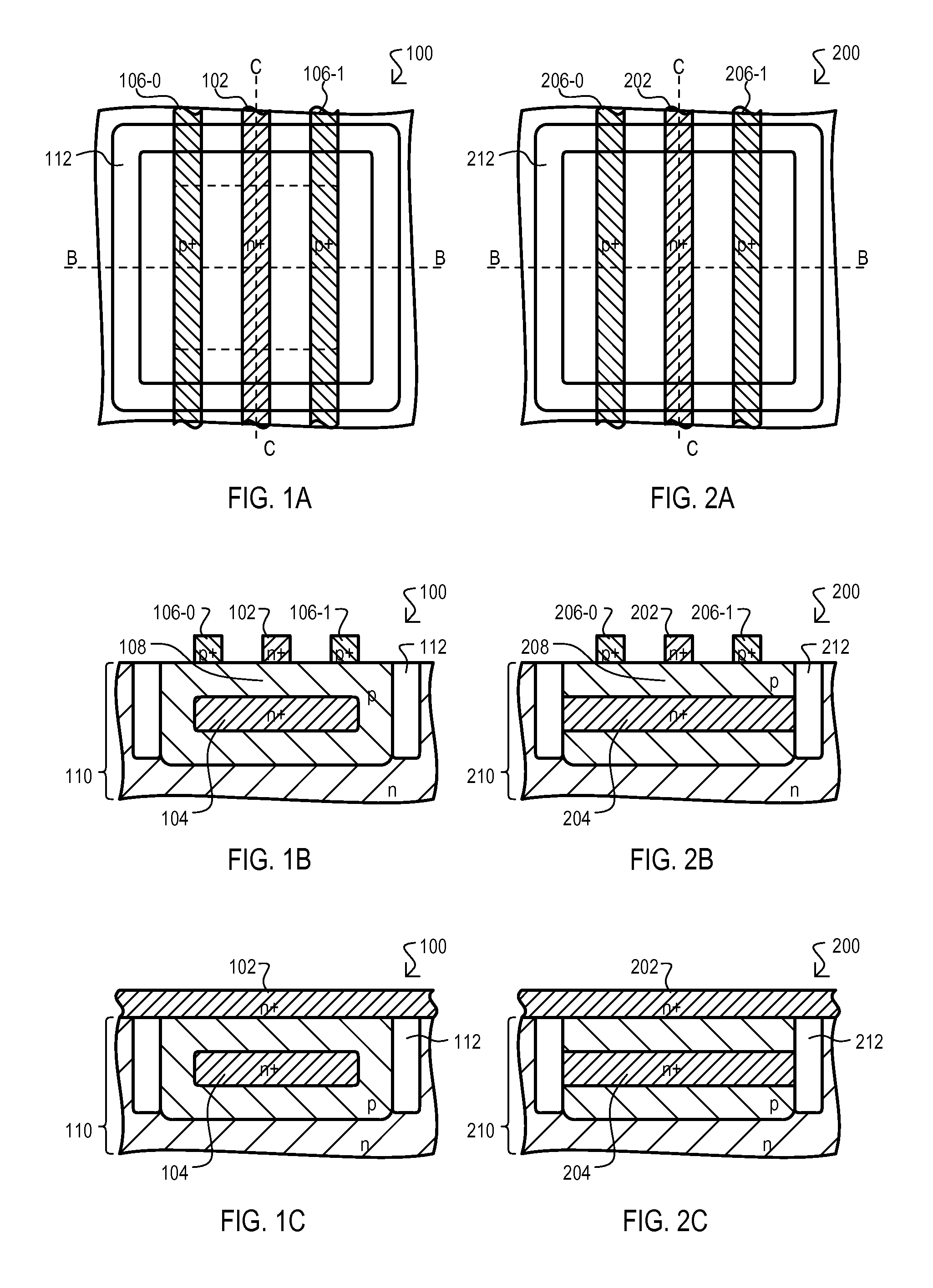

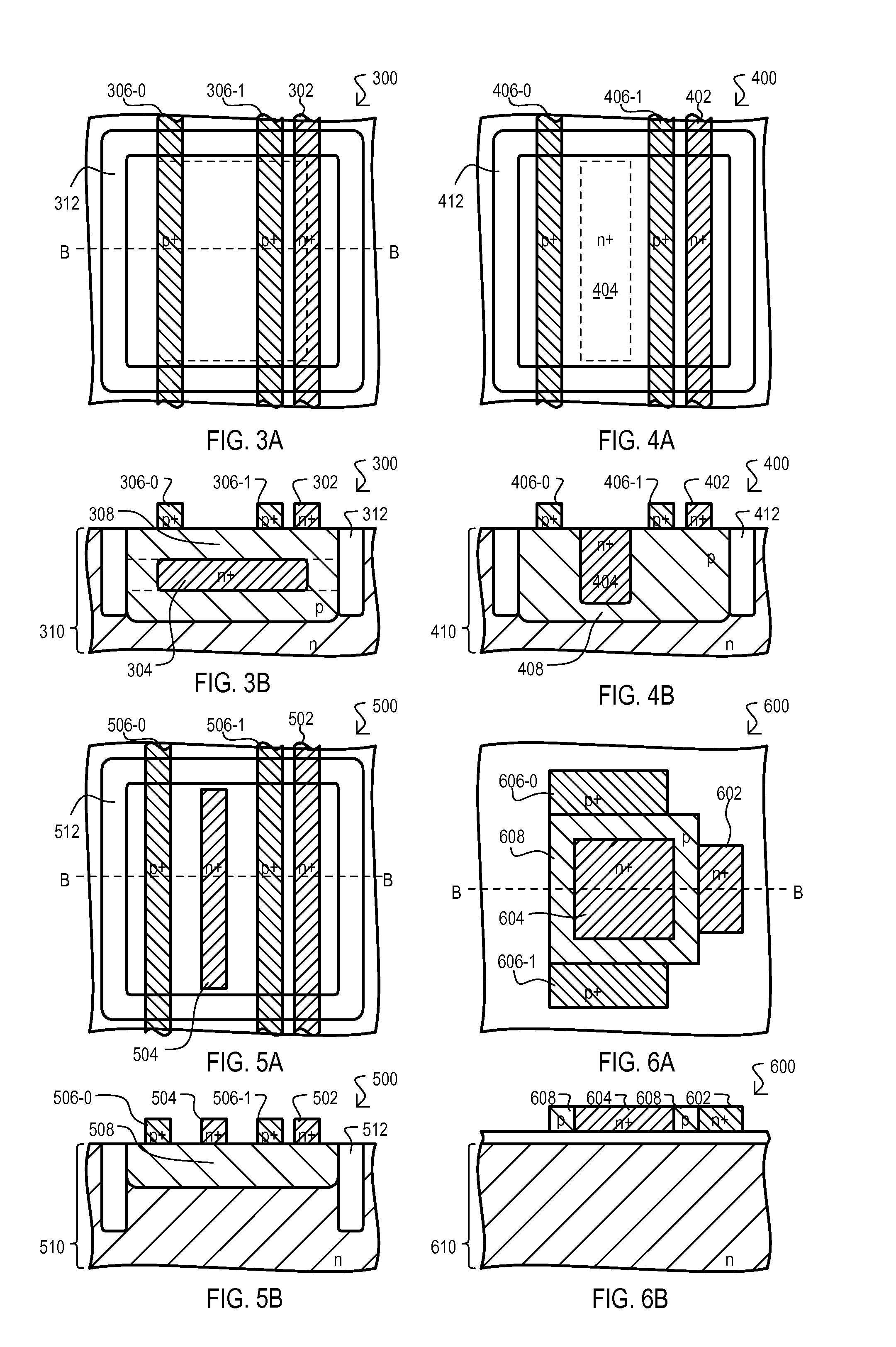

Semiconductor device storage cell structure, method of operation, and method of manufacture

A method of fabricating an integrated circuit device storage cell may include forming a channel region comprising a semiconductor material doped to a first conductivity type; forming a store gate structure comprising a semiconductor material doped to a second conductivity type in contact with the channel region; and forming a control gate terminal from at least a portion of a semiconductor layer deposited on a substrate surface in contact with the channel region, the portion of the semiconductor layer being doped to the second conductivity type.

Owner:SUVOLTA

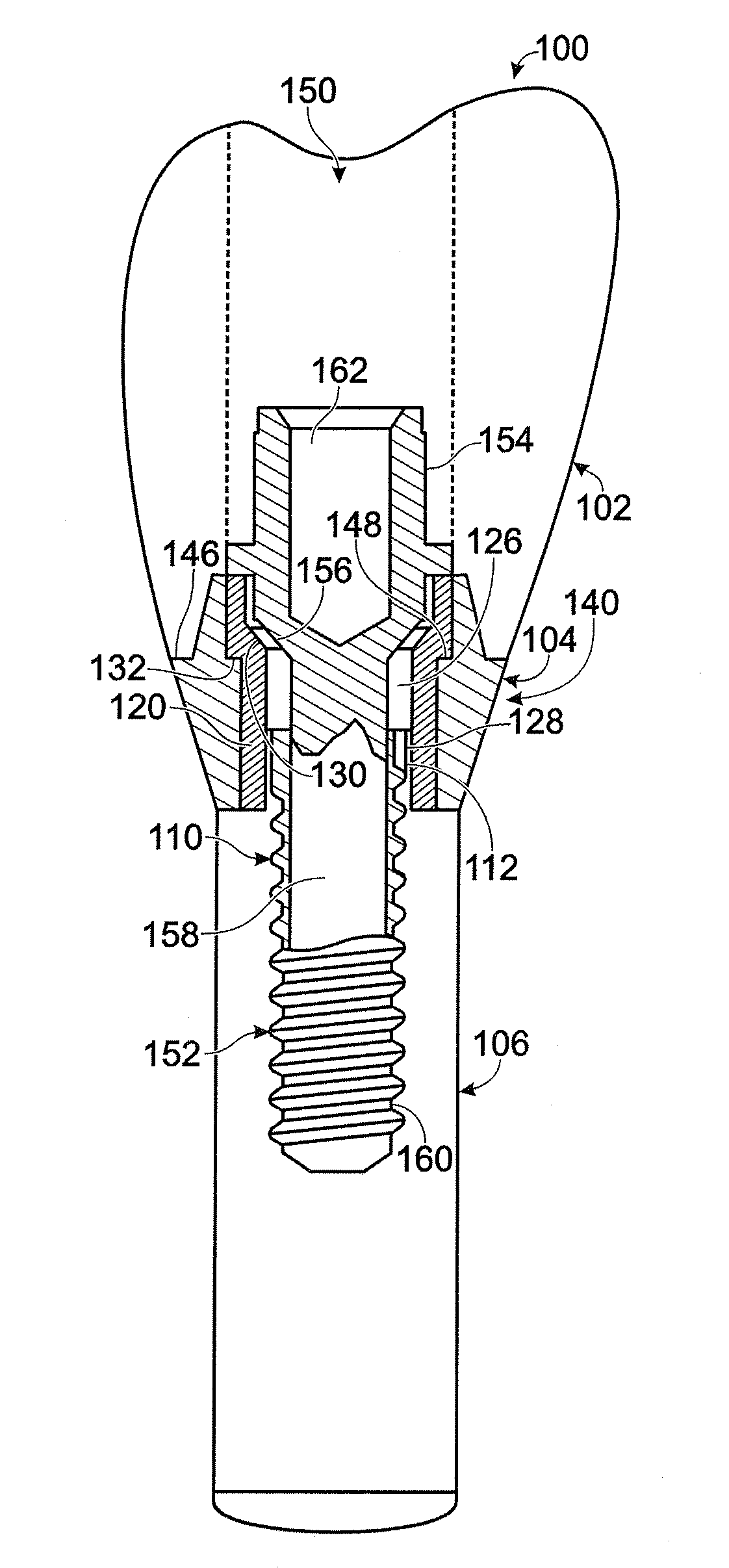

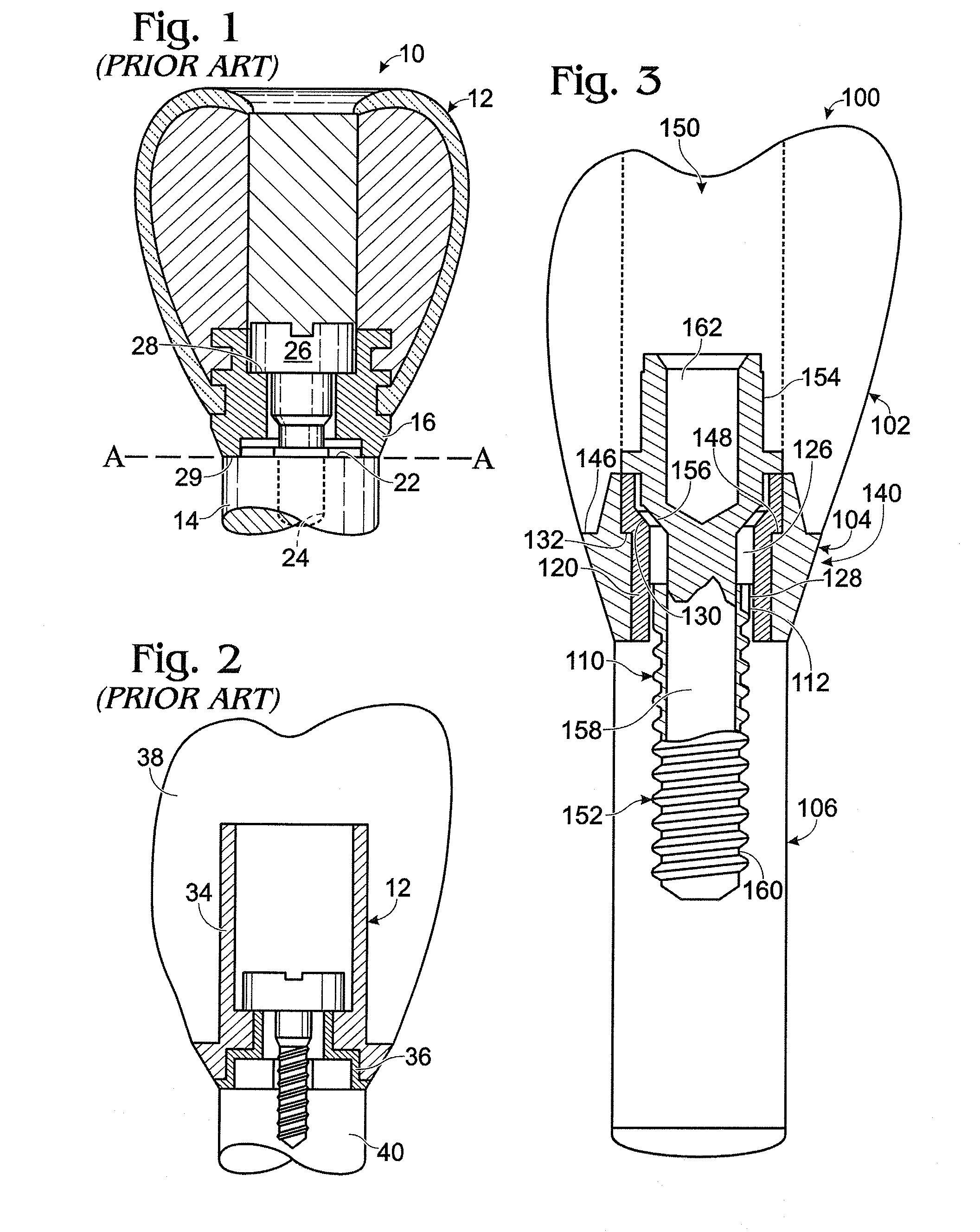

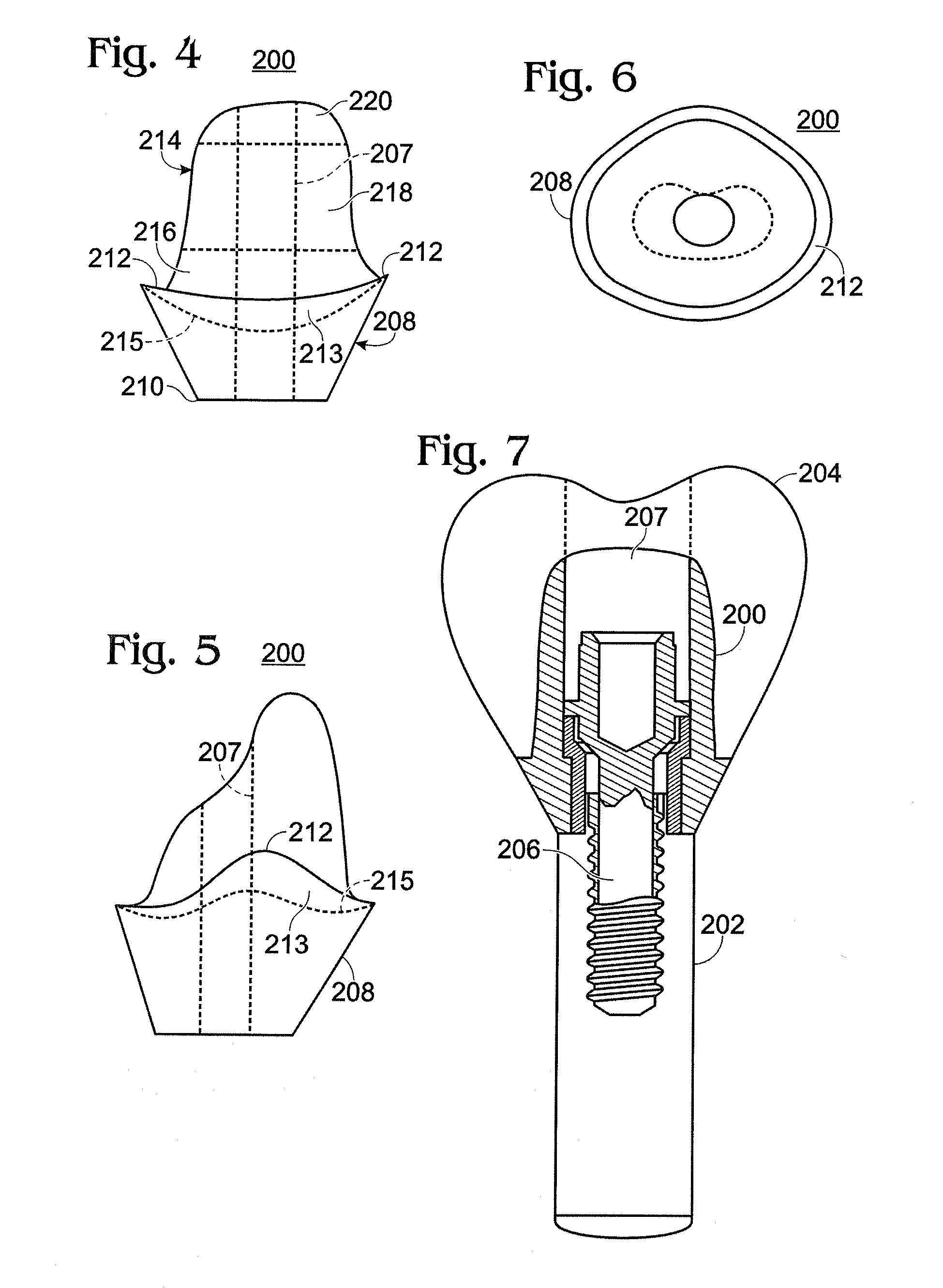

Dental Implant Abutment

A dental implant abutment for attaching a dental prosthesis within a patient's mouth. The abutment is a single unit structure fabricated of a ceramic material, multicolored throughout to match the color of the dental prosthesis, the surrounding dentition and the surrounding gingival tissue.

Owner:IVOCLAR VIVADENT AG

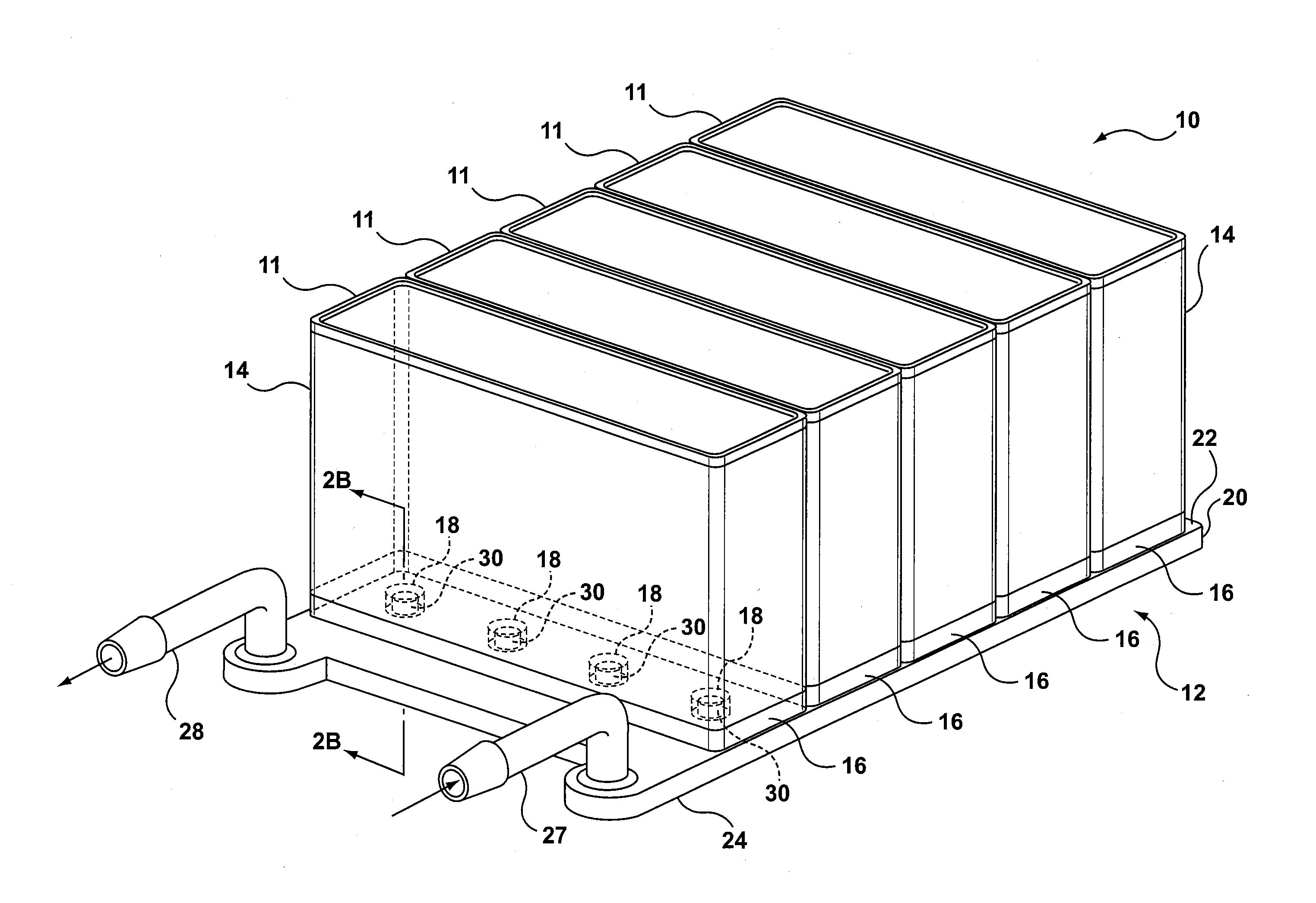

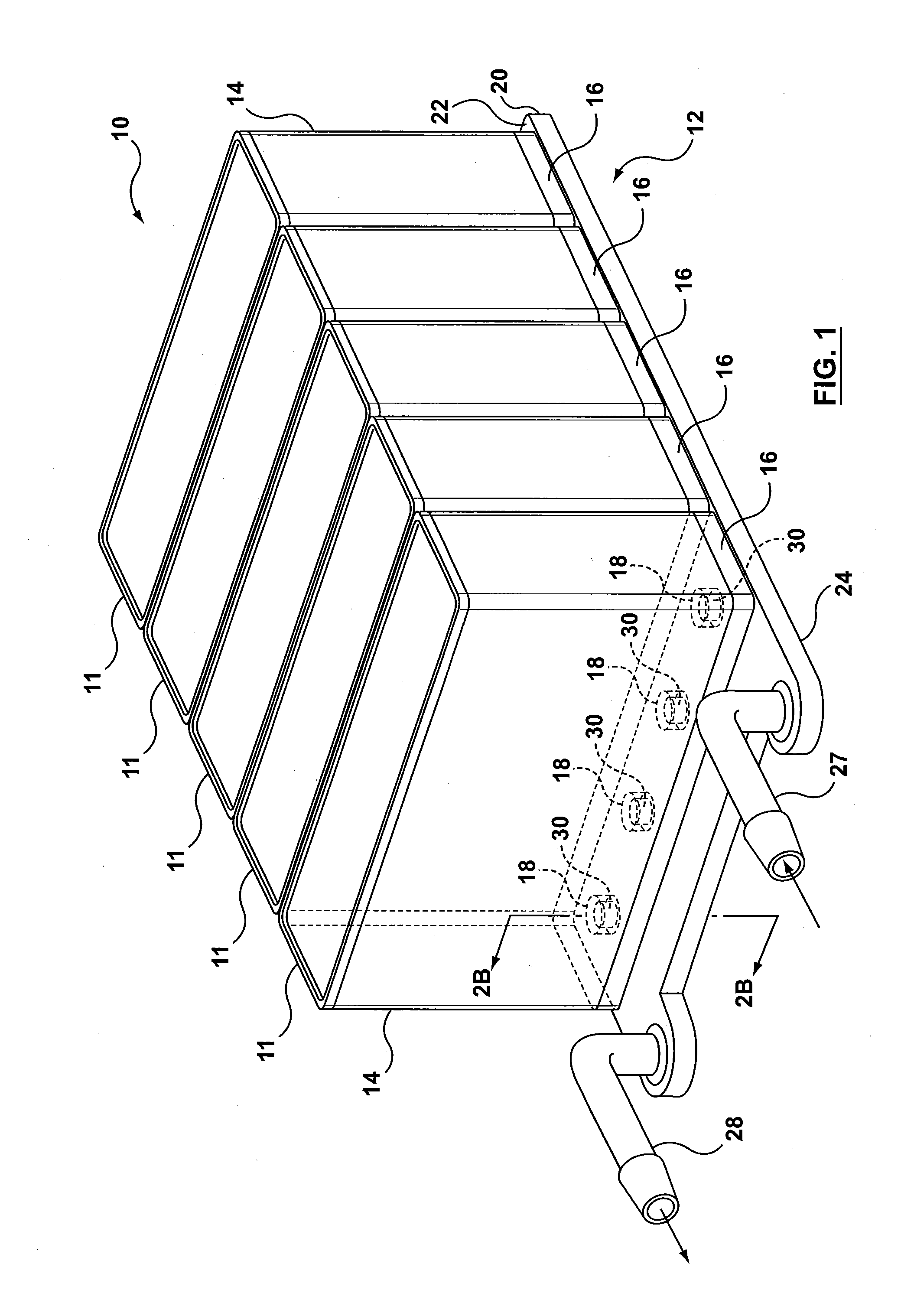

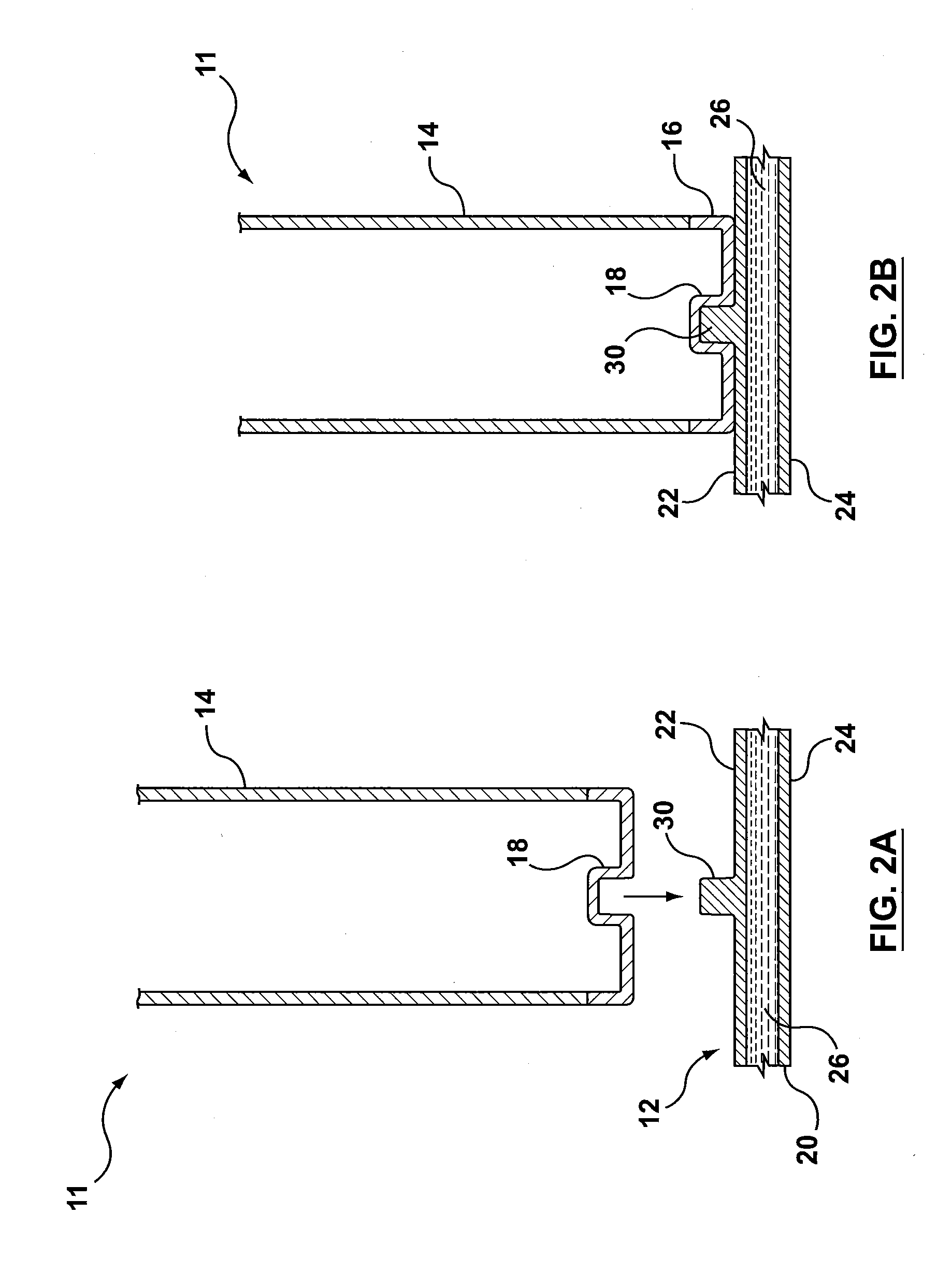

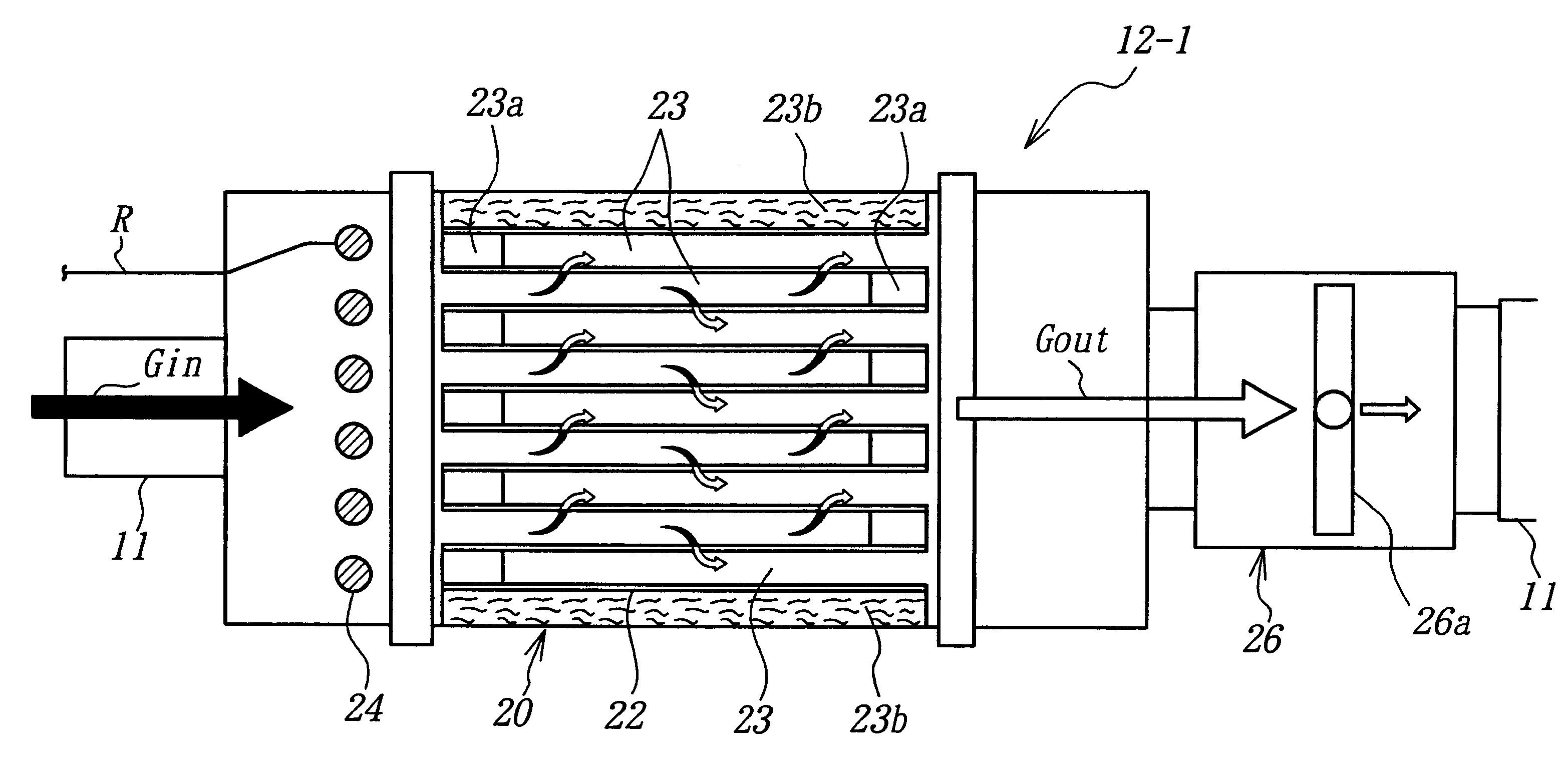

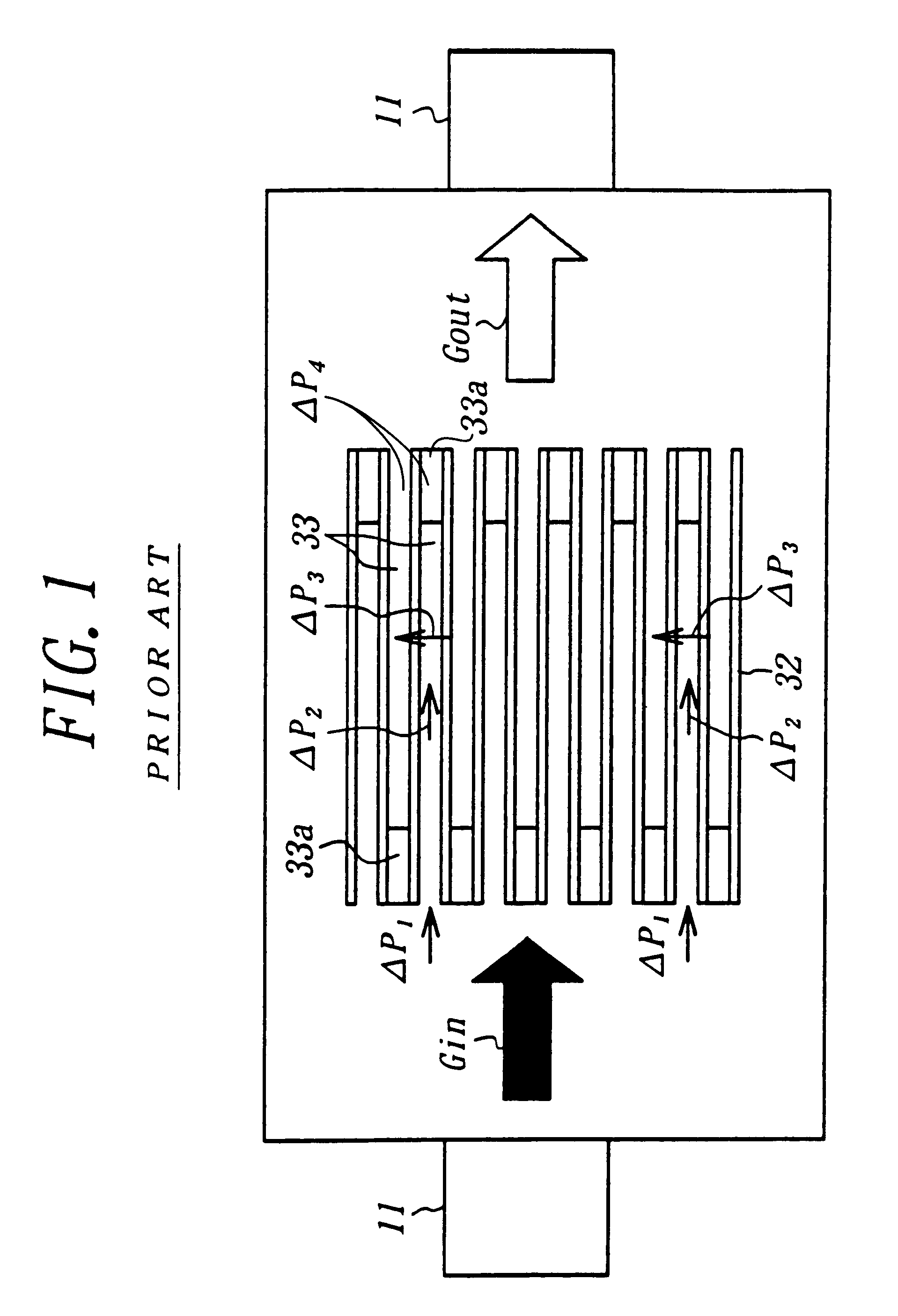

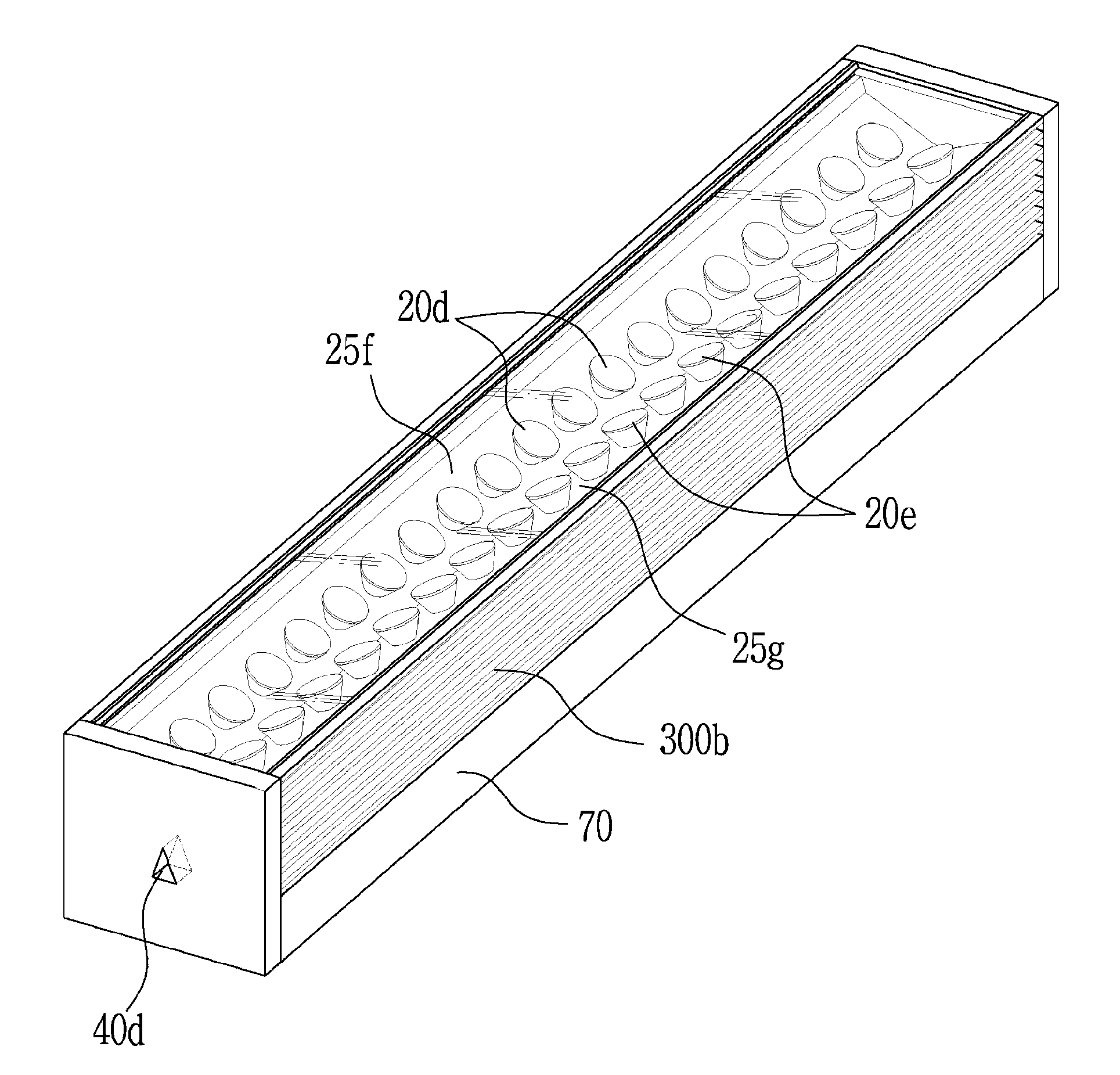

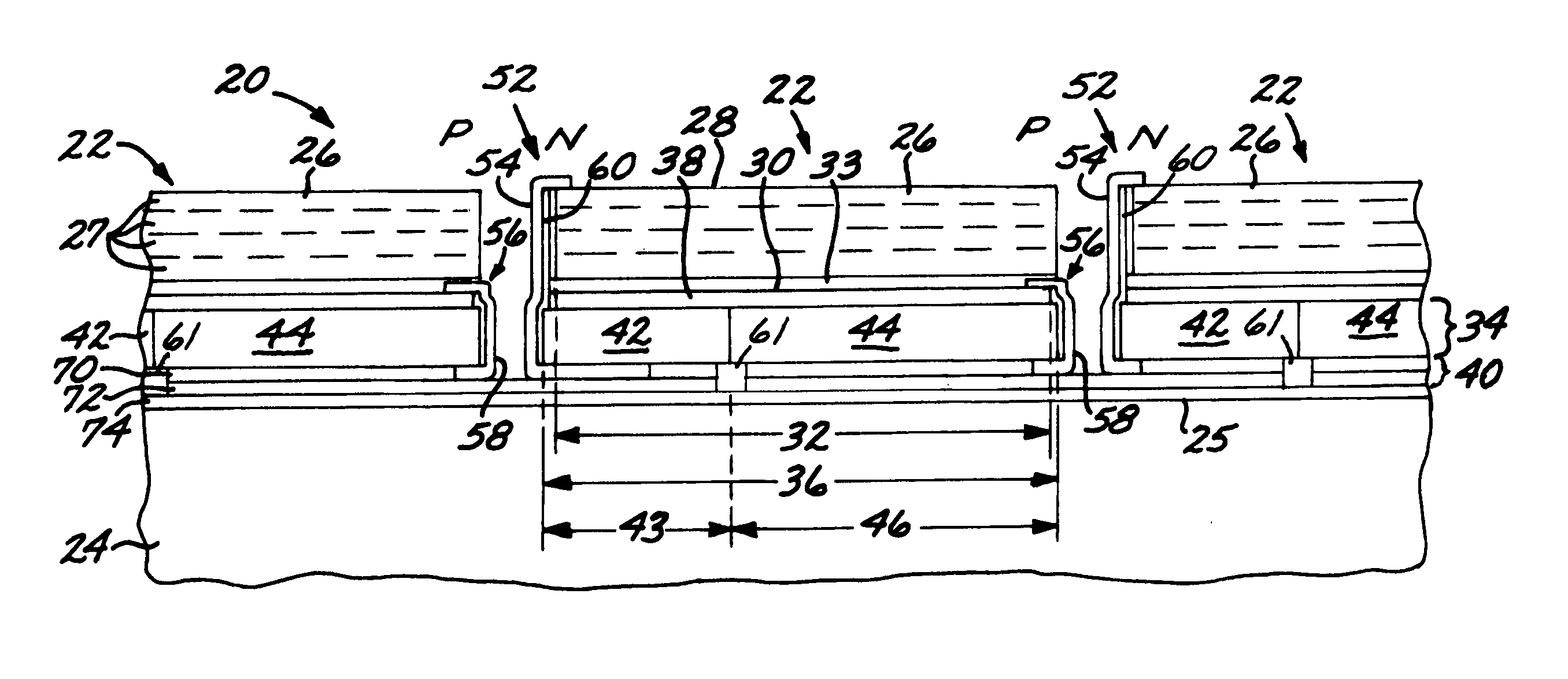

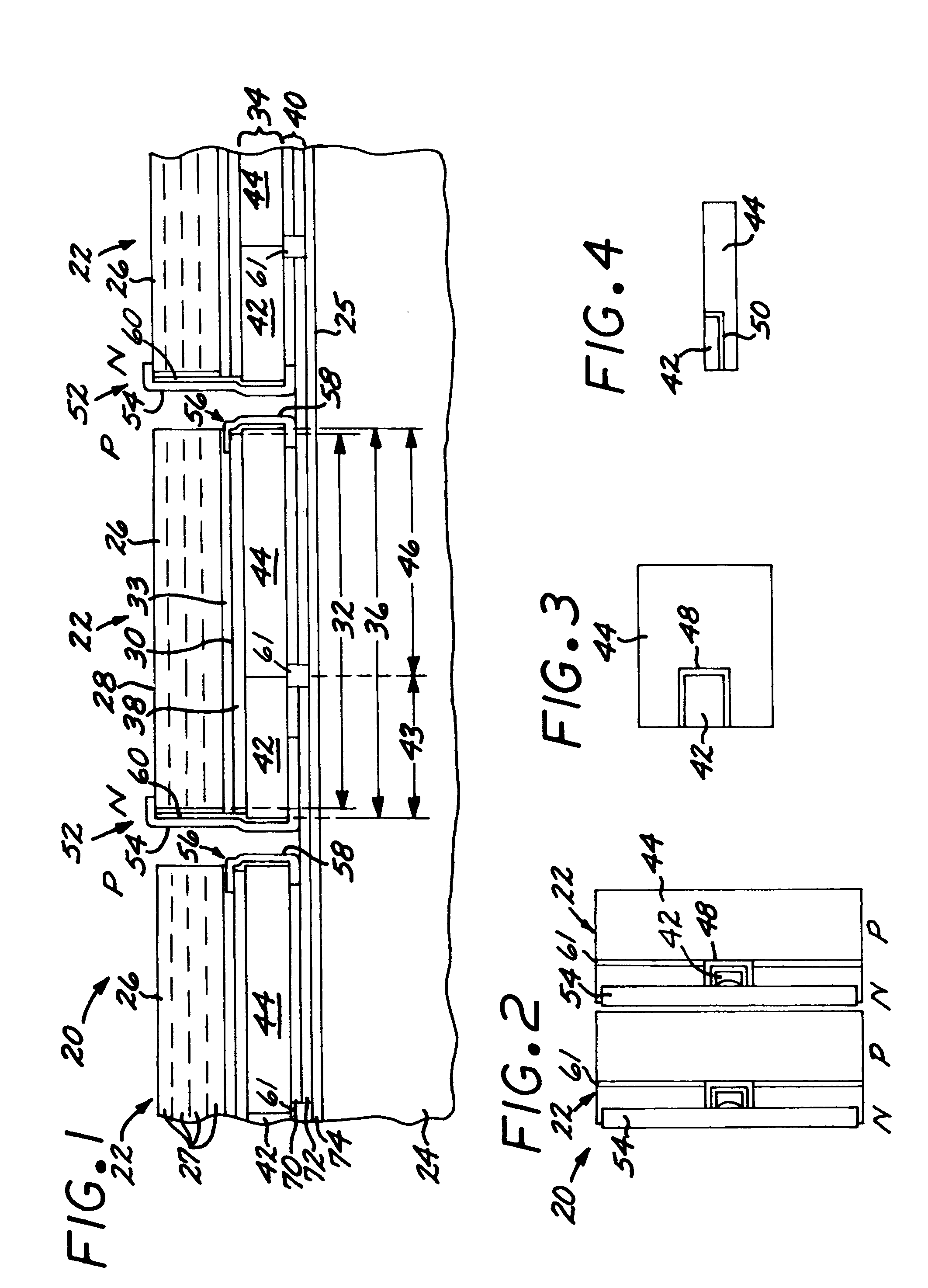

Heat Exchanger and Battery Unit Structure for Cooling Thermally Conductive Batteries

A heat exchanger and battery unit structure is provided for cooling battery units (or cells) where the thermally conductive nature of the battery forms a cooling path. The heat exchanger is in the form of a cooling element provided with an engaging device formed on or attached to an outer surface of the cooling plate for receiving and / or engaging with a corresponding engaging portion on a battery unit (or cell). The interconnection between the battery unit (or cell) and heat exchanger creates a mechanical interlock between the two components that results in improved heat transfer properties between the two components.

Owner:DANA CANADA CORP

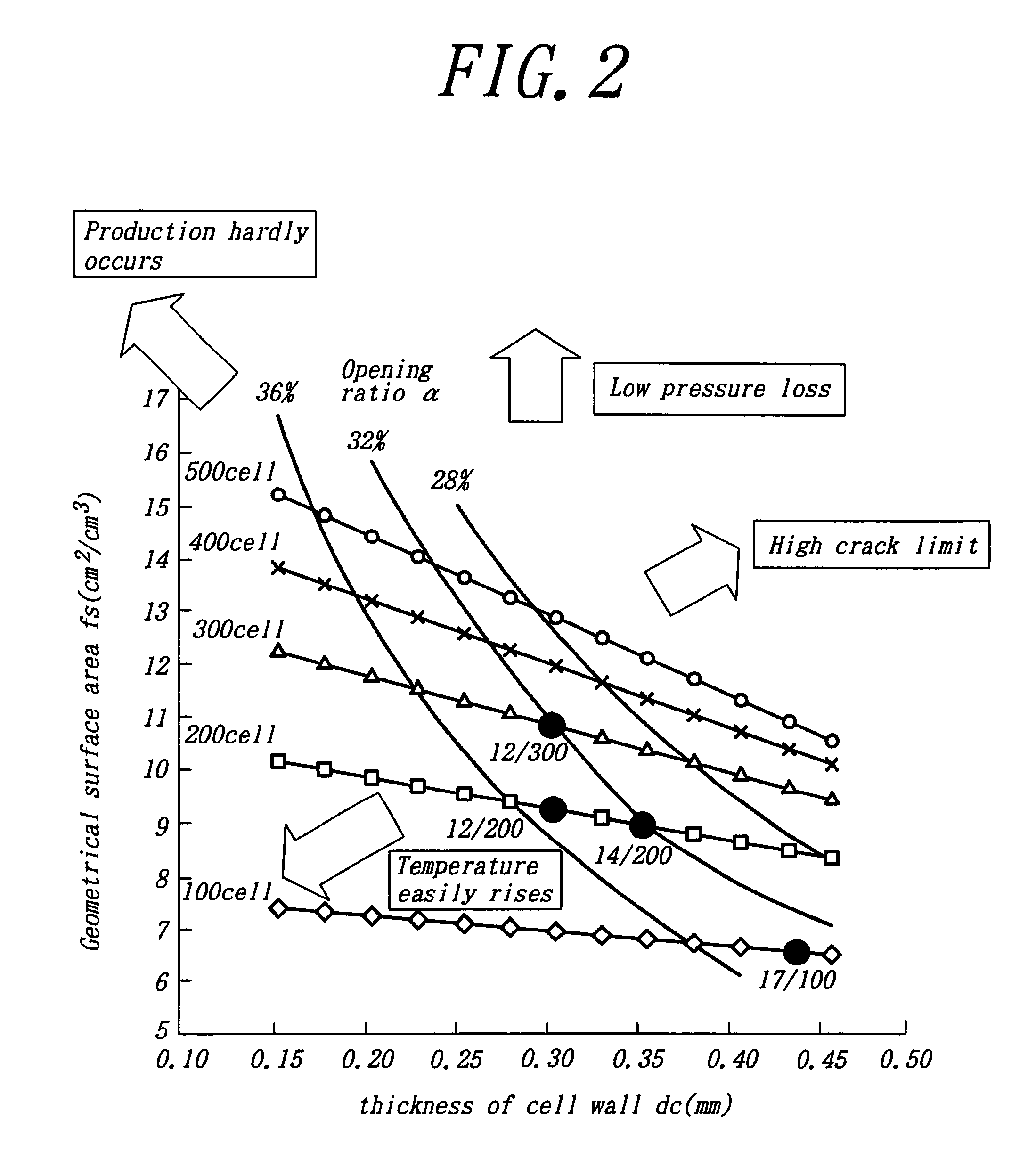

Regeneration system for an exhaust gas cleaning device

A regeneration system for an exhaust gas cleaning device disposed in an exhaust emission path of an internal combustion engine has an exhaust gas cleaning honeycomb filter and a heating element for the filter, wherein the filter is a checkered SiC honeycomb filter having a given cell structure, and the heating element is a heater or a glow plug when using a fuel containing fuel additive.

Owner:IBIDEN CO LTD

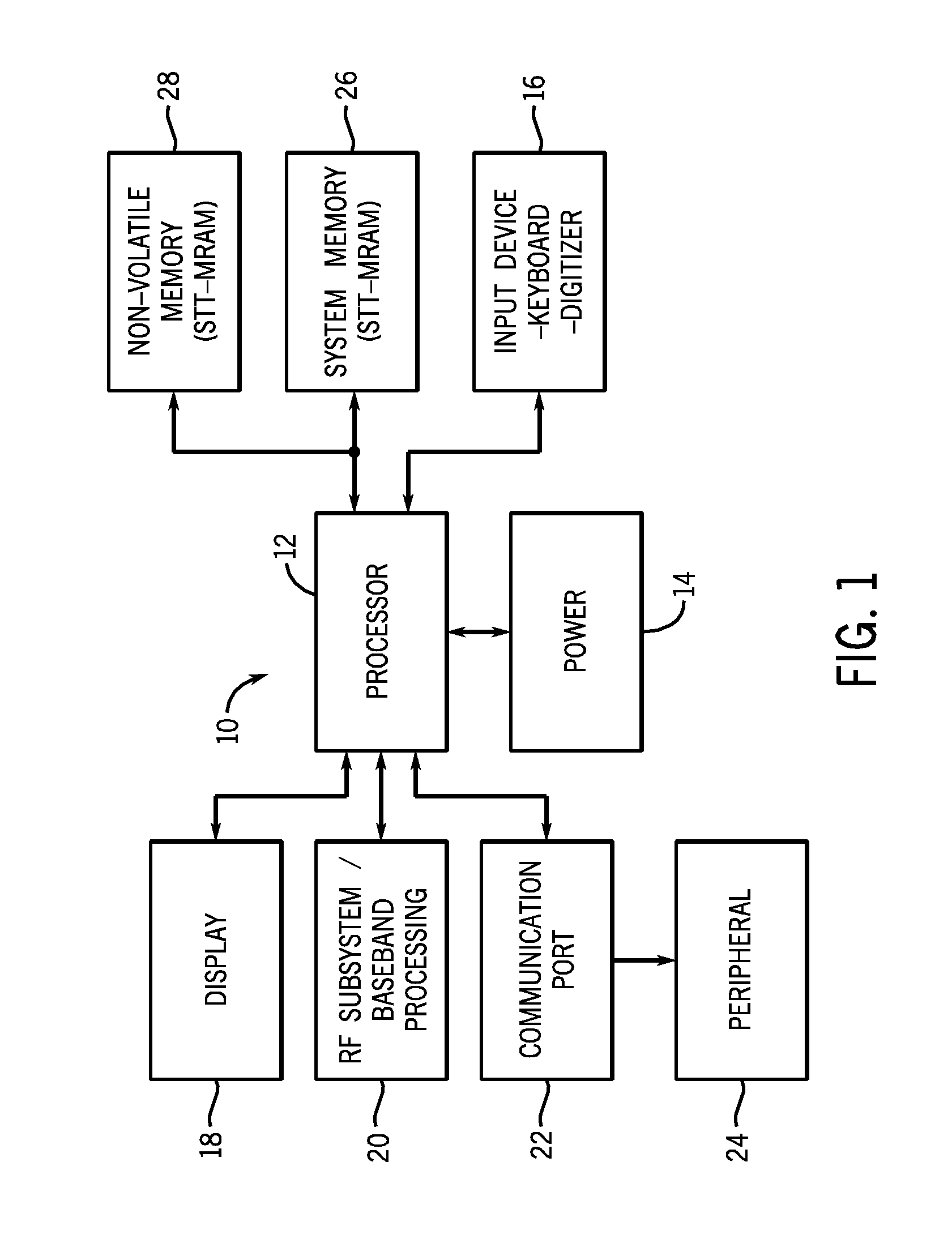

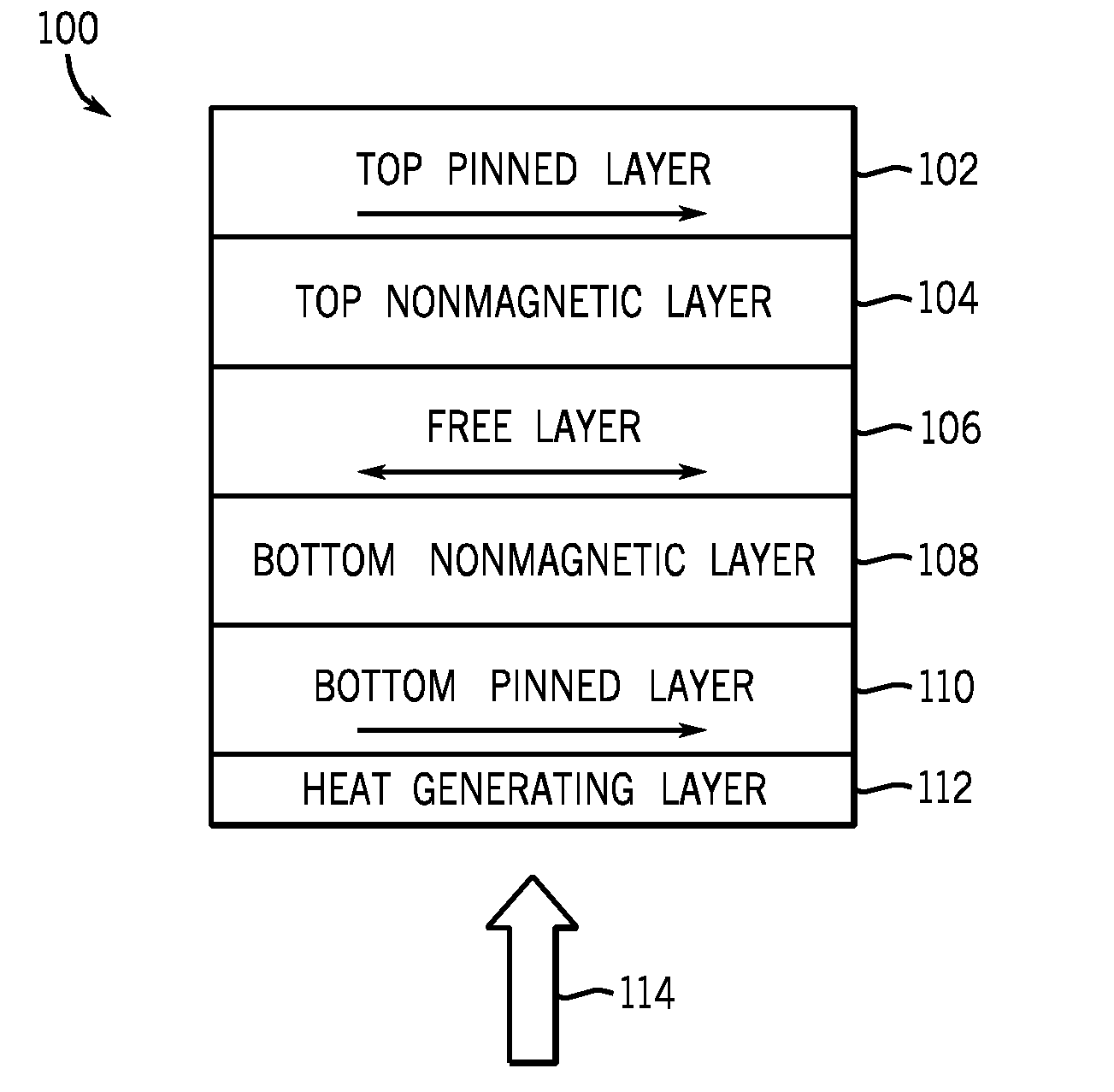

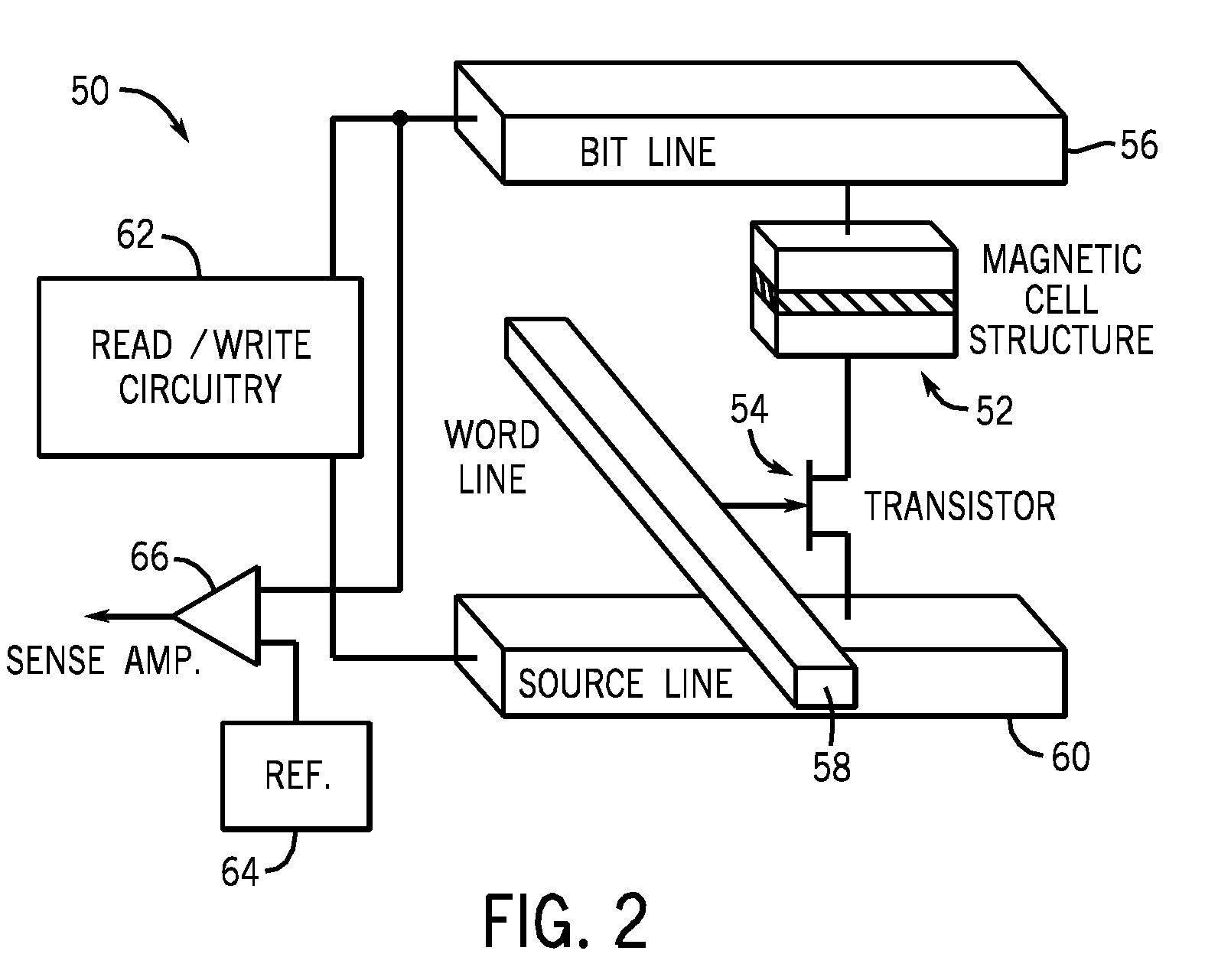

Spin torque transfer cell structure utilizing field-induced antiferromagnetic or ferromagnetic coupling

A magnetic memory cell including a soft magnetic layer and a coupling layer, and methods of operating the memory cell are provided. The memory cell includes a stack with a free ferromagnetic layer and a pinned ferromagnetic layer, and a soft magnetic layer and a coupling layer may also be formed as layers in the stack. The coupling layer may cause antiferromagnetic coupling to induce the free ferromagnetic layer to be magnetized in a direction antiparallel to the magnetization of the soft magnetic layer, or the coupling layer may cause ferromagnetic coupling to induce the free ferromagnetic layer to be magnetized in a direction parallel to the magnetization of the soft magnetic layer. The coupling layer, through a coupling effect, reduces the critical switching current of the memory cell.

Owner:OVONYX MEMORY TECH LLC

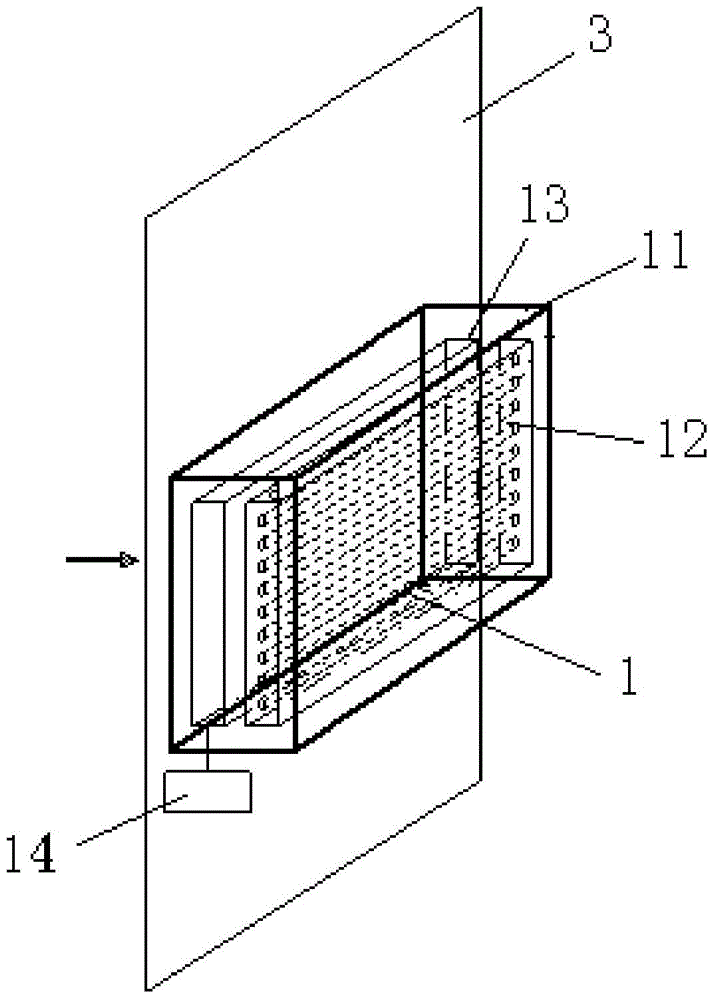

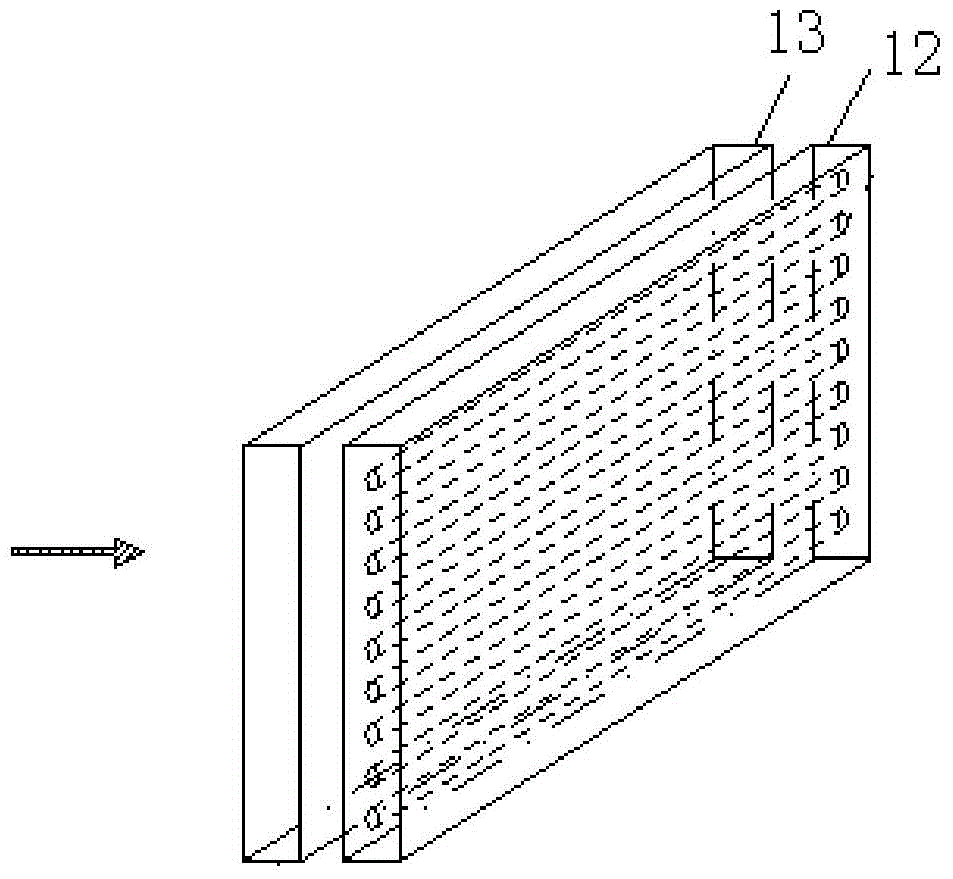

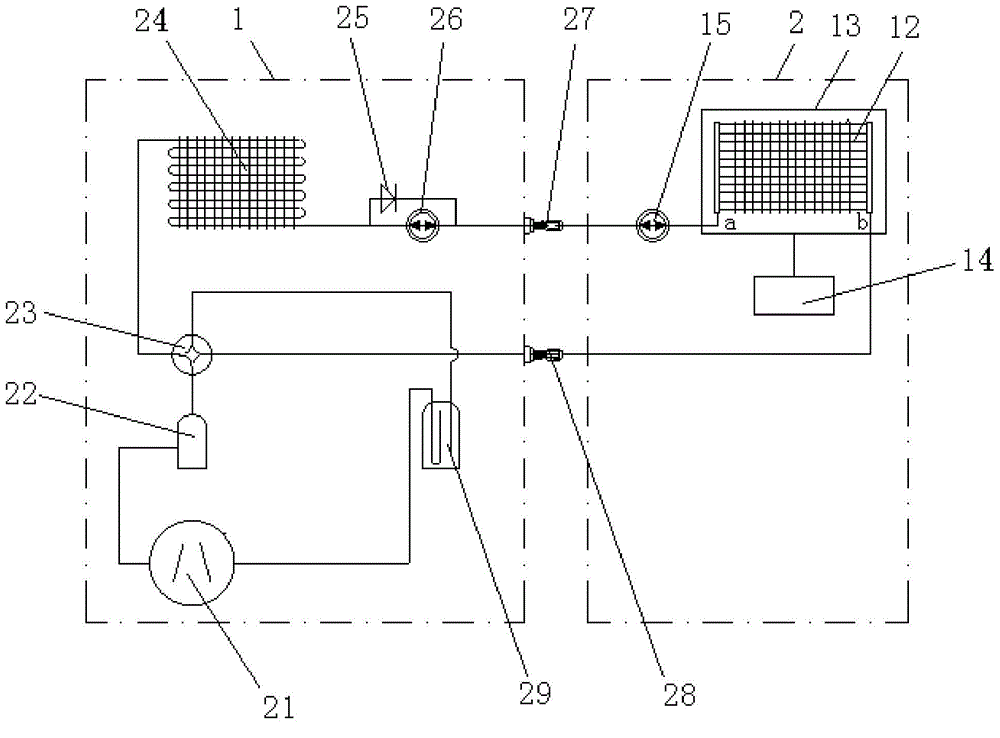

Ion wind indoor unit, ion wind air conditioner system and control method

InactiveCN105299744AReduce noiseSimple structureSpace heating and ventilation safety systemsLighting and heating apparatusEngineeringConvection heat

The invention discloses an ion wind indoor unit, an ion wind air conditioner system and a control method, and relates to the technical field of refrigerating and heating equipment. In order to solve the problems that an existing air conditioner indoor unit is large in occupation size, large in noise and the like, the ion wind indoor unit is designed. The ion wind indoor unit comprises a shell and an indoor heat exchanger arranged in the shell; an ion wind generator is arranged on the upwind side and / or downwind side of the indoor heat exchanger, and carries out corona on air entering the interior of the generator to generate ion wind and blow out the iron wind so as to achieve convection heat exchange of indoor air; and meanwhile, the ion wind air conditioner system with the ion wind indoor unit and the control method of the air conditioner system are provided. The ion wind indoor unit can reduce the starting noise of air and eliminate electromagnetic noise of a motor and vibration noise of a structural part; use comfort is greatly improved; and meanwhile, the indoor unit structure is simplified, the occupied size of the indoor unit is reduced, the attractiveness of the indoor unit is improved, and the production cost and the assembling cost are reduced.

Owner:QINGDAO HAIER AIR CONDITIONING ELECTRONICS CO LTD

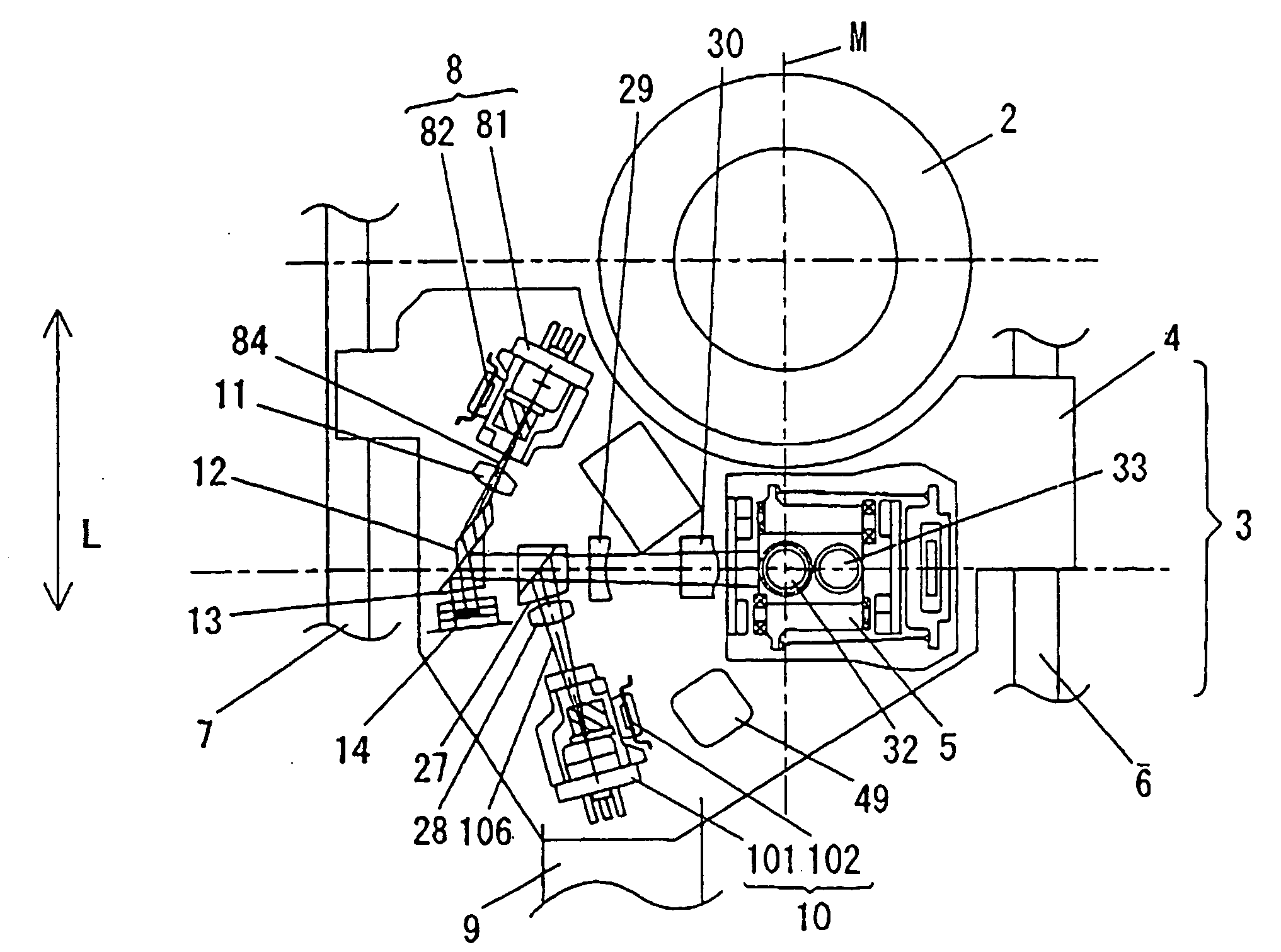

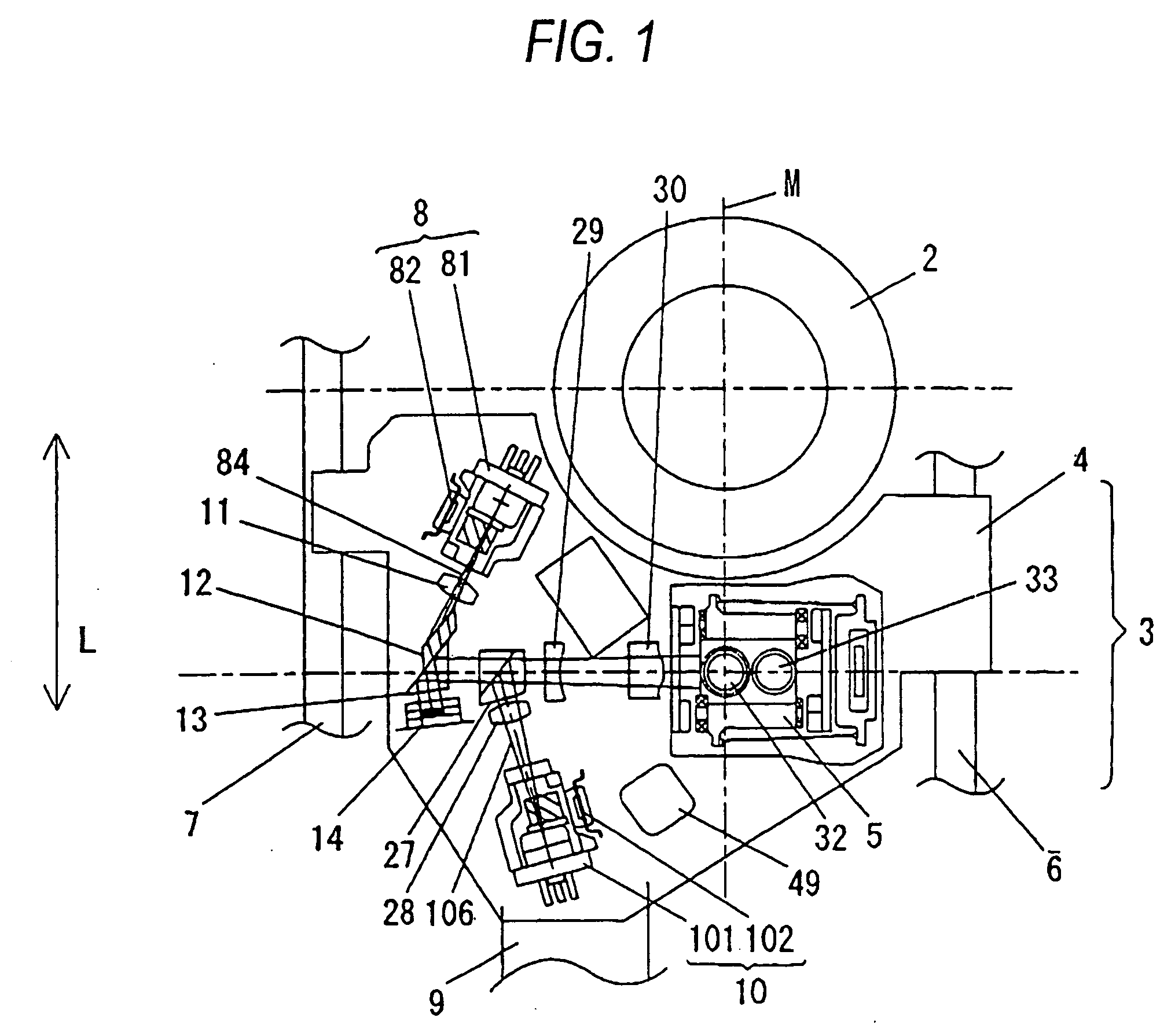

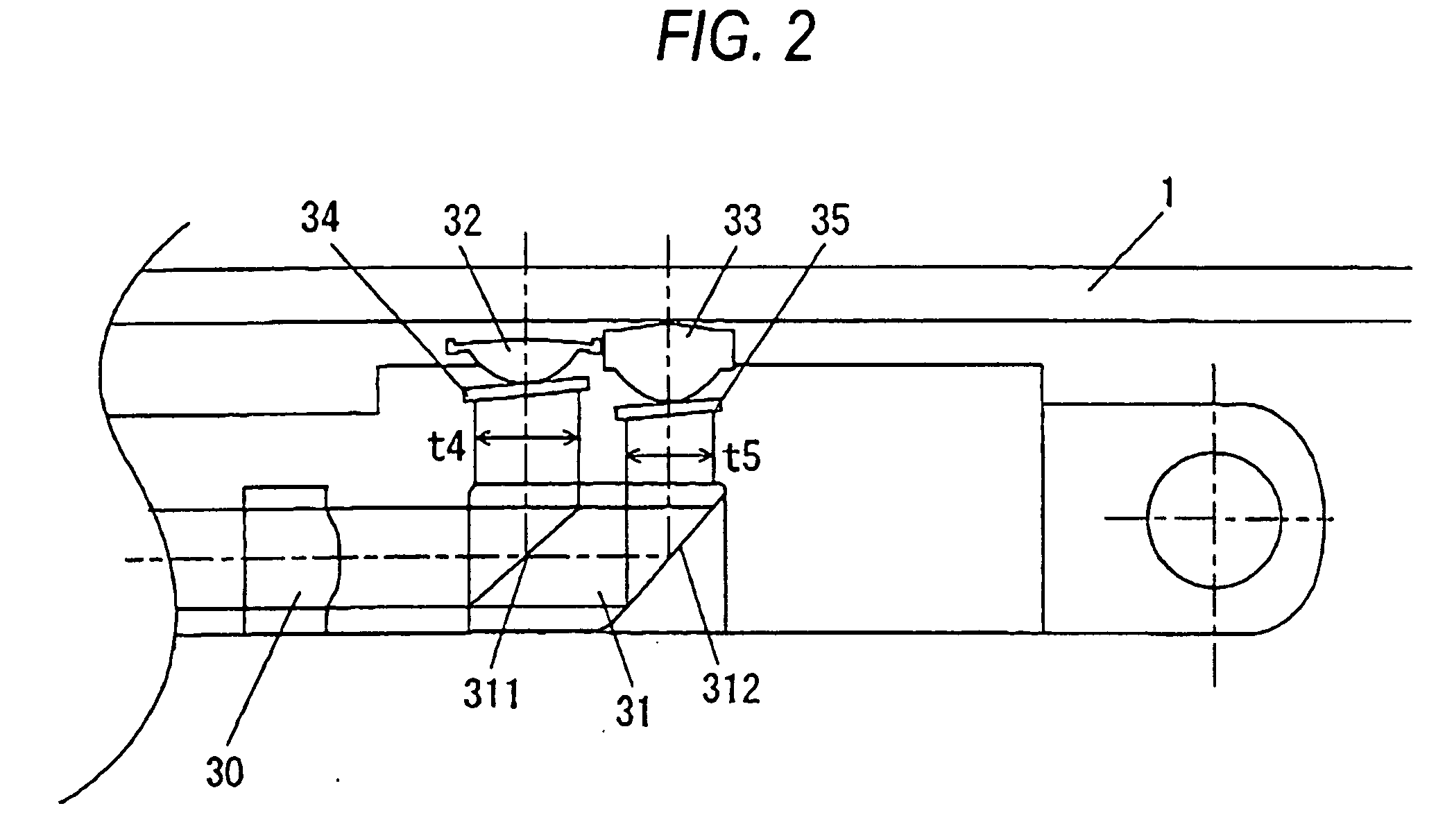

Objective lens, optical pick-up device, and optical disk device

InactiveUS20050007906A1Reduce thicknessSmall sizeOptical head protectionIntegrated optical head arrangementsOptical pickupMiniaturization

To provide an optical pickup device and optical disk device capable of realizing at least one of thickness reduction, size reduction and suppression against characteristic deterioration even where coping with various wavelengths of laser including a blue laser. An optical pickup device comprising light sources for respectively emitting a plurality of different wavelengths of light, unit structured for causing at least a part of the light emitted from the light sources to pass a same optical path; and focusing unit for focusing the light. The focusing unit includes at least first and second focusing parts, the first focusing part being to focus mainly a wavelength of light different from a wavelength of light to be mainly focused by the second focusing part.

Owner:PANASONIC CORP

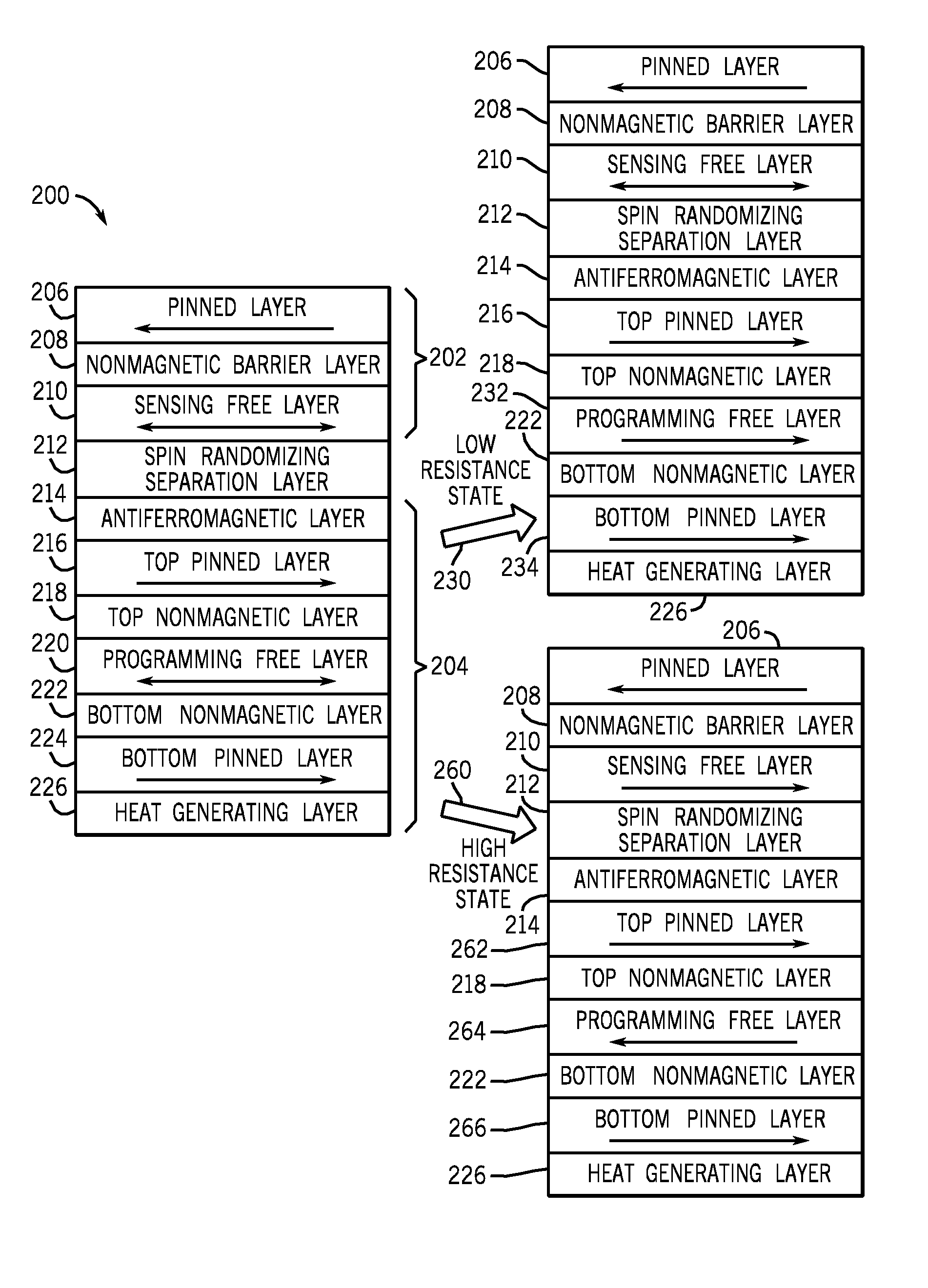

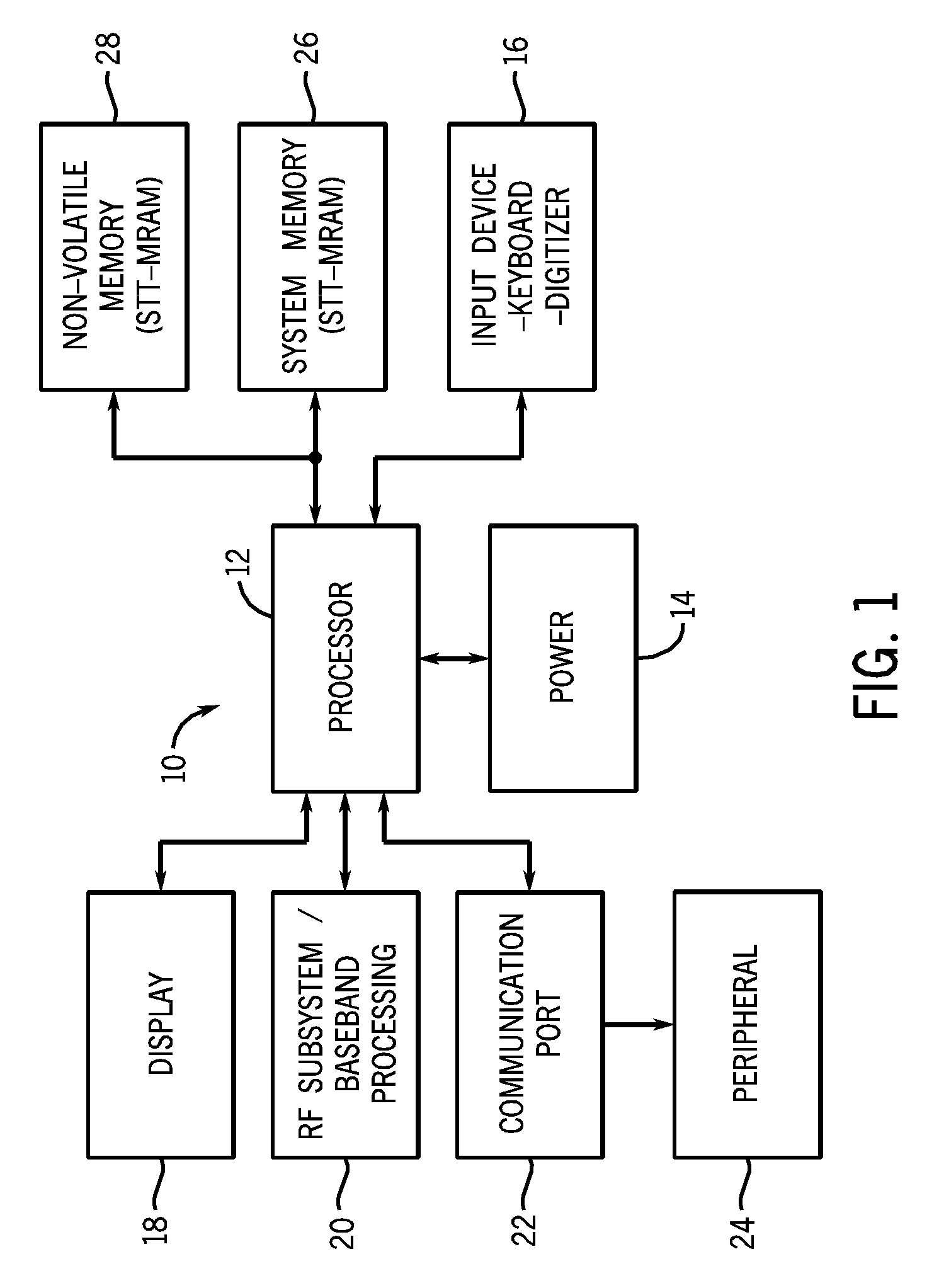

Unidirectional spin torque transfer magnetic memory cell structure

ActiveUS20100080036A1Galvano-magnetic device detailsDigital storageRandom access memoryMagnetic memory

Spin torque transfer magnetic random access memory devices configured to be programmed unidirectionally and methods of programming such devices. The devices include memory cells having two pinned layers and a free layer therebetween. By utilizing two pinned layers, the spin torque effect on the free layer from each of the two pinned layers, respectively, allows the memory cells to be programmed with unidirectional currents.

Owner:OVONYX MEMORY TECH LLC

Vertical memory cell for high-density memory

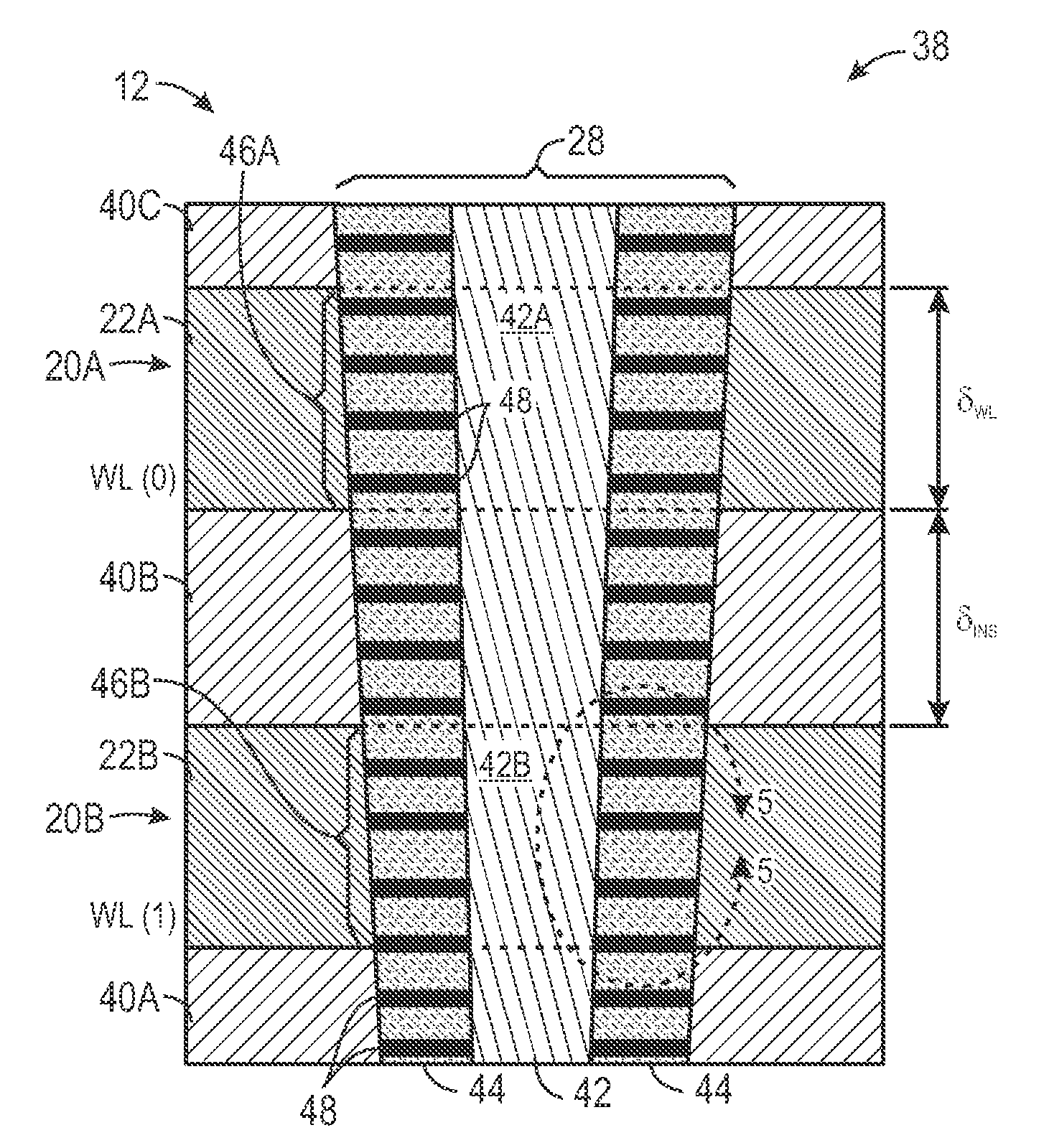

ActiveUS20120261638A1Solid-state devicesBulk negative resistance effect devicesHigh densityUnit structure

This disclosure provides embodiments for the formation of vertical memory cell structures that may be implemented in RRAM devices. In one embodiment, memory cell area may be increased by varying word line height and / or word line interface surface characteristics to ensure the creation of a grain boundary that is suitable for formation of conductive pathways through an active layer of an RRAM memory cell. This may maintain continuum behavior while reducing random cell-to-cell variability that is often encountered at nanoscopic scales. In another embodiment, such vertical memory cell structures may be formed in multiple-tiers to define a three-dimensional RRAM memory array. Further embodiments also provide a spacer pitch-doubled RRAM memory array that integrates vertical memory cell structures.

Owner:MICRON TECH INC

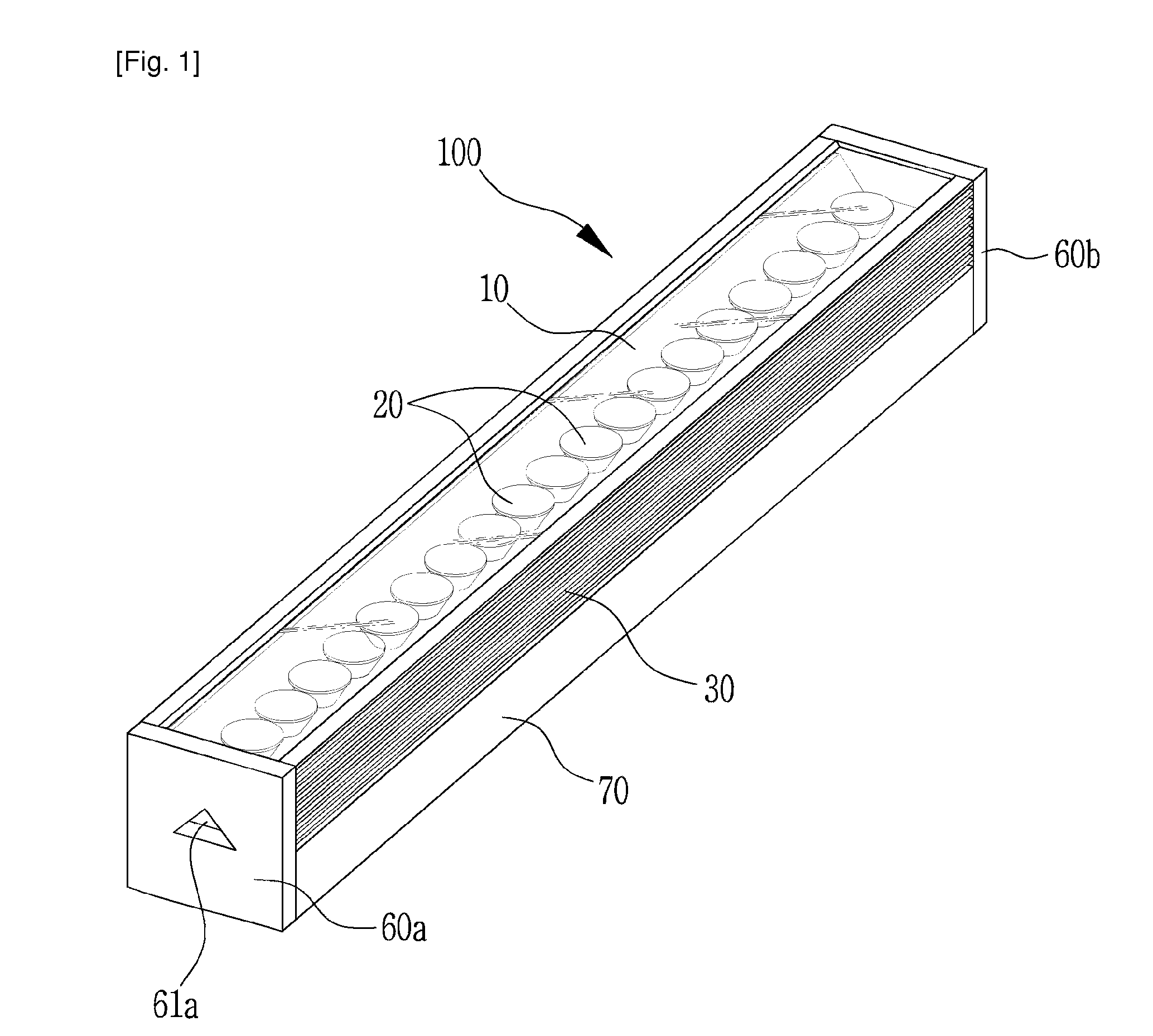

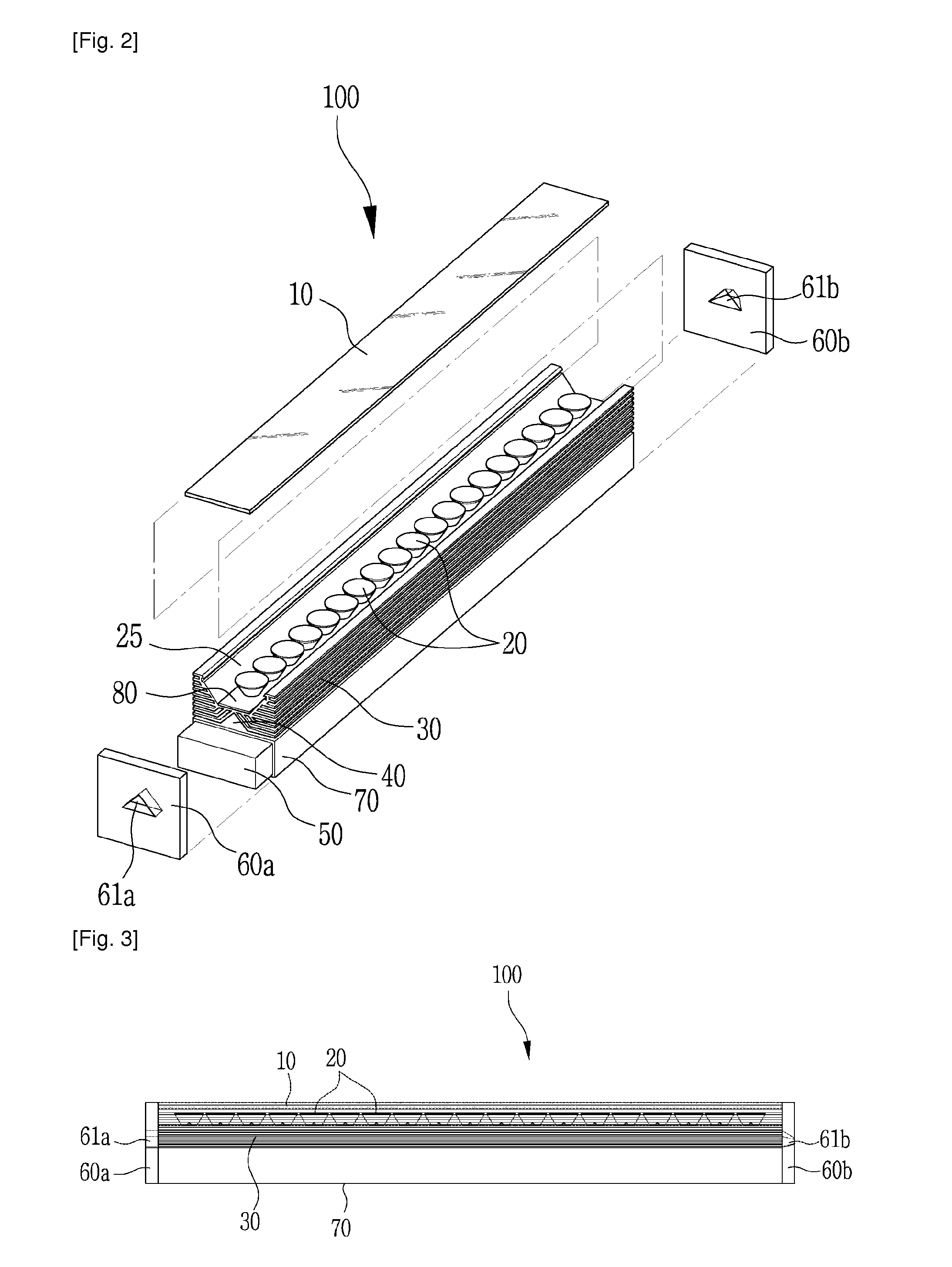

Lighting apparatus using light emitting diodes

ActiveUS20120218757A1Improve cooling effectEasy to implementNon-electric lightingPoint-like light sourceAir cycleAtmospheric air

Provided is a lighting apparatus using light emitting diodes (LEDs) having a lateral heat radiation unit structure that can maximize heat radiation effect by employing an air vent structure causing atmospheric pressure difference between both side ends of an air circulation path. The lighting apparatus comprising a housing having a power supply accommodation space therein, a heat radiation unit that comprises an LED module accommodation groove that is installed on the top of the housing and having at least one inclined surface or mounting surface on which the LED module is mounted, and a number of fins that are formed on the outer circumferential surface of the LED module accommodation groove, an air circulation path that is lengthily formed between the housing and the heat radiation unit.

Owner:AMOLUXE

Unidirectional spin torque transfer magnetic memory cell structure

Spin torque transfer magnetic random access memory devices configured to be programmed unidirectionally and methods of programming such devices. The devices include memory cells having two pinned layers and a free layer therebetween. By utilizing two pinned layers, the spin torque effect on the free layer from each of the two pinned layers, respectively, allows the memory cells to be programmed with unidirectional currents.

Owner:OVONYX MEMORY TECH LLC

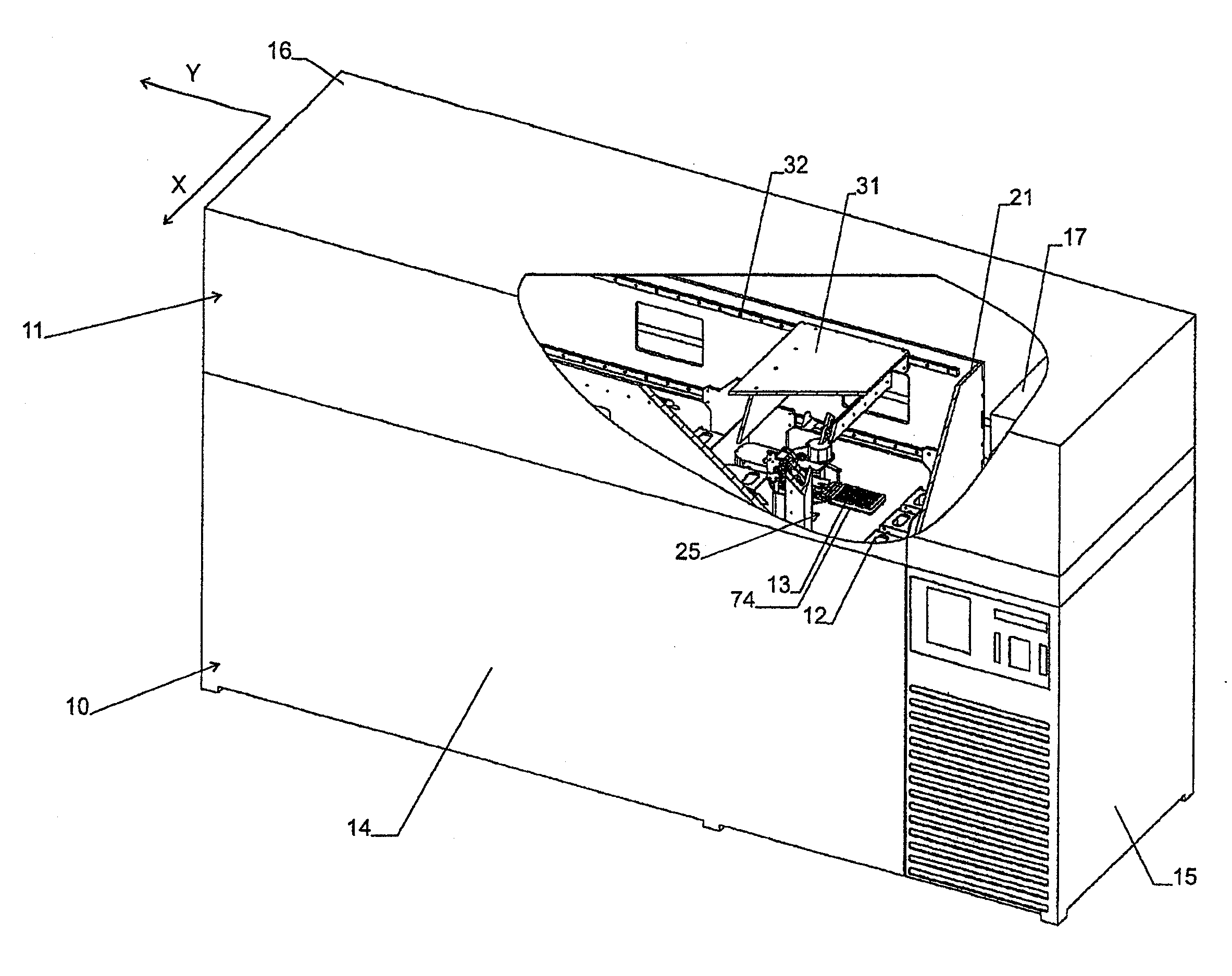

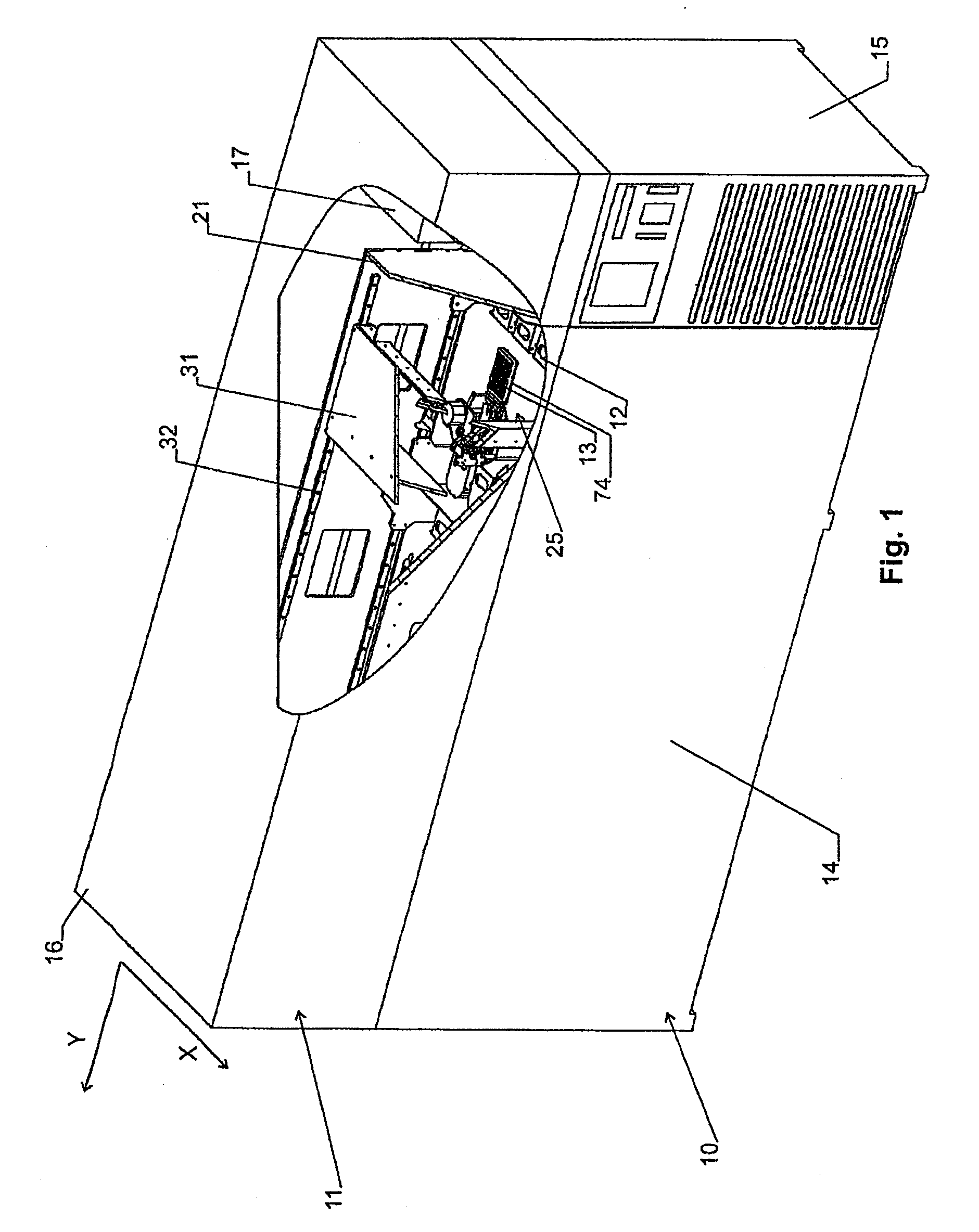

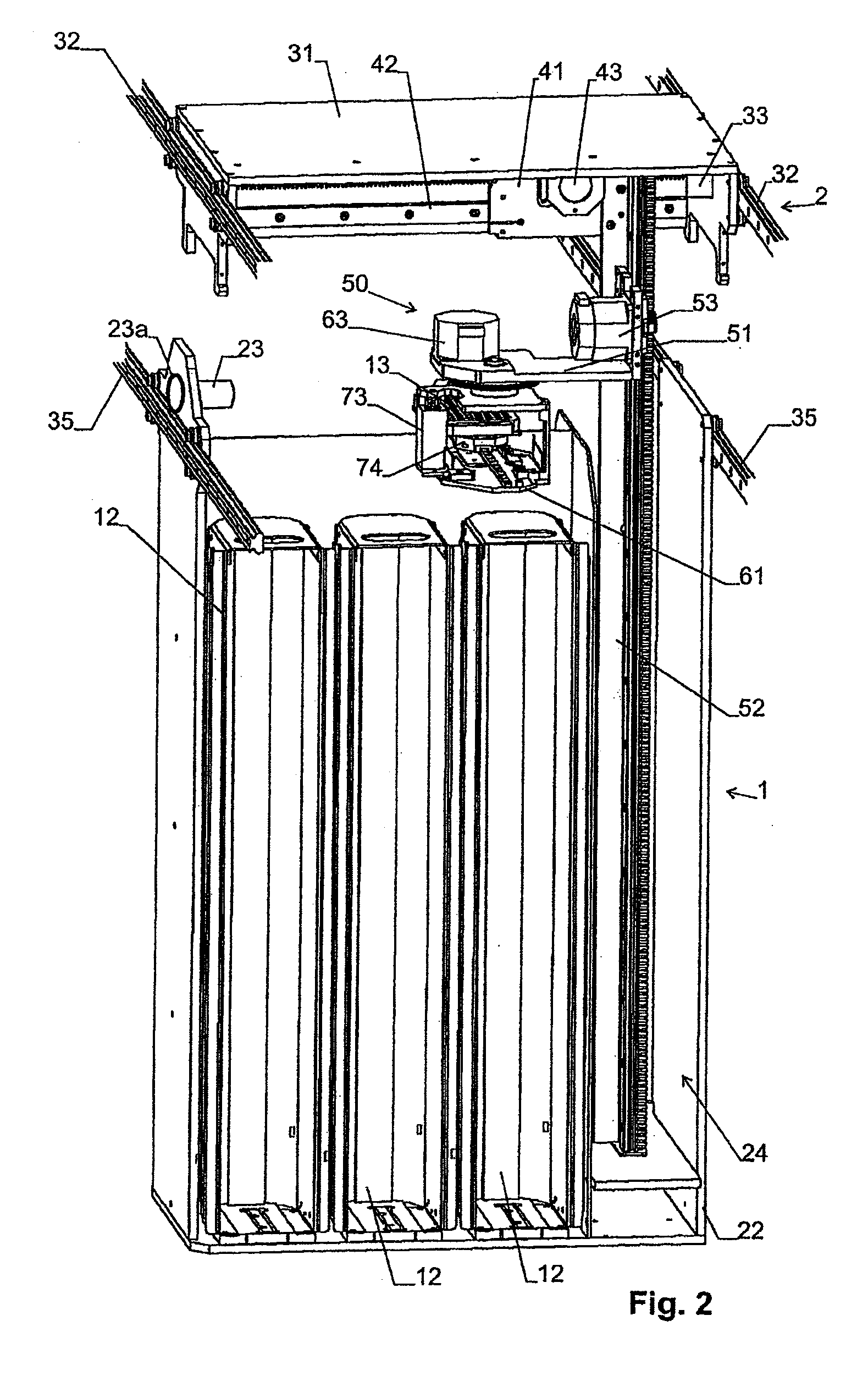

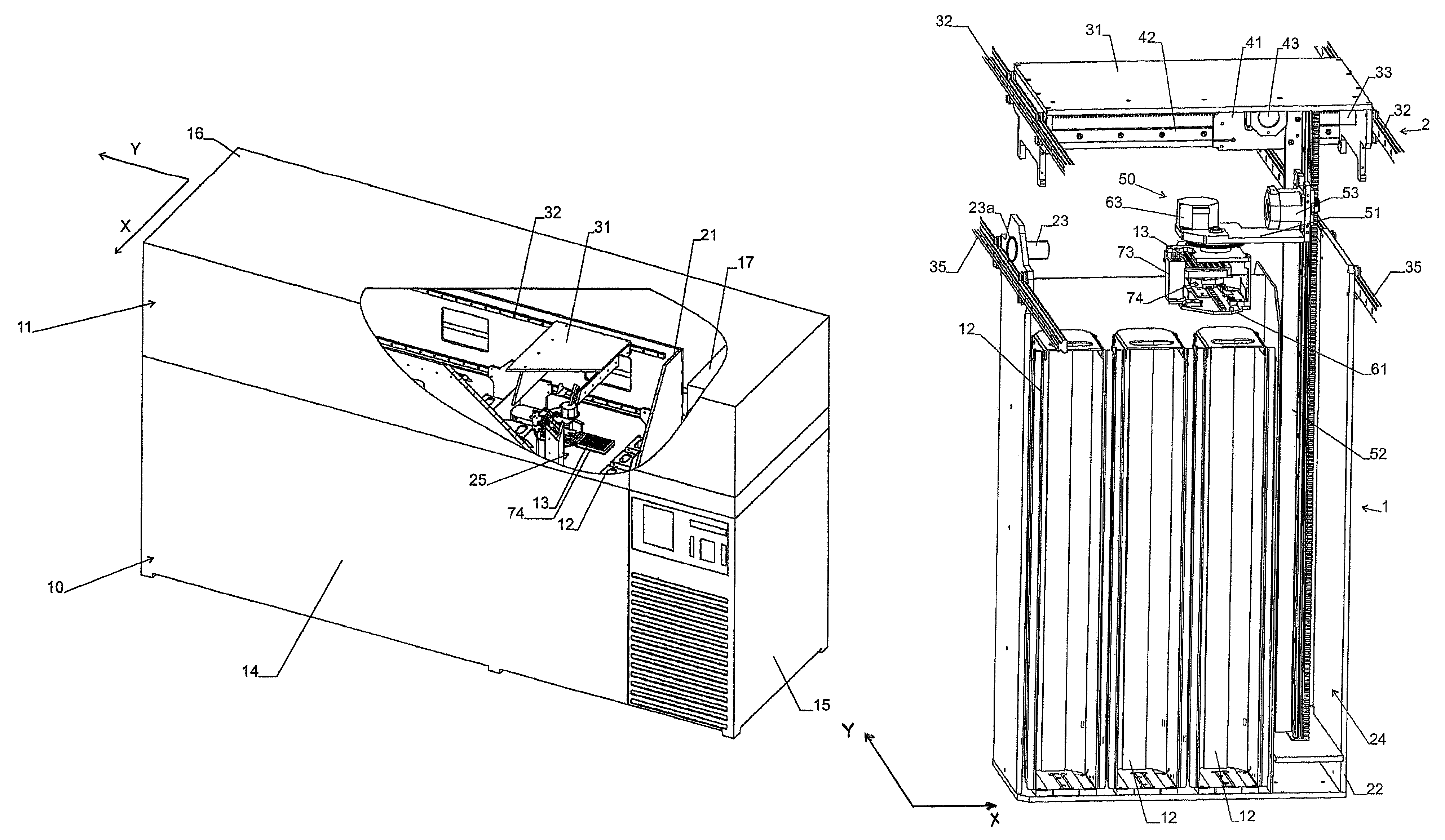

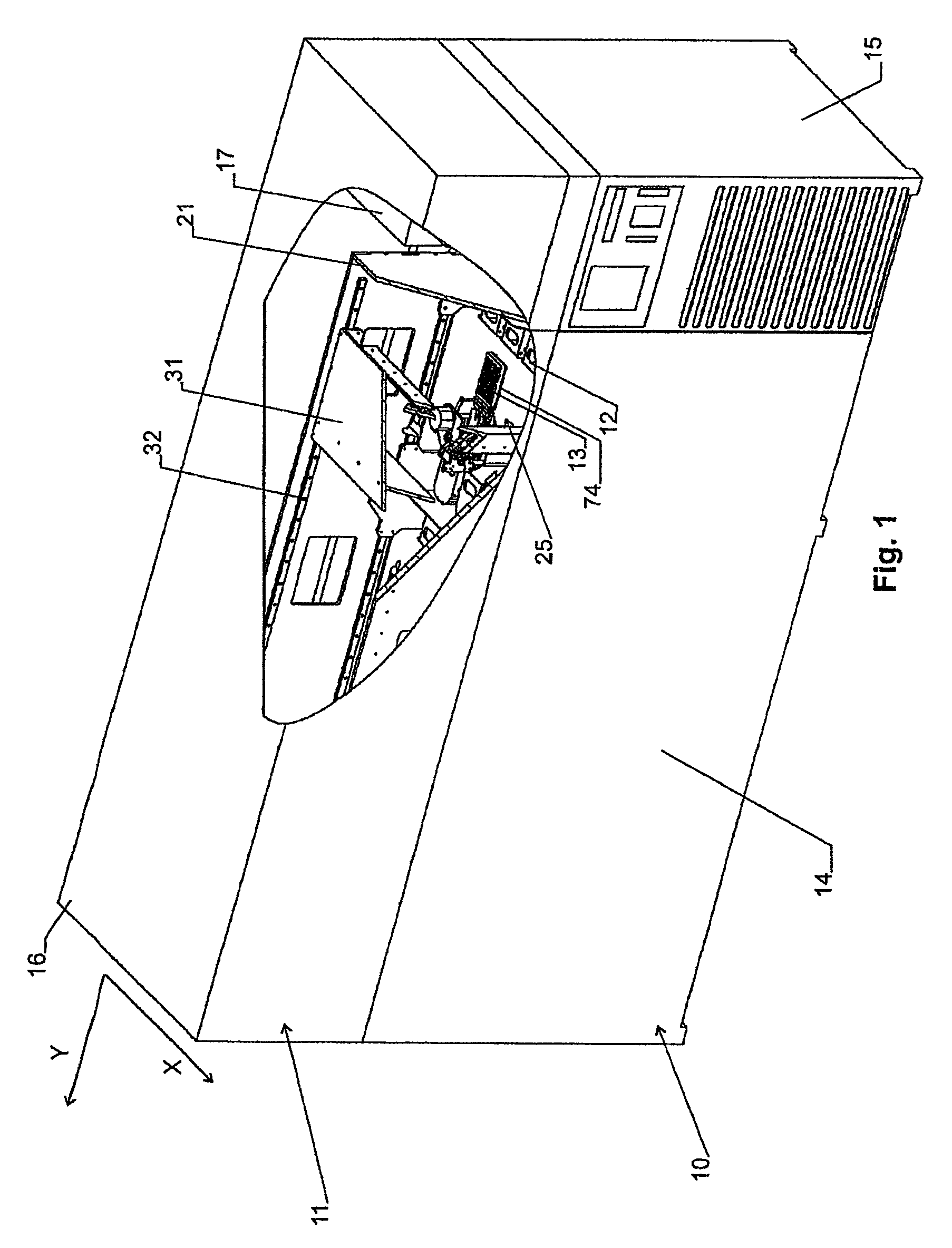

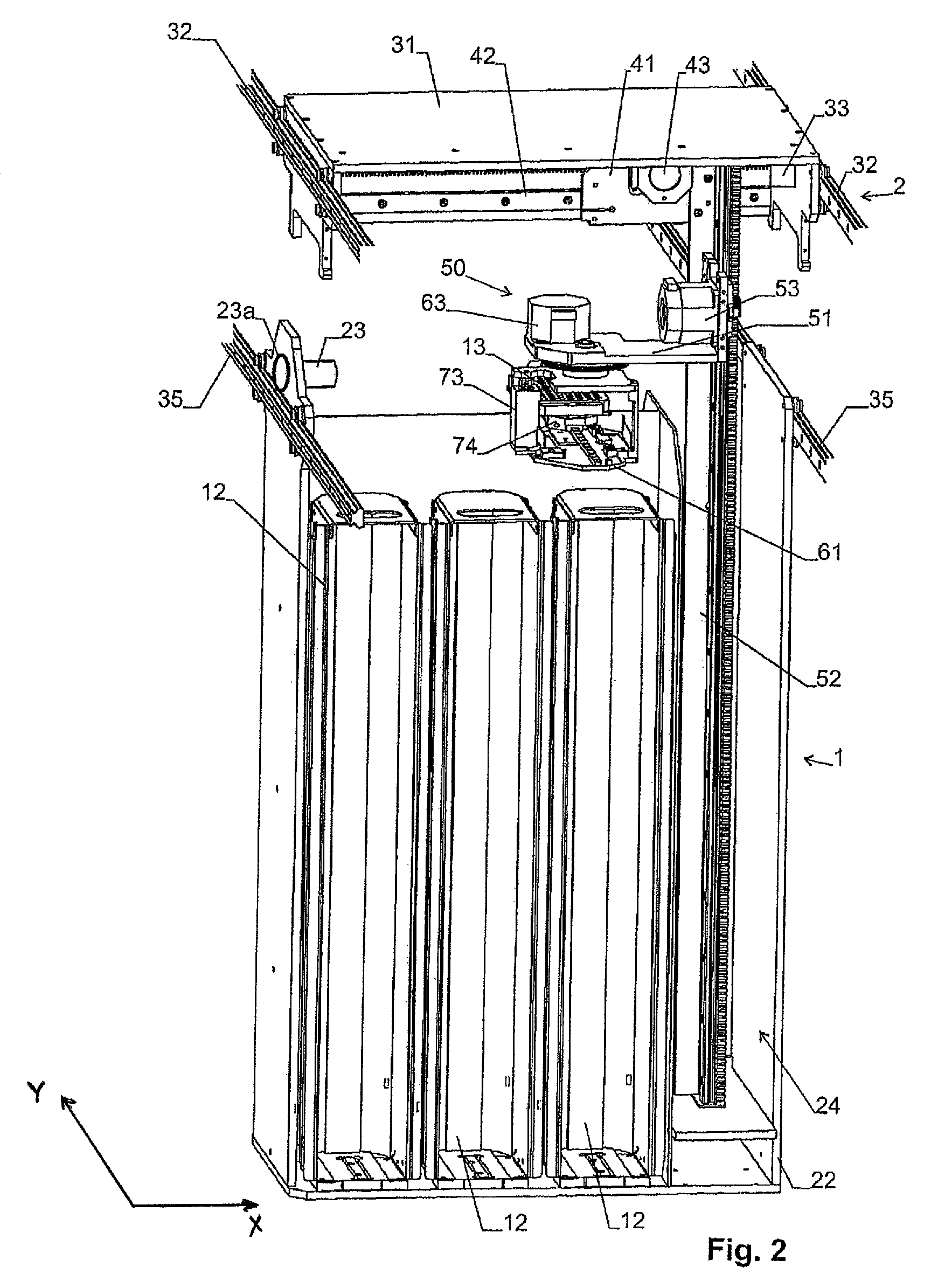

Automated substance storage

ActiveUS20080231152A1Compact storageImprove transportation capacityBook cabinetsLighting and heating apparatusTemperature controlEngineering

A climatic cabinet and storage cabinet that includes an upper zone, a lower zone, storage positions for storing objects in one of the upper and lower zone, and at least one temperature control unit structured and arranged to maintain a temperature in the one of the upper and lower zone different from the other of the upper and lower zone. The cabinet further includes a lock, a horizontal transport mechanism arranged at least in part in the other of the upper and lower zone to move the objects to and from the lock in a direction having a horizontal component, and a vertical transport mechanism structured and arranged to move the objects between the lower zone and the upper zone.

Owner:LICONIC

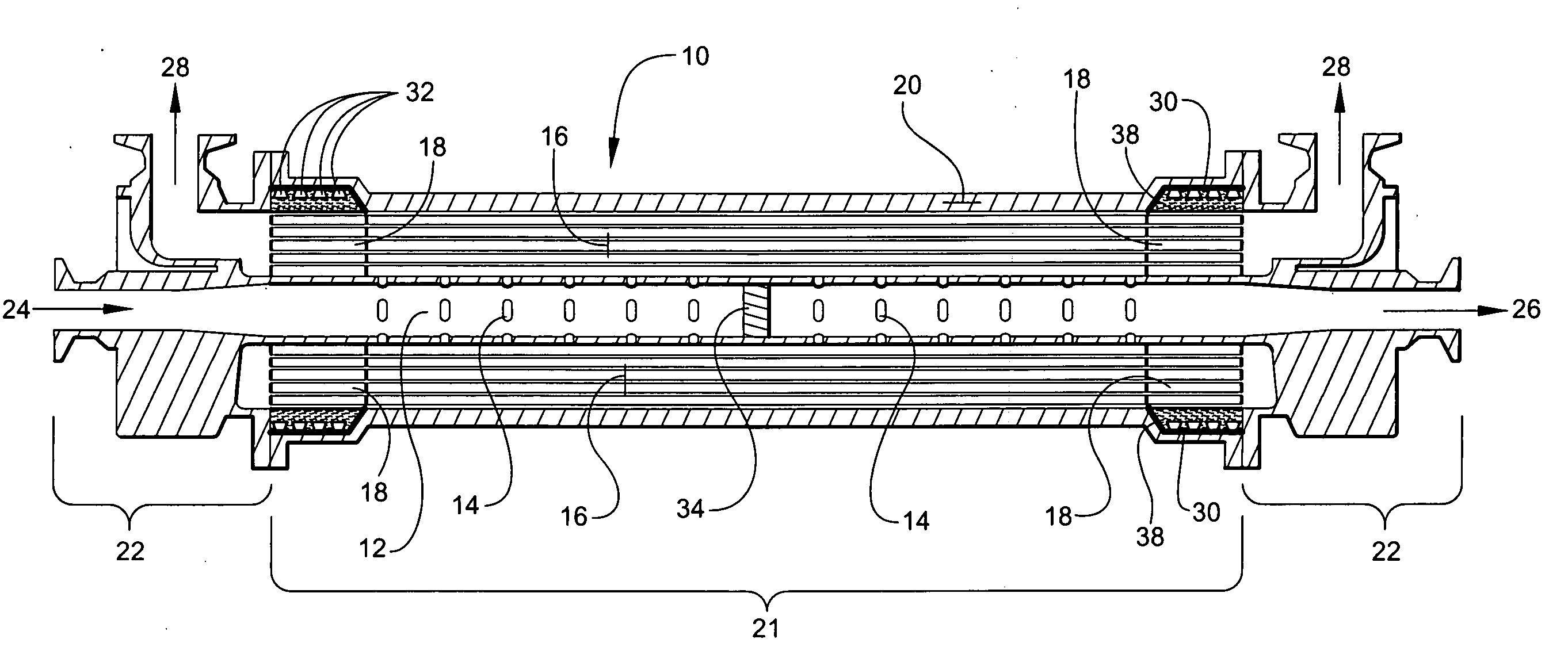

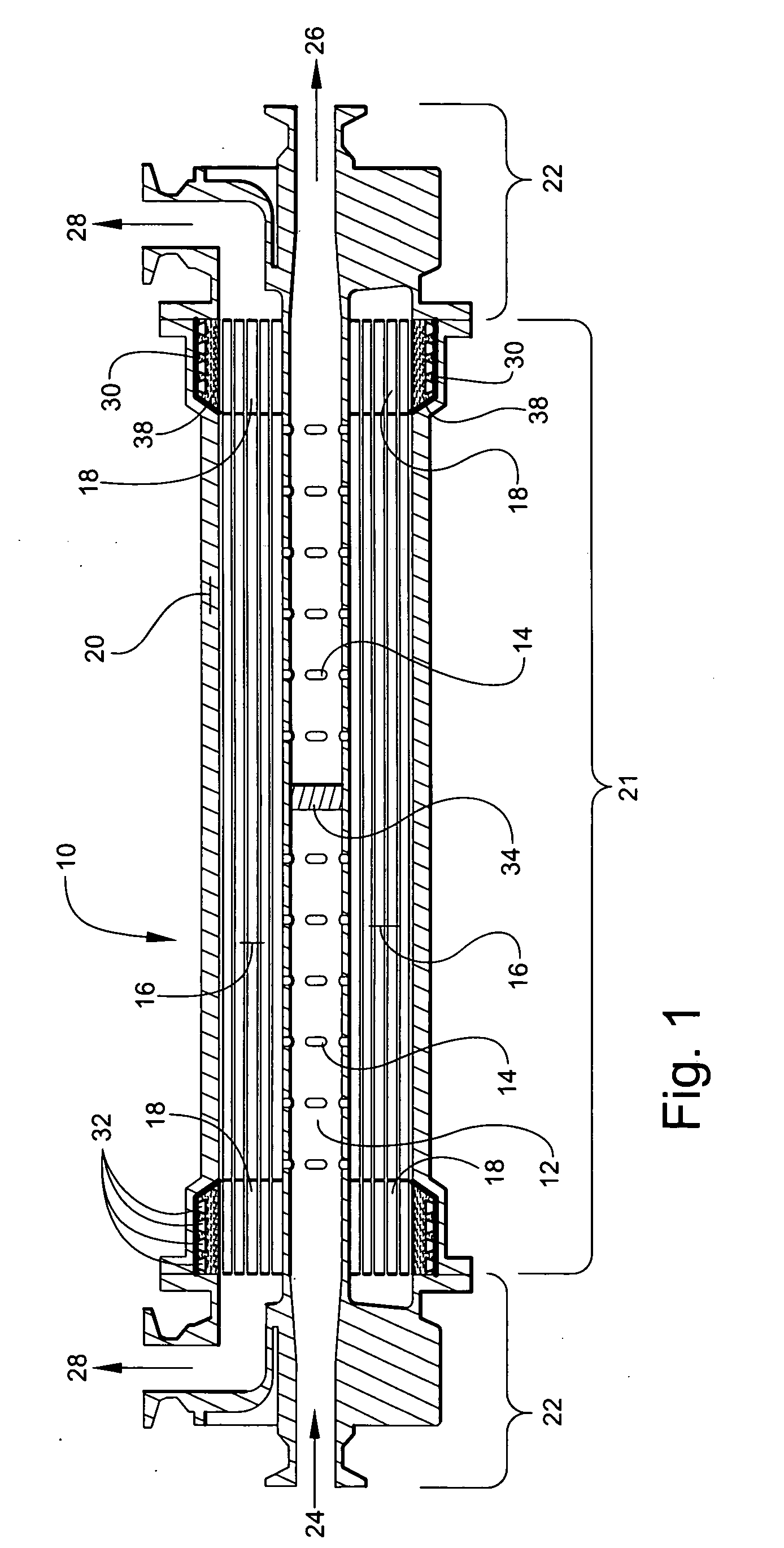

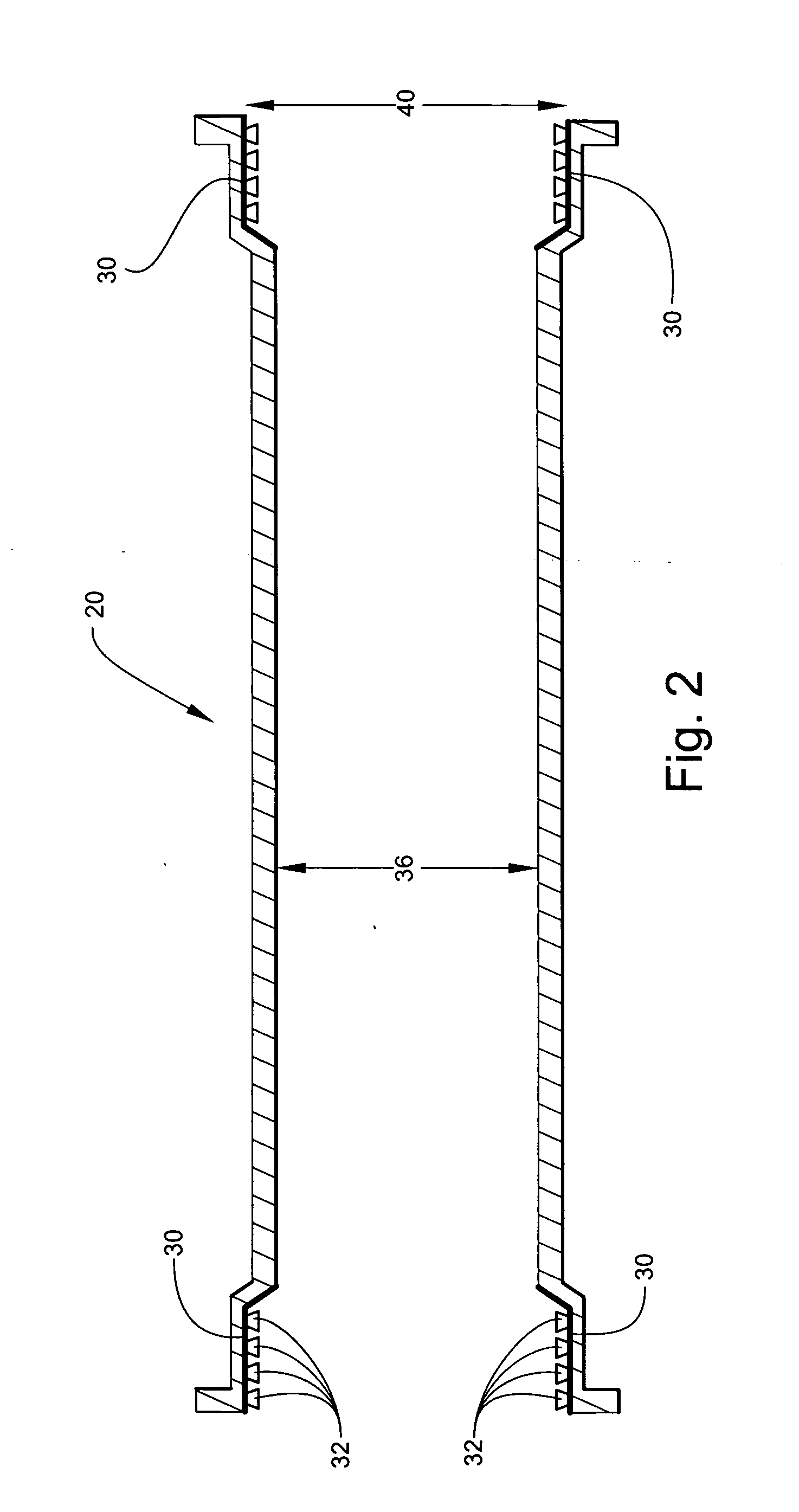

Hollow fiber membrane contactor and method of making same

The instant invention is a hollow fiber membrane contactor, and method of making same. The hollow fiber membrane contactor includes (1) a shell, said shell having a internal bonding surface, an interlocking geometry ring being provided on said internal bonding surface; (2) a unitized structure; (3) a potting material joining said unitized structure to said shell at said interlocking geometry ring thereby forming an interlocking seal therebetween; and (4) end caps, said end caps being adjoined to lateral ends of said shell. The method of making a hollow fiber membrane contactor includes (1) providing a shell, said shell having a internal bonding surface; (2) providing an interlocking geometry ring on said internal bonding surface; (3) forming a unitized structure; (4) placing the unitized structure into said shell (5) potting said unitized structure to said shell at said interlocking geometry ring thereby forming an interlocking seal therebetween; and (6) adjoining end caps to lateral ends of said shell.

Owner:3M INNOVATIVE PROPERTIES CO

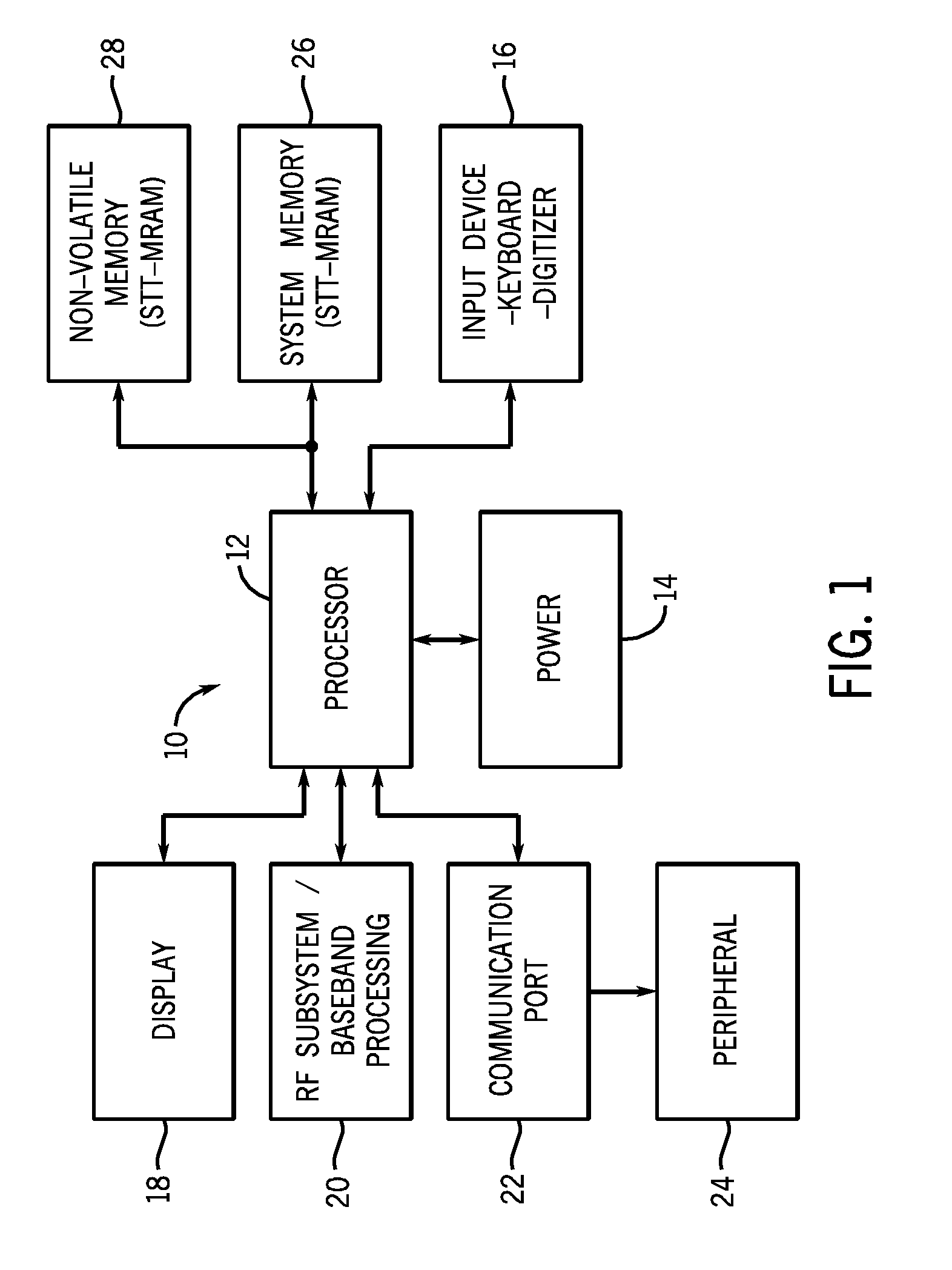

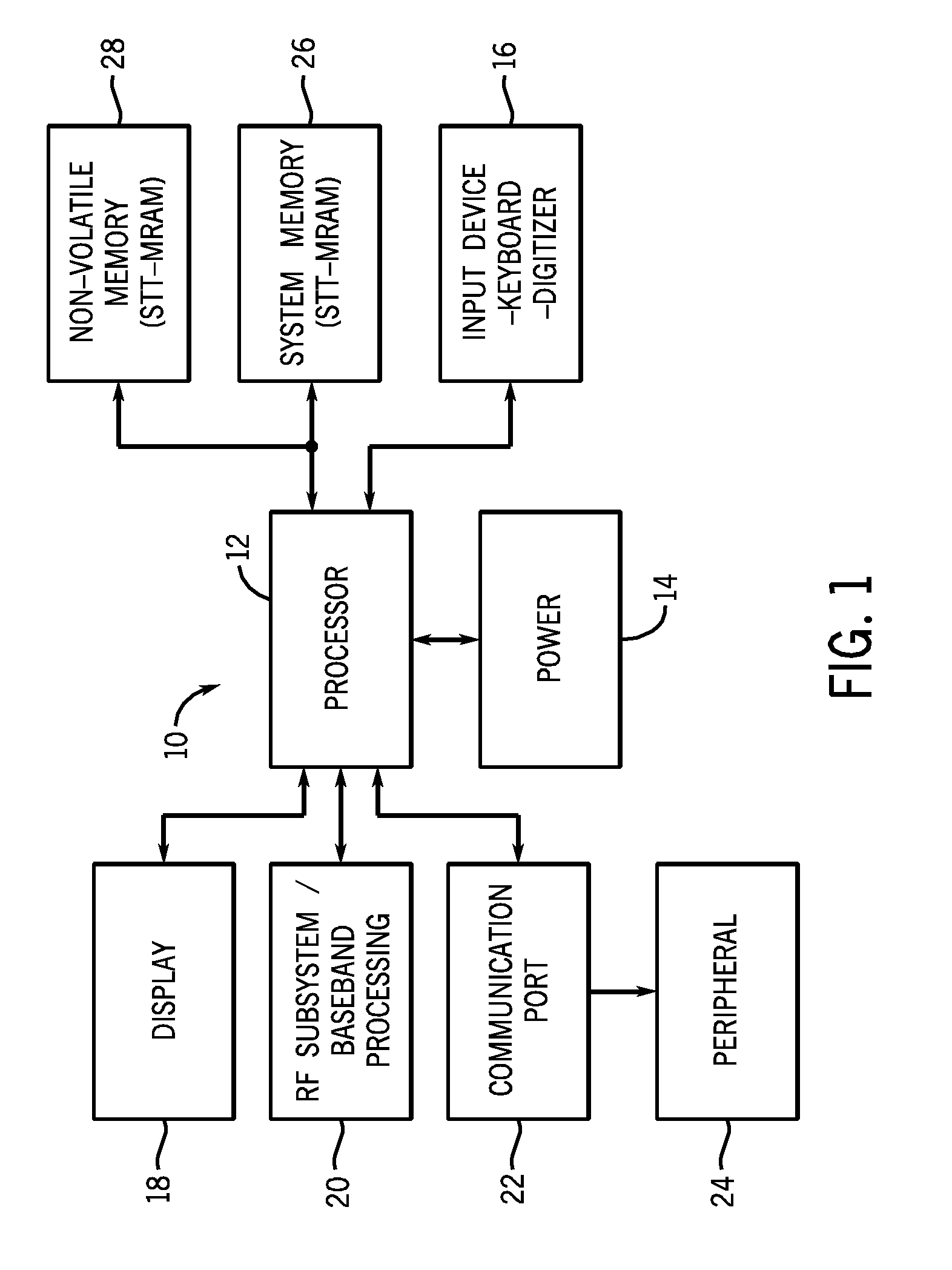

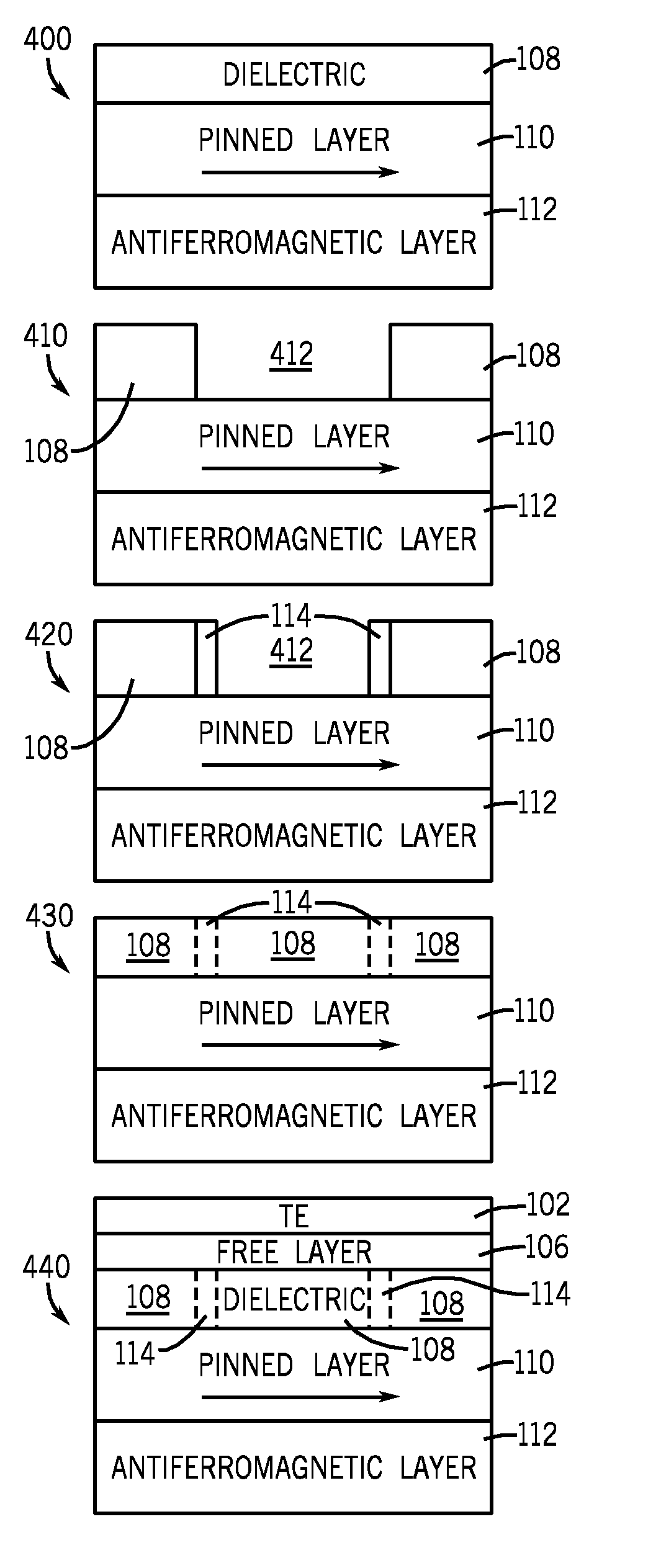

Stt-mram cell structures

A magnetic cell structure including a nonmagnetic bridge, and methods of fabricating the structure are provided. The magnetic cell structure includes a free layer, a pinned layer, and a nonmagnetic bridge electrically connecting the free layer and the pinned layer. The shape and / or configuration of the nonmagnetic bridge directs a programming current through the magnetic cell structure such that the cross sectional area of the programming current in the free layer of the structure is less than the cross section of the structure. The decrease in the cross sectional area of the programming current in the free layer enables a lower programming current to reach a critical switching current density in the free layer and switch the magnetization of the free layer, programming the magnetic cell.

Owner:OVONYX MEMORY TECH LLC

Automated substance storage

ActiveUS8857208B2Easy to useCost-effectiveLighting and heating apparatusTemperatue controlTemperature controlEngineering

A climatic cabinet and storage cabinet that includes an upper zone, a lower zone, storage positions for storing objects in one of the upper and lower zone, and at least one temperature control unit structured and arranged to maintain a temperature in the one of the upper and lower zone different from the other of the upper and lower zone. The cabinet further includes a lock, a horizontal transport mechanism arranged at least in part in the other of the upper and lower zone to move the objects to and from the lock in a direction having a horizontal component, and a vertical transport mechanism structured and arranged to move the objects between the lower zone and the upper zone.

Owner:LICONIC

Solar cell structure with integrated discrete by-pass diode

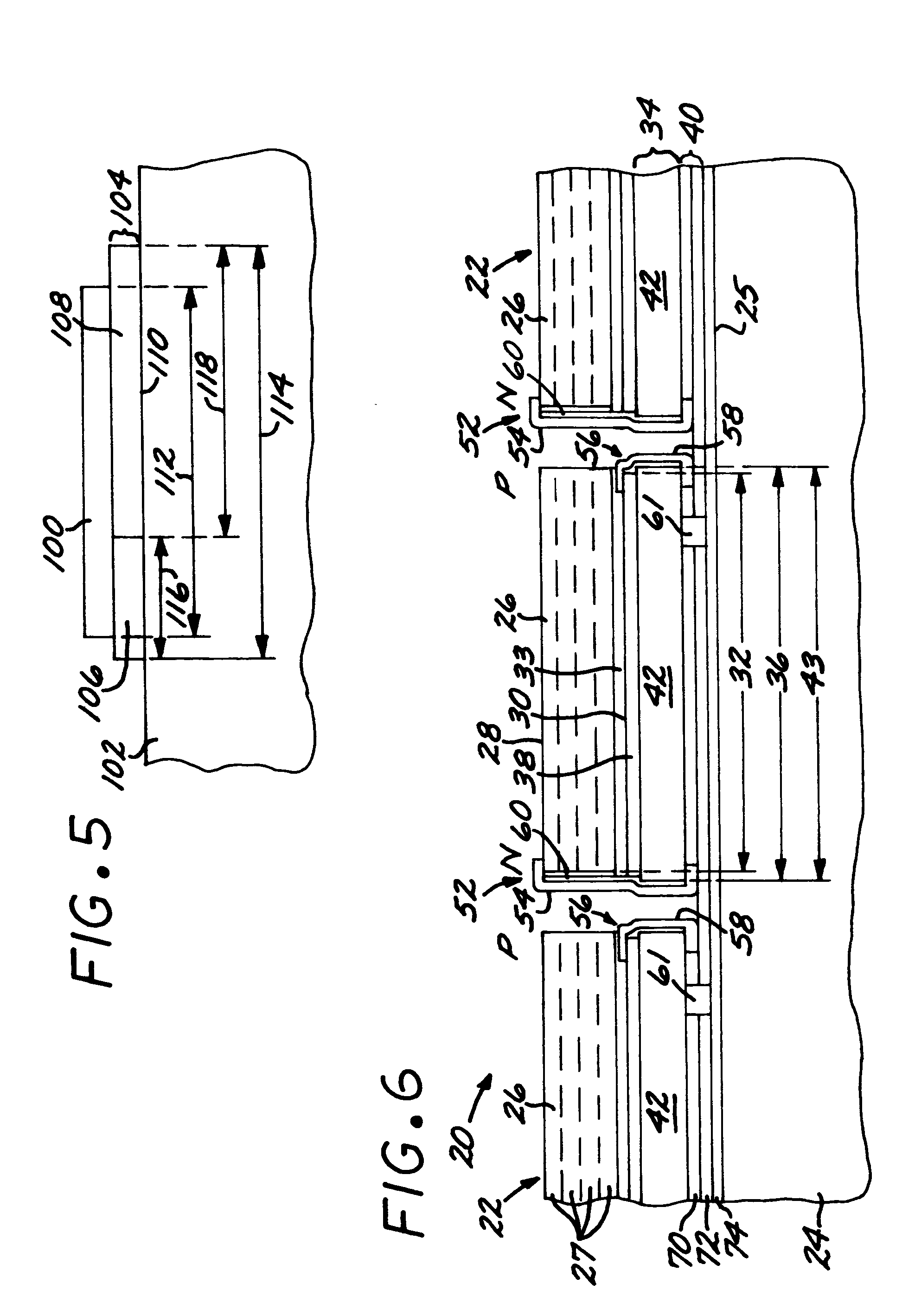

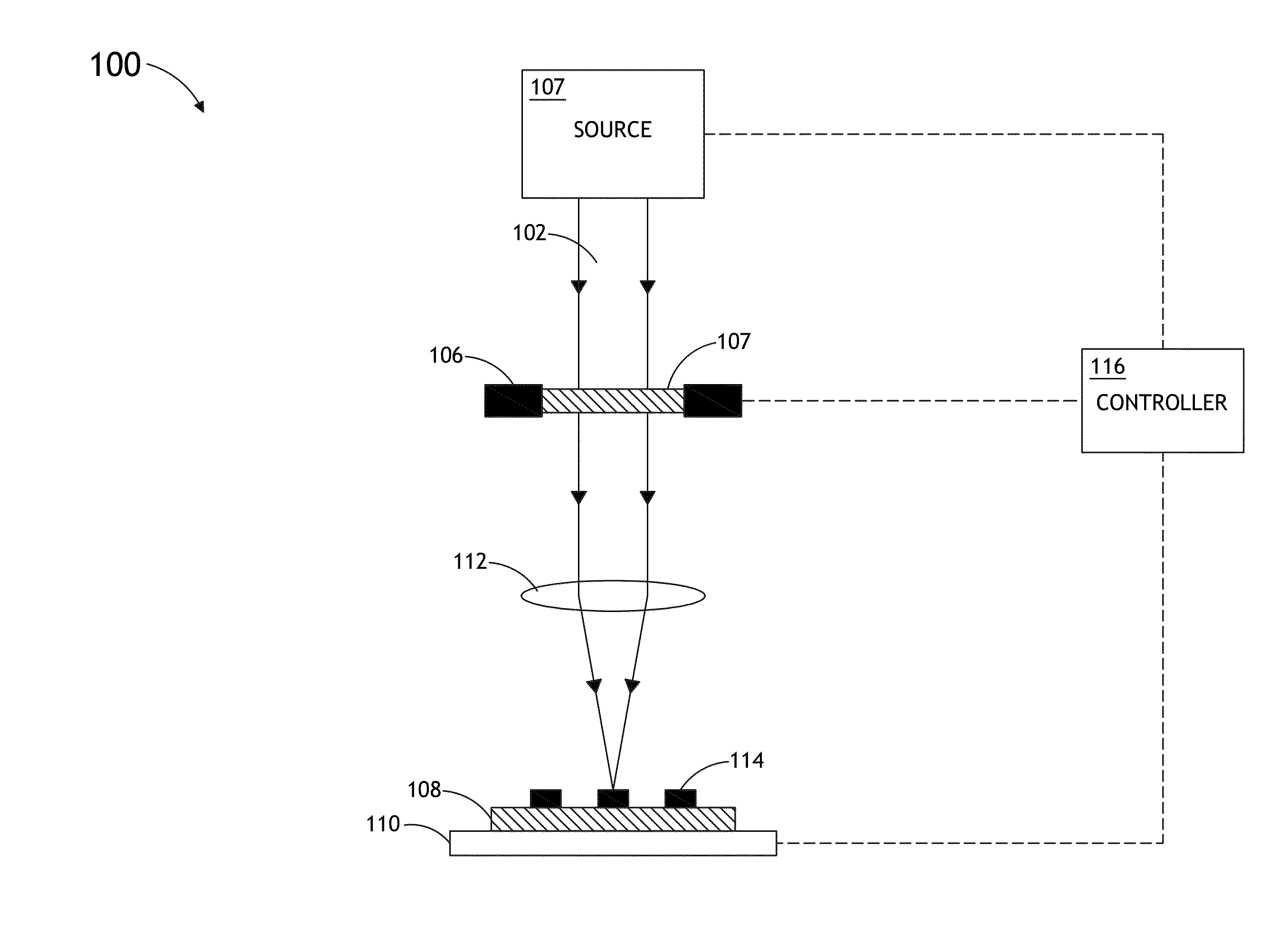

A solar cell structure has a solar cell unit structure including a heat sink, and a solar cell having a front side, a back side, and a solar-cell projected area coverage on the heat sink. The solar cell has an active semiconductor structure that produces a voltage between the front side and the back side when the front side is illuminated. An intermediate structure is disposed between and joined to the back side of the solar cell and to the heat sink. The intermediate structure has an intermediate-structure projected area coverage on the heat sink and includes a by-pass diode having a diode projected area coverage on the heat sink. The diode projected area coverage on the heat sink may be substantially the same as the intermediate-structure projected coverage on the heat sink. Alternatively, the diode projected area coverage on the heat sink maybe less than the solar-cell projected area coverage on the heat sink, and the intermediate structure further includes a substrate coplanar with the by-pass diode.

Owner:THE BOEING CO

Method and System for Providing a Target Design Displaying High Sensitivity to Scanner Focus Change

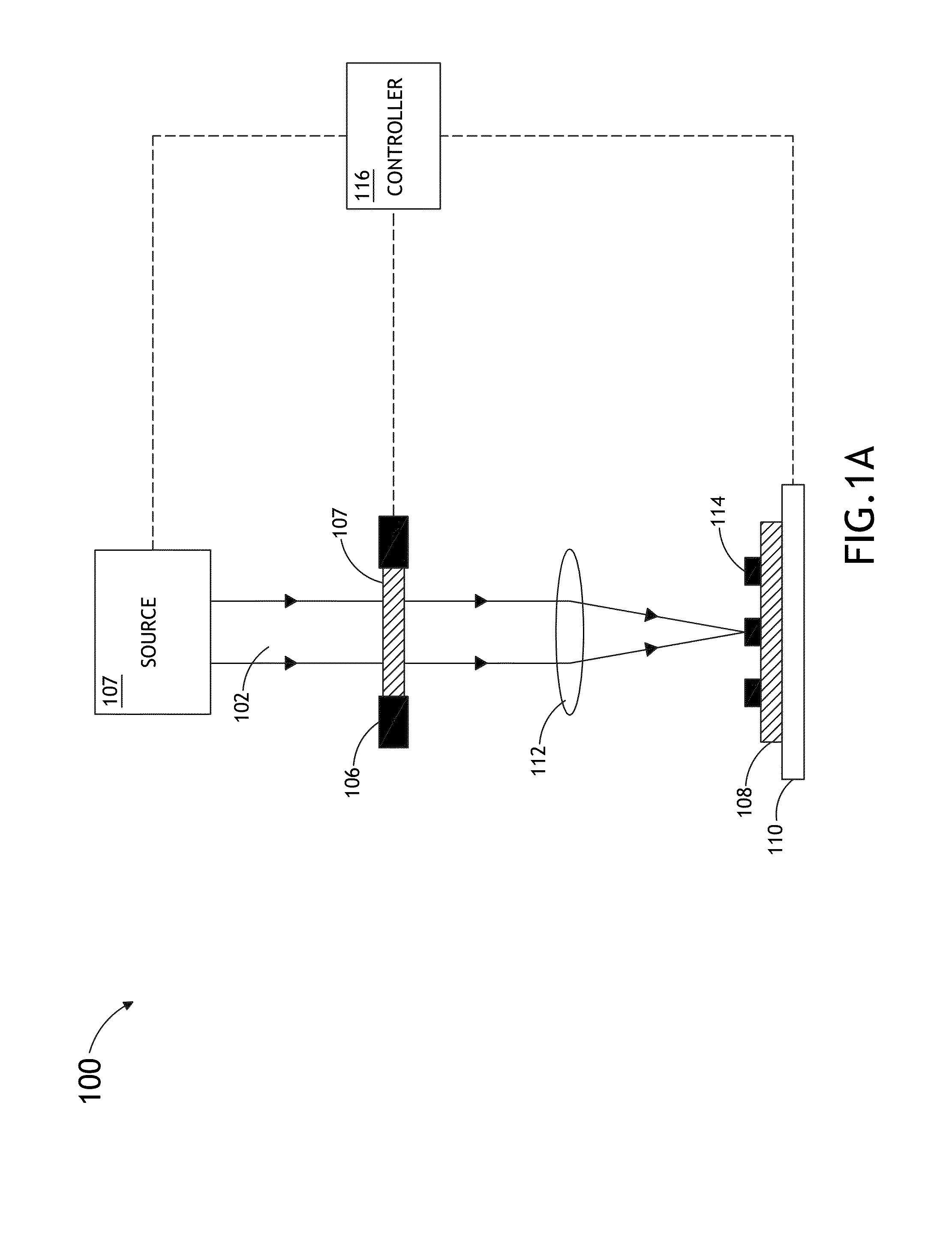

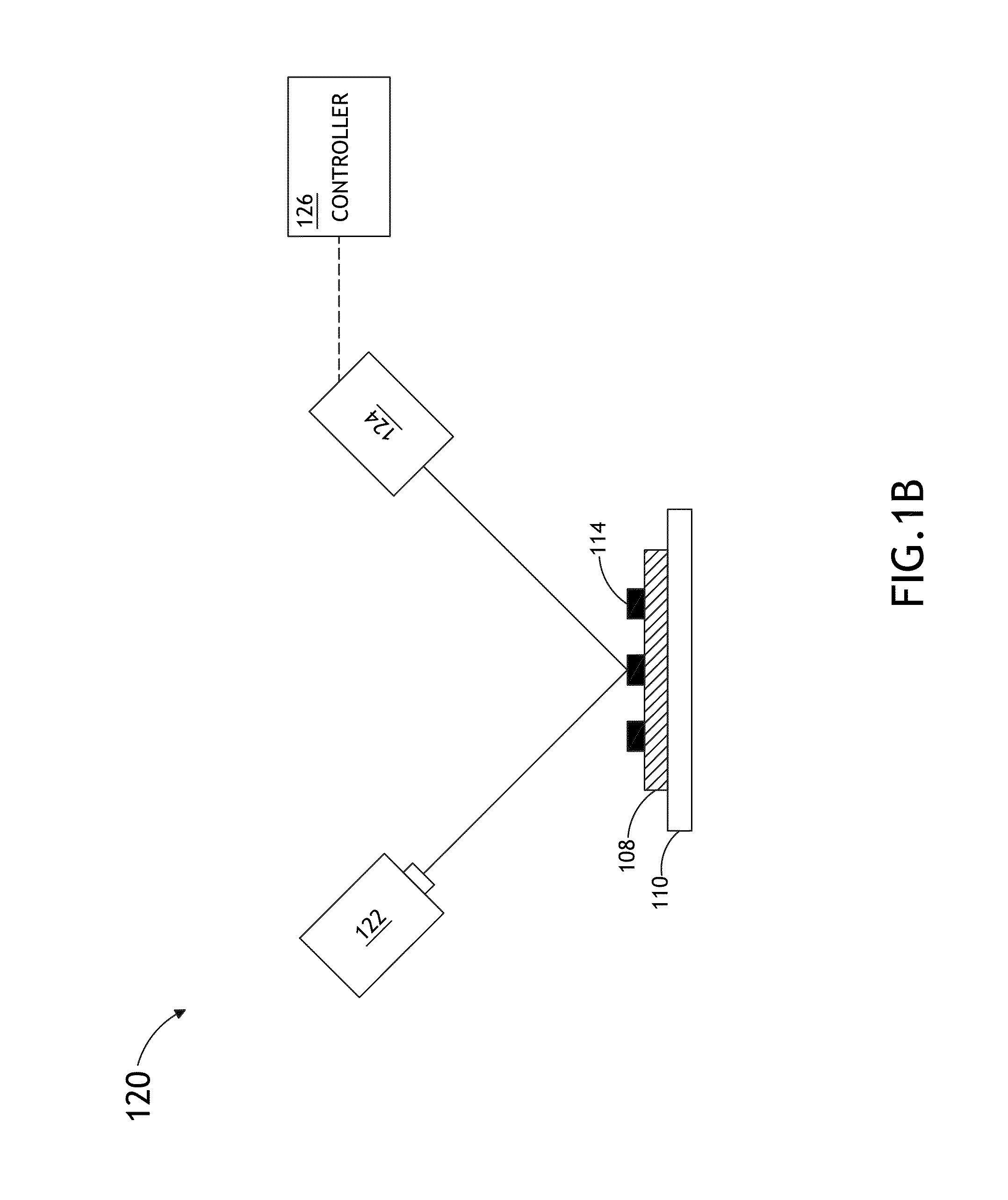

ActiveUS20140141536A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingUnit structureComputer science

A segmented mask includes a set of cell structures, wherein each cell structure includes a set of features having an unresolvable segmentation pitch along a first direction, wherein the unresolvable segmentation pitch along the first direction is smaller than the illumination of the lithography printing tool, wherein the plurality of cell structures have a pitch along a second direction perpendicular to the first direction, wherein the unresolvable segmentation pitch is suitable for generating a printed pattern for shifting the best focus position of the lithography tool by a selected amount to achieve a selected level of focus sensitivity.

Owner:KLA TENCOR TECH CORP