Patents

Literature

332 results about "Common word" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

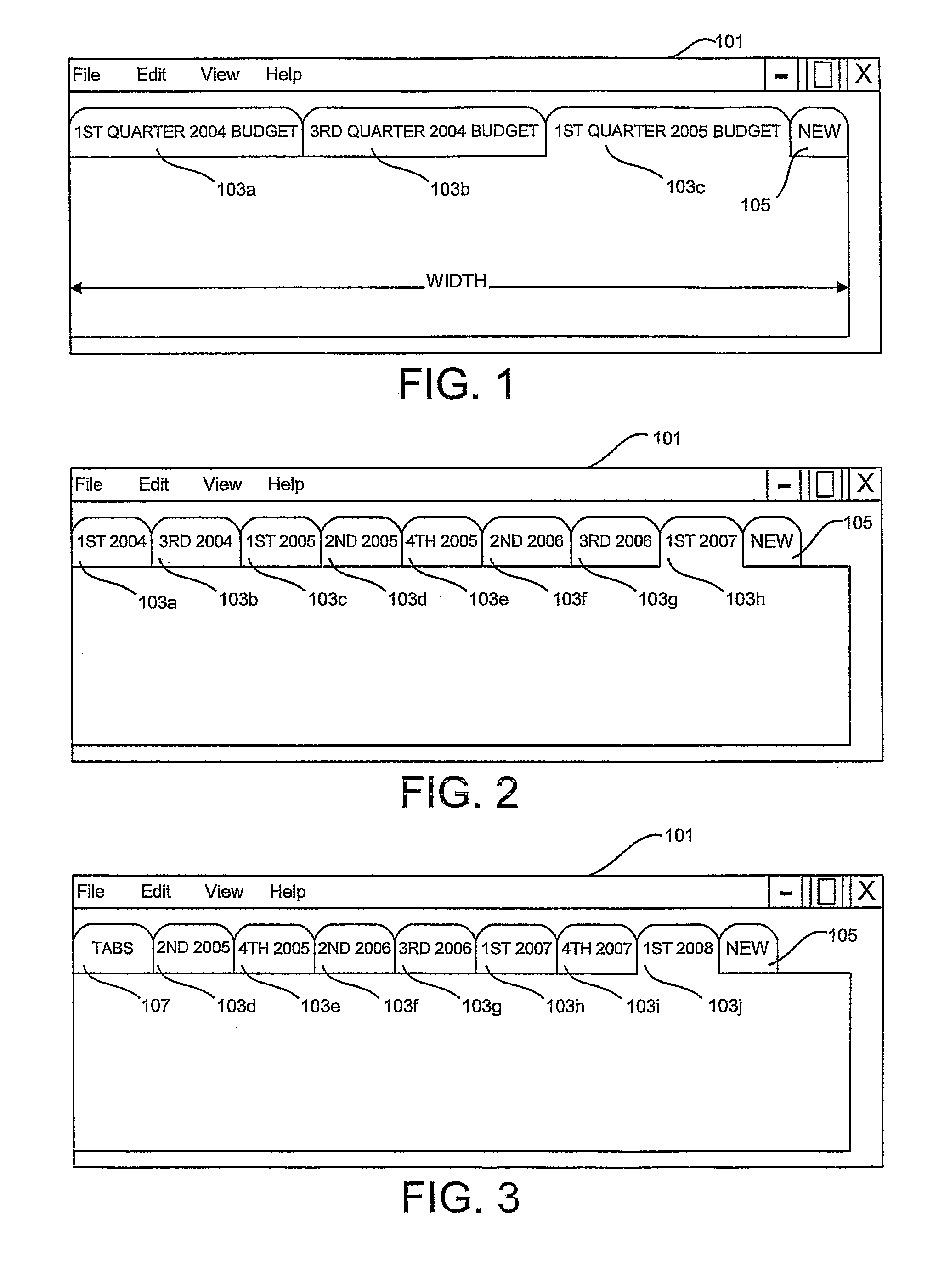

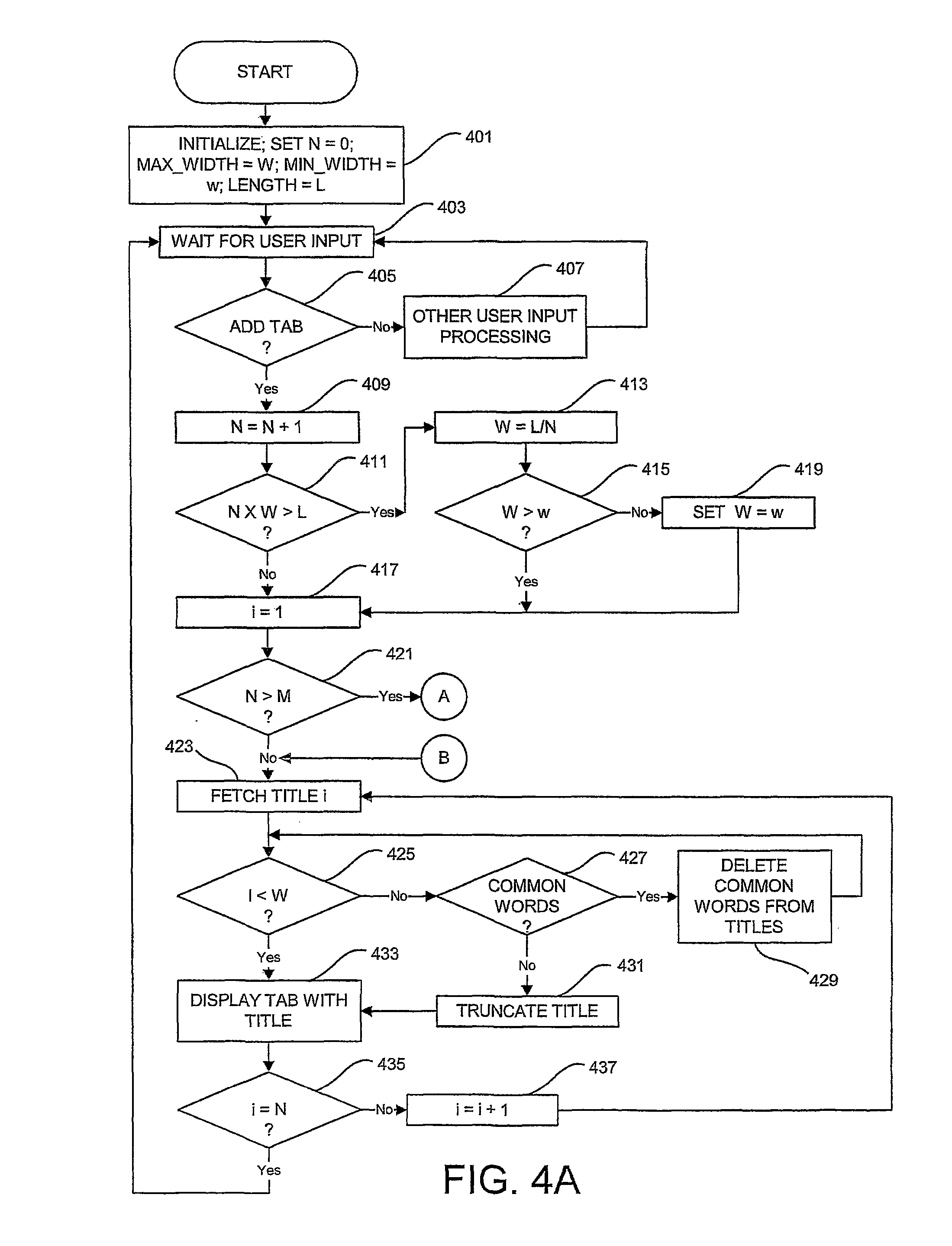

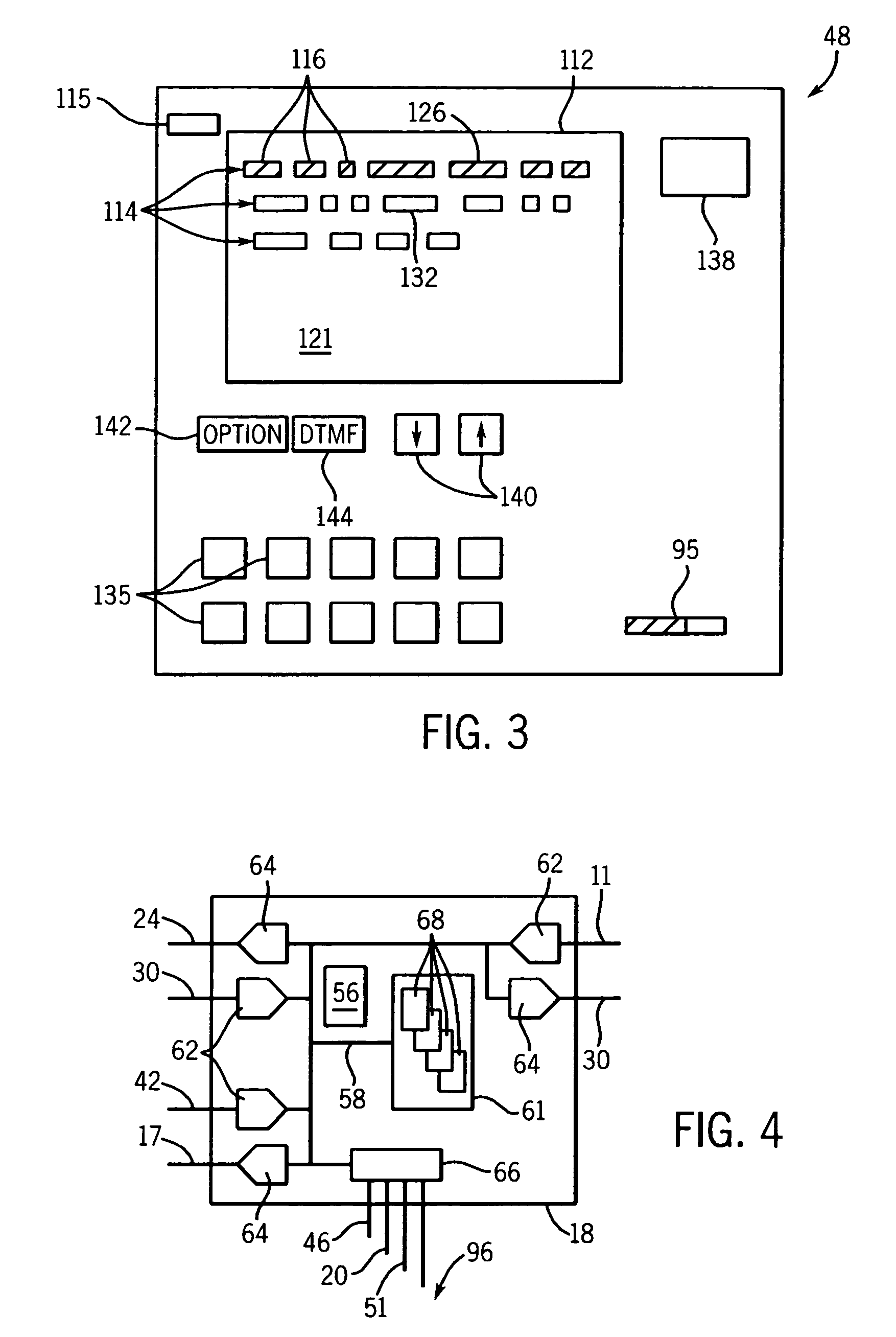

Method of displaying tab titles

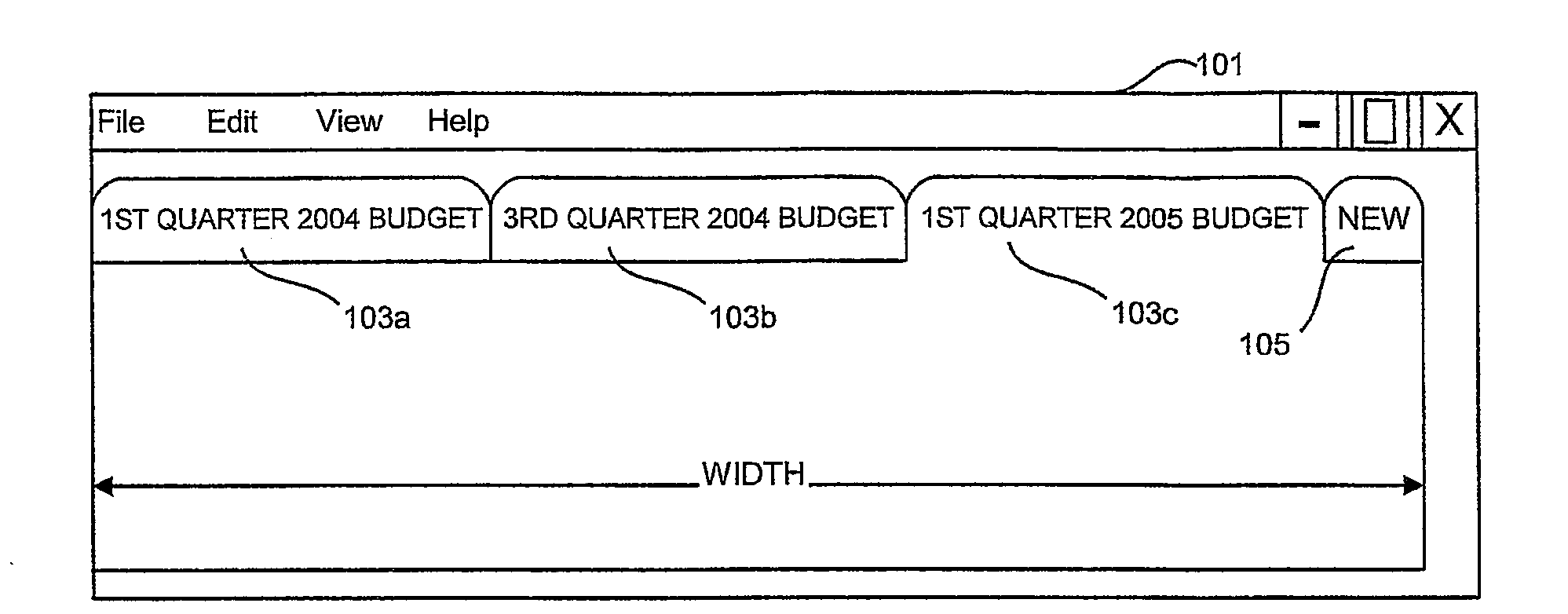

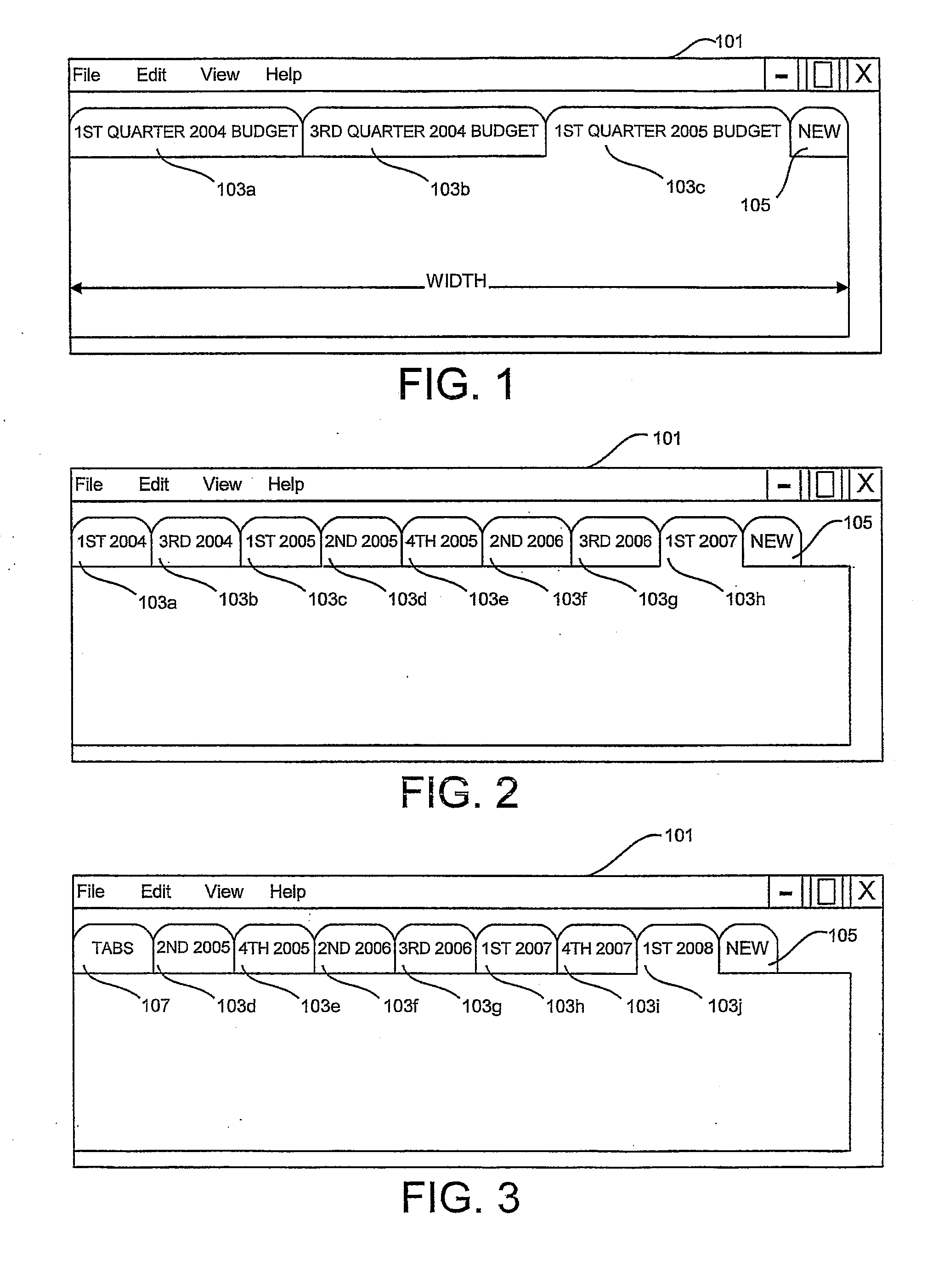

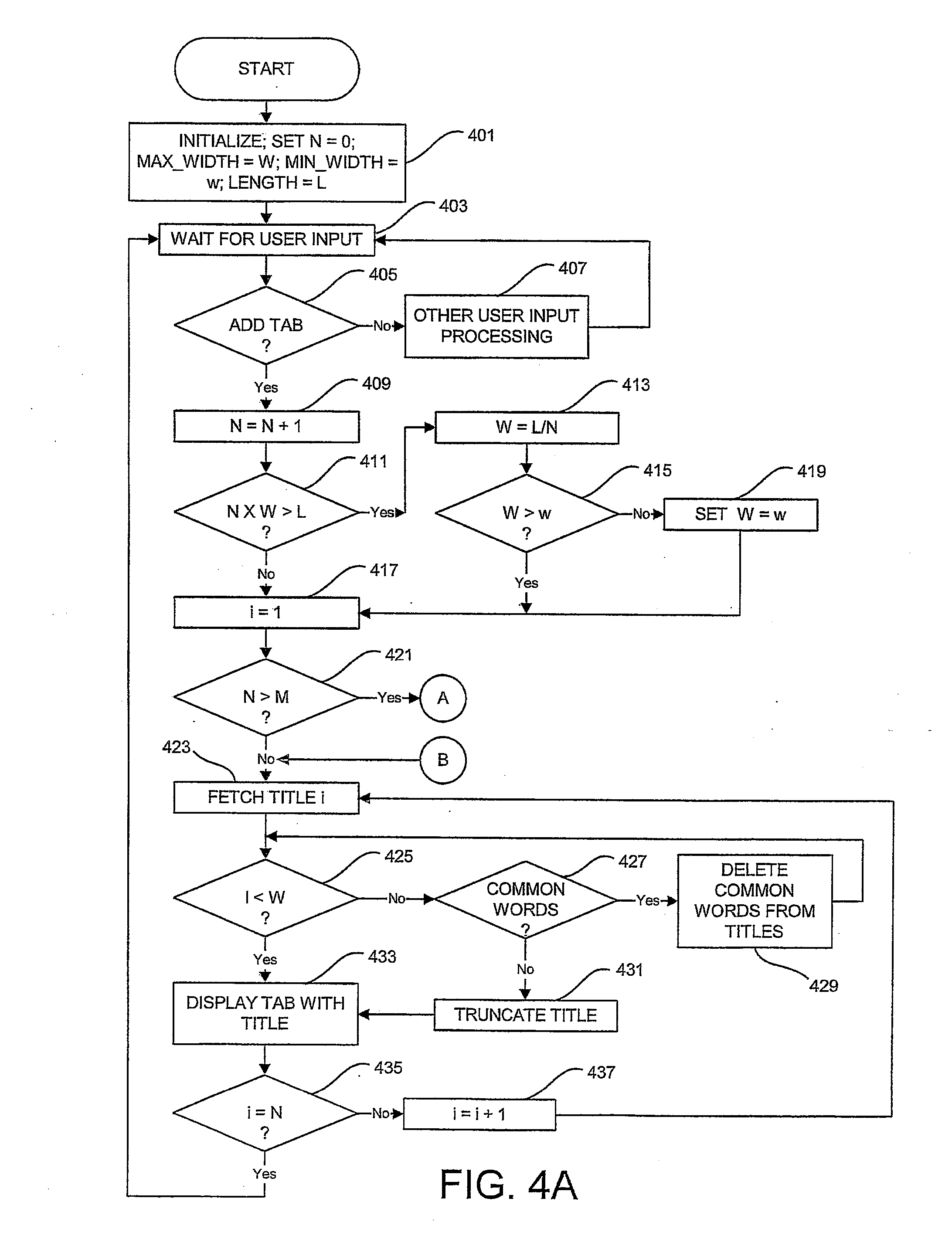

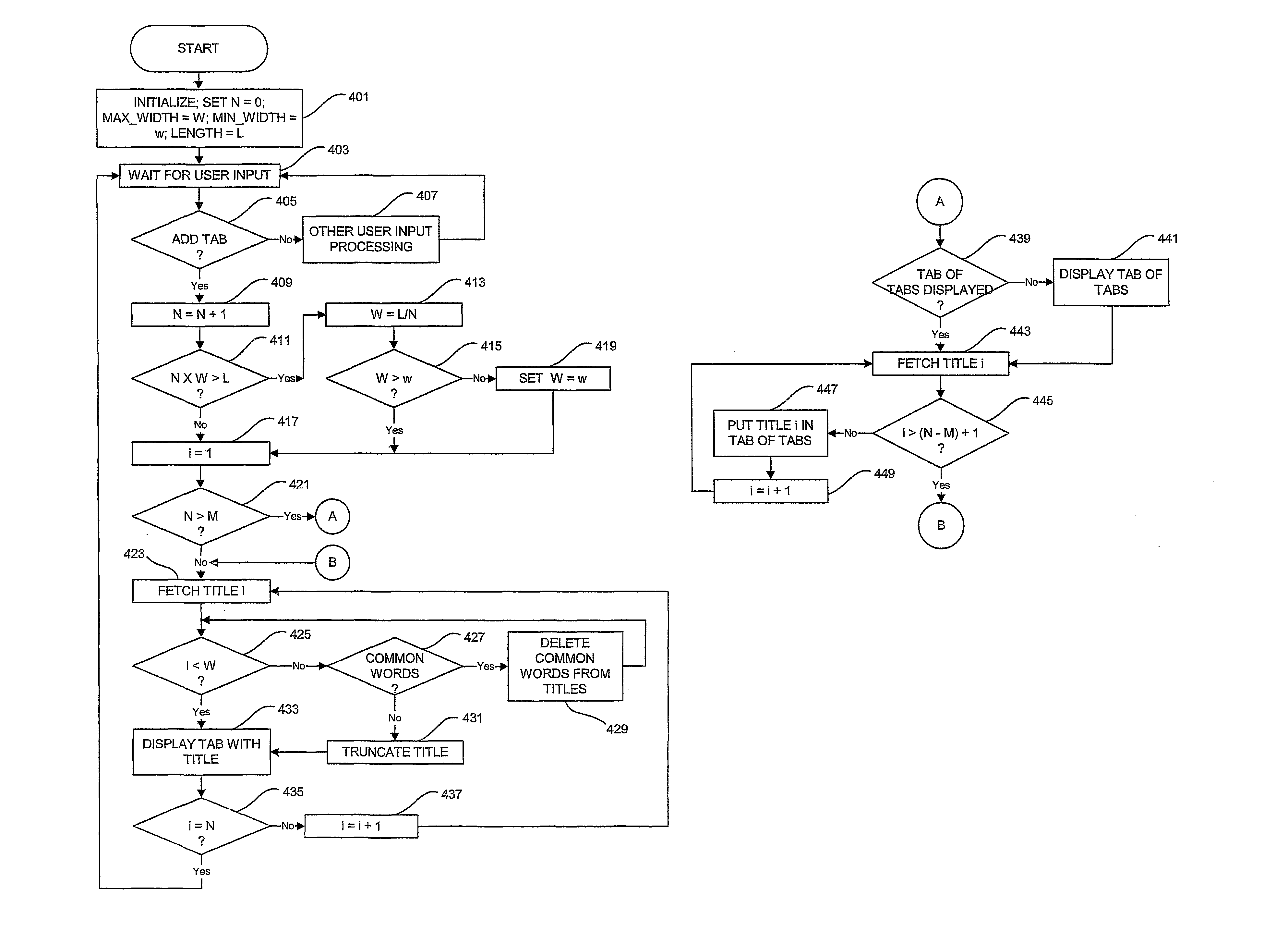

A method of displaying tab titles in a computer user interface receives a request to display a new tab in a tab area having a length. The new tab has a width and the new tab has a title having a length. The method determines a number of tabs to be displayed in the area and determines if the number of tabs to be displayed multiplied by the tab width is greater than the length of the tab area. If so, the method sets the tab width equal to the length of the tab area divided by the number of tabs. The method determines if the length of the title is greater than the tab width. If so, the method determines if the title has any words in common with any other titles of tabs. If so, the method deletes the common words from the titles, and displays the titles with the deleted common words in the tabs. The method may set a maximum number of tabs to be displayed in the tab area. The maximum number of tabs may be determined by the length of the tab area and a minimum tab width. If the number of tabs is greater than the maximum number of tabs is to be displayed, the method collapses some of the tabs in to a tab of tabs.

Owner:IBM CORP

Method of displaying tab titles

Owner:INT BUSINESS MASCH CORP

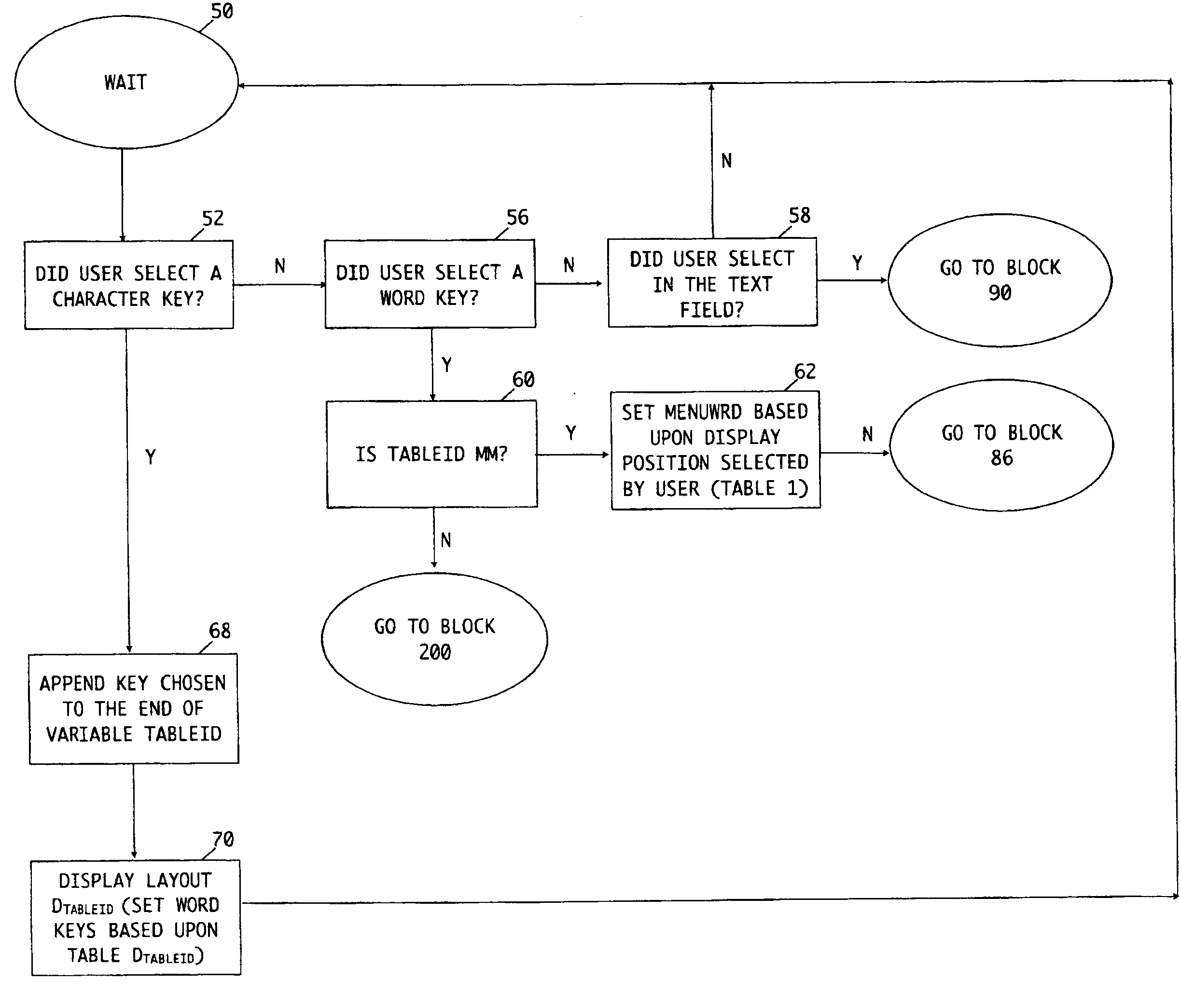

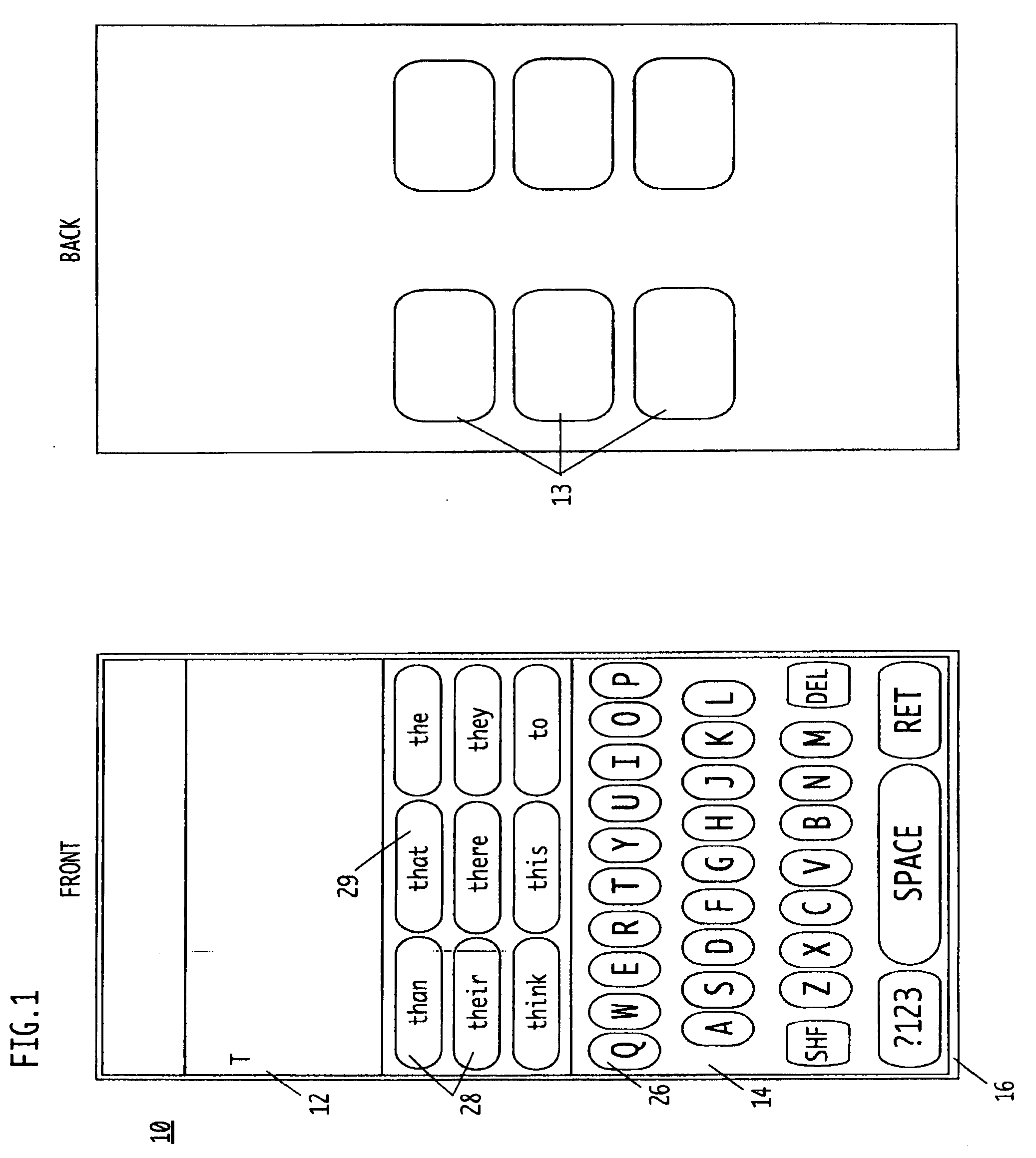

Methods and Systems for Improved Data Input, Compression, Recognition, Correction, and Translation through Frequency-Based Language Analysis

InactiveUS20100131900A1Improving optical character recognitionEfficient processingInput/output for user-computer interactionCathode-ray tube indicatorsCommon wordDocument preparation

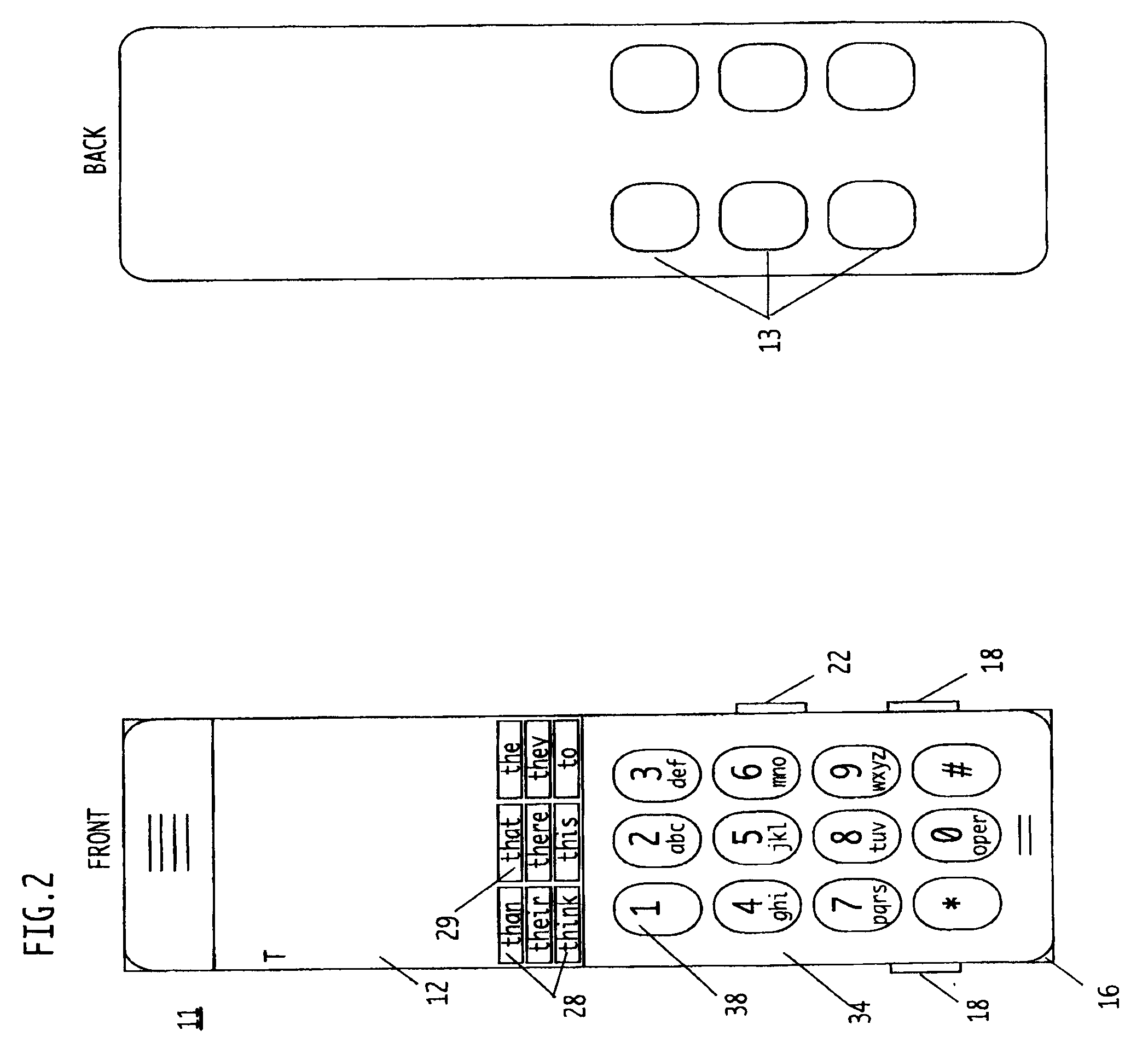

System and method for improving data input by using word frequency to text predict input. Other systems and methods include analyzing words already contained in a document (e.g. spell checking and OCR) and using word frequency to create a proxy system to reduce the space required to store data, allowing for more efficient usage of storage and enhancing the embedded content of matrix codes. The system displays the most common words in a language based upon the previously entered or displayed word(s), or the previously entered or displayed character or characters. Words with the most common frequency of use with the prior word(s) are displayed in a table to enable the user to quickly select one of the displayed words for rapid data entry. The input device can be a touch-sensitive display or non-touch sensitive type device.

Owner:SIEGEL ABBY L

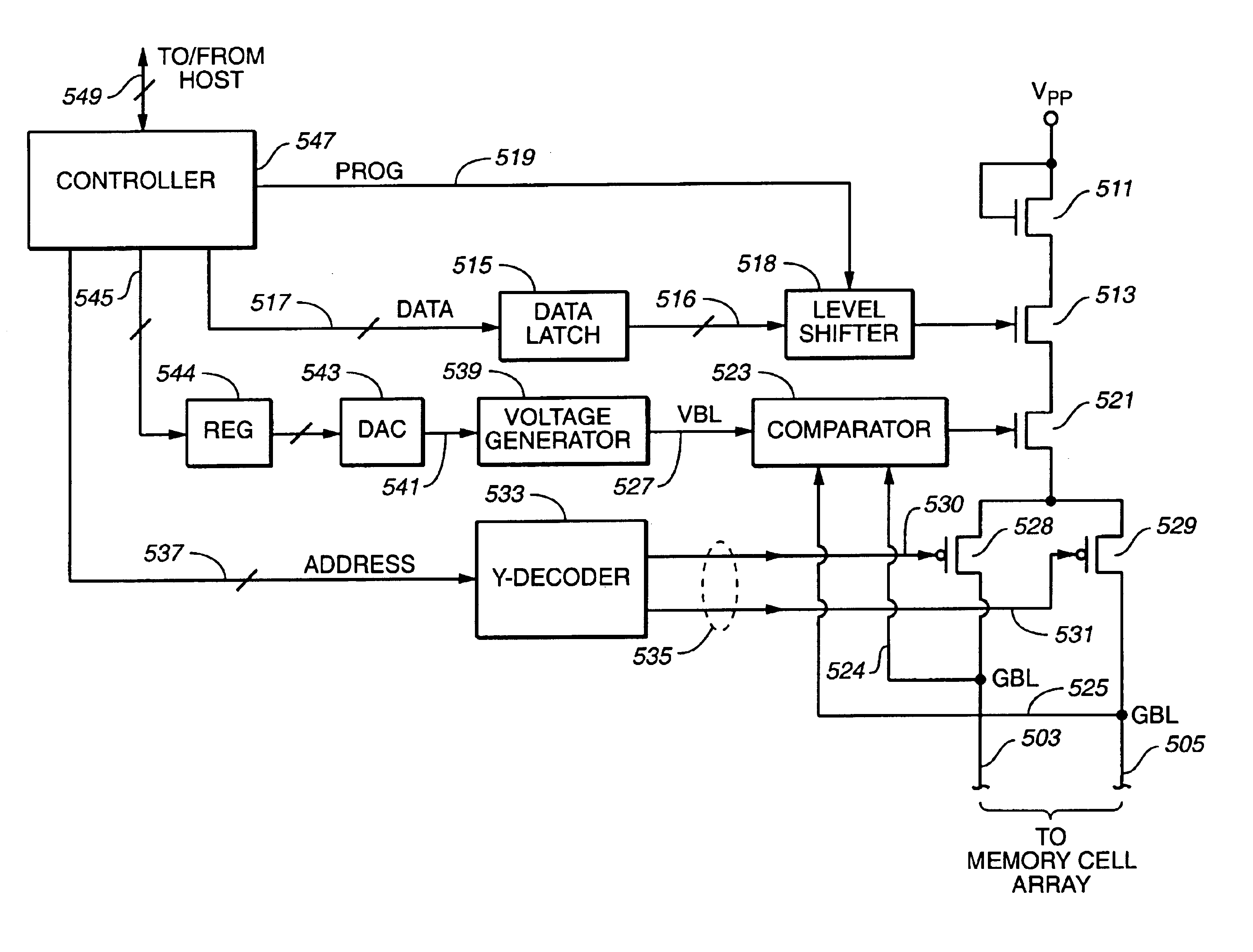

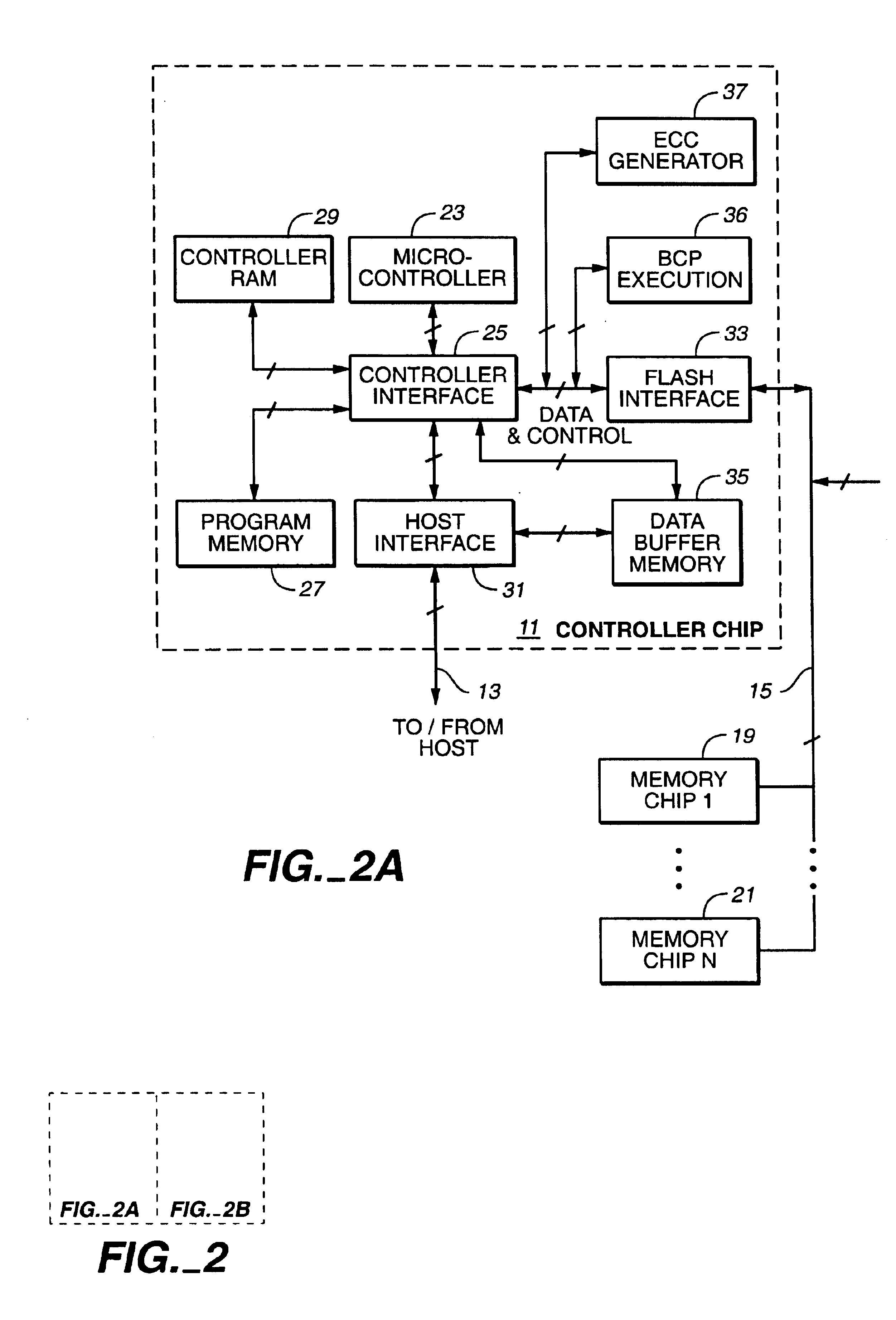

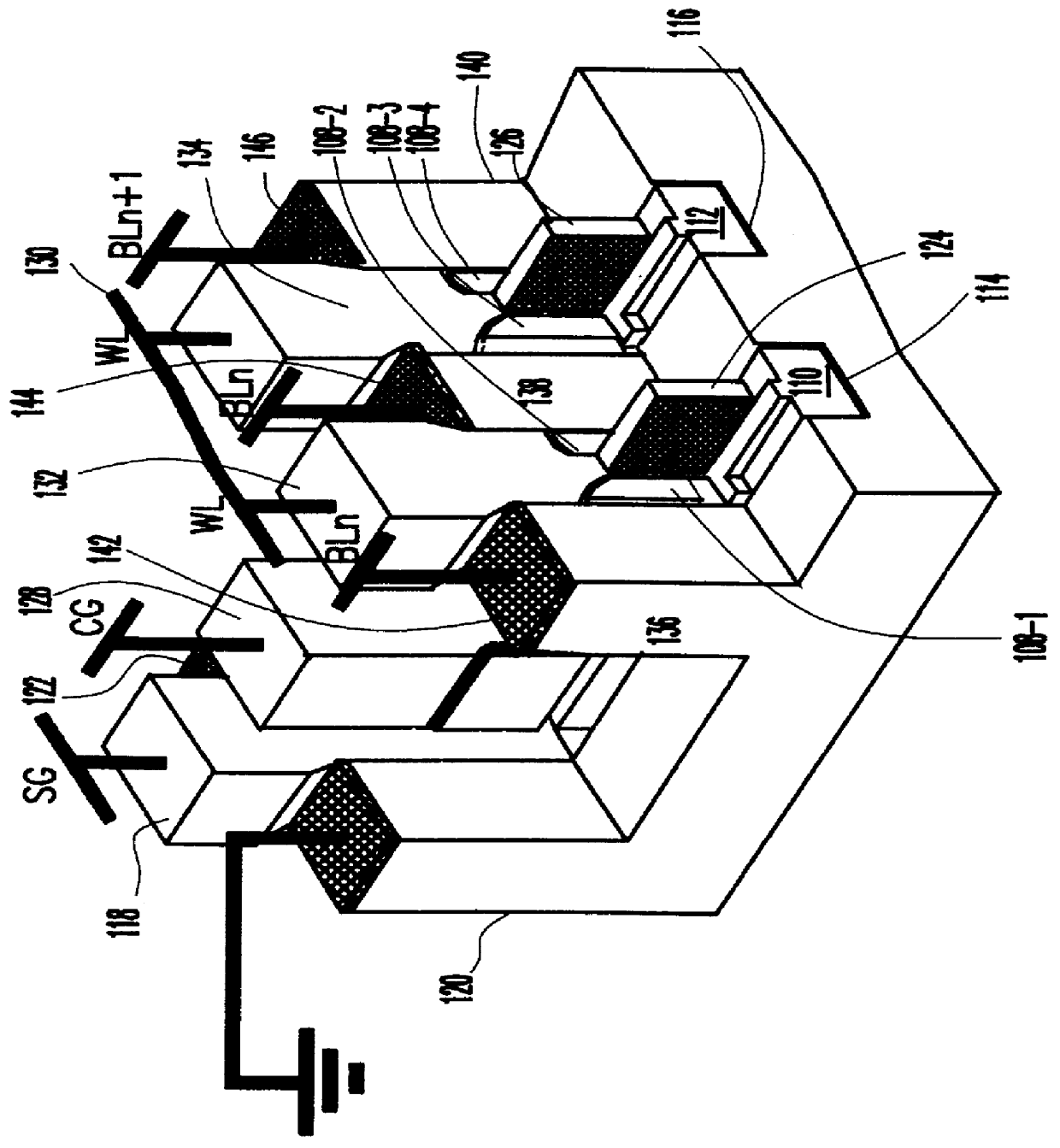

Method of reducing disturbs in non-volatile memory

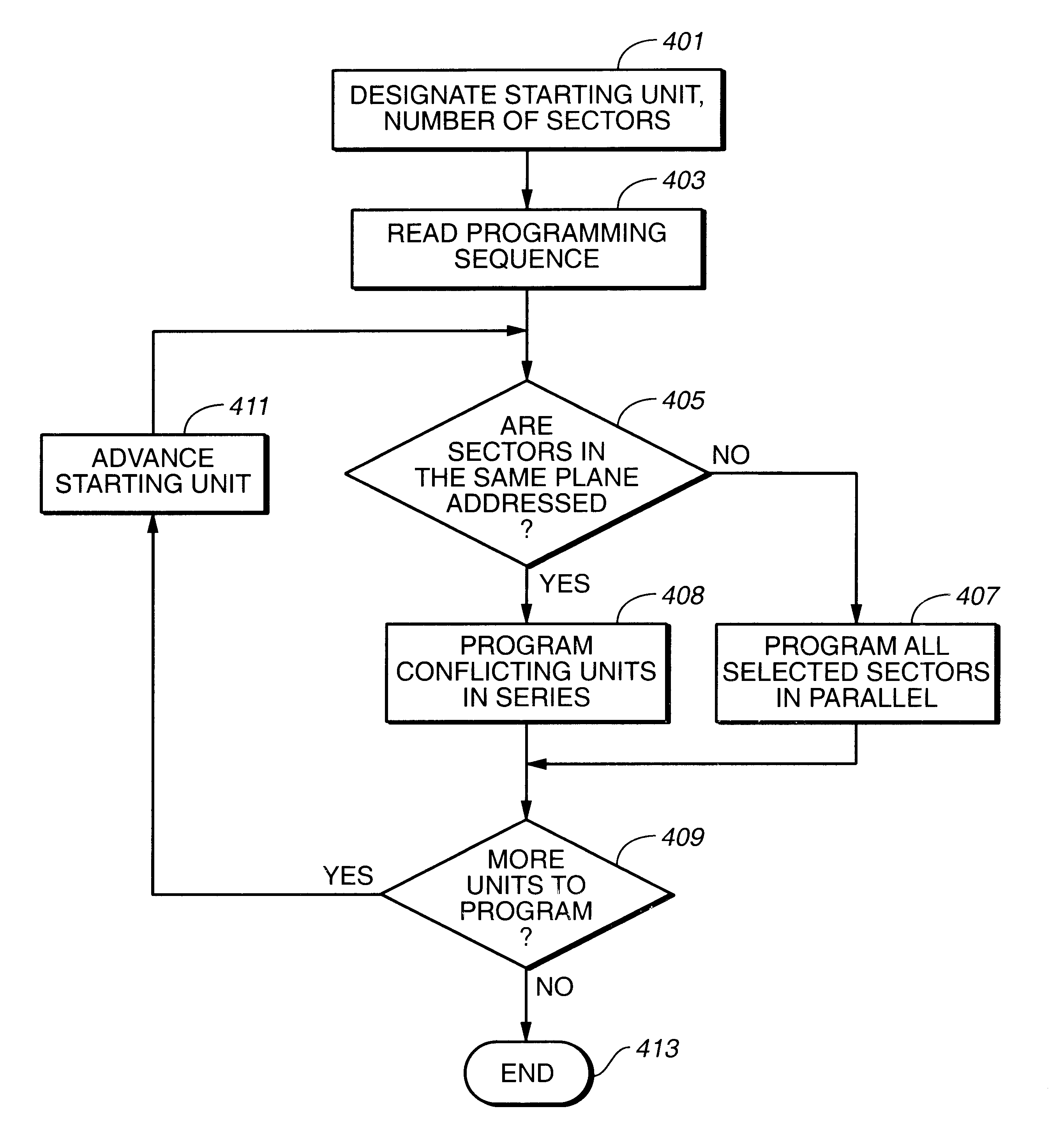

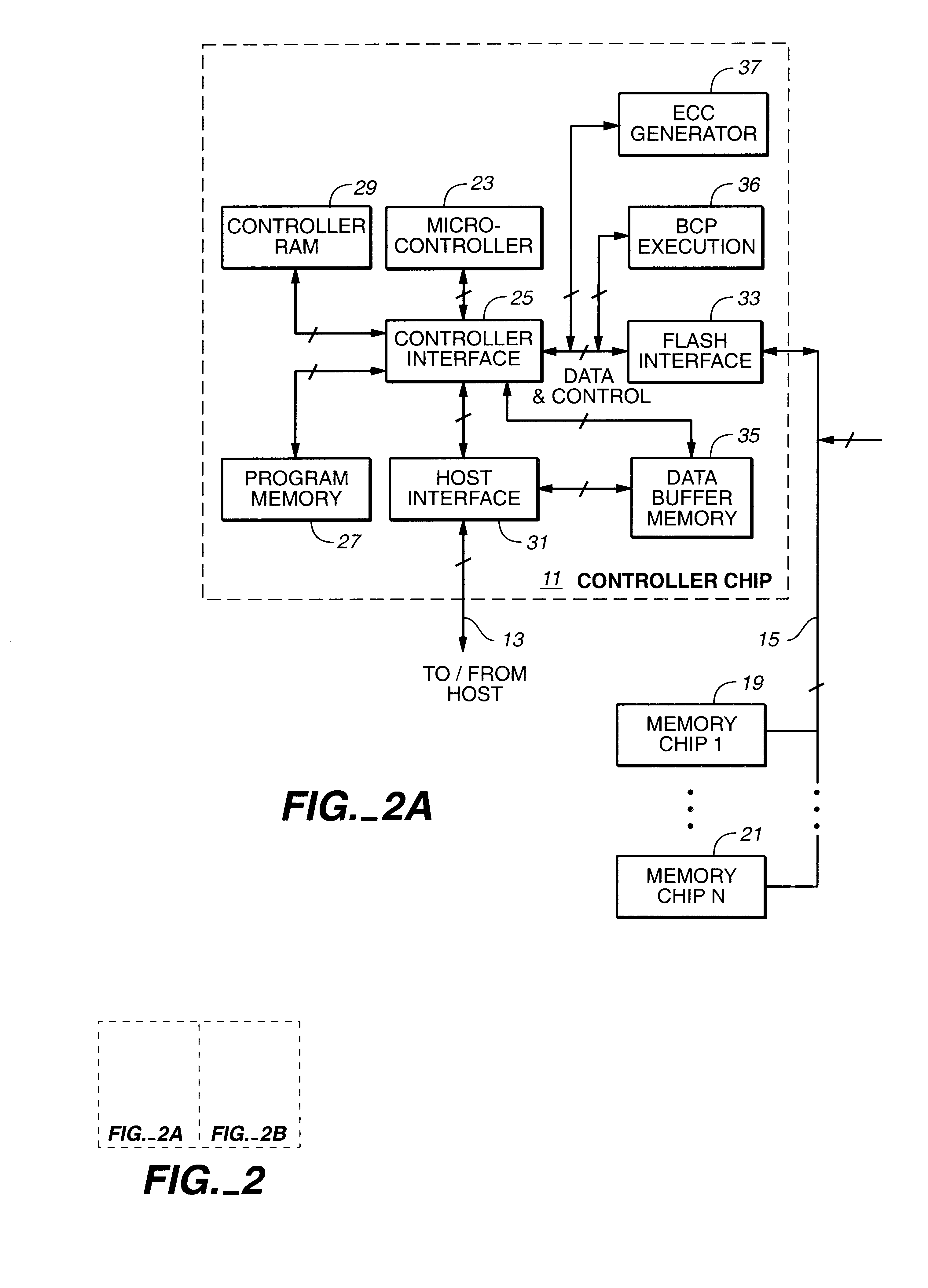

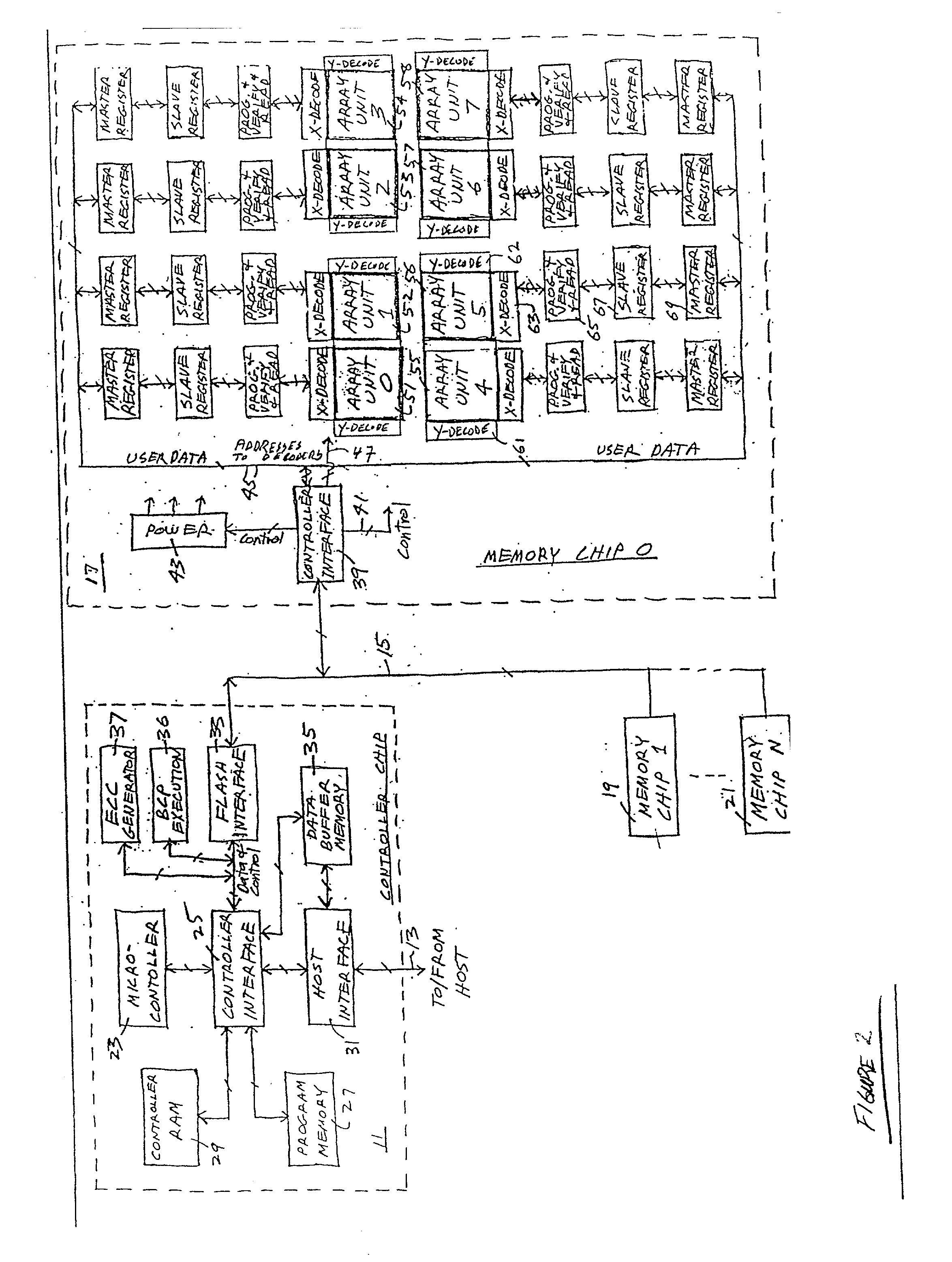

In a non-volatile memory, the displacement current generated in non-selected word lines that results when the voltage levels on an array's bit lines are changed can result in disturbs. Techniques for reducing these currents are presented. In a first aspect, the number of cells being simultaneously programmed on a word line is reduced. In a non-volatile memory where an array of memory cells is composed of a number of units, and the units are combined into planes that share common word lines, the simultaneous programming of units within the same plane is avoided. Multiple units may be programmed in parallel, but these are arranged to be in separate planes. This is done by selecting the number of units to be programmed in parallel and their order such that all the units programmed together are from distinct planes, by comparing the units to be programmed to see if any are from the same plane, or a combination of these. In a second, complementary aspect, the rate at which the voltage levels on the bit lines are changed is adjustable. By monitoring the frequency of disturbs, or based upon the device's application, the rate at which the bit line drivers change the bit line voltage is adjusted. This can be implemented by setting the rate externally, or by the controller based upon device performance and the amount of data error being generated.

Owner:SANDISK TECH LLC

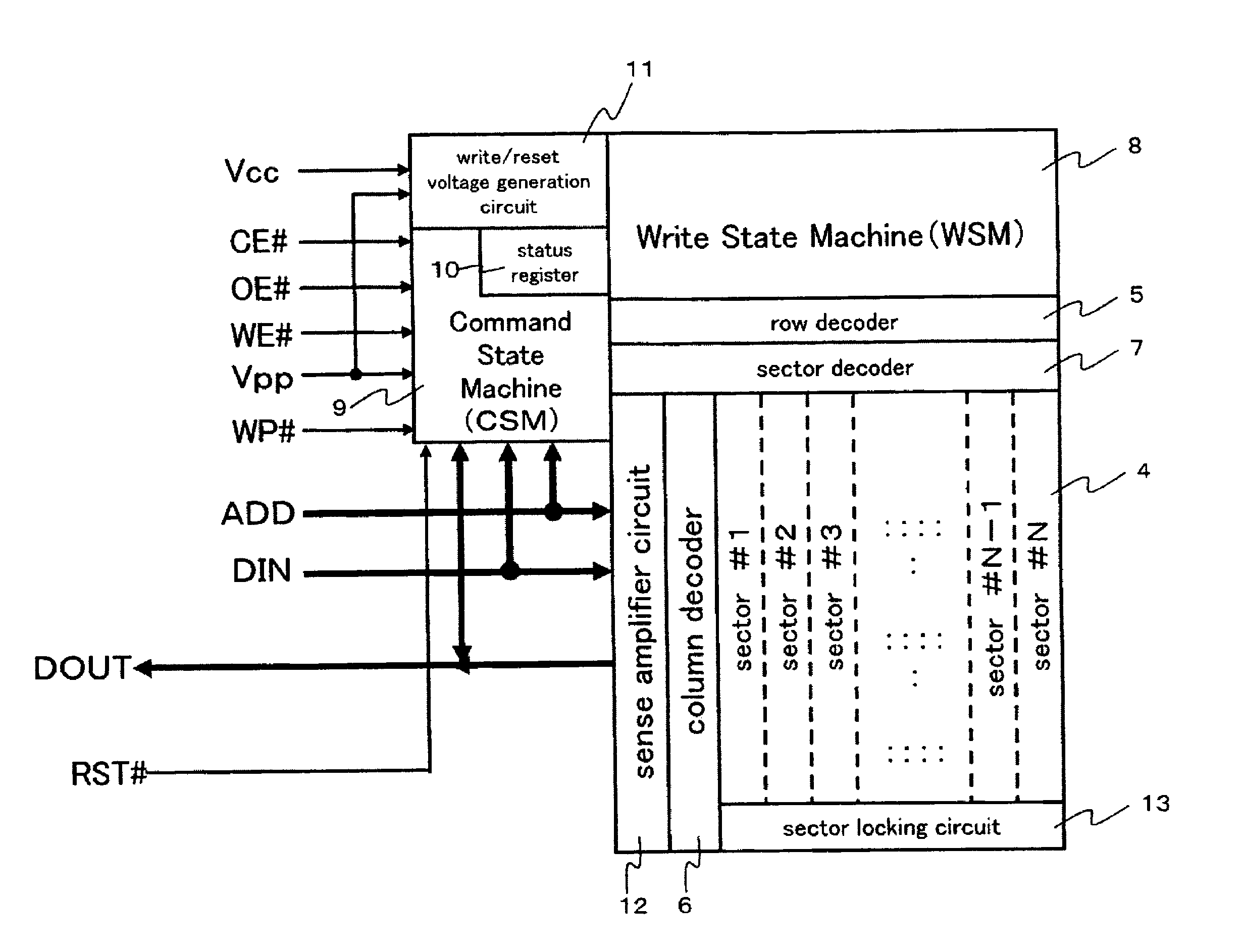

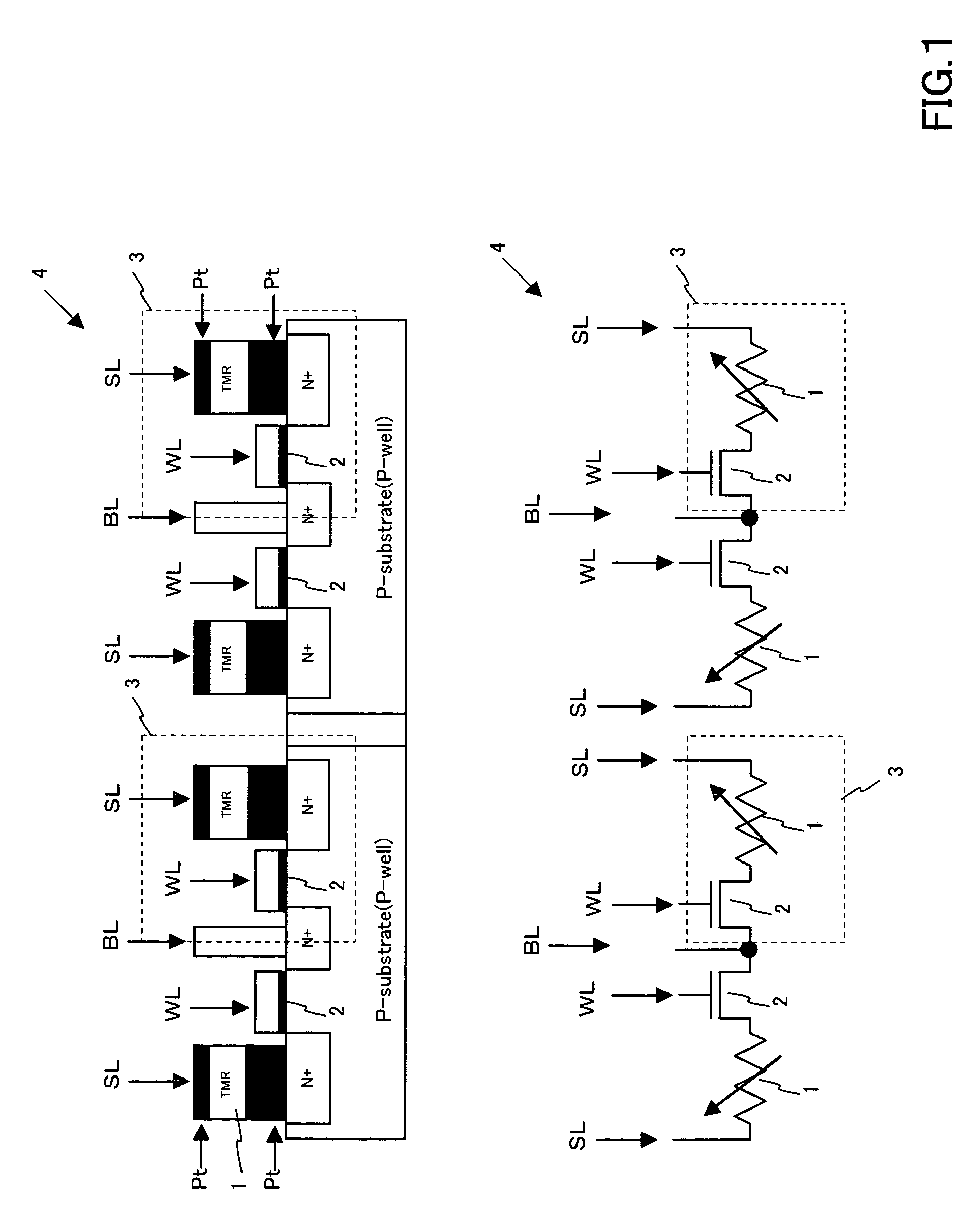

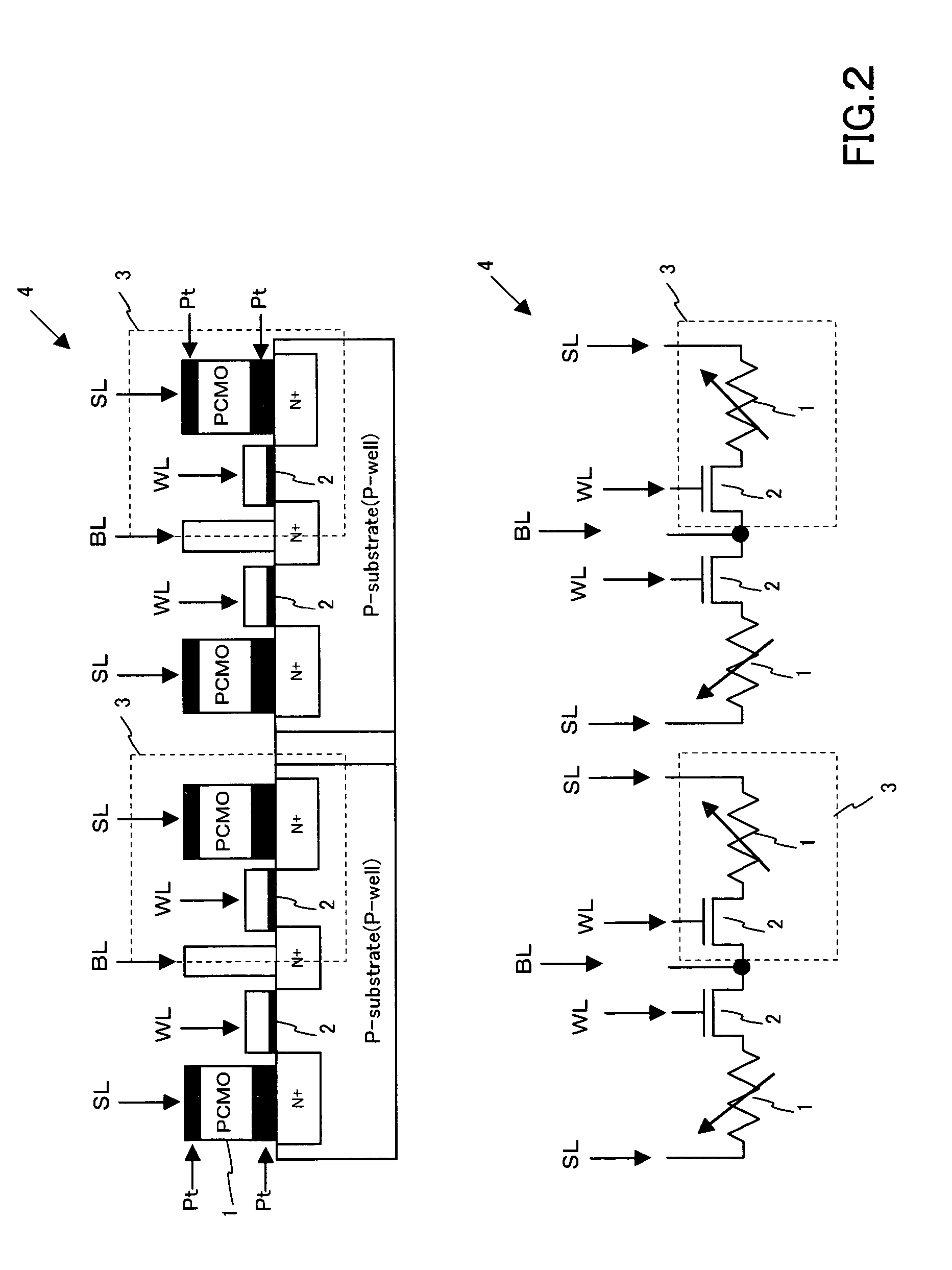

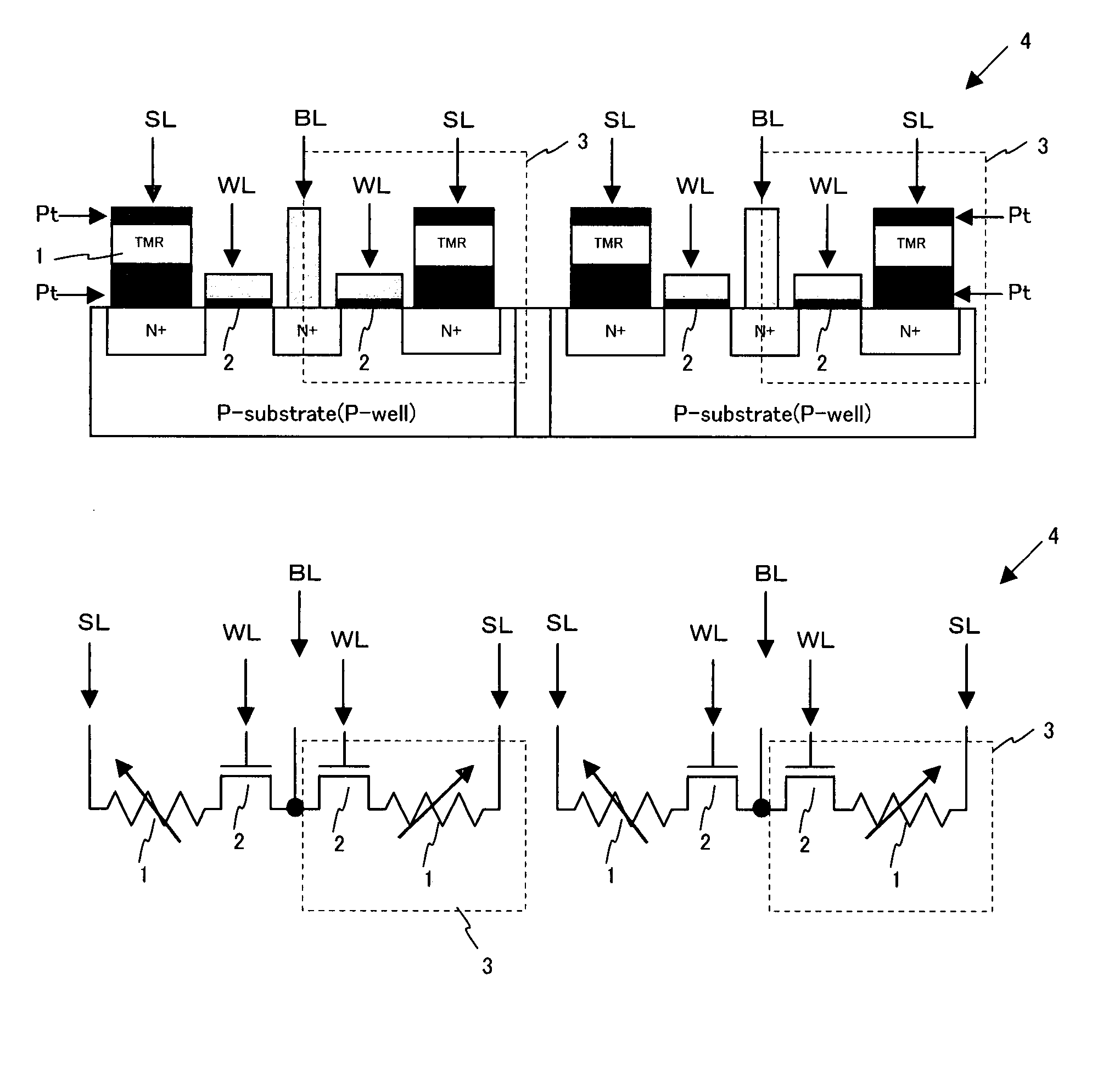

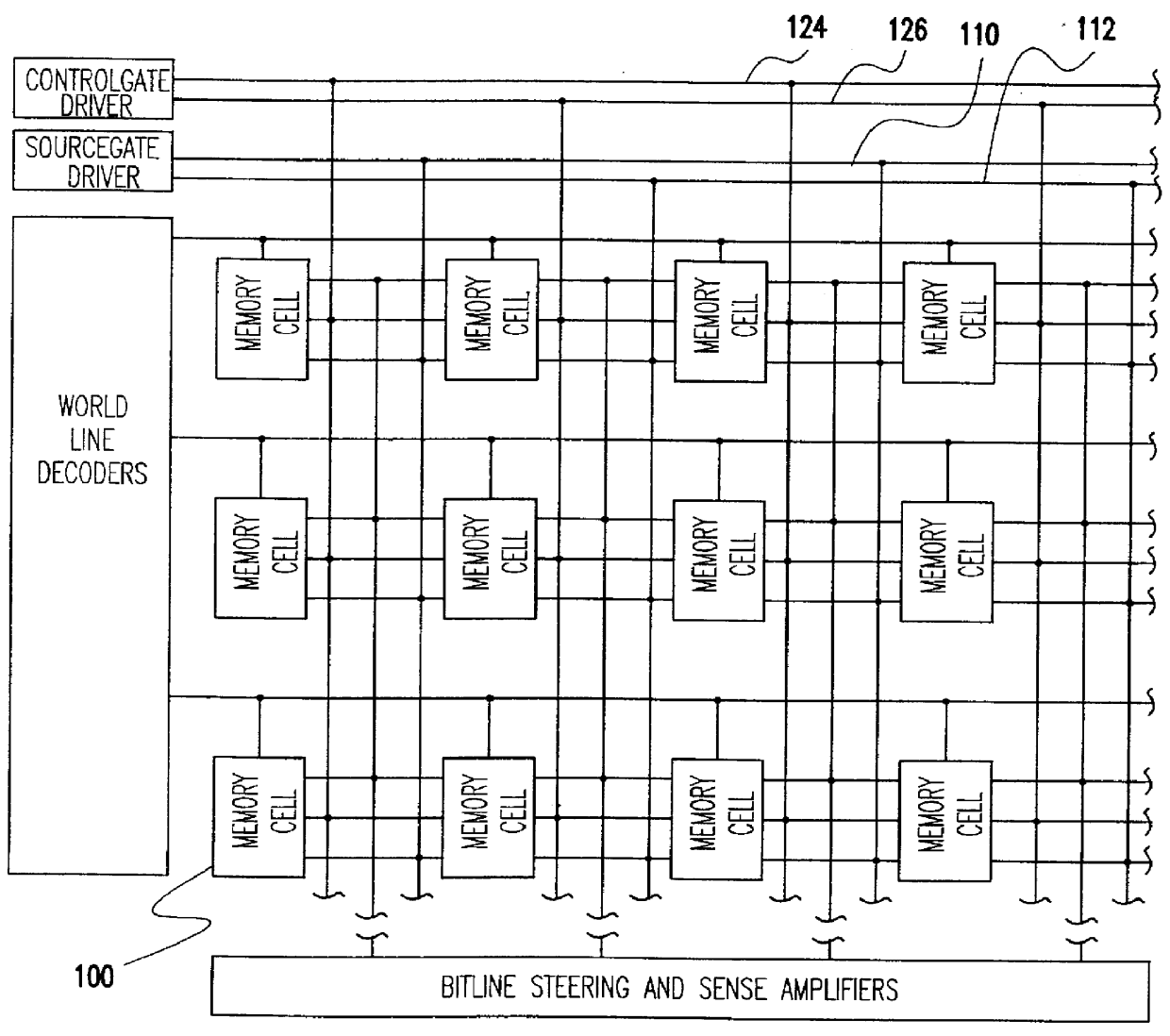

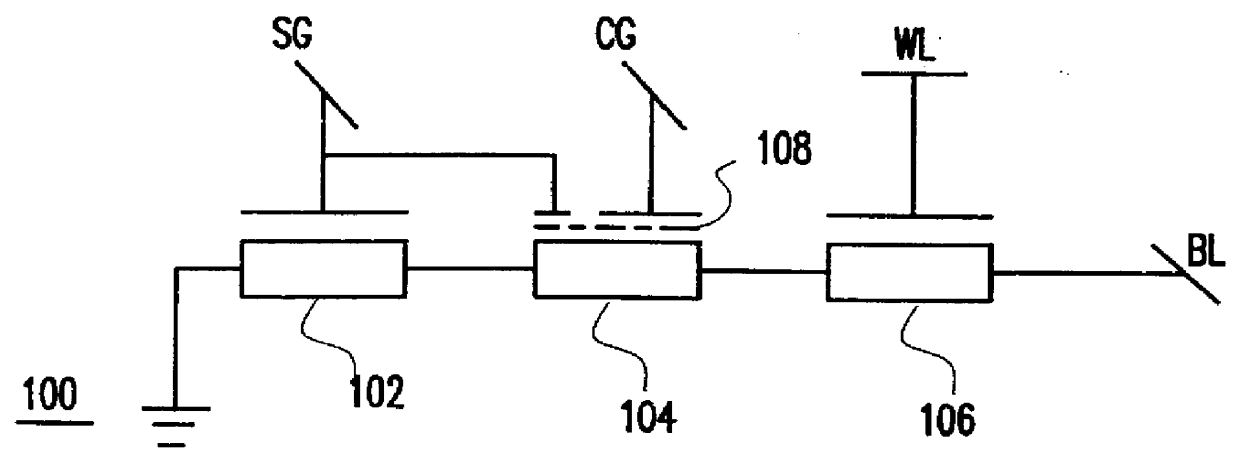

Nonvolatile semiconductor memory device

ActiveUS7057922B2Stress minimizationReliable dataNanoinformaticsSolid-state devicesBit lineEngineering

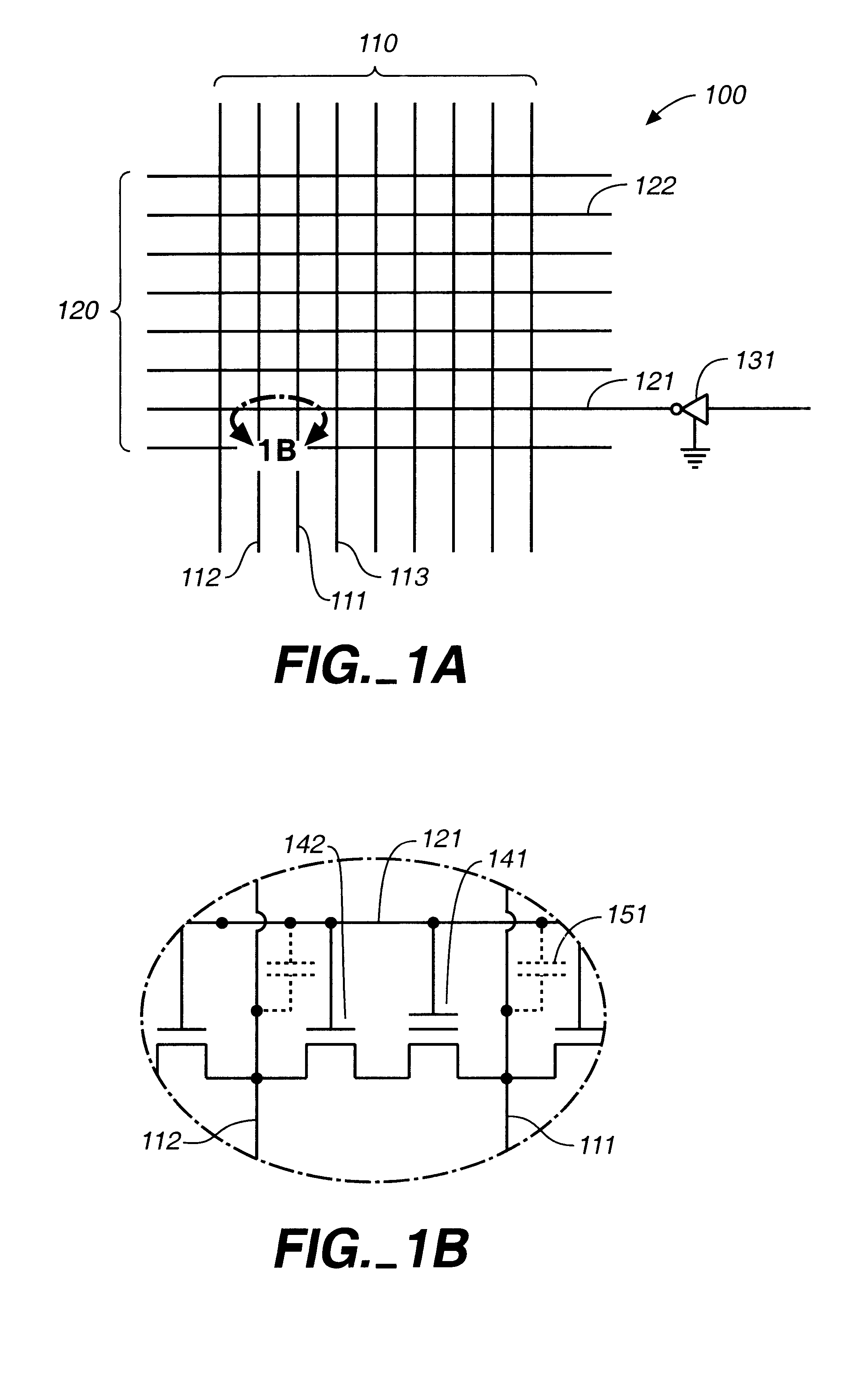

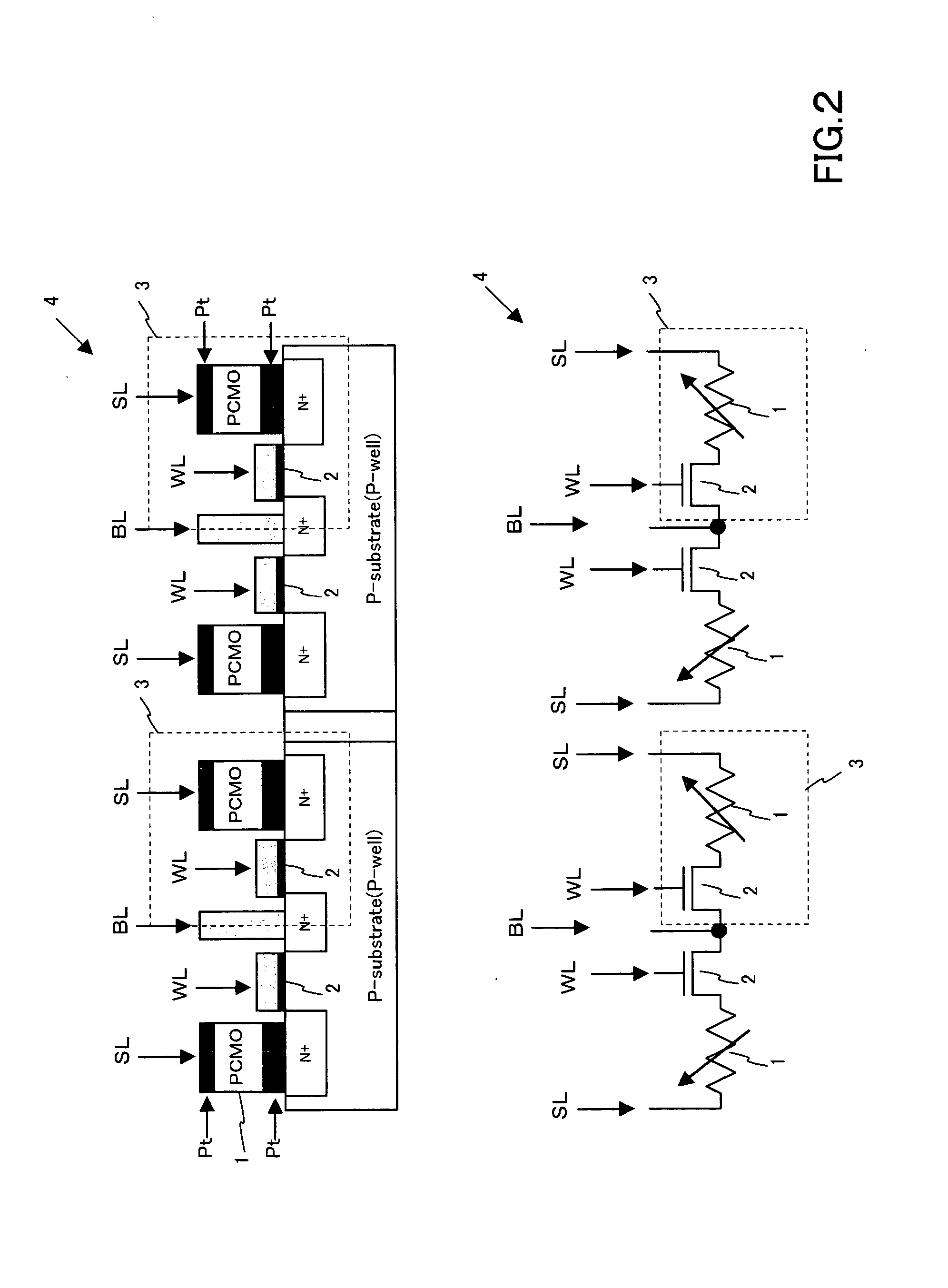

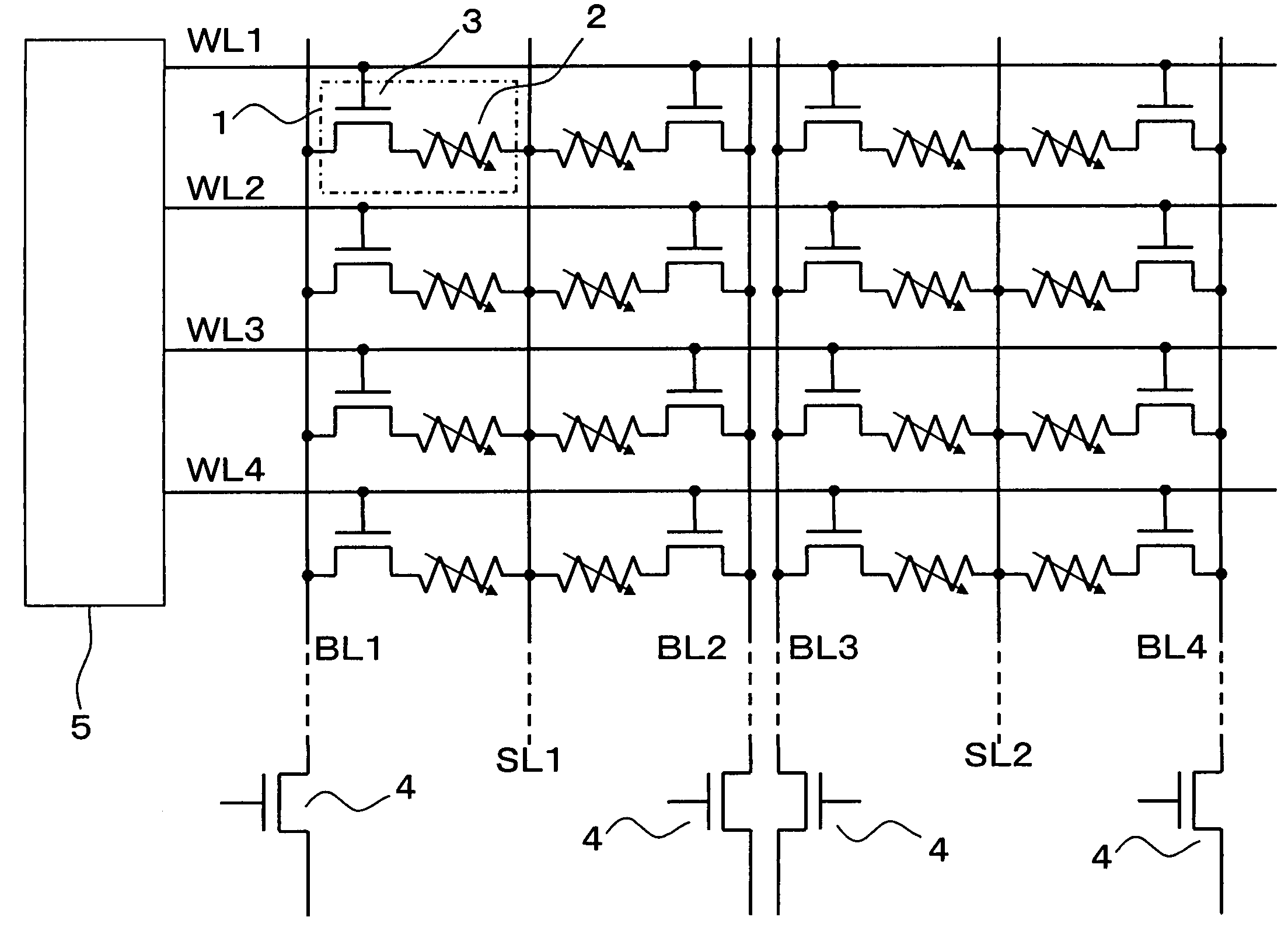

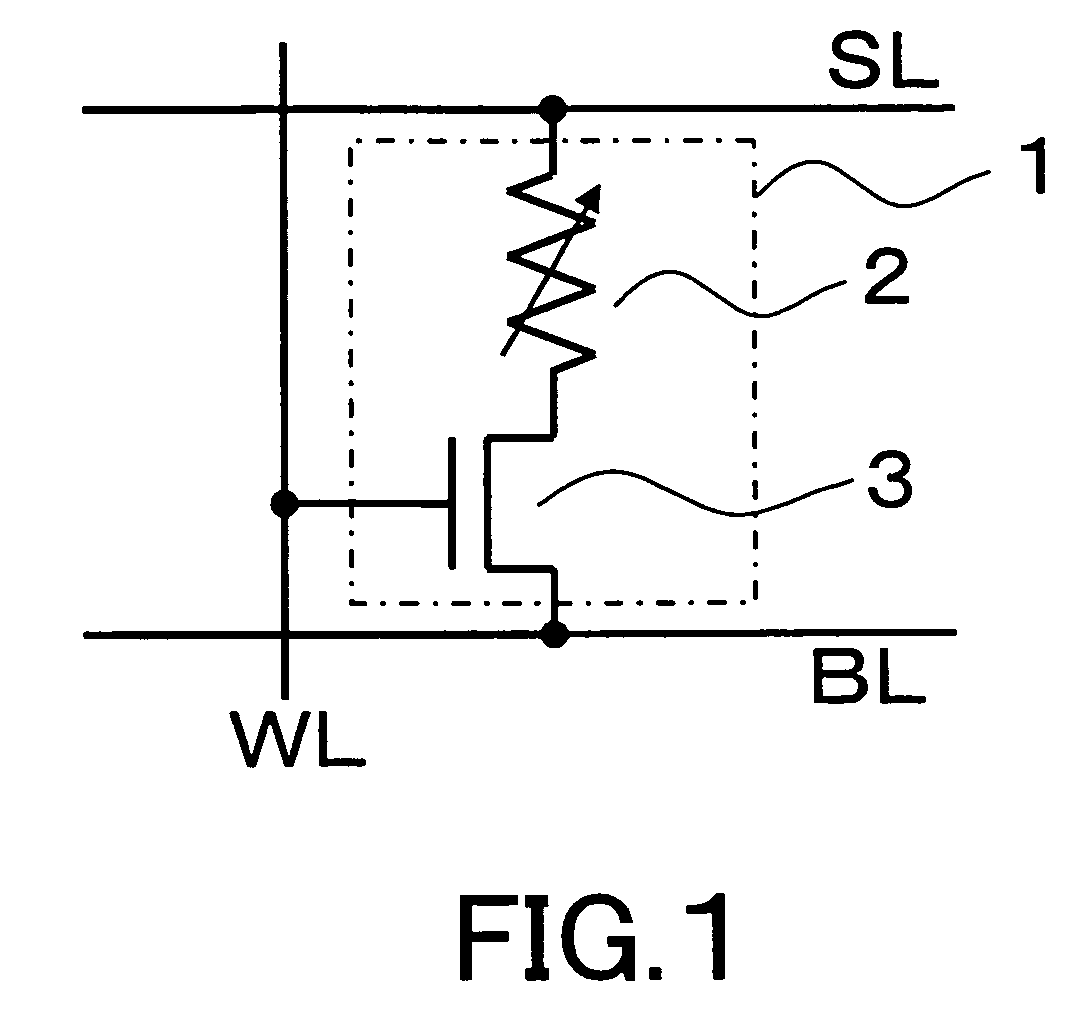

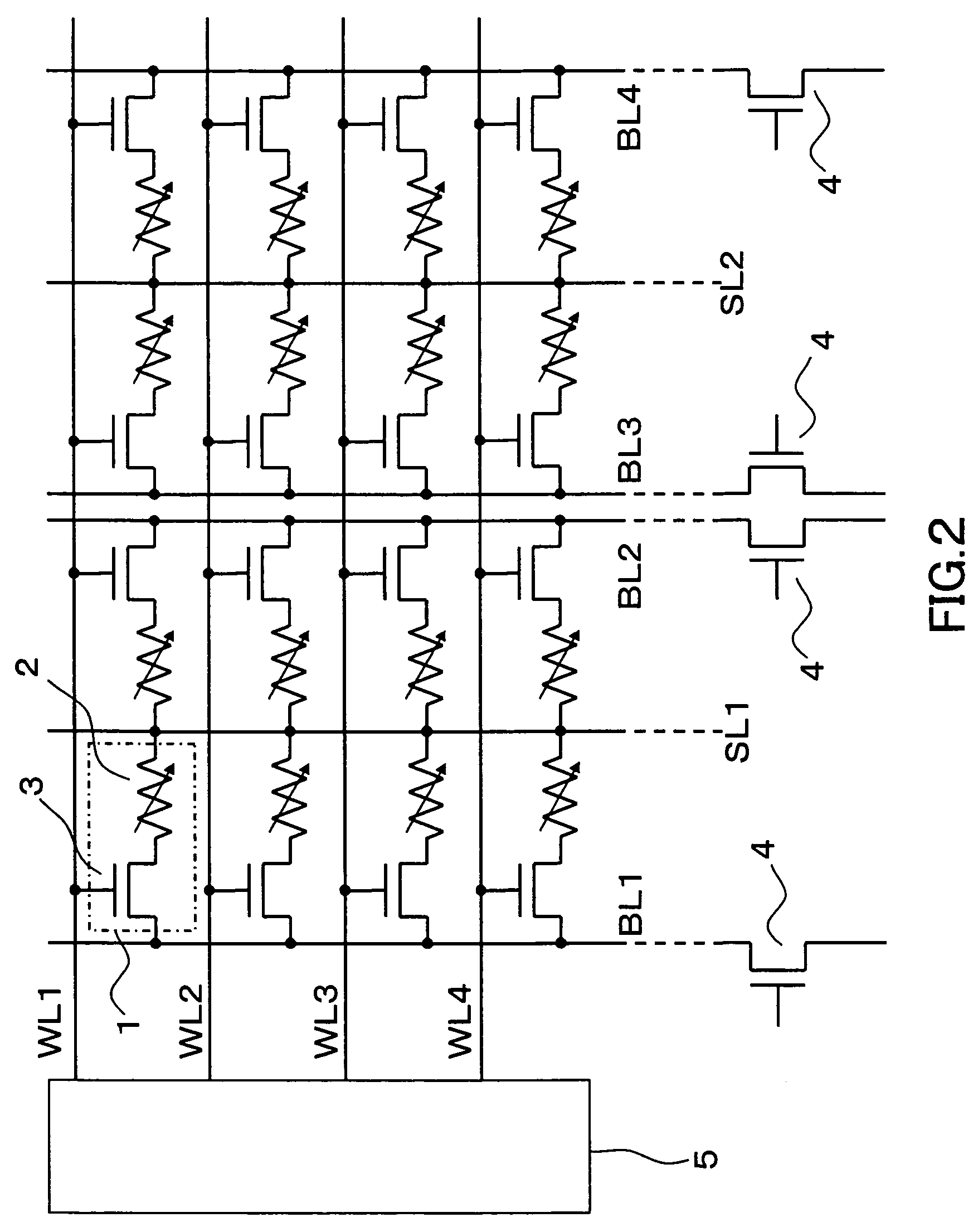

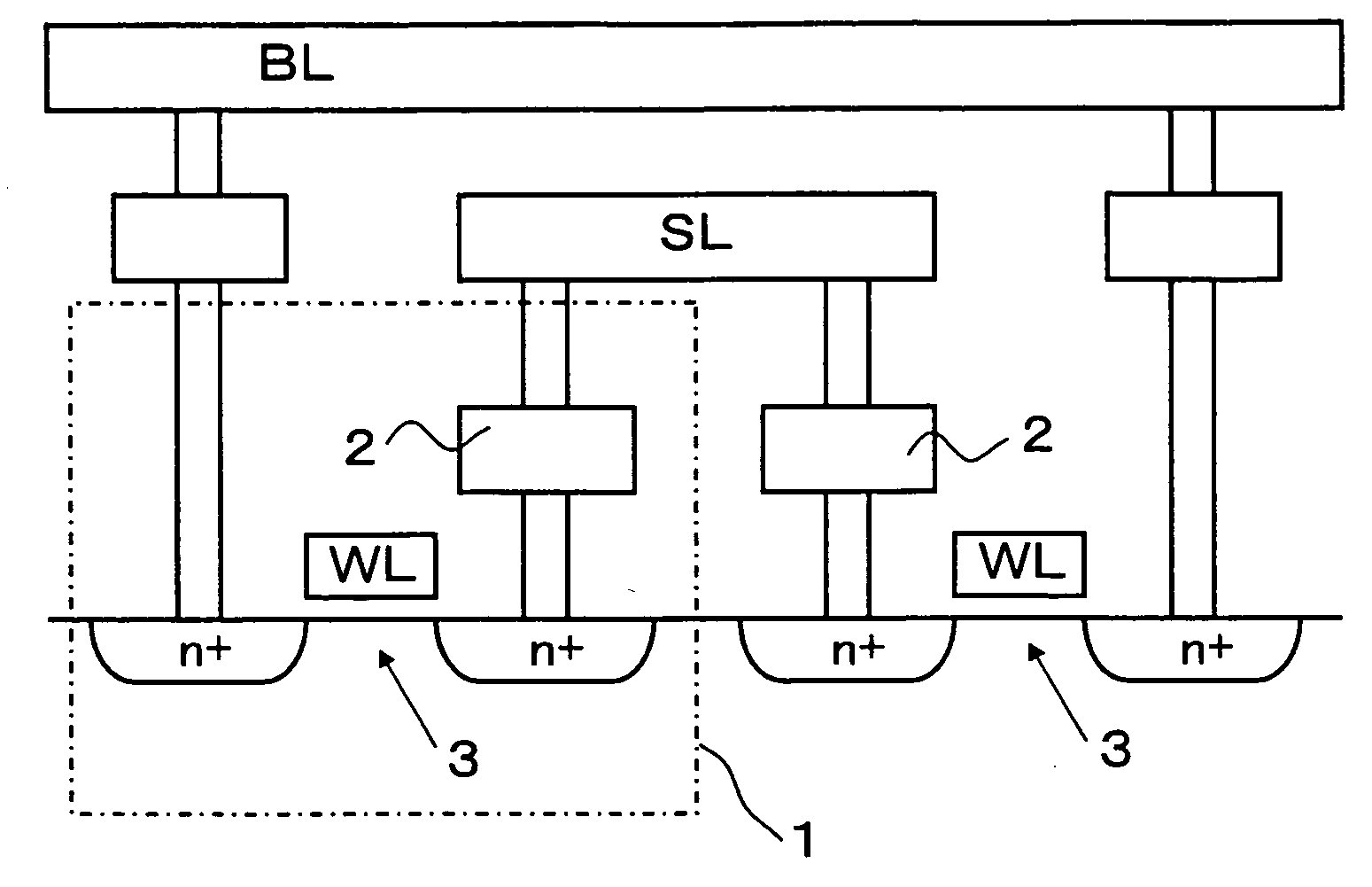

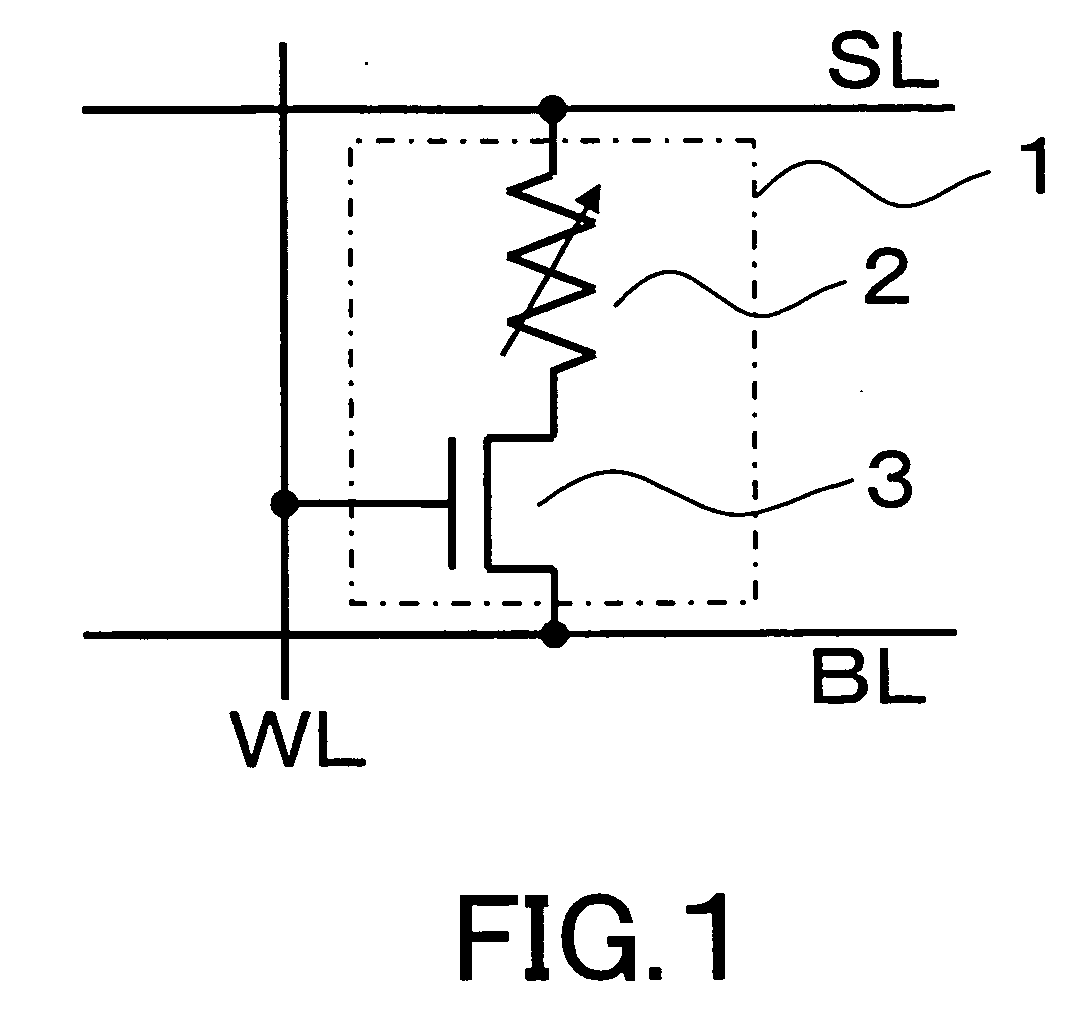

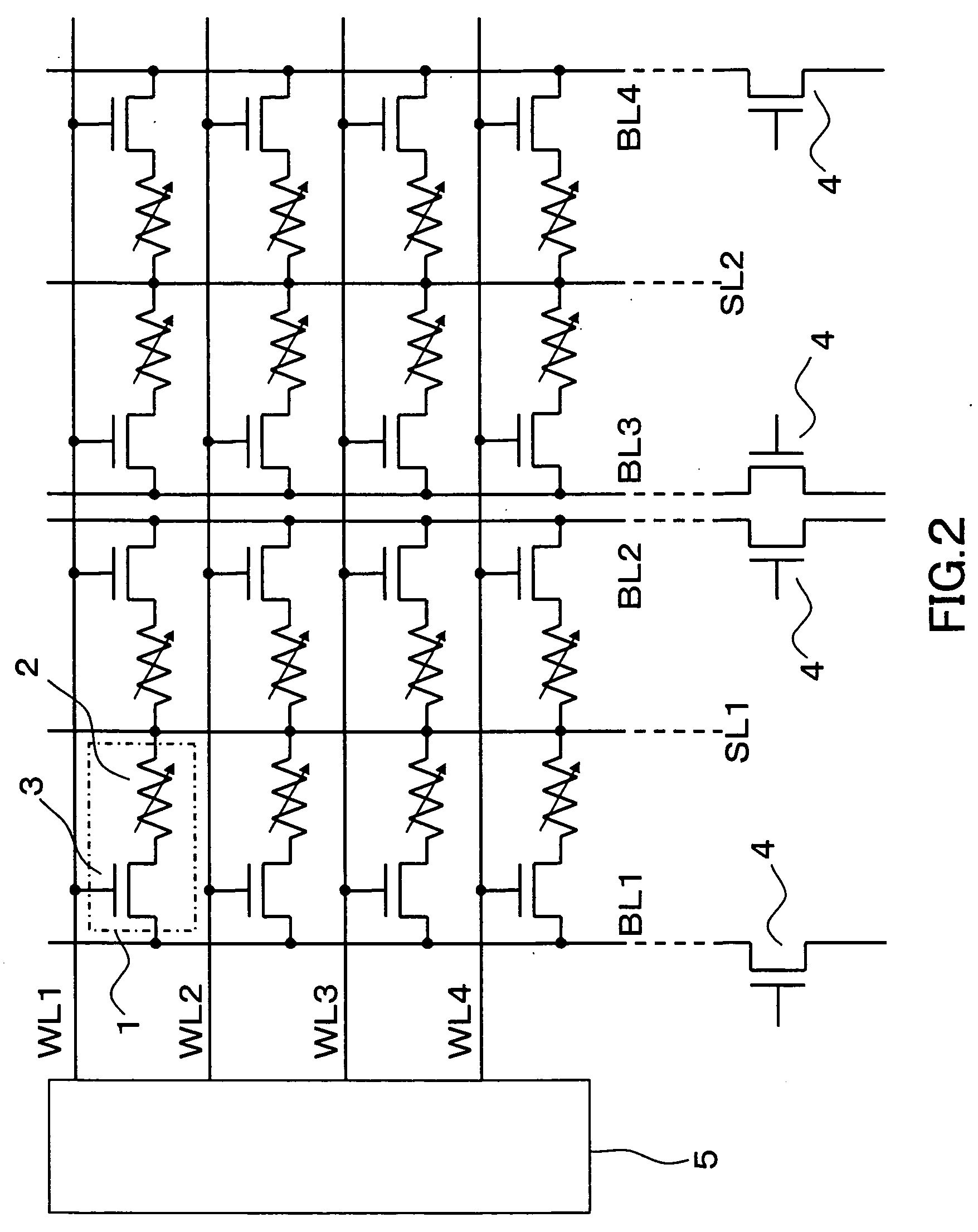

The present invention employs a memory cell structure in that one end of a variable resistance element (1) for storing information by change of electric resistance is connected to a source of a selection transistor (2) to form a memory cell (3) and, in a memory cell array (4), a drain of the selection transistor (2) is connected to a common bit line (BL) in a column direction, the other end of the variable resistance element (1) is connected to a source line (SL) and a gate of the selection transistor (2) is connected to a common word line (WL) in a row direction. In the memory cell structure, an operation of resetting data stored in the memory cell (3) is carried out for each of sectors including the plural memory cells (3) commonly connected to the source line (SL).

Owner:SAMSUNG ELECTRONICS CO LTD

Nonvolatile semiconductor memory device

ActiveUS20050122768A1Minimize of currentMinimize stress of voltageNanoinformaticsSolid-state devicesBit lineCommon word

The present invention employs a memory cell structure in that one end of a variable resistance element (1) for storing information by change of electric resistance is connected to a source of a selection transistor (2) to form a memory cell (3) and, in a memory cell array (4), a drain of the selection transistor (2) is connected to a common bit line (BL) in a column direction, the other end of the variable resistance element (1) is connected to a source line (SL) and a gate of the selection transistor (2) is connected to a common word line (WL) in a row direction. In the memory cell structure, an operation of resetting data stored in the memory cell (3) is carried out for each of sectors including the plural memory cells (3) commonly connected to the source line (SL).

Owner:SAMSUNG ELECTRONICS CO LTD

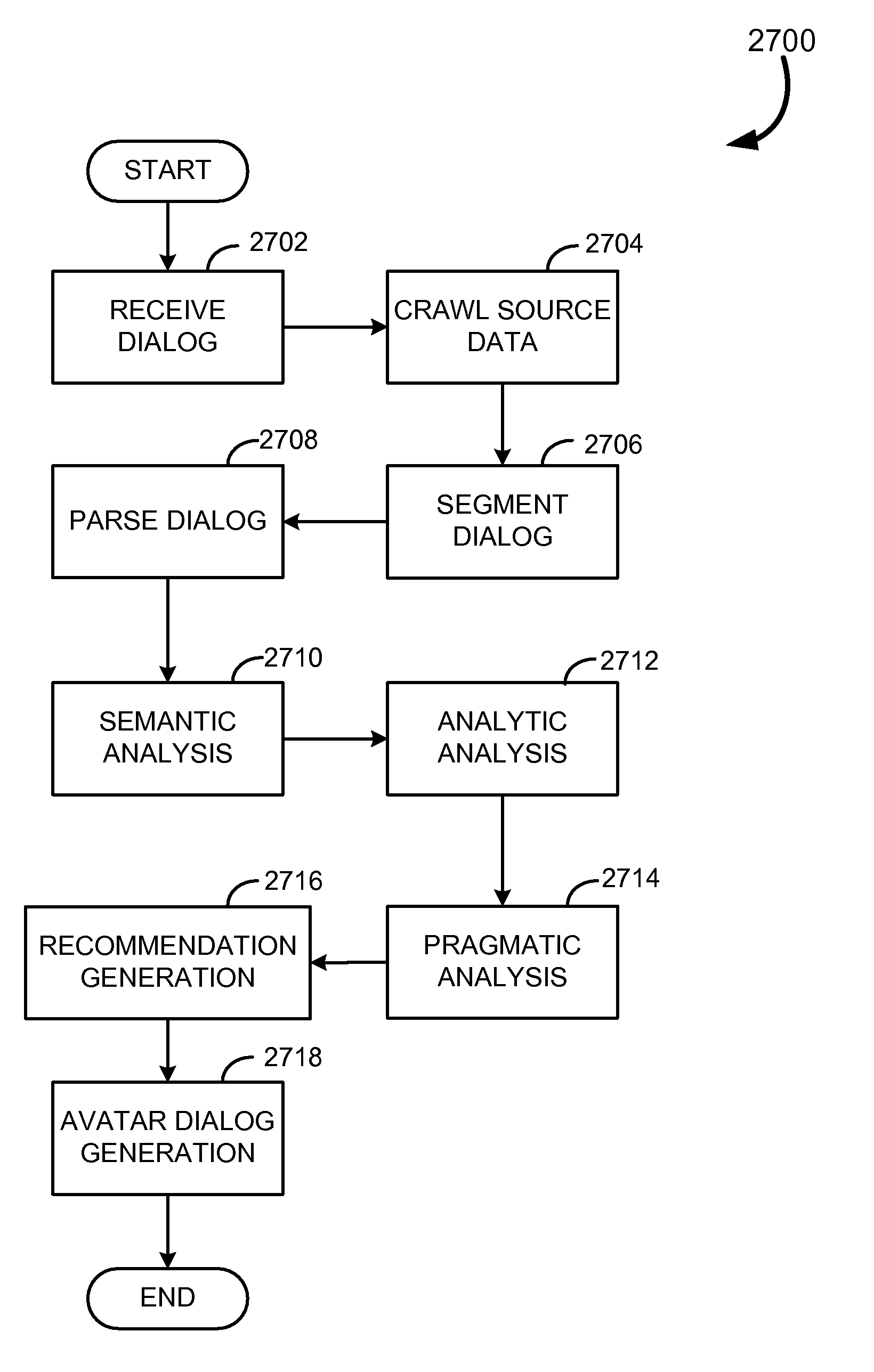

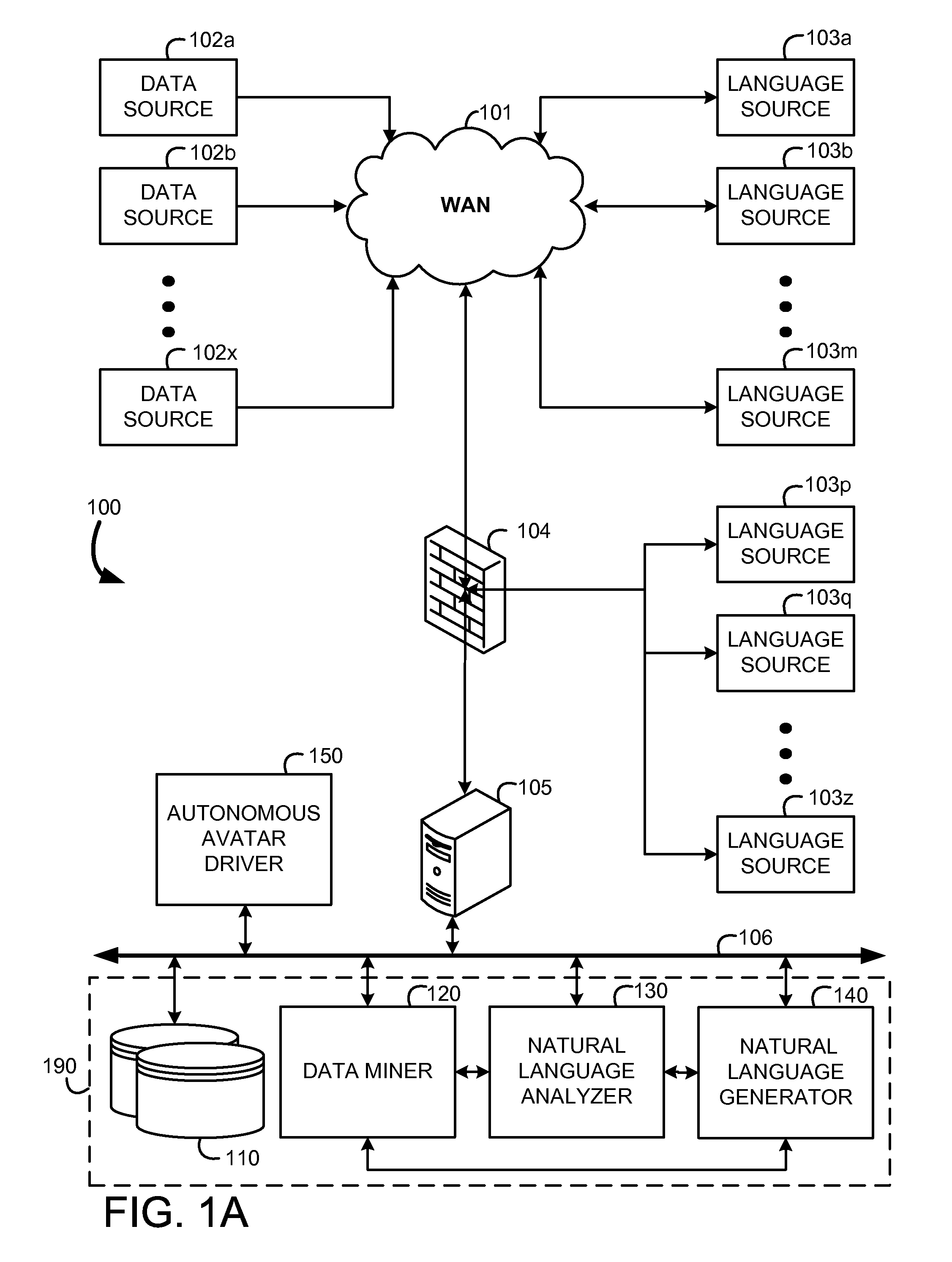

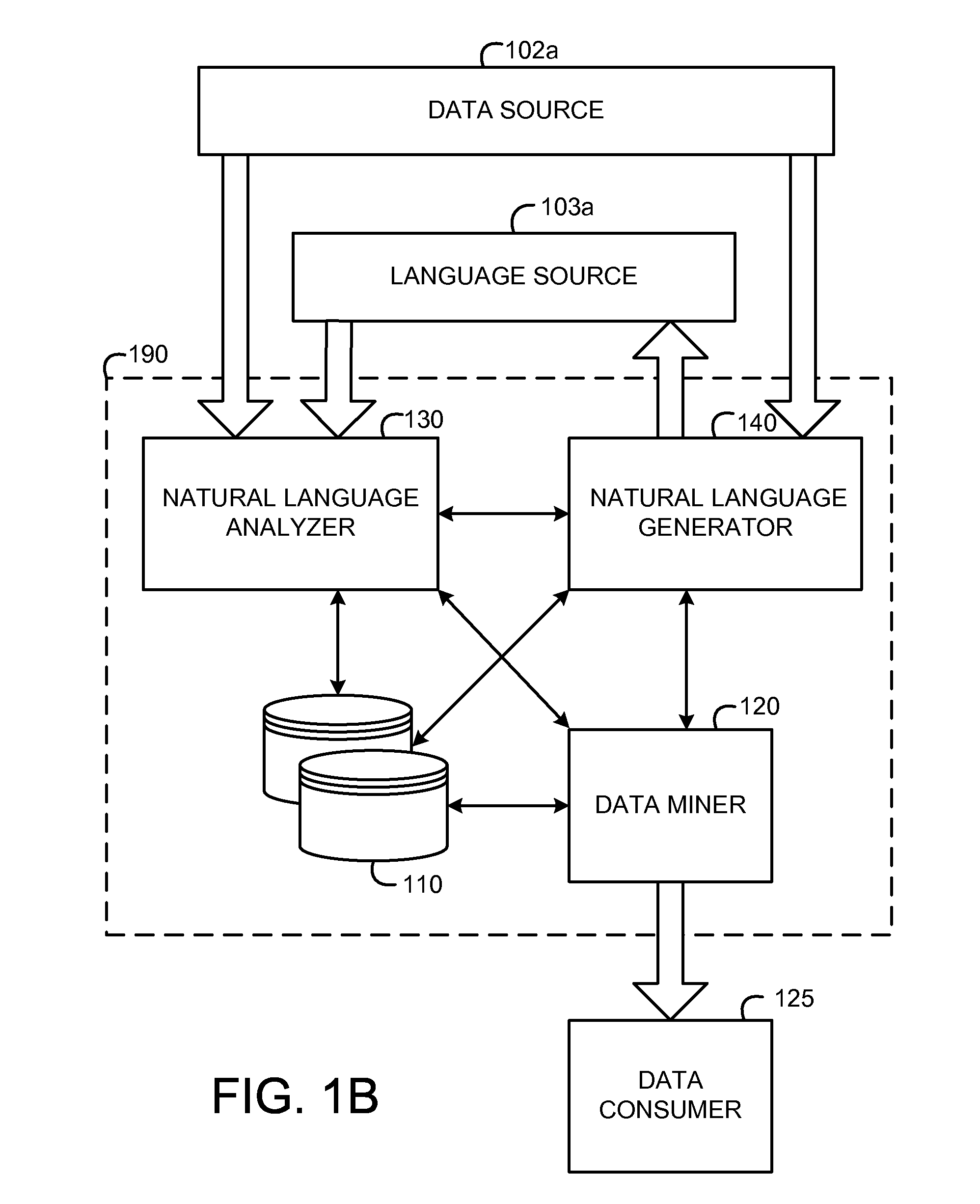

Systems and methods for an autonomous avatar driver

InactiveUS20080221892A1High reliabilityNatural language data processingAnimationSemantic lexiconCommon word

The autonomous avatar driver is useful in association with language sources. A sourcer may receive dialog from the language source. It may also, in some embodiments, receive external data from data sources. A segmentor may convert characters, represent particles and split dialog. A parser may then apply a link grammar, analyze grammatical mood, tag the dialog and prune dialog variants. A semantic engine may lookup token frames, generate semantic lexicons and semantic networks, and resolve ambiguous co-references. An analytics engine may filter common words from dialog, analyze N-grams, count lemmatized words, and analyze nodes. A pragmatics analyzer may resolve slang, generate knowledge templates, group proper nouns and estimate affect of dialog. A recommender may generate tag clouds, cluster the language sources into neighborhoods, recommend social networking to individuals and businesses, and generate contextual advertising. Lastly, a response generator may generate responses for the autonomous avatar using the analyzed dialog. The response generator may also incorporate the generated recommendations.

Owner:BOTANIC TECH INC

Method of reducing disturbs in non-volatile memory

Owner:SANDISK TECH LLC

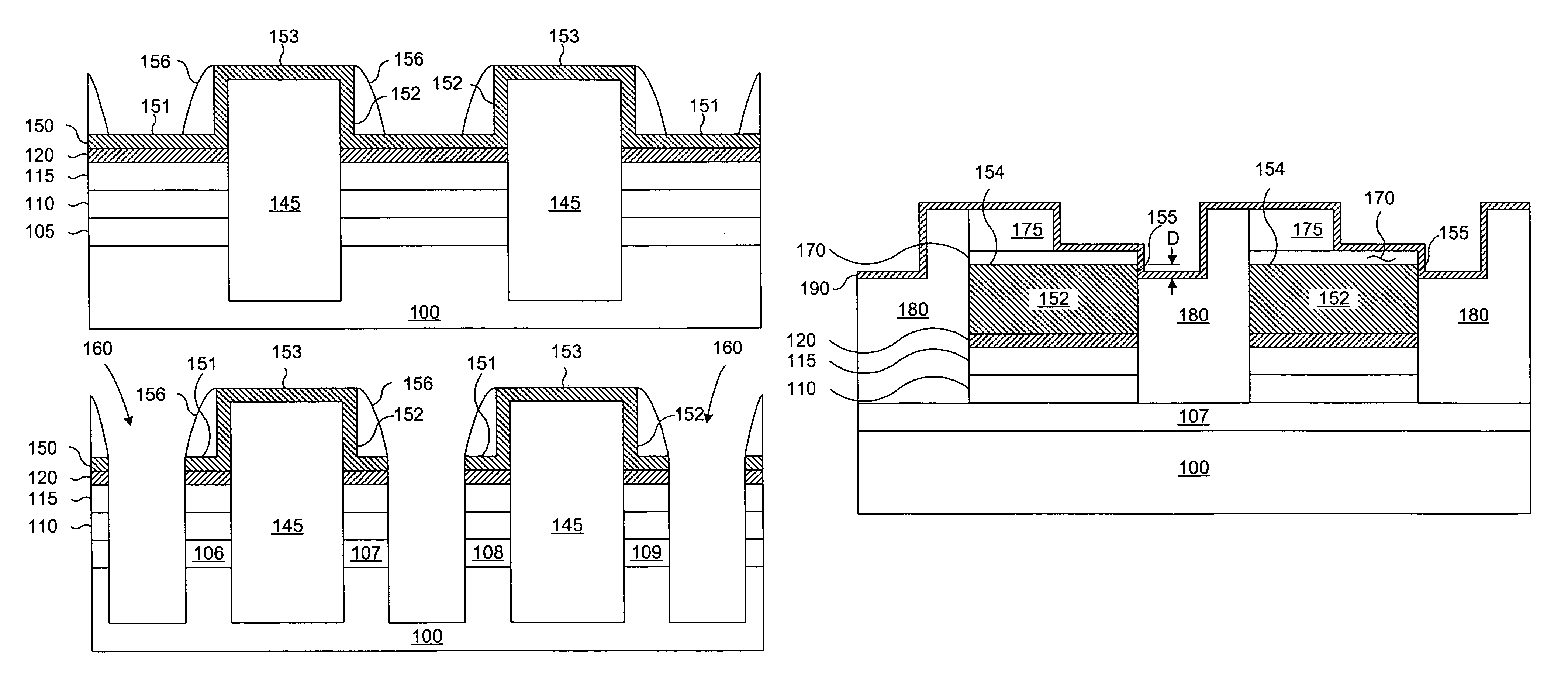

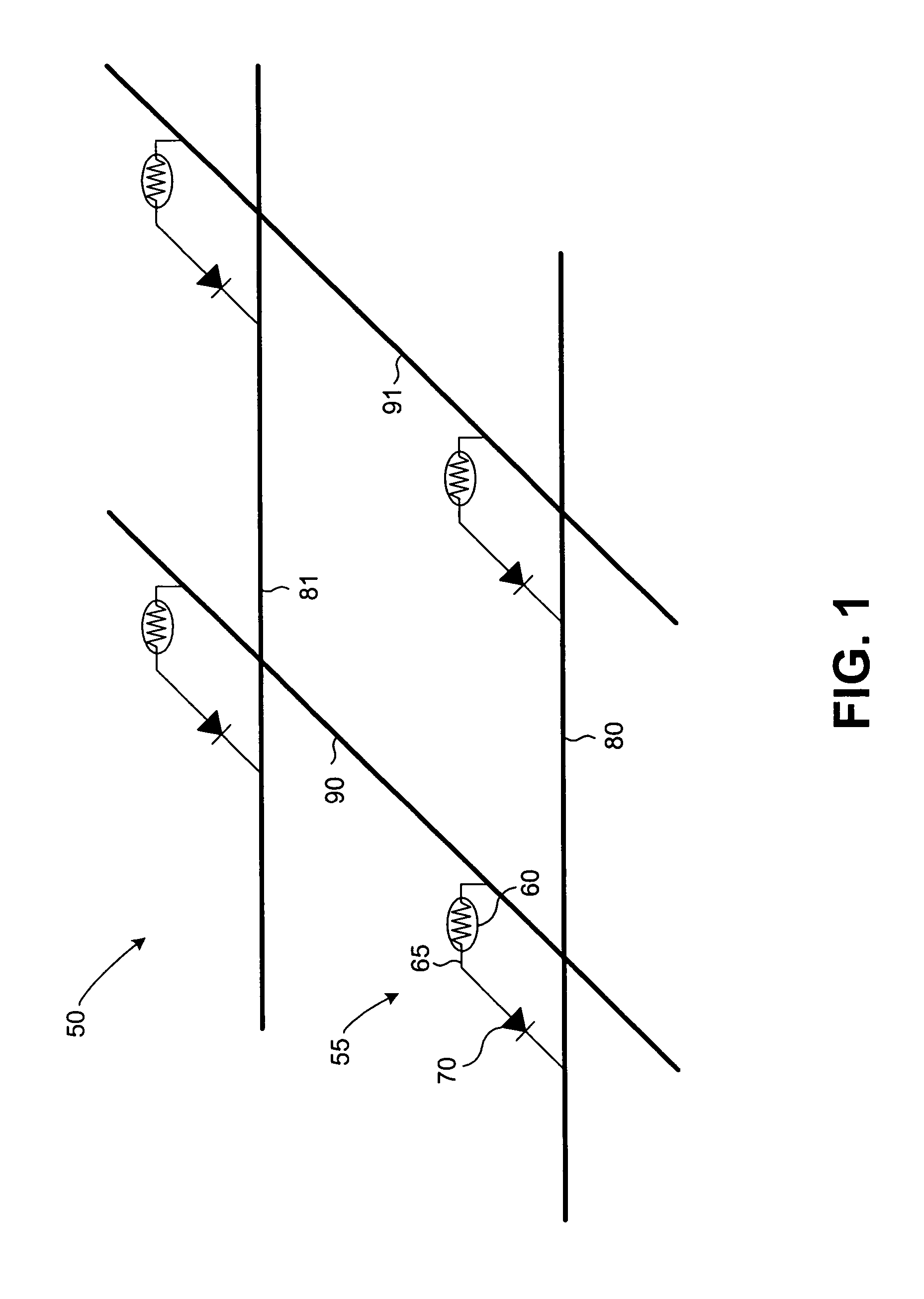

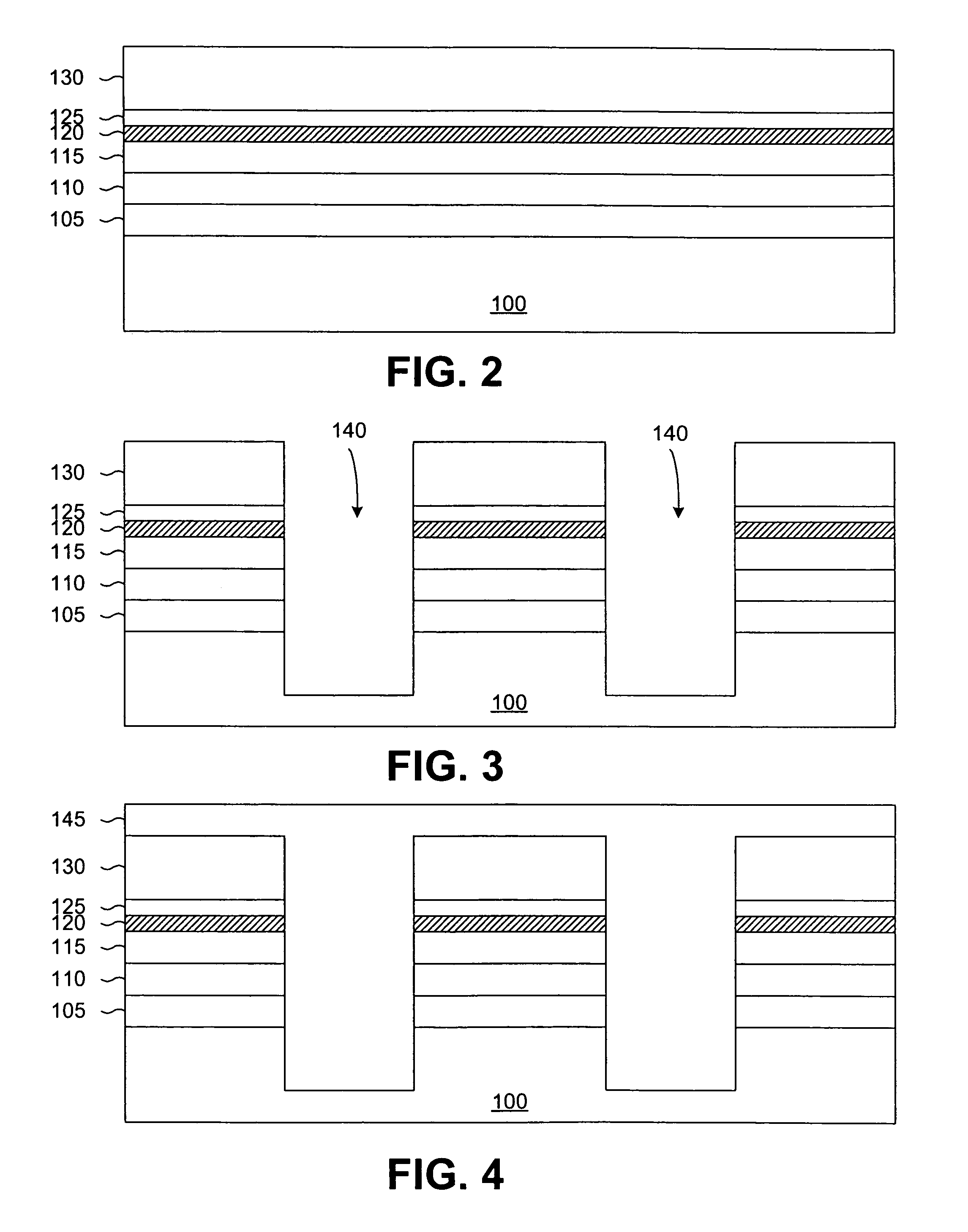

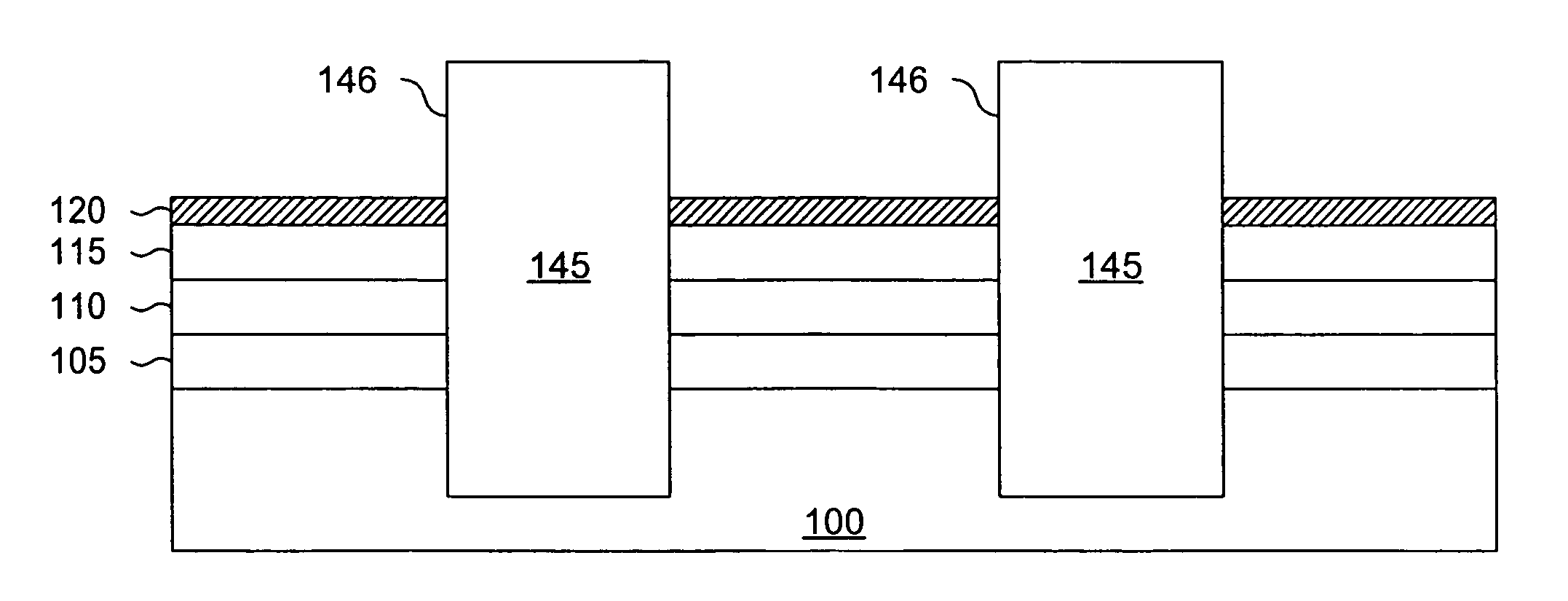

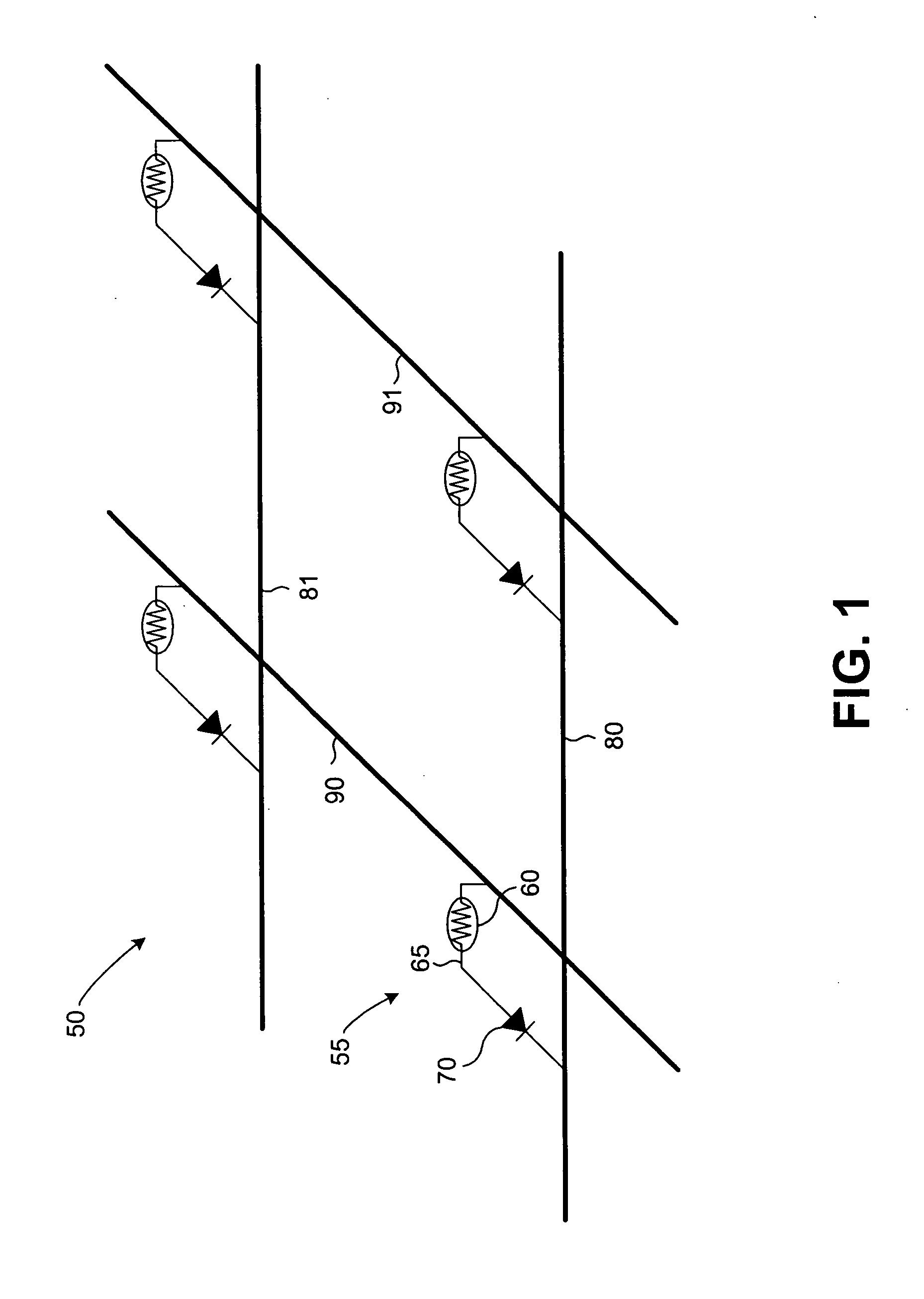

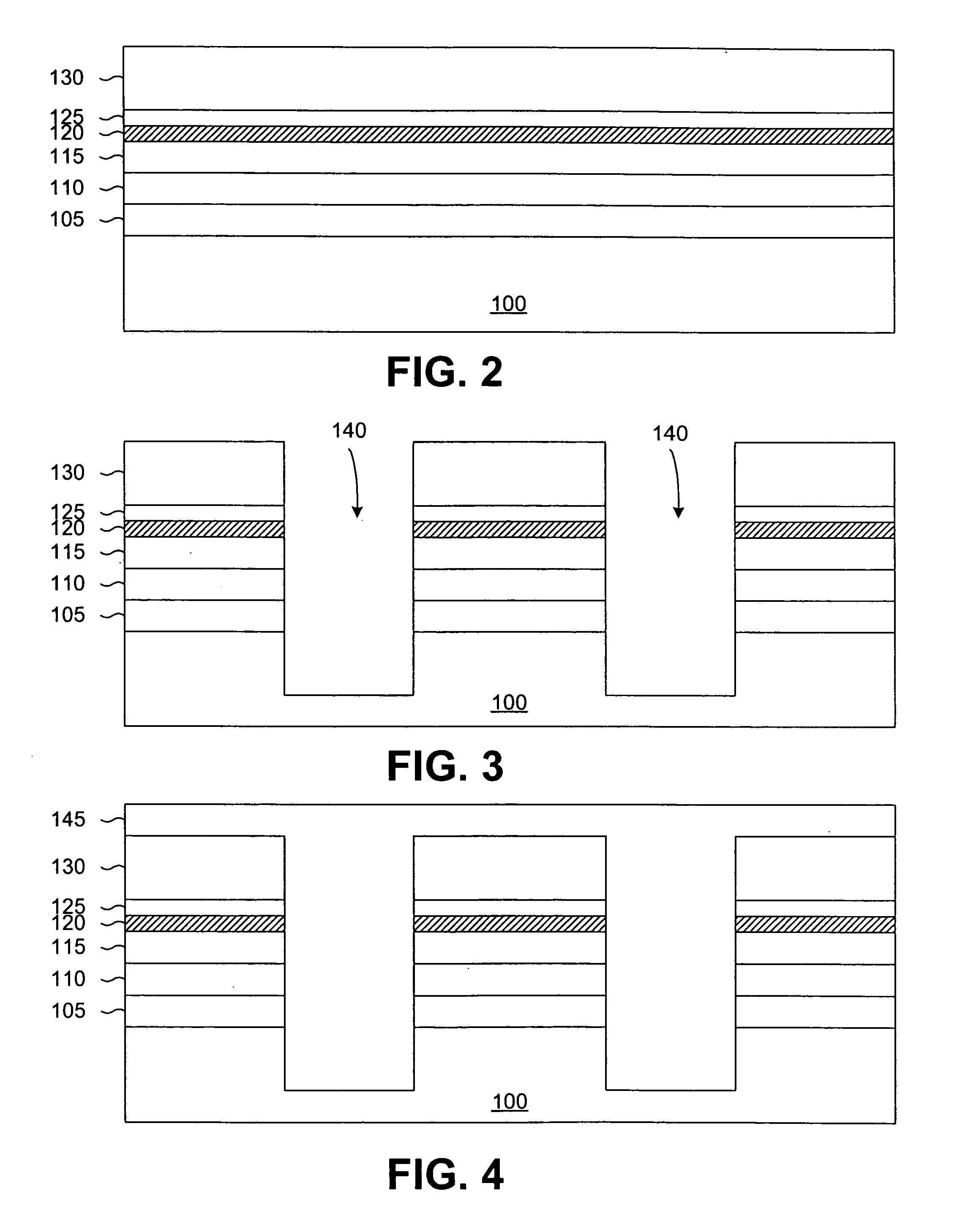

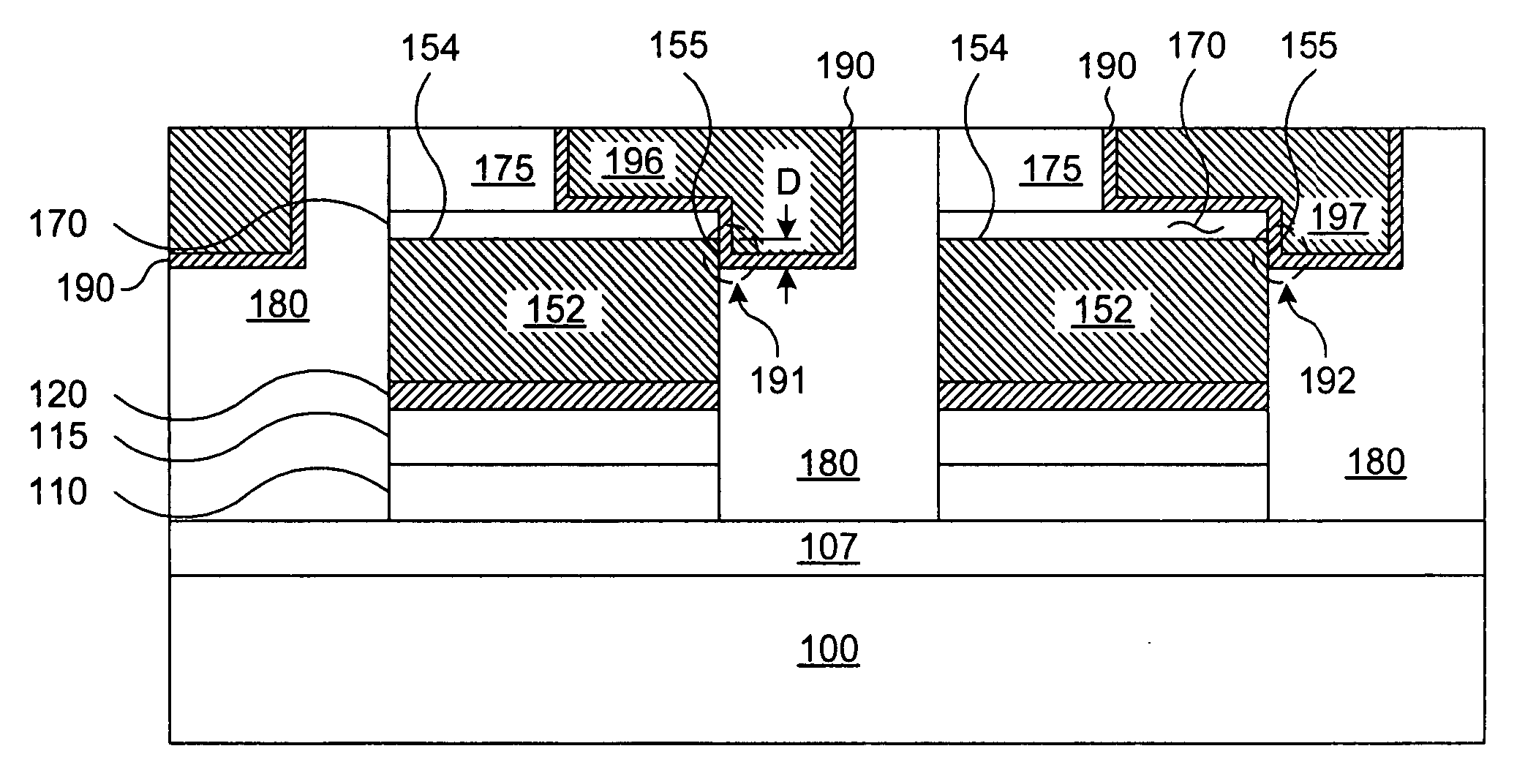

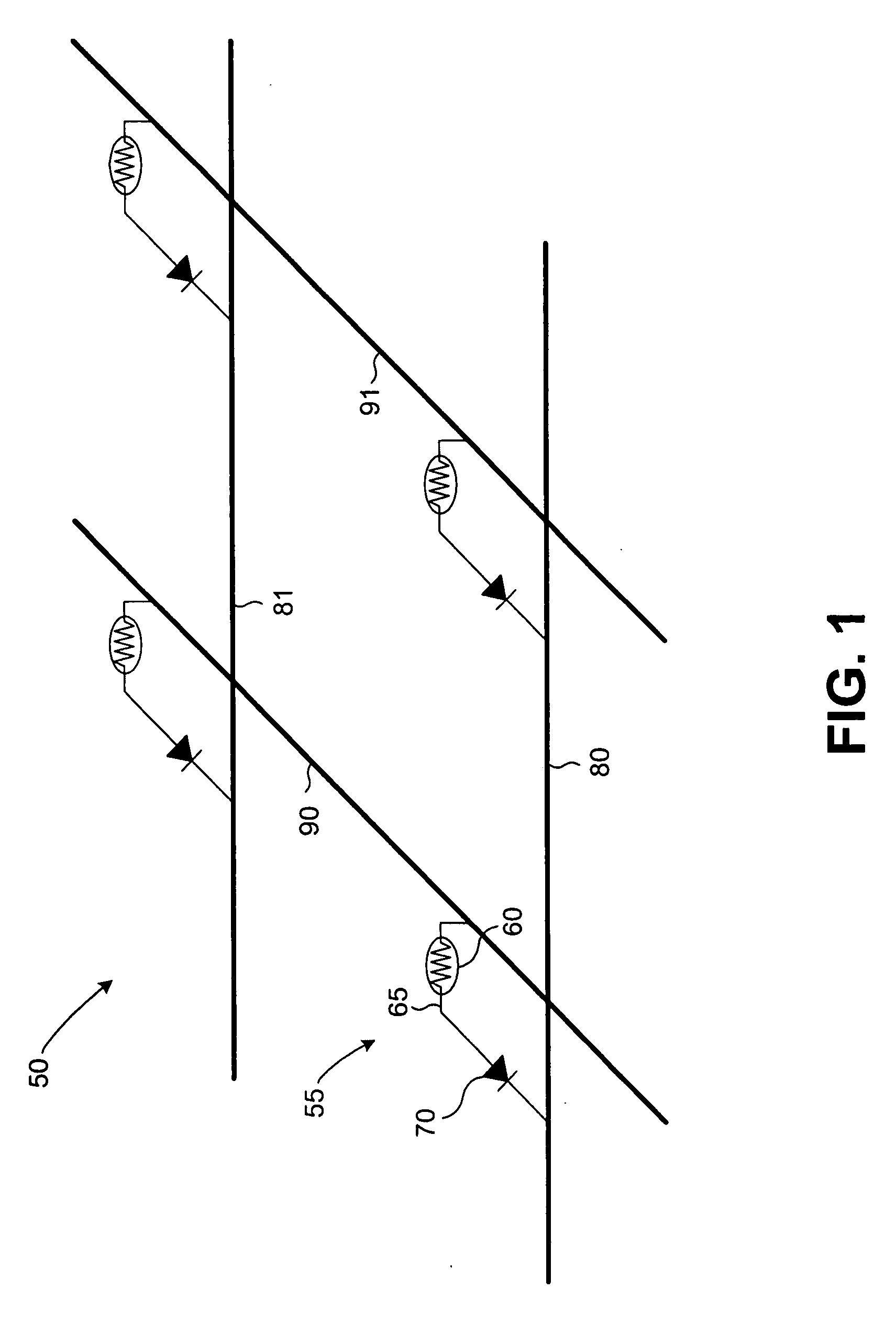

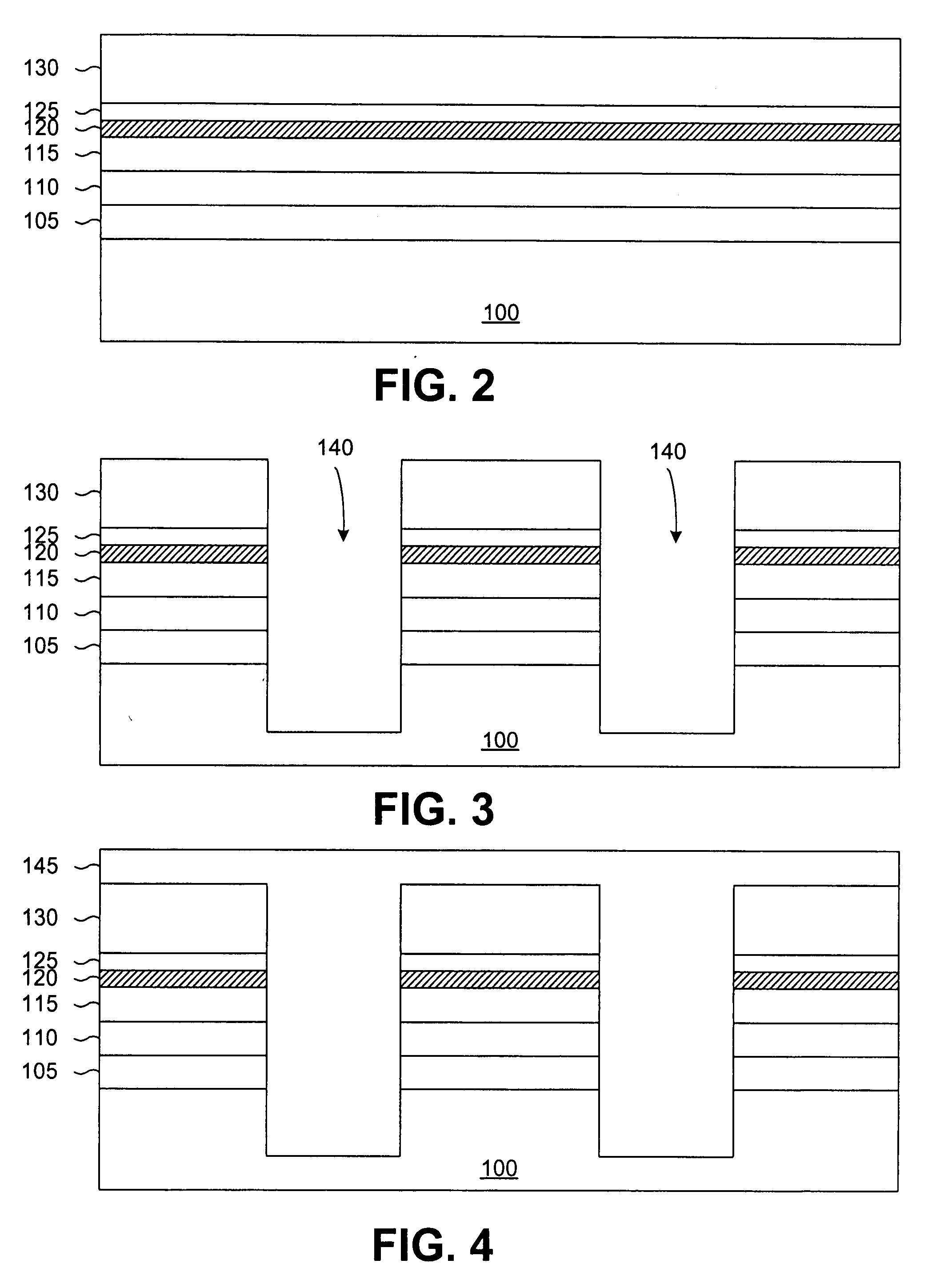

Common word line edge contact phase-change memory

InactiveUS7364935B2Solid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryCommon word

A method of fabricating a phase-change memory cell is described. The cross-sectional area of a contact with a phase-change memory element within the cell is controlled by a first dimension of a bottom electrode and a second dimension controlled by an etch process. The contact area is a product of the first dimension and the second dimension. The method allows the formation of very small phase-change memory cells.

Owner:MACRONIX INT CO LTD

Common word line edge contact phase-change memory

InactiveUS20060094154A1Need be addressSolid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryEngineering

A method of fabricating a phase-change memory cell is described. The cross-sectional area of a contact with a phase-change memory element within the cell is controlled by a first dimension of a bottom electrode and a second dimension controlled by an etch process. The contact area is a product of the first dimension and the second dimension. The method allows the formation of very small phase-change memory cells.

Owner:MACRONIX INT CO LTD

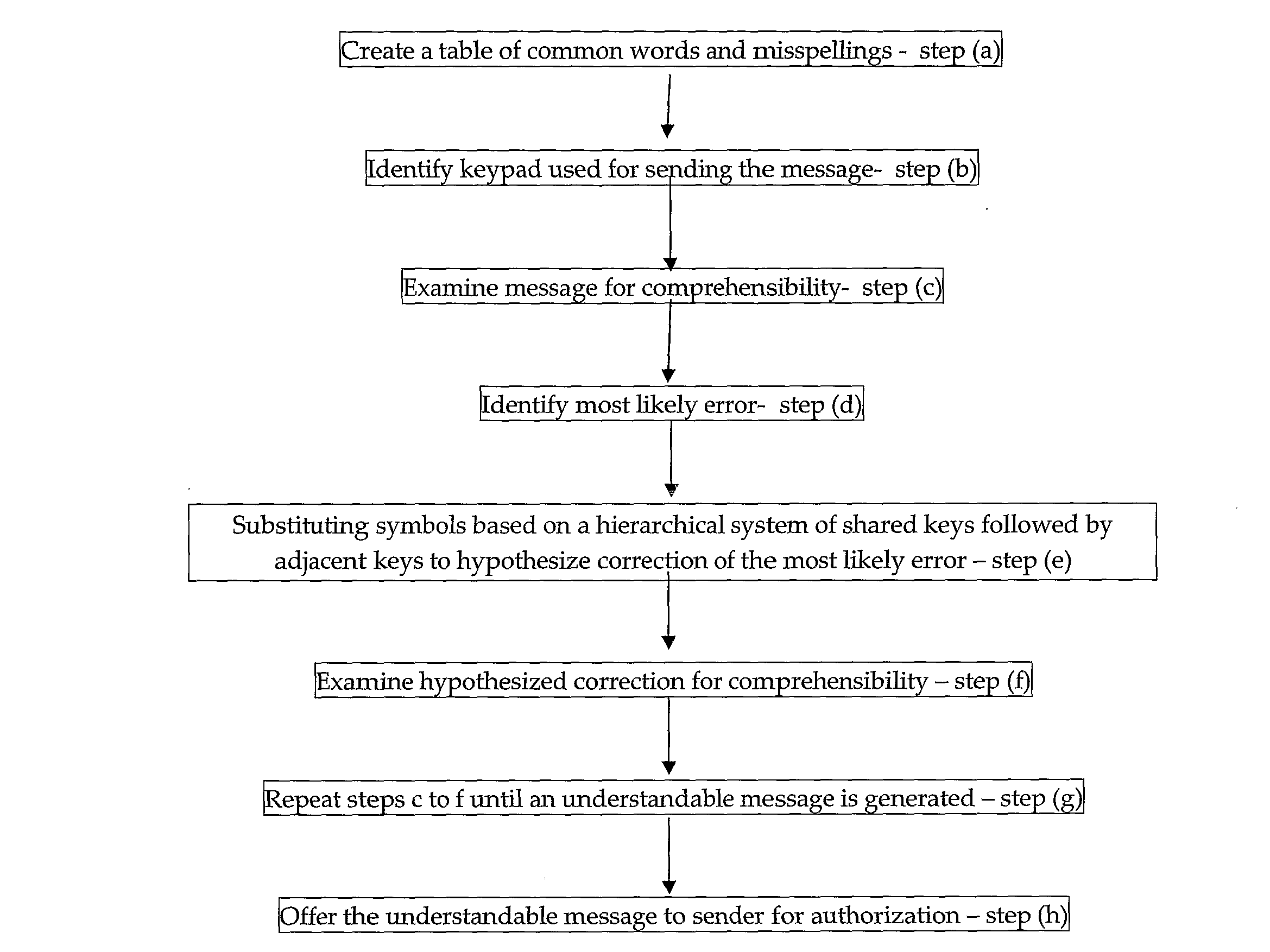

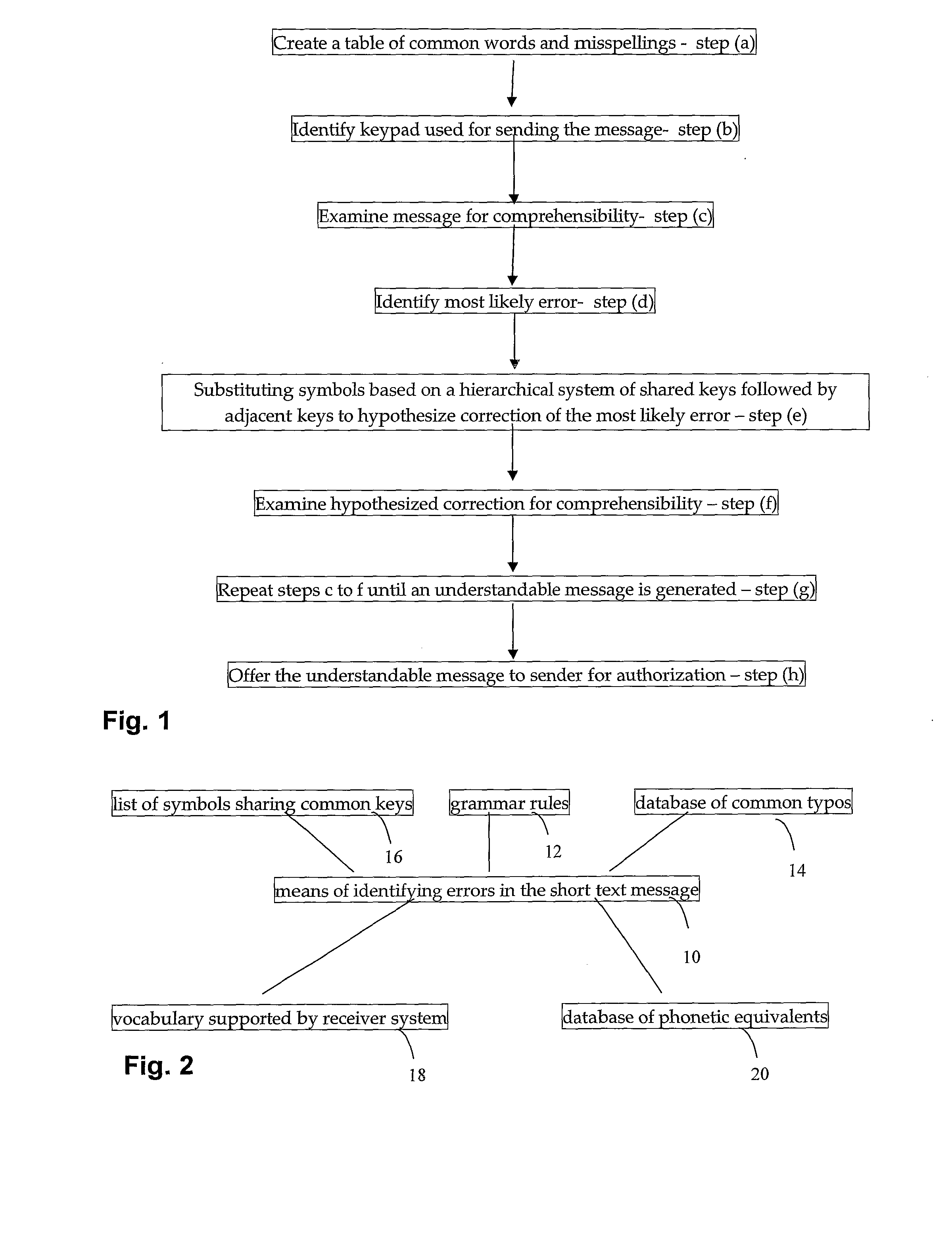

Context sensitive, error correction of short text messages

InactiveUS20100050074A1Efficient deploymentNatural language data processingSpecial data processing applicationsForward error correctionCommon word

A method for correcting a short text message comprising the steps of: creating a table of common words and misspellings; identifying keypad used for sending the message, examining message for comprehensibility; identifying most likely error, substituting symbols based on a hierarchical system of shared keys followed by adjacent keys to hypothesize correction of the most likely error; examining hypothesized correction for comprehensibility, and repeating steps (c) to (f) until an understandable message is generated.

Owner:CELLESENSE TECH

Common word line edge contact phase-change memory

Owner:MACRONIX INT CO LTD

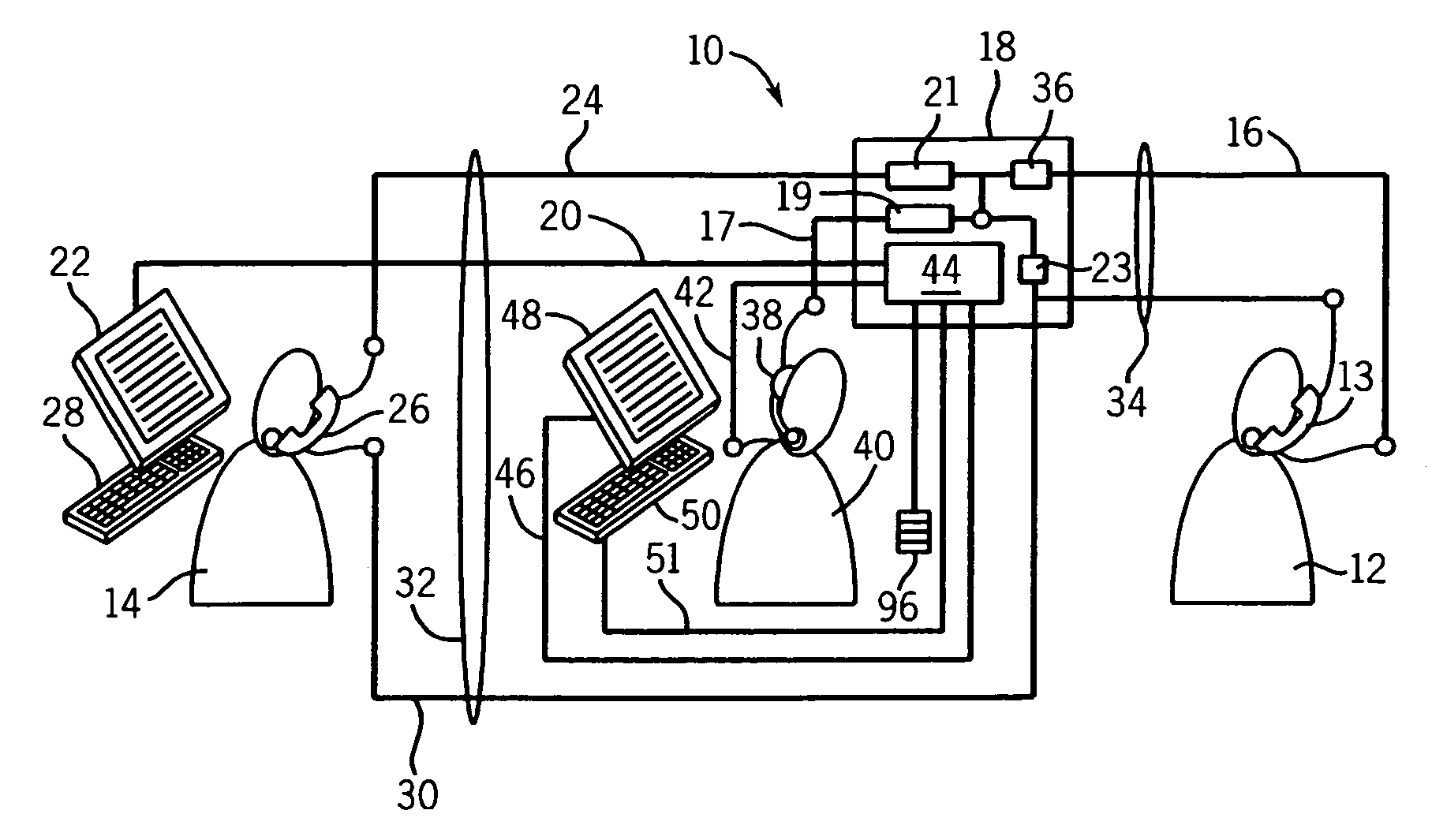

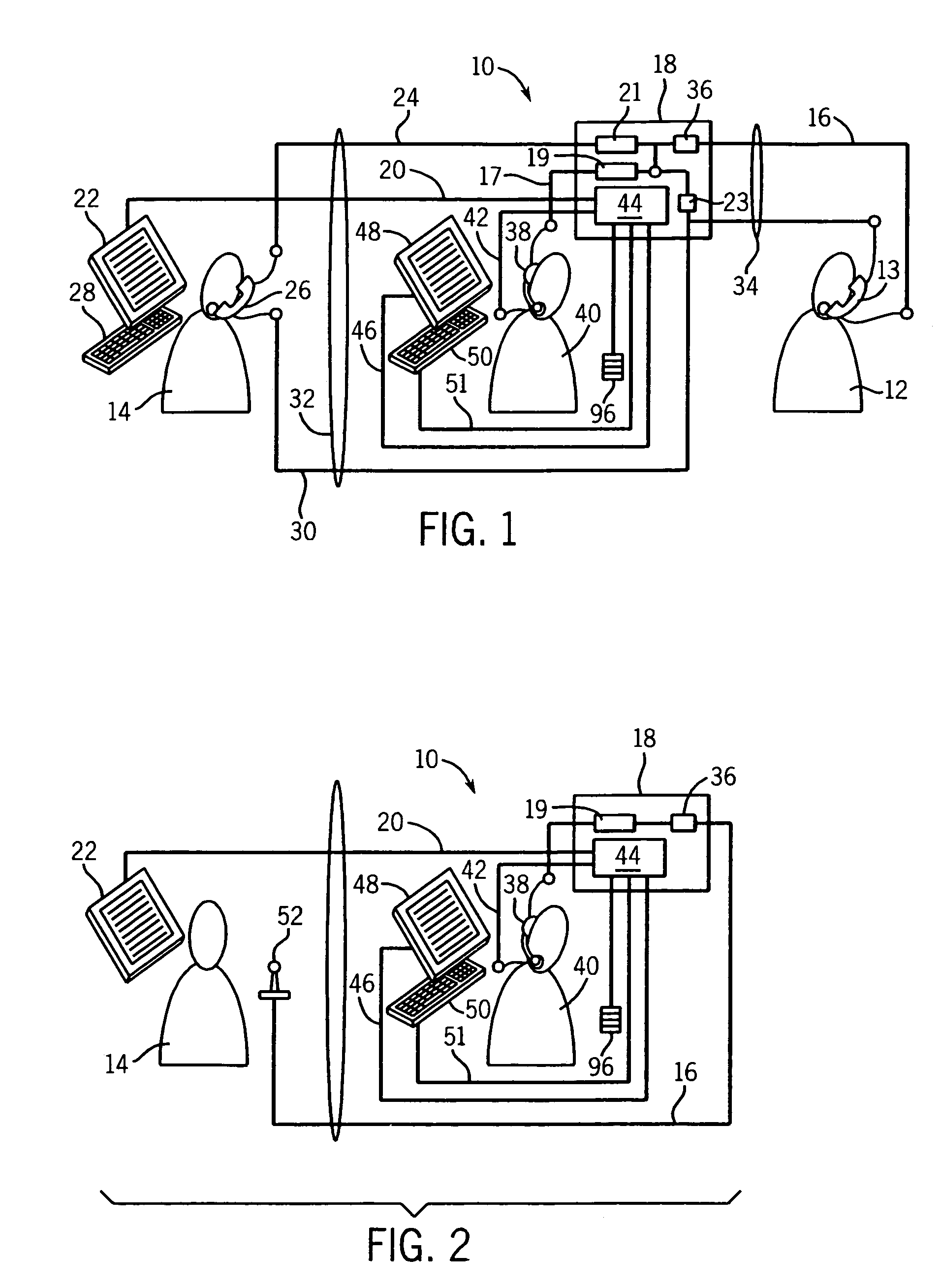

Real-time transcription correction system

InactiveUS7164753B2Simplify the editing processImprove accuracySpecial service for subscribersAutomatic call-answering/message-recording/conversation-recordingSpoken languageCommon word

A voice transcription system employing a speech engine to transcribe spoken words, detects the spelled entry of words via keyboard or voice to invoke a database of common words attempting to complete the word before all the letters have been input. This database is separate from the database of words used by the speech engine. A voice level indicator is presented to the operator to help the operator keep his or her voice in the ideal range of the speech engine.

Owner:ULTRATEC INC

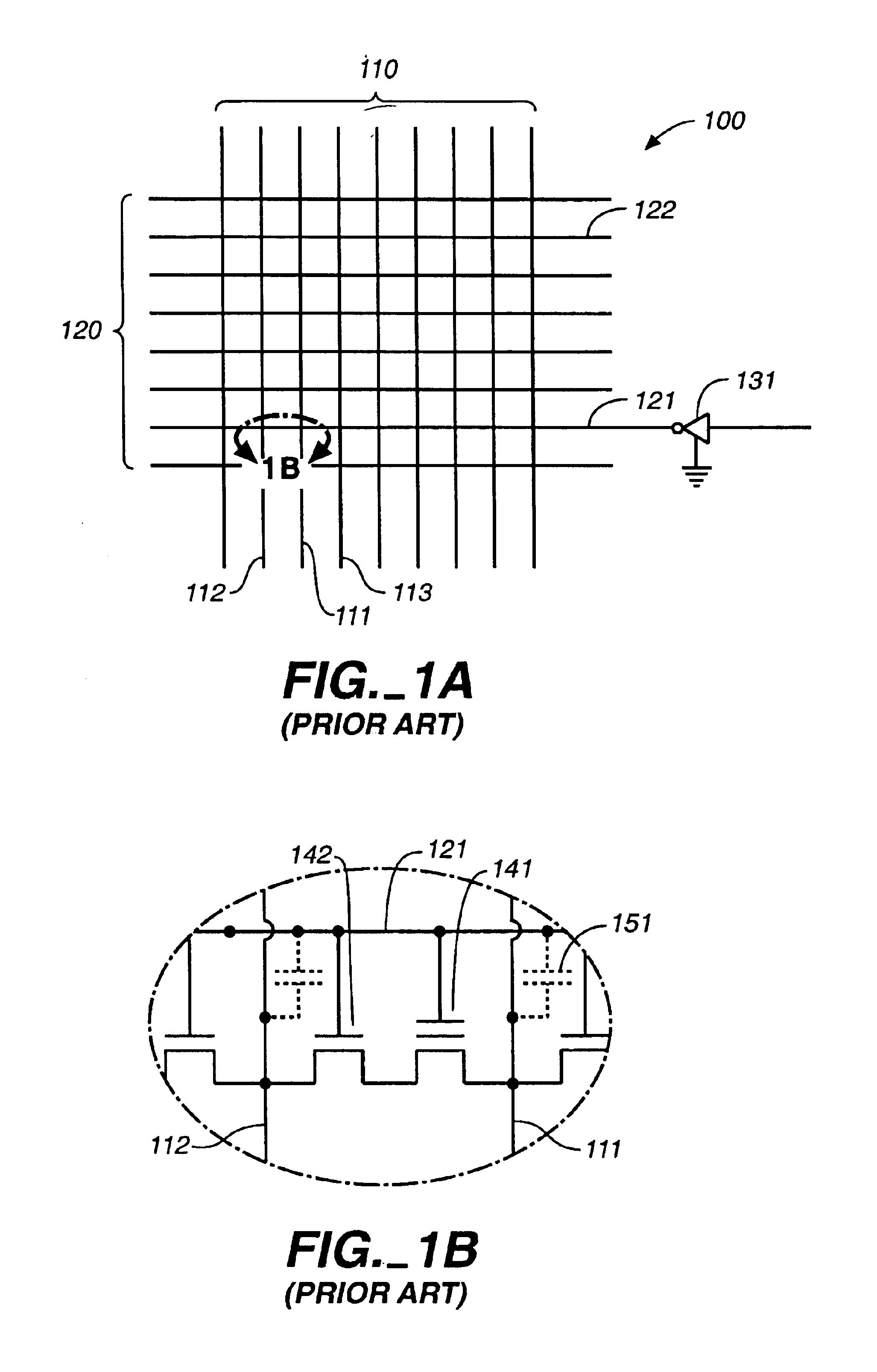

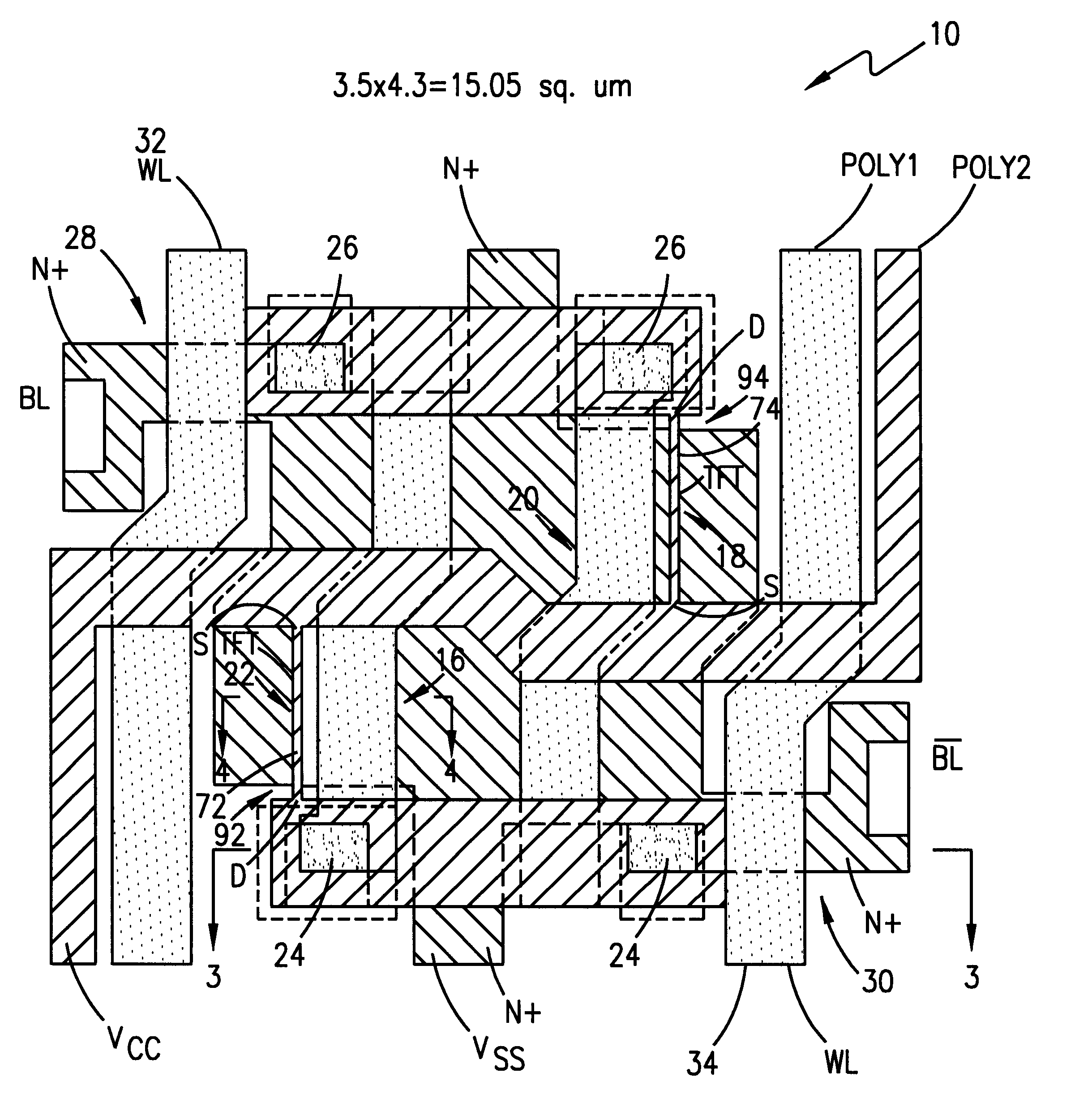

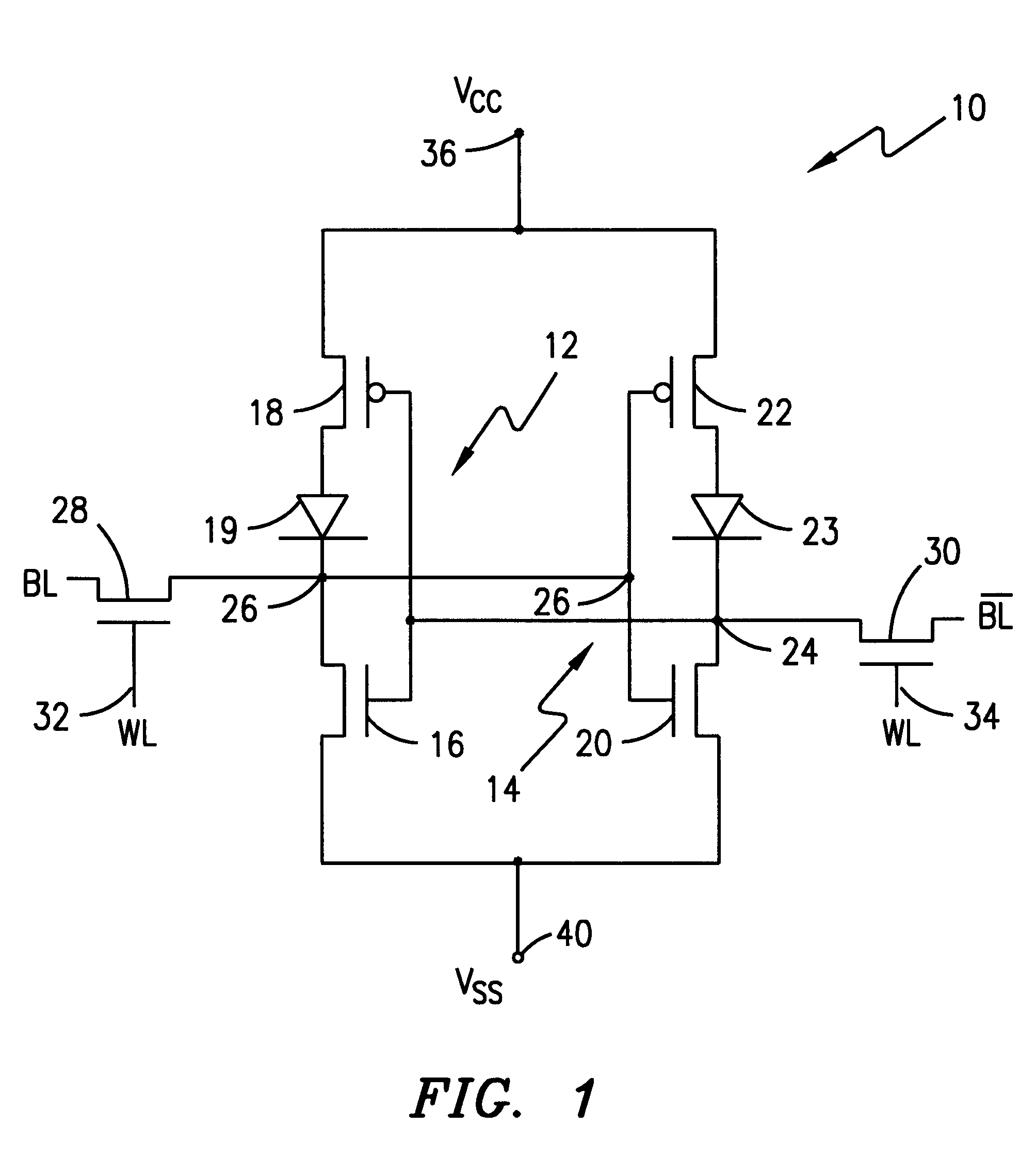

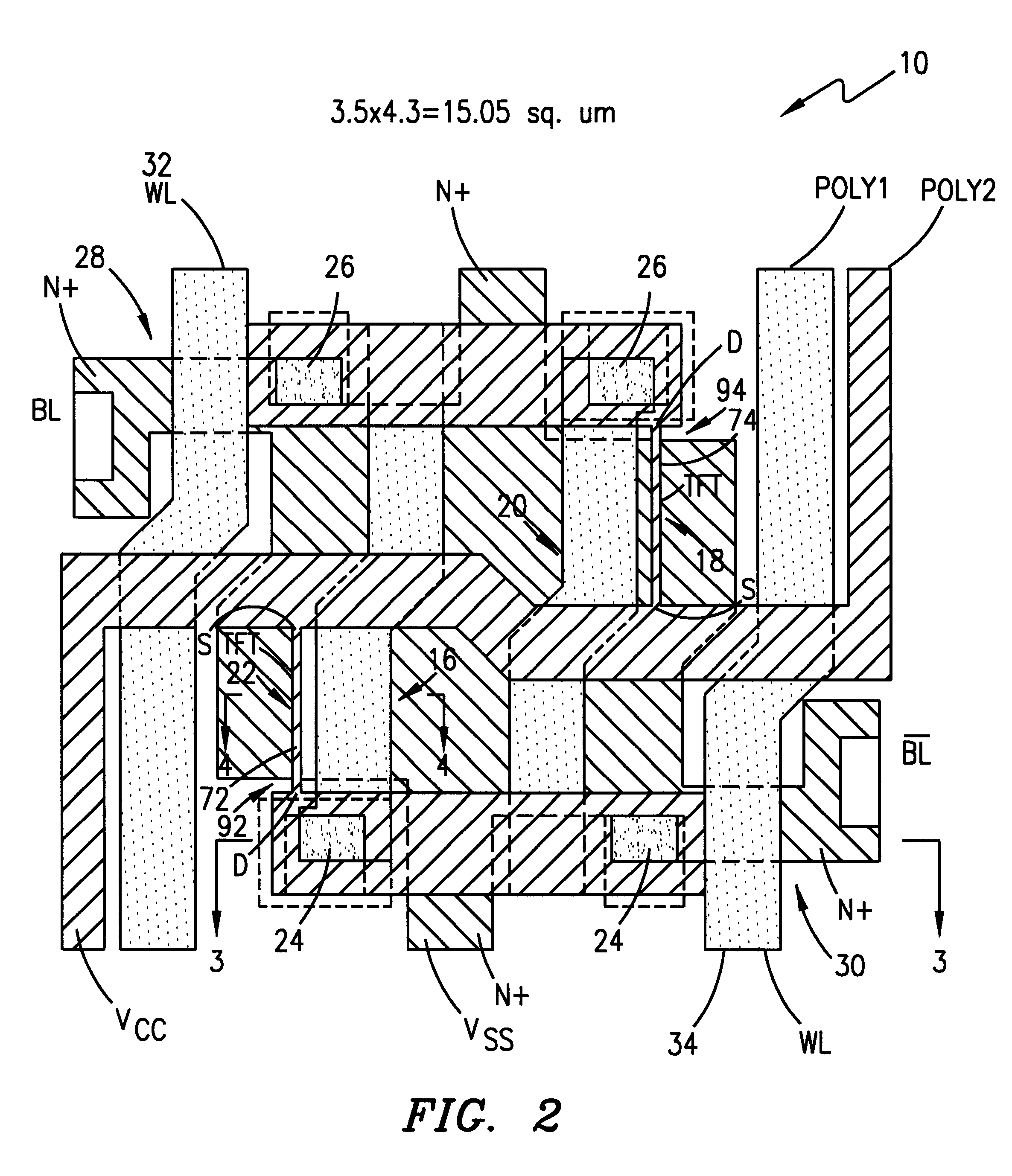

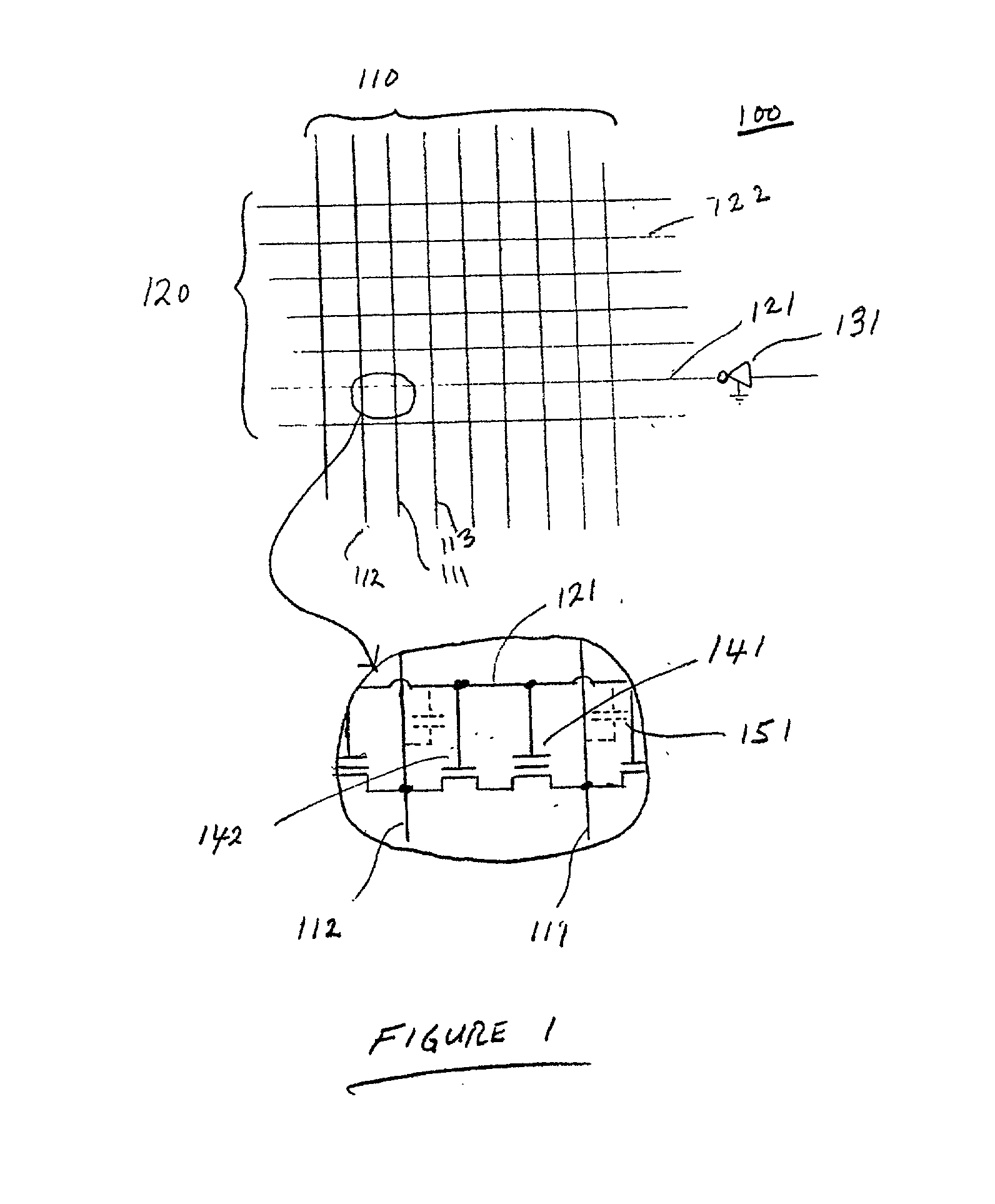

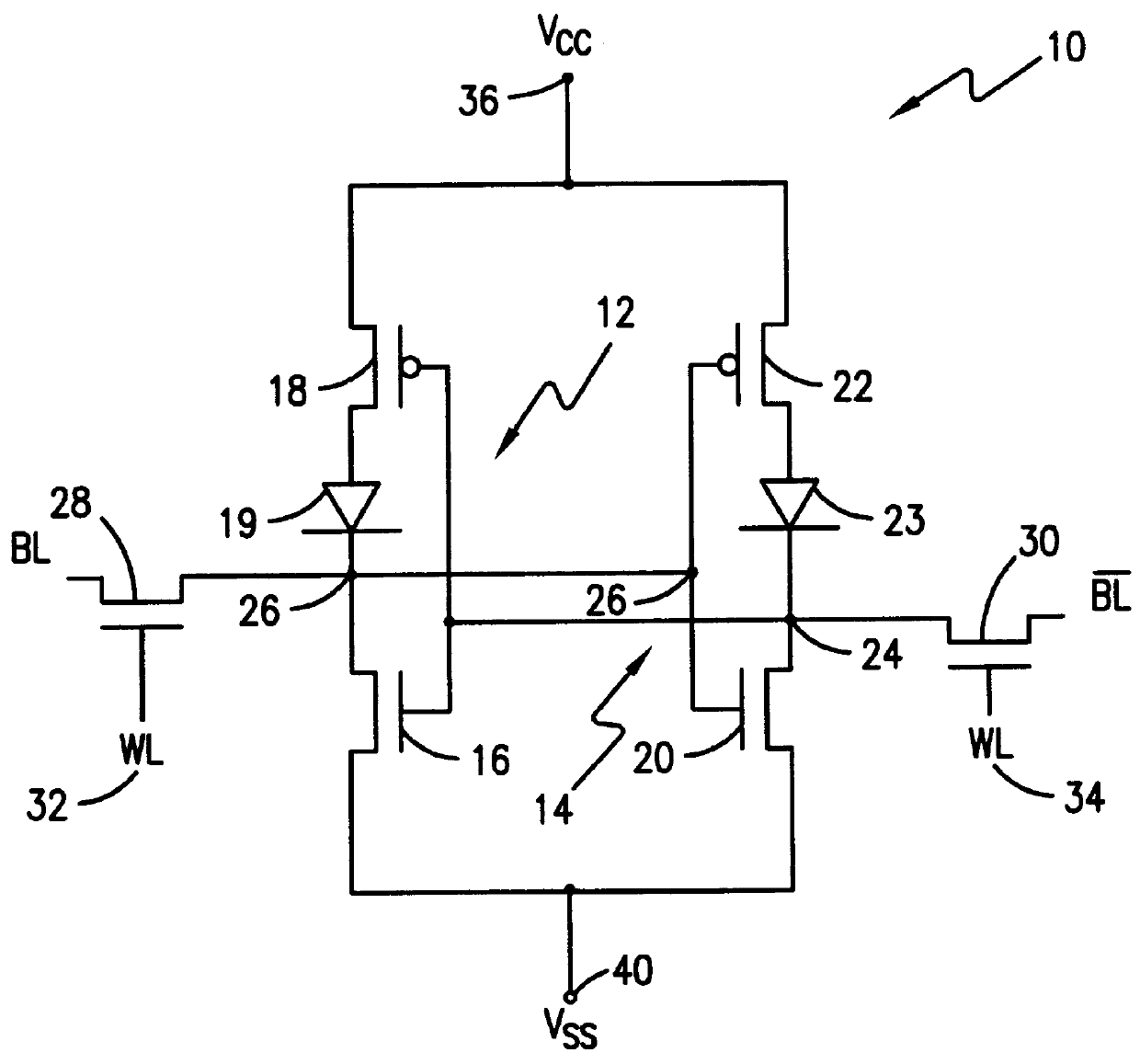

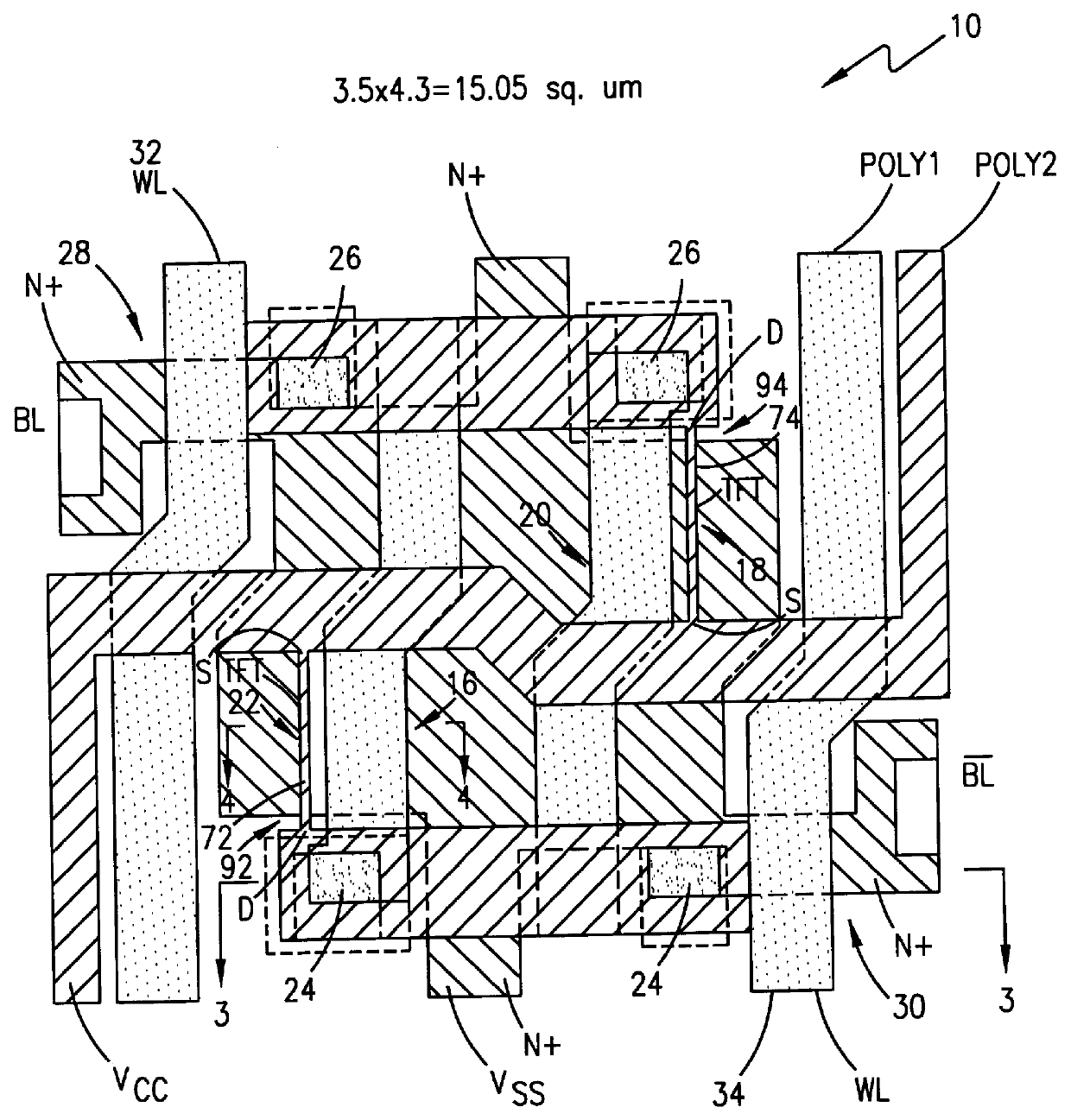

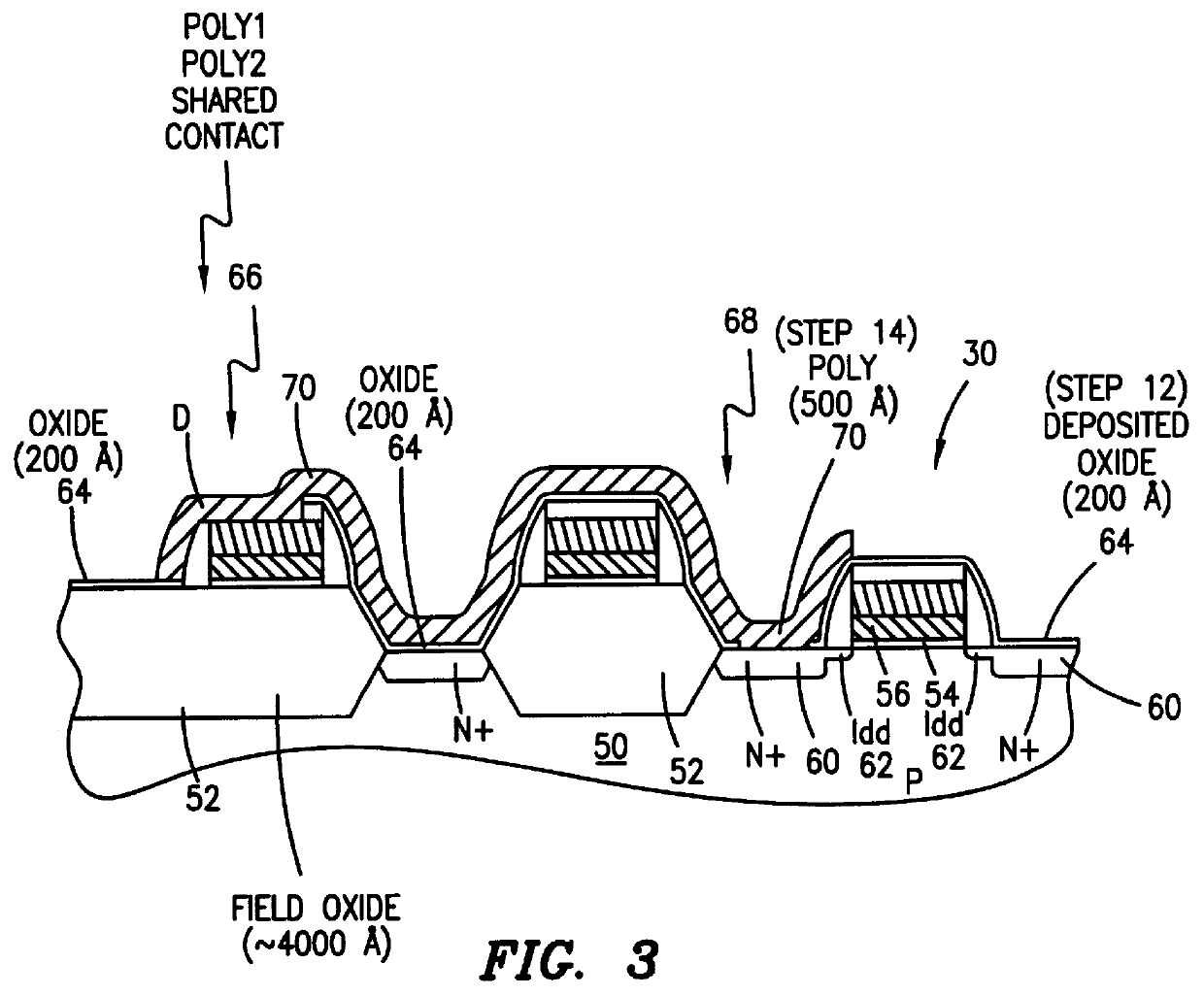

Method of making an SRAM cell and structure

A six transistor static random access memory (SRAM) cell with thin-film pull-up transistors and method of making the same includes providing two bulk silicon pull-down transistors of a first conductivity type, two active gated pull-up thin-film transistors (TFTs) of a second conductivity type, two pass gates, a common word line, and two bit line contacts. The bulk silicon pull-down transistors, two active gated pull-up TFTs, and two pass gates are connected at four shared contacts. In addition, the two bulk silicon pull-down transistors and the two active gated pull-up TFTs are formed with two polysilicon layers, a first of the polysilicon layers (poly1) is salicided and includes poly1 gate electrodes for the two bulk silicon pull-down transistors. A second of the polysilicon layers (poly2) includes desired poly2 stringers disposed along side edges of the poly1 gate electrodes, the desired poly2 stringers forming respective channel regions of the pull-up TFTs.

Owner:STMICROELECTRONICS SRL

Nonvolatile semiconductor memory device

ActiveUS7016222B2Higher-reliability data retention characteristicReduce voltage stressSolid-state devicesDigital storageComputer architectureCommon word

Owner:SAMSUNG ELECTRONICS CO LTD

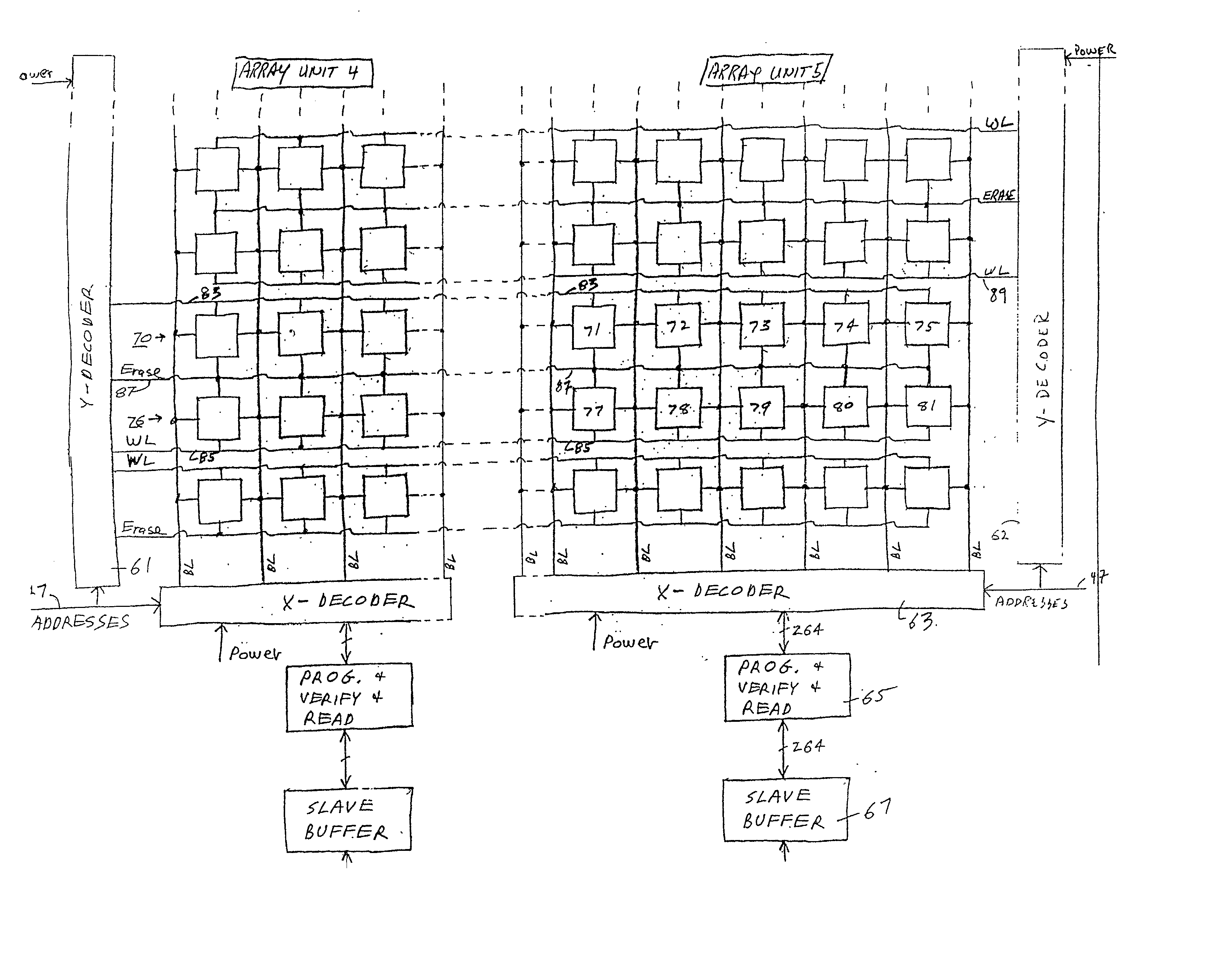

Method of reducing disturbs in non-volatile memory

In a non-volatile memory, the displacement current generated in non-selected word lines that results when the voltage levels on an array's bit lines are changed can result in disturbs. Techniques for reducing these currents are presented. In a first aspect, the number of cells being simultaneously programmed on a word line is reduced. In a non-volatile memory where an array of memory cells is composed of a number of units, and the units are combined into planes that share common word lines, the simultaneous programming of units within the same plane is avoided. Multiple units may be programmed in parallel, but these are arranged to be in separate planes. This is done by selecting the number of units to be programmed in parallel and their order such that all the units programmed together are from distinct planes, by comparing the units to be programmed to see if any are from the same plane, or a combination of these. In a second, complementary aspect, the rate at which the voltage levels on the bit lines are changed is adjustable. By monitoring the frequency of disturbs, or based upon the device's application, the rate at which the bit line drivers change the bit line voltage can be adjusted. This can be implemented by setting the rate externally, or by the controller based upon device performance and the amount of data error being generated.

Owner:SANDISK TECH LLC

Two square NVRAM cell

A non-volatile random access memory (NVRAM) cell and method of fabrication thereof. Pairs of NVRAM cells, each including three FETs stacked in a NAND-like structure are formed vertically in silicon pillars. Source devices at the bottom of the pillar selectively provide ground to one of the cells. A floating gate extends upward from the source device's gate line. A control gate plate extending between adjacent pillars selectively provides a programming voltage to the control gate. Both the source gate and the control gate are capacitively coupled through silicon rich oxide to the floating gate. Polysilicon plugs between silicon pillars are word line gates for cells in adjacent pillars. A diffusion at the top of each pillar is a bit line contact for both cells at the pillar. Each pair of cells on a pillar are on a common bit line and a common word line. The word line, control gate and source gate line select individual cells in the pair.

Owner:INT BUSINESS MASCH CORP

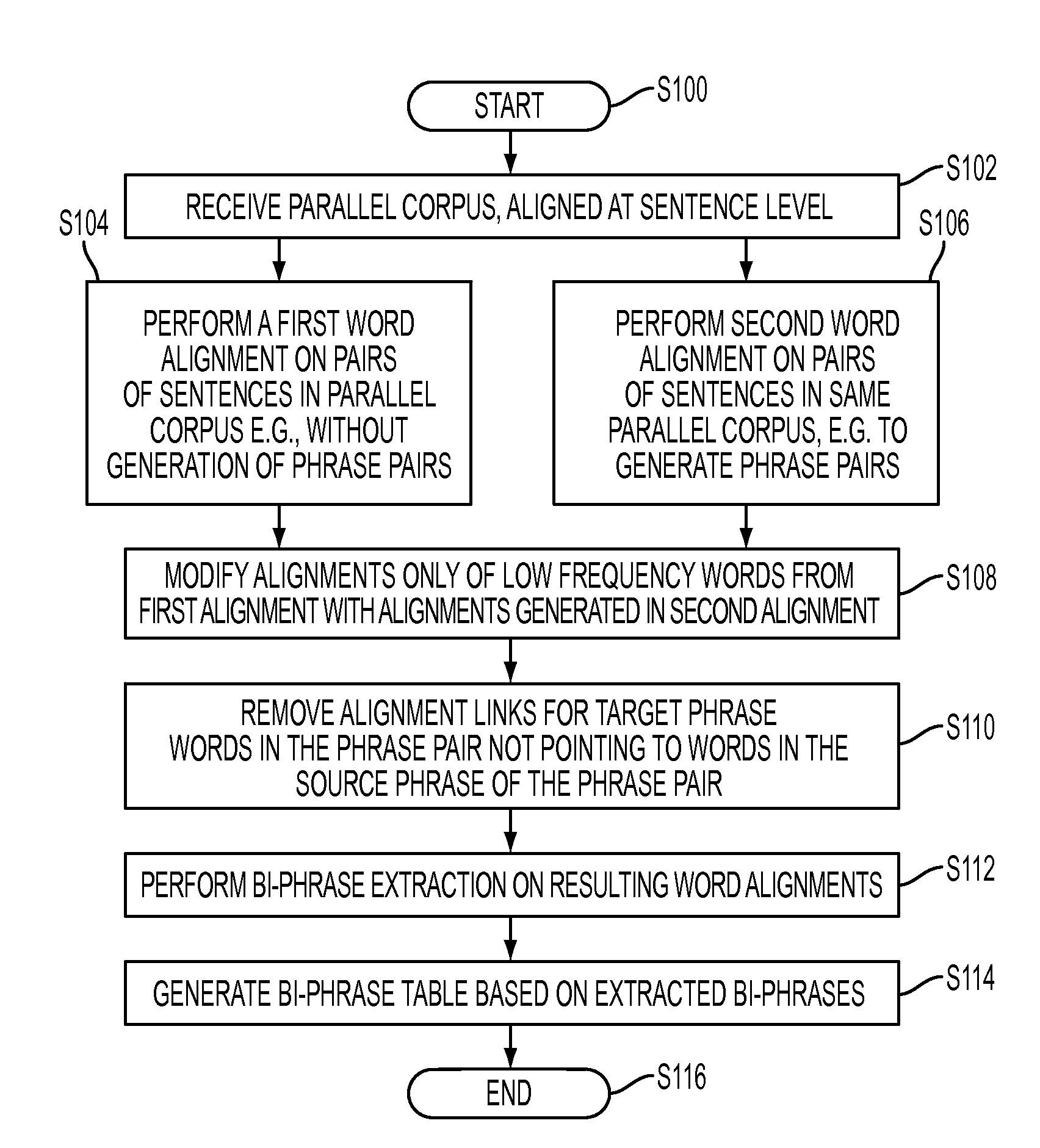

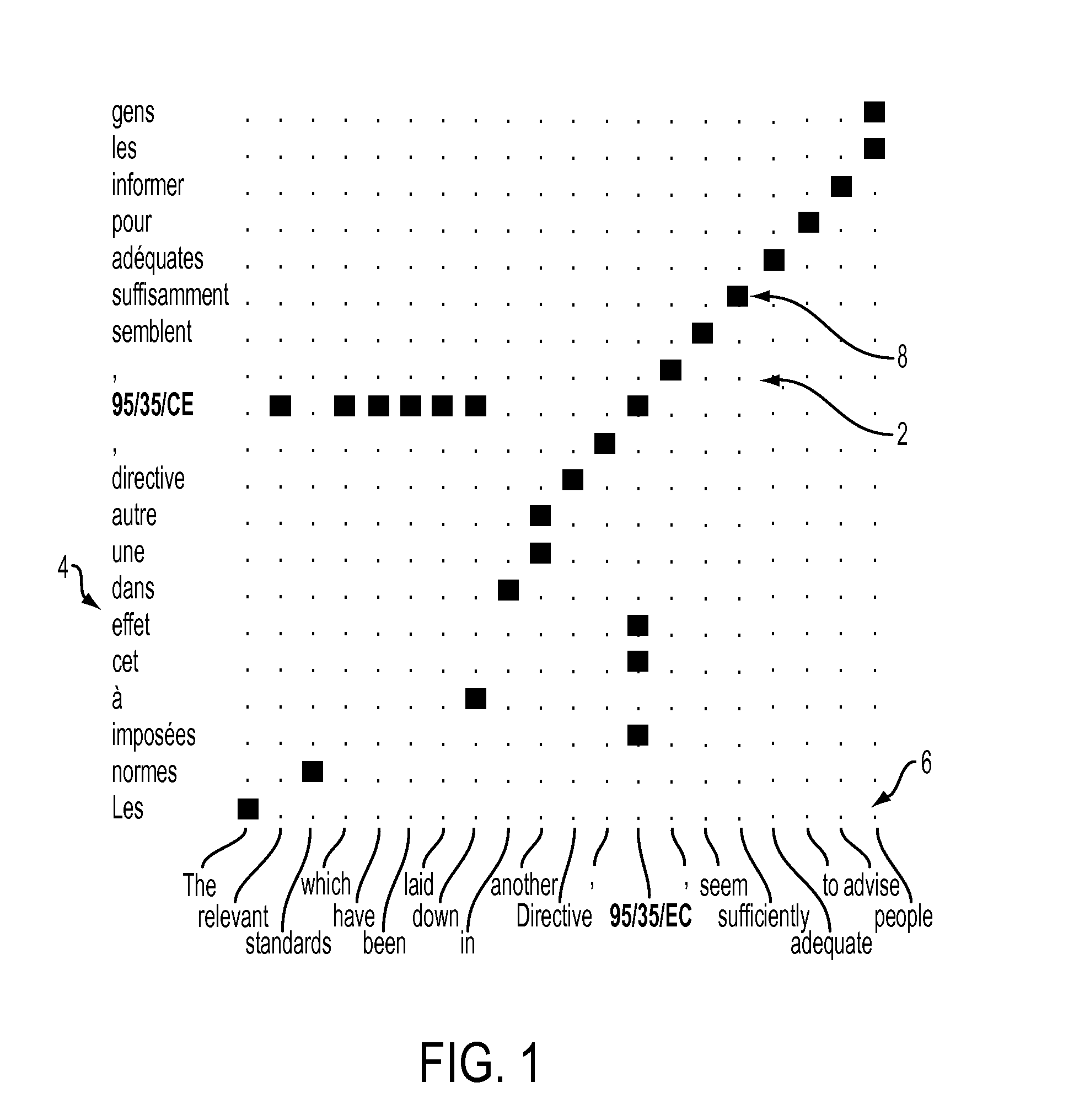

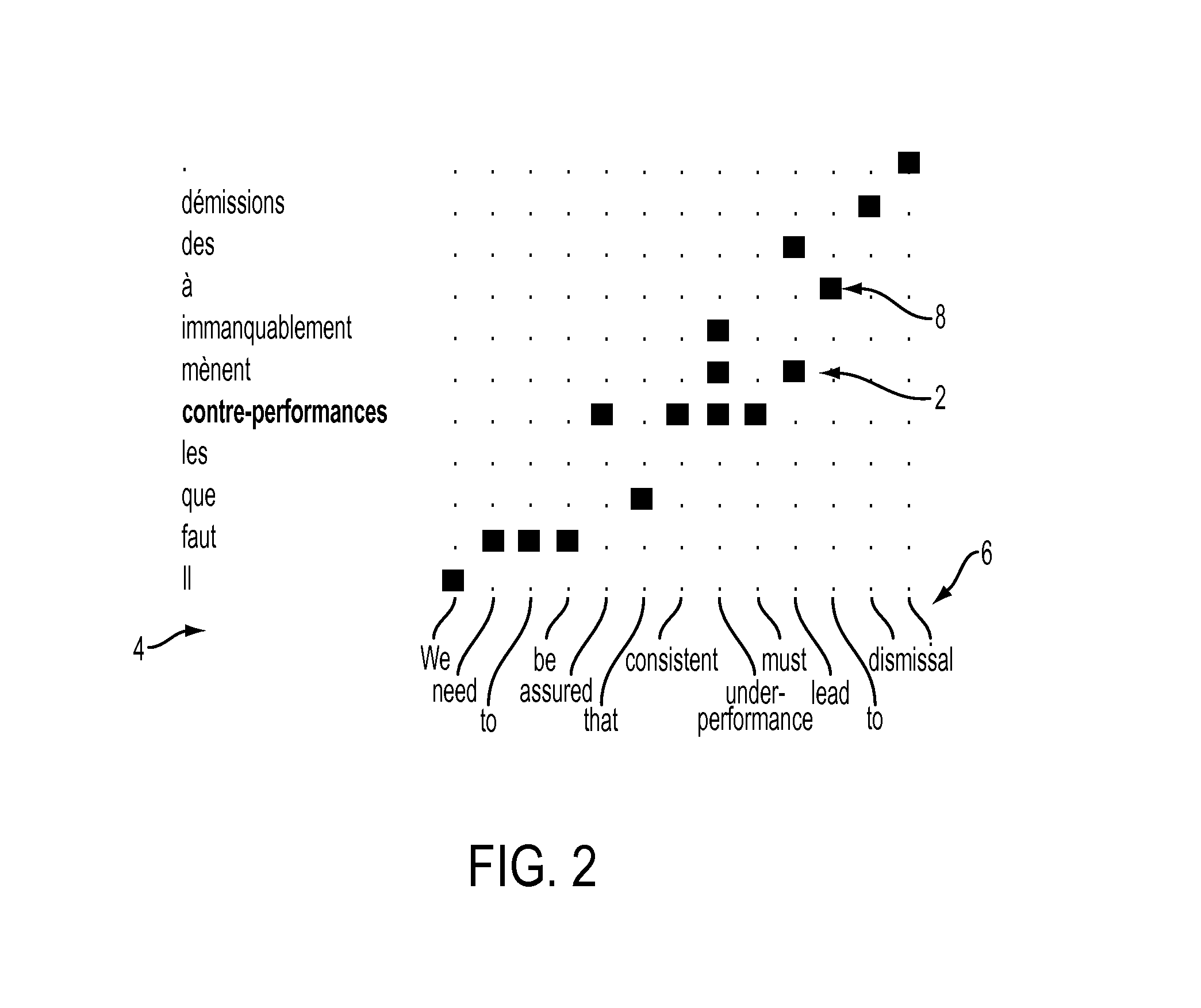

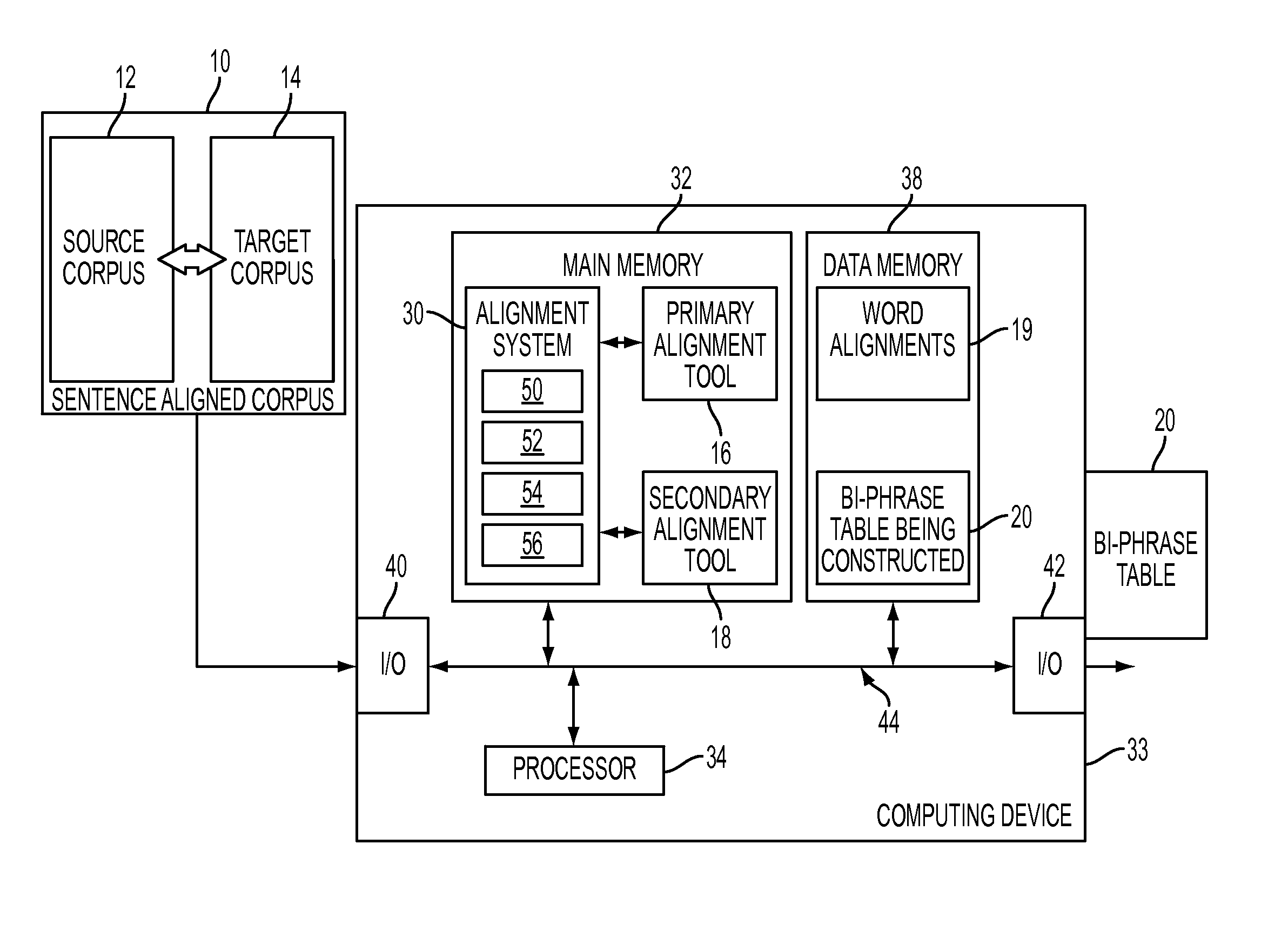

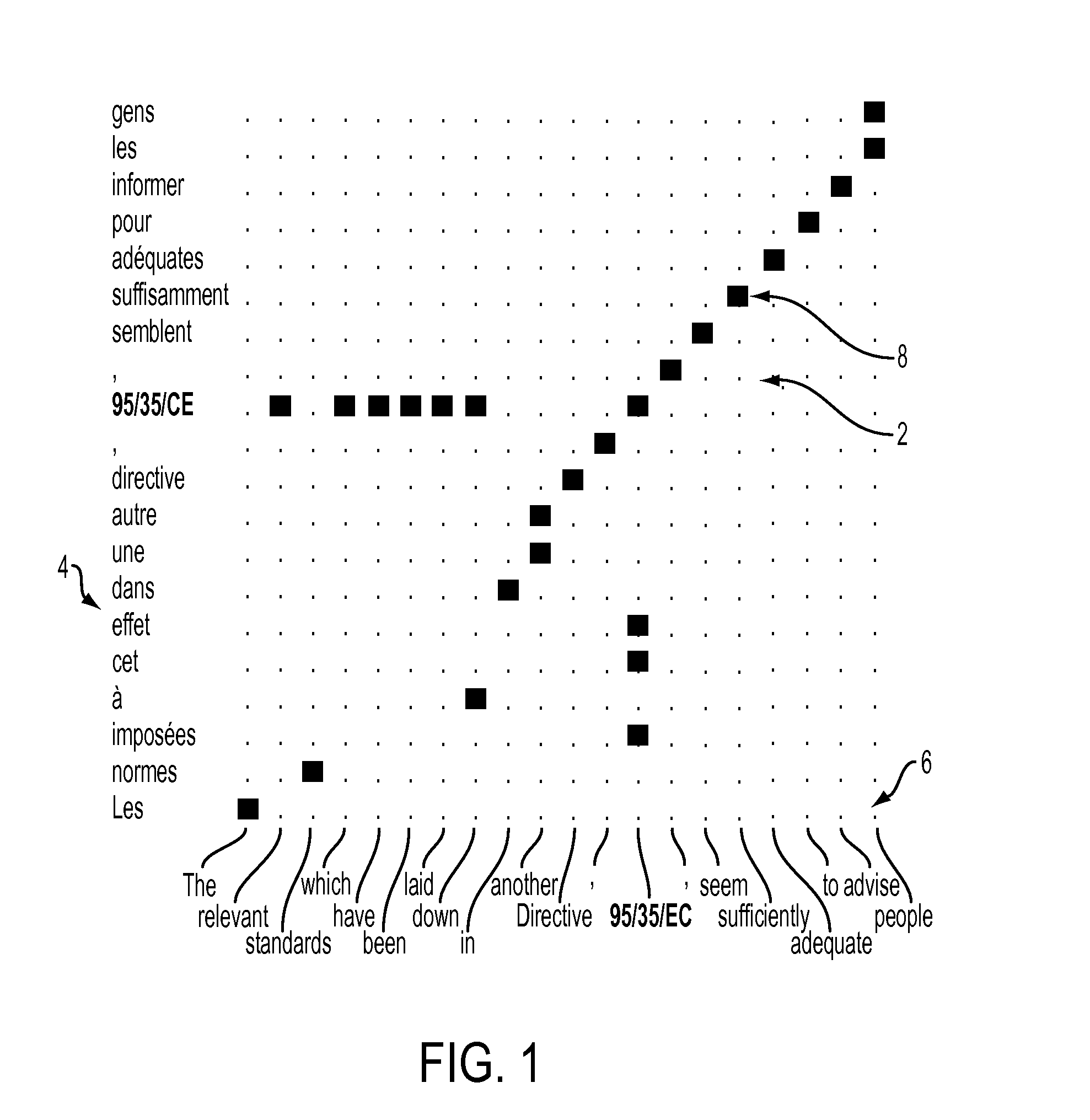

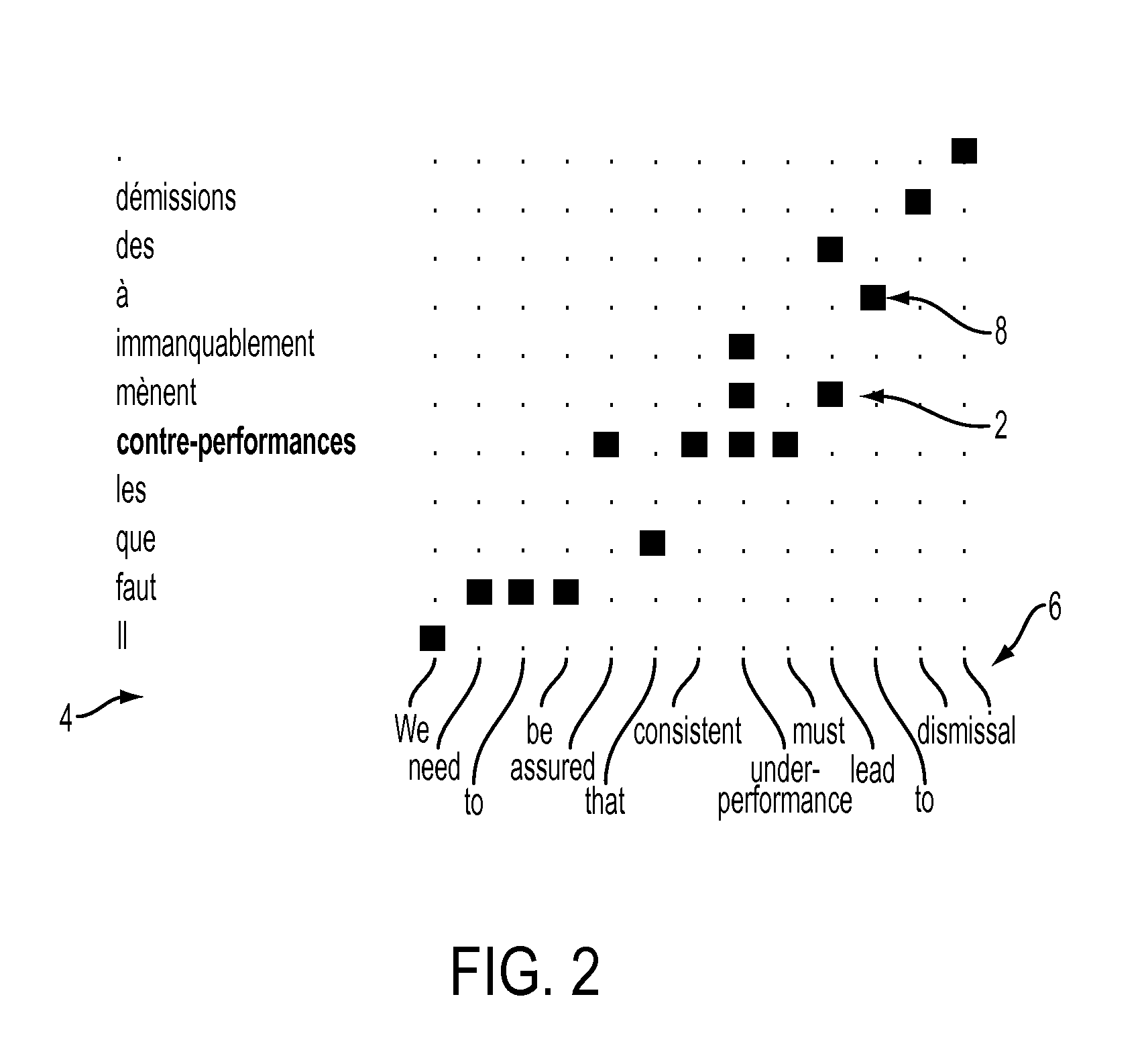

Word alignment method and system for improved vocabulary coverage in statistical machine translation

InactiveUS20110307245A1Natural language translationDigital data processing detailsMachine translation systemText string

A system and method for generating word alignments from pairs of aligned text strings are provided. A corpus of text strings provides pairs of text strings, primarily sentences, in source and target languages. A first alignment between a text string pair creates links therebetween. Each link links a single token of the first text string to a single token of the second text string. A second alignment also creates links between the text string pair. In some cases, these links may correspond to bi-phrases. A modified first alignment is generated by selectively modifying links in the first alignment which include a word which is infrequent in the corpus, based on links generated in the second alignment. This results in removing at least some of the links for the infrequent words, allowing more compact and better quality bi-phrases, with higher vocabulary coverage, to be extracted for use in a machine translation system.

Owner:XEROX CORP

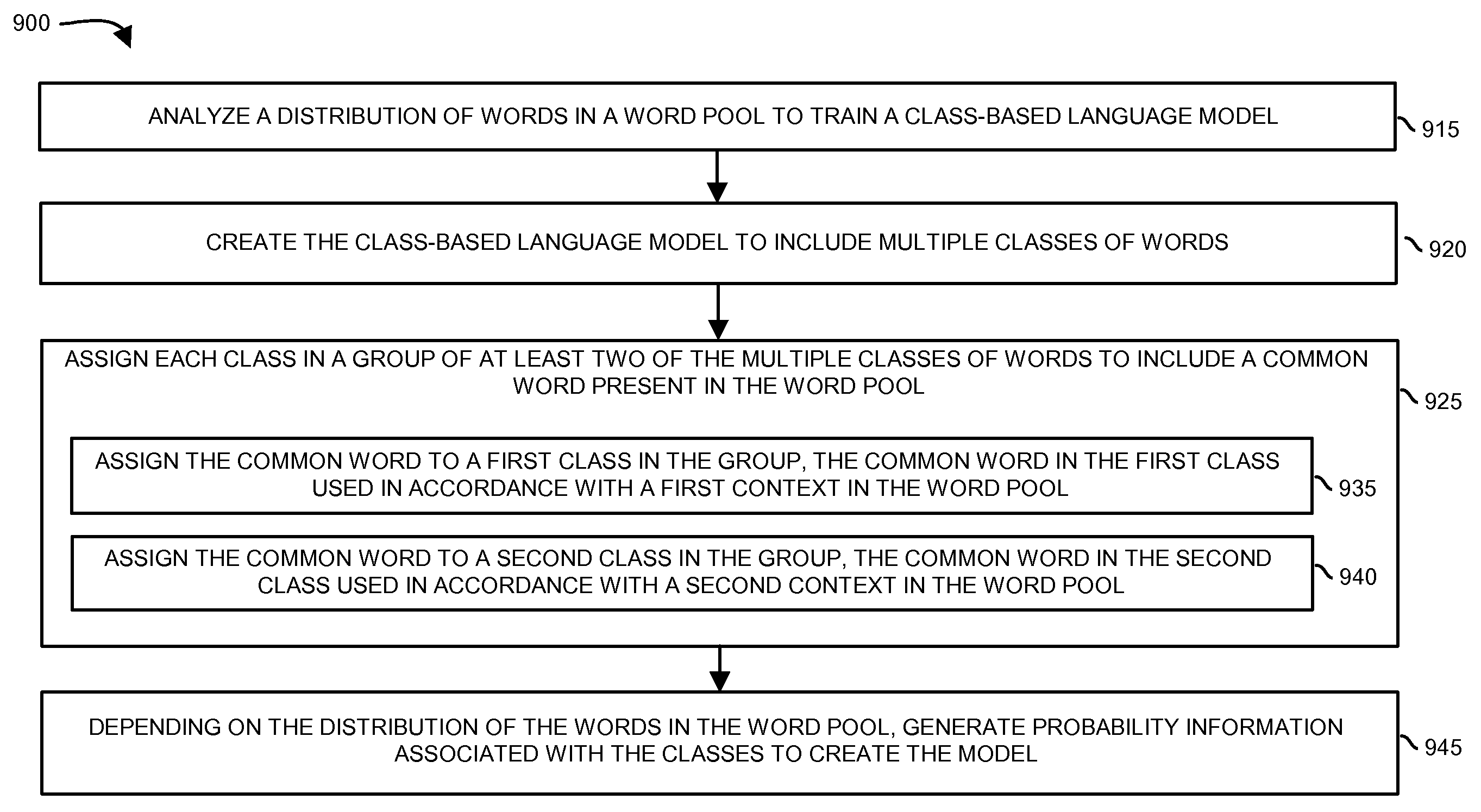

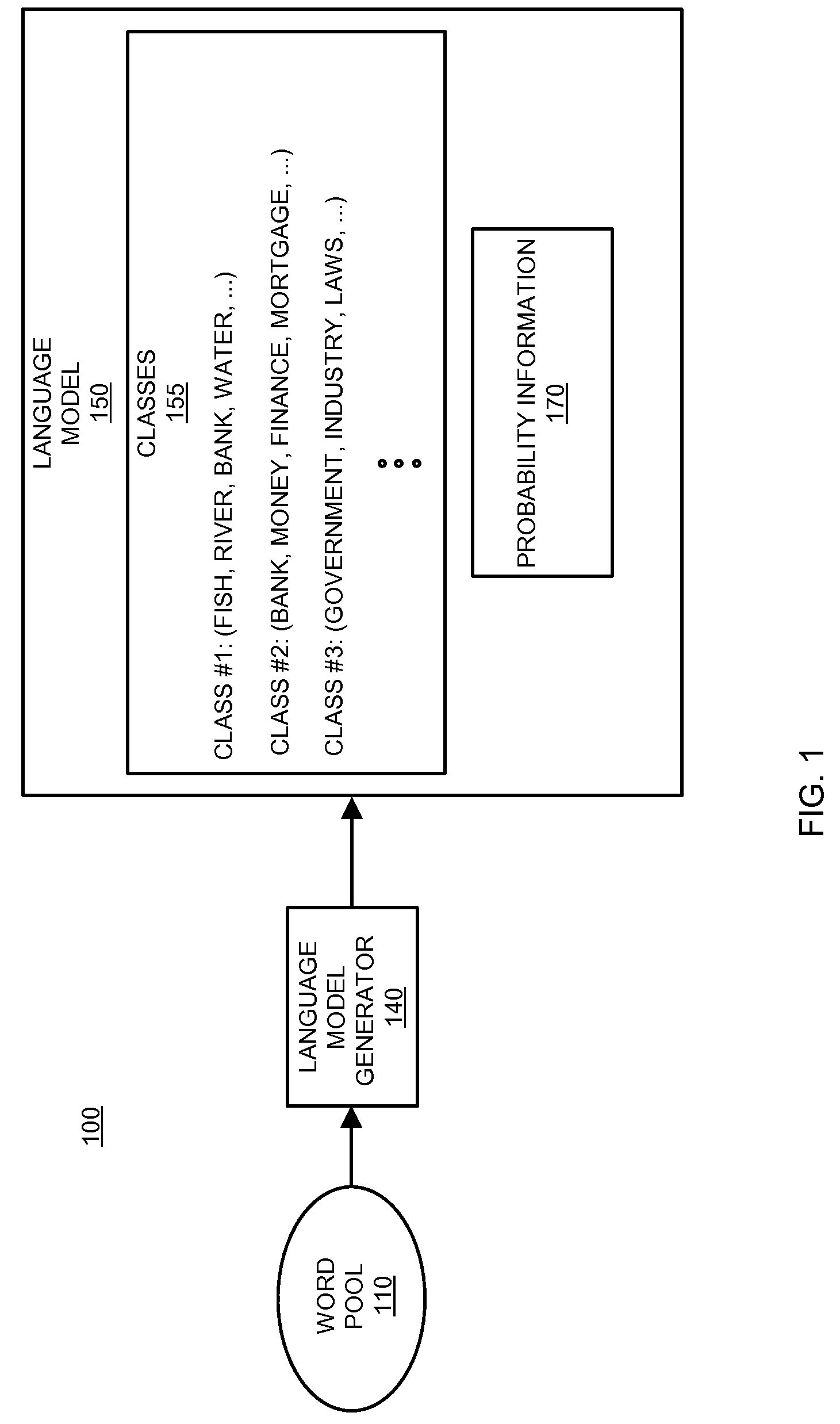

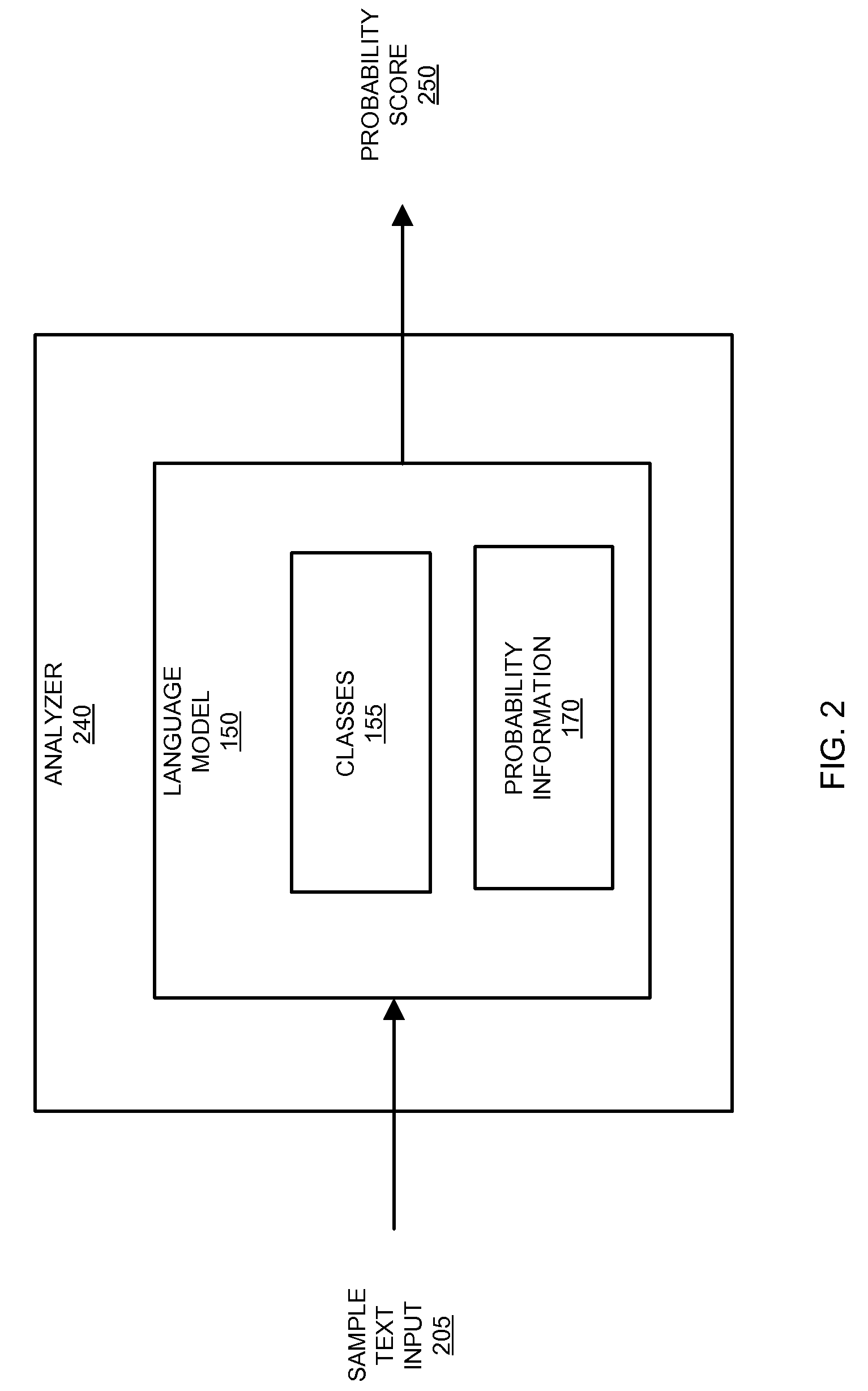

Class-based language model and use

InactiveUS8812299B1Probability is accurateNatural language translationSemantic analysisCommon wordHuman language

This disclosure describes novel generation and use of a class-based language model. For example, one embodiment herein includes detecting presence of a common word that is used in different contexts in a word pool and assigning the common word to each of multiple classes in a class-based language model. Generation of the class-based language model and assignment of the common word to multiple classes the class-based language model as discussed herein enables generation of a more accurate probability score indicating how likely the common word follows a give sequence of one or more words in a sample text input.

Owner:NUANCE COMM INC

SRAM cell structure with dielectric sidewall spacers and drain and channel regions defined along sidewall spacers

A six transistor static random access memory (SRAM) cell with thin-film pull-up transistors and method of making the same includes providing two bulk silicon pull-down transistors of a first conductivity type, two active gated pull-up thin-film transistors (TFTs) of a second conductivity type, two pass gates, a common word line, and two bit line contacts. The bulk silicon pull-down transistors, two active gated pull-up TFTs, and two pass gates are connected at four shared contacts. In addition, the two bulk silicon pull-down transistors and the two active gated pull-up TFTs are formed with two polysilicon layers, a first of the polysilicon layers (poly1) is salicided and includes poly1 gate electrodes for the two bulk silicon pull-down transistors. A second of the polysilicon layers (poly2) includes desired poly2 stringers disposed along side edges of the poly1 gate electrodes, the desired poly2 stringers forming respective channel regions of the pull-up TFTs.

Owner:STMICROELECTRONICS SRL

Nonvolatile semiconductor memory device

ActiveUS20040130939A1Securing higher-reliability data retention characteristicReduce voltage stressSolid-state devicesDigital storageComputer architectureCommon word

A memory cell array is included which is constituted by arranging the plurality of nonvolatile memory cells in a row direction and column direction respectively and arranging the plurality of word lines (WL) and the plurality of bit lines (BL) in the row direction and the column direction respectively in order to select a predetermined memory cell or a memory cell group out of the arranged nonvolatile memory cells, in which the memory cells are respectively constituted by connecting one end of a variable resistive element for storing information in accordance with a change of electrical resistances with the source of a selection transistor while in the memory cell array, the drain of the selection transistor is connected with a common bit line (BL) along the column direction, the other end of the variable resistive element is connected with a source line (SL), and the gate of the selection transistor is connected with the common word line (WL) along the row direction. According to the above memory cell configuration, it is possible to provide a nonvolatile semiconductor memory device capable of reducing voltage stresses applied to the variable resistive element of an unselected memory cell at the time of the reading and programming operations and securing a higher-reliability data holding characteristic.

Owner:SAMSUNG ELECTRONICS CO LTD

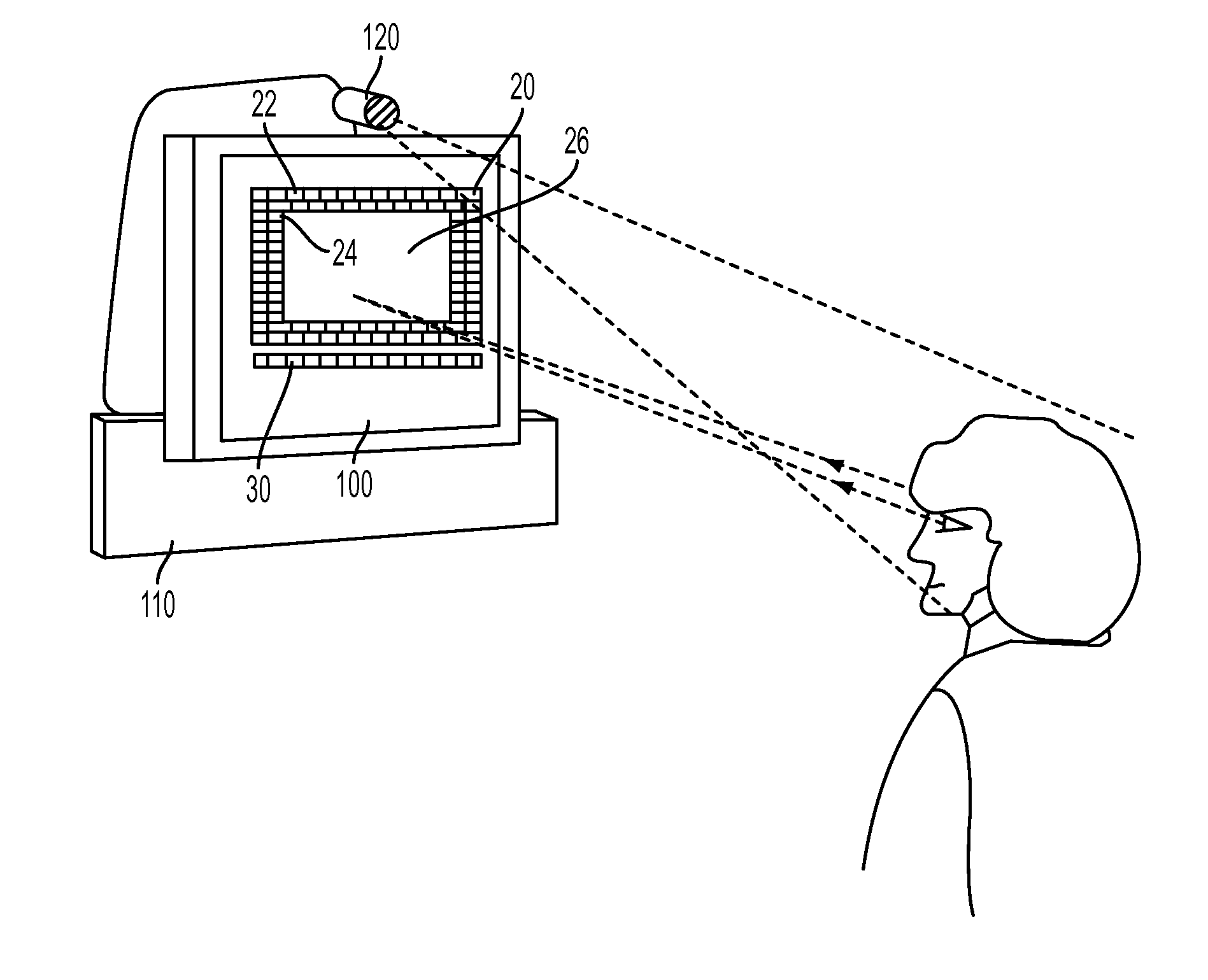

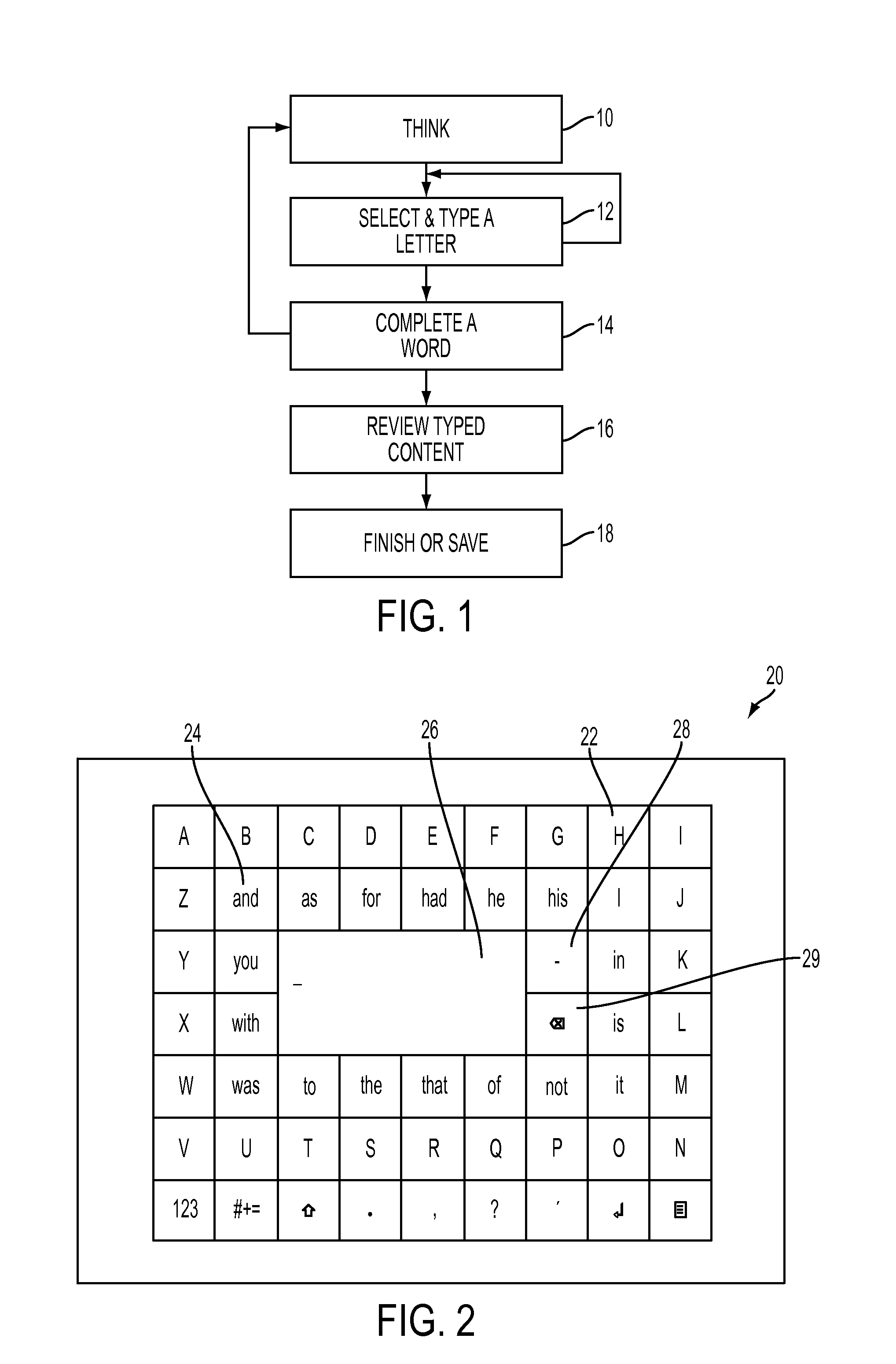

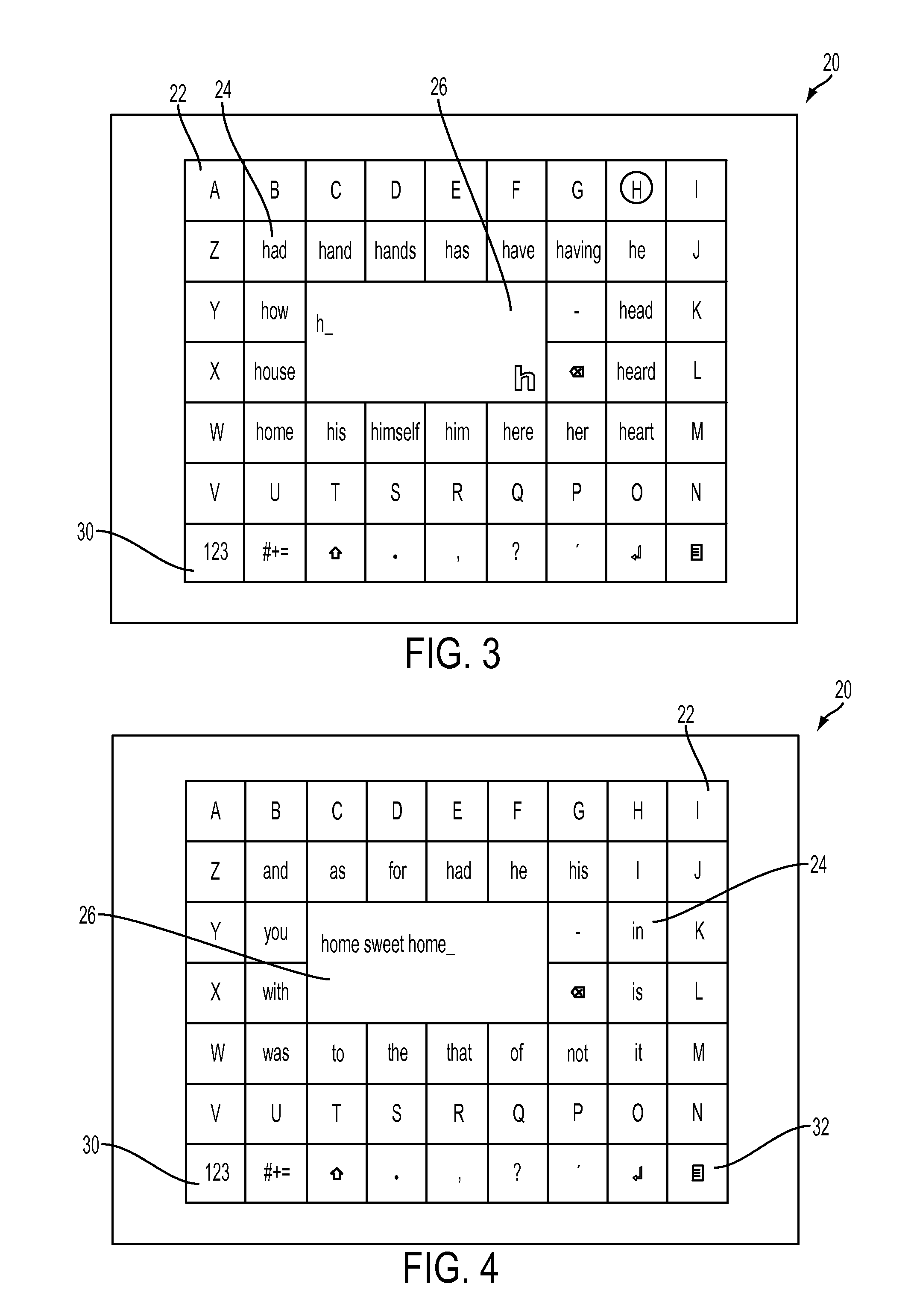

Eye typing system using a three-layer user interface

InactiveUS20120086645A1Effective and efficient controlMinimizing user fatigueInput/output for user-computer interactionCathode-ray tube indicatorsComputer graphics (images)Typing

A specially-configured interactive user interface for use in eye typing takes the form of a three-layer arrangement that allows for controlling computer input with eye gazes. The three-layer arrangement includes an outer, rectangular ring of letters, displayed clockwise in alphabetical order (forming the first layer). A group of “frequently-used words” associated with the letters being typed forms an inner ring (and is defined as the second layer). This second layer of words is constantly updated as the user continues to enter text. The third layer is a central “open” portion of the interface and forms the typing space—the “text box” that will be filled as the user continues to type. A separate row of control / function keys (including mode-switching for upper case vs. lower case, numbers and punctuation) is positioned adjacent to the three-layer on-screen keyboard display.

Owner:SIEMENS CORP

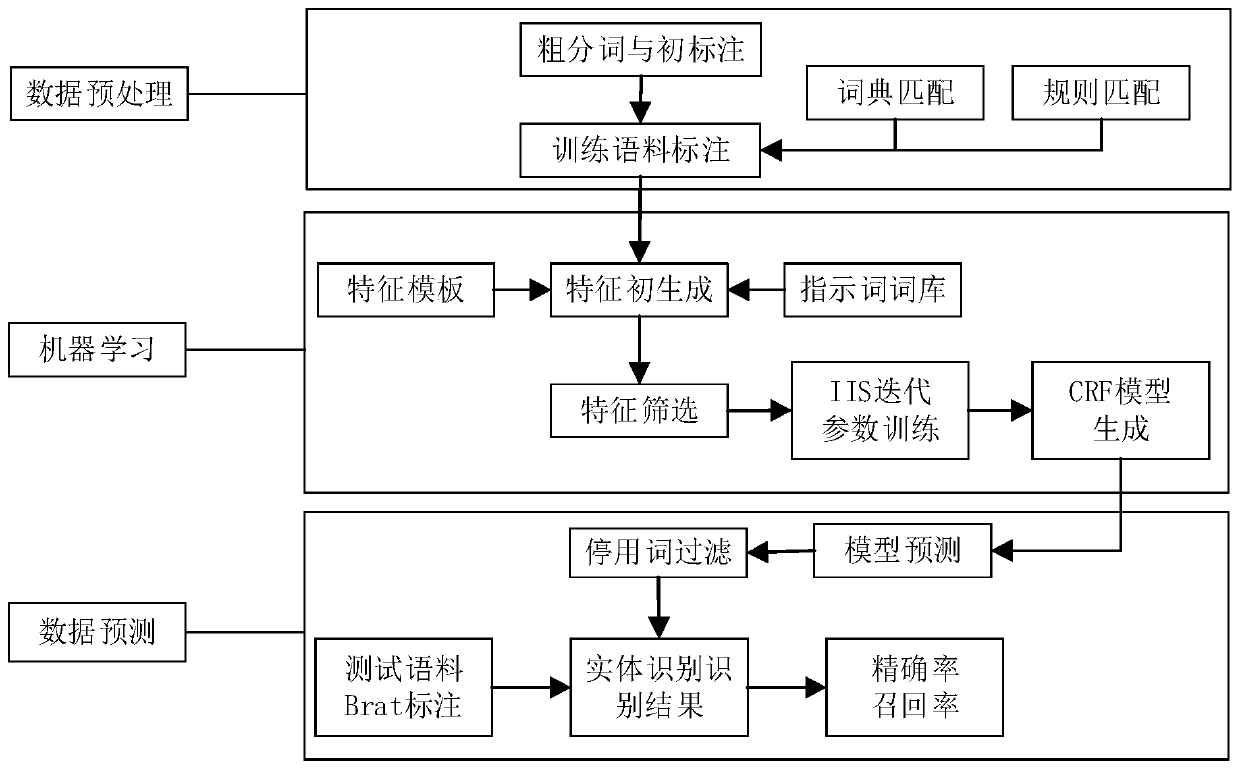

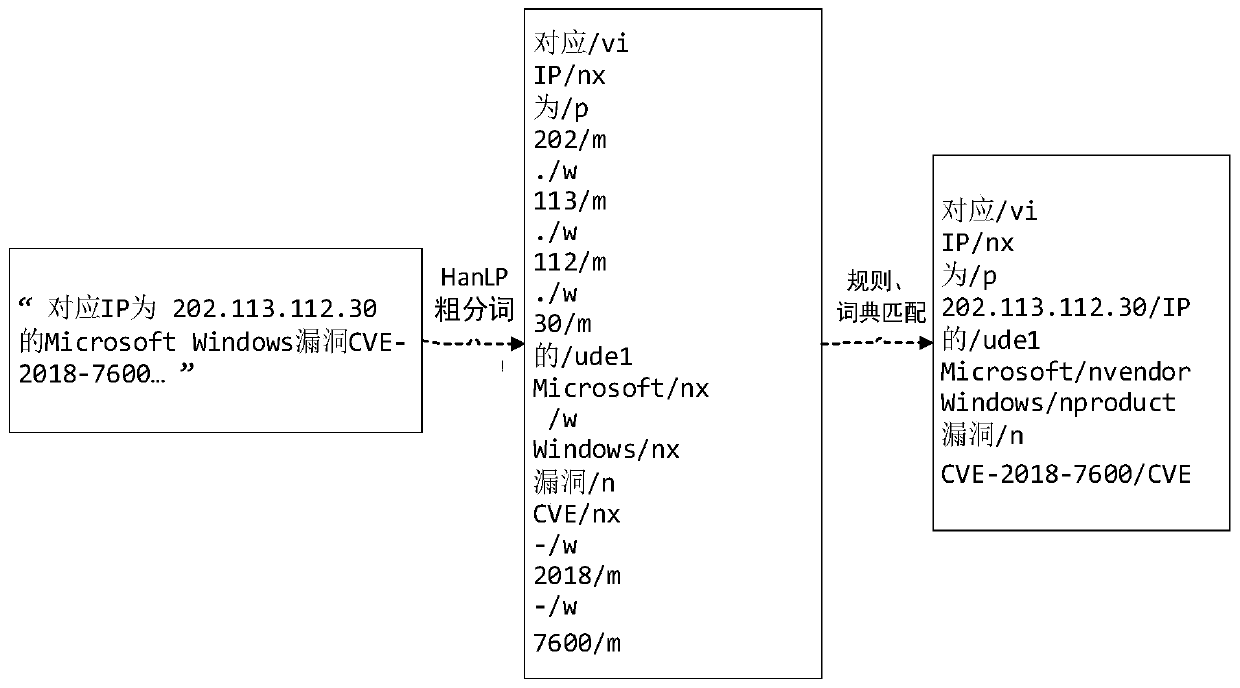

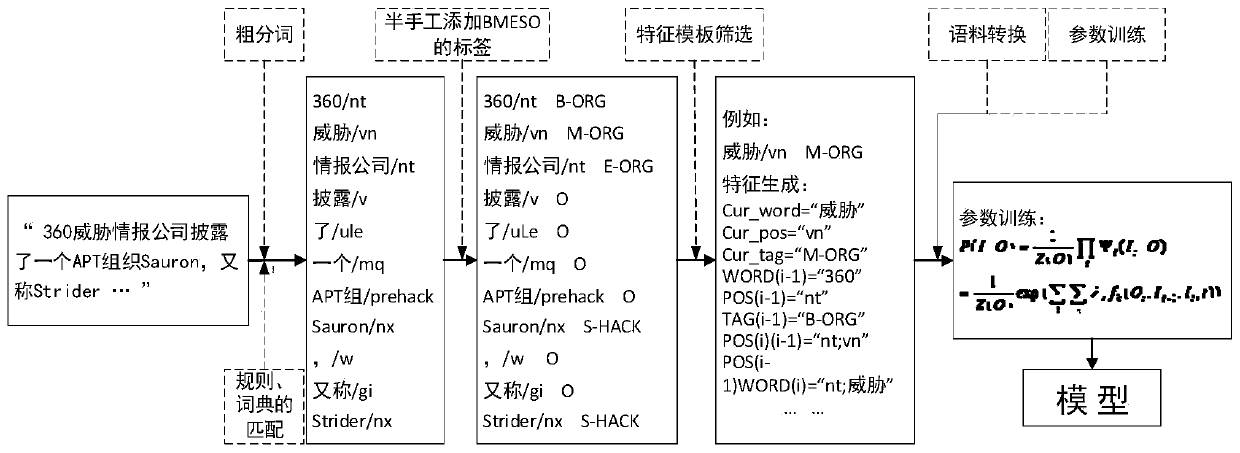

Threat intelligence oriented entity identification method and system

InactiveCN109858018AFitEasy to identifySpecial data processing applicationsCommon wordExtraction methods

The invention relates to a threat intelligence oriented entity identification method and system. The method comprises the following steps: 1) performing coarse word segmentation on a threat information text serving as a training corpus; 2) constructing a threat information entity common word dictionary library and a rule library, and performing dictionary matching and rule matching on a coarse word segmentation result; 3) marking an entity label for each word based on a matching result to form a training set; 4) constructing a feature template, establishing an indication word bank to perfect the screening form of the feature template, generating context features for the training set by using the feature template, screening, and inputting the screened features into a machine learning modelto carry out parameter iterative training; and 5) performing coarse word segmentation, dictionary matching and rule matching on the threat information text to be identified, and performing entity identification by using the trained machine learning model. According to the threat information entity extraction method, the threat information entity extraction is completed by adopting a means of combining a rule, a dictionary and a model, so that the entity identification precision of the threat information is remarkably improved.

Owner:INST OF INFORMATION ENG CHINESE ACAD OF SCI

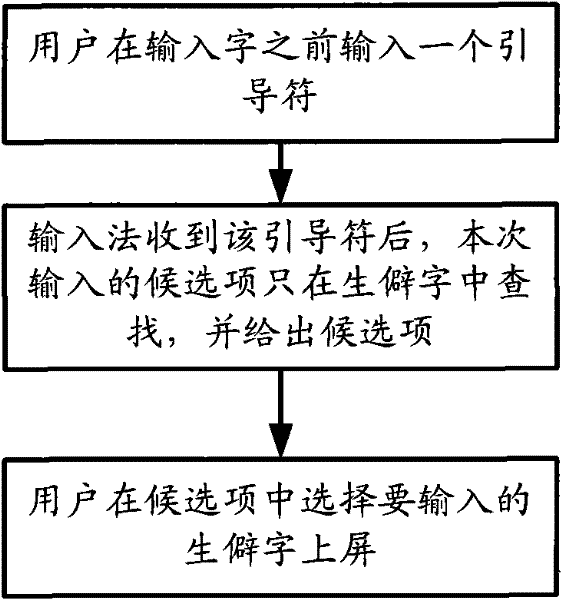

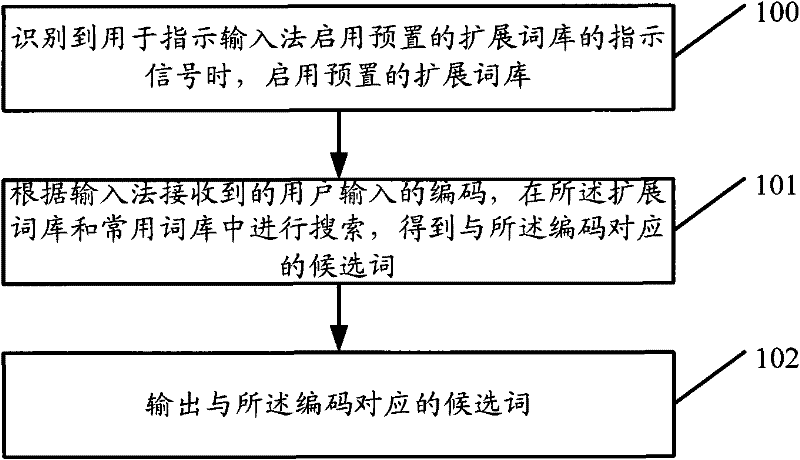

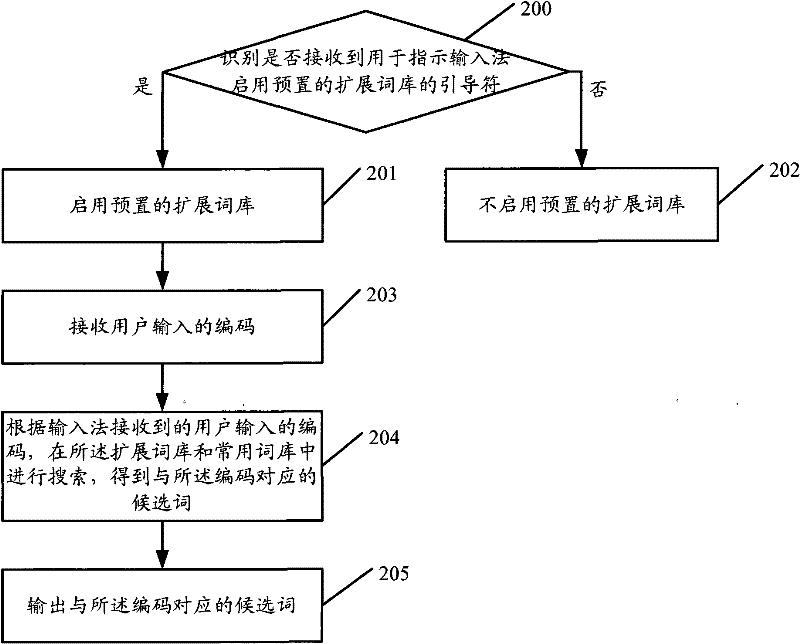

Input method and input method system

ActiveCN102346557ASolve the special needs of inputOvercoming scalabilityInput/output processes for data processingCommon wordAlgorithm

The invention provides an input method and an input method system. The input method comprises the following steps that: when indicating signals used for indicating that a preset expansion word stock is started by the input method are identified, the preset expansion stock is started; the searching is carried out in the expansion word stock and the common word stock according to the user input codes received by the input method, and candidate words corresponding to the codes are obtained; and the candidate words corresponding to the codes are output. When the input method and the input method system are implemented, the expansion searching is carried out in the preset word stock, in addition, the common use word stock can also be compatible with the expansion word stock, and more special input requirements of users can be met.

Owner:SHENZHEN SHI JI GUANG SU INFORMATION TECH

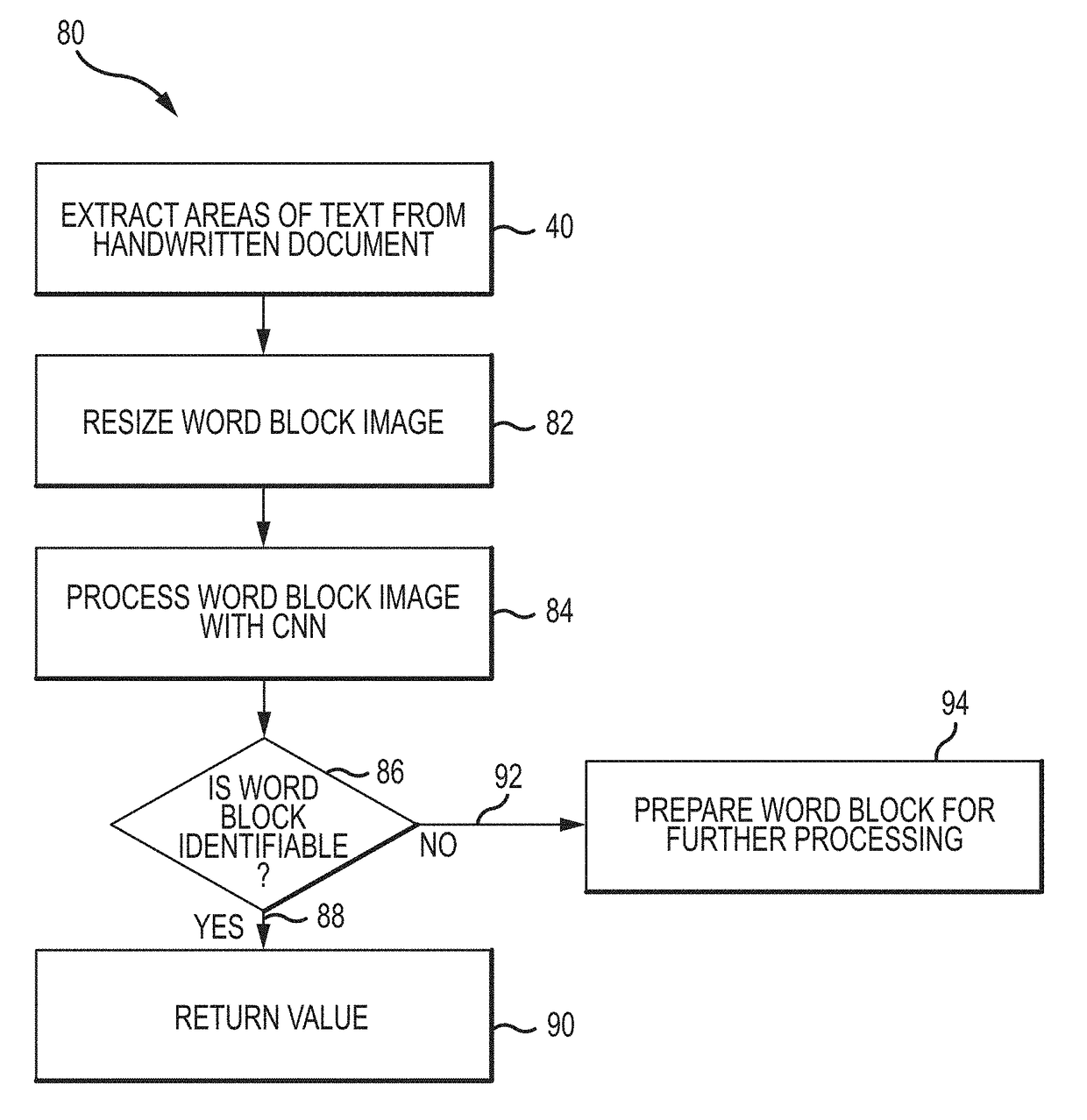

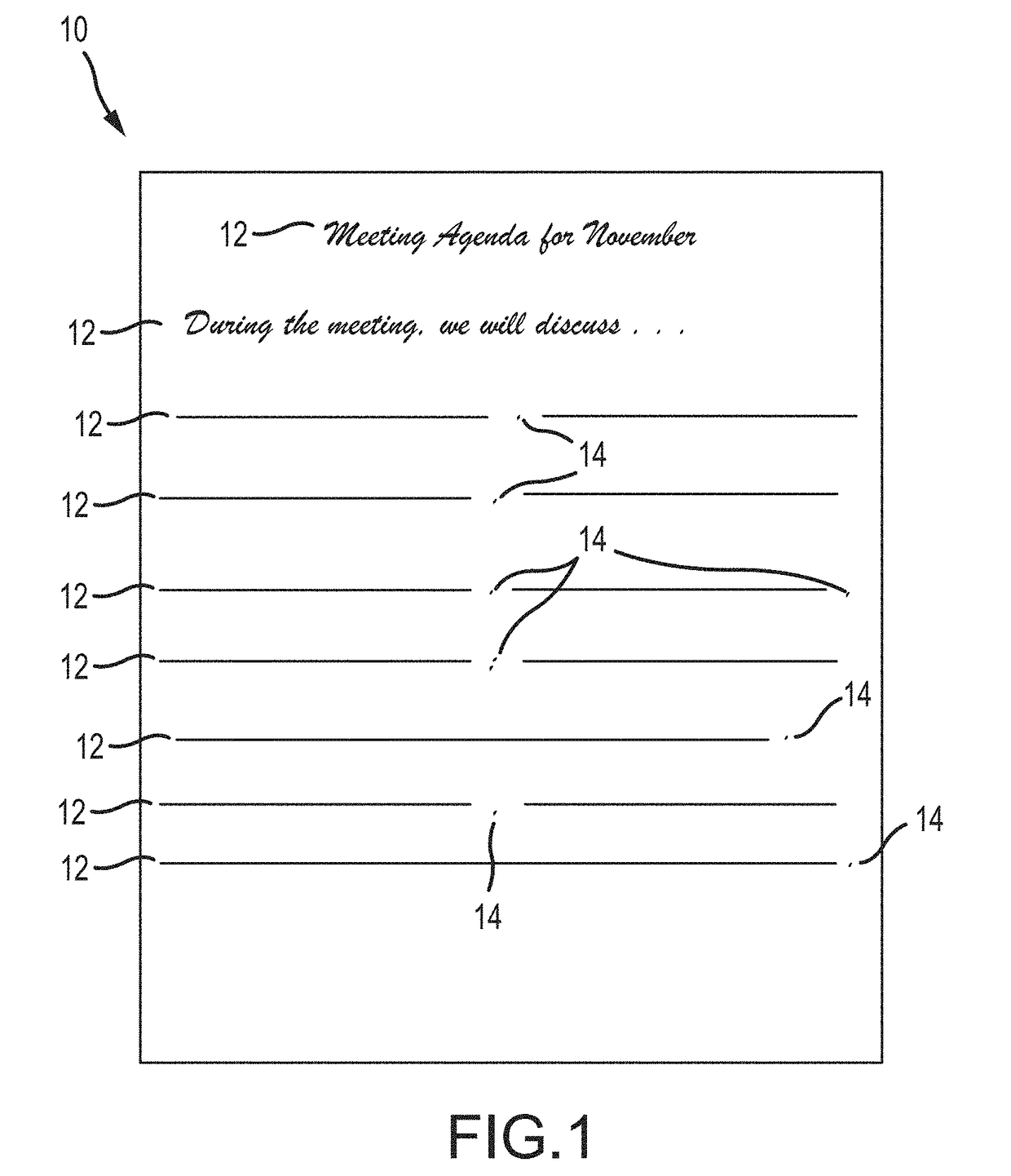

System and method of character recognition using fully convolutional neural networks with attention

ActiveUS20180137350A1Natural language data processingNeural architecturesConfidence factorDigital image

Embodiments of the present disclosure include a method that obtains a digital image. The method includes extracting a word block from the digital image. The method includes processing the word block by evaluating a value of the word block against a dictionary. The method includes outputting a prediction equal to a common word in the dictionary when a confidence factor is greater than a predetermined threshold. The method includes processing the word block and assigning a descriptor to the word block corresponding to a property of the word block. The method includes processing the word block using the descriptor to prioritize evaluation of the word block. The method includes concatenating a first output and a second output. The method includes predicting a value of the word block.

Owner:KODAK ALARIS INC

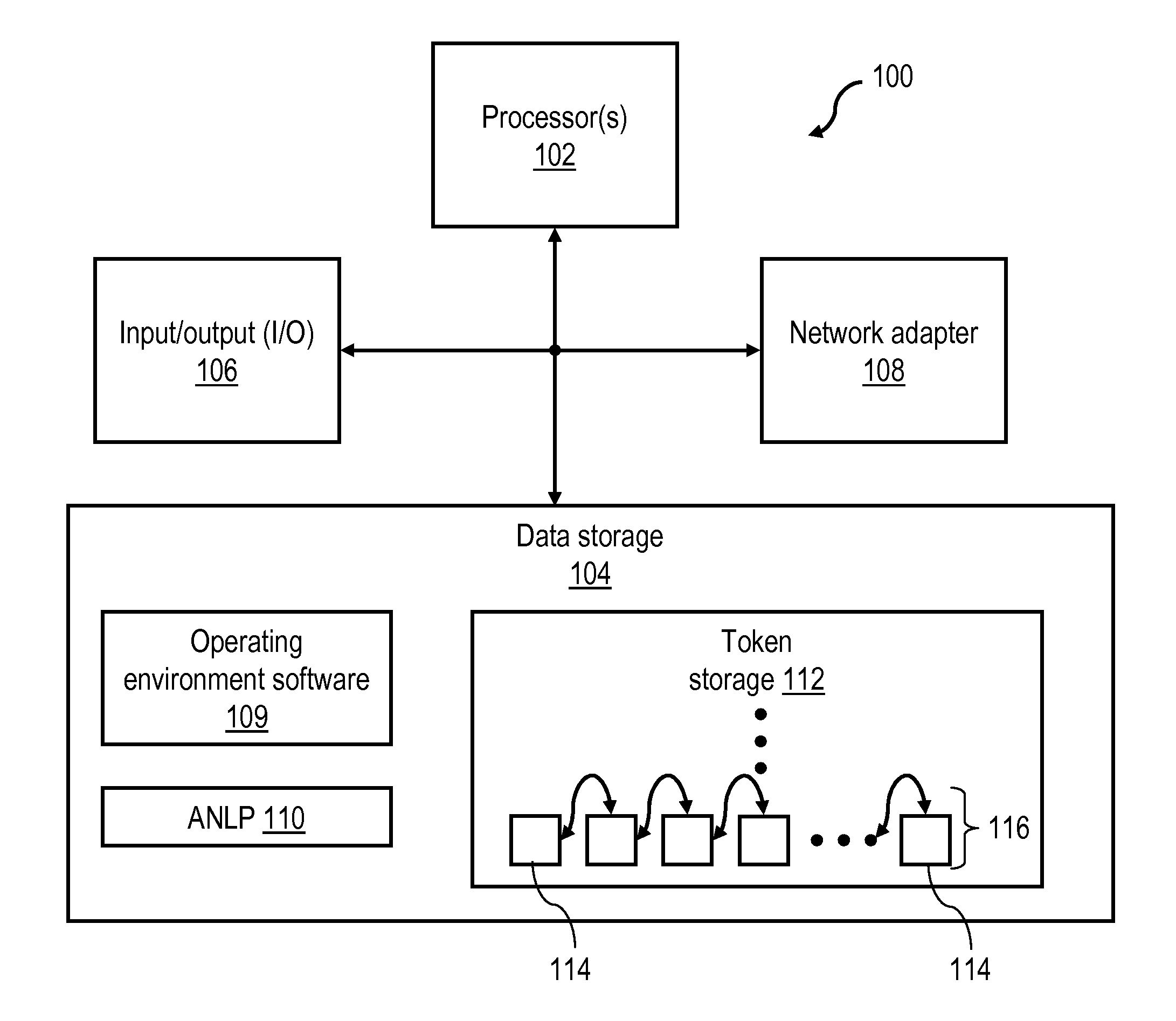

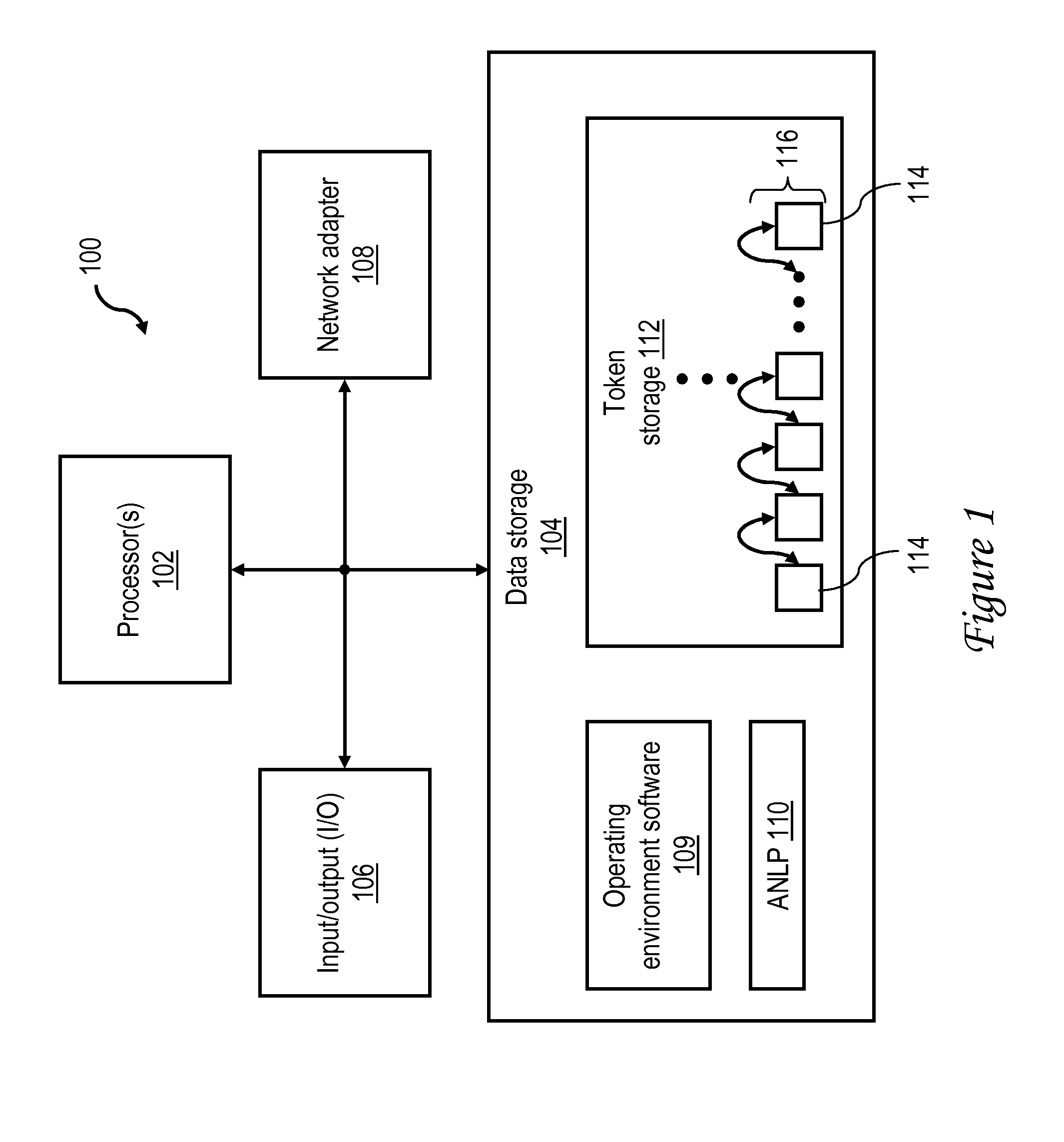

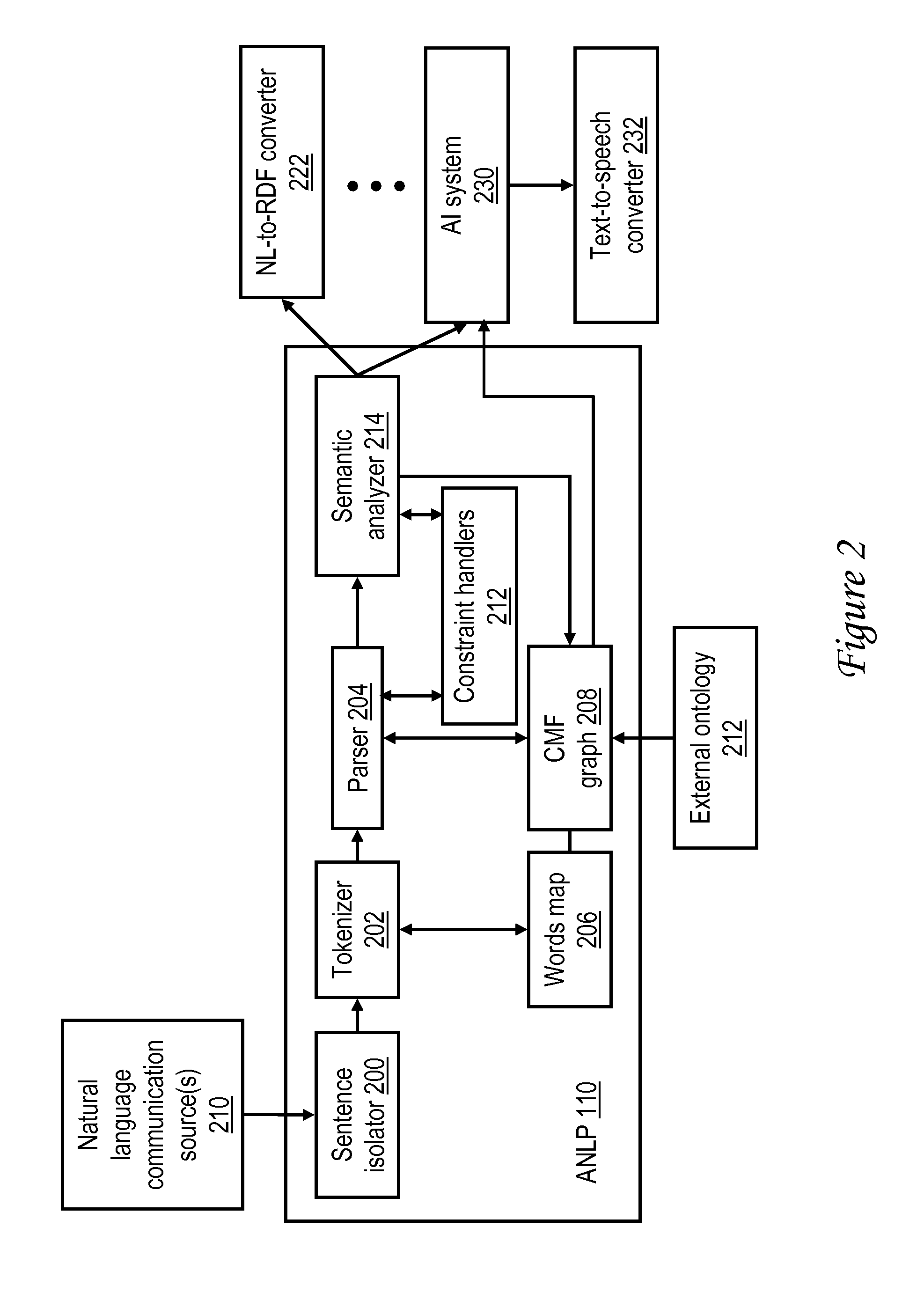

Automated comprehension of natural language via constraint-based processing

ActiveUS20150309992A1Semantic analysisSpecial data processing applicationsNODALData processing system

A consistent meaning framework (CMF) graph including a plurality of nodes linked by a plurality of edges is maintained in data storage of a data processing system. Multiple nodes among the plurality of nodes are meaning nodes corresponding to different word meanings for a common word spelling of a natural language. Each of the multiple word meanings has a respective one of a plurality of associated constraints. A natural language communication is processed by reference to the CMF graph. The processing includes selecting, for a word in the natural language communication, a selected word meaning from among the multiple word meanings based on which of the plurality of associated constraints is satisfied by the natural language communication. An indication of the selected word meaning is stored in data storage.

Owner:VISEL THOMAS A

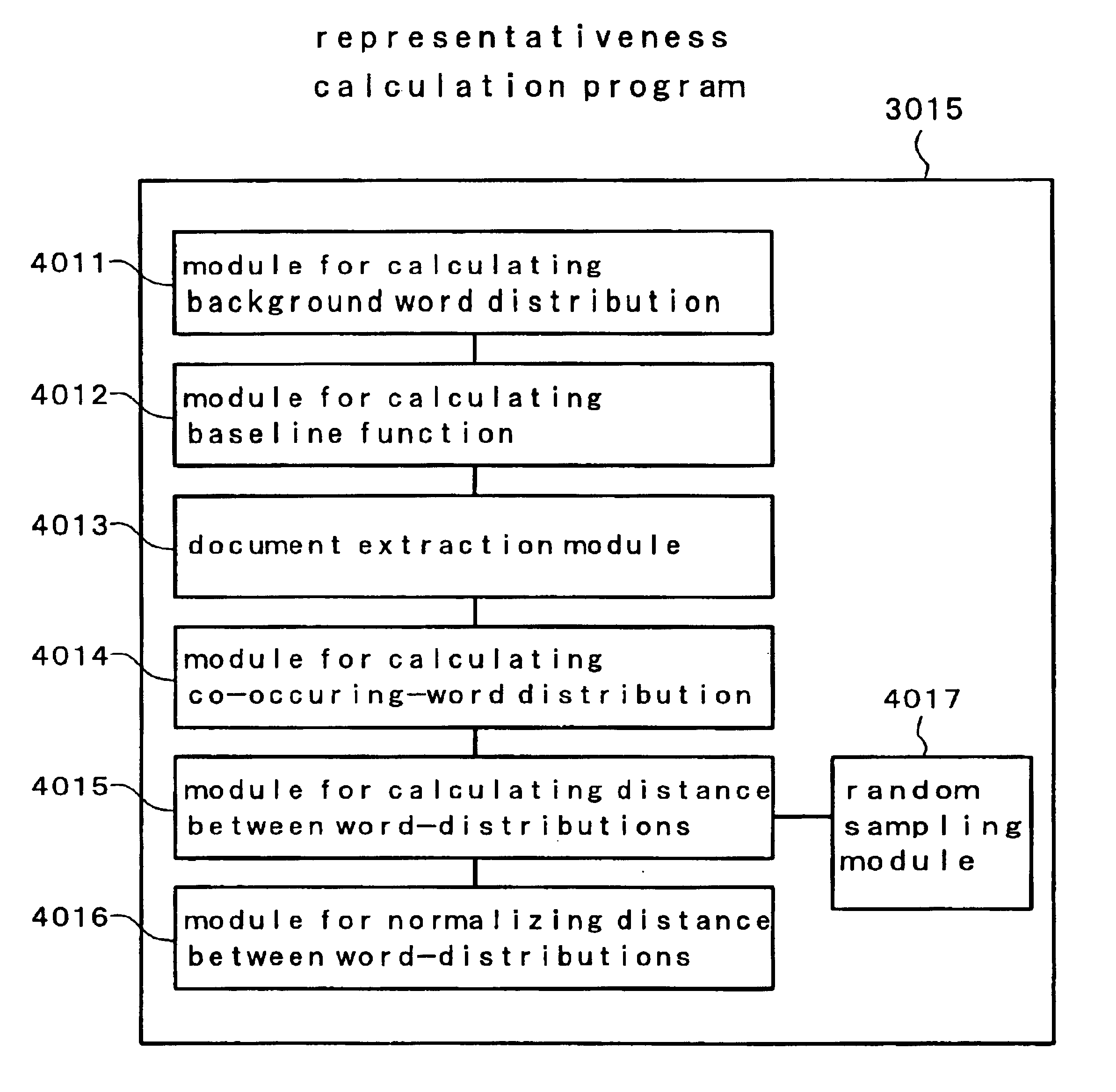

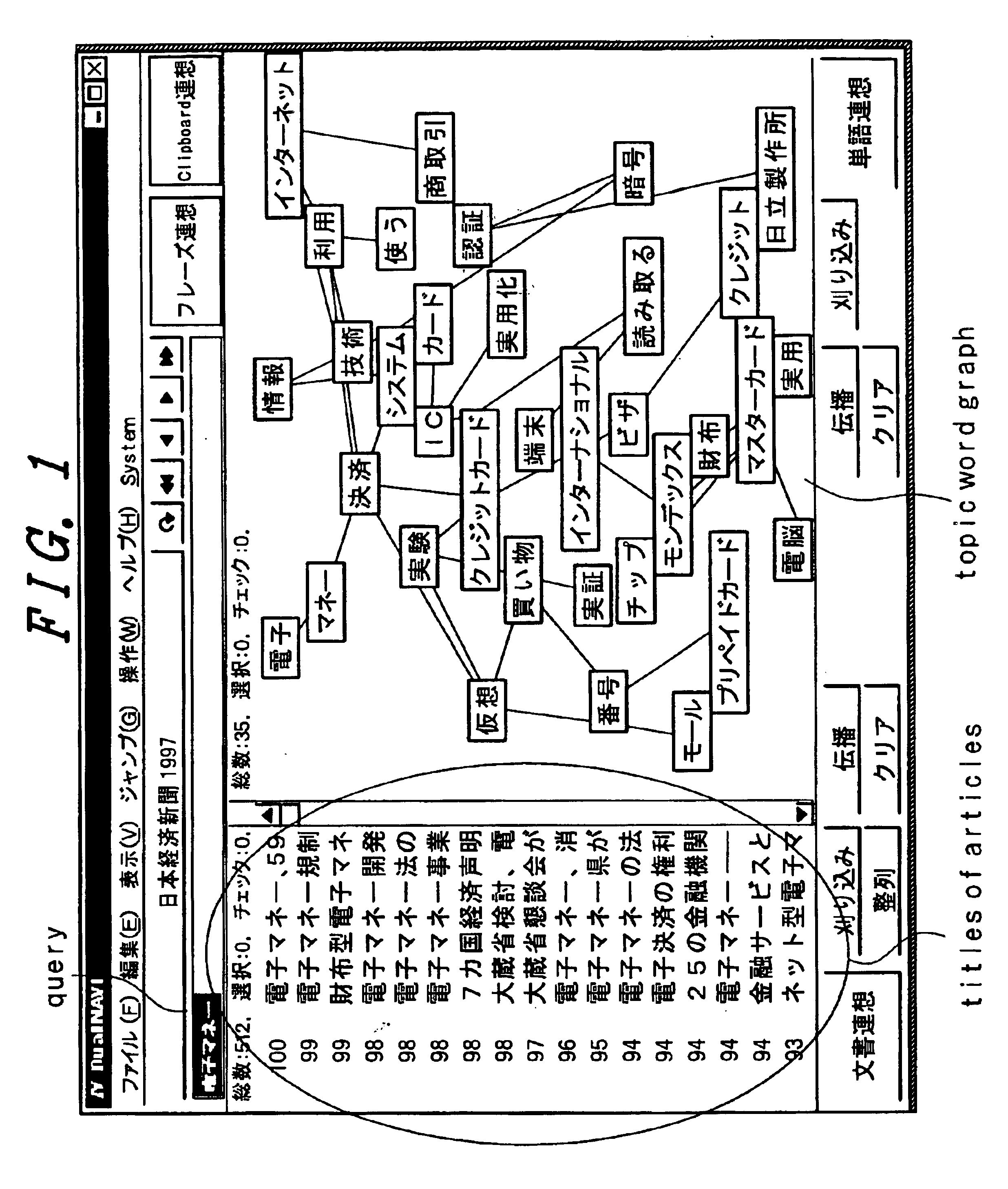

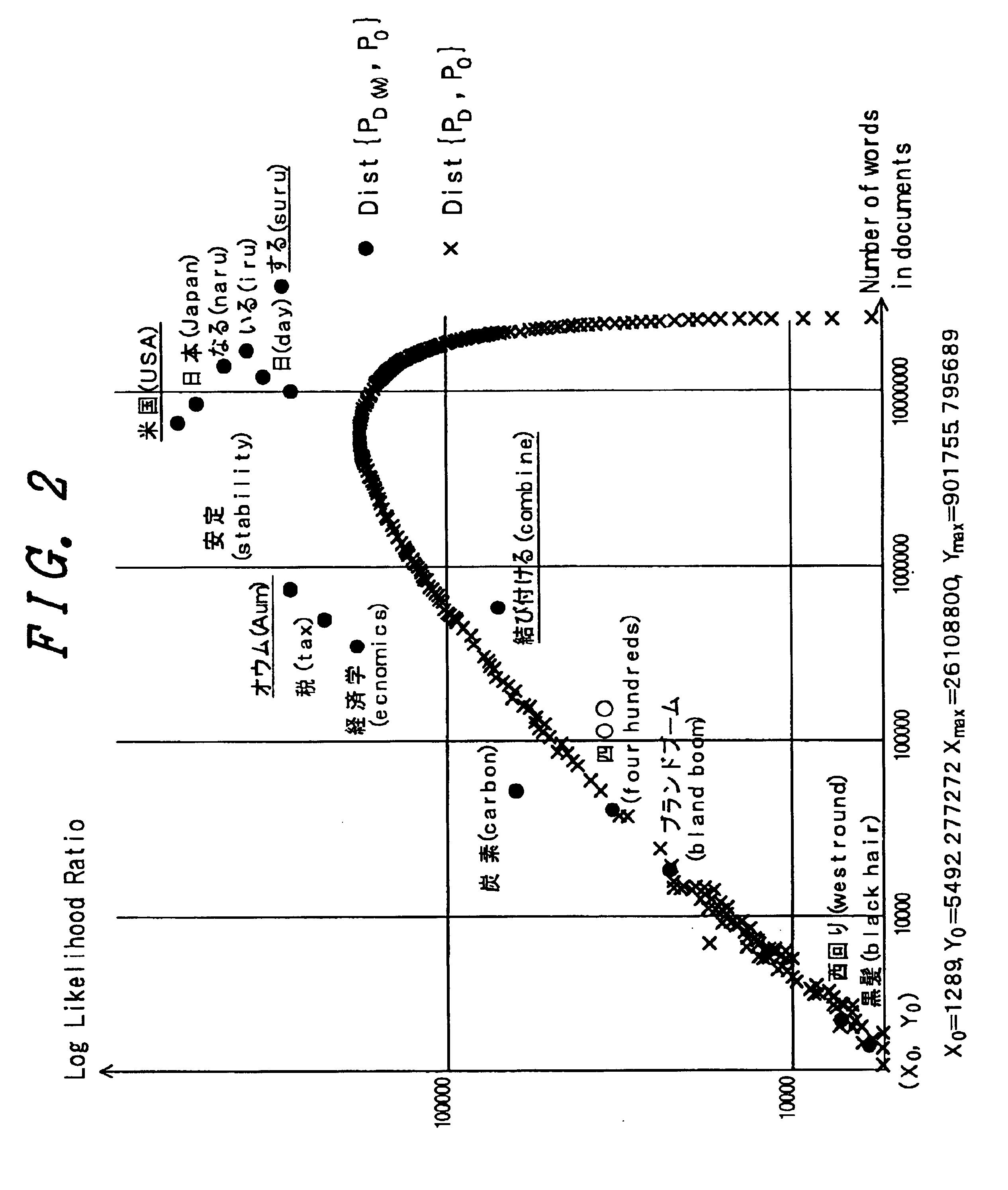

Word importance calculation method, document retrieving interface, word dictionary making method

InactiveUS6850937B1Not always easyDigital data information retrievalData processing applicationsAlgorithmCommon word

A known method for selecting words (or word sequences), which is an important aspect of information retrieval, involves the problems of inability to eliminate high-frequency common words and of often arbitrary setting of the threshold value for dividing important and unimportant words. These problems are solved by normalizing the difference between the word distribution in a subset of all documents containing a word to be extracted (or a subset of said document set) and the word distribution in the set of all documents with the number of words in the said subset of all documents containing the word as a parameter, and the accuracy of support information retrieval is thereby enhanced.

Owner:HITACHI LTD

Word alignment method and system for improved vocabulary coverage in statistical machine translation

InactiveUS8612205B2Natural language translationDigital data processing detailsMachine translation systemText string

A system and method for generating word alignments from pairs of aligned text strings are provided. A corpus of text strings provides pairs of text strings, primarily sentences, in source and target languages. A first alignment between a text string pair creates links therebetween. Each link links a single token of the first text string to a single token of the second text string. A second alignment also creates links between the text string pair. In some cases, these links may correspond to bi-phrases. A modified first alignment is generated by selectively modifying links in the first alignment which include a word which is infrequent in the corpus, based on links generated in the second alignment. This results in removing at least some of the links for the infrequent words, allowing more compact and better quality bi-phrases, with higher vocabulary coverage, to be extracted for use in a machine translation system.

Owner:XEROX CORP

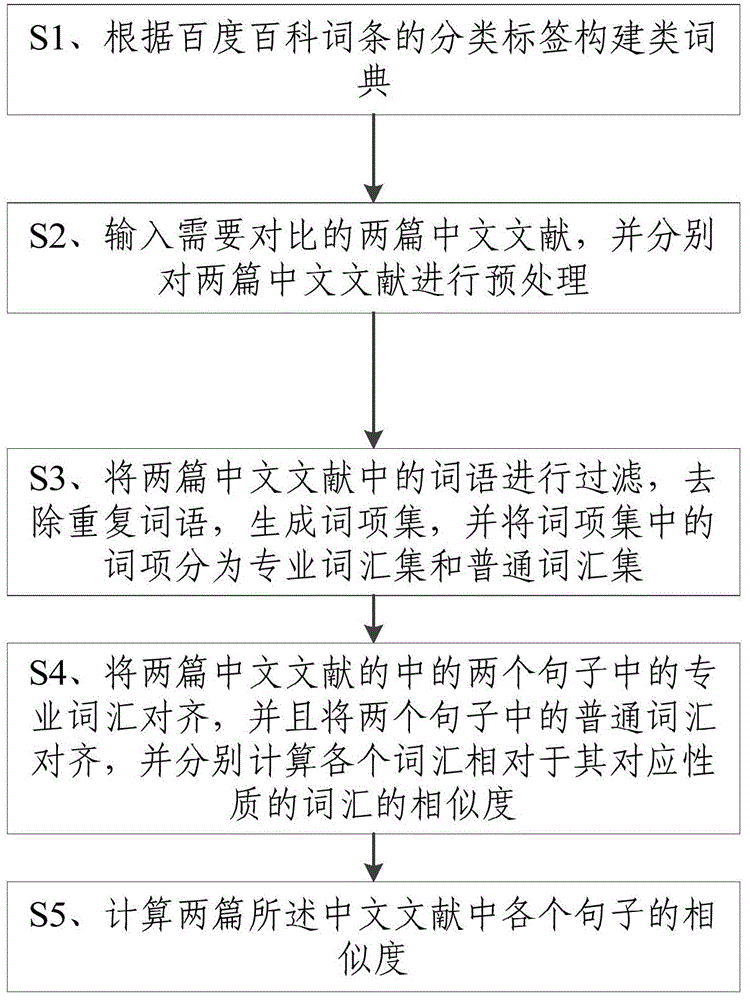

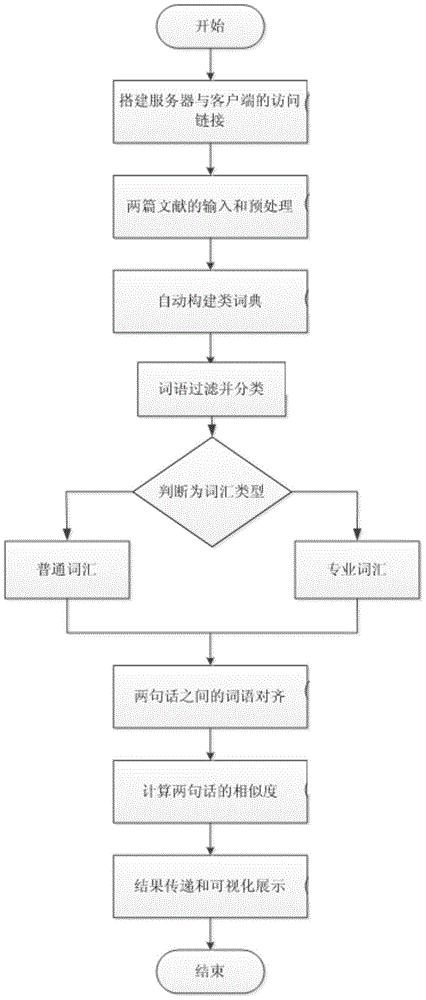

Text similarity detection device

InactiveCN104679728AImprove accuracyHigh speedSpecial data processing applicationsDegree of similarityCommon word

The invention discloses a text similarity detection device. The text similarity detection device comprises the following steps: constructing a thesaurus according to classification labels of Baidu Encyclopedia entries; inputting two Chinese documents needing to be compared, and pre-processing the two Chinese documents respectively; filtering words in the two Chinese documents and removing repeated words to generate a word item set; dividing word items in the word item set into a specialized word set and a common word set; aligning specialized words in two sentences in the two Chinese documents and aligning common words in the two sentences; calculating the similarity, relative to the word with the corresponding property, of each word respectively; and calculating the similarity of each sentence in the two Chinese documents. According to the method, manpower resources are saved to the greatest extent, and the judgment accuracy and the judgment speed of a computer network system to Chinese are improved.

Owner:CHINA AGRI UNIV