Patents

Literature

23145results about "Originals for photomechanical treatment" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

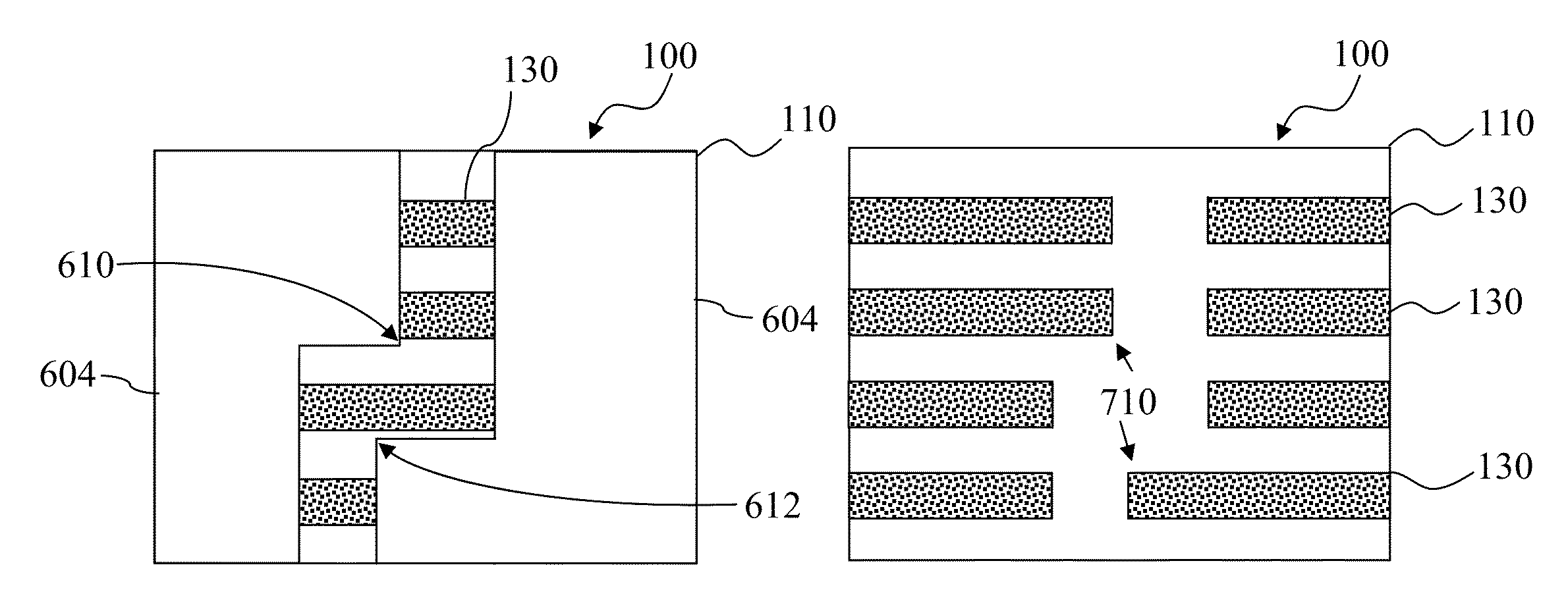

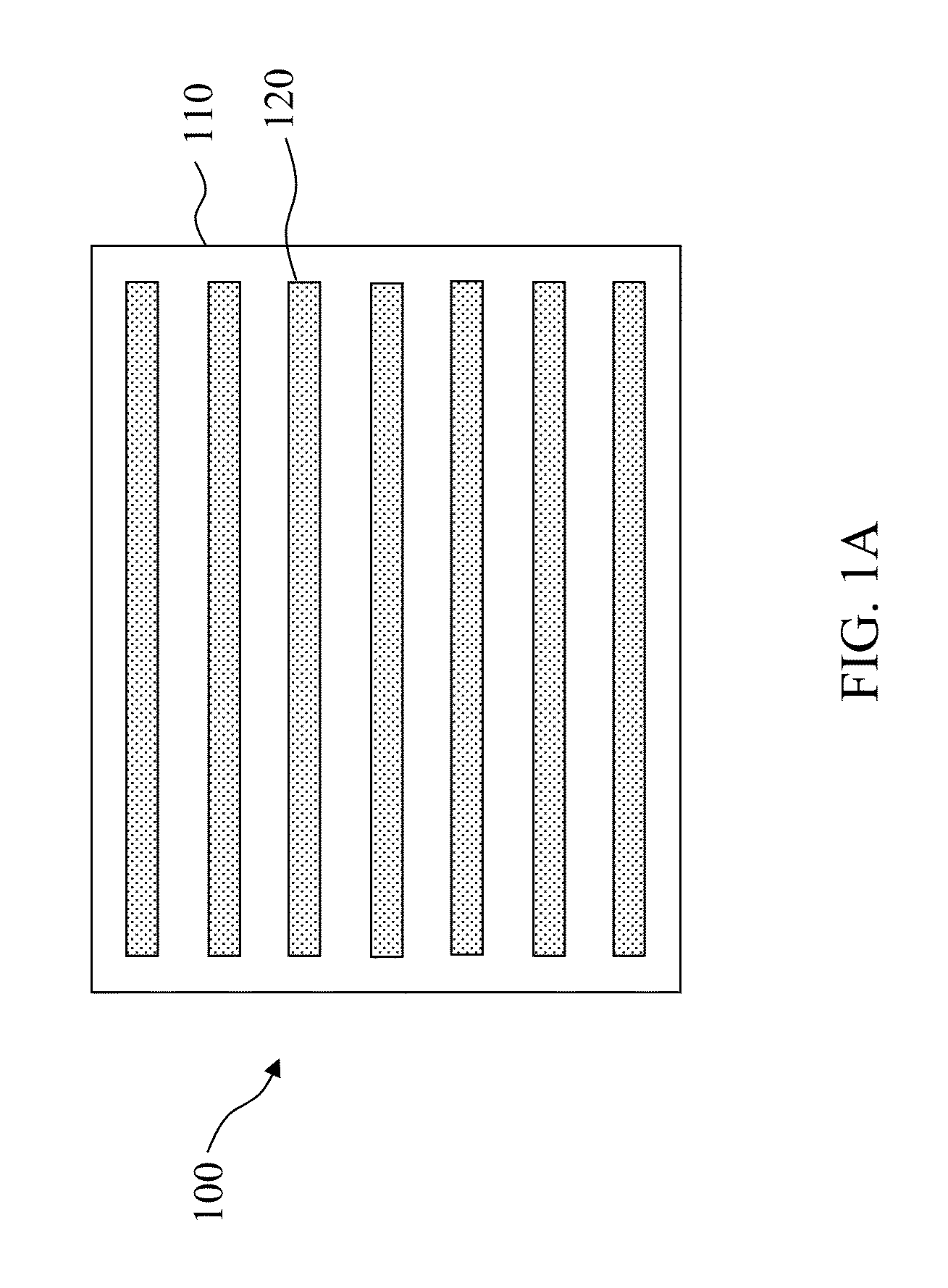

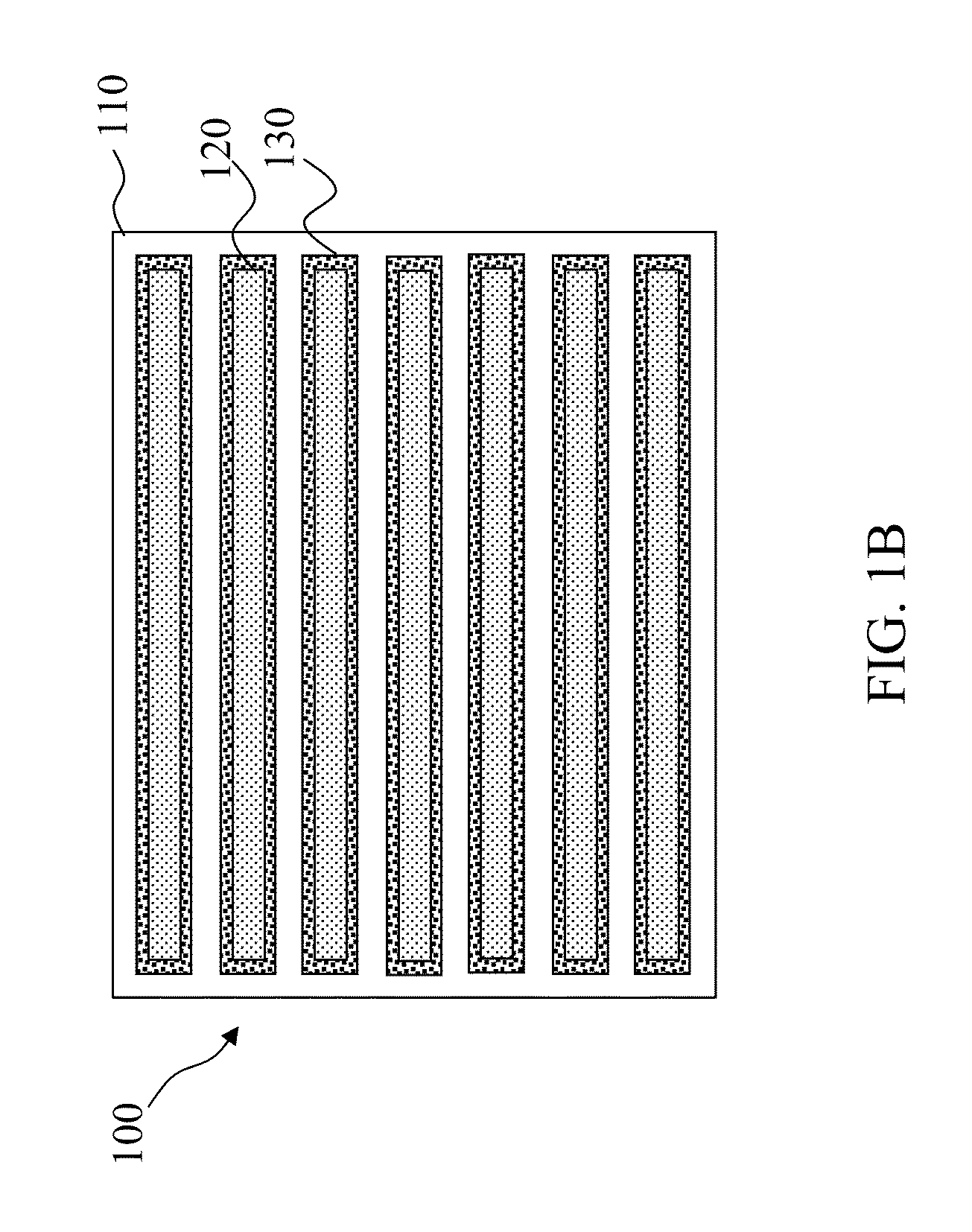

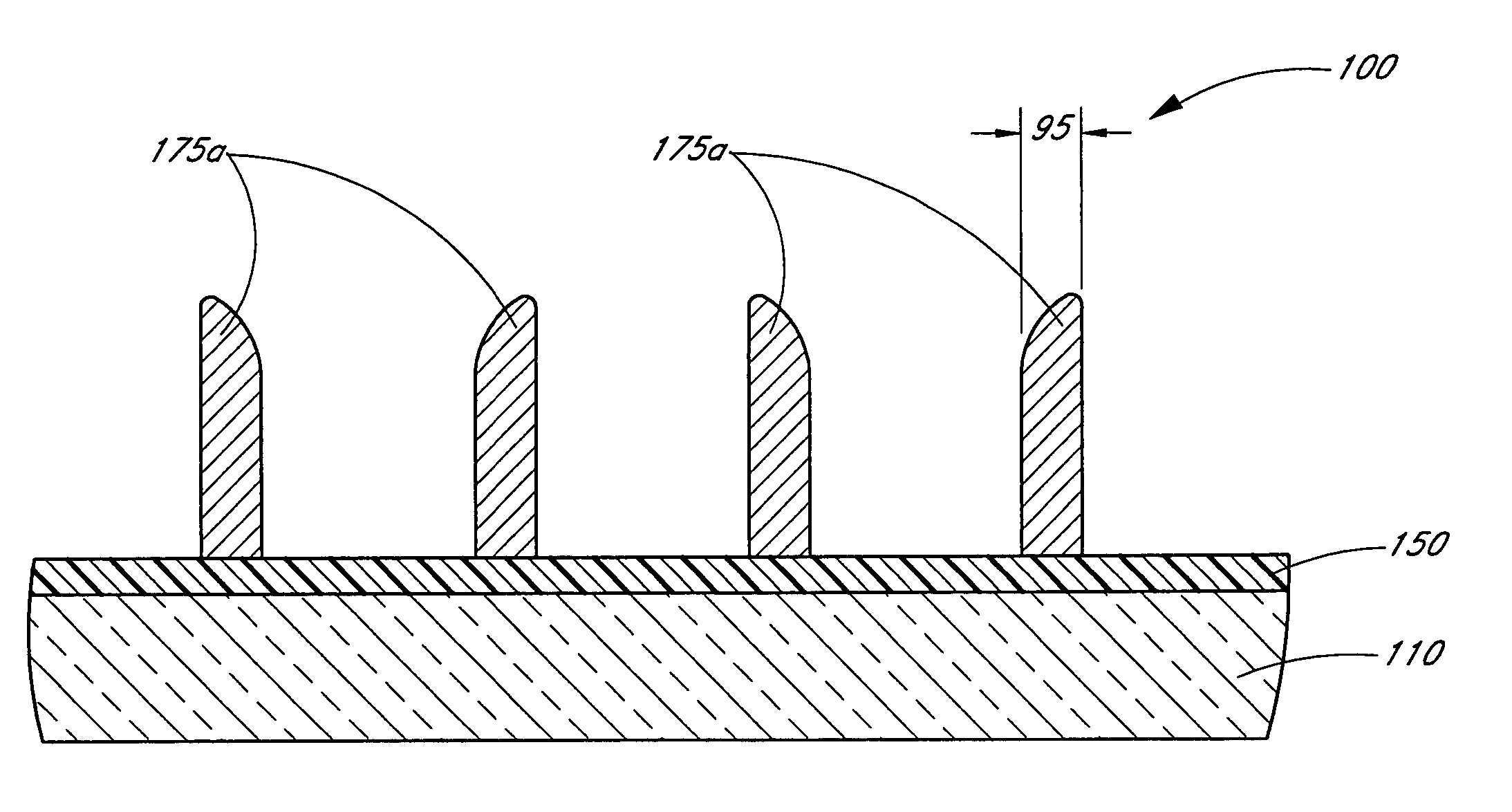

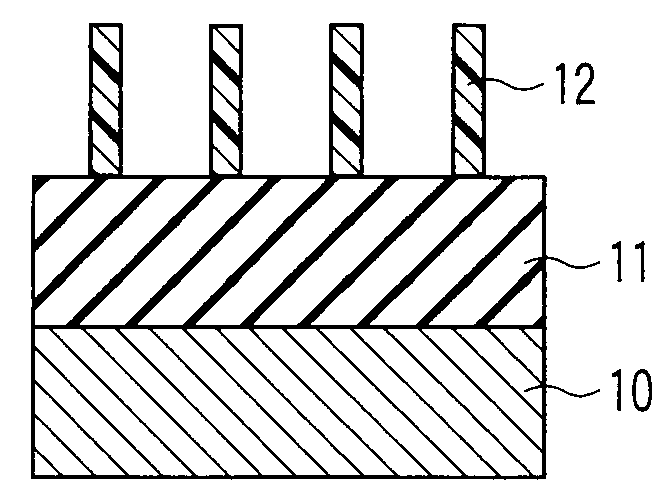

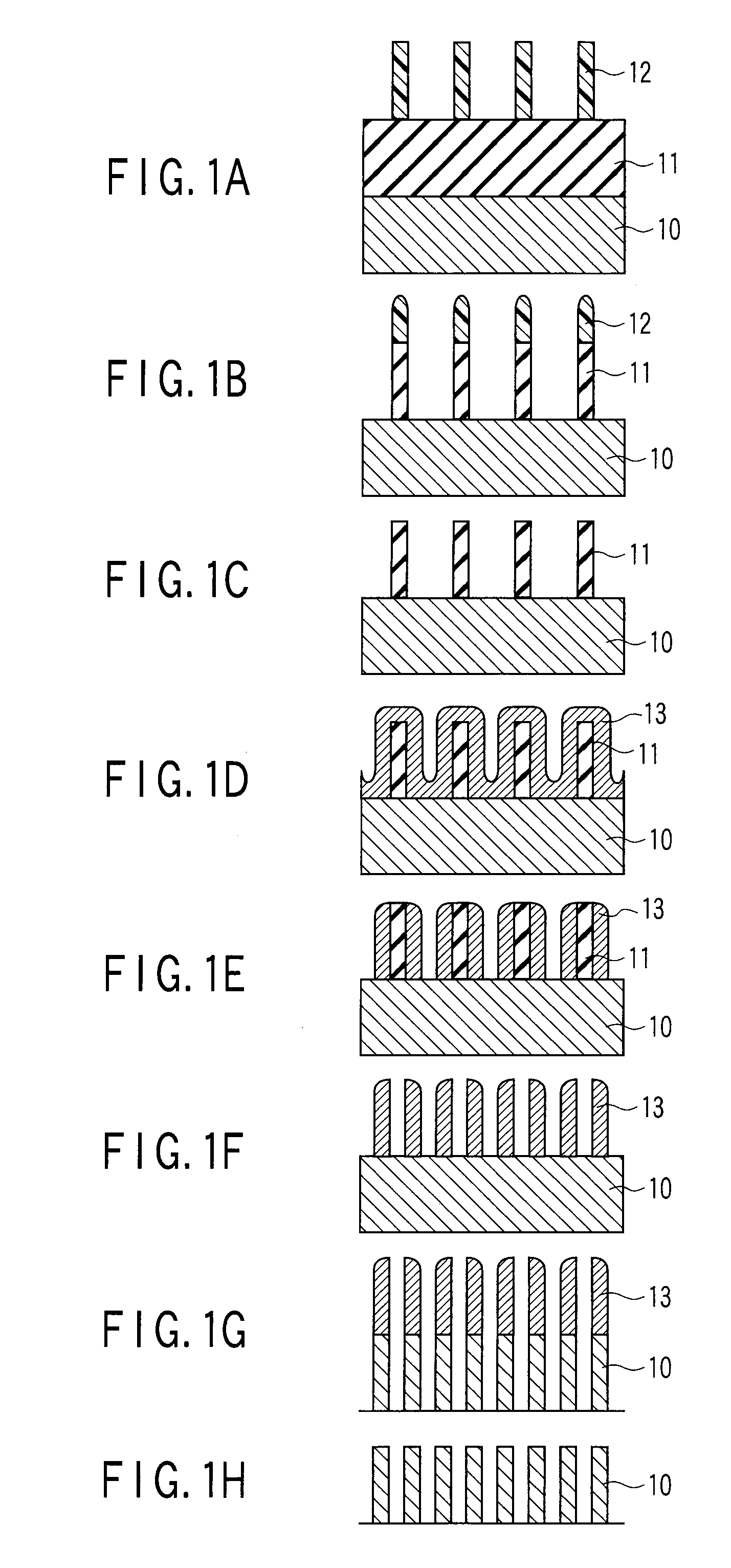

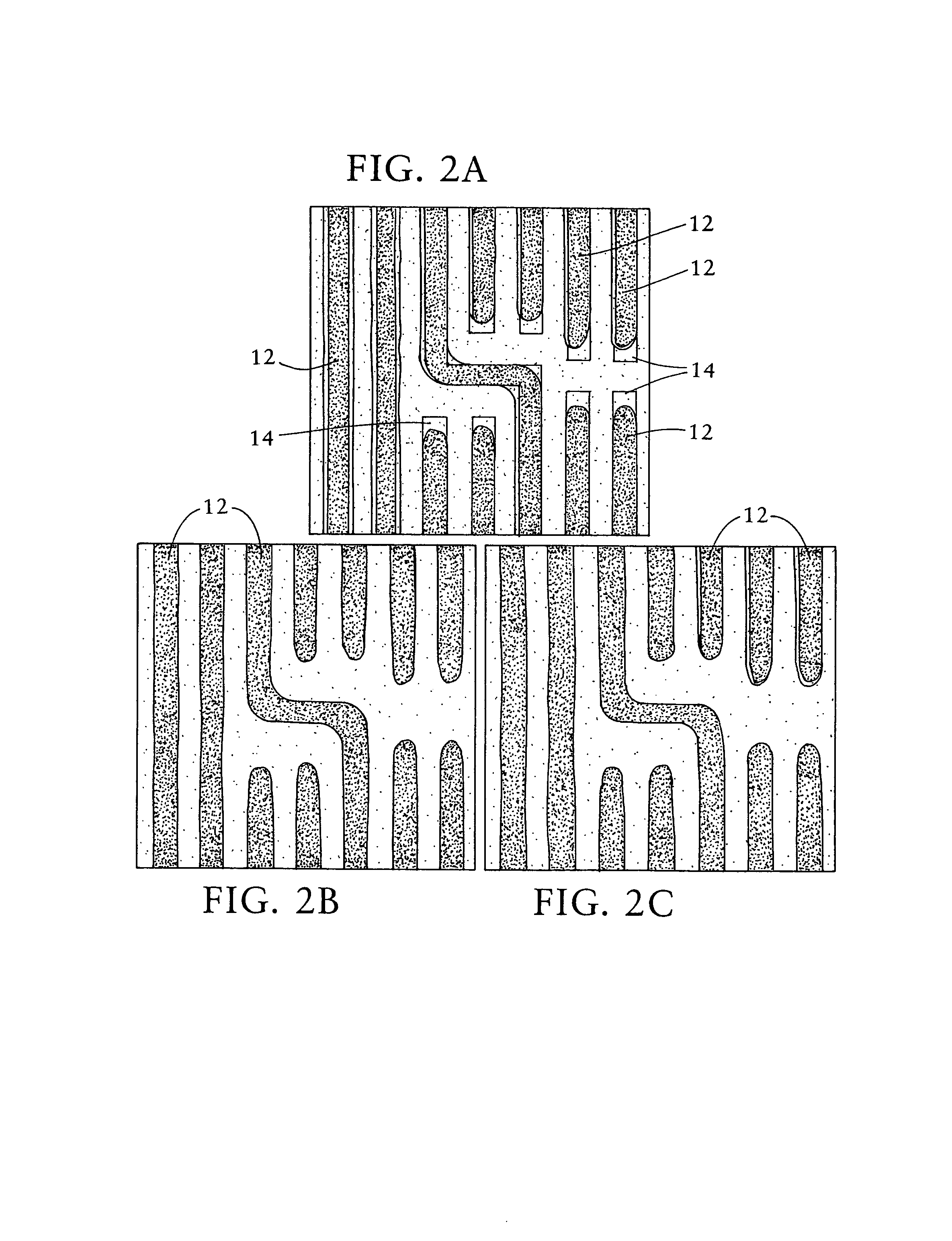

Cut-mask patterning process for fin-like field effect transistor (FinFET) device

ActiveUS9236267B2Liquid surface applicatorsSolid-state devicesImage resolutionField-effect transistor

A method for patterning a plurality of features in a non-rectangular pattern, such as on an integrated circuit device, includes providing a substrate including a surface with a plurality of elongated protrusions, the elongated protrusions extending in a first direction. A first layer is formed above the surface and above the plurality of elongated protrusions, and patterned with an end cutting mask. The end cutting mask includes two nearly-adjacent patterns with a sub-resolution feature positioned and configured such that when the resulting pattern on the first layer includes the two nearly adjacent patterns and a connection there between. The method further includes cutting ends of the elongated protrusions using the pattern on the first layer.

Owner:TAIWAN SEMICON MFG CO LTD

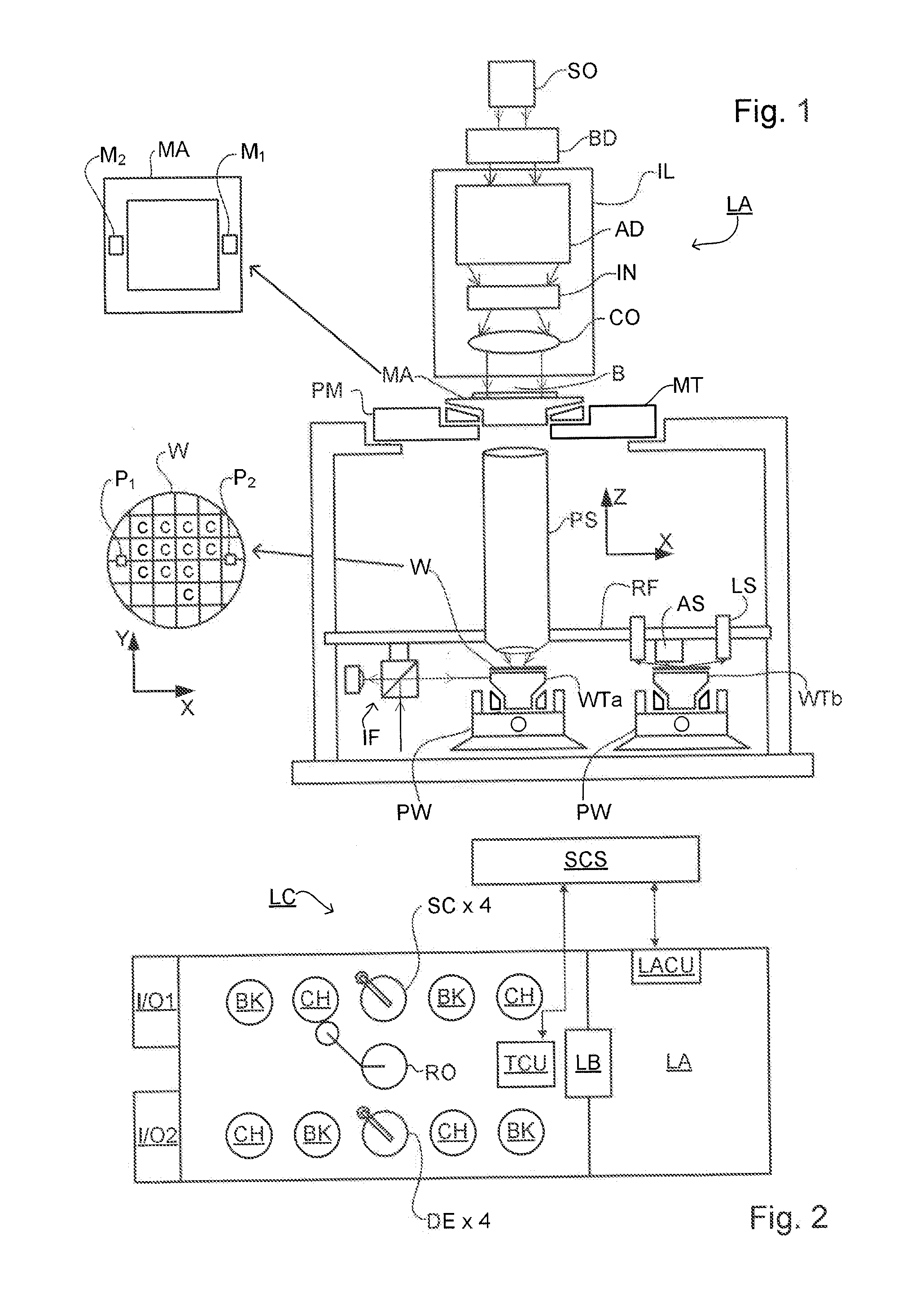

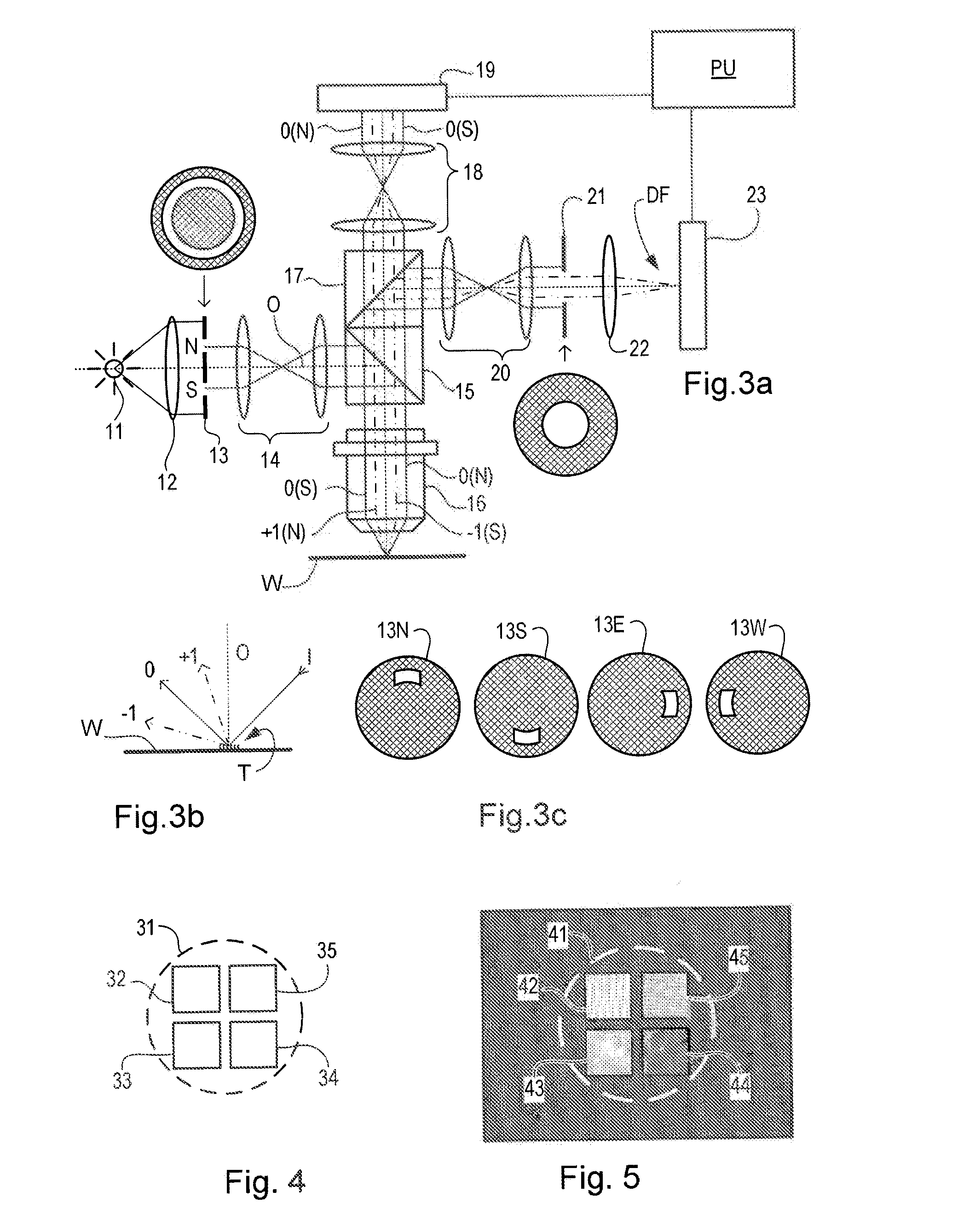

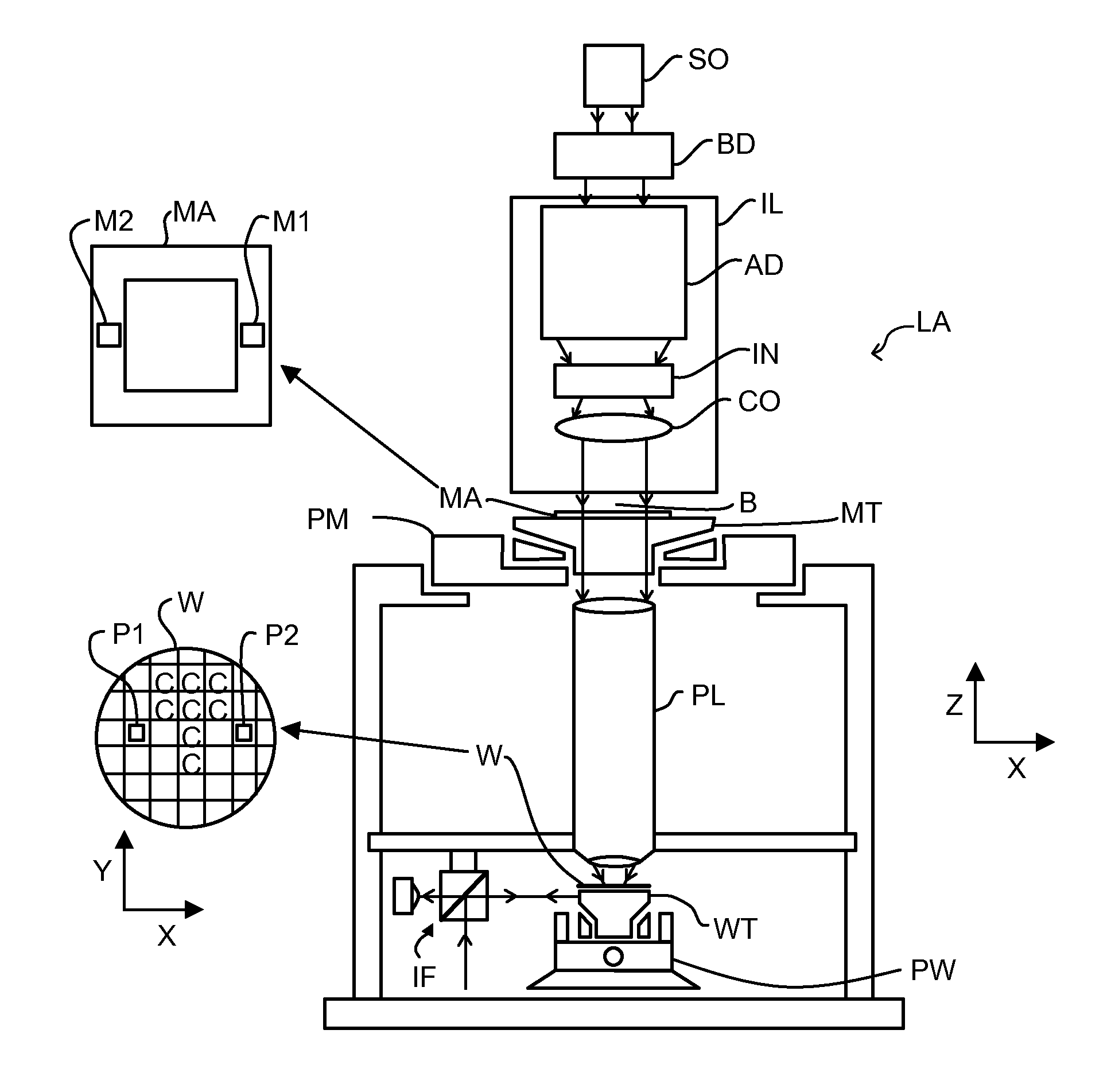

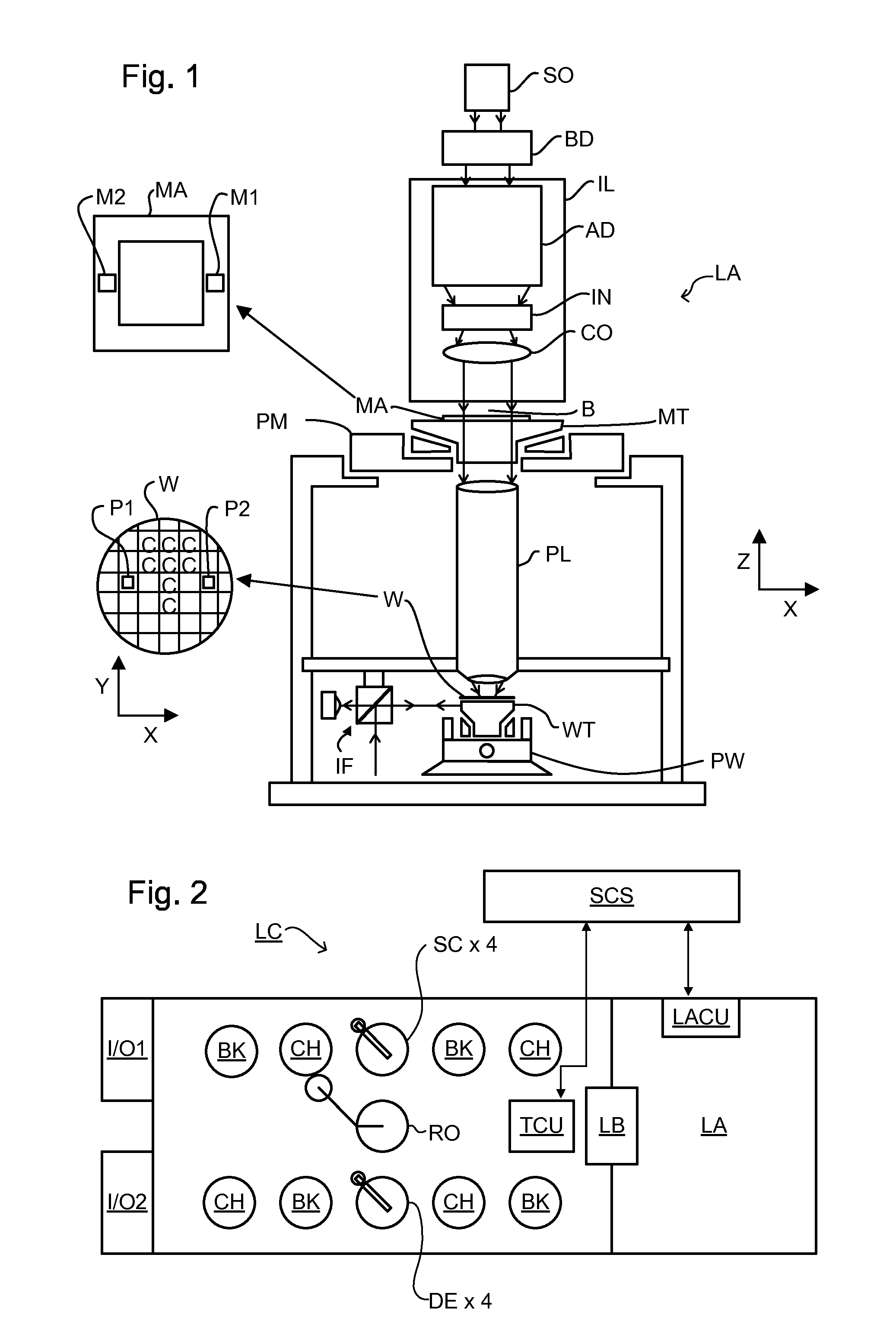

Substrate for Use in Metrology, Metrology Method and Device Manufacturing Method

InactiveUS20120044470A1Efficient packagingPhotomechanical apparatusMaterial analysis by optical meansMetrologyGrating

A pattern from a patterning device is applied to a substrate. The applied pattern includes device functional areas and metrology target areas. Each metrology target area comprises a plurality of individual grating portions, which are used for diffraction based overlay measurements or other diffraction based measurements. The gratings are of the small target type, which is small than an illumination spot used in the metrology. Each grating has an aspect ratio substantially greater than 1, meaning that a length in a direction perpendicular to the grating lines which is substantially greater than a width of the grating. Total target area can be reduced without loss of performance in the diffraction based metrology. A composite target can comprise a plurality of individual grating portions of different overlay biases. Using integer aspect ratios such as 2:1 or 4:1, grating portions of different directions can be packed efficiently into rectangular composite target areas.

Owner:ASML NETHERLANDS BV

Method and system for drying a substrate

ActiveUS20050046934A1Good pattern uniformityImprove uniformityMicroscopesPhotomechanical exposure apparatusCooking & bakingThin membrane

A method and system is described for drying a thin film on a substrate following liquid immersion lithography. Drying the thin film to remove immersion fluid from the thin film is performed prior to baking the thin film, thereby reducing the likely hood for interaction of immersion fluid with the baking process. This interaction has been shown to cause non-uniformity in critical dimension for the pattern formed in the thin film following the developing process.

Owner:TOKYO ELECTRON LTD

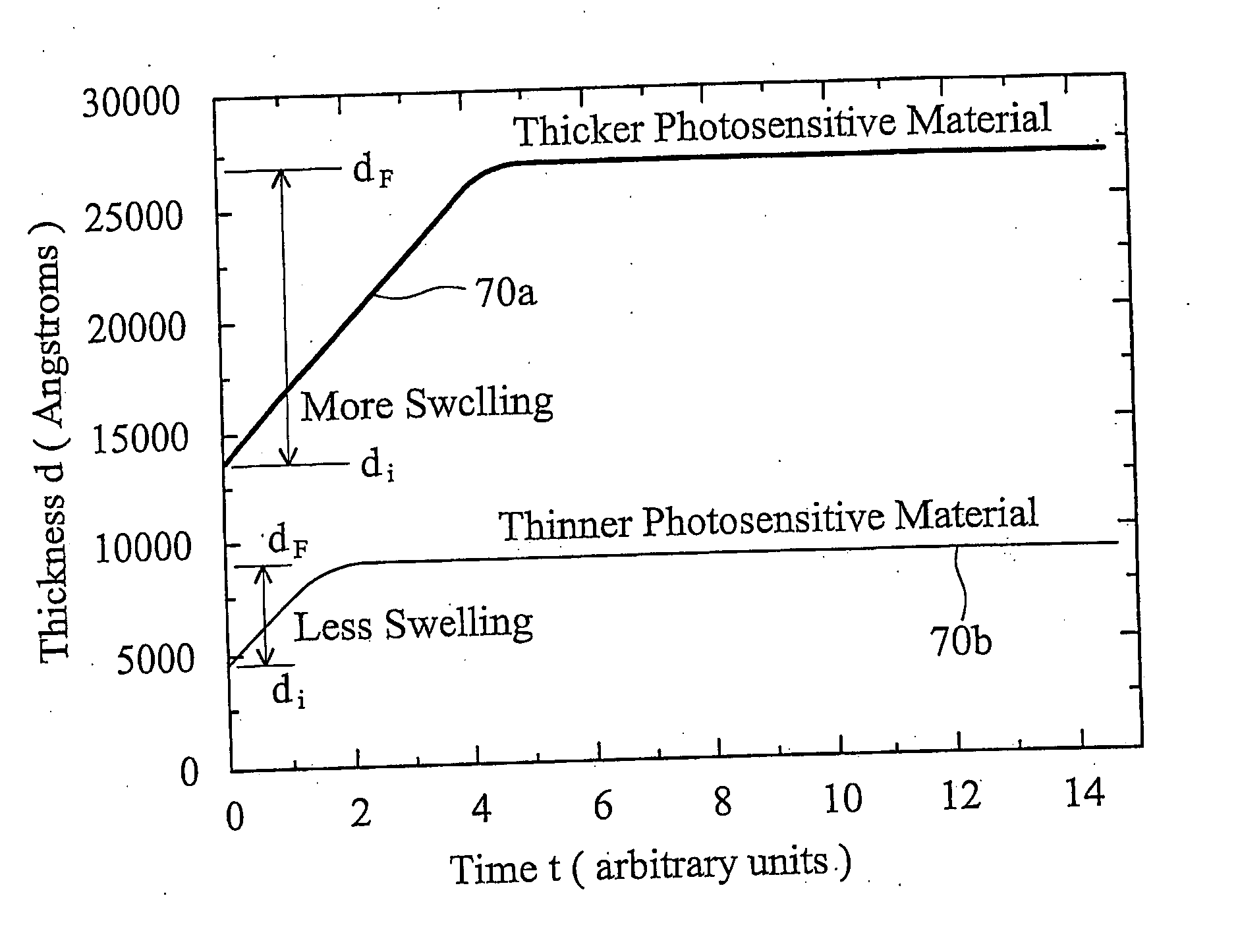

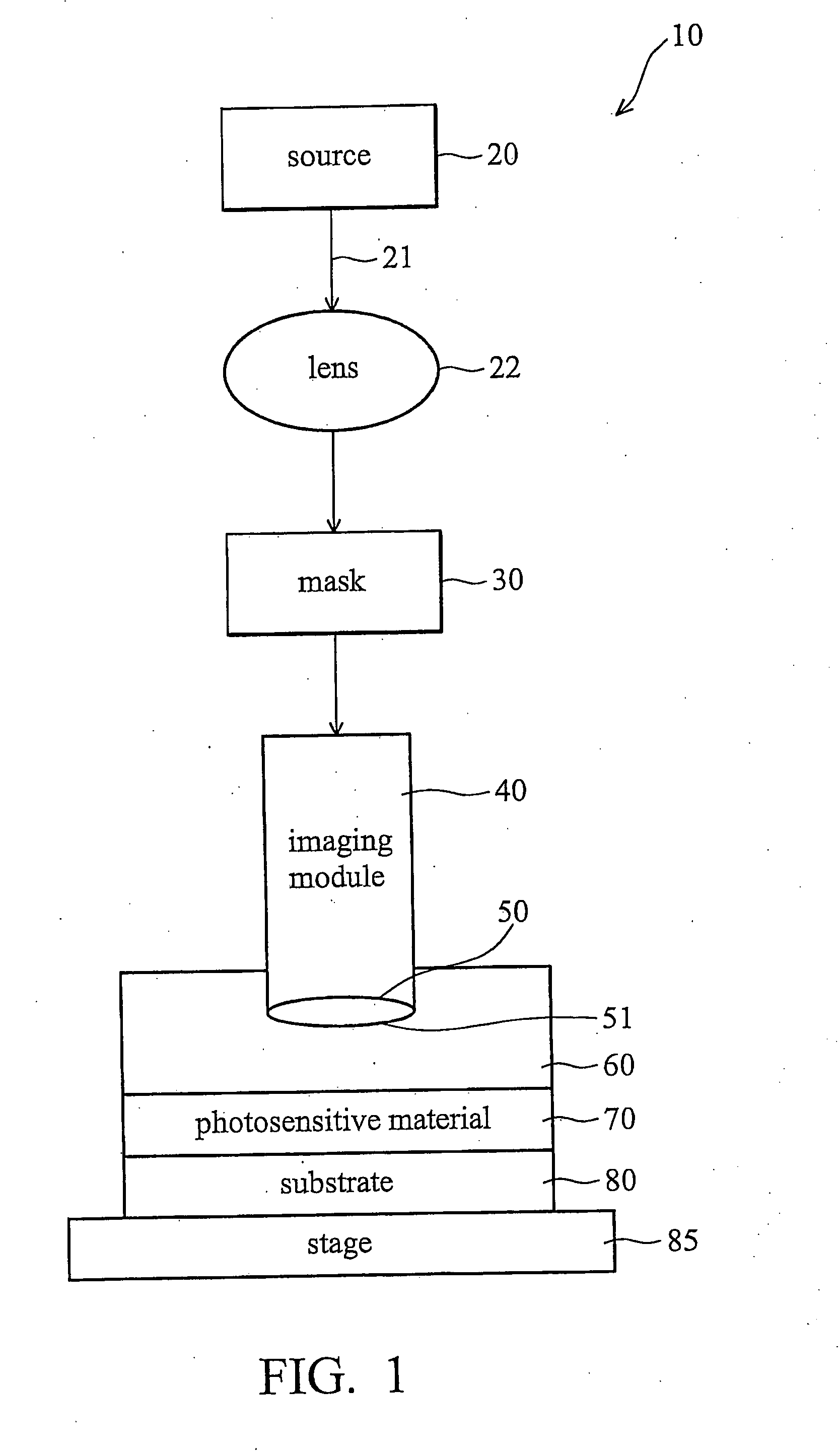

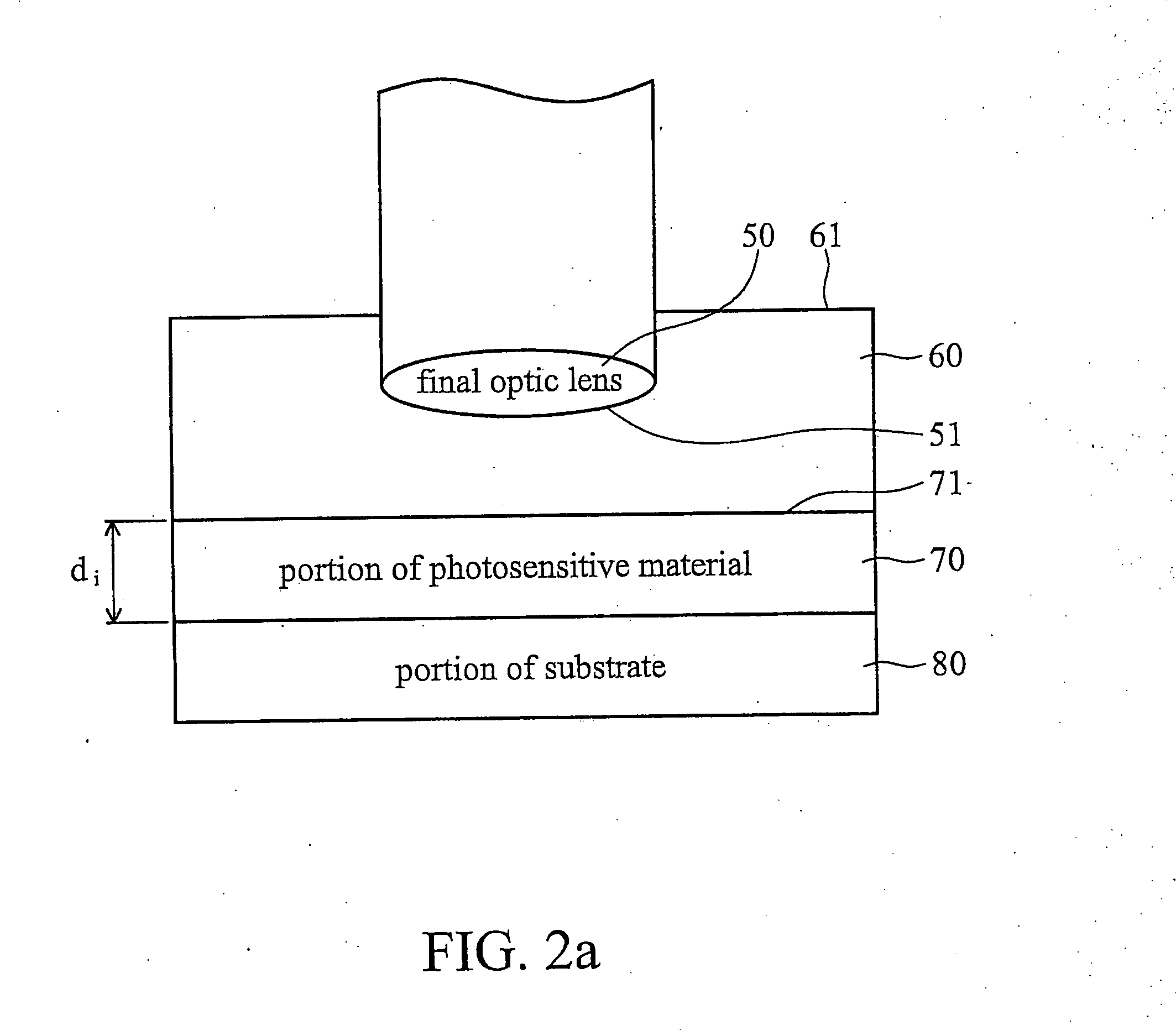

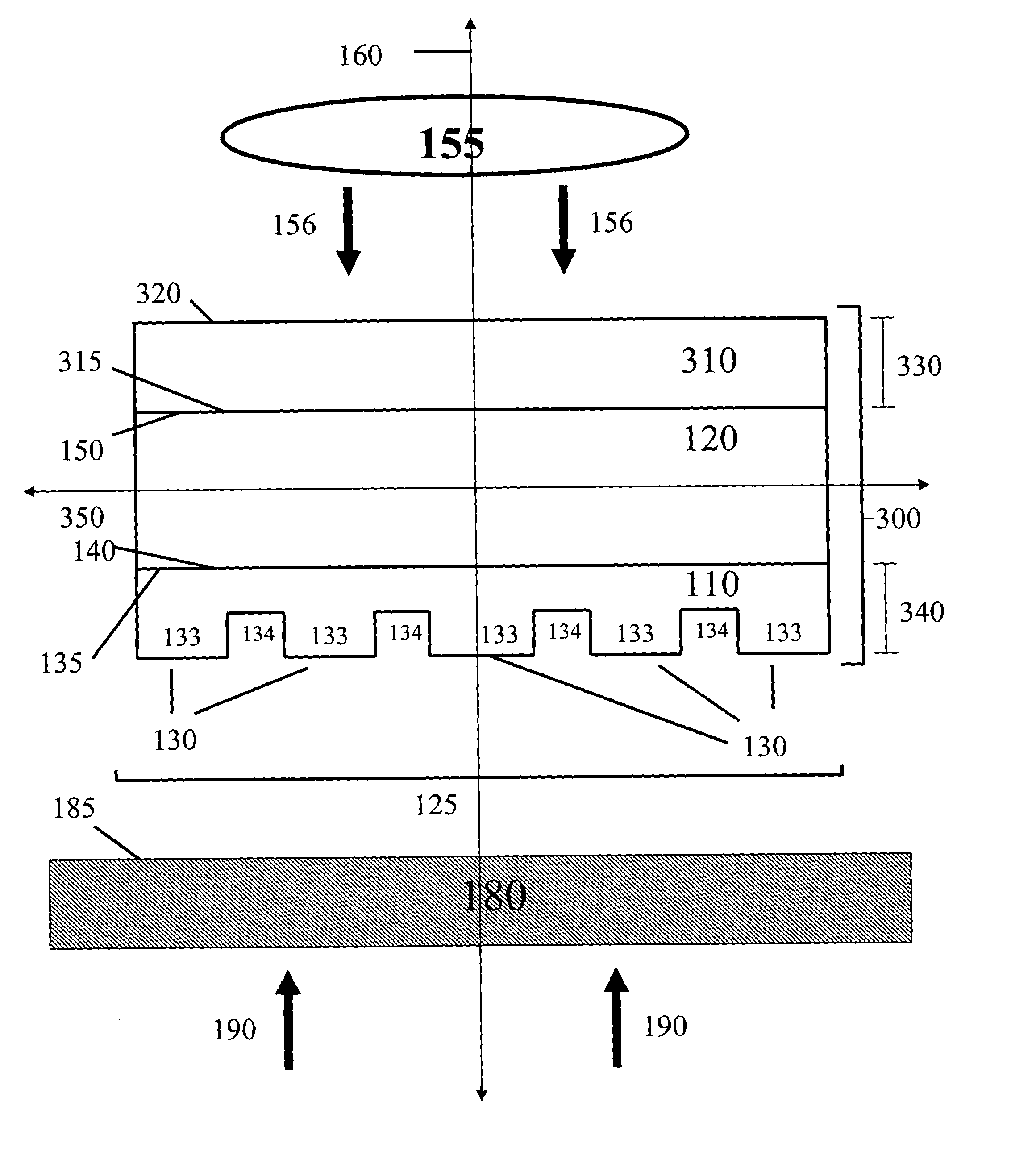

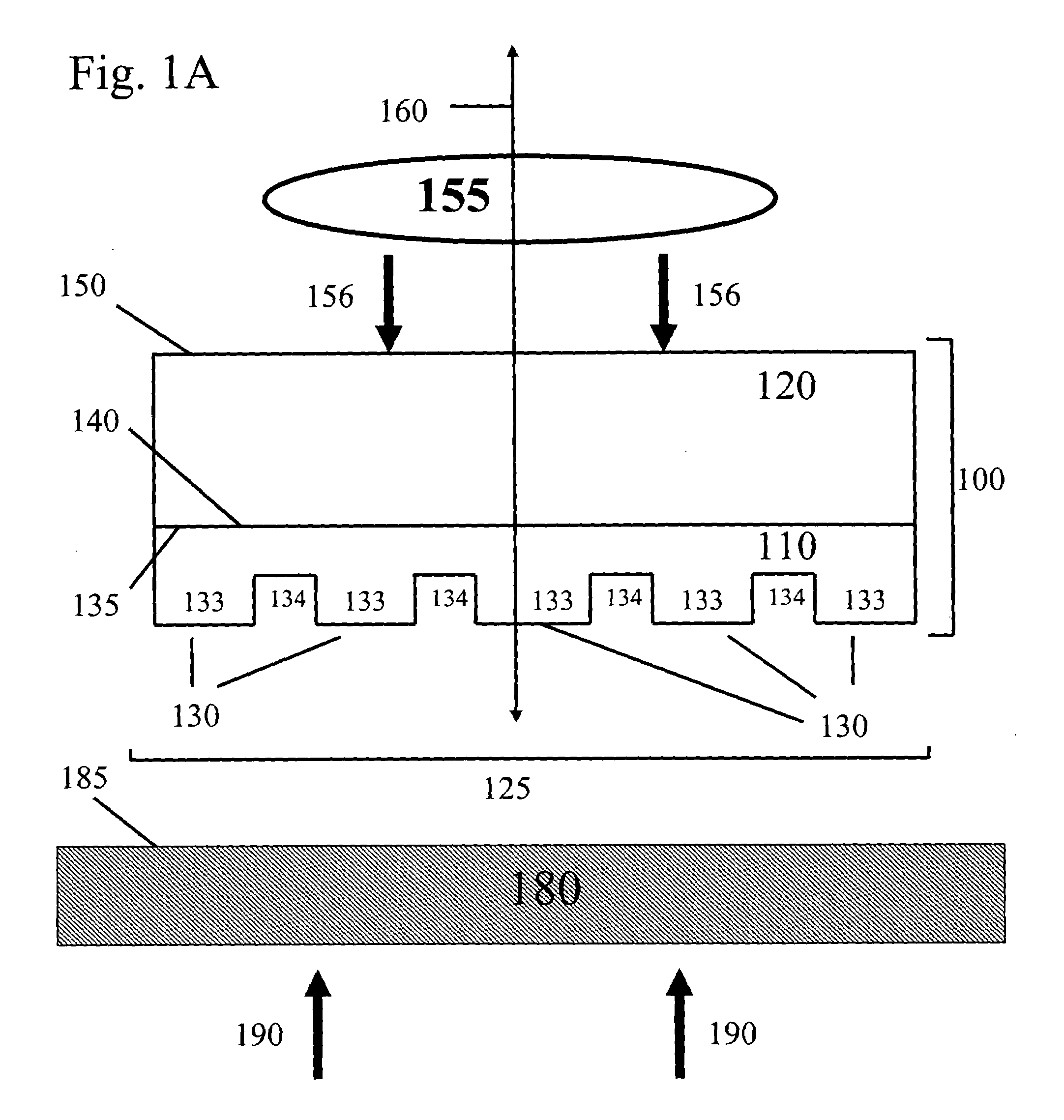

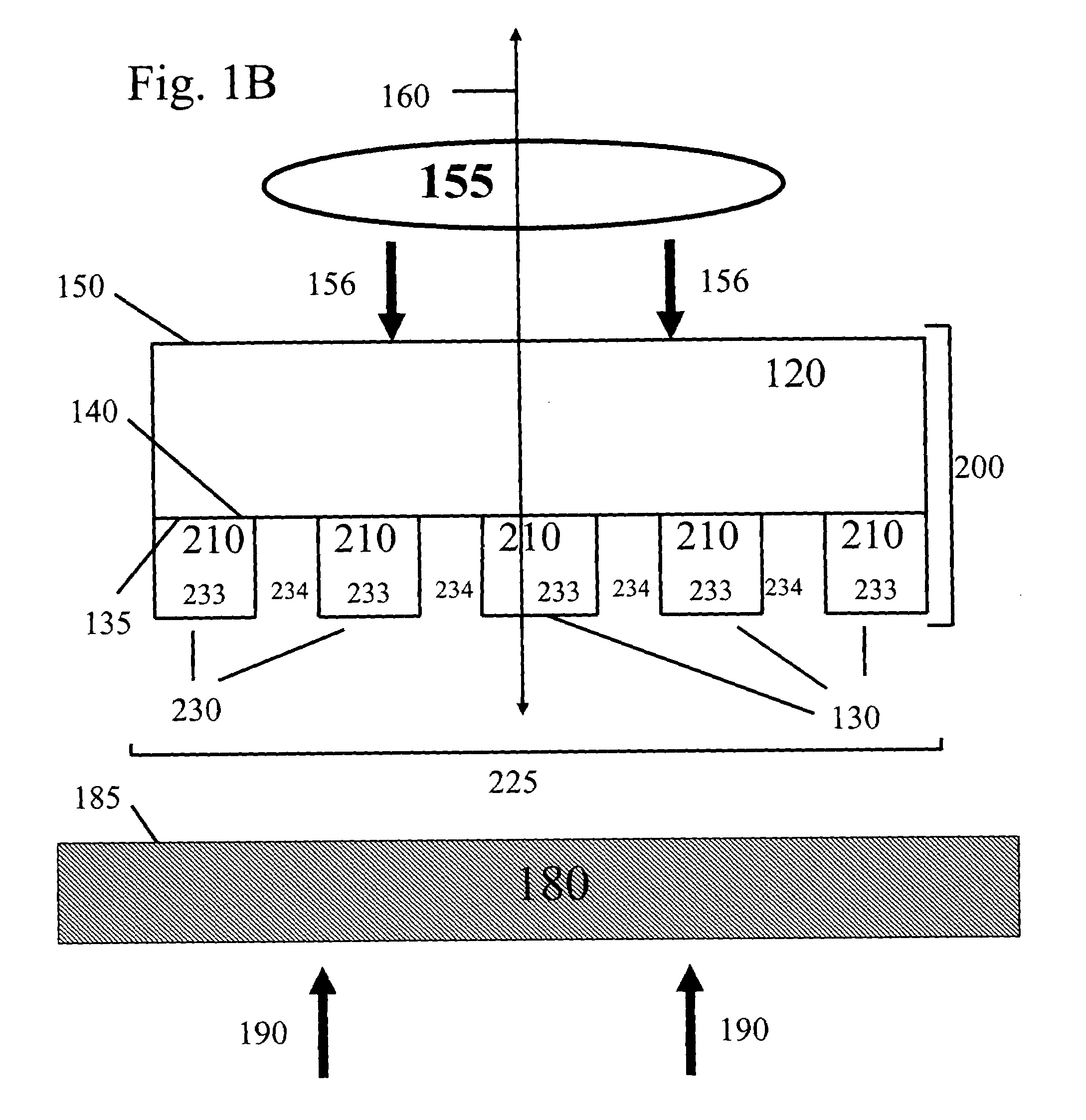

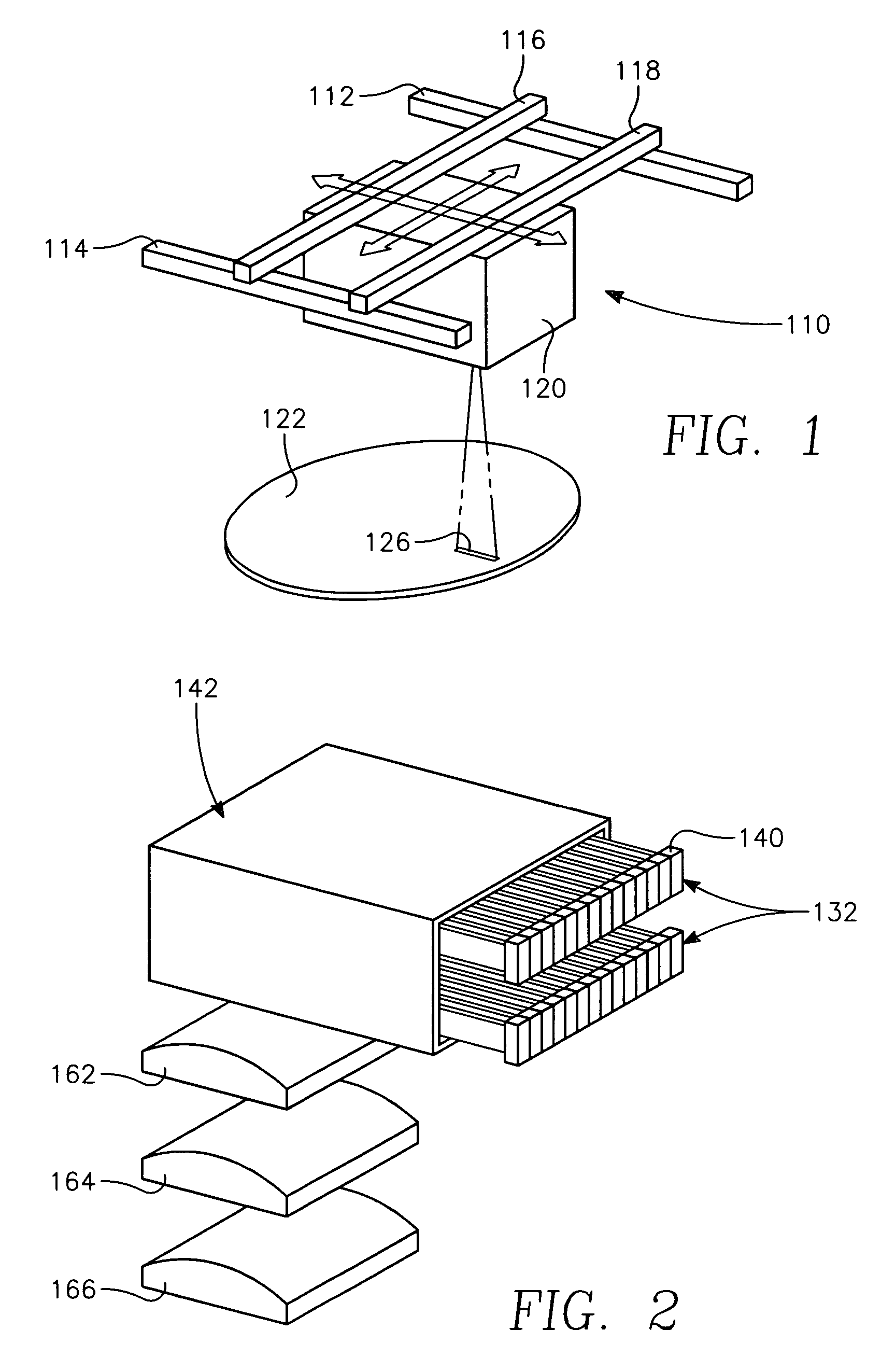

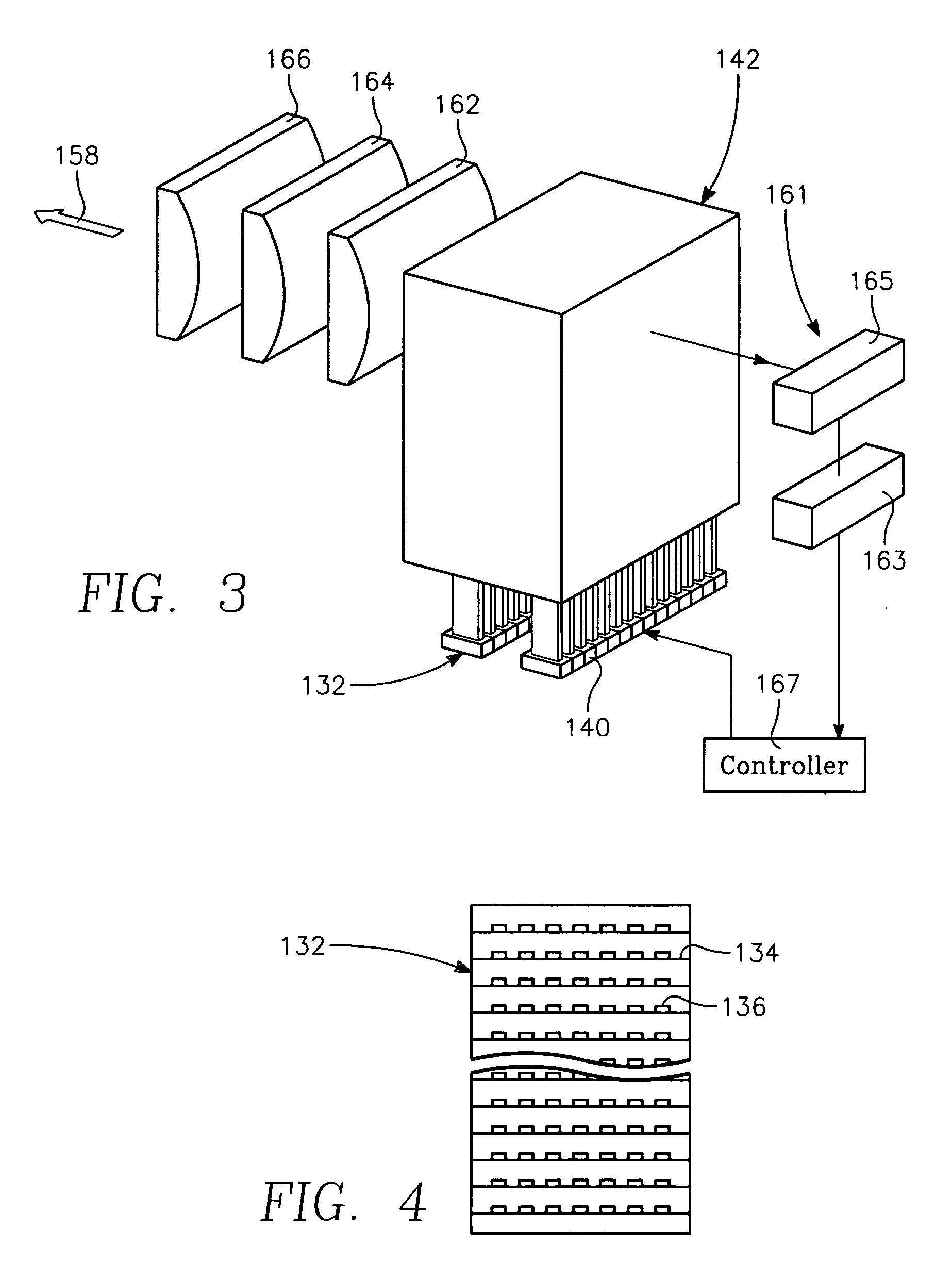

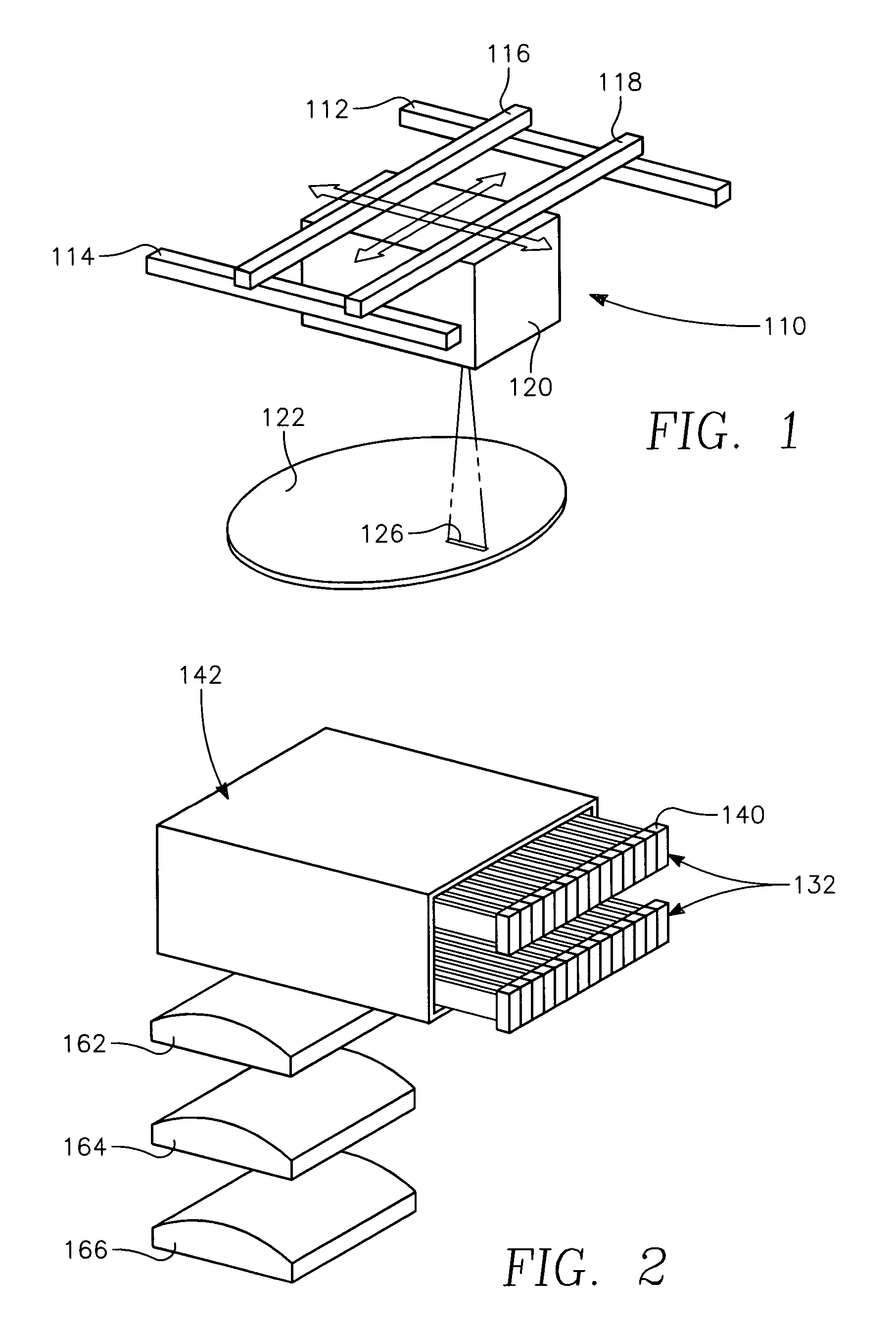

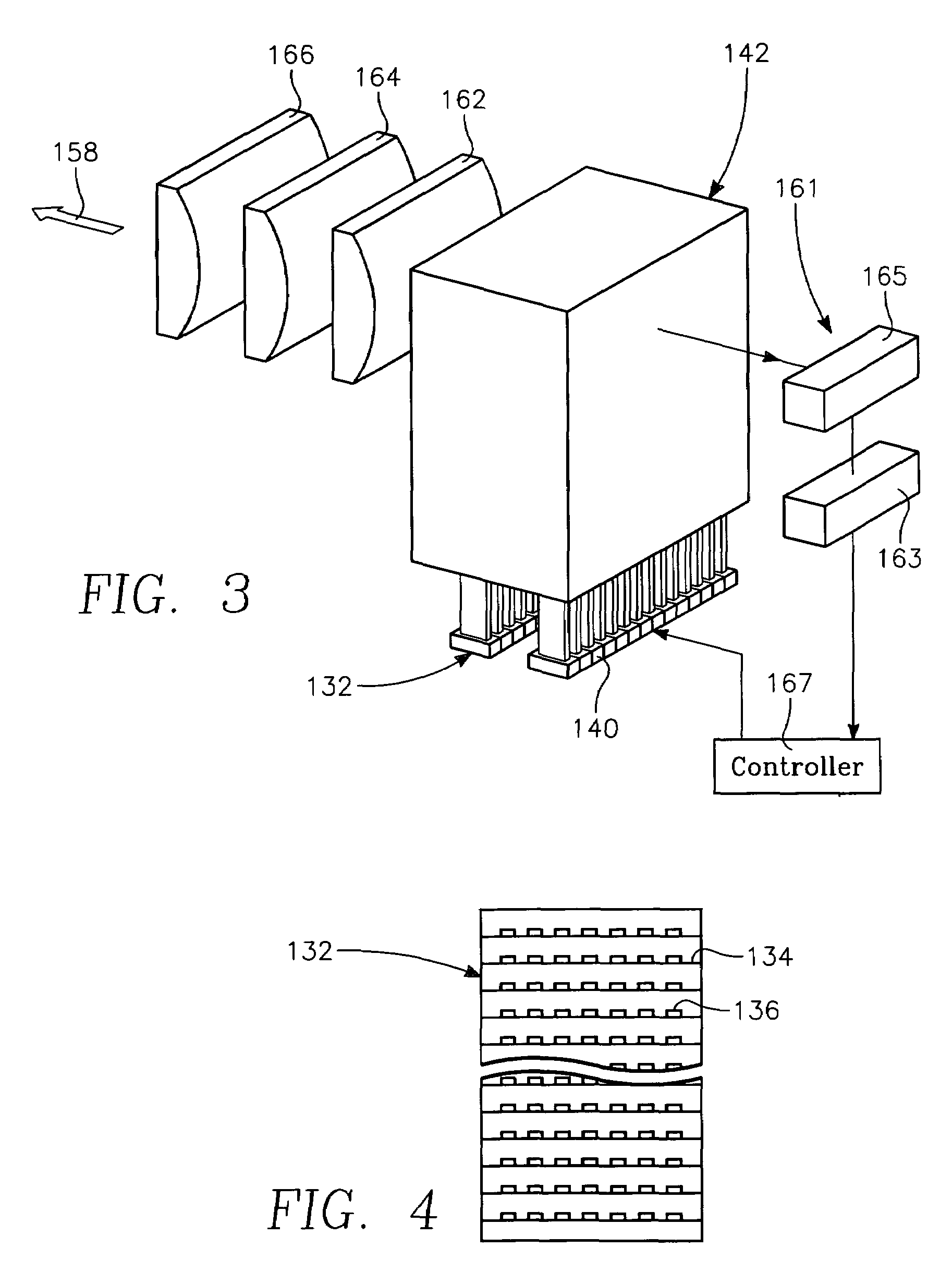

Lithography apparatus for manufacture of integrated circuits

ActiveUS20050036184A1Limit amount of swellingSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusLithographic artistSemiconductor structure

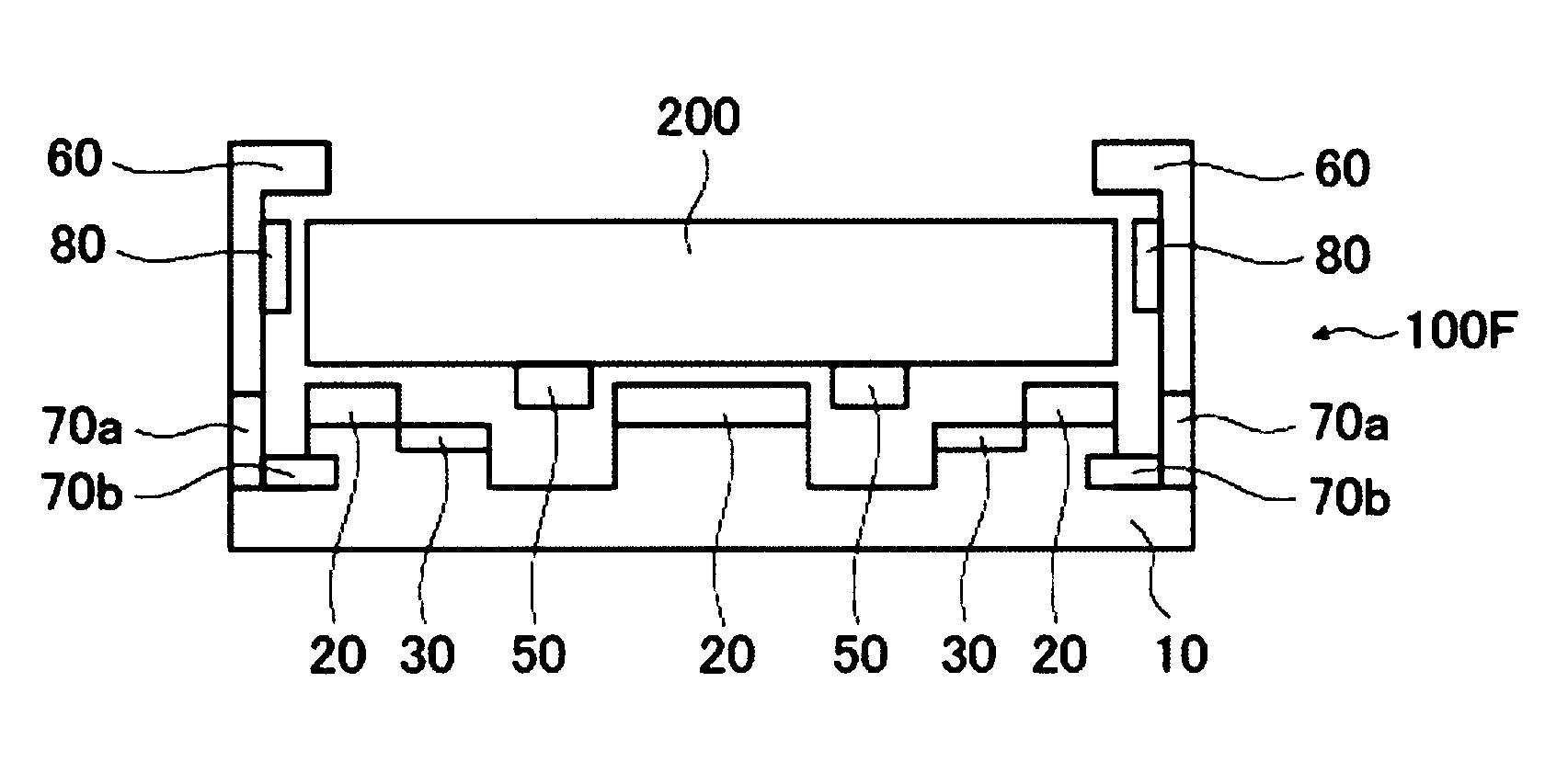

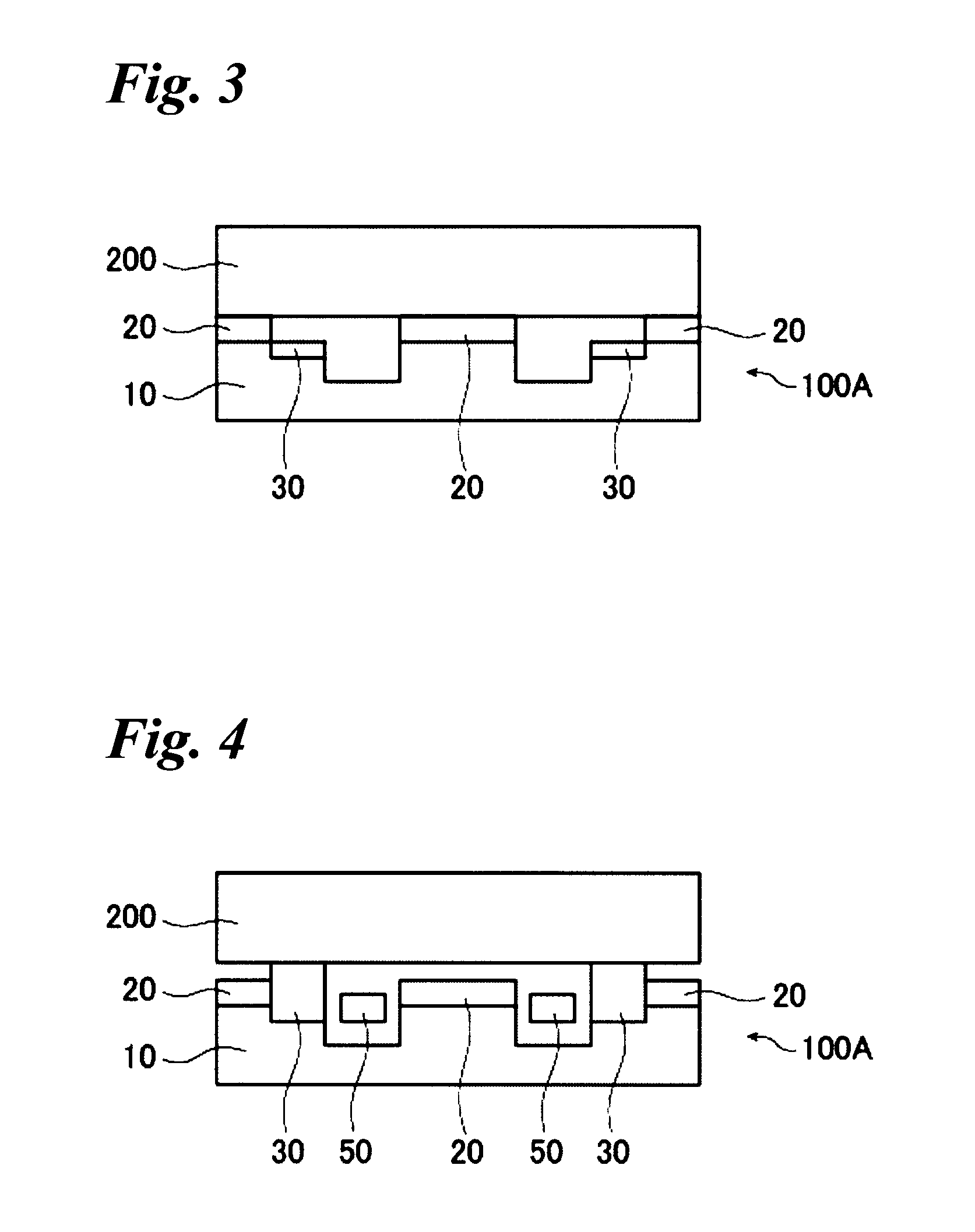

An immersion lithographic system 10 comprises an optical surface 51, an immersion fluid 60 contacting at least a portion of the optical surface, and a semiconductor structure 80 having a topmost photoresist layer 70 having a thickness of less than about 5000 angstroms, wherein a portion of the photoresist is in contact with the immersion fluid. Further, a method for illuminating a semiconductor structure 80 having a topmost photoresist layer 70 with a thickness of less than about 5000 angstroms, comprising introducing an immersion fluid 60 into a space between an optical surface 51 and the photoresist layer, and directing light preferably with a wavelength of less than about 450 nm through the immersion fluid and onto the photoresist.

Owner:TAIWAN SEMICON MFG CO LTD

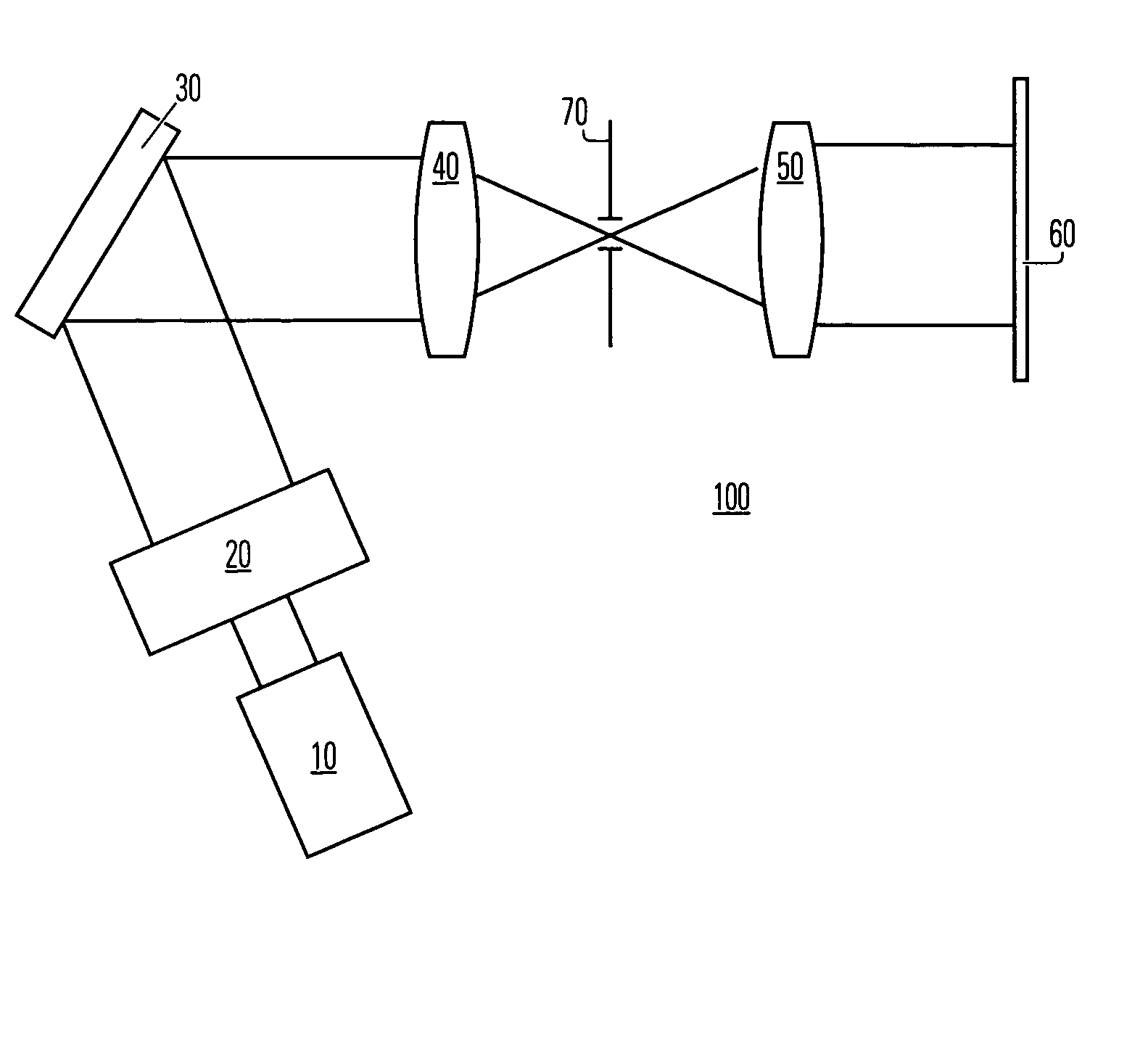

Method and device for immersion lithography

InactiveUS20050073670A1Reduce decreasePhotomechanical exposure apparatusMicrolithography exposure apparatusElectromagnetic radiationImage plane

The present invention relates to an immersion lithographic system for patterning a work piece arranged at an image plane and covered at least partly with a layer sensitive to electromagnetic radiation. Said system comprising a source emitting electromagnetic radiation onto an object plane, a mask, adapted to receive and modulate said electromagnetic radiation at said object plane and to relay said electromagnetic radiation toward said work piece, and an immersion medium contacting at least a portion of a final lens of said lithographic system and a portion of said work piece, wherein an area of said contacting is restricted by capillary forces. The invention further relates to a method for patterning a workpiece.

Owner:MICRONIC LASER SYST AB

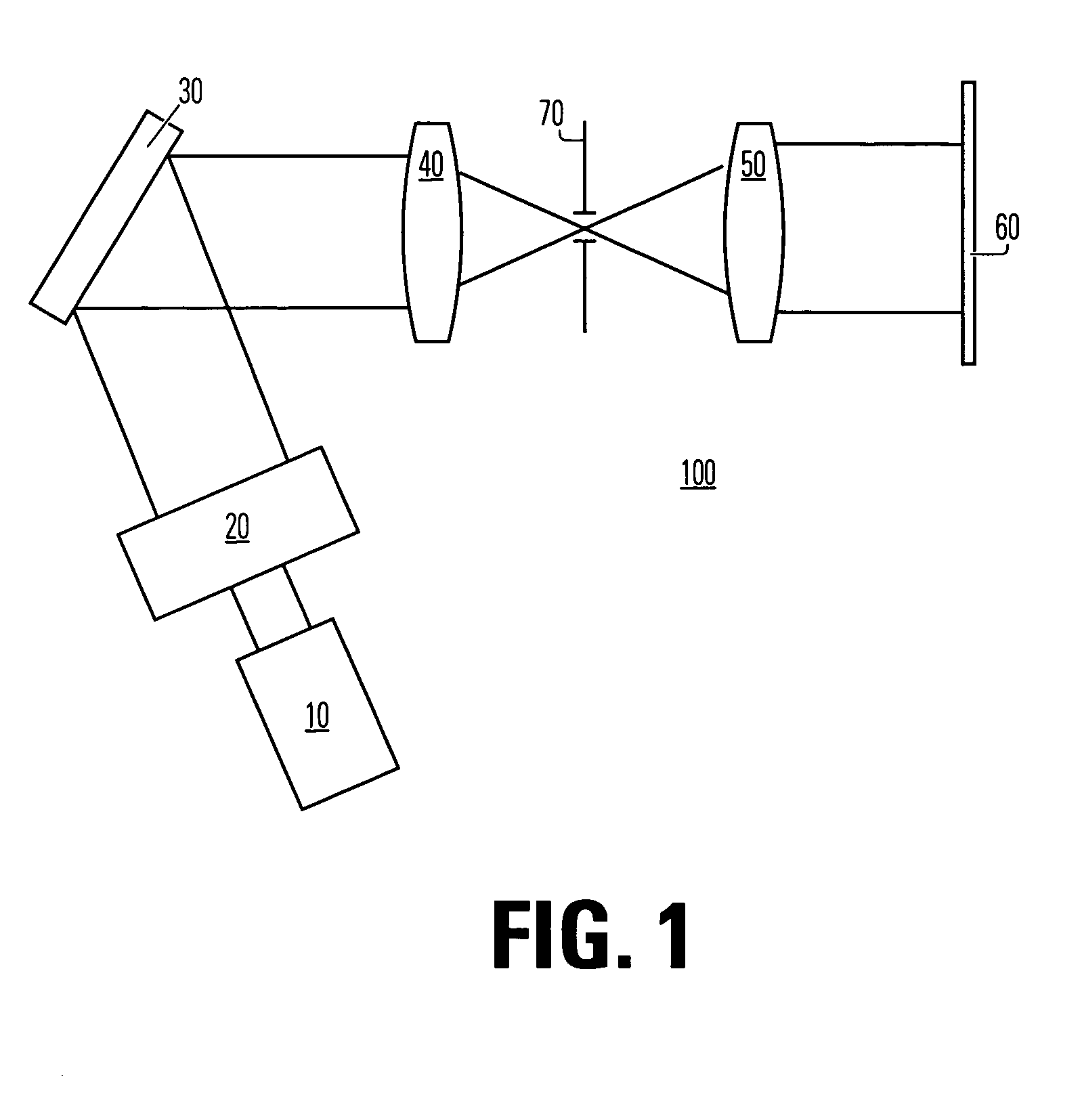

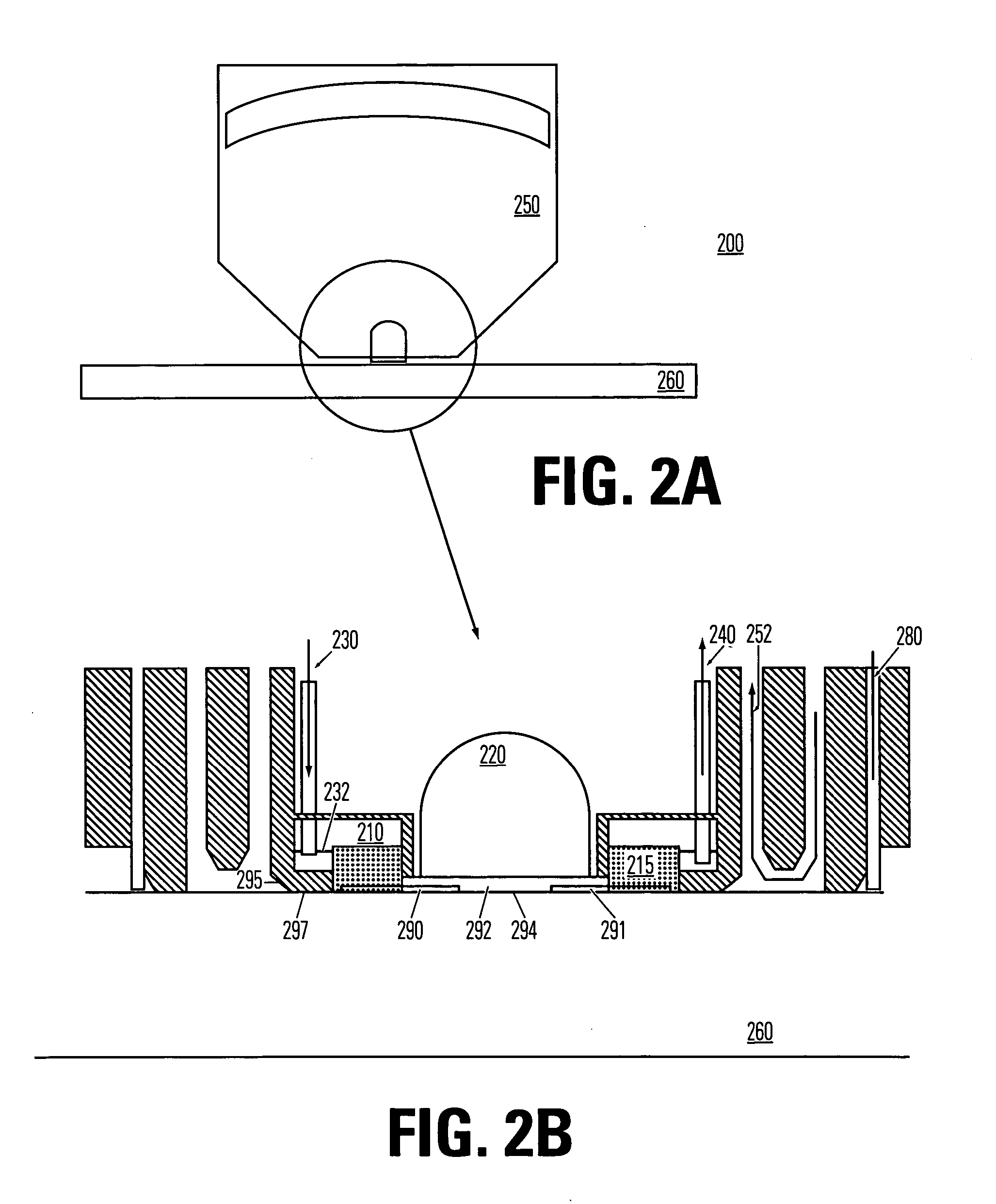

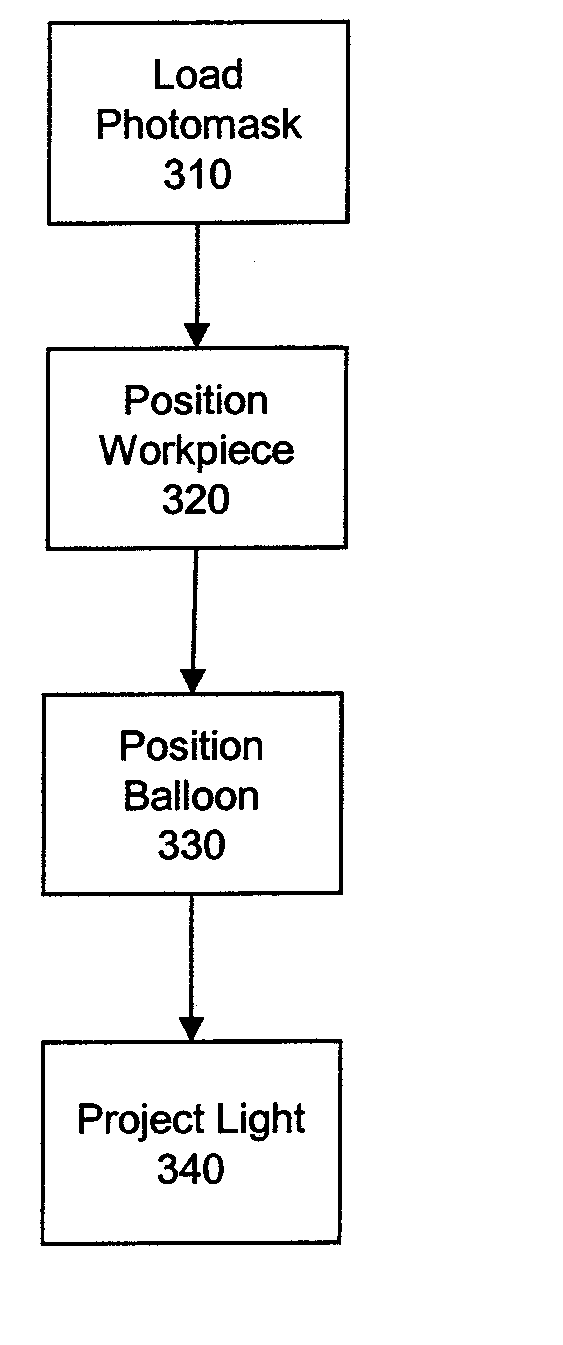

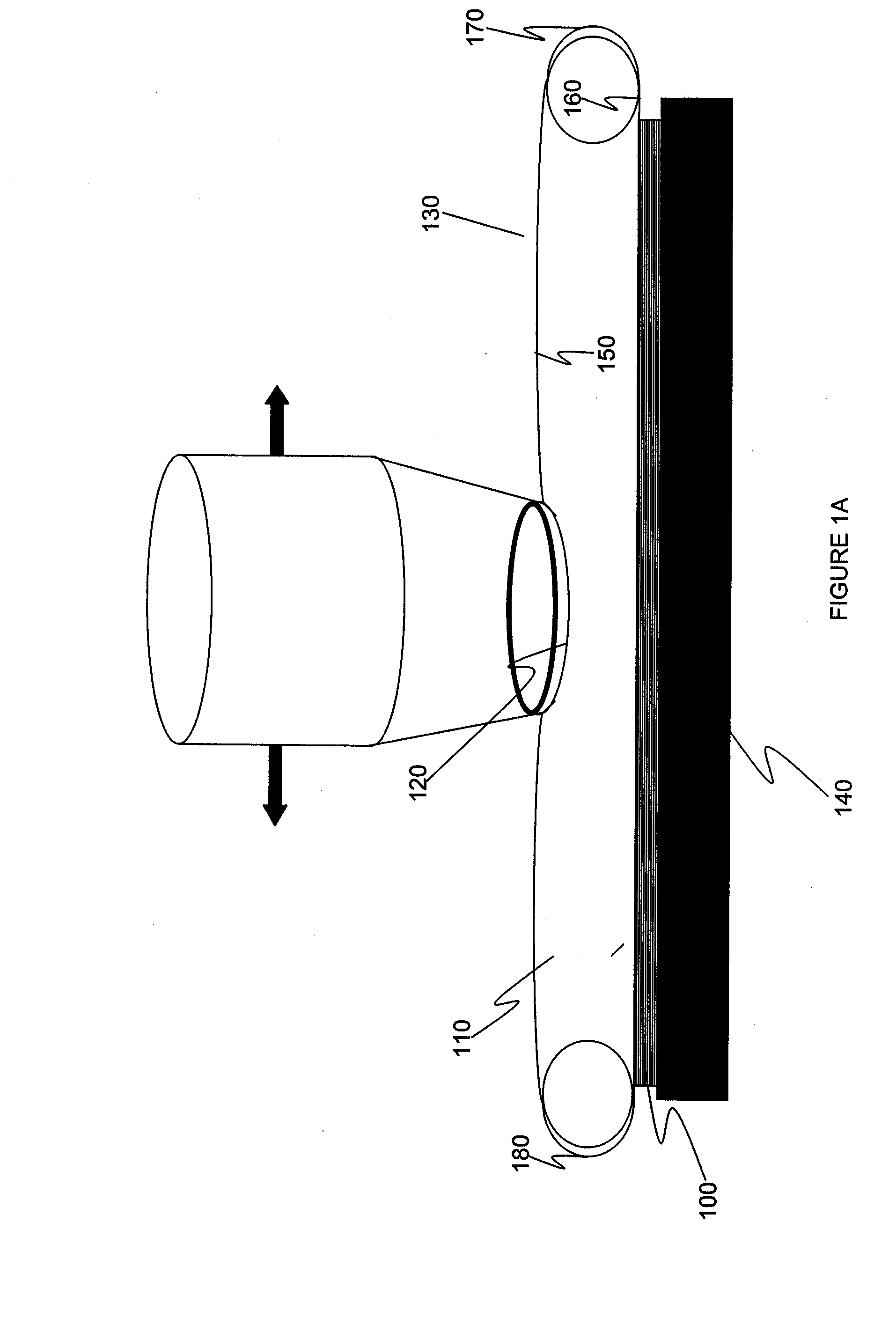

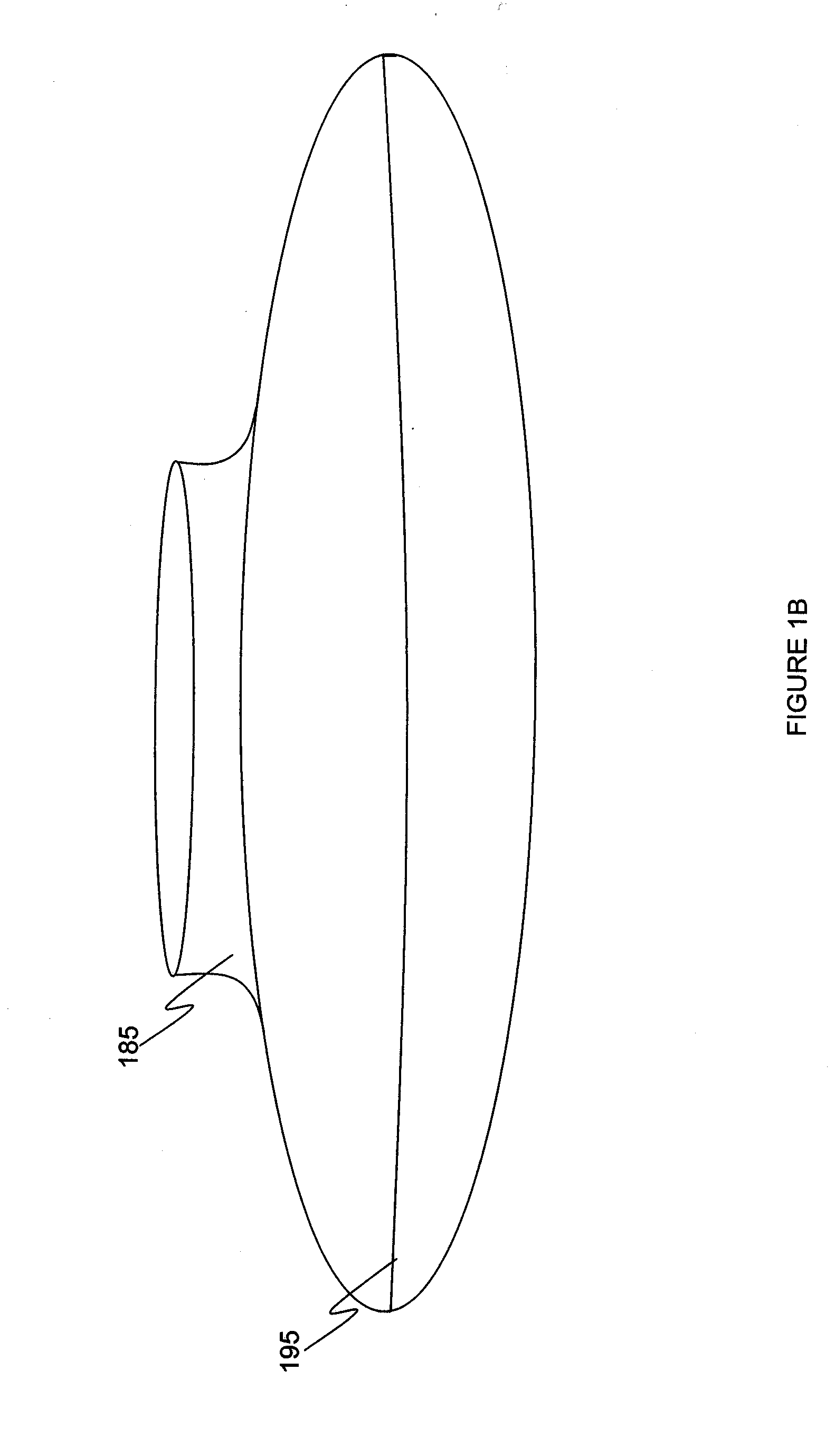

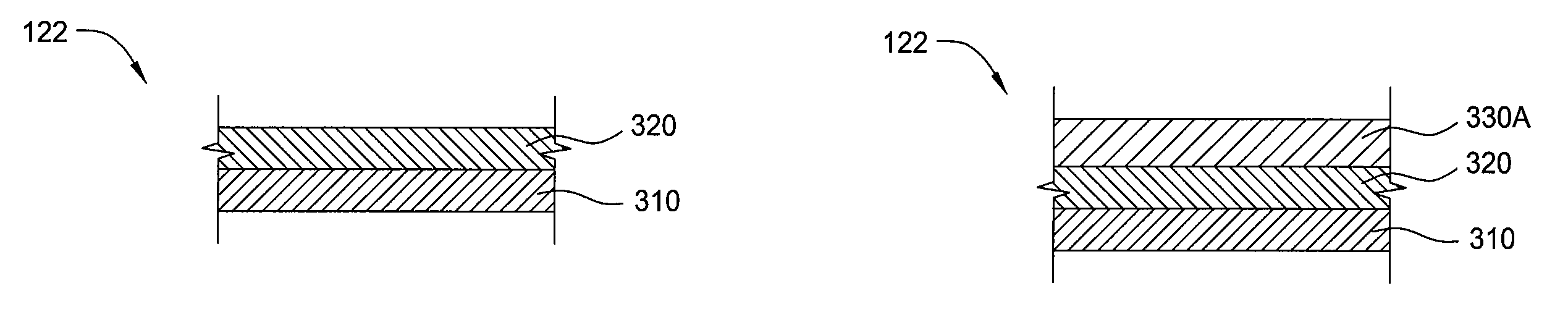

Liquid-filled balloons for immersion lithography

ActiveUS20050158673A1Suitable optical propertyPhotoprinting processesSemiconductor/solid-state device manufacturingOptical propertySemiconductor structure

A liquid-filled balloon may be positioned between a workpiece, such as a semiconductor structure covered with a photoresist, and a lithography light source. The balloon includes a thin membrane that exhibits good optical and physical properties. Liquid contained in the balloon also exhibits good optical properties, including a refractive index higher than that of air. Light from the lithography light source passes through a mask, through a top layer of the balloon membrane, through the contained liquid, through a bottom layer of the balloon membrane, and onto the workpiece where it alters portions of the photoresist. As the liquid has a low absorption and a higher refractive index than air, the liquid-filled balloon system enhances resolution. Thus, the balloon provides optical benefits of liquid immersion without the complications of maintaining a liquid between (and in contact with) a lithographic light source mechanism and workpiece.

Owner:TWITTER INC

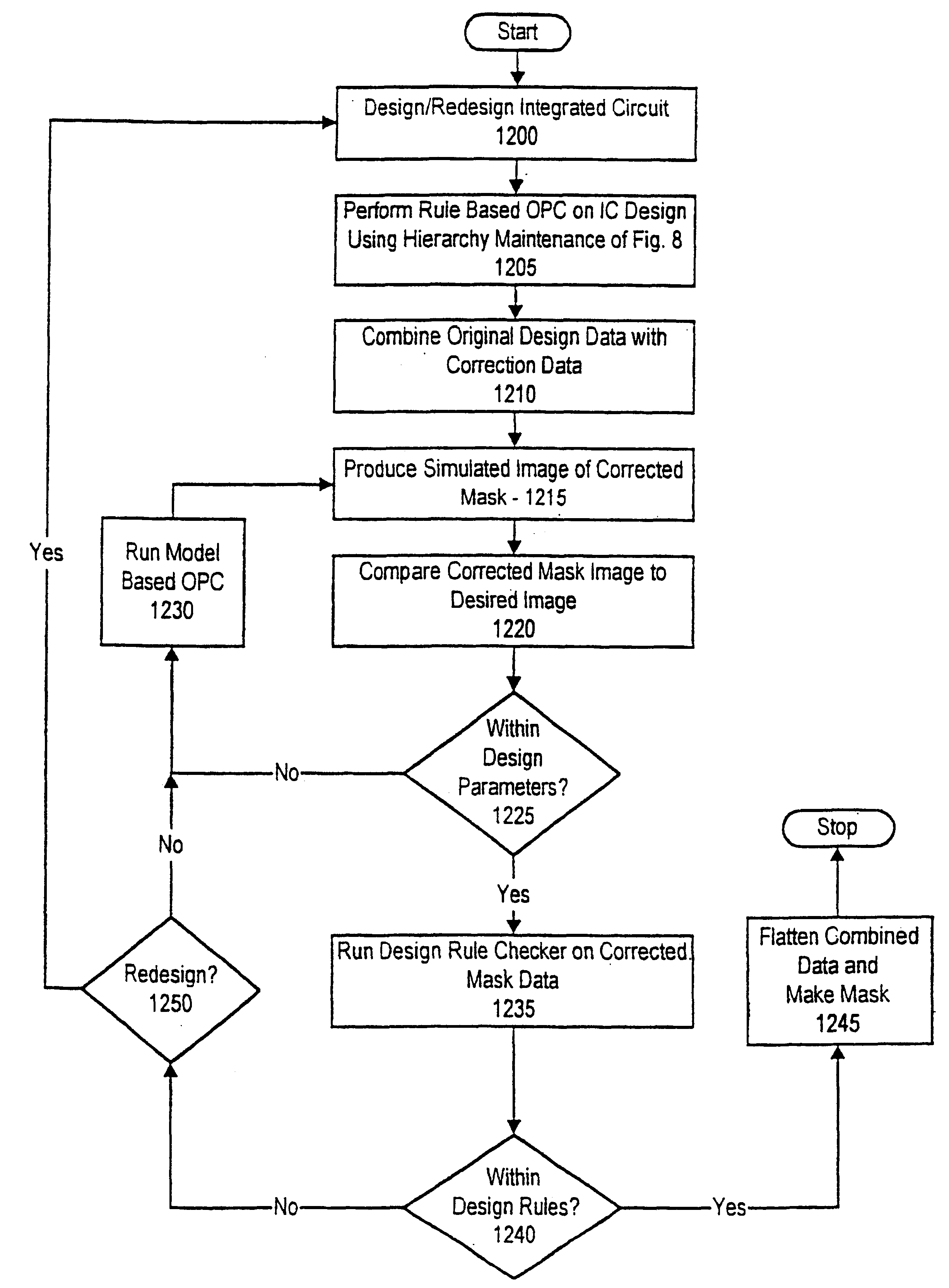

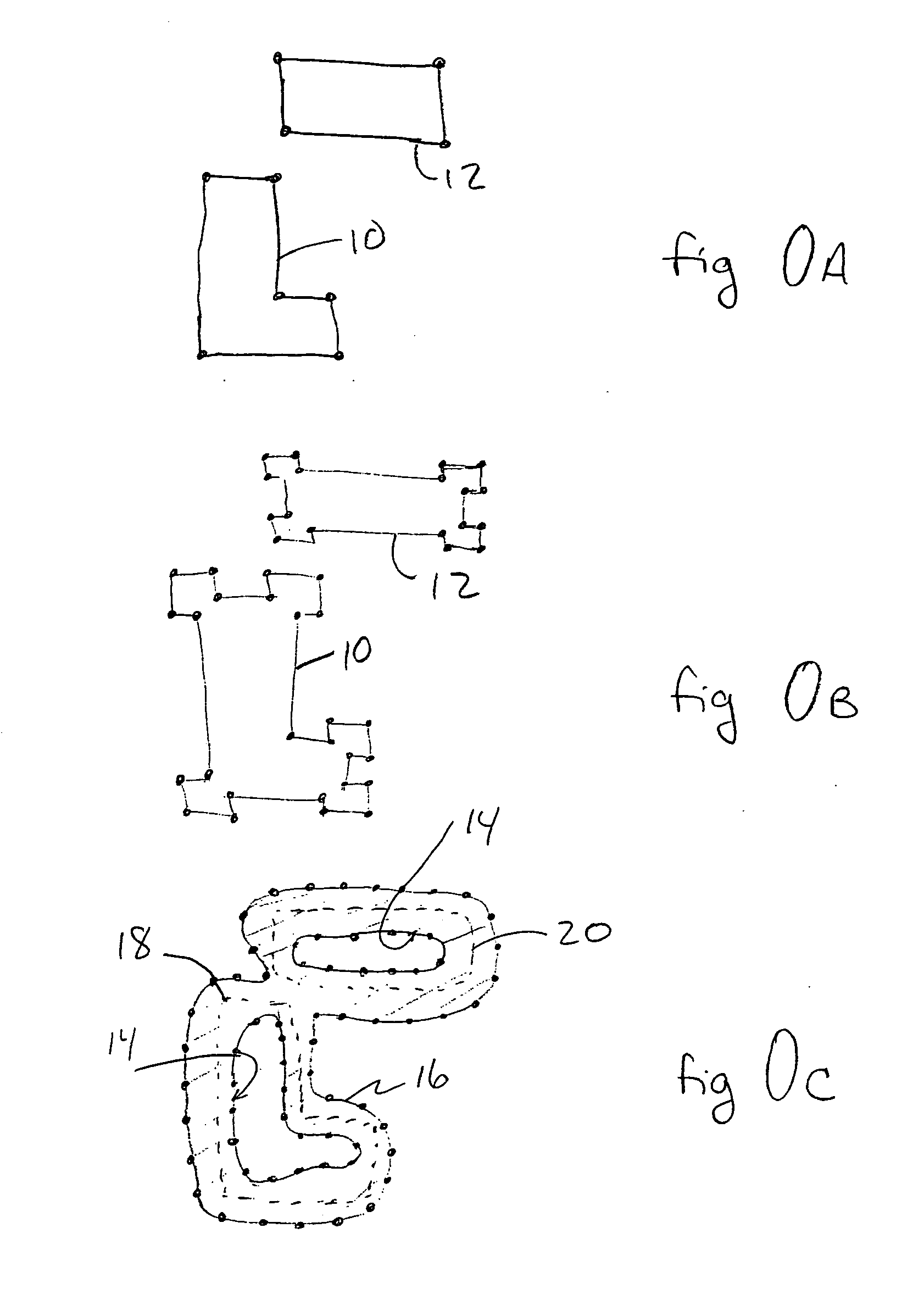

Design rule checking system and method

InactiveUS6470489B1Create efficientlyImprove system efficiencyOriginals for photomechanical treatmentComputer aided designDesign rule checkerLithography

A method for performing design rule checking on OPC corrected or otherwise corrected designs is described. This method comprises accessing a corrected design and generating a simulated image. The simulated image corresponds to a simulation of an image which would be printed on a wafer if the wafer were exposed to an illumination source directed through the corrected design. The characteristics of the illumination source are determined by a set of lithography parameters. In creating the image, additional characteristics can be used to simulate portions of the fabrication process. However, what is important is that a resulting simulated image is created. The simulated image can then be used by the design rule checker. Importantly, the simulated image can be processed to reduce the number of vertices in the simulated image, relative to the number of vertices in the OPC corrected design layout. Also, the simulated image can be compared with an idea layout image, the results of which can then be used to reduce the amount of information that is needed to perform the design rule checking.

Owner:SYNOPSYS INC

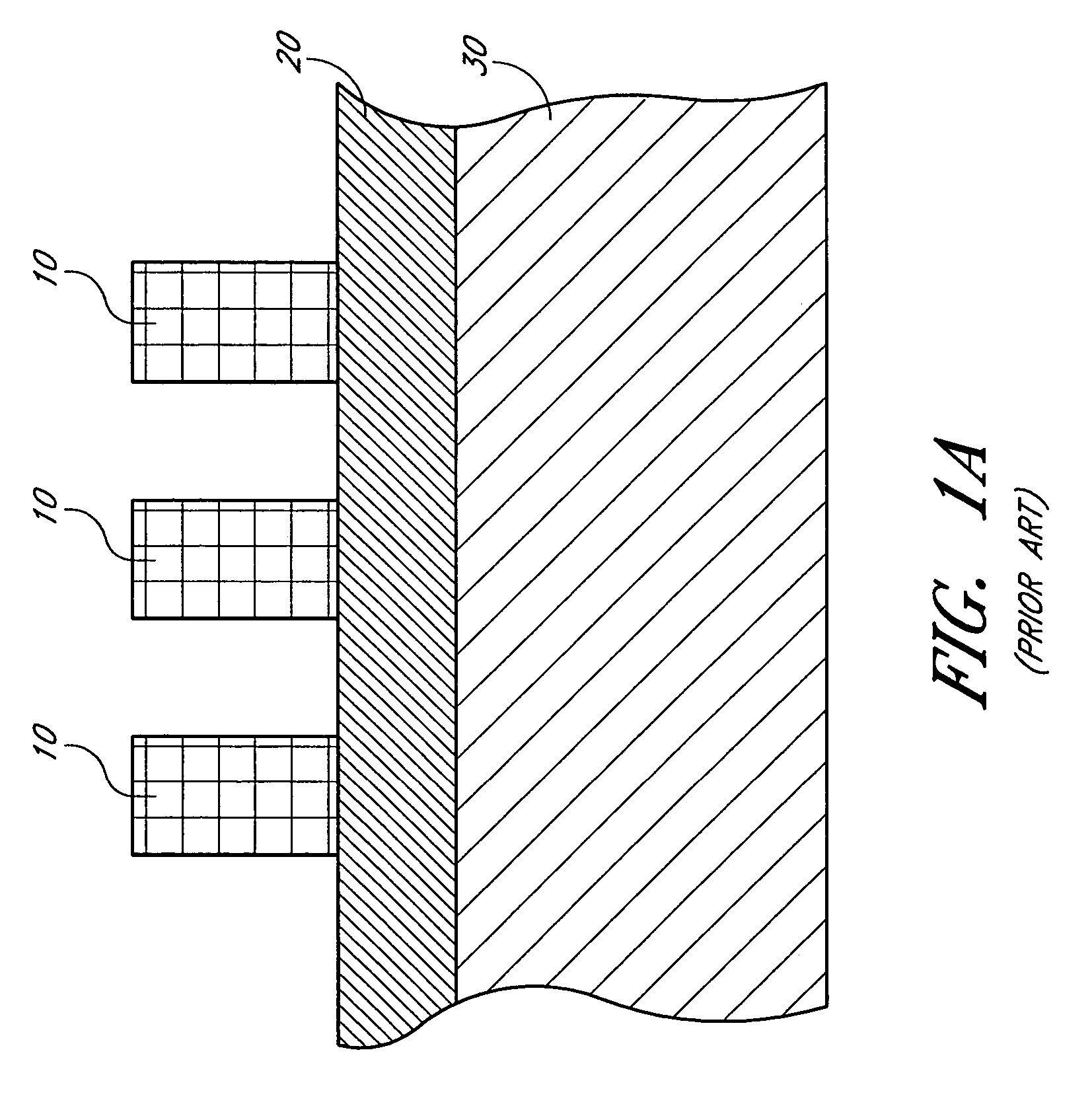

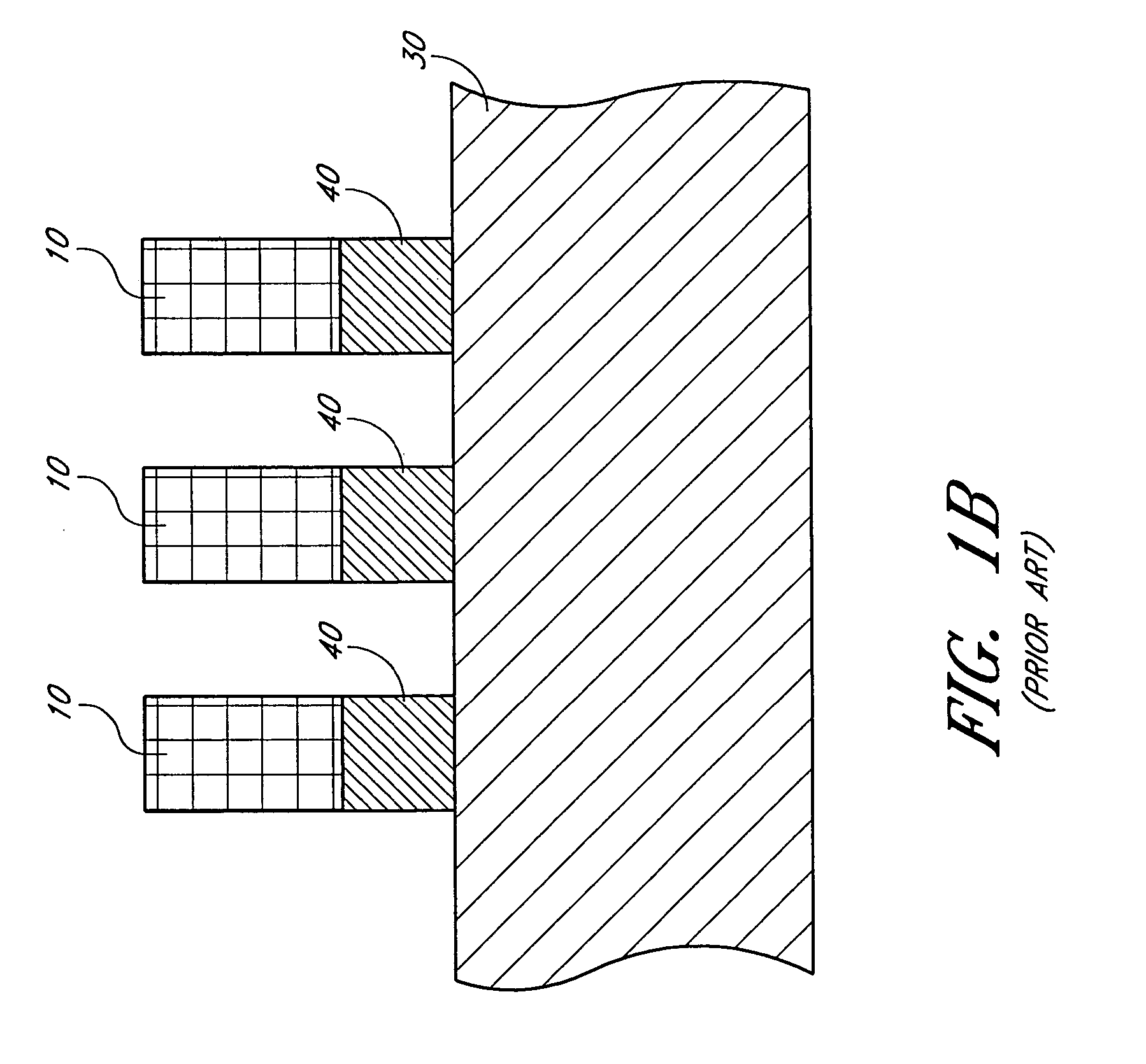

Composite patterning devices for soft lithography

ActiveUS7195733B2Improve fidelityIncrease resistanceMaterial nanotechnologyNanoinformaticsNano sizeYoung's modulus

The present invention provides methods, devices and device components for fabricating patterns on substrate surfaces, particularly patterns comprising structures having microsized and / or nanosized features of selected lengths in one, two or three dimensions. The present invention provides composite patterning devices comprising a plurality of polymer layers each having selected mechanical properties, such as Young's Modulus and flexural rigidity, selected physical dimensions, such as thickness, surface area and relief pattern dimensions, and selected thermal properties, such as coefficients of thermal expansion, to provide high resolution patterning on a variety of substrate surfaces and surface morphologies.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

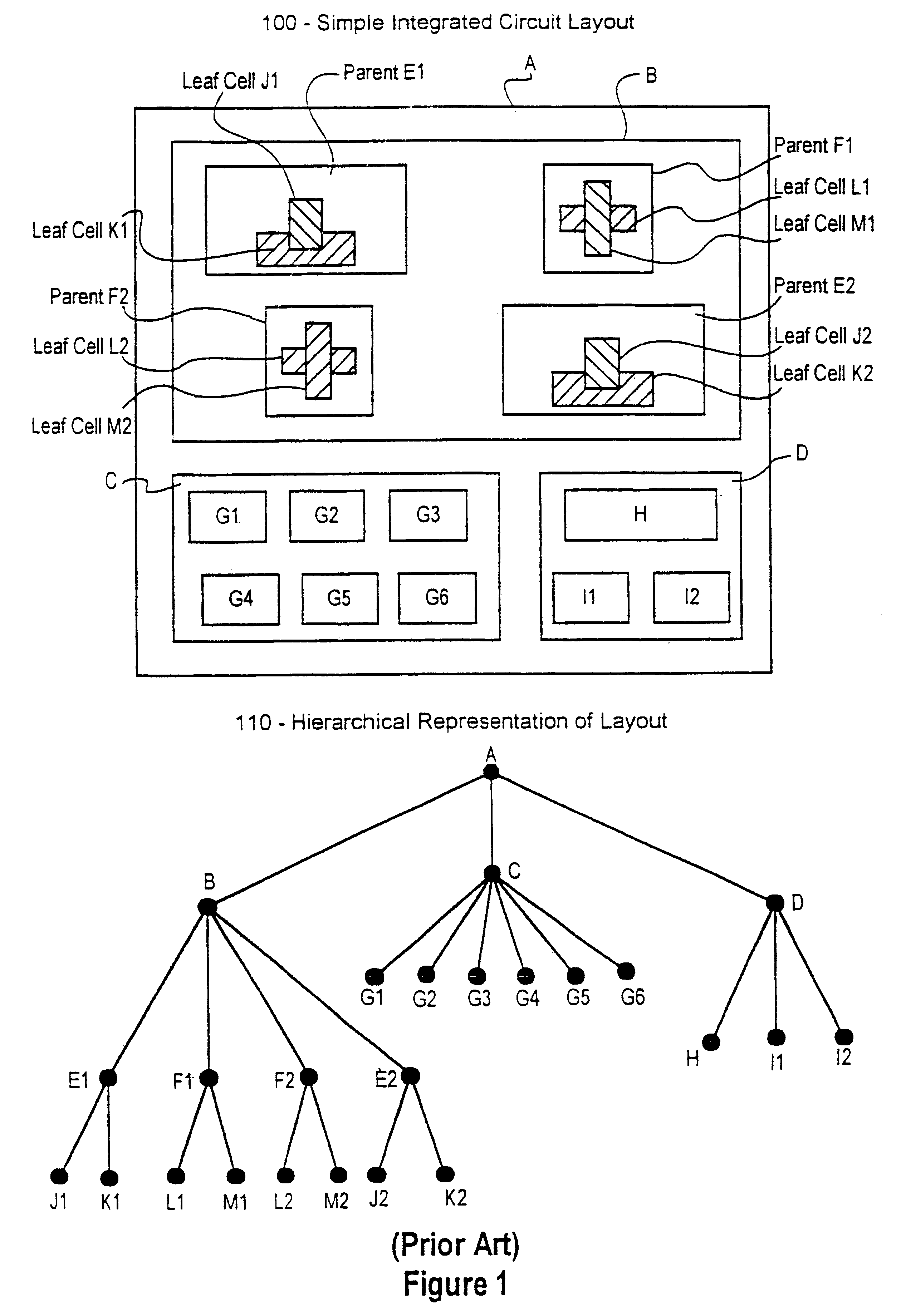

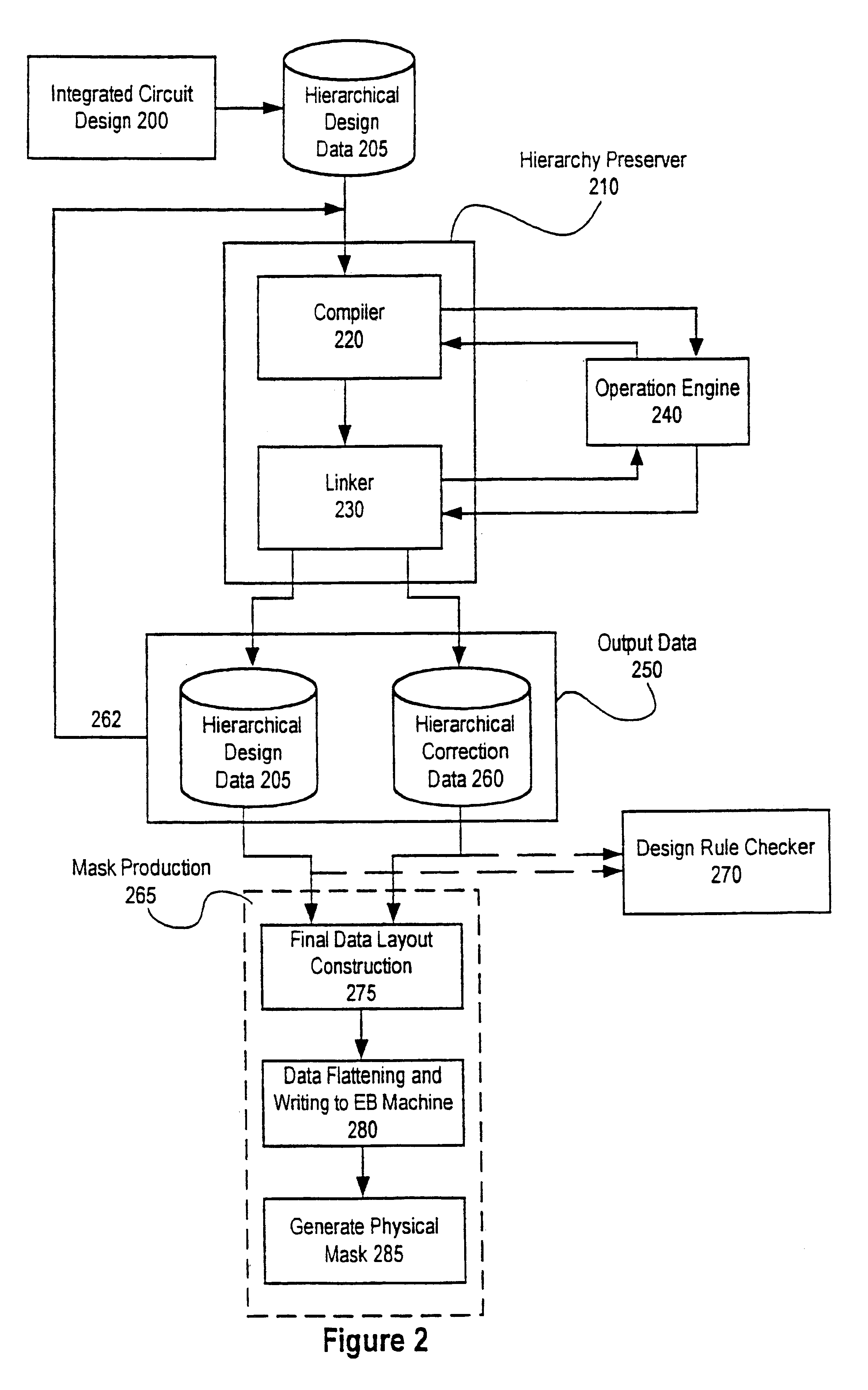

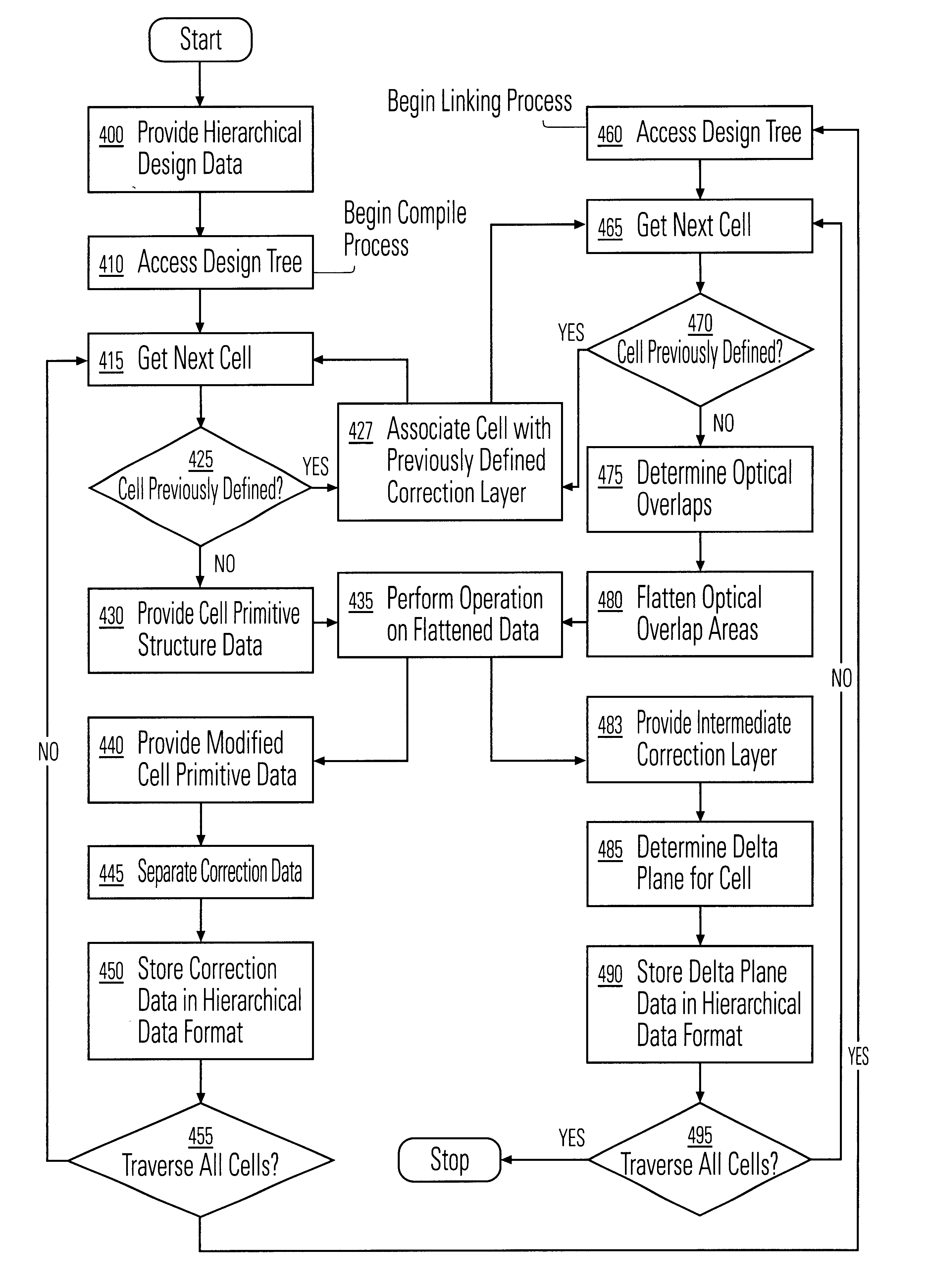

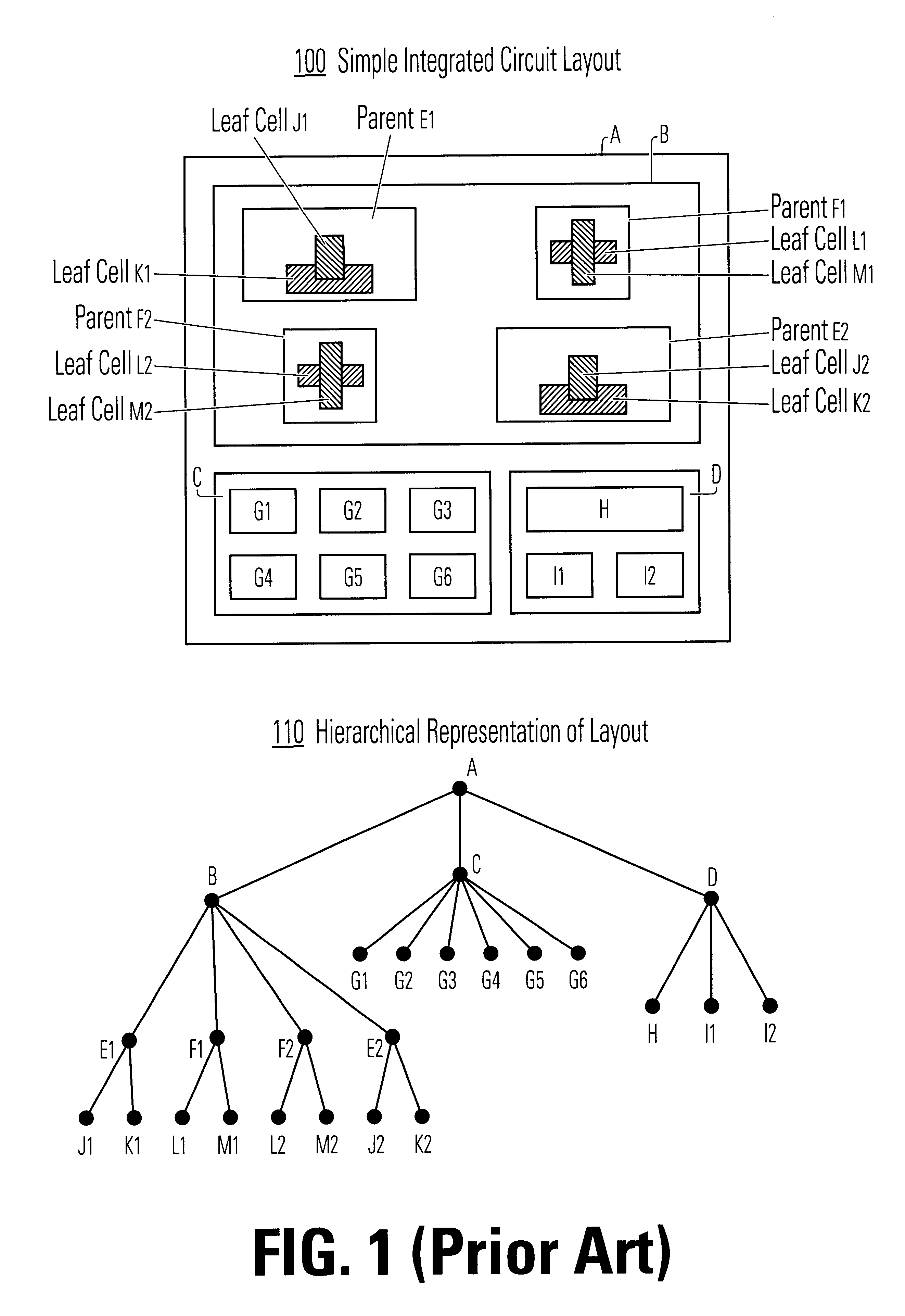

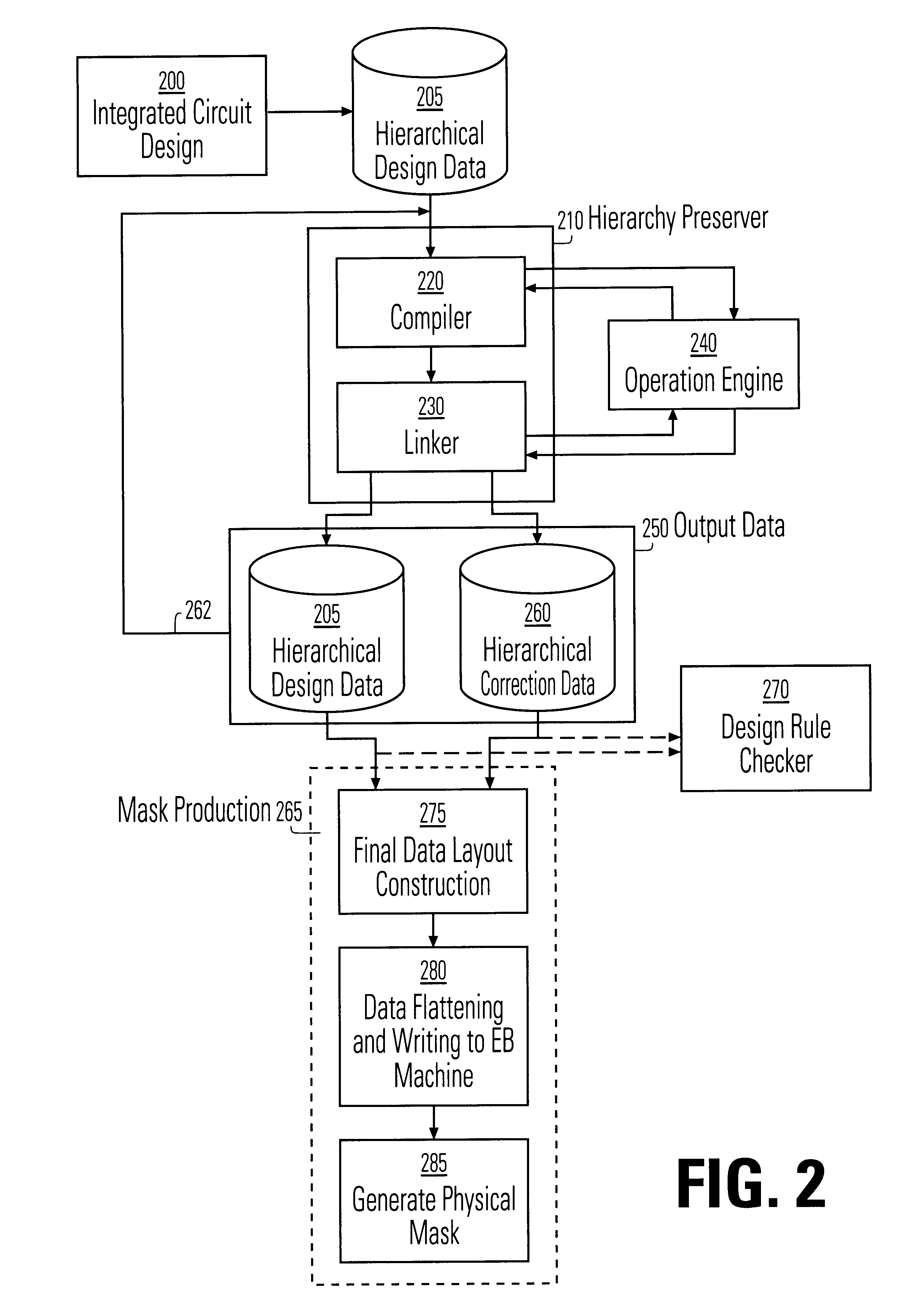

Data hierarchy layout correction and verification method and apparatus

InactiveUS6370679B1Computation using non-denominational number representationOriginals for photomechanical treatmentComputer architectureValidation methods

A method and apparatus for the correction of integrated circuit layouts for optical proximity effects which maintains the original true hierarchy of the original layout is provided. Also provided is a method and apparatus for the design rule checking of layouts which have been corrected for optical proximity effects. The OPC correction method comprises providing a hierarchically described integrated circuit layout as a first input, and a particular set of OPC correction criteria as a second input. The integrated circuit layout is then analyzed to identify features of the layout which meet the provided OPC correction criteria. After the areas on the mask which need correction have been identified, optical proximity correction data is generated in response to the particular set of correction criteria. Finally, a first program data is generated which stores the generated optical proximity correction data in a hierarchical structure that corresponds to the hierarchical structure of the integrated circuit layout. As the output correction data is maintained in true hierarchical format, layouts which are OPC corrected according to this method are able to be processed through conventional design rule checkers with no altering of the data.

Owner:SYNOPSYS INC

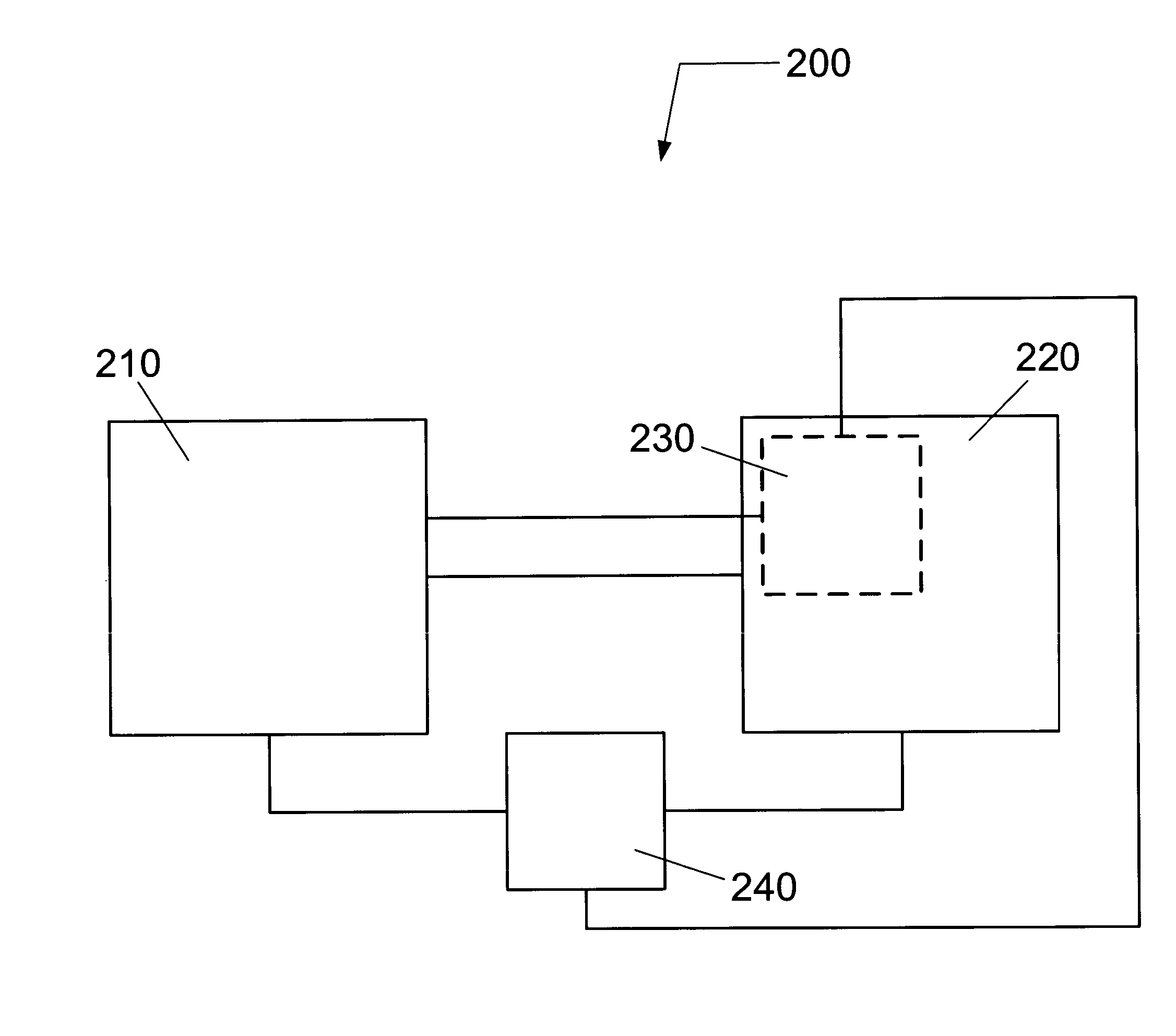

Lithographic Focus and Dose Measurement Using A 2-D Target

ActiveUS20110249244A1Minimize overall surface areaArea minimizationPhotomechanical apparatusSemiconductor/solid-state device manufacturingRadiologyScatterometer

In order to determine whether an exposure apparatus is outputting the correct dose of radiation and its projection system is focusing the radiation correctly, a test pattern is used on a mask for printing a specific marker onto a substrate. This marker is then measured by an inspection apparatus, such as a scatterometer, to determine whether there are errors in focus and dose and other related properties. The test pattern is configured such that changes in focus and dose may be easily determined by measuring the properties of a pattern that is exposed using the mask. The test pattern may be a 2D pattern where physical or geometric properties, e.g., pitch, are different in each of the two dimensions. The test pattern may also be a one-dimensional pattern made up of an array of structures in one dimension, the structures being made up of at least one substructure, the substructures reacting differently to focus and dose and giving rise to an exposed pattern from which focus and dose may be determined.

Owner:ASML NETHERLANDS BV

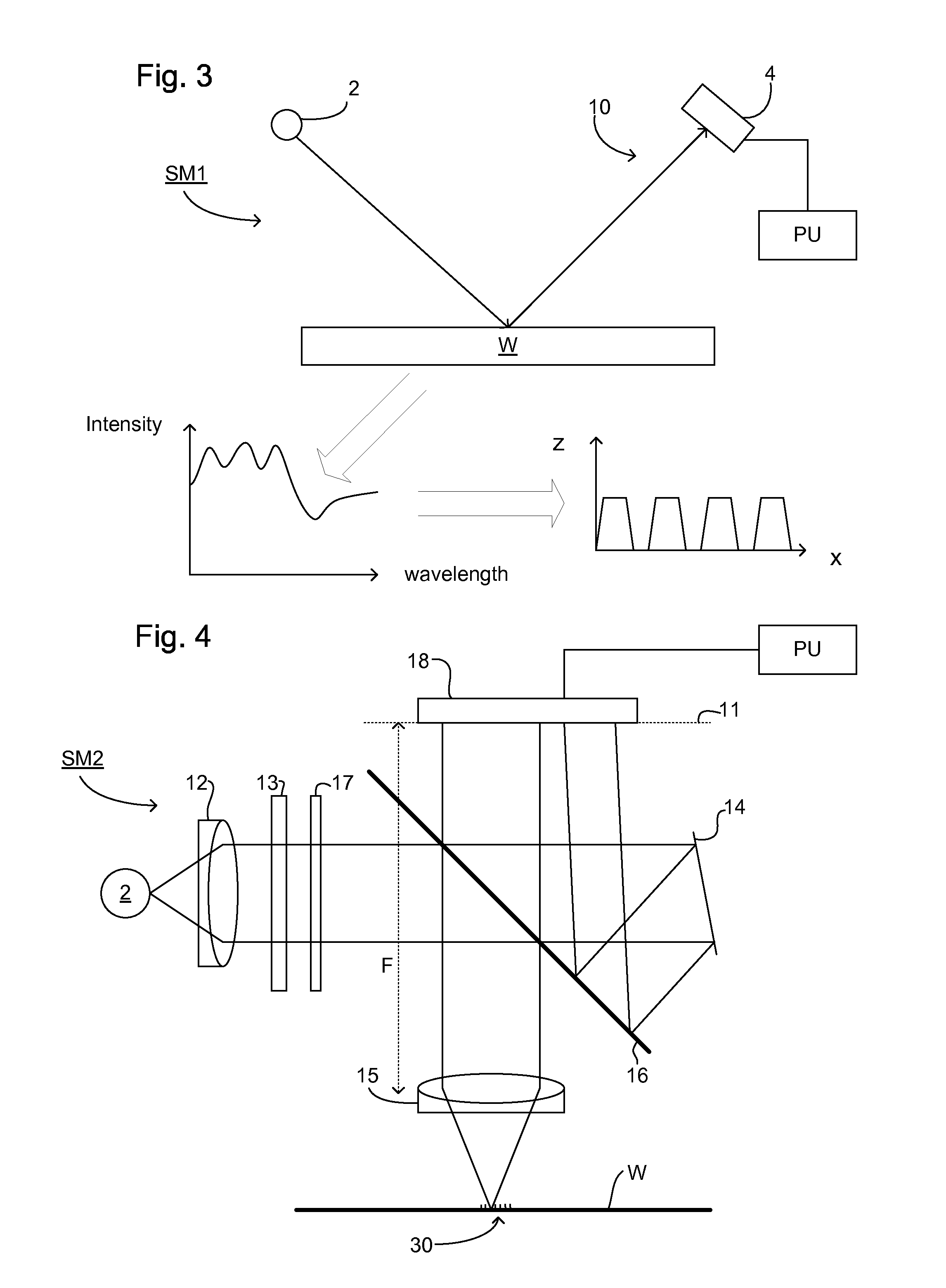

Integrated circuit layout design methodology with process variation bands

ActiveUS20050251771A1Constraint-based CADCAD circuit designSystems analysisIntegrated circuit layout

A system for analyzing IC layouts and designs by calculating variations of a number of objects to be created on a semiconductor wafer as a result of different process conditions. The variations are analyzed to determine individual feature failures or to rank layout designs by their susceptibility to process variations. In one embodiment, the variations are represented by PV-bands having an inner edge that defines the smallest area in which an object will always print and an outer edge that defines the largest area in which an object will print under some process conditions.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

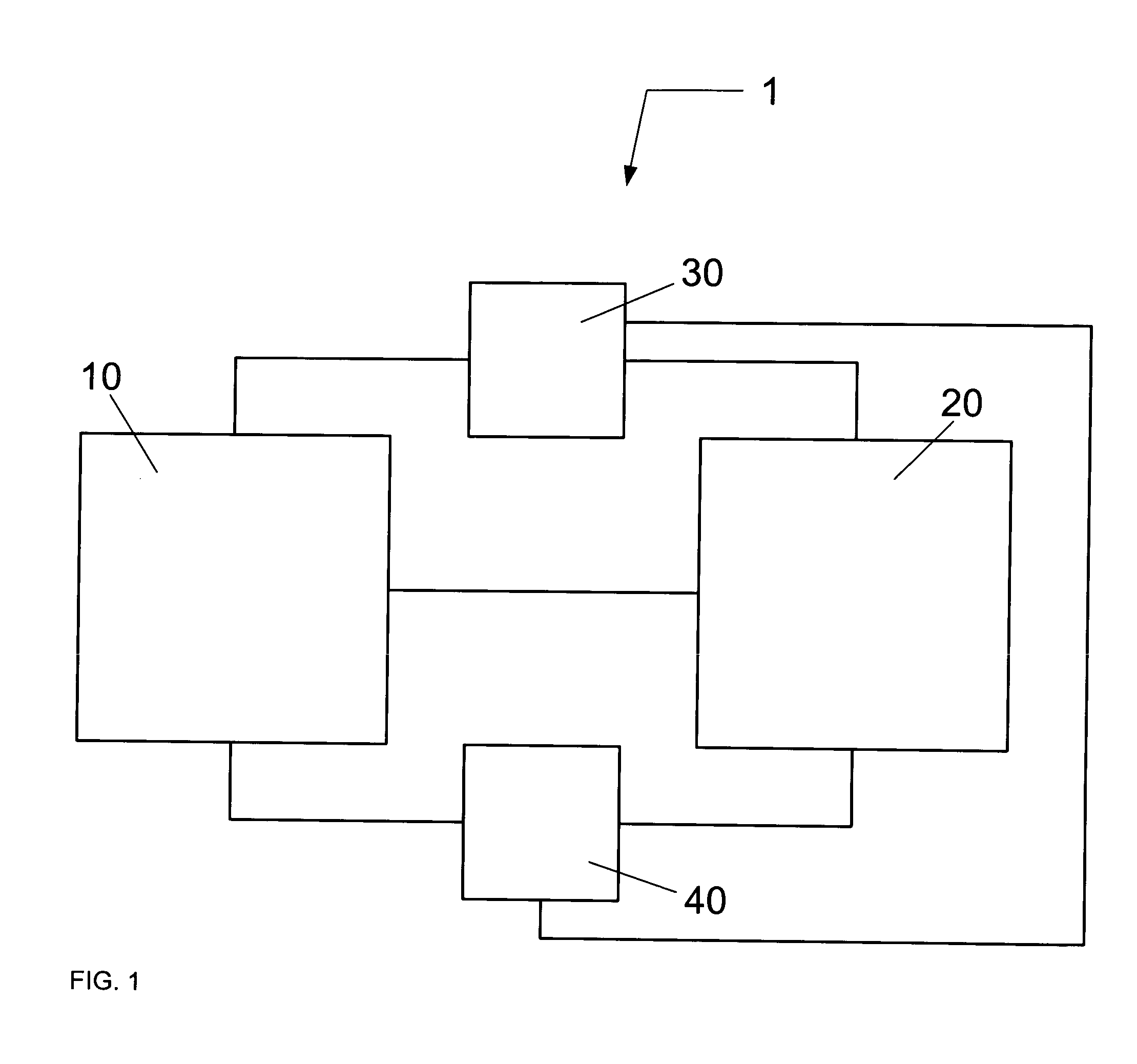

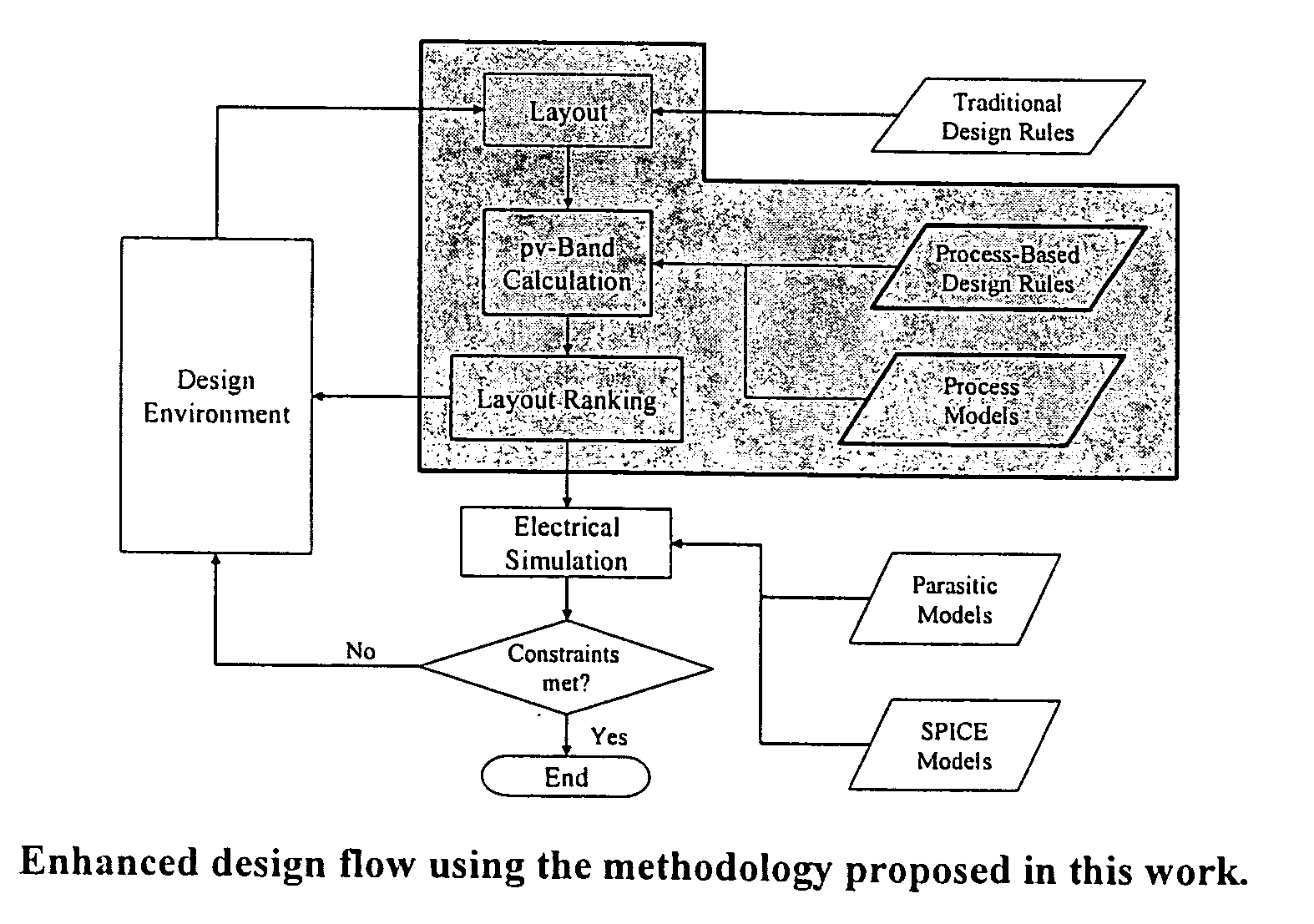

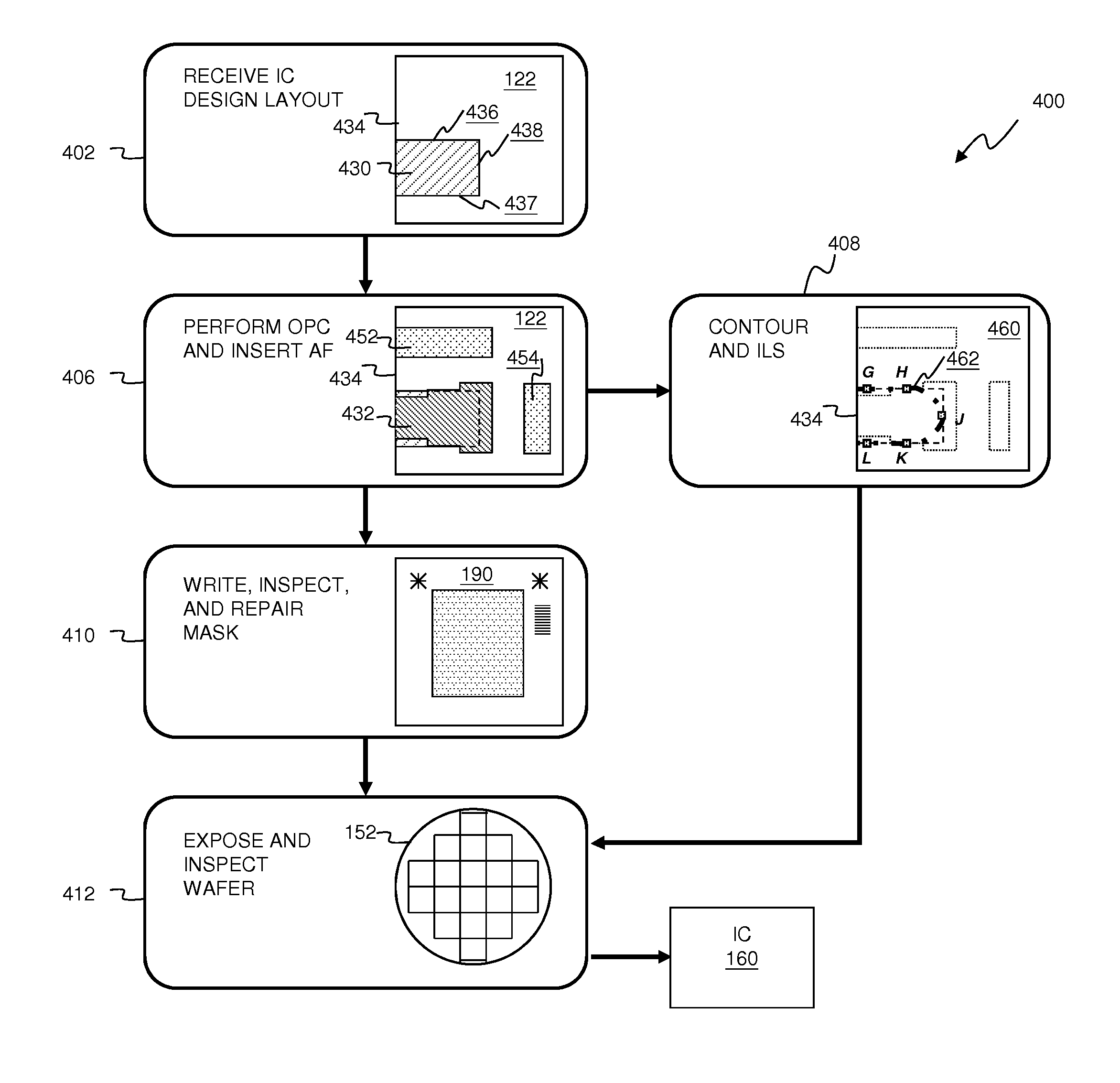

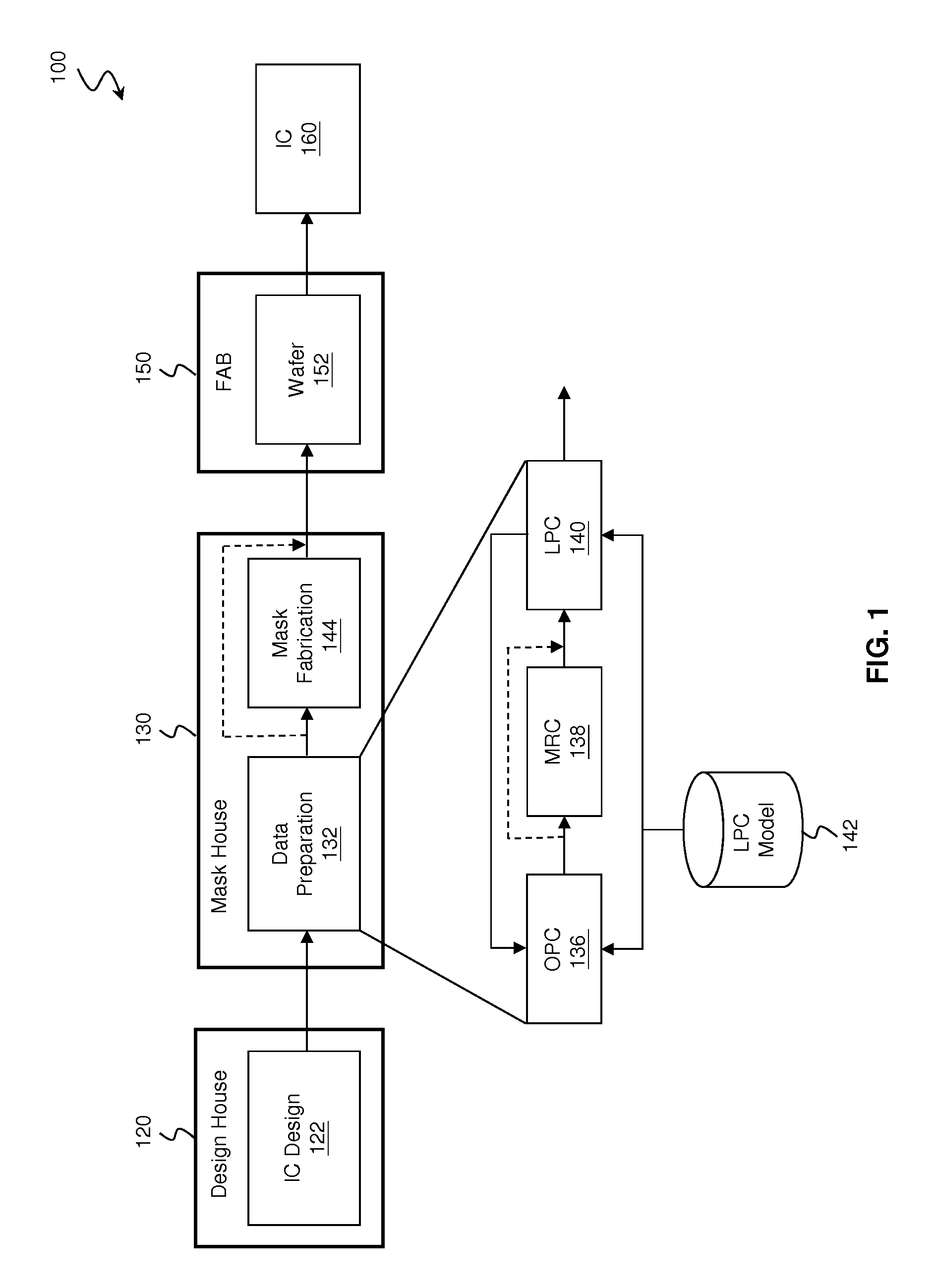

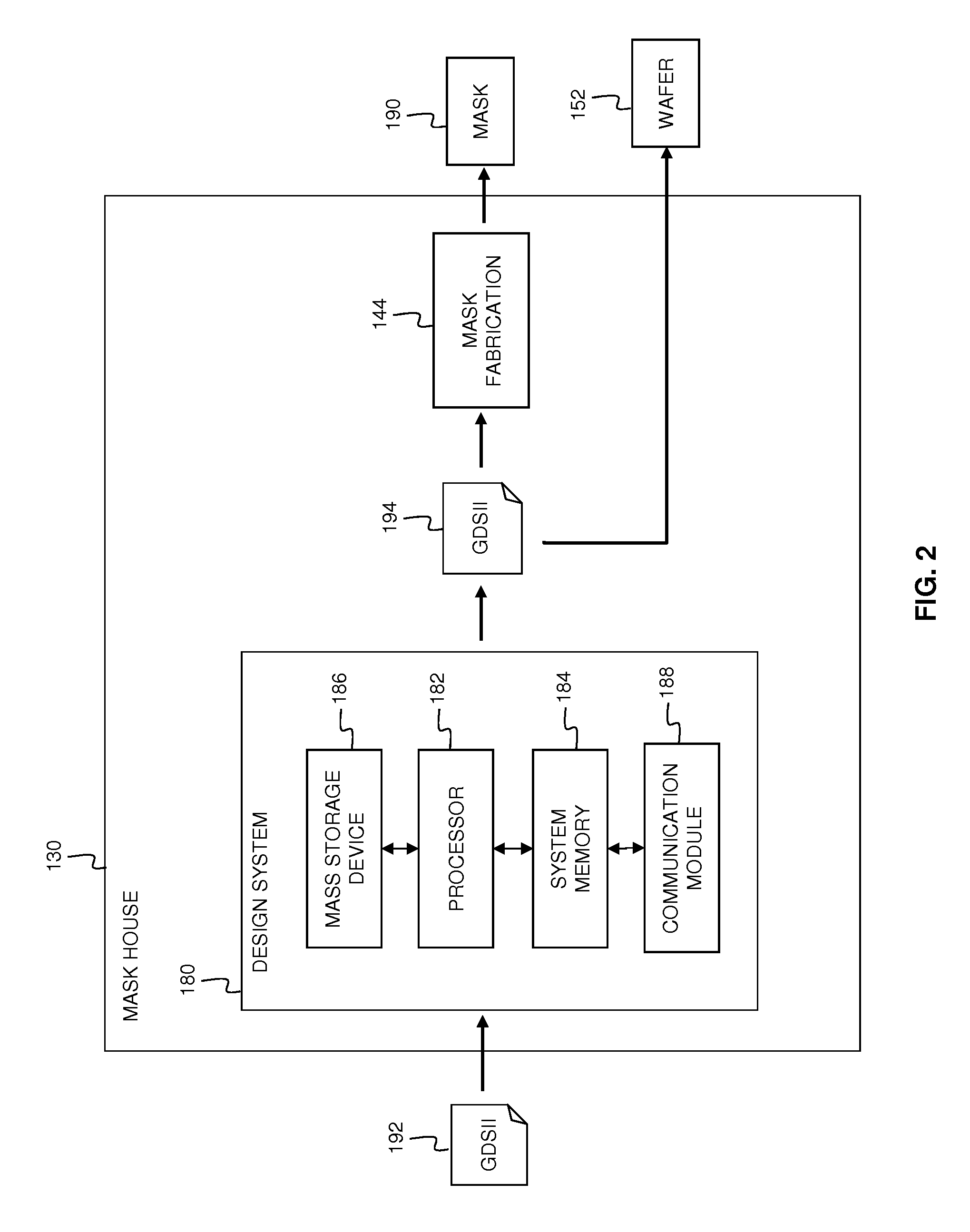

System and Method for Integrated Circuit Manufacturing

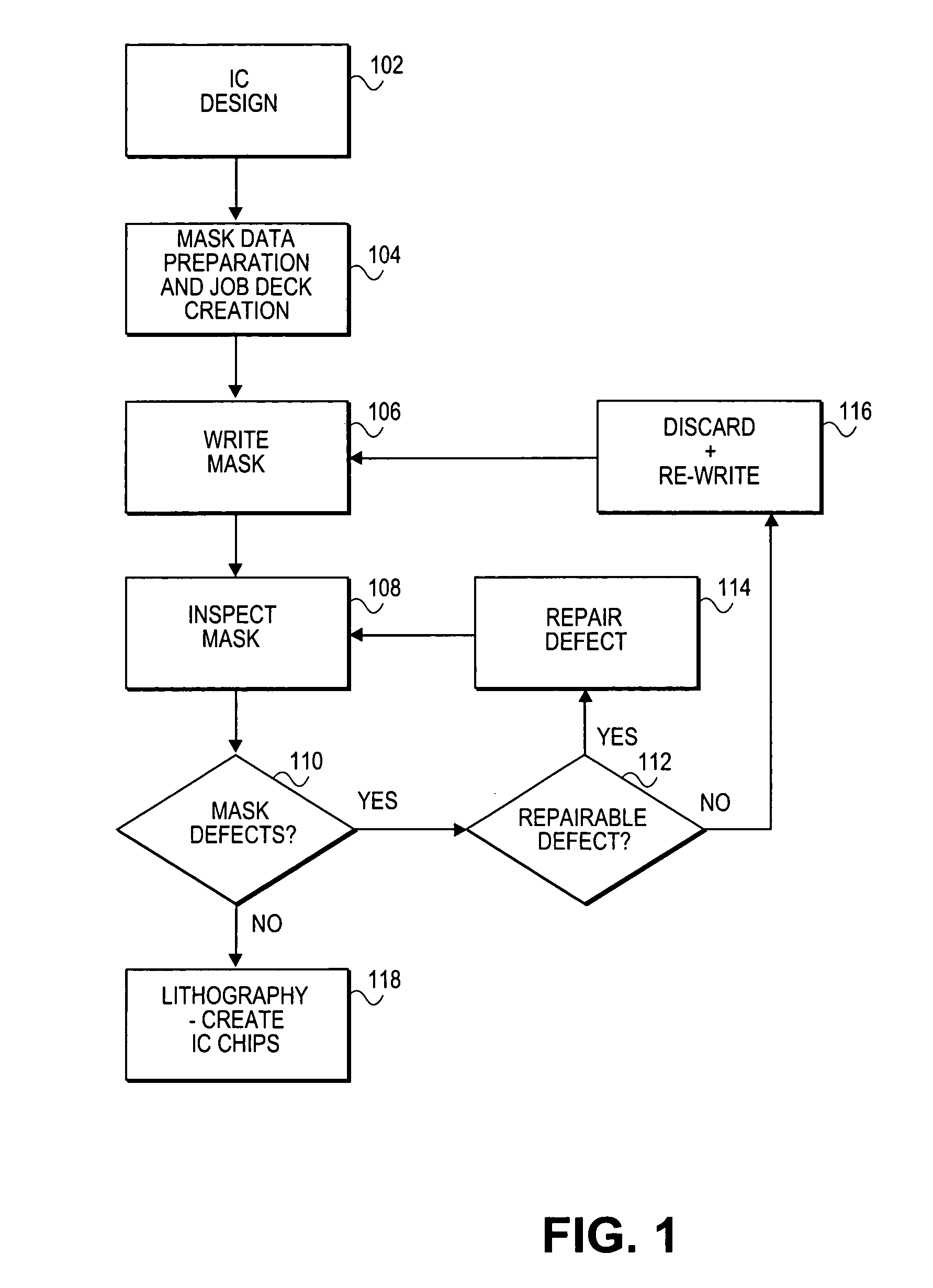

ActiveUS20150278429A1Photomechanical apparatusDesign optimisation/simulationMask inspectionIntegrated circuit manufacturing

Provided is an integrated circuit (IC) manufacturing method. The method includes receiving a design layout of an IC, the design layout having a main feature; performing a process correction to the main feature thereby generating a modified main feature; using a computer, generating a simulated contour of the modified main feature, the simulated contour having a plurality of points; generating a plurality of assistant data in computer readable format, wherein each assistant data includes at least one process performance factor associated with one of the points; and keeping the simulated contour and the assistant data for use by a further process stage, such as mask making, mask inspection, mask repairing, wafer direct writing, wafer inspection, and wafer repairing.

Owner:TAIWAN SEMICON MFG CO LTD

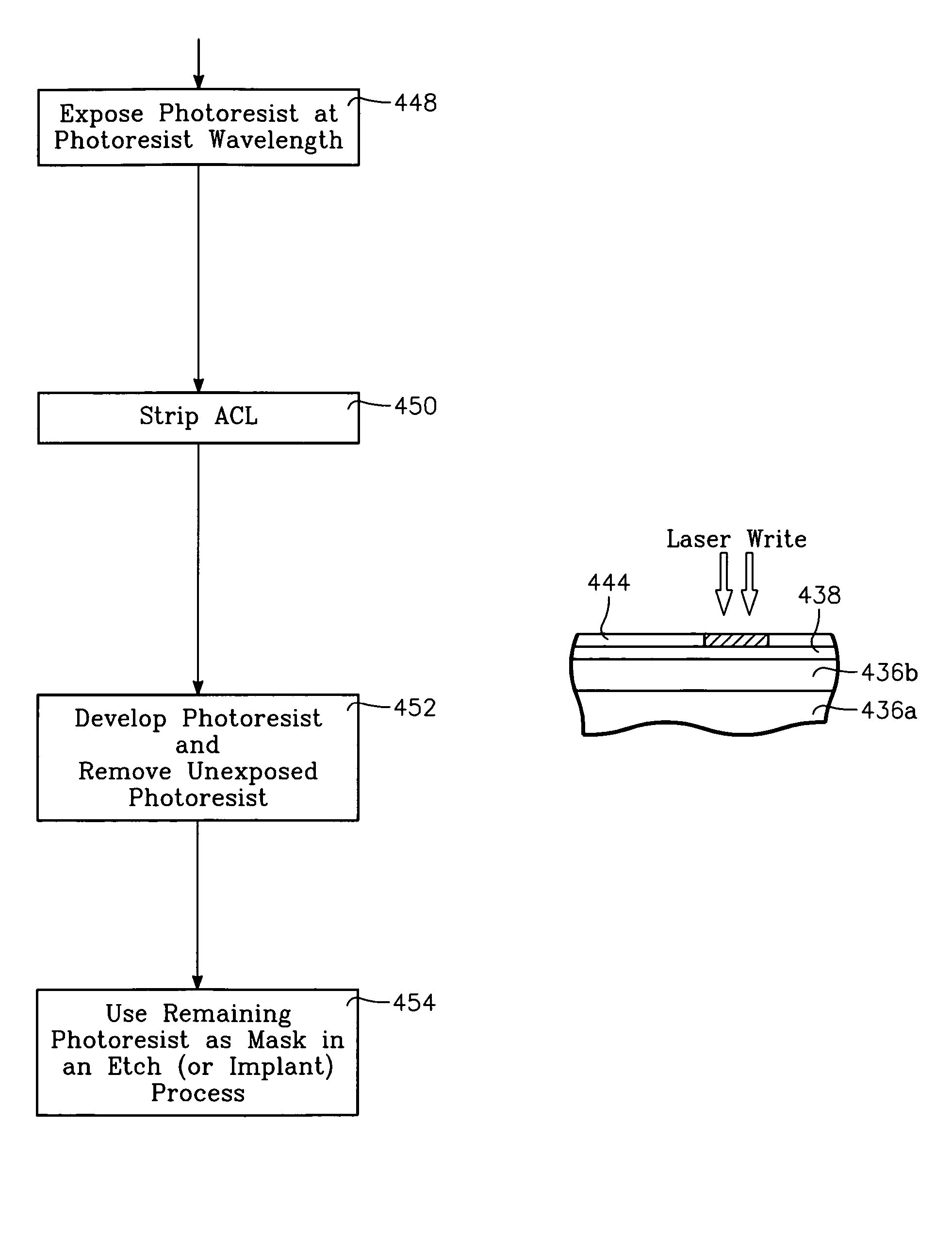

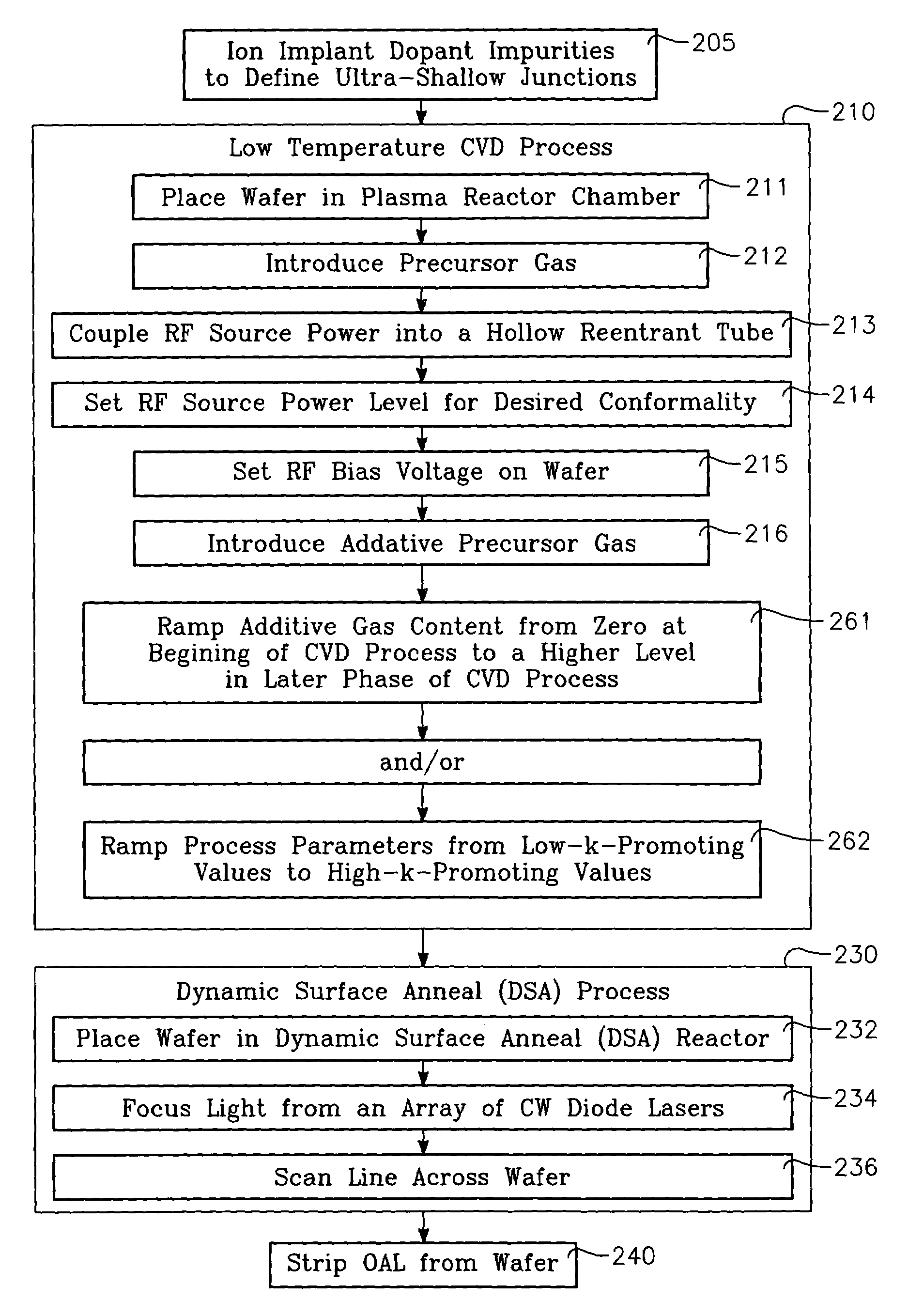

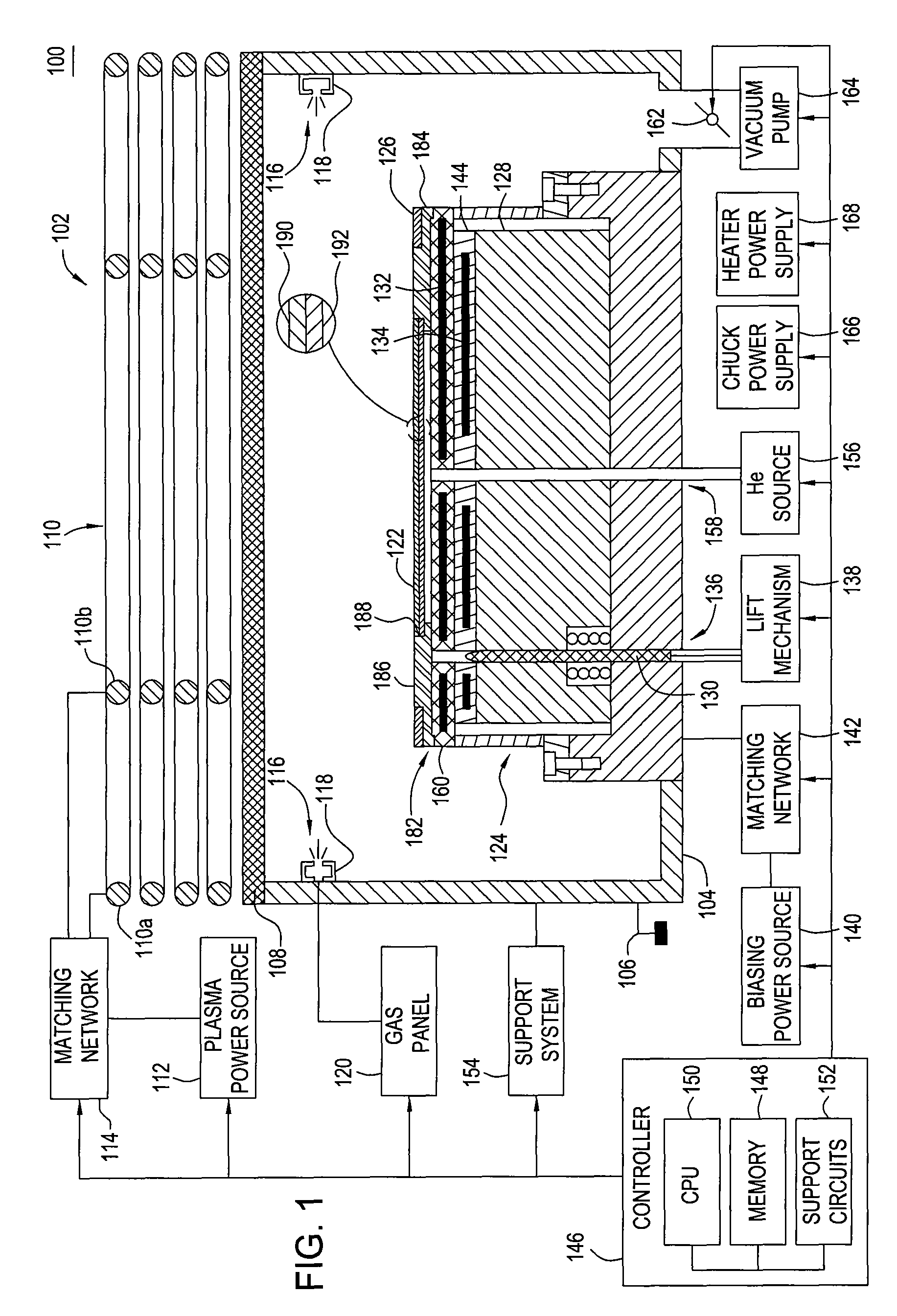

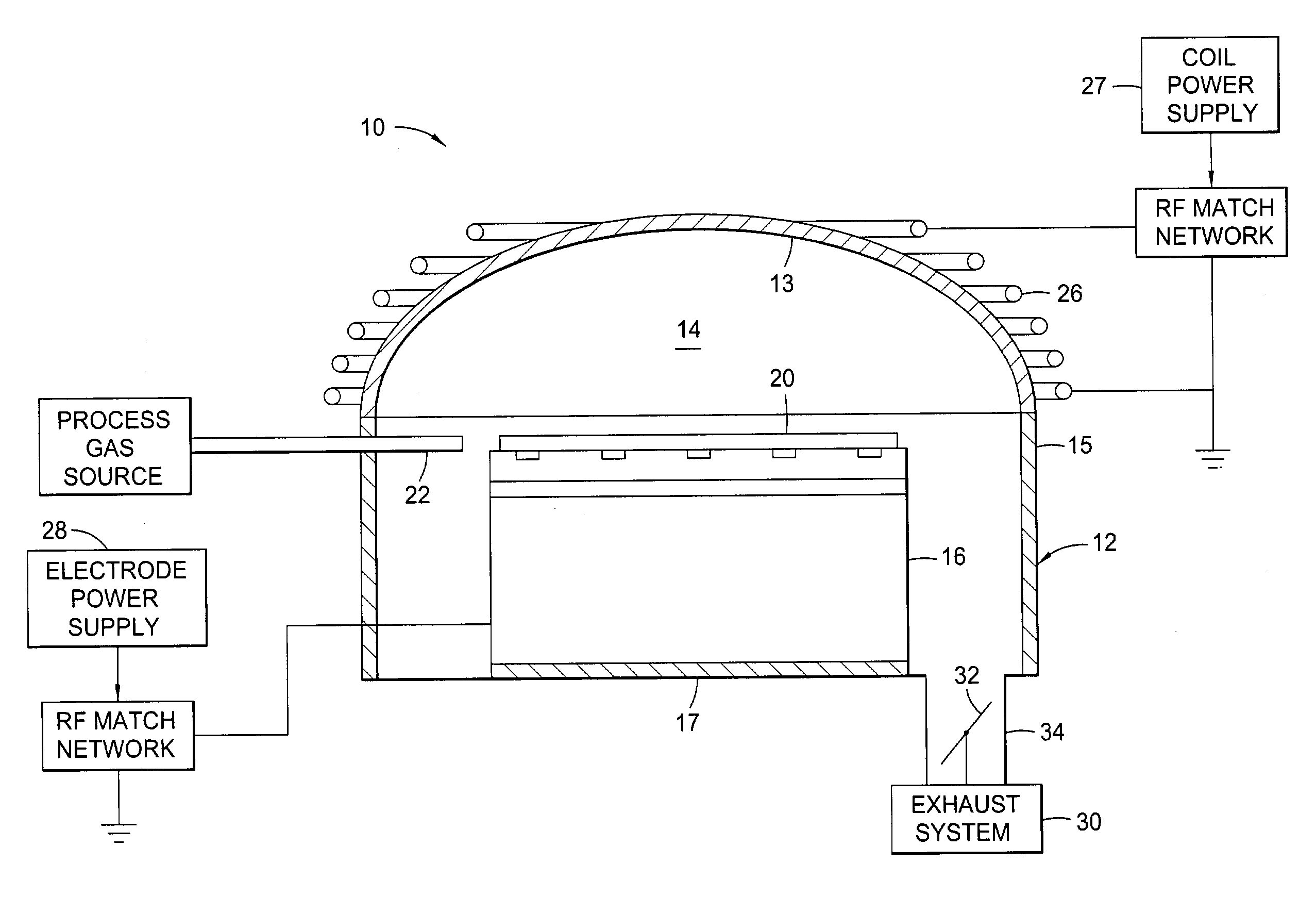

Semiconductor substrate process using a low temperature deposited carbon-containing hard mask

InactiveUS7323401B2Electric discharge tubesRadiation applicationsLow temperature depositionPlasma current

A method of processing a thin film structure on a semiconductor substrate using an optically writable mask includes placing the substrate in a reactor chamber, the substrate having on its surface a target layer to be etched in accordance with a predetermined pattern, and depositing a carbon-containing hard mask layer on the substrate by (a) introducing a carbon-containing process gas into the chamber, (b) generating a reentrant toroidal RF plasma current in a reentrant path that includes a process zone overlying the workpiece by coupling plasma RF source power to an external portion of the reentrant path, and (c) coupling RF plasma bias power or bias voltage to the workpiece. The method further includes photolithographically defining the predetermined pattern in the carbon-containing hard mask layer, and etching the target layer in the presence of the hard mask layer.

Owner:APPLIED MATERIALS INC

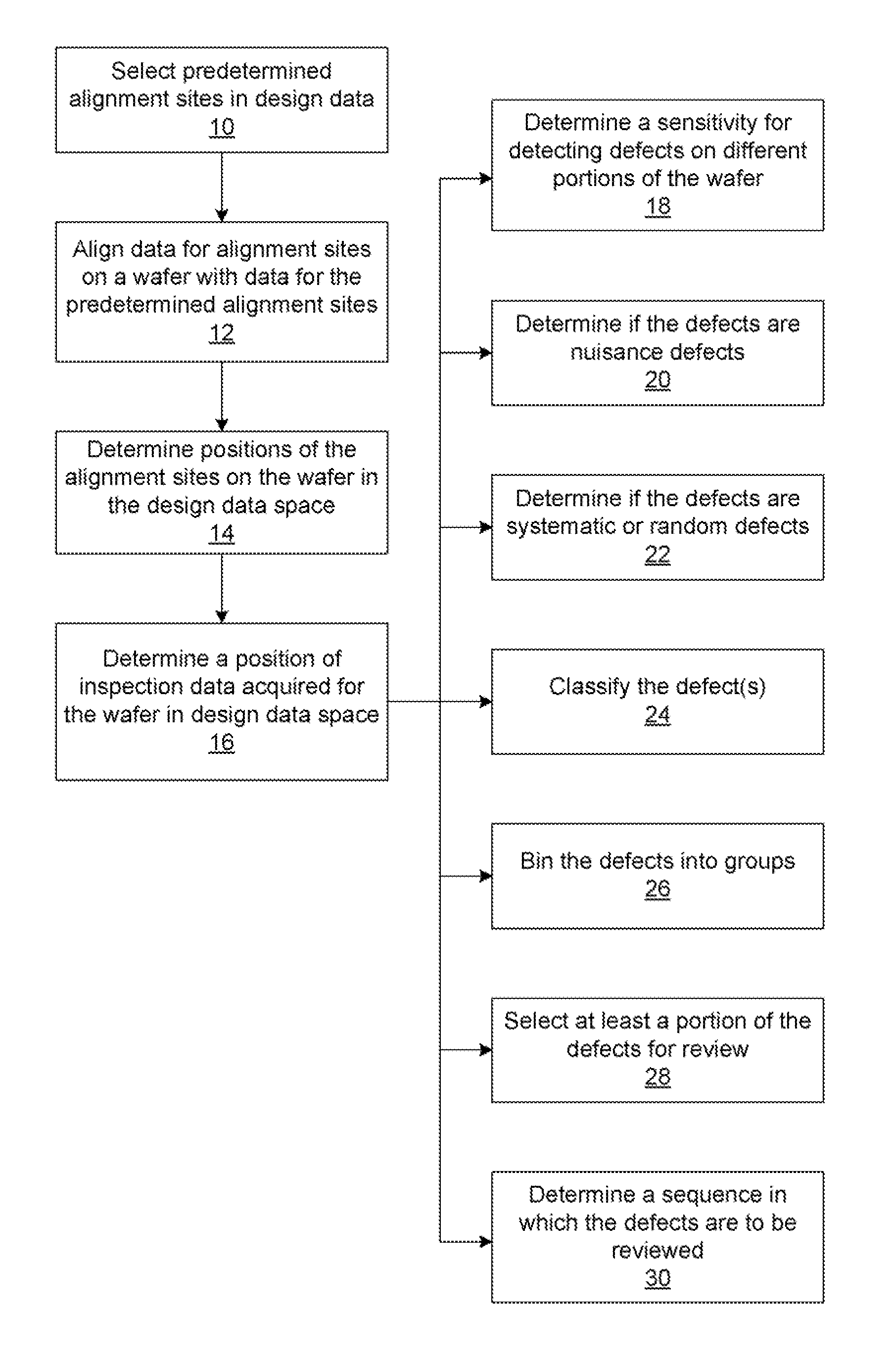

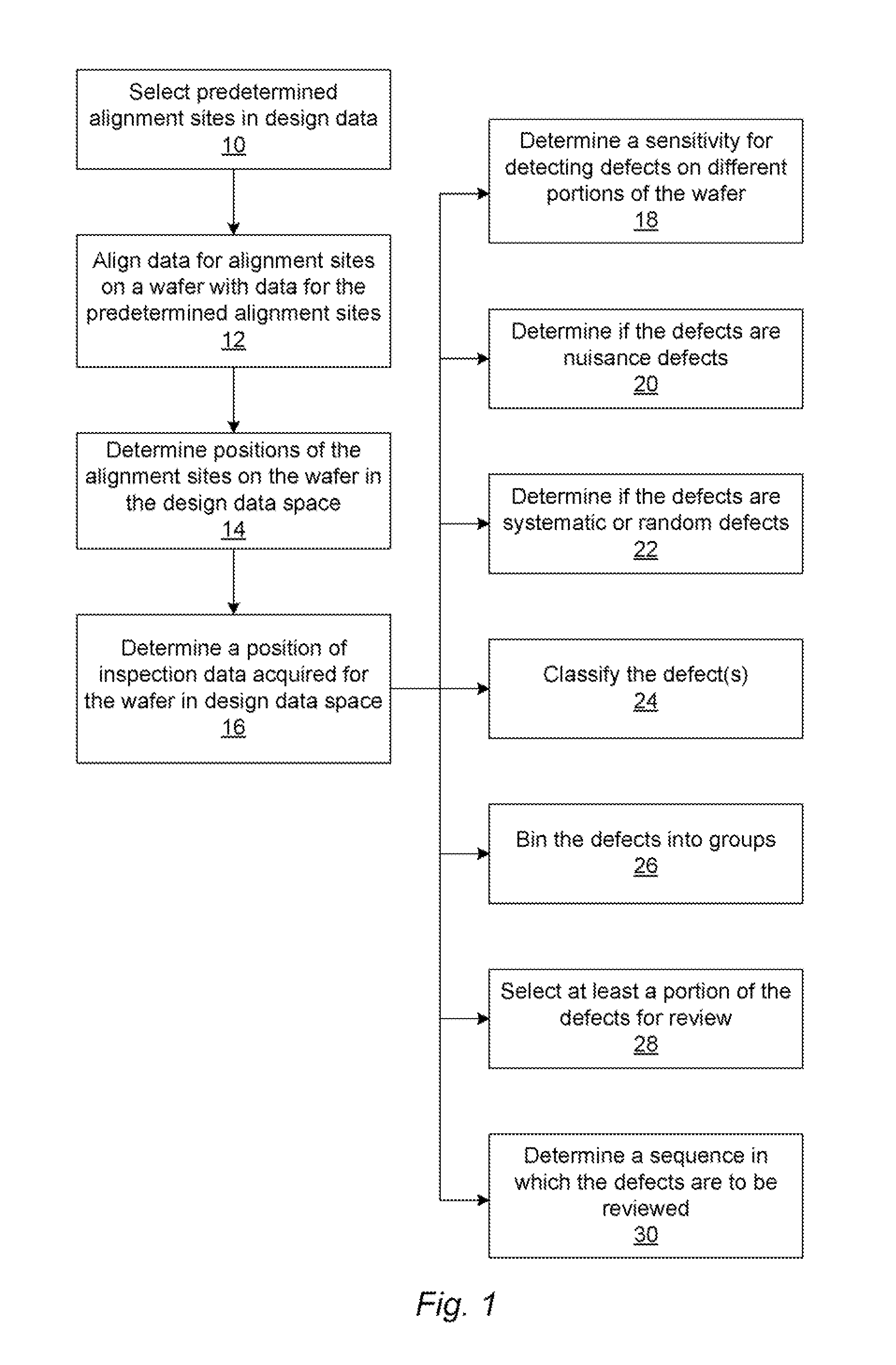

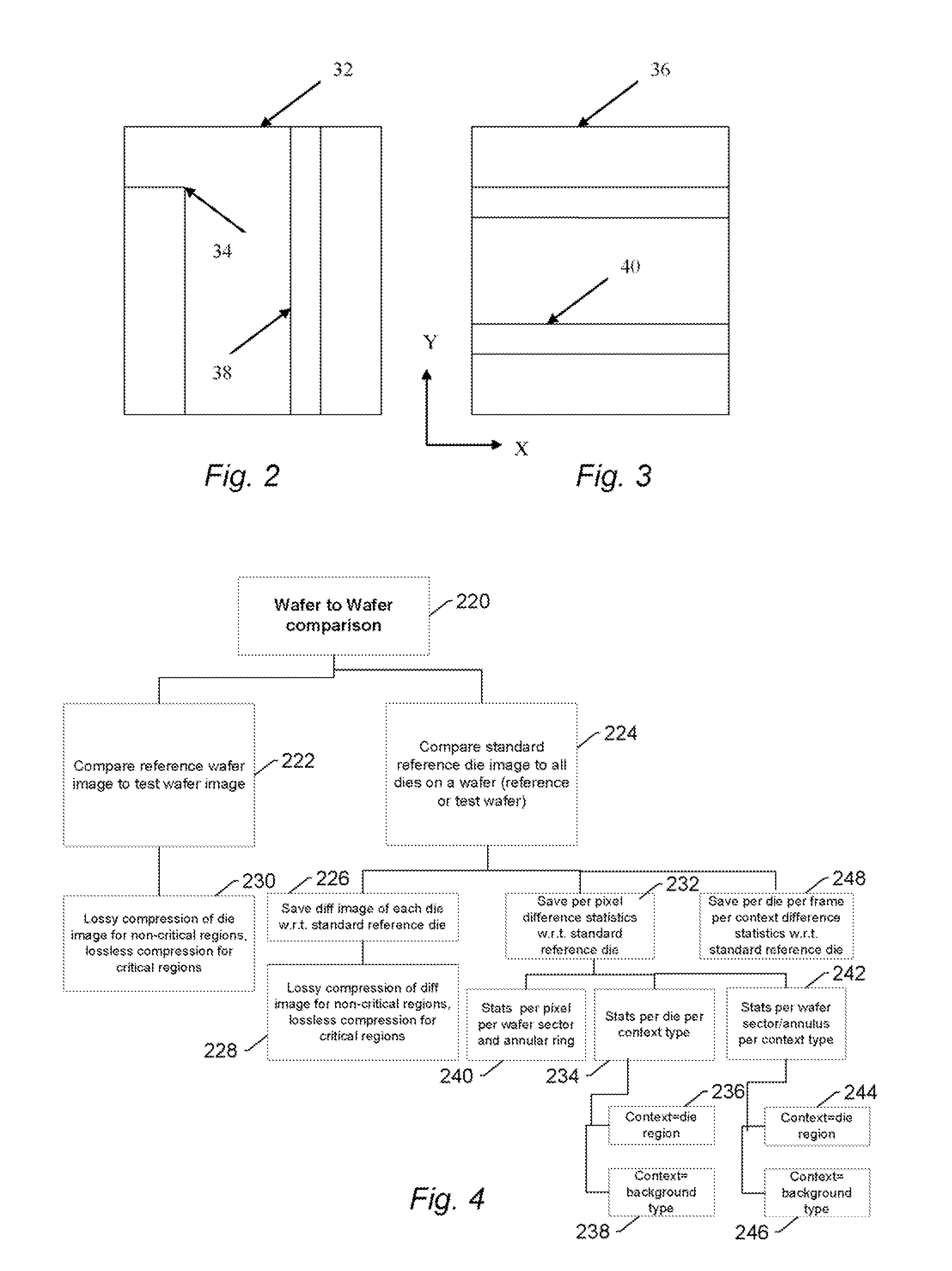

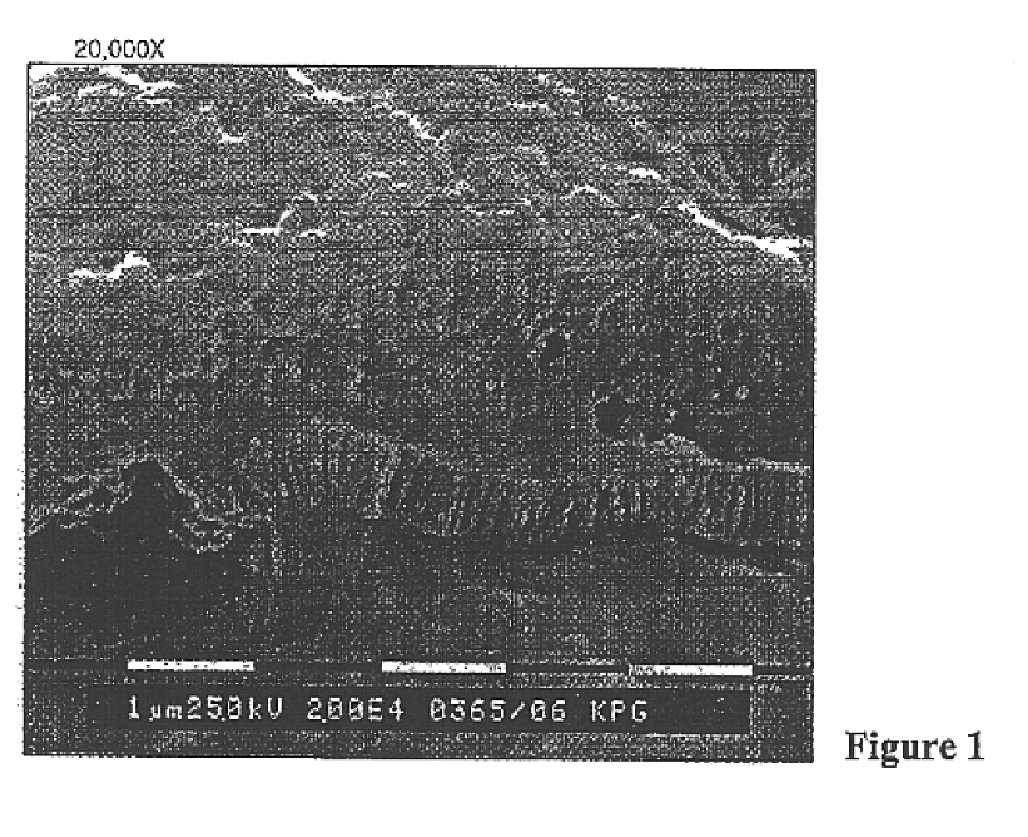

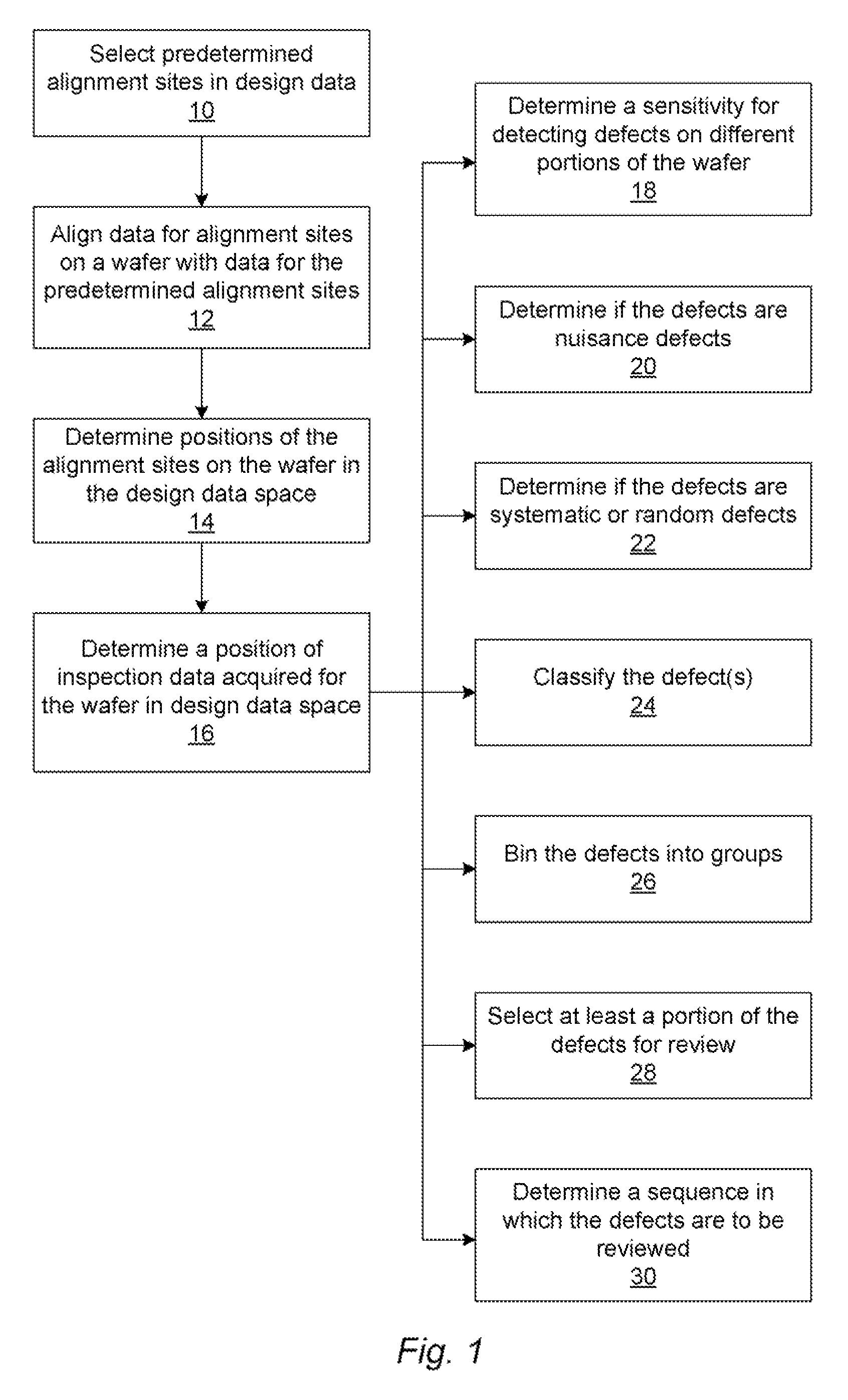

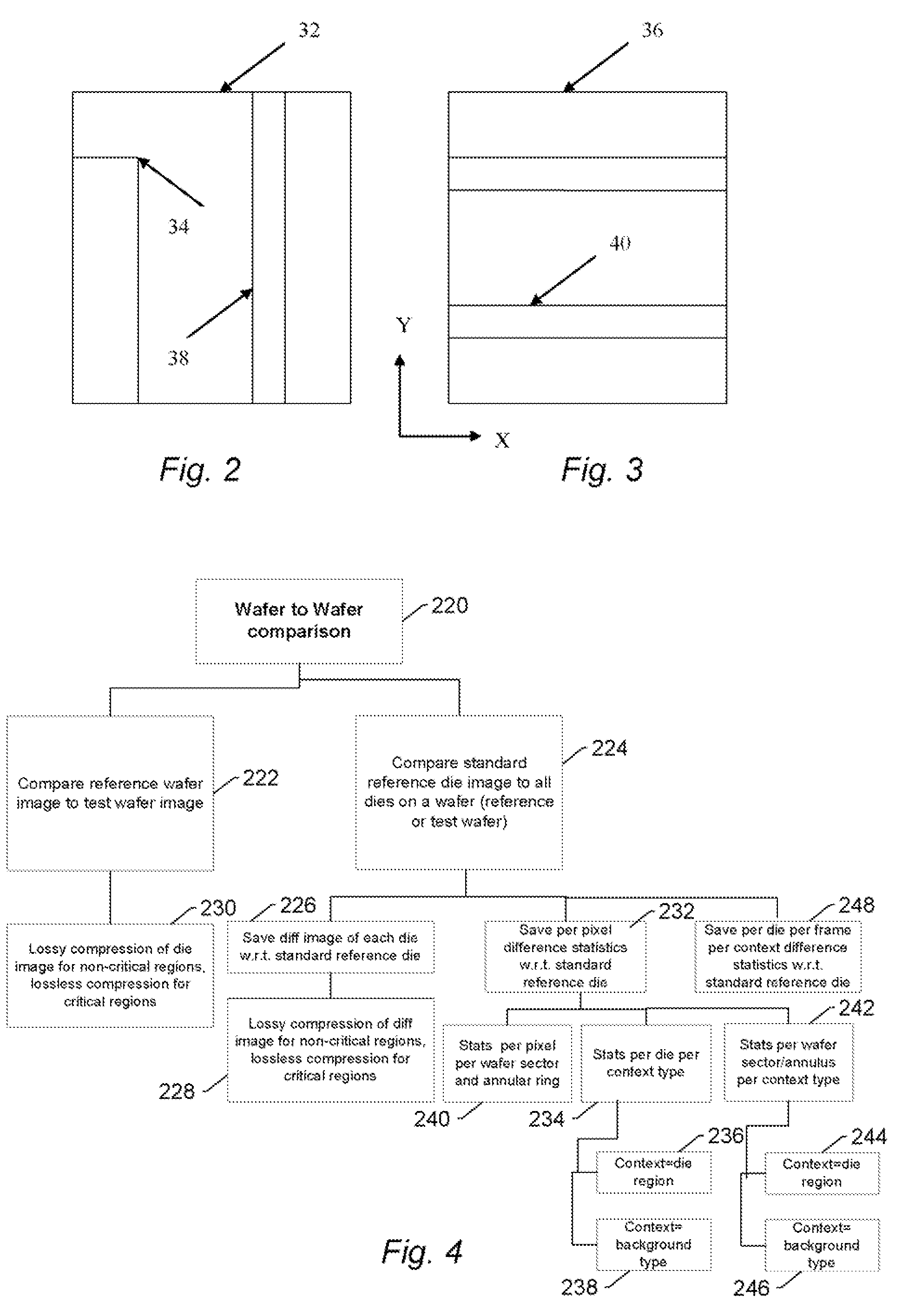

Methods and systems for utilizing design data in combination with inspection data

ActiveUS20070288219A1Increase catch rateReduce errorsImage enhancementImage analysisComputer scienceDesign data

Various methods and systems for utilizing design data in combination with inspection data are provided. One computer-implemented method for binning defects detected on a wafer includes comparing portions of design data proximate positions of the defects in design data space. The method also includes determining if the design data in the portions is at least similar based on results of the comparing step. In addition, the method includes binning the defects in groups such that the portions of the design data proximate the positions of the defects in each of the groups are at least similar. The method further includes storing results of the binning step in a storage medium.

Owner:KLA TENCOR CORP

On-press developable IR sensitive printing plates using binder resins having polyethylene oxide segments

InactiveUS6899994B2Prevent steppingRadiation applicationsSemiconductor/solid-state device manufacturingPolymer sciencePolyethylene oxide

The present invention relates to a polymerizable coating composition suitable for the manufacture of printing plates developable on-press. The coating composition comprises (i) a polymerizable compound and (ii) a polymeric binder comprising polyethylene oxide segments, wherein the polymeric binder is selected from the group consisting of at least one graft copolymer comprising a main chain polymer and polyethylene oxide side chains, a block copolymer having at least one polyethylene oxide block and at least one non-polyethylene oxide block, and a combination thereof. The invention is also directed to an imageable element comprising a substrate and the polymerizable coating composition.

Owner:KODAK POLYCHROME GRAPHICS

Methods and systems for utilizing design data in combination with inspection data

ActiveUS7570796B2Reduce errorsImprove signal-to-noise ratioImage enhancementImage analysisComputer scienceDesign data

Owner:KLA TENCOR TECH CORP

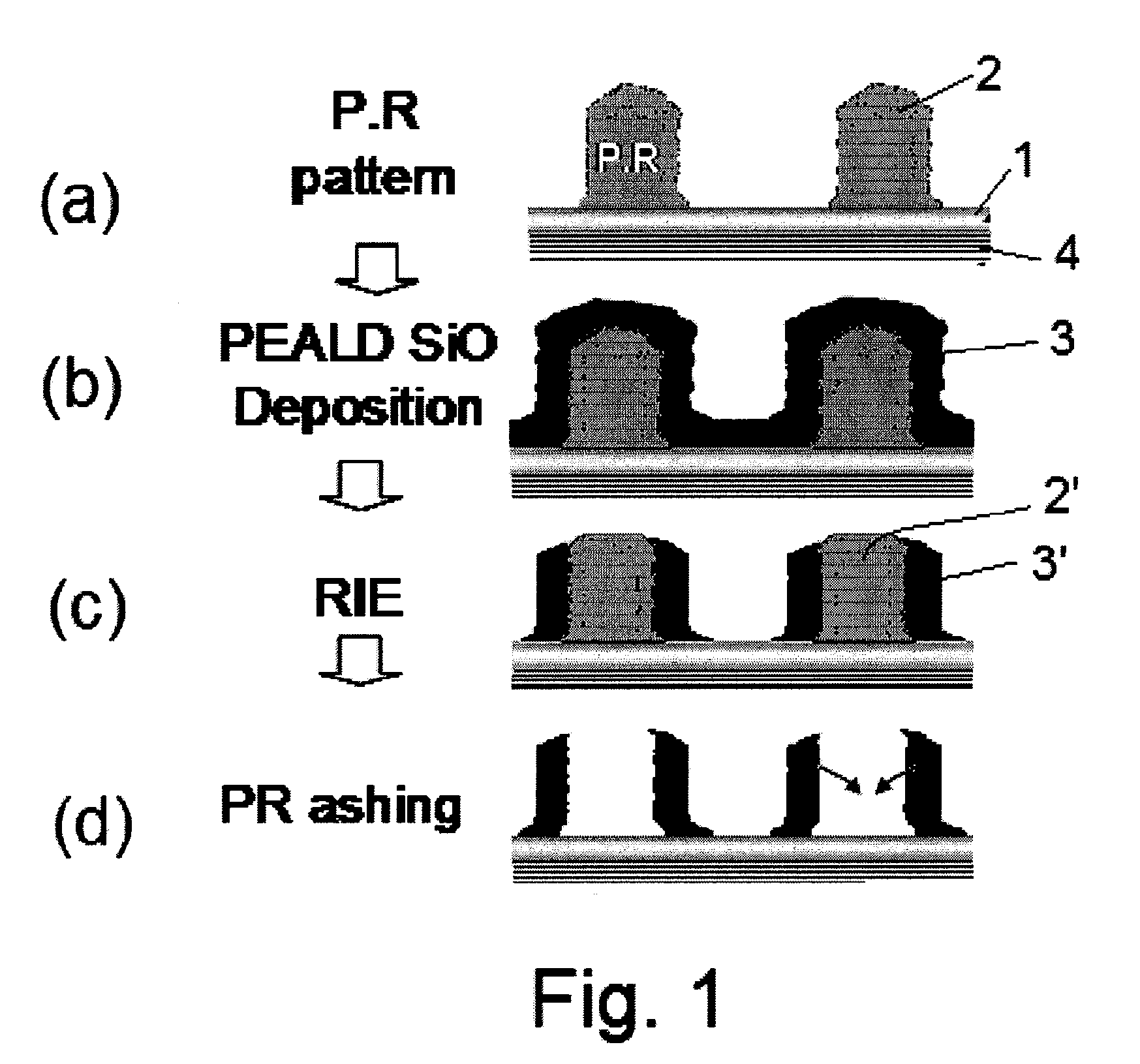

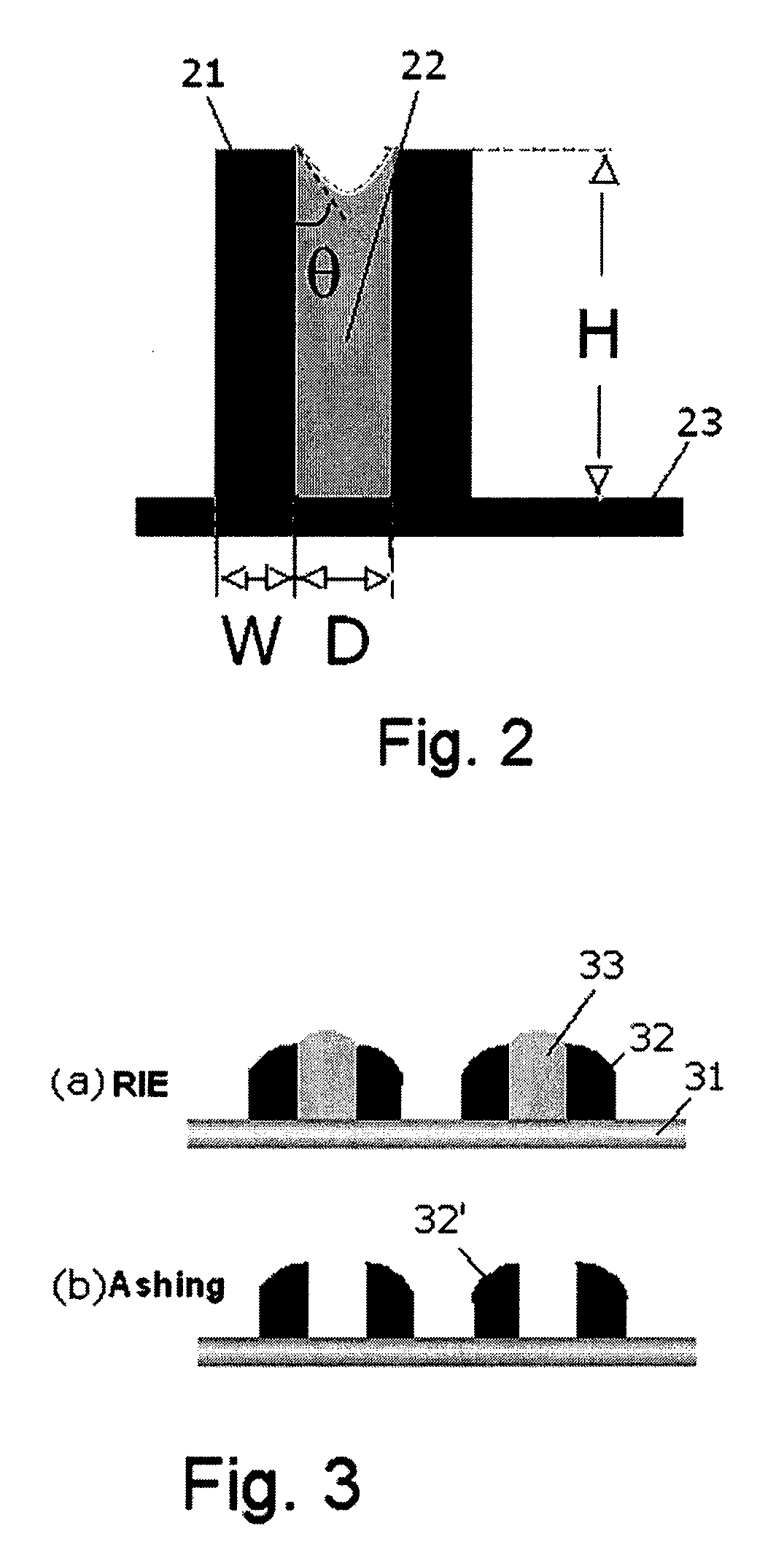

Mask material conversion

ActiveUS7910288B2Photomechanical apparatusSemiconductor/solid-state device manufacturingAmorphous siliconEngineering

The dimensions of mask patterns, such as pitch-multiplied spacers, are controlled by controlled growth of features in the patterns after they are formed. To form a pattern of pitch-multiplied spacers, a pattern of mandrels is first formed overlying a semiconductor substrate. Spacers are then formed on sidewalls of the mandrels by depositing a blanket layer of material over the mandrels and preferentially removing spacer material from horizontal surfaces. The mandrels are then selectively removed, leaving behind a pattern of freestanding spacers. The spacers comprise a material, such as polysilicon and amorphous silicon, known to increase in size upon being oxidized. The spacers are oxidized to grow them to a desired width. After reaching the desired width, the spacers can be used as a mask to pattern underlying layers and the substrate. Advantageously, because the spacers are grown by oxidation, thinner blanket layers can be deposited over the mandrels, thereby allowing the deposition of more conformal blanket layers and widening the process window for spacer formation.

Owner:MICRON TECH INC

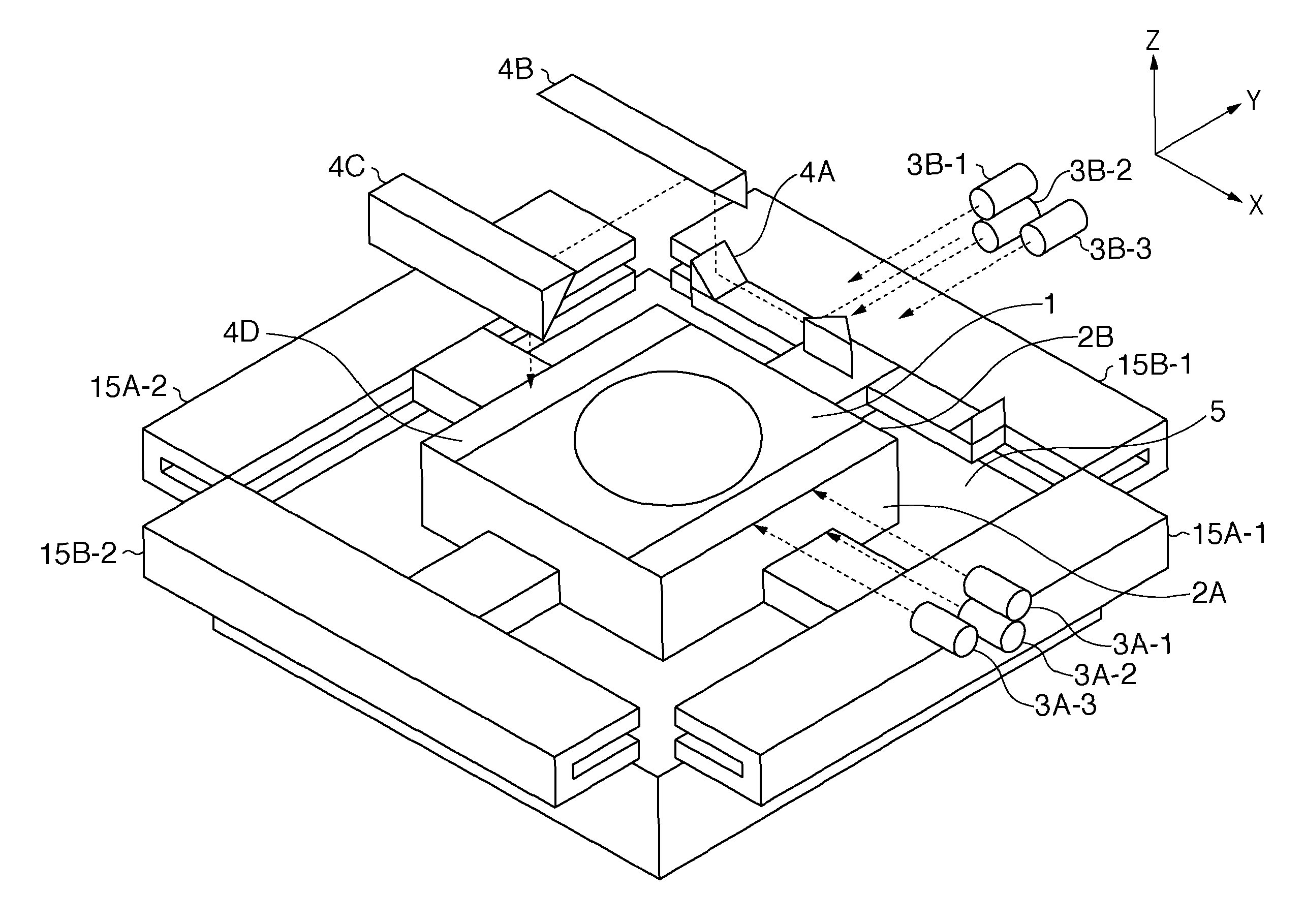

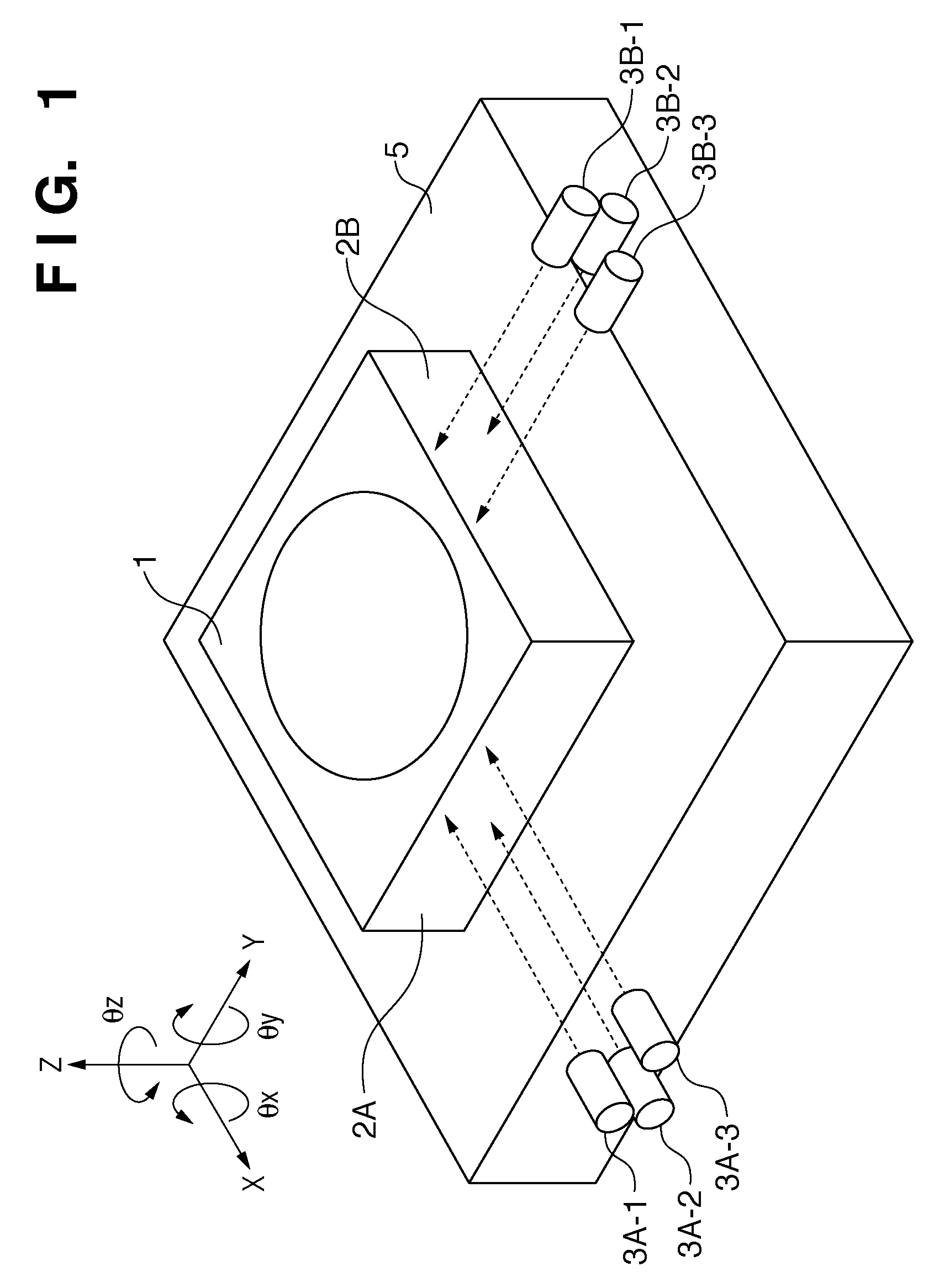

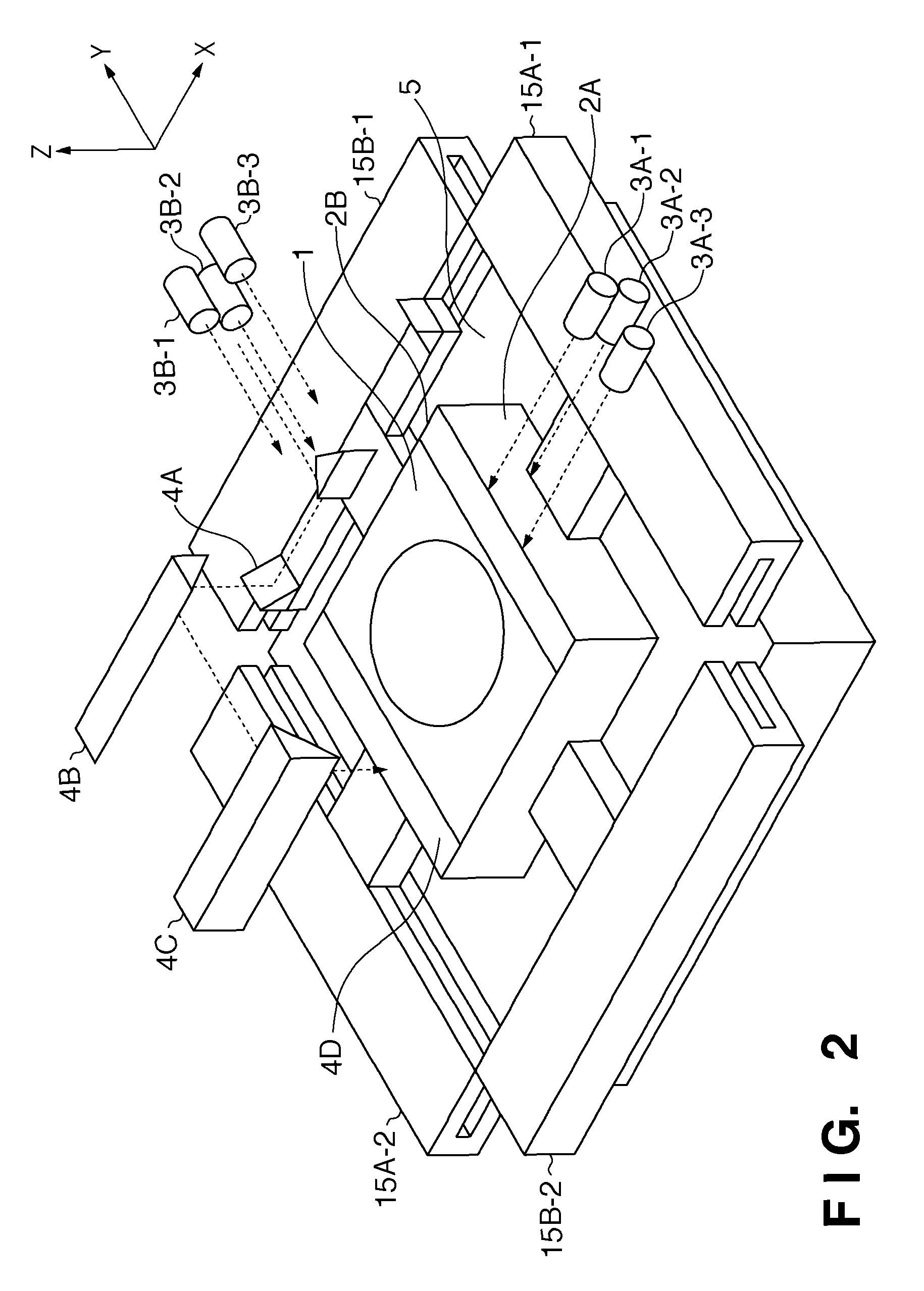

Exposure apparatus and method of manufacturing device

InactiveUS7884918B2Improve accuracyIncrease productivityPhotomechanical apparatusSemiconductor/solid-state device manufacturingObservational errorMeasurement device

Owner:CANON KK

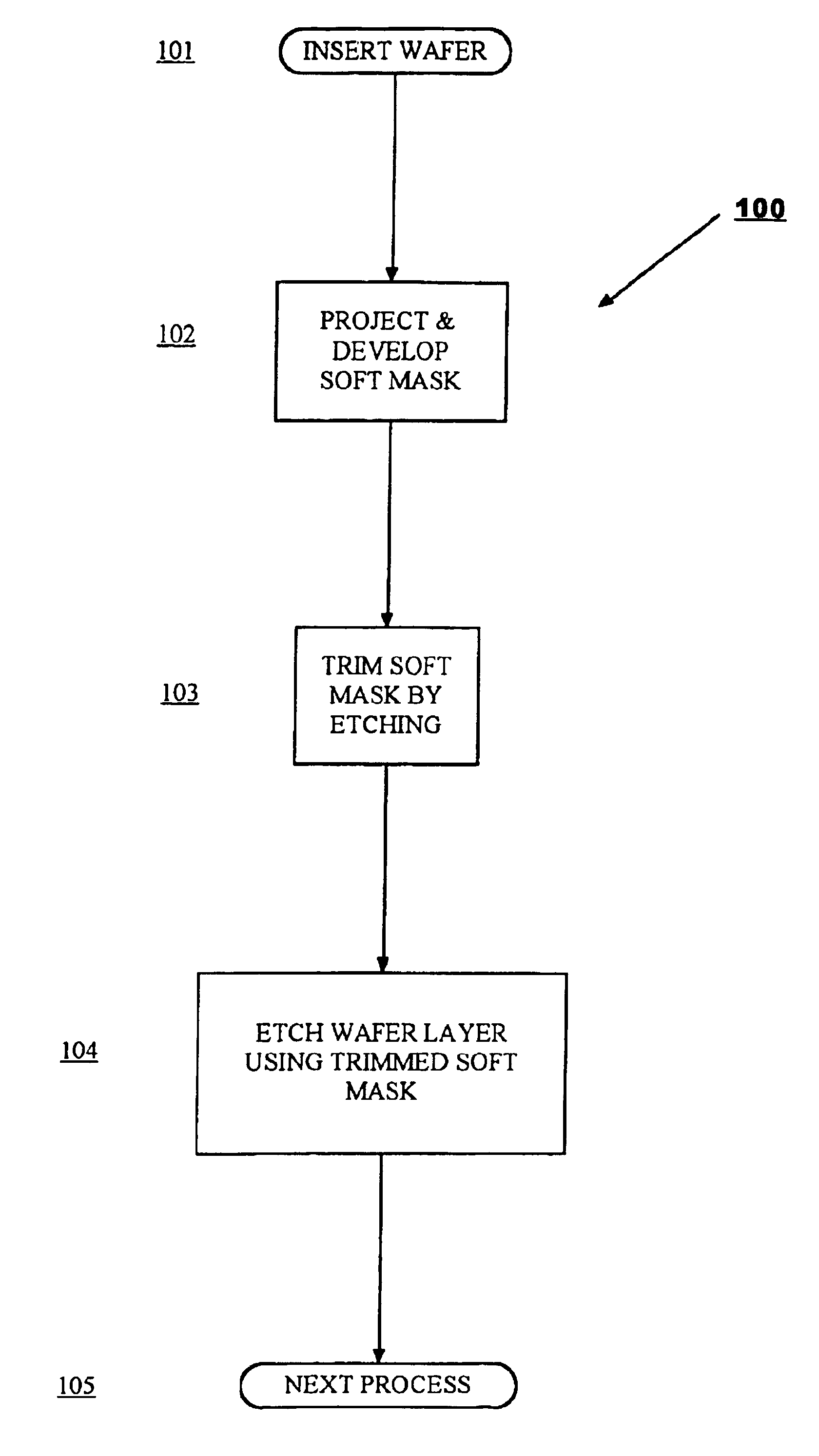

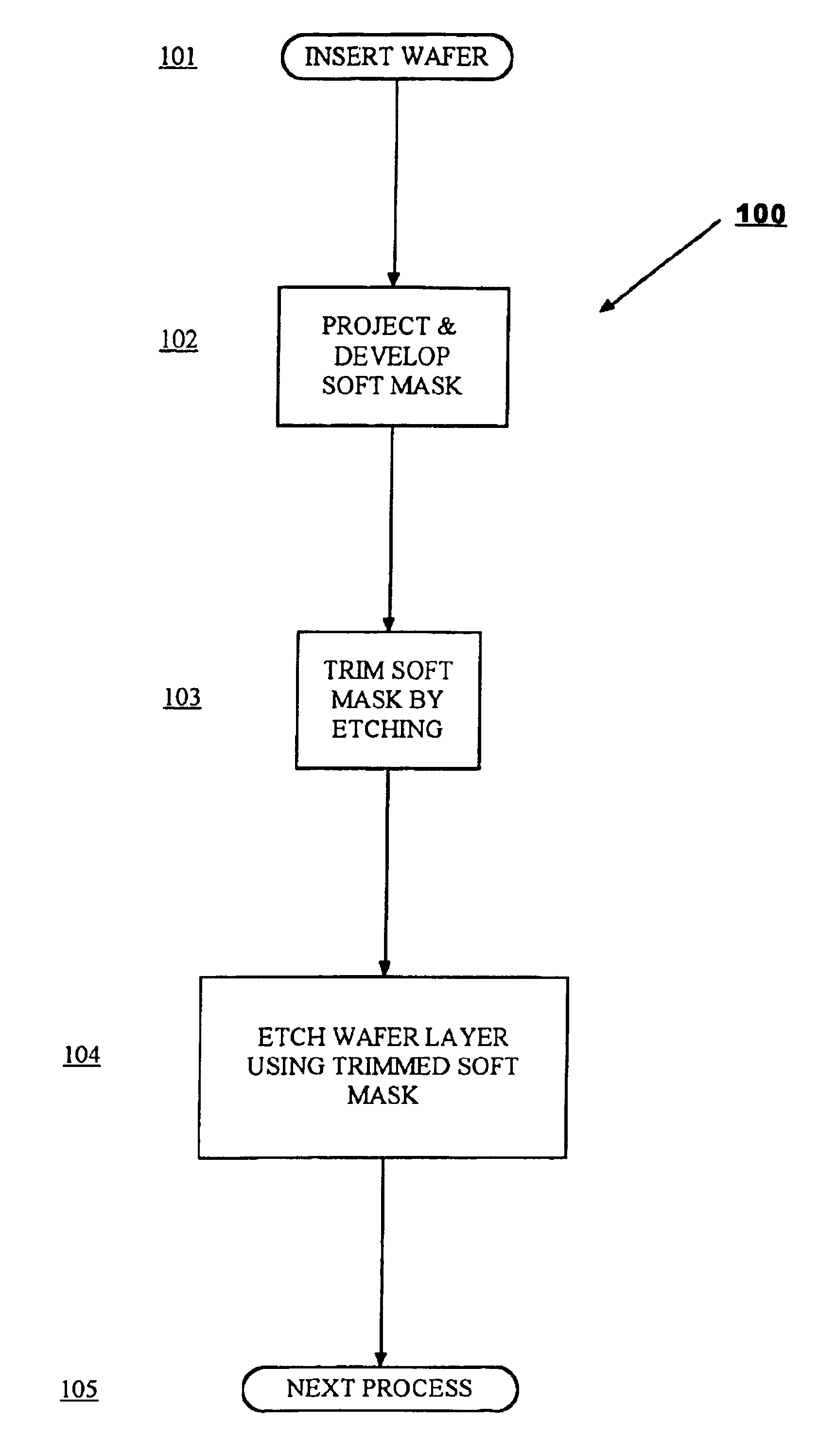

Gate linewidth tailoring and critical dimension control for sub-100 nm devices using plasma etching

InactiveUS6864041B2Tight tolerance variationMinimal variationVacuum gauge using ionisation effectsDecorative surface effectsImage resolutionLine width

A method of fabricating an electronic chip on a wafer in which a first mask at a predetermined lower resolution is developed on the wafer and then etched under a first set of conditions for a predetermined period to achieve a mask that is below the resolution limit of current lithography. The etched mask is then used as a hard mask for etching material on a lower layer.

Owner:INT BUSINESS MASCH CORP

Method of forming metal oxide hardmask

ActiveUS8901016B2Promote degradationSemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentAtomic layer depositionMetal

Owner:ASM JAPAN

Semiconductor substrate process using an optically writable carbon-containing mask

ActiveUS7429532B2Photomechanical apparatusSemiconductor/solid-state device manufacturingPlasma currentCoupling

A method of processing a thin film structure on a semiconductor substrate using an optically writable mask, the method includes placing the substrate in a reactor chamber, the substrate having on its surface a target layer to be exposed to a light source in accordance with a predetermined pattern, depositing an optically writable carbon-containing mask layer on the substrate by (a) introducing a carbon-containing process gas into the chamber, (b) generating a reentrant toroidal RF plasma current in a reentrant path that includes a process zone overlying the workpiece by coupling plasma RF source power to an external portion of the reentrant path, (c) coupling RF plasma bias power or bias voltage to the workpiece. The method further includes optically writing on the carbon-containing mask layer in accordance with the predetermined pattern with writing light of a characteristic suitable for transforming the transparency or opacity of the optically writable mask layer and exposing through the mask layer the target layer with reading light of a characteristic different from that of the writing light.

Owner:APPLIED MATERIALS INC

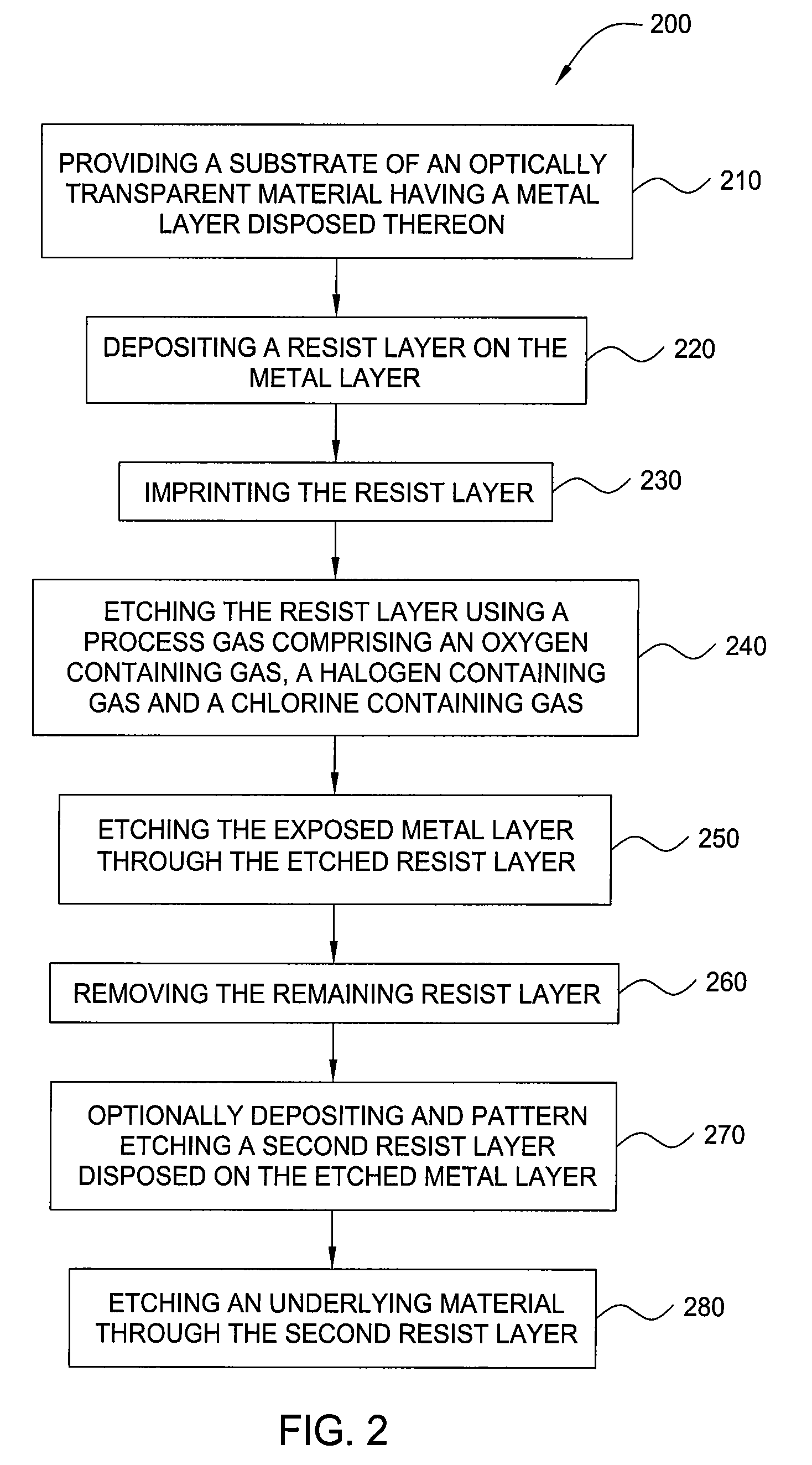

Etching of nano-imprint templates using an etch reactor

Owner:APPLIED MATERIALS INC

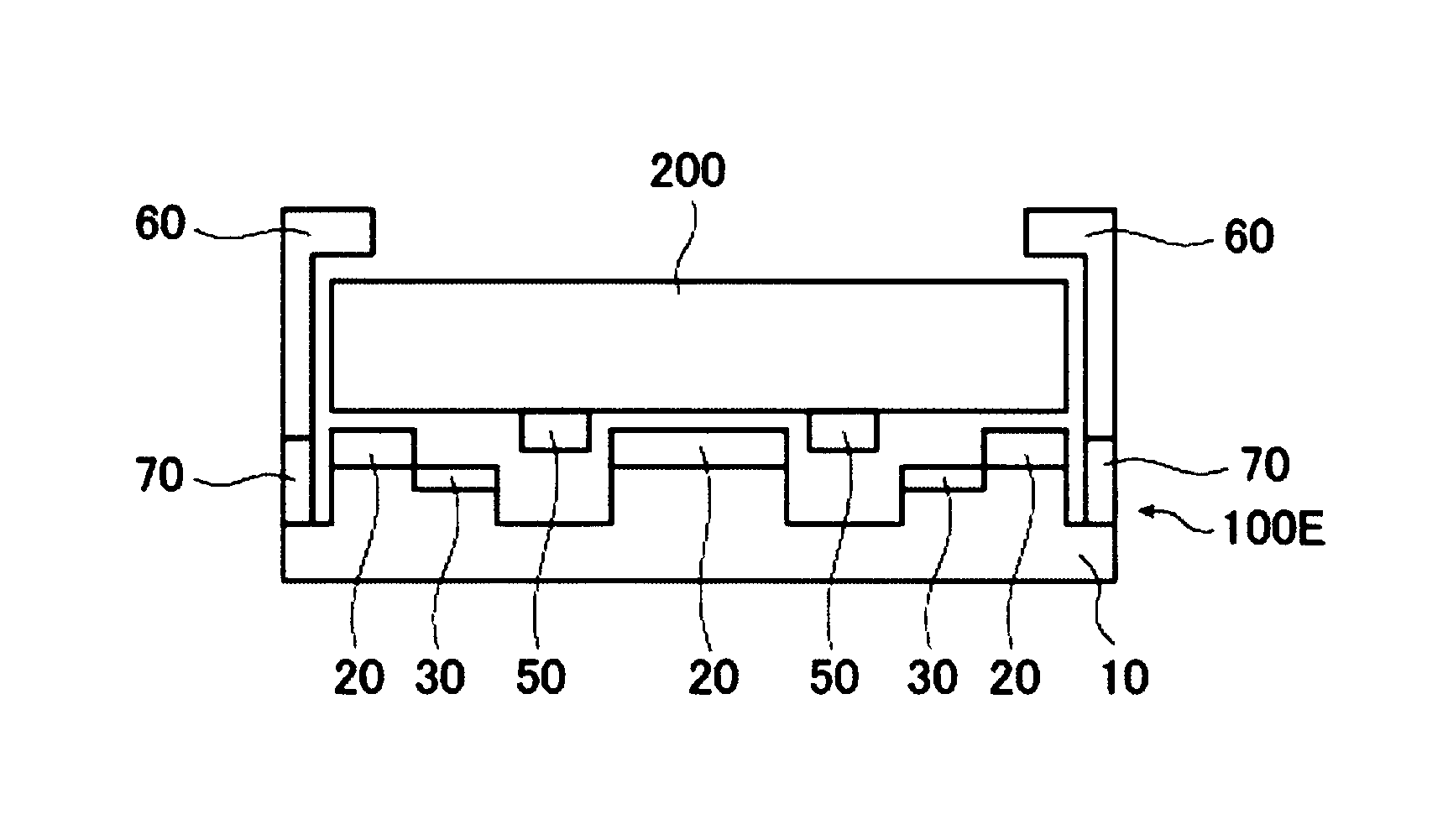

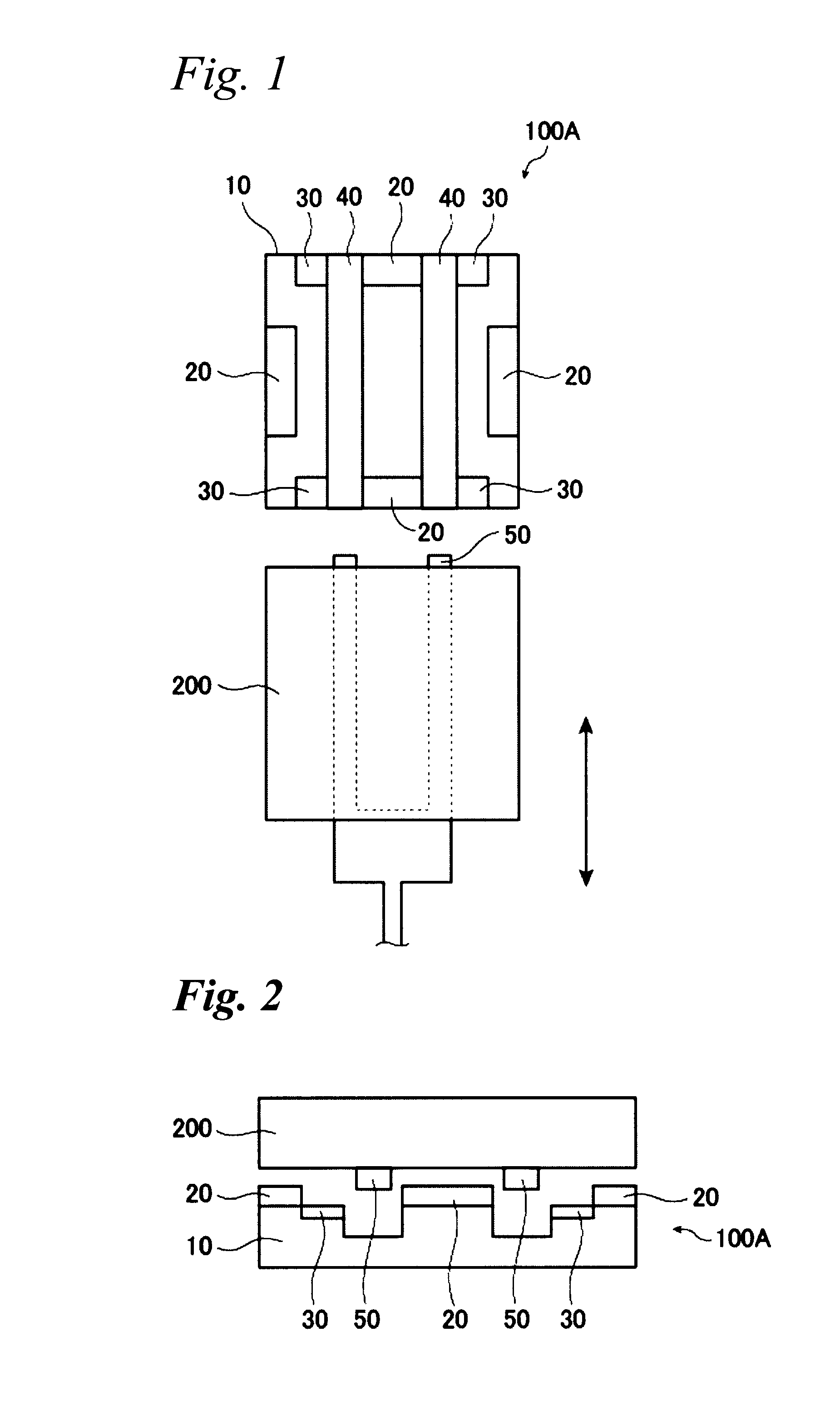

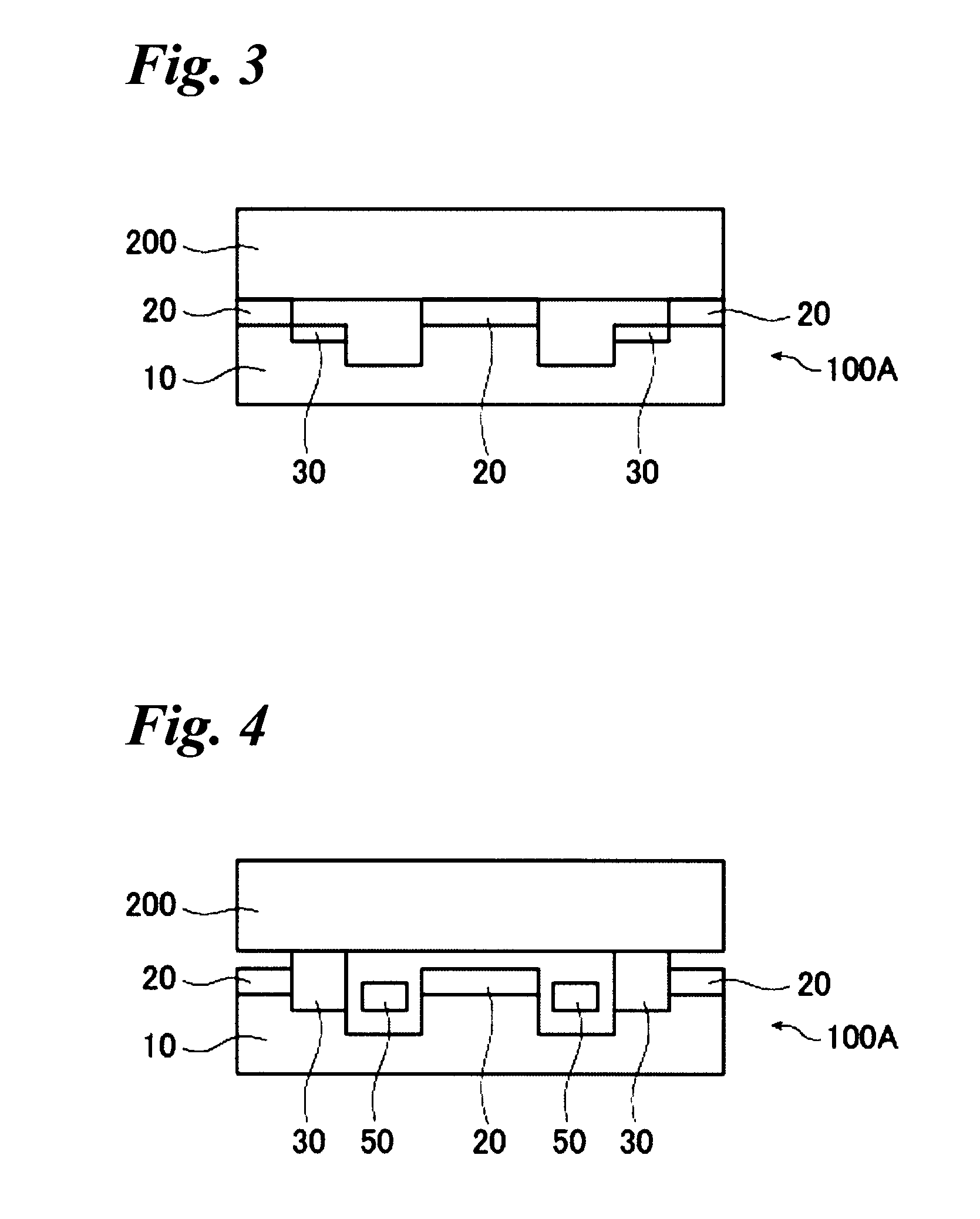

Glass substrate-holding tool

InactiveUS8192901B2Avoid dustAvoid depositionPhotomechanical apparatusSemiconductor/solid-state device manufacturingForeign matterEngineering

Owner:ASAHI GLASS CO LTD

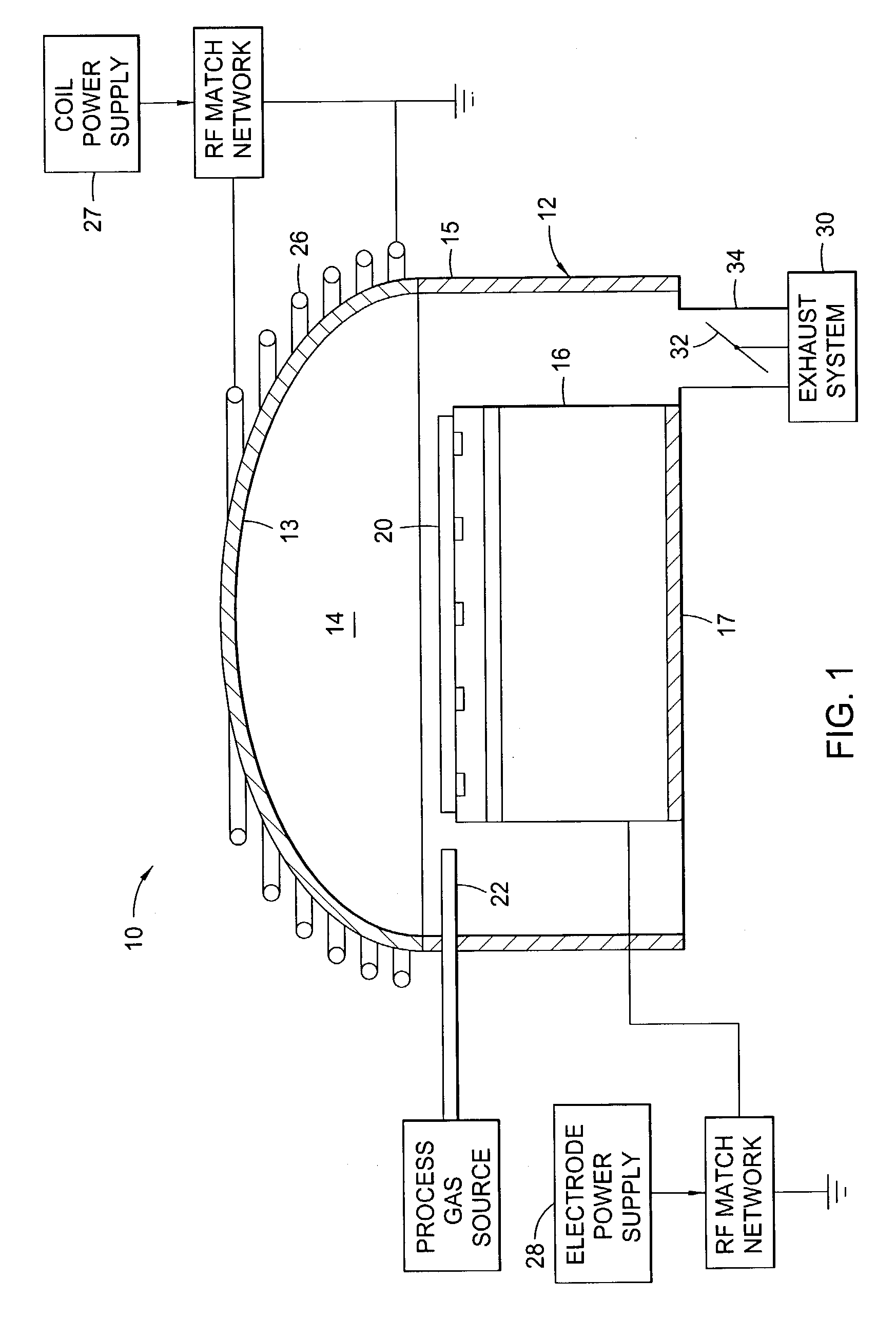

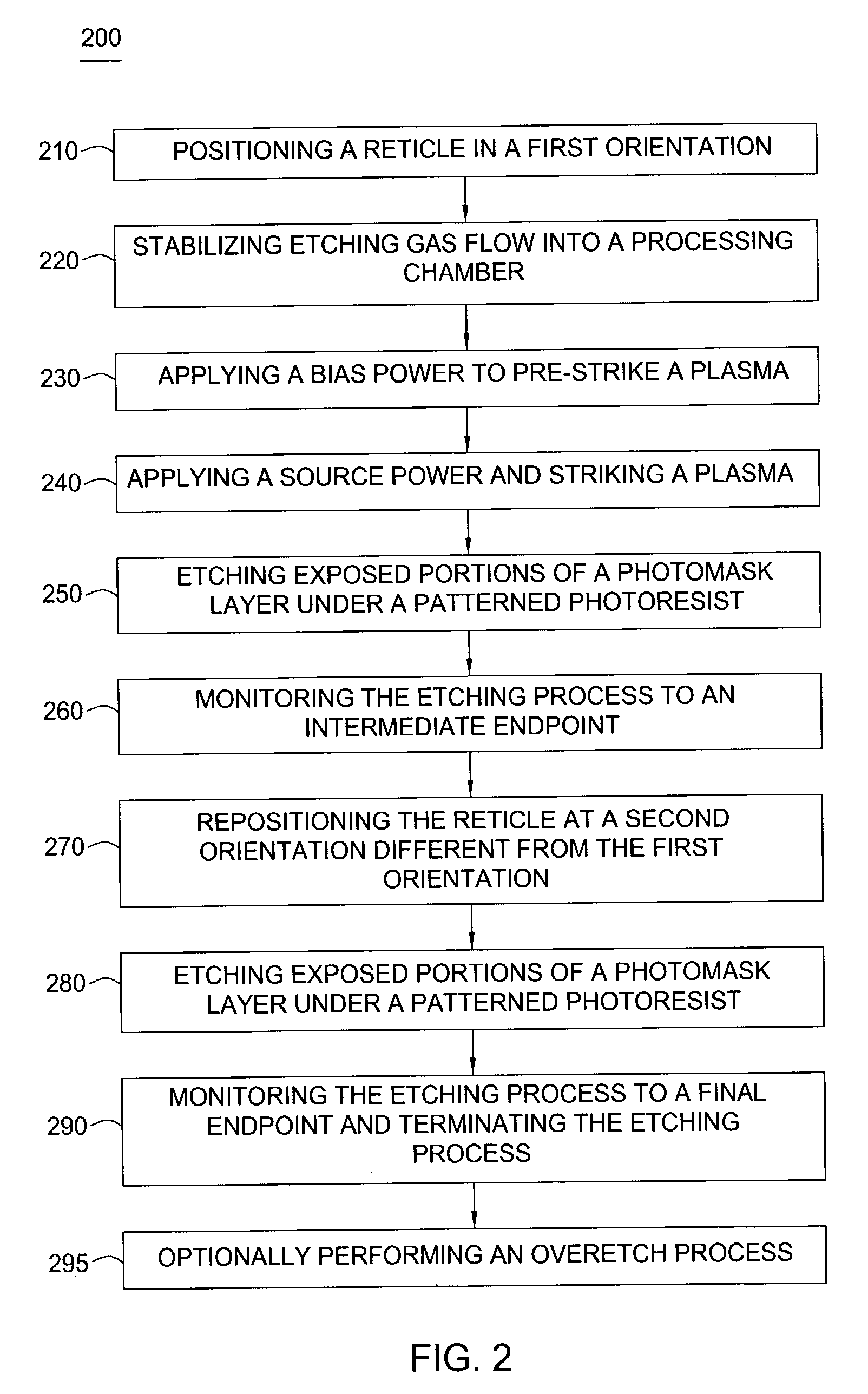

Methods for substrate orientation

Method and apparatus for etching a metal layer disposed on a substrate, such as a photolithographic reticle, are provided. In one aspect, a method is provided for processing a photolithographic reticle including positioning the reticle in a first orientation on a reticle support in a processing chamber, wherein the reticle comprises a metal photomask layer formed on an optically transparent substrate, and a patterned resist material deposited on the metal photomask layer, etching the metal photomask layer in the first orientation, positioning the reticle in at least a second orientation, and etching the metal photomask layer in the at least second orientation.

Owner:APPLIED MATERIALS INC

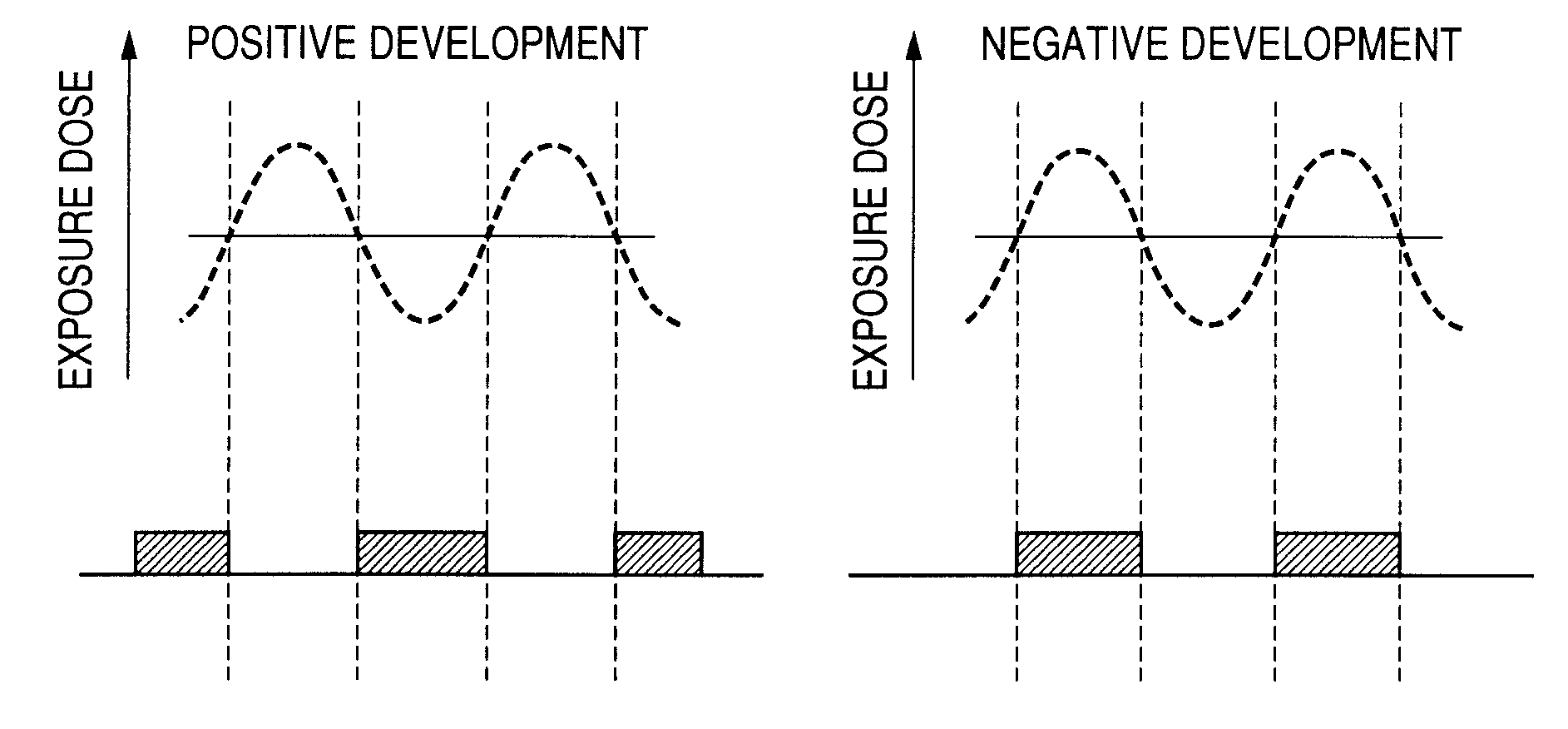

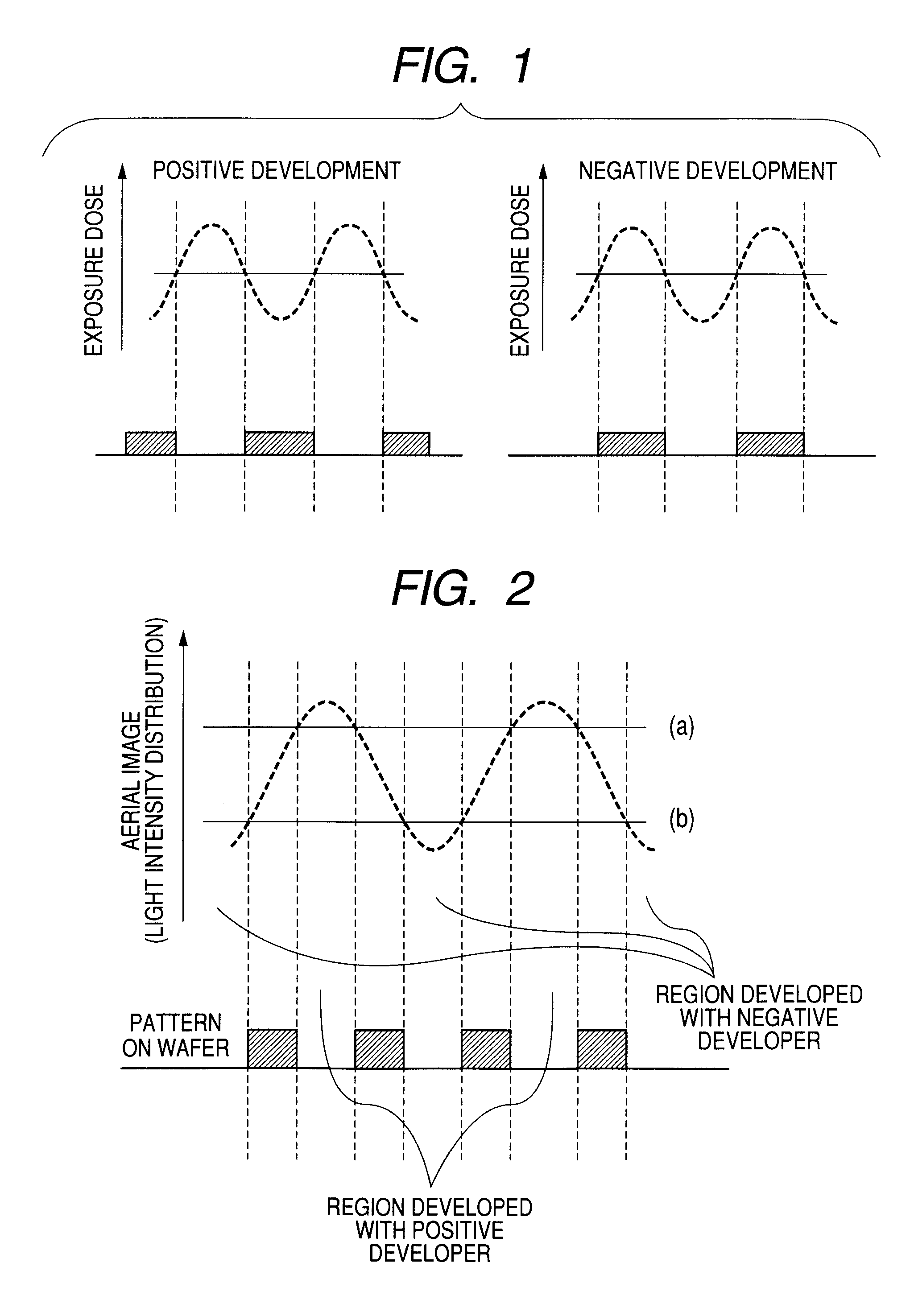

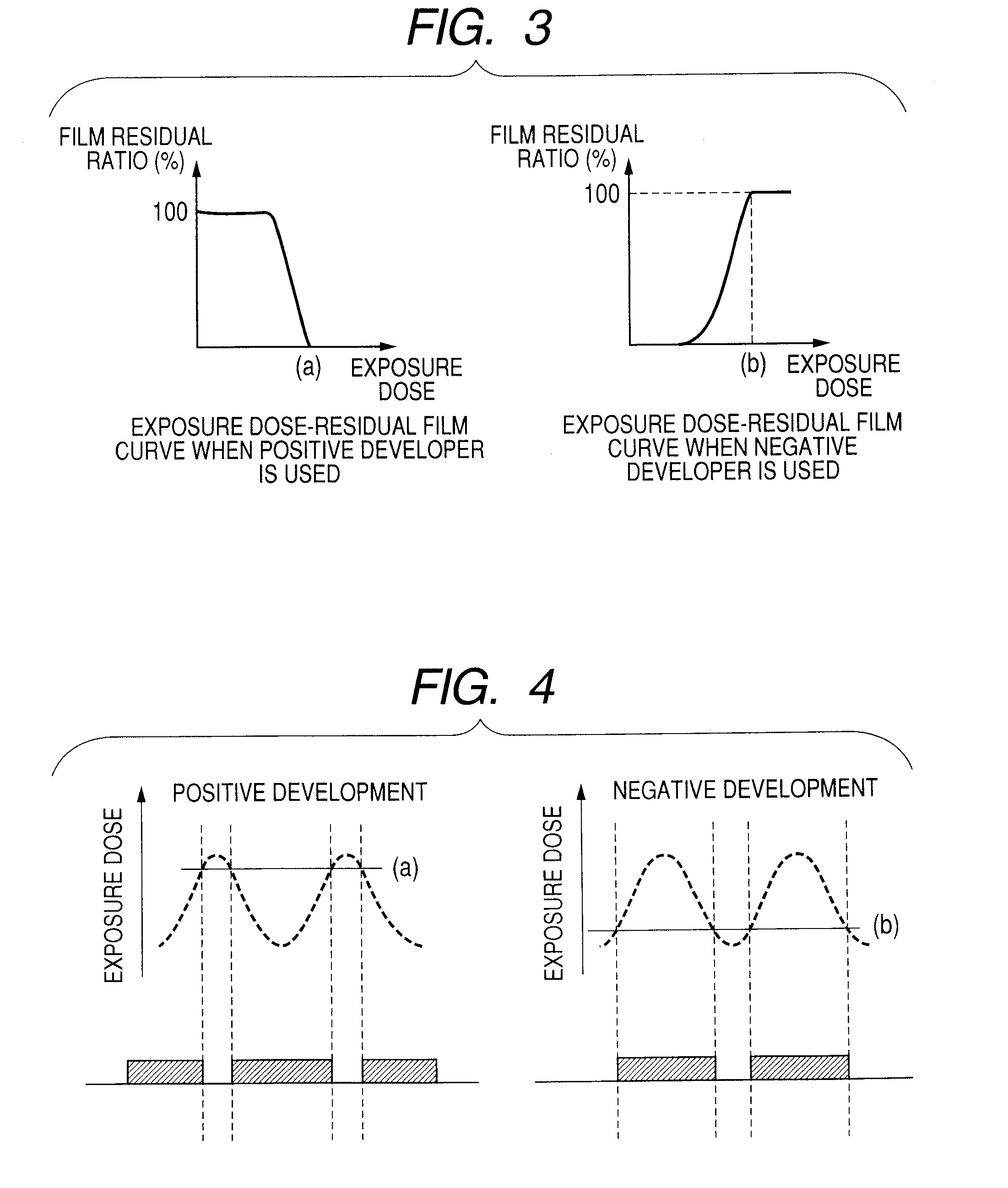

Pattern forming method, resist composition for multiple development used in the pattern forming method, developer for negative development used in the pattern forming method, and rinsing solution for negative development used in the pattern forming method

ActiveUS20080187860A1Improve accuracyMolding stabilityPhotosensitive materialsLayered productsActinic RaysPhotochemistry

A pattern forming method, including: (A) coating a substrate with a positive resist composition of which solubility in a positive developer increases and solubility in a negative developer decreases upon irradiation with actinic rays or radiation, so as to form a resist film; (B) exposing the resist film; and (D) developing the resist film with a negative developer; a positive resist composition for multiple development used in the method; a developer for use in the method; and a rinsing solution for negative development used in the method.

Owner:FUJIFILM CORP

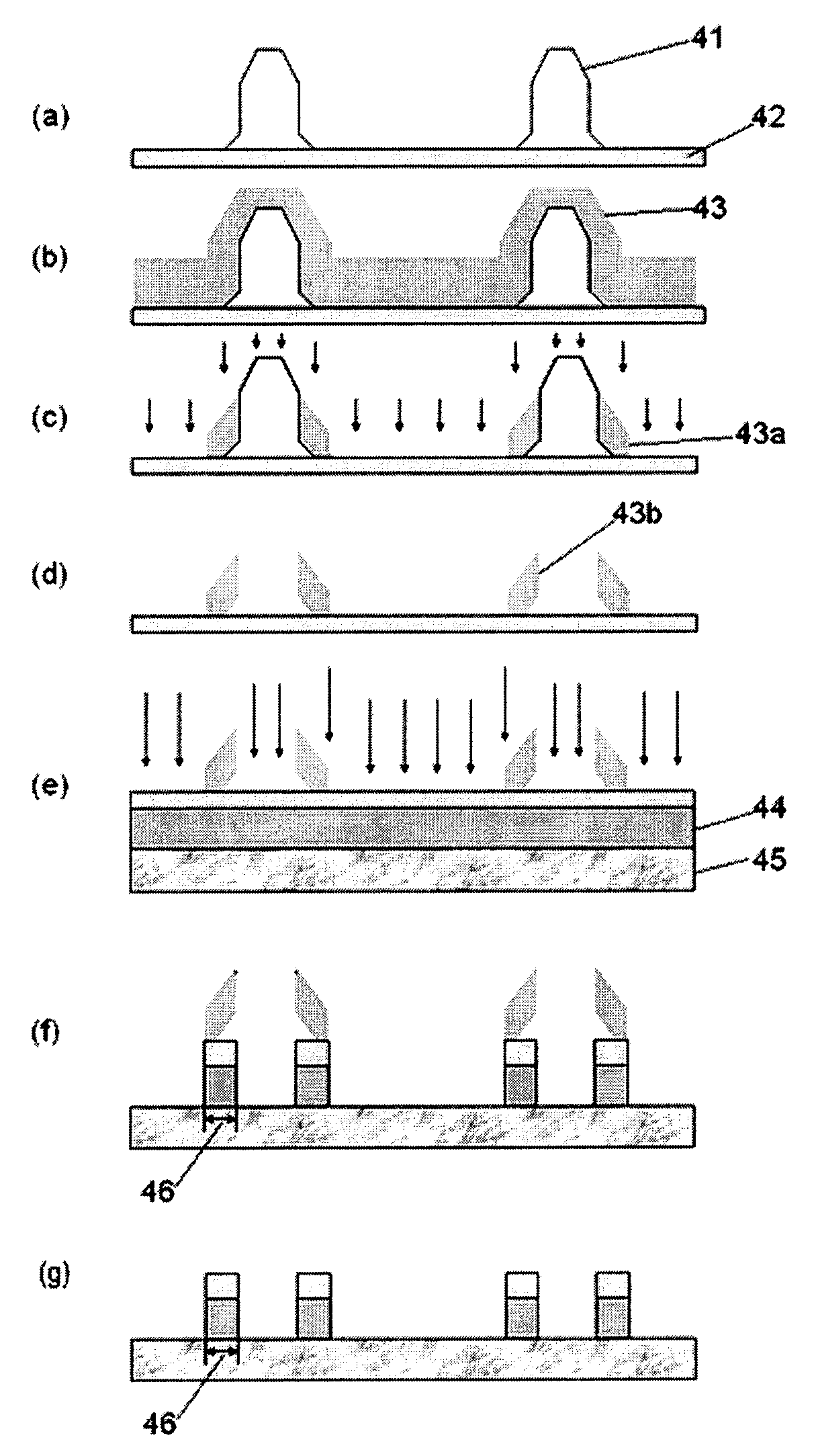

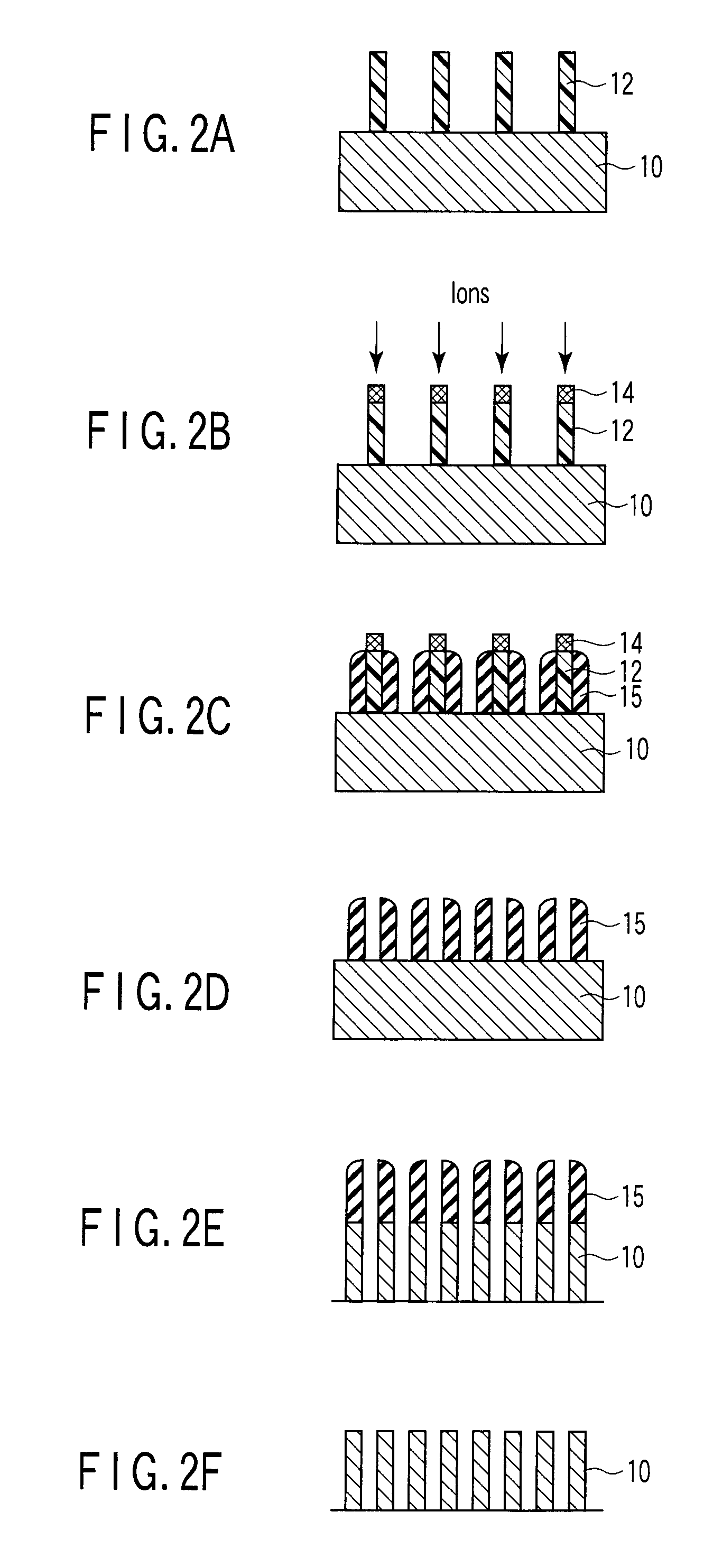

Pattern forming method using relacs process

InactiveUS20080305443A1Semiconductor/solid-state device manufacturingOriginals for photomechanical treatmentResistOrganic film

A resist pattern is formed on a to-be-processed film. Ions are implanted in the upper surface of the resist pattern. After ion implantation, an organic film is formed to cover the resist pattern and heated. A crosslinked resin film made of the organic film which has crosslinked is formed on the sidewall of the resist pattern by developing the organic film after heating. After formation of the crosslinked resin film, the resist pattern is removed. The to-be-processed film is processed using the crosslinked resin film as a mask.

Owner:KK TOSHIBA

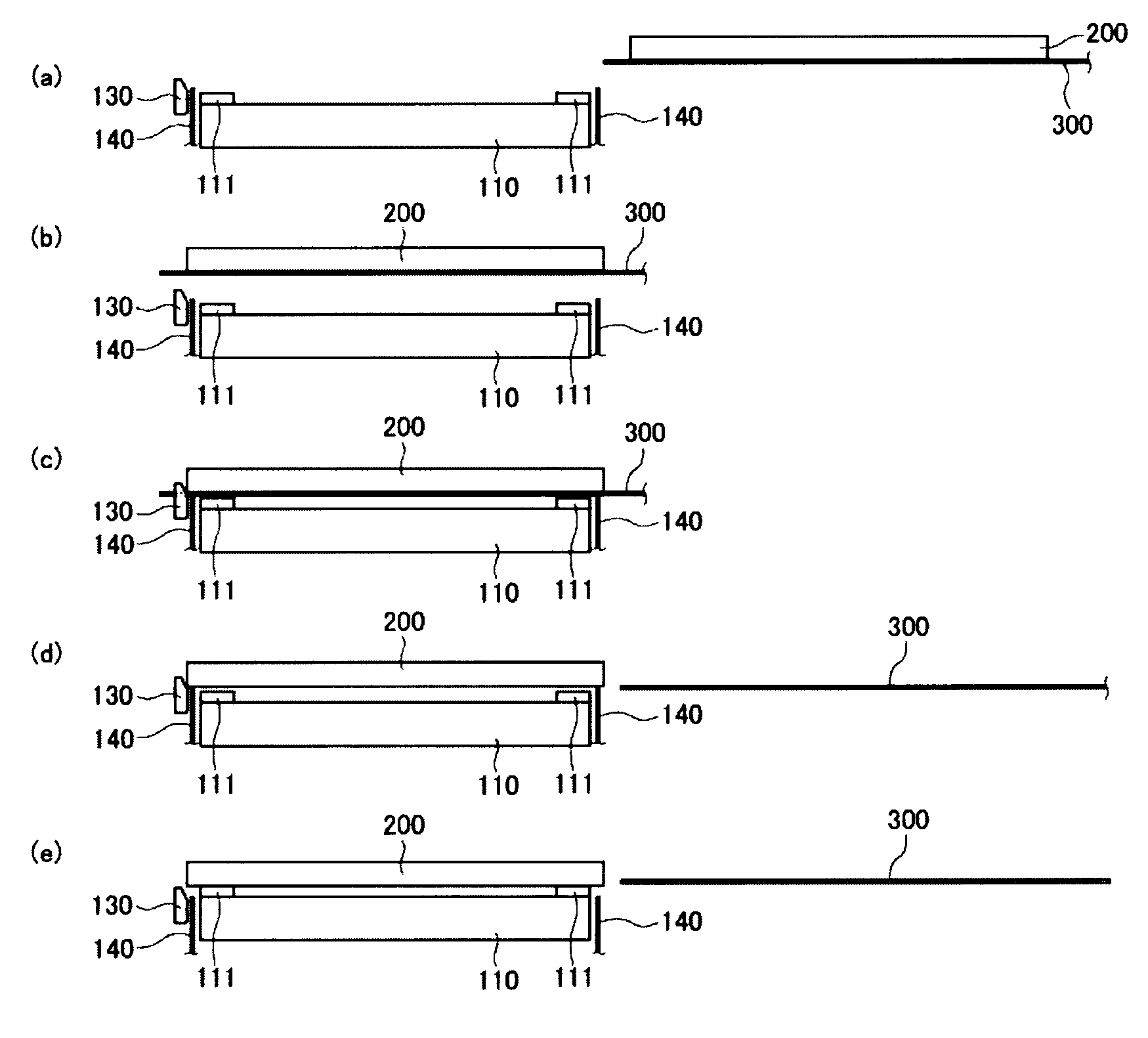

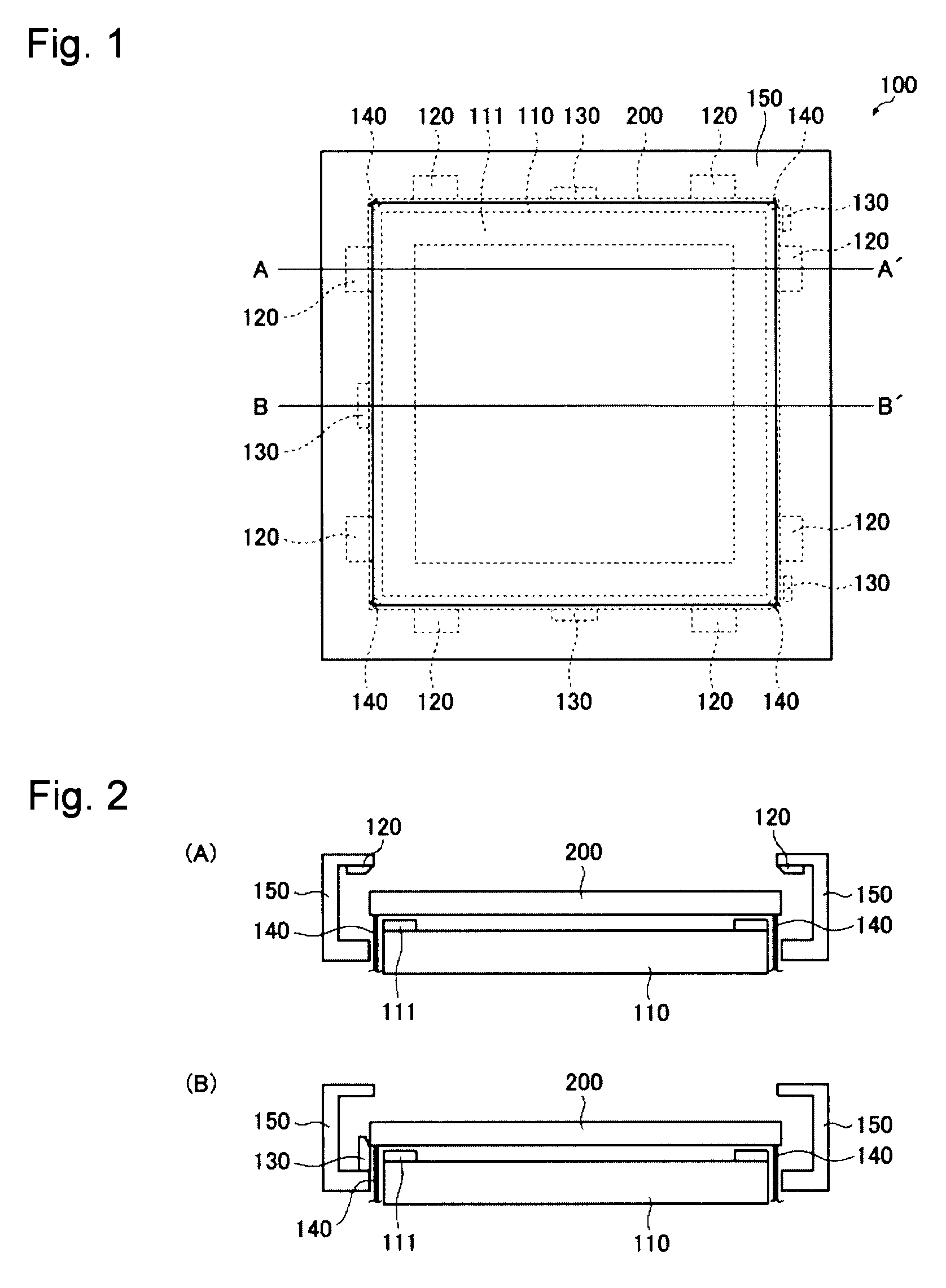

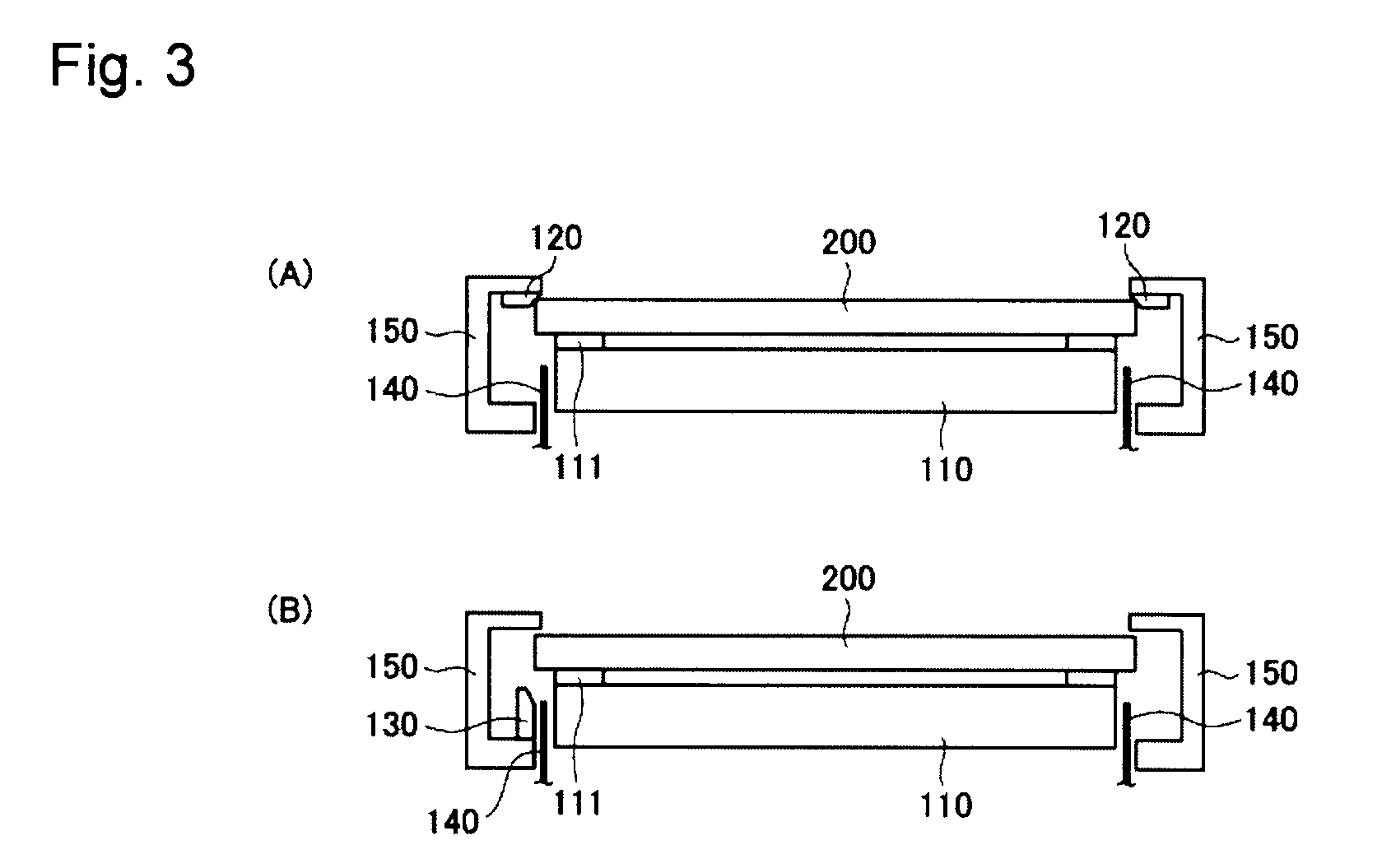

Glass substrate-holding tool and method for producing an EUV mask blank by employing the same

InactiveUS8967608B2InhibitionAccurate placementWorkpiece holdersVacuum evaporation coatingLithographic artistMaterials science

A glass substrate-holding tool employed during the production of a reflective mask blank for EUV lithography includes an electrostatic chuck and a mechanical chuck. A caught and held portion of a glass substrate caught and held by the electrostatic chuck, and pressed portions of the glass substrate pressed by the mechanical chuck are located outside a quality-guaranteed region on each of a film deposition surface and a rear surface of the glass substrate. The sum of a catching and holding force applied to the glass substrate by the electrostatic chuck and a holding force applied to the glass substrate by the mechanical chuck is at least 200 kgf. A pressing force per unit area applied to the glass substrate by the mechanical chuck is at most 25 kgf / mm2.

Owner:ASAHI GLASS CO LTD

Glass substrate-holding tool

InactiveUS20120100464A1Avoid dustAvoid depositionSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusEngineeringScratching

To provide a glass substrate-holding tool which is capable of avoiding scratching to the deposition surface of a glass substrate and dusting thereby caused as well as scratching and deposition of foreign substances at a center portion of the rear surface of the substrate and which is capable of suppressing dusting from the holding tool itself at the time of forming a multi-layered reflection film and an absorptive layer.A glass substrate-holding tool having, formed on a surface of a flat base, a catching portion for catching and holding by van der Waals forces, wherein the catching portion is in contact with only the periphery of the glass substrate.

Owner:ASAHI GLASS CO LTD

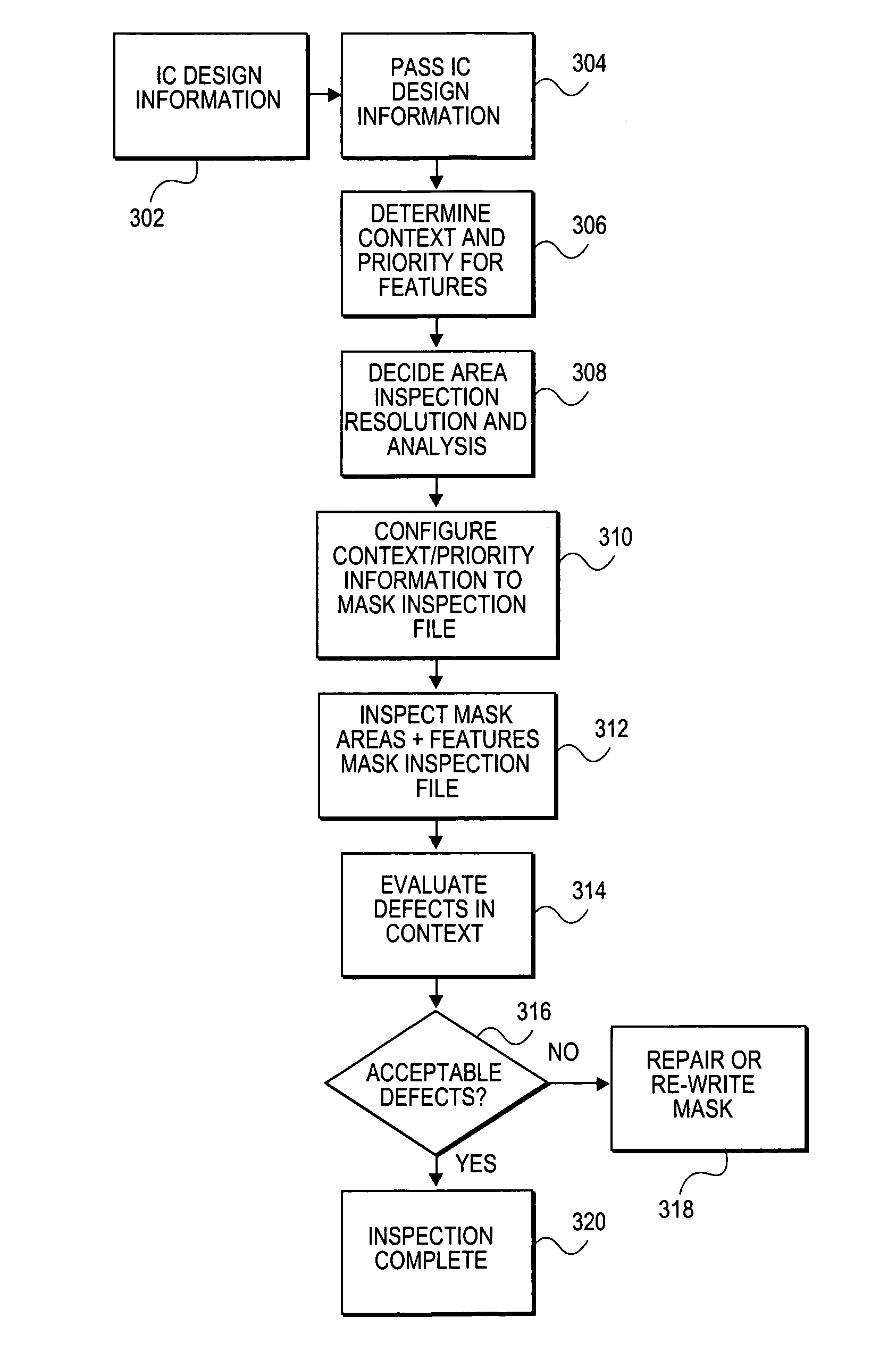

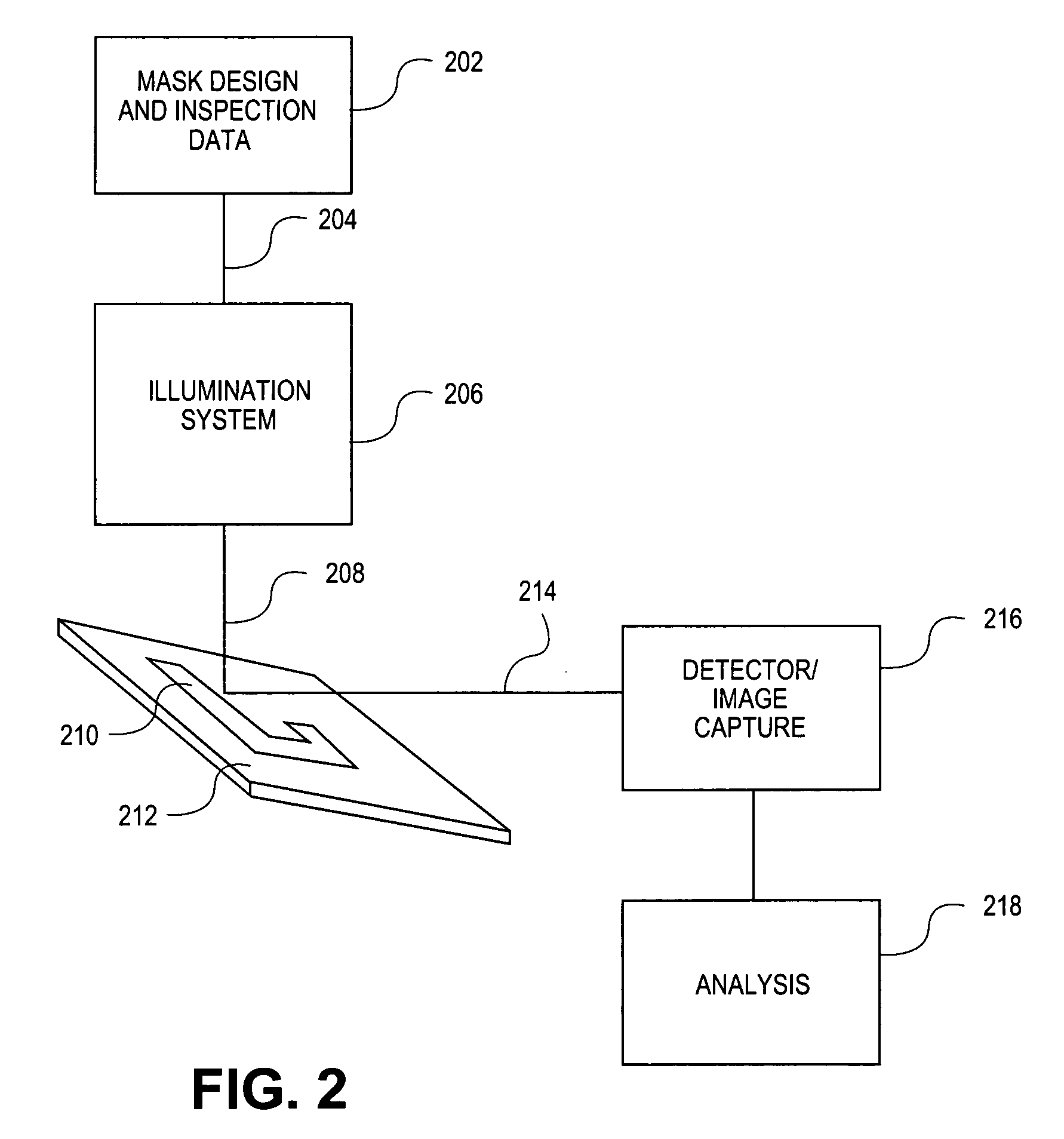

Method and system for context-specific mask inspection

InactiveUS7231628B2Electrical testingCharacter and pattern recognitionMask inspectionContext specific

A method for inspecting lithography masks includes generating integrated circuit design data and using context information from the integrated circuit design data to inspect a mask.

Owner:CADENCE DESIGN SYST INC

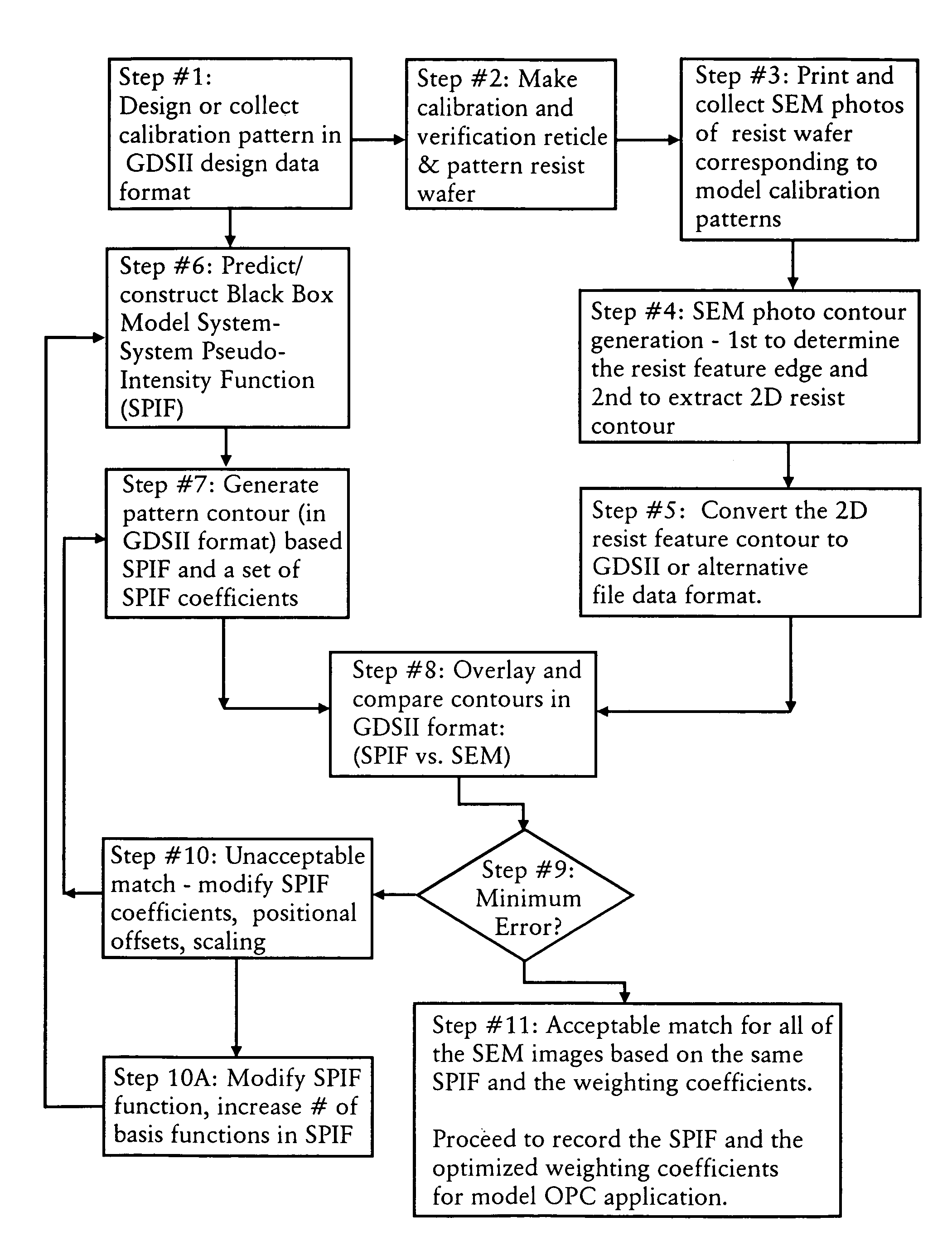

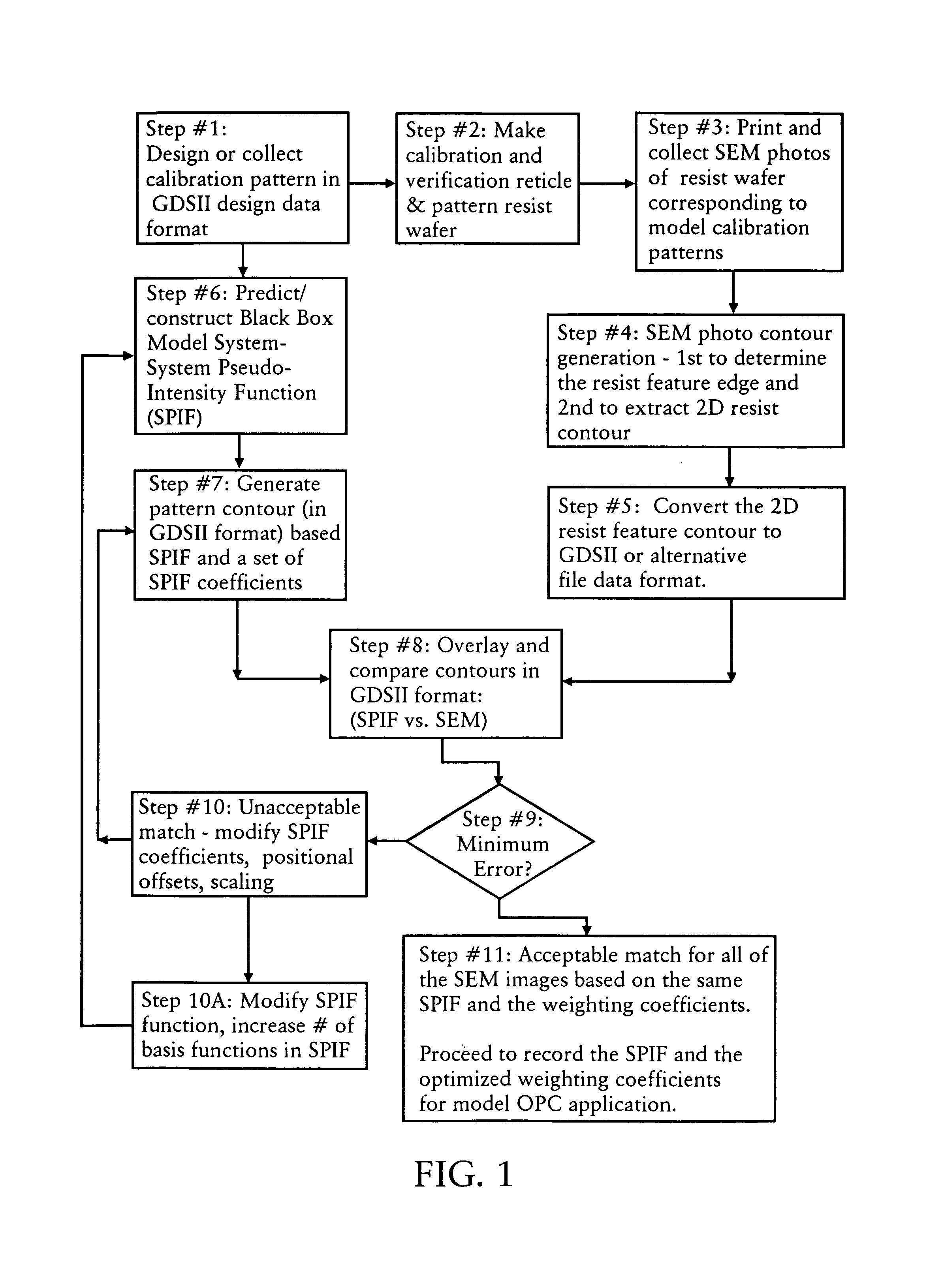

Method of two dimensional feature model calibration and optimization

InactiveUS7175940B2Minimize proximity effectAccurate performanceSemiconductor/solid-state device manufacturingCharacter and pattern recognitionPattern recognitionData format

A method for generating a photolithography mask for optically transferring a pattern formed in the mask onto a substrate utilizing an imaging system. The method includes the steps of: (a) defining a set of calibration patterns, which are represented in a data format; (b) printing the calibration patterns on a substrate utilizing the given imaging system; (c) determining a first set of contour patterns corresponding to the calibration patterns imaged on the substrate; (d) generating a system pseudo-intensity function, which approximates the imaging performance of the imaging system; (e) determining a second set of contour patterns by utilizing the system pseudo-intensity function to define how the calibration patterns will be imaged in the substrate; (f) comparing the first set of contour patterns and the second set of contour patterns to determine the difference therebetween; (g) adjusting the system pseudo-intensity function until the difference between the first set of contour patterns and the second set of contour patterns is below a predefined criteria; and (h) utilizing the adjusted system pseudo-intensity function to modify the mask so as to provide for optical proximity correction.

Owner:ASML NETHERLANDS BV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com