Patents

Literature

869 results about "Logic element" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

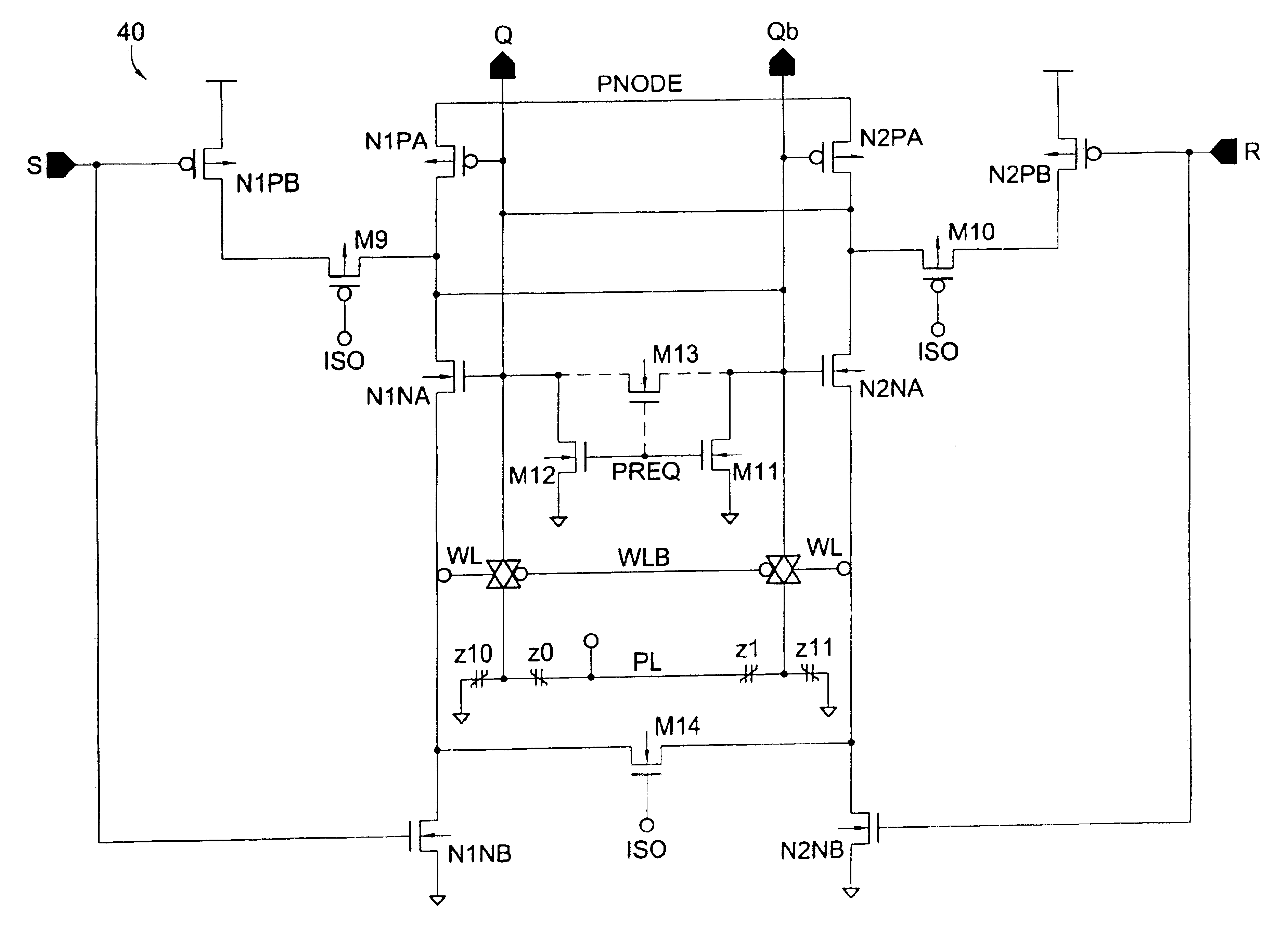

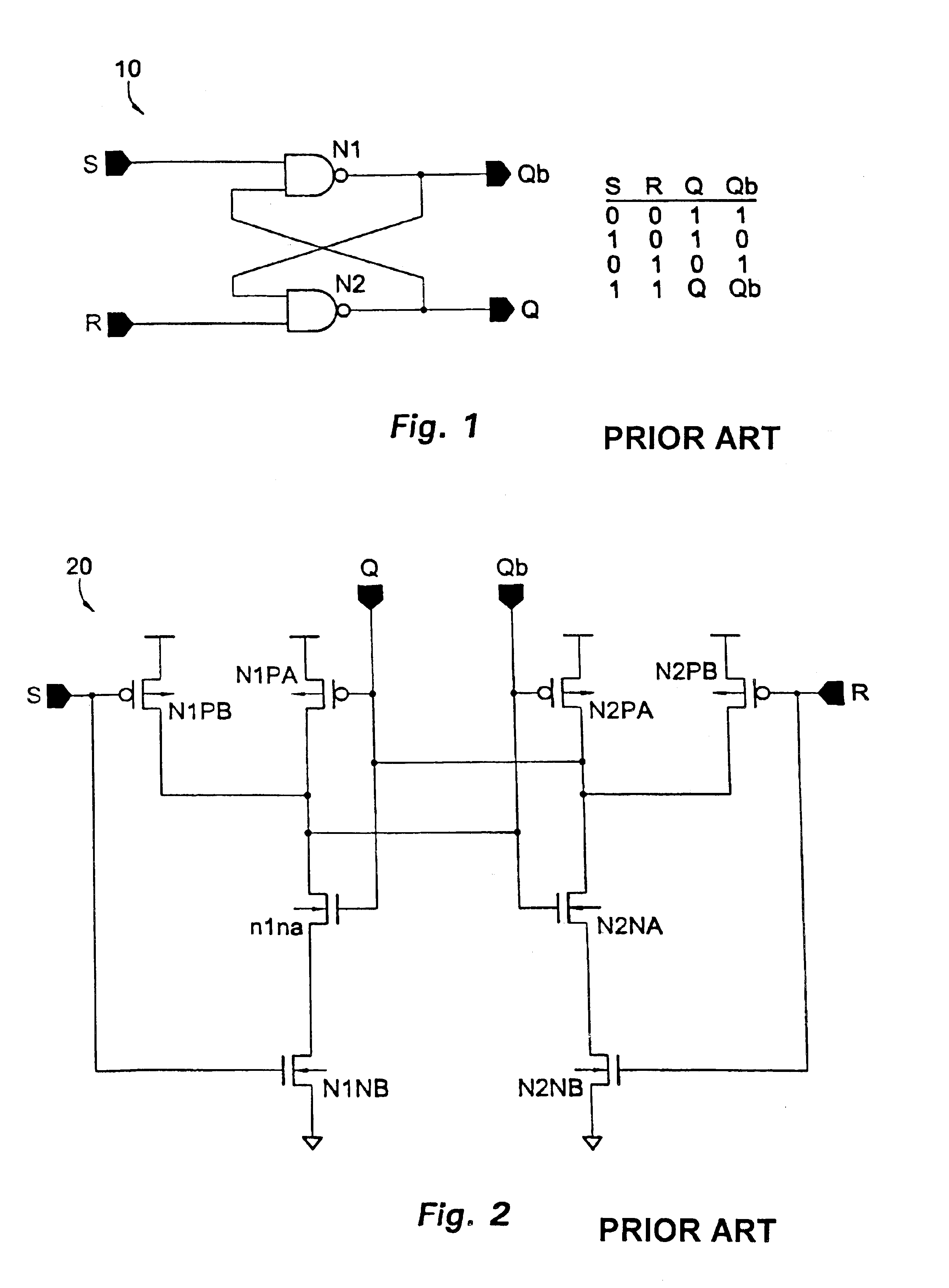

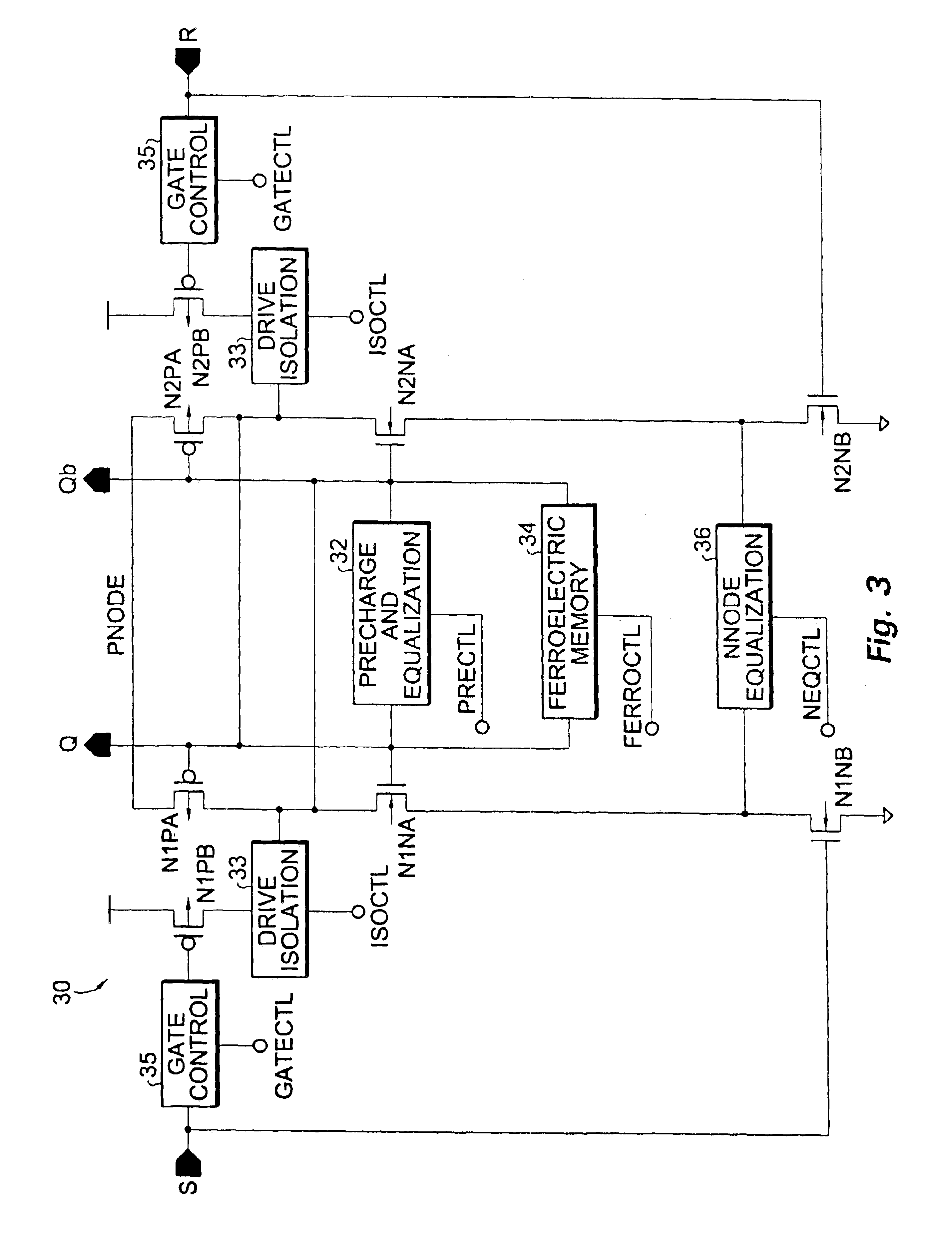

Ferroelectric non-volatile logic elements

InactiveUS6894549B2Easy translationImprove performanceTransistorPulse generation by non-linear magnetic/dielectric devicesShift registerAudio power amplifier

Various logic elements such as SR flip-flops, JK flip-flops, D-type flip-flops, master-slave flip-flops, parallel and serial shift registers, and the like are converted into non-volatile logic elements capable of retaining a current output logic state even though external power is removed or interrupted through the strategic addition of ferroelectric capacitors and supporting circuitry. In each case, the building blocks of a cross-coupled sense amplifier are identified within the logic element and the basic cell is modified and / or optimized for sensing performance.

Owner:MONTEREY RES LLC

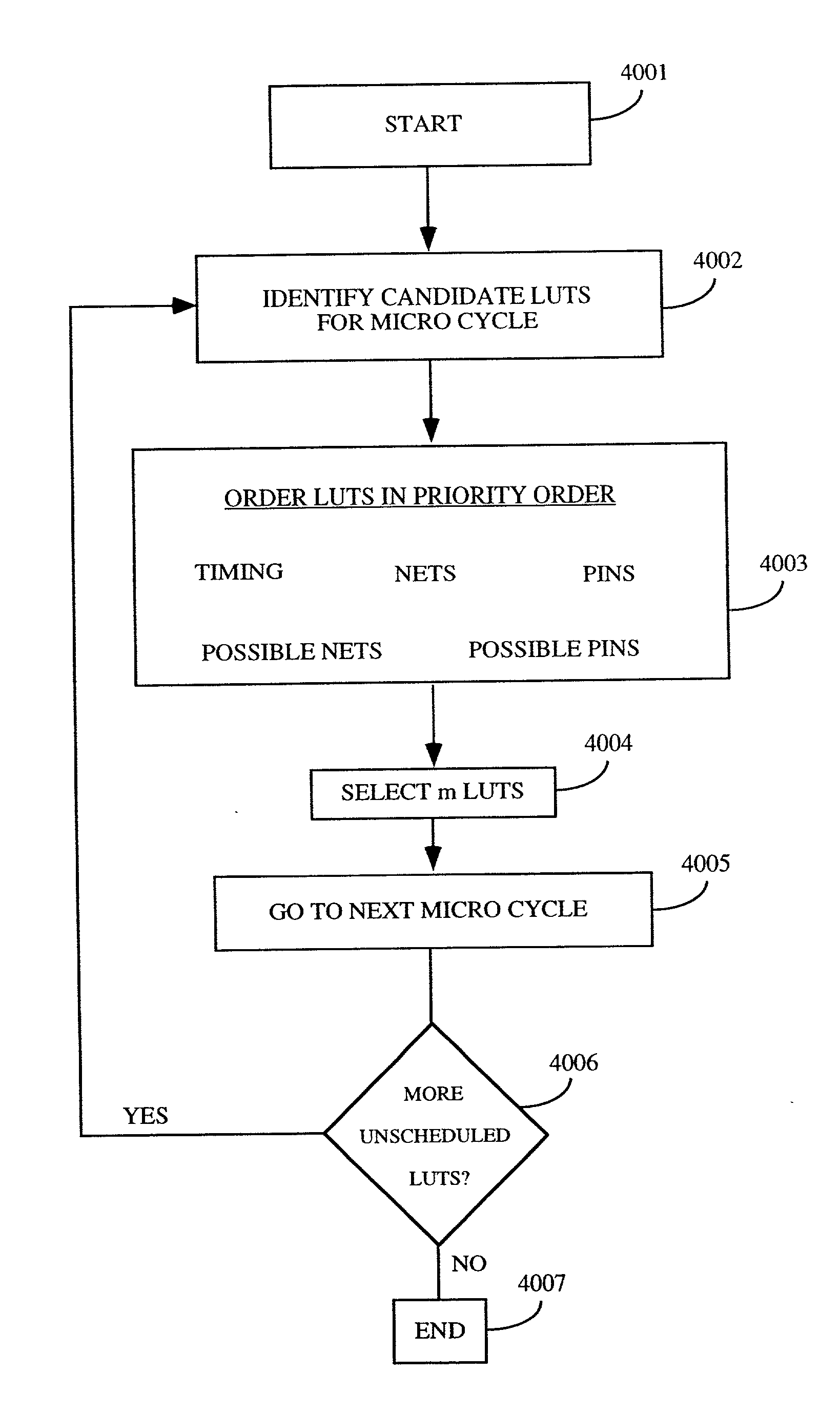

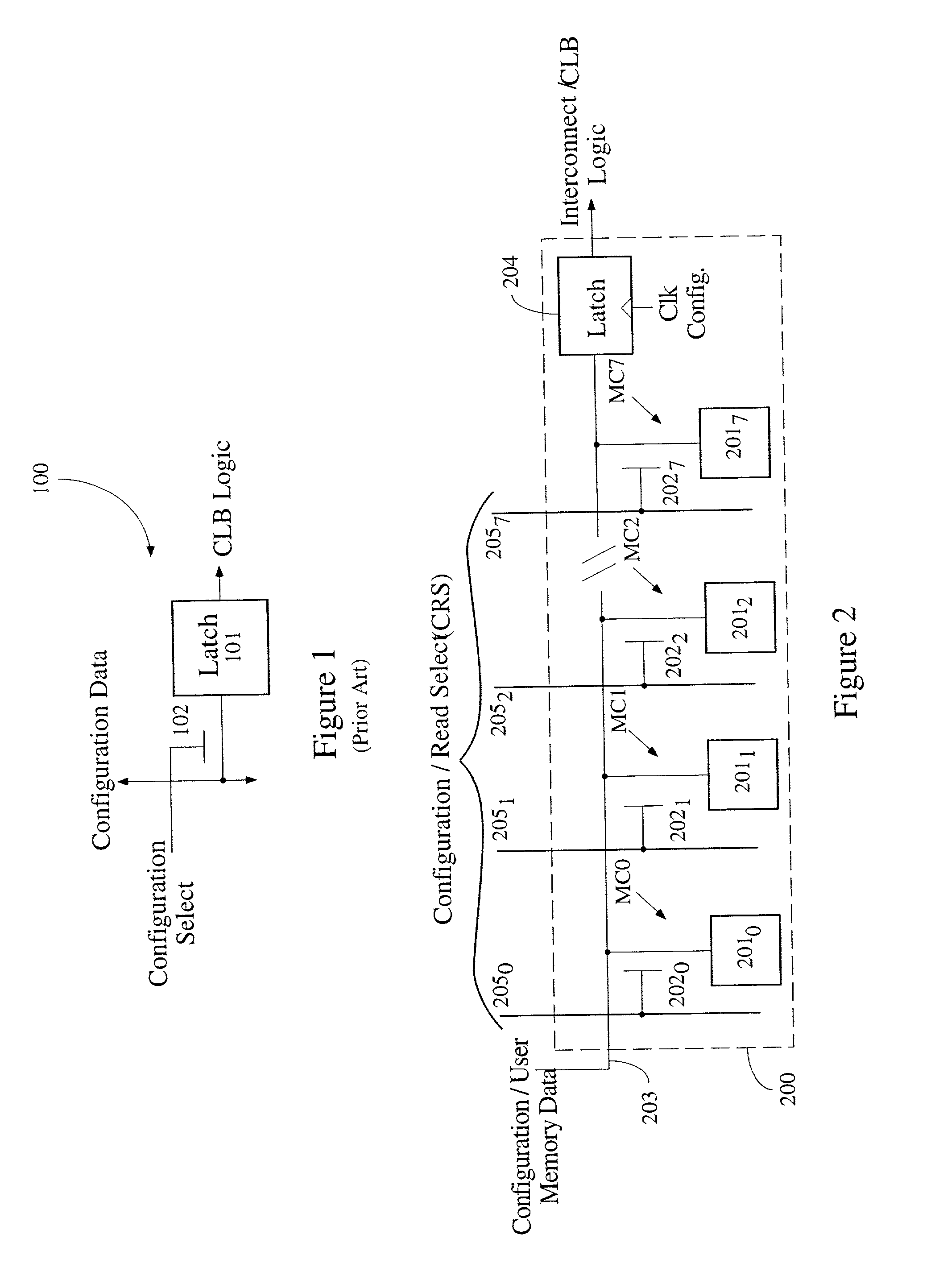

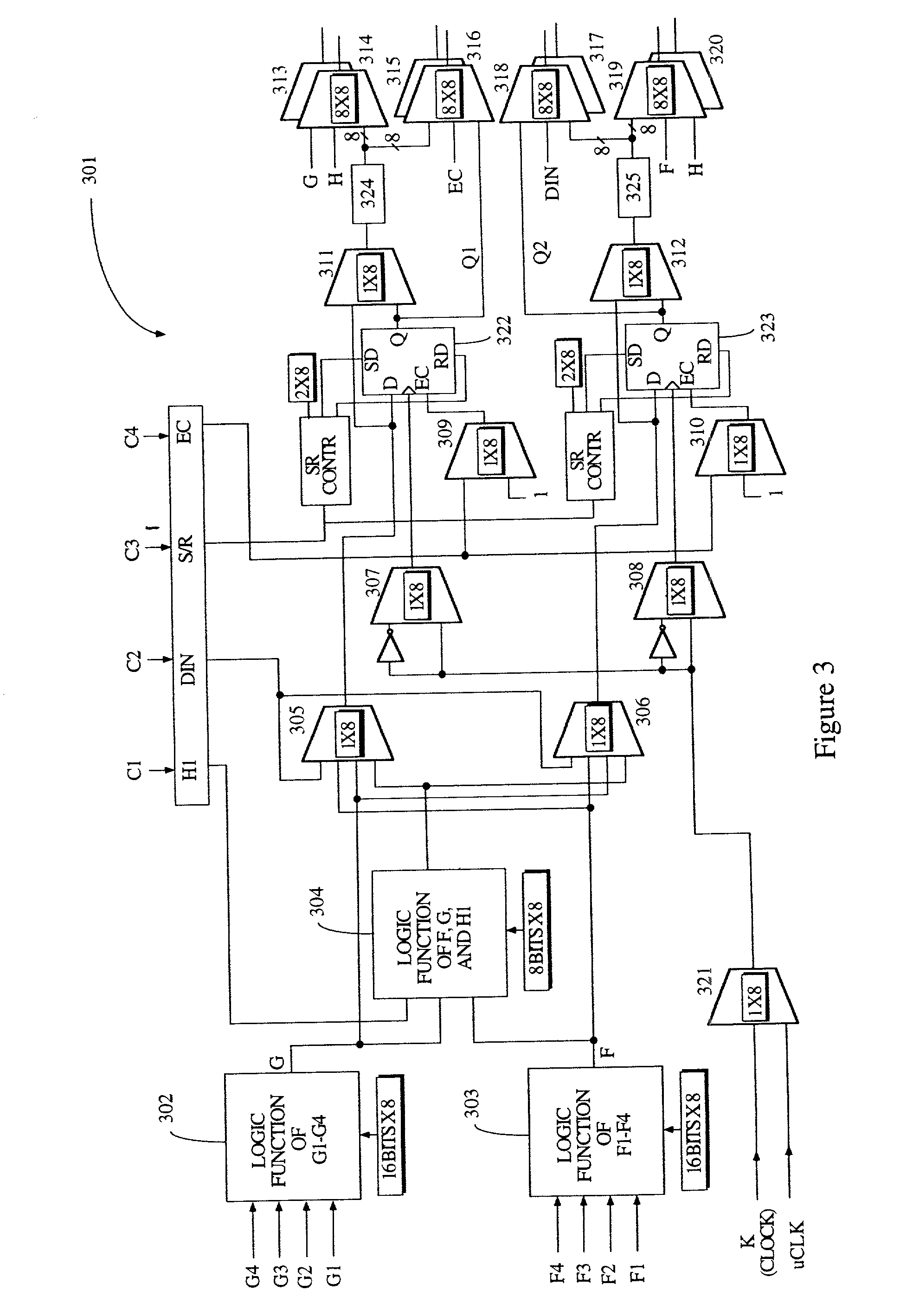

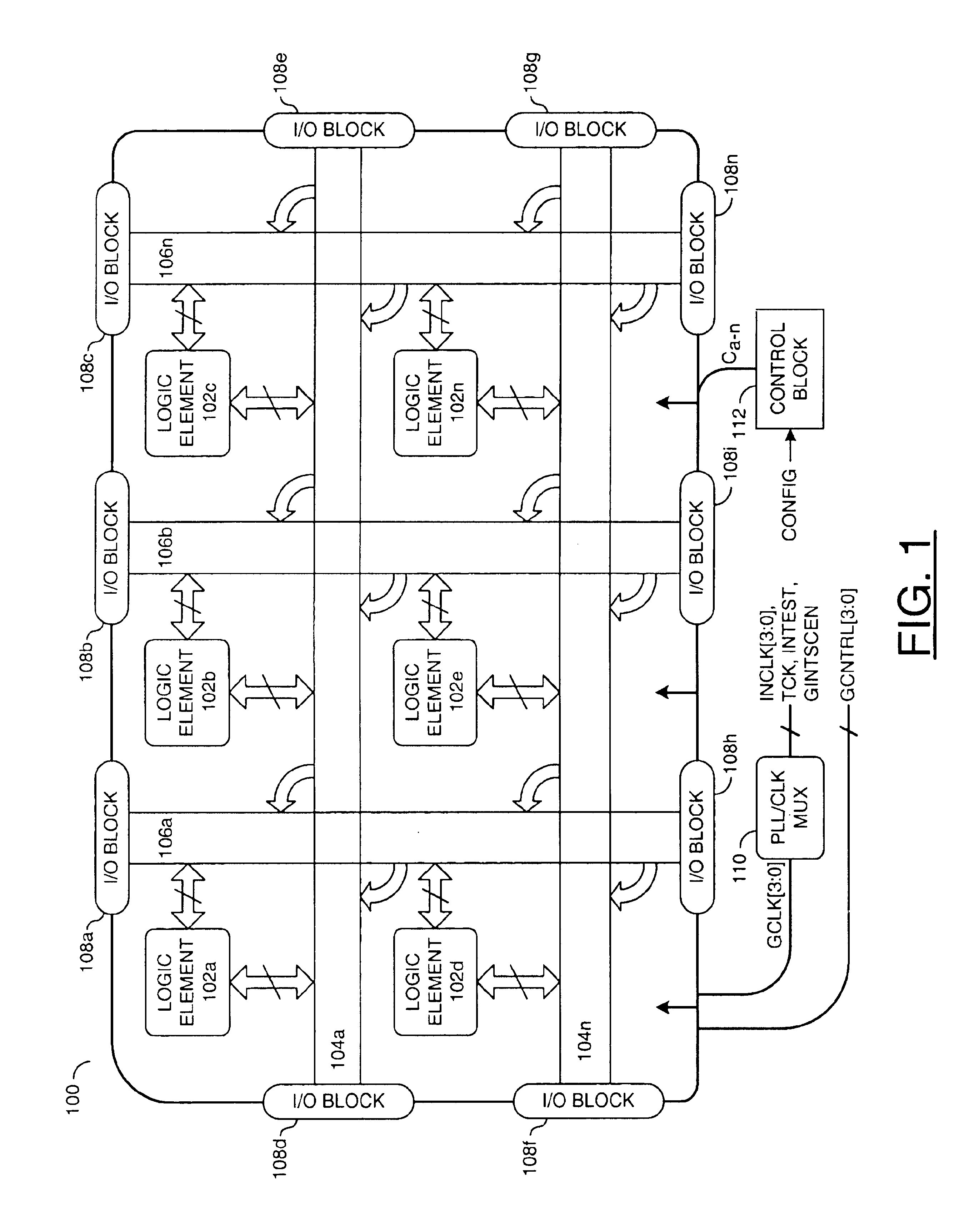

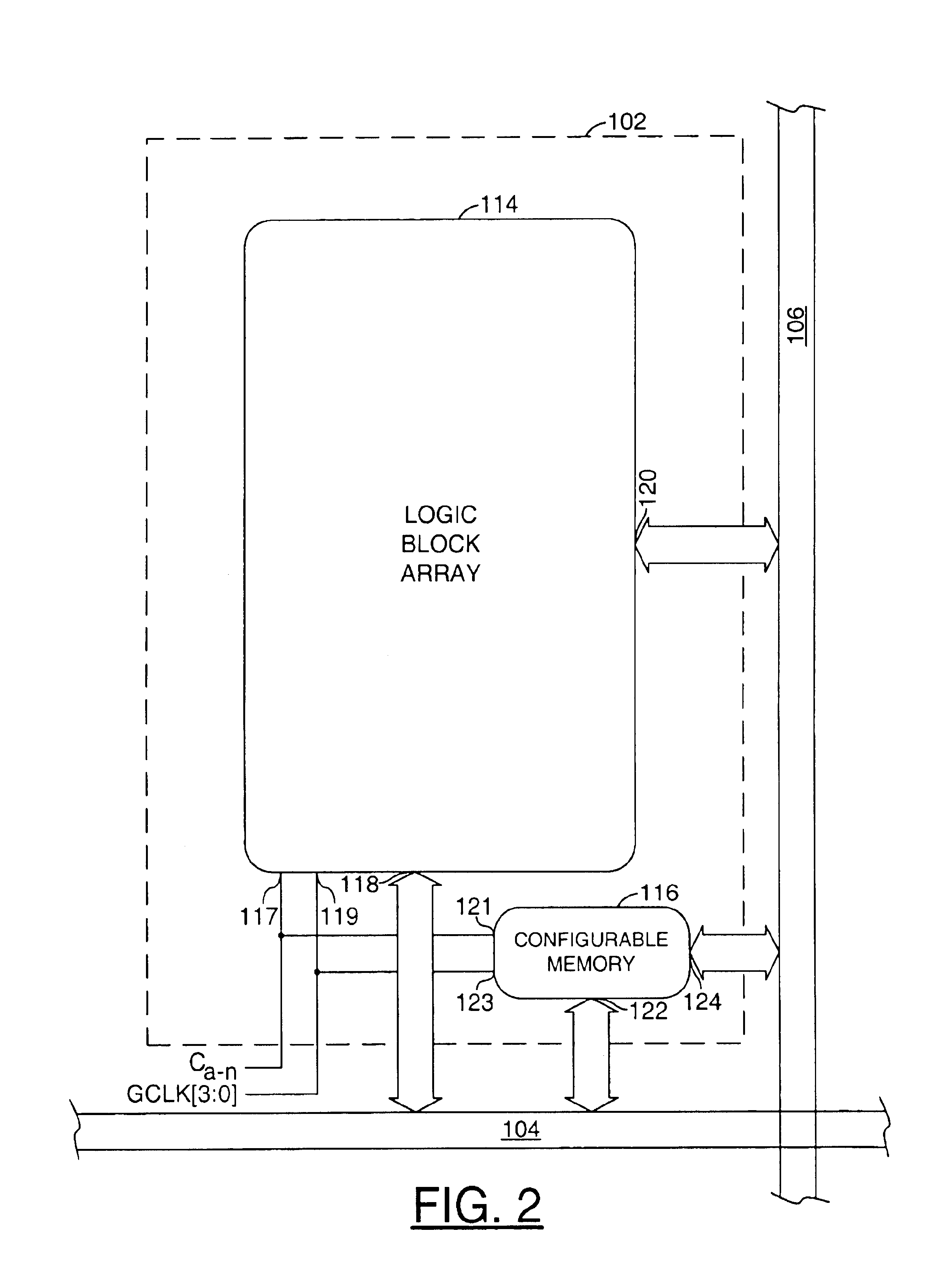

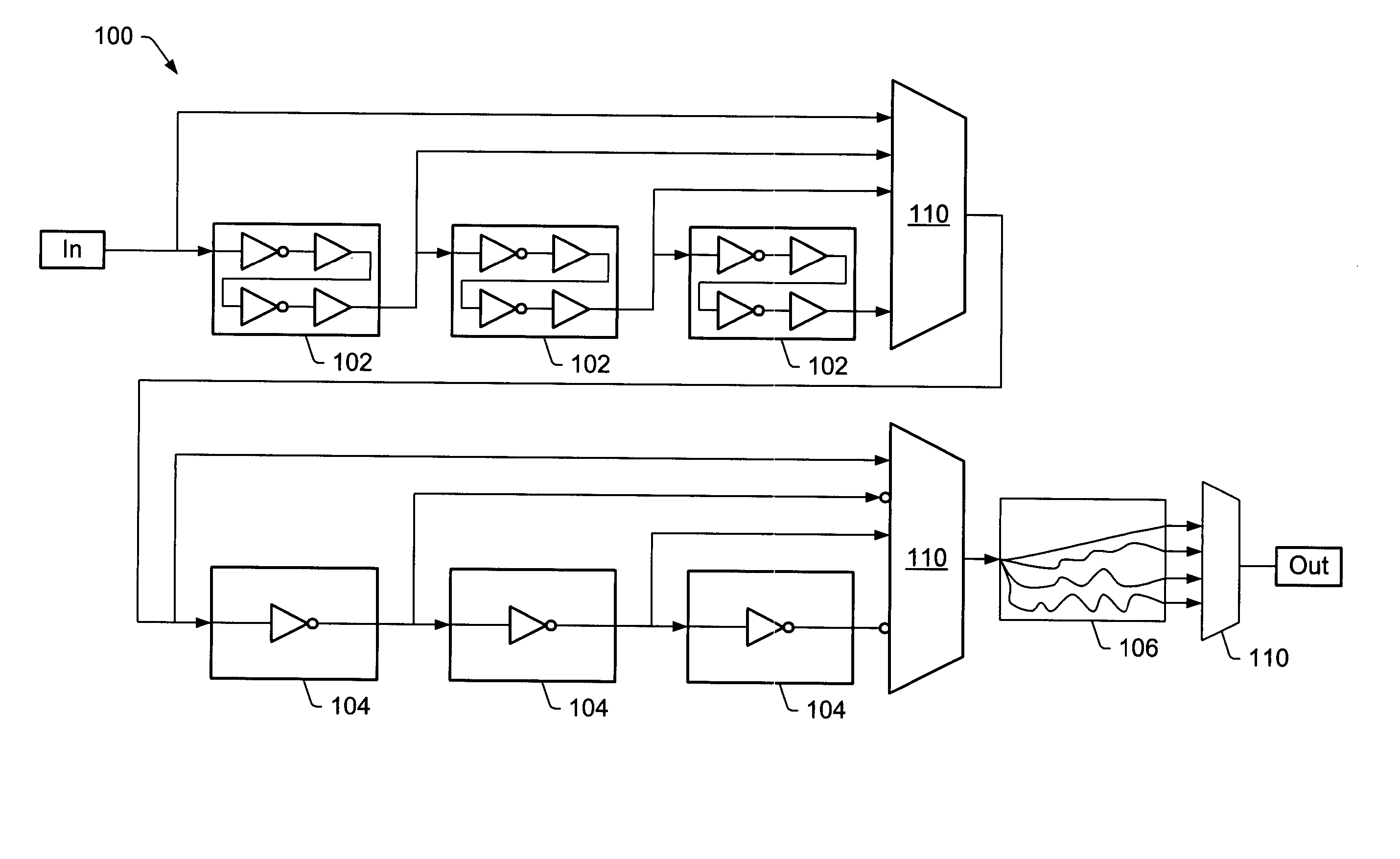

Method of time multiplexing a programmable logic device

InactiveUS20020010853A1Reduce in quantityEasy to reuseDigital computer detailsData resettingProgrammable logic deviceLogic element

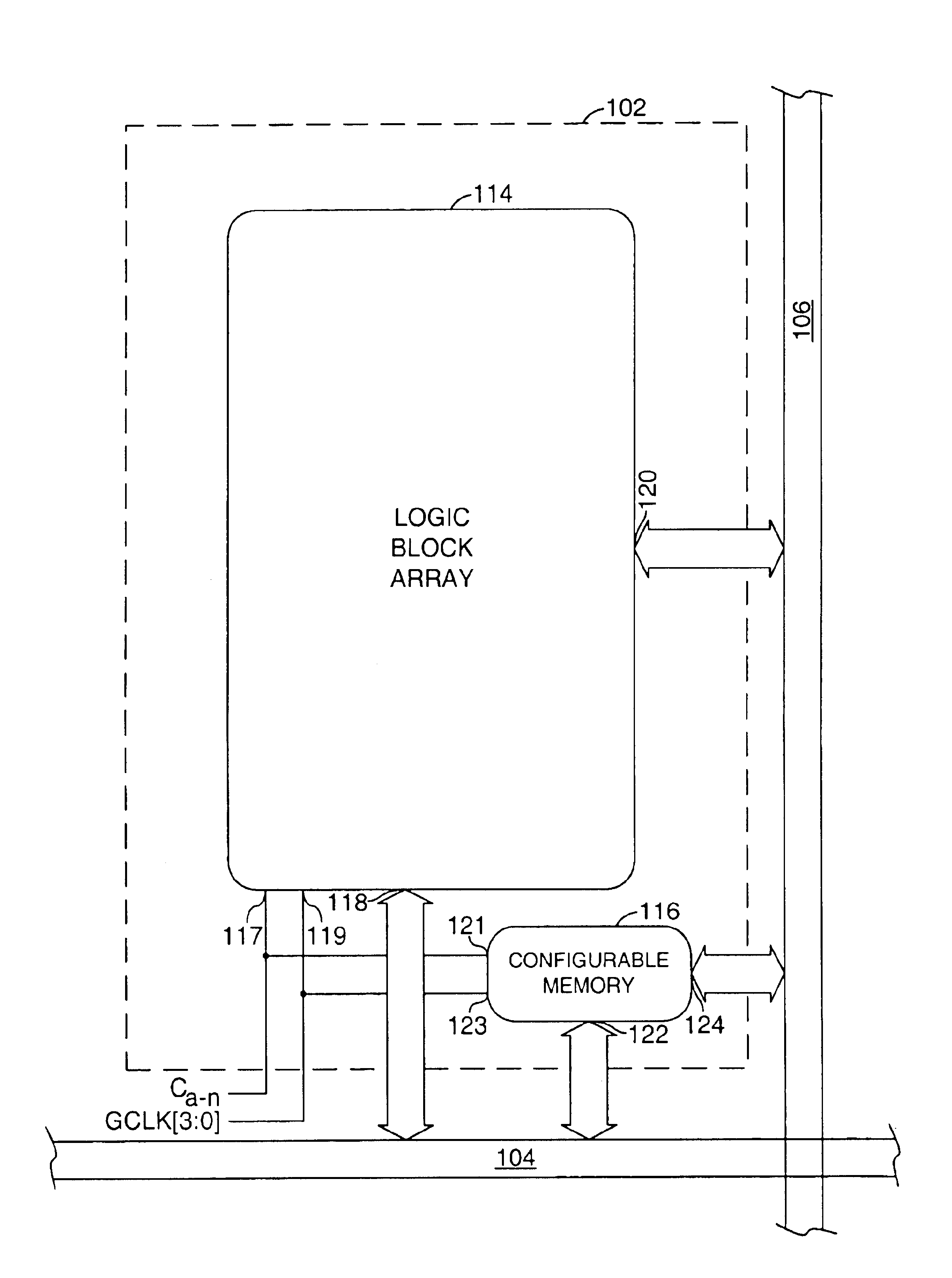

A programmable logic device (PLD) comprises at least one configurable element, and a plurality of programmable logic elements for configuring the configurable element(s). Alternatively, a PLD comprises an interconnect structure and a plurality of programmable logic elements for configuring the interconnect structure. In either embodiment, at least one of the programmable logic elements includes N memory cells. A predetermined one of the N memory cells forms part of a memory slice, wherein at least a portion of each slice of the programmable logic device is allocated to either configuration data or user data memory. Typically, one memory slice provides one configuration of the programmable logic device. In accordance with one embodiment, a memory access port is coupled between at least one of the N memory cells and either one configurable element or the interconnect, thereby facilitating loading of new configuration data into other memory slices during the one configuration. The new configuration data may include off-chip or on-chip data. The present invention typically allocates at least one slice to user data memory and includes means for disabling access to at least one of the N memory cells.

Owner:XILINX INC

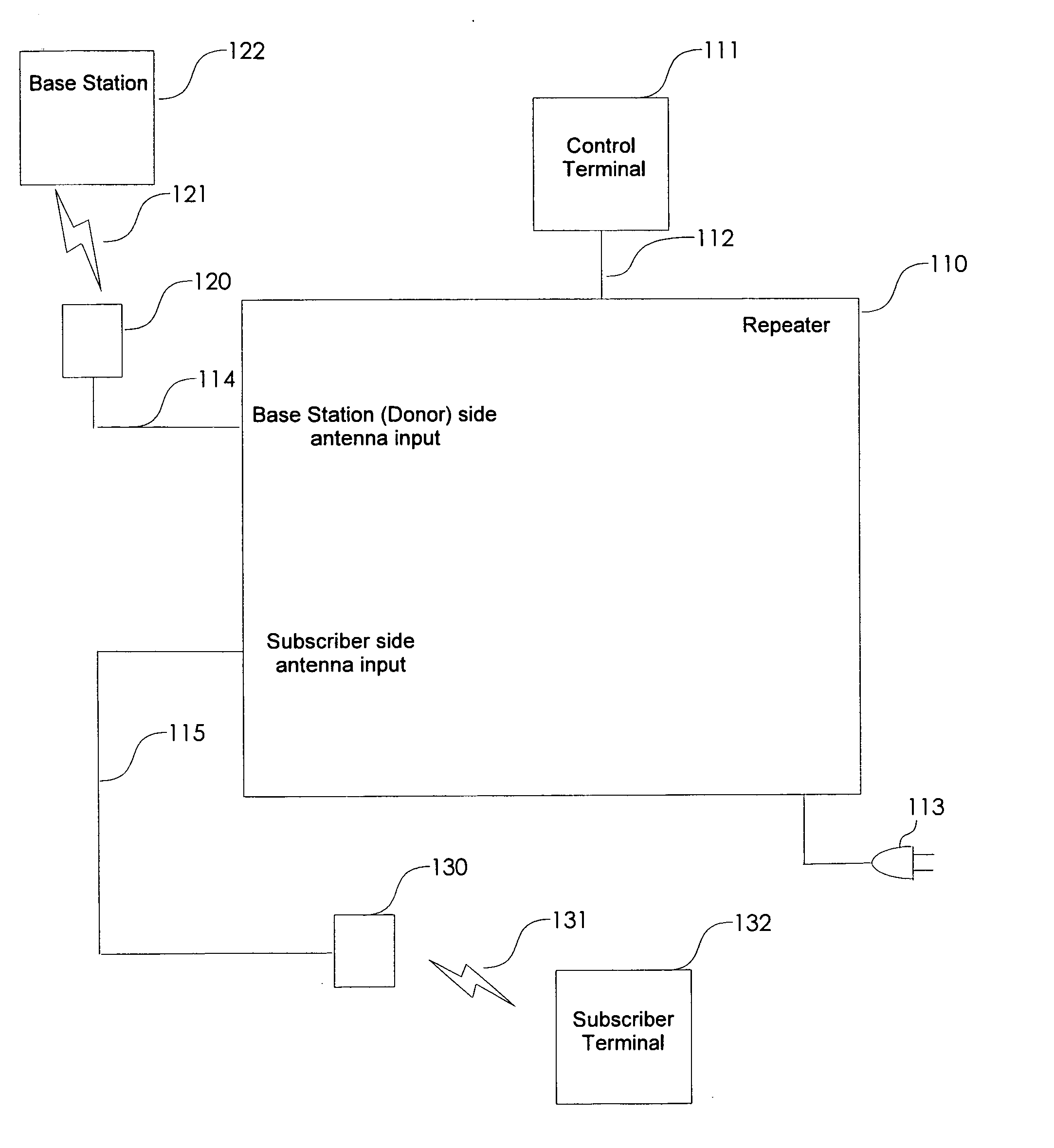

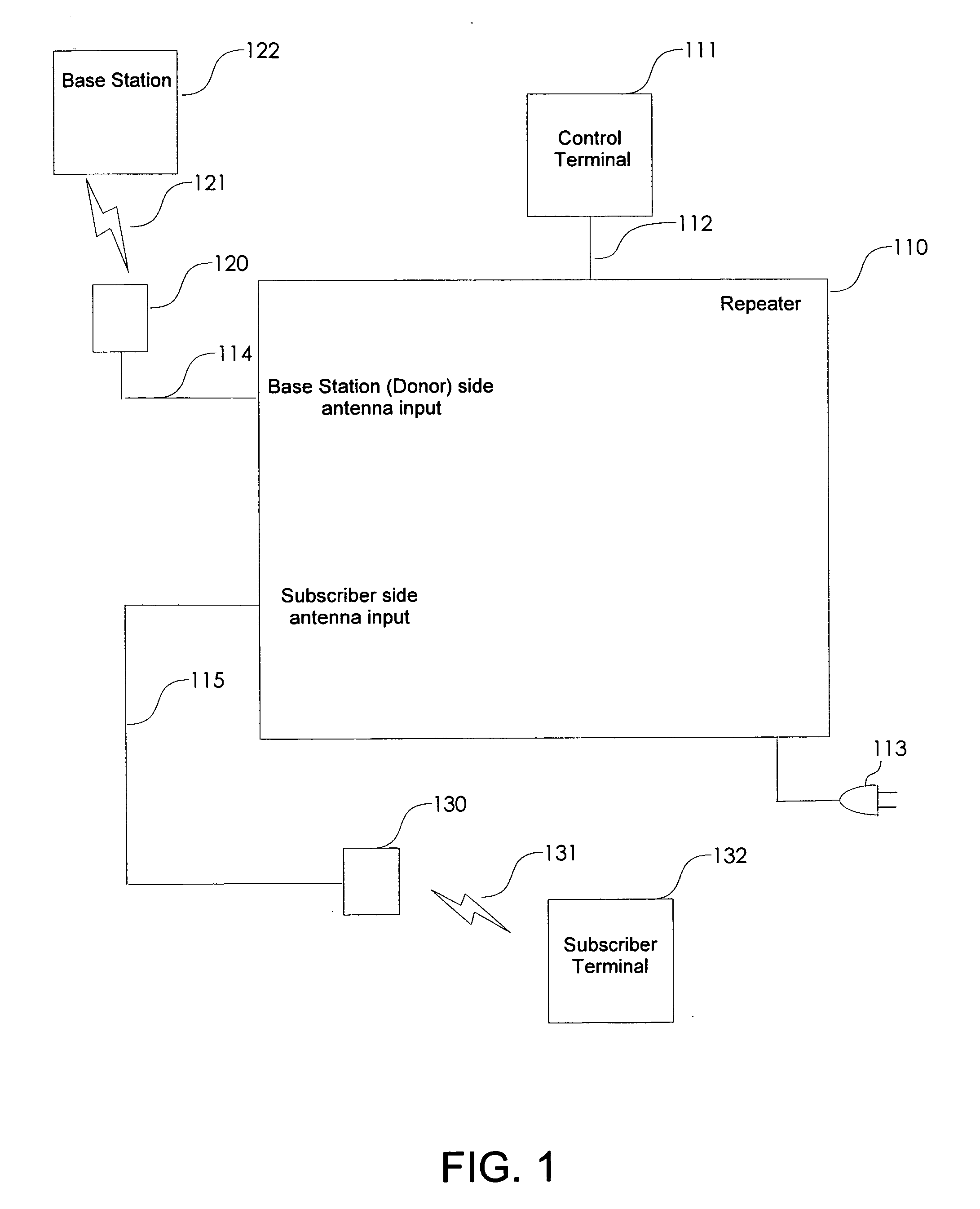

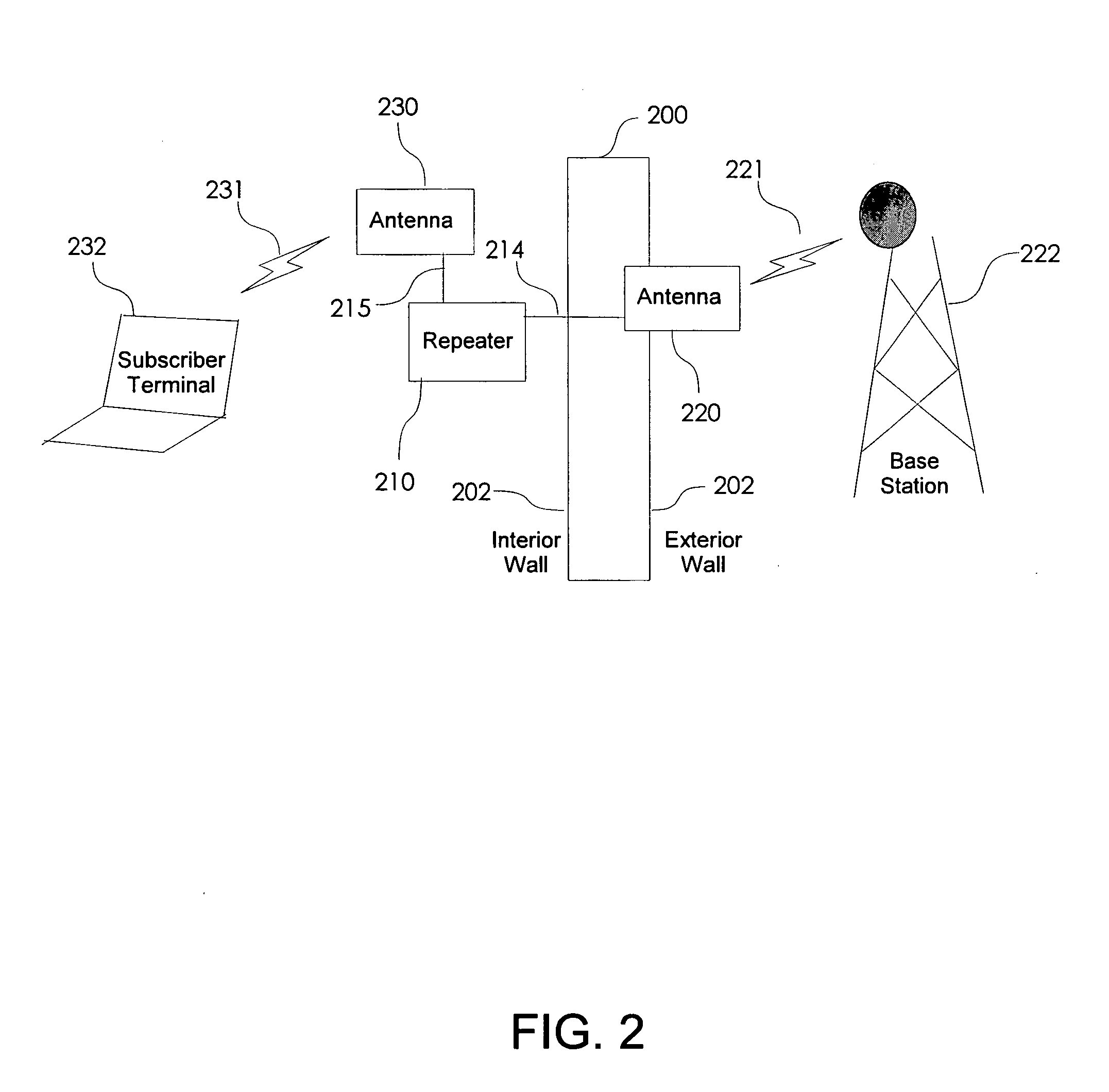

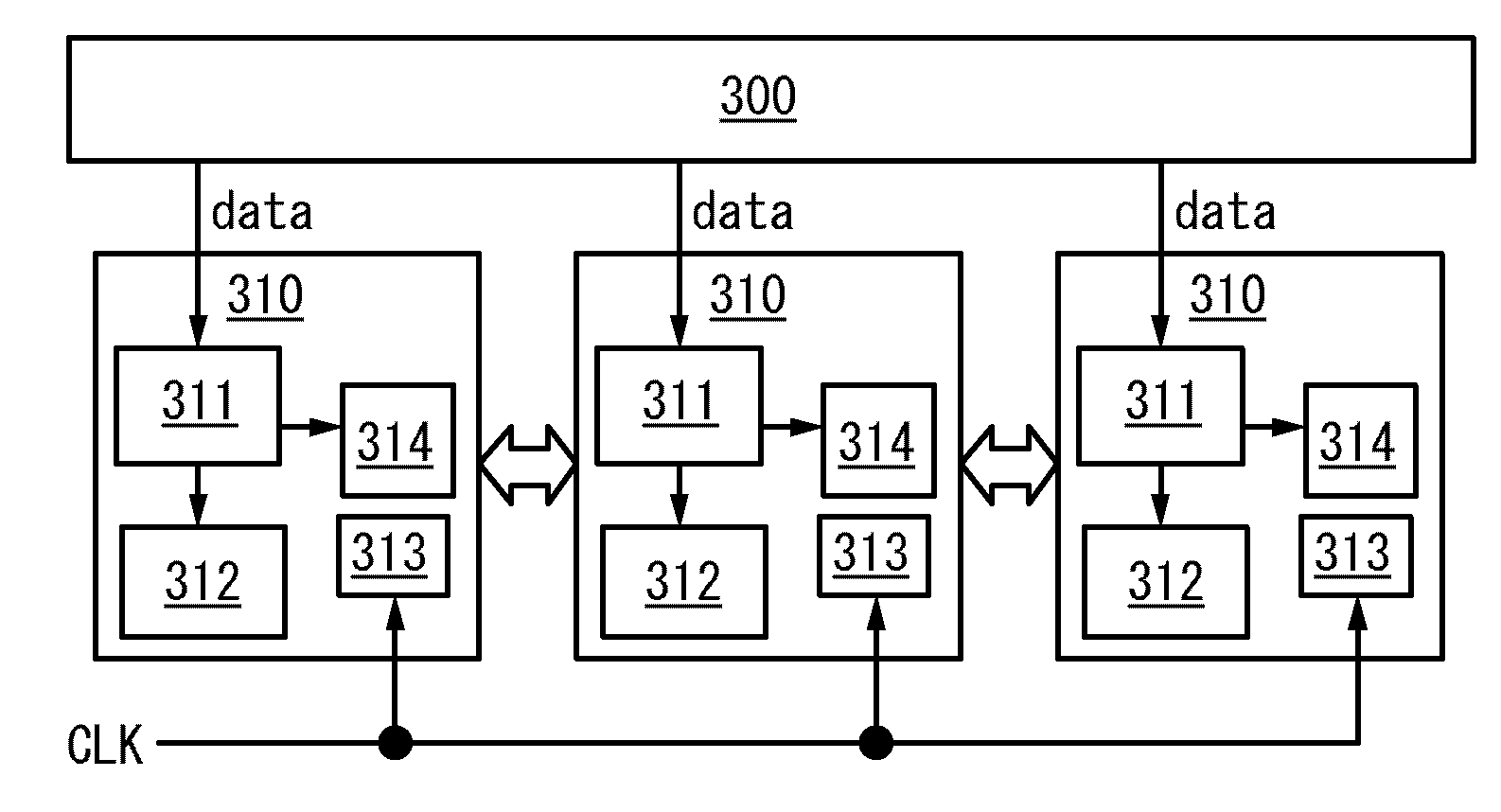

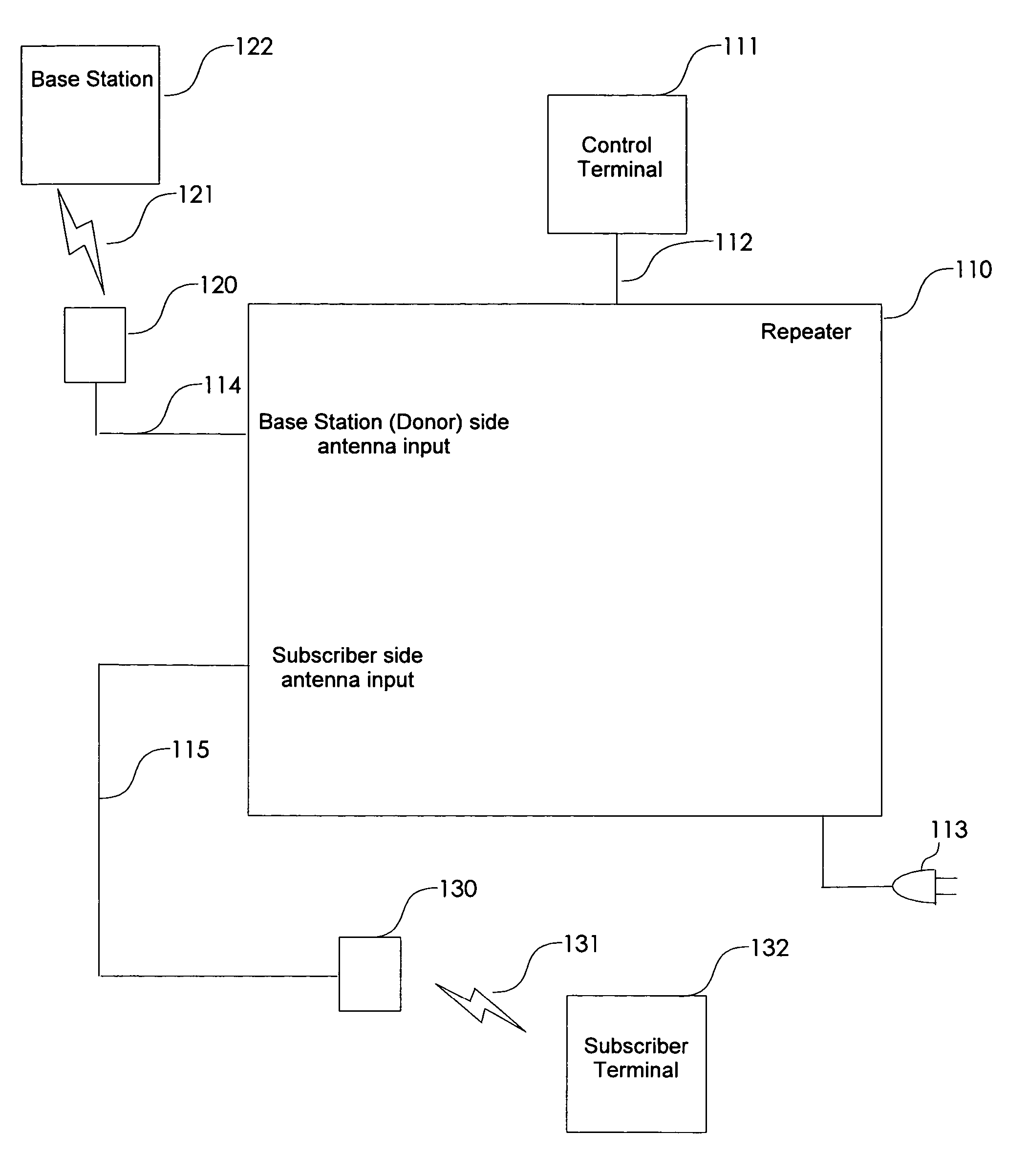

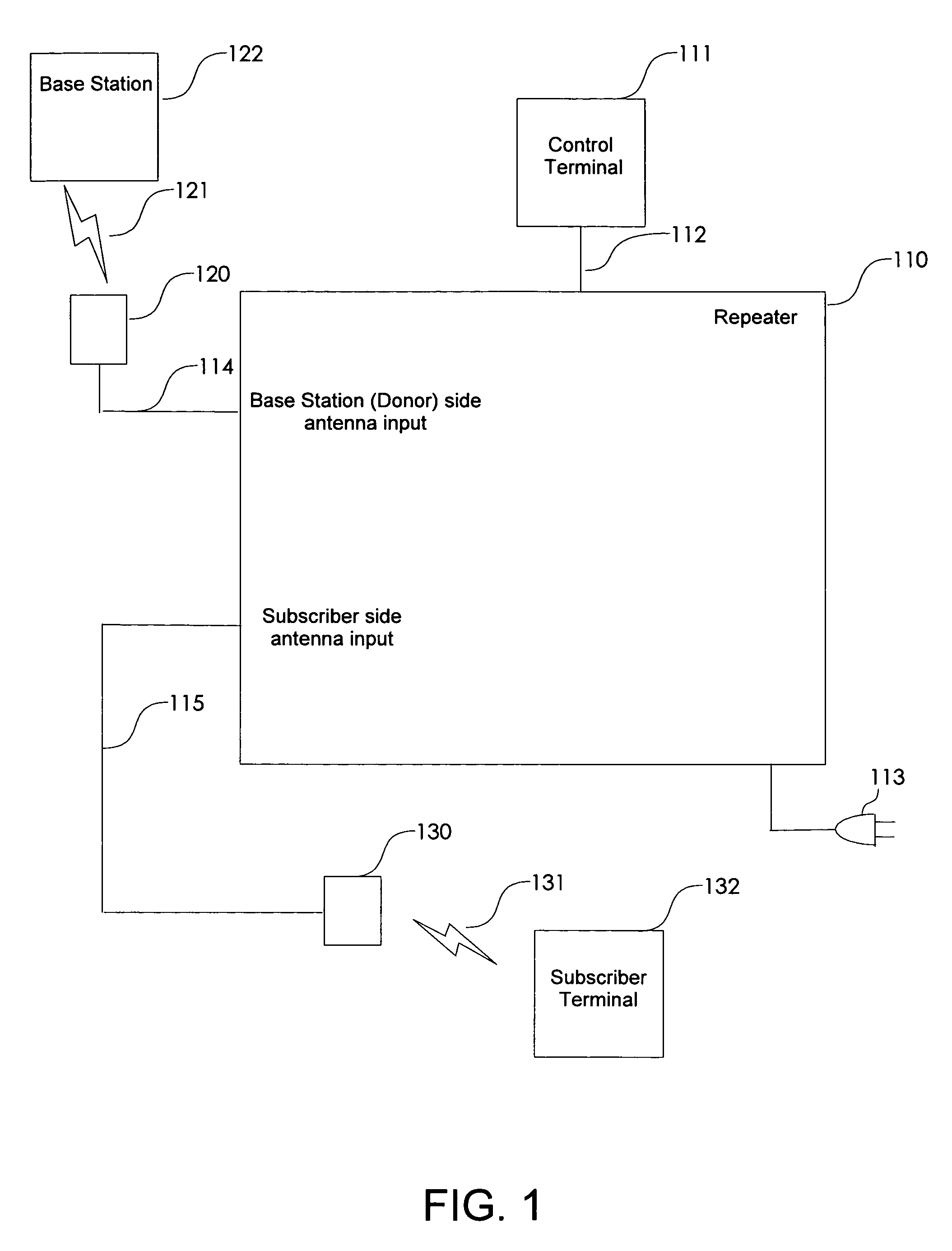

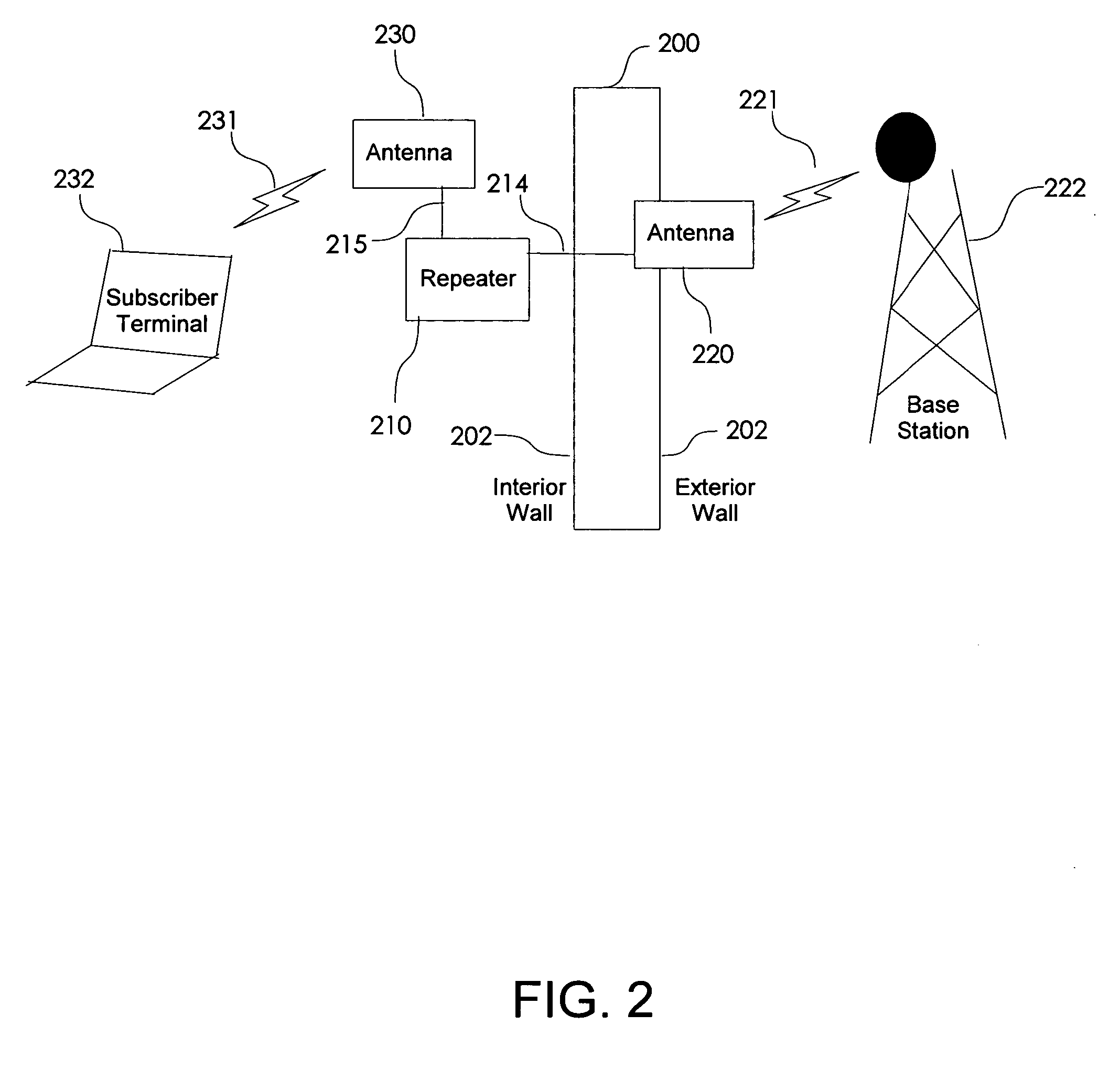

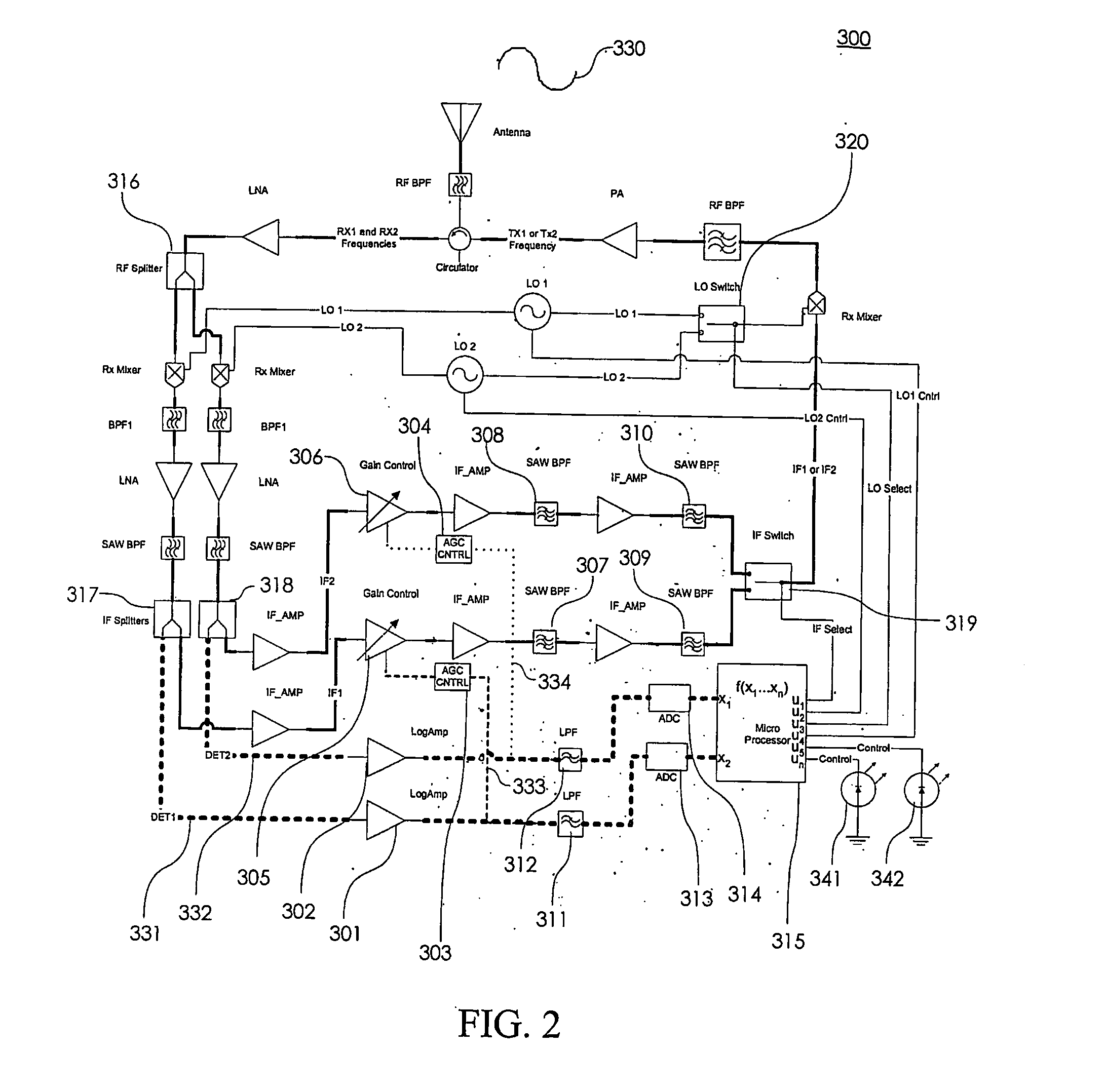

Non-frequency translating repeater with detection and media access control

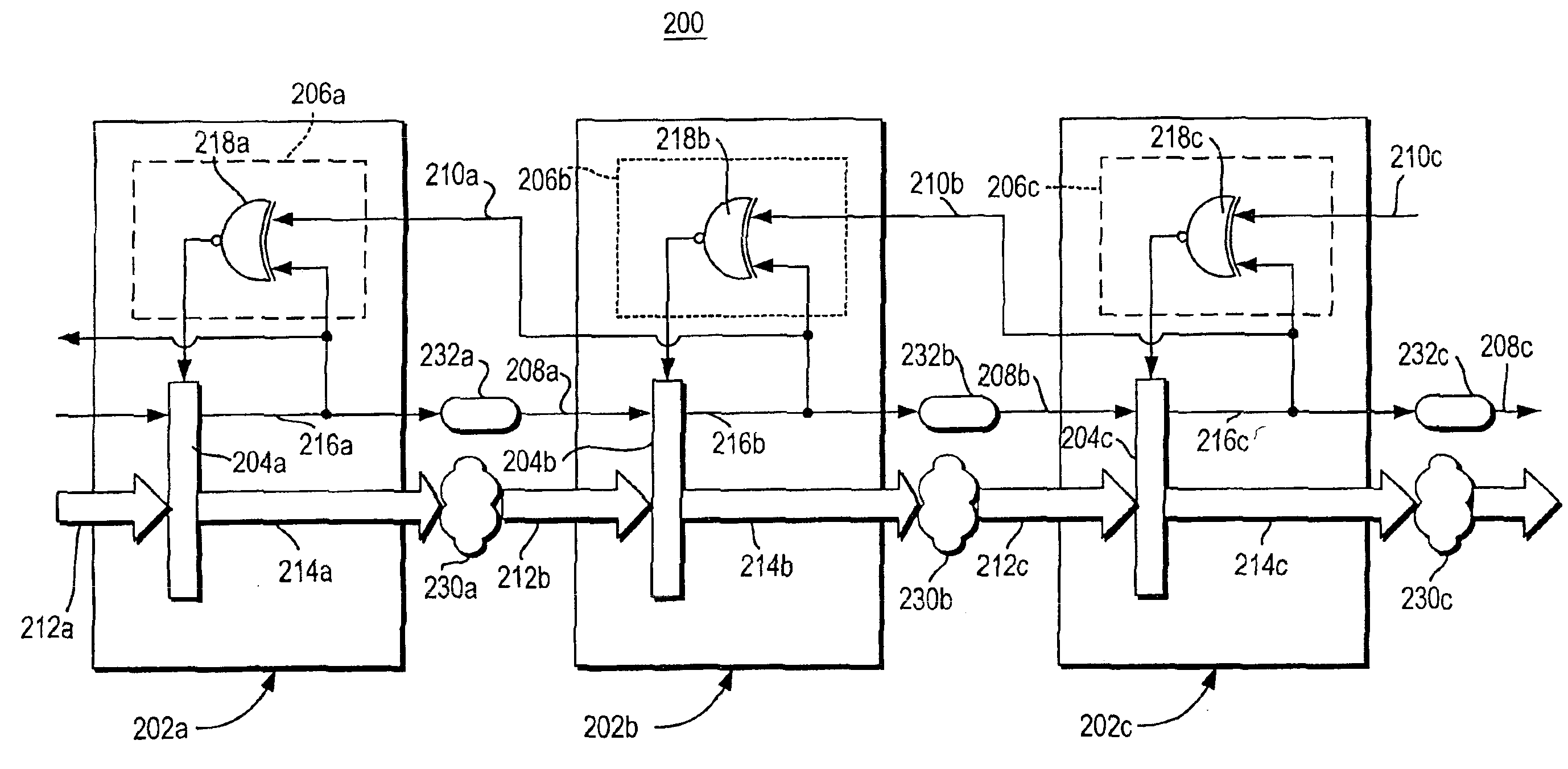

A non-frequency translating repeater (110, 210, 300) for use in a time division duplex (TDD) radio protocol communications system includes detection retransmission and automatic gain control. Detection is performed by detectors (309, 310) and a processor (313). Detection can be overridden by processor (313) using logic elements (314). Antennae (220, 230) having various form factors can be used to couple a base station (222) to a subscriber terminal (232) which can be located in a sub-optimal location such as deep inside a building or the like.

Owner:QUALCOMM INC

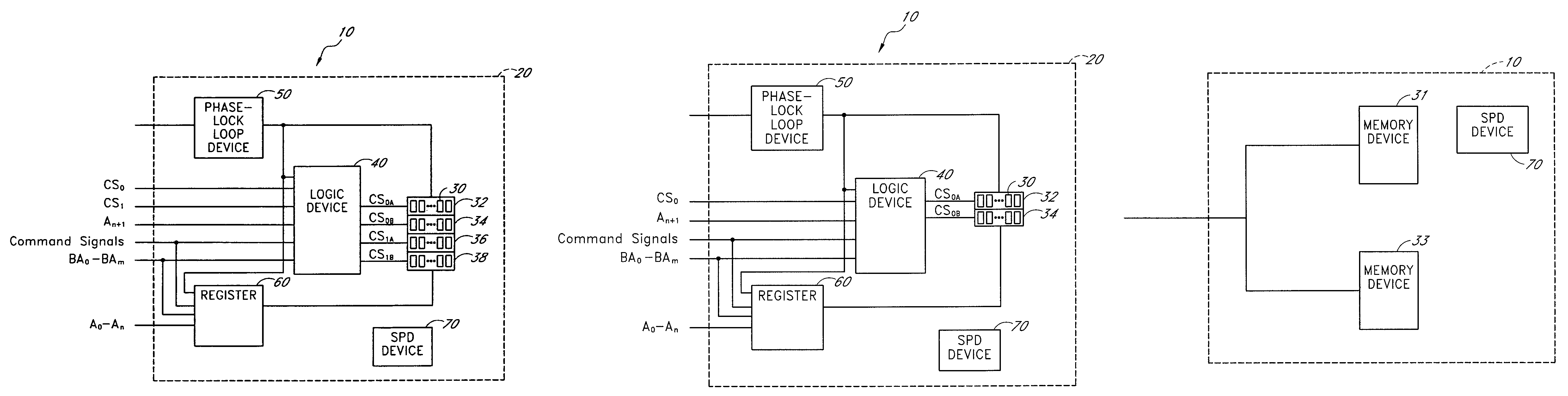

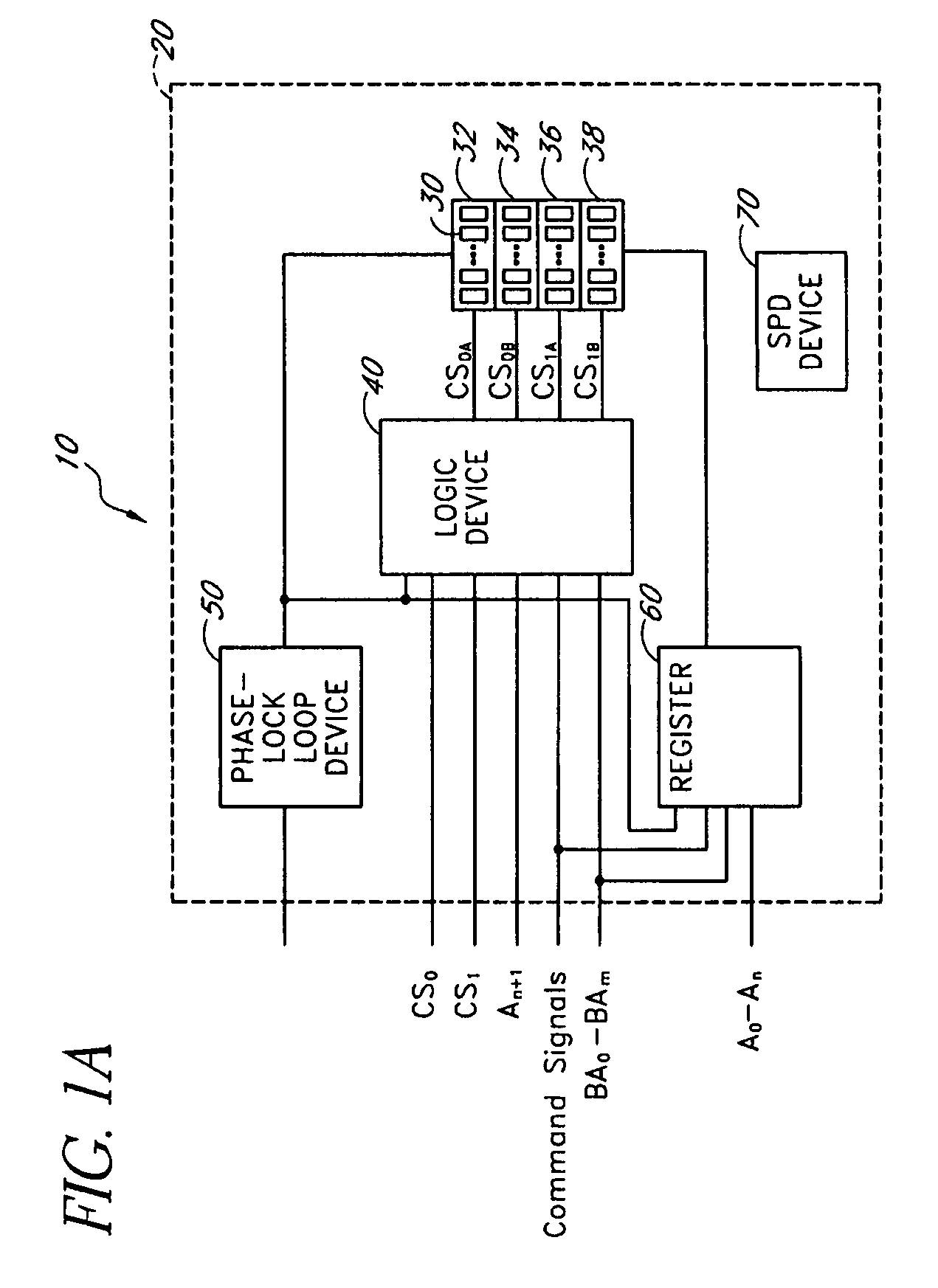

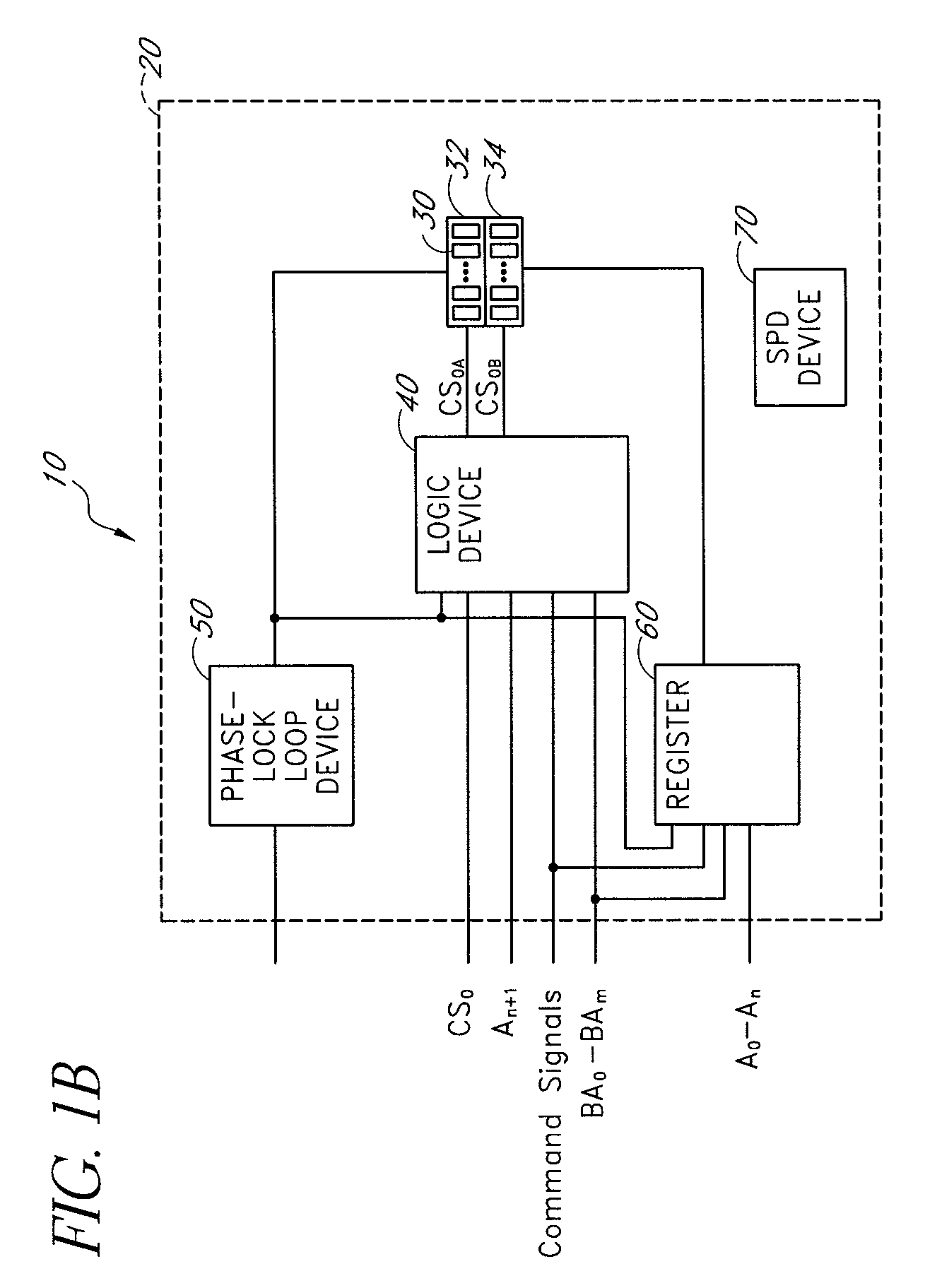

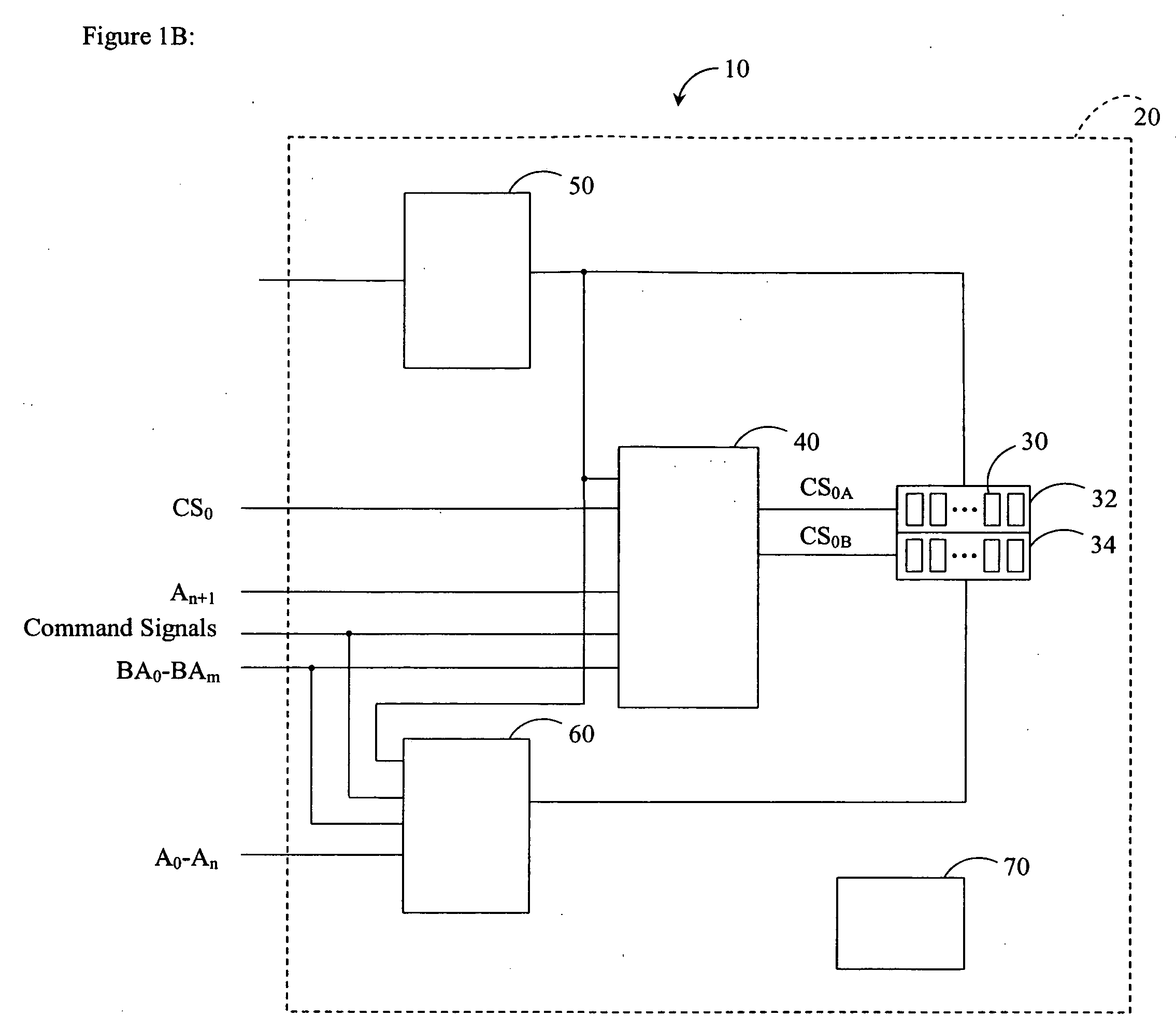

Memory module decoder

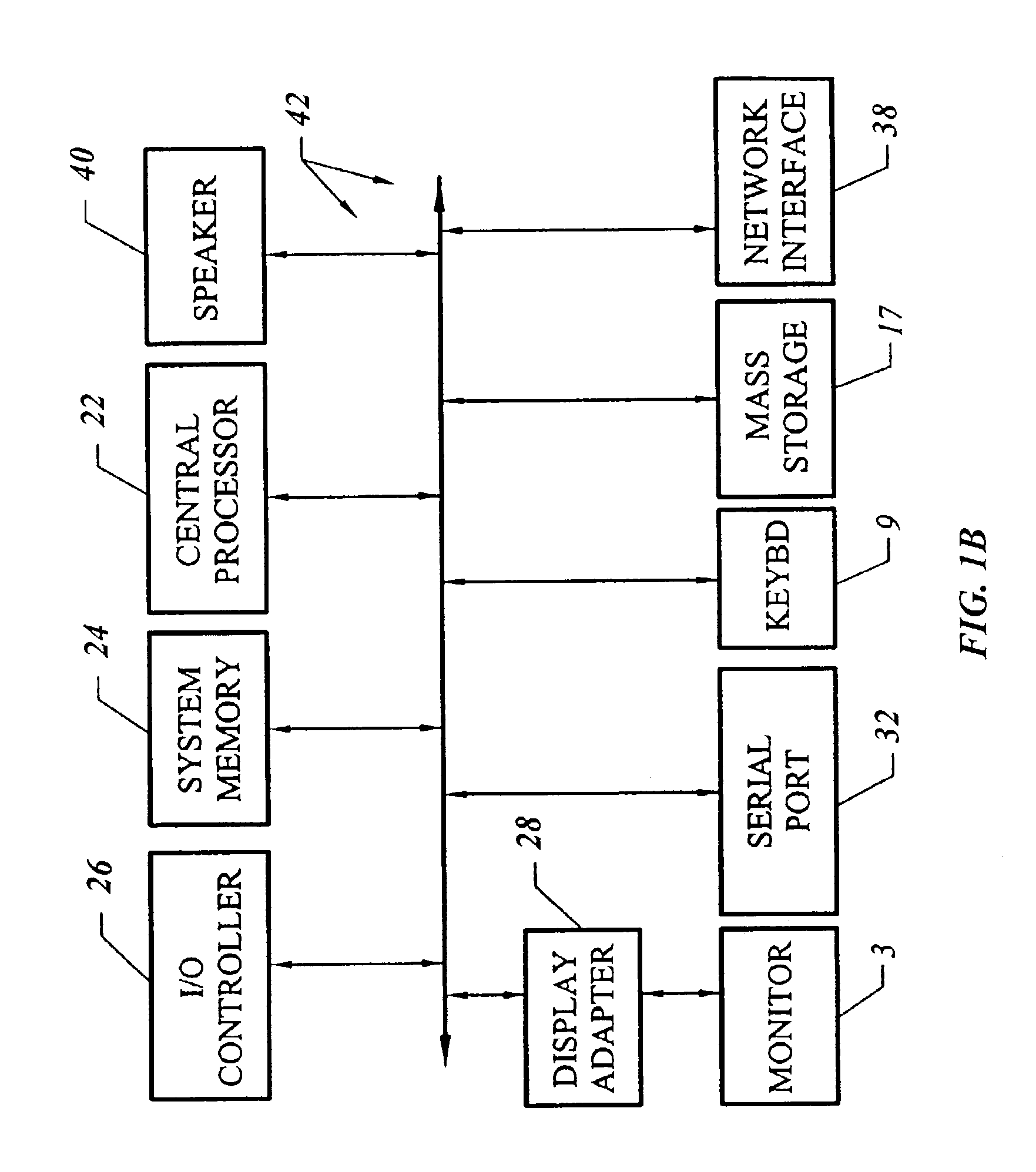

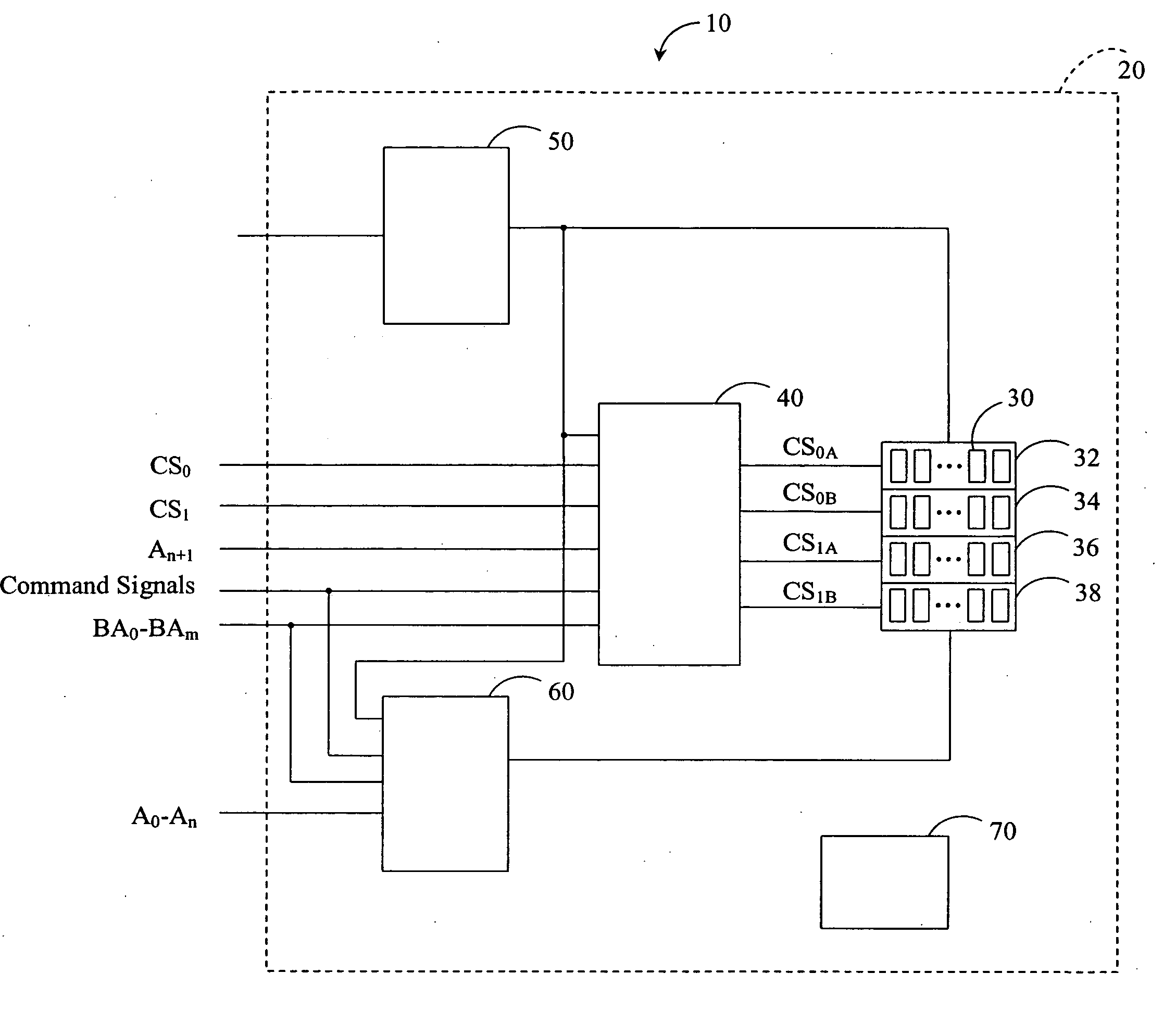

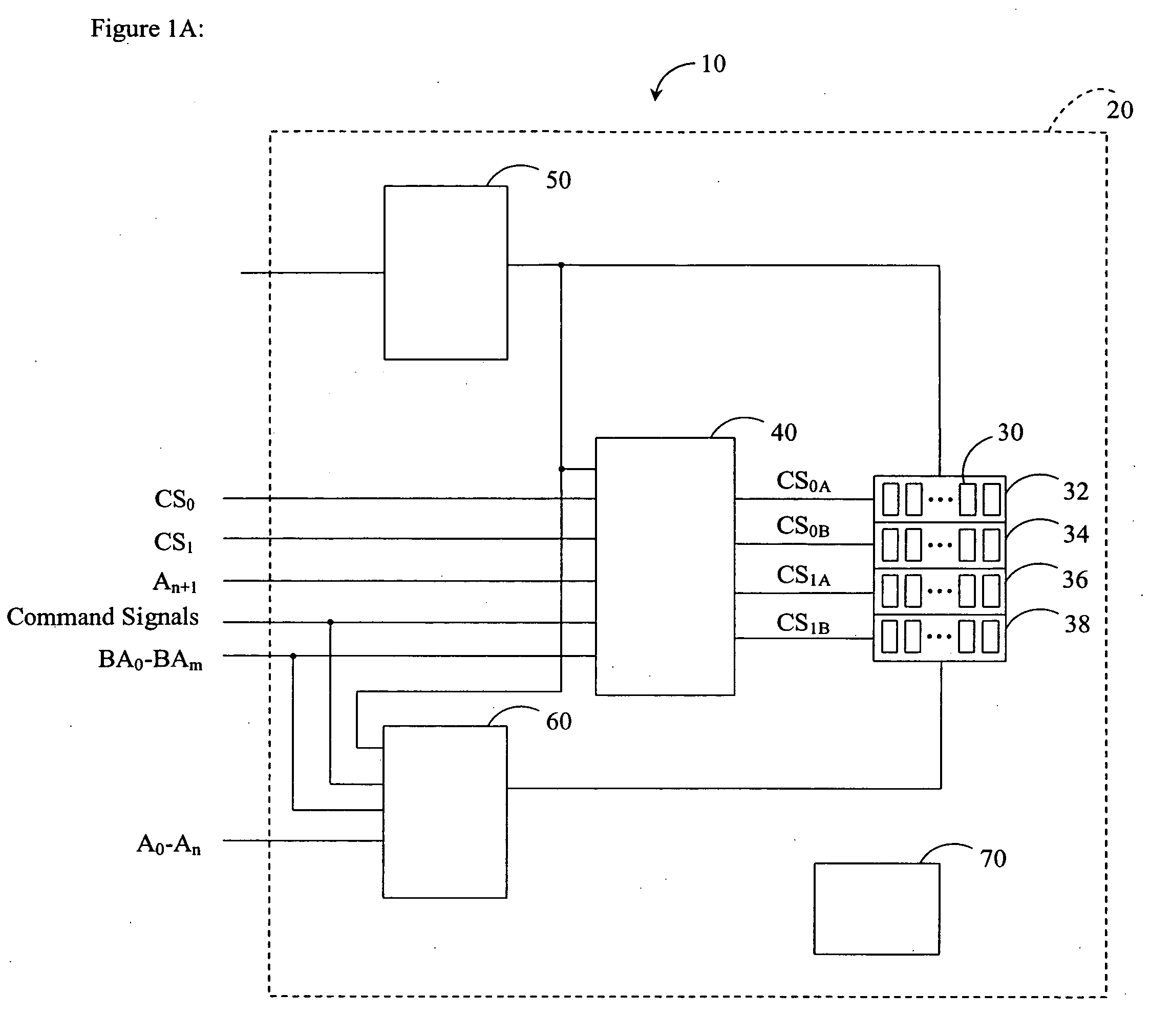

A memory module connectable to a computer system includes a printed circuit board, a plurality of memory devices coupled to the printed circuit board, and a logic element coupled to the printed circuit board. The plurality of memory devices has a first number of memory devices. The logic element receives a set of input control signals from the computer system. The set of input control signals corresponds to a second number of memory devices smaller than the first number of memory devices. The logic element generates a set of output control signals in response to the set of input control signals. The set of output control signals corresponds to the first number of memory devices.

Owner:NETLIST INC

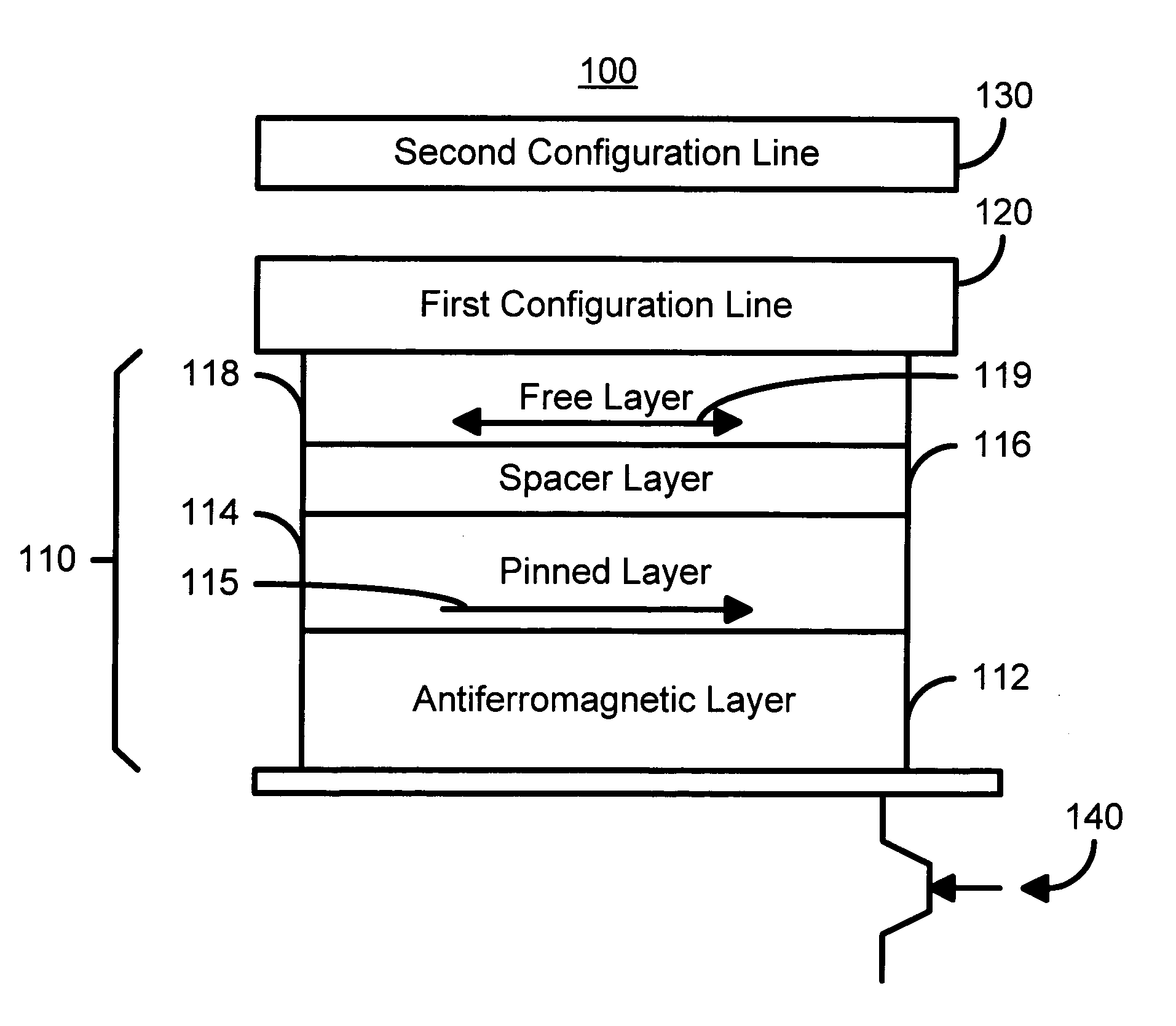

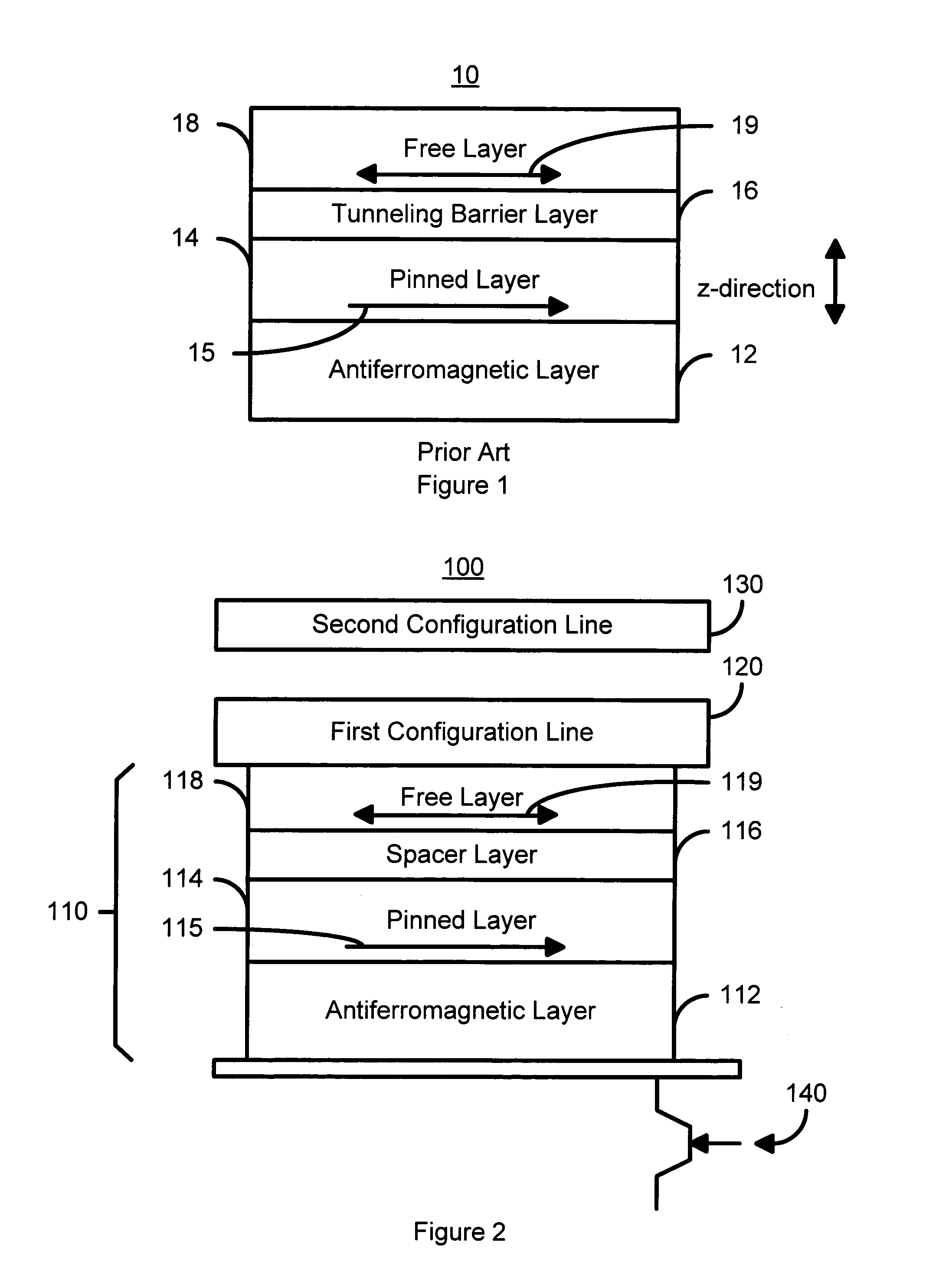

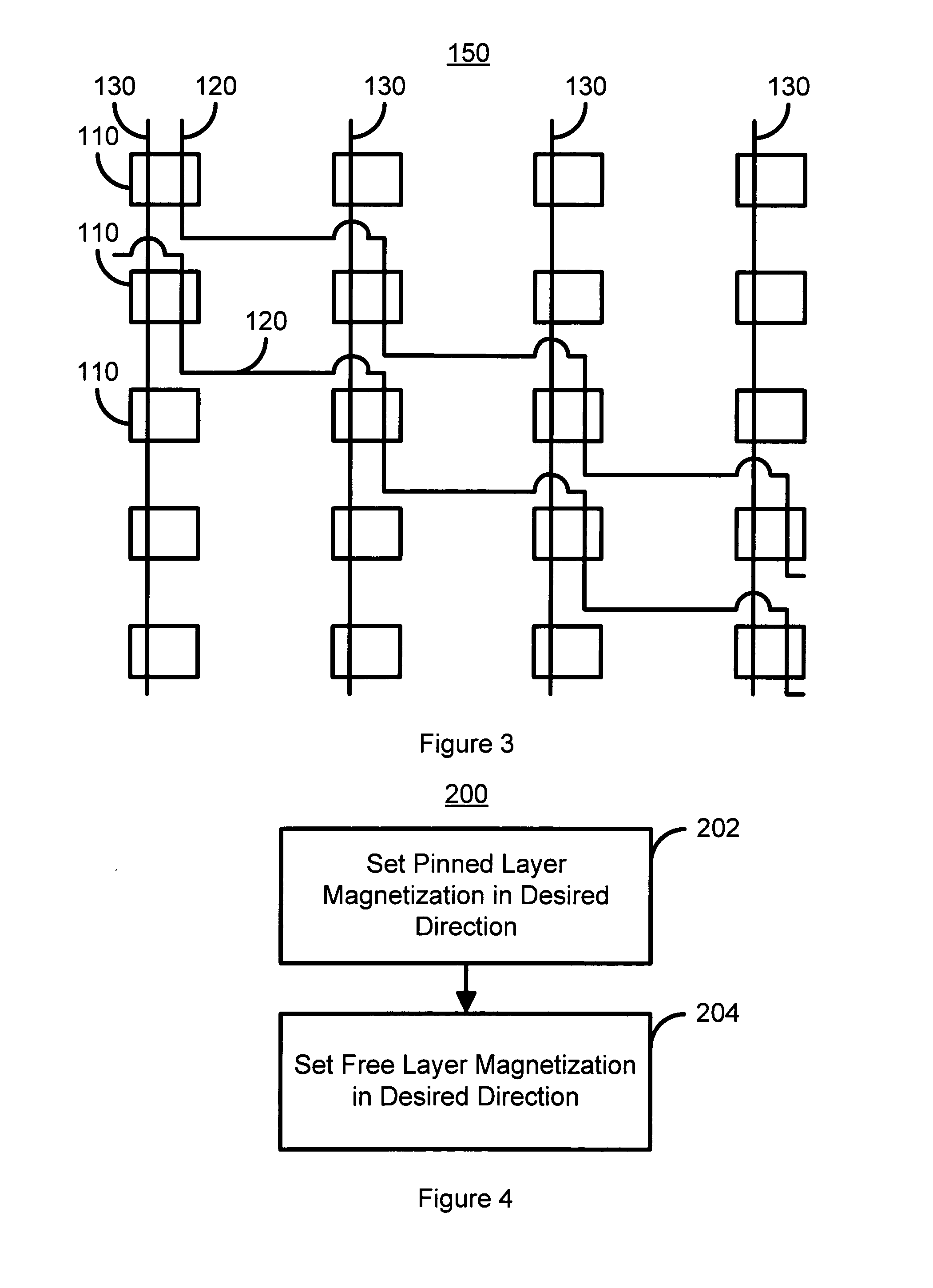

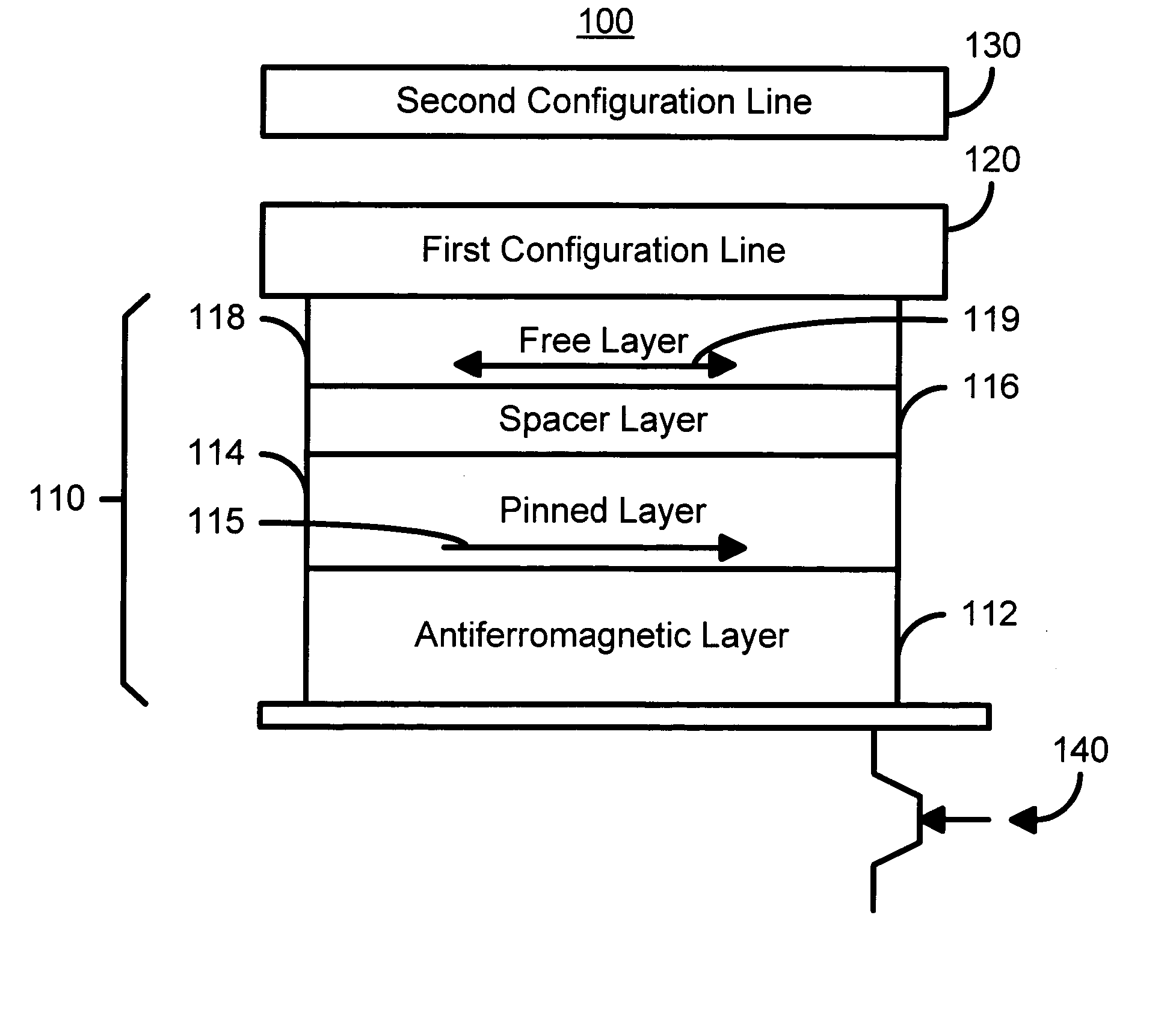

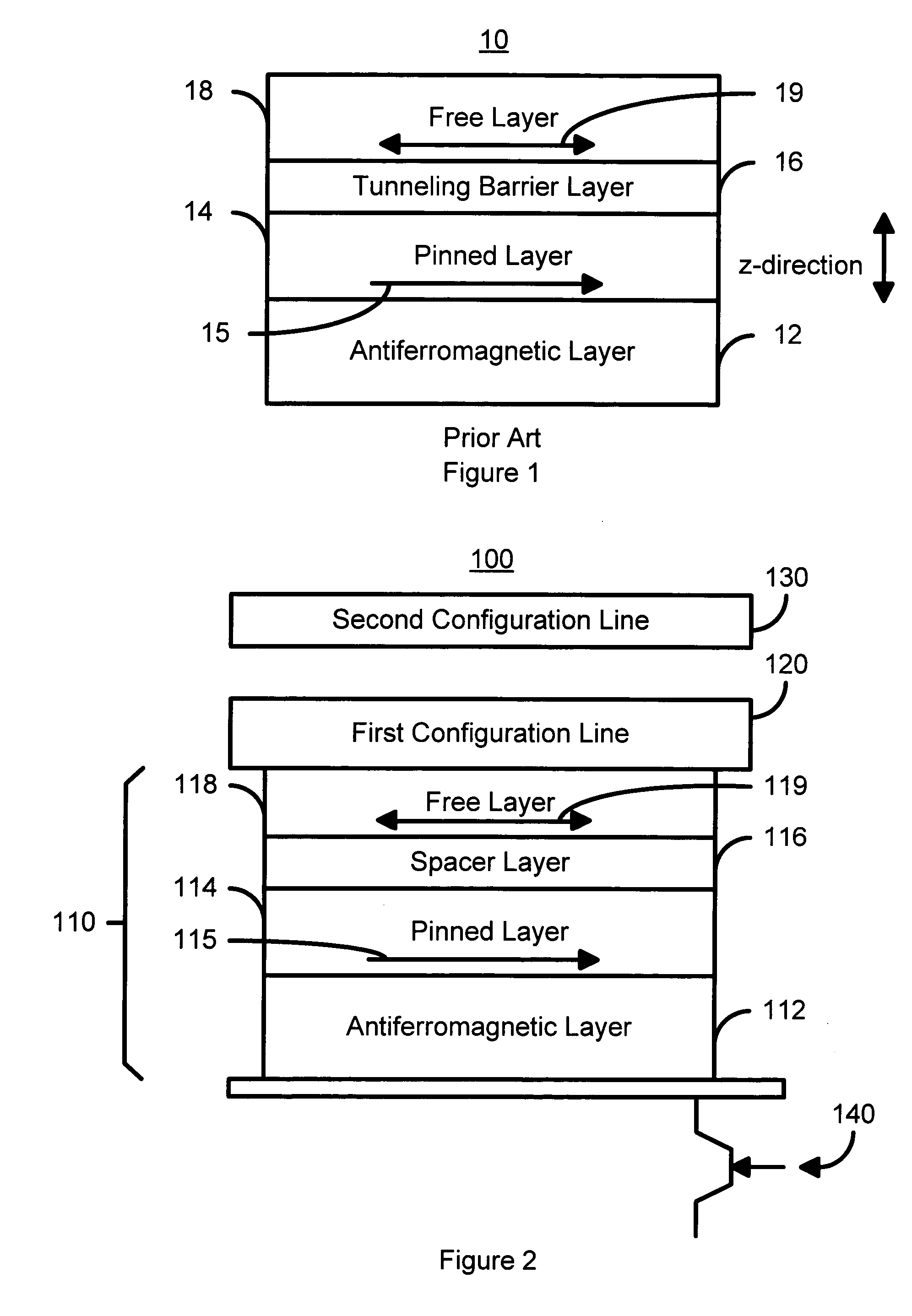

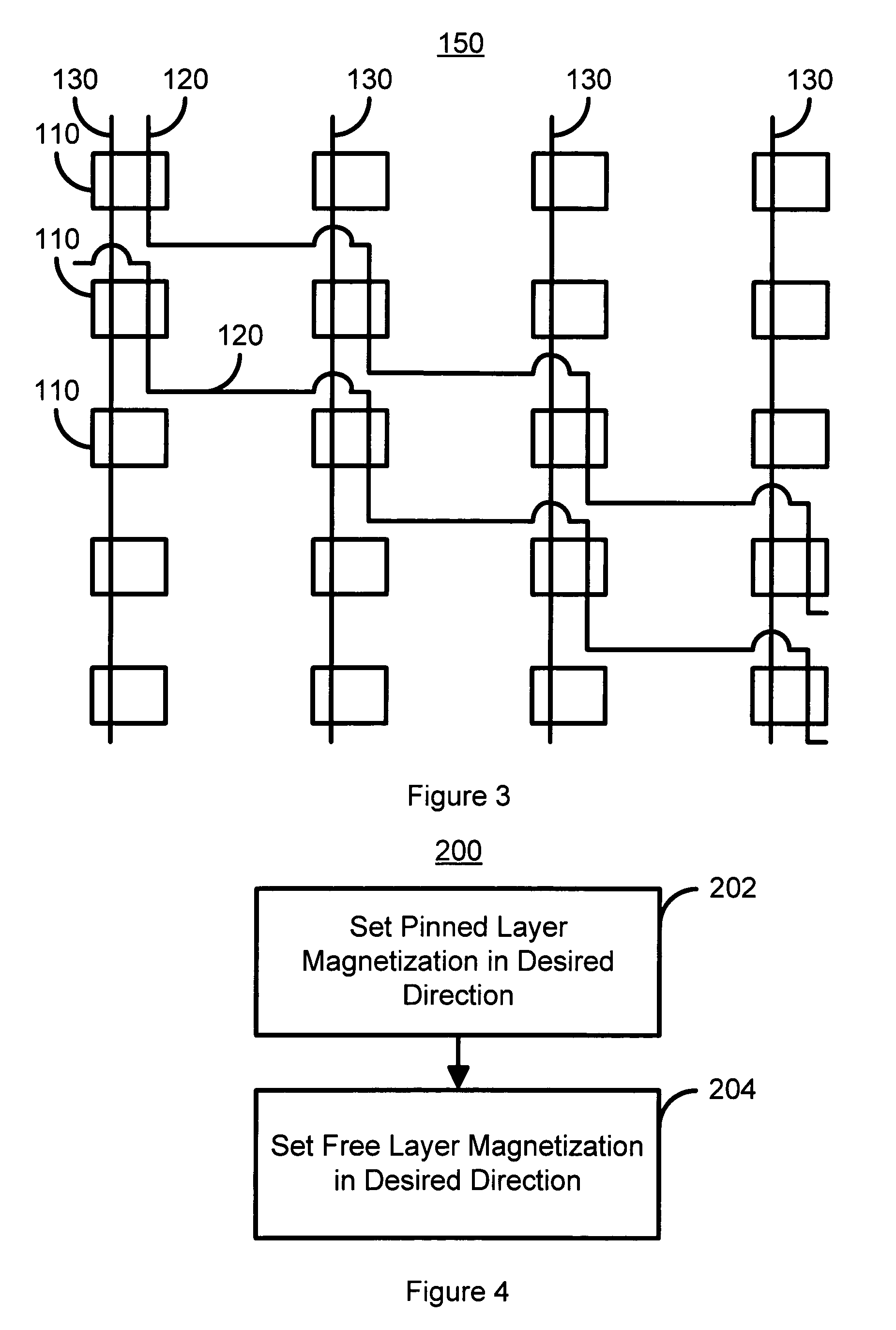

Re-configurable logic elements using heat assisted magnetic tunneling elements

A magnetic logic cell includes a magnetic element having a pinned layer, a free layer, and a spacer layer. The pinned and free layers have pinned and free layer magnetizations. The spacer layer resides between the pinned and free layers. In one aspect, the magnetic logic cell includes a first configuration line that is electrically connected to the magnetic element and carries a first current and a second configuration line electrically that is insulated from the magnetic element and the first configuration line and carries a second current. The first or second current alone cannot switch the free layer magnetization. The first and second currents together can switch the free layer magnetization. When the first current is driven through the magnetic element and the second current is provided, the combination sets the pinned layer magnetization direction. In one aspect, the pinned layer magnetization is set by heating the AFM layer to approximately at or above the blocking temperature. In order to configure the logic cell, an initial direction for the free layer magnetization is also set.

Owner:SAMSUNG SEMICON

Physical resynthesis of a logic design

InactiveUS7337100B1Simple designMinimize time delayElectronic circuit testingAnalogue computers for electric apparatusThird partyVisibility

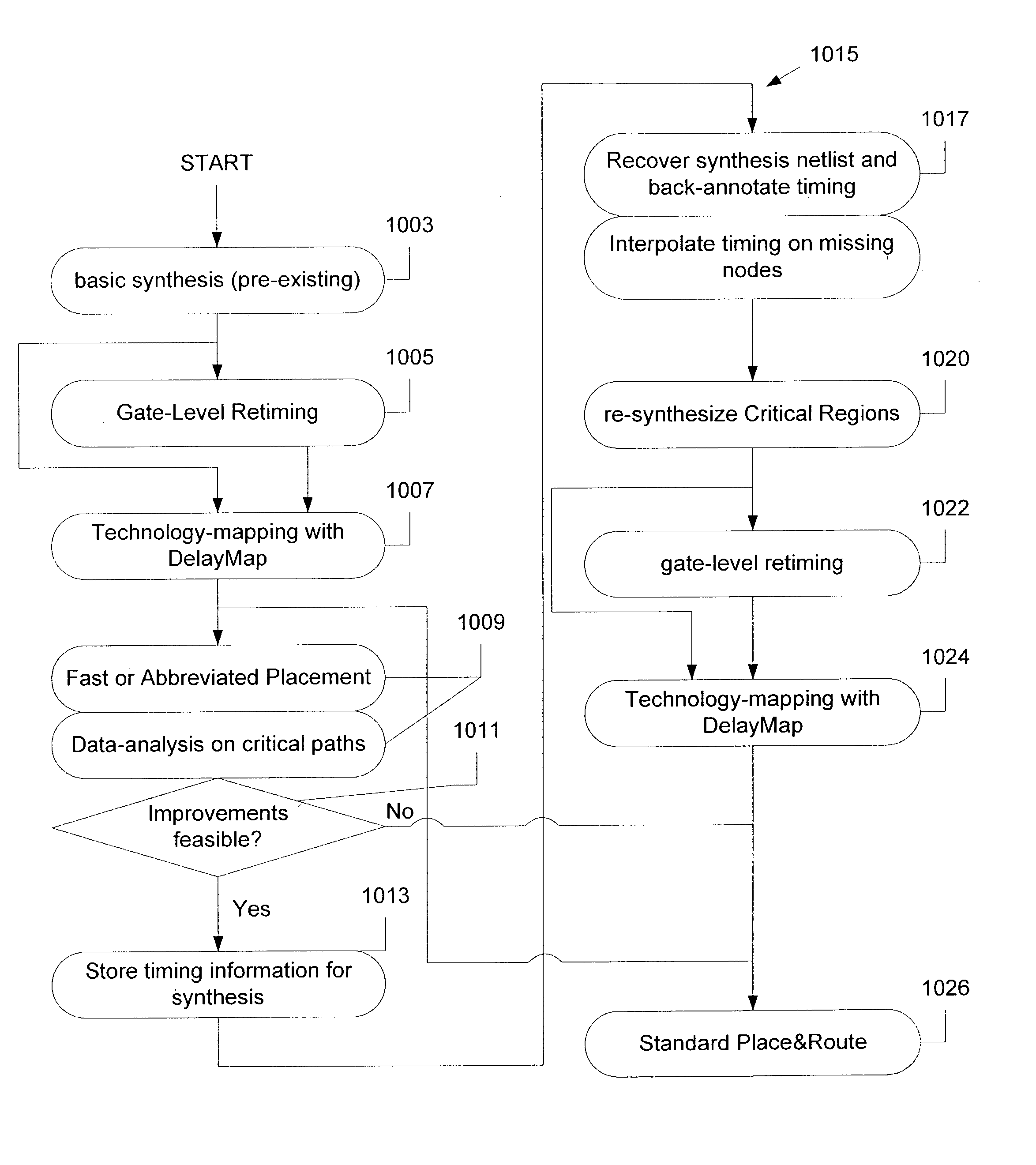

A multiple-pass synthesis technique improves the performance of a design. In a specific embodiment, synthesis is performed in two or more passes. In a first pass, a first synthesis is performed, and in a second or subsequent pass, a second synthesis or resynthesis is performed. During the first synthesis, the logic will be mapped to for example, the logic structures (e.g., logic elements, LUTs, synthesis gates) of the target technology such as a programmable logic device. Alternatively a netlist may be provided from a third party. Before the second synthesis, a fast or abbreviated fit may be performed of the netlist to a specific device (e.g., specific programmable logic device product). Before the second synthesis, the netlist obtained from the first synthesis (or provided by a third party) is unmapped and then the second synthesis is performed. Since a partial fit is performed, the second synthesis has more visibility and optimize the logic better than by using a single synthesis pass. After the second synthesis pass, a more detailed fit is performed.

Owner:ALTERA CORP

RE-PROGRAMMABLE ANTIFUSE FPGA UTILIZING RESISTIVE CeRAM ELEMENTS

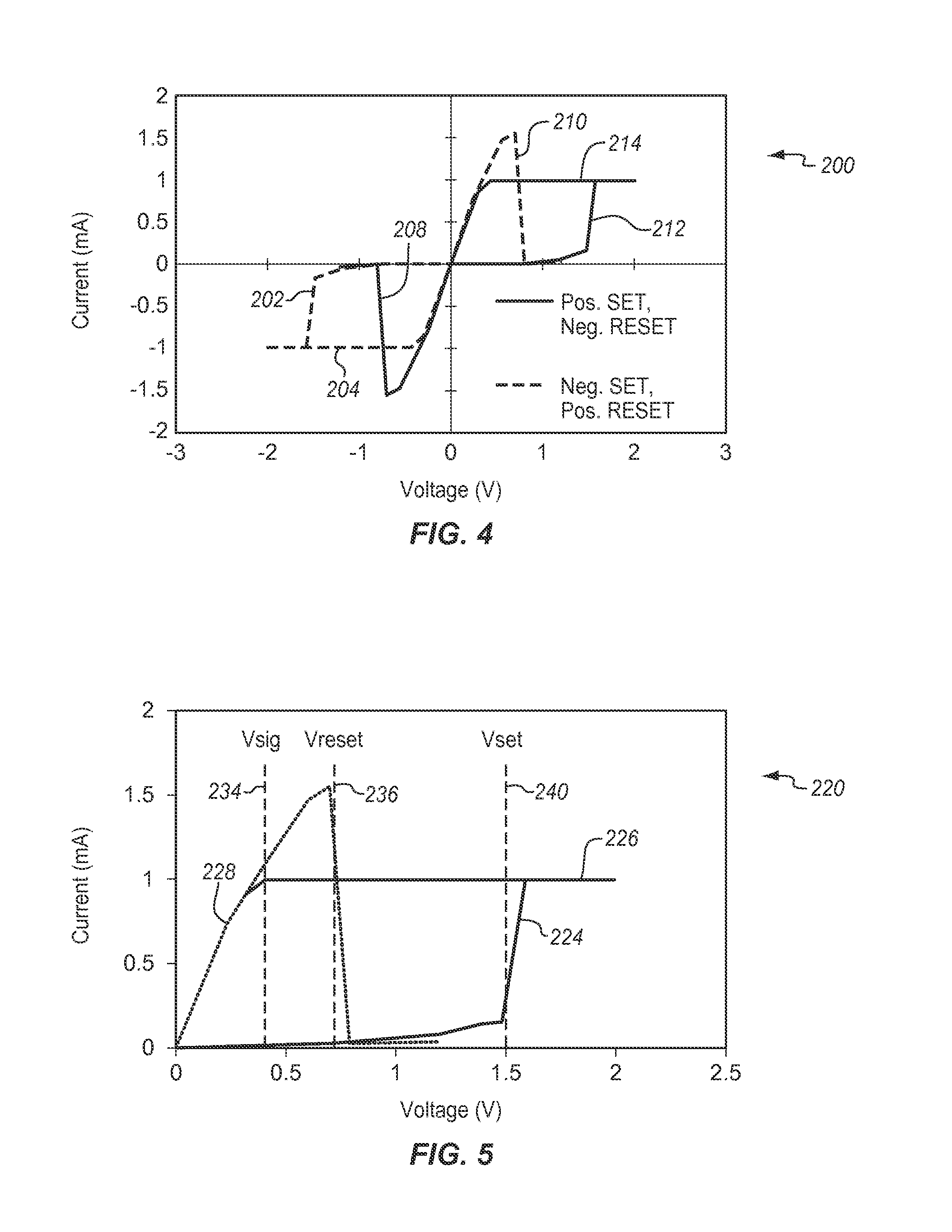

ActiveUS20130285699A1Solid-state devicesRead-only memoriesElectrical resistance and conductanceResistive switching

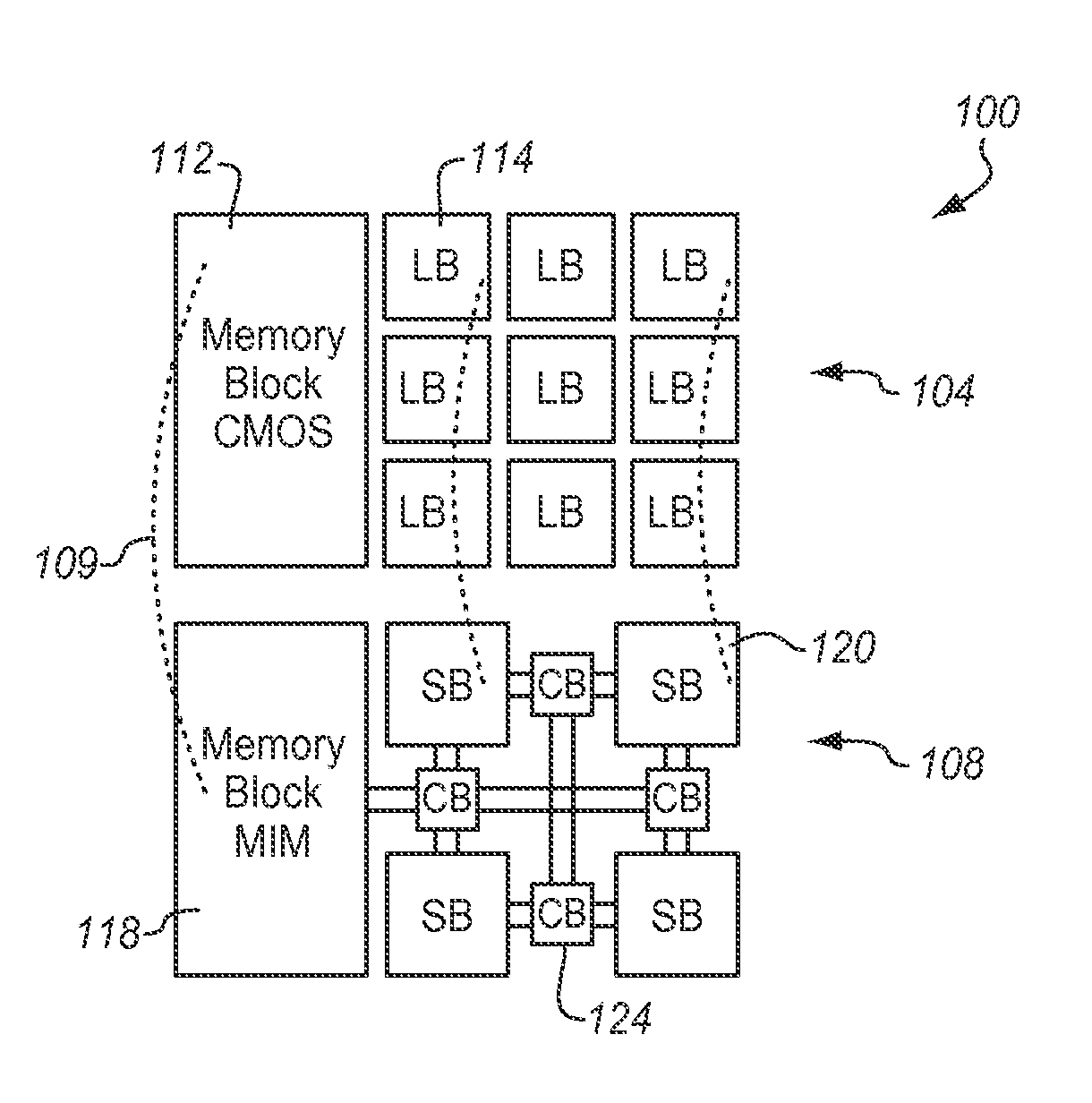

A re-programmable antifuse field programmable gate array (FPGA) integrated circuit, the FPGA comprising: a plurality of CeRAM resistive switching elements forming a connection block, the switching elements capable of being switched from a conductive (ON) state to a non-conductive (OFF) state and back to a conductive (ON) state; a plurality of logic elements forming a logic block; and a programming circuit for turning the CeRAM switching elements OFF and ON to connect the logic elements to form the FPGA.

Owner:SYMETRIX MEMORY

Apparatus and method for port polarity initialization in a shared I/O device

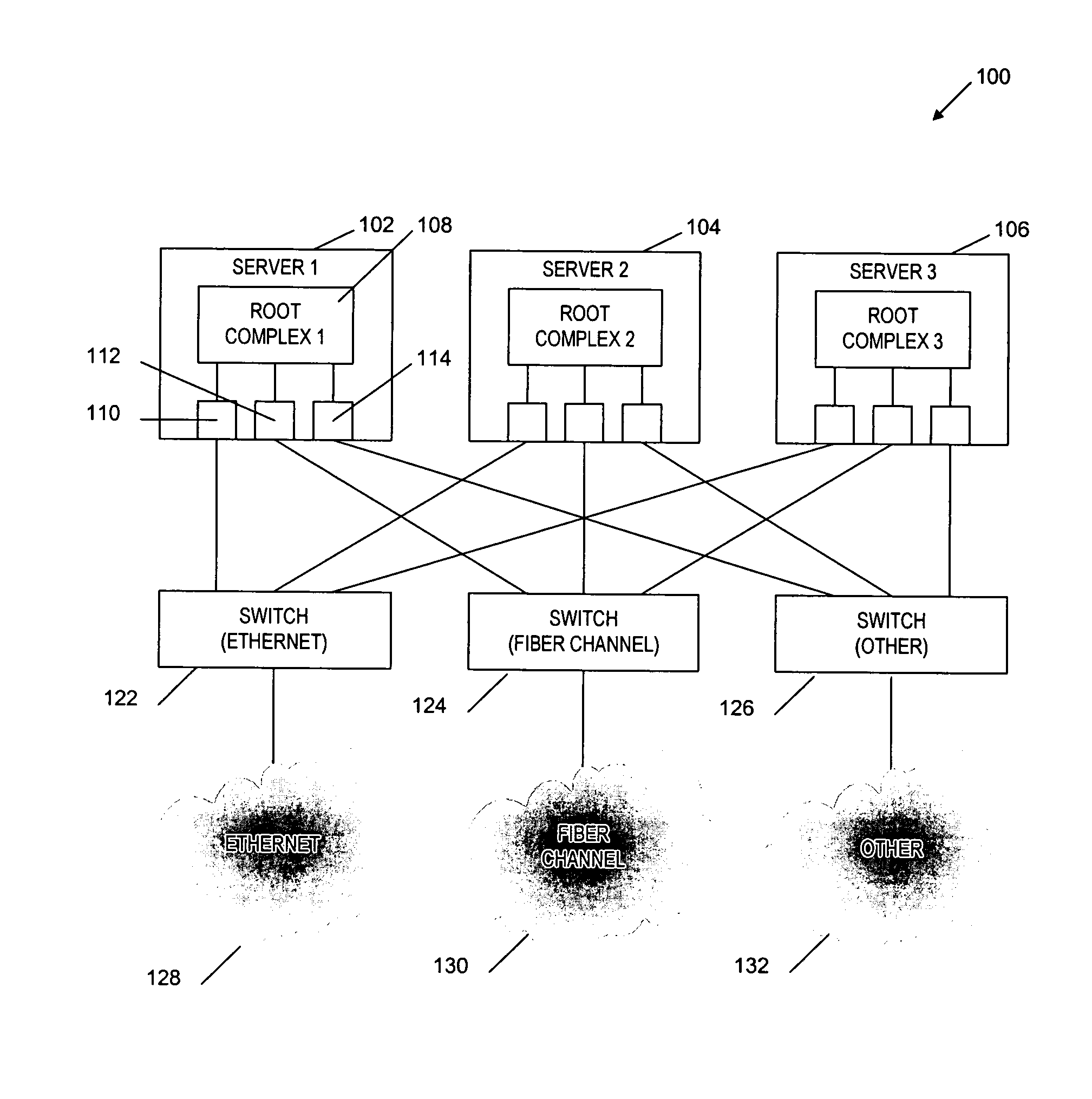

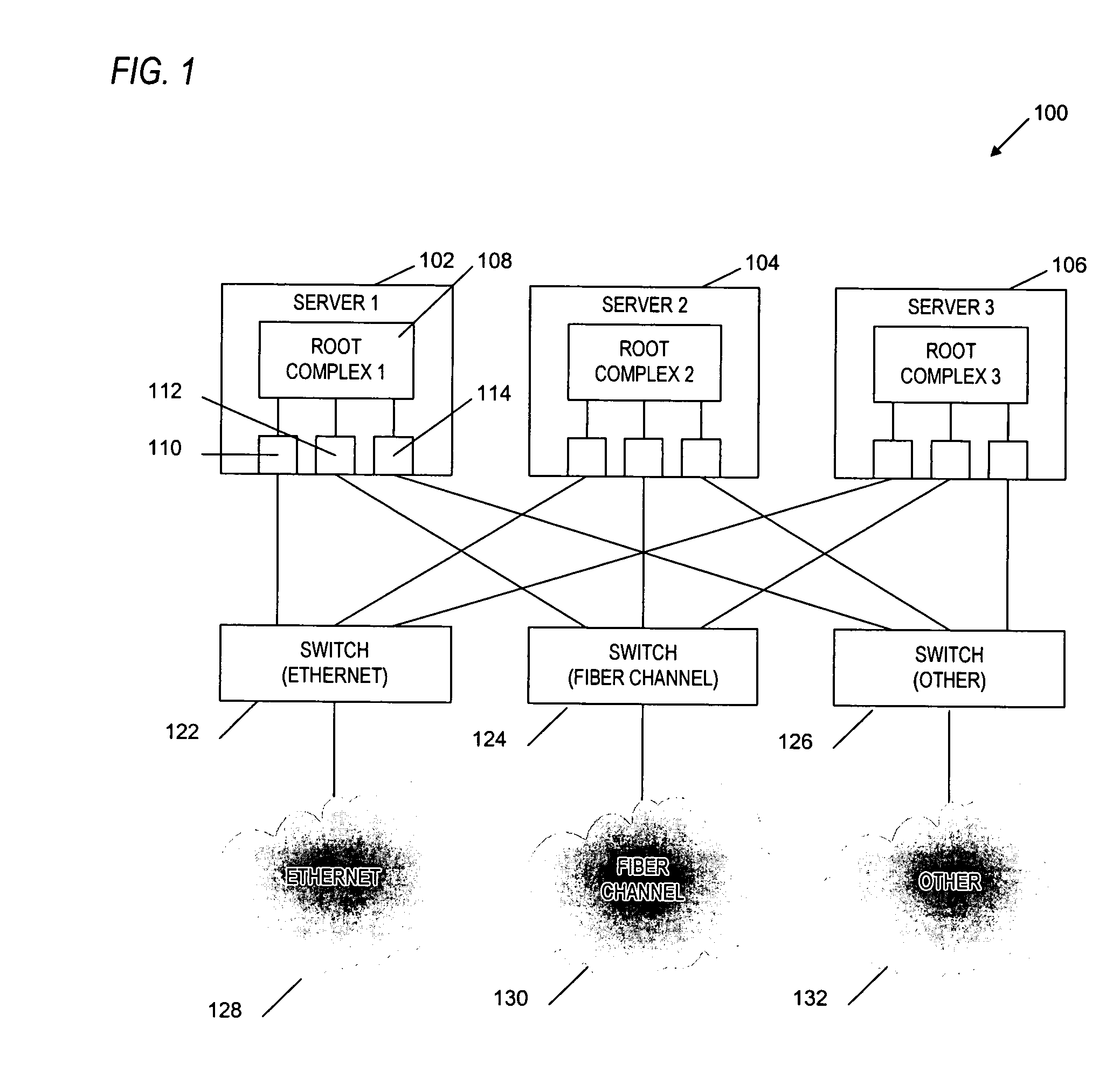

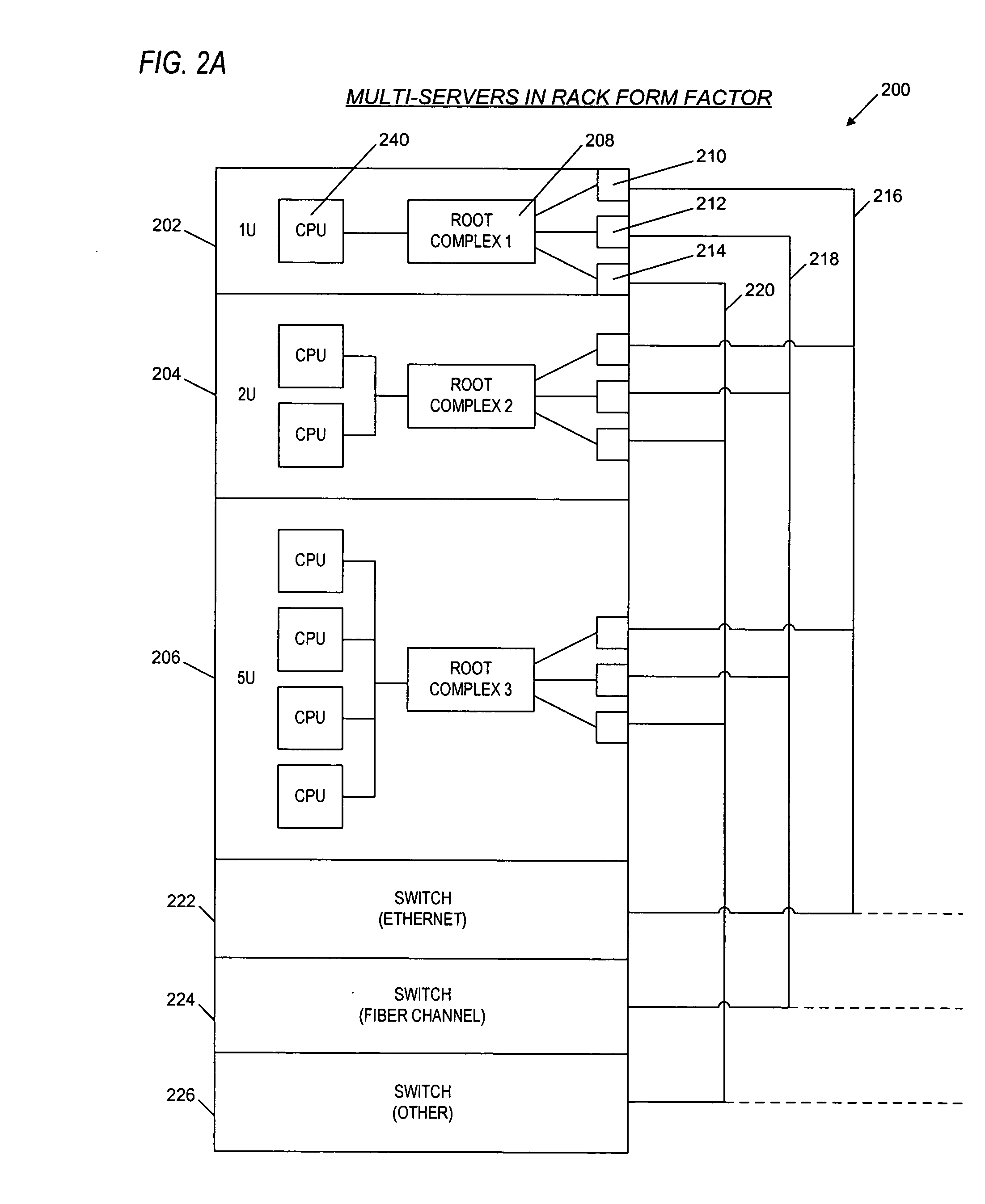

InactiveUS20050147117A1Multiplex system selection arrangementsData switching by path configurationOperational systemLogic cell

An apparatus and method are provided that enable I / O devices to be shared among multiple operating system domains. The apparatus includes a first plurality of I / O ports, a second I / O port, and a plurality of port initialization logic elements. The first plurality of I / O ports is coupled to a plurality of operating system domains through a load-store fabric. Each of the first plurality of I / O ports routes transactions between the plurality of operating system domains and the switching apparatus. The second I / O port is coupled to a first shared input / output endpoint. The first shared input / output endpoint is configured to request / complete the transactions for each of the plurality of operating system domains. One of the plurality of port initialization logic elements is coupled to the second I / O port and remaining ones of the plurality of port initialization logic elements are each coupled to a corresponding one of the first plurality of I / O ports. The plurality of port initialization logic elements is configured to initialize corresponding links between each of the plurality of operating system domains and the switching apparatus, and between the first shared input / output endpoint and the switching apparatus, to support the transactions, where each of the plurality of port initialization logic elements automatically configures a corresponding polarity for each of the first plurality of I / O ports and the second I / O port, and where the corresponding polarity is in a default polarity prior to being configured.

Owner:AVAGO TECH INT SALES PTE LTD

Re-configurable logic elements using heat assisted magnetic tunneling elements

A magnetic logic cell includes a magnetic element having a pinned layer, a free layer, and a spacer layer. The pinned and free layers have pinned and free layer magnetizations. The spacer layer resides between the pinned and free layers. In one aspect, the magnetic logic cell includes a first configuration line that is electrically connected to the magnetic element and carries a first current and a second configuration line electrically that is insulated from the magnetic element and the first configuration line and carries a second current. The first or second current alone cannot switch the free layer magnetization. The first and second currents together can switch the free layer magnetization. When the first current is driven through the magnetic element and the second current is provided, the combination sets the pinned layer magnetization direction. In one aspect, the pinned layer magnetization is set by heating the AFM layer to approximately at or above the blocking temperature. In order to configure the logic cell, an initial direction for the free layer magnetization is also set.

Owner:SAMSUNG SEMICON

Programmable logic device

InactiveUS6864710B1Increase capacityHigh voltageSolid-state devicesLogic circuits using elementary logic circuit componentsProgrammable logic deviceParallel computing

A programmable logic device comprising one or more horizontal routing channels, one or more vertical routing channels, and a logic element. Each logic element may be configured to connect between one of the horizontal routing channels and one of the vertical routing channels. The logic element may comprise a logic block cluster and a memory block.

Owner:MONTEREY RES LLC

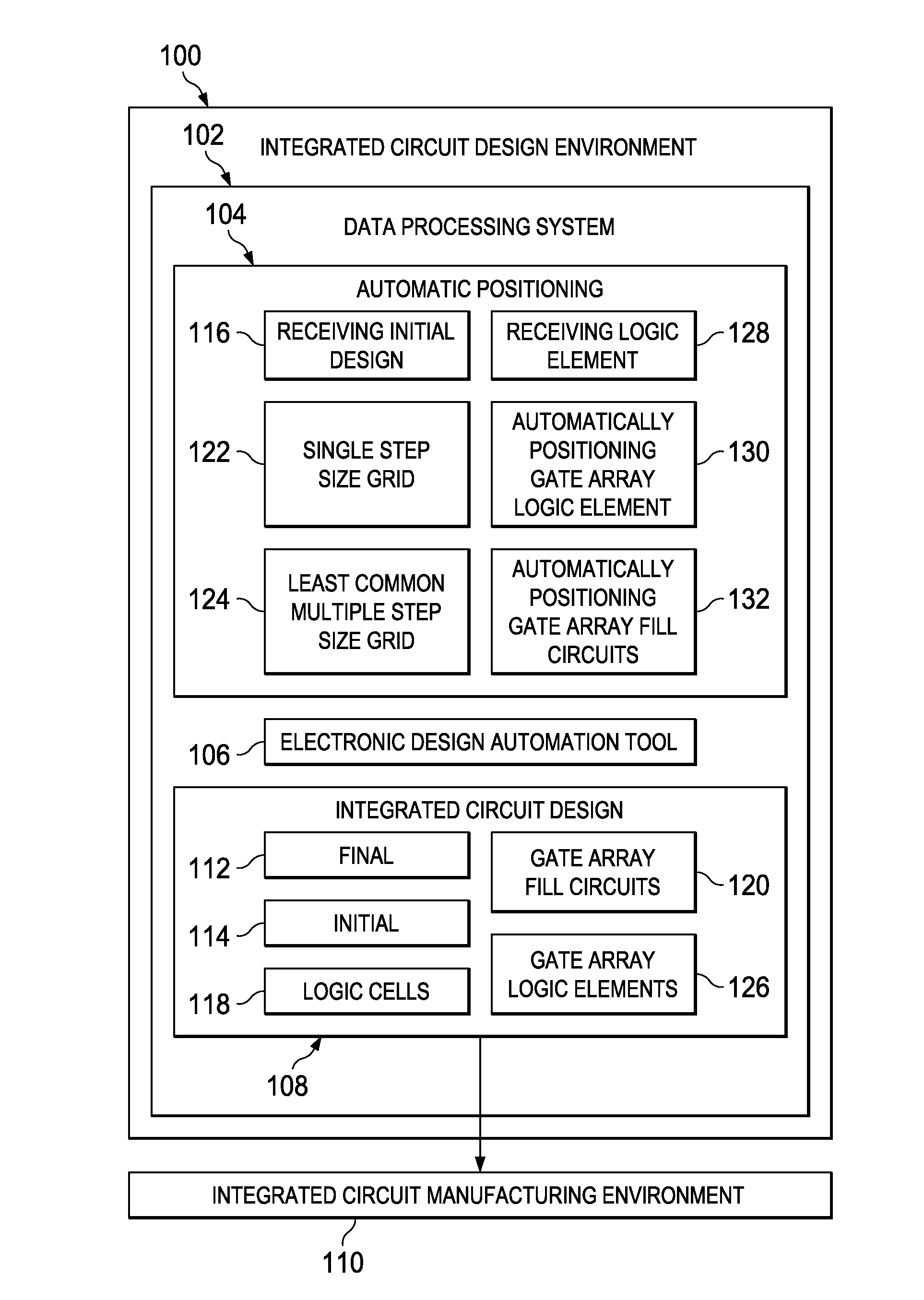

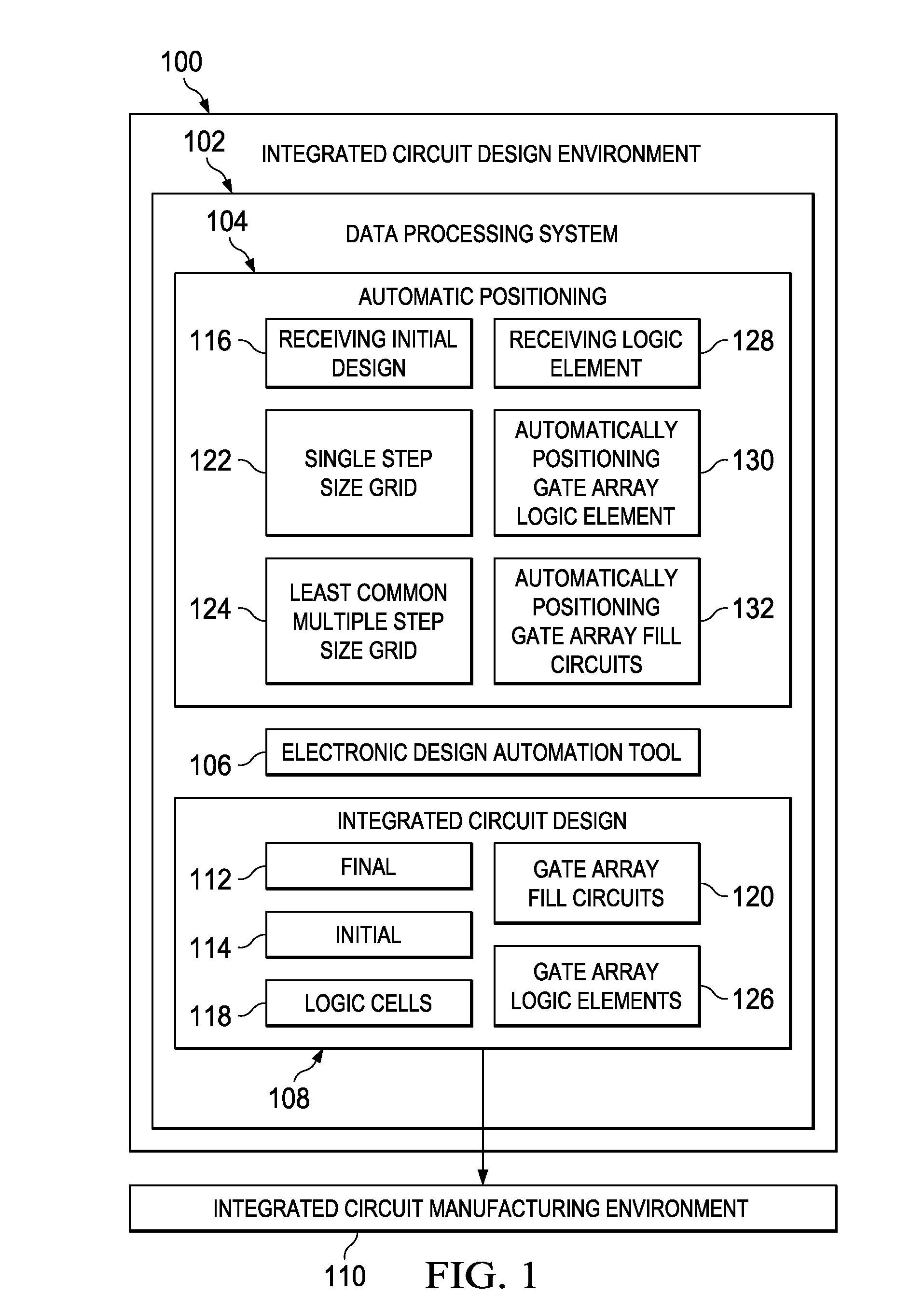

Automatic Positioning of Gate Array Circuits in an Integrated Circuit Design

ActiveUS20110072407A1Computer programmed simultaneously with data introductionComputer aided designLogic cellGate array

An automated method and apparatus for positioning gate array circuits in an integrated circuit design. An initial integrated circuit design includes logic cells and gate array fill circuits positioned thereon. The gate array fill circuits are positioned in available space between the adjacent logic cells so as to fill the available space with the maximum gate array fill circuits. A gate array logic element to be positioned in the integrated circuit design, such as may be required by an engineering change to the circuit design, is automatically positioned between adjacent logic cells so as to allow for full utilization of any space remaining between the adjacent logic cells by gate array fill circuits.

Owner:GLOBALFOUNDRIES US INC

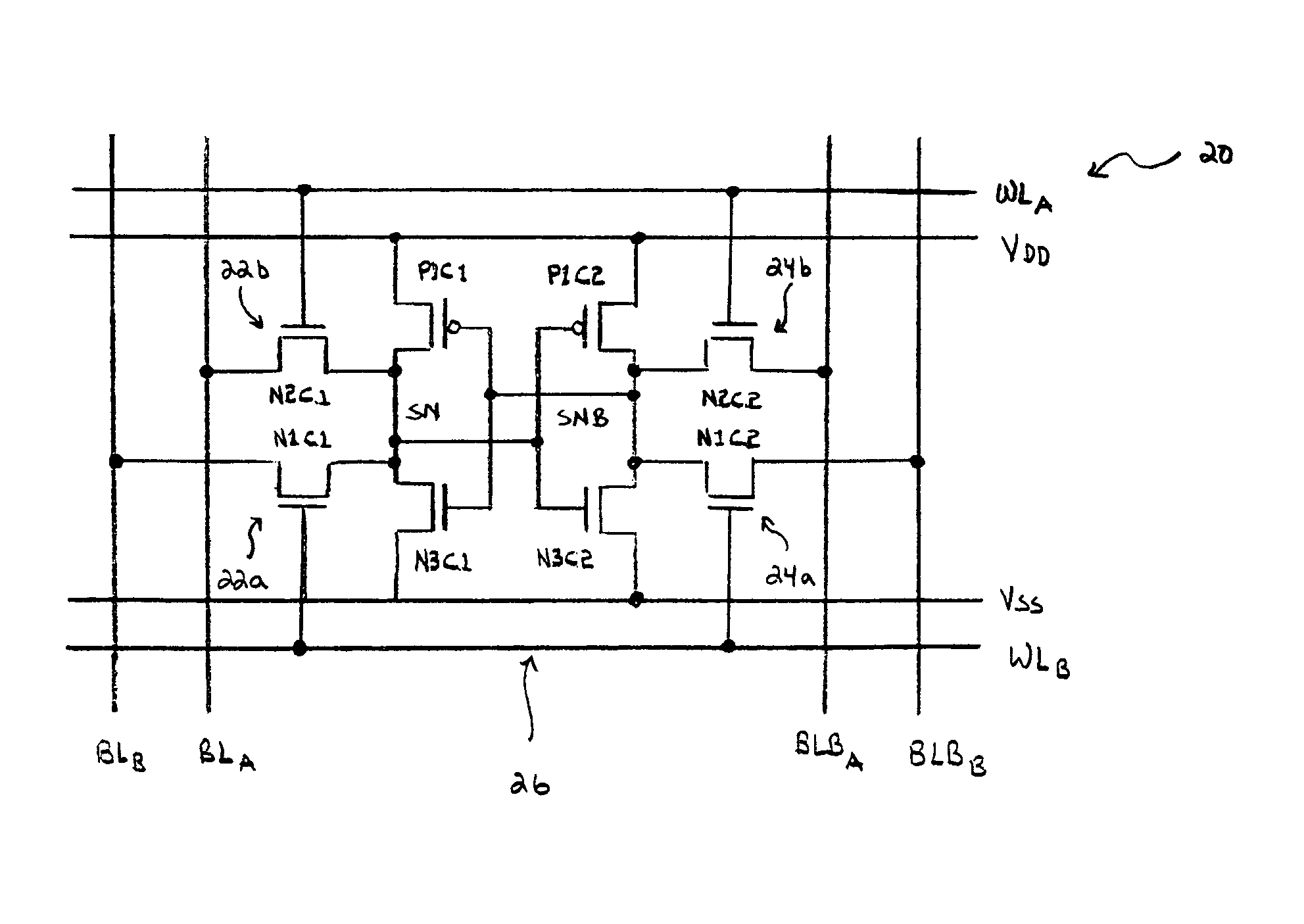

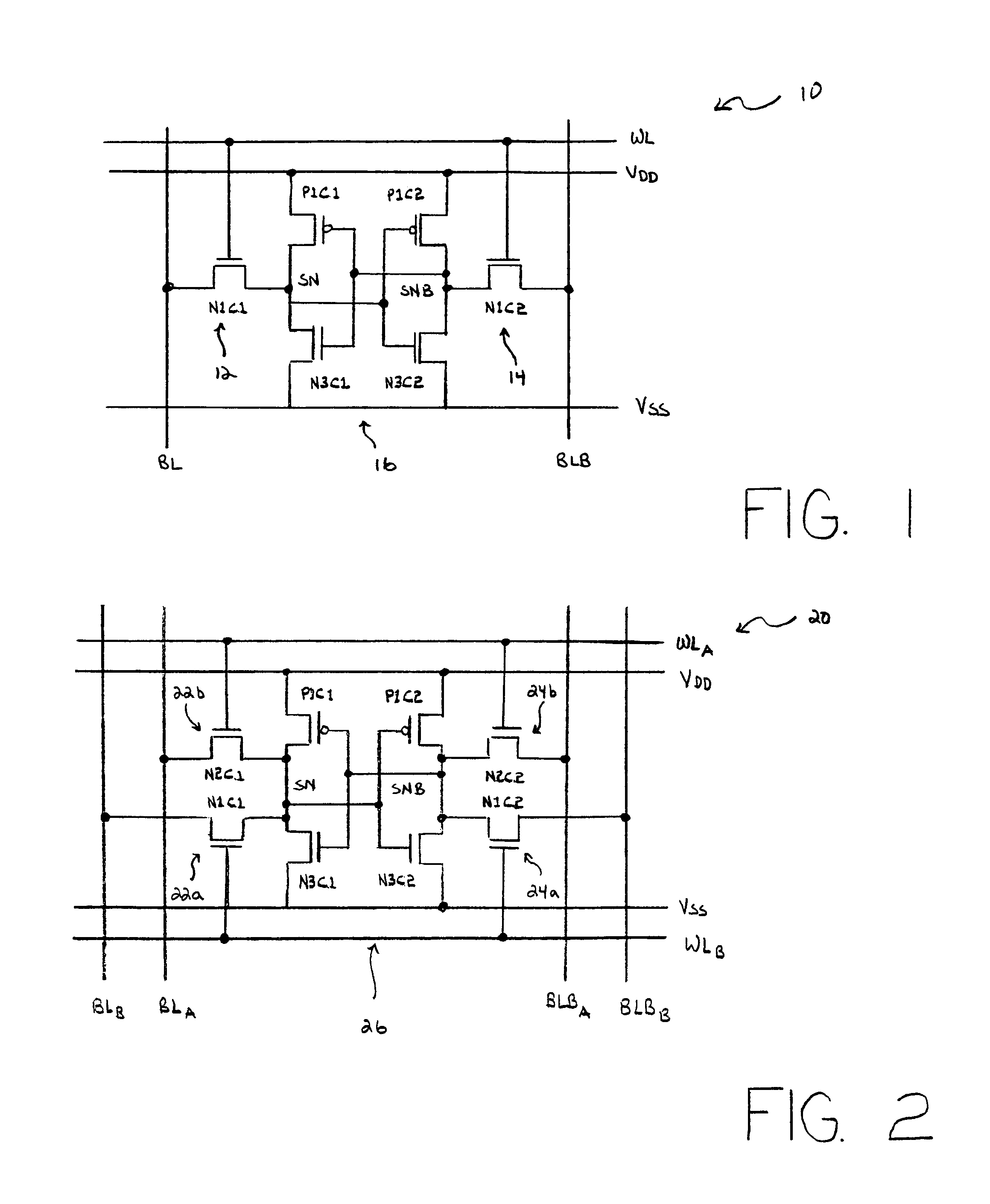

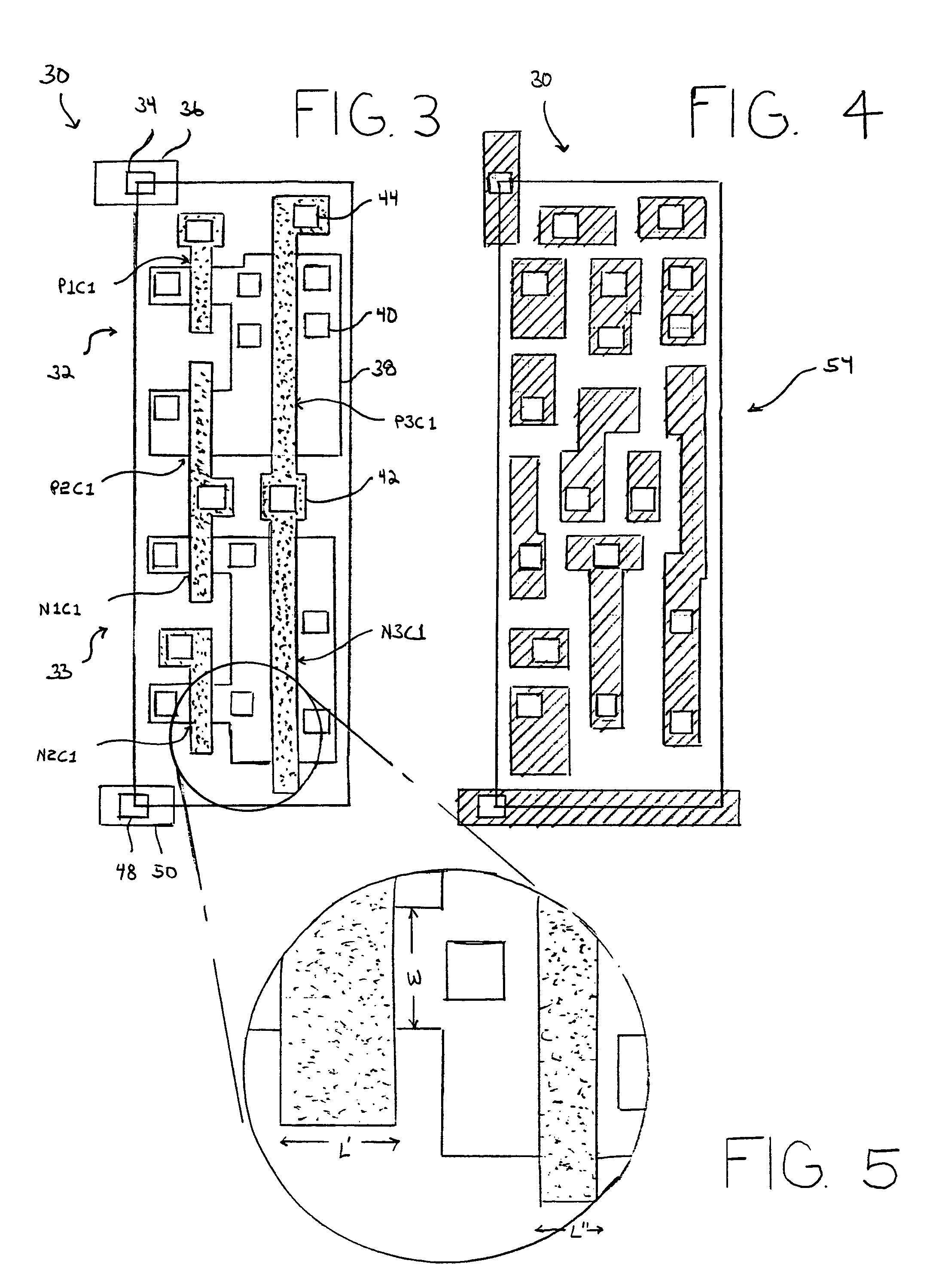

Integrated circuit cell architecture configurable for memory or logic elements

InactiveUS8044437B1Low costImprove performanceTransistorSemiconductor/solid-state device detailsBit lineEngineering

An improved integrated circuit cell architecture is provided for configurability between a memory cell or logic elements. The cell architecture is configured on variable layers above a first layer of metal, with the first layer of metal and layers therebelow reserved as fixed layers. By coupling a maximum of two layout cells together, a single-port or dual-port memory cell is realized. Likewise, by interconnecting transistors within a single cell or transistors among two or more cells, a logic device is realized. Within each cell, the bit lines are arranged on a layer separate from the wordlines, and extend orthogonal to each other.

Owner:AVAGO TECH INT SALES PTE LTD

Asynchronous pipeline with latch controllers

An asynchronous pipeline for high-speed applications uses simple transparent latches in its datapath and small latch controllers for each pipeline stage. The stages communicate with each other using request signals and acknowledgment signals. Each transition on the request signal indicates the arrival of a distinct new data item. Each stage comprises a data latch that is normally enabled to allow data to pass through, and a latch controller that enables and disables the data latch. The request signal and the data are inputs to the data latch. Once the stage has latched the data, a done signal is produced, which is sent to the latch controller, to the previous stage as an acknowledgment signal, and to the next stage as a request signal. The latch controller disables the latch upon receipt of the done signal, and re-enables the data latch upon receipt of the acknowledgment signal from the next stage. For correct operation, the request signal must arrive at the stage after the data inputs have stabilized. The asynchronous pipeline may incorporate logic elements to combine data, as well as matched delay elements for the request, acknowledgment, and done signals. The asynchronous pipeline may also incorporate clocked CMOS logic gates. Fork and join structures are also provided by the asynchronous pipeline design.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

Methodology for correlated memory fail estimations

ActiveUS8214190B2Adding excessive overheadAnalogue computers for electric apparatusProbabilistic CADStatistical analysisParallel computing

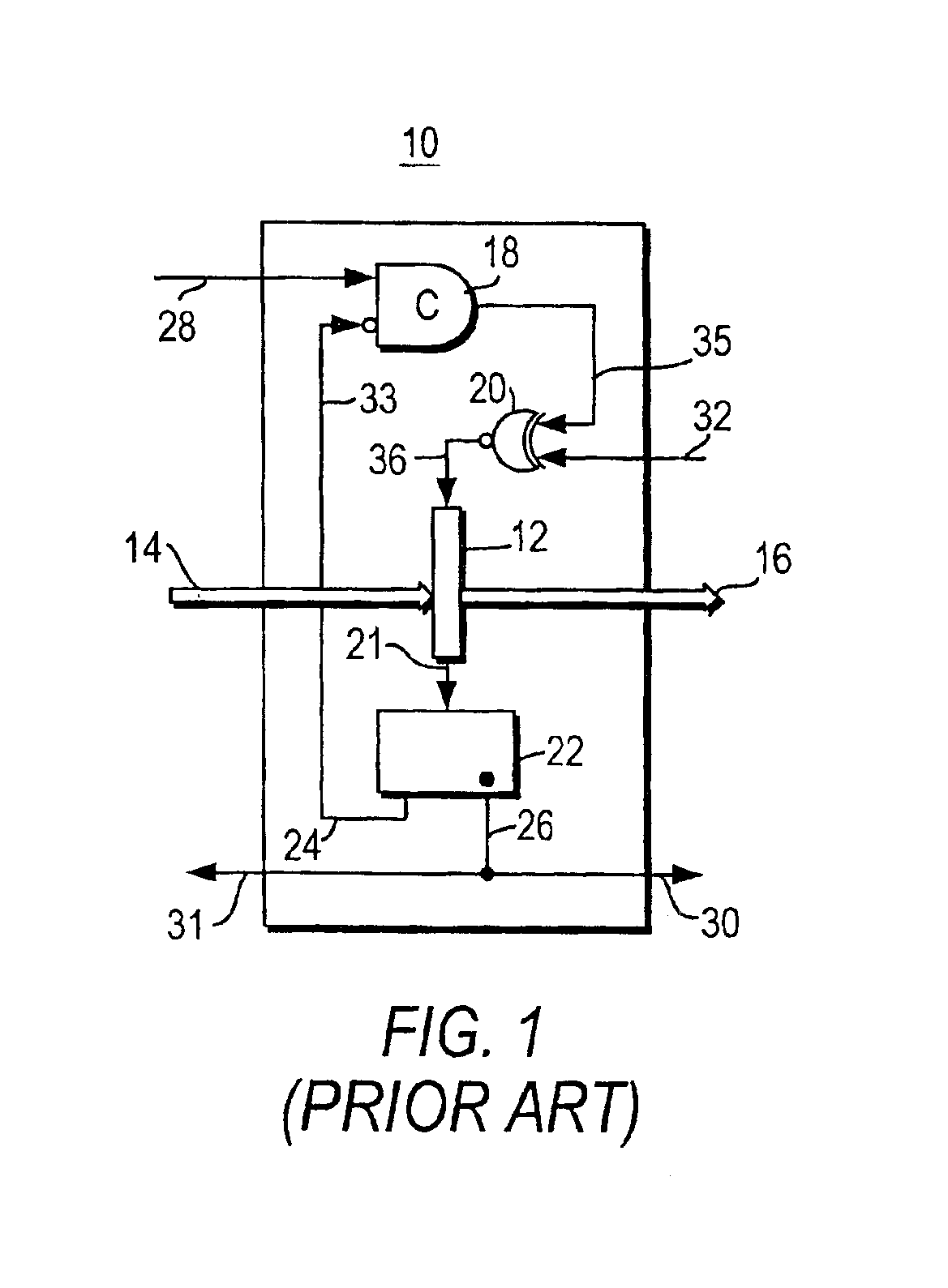

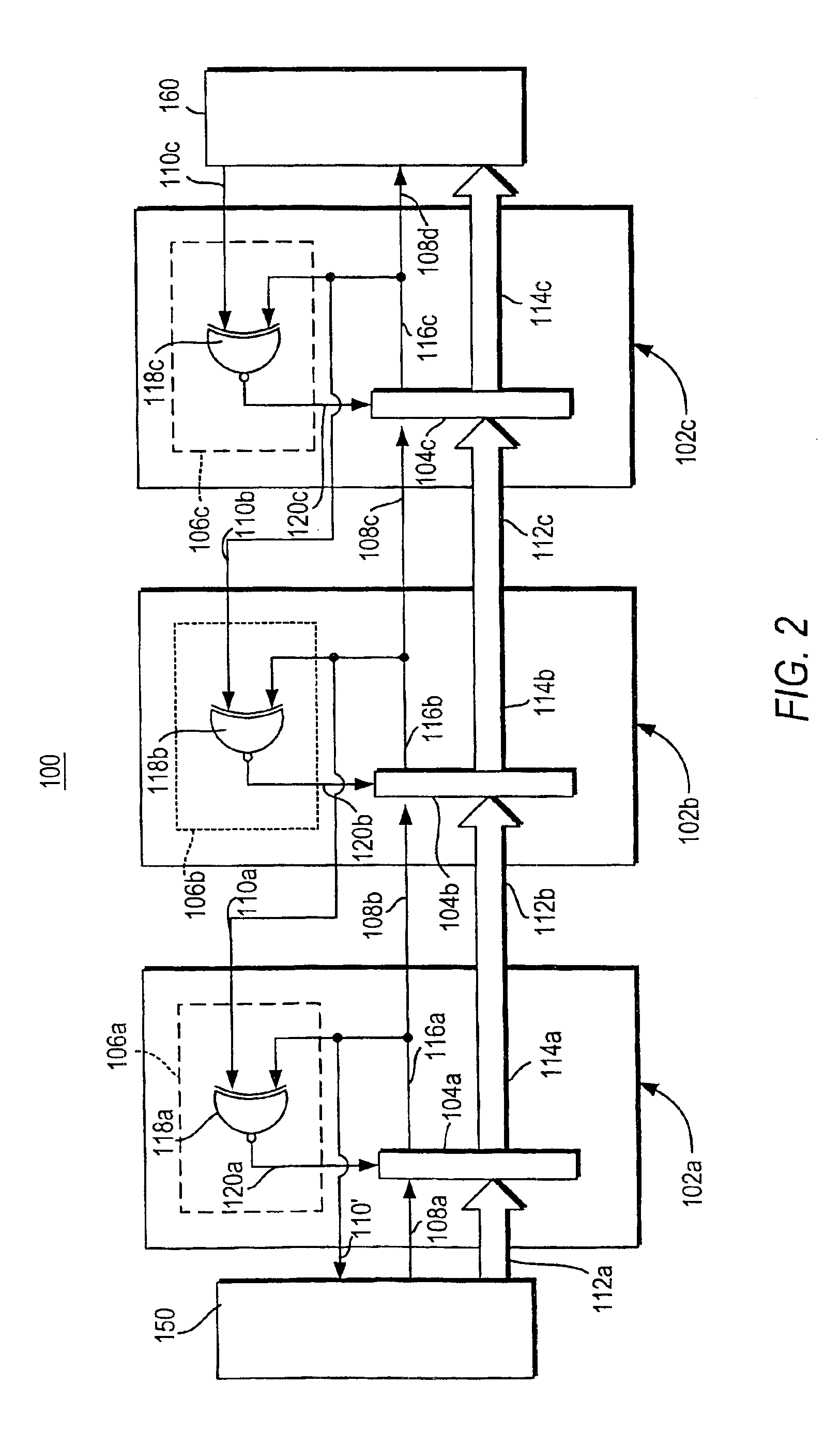

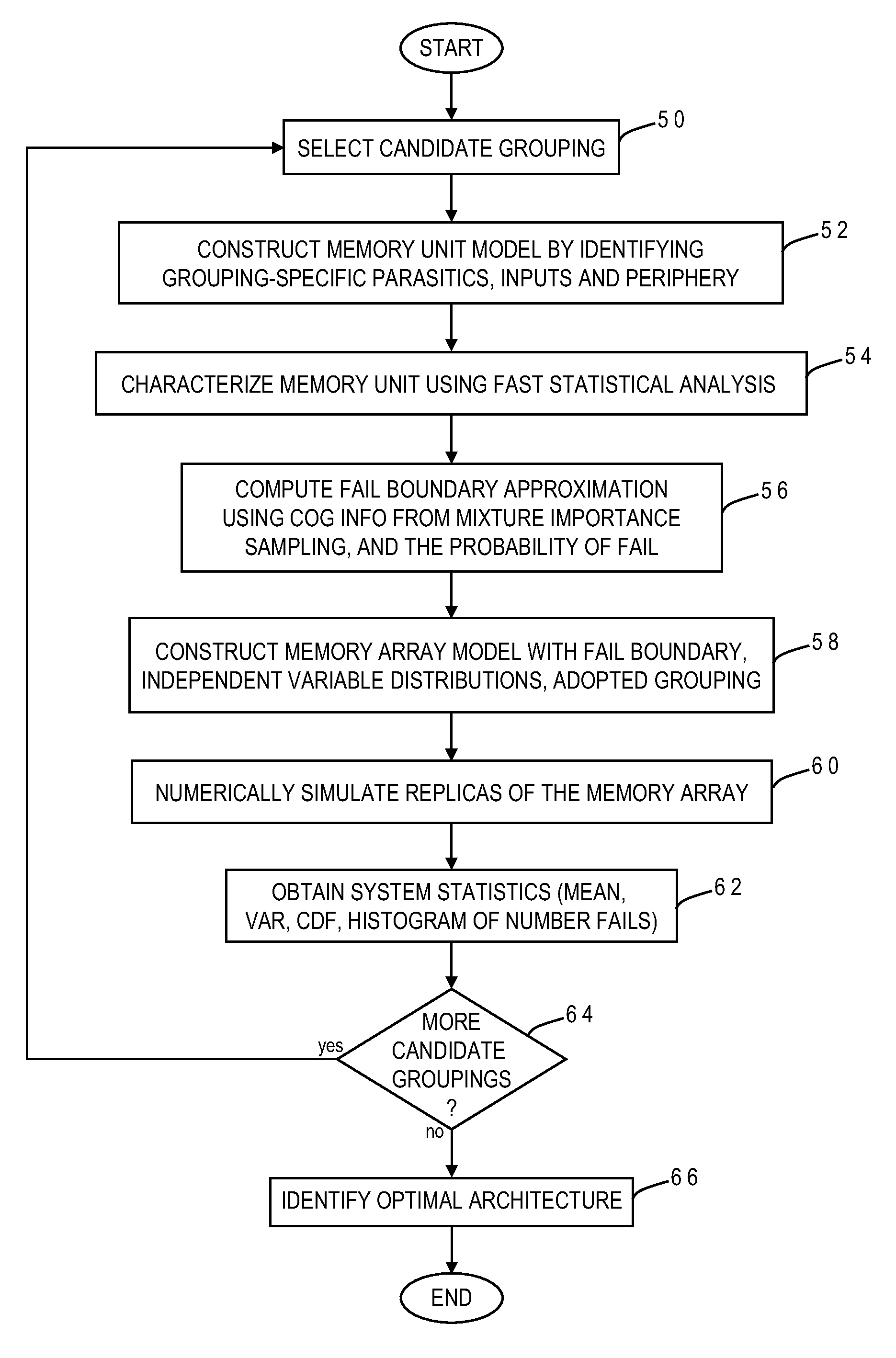

Correlated failure distribution for memory arrays having different groupings of memory cells is estimated by constructing memory unit models for the groupings based on multiple parameters, establishing failure conditions of the memory unit model using fast statistical analysis, calculating a fail boundary of the parameters for each memory unit model based on its corresponding failure conditions, and constructing memory array models characterized by the fail boundaries. Operation of a memory array model is repeatedly simulated with random values of the parameters assigned to the memory cells and peripheral logic elements to identify memory unit failures for each simulated operation. A mean and a variance is calculated for each memory array model, and an optimal architecture can thereafter be identified by selecting the grouping exhibiting the best mean and variance, subject to any other circuit requirements such as power or area.

Owner:GLOBALFOUNDRIES US INC

Memory module decoder

A memory module connectable to a computer system includes a printed circuit board, a plurality of memory devices coupled to the printed circuit board, and a logic element coupled to the printed circuit board. The plurality of memory devices has a first number of memory devices. The logic element receives a set of input control signals from the computer system. The set of input control signals corresponds to a second number of memory devices smaller than the first number of memory devices. The logic element generates a set of output control signals in response to the set of input control signals. The set of output control signals corresponds to the first number of memory devices.

Owner:NETLIST INC

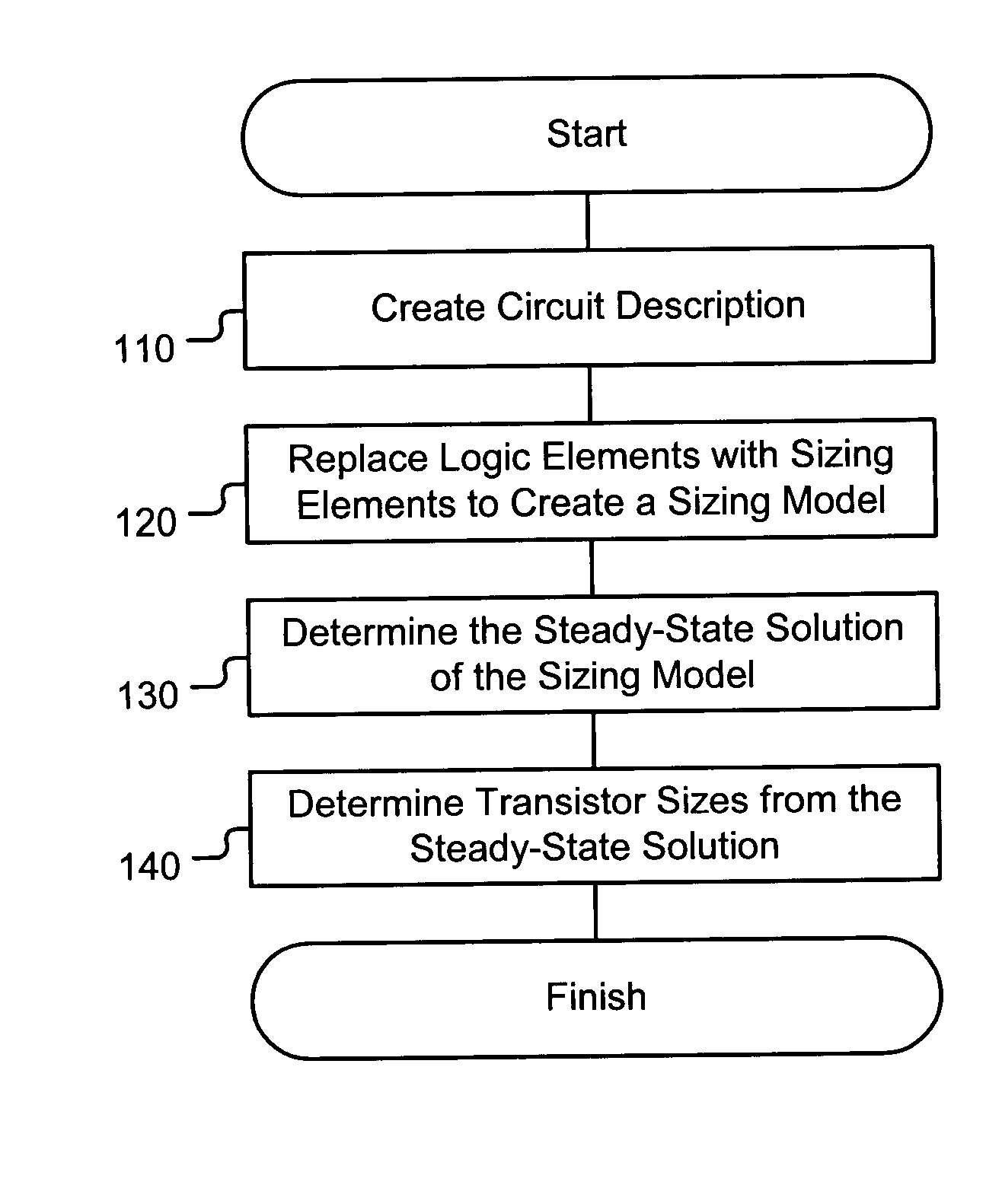

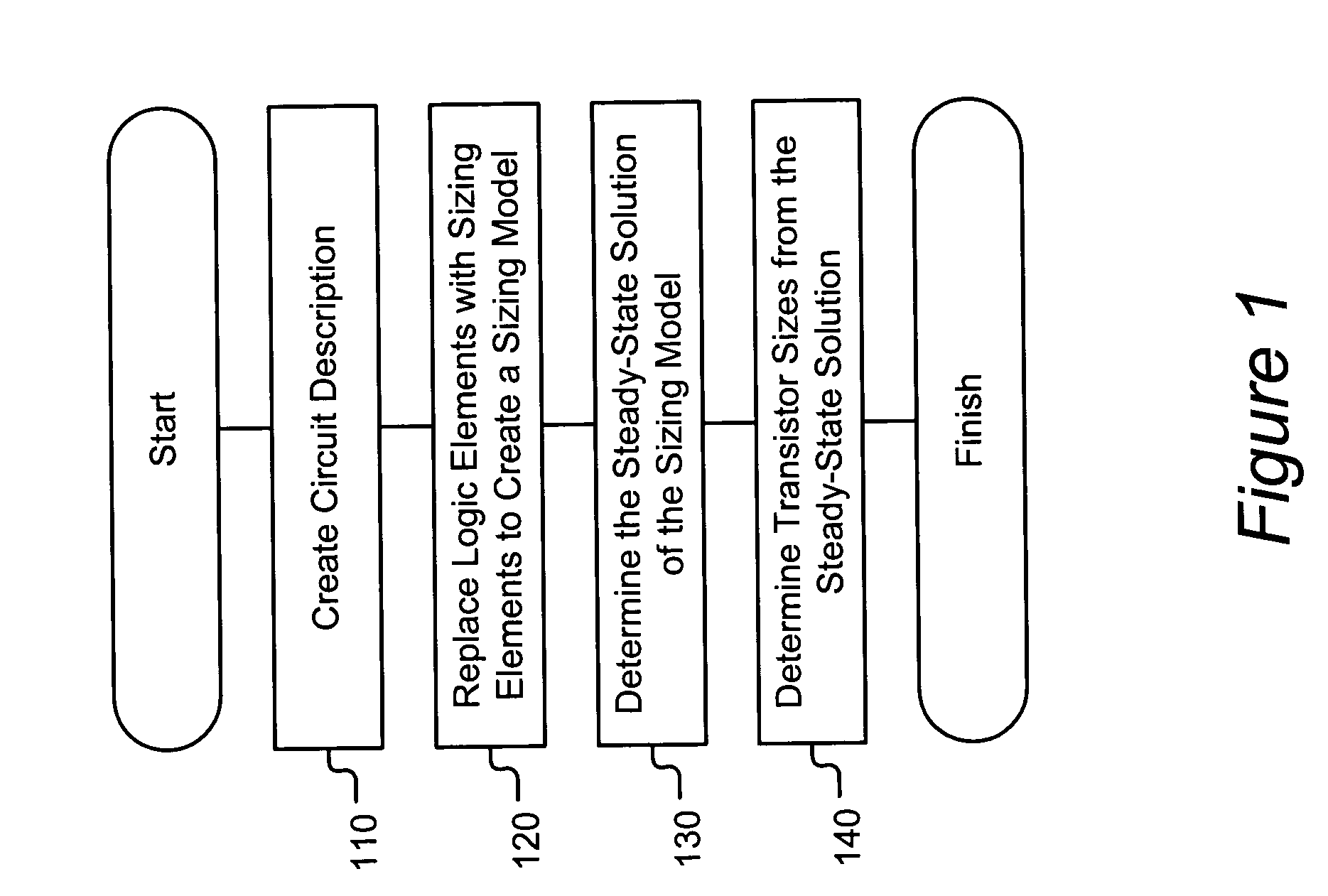

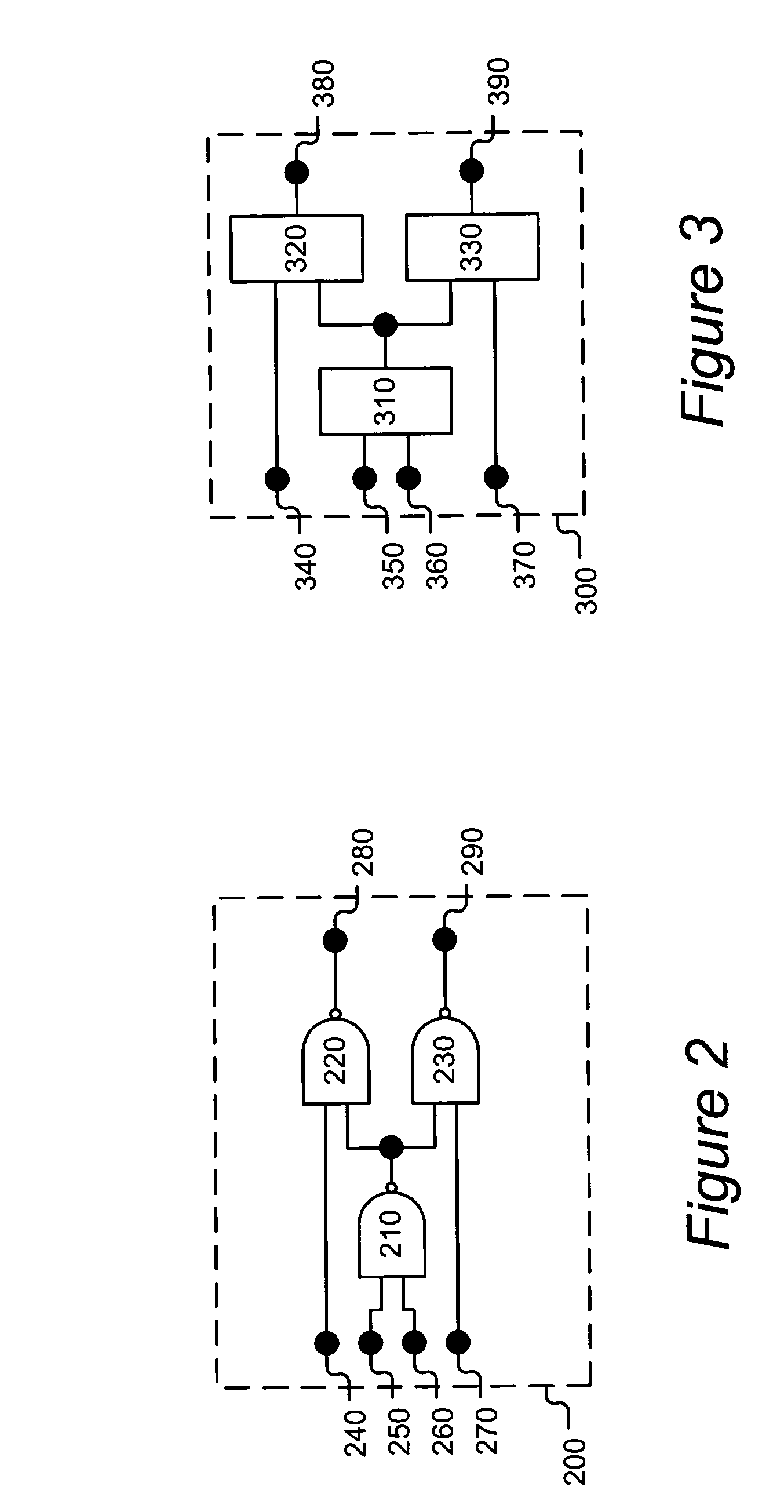

Method and apparatus for determining transistor sizes

A method of determining at least one ratio of transistor sizes. The method includes creating a sizing model by replacing at least one logic element in a circuit description with a sizing element that includes a piece-wise-linear current source. The method also includes determining a steady state solution to the sizing mode and determining at least one ratio of transistor sizes from the steady state solution. The method may also include determining at least one dimension of a transistor based at least in part upon the ratio of transistor sizes.

Owner:ORACLE INT CORP

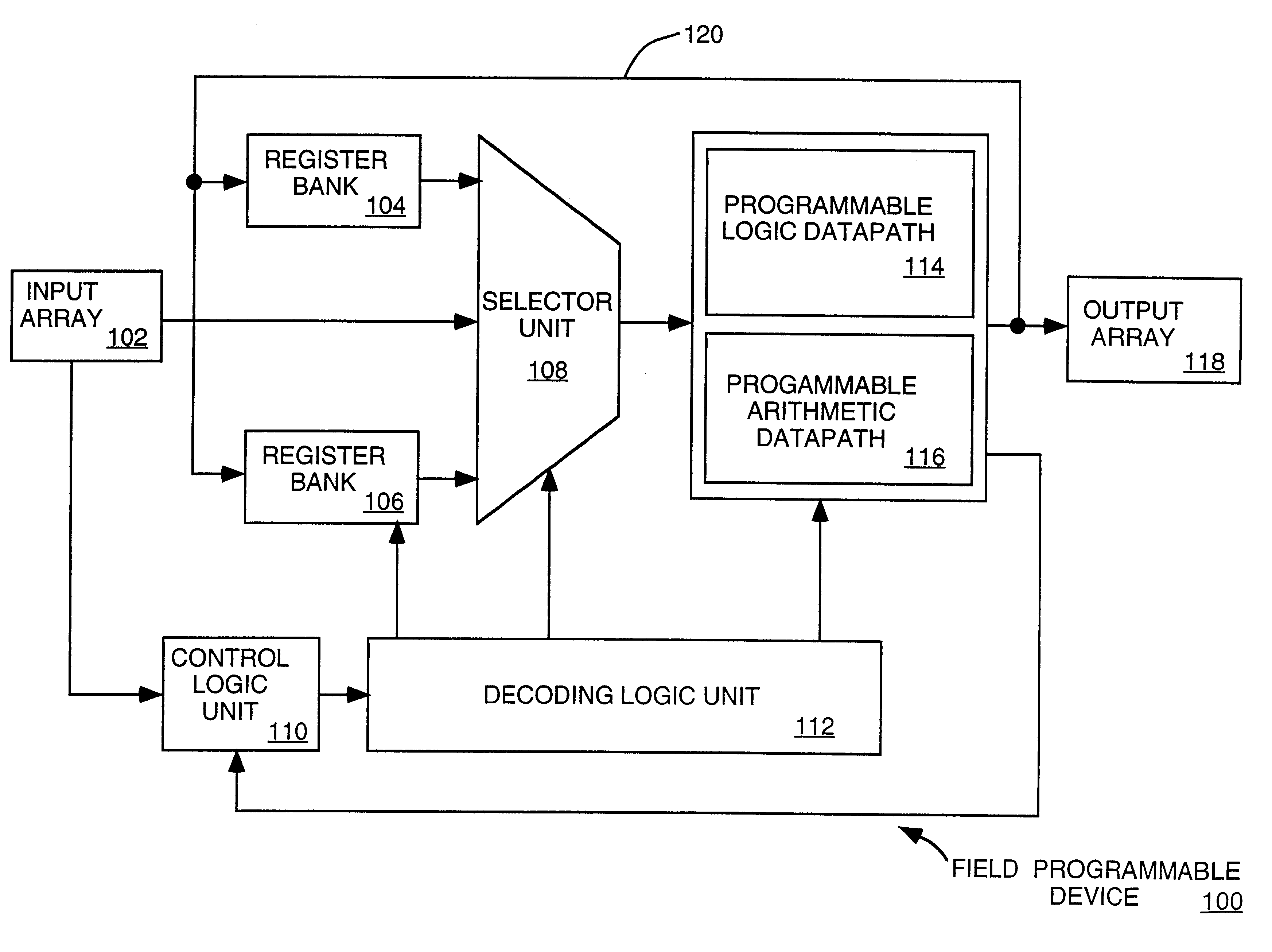

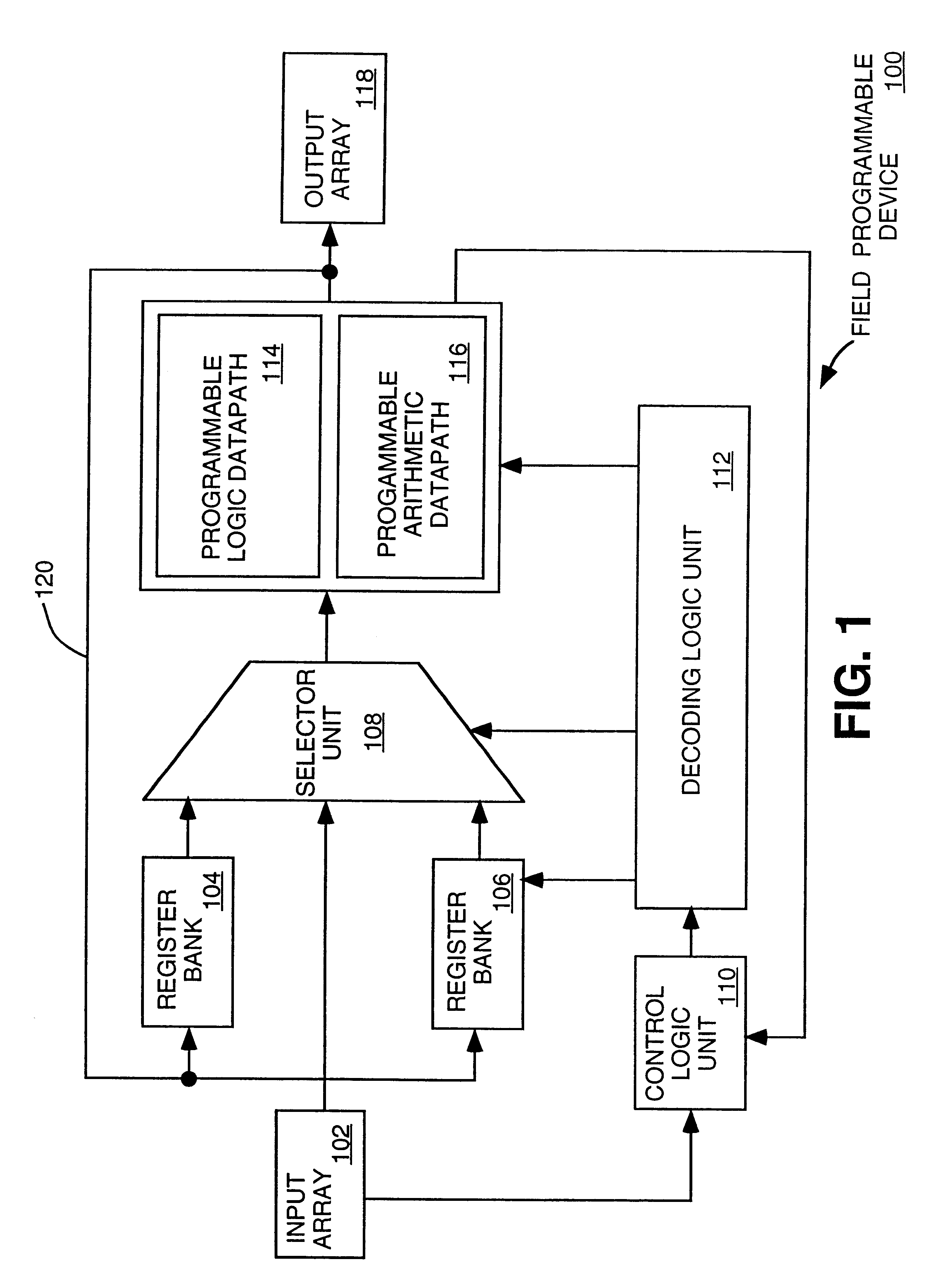

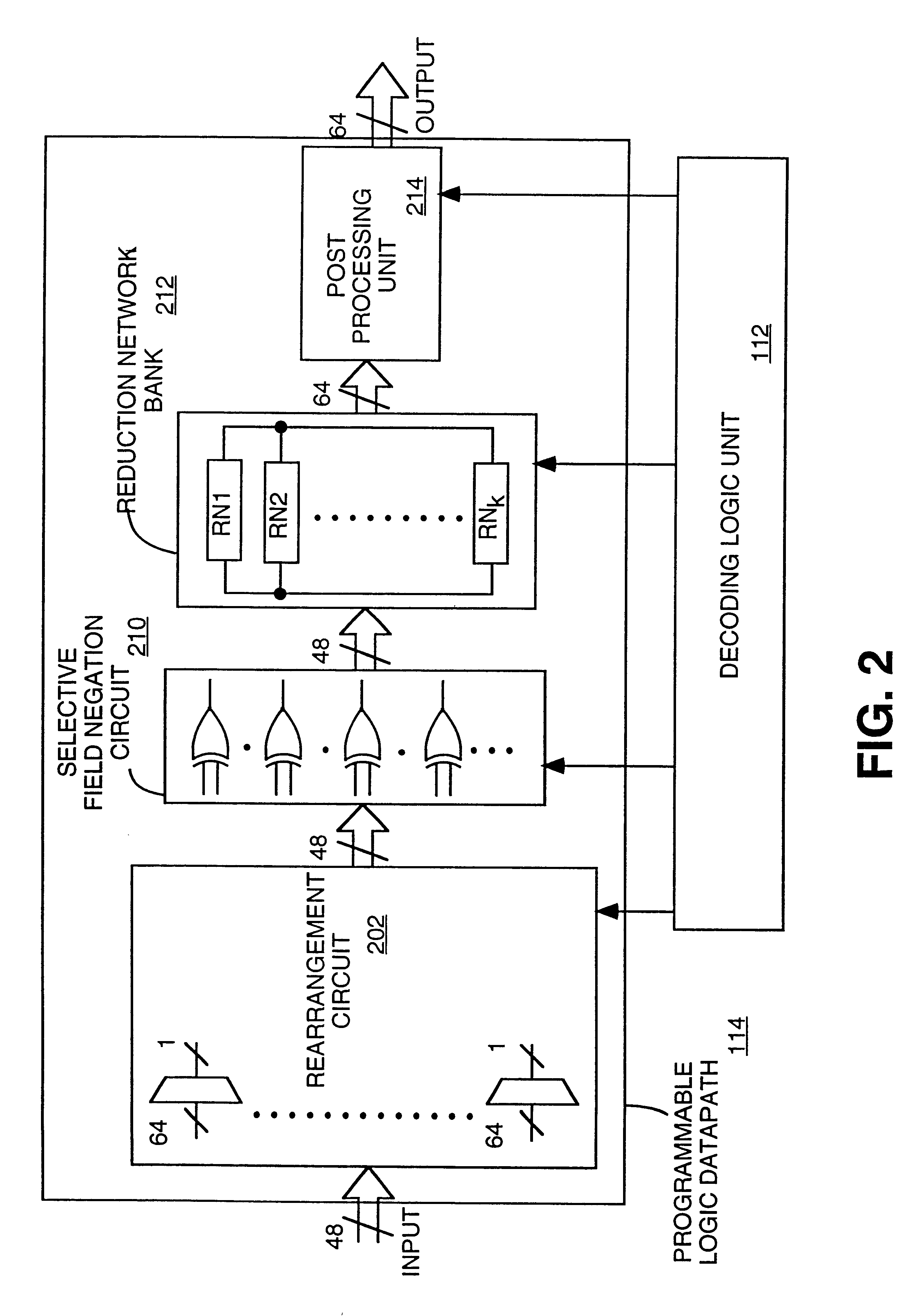

Programmable logic datapath that may be used in a field programmable device

A method and apparatus for providing a programmable logic datapath that may be used in a field programmable device. According to one aspect of the invention, a programmable logic datapath is provided that includes a plurality of logic elements to perform various (Boolean) logic operations. The programmable logic datapath further includes circuitry to selectively route and select operand bits between the plurality of logic elements (operand bits is used hereinafter to refer to input bits, logic operation result bits, etc., that may be generated within the logic datapath). In one embodiment, by providing control bits concurrently with operand bits to routing and selection (e.g., multiplexing) circuitry, the programmable logic datapath of the invention can provide dynamic programmability to perform a number of logic operations on inputs of various lengths on a cycle-by-cycle basis.

Owner:PMC-SIERRA

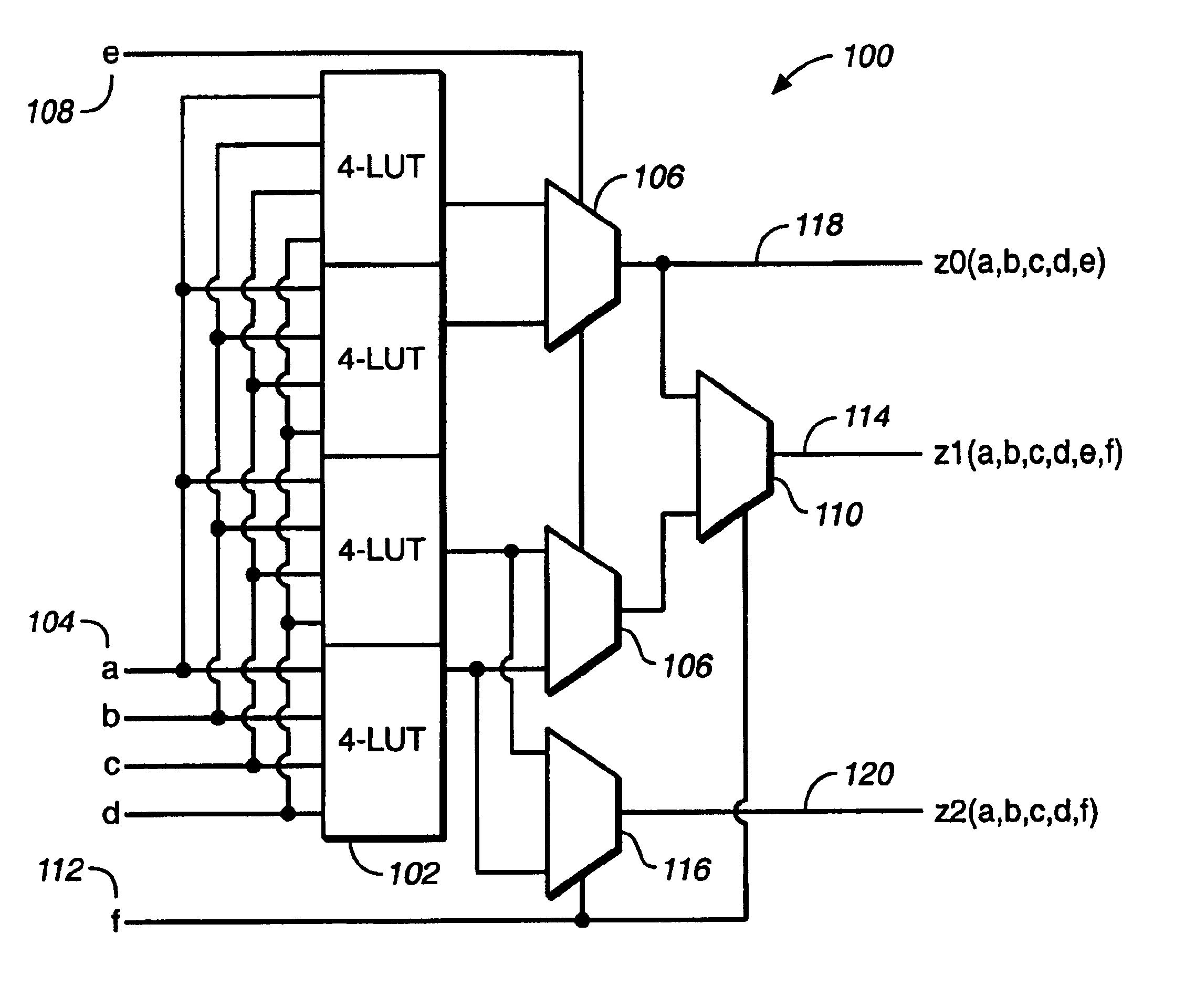

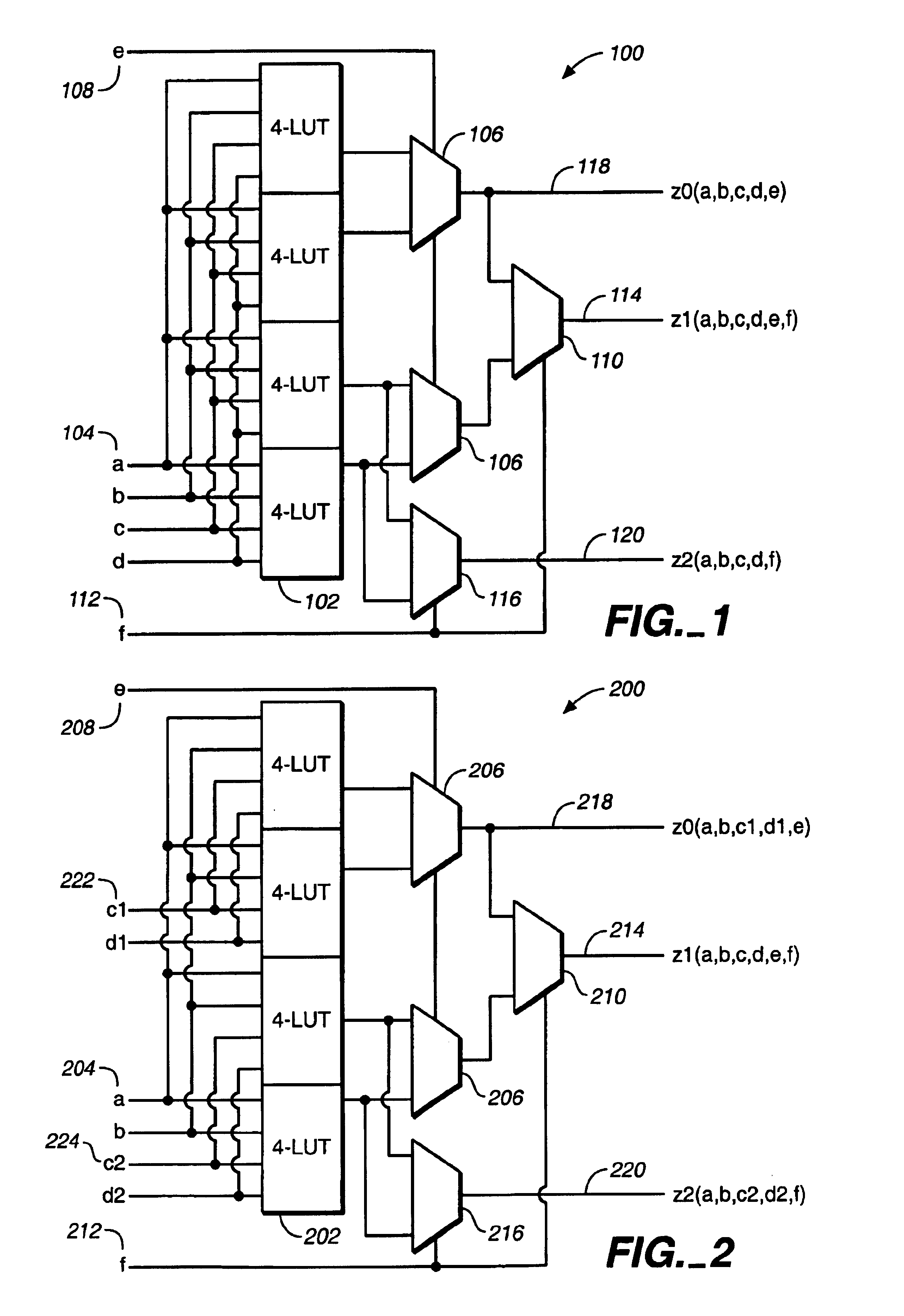

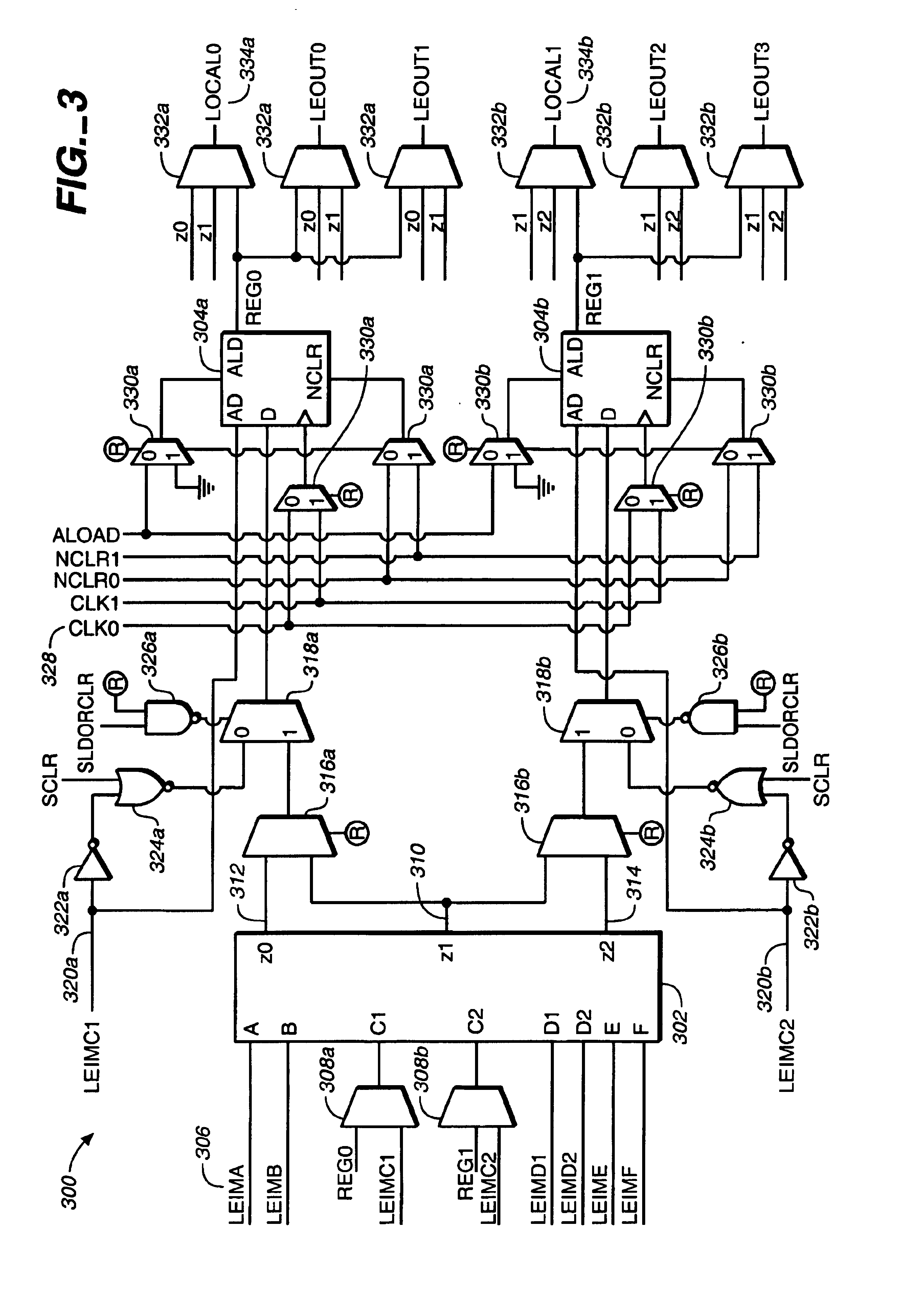

Fracturable lookup table and logic element

InactiveUS6943580B2Solid-state devicesLogic circuits using elementary logic circuit componentsMultiplexerEngineering

A logic element includes memory elements, multiplexers, and controls. The multiplexers are arranged in levels including a highest level of multiplexers with inputs connected to the memory elements and outputs connected to inputs of a next-to-highest level of multiplexers and a first level of multiplexers with inputs connected to outputs of a second level of multiplexers and at least one output. The controls are connected to the multiplexers. In a first operational mode the controls determine a first-mode output at the at least one output of the first level of multiplexers, and in a second operational mode the controls determine a plurality of second-mode outputs at selected outputs of multiplexers not at the first level of multiplexers.

Owner:ALTERA CORP

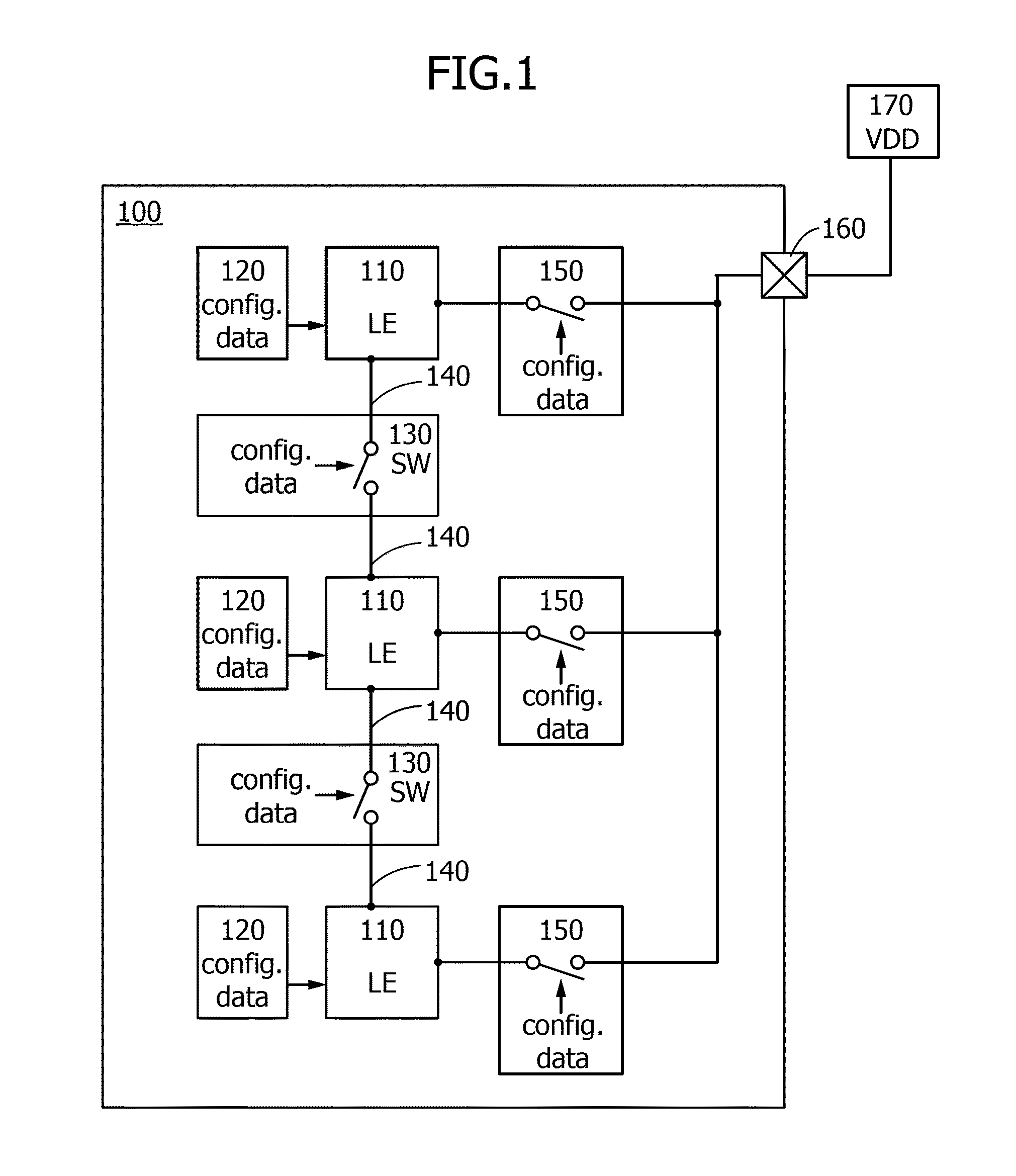

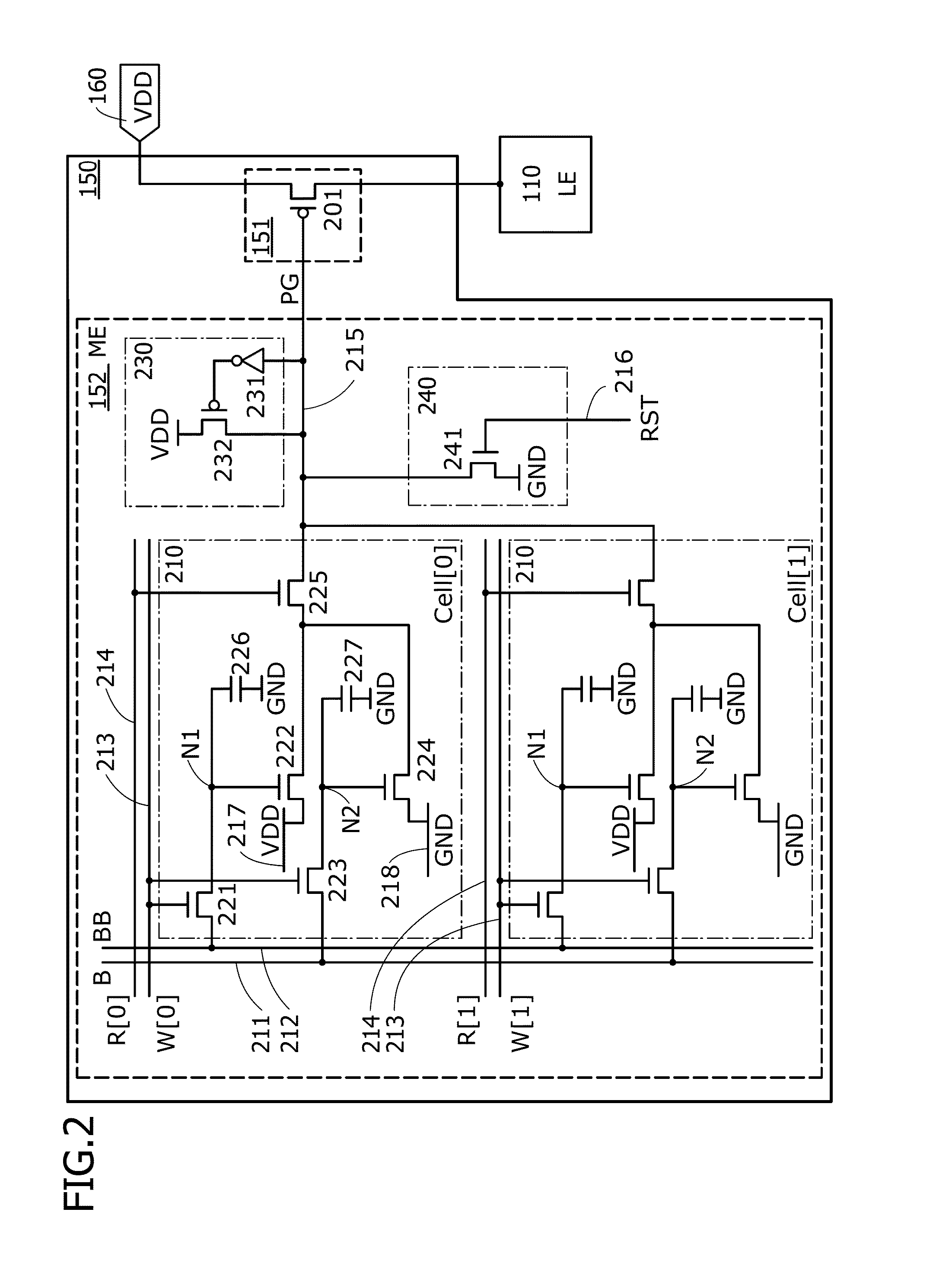

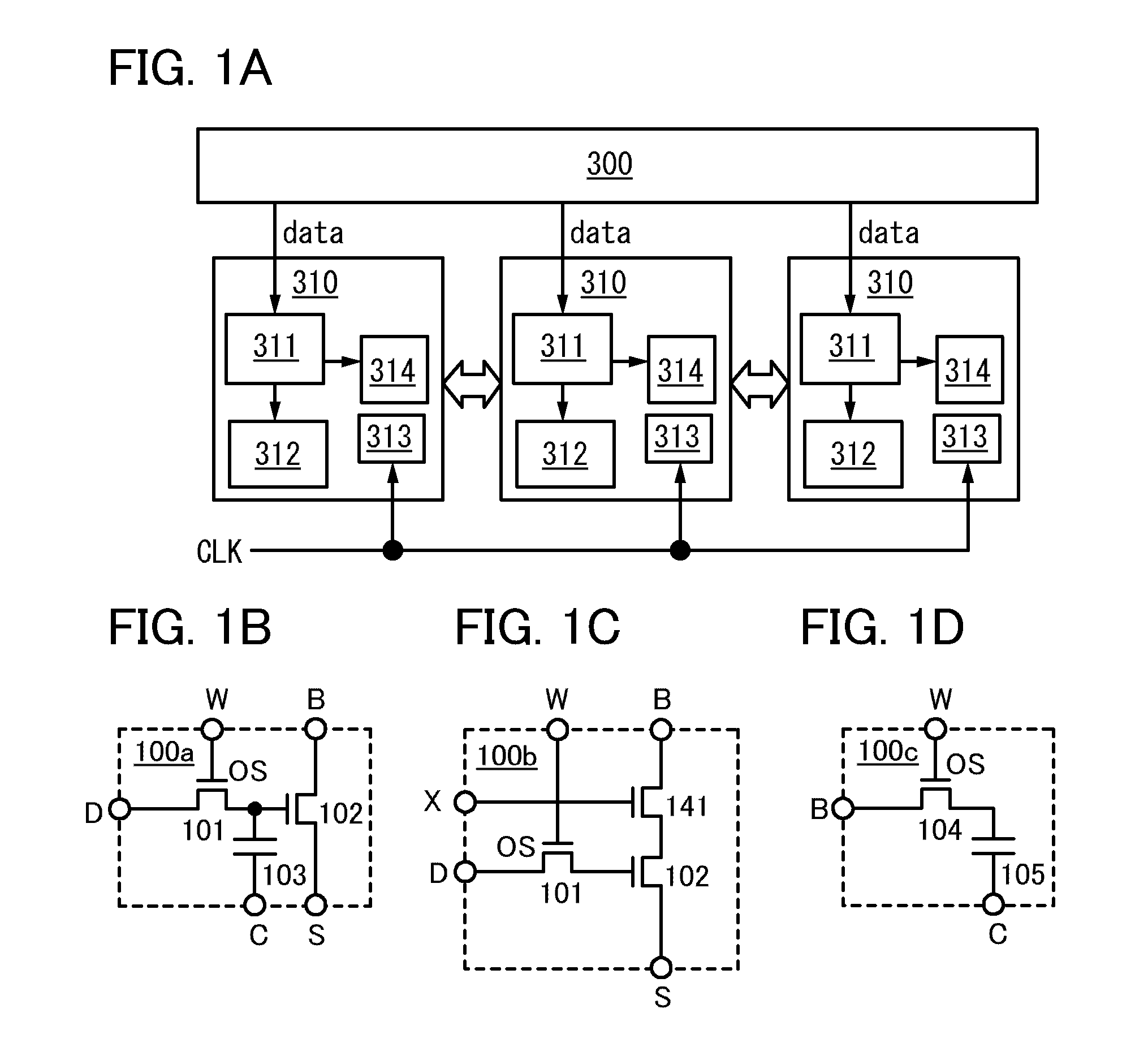

Semiconductor device

ActiveUS20140159771A1Less influenceImprove reliabilityPower reduction by control/clock signalSolid-state devicesPower semiconductor deviceControl signal

A programmable logic device (PLD) that can control whether to supply power in each logic element is provided. The PLD includes at least a programmable logic element, a terminal to which a potential is input from an external power source, a switch controlling conduction between the terminal and the logic element, and a memory outputting a control signal for setting the conduction state of the switch. The memory stores pieces of configuration data for setting the conduction state of the switch. Any one of the pieces of configuration data is output as the control signal from the memory to the switch.

Owner:SEMICON ENERGY LAB CO LTD

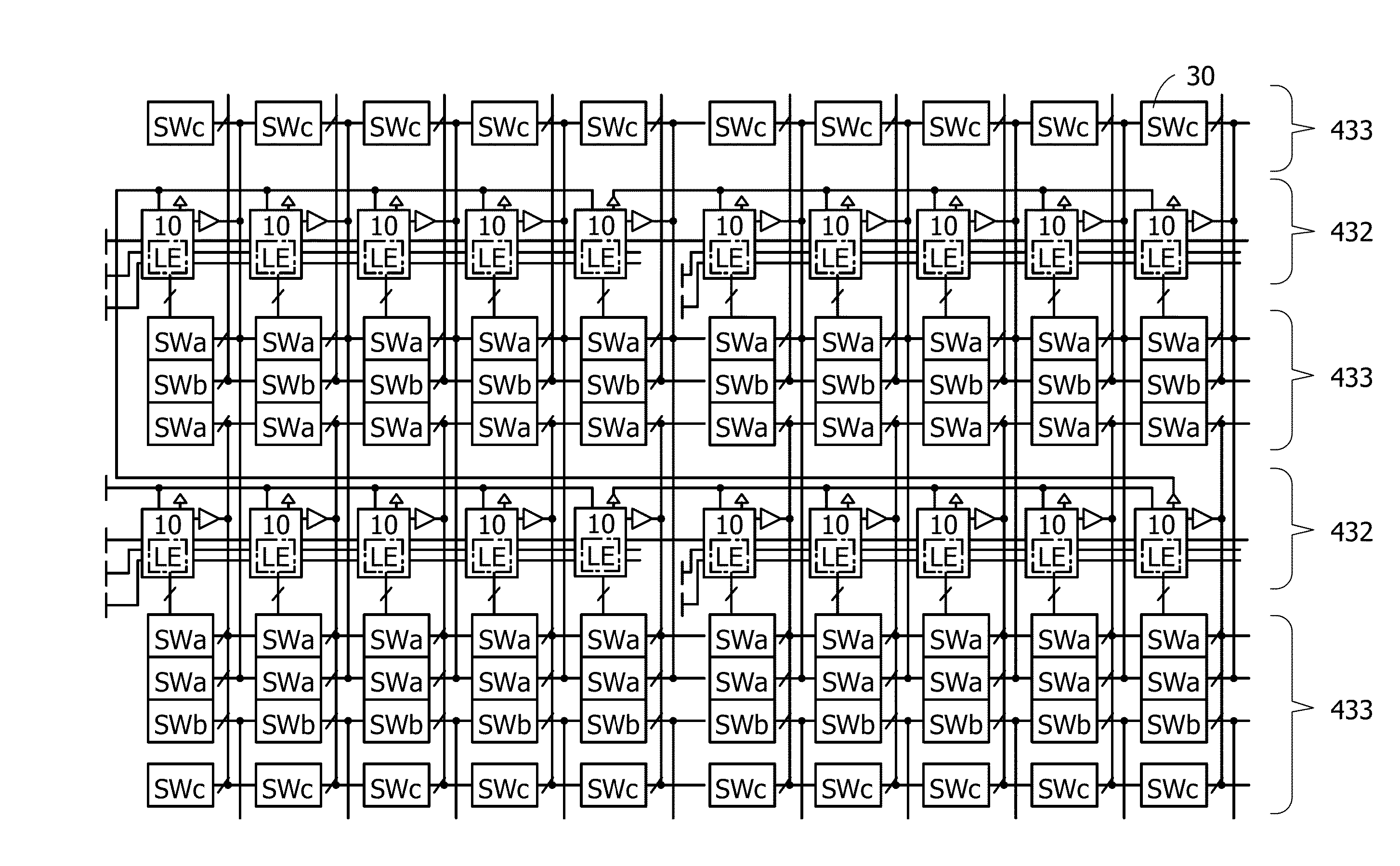

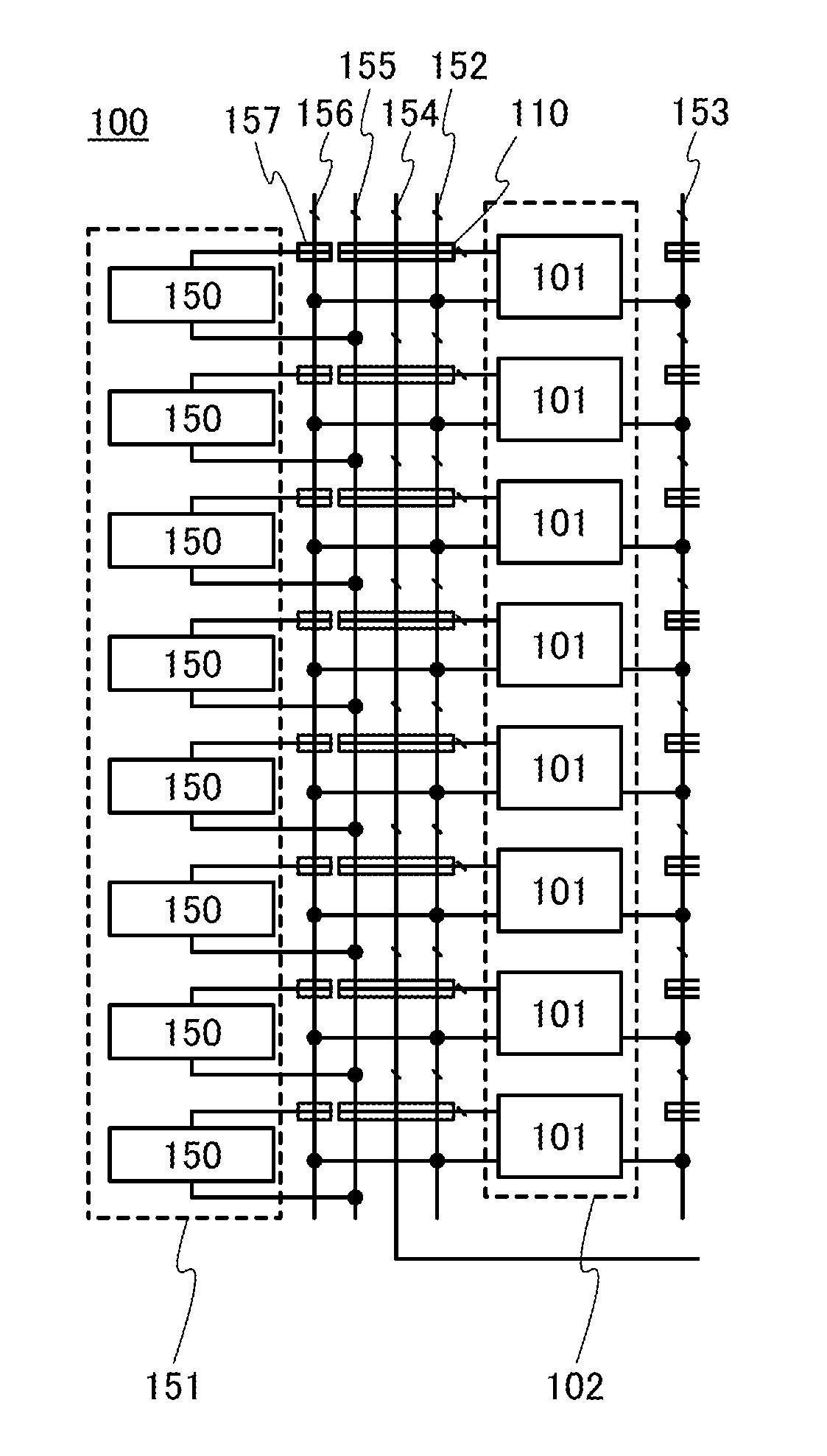

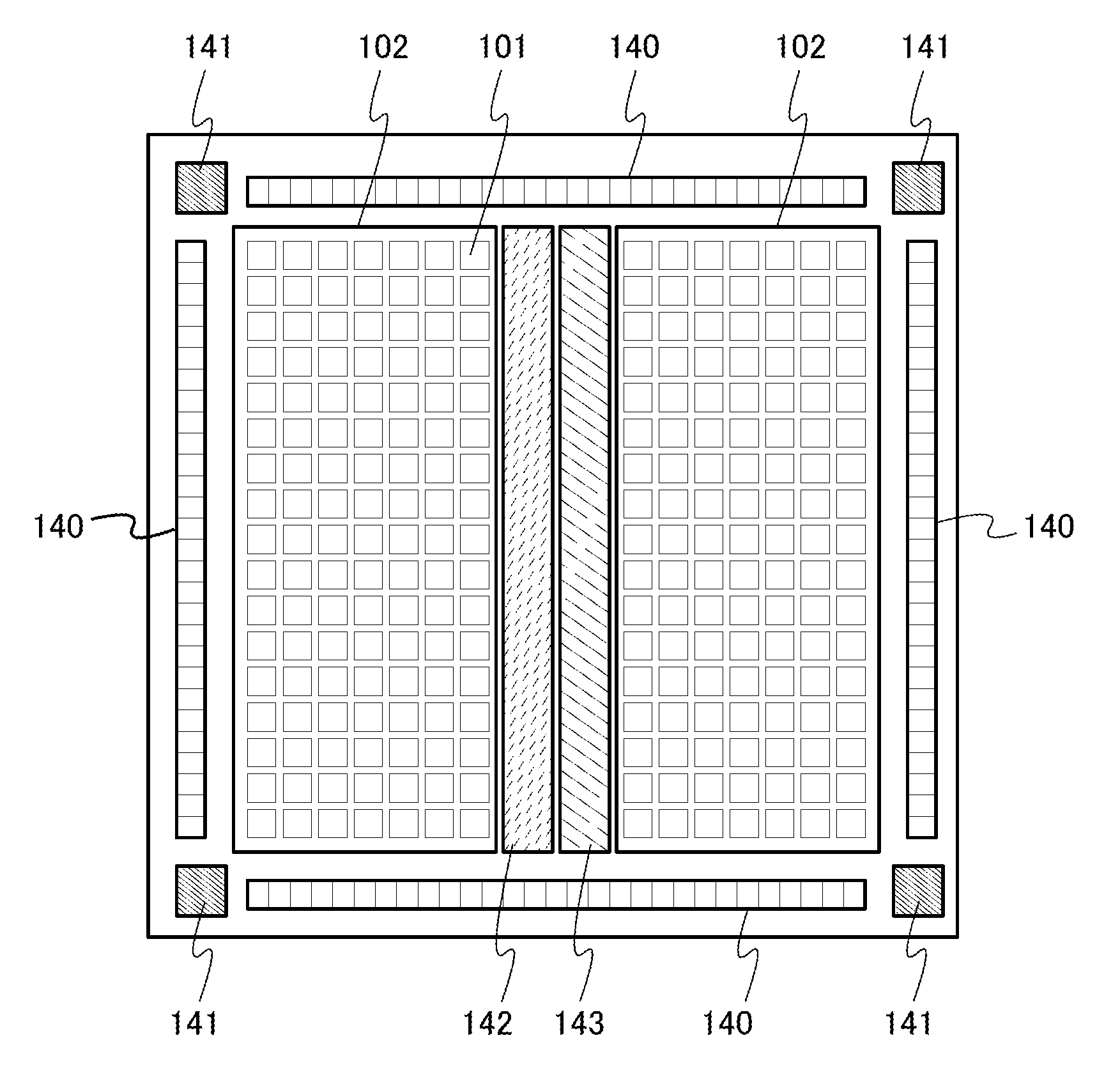

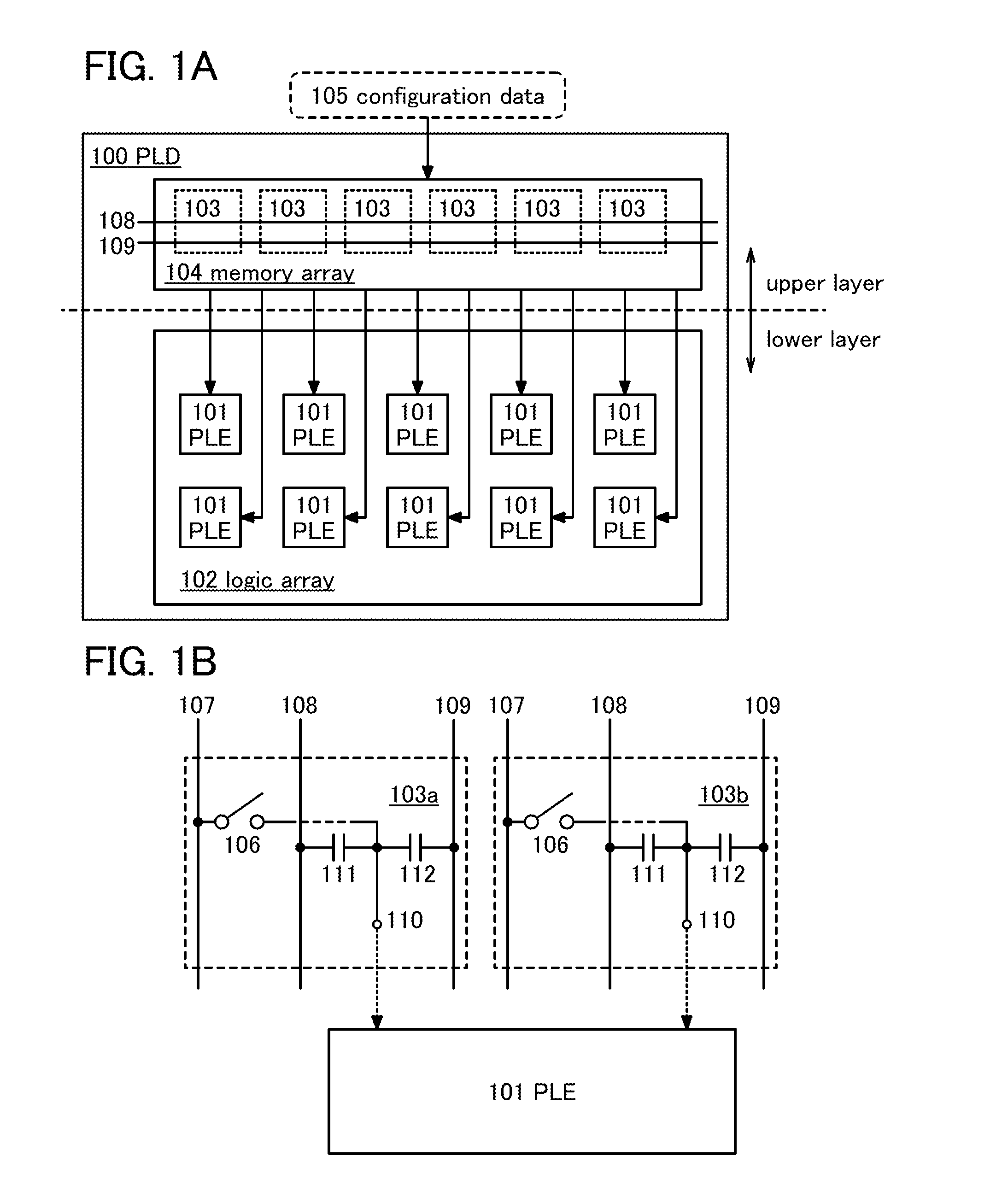

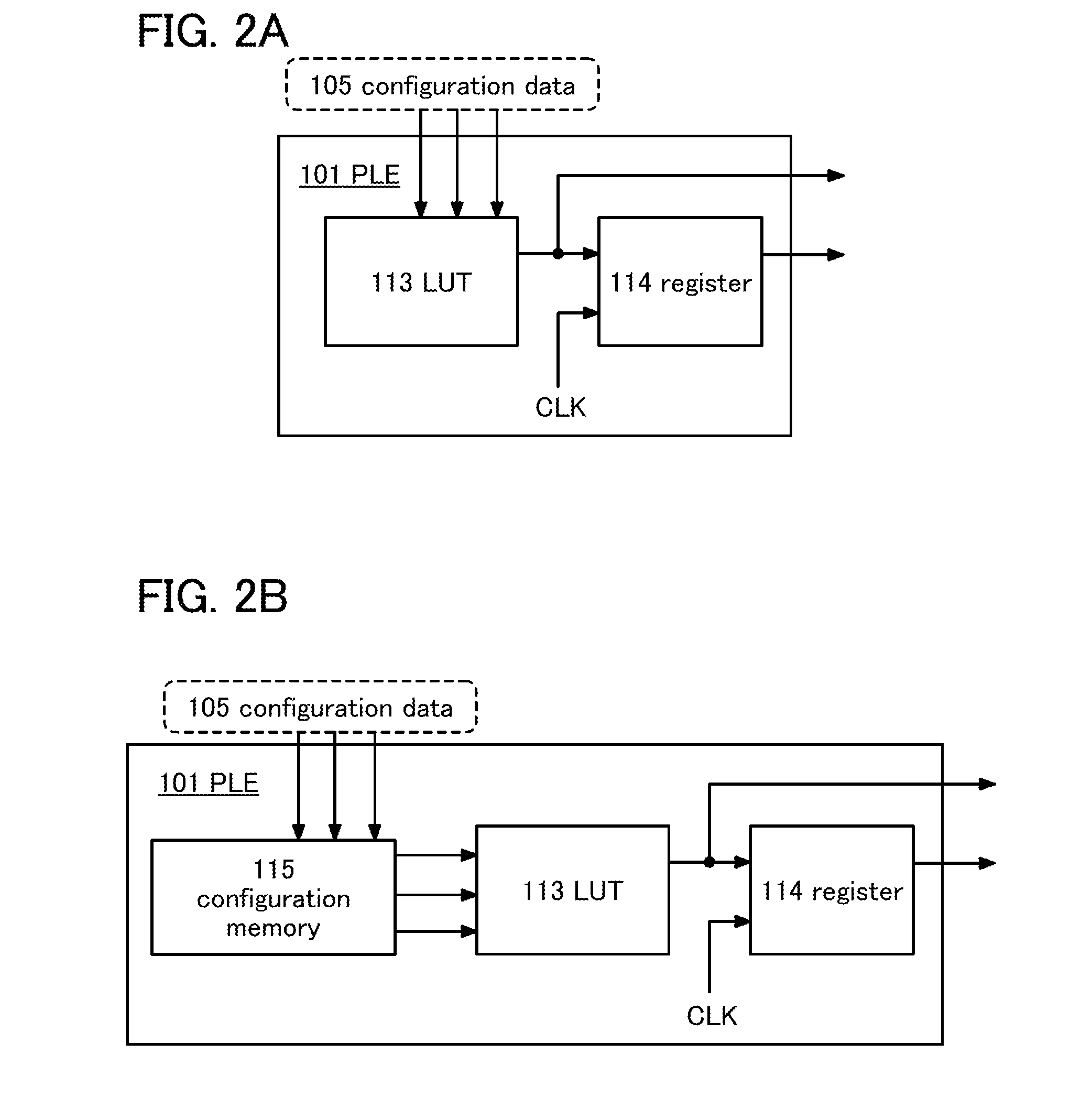

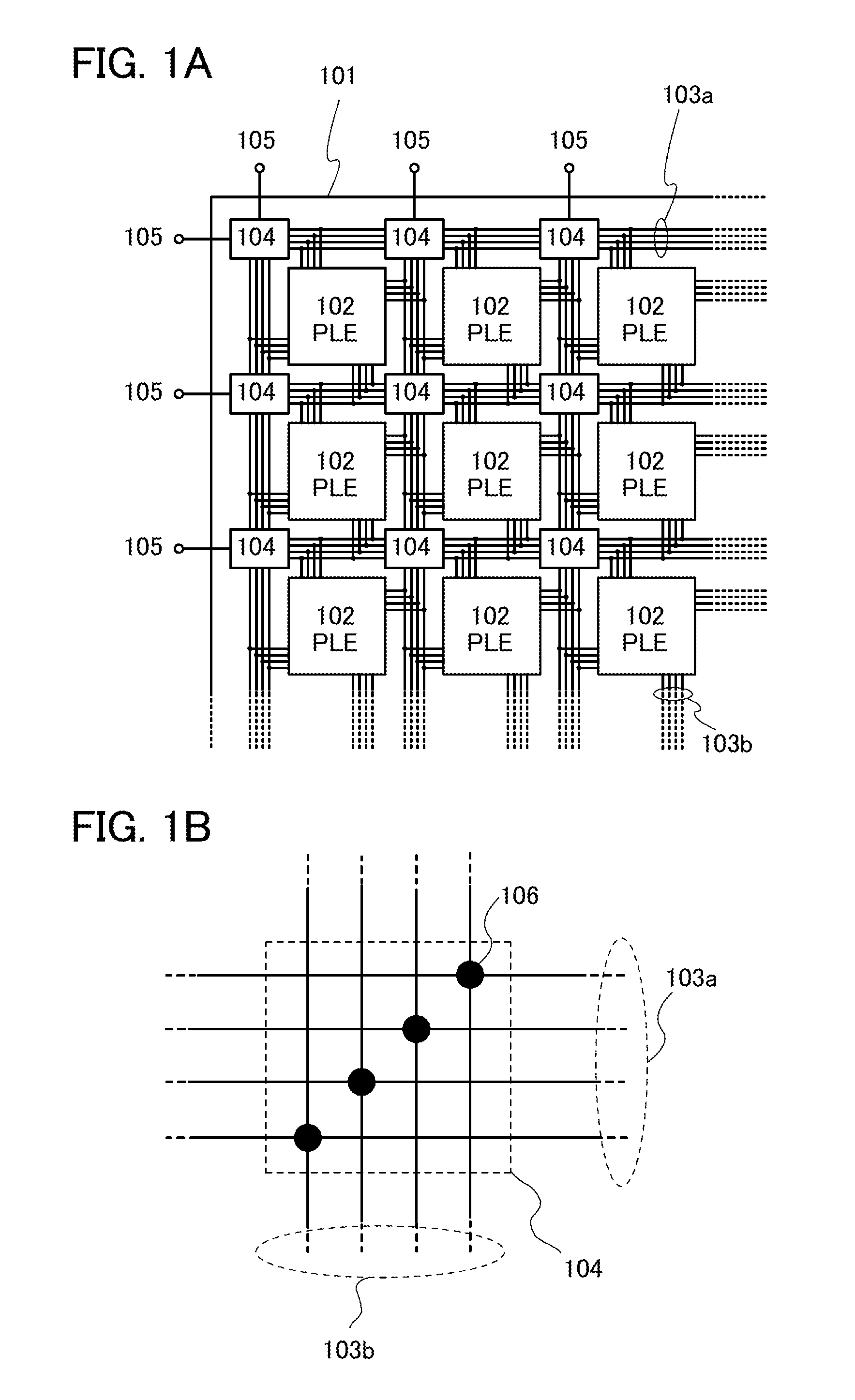

Programmable logic device and semiconductor device

ActiveUS20130314124A1Increase the areaRun at high speedSolid-state devicesLogic circuits using elementary logic circuit componentsProgrammable logic deviceLogic element

Provided is a programmable logic device that includes logic elements arranged in a plurality of columns. Wirings connecting logic elements are arranged between the plurality of columns. Switch circuits that control electrical connections between the wirings and the logic elements are also arranged between the plurality of columns. Each of the switch circuit selects an electrical connection between one of the wirings and an input terminal of one of the logic elements in accordance with configuration data.

Owner:SEMICON ENERGY LAB CO LTD

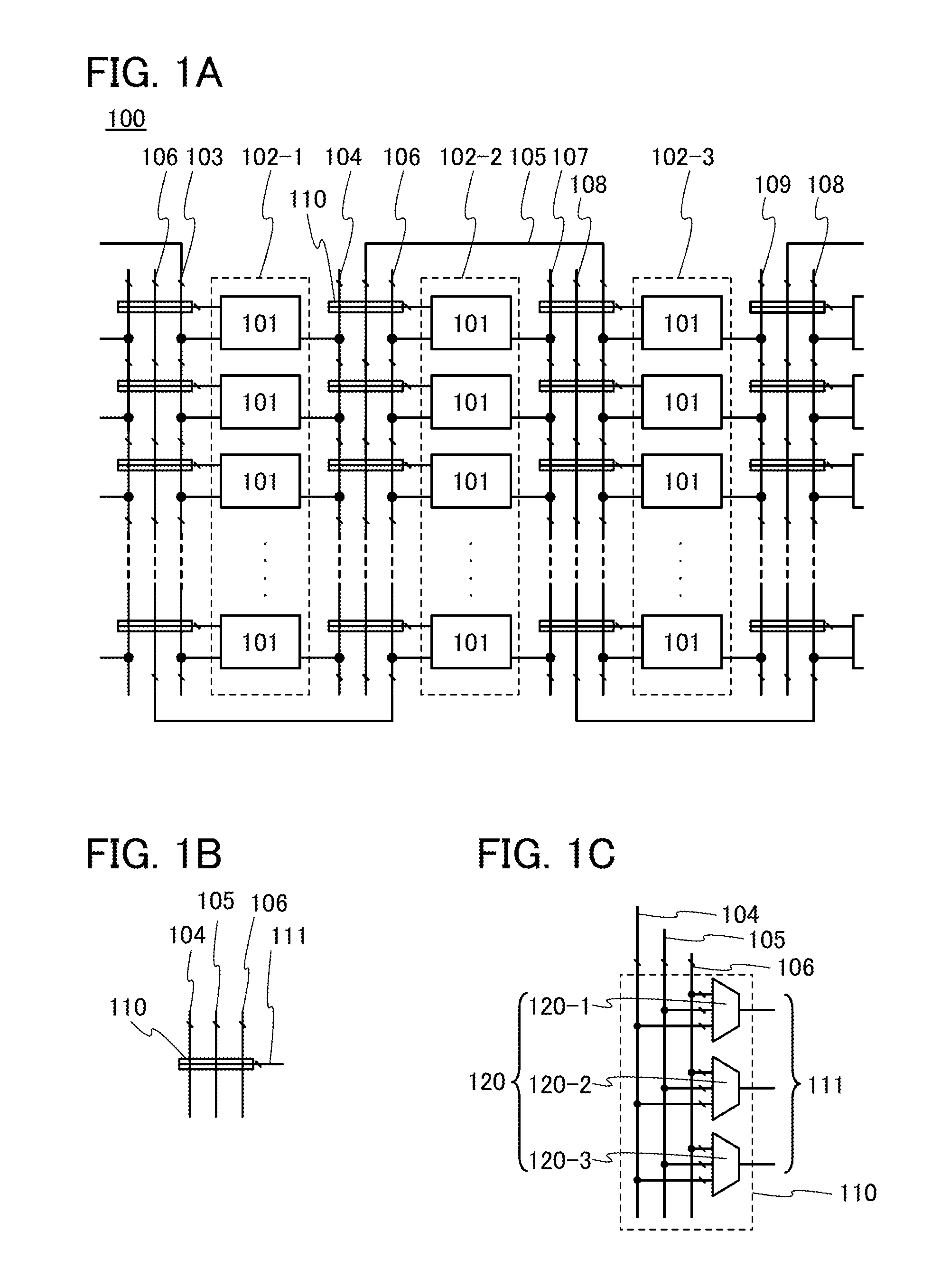

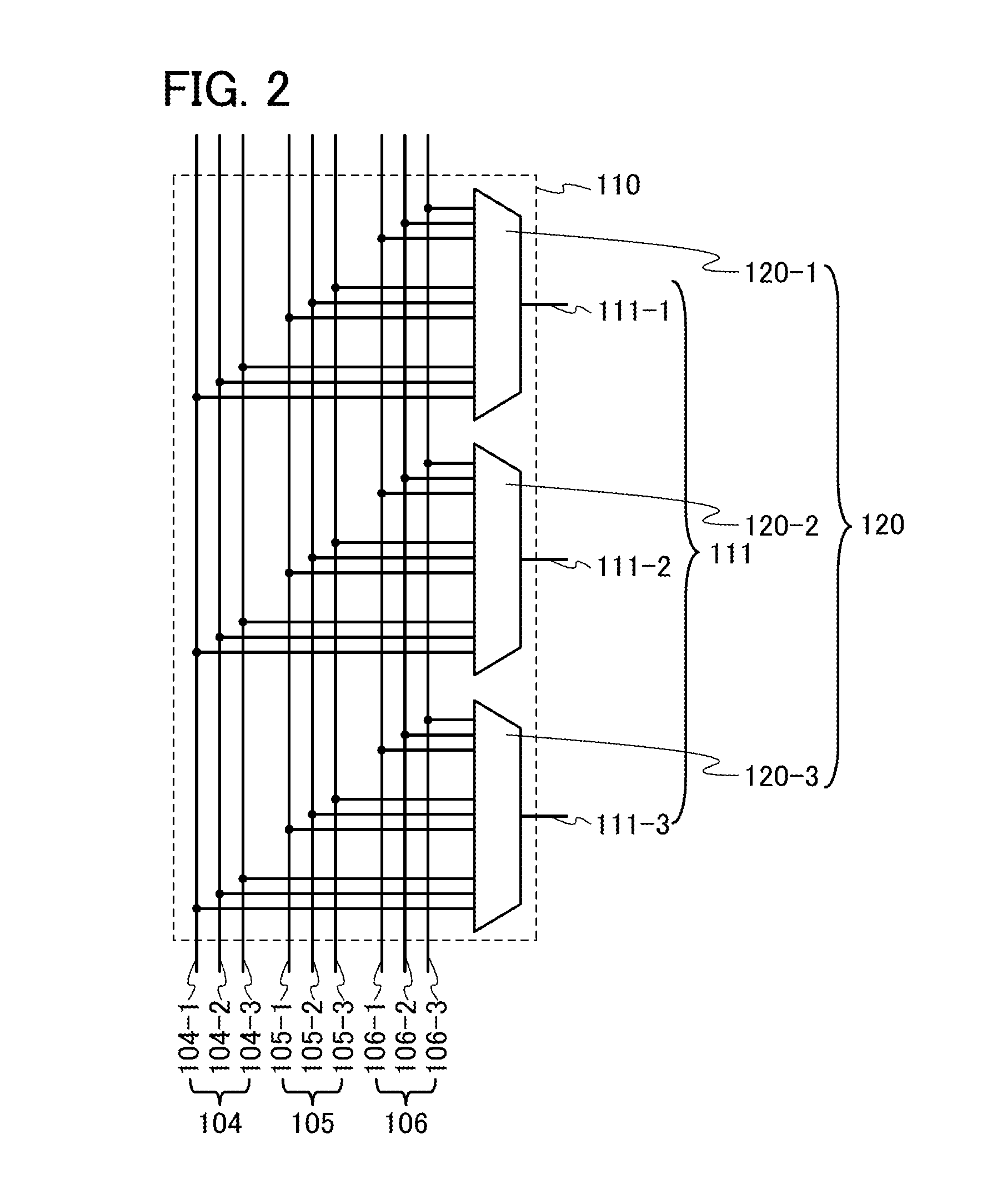

Programmable logic device and method for manufacturing semiconductor device

ActiveUS20130207170A1Reduce in quantityAccurate estimateTransistorPower consumption reductionCapacitanceProgrammable logic device

To provide a programmable logic device in which the number of elements per bit in a memory array can be reduced and with which power consumption or operation frequency can be estimated accurately at a testing stage. Provided is a programmable logic device including a plurality of programmable logic elements and a memory array which stores configuration data that determines logic operation executed in the plurality of programmable logic elements. The memory array includes a plurality of memory elements. The memory element includes a node which establishes electrical connection between the programmable logic element and the memory array, a switch for supplying charge whose amount is determined by the configuration data to the node, holding the charge in the node, or releasing the charge from the node, and a plurality of wirings. Capacitance is formed between the node and the wiring.

Owner:SEMICON ENERGY LAB CO LTD

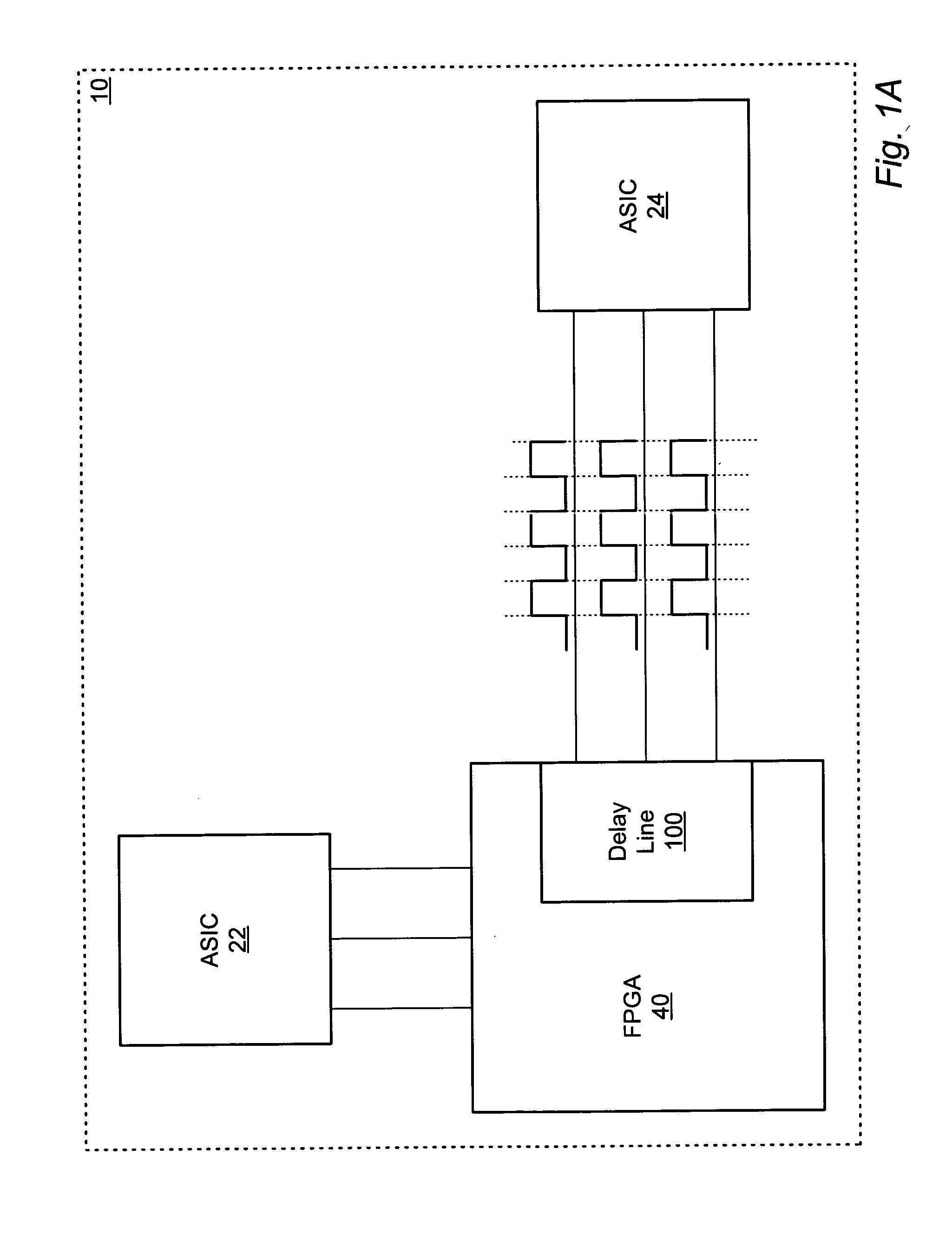

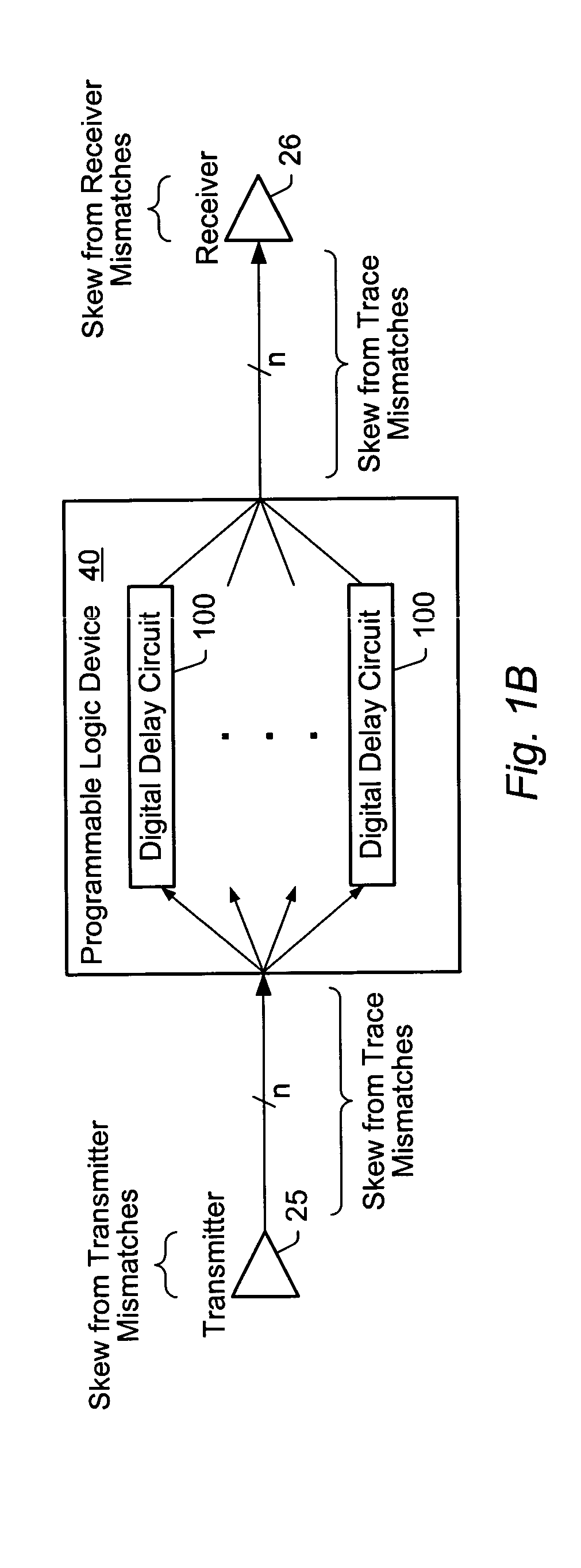

Digital delay elements constructed in a programmable logic device

InactiveUS20050046458A1Single output arrangementsGenerating/distributing signalsProgrammable logic deviceEngineering

A delay circuit. In one embodiment, a programmable logic device (PLD) is used to implement one or more delay circuits having a plurality of delay elements. Included in the plurality of elements are a balanced number of logic elements such that rising and falling edges of a signal passing through the delay circuit propagate with substantially the same amount of delay. The delay circuit may also include a selector circuit coupled to select an output from one of the plurality of delay elements. The delay circuit may be implemented such that it preserves the duty cycle and / or pulse width of signals to which the delay is applied.

Owner:NATIONAL INSTRUMENTS

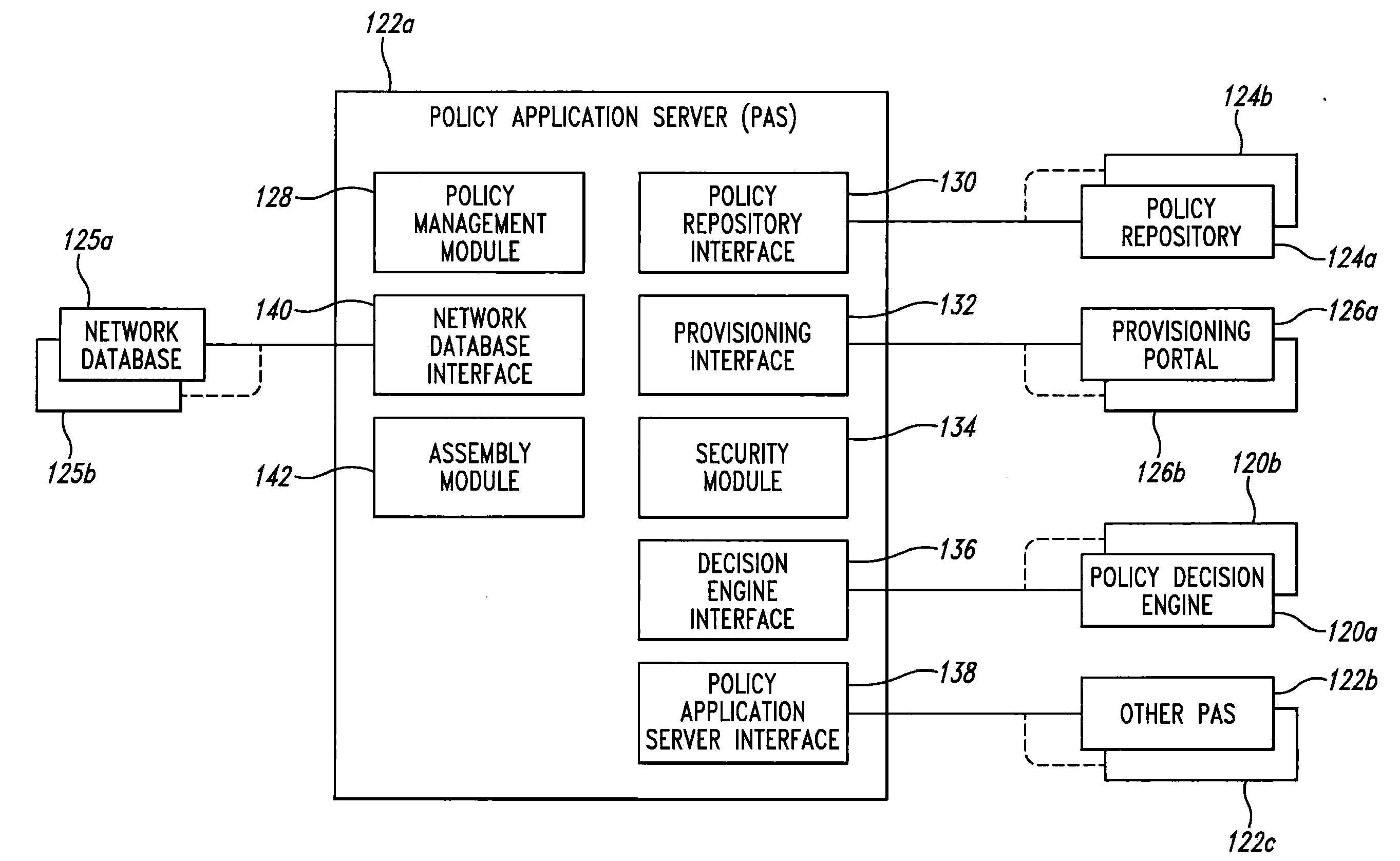

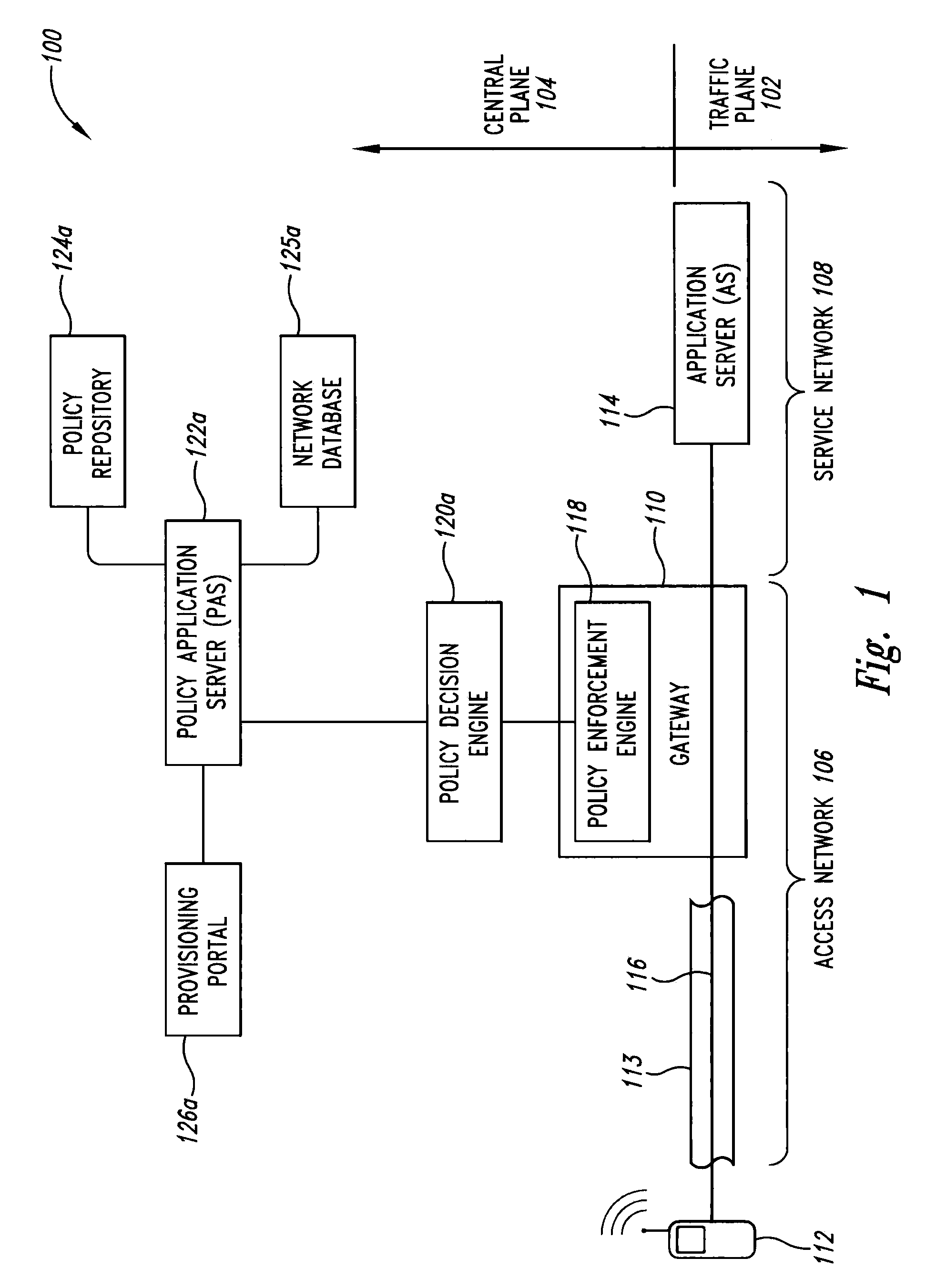

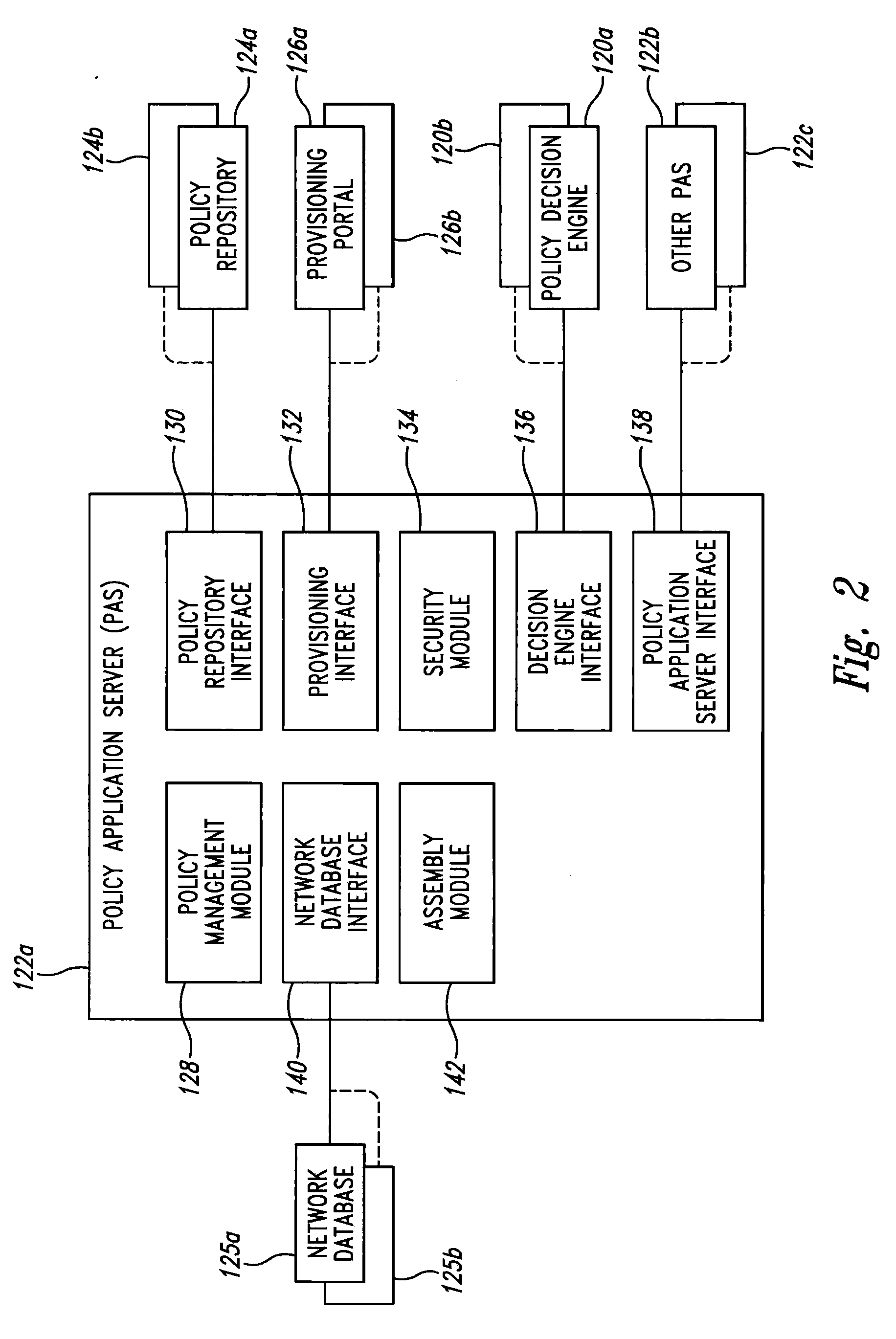

Policy application server for mobile data networks

ActiveUS20090228953A1Service provisioningMetering/charging/biilling arrangementsBilling systemApplication server

A policy application server and methods for use are described. The policy application server is a logical element of a policy-based control and charging system for a mobile data service network. The policy application server is configured to manage policies including creating, revising, formatting, and provisioning of policies. The policy application server is configured to assemble policy rules from policies and context data. Context data includes subscriber and service information needed to make a particular policy rule. The policy application server gathers context data from one or more network databases. The policy application server is configured to send policy rules to select ones of a plurality of policy decision engines. The policy application server manages the storing of policies, policy rules and formatted context data in select ones of a plurality of policy repositories.

Owner:AT&T MOBILITY II LLC

Programmable LSI

InactiveUS20120212995A1Lower average currentAvoid volatilityDigital storageLogic circuitsComputer architectureElectrical connection

A low-power programmable LSI that can perform configuration (dynamic configuration) at high speed and can quickly start is provided. The programmable LSI includes a plurality of logic elements and a memory element for storing configuration data to be input to the plurality of logic elements. The plurality of logic elements each include a configuration memory. Each of the plurality of logic elements performs different arithmetic processing and changes an electrical connection between the logic elements in accordance with the configuration data stored in the configuration memory. The memory element is formed using a storage element including a transistor whose channel is formed in an oxide semiconductor layer and a node set in a floating state when the transistor is turned off.

Owner:SEMICON ENERGY LAB CO LTD

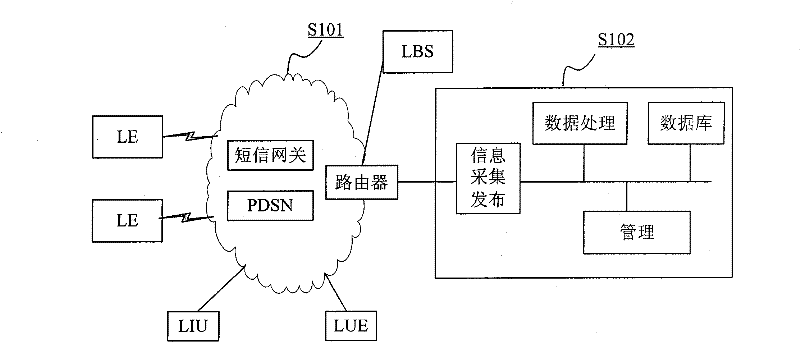

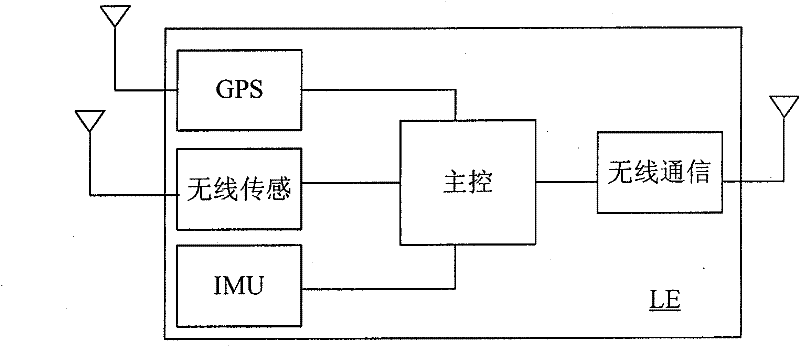

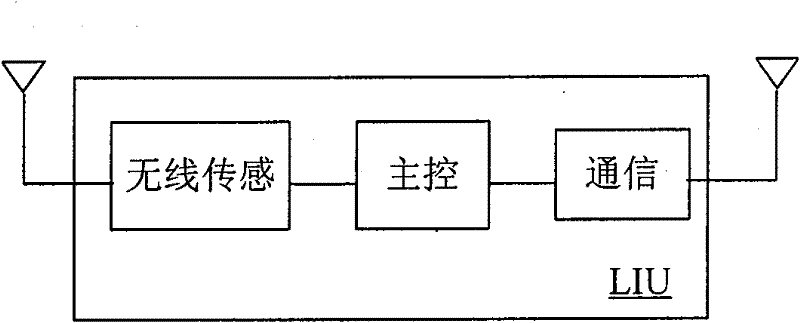

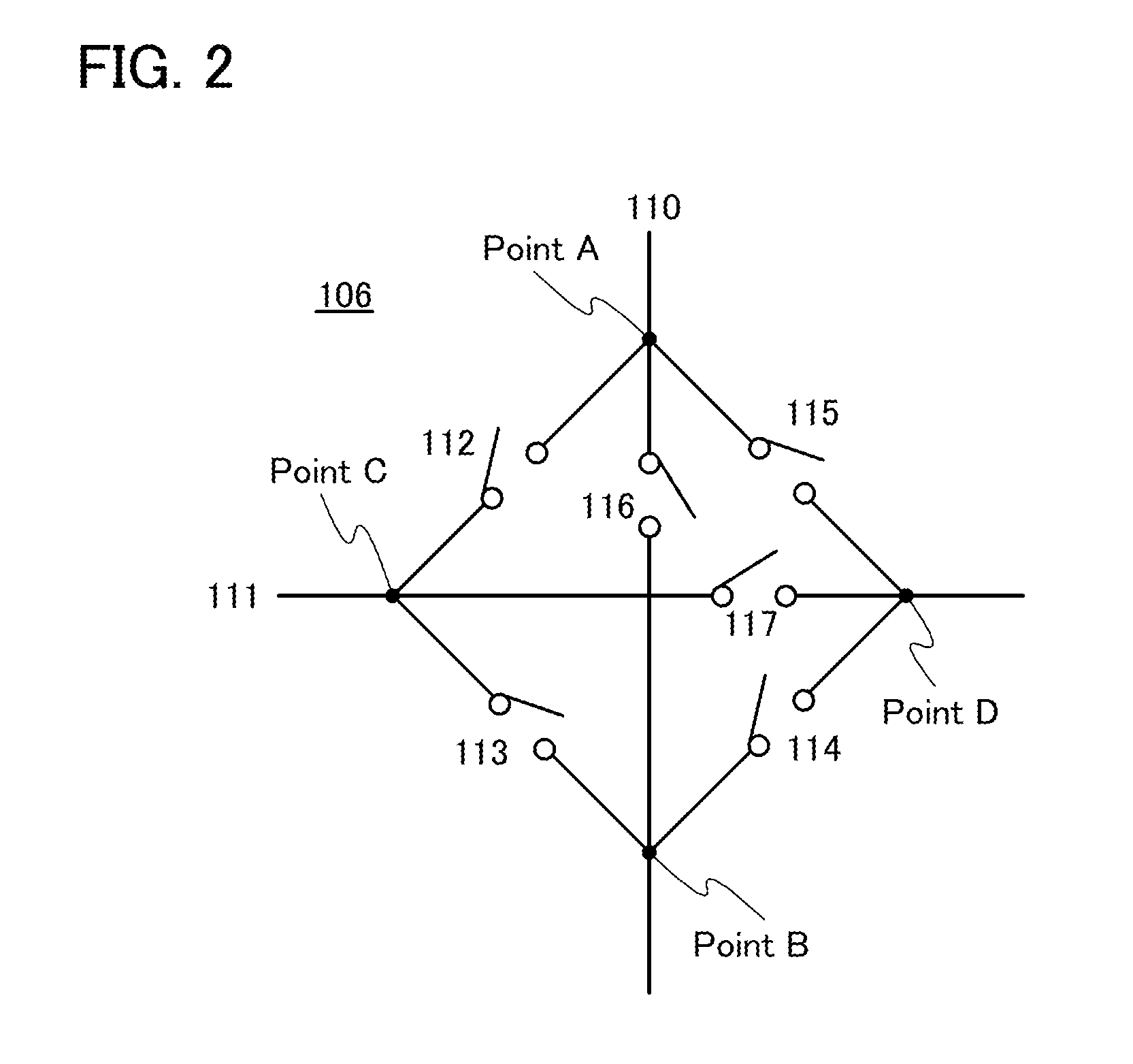

Mobile positioning service method

InactiveCN102223596AData processing is simpleReduce power consumptionPosition fixationLocation information based serviceThe InternetLogic element

The invention provides a positioning service method; firstly, a positioning management platform is connected with a plurality of LEs (logic elements) and LIUs (line internet units) through a communication network, wherein the LEs have the functions of positioning measurement, wireless sensing and communication, the LIUs have the functions of the wireless sensing and the communication; the LEs report positioning measurement data to the positioning management platform in a timing manner, and the positioning management platform obtains an optimal estimation of LE positions through an information fusion technology; when approaching a detection range of a wireless sensing unit of the LIUs, the LEs can be automatically identified, wherein an identification number ID-1 can be automatically read by the LIUs and is reported to the positioning management platform, and the positioning management platform corrects position data corresponding to the LEs. In the method of the invention, the data processing of the LEs can be greatly simplified, the power consumption is reduced, various positioning value-added services can be favorably developed, and particularly, the positioning services with requirements of low power consumption and hidden nature to the LEs can be favorably developed.

Owner:SHANGHAI QIDIAN INFORMATION TECH

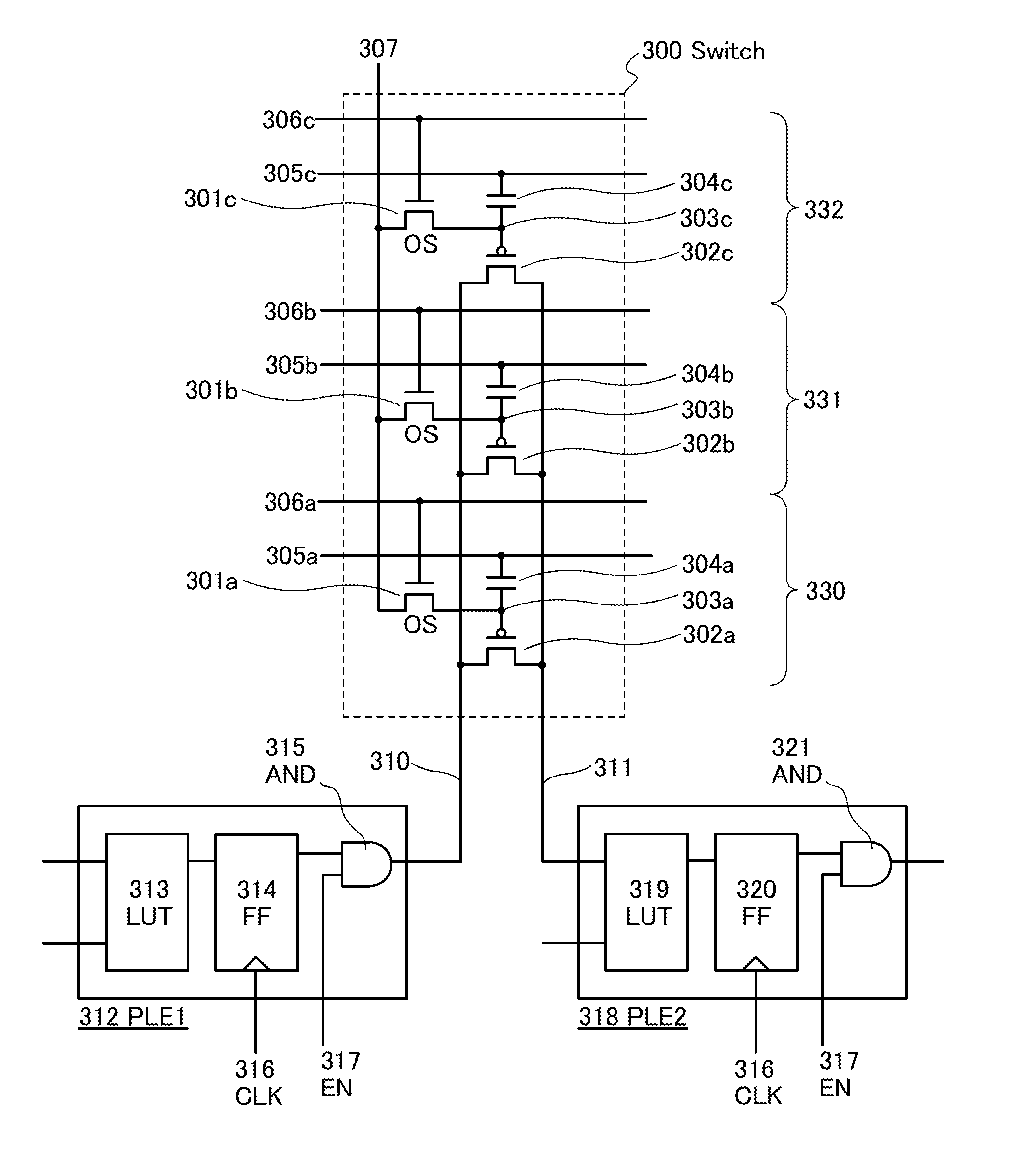

Programmable logic device

InactiveUS20130293263A1Reduce power consumptionShort startup timePower reduction in field effect transistorsSolid-state devicesProgrammable logic deviceSoftware engineering

Disclosed is a programmable logic device (PLD) which can undergo dynamic configuration at a high speed. The PLD includes a plurality of programmable logic elements (PLEs) and a switch for selecting electrical connection between the PLEs. The switch includes a plurality of circuit groups each of which includes first and second transistors. The second transistors of the circuit groups are electrically connected in parallel with one another. In each of the circuit groups, the electrical conduction between a source and a drain of the second transistor is determined based on configuration data held at a node between the gate of the second transistor and a drain of the first transistor, which allows the selection of the electrical connection and disconnection between the programmable logic elements by the selection of one of the circuit groups.

Owner:SEMICON ENERGY LAB CO LTD

Non-frequency translating repeater with downlink detection for uplink and downlink synchronization

ActiveUS20070066220A1Network topologiesActive radio relay systemsLogical elementCommunications system

A non-frequency translating repeater (110, 210, 300) for use in a time division duplex (TDD) radio protocol communications system includes detection retransmission and automatic gain control. Detection is performed by detectors (309, 310) and a processor (313). Detection can be overridden by processor (313) using logic elements (314). Antennae (220, 230) having various form factors can be used to couple a base station (222) to a subscriber terminal (232) which can be located in a sub-optimal location such as deep inside a building or the like.

Owner:QUALCOMM INC

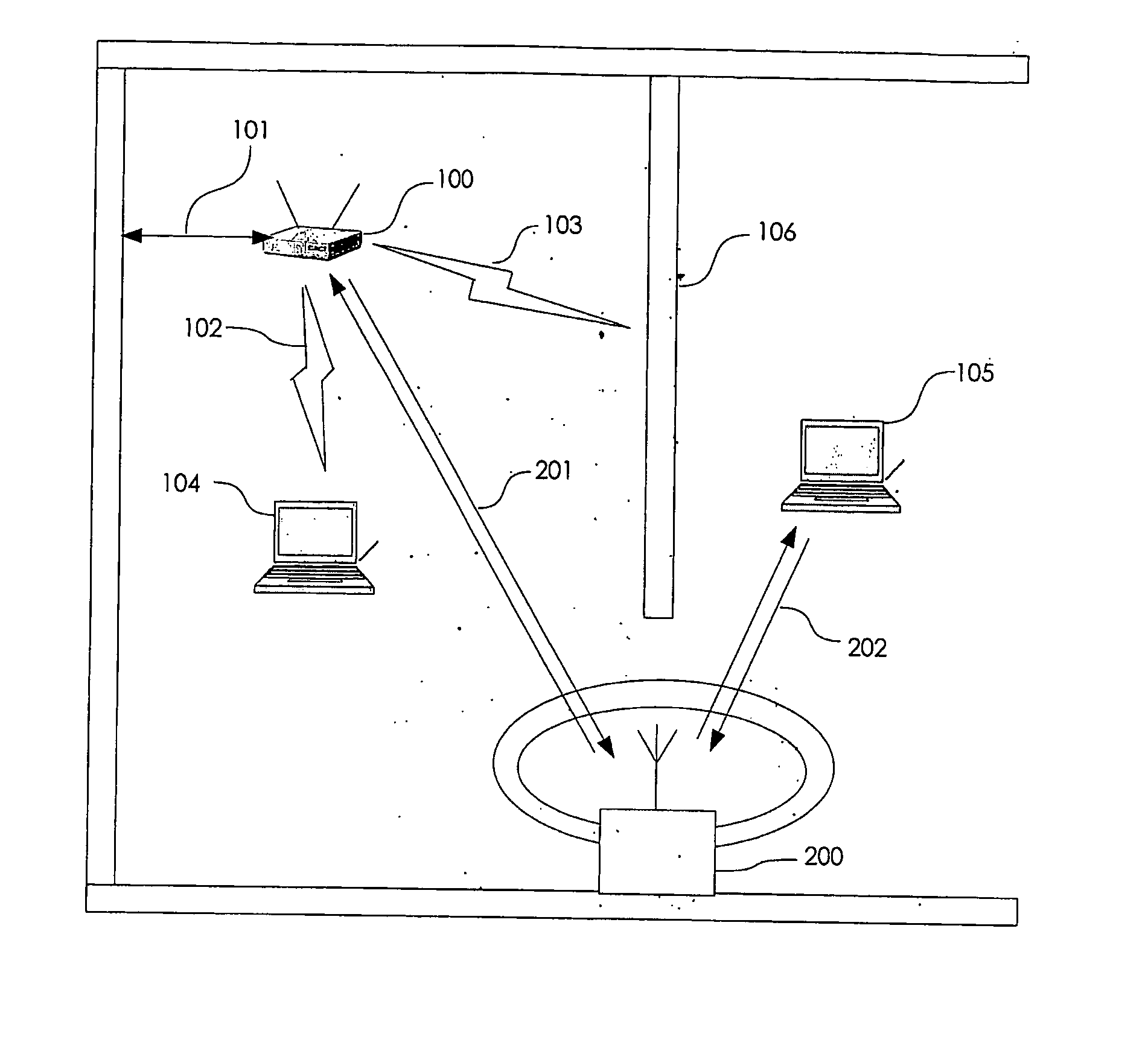

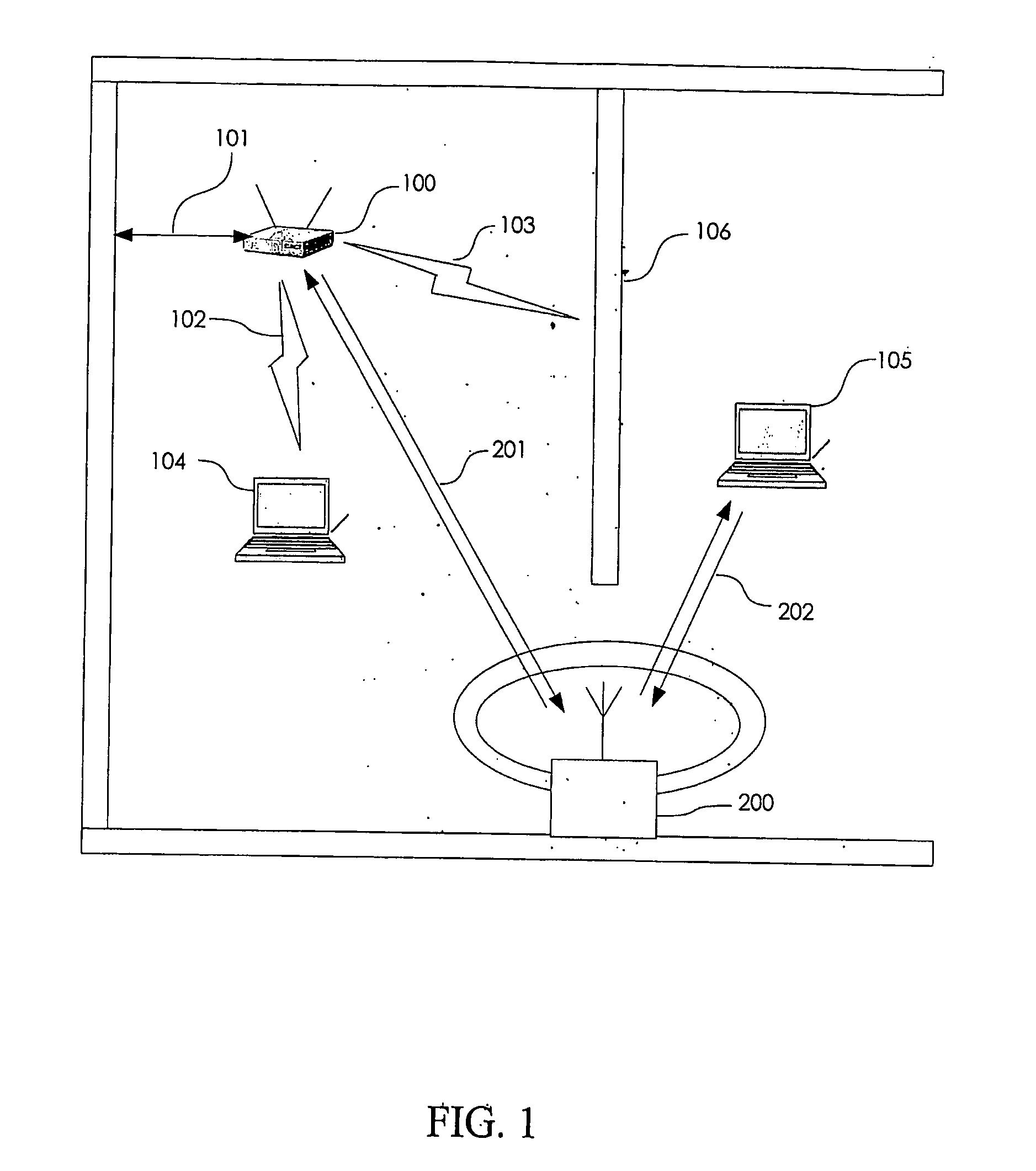

Wireless local area network repeater with detection

InactiveUS20060056352A1Fast initial decisionAccurate decisionNetwork topologiesActive radio relay systemsCommunications systemAudio power amplifier

A frequency translating repeater (200) for use in a time division duplex radio protocol communications system includes an automatic gain control feature. Detection is performed by comparators (401, 411) ADCs (402, 412); DACs (404, 414) and a processor (315). Detection can be overridden by processor (315) using logic elements (406, 416, 407, and 417) to control the generation of a Channel A / Channel B signal and a PA_ON signal for controlling a power amplifier associated with the transmitter.

Owner:QUALCOMM INC

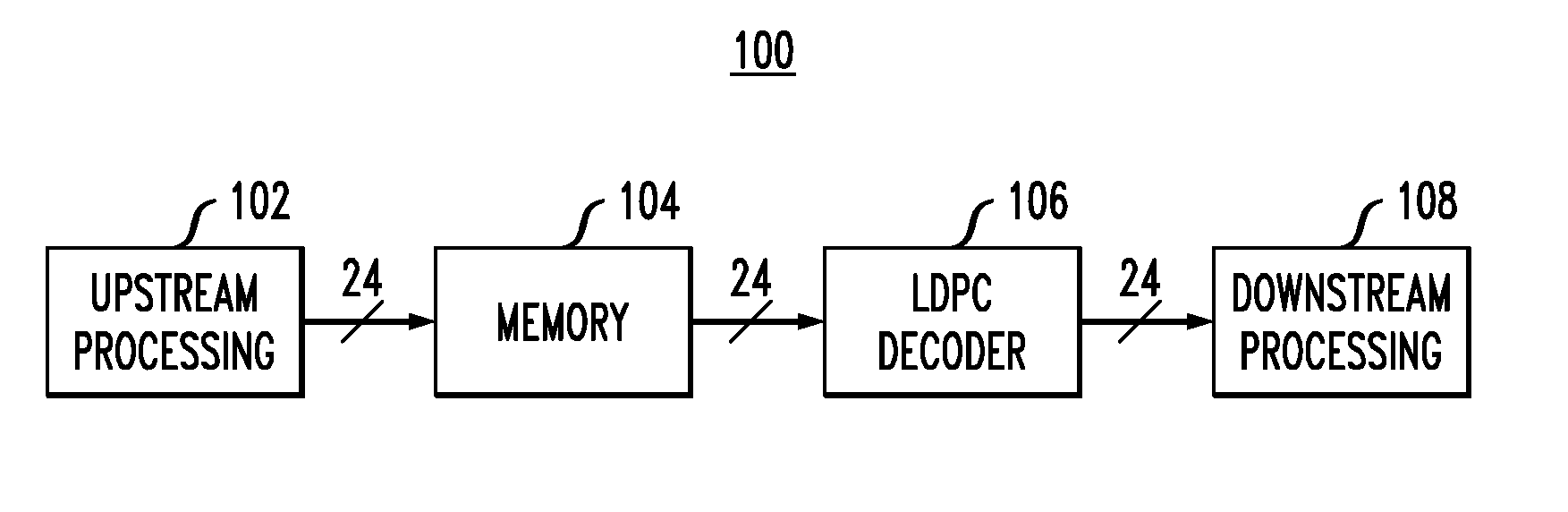

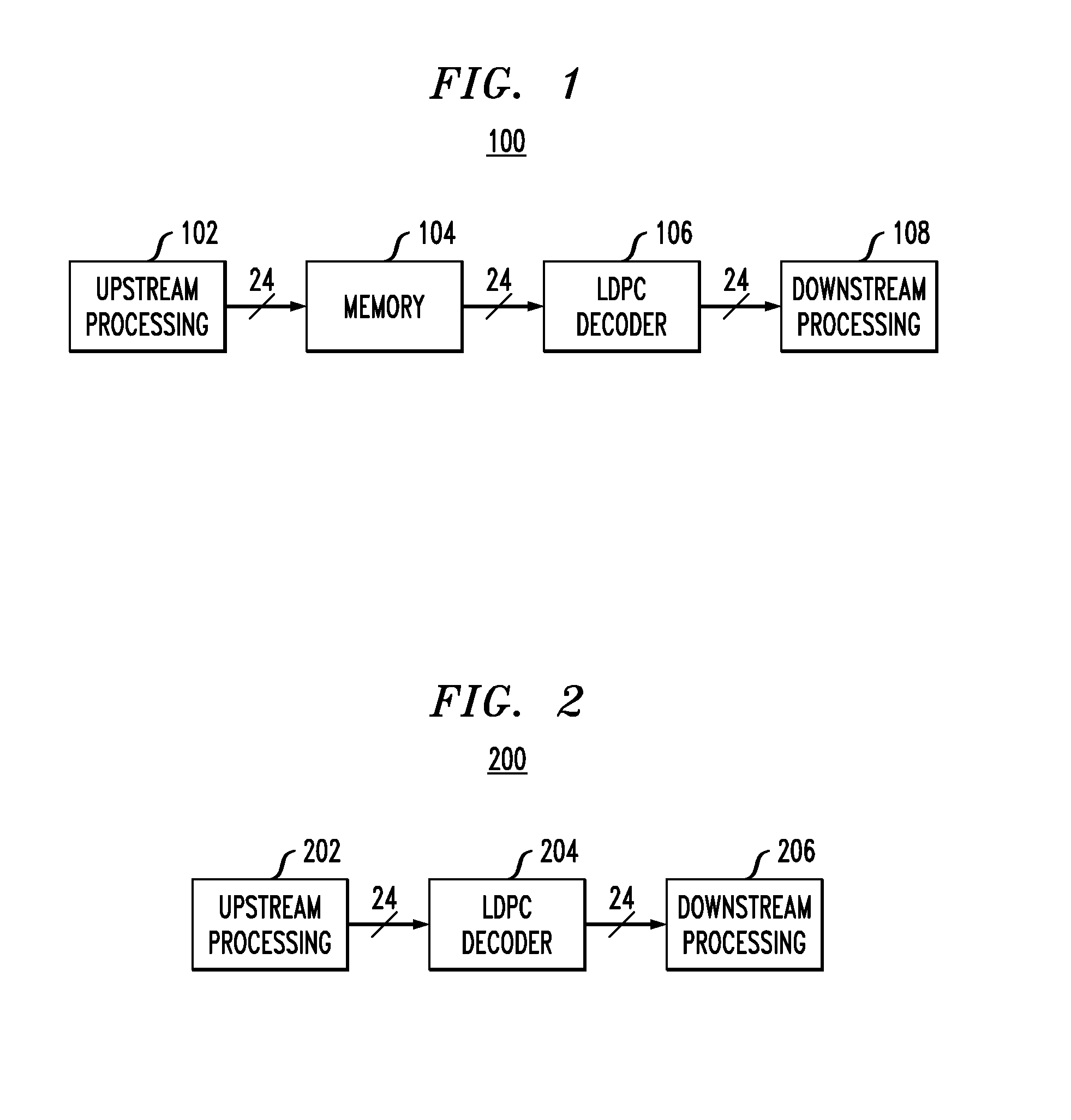

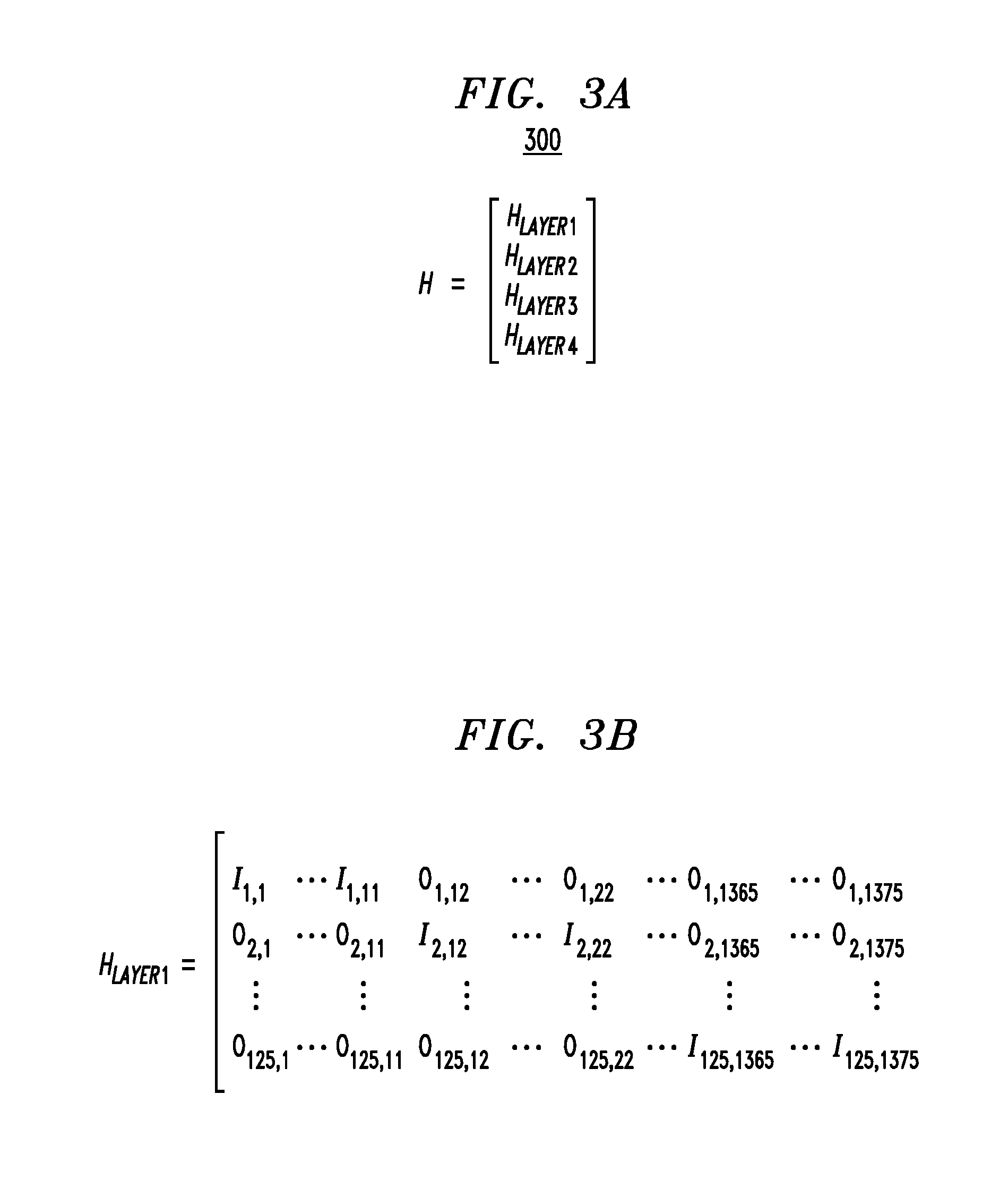

Hard input low density parity check decoder

A hard input low density parity check decoder is provided that shares logic between a bit-flipping decoder and a syndrome calculator. The hard-decision decoder decodes one or more error-correcting (EC) codewords and comprises a bit-flipping decoder that flips one or more bit nodes connected to one or more unsatisfied parity checks; and a syndrome calculator that performs a parity check to determine whether the bit-flipping decoder has converged on a valid codeword, wherein the bit-flipping decoder and the syndrome calculator share one or more logic elements. The decoder optionally includes means for updating a parity check equation of each flipped bit. Error-correcting (EC) codewords are decoded by flipping one or more bit nodes connected to one or more unsatisfied parity checks; and updating one or more parity check equations associated with the one or more bit nodes each time the one or more bit nodes are flipped. The parity check equations are updated whenever a bit is updated. The exemplary method terminates based on a predefined syndrome output.

Owner:AVAGO TECH INT SALES PTE LTD

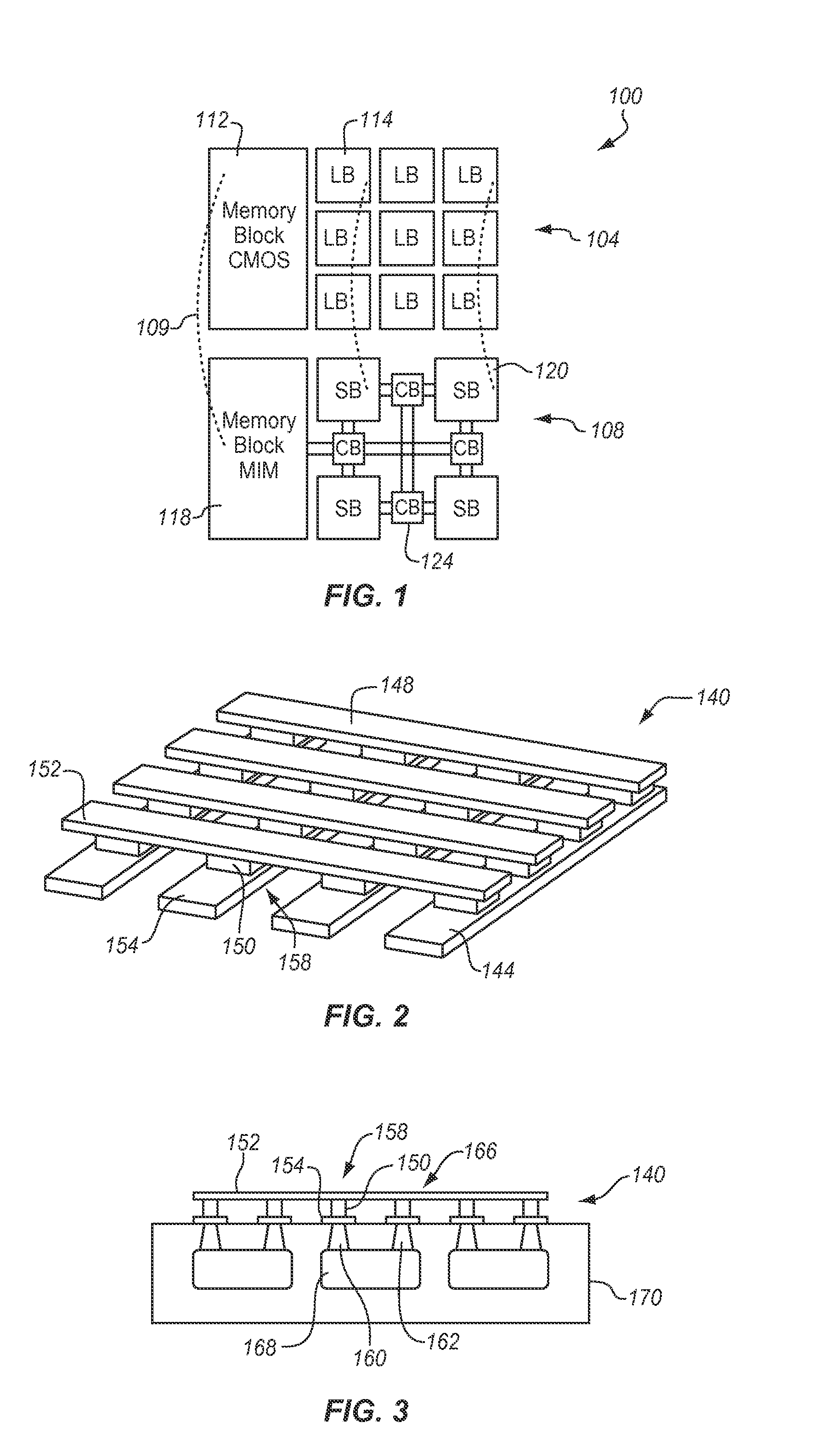

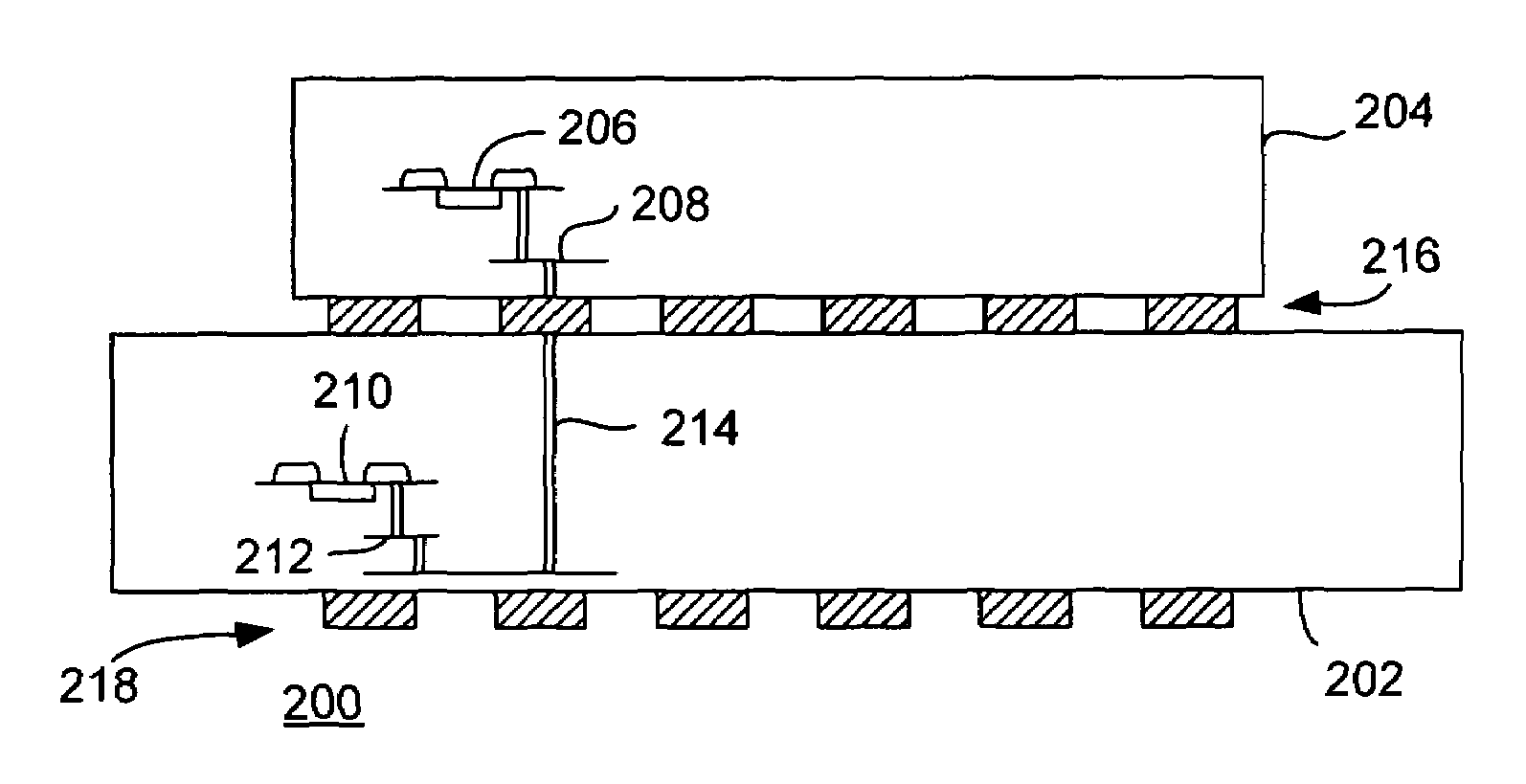

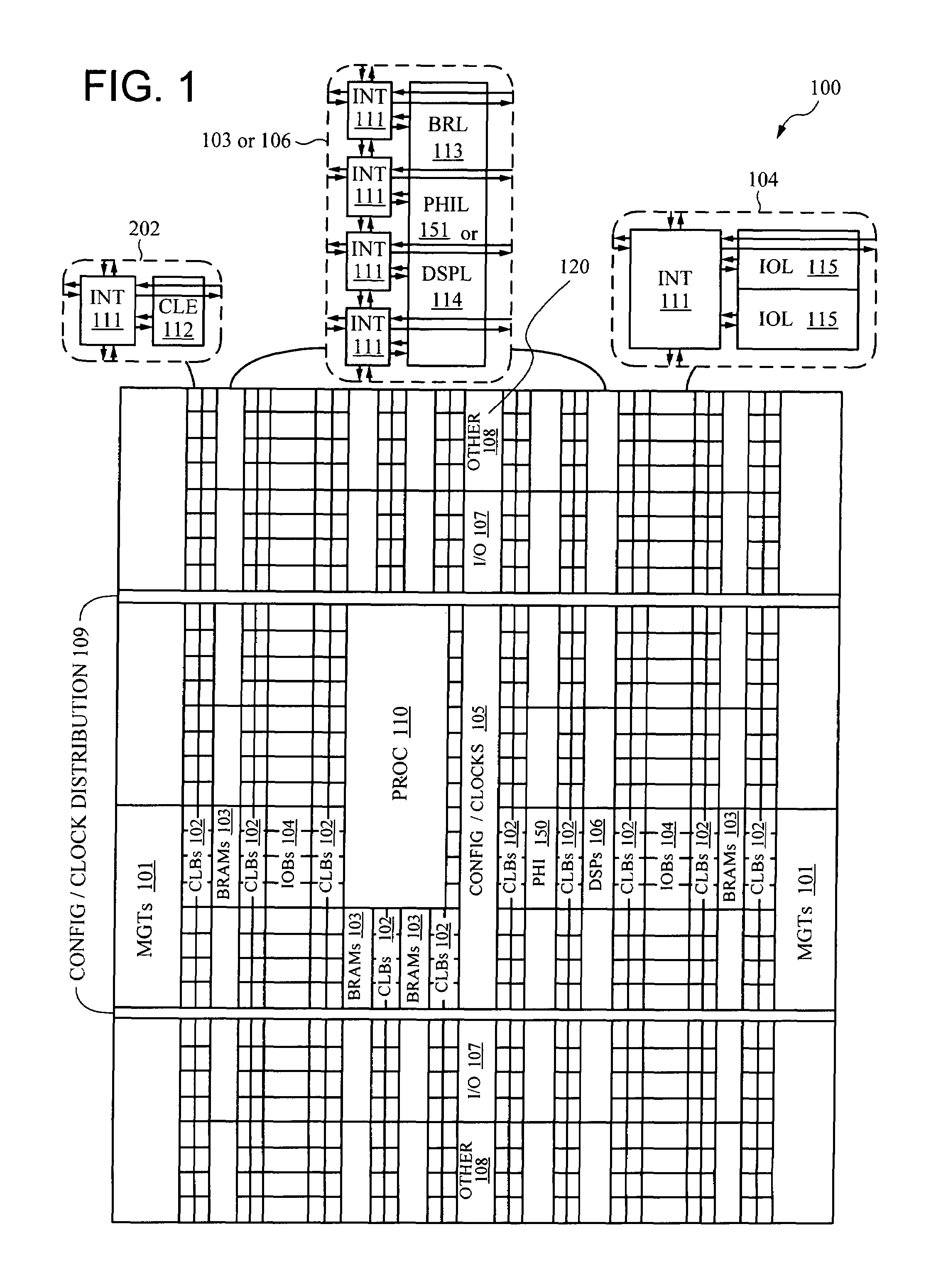

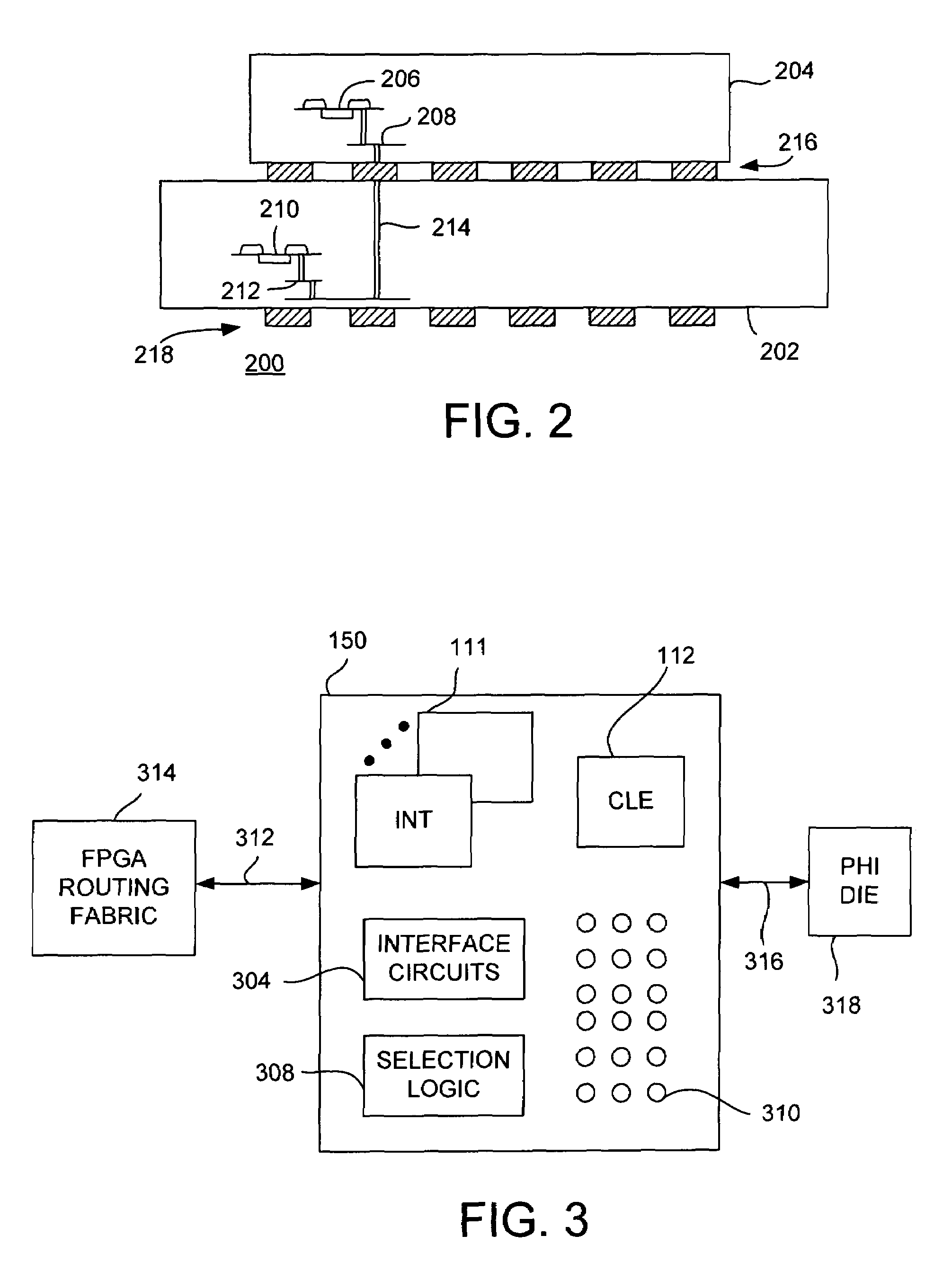

Integrated circuit with through-die via interface for die stacking

ActiveUS7518398B1Solid-state devicesLogic circuits using elementary logic circuit componentsEngineeringIntegrated circuit

An integrated circuit with a through-die via (TDV) interface for die stacking is described. One aspect of the invention relates to an integrated circuit die having an array of tiles arranged in columns. The integrated circuit die includes at least one interface tile. Each interface tile includes a logic element, contacts, and through die vias (TDVs). The logic element is coupled to a routing fabric of the integrated circuit die. The contacts are configured to be coupled to conductive interconnect of another integrated circuit die attached to the backside of the integrated circuit die. The TDVs are configured to couple the logic element to the contacts.

Owner:XILINX INC