Field-programmable gate array chip-based process mapping method

A gate array and chip technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of losing the ability to customize the FPGA chip architecture, spending a lot of time, and taking a long time to achieve the highest improvement The effect of working frequency, increasing fmax, and reducing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

[0016] The process mapping method based on the field programmable gate array FPGA chip provided by the present invention is applied in the mapping process after the logic synthesis process in the process flow of the FPGA chip. The method can retain the versatility of the process mapping algorithm to the greatest extent, and can quickly Supports the different characteristics of various new FPGA chip architectures. The following will introduce in detail through the embodiments.

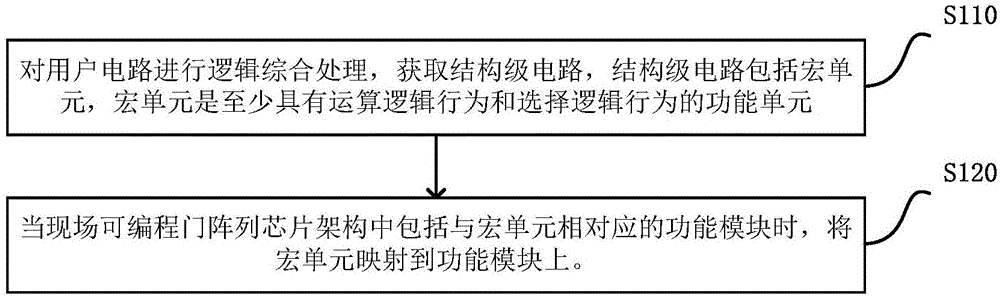

[0017] figure 1 A flow chart of a process mapping method based on a field programmable gate array chip provided by an embodiment of the present invention, such as figure 1 As shown, the method may include:

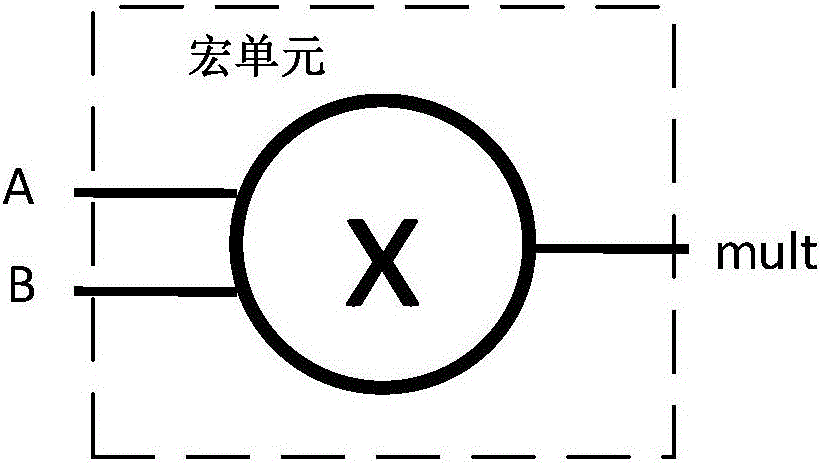

[0018] Step 110, perform logical synthesis processing on the user circuit to obtain a structural level circuit, the structural level cir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More