Patents

Literature

260 results about "Chip architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

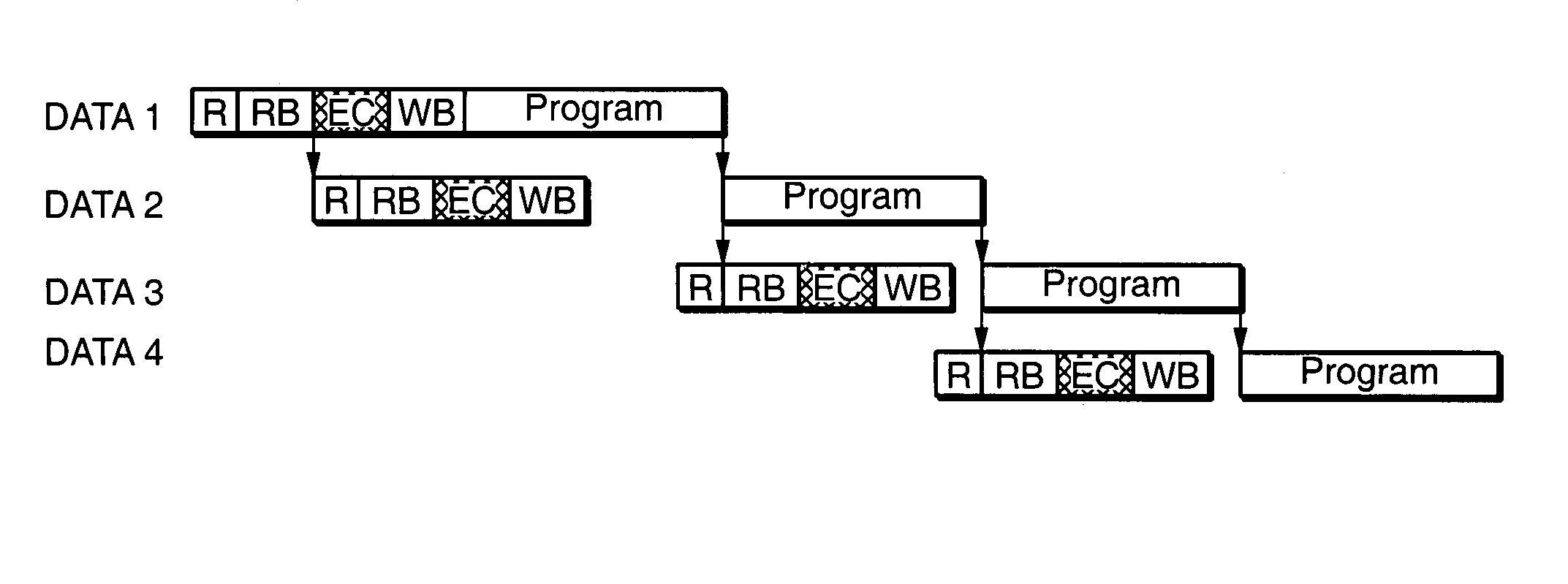

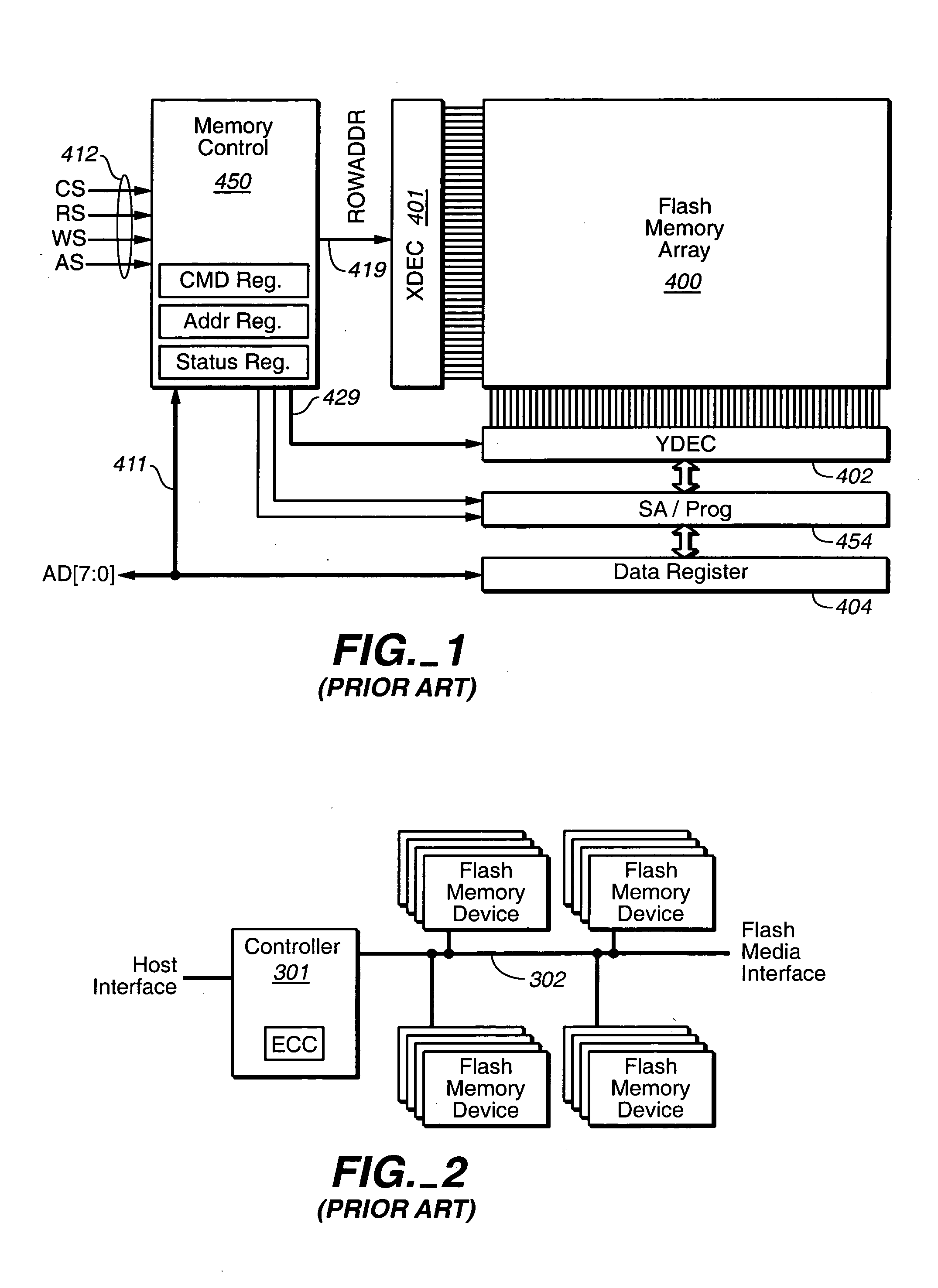

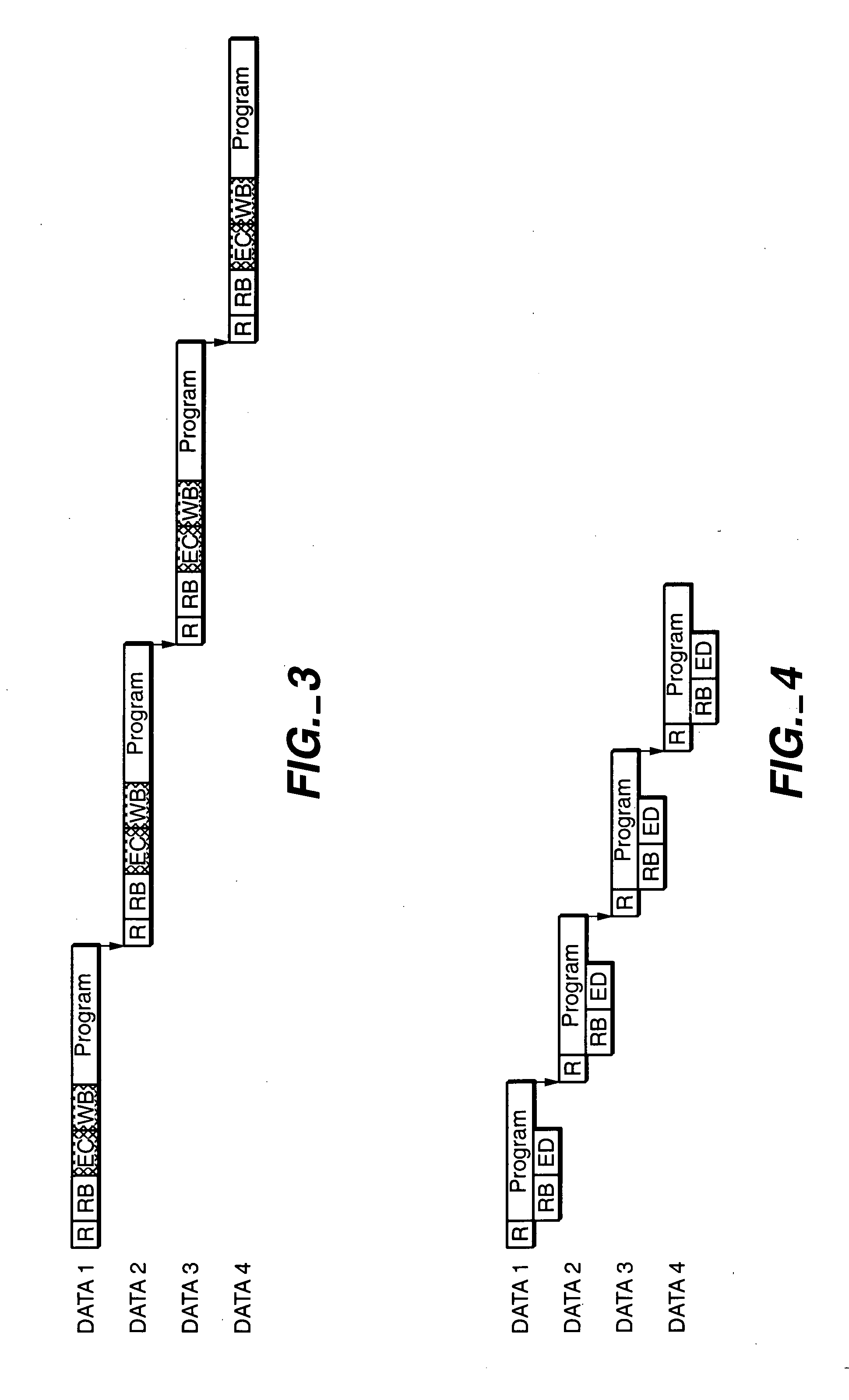

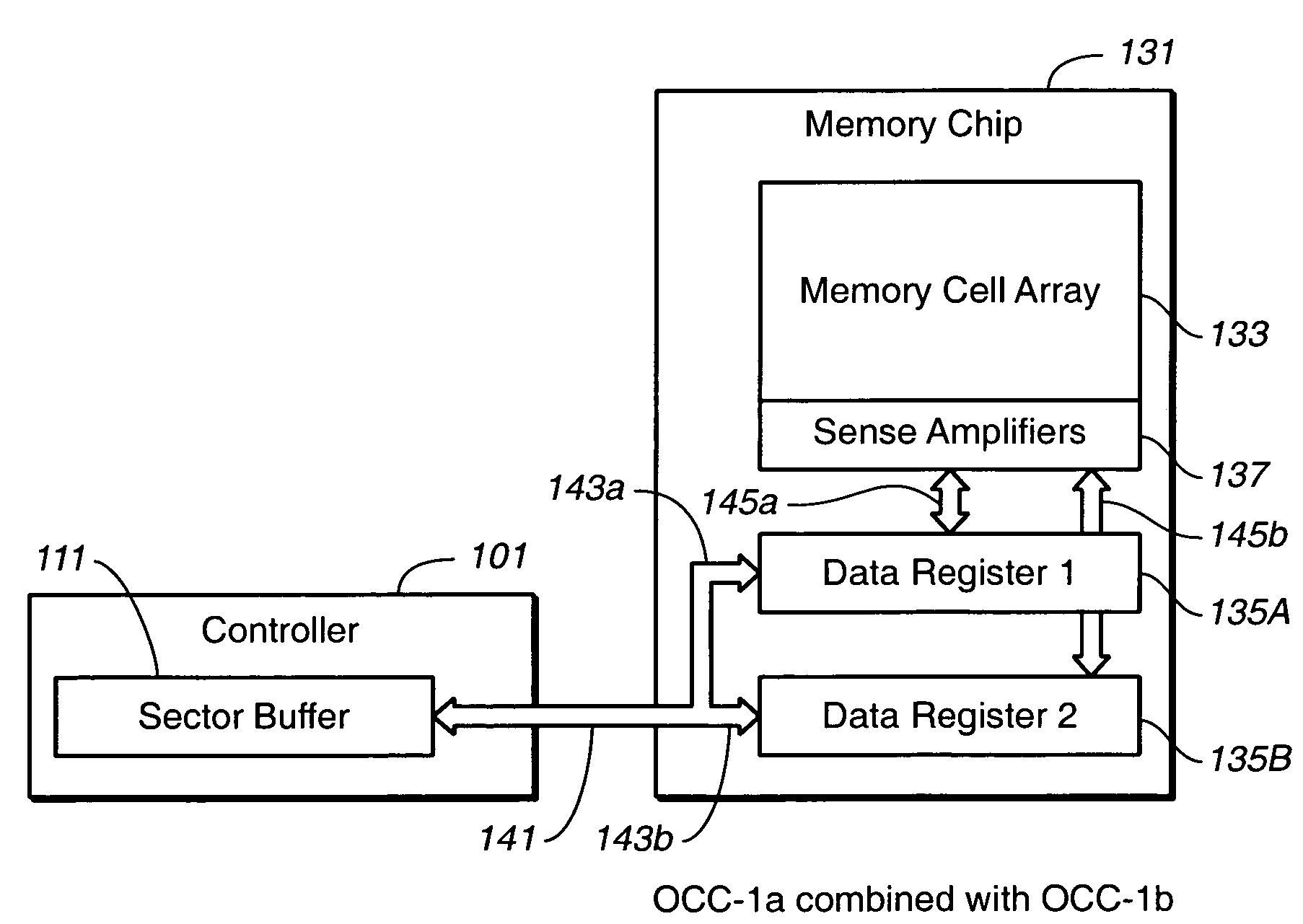

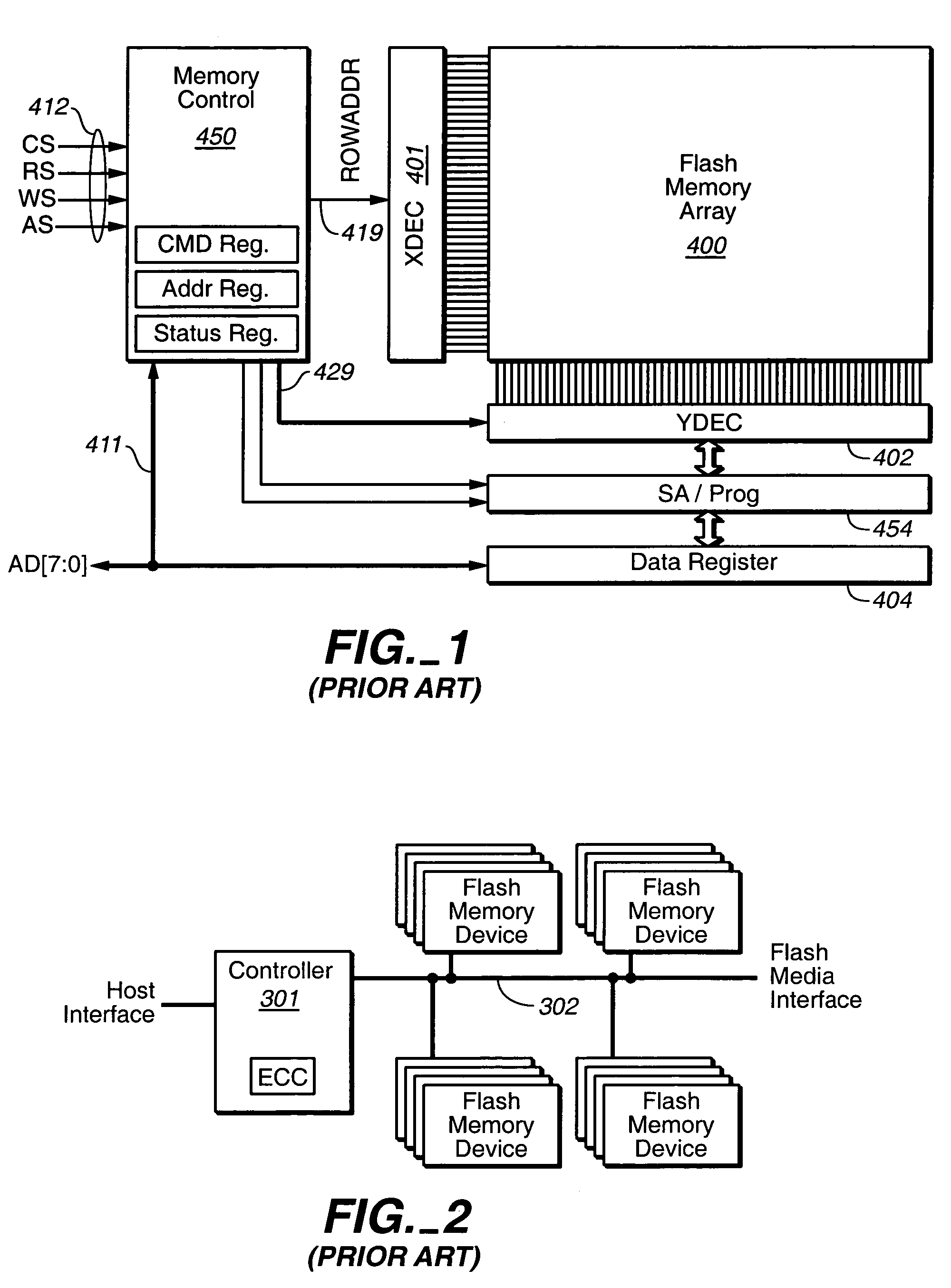

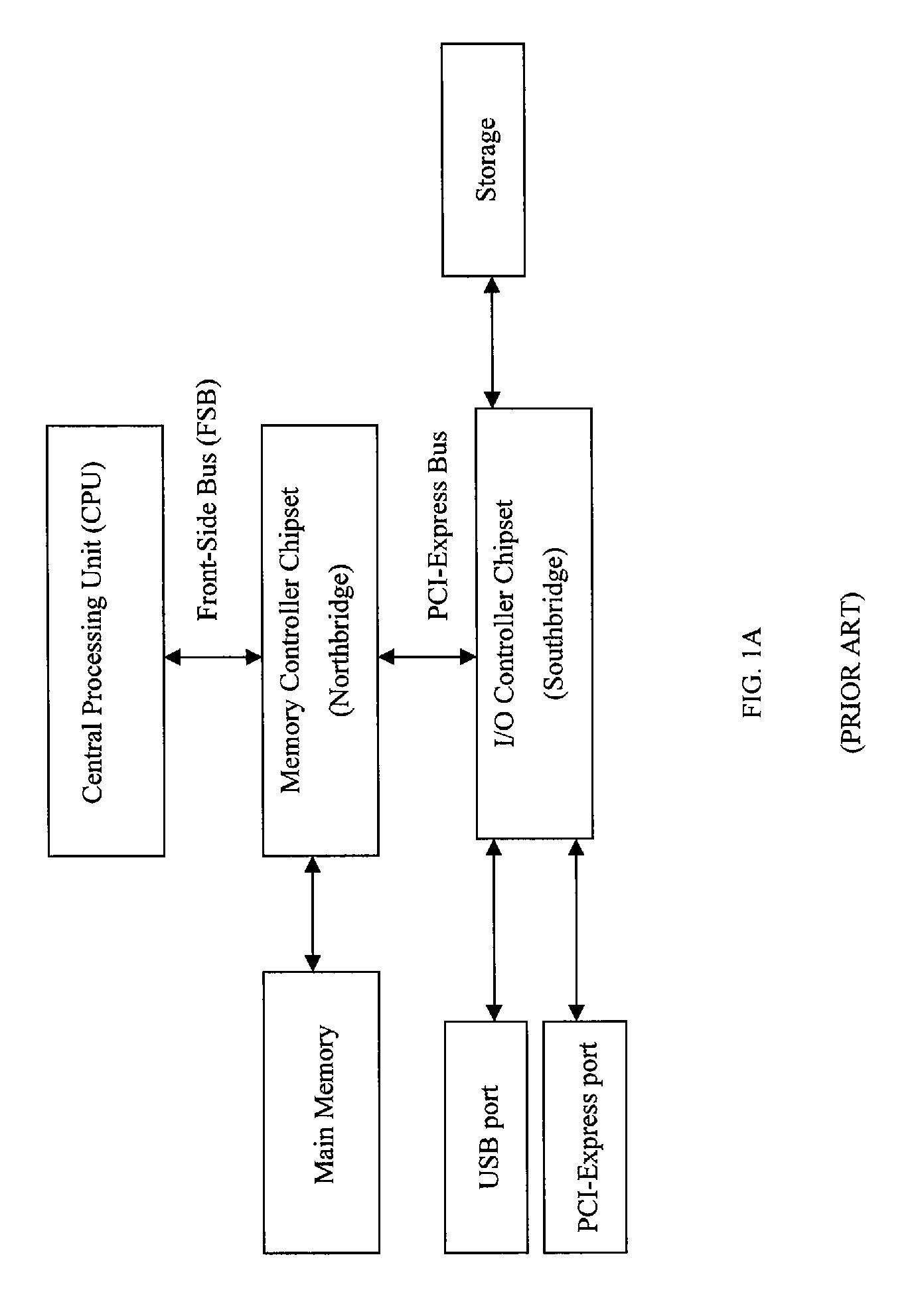

Pipelined data relocation and improved chip architectures

ActiveUS20050257120A1High error rateAccelerating complex data operationError detection/correctionRead-only memoriesPresent methodParallel computing

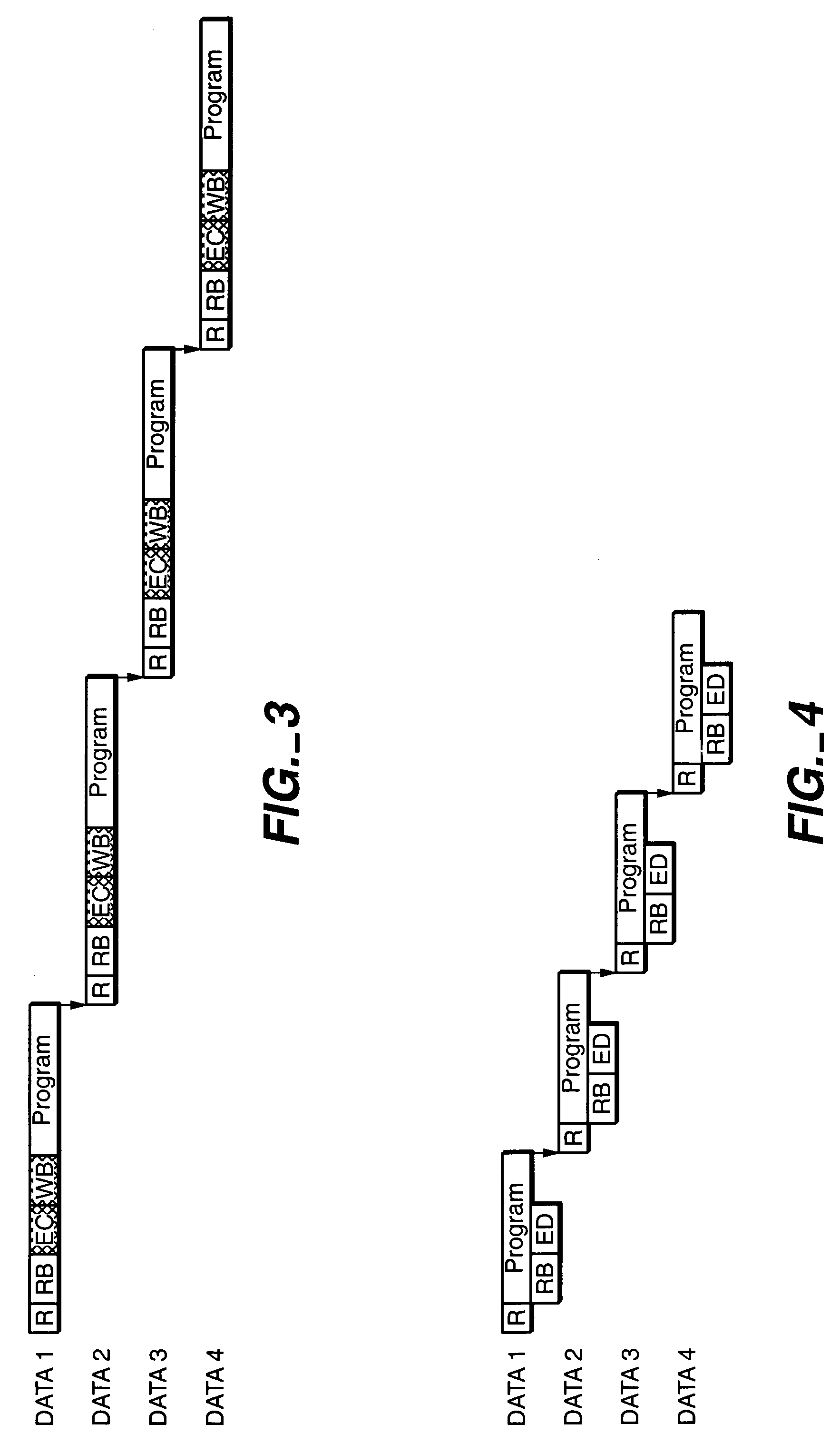

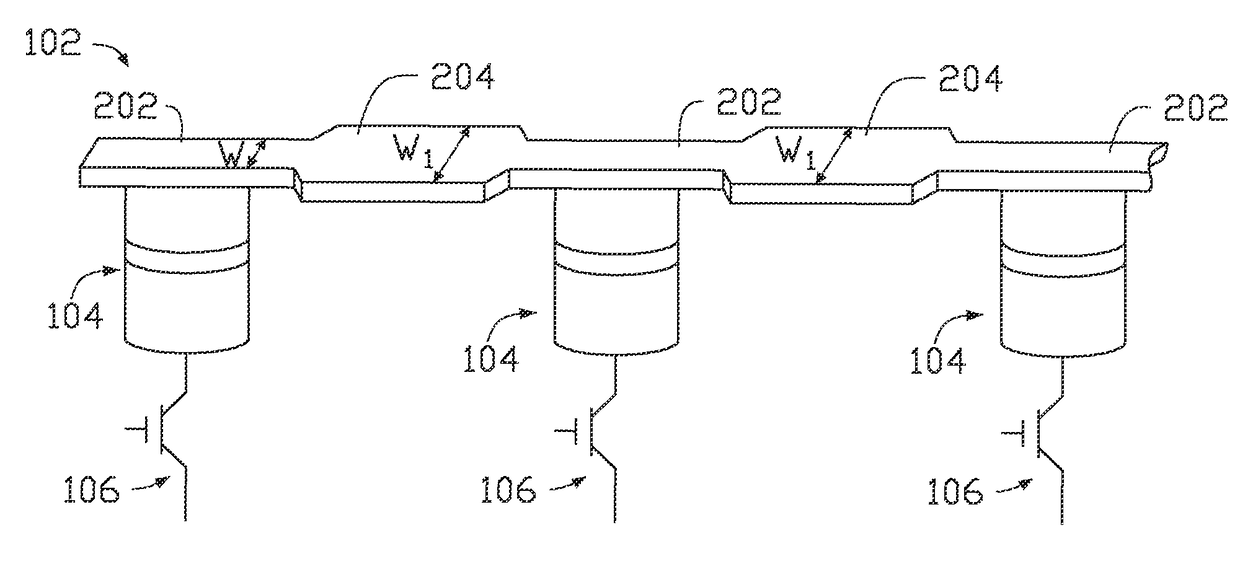

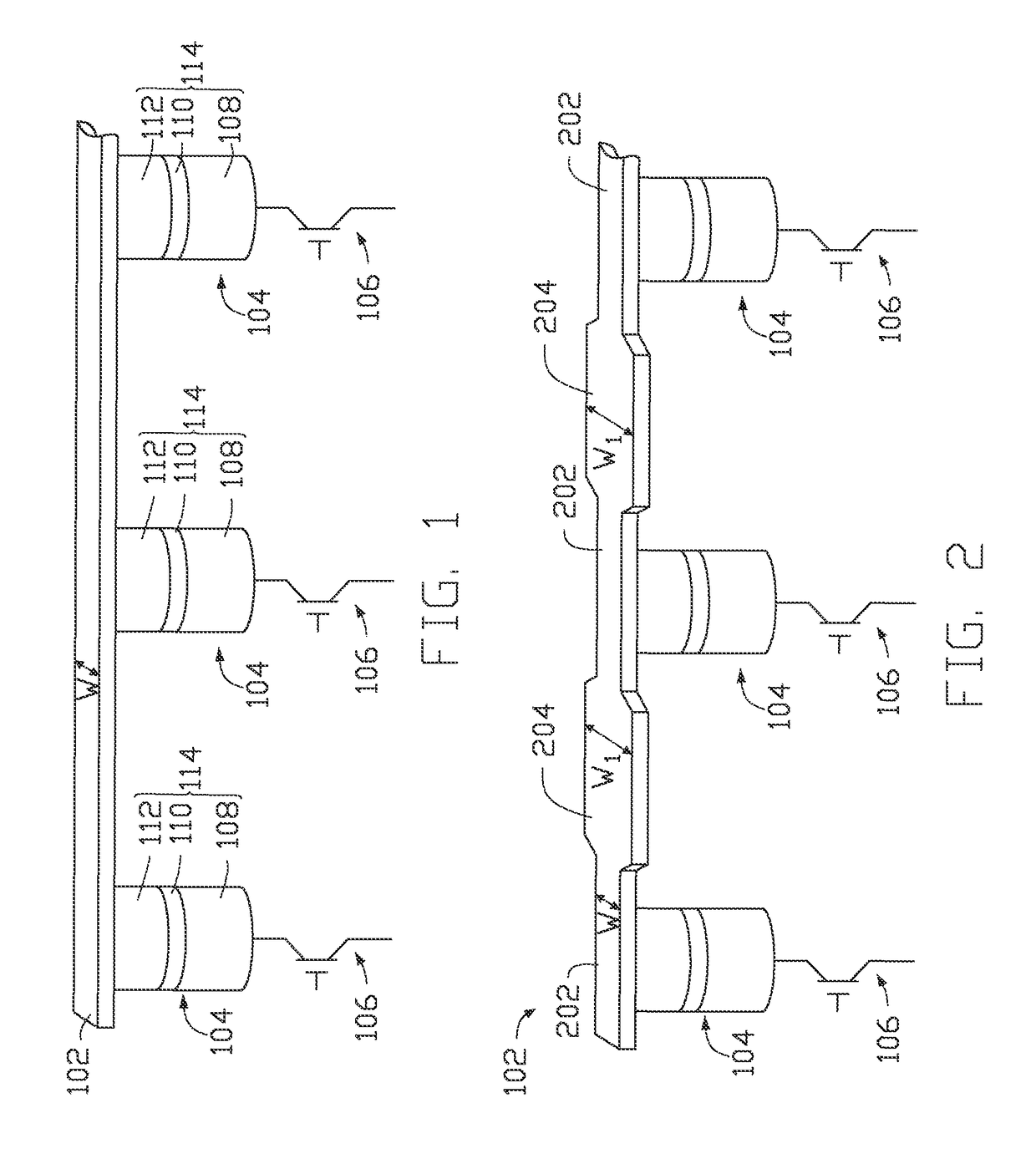

The present invention present methods and architectures for the pipelining of read operation with write operations. In particular, methods are presented for pipelining data relocation operations that allow for the checking and correction of data in the controller prior to its being re-written, but diminish or eliminate the additional time penalty this would normally incur. A number of architectural improve are described to facilitate these methods, including: introducing two registers on the memory where each is independently accessible by the controller; allowing a first memory register to be written from while a second register is written to; introducing two registers on the memory where the contents of the registers can be swapped.

Owner:SANDISK TECH LLC

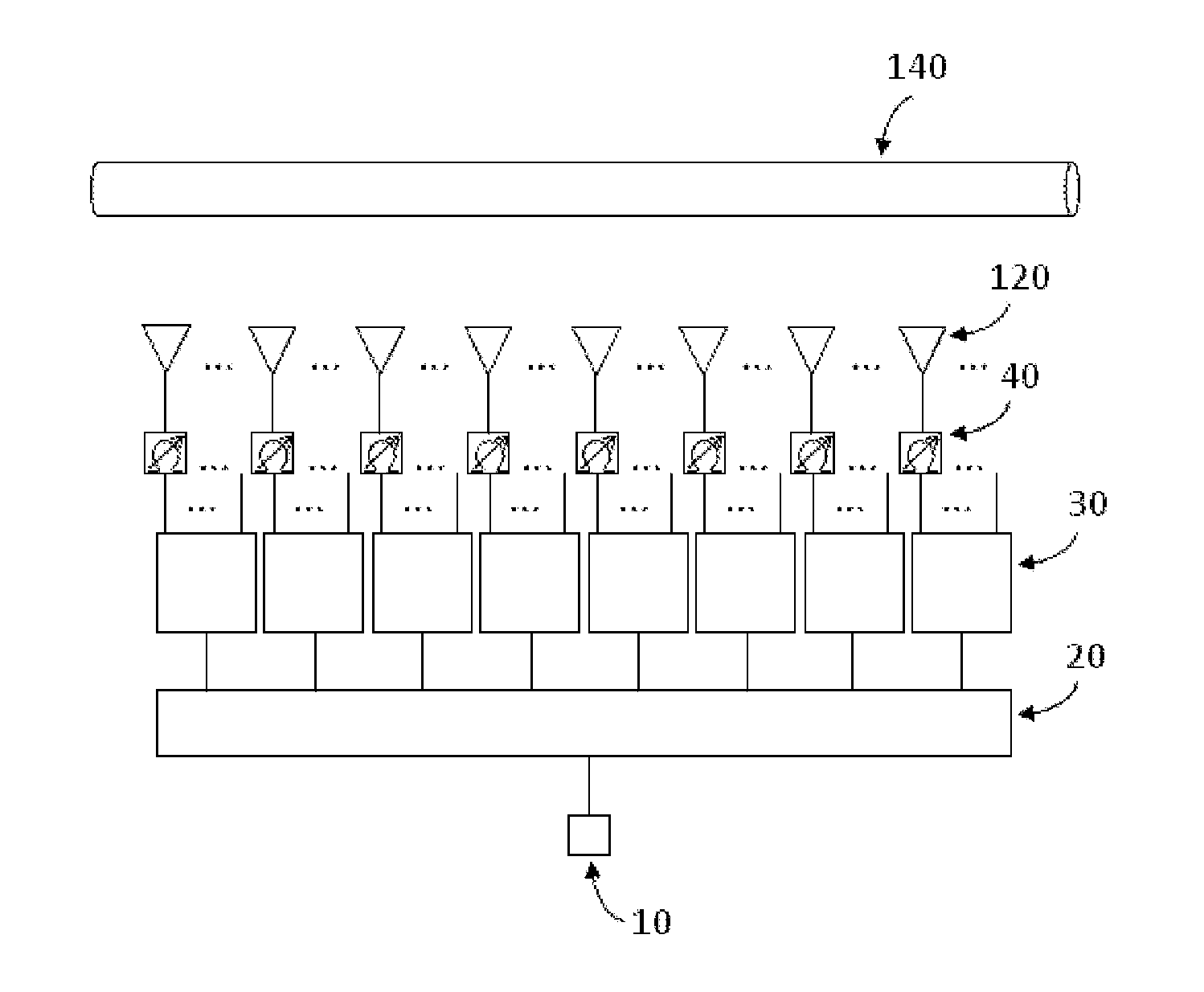

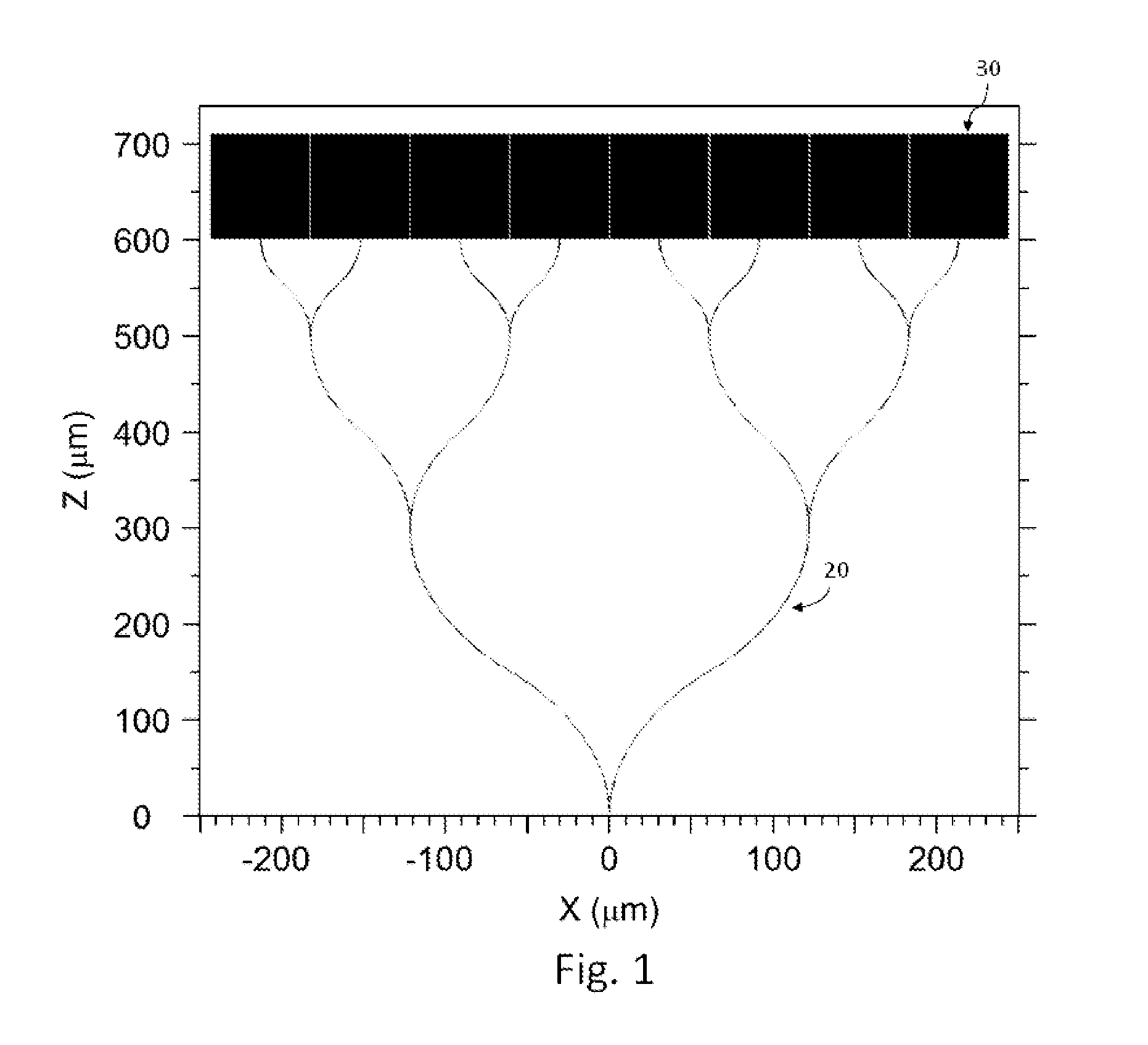

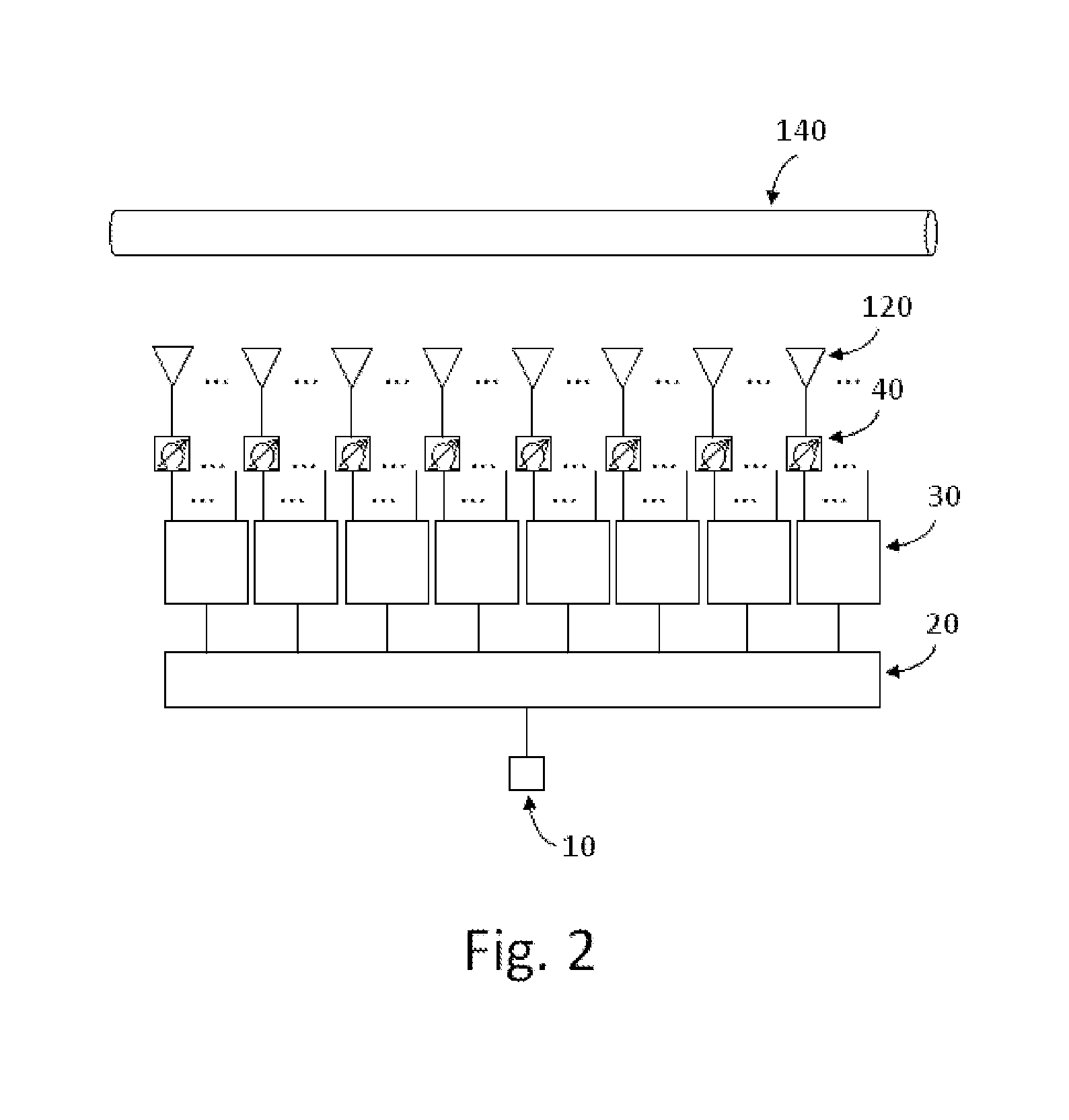

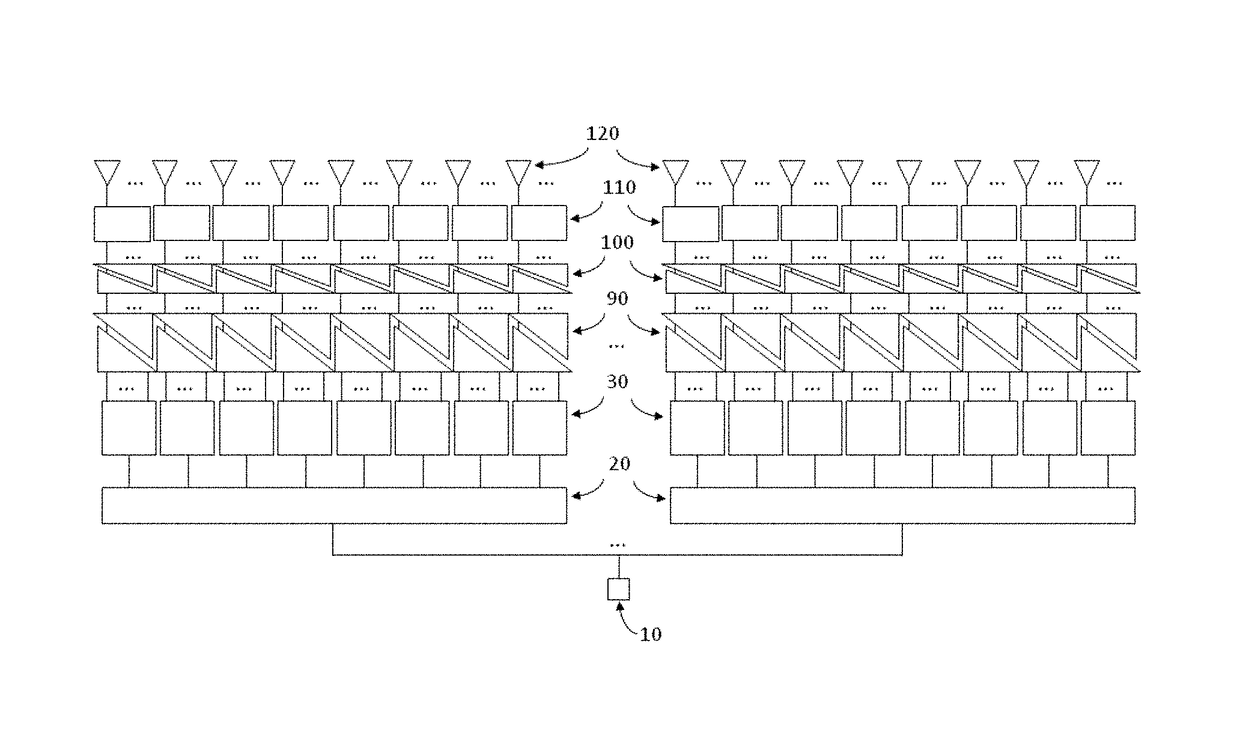

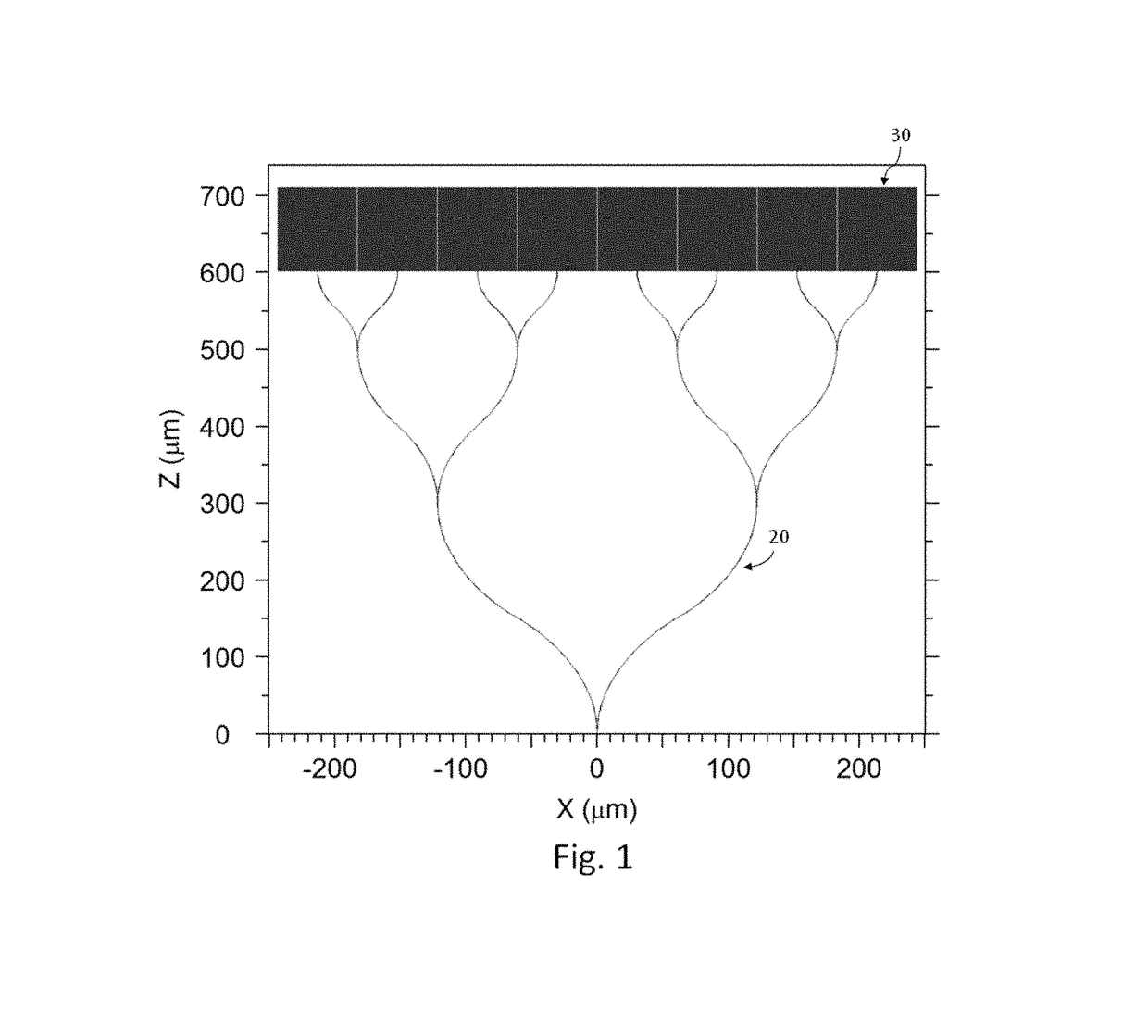

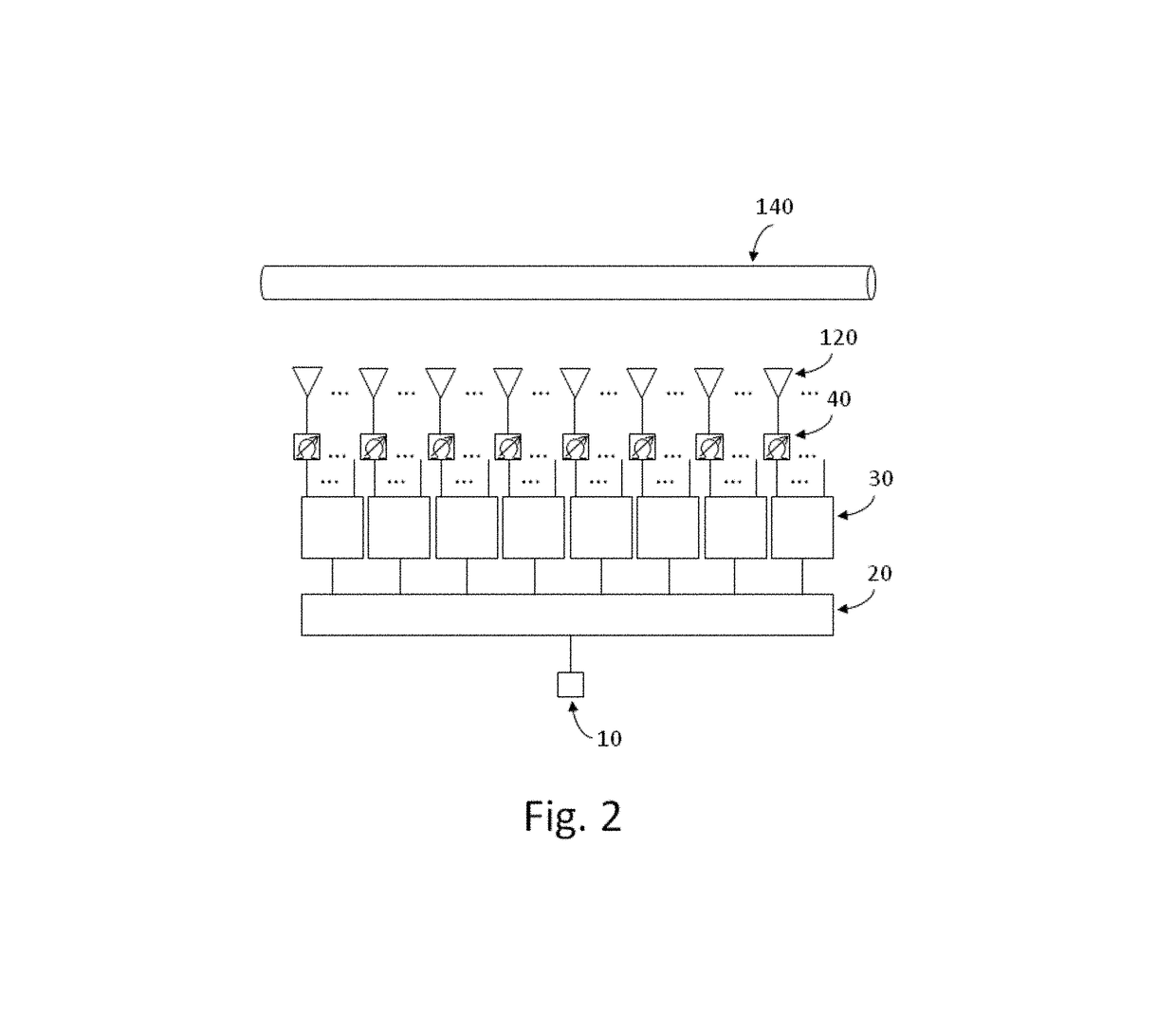

Planar beam forming and steering optical phased array chip and method of using same

ActiveUS20150378241A1High yieldLow costWave based measurement systemsNon-linear opticsRadarChip architecture

A one-dimensional planar beam forming and steering optical phased array chip is a simple building block of a two-dimensional beam forming and steering solid-state lidar, enabling manufacturing of said lidars at high yield and low cost through the use of a plurality of said chips. Innovative photonic integrated circuit chip architectures that follow design for manufacturing rules enable said building blocks.

Owner:QUANERGY SOLUTIONS INC

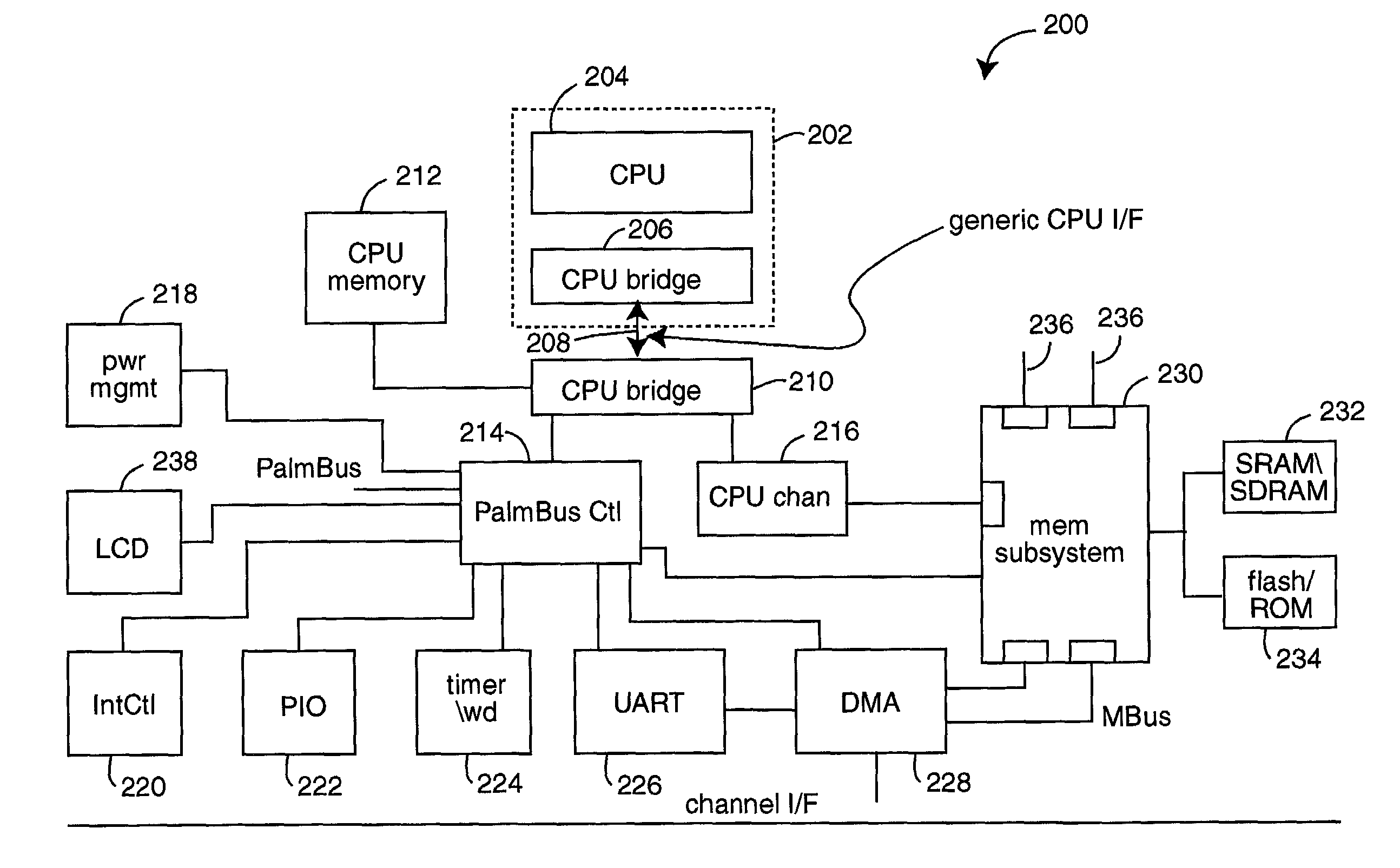

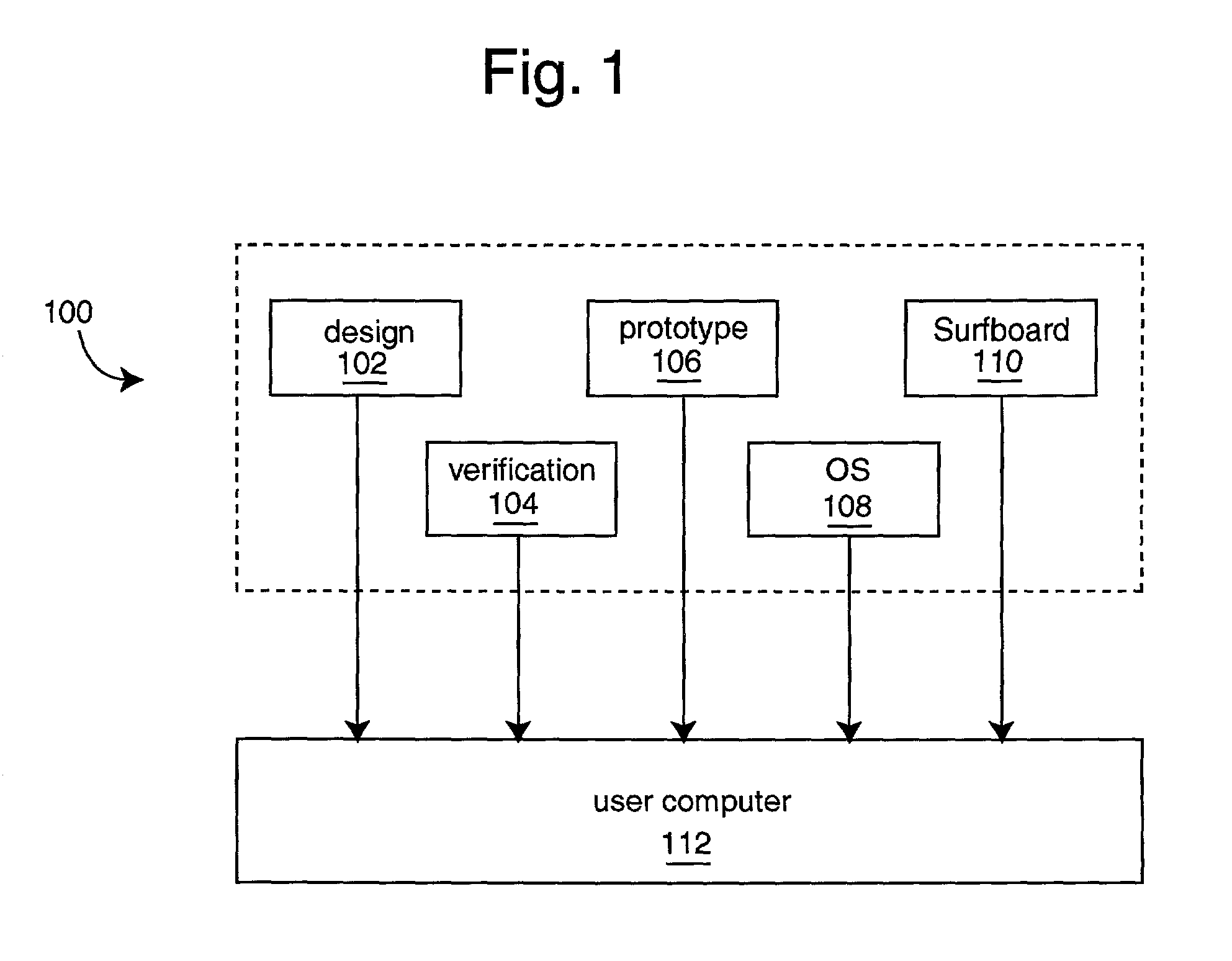

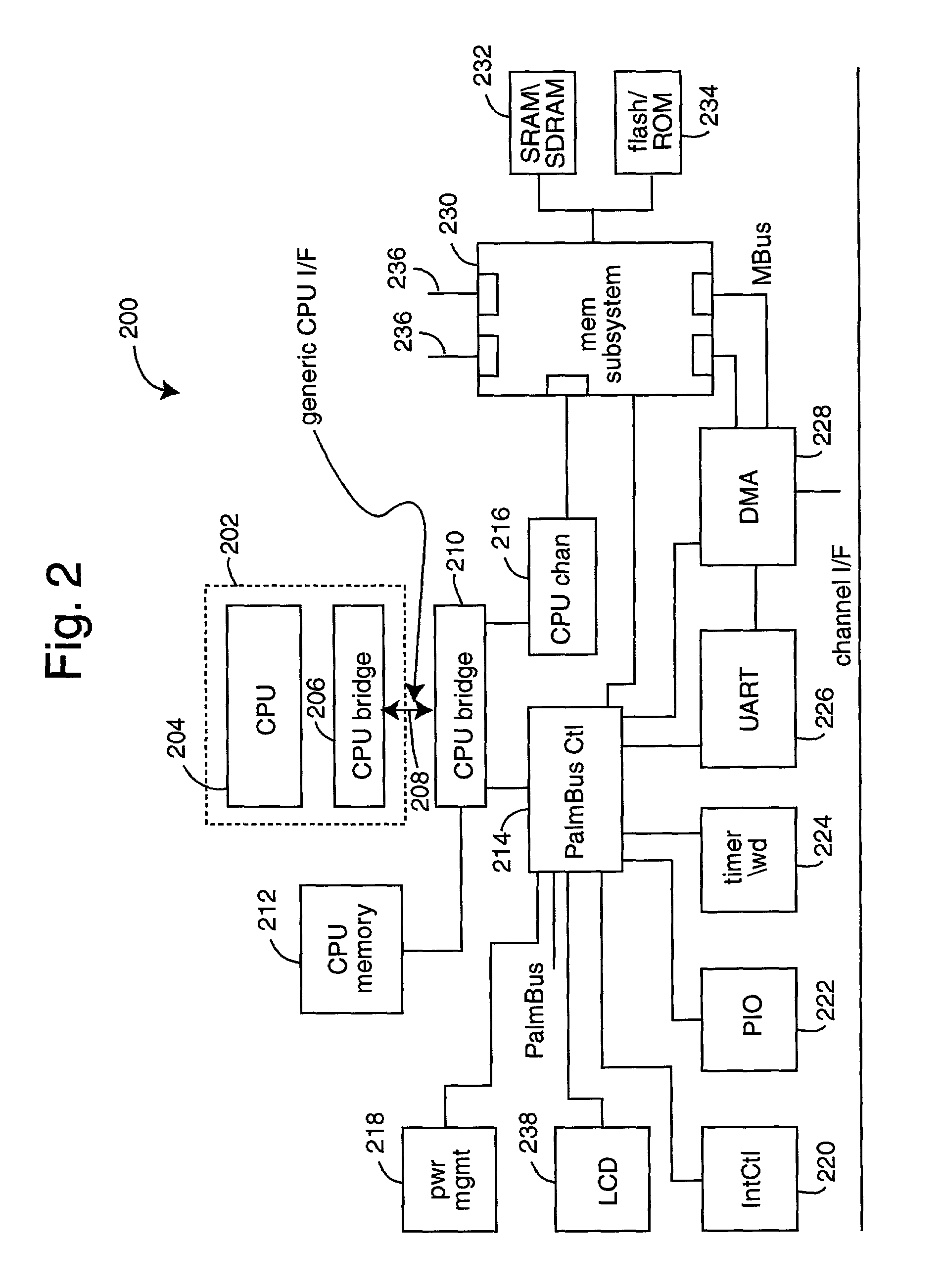

Design tool for systems-on-a-chip

InactiveUS7124376B2Promote rapid developmentReduce a user's time-to-marketCAD circuit designSoftware simulation/interpretation/emulationTest suiteMakefile

A pre-designed system-on-chip architecture and method includes several standard library devices, HDL source code, simulation environment and regression, synthesis scripts, software header files, software libraries, ASIC verification test suites, and makefiles. The standard library devices comprise an integrated CPU, a shared memory controller, a peripheral controller, system peripherals, a DMA controller, embedded memory, and general system control. CPU bridges are used to accommodate a variety of processor types and to insulate users from the complexities of interfacing to different kinds of processors. Such CPU bridges further allow the latest processors to be rapidly integrated into existing integration platforms and designs.

Owner:NETVINCI

Planar beam forming and steering optical phased array chip and method of using same

ActiveUS9753351B2High yieldLow costWave based measurement systemsNon-linear opticsRadarChip architecture

A one-dimensional planar beam forming and steering optical phased array chip is a simple building block of a two-dimensional beam forming and steering solid-state lidar, enabling manufacturing of said lidars at high yield and low cost through the use of a plurality of said chips. Innovative photonic integrated circuit chip architectures that follow design for manufacturing rules enable said building blocks.

Owner:QUANERGY SOLUTIONS INC

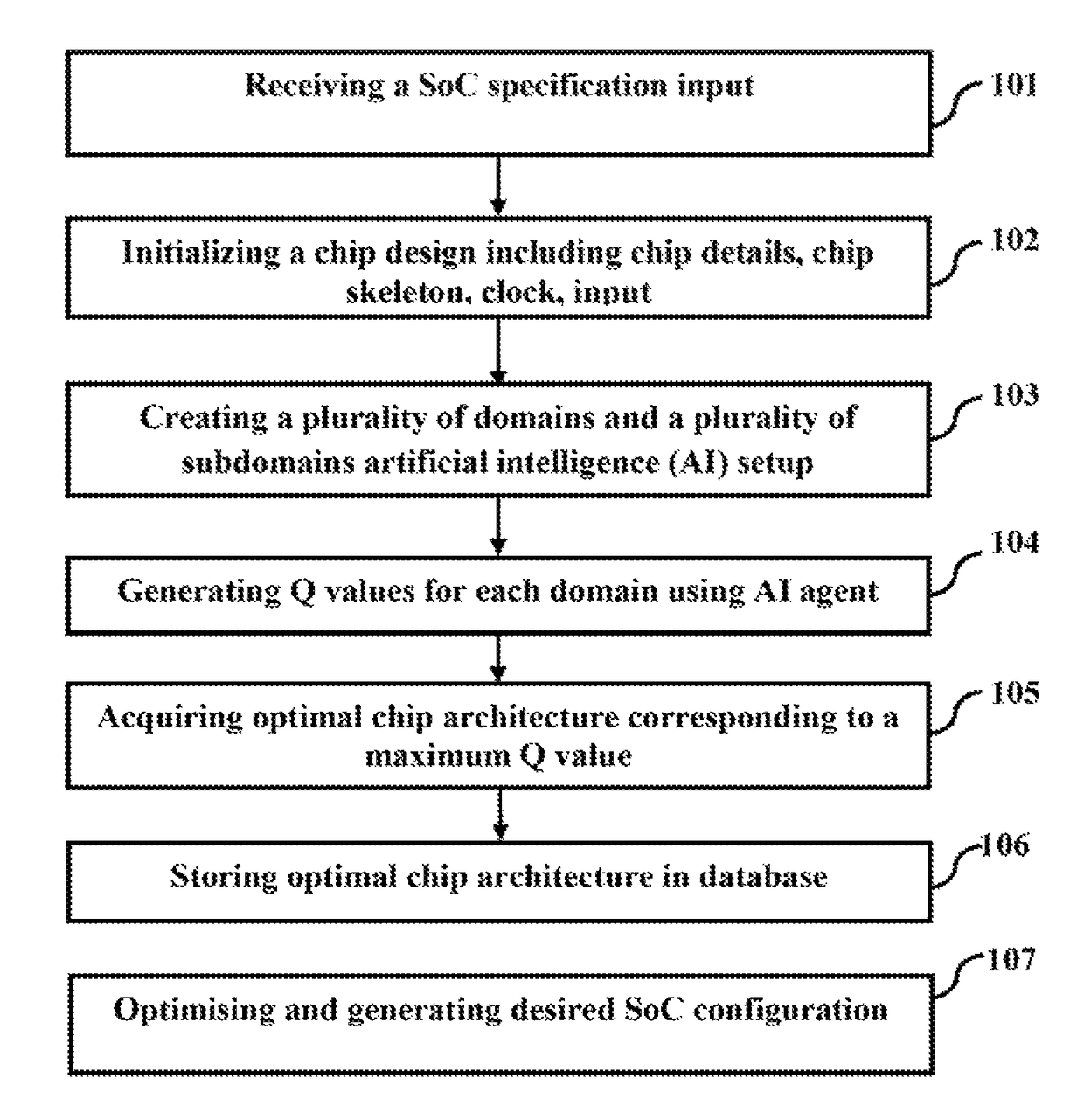

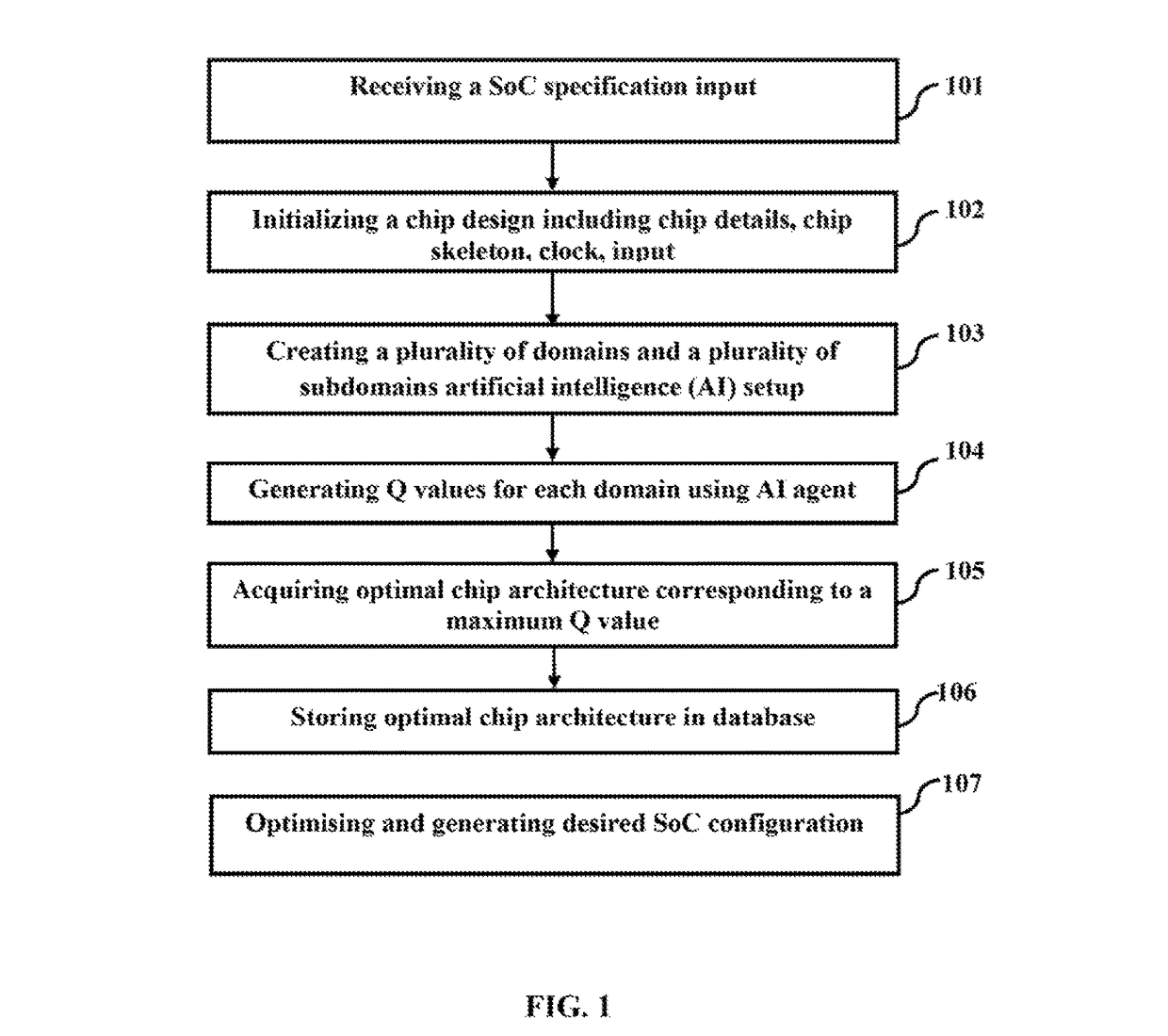

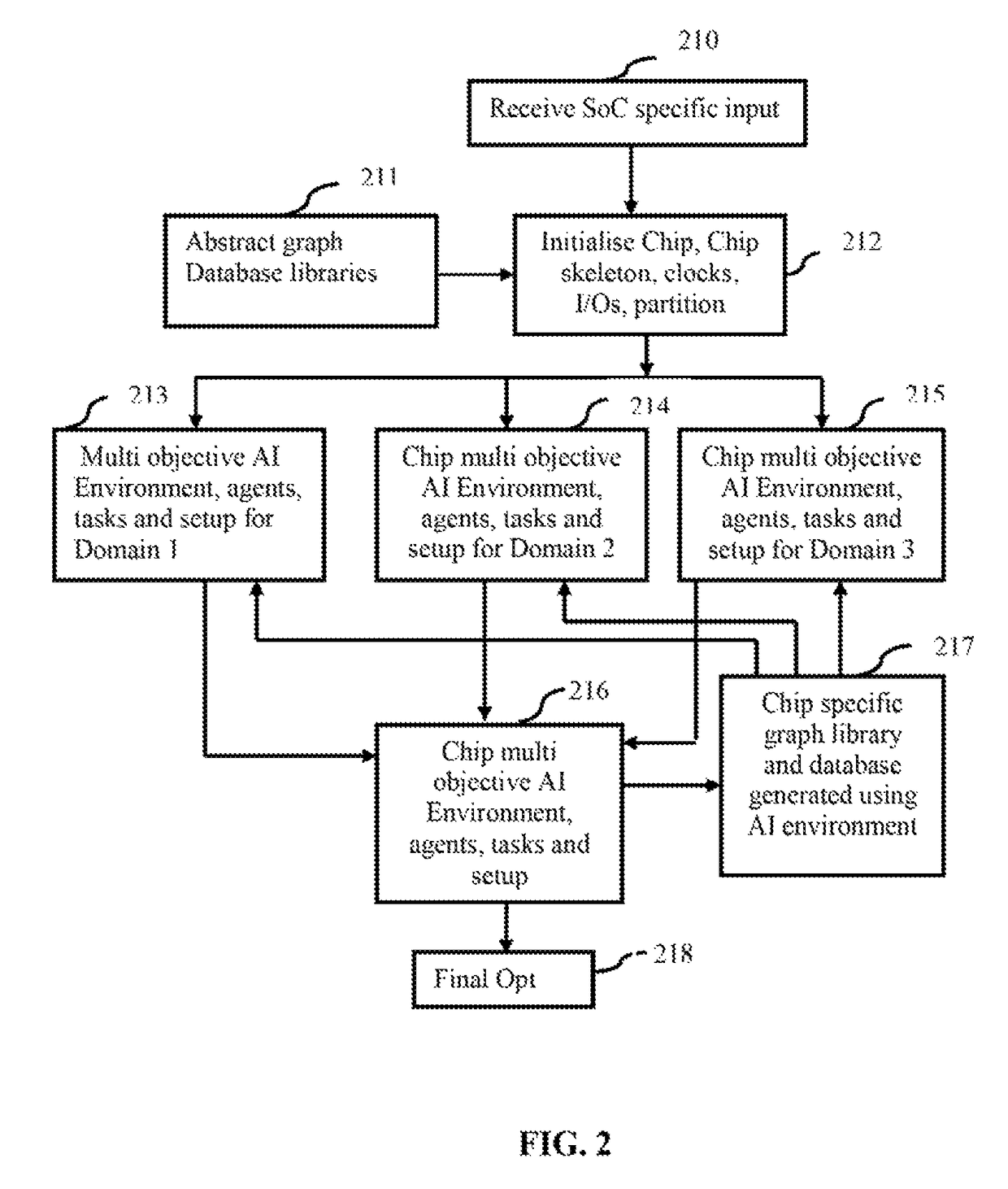

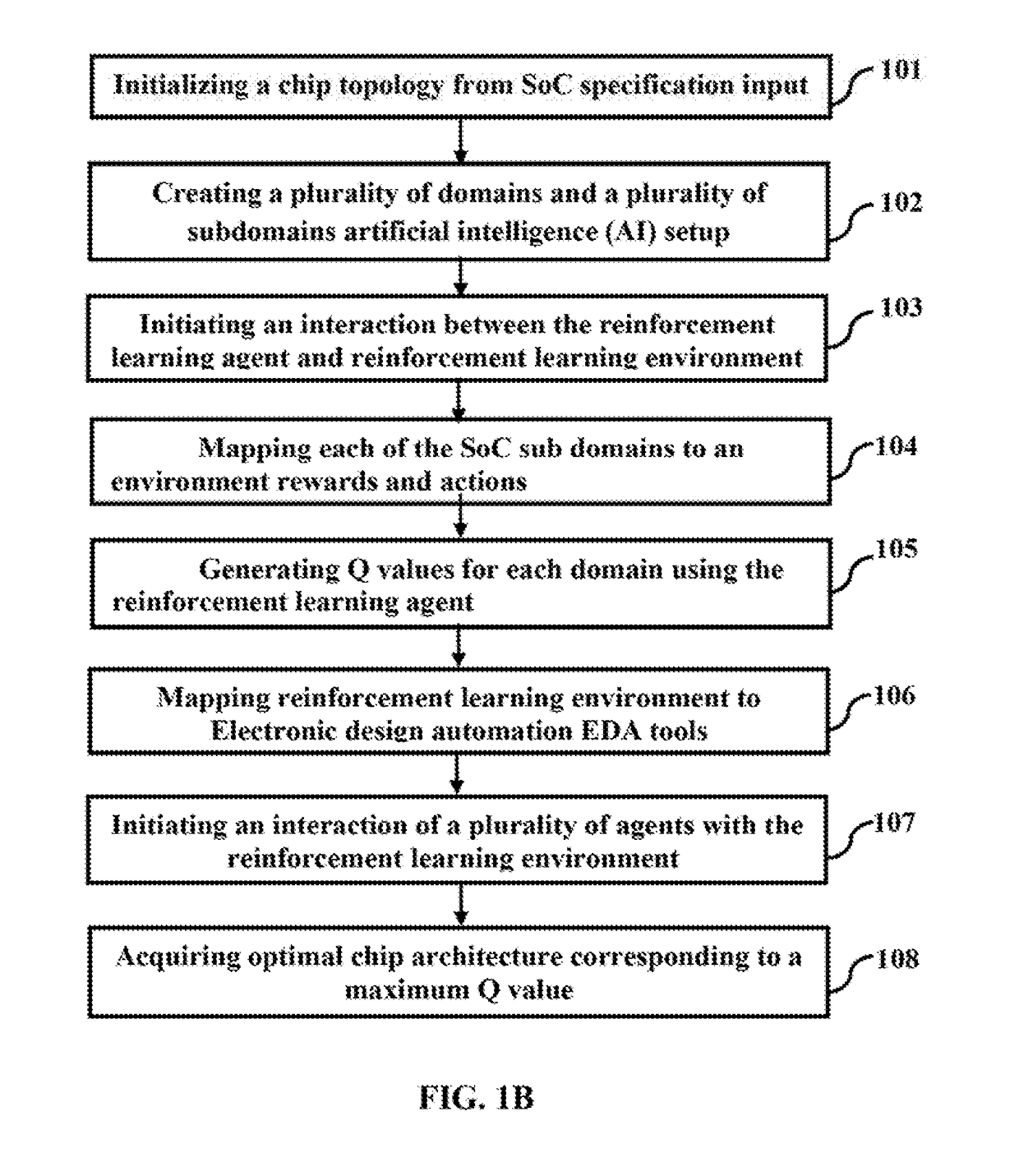

System and method for designing system on chip (SoC) circuits through artificial intelligence and reinforcement learning

ActiveUS9792397B1Reduce complexityGood decisionDesign optimisation/simulationCAD circuit designComputer architectureRelevant information

The embodiments herein discloses a system and method for designing SoC using AI and Reinforcement Learning (RL) techniques. Reinforcement Learning is done either hierarchically in several steps or in a single-step comprising environment, tasks, agents and experiments, to have access to SoC (System on a Chip) related information. The AI agent is configured to learn from the interaction and plan the implementation of a SoC circuit design. Q values generated for each domain and sub domain are stored in a hierarchical SMDP structure in a form of SMDP Q table in a big data database. An optimal chip architecture corresponding to a maximum Q value of a top level in the SMDP Q table is acquired and stored in a database for learning and inference. Desired SoC configuration is optimized and generated based on the optimal chip architecture and the generated chip specific graph library.

Owner:ALPHAICS CORP

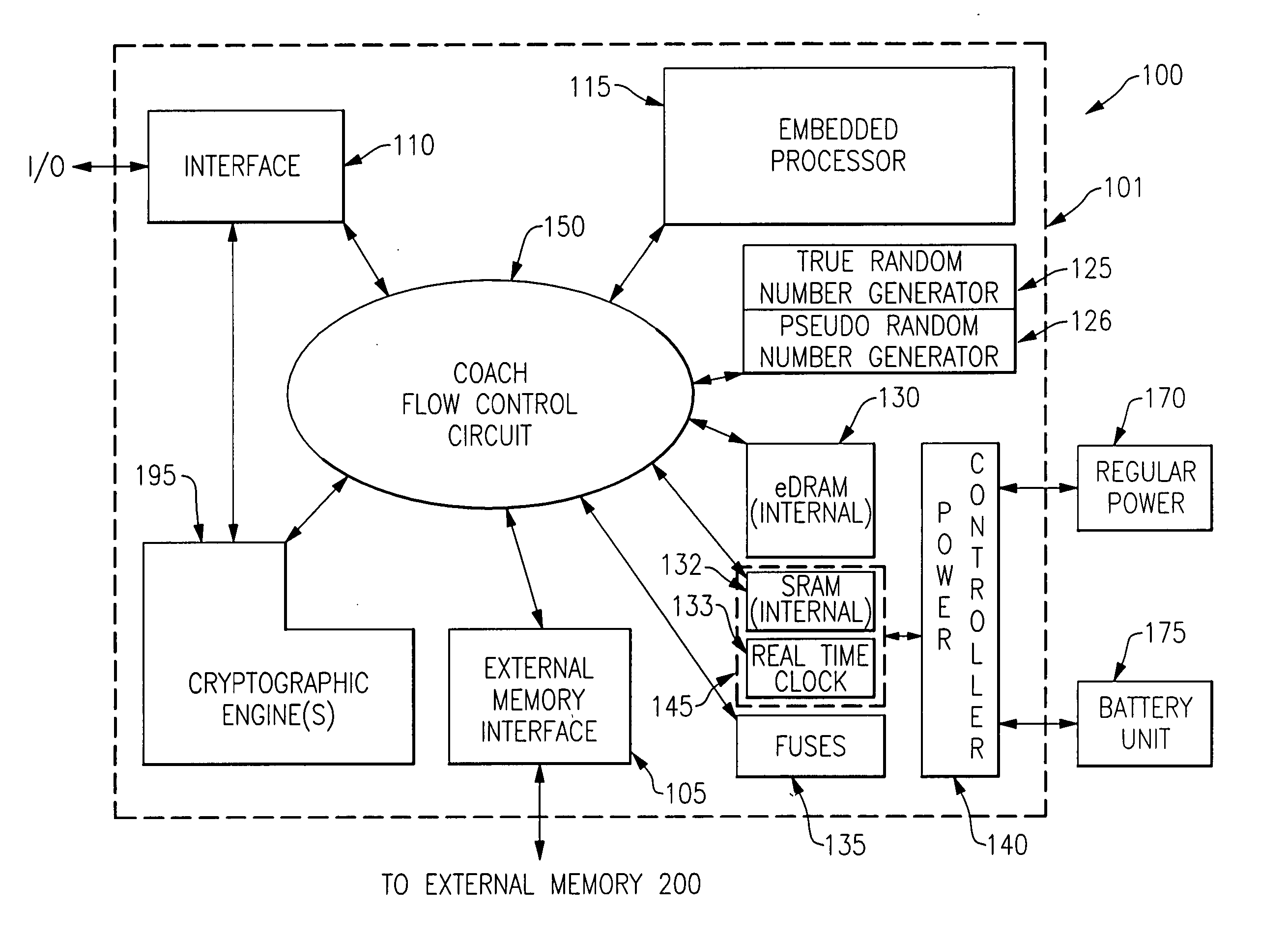

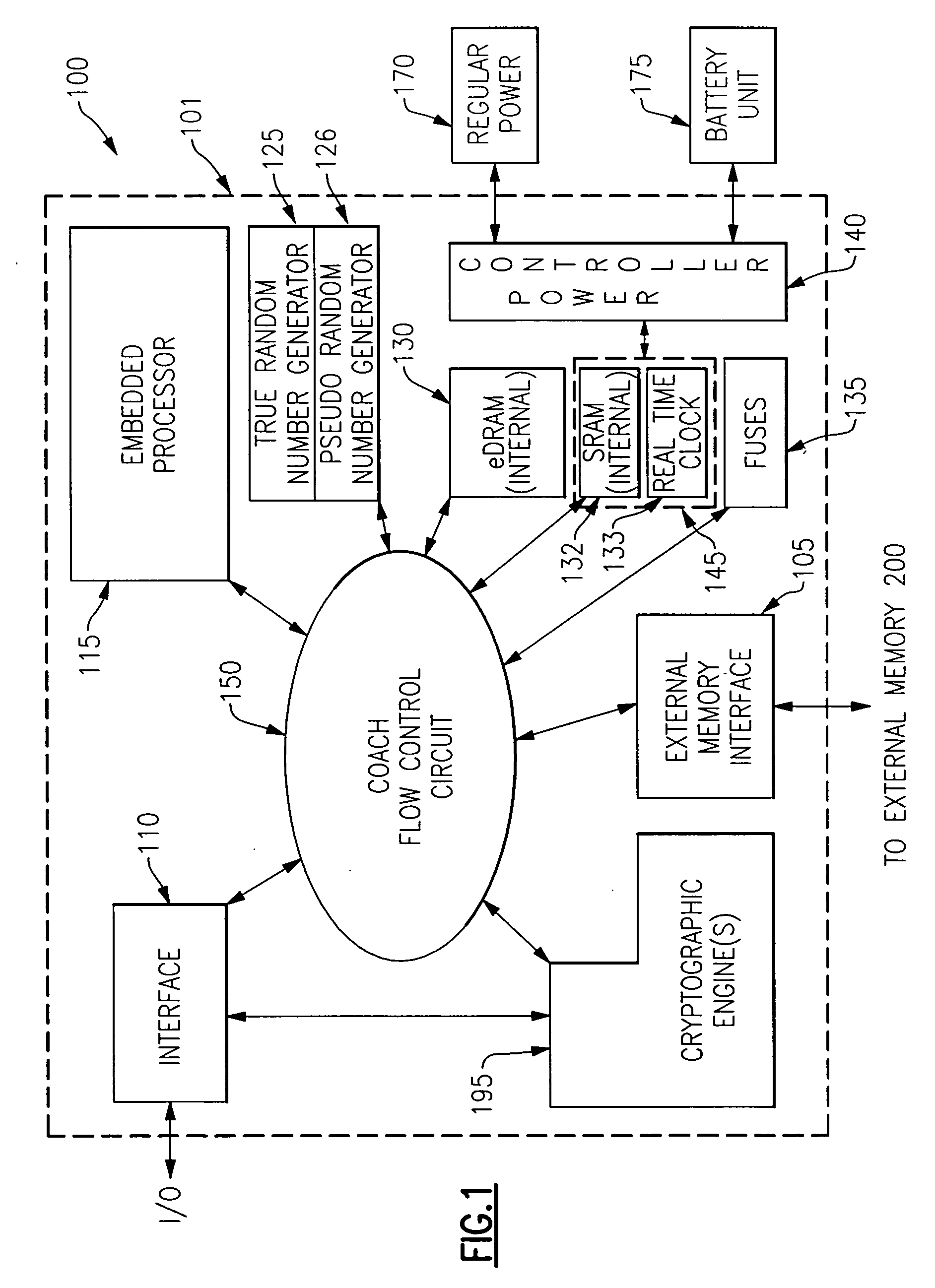

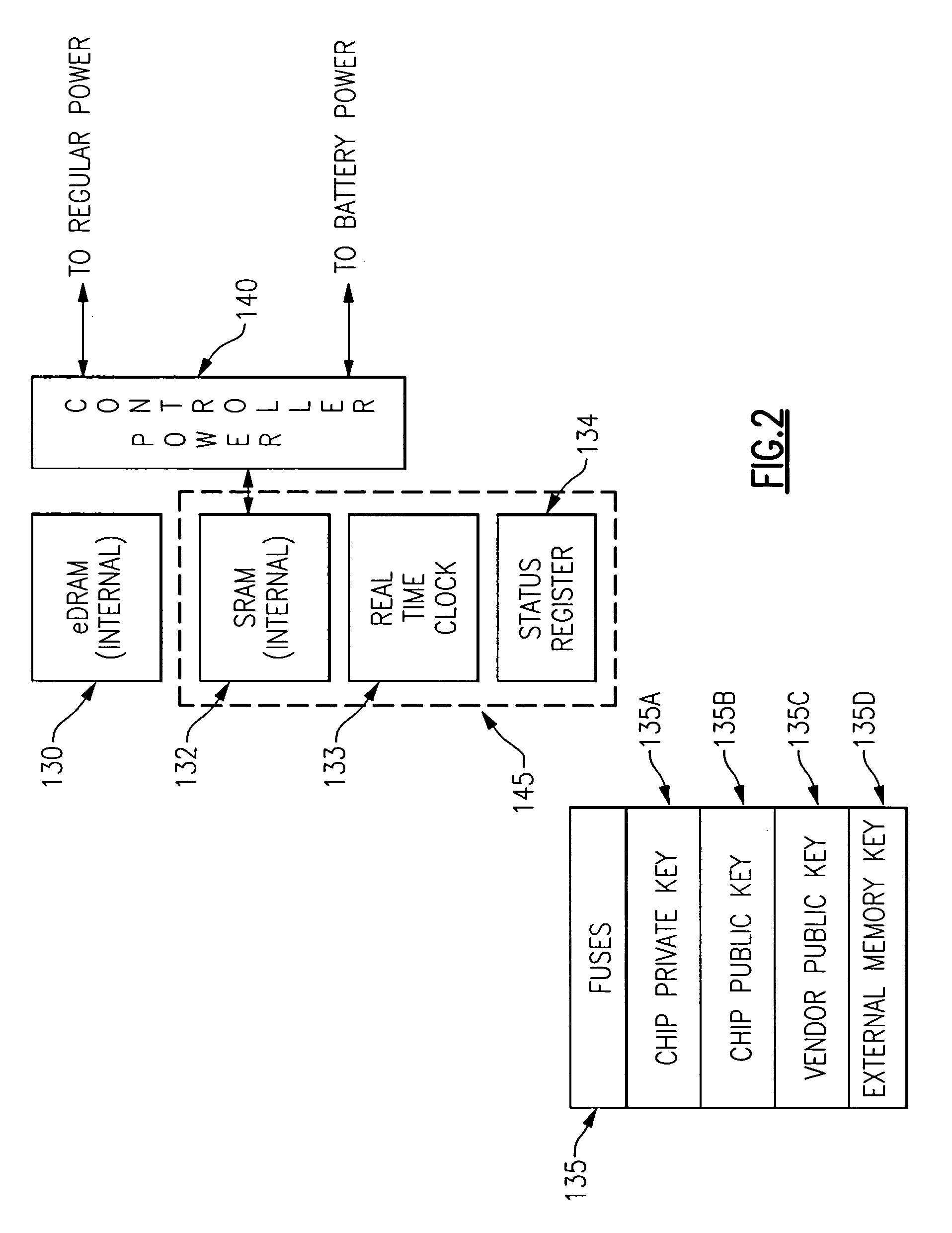

Integrated circuit chip for encryption and decryption having a secure mechanism for programming on-chip hardware

InactiveUS20060059372A1Improve process capabilityInhibit involvementUnauthorized memory use protectionHardware monitoringHard codingChip architecture

An integrated circuit chip is provided which contains one or more processors and one or more cryptographic engines. A flow control circuit having a command processor accepts requests and data via a secure external interface through which only encrypted information is passed. The flow control circuit mediates decryption of this information using cryptographic keys that are present in hard coded form on the chip. In particular the flow control circuit includes a programmable hardware portion which is configurable in a secure manner to create a flexible internal chip architecture. The chip also includes a volatile memory disposed on a voltage island on which is maintained either through a battery backup or from a fixed power source (mains). The chip is thus enabled to securely perform cryptographic operations with the processors controlling the cryptographic engines through the flow control circuit.

Owner:IBM CORP

Pipelined data relocation and improved chip architectures

ActiveUS7490283B2High error rateComplex data operationError detection/correctionRead-only memoriesPresent methodProcessor register

The present invention present methods and architectures for the pipelining of read operation with write operations. In particular, methods are presented for pipelining data relocation operations that allow for the checking and correction of data in the controller prior to its being re-written, but diminish or eliminate the additional time penalty this would normally incur. A number of architectural improvements are described to facilitate these methods, including: introducing two registers on the memory where each is independently accessible by the controller; allowing a first memory register to be written from while a second register is written to; introducing two registers on the memory where the contents of the registers can be swapped.

Owner:SANDISK TECH LLC

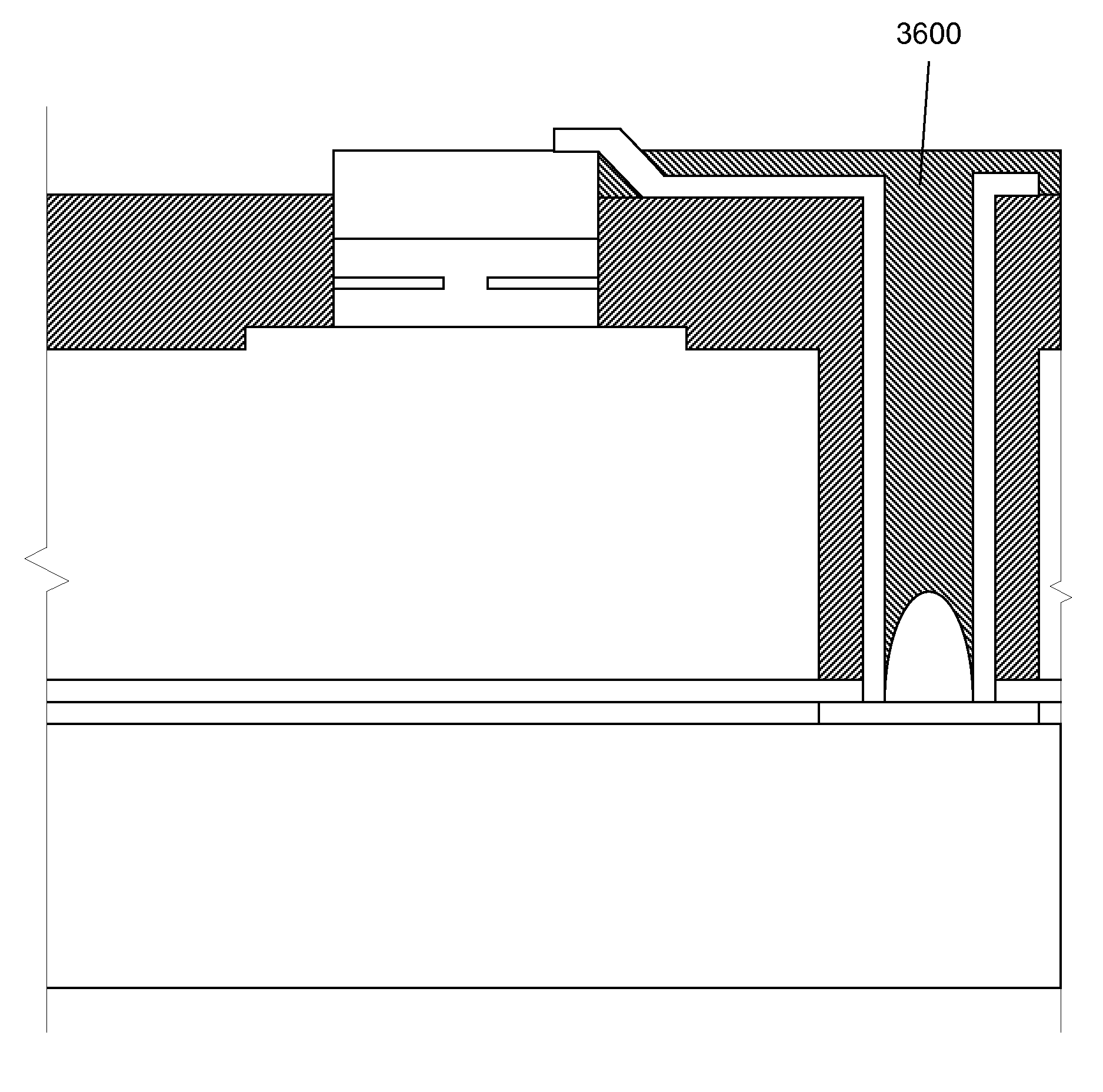

Structure and system-on-chip integration of a two-transistor and two-capacitor memory cell for trench technology

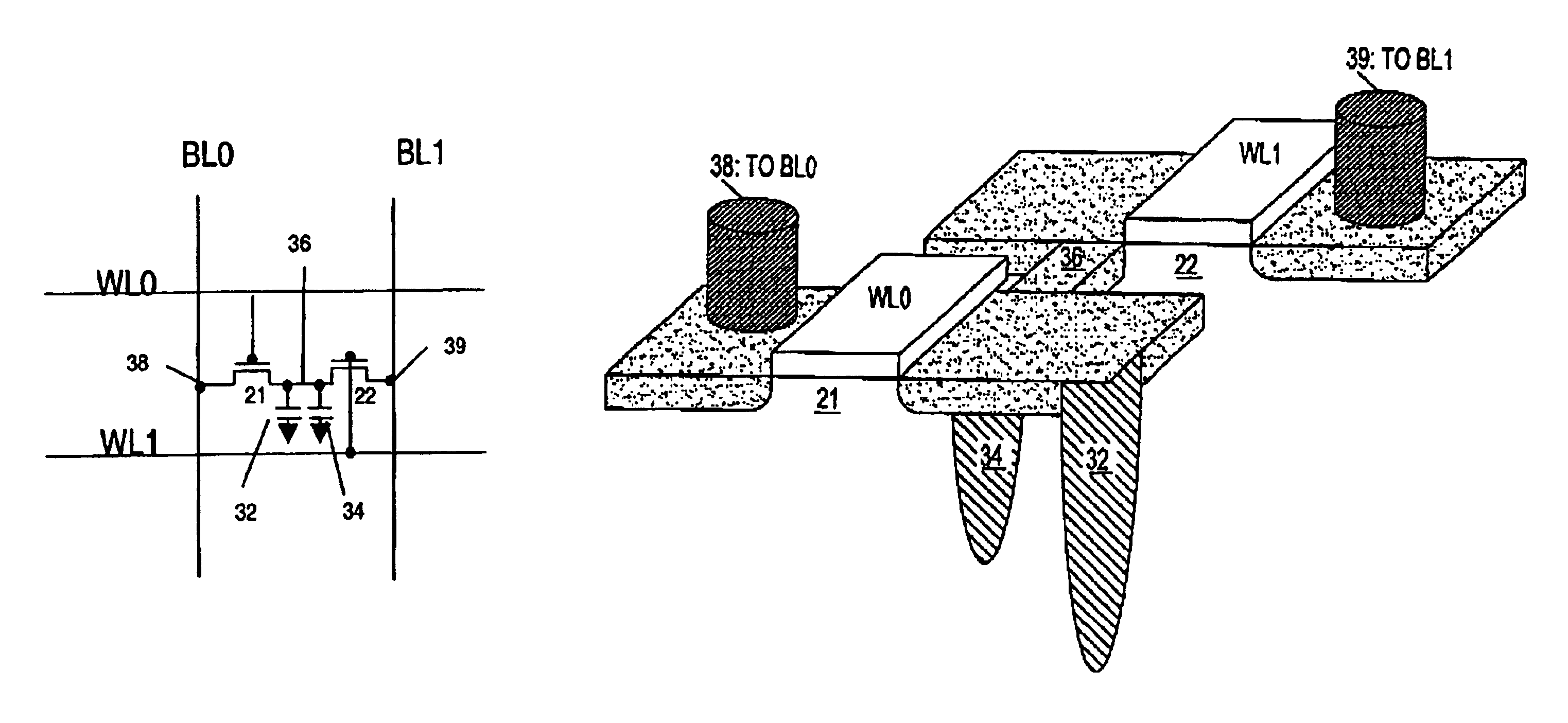

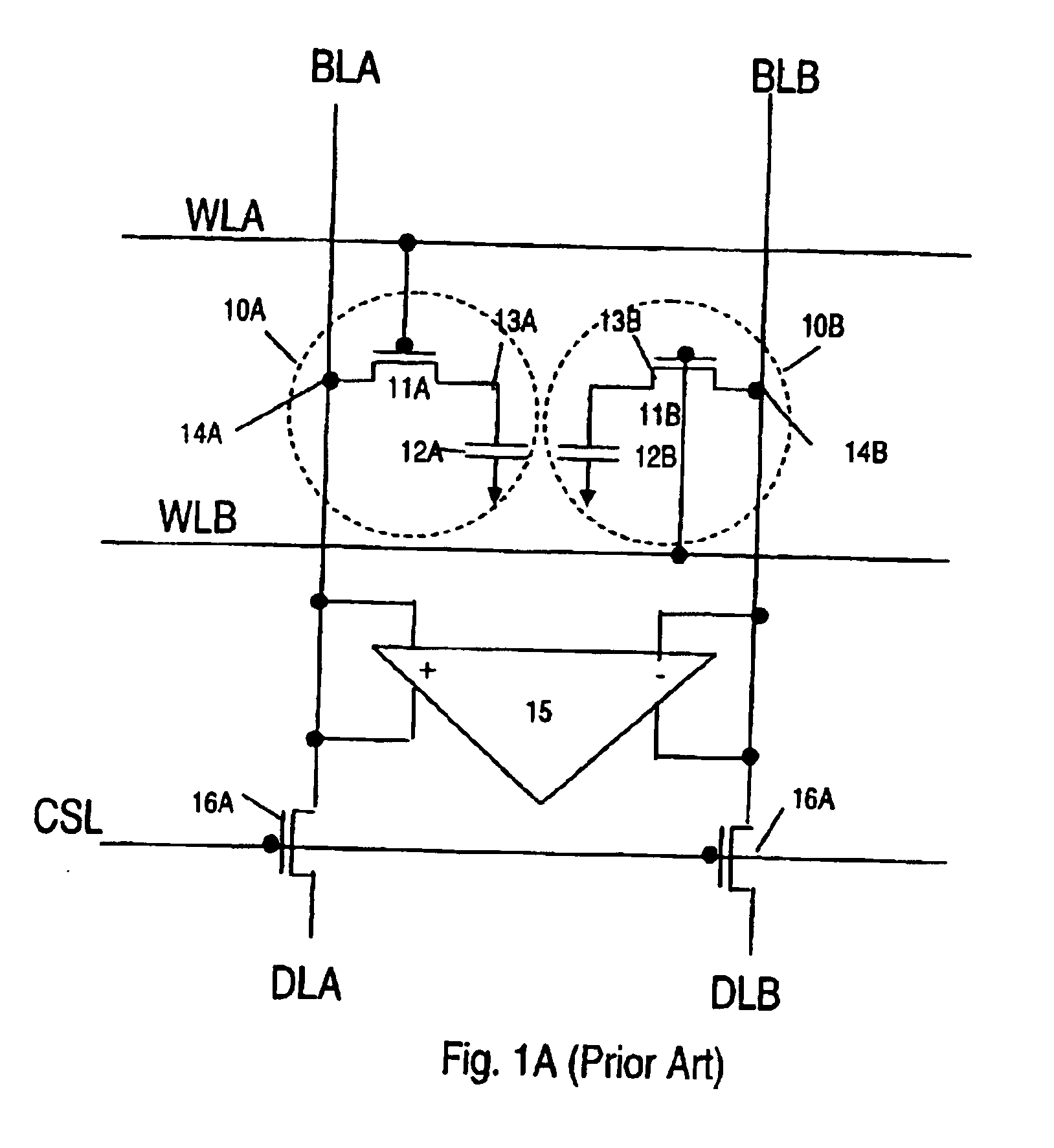

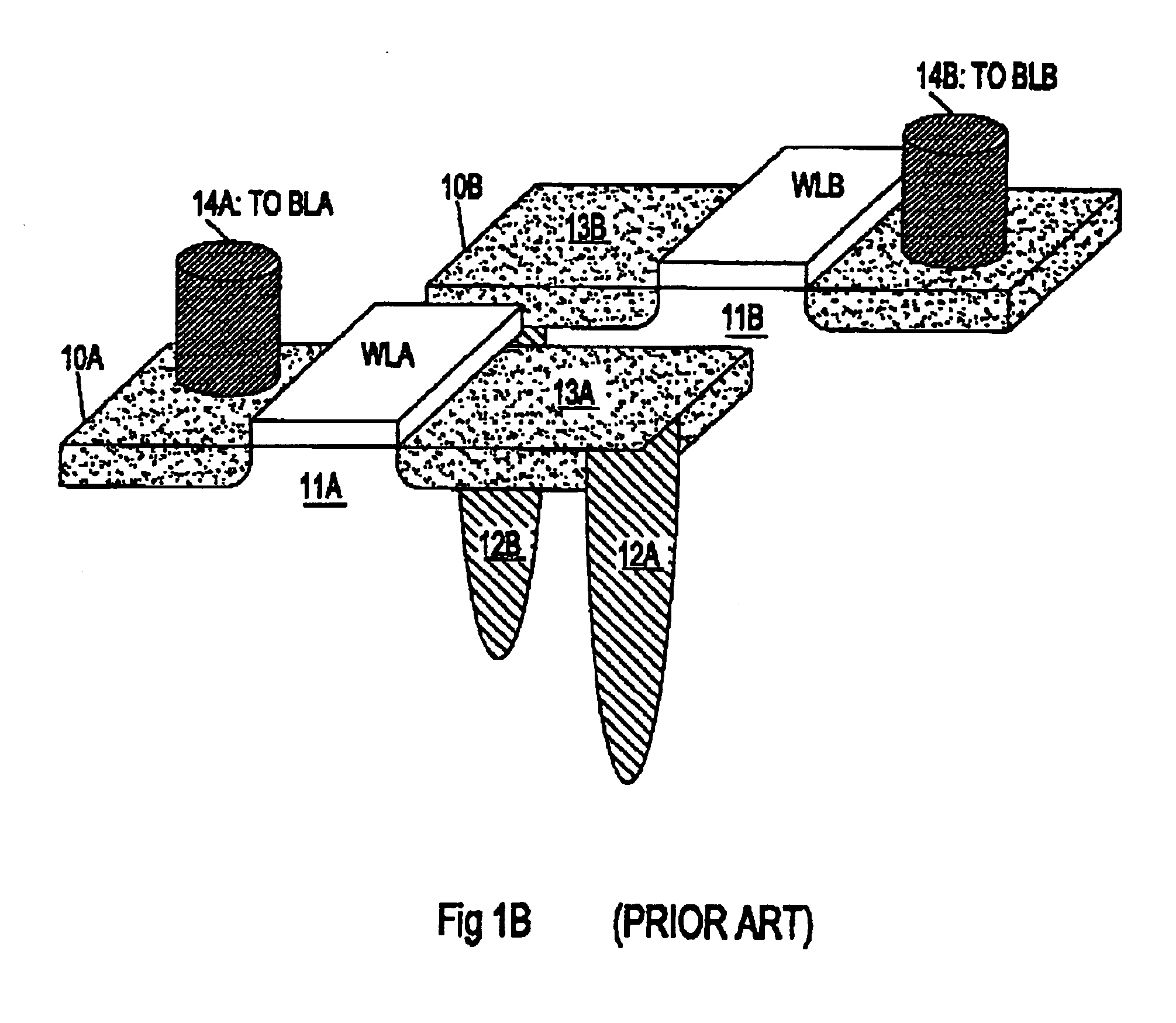

InactiveUS6845033B2Lower performance requirementsReducing storage chargeTransistorJoints with sealing surfacesRandom access memoryEngineering

A two-port dynamic random access memory (DRAM) cell consisting of two transistors and two trench capacitors (2T and 2C DRAM cell) connecting two one transistor and one capacitor DRAM cell (1T DRAM cell) is described. The mask data and cross-section of the 2T 2C DRAM and 1T DRAM cells are fully compatible to each other except for the diffusion connection that couples two storage nodes of the two 1T DRAM cells. This allows a one-port memory cell with 1T and 1C DRAM cell and a two-port memory cell with 2T and 2C DRAM cell to be fully integrated, forming a true system-on chip architecture. Alternatively, by halving the capacitor, the random access write cycle time is further reduced, while still maintaining the data retention time. The deep trench process time is also reduced by reducing by one-half the trench depth.

Owner:IBM CORP

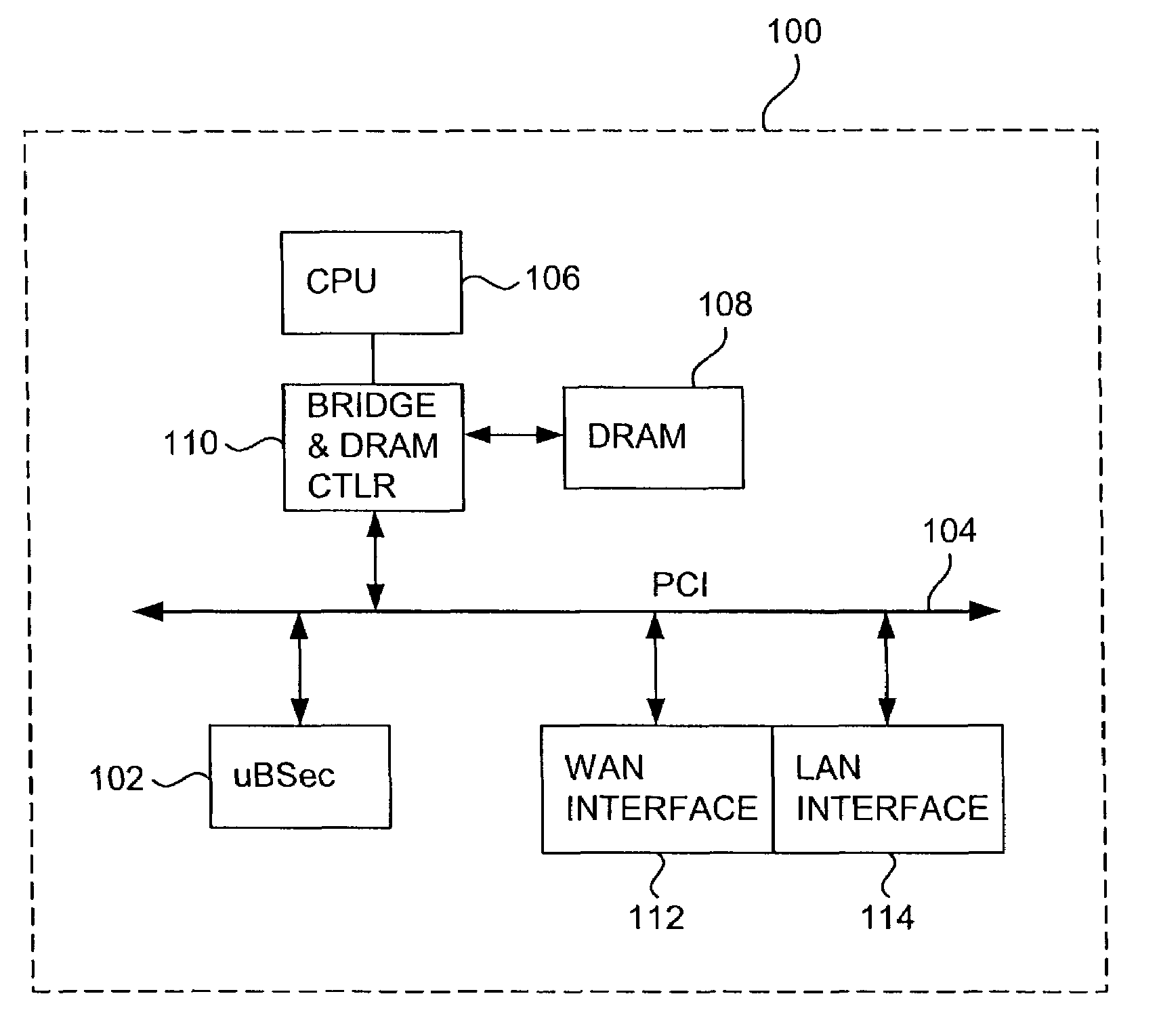

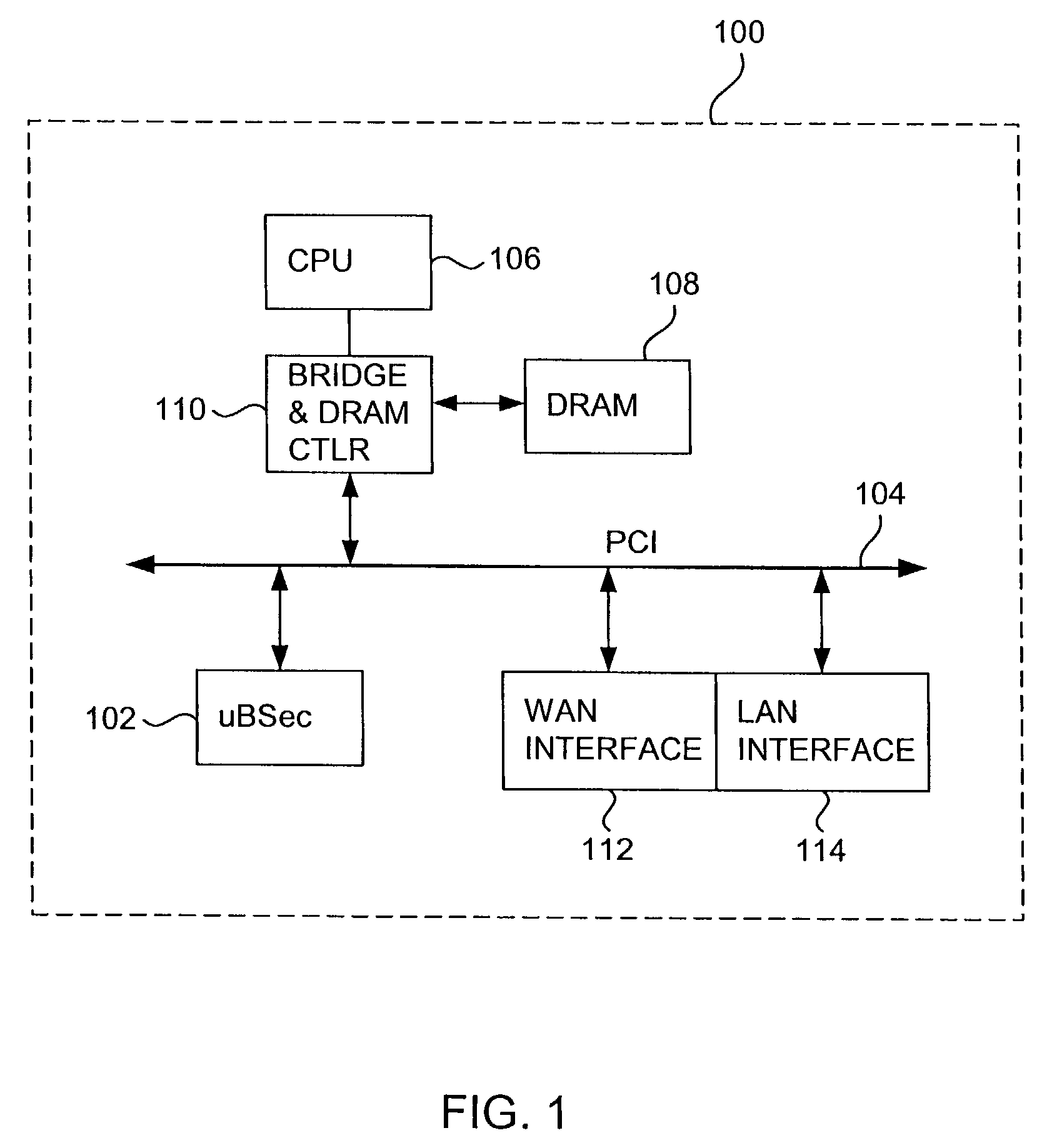

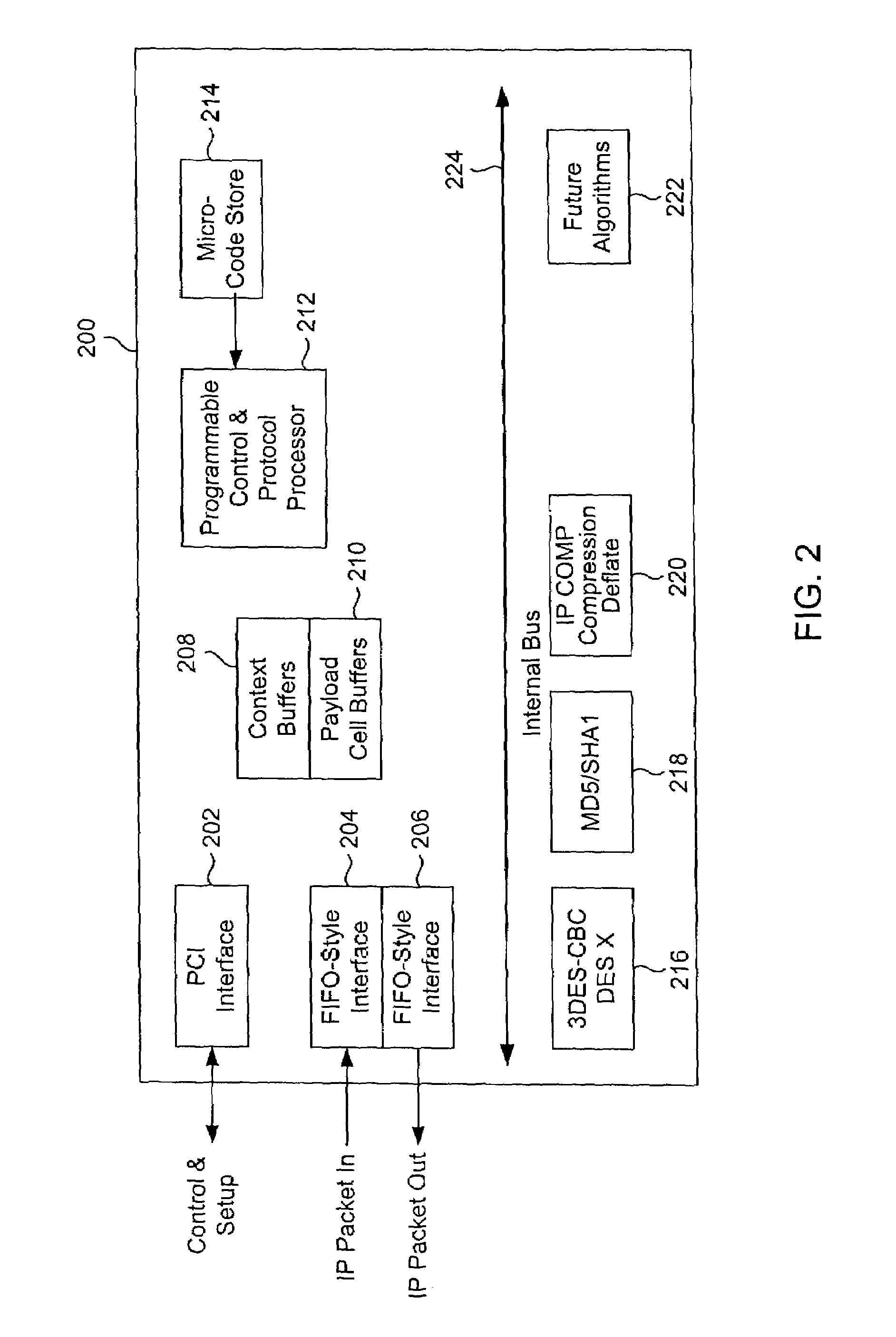

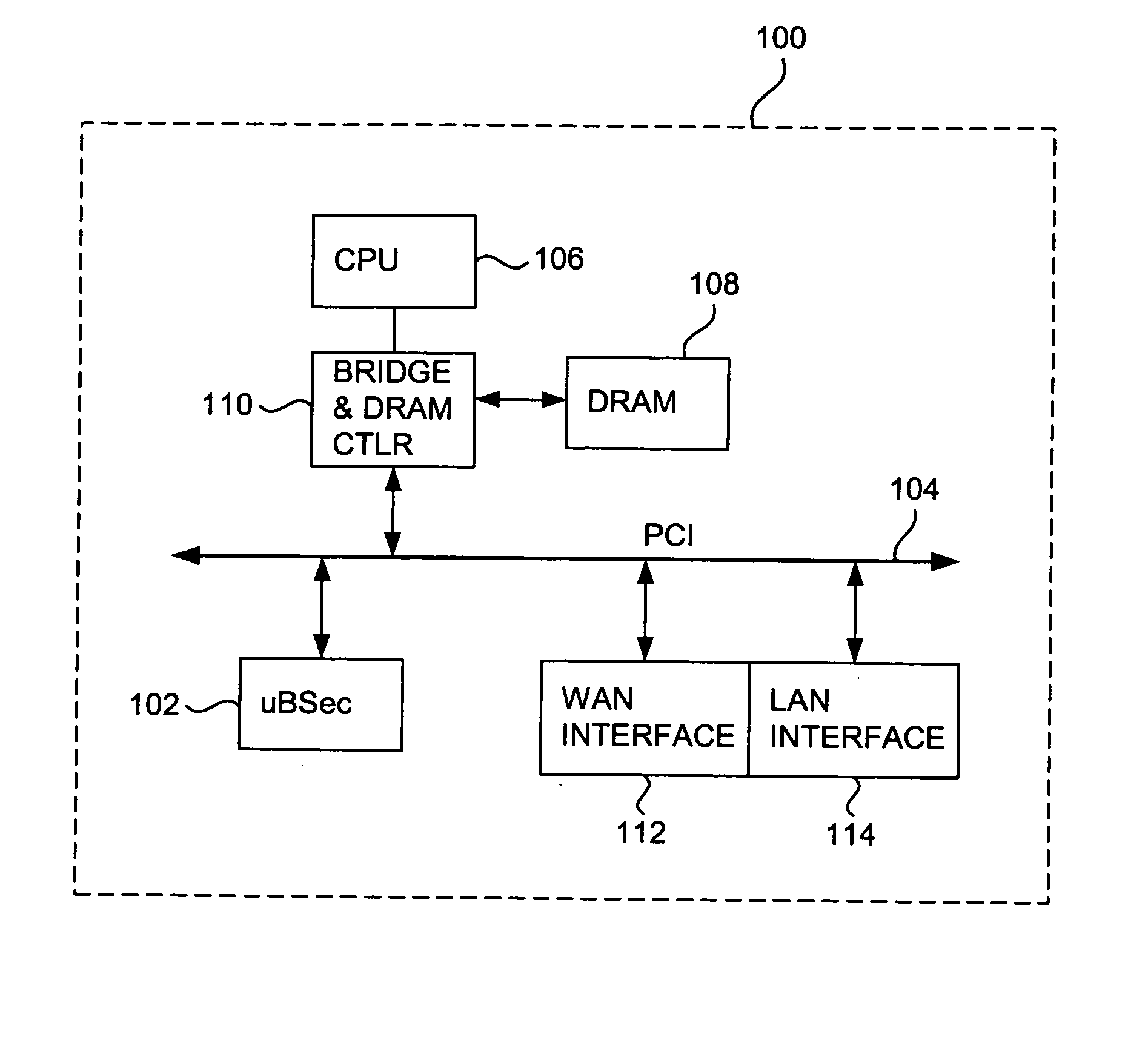

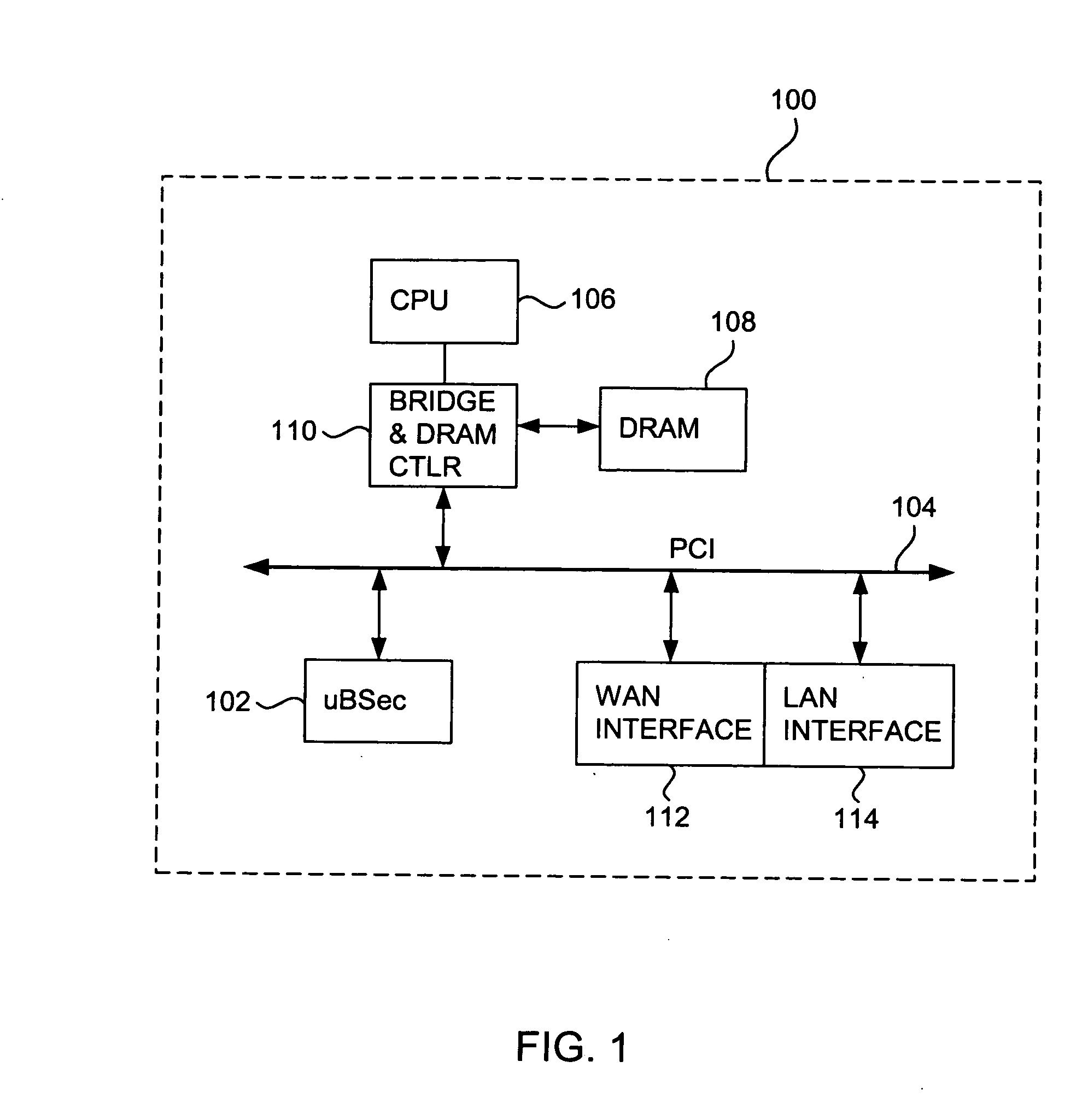

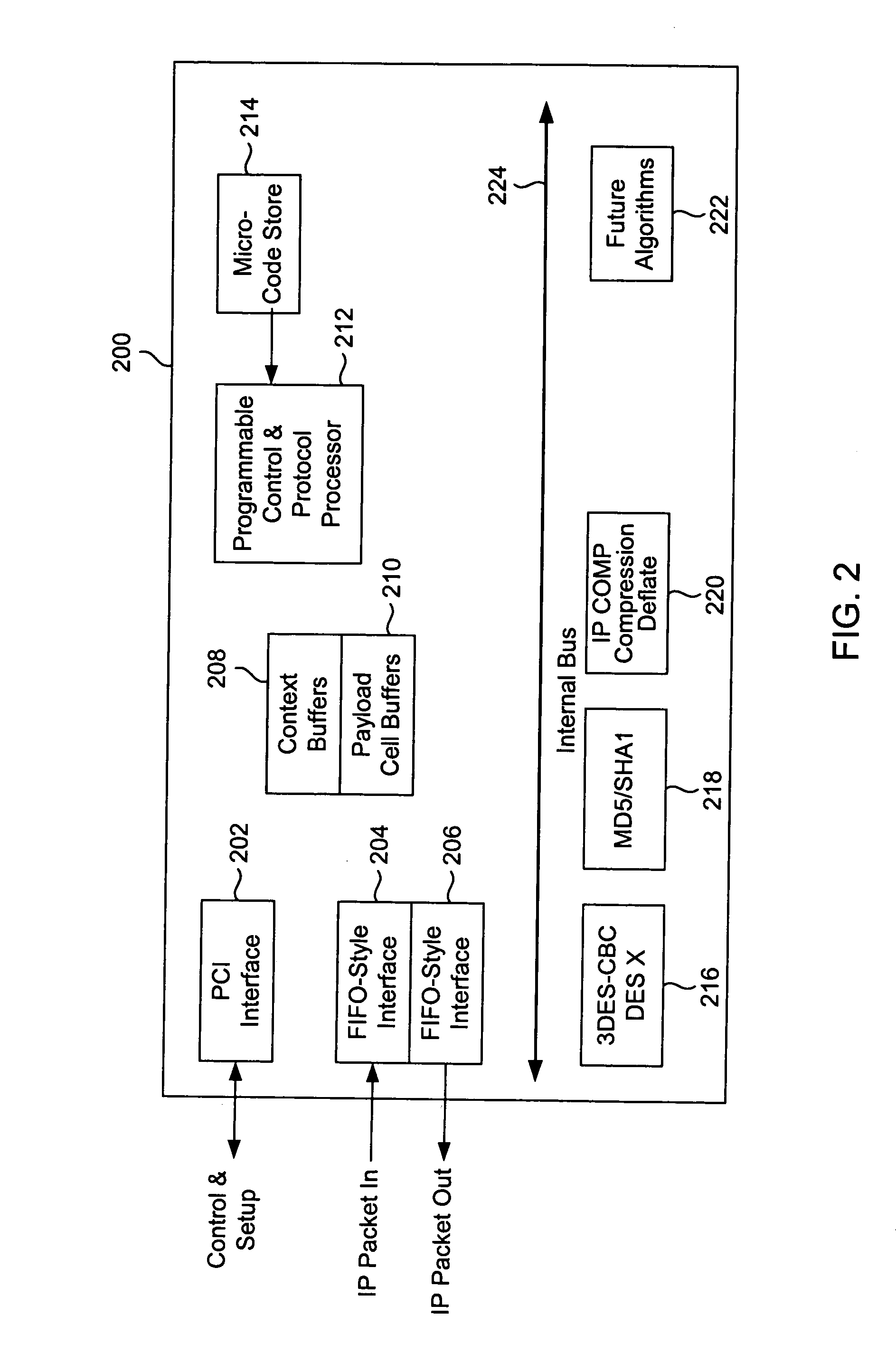

Security chip architecture and implementations for cryptography acceleration

InactiveUS6971006B2Maximum performanceImprove performanceDigital data processing detailsUser identity/authority verificationExternal storageChip architecture

An architecture and a method for a cryptography acceleration is disclosed that allows significant performance improvements without the use of external memory. Specifically, the chip architecture enables “cell-based” processing of random-length IP packets. The IP packets, which may be of variable and unknown size, are split into fixed-size “cells.” The fixed-sized cells are then processed and reassembled into packets. The cell-based packet processing architecture of the present invention allows the implementation of a processing pipeline that has known processing throughput and timing characteristics, thus making it possible to fetch and process the cells in a predictable time frame. The architecture is scalable and is also independent of the type of cryptography performed. The cells may be fetched ahead of time (pre-fetched) and the pipeline may be staged in such a manner that attached (local) memory is not required to store packet data or control parameters.

Owner:AVAGO TECH INT SALES PTE LTD

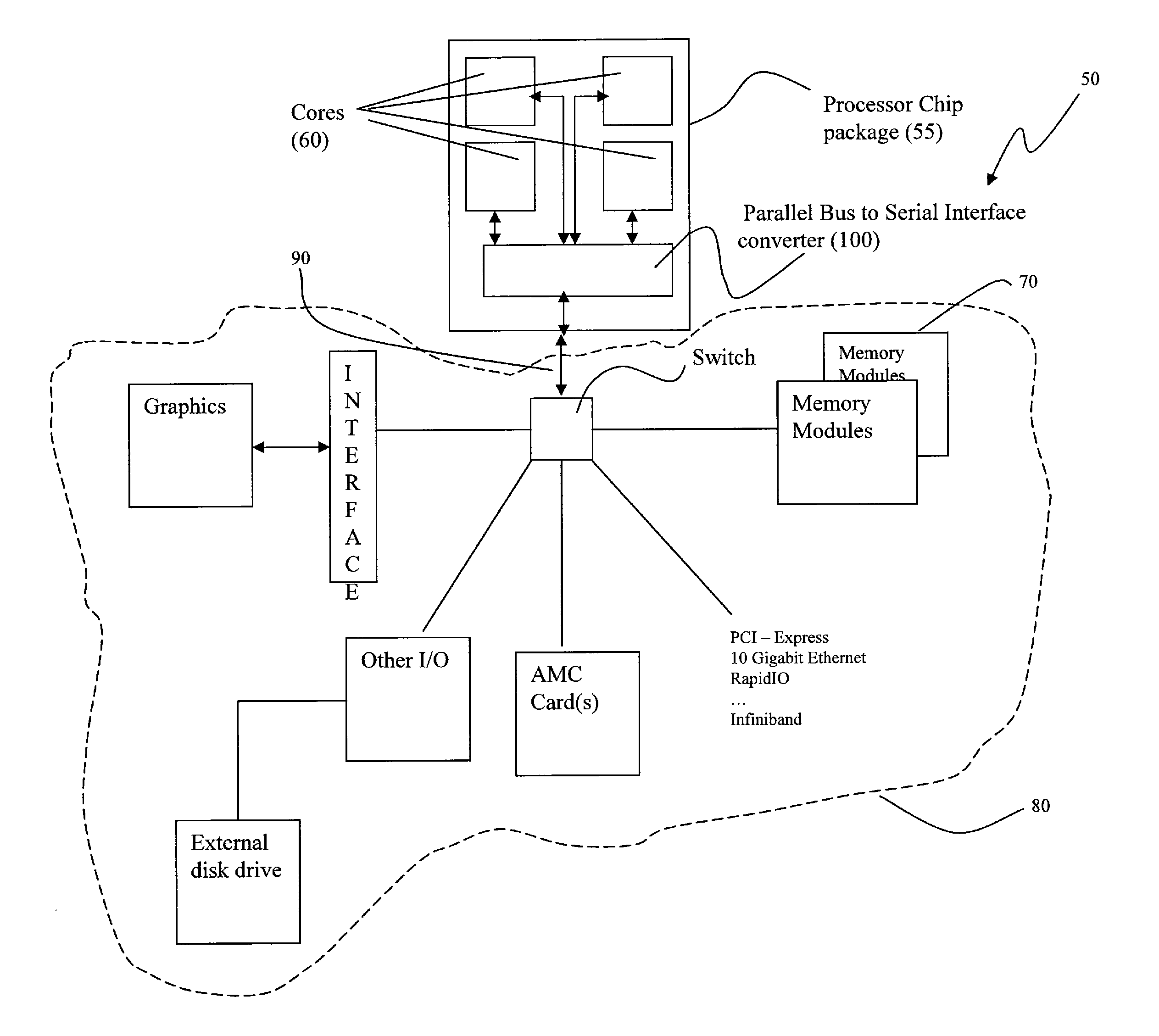

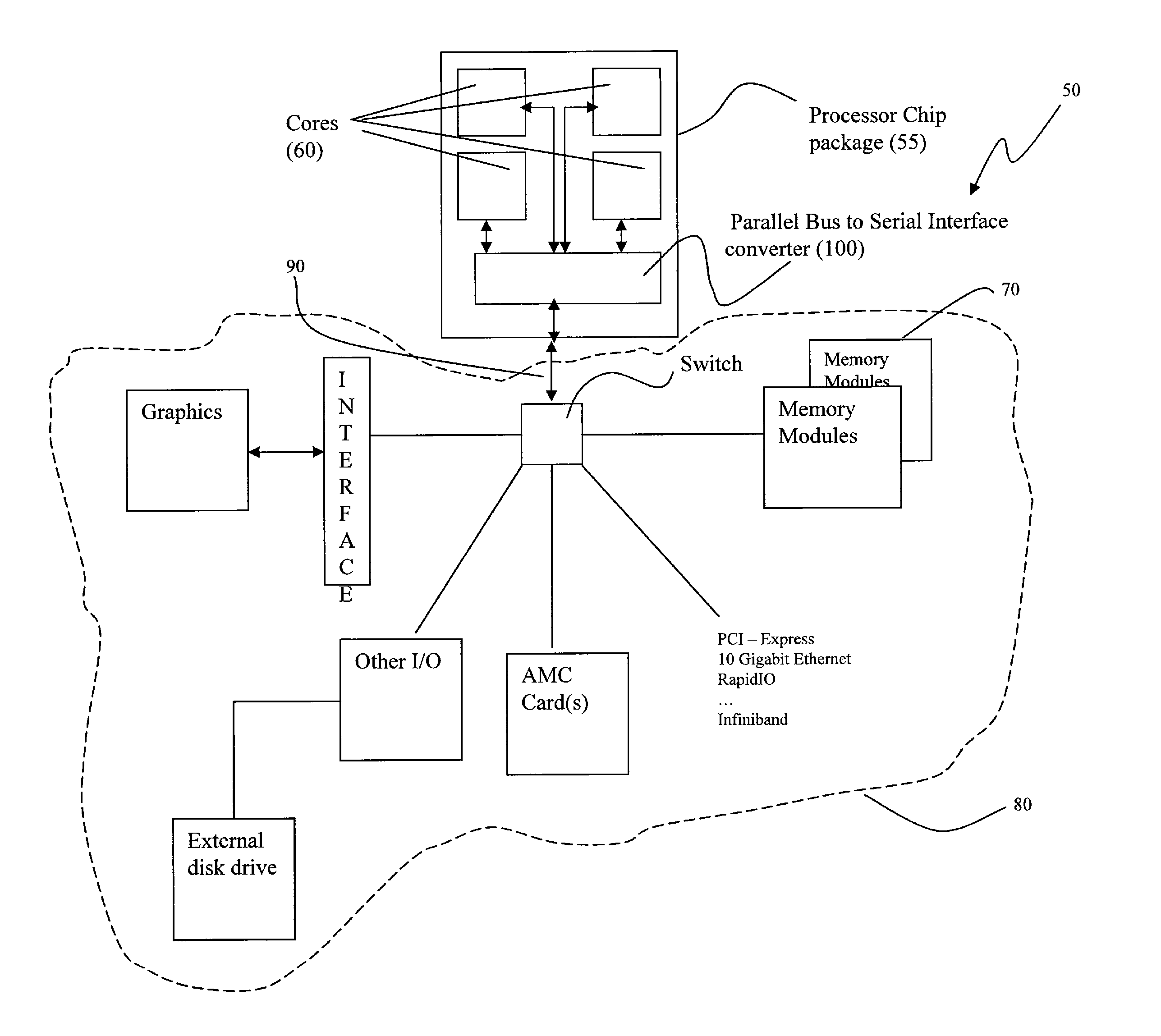

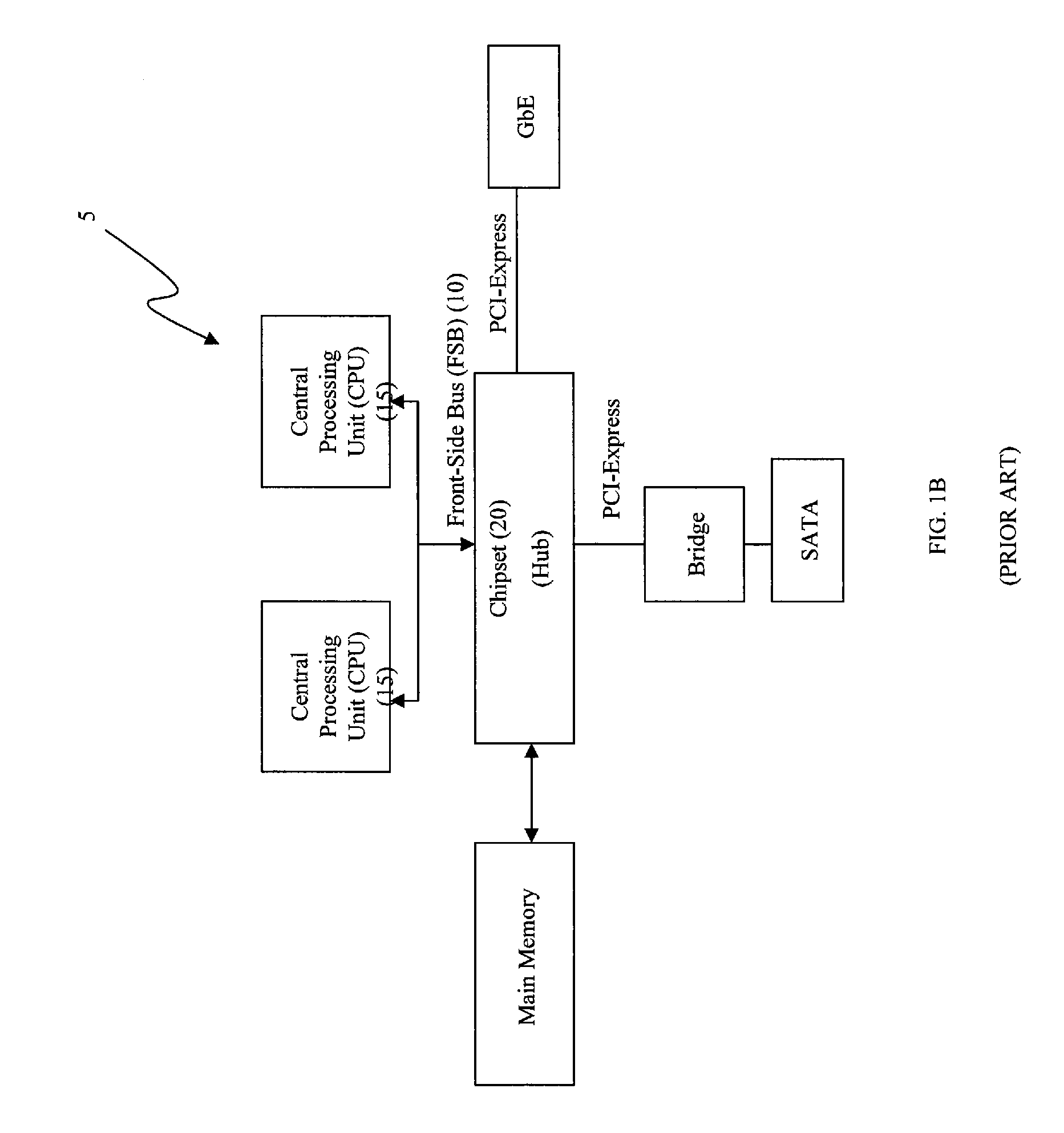

Processor chip arcitecture having integrated high-speed packet switched serial interface

InactiveUS20080244150A1Reduce communication overheadGeneral purpose stored program computerMultiple digital computer combinationsChip architectureProtocol processing

A computing and communication chip architecture is provided wherein the interfaces of processor access to the memory chips are implemented as a high-speed packet switched serial interface as part of each chip. In one embodiment, the interface is accomplished through a gigabit Ethernet interface provided by protocol processor integrated as part of the chip. The protocol processor encapsulates the memory address and control information like Read, Write, number of successive bytes etc, as an Ethernet packet for communication among the processor and memory chips that are located on the same motherboard, or even on different circuit cards. In one embodiment, the communication over head of the Ethernet protocol is further reduced by using an enhanced Ethernet protocol with shortened data frames within a constrained neighborhood, and / or by utilizing a bit stream switch where direct connection paths can be established between elements that comprise the computing or communication architecture.

Owner:KIRITIN INC

Top pinned sot-mram architecture with in-stack selector

InactiveUS20170117027A1Magnetic-field-controlled resistorsSolid-state devicesPower flowParallel computing

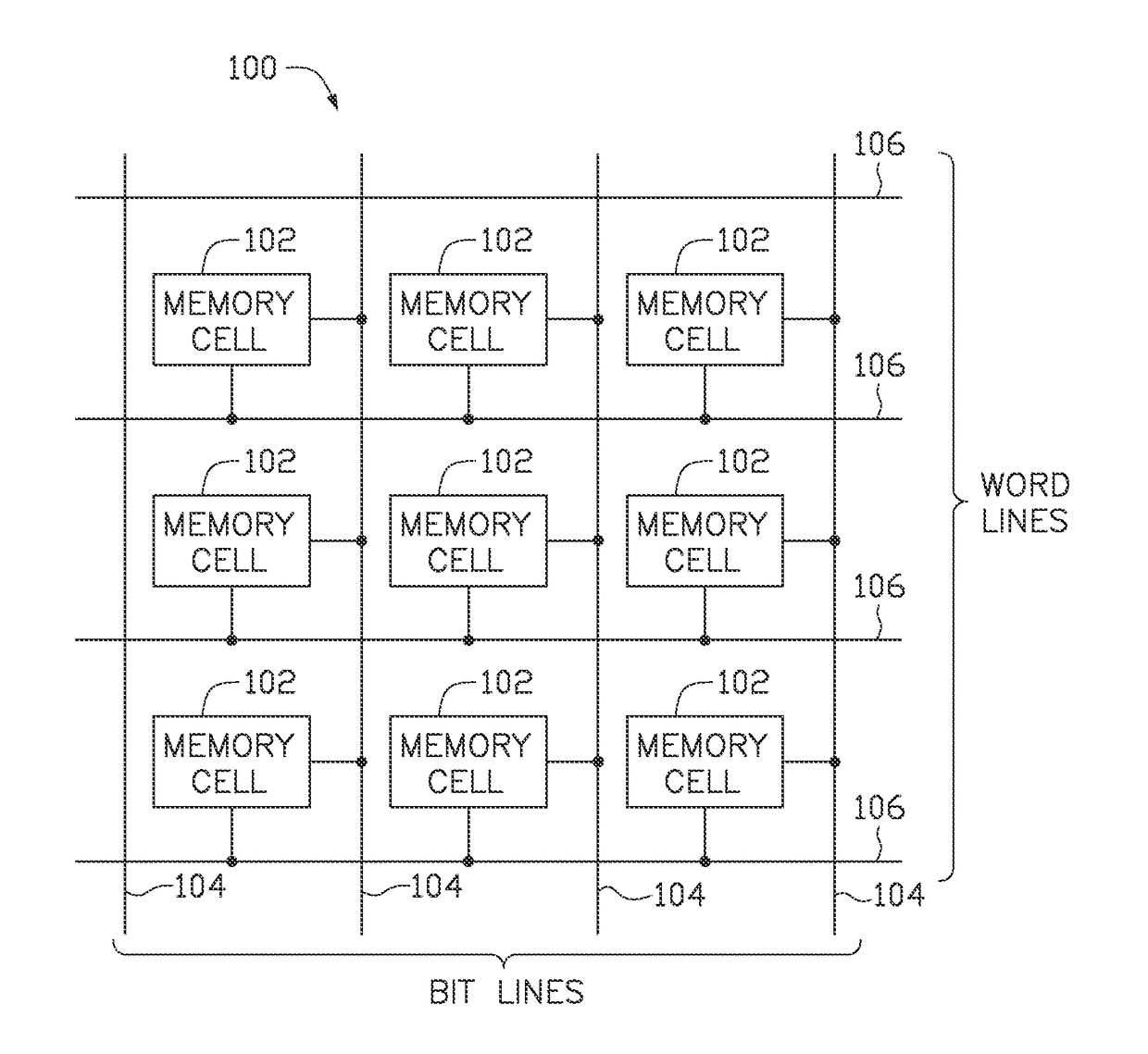

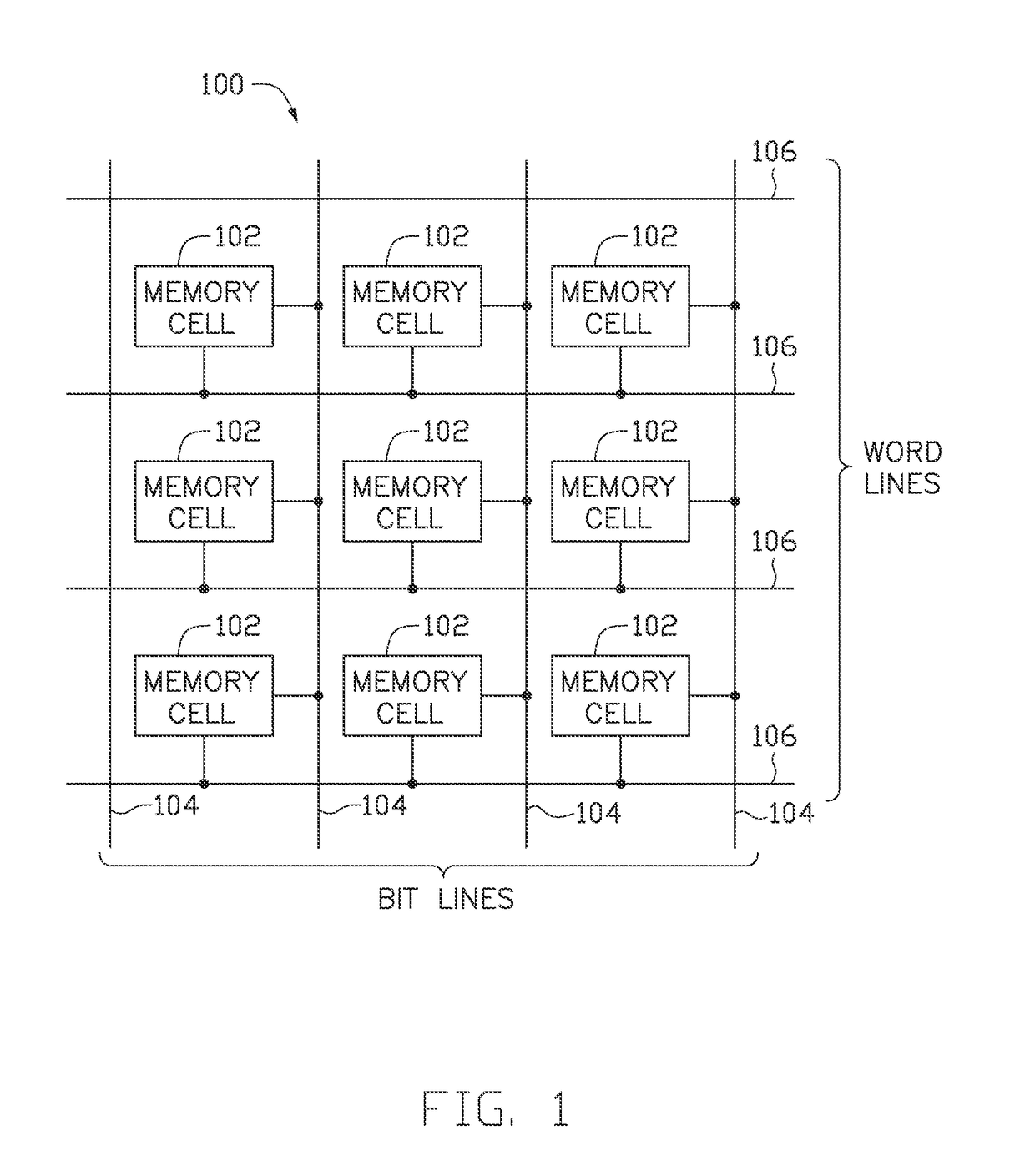

Embodiments of the present disclosure generally relate to data storage and computer memory systems, and more particularly, to a SOT-MRAM cell and chip architecture. The SOT-MRAM chip architecture includes a memory cell array having a plurality of first leads, a plurality of second leads, and a plurality of memory cells. Each memory cell of the plurality of memory cells includes a MTJ and a selector element. These SOT-MRAM cells eliminate the need to pass large currents through the barrier layer of the MTJ and the selector element eliminates the large transistors usually required for selecting a single memory cell without disturbing neighboring memory cells.

Owner:WESTERN DIGITAL TECH INC

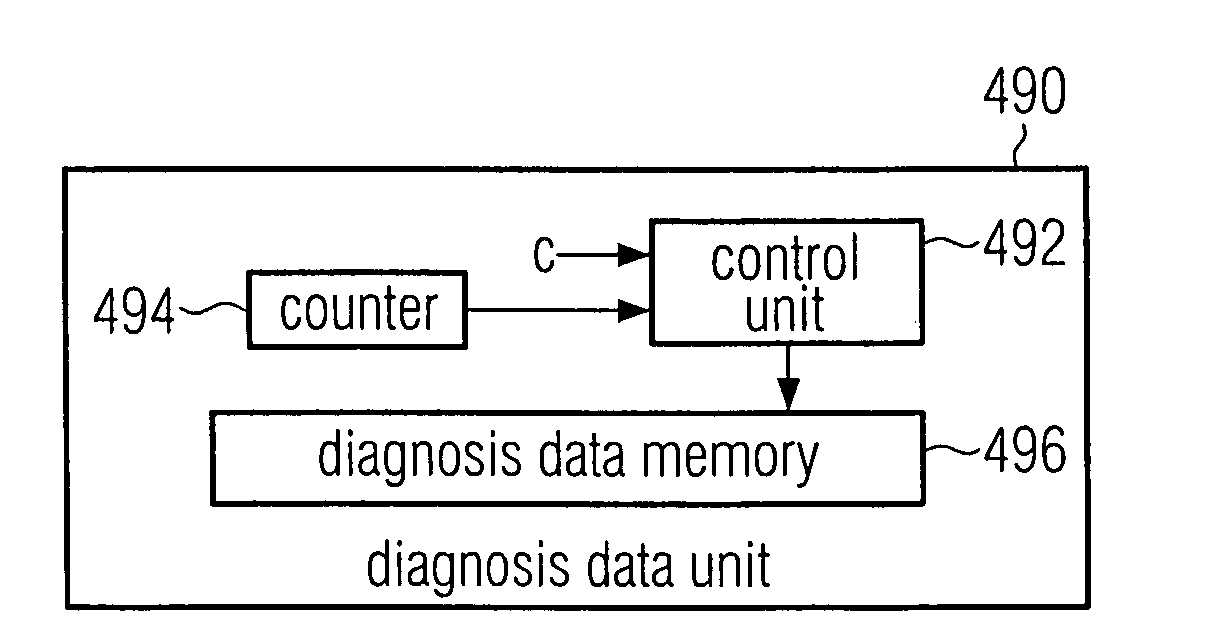

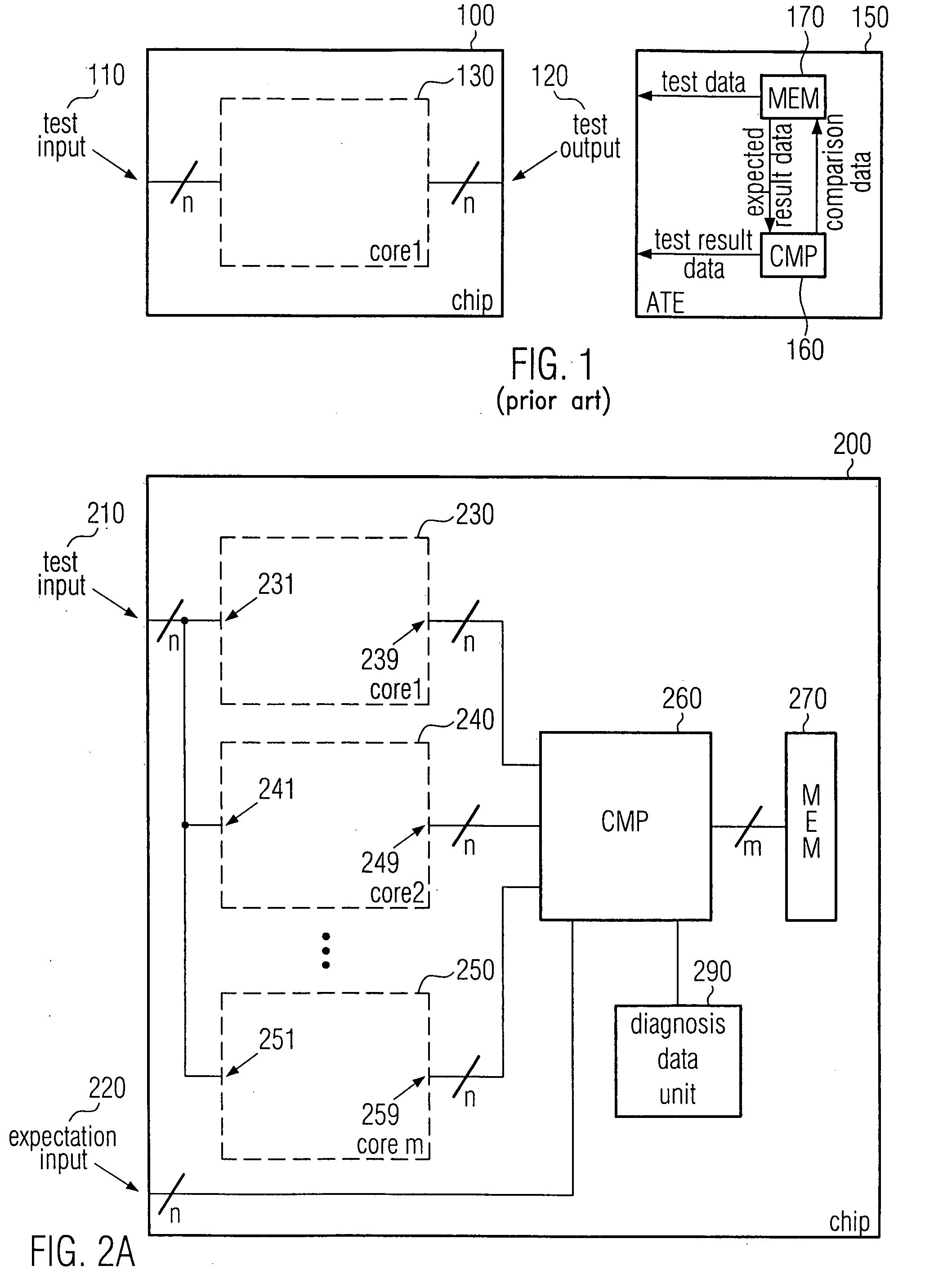

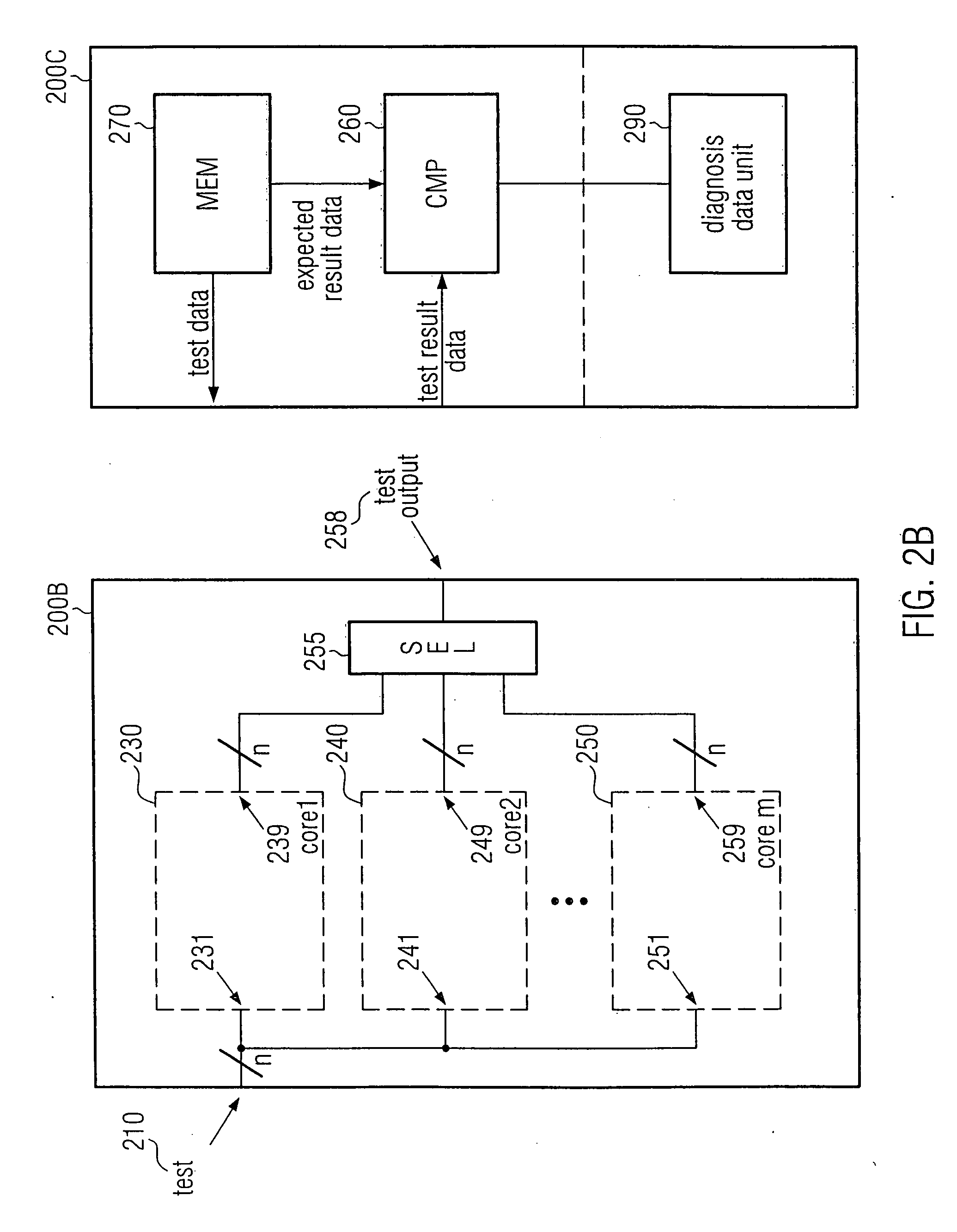

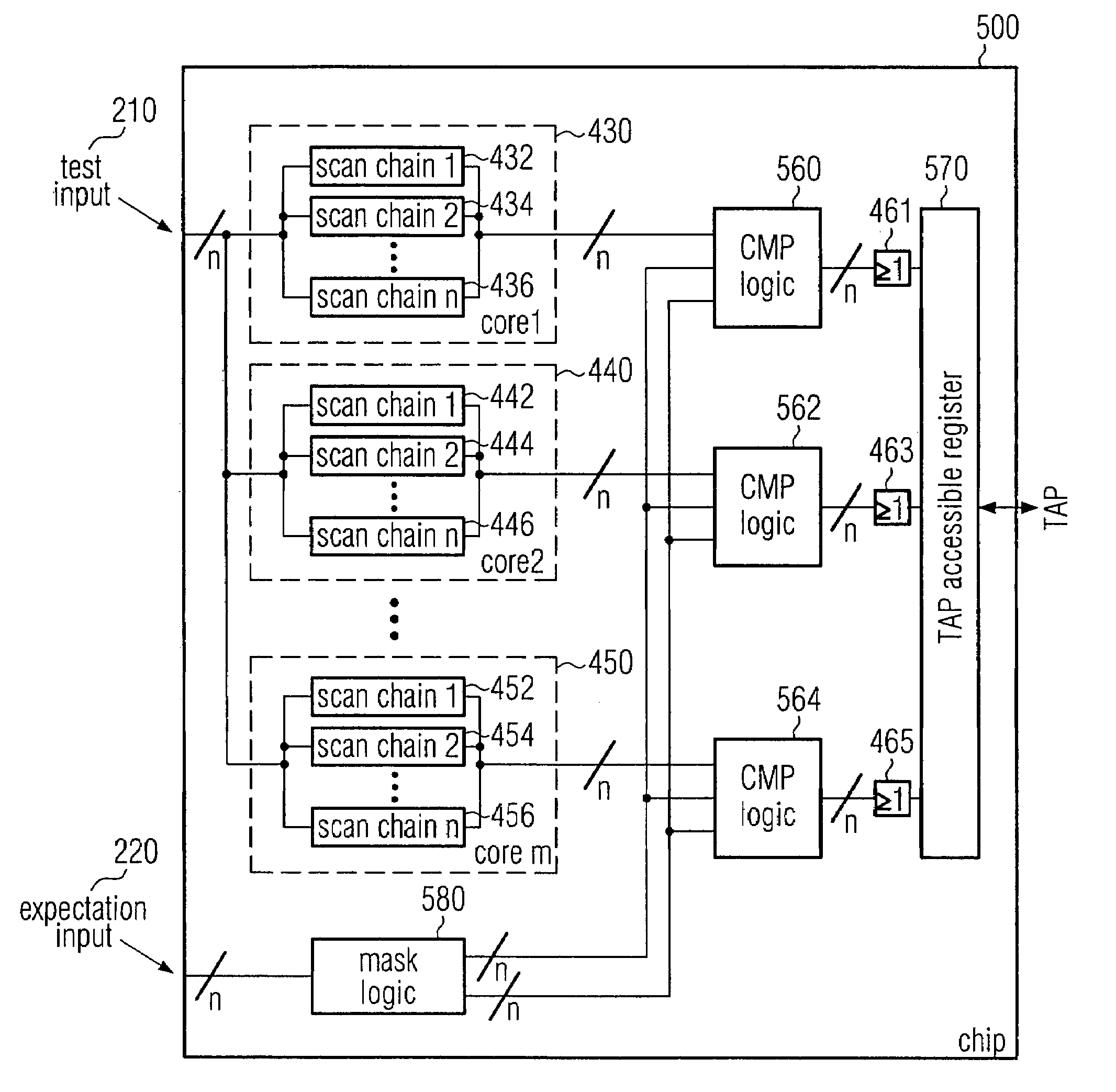

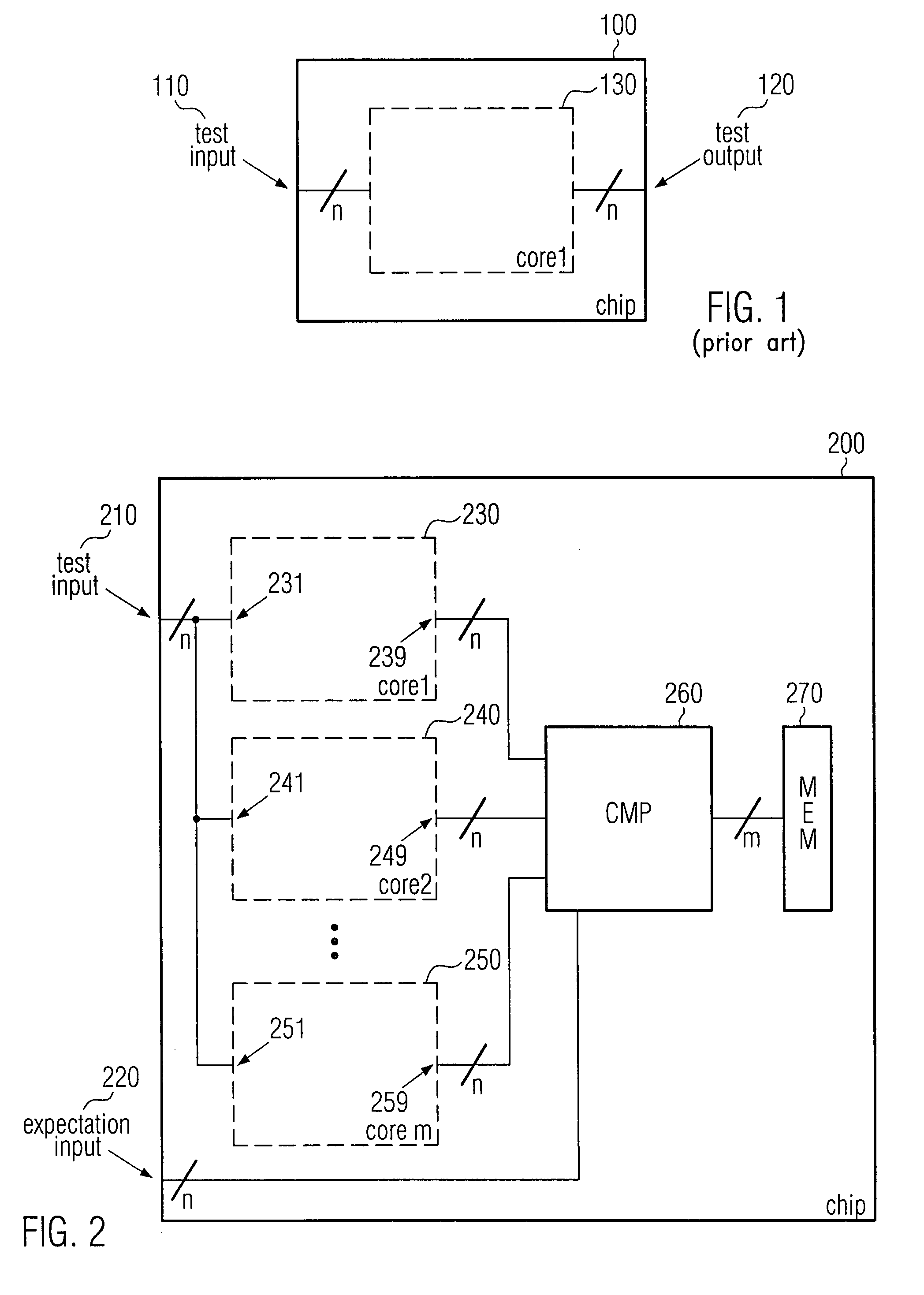

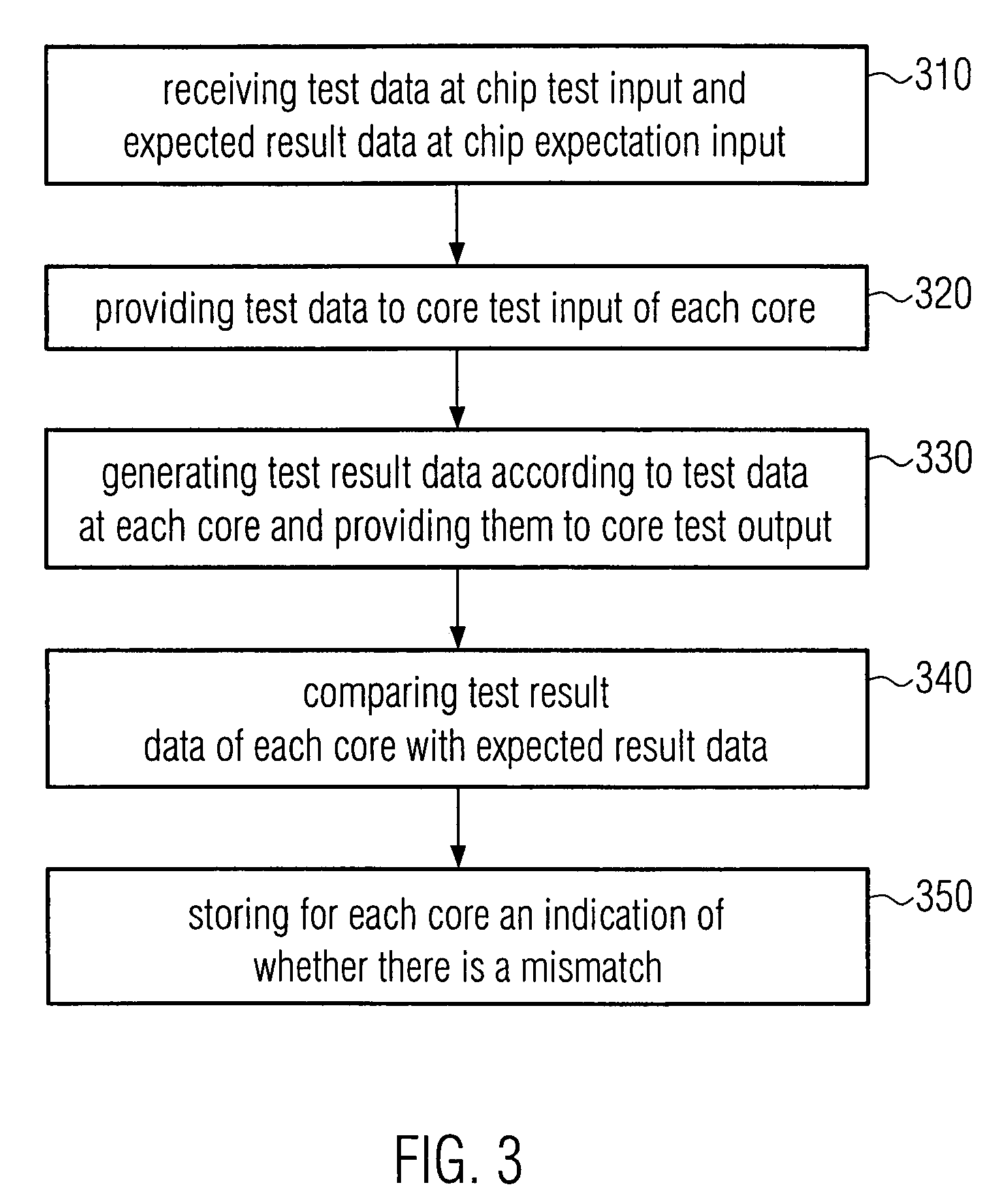

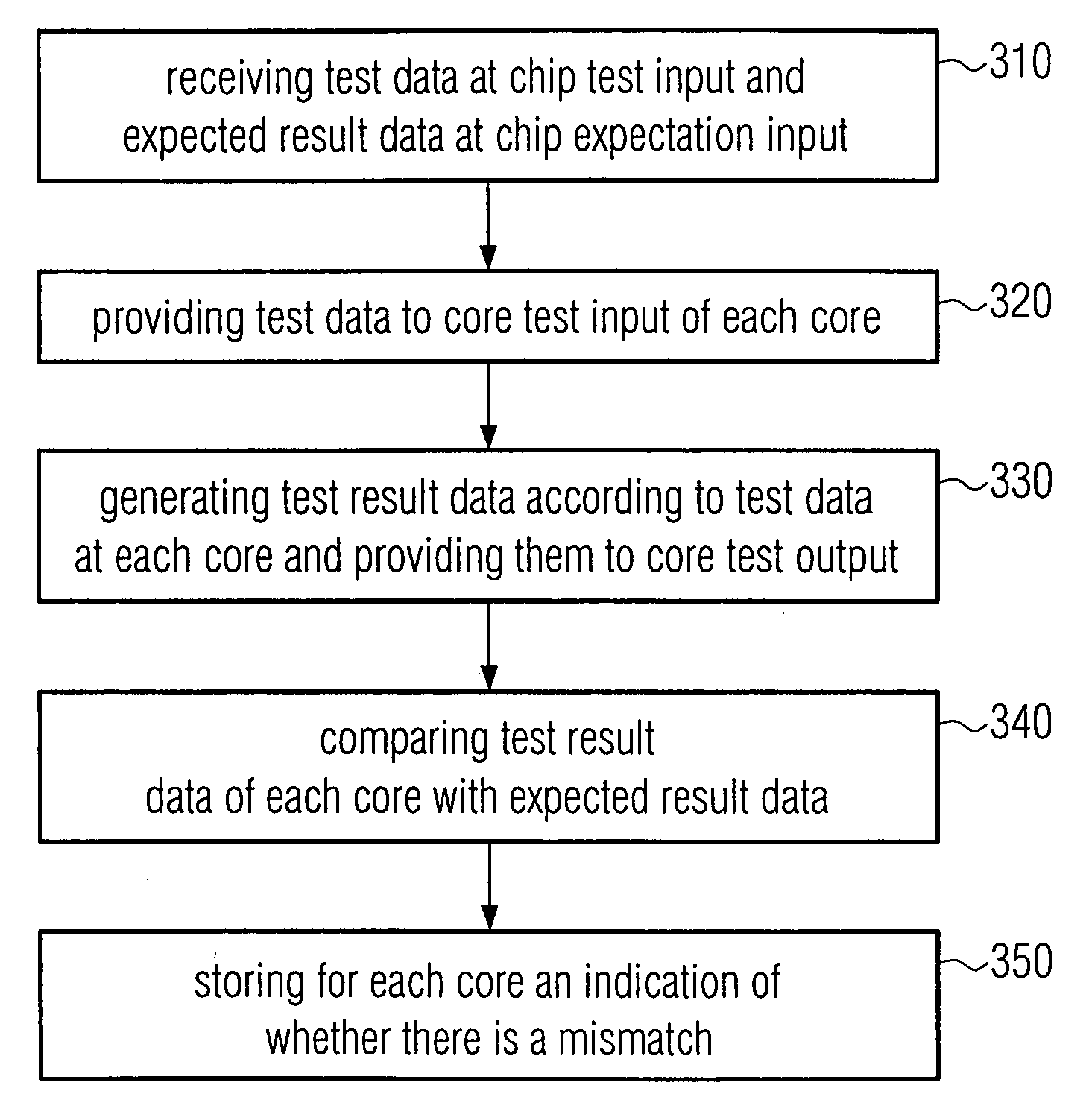

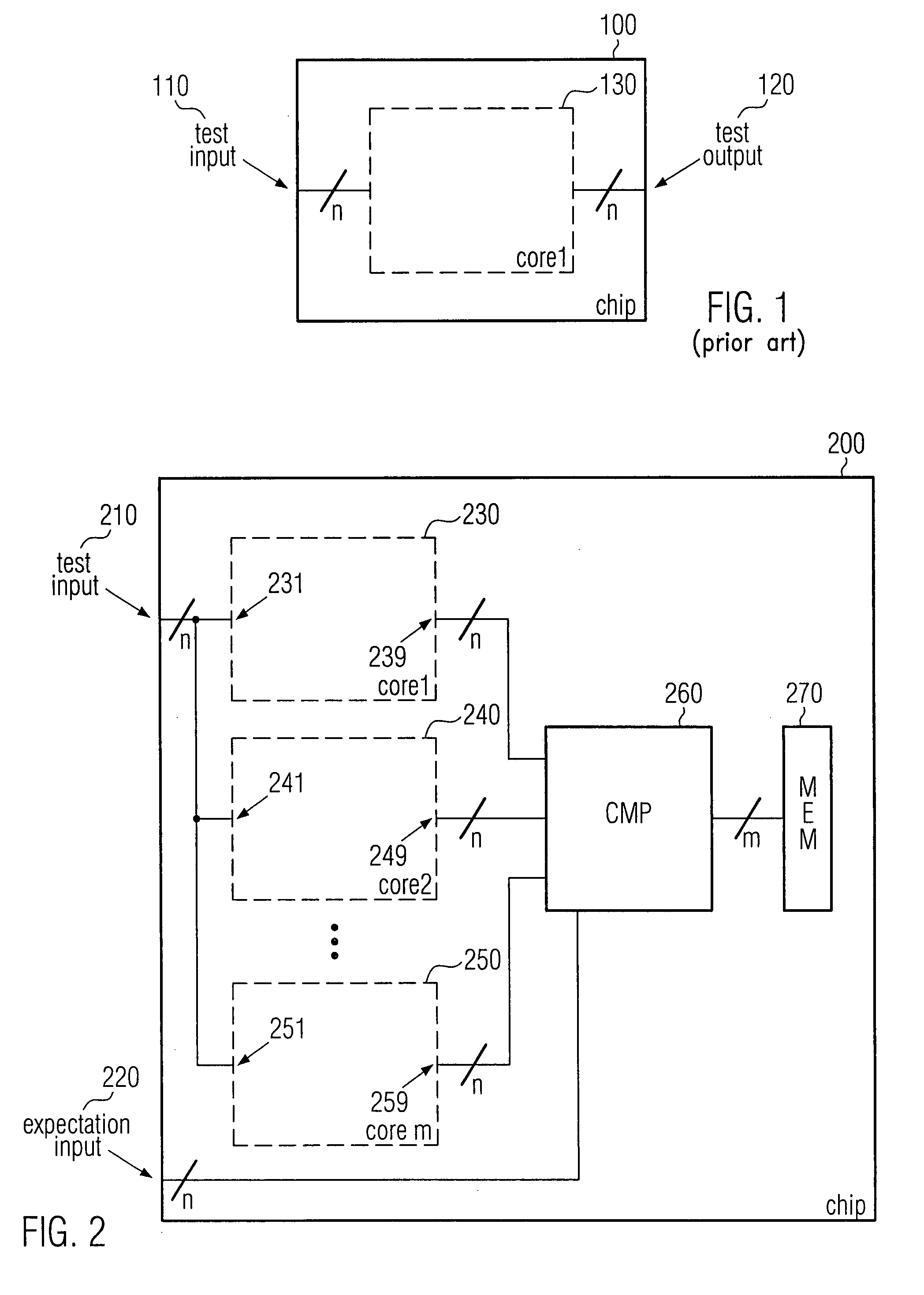

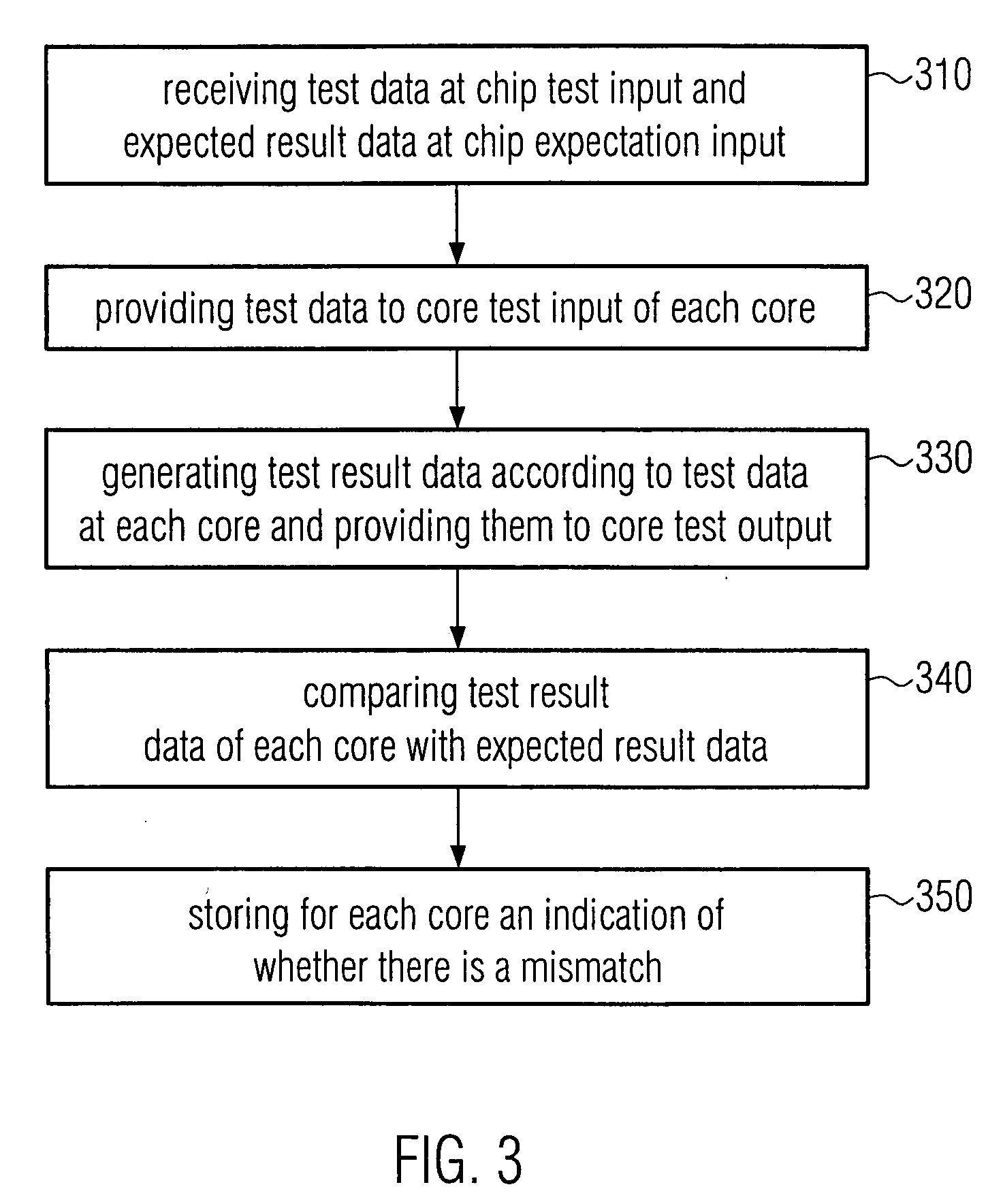

Storing multicore chip test data

ActiveUS20080148120A1Improve efficiencyElectronic circuit testingLogical operation testingDiagnostic dataTest analysis

An integrated chip architecture is provided which allows for efficiently testing multiple cores included in the integrated chip architecture and storing corresponding diagnosis data which include an indication of the failure-causing test data and the corresponding test analysis data. Embodiments are provided which enable that the test time and the number of required Input / Output test pins is nearly independent from the number of cores included in the multicore chip. The presented embodiments provide a multicore chip architecture which allows for providing input data to the multiple cores in parallel for simultaneously testing the multiple cores, and analyzing the resulting multiple test outputs on chip. As a result of this analysis embodiments may store on chip an indication for those cores that have not successfully passed the test, together with respective diagnosis data.

Owner:ADVANCED MICRO DEVICES INC

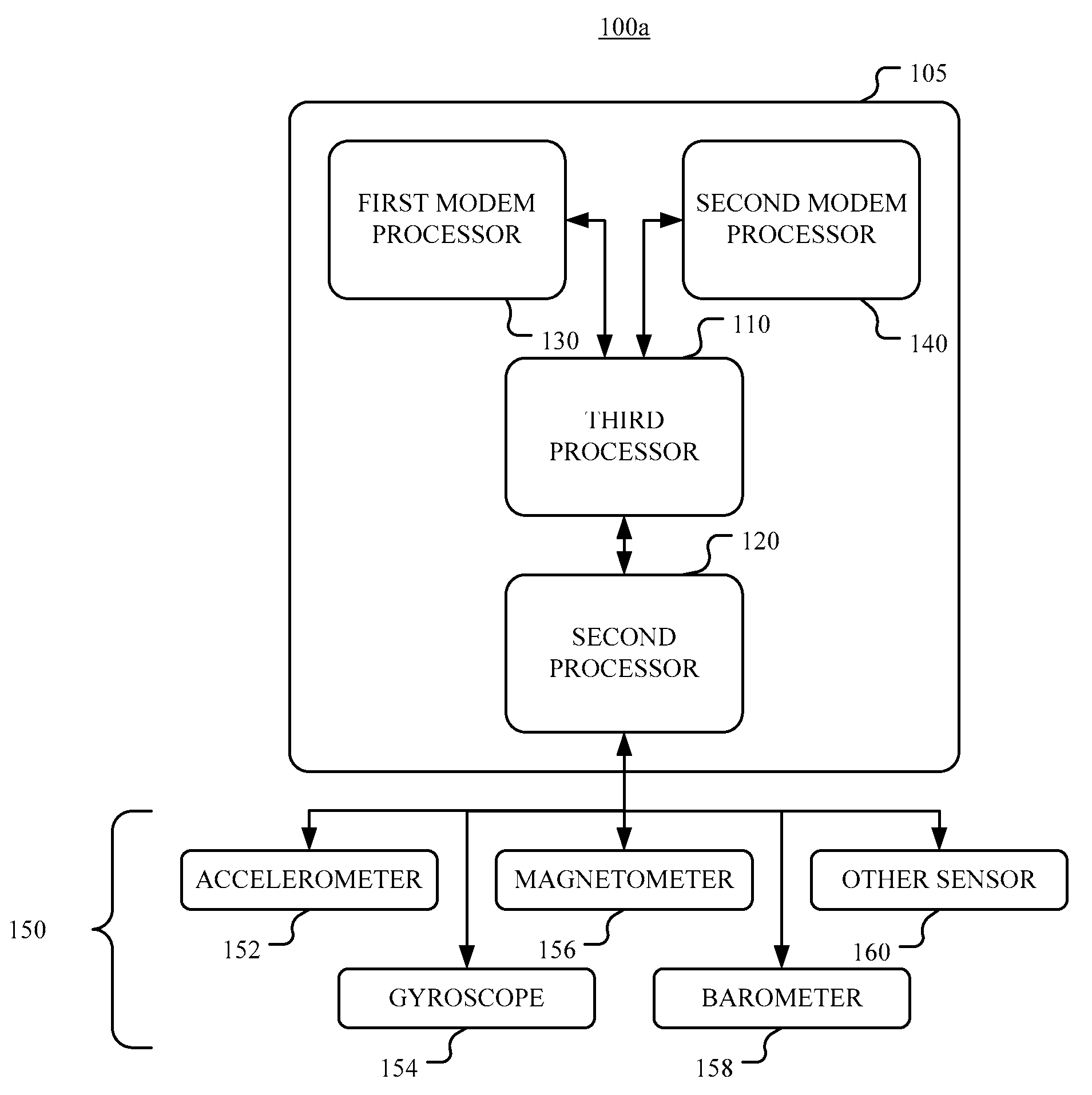

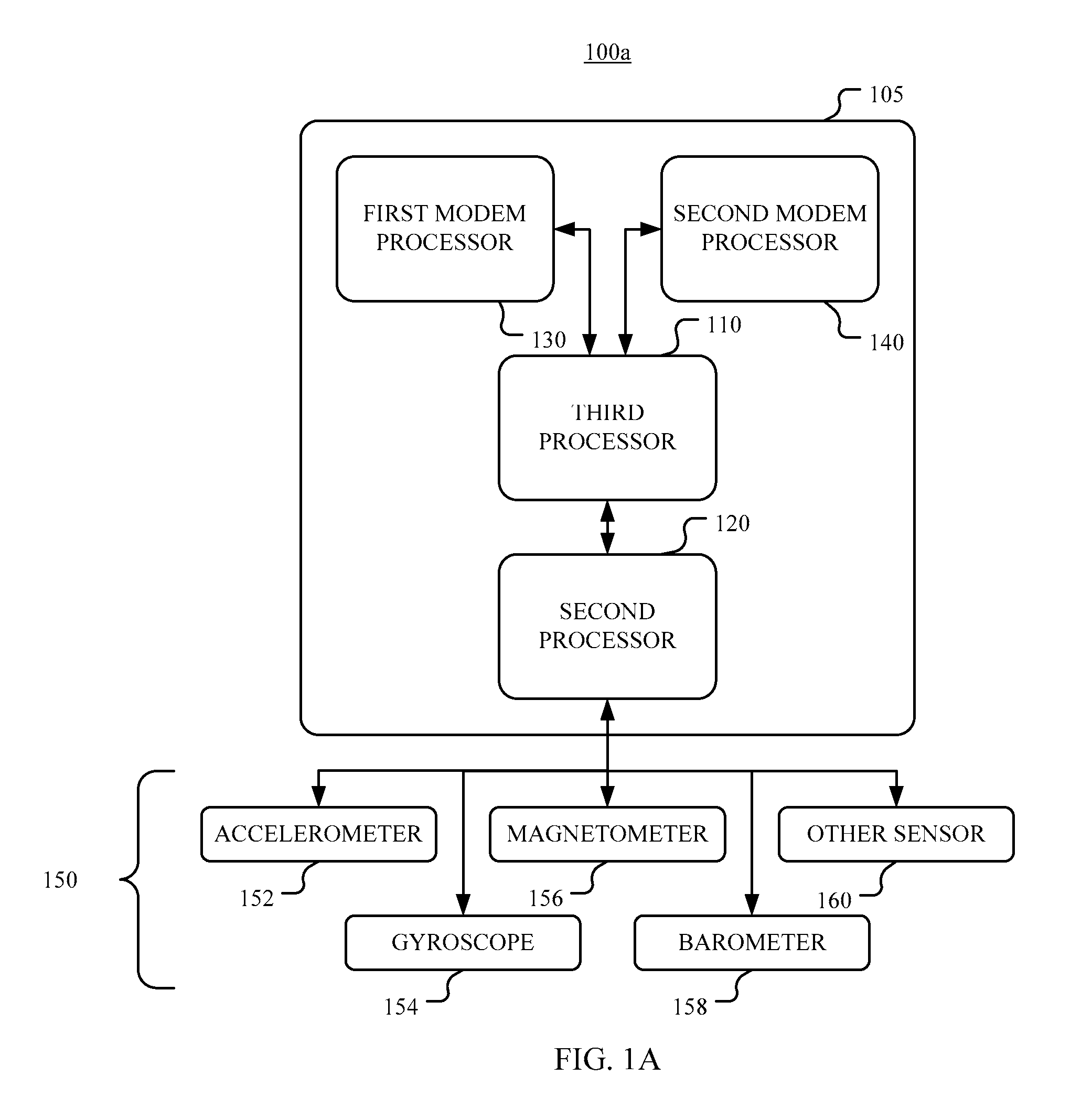

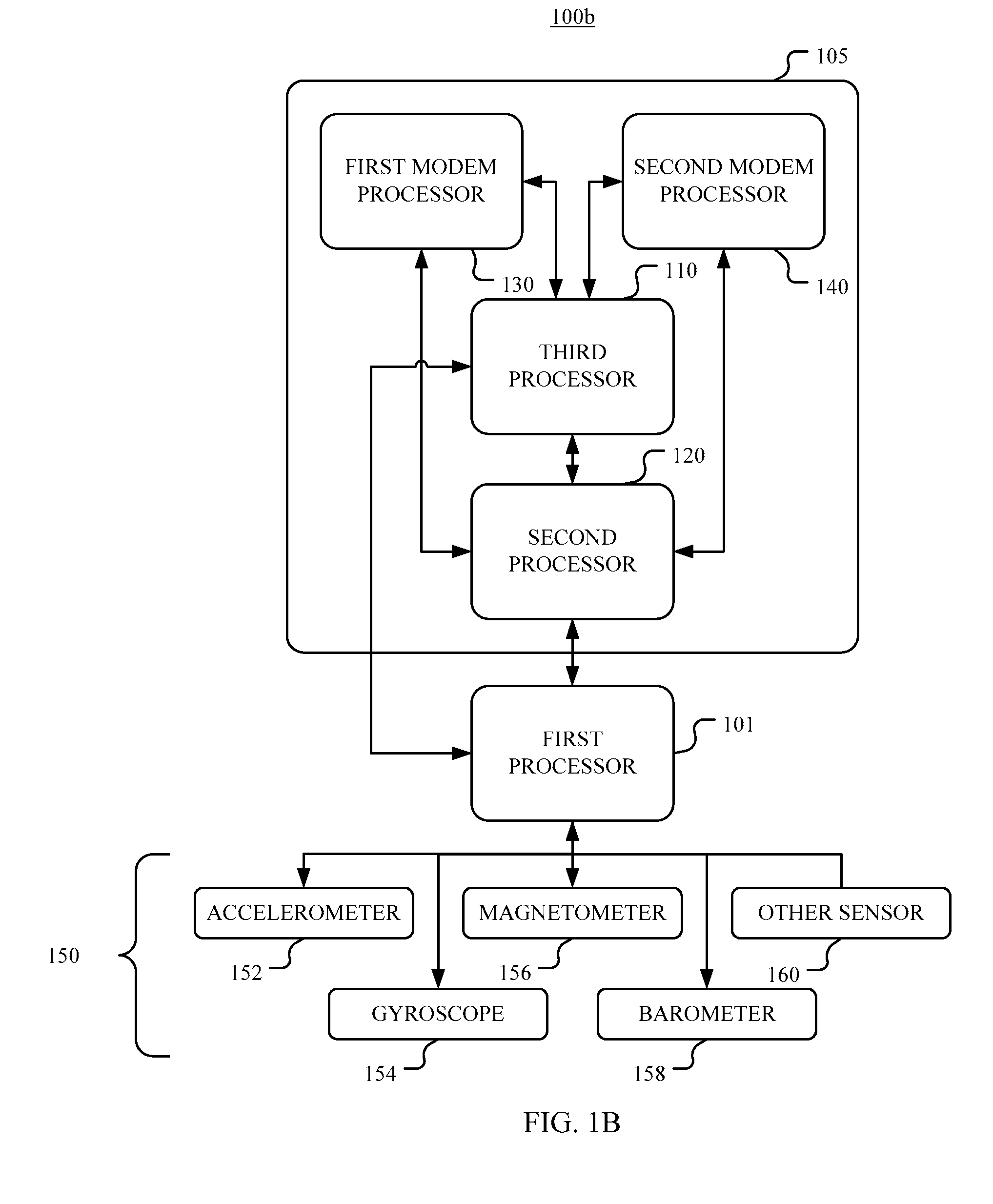

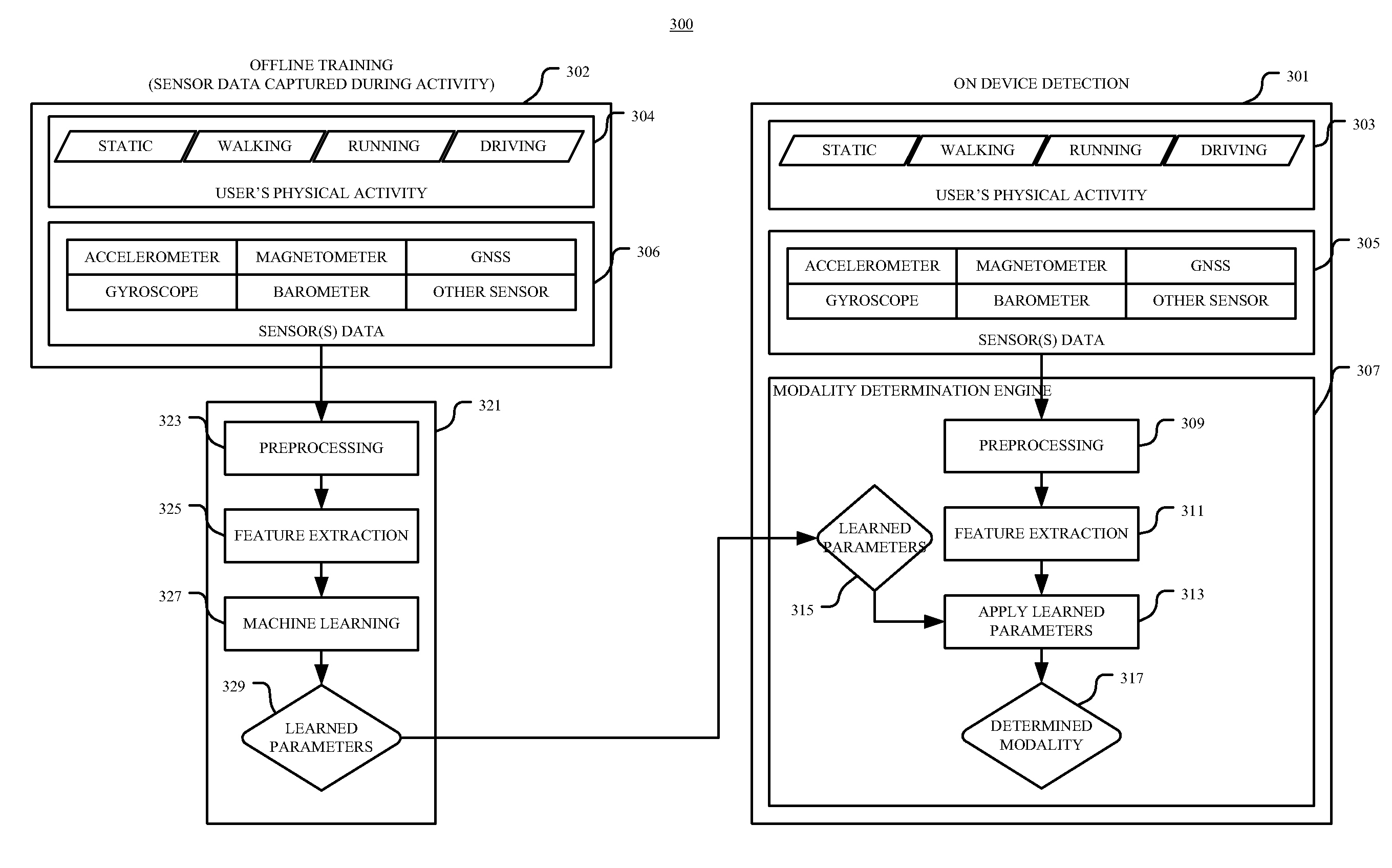

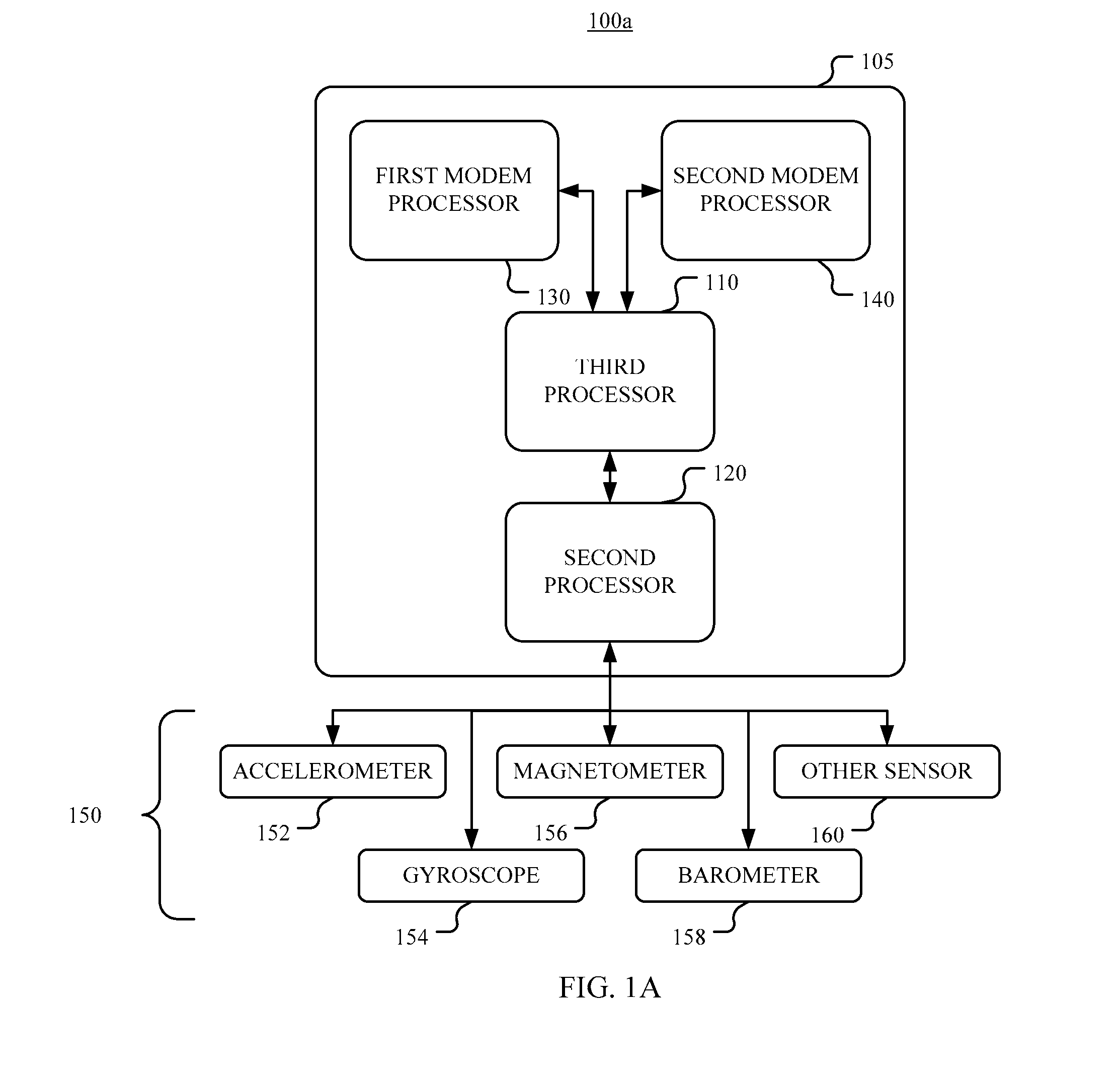

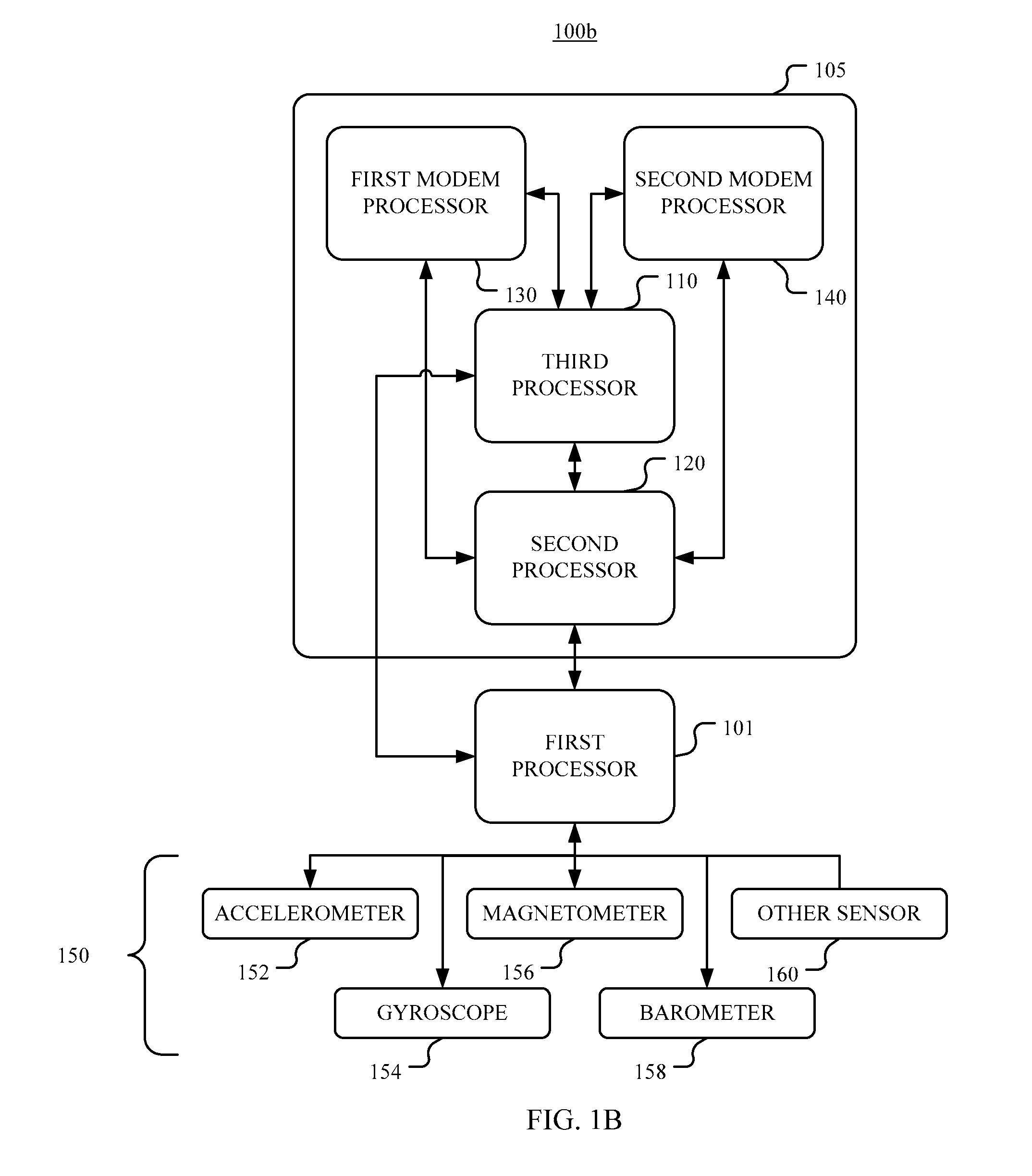

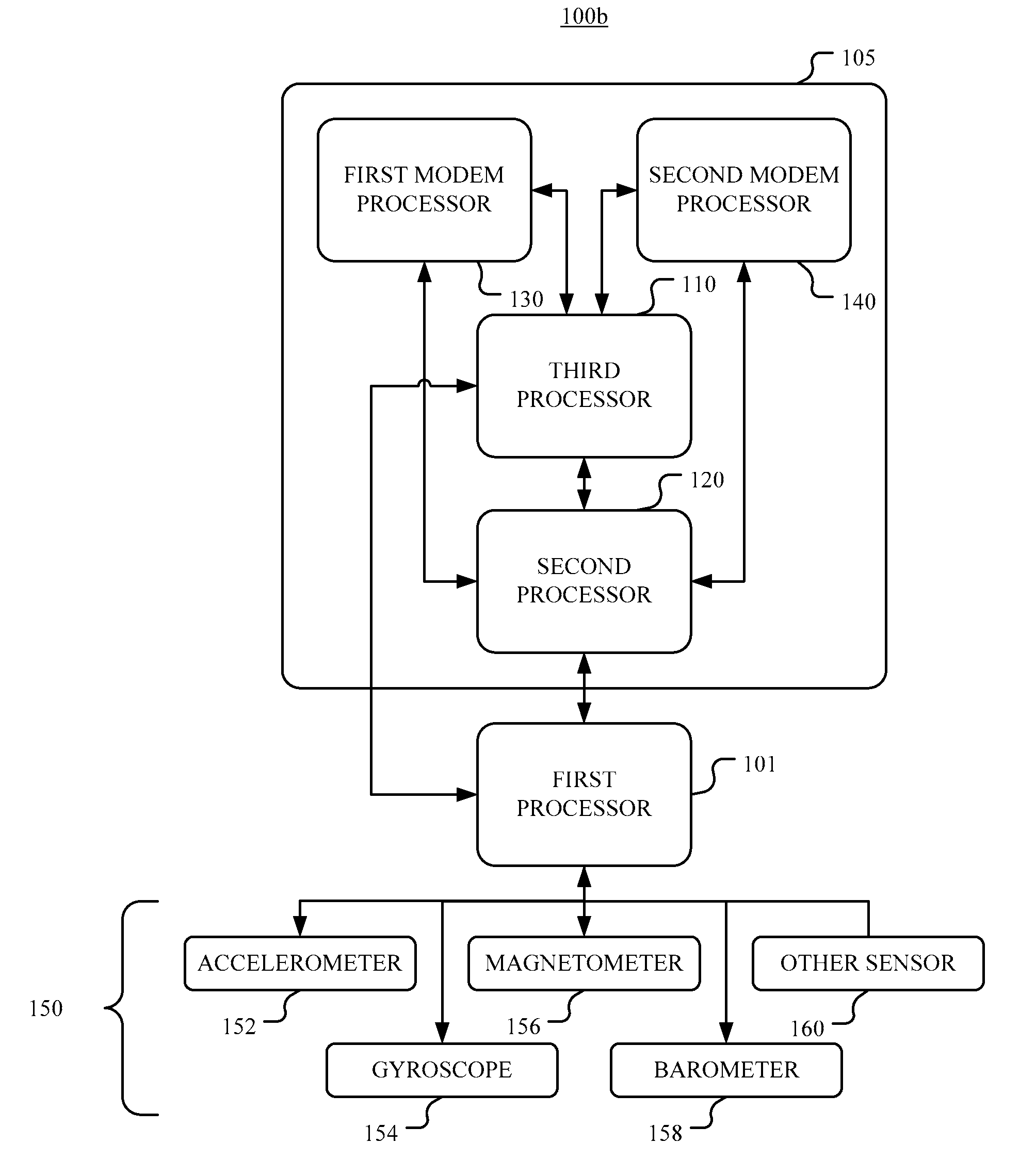

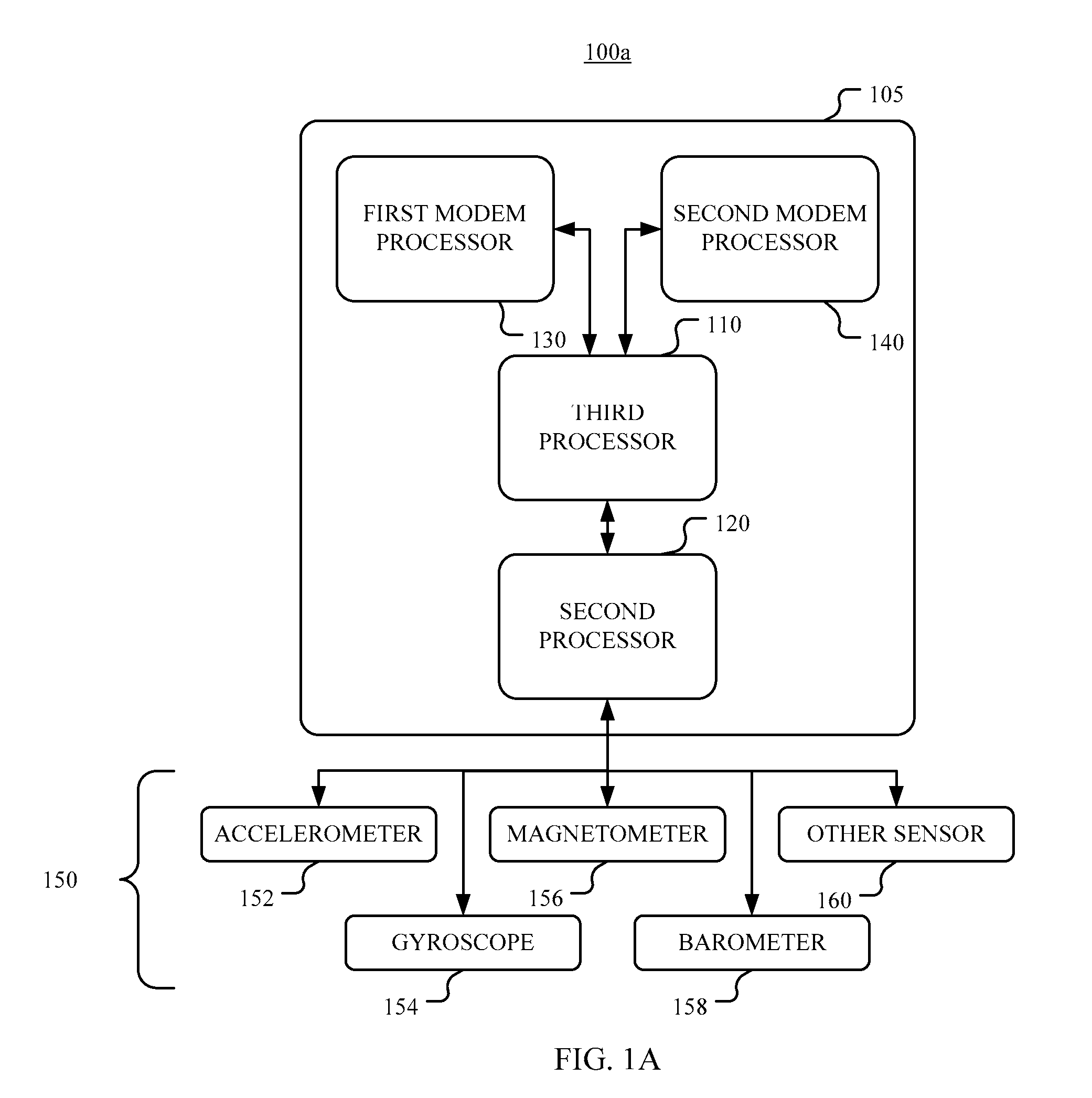

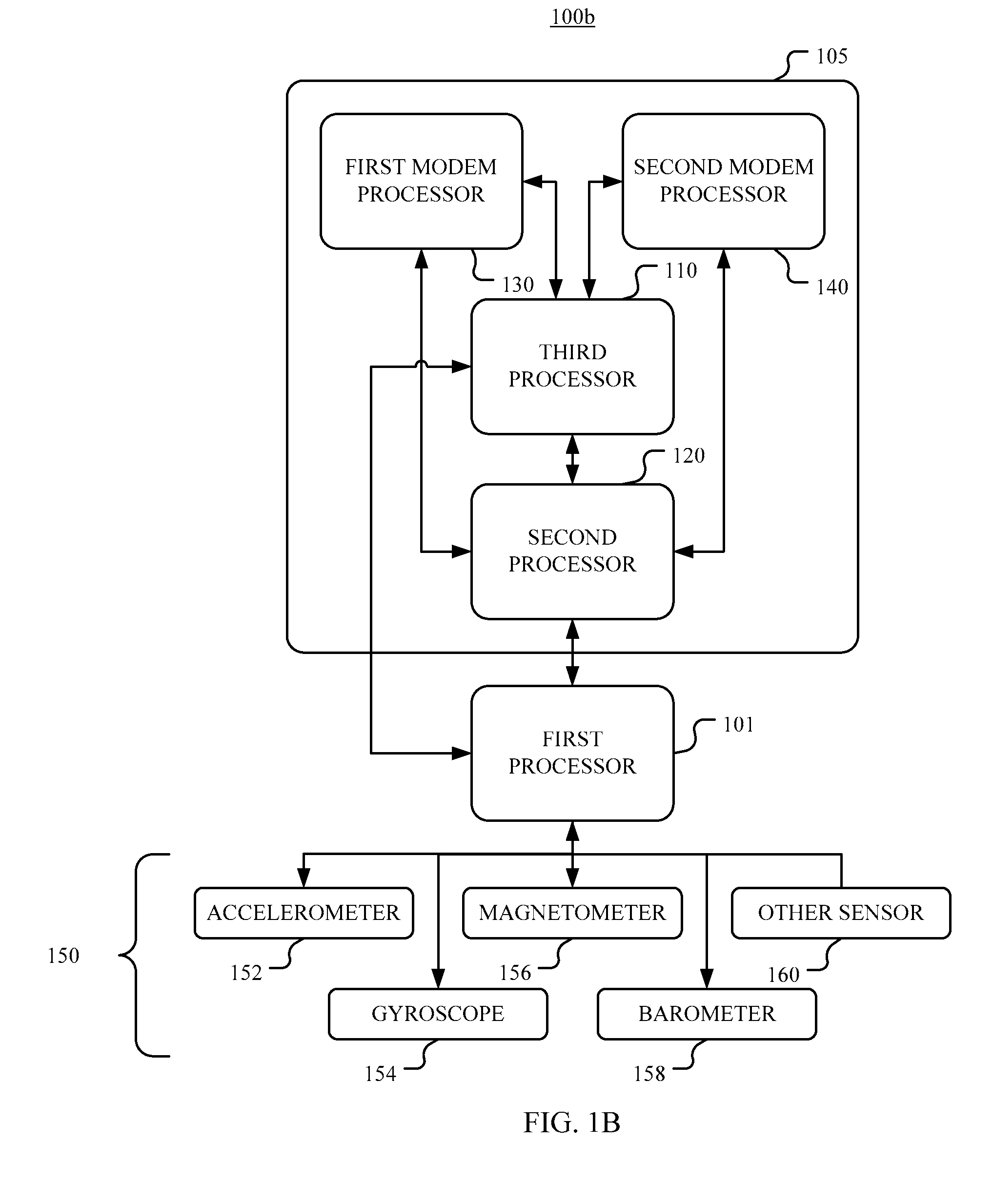

Low power management of multiple sensor chip architecture

A method, device, system, or article of manufacture is provided for low-power management of multiple sensor chip architecture. In one embodiment, a method comprises, at a computing device that includes a first processor, a second processor and a third processor, receiving, at the first processor, first sensor data from a first sensor; determining, at the first processor, a motion state of the computing device using the first sensor data; in response to determining that the motion state corresponds to a predetermined motion state, activating the second processor; receiving, at the second processor, second sensor data from a second sensor; determining, by the second processor, that the motion state corresponds to the predetermined motion state using the second sensor data; and, in response to determining that the motion state corresponds to the predetermined motion state using the second sensor data, sending the motion state to the third processor.

Owner:GOOGLE TECHNOLOGY HOLDINGS LLC

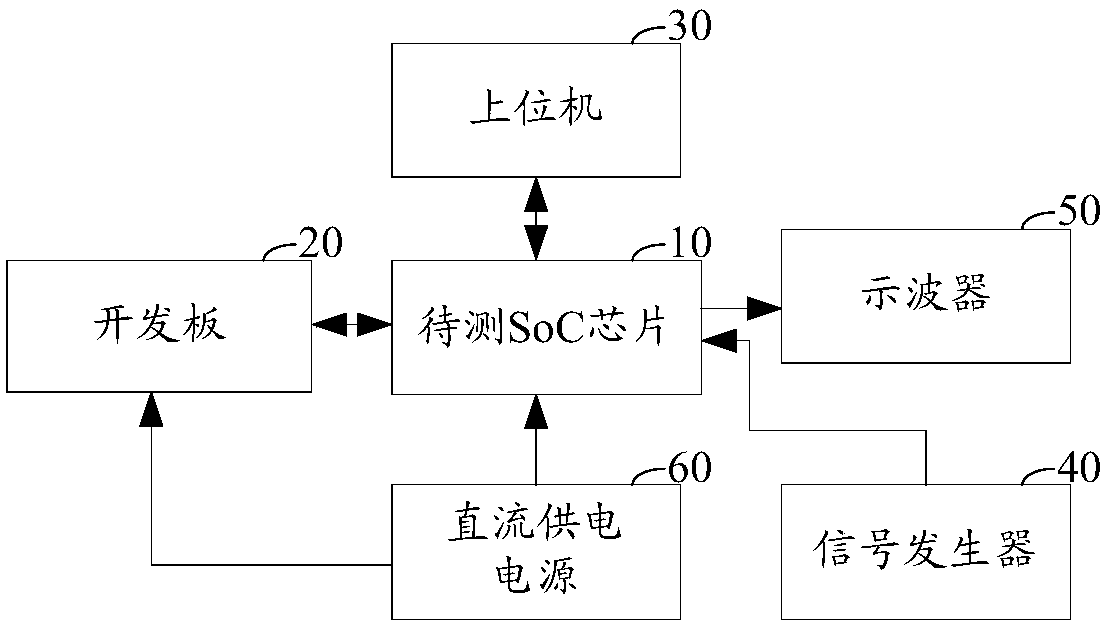

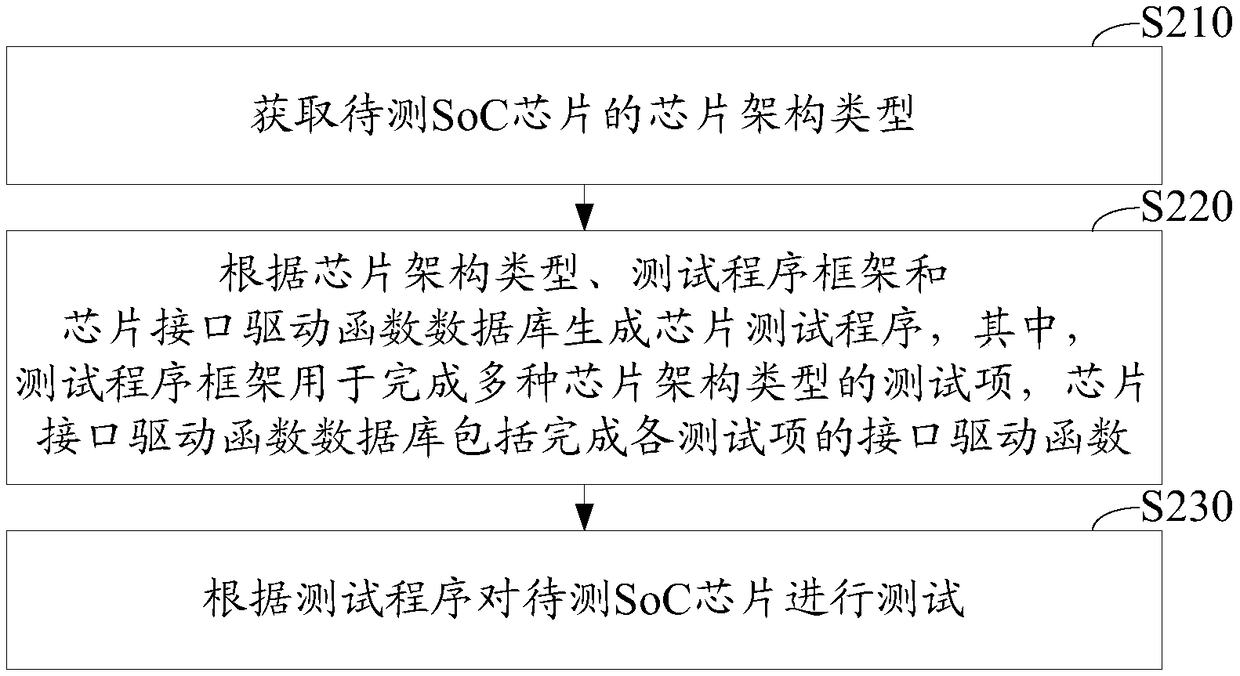

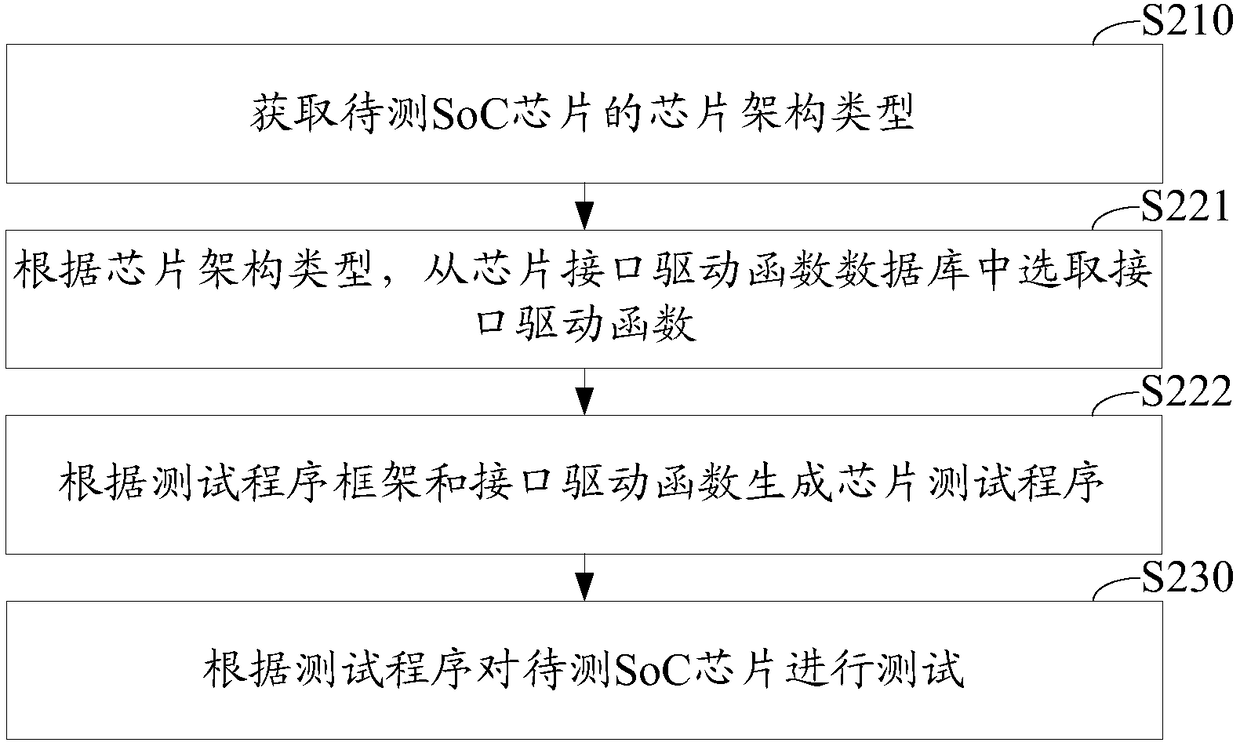

SoC chip test method, device and system and SoC chip test verification board

The invention relates to a SoC chip test method, device and system and a SoC chip test verification board. The method comprises the steps that the chip architecture type of a SoC chip to be tested isacquired; a chip test program is generated according to the chip architecture type, a test program framework and a chip interface driving function database, wherein the test program framework is usedto complete test items of various chip architecture types, and the chip interface driving function database comprises interface driving functions for completing various test item; and the SoC chip tobe tested is tested according to the test program. The method can generate the test program suitable for the SoC chip to be tested according to the chip architecture type of the chip to be tested, thetest program framework and the chip interface driving function database, so as to test the SoC chip to be tested. The method can be commonly used for testing to-be-tested chips of various different chip architecture types, which avoids separate test program development for various SoC chips. Labor and time, which are consumed by separate test program development, can be reduced, and the SoC chiptest cost is reduced.

Owner:CHINA ELECTRONICS PROD RELIABILITY & ENVIRONMENTAL TESTING RES INST

Low Power Management of Multiple Sensor Integrated Chip Architecture

ActiveUS20140347274A1Power managementDigital data processing detailsDiagnostic Radiology ModalityState dependent

A method, device, system, or article of manufacture is provided for low-power management of multiple sensor chip architecture. In one embodiment, a method comprises, at a computing device that includes a first processor, a second processor and a third processor, receiving, by the first processor, sensor data from a first sensor; determining, by the first processor, a movement by the computing device using the sensor data; receiving, by the first processor, a modality of the computing device; in response to determining that the modality corresponds to a predetermined state, determining, by the first processor, a modality move distance associated with the predetermined state; determining, by the first processor, a move distance of the computing device using the modality move distance; determining, by the first processor, that the move distance of the computing device is at least a move distance threshold; and, in response to determining that the move distance of the computing device is at least a move distance threshold, reporting, by the first processor, to at least one of the second processor and the third processor, that the move distance of the computing device is at least the move distance threshold.

Owner:GOOGLE TECH HLDG LLC

On-chip packet interface processor encapsulating memory access from main processor to external system memory in serial packet switched protocol

InactiveUS7822946B2Reduce communication overheadGeneral purpose stored program computerMultiple digital computer combinationsMemory addressMemory chip

A computing and communication chip architecture is provided wherein the interfaces of processor access to the memory chips are implemented as a high-speed packet switched serial interface as part of each chip. In one embodiment, the interface is accomplished through a gigabit Ethernet interface provided by protocol processor integrated as part of the chip. The protocol processor encapsulates the memory address and control information like Read, Write, number of successive bytes etc, as an Ethernet packet for communication among the processor and memory chips that are located on the same motherboard, or even on different circuit cards. In one embodiment, the communication over head of the Ethernet protocol is further reduced by using an enhanced Ethernet protocol with shortened data frames within a constrained neighborhood, and / or by utilizing a bit stream switch where direct connection paths can be established between elements that comprise the computing or communication architecture.

Owner:KIRITIN INC

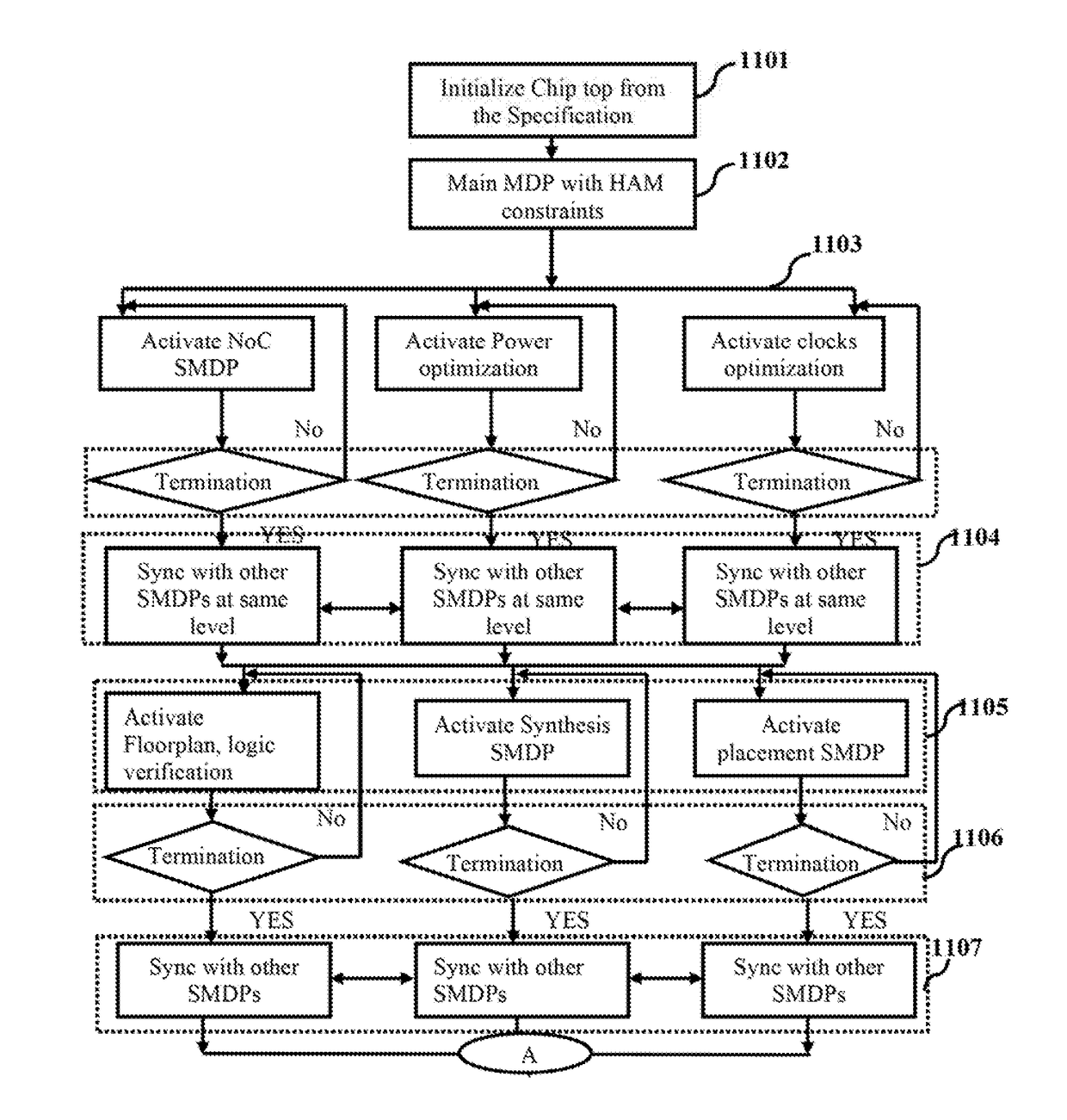

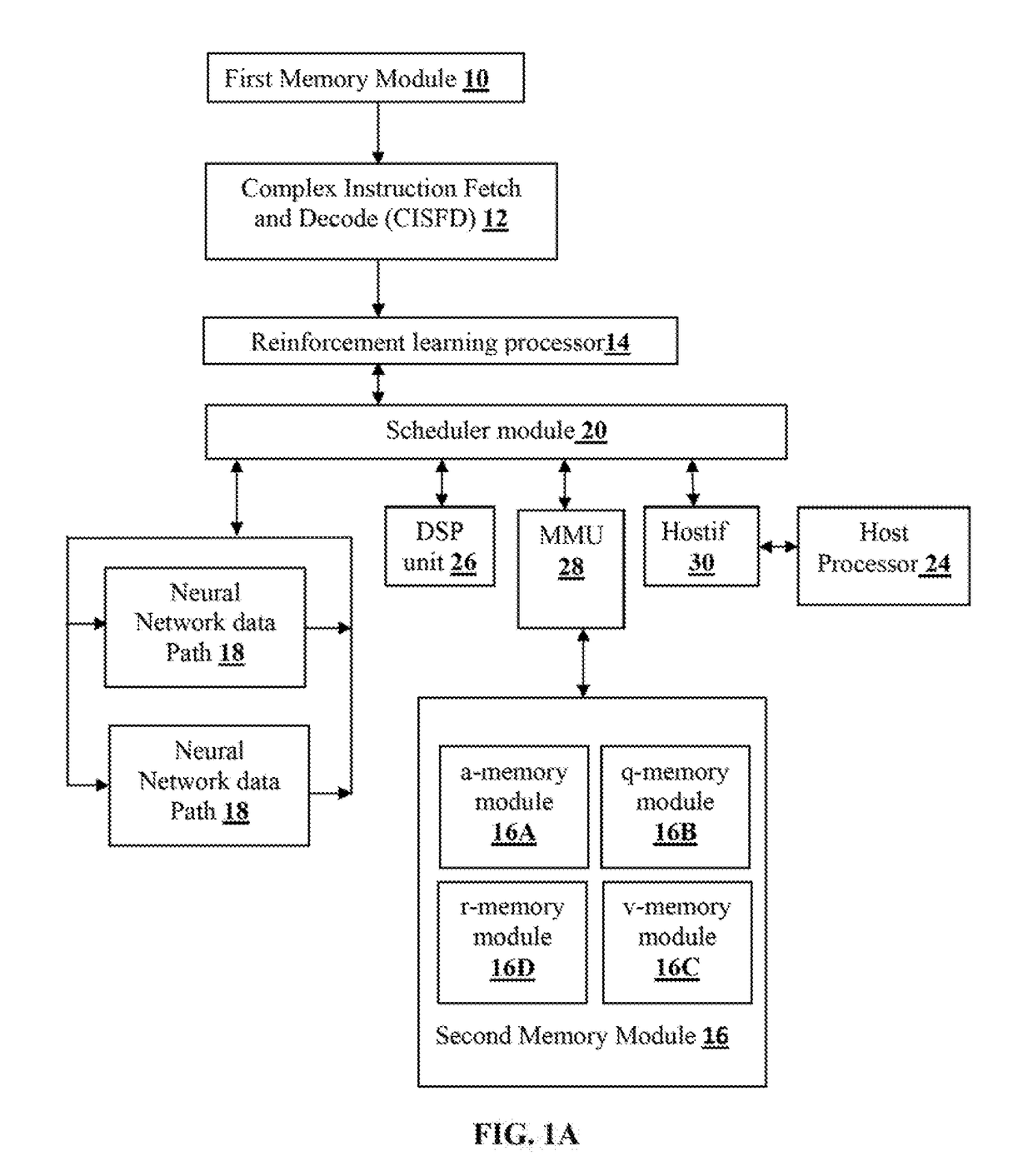

SYSTEM AND METHOD FOR DESIGNING SYSTEM ON CHIP (SoC) CIRCUITS USING SINGLE INSTRUCTION MULTIPLE AGENT (SIMA) INSTRUCTIONS

ActiveUS20180260498A1Computer aided designSpecial data processing applicationsComputer architectureChip architecture

The embodiments herein discloses a system and method for designing SoC by using a reinforcement learning processor. An SoC specification input is received and a plurality of domains and a plurality of subdomains is created using application specific instruction set to generate chip specific graph library. An interaction is initiated between the reinforcement learning agent and the reinforcement learning environ lent using the application specific instructions. Each of the SoC sub domains from the plurality of SoC sub domains is mapped to a combination of environment, rewards and actions by a second processor. Further, interaction of a plurality of agents is initiated with the reinforcement learning environment for a predefined number of times and further Q value, V value, R value, and A value is updated in the second memory module. Thereby, an optimal chip architecture for designing SoC is acquired using application-domain specific instruction set (ASI).

Owner:ALPHAICS CORP

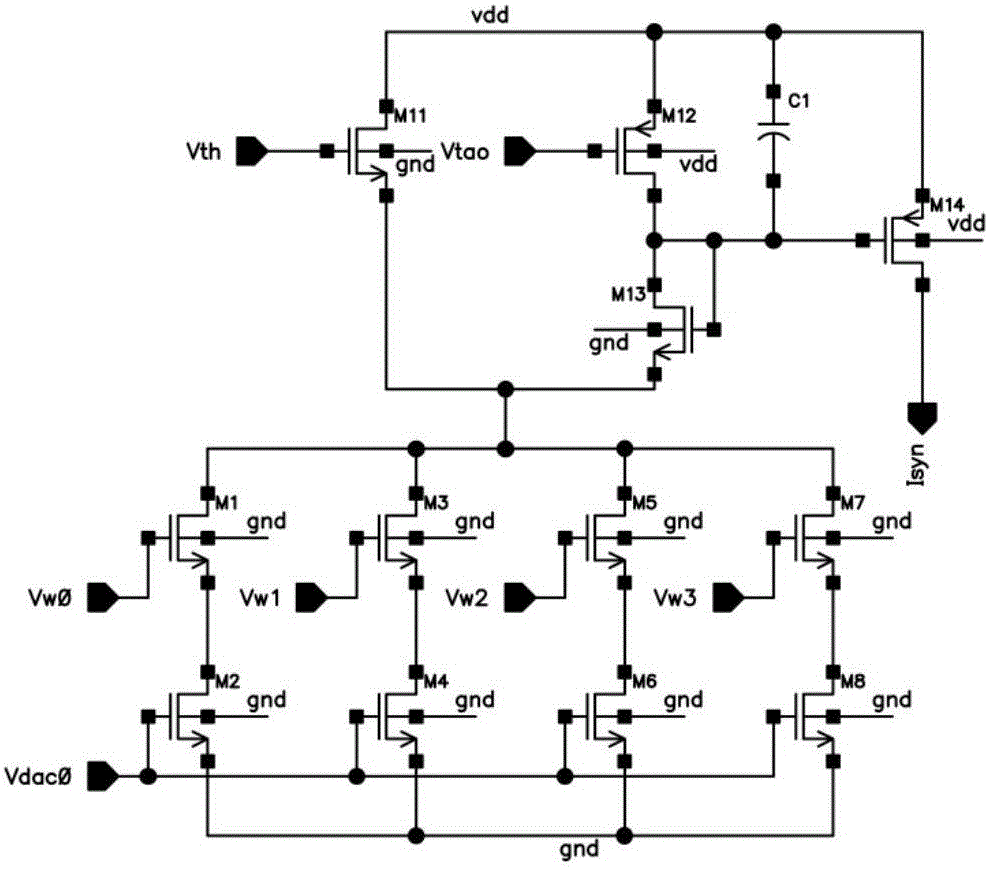

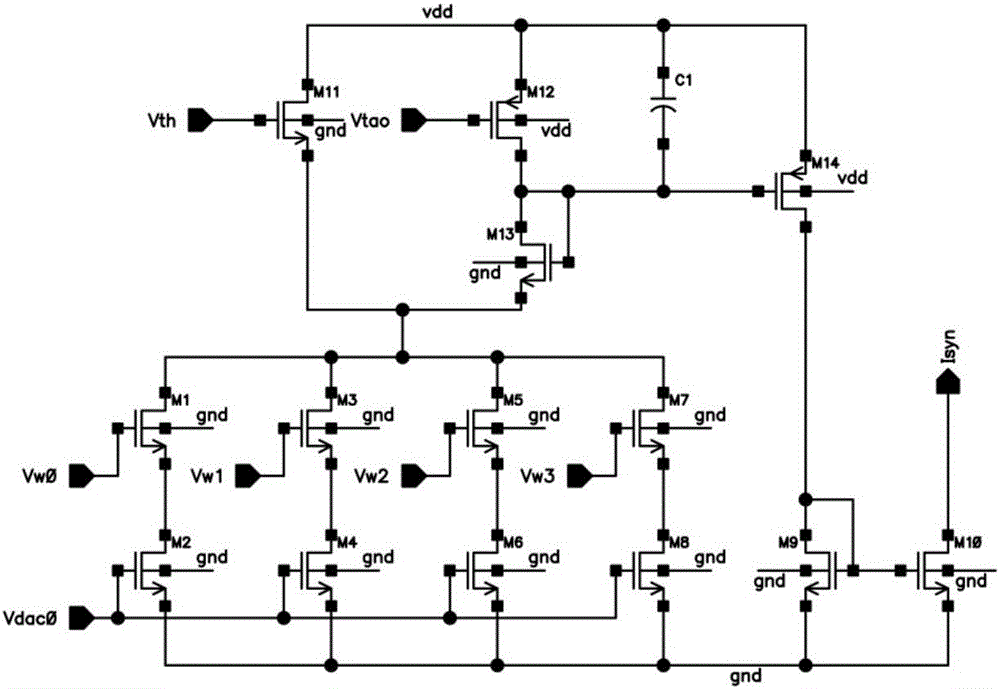

Digital-analog hybrid neural network chip architecture

The invention discloses a digital-analog hybrid neural network chip architecture. The architecture comprises a two-dimensional SRAM module, an analog synaptic circuit, a nerve cell circuit, an AER communication module, and a master control digital unit. The two-dimensional SRAM module is taken as a storage unit of neural network connection relation and a synaptic weight value. The analog synaptic circuit and the nerve cell circuit respectively consist of an MOSFET circuit working in a subthreshold section. The AER communication module serves as the input and output interfaces of a chip, and employs an AER protocol for communication. All control circuits in the architecture are synchronous digital circuits. The architecture is low in power consumption, is high in degree of parallelism, and can achieve a neural network algorithm in a reasonable chip area, wherein the neural network algorithm is more complex in nerve cell functions, is larger in network scale, and is more flexible in connection.

Owner:ZHEJIANG UNIV

Low Power Management of Multiple Sensor Chip Architecture

ActiveUS20140351559A1Power managementDigital data processing detailsMultiple sensorChip architecture

A method, device, system, or article of manufacture is provided for low-power management of multiple sensor chip architecture. In one embodiment, a method comprises, at a computing device that includes a first processor, a second processor and a third processor, receiving, at the first processor, first sensor data from a first sensor; determining, at the first processor, a motion state of the computing device using the first sensor data; in response to determining that the motion state corresponds to a predetermined motion state, activating the second processor; receiving, at the second processor, second sensor data from a second sensor; determining, by the second processor, that the motion state corresponds to the predetermined motion state using the second sensor data; and, in response to determining that the motion state corresponds to the predetermined motion state using the second sensor data, sending the motion state to the third processor.

Owner:GOOGLE TECH HLDG LLC

Security chip architecture and implementations for cryptography acceleration

InactiveUS20060021022A1Digital data processing detailsMultiple digital computer combinationsData packExternal storage

An architecture and a method for cryptography acceleration is disclosed that allows significant performance improvements without the use of external memory. Specifically, the chip architecture enables “cell-based” processing of random-length IP packets. The IP packets, which may be of variable and unknown size, are split into fixed size “cells.” The fixed-size cells are then processed and reassembled into packets. The cell-based packet processing architeture of the present invention allows the implementation of a processing pipeline that has known processing throughput and timing characteristics, thus making it possible to fetch and process the cells in a predictable time frame. The architecture is scalable and is also independent of the type of cryptography performed. The cells may be fetched ahead of time (pre-fetched) and the pipeline may be staged in such a manner that attached (local) memory is not required to store packet or control parameters.

Owner:AVAGO TECH INT SALES PTE LTD

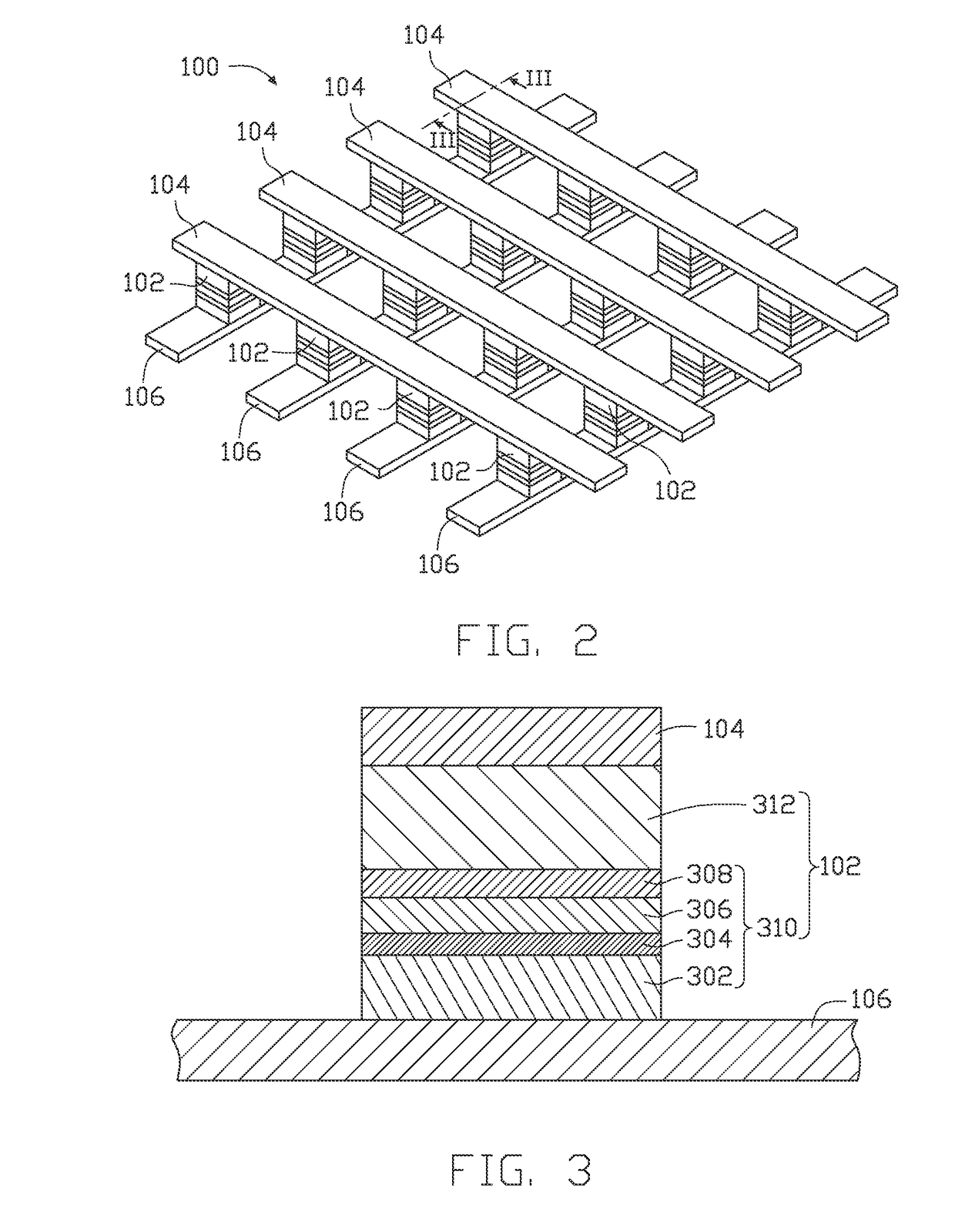

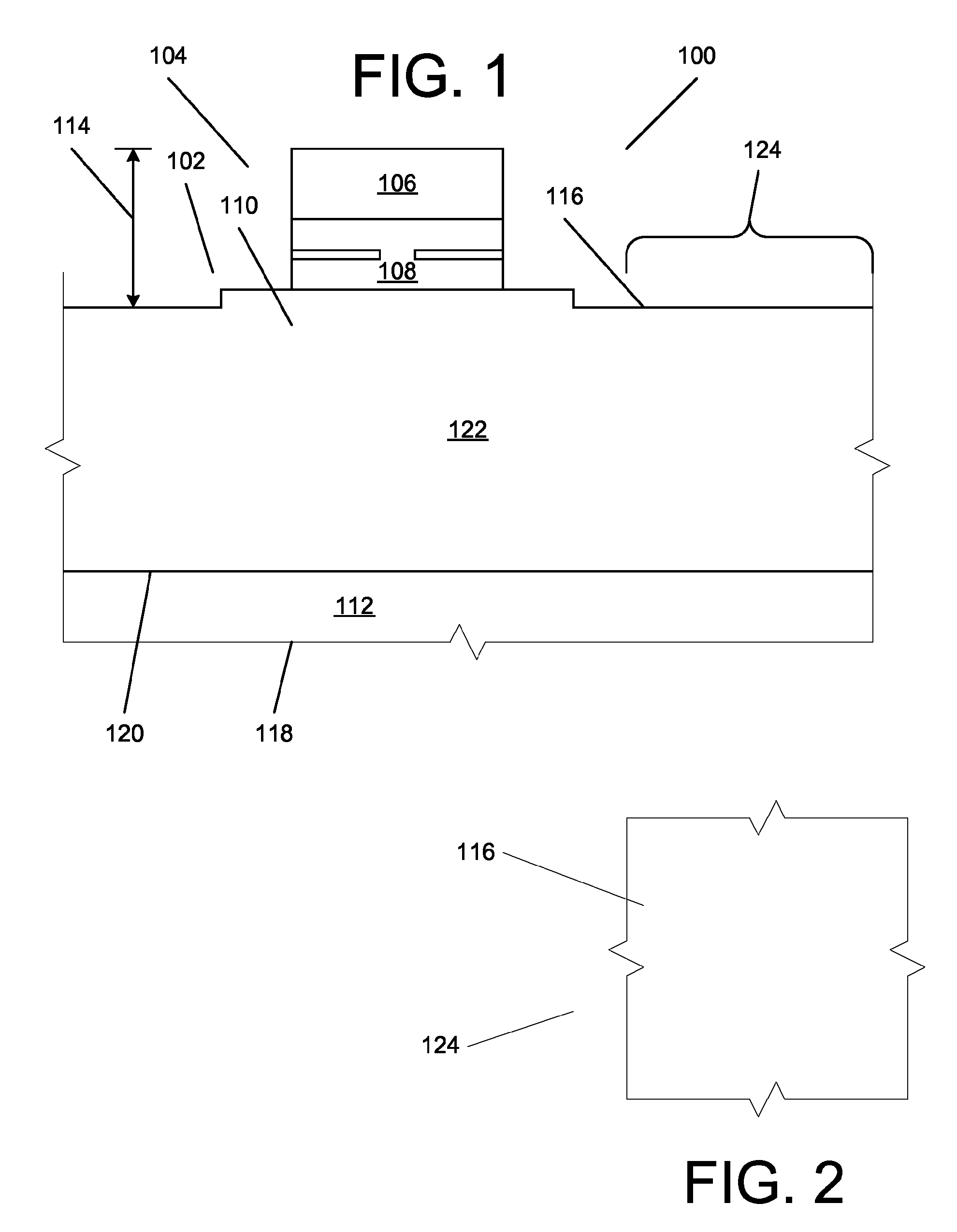

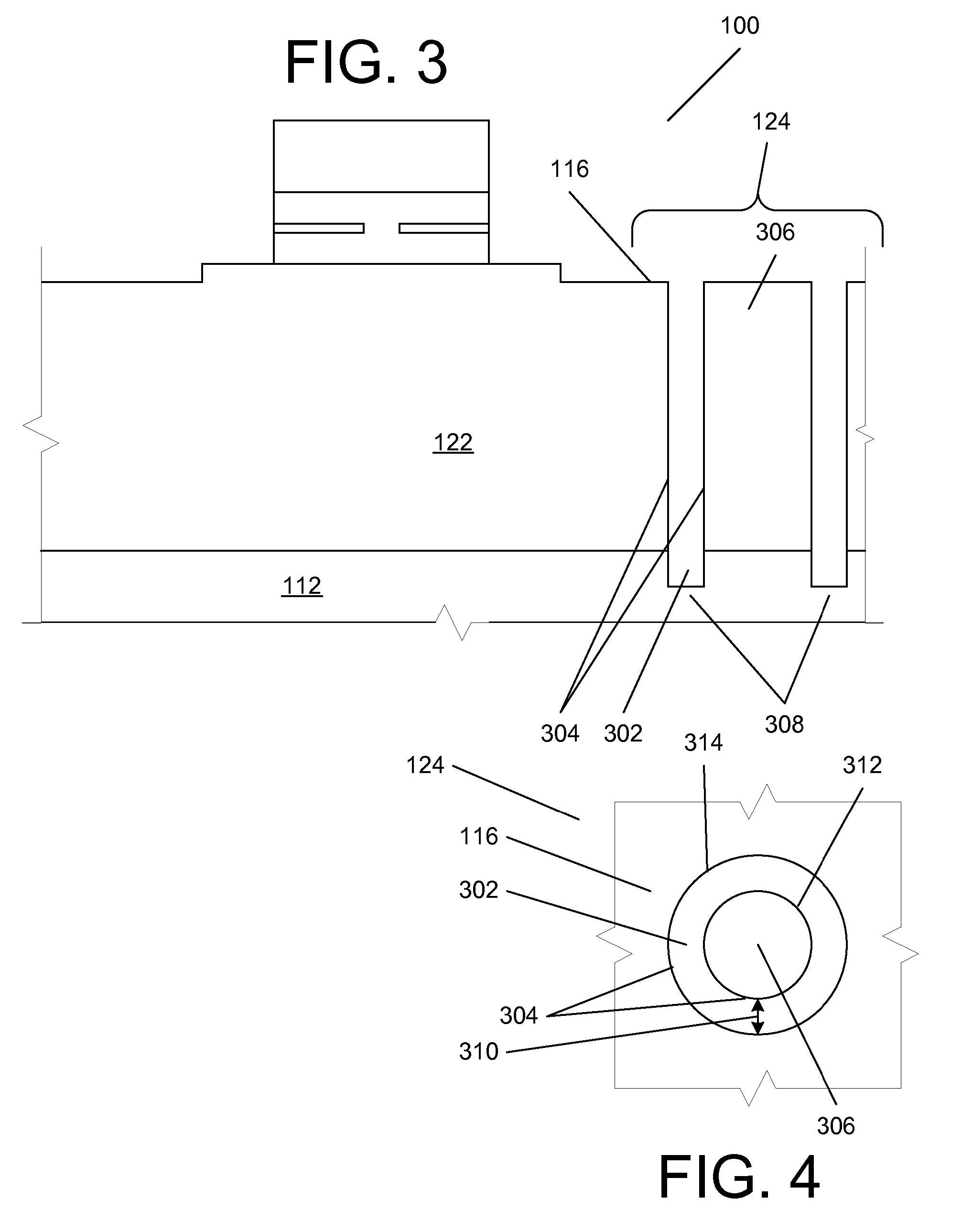

Routingless chip architecture

ActiveUS20060281296A1Easy to shapeSemiconductor/solid-state device detailsSolid-state devicesChip architectureWafer bonding

A method of creating a unified chip involves performing front-end processing on a first wafer, the front end processing creating multiple devices on the wafer, performing back-end processing on a second wafer, the back end processing creating layers of interconnected metal traces arranged to interconnect at least some of the multiple devices to each other, and bonding the first wafer to the second wafer such that the multiple devices on the first wafer are interconnected to each other by the metal traces of the second wafer.

Owner:CUFER ASSET LTD LLC

Multicore chip test

ActiveUS7689884B2Improve efficiencyElectronic circuit testingError detection/correctionParallel computingChip architecture

An integrated chip architecture is provided which allows for efficiently testing multiple cores included in the integrated chip architecture. In particular, the provided approach enables the test time and the number of required Input / Output test pins is nearly independent from the number of cores included in the multicore chip. The presented embodiments provide a multicore chip architecture which allows for providing input data to the multiple cores in parallel for simultaneously testing the multiple cores, and analyzing the resulting multiple test outputs on chip. As a result of this analysis embodiments may store on chip an indication for those cores that have not successfully passed the test.

Owner:ADVANCED MICRO DEVICES INC

Routingless chip architecture

ActiveUS7851348B2Semiconductor/solid-state device detailsSolid-state devicesChip architectureWafer bonding

A method of creating a unified chip involves performing front-end processing on a first wafer, the front end processing creating multiple devices on the wafer, performing back-end processing on a second wafer, the back end processing creating layers of interconnected metal traces arranged to interconnect at least some of the multiple devices to each other, and bonding the first wafer to the second wafer such that the multiple devices on the first wafer are interconnected to each other by the metal traces of the second wafer.

Owner:CUFER ASSET LTD LLC

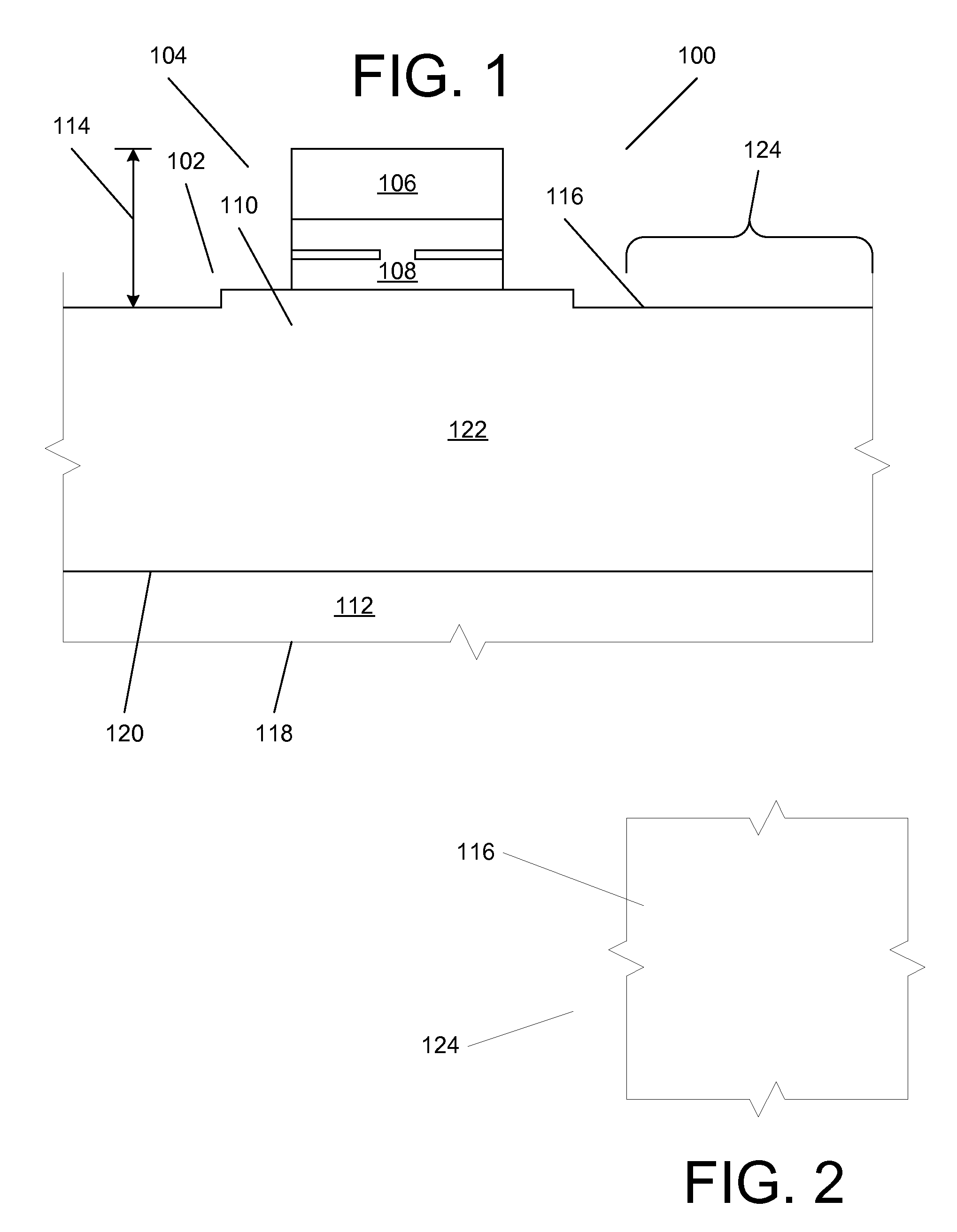

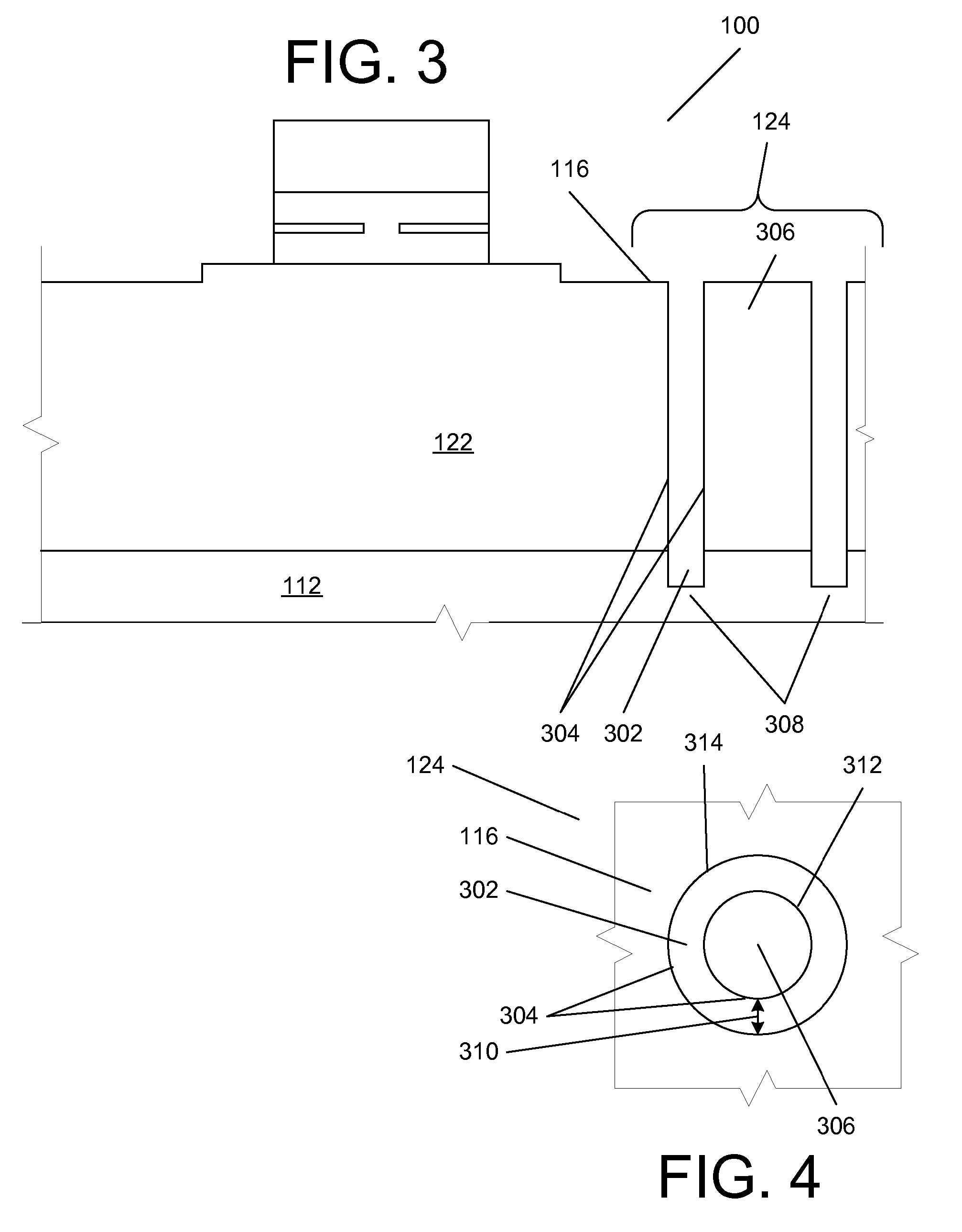

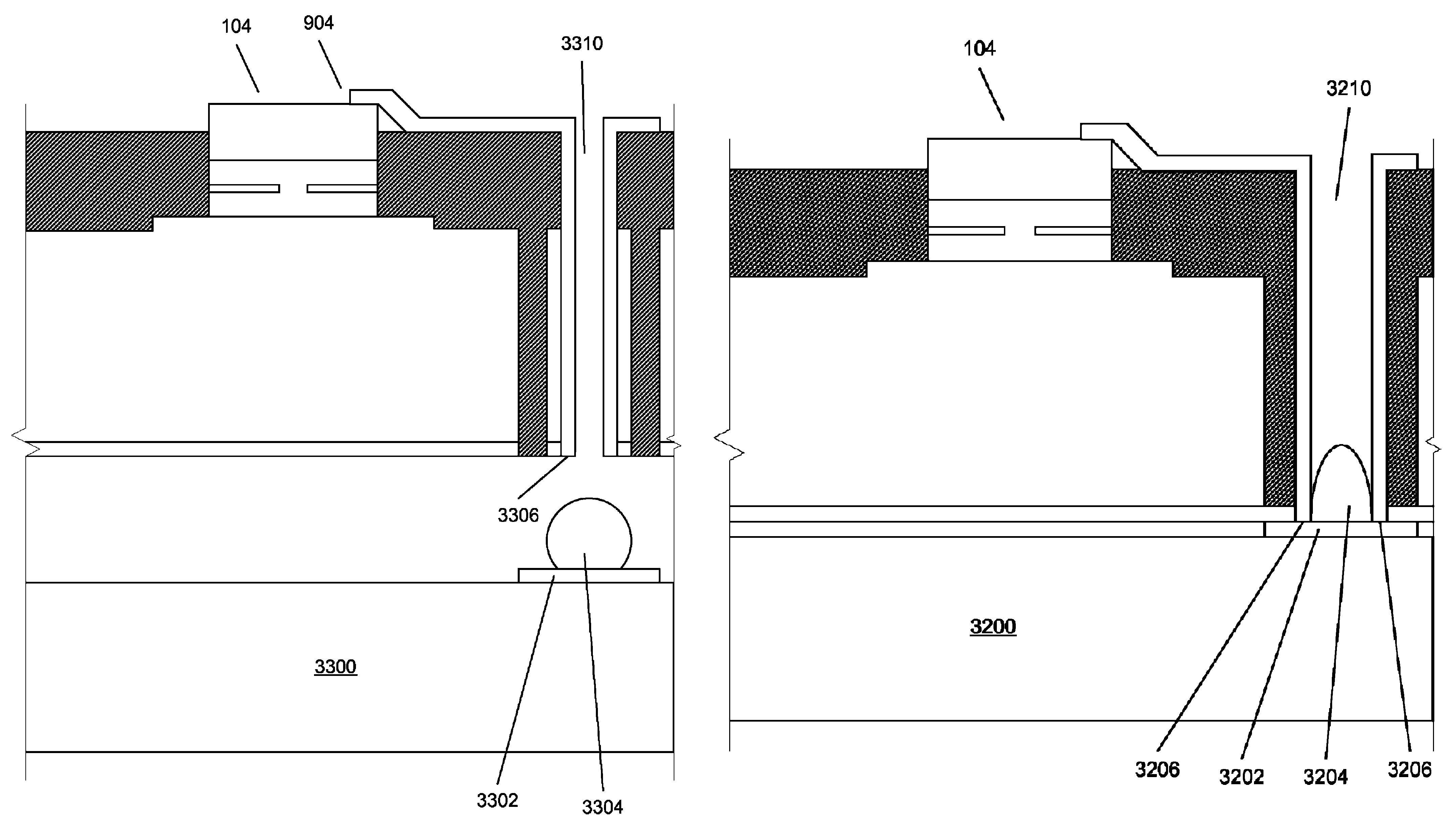

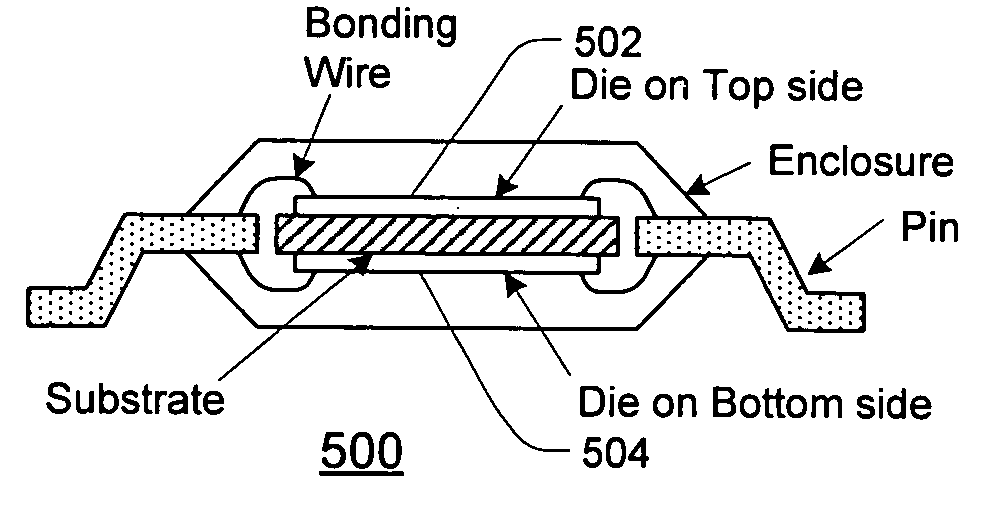

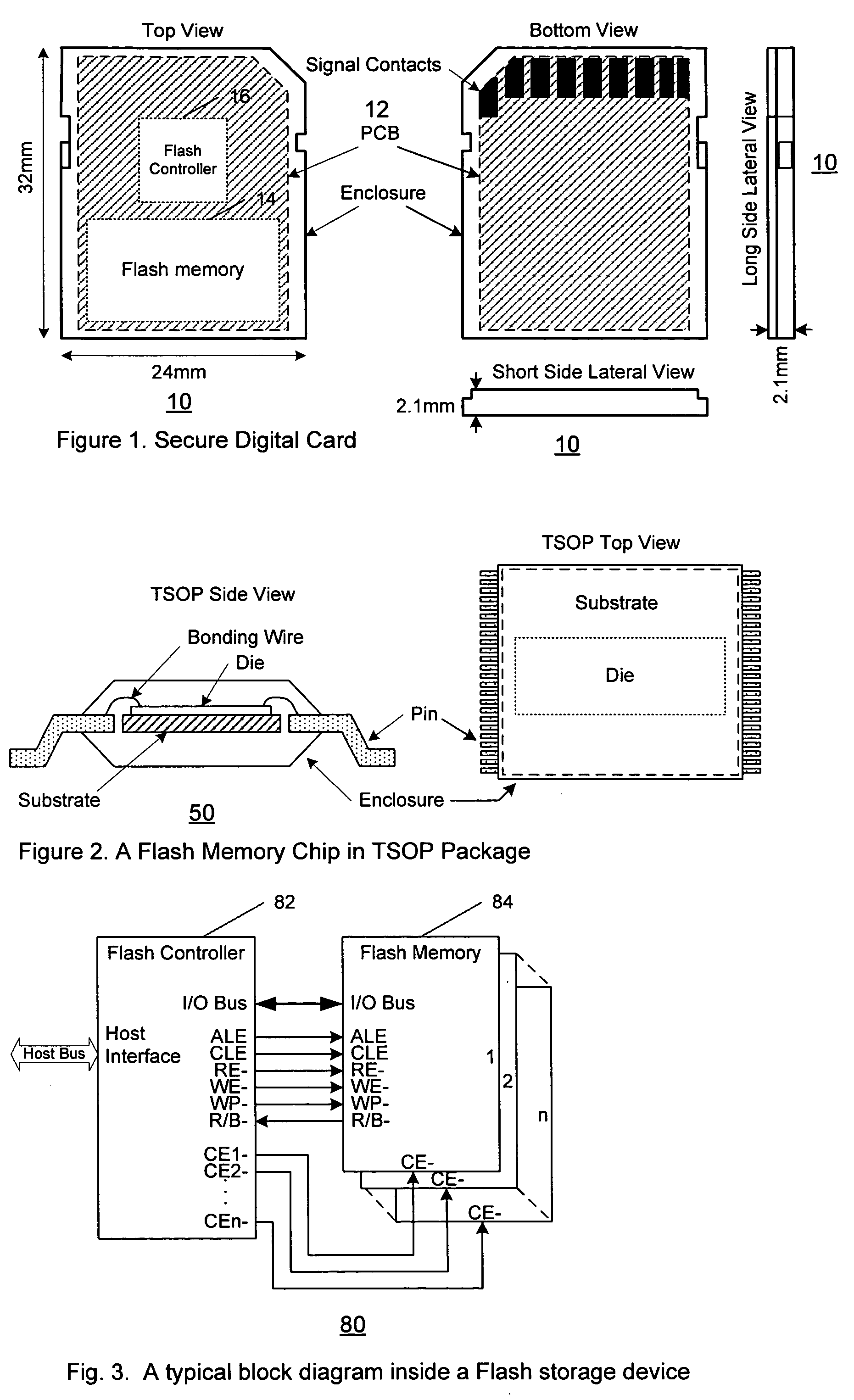

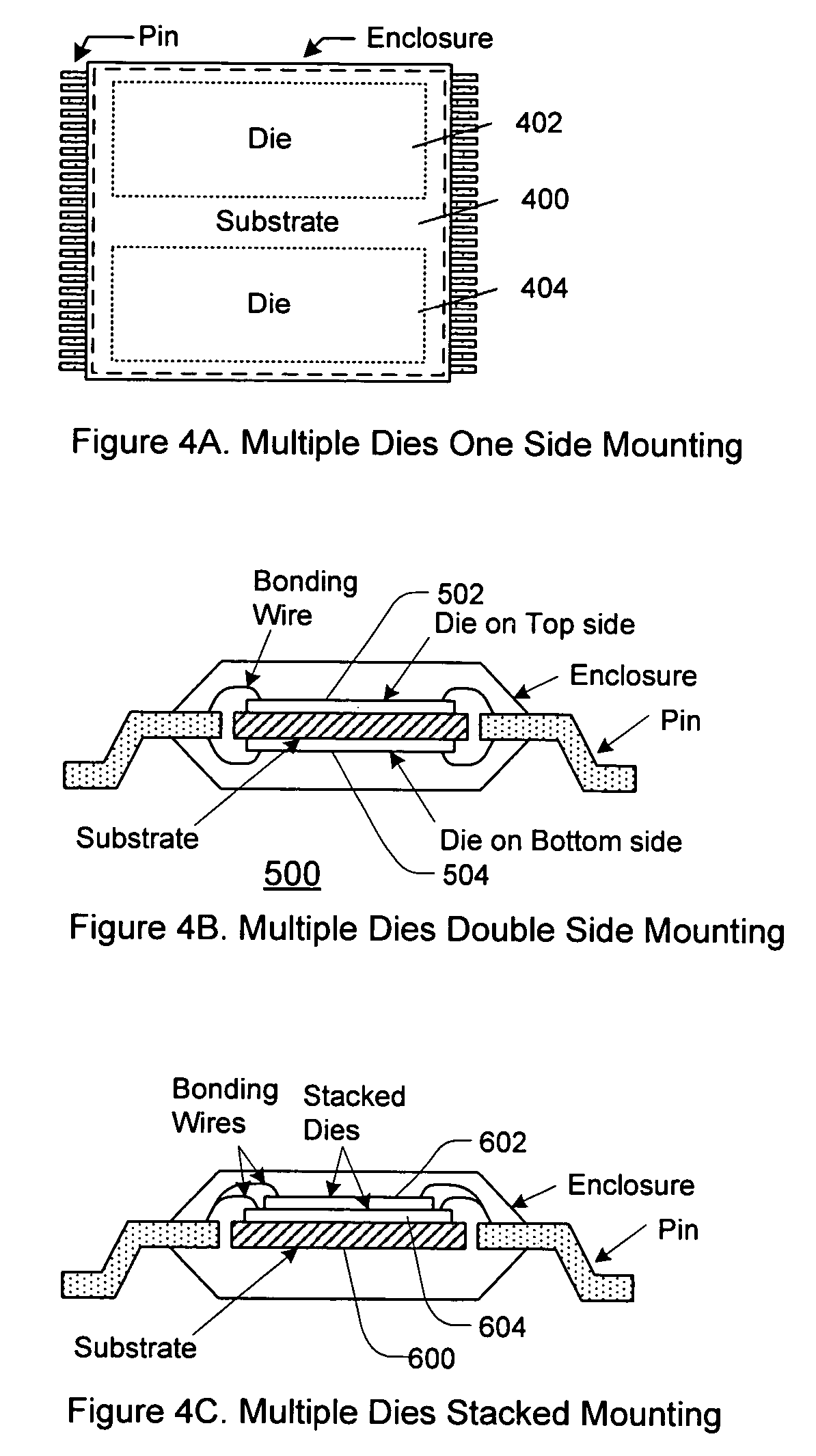

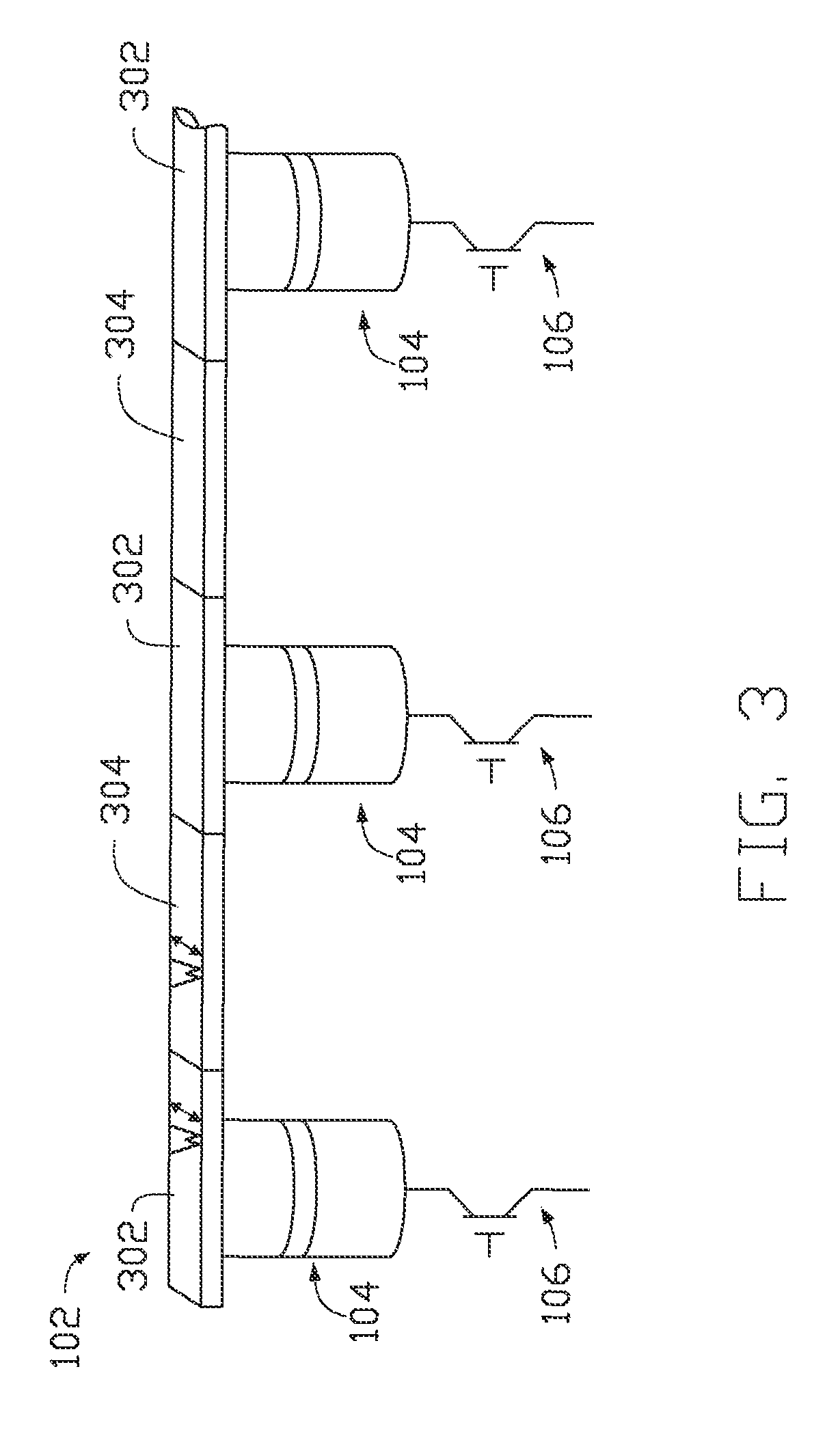

Method and system for expanding flash storage device capacity

InactiveUS20050285248A1Increase memory densityIncrease capacityFinal product manufactureSemiconductor/solid-state device detailsMemory chipChip architecture

A memory package and a chip architecture which includes stacked multiple memory chips is described. In a first aspect, a memory package comprises a substrate and a plurality of memory dies mounted on the substrate. Each die has a separate chip enable. In a second aspect, a chip architecture comprises a printed circuit board (PCB). The PCB includes a footprint. The footprint includes at least one no connect (NC) pad. The chip architecture includes a plurality of stacked memory chips mounted on the printed circuit board. Each of the plurality of stacked memory has a chip enable signal pin and also has at least one NC pin. At least one of the plurality of stacked memory chips utilizes an NC pin of another of the stacked memory chips to route the chip enable pin to at least one NC pad of the footprint. Accordingly, a system and method in accordance with the present invention provides for increased memory density within a particular space constraint by (1) providing multiple dies in a single memory package and (2) by providing stacked memory chips in a single PCB footprint. In so doing, the package / PCB will have increased memory density over a conventional package / PCB within the same space constraints, and the capacity of Flash storage devices is expanded accordingly.

Owner:SUPER TALENT ELECTRONICS

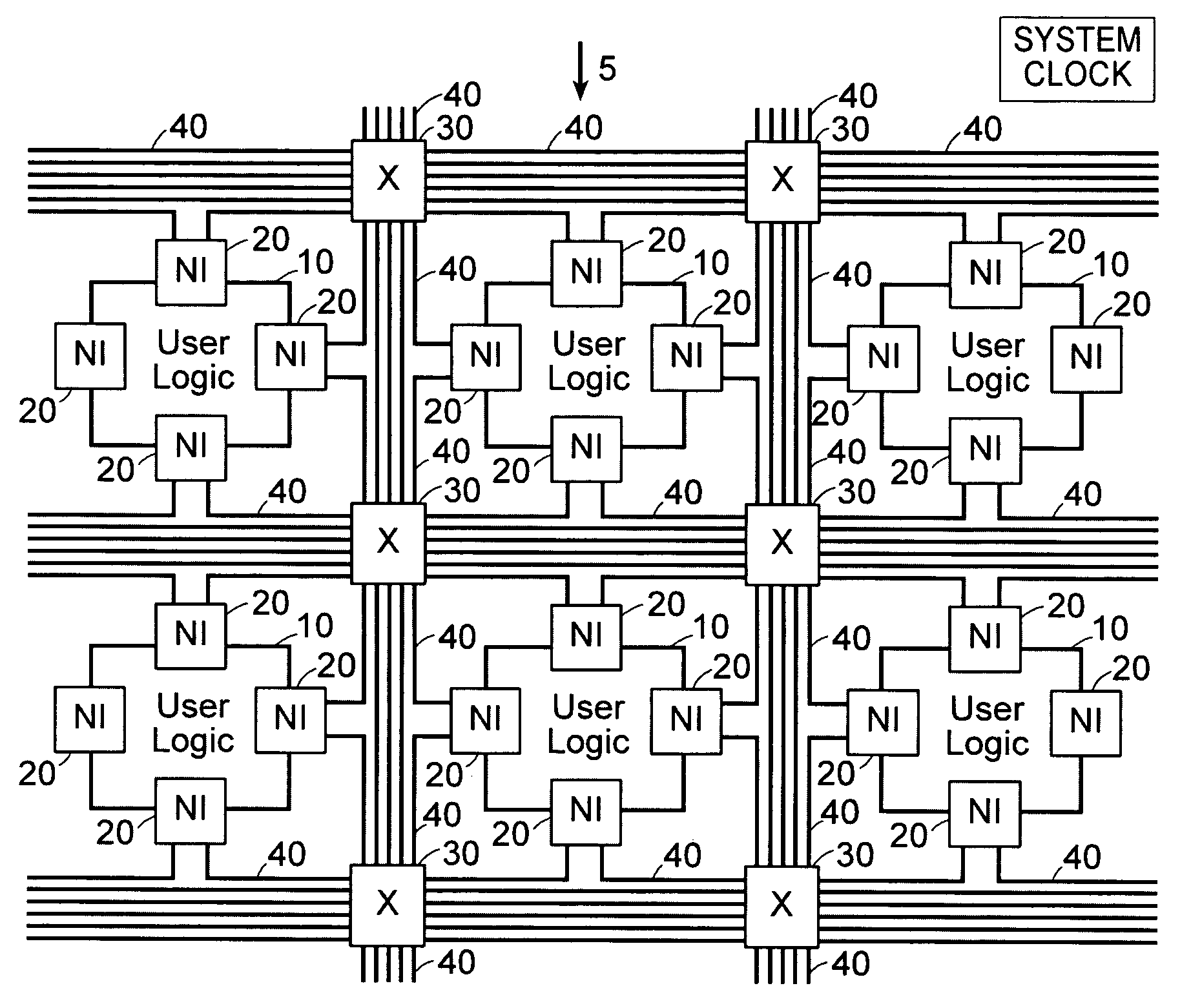

Integrated circuit and related improvements

InactiveUS7012448B2Improve reliabilitySolid-state devicesData switching networksChip architectureLogic gate

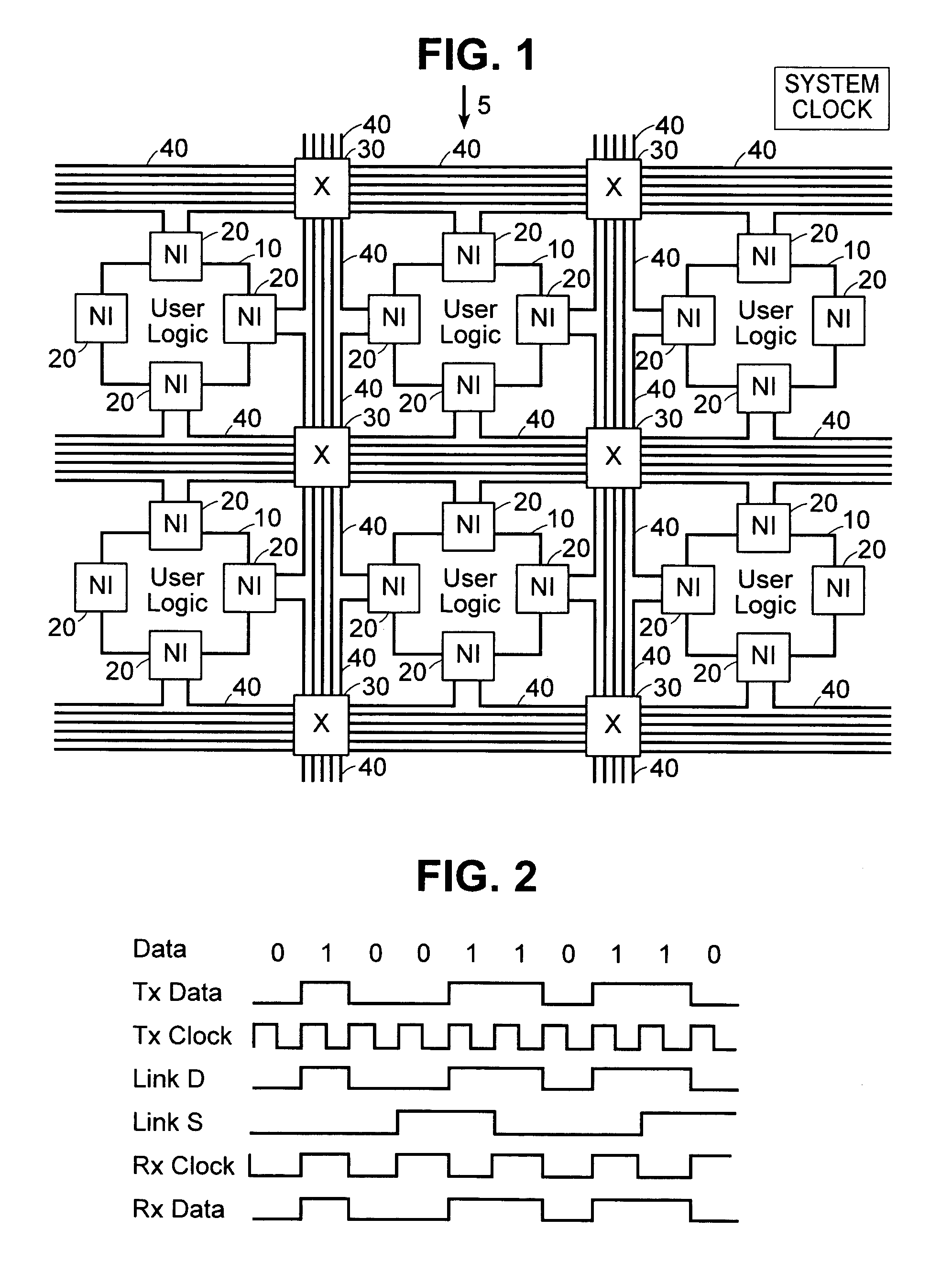

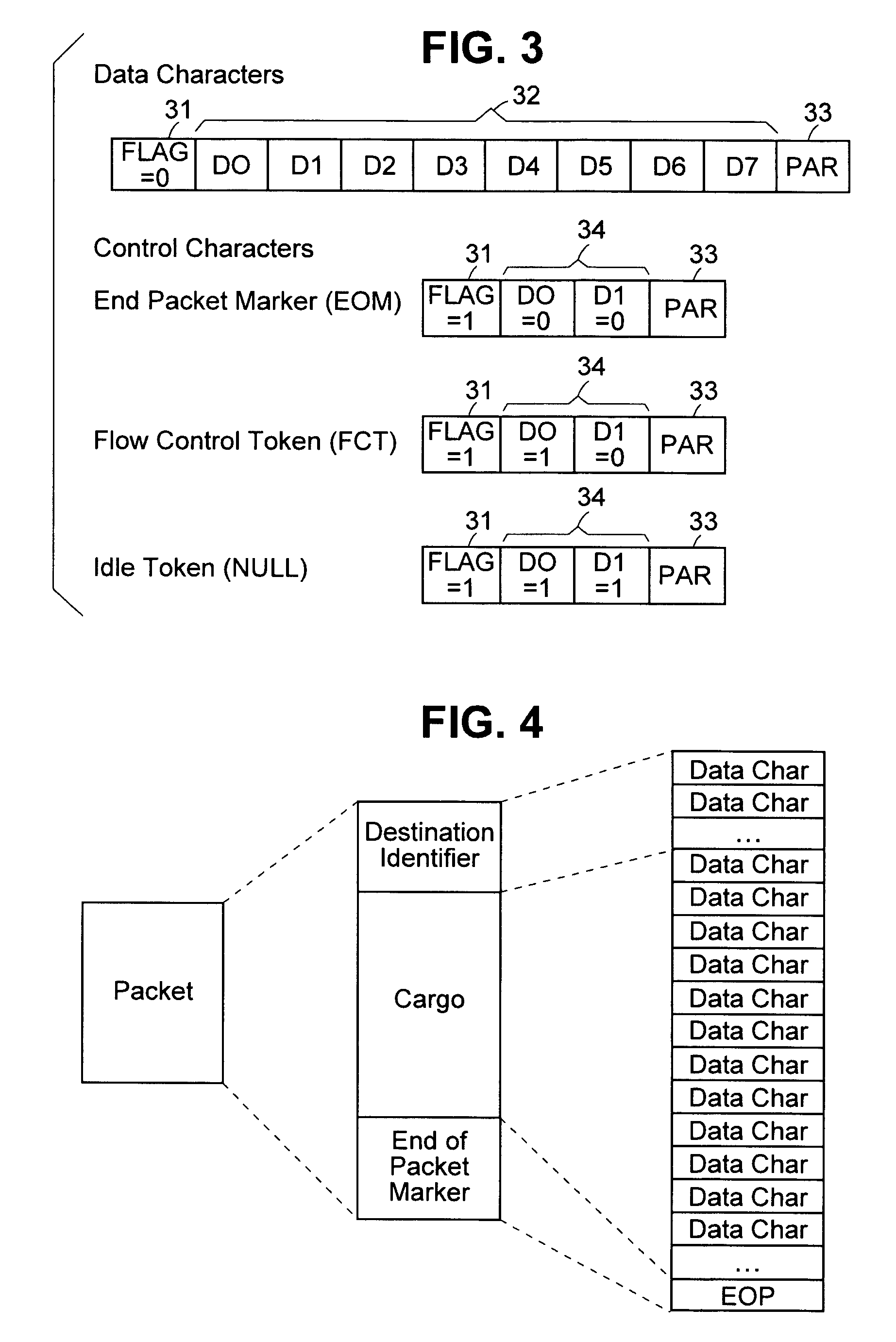

An improved integrated circuit and a related system apparatus and method. The integrated circuit includes a plurality of logic area or user logic areas; and an actively switchable network capable of selectively connecting at least one logic area with another logic area. In particular, the plurality of logic areas include an array of logic-gates or logic-blocks or custom logic which form functional blocks. The integrated circuit can provide a chip-architecture where the functional blocks are specific hardware functional blocks, hardware functional blocks that are parameterized, and / or programmable functional blocks including programmable processors. Also, the functional blocks can act as objects requesting and providing services to other objects on the actively switchable network so that, when a functional block is a programmable processor, the functional block optionally implements objects, with the programmable processor making one, some or all objects thereof visible to other objects connected to the actively switchable network.

Owner:UNIV COURT OF THE UNIV OF DUNDEE

Bottom pinned SOT-MRAM bit structure and method of fabrication

ActiveUS9768229B2Large spin-orbit coupling strengthHigh resistivityMagnetic-field-controlled resistorsSolid-state devicesSignal-to-noise ratio (imaging)Spins

Owner:WESTERN DIGITAL TECH INC

Multicore chip test

ActiveUS20080148117A1Improve efficiencyElectronic circuit testingError detection/correctionParallel computingChip architecture

An integrated chip architecture is provided which allows for efficiently testing multiple cores included in the integrated chip architecture. In particular, the provided approach enables the test time and the number of required Input / Output test pins is nearly independent from the number of cores included in the multicore chip. The presented embodiments provide a multicore chip architecture which allows for providing input data to the multiple cores in parallel for simultaneously testing the multiple cores, and analyzing the resulting multiple test outputs on chip. As a result of this analysis embodiments may store on chip an indication for those cores that have not successfully passed the test.

Owner:ADVANCED MICRO DEVICES INC

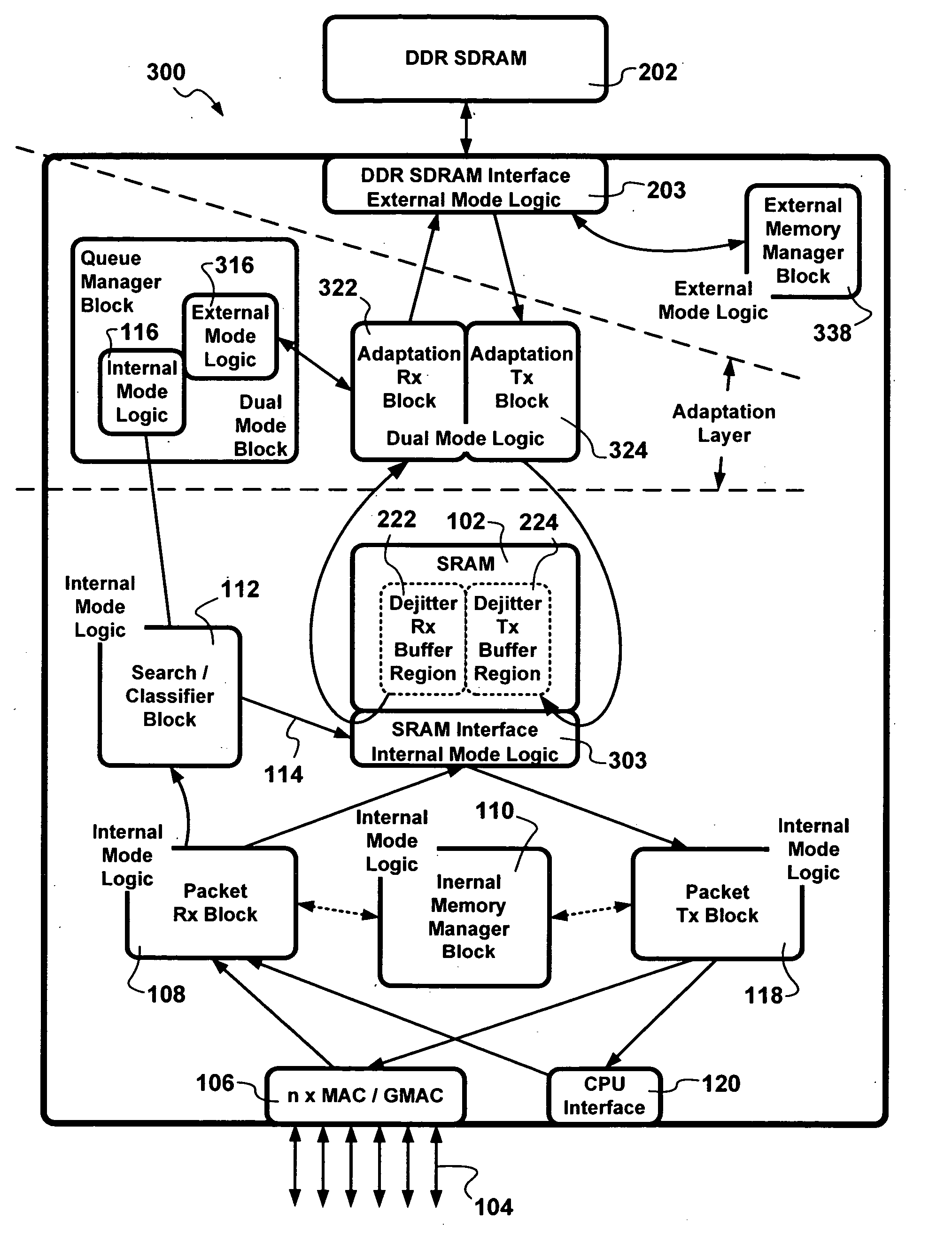

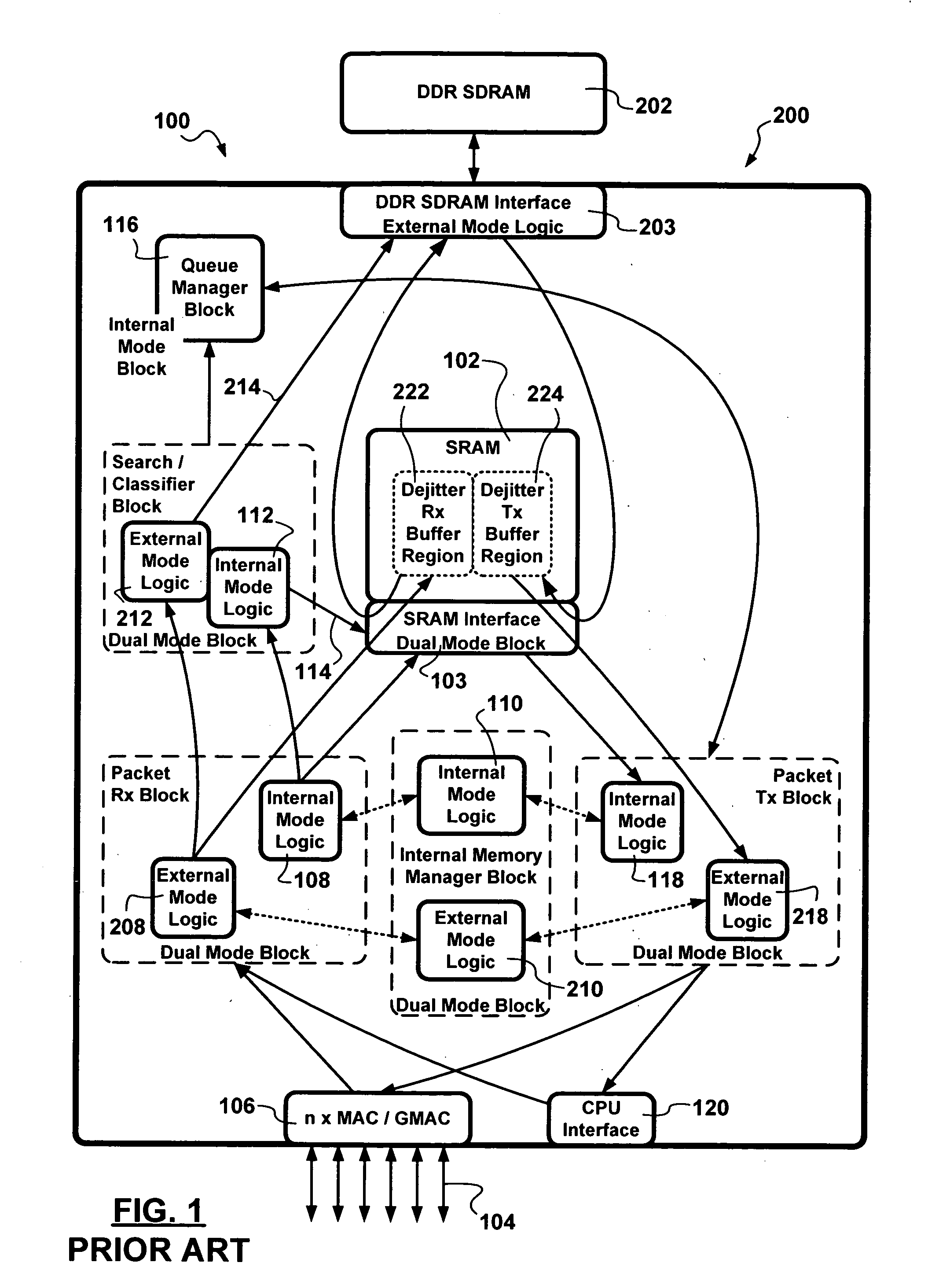

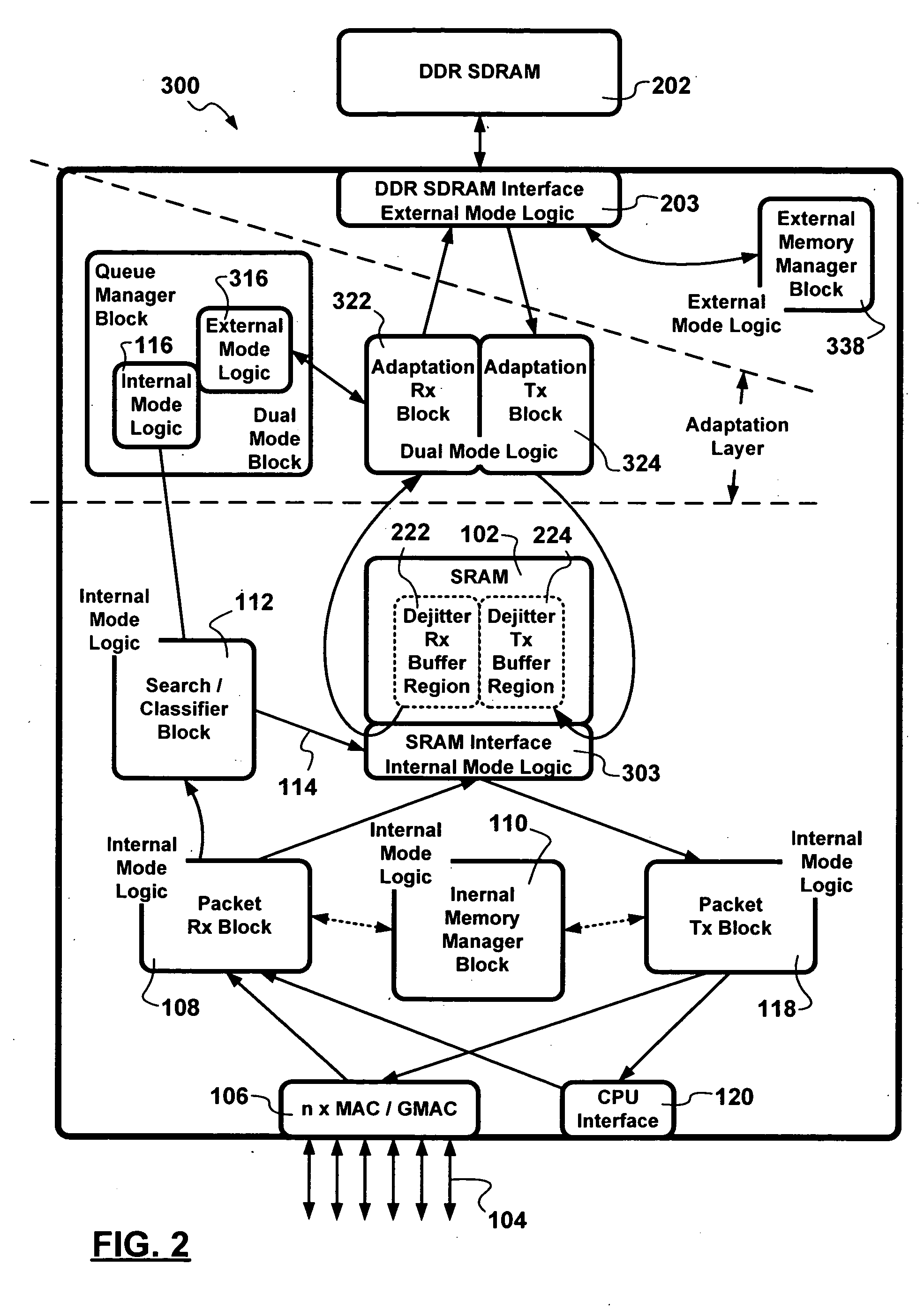

Compact packet switching node storage architecture employing double data rate synchronous dynamic RAM

A two-chip / single-die switch architecture and a method for accessing a DDR SDRAM memory store in a switching environment are presented. The two-chip / single-die architecture includes an internal memory storage block on the single-die, an external memory storage interface to a Double Data Rate Synchronous Dynamic Random Access Memory (DDR SDRAM), an external memory manager, and a packet data transfer engine effecting packet data transfers between an internal memory store and the external DDR SDRAM memory. The packet data transfer engine operates as an adaptation layer addressing issues related to employing appropriate: addressing schemes, granule sizes, memory transfer burst sizes, access timing, etc. The packet data transfer engine includes a minimal number of dual mode operational blocks such as: a queue manager, and adaptation receive and transmit blocks. The method relates to a packet data transfer discipline addressing random memory access latencies incurred in employing DDR SDRAM, using predictive bank switching to hide random access latencies, packet length dependent variable memory write burst lengths to minimize bank switching, and performing memory read and write operations during corresponding read and write windows. Advantages are derived from the a space-efficient two-chip / single-die switching node architecture implemented with a reduced amount of dual mode logic, and also from DDR SDRAM bandwidth utilization efficiencies.

Owner:IKANOS COMMUNICATIONS

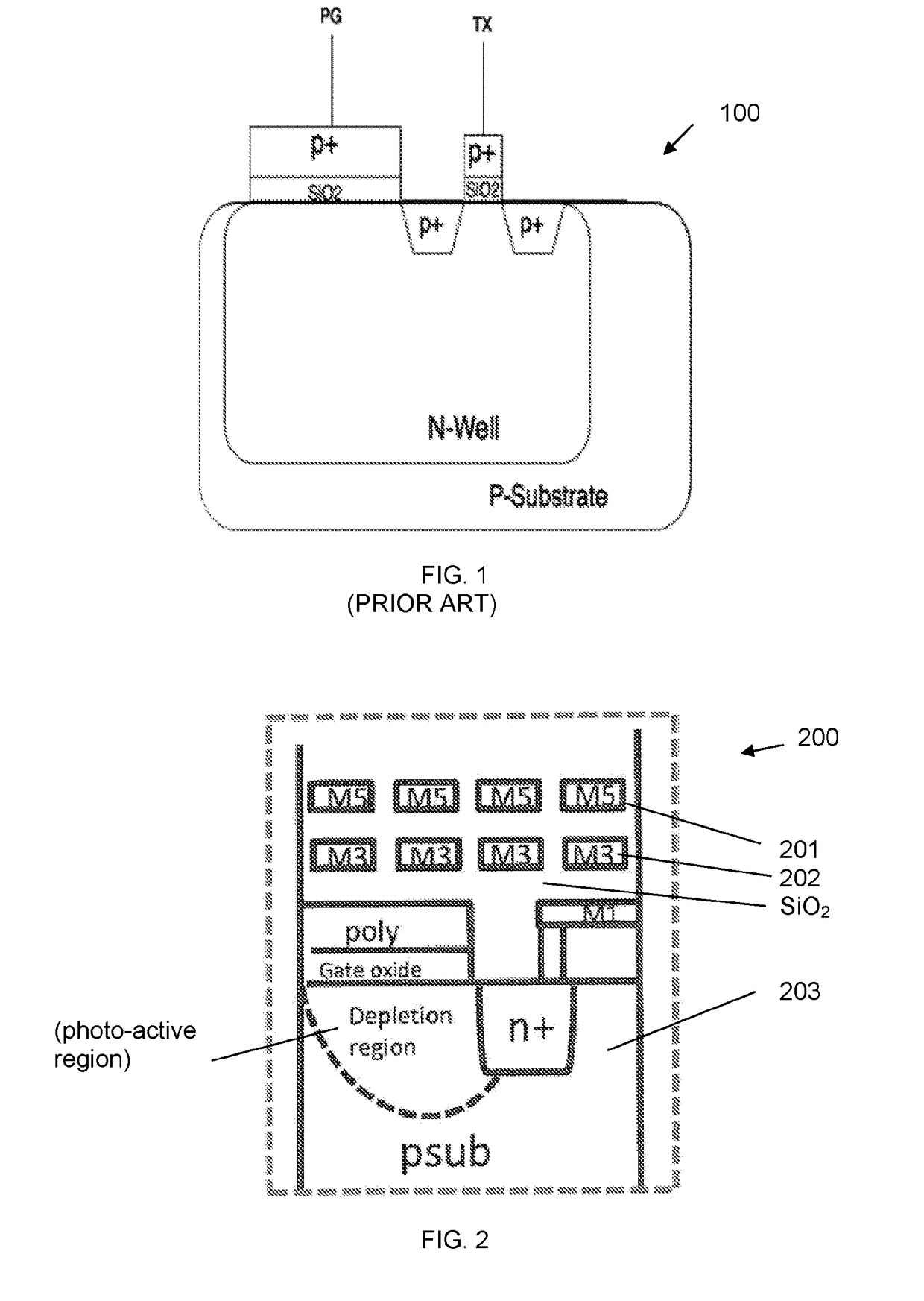

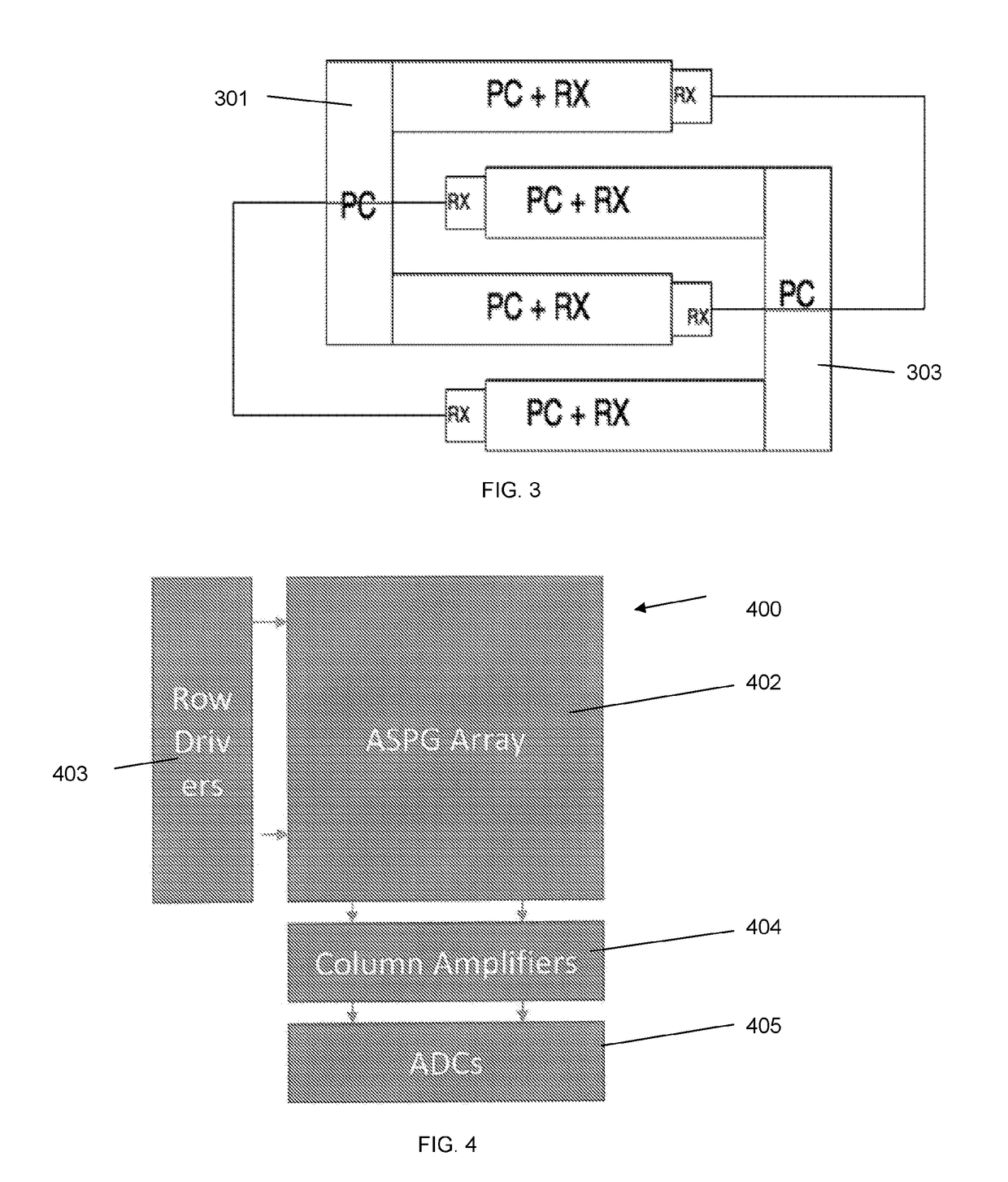

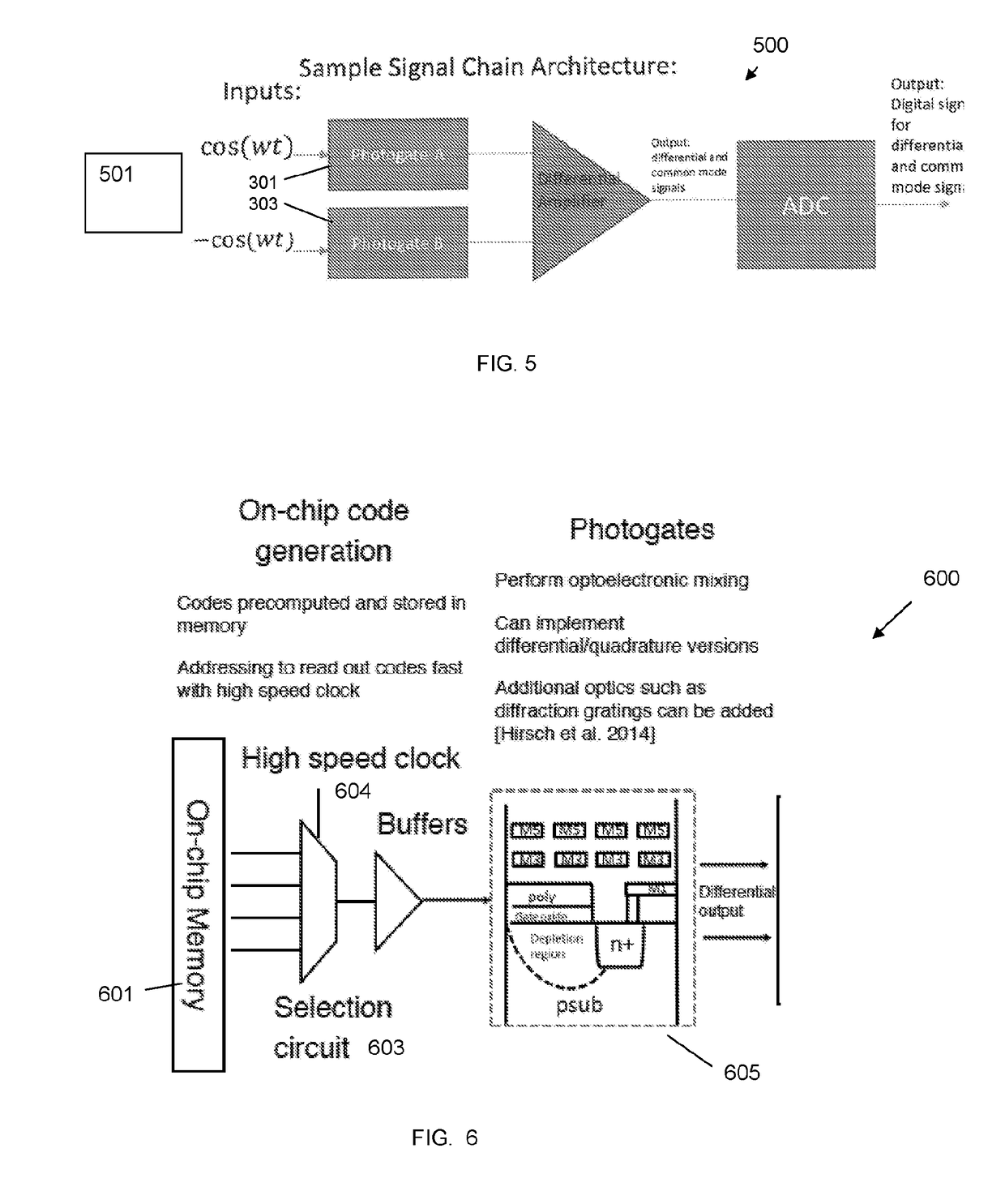

Depth field imaging apparatus, methods, and applications

ActiveUS20190033448A1Television system detailsColor television detailsDepth of fieldChip architecture

A depth of field imaging apparatus includes a light field imager and a time of flight imager combined in a single on-chip architecture. This hybrid device enables simultaneous capture of a light field image and a time of flight image of an object scene. Algorithms are described, which enable the simultaneous acquisition of light field images and a time of flight images. Associated hybrid pixel structures, device arrays (hybrid imaging systems), and device applications are disclosed.

Owner:CORNELL UNIVERSITY

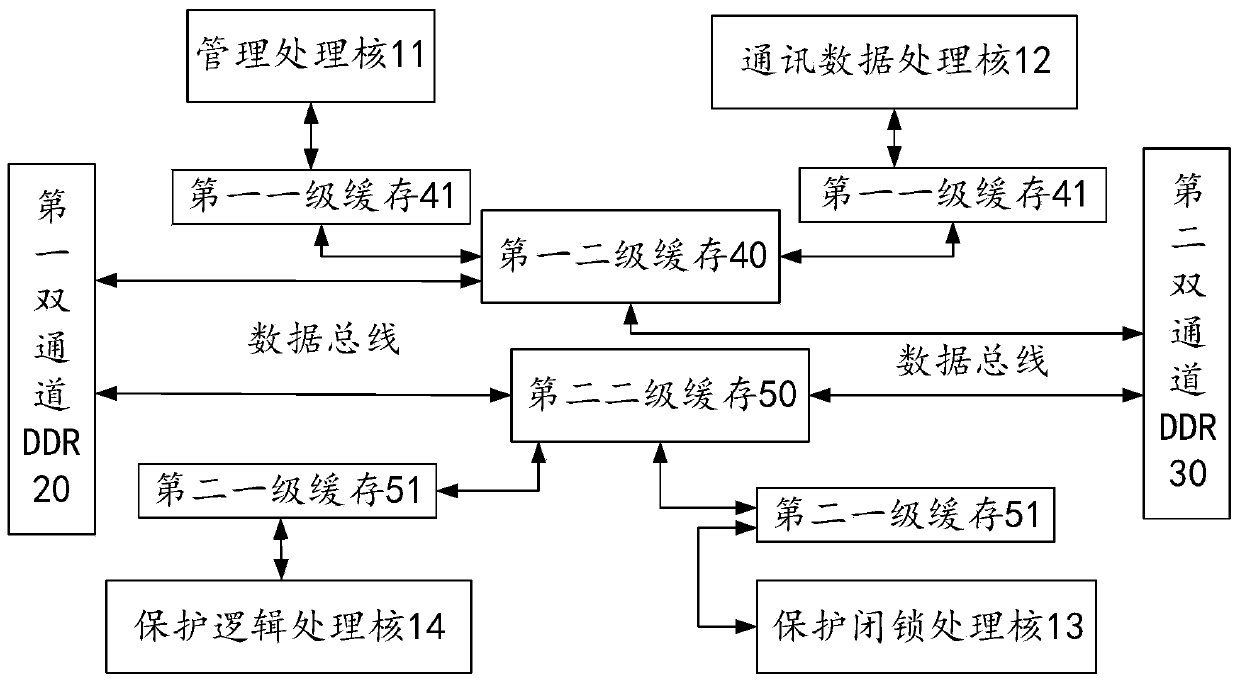

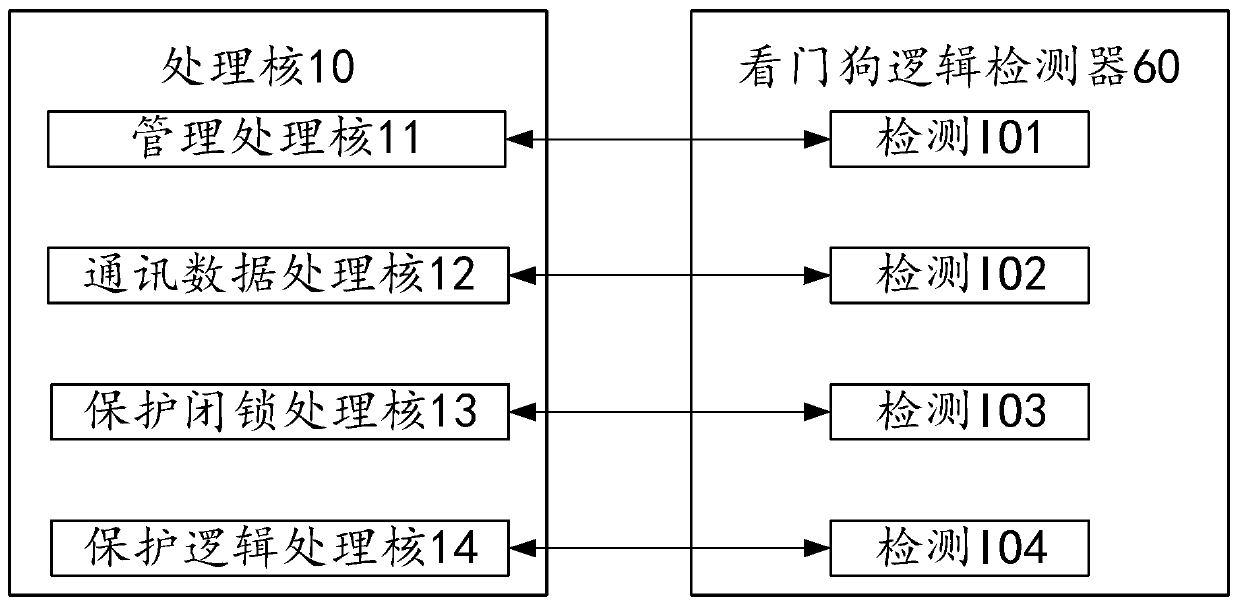

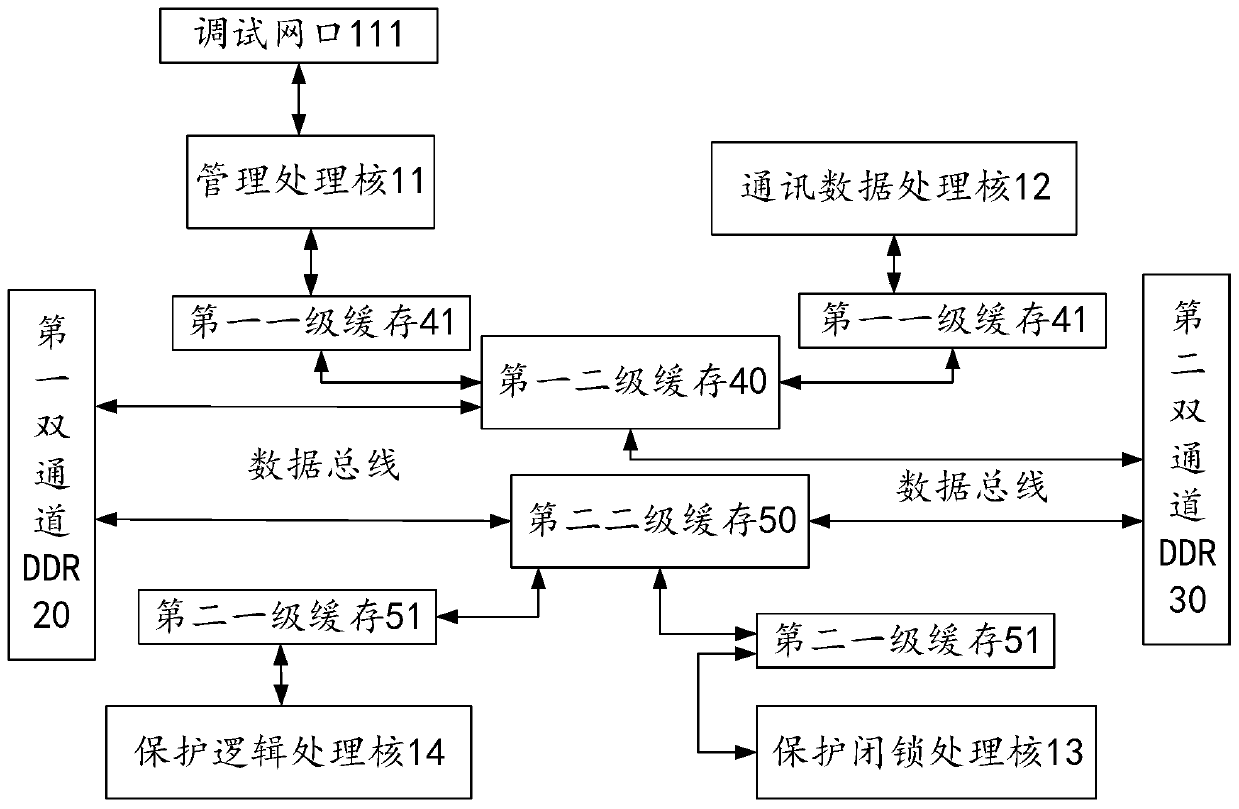

Relay protection system and special multi-core Soc chip architecture thereof

InactiveCN111427840AReduced operational reliabilityReduced operational stabilityFault responseArchitecture with single central processing unitComputer architectureProcessing core

The embodiment of the invention relates to a relay protection system and a special multi-core Soc chip architecture thereof. The special multi-core Soc chip architecture comprises a first dual-channelDDR, a second dual-channel DDR, a management processing core, a communication data processing core, a protection locking processing core, a protection logic processing core, a first secondary cache and a second secondary cache which are integrated on a chip. According to the special multi-core Soc chip architecture for the relay protection system, the four processing cores, the first dual-channelDDR, the second dual-channel DDR, the first secondary cache and the second secondary cache are integrally arranged on the chip, so that the original complex multi-chip hardware architecture is simplified; and low operation reliability and stability of the relay protection system caused by unstable connection of a multi-chip hardware structure are also avoided, and the operation reliability and stability of the relay protection system are improved. The technical problem that the operation stability and reliability of a relay protection product are influenced due to the fact that an existing relay protection multi-chip framework adopts a framework that a plurality of chips adopt a plurality of clamping plates and the multi-chip framework is complex is solved.

Owner:CHINA SOUTHERN POWER GRID DIGITAL GRID RES INST CO LTD