Digital-analog hybrid neural network chip architecture

A neural network and architecture technology, applied in the field of digital-analog hybrid neural network chip architecture, can solve the problems of high power consumption, low parallelism, small network scale, etc., achieve low power consumption, high parallelism, and avoid error signals Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

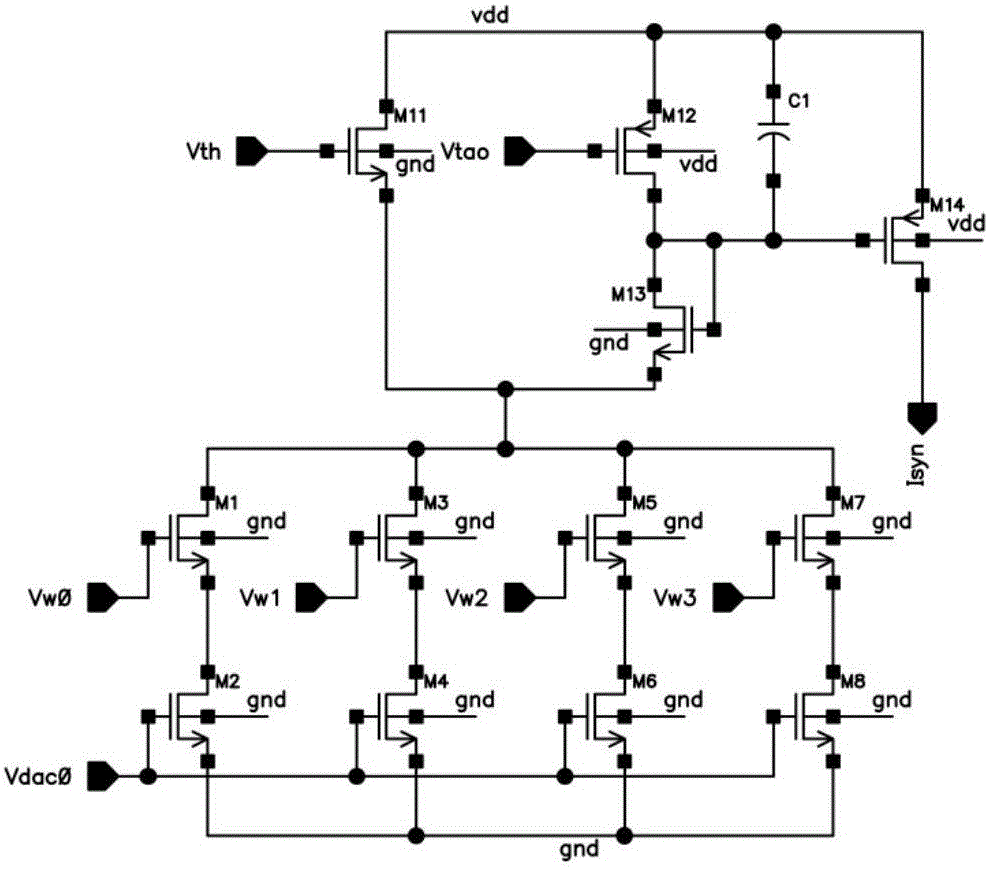

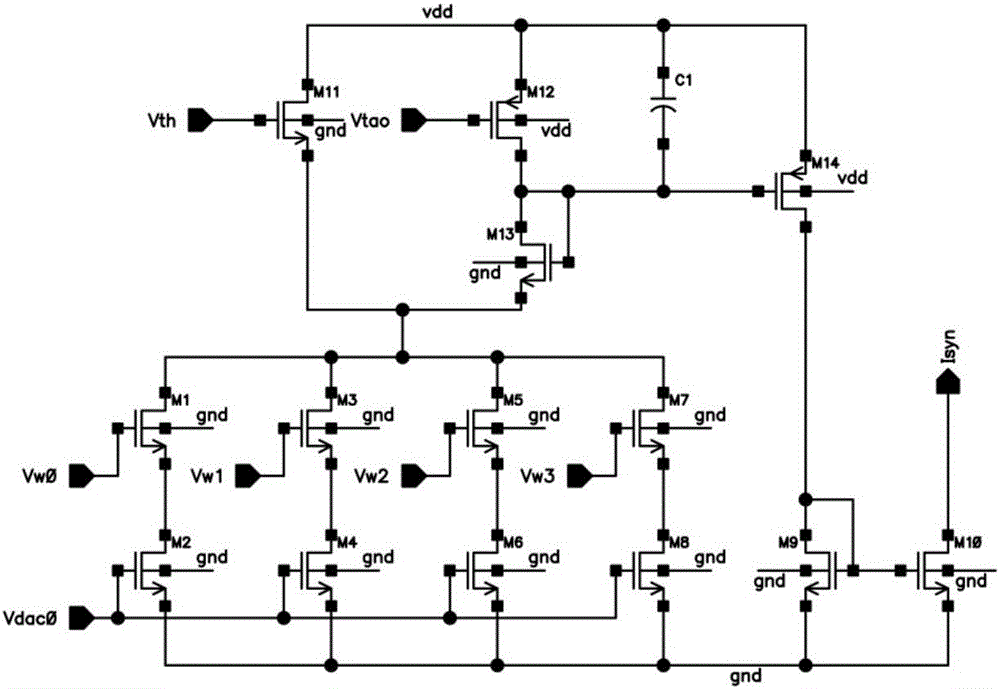

[0027] Such as figure 1 As shown, the chip of the present invention has an open-loop network structure, and the closed-loop of the chip itself, the connection between chips and the configuration of the chip by the off-chip system are flexibly realized through the AER input and output interfaces.

[0028] AER input interface includes req, ack pin and 16-bit address bus AER-IN, AER output interface includes req, ack pin, 9-bit address line AER-OUT and 1 additional configurable address. The input 16-bit bus consists of 8-bit X address, 7-bit Y address, and 1 broadcast address, and the output 9-bit bus is 8-bit X address (consisting of 7-bit output neuron address and 1 additional address) and 1 bit broadcast address.

[0029] When the corresponding req and ack between the AER input interface and output interface are respectively connect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More