Patents

Literature

600 results about "Embedded memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

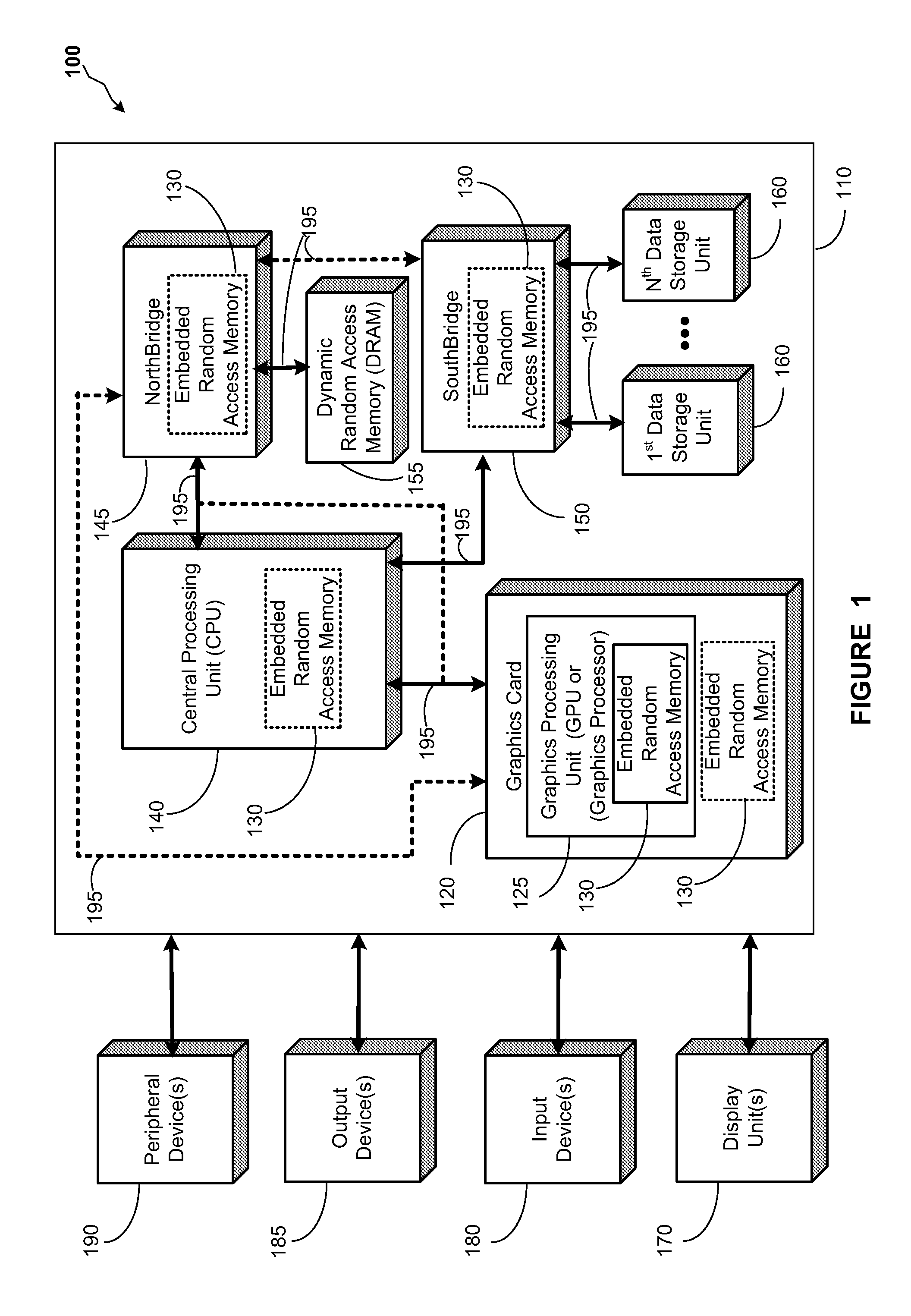

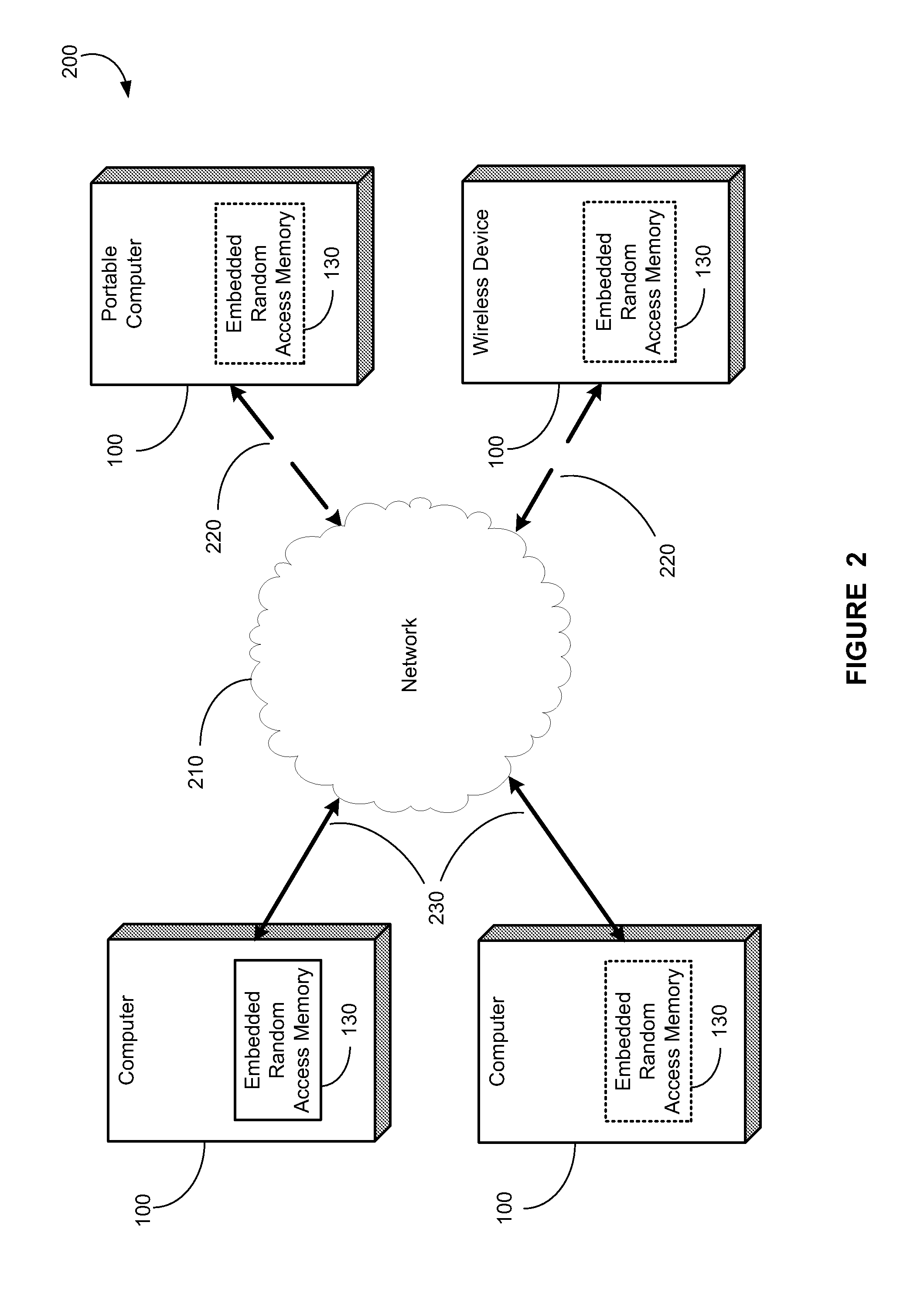

Embedded memory is any non-stand-alone memory. It is an integrated on-chip memory that sup-. ports the logic core to accomplish intended functions.

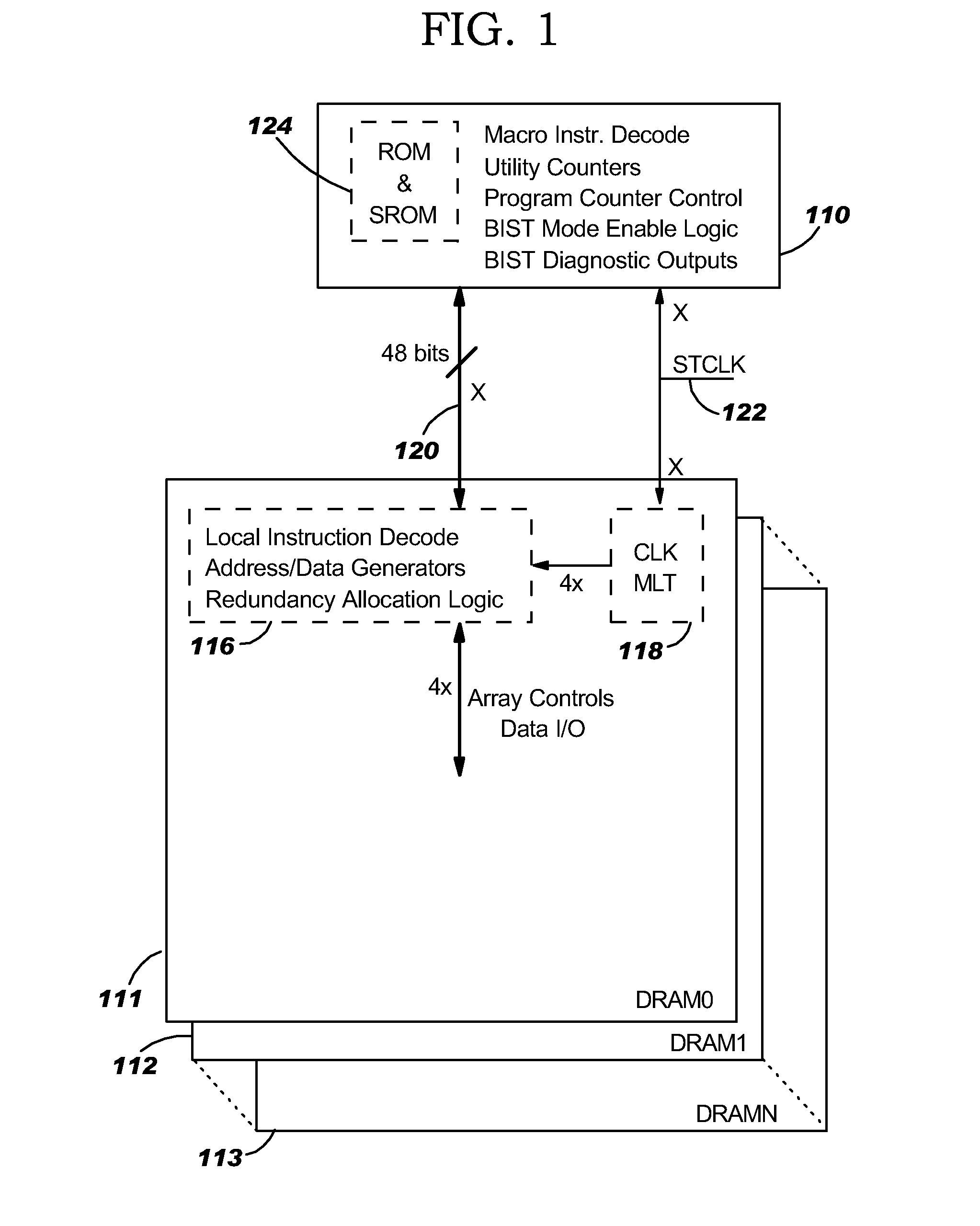

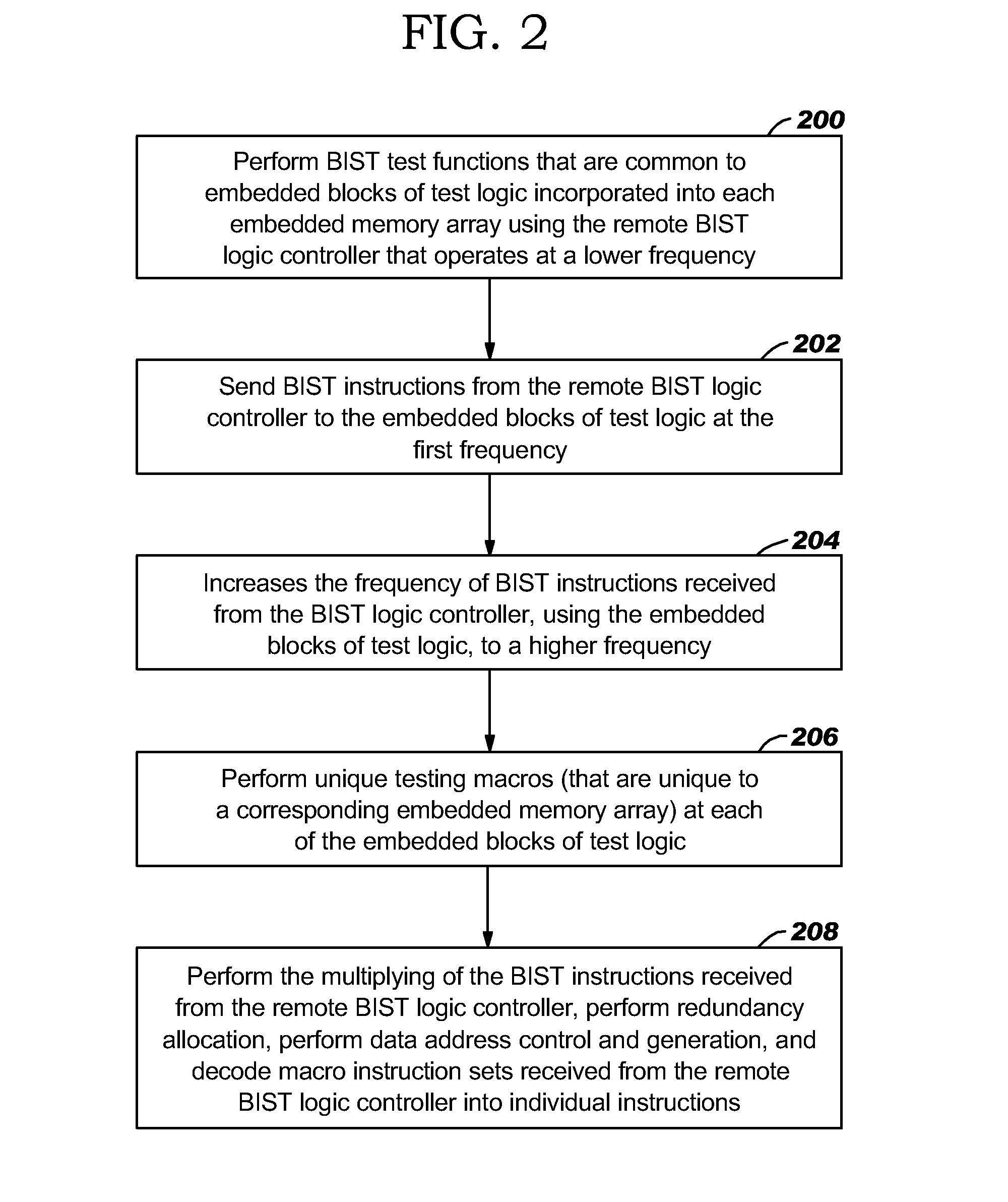

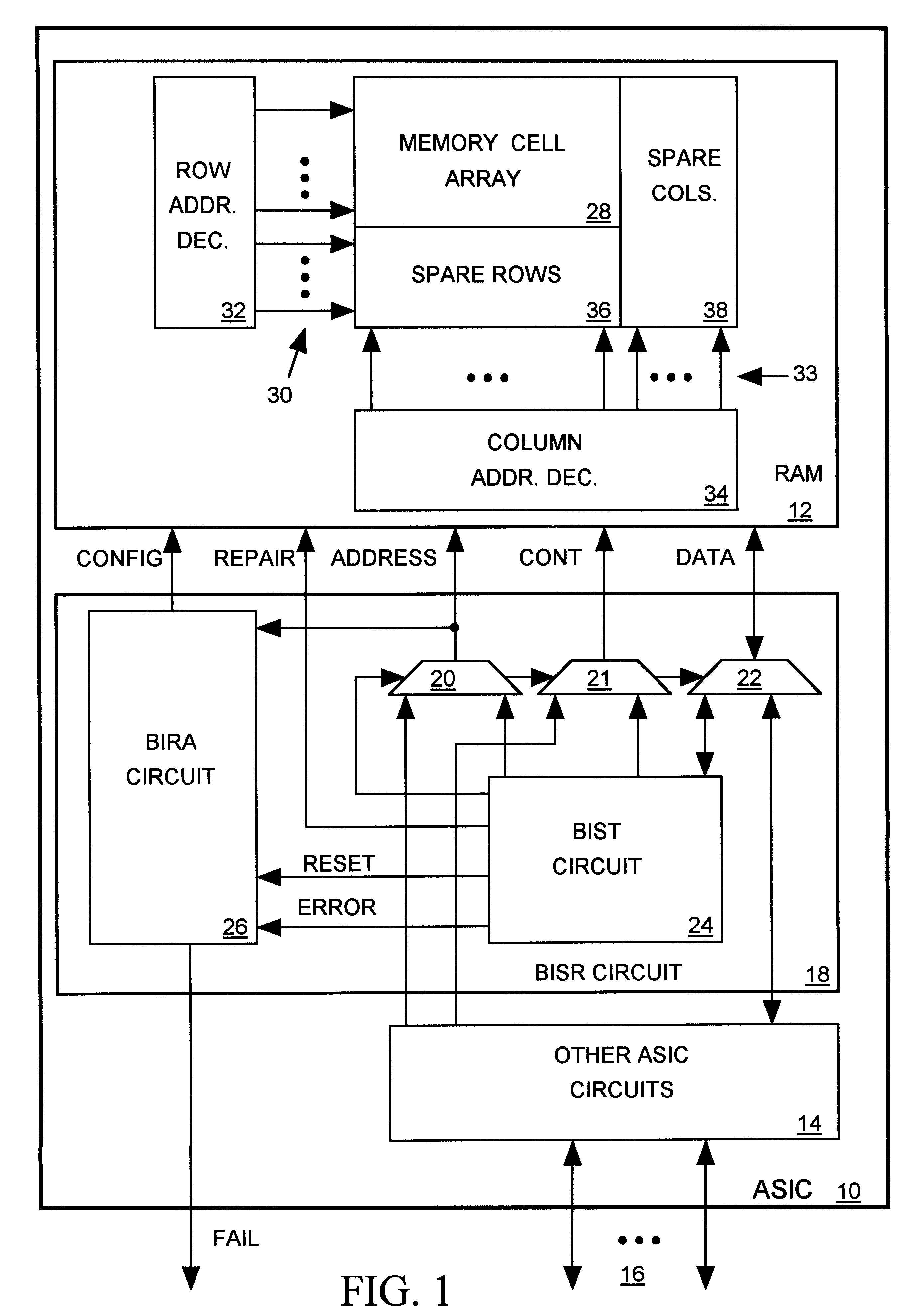

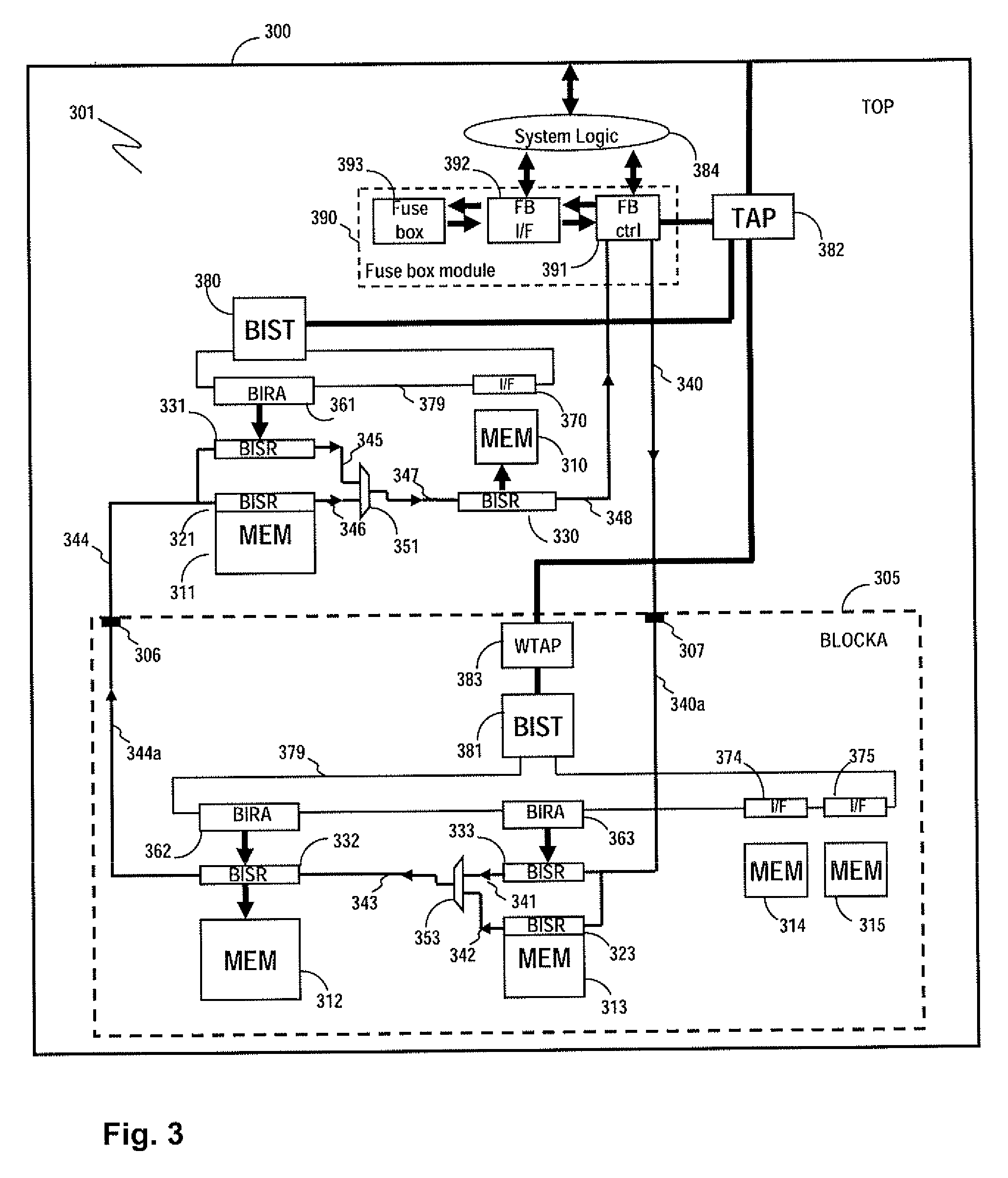

Hybrid built-in self test (BIST) architecture for embedded memory arrays and an associated method

ActiveUS20080178053A1Reduce frequencyMore test pattern flexibilityElectronic circuit testingFunctional testingSpecific testNormal mode

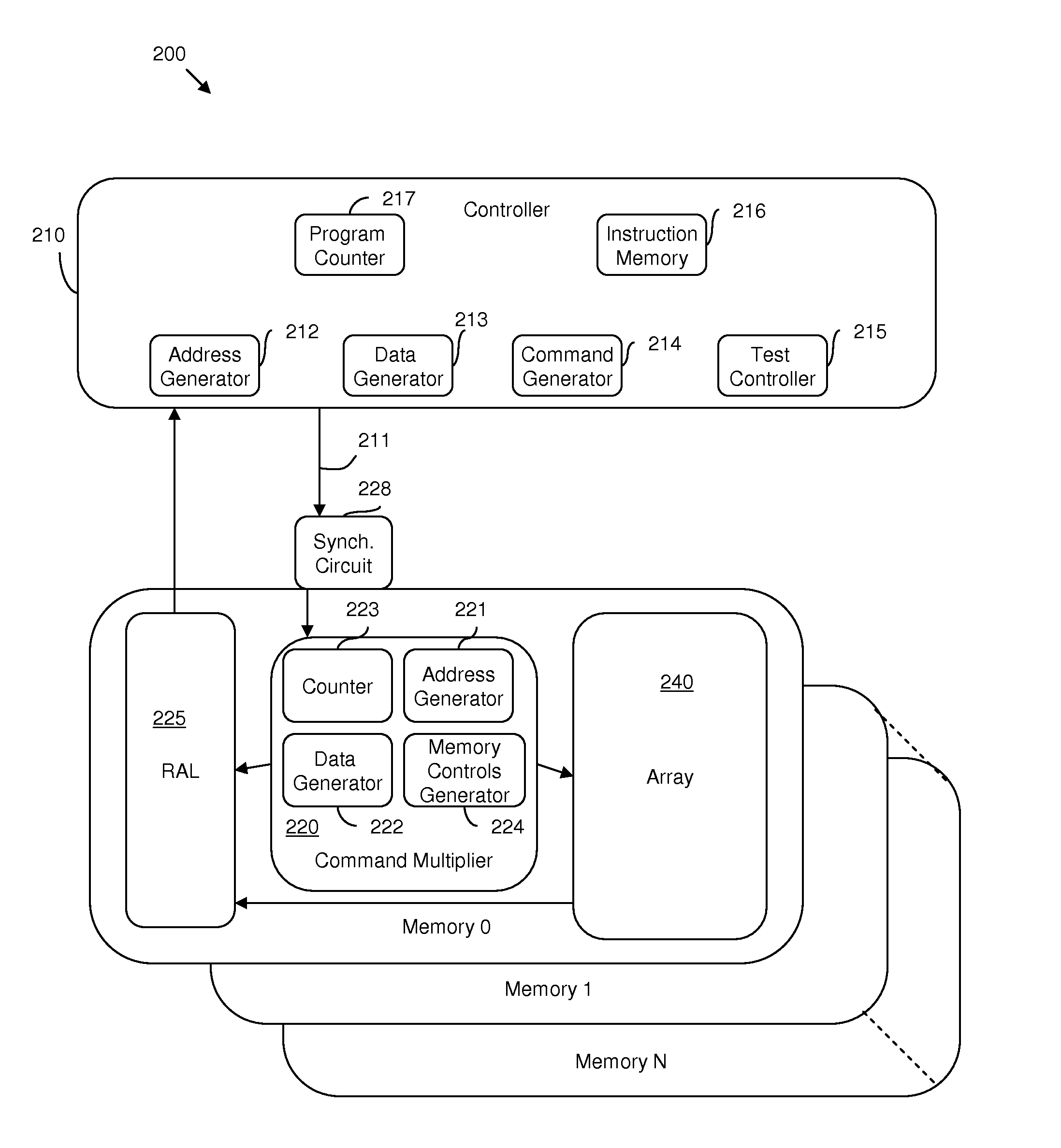

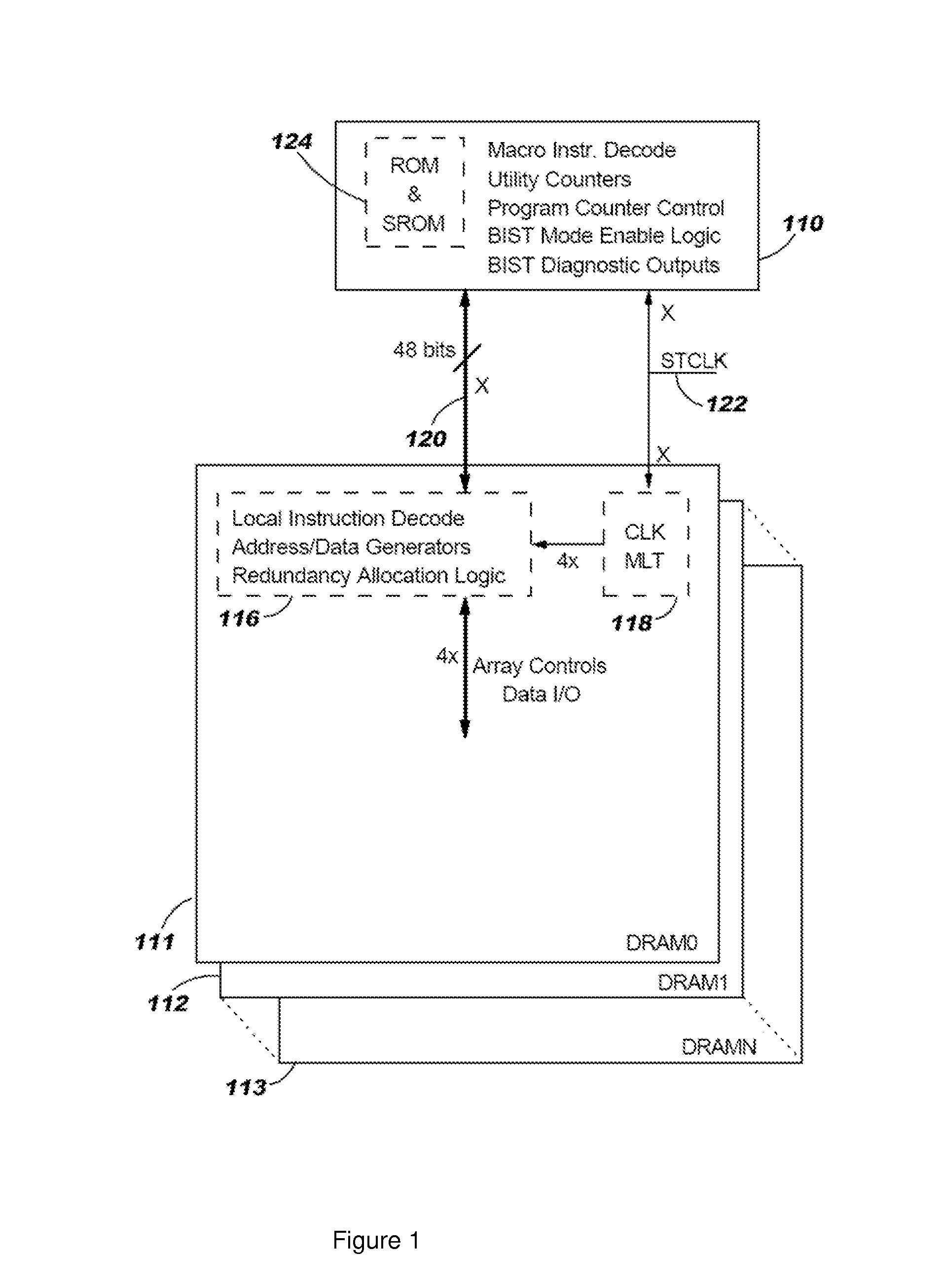

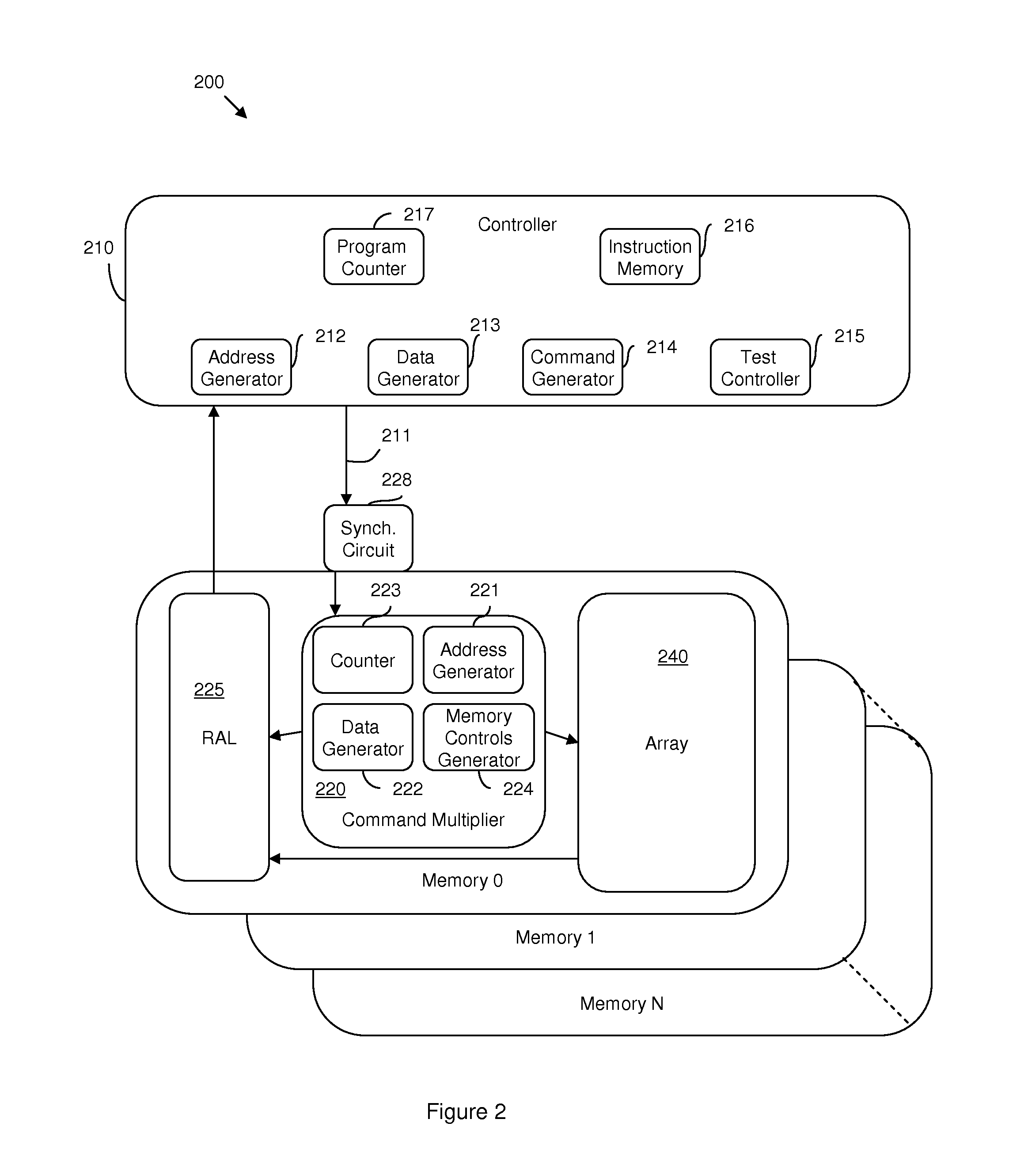

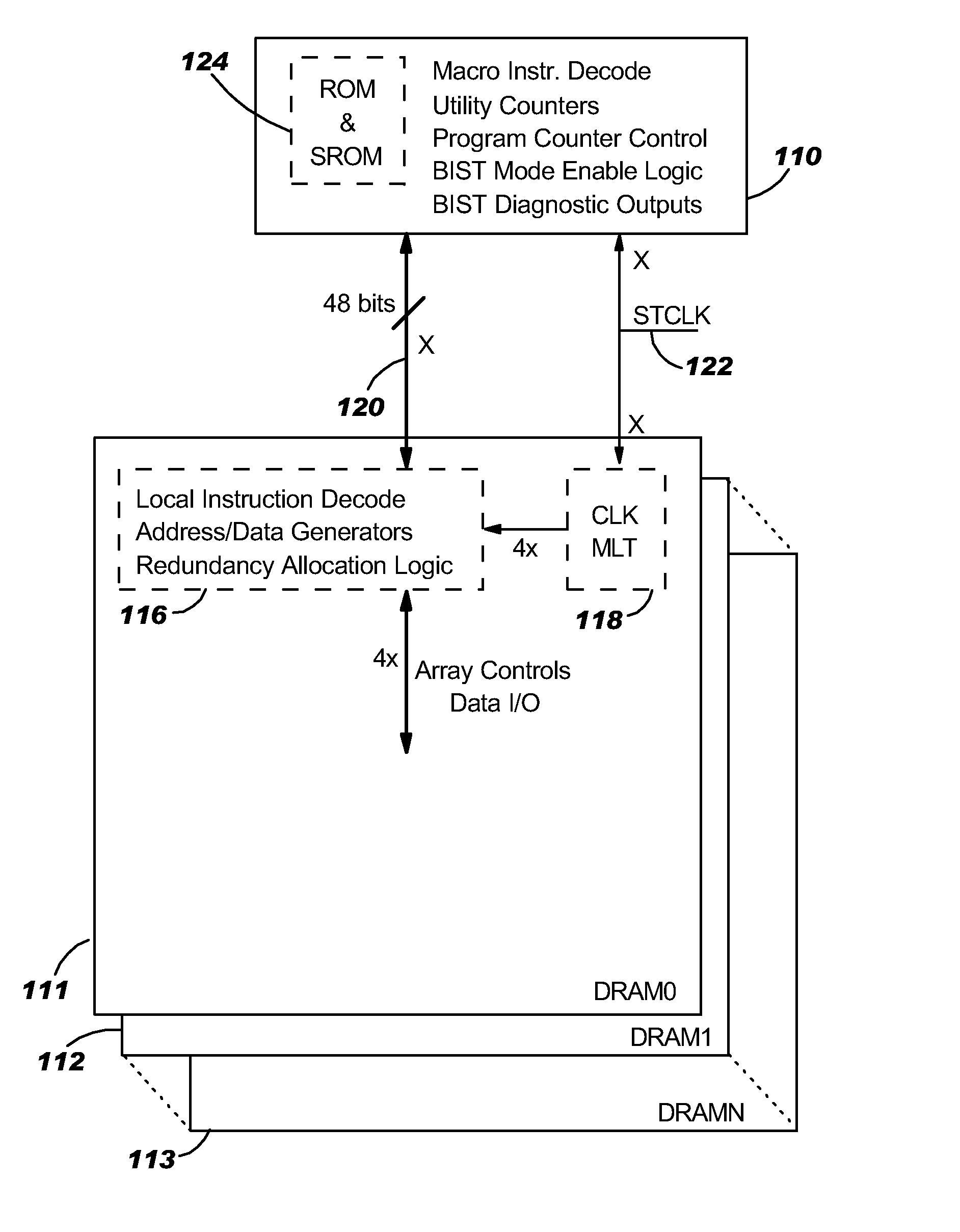

Disclosed are embodiments of a built-in self-test (BIST) architecture that incorporates a standalone controller that operates at a lower frequency to remotely perform test functions common to a plurality of embedded memory arrays. The architecture also incorporates command multipliers that are associated with the embedded memory arrays and that selectively operate in one of two different modes: a normal mode or a bypass mode. In the normal mode, instructions from the controller are multiplied so that memory array-specific test functions can be performed locally at the higher operating frequency of each specific memory array. Whereas, in the bypass mode, multiplication of the instructions is suspended so that memory array-specific test functions can be performed locally at the lower operating frequency of the controller. The ability to vary the frequency at which test functions are performed locally, allows for more test pattern flexibility.

Owner:META PLATFORMS INC

Remote bist for high speed test and redundancy calculation

InactiveUS20080215937A1Reduce frequencyIncrease processing frequencyDigital circuit testingFunctional testingLow speedSpeed test

Disclosed in a hybrid built-in self test (BIST) architecture for embedded memory arrays that segments BIST functionality into remote lower-speed executable instructions and local higher-speed executable instructions. A standalone BIST logic controller operates at a lower frequency and communicates with a plurality of embedded memory arrays using a BIST instruction set. A block of higher-speed test logic is incorporated into each embedded memory array under test and locally processes BIST instructions received from the standalone BIST logic controller at a higher frequency. The higher-speed test logic includes a multiplier for increasing the frequency of the BIST instructions from the lower frequency to the higher frequency. The standalone BIST logic controller enables a plurality of higher-speed test logic structures in a plurality of embedded memory arrays.

Owner:META PLATFORMS INC

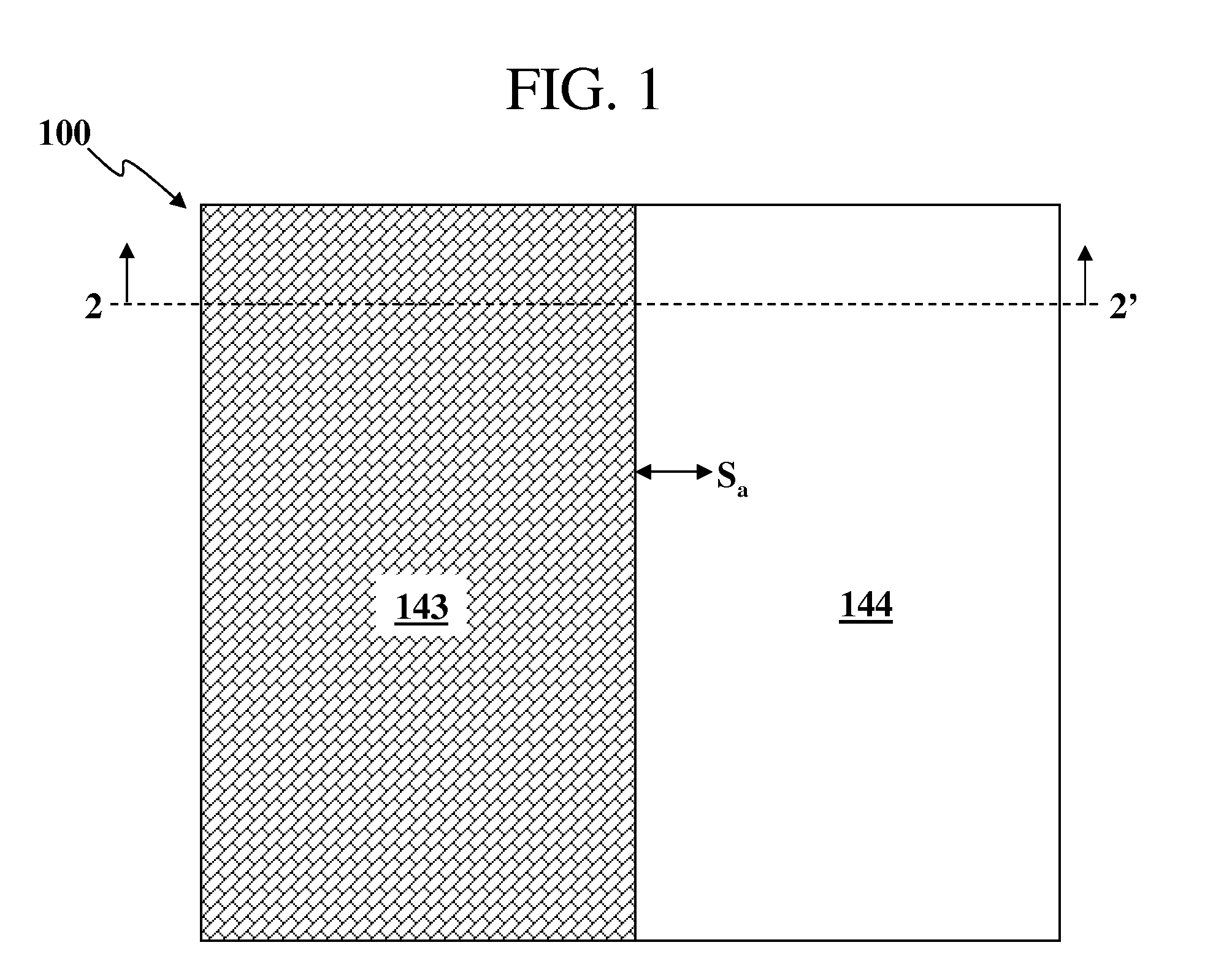

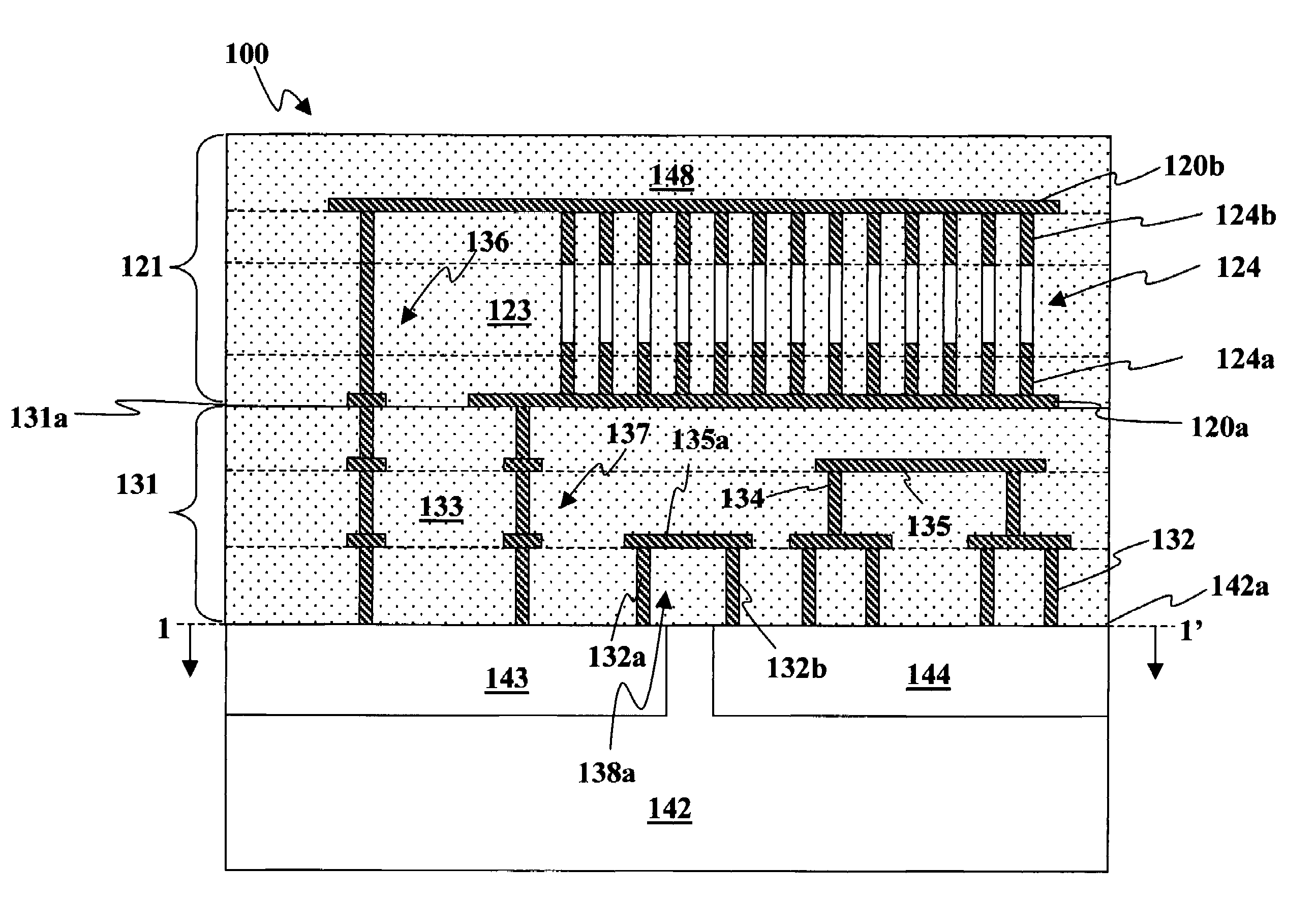

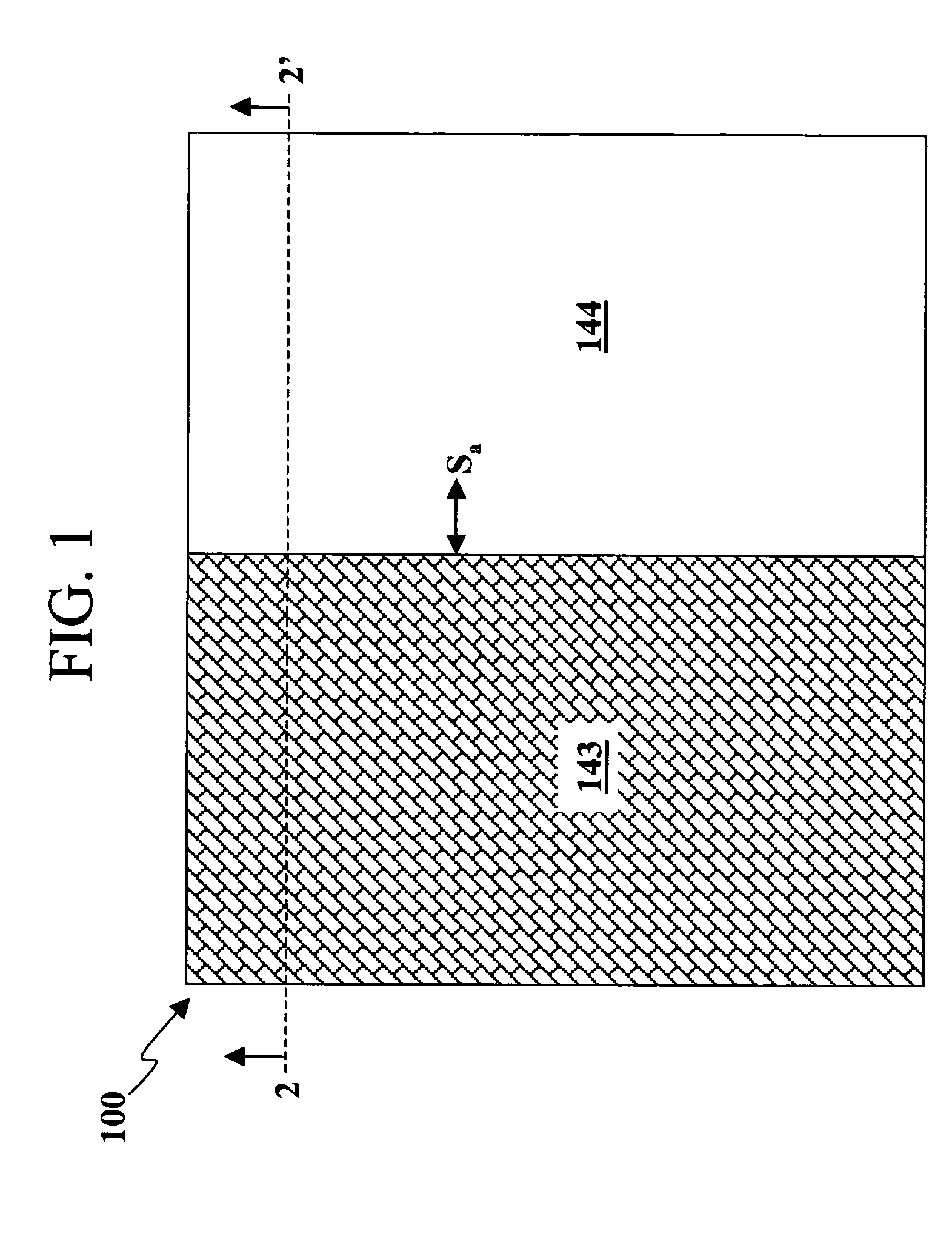

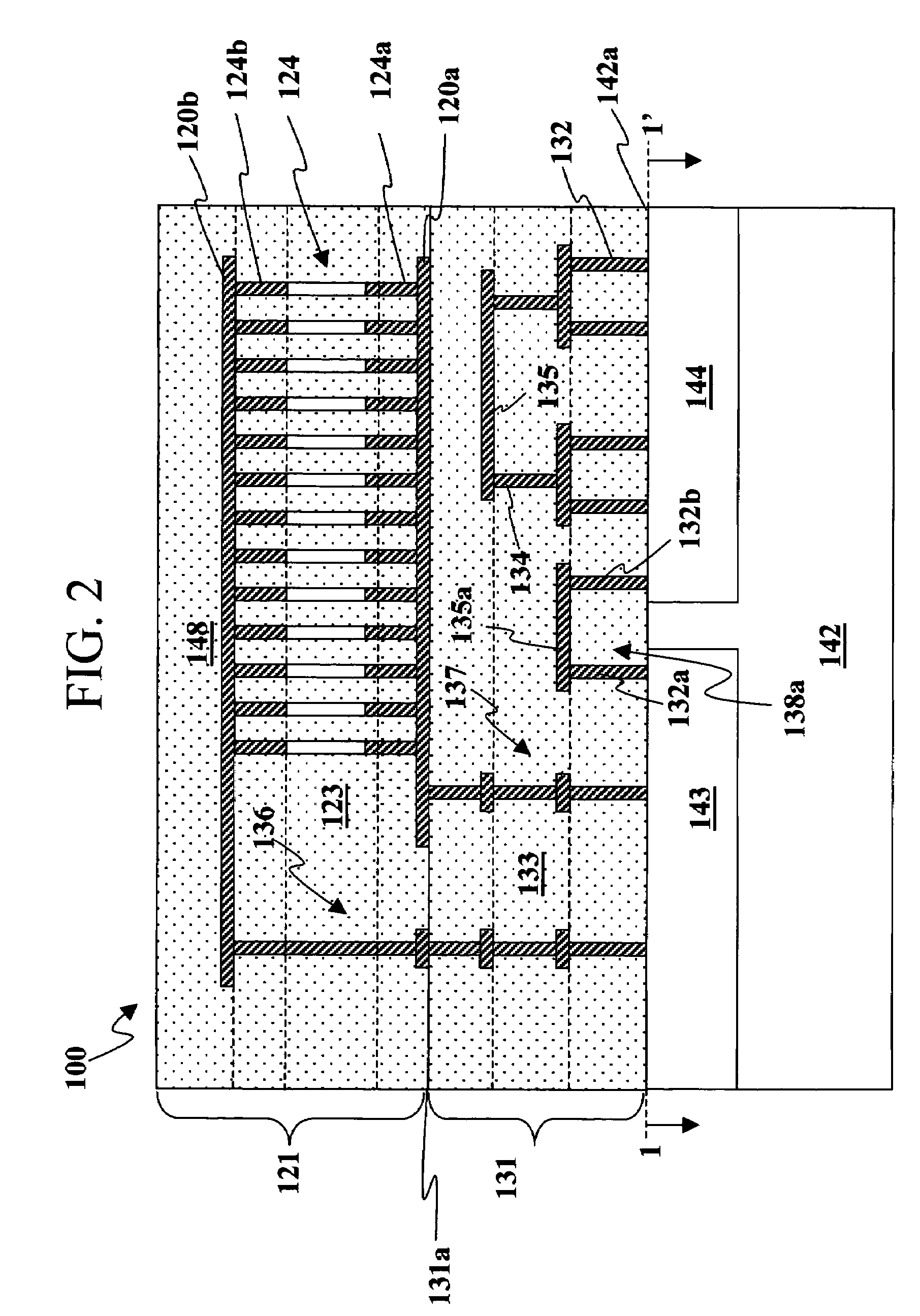

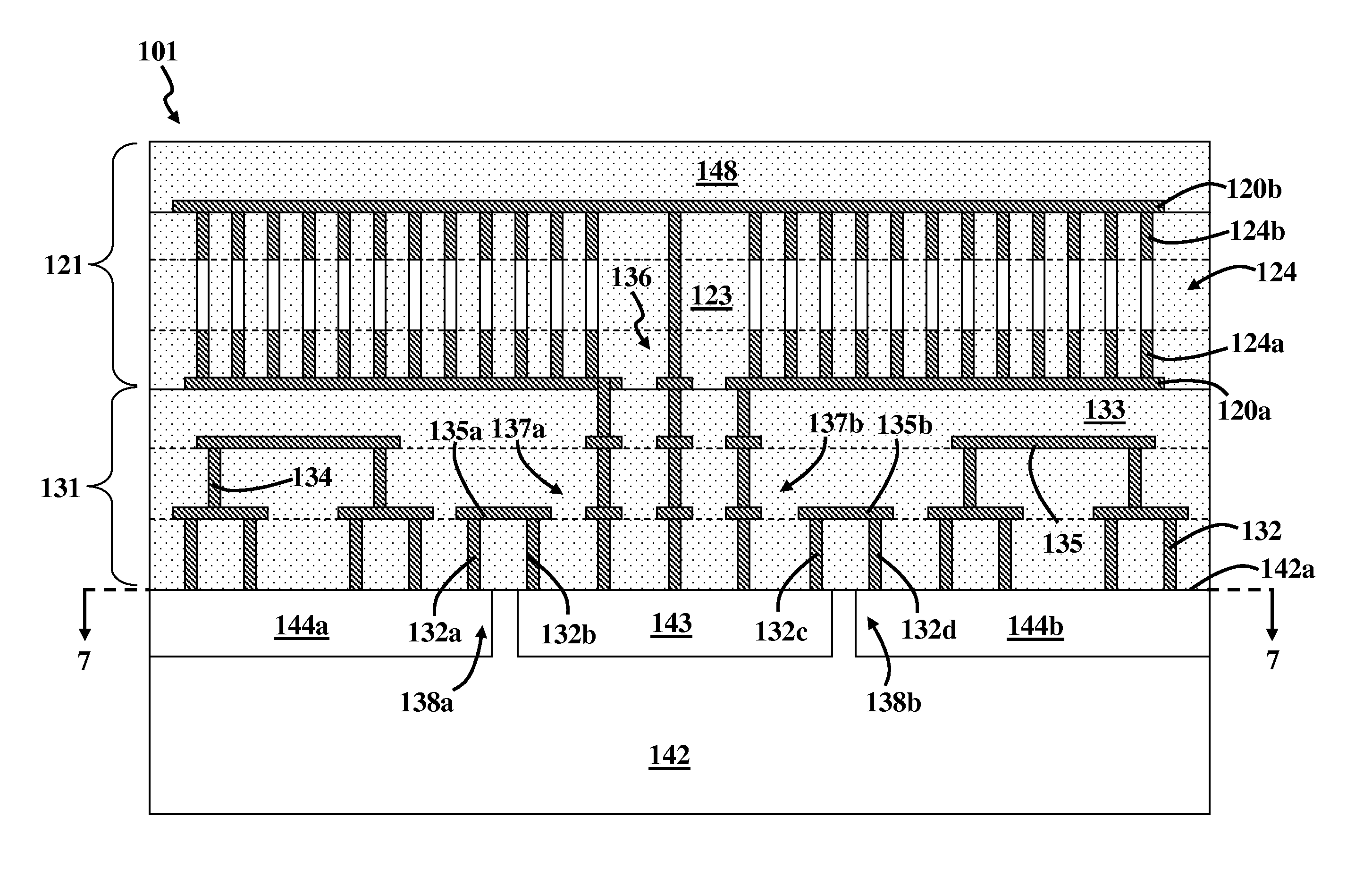

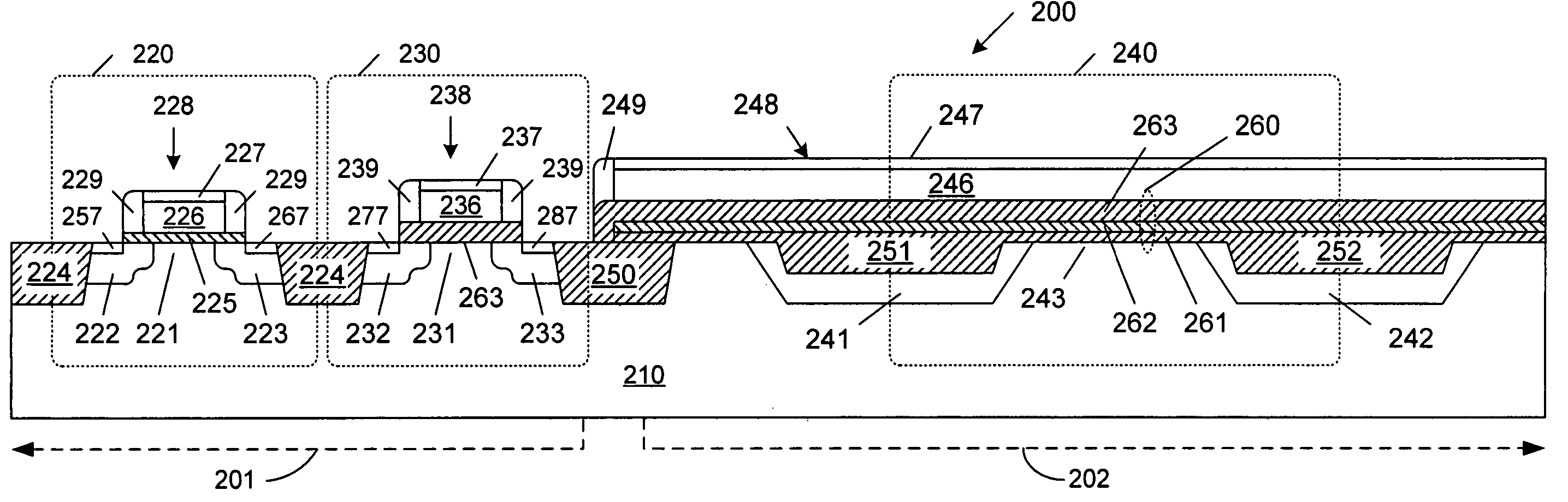

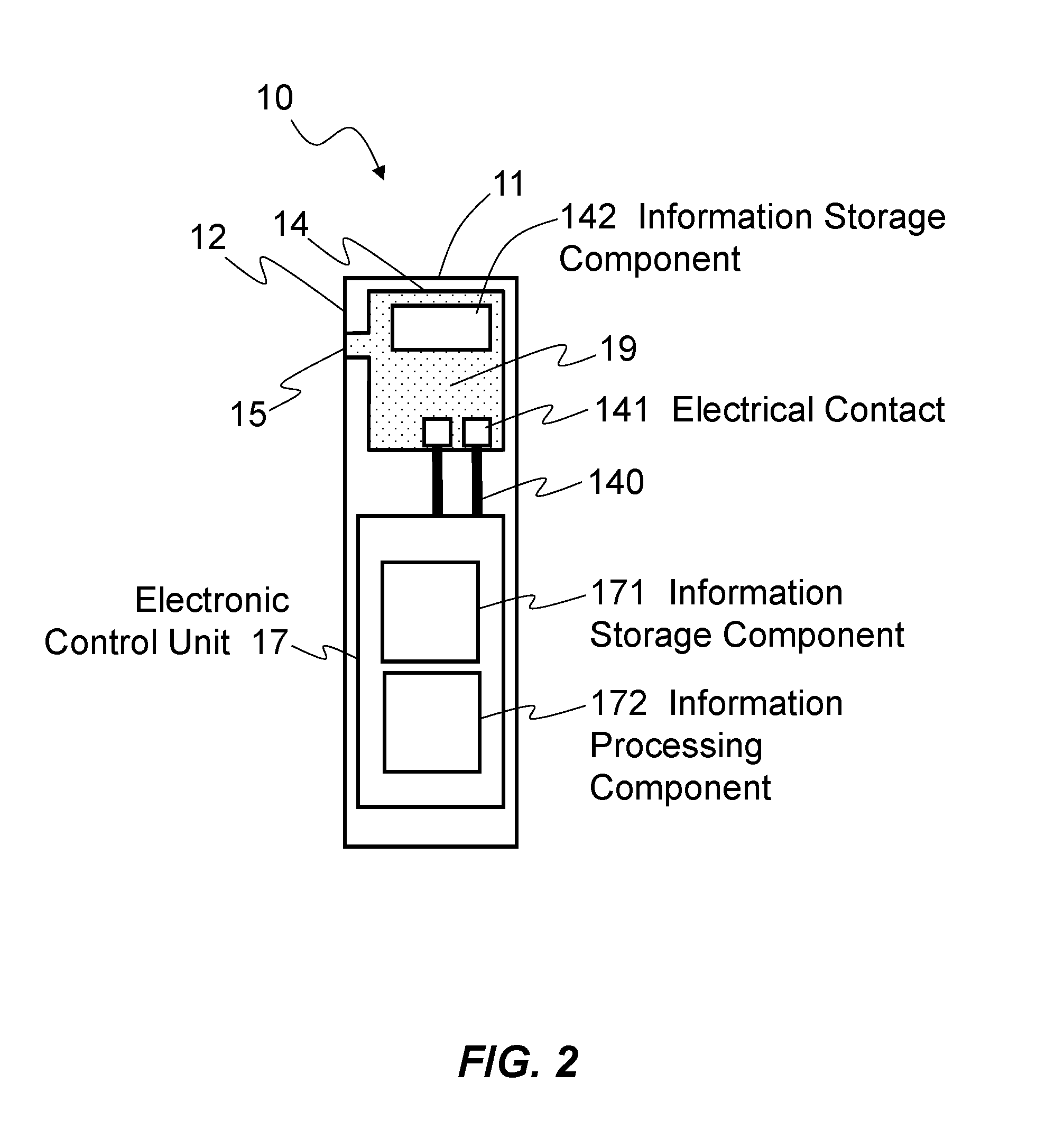

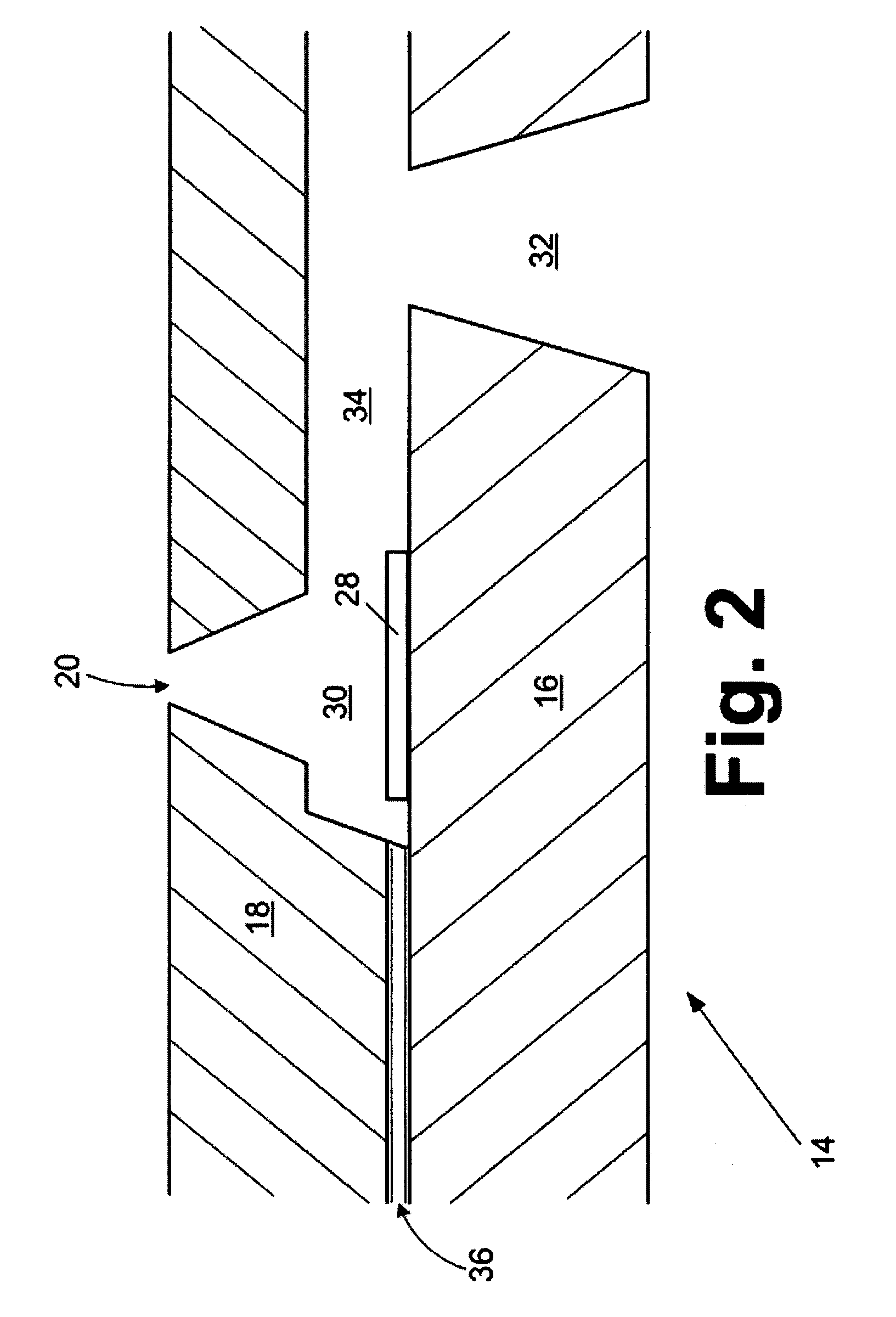

Electronic circuit with embedded memory

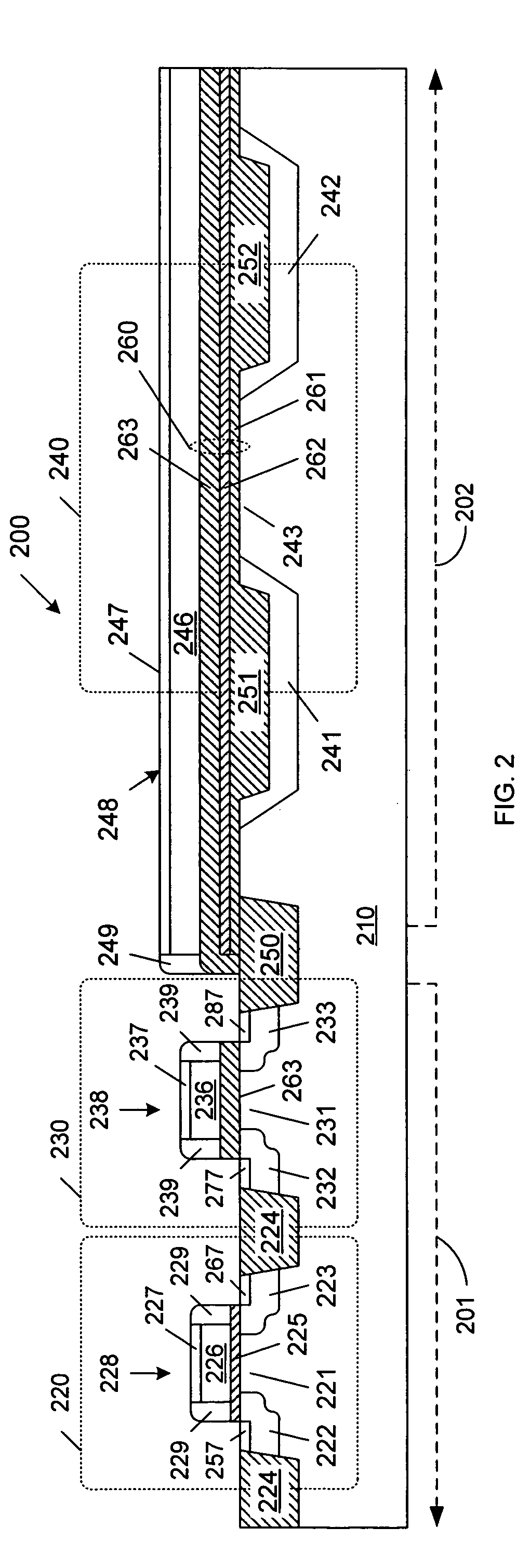

InactiveUS20080048327A1Semiconductor/solid-state device detailsSolid-state devicesMemory circuitsSemiconductor

Owner:BESANG

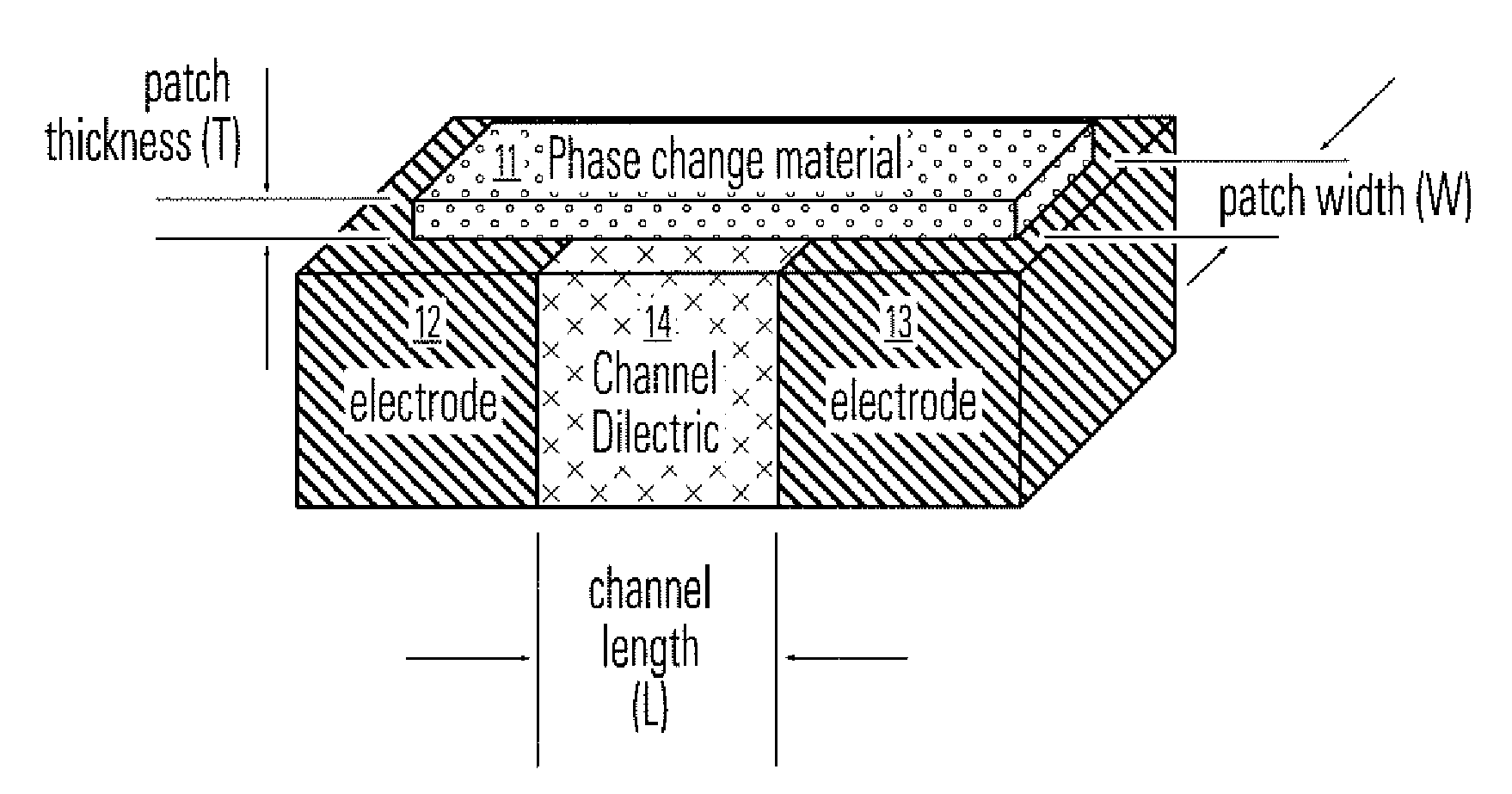

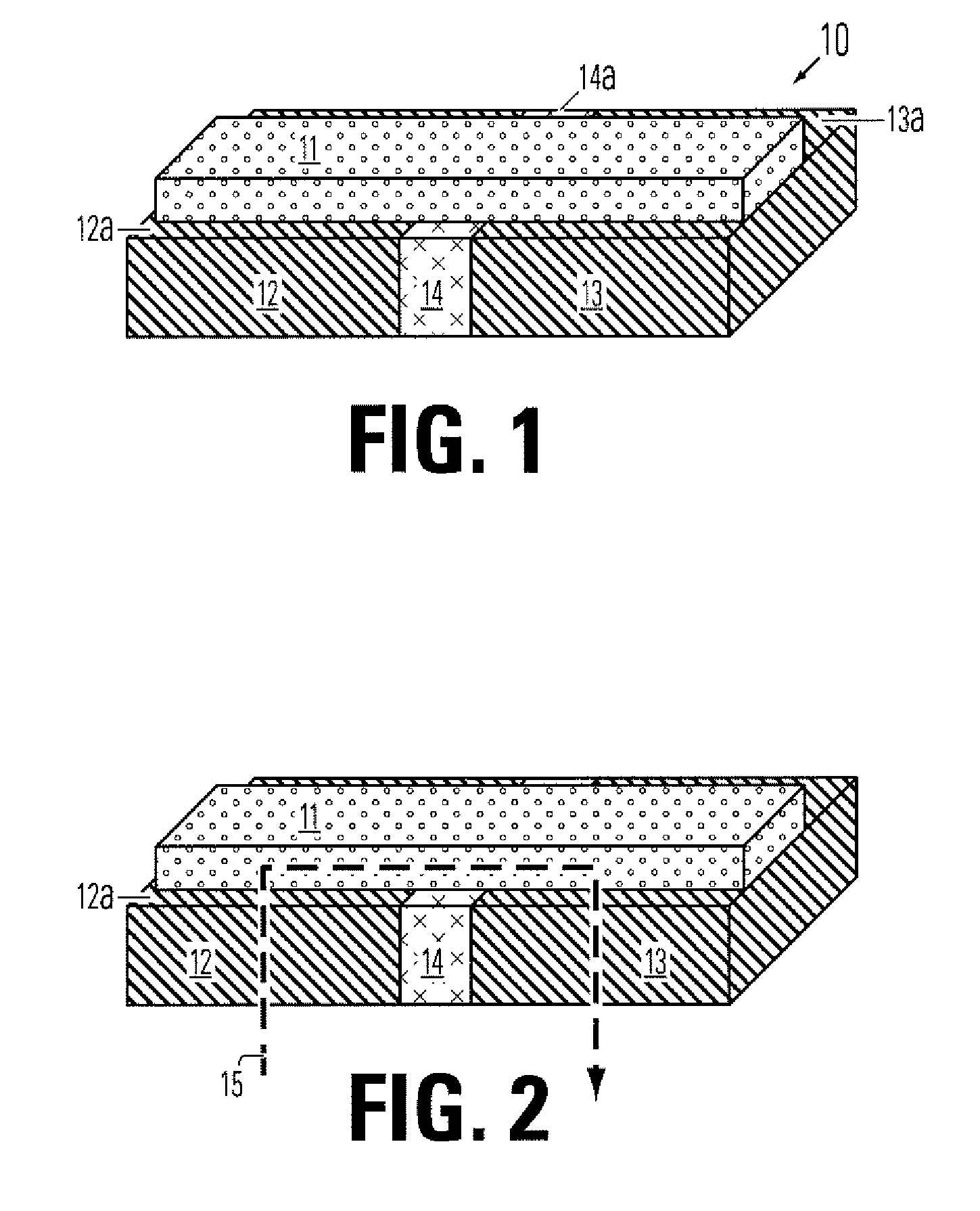

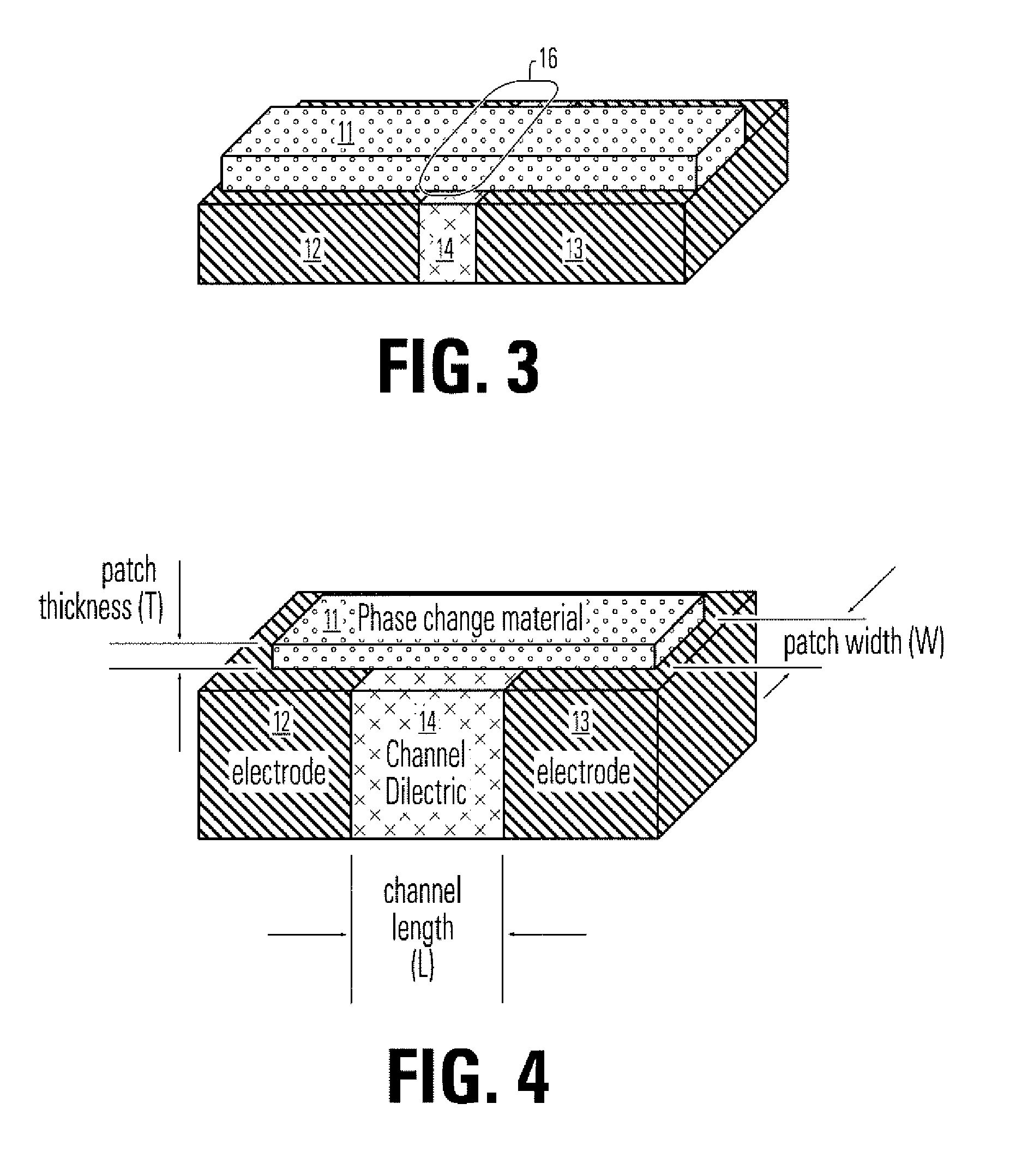

Self-aligned, embedded phase change ram and manufacturing method

ActiveUS20060284158A1Simple structureReduce power consumptionSolid-state devicesDigital storageElectrical conductorEngineering

An integrated circuit with an embedded memory comprises a substrate and a plurality of conductor layers arranged for interconnecting components of the integrated circuit. An intermediate layer in the plurality of conductor layers includes a first electrode having a top surface, a second electrode having a top surface, an insulating member between the first electrode and the second electrode. A bridge overlies the intermediate layer between the first and second electrodes across the insulating member, wherein the bridge comprises a programmable resistive memory material, such as a phase change material. A conductor in at least one layer in the plurality of conductor layers over said intermediate layer is connected to said bridge.

Owner:MACRONIX INT CO LTD

Electronic circuit with embedded memory

InactiveUS7633162B2Semiconductor/solid-state device detailsSolid-state devicesMemory circuitsSemiconductor

Owner:BESANG

Electronic circuit with embedded memory

InactiveUS20100133695A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringMemory circuits

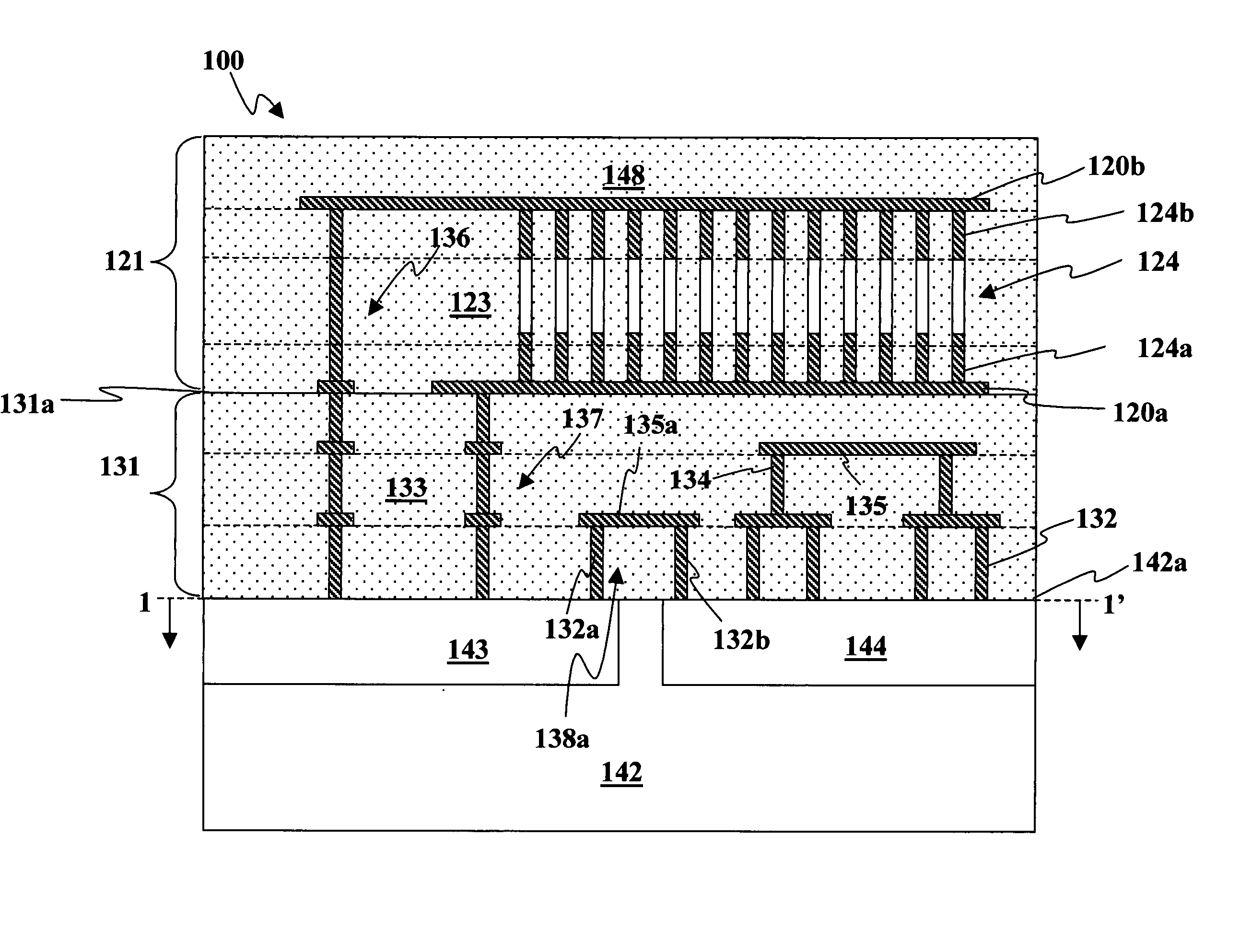

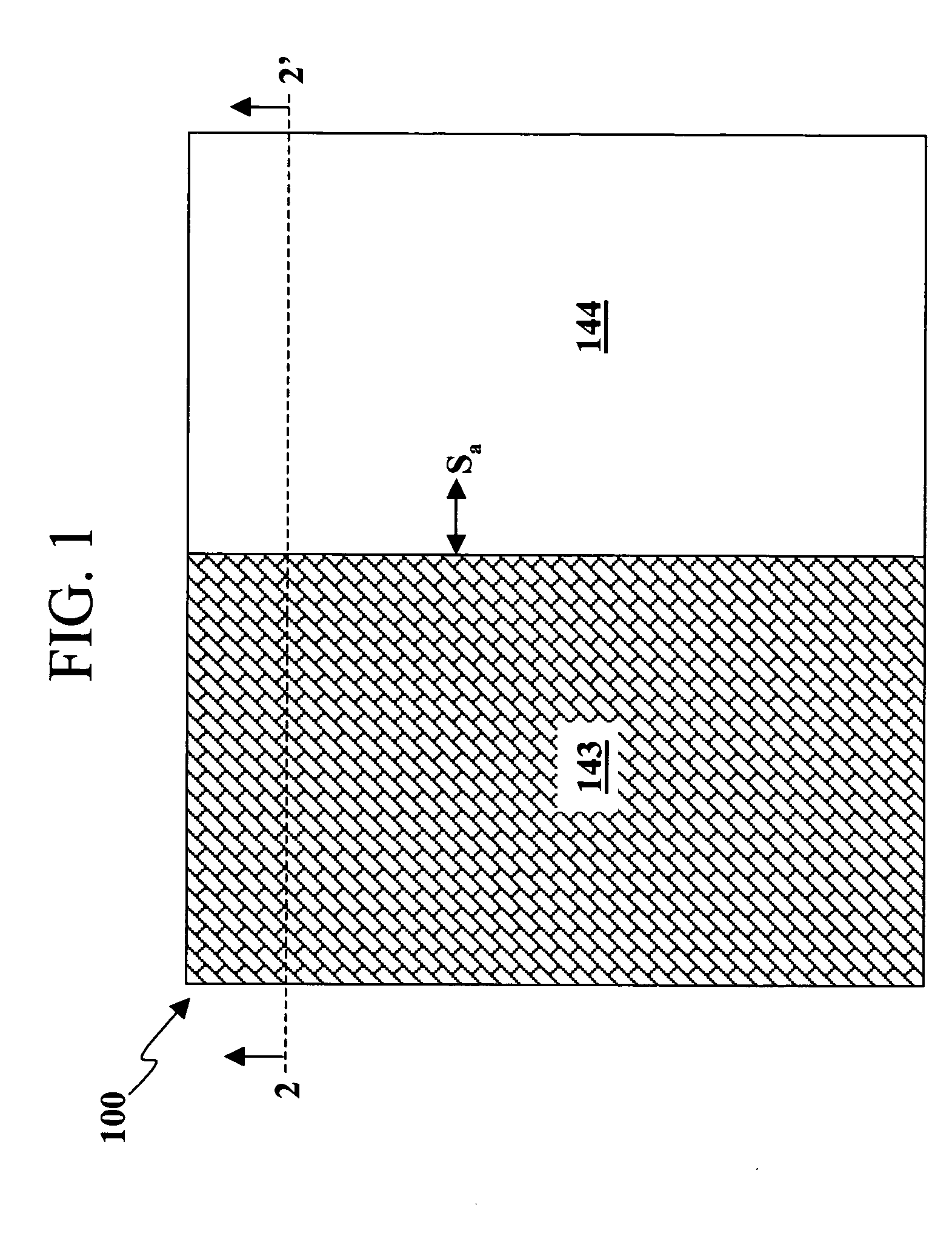

Circuitry includes first and second circuits spaced apart by an interconnect region. The interconnect region includes a first interconnect, and the second circuit includes a stack of semiconductor layers. The first interconnect extends between the first and second circuits to provide communication therebetween. The second circuit operates as a memory circuit.

Owner:BESANG

Electronic circuit with embedded memory

InactiveUS20050218521A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringMemory circuits

Circuitry includes first and second circuits spaced apart by an interconnect region. The interconnect region includes a first interconnect and the second circuit includes a stack of semiconductor layers. The first interconnect extends between the first and second circuits to provide communication therebetween. The second circuit operates as a memory circuit.

Owner:BESANG

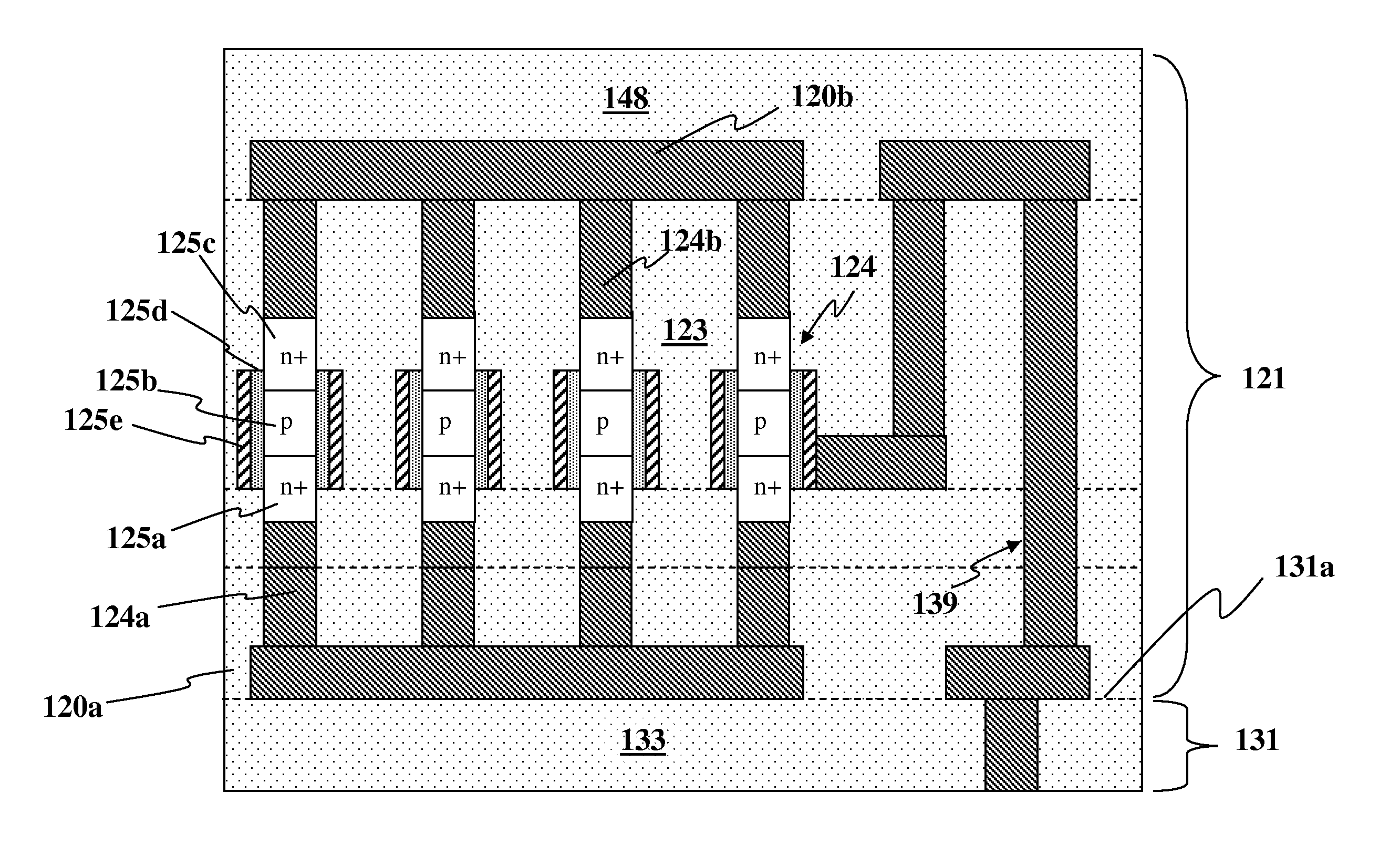

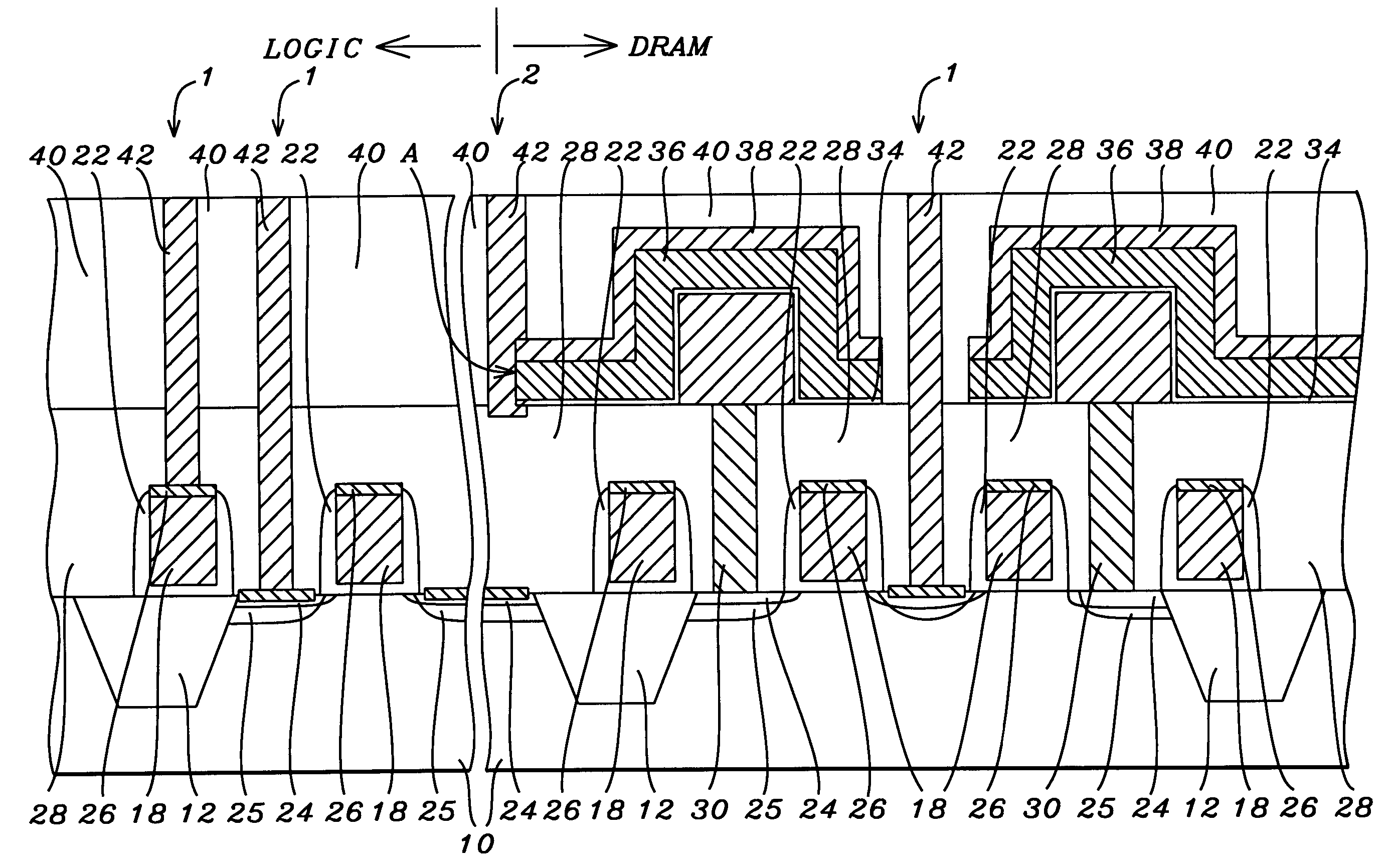

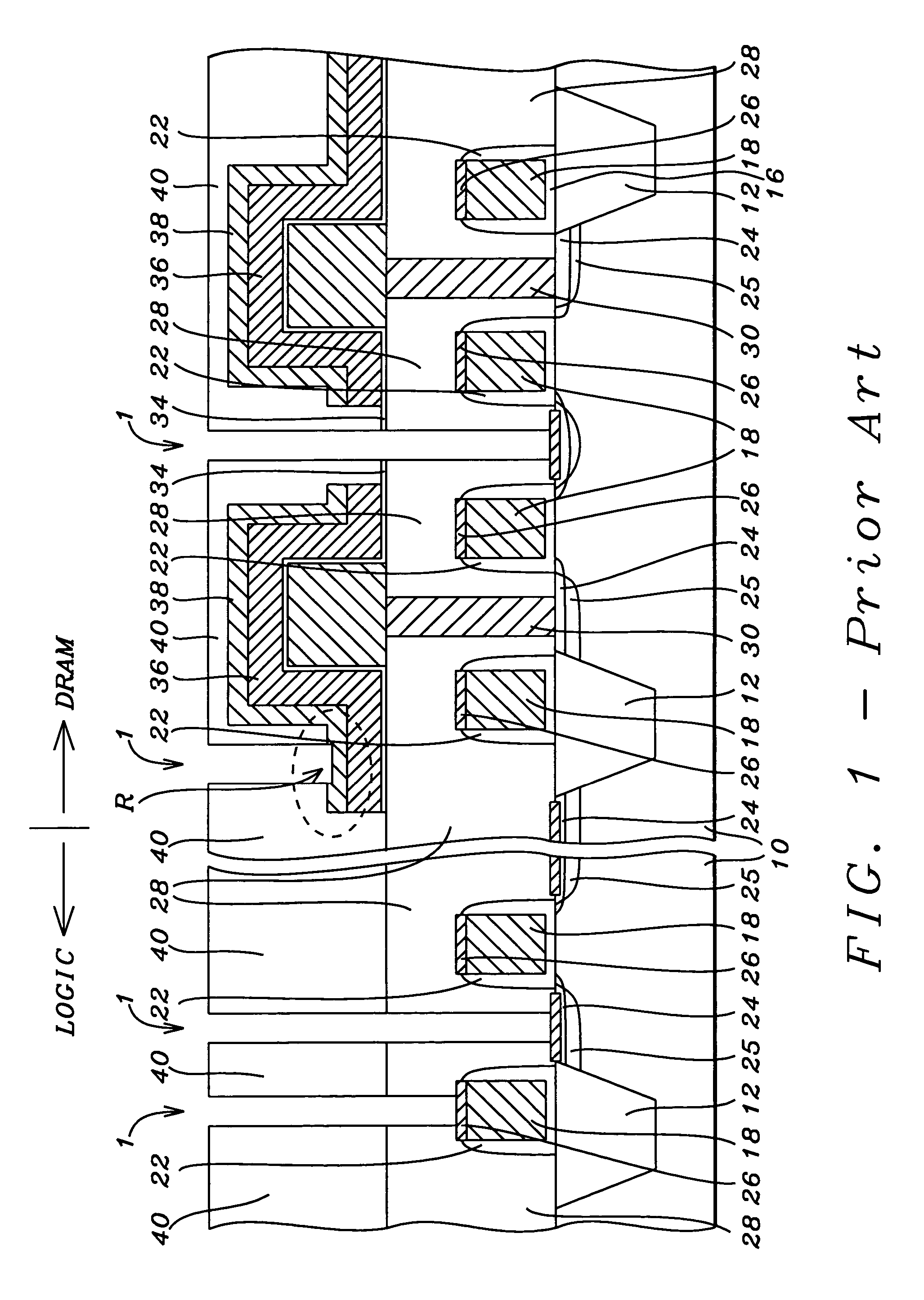

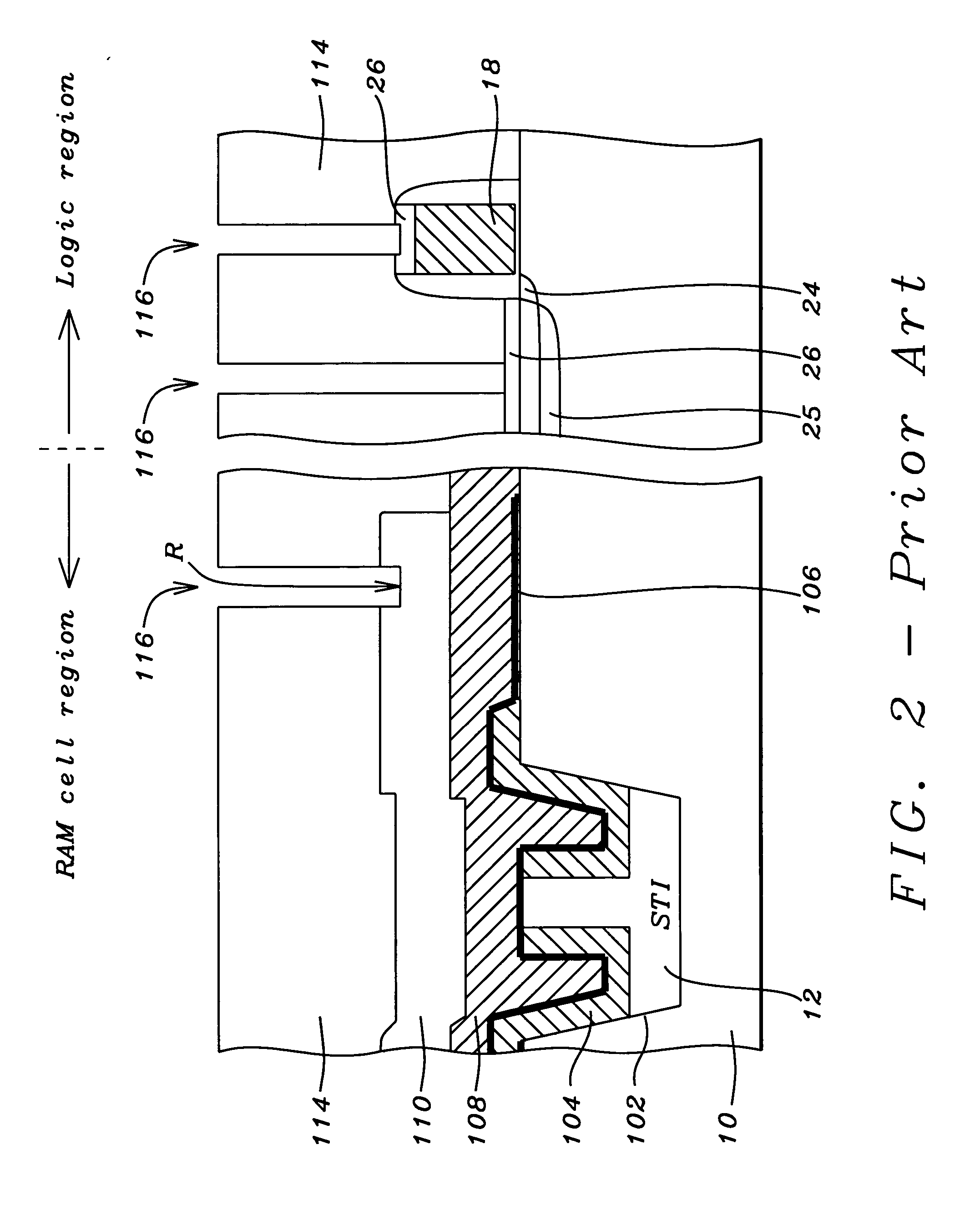

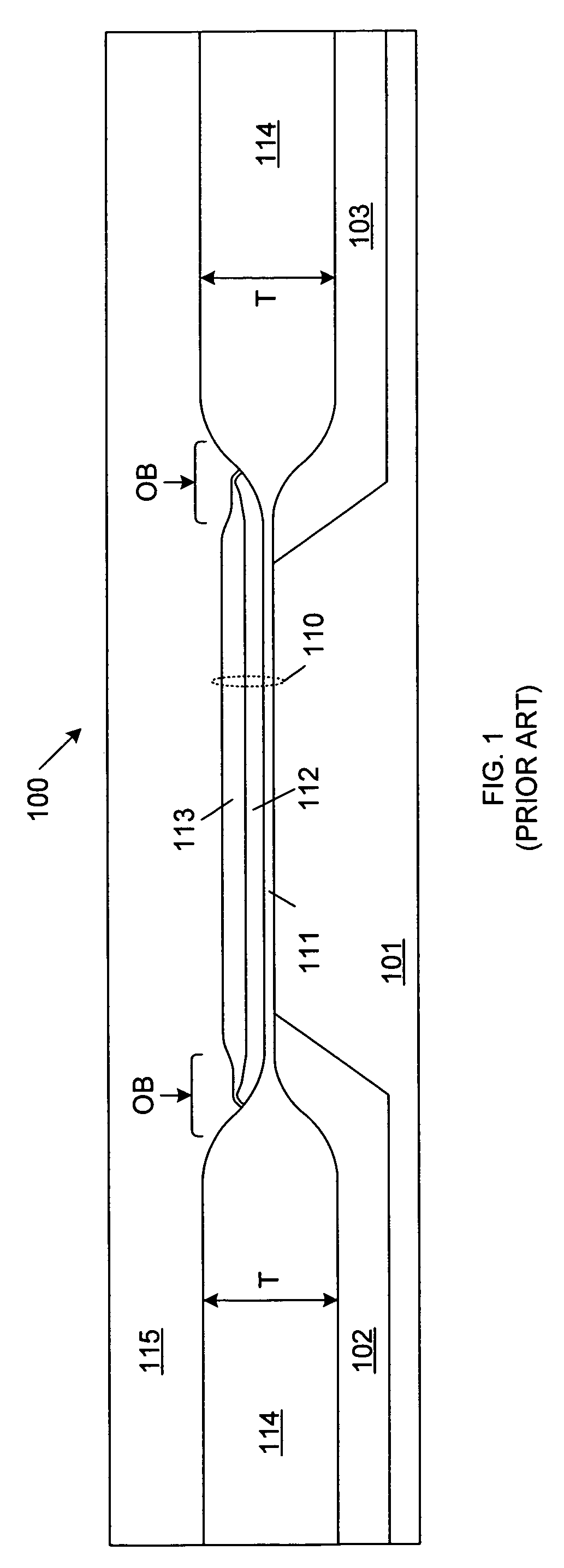

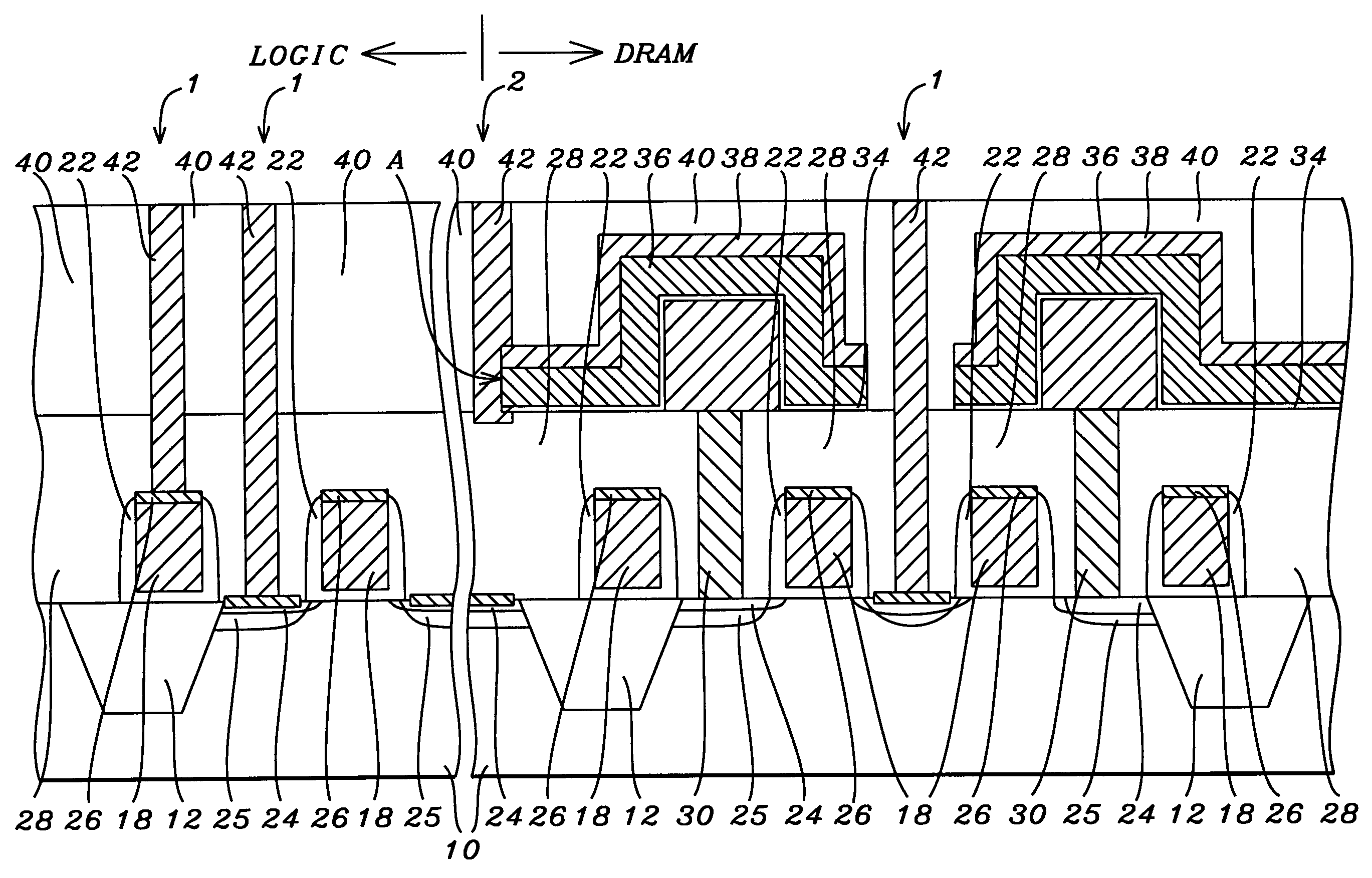

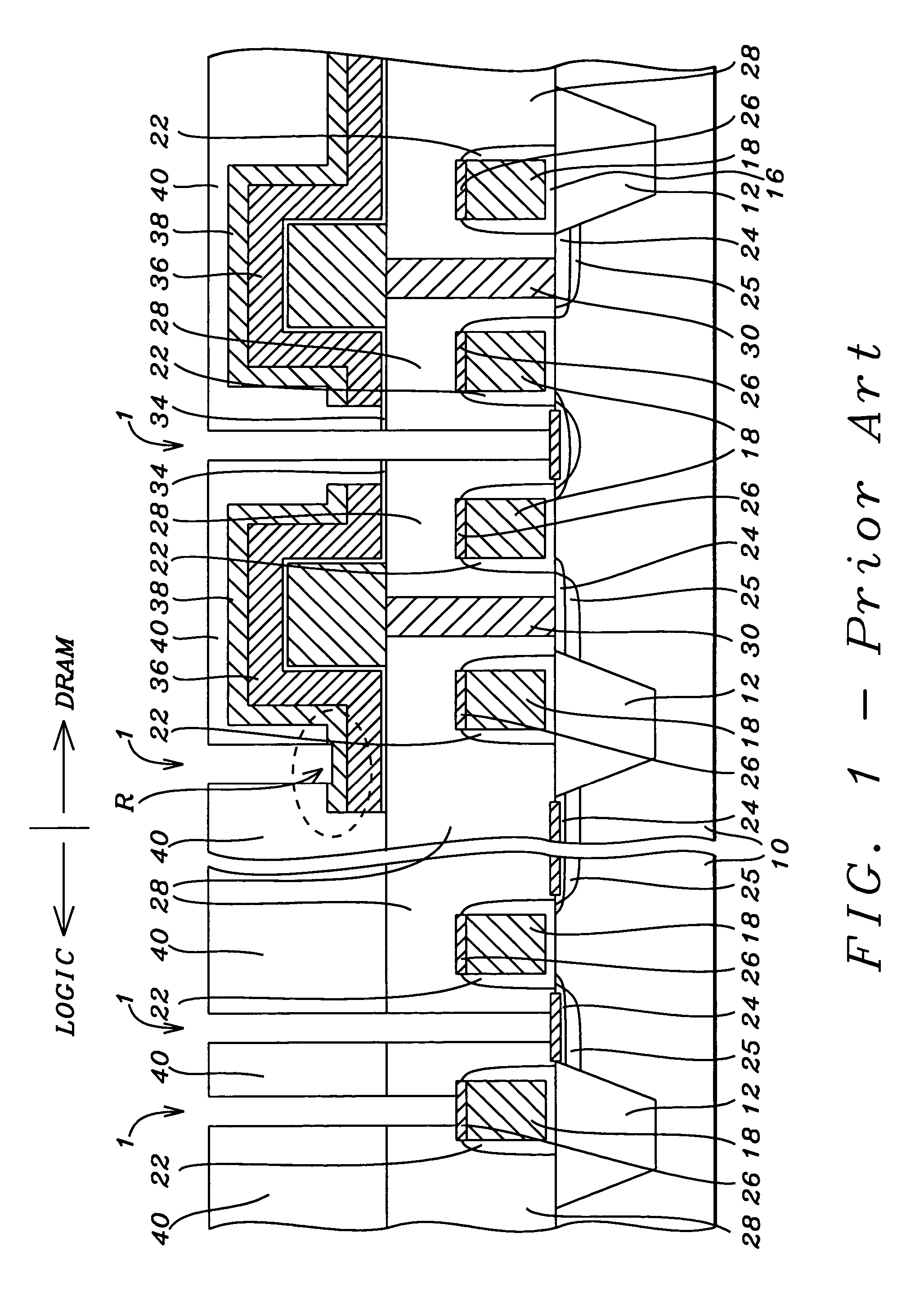

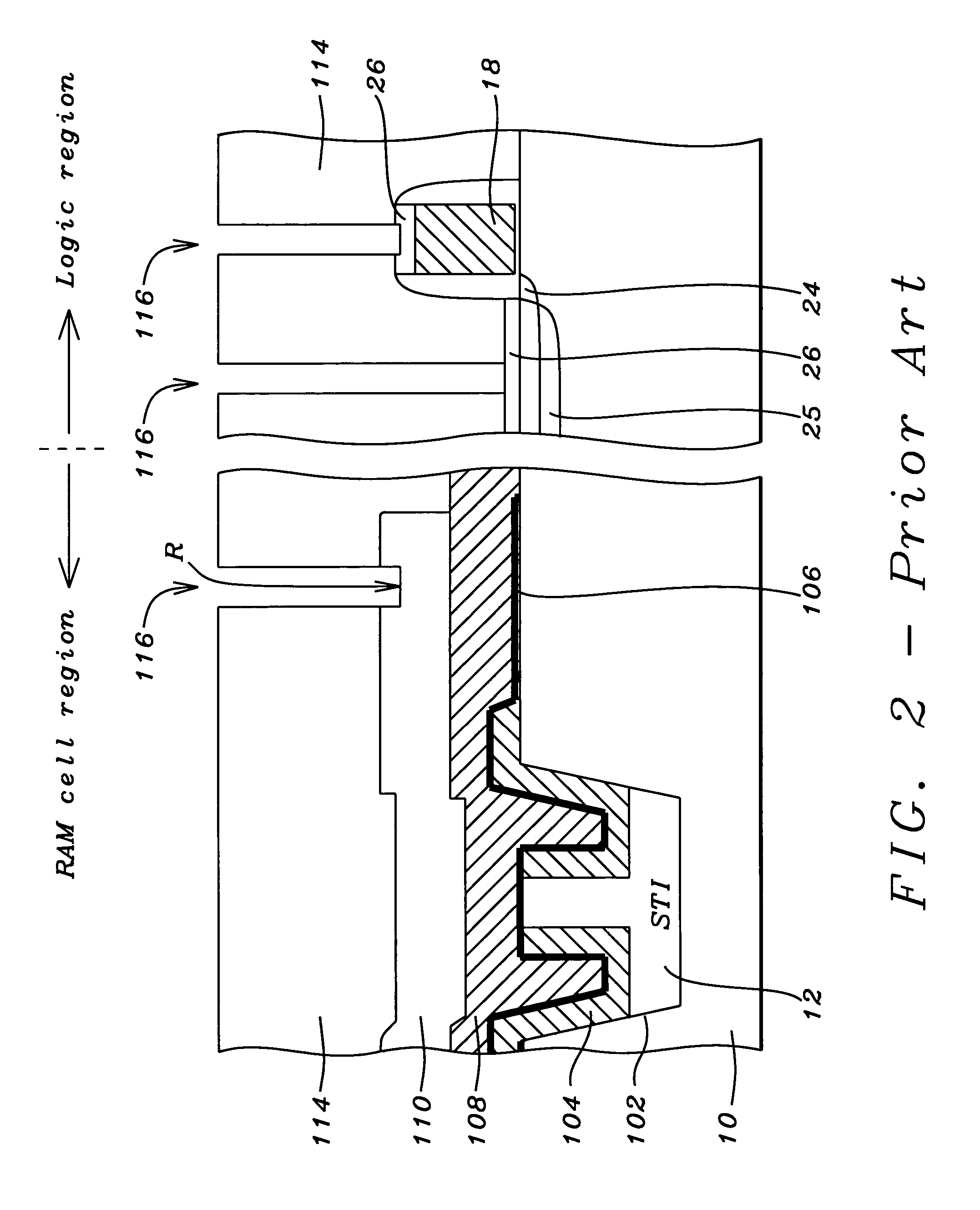

Structure for reducing leakage currents and high contact resistance for embedded memory and method for making same

ActiveUS20050093147A1More alignment toleranceReduce manufacturing costTransistorSemiconductor/solid-state device detailsDrain currentCapacitor

A method for fabricating an insulating layer having contact openings of varying depths for logic / DRAM circuits is achieved using a single mask and etch step. After forming stacked or trench capacitors, a planar insulating layer is formed. Contact openings are etched in the planar insulating layer to the substrate, and contact openings that extend over the edge of the stacked or trench capacitor top electrode, having an ARC, are etched using a novel mask design and a single etching step. This allows one to make contacts to the substrate without overetching while making low-resistance contacts to the sidewall of the capacitor top electrode. In the trench capacitor open areas are formed to facilitate making contact openings that extend over the top electrode. A series of contact openings that are skewed or elongated also improve the latitude in alignment tolerance.

Owner:TAIWAN SEMICON MFG CO LTD

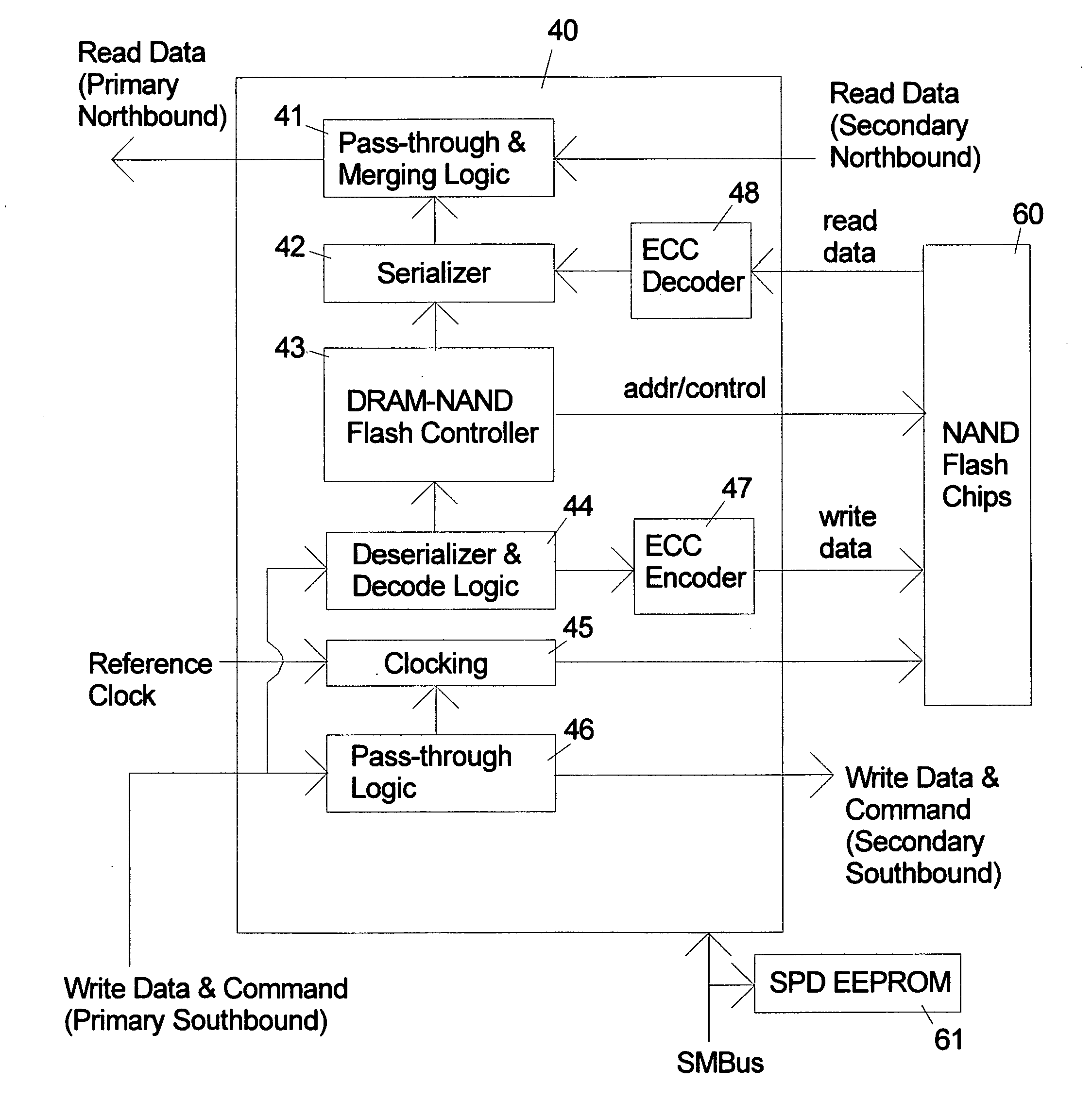

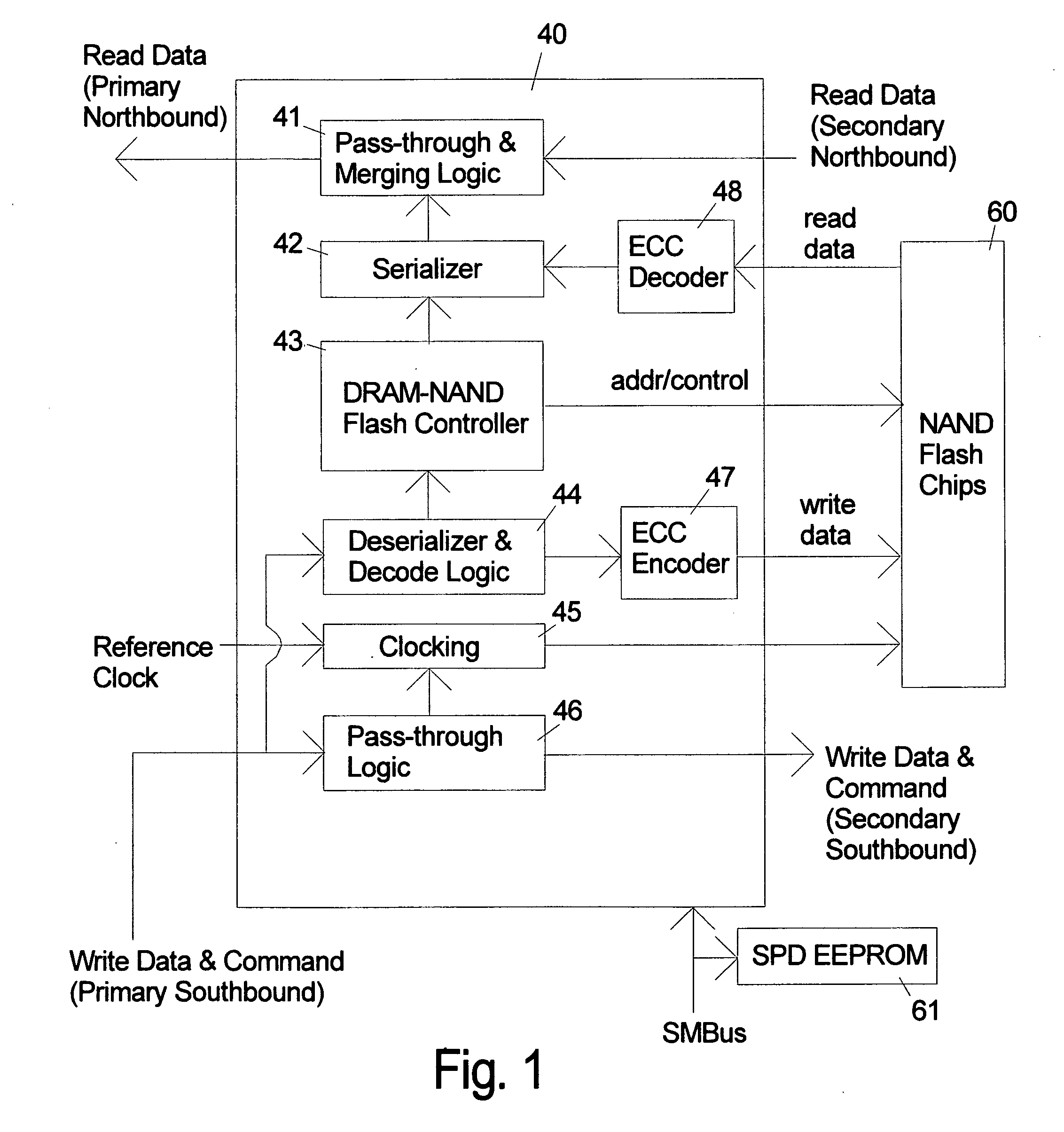

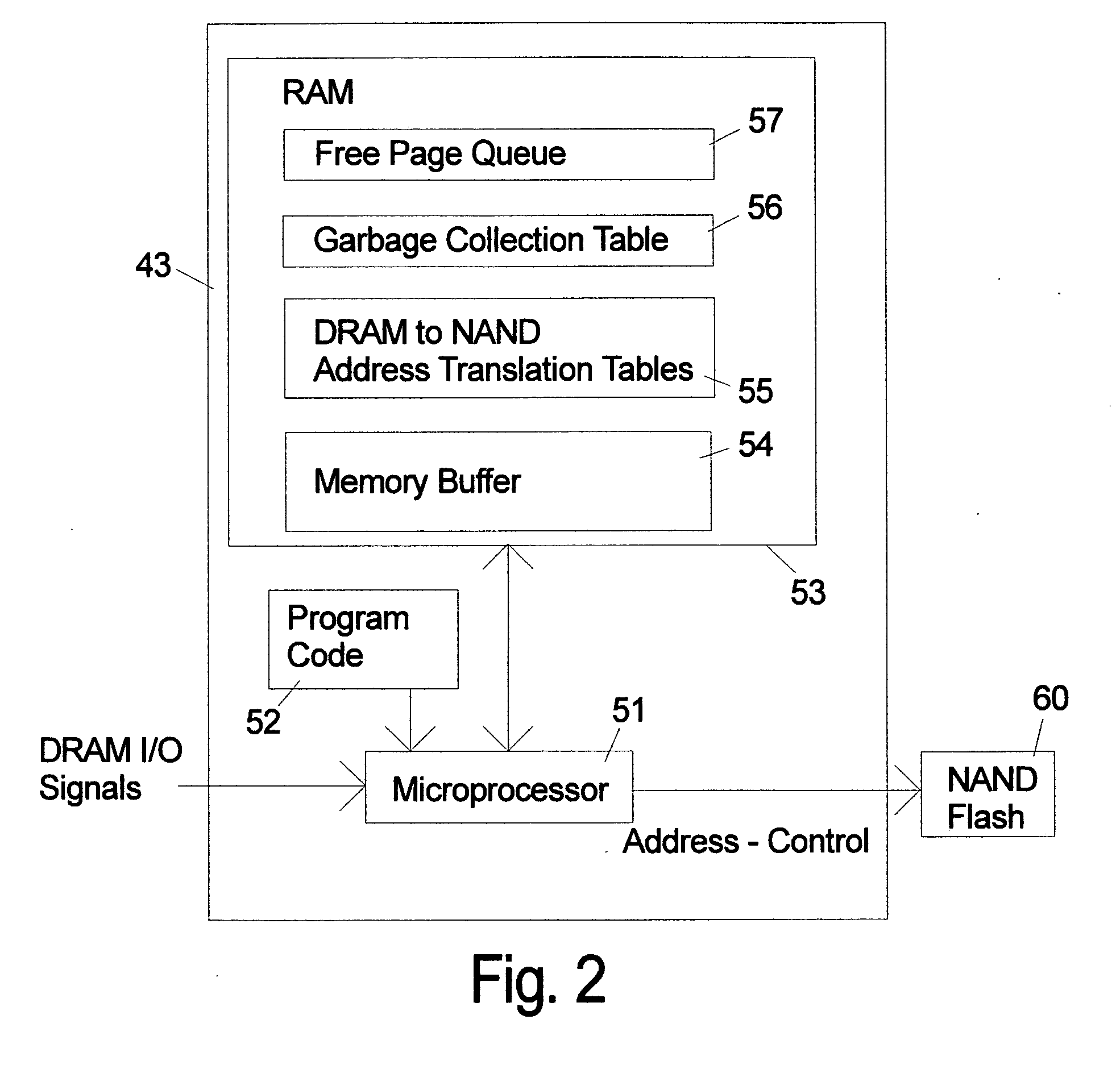

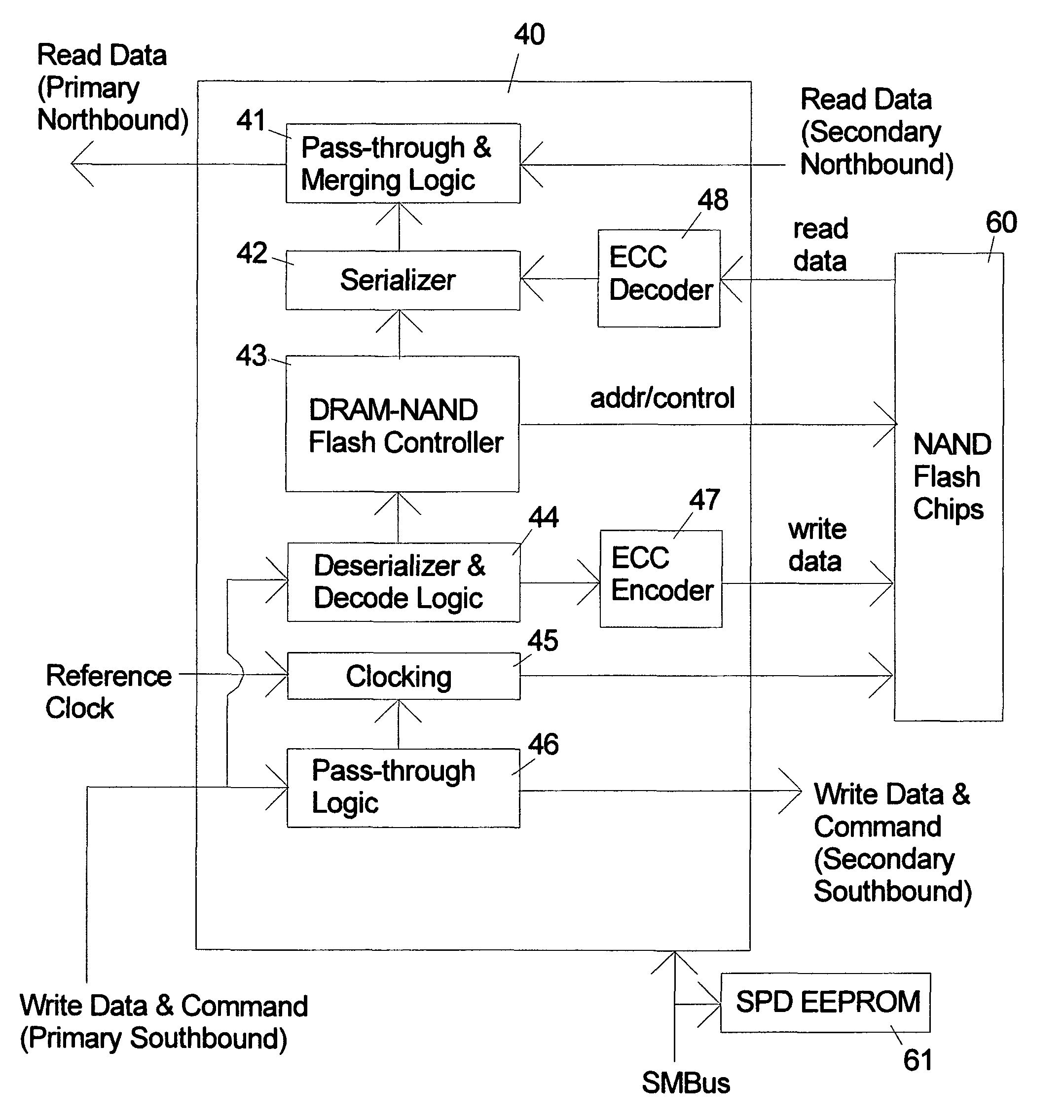

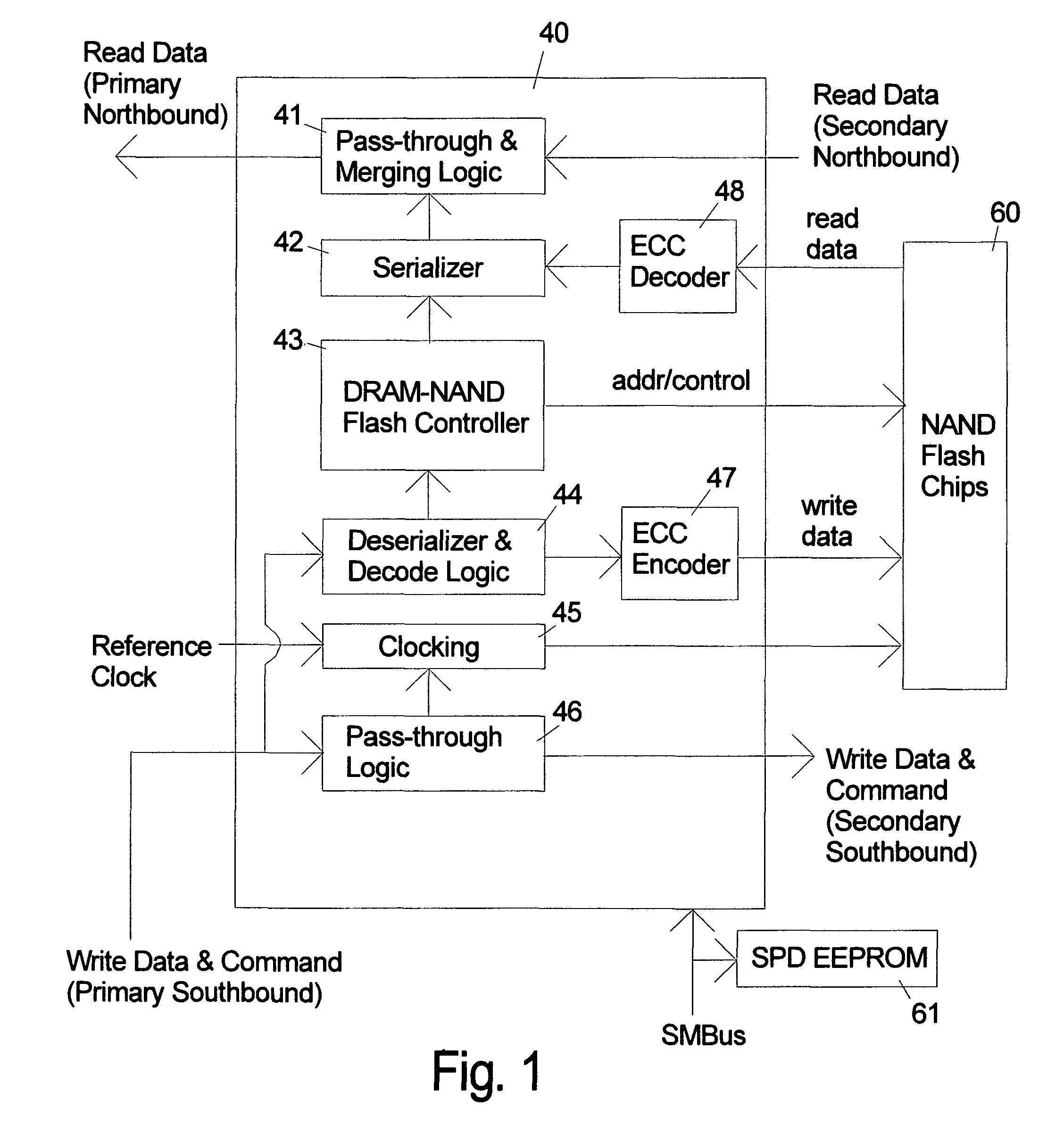

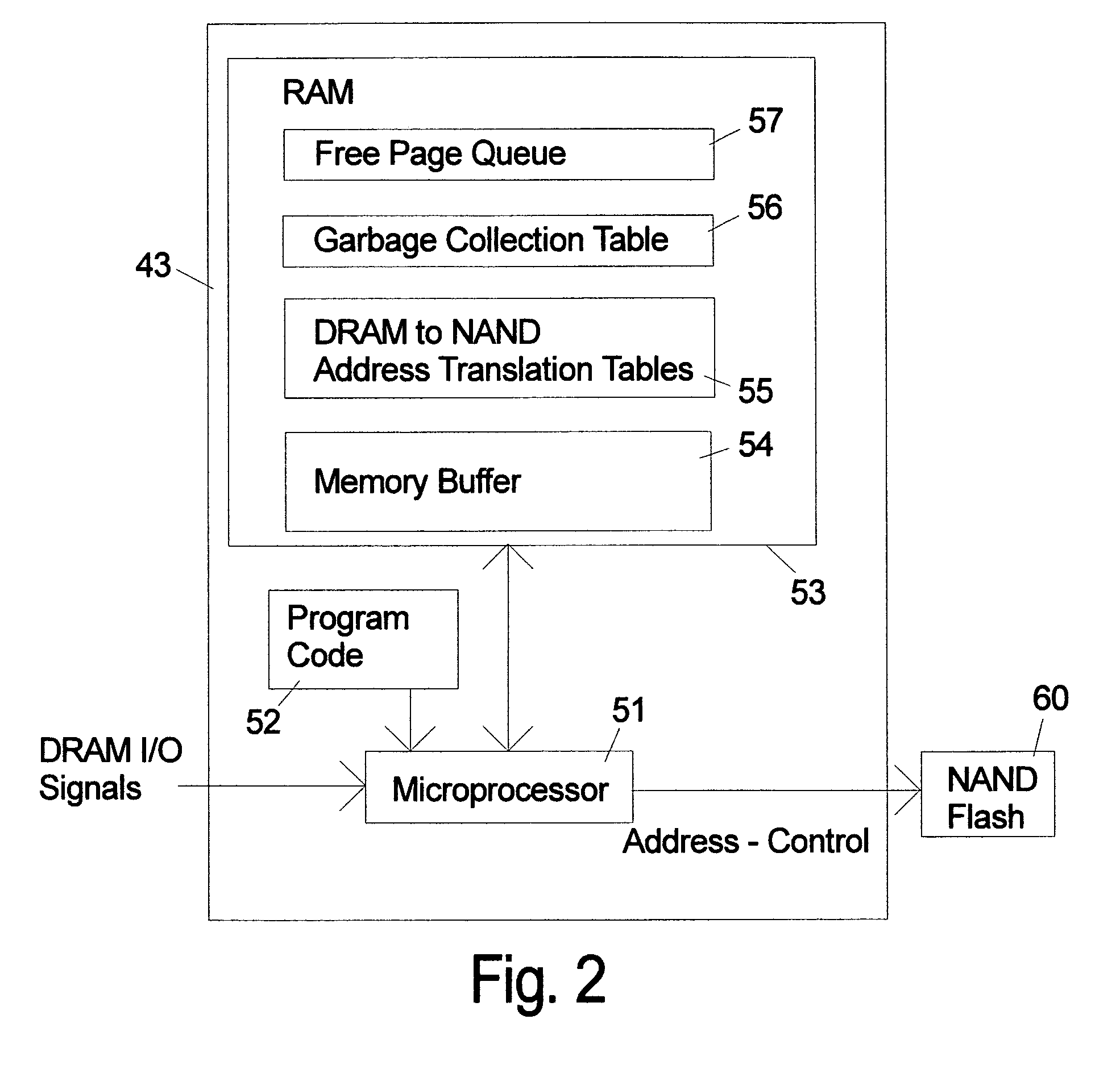

NAND flash module replacement for DRAM module

ActiveUS20090157950A1Most efficientAddressing slow performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationControl signalFlash memory controller

An electronic memory module according to the invention provides non-volatile memory that can be used in place of a DRAM module without battery backup. An embodiment of the invention includes an embedded microprocessor with microcode that translates the FB-DIMM address and control signals from the system into appropriate address and control signals for NAND flash memory. Wear-leveling, bad block management, garbage collection are preferably implemented by microcode executed by the microprocessor. The microprocessor, additional logic, and embedded memory provides the functions of a flash memory controller. The microprocessor memory preferably contains address mapping tables, free page queue, and garbage collection information.

Owner:WESTERN DIGITAL TECH INC

NAND flash module replacement for DRAM module

ActiveUS8185685B2Reduce speedMost efficientMemory architecture accessing/allocationMemory adressing/allocation/relocationProcess memoryControl signal

An electronic memory module according to the invention provides non-volatile memory that can be used in place of a DRAM module without battery backup. An embodiment of the invention includes an embedded microprocessor with microcode that translates the FB-DIMM address and control signals from the system into appropriate address and control signals for NAND flash memory. Wear-leveling, bad block management, garbage collection are preferably implemented by microcode executed by the microprocessor. The microprocessor, additional logic, and embedded memory provides the functions of a flash memory controller. The microprocessor memory preferably contains address mapping tables, free page queue, and garbage collection information.

Owner:WESTERN DIGITAL TECH INC

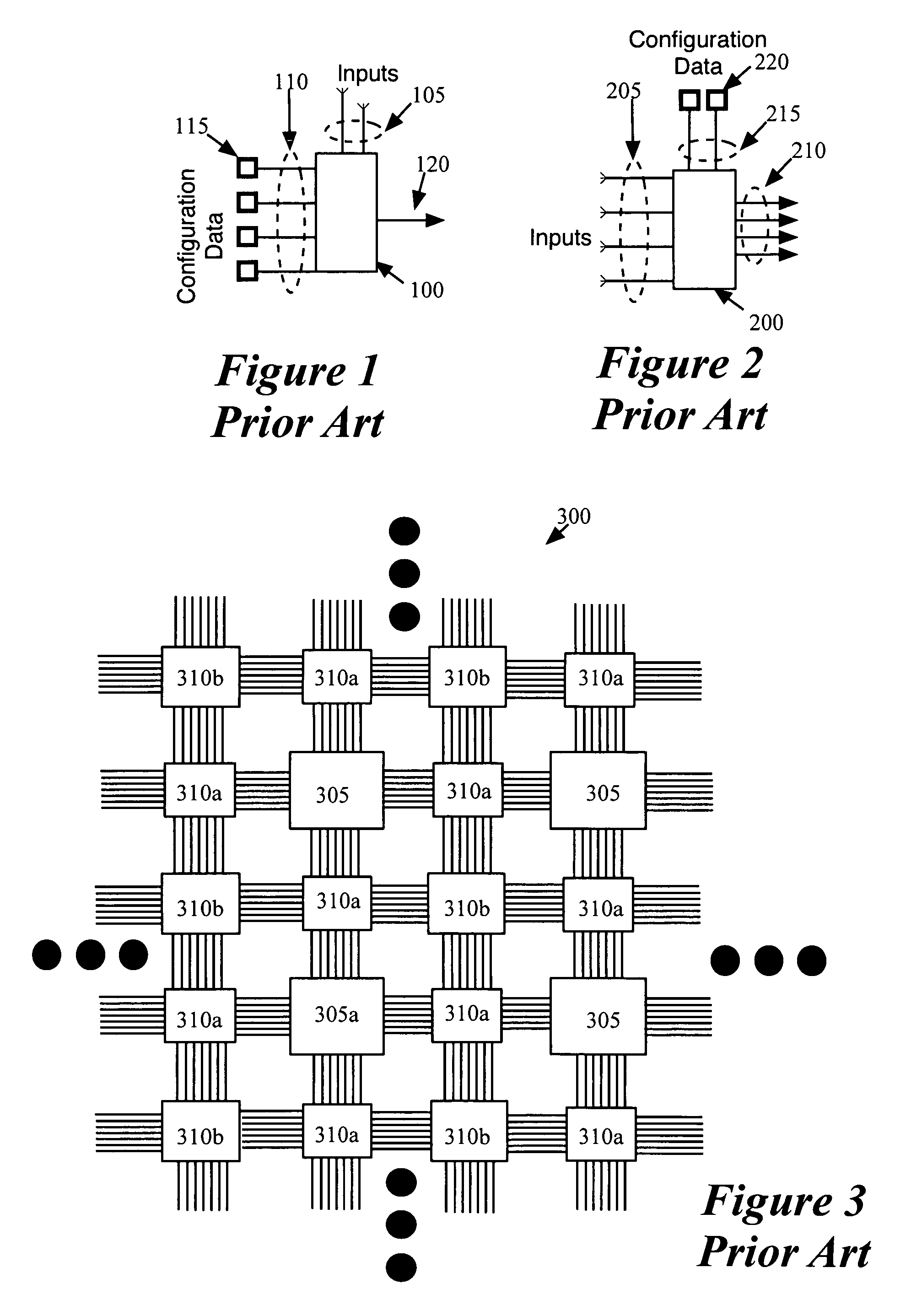

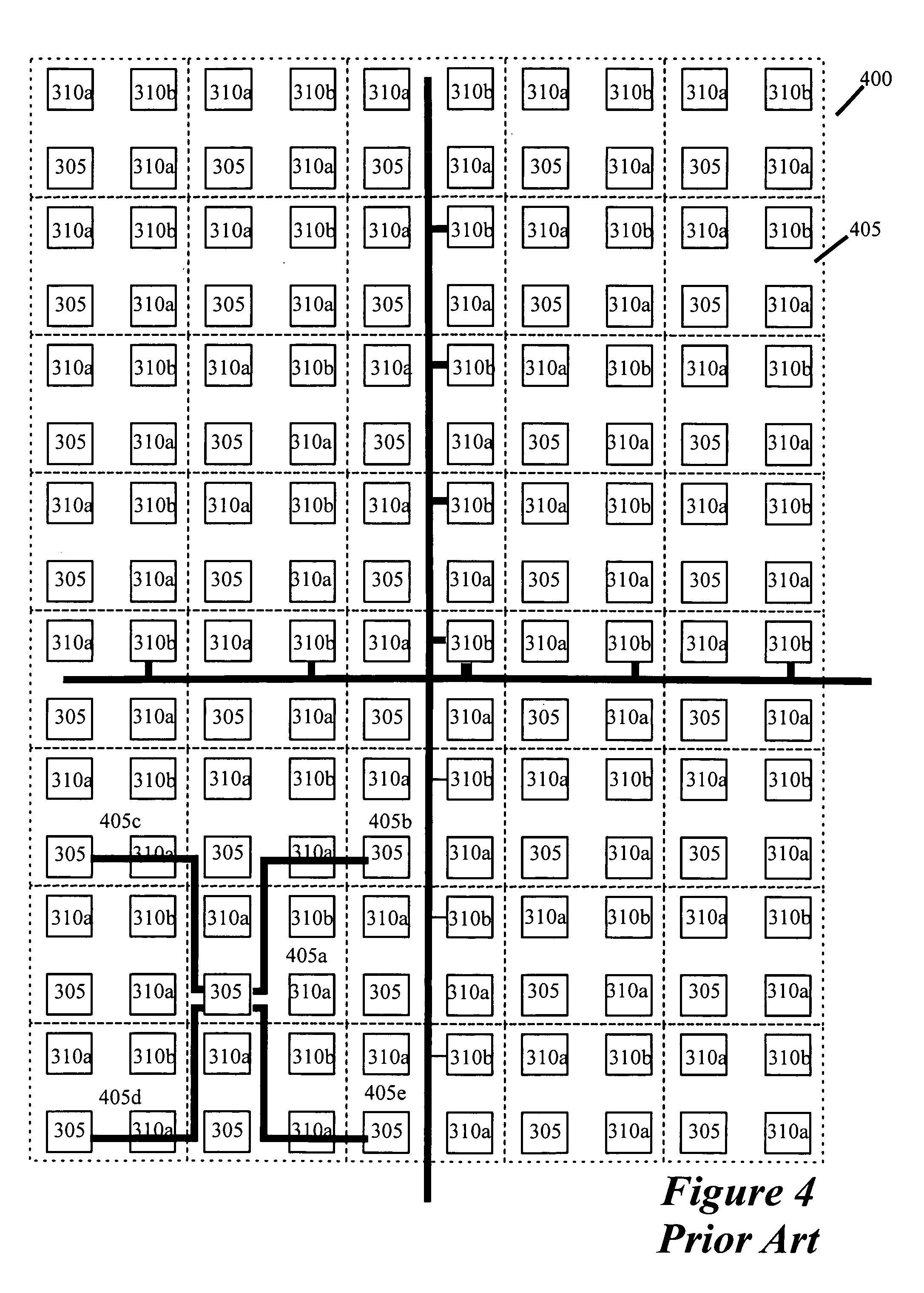

Error correction for programmable logic integrated circuits

InactiveUS7328377B1Increase delayReduces static hazardsError detection/correctionProgrammable logic controllerProgrammable logic device

Systems and methods for detecting and correcting errors in programmable logic ICs are provided. In one embodiment, a scrubber periodically reads the memory cells in a programmable logic IC, detects and corrects any errors, and writes the corrected contents back into the memory cell. In another embodiment, regions of memory cells in a programmable logic IC each have associated error correcting circuitry which operates to continuously detect and correct errors as they occur. Error correcting circuitry can further be designed to reduce static hazards. It may be more desirable to design programmable logic IC routing architectures that reduce the number of memory cells needed to implement a given function. Error correcting circuitry can be provided for configuration memory or for an embedded memory block on a programmable logic IC.

Owner:ALTERA CORP

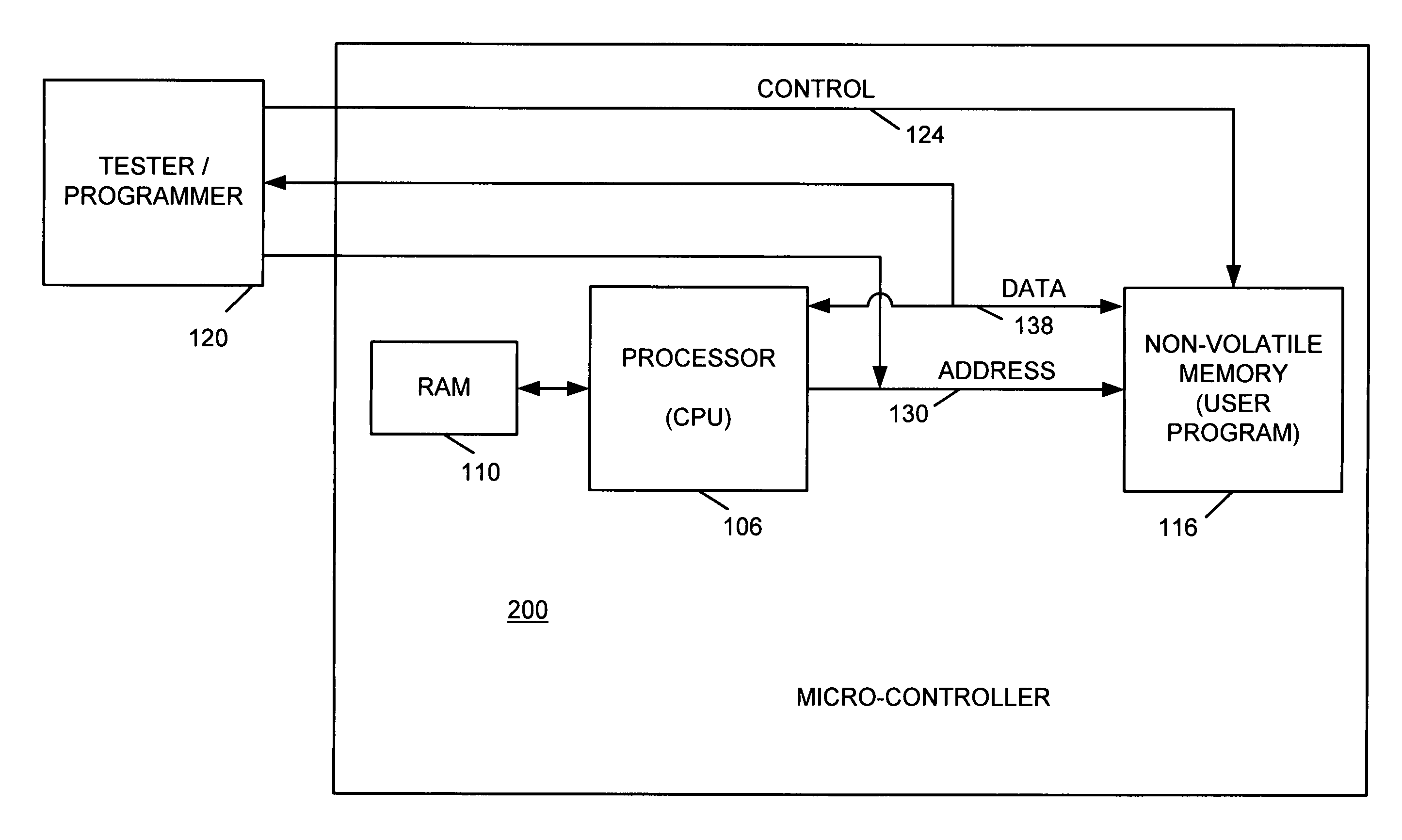

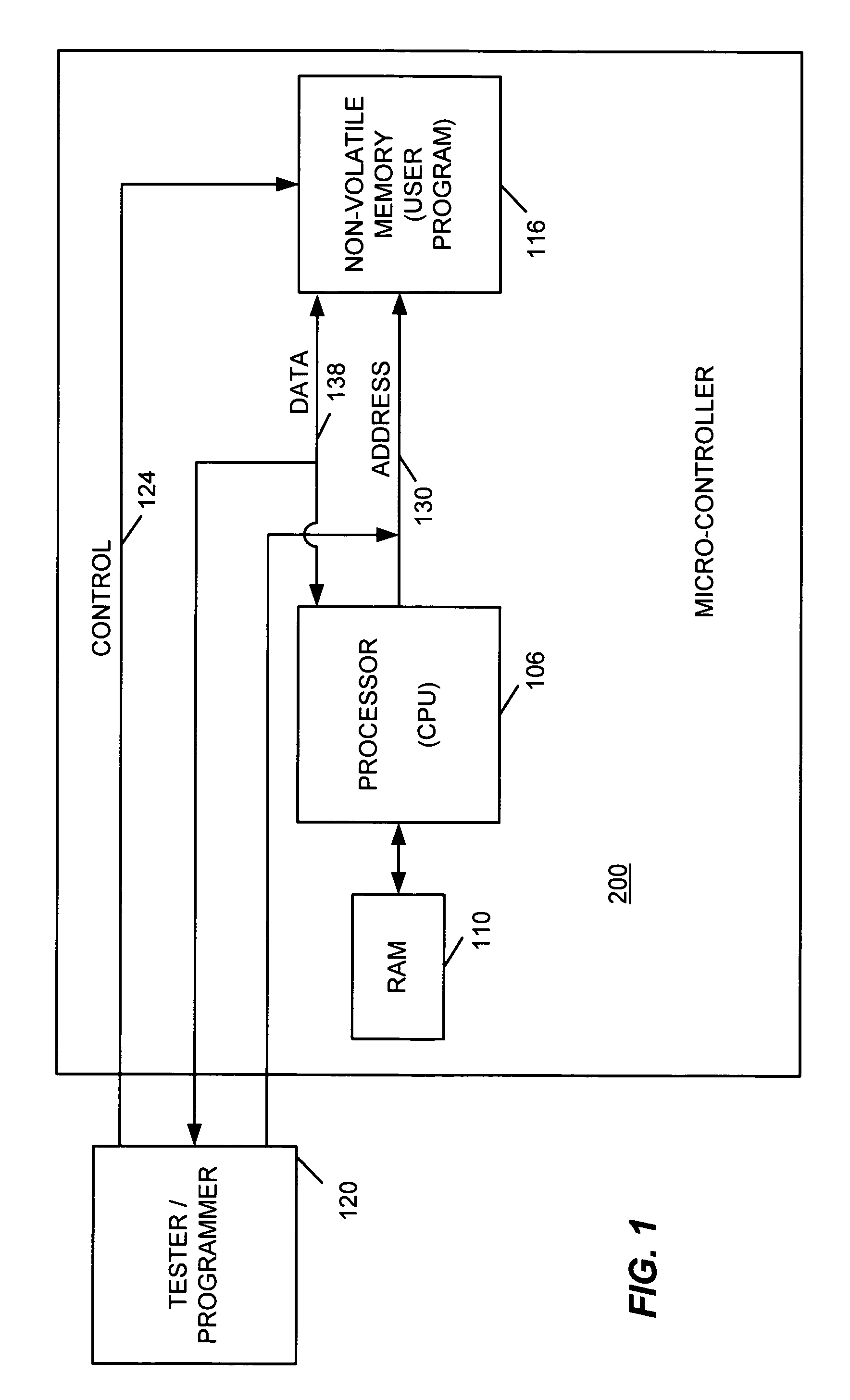

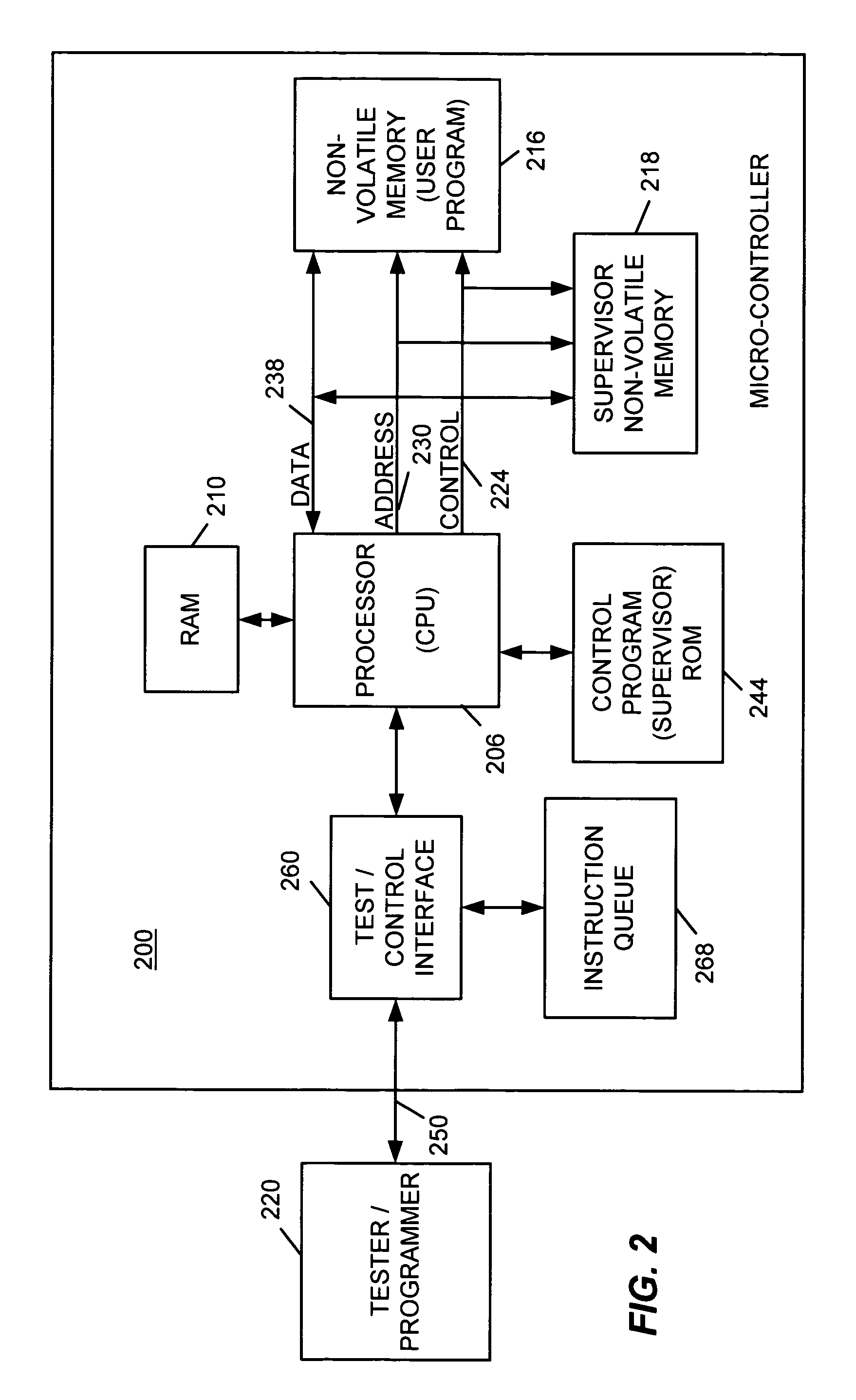

Protecting access to microcontroller memory blocks

InactiveUS6952778B1Security levels can be modifiedImprove security levelDigital data processing detailsUser identity/authority verificationMicrocontrollerSecurity level

A microcontroller provides protection to memory blocks in an embedded memory. A set of rules such as security levels mapped to memory blocks are stored in a nonvolatile supervisory memory. An algorithm for application of the rules is stored in a supervisory ROM. When a read or write operation is to be carried out, the rules are applied according to the algorithm in order to authorize or reject the read or write operation. Security levels can be modified, but only according to defined rules. In one embodiment, the security levels can only be increased.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

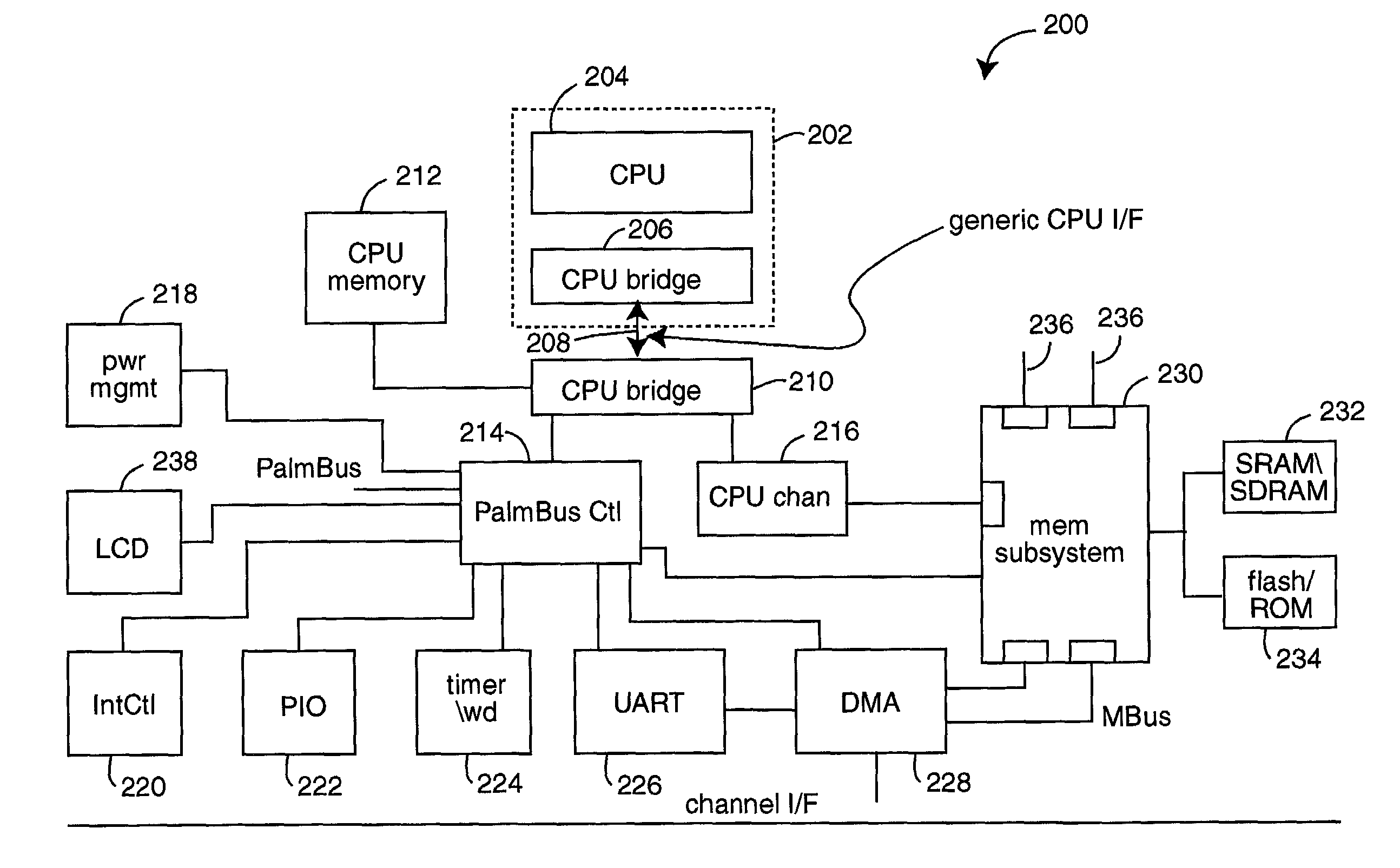

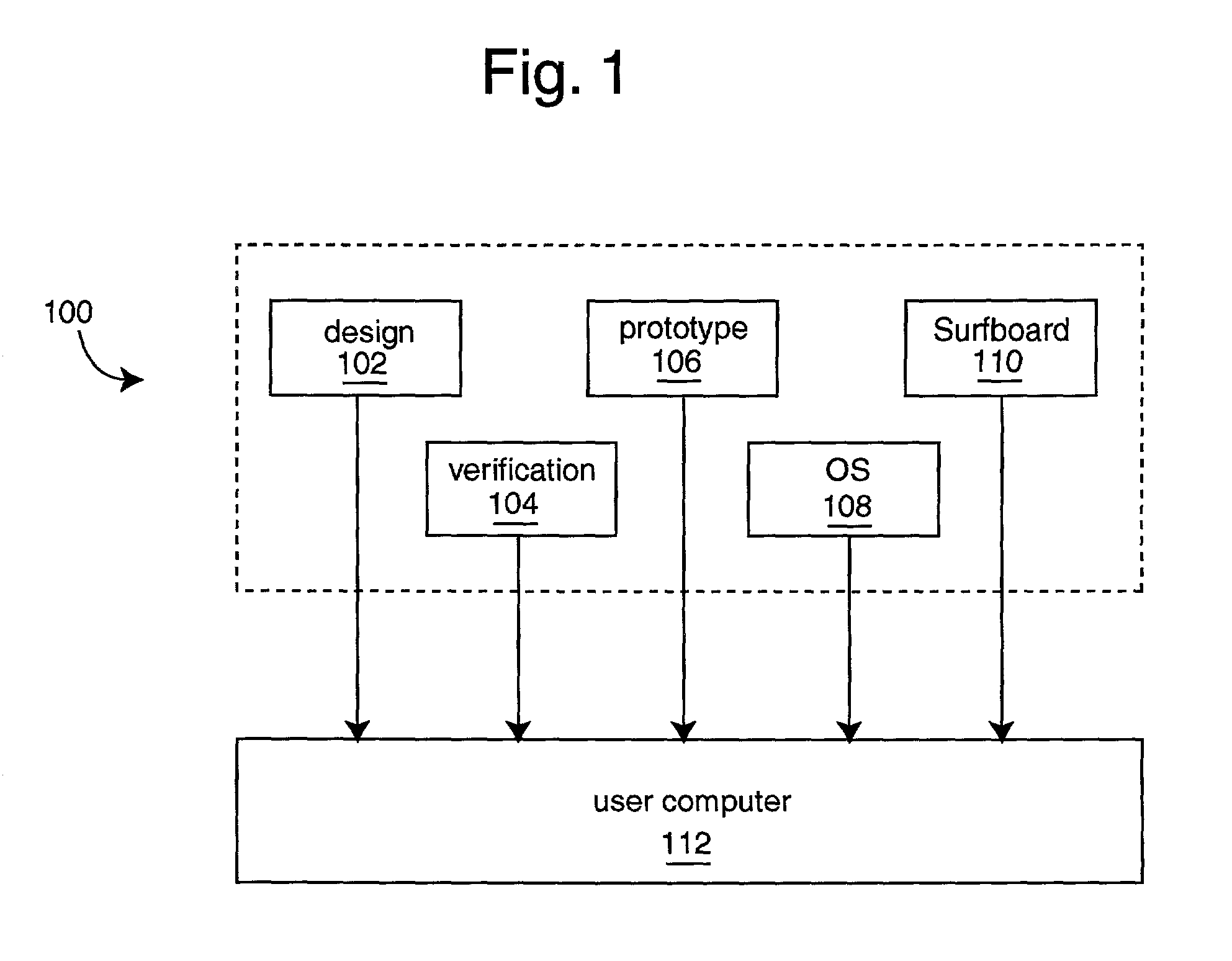

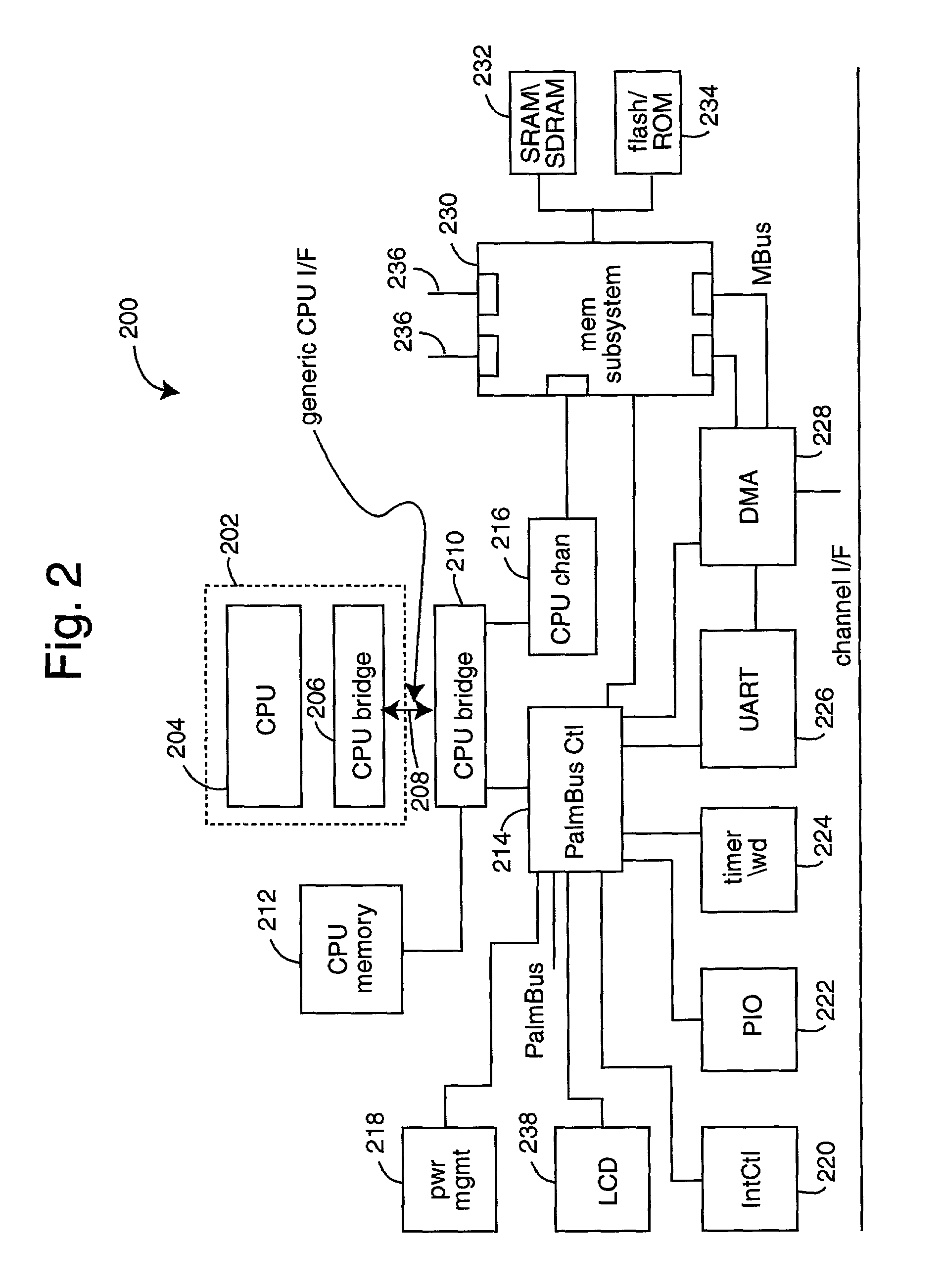

Design tool for systems-on-a-chip

InactiveUS7124376B2Promote rapid developmentReduce a user's time-to-marketCAD circuit designSoftware simulation/interpretation/emulationTest suiteMakefile

A pre-designed system-on-chip architecture and method includes several standard library devices, HDL source code, simulation environment and regression, synthesis scripts, software header files, software libraries, ASIC verification test suites, and makefiles. The standard library devices comprise an integrated CPU, a shared memory controller, a peripheral controller, system peripherals, a DMA controller, embedded memory, and general system control. CPU bridges are used to accommodate a variety of processor types and to insulate users from the complexities of interfacing to different kinds of processors. Such CPU bridges further allow the latest processors to be rapidly integrated into existing integration platforms and designs.

Owner:NETVINCI

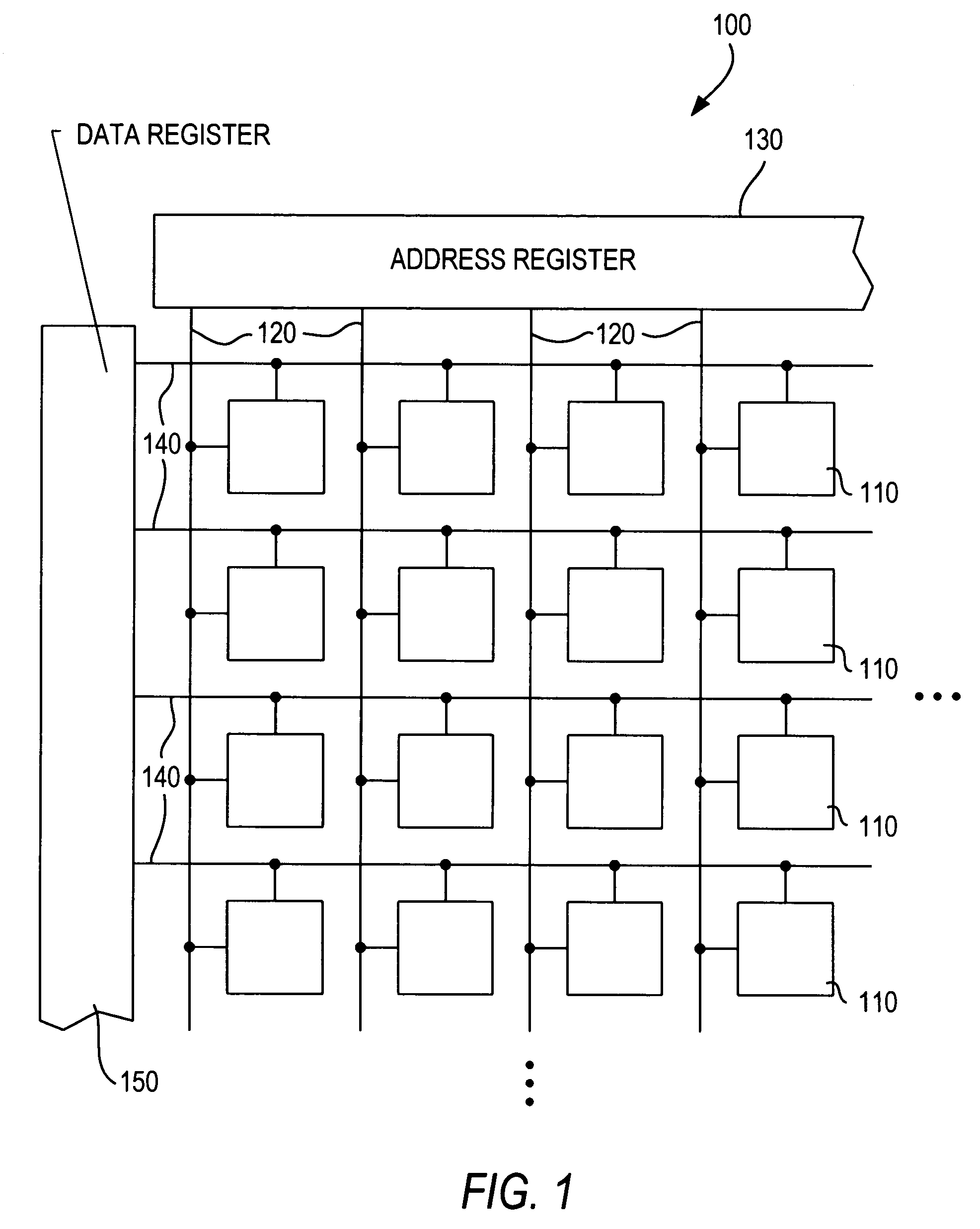

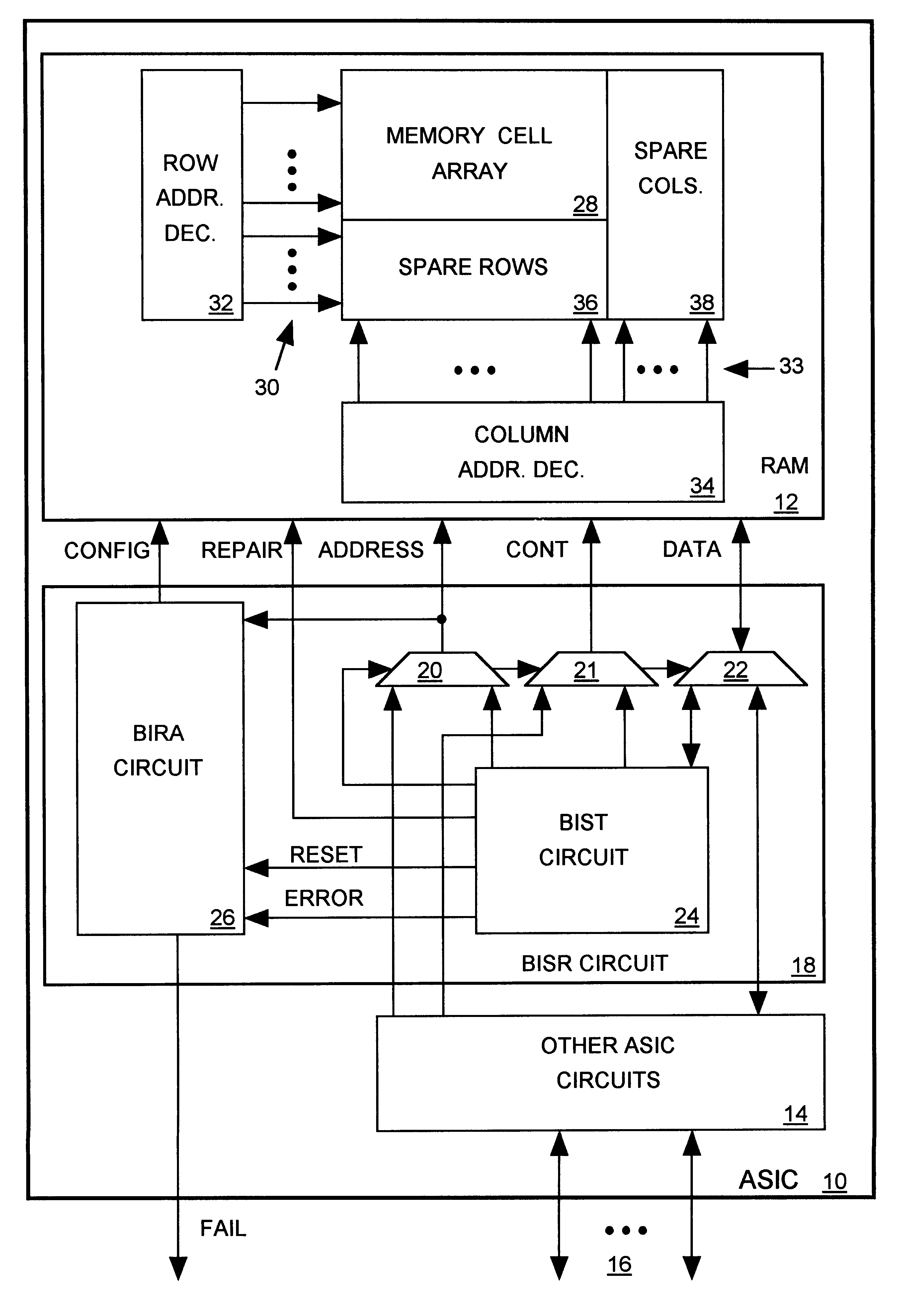

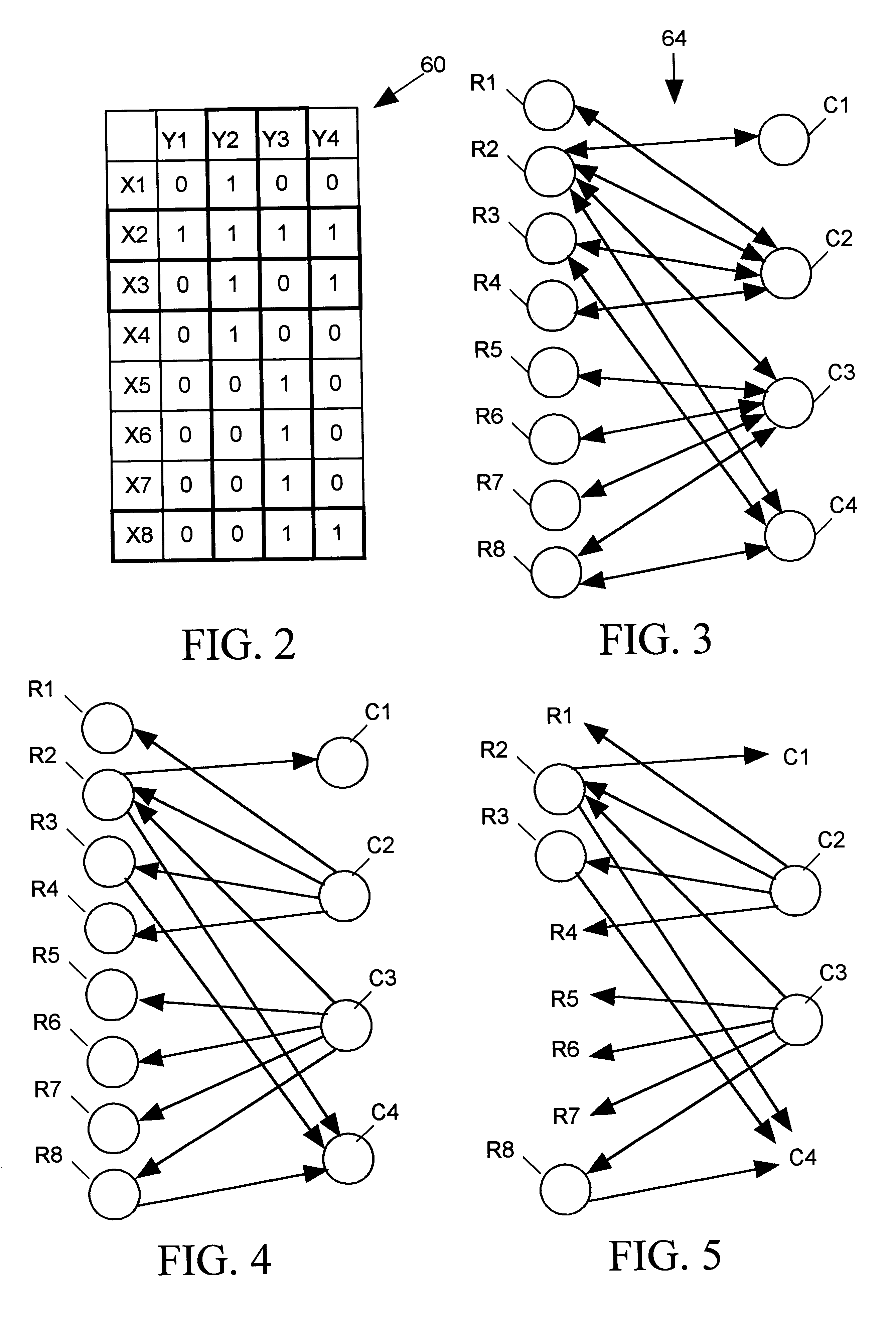

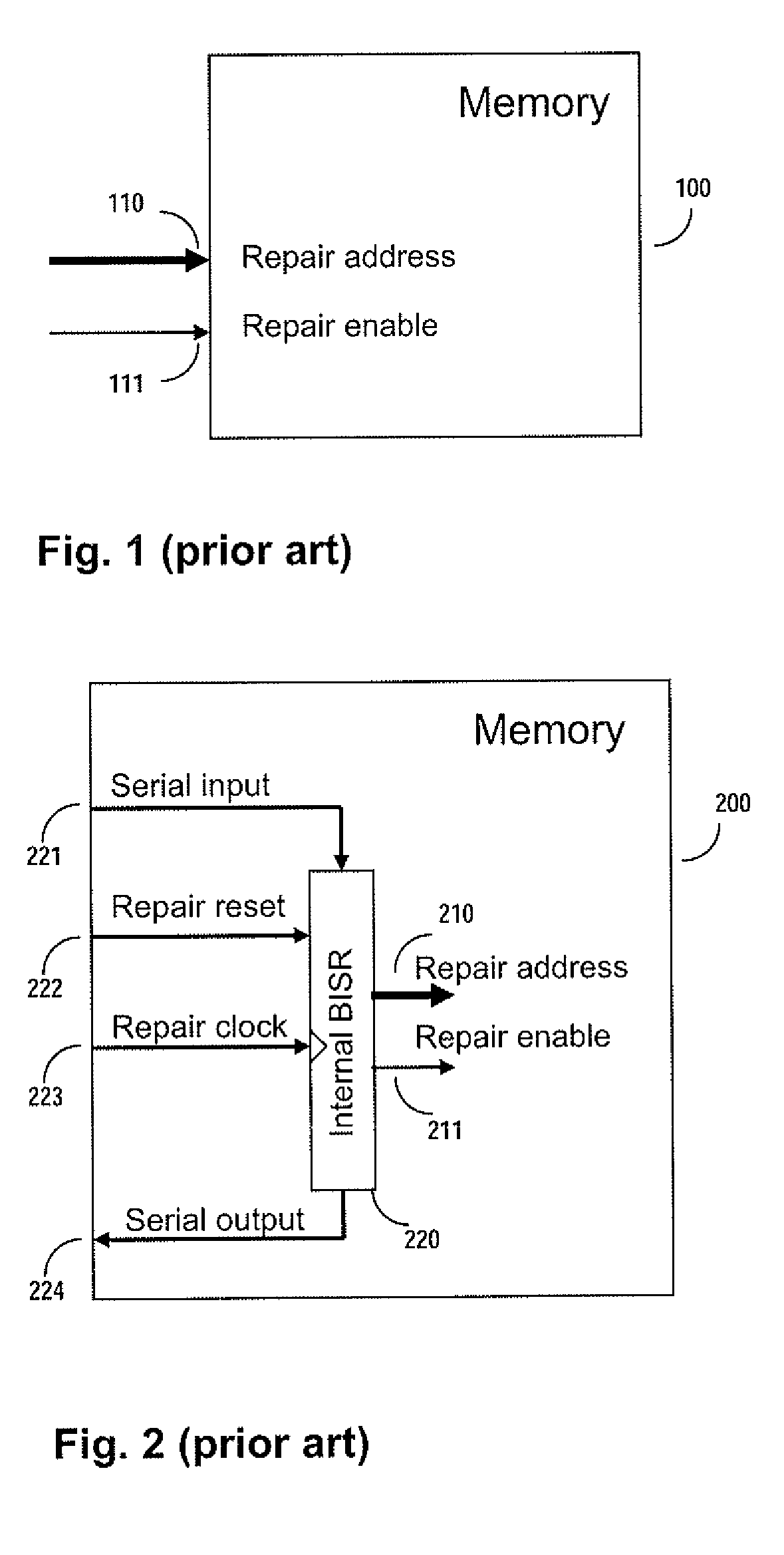

Built-in spare row and column replacement analysis system for embedded memories

InactiveUS6304989B1OptimizationElectronic circuit testingStatic storageProcessor registerData storing

A built-in replacement analysis (BIRA) circuit allocates spare rows and columns of cells for replacing rows and columns of an array of memory cells in response to an input sequence of cell addresses, each identifying a row address and a column address of each defective cell of the cell array. The BIRA subsystem, including a row register corresponding each spare row and a column register corresponding to each spare column, responds to incoming cell addresses by writing their included row address into the row registers, by writing their column addresses into the column registers, and by writing link bits into the column registers. Each link bit links a row and a column register by storing row and column addresses of a defective cell. The BIRA subsystem also writes a "multiple cell" bit into each row register to indicate when the row address it stores includes more than one defective cell. The row and column addresses stored in these registers indicate the array rows and columns for which spare rows and columns are to be allocated. Each row and column register also includes a "permanent" bit the BIRA subsystem sets to indicate when the spare row or column allocation indicated by its stored row or column address is permanent. The BIRA subsystem efficiently allocates spare row and columns by manipulating the data stored in the row and column registers in response to a sequence of defective cell address.

Owner:CREDENCE SYSTEMS

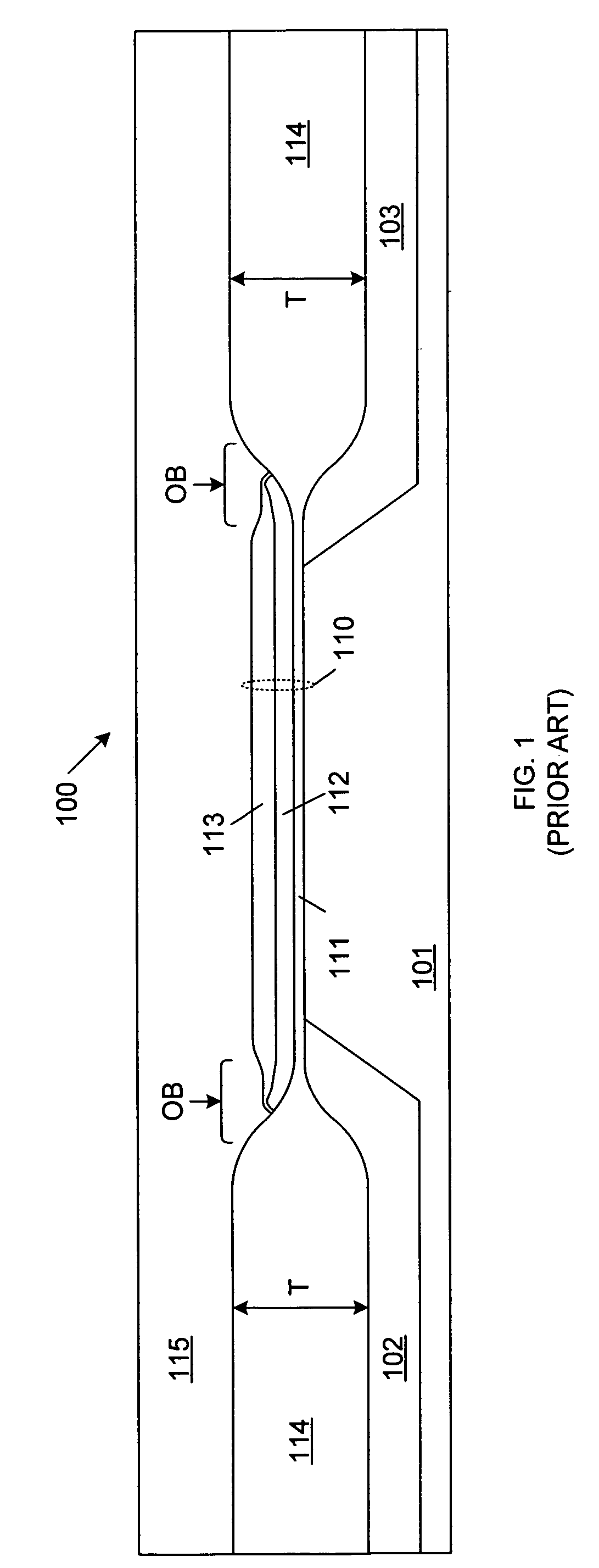

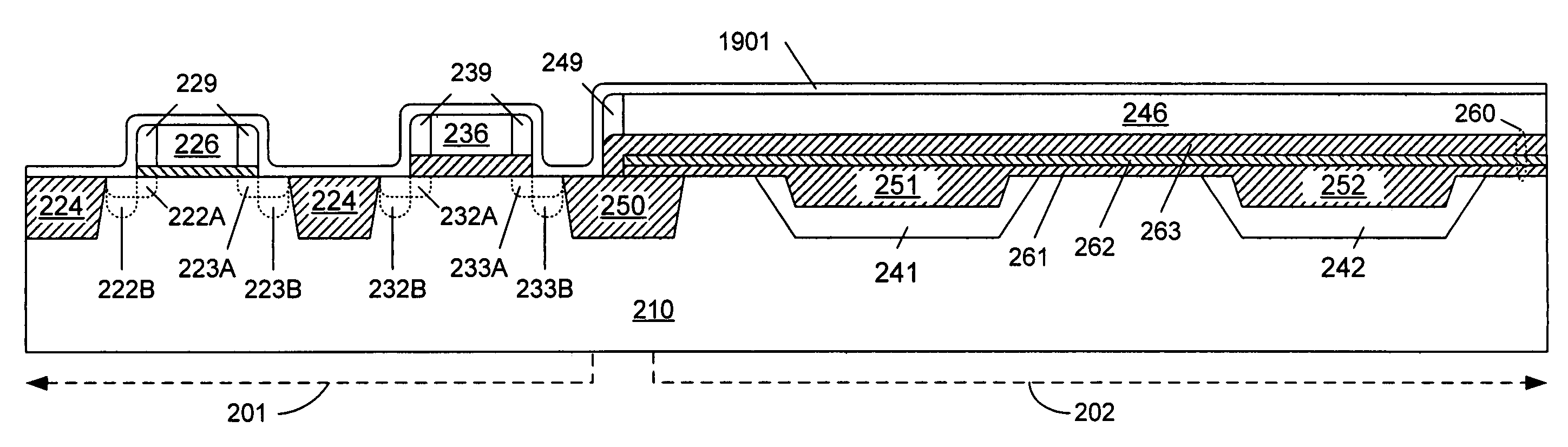

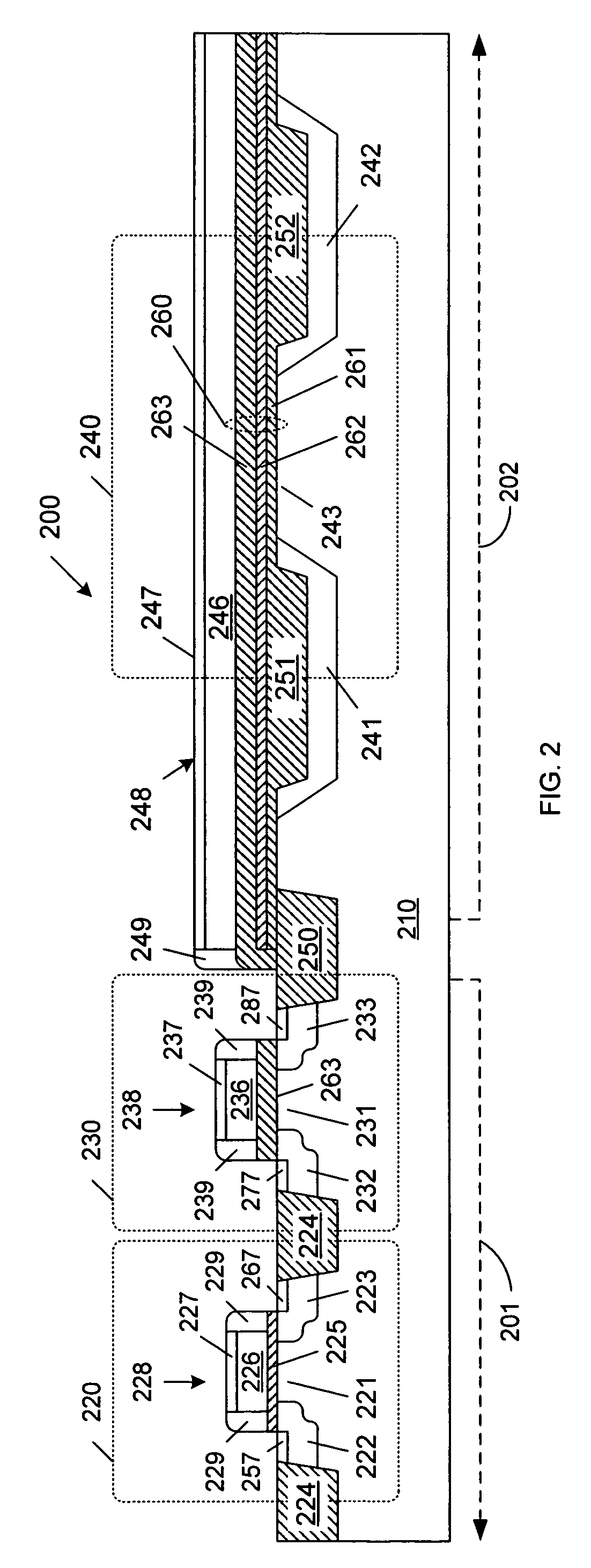

SONOS embedded memory with CVD dielectric

InactiveUS20050186741A1Faster rateRegion of becomes thinSolid-state devicesSemiconductor/solid-state device manufacturingCMOSBit line

An embedded semiconductor memory is fabricated by: forming diffusion bit line regions in a semiconductor substrate; then thermally oxidizing the upper surface of the substrate, thereby forming a bottom oxide layer over the substrate and simultaneously forming bit line oxide regions over each of the diffusion bit line regions; and then forming an intermediate dielectric layer (e.g., silicon nitride), over the bottom oxide layer and the bit line oxide regions. CMOS well implants are then performed in a CMOS section of the device through the silicon nitride layer and bottom oxide layer. The silicon nitride layer and bottom oxide layer are then removed in the CMOS section, and a top dielectric layer, such as a high-temperature oxide or a high-k dielectric, is deposited. The top dielectric layer completes a memory stack of the memory device, and forms a gate dielectric layer of a high voltage transistor in the CMOS section.

Owner:PS4 LUXCO SARL

Method and apparatus for storing and distributing memory repair information

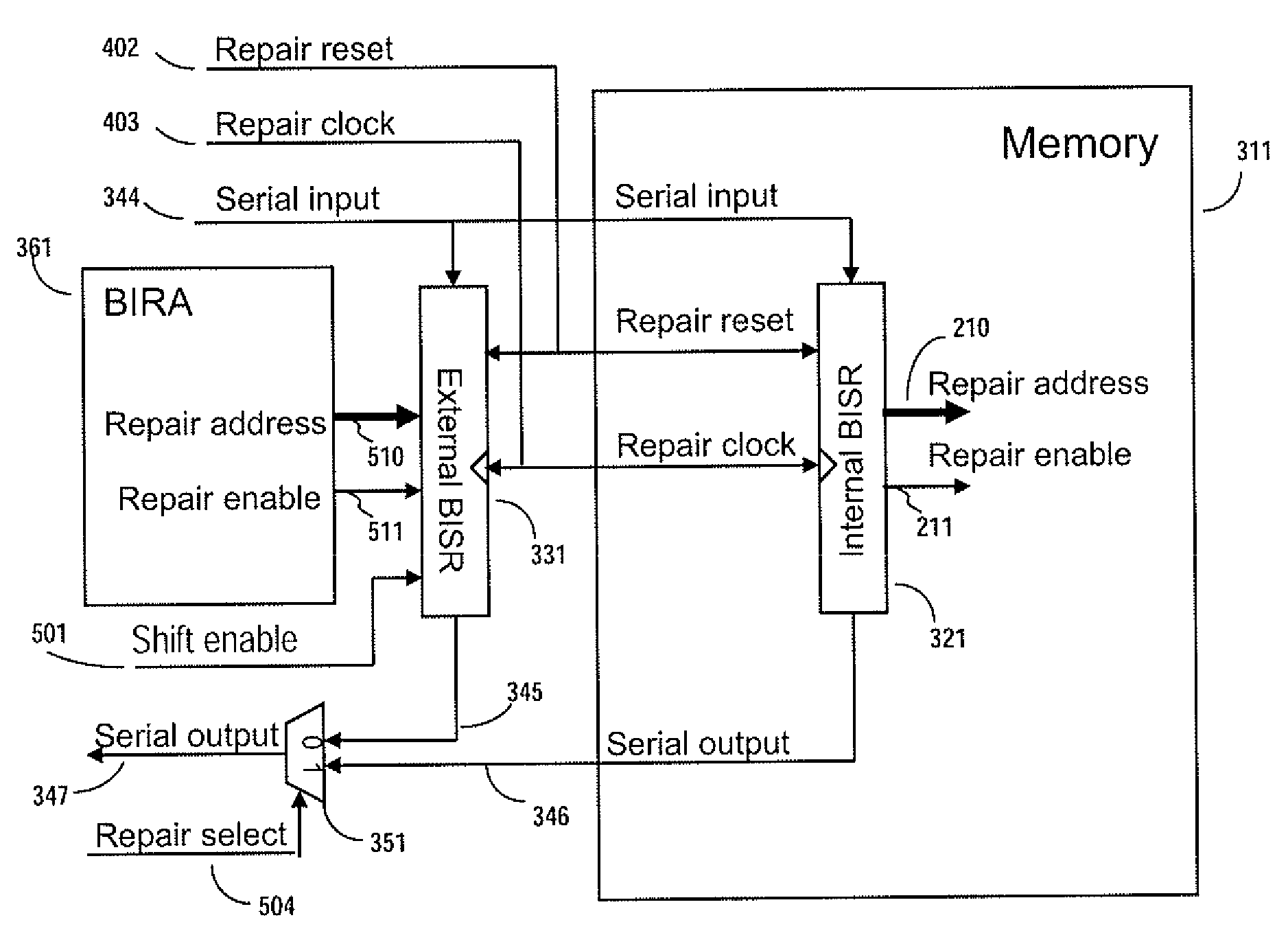

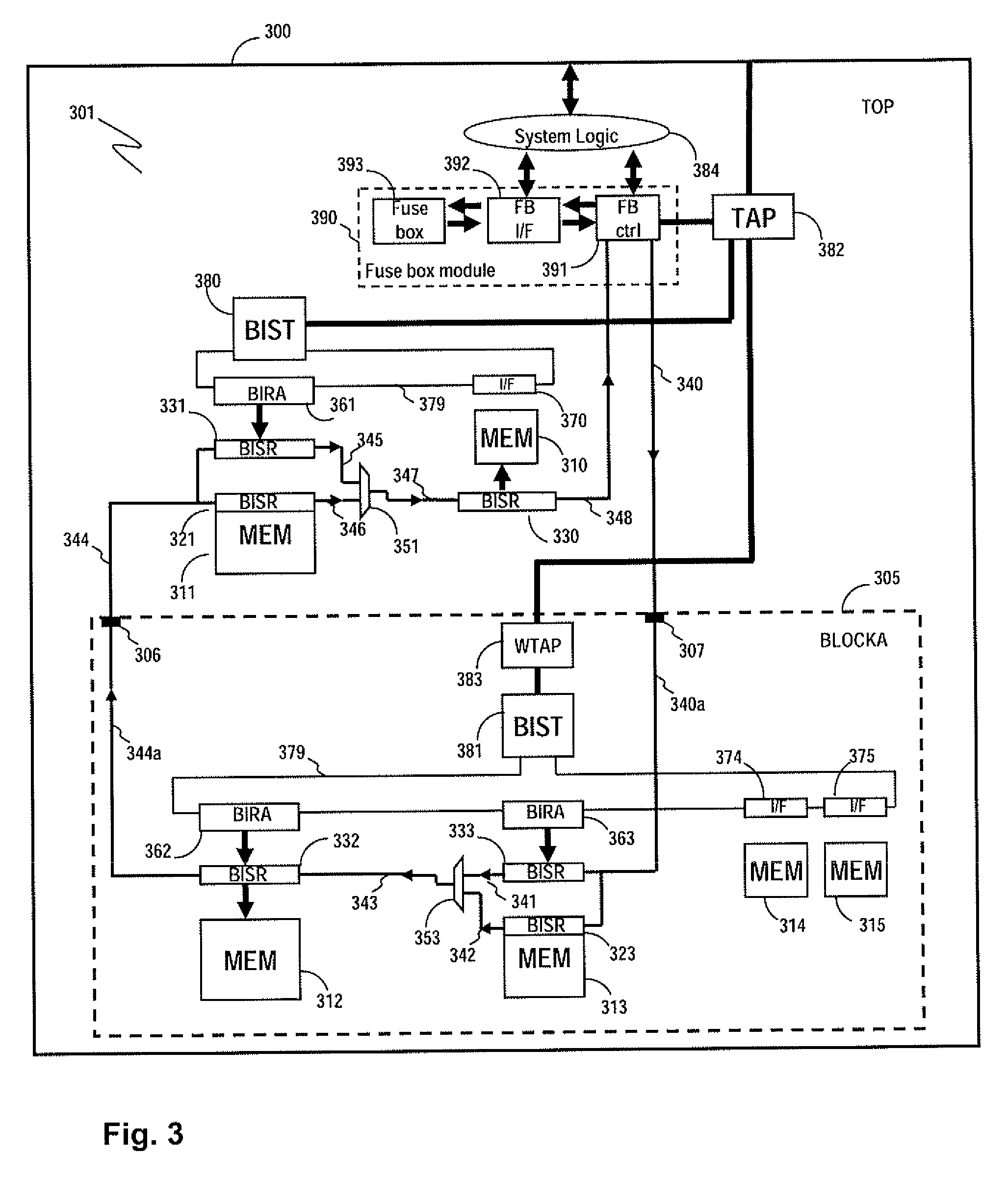

ActiveUS7757135B2Easy to integrateConvenient to accommodateElectronic circuit testingError detection/correctionDistributed memoryProcessor register

A system for repairing embedded memories on an integrated circuit includes an external Built-In Self-repair Register (BISR) associated with every reparable memory. Each BISR is serially configured in a daisy chain with a fuse box controller. The controller determines the daisy chain length upon power up. The controller may perform a corresponding number of shift operations to move repair data between BISRs and a fuse box. Memories can have a parallel or serial repair interface. The BISRs may have a repair analysis facility into which fuse data may be dumped and uploaded to the fuse box or downloaded to repair the memory. Pre-designed circuit blocks provide daisy chain inputs and access ports to effect the system or to bypass the circuit block.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

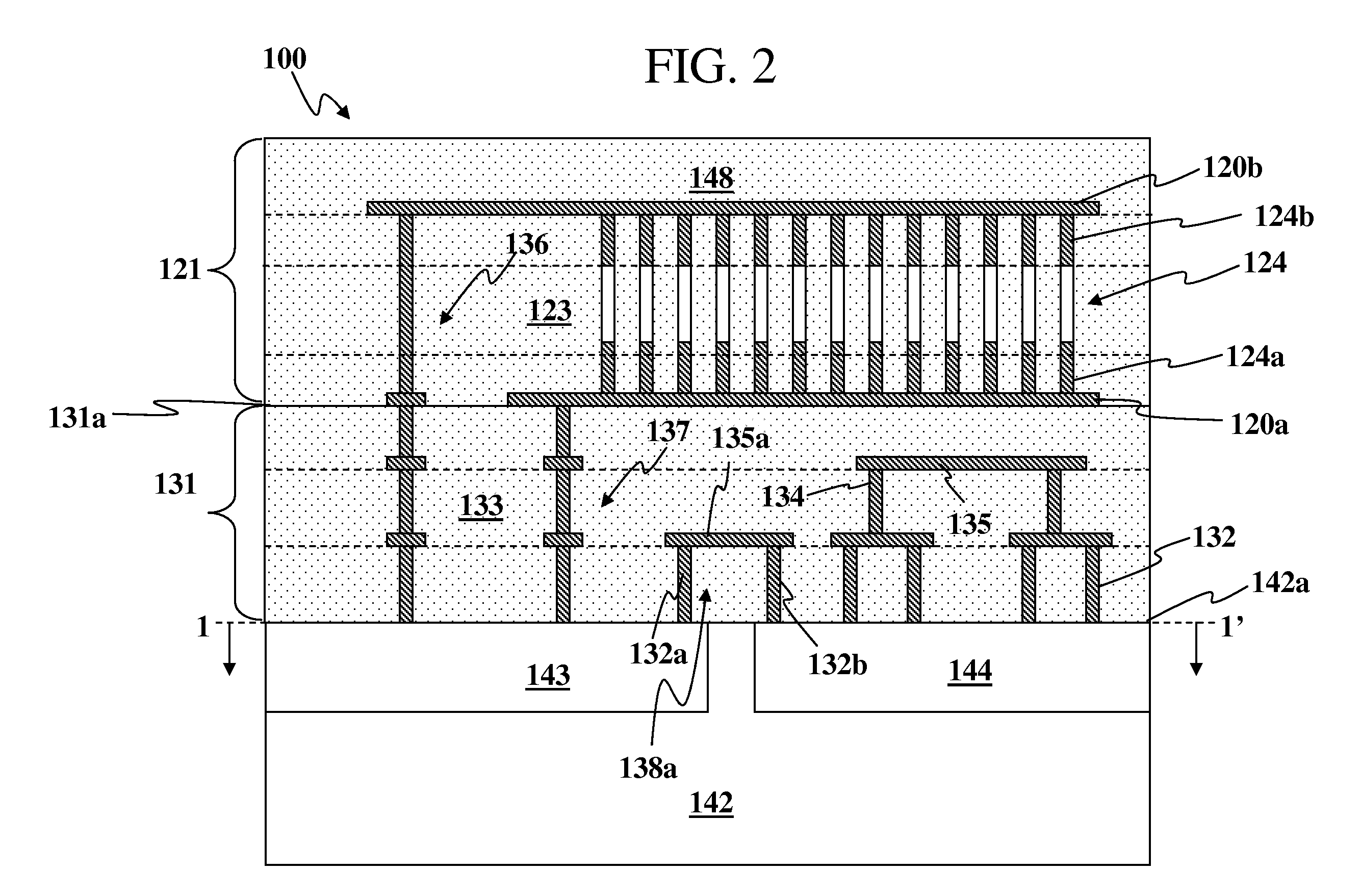

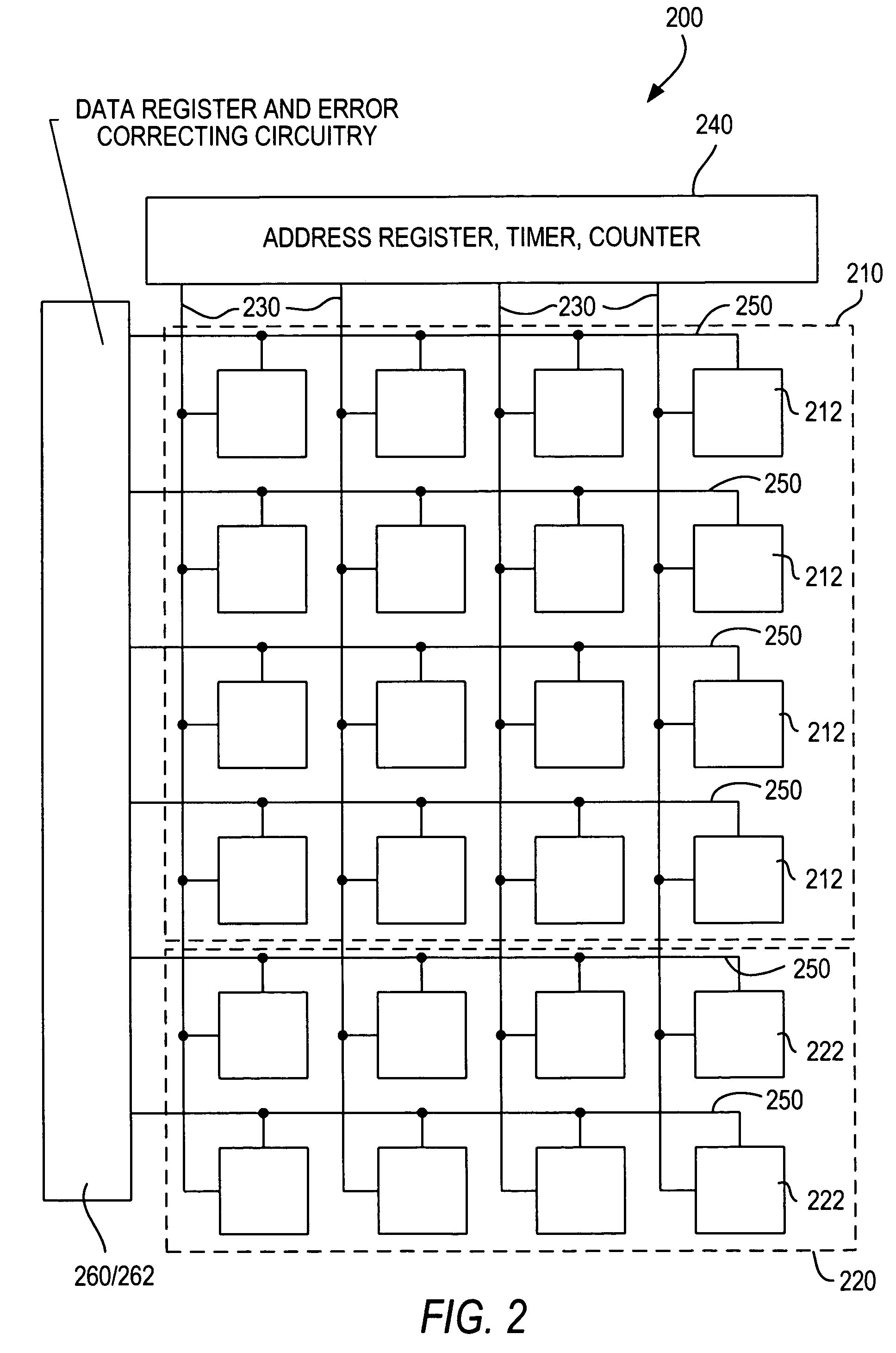

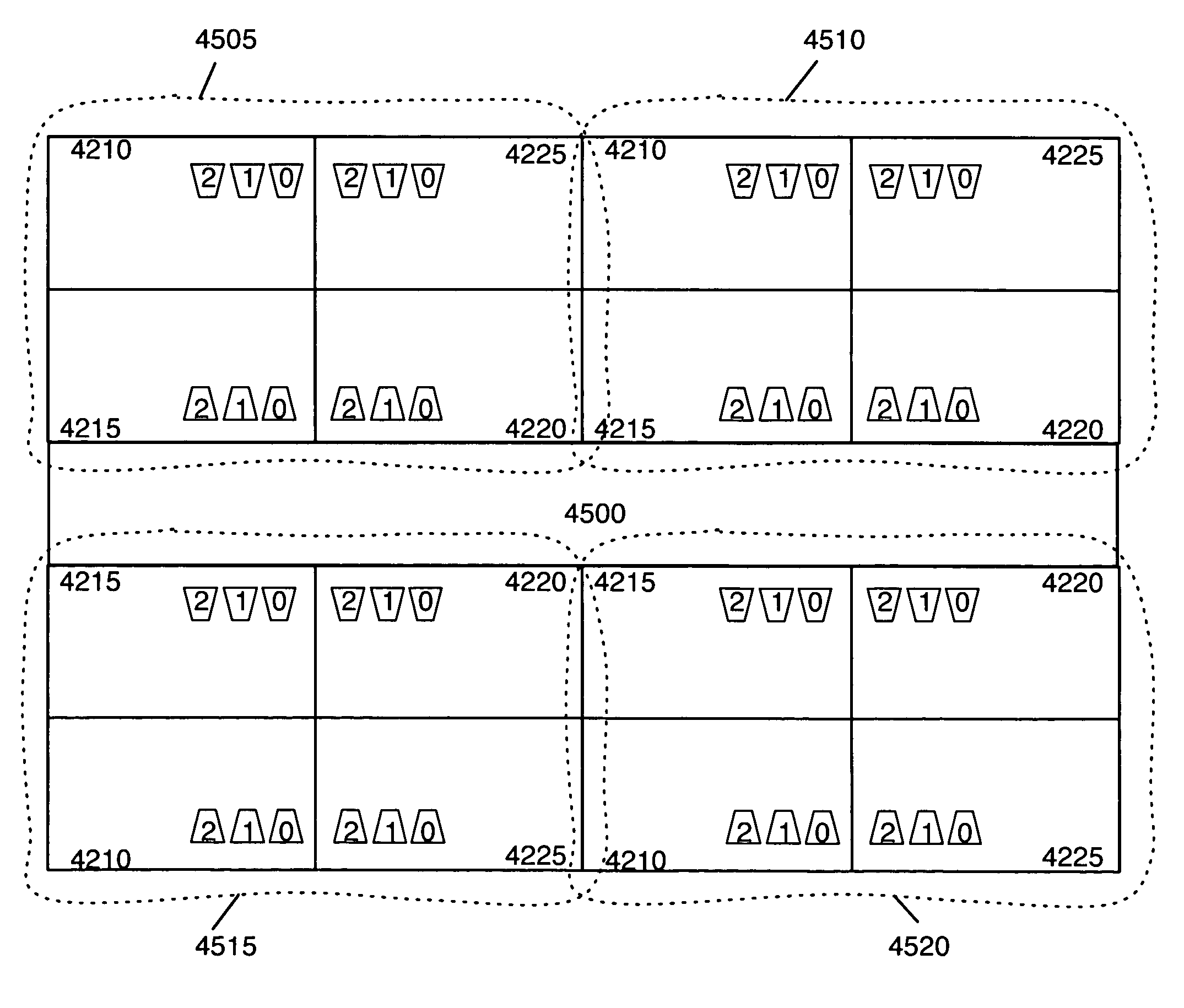

Embedding memory between tile arrangement of a configurable IC

Some embodiments of the invention provide a configurable IC that includes several configurable computational tiles and several memory tiles. These tiles are arranged in a particular tile arrangement. Each computational tile has a set of configurable logic circuits for configurably performing a plurality of computations and a set of configurable routing circuits. The routing circuits of the tiles configurably route signals between configurable logic circuits. The configurable IC also has several memory arrays for storing data on which the logic circuit perform computation. The memory arrays are embedded in the tile arrangement between two sets of memory tiles, where each set of memory tiles includes a set of routing circuits. In this IC, at least a first memory tile has the same set of configurable routing circuits as at least a second computational tile.

Owner:ALTERA CORP

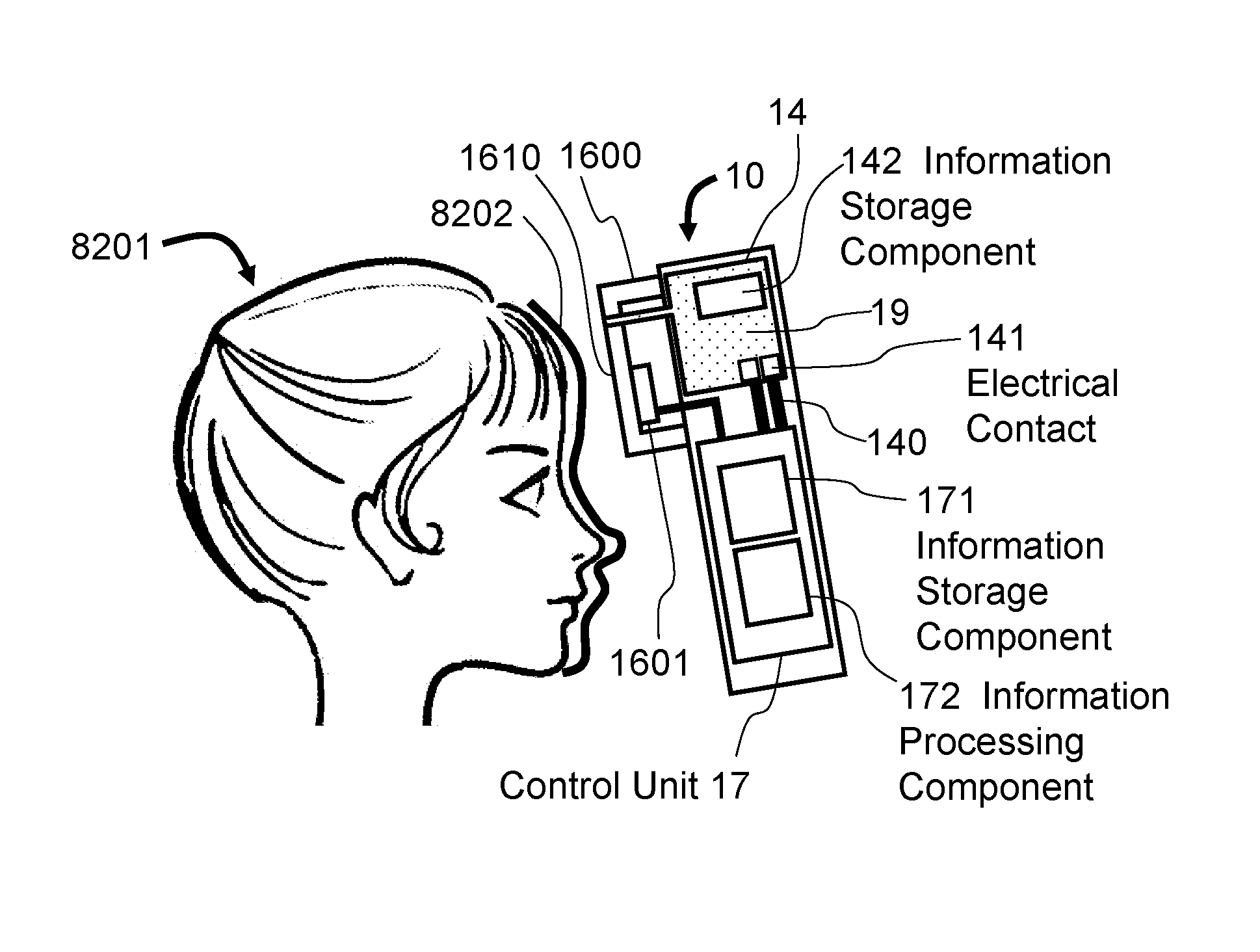

Customized skin care and method to provide same

InactiveUS20160331308A1Improve health careImprovement in care personal care effectivenessElectrotherapyDrug and medicationsElectricityPersonal care

Methods to provide customized skin care by using specimen dispensing device to dispense specimens from removable dispensers for the purpose of treating skin of a user are presented. Methods to utilize the embedded memory and electrical interface of the dispensing device and dispensers to produce customizable skin care products that give better skin treatment results are also presented. The invention may also be applied to health care and personal care needs.

Owner:LA PIERRES

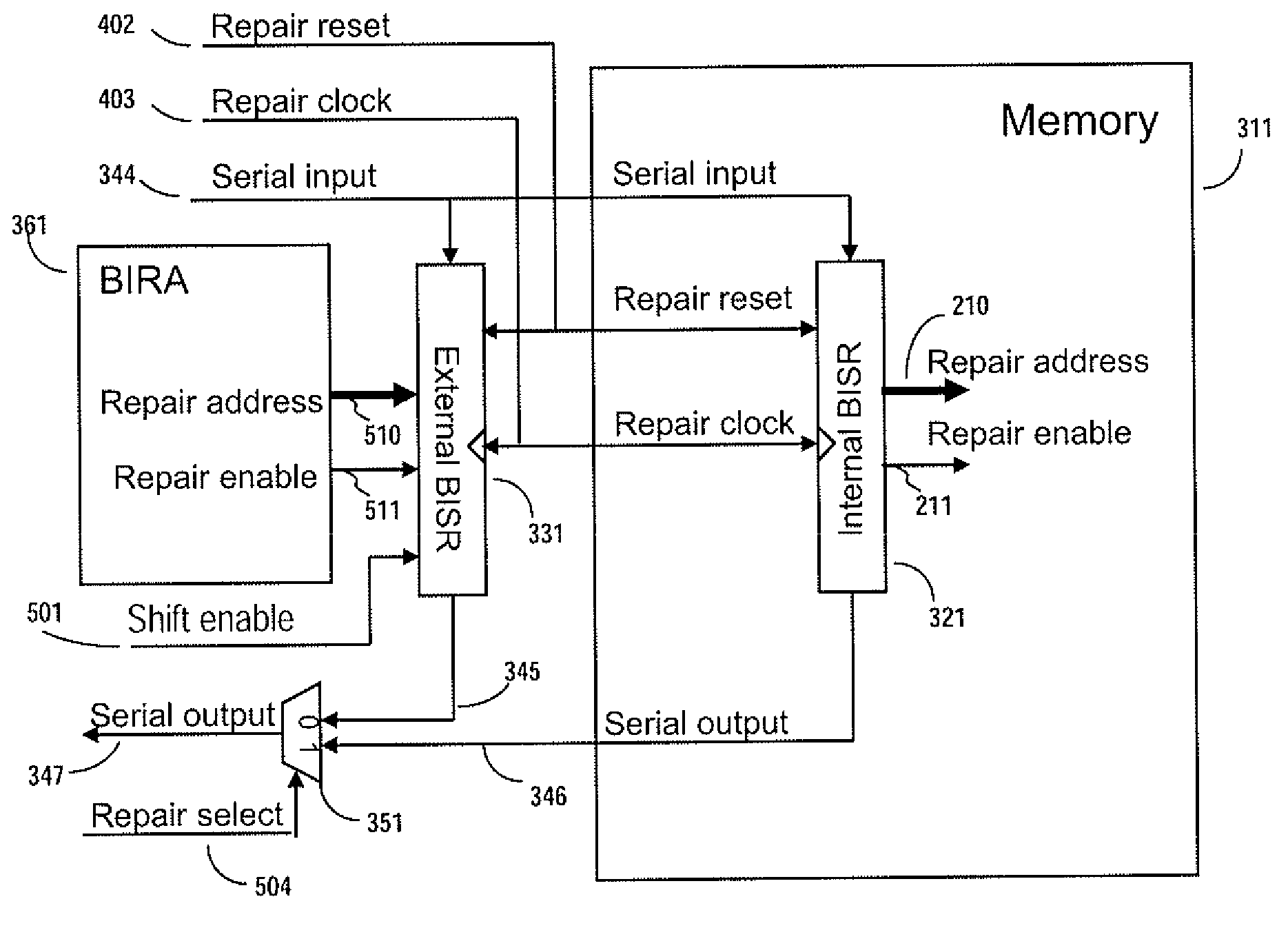

Method and apparatus for storing and distributing memory repair information

ActiveUS20080065929A1Easy to integrateConvenient to accommodateElectronic circuit testingStatic storageDistributed memoryControl signal

A system for repairing embedded memories on an integrated circuit is disclosed. The system comprises an external Built-In Self-repair Register (BISR) associated with every reparable memory on the circuit. Each BISR is configured to accept a serial input from a daisy chain connection and to generate a serial output to a daisy chain connection, so that a plurality of BISRs are connected in a daisy chain with a fuse box controller. The fuse box controller has no information as to the number, configuration or size of the embedded memories, but determines, upon power up, the length of the daisy chain. With this information, the fuse box controller may perform a corresponding number of serial shift operations to move repair data to and from the BISRs and into and out of a fuse box associated with the controller. Memories having a parallel repair interface are supported by a parallel address bus and enable control signal on the BISR, while those having a serial repair interface are supported by a parallel daisy chain path that may be selectively cycled to shift the contents of the BISR to an internal serial register in the memory. Preferably, each of the BISRs has an associated repair analysis facility having a parallel address bus and enable control signal by which fuse data may be dumped in parallel into the BISR and from there, either uploaded to the fuse box through the controller or downloaded into the memory to effect repairs. Advantageously, pre-designed circuit blocks may provide daisy chain inputs and access ports to effect the inventive system therealong or to permit the circuit block to be bypassed for testing purposes.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

SONOS embedded memory with CVD dielectric

InactiveUS7390718B2Faster rateSolid-state devicesSemiconductor/solid-state device manufacturingBit lineCMOS

An embedded semiconductor memory is fabricated by: forming diffusion bit line regions in a semiconductor substrate; then thermally oxidizing the upper surface of the substrate, thereby forming a bottom oxide layer over the substrate and simultaneously forming bit line oxide regions over each of the diffusion bit line regions; and then forming an intermediate dielectric layer (e.g., silicon nitride), over the bottom oxide layer and the bit line oxide regions. CMOS well implants are then performed in a CMOS section of the device through the silicon nitride layer and bottom oxide layer. The silicon nitride layer and bottom oxide layer are then removed in the CMOS section, and a top dielectric layer, such as a high-temperature oxide or a high-k dielectric, is deposited. The top dielectric layer completes a memory stack of the memory device, and forms a gate dielectric layer of a high voltage transistor in the CMOS section.

Owner:PS4 LUXCO SARL

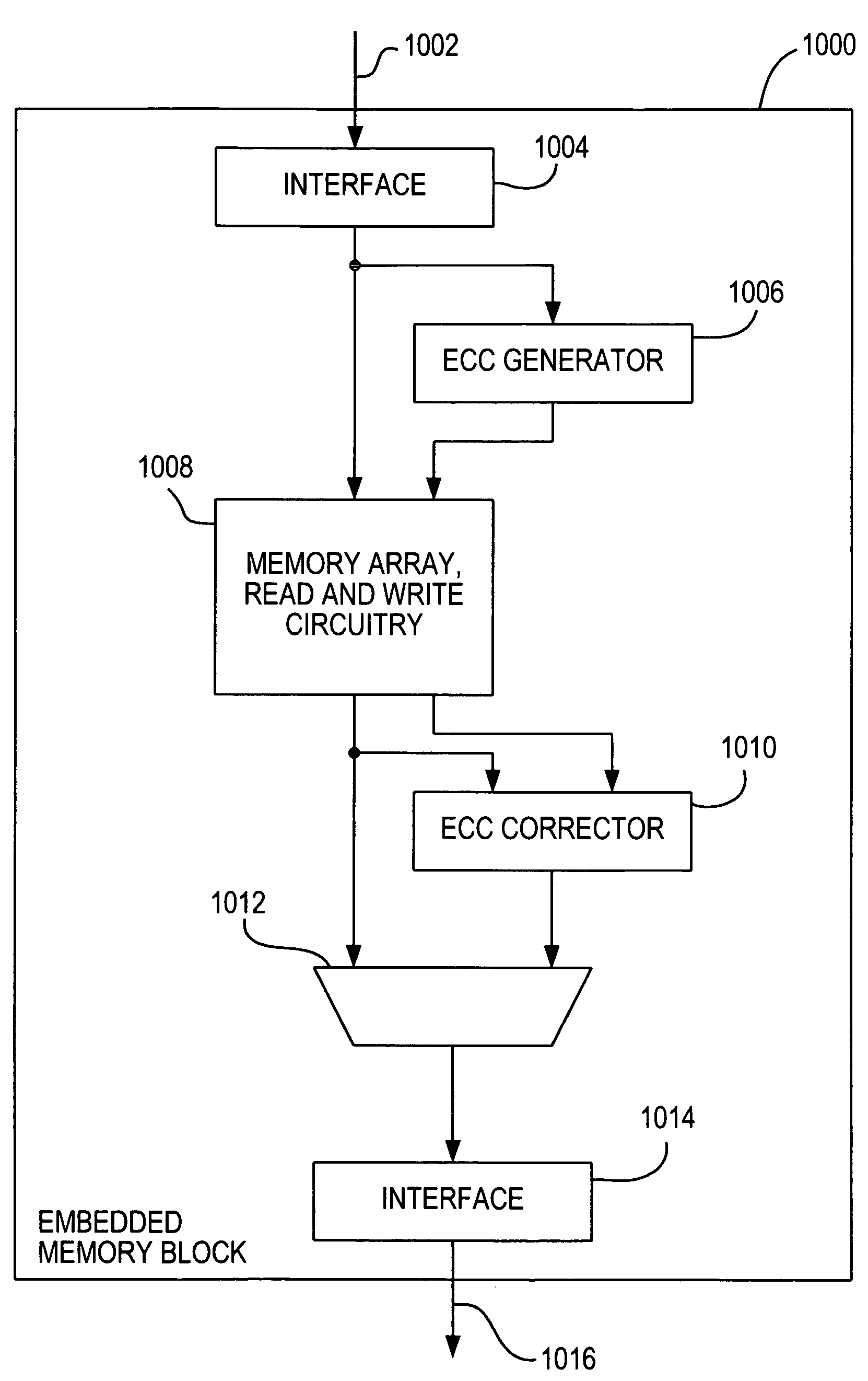

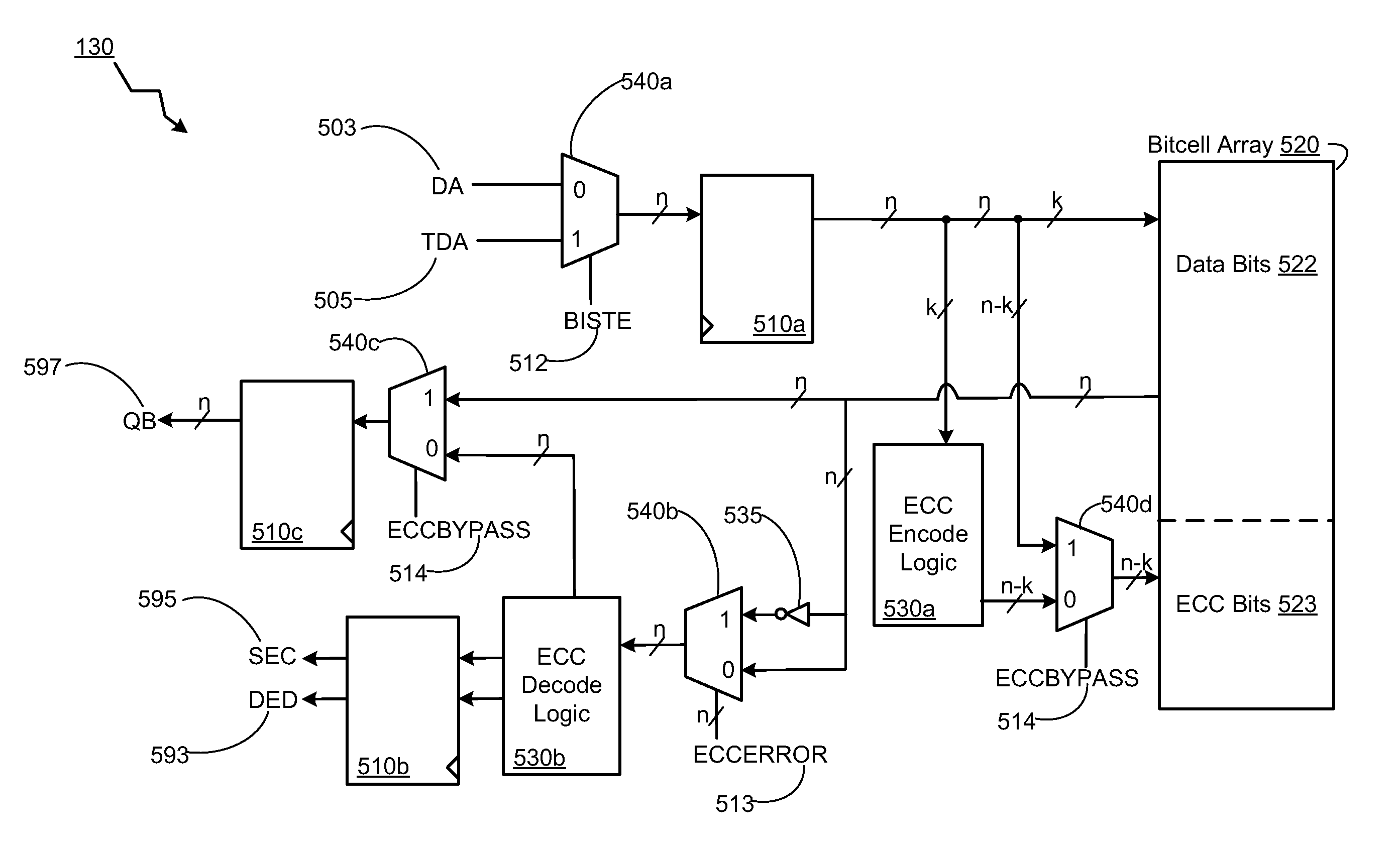

Providing test coverage of integrated ecc logic en embedded memory

A method is provided in which a first error test may be performed on a memory that includes an integrated error correcting code (ECC) portion. The functionality of the ECC portion may be bypassed in the first error test. A second error test may be performed on the memory, where the second error test includes testing the functionality of the ECC portion. Also provided is an apparatus including a memory device and an error correcting code (ECC) circuit. The apparatus also includes a first switching device adapted to select a first input signal or a second input signal and a second switching device adapted to select one of a signal from the memory device or a signal from a portion of the ECC circuit. Also provided are computer readable storage devices encoded with data for adapting a manufacturing facility to create the apparatus and for adapting a processor to perform the method above.

Owner:ADVANCED MICRO DEVICES INC

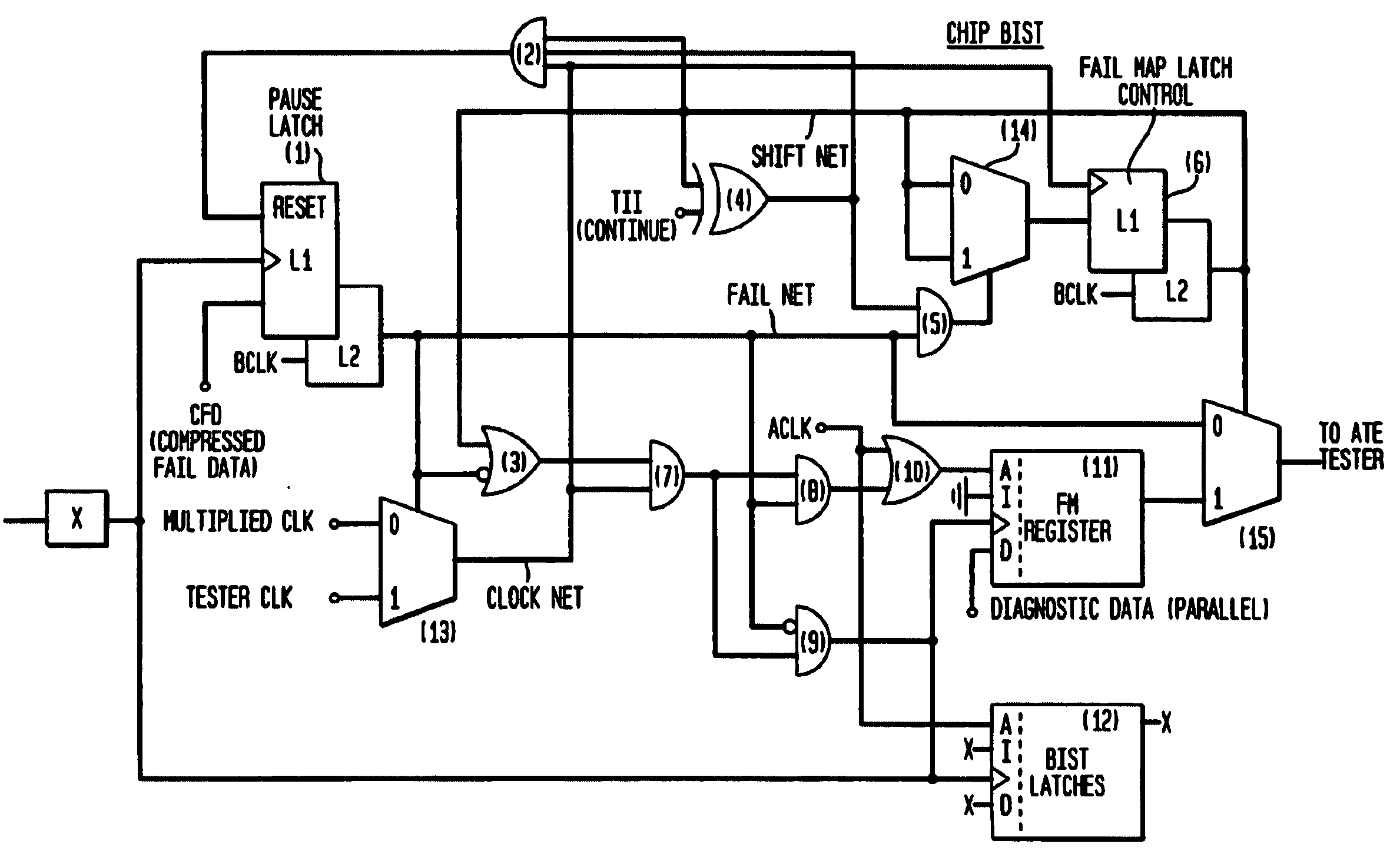

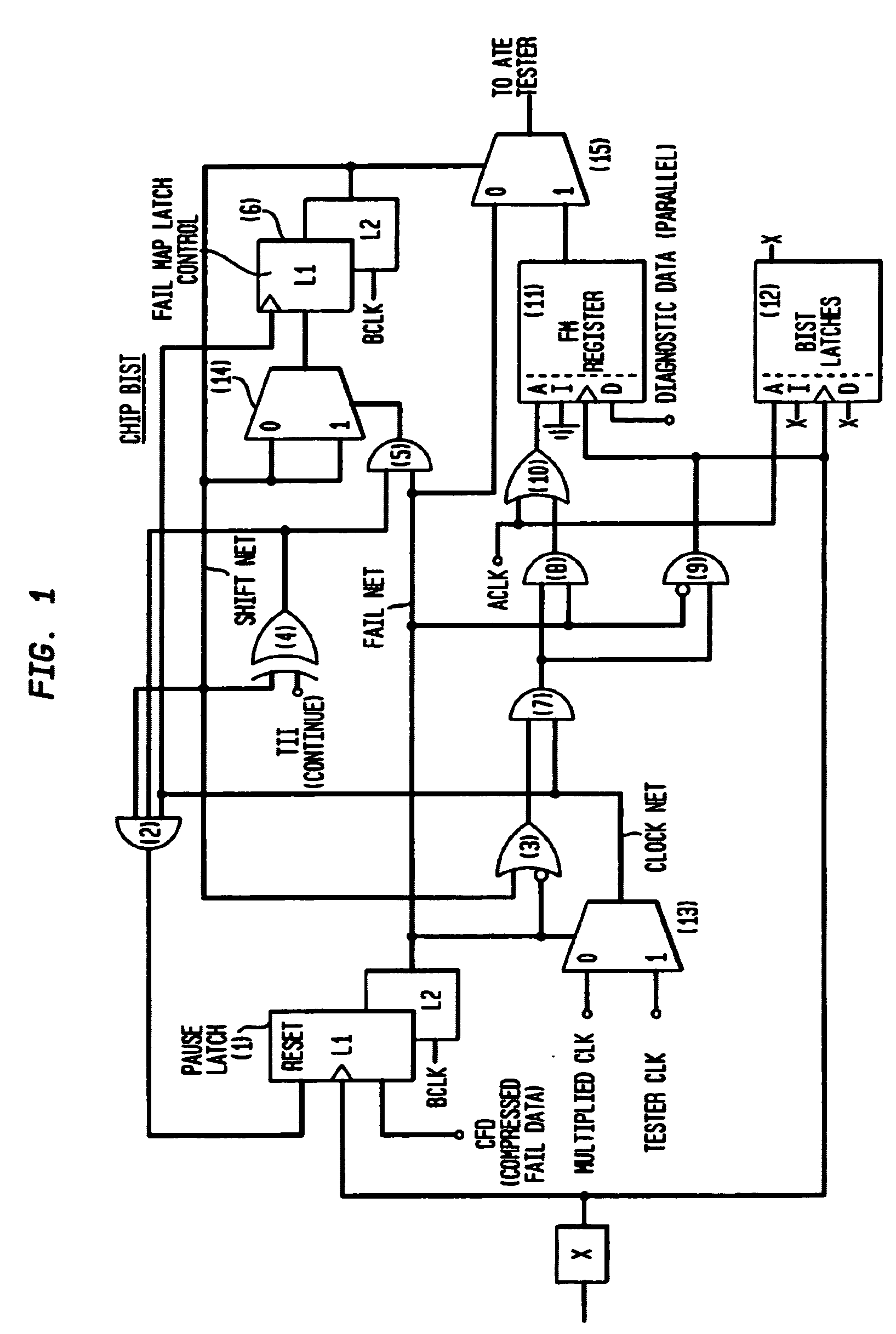

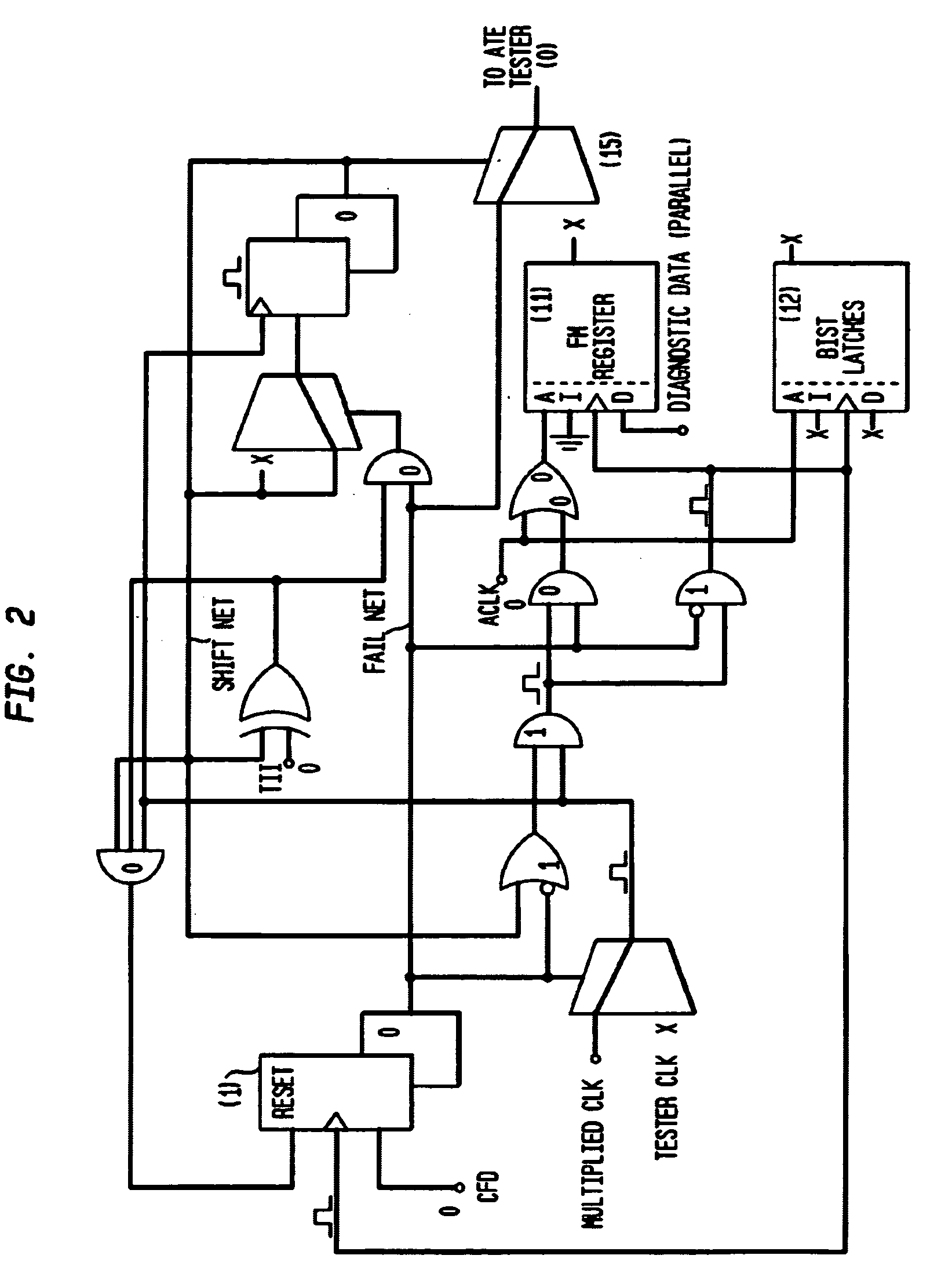

Automatic bit fail mapping for embedded memories with clock multipliers

A bit fail map circuit accurately generates a bit fail map of an embedded memory such as a DRAM by utilizing a high speed multiplied clock generated from a low-speed Automated Test Equipment (ATE) tester. The circuit communicates between the ATE tester, the embedded memory under test, Built-In Self-Test (BIST) and Built-In Redundancy Analysis (BIRA). An accurate bit fail map of an embedded DRAM memory is provided by pausing the BIST test circuitry at a point when a fail is encountered, namely a mismatch between BIST expected data and the actual data read from the array, and then shifting the bit fail data off the chip using the low-speed ATE tester clock. Thereafter, the high-speed test is resumed from point of fail by again running the BIST using the high-speed internal clock, to provide at-speed bit Fail Maps.

Owner:IBM CORP

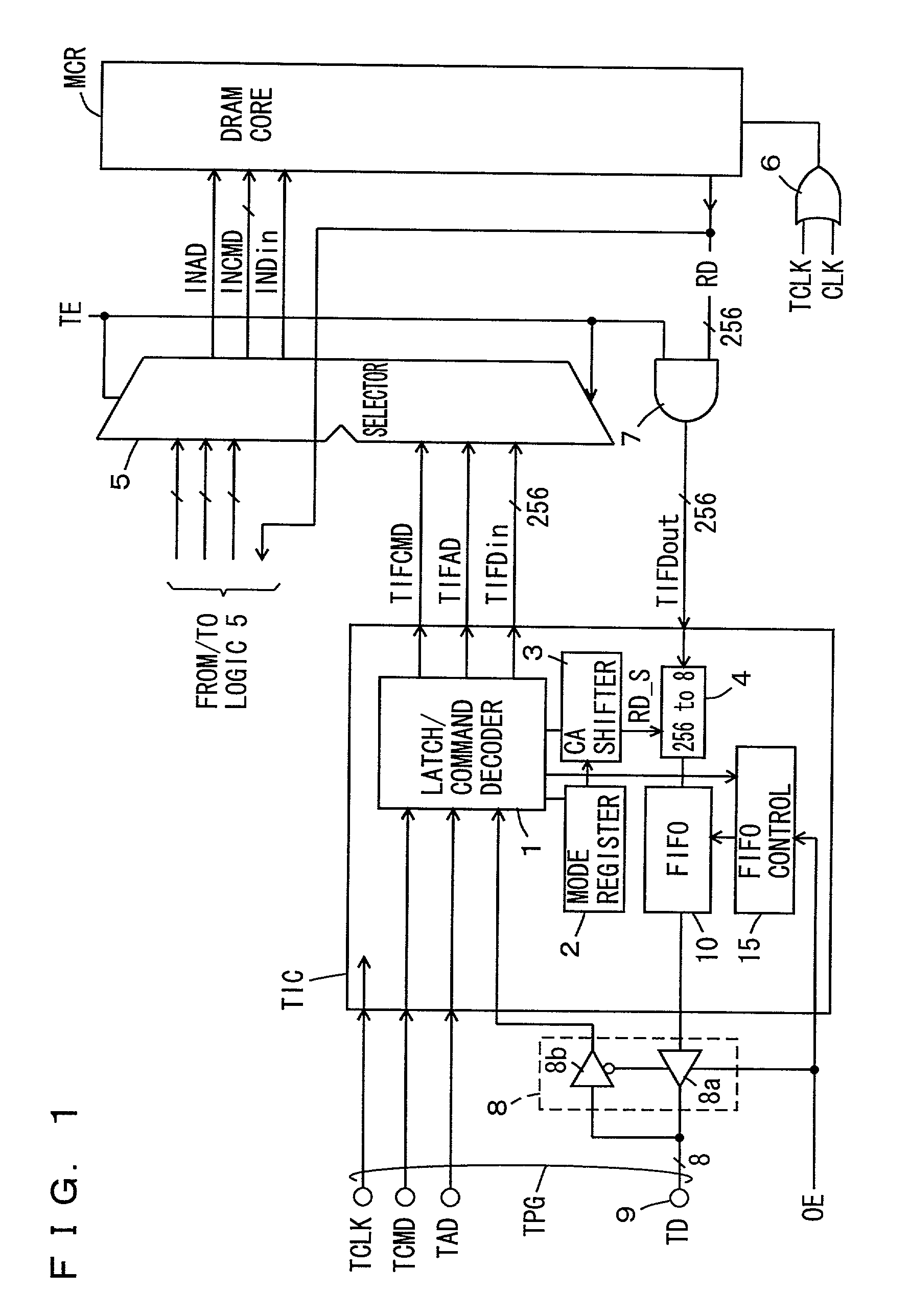

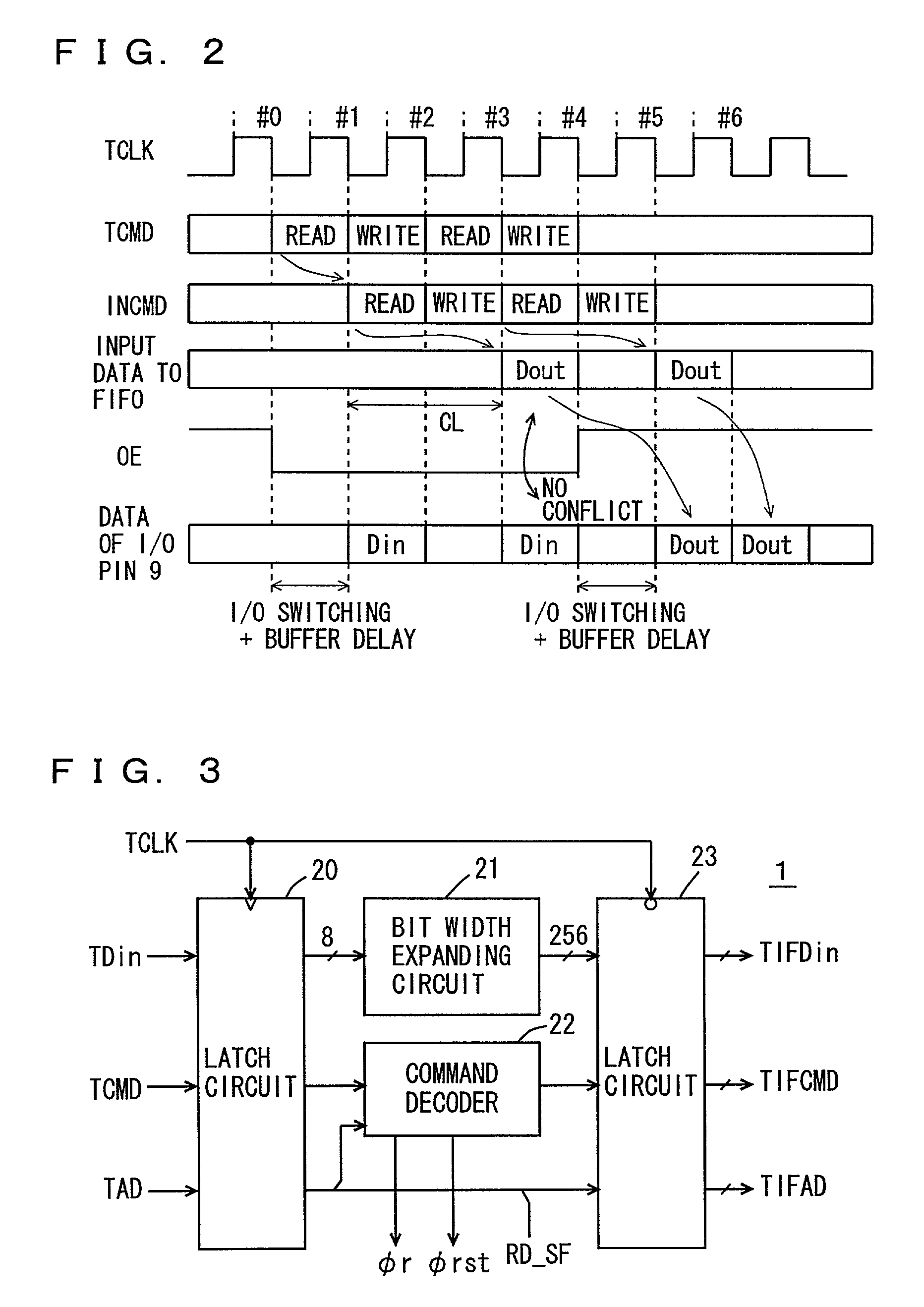

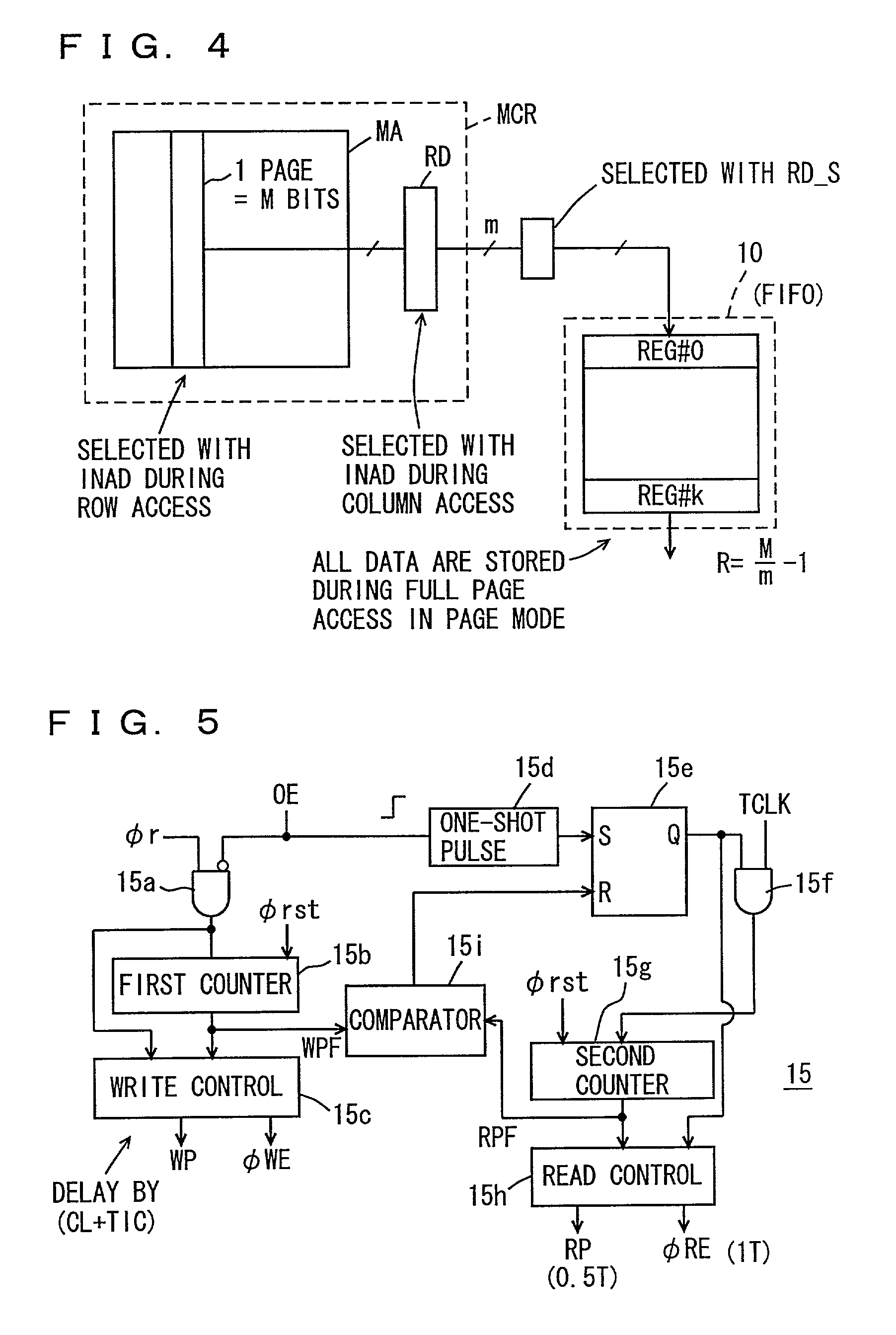

Test interface circuit and semiconductor integrated circuit device including the same

In a test interface circuit arranged between an embedded memory and a test data input / output (I / O) terminal, a first-in first-out circuit for successively storing test data is arranged for controlling a latency of data read from the embedded memory. The test interface circuit for the embedded memory can reduce the number of test data I / O terminals, and can increase the executable test patterns.

Owner:RENESAS ELECTRONICS CORP

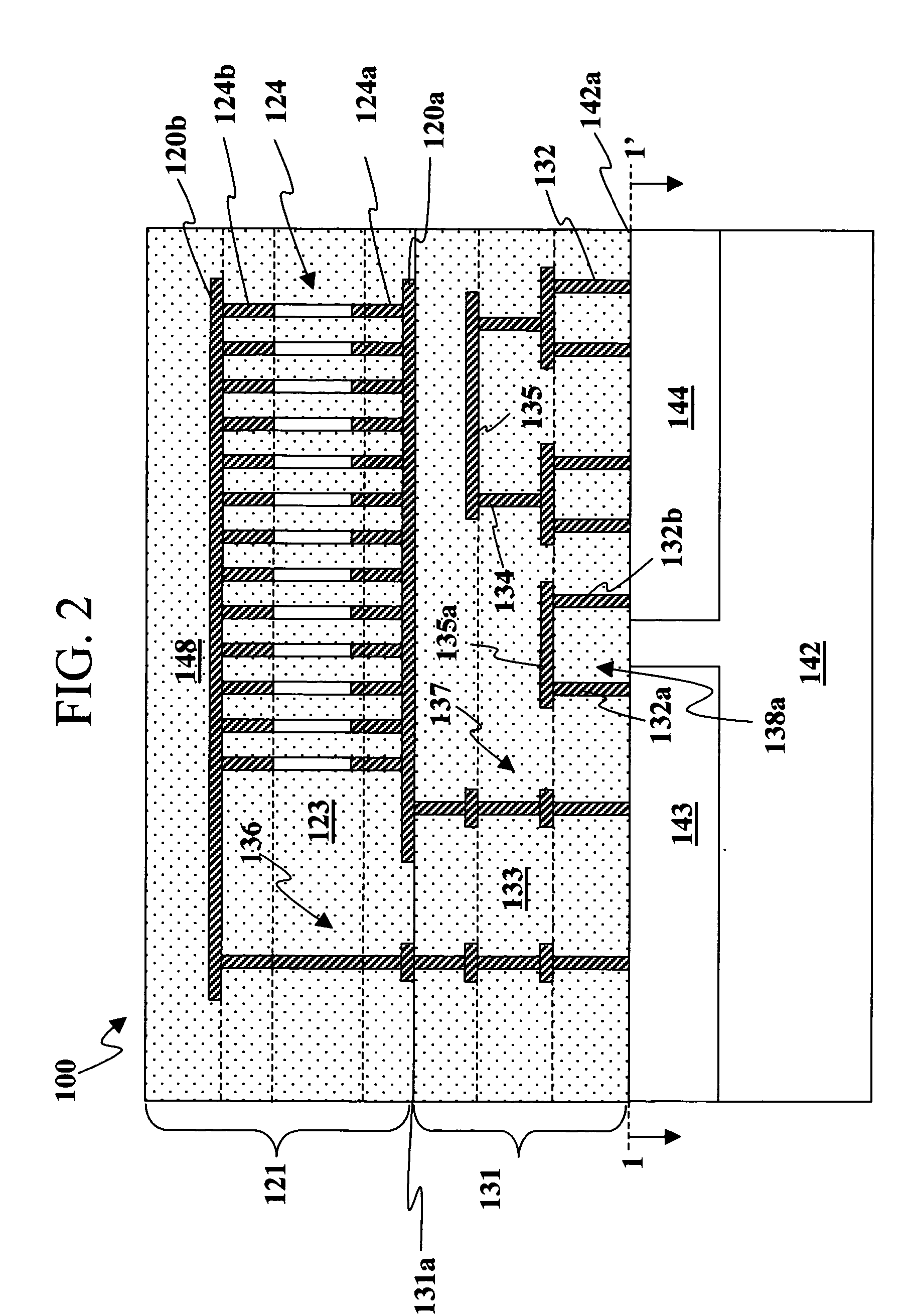

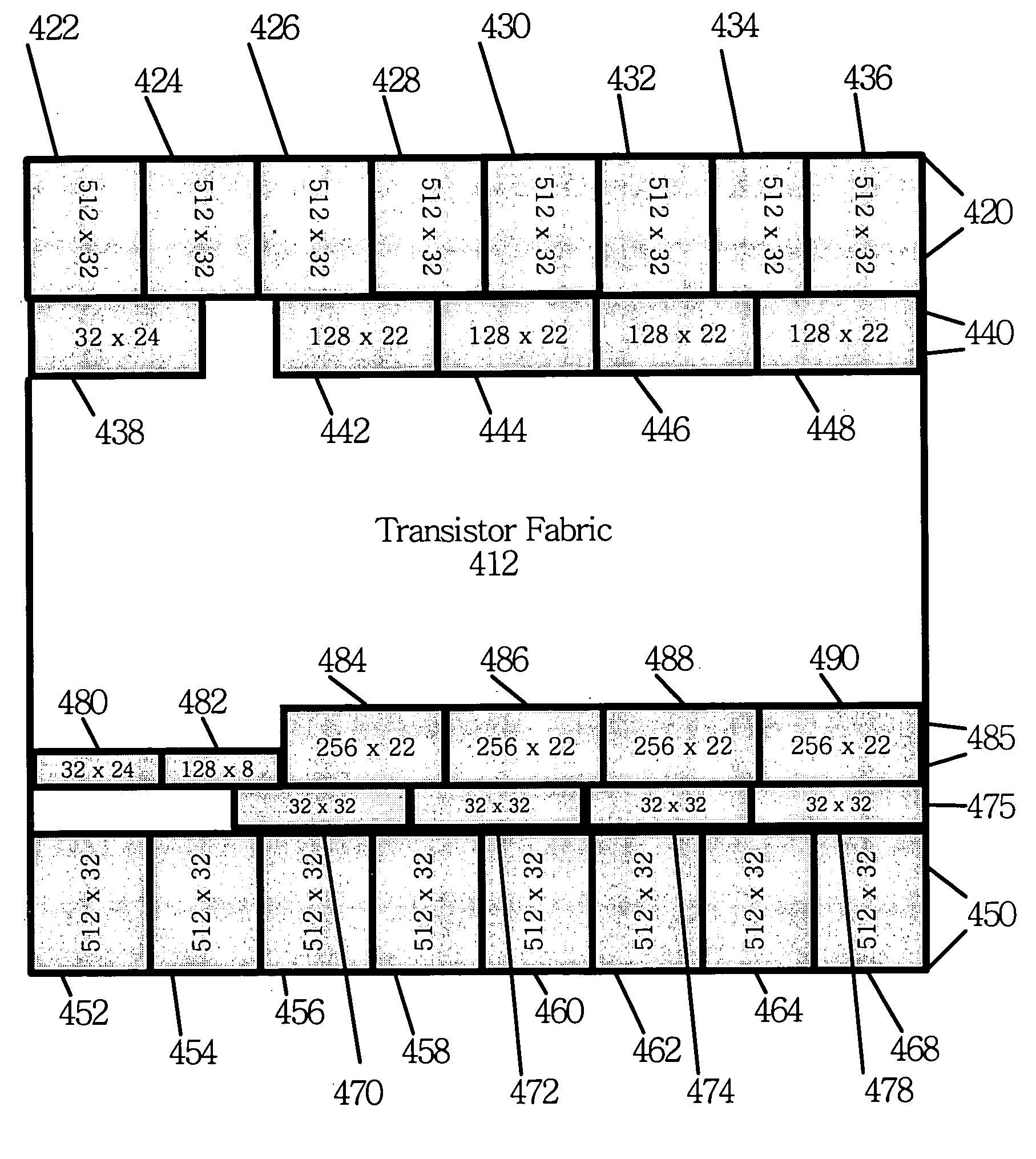

Flexible design for memory use in integrated circuits

A method for designing and using a partially manufactured semiconductor product is disclosed. The partially manufactured semiconductor product, referred to as a slice, contains a fabric of configurable transistors and at least an area of embedded memory. The method contemplates that a range of processors, processing elements, processing circuits exists which might be manufactured as a hardmacs or configured from the transistor fabric of the slice. The method then evaluates all the memory requirements of all the processors in the range to create a memory superset to be embedded into the slice. The memory superset can then be mapped and routed to a particular memory for one of the processors within the range; ports can be mapped and routed to access the selected portions of the memory superset. If any memory is not used, then it and / or its adjoining transistor fabric can become a landing zone for other functions or registers or memories.

Owner:BELL SEMICON LLC

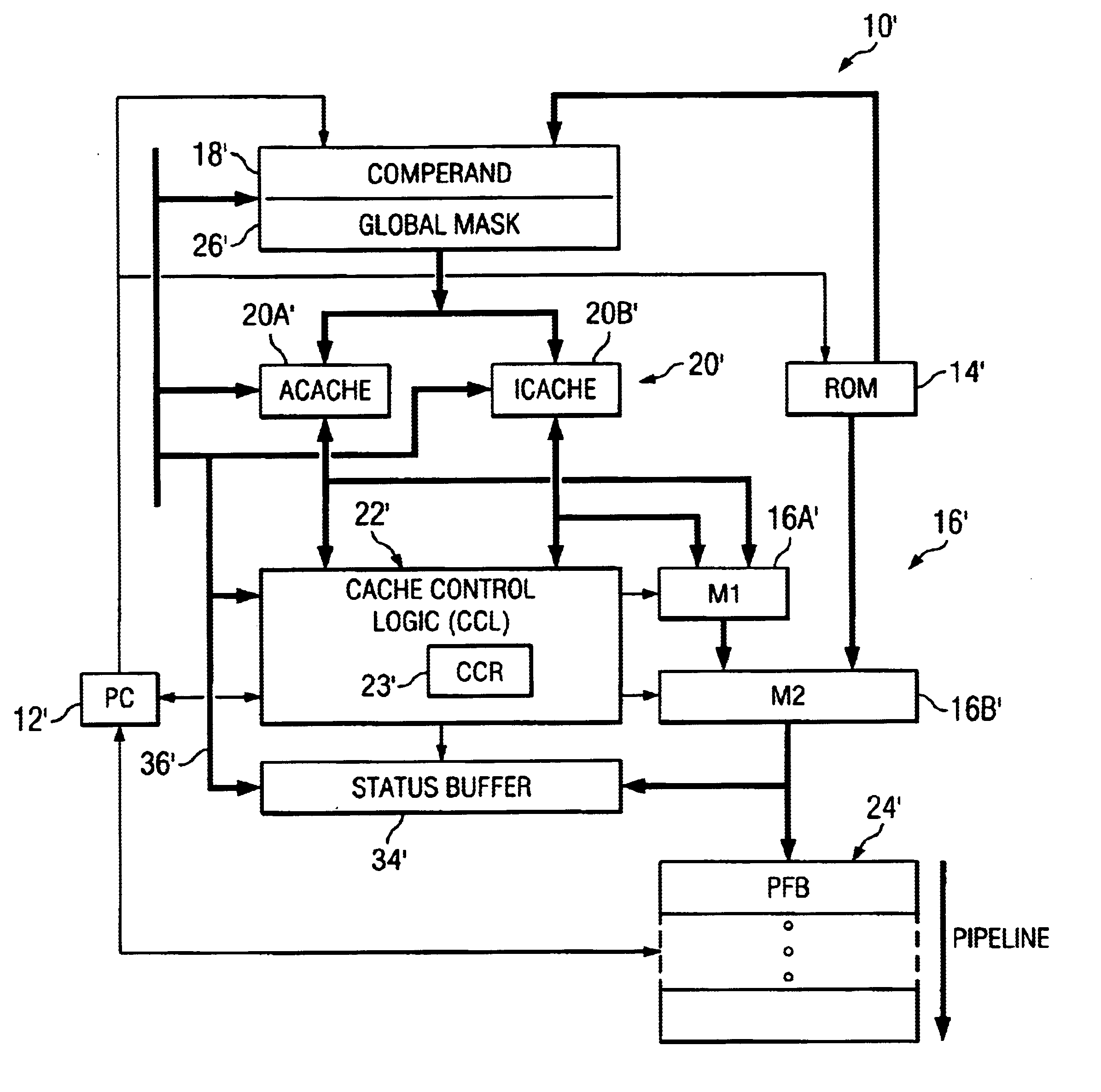

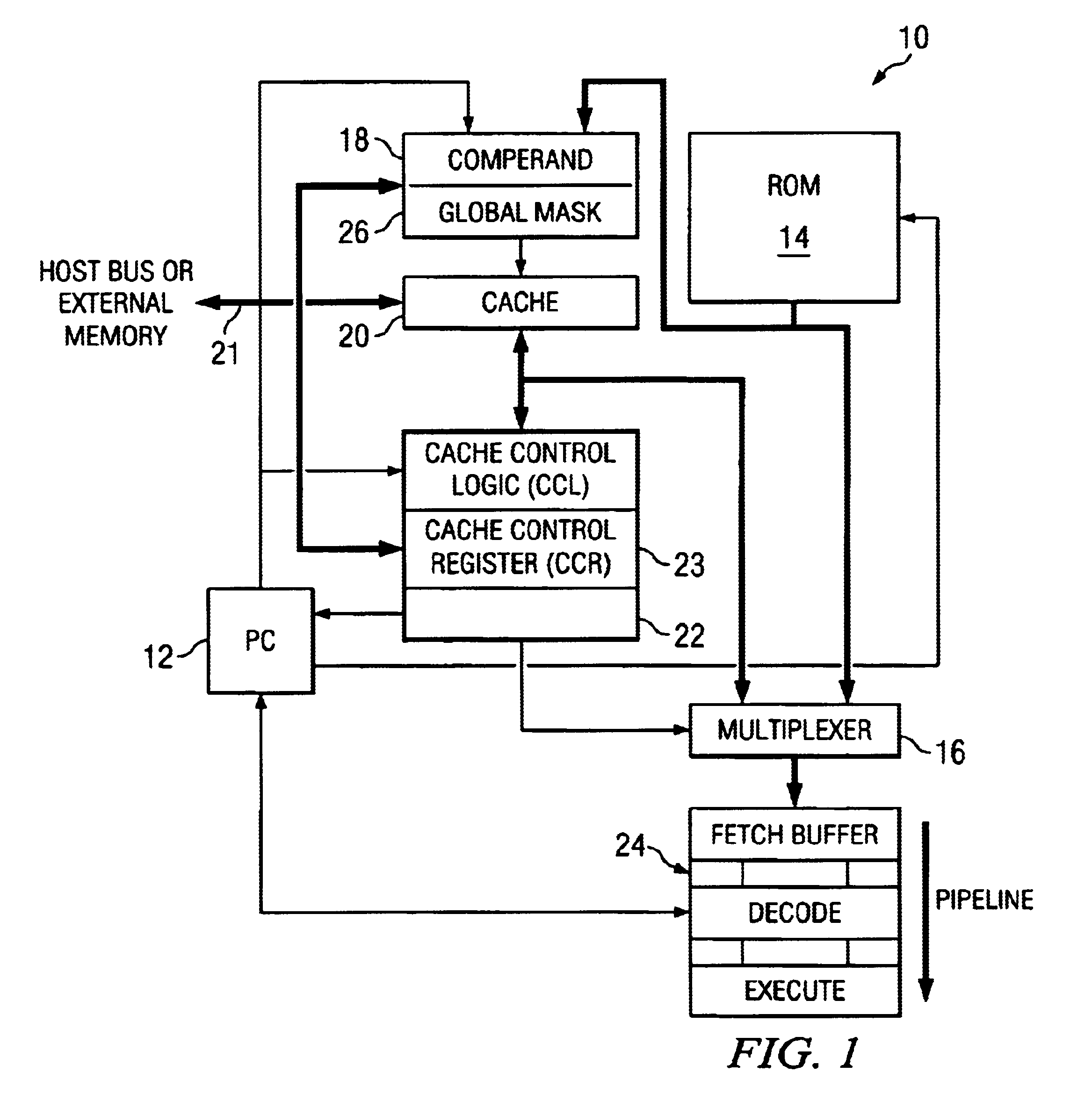

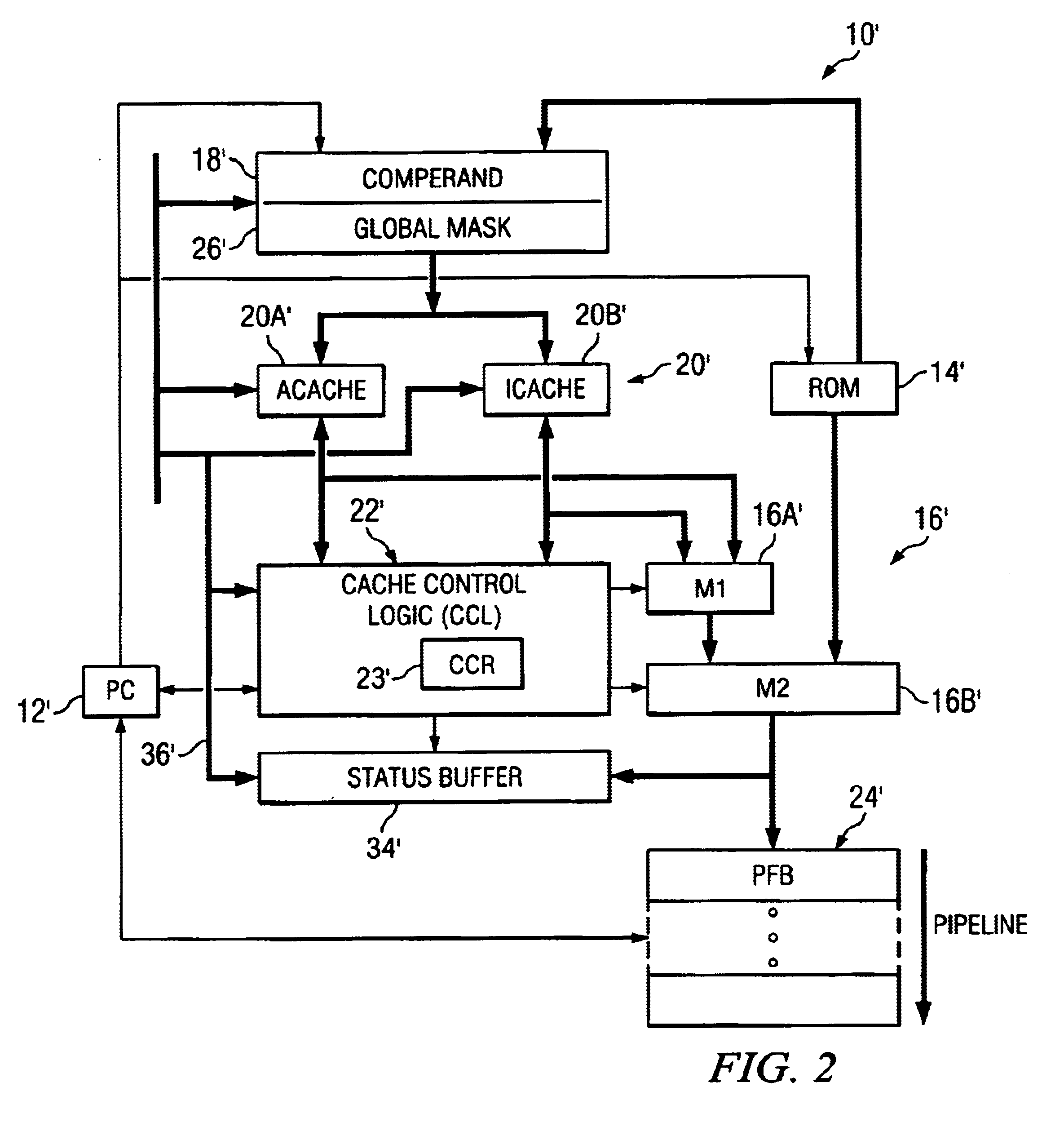

Method and apparatus for changing microcode to be executed in a processor

InactiveUS6691308B1Runtime instruction translationGeneral purpose stored program computerComputer architectureEngineering

A Central Processing Unit (CPU) hotpatch circuit compares the run-time instruction stream against an internal cache. The internal cache stores embedded memory addresses with associated control flags, executable instruction codes, and tag information. In the event that a comparison against the current program counter succeeds, then execution is altered as required per the control flags. If no comparison match is made, then execution of the instruction that was accessed by the program counter is executed.

Owner:MICROELECTRONIC INNOVATIONS LLC

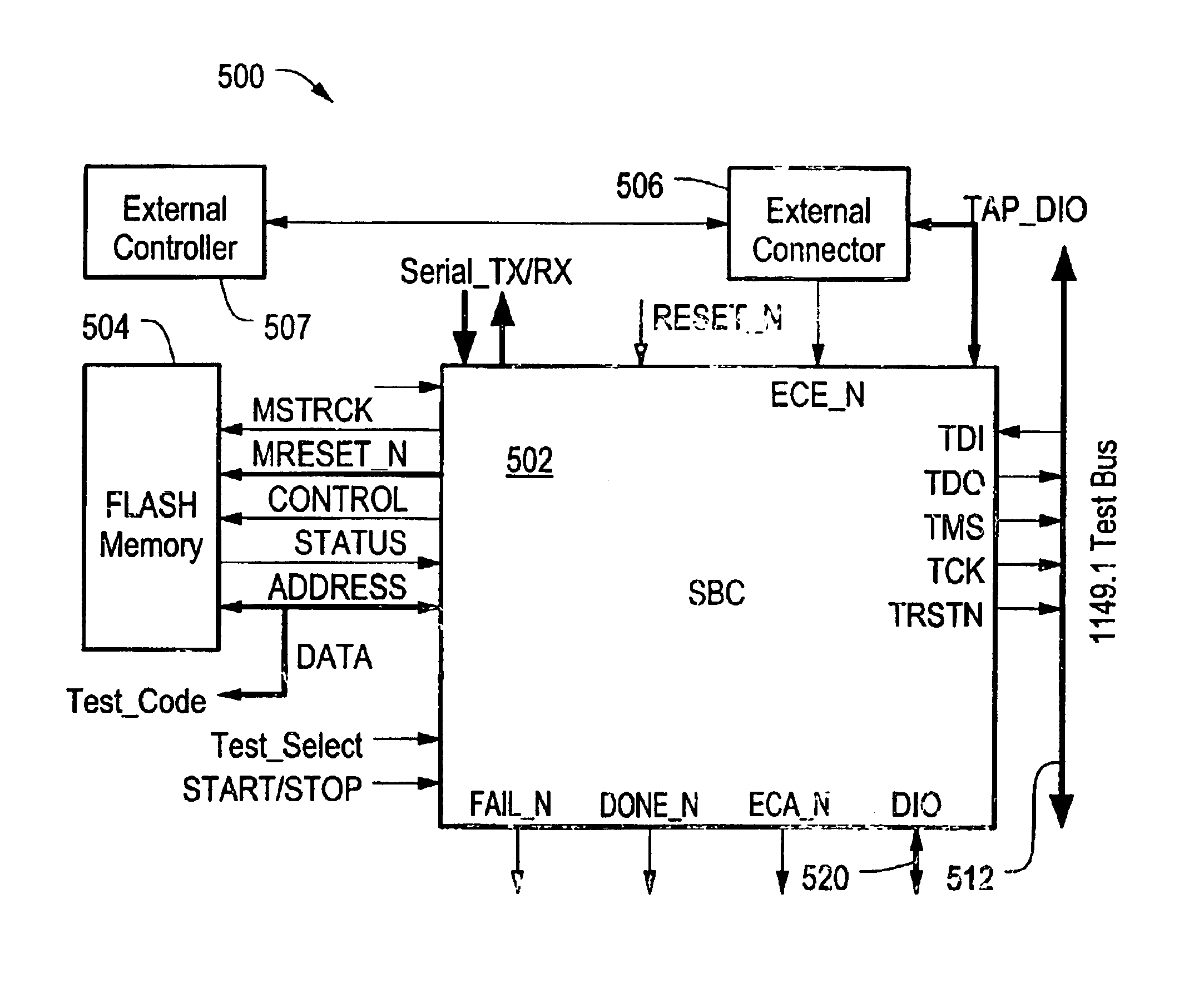

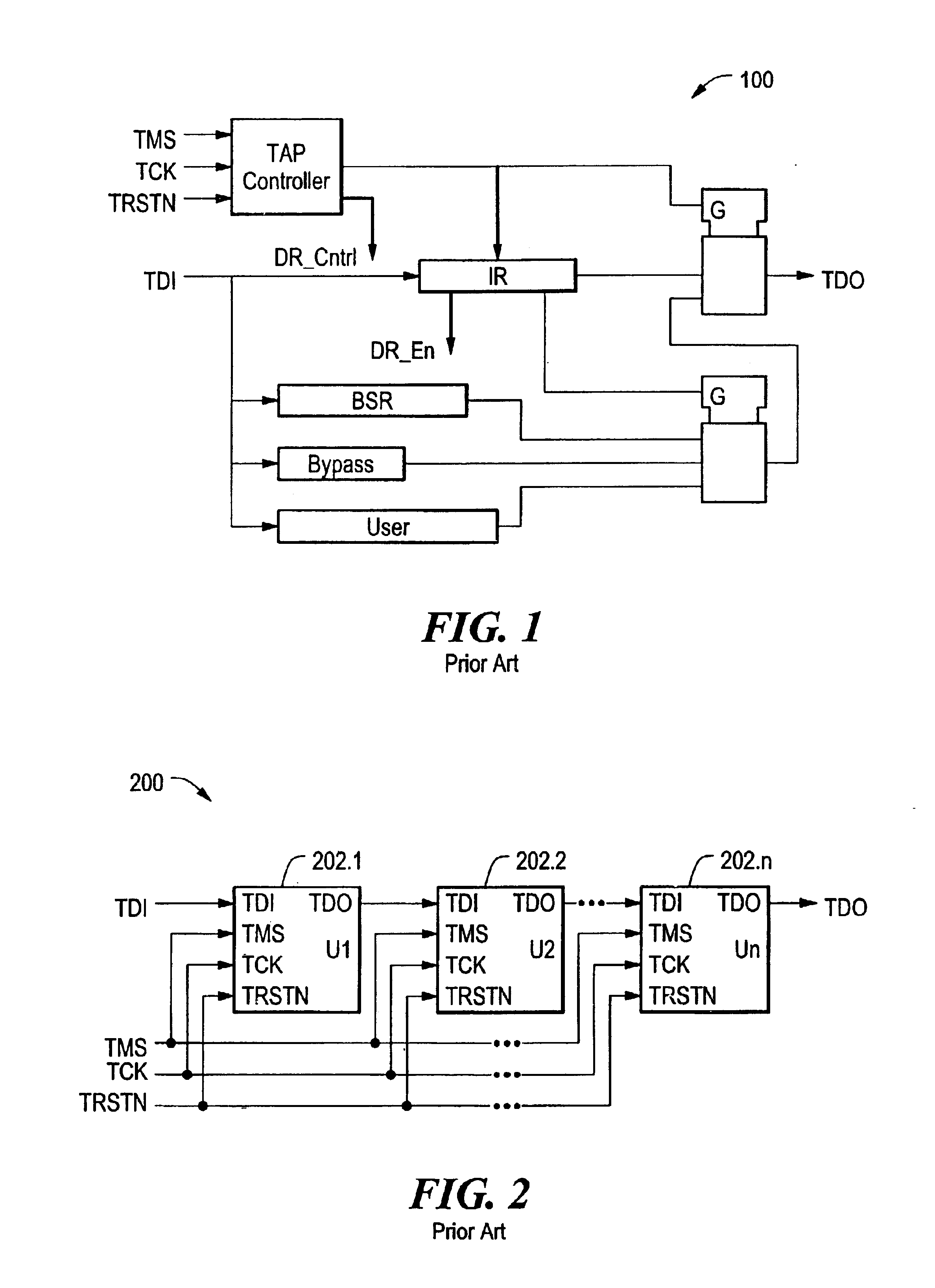

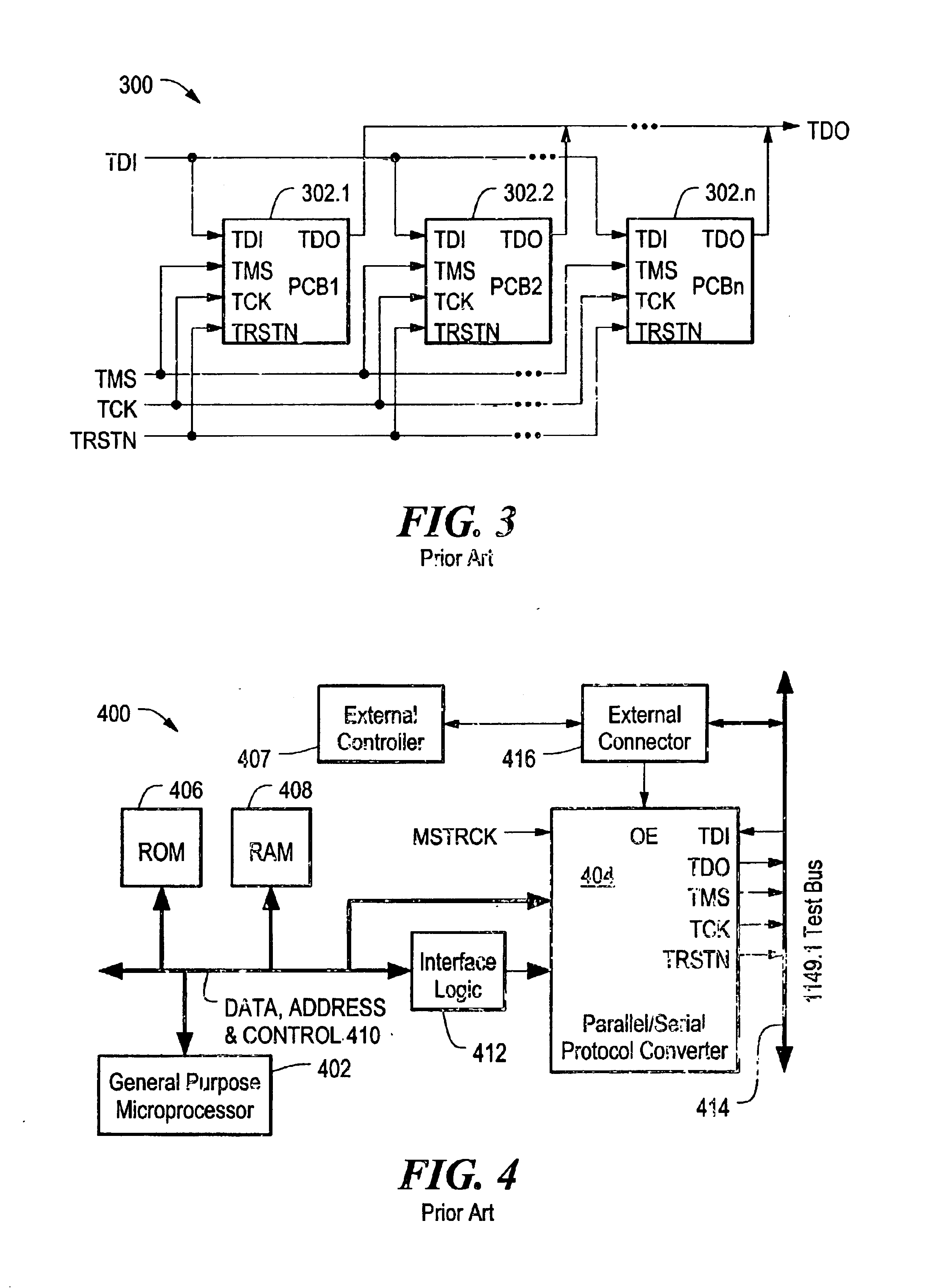

Method and apparatus for embedded built-in self-test (BIST) of electronic circuits and systems

InactiveUS6957371B2Facilitates testing and debuggingLow costElectronic circuit testingError detection/correctionController architectureElectronic systems

An embedded electronic system built-in self-test controller architecture that facilitates testing and debugging of electronic circuits and in-system configuration of programmable devices. The system BIST controller architecture includes an embedded system BIST controller, an embedded memory circuit, an embedded IEEE 1149.1 bus, and an external controller connector. The system BIST controller is coupled to the memory circuit and the IEEE 1149.1 bus, and coupleable to an external test controller via the external controller connector. The external test controller can communicate over the IEEE 1149.1 bus to program the memory and / or the system BIST controller circuitry, thereby enabling scan vectors to be debugged by the external test controller and then downloaded into the memory for subsequent application to a unit under test by the system BIST controller.

Owner:INTELLITECH INC

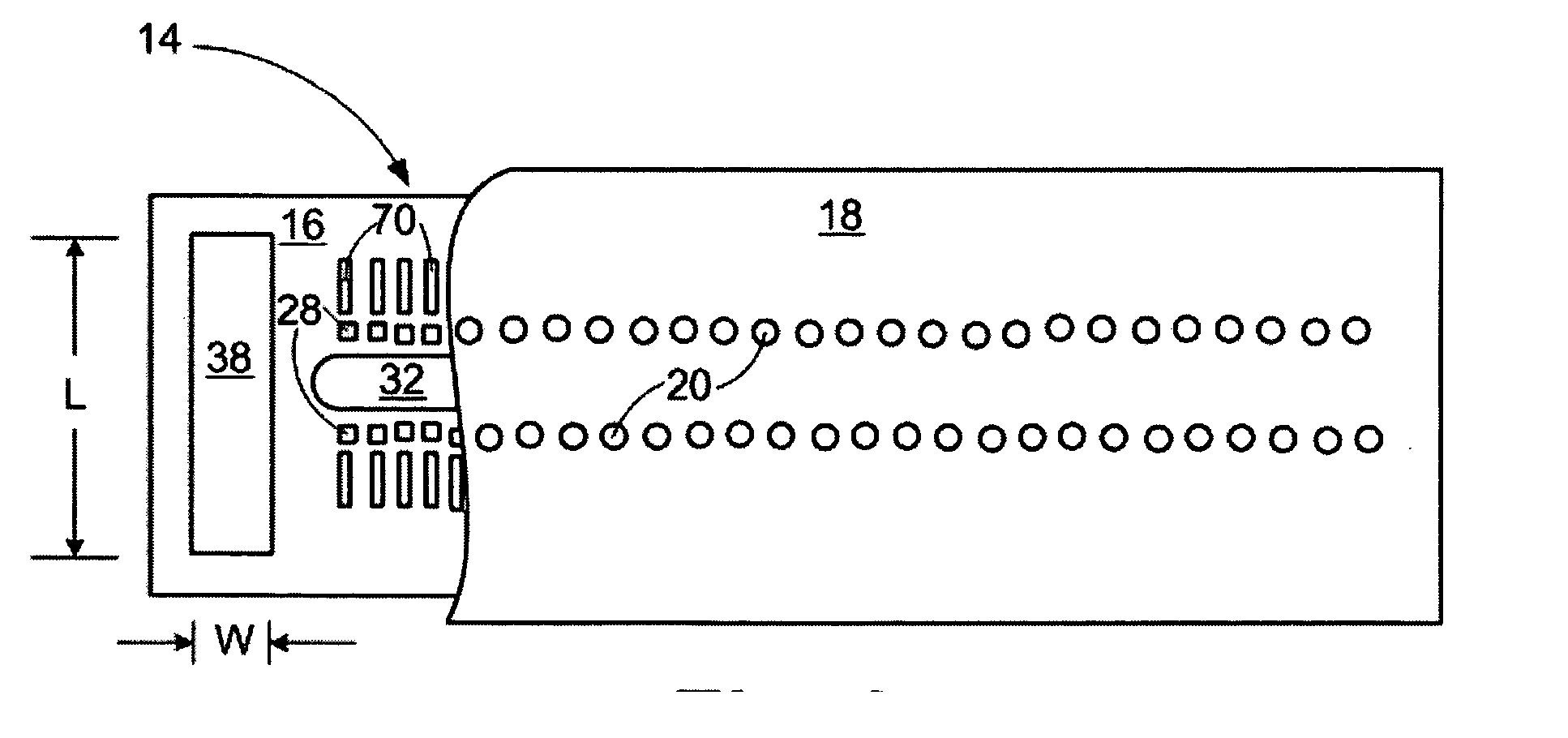

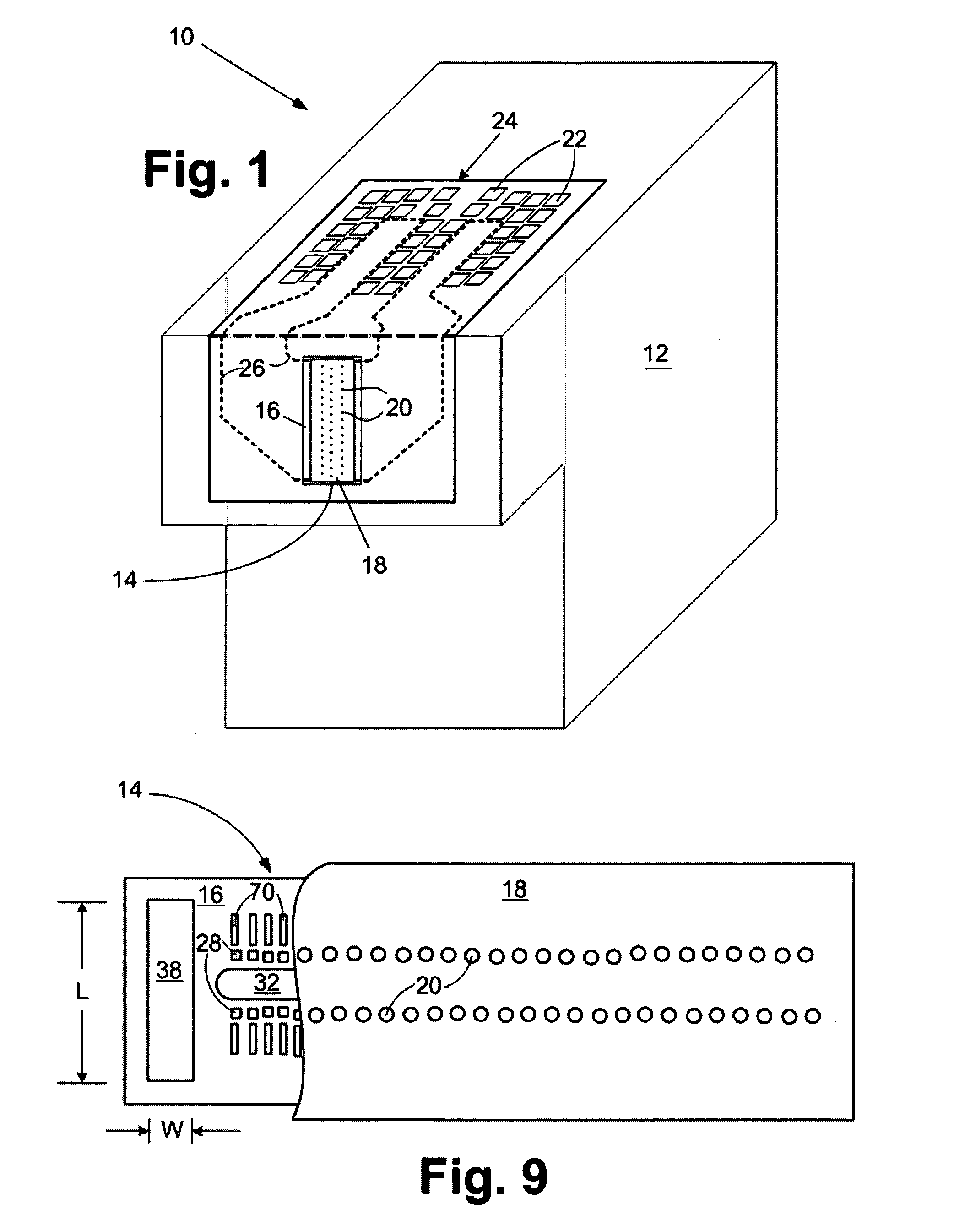

Printhead having embedded memory device

A semiconductor substrate for a micro-fluid ejecting device. The semiconductor substrate includes a plurality of fluid ejection devices disposed on the substrate. A plurality of driver transistors are disposed on the substrate for driving the plurality of fluid ejection devices. A programmable memory matrix containing embedded programmable memory devices is operatively connected to the micro-fluid ejecting device for collecting and storing information on the semiconductor substrate for operation of the micro-fluid ejecting device. The programmable memory matrix provides a high density of memory bits embedded on the substrate for storing information about the micro-fluid ejecting device.

Owner:SLINGSHOT PRINTING LLC

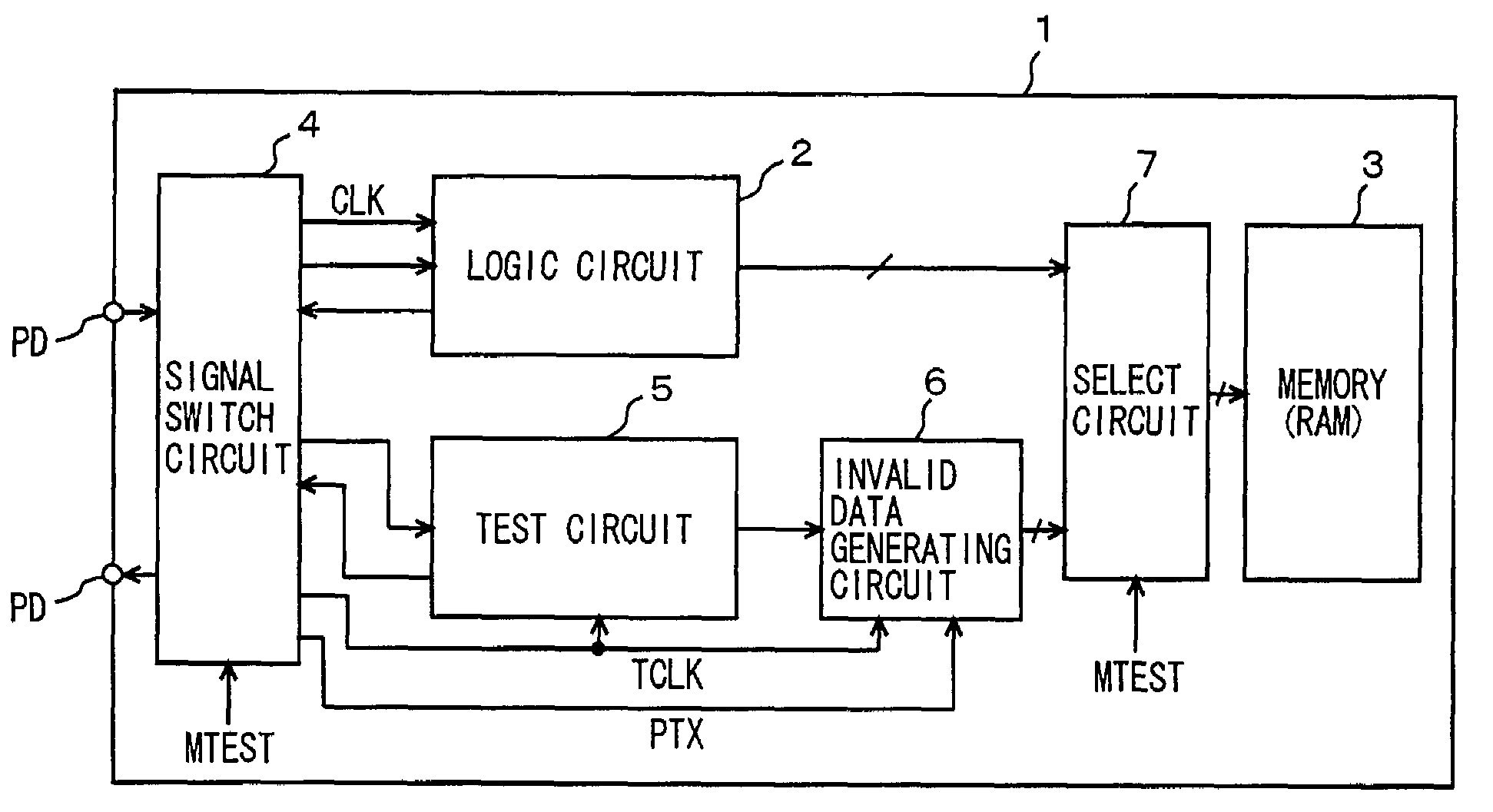

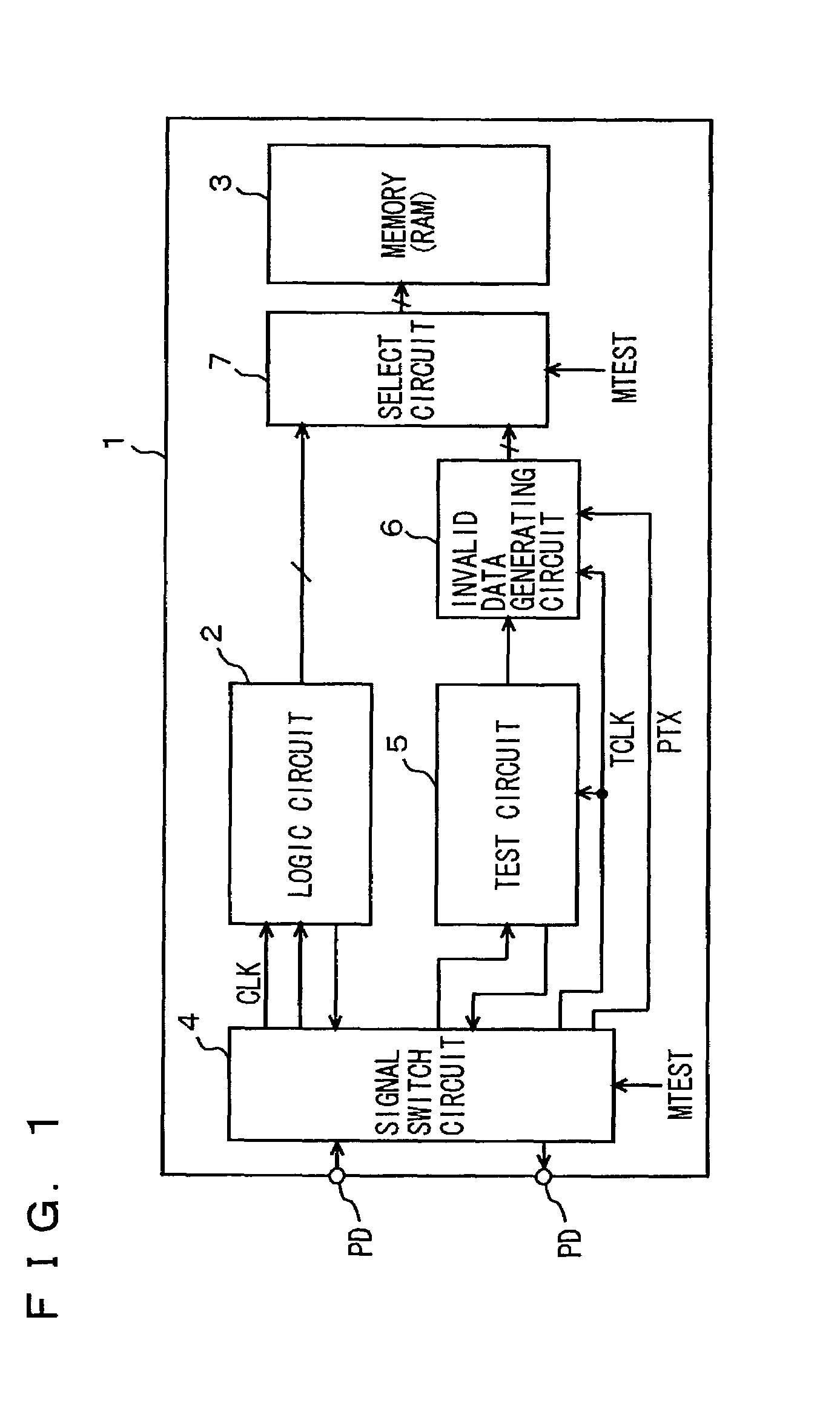

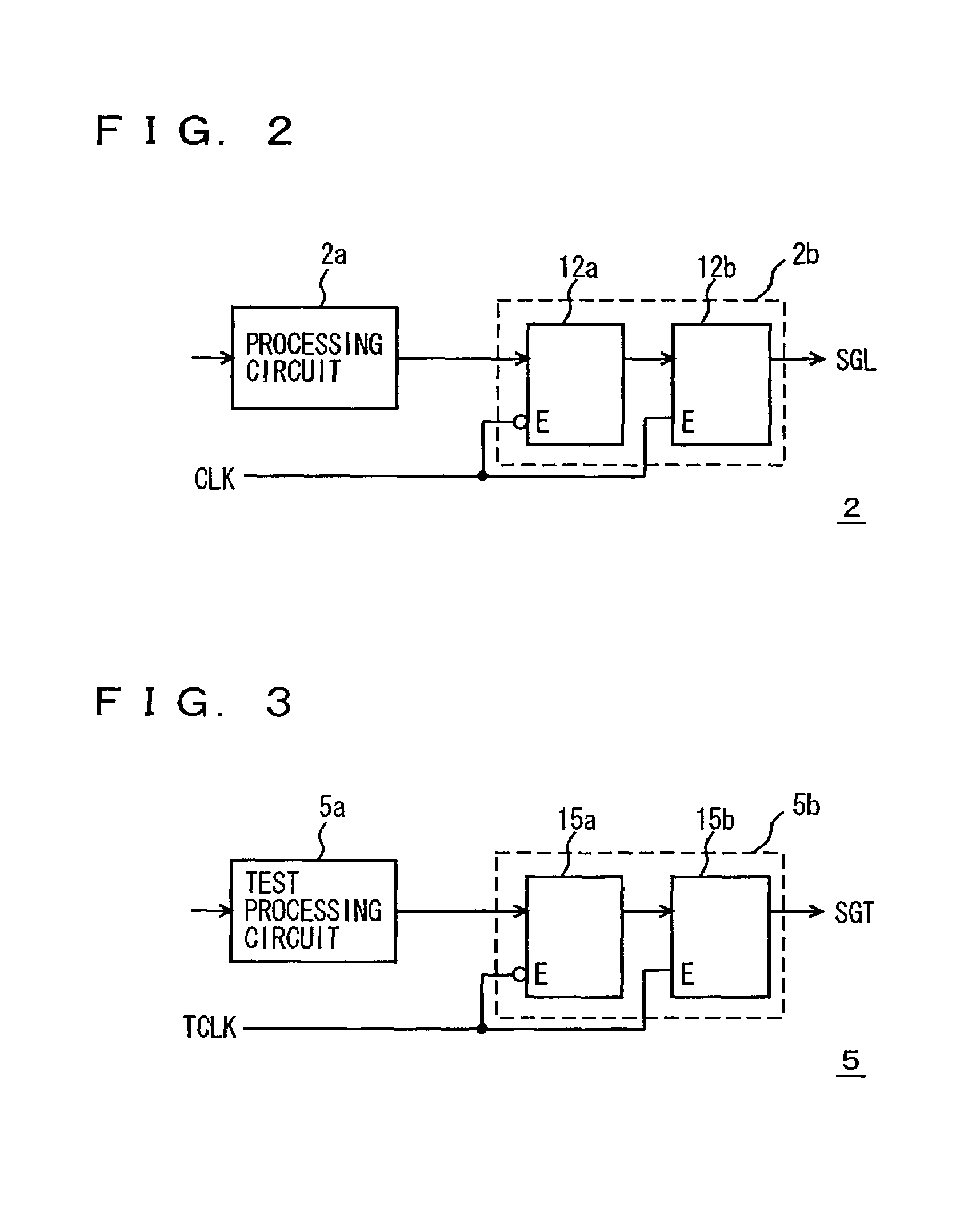

Test circuit capable of testing embedded memory with reliability

InactiveUS7007215B2Accurate conditionAccurate measurementError preventionTransmission systemsAccess timeControl signal

A test signal applied to an embedded memory is changed in synchronization with a test clock signal, set to an invalidated state by an asynchronous control signal asynchronous to the test clock signal and then is applied to a memory. The memory takes in a received signal in synchronization with a memory clock signal. An invalid data generating circuit modifies the test signal in accordance with the asynchronous control signal and generates a test signal and to apply the test signal to the memory. A period of an invalid state of the modified test signal can be adjusted and therefore, by monitoring a changing timing of the asynchronous control signal PTX with an external tester, setup and hold times of a signal for the memory can be measured. Setup and hold times and an access time for an embedded memory can be correctly measured.

Owner:RENESAS TECH CORP

Structure for reducing leakage currents and high contact resistance for embedded memory and method for making same

ActiveUS7329953B2Reduce manufacturing costEliminate needTransistorSemiconductor/solid-state device detailsDrain currentCapacitor

Owner:TAIWAN SEMICON MFG CO LTD

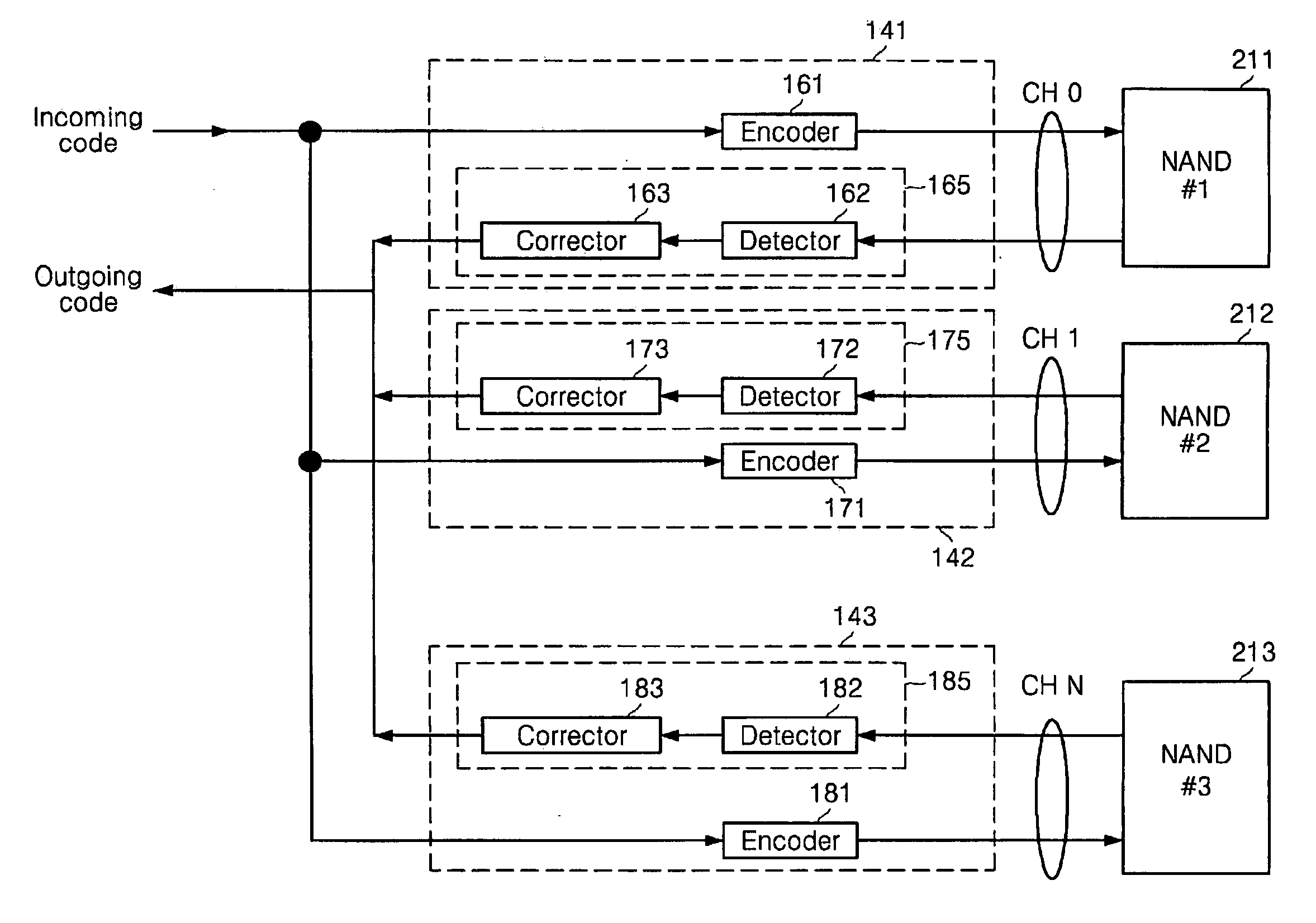

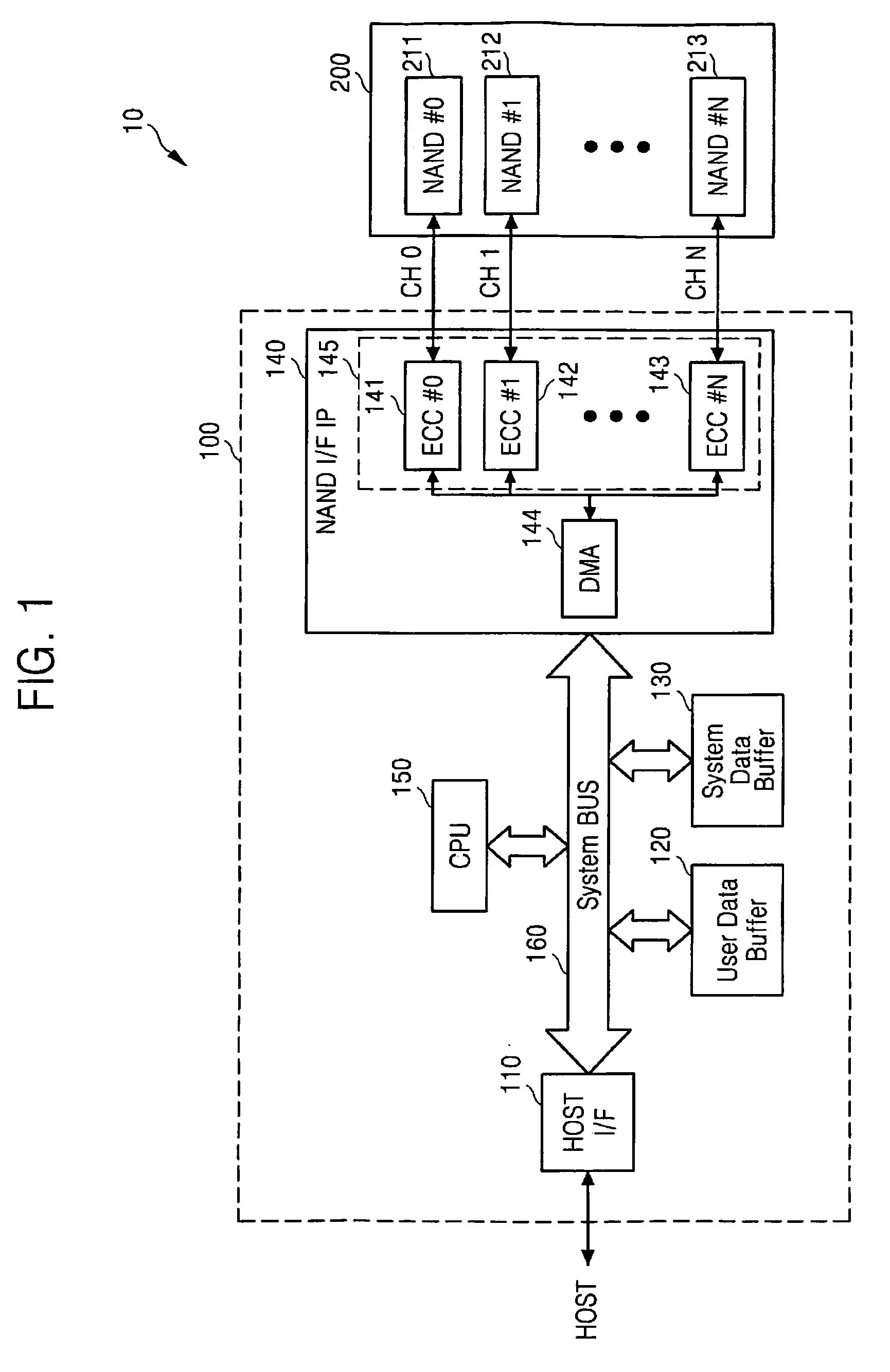

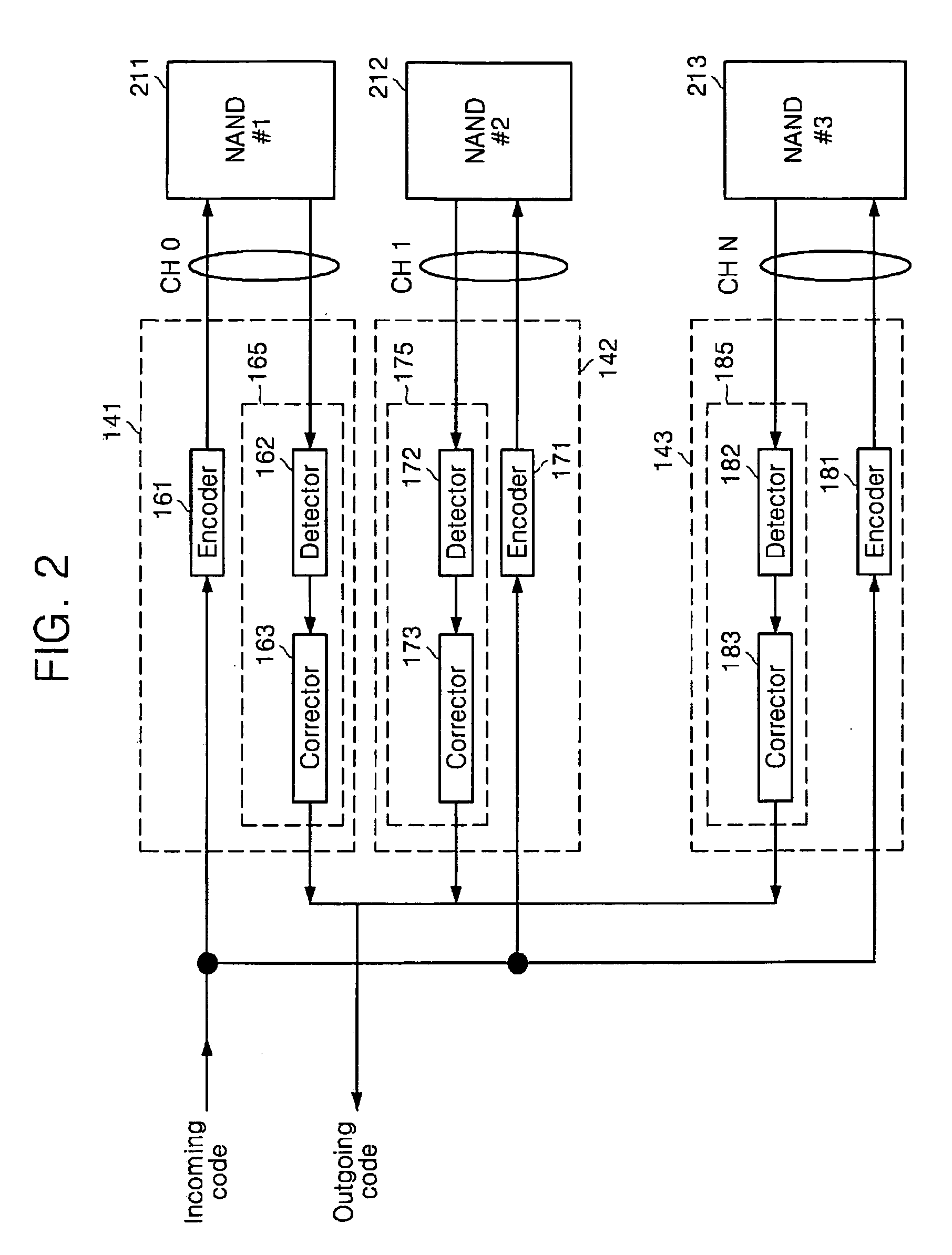

Multi-channel error correction coder architecture using embedded memory

InactiveUS20090024902A1Data representation error detection/correctionMemory loss protectionControl storeMemory controller

A memory system includes a plurality of memory devices; and a memory controller having a plurality of communication channels for communicating data with the plurality of memory devices. The memory controller includes an error correction encoder that is adapted to encode data to be communicated from the memory controller via the plurality of communication channels, and / or an error correction decoder that is adapted to detect and correct errors in data communicated to the memory controller via the plurality of communication channels.

Owner:SAMSUNG ELECTRONICS CO LTD