Patents

Literature

130 results about "Controller architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

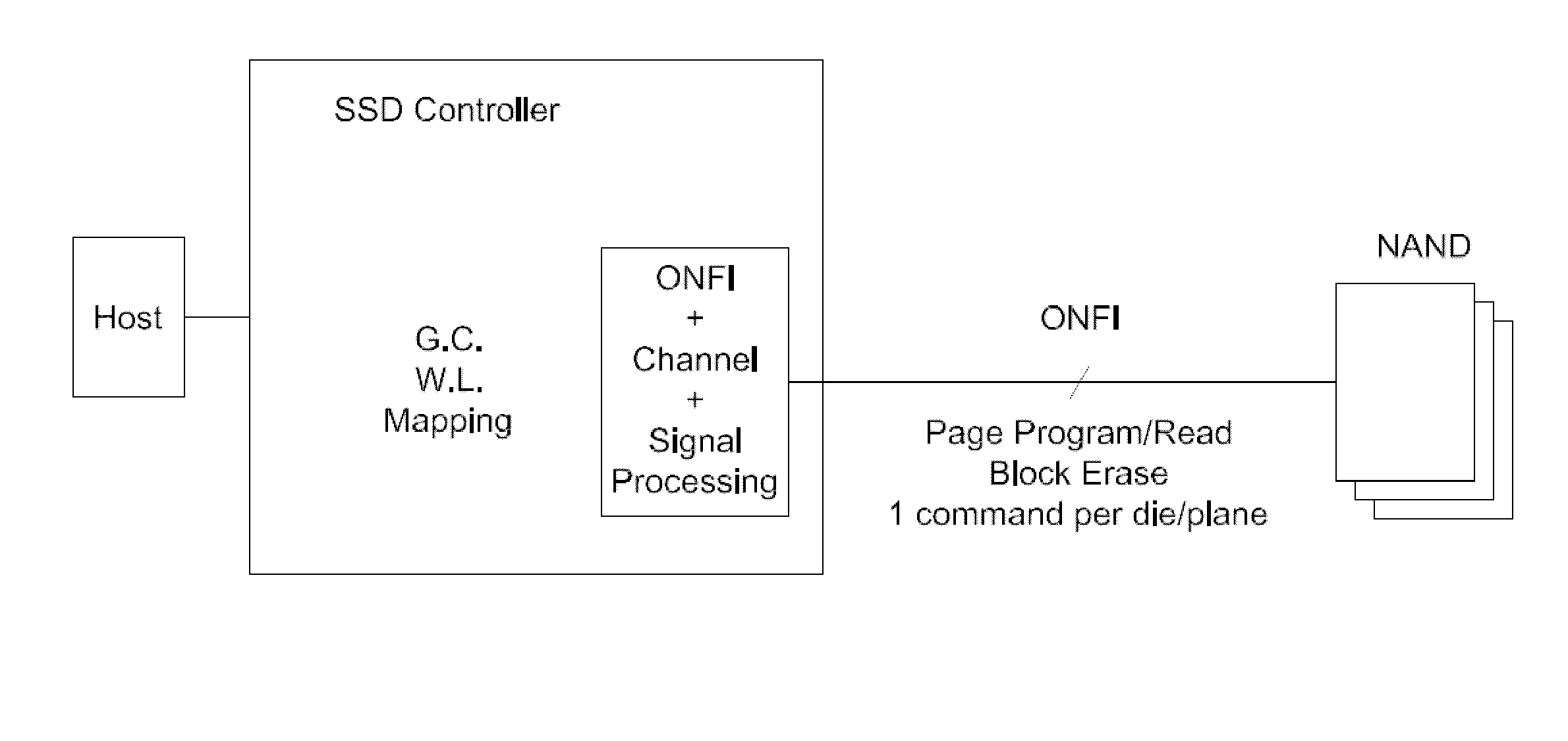

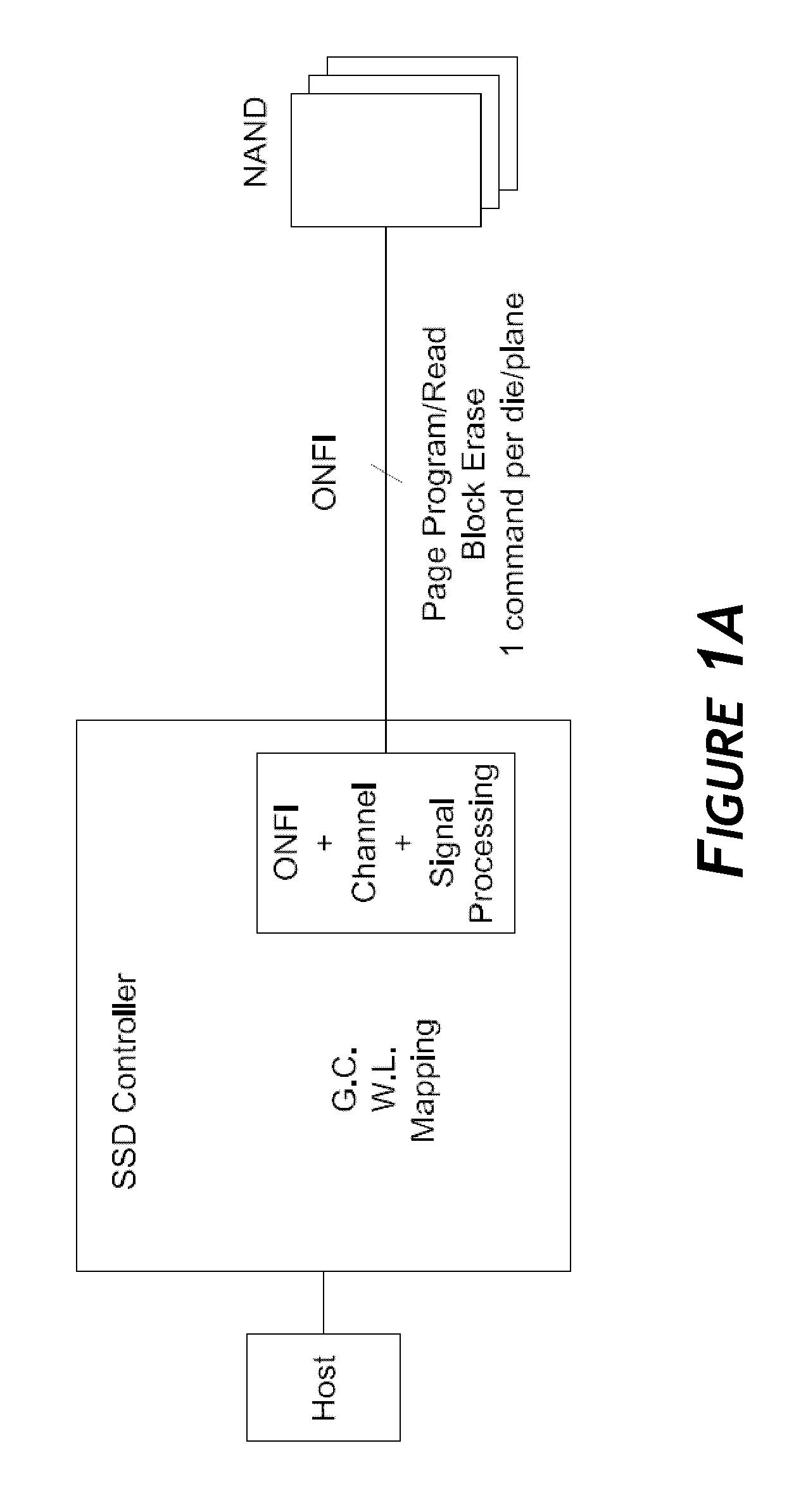

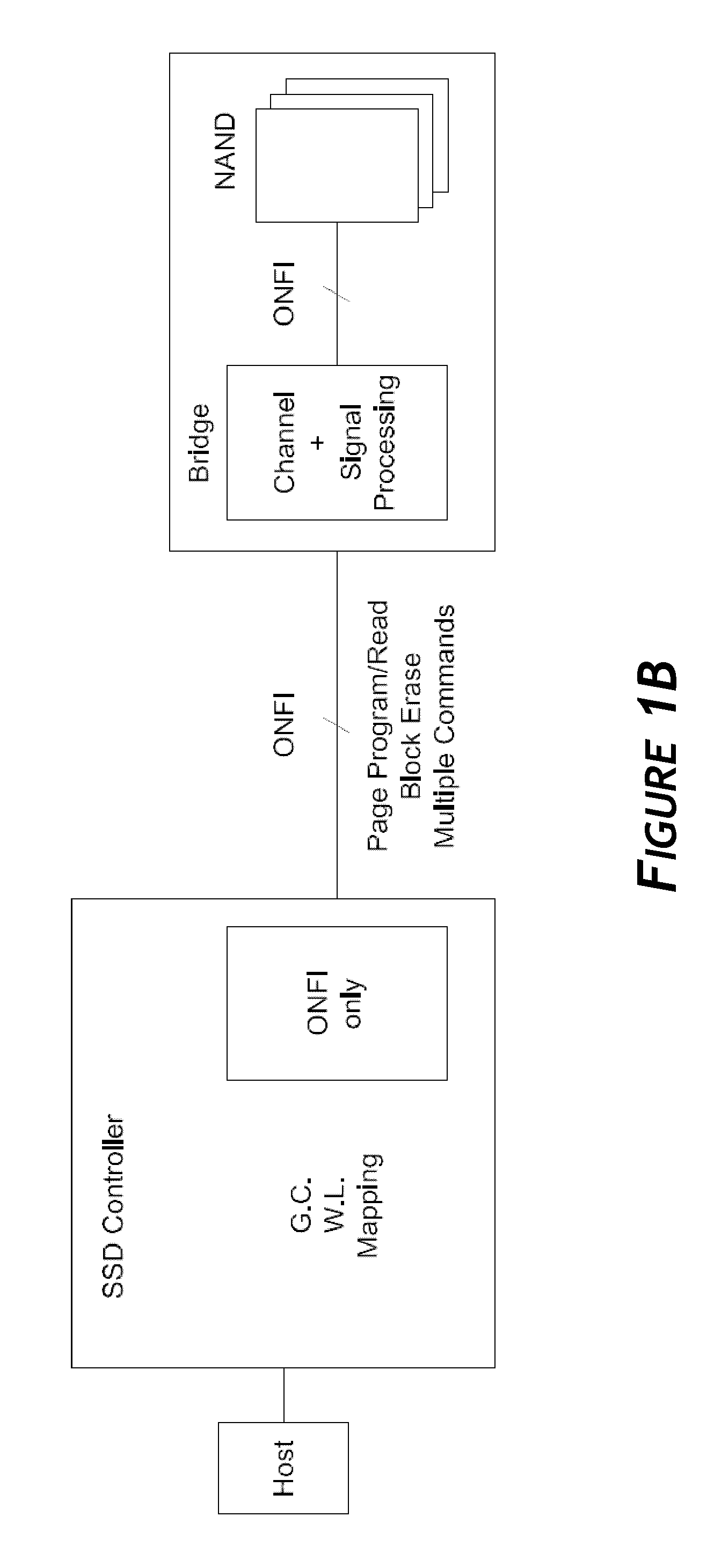

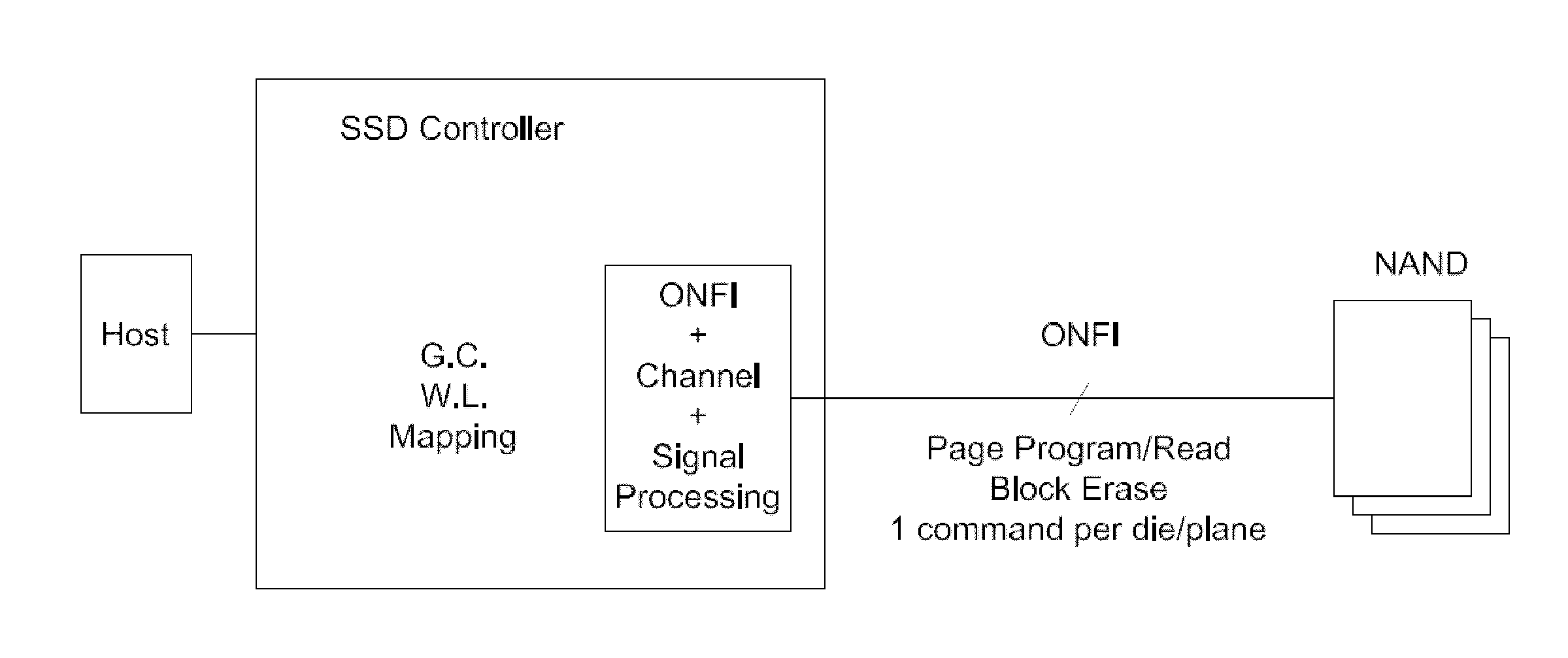

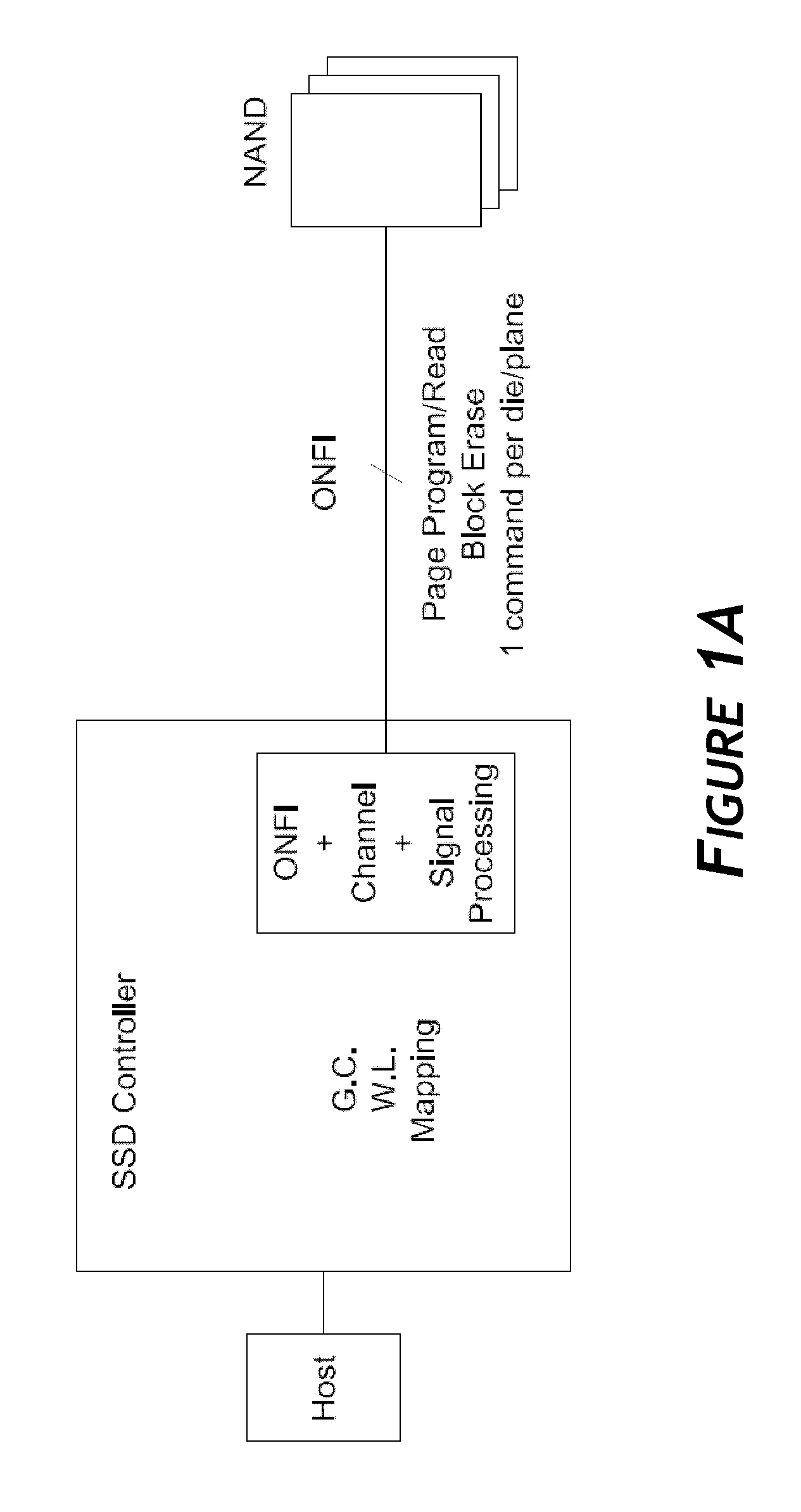

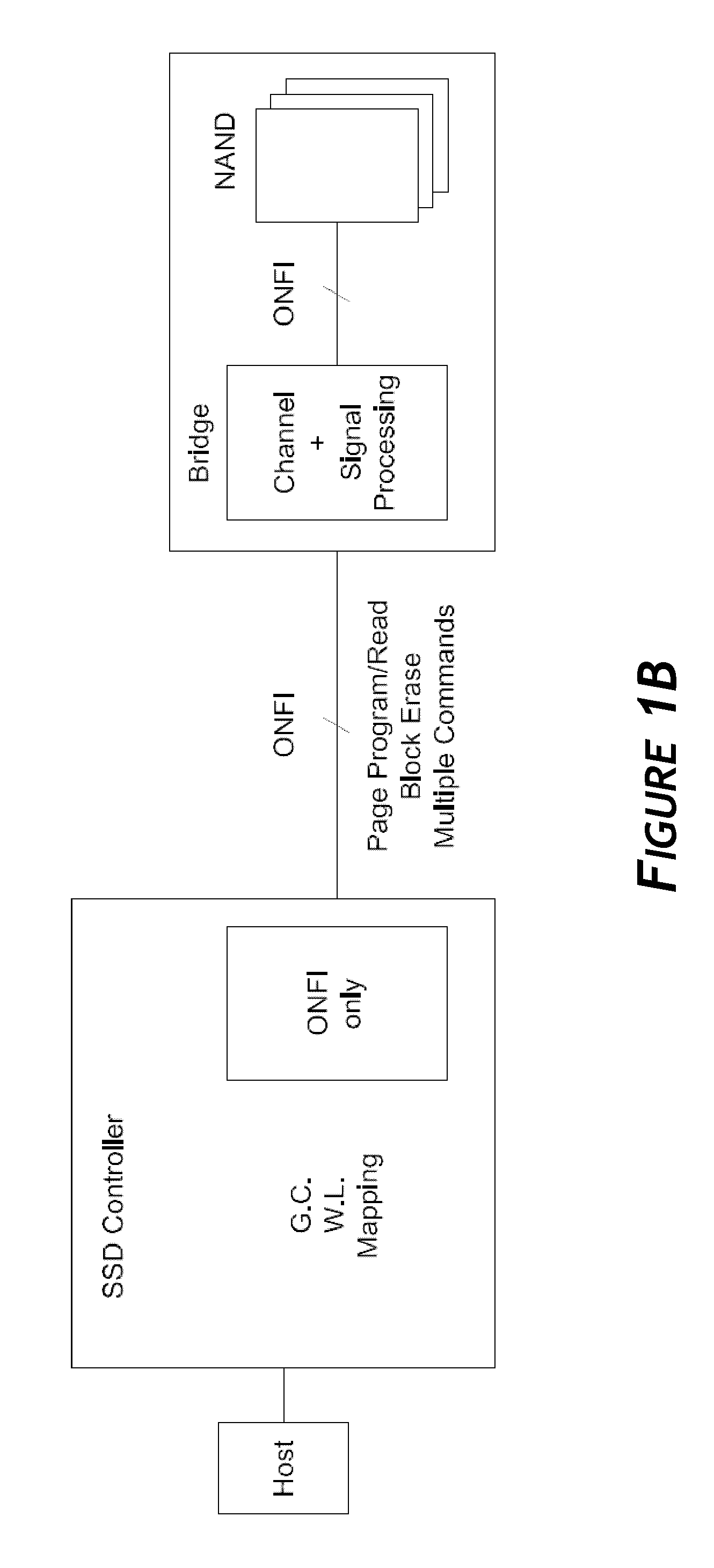

Systems and methods for an enhanced controller architecture in data storage systems

Disclosed herein is a controller architecture that pairs a controller with a NVM (non-volatile memory) storage system over a high-level, high speed interface such as PCIe. In one embodiment, the NVM storage system includes a bridge that communicates with the controller via the high-level interface, and controls the NVM via an interface (e.g., ONFI). The controller is provided a rich set of physical level of controls over individual elements of the NVM. In one embodiment, the controller is implemented in a higher powered processor that supports advanced functions such as mapping, garbage collection, wear leveling, etc. In one embodiment, the bridge is implemented in a lower powered processor and performs basic signal processing, channel management, basic error correction functions, etc. This labor division provides the controller physical control of the NVM over a fast, high-level interface, resulting in the controller managing the NVM at both the page and block level.

Owner:WESTERN DIGITAL TECH INC

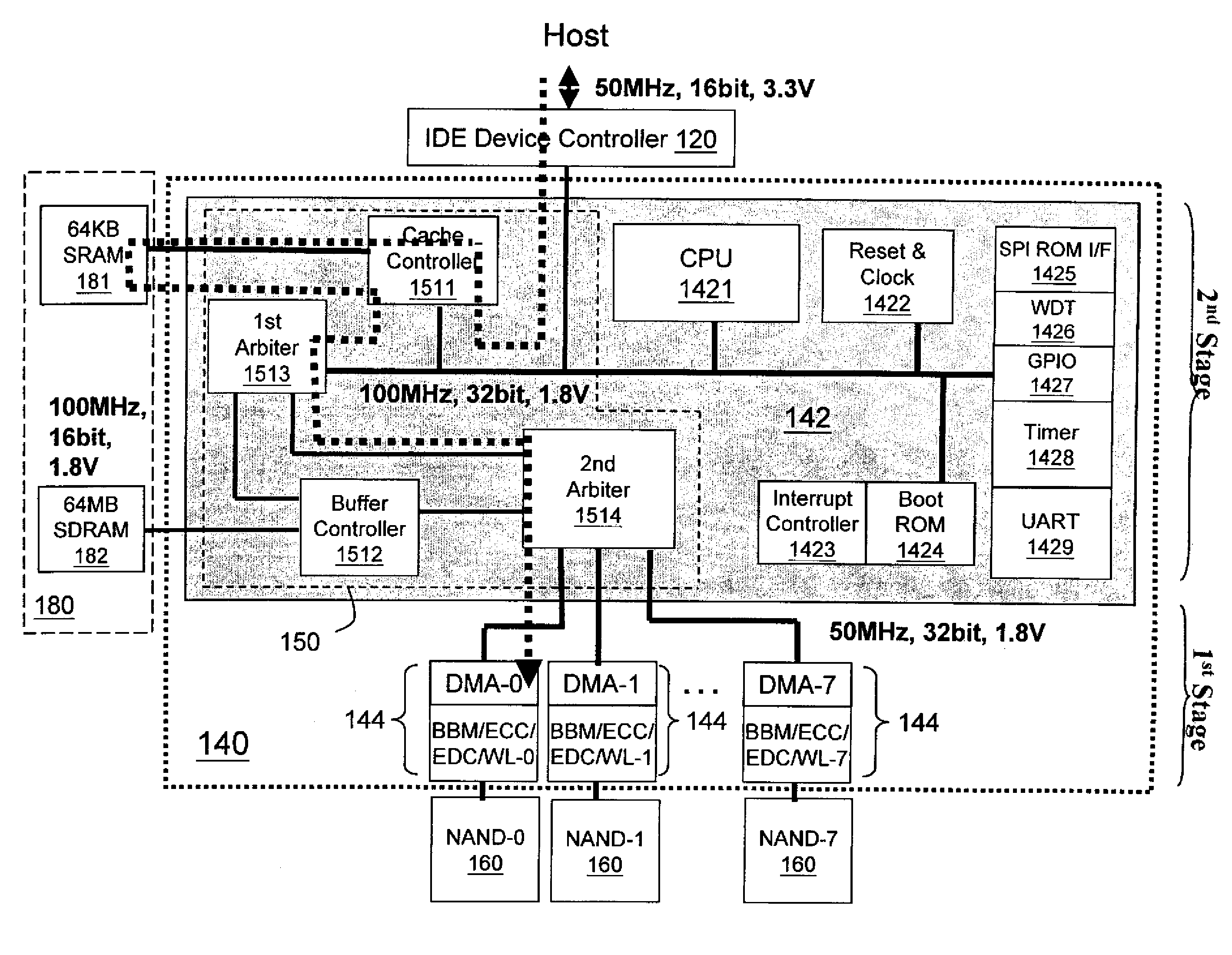

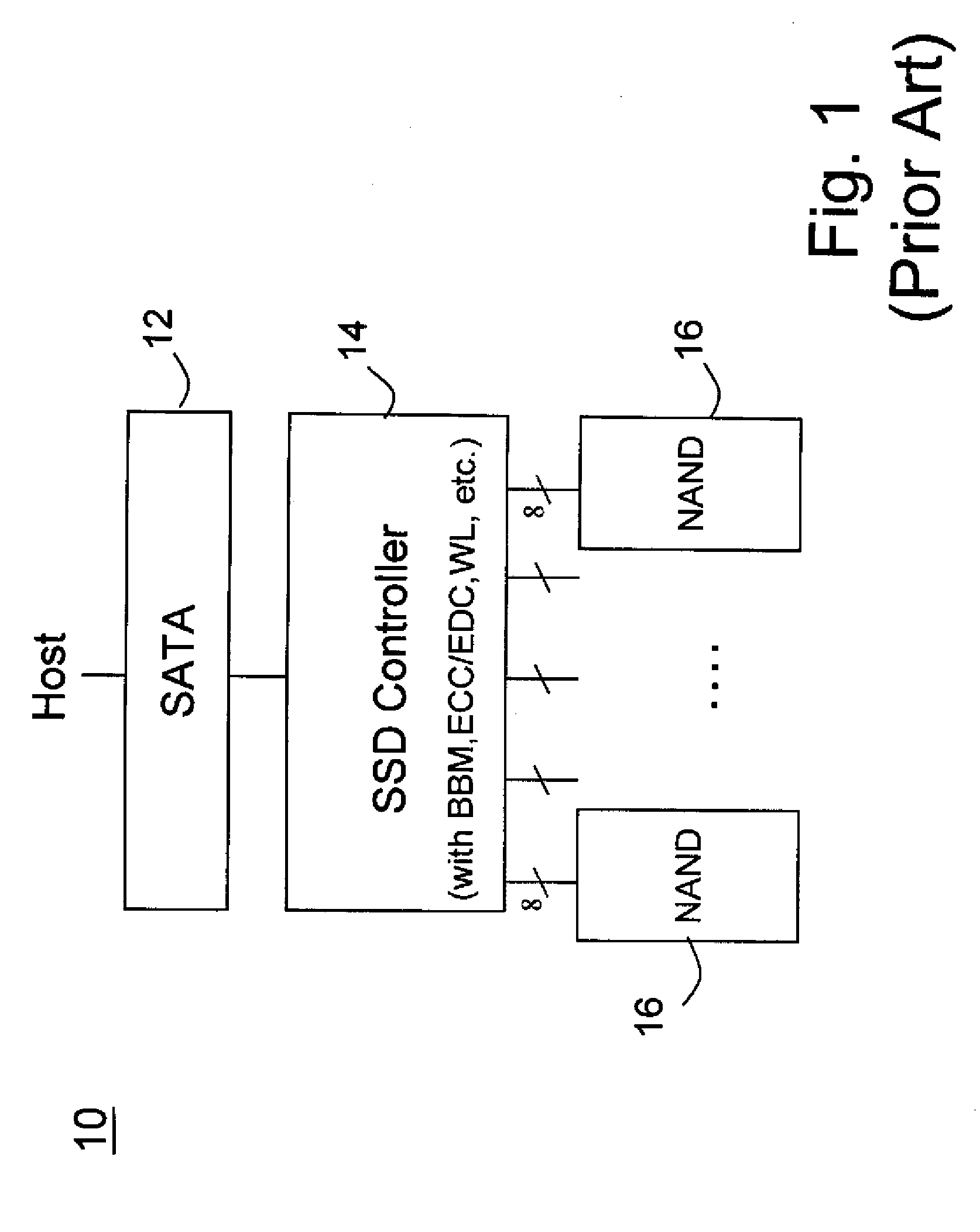

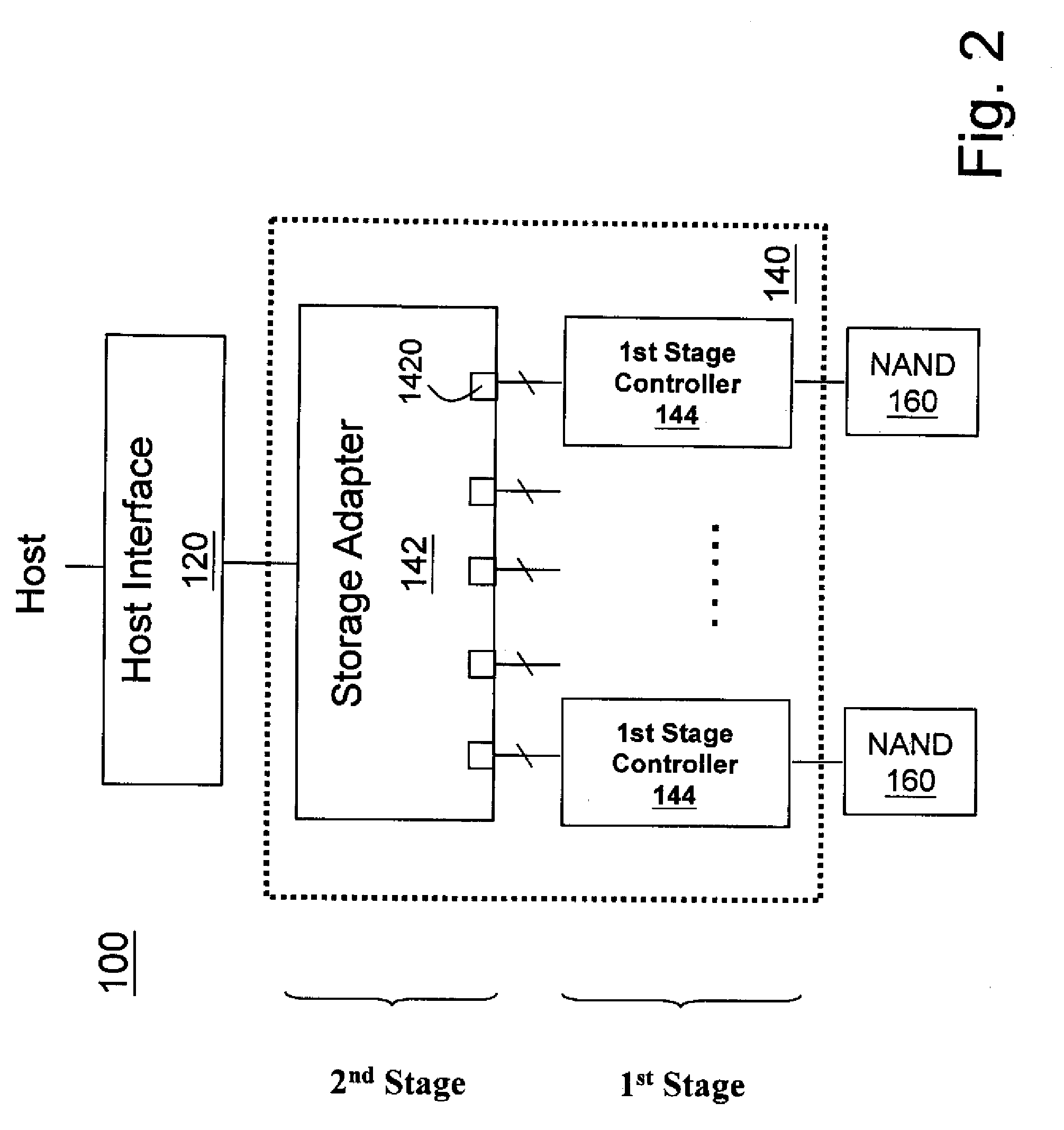

Non-volatile memory storage system with two-stage controller architecture

InactiveUS20100017556A1Improve performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationNon-volatile memoryController architecture

The present invention discloses a non-volatile memory storage system with two-stage controller, comprising: a plurality of flash memory devices; a plurality of first stage controllers coupled to the plurality of flash memory devices, respectively, wherein each of the first stage controllers performs data integrity management as well as writes and reads data to and from a corresponding flash memory device; and a storage adapter communicating with the plurality of first stage controllers through one or more internal interfaces.

Owner:NANOSTAR CORP

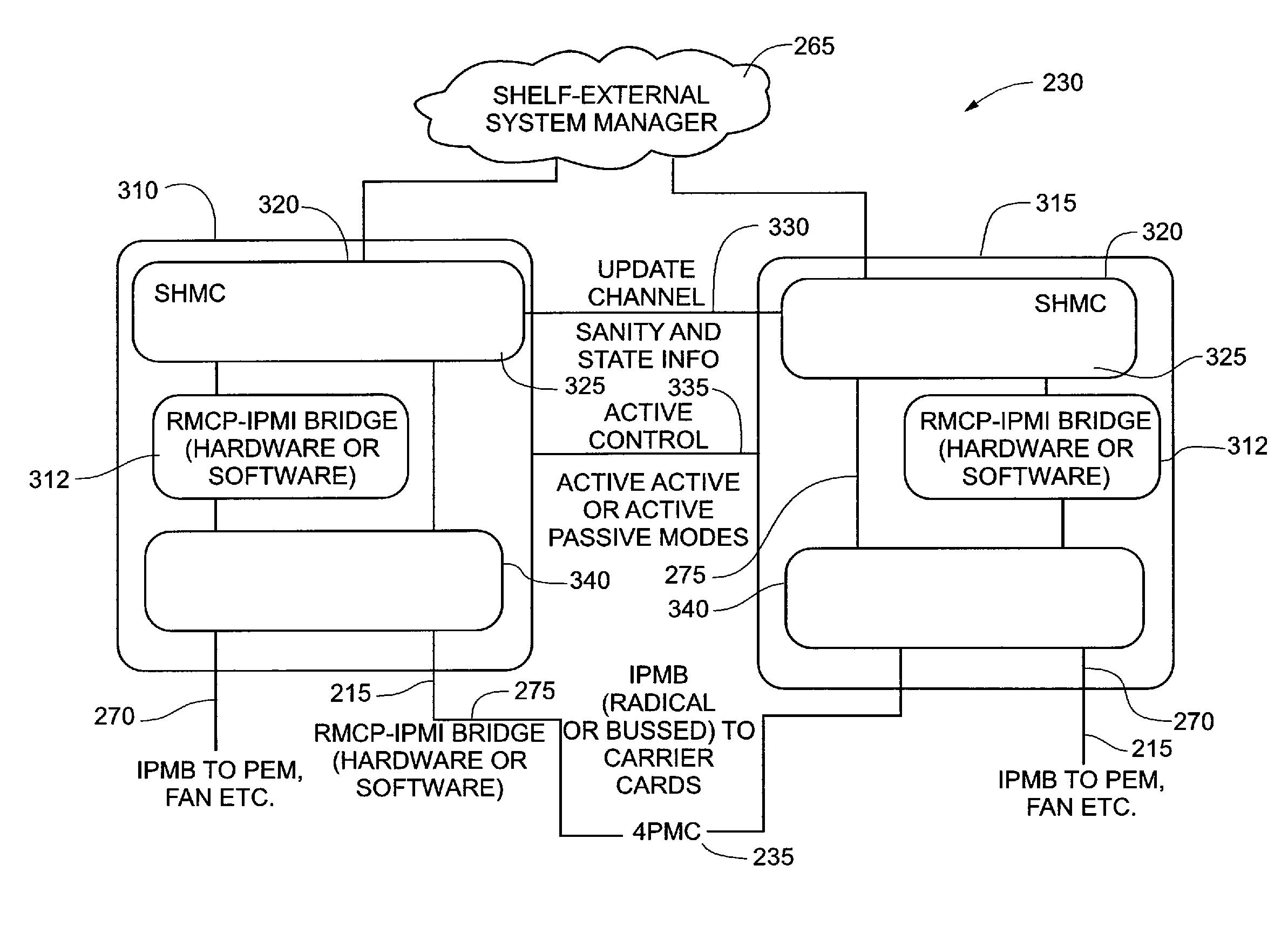

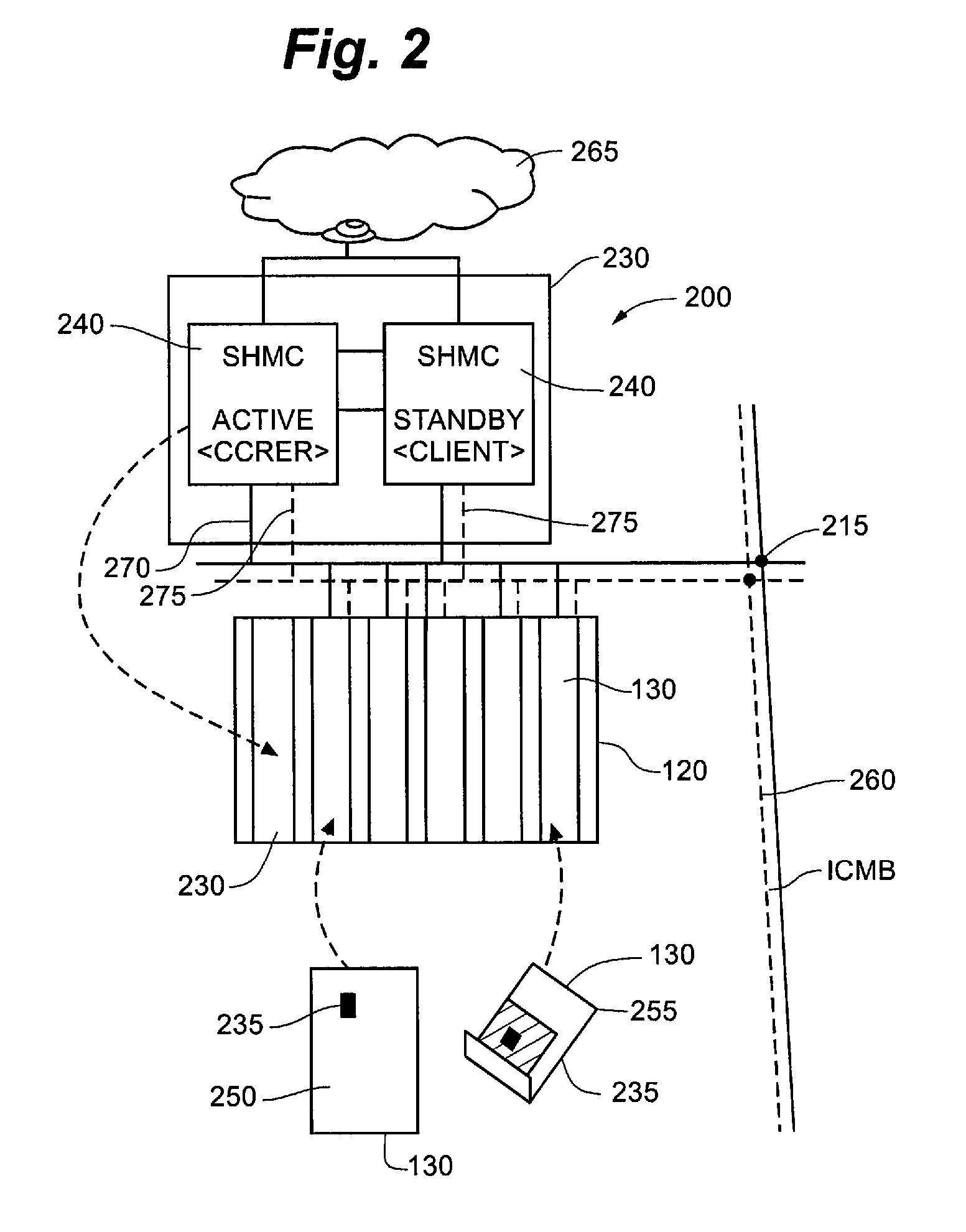

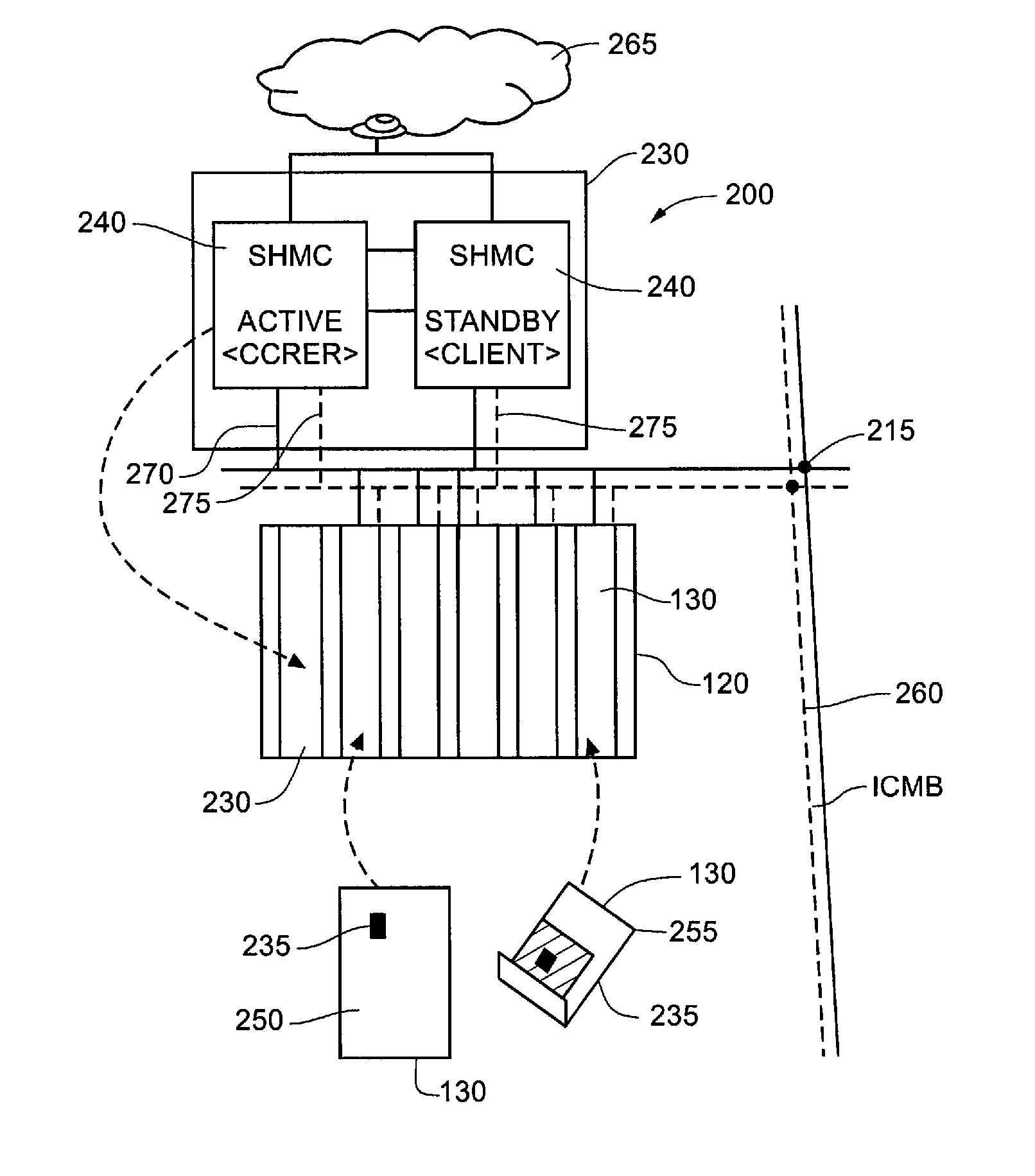

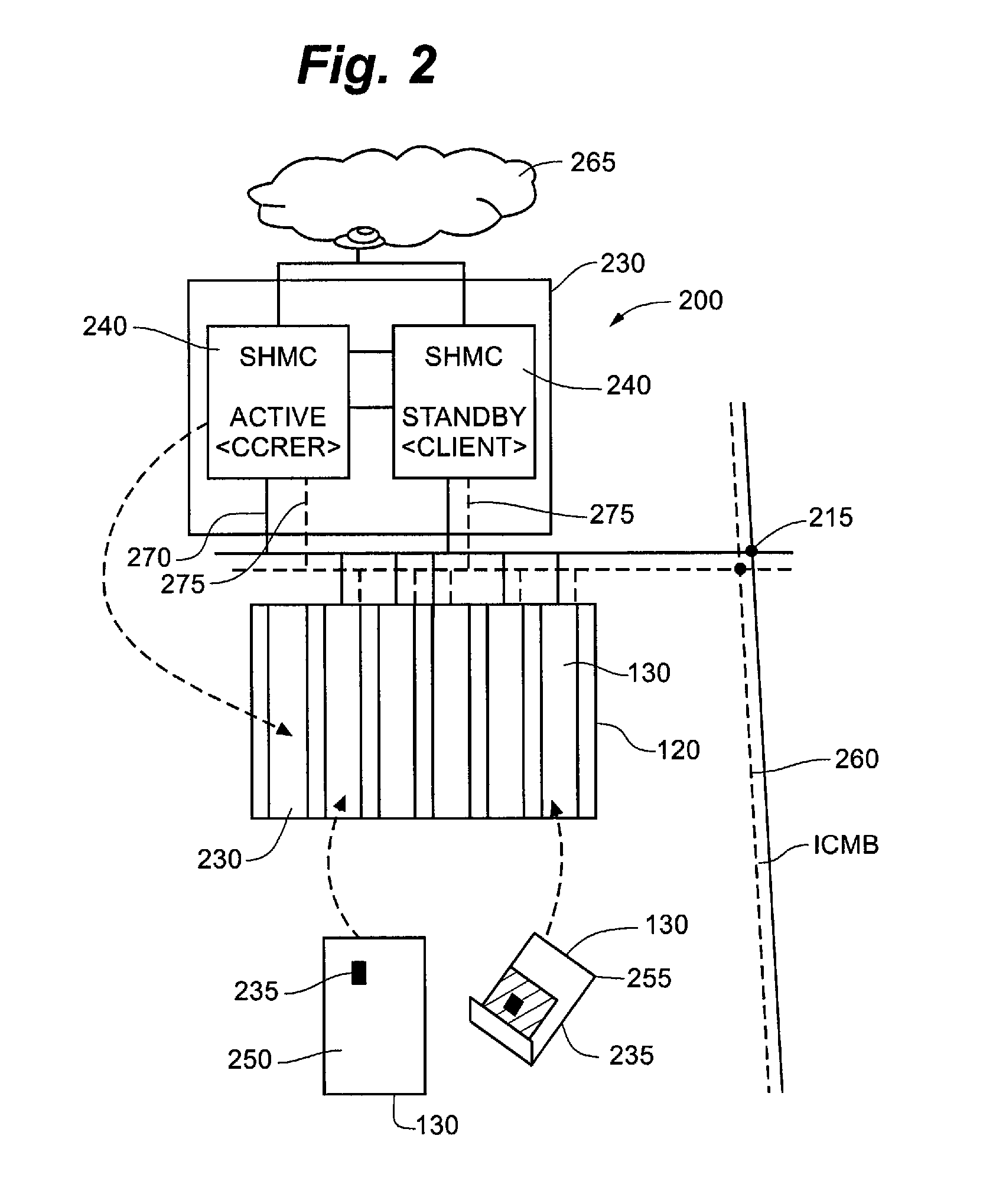

Shelf management controller with hardware/software implemented dual redundant configuration

InactiveUS7827442B2Safety arrangmentsElectric controllersController architectureIntelligent Platform Management Interface

A fault tolerant, multi-protocol shelf management controller architecture that is extensible provides an intelligent platform management interface that is version indifferent as well as programmable and reconfigurable. The shelf management controller is arranged in a dual redundant configuration in a client-server mode and has a message driven configuration with the messages conforming to the Intelligent Platform Management Interface (IPMI) specification as extended by PICMG 3.0. In one embodiment, each shelf management controller includes at least one bit stream processor comprising sequenced stage machines implementing one or more finite state machines associated with one or more devices that are under control of the shelf management controller. The finite state machines could be hardware or software based. The shelf management controller is also modeled as a layered architecture that includes an IPMI API layer. The IPMI API layer enables the shelf manager to interface with legacy and future IPMI specifications.

Owner:RPX CORP

Systems and methods for an enhanced controller architecture in data storage systems

ActiveUS20130060981A1Memory adressing/allocation/relocationDigital computer detailsController architectureEngineering

Disclosed herein is a controller architecture that pairs a controller with a NVM (non-volatile memory) storage system over a high-level, high speed interface such as PCIe. In one embodiment, the NVM storage system includes a bridge that communicates with the controller via the high-level interface, and controls the NVM via an interface (e.g., ONFI). The controller is provided a rich set of physical level of controls over individual elements of the NVM. In one embodiment, the controller is implemented in a higher powered processor that supports advanced functions such as mapping, garbage collection, wear leveling, etc. In one embodiment, the bridge is implemented in a lower powered processor and performs basic signal processing, channel management, basic error correction functions, etc. This labor division provides the controller physical control of the NVM over a fast, high-level interface, resulting in the controller managing the NVM at both the page and block level.

Owner:WESTERN DIGITAL TECH INC

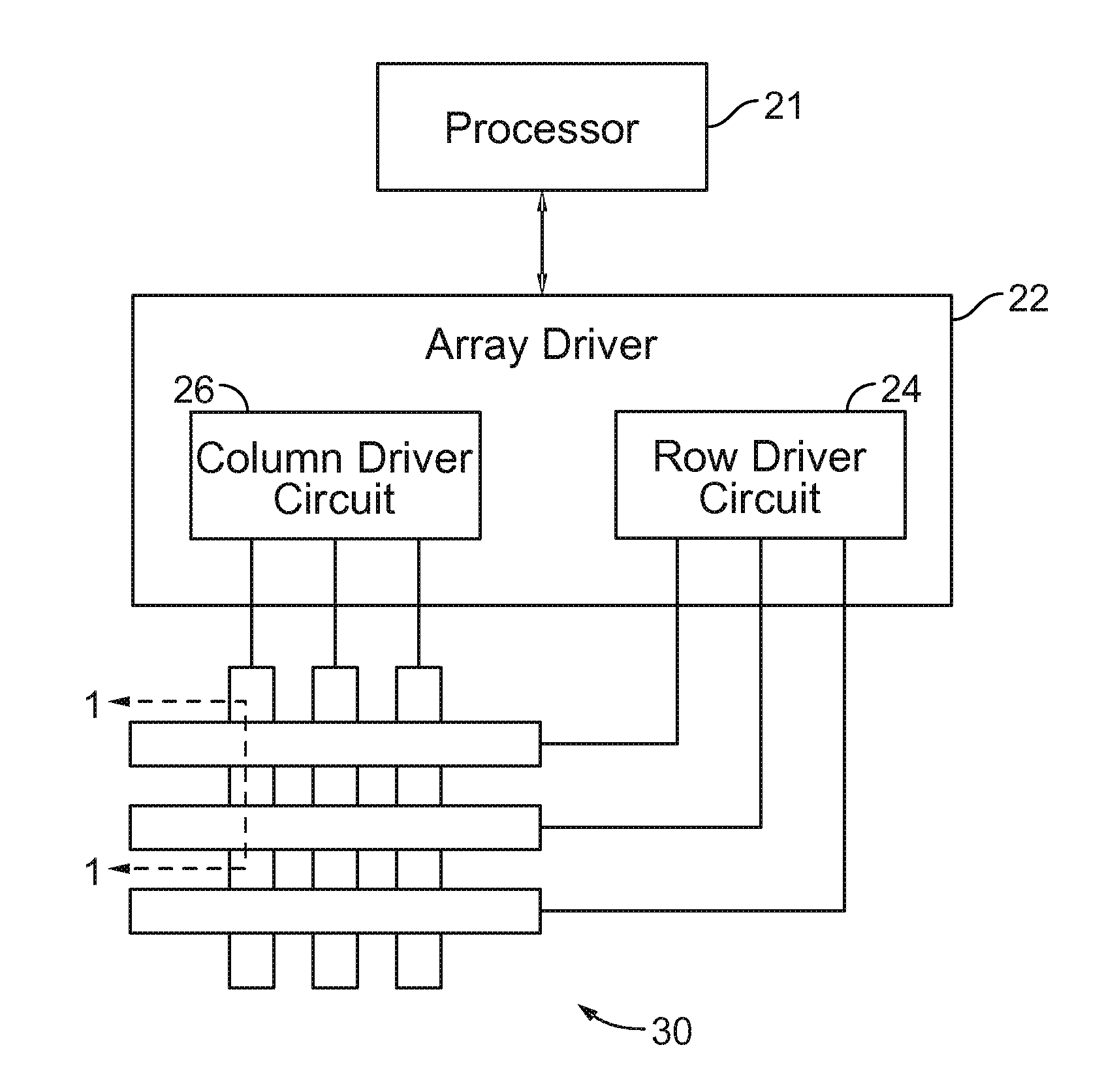

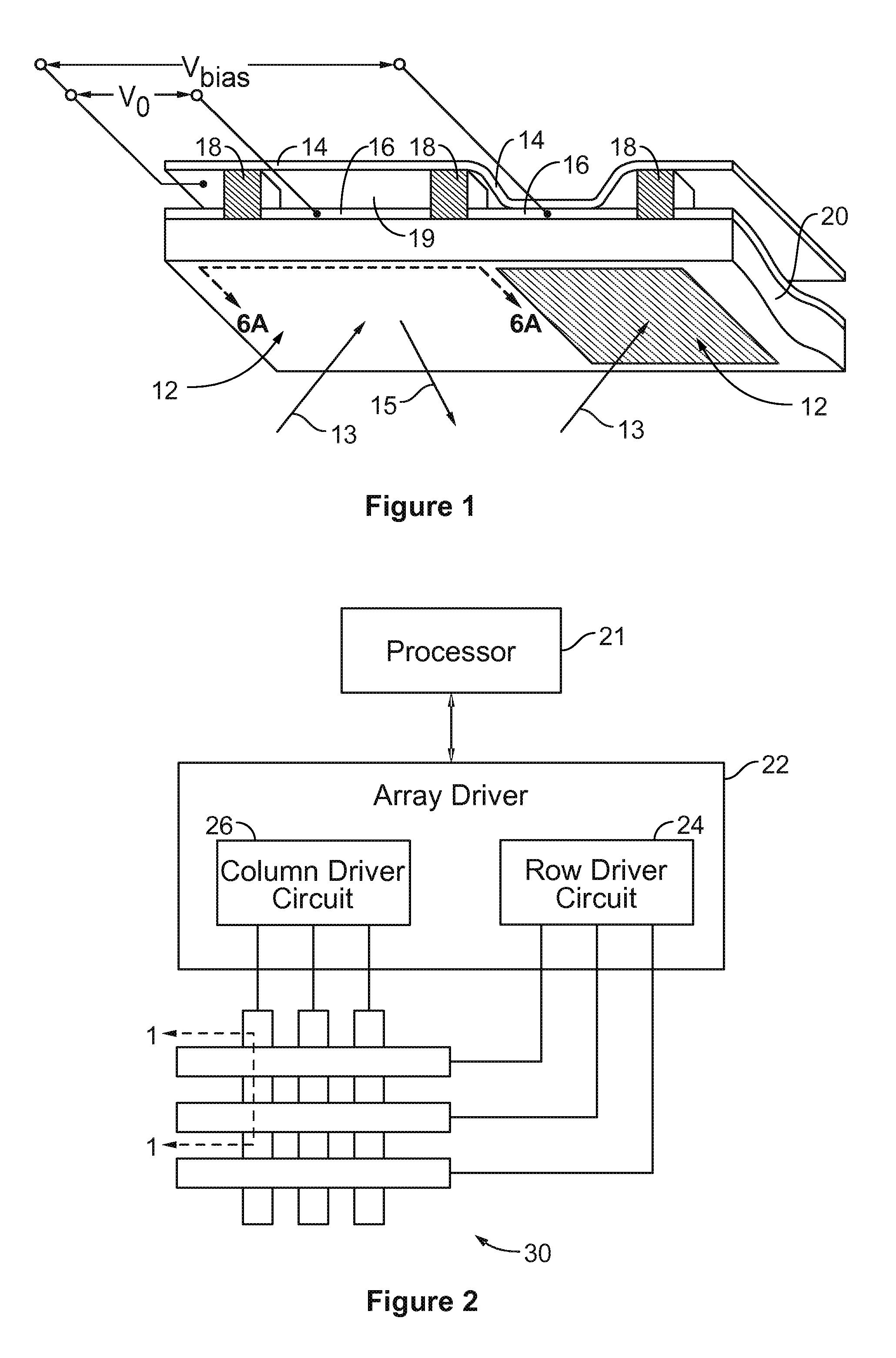

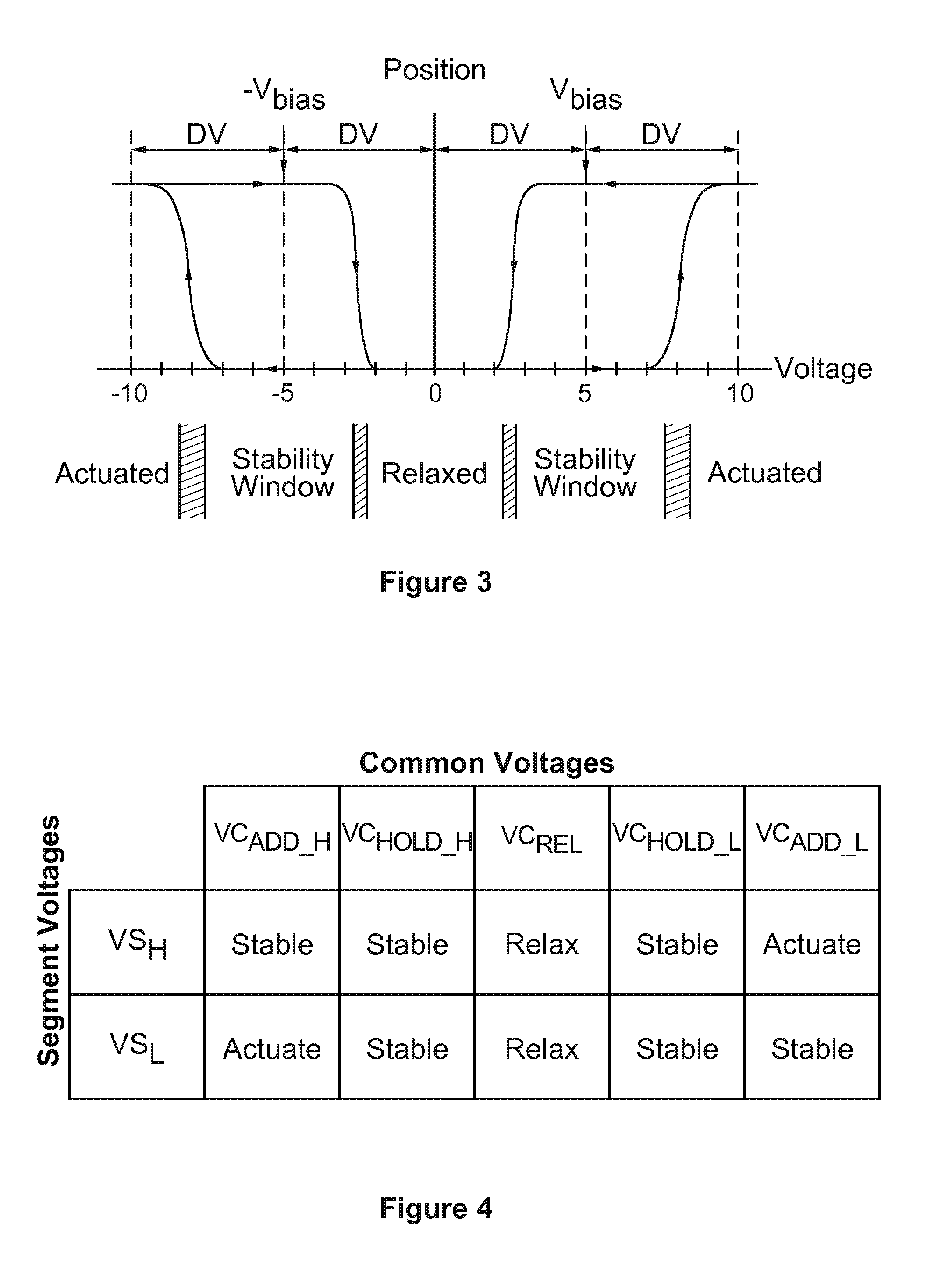

Controller architecture for combination touch, handwriting and fingerprint sensor

InactiveUS20120092293A1Reduce power consumptionInternal/peripheral component protectionDigital data authenticationController architectureHandwriting

A separate control system may be configured for a combined sensor device. Alternatively, at least part of the control system may be included in another device, such as a processor of a mobile device. Software for handwriting, touch and fingerprint detection may be included in the control system. Low, medium and high resolution may be obtained with a single combined sensor device by scanning a subset of the sensels, or by aggregating lines or columns. Power consumption may be reduced by aggregating sensor pixels (or rows or columns) electrically using the controller, so that they perform as a low power small array until higher resolution with a larger array is needed. Power consumption may be reduced by turning off portions or all of the sensor device, turning off parts of the control system, and / or employing first-level screening at a reduced frame rate.

Owner:SNAPTRACK

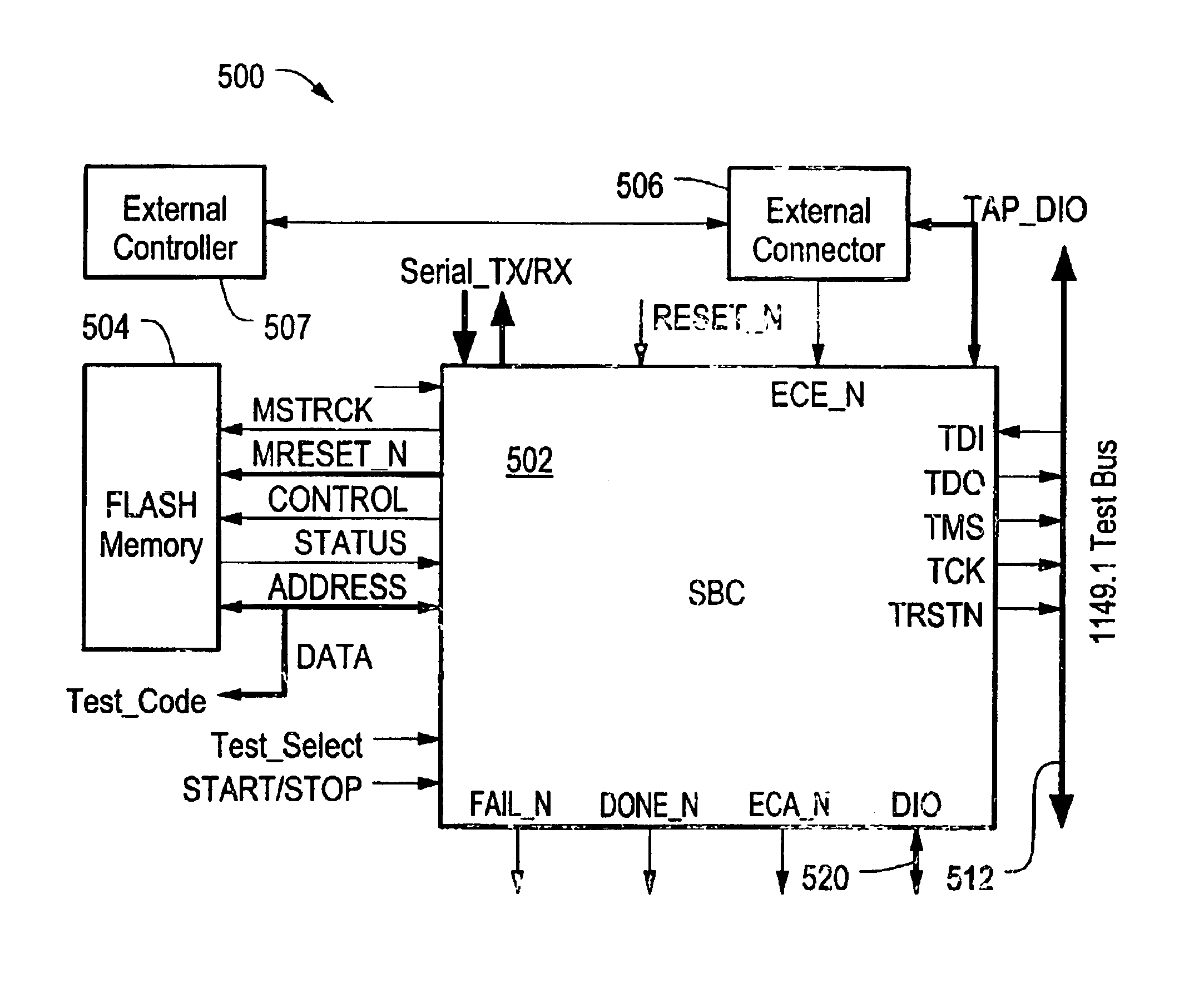

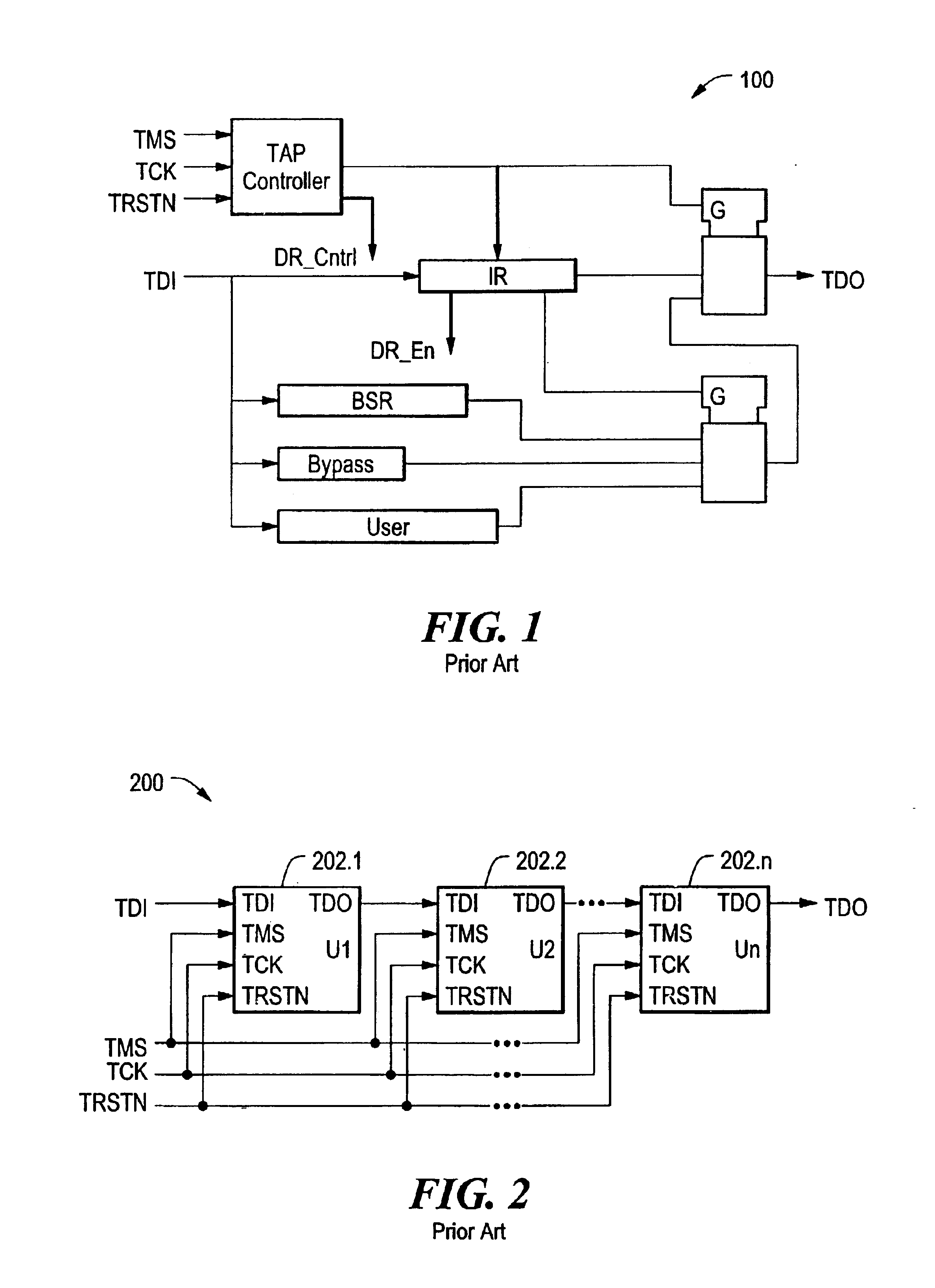

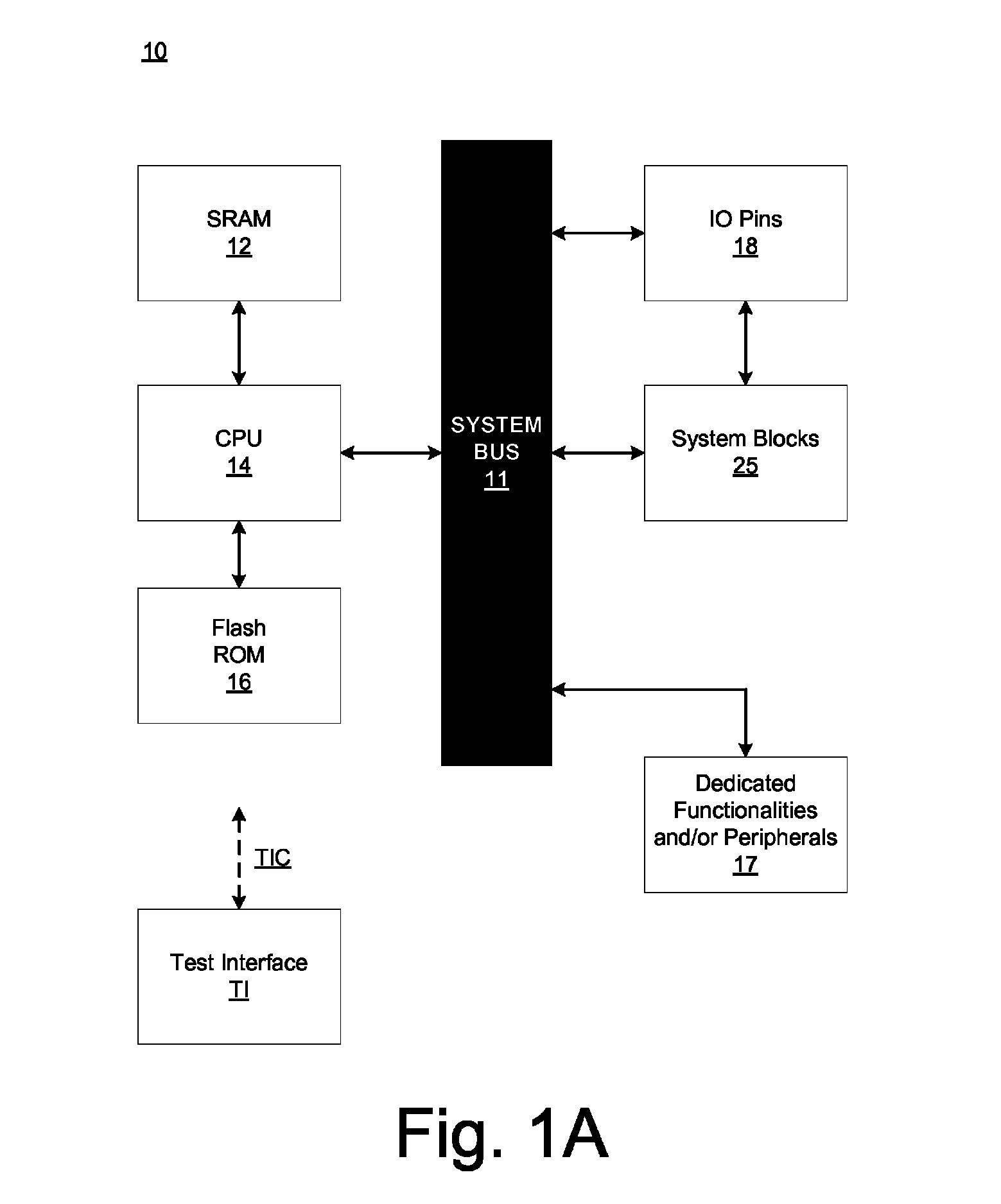

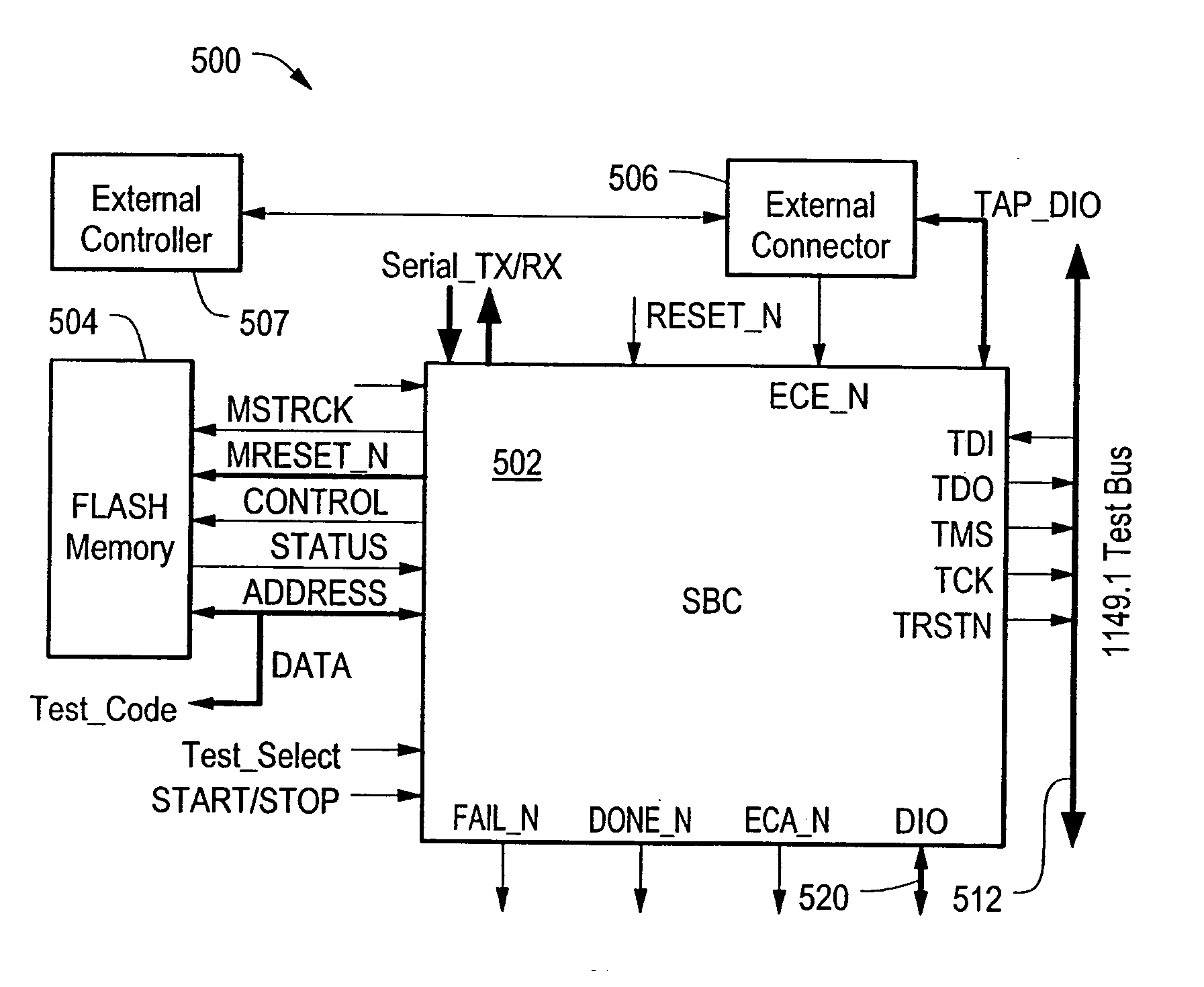

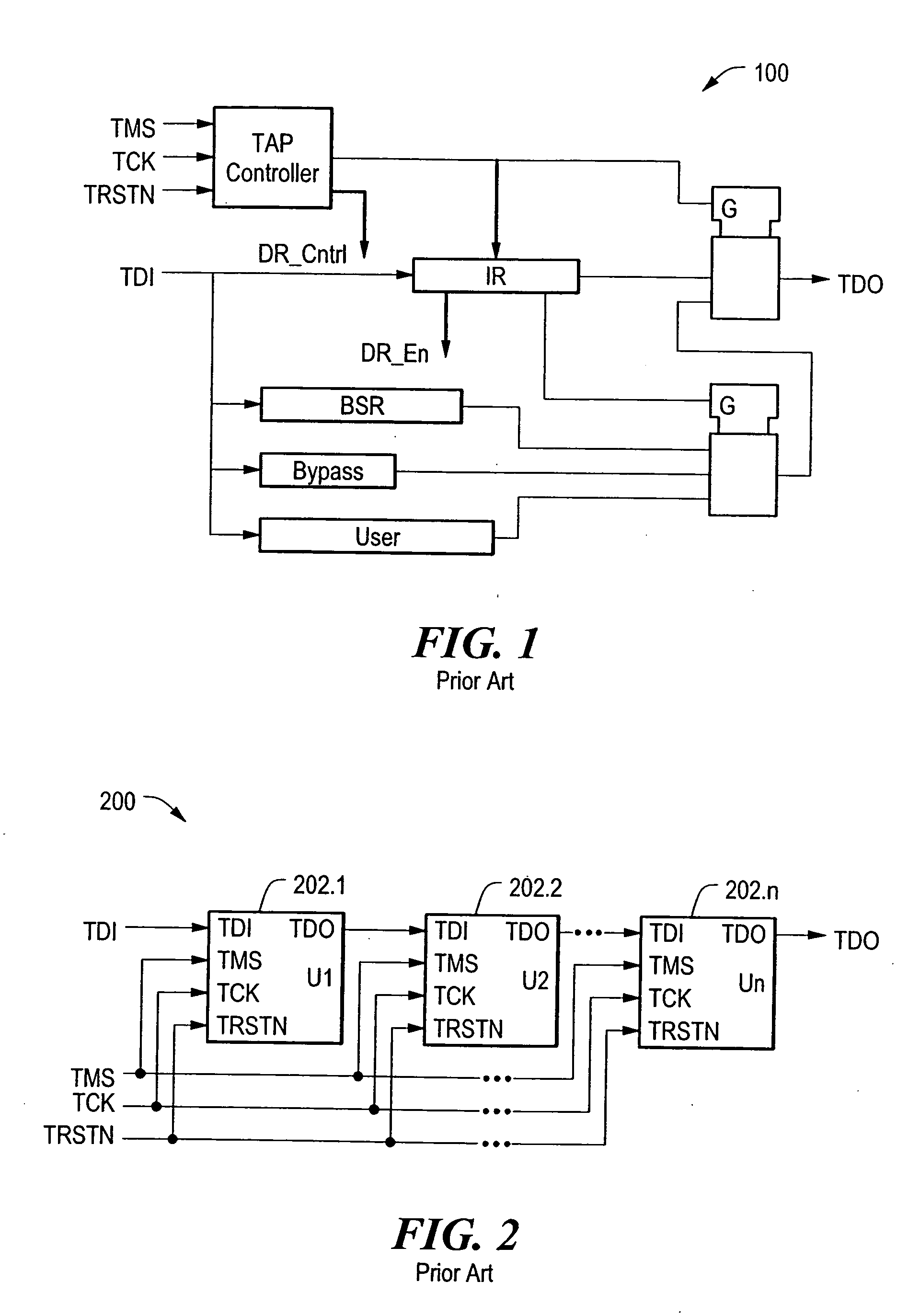

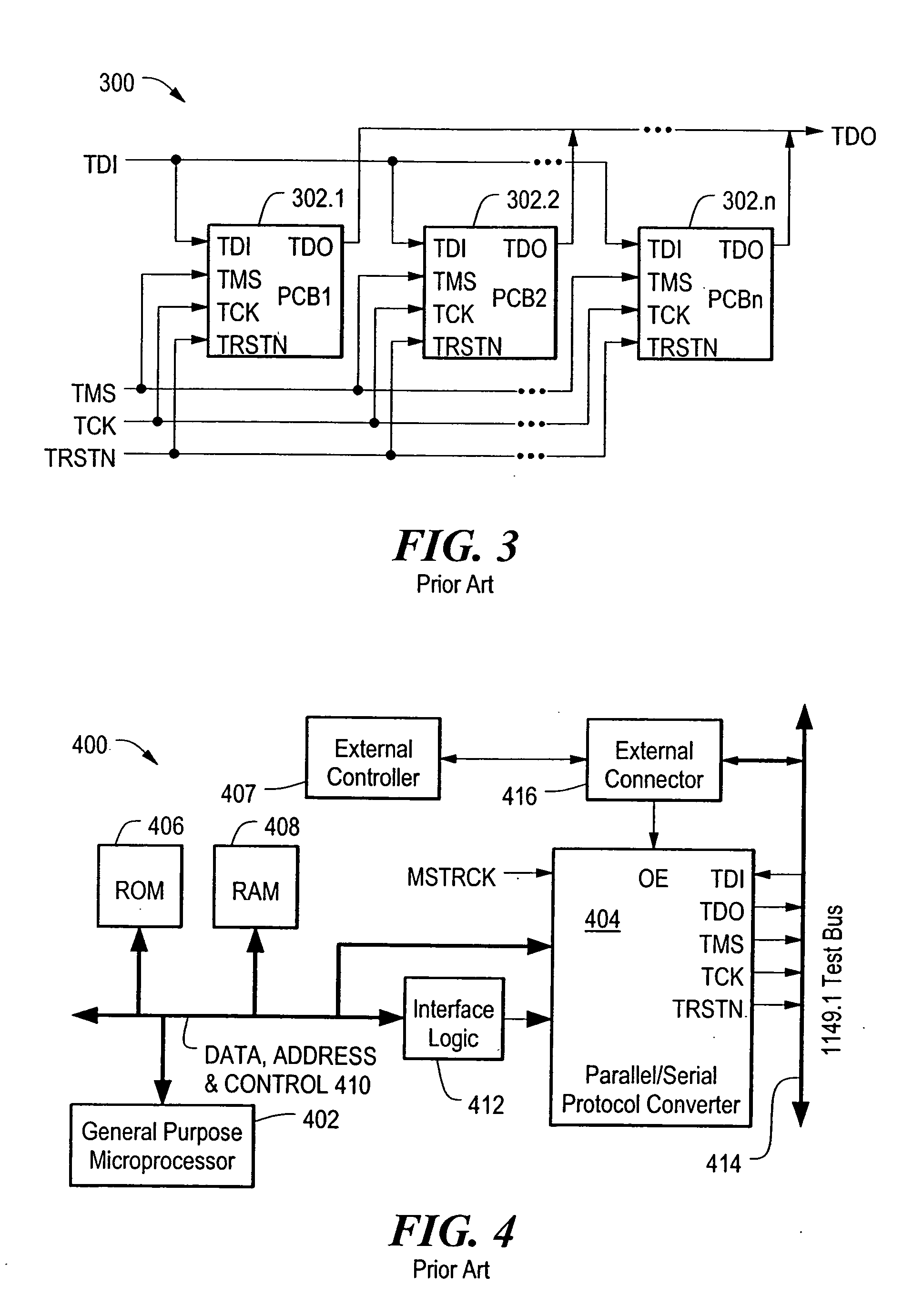

Method and apparatus for embedded built-in self-test (BIST) of electronic circuits and systems

InactiveUS6957371B2Facilitates testing and debuggingLow costElectronic circuit testingError detection/correctionController architectureElectronic systems

An embedded electronic system built-in self-test controller architecture that facilitates testing and debugging of electronic circuits and in-system configuration of programmable devices. The system BIST controller architecture includes an embedded system BIST controller, an embedded memory circuit, an embedded IEEE 1149.1 bus, and an external controller connector. The system BIST controller is coupled to the memory circuit and the IEEE 1149.1 bus, and coupleable to an external test controller via the external controller connector. The external test controller can communicate over the IEEE 1149.1 bus to program the memory and / or the system BIST controller circuitry, thereby enabling scan vectors to be debugged by the external test controller and then downloaded into the memory for subsequent application to a unit under test by the system BIST controller.

Owner:INTELLITECH INC

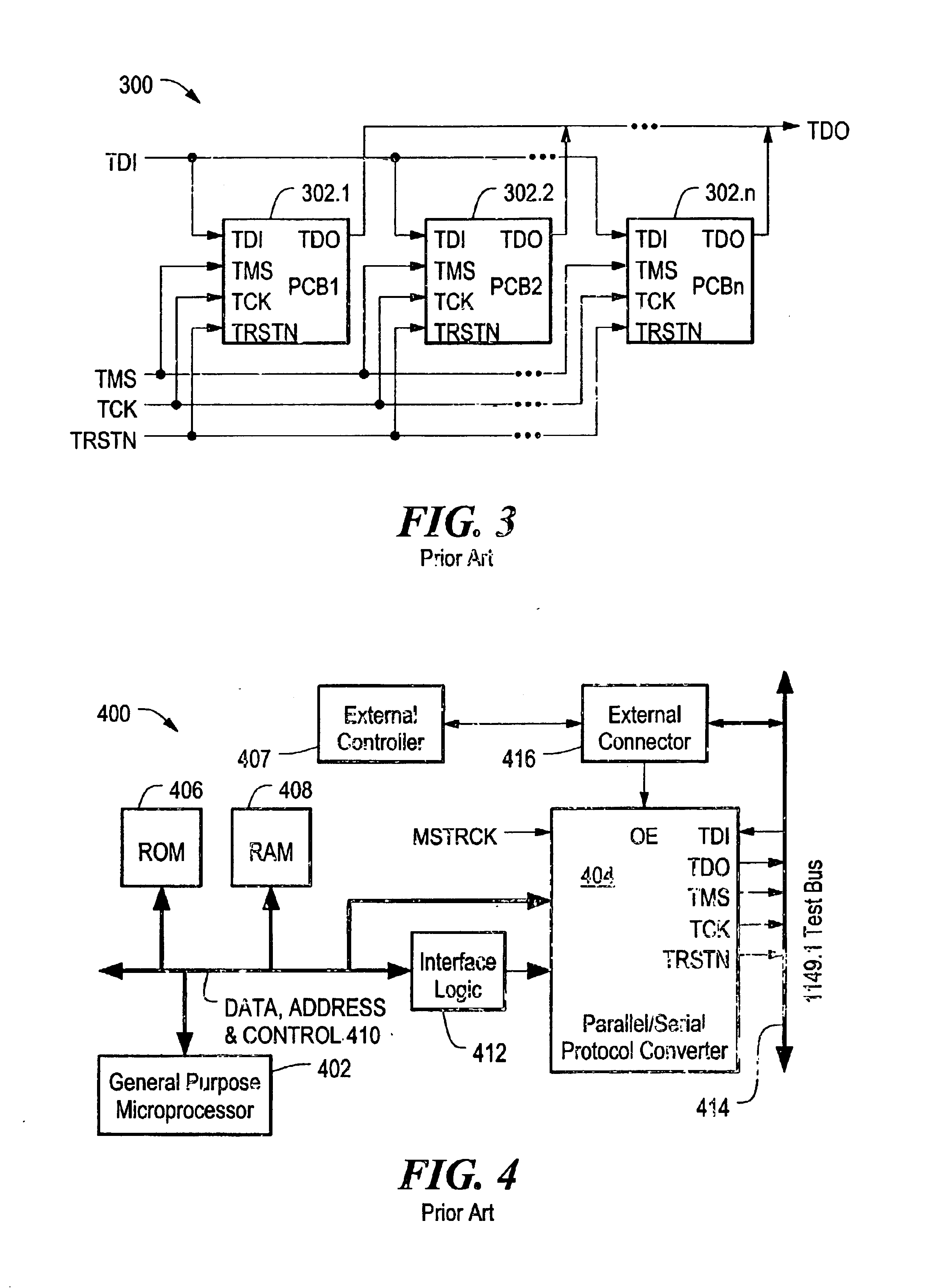

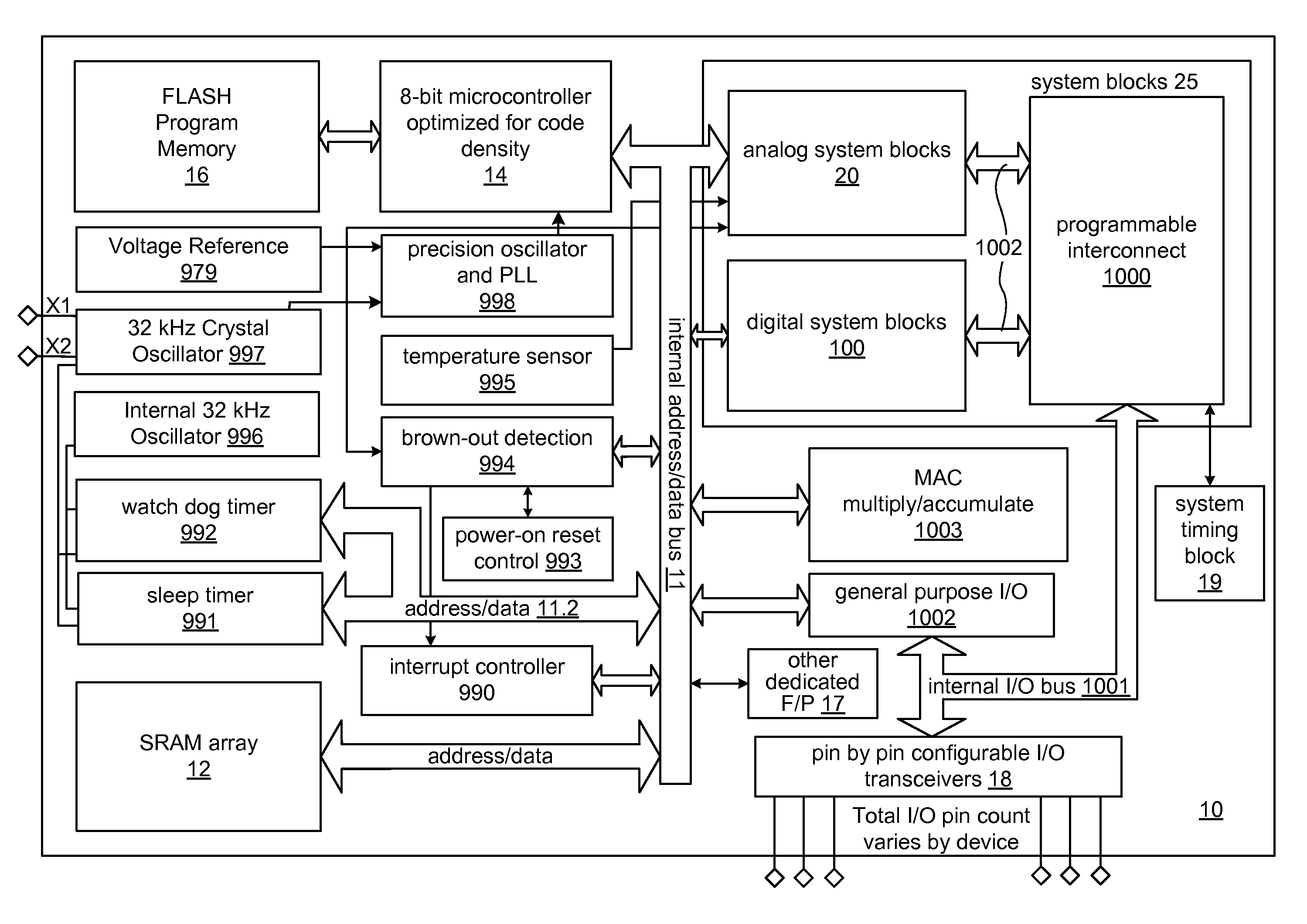

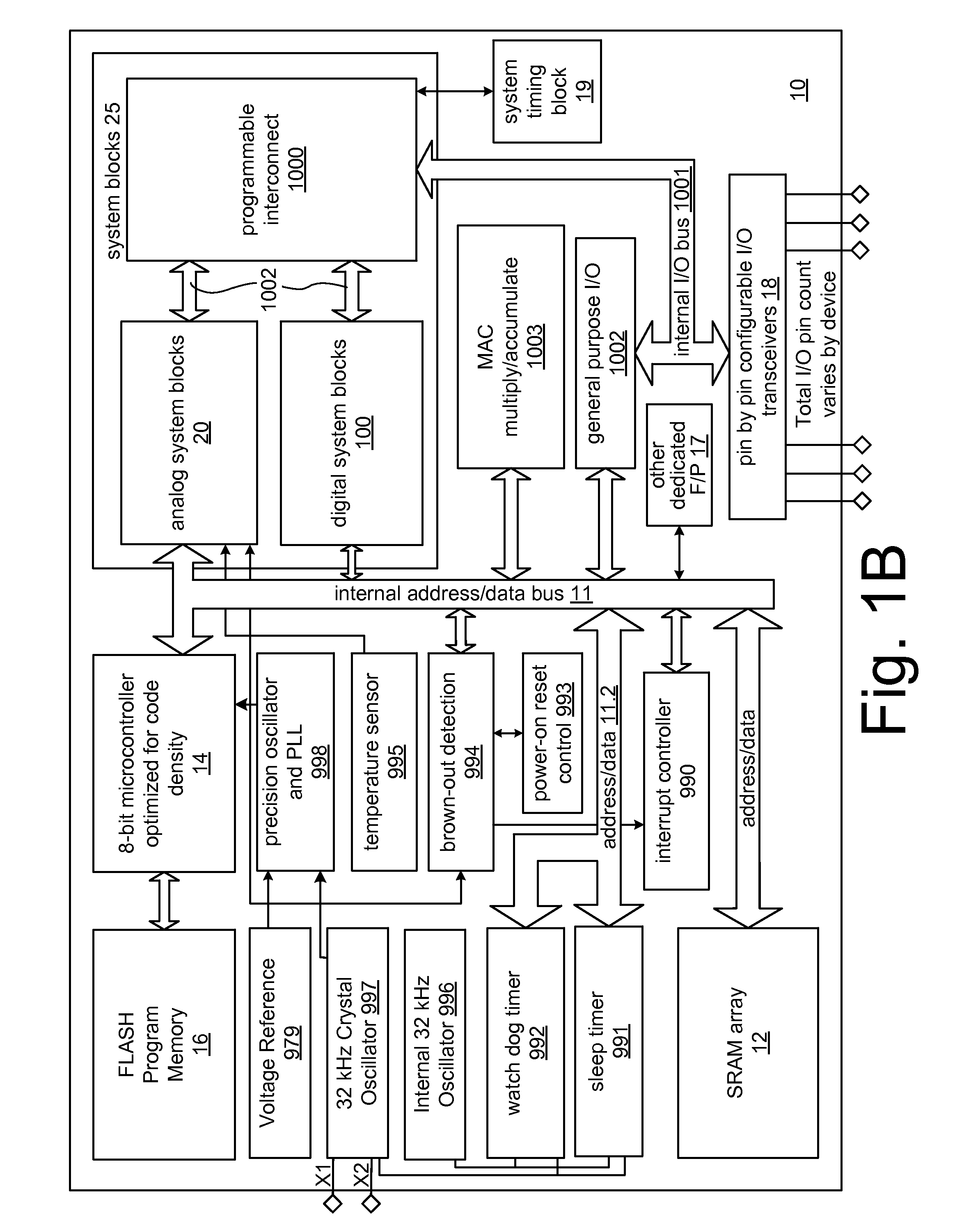

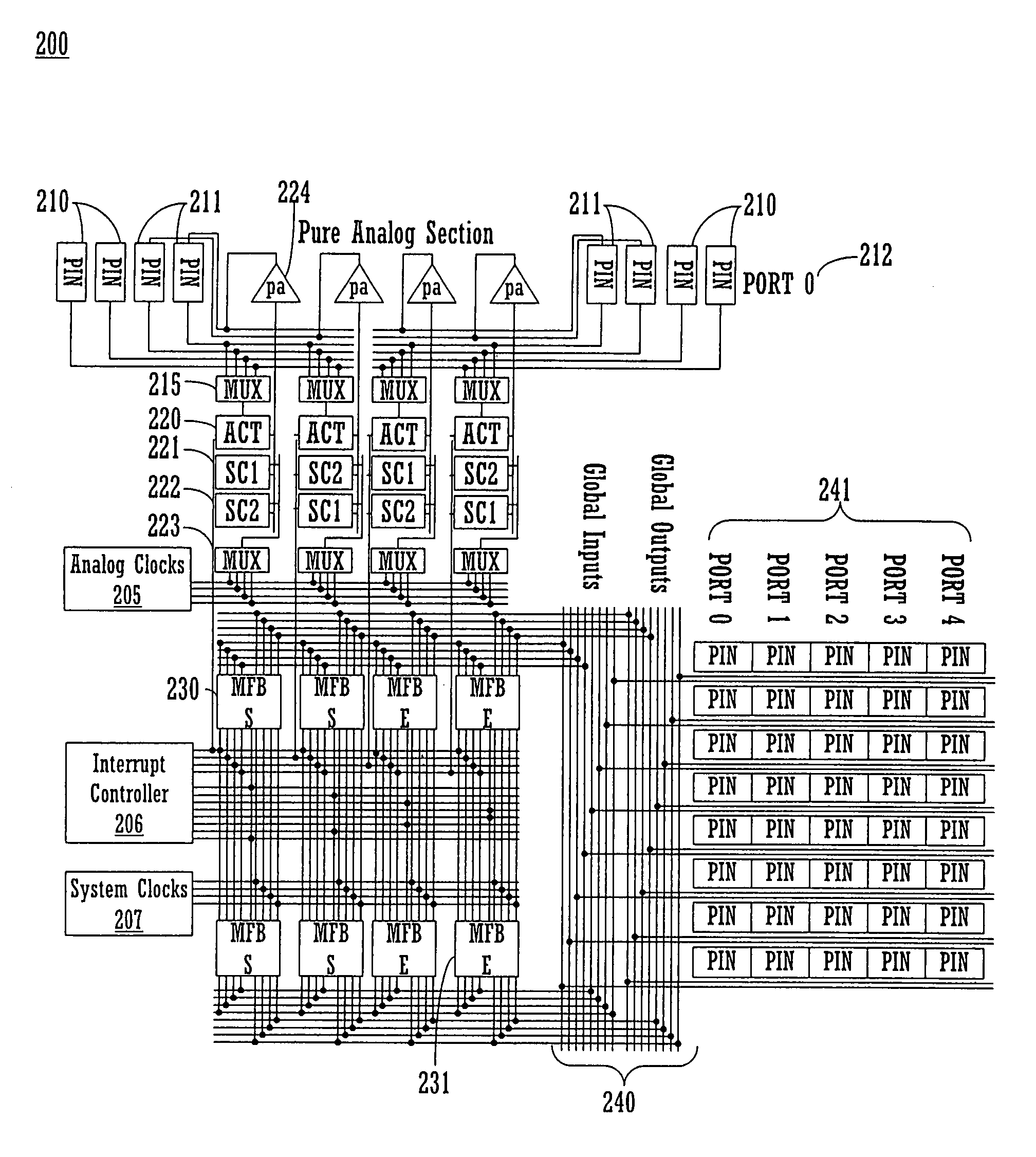

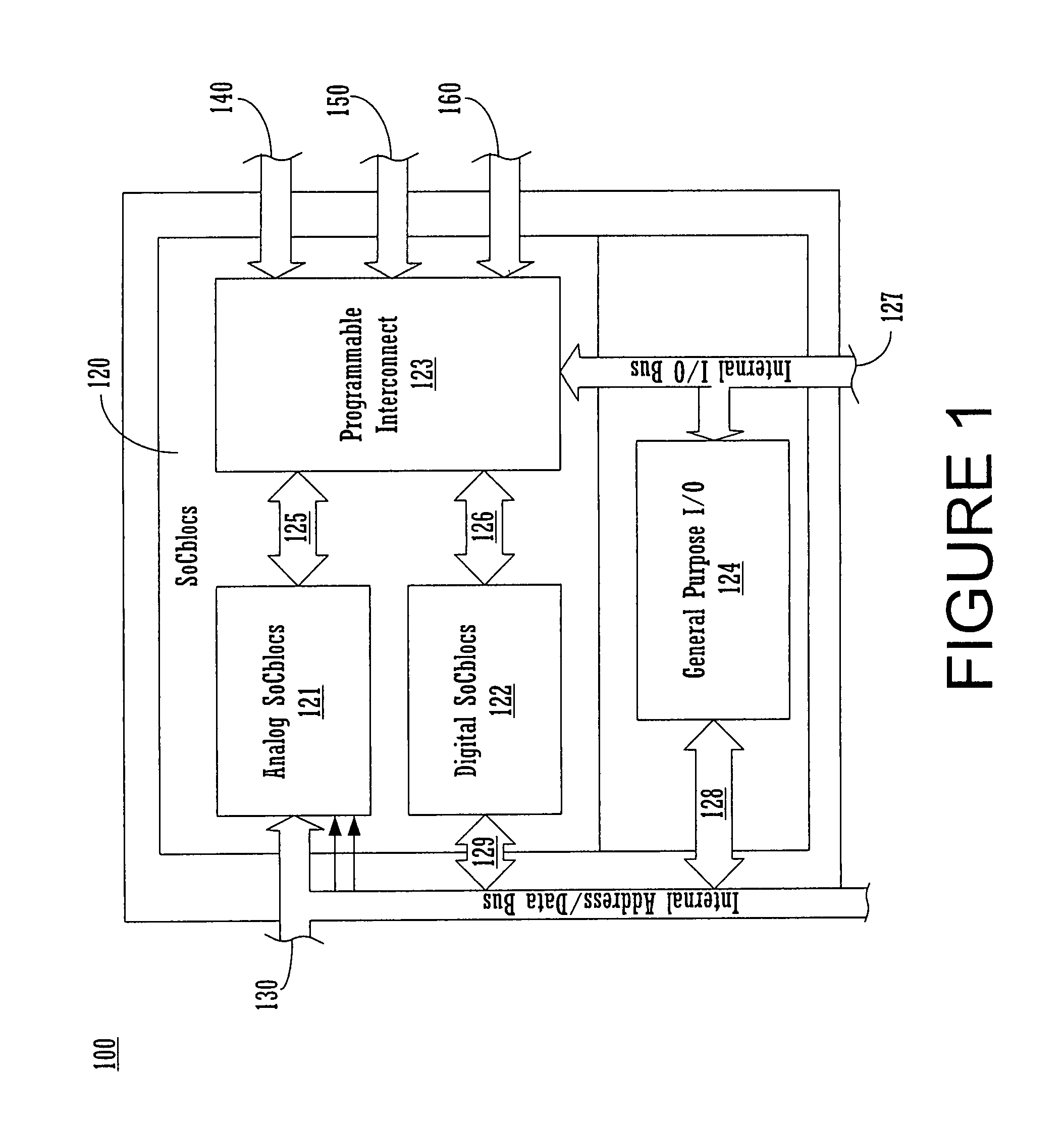

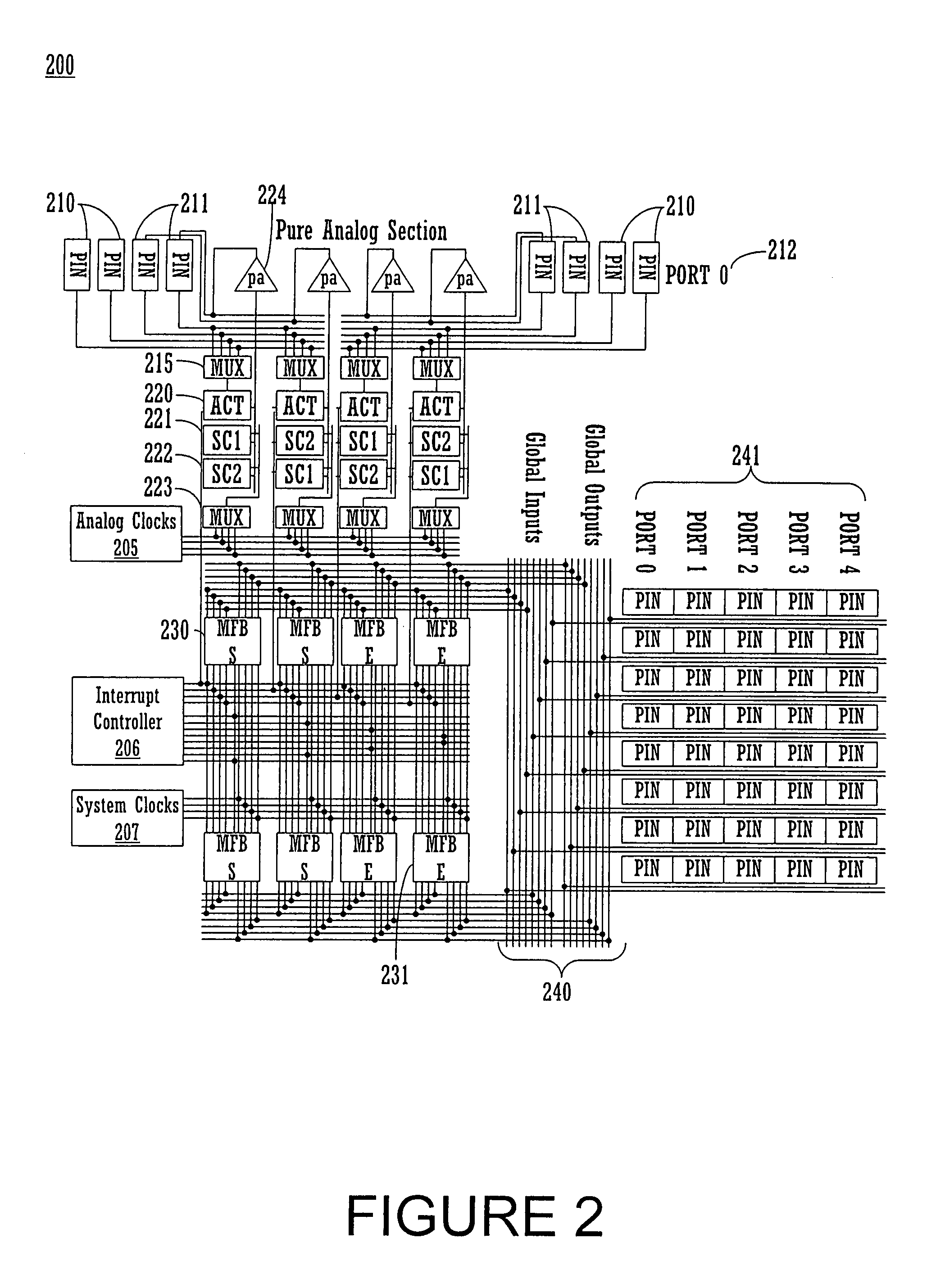

Programmable microcontroller architecture

ActiveUS8176296B2Little timeInexpensive and simple to and applyProgramme controlDigital technique networkController architectureMicrocontroller

Embodiments of the present invention are directed to a microcontroller device having a microprocessor, programmable memory components, and programmable analog and digital blocks. The programmable analog and digital blocks are configurable based on programming information stored in the memory components. Programmable interconnect logic, also programmable from the memory components, is used to couple the programmable analog and digital blocks as needed. The advanced microcontroller design also includes programmable input / output blocks for coupling selected signals to external pins. The memory components also include user programs that the embedded microprocessor executes. These programs may include instructions for programming the digital and analog blocks “on-the-fly,” e.g., dynamically. In one implementation, there are a plurality of programmable digital blocks and a plurality of programmable analog blocks.

Owner:MONTEREY RES LLC

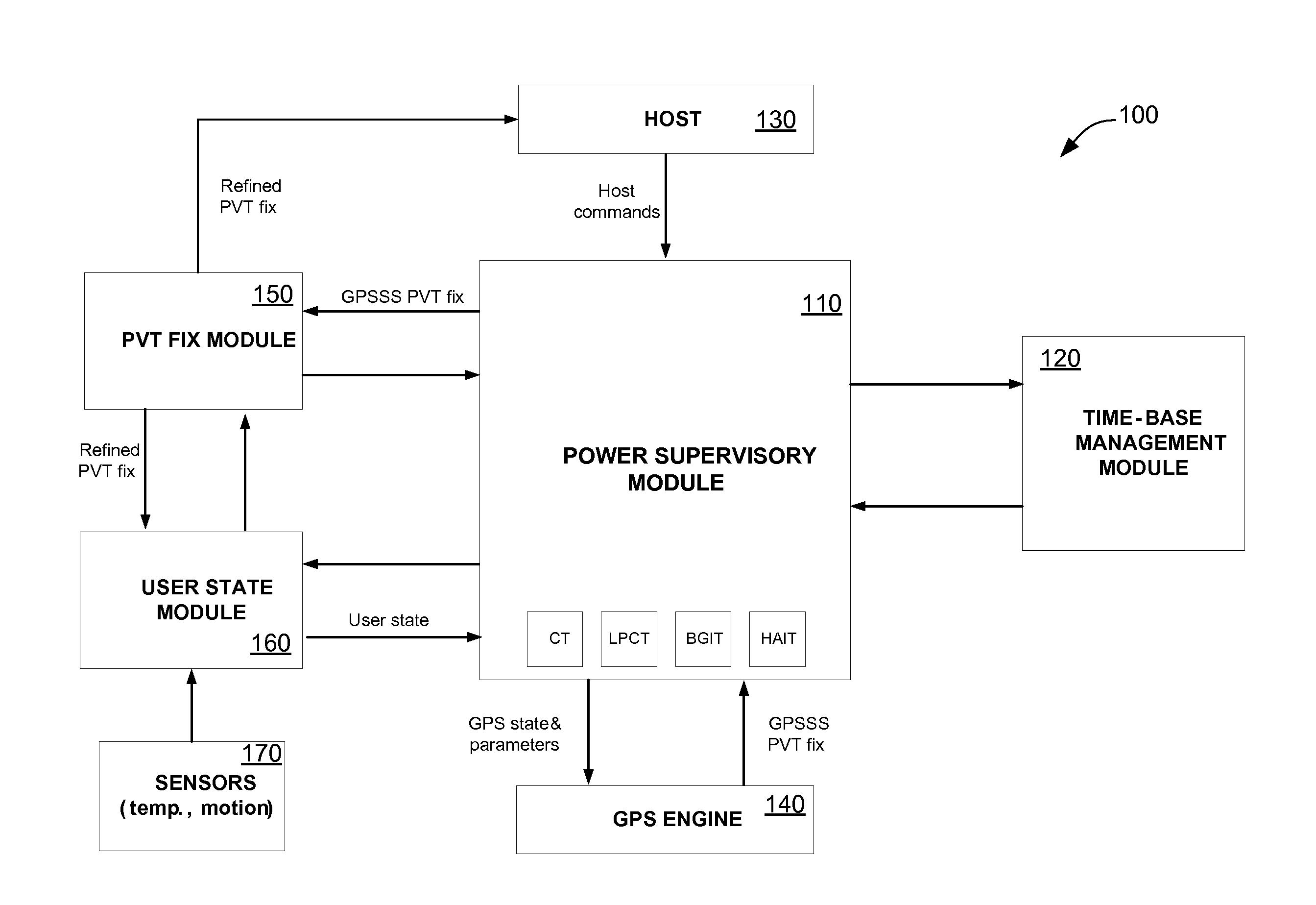

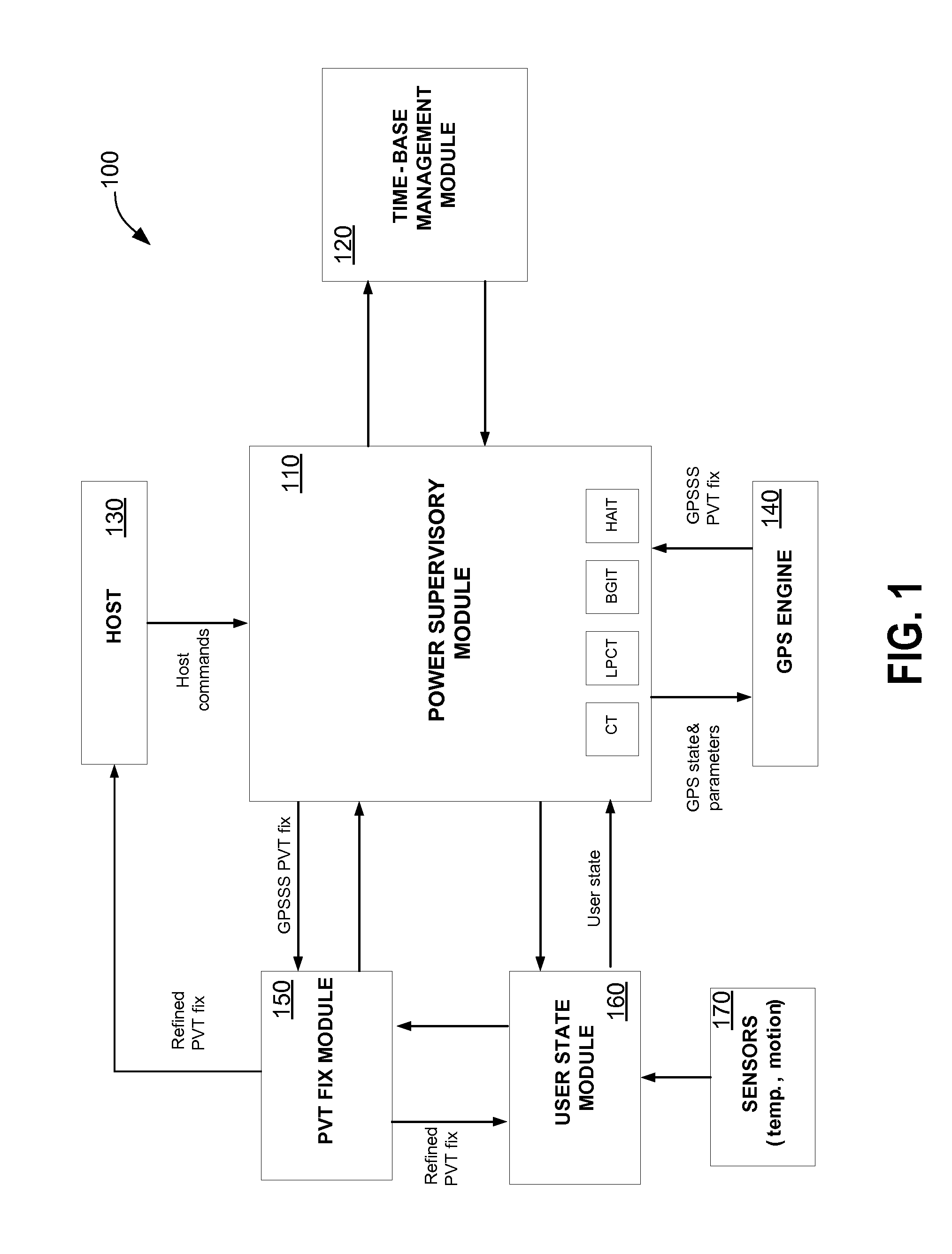

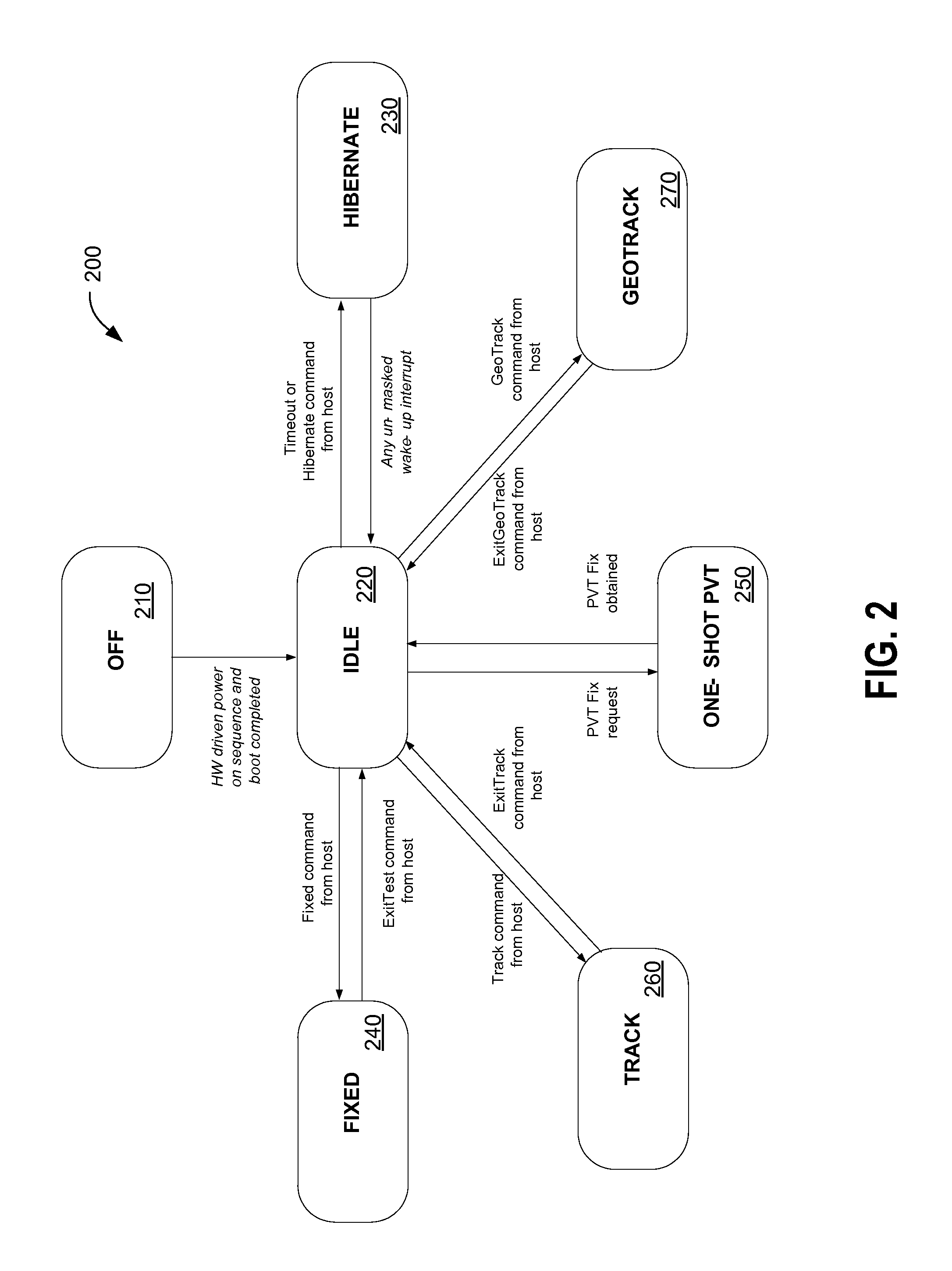

GPS baseband controller architecture

A GPS receiver includes an RF front end for acquiring and tracking a satellite signal and a baseband processor configured to preserve power. The baseband processor includes a GPS engine configured to process the satellite signal and generate a PVT fix, a power supervisory module for receiving the PVT fix, and a user state module that determines an environmental state, wherein the power supervisory module may power down the GPS receiver for a period of time based on a result of the determined environment state. The baseband processor also includes a time-based management module that adjusts the TCXO in response to the determined environmental state. The GPS receiver includes a plurality of operation modes, each of which is associated with a plurality of tracking profiles.

Owner:MAXLINEAR INC

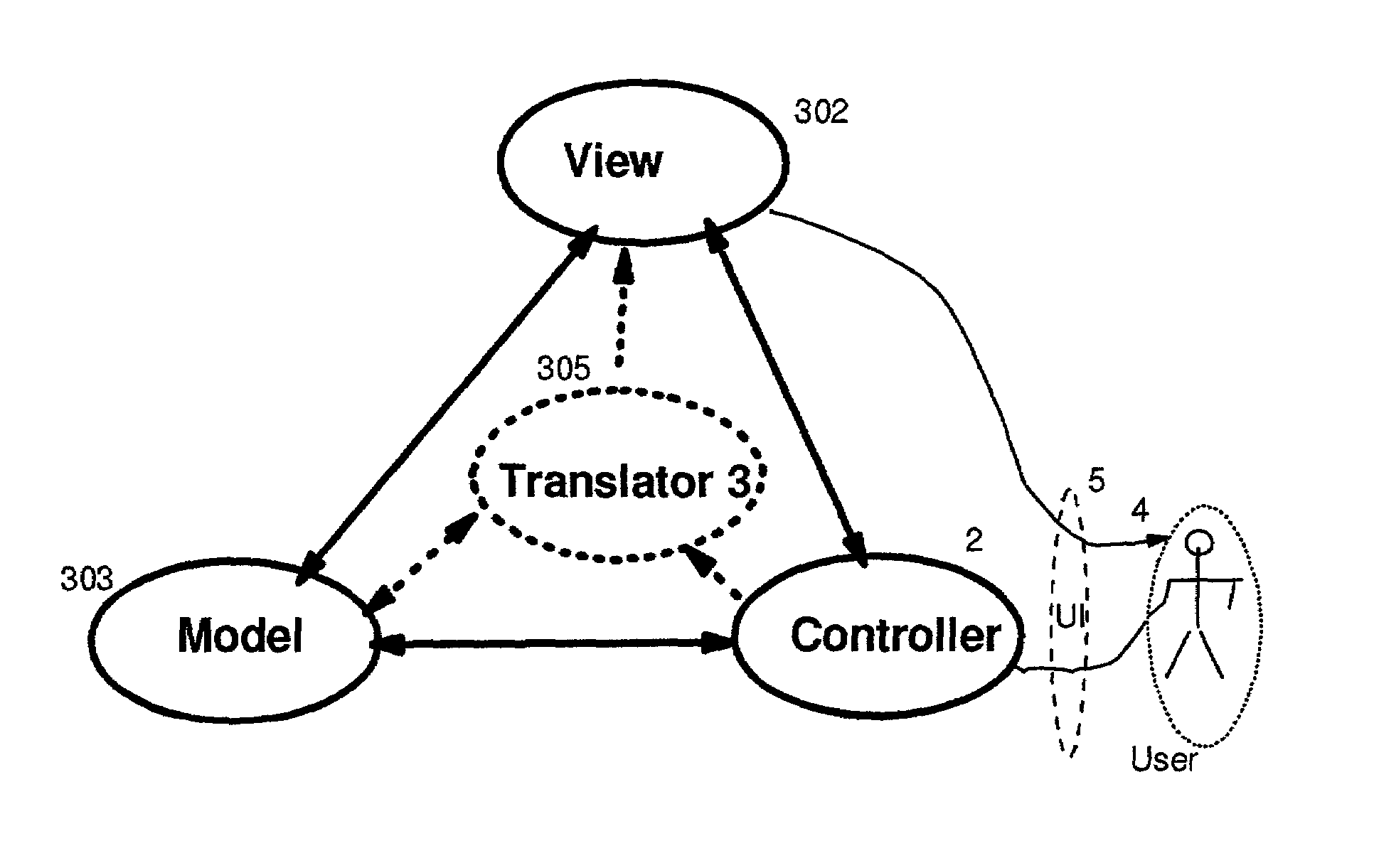

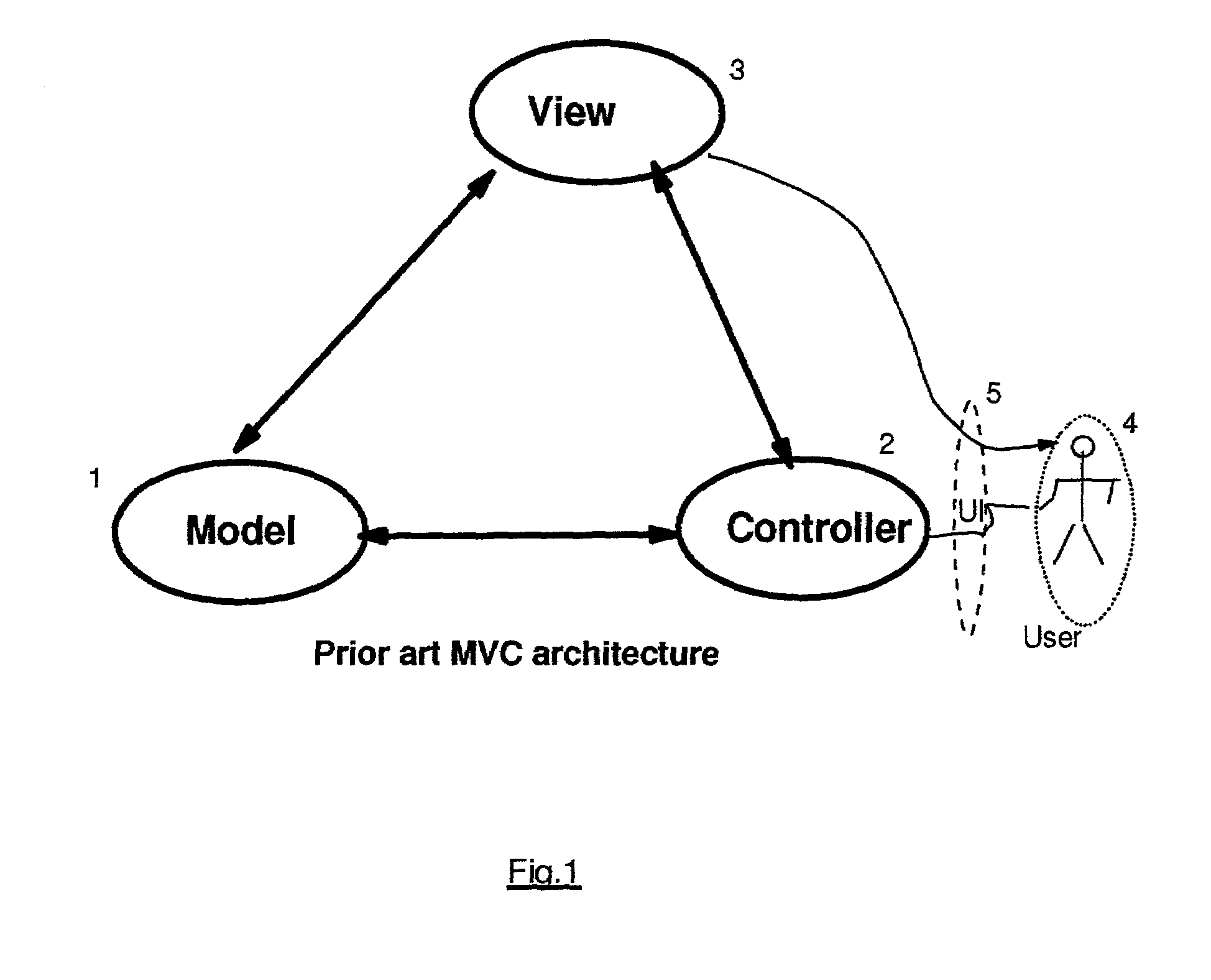

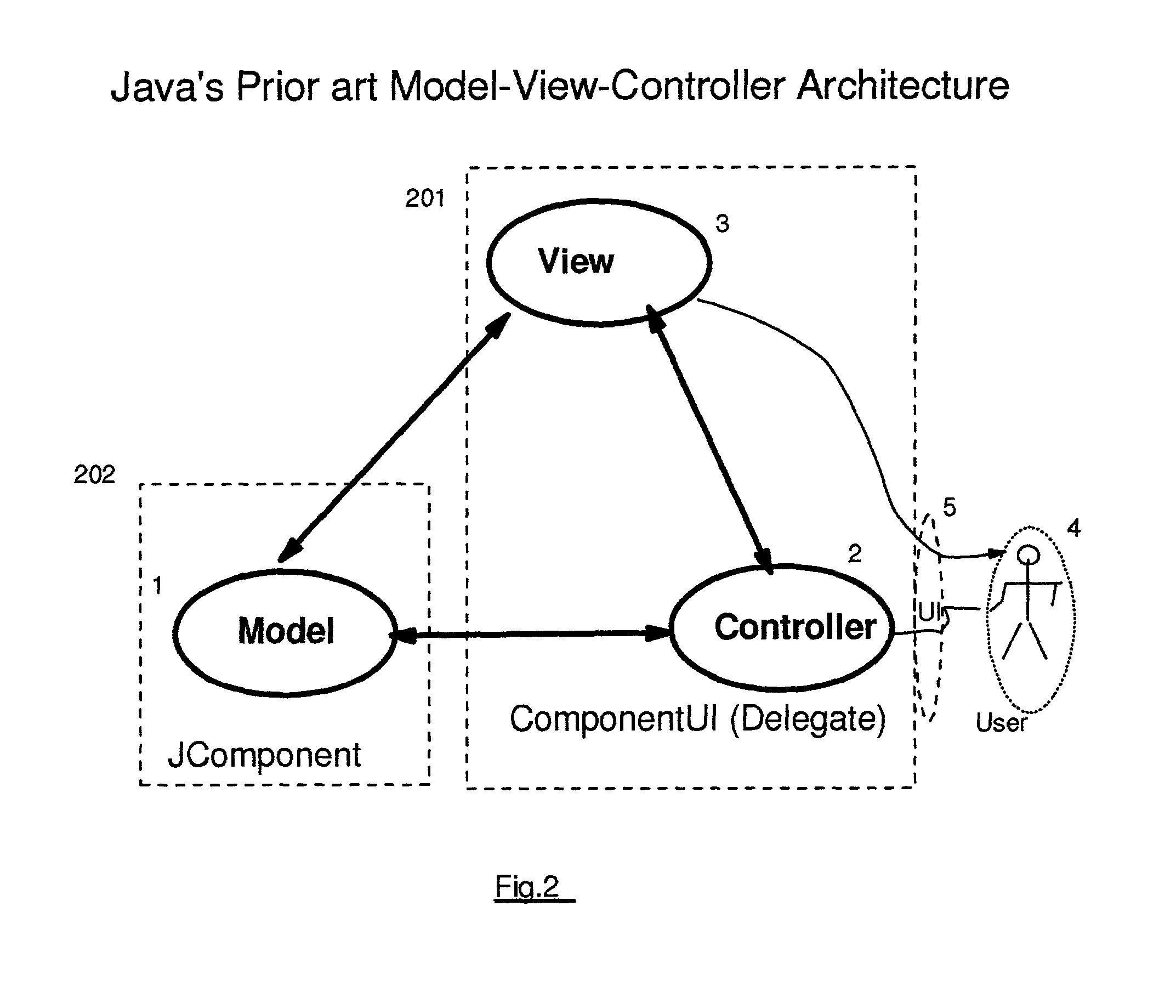

Method, system and program product in a model-view-controller (MVC) programming architecture for inter-object communication with transformation

ActiveUS7114127B2Facilitate communicationEasy to handleCathode-ray tube indicatorsRequirement analysisController architectureData type

A system, method and program product in a Model-View-Controller architecture for communicating between objects such as a Model object and a View object. A transform object is provided in the interface between any of the conventional Model, View and Controller objects such that transformation of data types into appropriate other data types is accomplished outside of the MVC object. This relieves the recipient MVC object of the responsibility of being designed to support multiple data types in order to perform a function.

Owner:IBM CORP

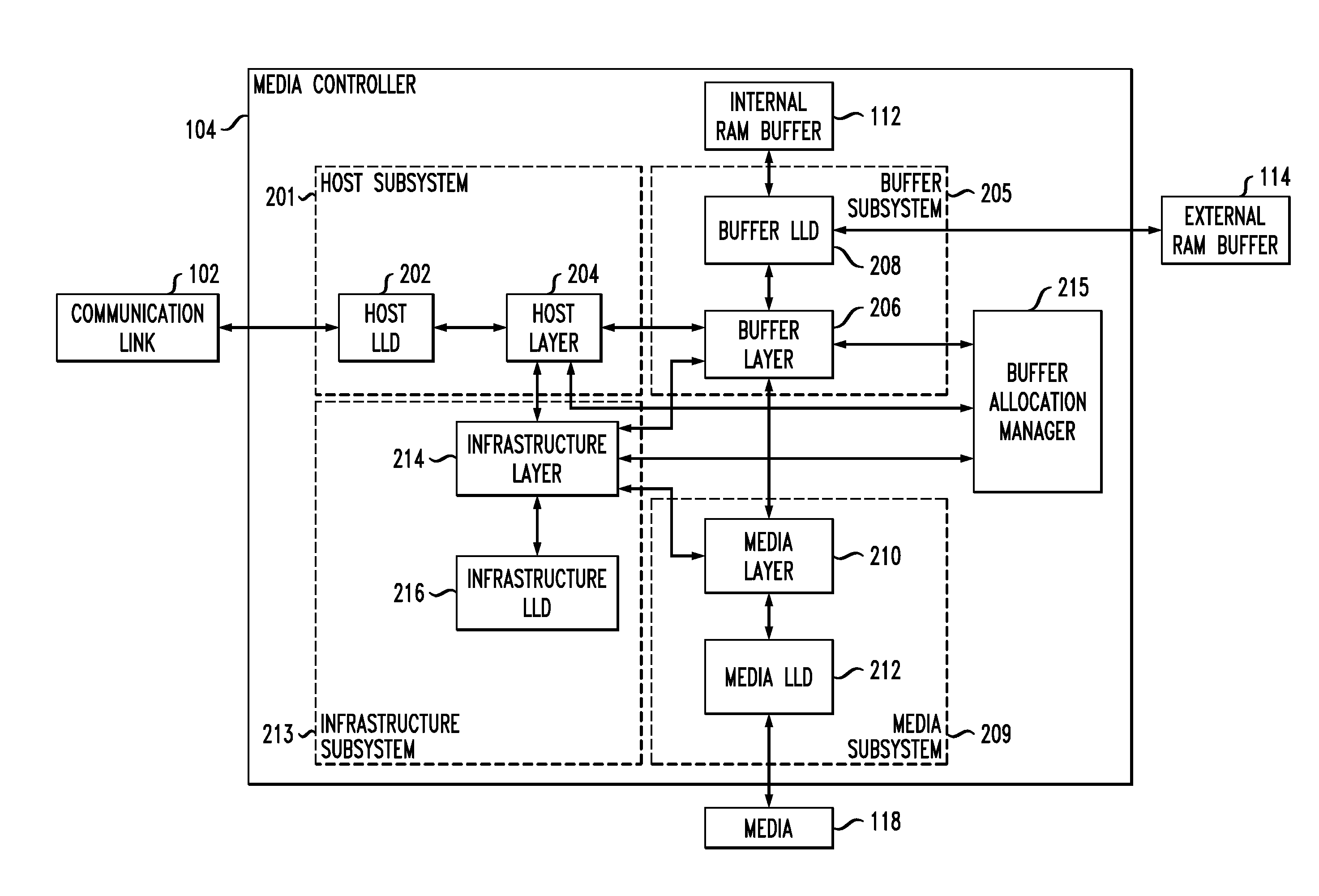

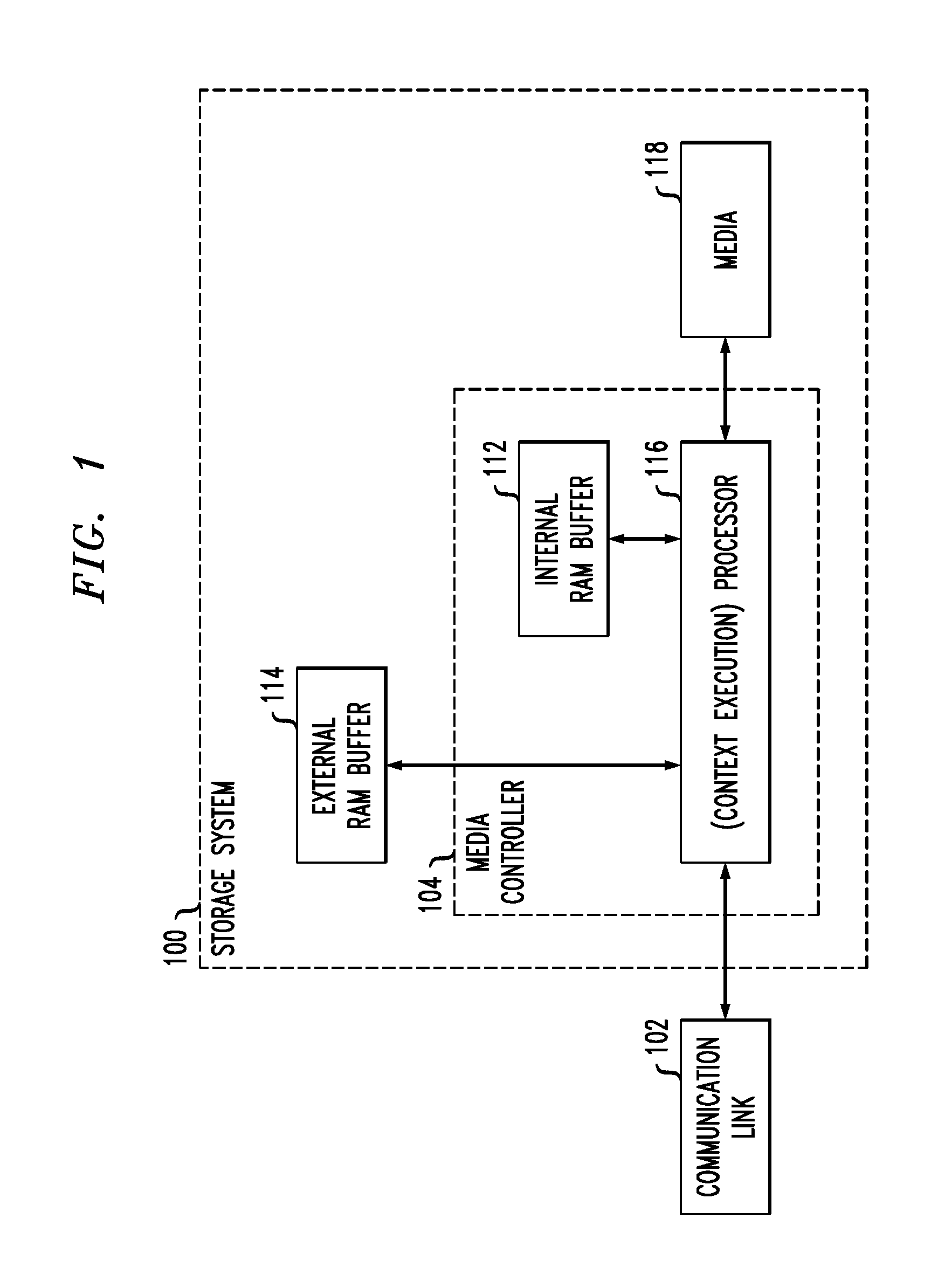

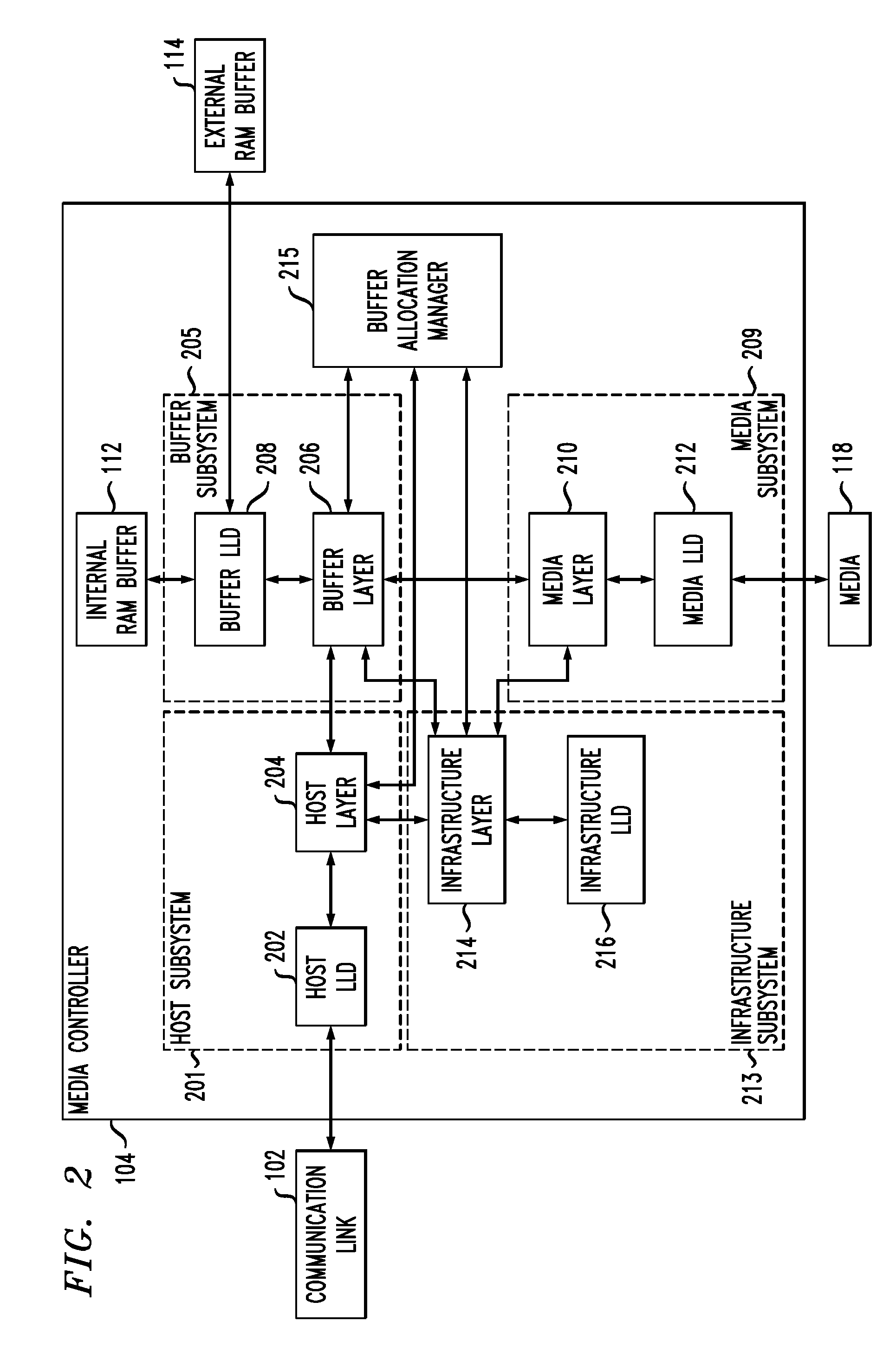

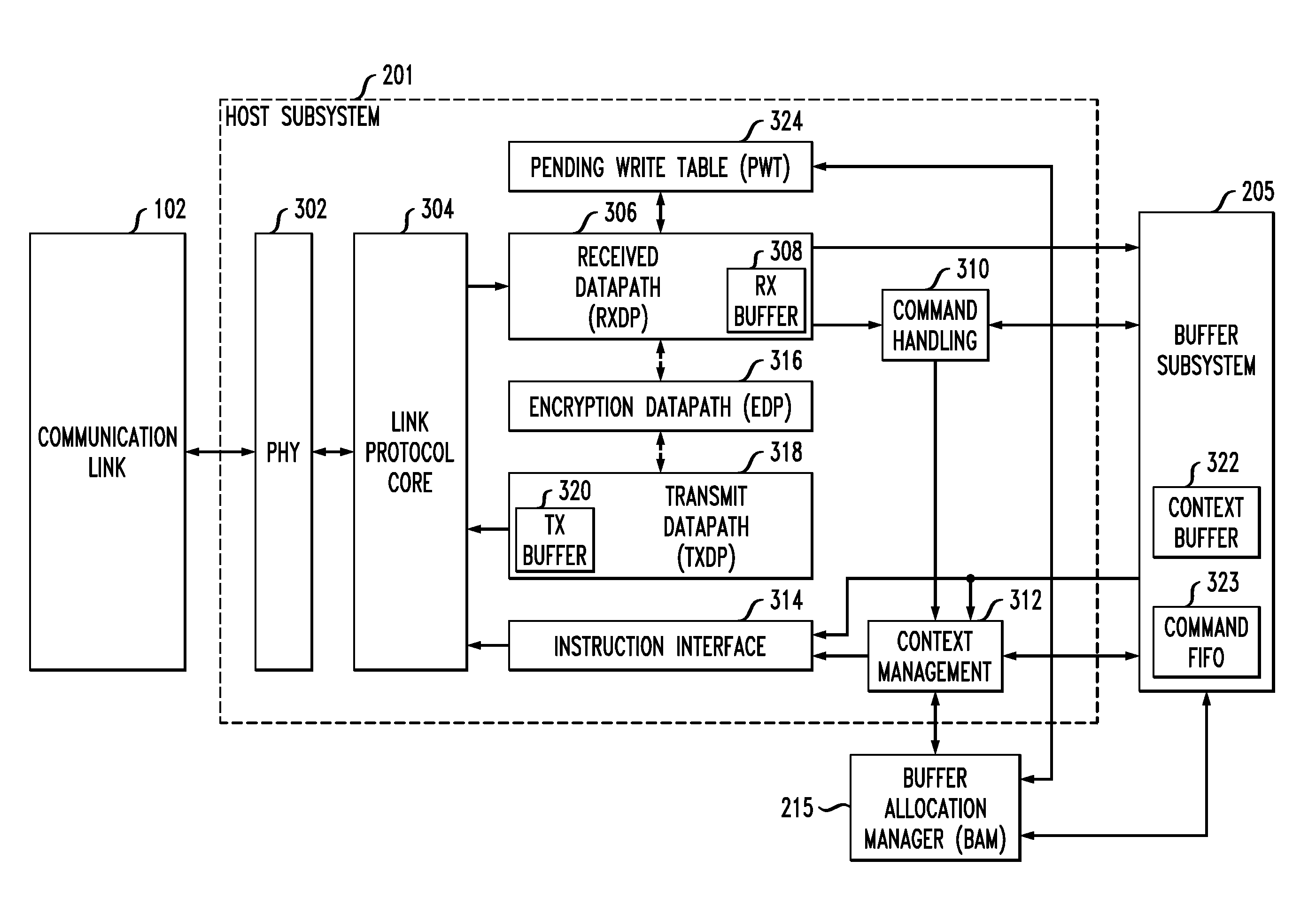

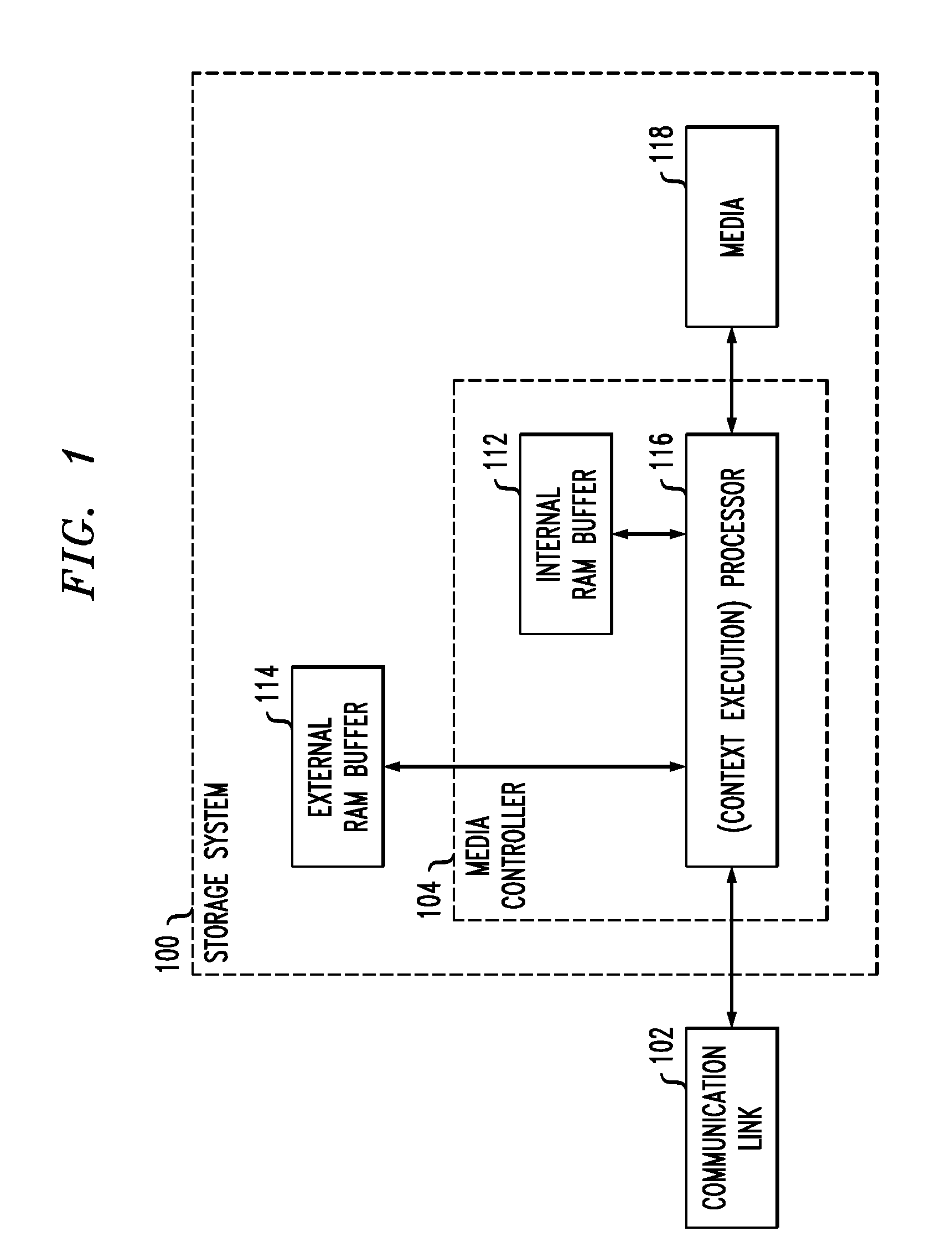

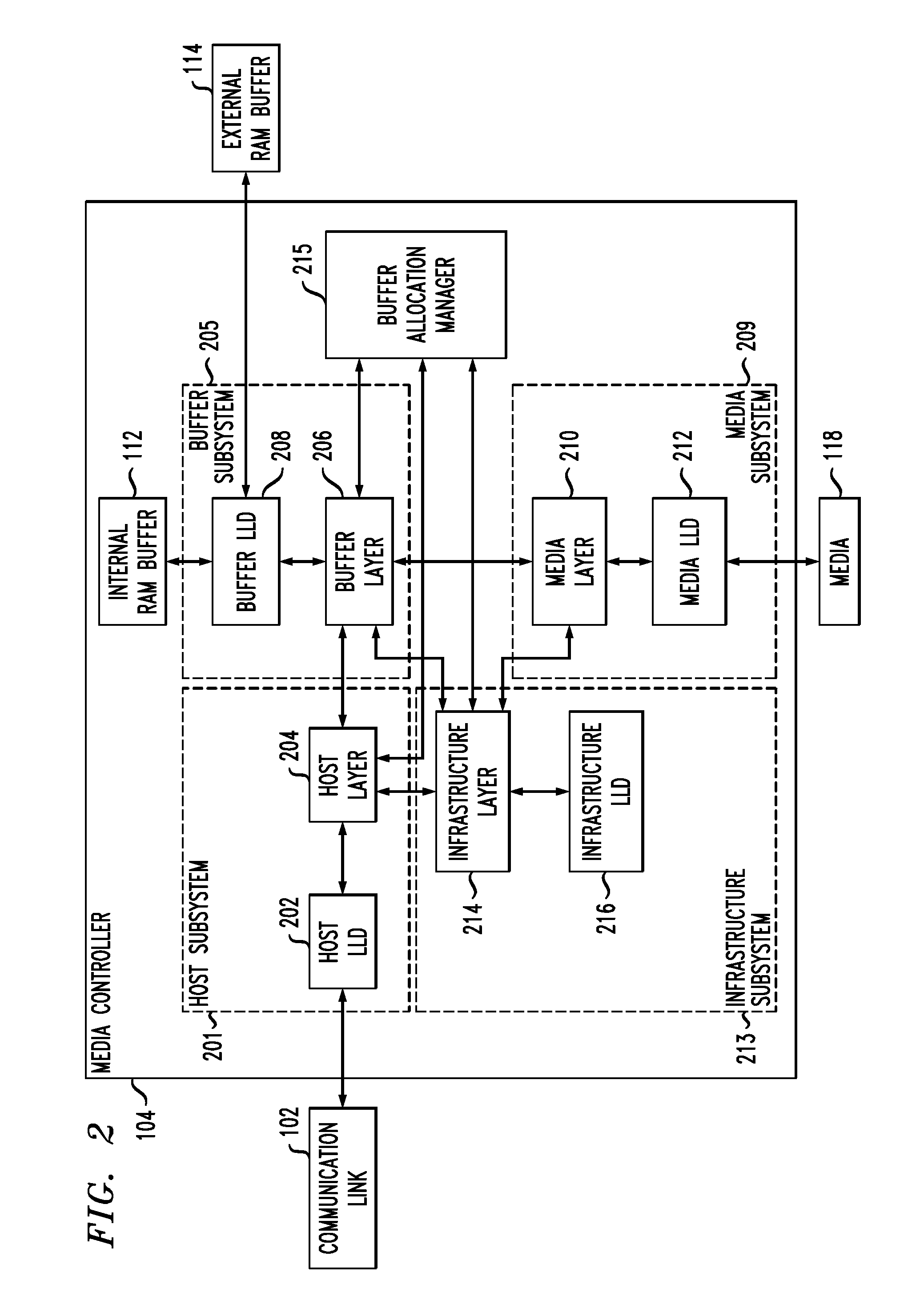

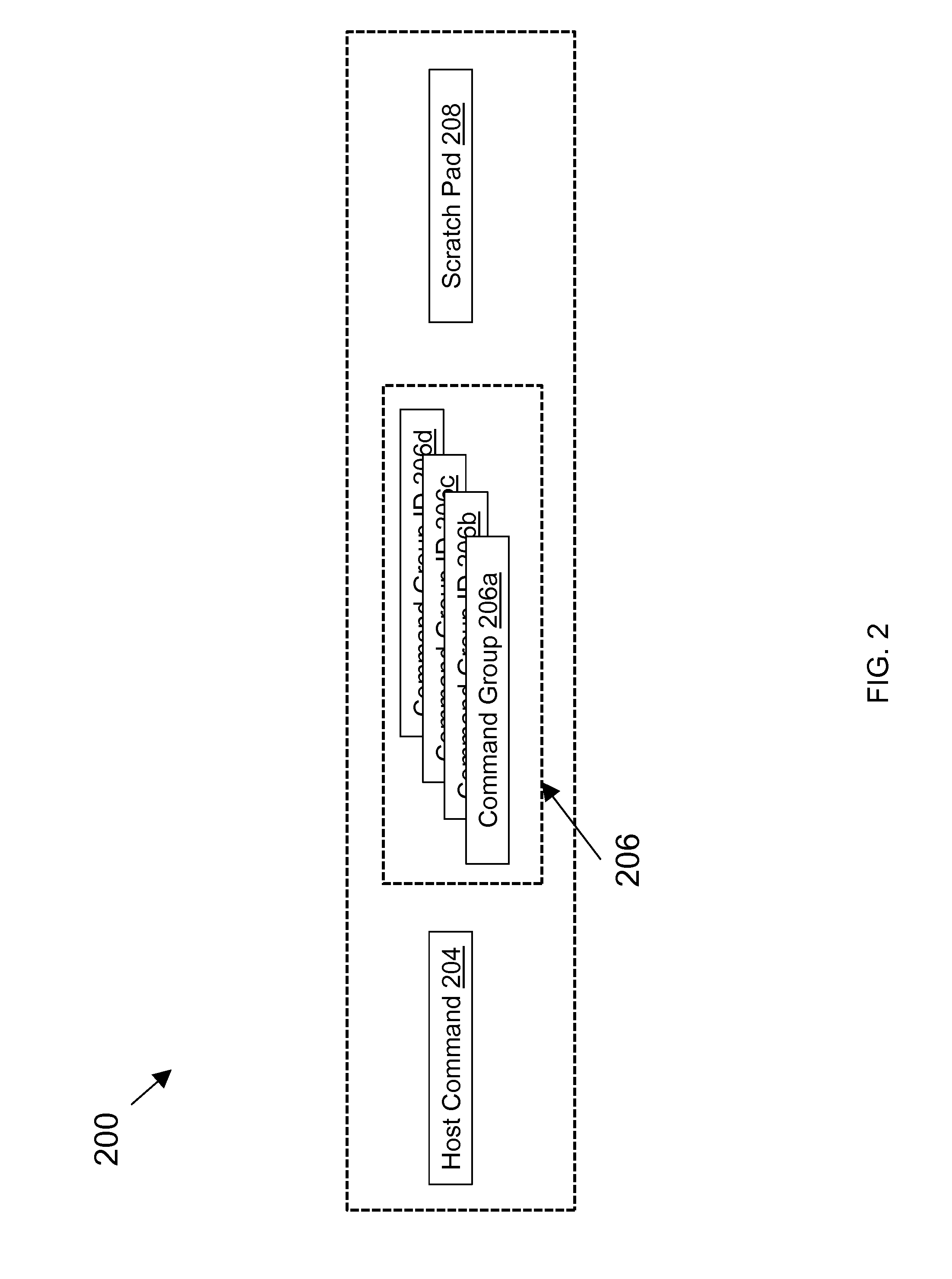

Context Processing for Multiple Active Write Commands in a Media Controller Architecture

Described embodiments provide a method of transferring data from host devices to a media controller. The media controller generates a transfer context for each write request received from a host device. Receive-data threads corresponding to data transfer contexts for each transfer context are generated, each receive-data thread corresponding to a data transfer between a host device and the media controller. Buffer threads corresponding to data transfer contexts for each transfer context are generated, each buffer thread corresponding to a data transfer between the receive data path and a buffer subsystem. The receive-data and buffer threads are tracked for each transfer context. For each tracked transfer context, data from the receive datapath is iteratively transferred to the buffer subsystem for a previous data transfer context of the buffer thread while data from the host device is transferred to the receive datapath for a subsequent data transfer context of the receive-data thread.

Owner:SEAGATE TECH LLC

Shelf management controller with hardware/software implemented dual redundant configuration

InactiveUS20070255430A1Low costSafety arrangmentsElectric controllersController architectureIntelligent Platform Management Interface

A fault tolerant, multi-protocol shelf management controller architecture that is extensible provides an intelligent platform management interface that is version indifferent as well as programmable and reconfigurable. The shelf management controller is arranged in a dual redundant configuration in a client-server mode and has a message driven configuration with the messages conforming to the Intelligent Platform Management Interface (IPMI) specification as extended by PICMG 3.0. In one embodiment, each shelf management controller includes at least one bit stream processor comprising sequenced stage machines implementing one or more finite state machines associated with one or more devices that are under control of the shelf management controller. The finite state machines could be hardware or software based. The shelf management controller is also modeled as a layered architecture that includes an IPMI API layer. The IPMI API layer enables the shelf manager to interface with legacy and future IPMI specifications.

Owner:RPX CORP

Programmable microcontroller architecture(mixed analog/digital)

InactiveUS7825688B1Simple interfaceDigital technique networkSolid-state devicesController architectureCapacitance

Owner:MONTEREY RES LLC

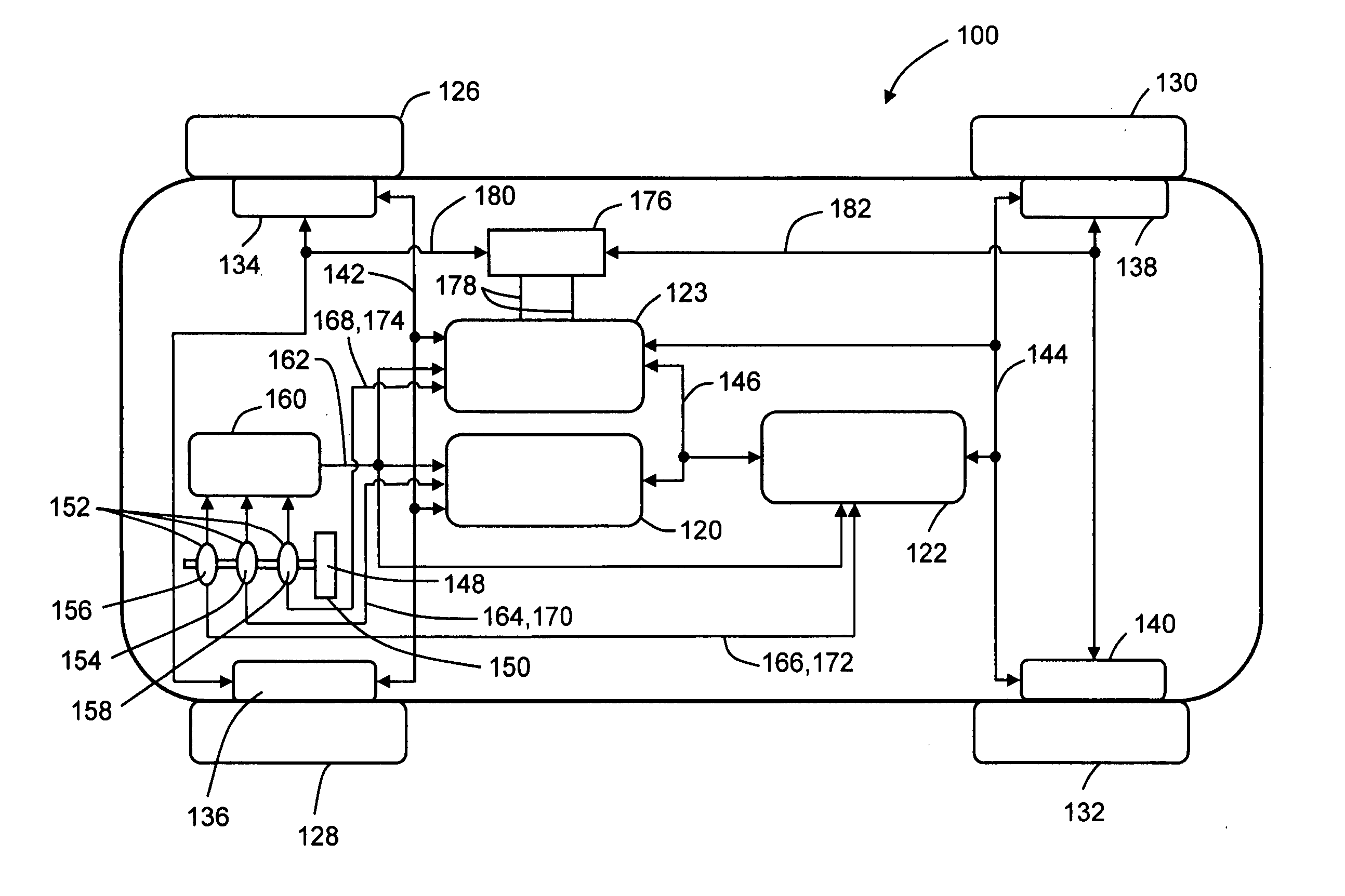

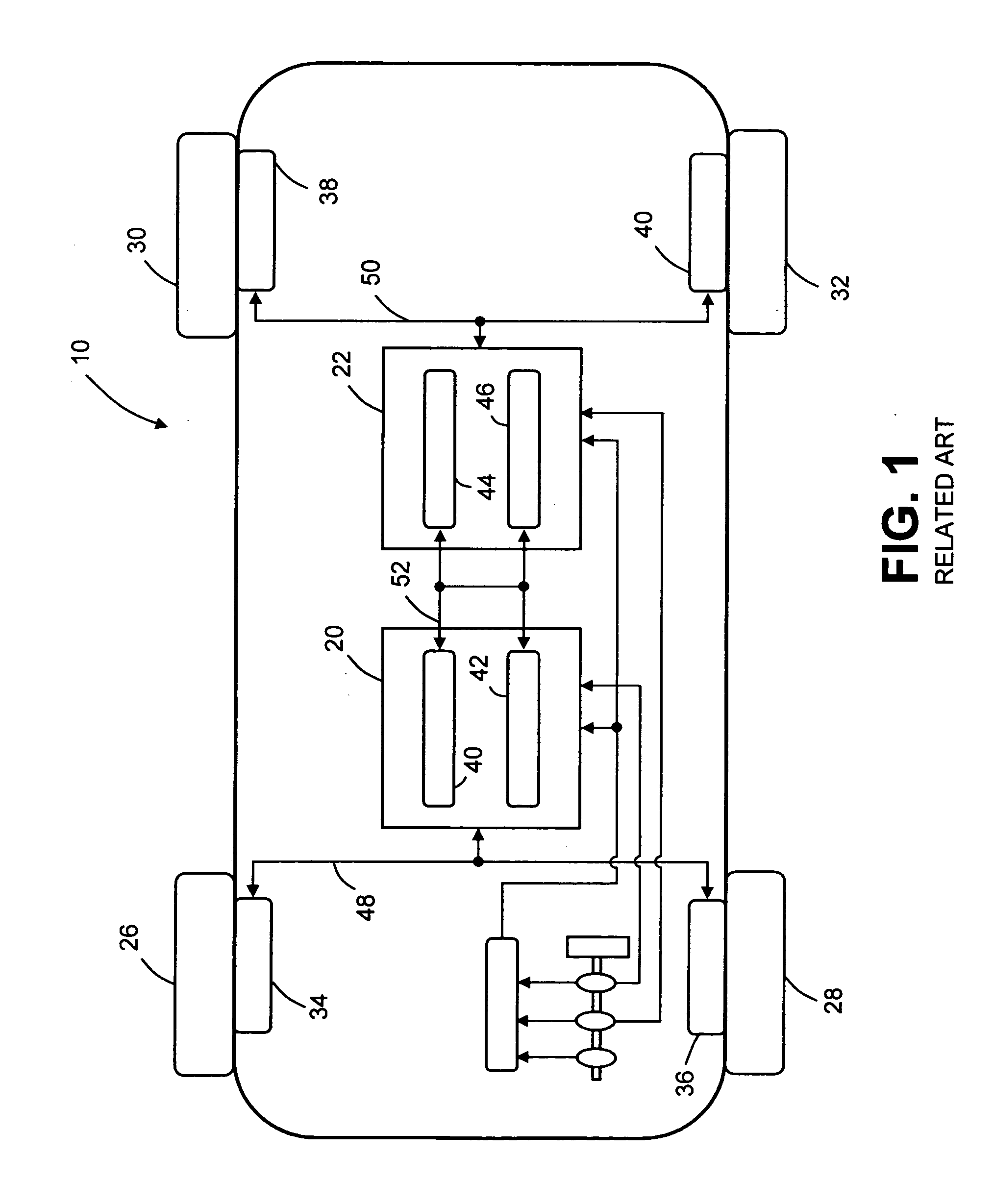

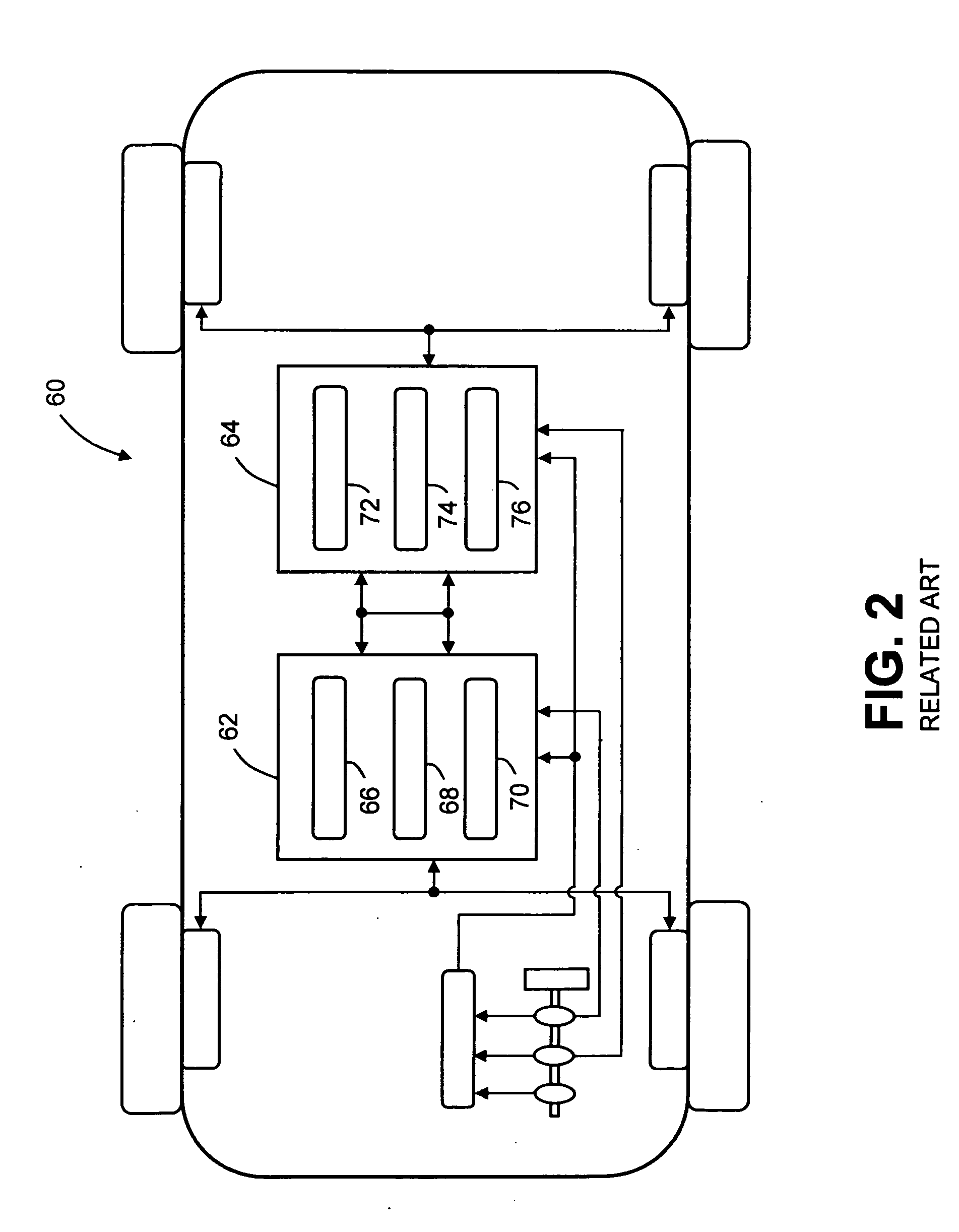

Brake by-wire control system

InactiveUS20050225165A1Reduce system complexityIncrease redundancyBraking action transmissionBrake control systemsController architectureControl system

A brake control system for brake by wire applications having a dual fail-silent pair controller architecture. The system utilizes two supervisory controllers and a shared monitoring controller to achieve the dual fail-silent pair configuration. The brake control system also features a mechanism whereby the monitoring controller ensures the fail-silent operation of the brake control units in the event of certain undesired events occurring within the system by assuming control of the affected brake control units. The control system further assures that no single event, including an event related to the monitoring controller, causes loss of more than half the braking functionality. The control system also features additional redundancy with regard to the brake command signals by sharing a separate unprocessed brake command signal with each of the supervisory controllers and the monitoring controller.

Owner:GENERAL MOTORS COMPANY

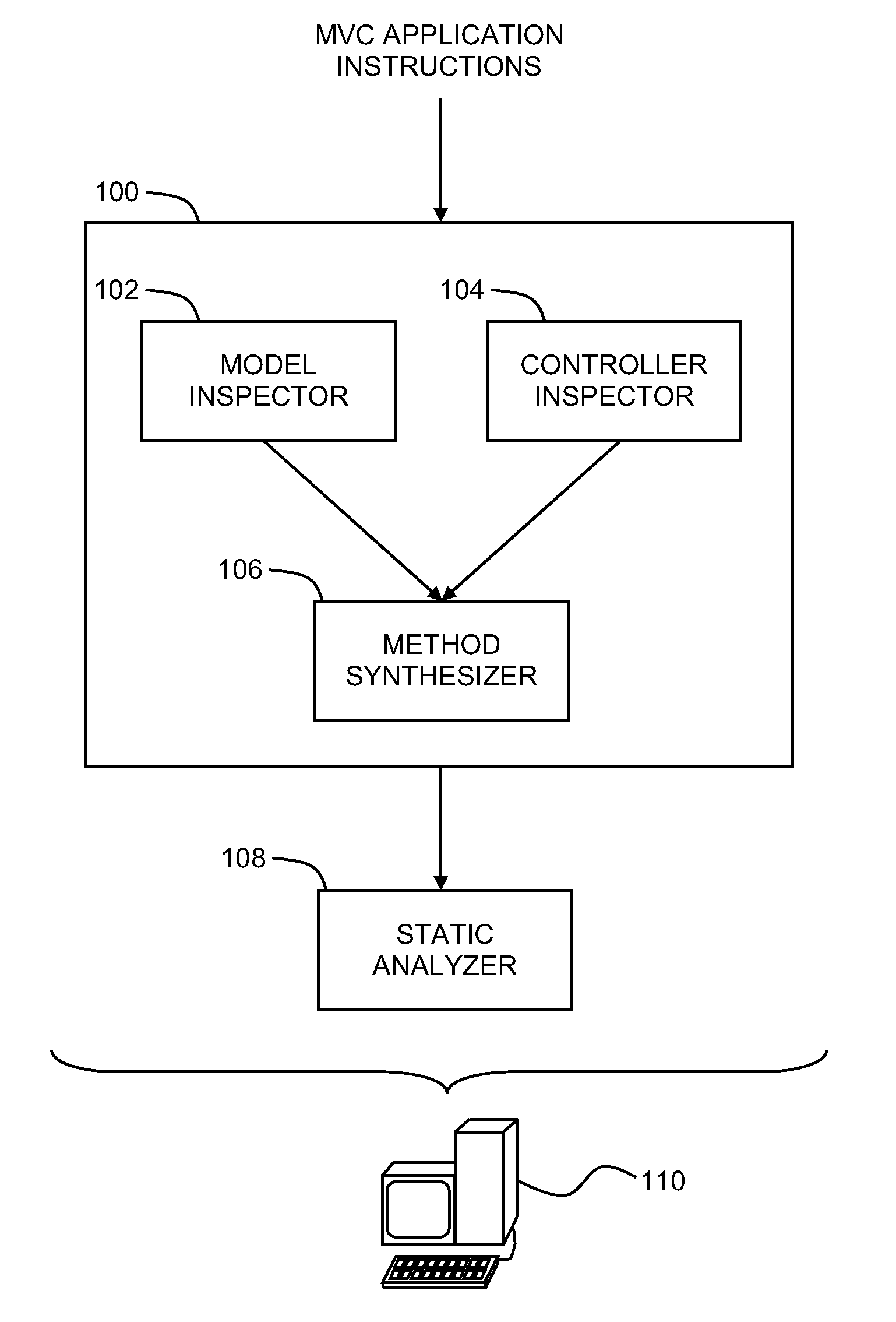

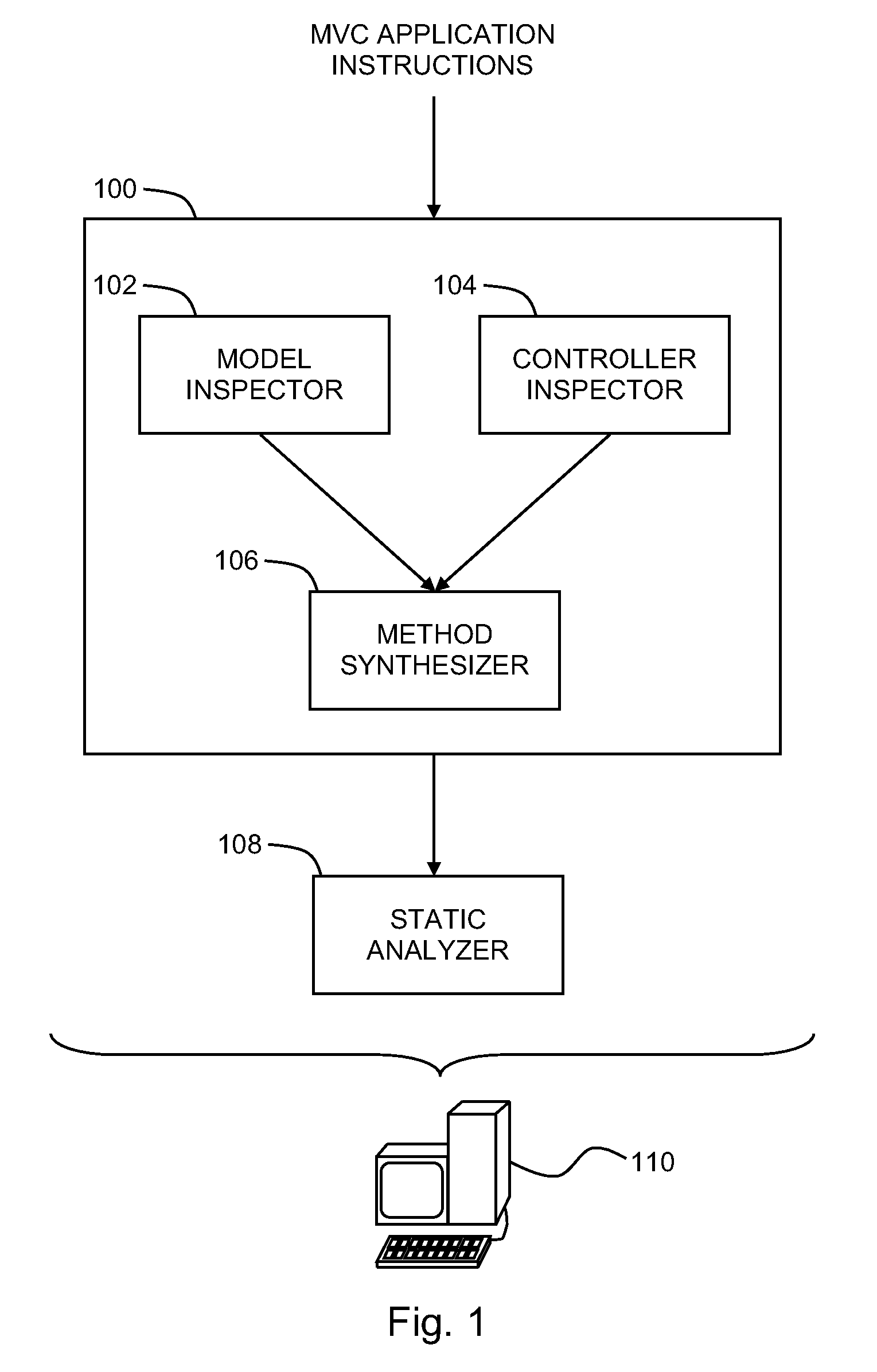

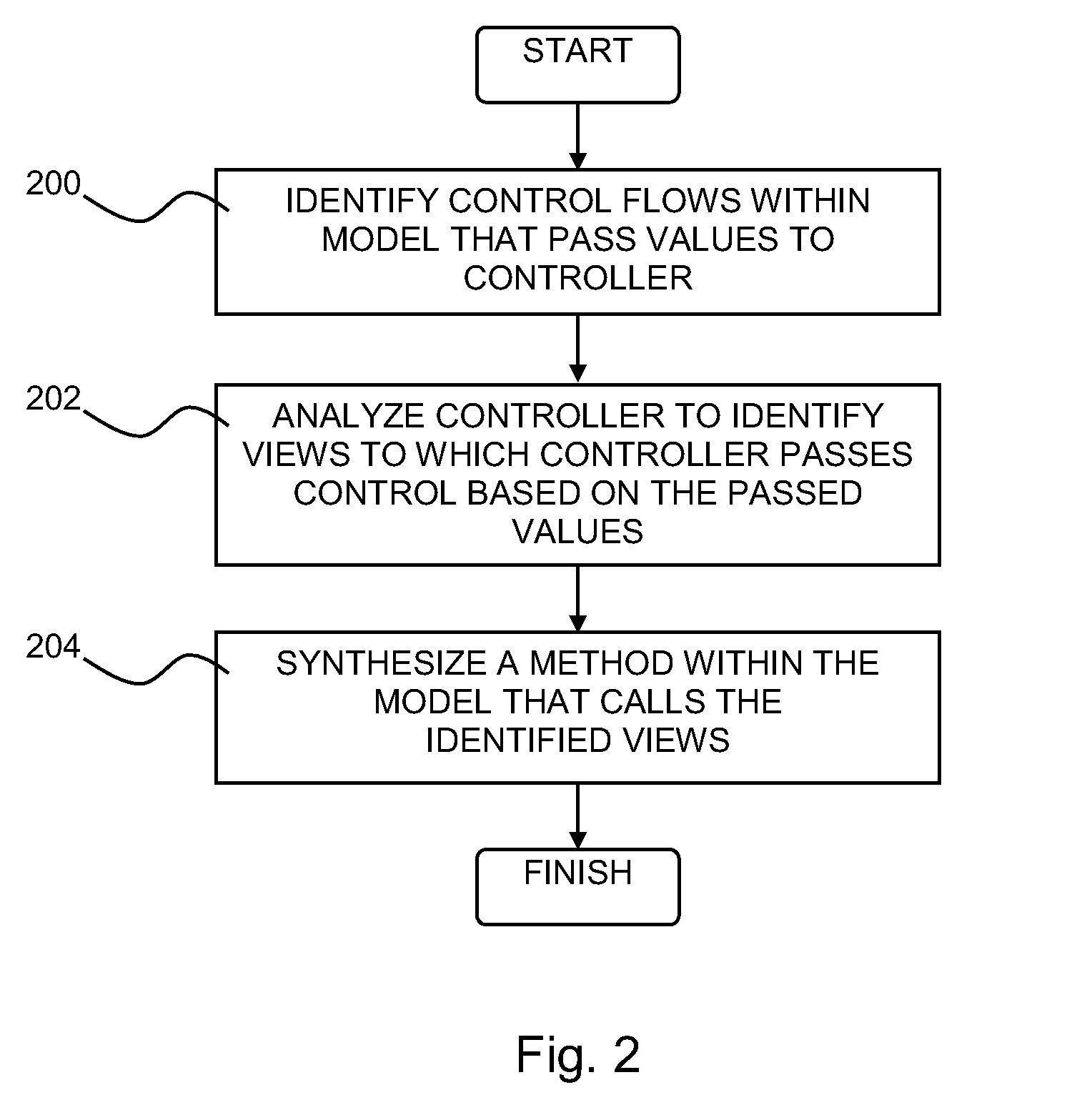

Static Analysis of Computer Software Applications Having A Model-View-Controller Architecture

Preparing a computer software application for static analysis by identifying a control flow within a model portion of a computer software application having a model-view-controller architecture, where the control flow passes a value to a controller portion of the computer software application, analyzing a declarative specification of the controller portion of the computer software application to identify a view to which the controller portion passes control based on the value, and synthesizing a method within the computer software application, where the method calls the view.

Owner:IBM CORP

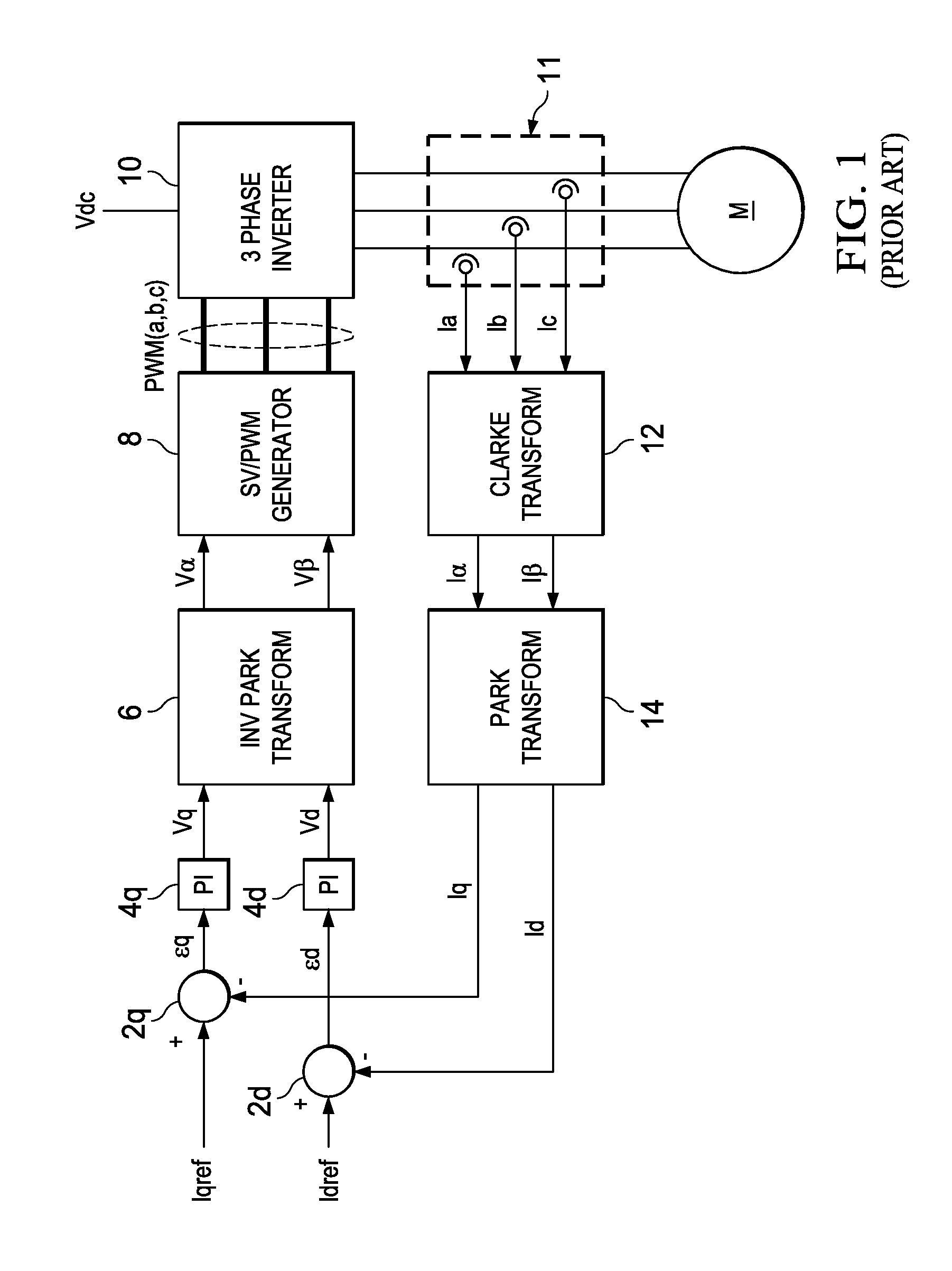

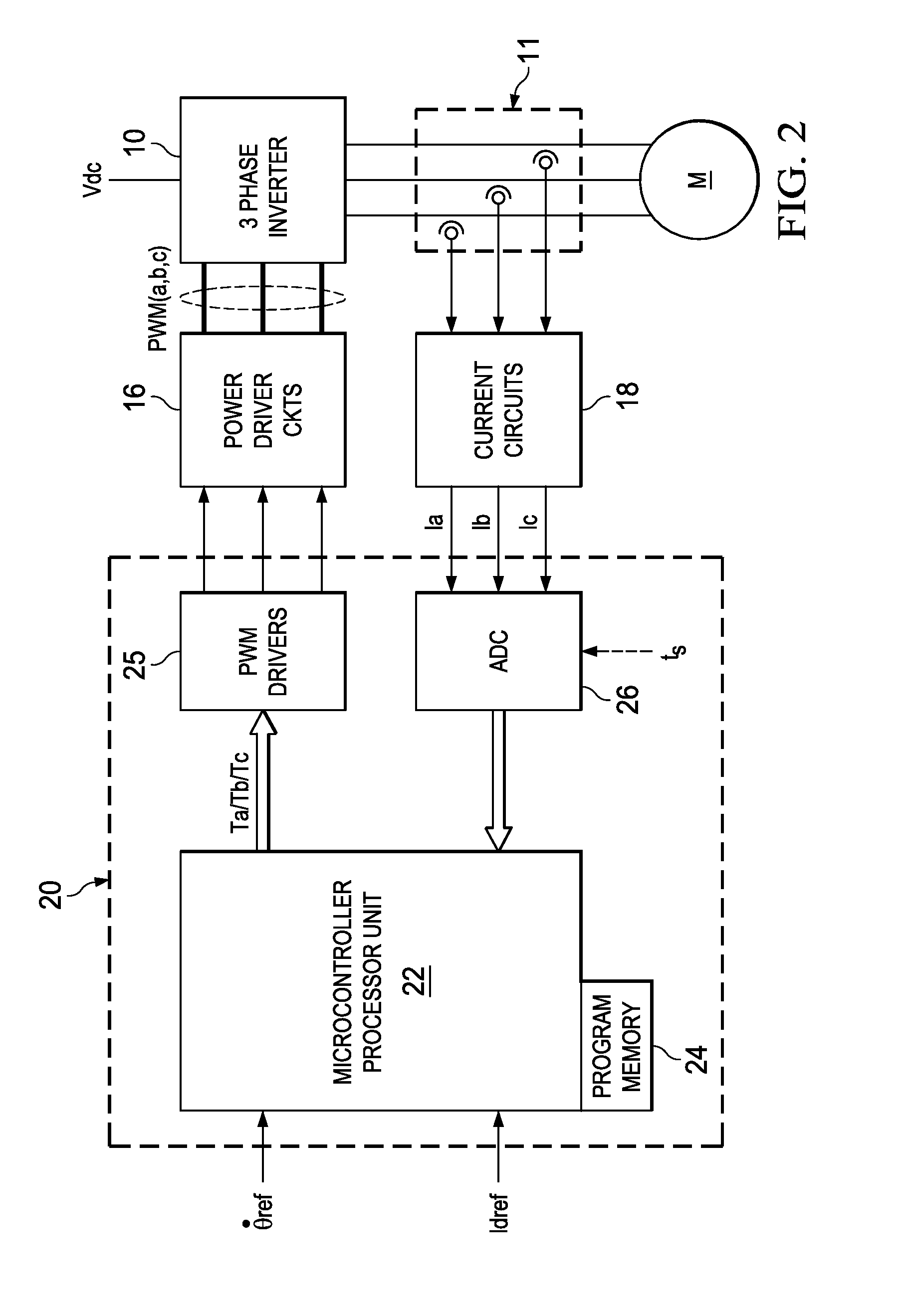

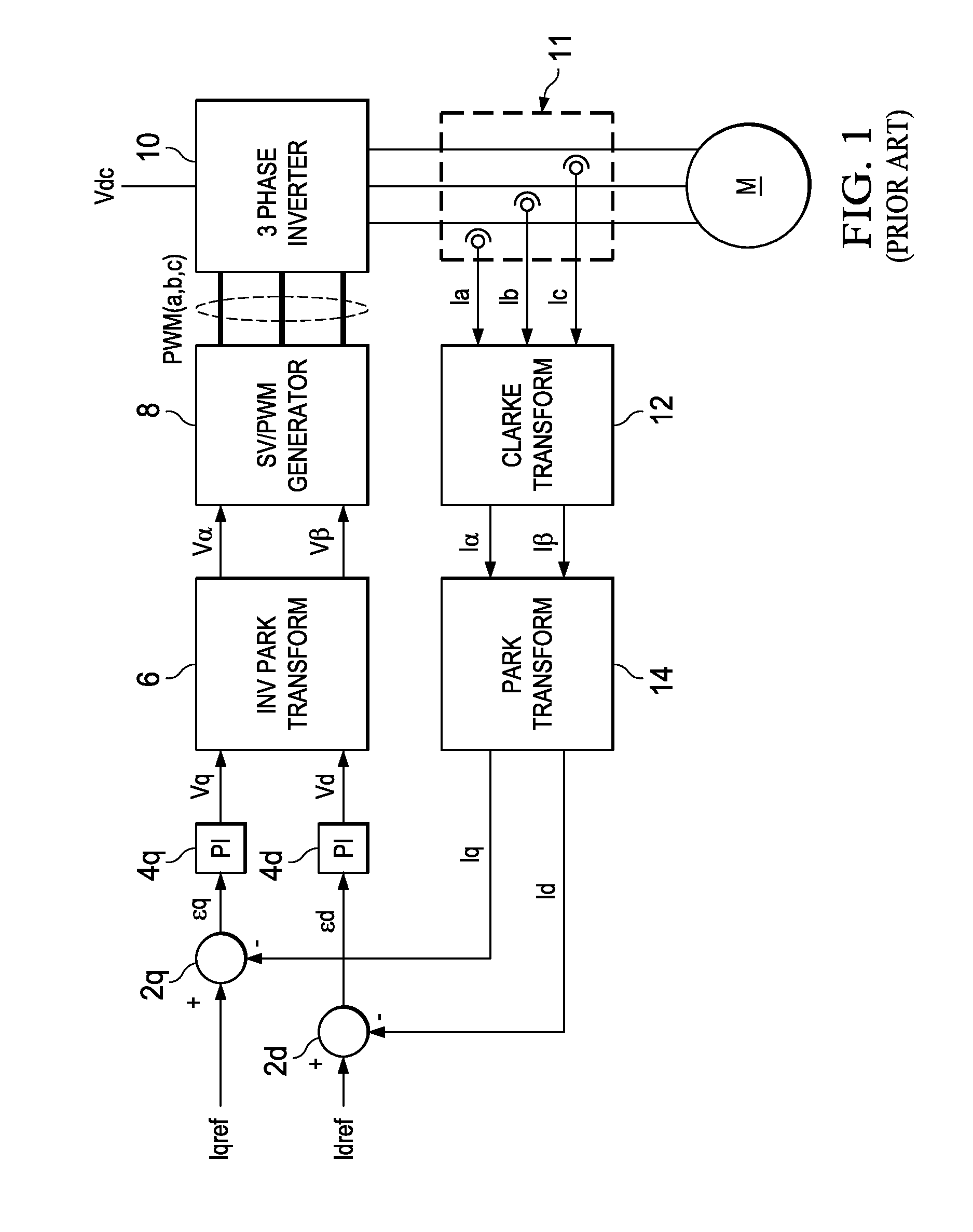

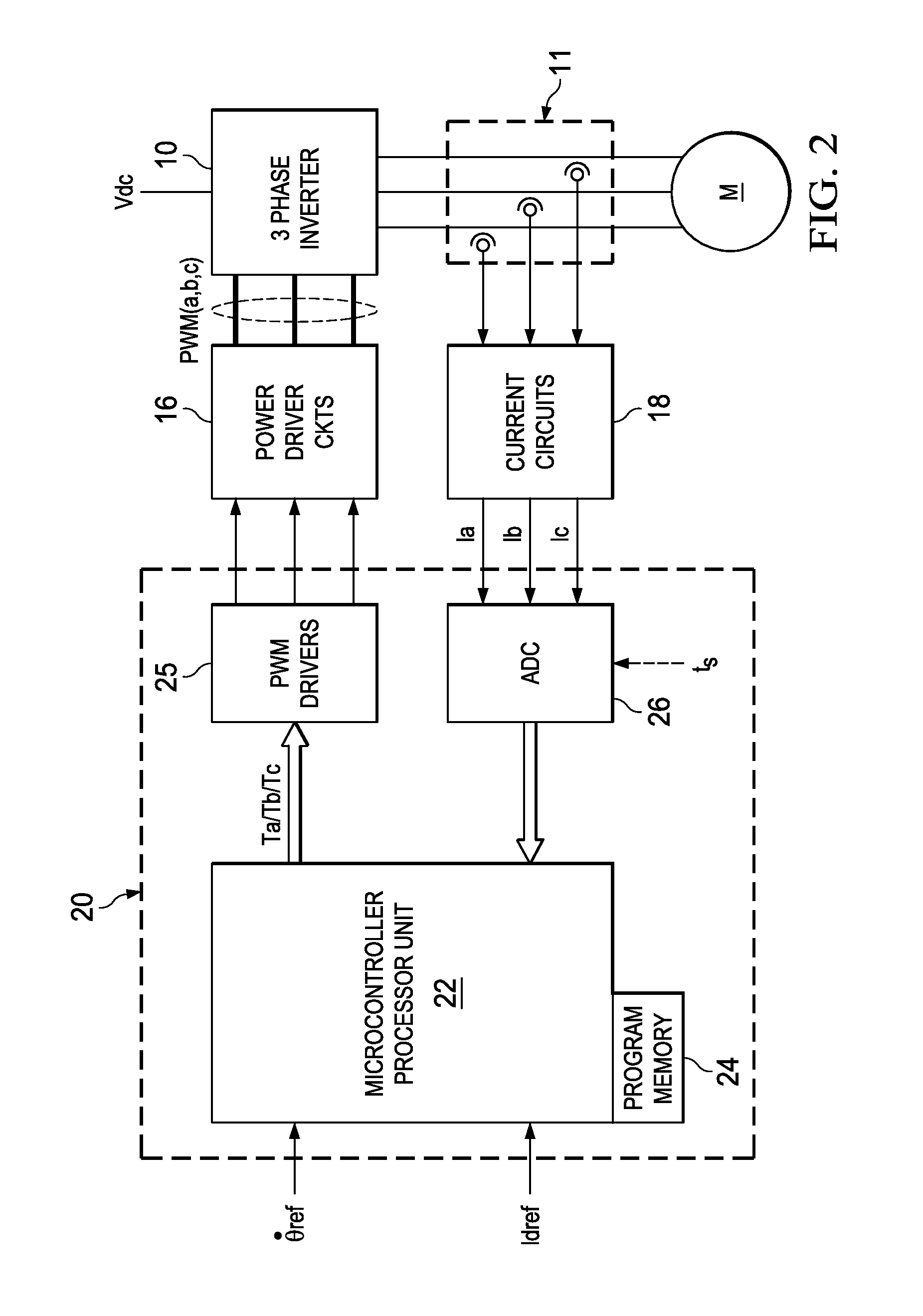

Angle/Frequency Selector in an Electric Motor Controller Architecture

ActiveUS20150084575A1Smooth and precise controlEfficient implementationElectronic commutation motor controlMotor/generator/converter stoppersController architecturePeriodic excitation

A motor controller architecture and method of operating the same. The motor controller includes a function for estimating the low speed operation of the motor, for example by evaluating the response to a periodic excitation signal injected into the control loop of the controller architecture. A periodic excitation signal in the form of a square wave allows for analysis of the response of the motor without requiring demodulation, which allows the frequency of the excitation signal to be above the audible range. Control logic for controlling the motor at transitional speeds between low speed control and high speed (back emf) control is provided in some embodiments.

Owner:TEXAS INSTR INC

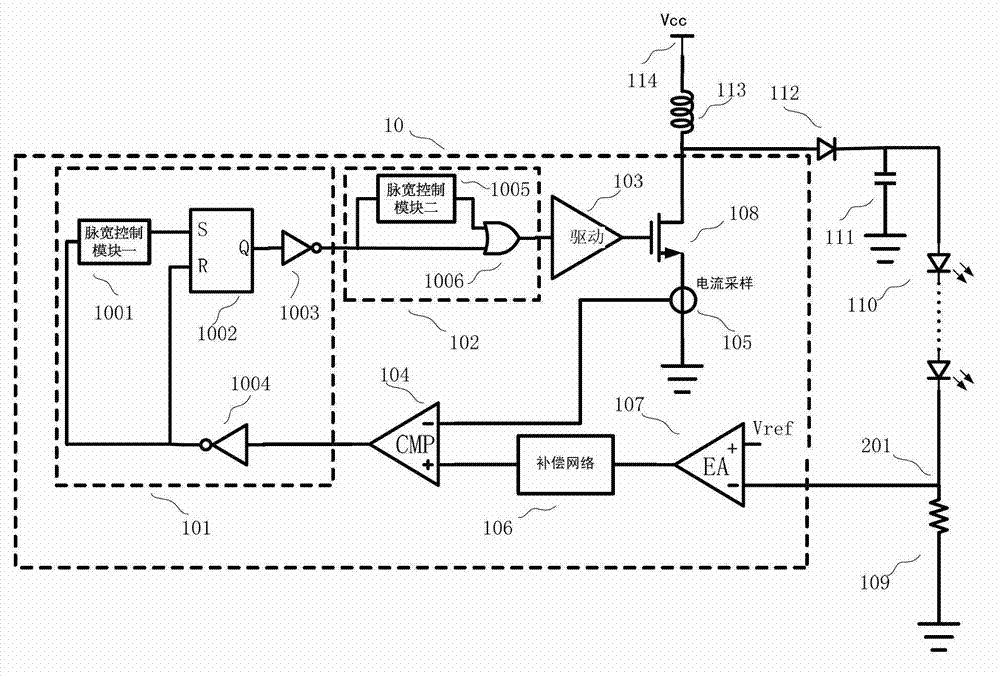

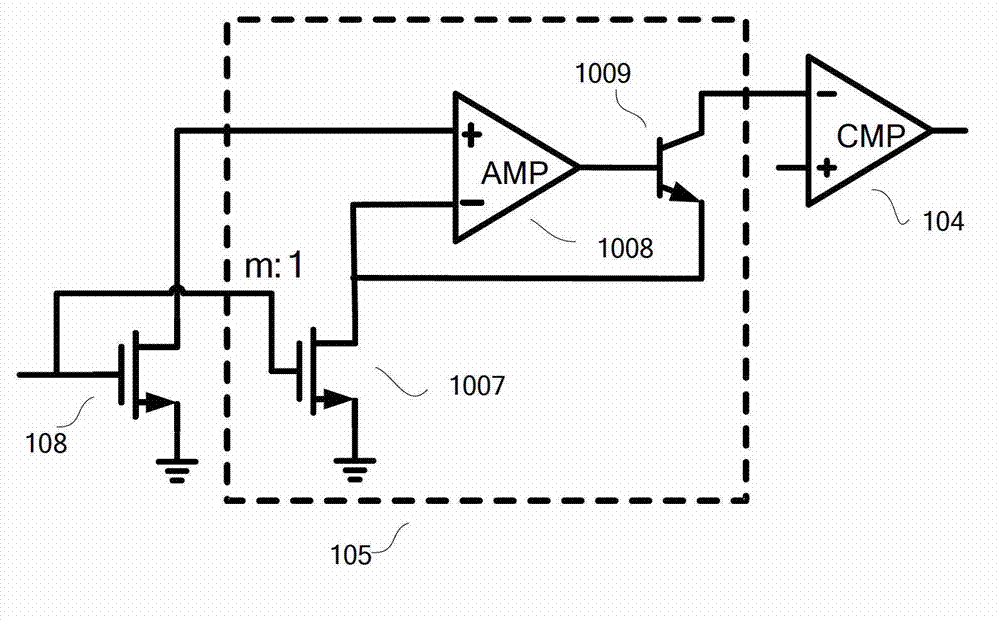

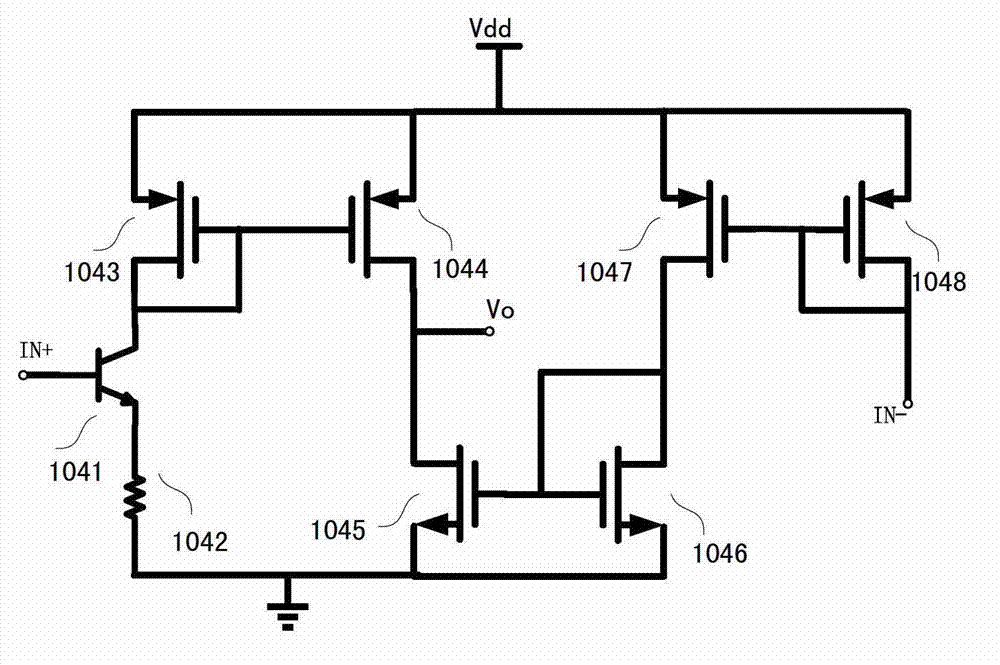

Deadline-fixed PFM (pulse frequency modulation) mode switching power supply controller

InactiveCN102868297ASimple structureReduce lossApparatus without intermediate ac conversionElectric light circuit arrangementController architectureExternal energy

The invention relates to a deadline-fixed PFM (pulse frequency modulation) mode switching power supply controller belonging to the technical field of power integrated circuits, and mainly relates to the application area of BOOST switching power supplies. The switching power supply controller comprises an error amplifier (107), a frequency compensation network (106), a comparator (104), a deadline-fixed PFM control module (101), a maximum frequency limit module (102), a power switching tube drive circuit (103), a current sampling module (105) and a power switch (108). The PFM controller architecture is simple in implementation mode, can work in an interrupted current mode and can also work in a continuous current mode; and in practical application, the controller has the advantages of small size of external energy storage elements, low ripple voltage in case of a light load, low switching loss and high efficiency in case of a heavy load, and the like.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

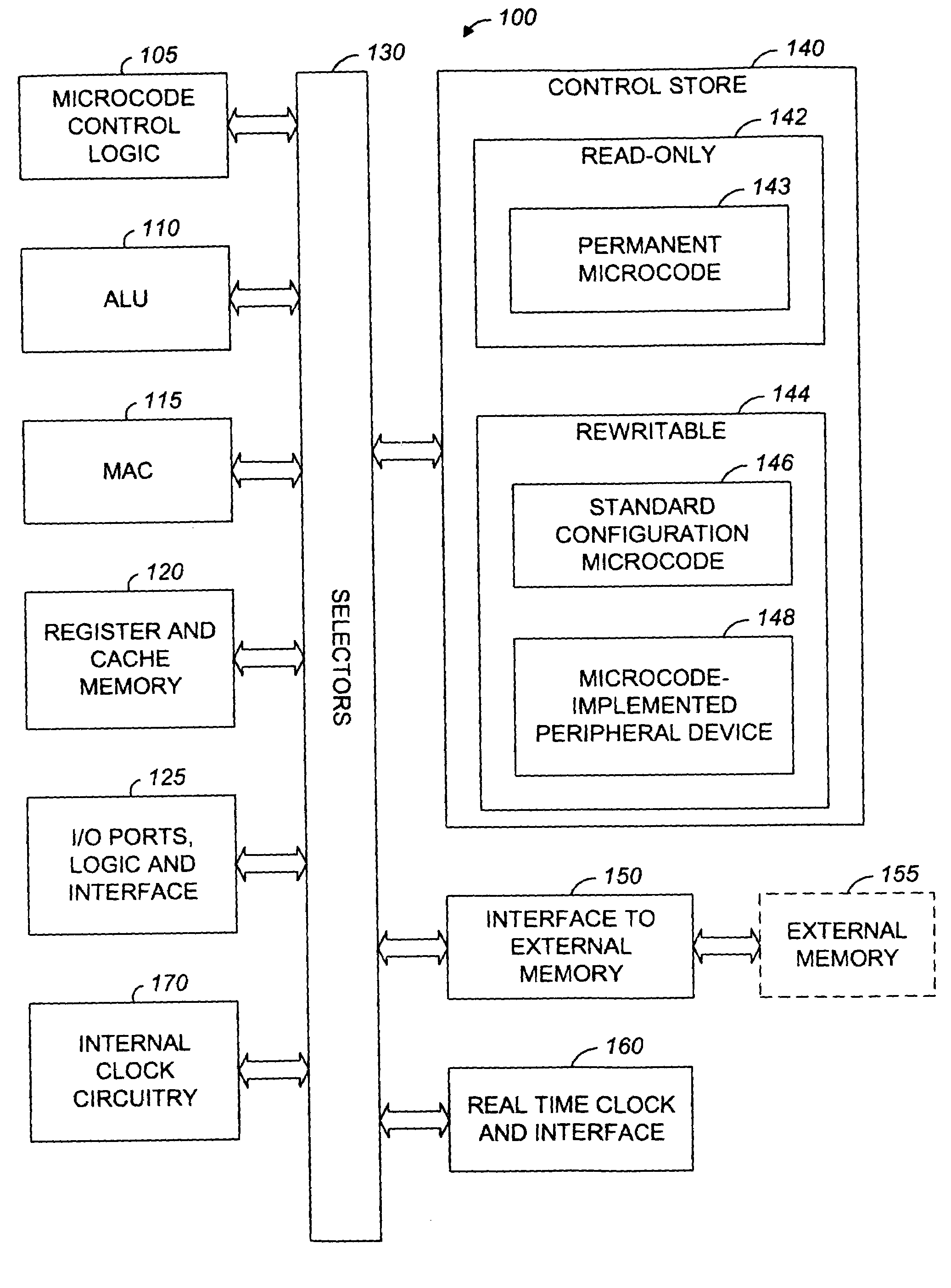

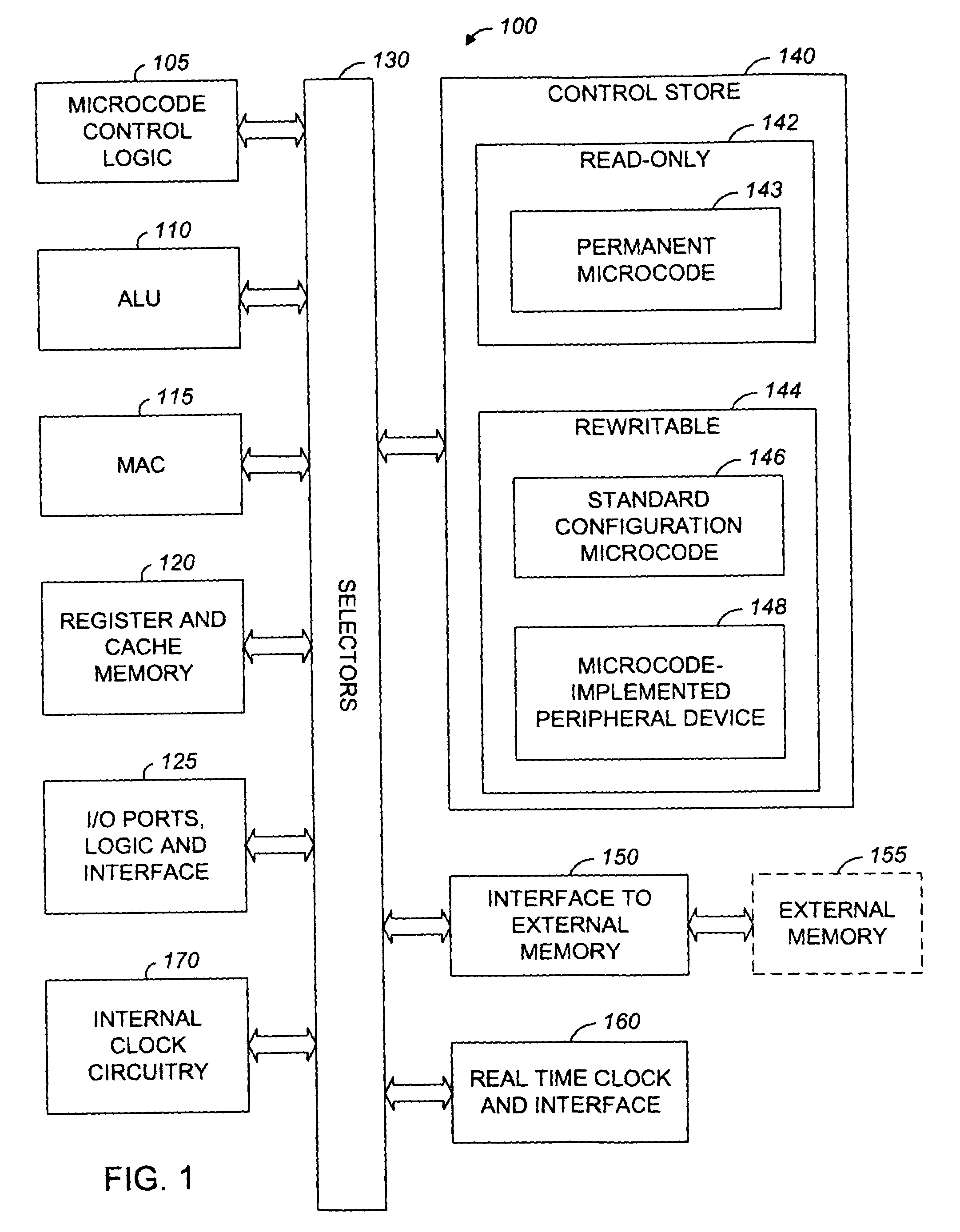

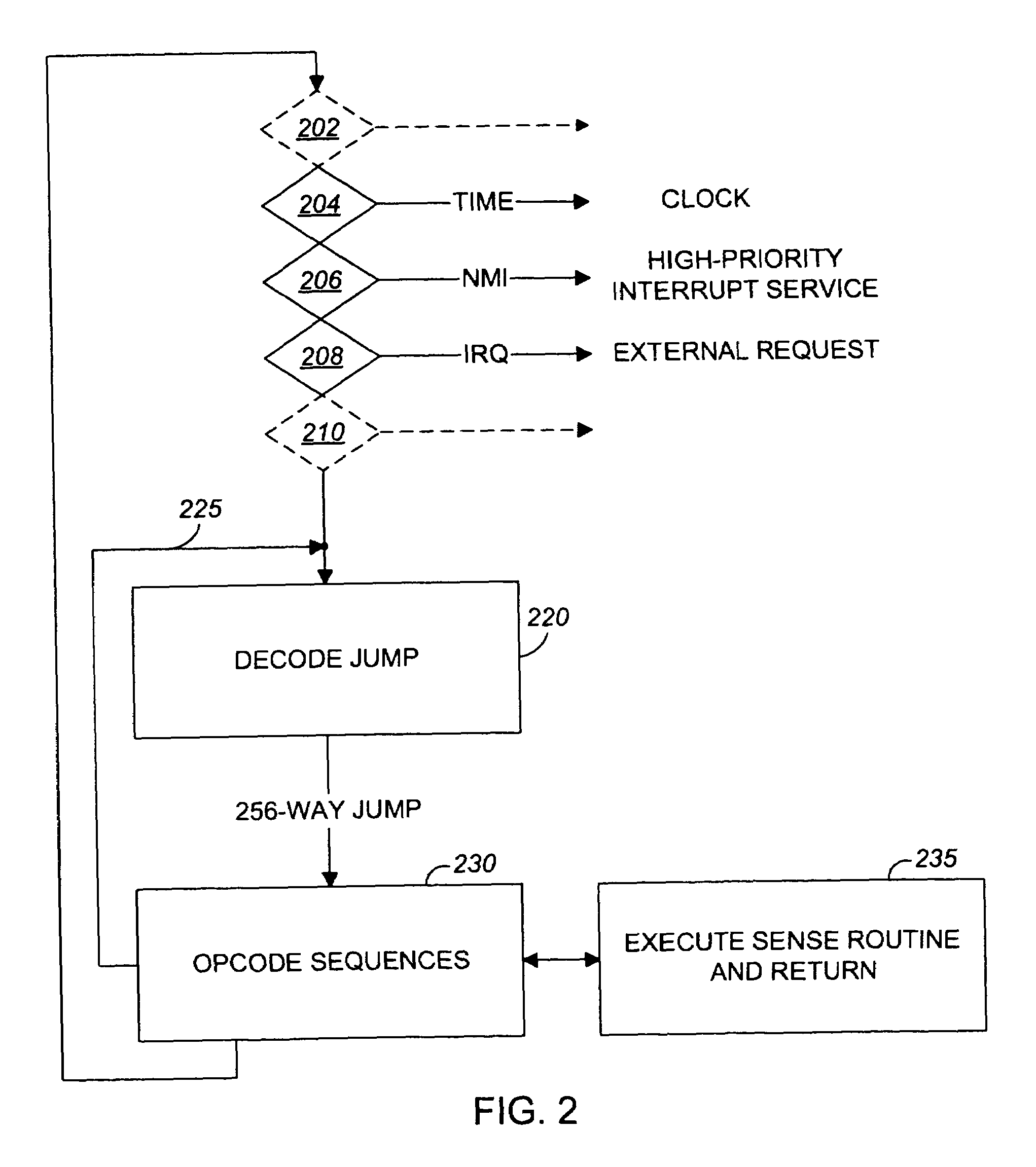

Microcontroller architecture supporting microcode-implemented peripheral devices

InactiveUS7103759B1Reduce demandLow costDigital computer detailsConcurrent instruction executionMicrocontrollerController architecture

Methods and apparatus for creating microcode-implemented peripheral devices for a microcontroller core formed in a monolithic integrated circuit. The microcontroller core has a control store for storing microcode instructions; execution circuitry operable to execute microcode instructions from the control store; and means for loading a suite of one or more microcode-device modules defining an optional peripheral device, the optional peripheral device being implemented by microcode instructions executed by the execution circuitry in accordance with the definition provided by the microcode-device modules.

Owner:CONEMTECH +1

Method and apparatus for embedded Built-In Self-Test (BIST) of electronic circuits and systems

InactiveUS20050210352A1Facilitates testing and debuggingLow costElectronic circuit testingError detection/correctionController architectureElectronic systems

An embedded electronic system built-in self-test controller architecture that facilitates testing and debugging of electronic circuits and in-system configuration of programmable devices. The system BIST controller architecture includes an embedded system BIST controller, an embedded memory circuit, an embedded IEEE 1149.1 bus, and an external controller connector. The system BIST controller is coupled to the memory circuit and the IEEE 1149.1 bus, and coupleable to an external test controller via the external controller connector. The external test controller can communicate over the IEEE 1149.1 bus to program the memory and / or the system BIST controller circuitry, thereby enabling scan vectors to be debugged by the external test controller and then downloaded into the memory for subsequent application to a unit under test by the system BIST controller.

Owner:INTELLITECH INC

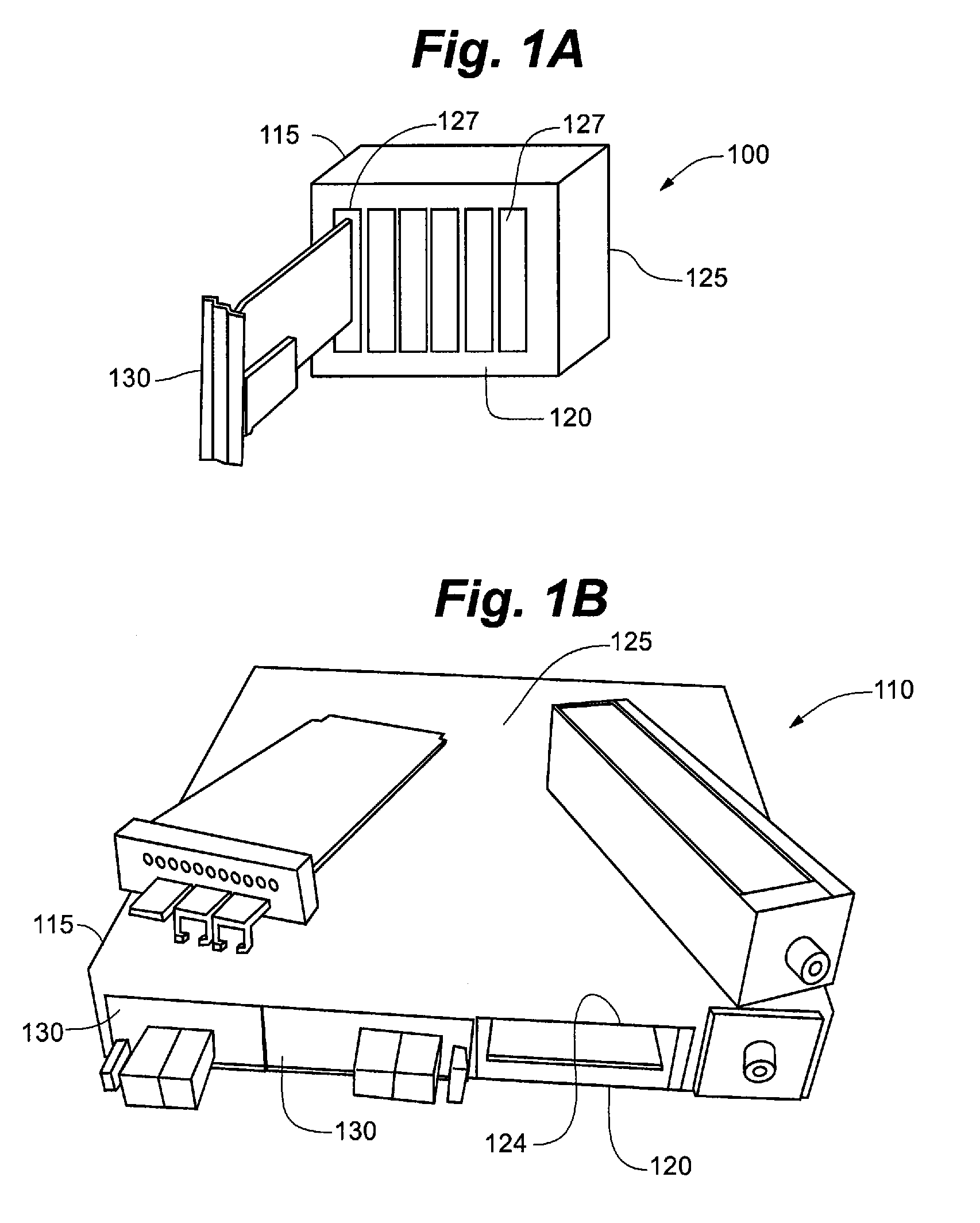

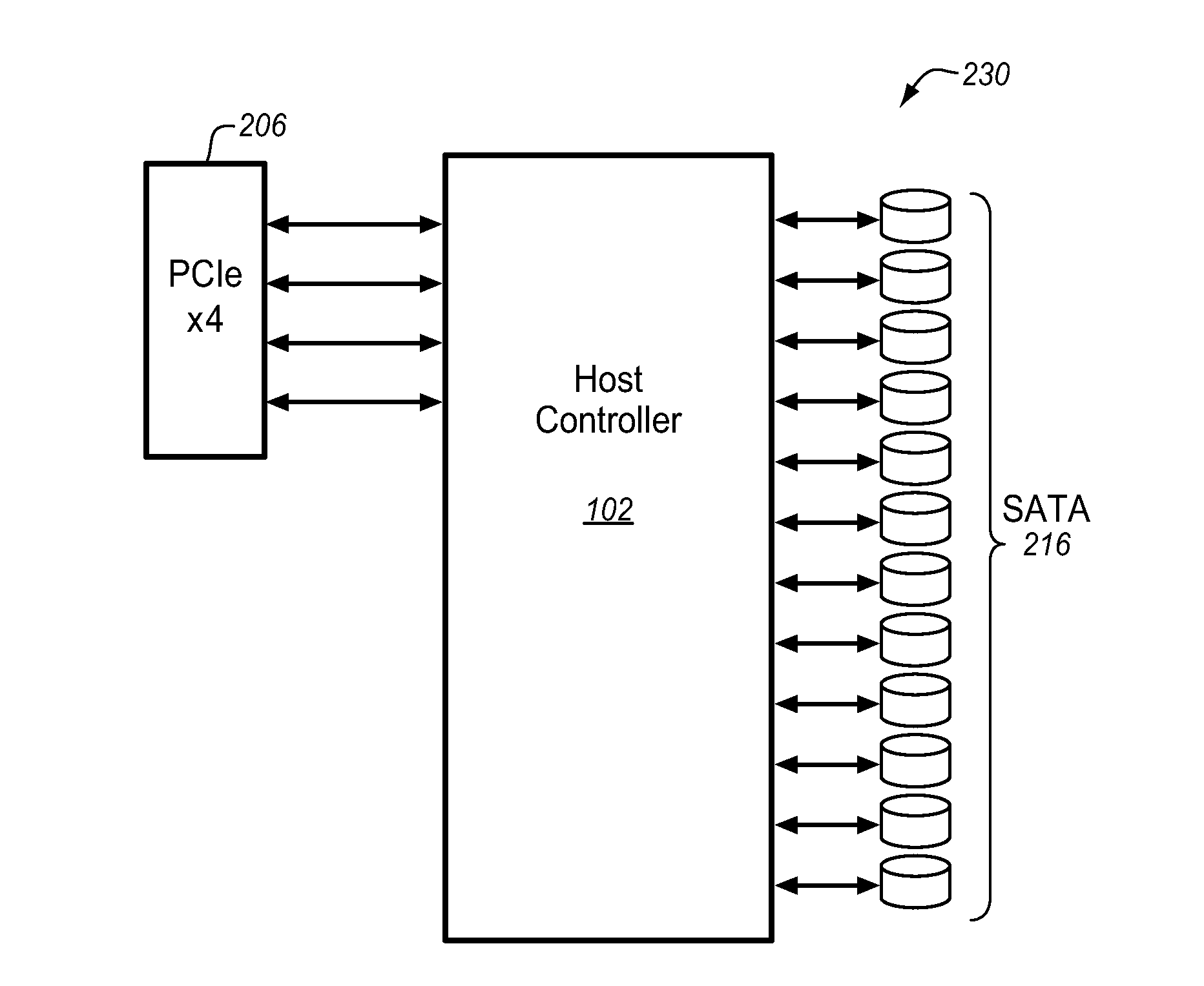

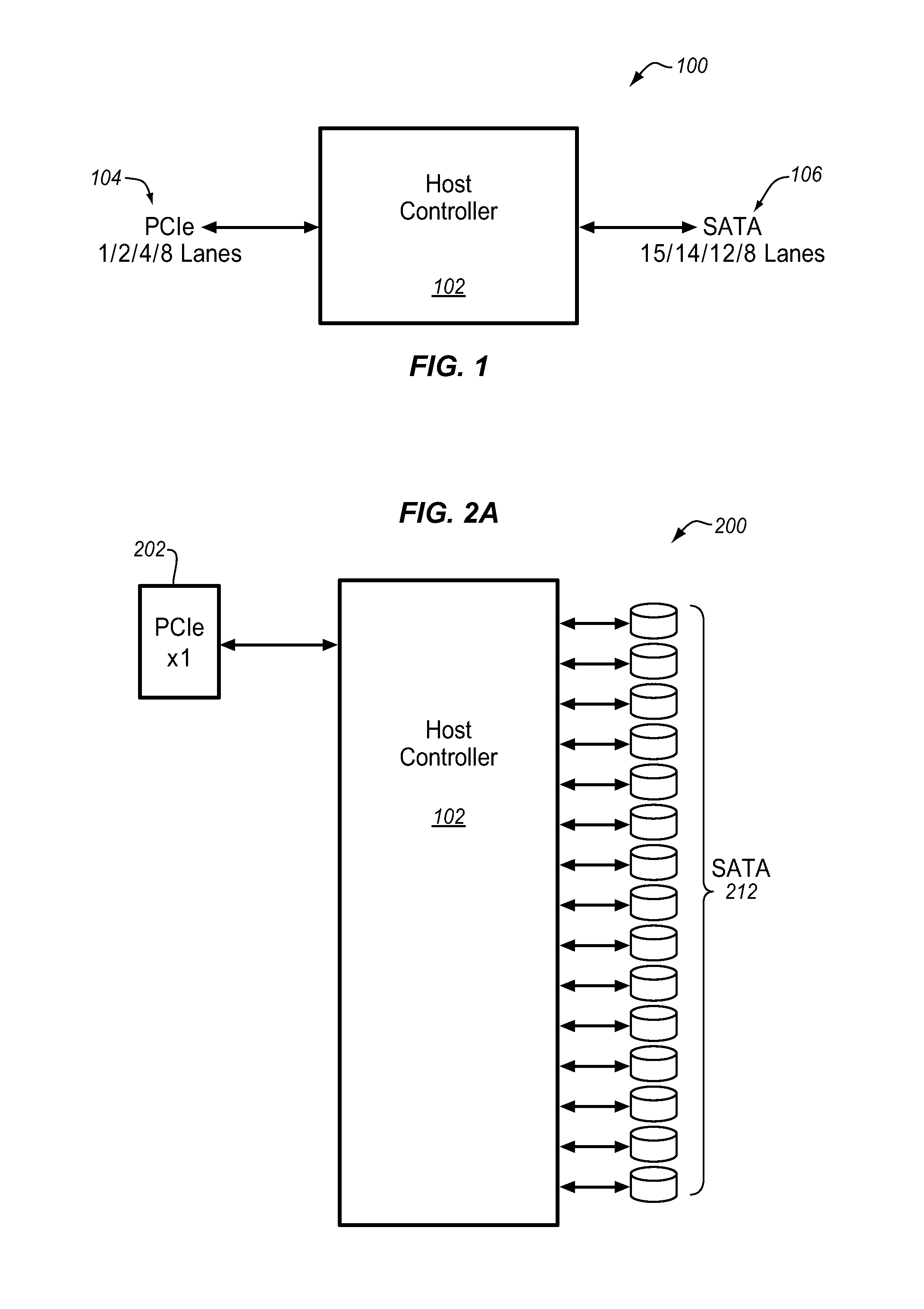

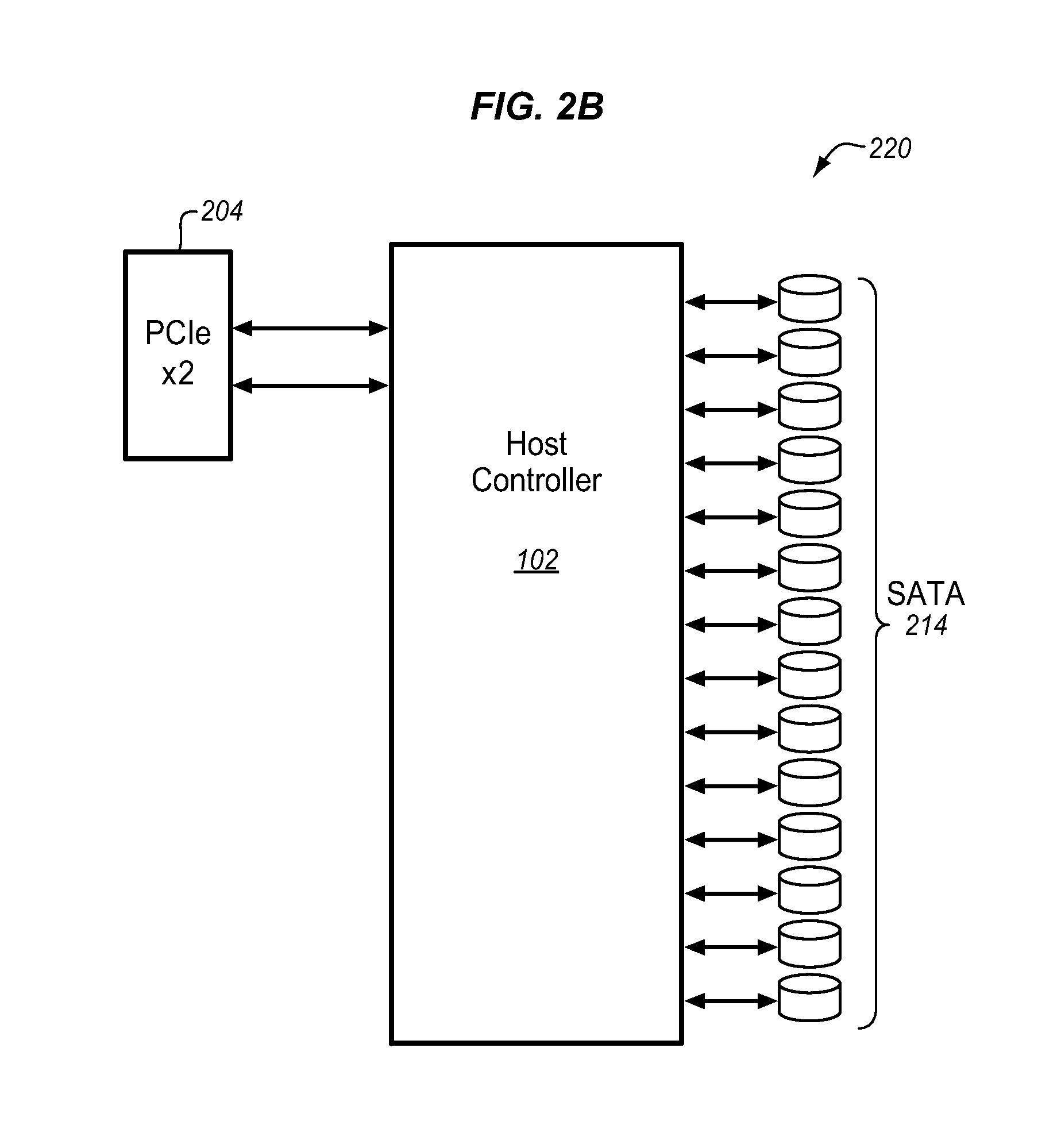

Mechanism for facilitating a configurable port-type peripheral component interconnect express/serial advanced technology attachment host controller architecture

ActiveUS20120166701A1Energy efficient computingElectric digital data processingController architectureSerial advanced technology attachment

A mechanism for facilitating configuration of port-type Peripheral Component Interconnect Express / Serial Advanced Technology Attachment host controller architecture is described. In one embodiment, an apparatus includes a plurality of PHYs to be used as Peripheral Component Interconnect Express (PCIe) ports and Serial Advanced Technology Attachment (SATA) ports, and logic to facilitate swapping of one or more of the plurality of PHYs between being the PCIe ports and the SATA ports.

Owner:LATTICE SEMICON CORP

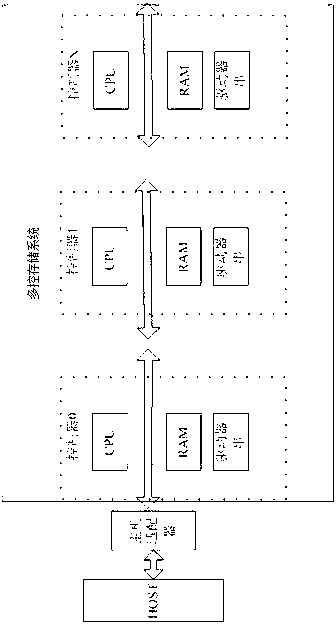

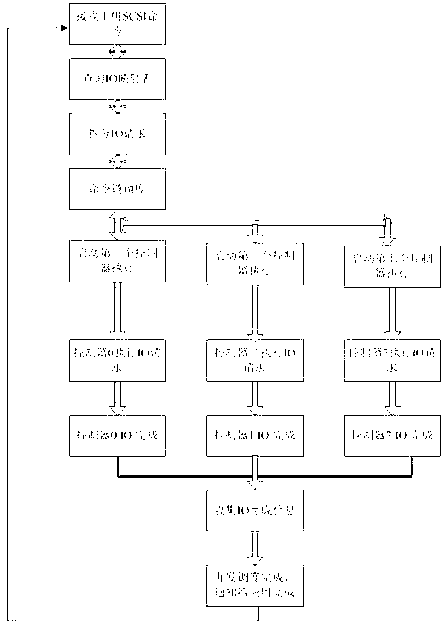

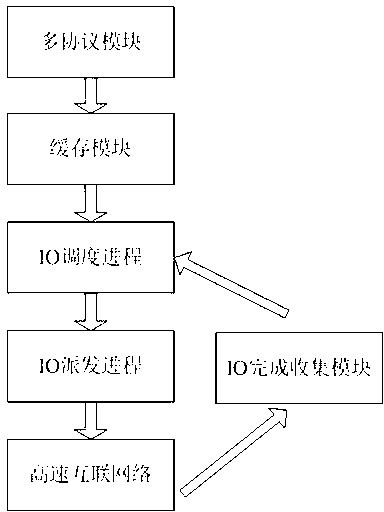

Self-adaptive IO (Input Output) scheduling method of multi-control storage system

ActiveCN103135943AImprove load statusLoad balancingInput/output to record carriersController architectureNetwork connection

The invention provides a self-adaptive I / O (Input / Output) scheduling method of a multi-control storage system. The self-adaptive I / O scheduling method of the multi-control storage system has the advantages of being capable of achieving load balance of a multiple controller architecture and among controllers; avoiding risk and performance choke points caused by single controller failure; supporting a plurality of host connecting interfaces; supporting an ISCSI (Internet Small Computer System Interface), an FC (Fibre Channel), an InfiniBand and 10 gigabit network connection; being capable of providing high bandwidth IB (InfiniBand) and the 10 gigabit network connection for users at the same time; and meeting the differentiation requirements of customers for high bandwidth and high performance. The invention relates to I / O scheduling of the multi-control storage system and provides the I / O scheduling method among multiple controllers. When the multi-control storage system accepts an I / O request from an application layer, the self-adaptive I / O scheduling method of the multi-control storage system can be utilized to schedule the I / O request to the multiple controllers to perform simultaneous concurrent execution, not only allocates unallocated I / O requests to low load controllers, but also reschedules I / O requests to lower load controllers from overload controllers, so that the load state of every controller in a system is improved, I / O load scheduling and balance on multi-control nodes are achieved, potentials of equipment are fully scheduled, and the performance of the system is improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

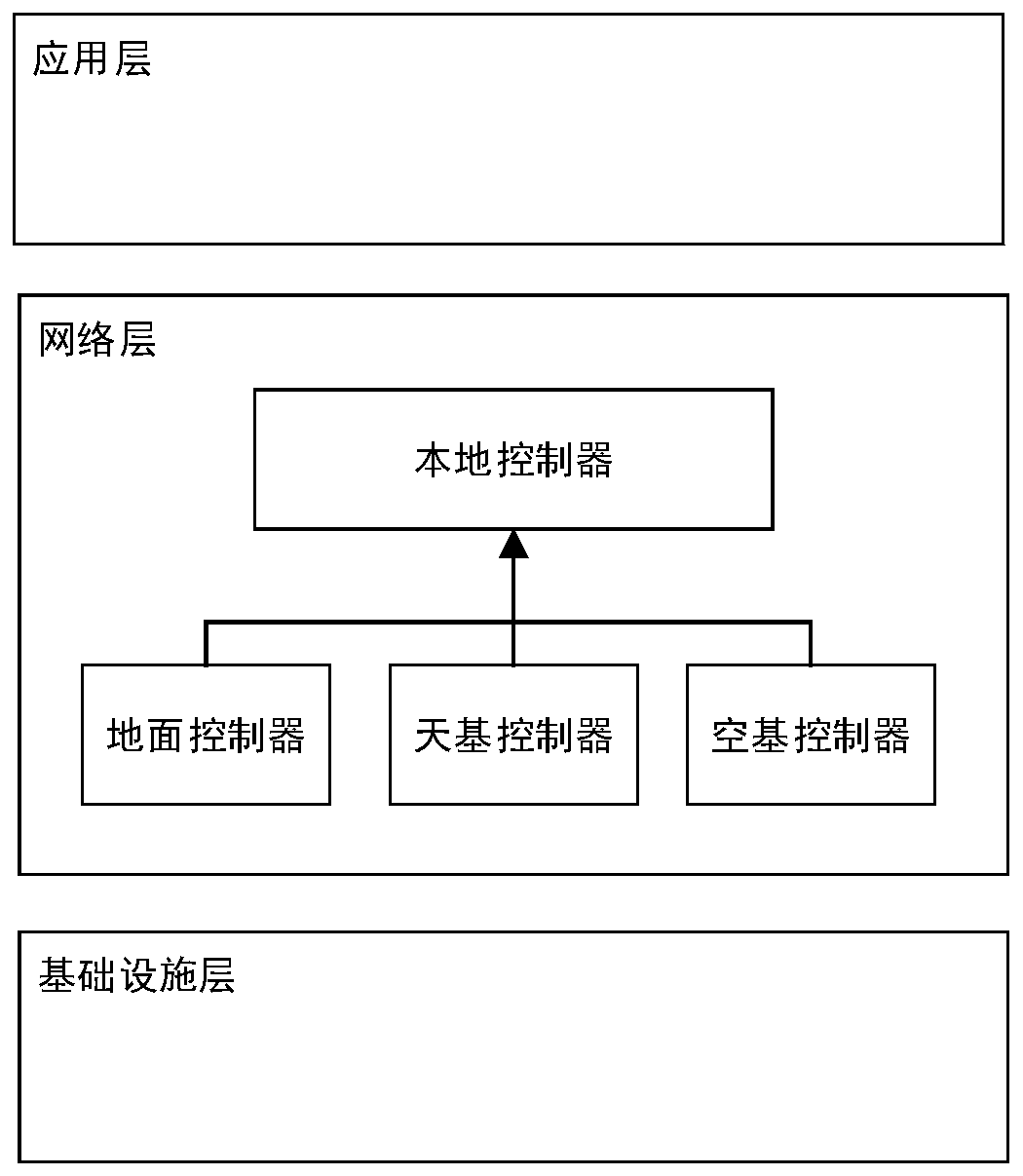

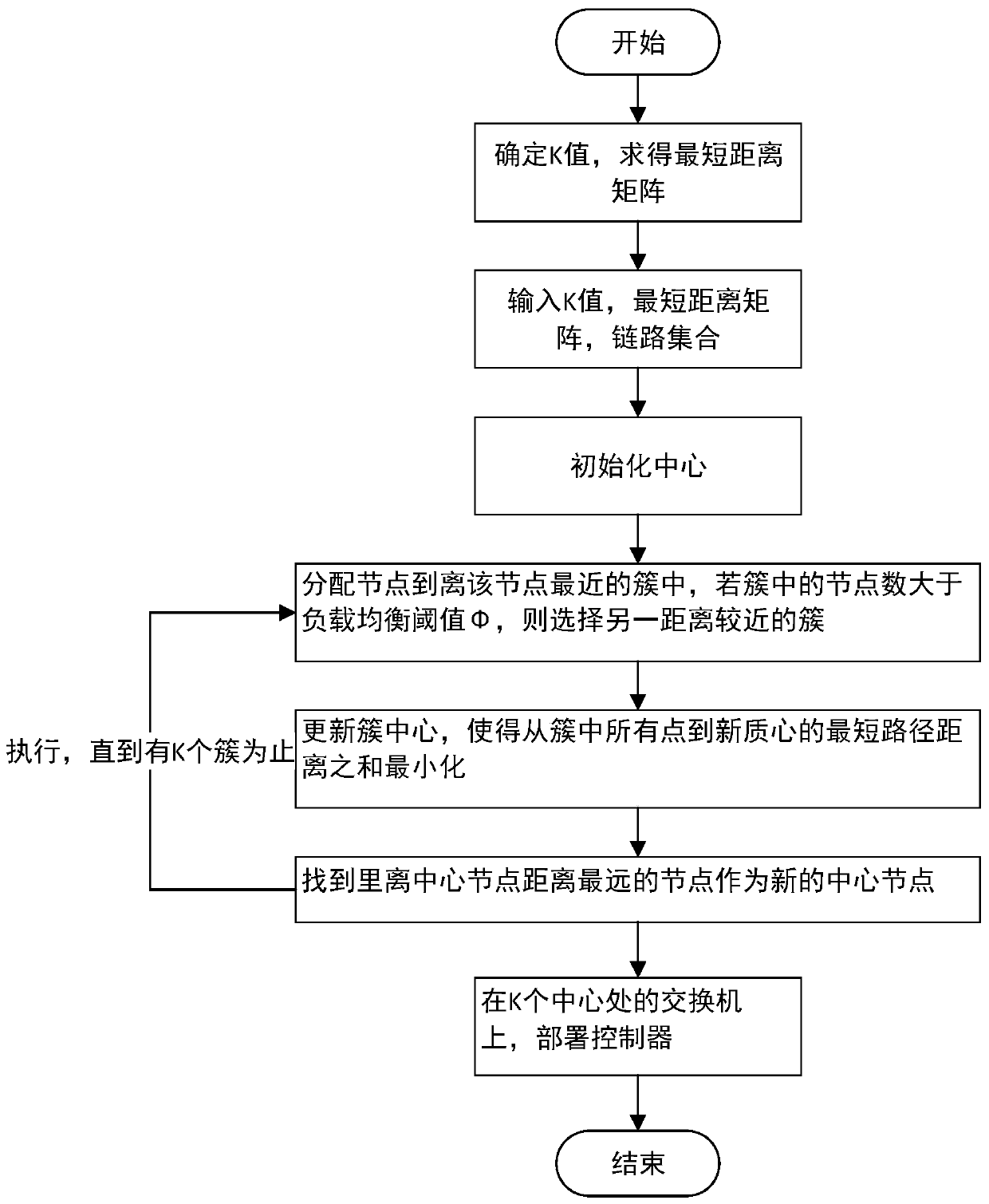

SDN-based space-air-ground controller deployment architecture and control method

ActiveCN111342993AMinimize Propagation DelayPropagation Delay EqualizationData switching networksController architectureNetwork control

The invention discloses an SDN-based space-space-ground controller deployment architecture and a control method, the controller architecture comprises three network segments of a space-based network,a space-based network and a foundation network, and the space-based network realizes controller dynamic deployment on an unmanned aerial vehicle; introducing an upper SDN controller to the top of eachnetwork segment controller; wherein the SDN network architecture of the upper SDN controller comprises an infrastructure layer, a network control layer and an application layer from bottom to top; the network control layer is used for collecting and maintaining a global topological structure, a link state and flow state information, issuing a control message, introducing an SDN architecture, decoupling a data plane and a control plane, providing a unified programming interface, and configuring and managing nodes in a network in a unified manner. According to the invention, multiple optimization objectives of minimizing the propagation time delay between the switch and the controller and improving the load balance degree of the controller are realized.

Owner:XI AN JIAOTONG UNIV

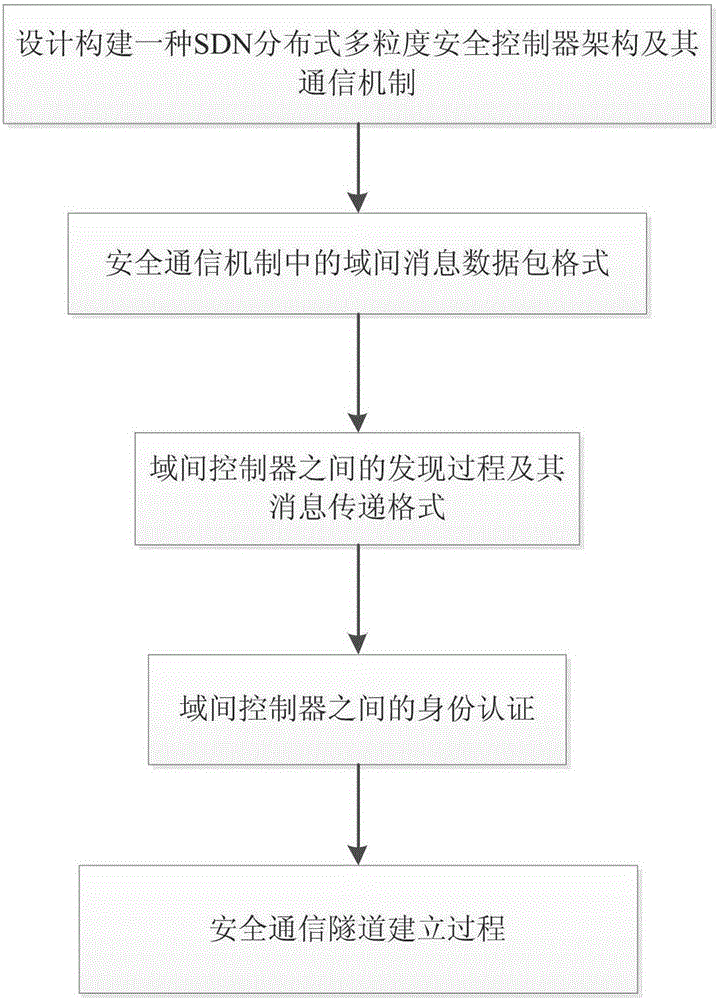

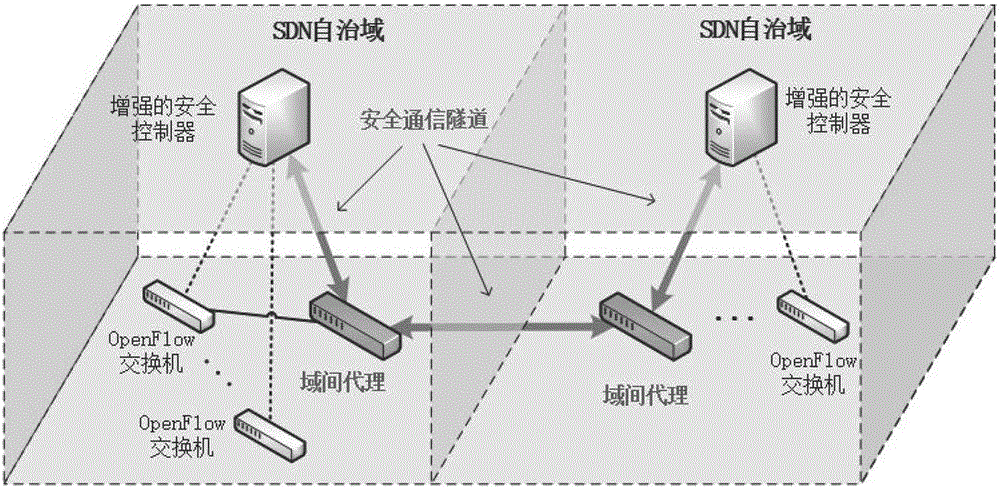

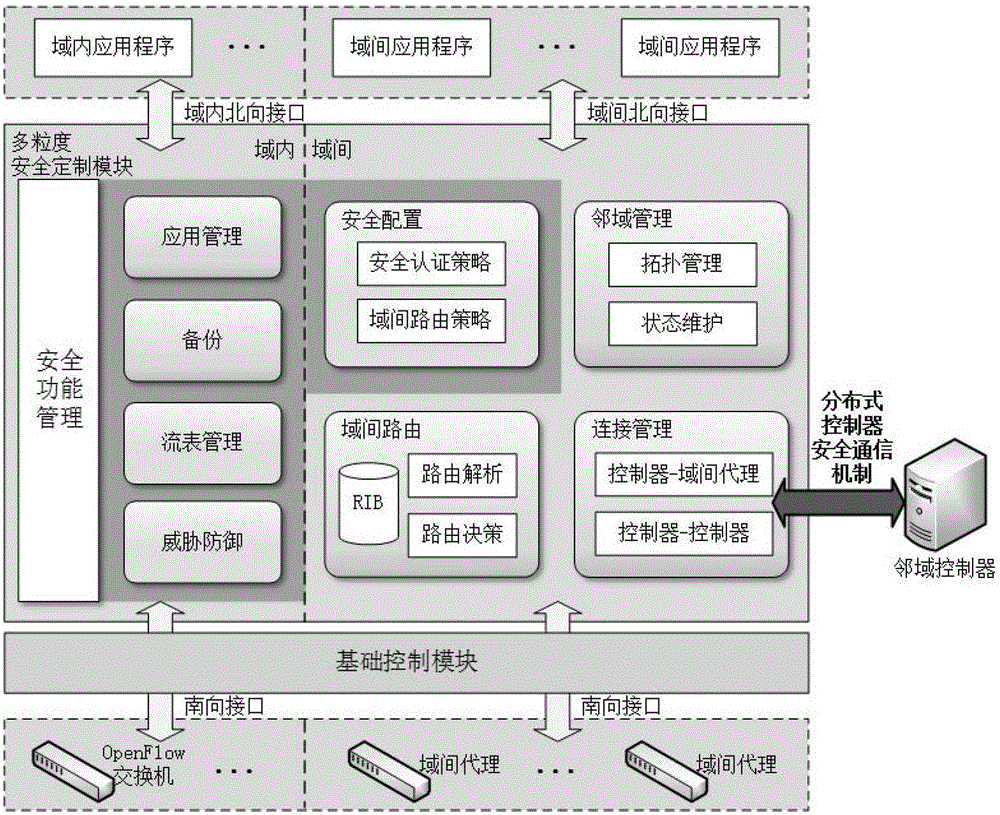

Secure communication method for distributed multi-granularity controller of software defined network based on proxy

ActiveCN106209897ASolve communication problemsImprove securityTransmissionController architectureDirect communication

The invention relates to a secure communication method for a distributed multi-granularity controller of a software defined network based on proxy, and belongs to the technical field of inter-domain secure communication of a multi-domain SDN. The method comprises the following steps: designing architecture of a distributed multi-granularity security controller, wherein the architecture comprises a message data packet format between controllers, establishing a communication tunnel via the connection between a controller domain and inter-domain proxies and the connection between the inter-domain proxies, and completing neighbor discovery between the controller, two-step identity authentication and encrypted transmission to achieve direct communication between multi-domain network controllers. In the communication method, the infrastructure is based on the security controller and the inter-domain proxies, a message of a control plane is released to a data plane by the inter-domain proxies for transmission, and thus the communication problem between independent control planes is solved; and meanwhile, the two-step authentication scheme of communication of the controller is given based on a challenge response mechanism and a DTLS protocol, service supply can be defended and refused, and the identity authentication is completed to improve the security.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

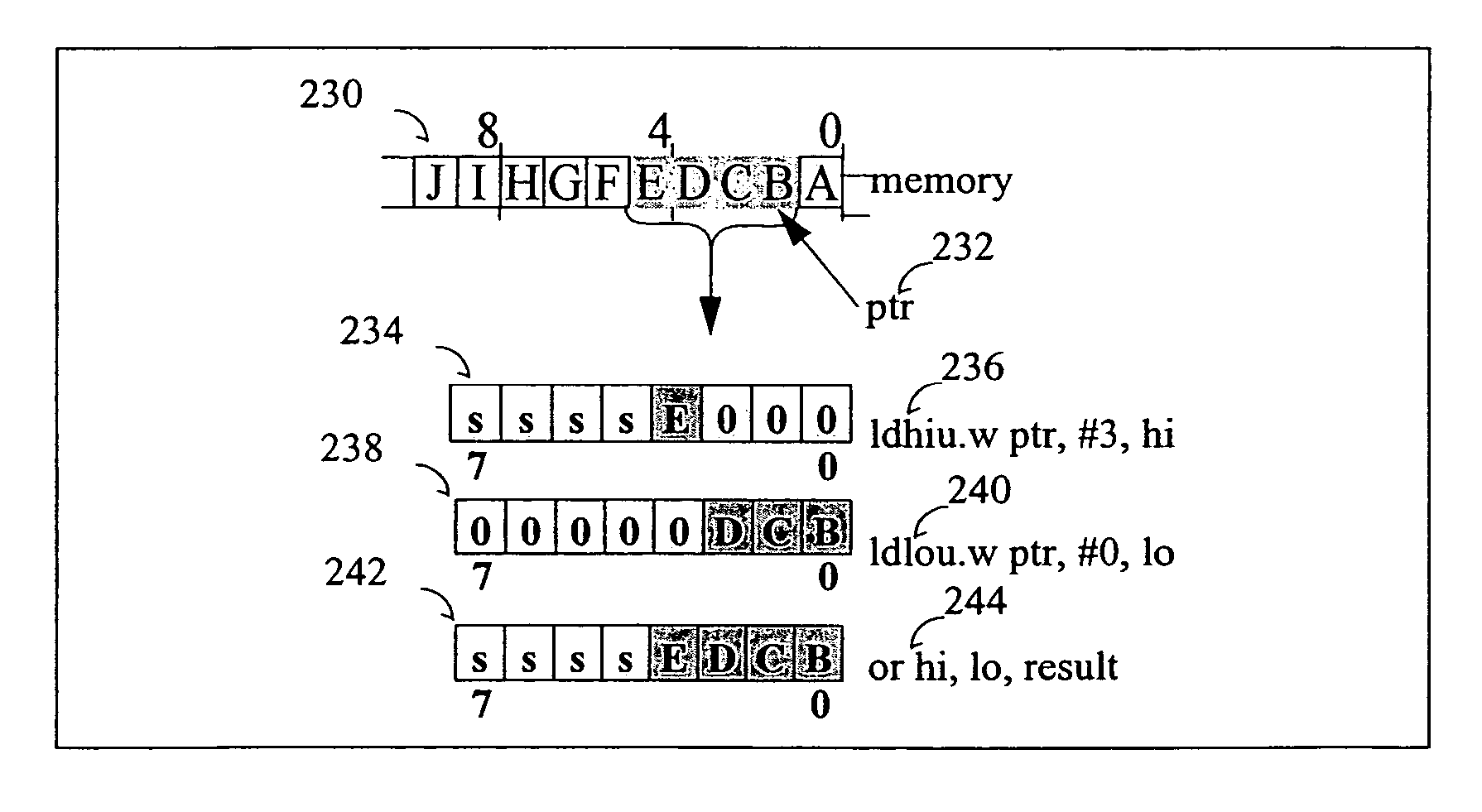

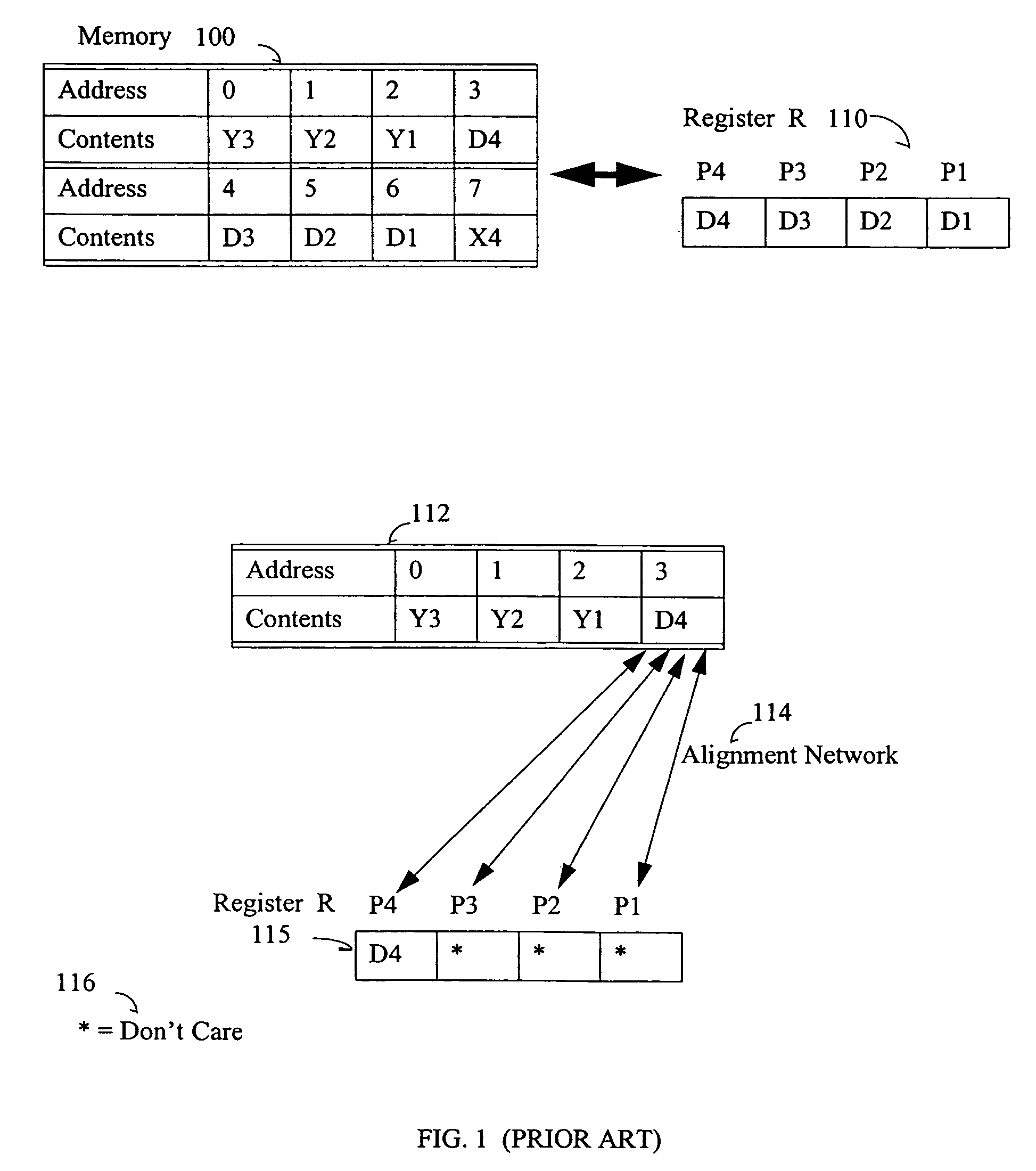

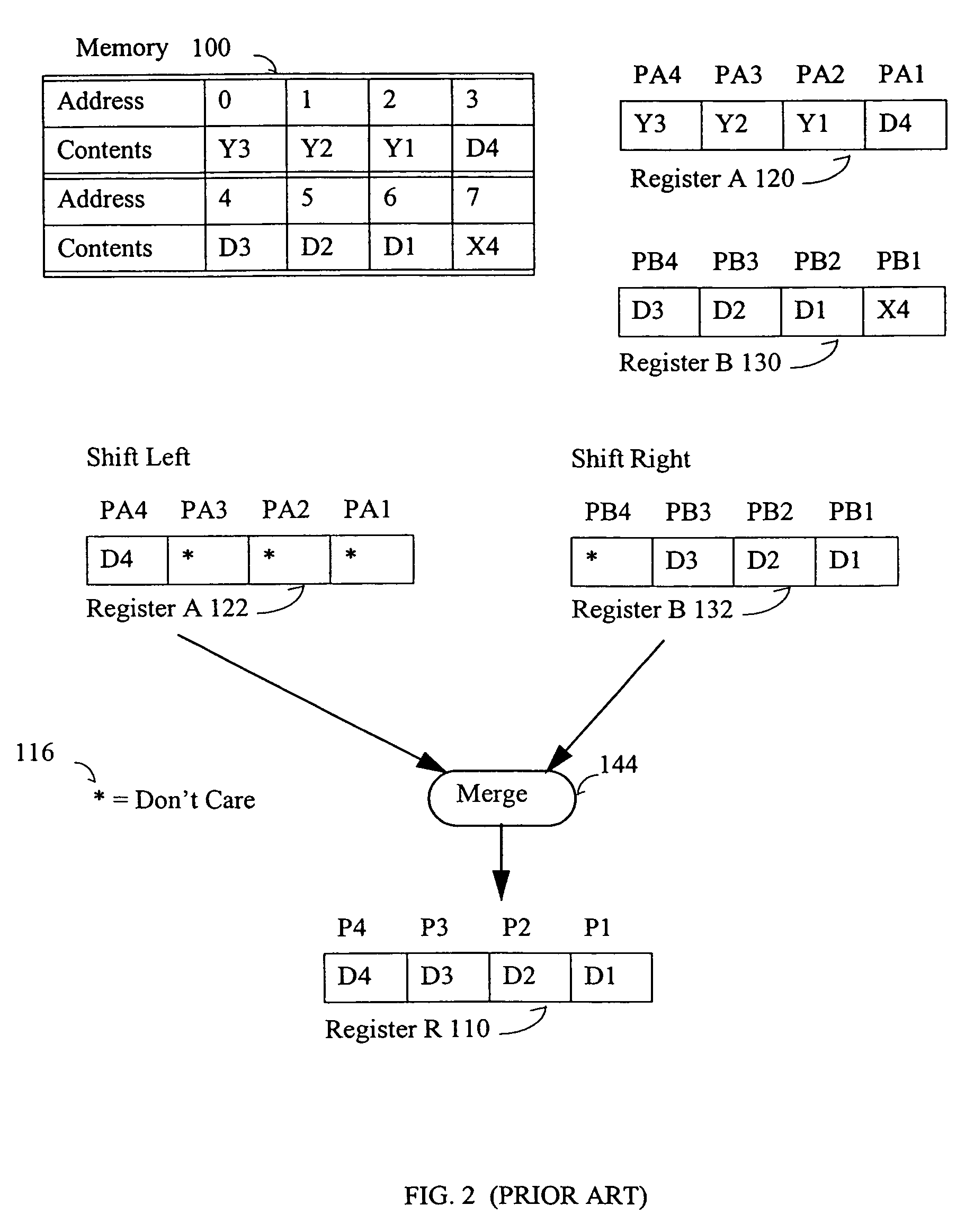

Aligning load/store data using rotate, mask, zero/sign-extend and or operation

InactiveUS7254699B2Memory adressing/allocation/relocationDigital computer detailsController architectureMicrocontroller

The present invention relates generally to microprocessor or microcontroller architecture, and particularly to an architecture structured to handle unaligned memory references. A method is disclosed for loading unaligned data stored in several memory locations, including a step of loading a first part of the unaligned data into a first storage location and rotating the first part from a first position to a second position in the first memory location. Next a second part of the unaligned data is loaded into a second storage location and rotated from one position to another position. Then the first storage location is combined with the second storage location using a logical operation into a result storage location. The storage locations may be, for example, 64-bit registers. The logical operation may be a bit-wise OR operation. The method may optionally include, performing masking, zero-extending and / or sign extending operations on the first storage location, when the first part of the unaligned data is in the second position of the first storage location.

Owner:RENESAS ELECTRONICS CORP

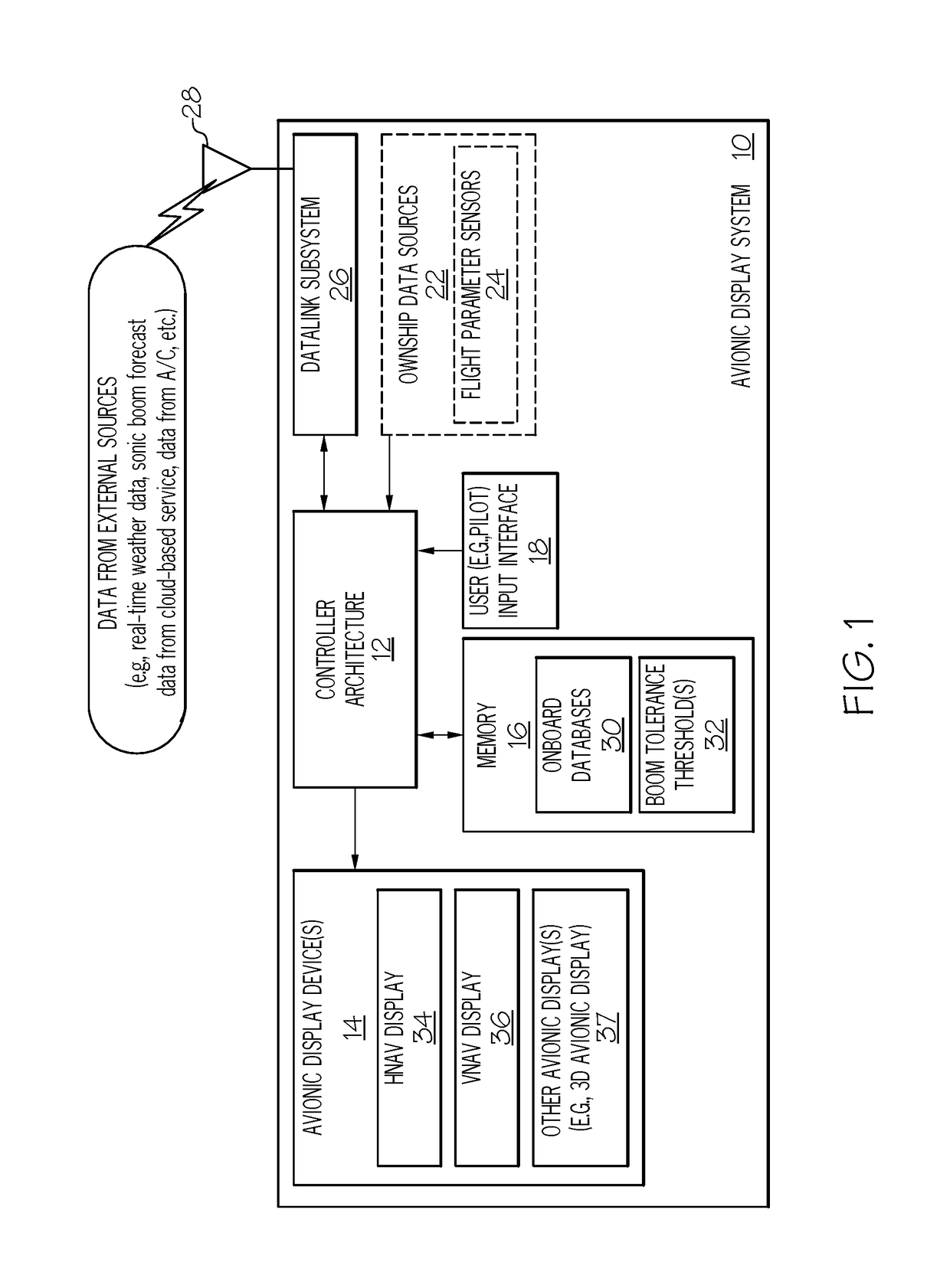

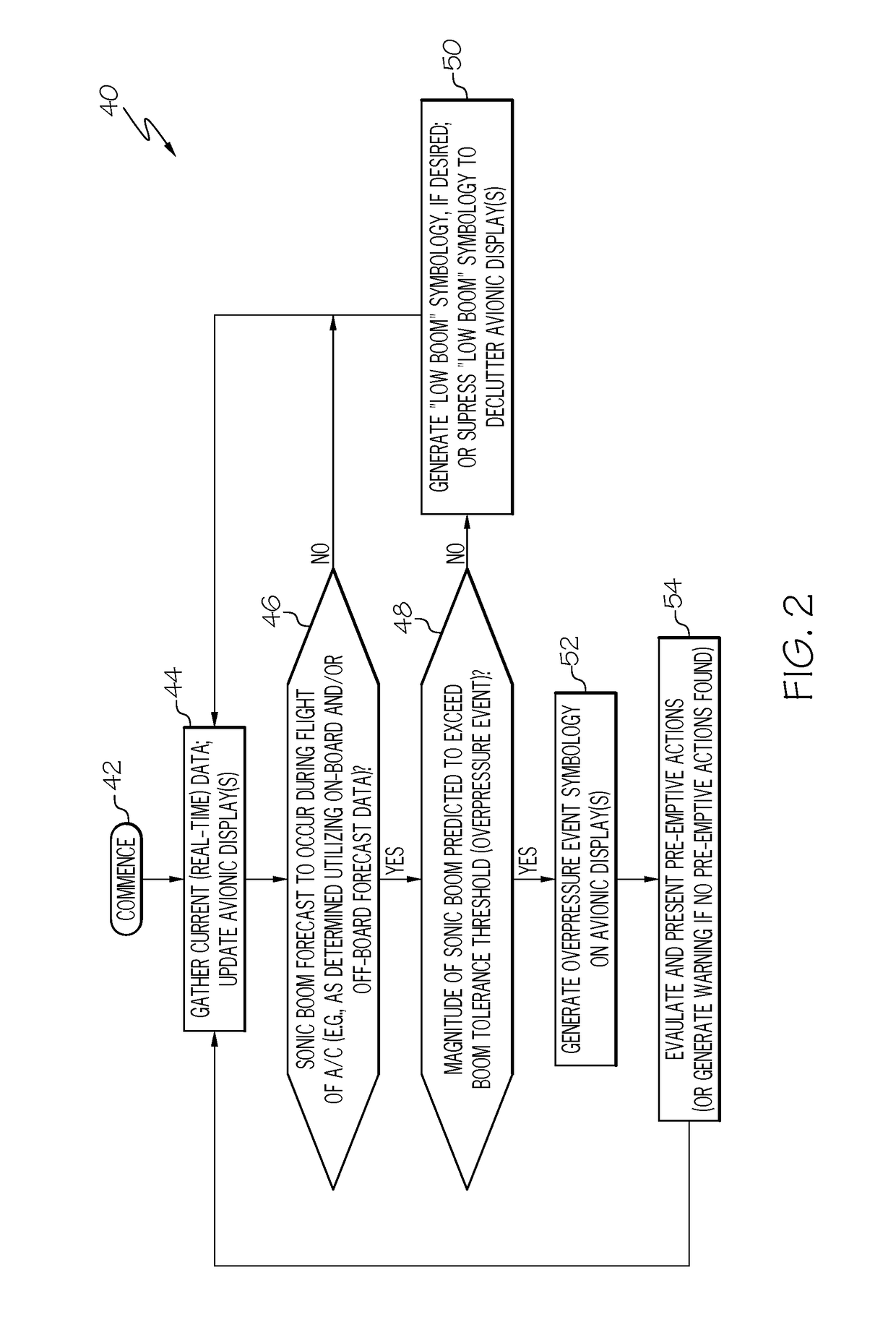

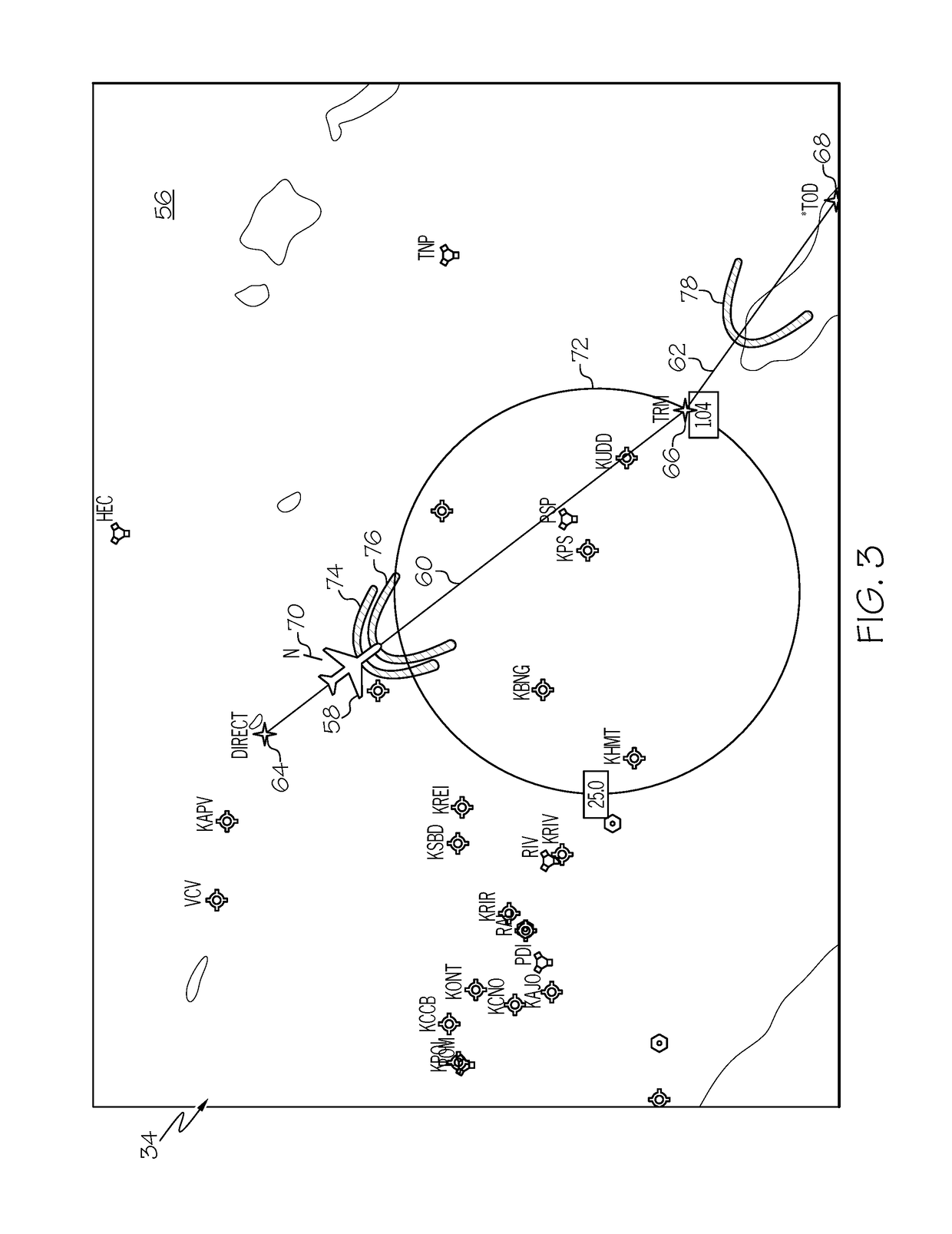

Systems and methods for generating avionic displays including forecast overpressure event symbology

ActiveUS10209122B1Avoid it happening againVibration measurement in solidsVelocity propogationSymbolic SystemsController architecture

Avionic display systems and methods are provided for generating avionic displays, which include symbology and other graphics pertaining to forecast overpressure events, which are forecast to occur during supersonic aircraft flight. In various embodiments, the avionic display system includes a display device on which an avionic display is produced. A controller architecture is operably coupled to the display device. Storage media contains computer-readable code or instructions that, when executed by the controller architecture, cause the avionic display system to determine whether an overpressure event is forecast to occur due to the predicted future occurrence of a sonic boom, which has a magnitude exceeding a boom tolerance threshold. When the controller architecture determines that an overpressure event is forecast to occur, the avionic display system further generates symbology on the avionic display indicative of or visually signifying the forecast overpressure event.

Owner:HONEYWELL INT INC

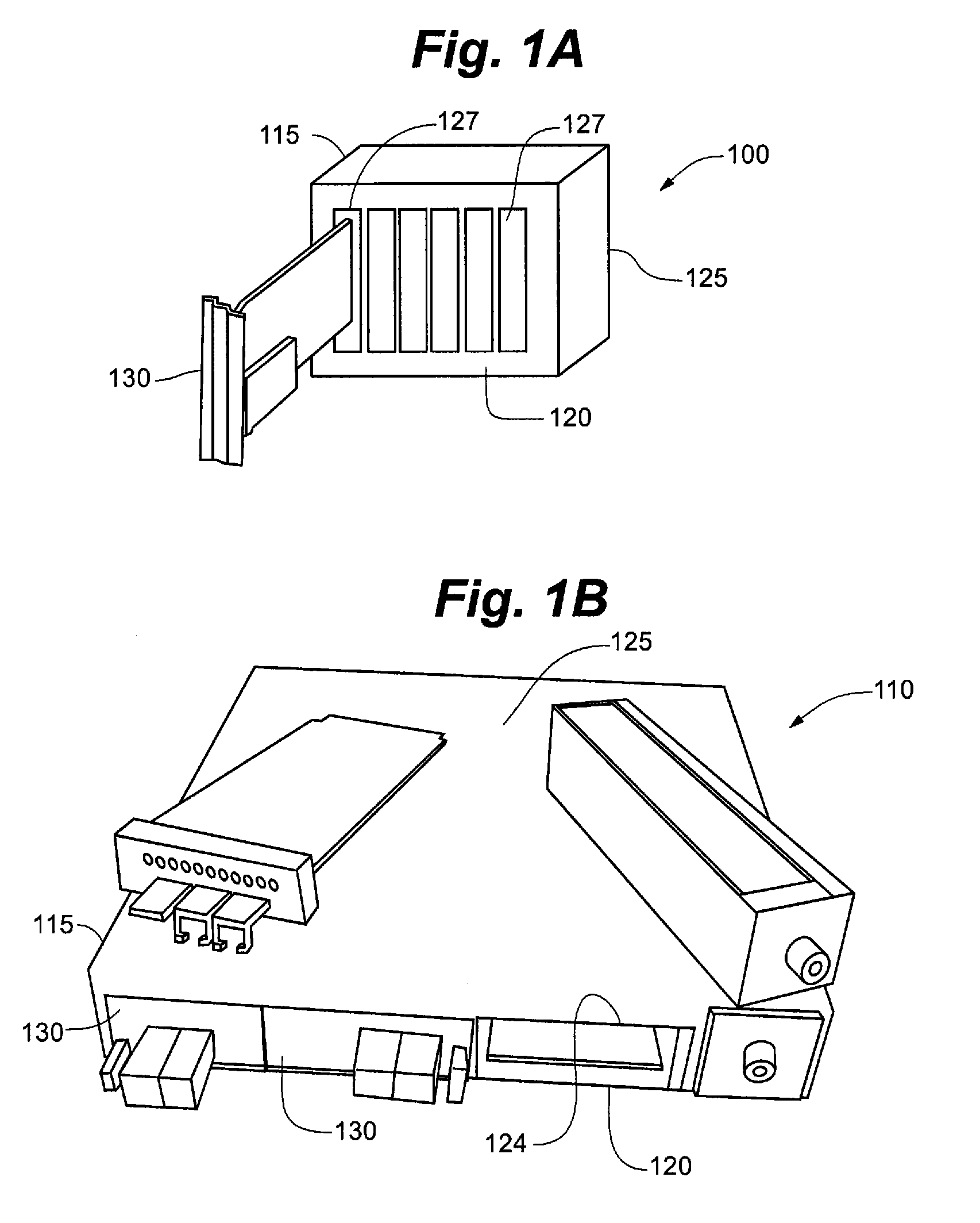

Coalescing Multiple Contexts into a Single Data Transfer in a Media Controller Architecture

InactiveUS20110131351A1Well formedTime-division multiplexMemory systemsMultiple contextController architecture

Owner:SEAGATE TECH LLC

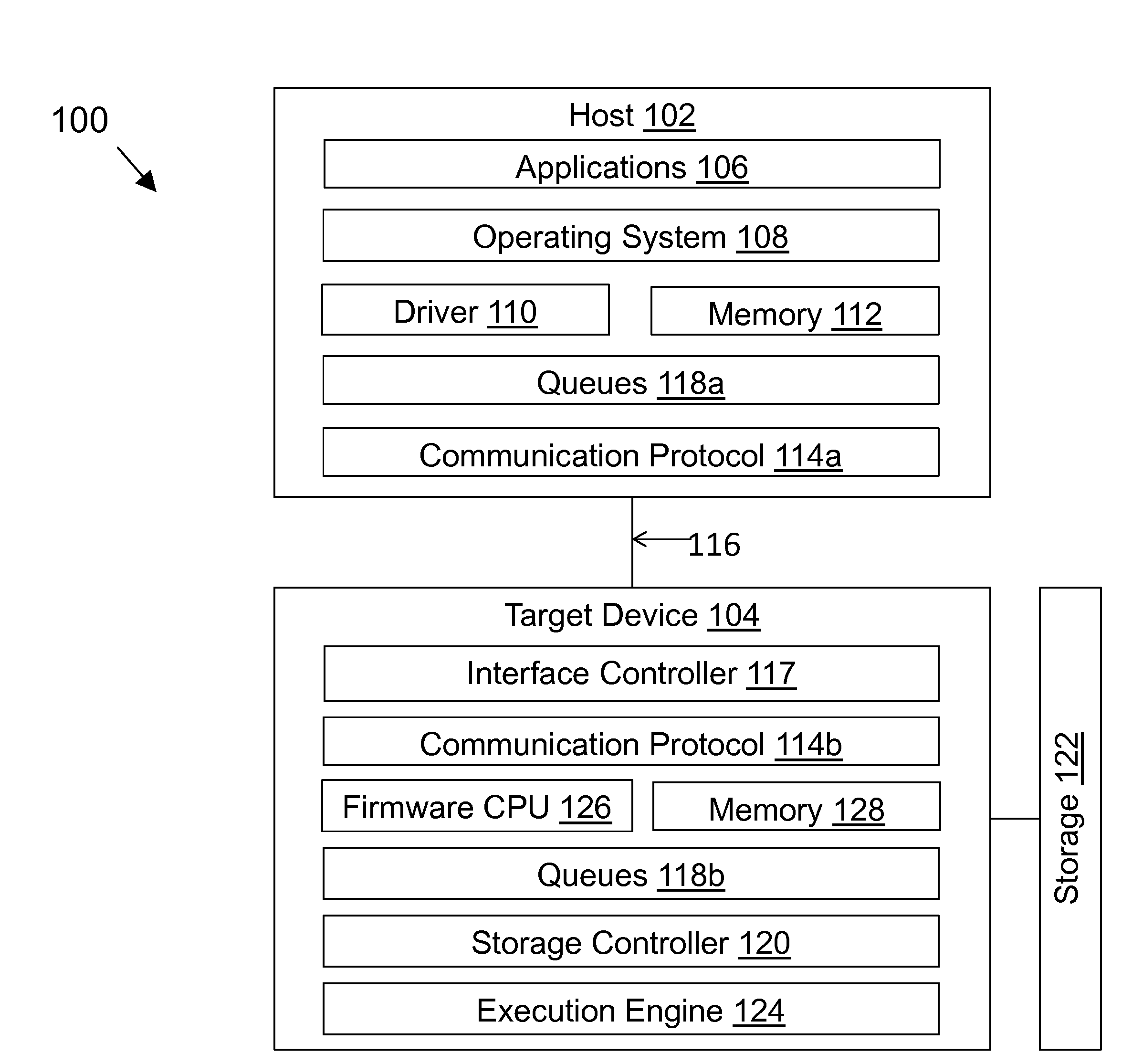

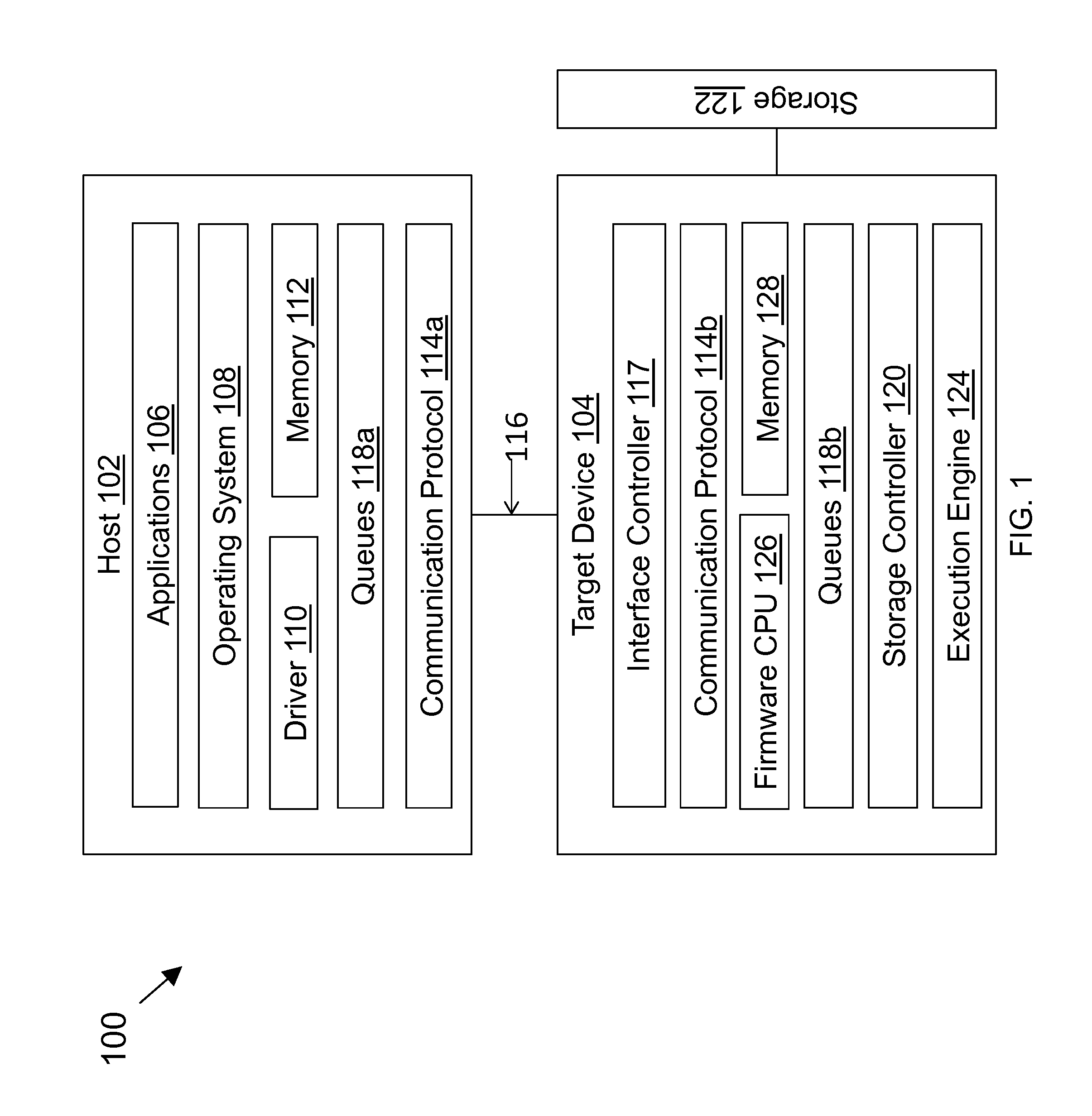

Programmable, high performance solid state drive controller architecture

ActiveUS20160162202A1Input/output to record carriersNon-redundant fault processingController architectureControl flow

Systems and methods for designing a programmable solid state drive (SSD) controller and a non-volatile memory apparatus are provided. The disclosed systems and methods utilize data structures, termed “Superbufs” for organizing internal activities in an SSD controller. Superbufs can be used for providing control flow services, such as, sequencing, synchronization, completion, and interrupt generation, as well as data flow services, for example, data transfer, data transformation, and data distribution.

Owner:WESTERN DIGITAL TECH INC

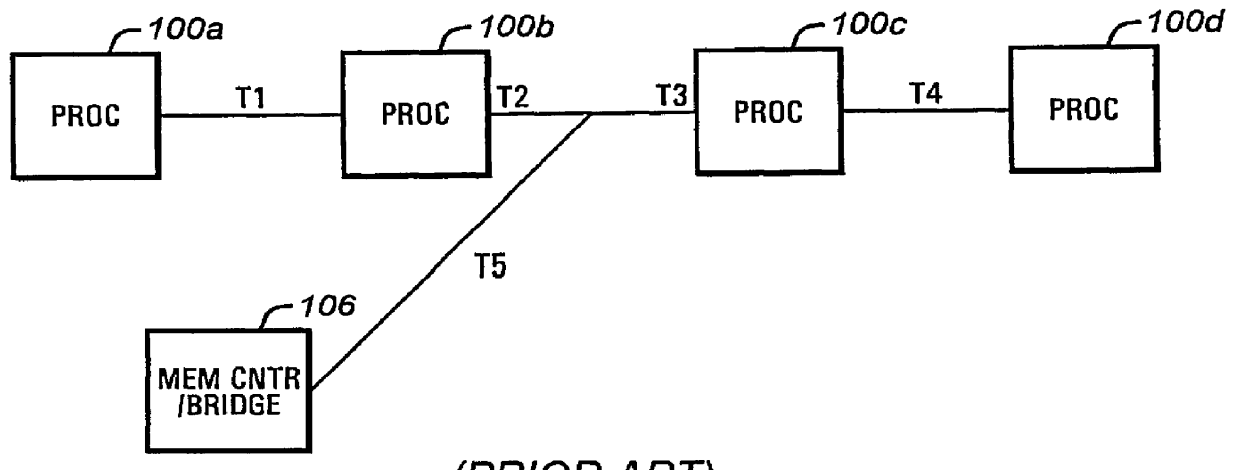

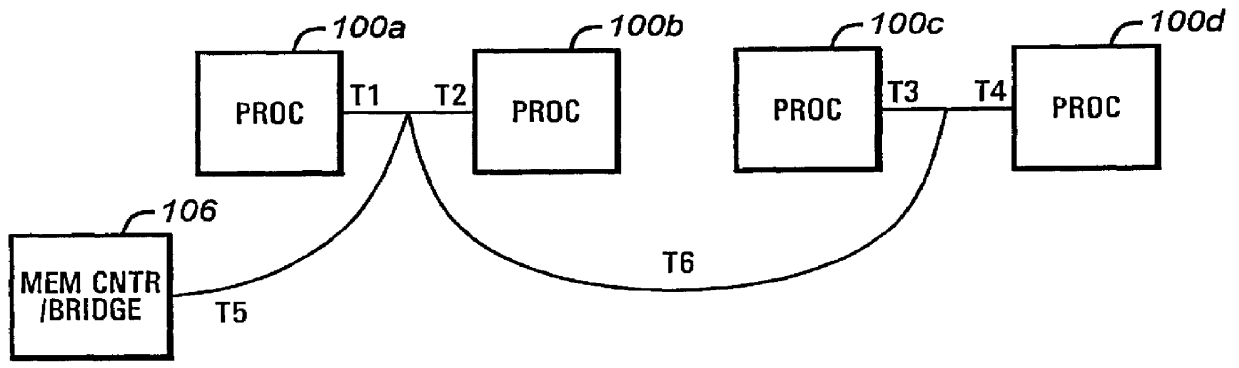

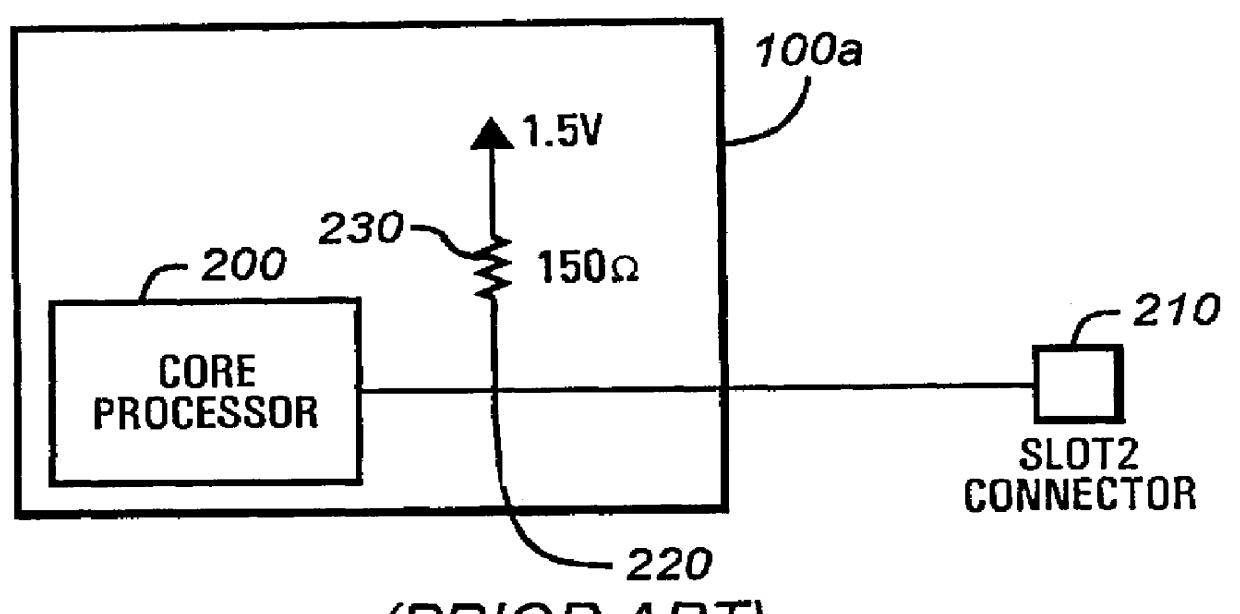

Flexible placement of GTL end points using double termination points

InactiveUS6067596ATightly coupledMaintain impedance matchReliability increasing modificationsElectronic switchingController architectureGunning transceiver logic

A highly parallel computer system including dual processors and dual memory controllers are coupled to an Assisted Gunning Transceiver Logic Plus (AGTL+) high speed system bus. The microprocessors are designed for a quad processor architecture requiring four processors and four connectors for the processors. To maintain signal timing and integrity in a dual processor / dual memory controller architecture, additional terminations are inserted. Printed circuit board space is conserved with a dual processor architecture. The additional connectors and traces to the additional connectors for the processors are no longer needed. Furthermore, with the dual processor design, there is no need for two additional termination cards.

Owner:SAMSUNG ELECTRONICS CO LTD

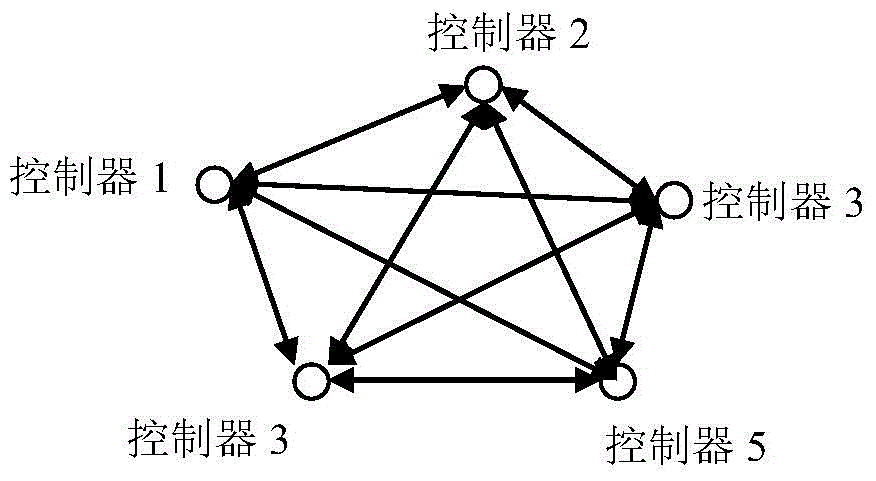

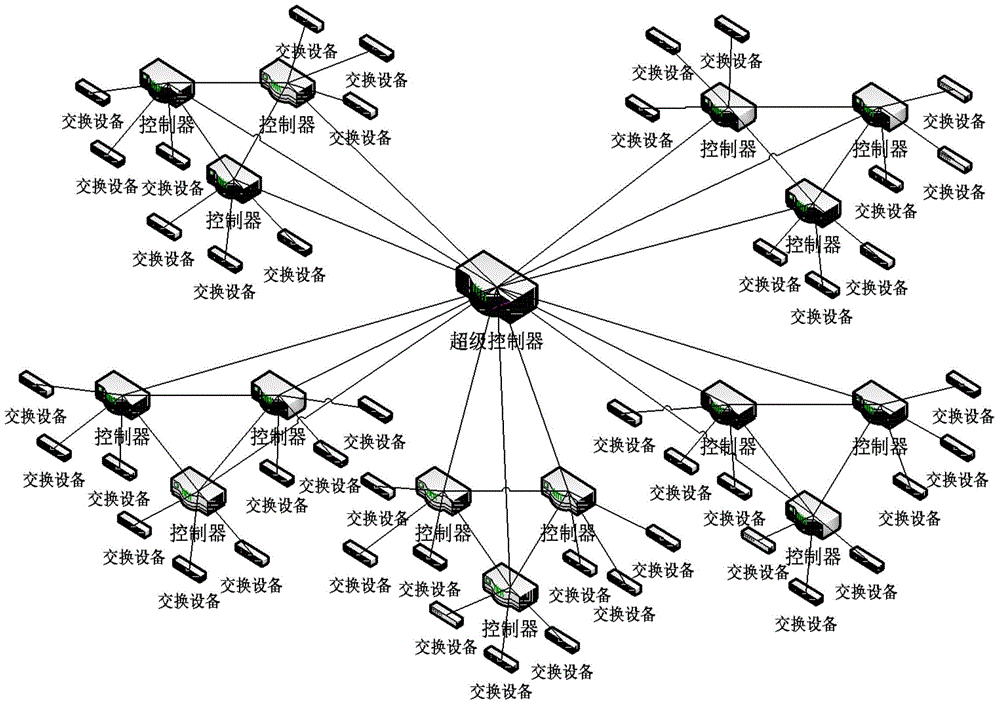

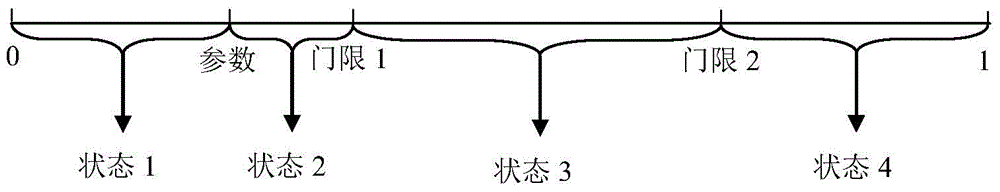

Multi-controller load balancing method and system based on distributed-centralized type architecture model in software defined networking

At present, two multi-controller architecture models mainly exist in software defined networking, namely, a distributed multi-controller architecture model and a centralized multi-controller architecture model. The two architecture models have advantages and defects. Even though the distributed multi-controller architecture model can effectively solve the problem of a single controller in performance and reliability, time delay of message transmission among a plurality of distributed controllers is long. Even though the centralized multi-controller architecture model can effectively reduce time delay of message transmission among the controllers, the defects of centralized control still exist. Therefore, the invention provides a distributed-centralized type multi-controller architecture model to avoid the defects of the previous architecture models. On this basis, a multi-controller load balancing method based on the distributed-centralized type architecture model is provided. Therefore, the load of the whole networking can be distributed in a balanced mode.

Owner:BEIJING UNIV OF POSTS & TELECOMM

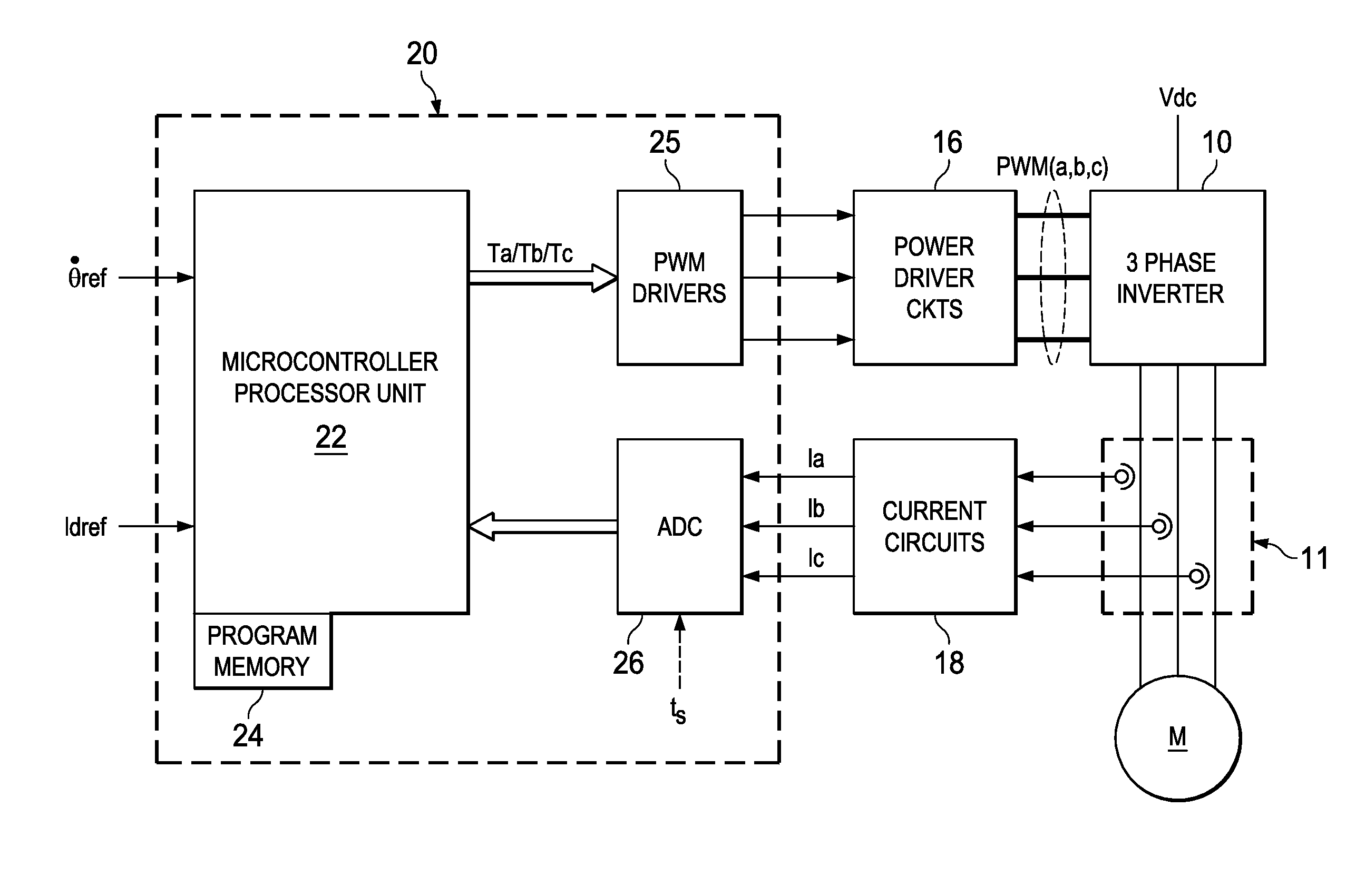

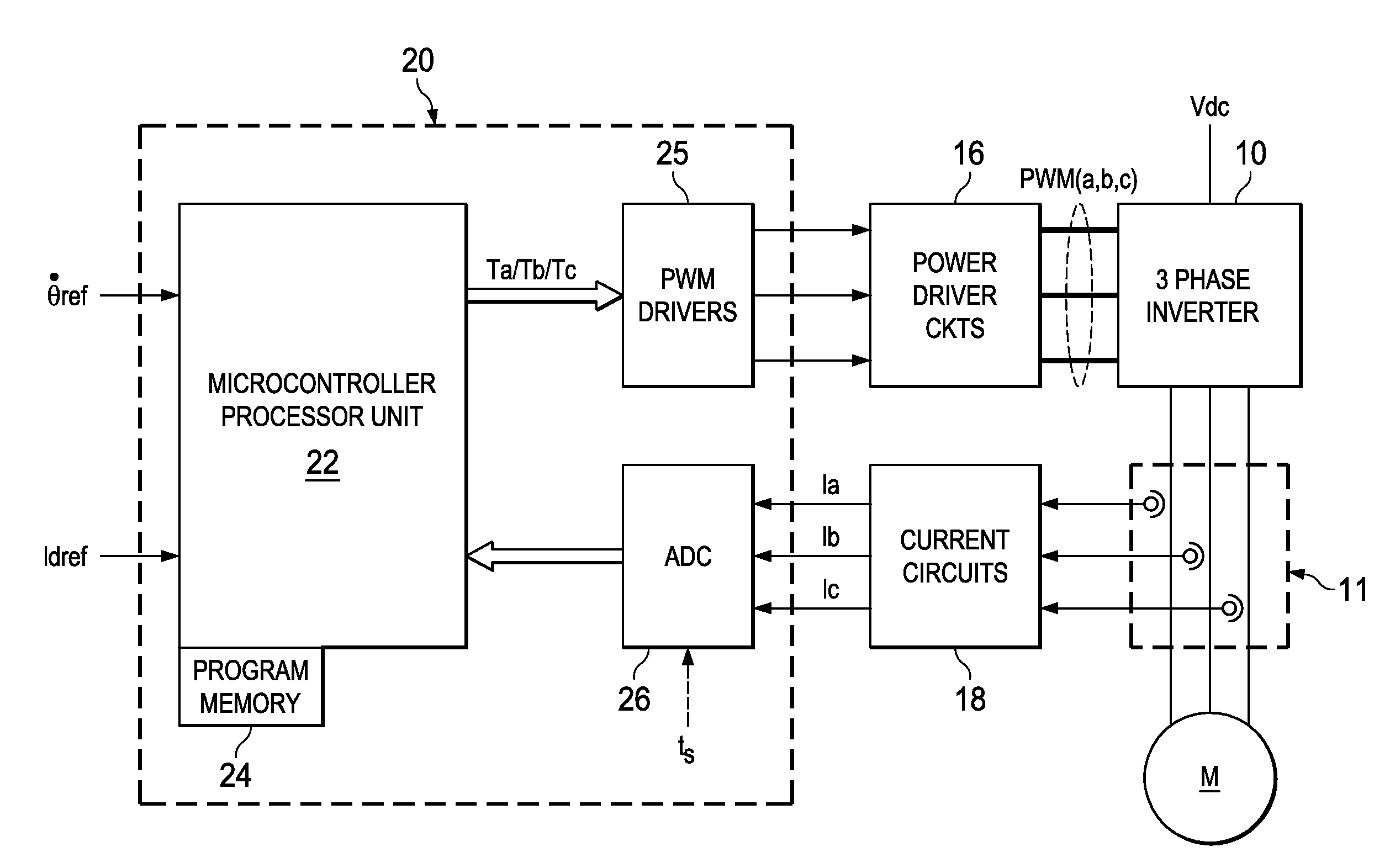

Low Speed and High Speed Controller Architecture for Electric Motors

InactiveUS20150084576A1Accurate low speed controlEfficient implementationElectronic commutation motor controlMotor/generator/converter stoppersPeriodic excitationController architecture

A motor controller architecture and method of operating the same. The motor controller includes a function for estimating the low speed operation of the motor, for example by evaluating the response to a periodic excitation signal injected into the control loop of the controller architecture. A periodic excitation signal in the form of a square wave allows for analysis of the response of the motor without requiring demodulation, which allows the frequency of the excitation signal to be above the audible range. Control logic for controlling the motor at transitional speeds between low speed control and high speed (back emf) control is provided in some embodiments.

Owner:TEXAS INSTR INC

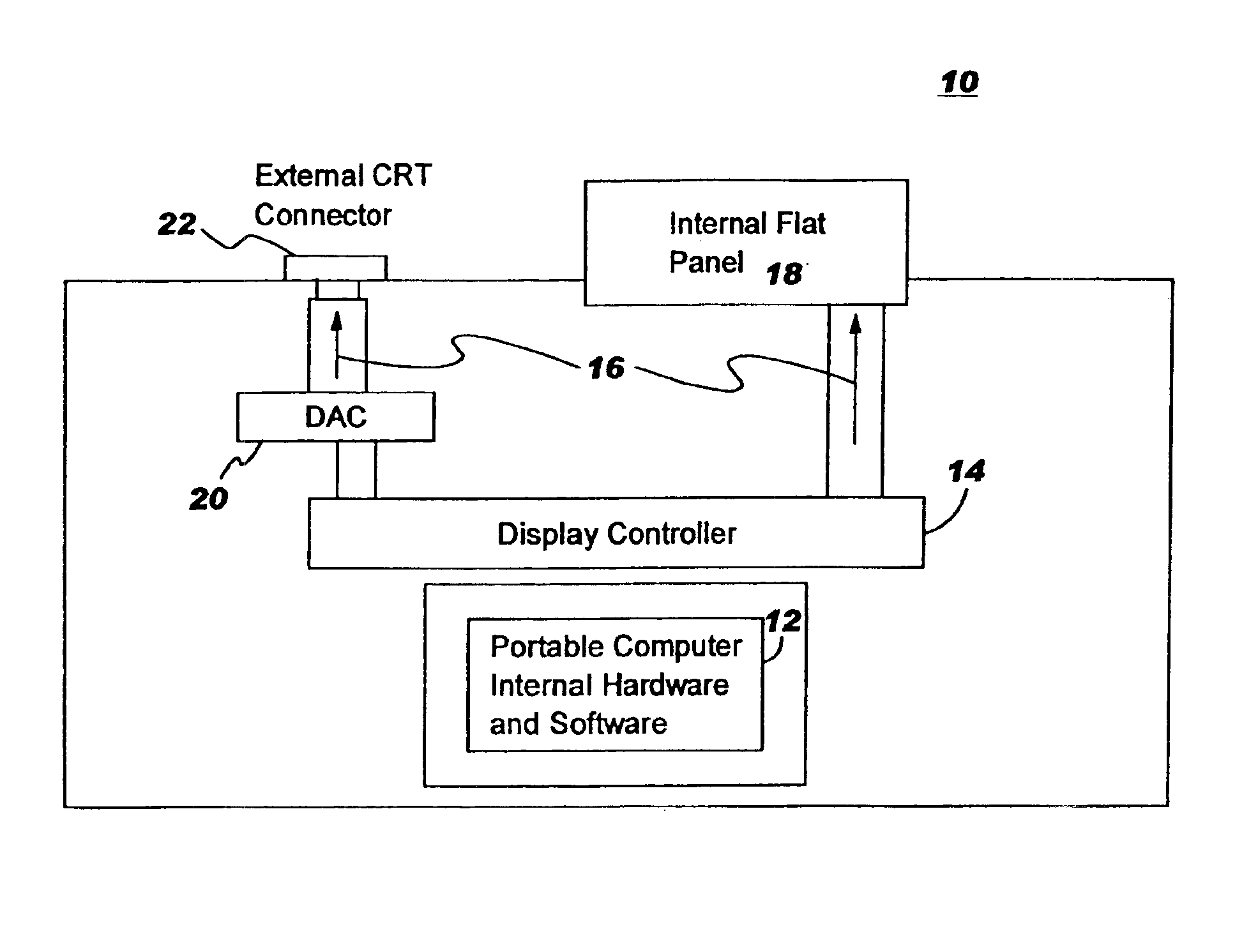

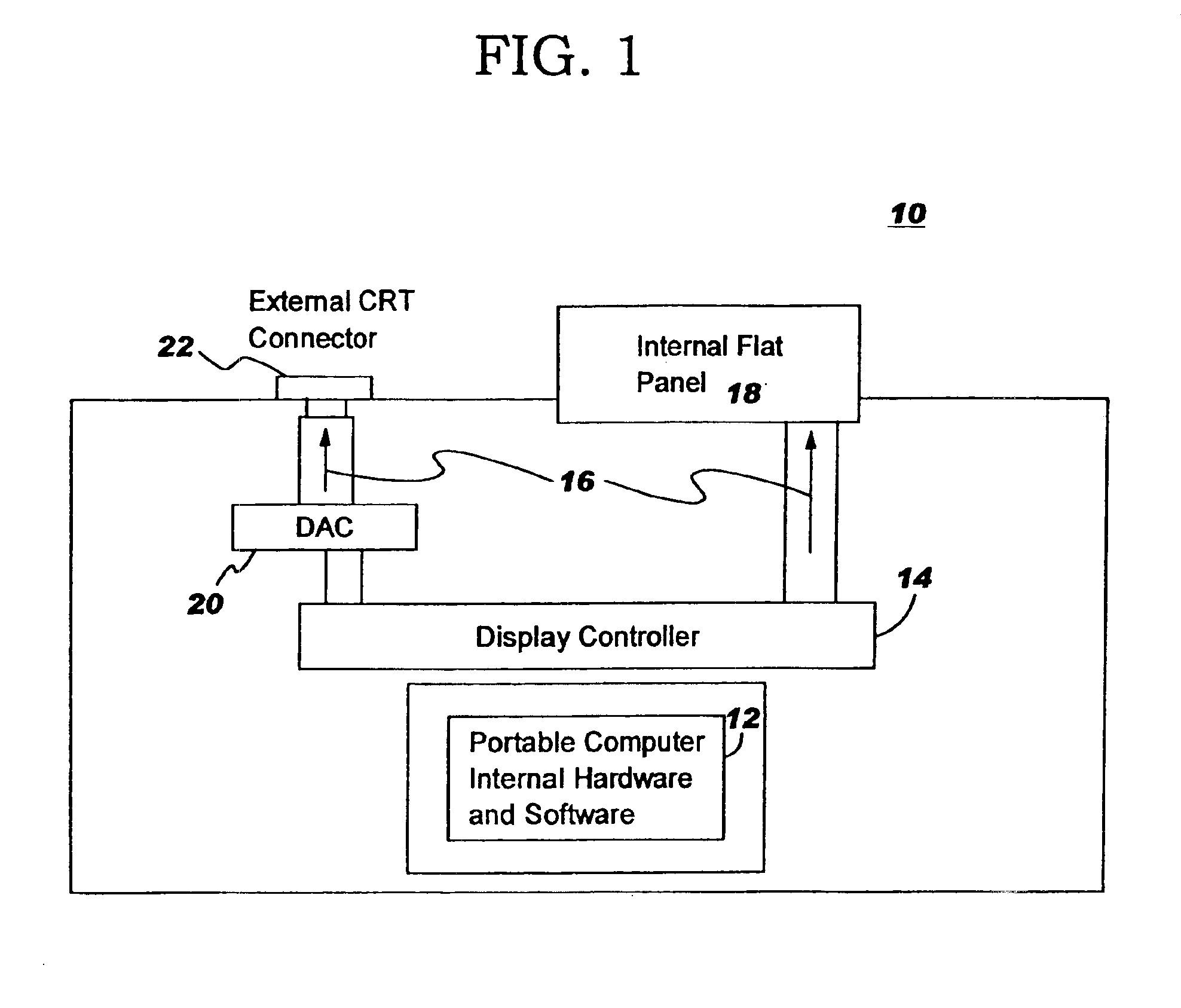

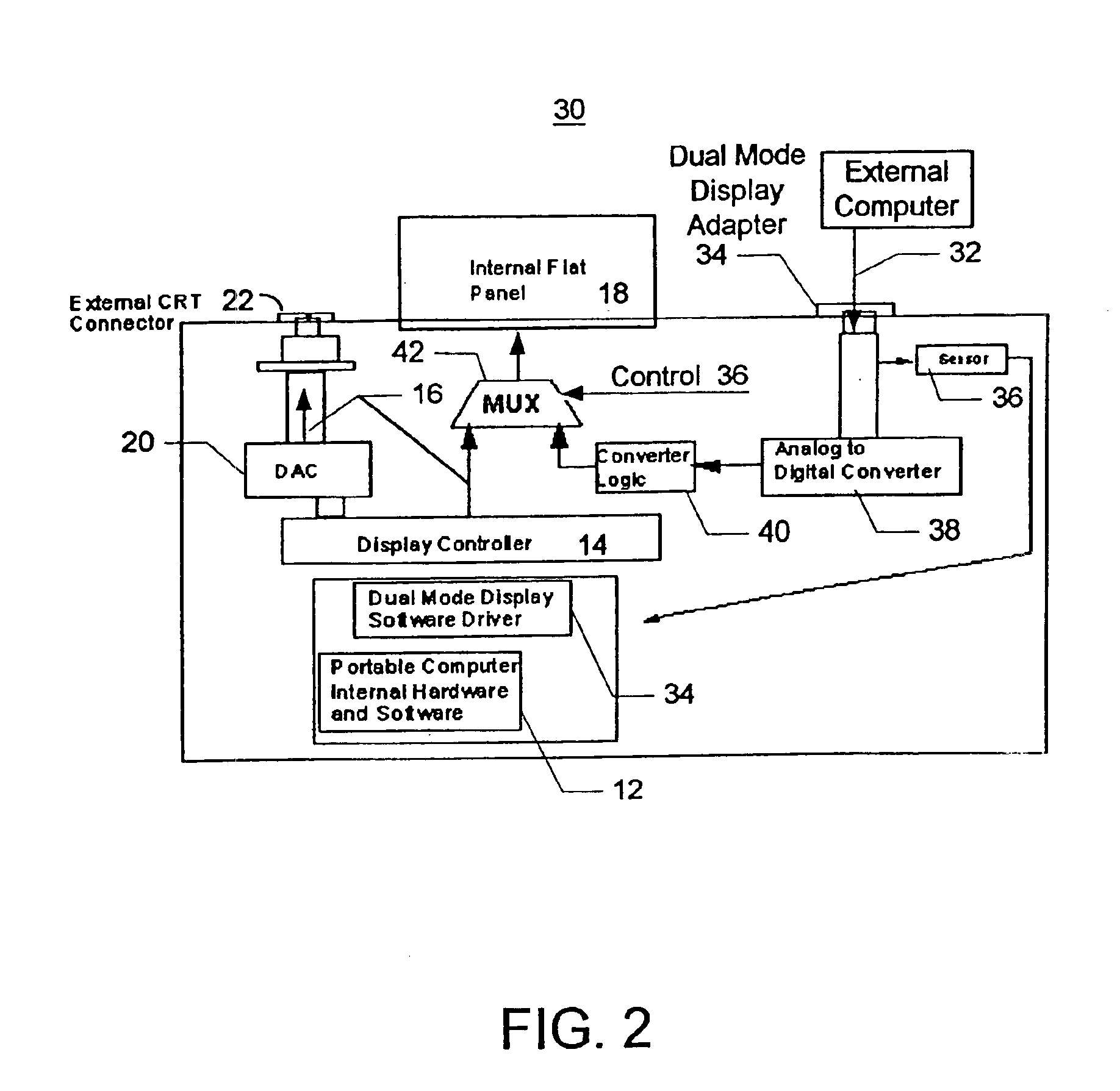

Display controller architecture for portable computers

InactiveUS6873306B2Cathode-ray tube indicatorsDetails for portable computersController architectureMultiplexer

A dual display mode portable computer is disclosed. The portable computer includes a flat-panel display, and a display controller for outputting an internal video signal to the flat panel display. The portable computer further includes means for receiving an external video signal, and a multiplexer for outputting the internal video signal to the flat-panel display during a first display mode, and for outputting the external video signal to the flat-panel display during a second display mode, thereby enabling the portable computer to act as a display device for an external computer.

Owner:LENOVO PC INT