Patents

Literature

284 results about "InfiniBand" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

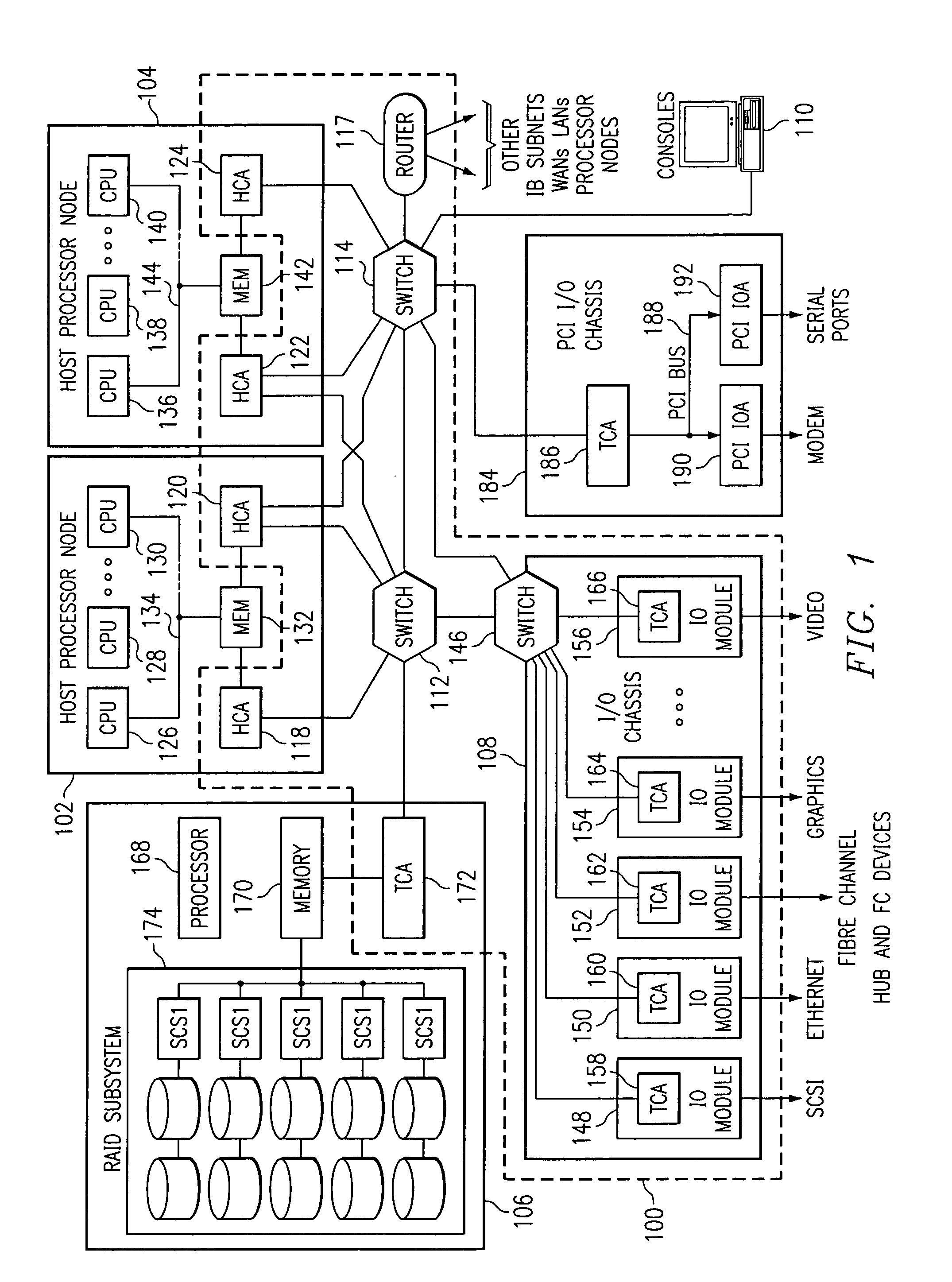

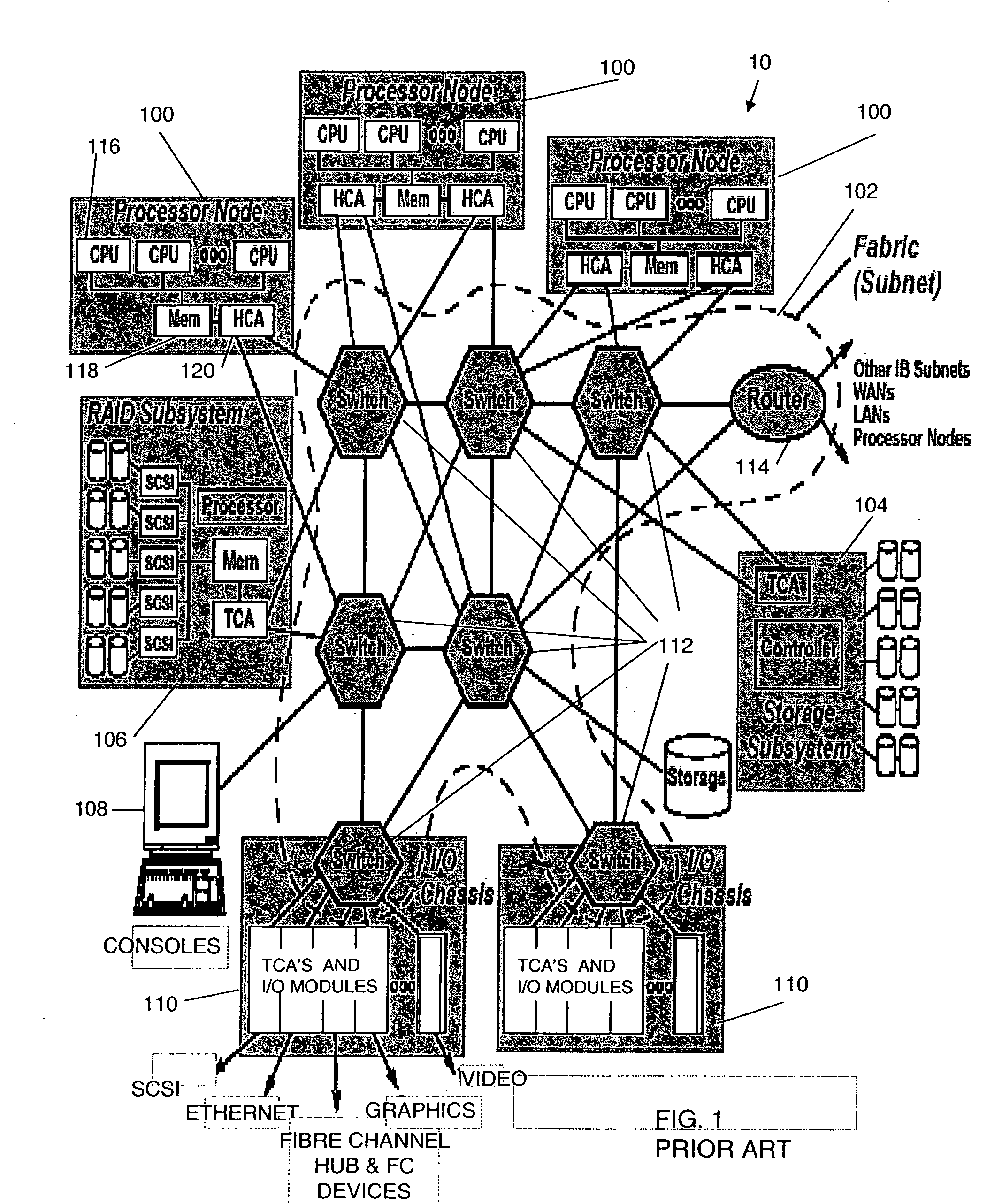

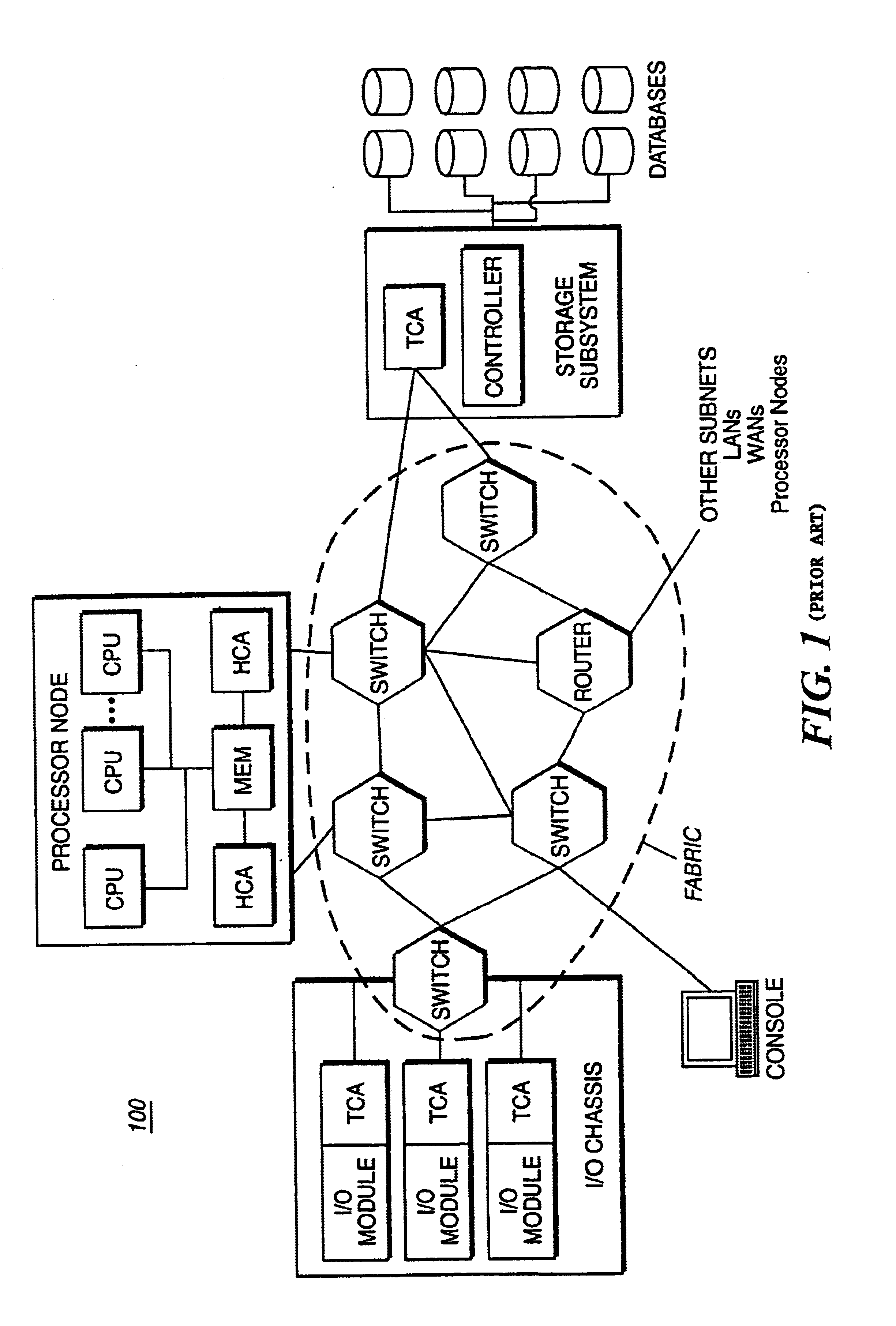

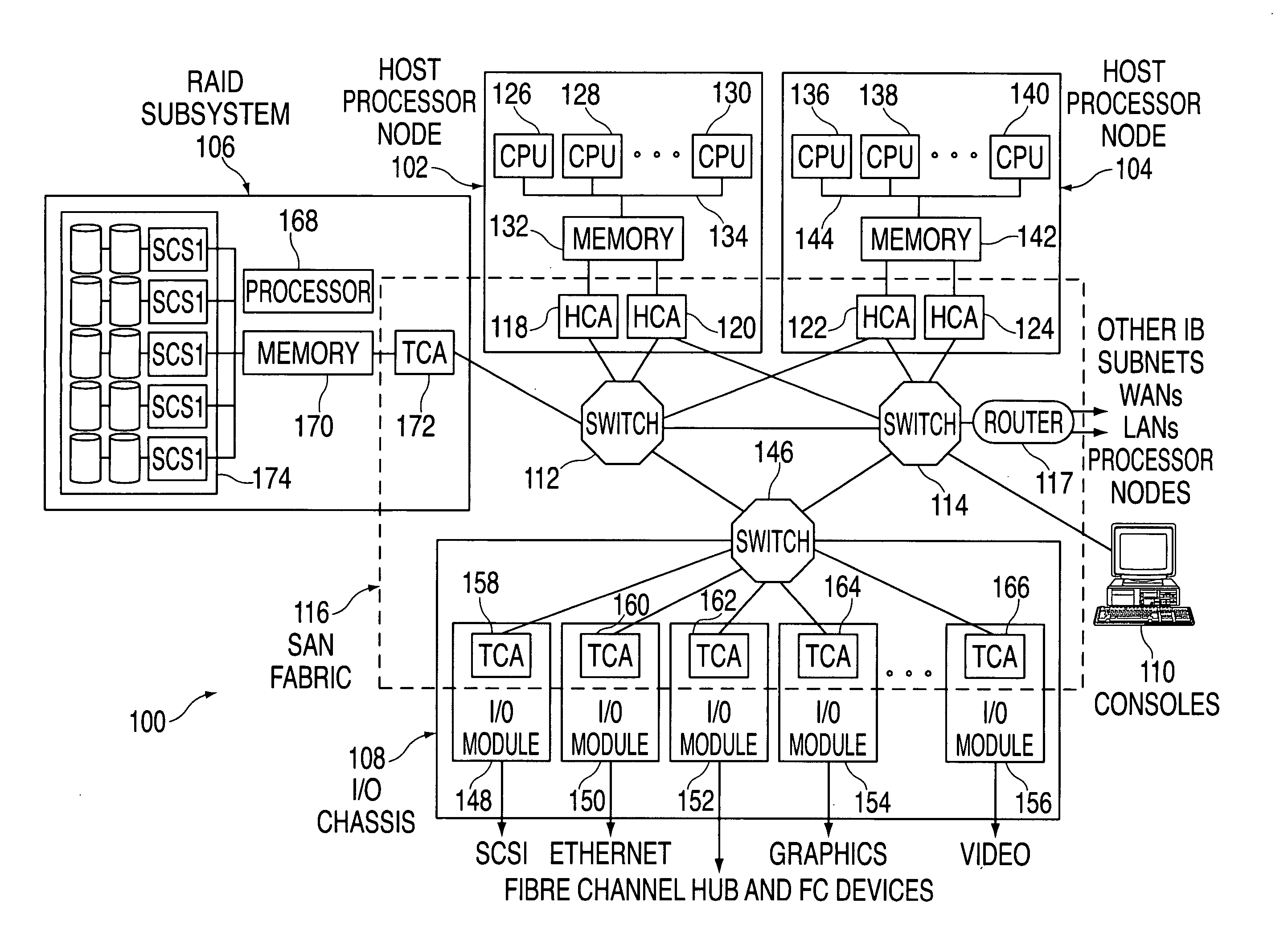

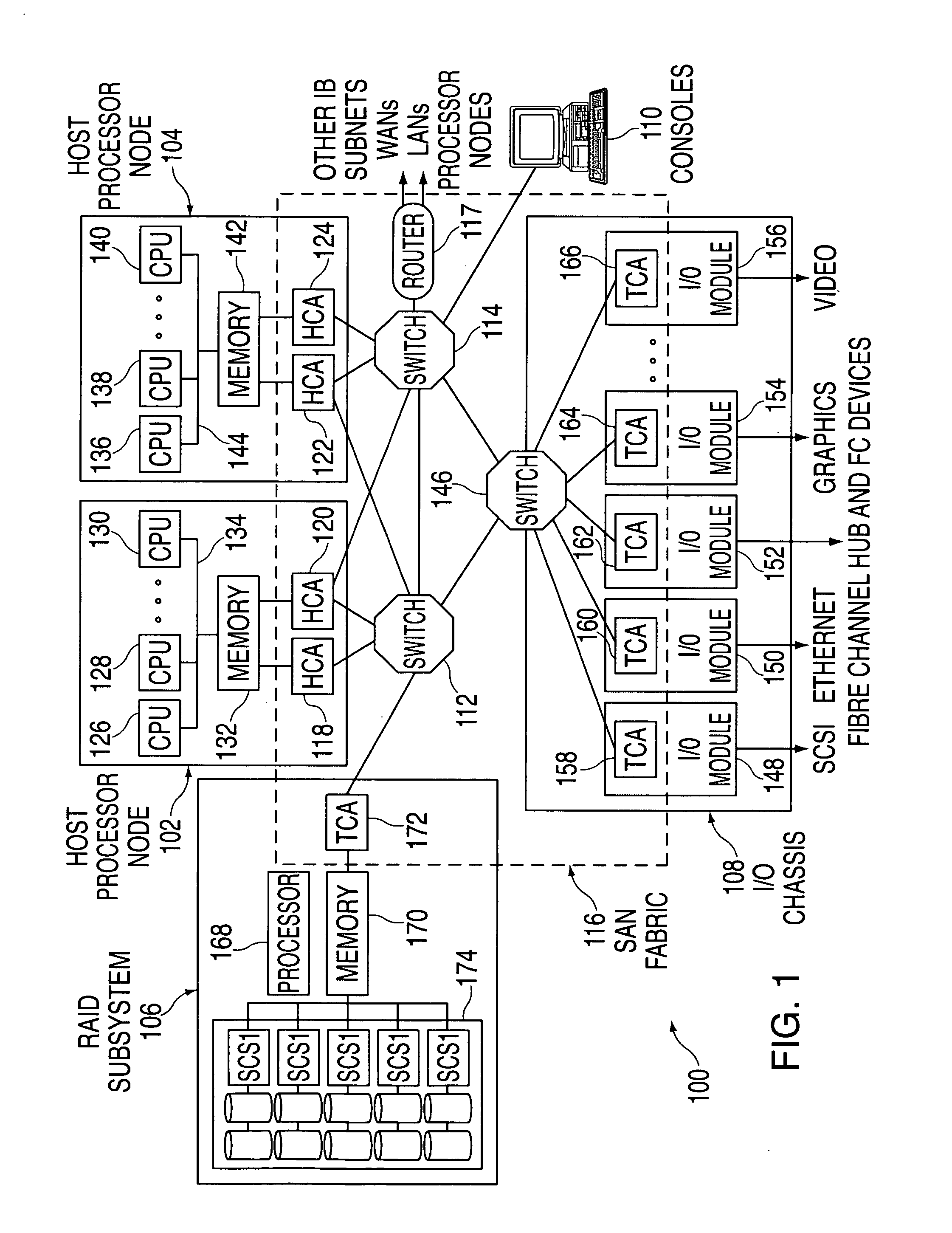

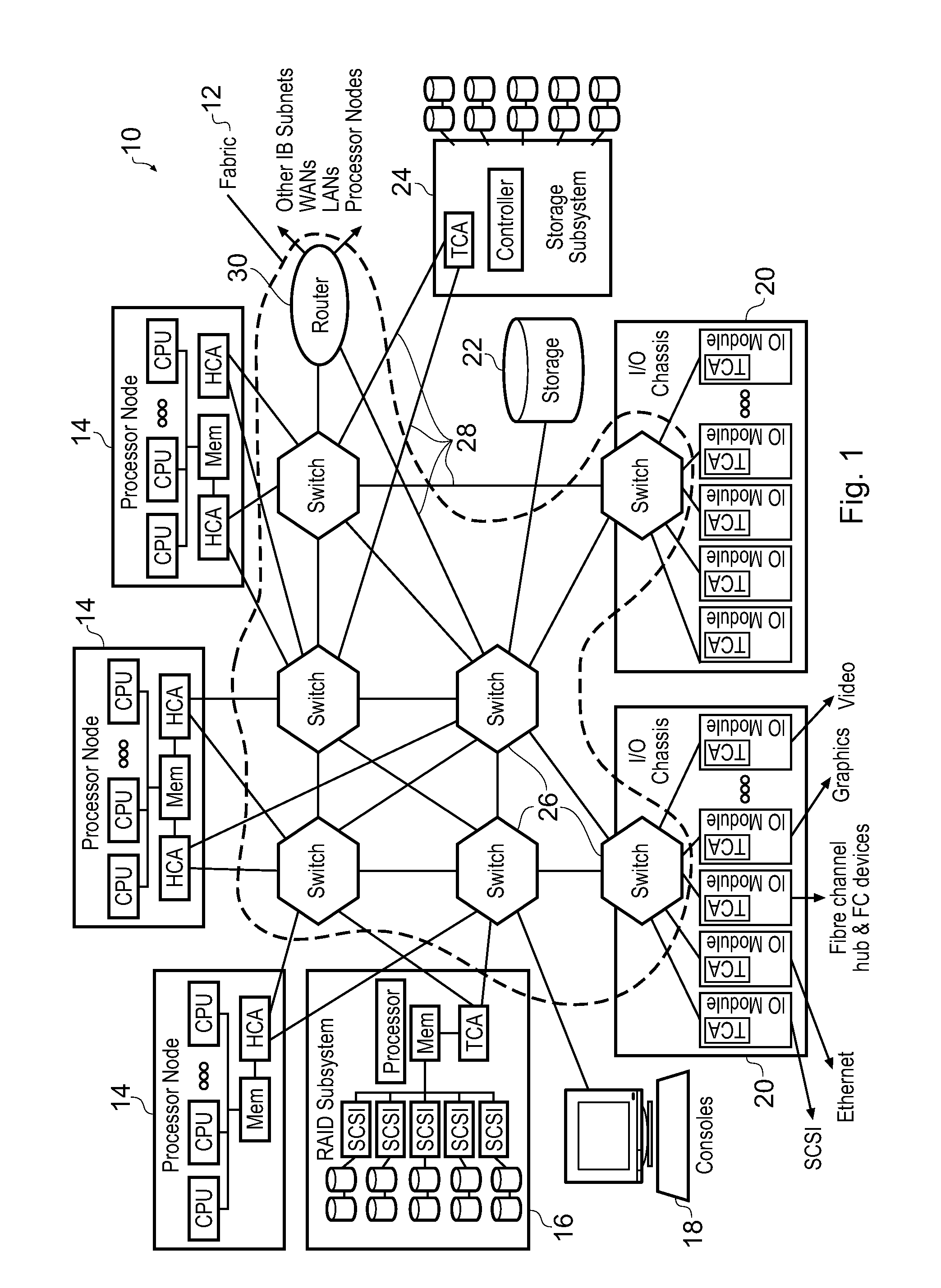

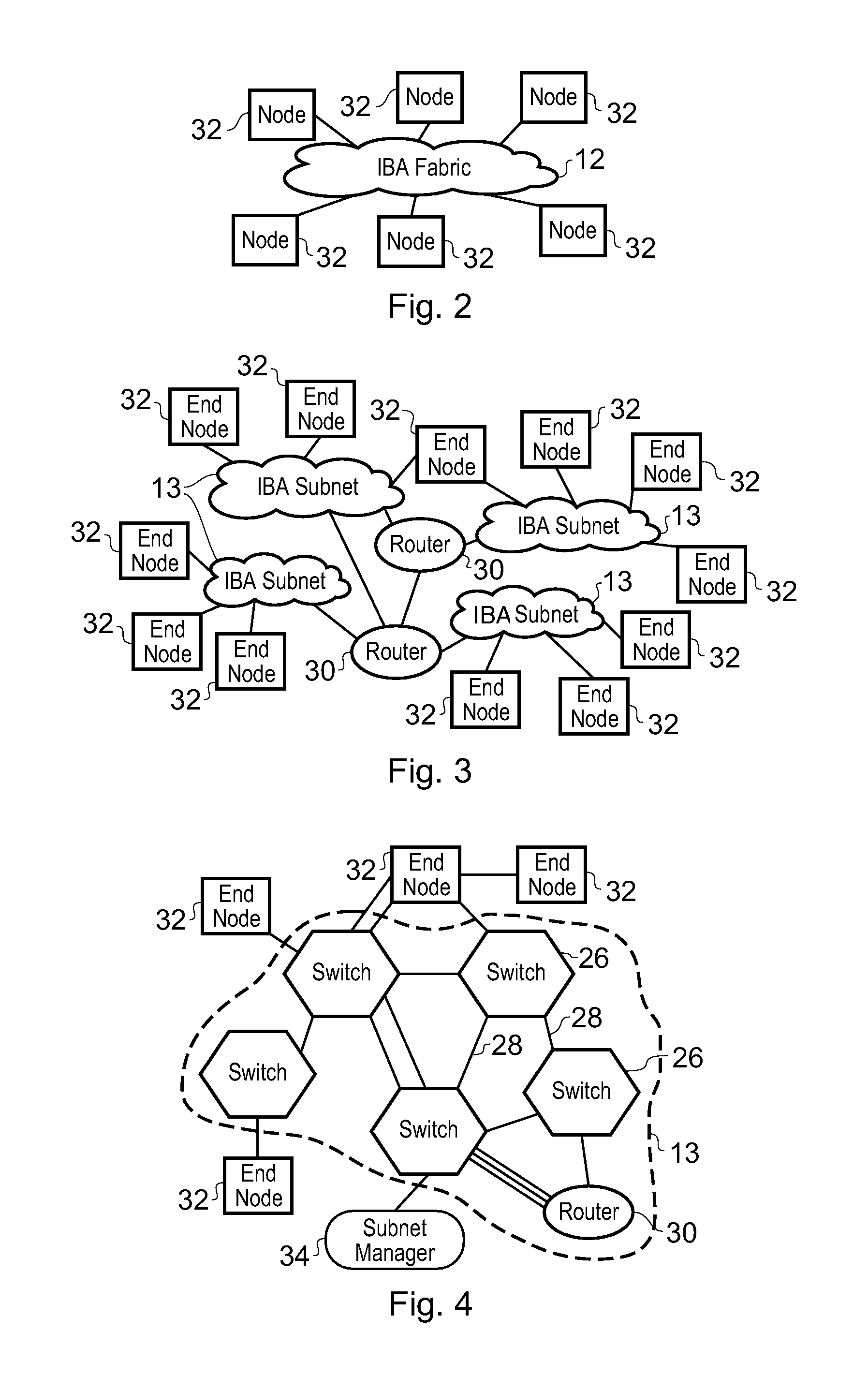

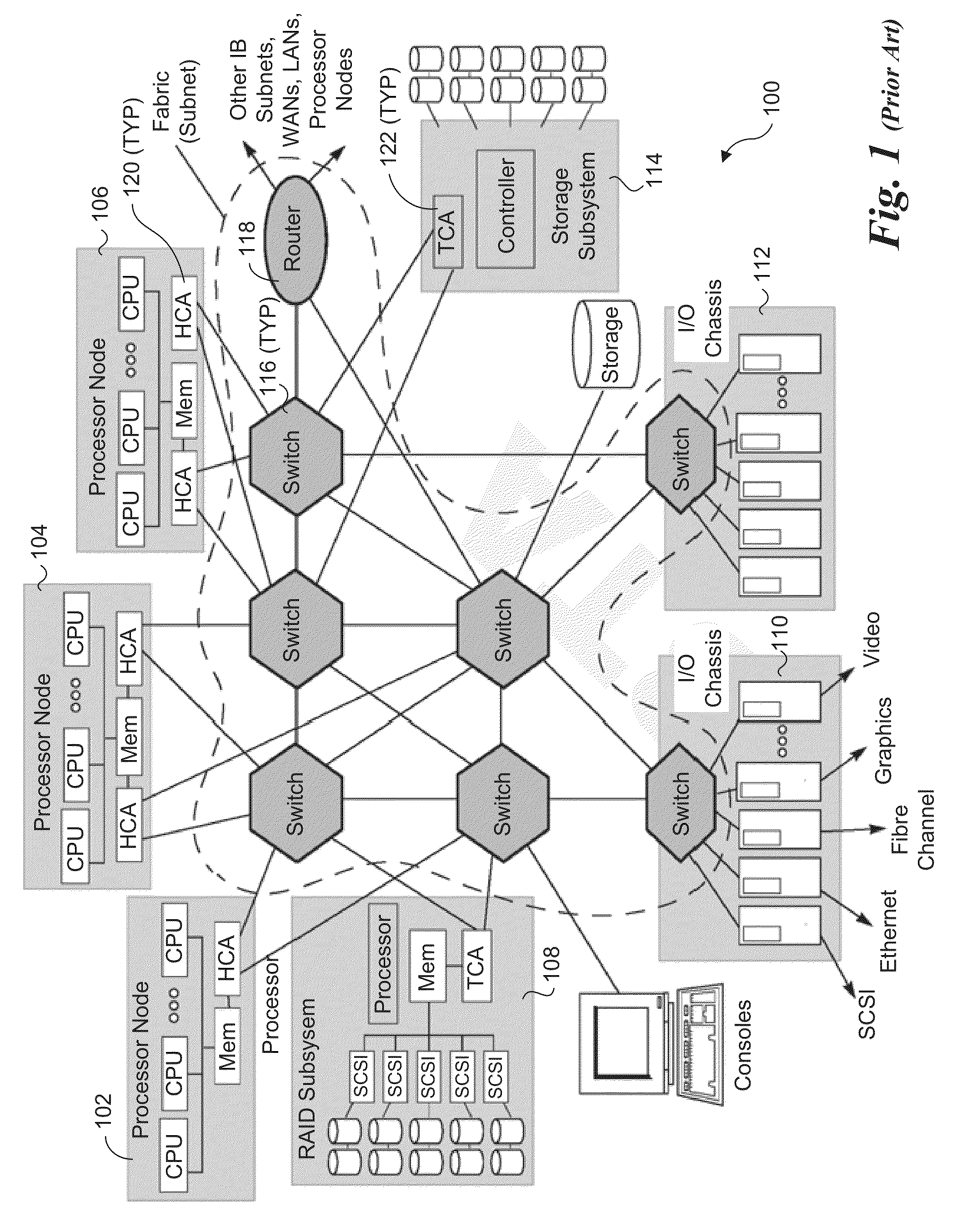

InfiniBand (IB) is a computer networking communications standard used in high-performance computing that features very high throughput and very low latency. It is used for data interconnect both among and within computers. InfiniBand is also used as either a direct or switched interconnect between servers and storage systems, as well as an interconnect between storage systems.

Immediate ready implementation of virtually congestion free guaranteed service capable network: external internet nextgentcp (square waveform) TCP friendly san

InactiveUS20080037420A1Guaranteed service qualityGood serviceFrequency-division multiplex detailsTransmission systemsSquare waveformThe Internet

Various techniques of simple modifications to TCP / IP protocol and other susceptible protocols and related network's switches / routers configurations, are presented for immediate ready implementations over external Internet of virtually congestion free guaranteed service capable network, without requiring use of existing QoS / MPLS techniques nor requiring any of the switches / routers softwares within the network to be modified or contribute to achieving the end-to-end performance results nor requiring provision of unlimited bandwidths at each and every inter-node links within the network.

Owner:TANG BOB

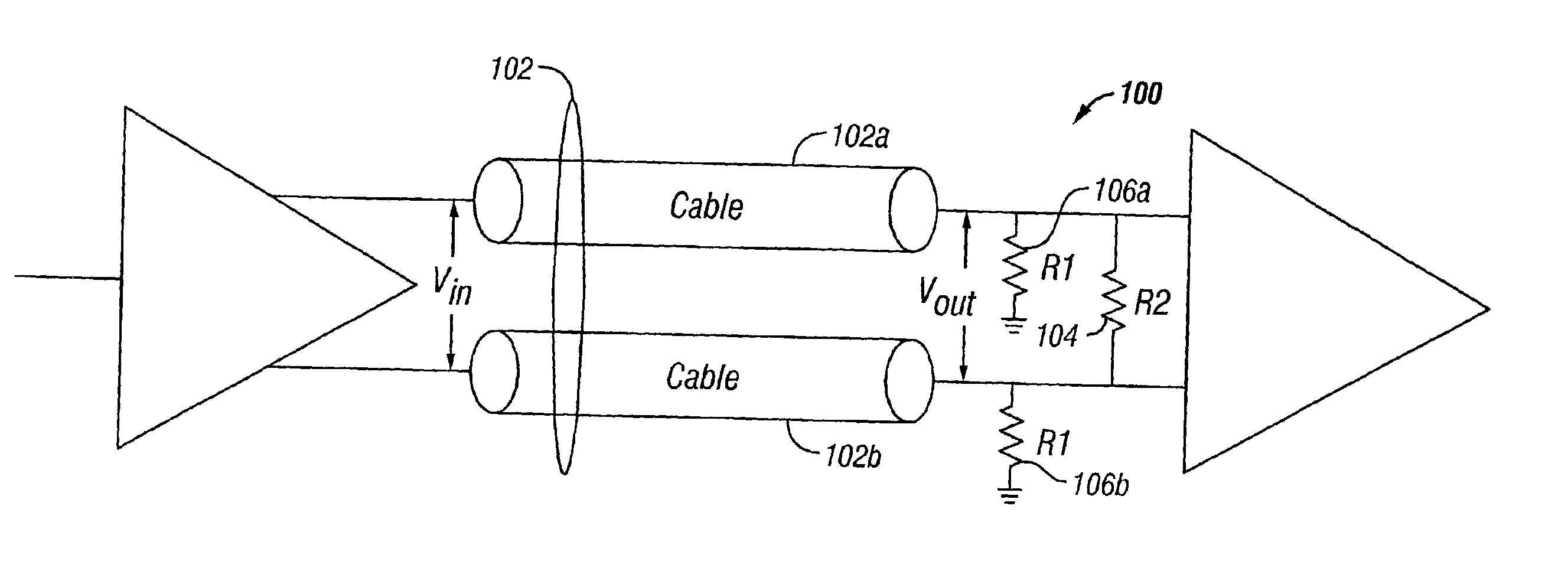

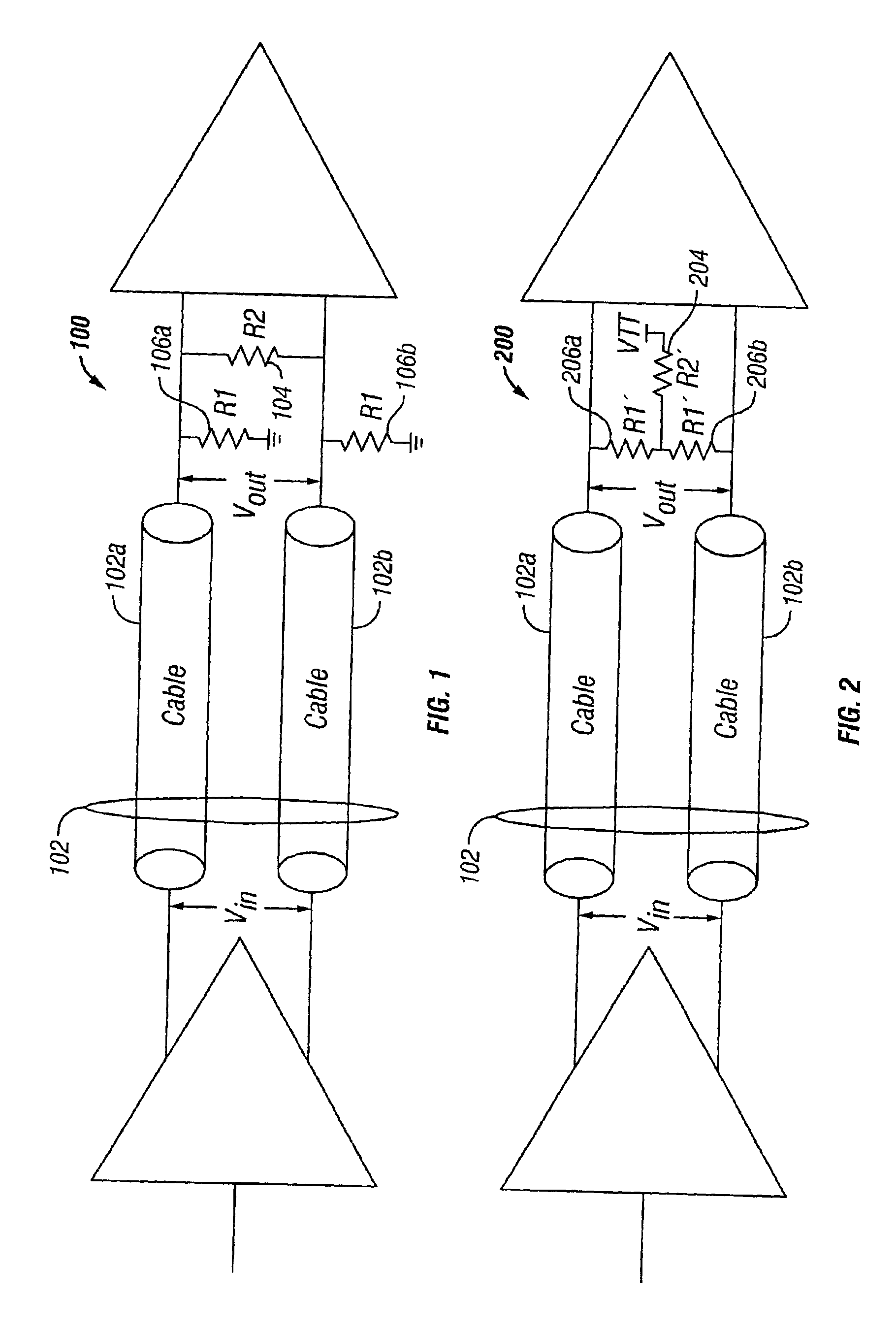

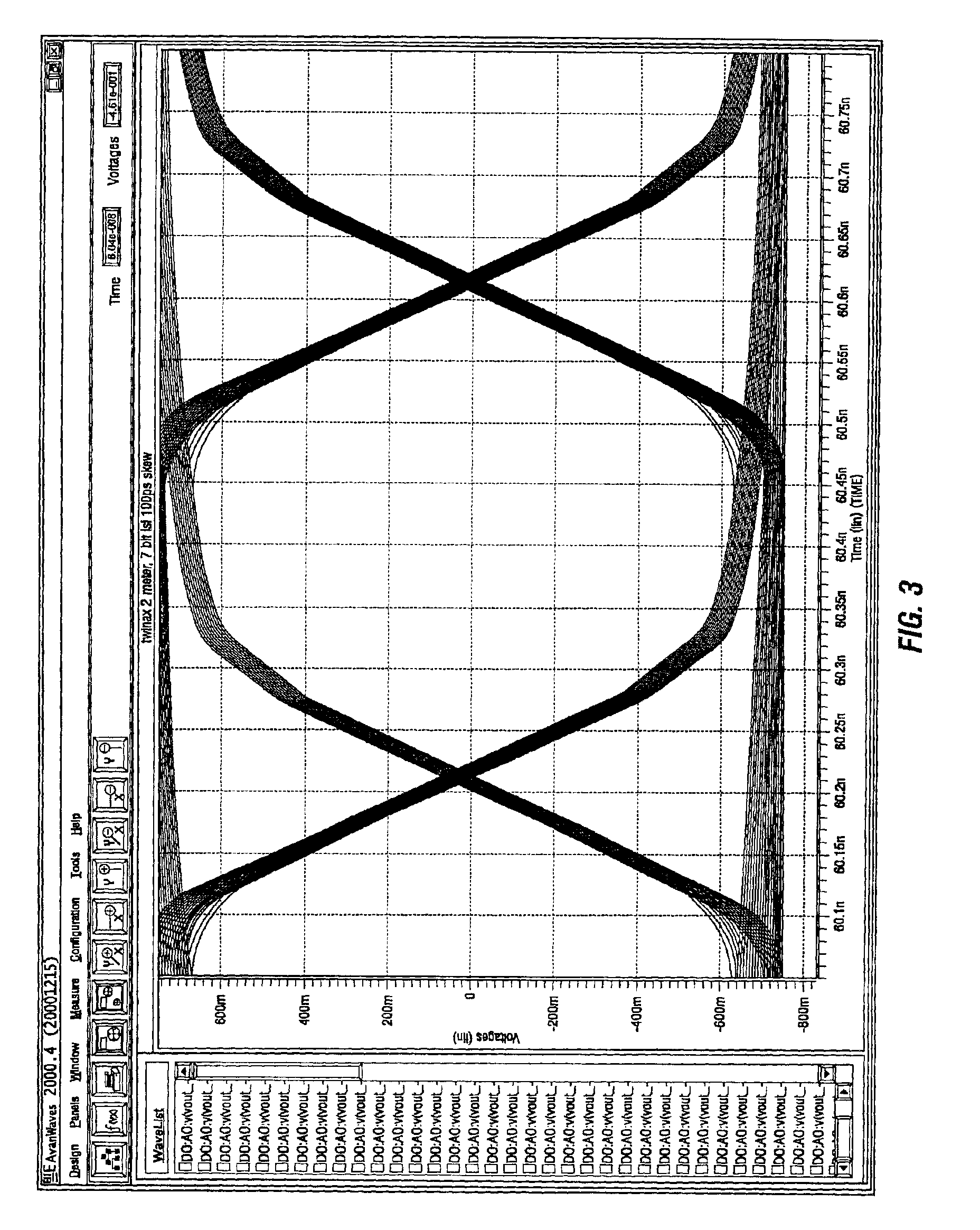

Improving signal integrity in differential signal systems

InactiveUS6886065B2Improves differential signal integrityEnhanced signalReliability increasing modificationsBaseband system detailsSignal qualityDifferential signaling

Over-terminating the differential mode impedance of a differential transmission line, such as an INFINIBAND™ cable, at the receiving end, improves the differential signal integrity for typical variations in termination network impedance component (e.g., resistor) and transmission line characteristics. Eye opening of the differential signal can be made larger with reduced attenuation but increased jitter compared to under-terminating the differential mode impedance. Because the differential signal quality (larger eye opening) is improved, data can be transmitted over a longer transmission line with the same transmitter and receiver.

Owner:VALTRUS INNOVATIONS LTD

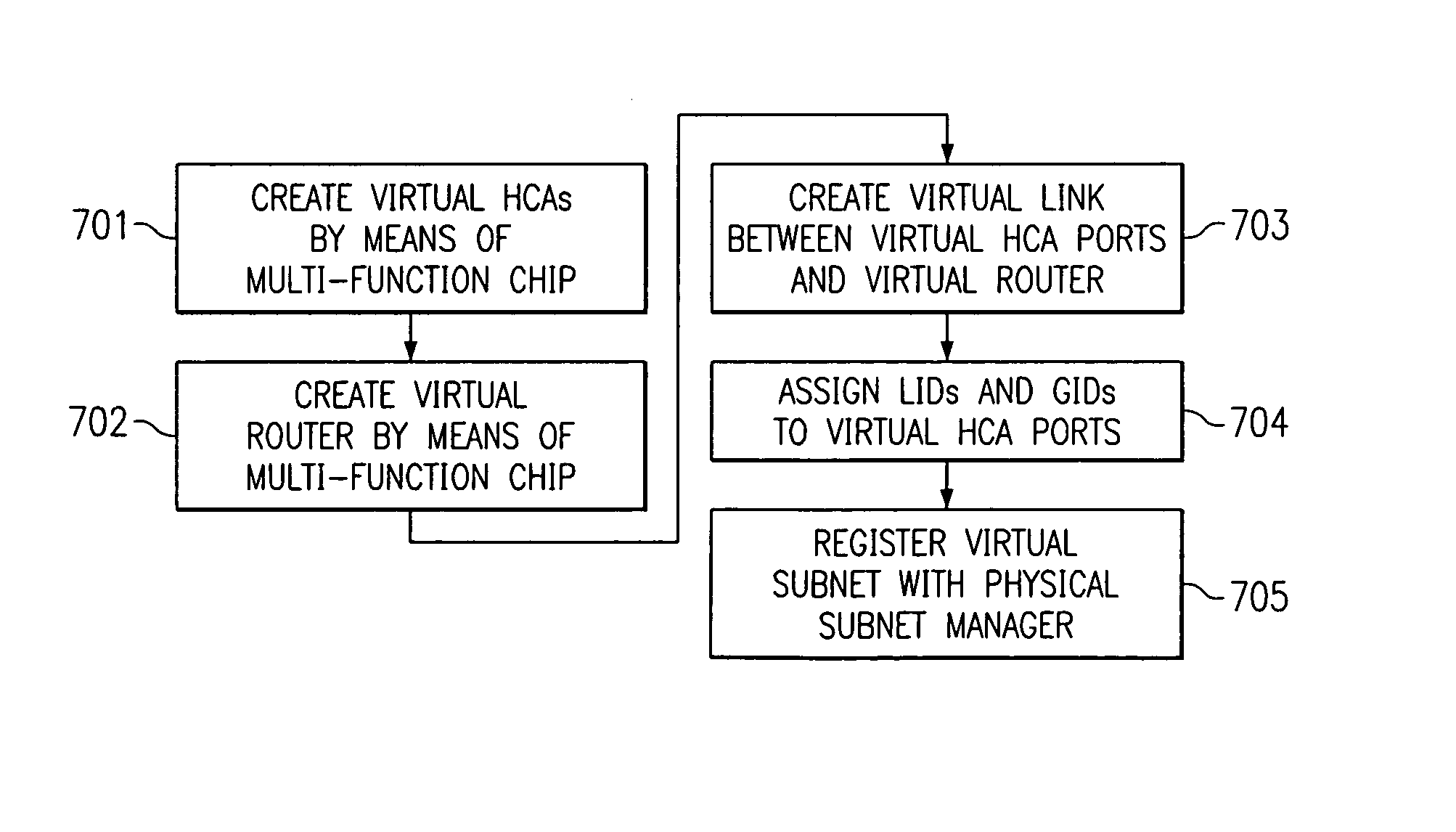

End node partitioning using virtualization

ActiveUS7093024B2Increases horizontal scaling capabilityMultiple digital computer combinationsWireless commuication servicesVirtualizationVirtual hosting

A mechanism for allowing a single physical IB node to virtualize a plurality of host channel adapters is provided. This includes providing the appearance of both a router and multiple virtual HCA's residing behind that router, to the external REAL subnet components. Each virtual host channel adapter will have unique access control levels. One or more InfiniBand subnets are virtualized in such a way that nodes residing both within the virtual subnets and in separate physical subnets are completely unaware of the virtualization. This virtualization of InfiniBand subnets significantly increases the horizontal scaling capabilities of a single InfiniBand physical component, while at the same time provides “native” network throughput for all the virtual hosts.

Owner:IBM CORP

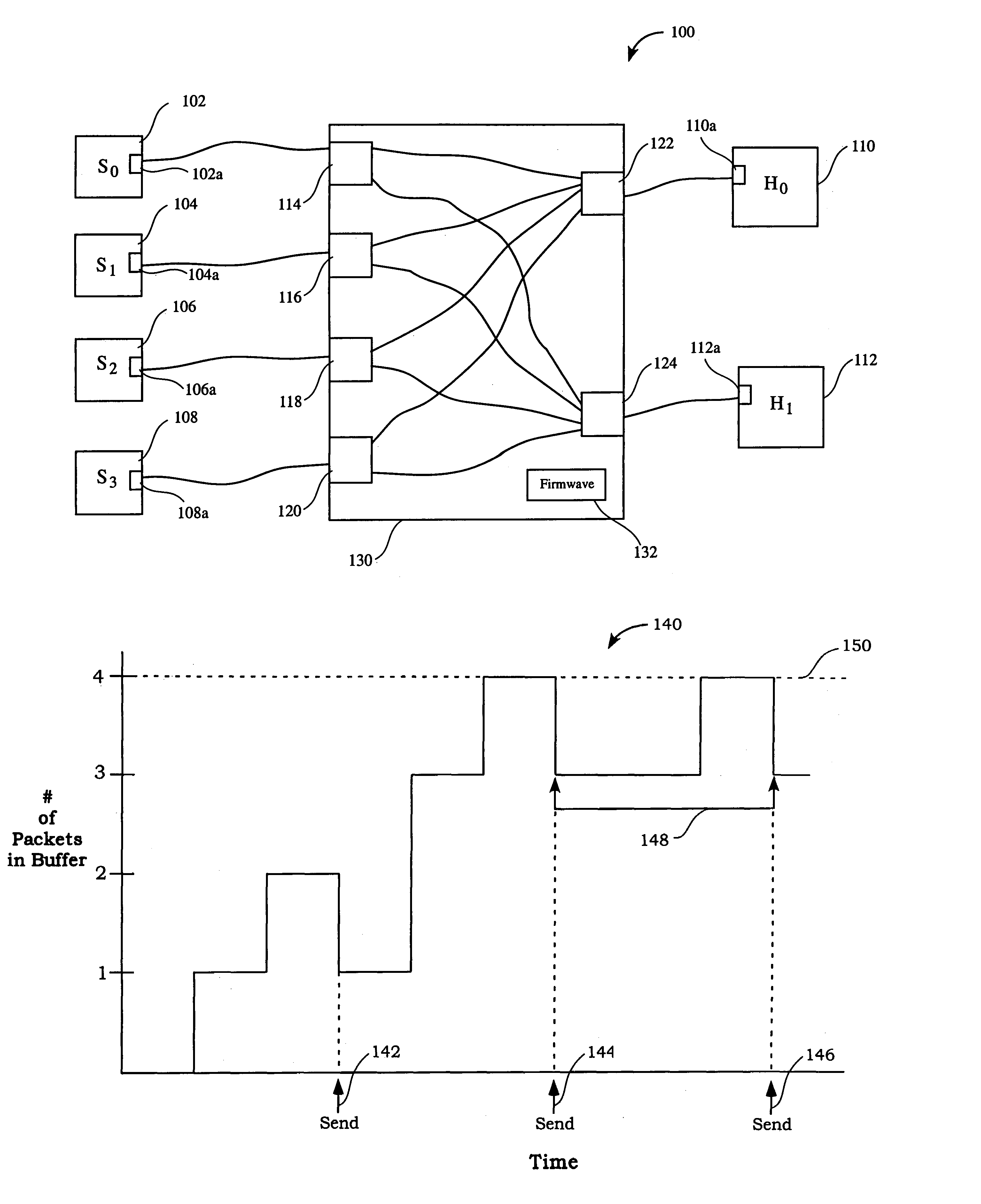

Methods for congestion mitigation in infiniband

ActiveUS7000025B1Reduce congestionEasy data transferEnergy efficient ICTMultiple digital computer combinationsTransfer systemTransmission equipment

A method for optimizing data transmission in a data transfer system is provided where the data transfer system includes a transmitting device that transmits data to a receiving device through a switch. The method includes monitoring data transfer congestion in a buffer of the switch. The monitoring includes marking the data when data transfer congestion is detected. If data transfer congestion is detected, the method includes marking an acknowledgement (ACK) data after the marked data is received by the receiving device. The method further includes transmitting the ACK data from the receiving device to the transmitting device. The method also includes adjusting a data transfer rate between the transmitting device and the receiving device based on data transfer congestion. Monitoring data transfer congestion includes marking the data according to a probability corresponding to a percentage of time that the buffer is full.

Owner:RPX CORP

Filtered application-to-application communication

ActiveUS7216225B2User identity/authority verificationDigital computer detailsComputer hardwareCommunications software

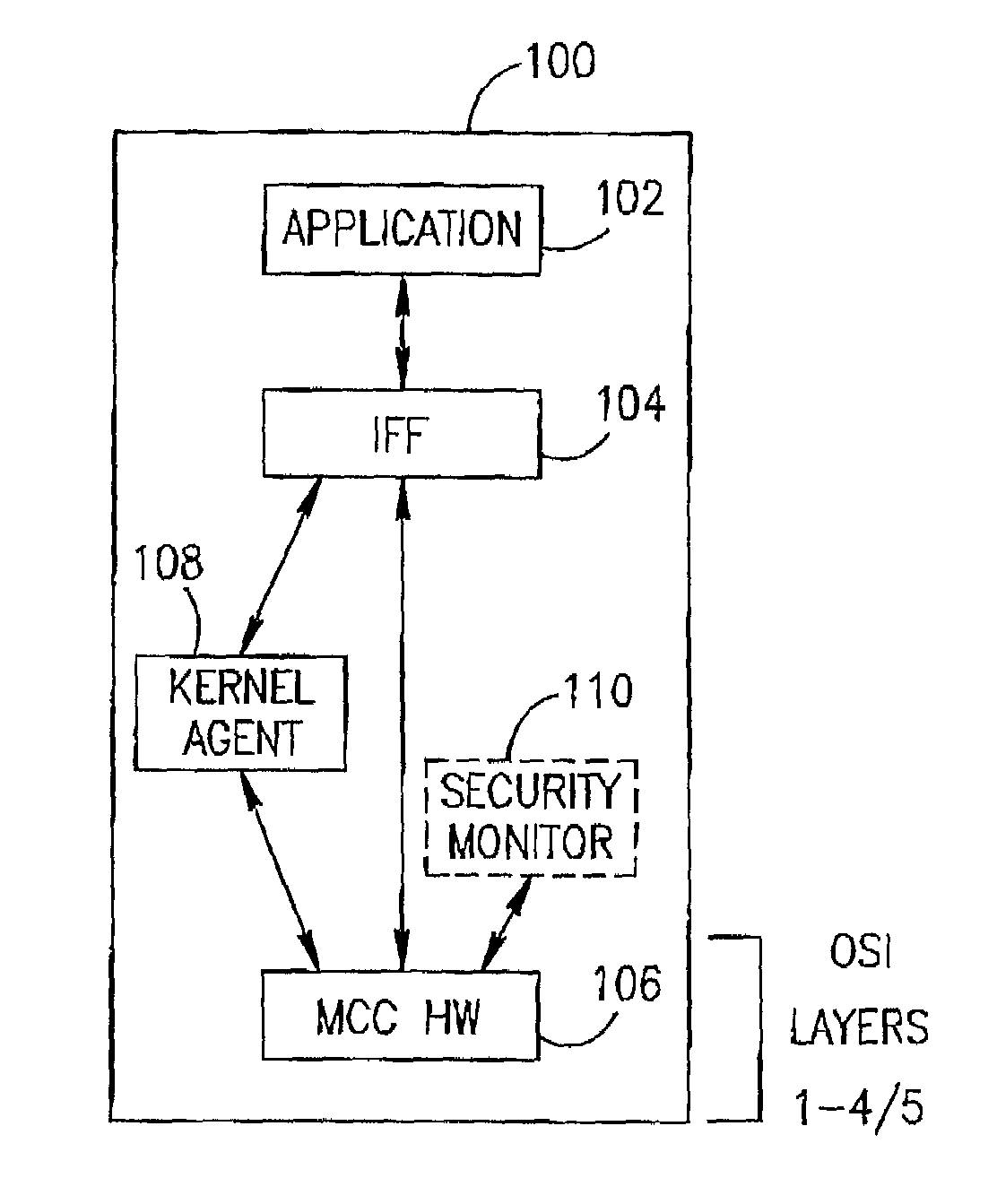

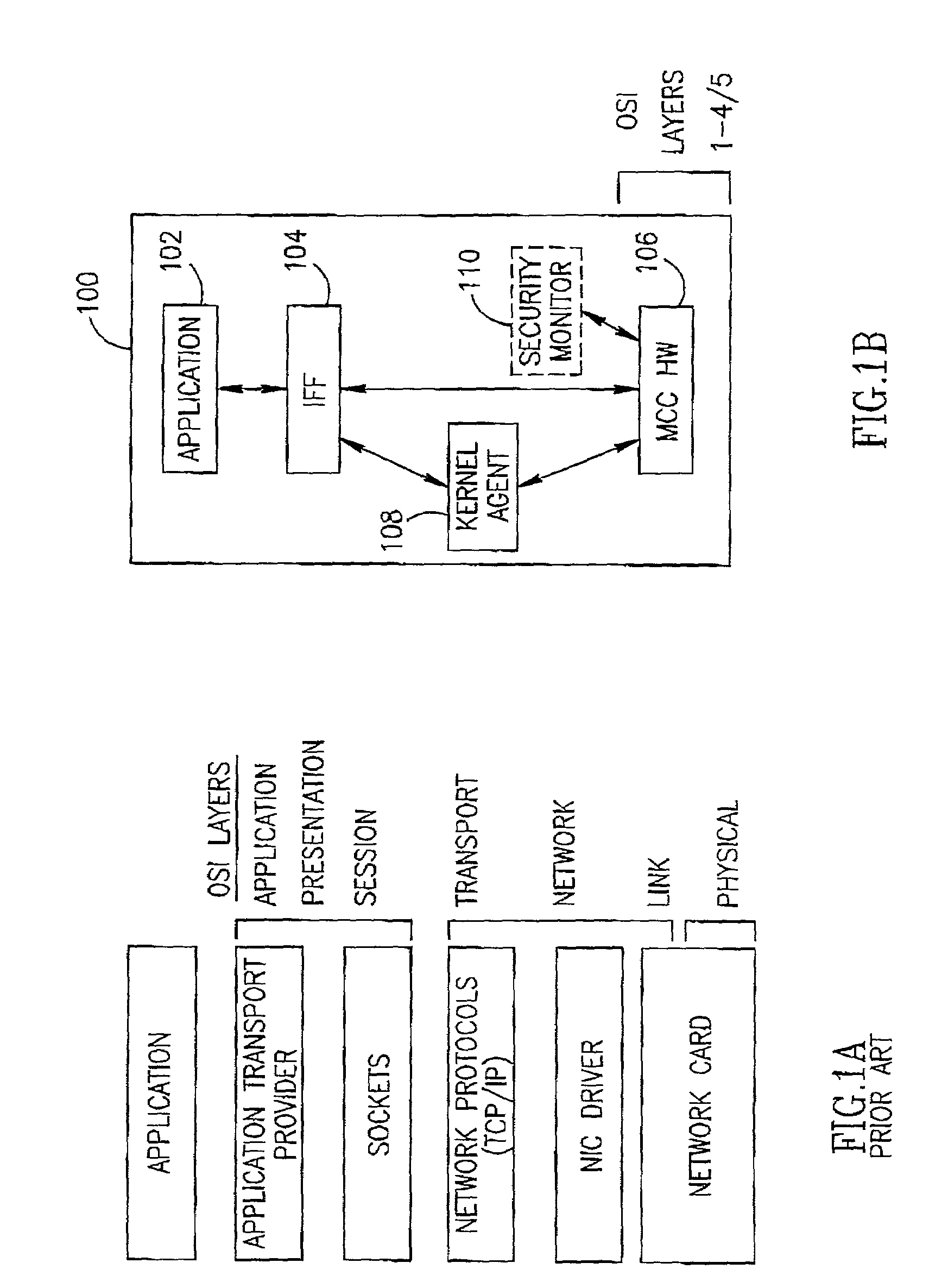

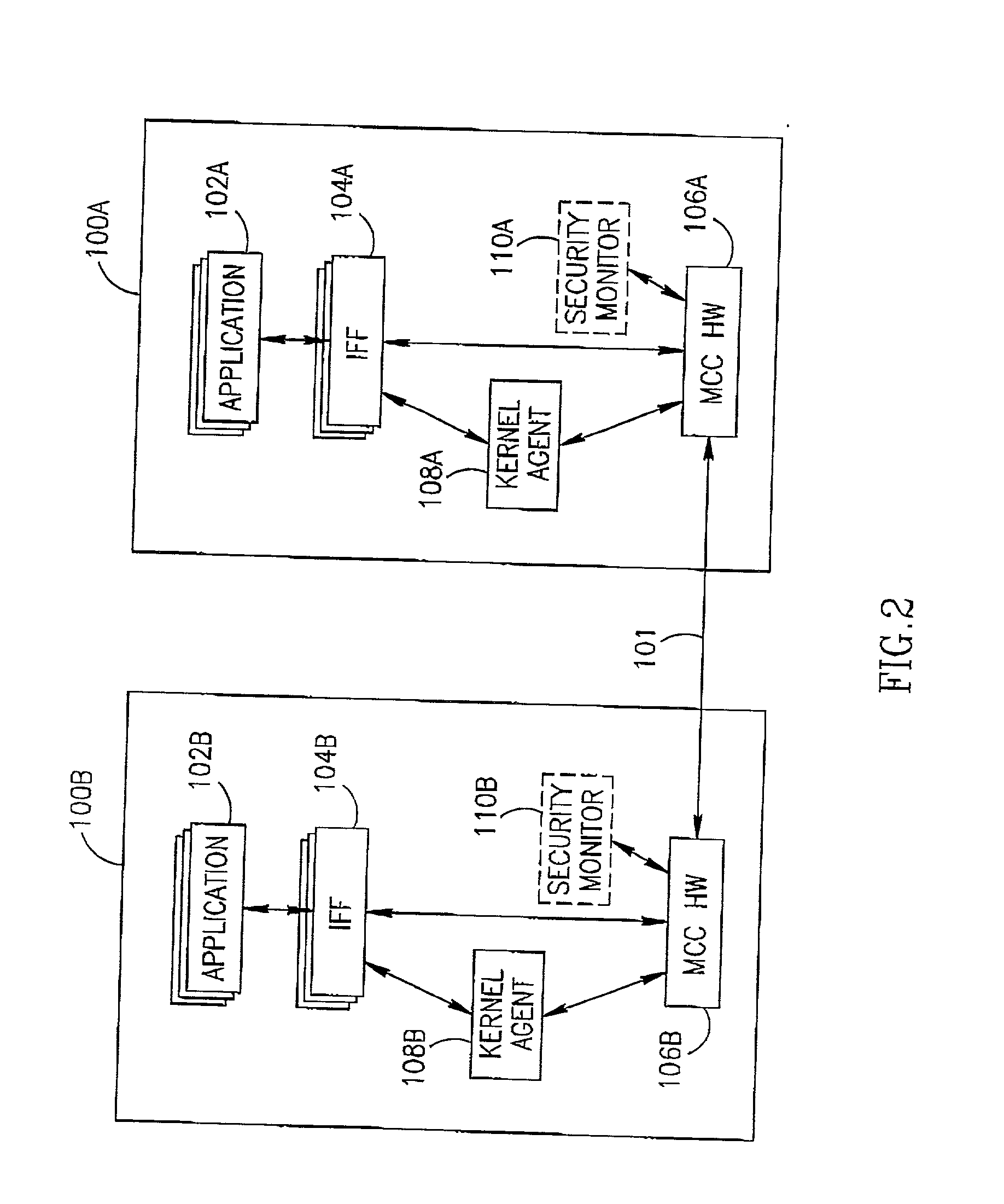

Some embodiments of the present invention are directed to a system that enables filtered application-to-application communication in a server farm in a multi-channel reliable hardware environment (e.g. InfiniBand). The system may also improve the performance of application-to-application communication between servers in the farm. The implementation of multi-channel reliable communication hardware may reduce the number of communication software layers above.

Owner:MELLANOX TECH TLV

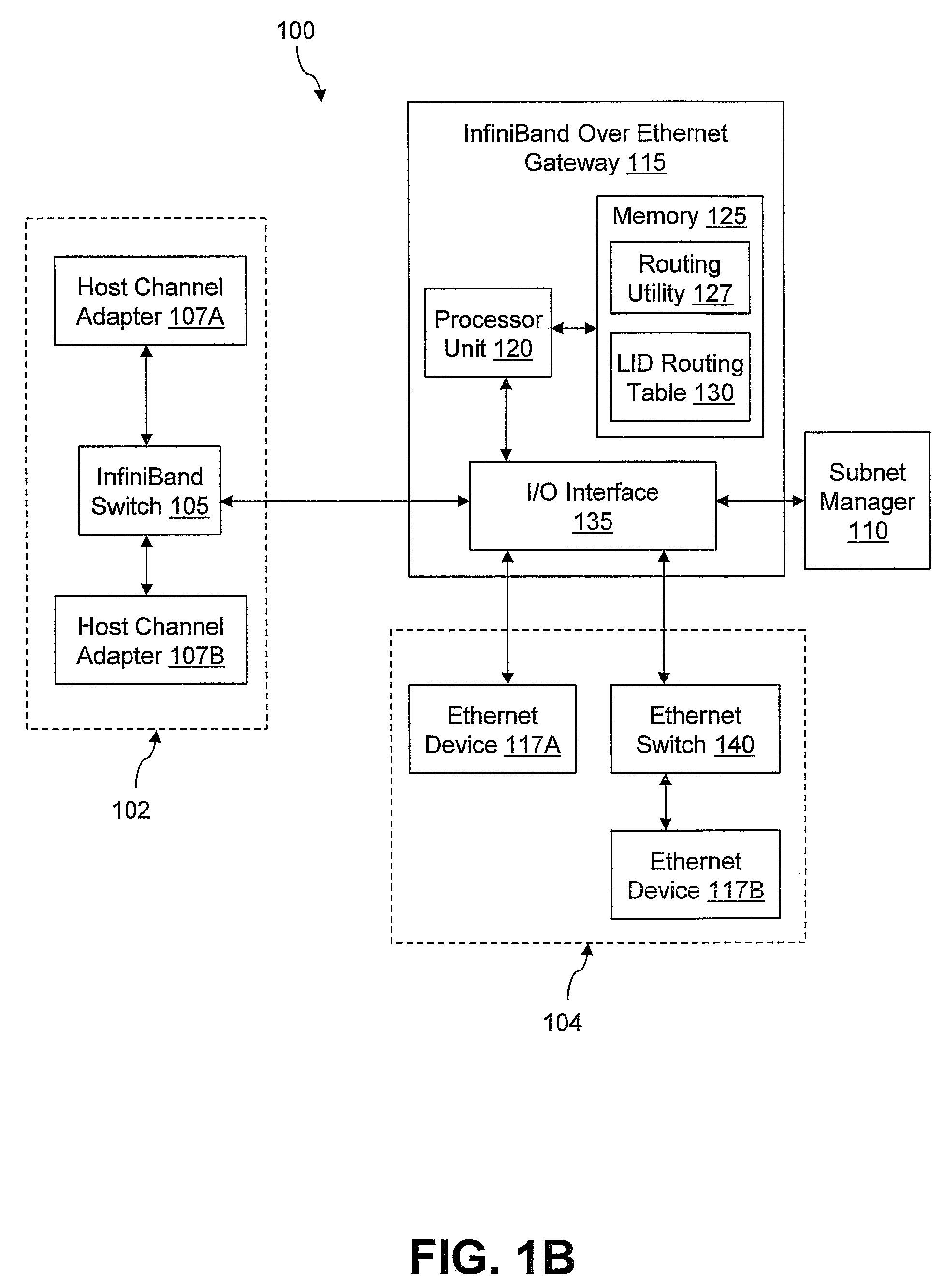

Methods and apparatus for encapsulating a frame for transmission in a storage area network

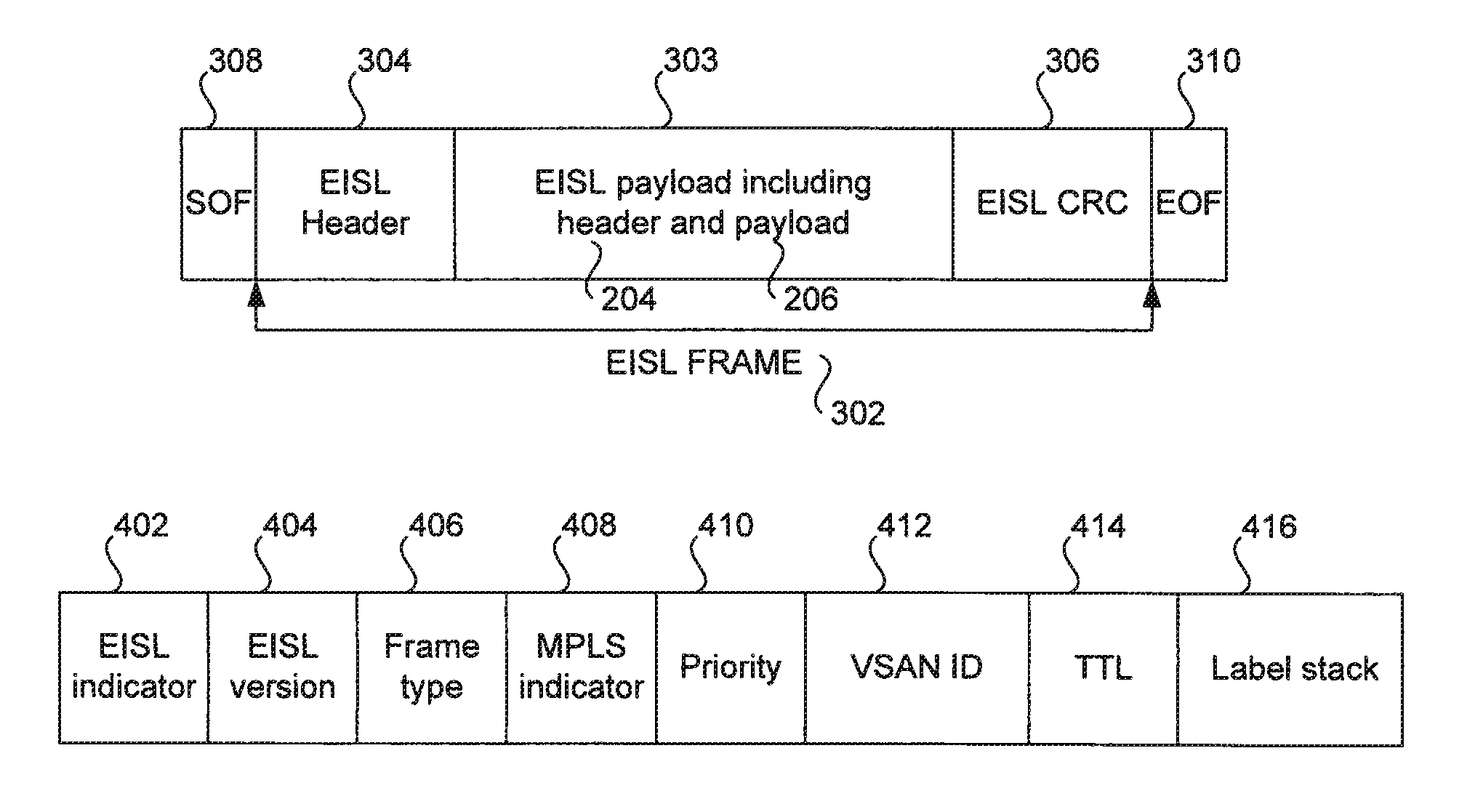

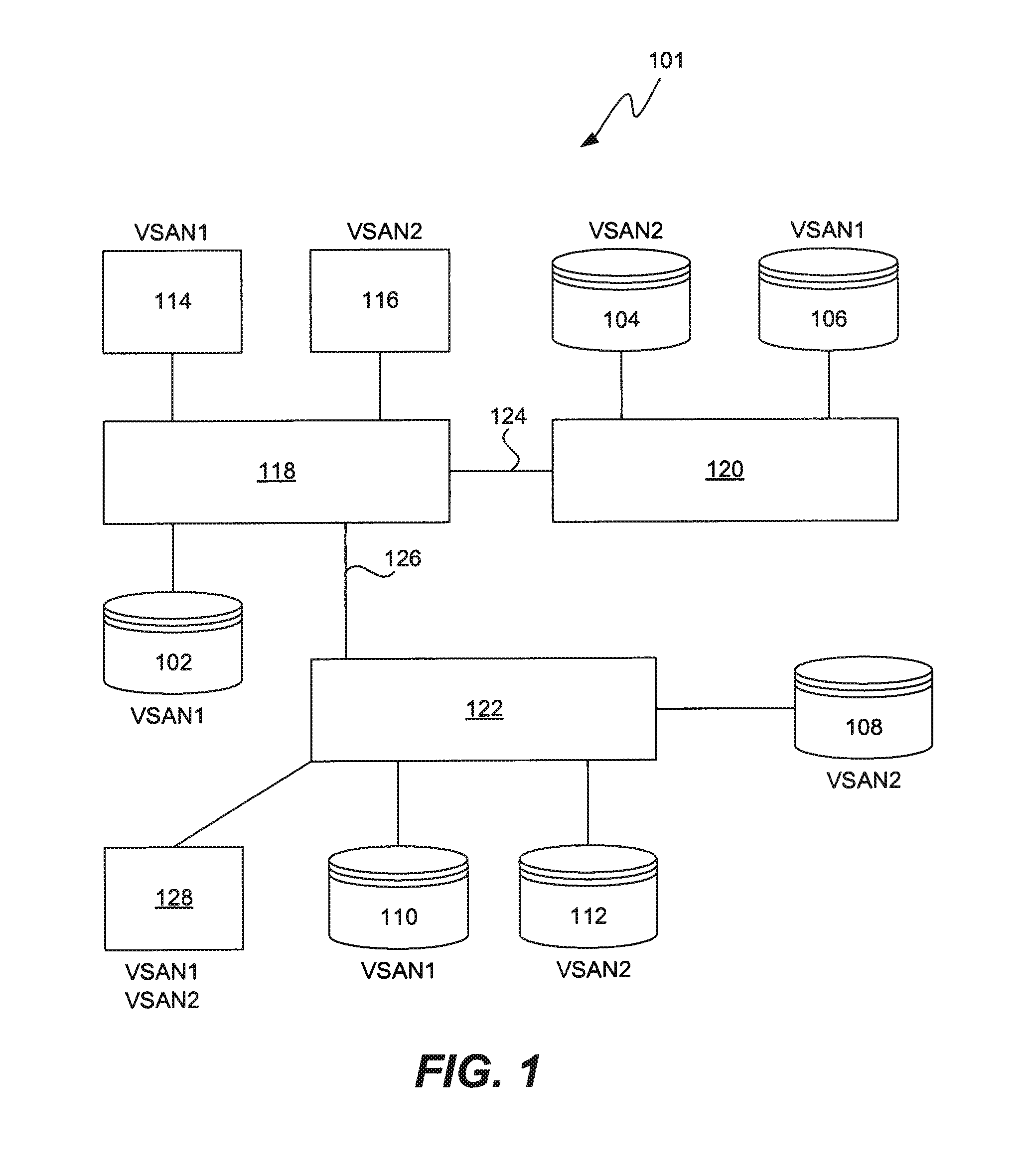

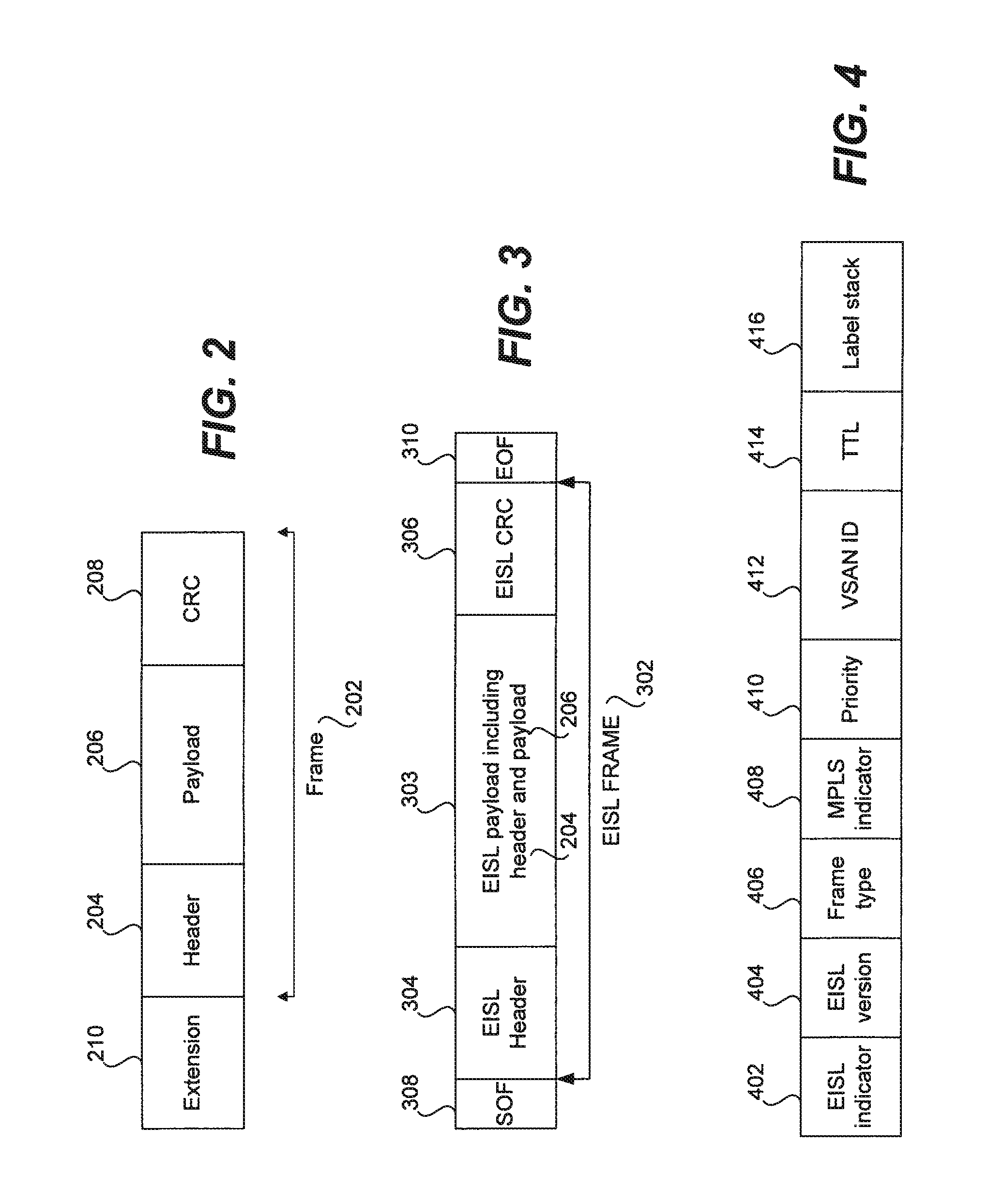

Methods and apparatus for encapsulating a packet or frame for transmission in a storage area network are disclosed. A packet or frame compatible with a standard protocol employed in the storage area network is received or generated. The packet or frame is then encapsulated with a virtual storage area network identifier. The packet or frame may further be encapsulated with at least one of a TTL value, MPLS information, and a type of traffic to be carried by the packet or frame. For instance, the type of traffic to be carried by the packet or frame may include Ethernet, Fibre Channel, and Infiniband. Once encapsulated, the encapsulated packet or frame is sent over the storage area network. For instance, the encapsulated packet or frame may be generated as well as transmitted by a switch over an inter-switch link in the storage area network.

Owner:CISCO TECH INC

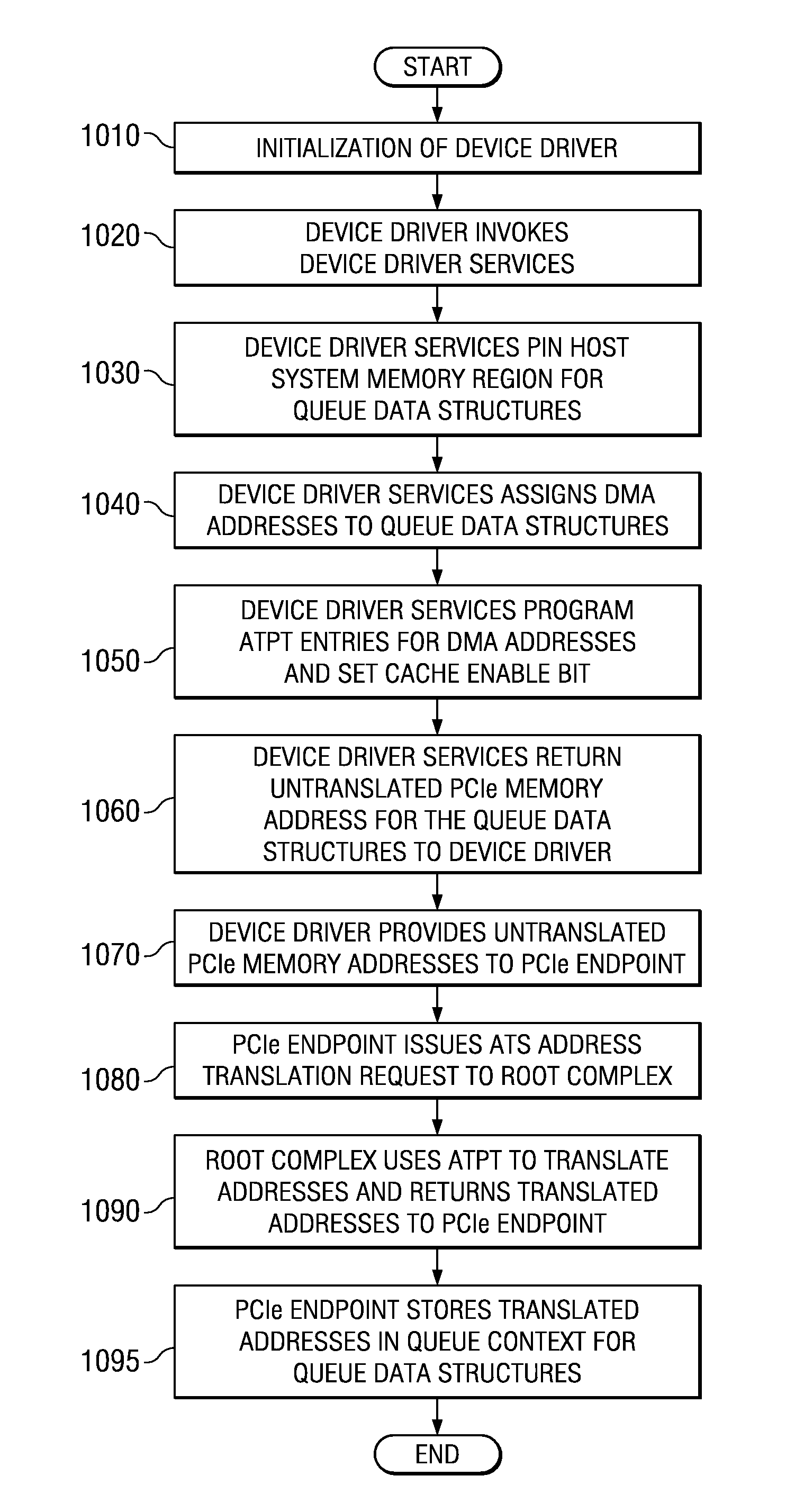

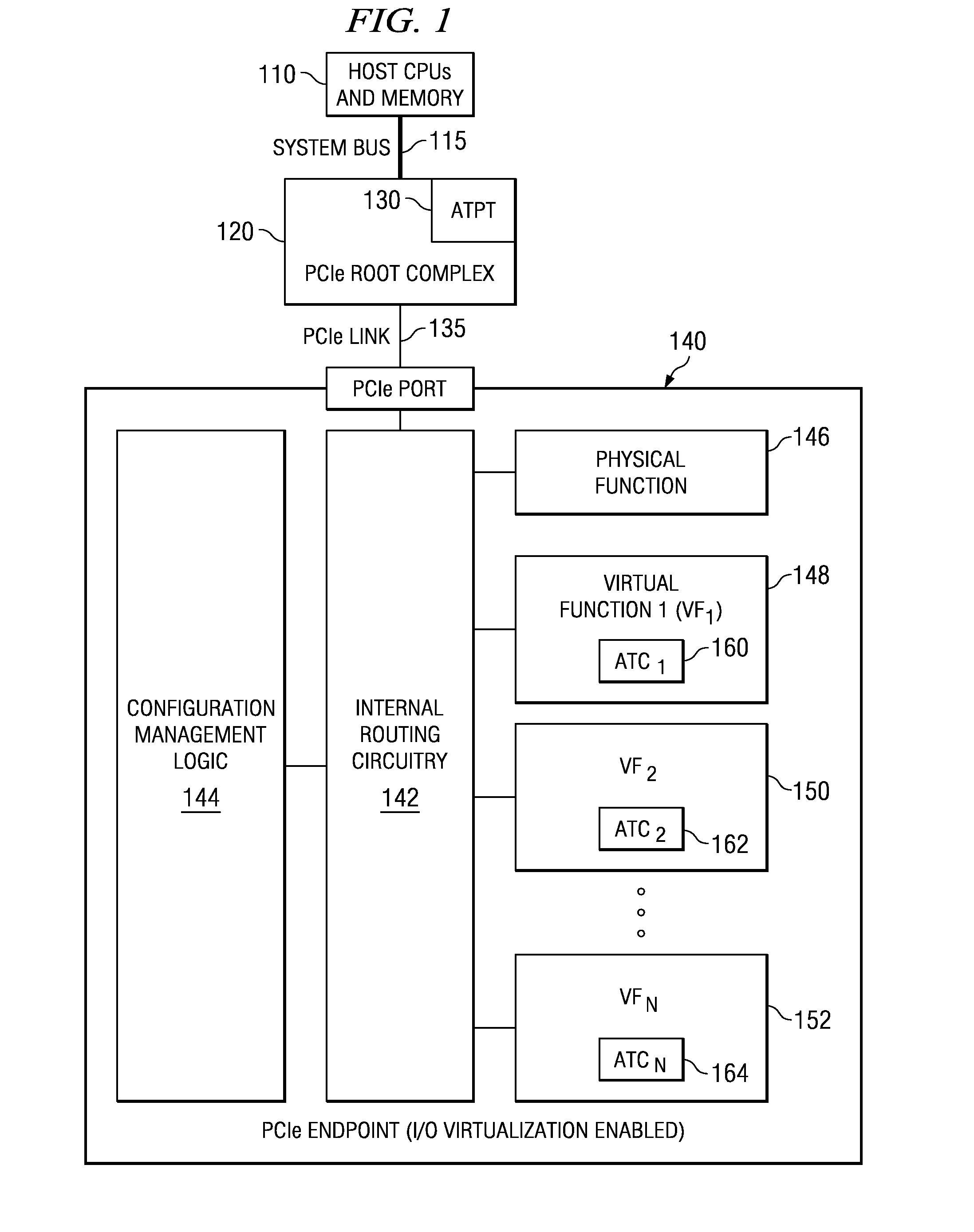

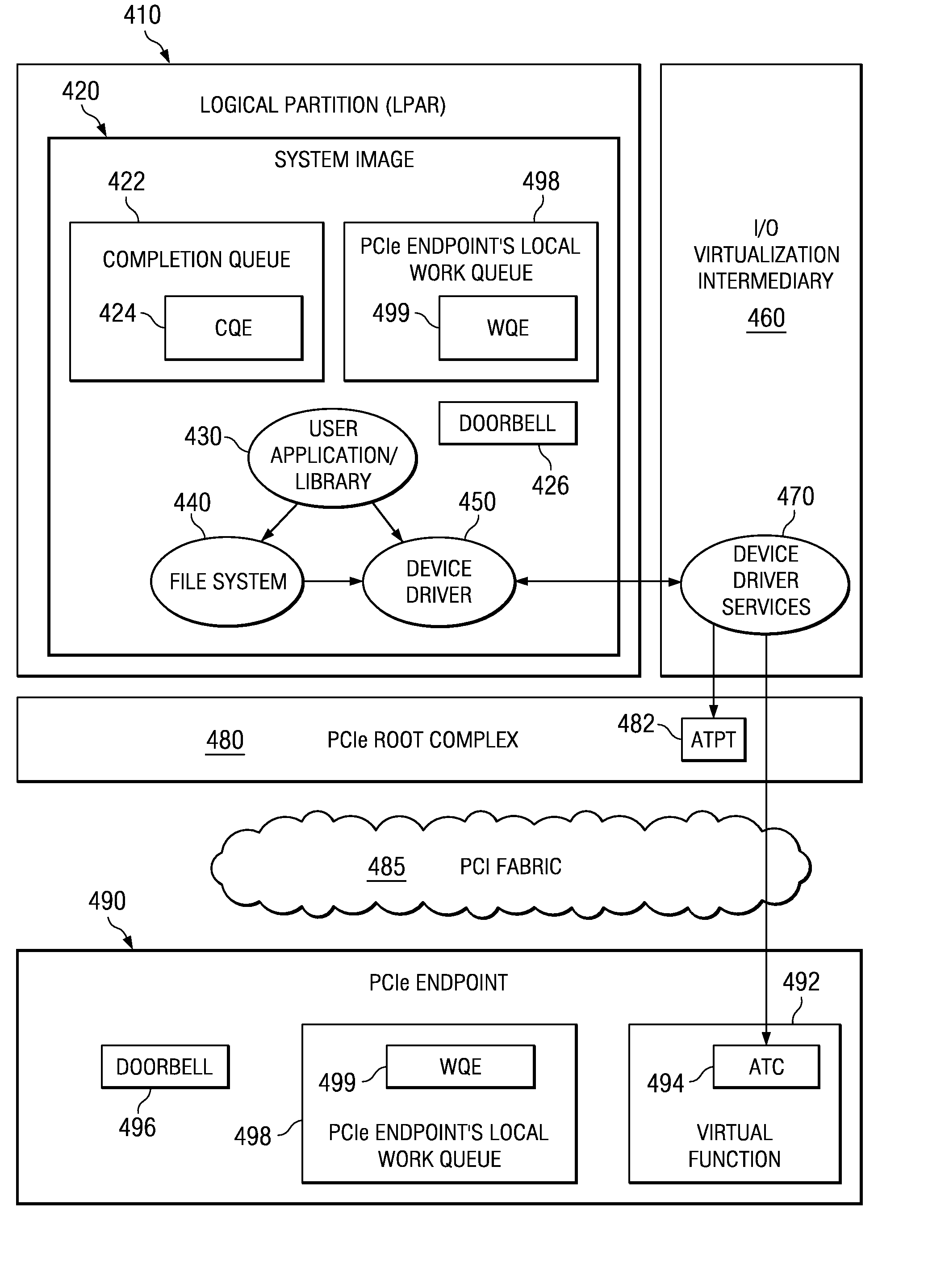

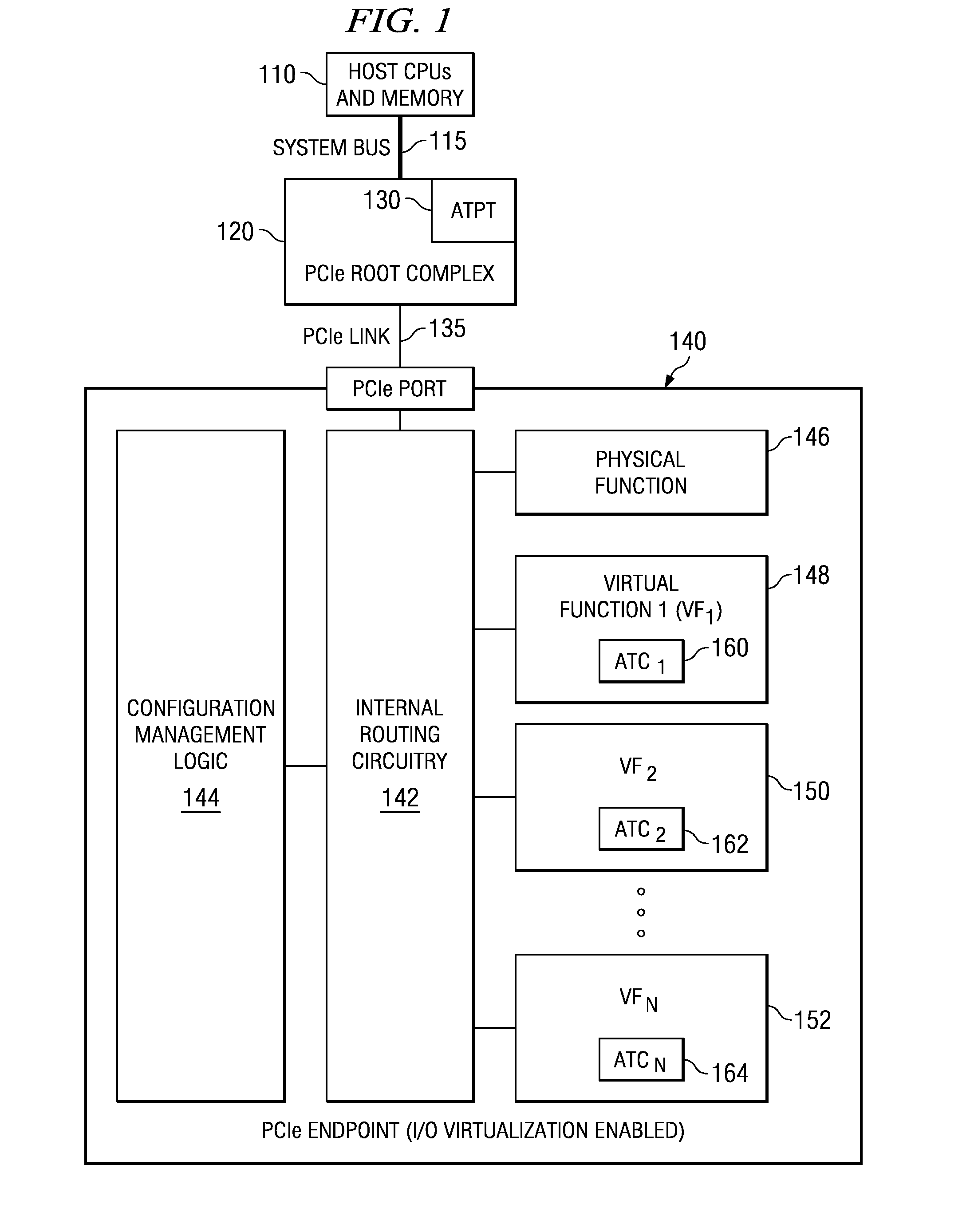

Apparatus and Method for Communicating with a Memory Registration Enabled Adapter Using Cached Address Translations

InactiveUS20080091915A1Lower latencyReduce DMA read latencyComputer security arrangementsMemory systemsRoot complexImage registration

An apparatus and method for communicating with a memory registration enabled adapter, such as an InfiniBand™ host channel adapter, are provided. With the apparatus and method, device driver services may be invoked by a device driver for initializing address translation entries in an address translation data structure of a root complex. An address of a device driver data buffer data structure and registration modifiers may be passed by the device driver to the device driver services. The device driver services may create address translation data structure entries in the address translation data structure associated with the root complex and memory registration (MR) address translation entries in a MR address translation data structure of the adapter. The MR address translation data structure may then be used with I / O operations to bypass the address translation data structure associated with the root complex.

Owner:IBM CORP

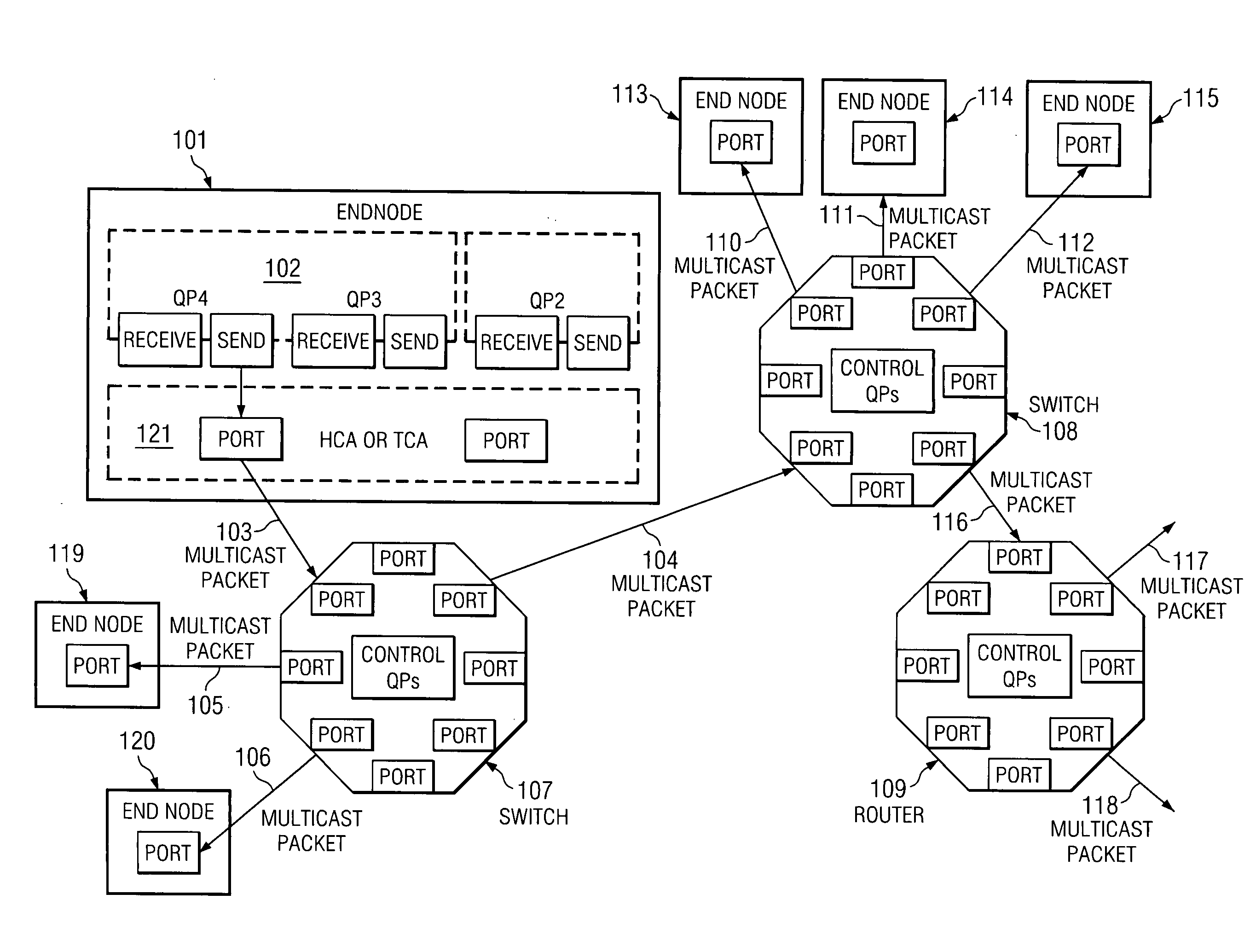

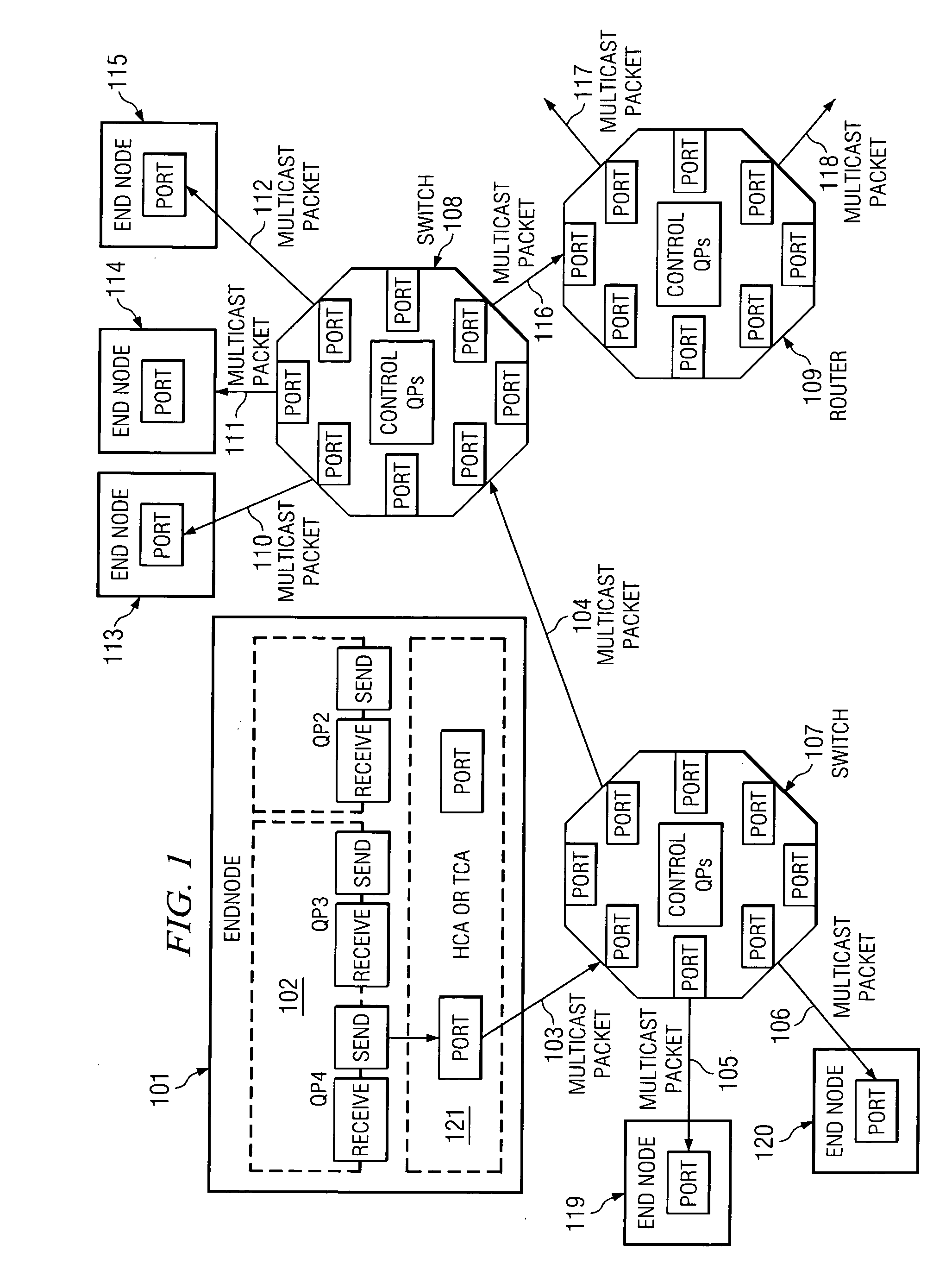

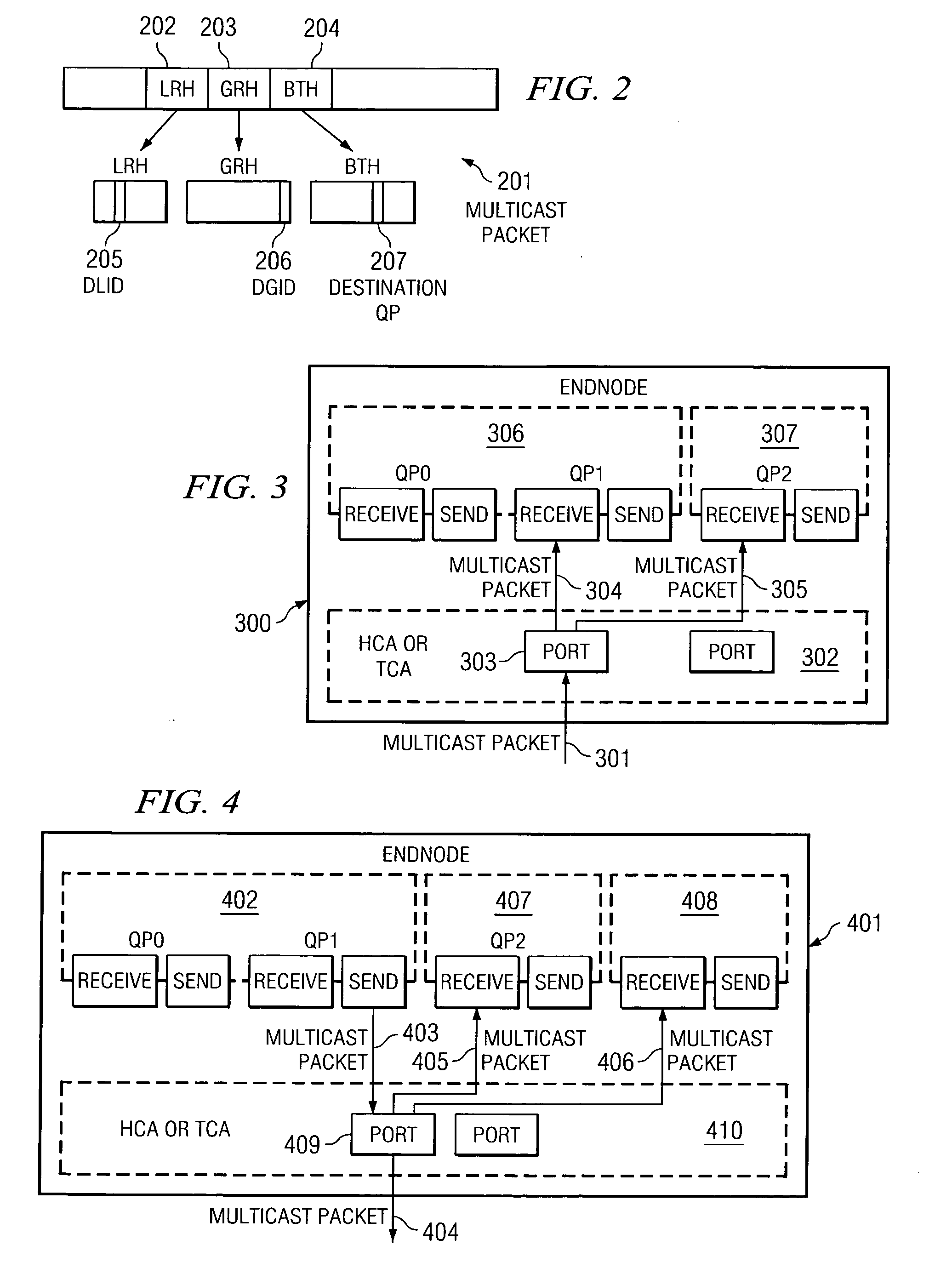

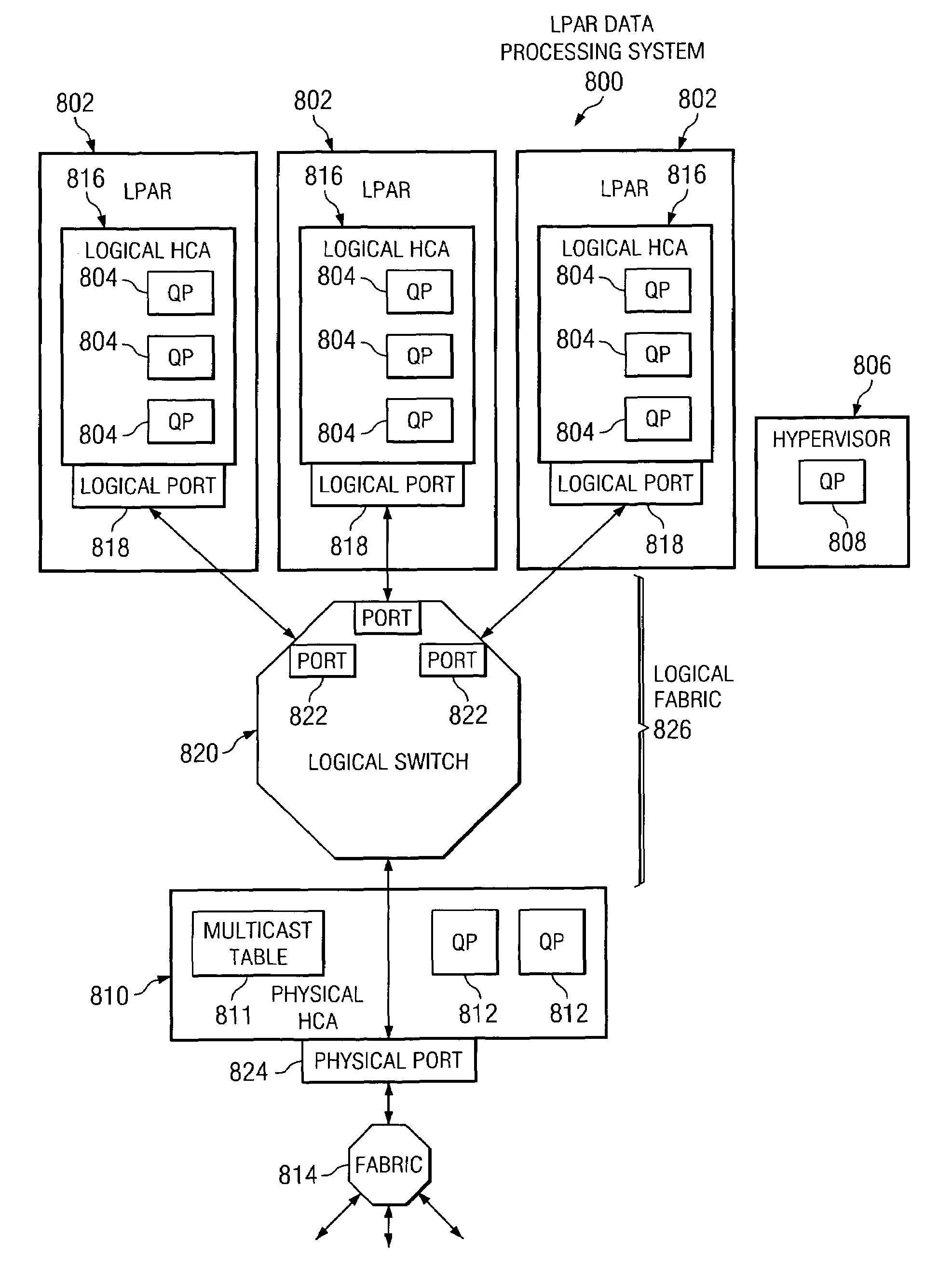

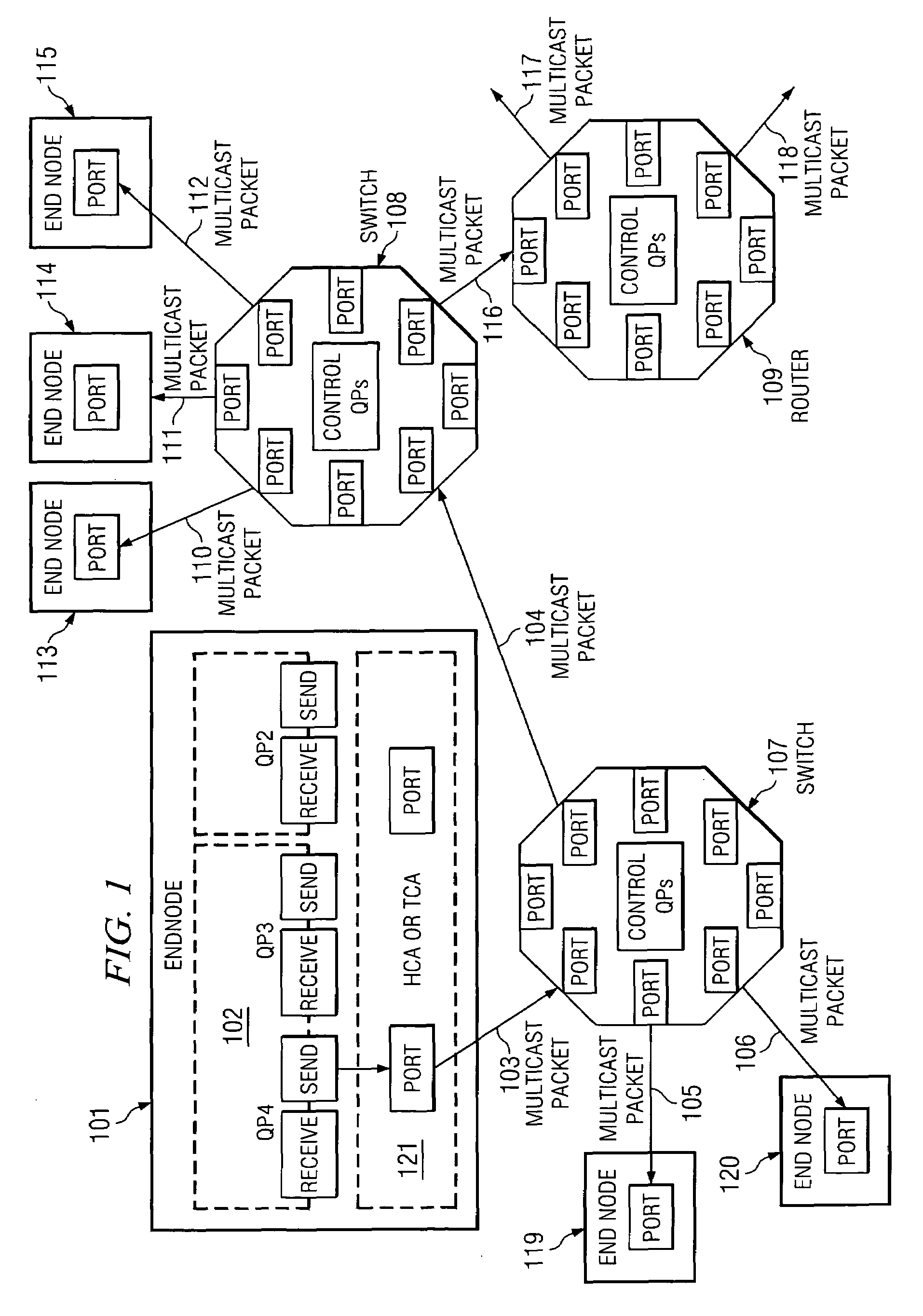

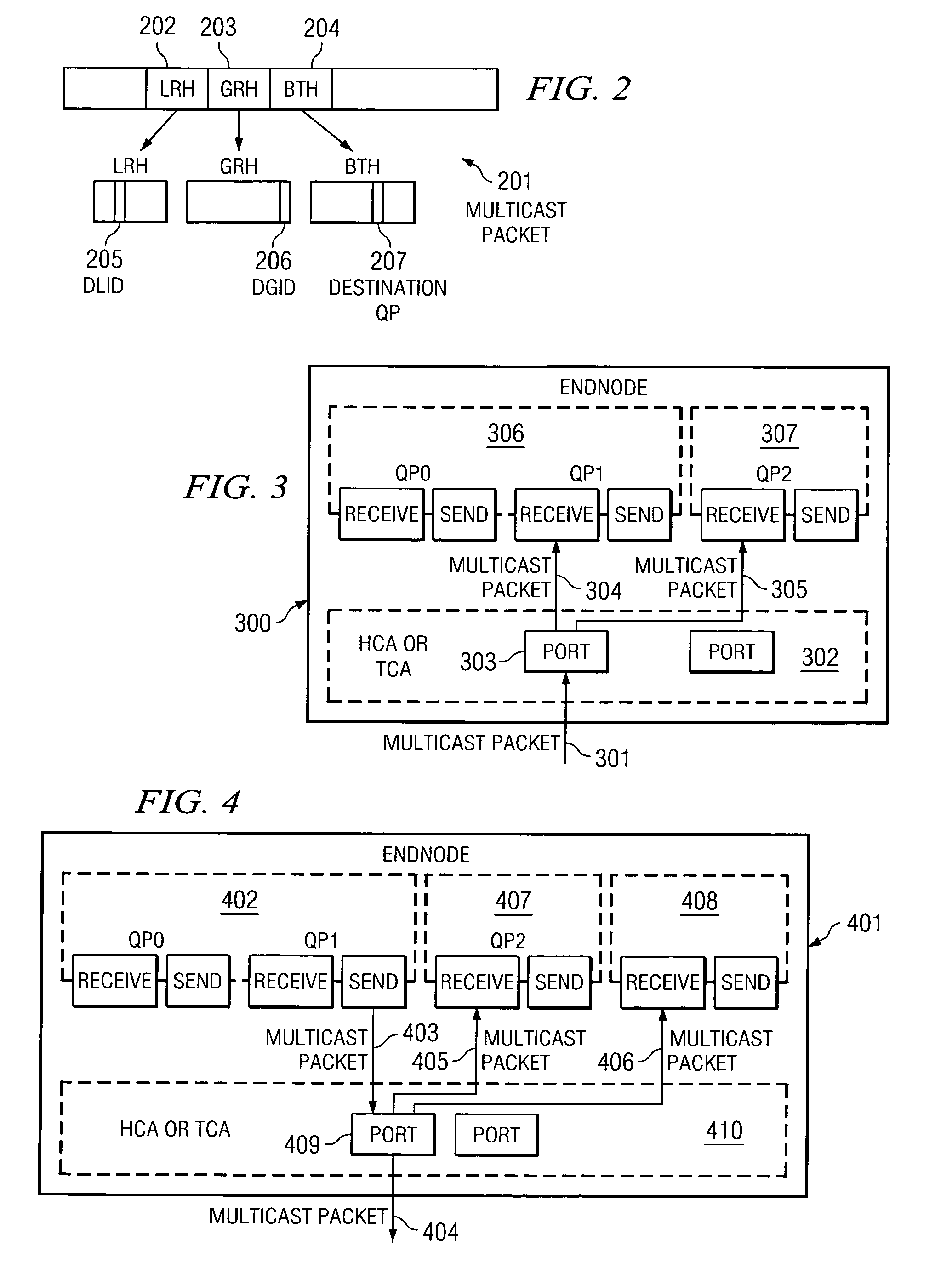

Infiniband multicast operation in an LPAR environment

InactiveUS20050144313A1Special service provision for substationData switching by path configurationData treatmentHandling system

A method, computer program product, and data processing system for providing system-area network (SAN) multicasting functionality in a logically partitioned (LPAR) data processing system in which a channel adapter is shared among a plurality of logical partitions is disclosed. A preferred embodiment of the present invention allows LPAR “hypervisor” firmware to assume the responsibility for multicast protocol handling and distribution of packets among logical partitions.

Owner:IBM CORP

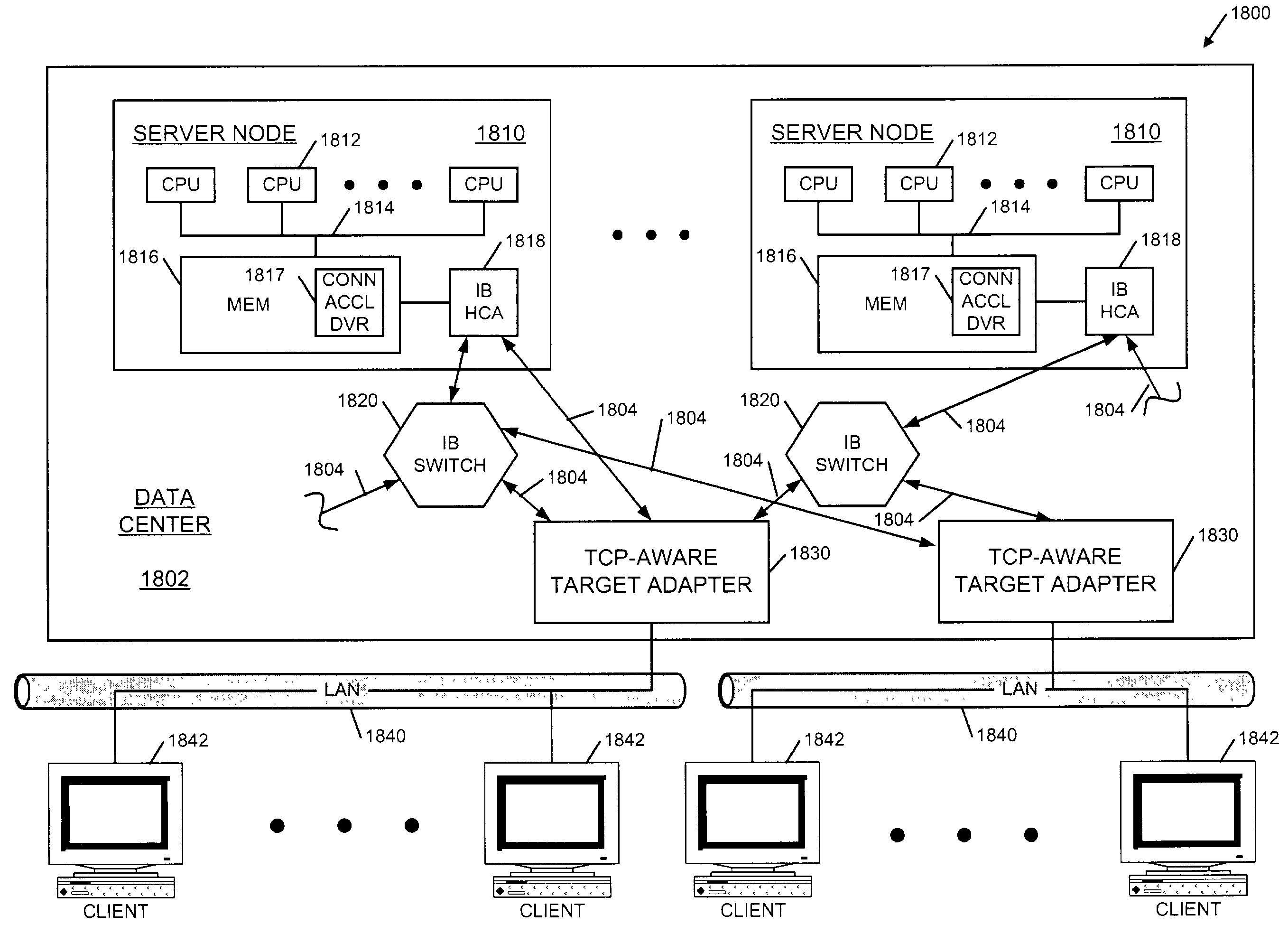

Infiniband TM work queue to TCP/IP translation

InactiveUS7149817B2Increase capacityFast data transferMultiple digital computer combinationsMemory systemsDirect memory accessIp processing

A TCP-aware target adapter for accelerating TCP / IP connections between clients and servers, where the servers are interconnected over an Infiniband™ fabric and the clients are interconnected over a TCP / IP-based network. The TCP-aware target adapter includes an accelerated connection processor and a target channel adapter. The accelerated connection processor bridges TCP / IP transactions between the clients and the servers. The accelerated connection processor accelerates the TCP / IP connections prescribing Infiniband remote direct memory access operations to retrieve / provide transaction data from / to the servers. The target channel adapter is coupled to the accelerated connection processor. The target channel adapter supports Infiniband operations with the servers, including execution of the remote direct memory access operations to retrieve / provide the transaction data. The TCP / IP connections are accelerated by offloading TCP / IP processing otherwise performed by the servers to retrieve / provide said transaction data.

Owner:INTEL CORP

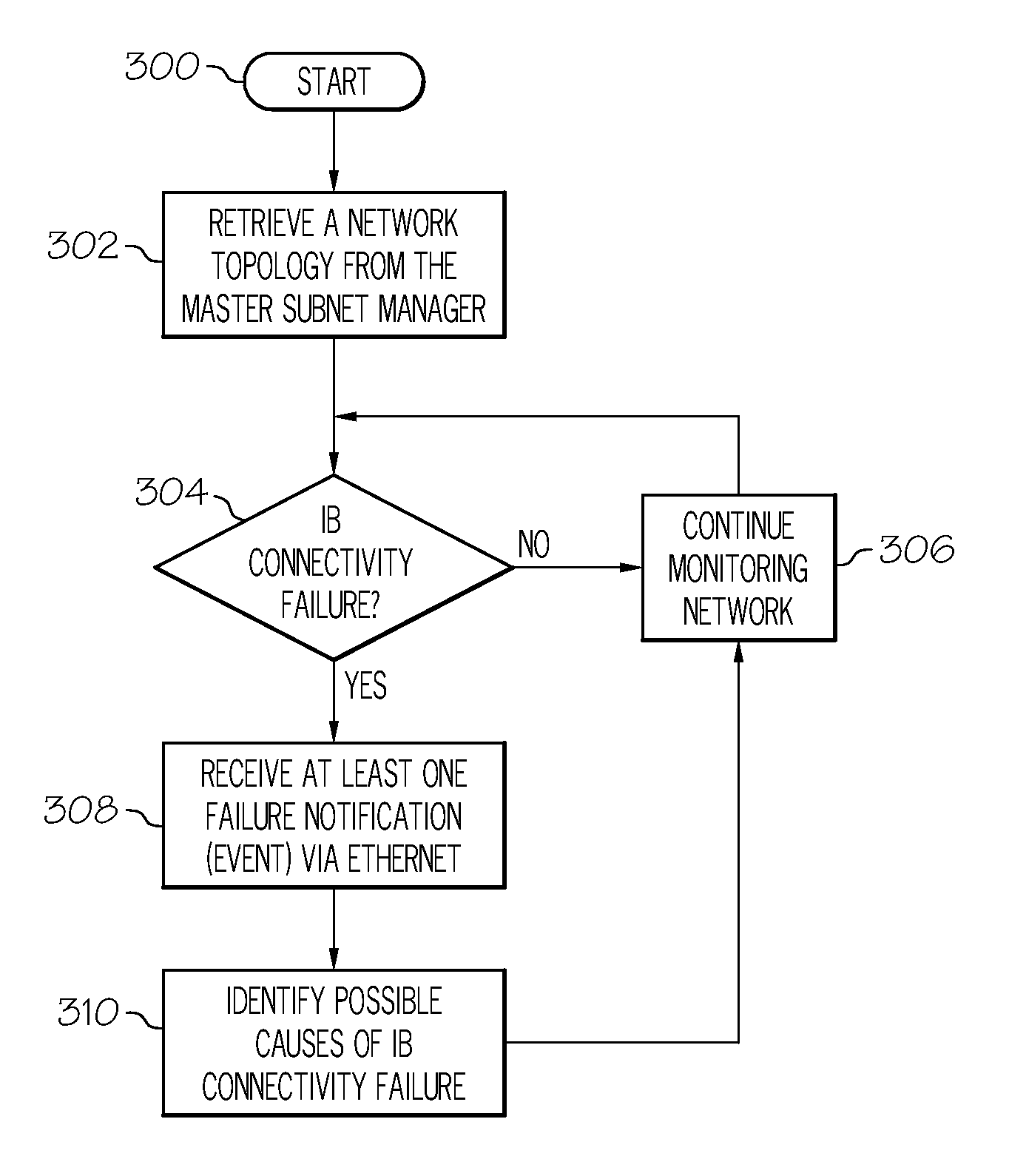

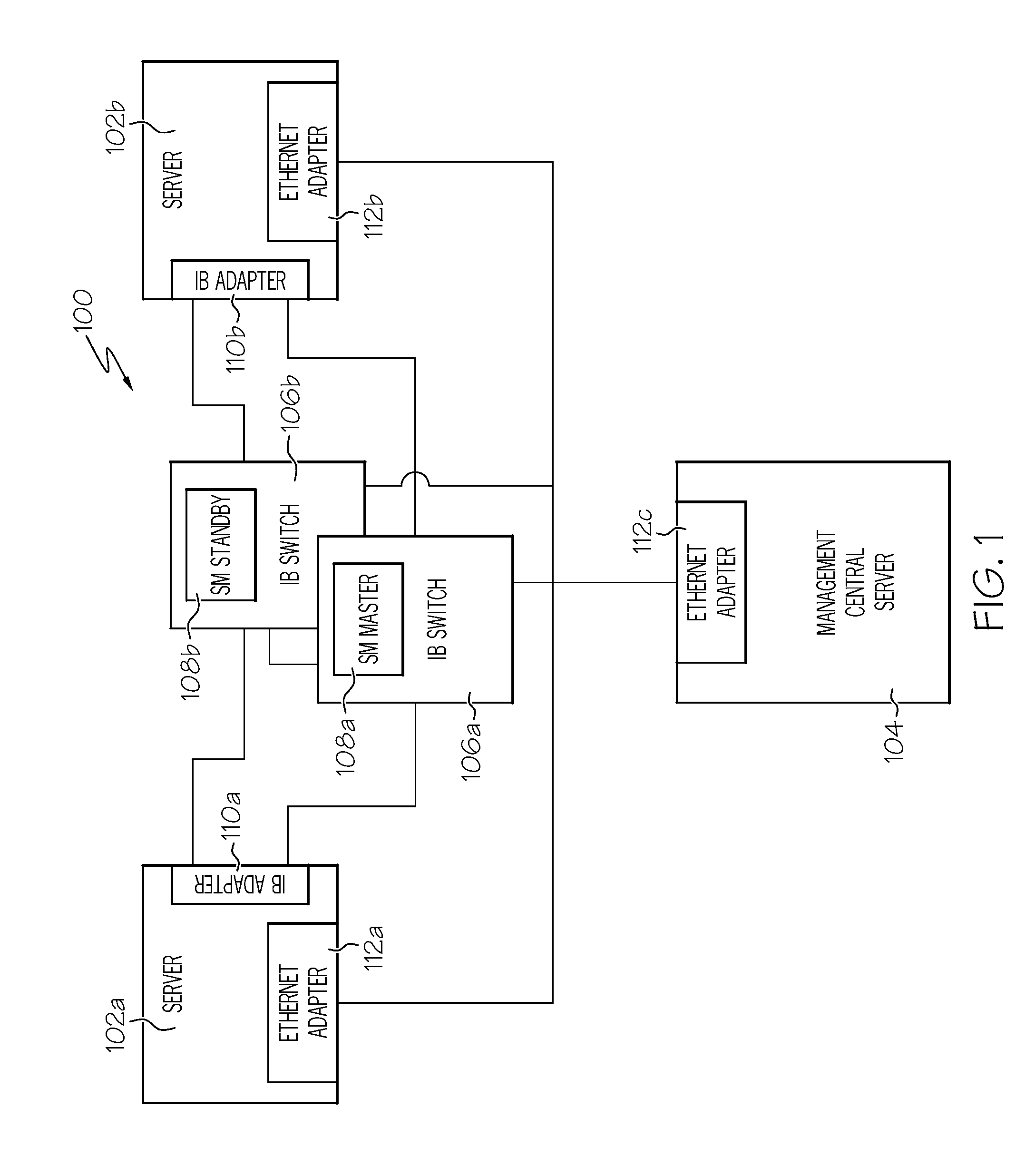

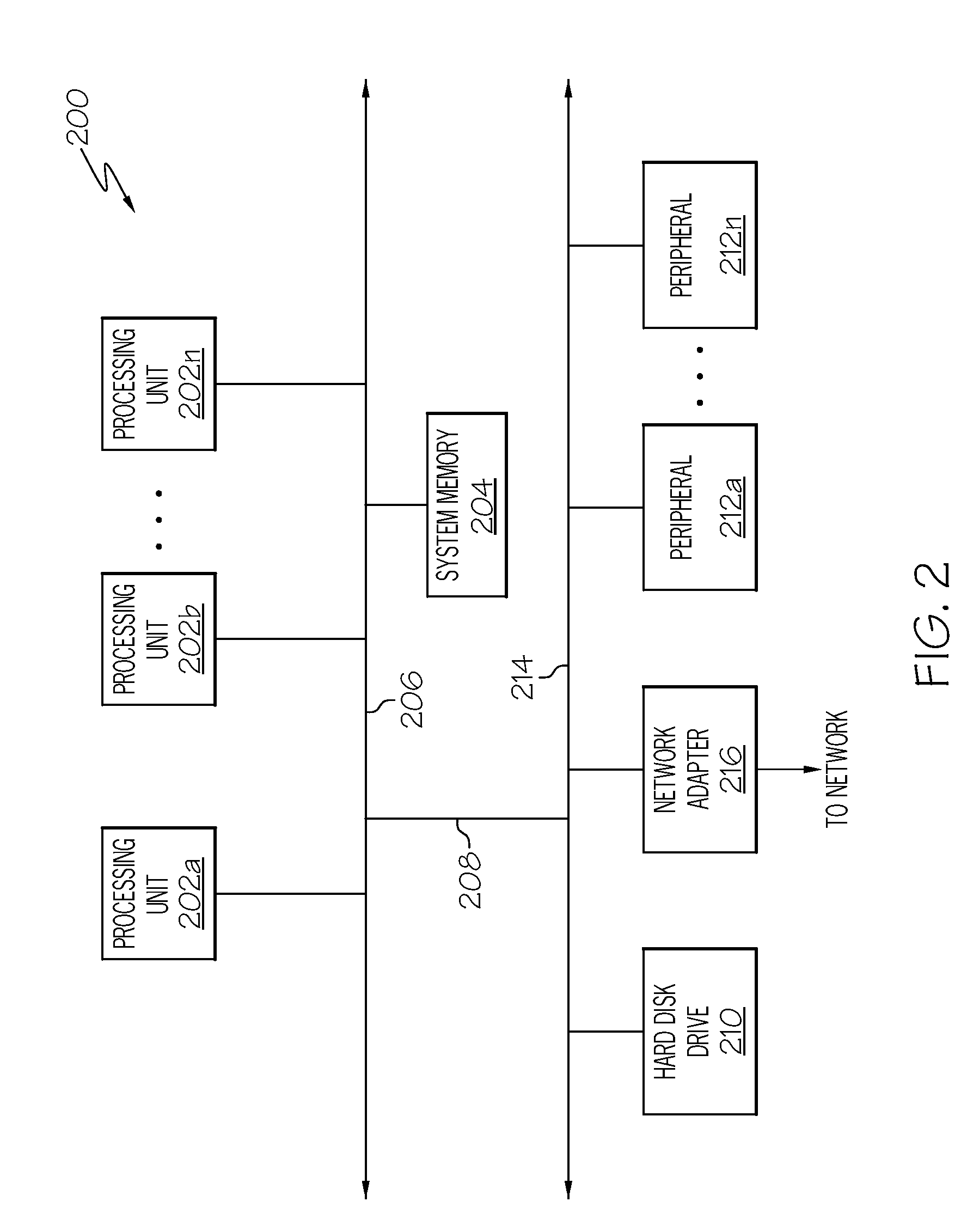

System and method for implementing an infiniband error log analysis model to facilitate faster problem isolation and repair

InactiveUS20080080384A1Error preventionFrequency-division multiplex detailsNetwork topologyNetwork error

A system, method, and computer-readable medium for detecting errors on a network. According to a preferred embodiment of the present invention, a network error manager retrieves a network topology from a master subnet manager, wherein the network includes a collection of devices coupled by a first interconnect type. When a connectivity failure is detected in the first interconnect type, the network error manager receives from the master subnet manager at least one event notification via a second interconnect type. An error log analysis component identifies at least one device among the collection of devices as a possible cause of the connectivity failure in the first interconnect type. The network error manager retrieves events from at least one device among the collection of devices that can influence a state of the first interconnect type.

Owner:IBM CORP

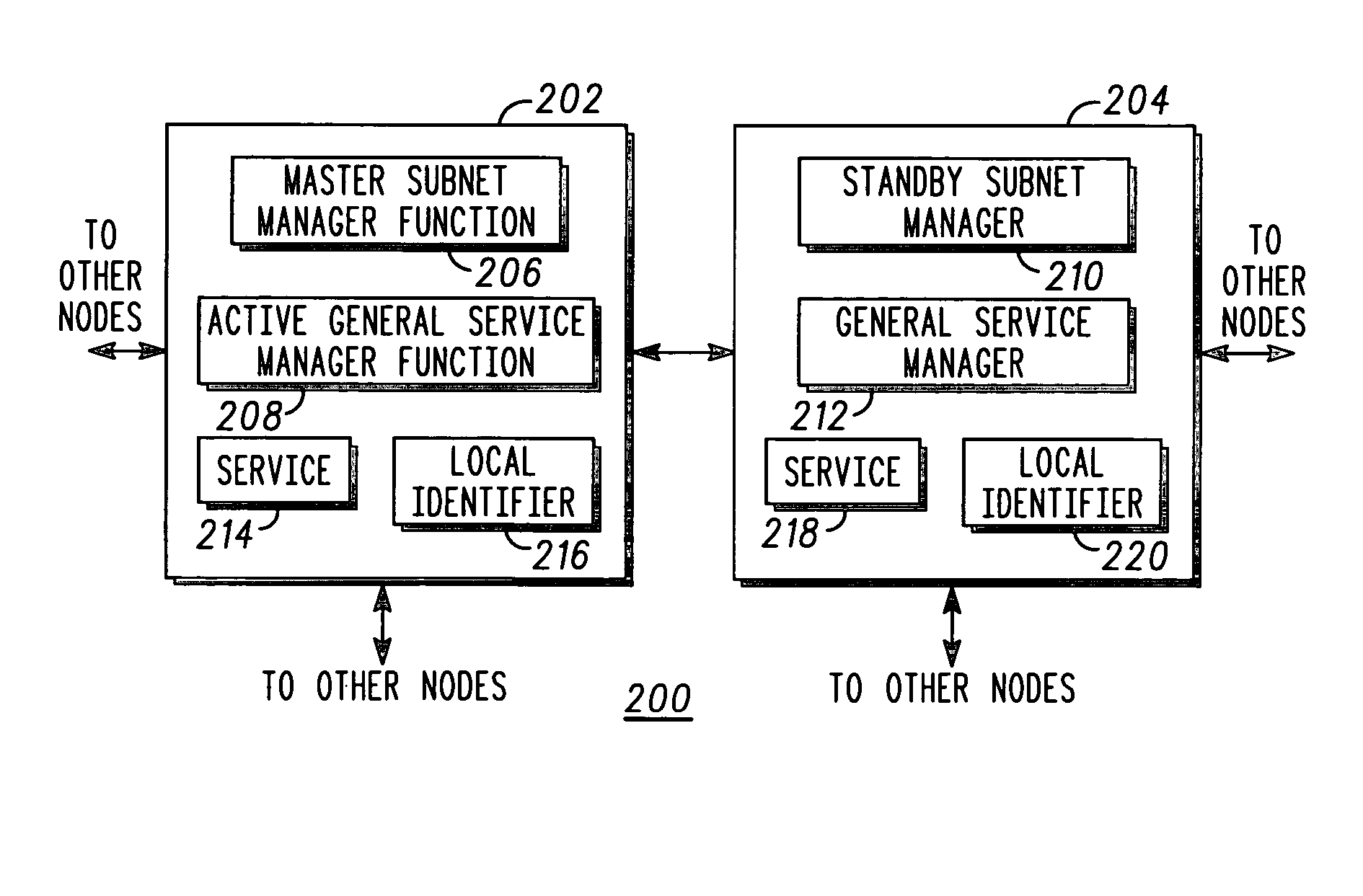

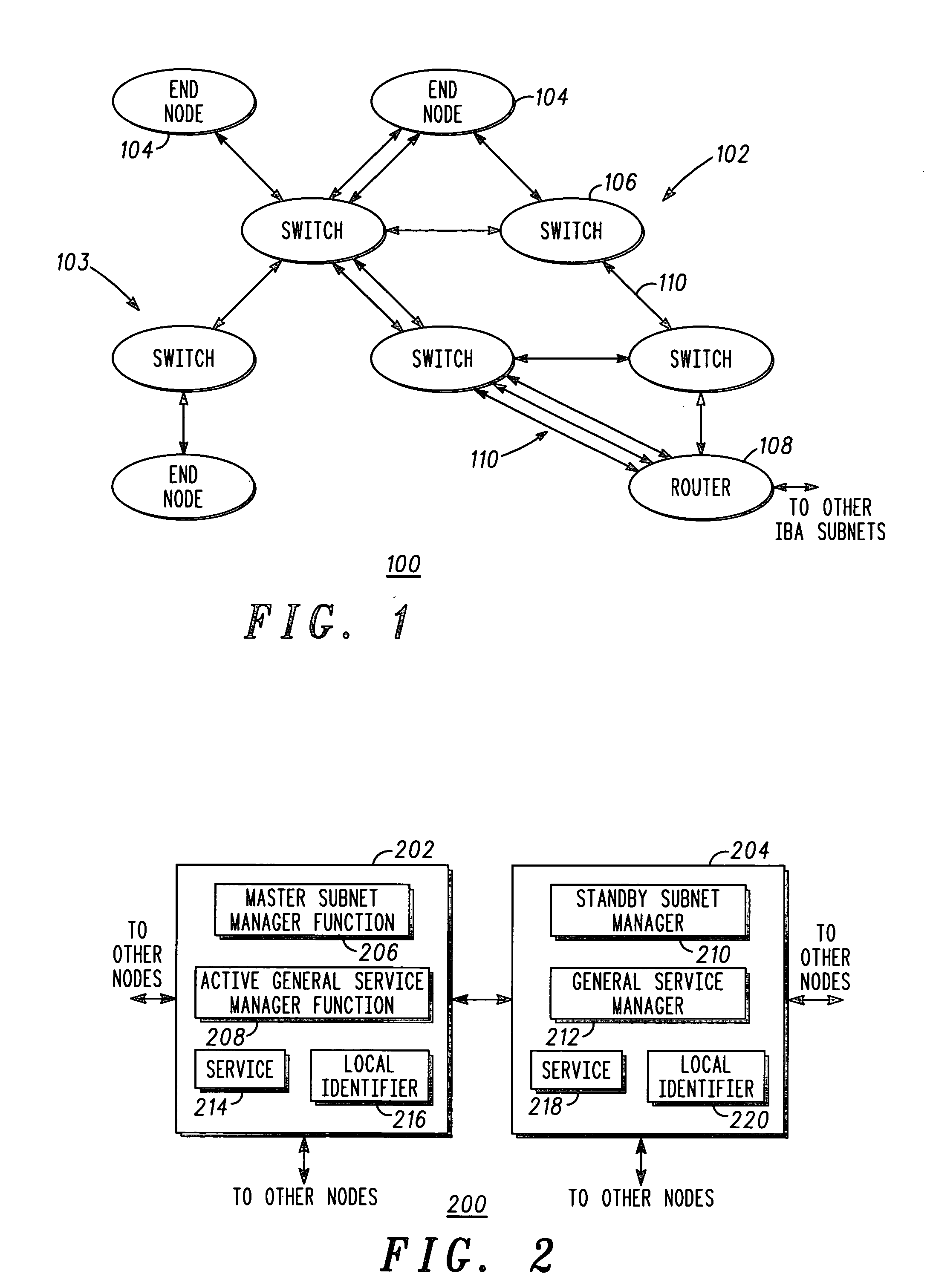

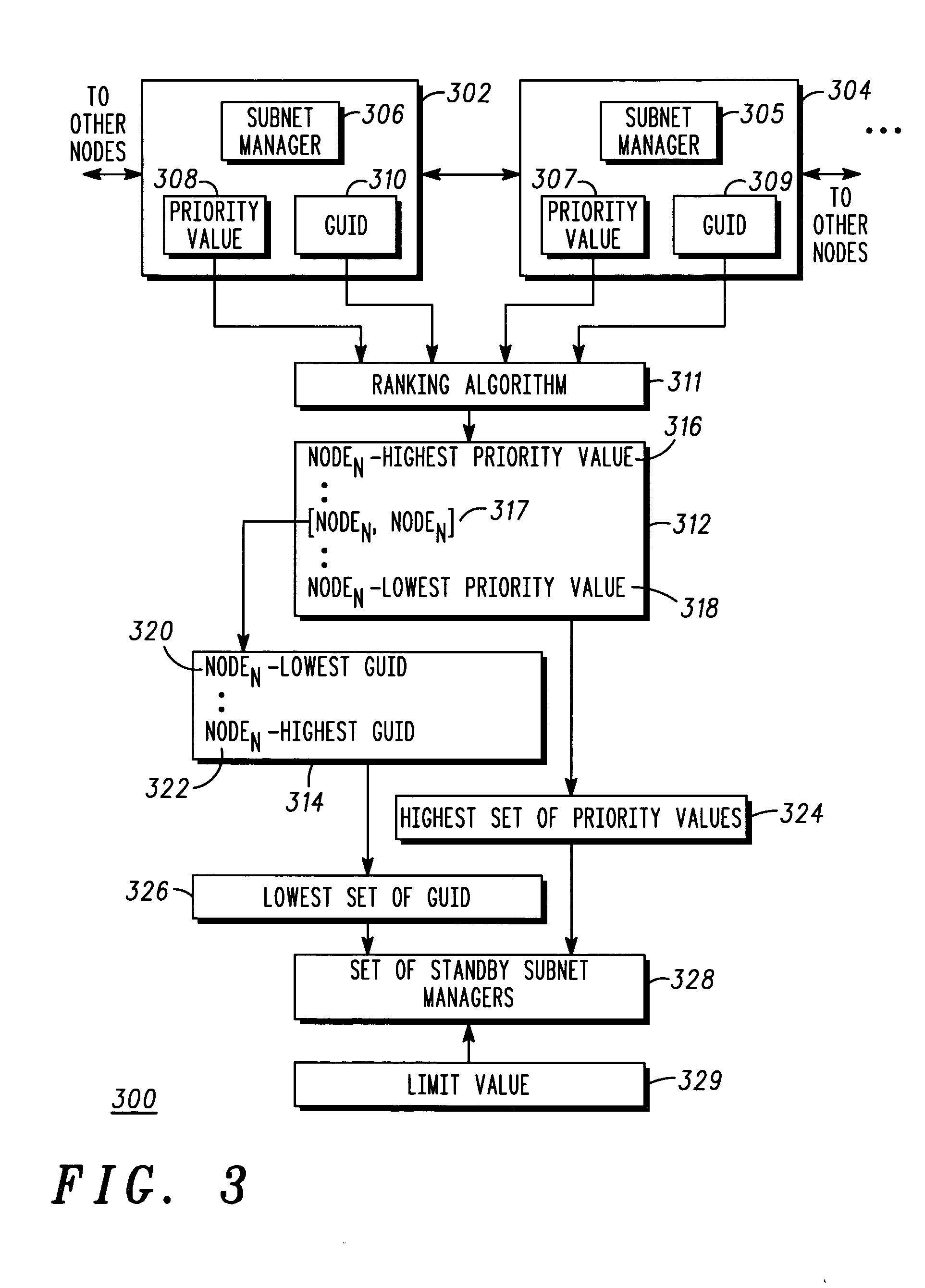

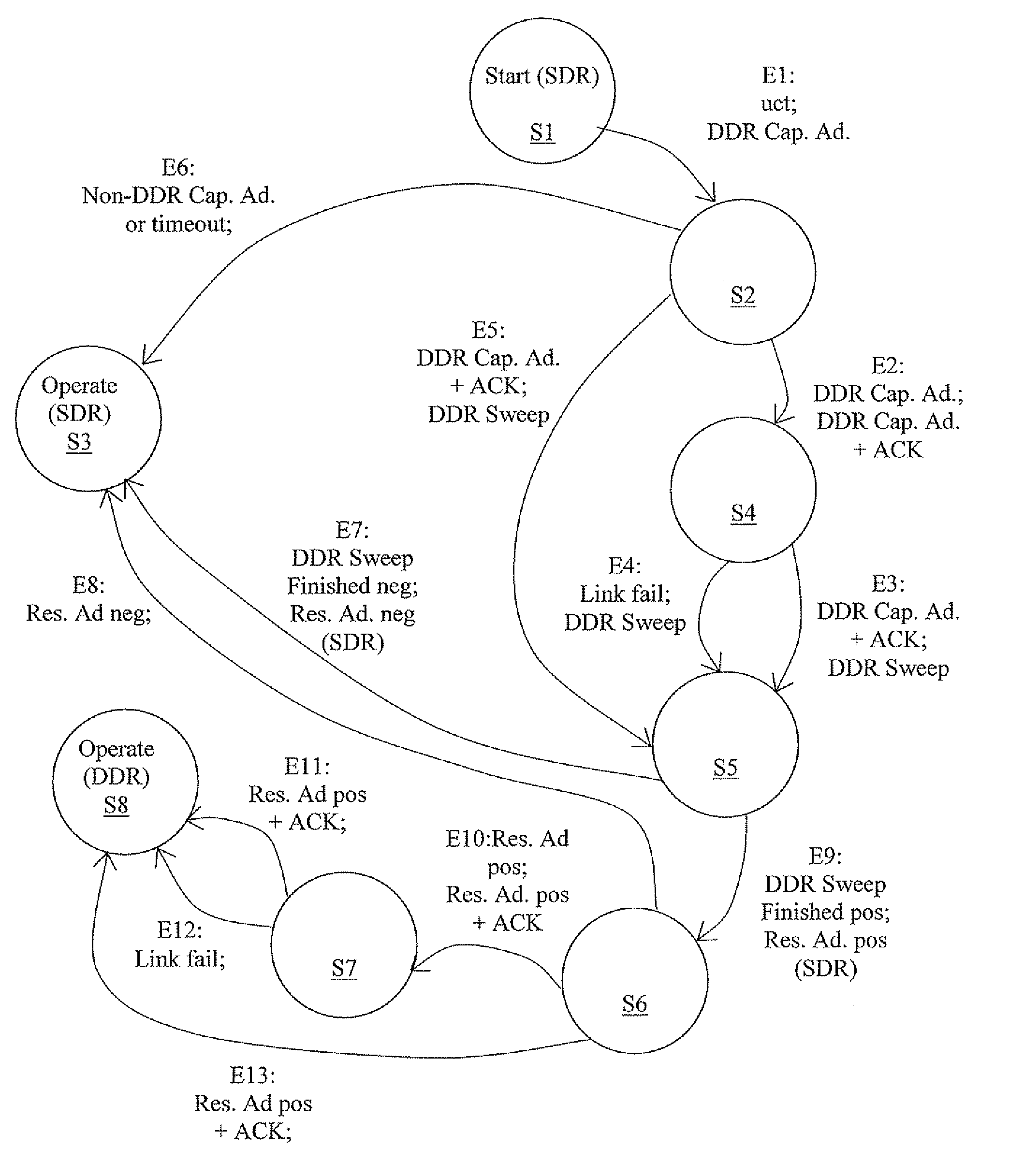

InfiniBand architecture subnet derived database elements

A method providing derived database elements (752) includes providing an InfiniBand architecture subnet (700) having a plurality of subnet managers, where one of the plurality of subnet managers assuming a master subnet manager function (706). Computing derived database elements independent of which of the plurality of subnet managers assumes the master subnet manager function.

Owner:EMERSON NETWORK POWER EMBEDDED COMPUTING

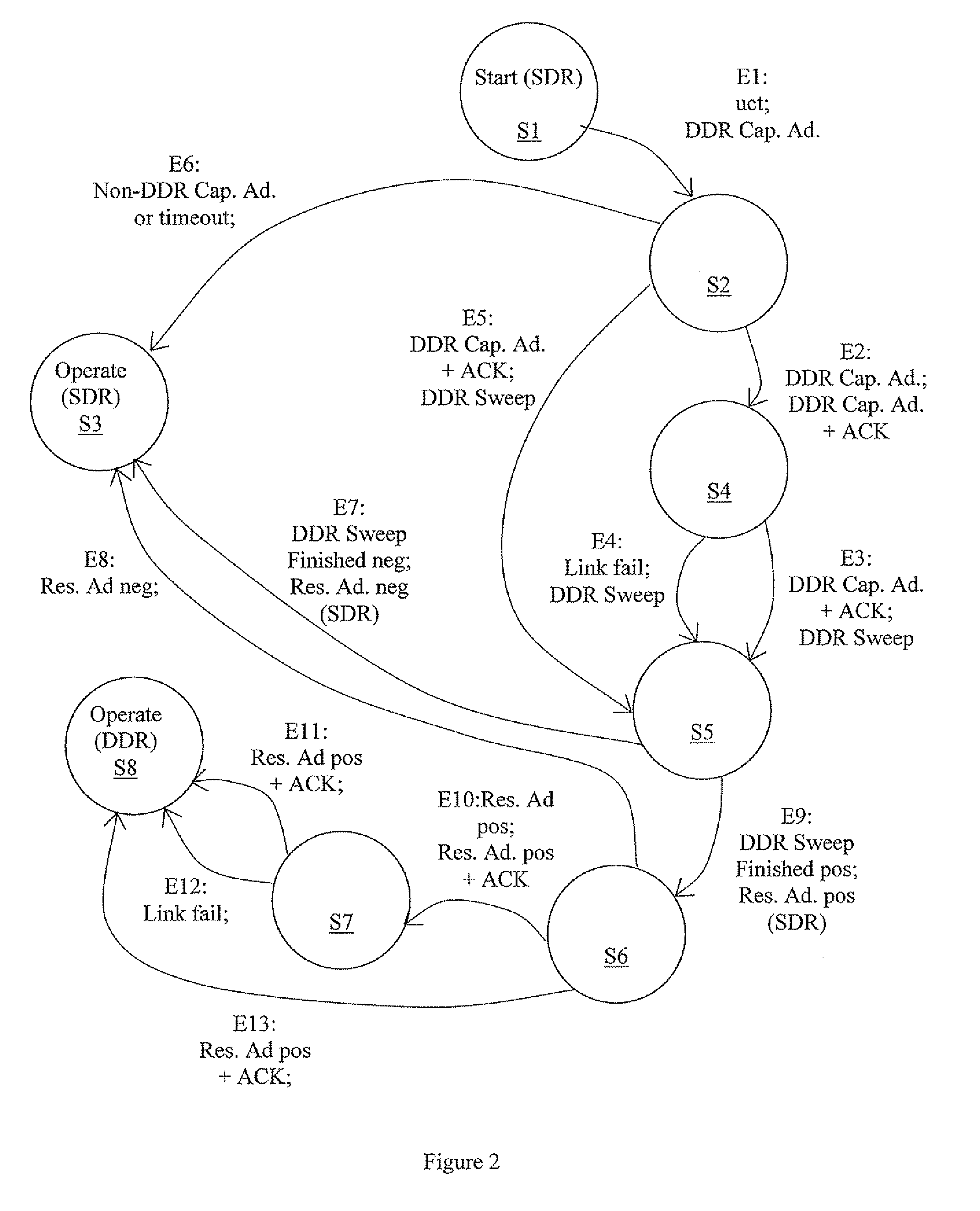

Auto-negotiation by nodes on an infiniband fabric

A method and system for digital communication wherein nodes exchange messages at a first data rate in order to coordinate testing at a second, higher data rate. After testing is completed, the nodes exchange test results at the first data rate, and if conditions are satisfactory for operation at the second data rate user data are transmitted at the second data rate. Otherwise, user data are transmitted at the first data rate.

Owner:MELLANOX TECHNOLOGIES LTD

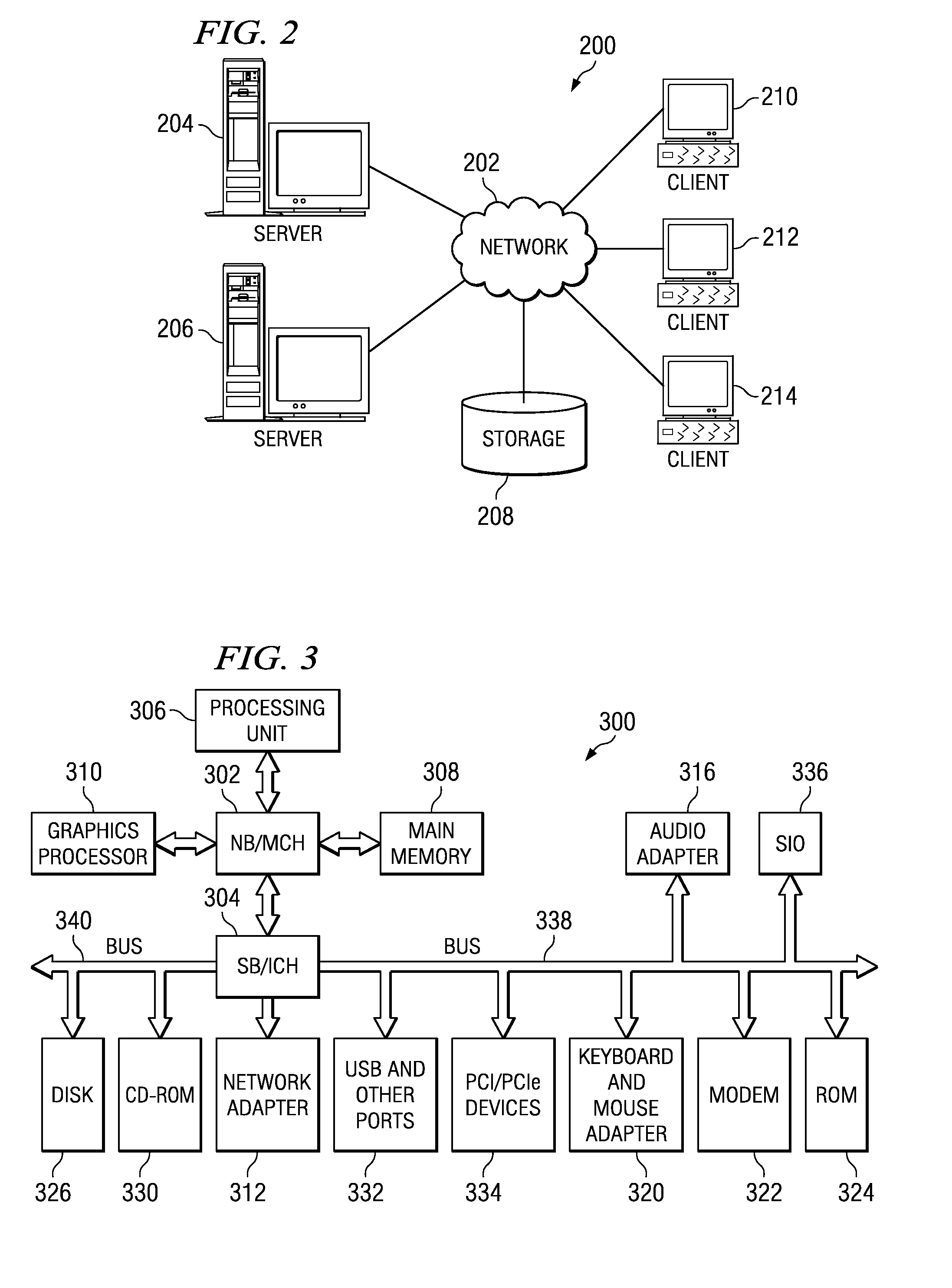

Virtual machine spanning multiple computers

ActiveUS7596654B1Reduce operating costsMemory architecture accessing/allocationMultiprogramming arrangementsOperational systemComputerized system

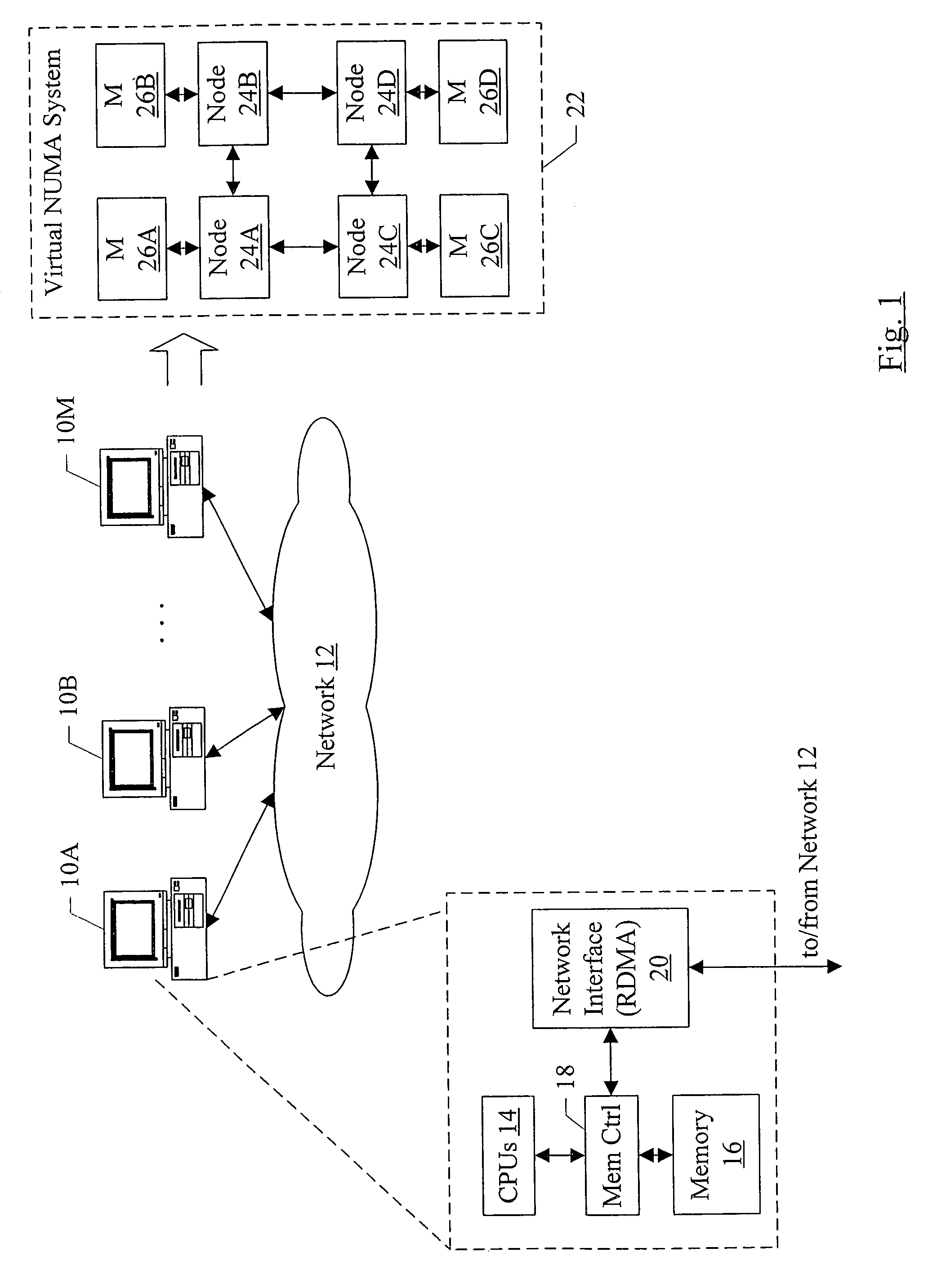

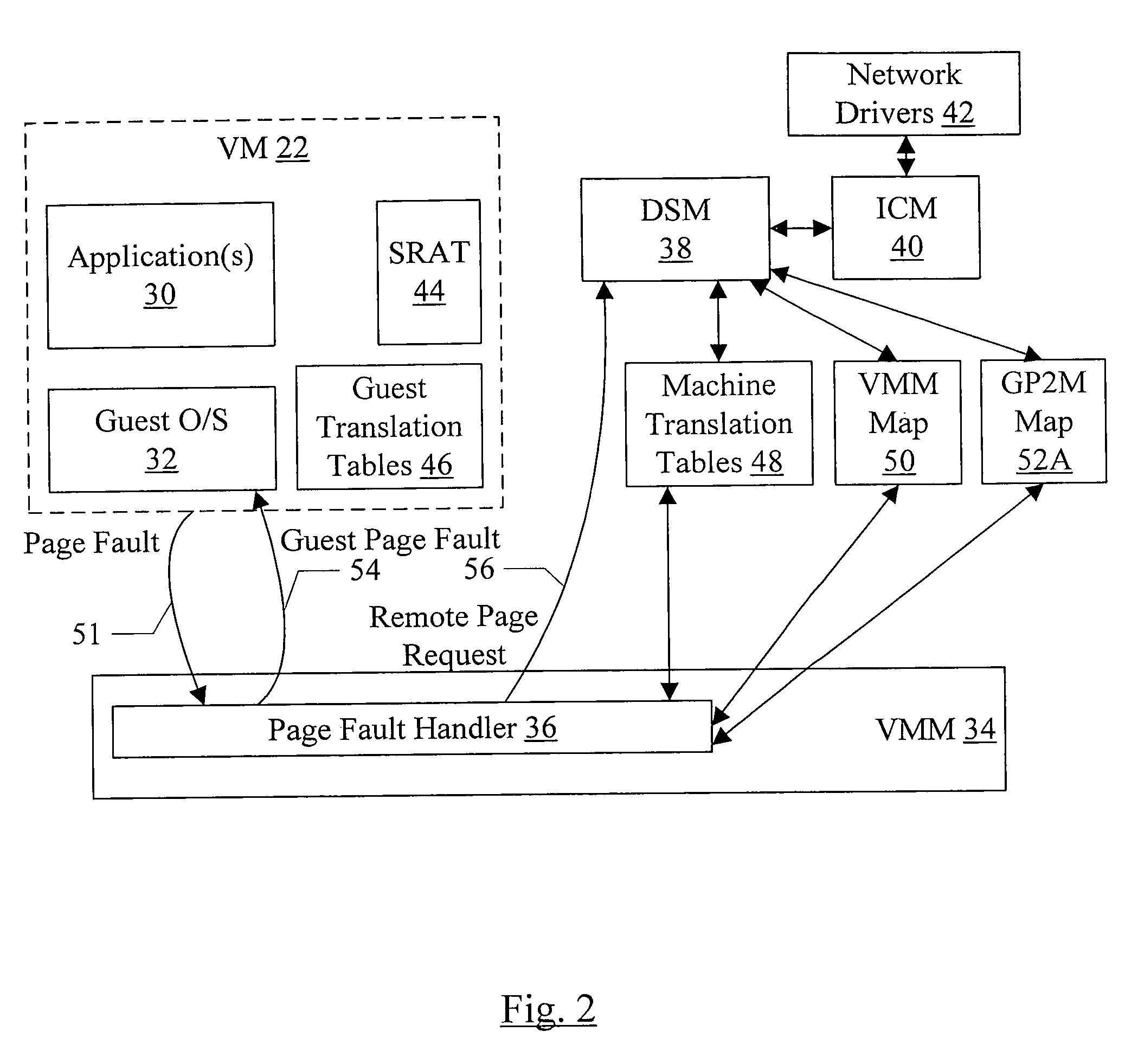

In one embodiment, a virtual NUMA system may be formed from multiple computer systems coupled to a network such as InfiniBand, Ethernet, etc. Each computer includes one or more software modules which present the resources of the computers as a virtual NUMA machine. A single instance of a guest operating system executes on the virtual NUMA machine. The guest operating system is designed to execute on a NUMA system and executes without modification on the virtual machine. The memory model of the virtual NUMA machine includes a single writer, multiple reader memory model.

Owner:SYMANTEC OPERATING CORP

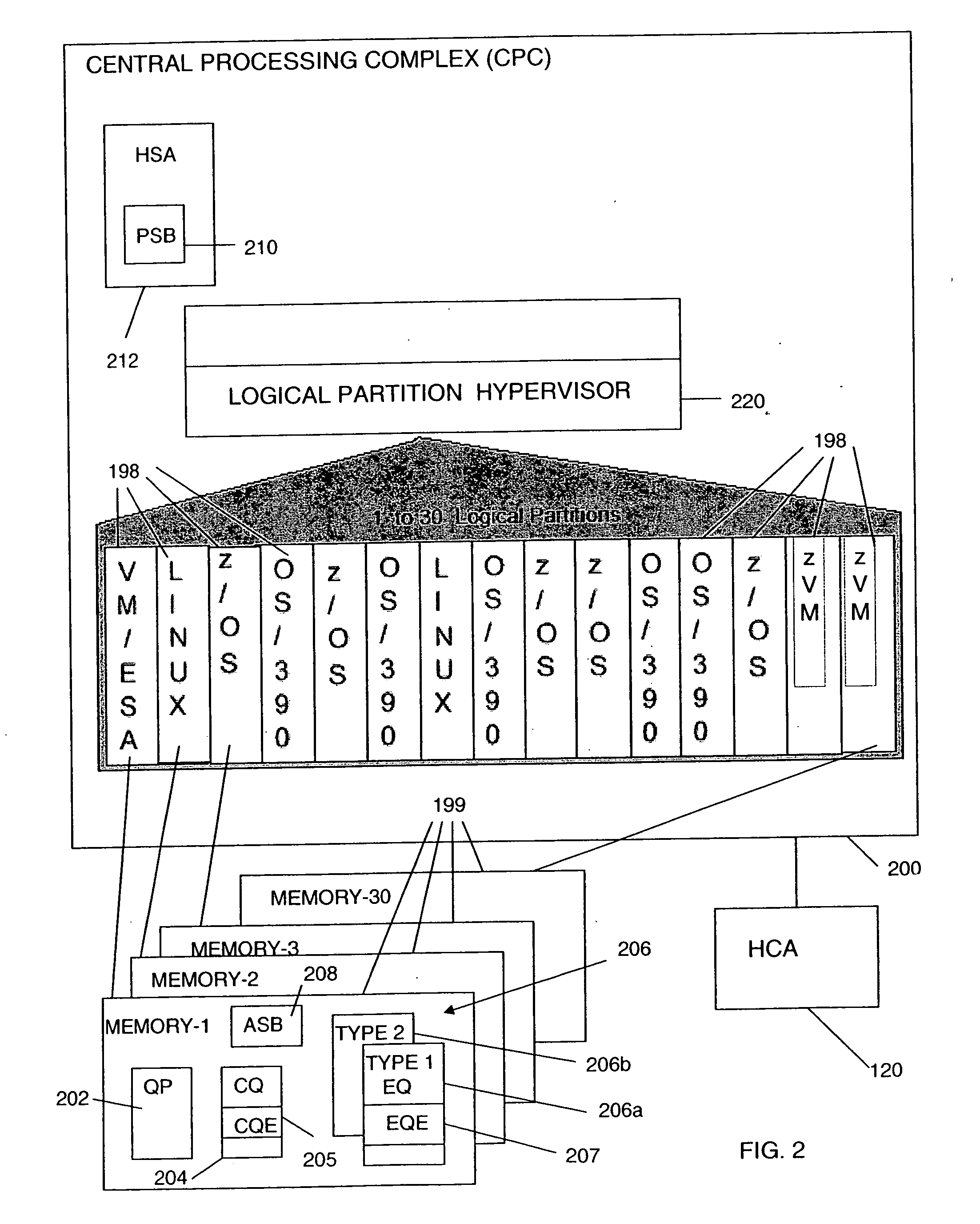

Virtualization of infiniband host channel adapter interruptions

InactiveUS20070271559A1Significant competitive advantageEfficient and cost-effective mechanismSoftware simulation/interpretation/emulationMemory systemsGrouped EventsEvent queue

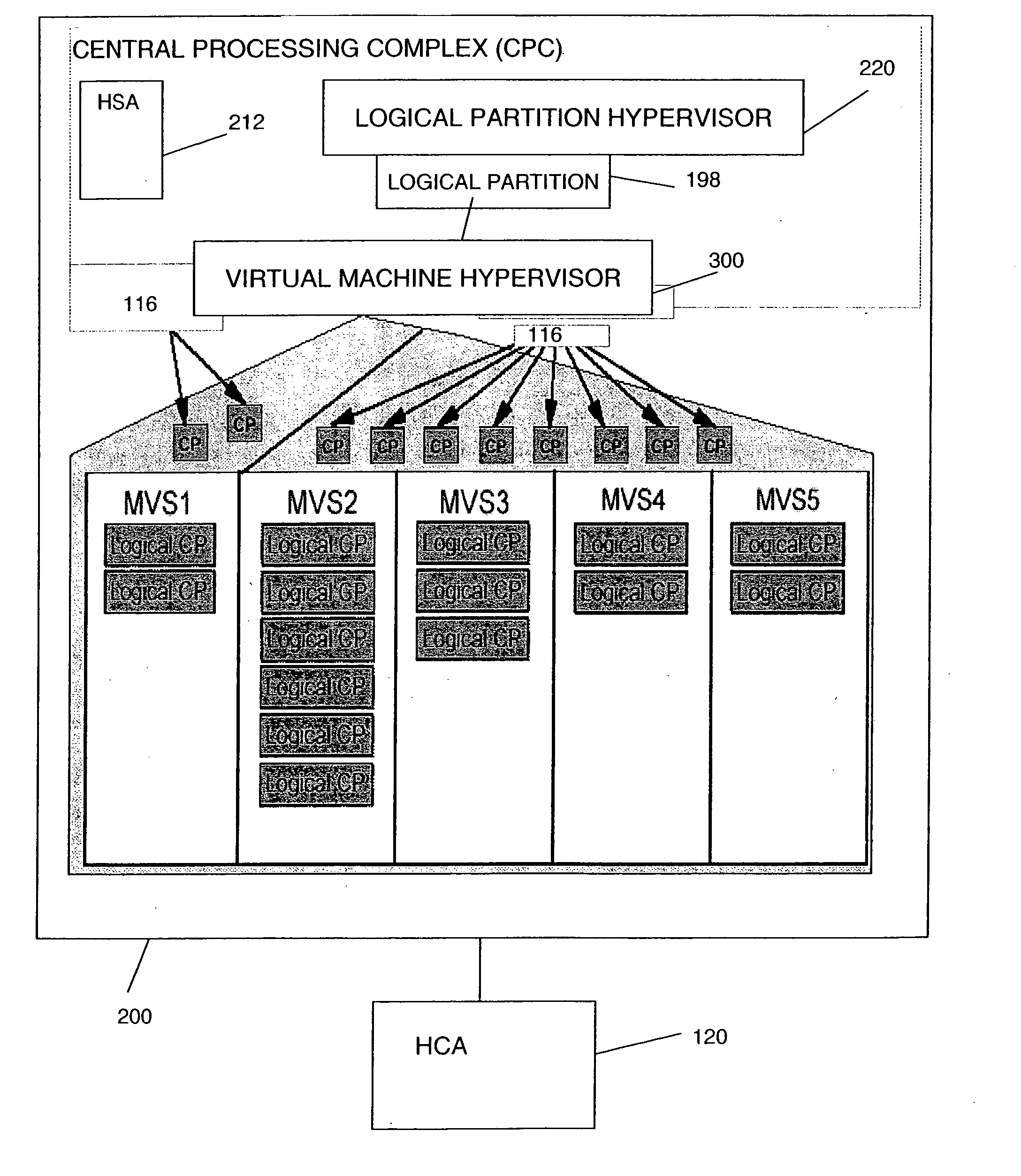

A method, system, program product and computer data structure for providing for two levels of server virtualization. A first hypervisor enables multiple logical partitions to share a set of resources and provides a first level of virtualization. A second hypervisor enables multiple, independent virtual machines to share the resources that are assigned to a single logical partition and provides a second level of virtualization. All events for all of the virtual machines within said single logical partition are grouped into a single partition-owned event queue for receiving event notifications from the shared resources for that single logical partition. A request for an interrupt is signaled for the grouped events from the partition-owned event queue for the demultiplexing of grouped events, by the machine, from the partition-owned event queue into individual, virtualized event queues that are allocated on a per virtual machine basis.

Owner:IBM CORP

Communicating with a memory registration enabled adapter using cached address translations

InactiveUS7587575B2Memory adressing/allocation/relocationComputer security arrangementsRoot complexData buffer

Mechanisms for communicating with a memory registration enabled adapter, such as an InfiniBand™ host channel adapter, are provided. With the mechanisms, device driver services may be invoked by a device driver for initializing address translation entries in an address translation data structure of a root complex. An address of a device driver data buffer data structure and registration modifiers may be passed by the device driver to the device driver services. The device driver services may create address translation data structure entries in the address translation data structure associated with the root complex and memory registration (MR) address translation entries in a MR address translation data structure of the adapter. The MR address translation data structure may then be used with I / O operations to bypass the address translation data structure associated with the root complex.

Owner:IBM CORP

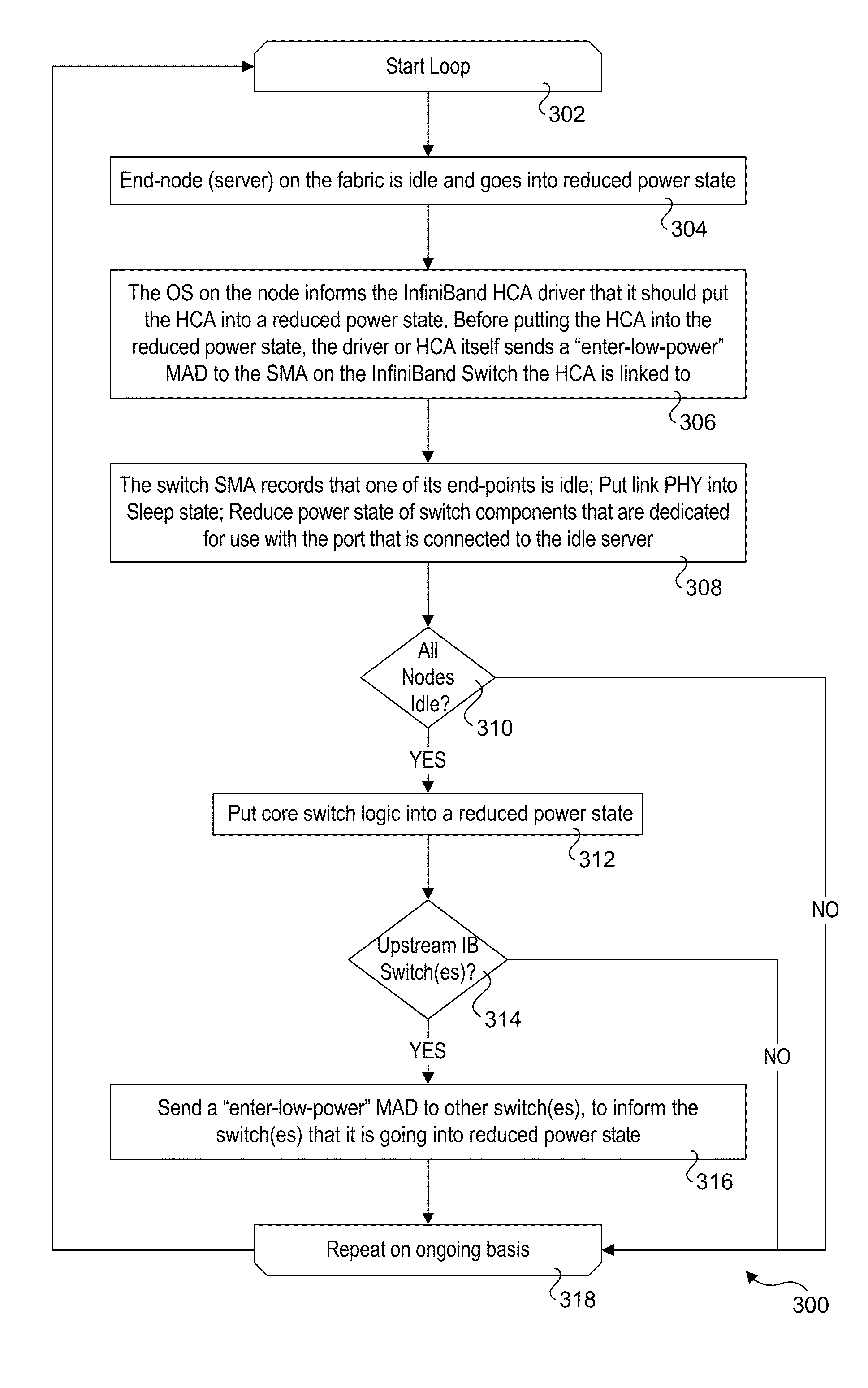

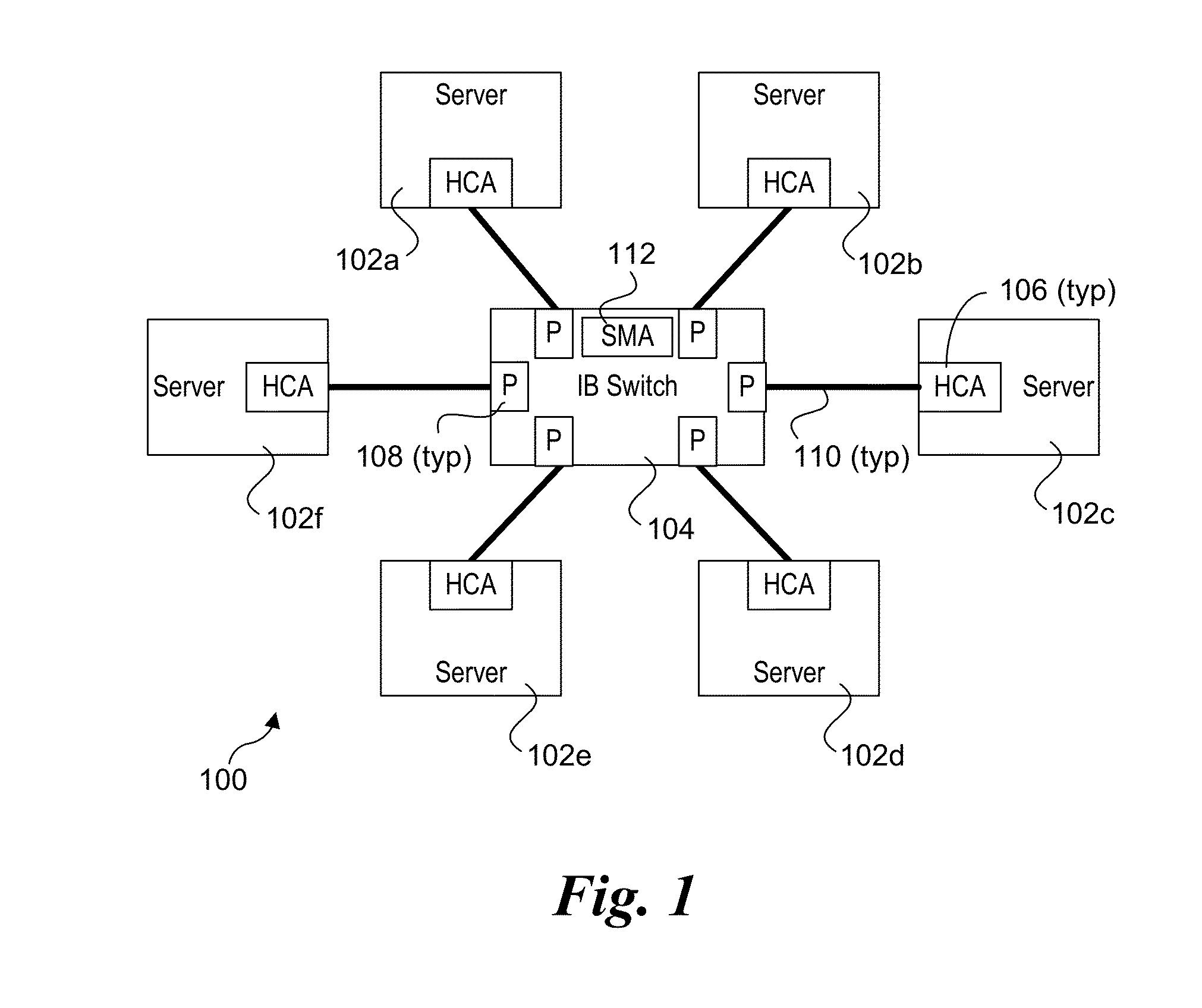

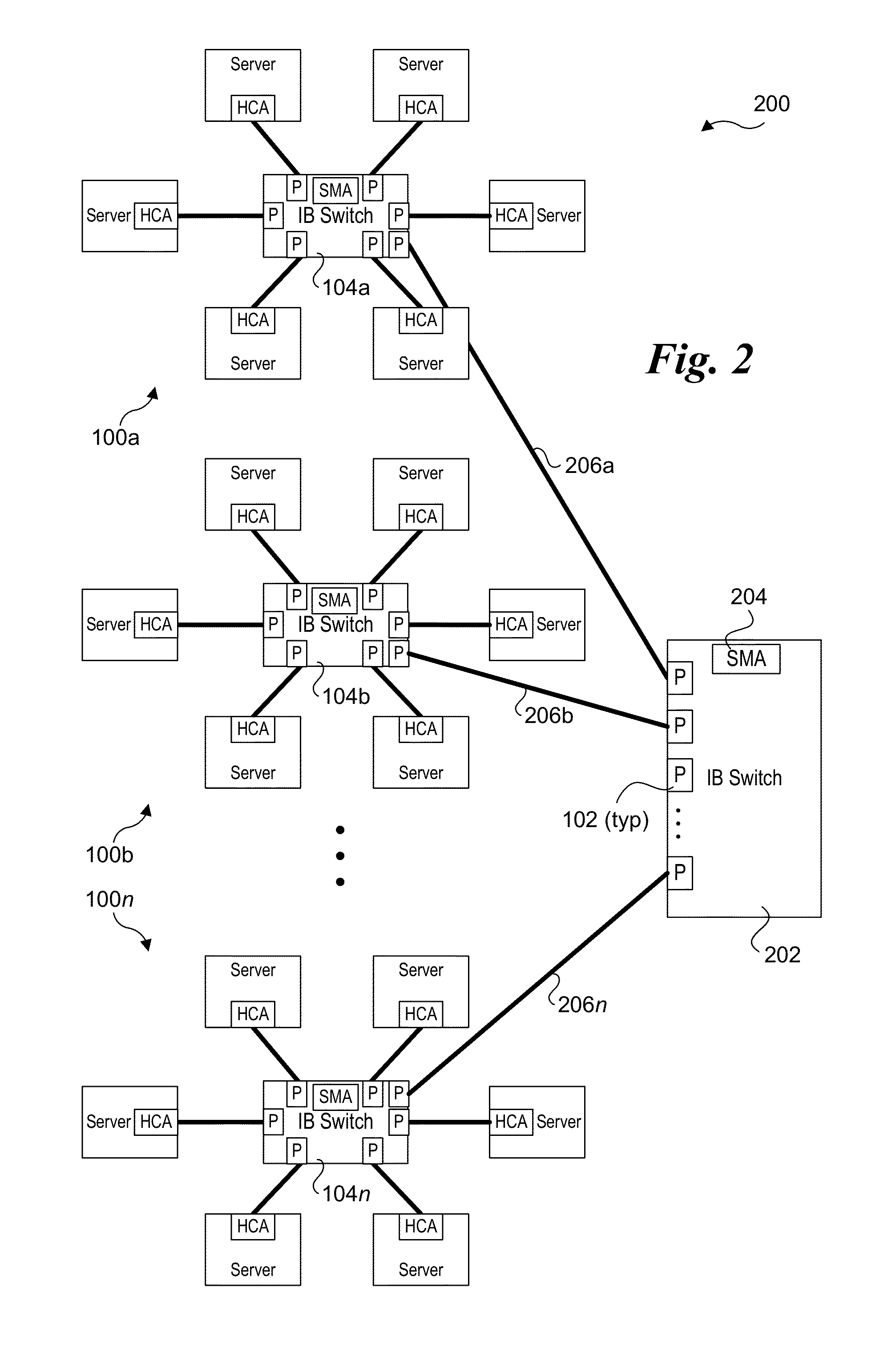

Power management of infiniband switches

ActiveUS20150338909A1Power supply for data processingEnergy efficient computingMulti portComputer science

Methods for performing power management of InfiniBand (IB) switches and apparatus and software configured to implement the methods. Power management datagrams (MADs) are used to inform IB switches that host servers connected to the IB switch's ports are to transition to a reduced-power or offline state or have returned to a normal operating state. A subnet management agent (SMA) on the IB switch receives the power MADs from the host servers and tracks each server's operating state. In response to power down MADs, the SMA coordinates power reduction of the switch's ports and other switch circuitry. For switches with multi-port IB interfaces, a multi-port interface is caused to enter a reduced-power state when all of its ports are connected to host servers that are idle or offline. Additionally, when all of a switch's ports are connected to idle or offline servers the SMA may put the switch's core switch logic into a reduced-power state. Power MADs are also used to inform upstream IB switches when a switch is to transition to a reduced power state or has returned to a normal operating state.

Owner:INTEL CORP

Mapping layer 2 LAN priorities to a virtual lane in an Infiniband(TM) network

A router is configured for sending and receiving data packets on an InfiniBand™ network. When placed between an Ethernet network and an InfiniBand™ network, the router is configured to receive an Ethernet data packet having a VLAN tag indicative of layer 2 priority data of the Ethernet packet. The router includes a mapping table having multiple entries, each entry specifying a VLAN tag and a corresponding service level. A controller is configured for parsing the VLAN tag and determining the service level for the VLAN tag. The controller outputs the Ethernet packet on the InfiniBand™ network within an InfiniBand™ packet according to the determined service level.

Owner:ADVANCED MICRO DEVICES INC

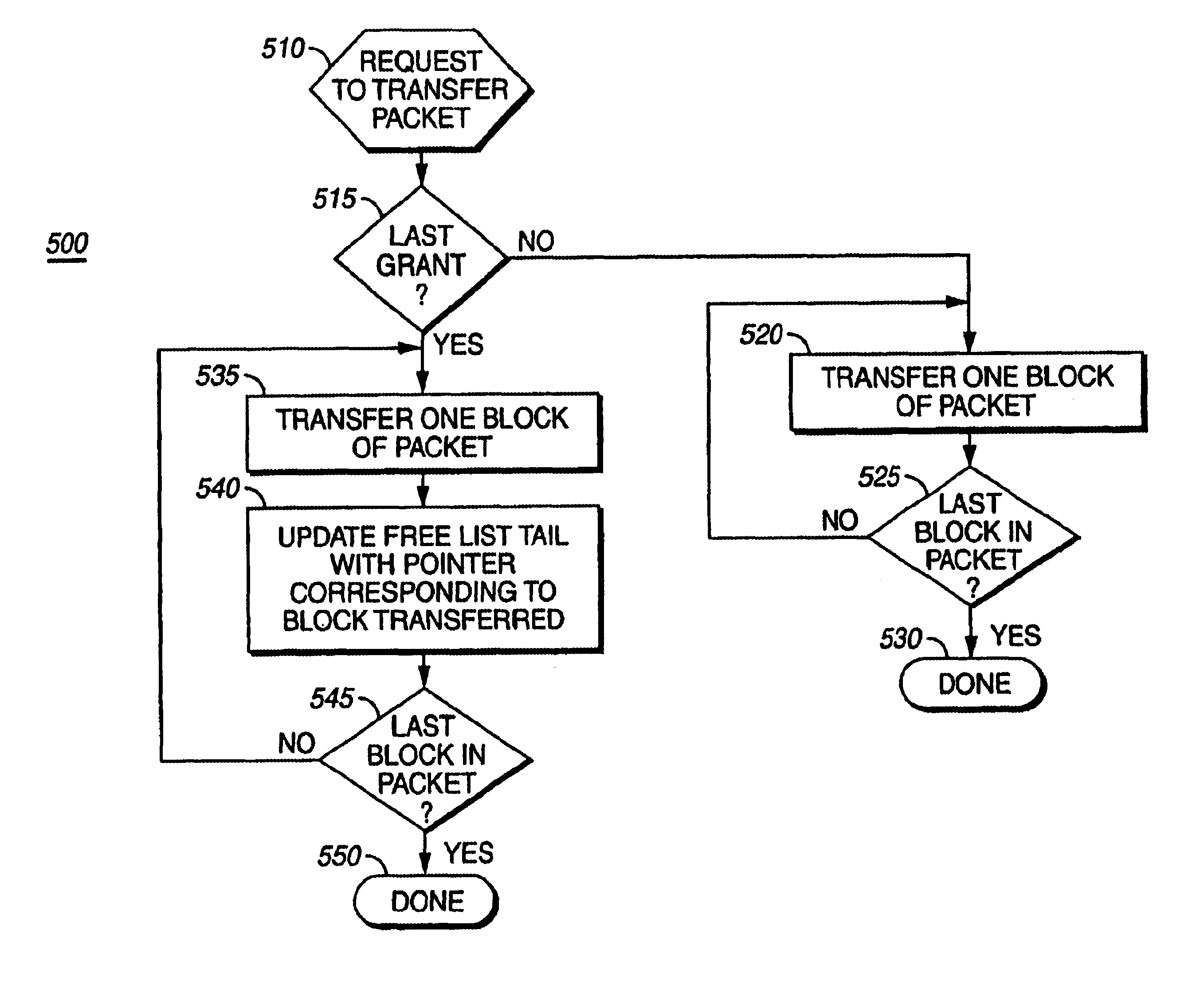

Buffer management architecture and method for an infiniband subnetwork

InactiveUS6904507B2Error preventionFrequency-division multiplex detailsData informationNetwork packet

An architecture and method for dynamically allocating and deallocating memory for variable length packets with a variable number of virtual lanes in an Infiniband subnetwork. This architecture uses linked lists and tags to handle the variable number of Virtual Lanes and the variable packet sizes. The memory allocation scheme is independent of Virtual Lane allocation and the maximum Virtual Lane depth. The disclosed architecture is also able to process Infiniband packet data comprising variable packet lengths, a fixed memory allocation size, and deallocation of memory when packets are either multicast or unicast. The memory allocation scheme uses linked lists to perform memory allocation and deallocation, while tags are used to track Infiniband subnetwork and switch-specific issues. Memory allocation and deallocation is performed using several data and pointer tables. These tables store packet data information, packet buffer address information, and pointer data and point addresses. The tags allow the memory allocation and deallocation process to correctly handle good and bad packets, as well as successive blocks within a data packet.

Owner:MICROSEMI SOLUTIONS (US) INC

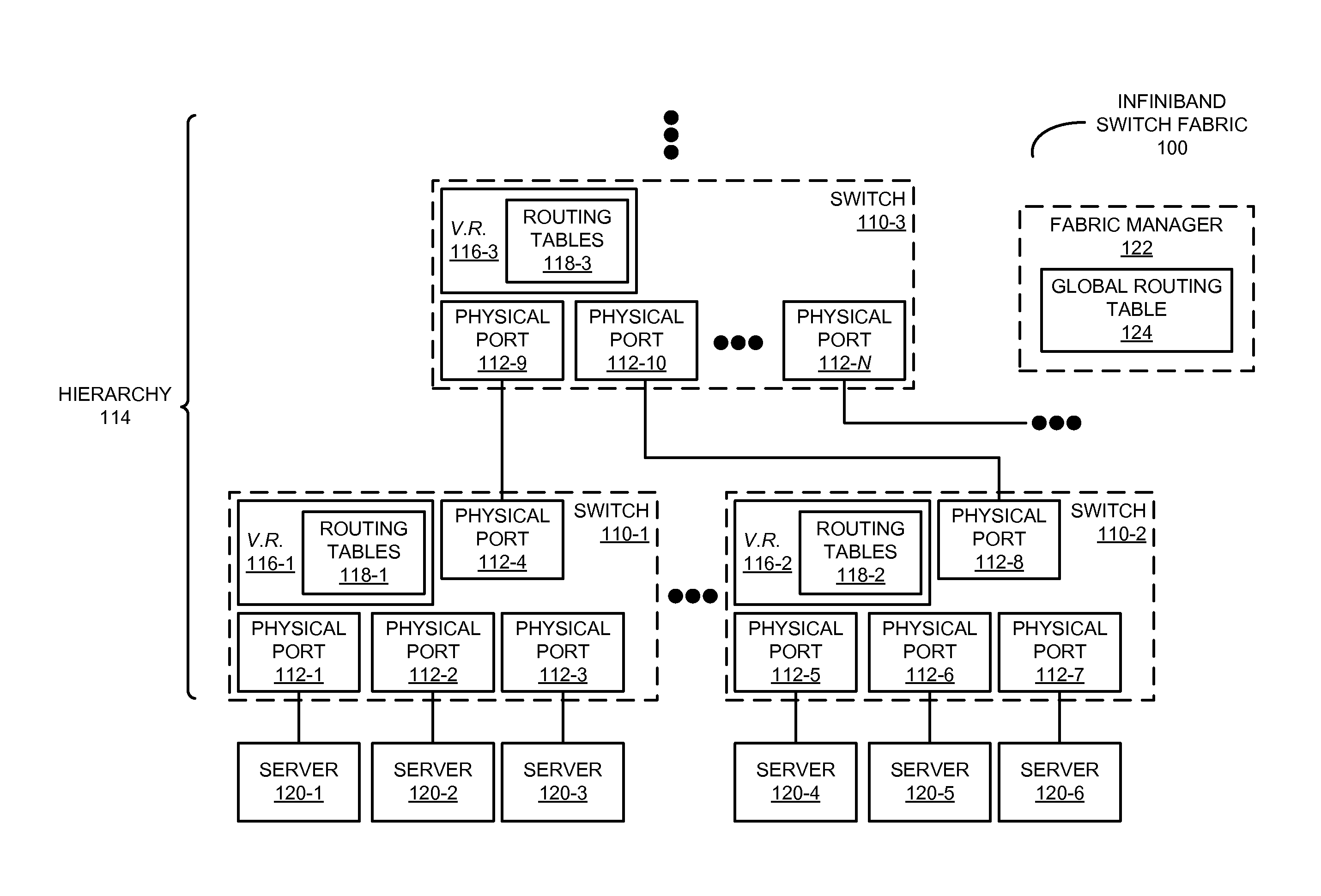

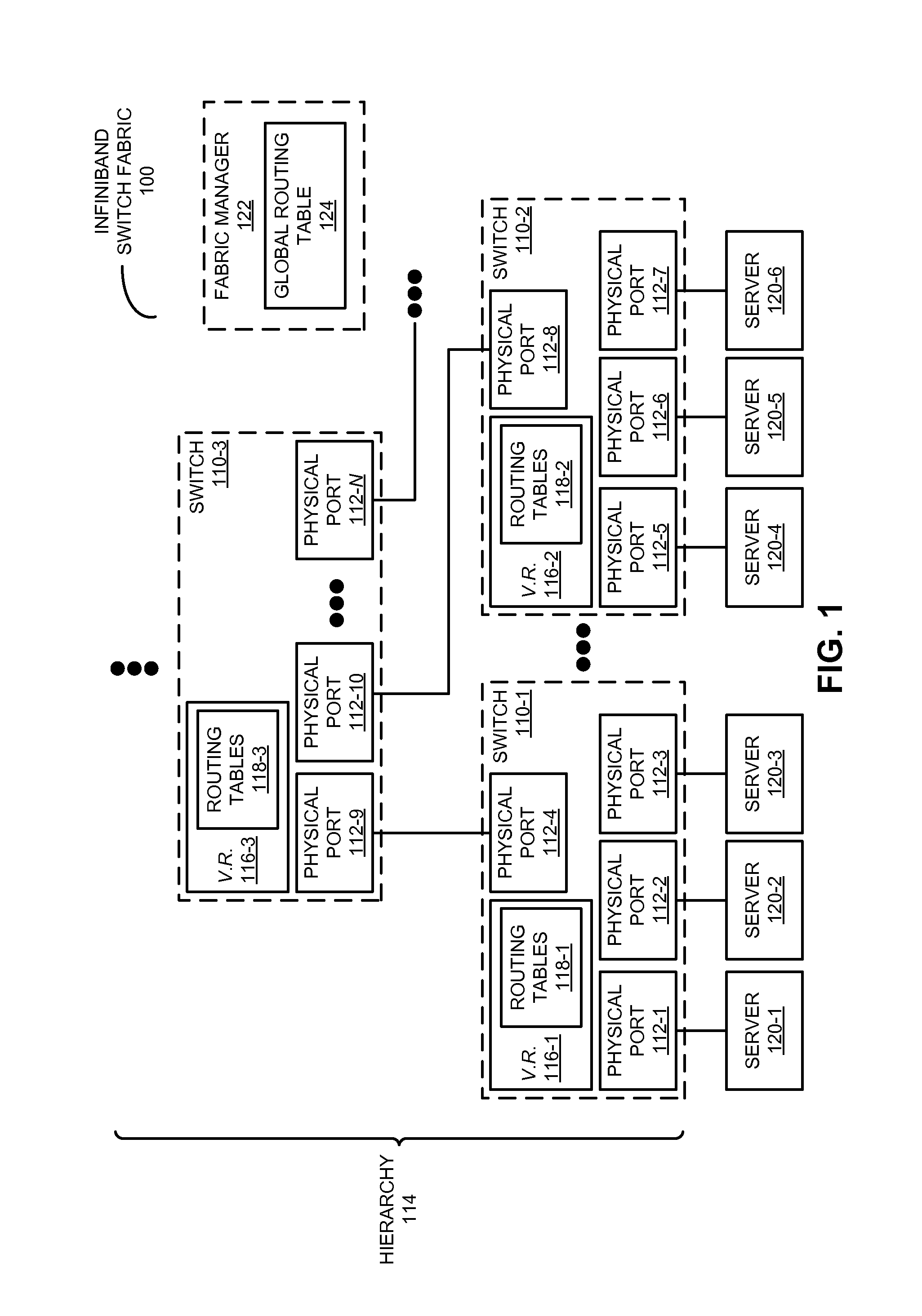

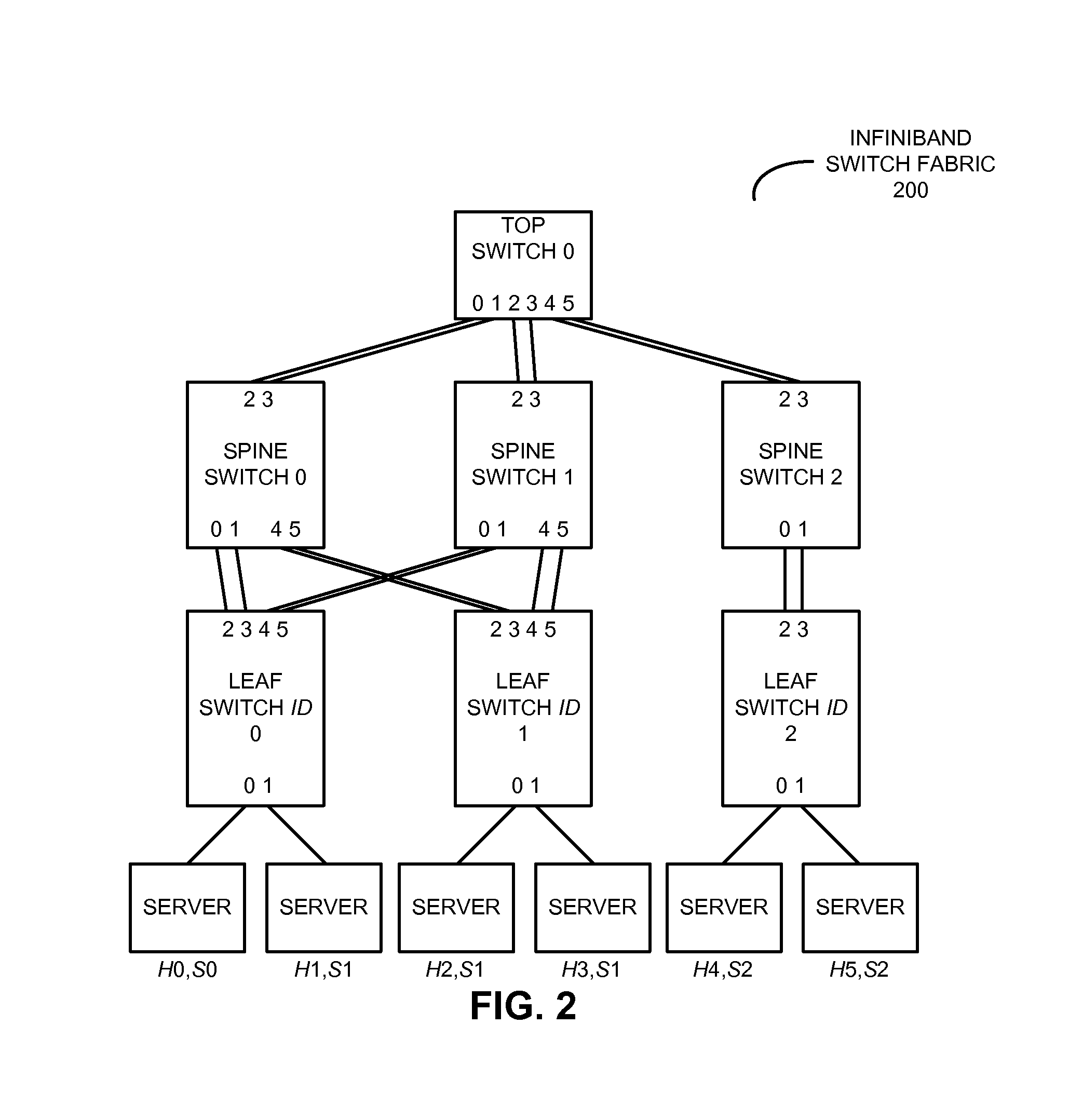

Scalable infiniband packet-routing technique

ActiveUS20140269720A1Optimization pathData switching by path configurationRouting tableNear neighbor

An InfiniBand switch fabric is described. This InfiniBand switch fabric includes a hierarchy of switches having physical ports. These physical ports have associated local routing tables for nearest-neighbor connections to the physical ports. Moreover, relationships between the nearest-neighbor connections to each of the physical ports specified in the local routing tables are based in part on network-layer global identifiers that are assigned based on the hierarchy. Furthermore, local routing tables in the switches facilitate paths or routes for packets through the InfiniBand switch fabric without using a global routing table in the switches. In addition, the InfiniBand switch fabric includes a fabric manager, coupled to the switches, having the global routing table to assign the network-layer global identifiers.

Owner:ORACLE INT CORP

System, method, and storage medium for shared key index space for memory regions

InactiveUS20060095690A1Memory systemsMicro-instruction address formationOperational systemTerm memory

In a logical partitioning (LPAR) environment with InfiniBand™ host channel adapters (HCAs), multiple operating systems share the resources of a physical HCA. A mechanism for efficiently allocating memory regions (or memory windows) to different LPARs is provided, while ensuring that a memory region assigned to one LPAR is not accessible from another LPAR.

Owner:IBM CORP

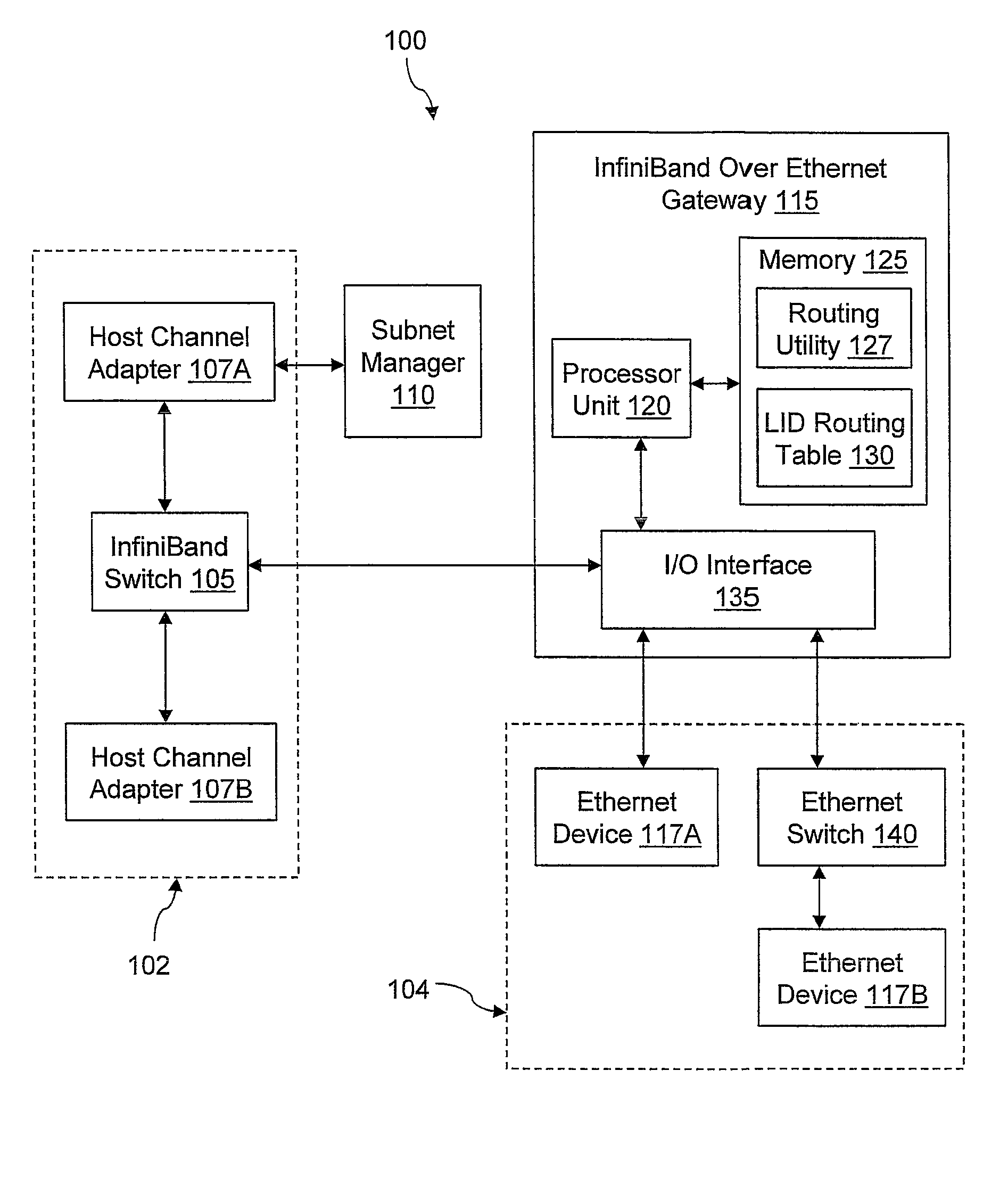

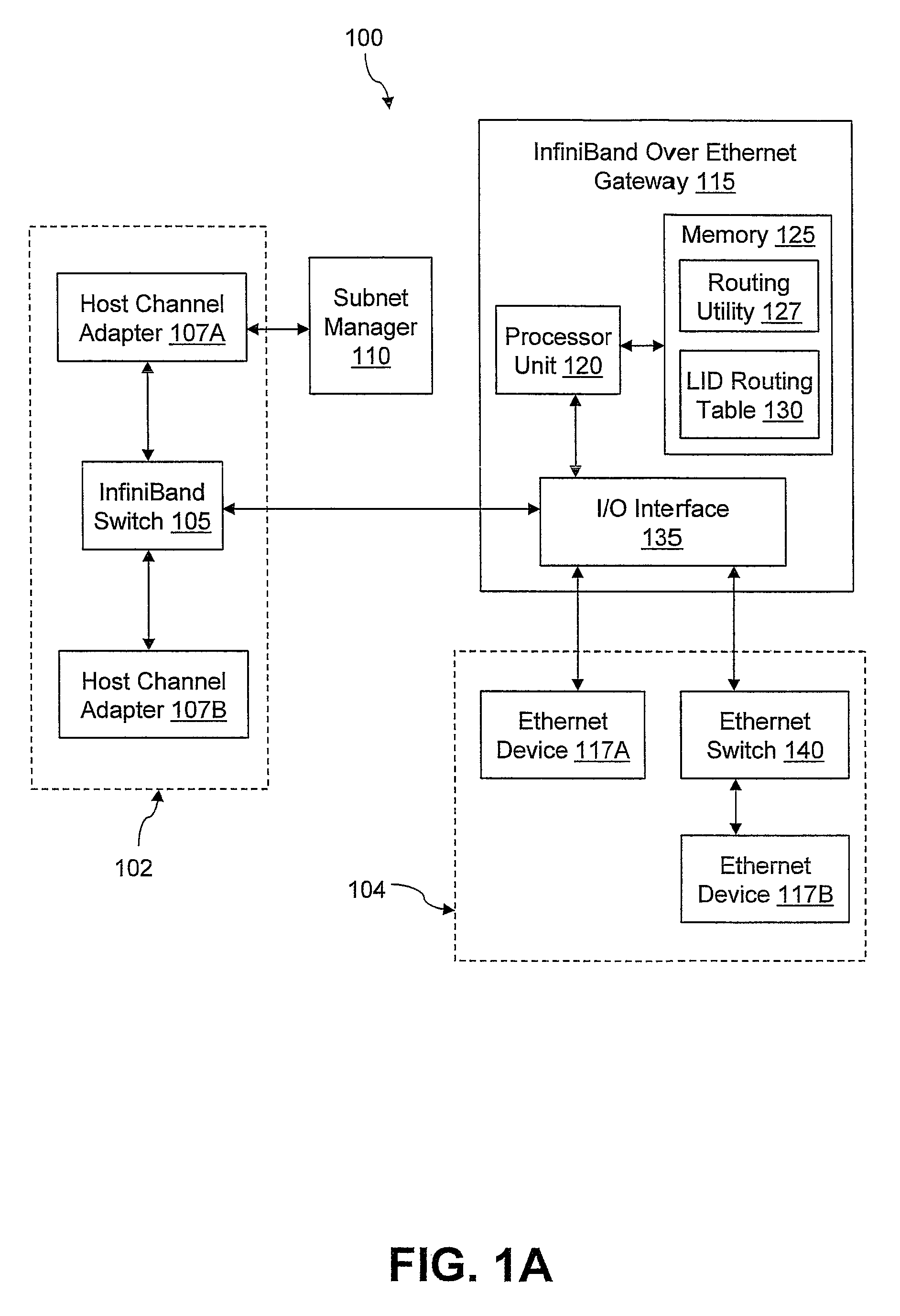

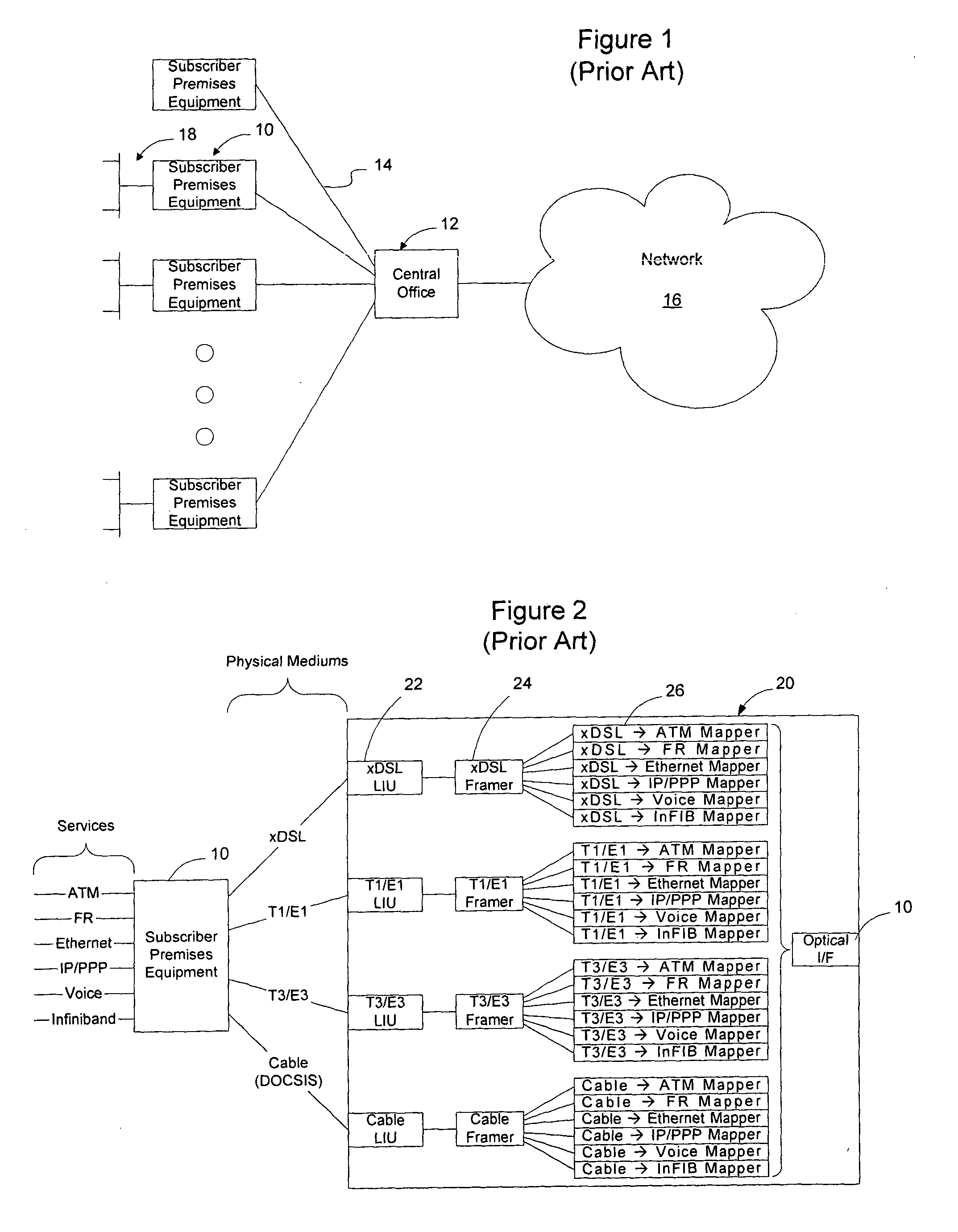

Providing visibility of Ethernet components to a subnet manager in a converged InfiniBand over Ethernet network

A method of providing visibility of Ethernet components to a subnet manager in a converged InfiniBand over Ethernet (IBOE) network. If a port of an IBOE gateway corresponds to one or more InfiniBand devices, the subnet manager sends fabric management packets (FMPs) to discover the InfiniBand network and assigns physical local identifiers (LIDs) to the InfiniBand devices. If a port of the IBOE gateway corresponds to one or more Ethernet devices, the subnet manager sends FMPs to discover the Ethernet network. The subnet manager adds the Ethernet Media Access Control (MAC) addresses of any responding devices to an LID routing table and assigns LIDs to the Ethernet devices. The subnet manager configures one or more virtual Host Channel Adapters (HCAs) corresponding to the one or more Ethernet MAC addresses in the LID routing table.

Owner:IBM CORP

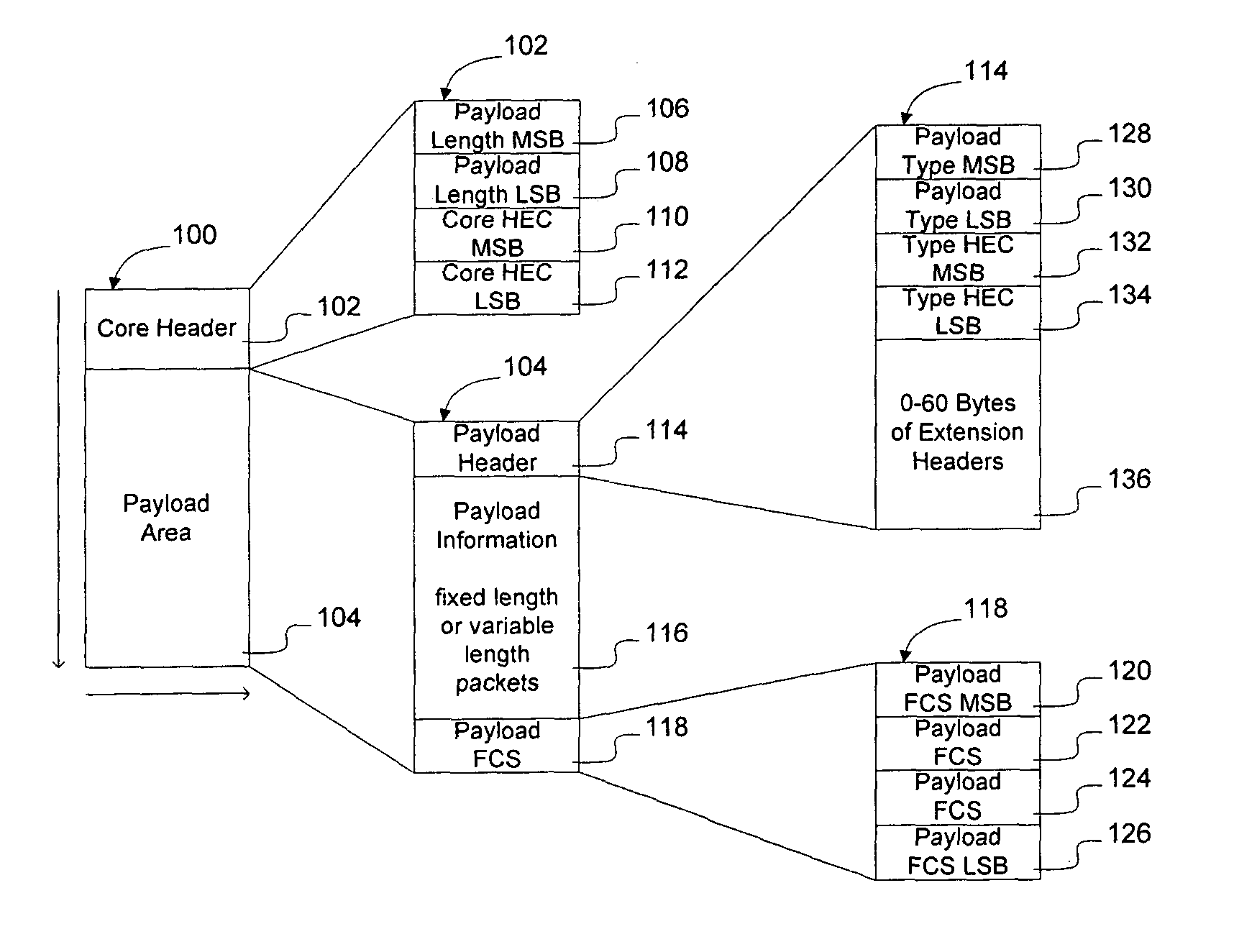

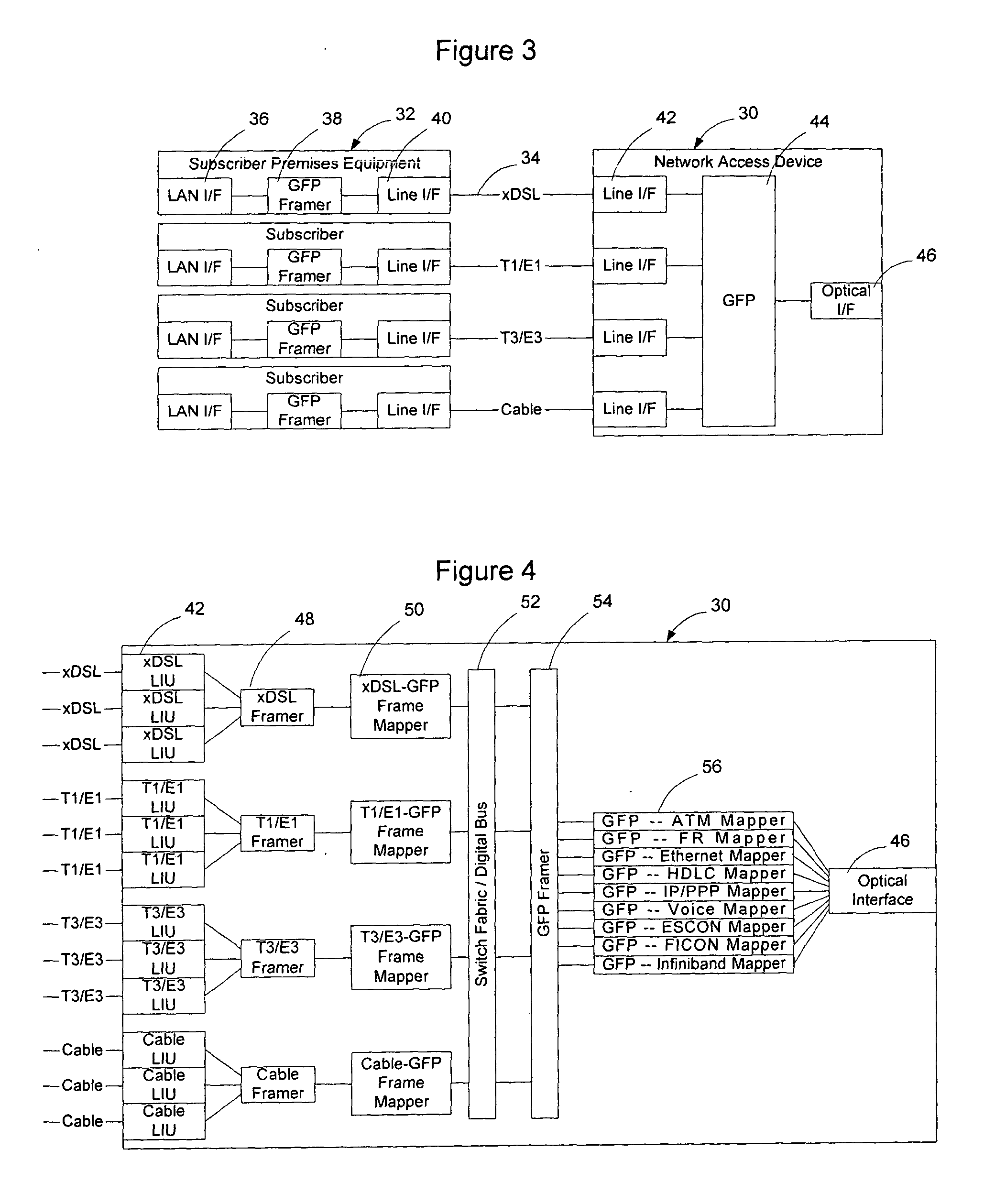

Method and apparatus for encapsulating services for transportation over metallic physical mediums

InactiveUS20050053064A1Reduce the amount requiredReduce complexityTime-division multiplexData switching by path configurationFrame RelayPhysical layer

A network element employing a universal mapper enables multiple services to be mapped onto a physical medium (metallic link with a particular physical layer protocol) so that the number of service mappers, and hence the complexity of the network element, may be reduced, the cost of provisioning the device may be reduced, and new services may be deployed, such as Ethernet over T1. The universal mapper may be configured to generate frames for transmission over multiple physical mediums utilizing a protocol known as Generic Framing Procedure (GFP). Using this embodiment, services such as ATM, Frame Relay, Ethernet, IP / PPP, Voice, and Infiniband may be transported in GFP frames over metallic links operating using xDSL, T1 / E1, T3 / E3, or cable access technologies by utilizing a single GFP framer and a single set of service mappers.

Owner:INT LICENSE EXCHANGE OF AMERICA LLC

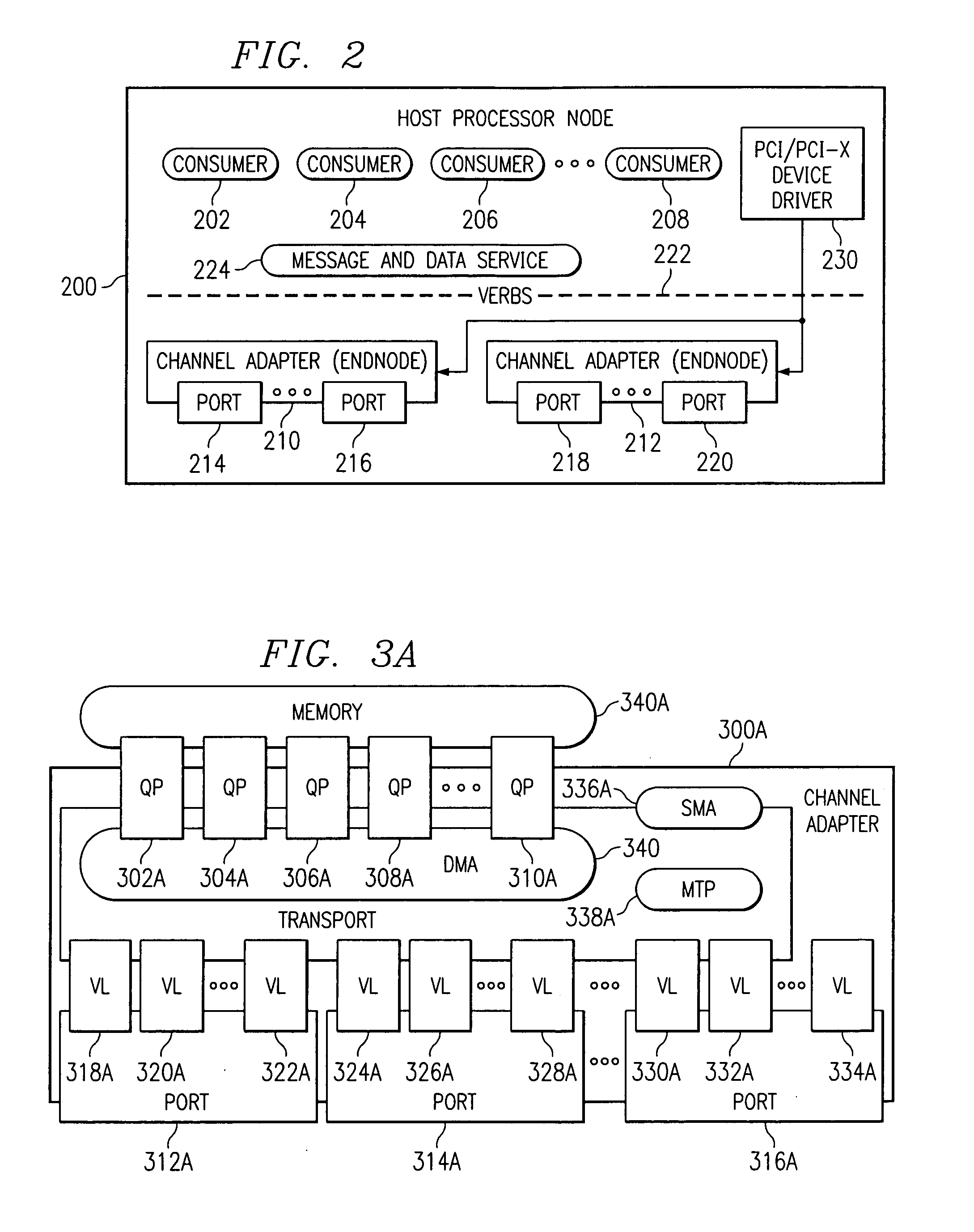

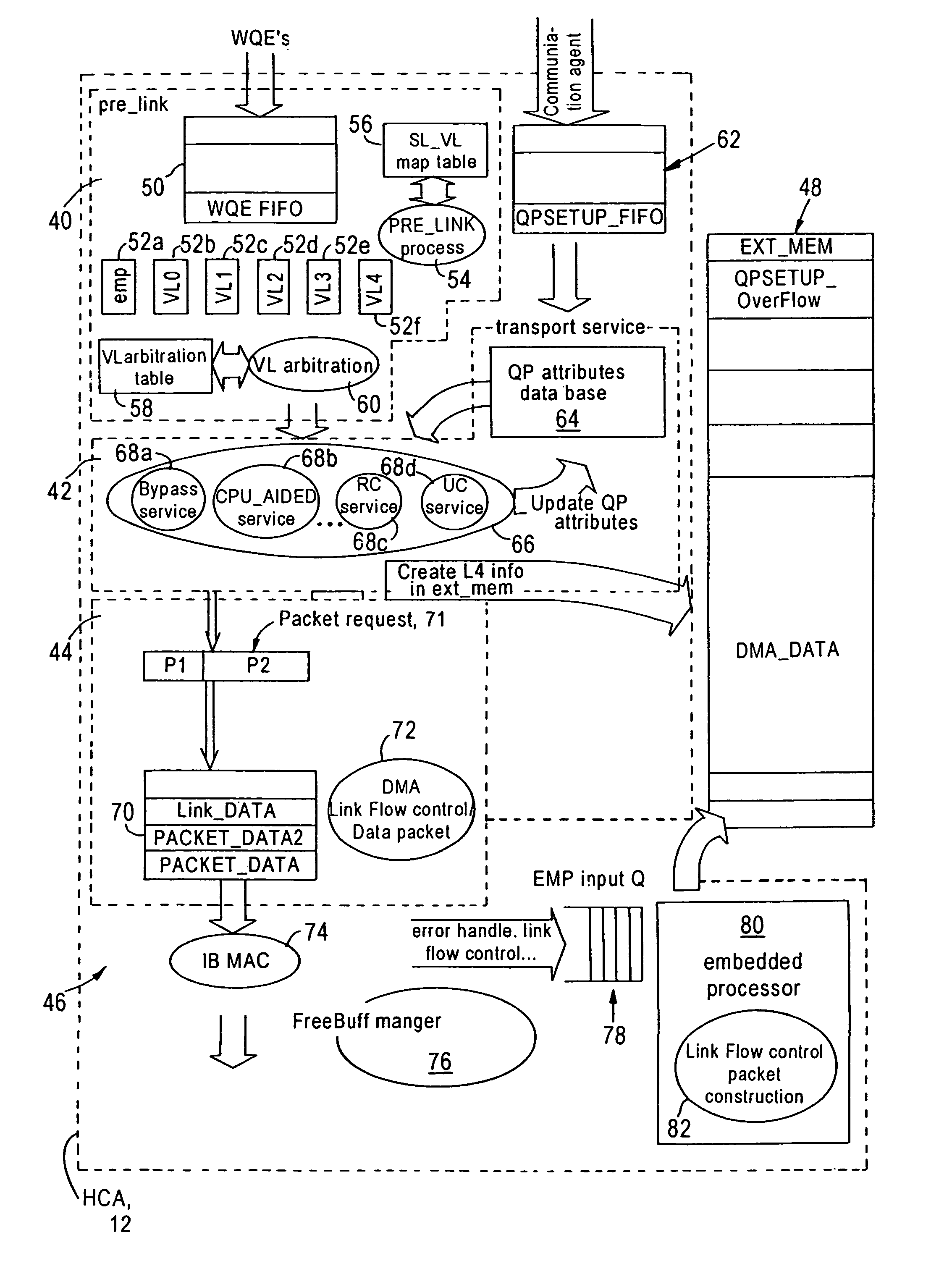

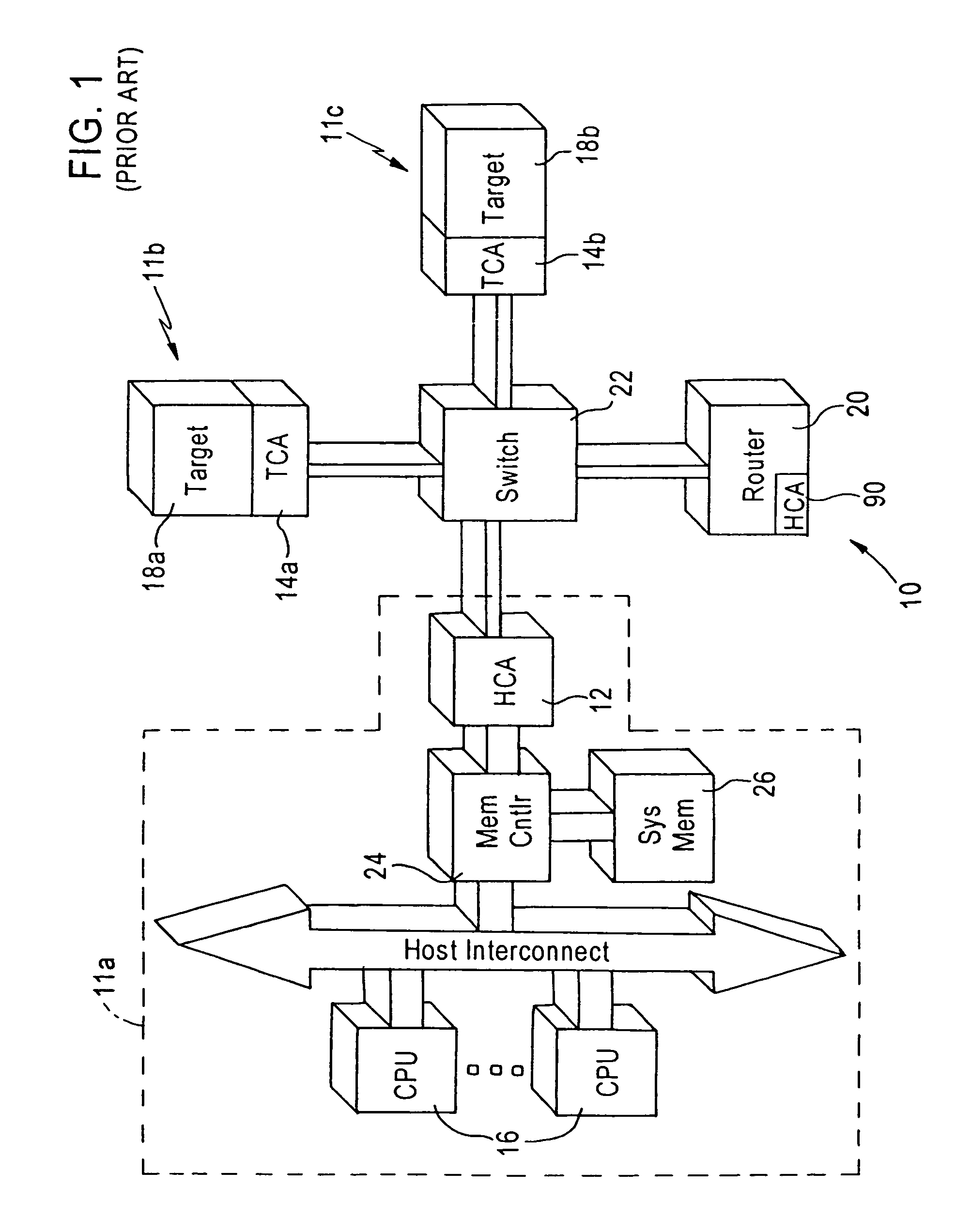

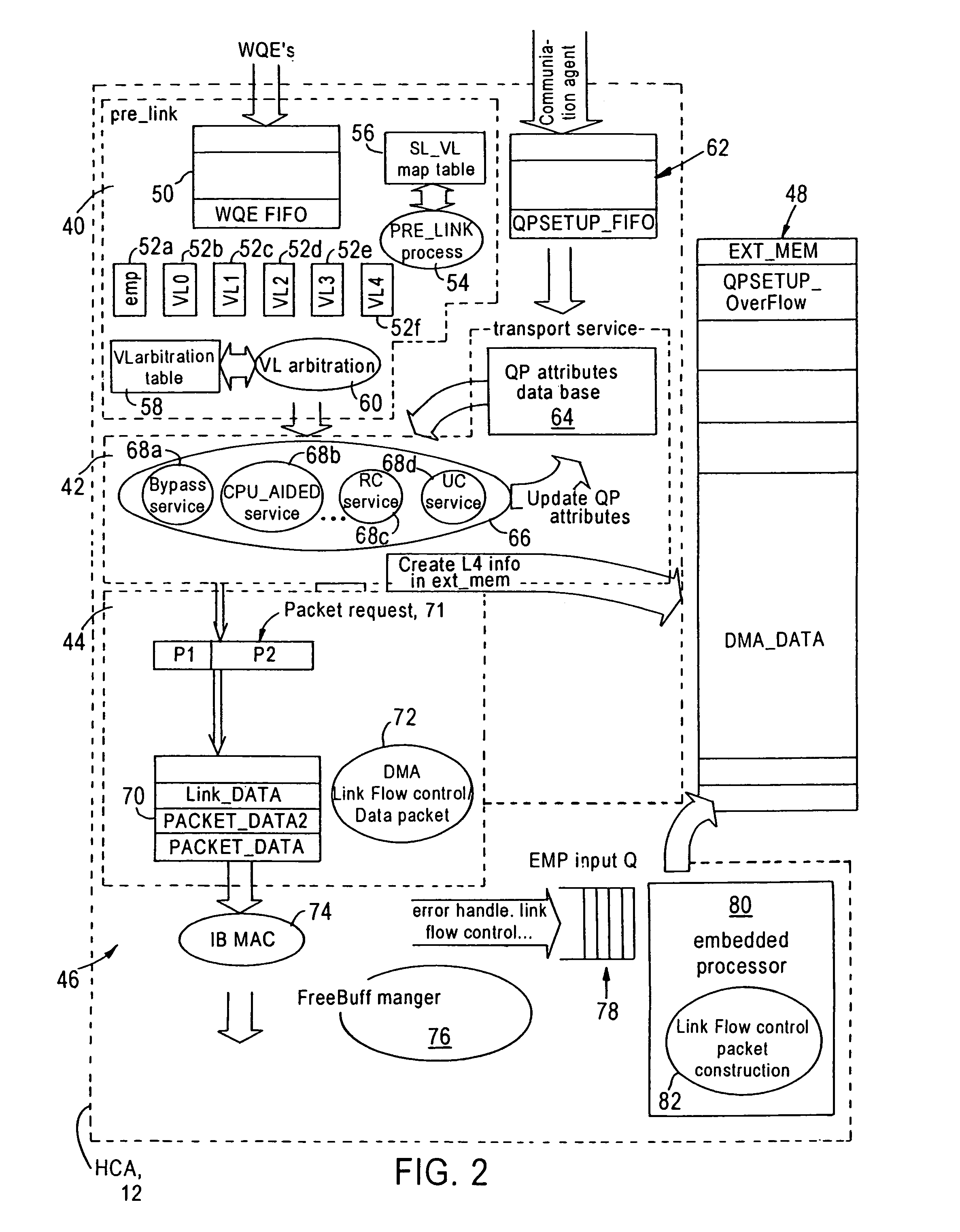

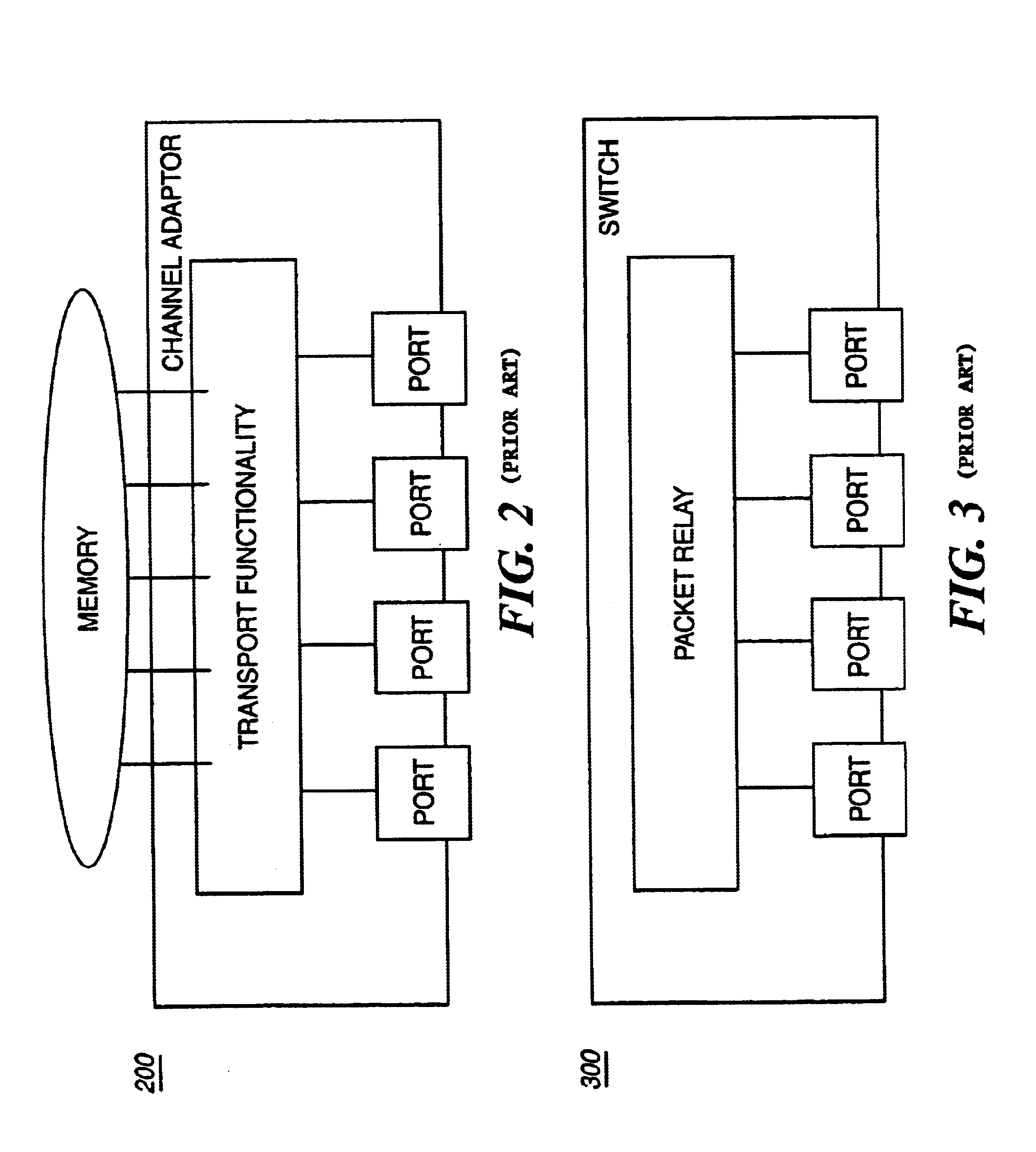

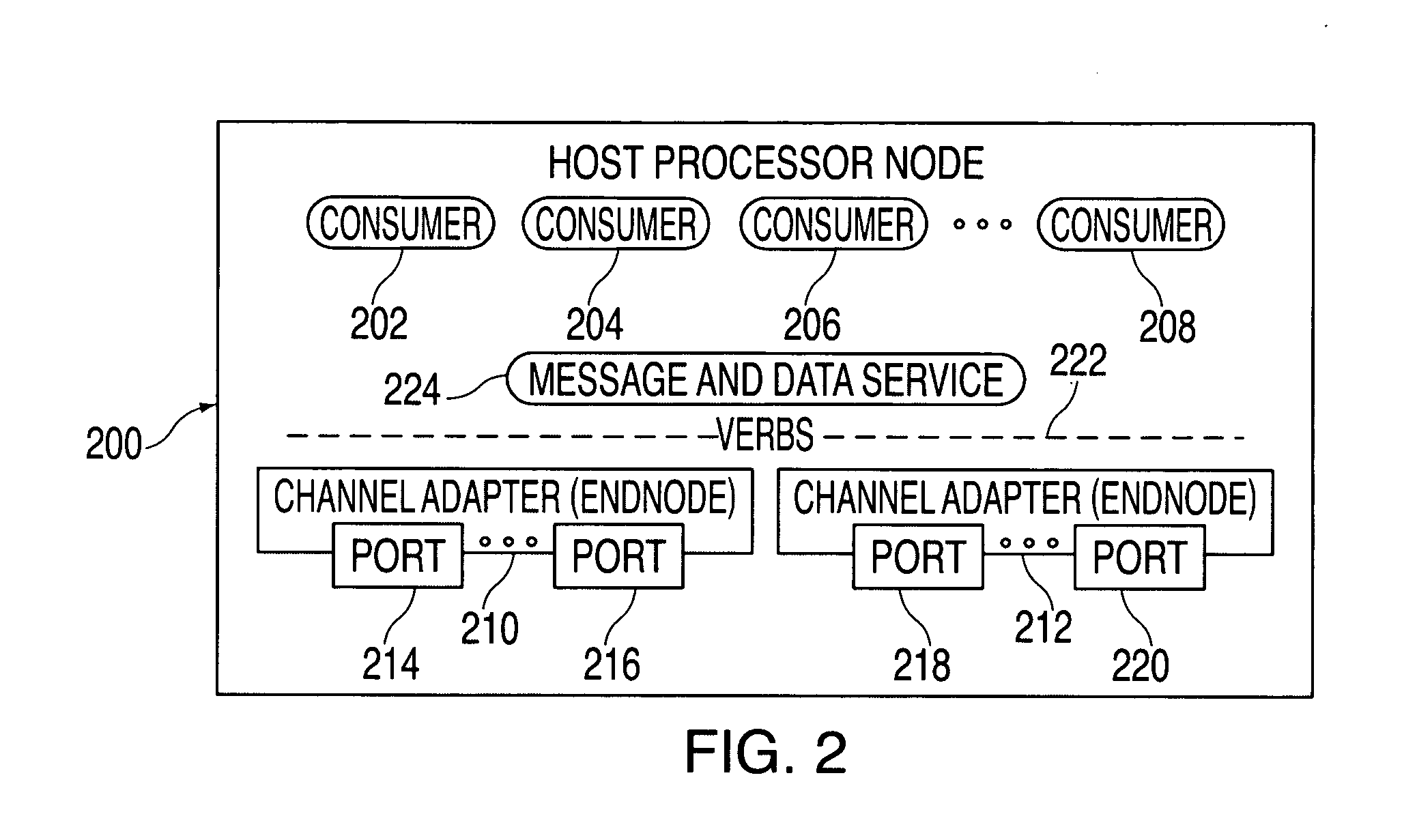

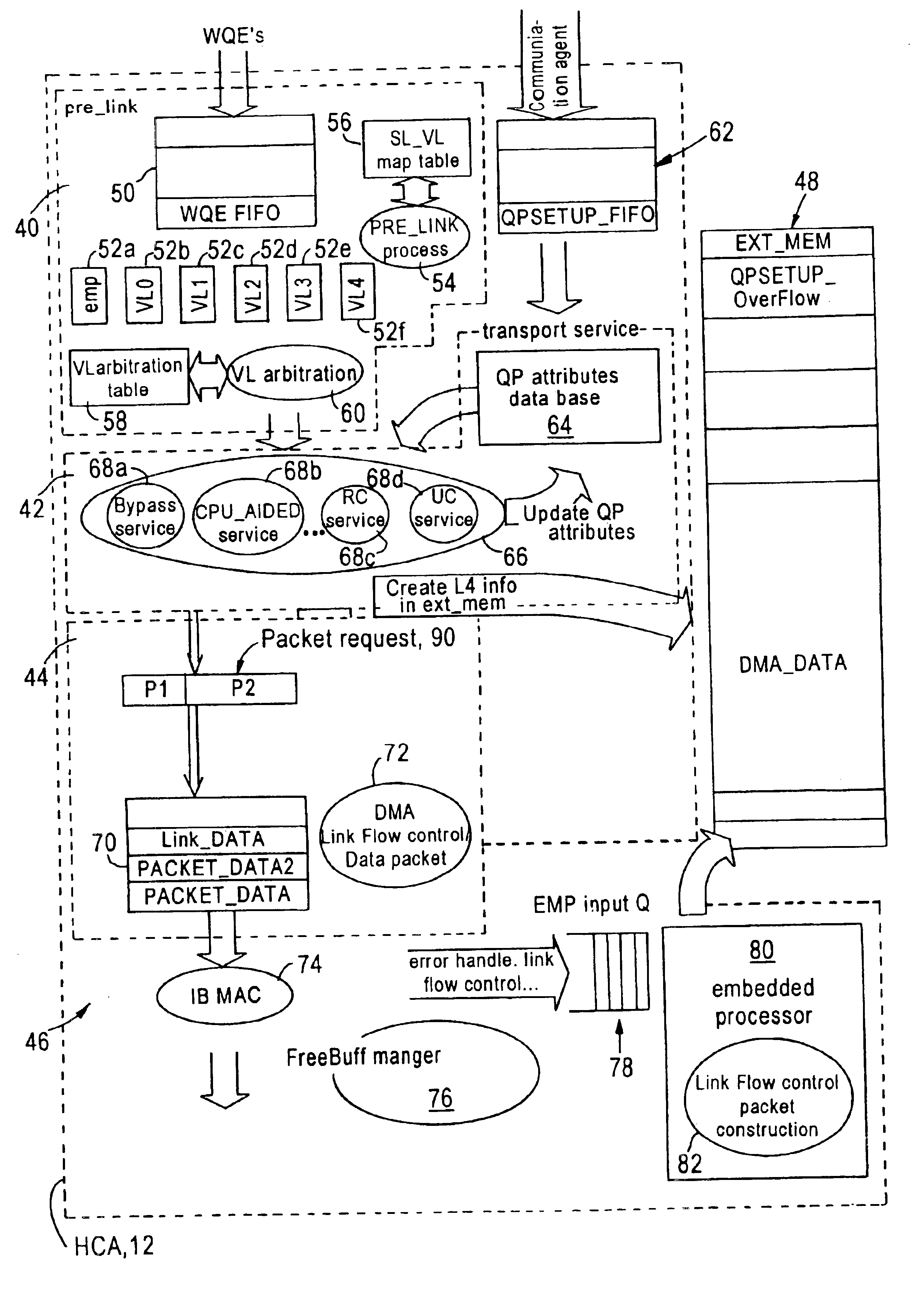

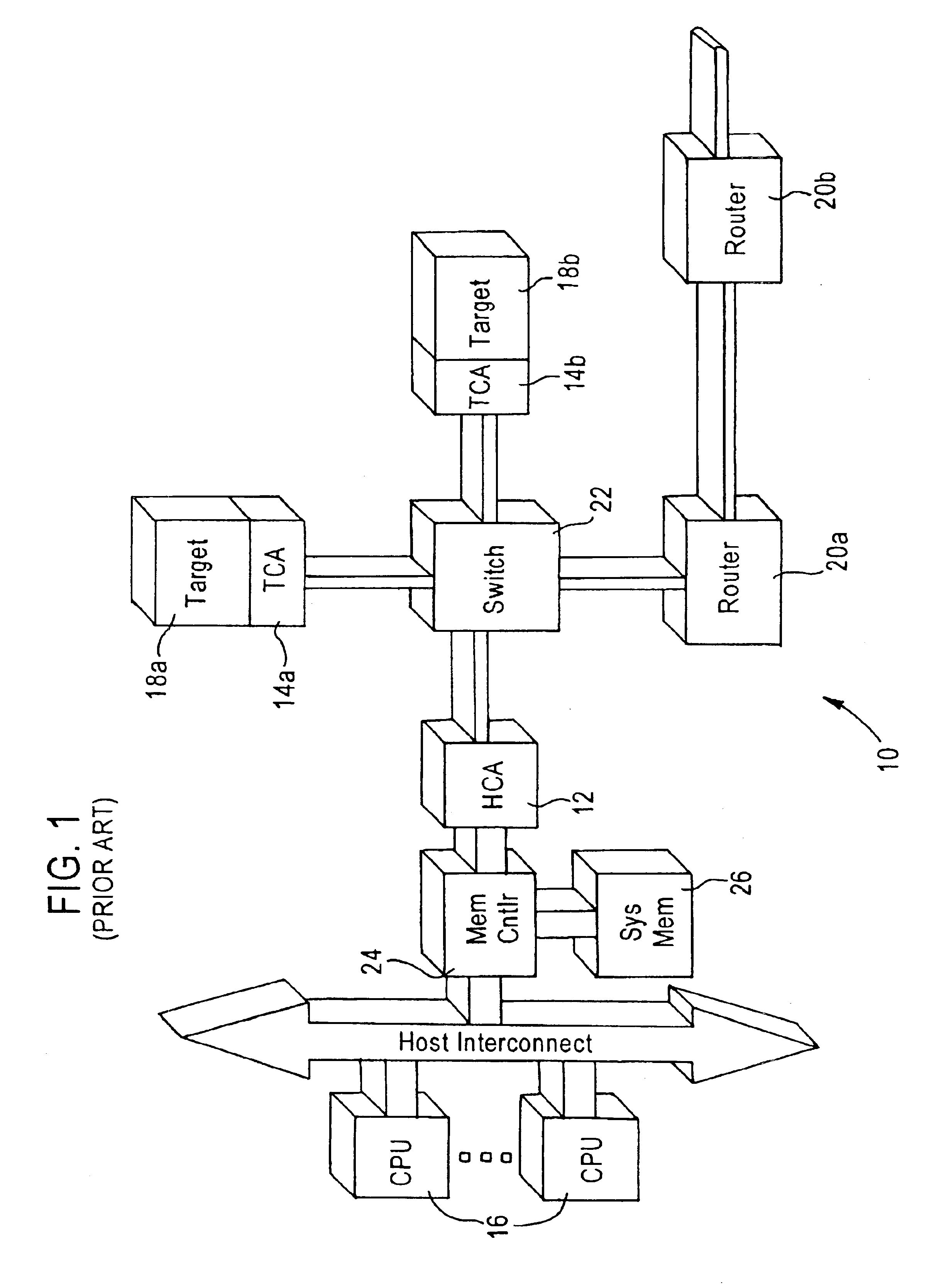

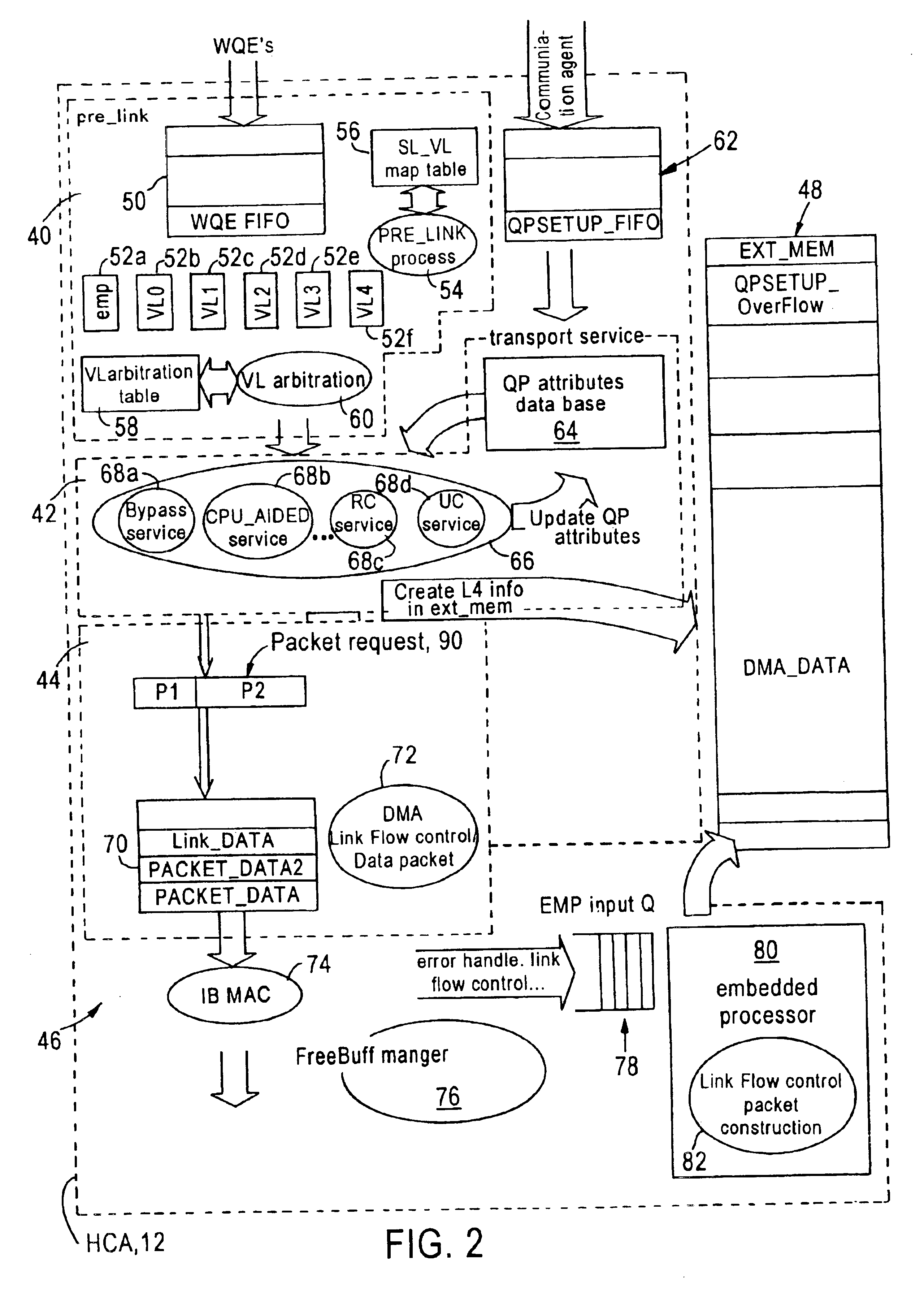

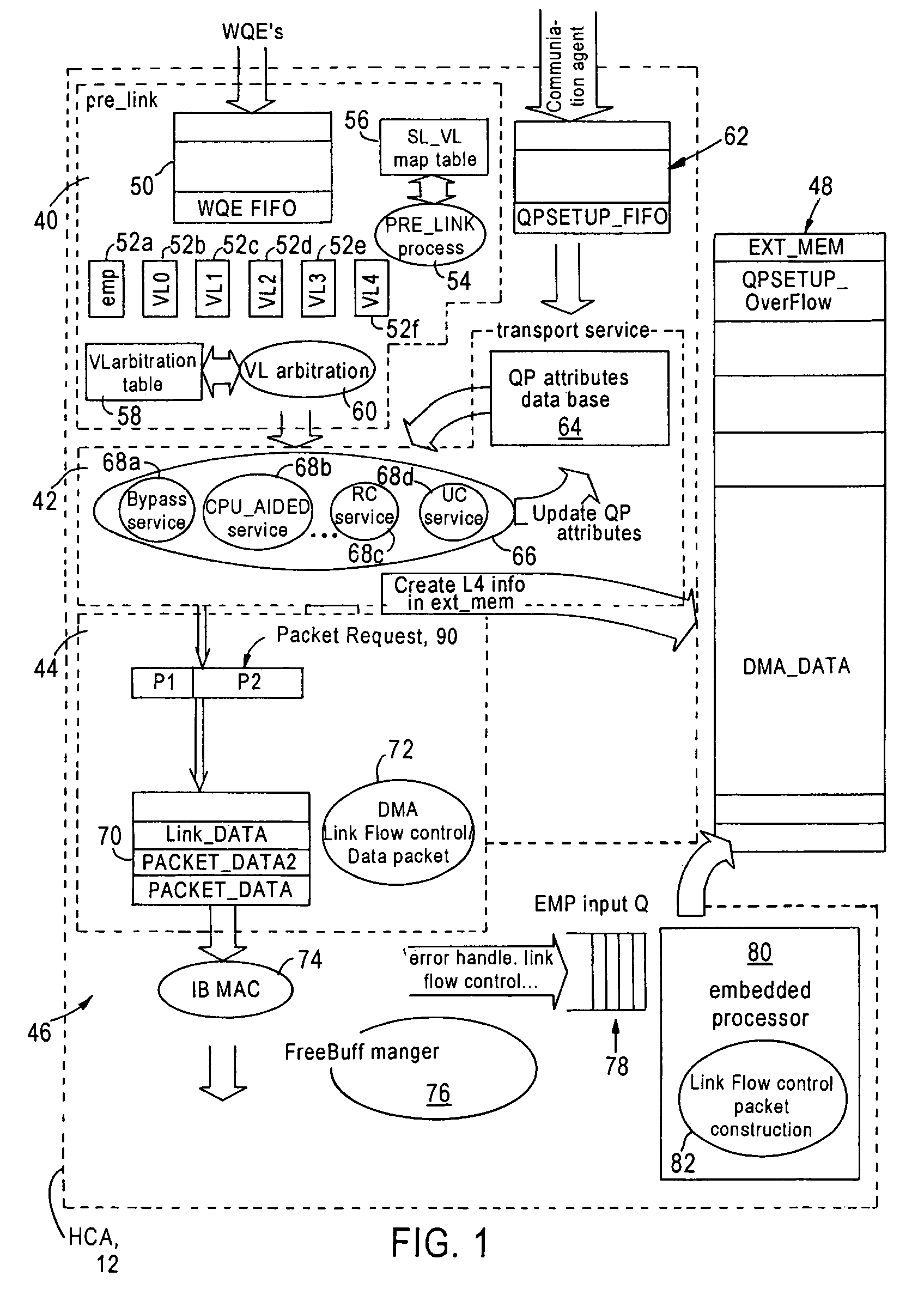

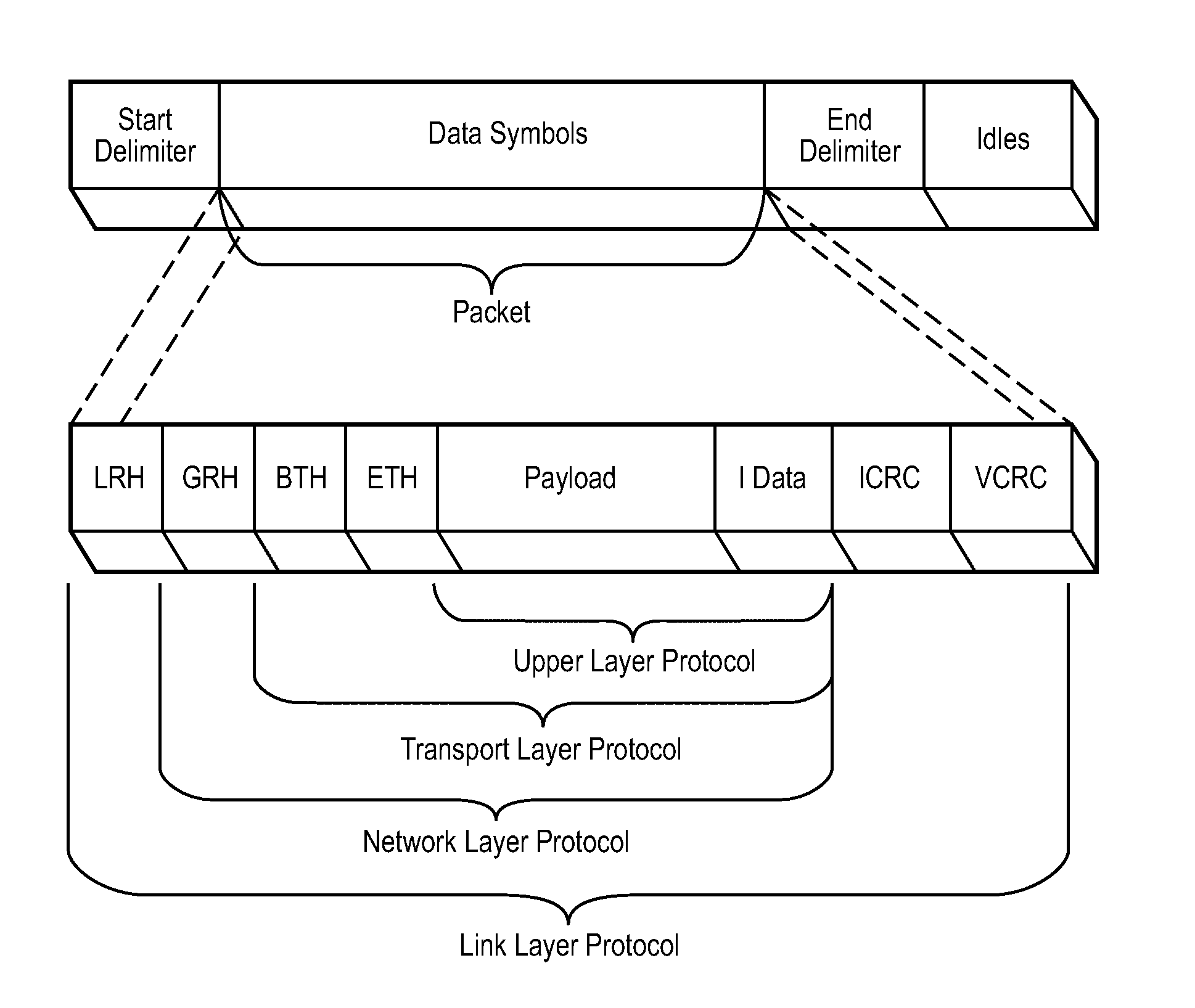

Host channel adapter having partitioned link layer services for an infiniband server system

InactiveUS6912604B1Sufficient flexibilityWithout compromising HCA performanceData switching by path configurationStore-and-forward switching systemsTransport layerComputer module

A host channel adapter configured for outputting packets according to InfiniBand™ protocol is implemented using partitioned link modules configured for performing selected link operations prior to outputting the packets. A pre-link module is configured for ordering work queue entries in an order based on determined service level and virtual lane priorities. The pre-link module outputs the ordered work queue entries to a transport service module configured for generating a transport layer header for the packets based on the respective work queue entries. Once the transport layer headers have been generated, a post-link module is configured for retrieval of the transport layer header and transport data and preparing the transmit data packets for transmission on the network by constructing the link layer fields. The post-link module outputs the transmit data packets based on the ordering and the flow control protocol for the appropriate virtual lanes.

Owner:ADVANCED MICRO DEVICES INC

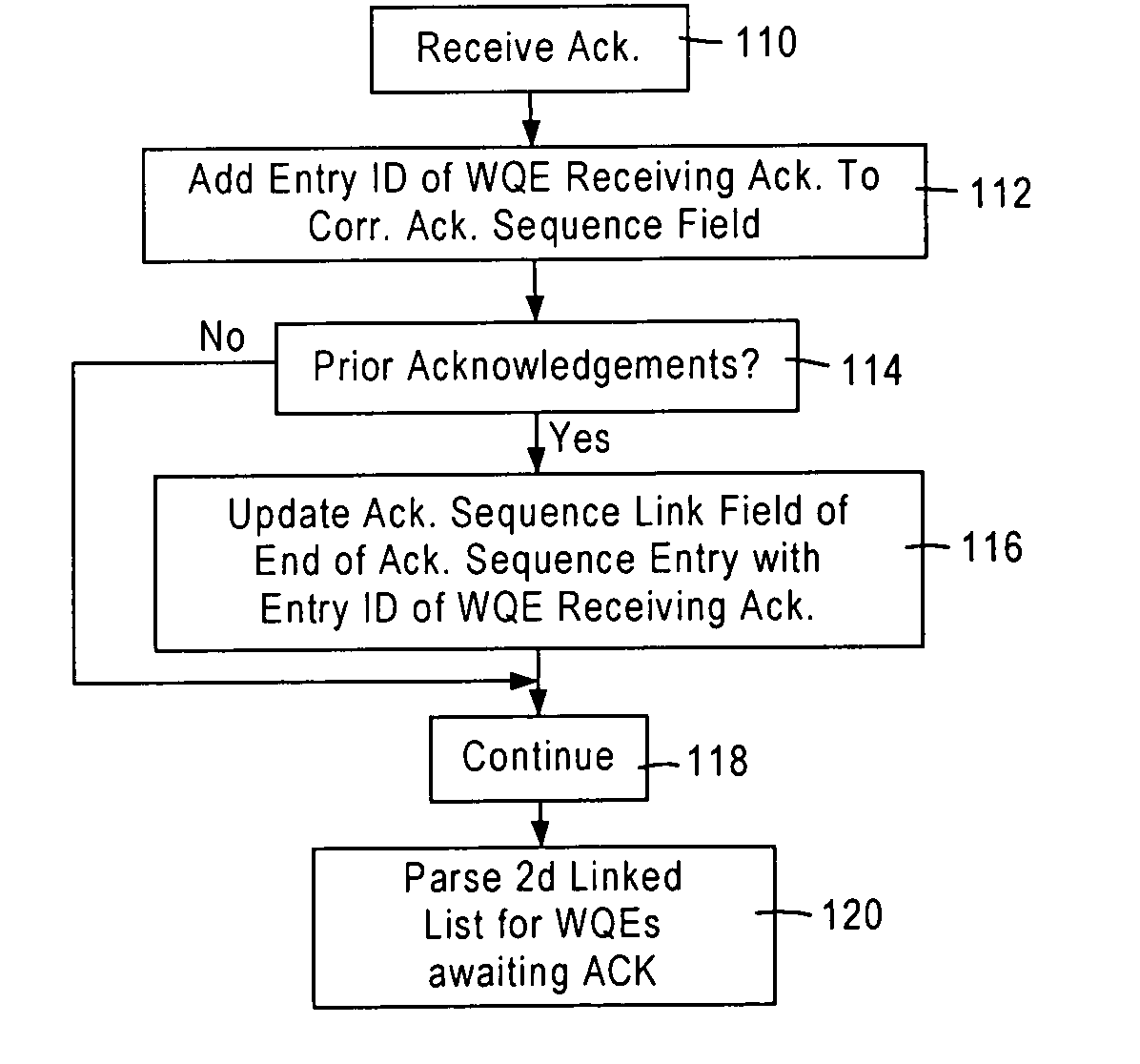

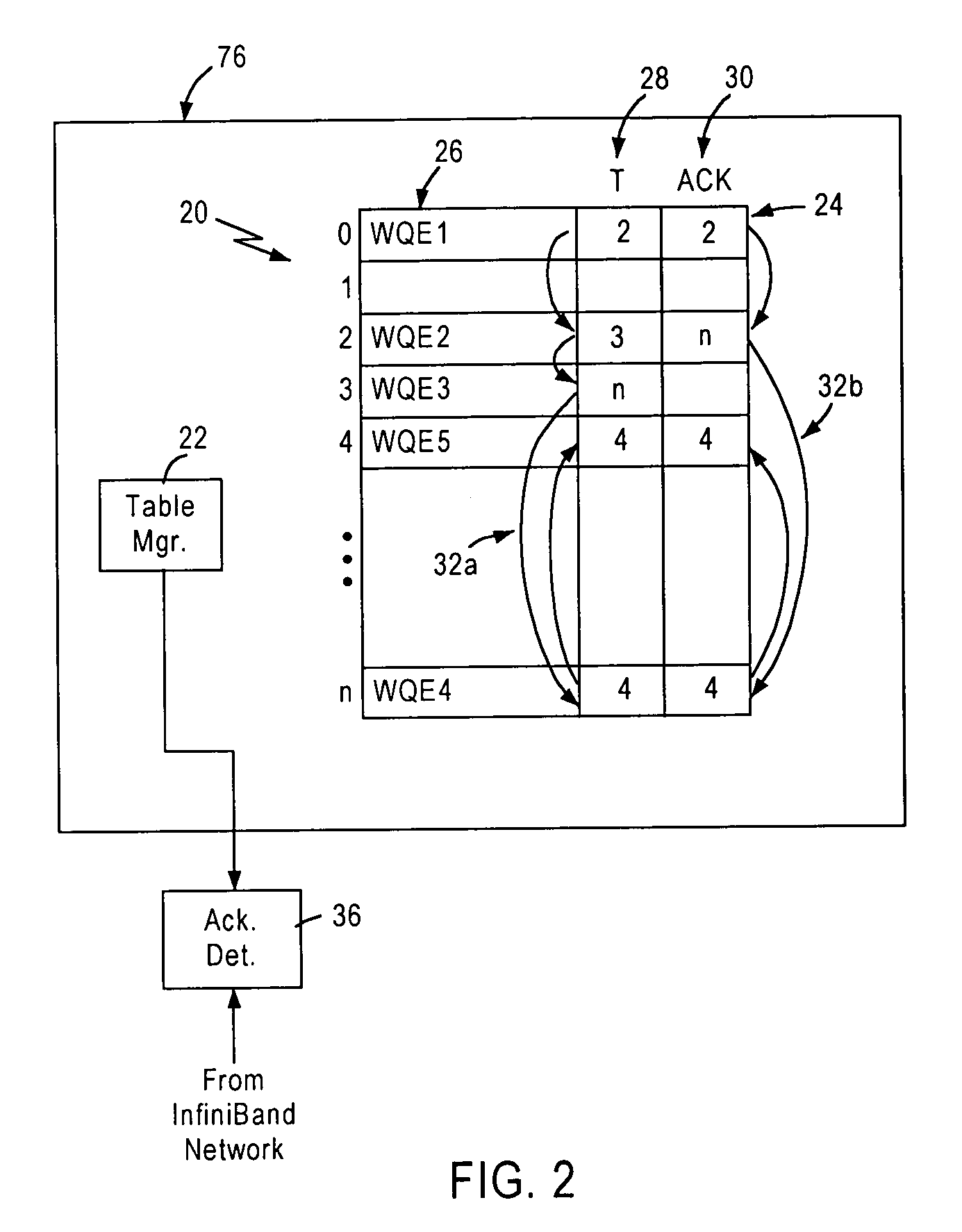

Arrangement in an infiniband channel adapter for sharing memory space for work queue entries using multiply-linked lists

InactiveUS7346707B1Economical and efficientMultiple digital computer combinationsInput/output processes for data processingNetwork conditionsDatabase

A channel adapter includes a work queue entry table having entries configured for storing work queue entries awaiting respective acknowledgements. Each entry includes a work queue entry field for storing a corresponding work queue entry, and first and second link fields for respective linked lists. The channel adapter also includes a table manager configured for creating the linked lists, based on prescribed network conditions, for example for storage of a first list specifying a transmission order of the work queue entry fields and a second list specifying an acknowledgement order. Hence, the multiple link fields enable the work queue entry table to be shared for respective linked lists specifying respective attributes relative to the stored work queue entries.

Owner:ADVANCED MICRO DEVICES INC

Service level to virtual lane mapping

An Infiniband device can be provided. The device can have an input port for receiving a packet. The port can be operable to extract a destination descriptor and a quality of service requirement descriptor for the packet and simultaneously to determine an output port of the device for onward transmission of the packet on the basis of the destination descriptor and to determine an output port virtual lane for each output port of the device on the basis of the quality of service requirement descriptor. The port can additionally be operable subsequently to use the determined output port to select between the determined output port virtual lanes.

Owner:ORACLE INT CORP

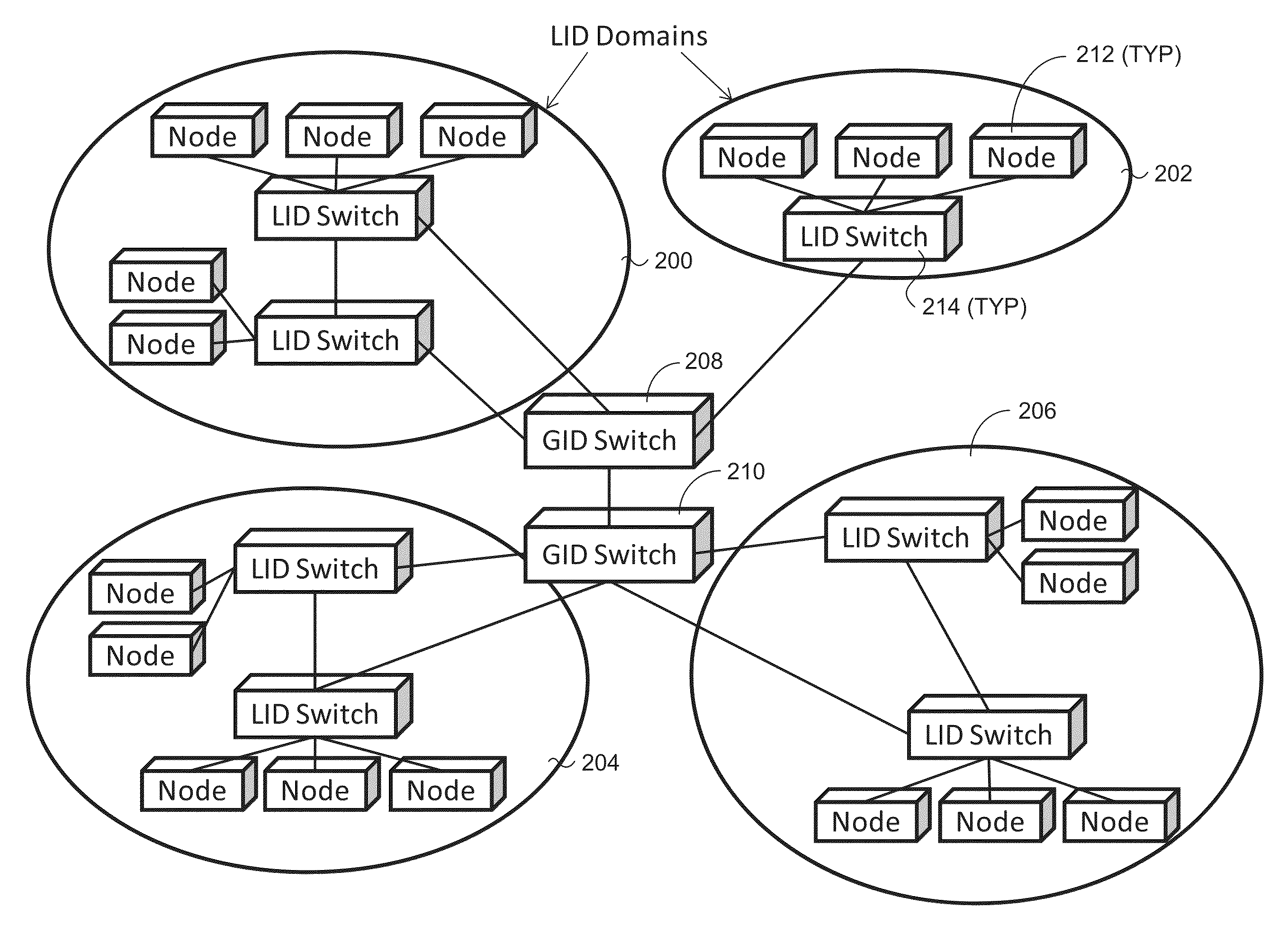

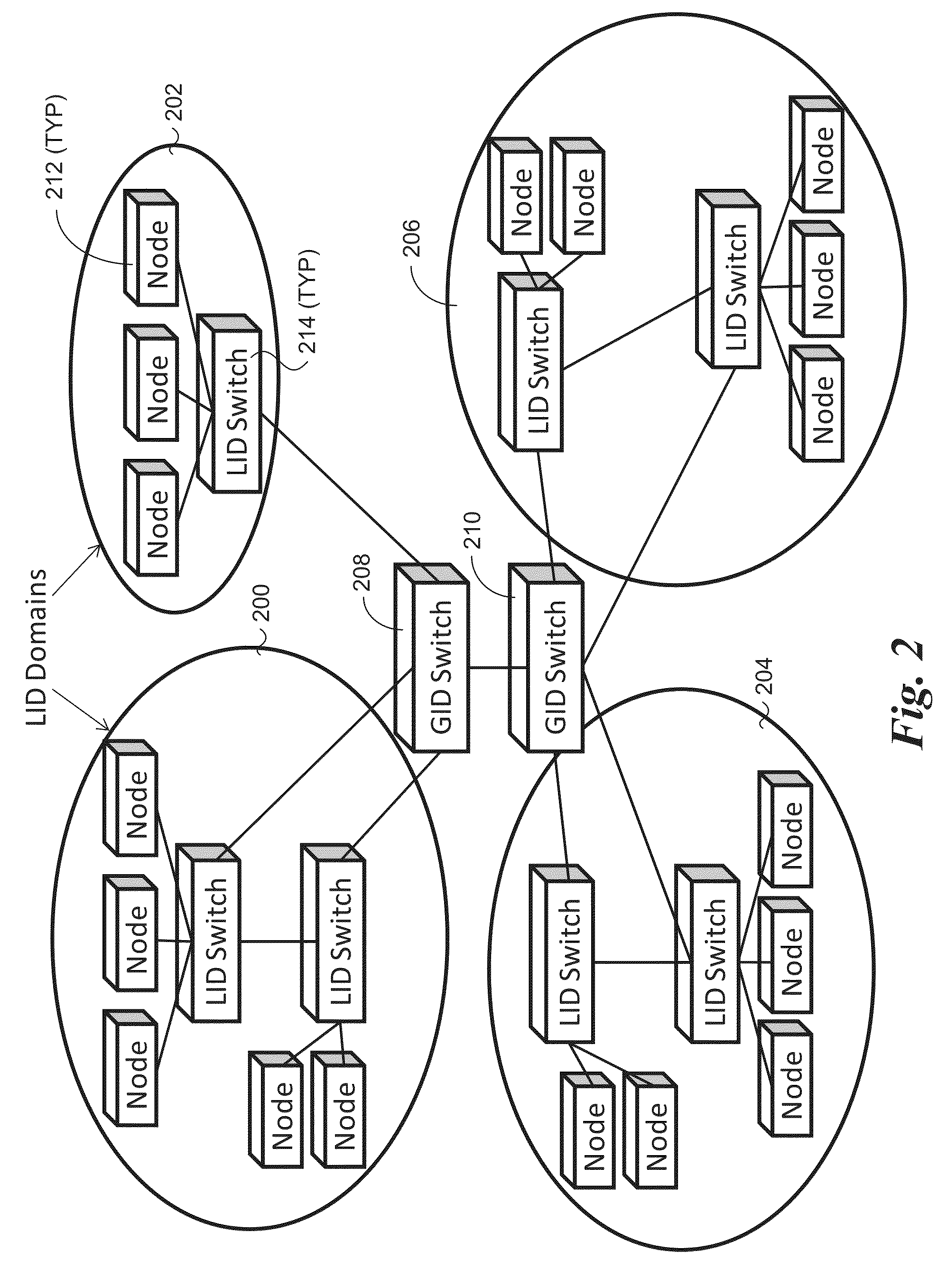

Gid capable switching in an infiniband fabric

Methods, systems, and apparatus for extending the size of Infiniband subnets using GID switching in an Infiniband fabric. An Infiniband subnet is defined to include multiple local identifier (LID) domains, each including multiple nodes interconnected via one or more LID switches. In turn, the LID domains are interconnected via one or more GID switches. Messages may be transferred between nodes in a given LID domain using LID switches in the domain. Messages may be transferred between nodes in separate LID domains by routing the messages via one or more GID switches. In various embodiments, GID switches may be implemented to also operate as LID switches and perform routing based on selected packet header fields.

Owner:INTEL CORP

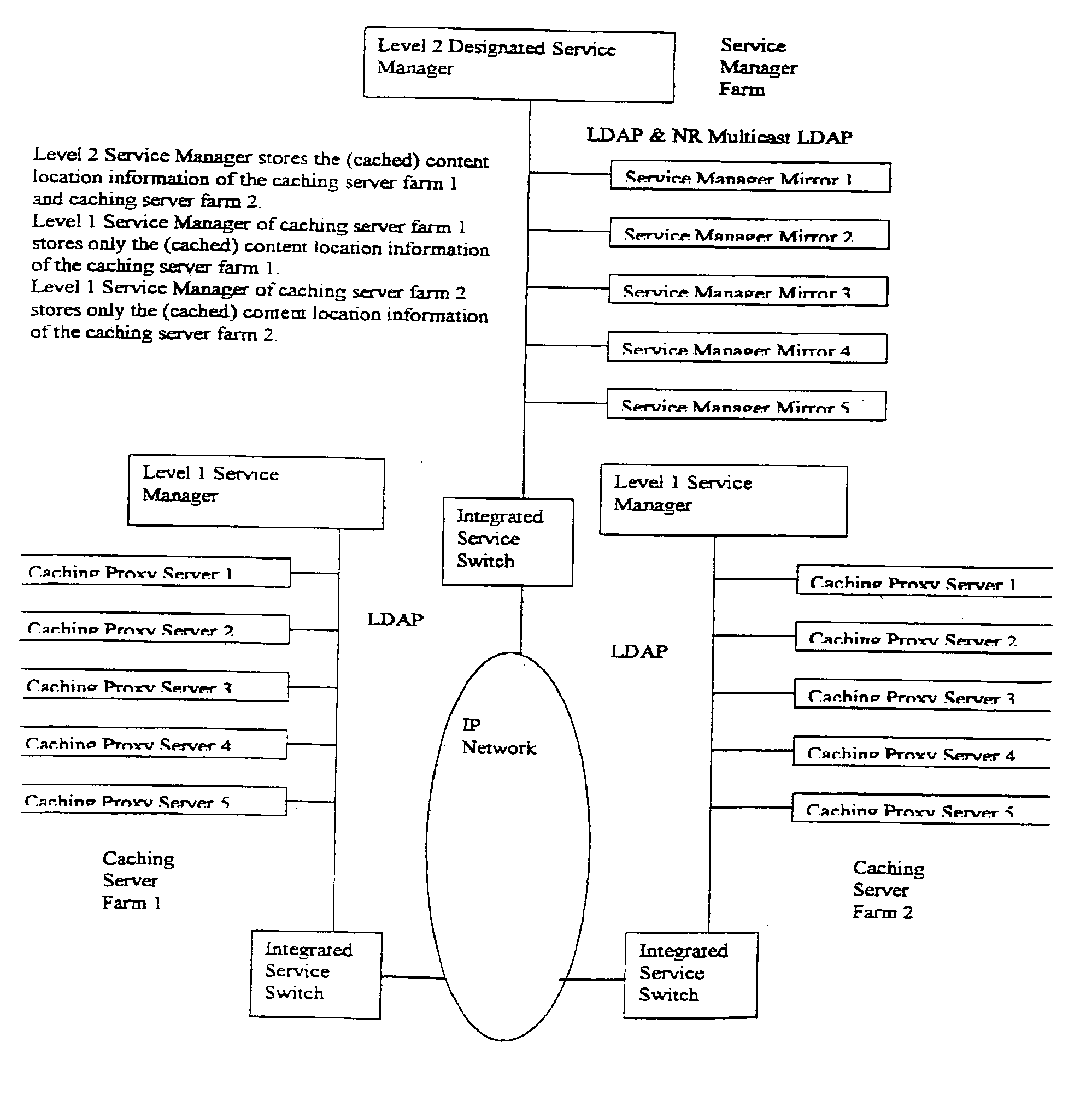

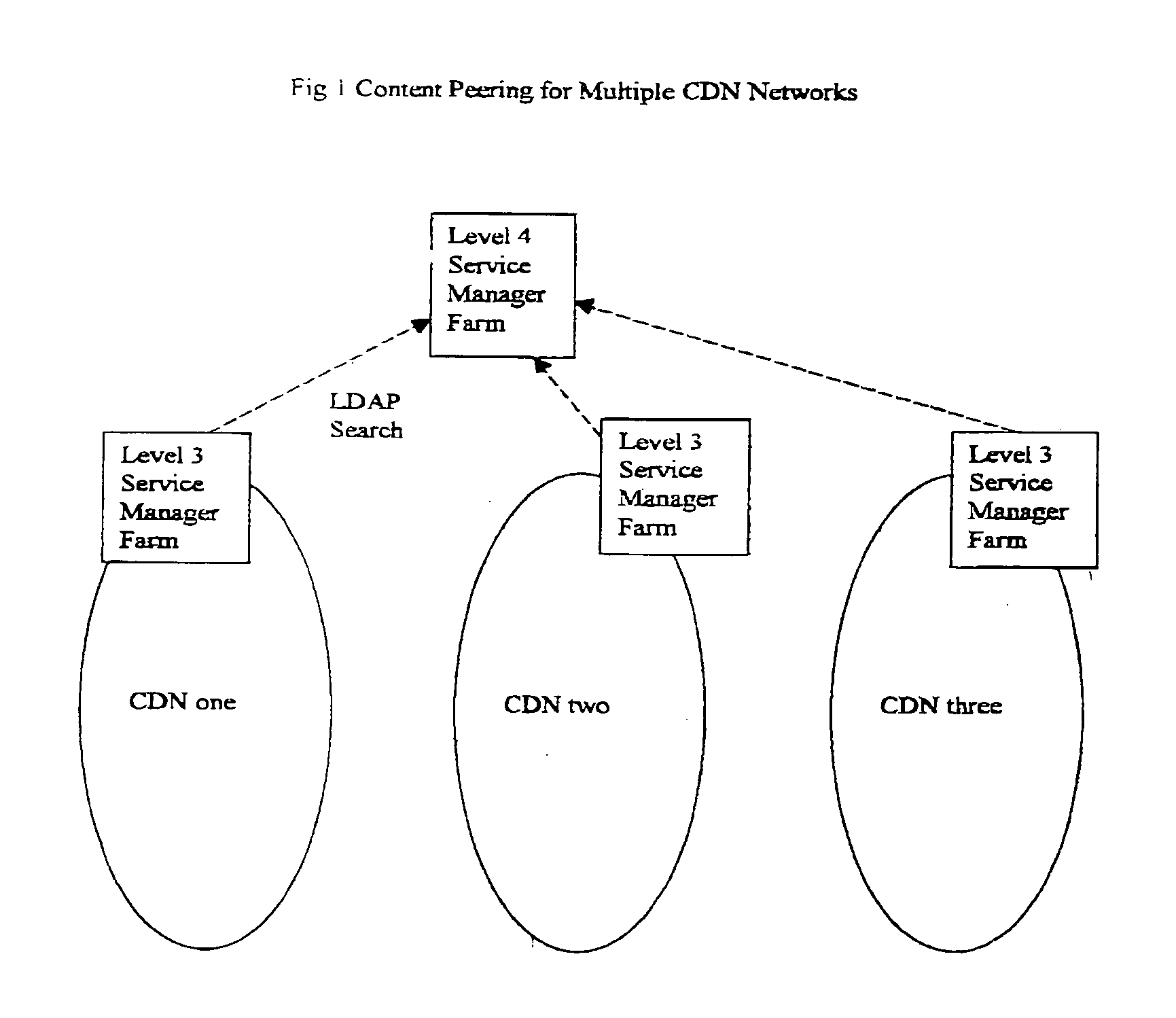

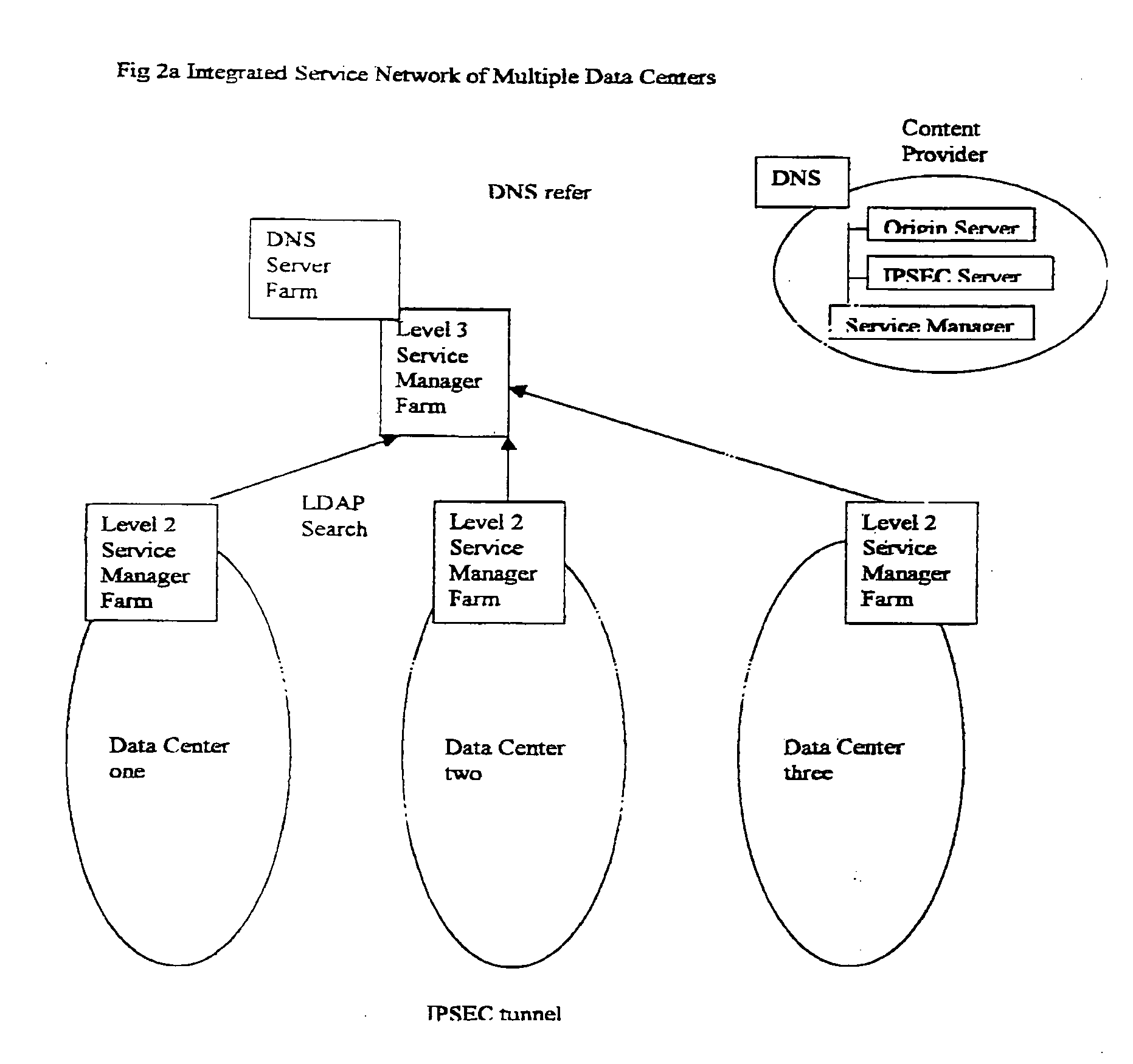

Network system, method and protocols for hierarchical service and content distribution via directory enabled network

InactiveUS20050198250A1Improve performanceBetter and scalable service provisioning and managementDigital computer detailsData switching networksContent distributionData center

A network system manages hierarchical service and content distribution via a directory enabled network to improve performance of the content delivery network with a hierarchical service network infrastructure design. The network system allows a user to obtain various Internet services, especially the content delivery service, in a scalable and fault tolerant way. In particular the network system is divided into 4 layers, each layer being represented and managed by a service manager with back up mirrored managers. The layer 4 service manager is responsible for management of multiple content delivery networks (CDNs). The layer 3 service manager is responsible for management of one CDN network that has multiple data centers. The layer 2 service manager is responsible for management of one data center that has multiple server farms or service engine farms. The layer 1 service manager is responsible for all servers in a server farm. Each server of the server farm can be connected by a LAN Ethernet Switch Network that supports the layer 2 multicast operations or by an Infiniband switch.

Owner:TERITED INT

Infiniband multicast operation in an LPAR environment

InactiveUS7428598B2Special service provision for substationData switching by path configurationData processing systemData treatment

A method, computer program product, and data processing system for providing system-area network (SAN) multicasting functionality in a logically partitioned (LPAR) data processing system in which a channel adapter is shared among a plurality of logical partitions is disclosed. A preferred embodiment of the present invention allows LPAR “hypervisor” firmware to assume the responsibility for multicast protocol handling and distribution of packets among logical partitions.

Owner:IBM CORP

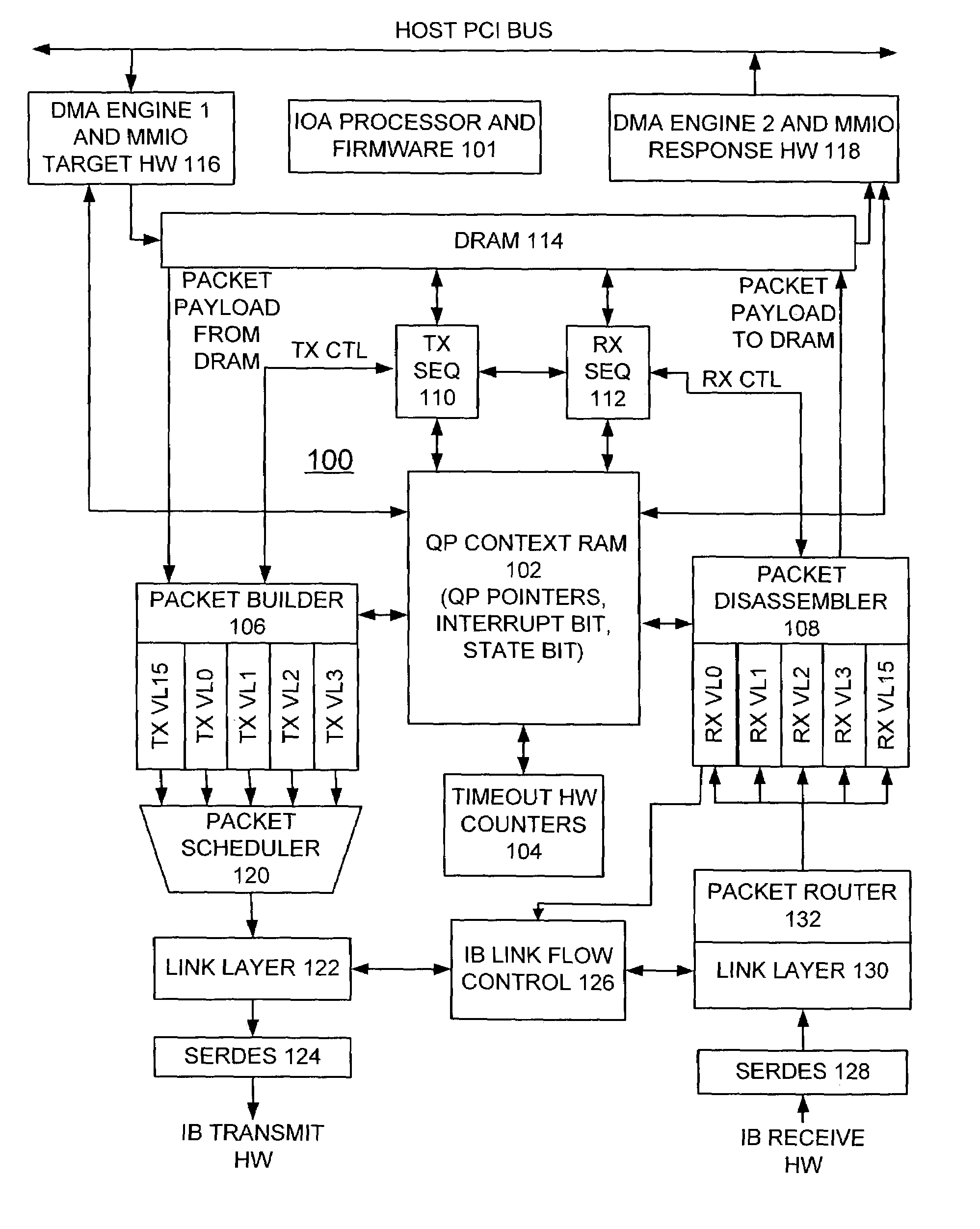

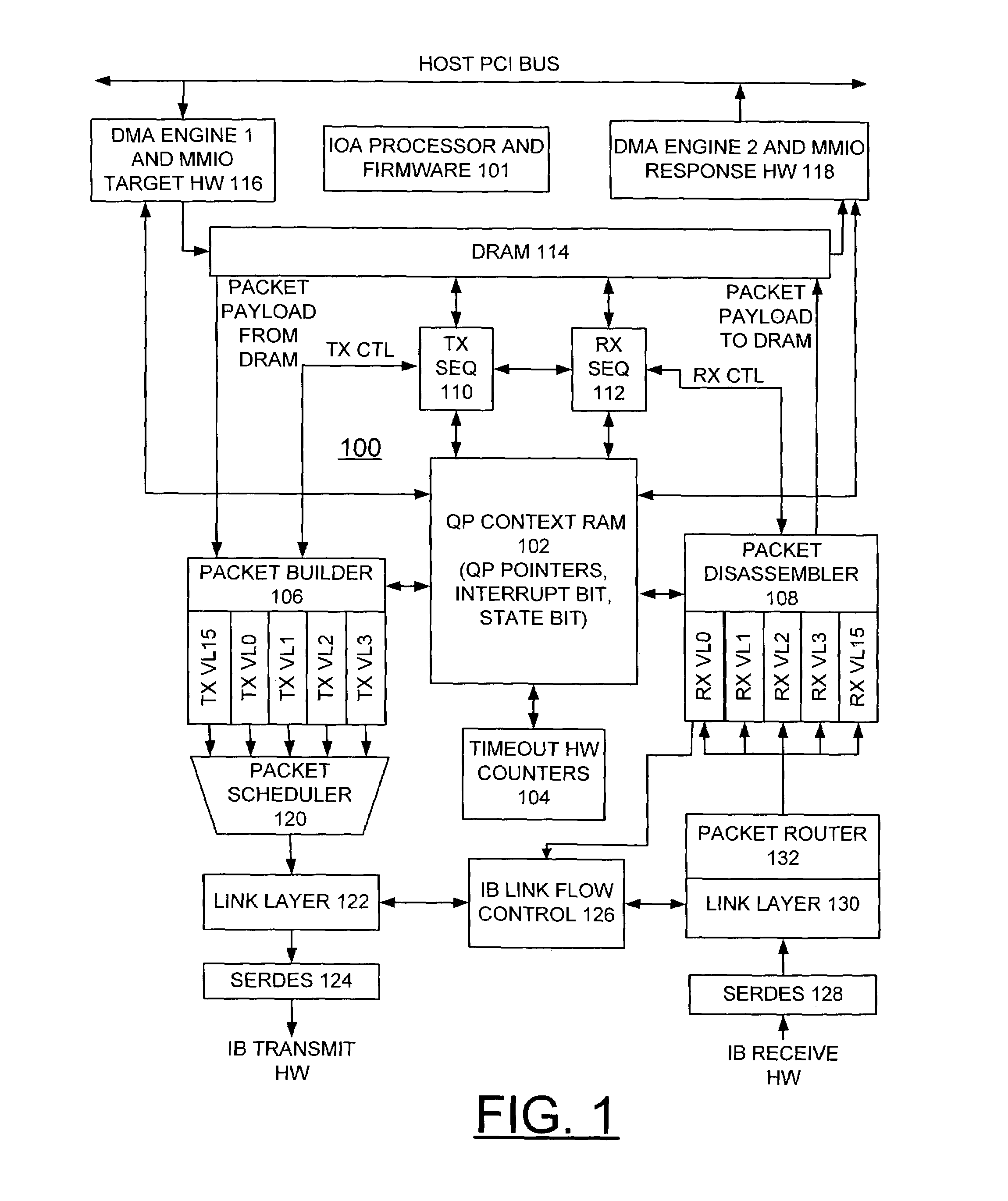

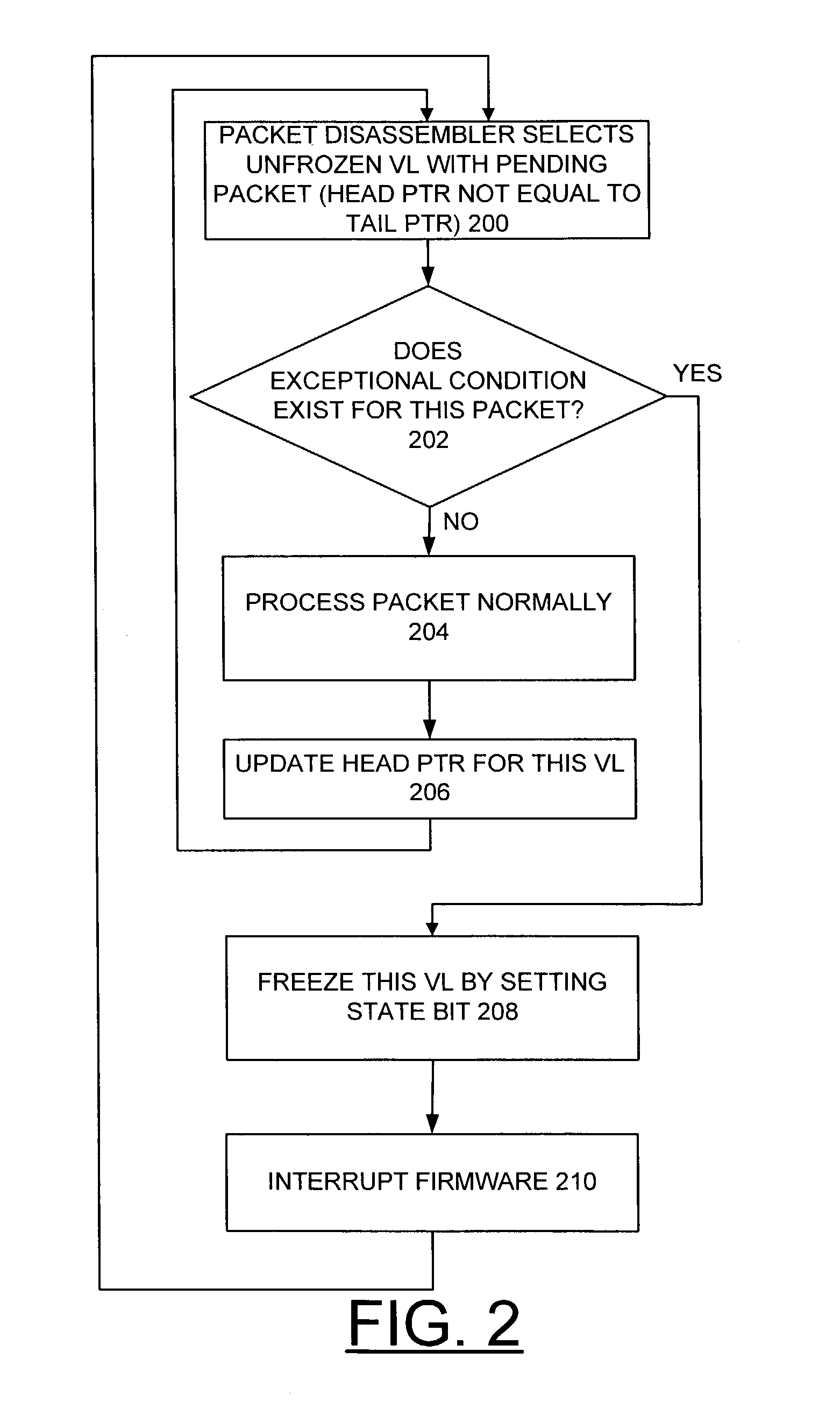

Method and apparatus for implementing infiniband receive function

InactiveUS7225364B2Negative effectError detection/correctionData switching by path configurationNetwork packetApplication software

A method, apparatus, and computer program product are provided for implementing a receive function over an interconnect network, such as InfiniBand. A virtual lane (VL) with a pending packet for a queue pair (QP) is selected. Then the pending packet is checked for an exceptional condition. Responsive to identifying the exceptional condition for the pending packet, a state bit is set for freezing the selected VL; and an interrupt is generated to firmware. Responsive to receiving the interrupt, the firmware determines a cause for freezing the selected VL and performs a responsive action. For example, the responsive action performed by firmware includes firmware performing an error recovery procedure (ERP) for the QP; firmware updating a state for the QP; or firmware performing application unique processing for the QP.

Owner:GOOGLE LLC

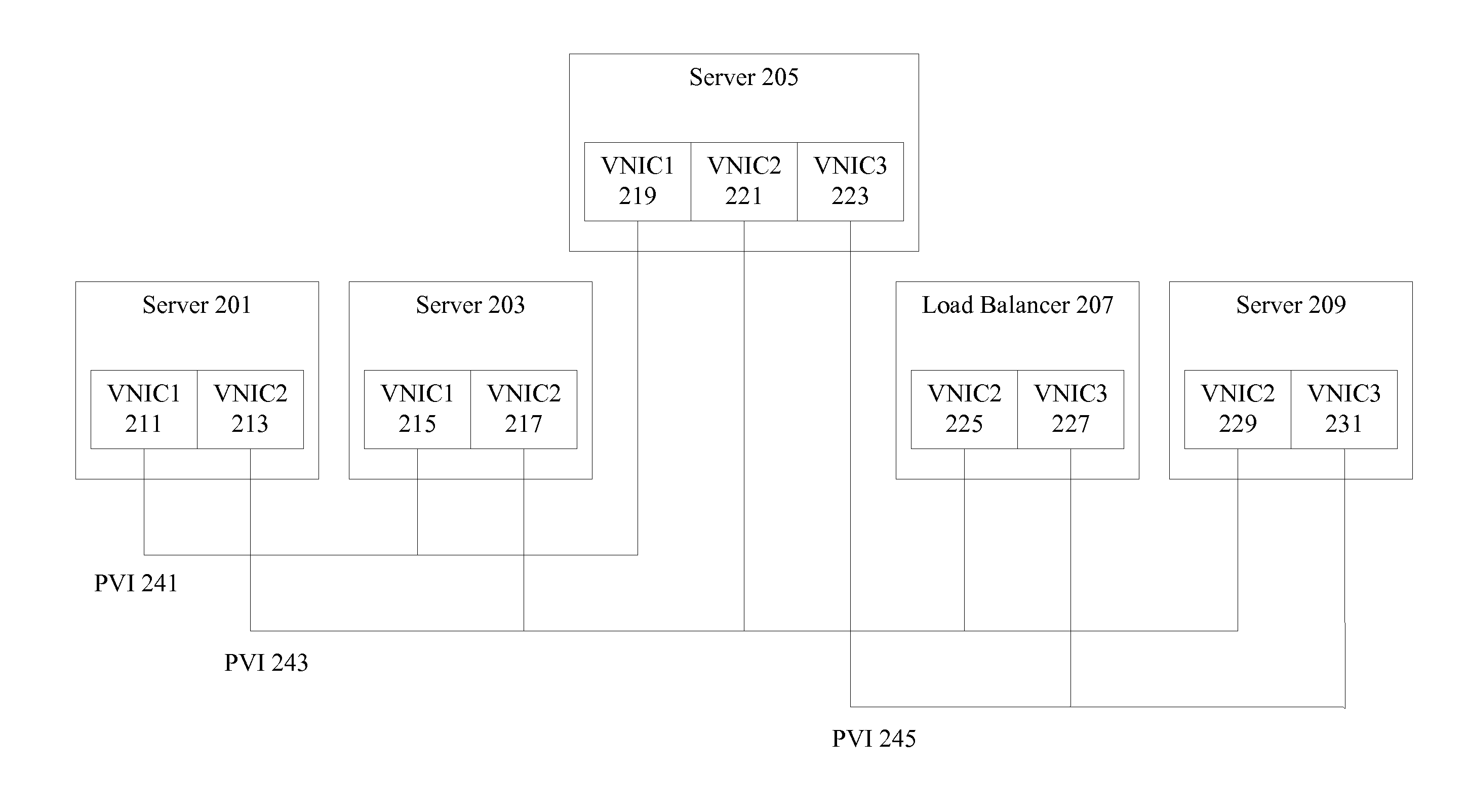

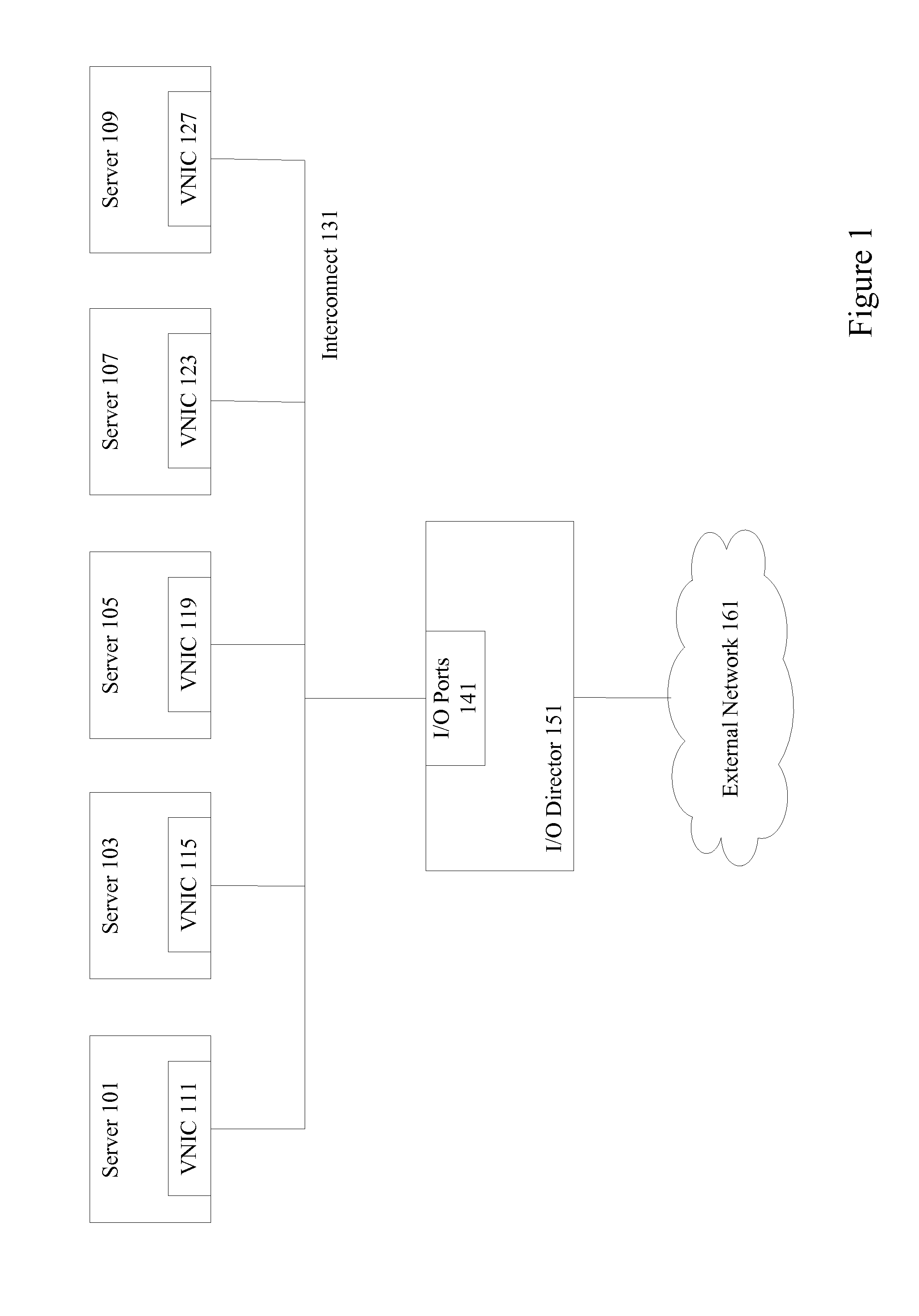

Network virtualization over infiniband

ActiveUS20140122675A1Digital computer detailsData switching networksBroadcastingNetwork virtualization platform

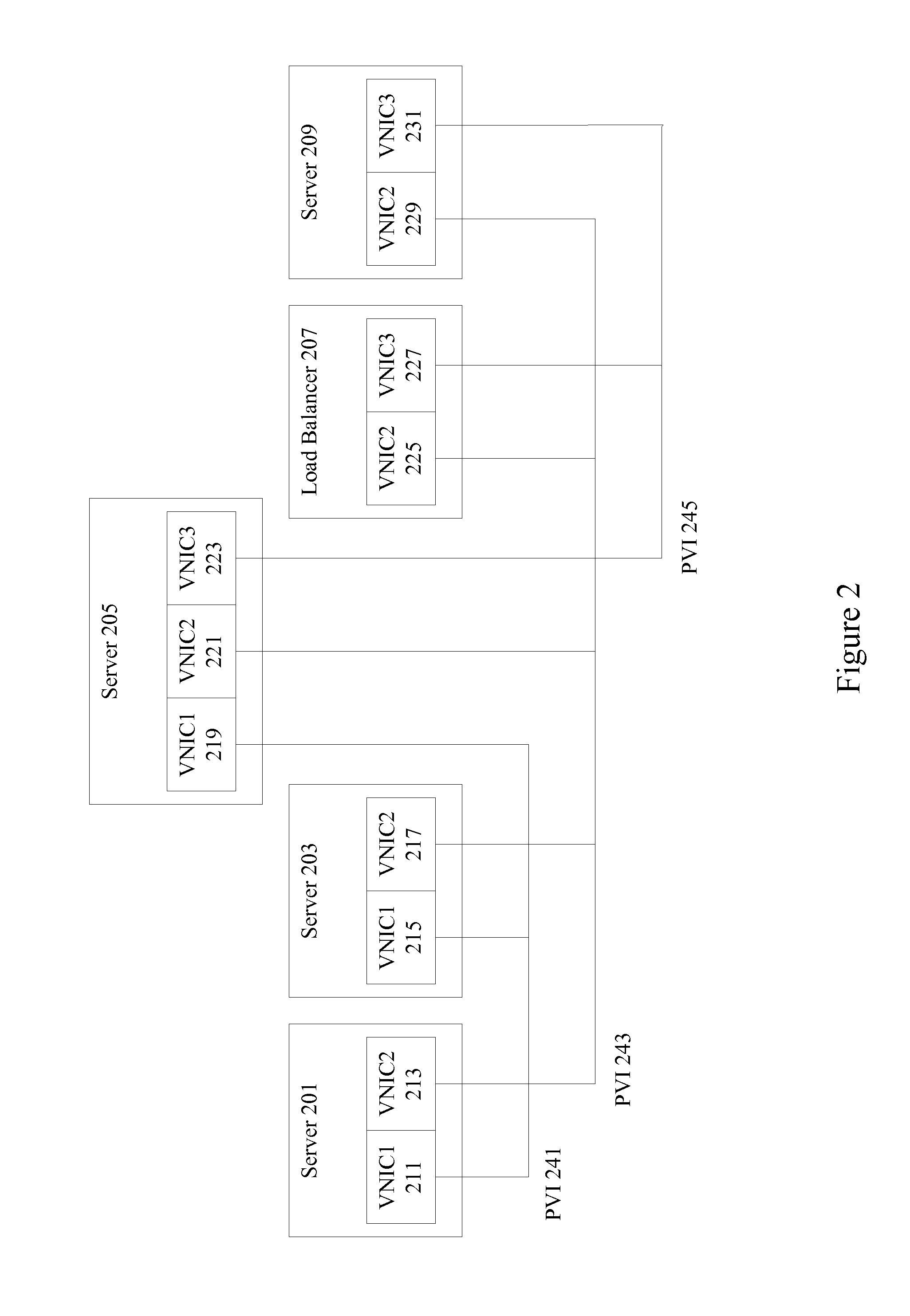

Mechanisms are provided to allow servers connected over an InfiniBand fabric to communicate using multiple private virtual interconnects (PVIs). In particular embodiments, the PVIs appear as virtual Ethernet networks to users on individual servers and virtual machines running on the individual servers. Each PVI is represented on the server by a virtual network interface card (VNIC) and each PVI is mapped to its own InfiniBand multicast group. Data can be transmitted on PVIs as Ethernet packets fully encapsulated, including the layer 2 header, within InfiniBand messages. Broadcast and multicast frames are propagated using InfiniBand.

Owner:ORACLE INT CORP