Patents

Literature

6500results about "Baseband system details" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

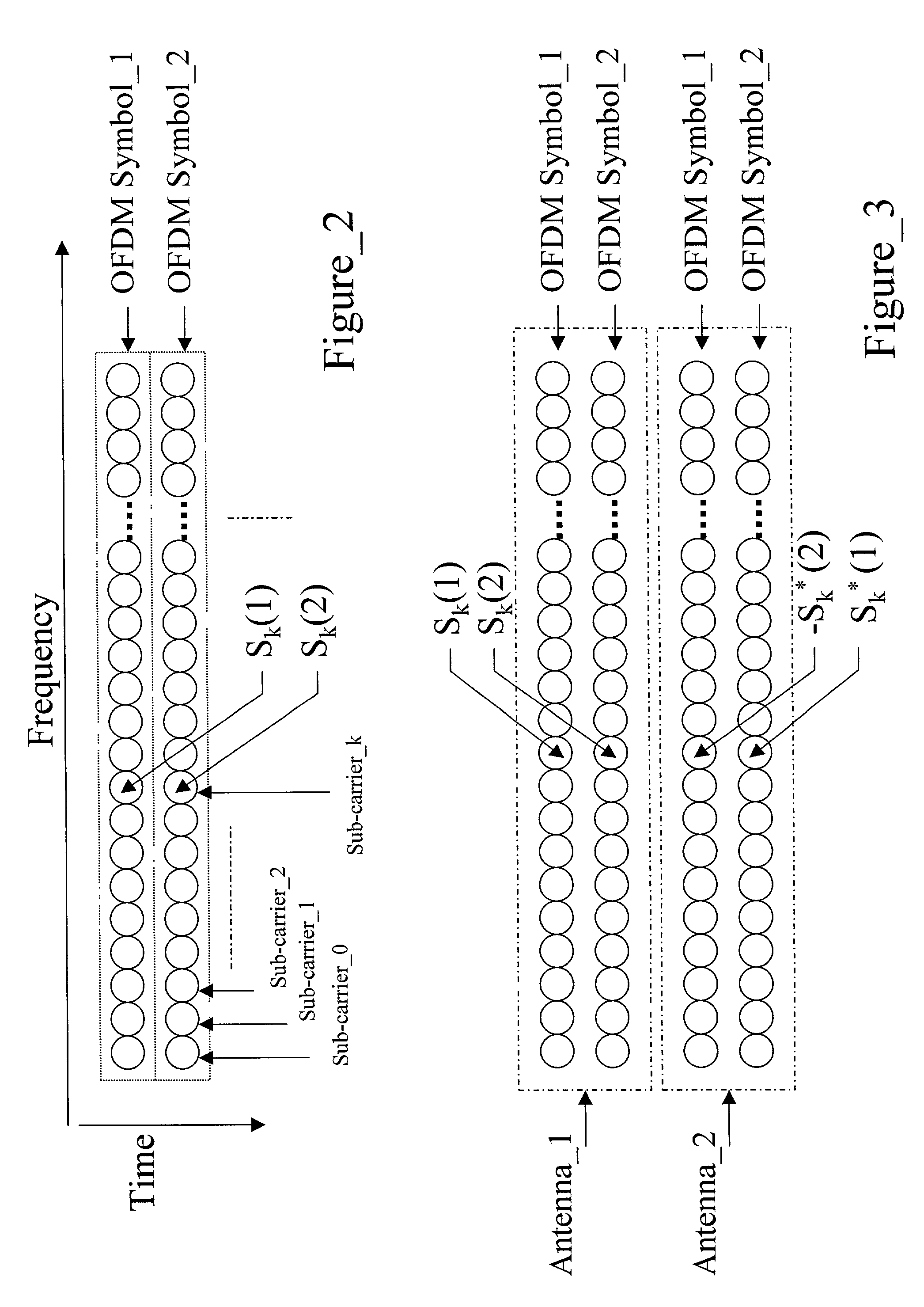

Apparatus for OFDMA transmission and reception for coherent detection in uplink of wireless communication system and method thereof

InactiveUS20050135324A1Improve channel estimation performanceFrequency-division multiplexSecret communicationCommunications systemResource block

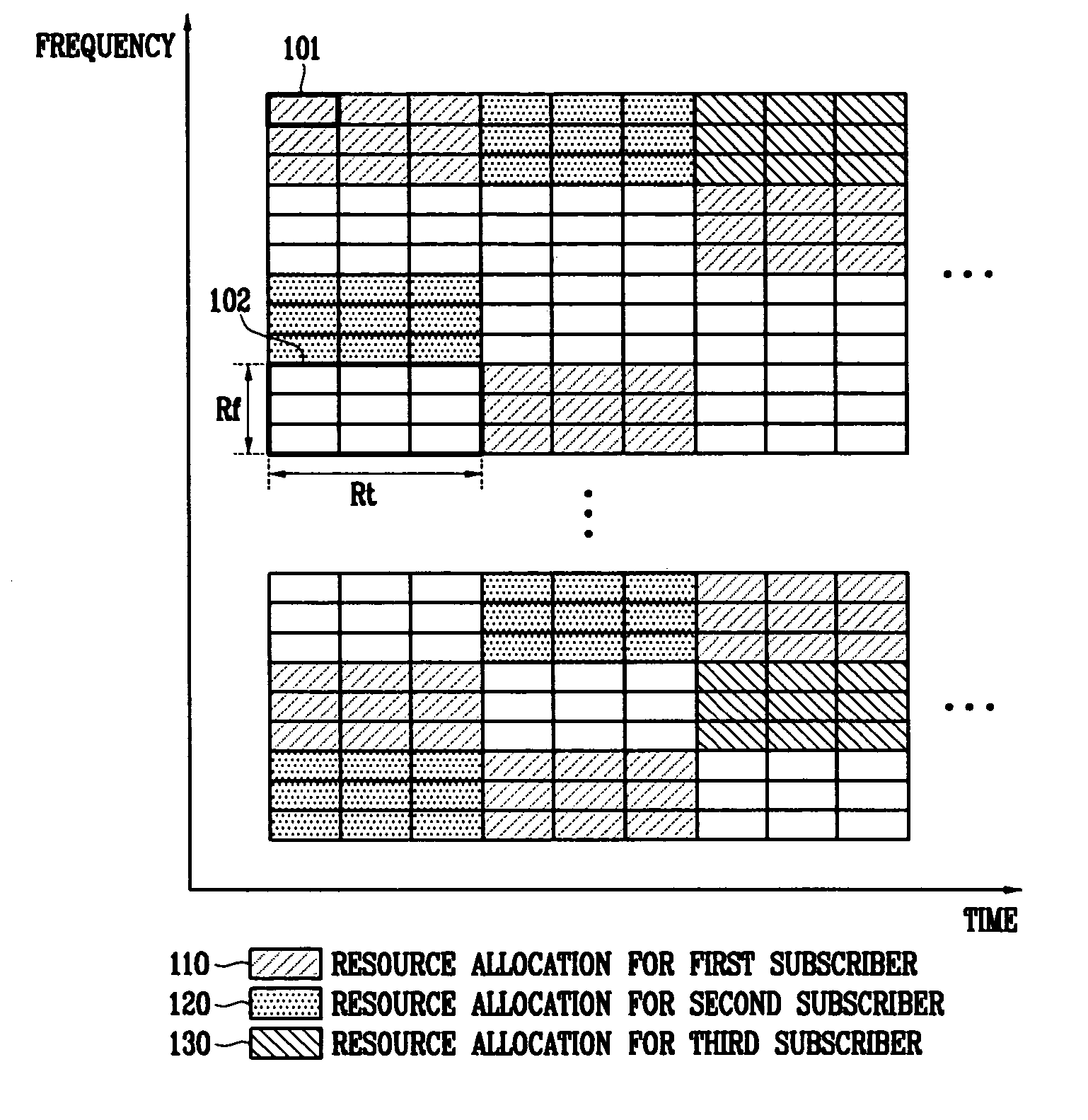

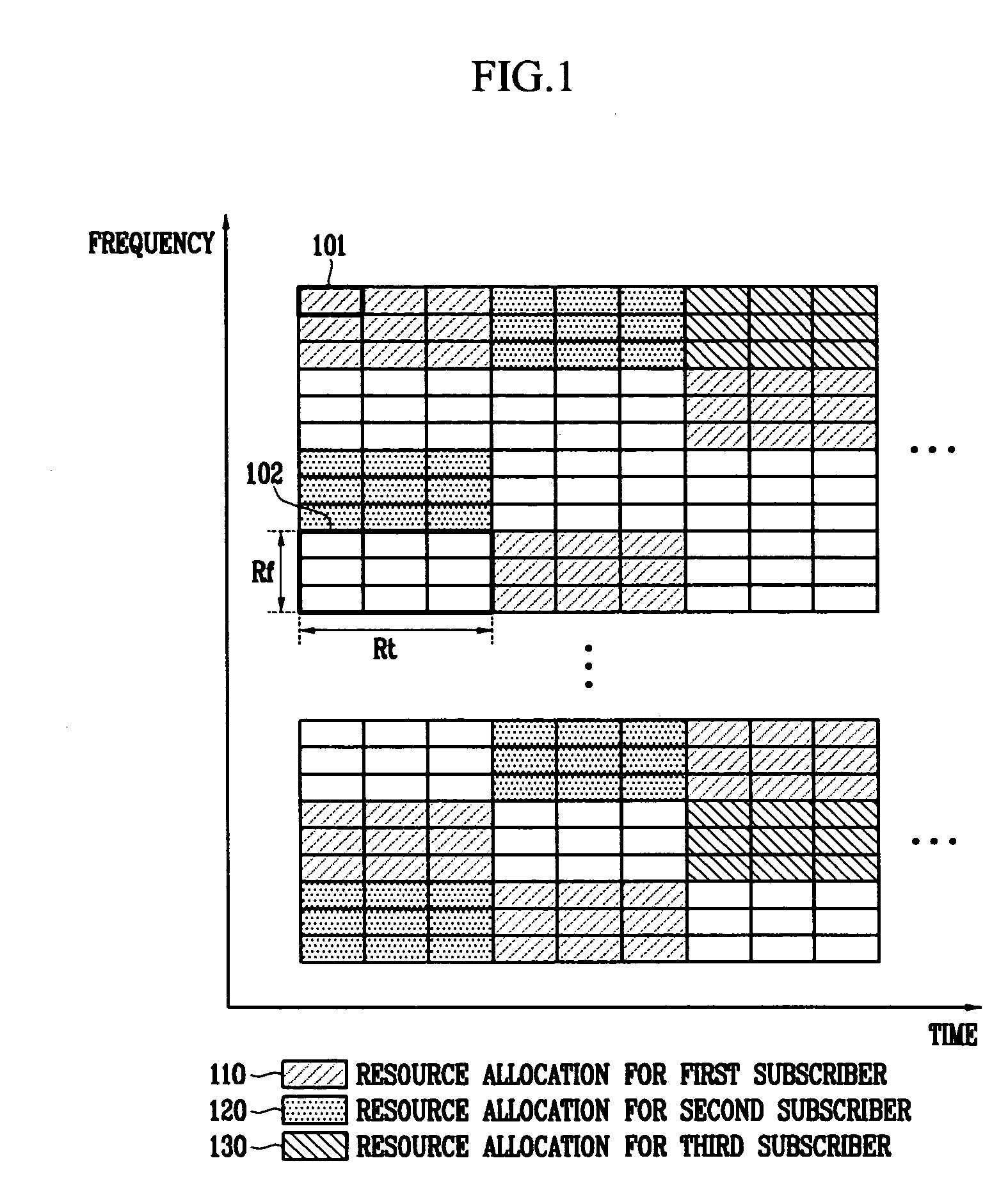

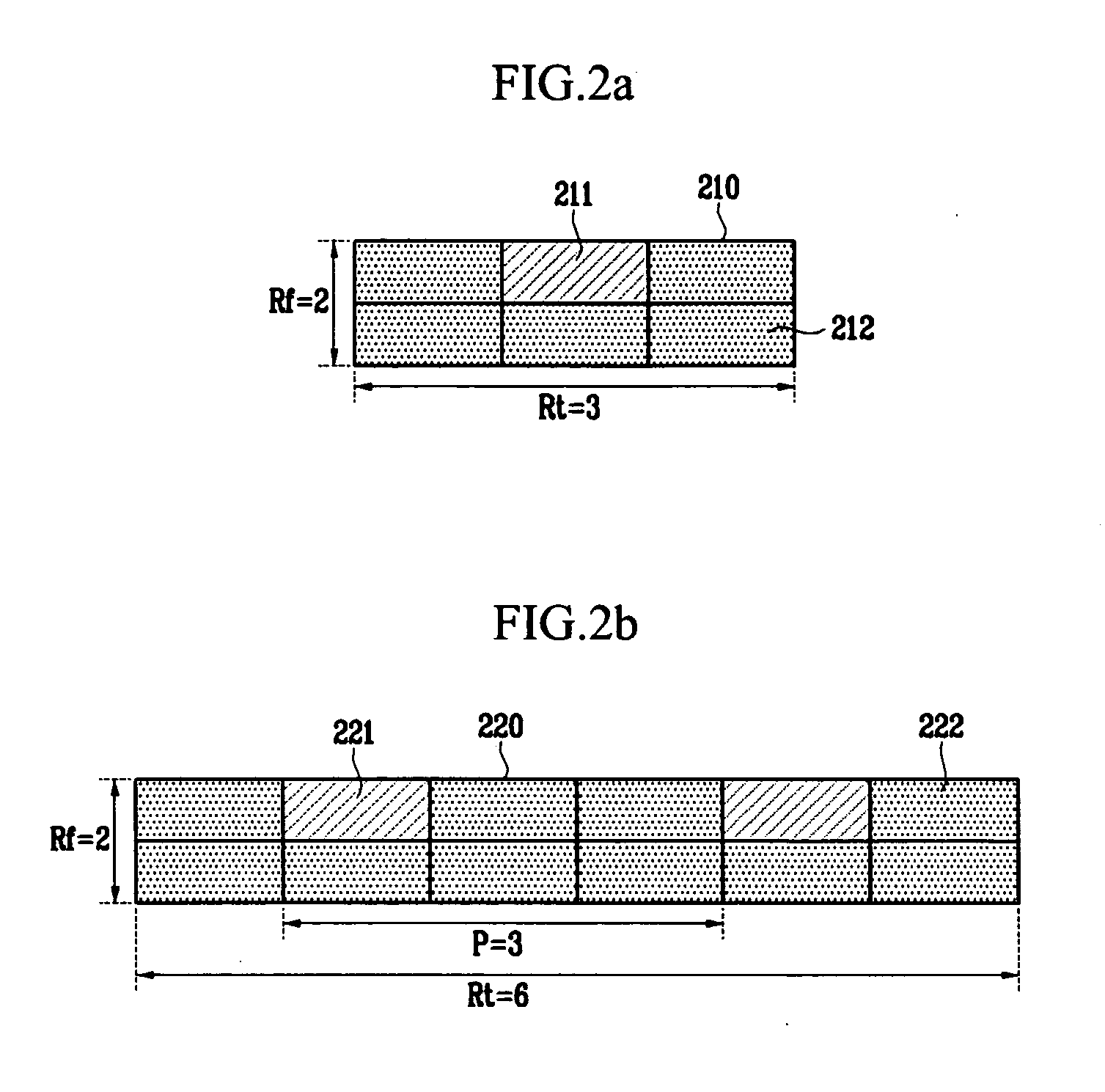

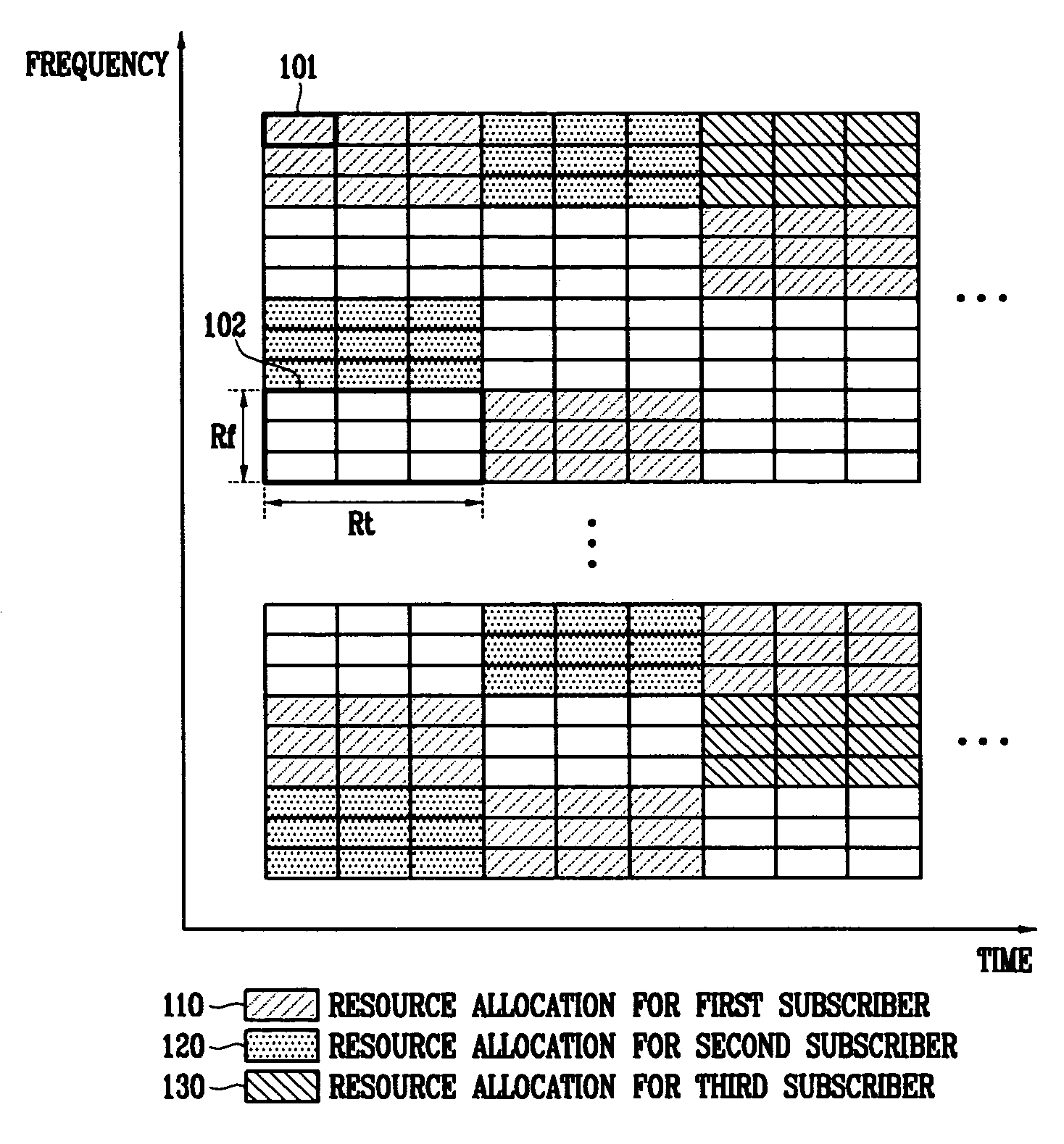

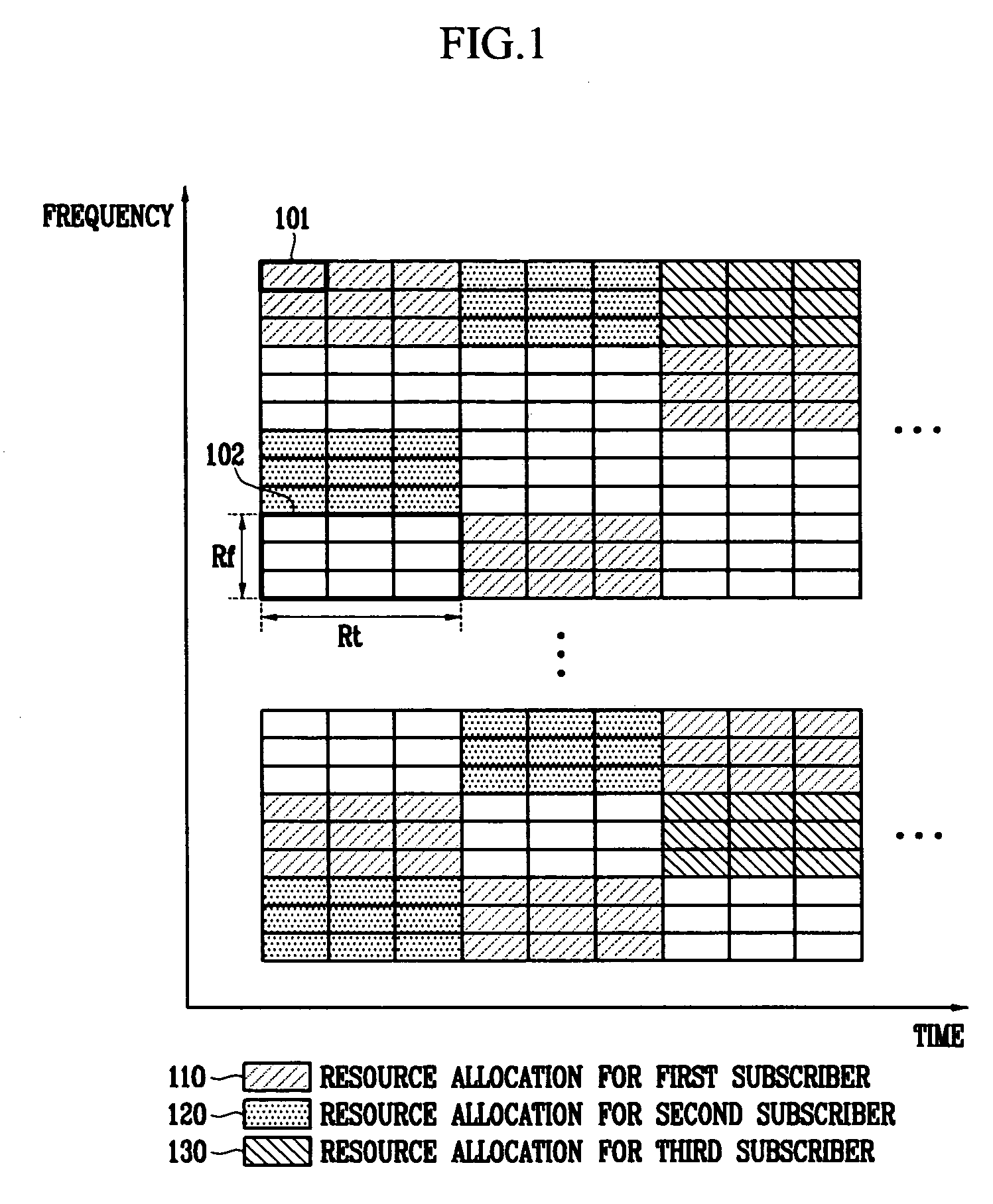

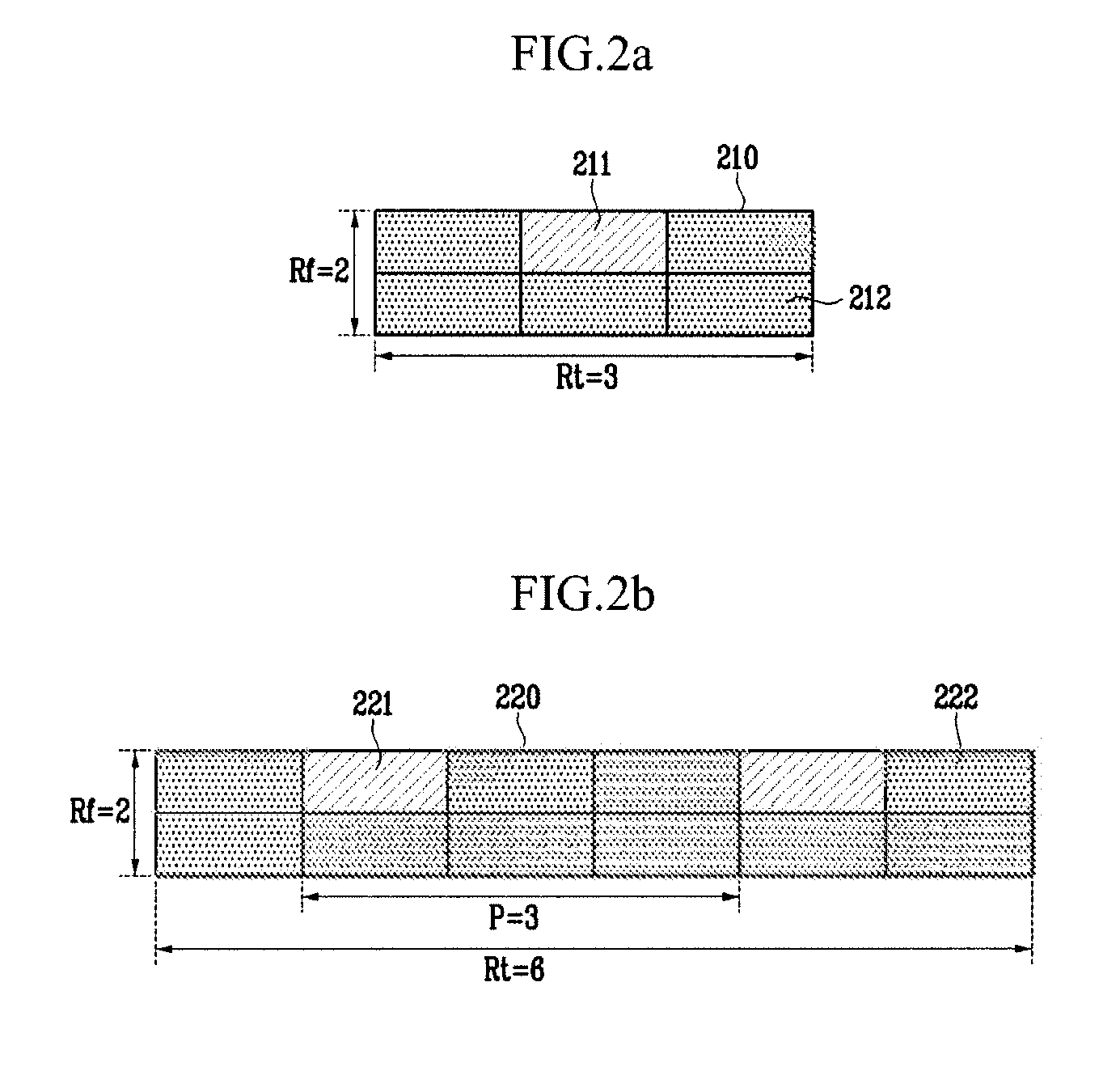

In the resource mapping method for data transmission, a time-frequency resource of a slot interval including OFDM symbols is divided into traffic channels and shared among the subscribers, the traffic channel including resource blocks uniformly distributed in the whole transmit frequency band, the resource block including consecutive subcarriers of consecutive received symbols having at least one inserted pilot symbol. The pilot symbols and the channel-encoded and modulated data symbols are processed by time-frequency mapping according to the resource-block-based mapping method to generate received symbols. The receiver separates the received symbols by subscribers according to the resource-block-based mapping method in a frequency domain, and performs iterative channel estimation, demodulation, and decoding by using the pilot and a data reference value after decoding for each traffic channel.

Owner:ELECTRONICS & TELECOMM RES INST

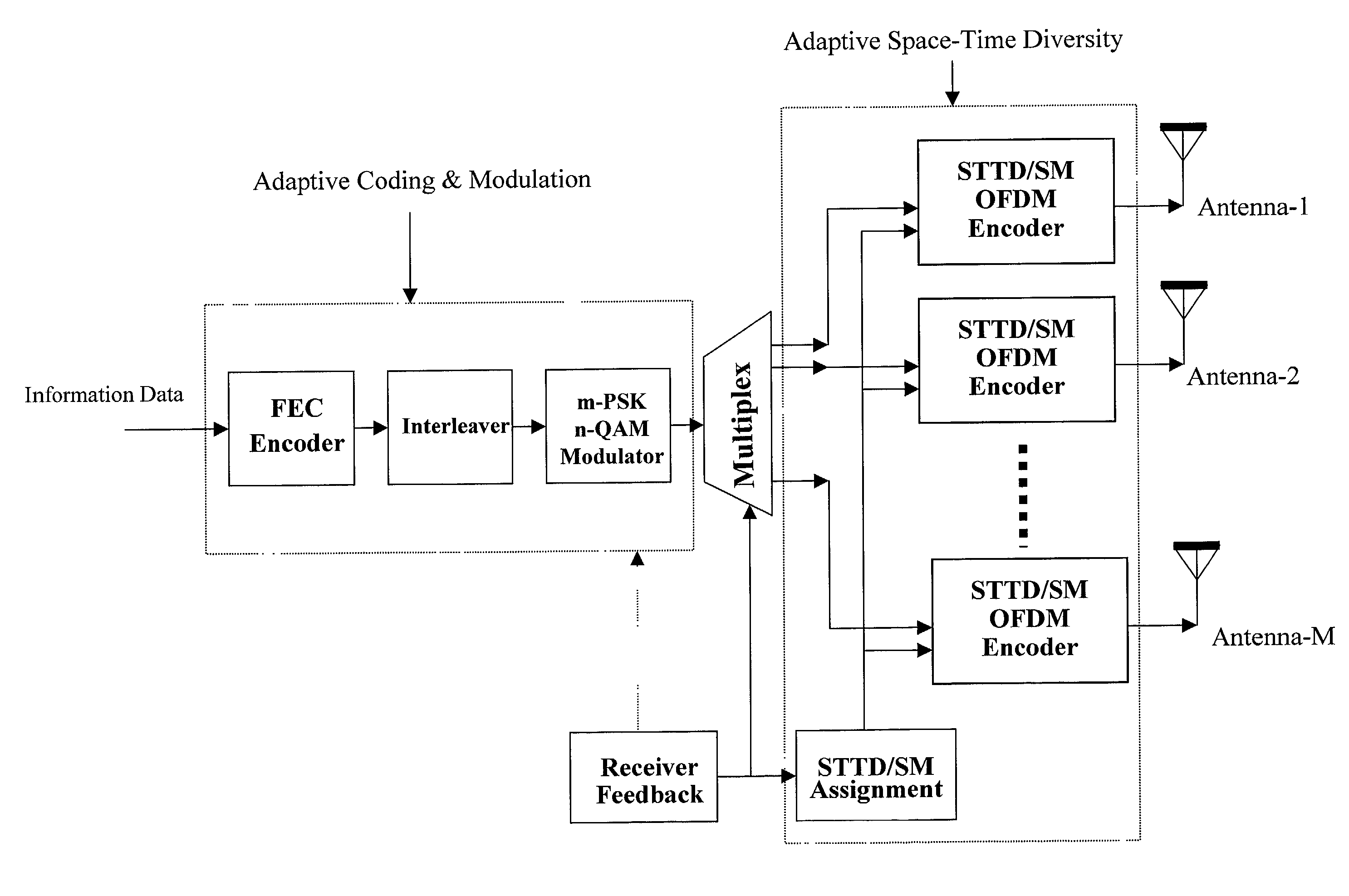

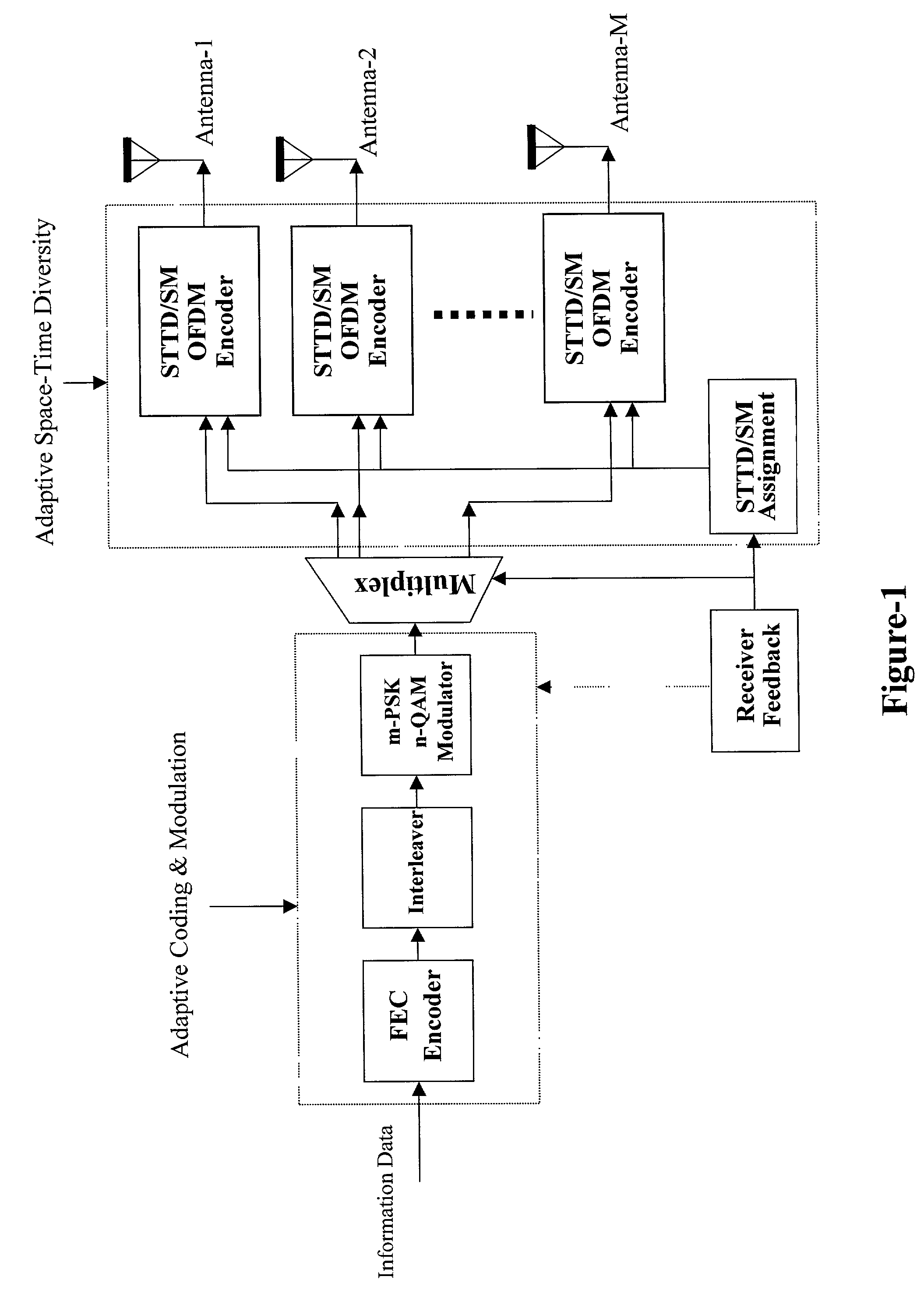

Adaptive time diversity and spatial diversity for OFDM

InactiveUS6985434B2Gain is assured with time diversityReduce signalingSpatial transmit diversityMultiple modulation transmitter/receiver arrangementsCarrier signalData rate

An adaptable orthogonal frequency-division multiplexing system (OFDM) that uses a multiple input multiple output (MIMO) to having OFDM signals transmitted either in accordance with time diversity to reducing signal fading or in accordance with spatial diversity to increase the data rate. Sub-carriers are classified for spatial diversity transmission or for time diversity transmission based on the result of a comparison between threshold values and at least one of three criteria. The criteria includes a calculation of a smallest eigen value of a frequency channel response matrix and a smallest element of a diagonal of the matrix and a ratio of the largest and smallest eigen values of the matrix.

Owner:APPLE INC

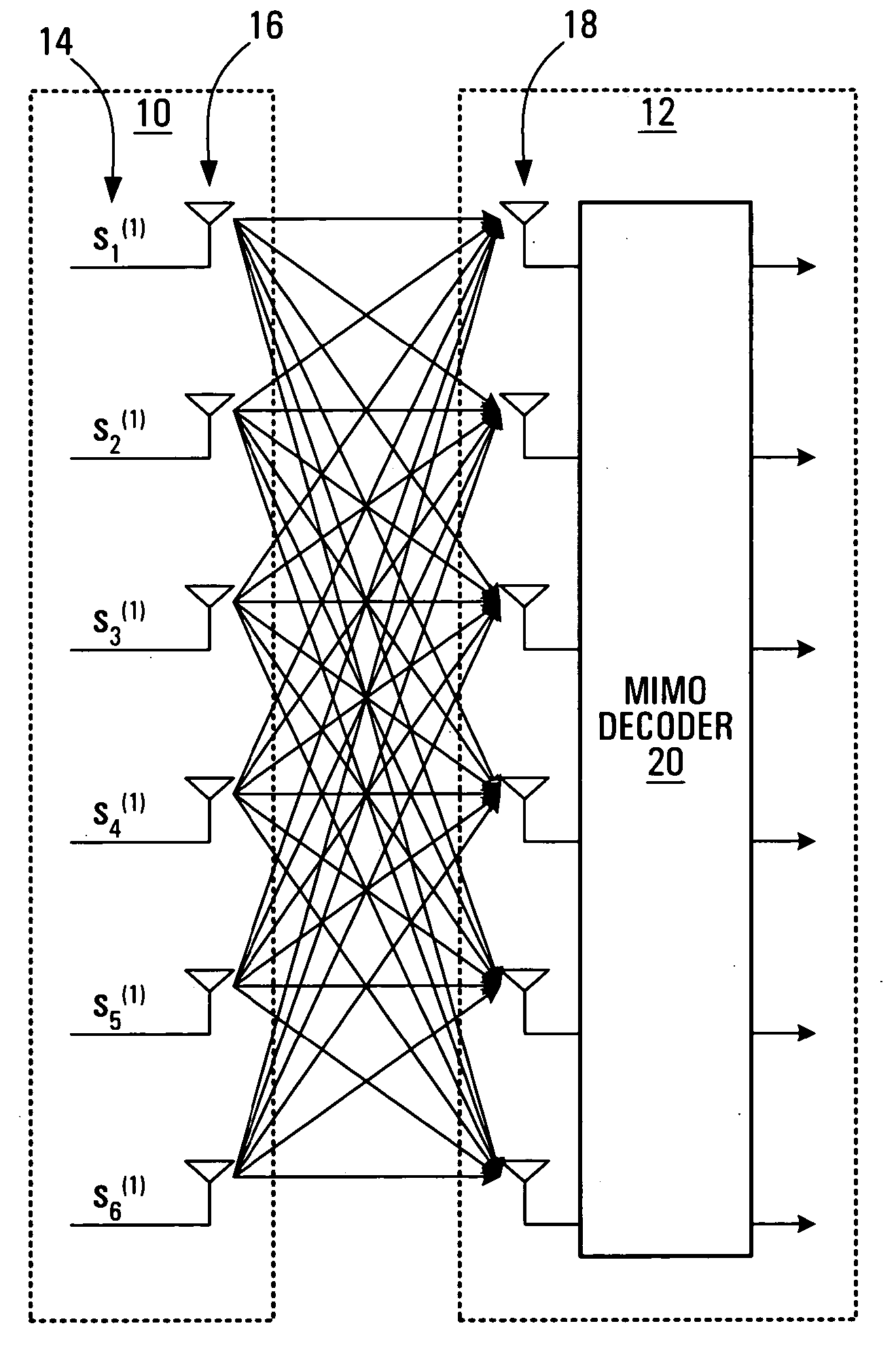

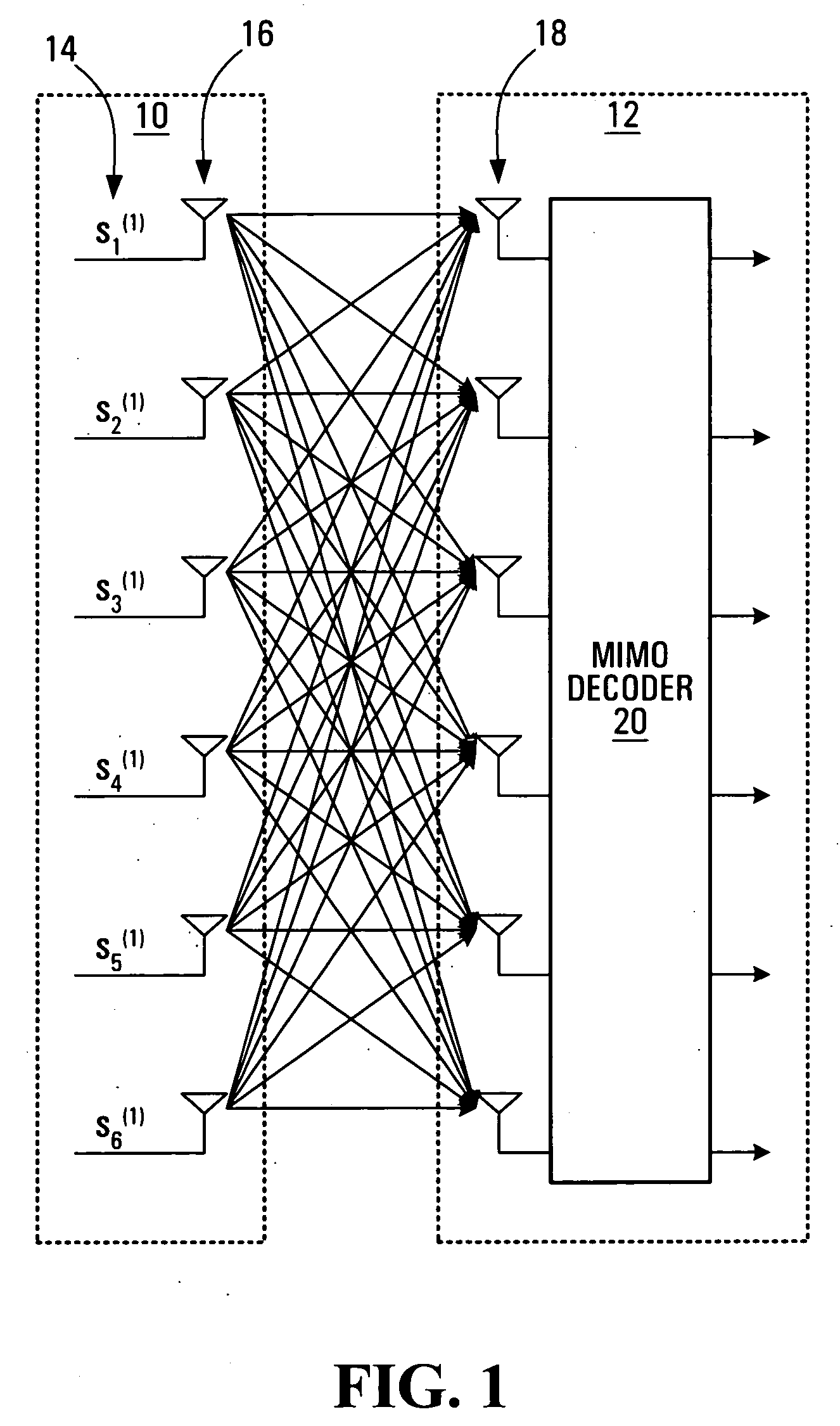

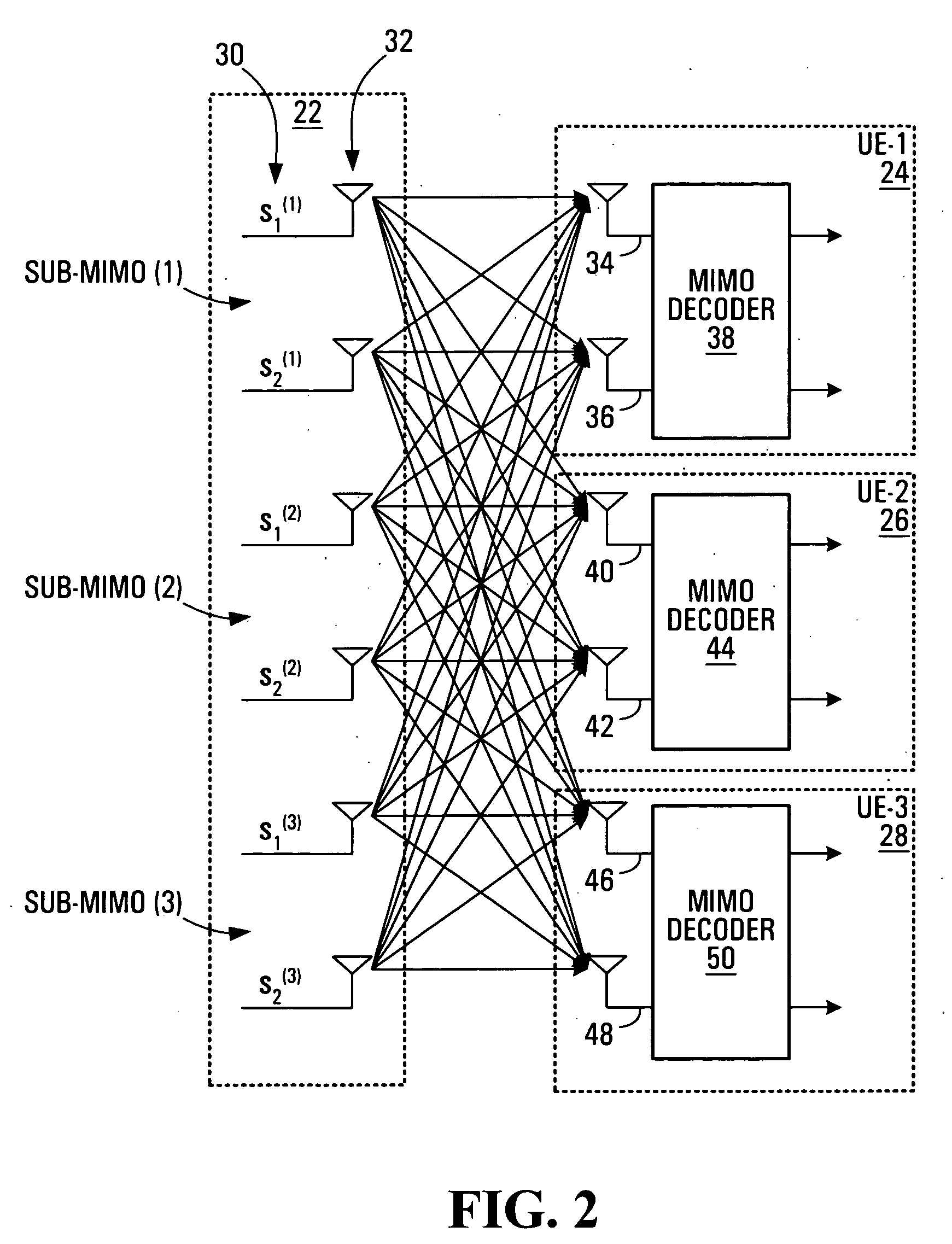

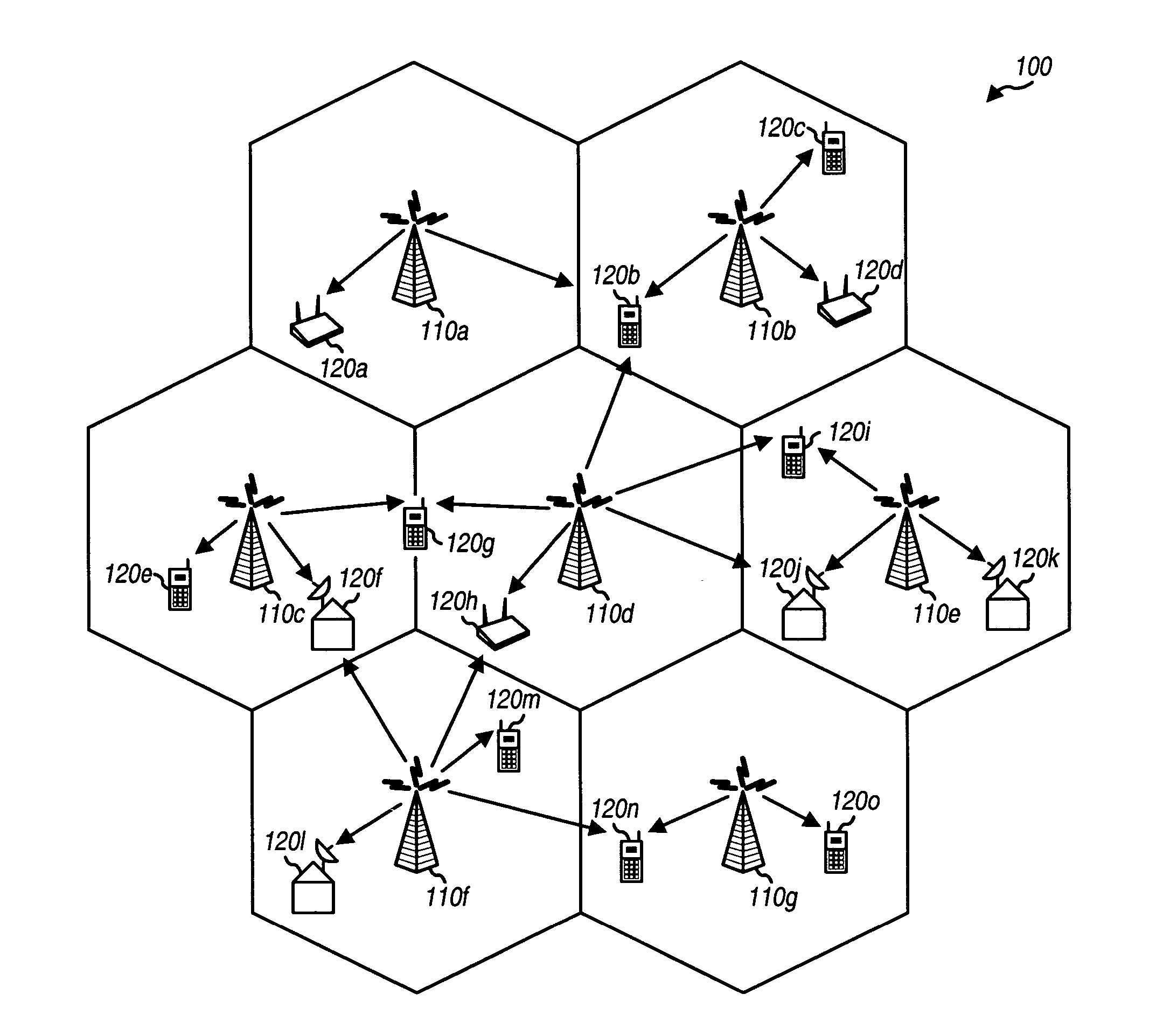

Communication channel optimization systems and methods in multi-user communication systems

ActiveUS20050101259A1Spatial transmit diversityBaseband system detailsChannel state informationCommunications system

Systems and methods of optimizing communication channels in multi-user communication systems are provided. Coding weights are determined based on communication channel state information for communication channels between a transmitter and multiple receivers. The coding weights are applied to communication signals to be transmitted from the transmitter to the receivers. Each receiver decodes received signals using inverses of the coding weights. Embodiments of the invention support multi-user MIMO (Multiple Input Multiple Output) where each receiver has fewer antennas than the transmitter, and enhance system performance if the total number of antennas at all of the receivers exceeds the number of antennas at the transmitter.

Owner:APPLE INC

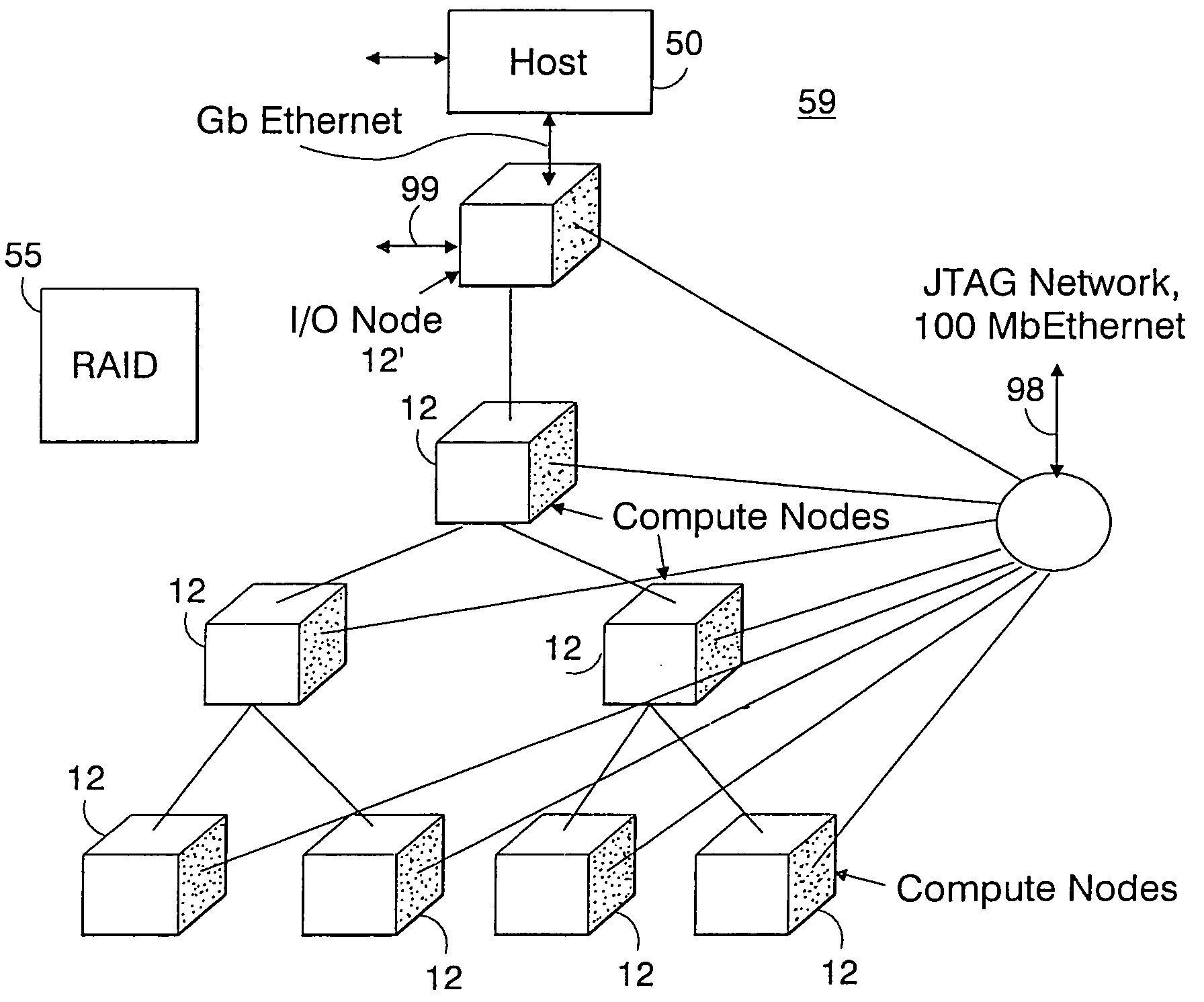

Novel massively parallel supercomputer

InactiveUS20090259713A1Low costReduced footprintError preventionProgram synchronisationSupercomputerPacket communication

Owner:INT BUSINESS MASCH CORP

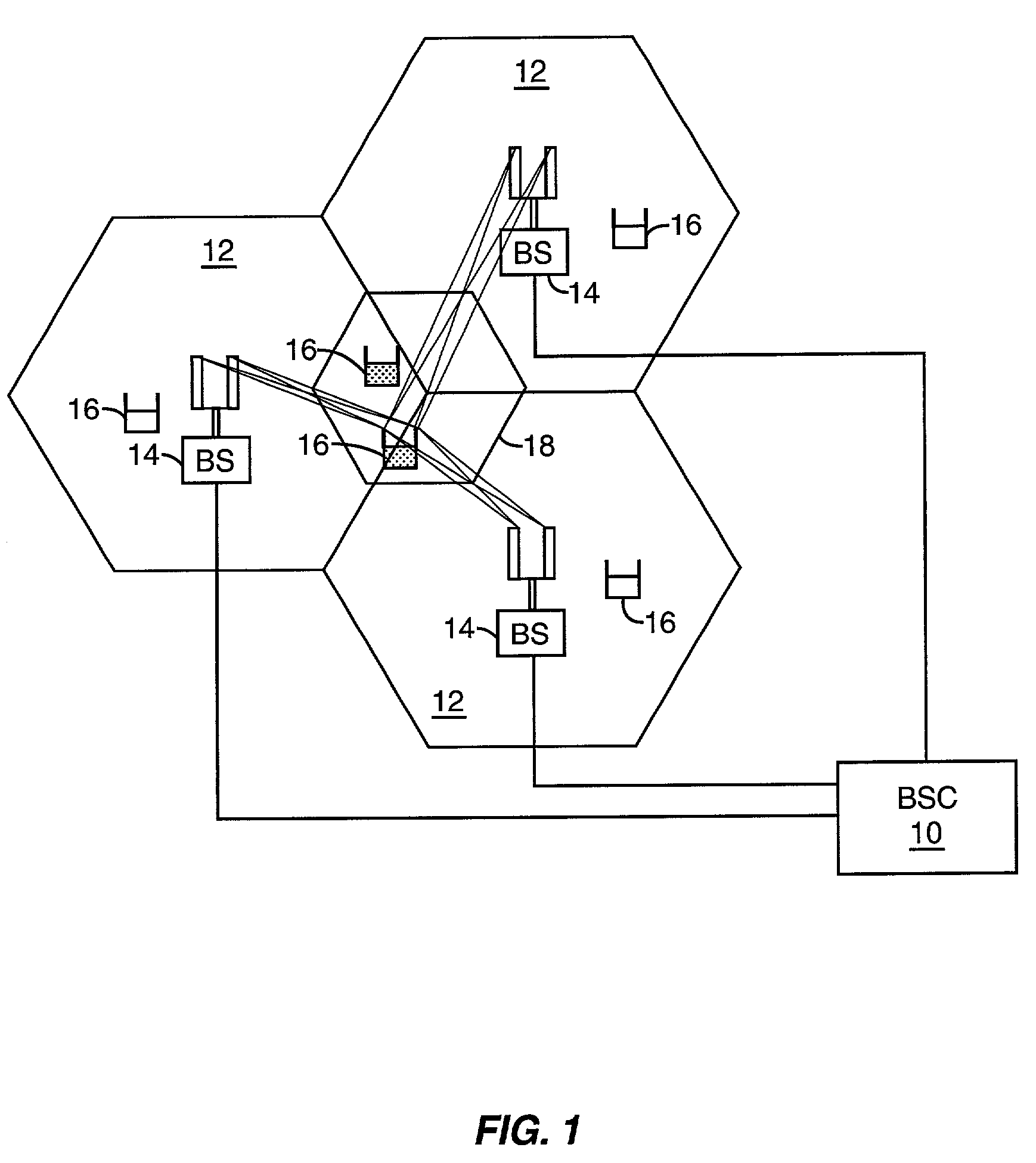

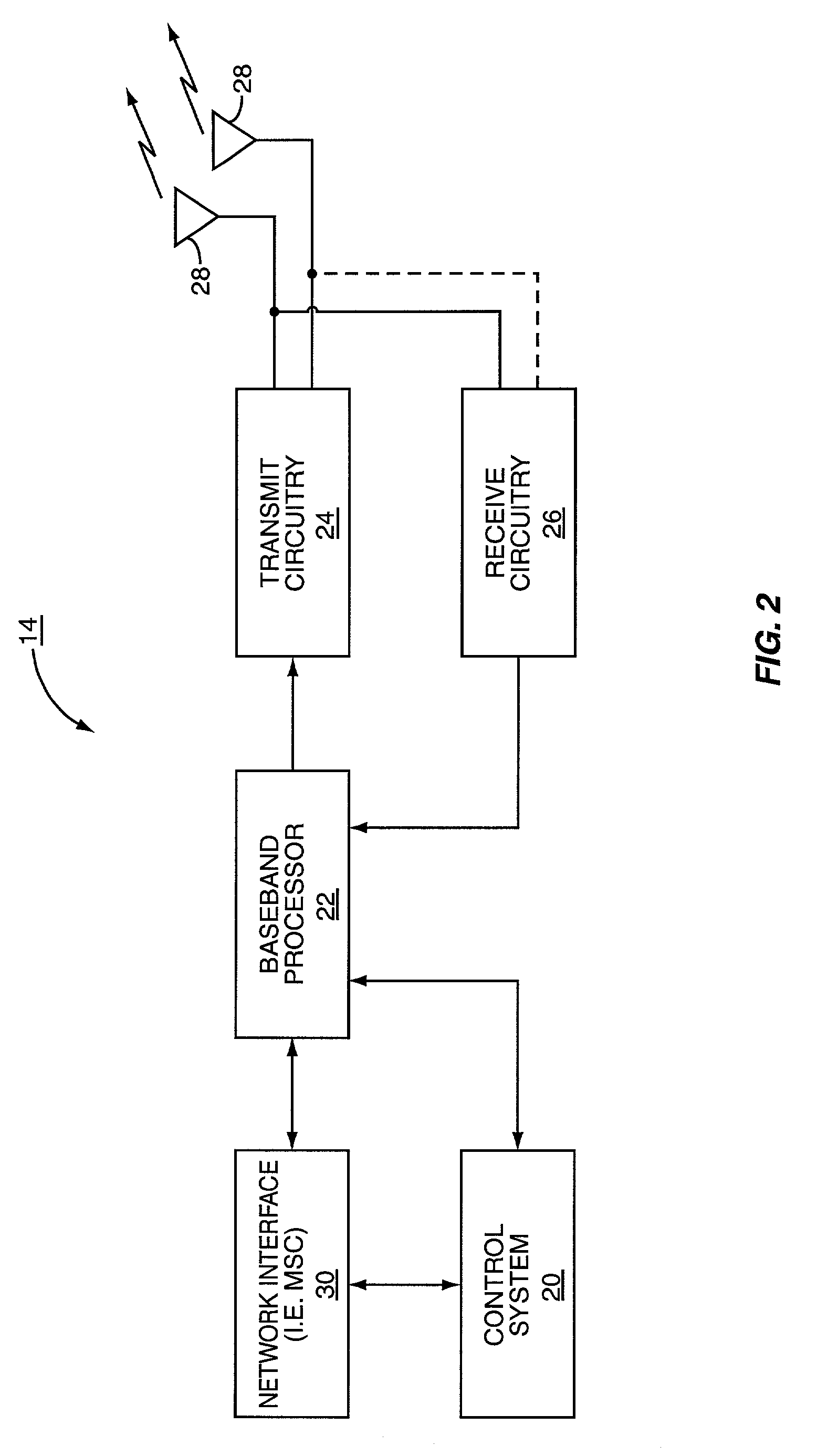

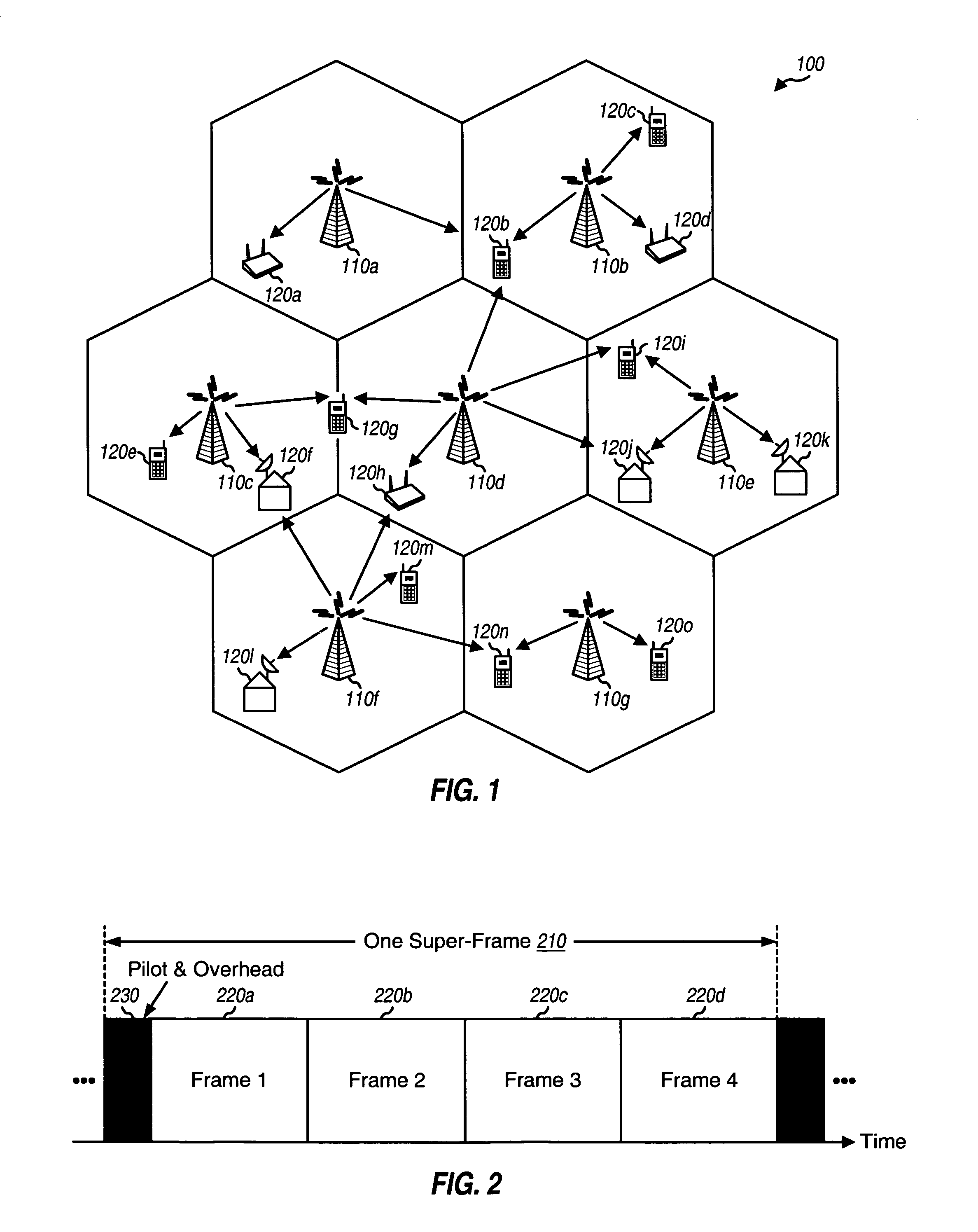

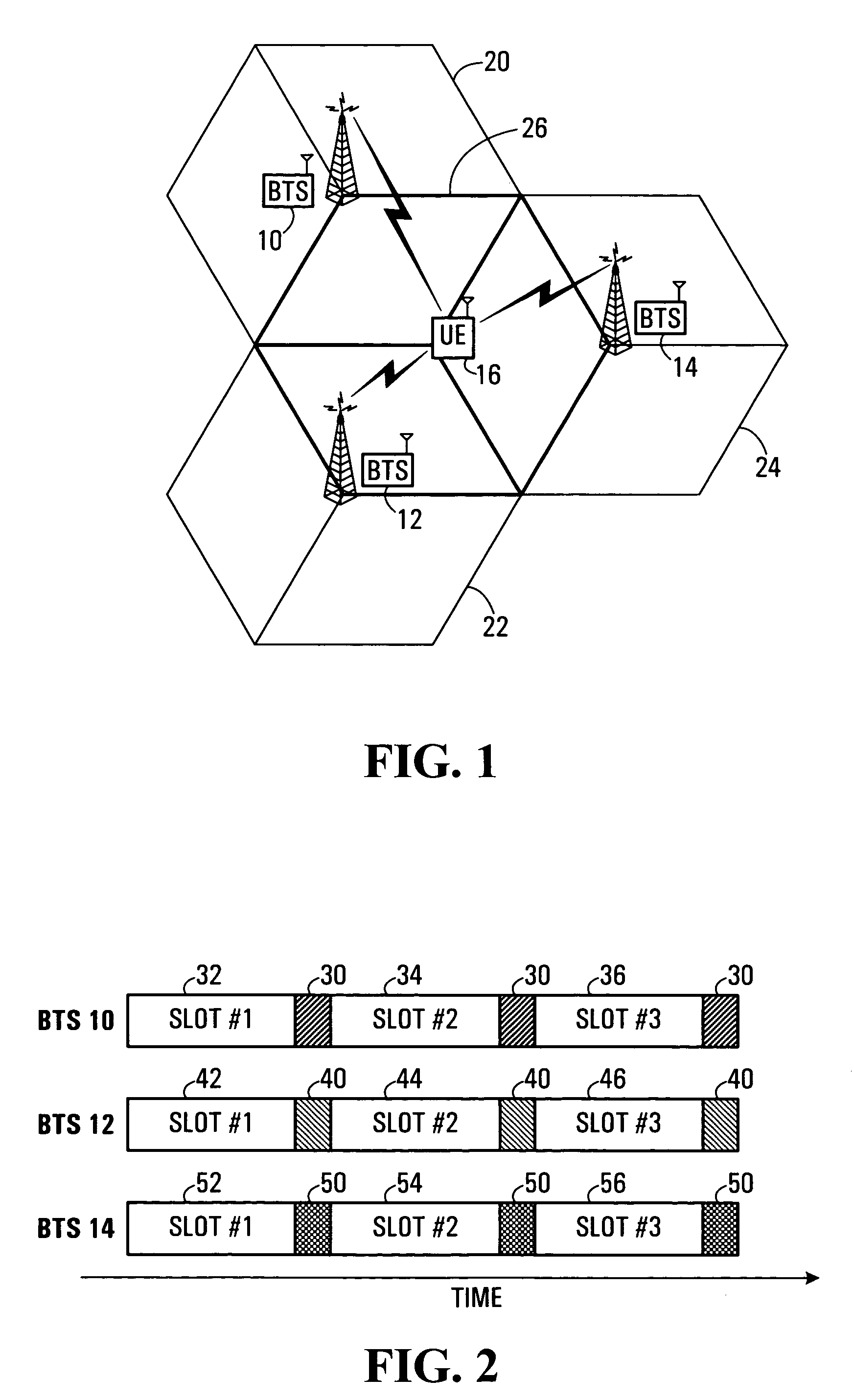

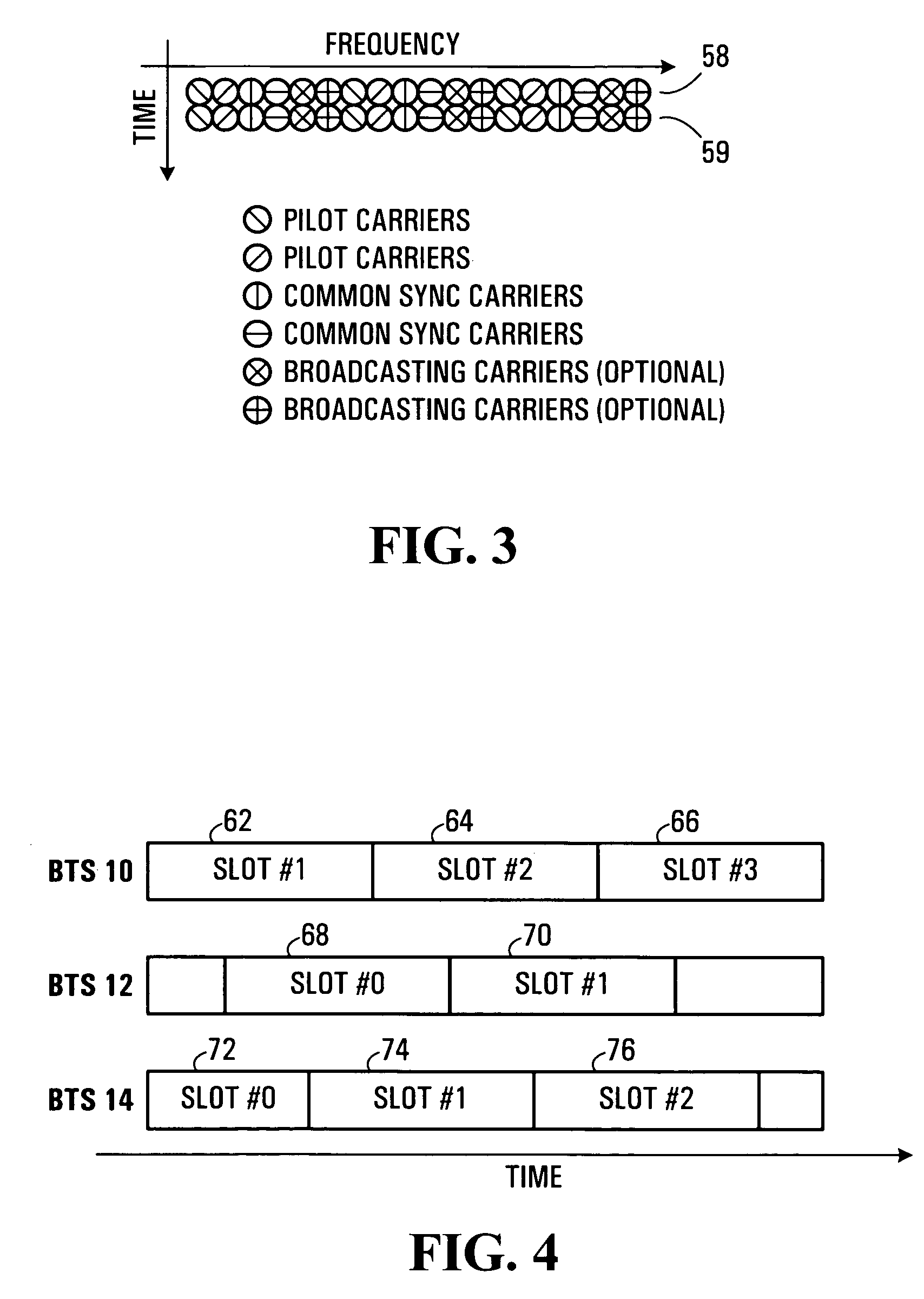

Soft handoff for OFDM

The present invention relates to soft handoffs in an OFDM system. Each mobile terminal measures pilot signal strengths of transmissions from adjacent base stations. If the pilot signal strength for a base station exceeds the defined threshold, that base station is added to an active set list. Each mobile terminal notifies the base stations of their active set lists. By providing the set list to the base station controller and the servicing base station, the mobile terminal identifies the sole servicing base station or triggers a soft handoff mode when multiple base stations appear on the active set list. The soft handoff mode uses a combination of scheduling and space-time coding to affect efficient and reliable handoffs.

Owner:MICROSOFT TECH LICENSING LLC

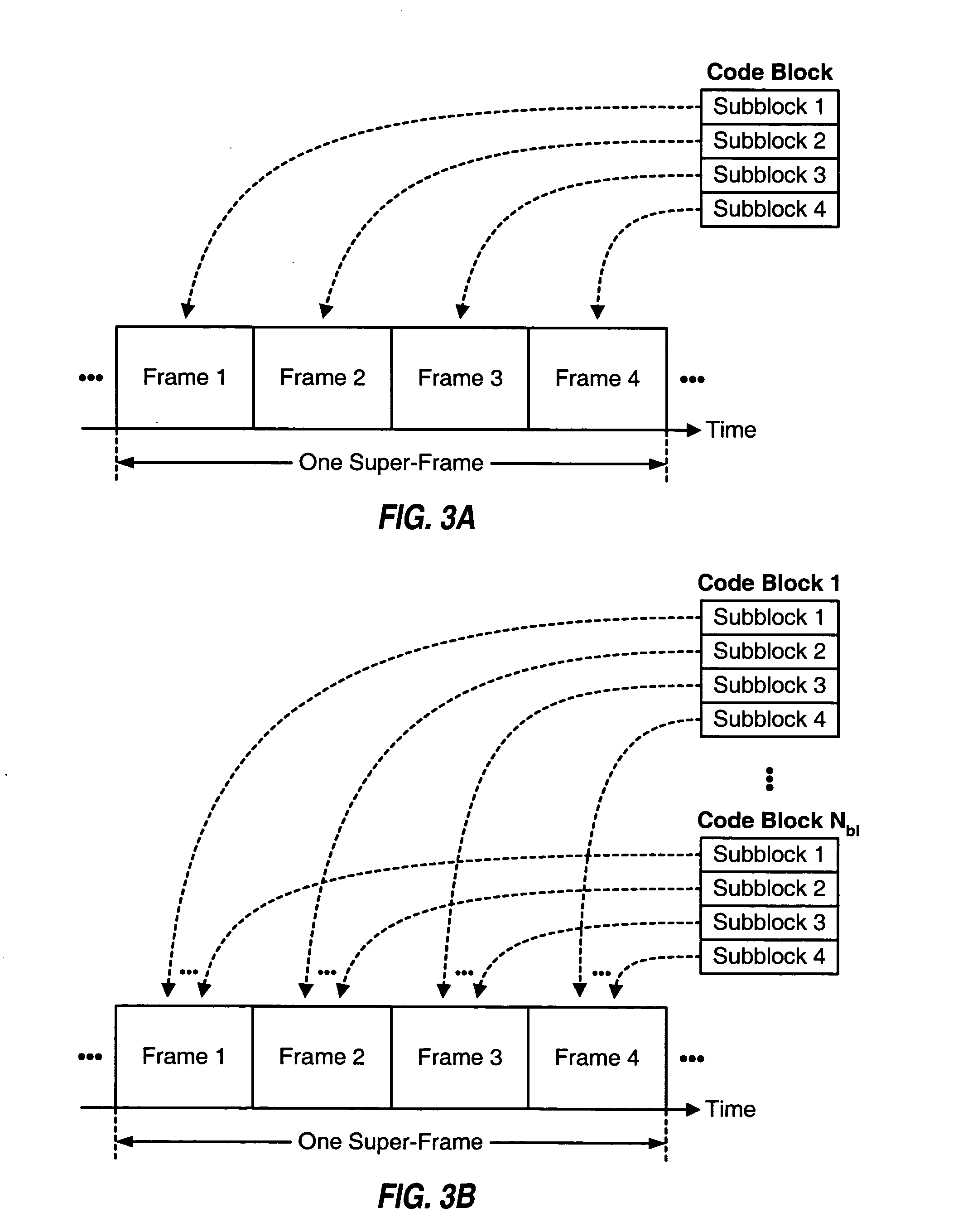

Multiplexing and transmission of multiple data streams in a wireless multi-carrier communication system

ActiveUS20050058089A1Facilitate power-efficientFacilitate robust receptionEnergy efficient ICTTransmission path divisionMultiplexingCoding block

Techniques for multiplexing and transmitting multiple data streams are described. Transmission of the multiple data streams occurs in “super-frames”. Each super-frame has a predetermined time duration and is further divided into multiple (e.g., four) frames. Each data block for each data stream is outer encoded to generate a corresponding code block. Each code block is partitioned into multiple subblocks, and each data packet in each code block is inner encoded and modulated to generate modulation symbols for the packet. The multiple subblocks for each code block are transmitted in the multiple frames of the same super-frame, one subblock per frame. Each data stream is allocated a number of transmission units in each super-frame and is assigned specific transmission units to achieve efficient packing. A wireless device can select and receive individual data streams.

Owner:QUALCOMM INC

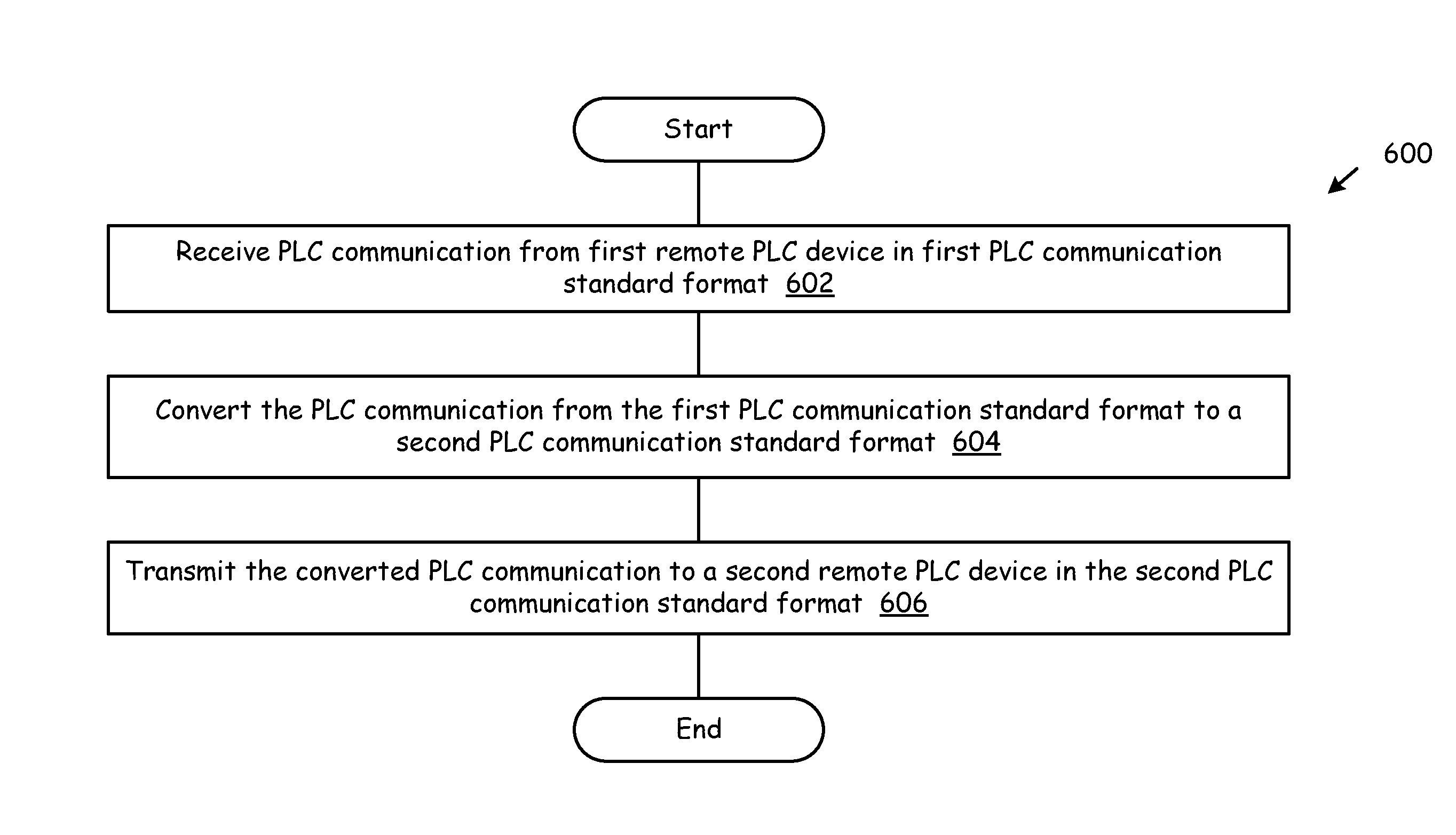

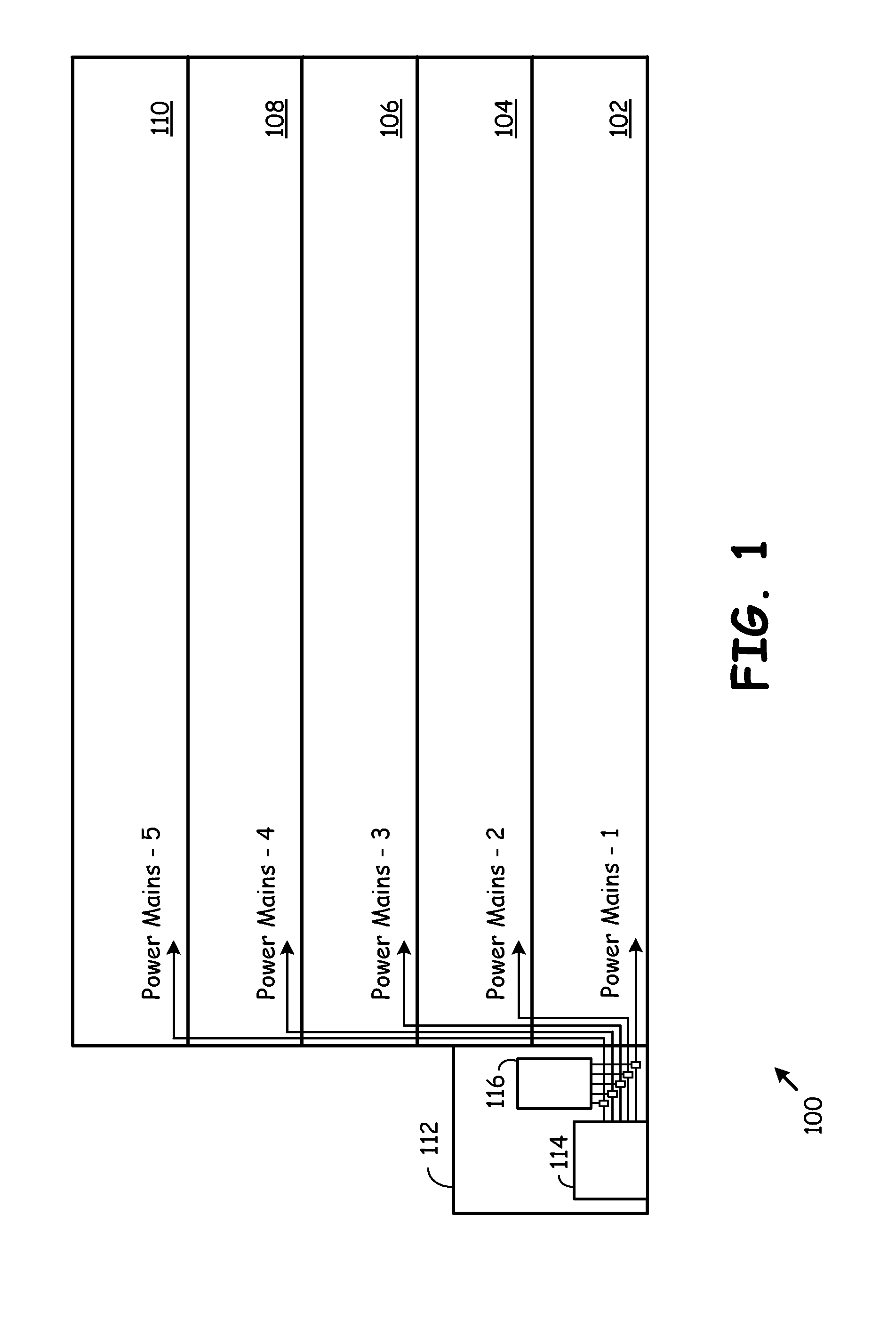

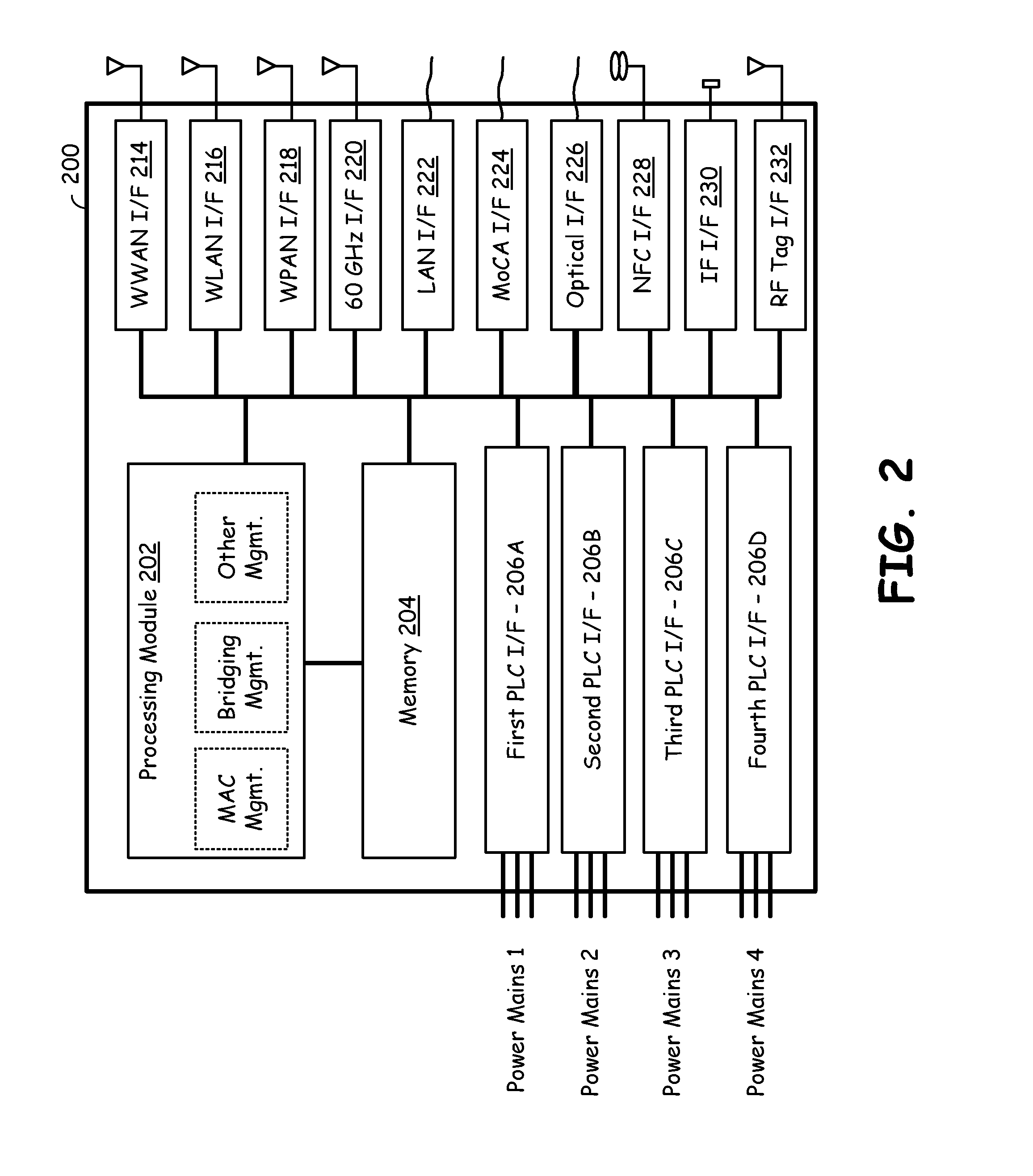

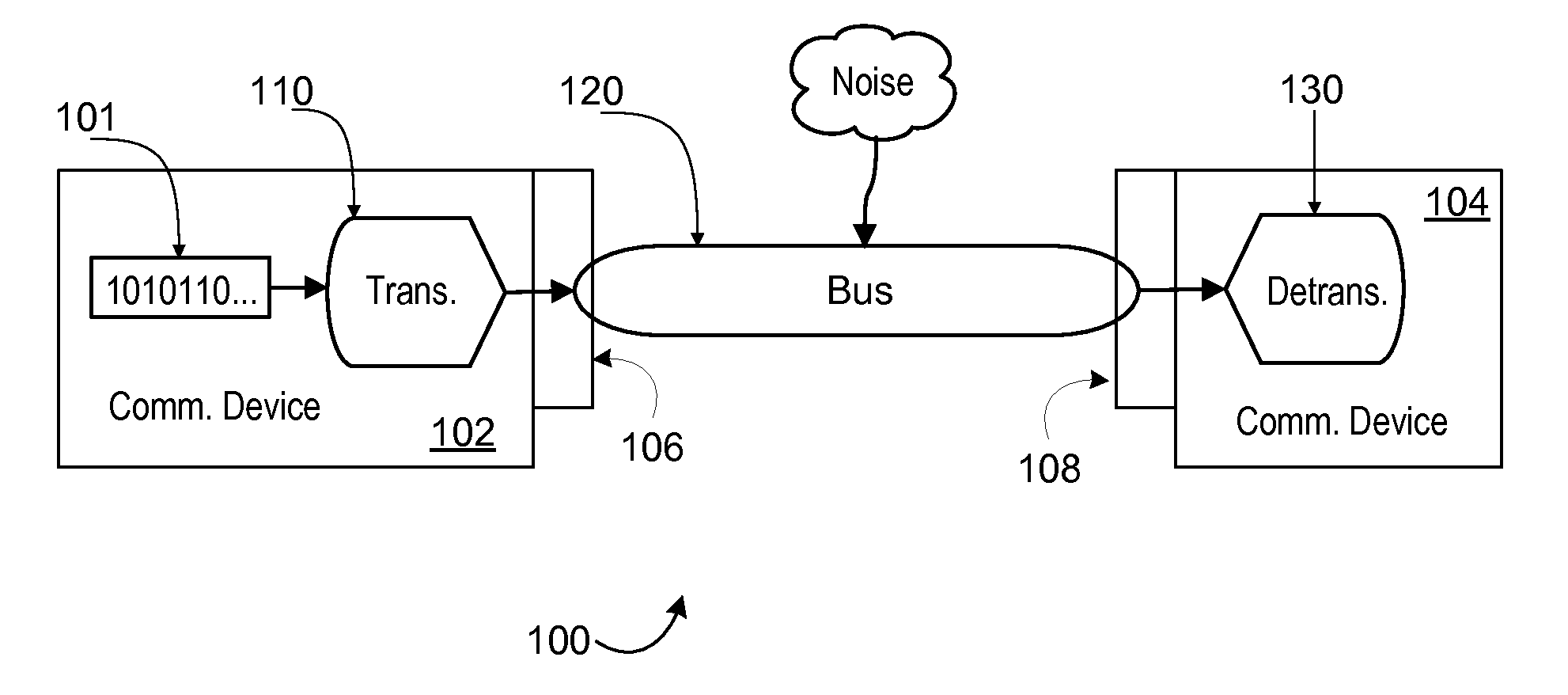

Breaker box powerline communication device

InactiveUS20130003876A1Analogue/digital conversionBaseband system detailsPower-line communicationCommunication interface

A Power Line Communications (PLC) device includes a processing module, memory, and a plurality of PLC communication interfaces coupled to the processing module. Each PLC communication interface couples to a respective PLC media segment. The processing module, the plurality of PLC communication interfaces, and the memory are operable to receive a PLC communication from a first PLC device via a first PLC communication interface of the plurality of communication interfaces, process the PLC communication to identify a second PLC device, and transmit the PLC communication to the second PLC device via a second PLC communication interface of the plurality of communication interfaces. The PLC device may include one or more non-PLC interfaces that support non-PLC communications.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

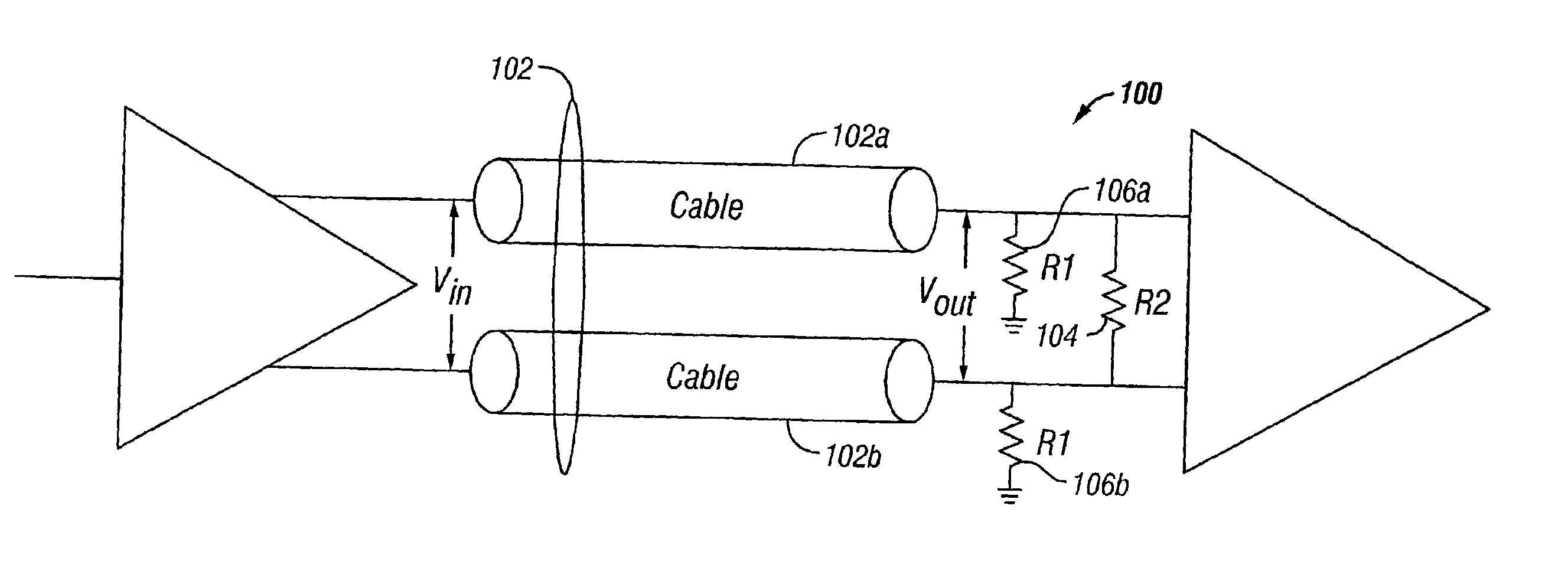

Improving signal integrity in differential signal systems

InactiveUS6886065B2Improves differential signal integrityEnhanced signalReliability increasing modificationsBaseband system detailsSignal qualityDifferential signaling

Over-terminating the differential mode impedance of a differential transmission line, such as an INFINIBAND™ cable, at the receiving end, improves the differential signal integrity for typical variations in termination network impedance component (e.g., resistor) and transmission line characteristics. Eye opening of the differential signal can be made larger with reduced attenuation but increased jitter compared to under-terminating the differential mode impedance. Because the differential signal quality (larger eye opening) is improved, data can be transmitted over a longer transmission line with the same transmitter and receiver.

Owner:VALTRUS INNOVATIONS LTD

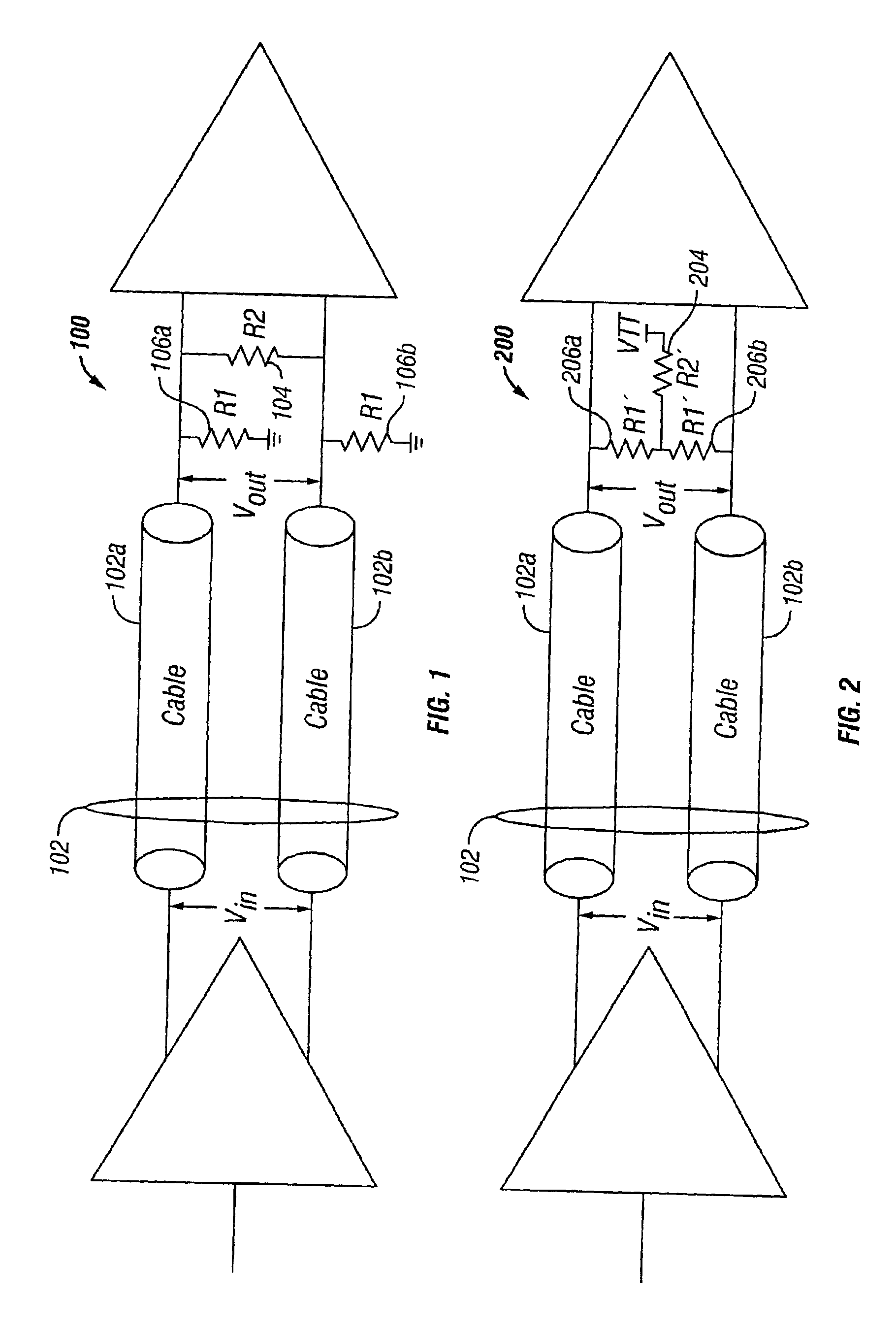

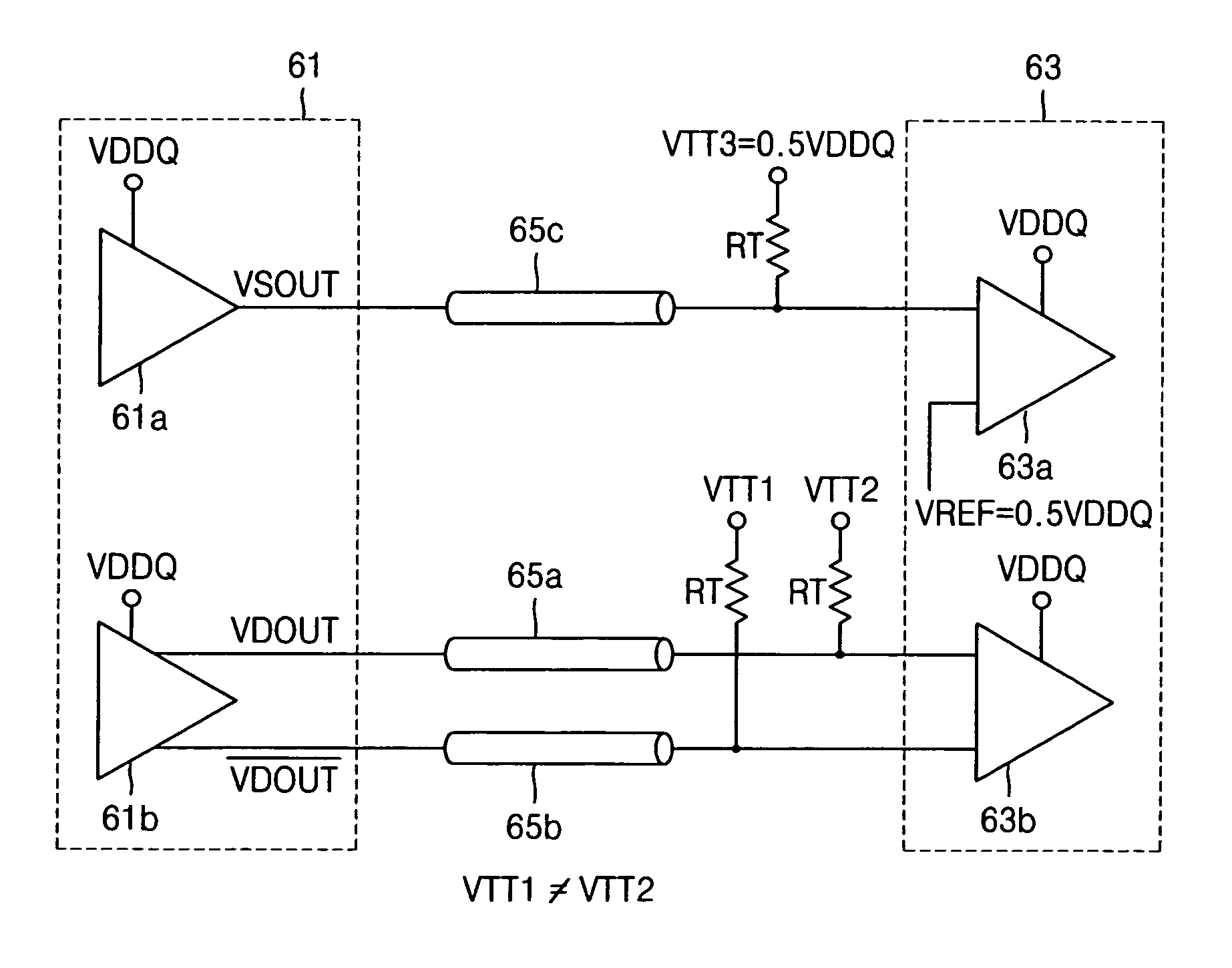

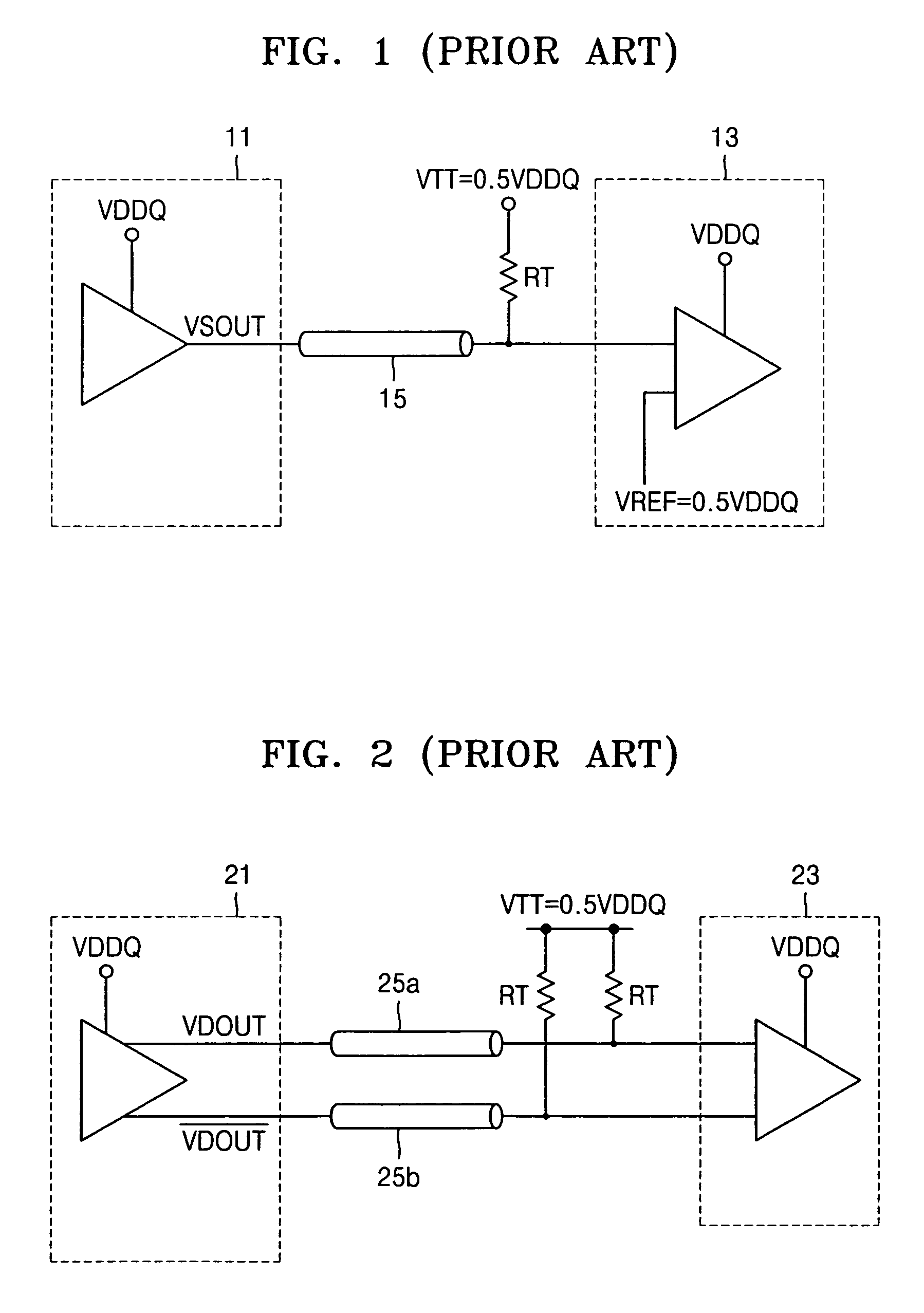

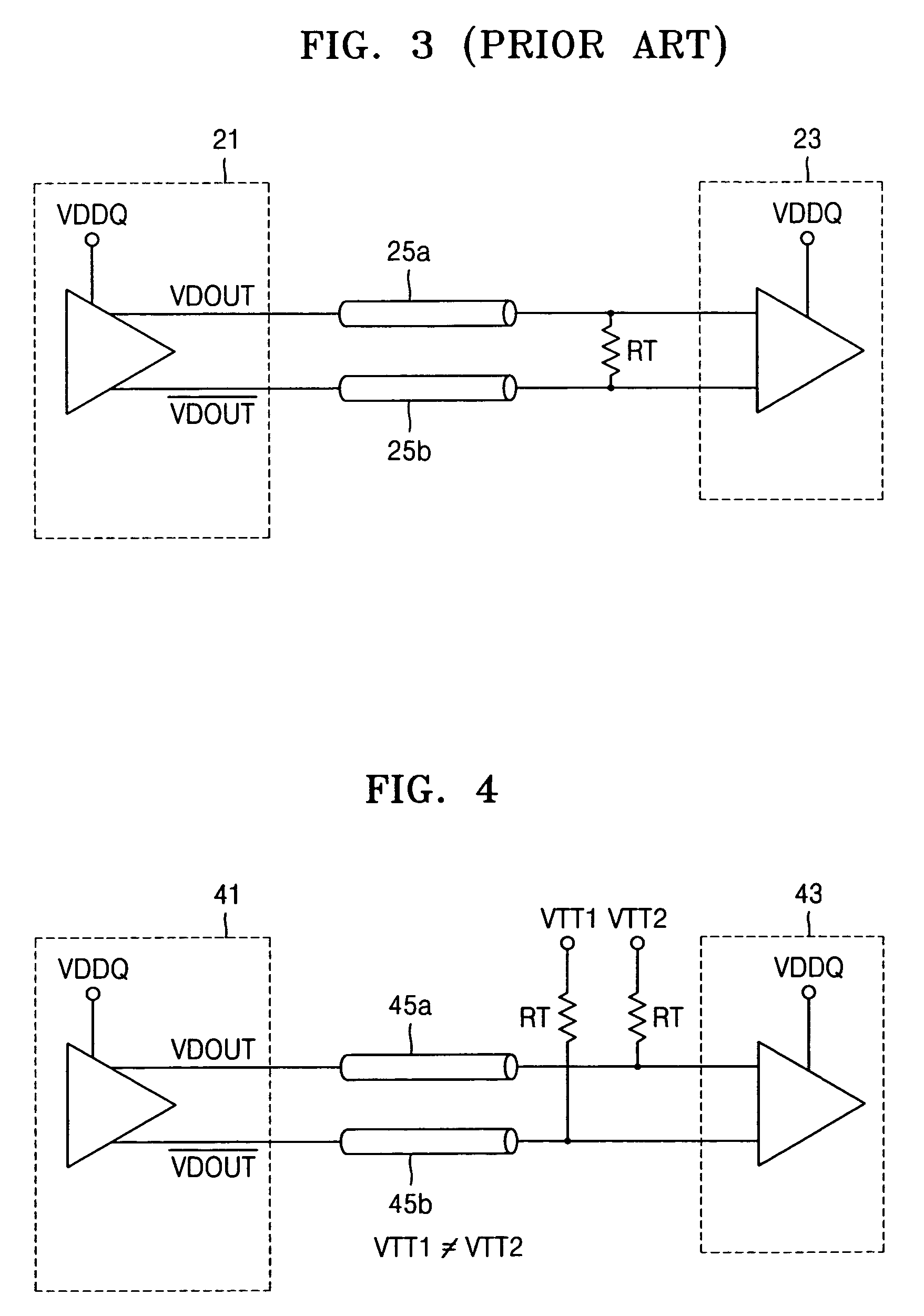

Memory system with stable termination of a pair of differential signals transmitted via a pair of transmission lines

InactiveUS7456650B2Avoid instabilityReliability increasing modificationsBaseband system detailsEngineeringTransmitter

Provided is a memory system in which a pair of differential signals transmitted via a pair of transmission lines are prevented from being terminated at the same voltage during a standby mode, thereby preventing a receiver from entering an unstable state. The memory system includes a pair of transmission lines, a transmitter that outputs a pair of differential signals to the pair of transmission lines, and a receiver that receives the pair of differential signals via the pair of transmission lines. A first termination voltage is applied to one of the pair of transmission lines, and a second termination voltage is applied to the other transmission line. The first termination voltage is determined to be different from the second termination voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

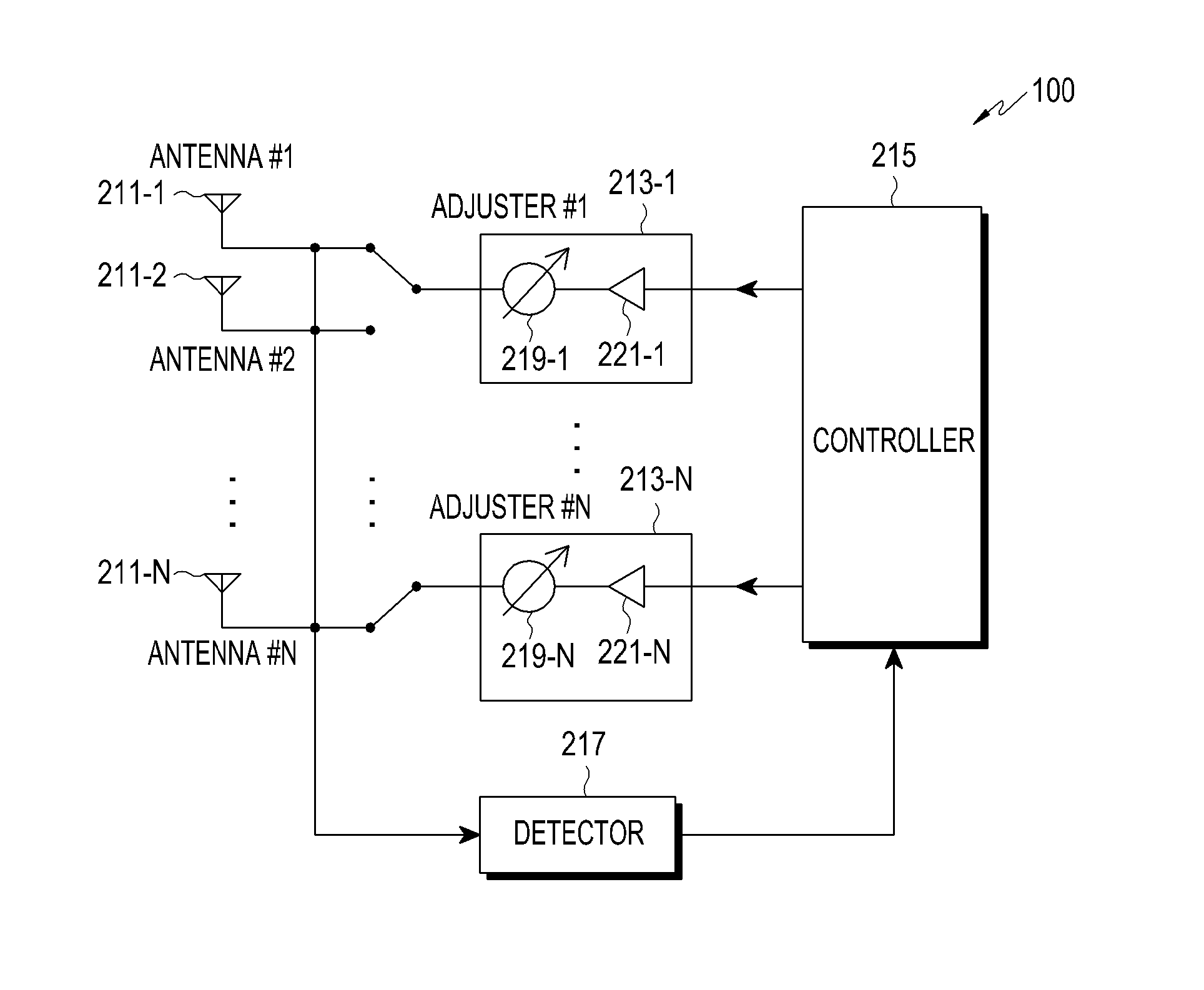

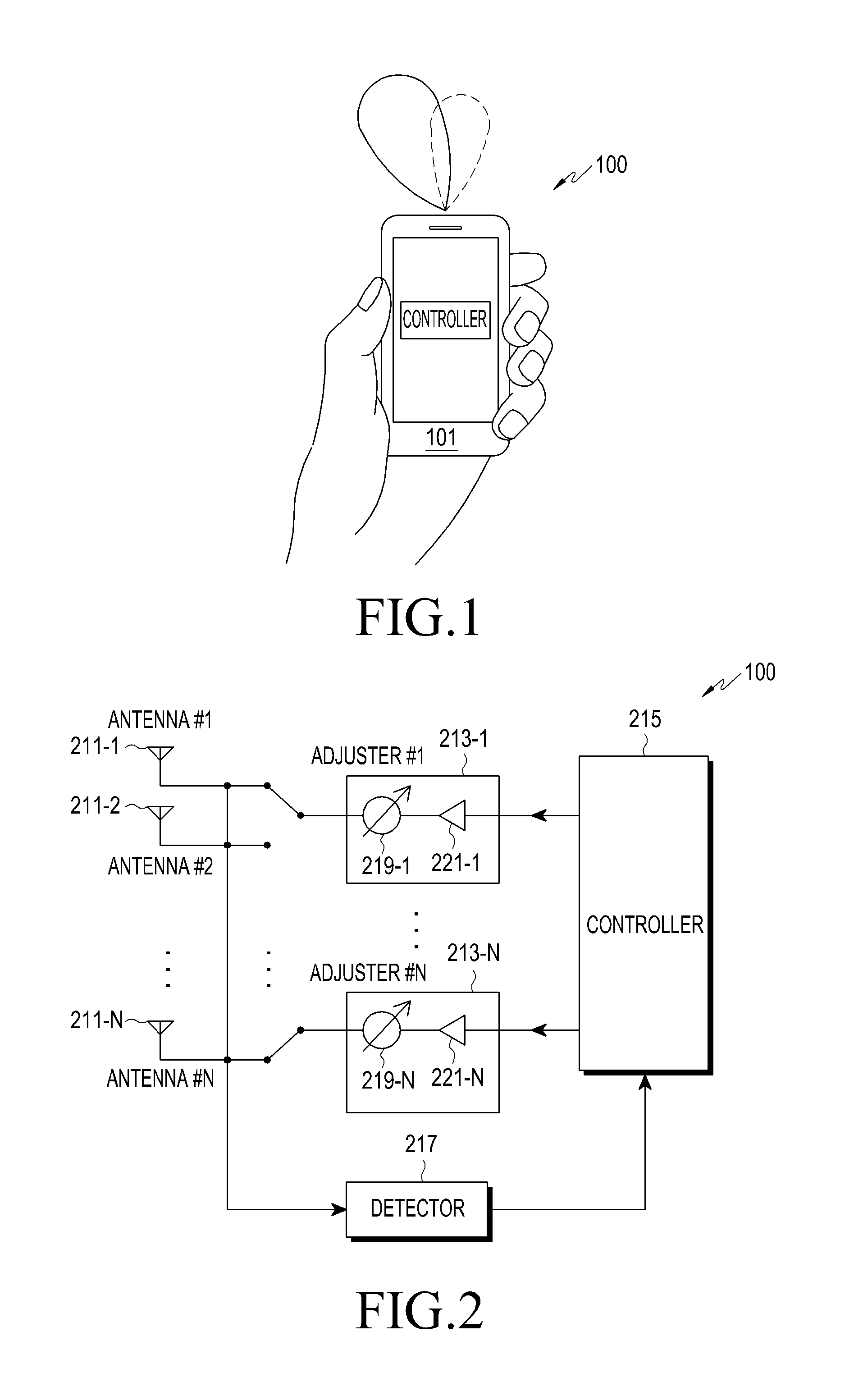

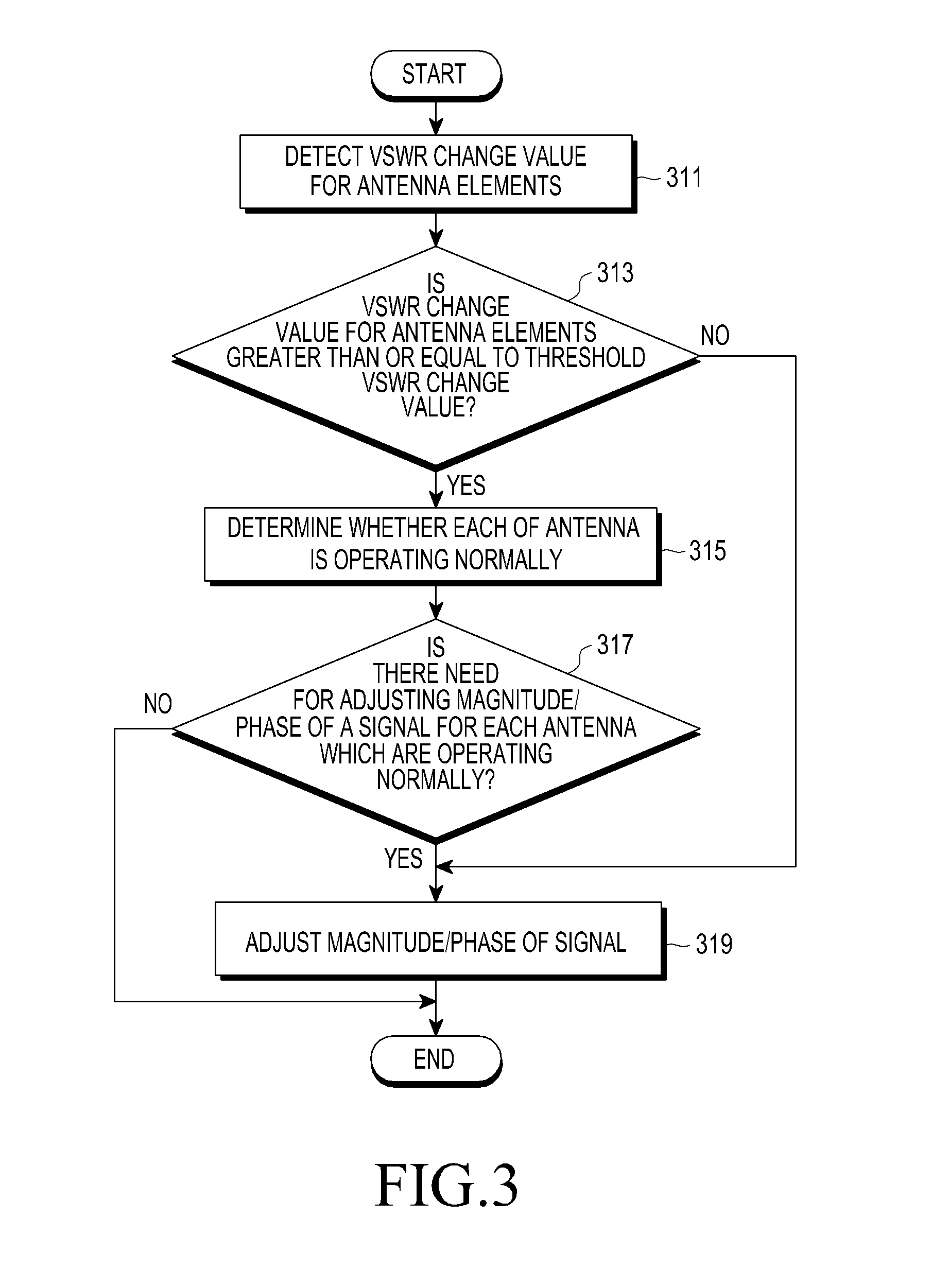

Apparatus and method for adjusting beam pattern in communication system supporting beam division multipile access scheme

ActiveUS20150318610A1Reduce degradationImprove communication system performanceTransmitters monitoringSpatial transmit diversityCommunications systemBeam pattern

A method for adjusting a beam pattern in a beam pattern adjusting apparatus in a communication system supporting a Beam Division Multiple Access (BDMA) scheme is provided. The method includes determining whether a Voltage Standing Wave Ratio (VSWR) value for each antenna included in an antenna array included in the beam pattern adjusting apparatus is greater than or equal to a threshold VSWR value, if it is determined that an antenna of the antenna array has a VSWR value that is greater than or equal to the threshold VSWR, detecting whether each of the antenna elements is operable, and if it is determined that at least one of the antennas is inoperable, adjusting a beam pattern of at least one of the antennas that is operable.

Owner:SAMSUNG ELECTRONICS CO LTD +1

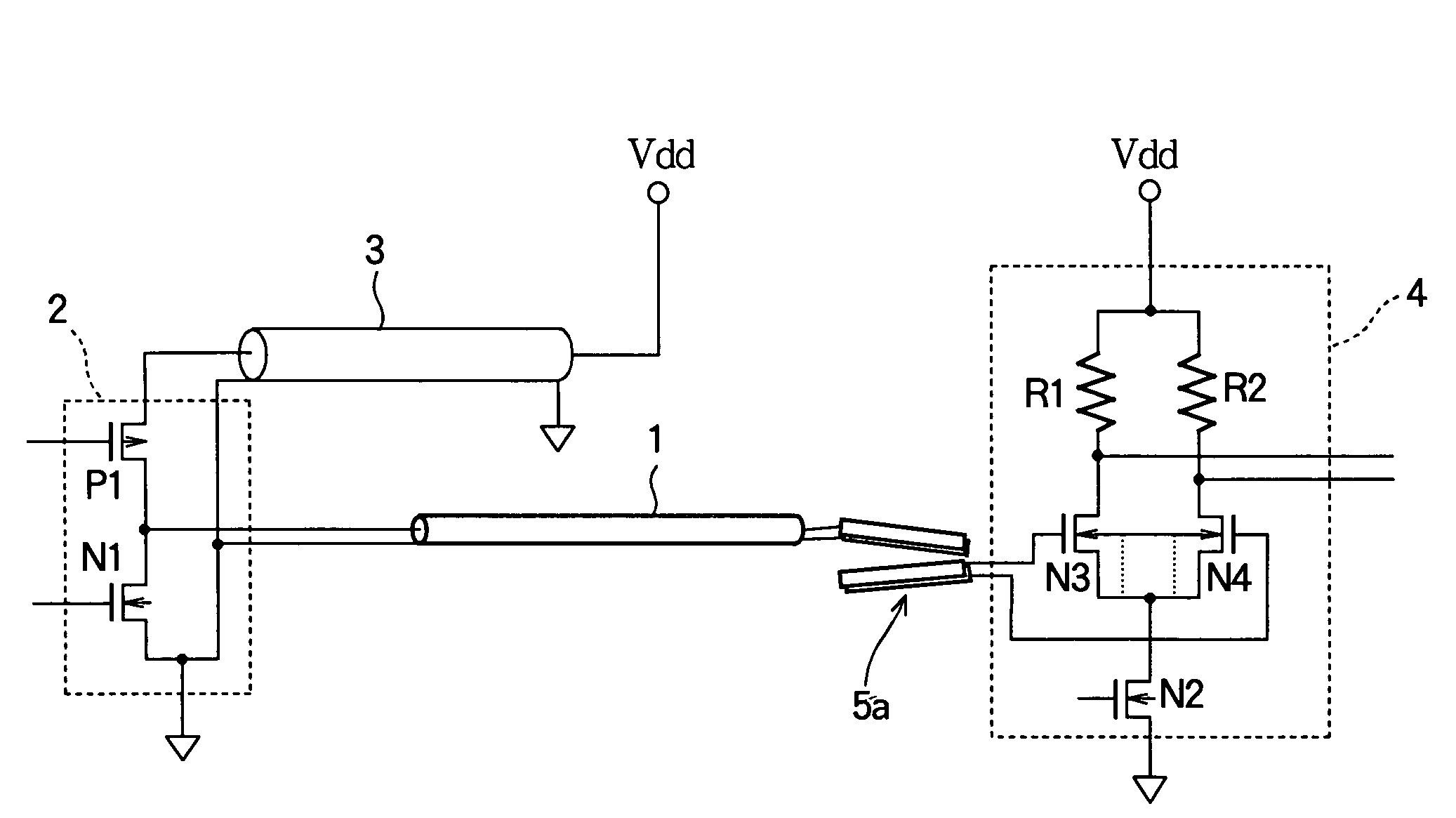

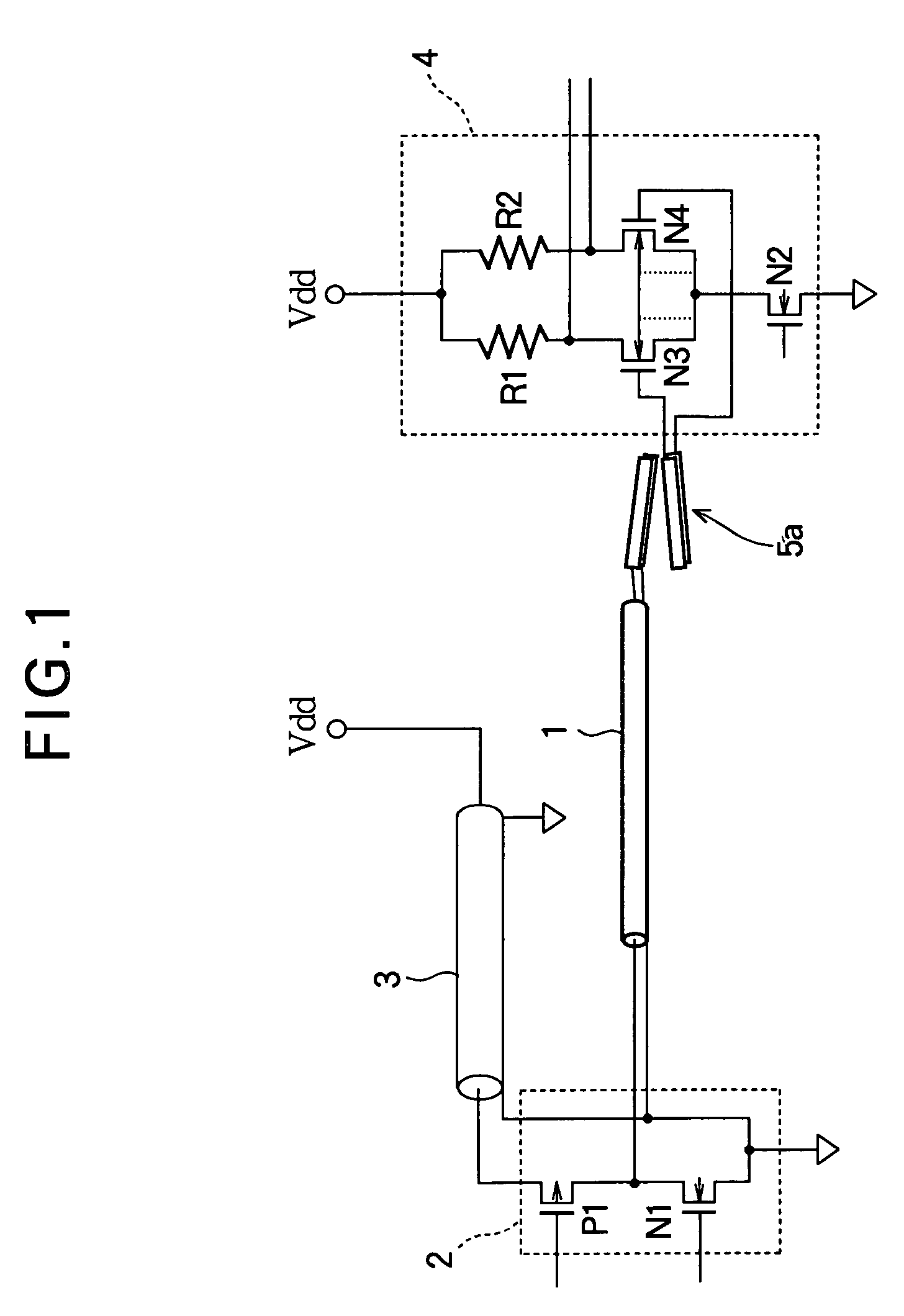

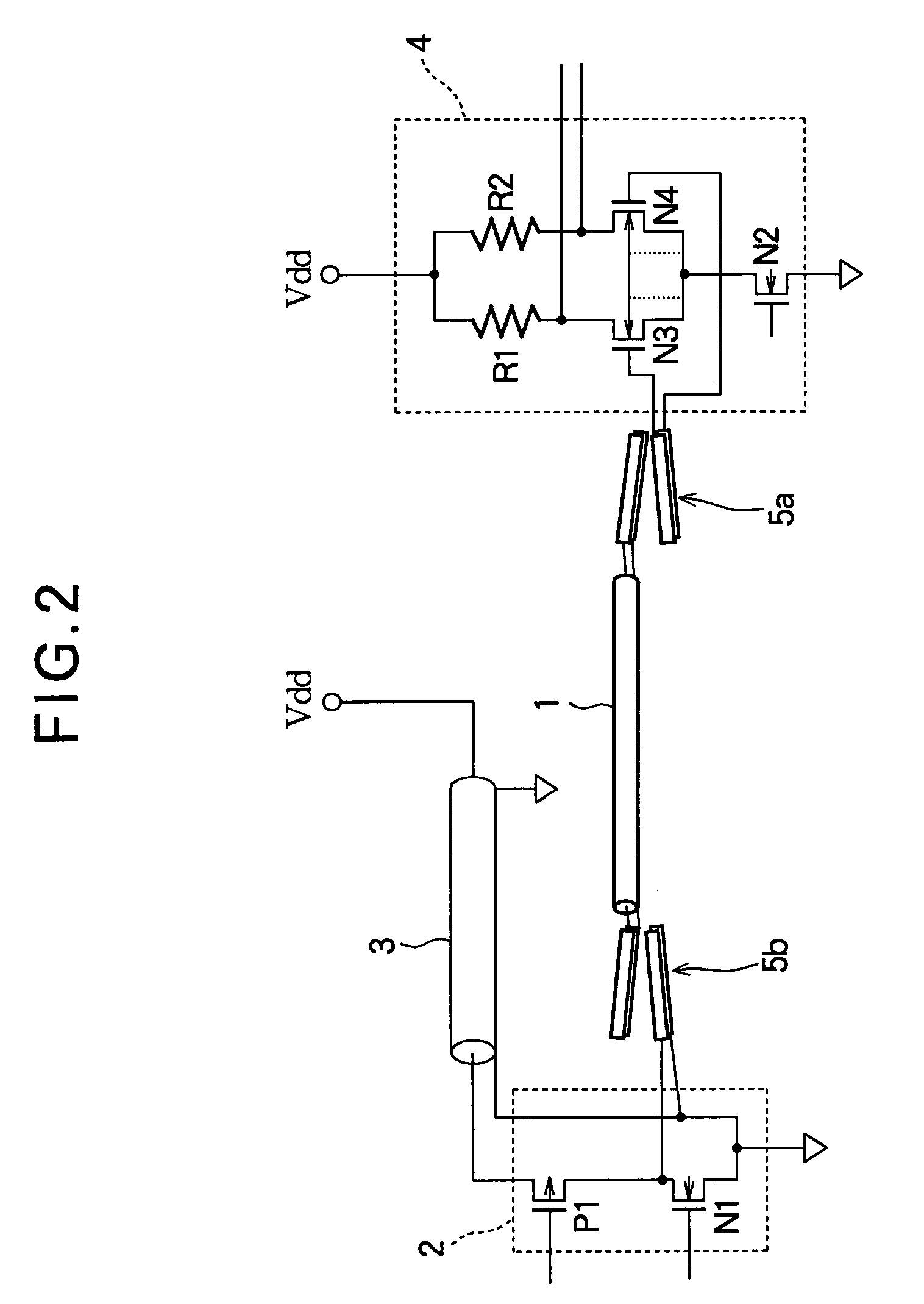

Signal transmission apparatus and interconnection structure

ActiveUS7446567B2Sufficient capabilitySimple and scalableReliability increasing modificationsBatteries circuit arrangementsLine pairHarmonic

Apparatus for transmitting a digital signal within, for example, an integrated circuit includes a signal transmission line with a directional coupler at one or both ends. The directional coupler blocks the direct-current component of the digital signal while transmitting the alternating-current component, including enough higher harmonics to transmit a well-defined pulse waveform. A suitable directional coupler consists of two adjacent line pairs in materials with different dielectric constants. The apparatus may also include a driver of the inverter type, a receiver of the differential amplifier type, a terminating resistor, and a power-ground transmission line pair for supplying power to the driver. An all-metallic transmission-line structure is preferably maintained from the output interconnections in the driver to the input interconnections in the receiver.

Owner:PANASONIC CORP +11

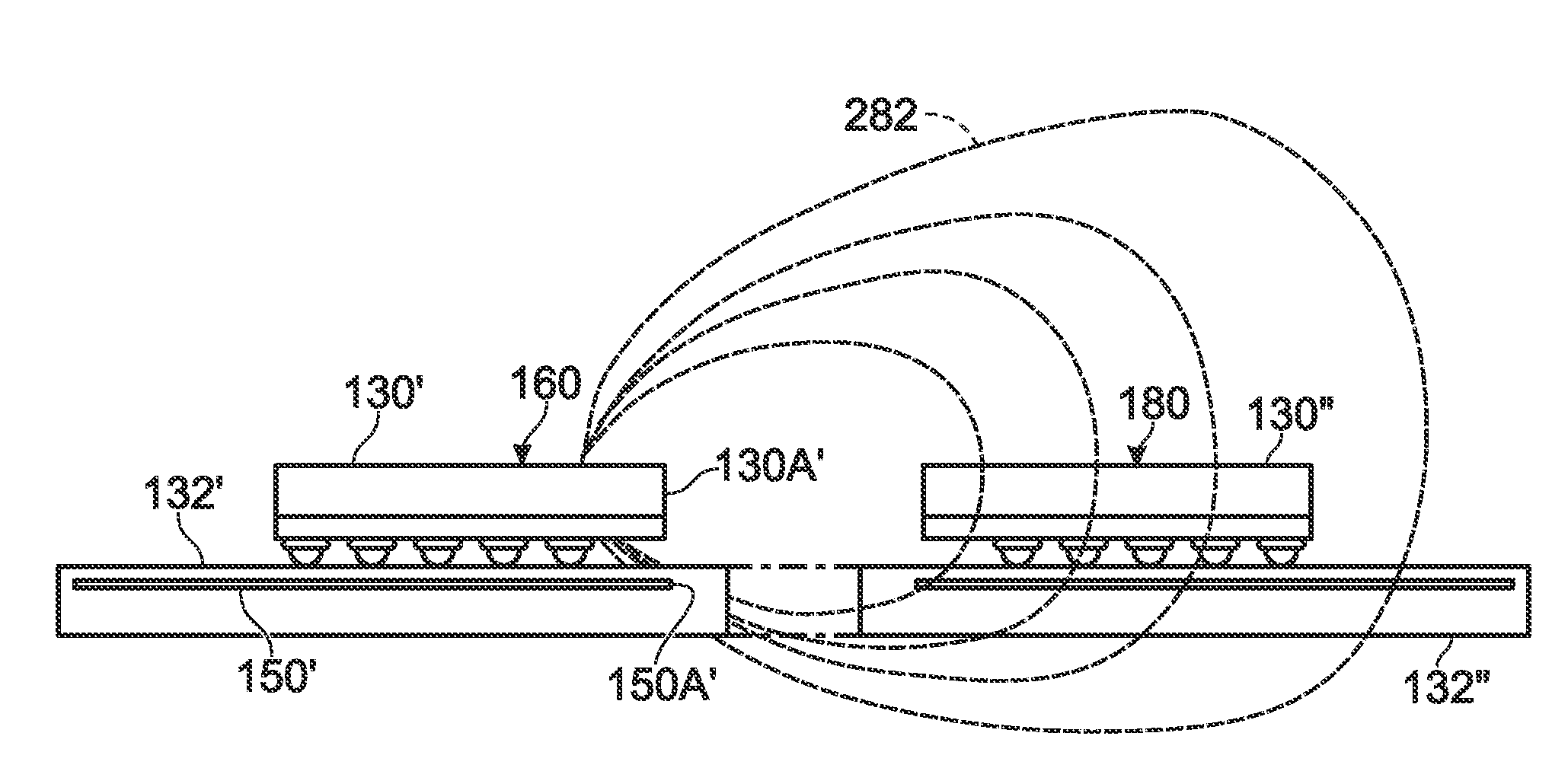

Integrated circuit with electromagnetic communication

ActiveUS20120263244A1Baseband system detailsModulated-carrier systemsElement spaceElectrical conductor

A system for transmitting or receiving signals may include an integrated circuit (IC), a transducer operatively coupled to the IC for converting between electrical signals and electromagnetic signals; and insulating material that fixes the locations of the transducer and IC in spaced relationship relative to each other. The system may further include a lead frame providing external connections to conductors on the IC. An electromagnetic-energy directing assembly may be mounted relative to the transducer for directing electromagnetic energy in a region including the transducer and in a direction away from the IC. The directing assembly may include the lead frame, a printed circuit board ground plane, or external conductive elements spaced from the transducer. In a receiver, a signal-detector circuit may be responsive to a monitor signal representative of a received first radio-frequency electrical signal for generating a control signal that enables or disables an output from the receiver.

Owner:MOLEX INC

Apparatus for OFDMA transmission and reception for coherent detection in uplink of wireless communication system and method thereof

InactiveUS7639660B2Improve channel estimation performanceFrequency-division multiplexSecret communicationCommunications systemResource block

In the resource mapping method for data transmission, a time-frequency resource of a slot interval including OFDM symbols is divided into traffic channels and shared among the subscribers, the traffic channel including resource blocks uniformly distributed in the whole transmit frequency band, the resource block including consecutive subcarriers of consecutive received symbols having at least one inserted pilot symbol. The pilot symbols and the channel-encoded and modulated data symbols are processed by time-frequency mapping according to the resource-block-based mapping method to generate received symbols. The receiver separates the received symbols by subscribers according to the resource-block-based mapping method in a frequency domain, and performs iterative channel estimation, demodulation, and decoding by using the pilot and a data reference value after decoding for each traffic channel.

Owner:ELECTRONICS & TELECOMM RES INST

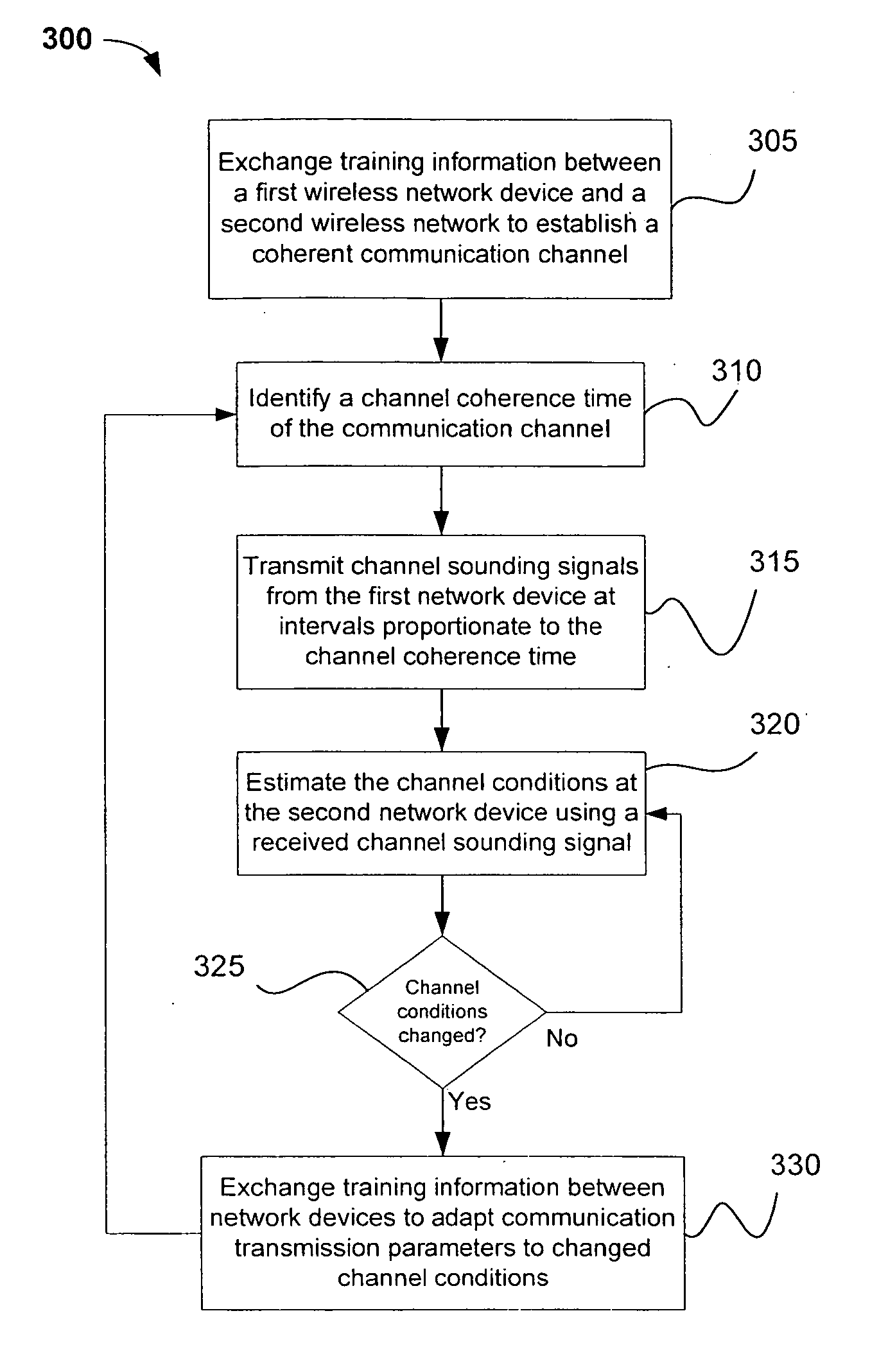

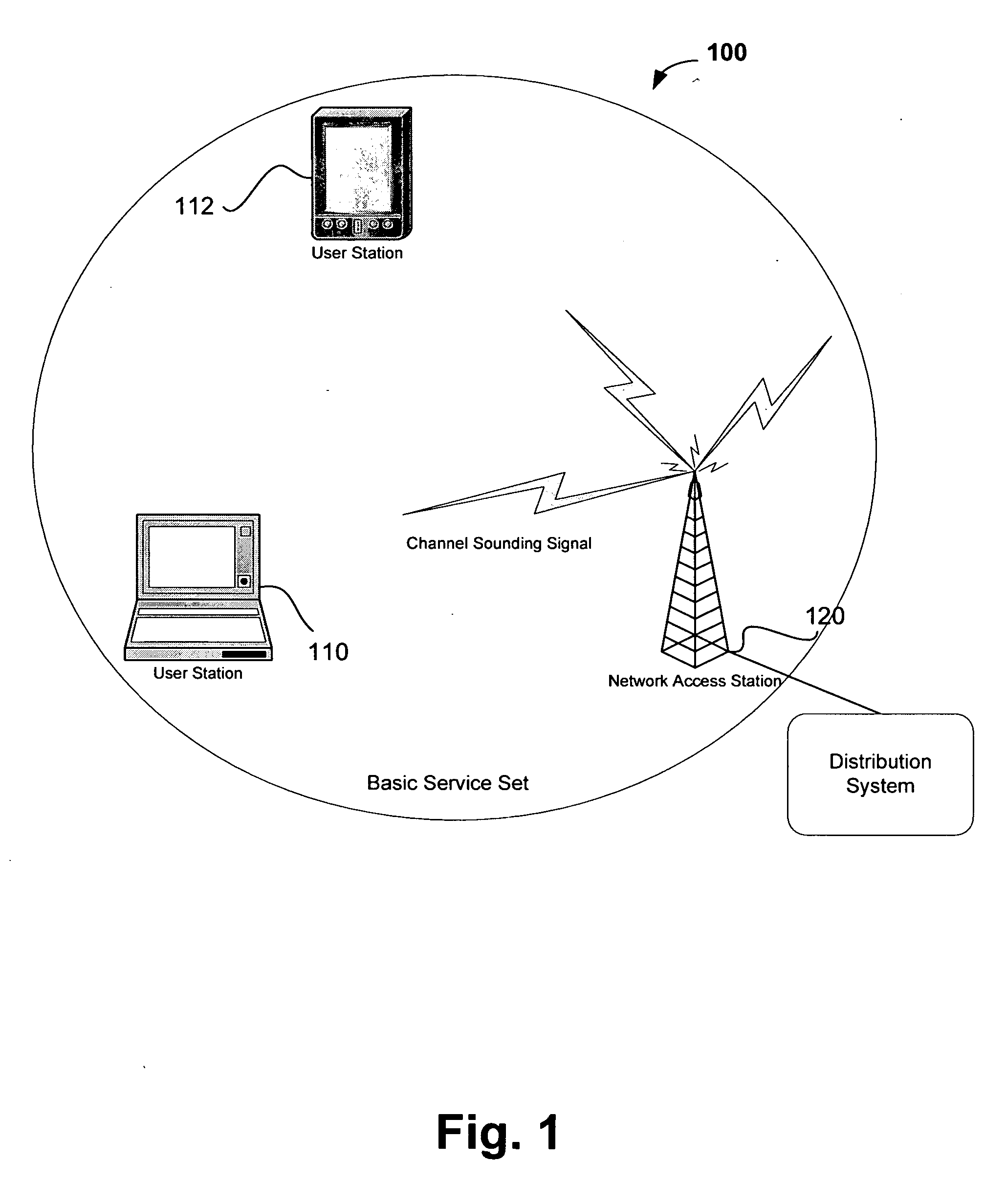

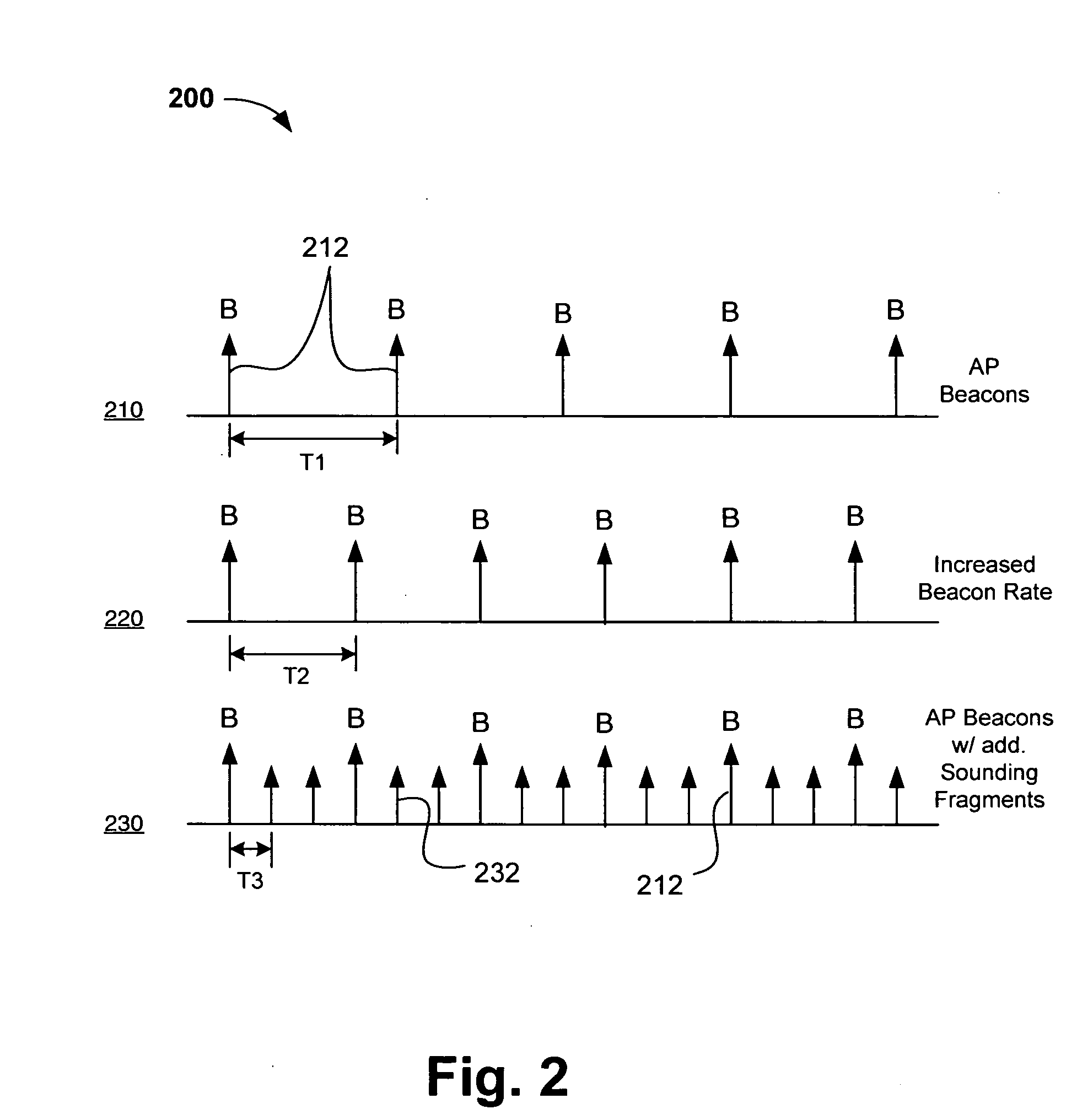

Channel adaptation using variable sounding signal rates

InactiveUS20050170781A1Error detection/prevention using signal quality detectorFrequency-division multiplex detailsCoherence timeLink adaptation

Systems, devices and methods for updating link adaptations in multi-carrier modulated signals between an access point (AP) and a wireless local area network (WLAN) station (STA) include (are configured for) periodically transmitting a channel sounding signal from the AP. The STA receives each unsolicited channel sounding signal and evaluates the current channel conditions between the AP and STA. The AP adjusts a rate of transmission of the channel sounding signals in accordance with the channel coherence time so that the channel estimates performed by the STA will be valid within the time varying characteristics of the channel. Depending on the length of the coherence time for network environment, the channel sounding signals may be AP beacons, low overhead signal fragments with no payload, or a combination of both.

Owner:INTEL CORP

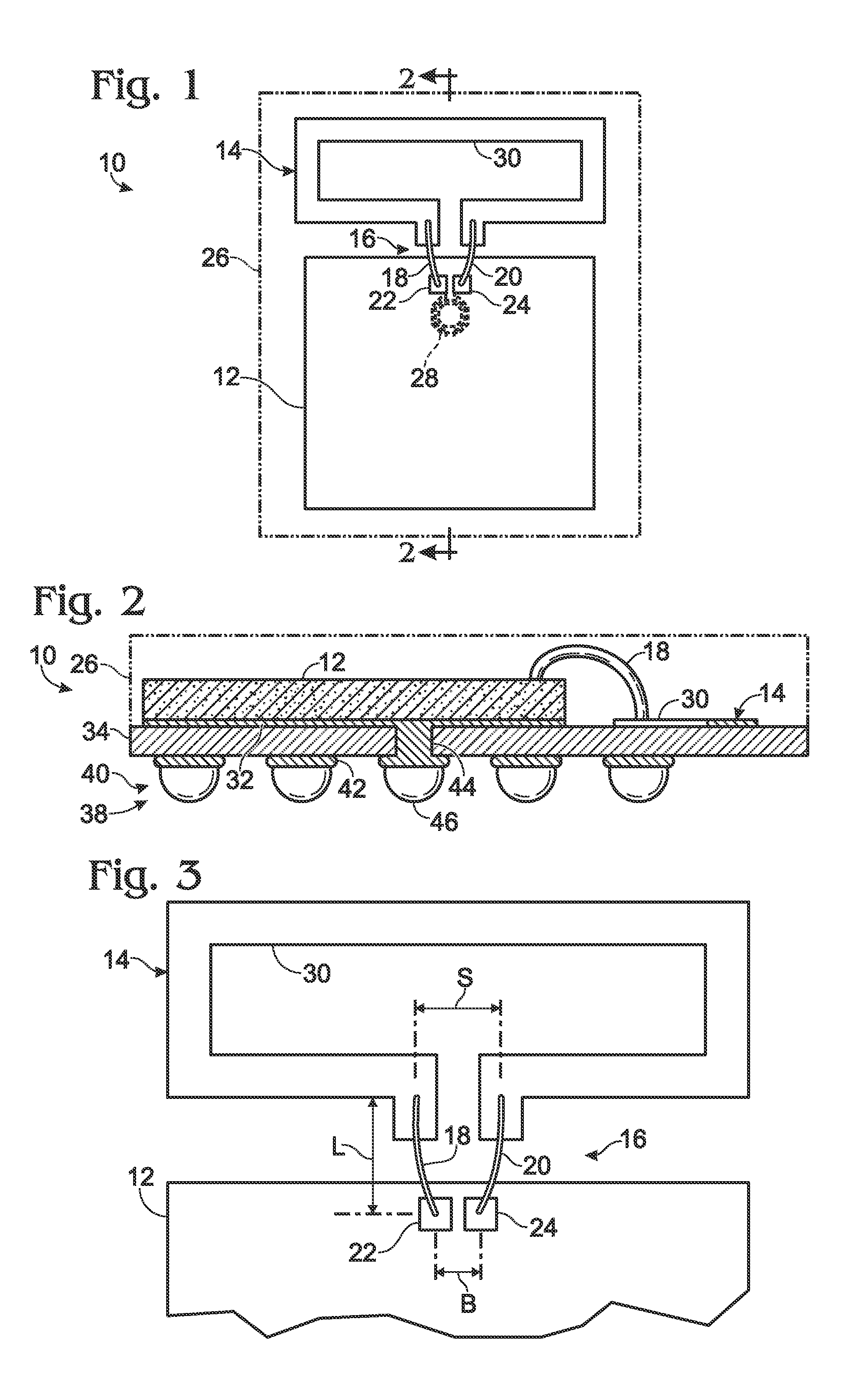

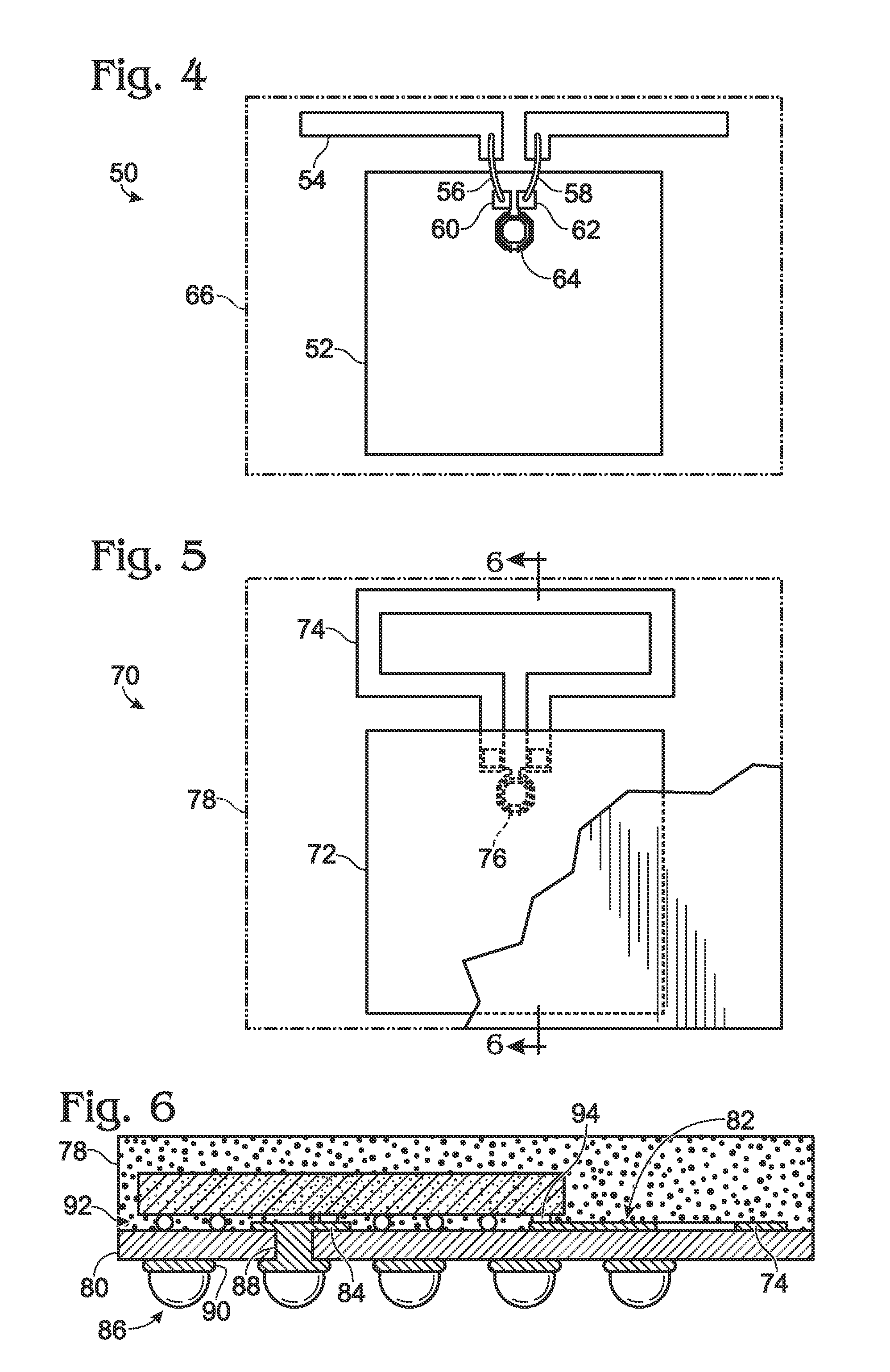

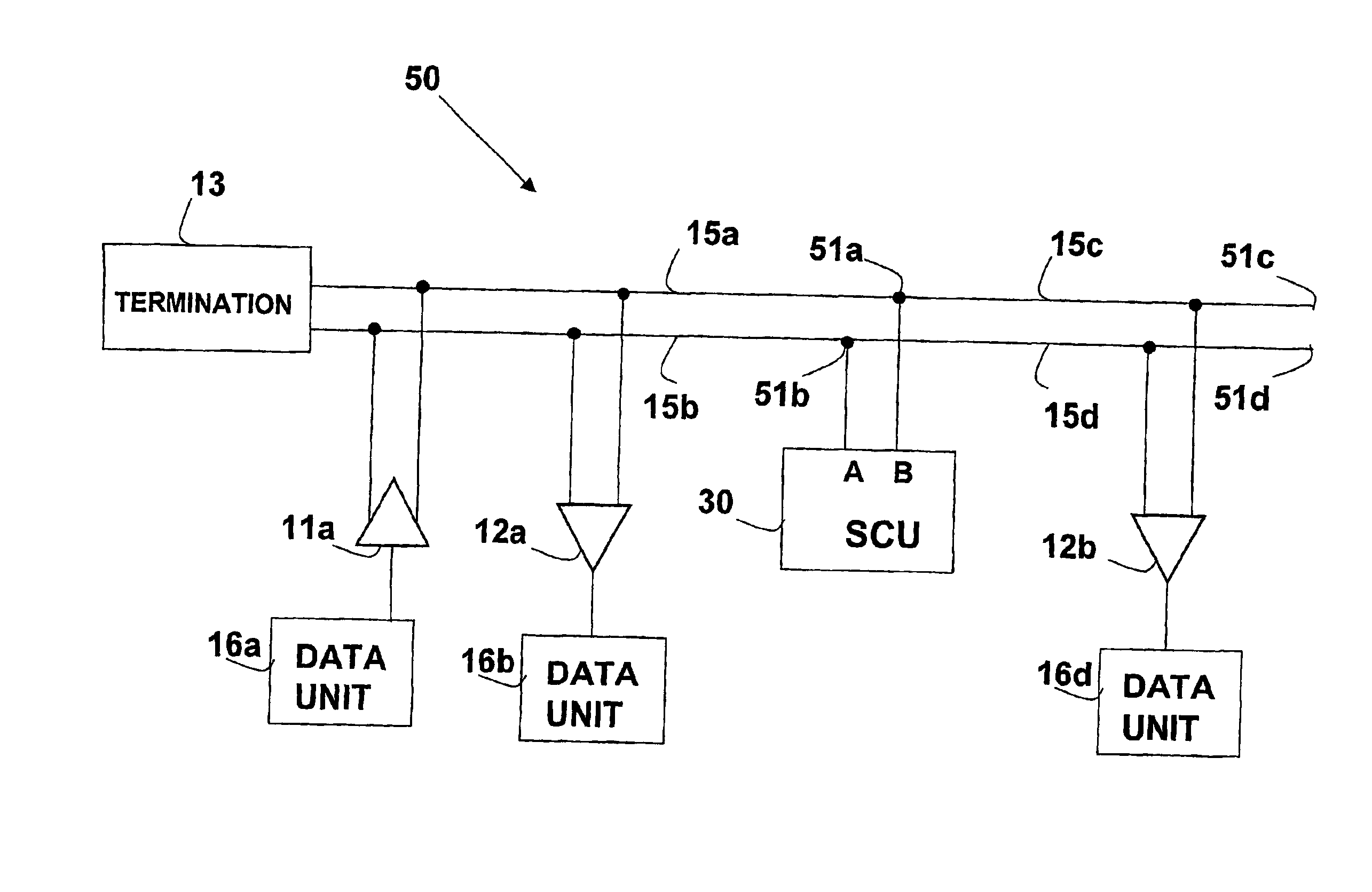

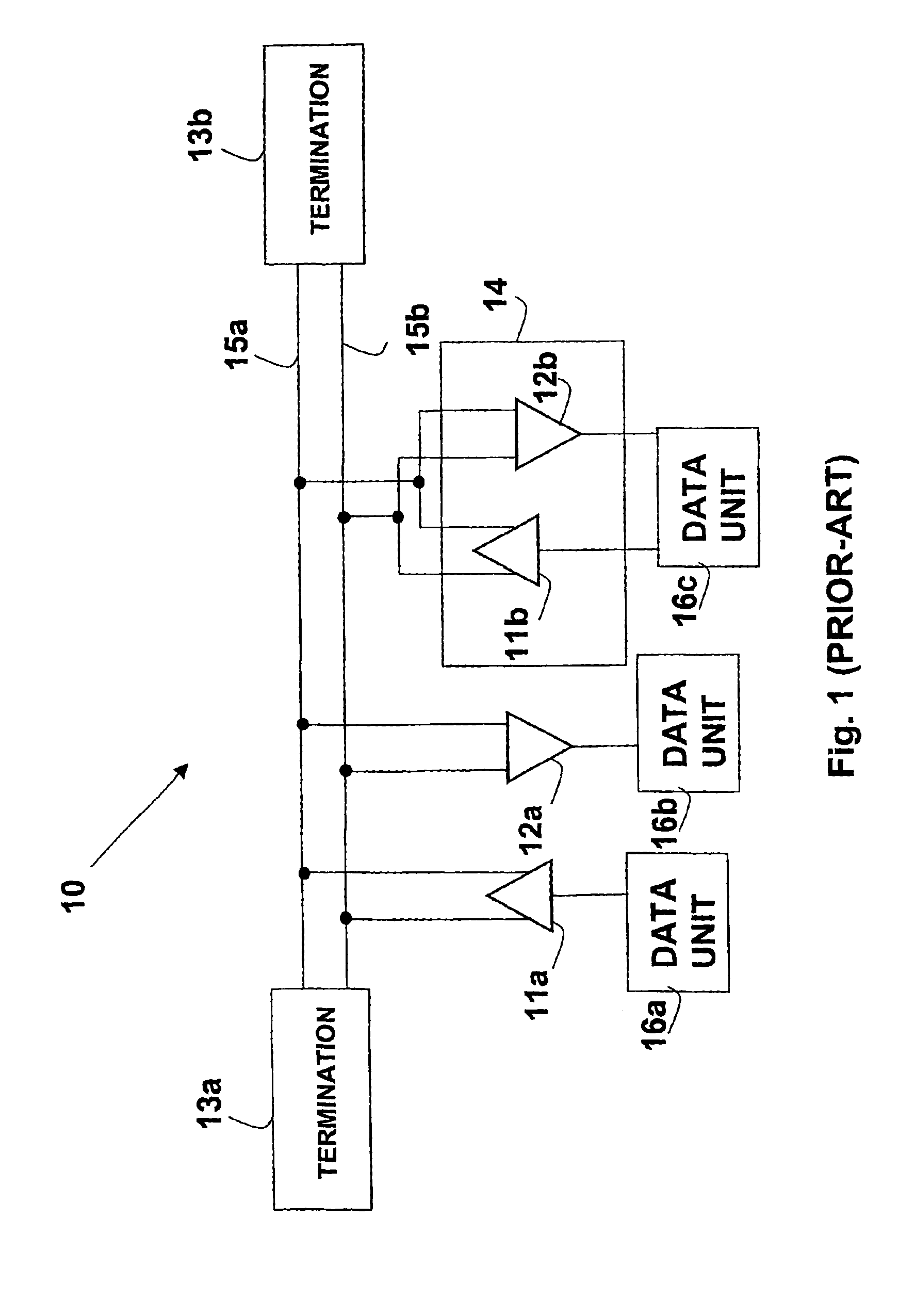

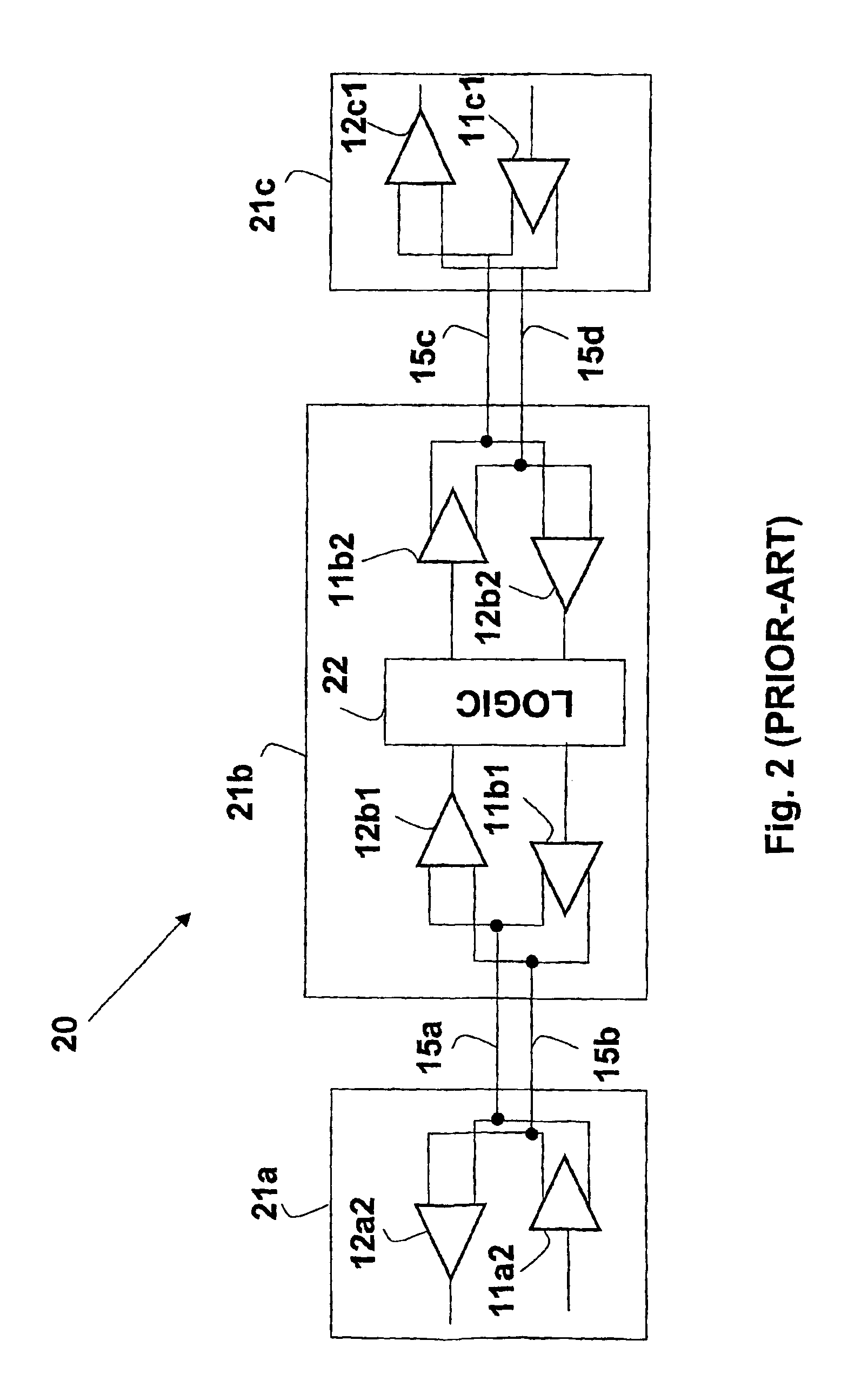

System and method for transmission-line termination by signal cancellation, and applications thereof

InactiveUS6937056B2Effective segmentationInput/output impedence modificationReliability increasing modificationsElectric power transmissionNetwork termination

An active terminating device (30) for an electrical transmission line with optional line-receiving and line-driving capabilities. The basic device is a two-terminal unit, denoted as a Signal Canceling Unit (SCU), which sensesthe signal available at its terminals (34a, 34b), and applies negative feedback in order to cancel and absorb the signal. When applied to the end of a transmission line (15a, 15b) as part of wired communication network, the SCU functions as a terminator. When connected in the middle of such wired transmission line, the SCU splits the transmission line into two separate and isolated segments. In such a configuration, the SCU can be used to isolate a portion of a network from signal degradation due to noise or bridge-tap. Furthermore, the two isolated segments may each employ independent communications, such that no interference exists between the segments. In another embodiment, line receiver functionality is integrated into the SCU, designated as a Signal Canceling and Receiving Unit (SCRU) (90). The SCRU can perform all the SCU functions, and also serves as a line receiver in the communication network. In yet another embodiment, line driver functionality is integrated into the SCRU, designated as a Signal Canceling, Receiving and Transmitting Unit (SCRTU) (120). The SCRTU can perform all the SCRU functions, and also serves as a line driver in the communication network. Upon connecting multiple SCRTU's to a continuous transmission line, terminated independent point-to-point communication segments are formed.

Owner:CONVERSANT INTPROP MANAGEMENT INC

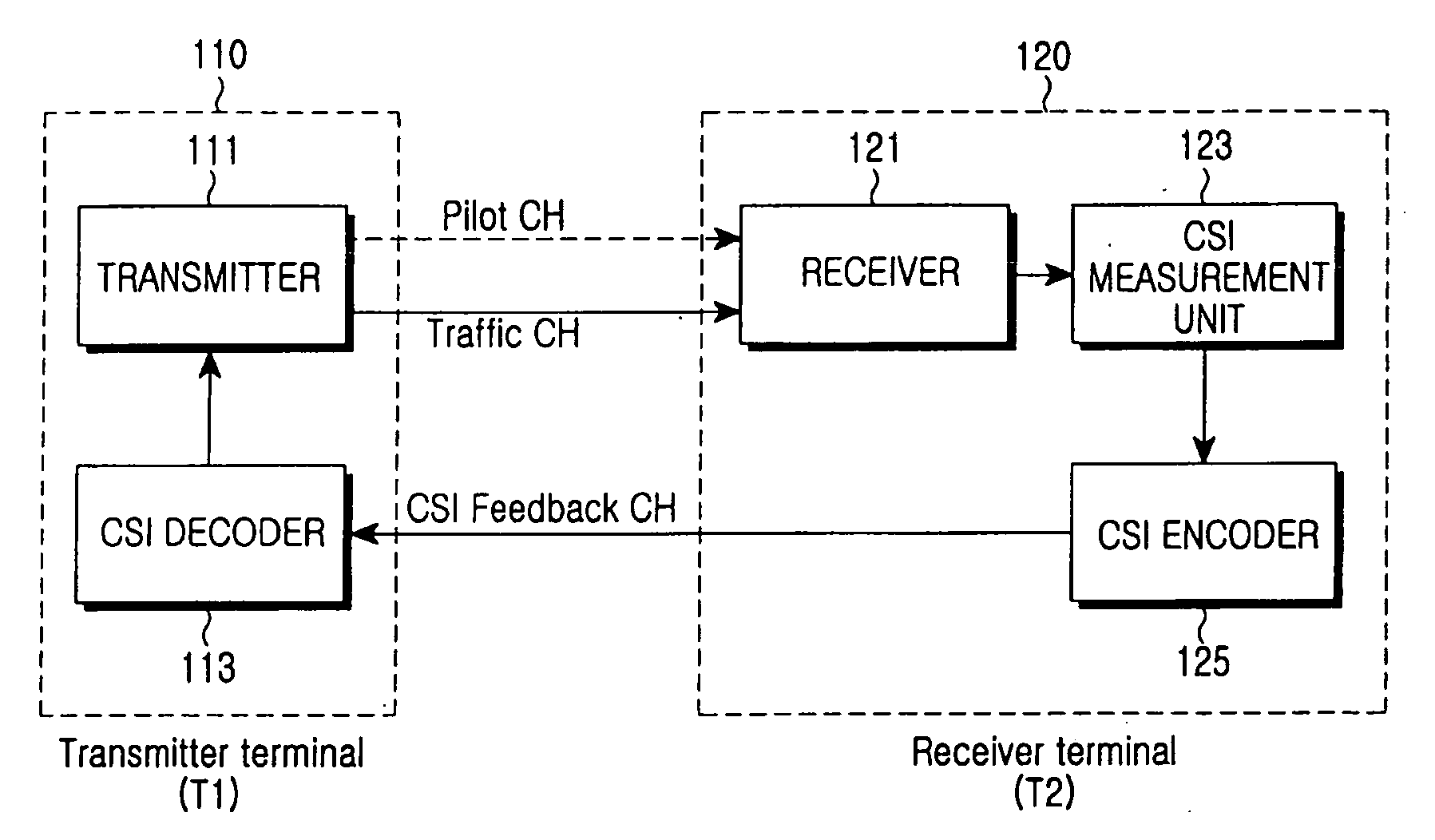

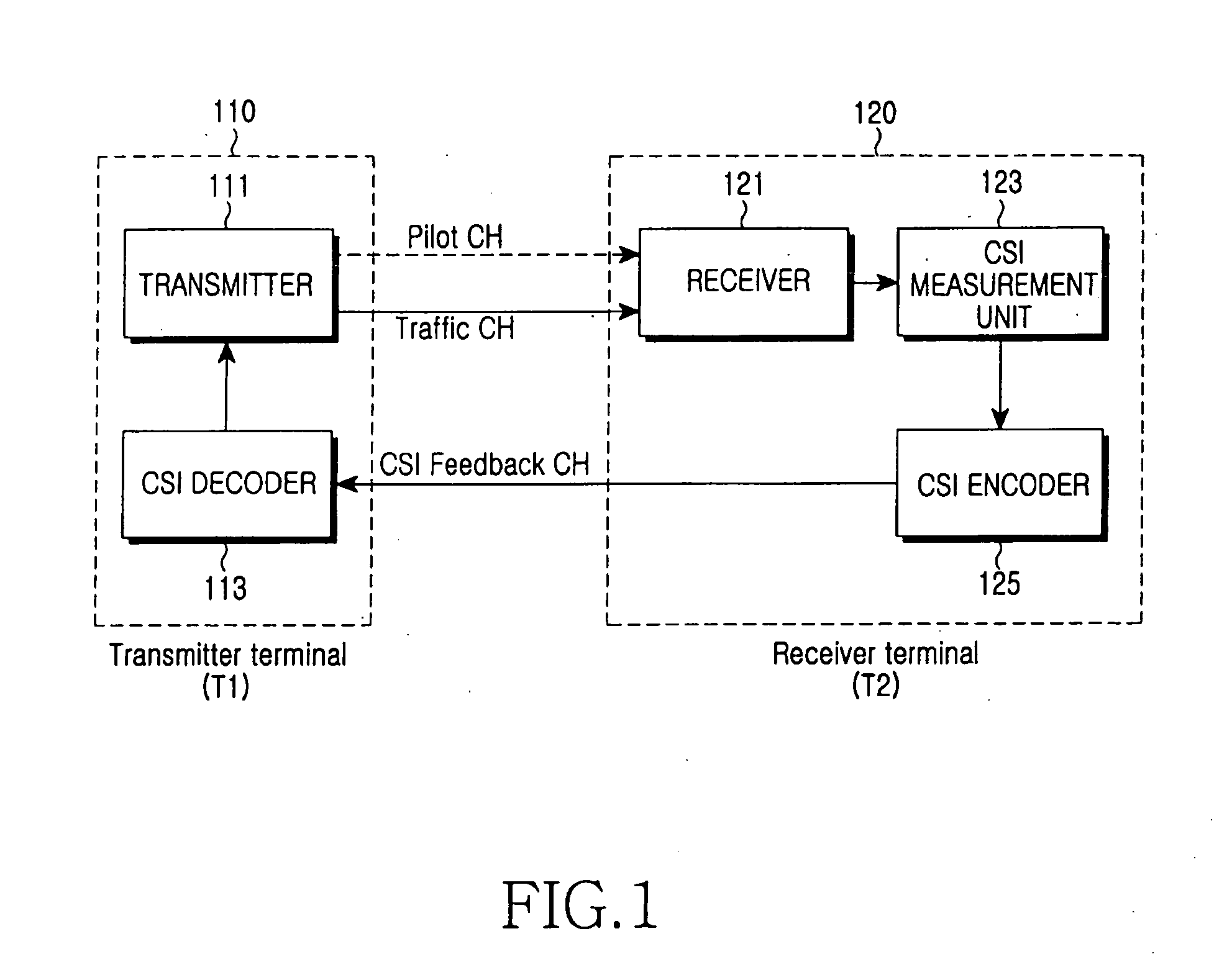

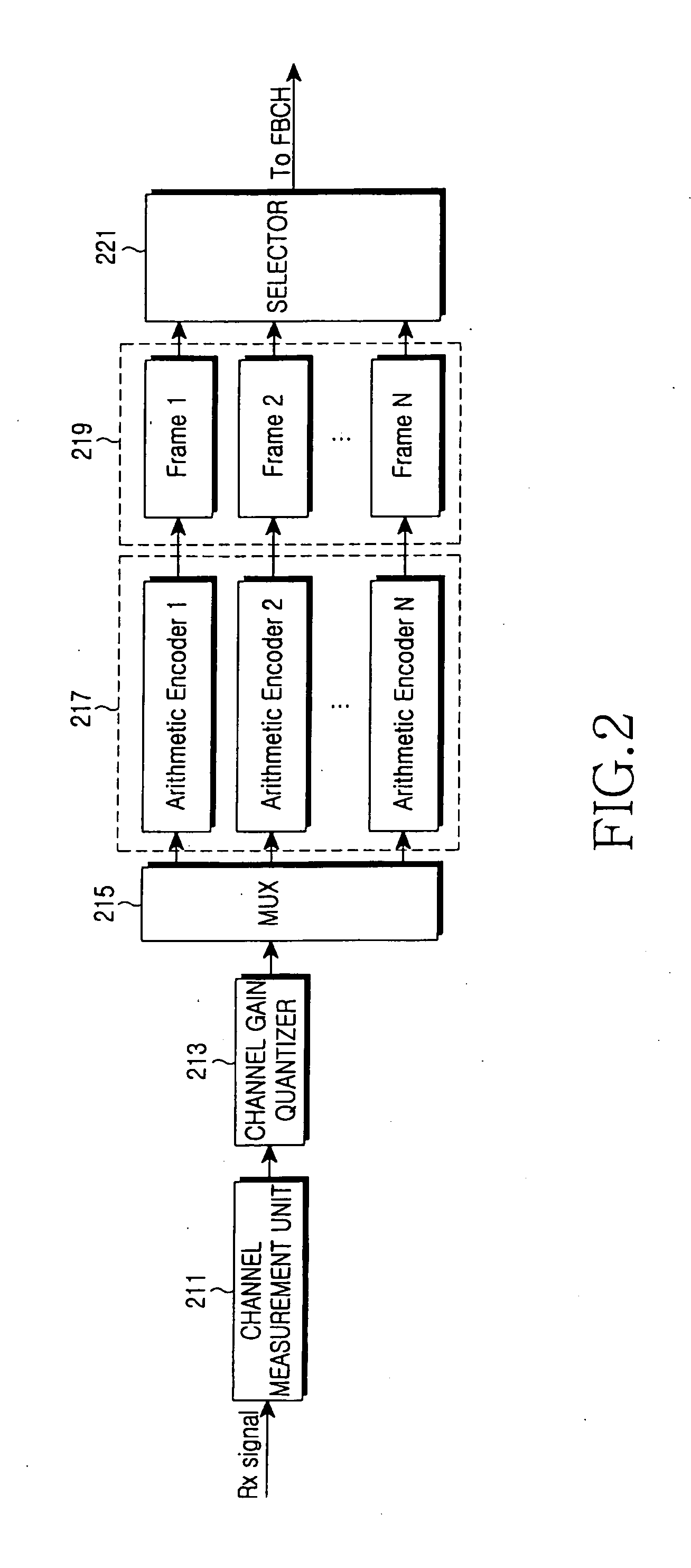

Method and apparatus for channel state feedback using arithmetic coding

ActiveUS20050265436A1Reduce the impactImprove system performanceModulated-carrier systemsFrequency-division multiplex detailsCommunications systemArithmetic coding

Disclosed are the design and implementation of a CSI feedback channel in a multi-carrier wireless communication system. An apparatus and a method for channel state feedback using arithmetic coding are provided to ensure efficiency and reliability of a system by transmitting the CSI while compressing the CSI with a predetermined compression rate selected depending on a channel state. The apparatus for CSI feedback in a wireless communication system performing channel estimation at a transmitter or a receiver by using a communication channel includes a transmitter terminal transmitting a signal for CSI measurement by using the communication channel, and a receiver terminal receiving the signal from the transmitter terminal, checking a channel state based on the received signal, and transmitting the signal to the transmitter terminal after compressing the signal according to the channel state.

Owner:SAMSUNG ELECTRONICS CO LTD +1

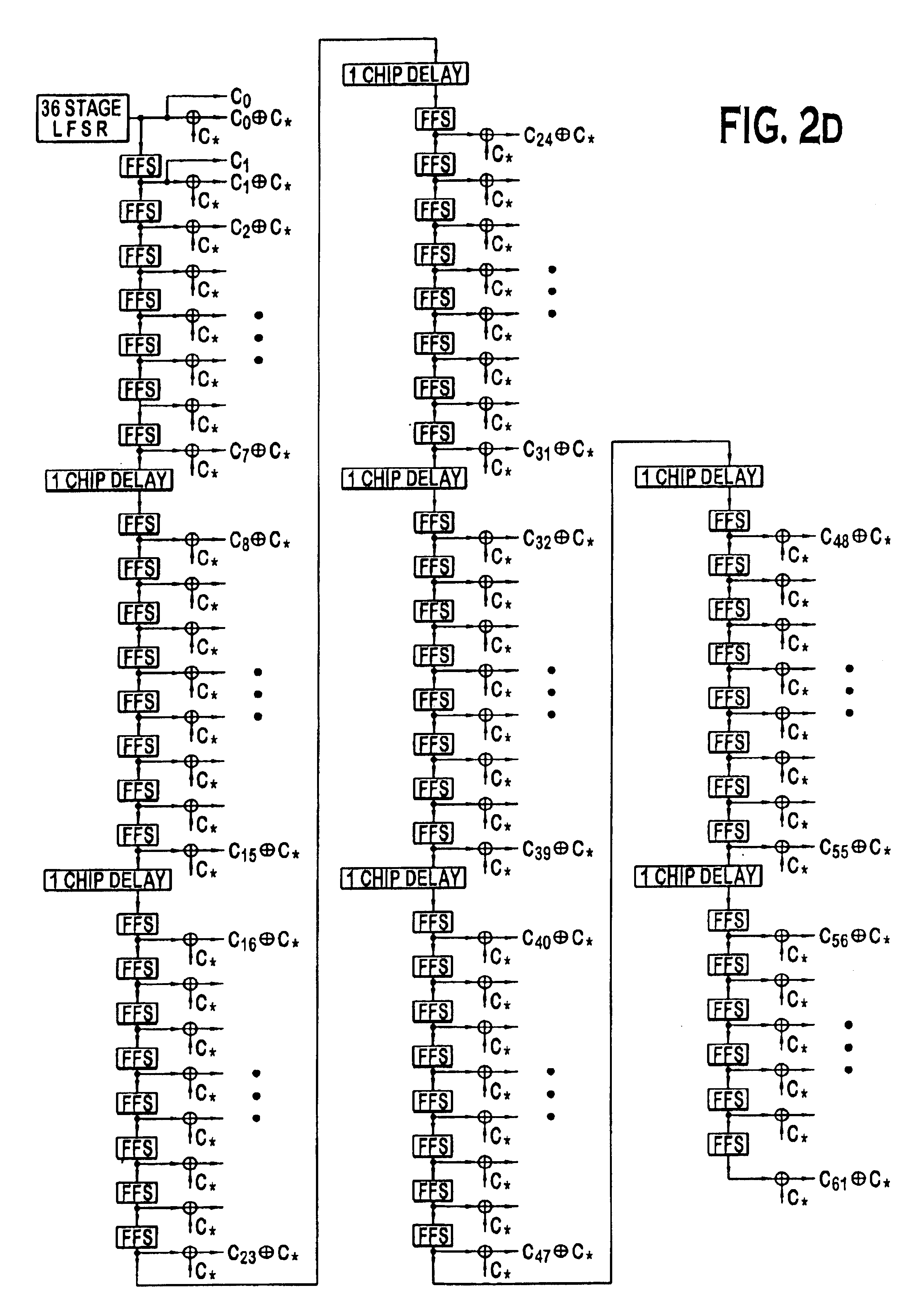

System for using rapid acquisition spreading codes for spread-spectrum communications

InactiveUS20050265430A1Increase profitEnergy efficient ICTRadio transmission for post communicationCode division multiple accessCarrier signal

A system for rapidly acquiring a spreading code, used in a code division multiple access (CDMA) system, comprises a generator for generating a first long code and a second long code, with each long code having a length of N chips. The first long code is different from the second long code. A transmitter transmits the first long code and the second long code at a first phase angle and at a second phase angle, respectively, on a carrier signal over a communications channel using radio waves. The first long code and the second long code may be transmitted at an in-phase (I) angle and at a quadrature-phase (Q) angle, respectively, on the carrier signal. From the communications channel, an I acquisition circuit and a Q acquisition circuit may acquire, in parallel, the first long code and the second long code from the I angle and the Q angle, respectively, of the carrier signal by searching, in parallel, N / 2 chips of the first long code and the second long code.

Owner:INTERDIGITAL TECH CORP

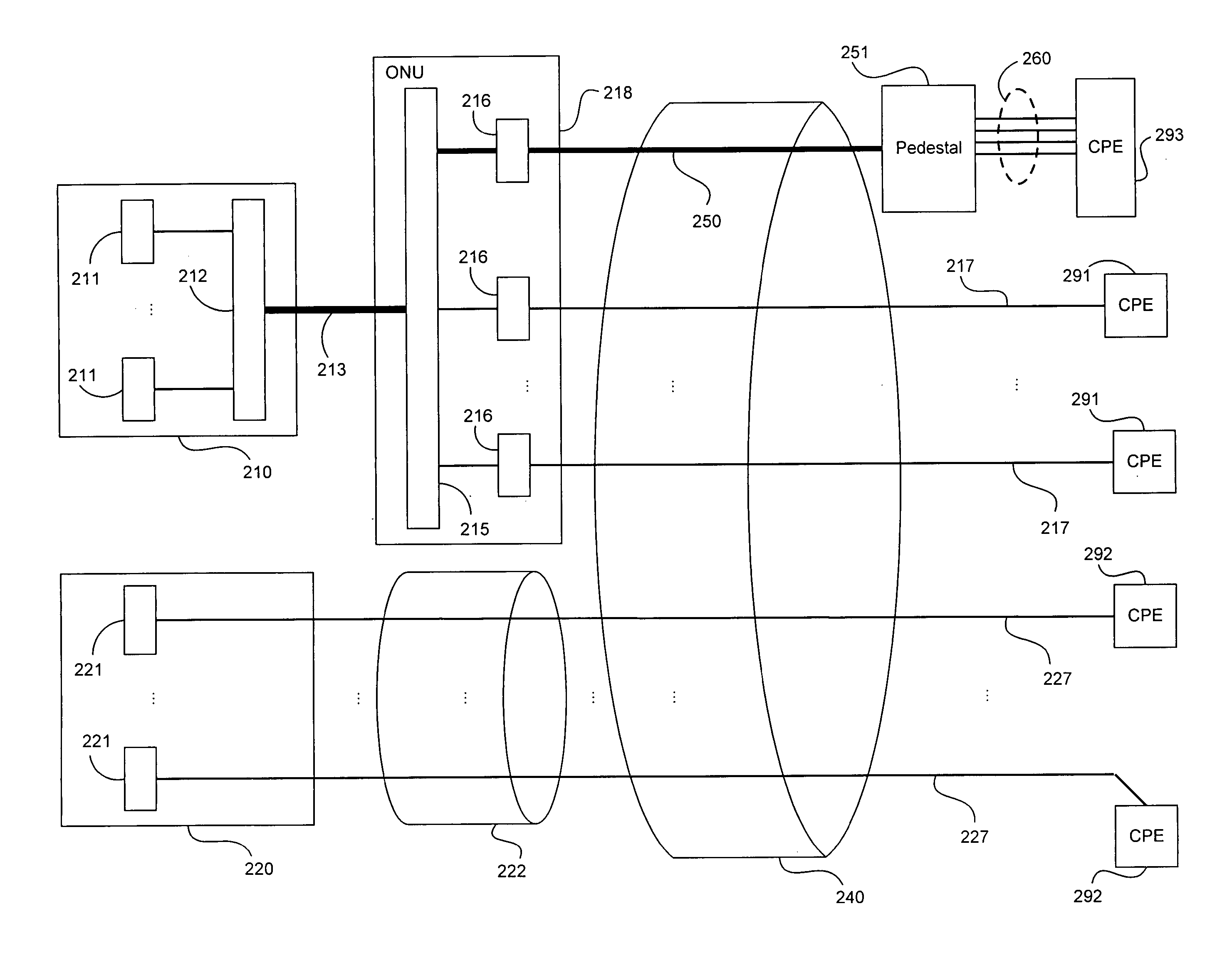

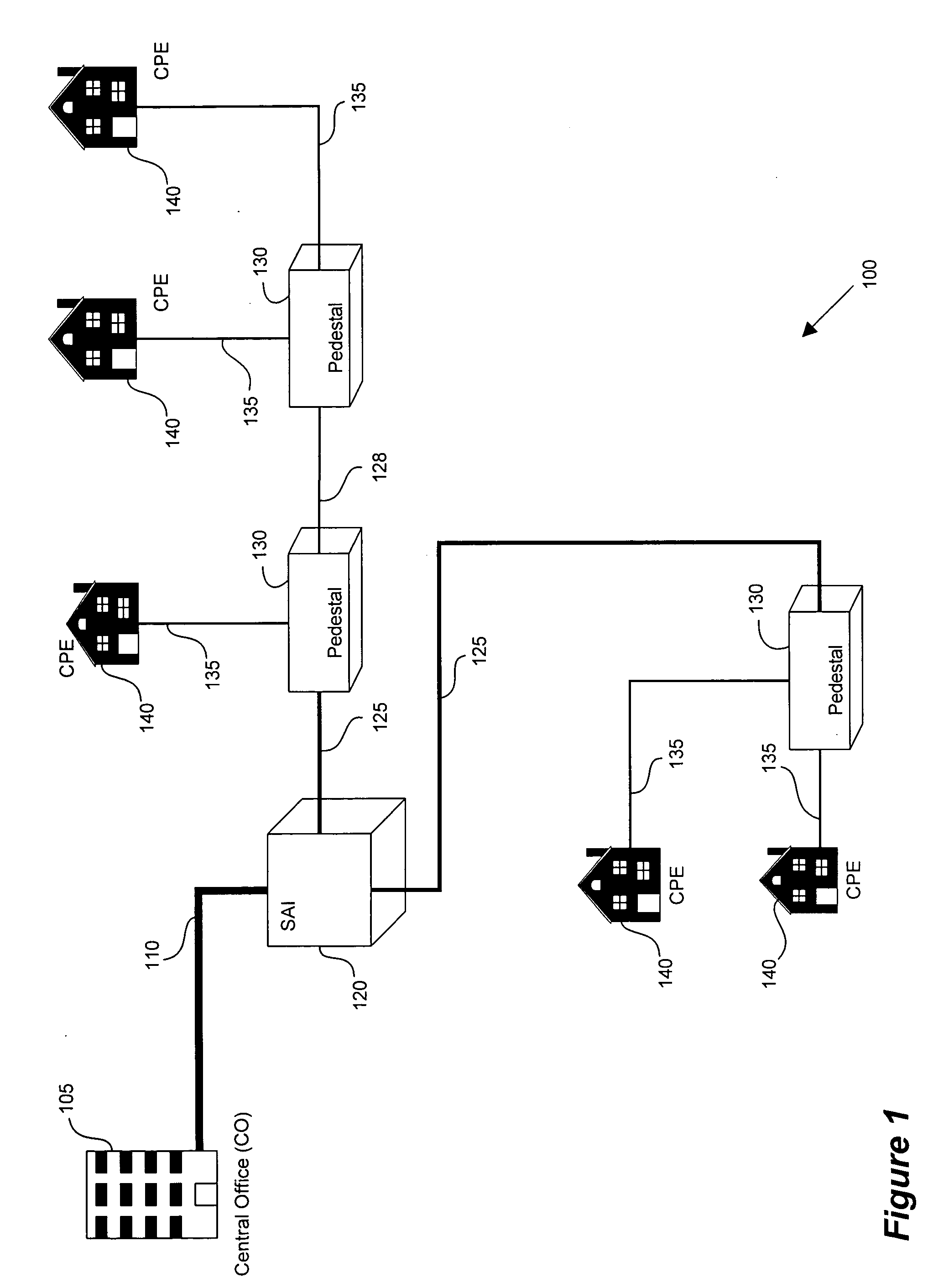

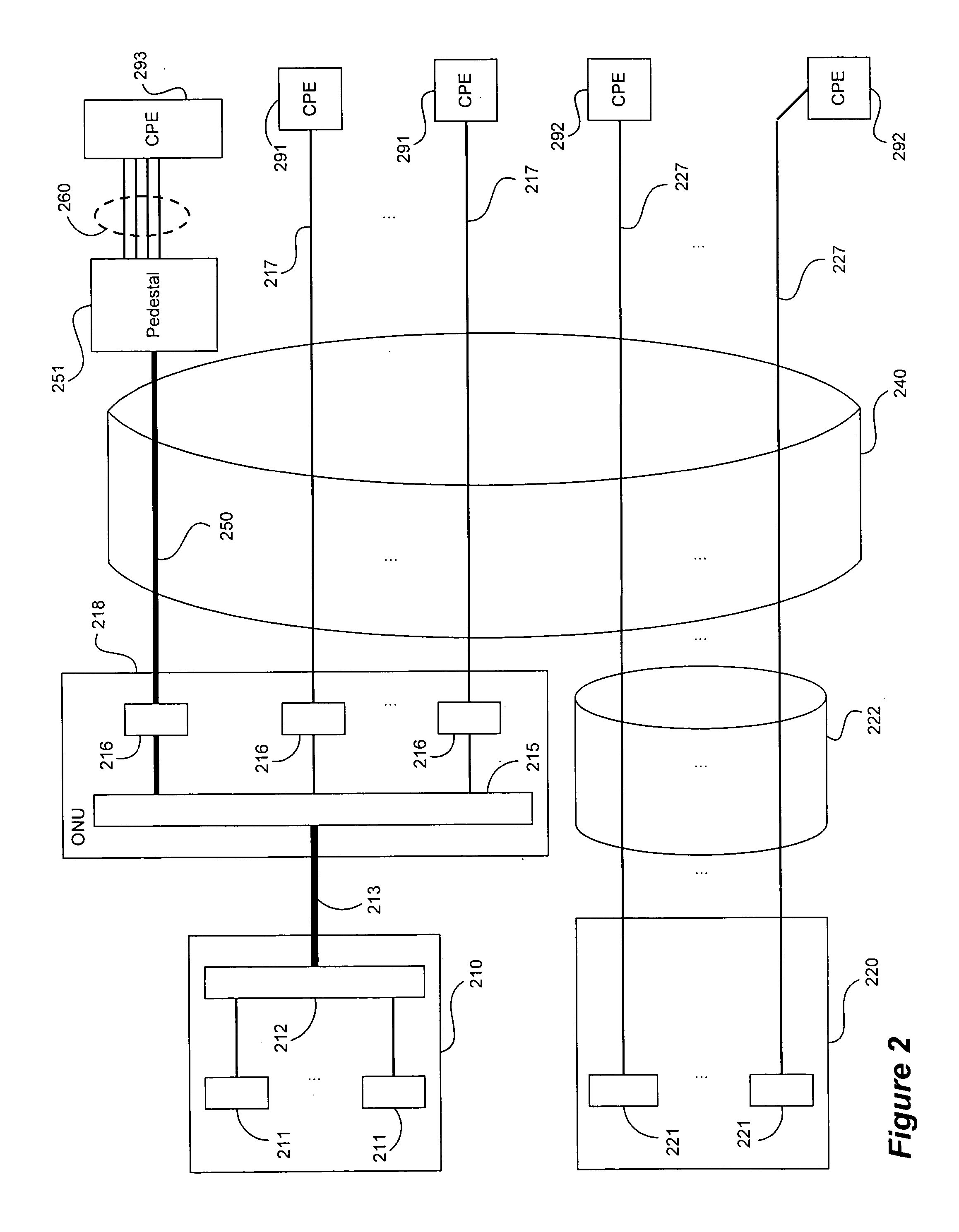

High speed multiple loop DSL system

ActiveUS20050152385A1Increase speedIncrease data carrying capabilityTwo-way loud-speaking telephone systemsFrequency-division multiplex detailsFrequency spectrumDynamic spectrum management

A DSL system includes a multiple loop segment where K loops are bonded to provide a multiple loop segment having up to (2K−1) communication channels on which transmissions are vectored. The segment may be a drop to a customer premises, an inter-pedestal link, or any other suitable part of a larger DSL system. Generally the bonded loops are relatively short, being 300 meters or less. Signal vectoring is used to increase the speed and data carrying capability of the channels. In some embodiments, an expanded frequency spectrum also can be used to increase the data carrying capability of one or more of the channels. An impedance matching circuit may be coupled to each end of the segment to provided efficient transmission of data across the segment. A controller may provide control signals used to operate the segment as a vectored system and, if desired, frequency bandwidth control signals. The controller may monitor and / or collect data and information from the DSL system to assist in generating control signals. The controller can be a dynamic spectrum manager or DSM Center that includes a computer system and / or other hardware to assist in performing the required functions.

Owner:ASSIA SPE LLC CO THE CORP TRUST CO

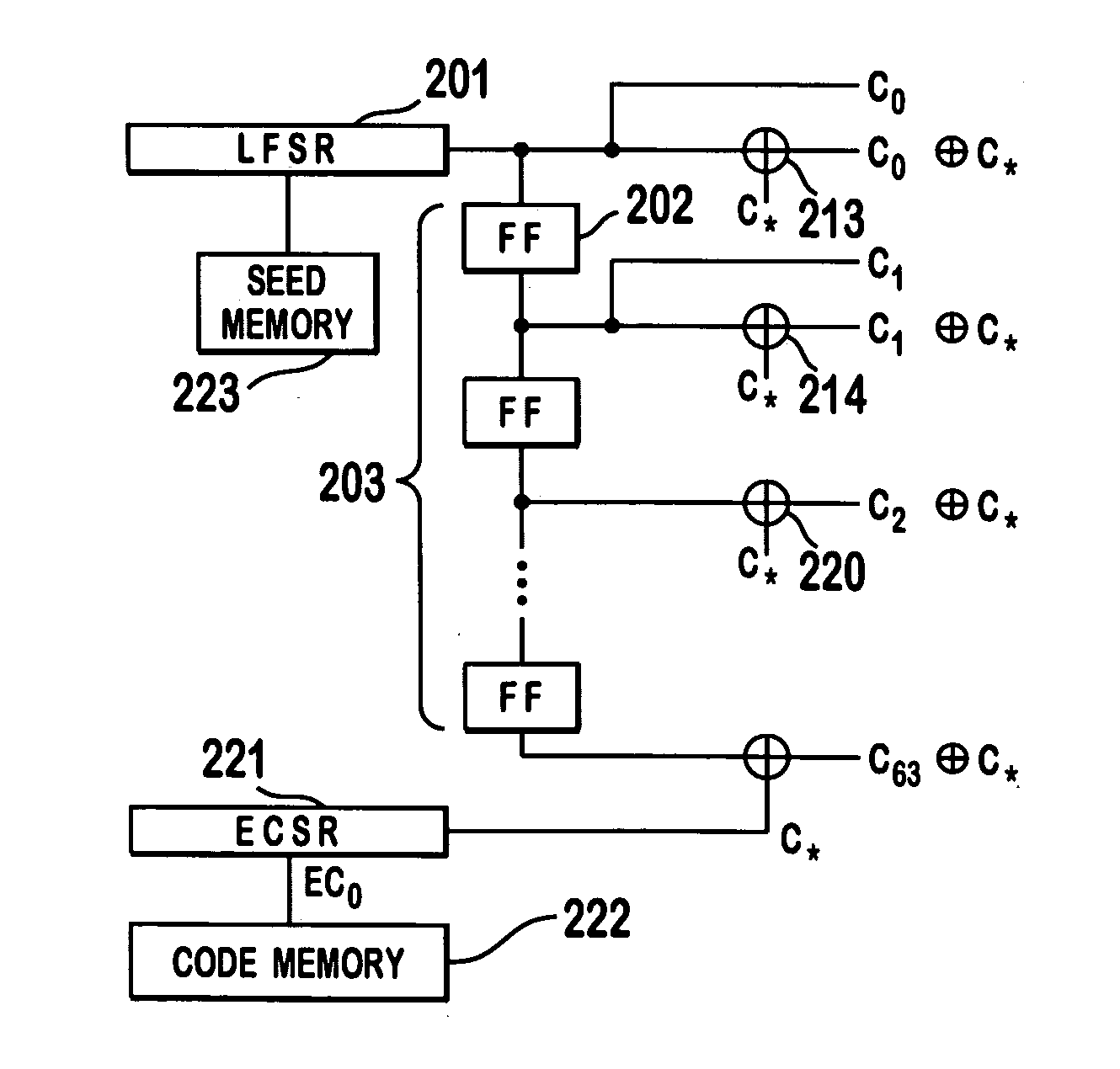

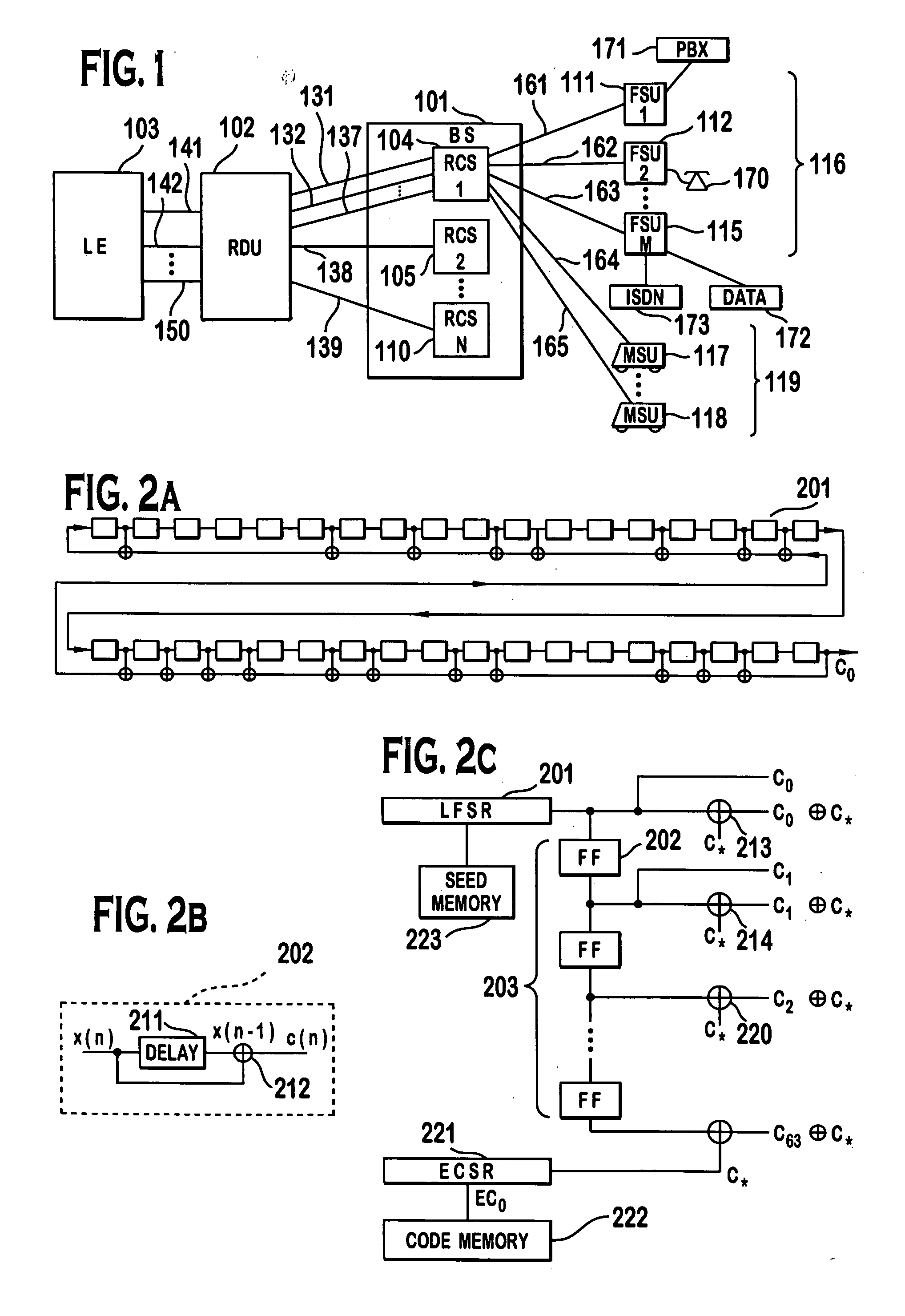

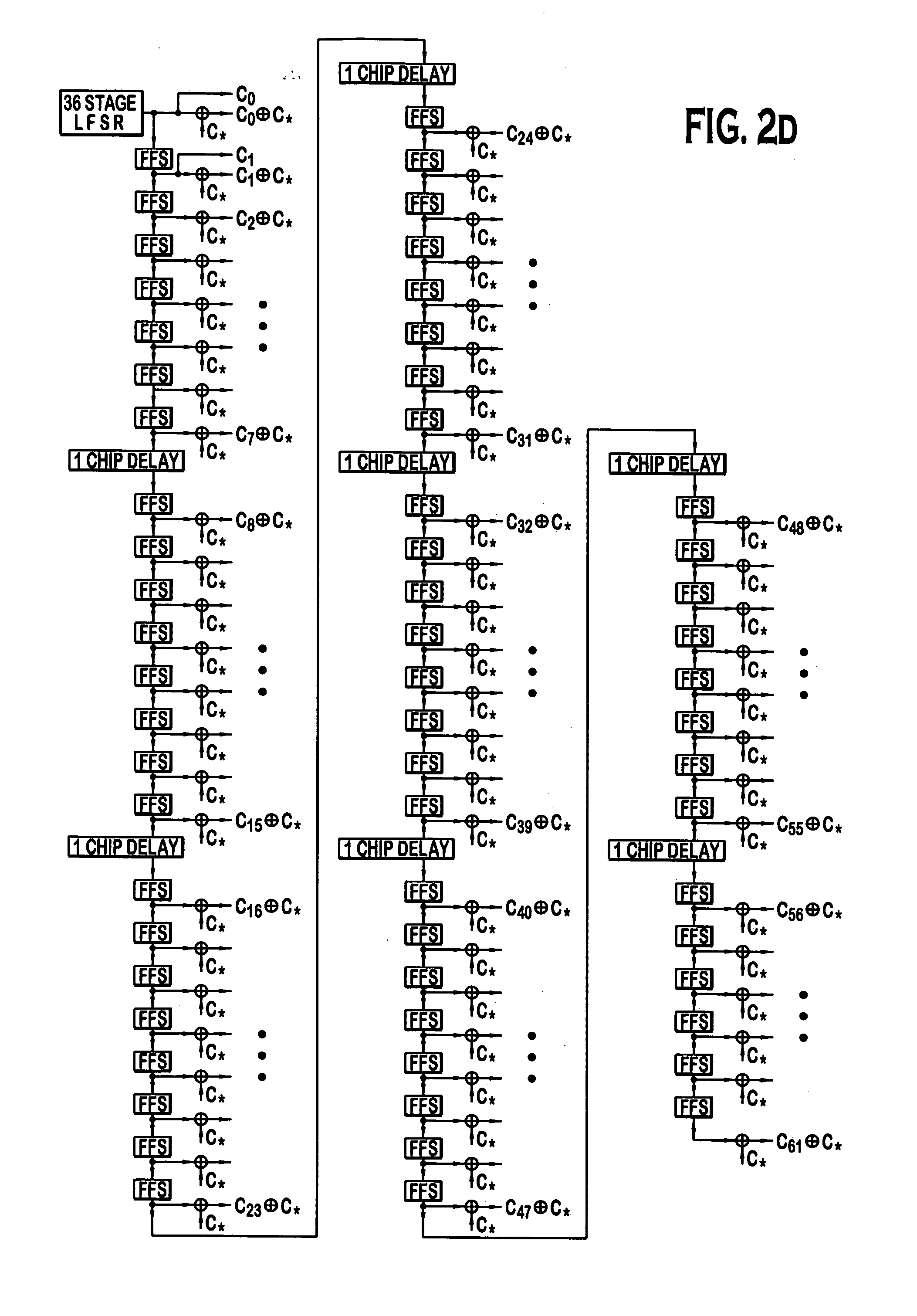

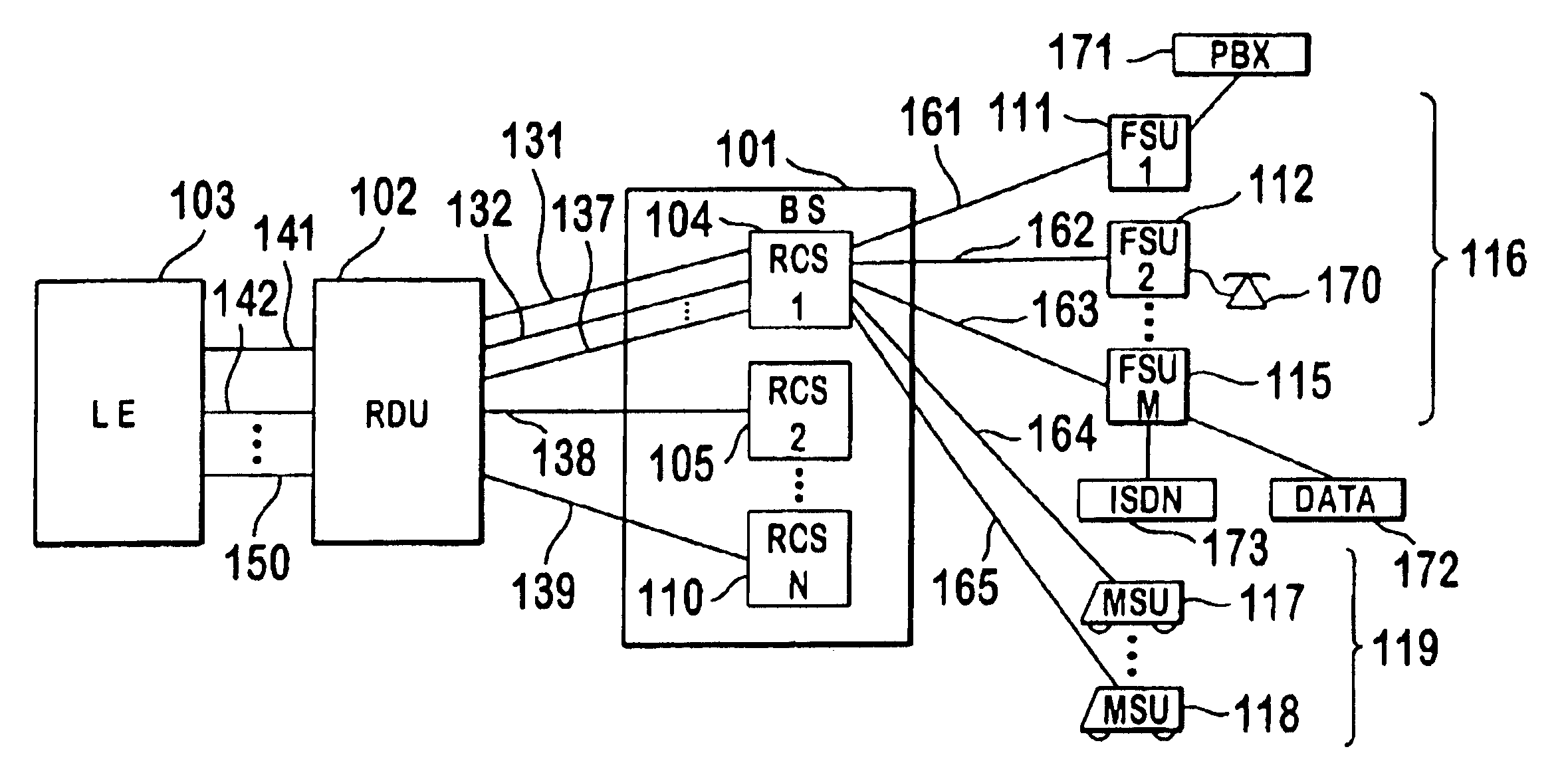

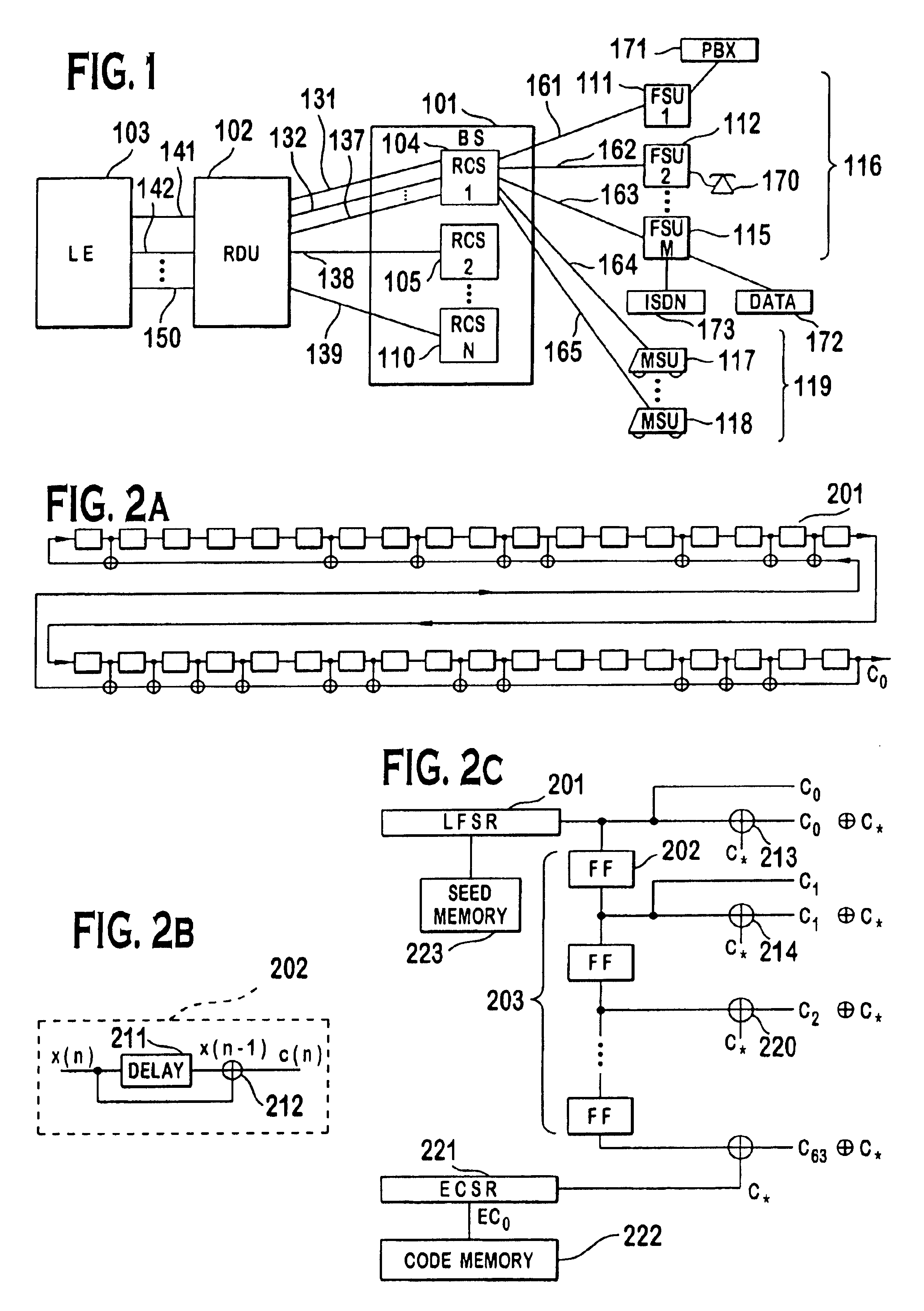

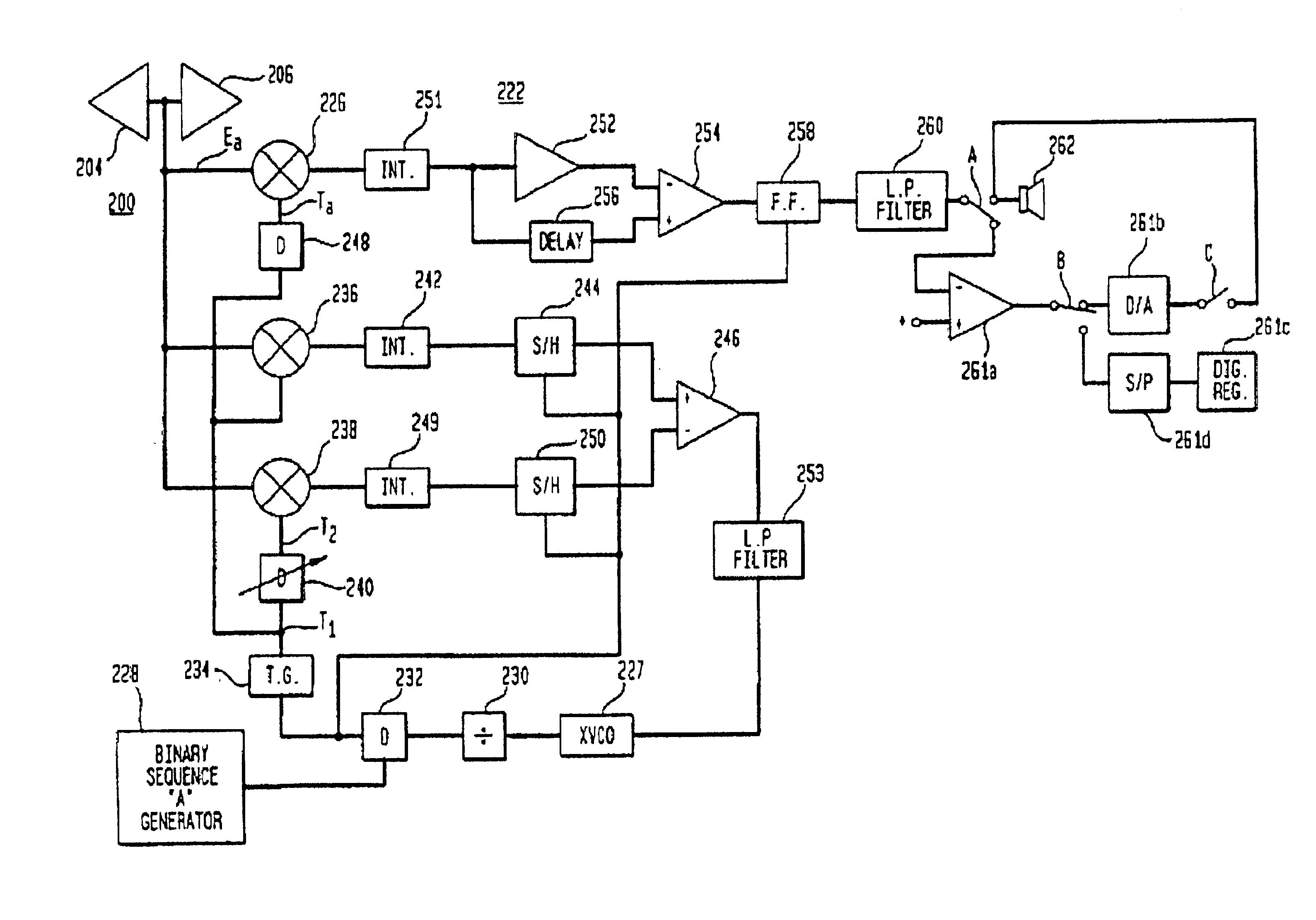

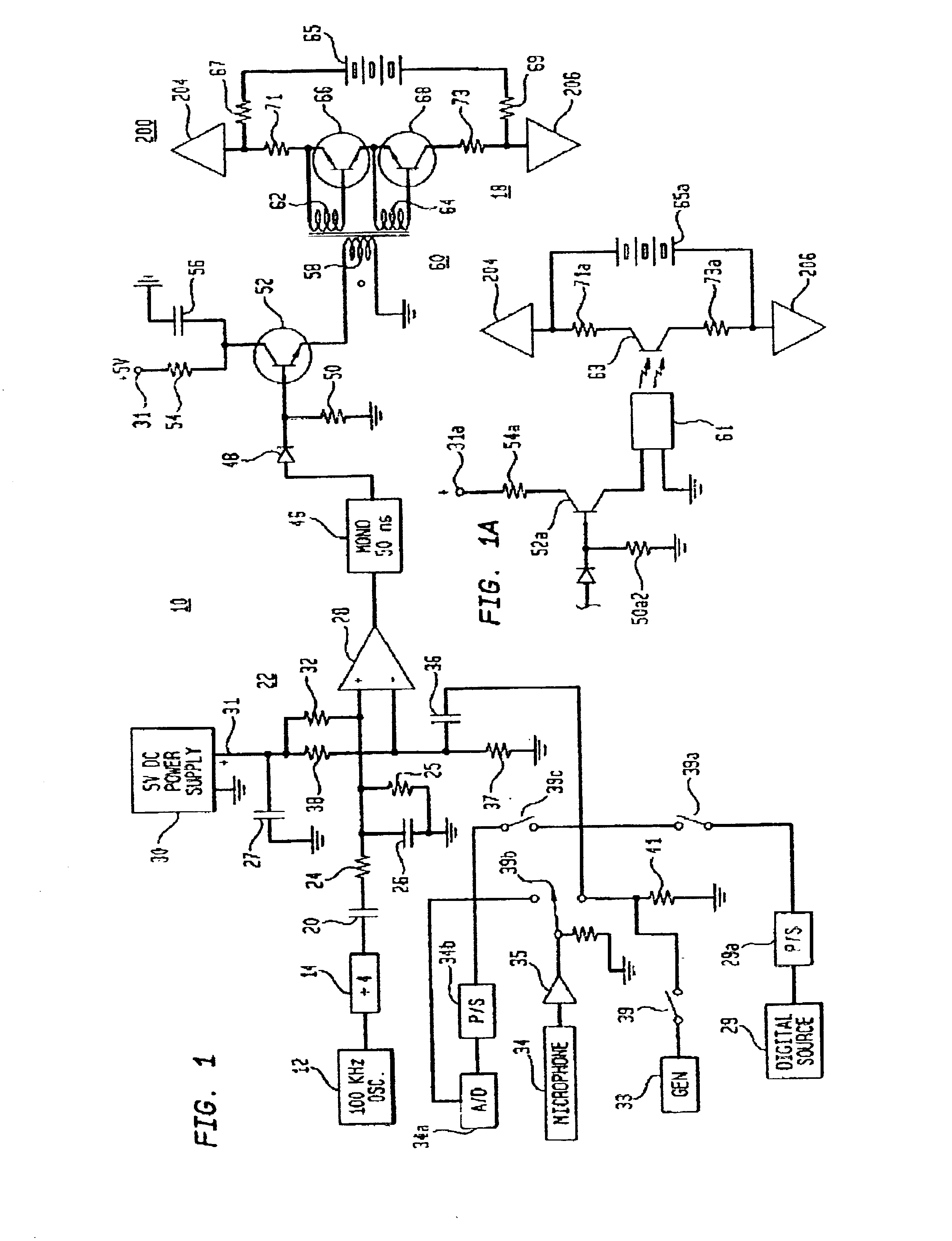

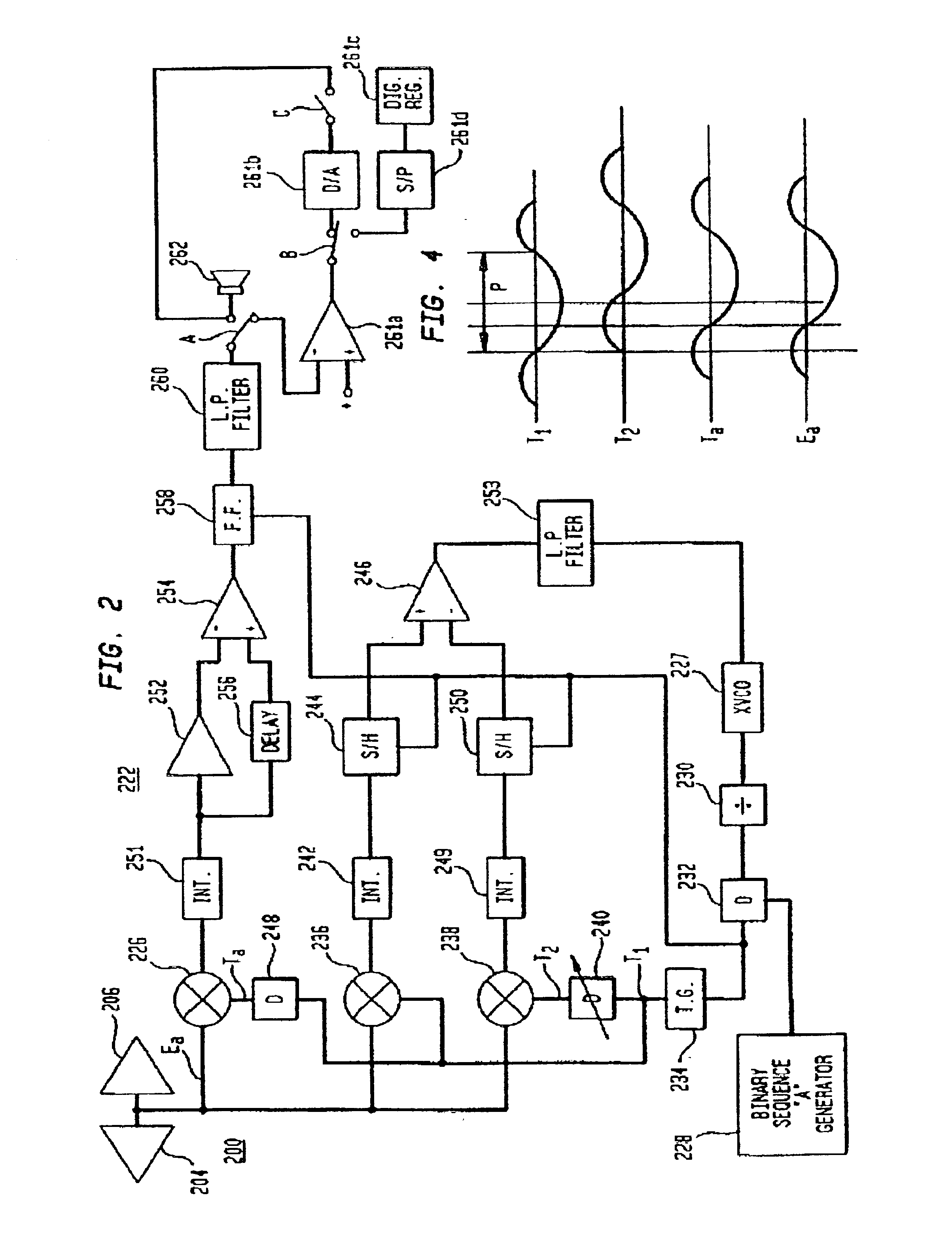

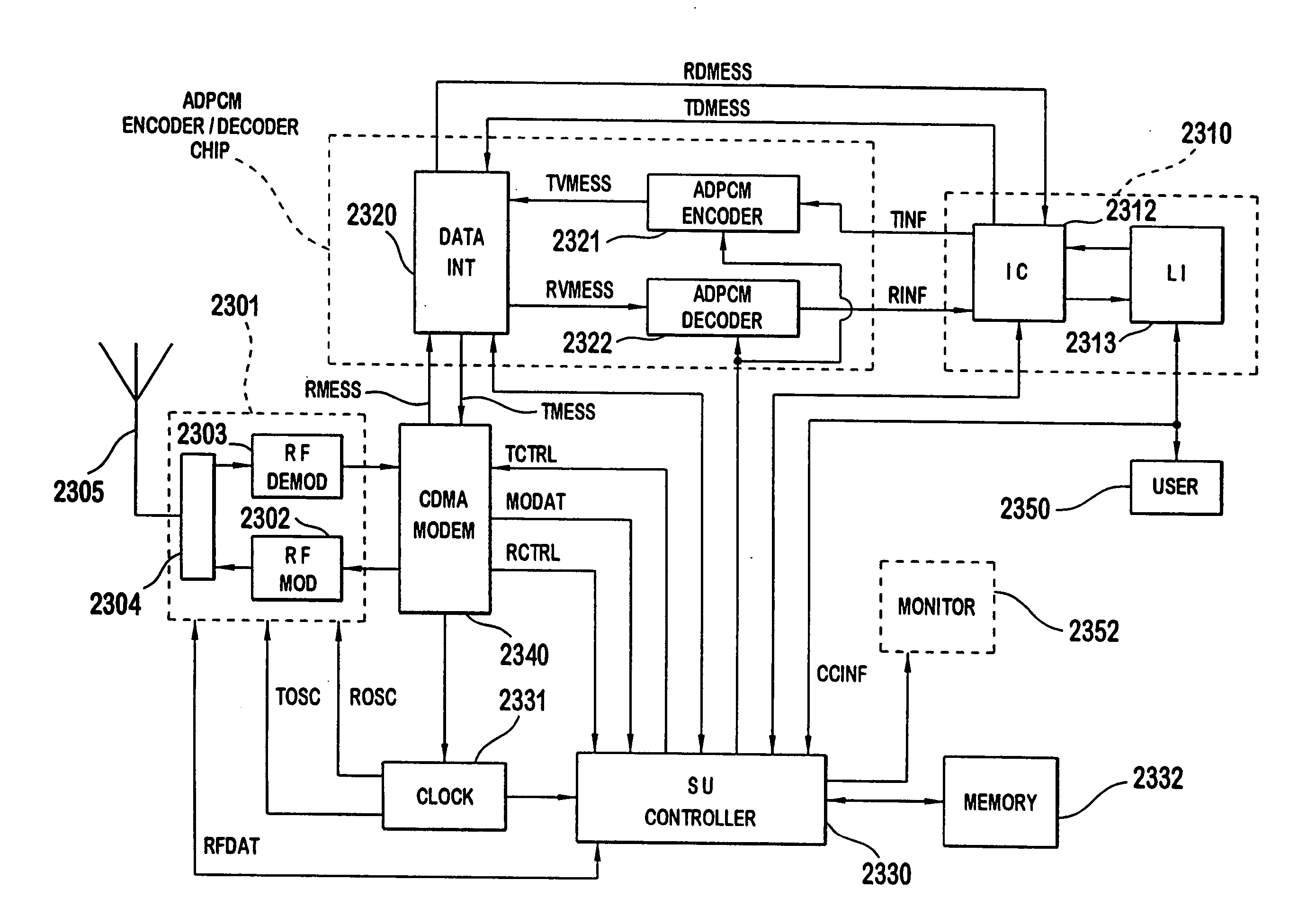

Code division multiple access (CDMA) communication system

InactiveUS6885652B1Increase profitPower managementBaseband system detailsModem deviceSystem capacity

A multiple access, spread-spectrum communication system processes a plurality of information signals received by a Radio Carrier Station (RCS) over telecommunication lines for simultaneous transmission over a radio frequency (RF) channel as a code-division-multiplexed (CDM) signal to a group of Subscriber Units (SUs). The RCS receives a call request signal that corresponds to a telecommunication line information signal, and a user identification signal that identifies a user to receive the call. The RCS includes a plurality of Code Division Multiple Access (CDMA) modems, one of which provides a global pilot code signal. The modems provide message code signals synchronized to the global pilot signal. Each modem combines an information signal with a message code signal to provide a CDM processed signal. The RCS includes a system channel controller is coupled to receive a remote call. An RF transmitter is connected to all of the modems to combine the CDM processed signals with the global pilot code signal to generate a CDM signal. The RF transmitter also modulates a carrier signal with the CDM signal and transmits the modulated carrier signal through an RF communication channel to the SUs. Each SU includes a CDMA modem which is also synchronized to the global pilot signal. The CDMA modem despreads the CDM signal and provides a despread information signal to the user. The system includes a closed loop power control system for maintaining a minimum system transmit power level for the RCS and the SUs, and system capacity management for maintaining a maximum number of active SUs for improved system performance.

Owner:INTERDIGITAL TECH CORP

Time domain radio transmission system

InactiveUS6882301B2Easy to detectImprove signal-to-noise ratioBaseband system detailsModulated-carrier systemsTime domainCommunications system

A time domain communications system wherein a broadband of time-spaced signals, essentially monocycle-like signals, are derived from applying stepped-in-amplitude signals to a broadband antenna, in this case, a reverse bicone antenna. When received, the thus transmitted signals are multiplied by a D.C. replica of each transmitted signal, and thereafter, they are, successively, short time and long time integrated to achieve detection.

Owner:TIME DOMAIN

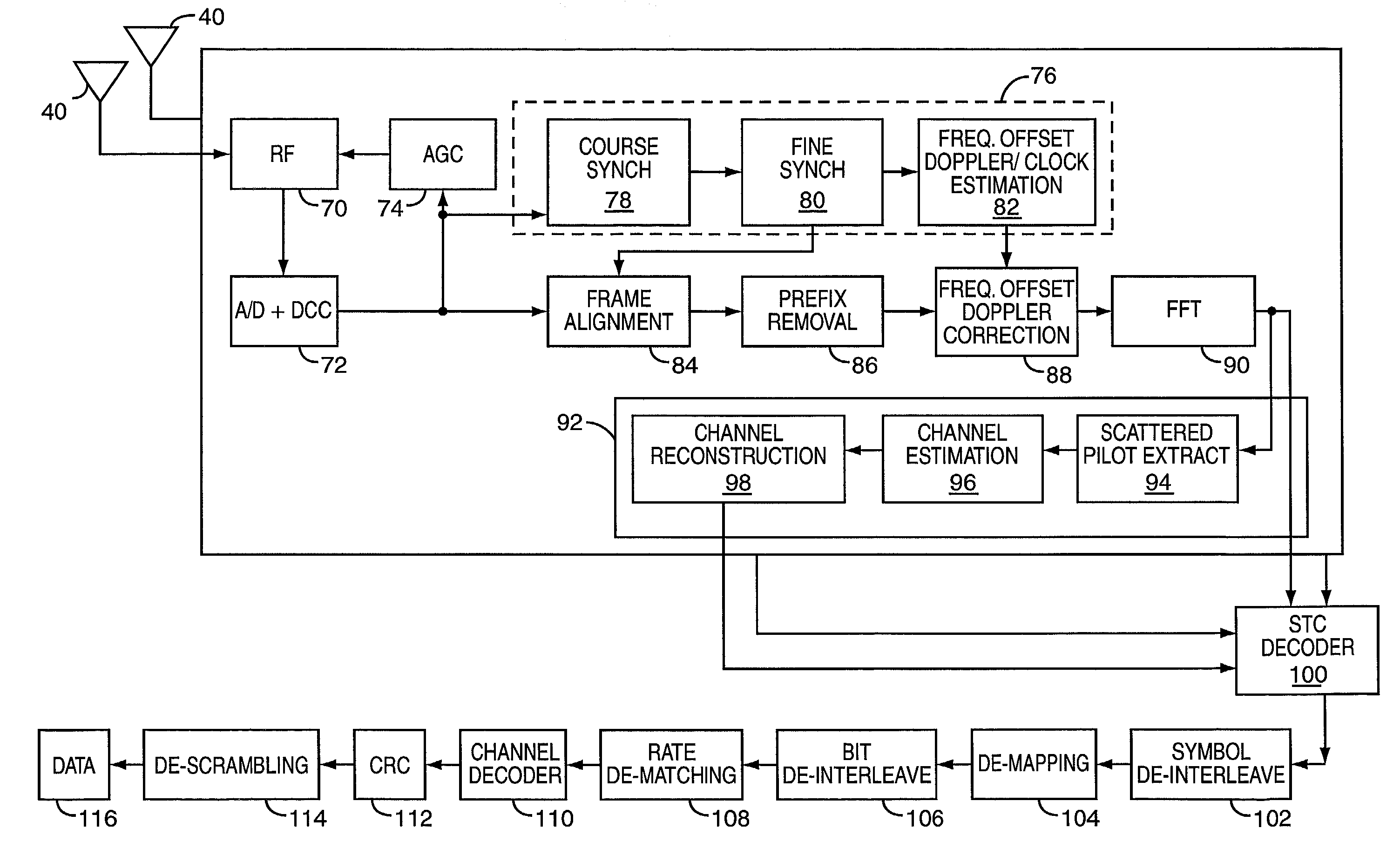

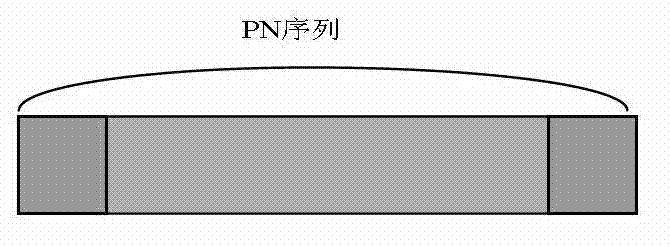

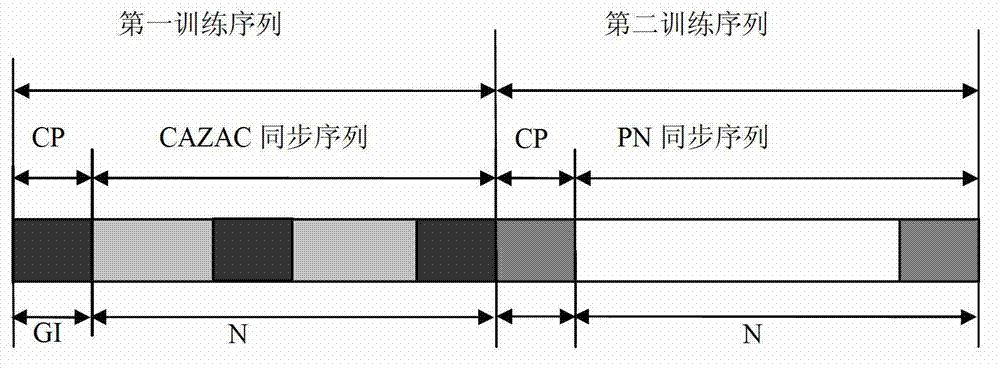

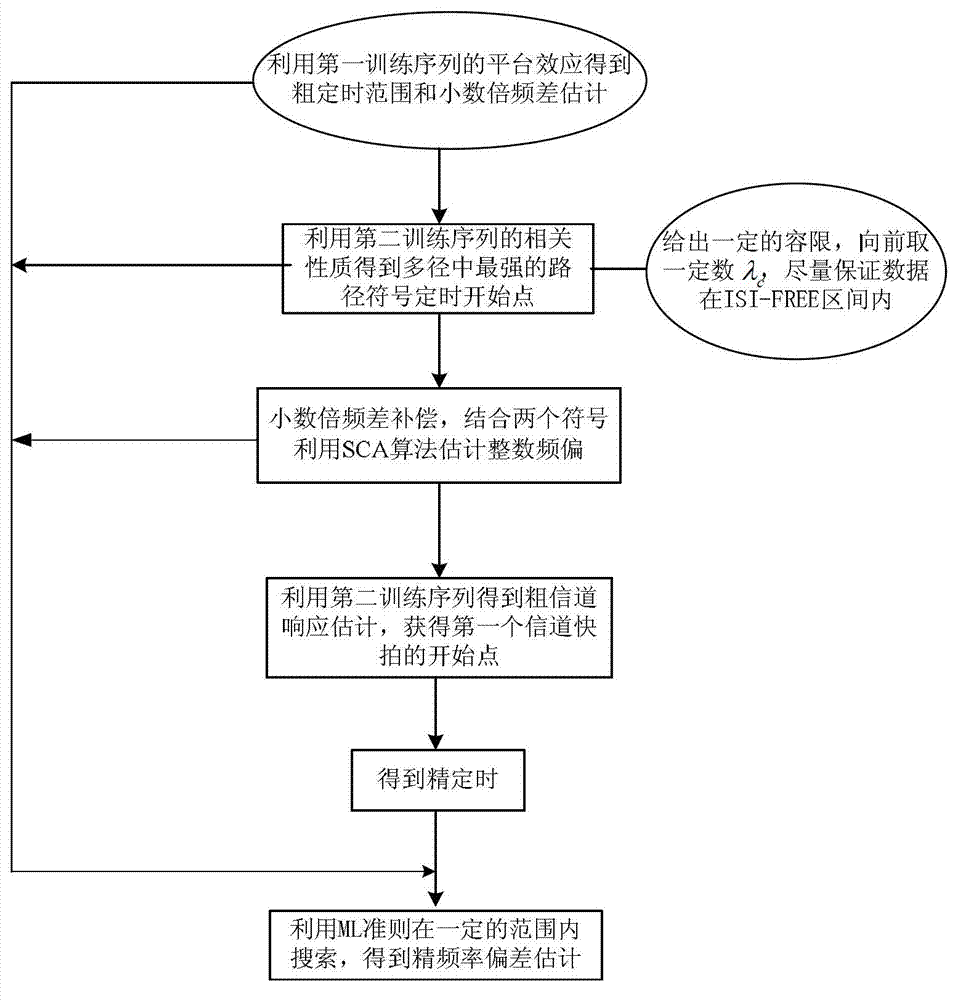

Synchronous processing method based on CMMB signals

InactiveCN102882670AHigh synchronization accuracyGood synchronizationBaseband system detailsMulti-frequency code systemsFast Fourier transformTime delays

The invention provides a synchronous processing method based on new CMMB (China Mobile Multimedia Broadcasting) synchronous signals. The CMMB synchronous signals comprise first training sequences and second training sequences; the first training sequences comprise CAZAC (Constant Amplitude Zero Auto Correlation) sequences, and the second training sequences comprise PN (Pseudo-Noise) sequences; in the synchronous processing method, the CAZAC sequences are utilized to achieve coarse symbol timing offset estimation and decimal frequency offset coarse estimation; the PN sequences are utilized to achieve the estimation of strongest path time delay in multipath, and the multipath is taken as coarse symbol timing positioning; the CAZAC sequences and the PN sequences are utilized to achieve the integer frequency offset estimation; the fast Fourier transform (FFT) is performed on the PN sequences to achieve the channel response estimation so as to estimate a first path time delay and achieve the fine symbol timing position estimation; and a maximum likelihood (ML) criterion is utilized to process the PN sequences in the second training sequences to obtain the decimal frequency offset fine estimation. The synchronous processing method can effectively improve the synchronous accuracy and can achieve better synchronization performance in the mobile communication environment with low signal-to-noise ratio.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

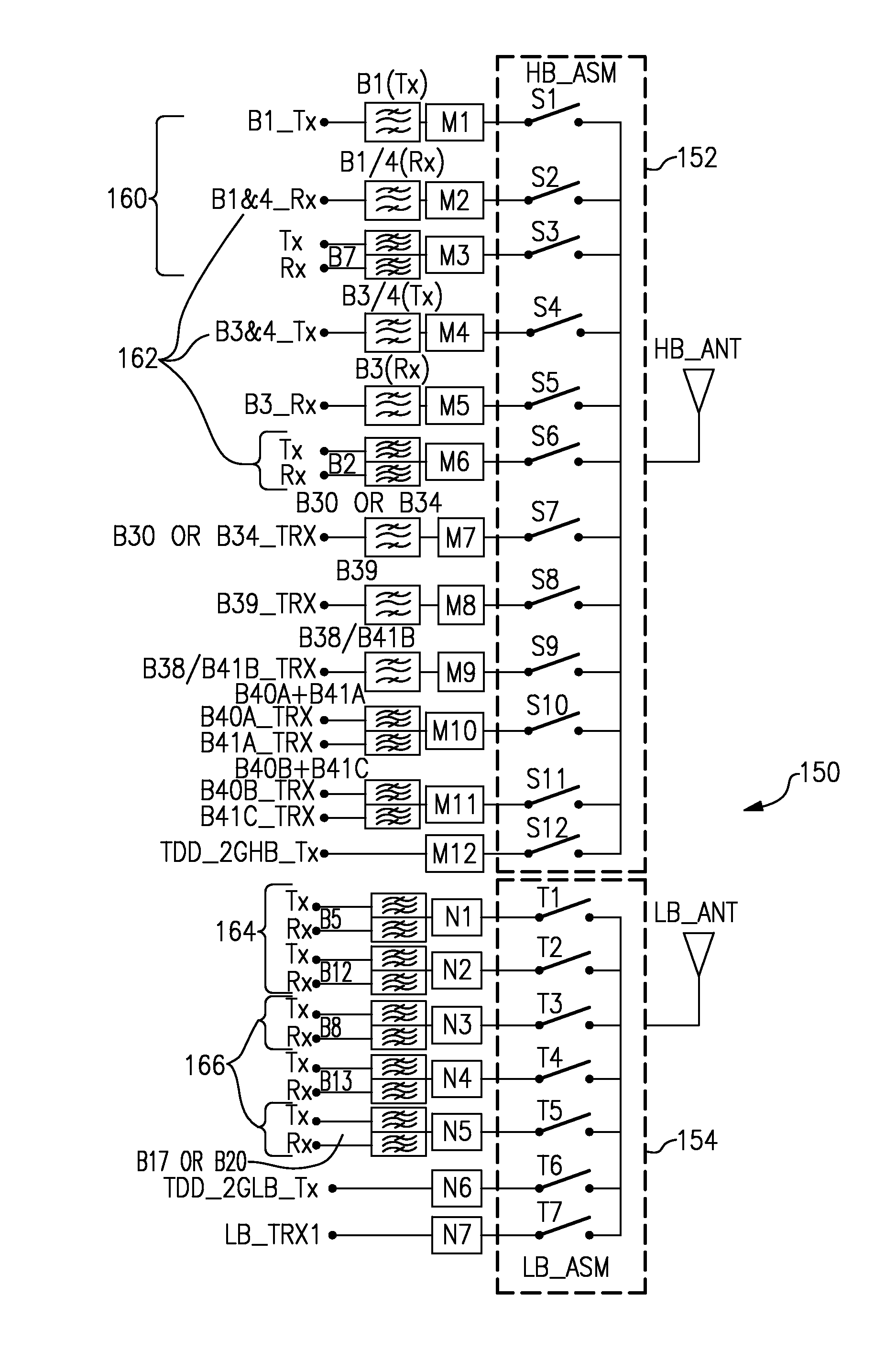

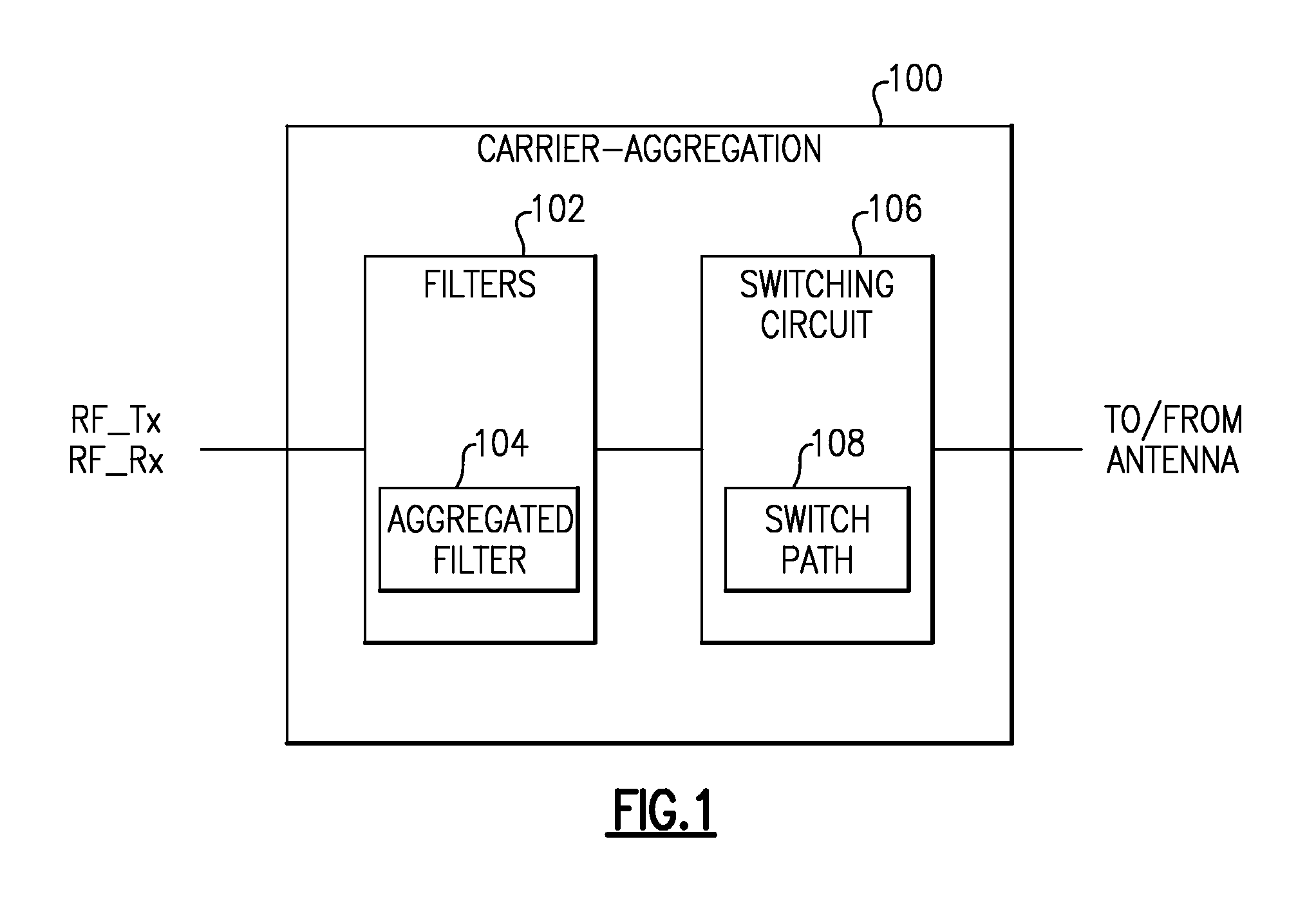

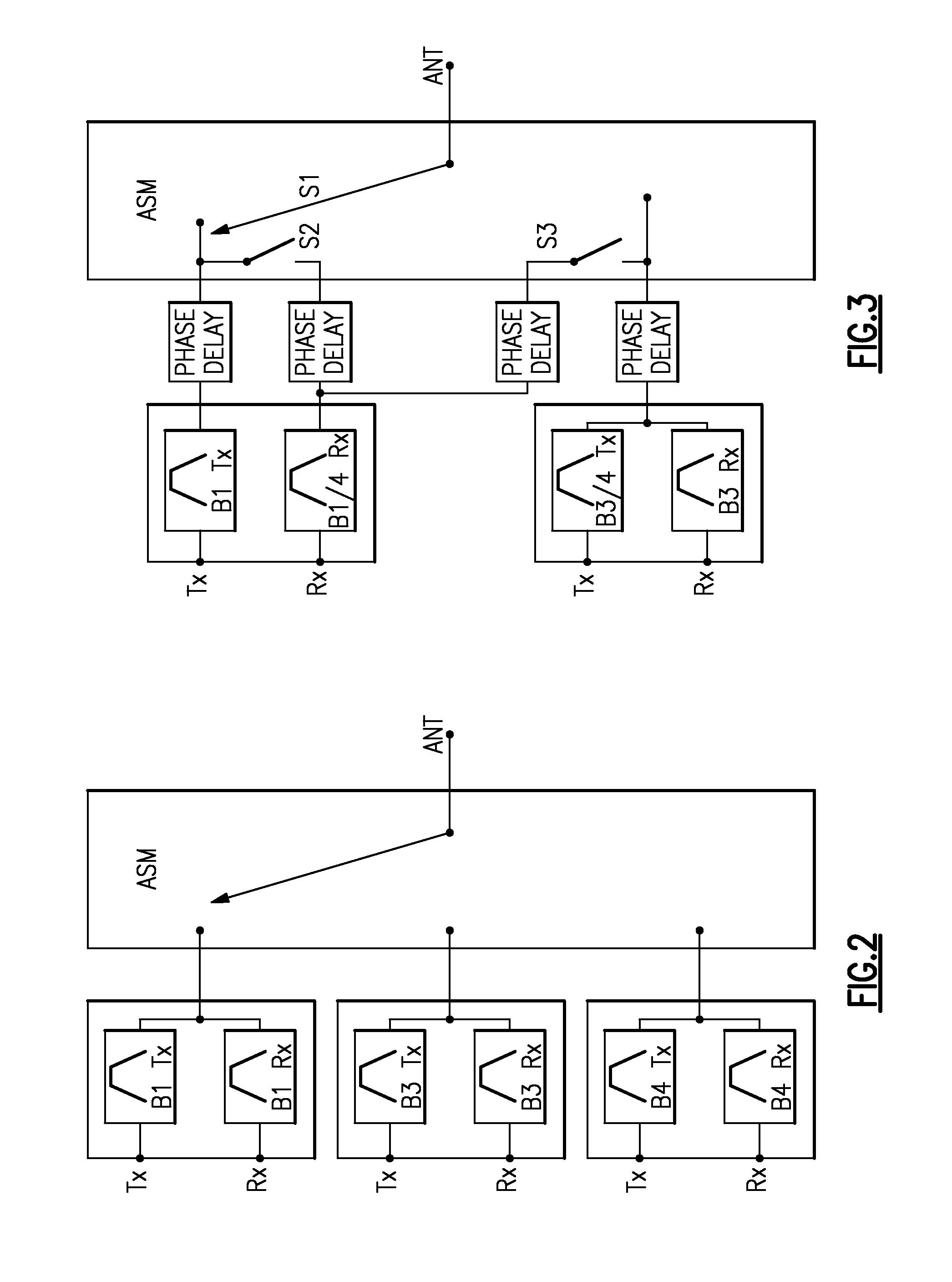

Systems and methods related to carrier aggregation front-end module applications

Improved switched multiplexer architecture for supporting carrier aggregation in front-end applications. In some embodiments, an N-plexing system can include an assembly of filters configured to provide N filtered paths, and a switching circuit in communication with the assembly of filters. The switching circuit can be configured to provide a plurality of switchable paths between the assembly of filters and an antenna port to allow simultaneous operation between the N filtered paths and the antenna port. In some embodiments, N can be 4 for a quadruplexing system or 2 for a duplexing system, and such a system can be implemented in a front-end module (FEM) for wireless devices.

Owner:SKYWORKS SOLUTIONS INC

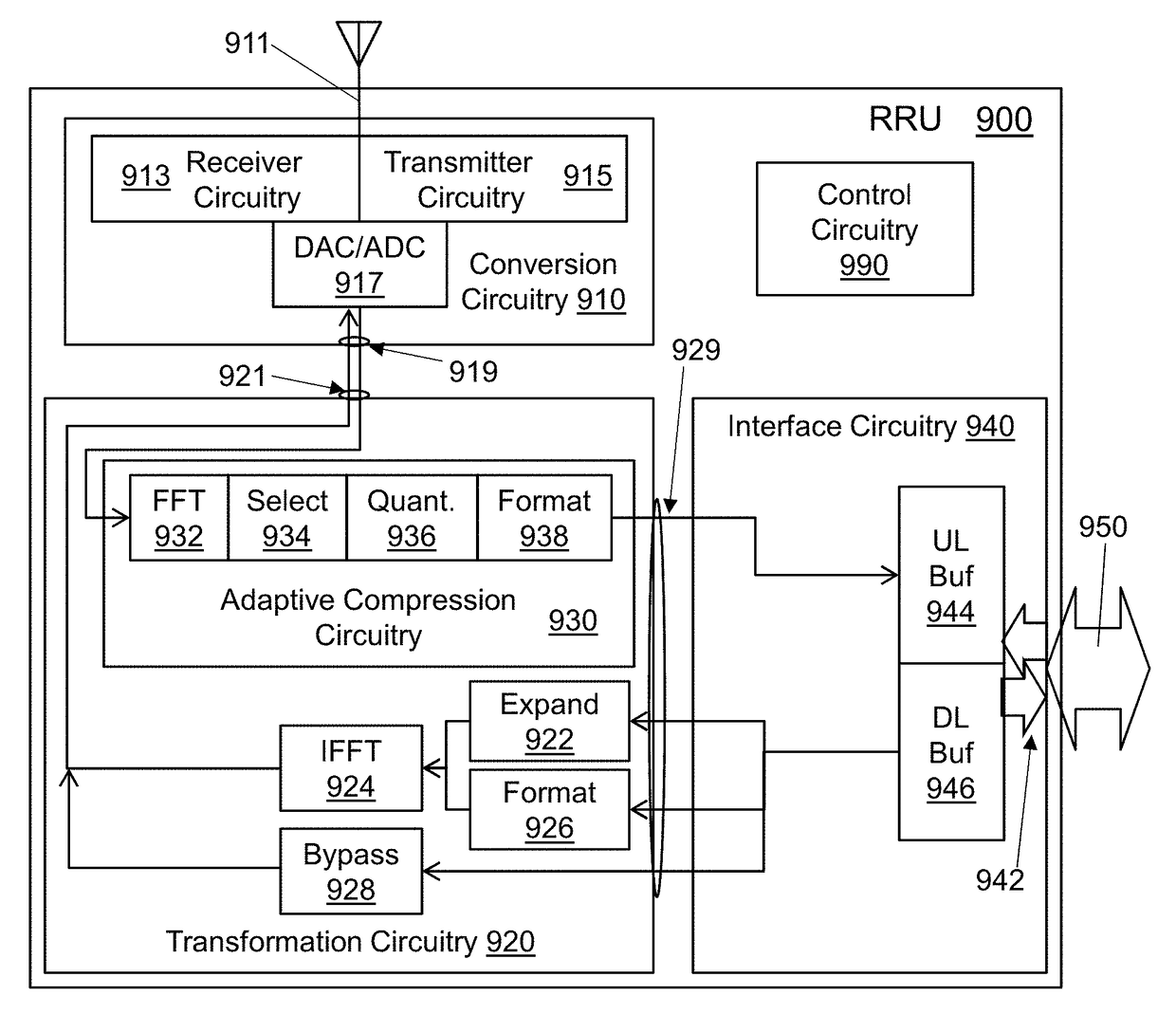

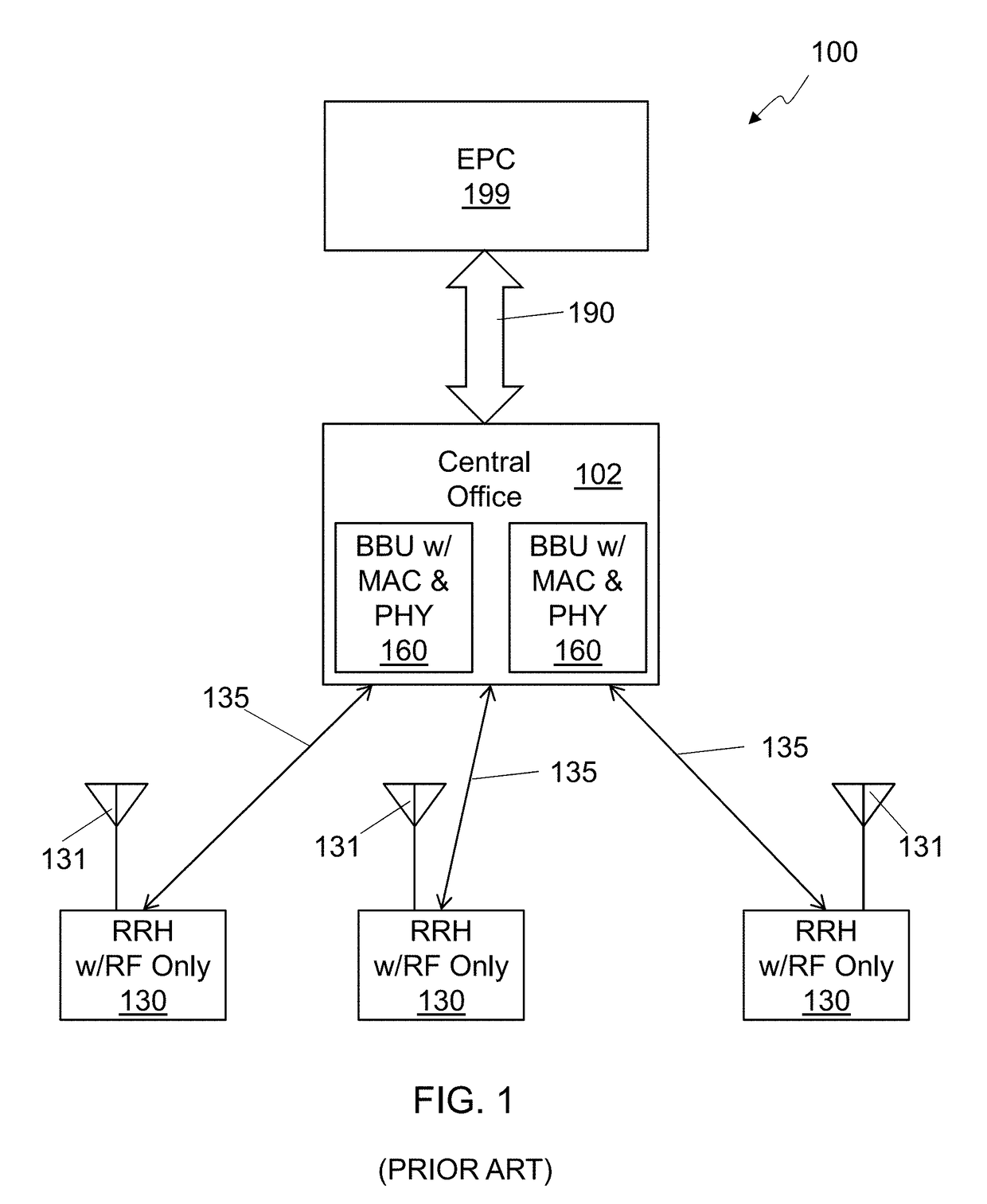

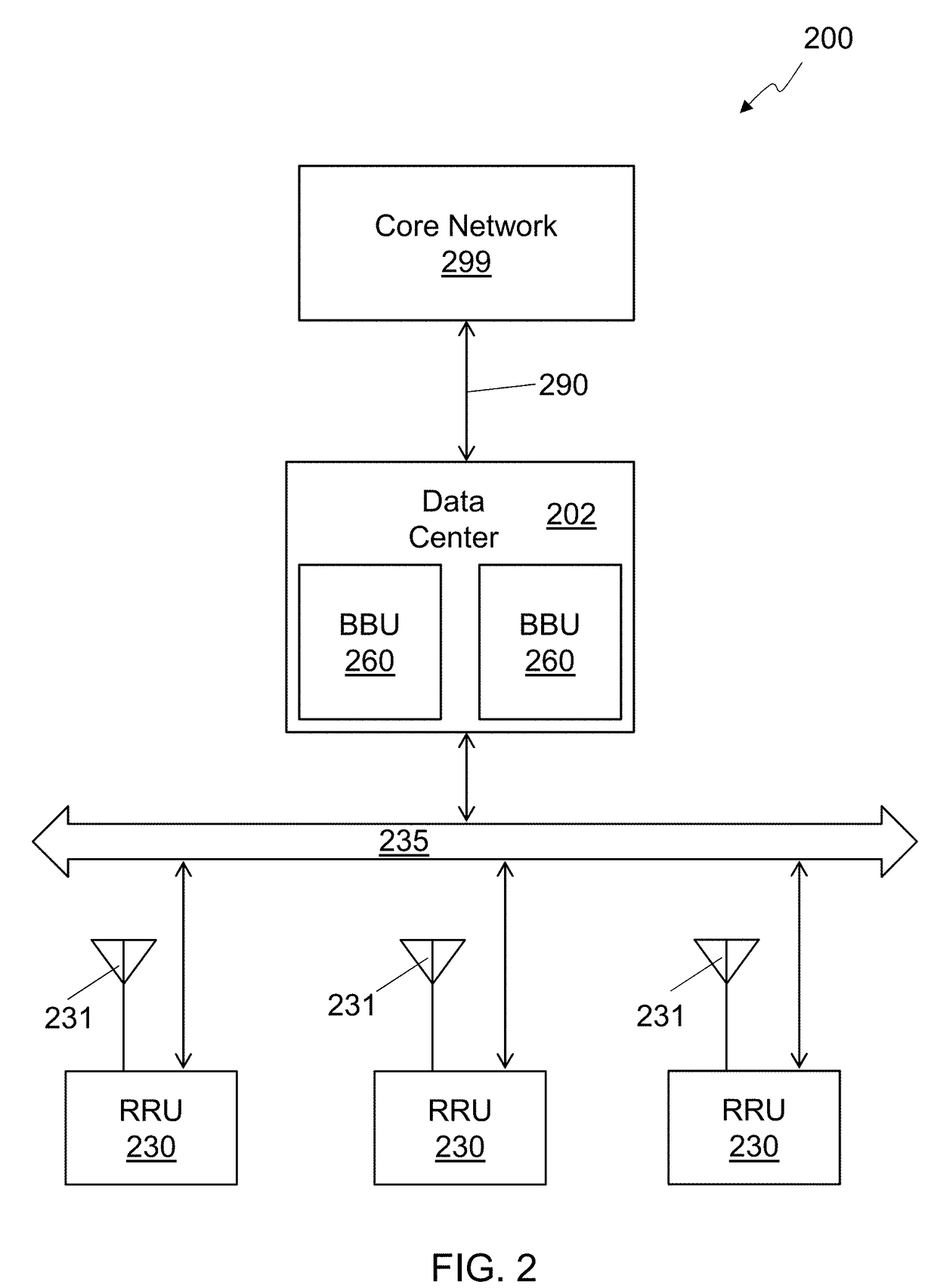

Remote Radio Unit with Adaptive Fronthaul Link for a Distributed Radio Access Network

ActiveUS20170373890A1Error prevention/detection by using return channelBaseband system detailsGPRS core networkRadio networks

A distributed radio frequency communication system facilitates communication between a wireless terminal and a core network. The system includes a remote radio unit (RRU) coupled to at least one antenna to communicate with the wireless terminal. The RRU includes electronic circuitry to perform at least a first portion of a first-level protocol of a radio access network (RAN) for communicating between the wireless terminal and the core network. The system also includes a baseband unit (BBU) coupled to the core network, and configured to perform at least a second-level protocol of the RAN. A fronthaul link is coupled to the BBU and the RRU. The fronthaul link utilizes an adaptive fronthaul protocol for communication between the BBU and the RRU. The adaptive fronthaul protocol has provisions for adapting to conditions of the fronthaul link and radio network by changing the way data is communicated over the fronthaul link.

Owner:COMMSCOPE TECH LLC

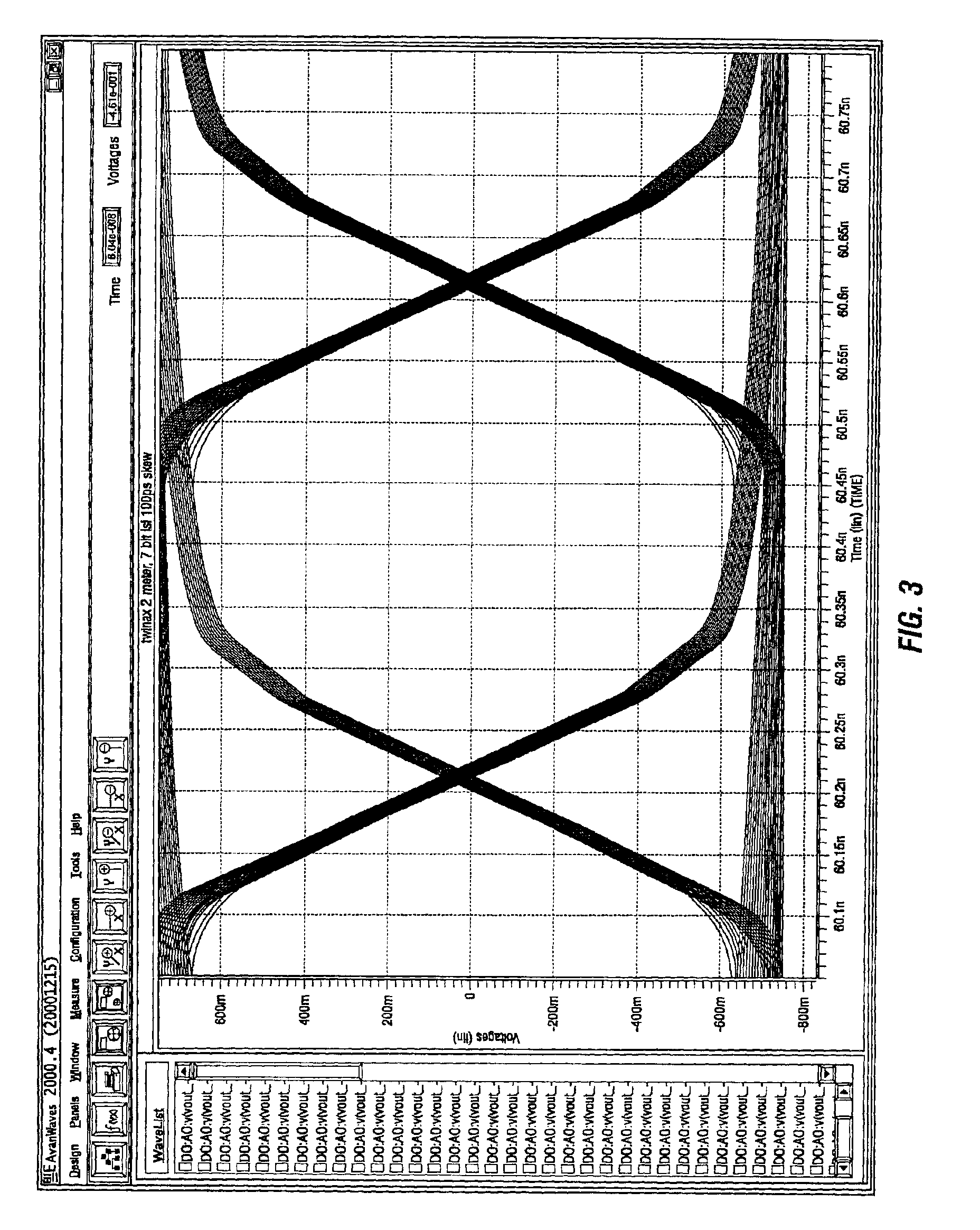

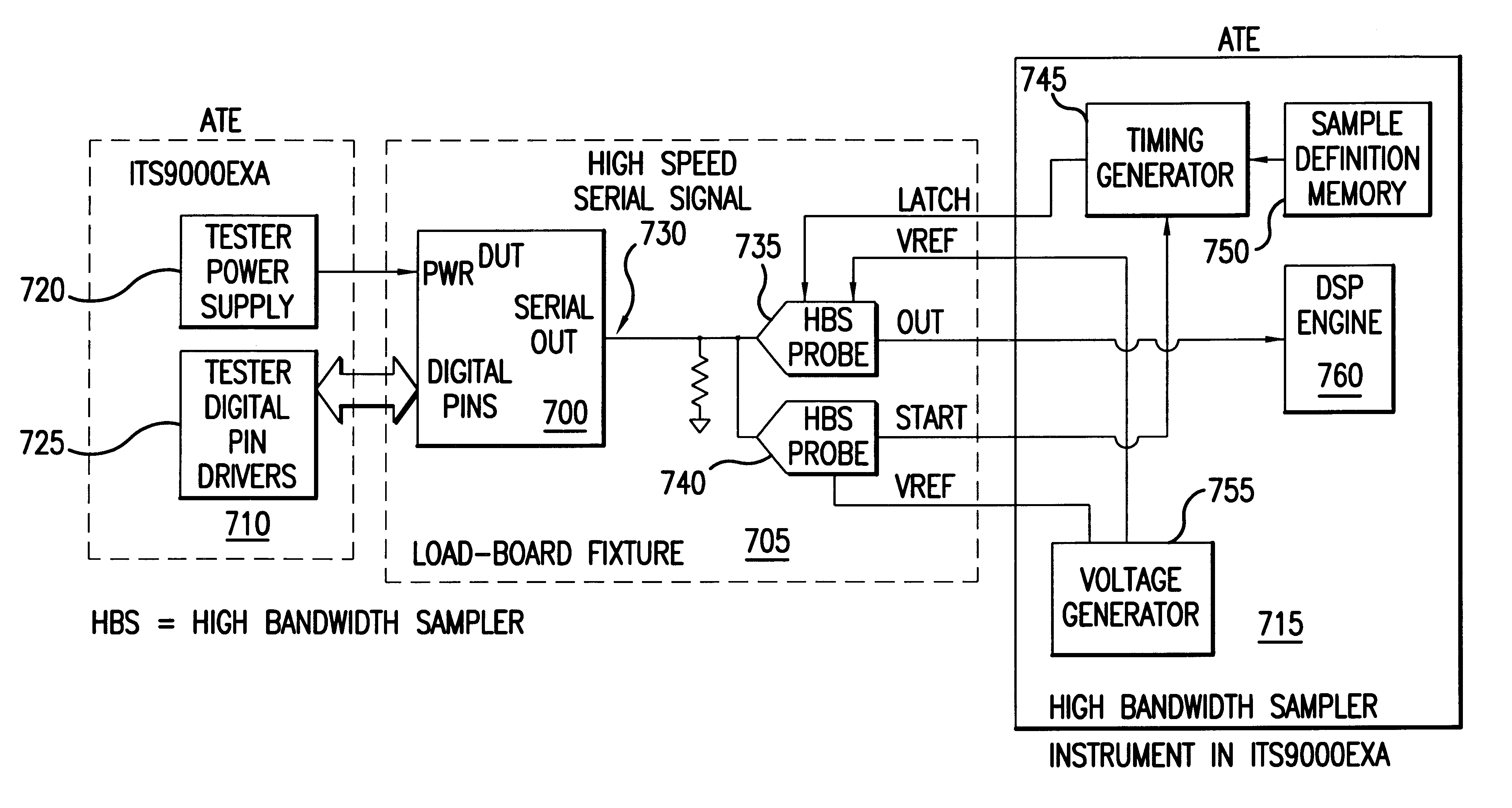

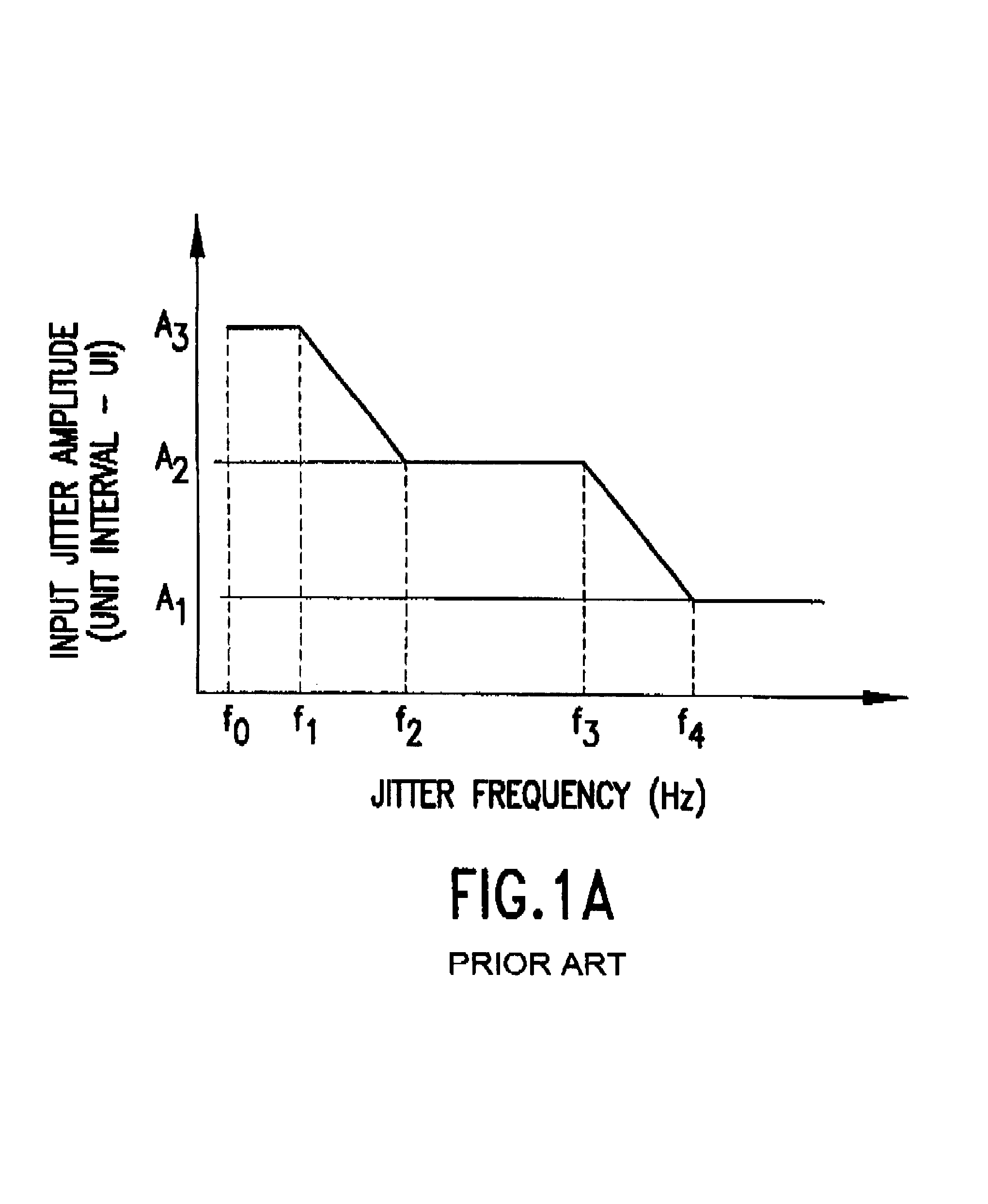

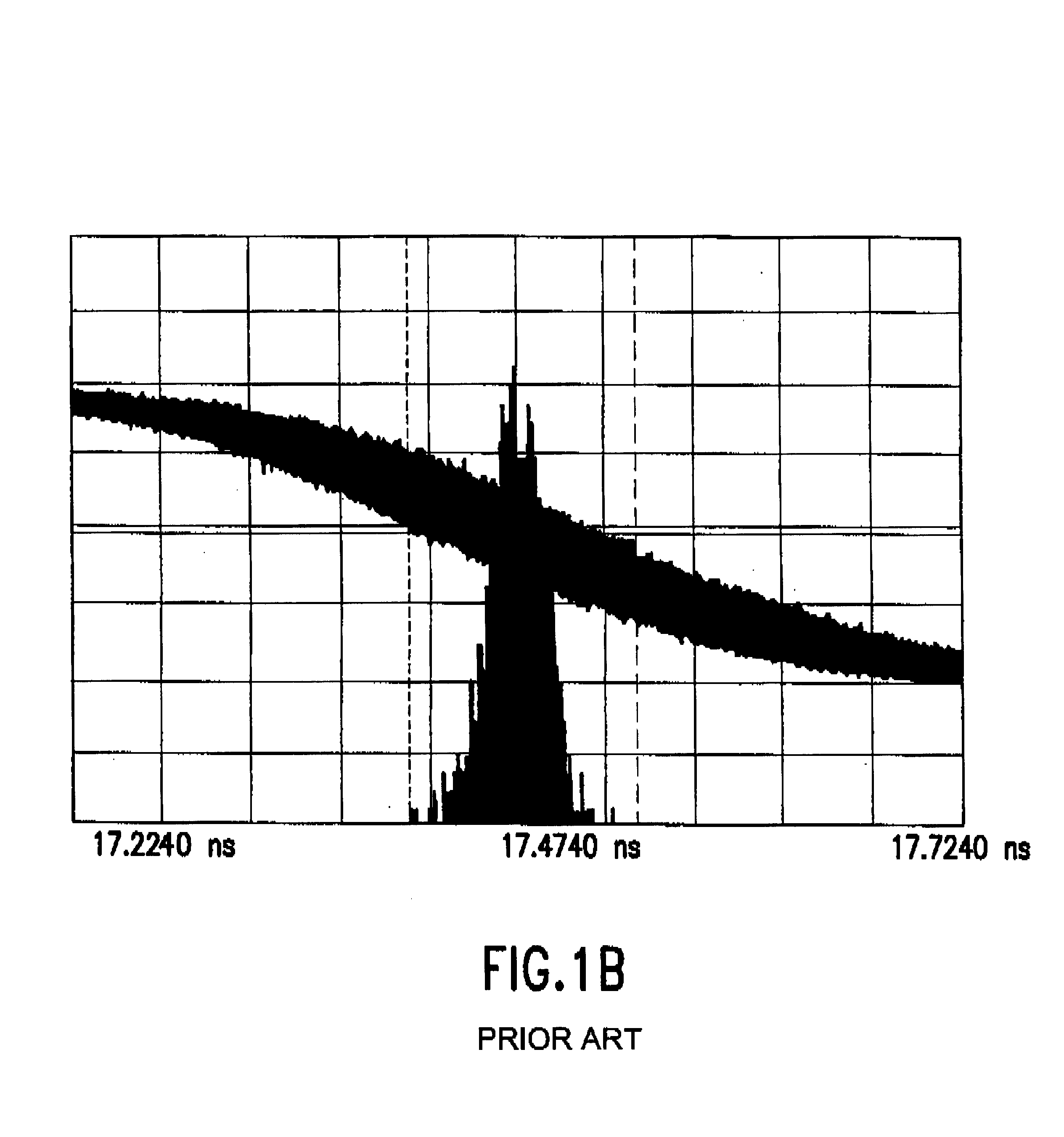

Measuring jitter of high-speed data channels

A jitter measurement technique utilizing a high-bandwidth undersampling voltage measurement instrument is presented. A trigger is derived from the a signal having a repetitive signal pattern. The signal is compared with a threshold at a plurality of times relative to the trigger during multiple repetitions of the signal pattern to produce measurement samples indicative of signal level relative to the threshold. The measurement samples are used to determine the probability of signal edge states as a function of time for the multiple repetitions. The probability of signal edge states are used to determine an edge probability density as a function of time. A histogram of signal state transition times can be prepared from the edge probability density. Mean deviation of edge transitions of the signal can be estimates, and standard deviation of edge transitions of the signal can be estimated to give the root-mean-square (rms) jitter of the signal.

Owner:CREDENCE SYSTEMS

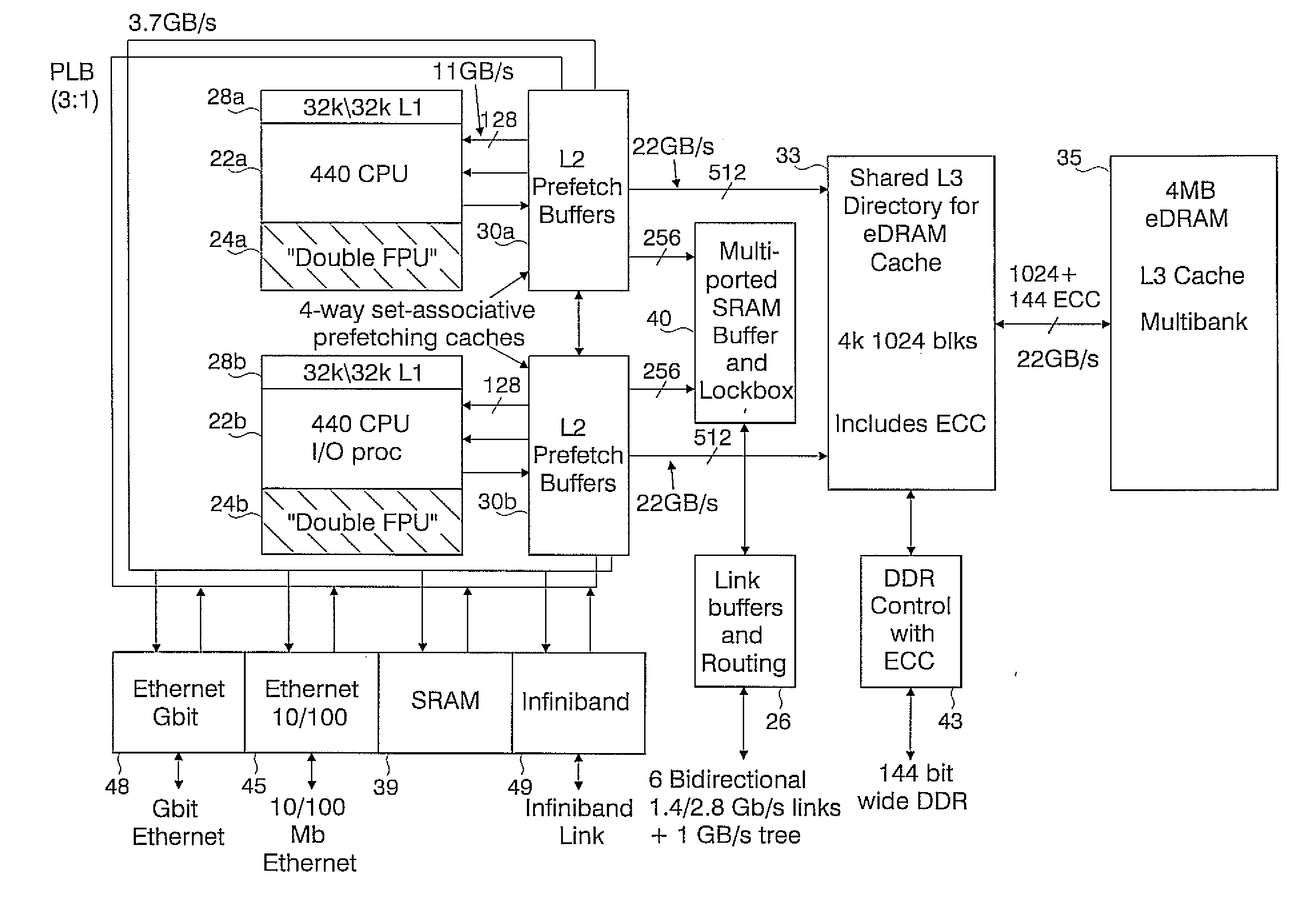

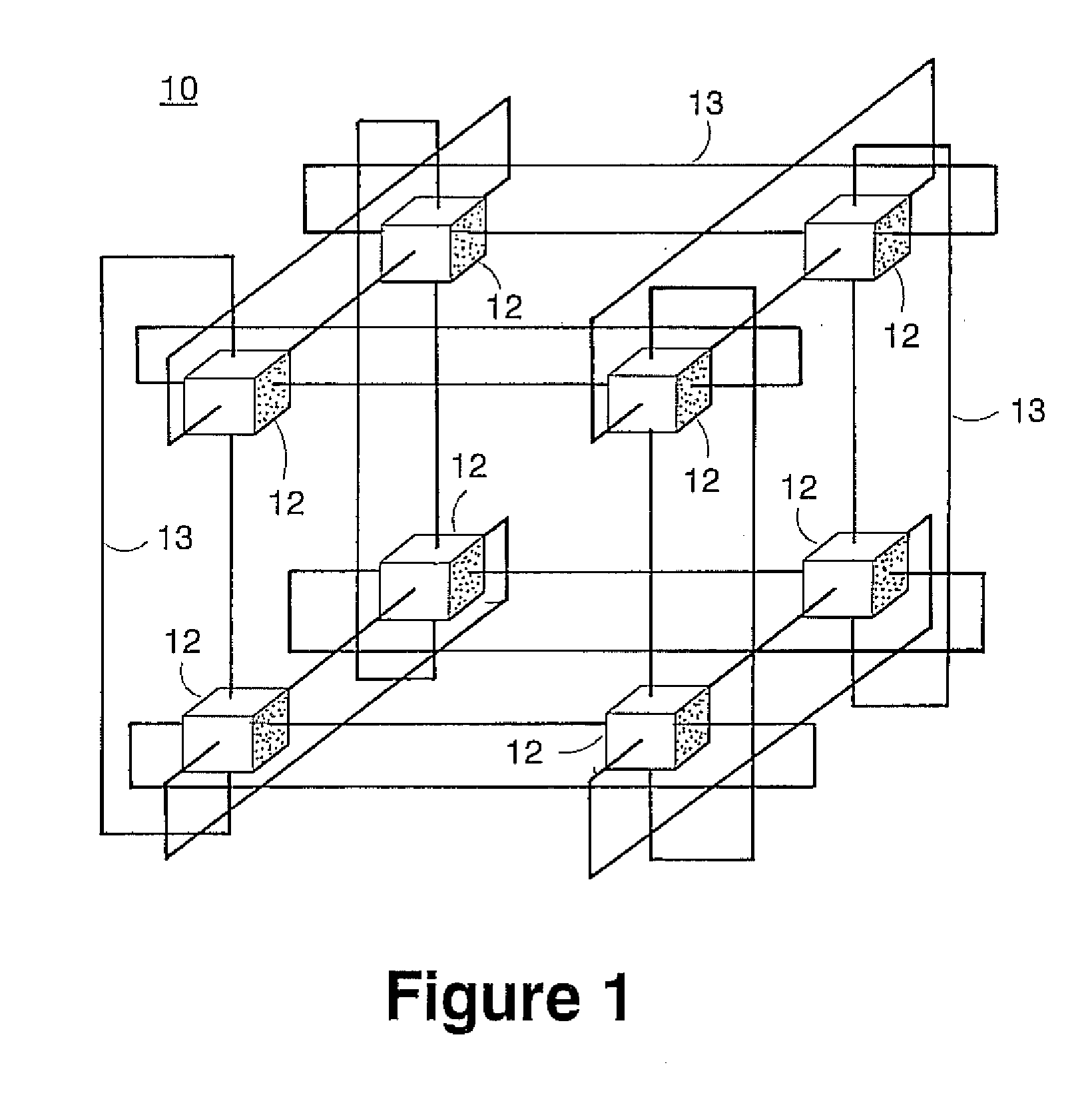

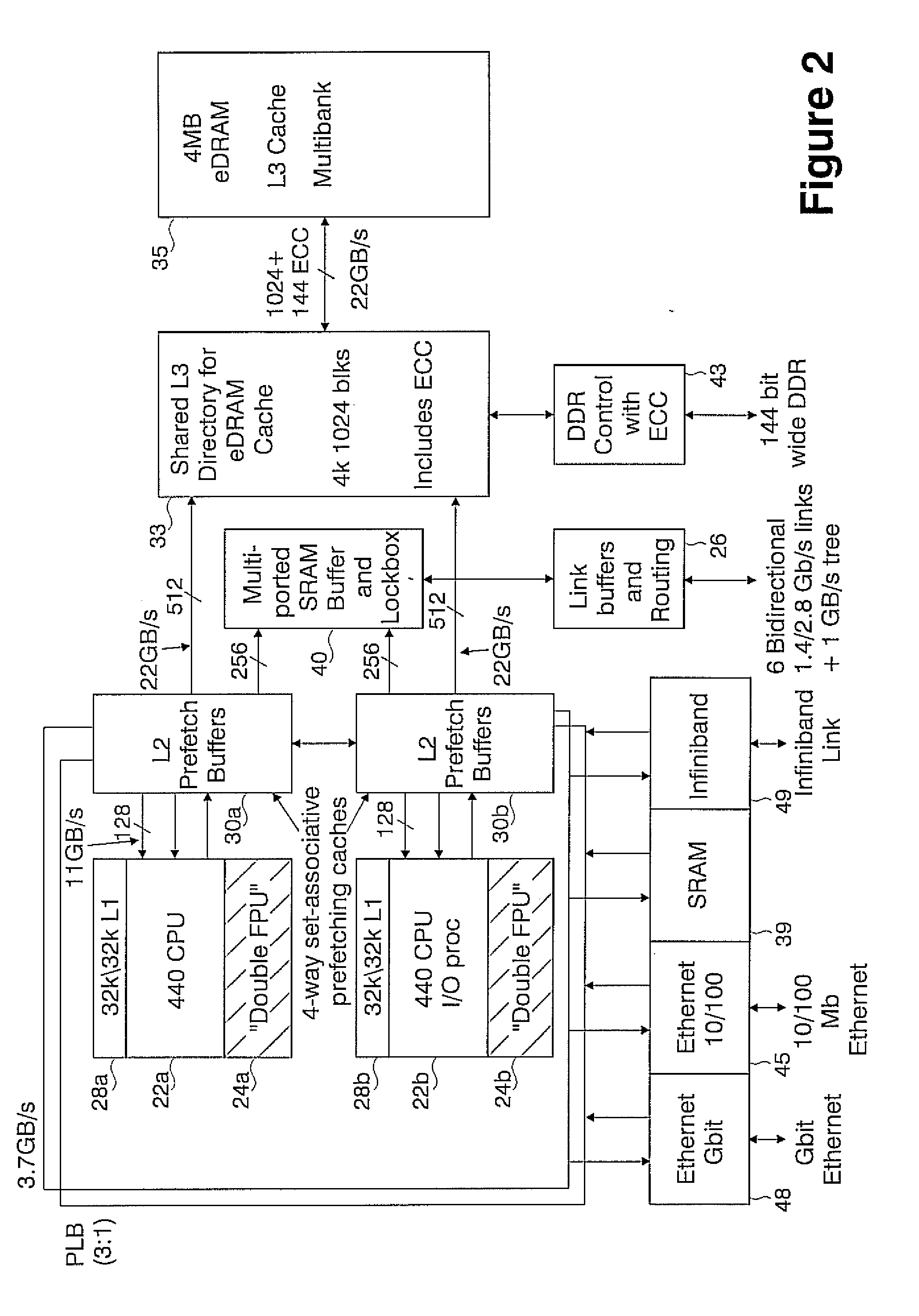

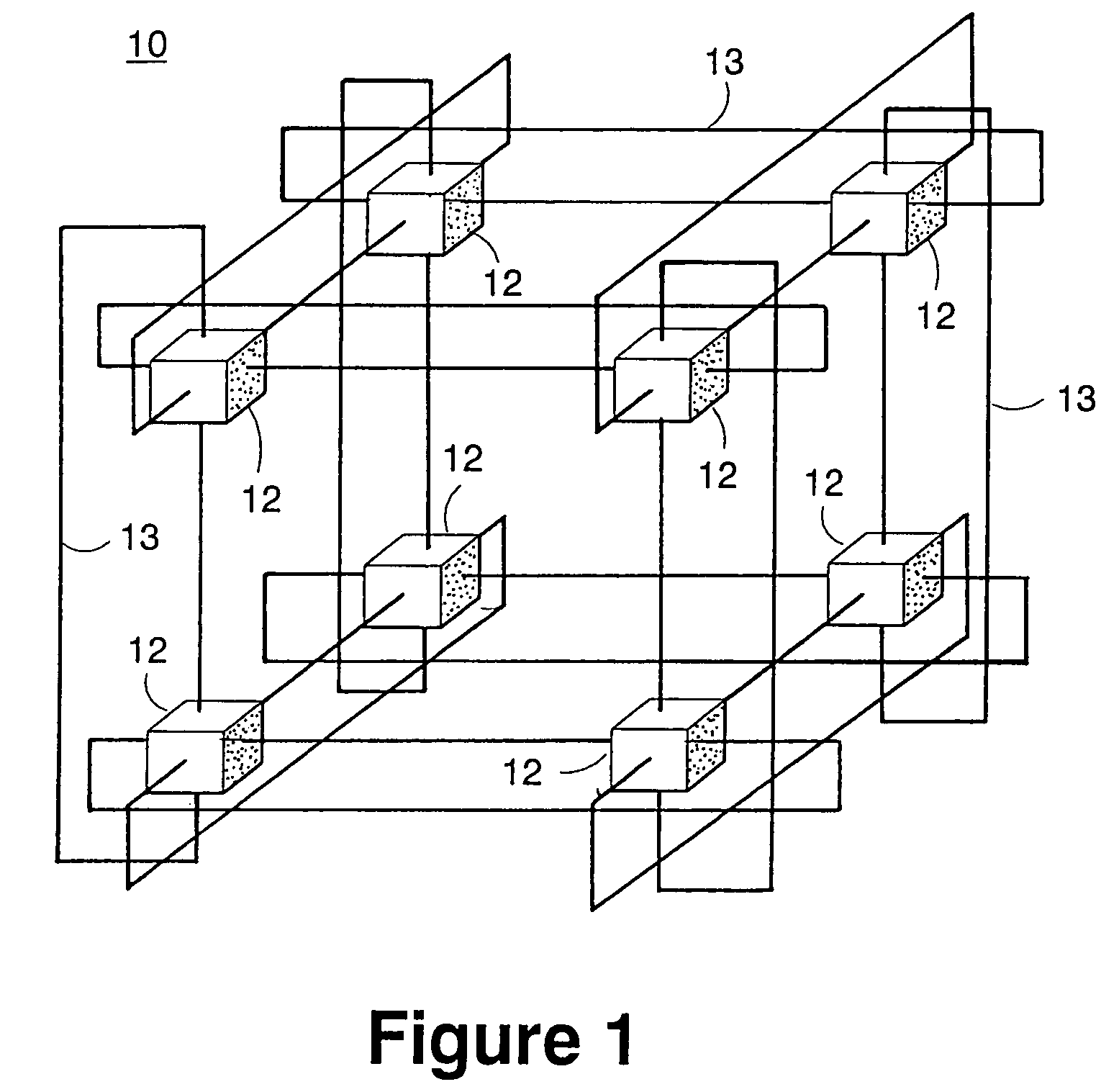

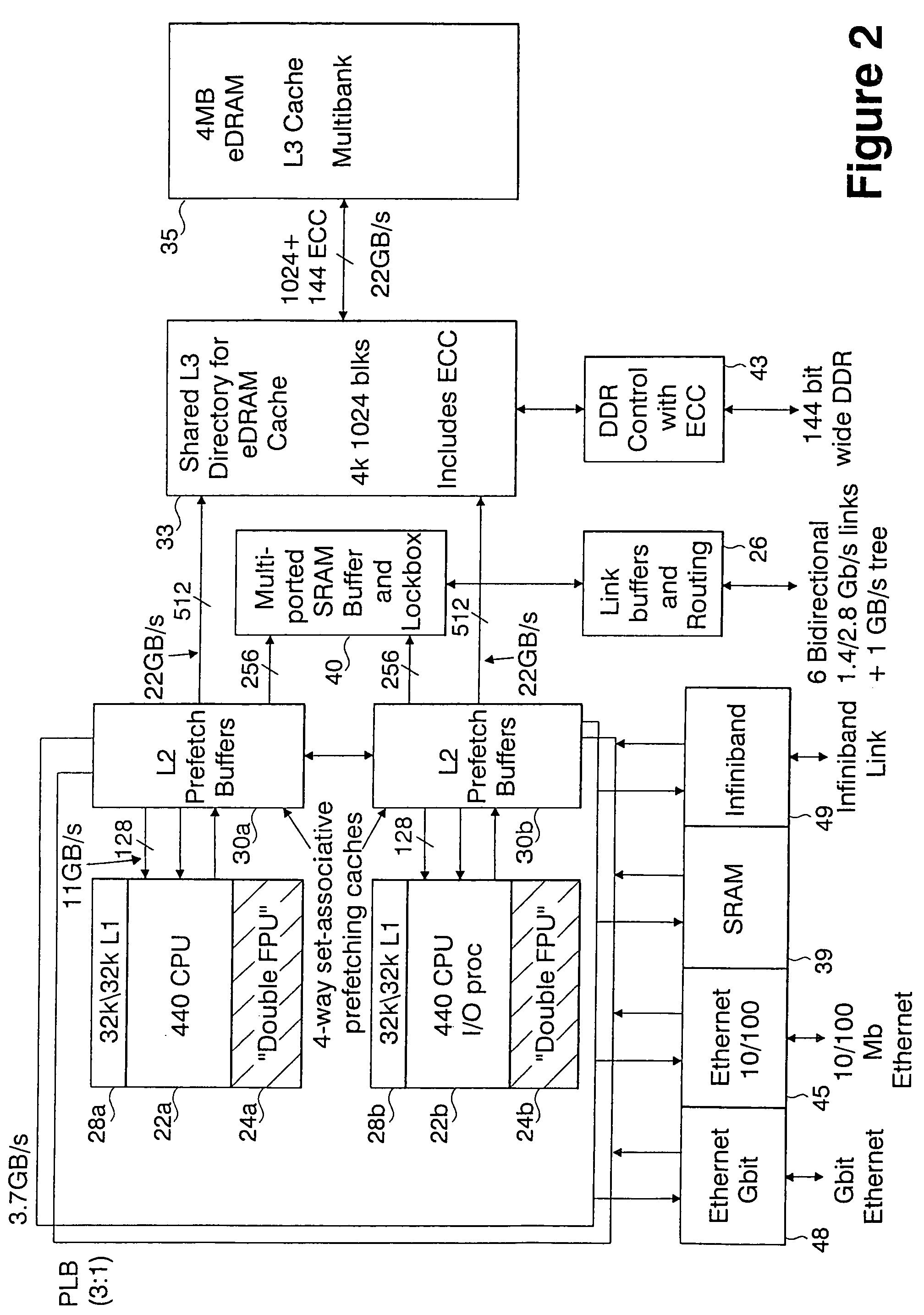

Massively parallel supercomputer

InactiveUS7555566B2Massive level of scalabilityUnprecedented level of scalabilityError preventionProgram synchronisationPacket communicationSupercomputer

A novel massively parallel supercomputer of hundreds of teraOPS-scale includes node architectures based upon System-On-a-Chip technology, i.e., each processing node comprises a single Application Specific Integrated Circuit (ASIC). Within each ASIC node is a plurality of processing elements each of which consists of a central processing unit (CPU) and plurality of floating point processors to enable optimal balance of computational performance, packaging density, low cost, and power and cooling requirements. The plurality of processors within a single node may be used individually or simultaneously to work on any combination of computation or communication as required by the particular algorithm being solved or executed at any point in time. The system-on-a-chip ASIC nodes are interconnected by multiple independent networks that optimally maximizes packet communications throughput and minimizes latency. In the preferred embodiment, the multiple networks include three high-speed networks for parallel algorithm message passing including a Torus, Global Tree, and a Global Asynchronous network that provides global barrier and notification functions. These multiple independent networks may be collaboratively or independently utilized according to the needs or phases of an algorithm for optimizing algorithm processing performance. For particular classes of parallel algorithms, or parts of parallel calculations, this architecture exhibits exceptional computational performance, and may be enabled to perform calculations for new classes of parallel algorithms. Additional networks are provided for external connectivity and used for Input / Output, System Management and Configuration, and Debug and Monitoring functions. Special node packaging techniques implementing midplane and other hardware devices facilitates partitioning of the supercomputer in multiple networks for optimizing supercomputing resources.

Owner:IBM CORP

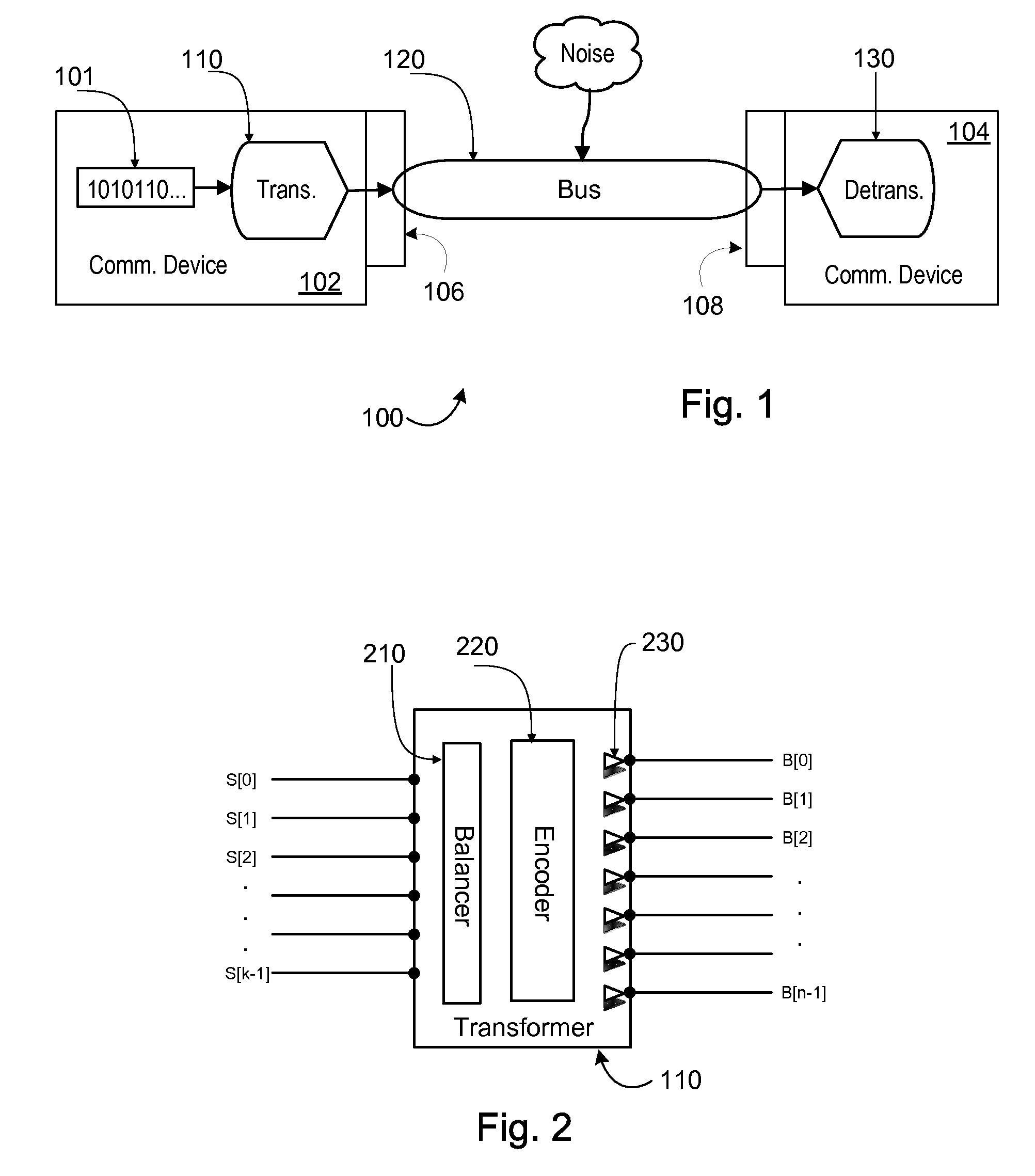

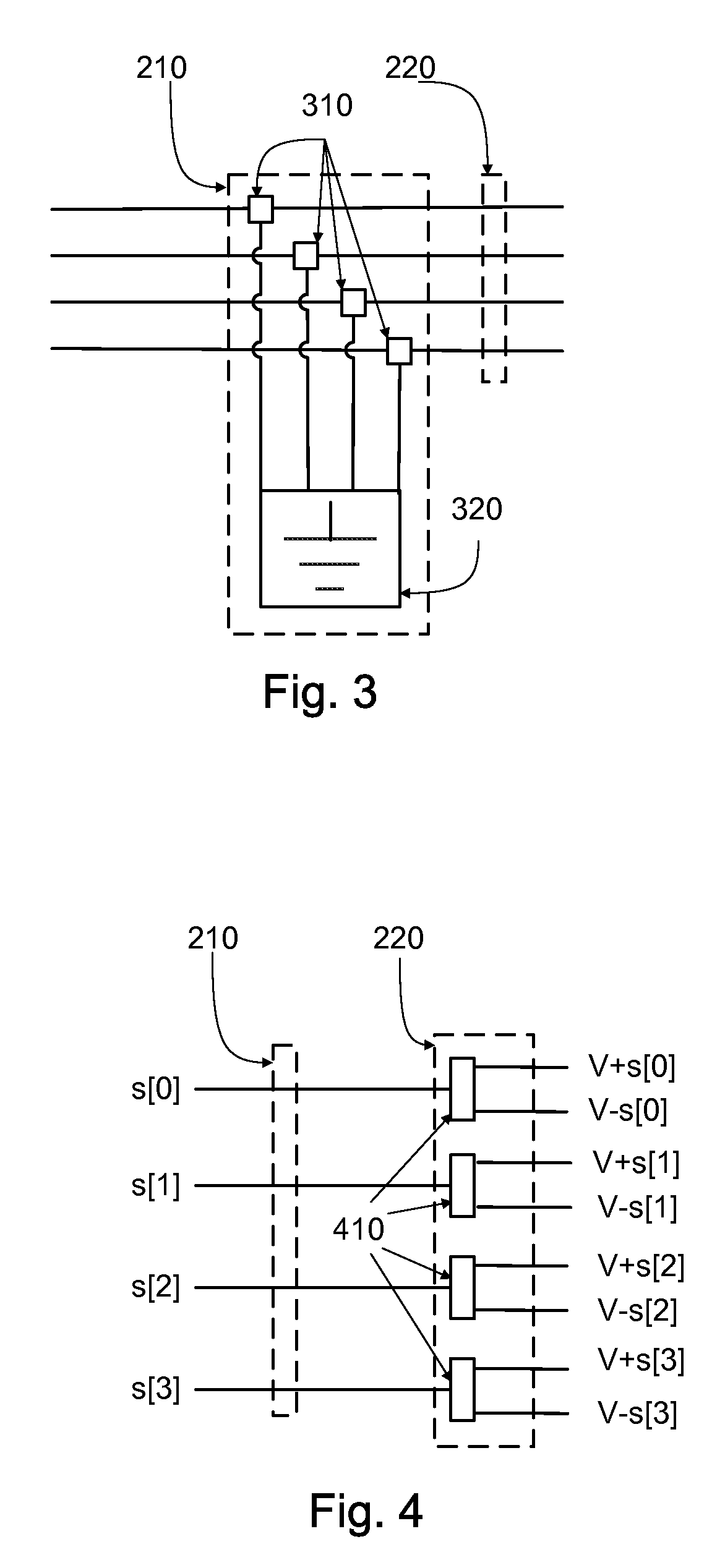

Orthogonal differential vector signaling

ActiveUS9288089B2Increase valueImprove energy consumptionBaseband system detailsTransmission path divisionPhysical spaceAlgorithm

Using a transformation based at least in part on a non-simple orthogonal or unitary matrix, data may be transmitted over a data bus in a manner that is resilient to one or more types of signal noise, that does not require a common reference at the transmission and acquisition points, and / or that has a pin-efficiency that is greater than 50% and may approach that of single-ended signaling. Such transformations may be implemented in hardware in an efficient manner. Hybrid transformers that apply such transformations to selected subsets of signals to be transmitted may be used to adapt to various signal set sizes and / or transmission environment properties including noise and physical space requirements of given transmission environments.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

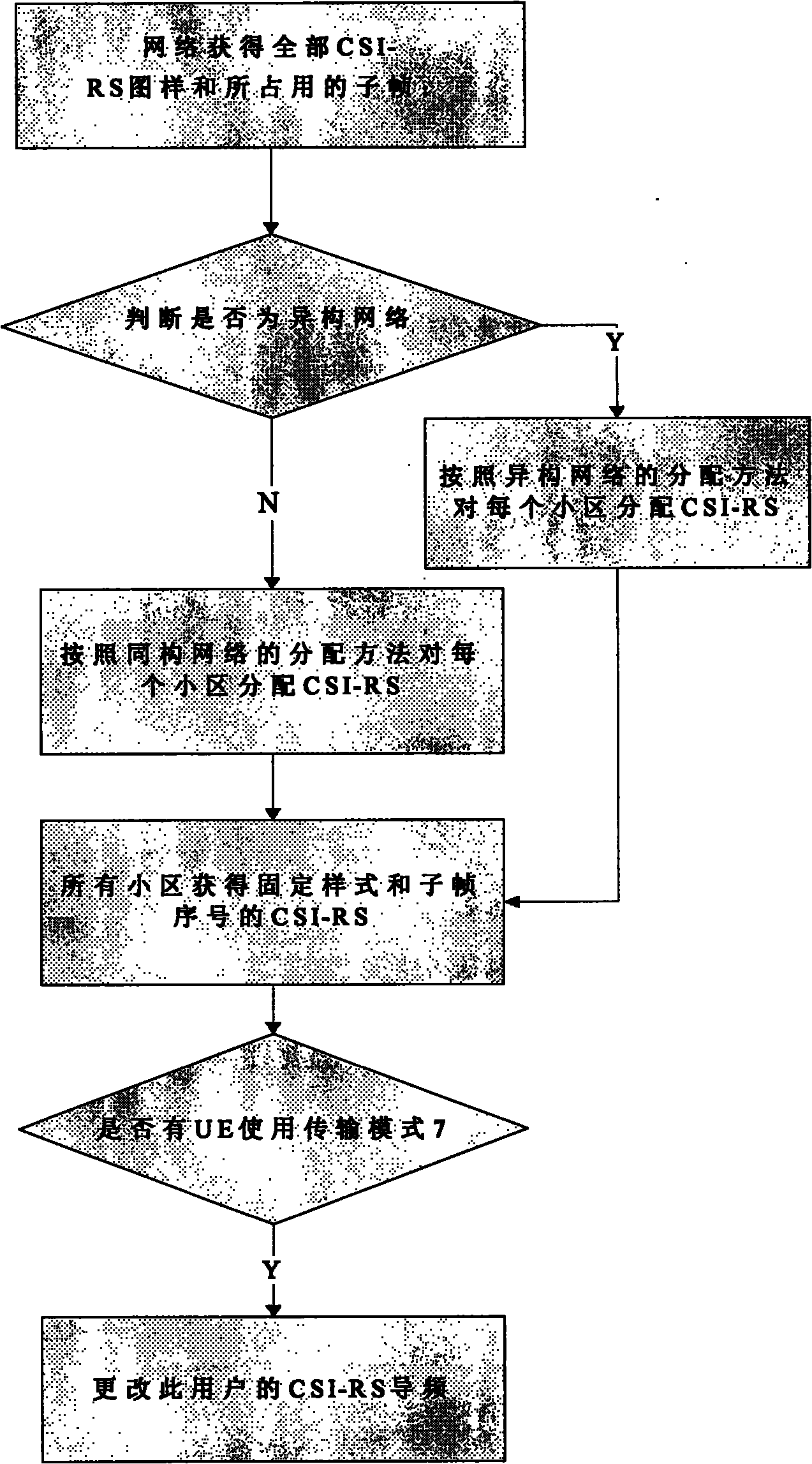

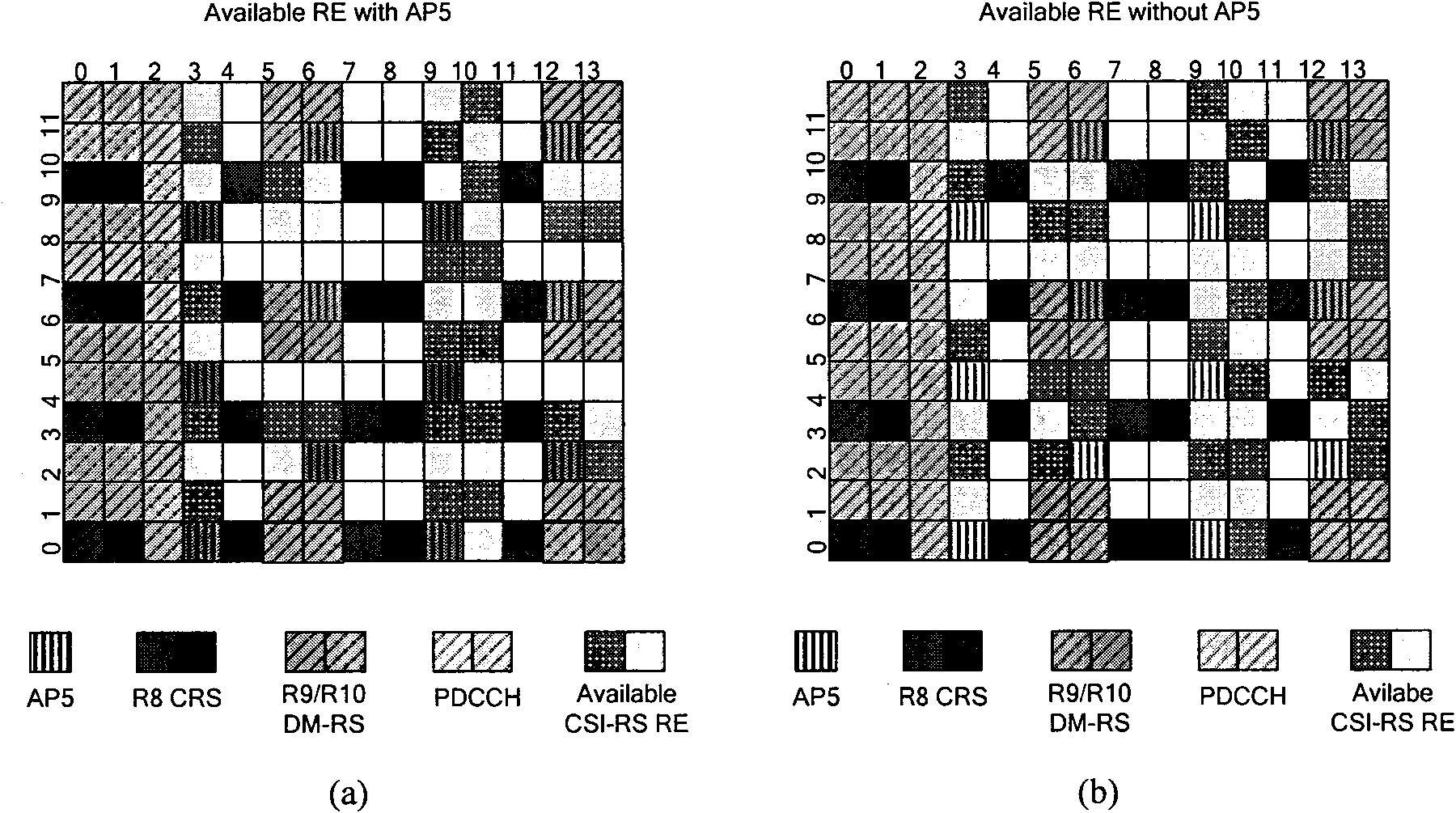

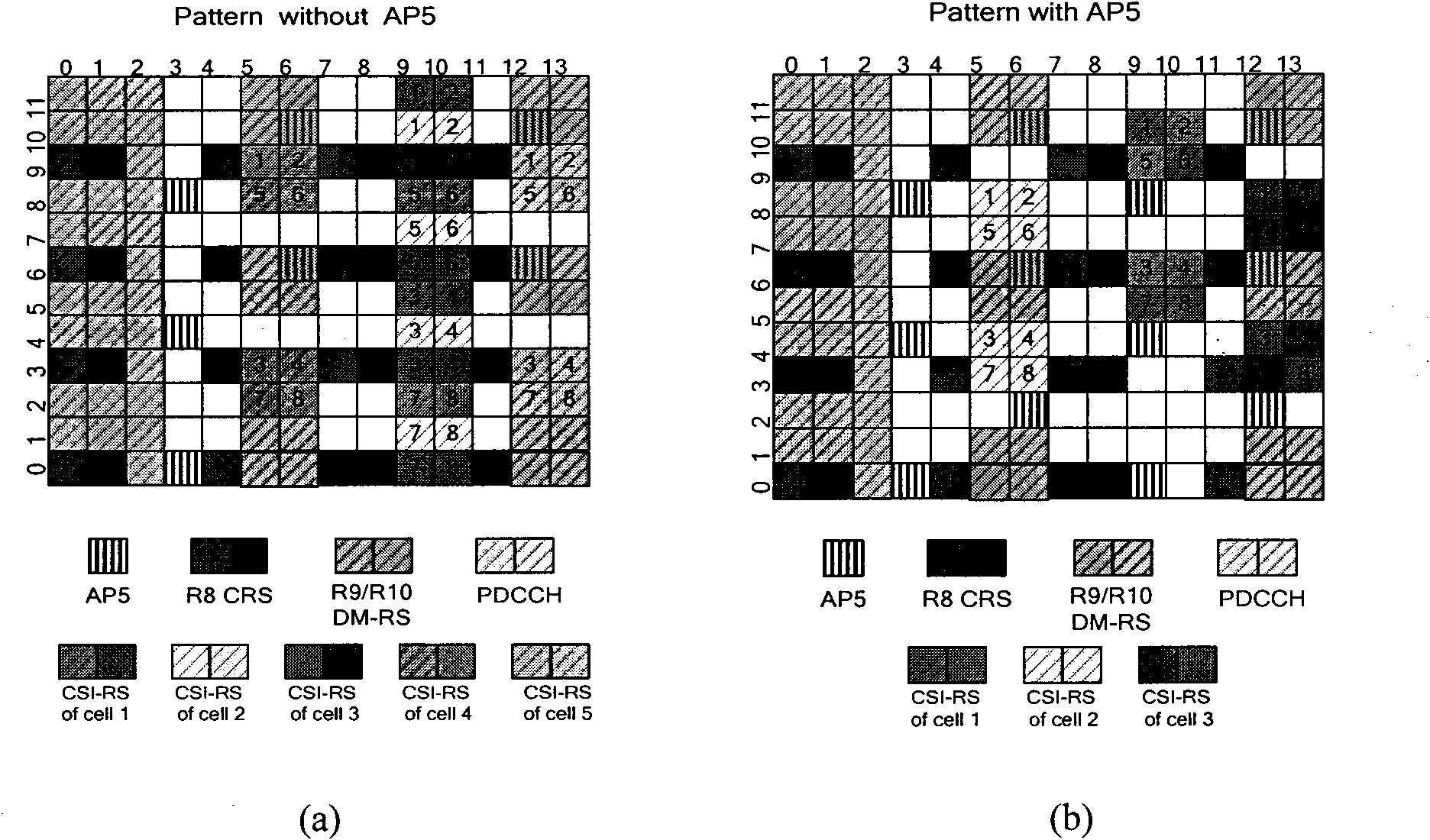

Method for designing channel state information reference signal (CSI-RS) in LTE-A (Long Term Evolution-Advanced) system

InactiveCN101924610AImprove performanceImprove compatibilityBaseband system detailsError prevention/detection by diversity receptionChannel state informationMultiplexing

The invention discloses a method for designing a channel state information reference signal (CSI-RS) in an LTE-A (Long Term Evolution-Advanced) system, belonging to the communication field and being used for measuring the CSI. The method comprises the following steps of: 1, RE capable of being used by the CSI-RS in a PRB; 2, multiplexing mode of the CSI-RS among ports of a cell; 3, CSI-RS mode when the port 5 is not used; 4, CSI-RS mode when the port 5 is used; and 5, allocation of the CSI-RS in a homogeneous network and a heterogeneous network. The method for designing the CSI-RS can not only ensure that a user of an LTE works well in an LTE-A network, reduce the influences on the user of the LTE because of adding the CSI-RS, but also ensures that the CSI-RS in the LTE-A system obtains abigger multiplexing factor, reduces the interference among the CSI-RSs, provides an orthorhombic CSI-RS for a CoMP measuring set, improves the accuracy of channel estimation and enhances the propertyof the system.

Owner:XIDIAN UNIV

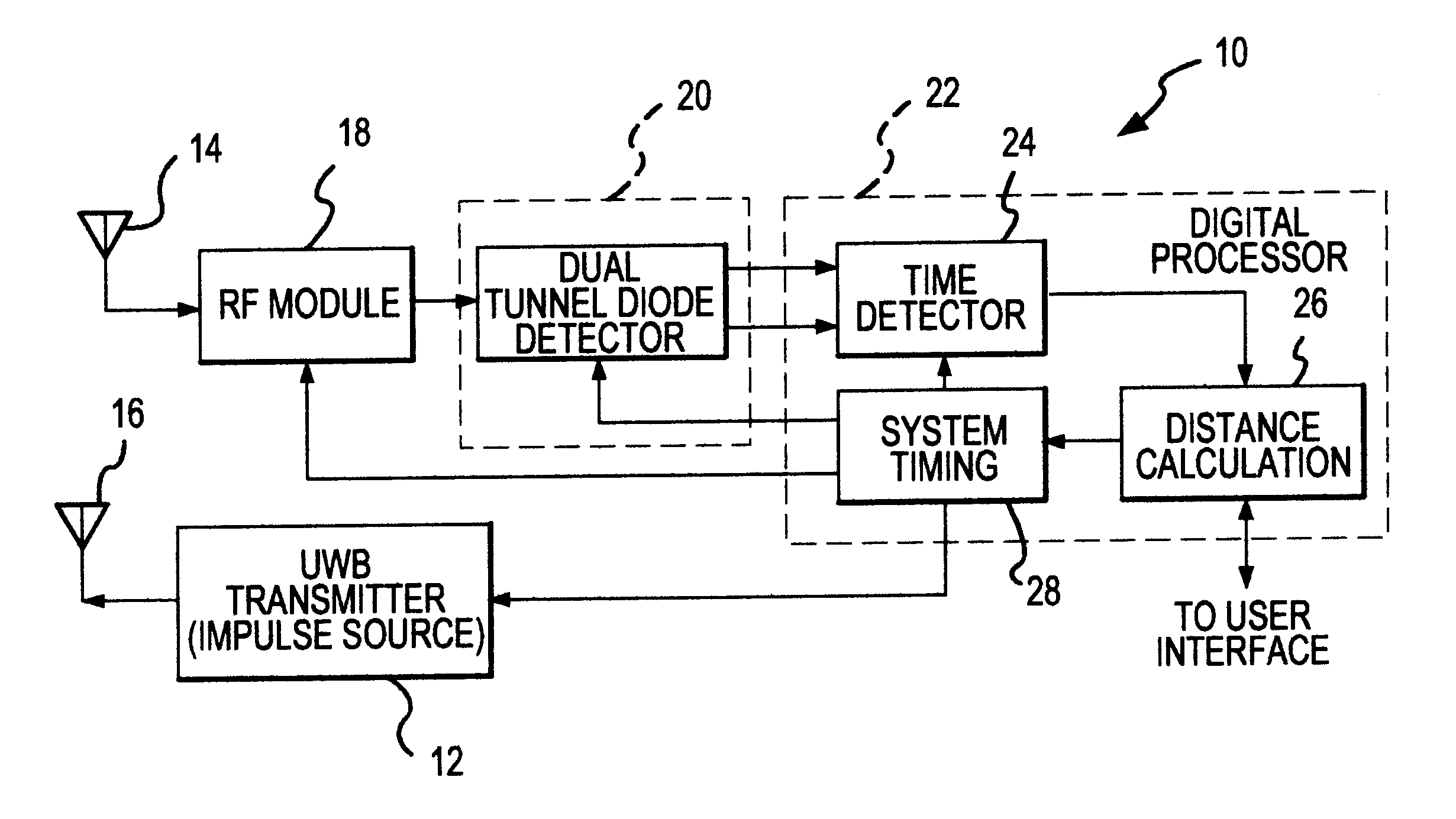

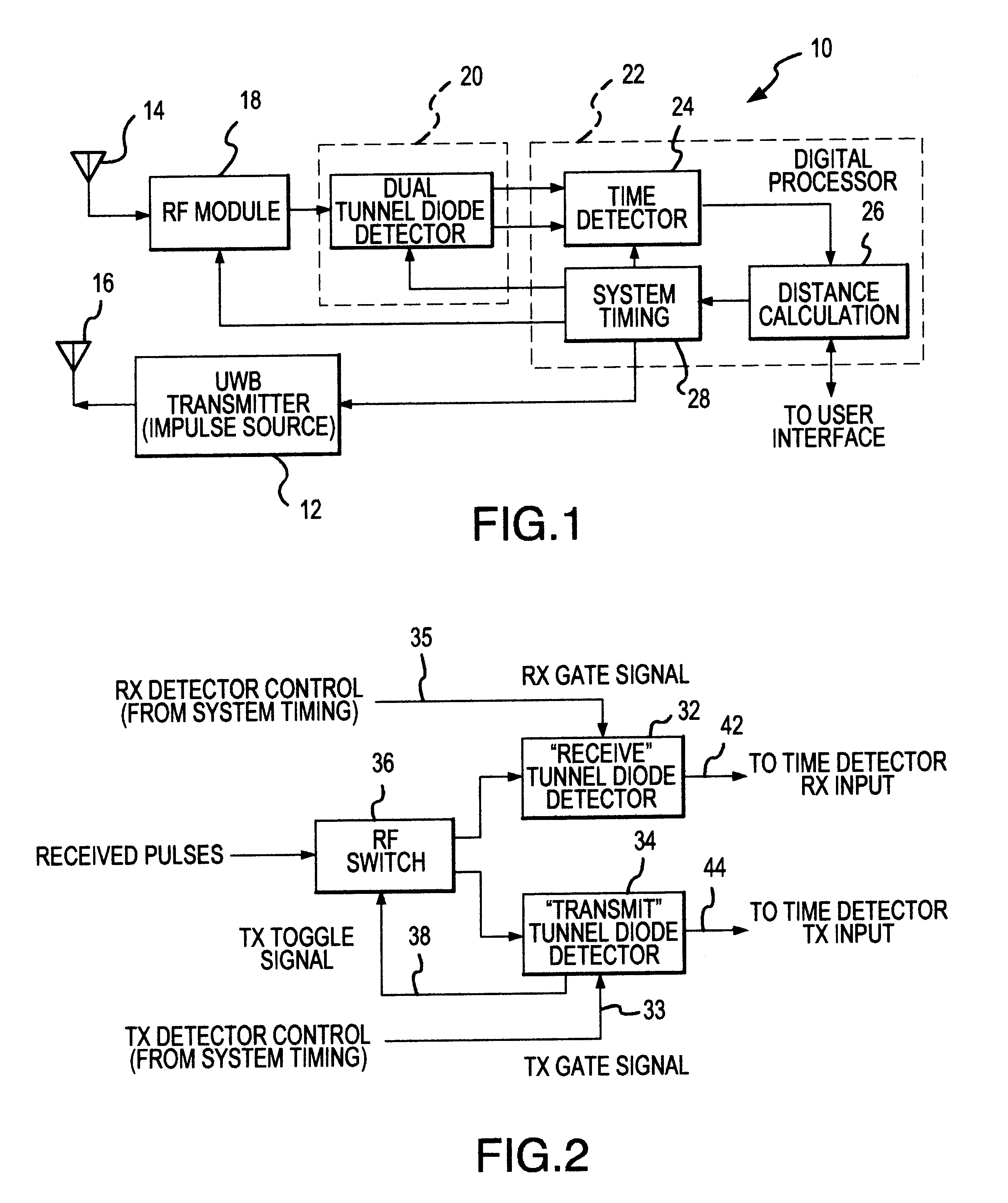

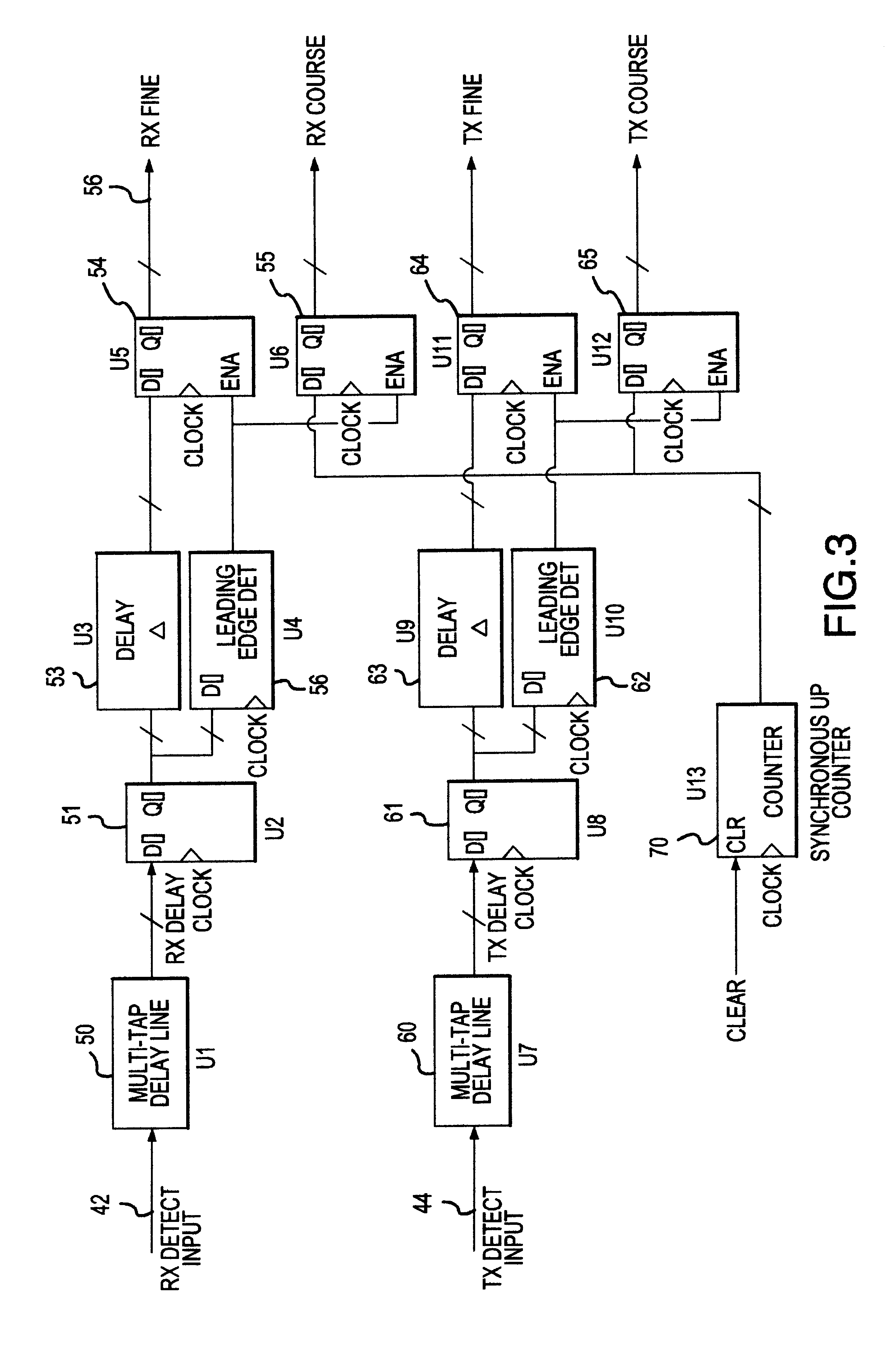

UWB dual tunnel diode detector for object detection, measurement, or avoidance

InactiveUS6239741B1Baseband system detailsAmplitude-modulated carrier systemsUltra-widebandTunnel diode

A highly sensitive, high-speed dual tunnel diode detector is described for use in Ultra Wideband (UWB) object detection systems, such as a radar. The extended capability of the detector to both extremely short (sub-foot) and long distance (tens of thousands of feet) ranges is unique and permits the application of low power UWB radar to a wide variety of applications including high resolution radar altimetry at altitudes exceeding 10,000 feet and for autonomous on-deck landing operations (e.g., one-foot altitudes), the detection of extremely low radar cross section (RCS) targets for such applications as suspended wire detection for helicopters and other manned and unmanned craft, etc. High noise and interference immunity of the detector permits co-location of a UWB radar sensor with other active systems. The invention has immediate and significant application to all areas, both military and commercial, of precision distance measurement, intrusion detection, targeting, etc. over a wide range of distances.

Owner:ZEBRA TECH CORP

Code division multiple access (CDMA) communication system

InactiveUS20040252668A1Easy to liftMaximize signal to noisePower managementBaseband system detailsSystem capacityCode division multiple access

A subscriber unit for use in a multiple access spread-spectrum communication system includes a spread spectrum radio interface, responsive to a rate function signal from a base station, and first and second despreaders. The base station assigns the rate function spread-spectrum message channels and the first despreader recovers and modifies an information signal one of the spread spectrum message channels. The information channel mode is then modified for processing by the second despreader, with the second despreader supporting a different information signal rate. The subscriber unit has a capability of communicating with a dynamically changing a transmission rate of an information signal which includes multiple spread spectrum message channels. The system includes a closed loop power control system for maintaining a minimum system transmit power level for a radio carrier station and the subscriber units, and system capacity management for maintaining a maximum number of active subscriber units for improved system performance.

Owner:INTERDIGITAL TECH CORP

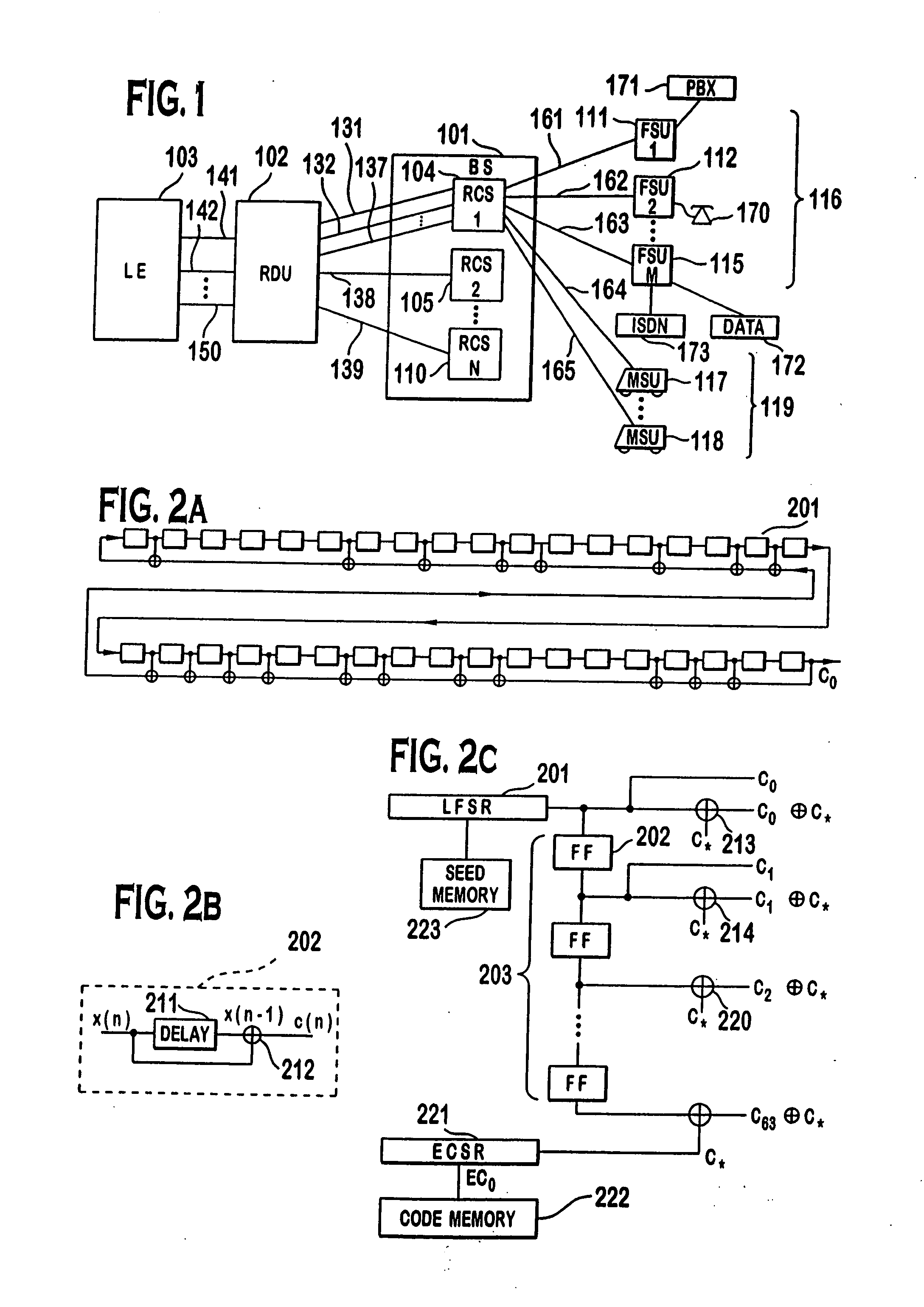

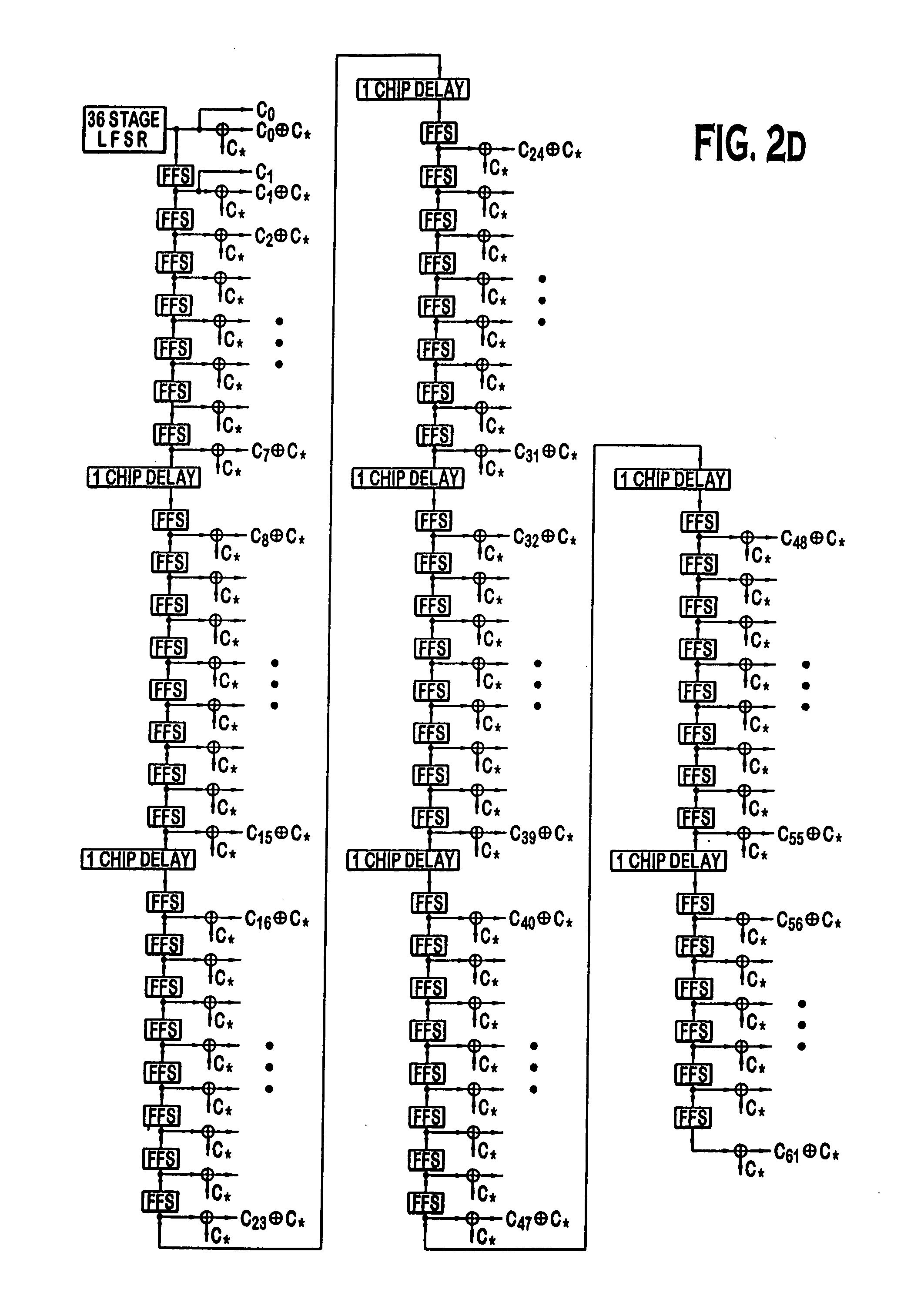

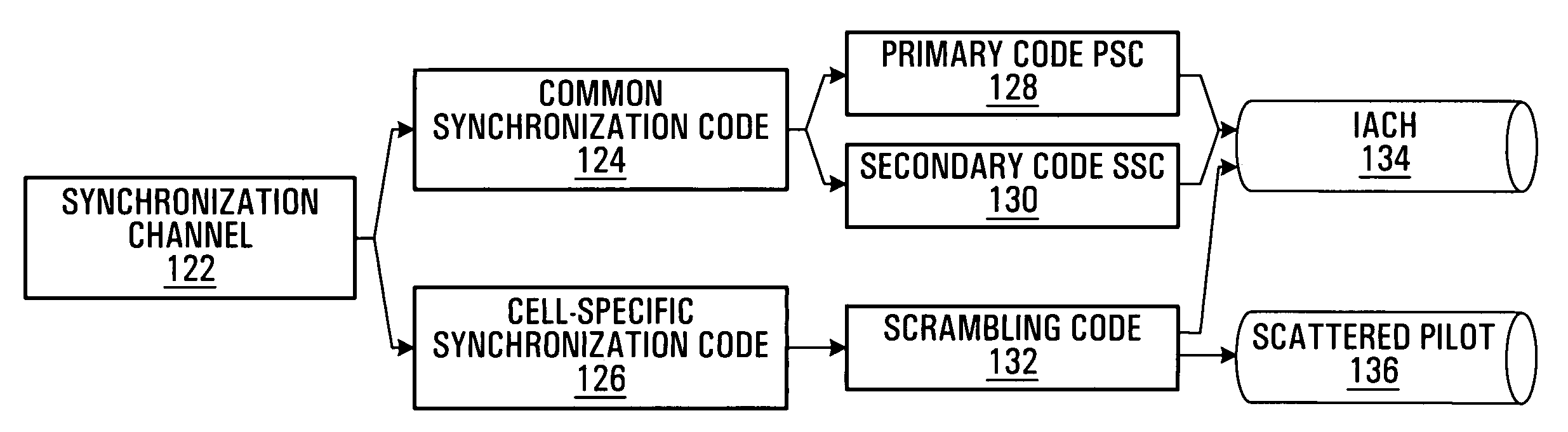

Physical layer structures and initial access schemes in an unsynchronized communication network

Physical layer structures and related access schemes for unsynchronized communication networks are provided. Access channel information, preferably including a common synchronization code associated with all transceiver stations in a communication network and a cell-specific synchronization code uniquely associated with one of the transceiver stations, is modulated onto at least one set of time-continuous signal components of a communication signal. In order to access the communication network, communication terminals search for the access channel information in one or more sets of time-continuous signal components and synchronization parameters are then determined based on a location of the access channel information in the sets of time-continuous signal components. Some embodiments of the invention provide for joint frame synchronization and coarse timing synchronization. In further embodiments, the communication signal also includes a scattered pilot channel onto which a portion of the access channel information, preferably the cell-specific synchronization code, is modulated. The pilot channels may then be re-used for initial access operations in addition to its conventional uses for such operations as channel estimation.

Owner:APPLE INC