Patents

Literature

329 results about "Signal edge" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronics, a signal edge is a transition of a digital signal from low to high (0 to 1) or from high to low (1 to 0)...

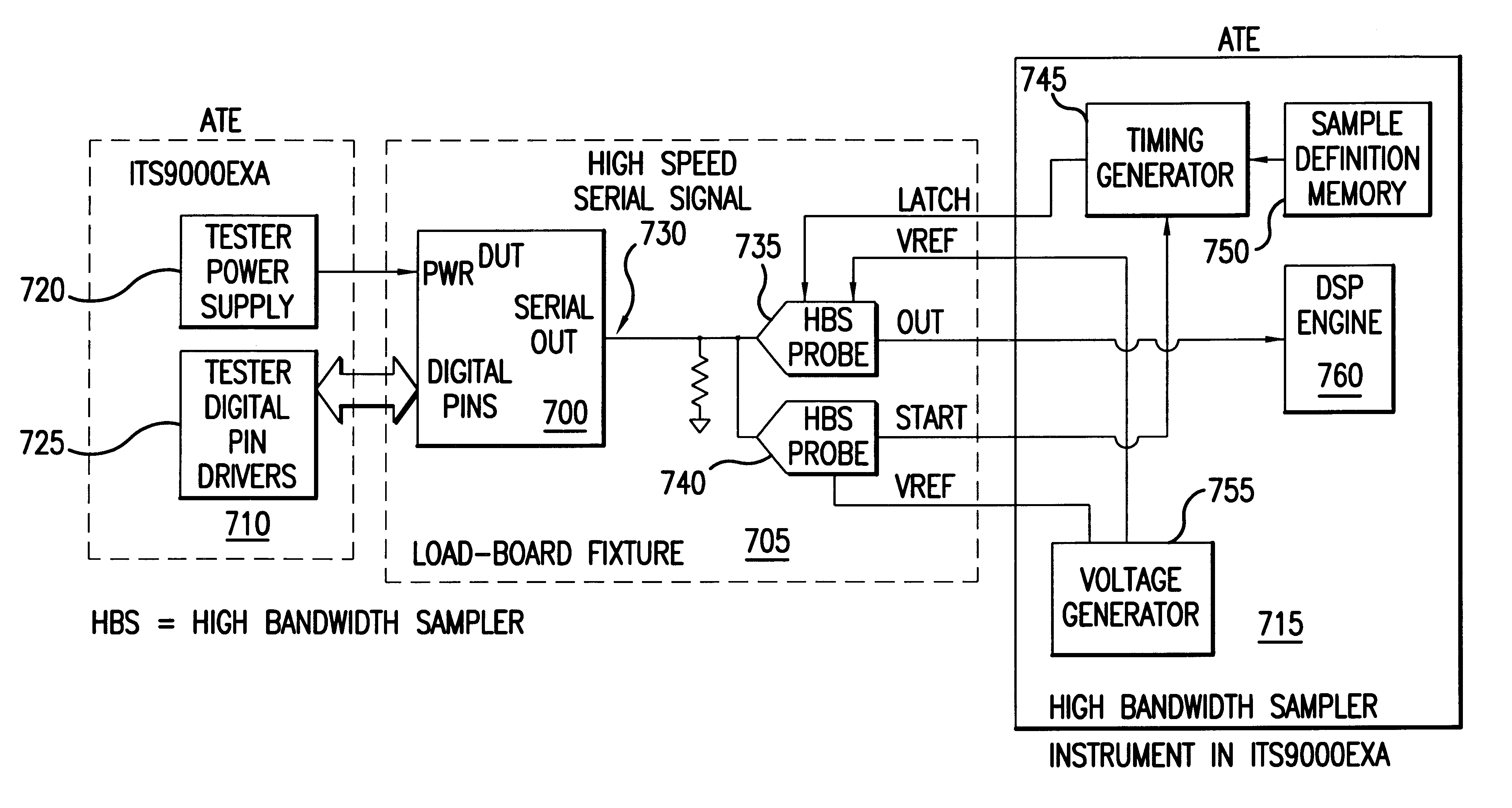

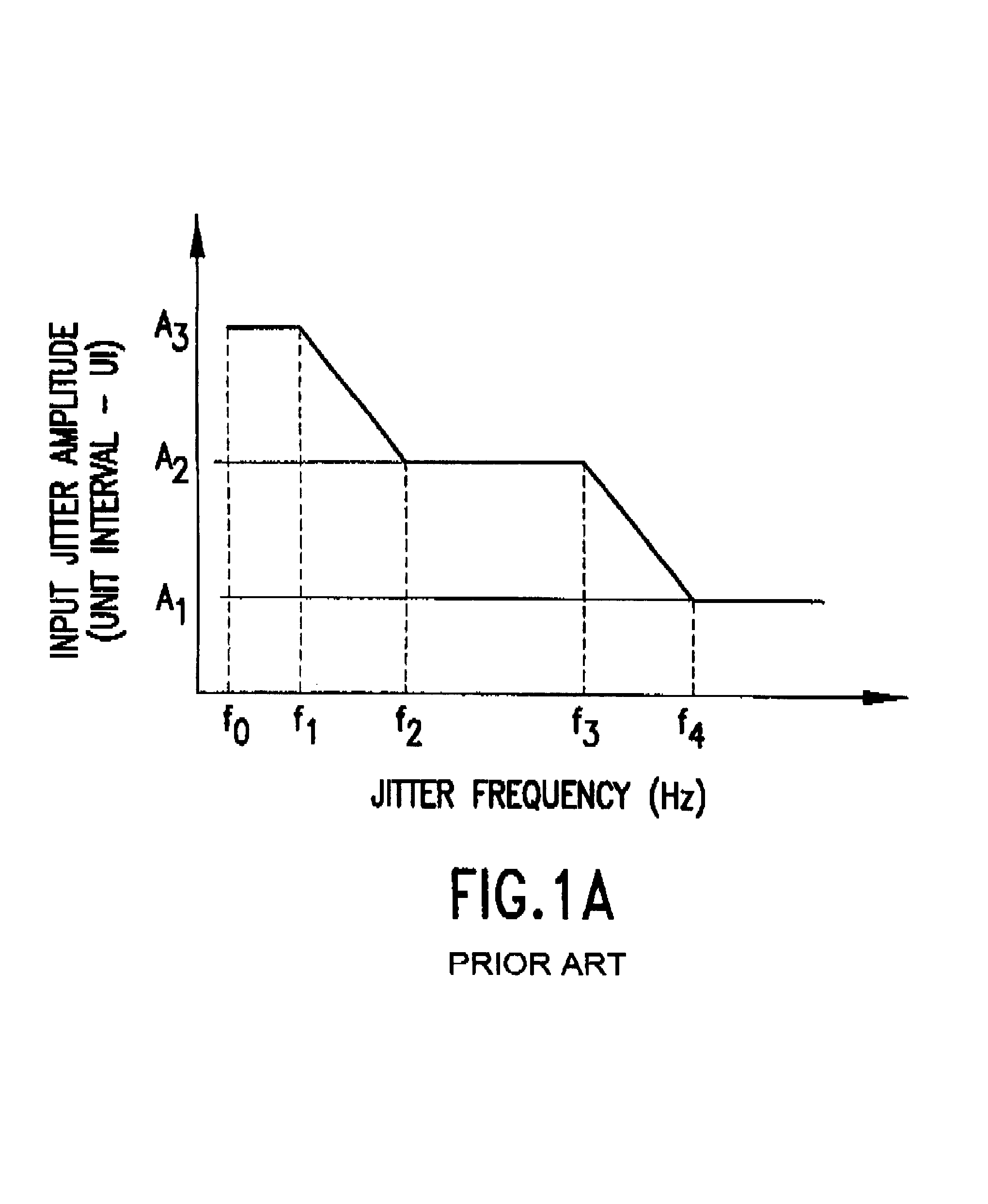

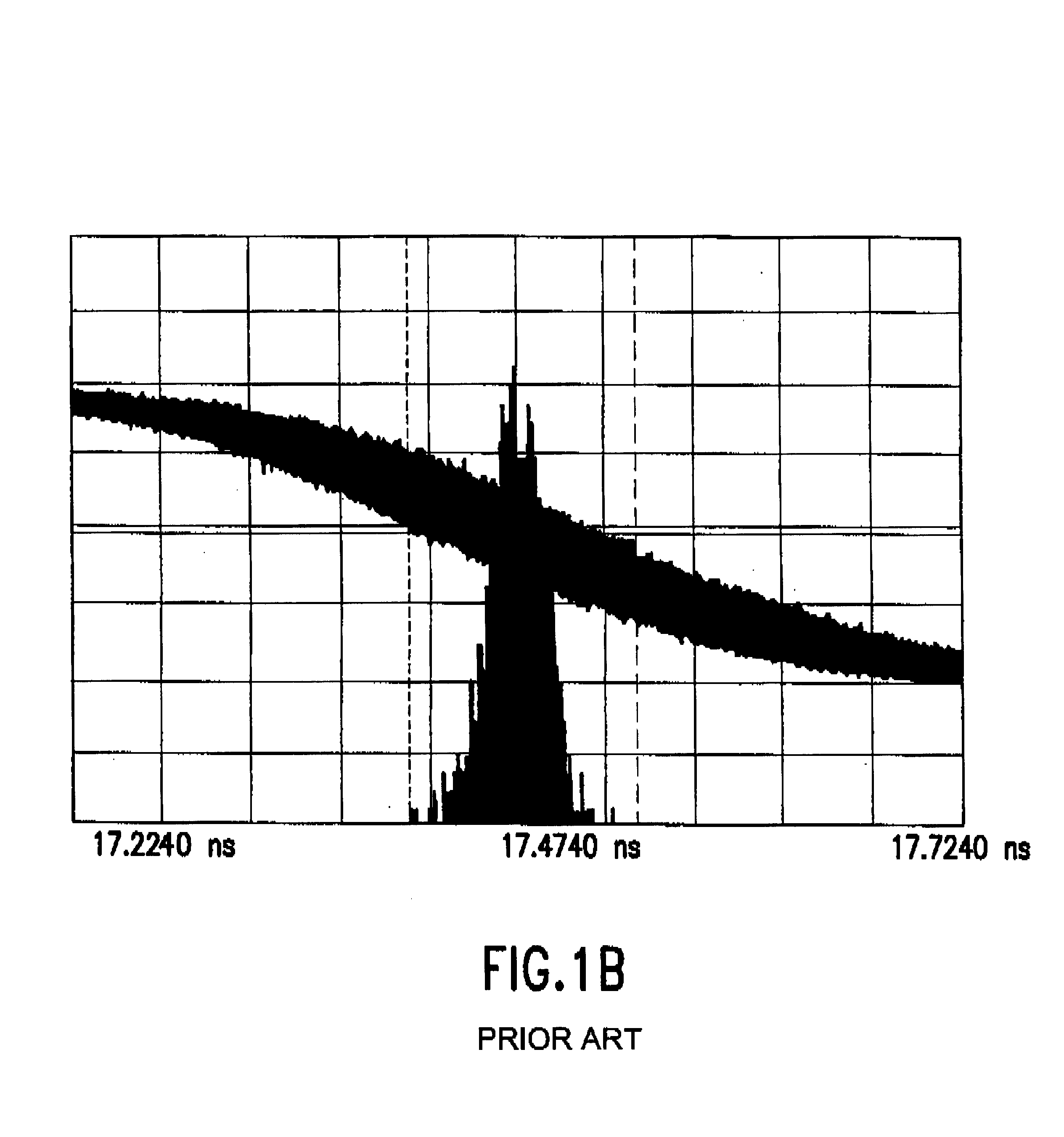

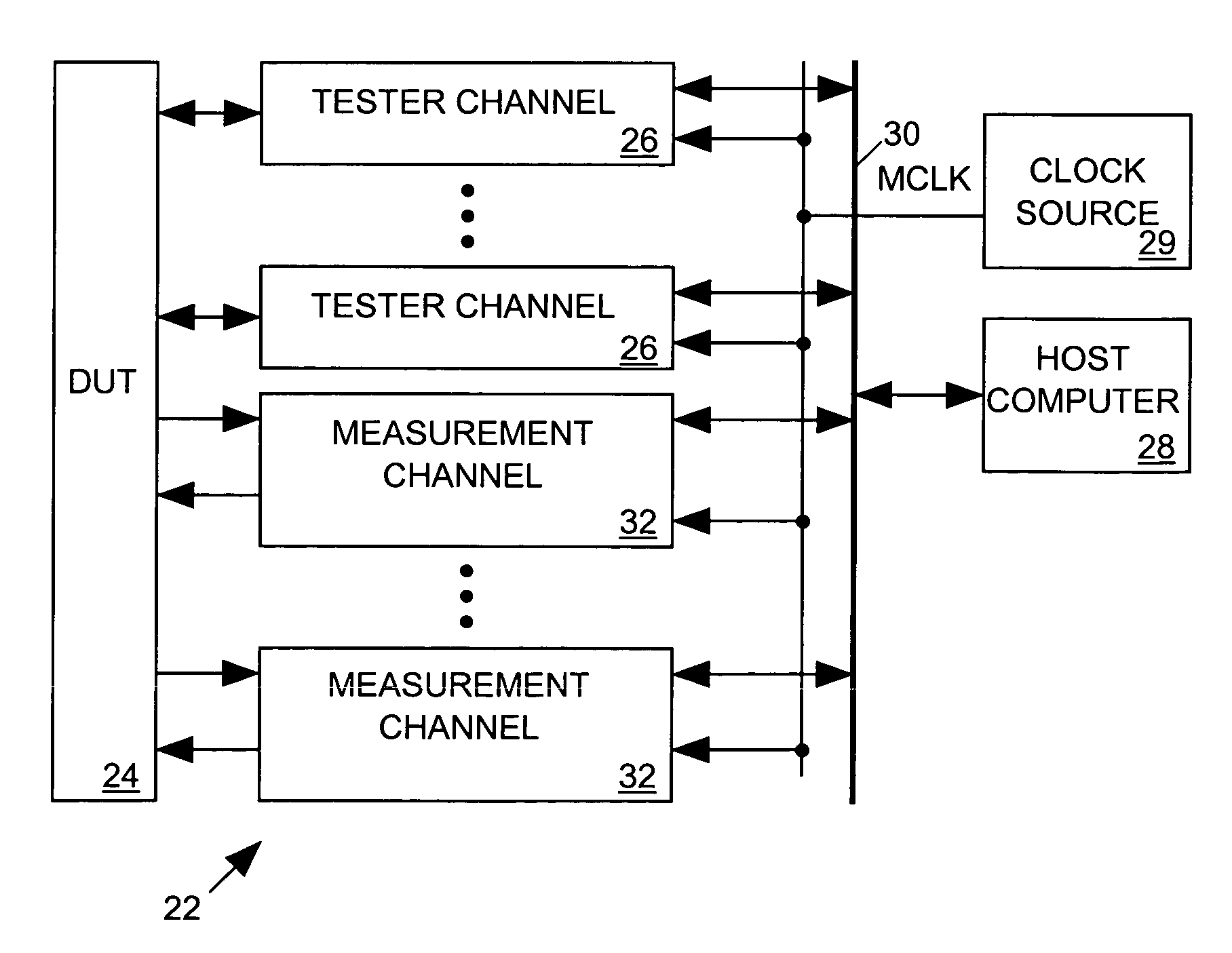

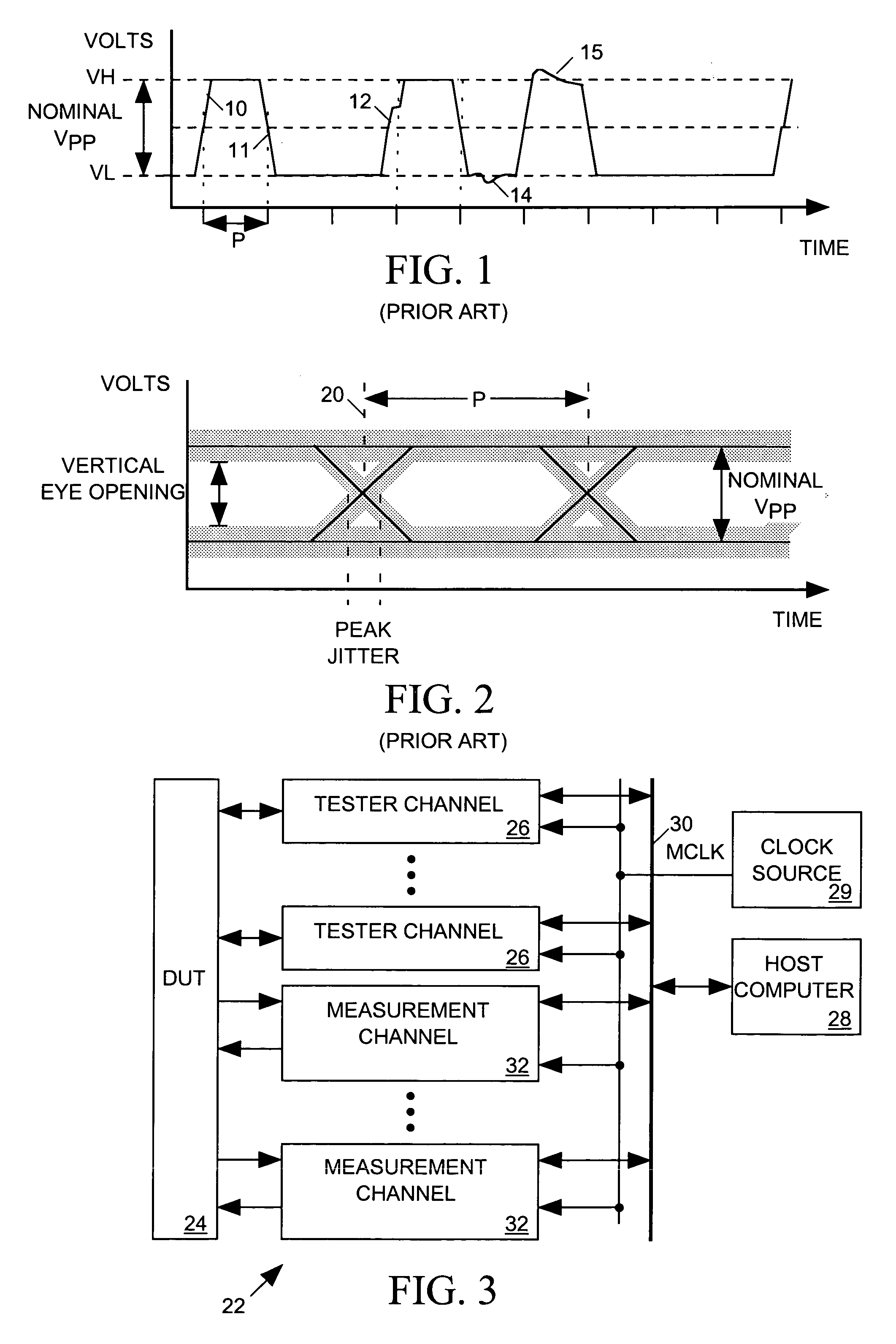

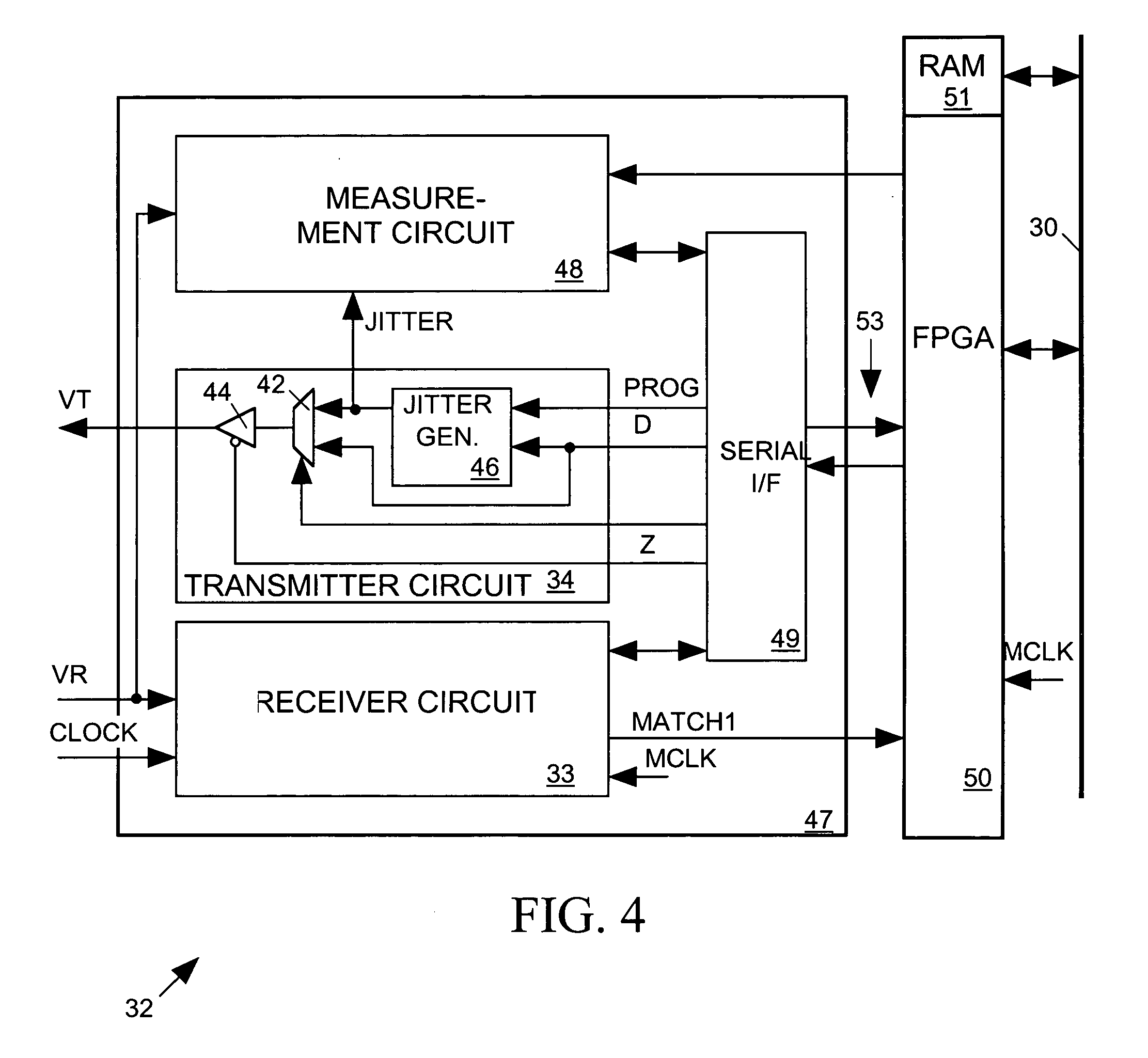

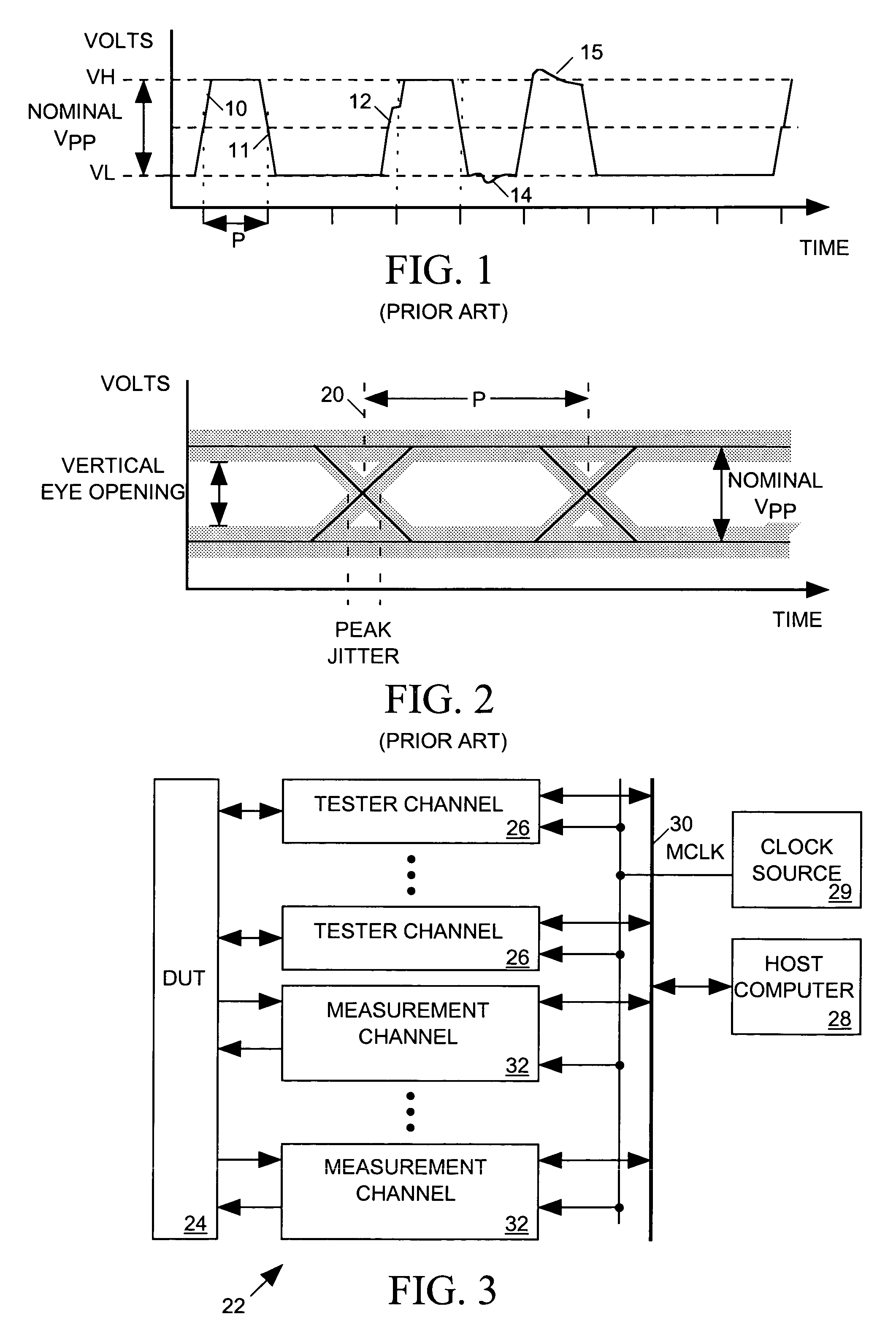

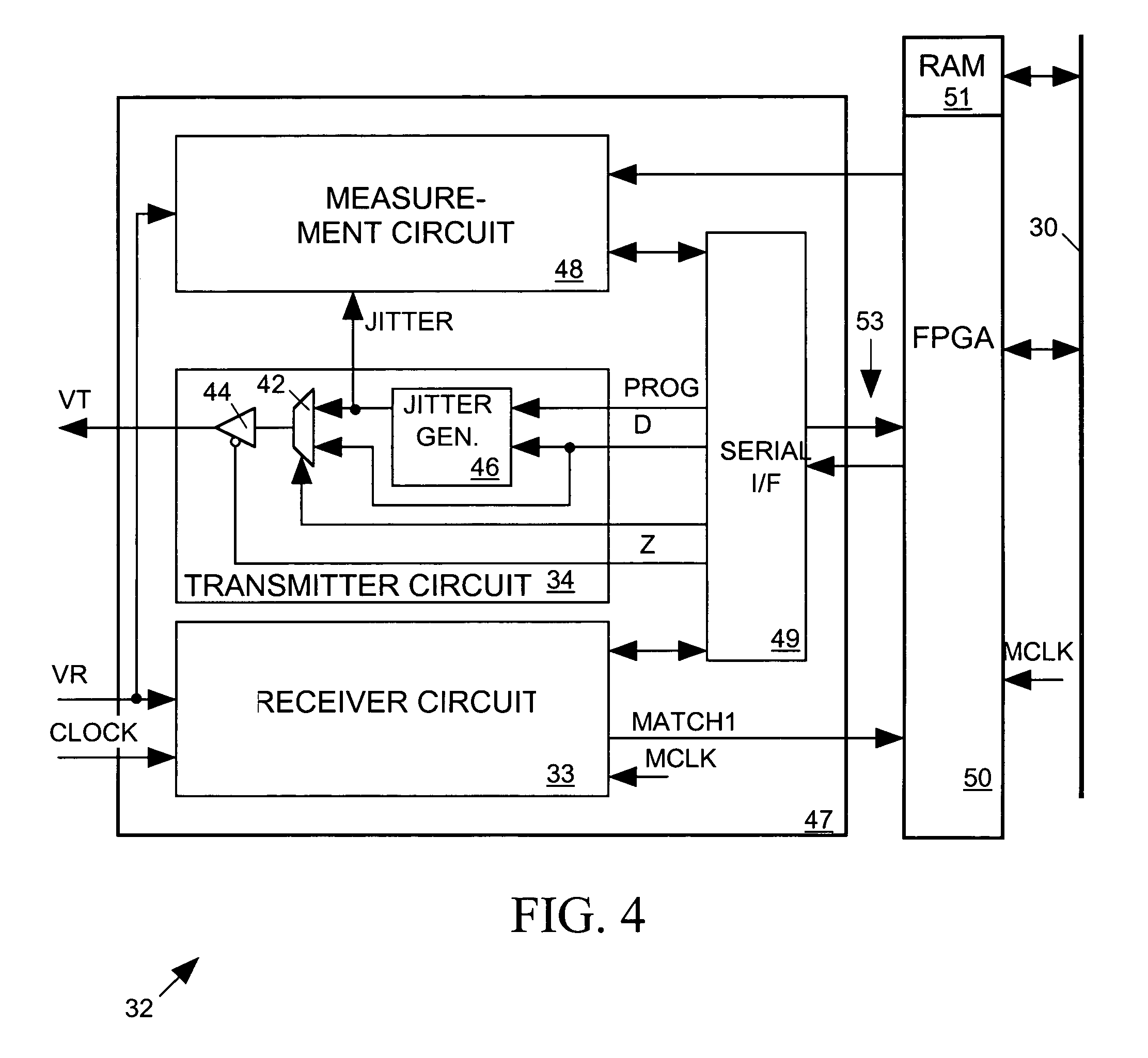

Measuring jitter of high-speed data channels

A jitter measurement technique utilizing a high-bandwidth undersampling voltage measurement instrument is presented. A trigger is derived from the a signal having a repetitive signal pattern. The signal is compared with a threshold at a plurality of times relative to the trigger during multiple repetitions of the signal pattern to produce measurement samples indicative of signal level relative to the threshold. The measurement samples are used to determine the probability of signal edge states as a function of time for the multiple repetitions. The probability of signal edge states are used to determine an edge probability density as a function of time. A histogram of signal state transition times can be prepared from the edge probability density. Mean deviation of edge transitions of the signal can be estimates, and standard deviation of edge transitions of the signal can be estimated to give the root-mean-square (rms) jitter of the signal.

Owner:CREDENCE SYSTEMS

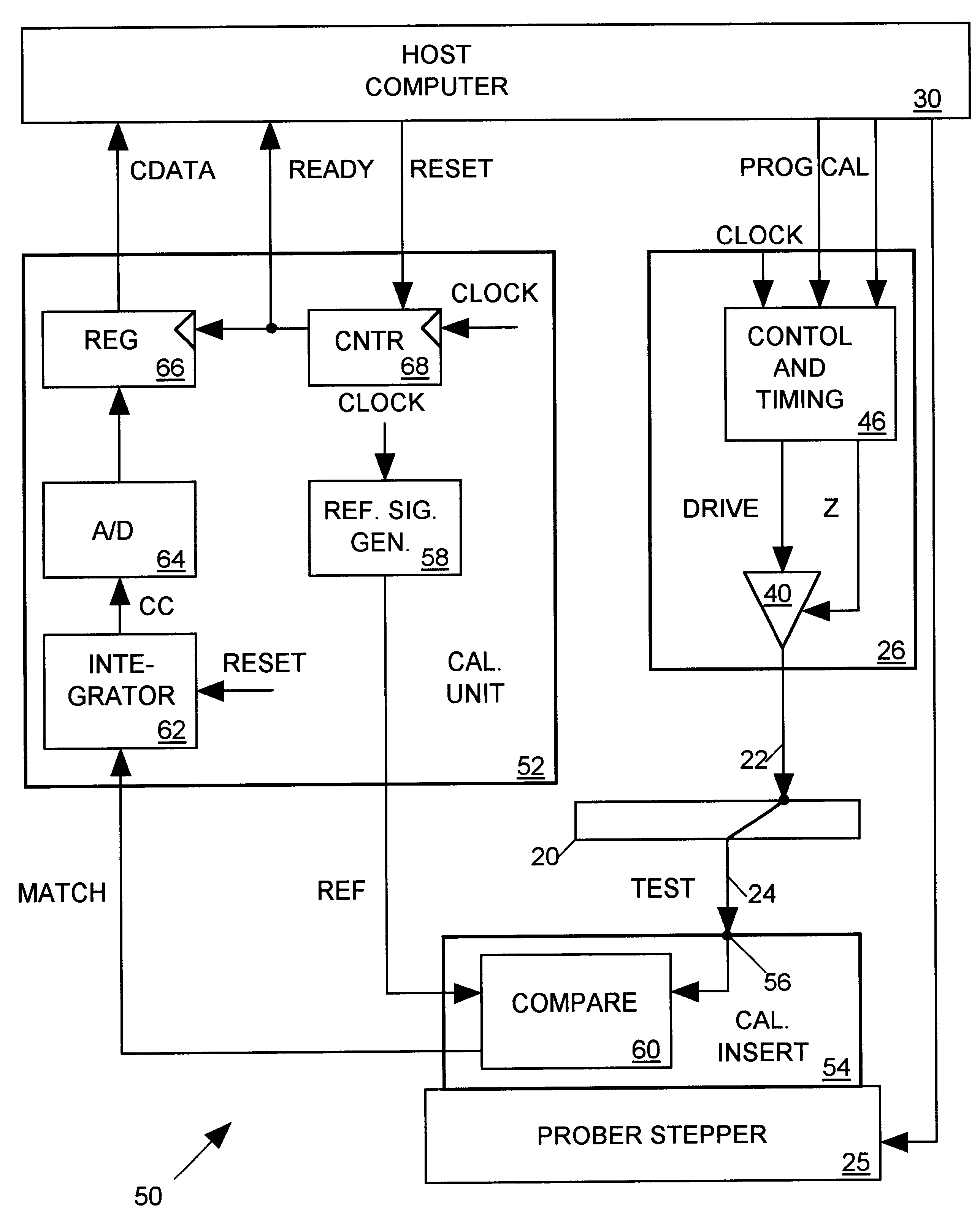

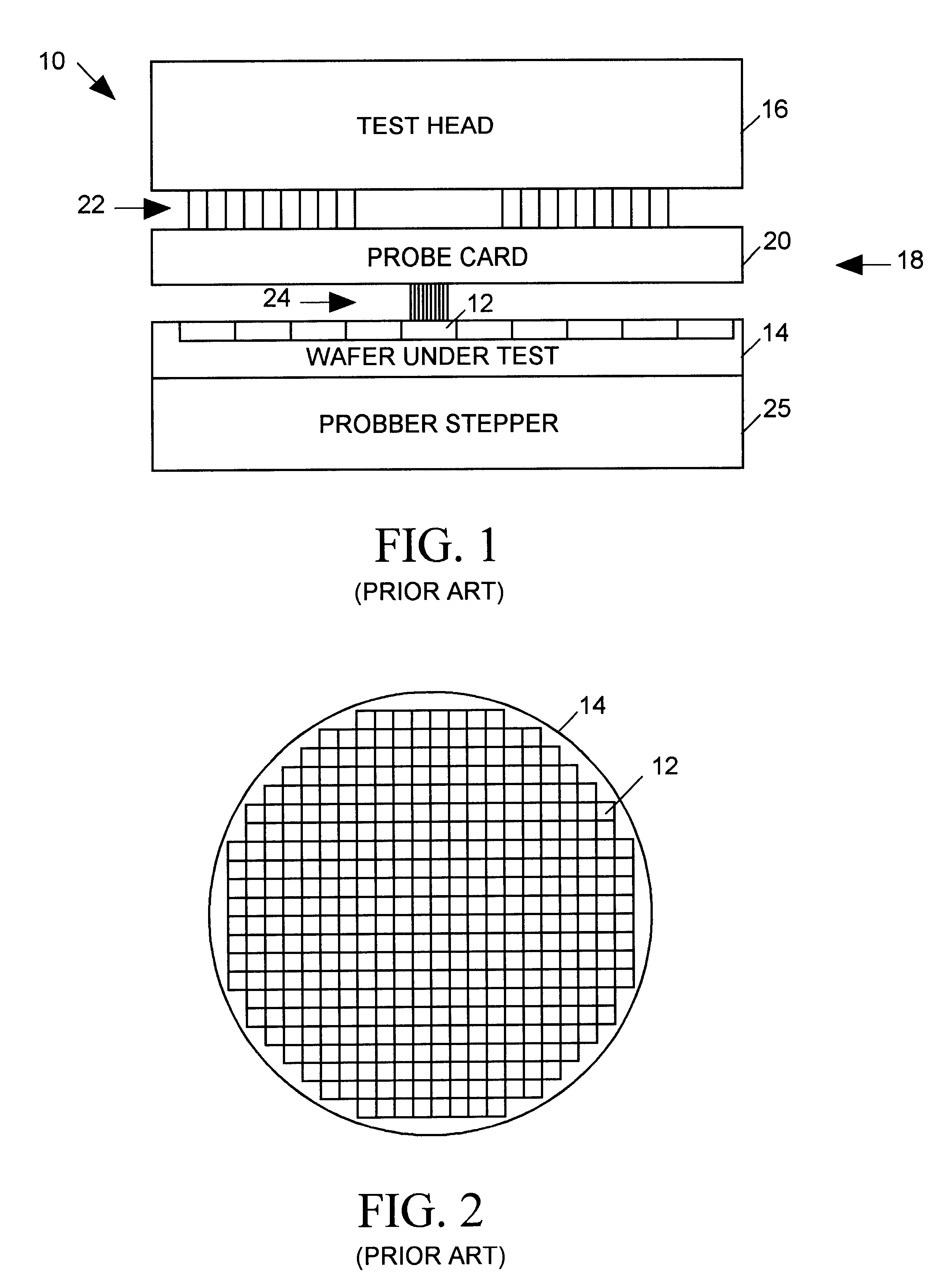

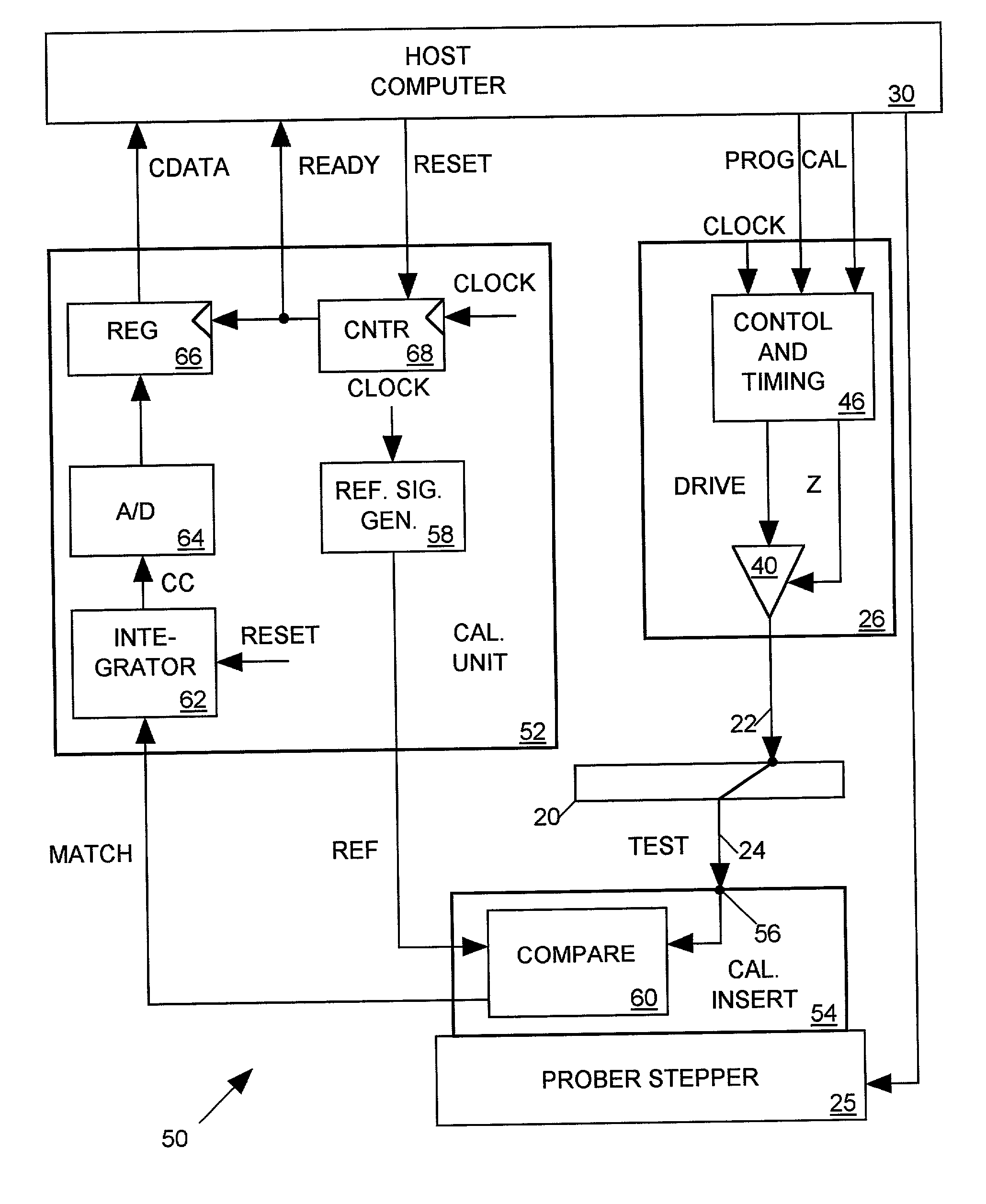

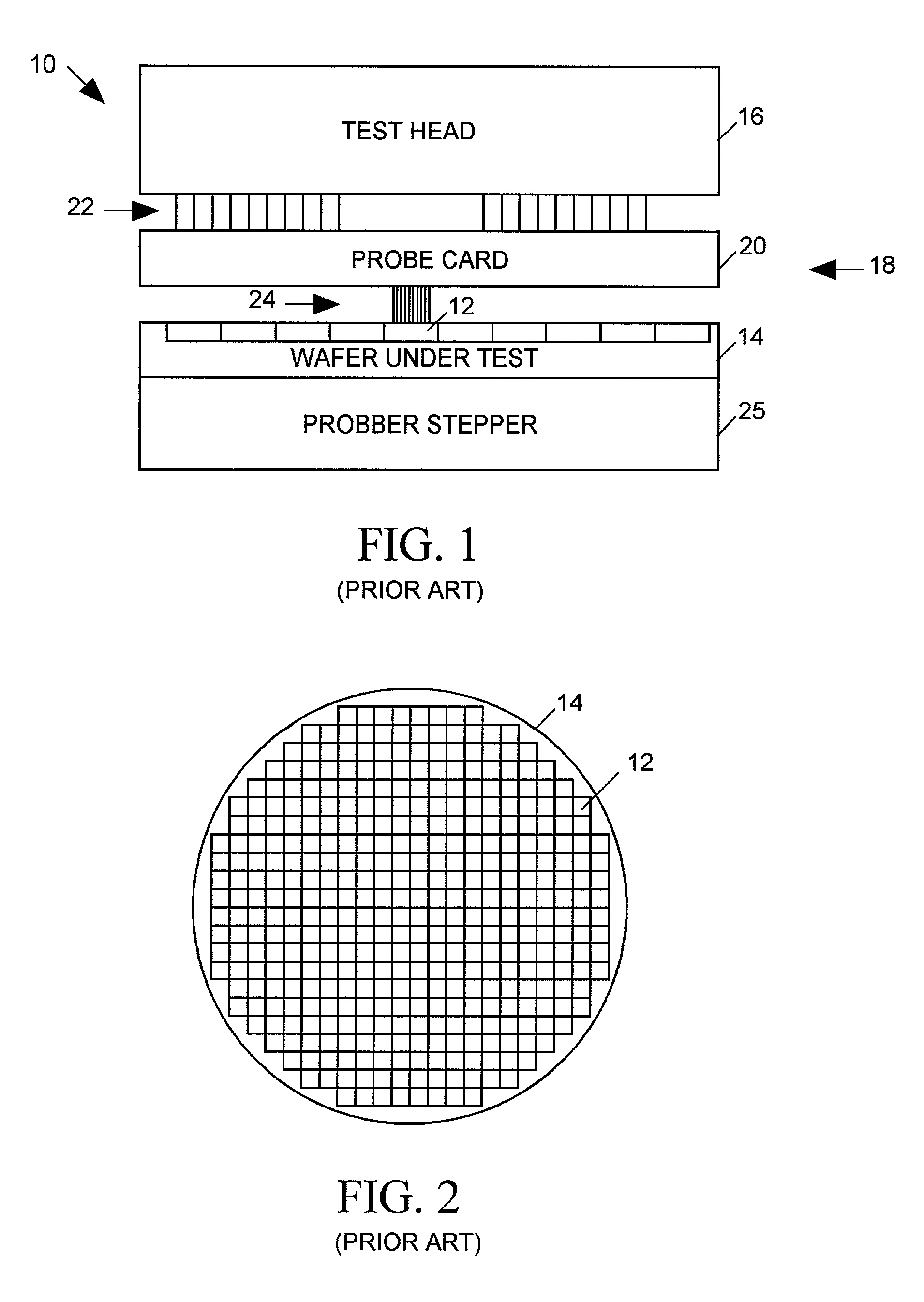

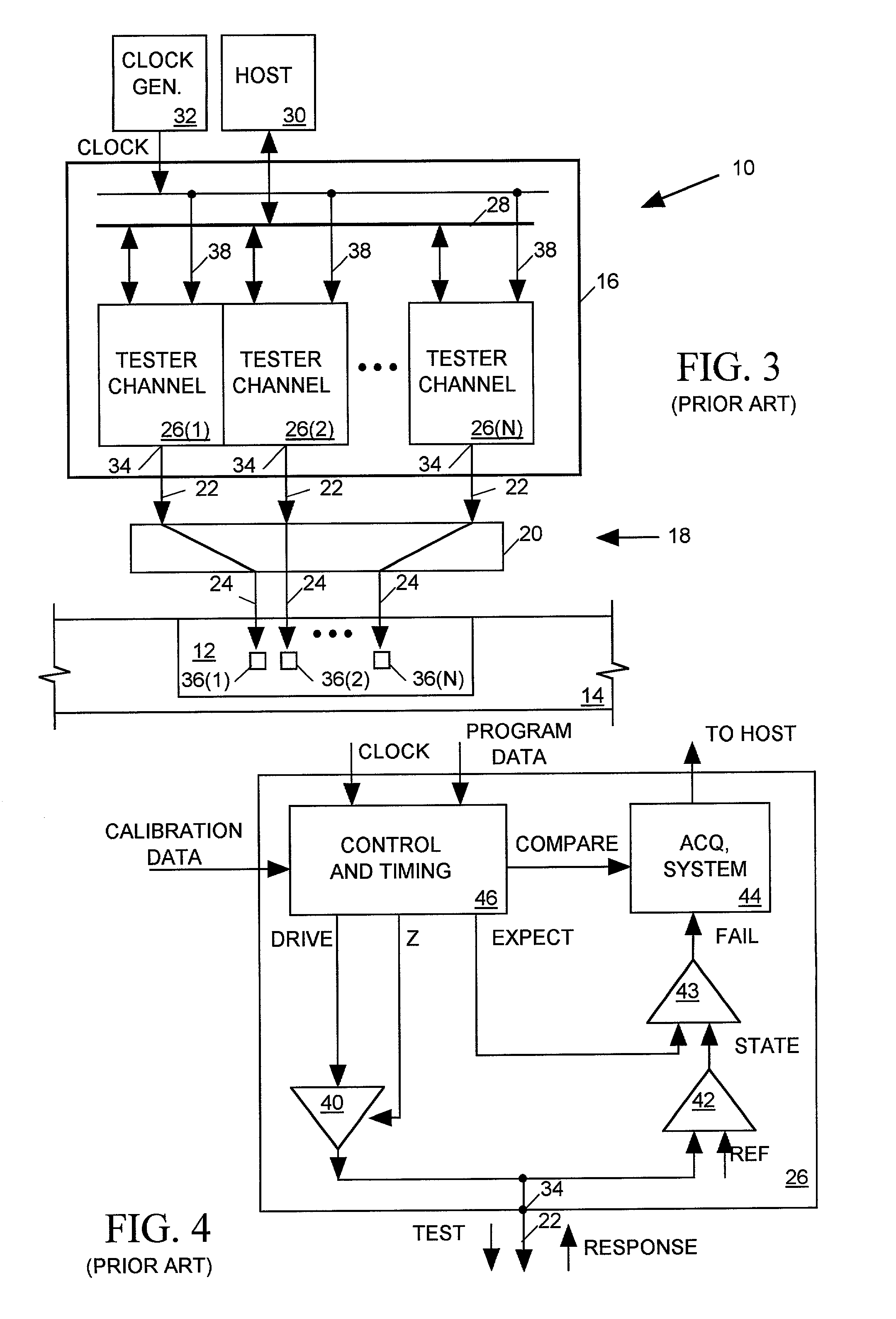

Cross-correlation timing calibration for wafer-level IC tester interconnect systems

InactiveUS6606575B2Easy accessDigital circuit testingTesting/calibration apparatusEngineeringSignal edge

To calibrate timing of test signals generated by all channels of an integrated circuit, each channel is programmed to generate a test signal having a repetitive pseudo-random test signal edge pattern. The test signal pattern of each channel is compared to a reference signal having the same edge pattern and the delay of each channel is adjusted to maximize cross-correlation between the test signal and the reference signal.

Owner:FORMFACTOR INC

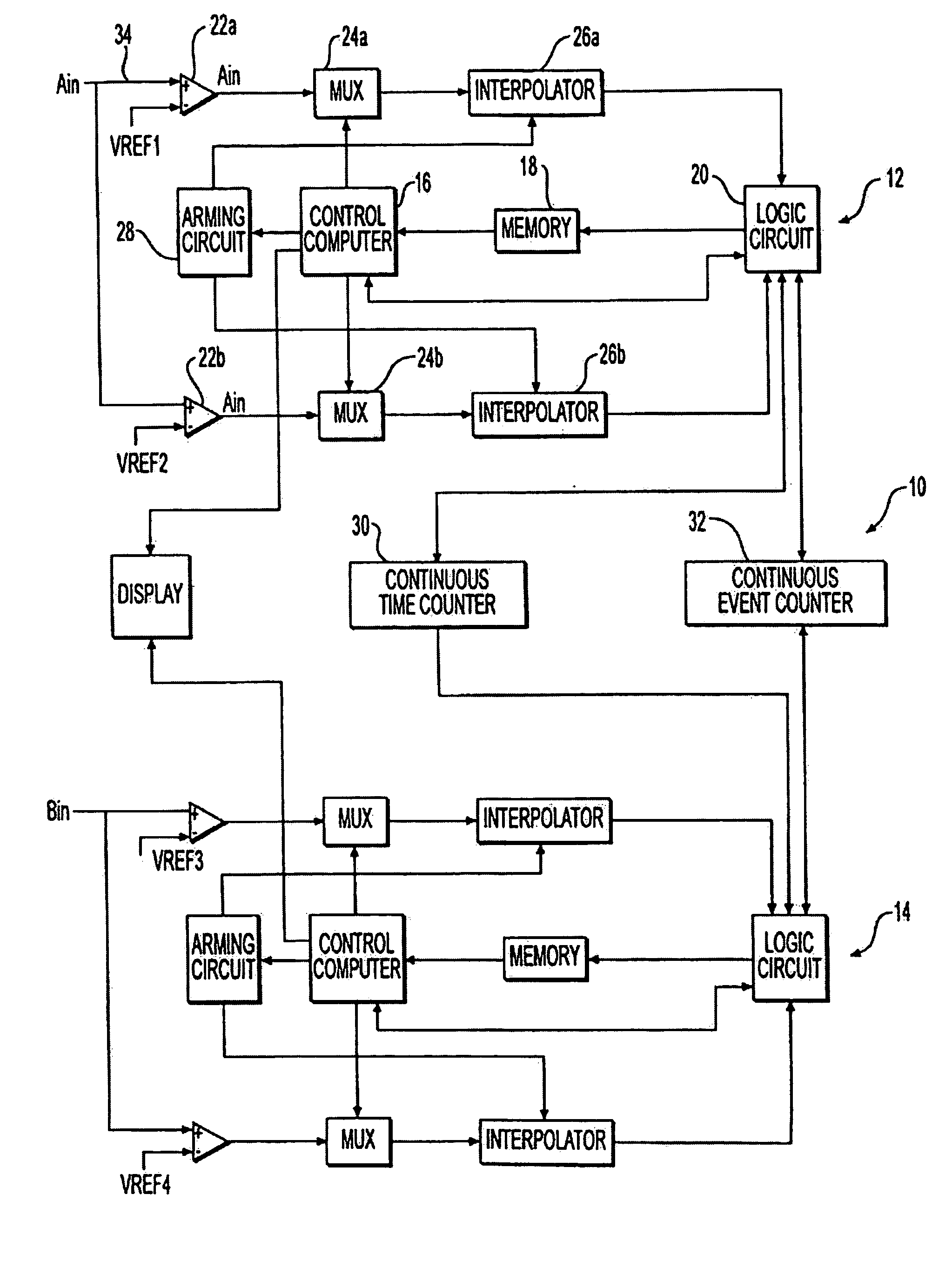

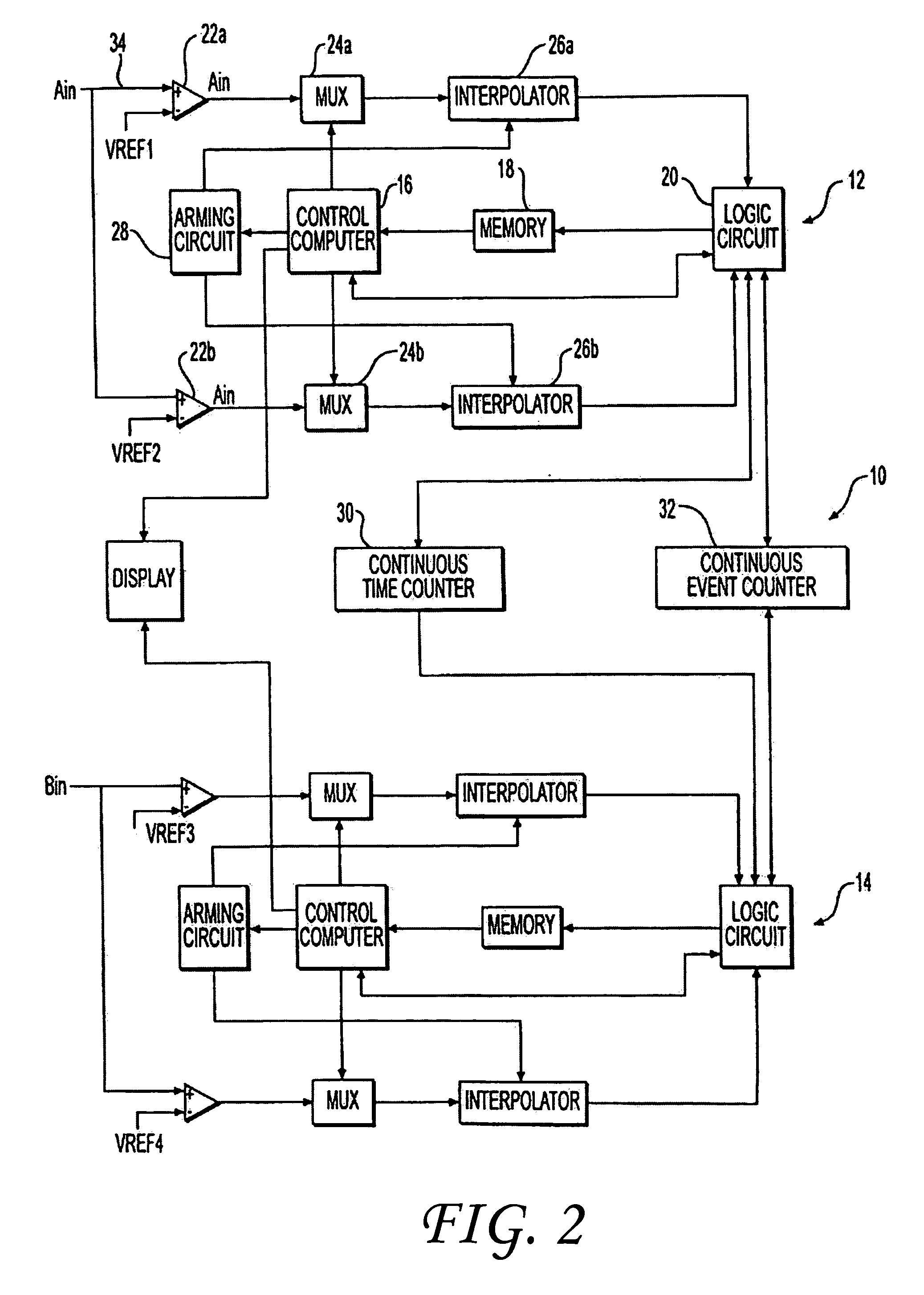

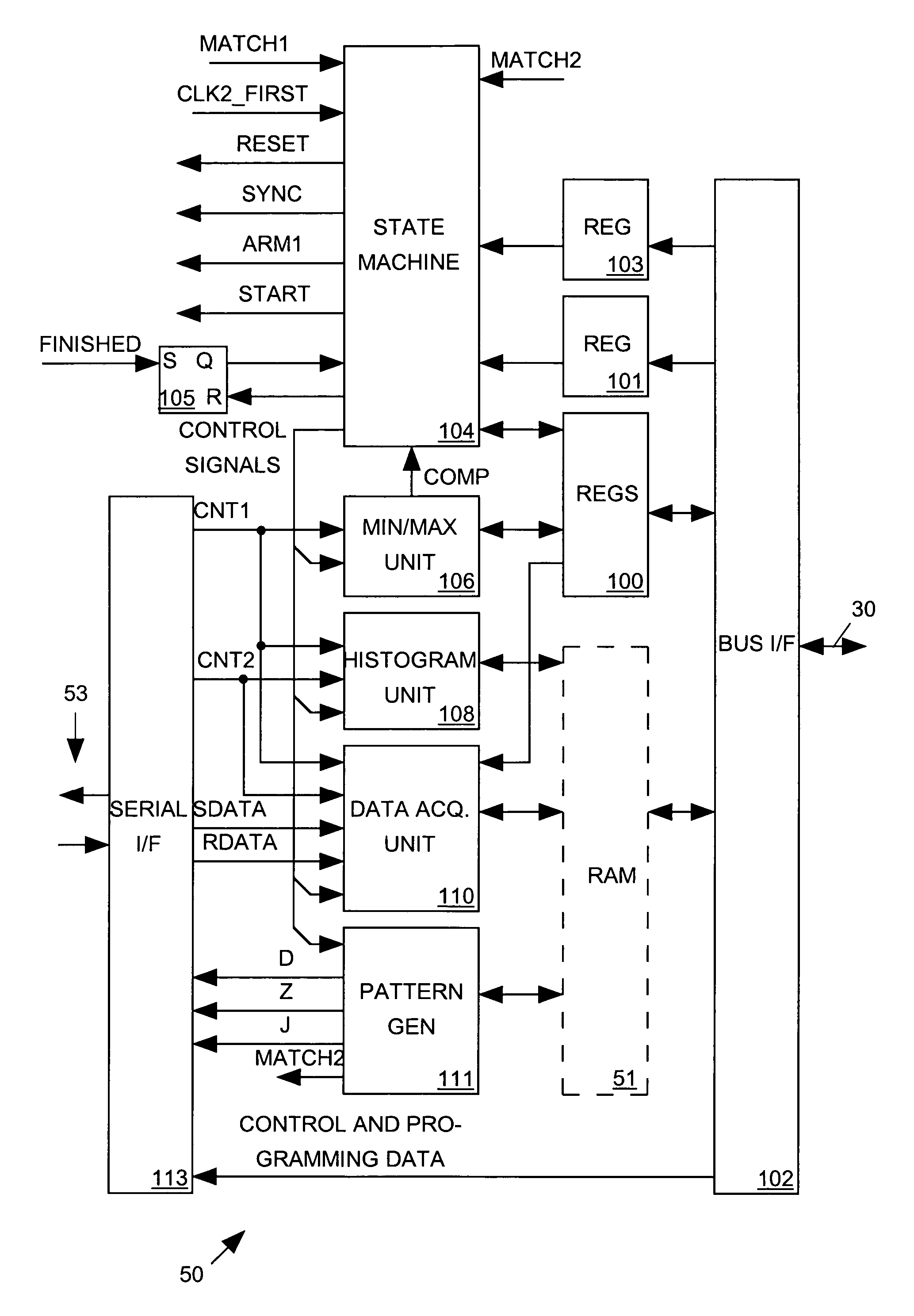

System for measuring characteristics of a digital signal

An electronic device under test (DUT) responds to a digital input signal by generating a digital DUT output signal conveying a repetitive digital signal pattern. An apparatus for measuring various characteristics of the DUT output signal includes a trigger generator for generating a series of trigger signal edges in response to selected DUT output signal edges occurring during separate repetitions of the digital signal pattern. The trigger generator can be configured to generate each trigger signal edge in response to the same or a different edge of the digital signal pattern. The apparatus determines when a DUT output signal edge occurs by determining when the DUT output signal rises above or falls below adjustable reference voltages. The apparatus alternatively responds to each trigger signal edge by measuring a period between two different edges of the digital signal pattern and or by repetitively sampling the DUT output signal to determine its state.

Owner:CREDENCE SYSTEMS

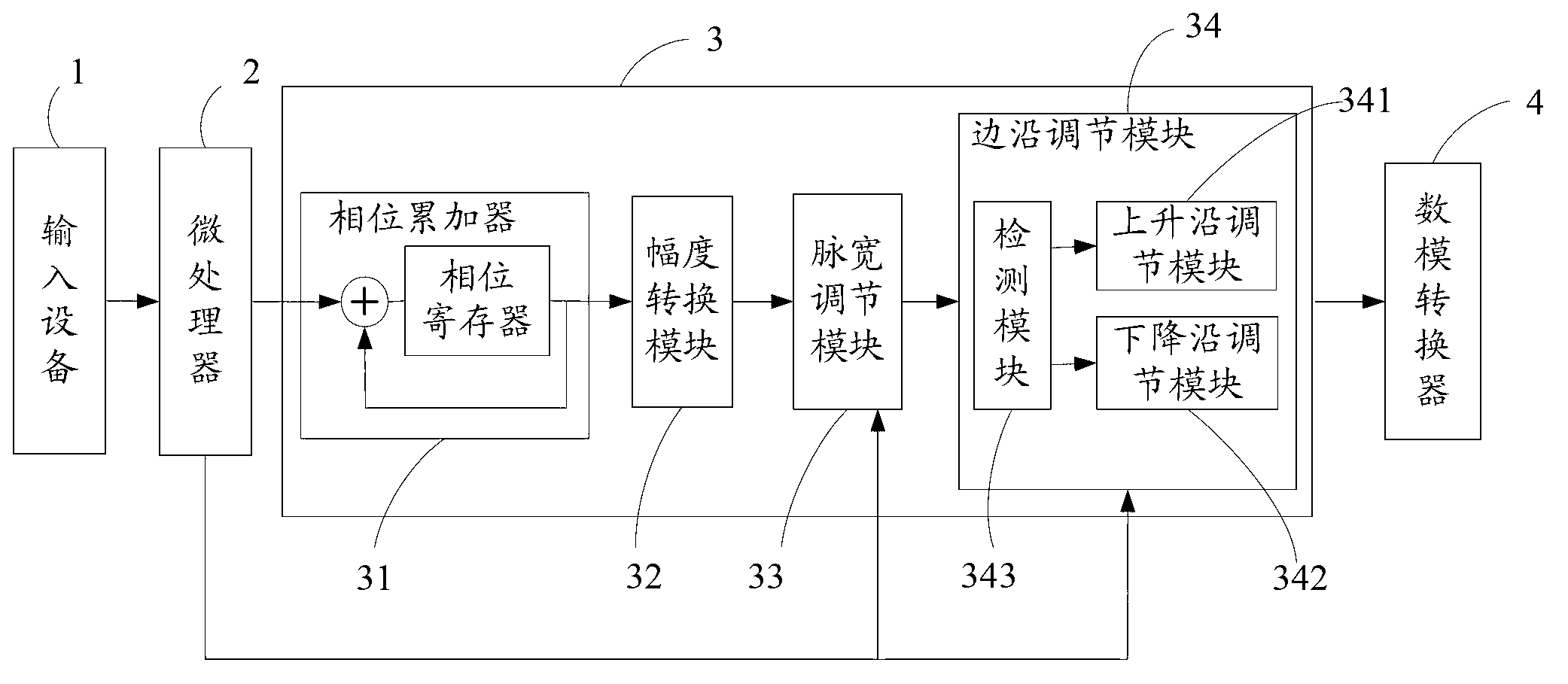

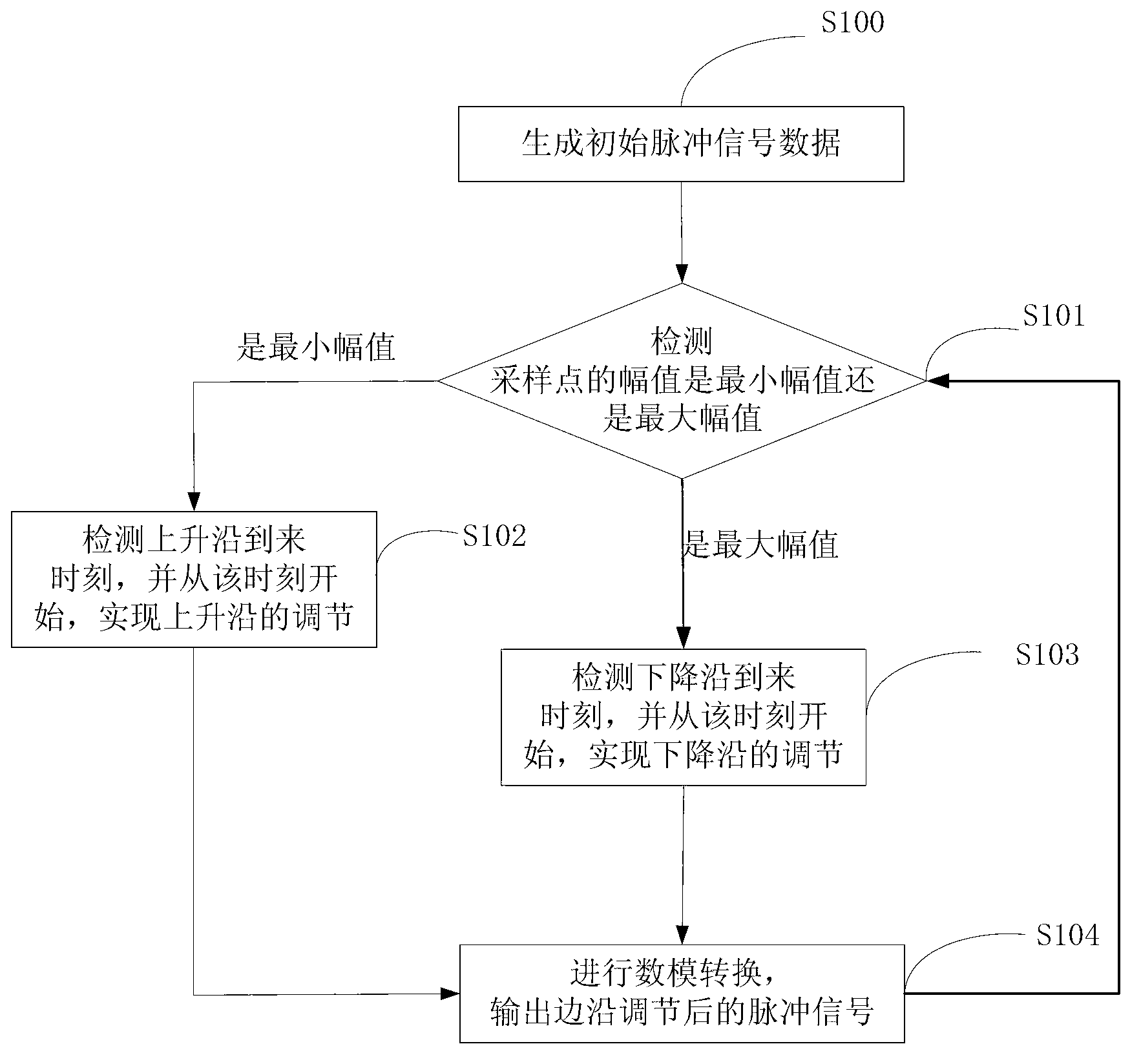

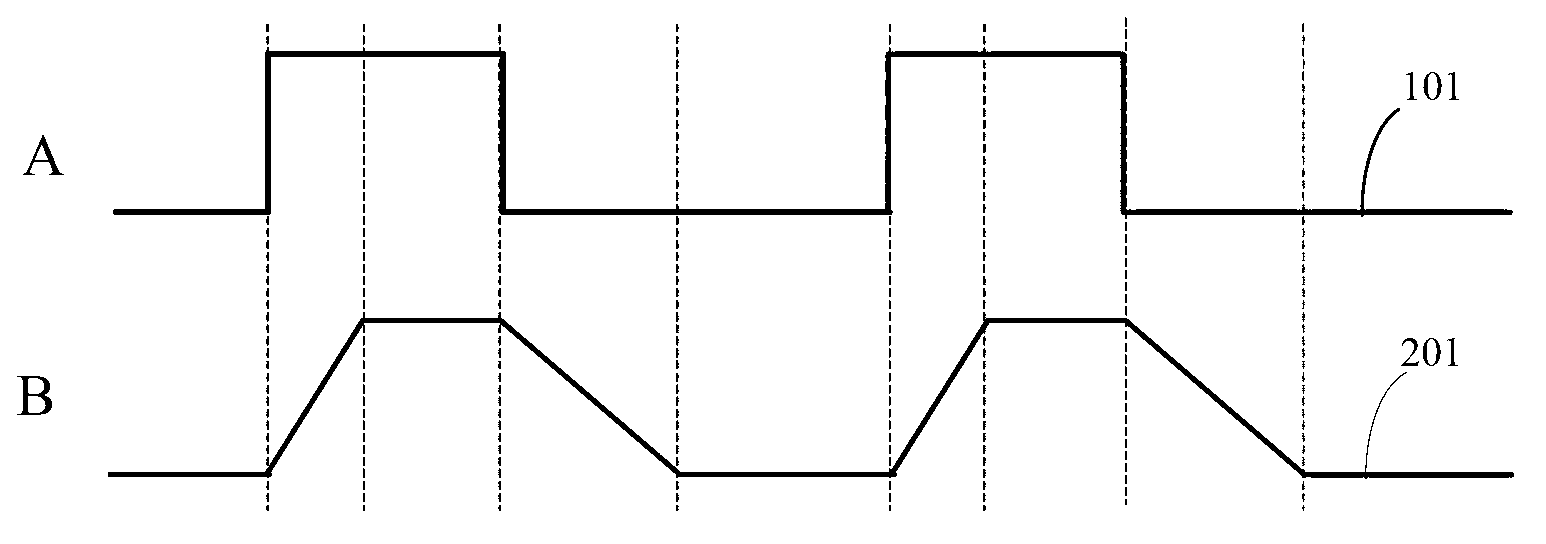

Method and module for DDS (direct digital synthesizer) pulse edge adjusting and pulse signal generator

ActiveCN103178809AEasy to adjustGrow fastElectric pulse generator circuitsPulse manipulationDigital analog converterArrival time

The invention discloses a method and a system for DDS (direct digital synthesizer) pulse edge adjusting and a pulse signal generator. The pulse signal generator comprises input equipment, a microprocessor, a DDS module and a digital-analog converter in sequential connection, the DDS module comprises a phase accumulator, an amplitude converting module, a pulse-width adjusting module and an edge adjusting module, the edge adjusting module comprises a detection module, a rising edge adjusting module and a falling edge adjusting module, the detection module is used for detecting arrival time of a rising edge and arrival time of a falling edge of initial pulse signal data, the rising edge adjusting module is used for realizing rising edge adjusting of the initial pulse signal data according to an upper stepping value, and the falling edge adjusting module is used for realizing falling edge adjusting of the initial pulse signal data according to a lower stepping value. Compared with the prior art, by the technical scheme, quick rising and falling of pulse signal edges can be realized when frequency is low, the duty ratio is extremely low, and large-scale accurate pulse signal edge adjusting can also be realized.

Owner:SHENZHEN CITY SIGLENT TECH

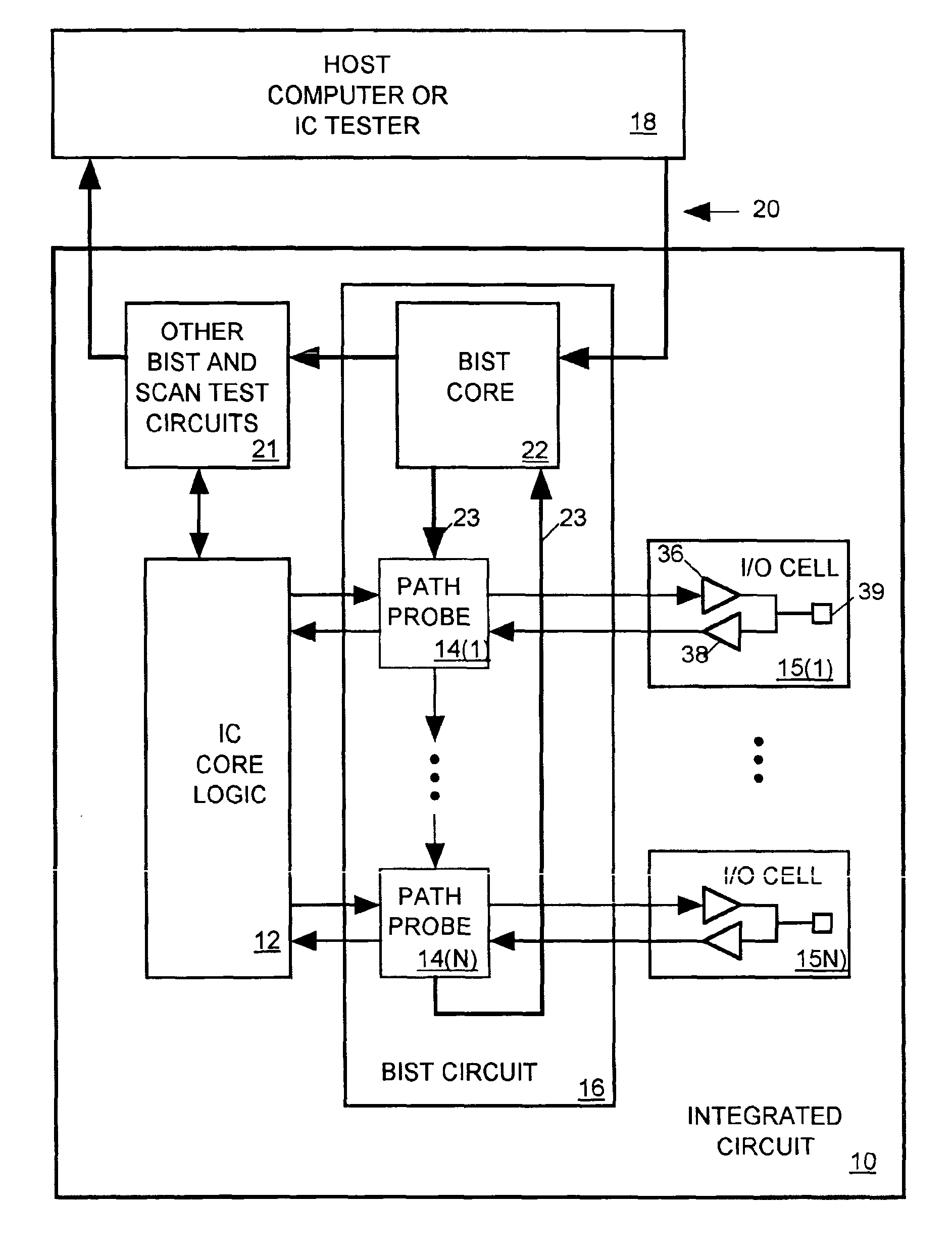

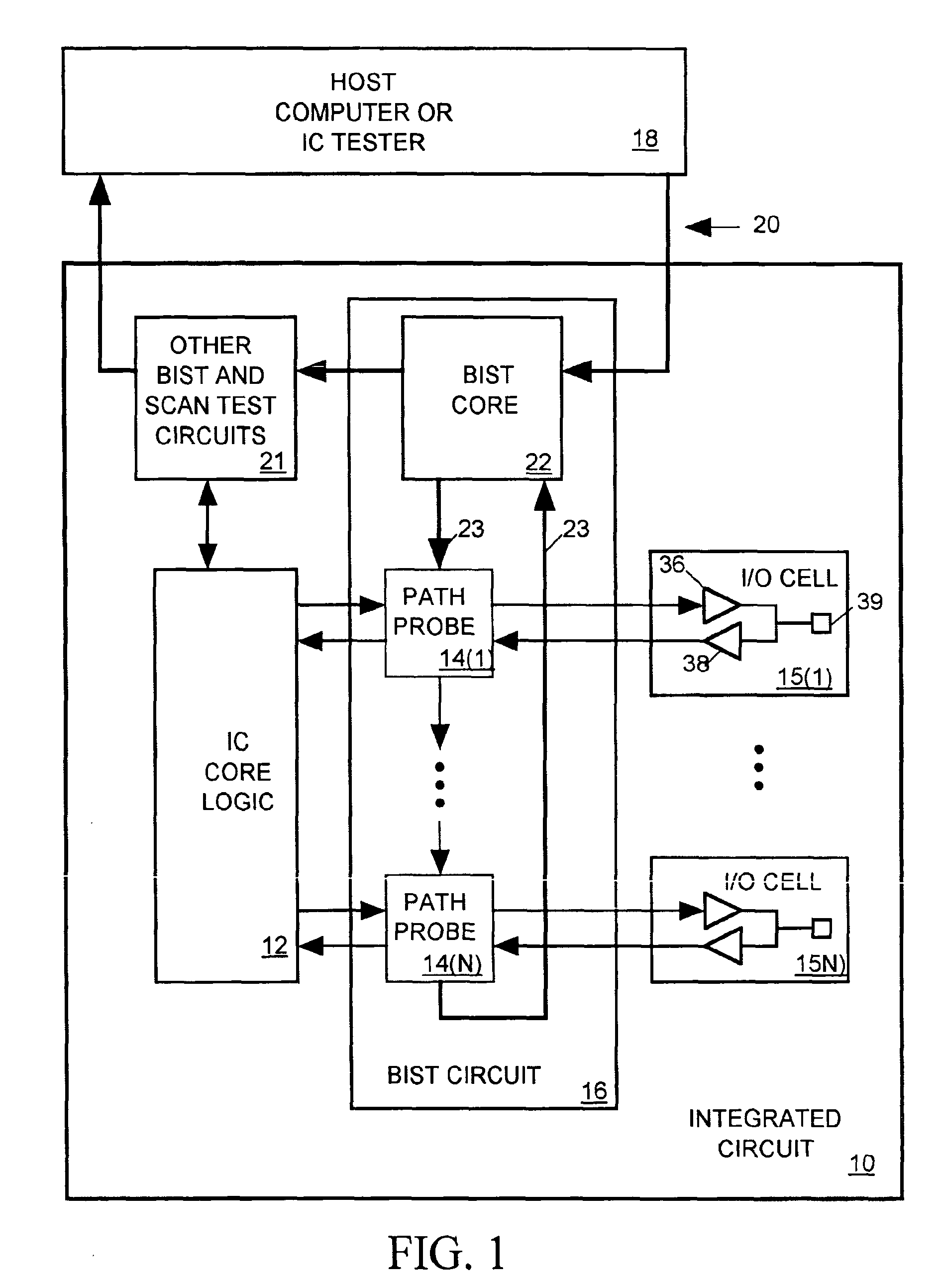

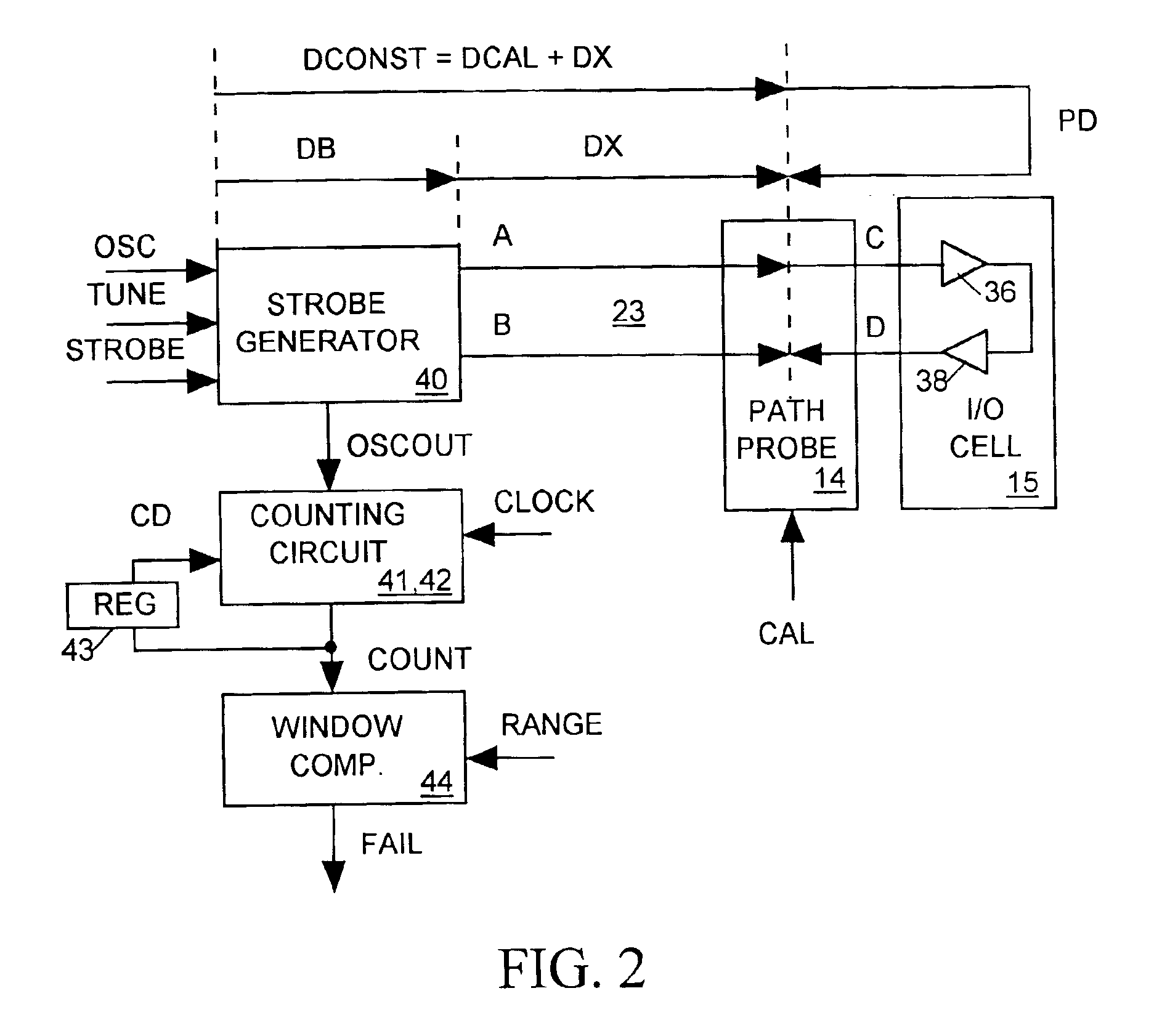

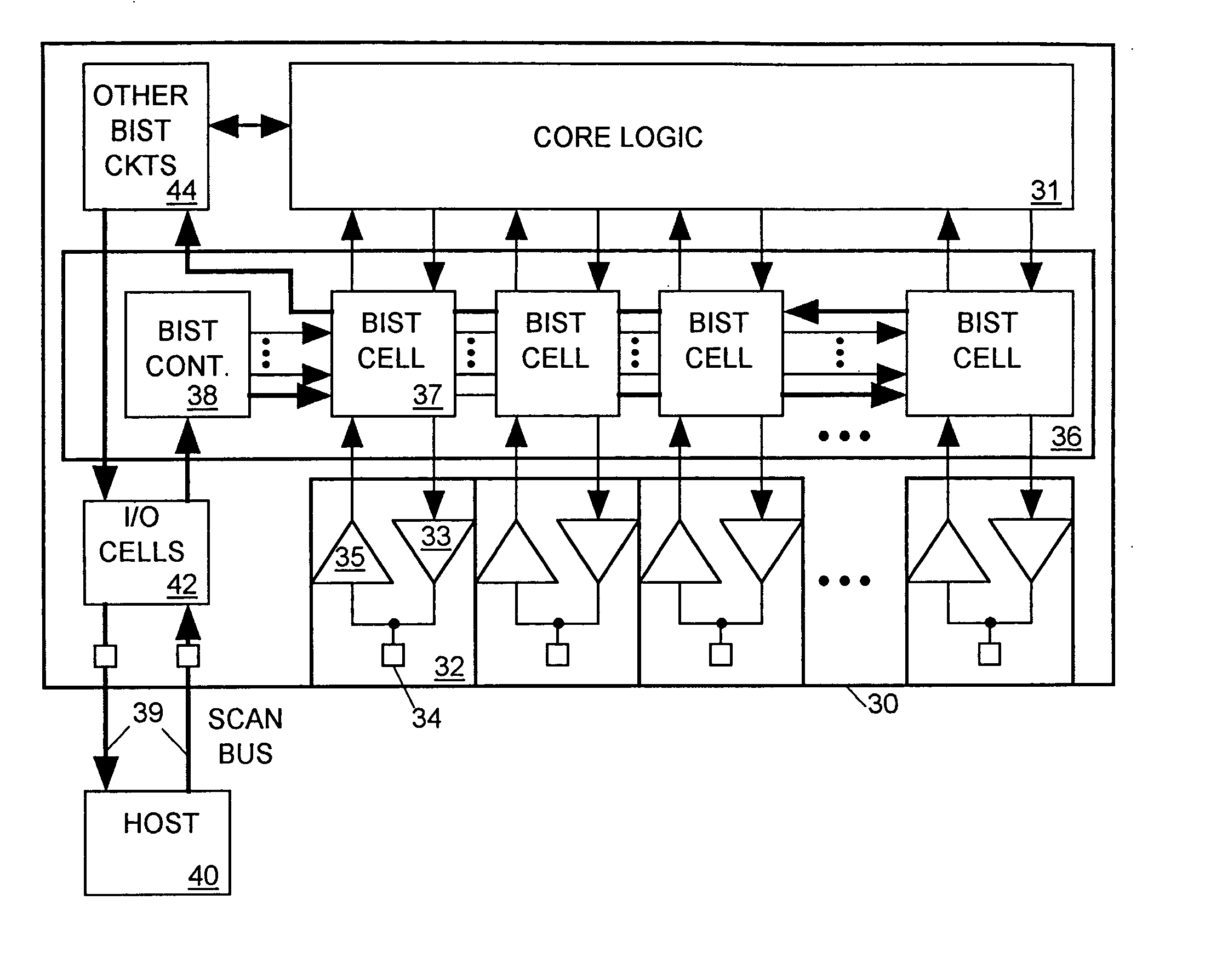

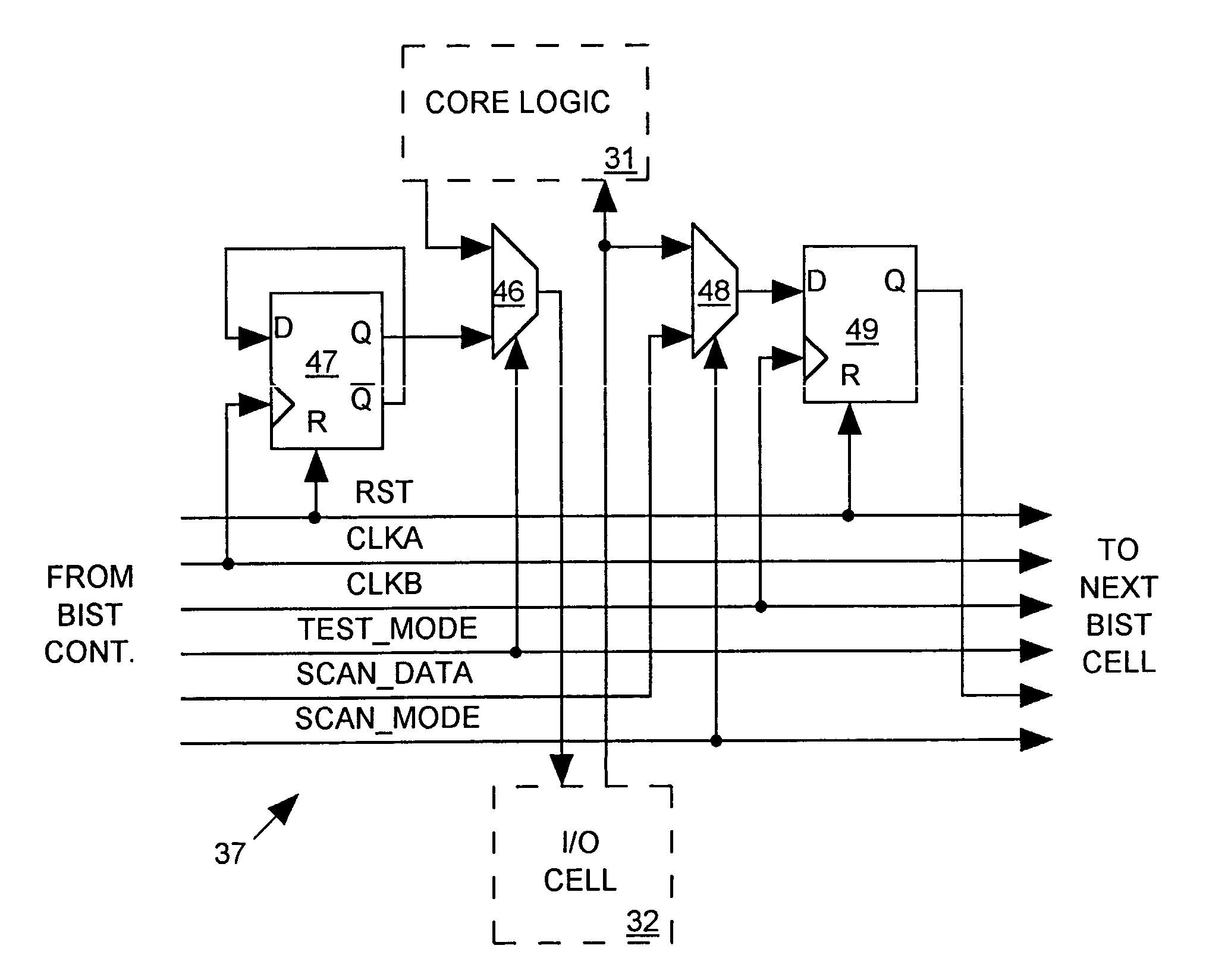

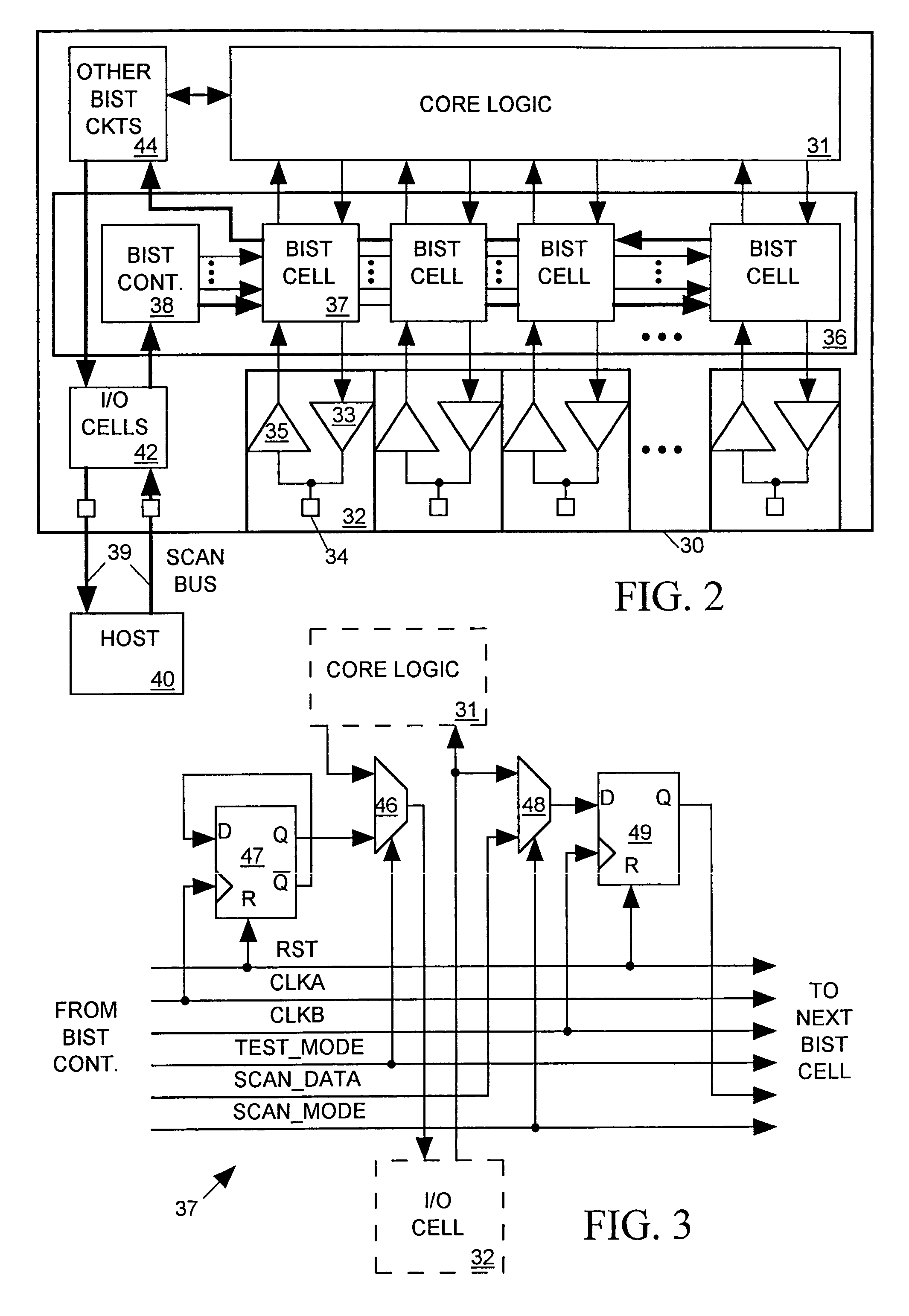

BIST circuit for measuring path delay in an IC

InactiveUS6996032B2Digital circuit testingElectromechanical unknown time interval measurementDelayed responseTime delays

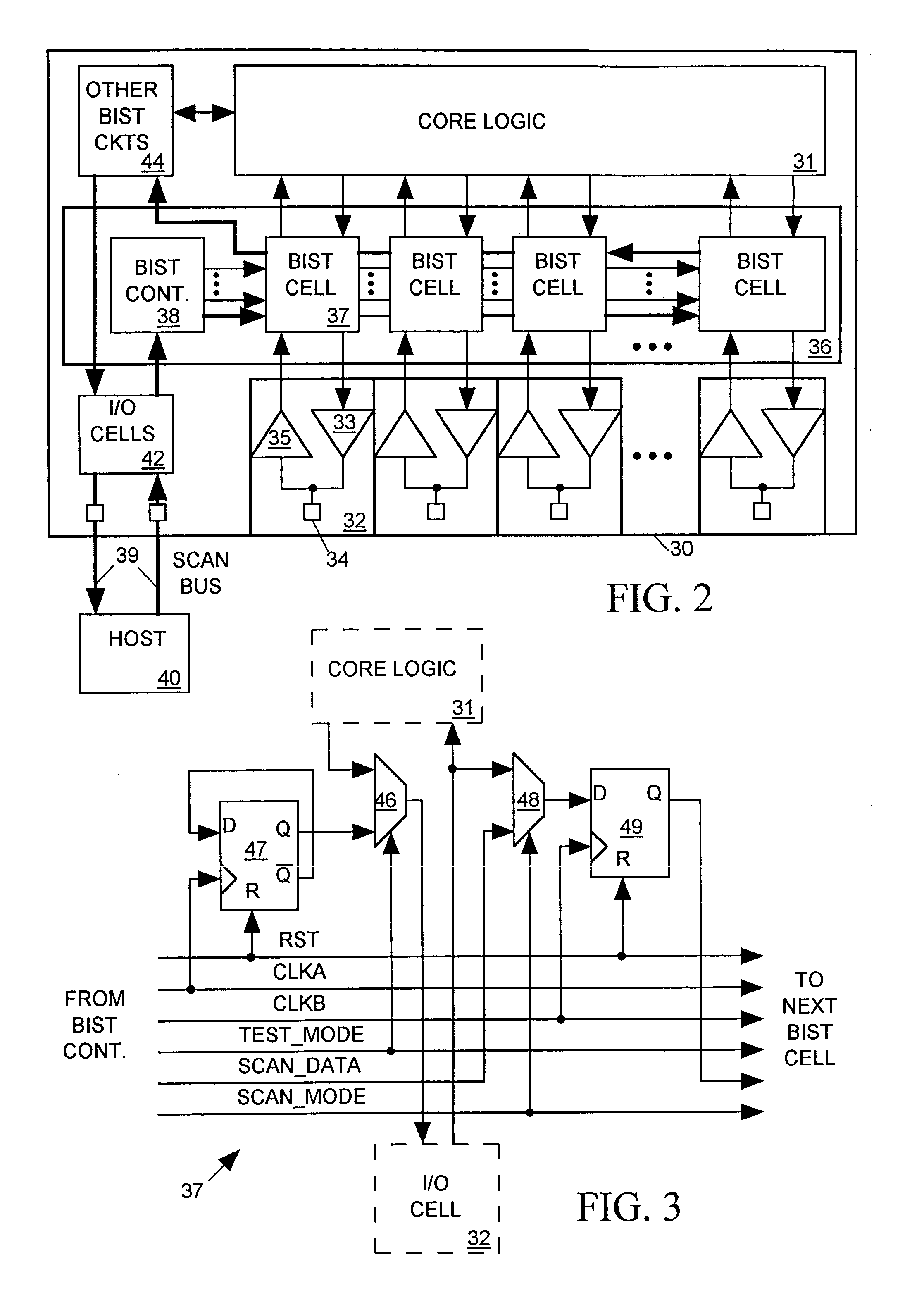

A BIST circuit for an IC measures the time delay a rising or falling edge experiences as it passes through a signal path within the IC. A strobe circuit within the BIST circuit generates edges in two signals A and B in delayed response to edges of a STROBE signal. A path probe generates a signal C edge at the signal path input in response to each signal A edge. The STROBE-to-B edge delay within the strobe generator is iteratively adjusted to determine a first delay for which the path probe detects the B and C signal edges at nearly the same time and thereafter iteratively adjusted to determine a second delay for which the path probe detects the B and D signal edges at nearly the same time. The first delay is measured by causing the strobe signal generator to produce a periodic signal having a period proportional to the first delay and counting the number of cycles of a reference clock occurring during K cycles of the periodic signal. The second delay is measured in a similar manner. The path delay is determined as a difference between the measured first and second delays.

Owner:CREDENCE SYSTEMS

Cross-correlation timing calibration for wafer-level IC tester interconnect systems

InactiveUS20020049554A1Easy accessDigital circuit testingTesting/calibration apparatusContact padTester device

A timing calibration system for a wafer level integrated circuit (IC) tester is disclosed. The tester includes a set of probes for contacting pads on a surface of an IC and having a plurality of tester channels. Each channel generates a TEST signal at a tip of a corresponding probe in response to a periodic CLOCK signal with a delay adjusted by drive calibration data supplied as input to the tester channel. The TEST signal produced by each channel includes edges occurring in a timing pattern controlled by programming data provided as input to each tester channel. To calibrate test signal timing of all channels, each channel is programmed to generate a test signal having the same repetitive edge timing pattern at the tester channel's corresponding probe tip. The test signal produced at each probe tip is then cross-correlated to a periodic reference signal having the same repetitive edge timing pattern. The drive calibration data of each channel is then iteratively adjusted to determine a value which maximizes the cross-correlation between its output test signal and the reference signal. To maximize the accuracy of the timing calibration, each repetition of the test and reference signal edge pattern provides pseudo-randomly distributed time intervals between successive signal edges.

Owner:FORMFACTOR INC

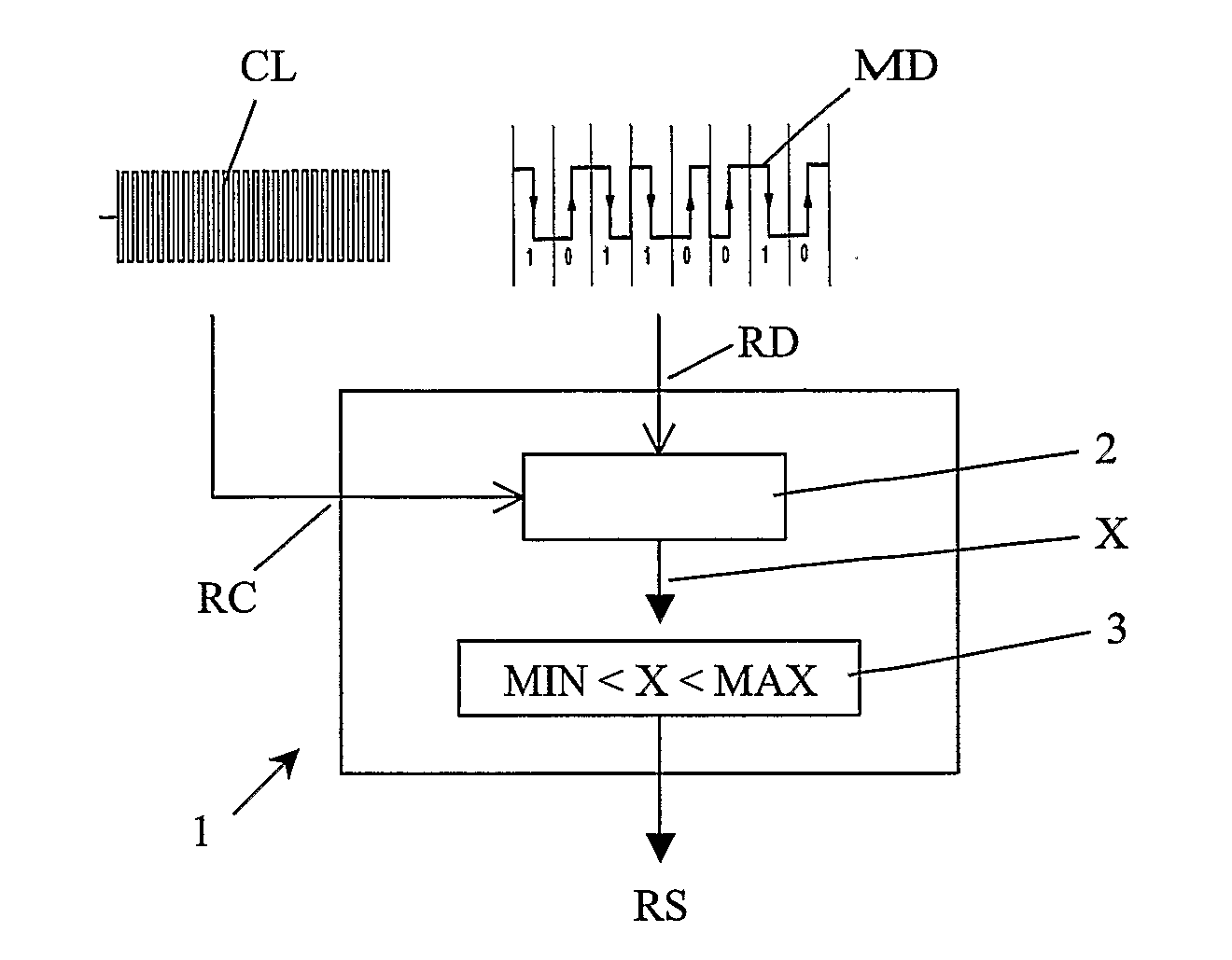

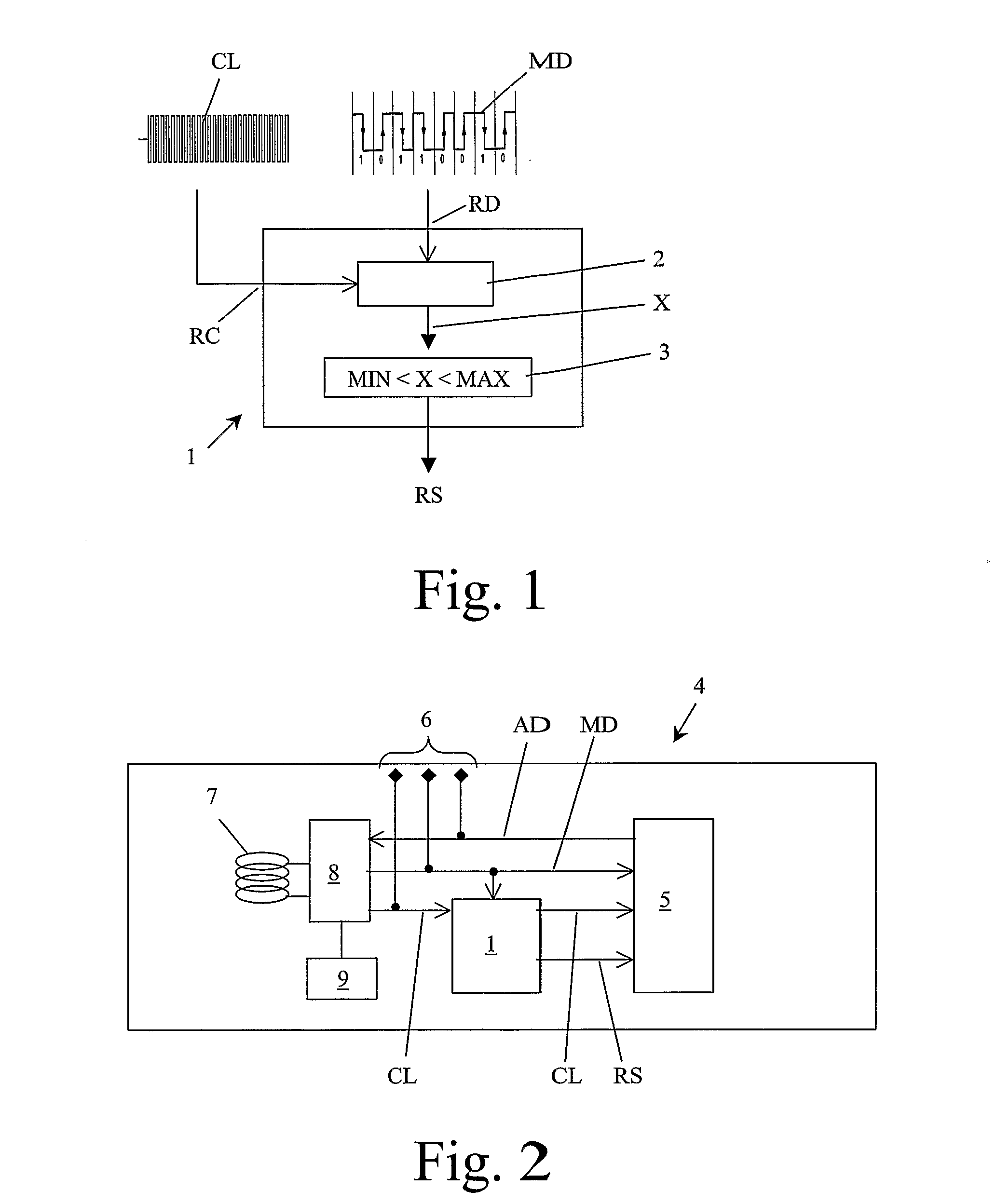

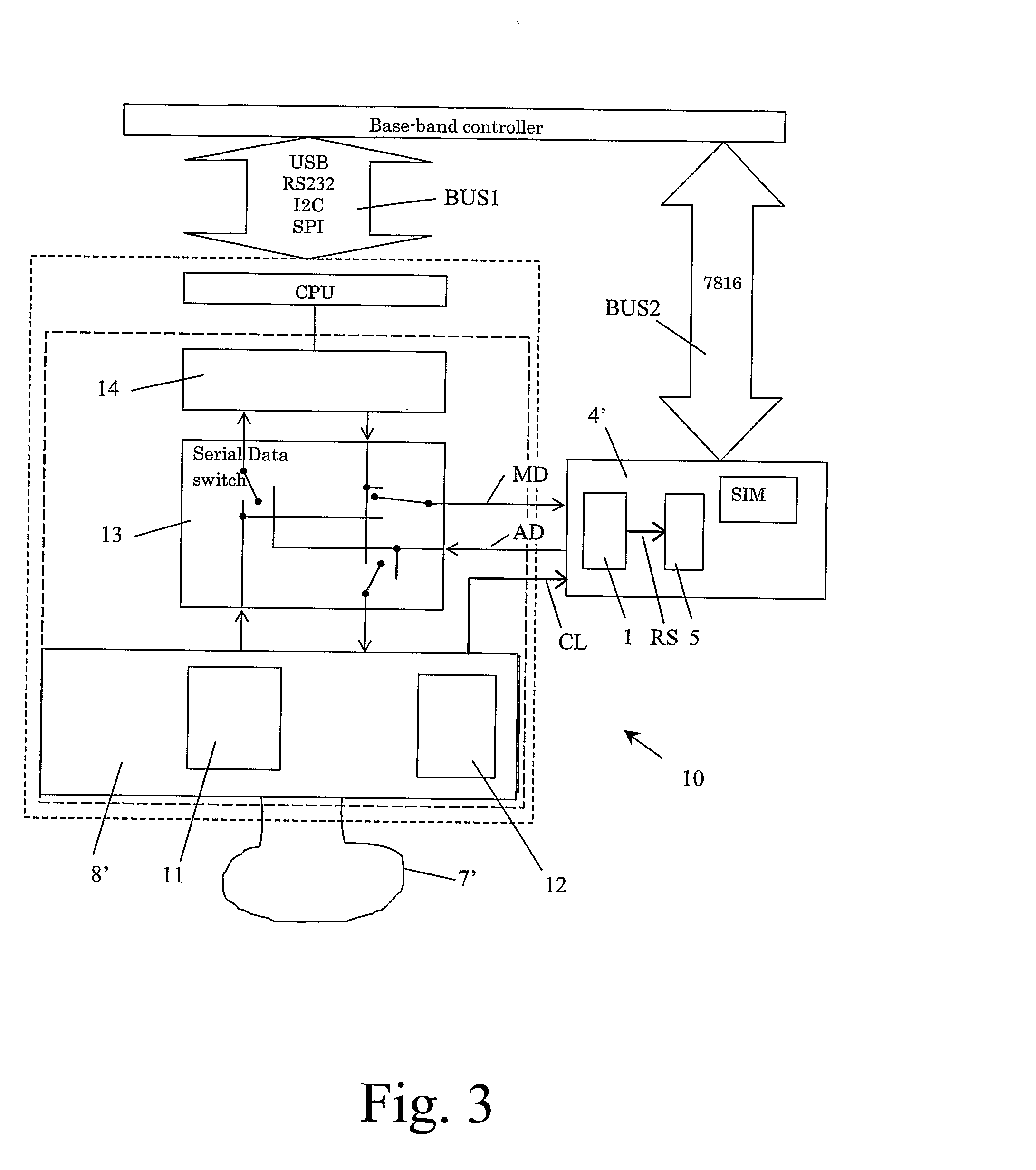

Reset circuit, data carrier and communication device

InactiveUS20070170256A1Long workWide rangeCorrect operation testingSensing record carriersDigital dataLower limit

In a reset circuit (1) comprising a clock signal input (RC) for receiving a clock singal CL MD signal (CL) consisting of a sequence of clock signal cycles, and comprising a data signal input (RD) for receiving digital data signals (MD), which are encoded in such a manner that at least one signal edge (0→1, 1→ 0) appears per data bit in the data signal, are provided a counter (2) being connected to the data signal input (RD) and the clock signal input (RC) and being designed for counting the number (X) of clock signal cycles, which appear between a defined number of data signal edges, and comparing means (3), which comparing means (3) being designed for comparing the number (X) of clock signal cycles counted by the counter (2) with a lower limit (MIN) and / or with an upper limit (MAX) and which comparing means (3) being designed to produce a reset signal (RS), if the number (X) either remains below the lower object (MIN) or exceeds the upper limit (MAX), depending on the limit value (MIN, MAX) taken for comparison.

Owner:NXP BV

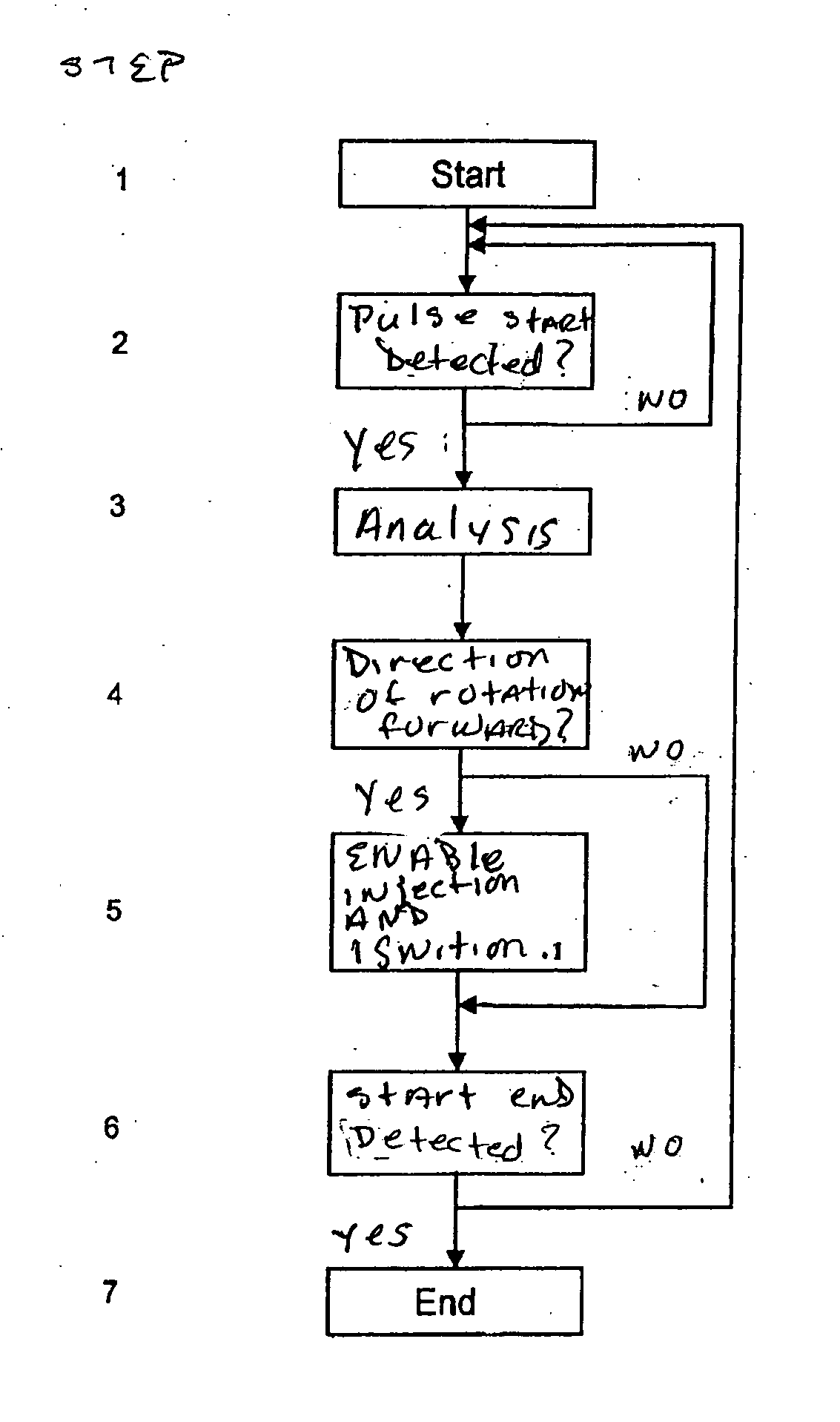

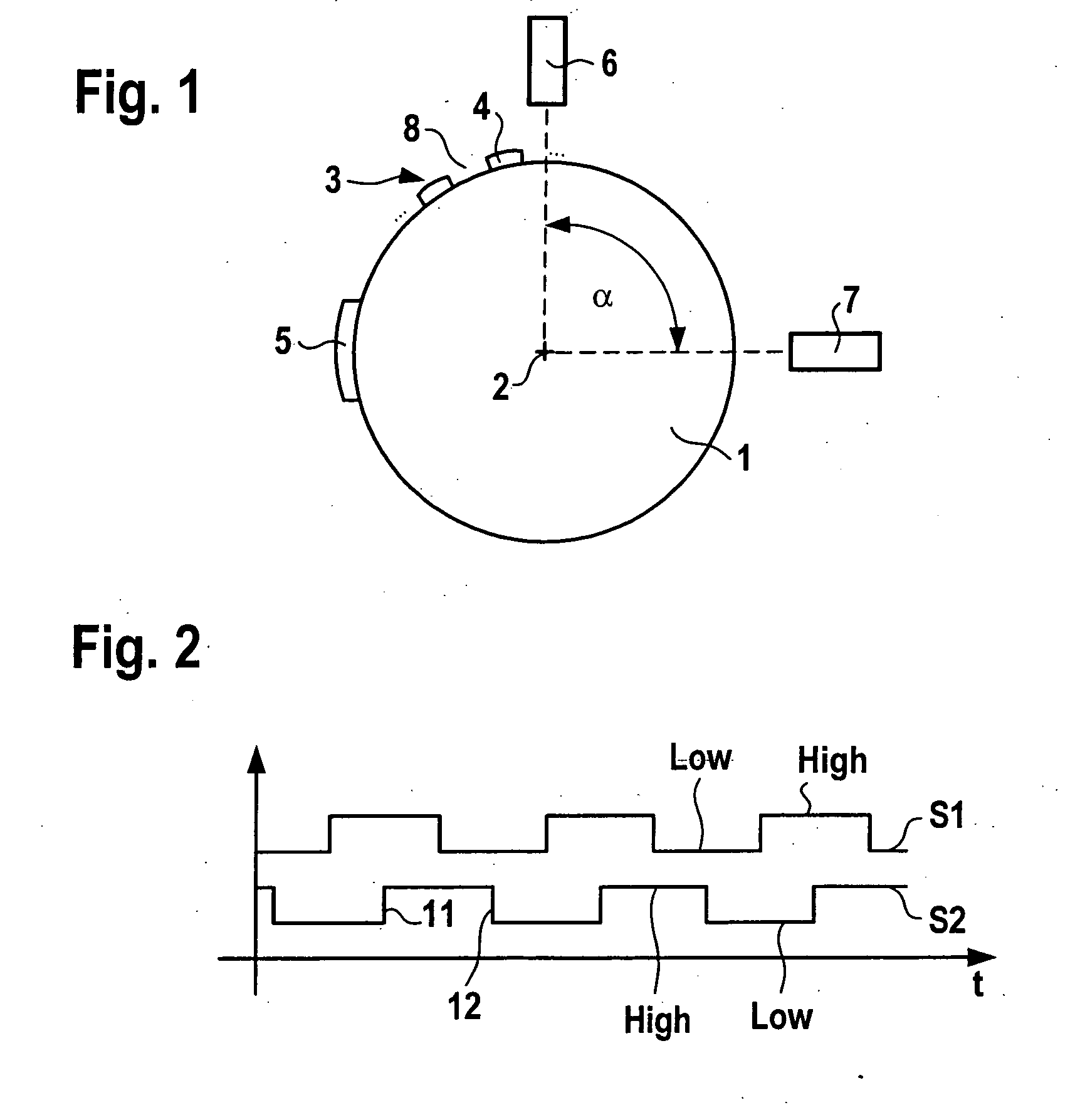

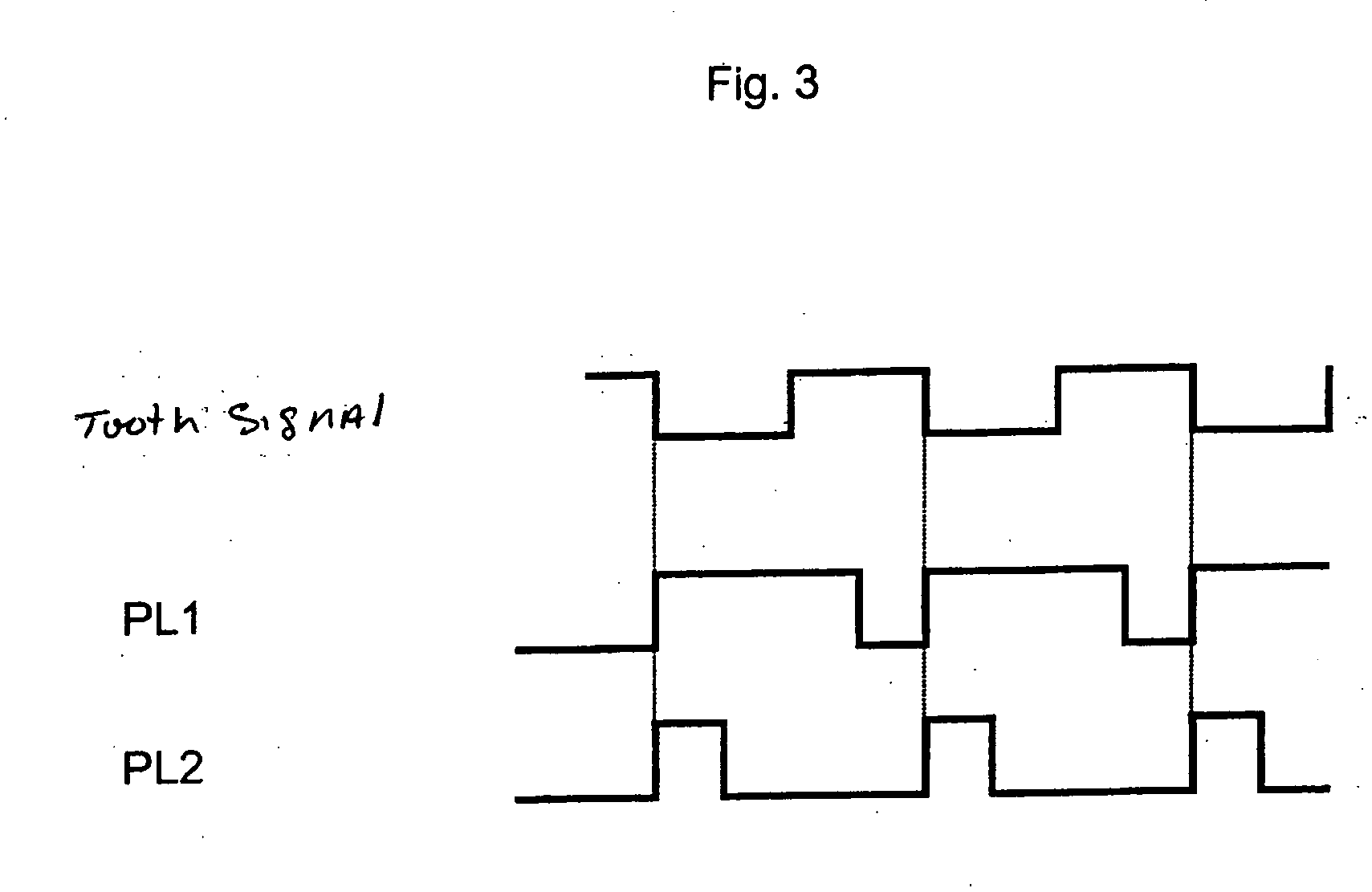

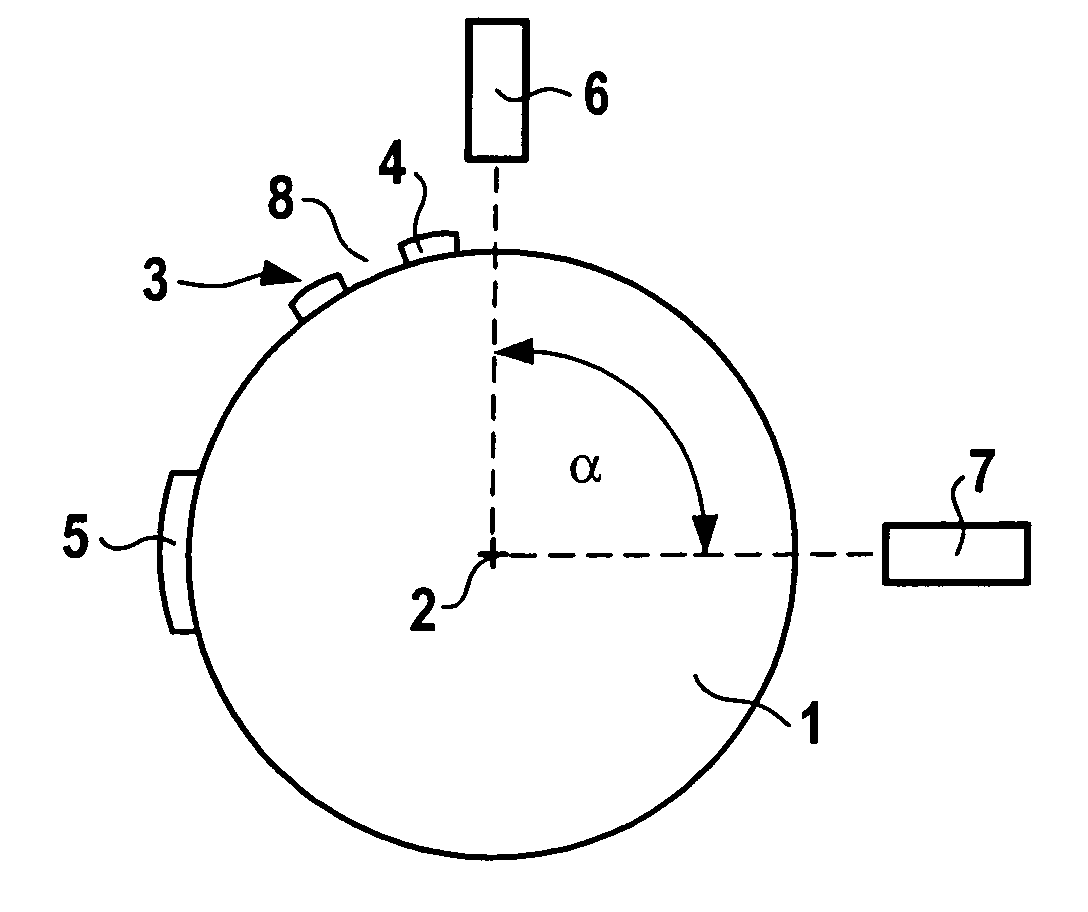

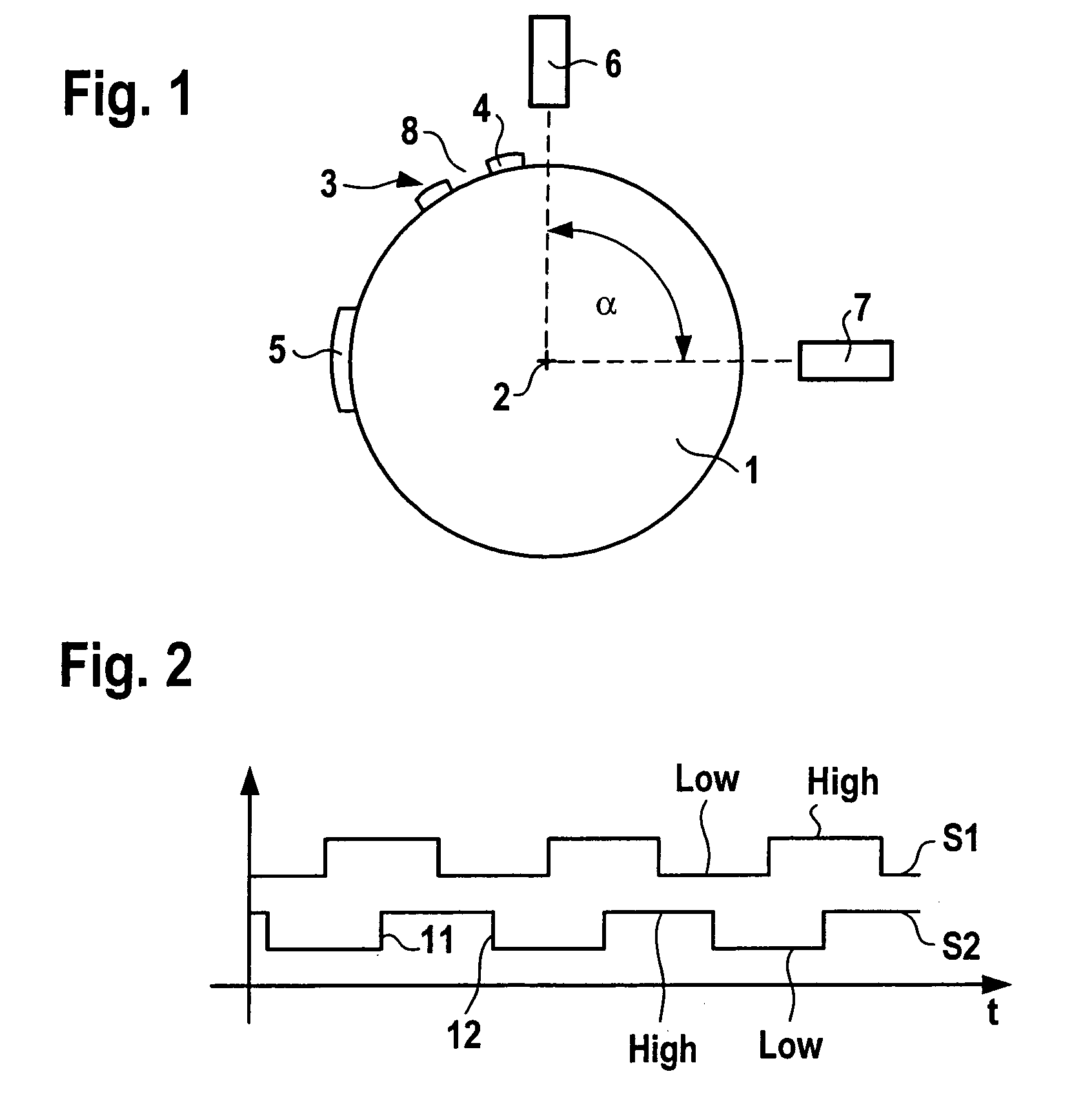

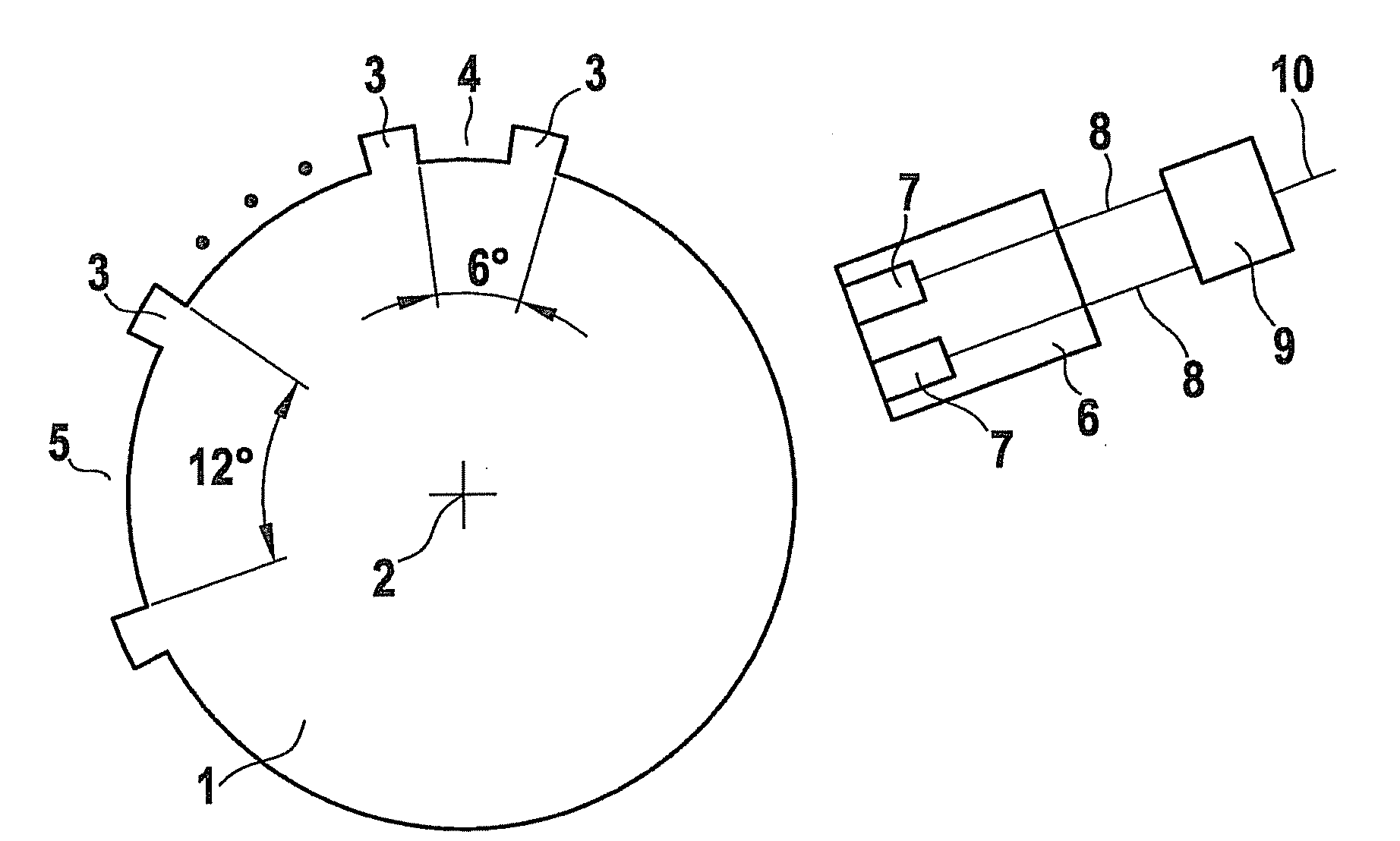

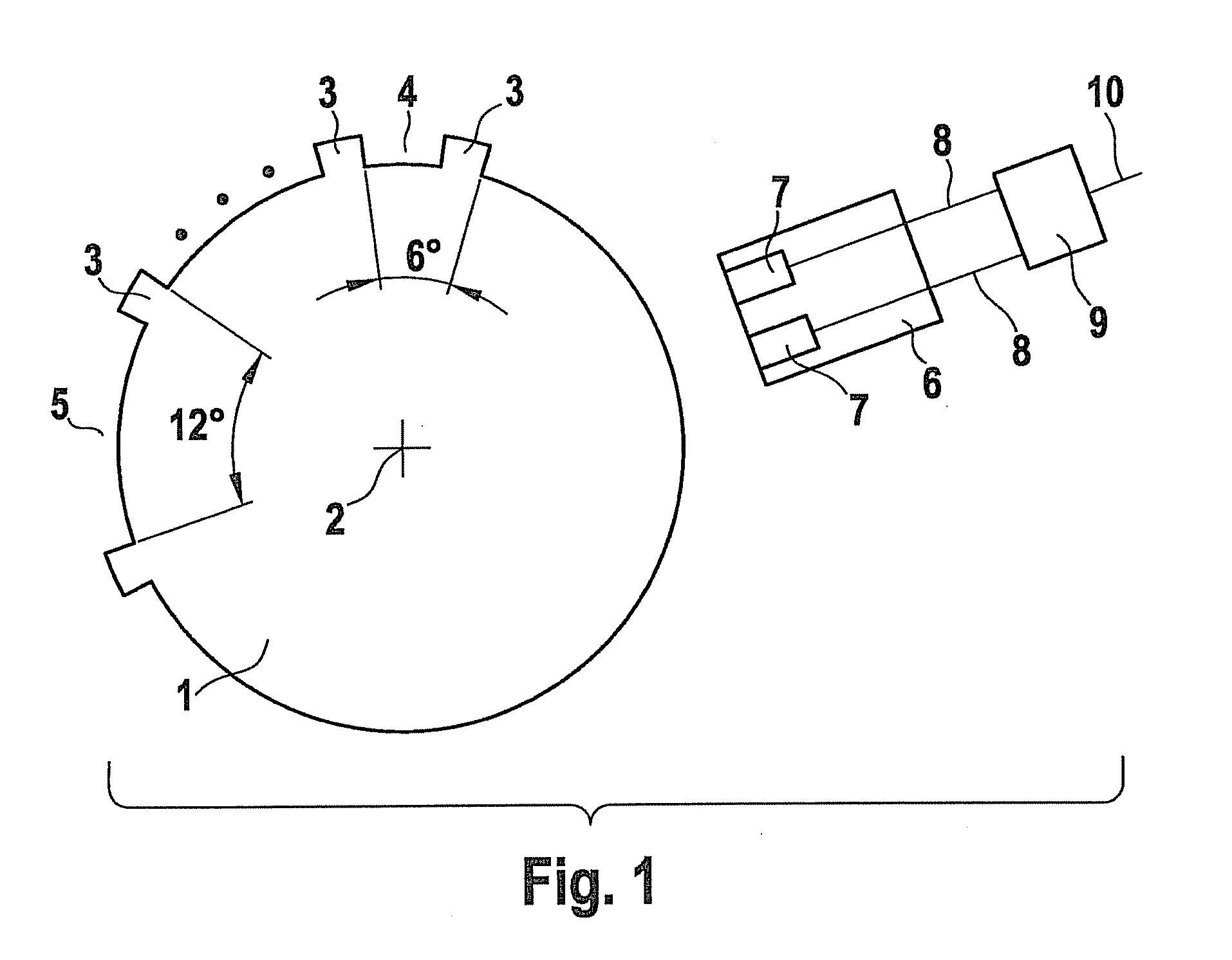

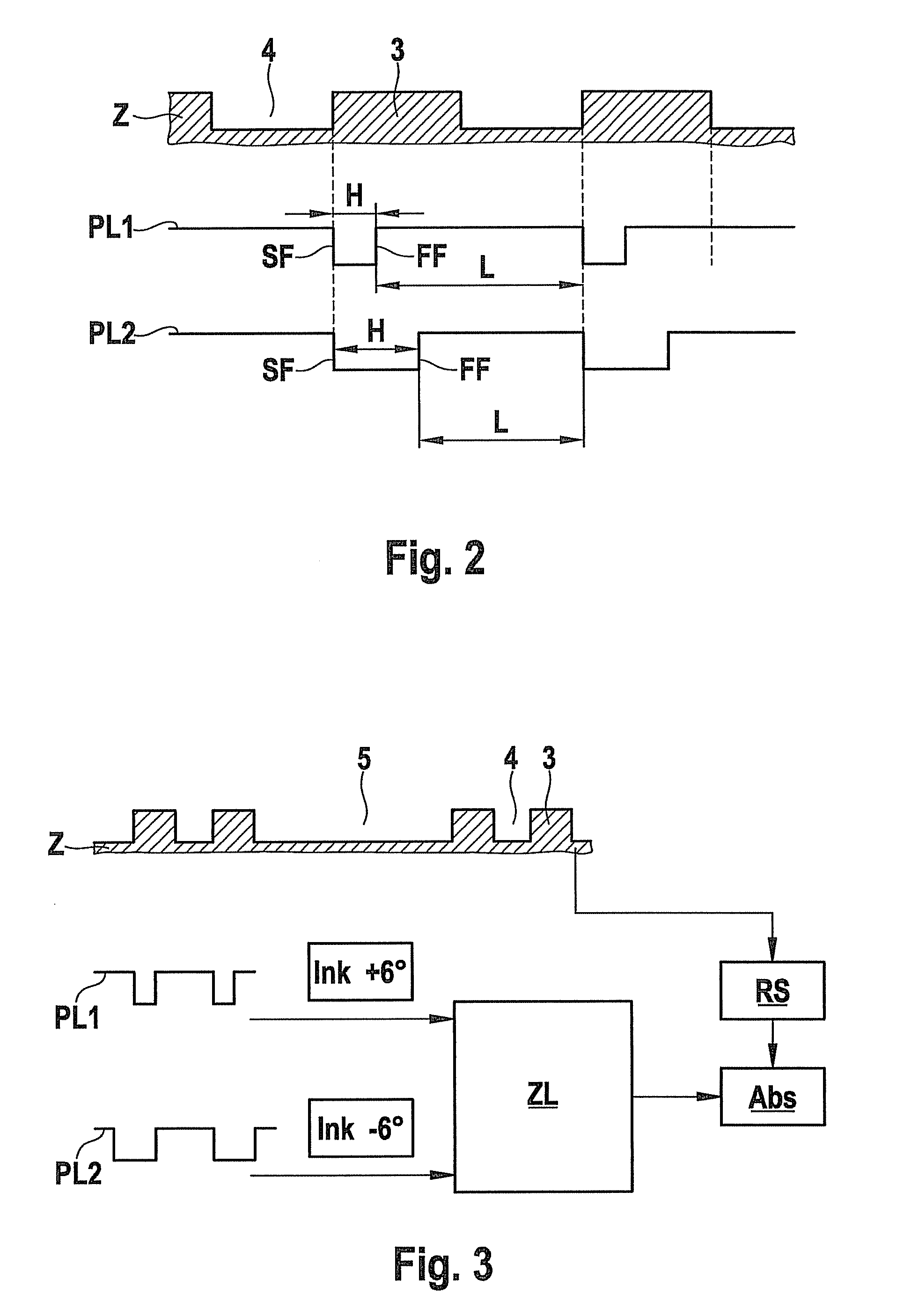

Method for detecting reverse rotation for internal combustion engines

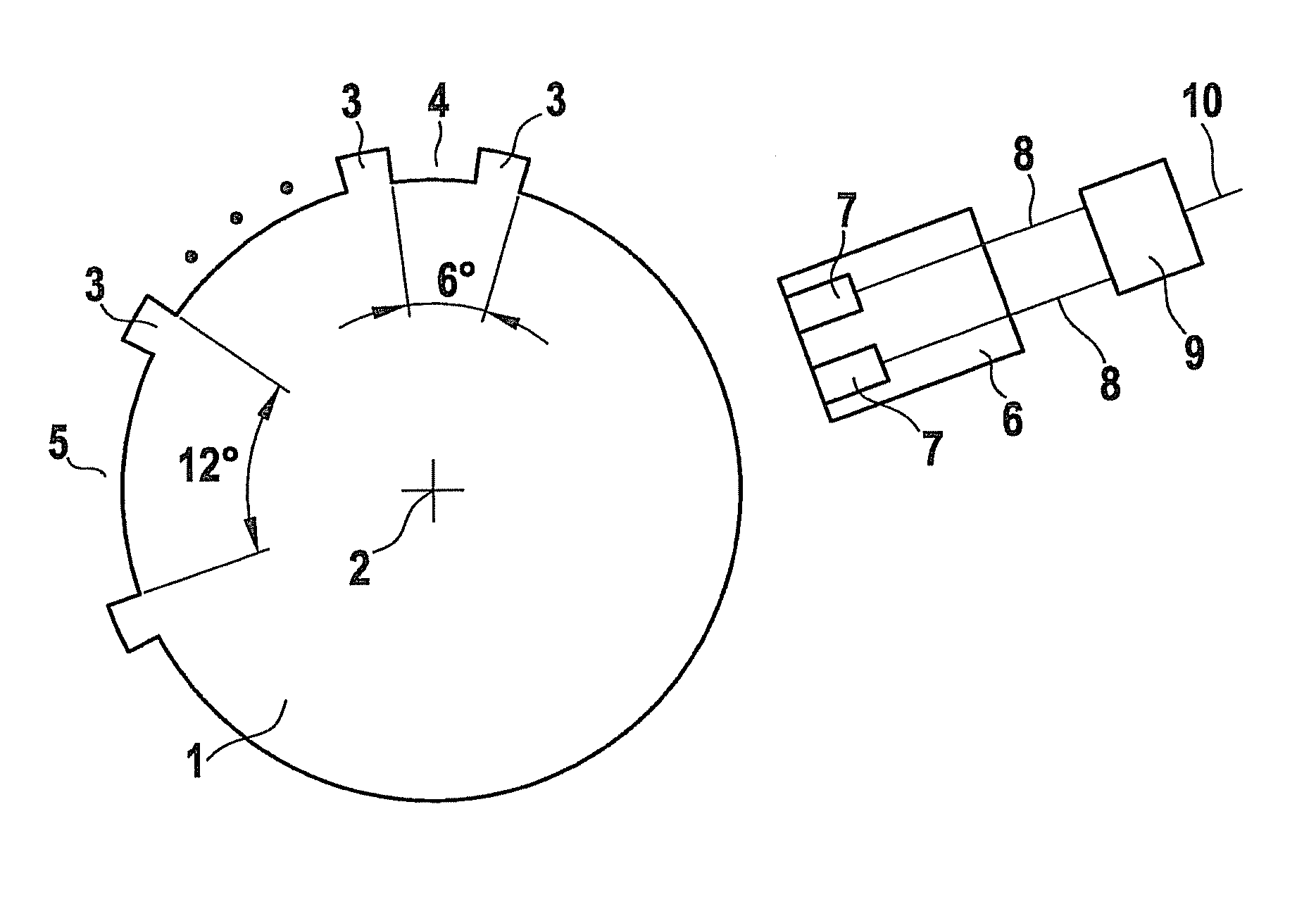

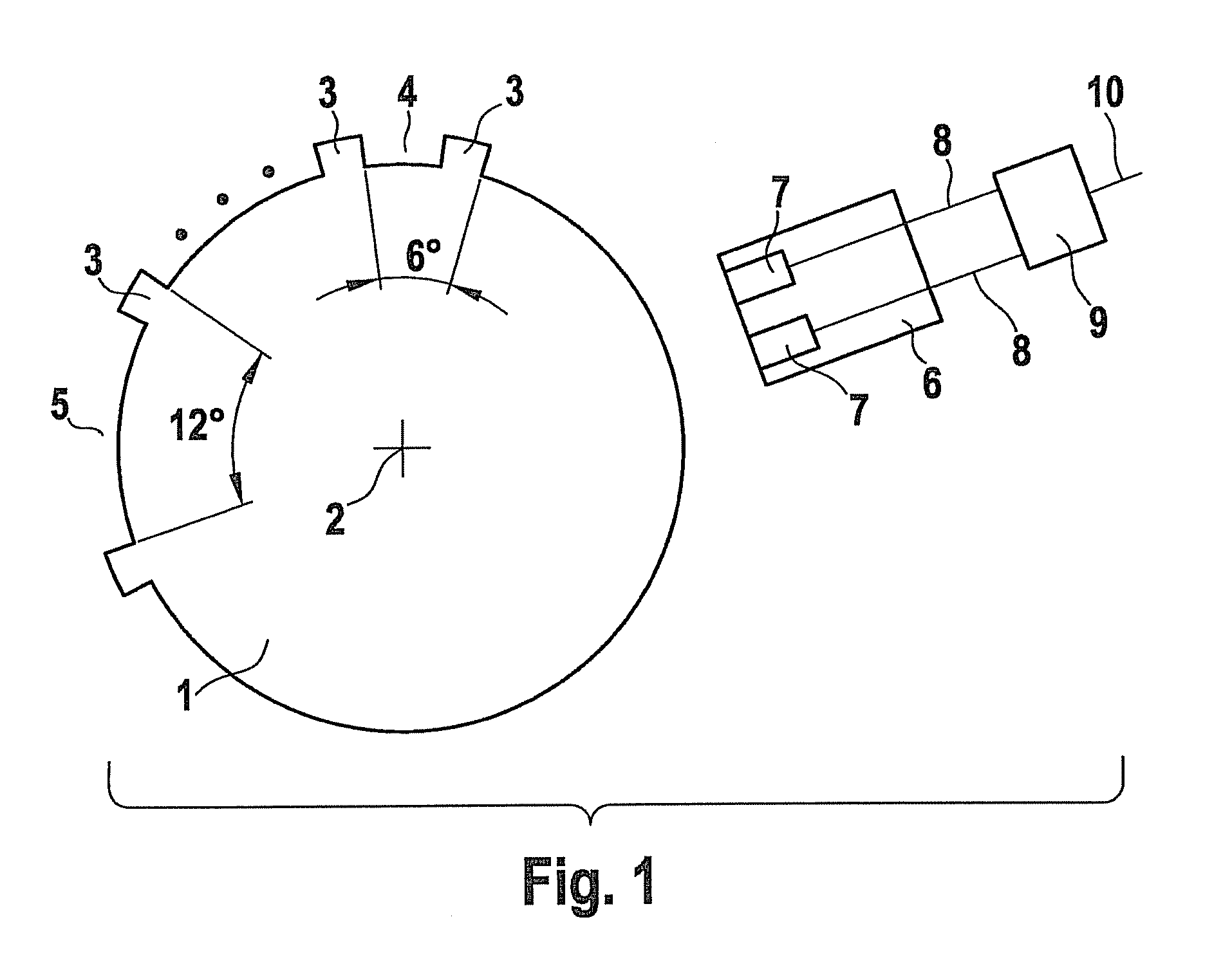

In a method for detecting reverse rotation when starting an internal combustion engine having a sensor disk which is coupled to a crankshaft of the engine, the sensor disk having a marking via an alternating arrangement of teeth and tooth spaces, and a first sensor and a second sensor each capable of generating an electric signal which may assume at least two signal levels, being associated with the sensor disk, one of the signal levels being associated with a tooth and the other signal level with a tooth space, a rising or falling signal edge of the one signal and the signal level of the other signal being used for determining the direction of rotation and increment of the angle of rotation of the crankshaft, the start characteristics are improved by determining the direction of rotation during the start of the engine as early as at the first signal edge.

Owner:ROBERT BOSCH GMBH

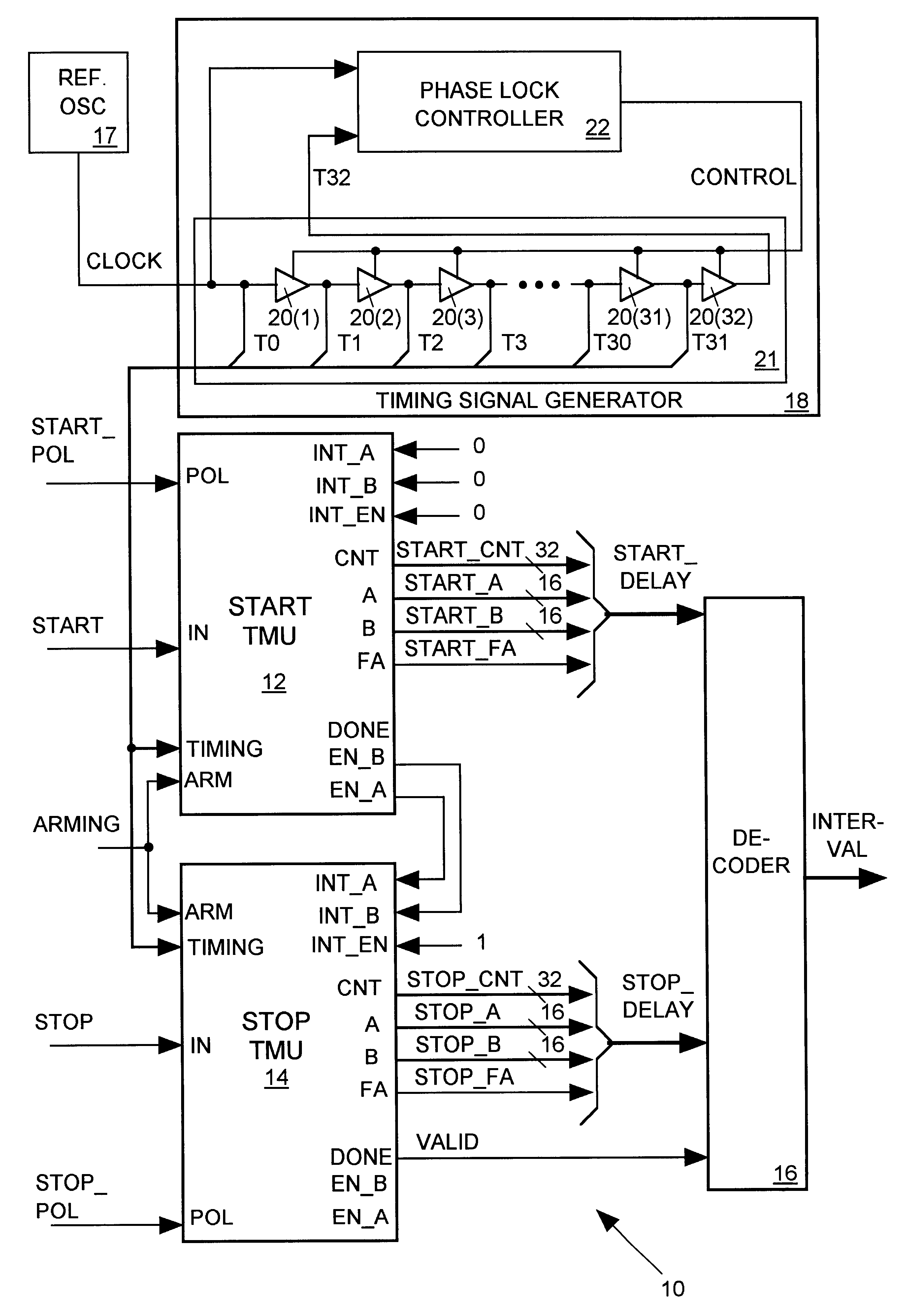

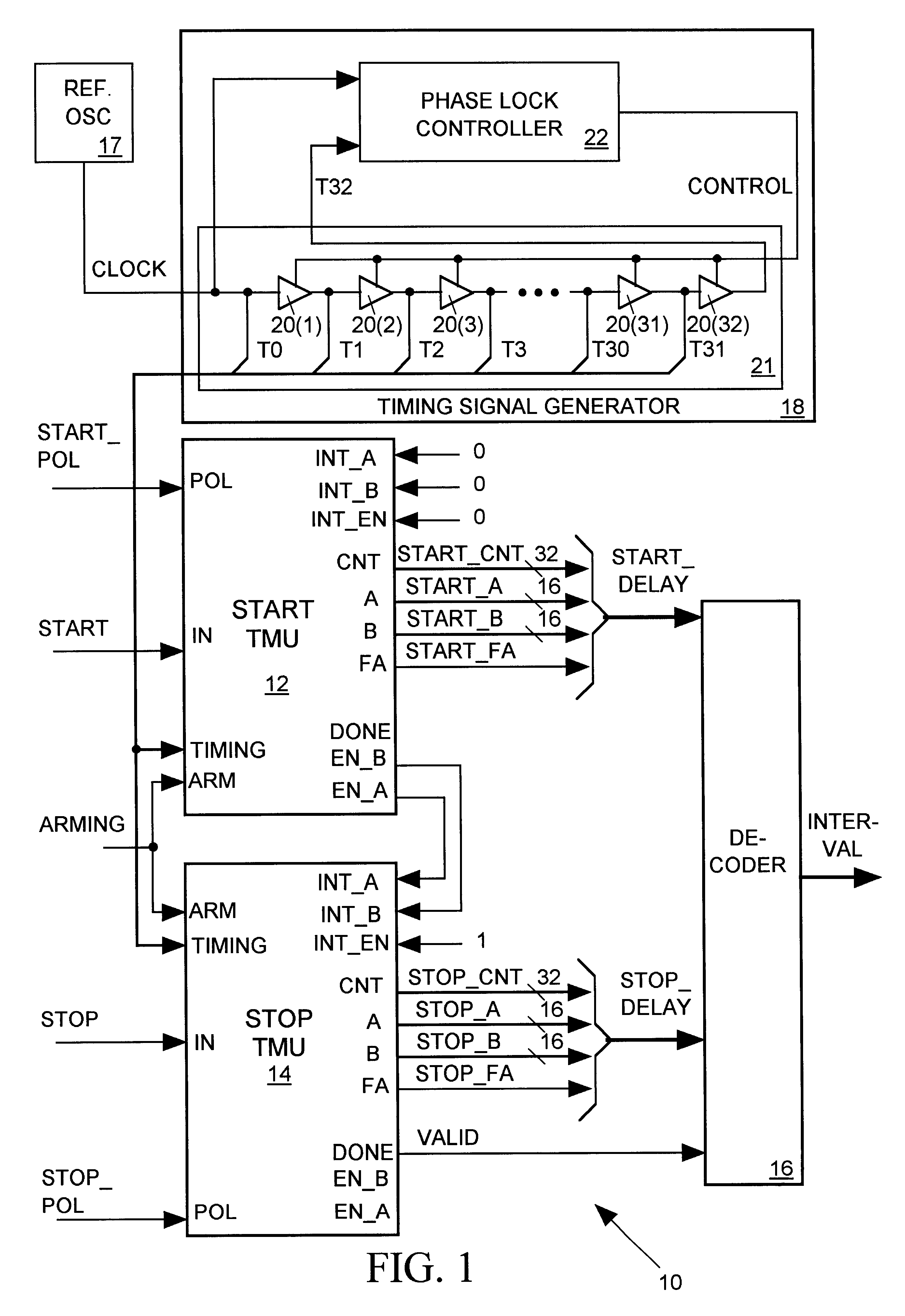

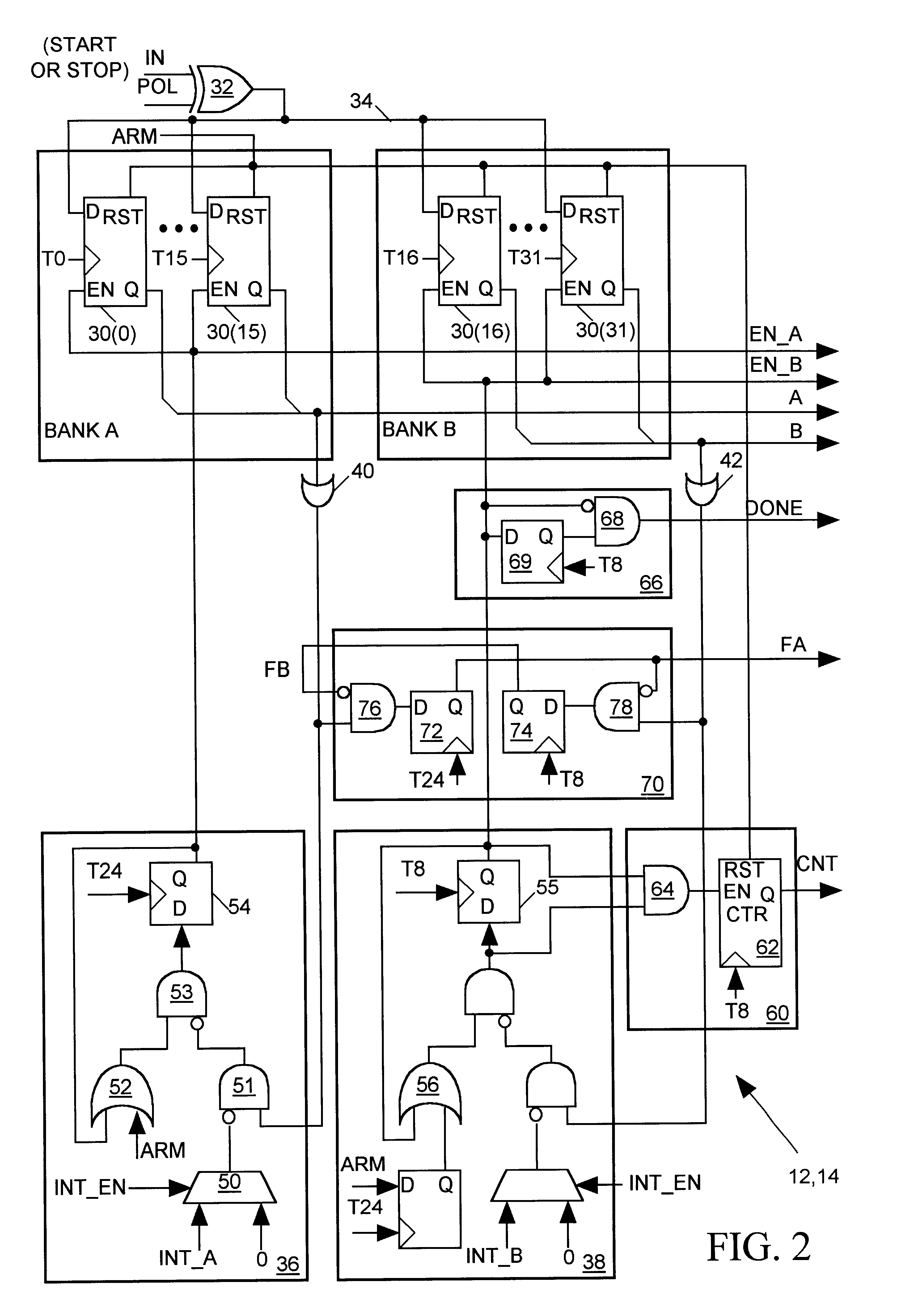

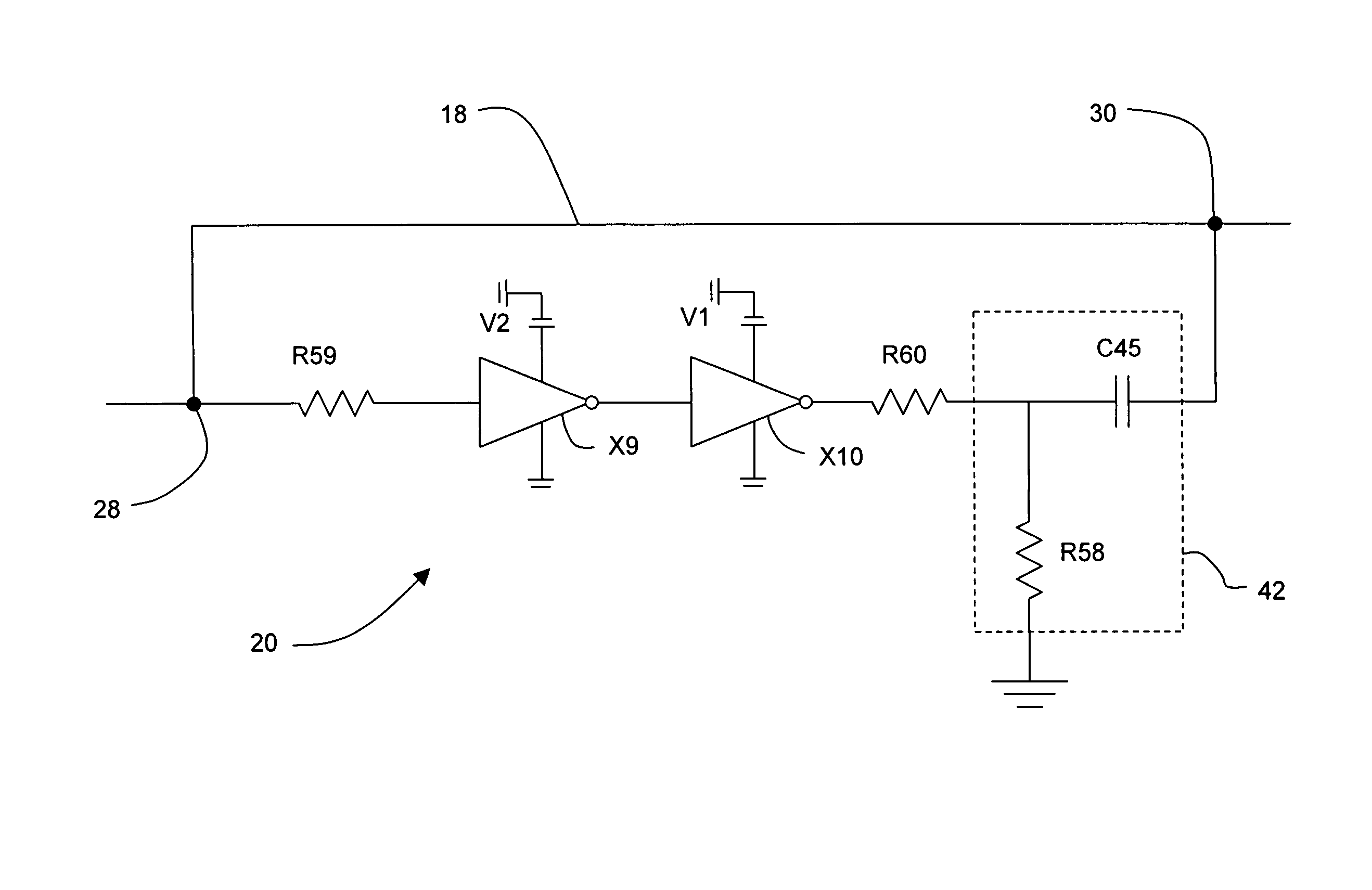

Apparatus for measuring intervals between signal edges

InactiveUS6246737B1Pulse automatic controlElectromechanical unknown time interval measurementStart timeTime delays

An apparatus for measuring a time interval between a start signal edge and a stop signal edge provides a stable clock signal as input to a delay line formed by a series of similar logic gates. The output signal of the last gate of the series is phase locked to the clock signal by adjusting a bias signal controlling the switching speed of all gates. The clock signal and the output signal of each gate form a set of phase distributed periodic timing signals applied to a start time measurement unit (TMU) and a similar stop TMU. The start TMU counts edges of one of the timing signals occurring between an edge of an arming signal and the start signal edge and generates output data representing a time delay between the arming signal and the start signal edge. The data represents the start delay as a whole and fractional number of clock signal periods by conveying the counter output and by indicating which of the timing signals had an edge most closely following the start signal edge. The stop TMU similarly produces output data indicating a whole an fractional number of clock cycles occurring between the arming signal and the stop signal edge. The delay represented by the start TMU output data is subtracted from the delay represented by the stop TMU output data to determine the interval between the start and stop signal edges.

Owner:CREDENCE SYSTEMS

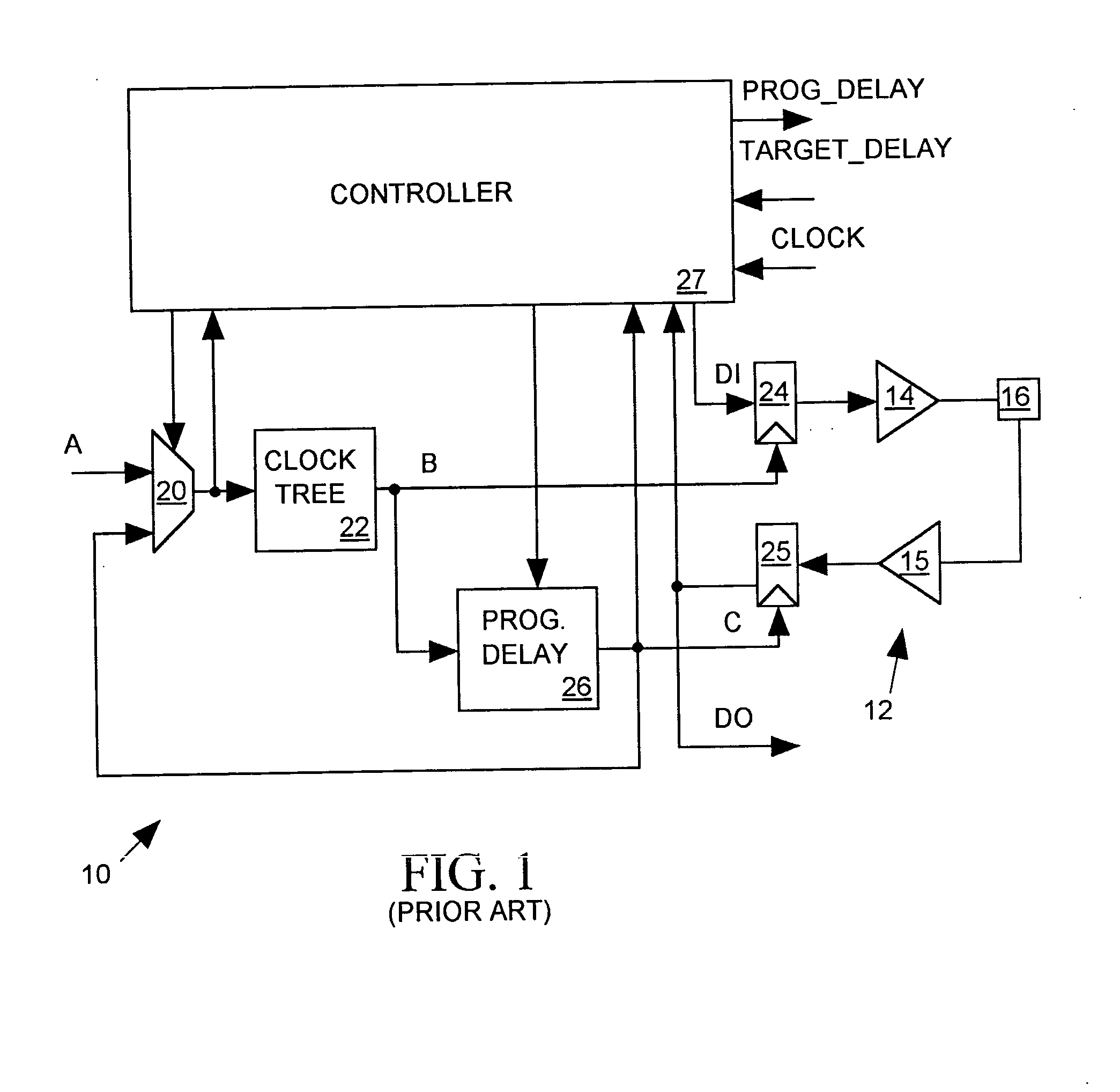

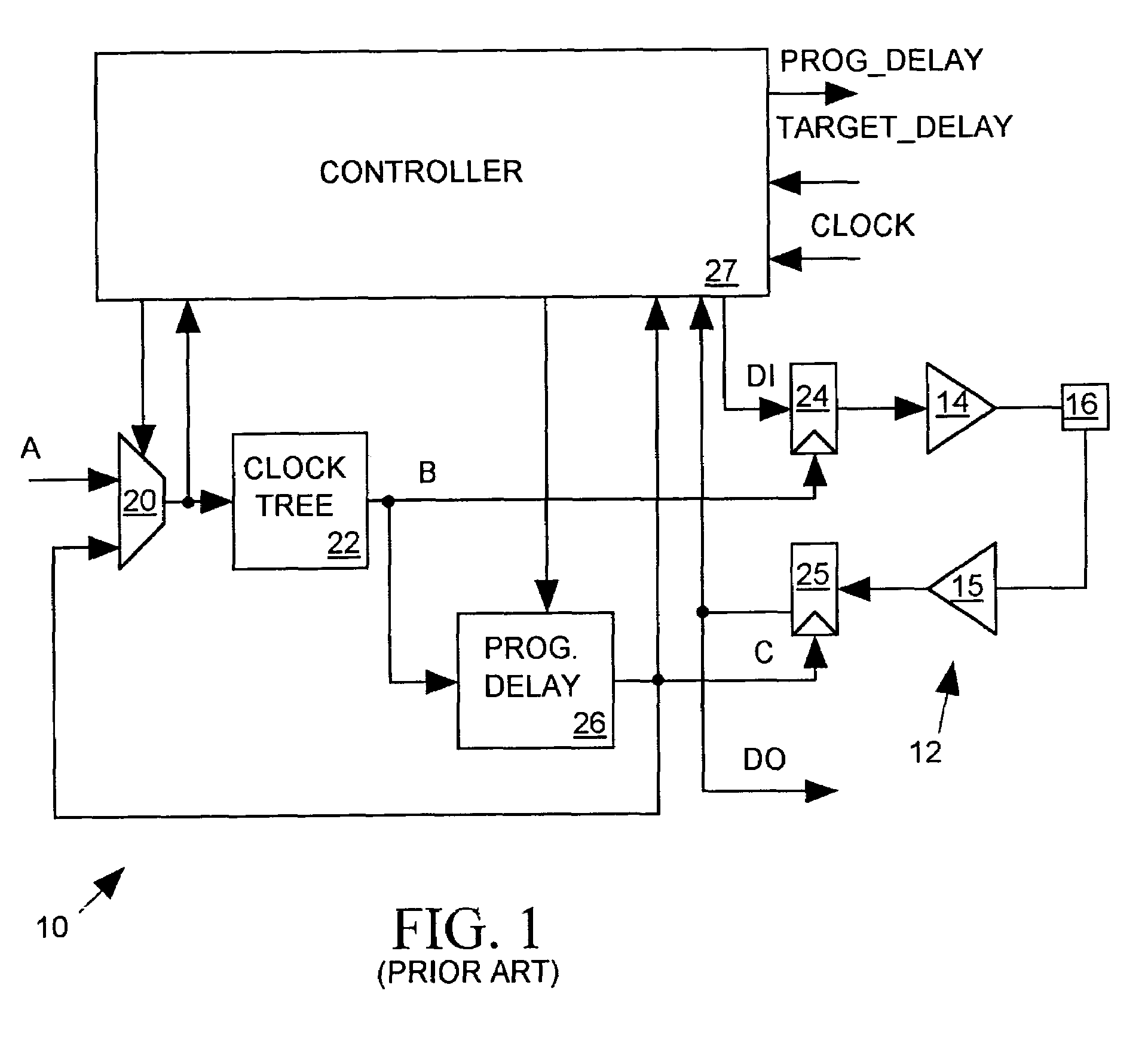

Self-calibrating strobe signal generator

A self-calibrating strobe signal generator for a BIST circuit responds to an edge of an input strobe signal by generating corresponding edges of first and second strobe signals separated in time by a target delay specified by input data. The strobe signal generator includes a multiplexer, a delay circuit and a controller. The multiplexer normally provides the input strobe signal as a multiplexer output signal to the delay circuit which generates edges in each of the first and second strobe signals in response to each edge in the multiplexer output signal with a programmable delay between corresponding first and second strobe signal edges. During a calibration process the control circuit adjusts the programmable delay by counting cycles of a reference clock signal occurring during a predetermined number of cycles of the multiplexer output signal when the multiplexer is set to select the first strobe signal and then the second strobe signal as the source of the multiplexer output signal such that the multiplexer output signal oscillates, and by incrementing or decrementing the programmable delay depending on whether a difference between the counts matches the input data.

Owner:CREDENCE SYSTEMS

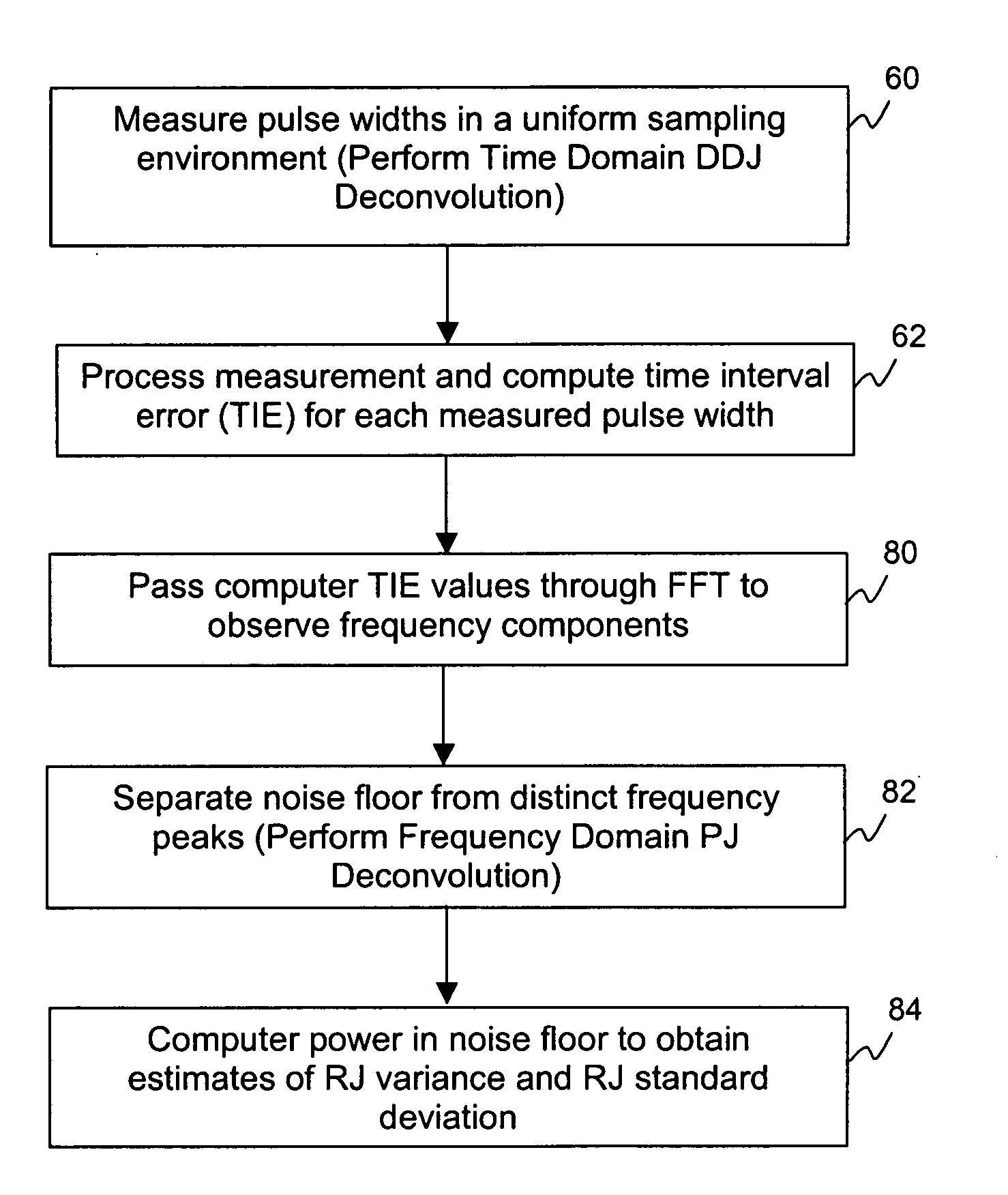

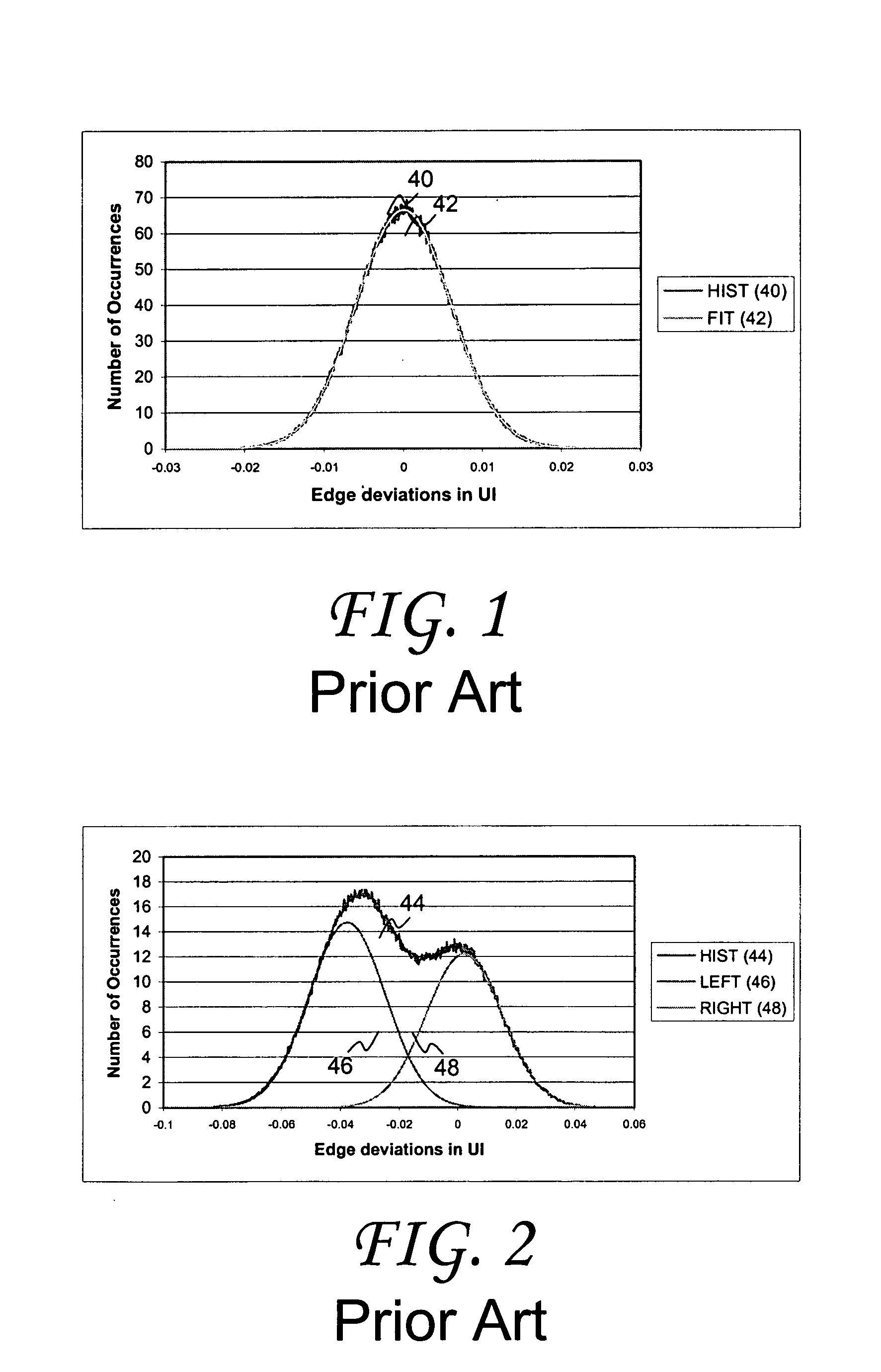

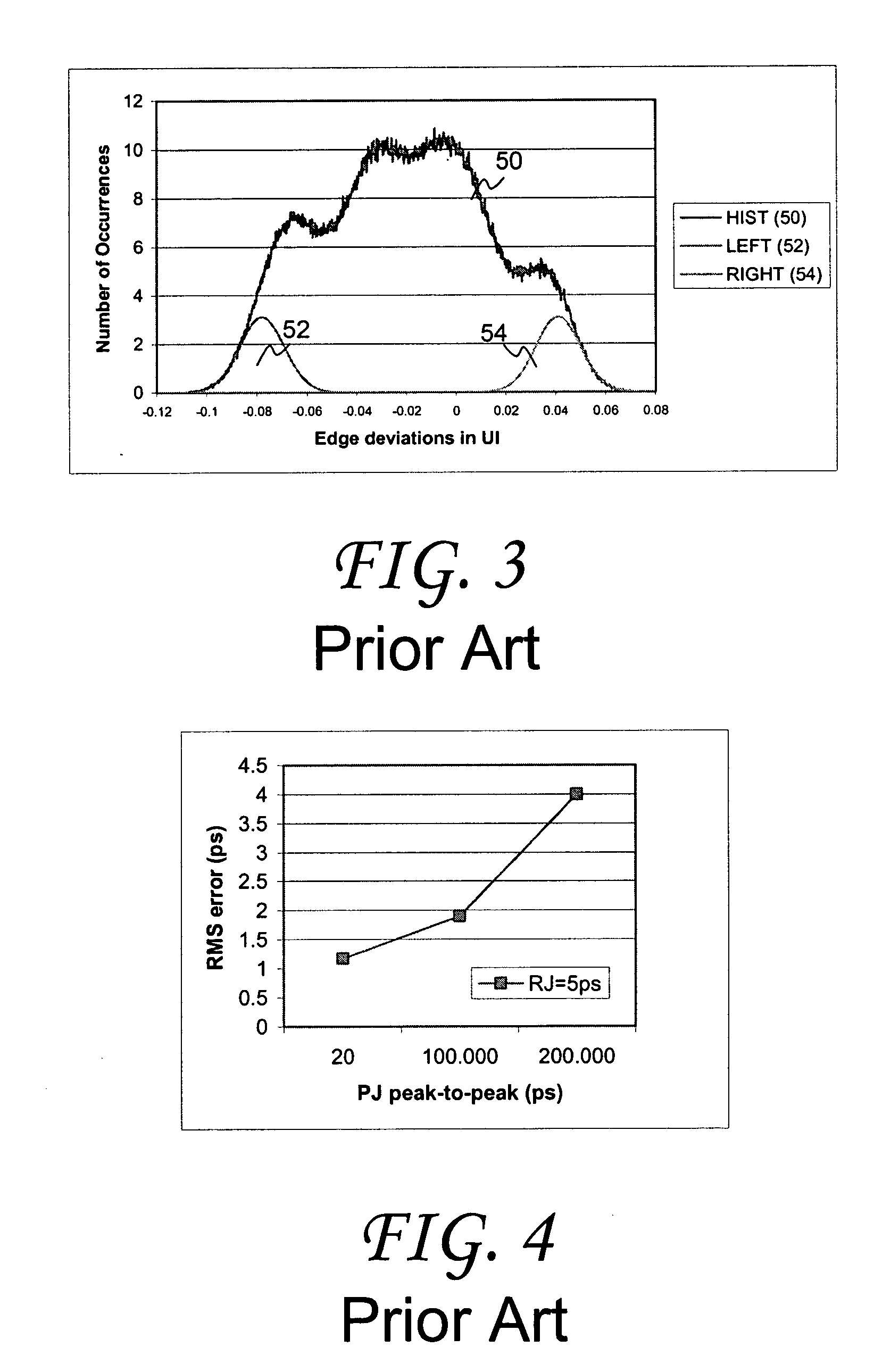

System and method of obtaining random jitter estimates from measured signal data

InactiveUS20050286627A1Convenient to accommodateData-dependent jitter can be eliminated or significantly minimizedDigital circuit testingNoise figure or signal-to-noise ratio measurementData streamData signal

A method of estimating random jitter from measured samples of a transmitted data signal includes a first step of obtaining a plurality of measurements (e.g., pulse widths) for a plurality of selected signal edges within a transmitted data stream, where the data stream comprises a repeating data pattern having a known bit length and known number of rising edges, and wherein the time difference between adjacent measurements is determined by an event count increment equal to an integer multiple of the known number of rising edges. A time interval error value is then computed for each measured signal edge. Time interval error values are then transformed into corresponding TIE frequency components (via, for example, an FFT) for selected of the measured signal edges, wherein the TIE frequency components are representative of both noise floor as well as multiple distinct frequency peaks. Noise floor is separated from the multiple distinct frequency peaks representative of periodic jitter by replacing each TIE frequency component greater than a predetermined value with a lower predetermined replacement value. The power of the noise floor may be computed to provide an estimate of random jitter variance, from which the standard deviation may be calculated.

Owner:GUIDE TECH

Method and device for estimating signal noise ratio

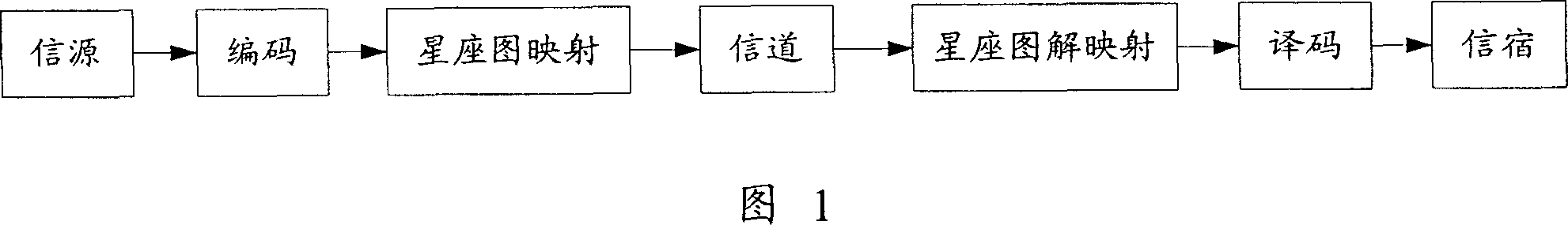

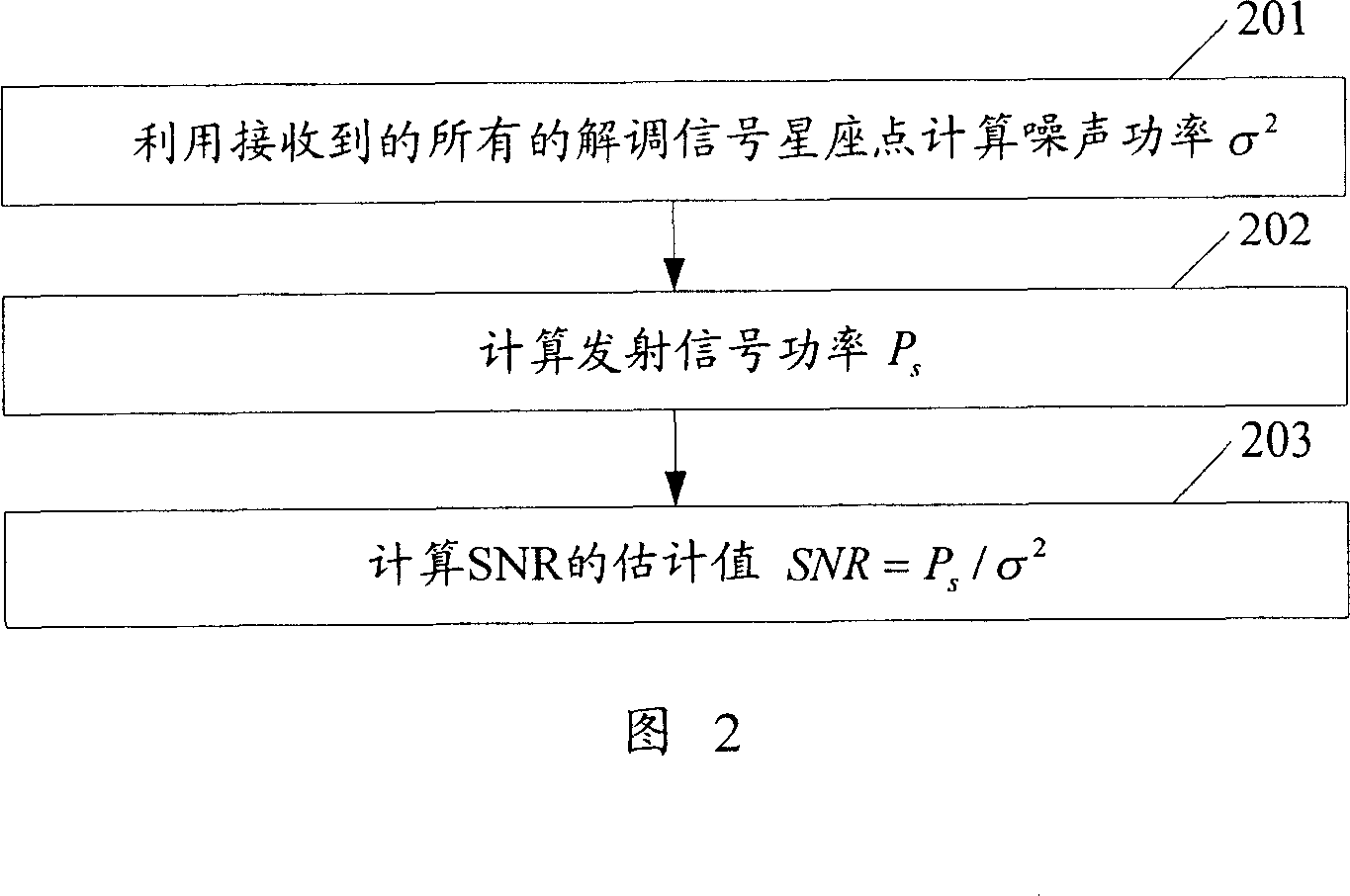

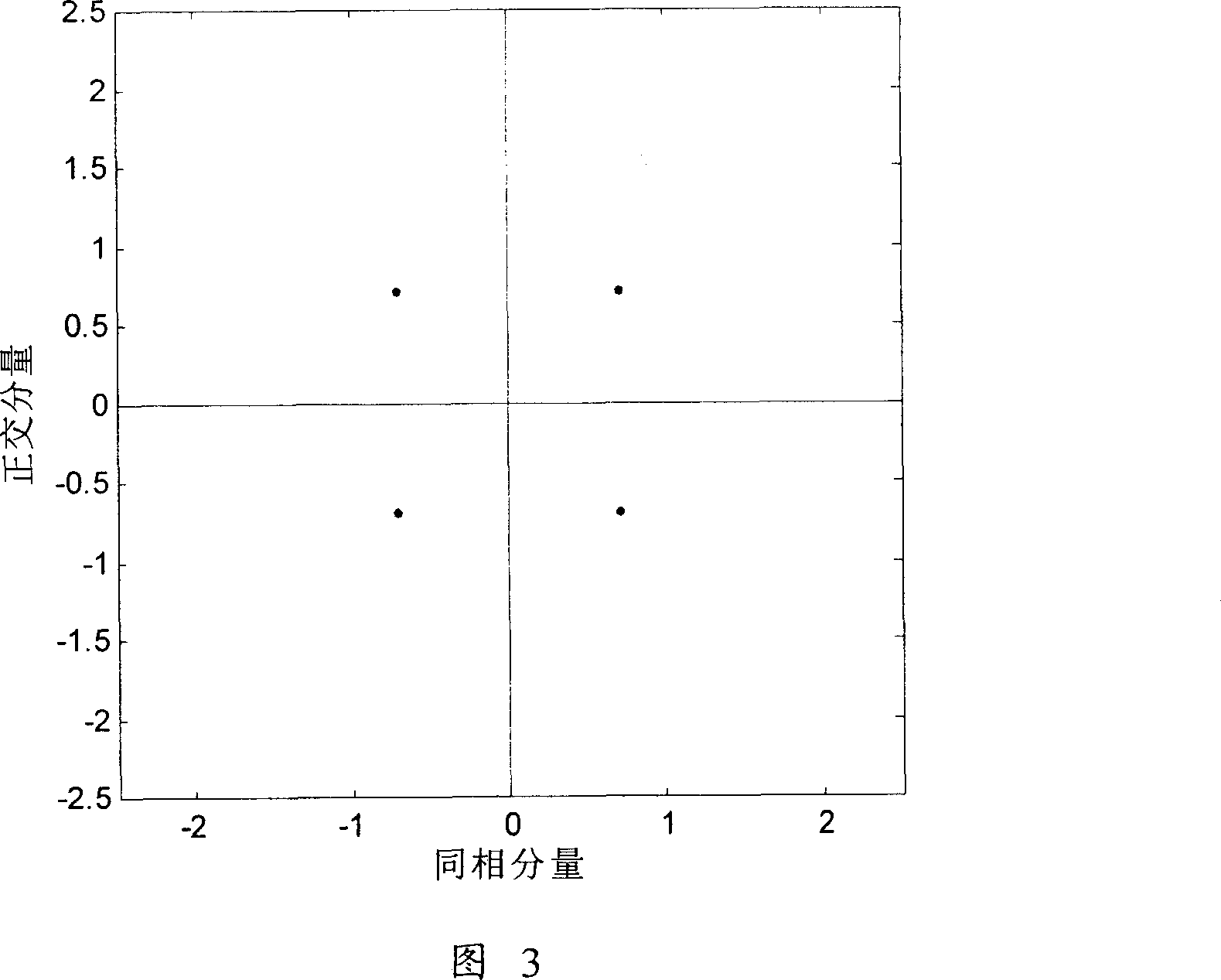

InactiveCN101047688AImprove accuracyAvoid noise power errorsBaseband system detailsPhase-modulated carrier systemsSignal-to-noise ratio (imaging)Signal edge

This invention discloses a method for estimating S / N ratio including: selecting demodulation signal constellation points with the absolute value of the signal component greater than that of the edge constellation point of the modulation signal to compute noise power utilizing the selected demodulated signal constellation points, computing emission power and the ratio with noise power to get an estimated value of the S / N ratio. This invention also discloses a device estimating S / N ratio including: a constellation scheme mapping unit, a constellation point selection unit, a noise power computation unit, an emission signal power computation unit and S / N ratio computation unit.

Owner:HUAWEI TECH CO LTD

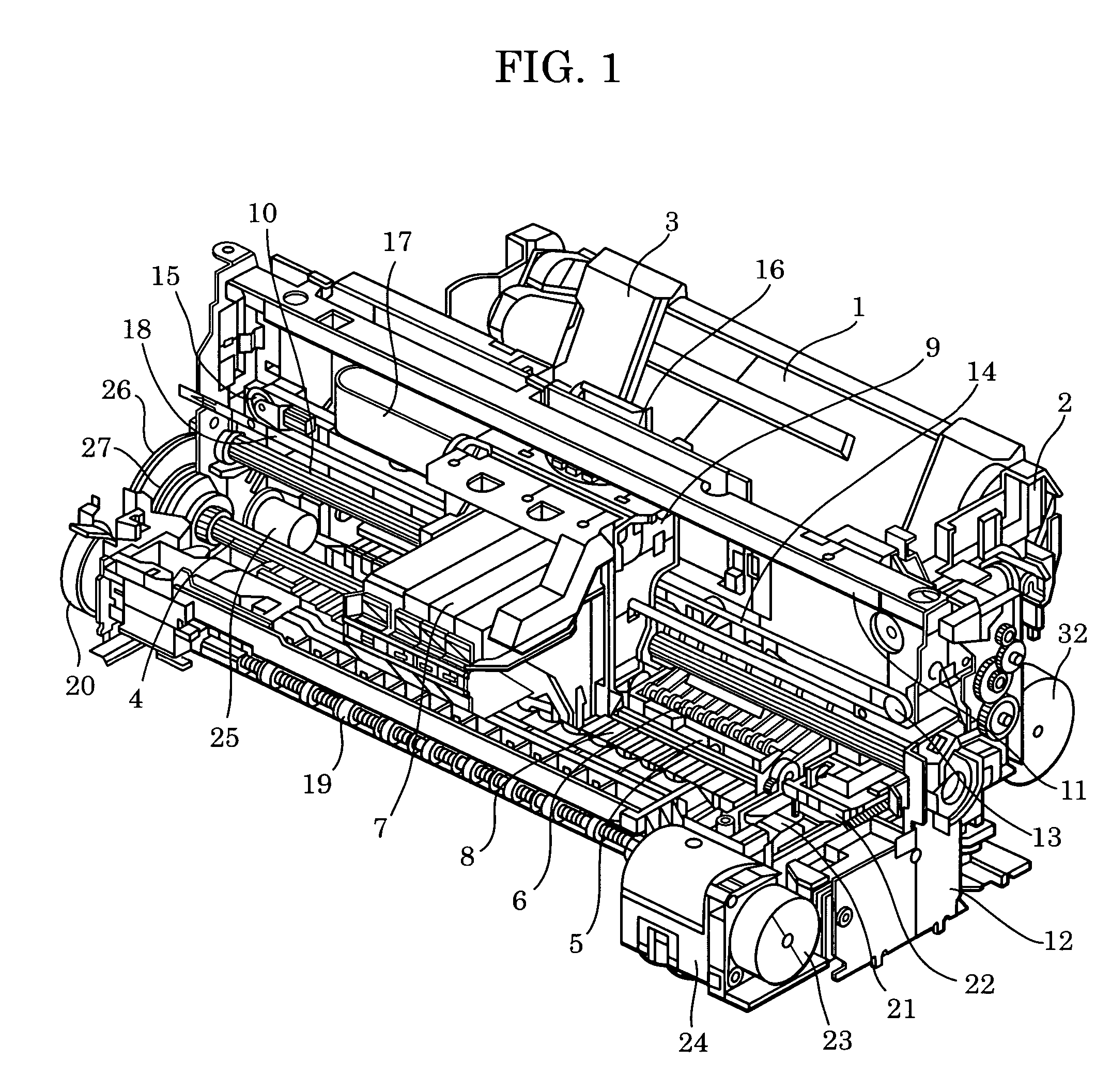

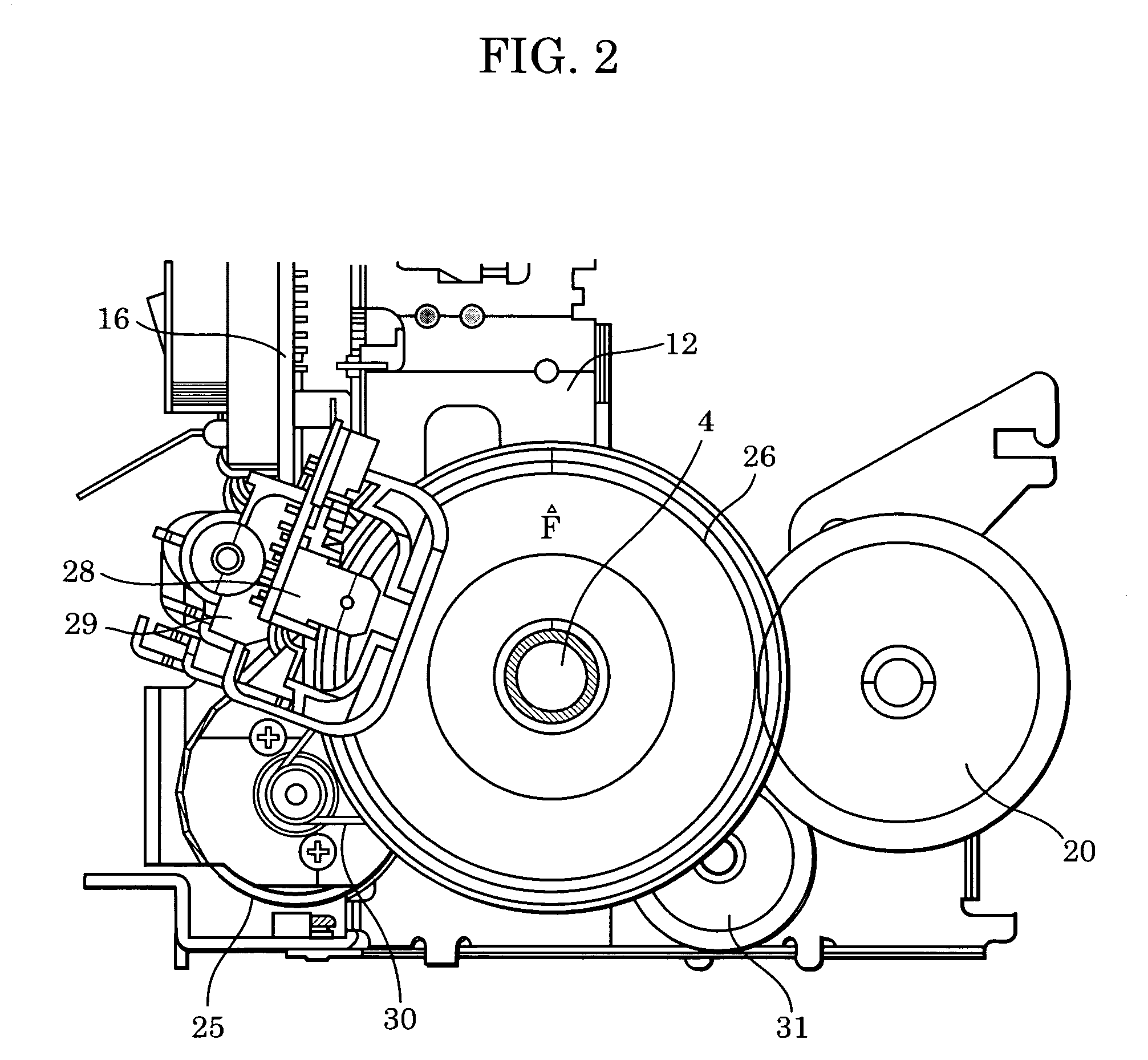

Printer and paper feed controller

InactiveUS7014378B2High resolutionPrecise feedingSpacing mechanismsOther printing apparatusControl signalSignal edge

High accuracy is achieved in paper feed control without increasing the size of an encoder, which would result in an increase in cost. The velocity of a paper feeding mechanism is calculated from an edge signal that is generated by the encoder in response to the motion of the paper feeding mechanism. Based on the calculated velocity, a calculation is performed as to the time needed to reach a stop position since a detection of an encoder signal edge immediately before the stop position. Based on the calculated time, a control signal for stopping the paper feeding mechanism is generated.

Owner:CANON KK

Self-calibrating strobe signal generator

A self-calibrating strobe signal generator for a BIST circuit responds to an edge of an input strobe signal by generating corresponding edges of first and second strobe signals separated in time by a target delay specified by input data. The strobe signal generator includes a multiplexer, a delay circuit and a controller. The multiplexer normally provides the input strobe signal as a multiplexer output signal to the delay circuit which generates edges in each of the first and second strobe signals in response to each edge in the multiplexer output signal with a programmable delay between corresponding first and second strobe signal edges. During a calibration process the control circuit adjusts the programmable delay by counting cycles of a reference clock signal occurring during a predetermined number of cycles of the multiplexer output signal when the multiplexer is set to select the first strobe signal and then the second strobe signal as the source of the multiplexer output signal such that the multiplexer output signal oscillates, and by incrementing or decrementing the programmable delay depending on whether a difference between the counts matches the input data.

Owner:CREDENCE SYSTEMS

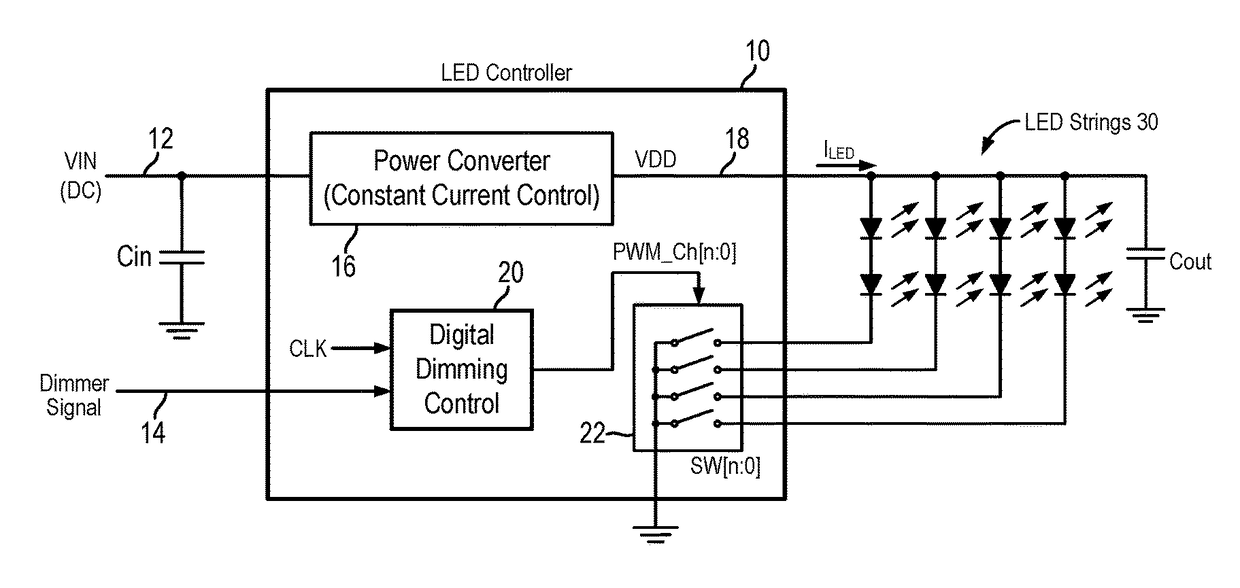

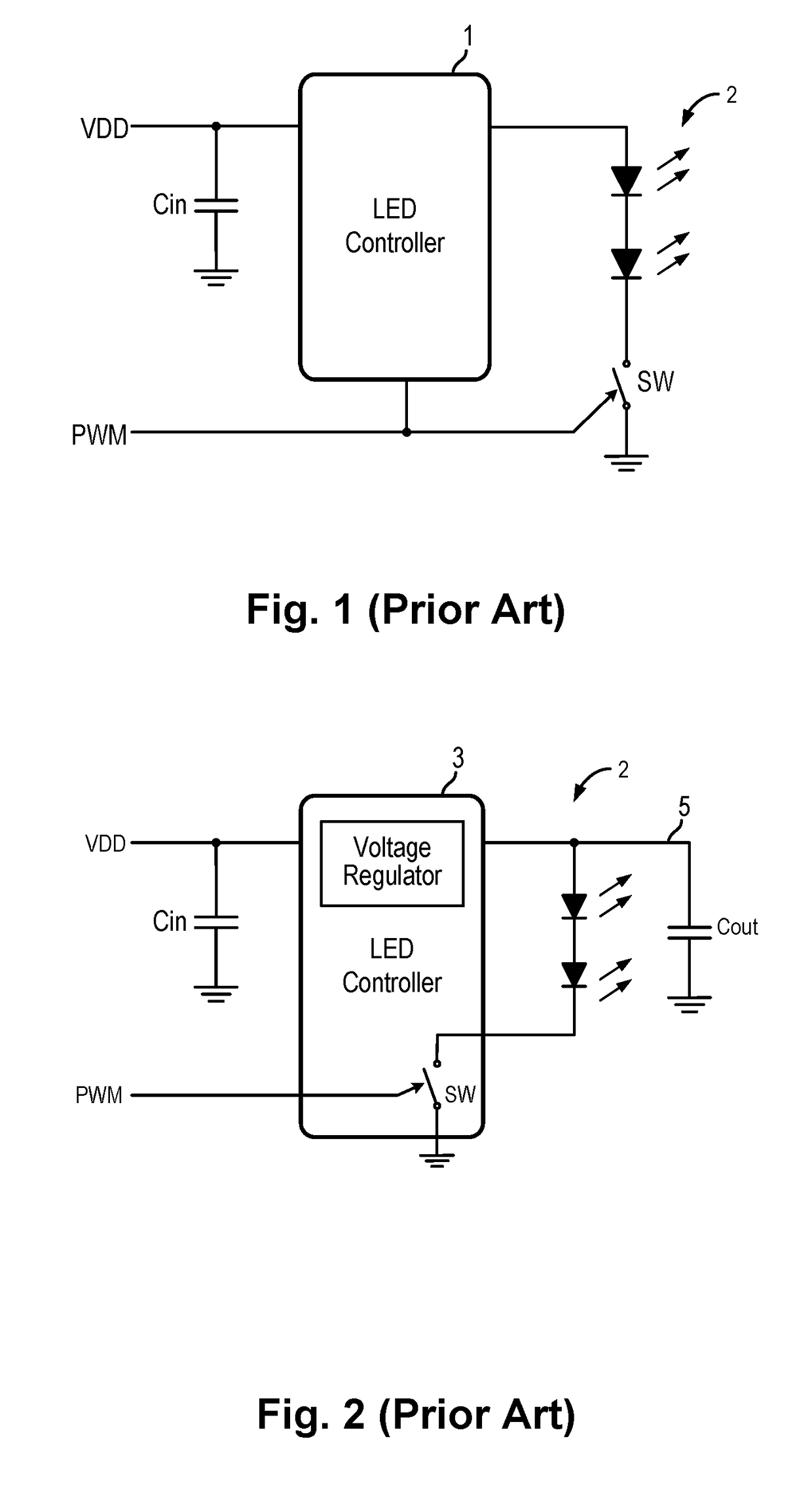

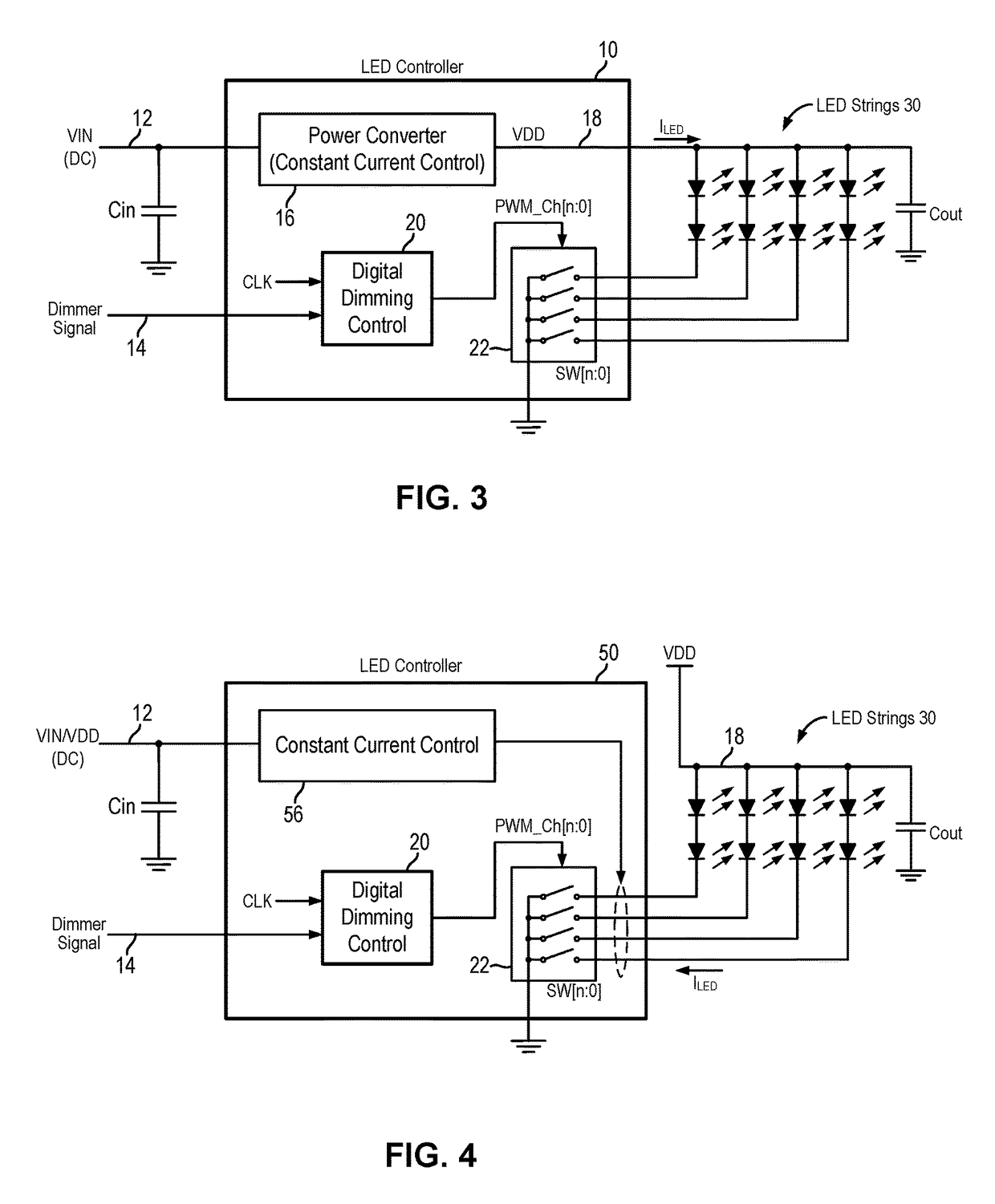

Audible noise reduction method for multiple LED channel systems

An LED controller for a multiple LED channel system using PWM method for LED dimming function incorporates a digital dimming control circuit to generate the PWM signals for driving the LED channels to spread out or cancel out the power supply transients generated by the LED transient current during PWM modulation for dimming operation. The digital dimming control circuit implements an audible noise reduction method whereby the active period of the PWM signals for some of the LED channels are shifted within the switching cycle to align at least some of the rising signal edges with some of the falling signal edges so as to cancel out the voltage transients on the LED power rails generated at the signal transitions. Furthermore, the rising and falling signal edges that are not lined up are spread out through the PWM switching cycle so that the power supply transients are spread out.

Owner:INTEGRATED SILICON SOLUTION

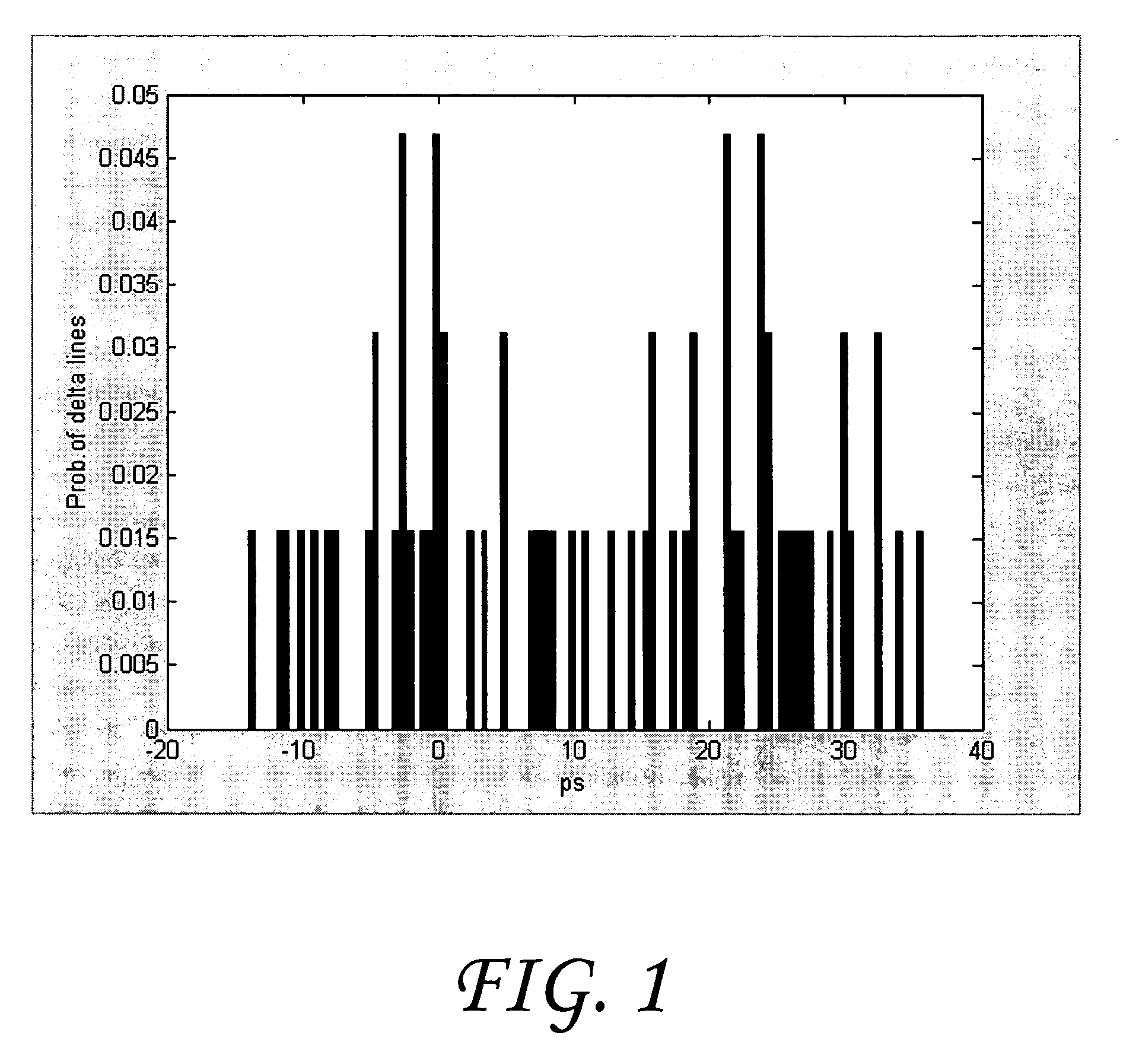

System and method of obtaining data-dependent jitter (DDJ) estimates from measured signal data

InactiveUS7203610B2Enhanced low frequencyImprove the measurement effectNoise figure or signal-to-noise ratio measurementVoltage-current phase angleDuty cycle distortionData signal

Methods for estimating data-dependent jitter (DDJ) from measured samples of a transmitted data signal include a first exemplary step of obtaining a plurality of measurements (e.g., time tags and event counts for selected pulse widths in the data signal). Such measurements may be obtained at predetermined intervals within a transmitted signal or may be obtained at randomly selected intervals, and should yield measurements for each data pulse in a repeating data pattern. An average unit interval value representative of the average bit time of the transmitted signal is determined. Time interval error estimates representative of the timing deviation from each signal edge's measured value relative to its ideal value (determined in part from the calculated average unit interval value) are also determined, as well as a classification for each measured signal edge relative to a corresponding data pulse in the repeating data pattern. DDJ delta lines are then calculated for signal edges of each pulse width in the transmitted data pattern, from which peak-to-peak DDJ values and / or estimates of duty-cycle-distortion (DCD) can be determined.

Owner:GUIDE TECH

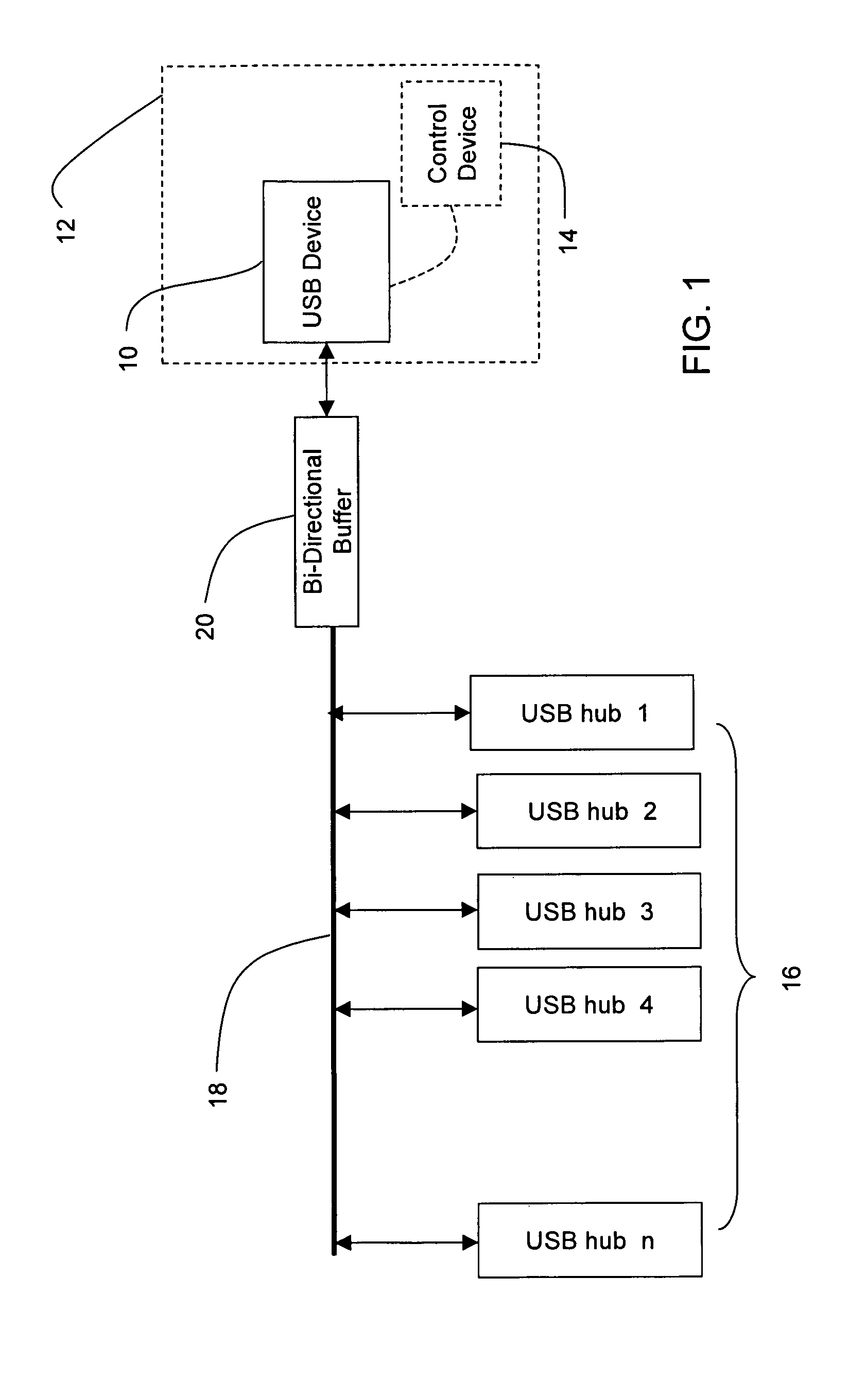

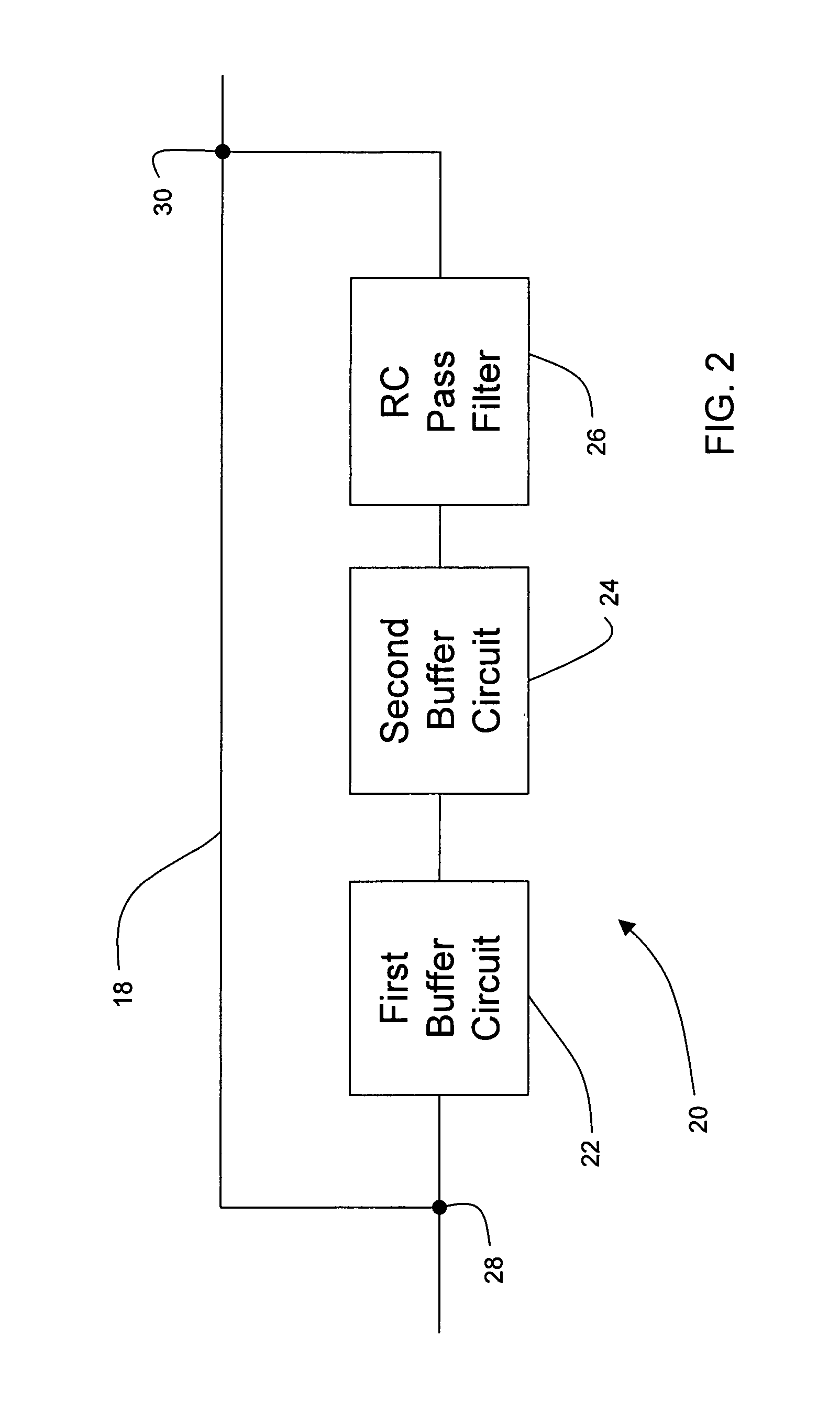

Bi-directional universal serial bus booster circuit

A bi-directional universal serial bus (“USB”) circuit for boosting a signal on a USB bus disclosed. The circuit includes a first stage inverting buffer coupled to a second stage inverting buffer to form a non-inverting buffer circuit. A high pass filter is coupled in series with the non-inverting buffer circuit to provide AC coupling to the USB bus and to allow fast signal edges through the circuit. The booster circuit is arranged to improve signal quality over a USB bus to allow additional USB devices and longer USB busses to be utilized.

Owner:IBM CORP

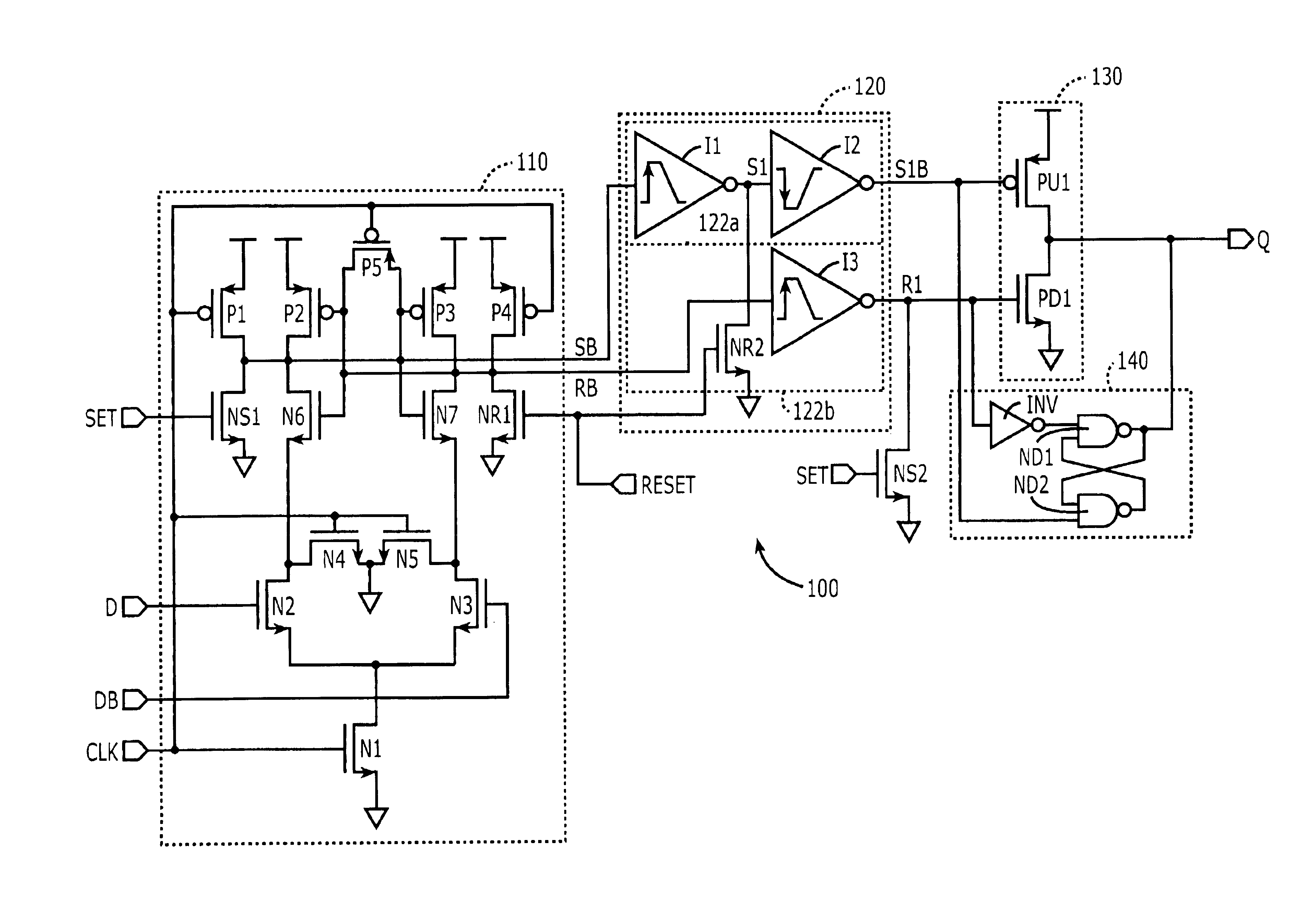

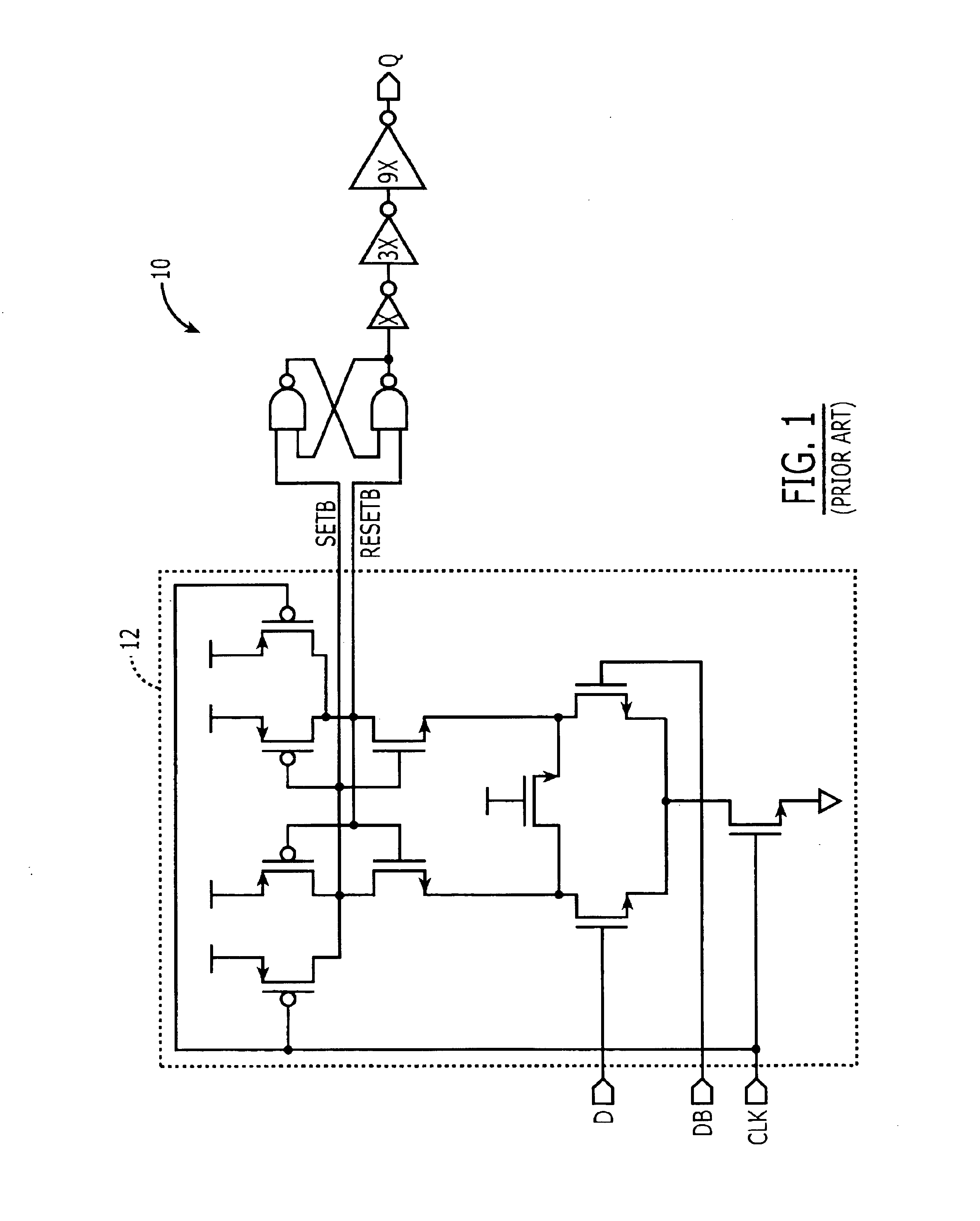

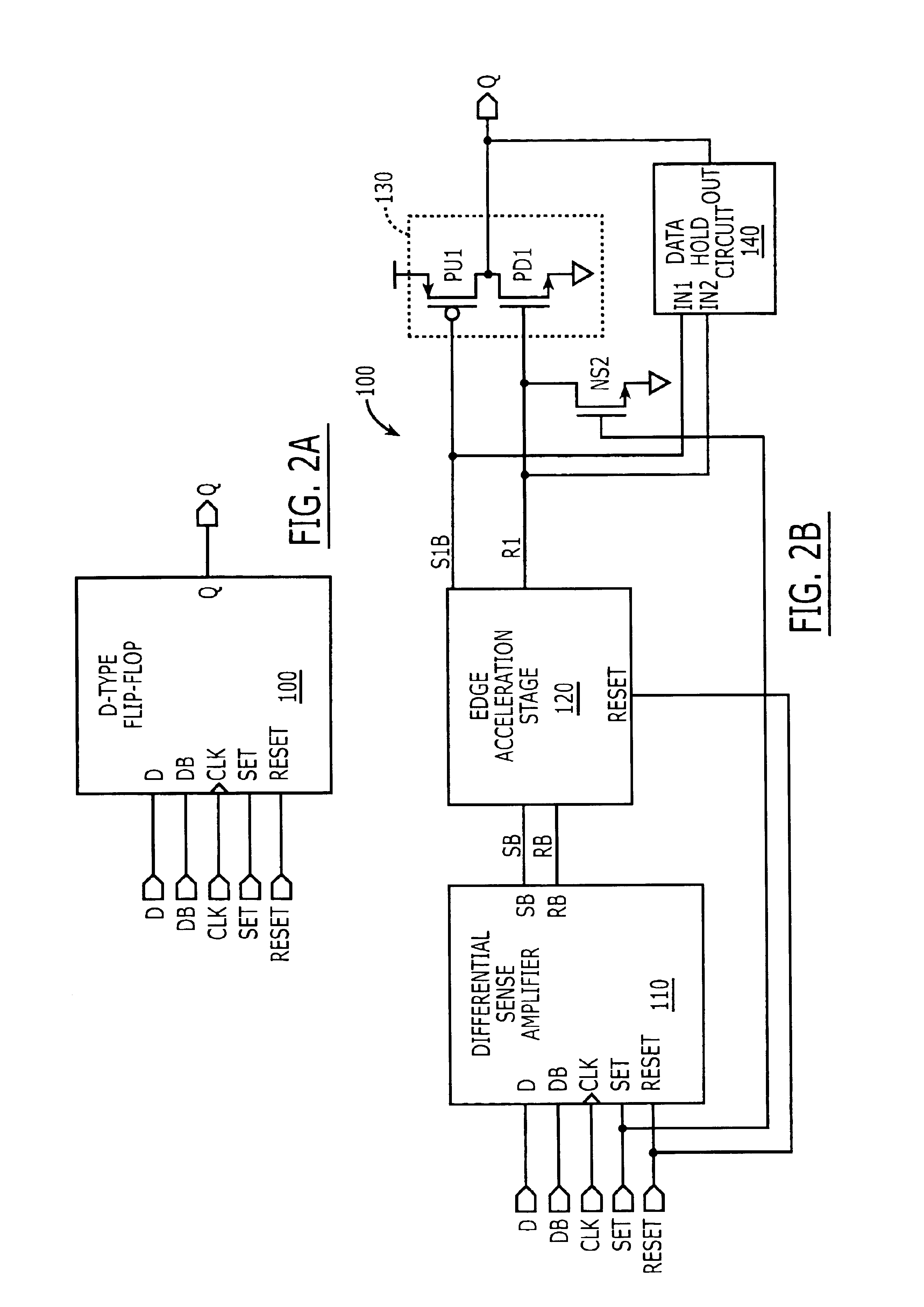

Edge accelerated sense amplifier flip-flop with high fanout drive capability

ActiveUS6924683B1High fanout drive capabilityFast timeElectric pulse generatorLeading edgeAudio power amplifier

Flip-flop devices provide fast clock-to-Q timing that exploits the pulsed nature of outputs generated by a clocked sense amplifier. These flip-flop devices include an output stage, which has a PMOS pull-up transistor and an NMOS pull-down transistor therein, and a clocked sense amplifier at an input stage. The clocked sense amplifier is configured to generate first and second data output signals ( / SET and / RESET). These data output signals are provided to a signal edge acceleration stage. This signal edge acceleration stage is configured to generate the pull-up and pull-down control pulses in response to the first and second data output signals, respectively. This leading edge acceleration stage includes a pull-up buffer having an odd (even) number of inverters therein that are skewed to accelerate the leading edge of the pull-up control pulse relative to a trailing edge of the pull-up control pulse. The leading edge acceleration stage also includes a pull-down buffer having an even (odd) number of inverters therein that are skewed to accelerate the leading edge of the pull-down control pulse relative to a trailing edge of the pull-down control pulse. Accordingly, the pull-up buffer accelerates the clock-to-Q timing when driving Q high and the pull-down buffer accelerates the clock-to-Q timing when driving Q low.

Owner:INTEGRATED DEVICE TECH INC

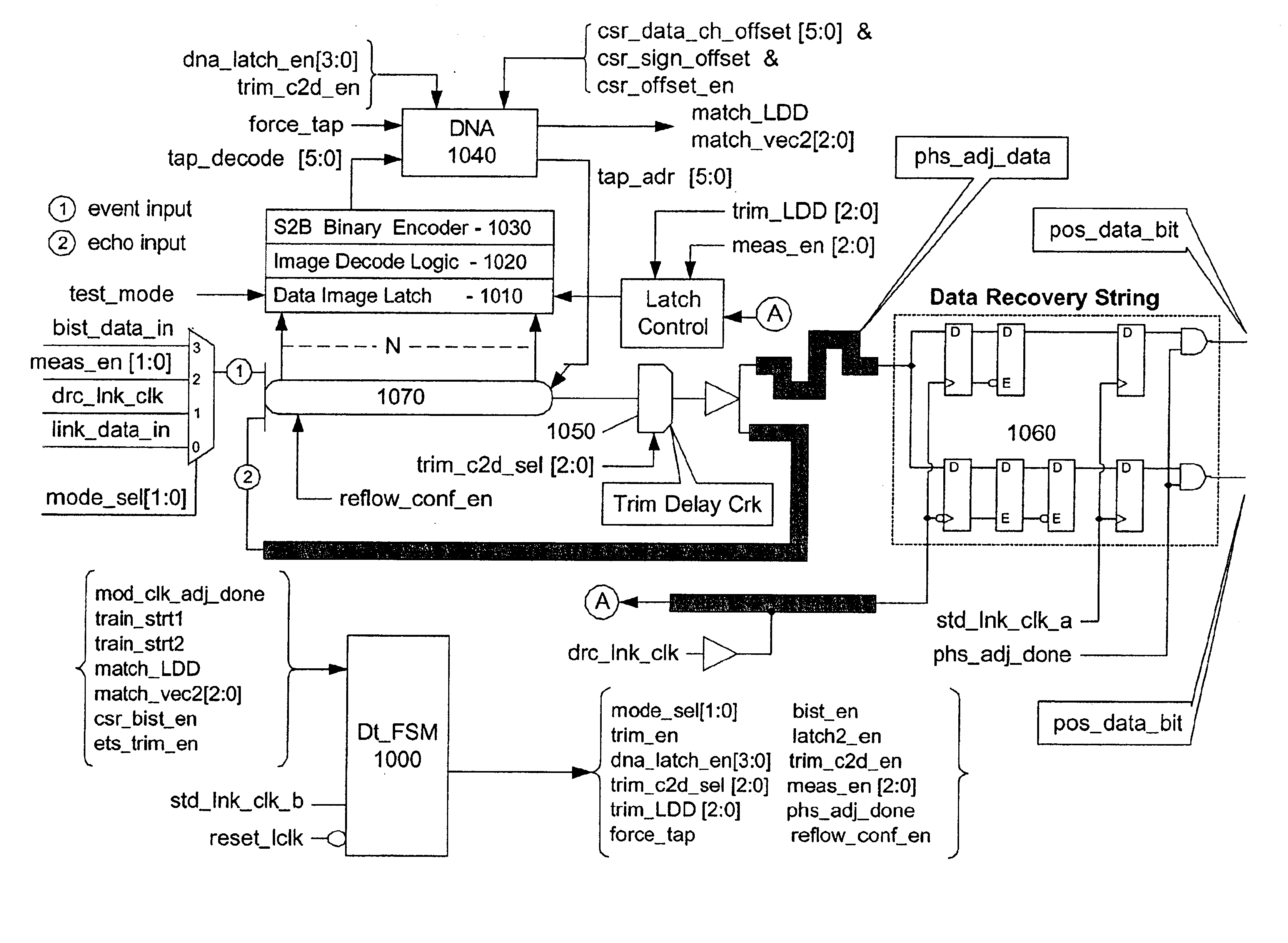

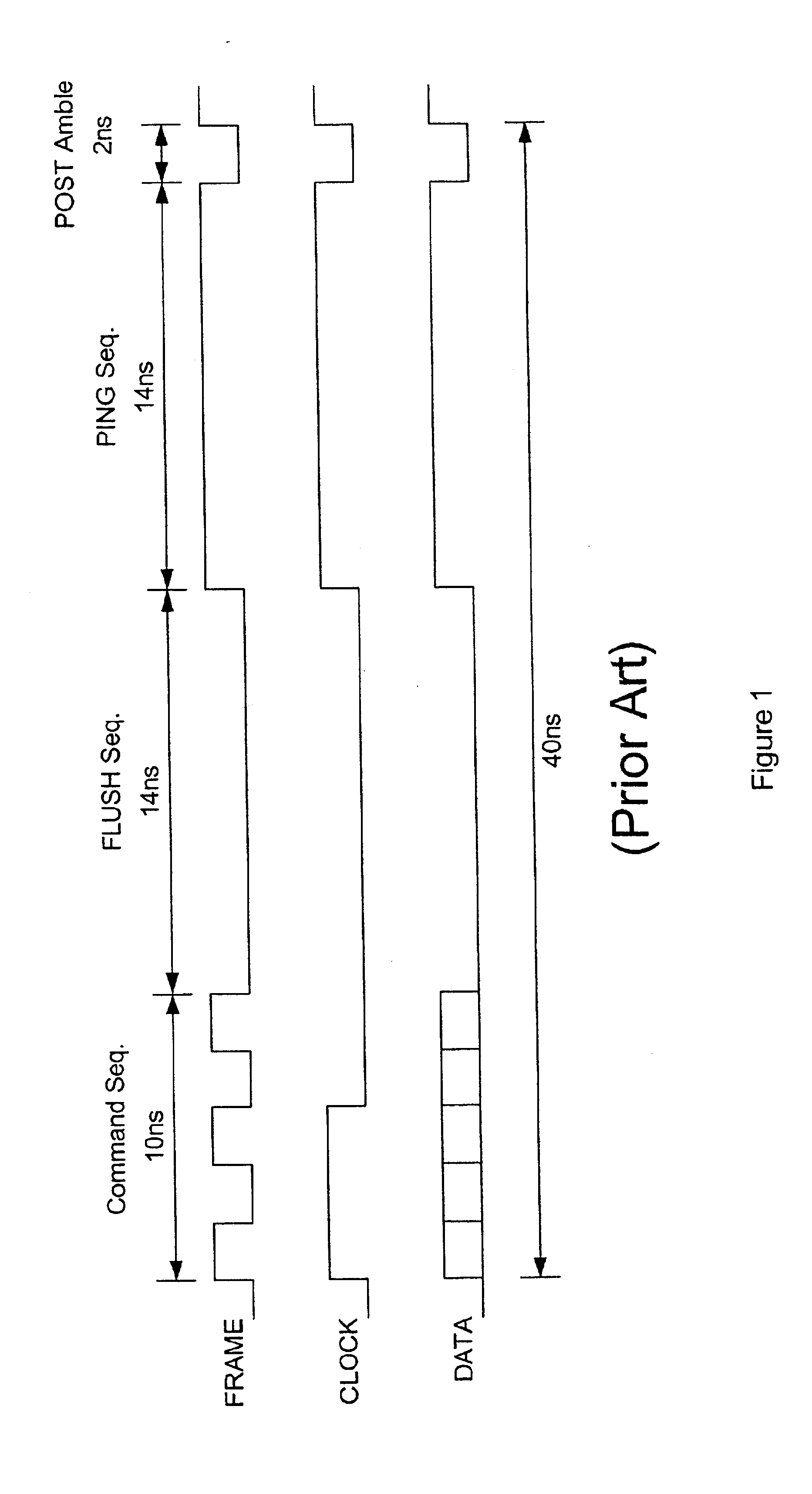

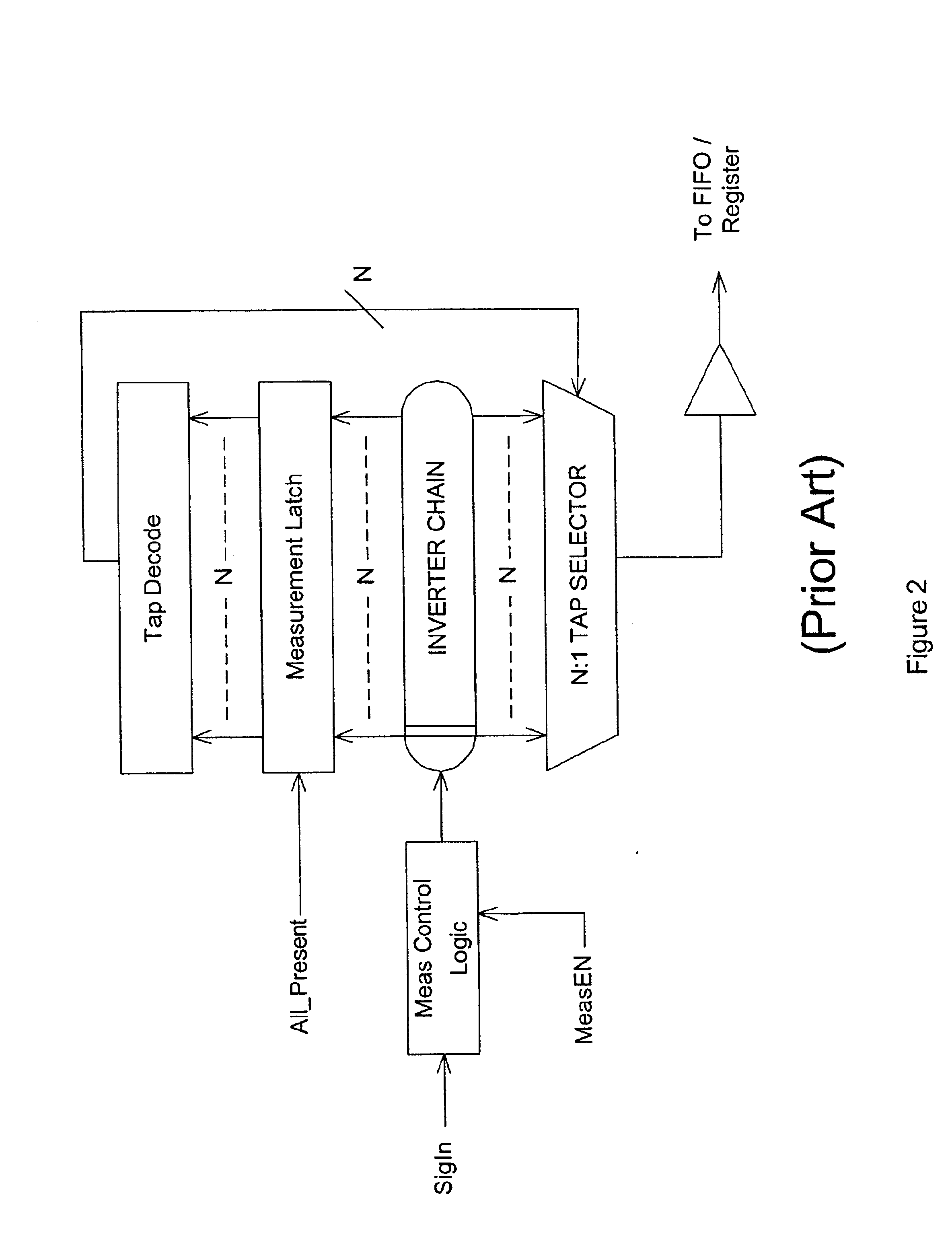

Relative dynamic skew compensation of parallel data lines

InactiveUS6907552B2Add supportDelay powerChannel dividing arrangementsError detection/correctionData signalSignal edge

A system performs a two-step skew compensation procedure by first correcting for any phase error alignment between a parallel link clock and data signal edges of each data channel, thereby allowing the received data bits to be correctly sampled. Then, a second step is performed to “word-align” the bits into the original format, which is accomplished with a Skew Synchronizing Marker (SSM) byte in a data FIFO of each data channel. The SSM byte is transmitted on each data channel and terminates the skew compensation procedure. When the SSM byte is detected by logic in the data FIFO of each data channel, the data FIFO employs the SSM byte to initialize the read and write pointers to properly align the output data.

Owner:SYNOPSYS INC

Method for detecting reverse rotation for internal combustion engines

In a method for detecting reverse rotation when starting an internal combustion engine having a sensor disk which is coupled to a crankshaft of the engine, the sensor disk having a marking via an alternating arrangement of teeth and tooth spaces, and a first sensor and a second sensor each capable of generating an electric signal which may assume at least two signal levels, being associated with the sensor disk, one of the signal levels being associated with a tooth and the other signal level with a tooth space, a rising or falling signal edge of the one signal and the signal level of the other signal being used for determining the direction of rotation and increment of the angle of rotation of the crankshaft, the start characteristics are improved by determining the direction of rotation during the start of the engine as early as at the first signal edge.

Owner:ROBERT BOSCH GMBH

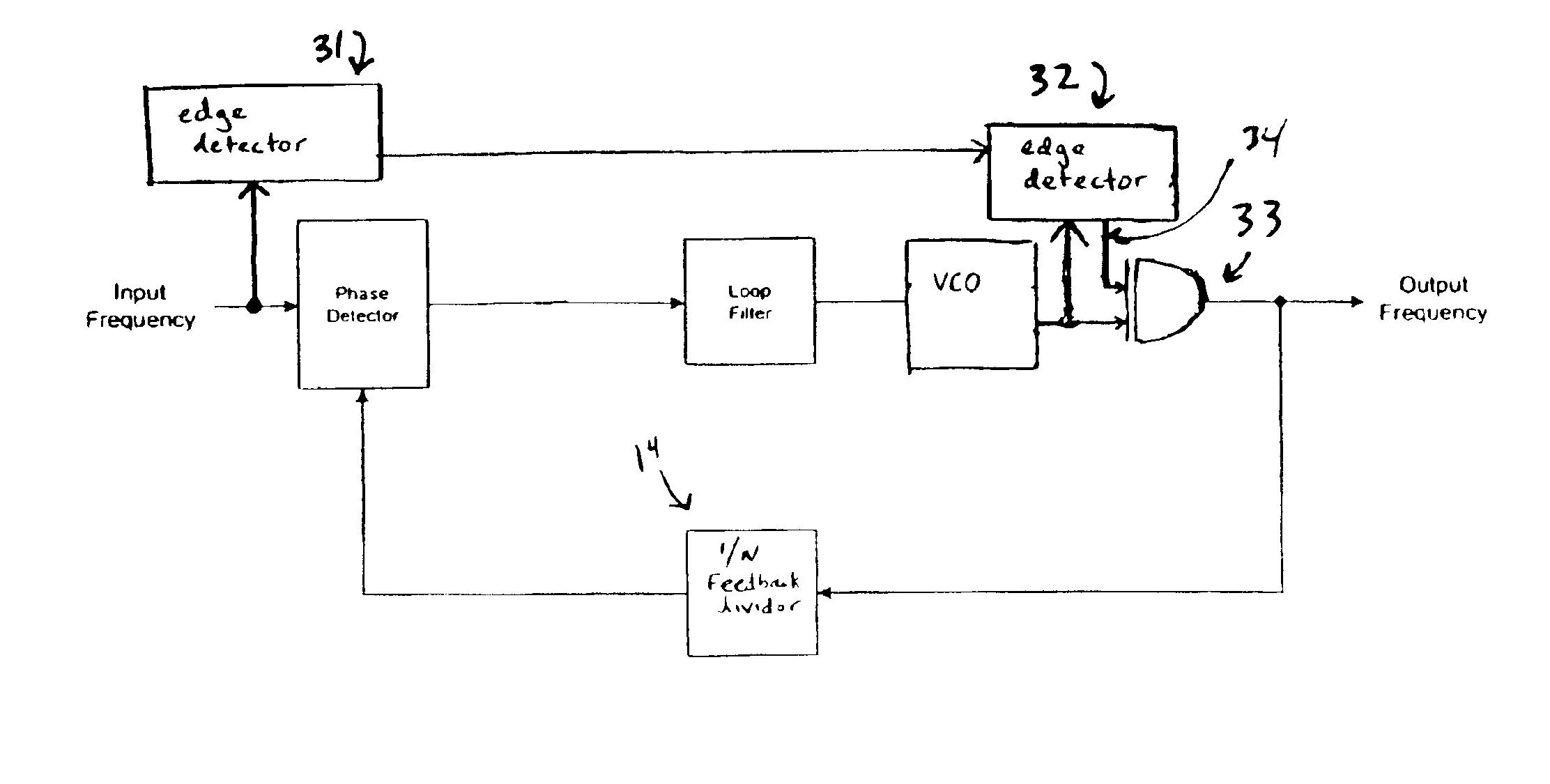

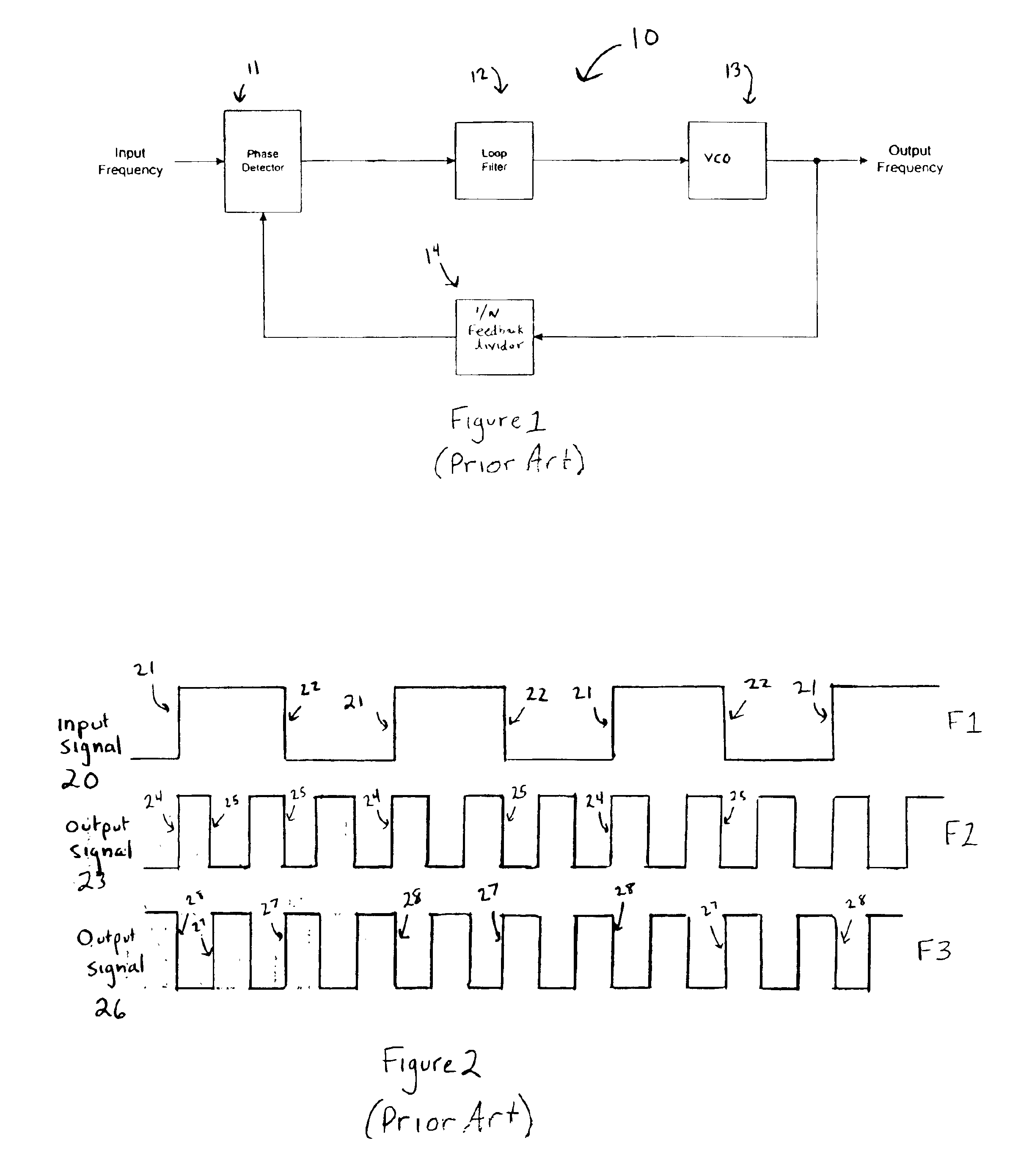

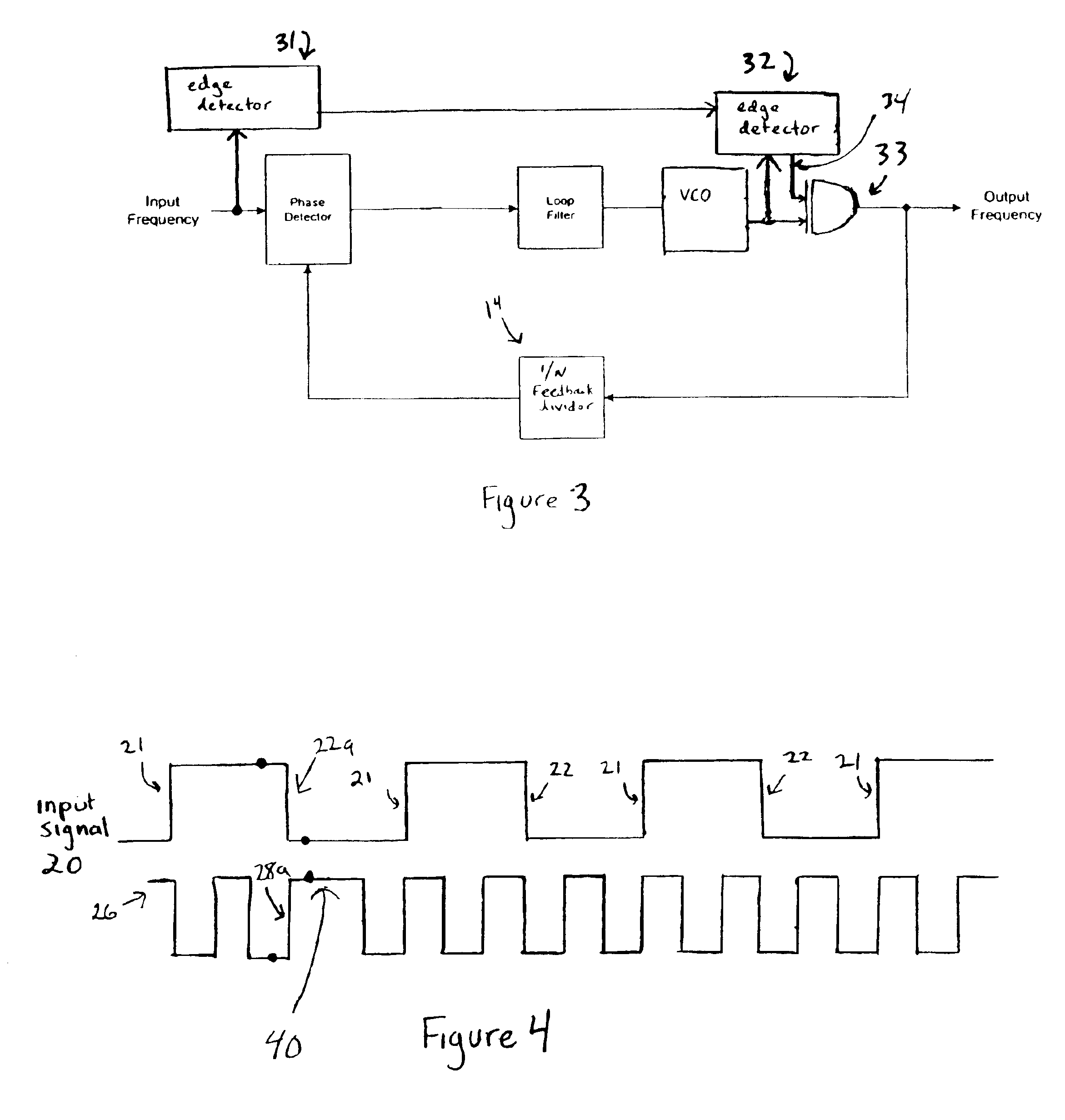

Edge synchronized phase-locked loop circuit

InactiveUS6891441B2Efficient productionPulse automatic controlAmplitude demodulationPhase locked loop circuitSignal edge

A phase-locked loop circuit for synchronizing an edge of an output signal with an edge of an input signal. The circuit detects an edge of an input clock signal, and a corresponding edge on an output signal. If the output signal edge is out of phase with the input clock edge, the circuit shifts the output signal by 180 degrees to effectively produce a single double-length clock phase. The synchronized phase-locked loop circuit provides predictable phase-locked loop output phase synchronization with an input clock.

Owner:ZORAN CORPORATION

System for measuring characteristics of a digital signal

An electronic device under test (DUT) responds to a digital input signal by generating a digital DUT output signal conveying a repetitive digital signal pattern. An apparatus for measuring various characteristics of the DUT output signal includes a trigger generator for generating a series of trigger signal edges in response to selected DUT output signal edges occurring during separate repetitions of the digital signal pattern. The trigger generator can be configured to generate each trigger signal edge in response to the same or a different edge of the digital signal pattern. The apparatus determines when a DUT output signal edge occurs by determining when the DUT output signal rises above or falls below adjustable reference voltages. The apparatus alternatively responds to each trigger signal edge by measuring a period between two different edges of the digital signal pattern and or by repetitively sampling the DUT output signal to determine its state.

Owner:CREDENCE SYSTEMS

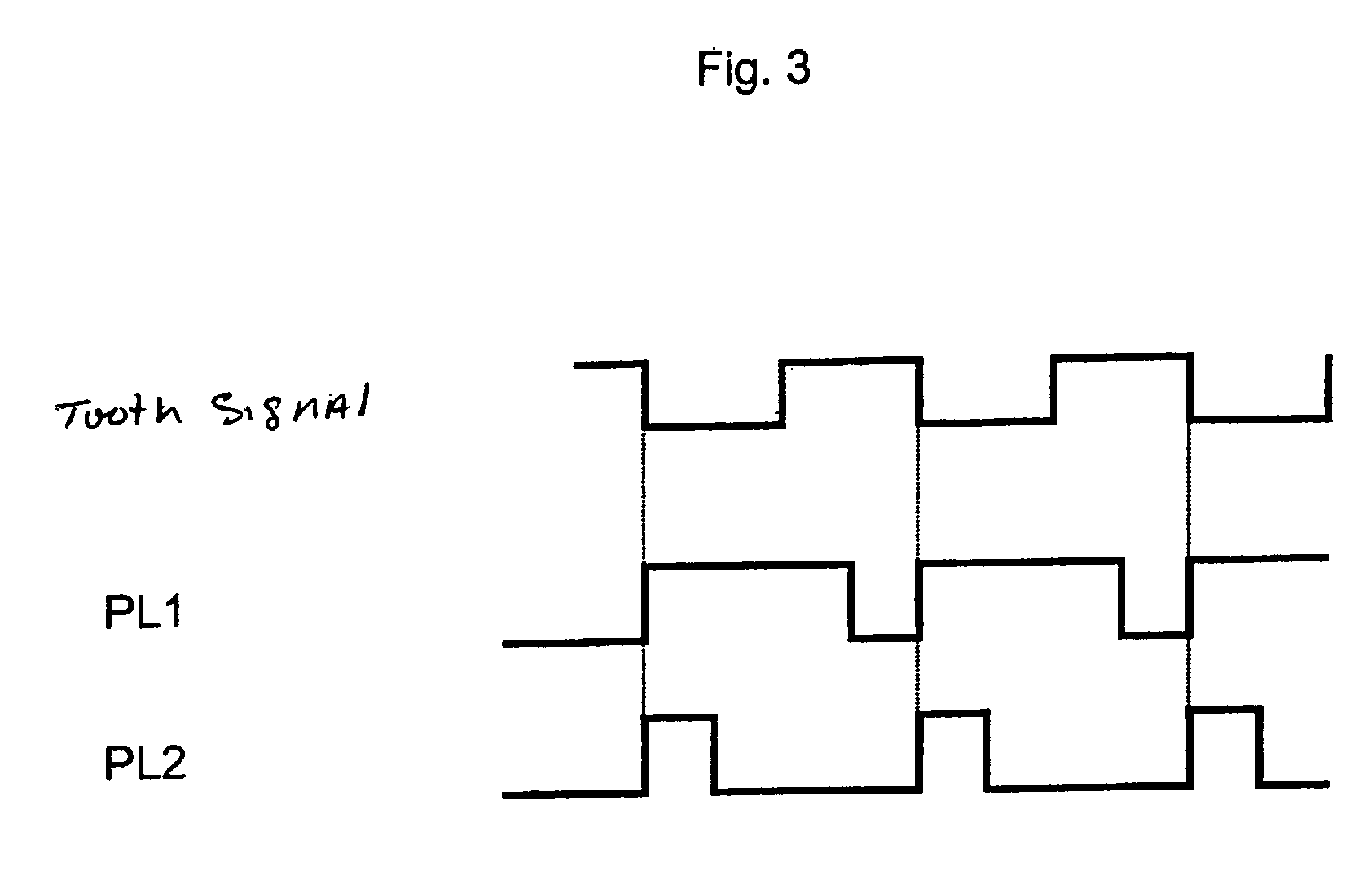

Method for incrementally ascertaining a rotation angle of a shaft

A method for incrementally ascertaining a rotation angle of a shaft, in particular of a crankshaft of an internal combustion engine, the shaft being connected to a sensor wheel having teeth and tooth gaps, and at least one sensor being associated with the sensor wheel, the sensor generating a square-wave signal as an output signal which may assume a first value or a second value, and a signal edge being associated with a tooth edge, and the position in time of a counteredge with respect to the edge encoding a direction of rotation, an assignment of a direction of rotation reversal point to a tooth of the sensor wheel or a tooth gap of the sensor wheel being encoded by the position in time of the counteredge with respect to the edge, the rotation angle being ascertained by adding an increment for each signal edge to a counter, after a direction of rotation reversal while a tooth passes the sensor, a half-increment, having a sign of the direction of rotation after the direction of rotation reversal, being incremented once and in the event of a direction of rotation reversal while a tooth gap passes the sensor, a half-increment, having a sign of the direction of rotation prior to the direction of rotation reversal, being incremented once.

Owner:ROBERT BOSCH GMBH

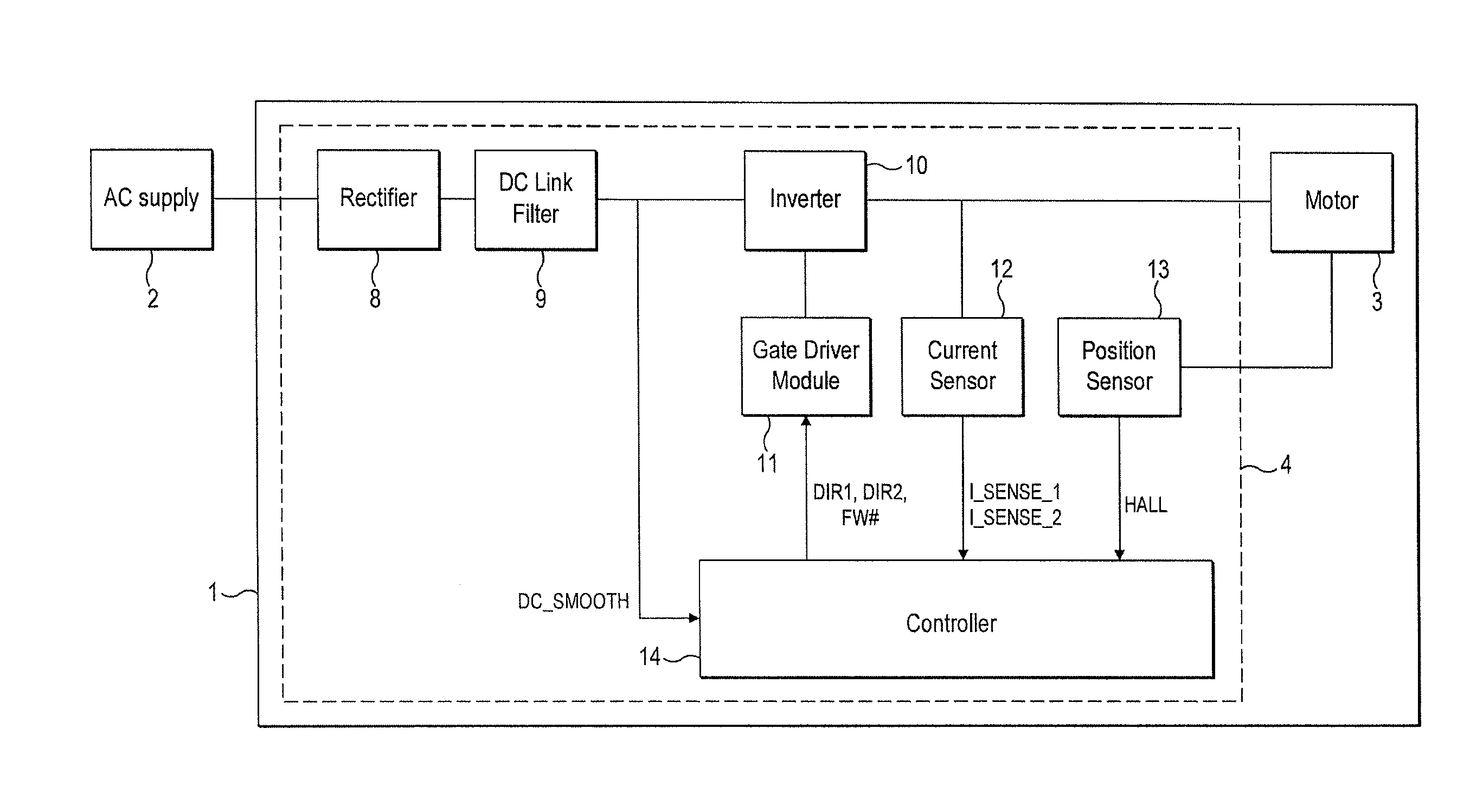

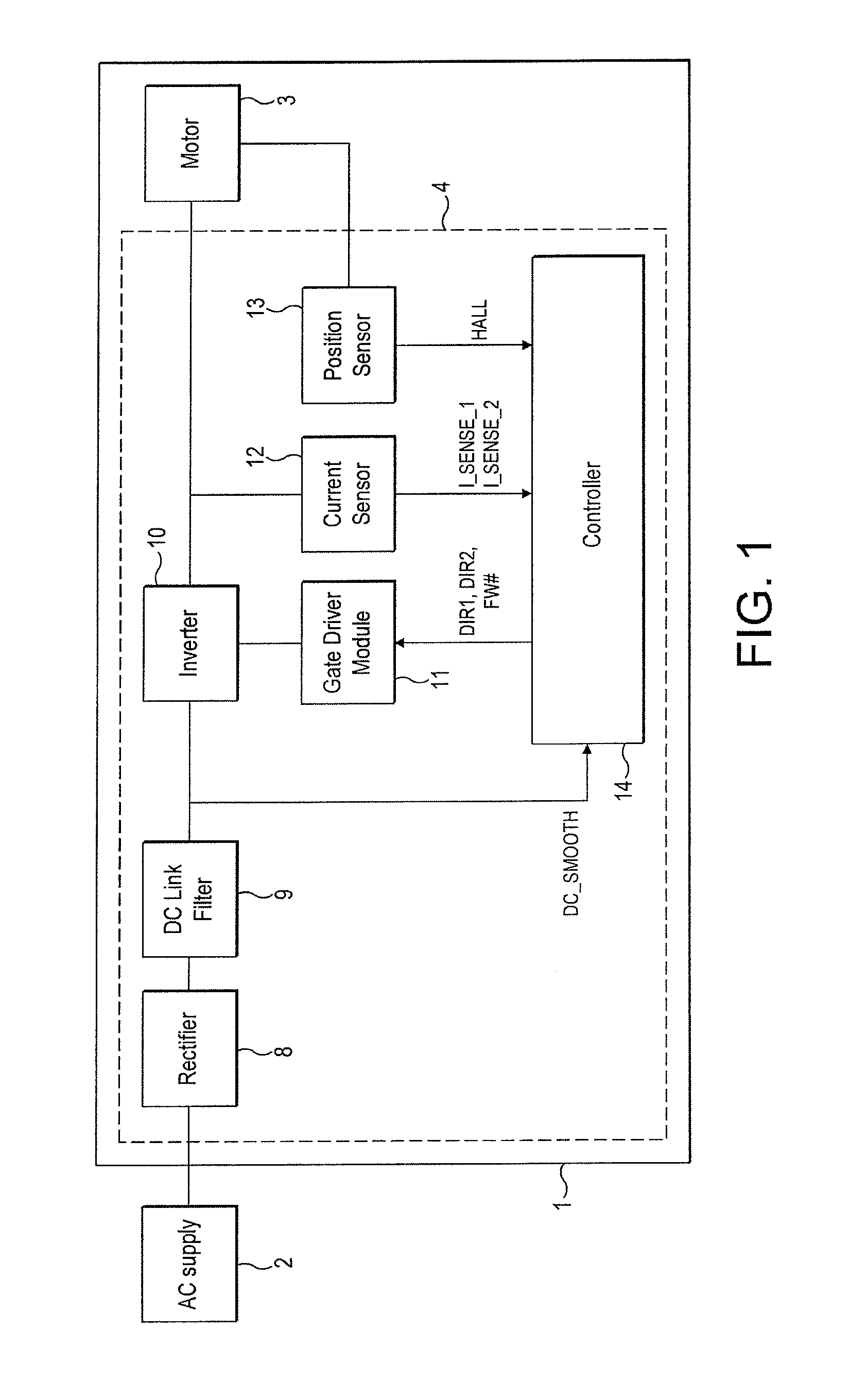

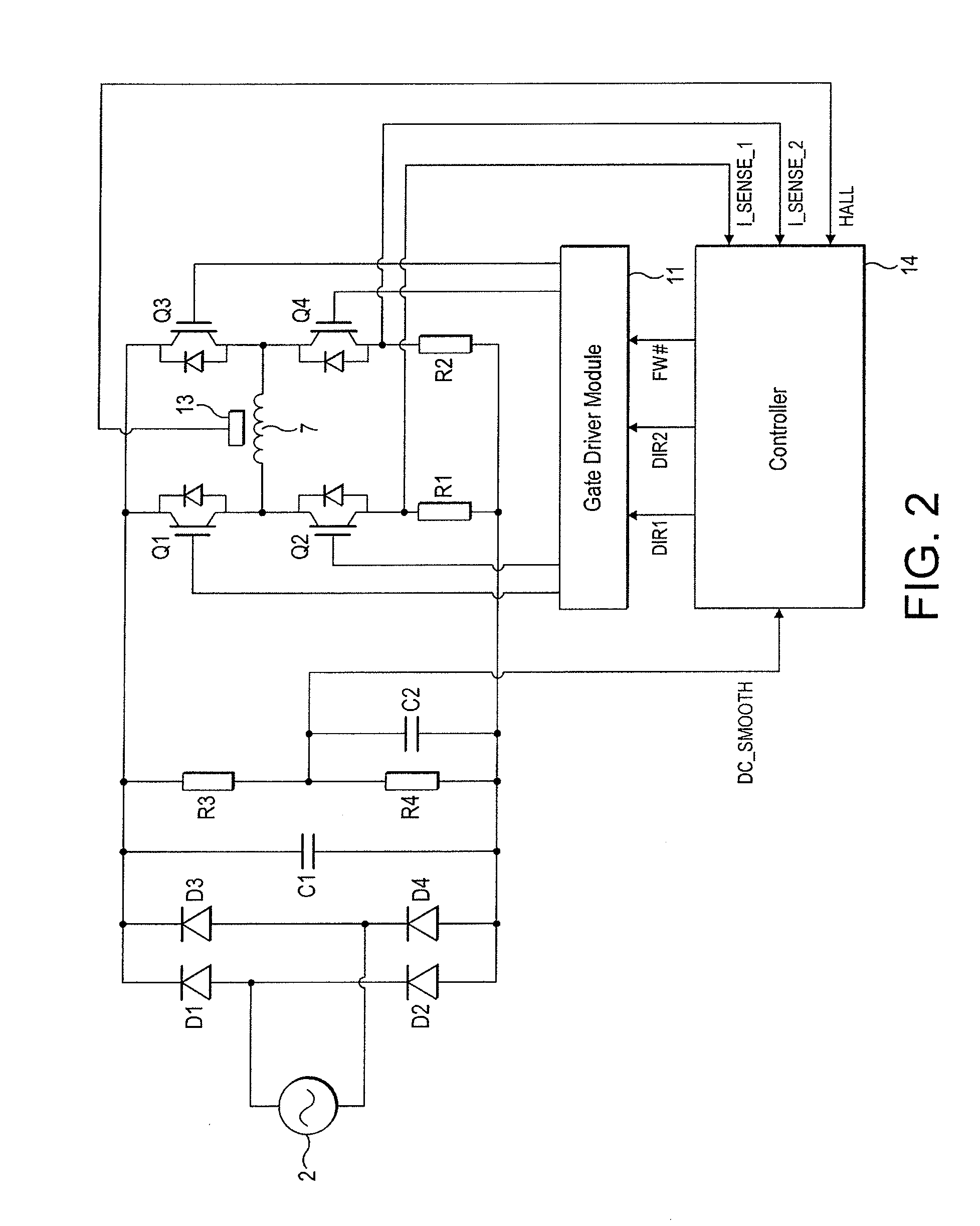

Control of an electrical machine

ActiveUS20120081050A1Stable electrical machineImprove efficiencySynchronous motors startersDC motor speed/torque controlControl systemElectric machine

A method of controlling an electrical machine that includes commutating a phase winding of the electrical machine at a time T_COM(1) after a first edge and at a time T_COM(2) after a second edge of a rotor-position signal. T_COM(2) is defined by the equation: T_COM(2)=T_COM(1)+T_AVE−T_PD, where T_AVE is an average period between edges of the rotor-position signal, and T_PD is the period between the first and second edges. Additionally, a controller and control system that implement the method.

Owner:DYSON TECH LTD

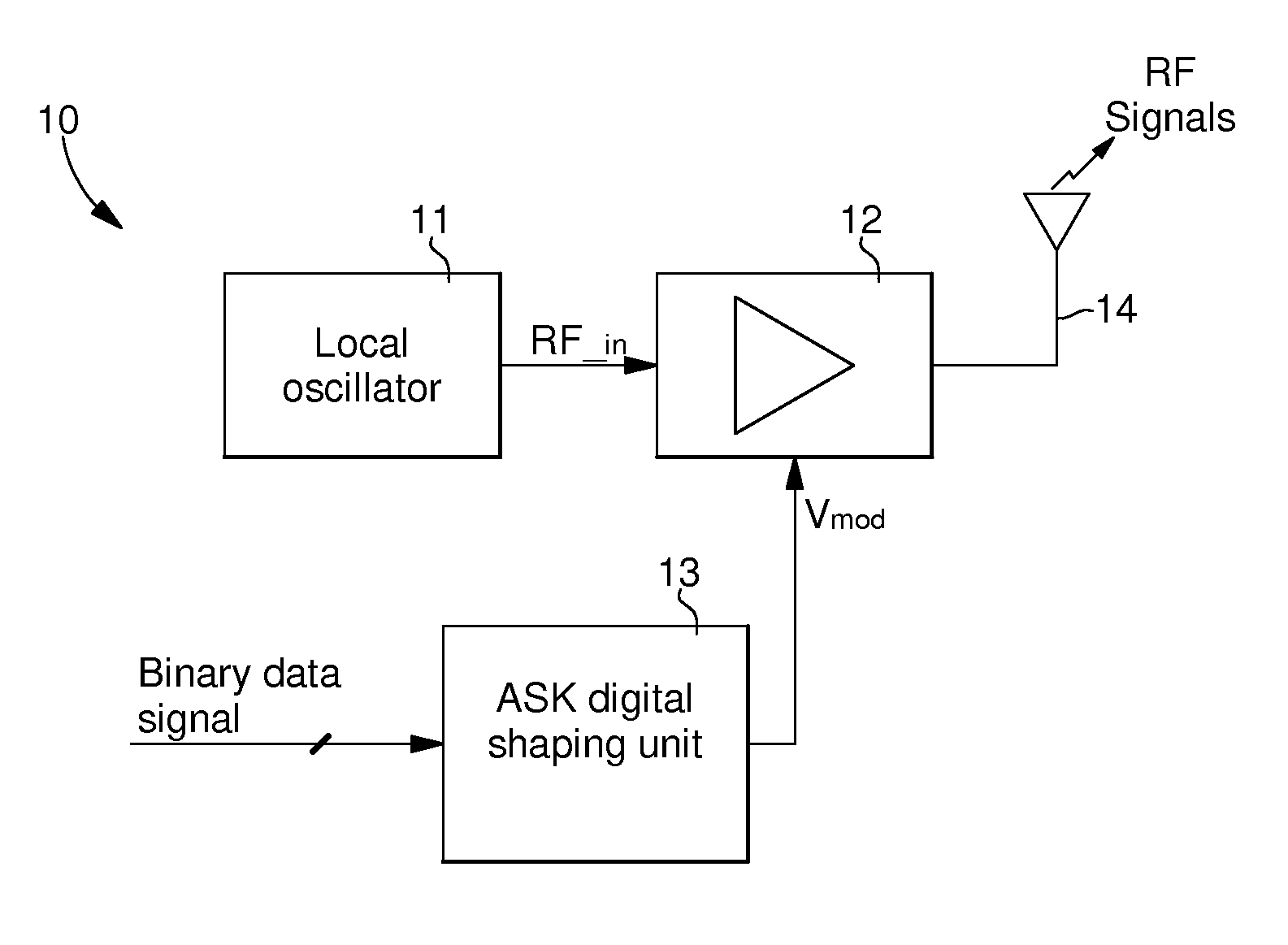

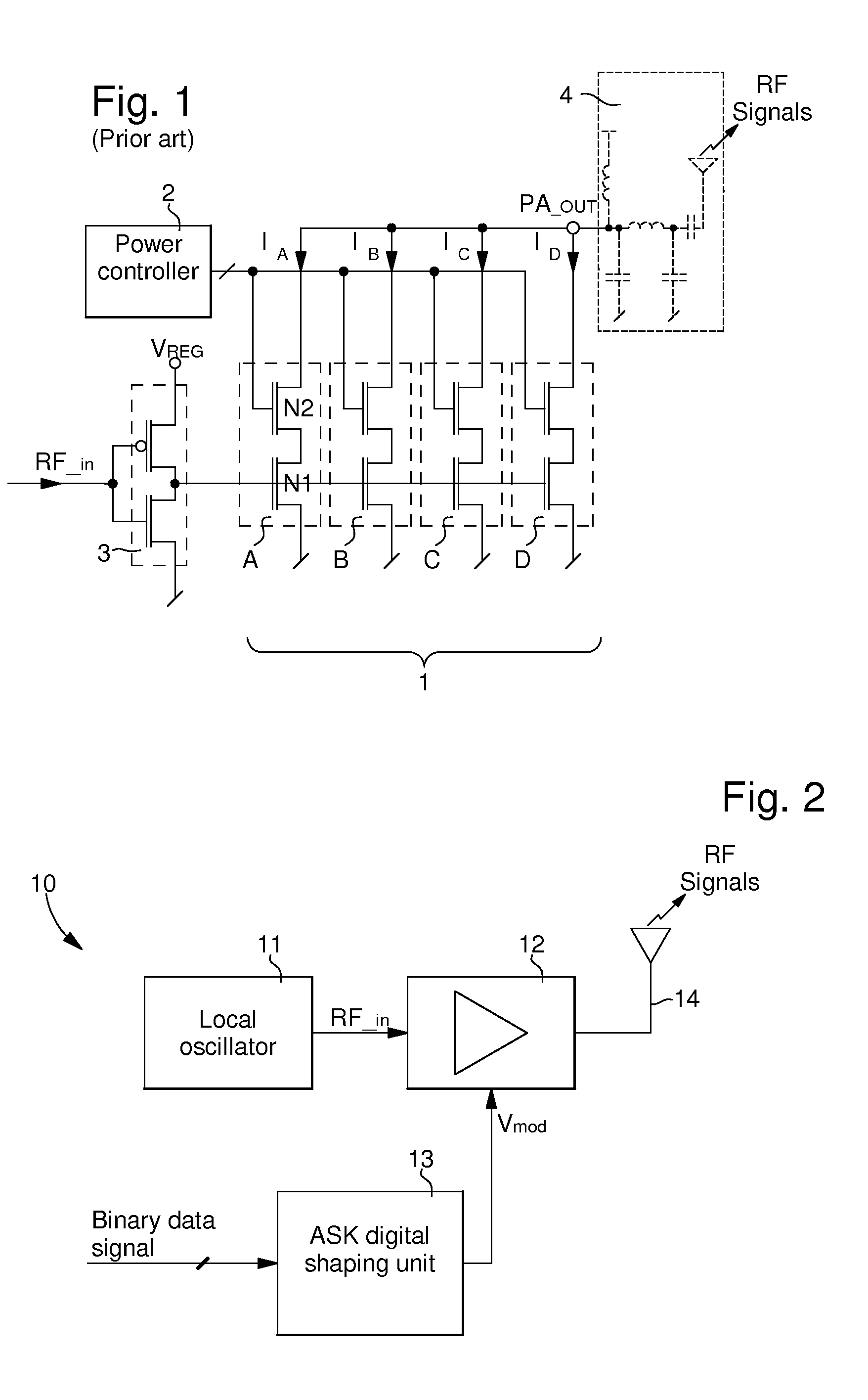

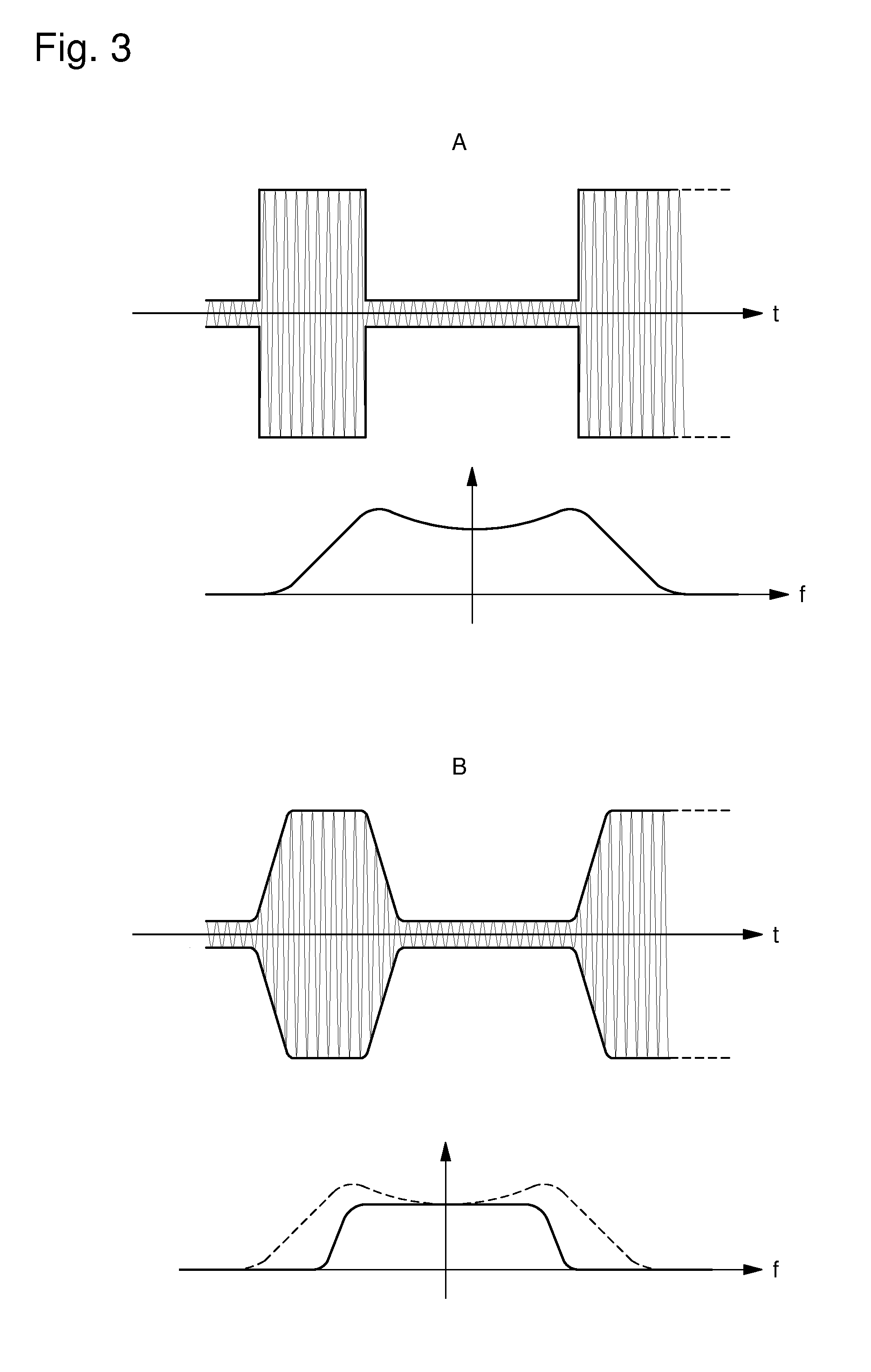

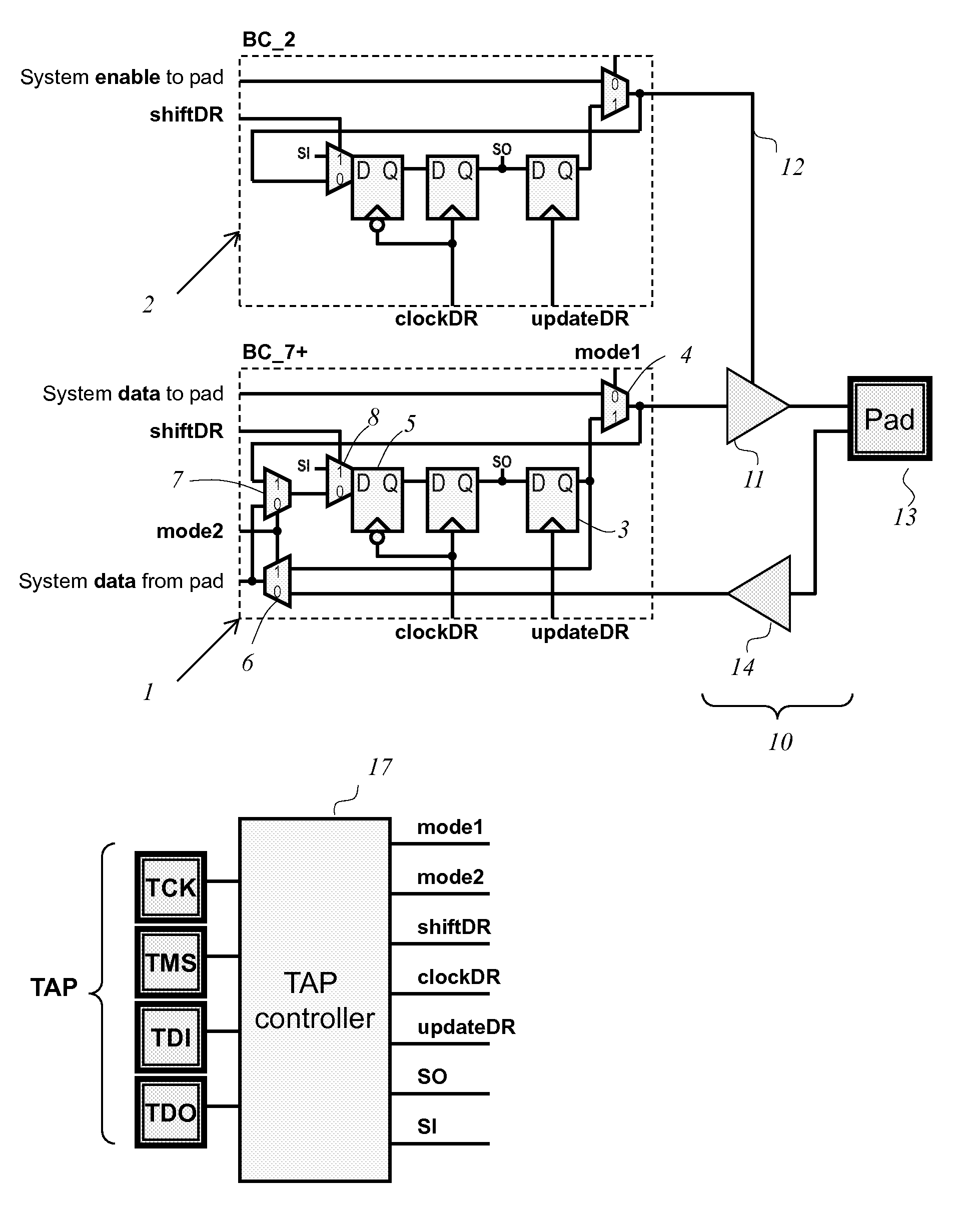

Circuit for transmitting ask RF signals with data signal edge adaptation

ActiveUS20130163697A1Raise the cutoff frequencyEasy to integrateHigh frequency amplifiersGated amplifiersDigital dataControl signal

The circuit is provided for the transmission of data amplitude modulated radio frequency signals. The circuit includes a local oscillator for generating an oscillating signal at a determined carrier frequency, a unit for shaping data pulses to supply a data amplitude modulation control signal (Vmod), and a power amplifier receiving the oscillating signal and the data amplitude modulation control signal (Vmod) for the transmission of data amplitude modulated radio frequency signals by an antenna or an antenna arrangement. The data pulse shaping unit (13) includes a pulse shaper (21) for digitally adapting the data transition edges on the basis of an incoming digital data signal (d), and a digital-analogue conversion stage (26, 27) for converting a digital data signal shaped in the unit, in order to supply the data amplitude modulation control signal (Vmod) to the power amplifier.

Owner:EM MICROELECTRONIC-MARIN

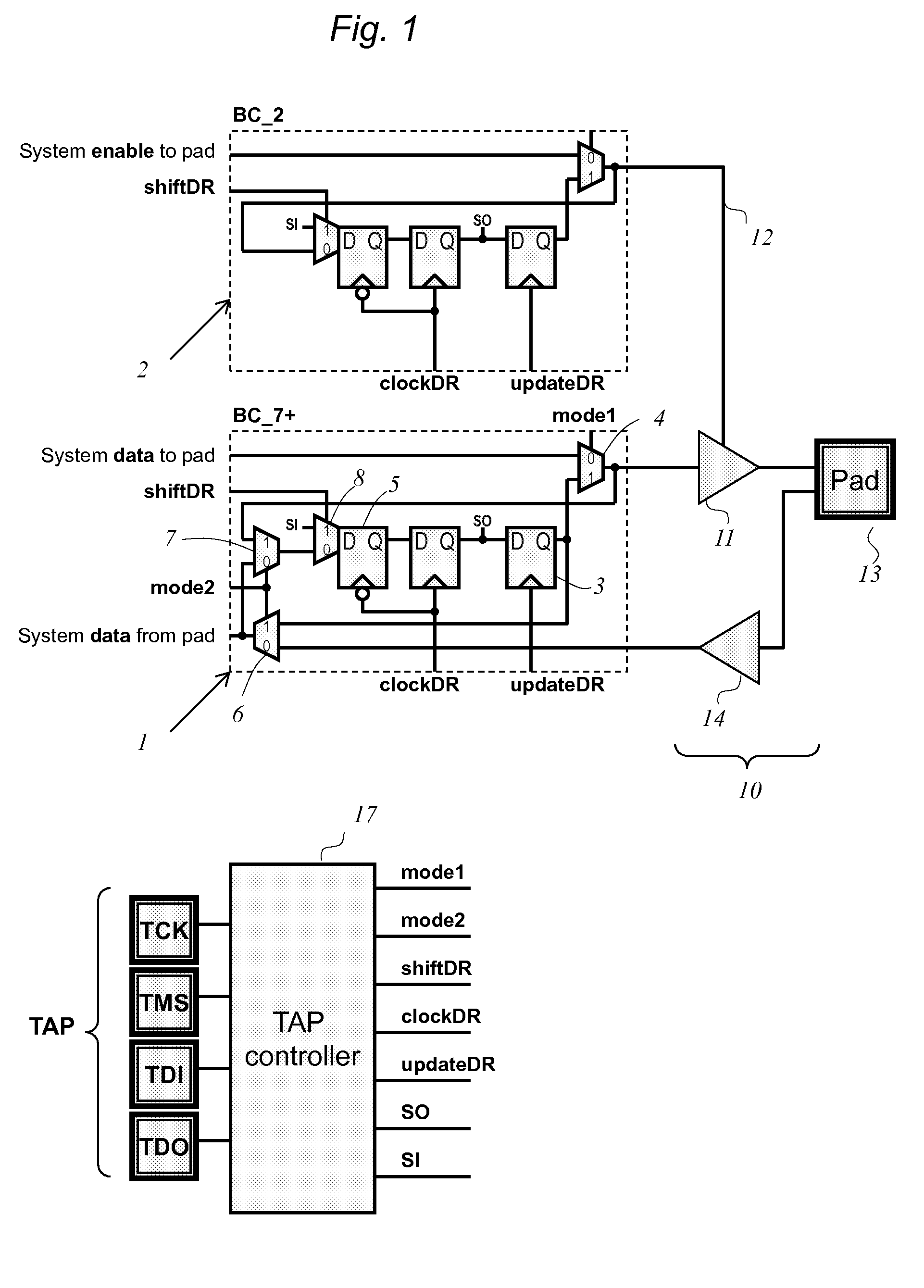

Circuit and Method for Measuring Delays between Edges of Signals of a Circuit

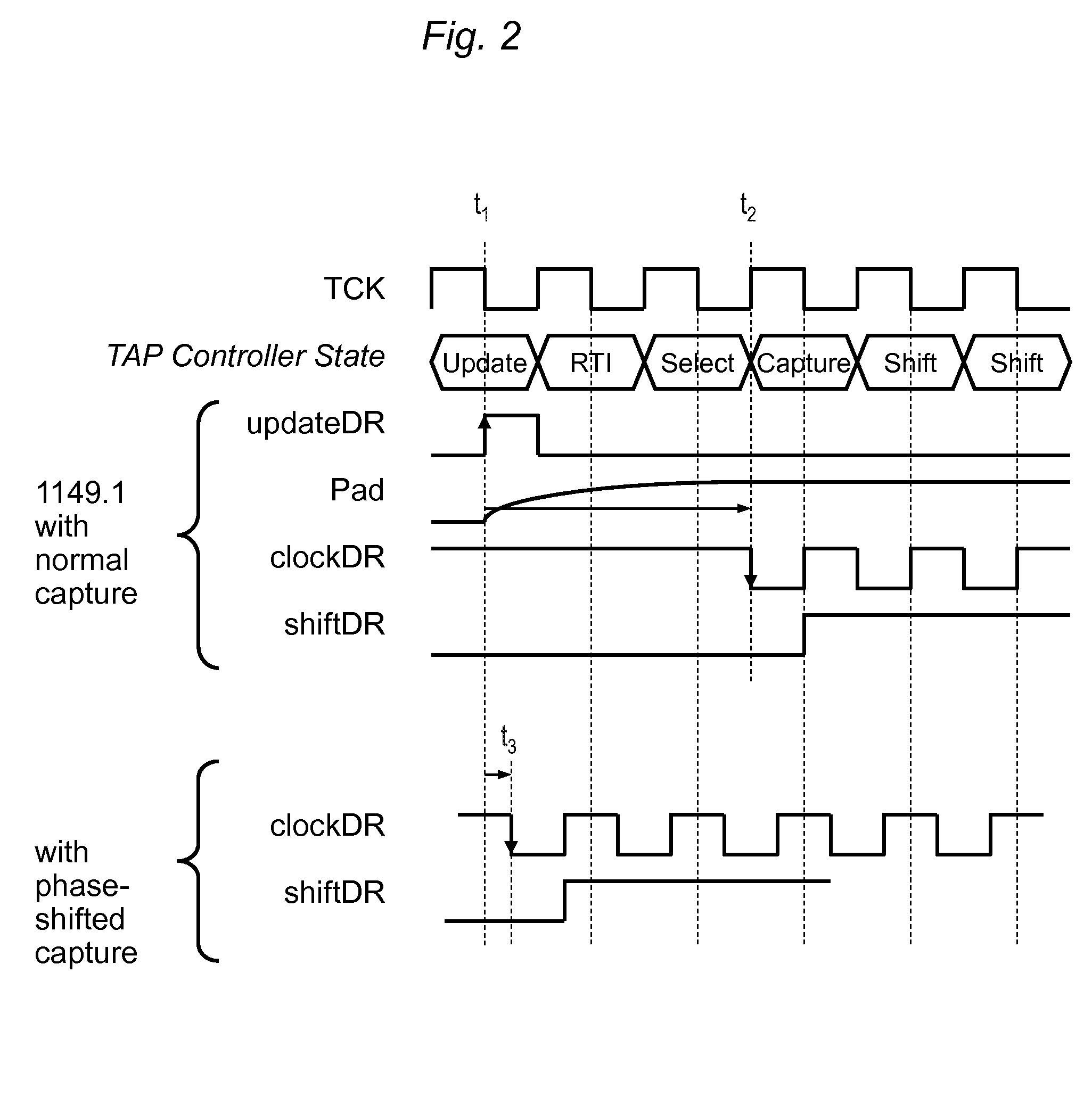

Various aspects of the present invention relate to techniques of measuring delays between edges of signals of a circuit. Alternating signals, synchronous to a first clock, are supplied to a plurality of nodes of the circuit. First samples of a plurality of signals associated with the alternating signals are captured using a first capture clock, of which sampling instants are synchronous to a second clock. Second samples of the first samples are then captured using a second capture clock, of which sampling instants are also synchronous to the second clock. The captured second samples are conveyed via a shift register to a plurality of modulo counters. The measured signal delay includes a timing skew associated with the first clock and a timing skew of the first capture clock but not a timing skew of the second capture clock.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Method for incrementally ascertaining a rotation angle of a shaft

A method for incrementally ascertaining a rotation angle of a shaft, in particular of a crankshaft of an internal combustion engine, the shaft being connected to a sensor wheel having teeth and tooth gaps, and at least one sensor being associated with the sensor wheel, the sensor generating a square-wave signal as an output signal which may assume a first value or a second value, and a signal edge being associated with a tooth edge, and the position in time of a counteredge with respect to the edge encoding a direction of rotation, an assignment of a direction of rotation reversal point to a tooth of the sensor wheel or a tooth gap of the sensor wheel being encoded by the position in time of the counteredge with respect to the edge, the rotation angle being ascertained by adding an increment for each signal edge to a counter, after a direction of rotation reversal while a tooth passes the sensor, a half-increment, having a sign of the direction of rotation after the direction of rotation reversal, being incremented once and in the event of a direction of rotation reversal while a tooth gap passes the sensor, a half-increment, having a sign of the direction of rotation prior to the direction of rotation reversal, being incremented once.

Owner:ROBERT BOSCH GMBH

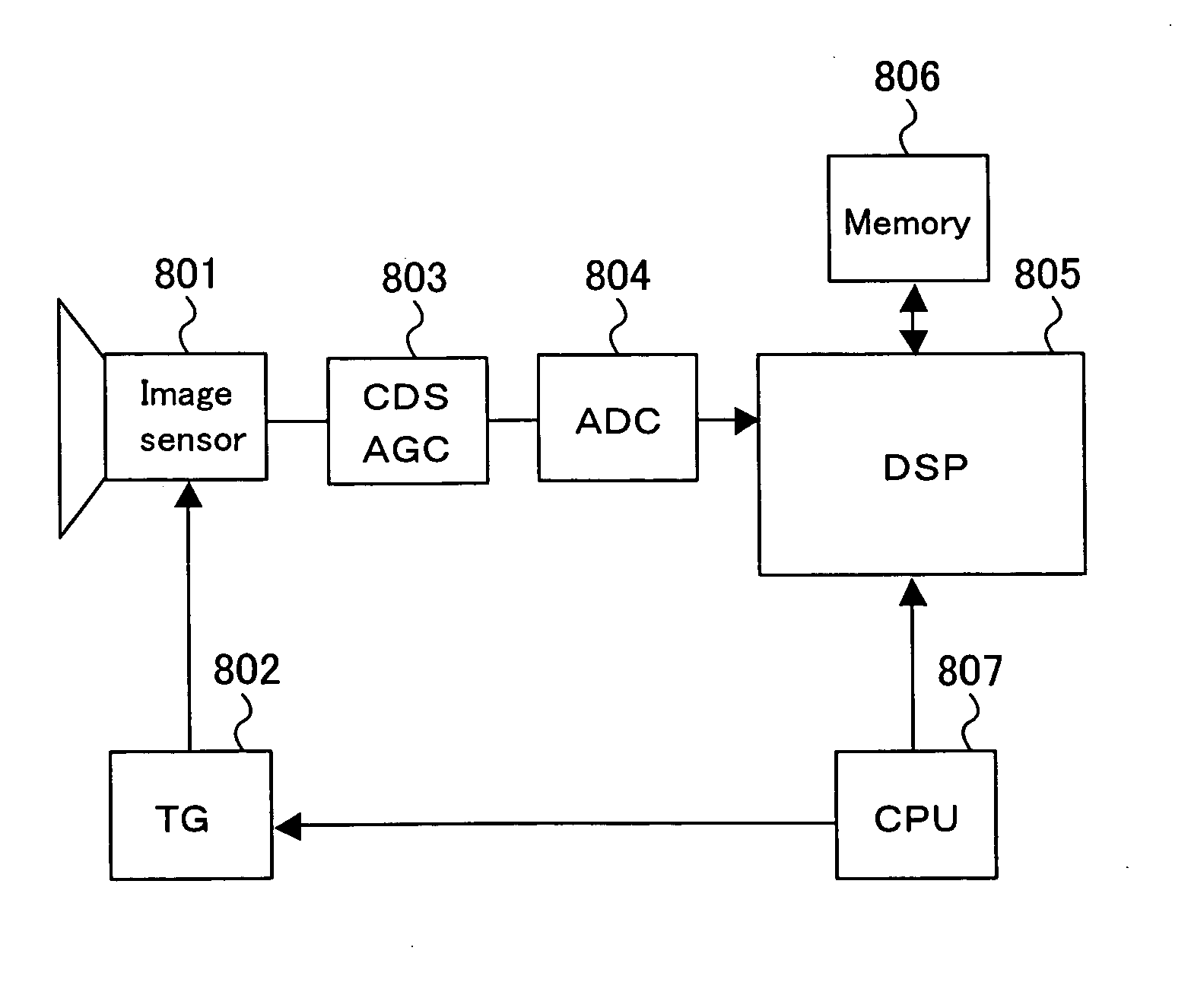

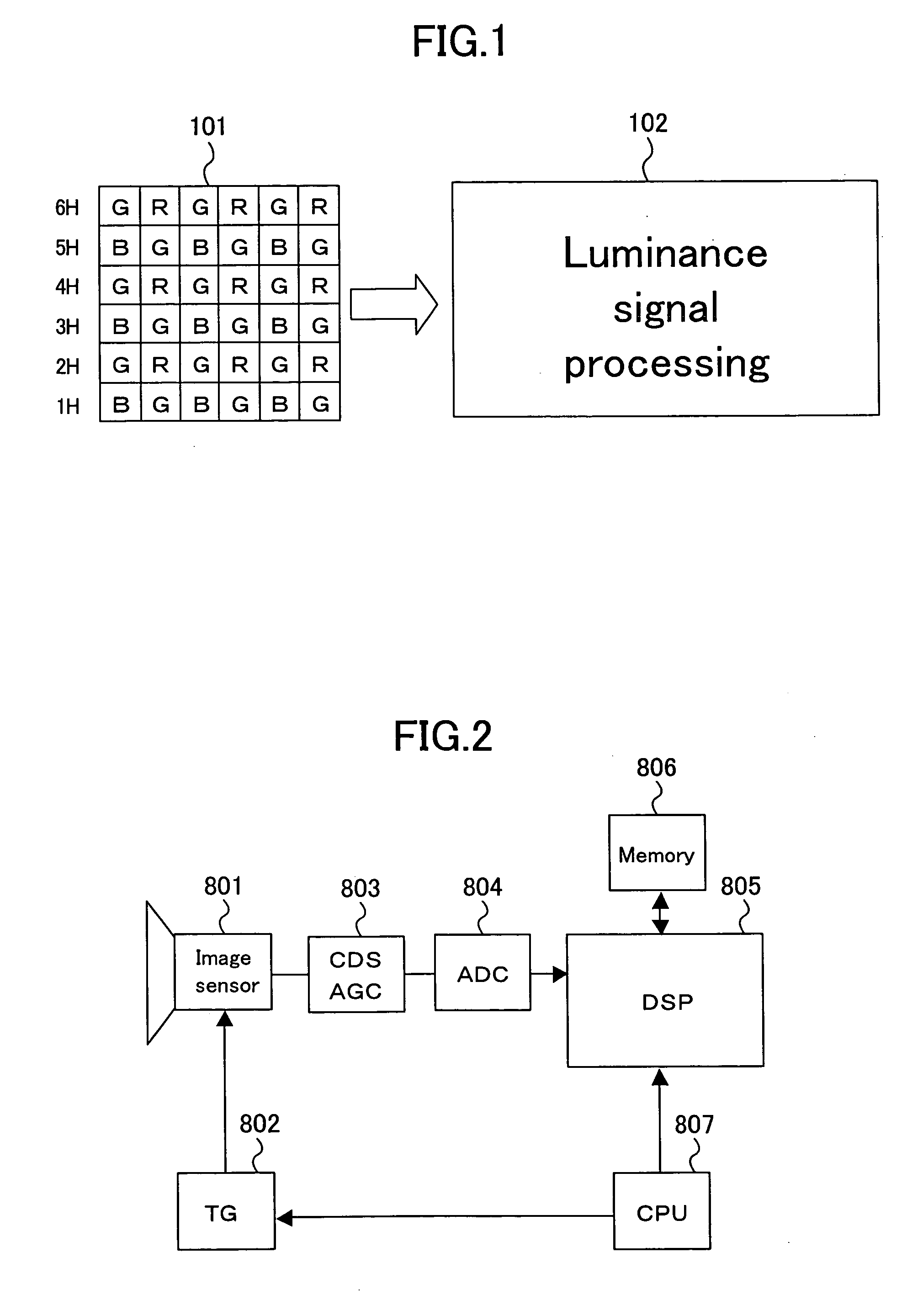

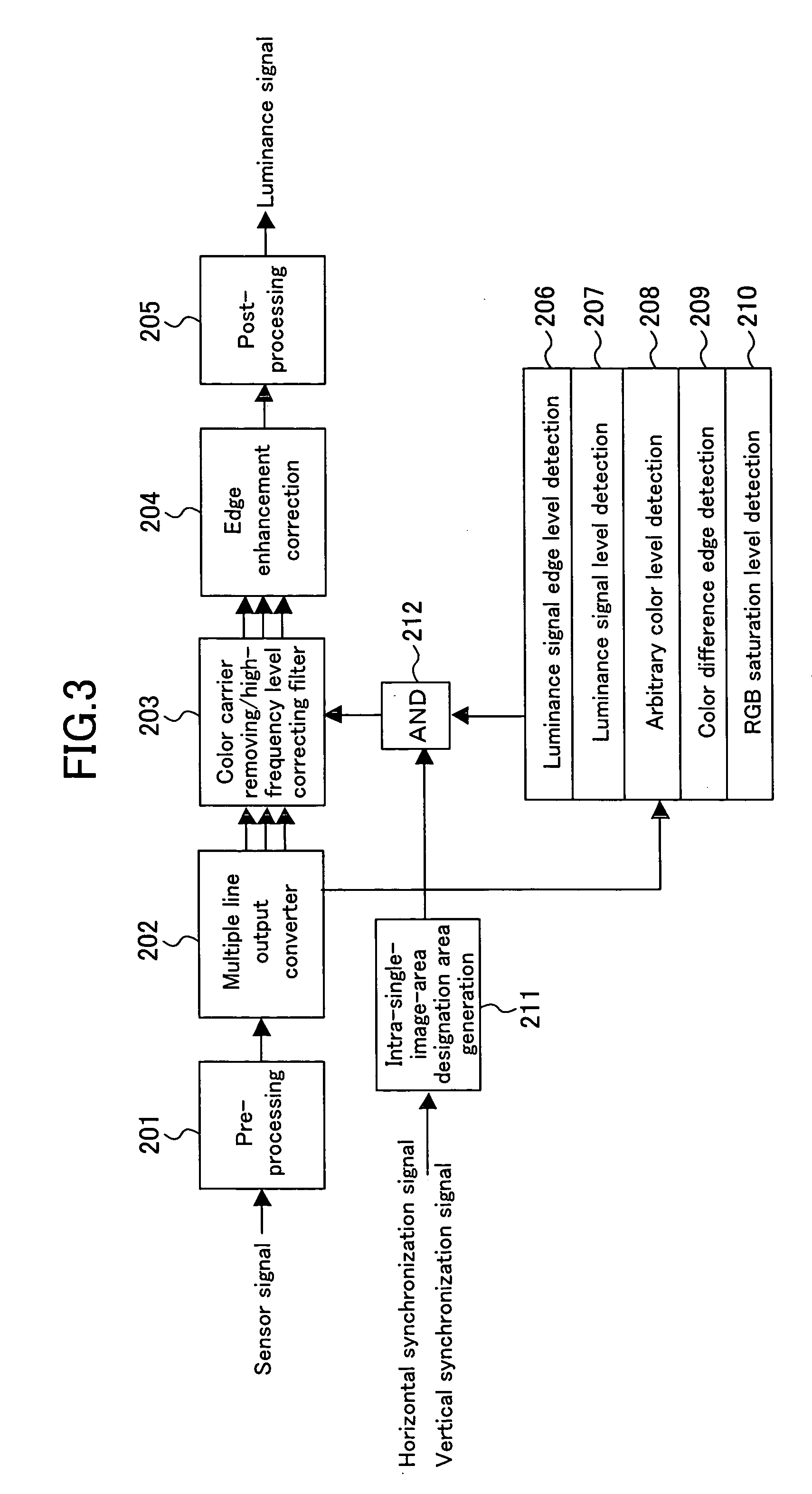

Luminance signal processing device

InactiveUS20060256217A1High resolutionInhibitionTelevision system detailsColor signal processing circuitsColor imageSignal edge

A filter section performs color carrier component removal and high-frequency level correction according to color image signal data, and a correction section performs edge enhancement correction. By these operations, luminance signal data is obtained. The characteristics of the filter section are established adaptively in accordance with the luminance signal level of low spatial frequency components in the color image signal data, the luminance signal edge level in the color image signal data, whether or not a predetermined color is exhibited in the color image signal data, a color difference edge level in the color image signal data, or whether or not the RGB data reaches the saturation level in the color image signal data.

Owner:COLLABO INNOVATIONS INC

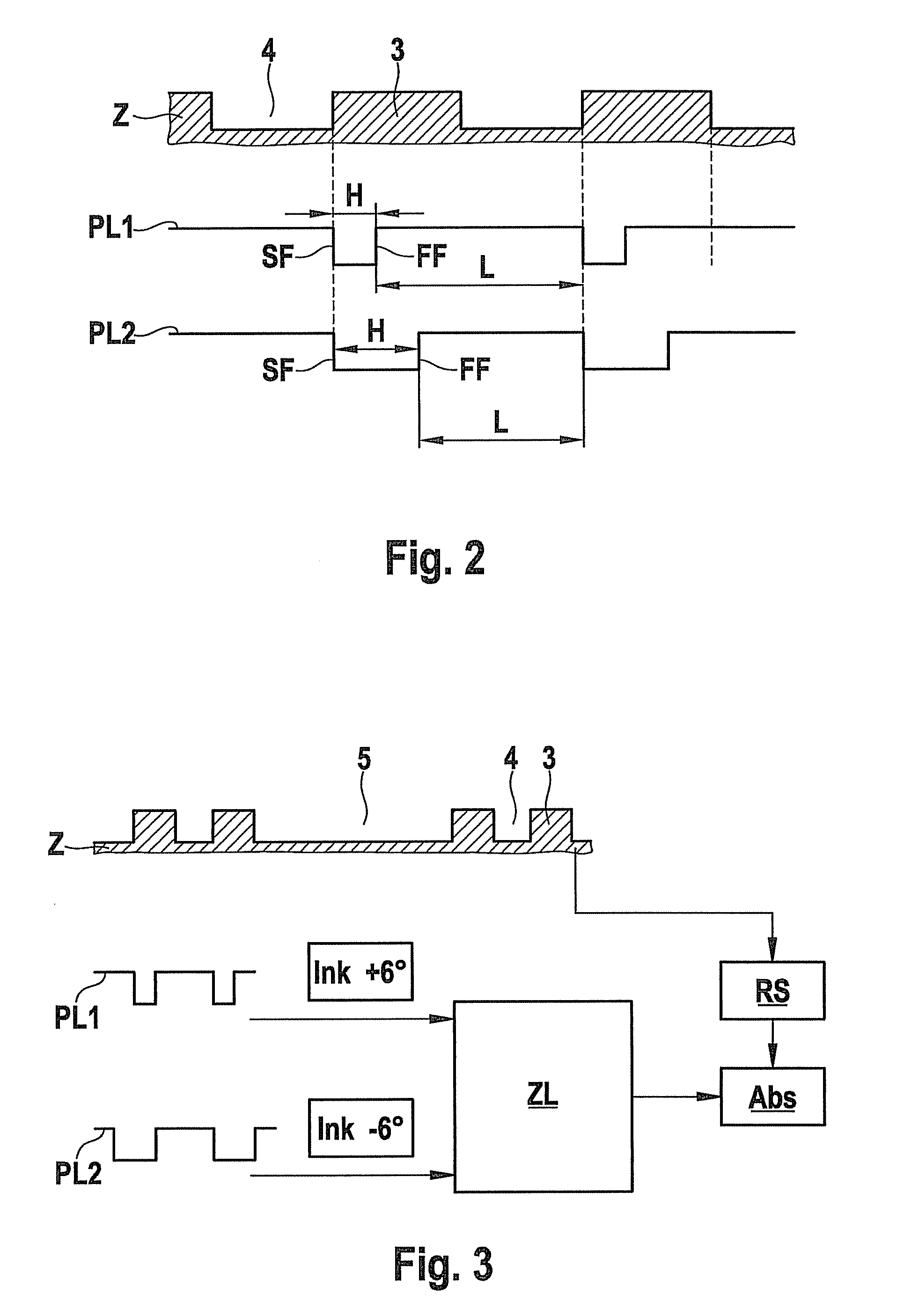

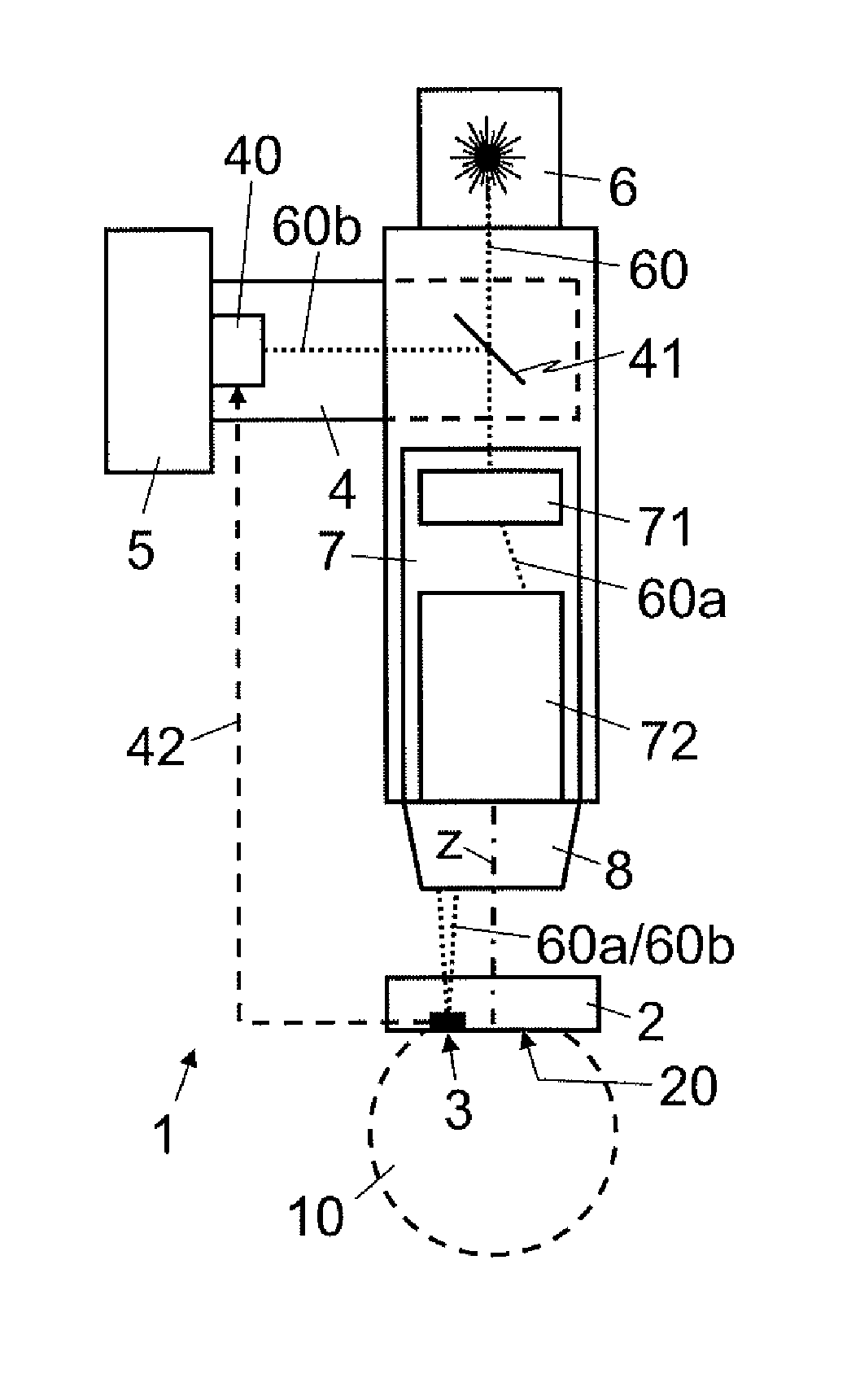

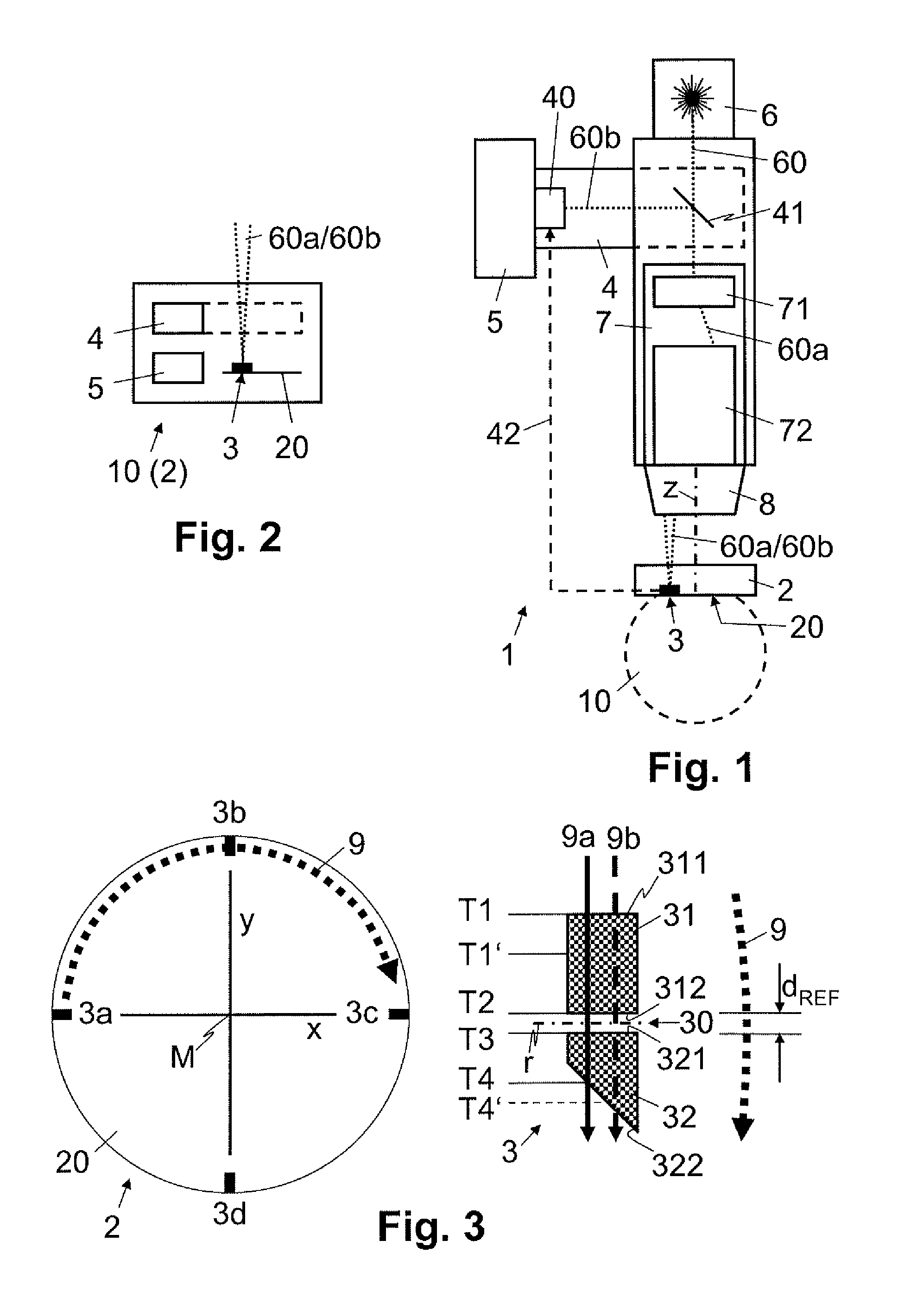

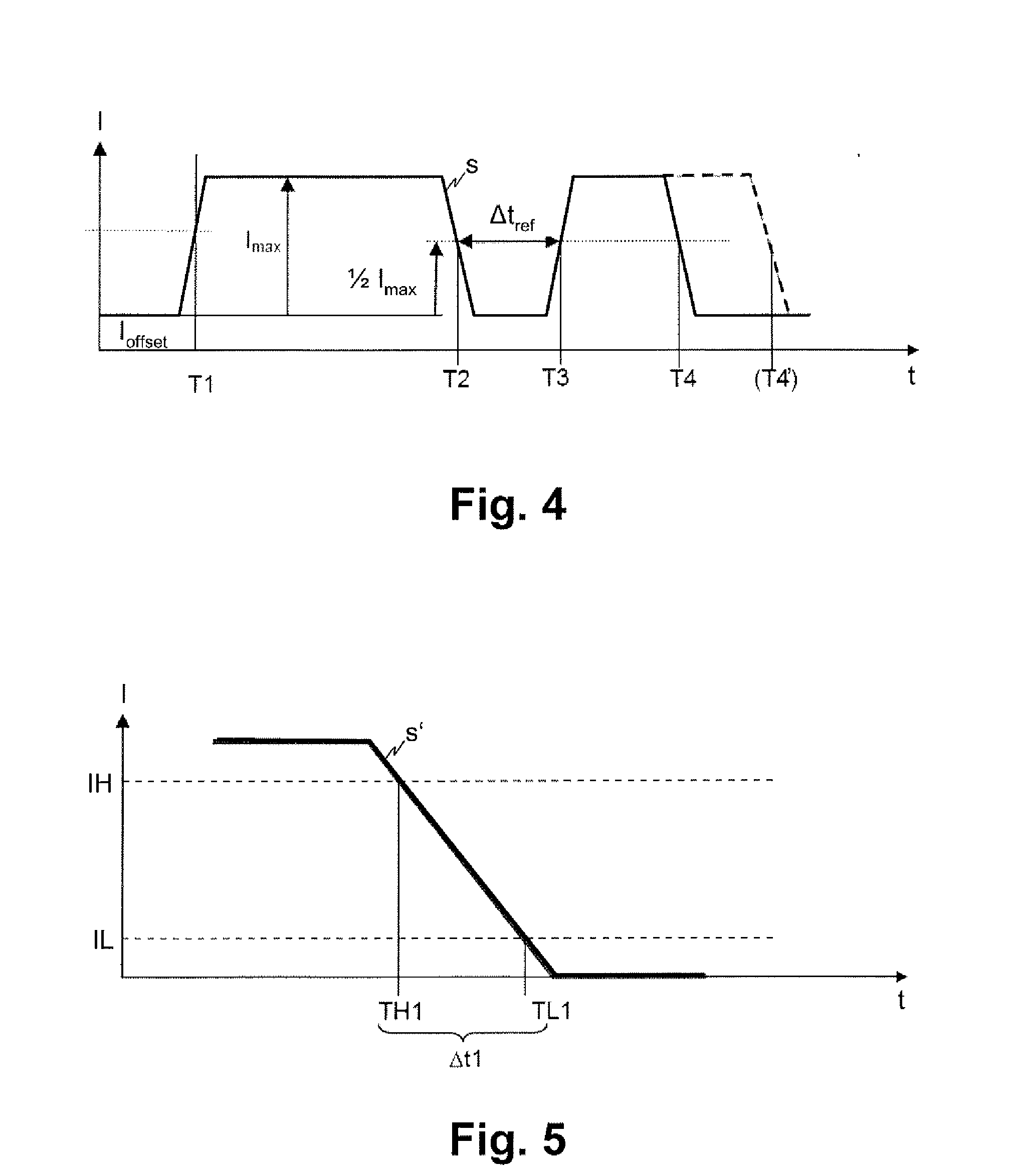

Device and method for determining the focus position of a laser beam

In order to determine the focus position of a laser beam (60, 60a) in an ophthalmological laser projection system (1), at least one measurement marking (3) applied to a reference area (20) is passed over by means of the laser beam (60, 60a) along a scanning path. A measurement signal created by passing over the measurement marking (3) is captured. Time values from at least one signal edge created in the measurement signal when passing over edges of the measurement marking (3) are determined and the focus position is established on the basis of the time values. By scanning defined measurement markings (3) and establishing time values of signal edges created when edges of the measurement marking (3) are passed over, it is possible to determine the focus position of the laser beam (60, 60a) without focusing movements being required for this during the measurement.

Owner:ZIEMER OPHTHALMIC SYST

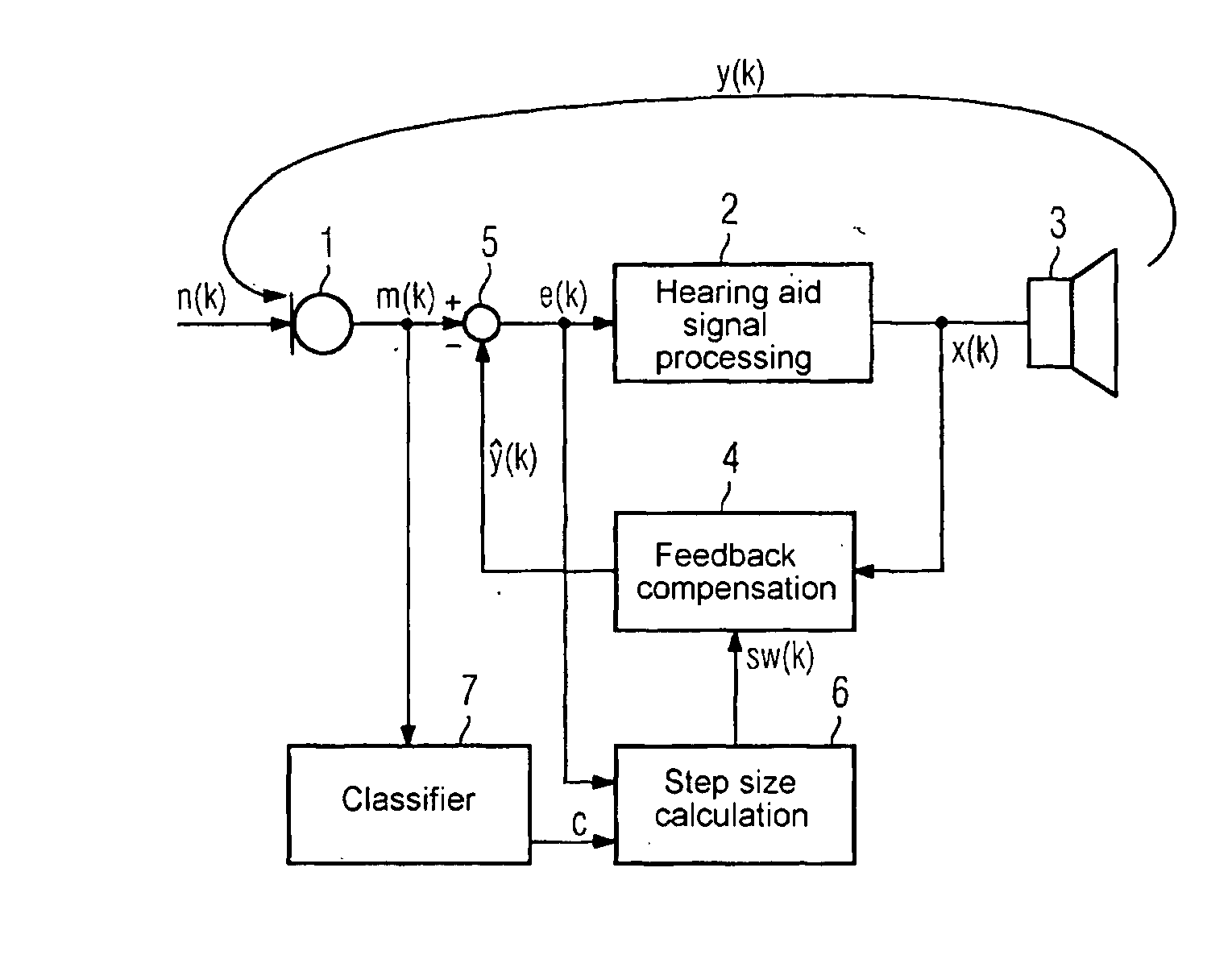

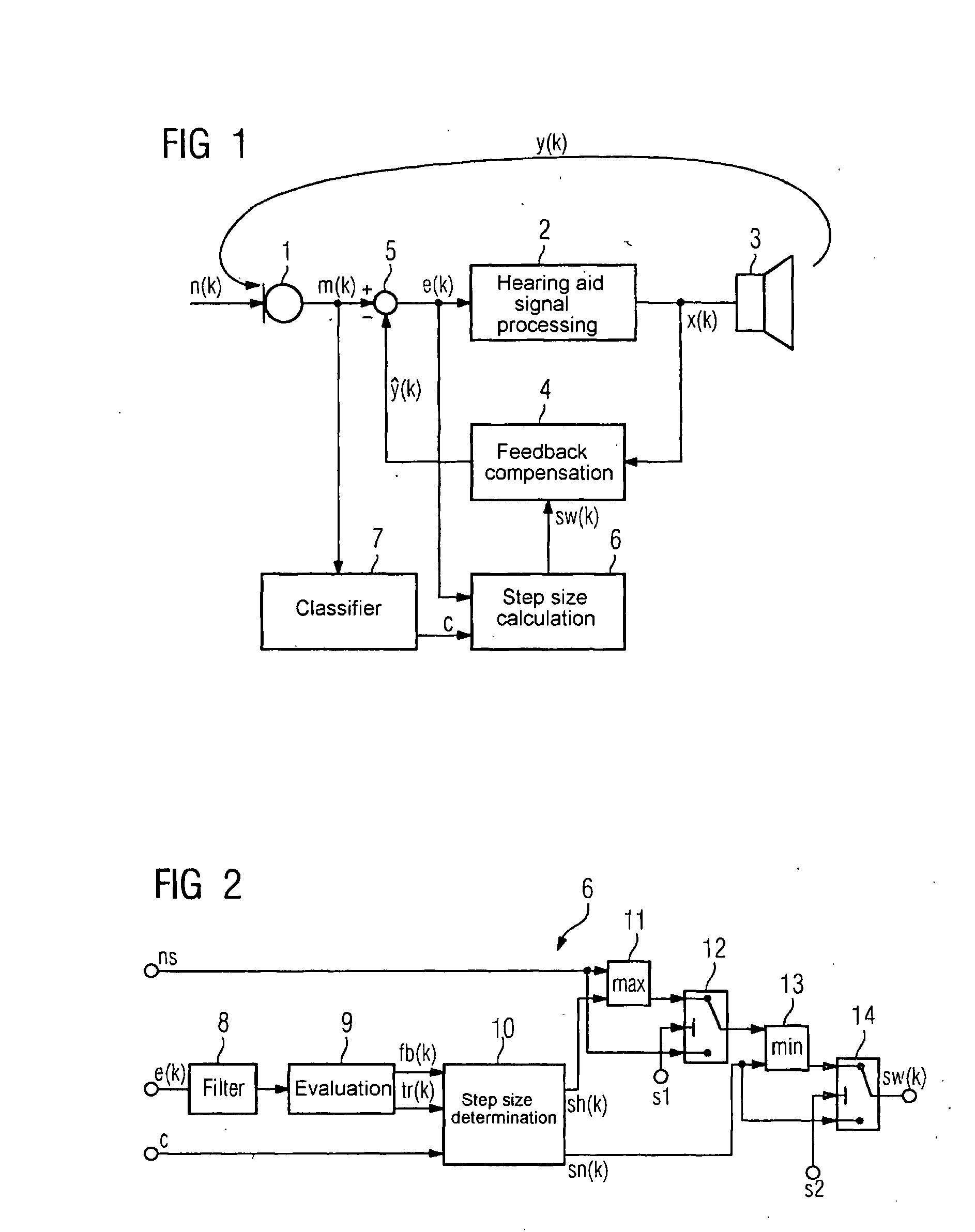

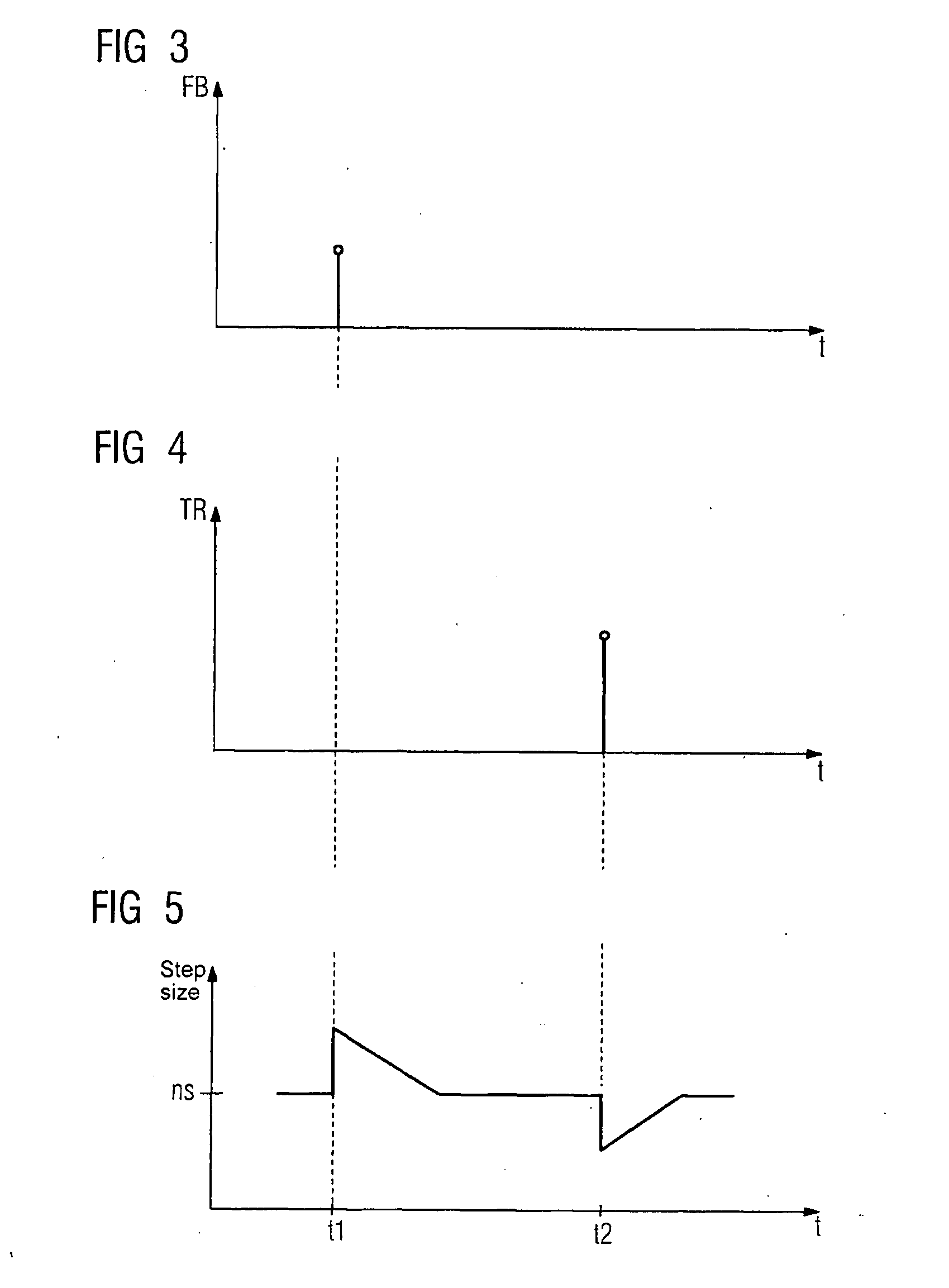

Device and method for controlling the step size of an adaptive filter

InactiveUS20070297627A1Easy to adaptPublic address systemsTransducer acoustic reaction preventionHearing aidSignal edge

Owner:SIVANTOS PTE LTD