Patents

Literature

170 results about "Ic testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Ion Chromatography Testing (IC Testing) Ion Chromatography Testing provides cleanliness-related information, specifically individual ionic data values, for various types of samples, including, but not limited to, printed circuit boards, printed circuit assemblies, and soldering fluxes..

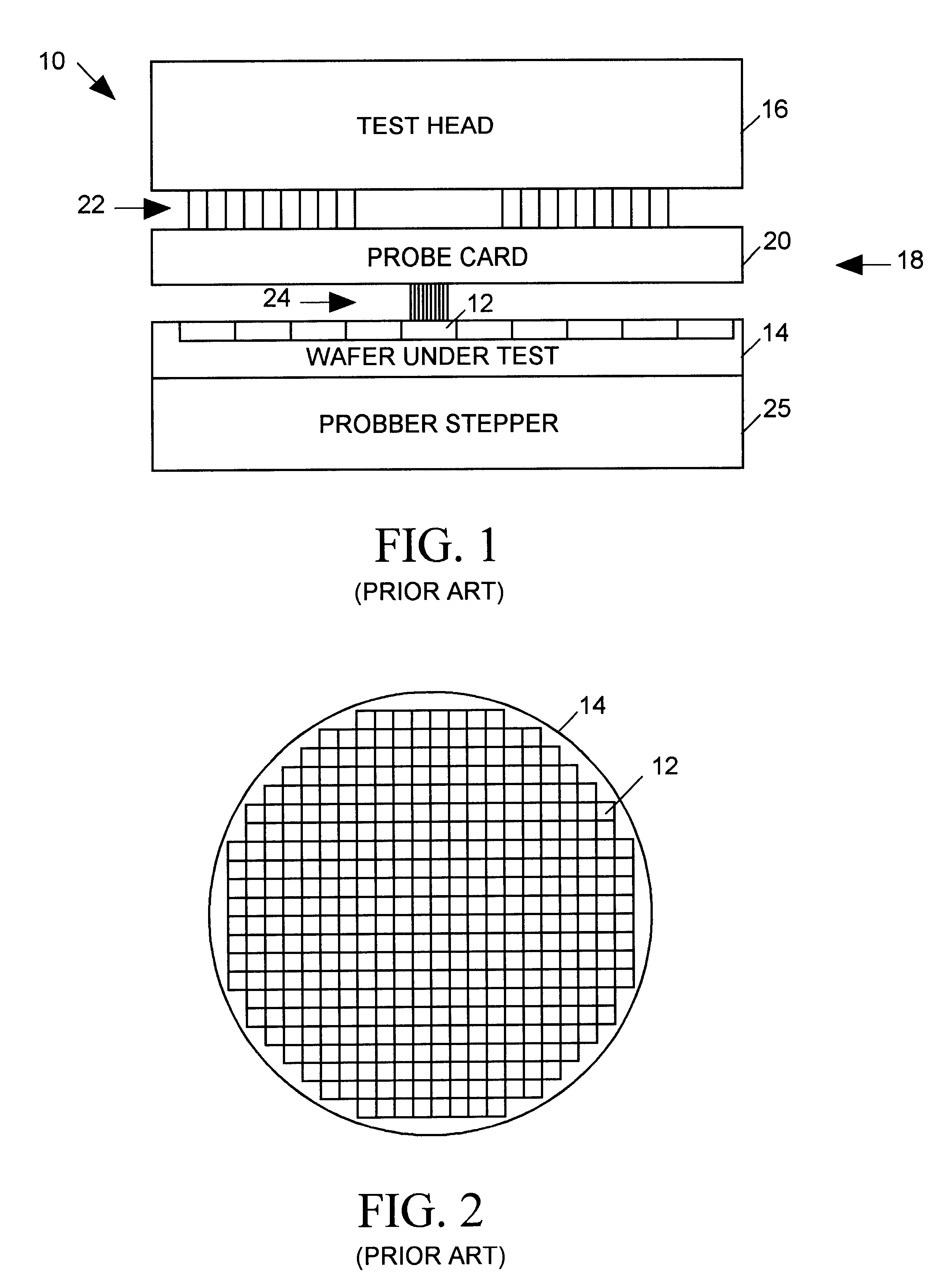

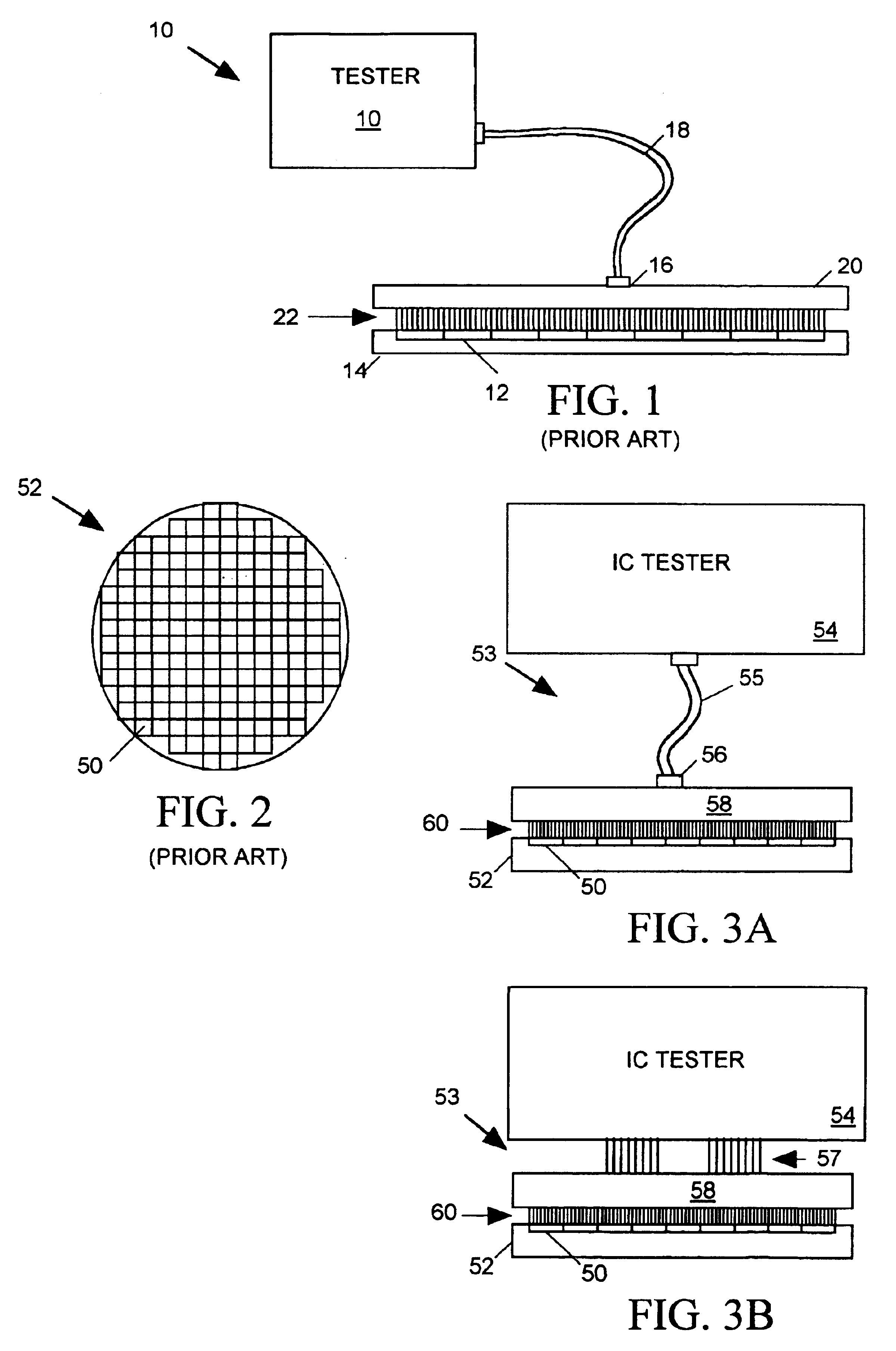

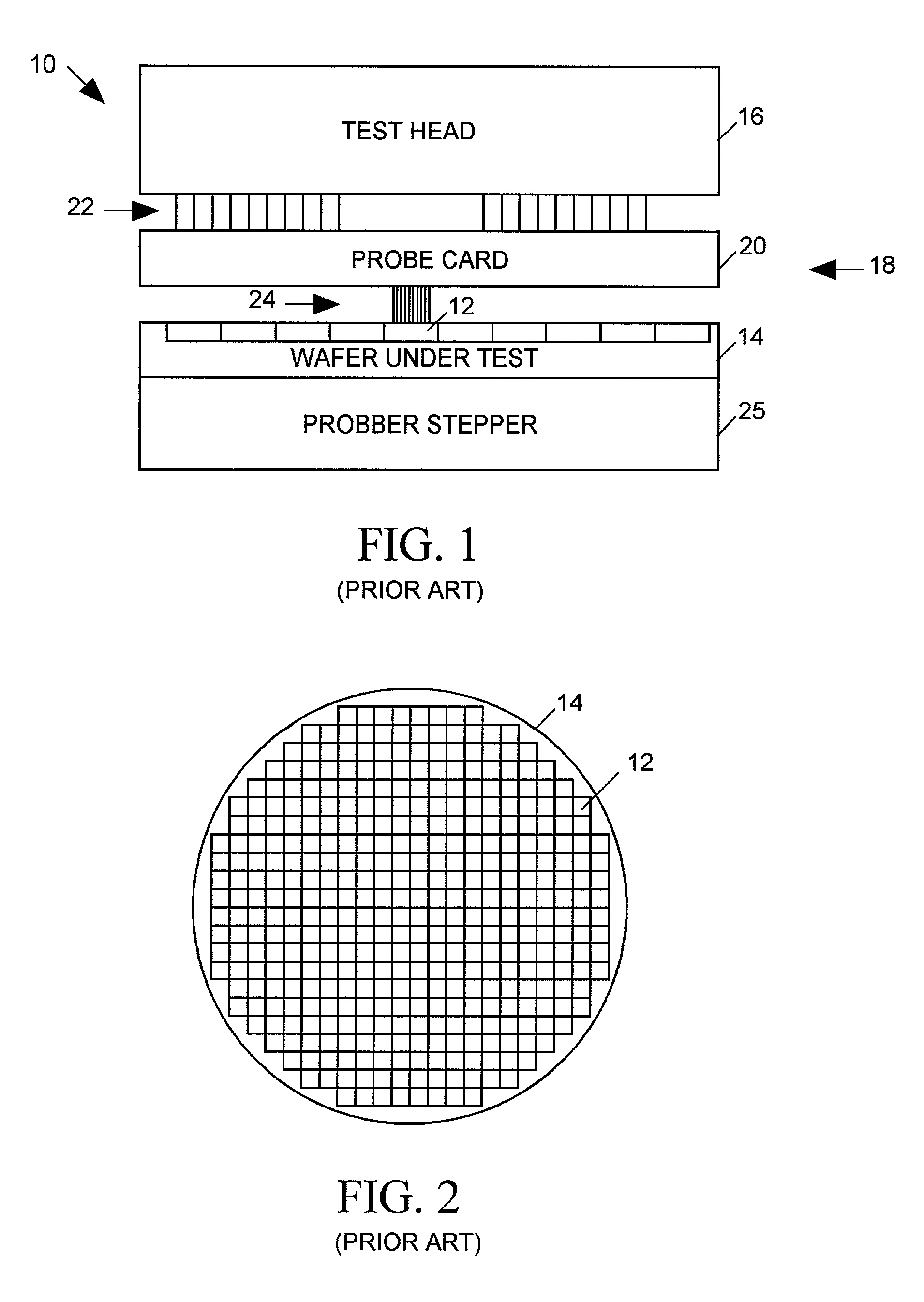

High bandwidth passive integrated circuit tester probe card assembly

InactiveUS6218910B1Multiple-port networksElectrical measurement instrument detailsCapacitanceProbe card

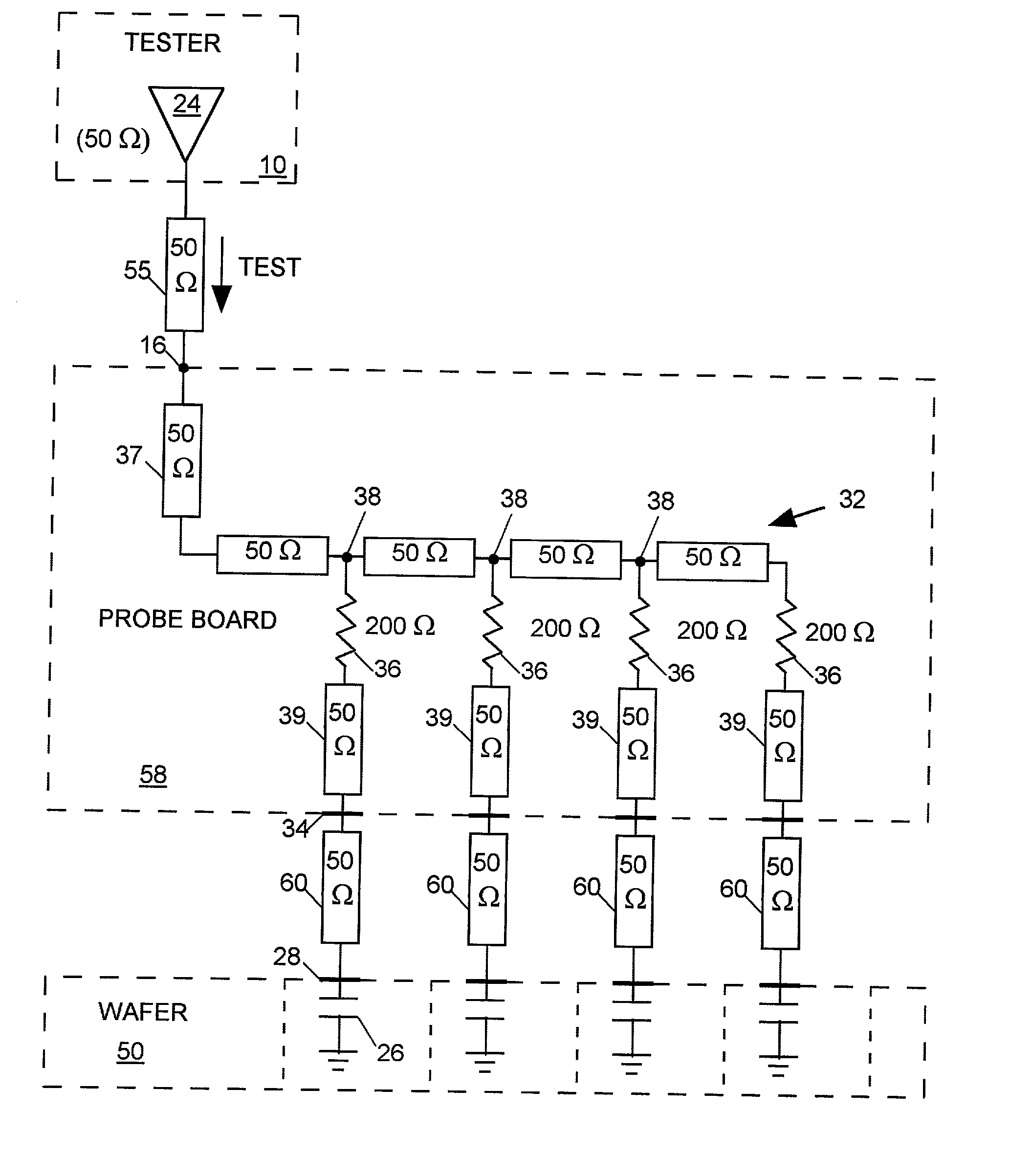

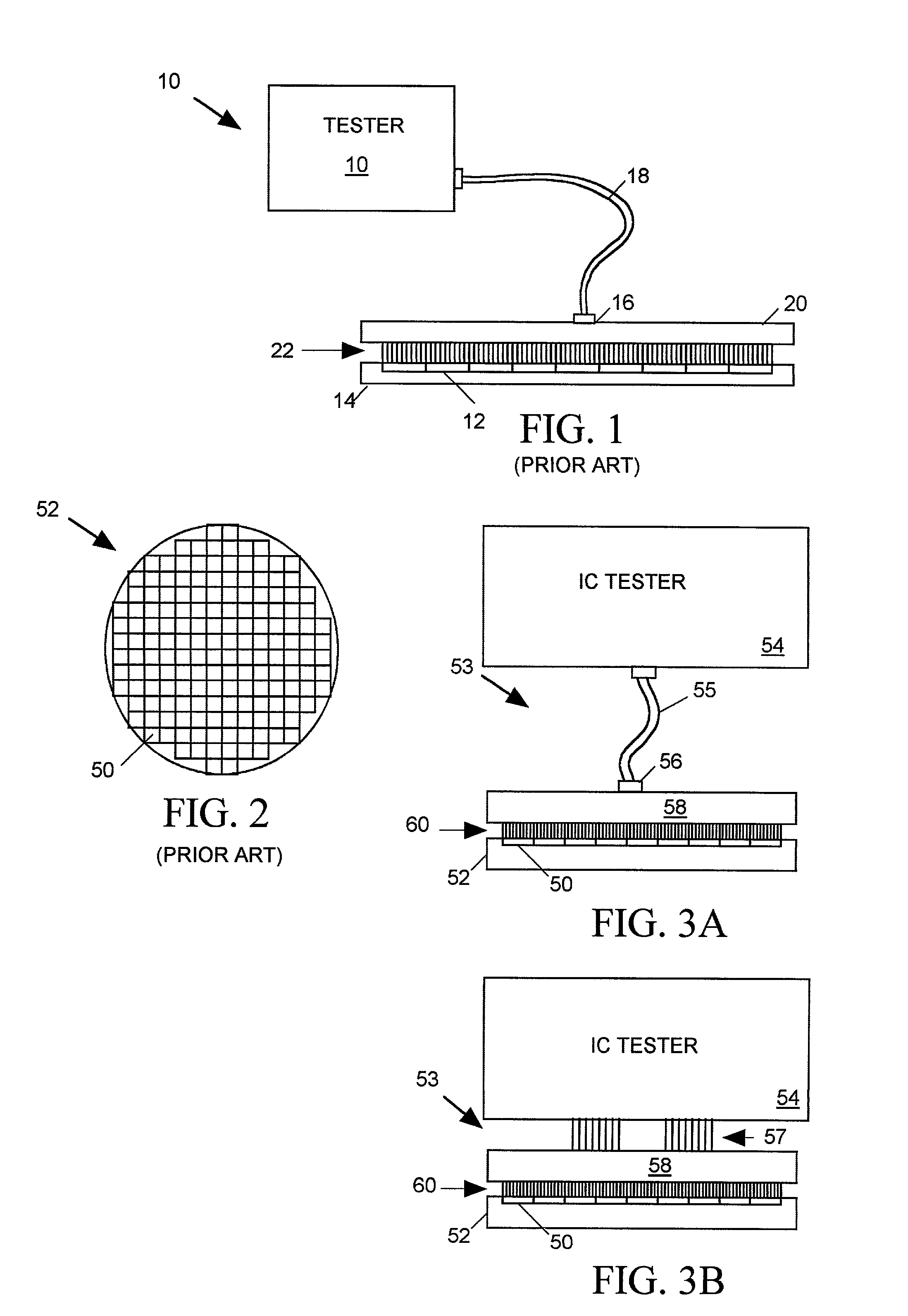

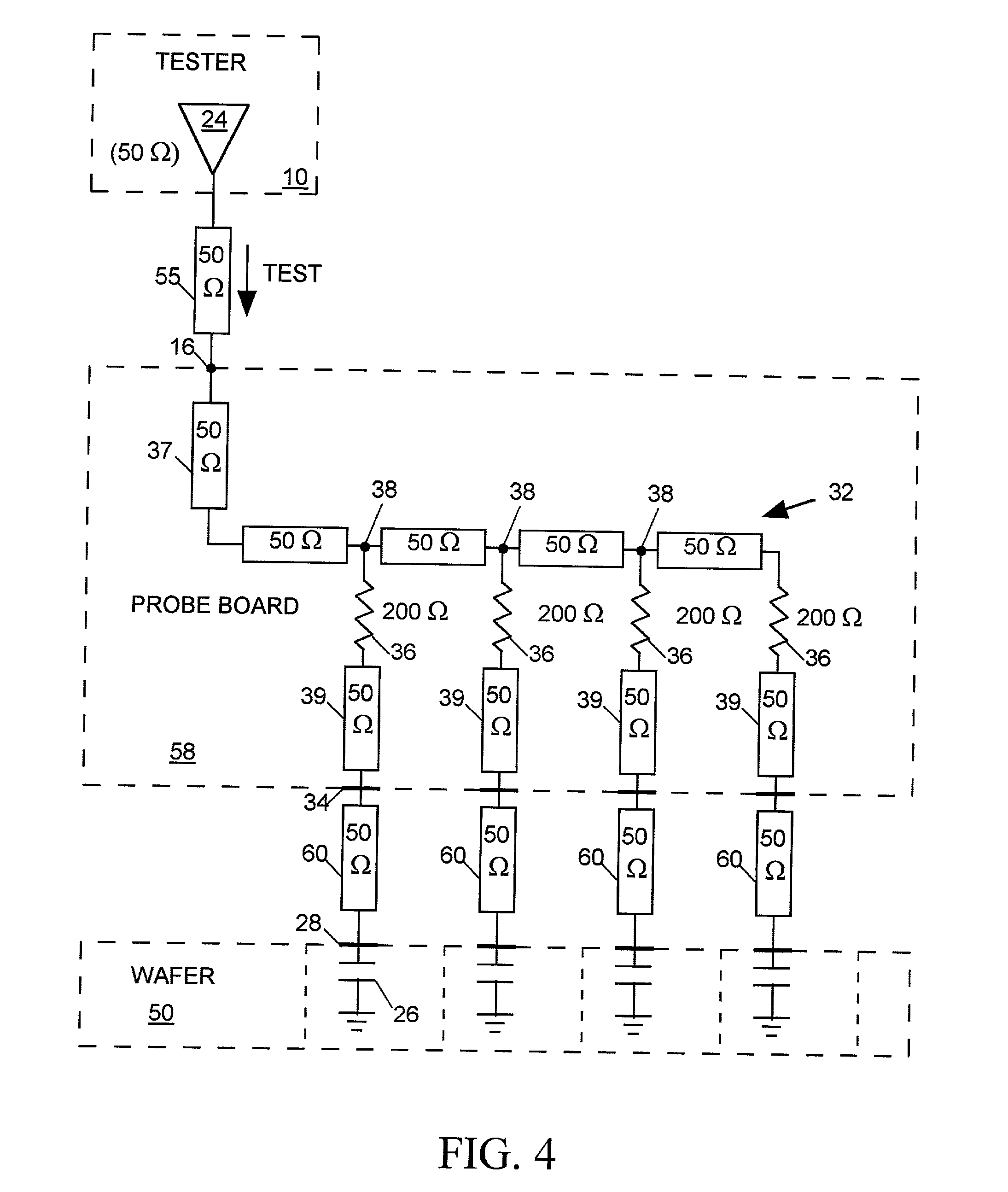

Described herein is a probe card assembly providing signal paths for conveying high frequency signals between bond pads of an integrated circuit (IC) and an IC tester. The frequency response of the probe card assembly is optimized by appropriately distributing, adjusting and impedance matching resistive, capacitive and inductive impedance values along the signal paths so that the interconnect system behaves as an appropriately tuned Butterworth or Chebyshev filter.

Owner:FORMFACTOR INC

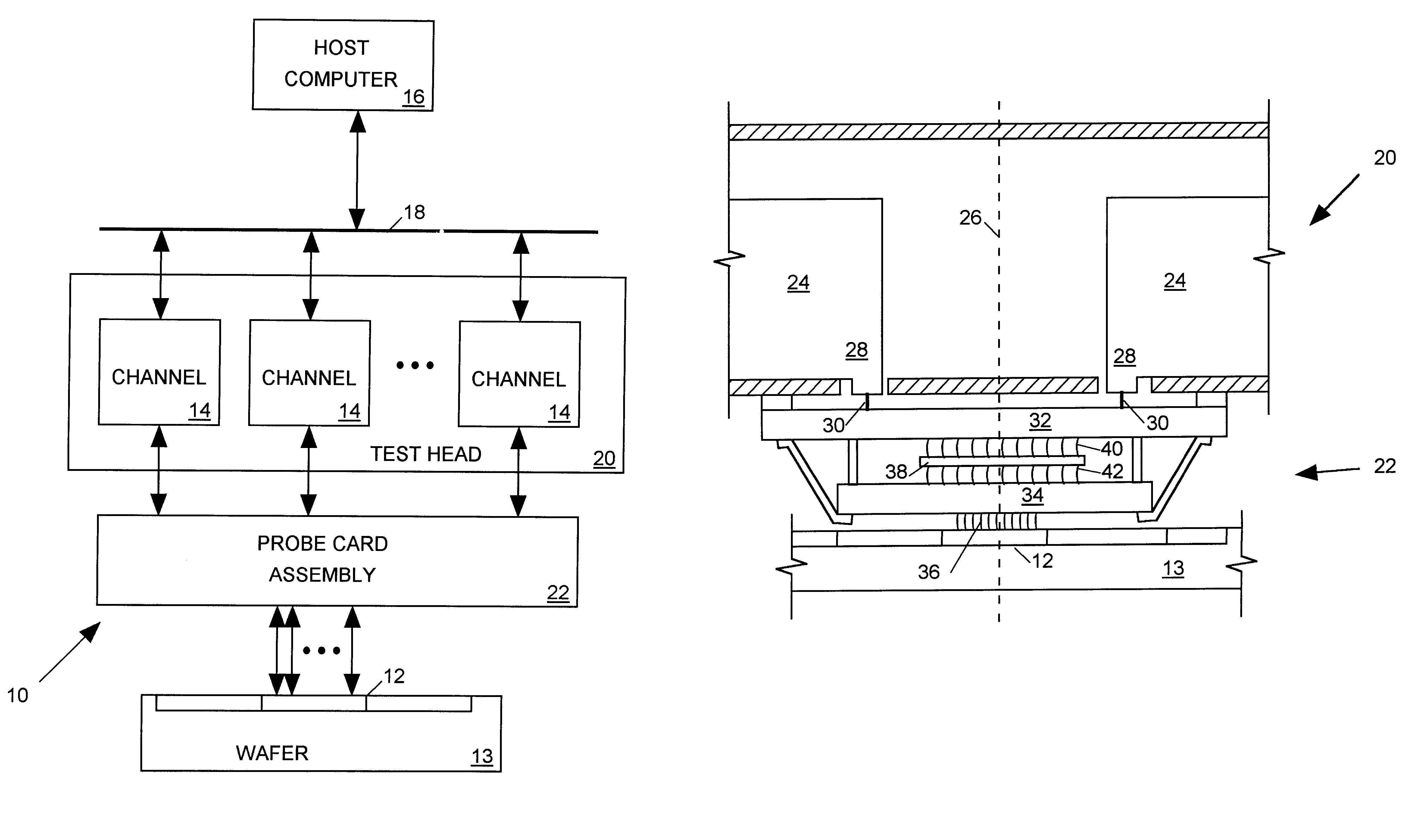

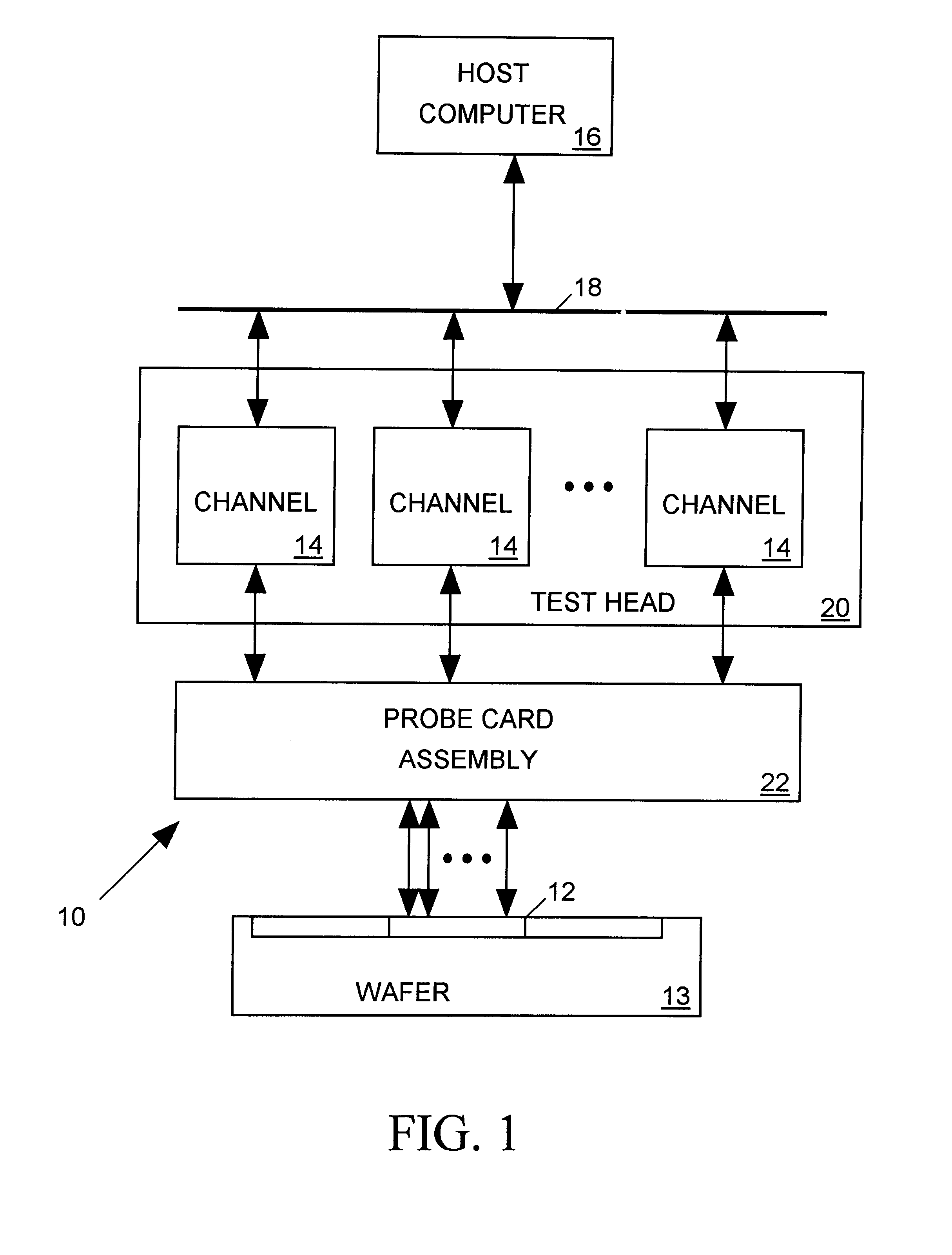

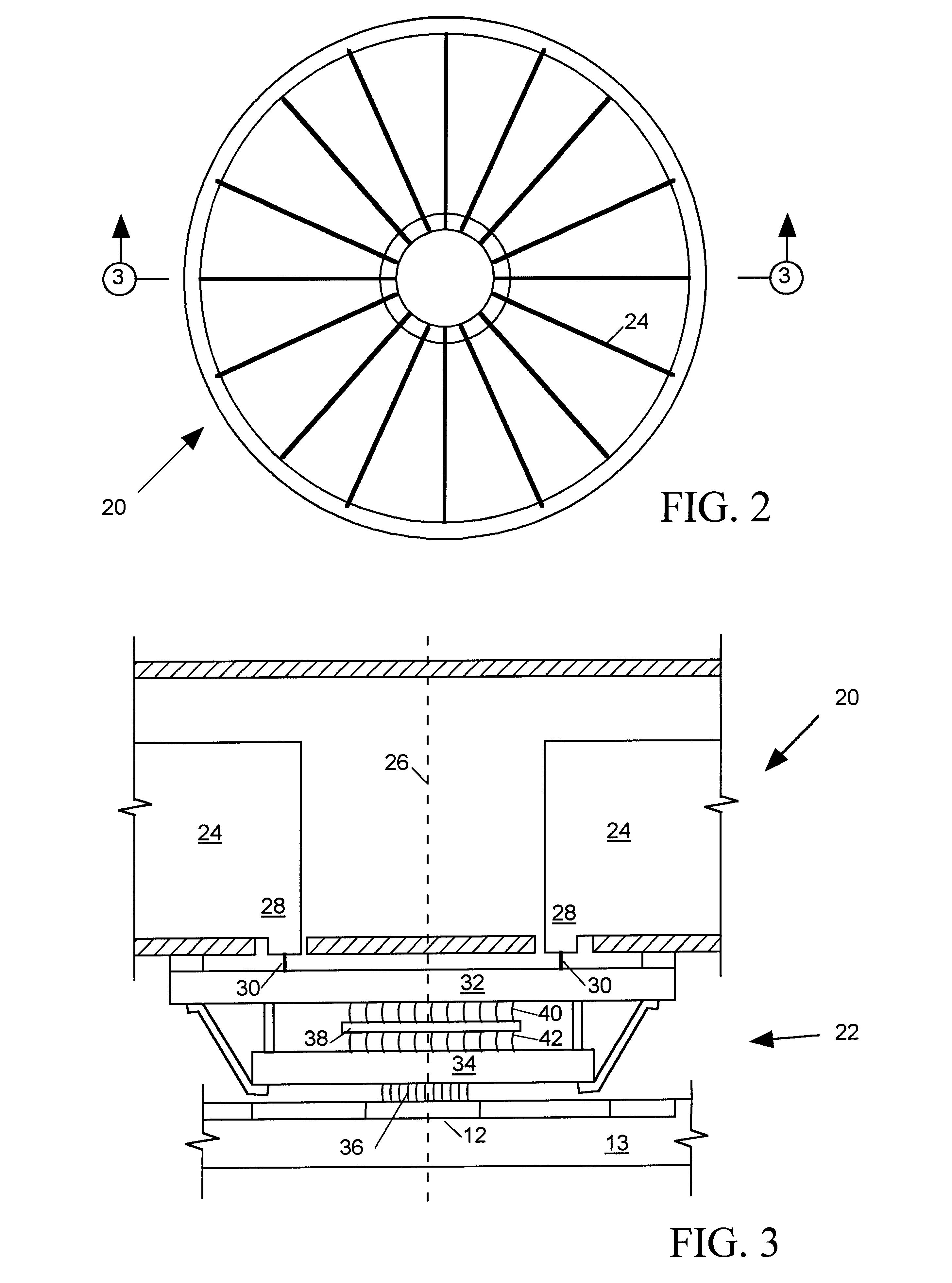

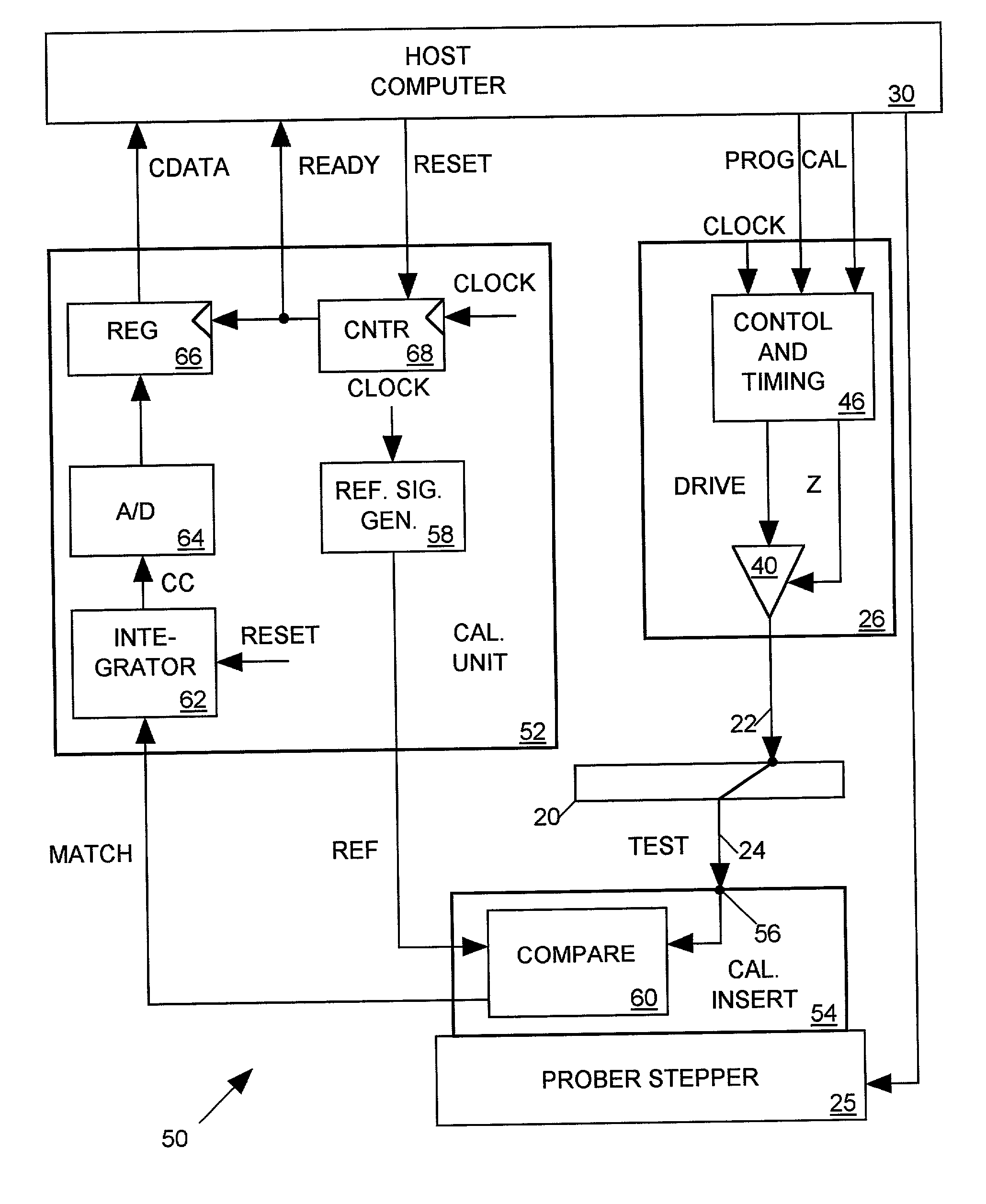

Cross-correlation timing calibration for wafer-level IC tester interconnect systems

InactiveUS6606575B2Easy accessDigital circuit testingTesting/calibration apparatusEngineeringSignal edge

To calibrate timing of test signals generated by all channels of an integrated circuit, each channel is programmed to generate a test signal having a repetitive pseudo-random test signal edge pattern. The test signal pattern of each channel is compared to a reference signal having the same edge pattern and the delay of each channel is adjusted to maximize cross-correlation between the test signal and the reference signal.

Owner:FORMFACTOR INC

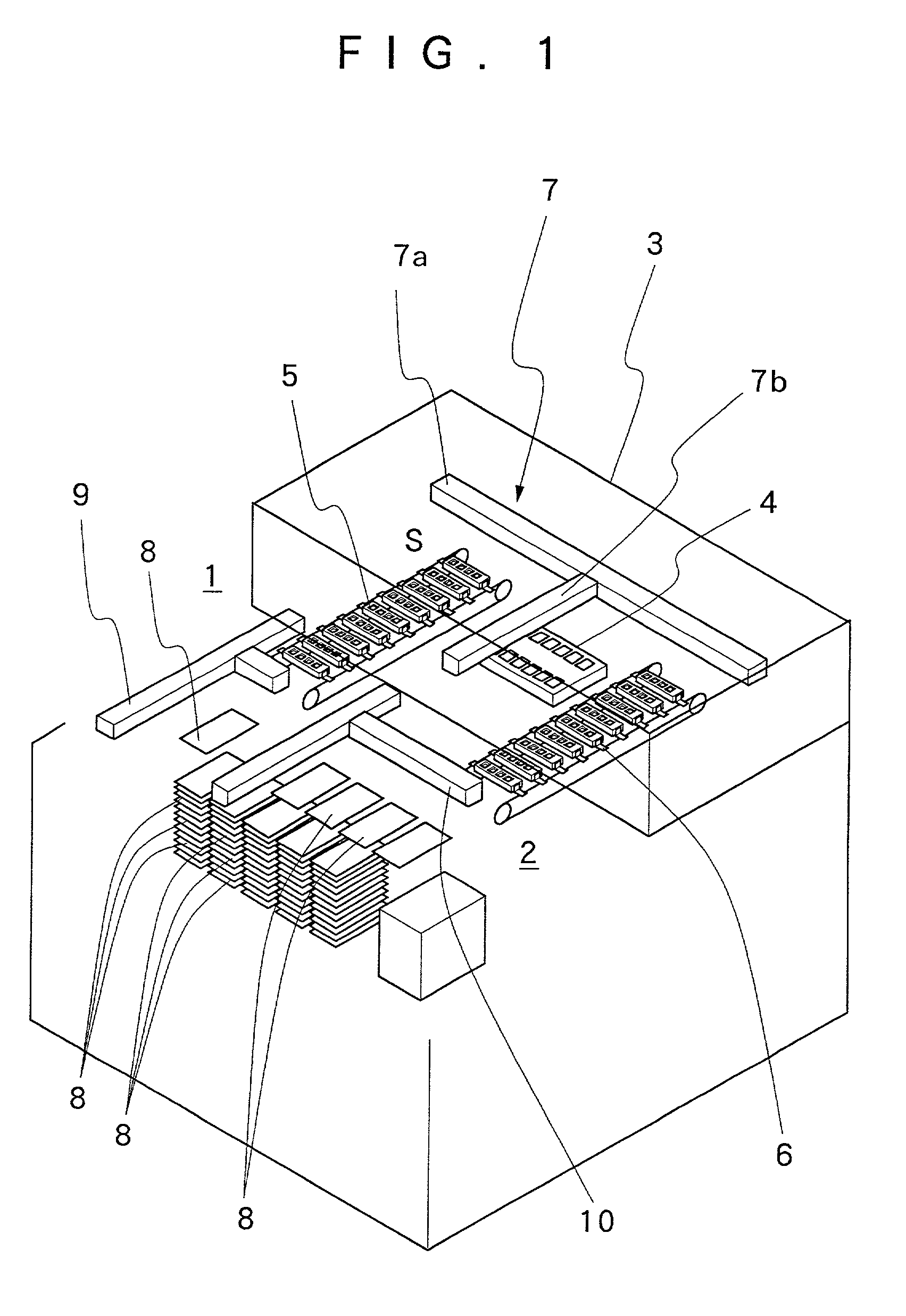

Method and apparatus for testing IC device

InactiveUS6515470B2Semiconductor/solid-state device testing/measurementDigital data processing detailsElectricityEngineering

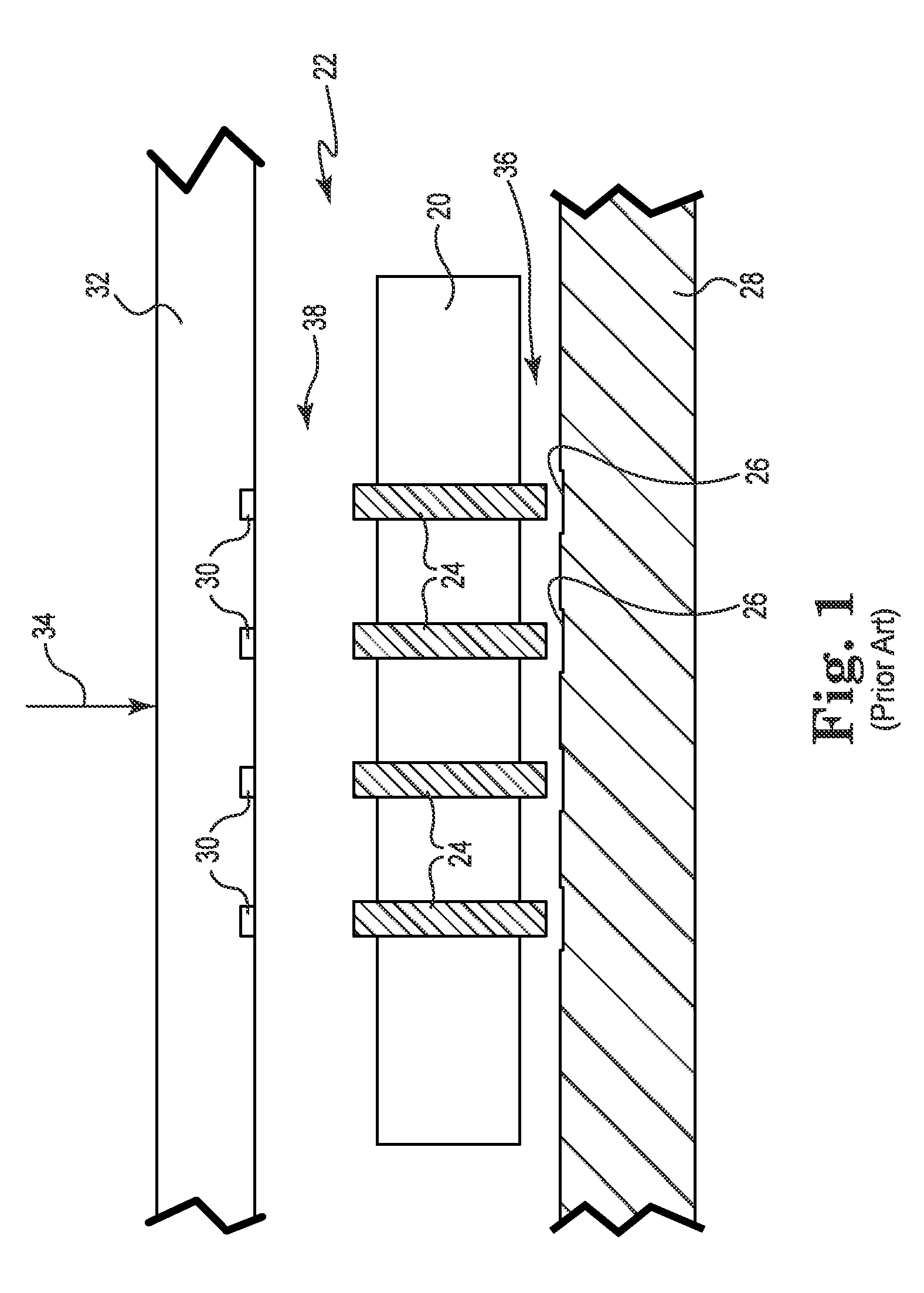

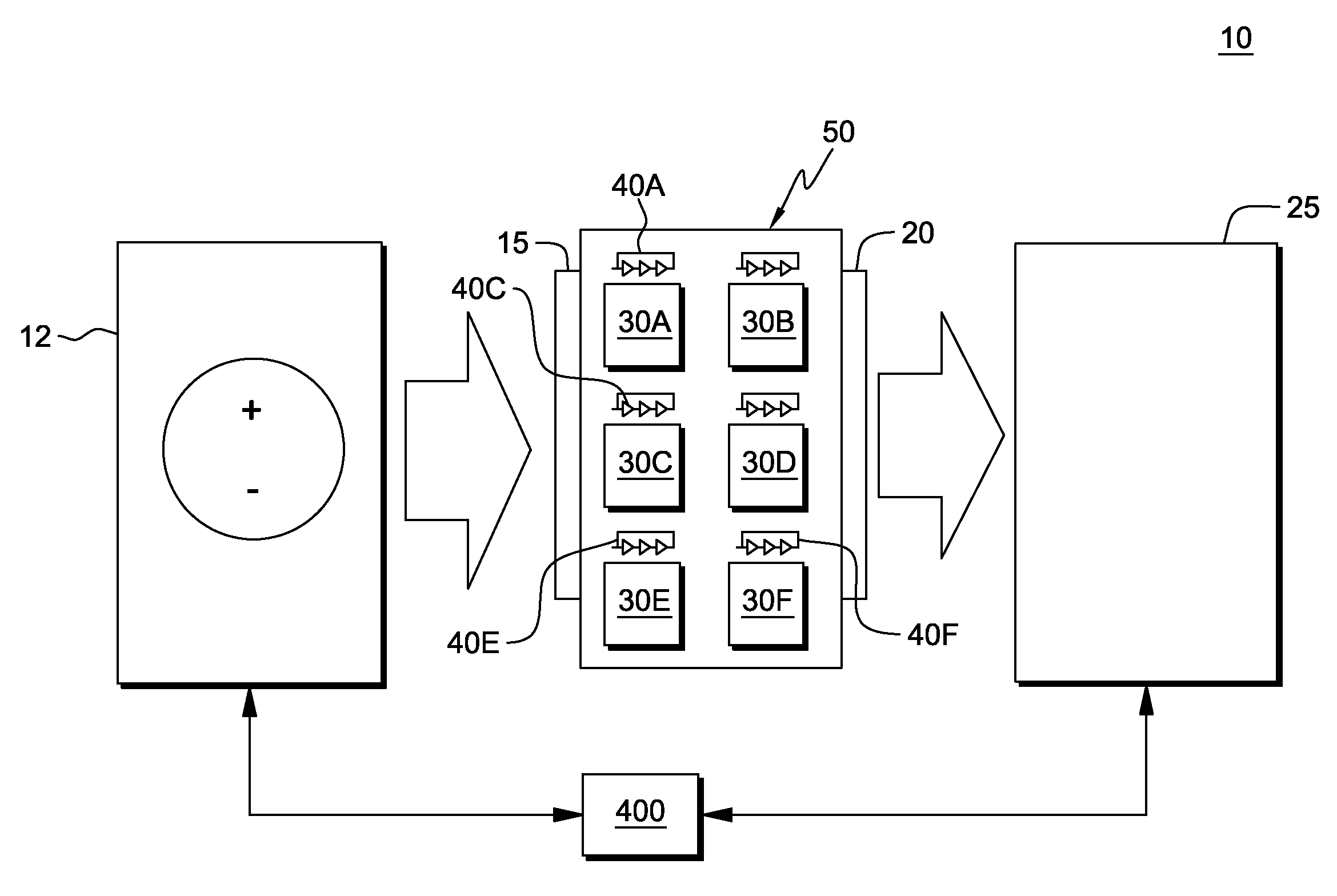

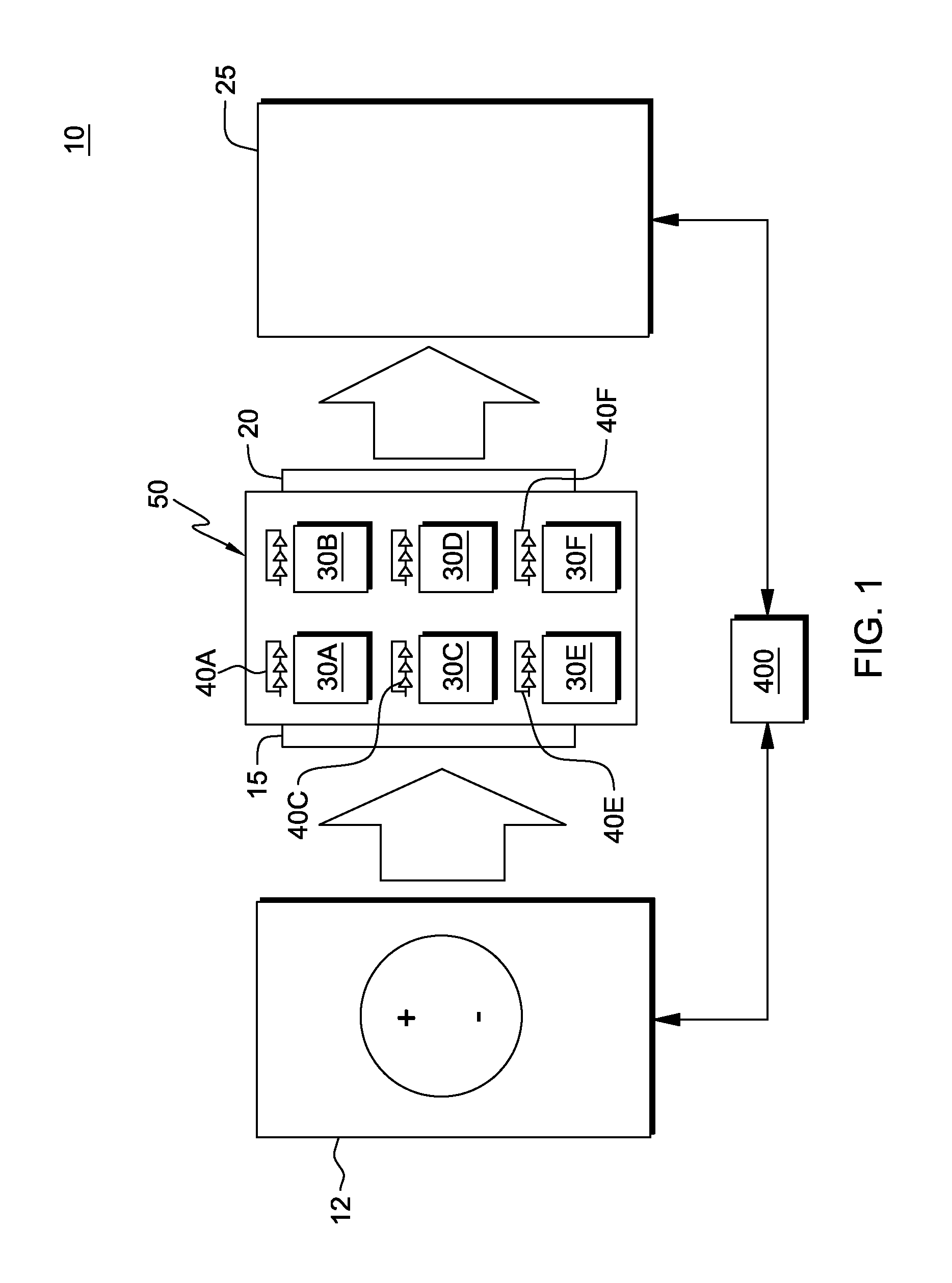

For testing electrical properties of packaged IC devices, there is provided an apparatus which includes a test board which is located at a testing station and provided with a plural number of contacting sockets for connecting individual IC devices to an IC tester separately and independently of each other, a loader which is located at a loading station and adapted to feed untested IC devices toward the test board, an unloader which is located at an unloading station and adapted to discharge tested IC devices from the test board at the testing station, and a device transfer mechanism which is movable across the testing station to transfer untested IC devices from the loader to the test board and also to transfer tested IC devices from the test board to the unloader. Upon detecting completion of a test on one of IC devices in one socket of the test board, a fresh untested IC device is transferred to the testing station to replace the tested IC device. As soon as the fresh IC device is set in position in that socket, execution of a test program is started with respect to that socket on the test board.

Owner:HITACHI ELECTRONICS ENG CO LTD

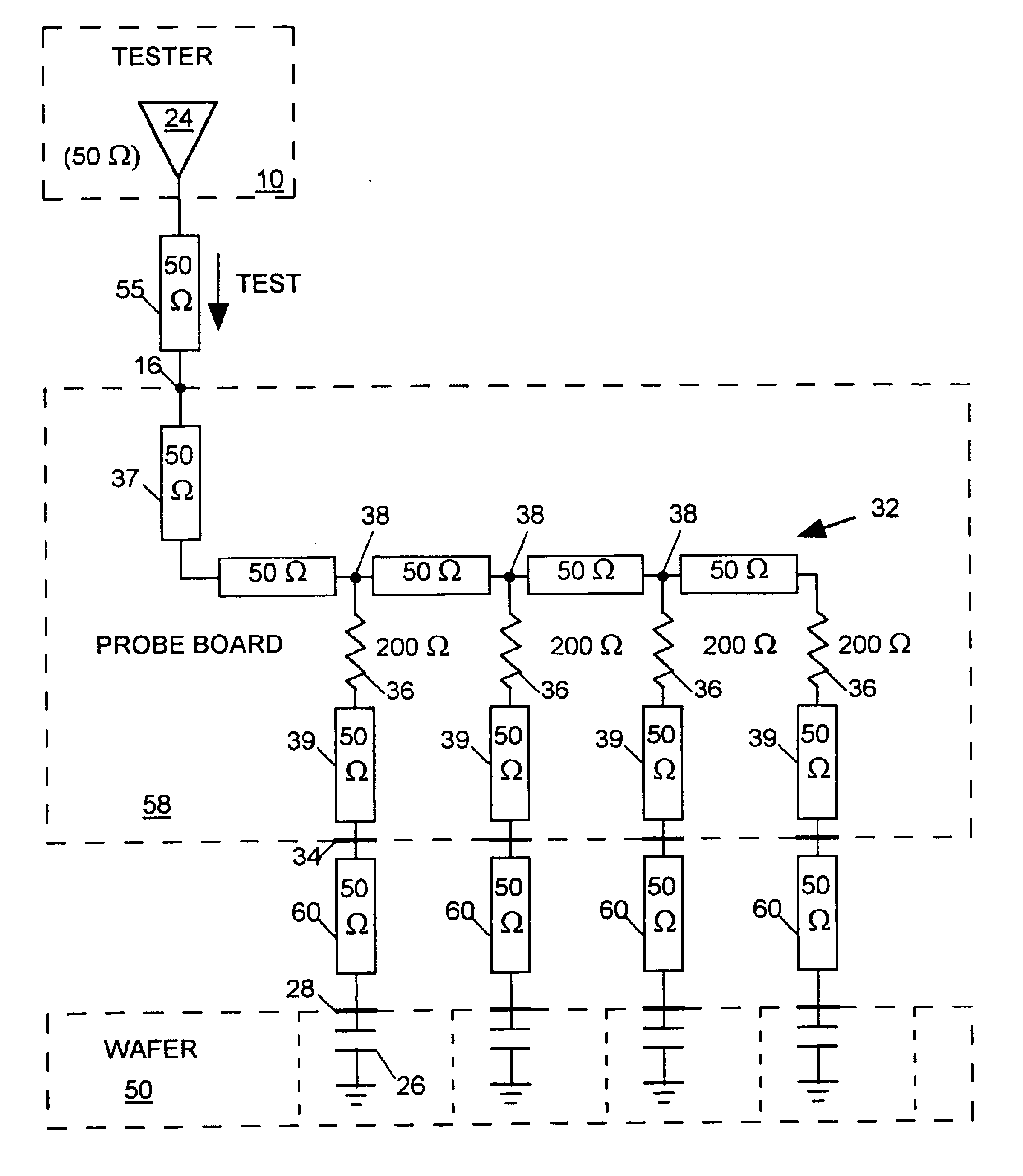

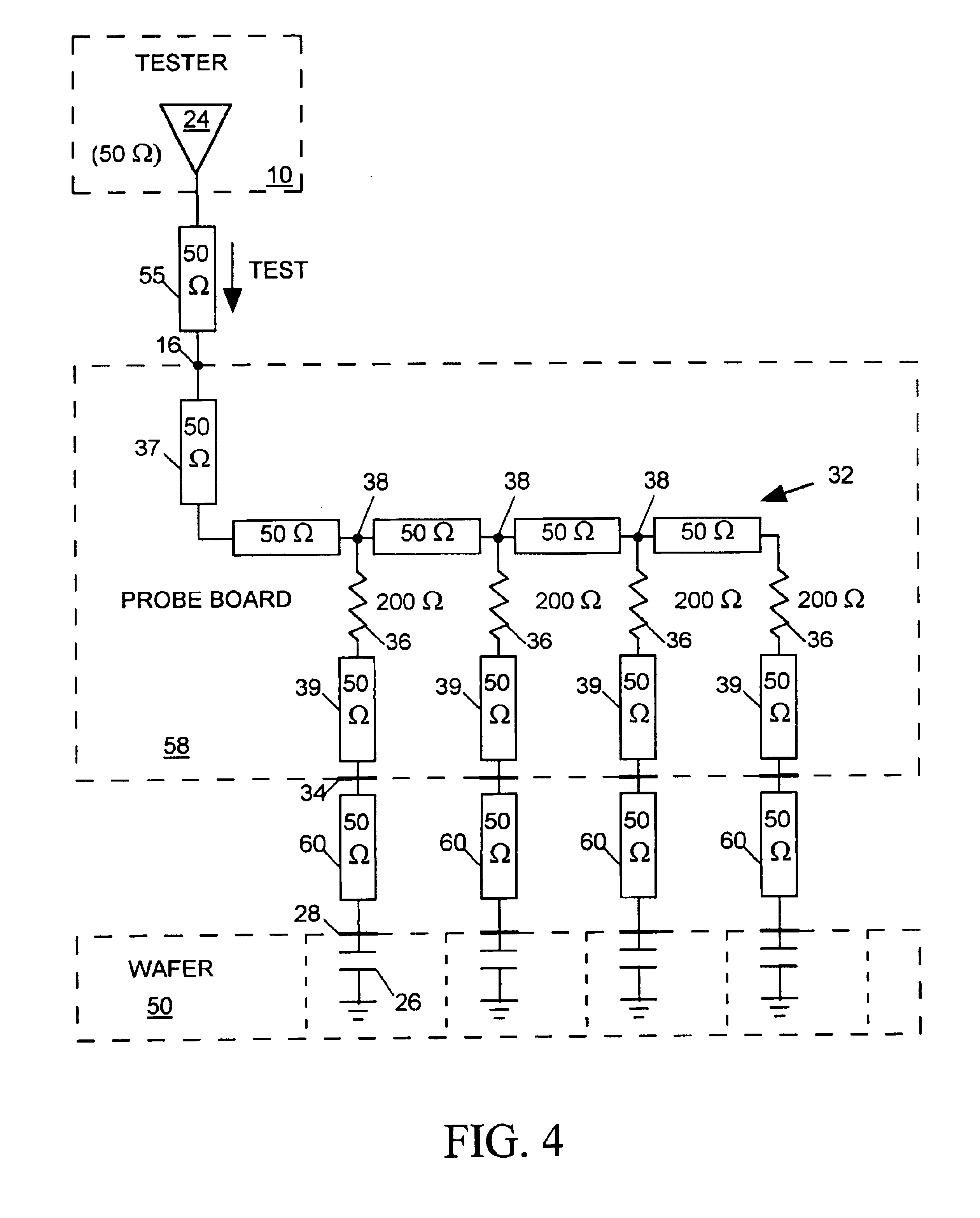

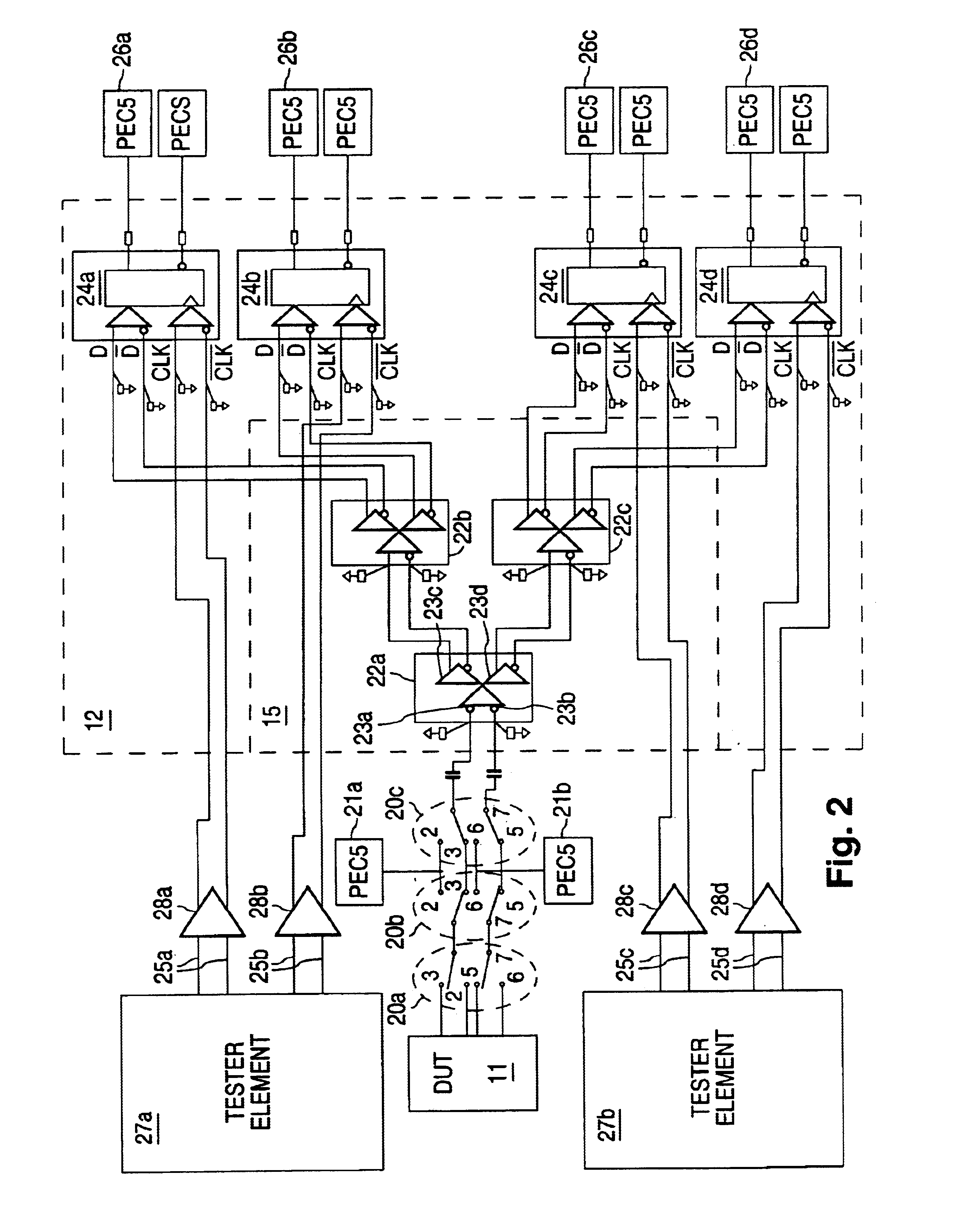

Test signal distribution system for IC tester

InactiveUS6784674B2Digital circuit testingElectrical measurement instrument detailsDistribution systemEngineering

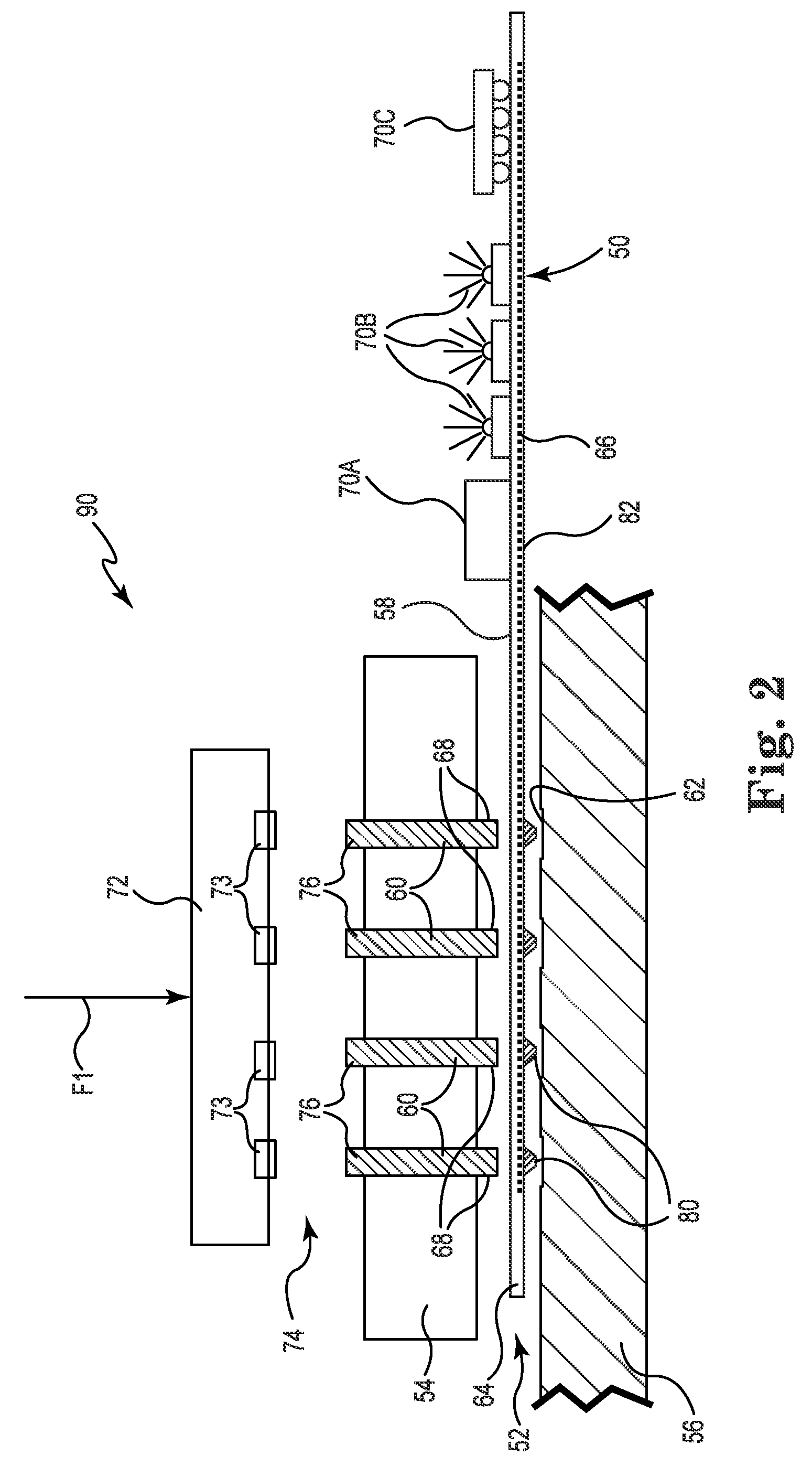

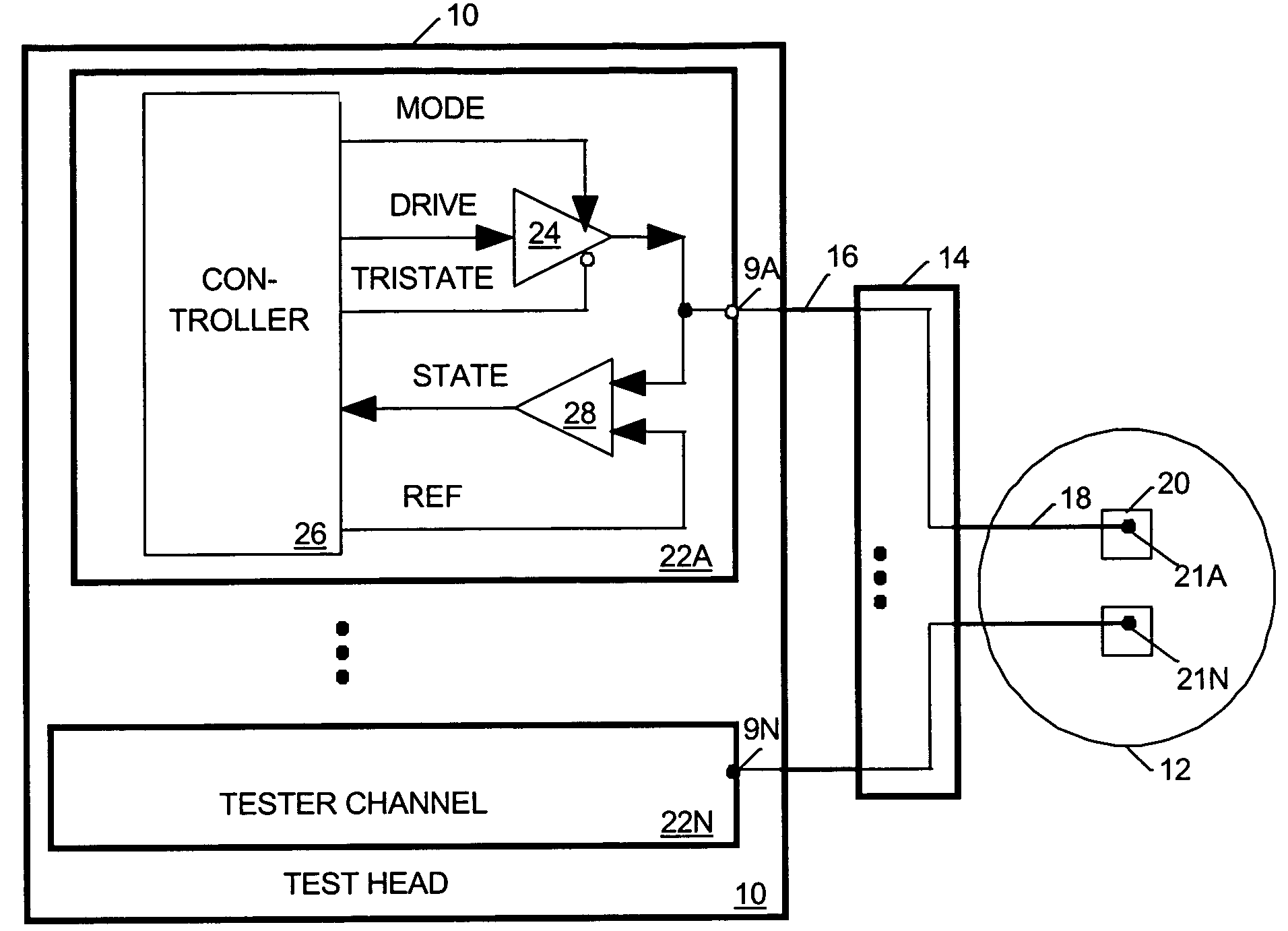

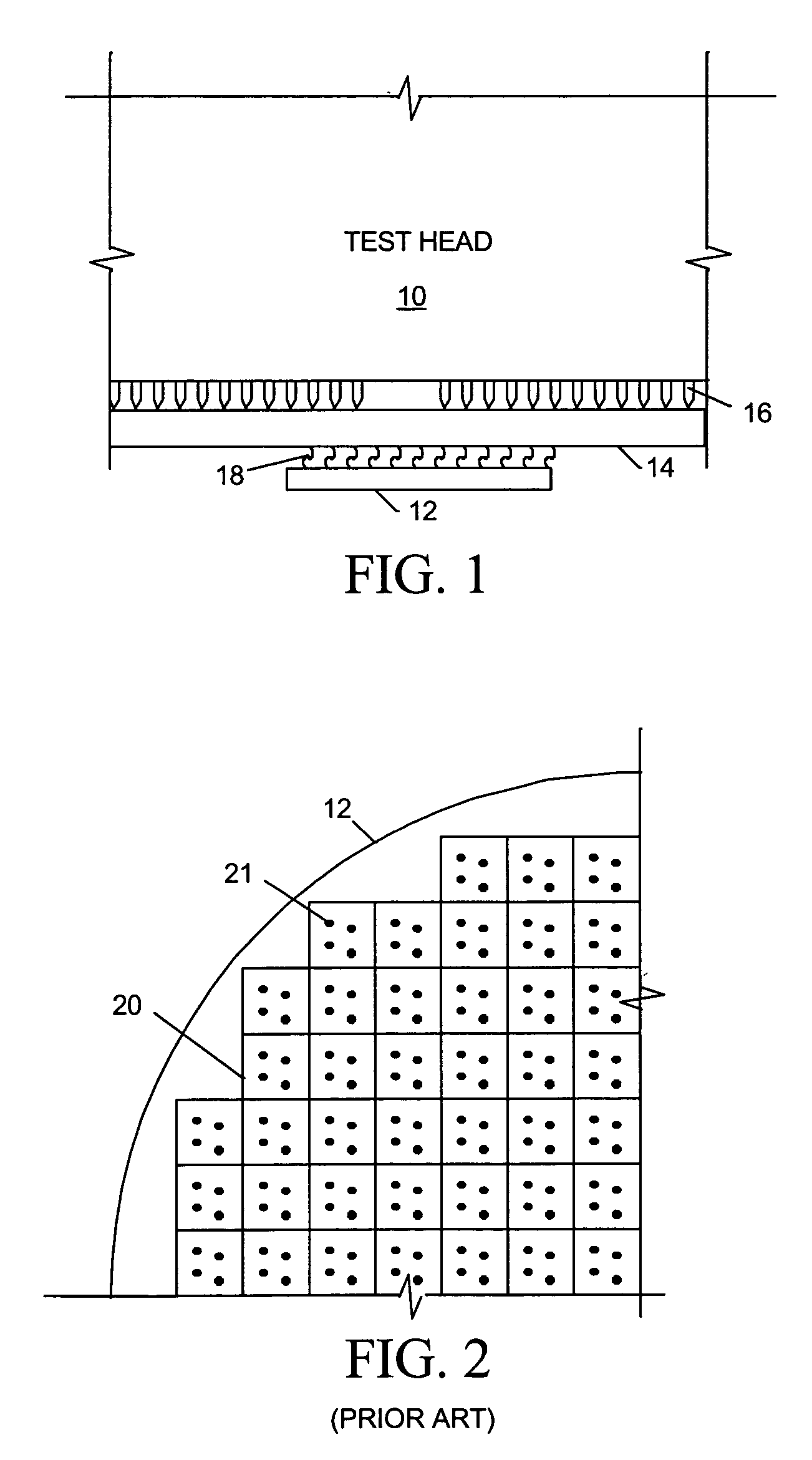

A probe board provides signal paths between an integrated circuit (IC) tester and probes accessing terminals on the surfaces of ICs formed on a semiconductor wafer for receiving test signals form the IC tester. A branching signal path within the probe board distributes a test signal produced by one channel of the IC tester to several probes. Resistors within the branching signal path resistively isolate the probes from one another so that a fault occurring at any one IC terminal will not affect the logic state of the test signal arriving at any other IC terminal. The isolation resistors are sized relative to signal path characteristic impedances so as to substantially minimize test signal reflections at the branch points.

Owner:FORMFACTOR INC

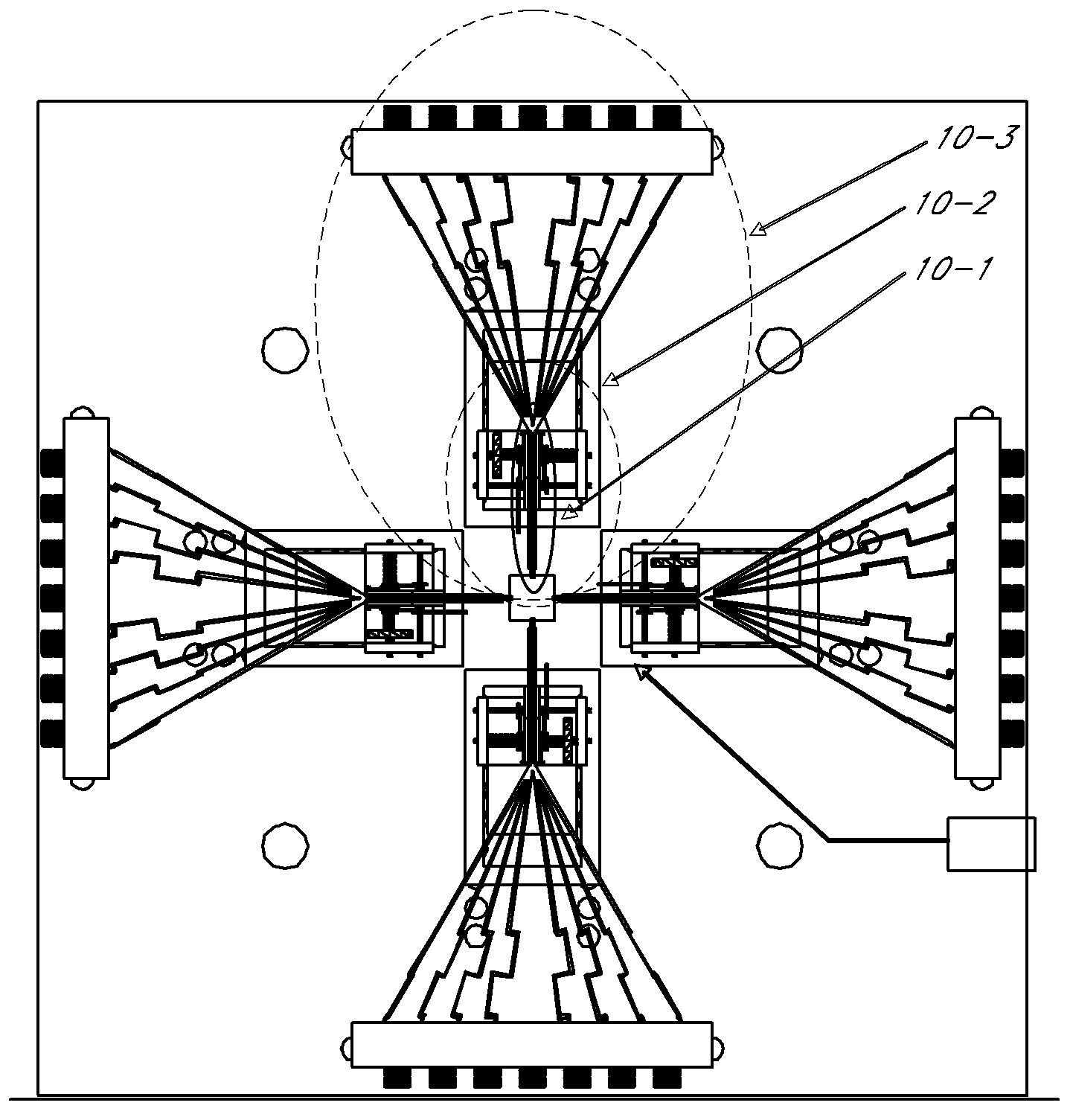

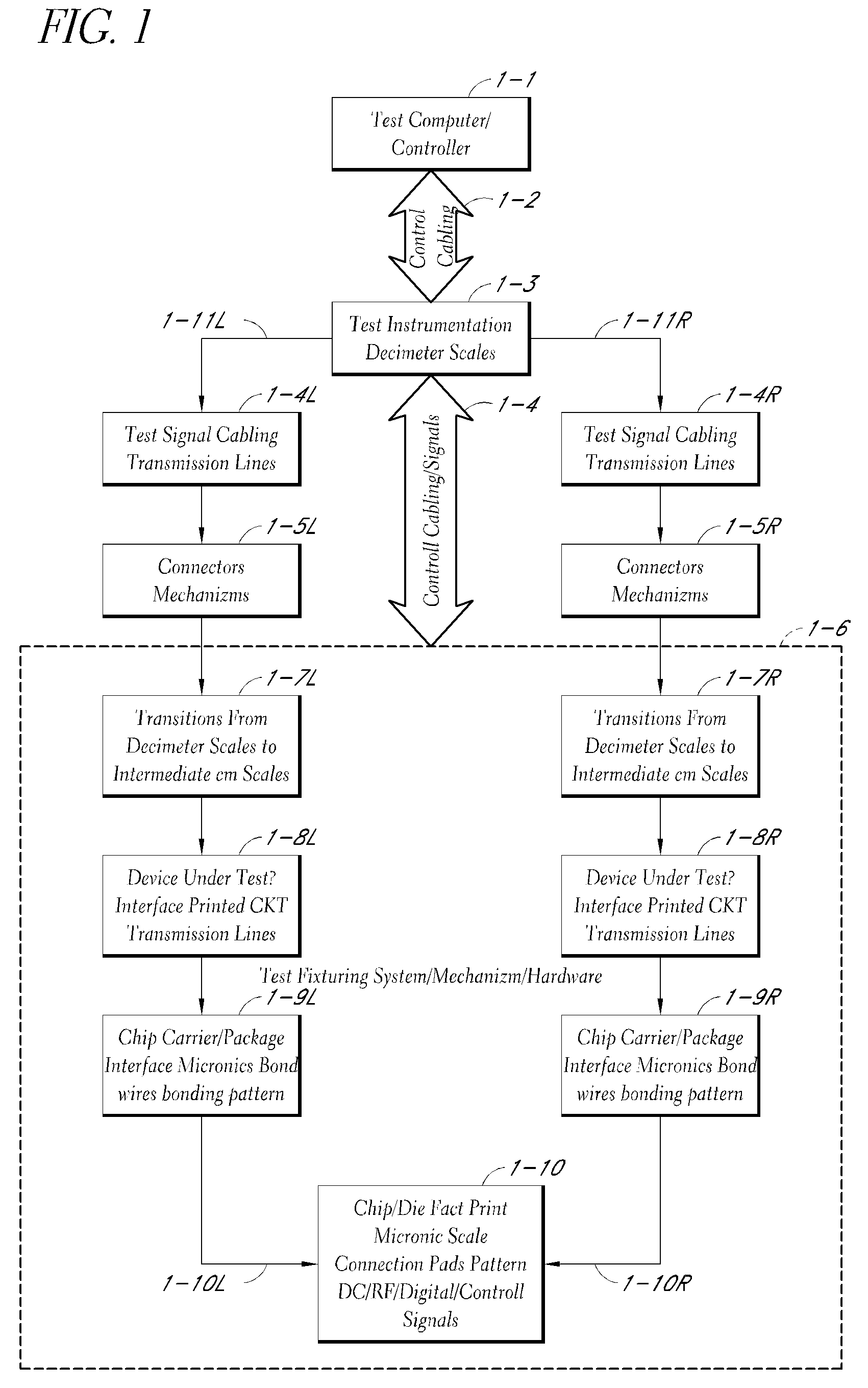

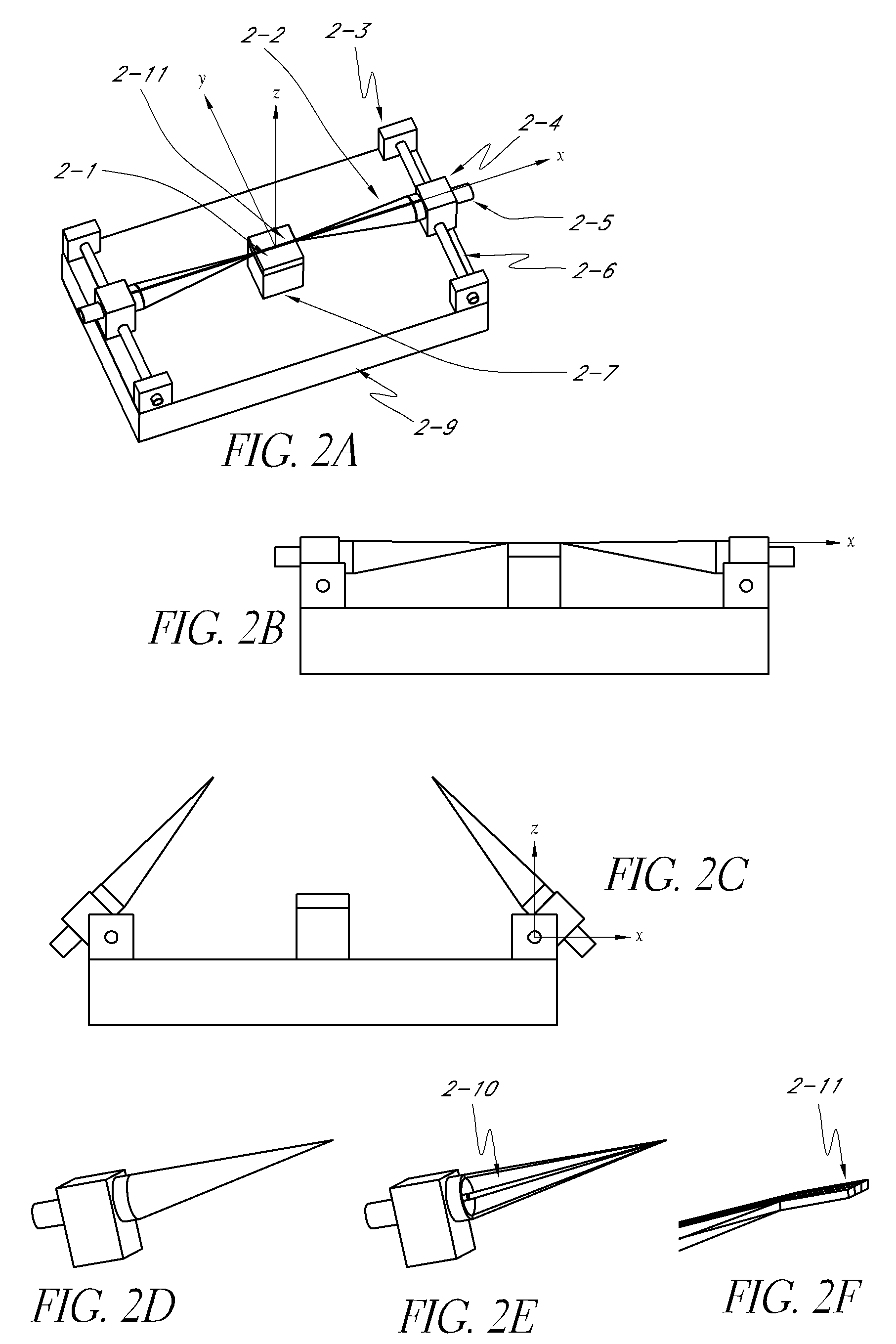

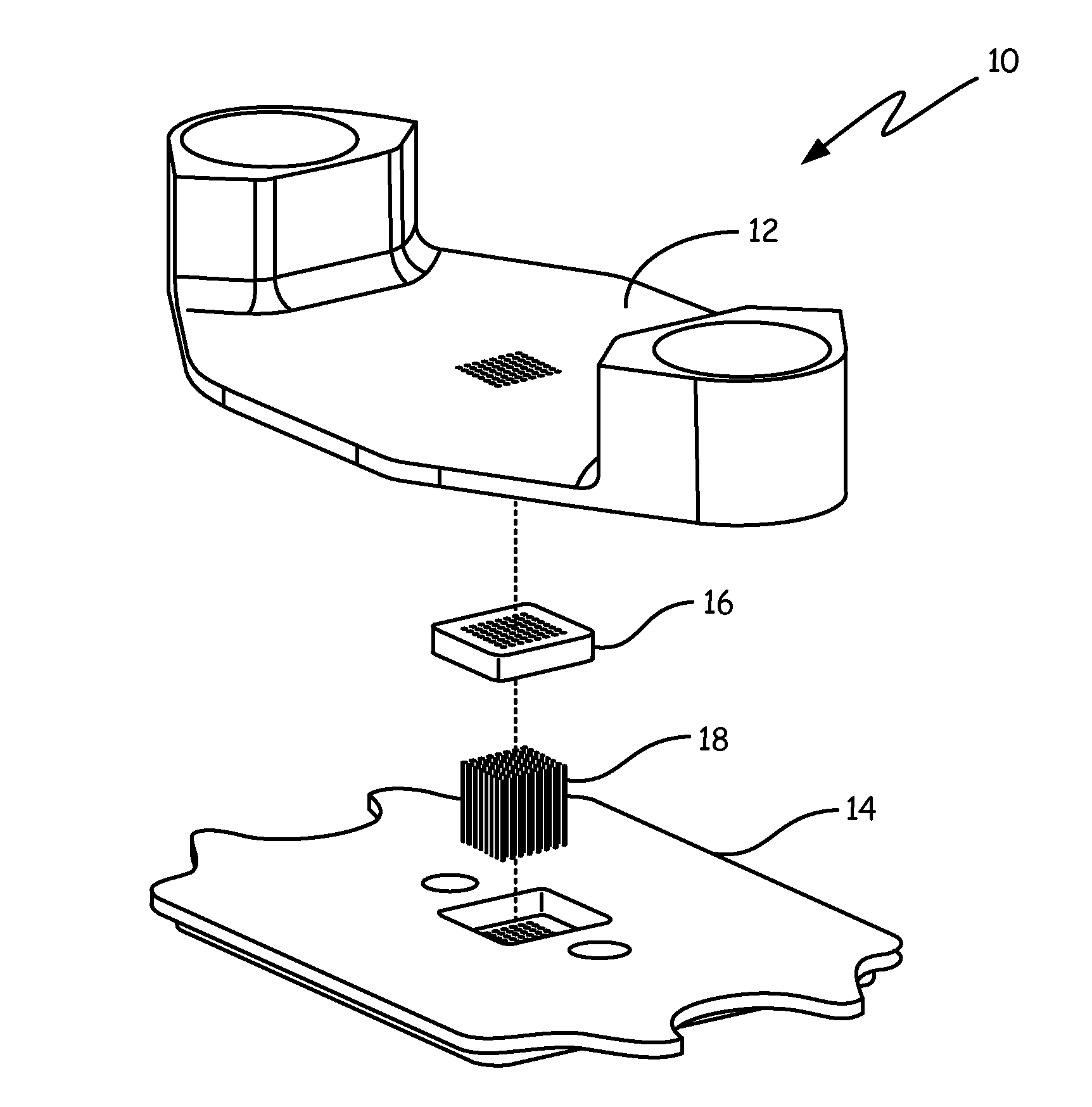

Scalable wideband probes, fixtures, and sockets for high speed IC testing and interconnects

ActiveUS20080265919A1Reducing cross talk and prasiticsIncrease speedElectrical measurement instrument detailsSolid-state devicesRadiation lossPicosecond

We introduce a new Periodic micro coaxial transmission line (PMTL) that is capable of sustaining a TEM propagation mode up to THz band. The PMTL can be manufactured using the current photolithographic processes. This transmission line can be embedded in microscopic layers that allow many new applications. We use the PMTL to develop a wideband highly scalable connector that is then used in a Probe that can be used for connecting to microscopic scale Integrated Circuits with picoseconds High Speed Digital and near THz Analogue performance in various stages of development from R&D to production testing. These probes, in one embodiment, provide a thin pen-like vertical probe tip that matches the die pad pattern precisely that can be as agile as a high speed plotter pen, connecting on the fly to any die pattern on a wafer. This approach allows the most valuable part of the test, namely the wafer to remain stationary and safe, and the least costly part of the test, namely the probe to take most of the wear and tear. We further use the embedded PMTL to develop a modular, scaleable and fully automated Universal Test Fixture for testing chips in various stages of development mainly for digital IC chips that can be utilized in production lines with pick and place of chips on tape to test every chip before insertion into circuits. One embodiment includes a low profile wideband Signal Launcher and an alligator type RF Clip that can be used at the edge of PCB's directly for validation broads. The Signal Launcher is used to develop a new versatile Flush Top Test Fixtures for individual device testing in various stages of development from die, to packaged, to Module, to Circuit Boards. The PMTL can also provide Confined Field Interconnects (CFI) between various elements on semiconductor wafers to reduce parasitic and radiation losses and practically eliminating cross talk, thus, increasing the speed of digital IC's. The PMTL is also used to develop a Universal Test Socket, and a Hand Probe with performance up to 220 GHz.

Owner:WAYMO LLC

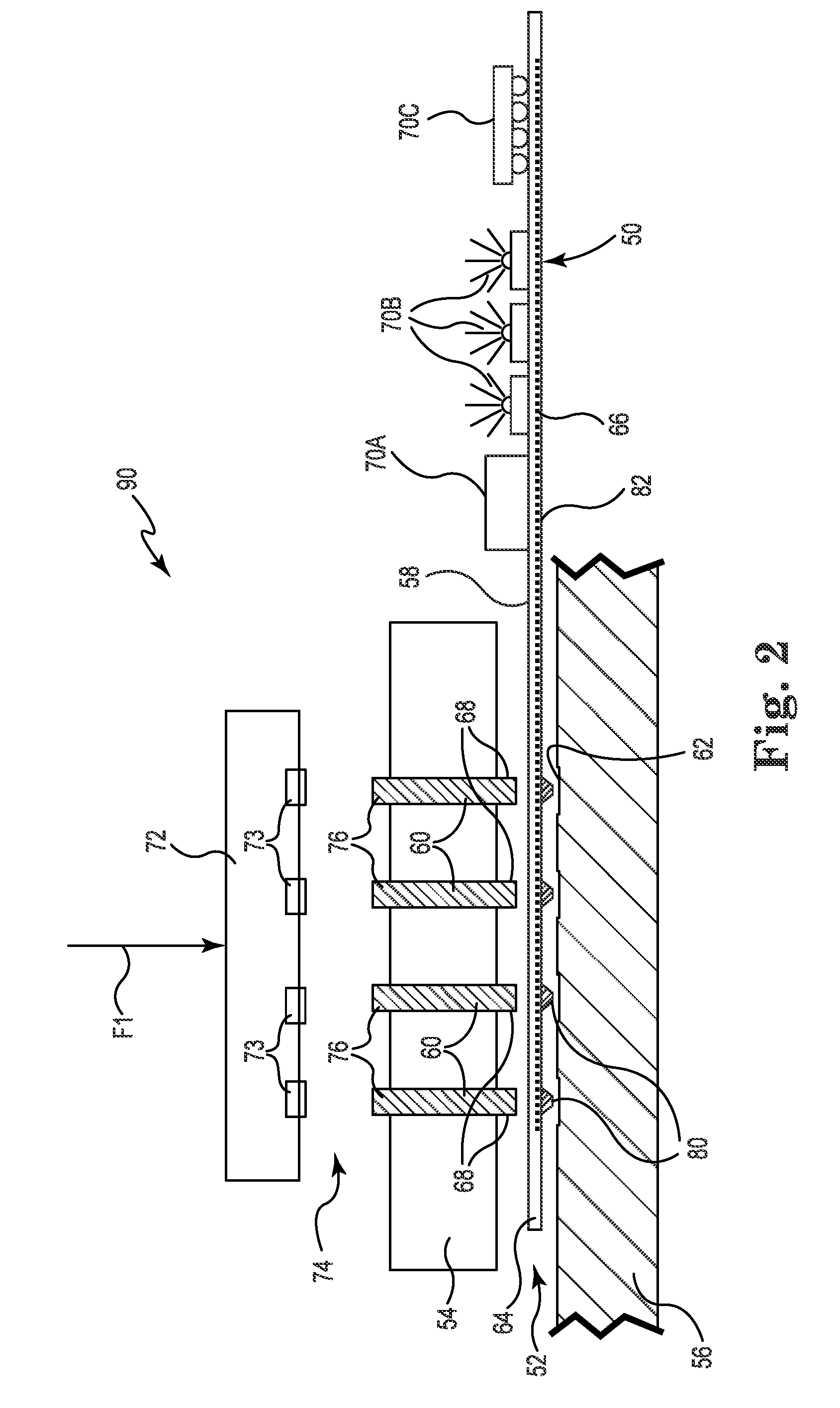

Compliant printed circuit wafer probe diagnostic tool

InactiveUS20120062270A1Improve performanceIncrease valueElectrical measurement instrument detailsSolid-state devicesContact padElectrical devices

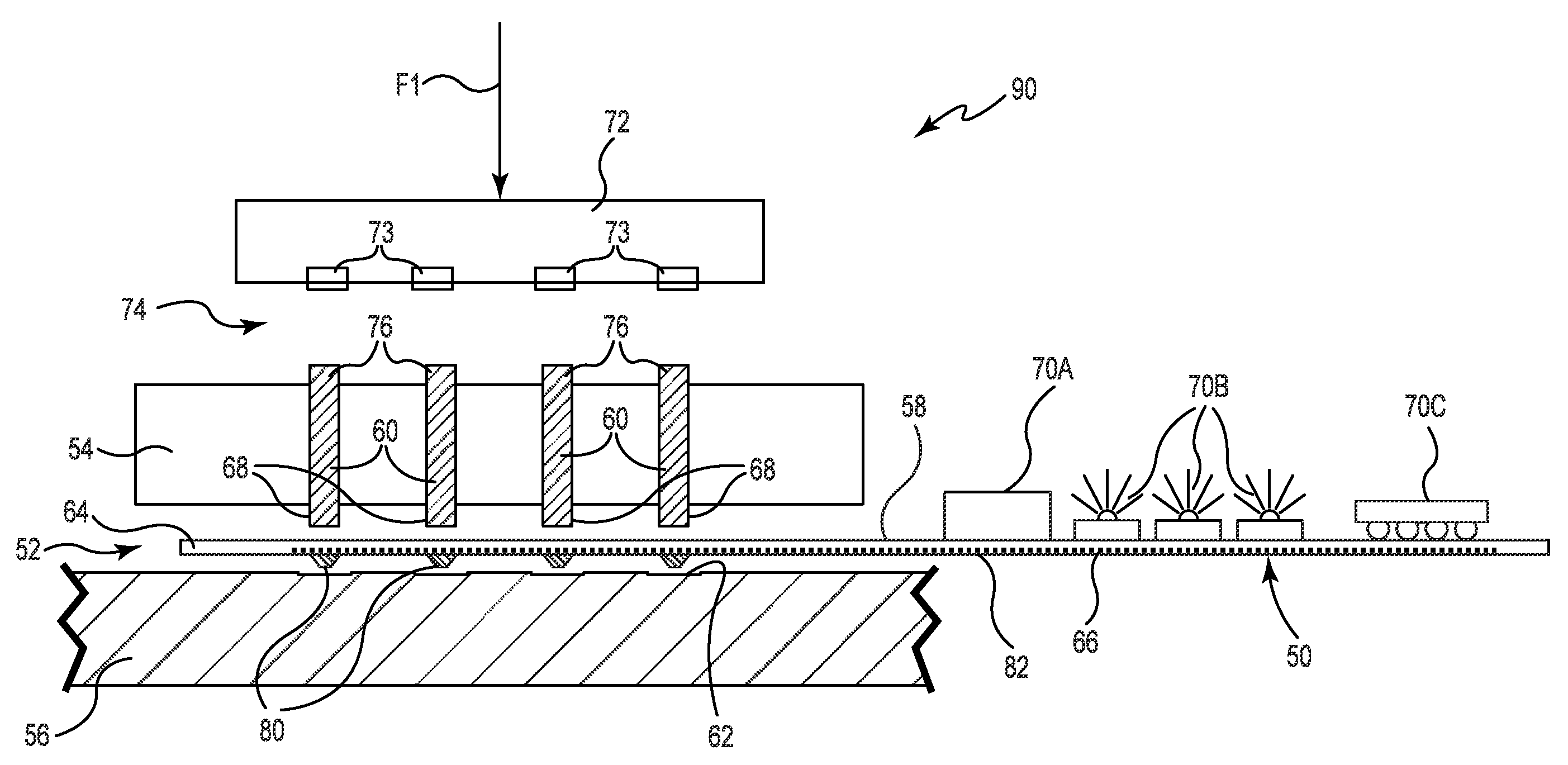

Diagnostic tools for testing wafer-level IC devices, and a method of making the same. The first diagnostic tool can include a first compliant printed circuit with a plurality of contact pads configured to form an electrical interconnect at a first interface between distal ends of probe members in the wafer probe and contact pads on a wafer-level IC device. A plurality of printed conductive traces electrically couple to a plurality of the contact pads on the first compliant printed circuit. A plurality of electrical devices are printed on the first compliant printed circuit at a location away from the first interface. The electrical devices are electrically coupled to the conductive traces and are configured to provide one or more of continuity testing or functionality of the wafer-level IC devices. A second diagnostic tool includes a second compliant printed circuit electrically coupled to a dedicated IC testing device. A plurality of electrical devices are printed on the second compliant printed circuit and electrically coupled to the dedicated IC device.

Owner:HSIO TECH

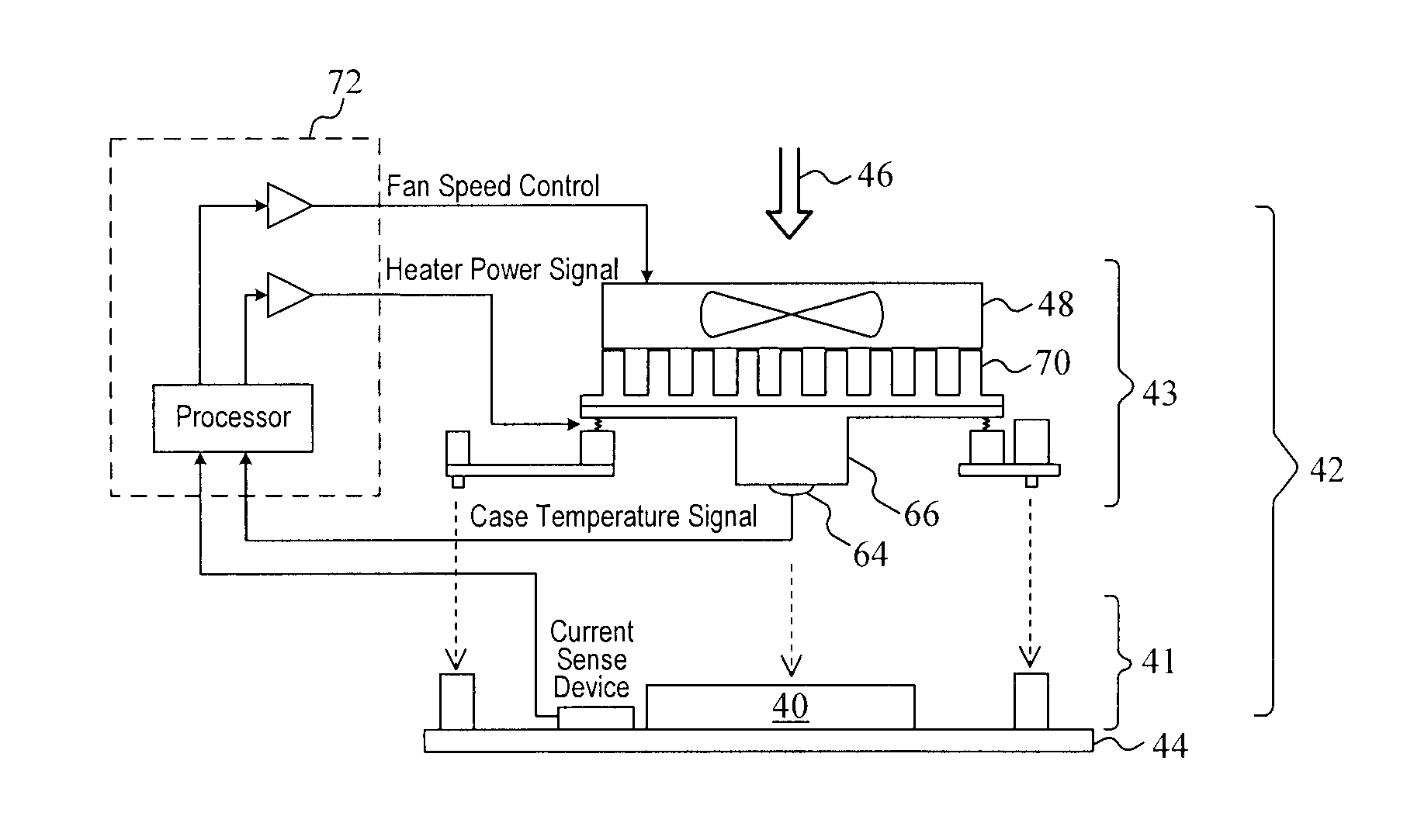

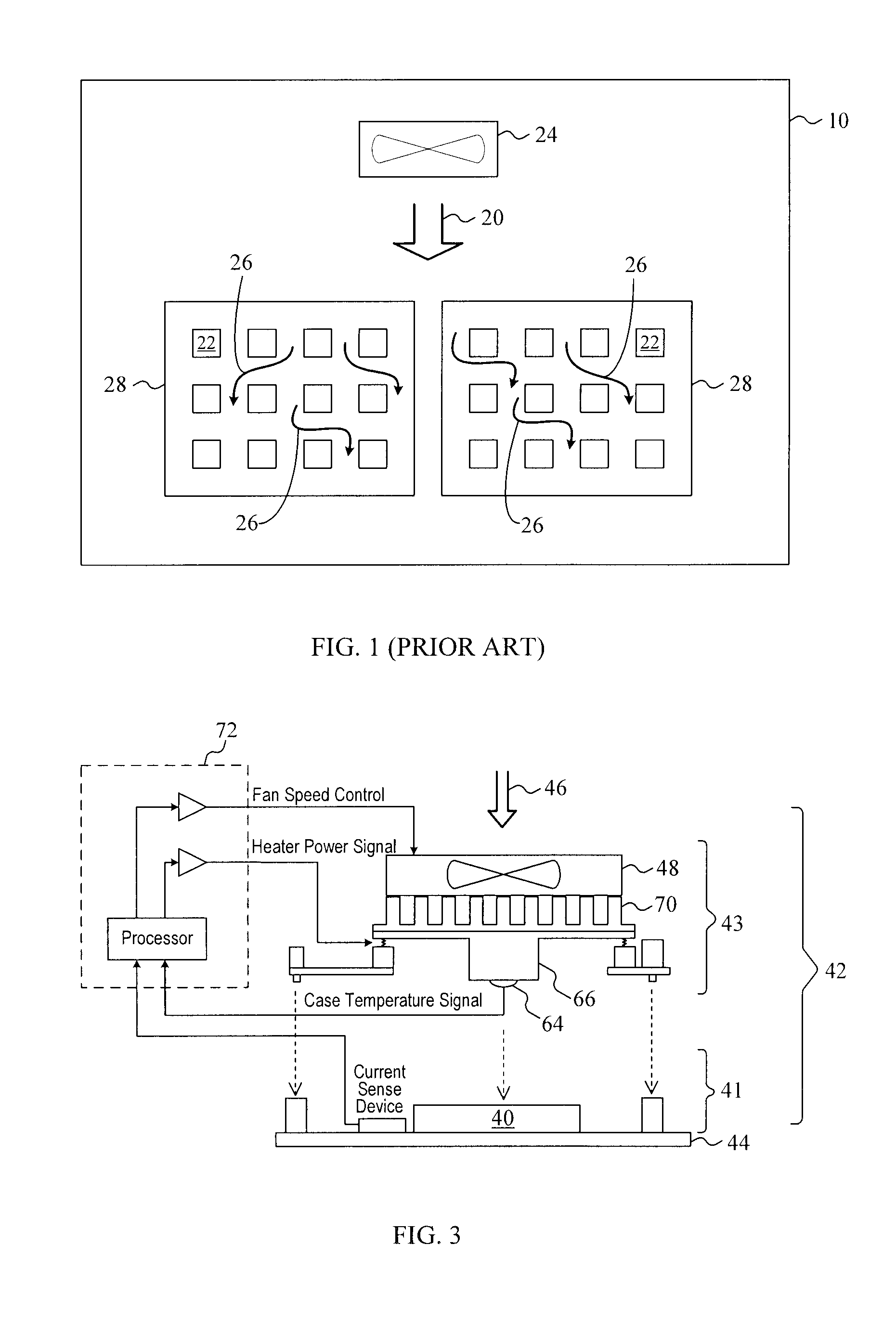

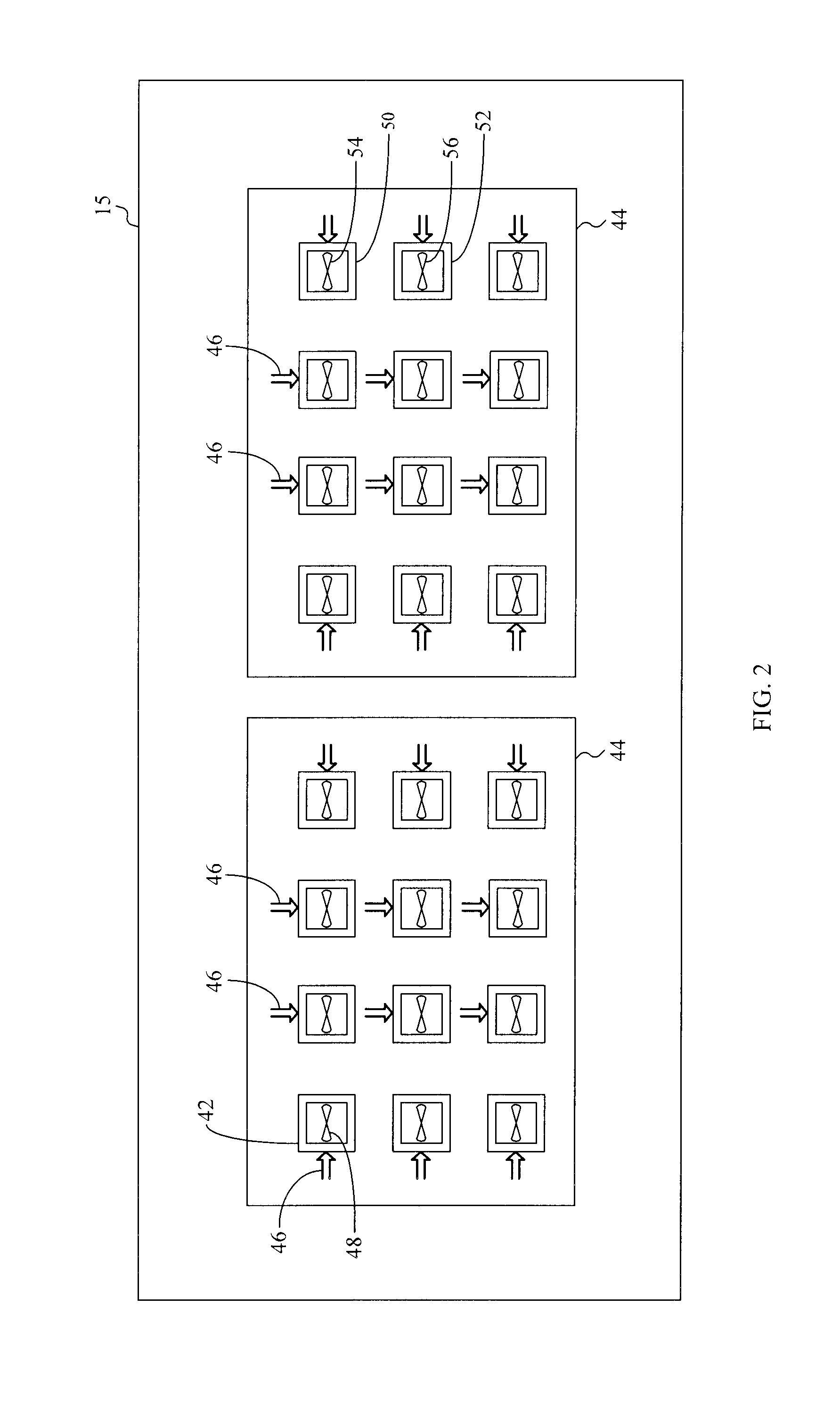

Temperature control in IC sockets

InactiveUS20060290370A1Maintain surface temperatureMaintain temperatureElectrical measurement instrument detailsFault location by increasing destruction at faultTemperature controlElectronic controller

A system and method are provided which provides more accurate temperature control of integrated circuits. A system for testing integrated circuit (IC) packages comprises a plurality of IC testing socket bases arranged on a testing board and configured to receive a plurality of IC packages. A plurality of IC testing socket lids are arranged to attach to the testing board. Each IC testing socket lid comprises a temperature sensor to thermally contact the IC package and measure a surface temperature of the IC package, a heater or cooler to directly contact the IC package, and an electronic controller to receive signals from the temperature sensor. The electronic controller is programmed to change the temperature of the heater or cooler responsive to the measured surface temperature of the IC package. A plurality of cooling devices individually removes heat generated by the plurality of IC packages. The electronic controller in each IC testing socket lid is further programmed to control a corresponding cooling device to maintain the surface temperature of the plurality of IC packages within a desired temperature range.

Owner:WELLS CTI LLC

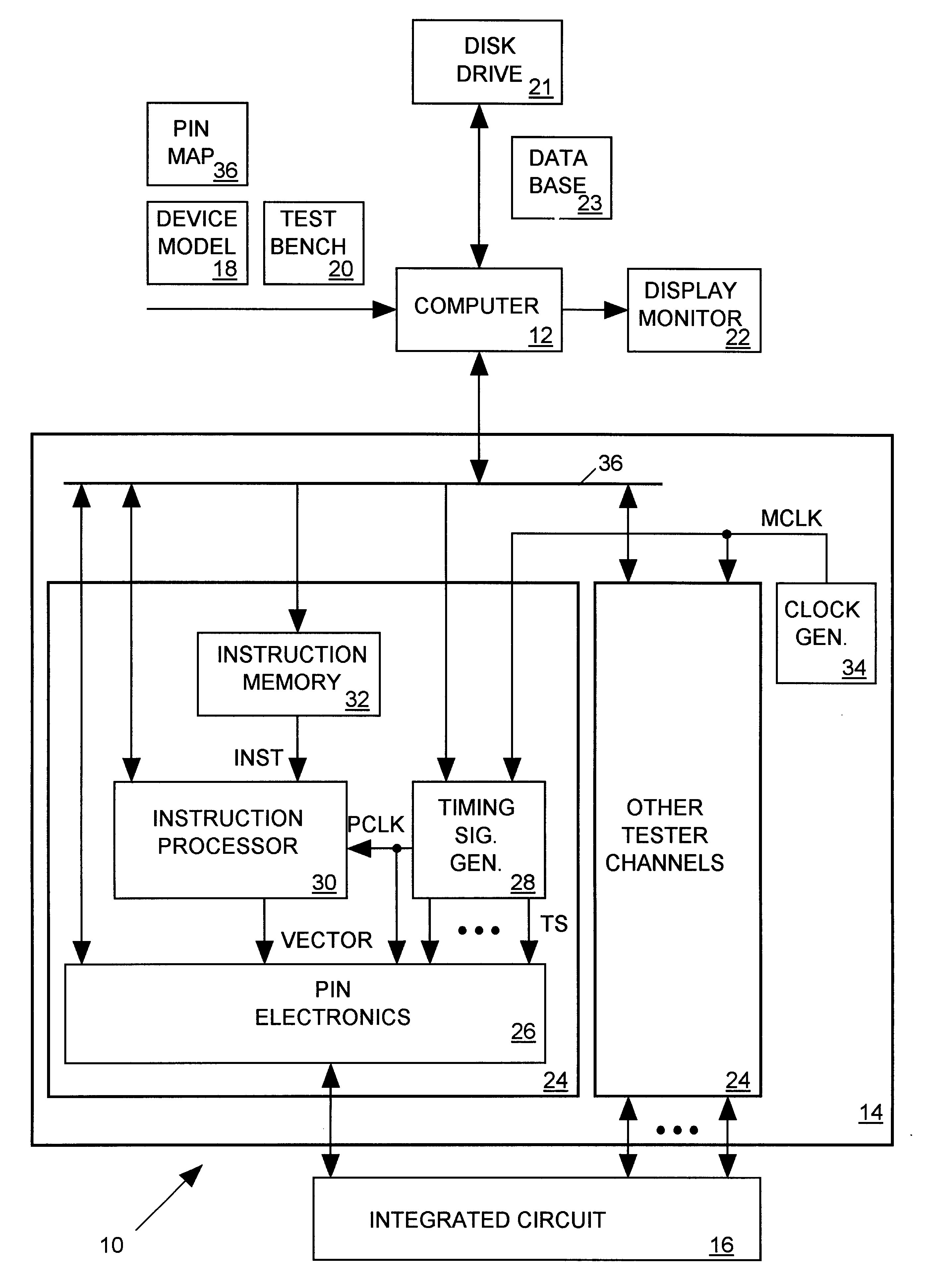

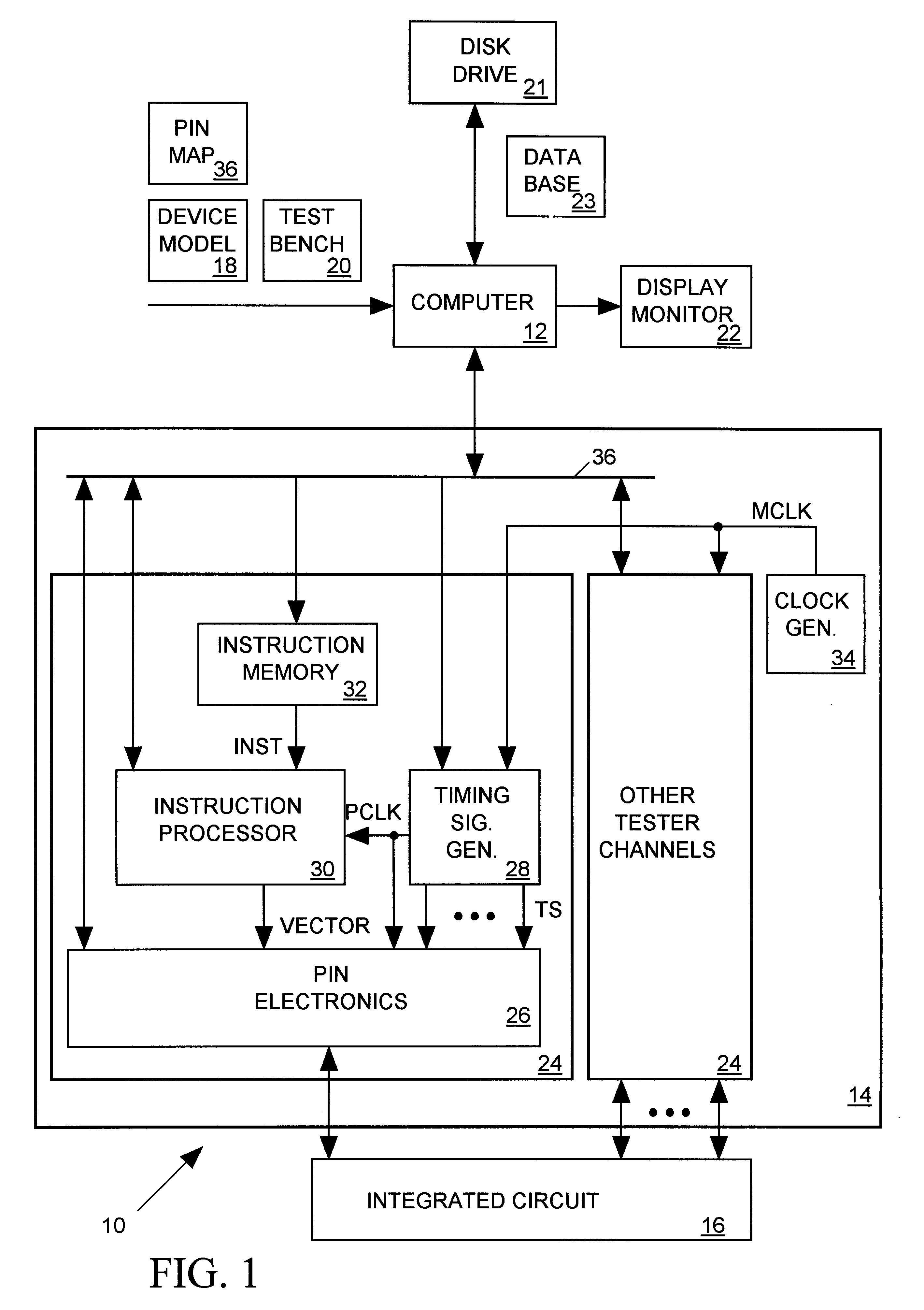

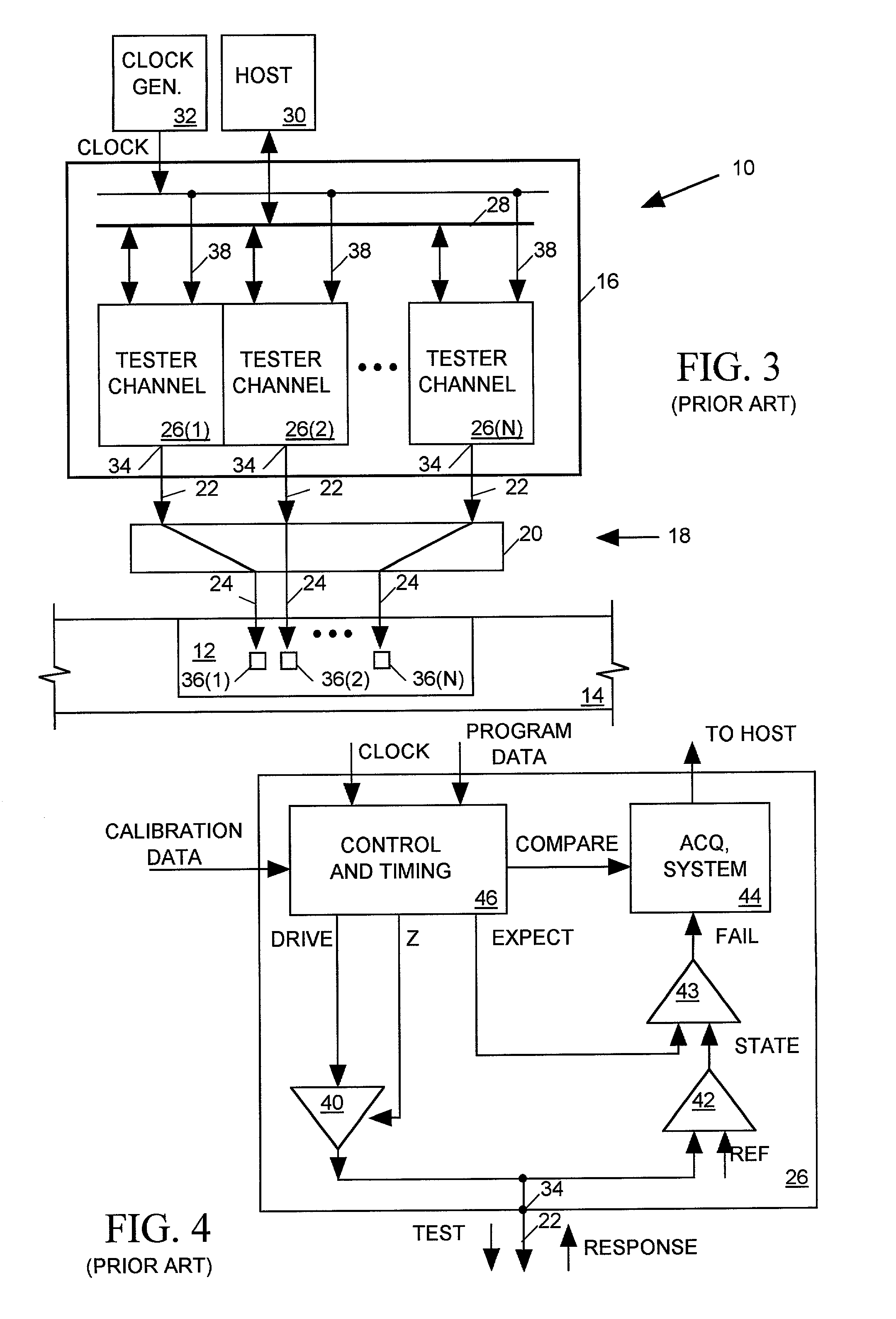

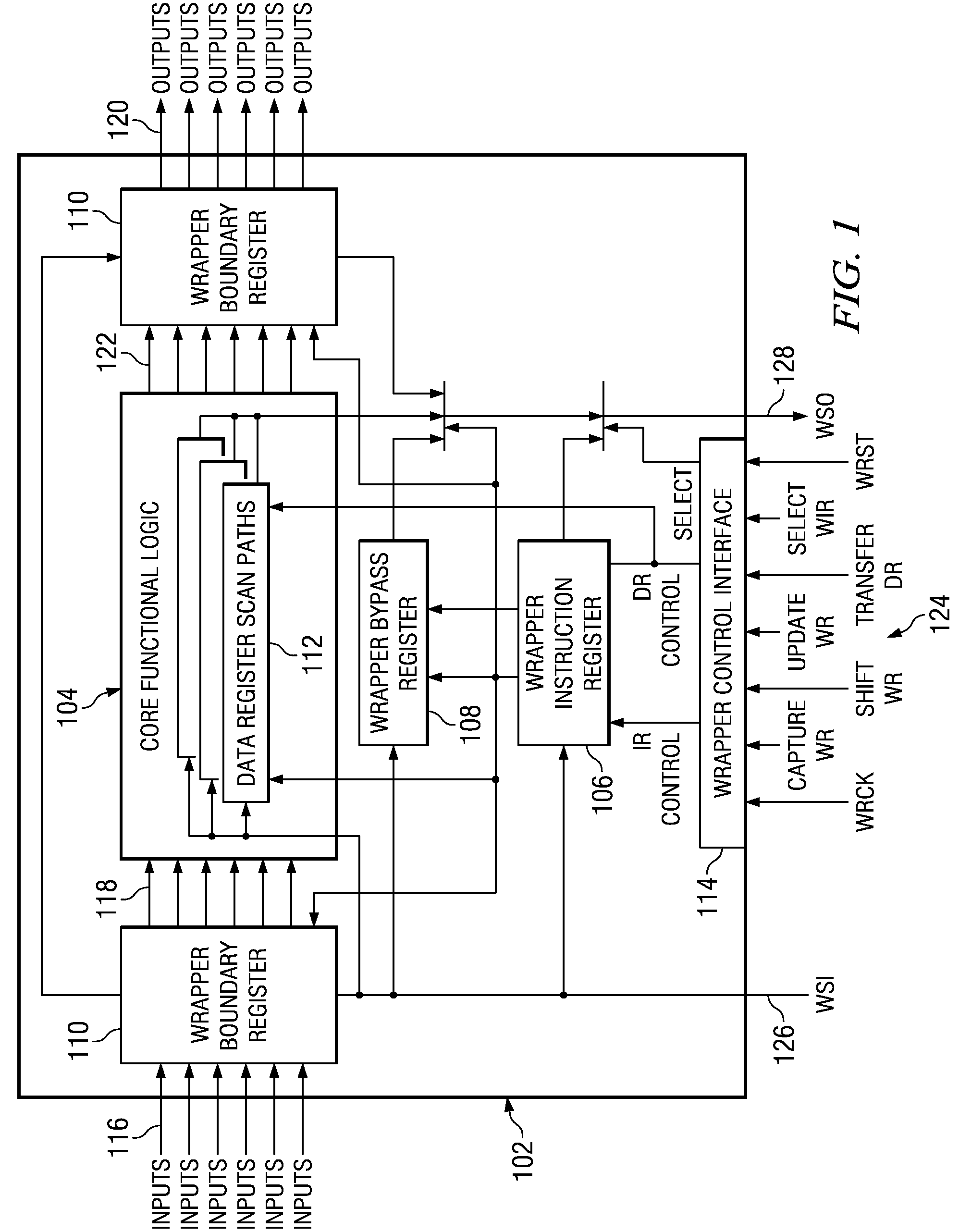

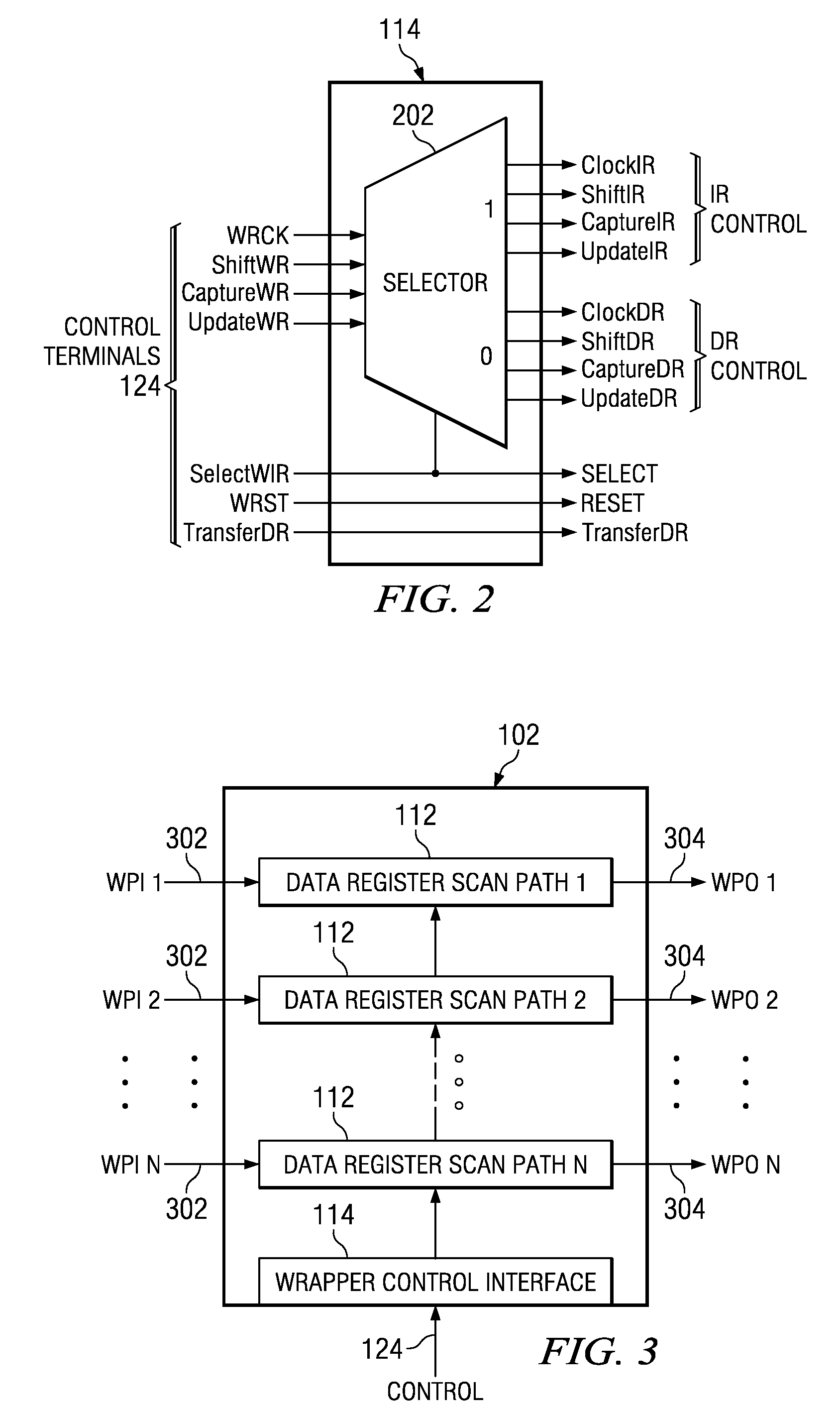

System for testing real and simulated versions of an integrated circuit

A system for testing both simulated and real versions of an integrated circuit (IC) includes an IC simulator, a simulator manager, an IC tester, and a tester manager. The IC simulator simulates response of the IC to a set of simulated IC input signals by producing a set of simulated IC output signals. The simulator manager, programmed by a user-supplied test bench file, provides the simulated IC input signals to the simulator during the simulation. During the simulation, the simulator manager also generates a set of waveform data sequences, each representing periodically sampled values of a corresponding one of the simulated IC input and output signals. The IC tester includes a separate channel corresponding to each real IC input and output signal. The tester manager converts the waveform data sequence corresponding to each simulated IC input and output signal to a separate set of instructions provided as input to a corresponding one of the IC tester channels. When testing the real IC, each IC tester channel corresponding to a real IC input signal responds to its input instructions by generating and supplying to the IC an input signal having the sequence of values indicted by the waveform data sequence representing the corresponding simulated IC input signal. Each IC tester channel corresponding to an IC output signal responds to its input instructions by periodically sampling the corresponding IC output signal to determine whether the IC output signal has the sequence of values indicated by the waveform data sequence representing the corresponding simulated IC output signal.

Owner:CREDENCE SYSTEMS

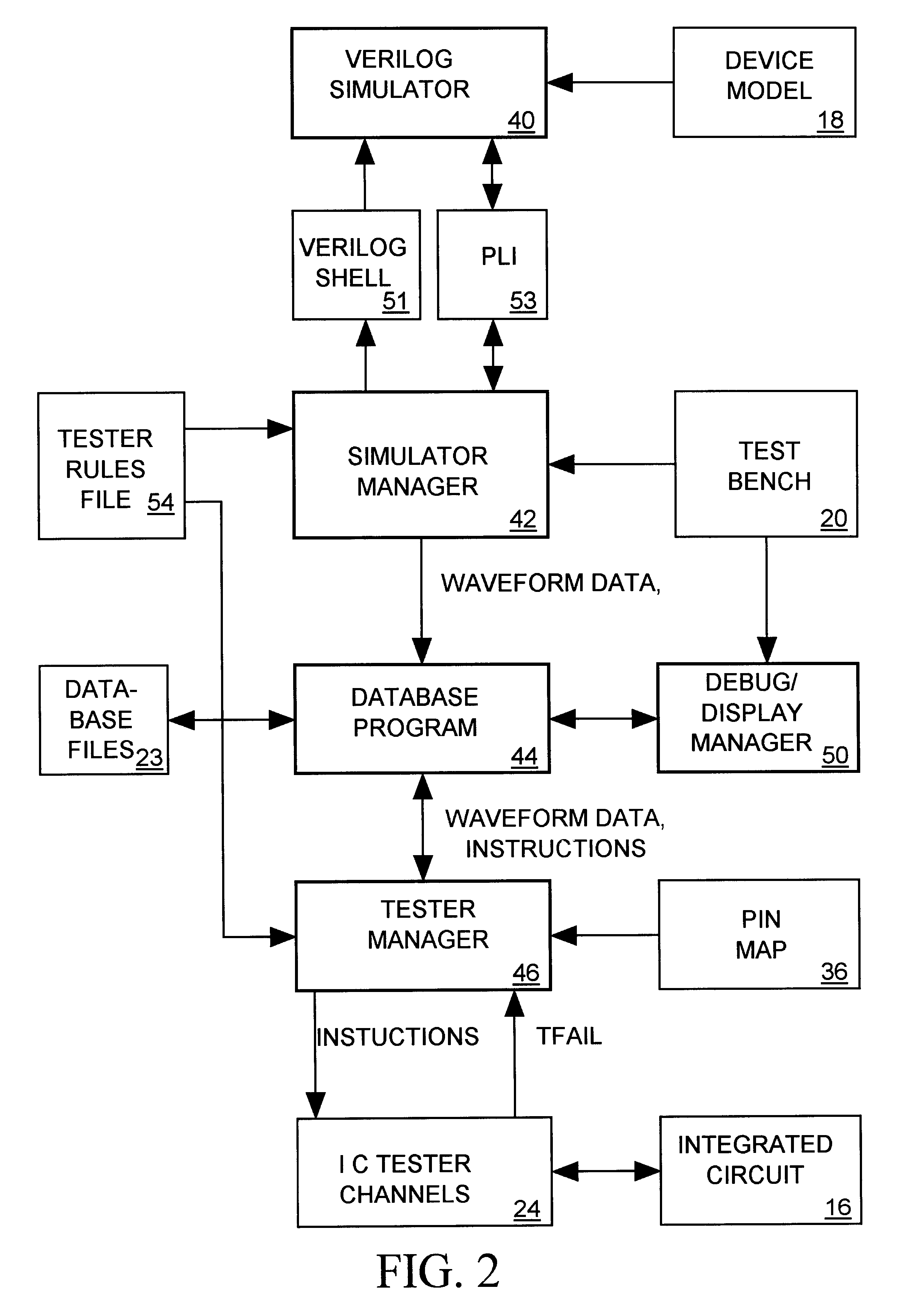

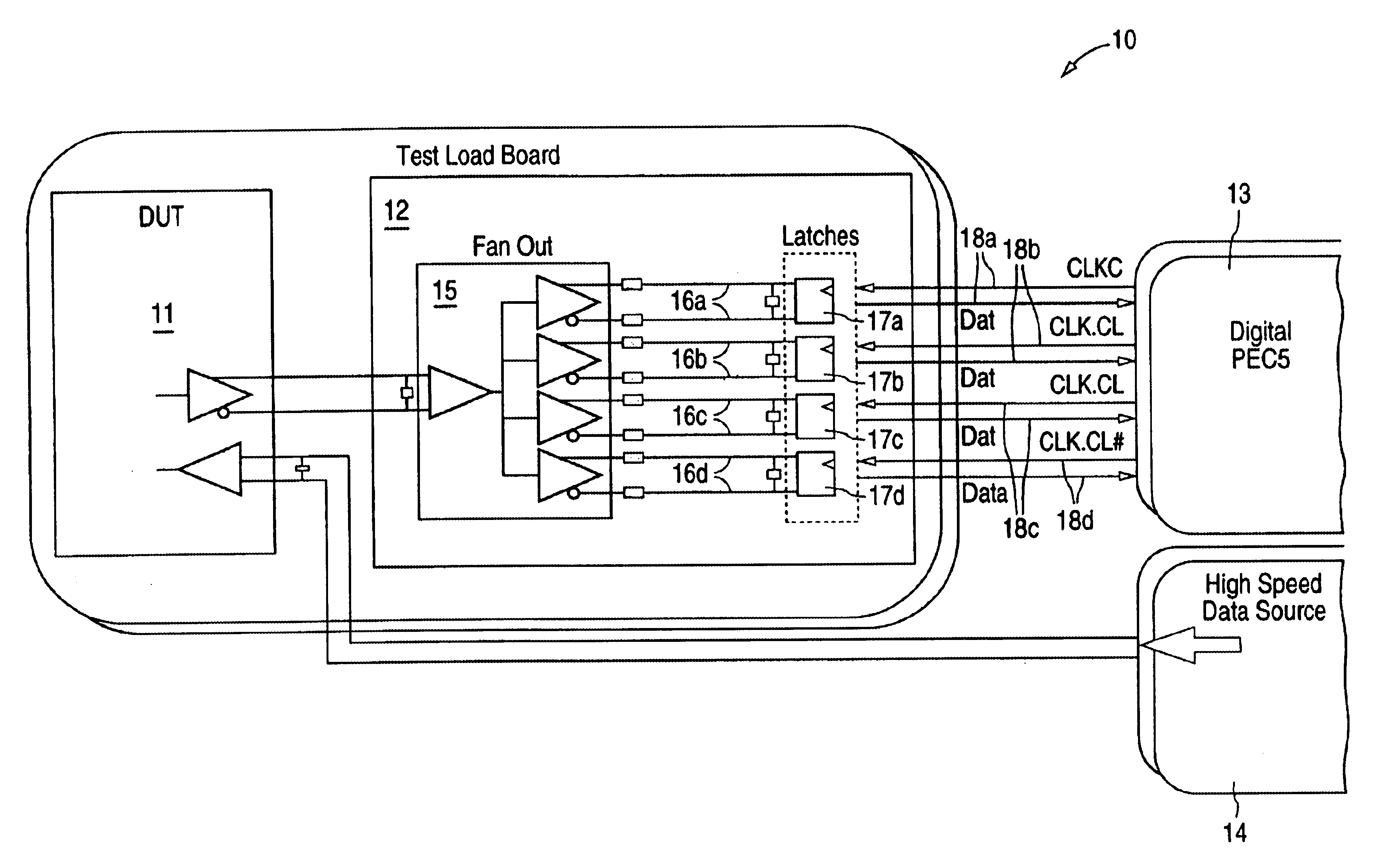

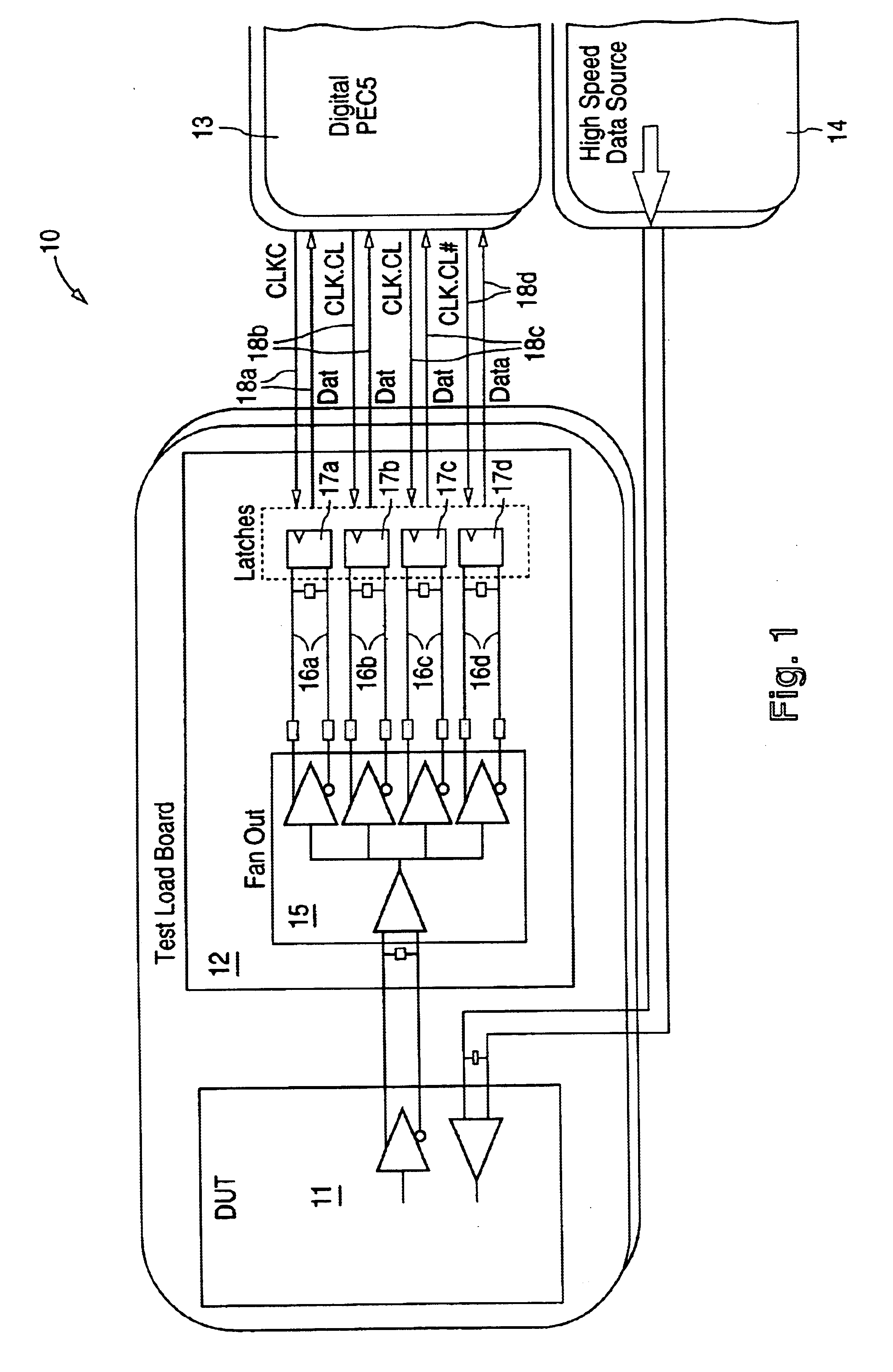

Method and apparatus for high speed IC test interface

InactiveUS6859902B1Save the total testing timeEffective real-time captureDigital circuit testingError detection/correctionData streamCommunication device

A testing method and circuit used to test high-speed communication devices on Automatic Test Equipment—ATE. The method and circuit provide a solution to testing very high speed (2.5 Gbps and above) integrated circuits. The circuit fans out the data streams from the output of the Device Under Test (DUT) to multiple tester channels which under-sample the streams. The testing method and circuit also allow for the injection of jitter into to the DUT at the output of the DUT. The skipping of data bits inherent in multi-pass testing is avoided by duplicating the tester resources to achieve effective real-time capture (saving test time and improving Bit Error Rate). Moreover the circuit synchronizes different DUTs with the timing of ATE hardware independent of DUT output data. Also, a calibration method is used compensate for differing trace lengths and propagation delay characteristics of test circuit components.

Owner:CREDENCE SYSTEMS

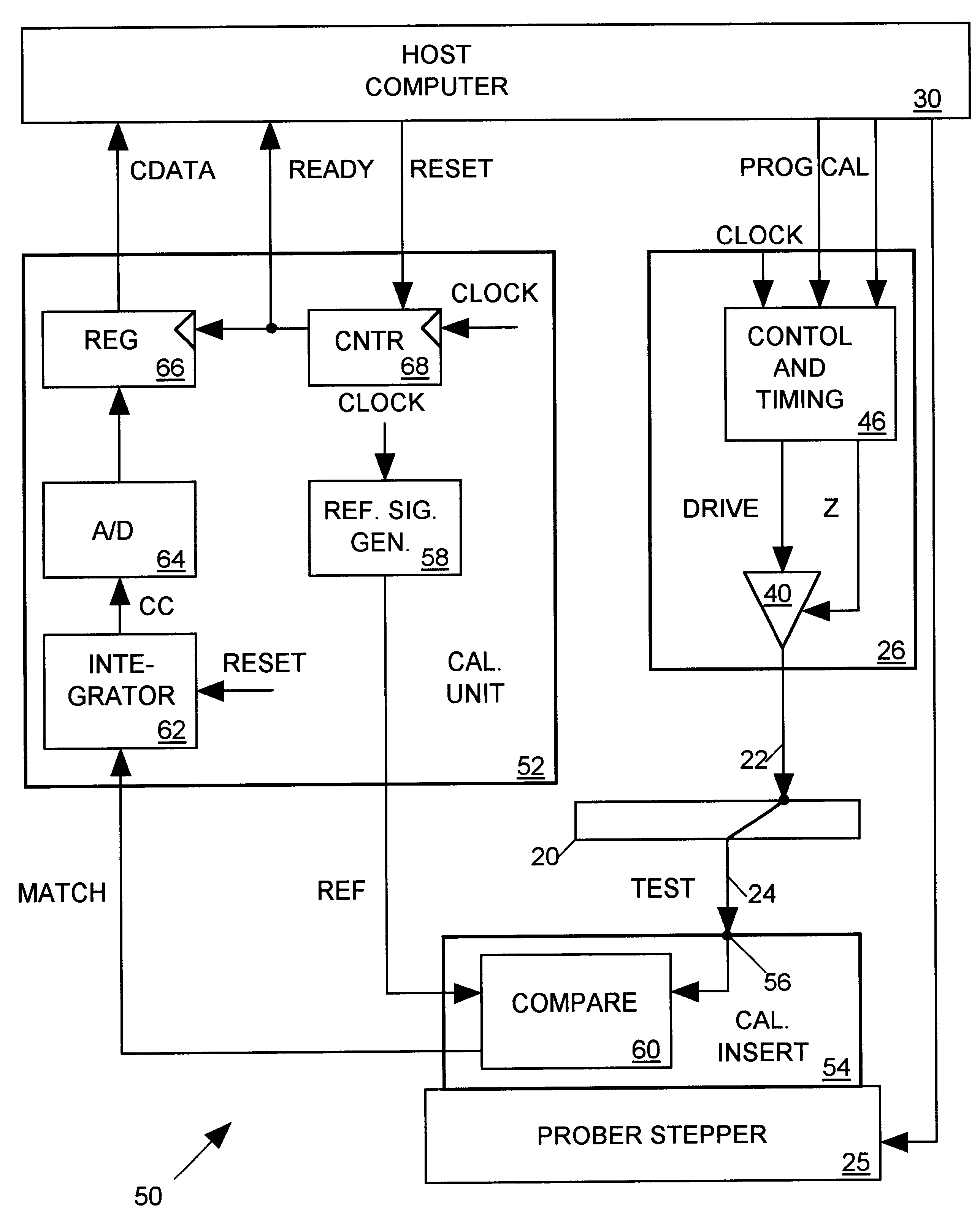

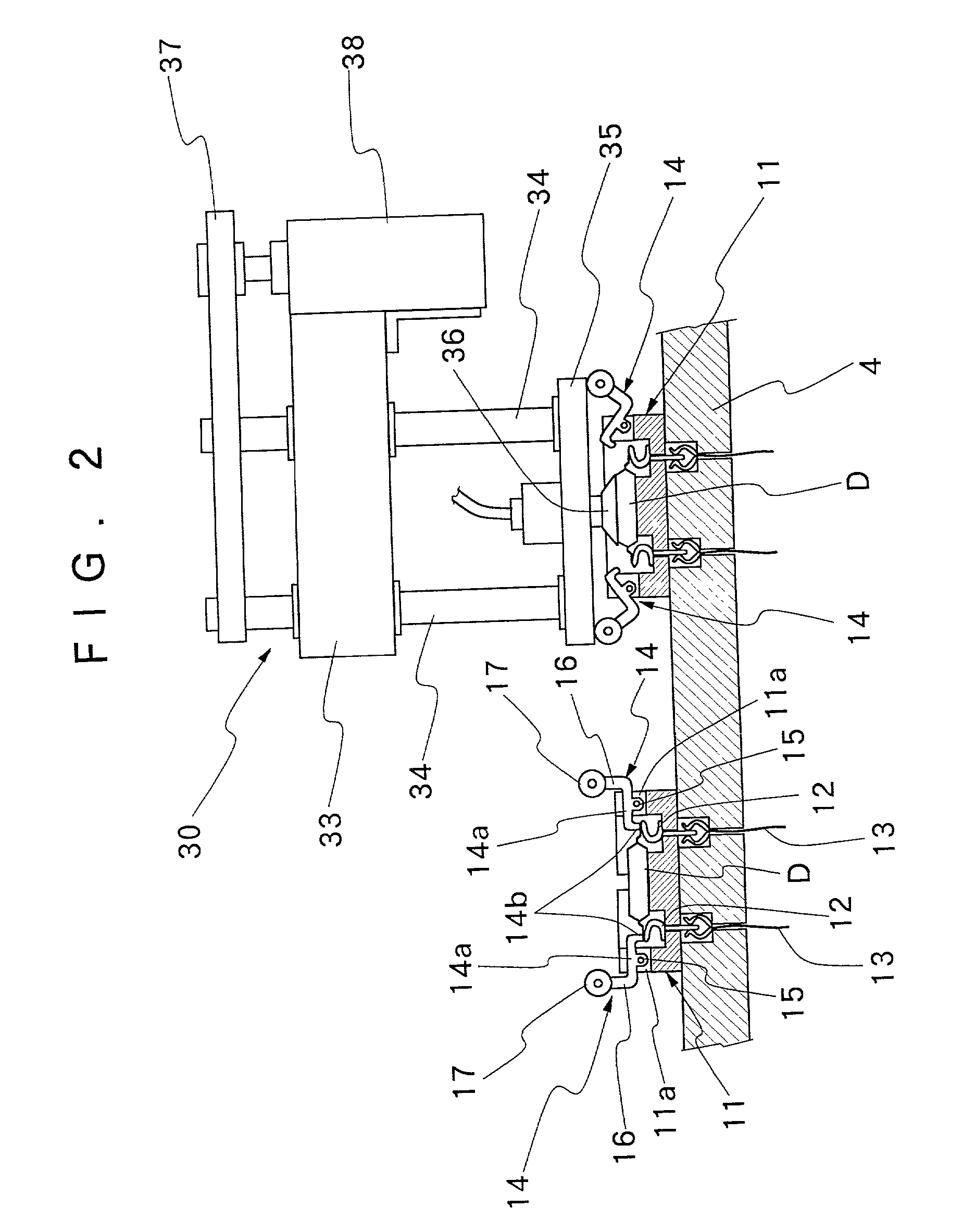

Cross-correlation timing calibration for wafer-level IC tester interconnect systems

InactiveUS20020049554A1Easy accessDigital circuit testingTesting/calibration apparatusContact padTester device

A timing calibration system for a wafer level integrated circuit (IC) tester is disclosed. The tester includes a set of probes for contacting pads on a surface of an IC and having a plurality of tester channels. Each channel generates a TEST signal at a tip of a corresponding probe in response to a periodic CLOCK signal with a delay adjusted by drive calibration data supplied as input to the tester channel. The TEST signal produced by each channel includes edges occurring in a timing pattern controlled by programming data provided as input to each tester channel. To calibrate test signal timing of all channels, each channel is programmed to generate a test signal having the same repetitive edge timing pattern at the tester channel's corresponding probe tip. The test signal produced at each probe tip is then cross-correlated to a periodic reference signal having the same repetitive edge timing pattern. The drive calibration data of each channel is then iteratively adjusted to determine a value which maximizes the cross-correlation between its output test signal and the reference signal. To maximize the accuracy of the timing calibration, each repetition of the test and reference signal edge pattern provides pseudo-randomly distributed time intervals between successive signal edges.

Owner:FORMFACTOR INC

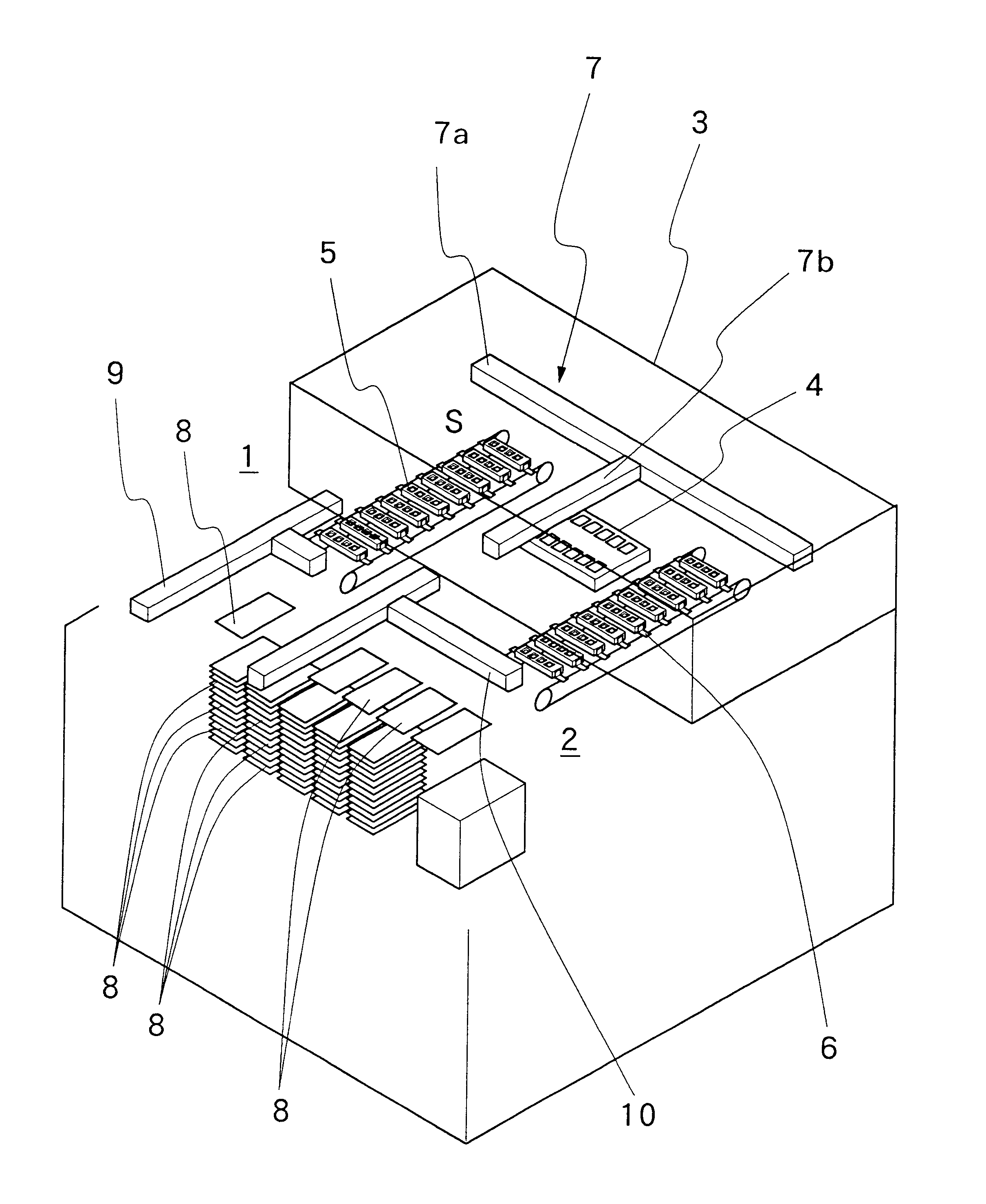

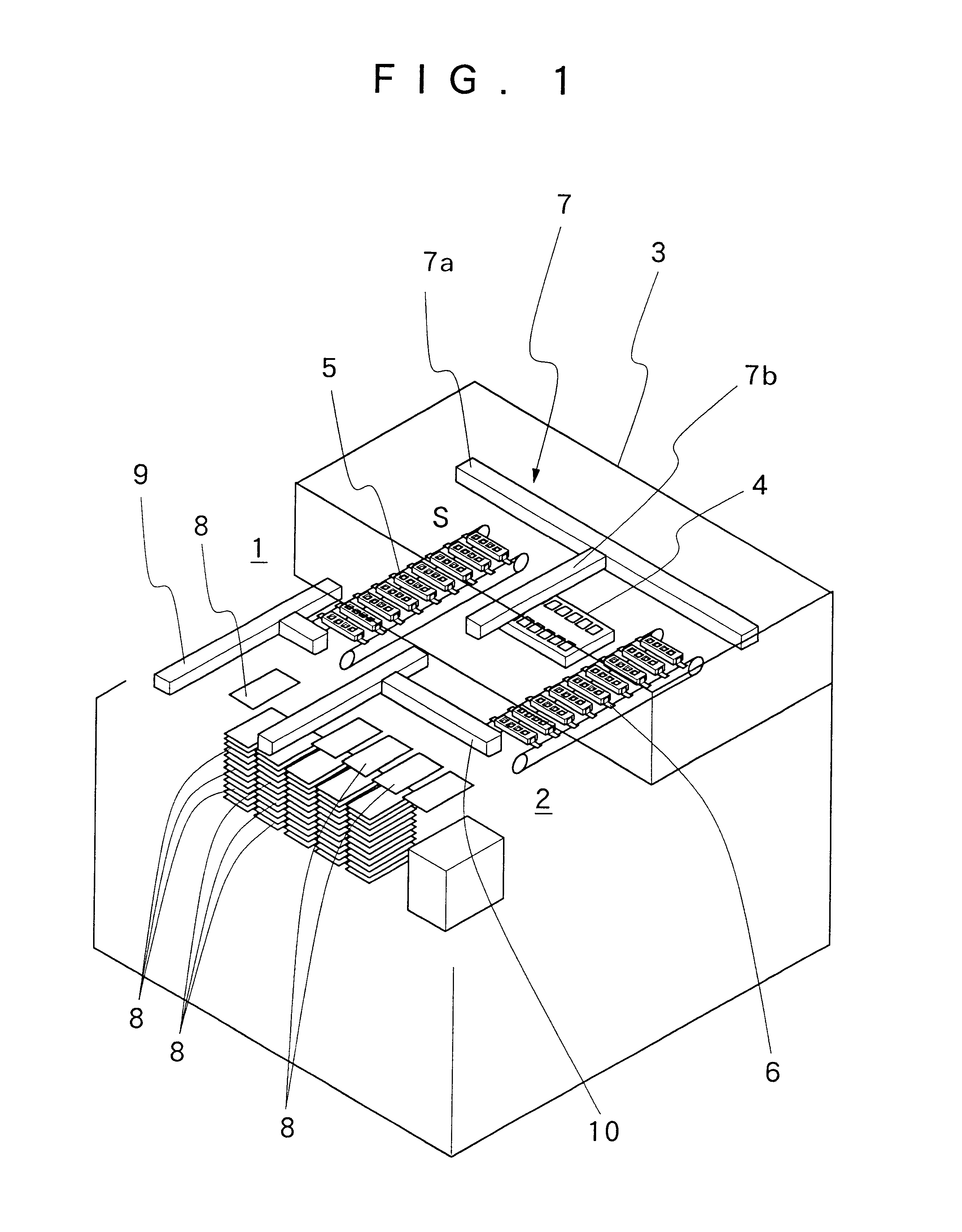

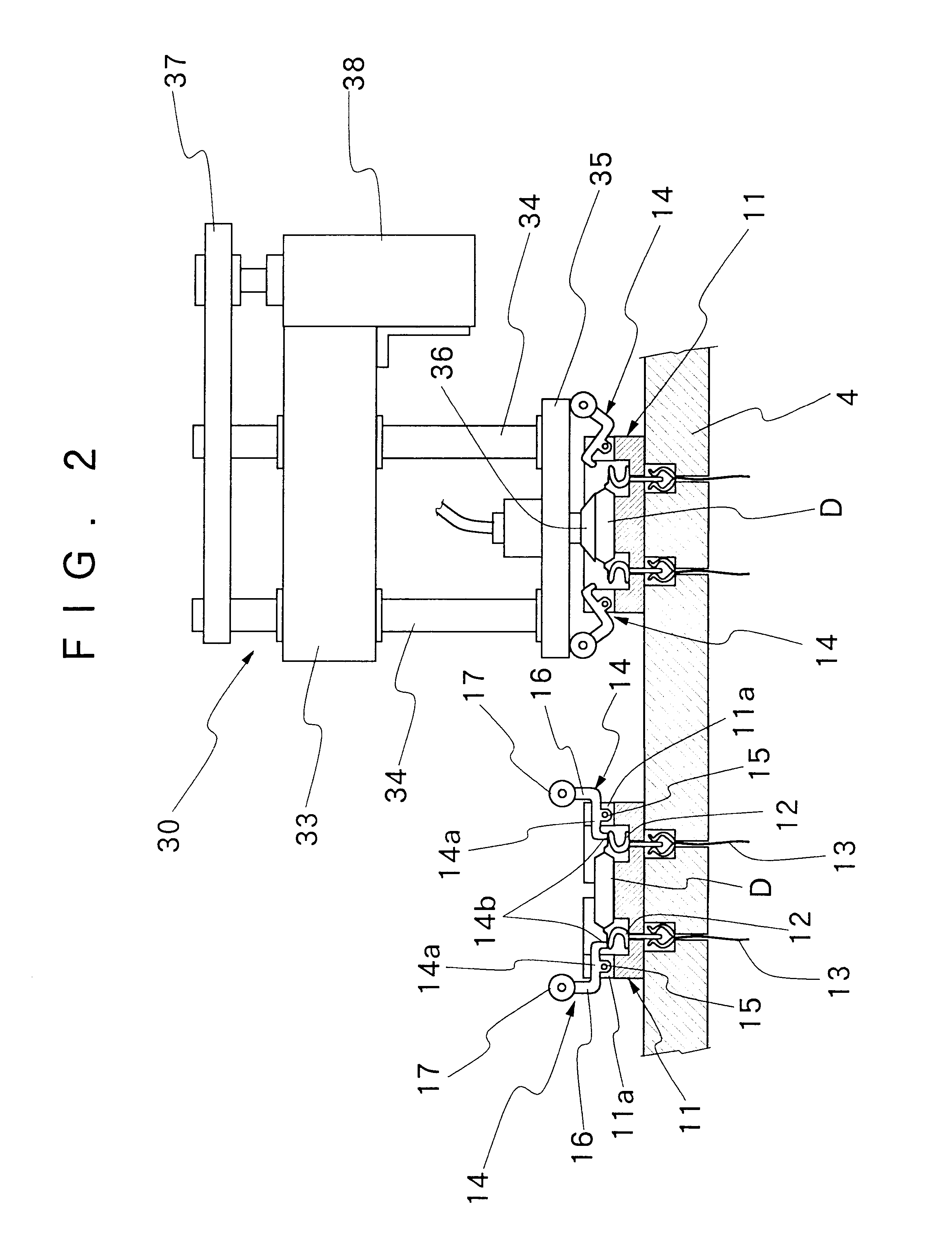

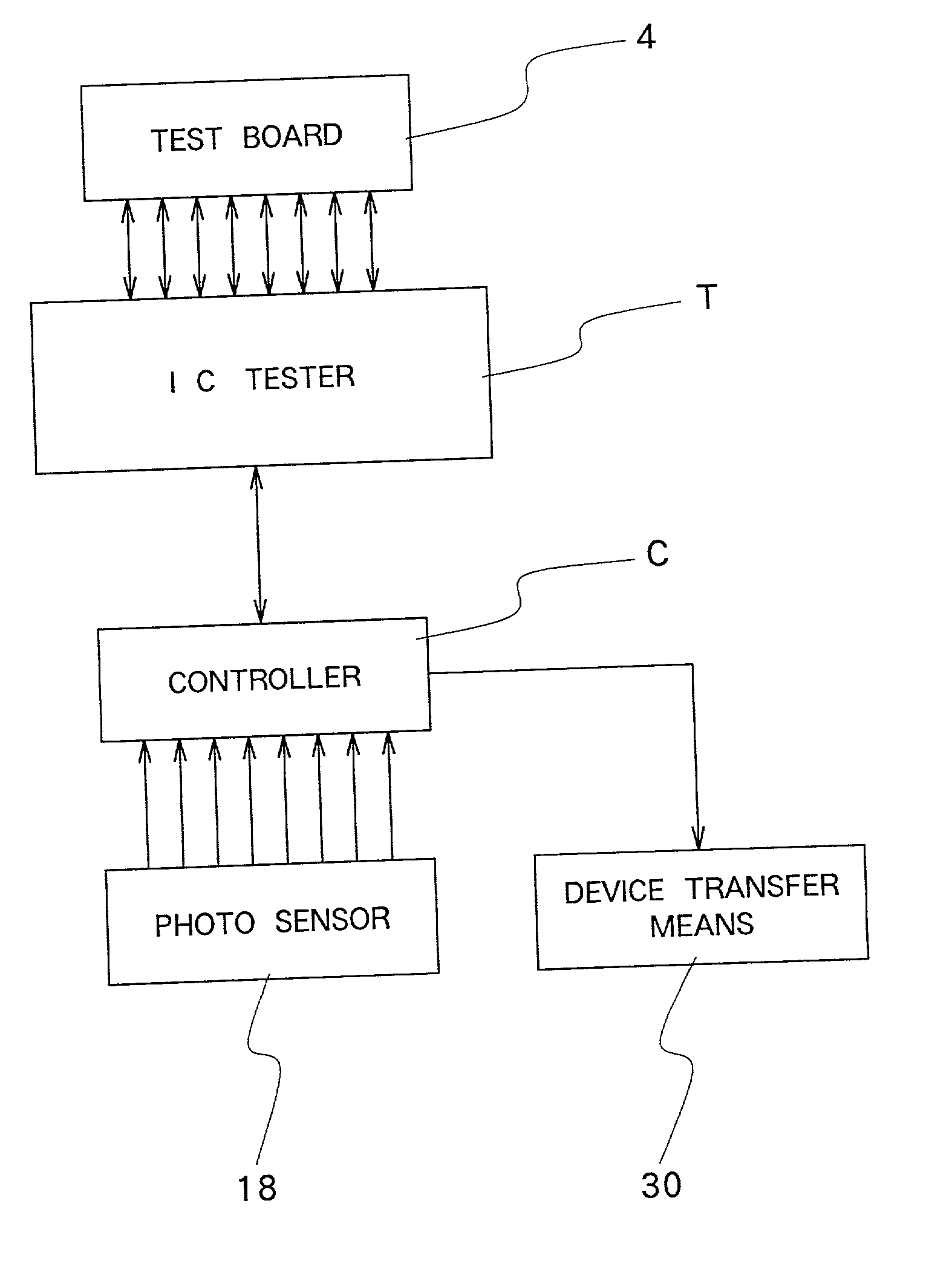

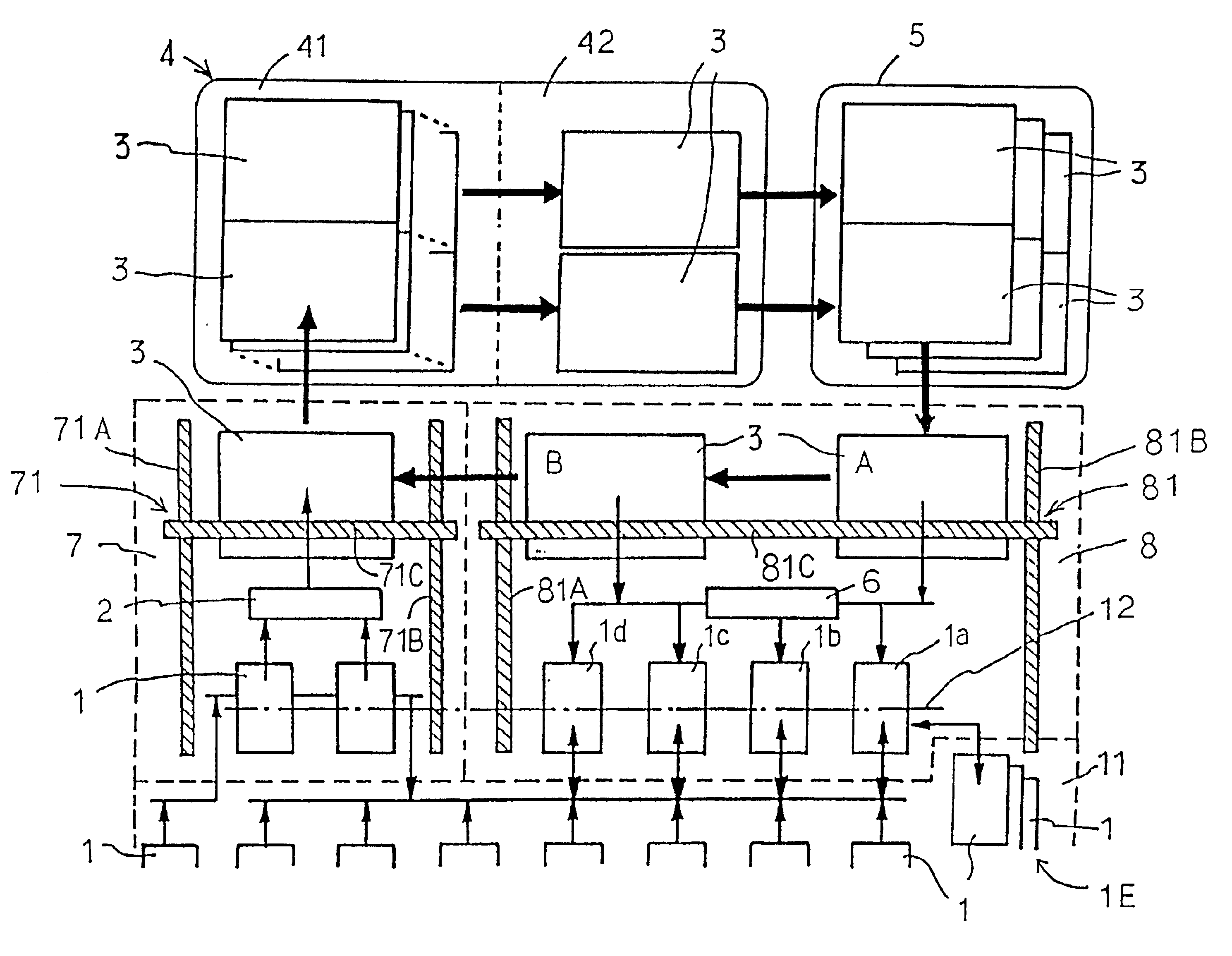

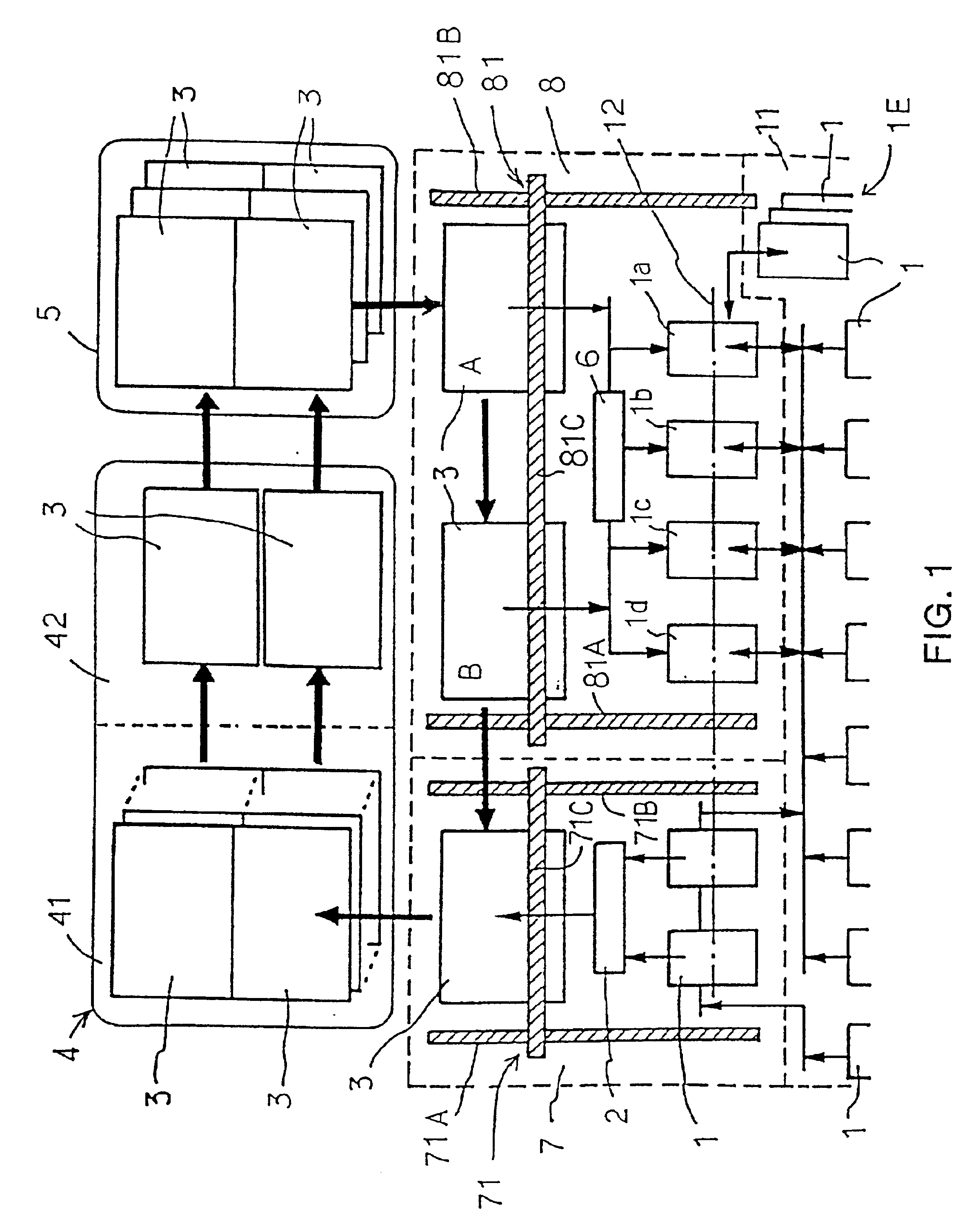

Method and apparatus for testing IC device

InactiveUS20020026258A1Semiconductor/solid-state device testing/measurementDigital data processing detailsTransfer mechanismIc devices

For testing electrical properties of packaged IC devices, there is provided an apparatus which includes a test board which is located at a testing station and provided with a plural number of contacting sockets for connecting individual IC devices to an IC tester separately and independently of each other, a loader which is located at a loading station and adapted to feed untested IC devices toward the test board, an unloader which is located at an unloading station and adapted to discharge tested IC devices from the test board at the testing station, and a device transfer mechanism which is movable across the testing station to transfer untested IC devices from the loader to the test board and also to transfer tested IC devices from the test board to the unloader. Upon detecting completion of a test on one of IC devices in one socket of the test board, a fresh untested IC device is transferred to the testing station to replace the tested IC device. As soon as the fresh IC device is set in position in that socket, execution of a test program is started with respect to that socket on the test board.

Owner:HITACHI ELECTRONICS ENG CO LTD

Compliant printed circuit wafer probe diagnostic tool

InactiveUS8912812B2Improve performanceIncrease valueElectrical measurement instrument detailsSolid-state devicesElectricityContact pad

Owner:HSIO TECH

Test signal distribution system for IC tester

InactiveUS20030210067A1Digital circuit testingElectrical measurement instrument detailsDistribution systemEngineering

A probe board provides signal paths between an integrated circuit (IC) tester and probes accessing terminals on the surfaces of ICs formed on a semiconductor wafer for receiving test signals form the IC tester. A branching signal path within the probe board distributes a test signal produced by one channel of the IC tester to several probes. Resistors within the branching signal path resistively isolate the probes from one another so that a fault occurring at any one IC terminal will not affect the logic state of the test signal arriving at any other IC terminal. The isolation resistors are sized relative to signal path characteristic impedances so as to substantially minimize test signal reflections at the branch points.

Owner:FORMFACTOR INC

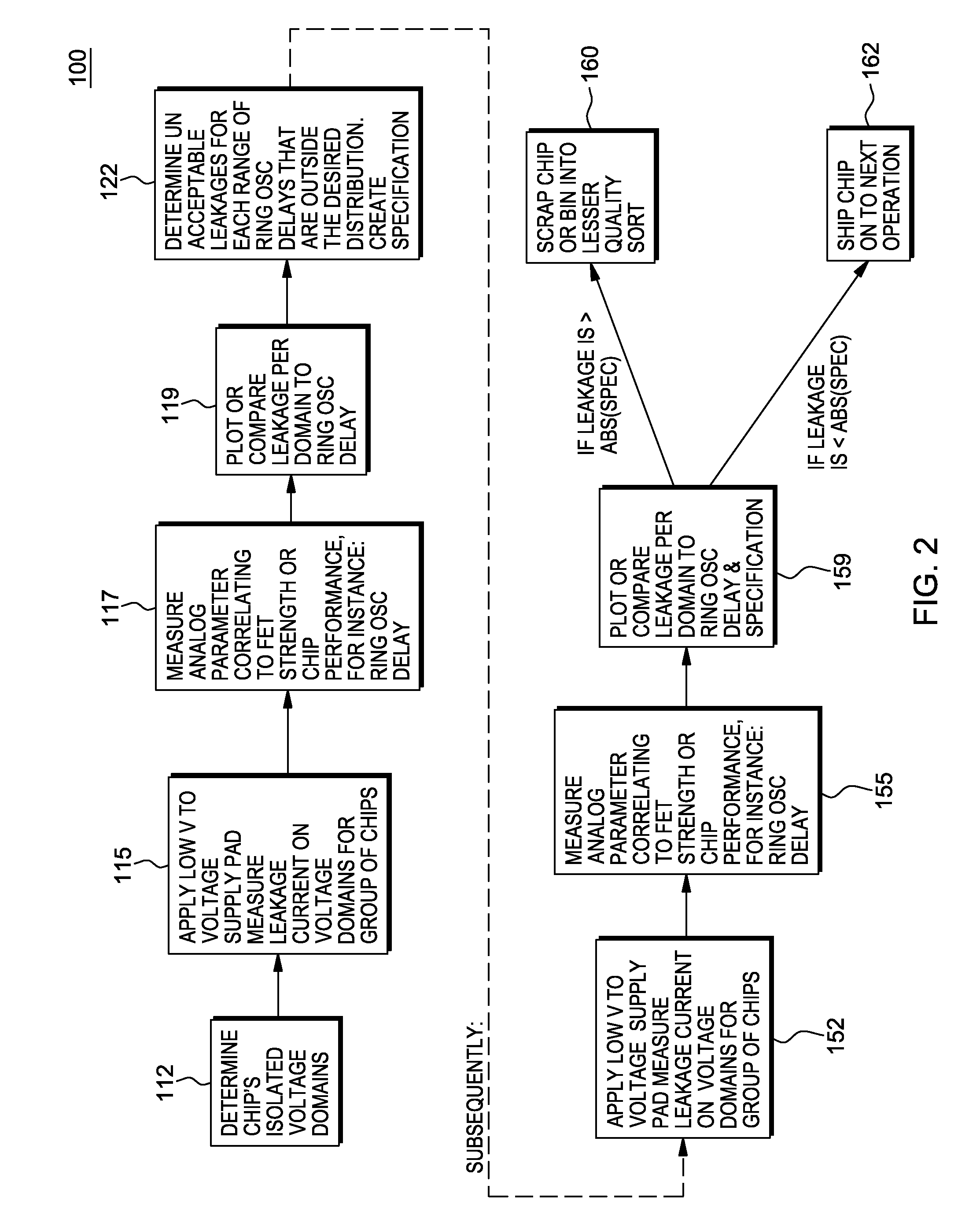

Low-voltage IC test for defect screening

InactiveUS20140184262A1Strong signalDetection moreElectronic circuit testingSolid-state devicesTest flowLow voltage

System and method using low voltage current measurements to measure voltage network currents in an integrated circuit (IC). In one aspect, a low voltage current leakage test is applied voltage networks for the IC or microchip via one or more IC chip connectors. One or multiple specifications are developed based on chip's circuit delay wherein a chip is aborted or sorted into a lesser reliability sort depending whether the chip fails specification. Alternately, a low voltage current leakage test begins an integrated circuit test flow. Then there is run a high voltage stress, and a second low voltage current leakage test is thereafter added. Then, there is compared the second low voltage test to the first low V test, and if the measured current is less on second test, this is indicative of a defect present which may result in either a scrap or downgrade reliability of chip.

Owner:ALSEPHINA INNOVATIONS INC

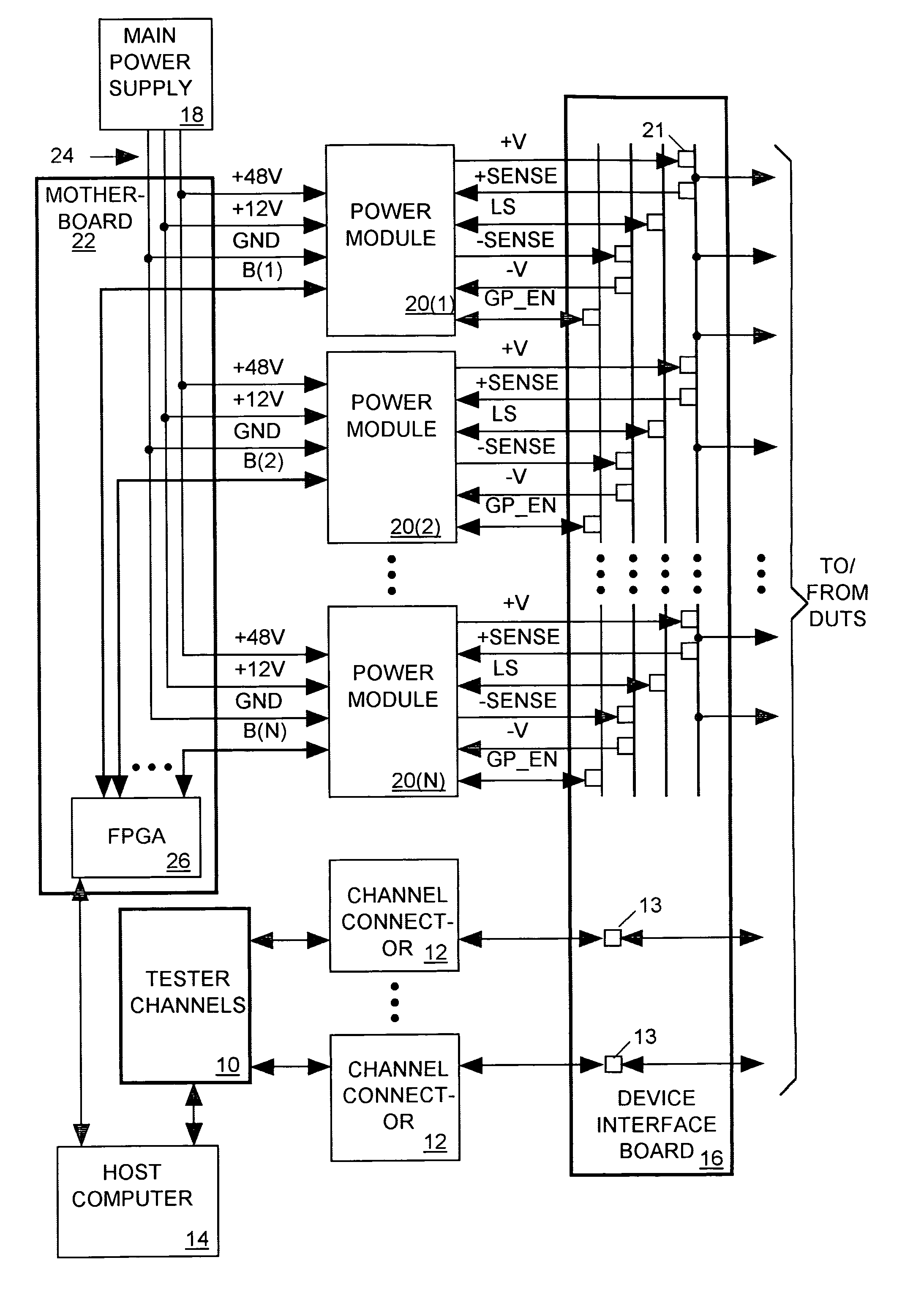

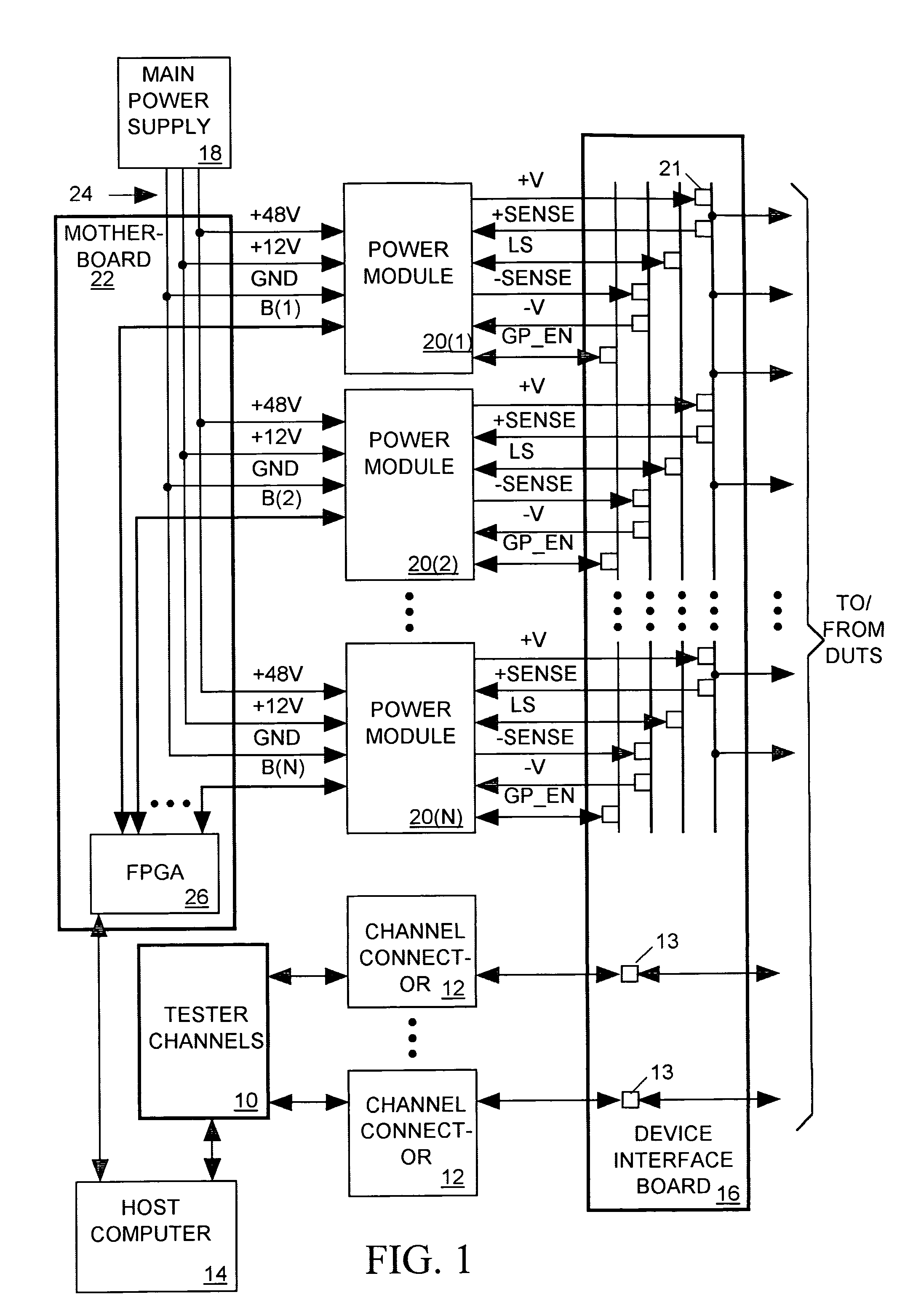

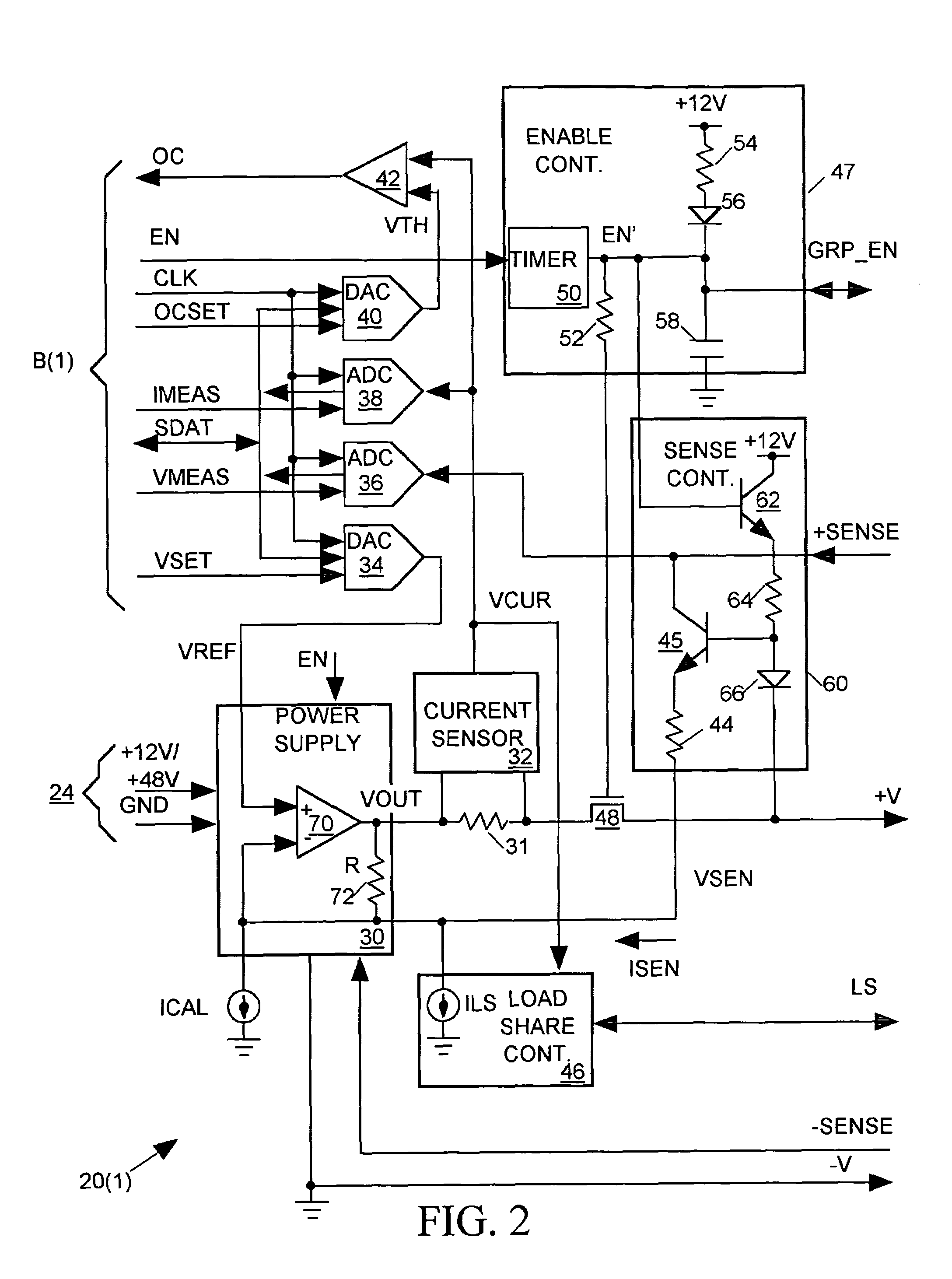

Distributed, load sharing power supply system for IC tester

InactiveUS7053648B2Digital circuit testingIndividual semiconductor device testingComputer moduleElectrical current

An integrated circuit (IC) tester includes a set of power modules mounted in a test head, each contacting a device interface board (DIB). The DIB provides power paths for delivering an output current generate by each power module to a power input terminals of one or more IC devices under test (DUTs). Power modules that supply current to the same set of DUTs communicate with one another though conductive paths provided by the DIB to ensure that all power modules begin supplying load current to that set of DUTs at the same time and to ensure that all power modules supply substantially the same amount of load current to those DUTs.

Owner:CREDENCE SYSTEMS

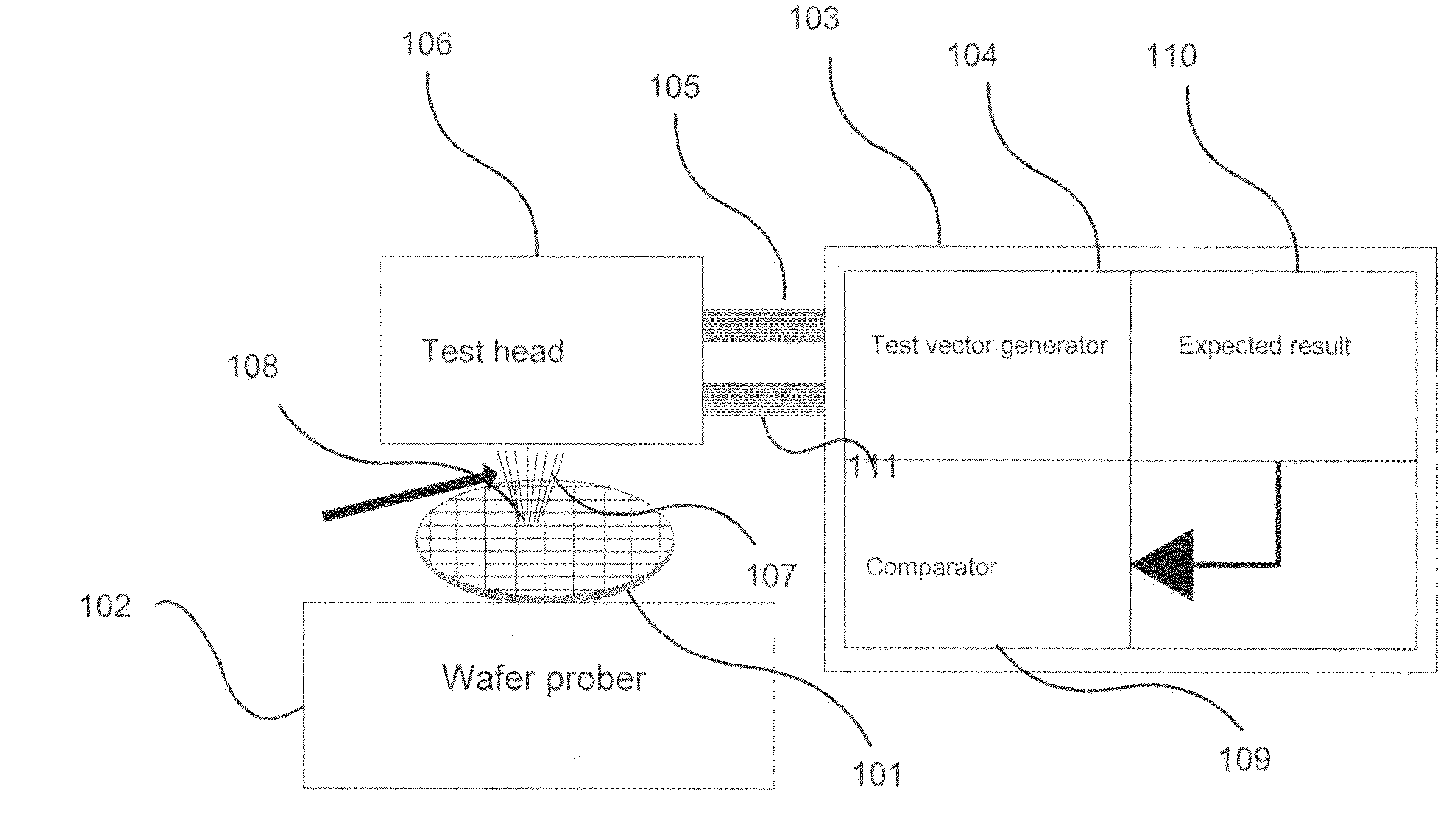

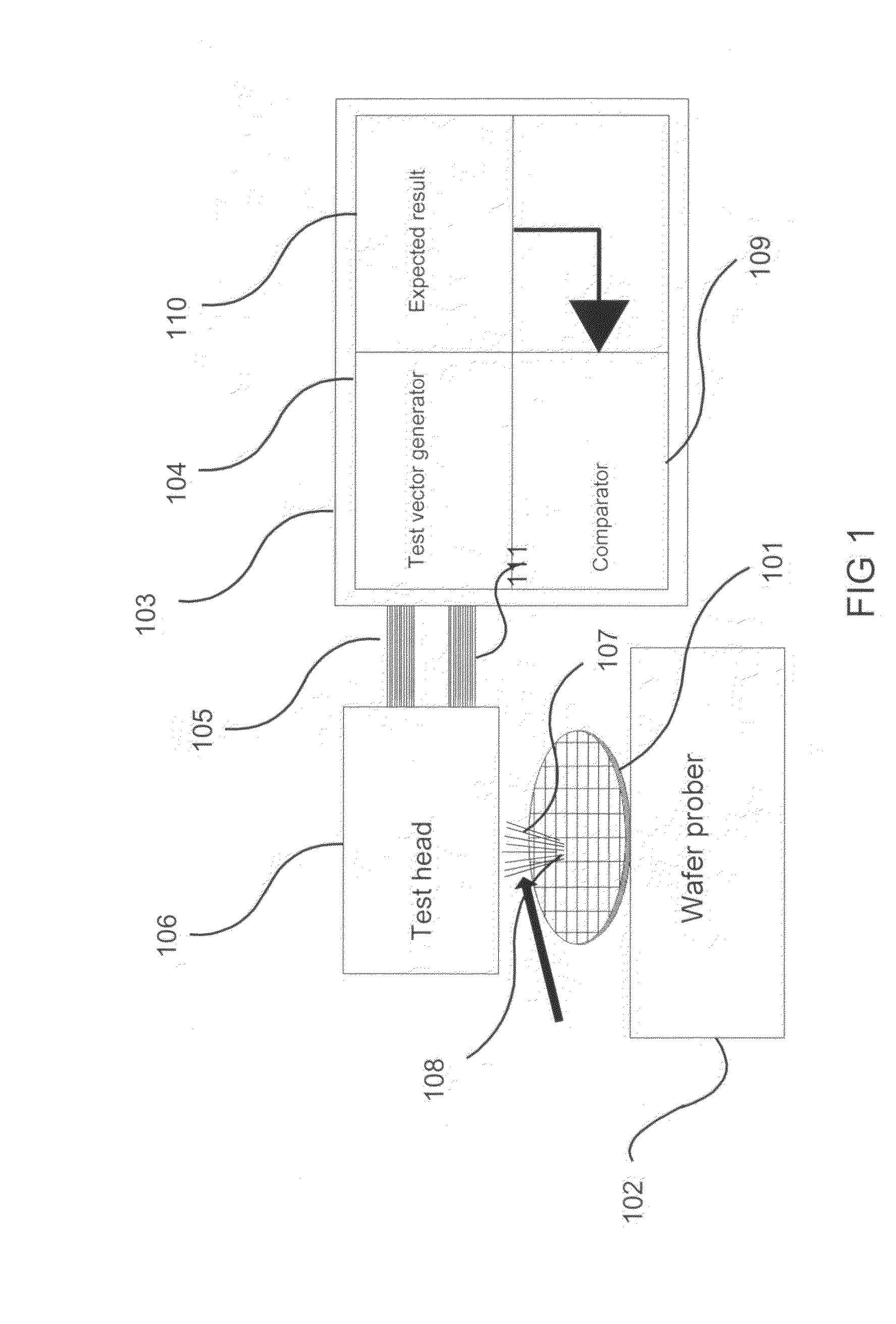

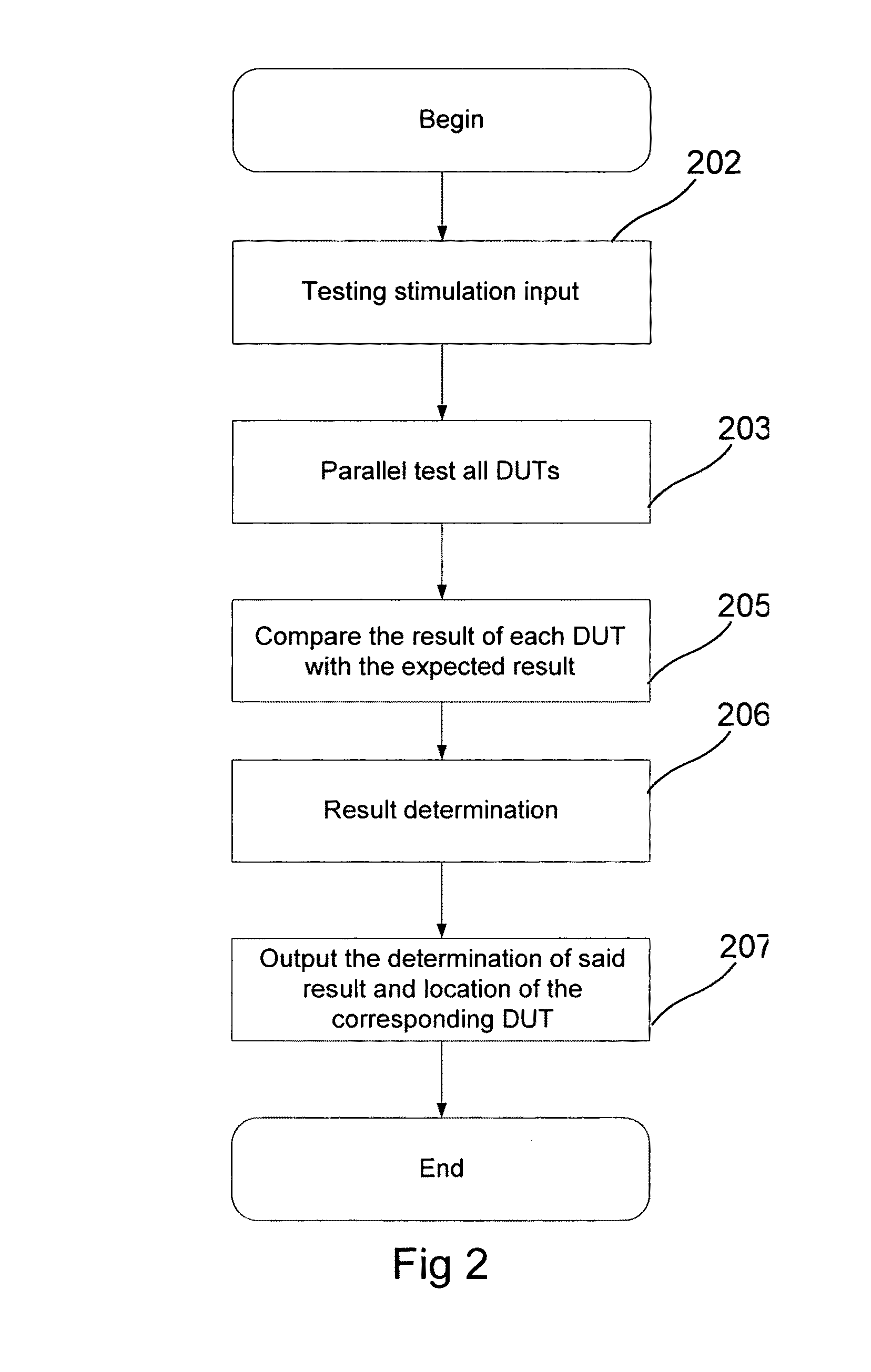

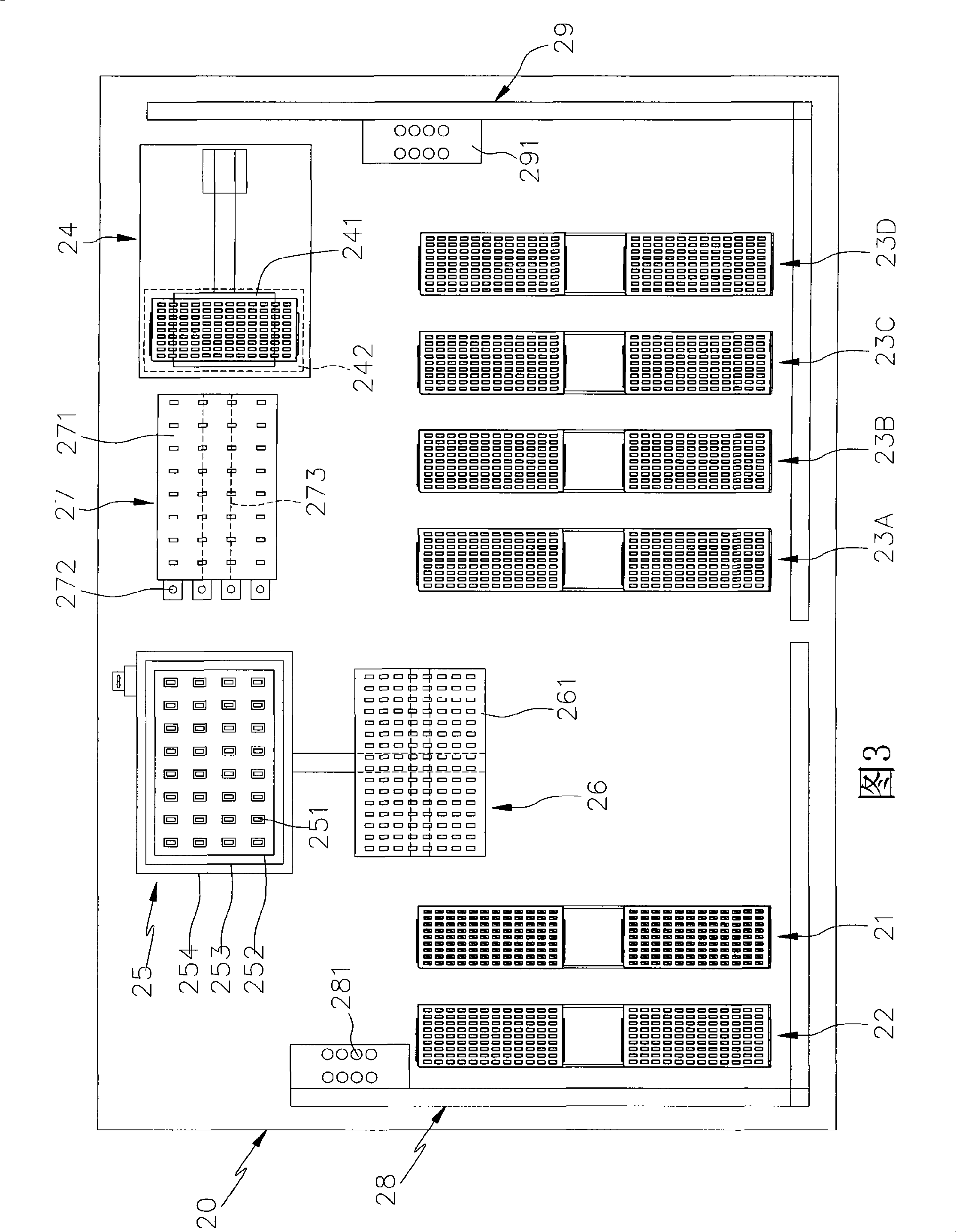

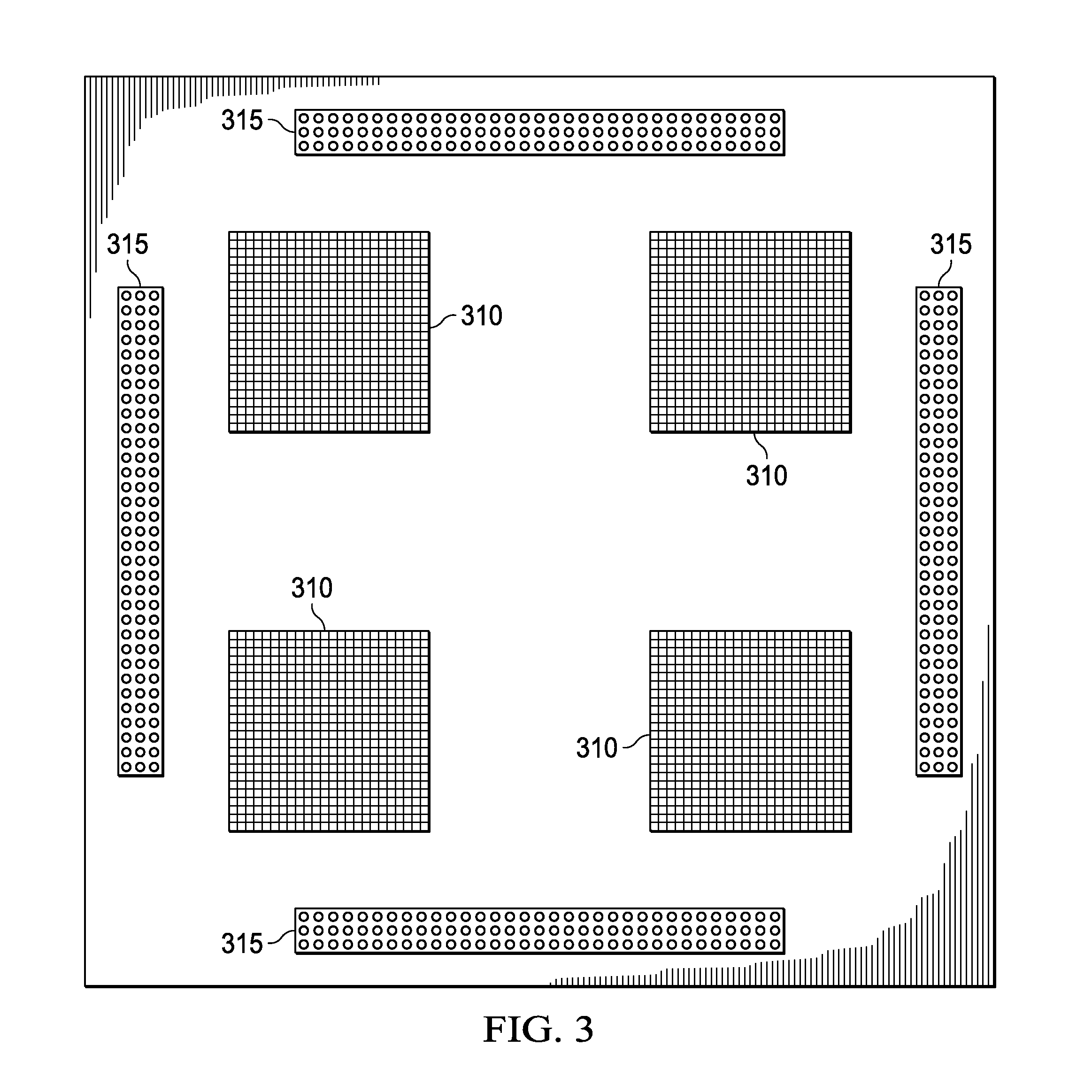

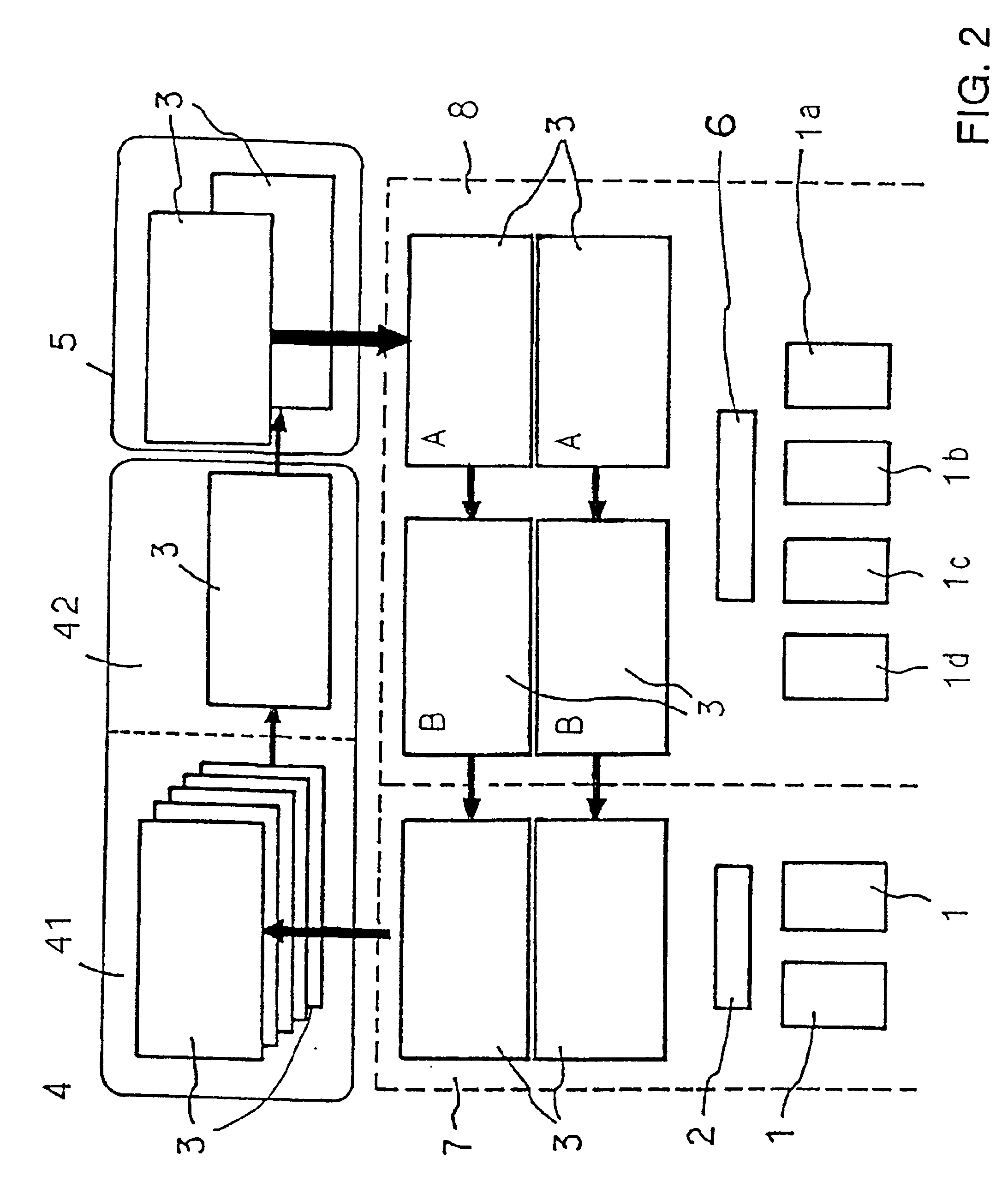

Method, apparatus and system of parallel IC test

ActiveUS20100237891A1Test accurateShorten test timeCurrent/voltage measurementElectrical testingEngineeringIc testing

A method, apparatus and system for integrated circuit testing, wherein a plural number of devices under test (DUTs) and a plural number of comparison apparatuses are placed on a common substrate. The DUTs all operate under the same input stimulation and each produce its own operation output. The outputs are compared by the comparison apparatuses to generate comparison characteristics which are used to filter-out the failed devices. This invention lowers the testing cost, shortens time to product mass-production, and lowers the miss rate of failed devices passed as good ones.

Owner:SHANGHAI XINHAO MICROELECTRONICS

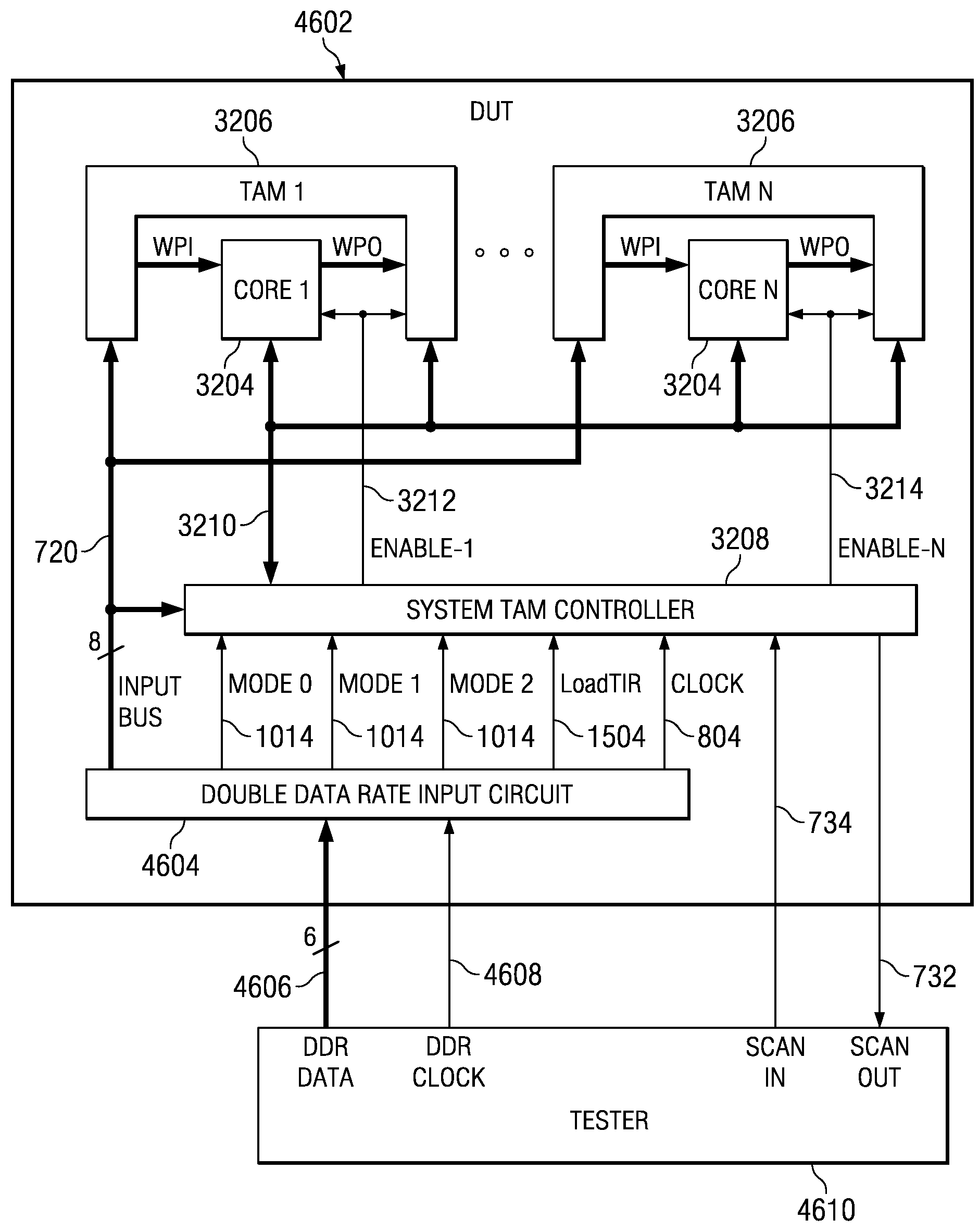

DDR input interface to IC test controller circuitry

ActiveUS7529996B2Efficient testingSimplifies testerElectronic circuit testingDouble data rateProgrammable logic controller

Owner:TEXAS INSTR INC

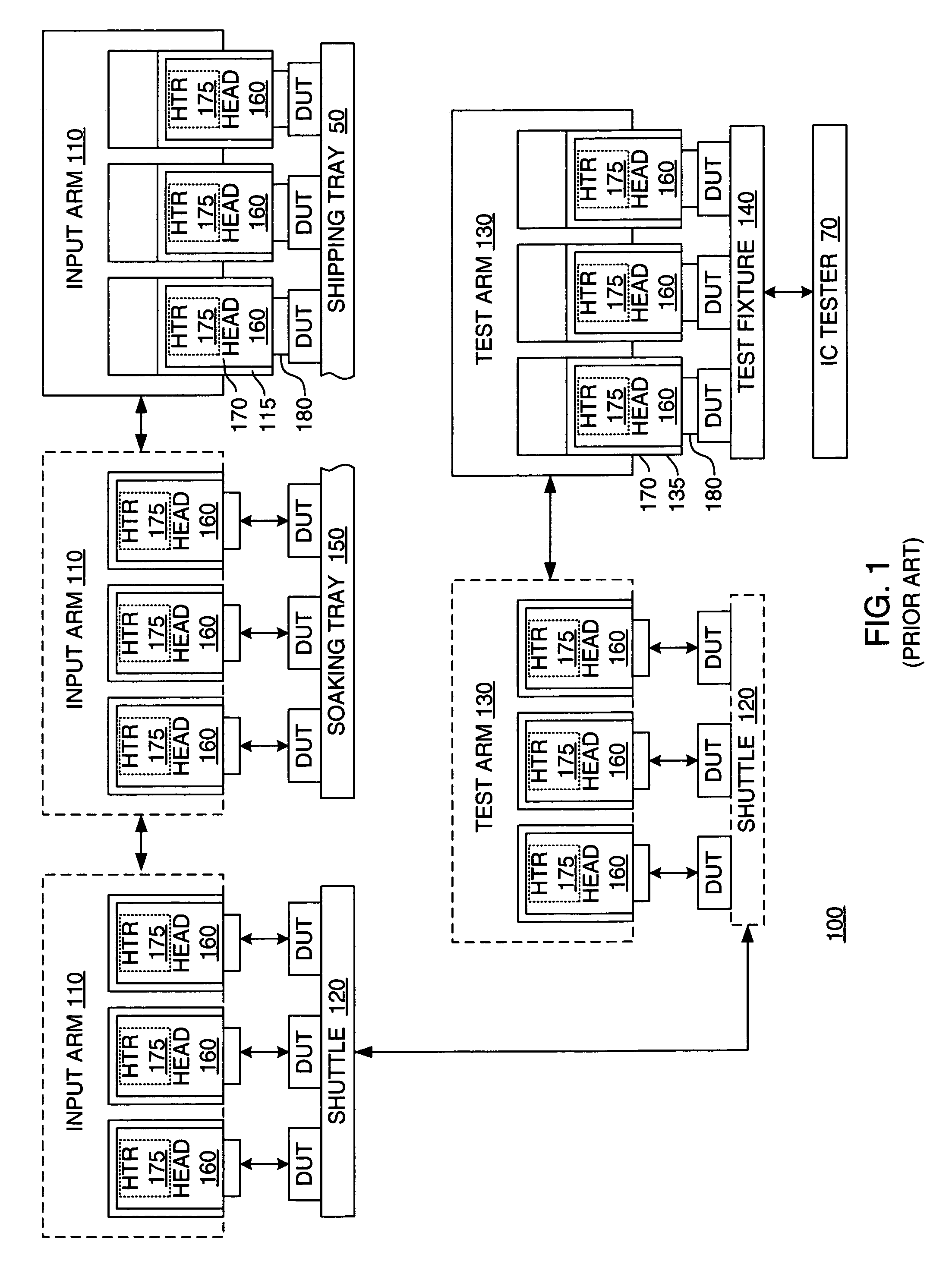

Machine allocation of IC test processor and process for making the same

InactiveCN1464312ASemiconductor/solid-state device testing/measurementElectronic circuit testingTest benchIc testing

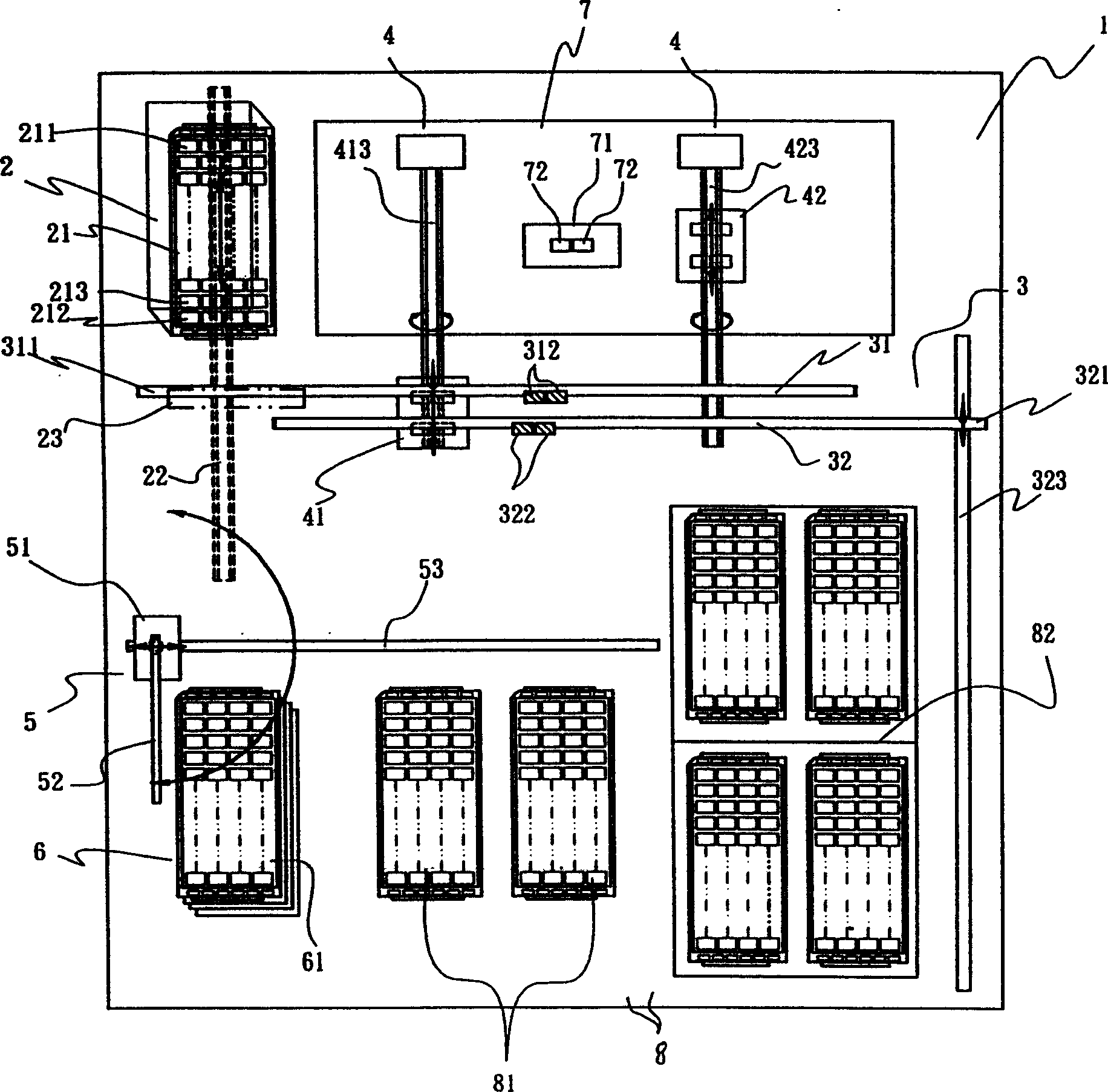

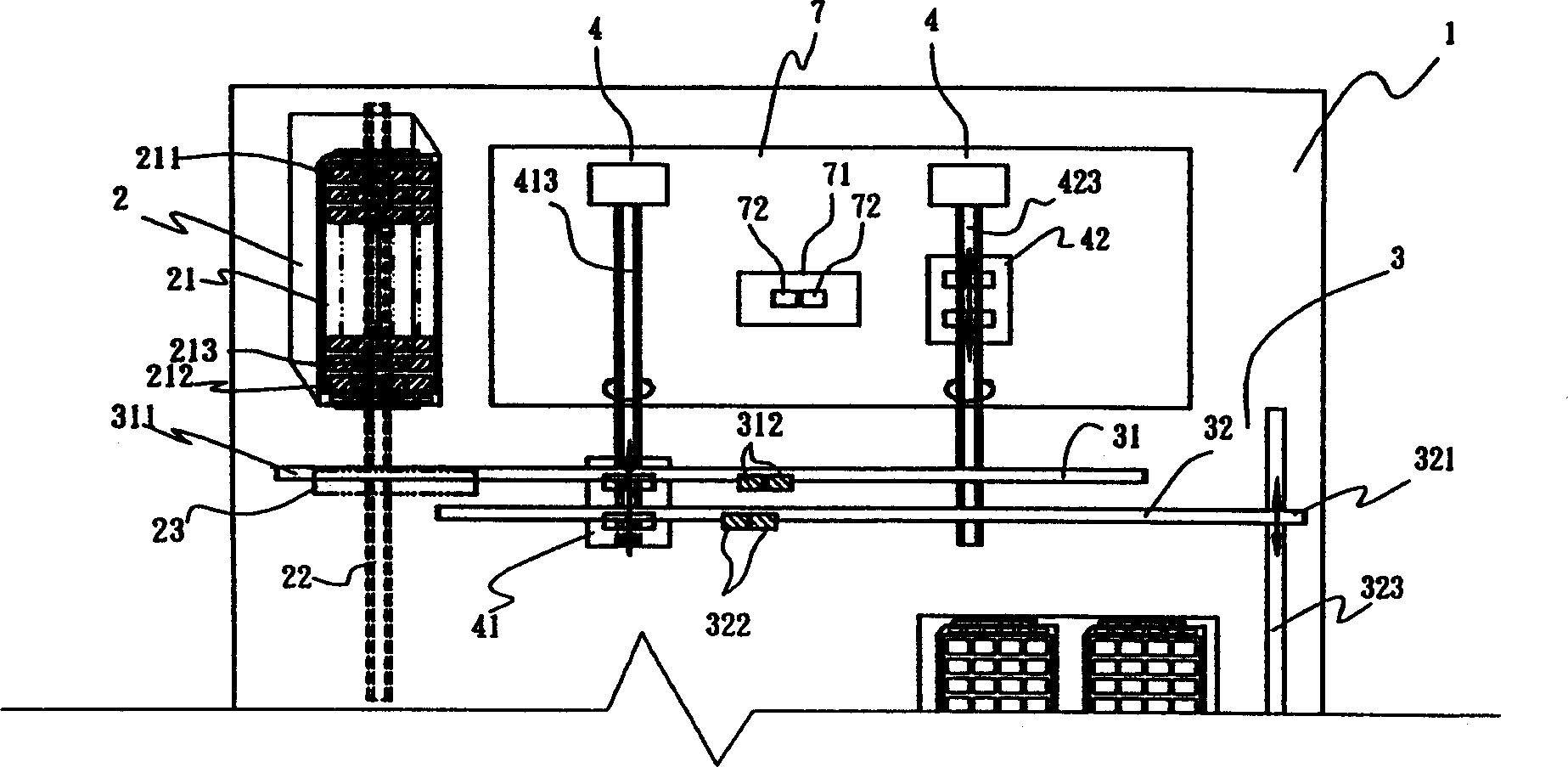

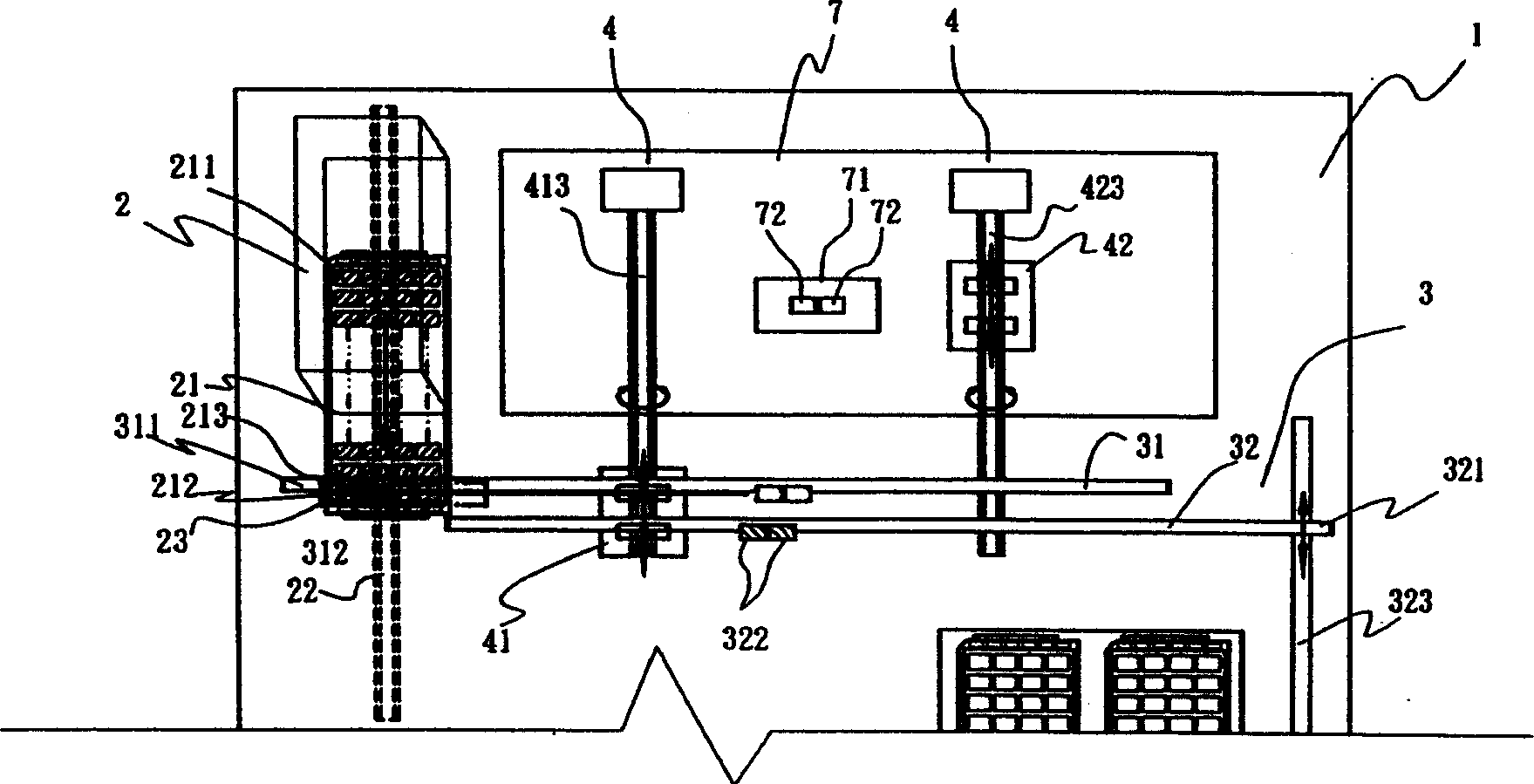

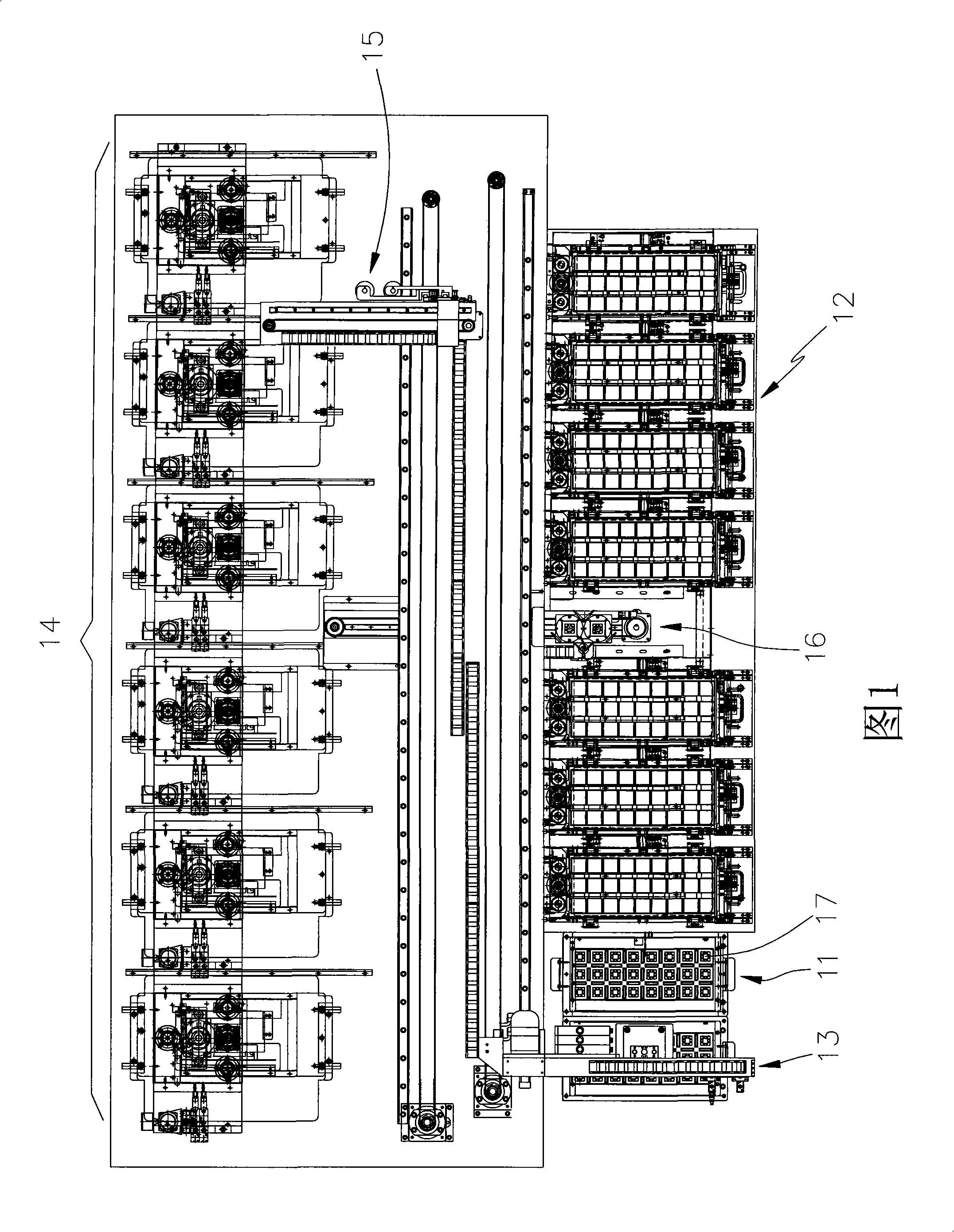

The present invention is test bench configuration and measurement process for IC test. The test bench includes material stacking and feed buffering area for stacking ICs to be tested; empty IC tray dispatching mechanism for sucking empty tray for concentration in the empty IC tray area; double-IC conveying arm with double sucking heads to suck one pair of ICs; one pair of alternately conveyed temporary storing trays for conveying ICs to IC test area for continuous test; and tested IC setting area. In the test bench, all tested ICs are set based on their parameters. The present invention has high efficiency, small covered area and short processing path.

Owner:TASK TECH

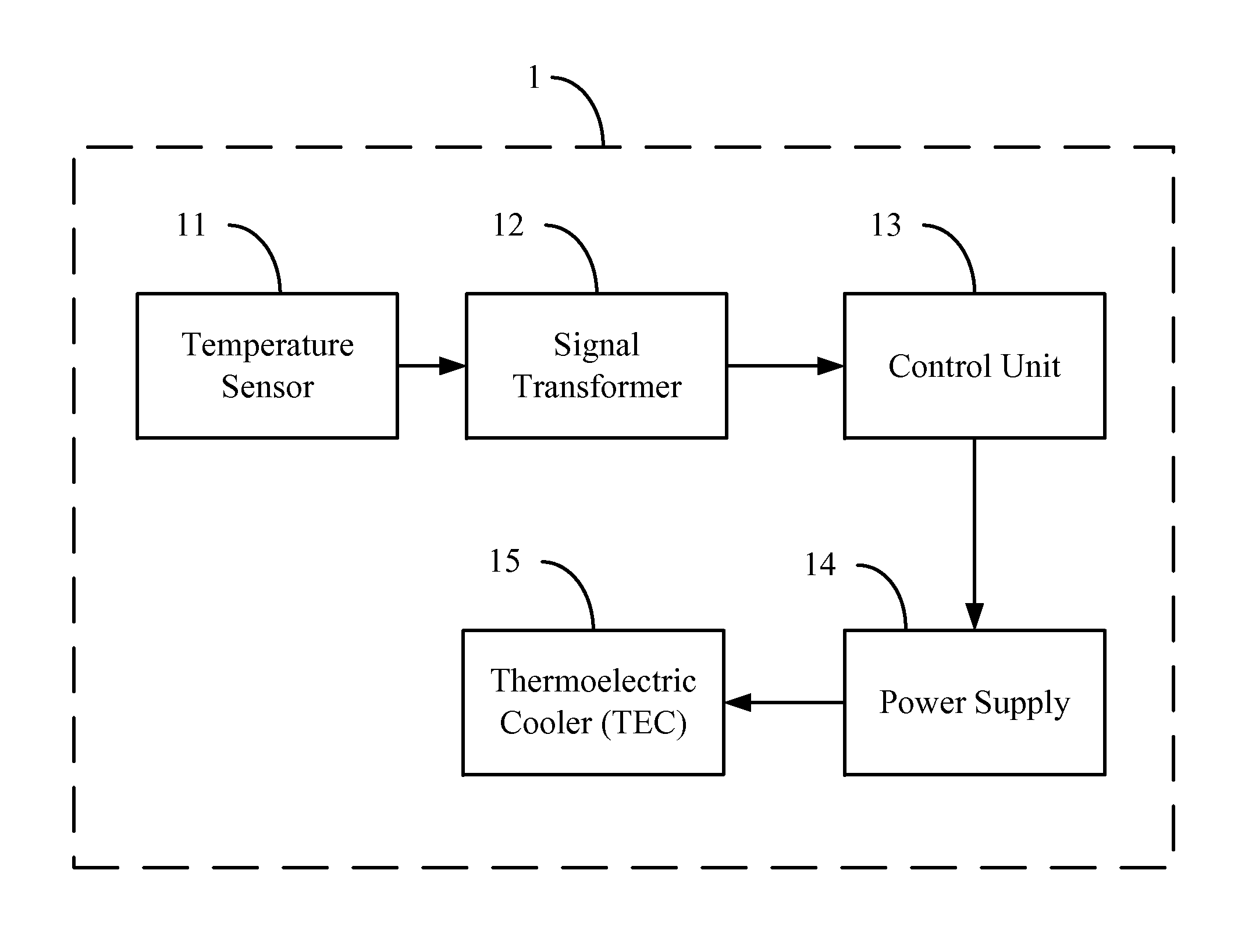

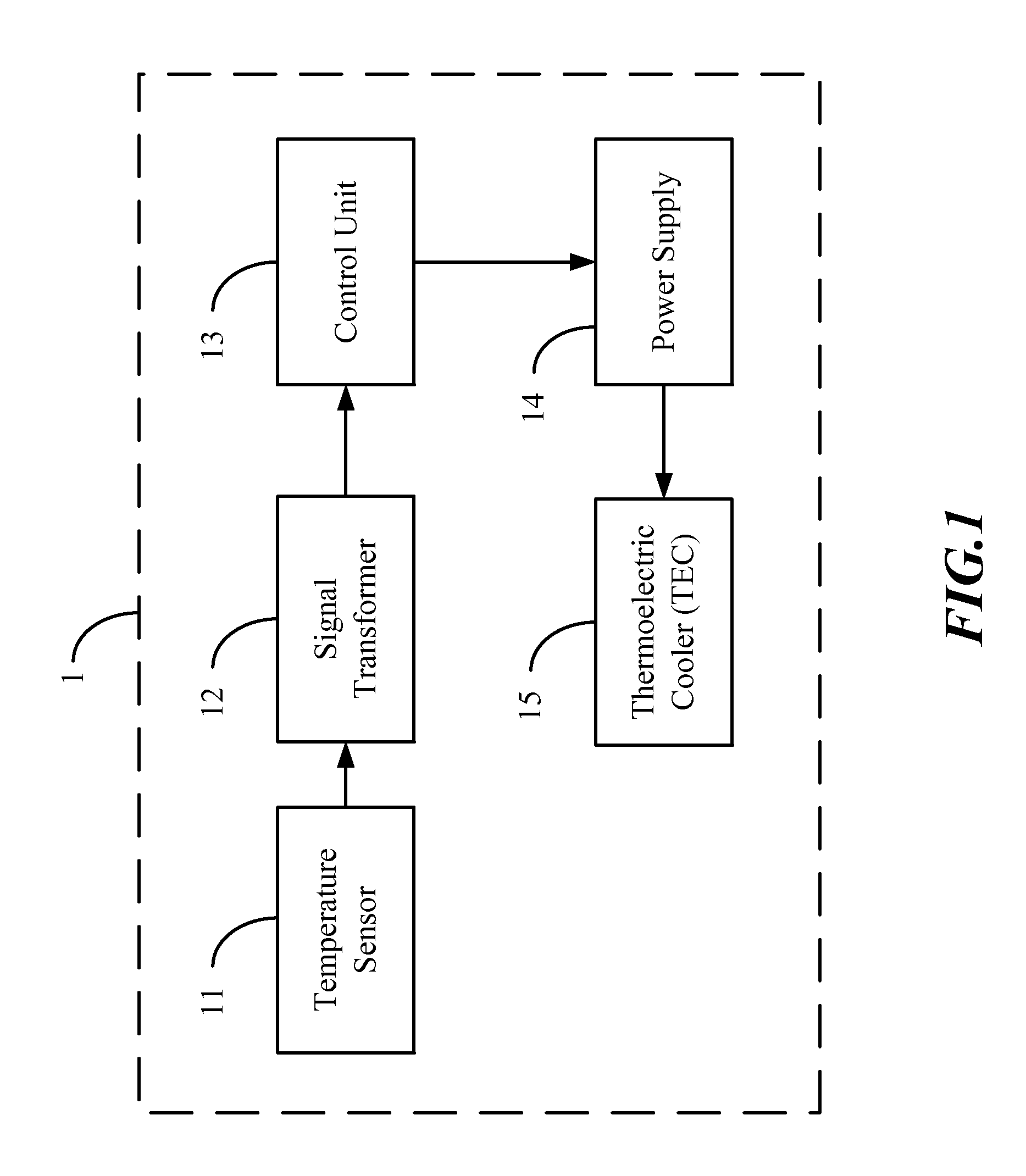

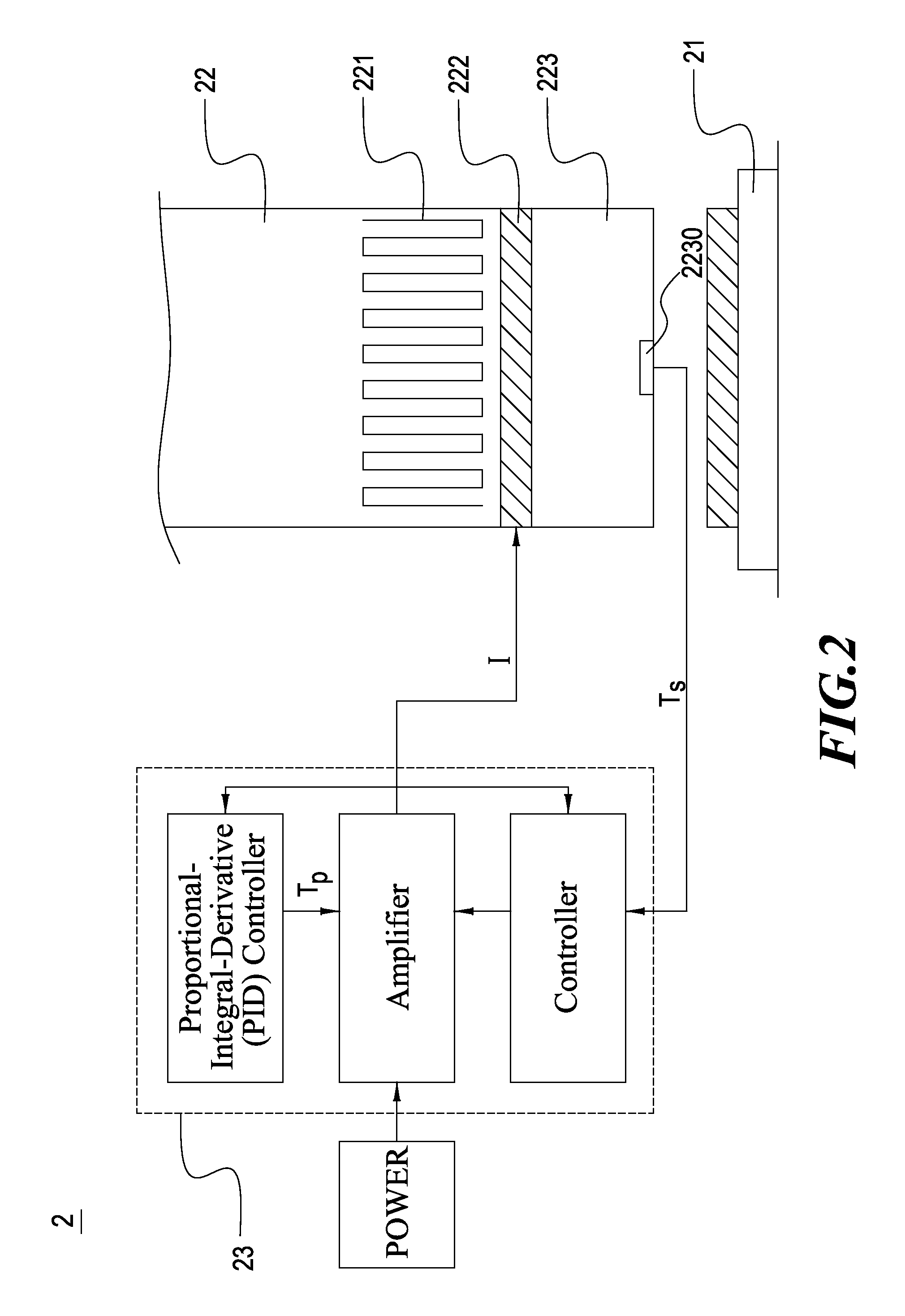

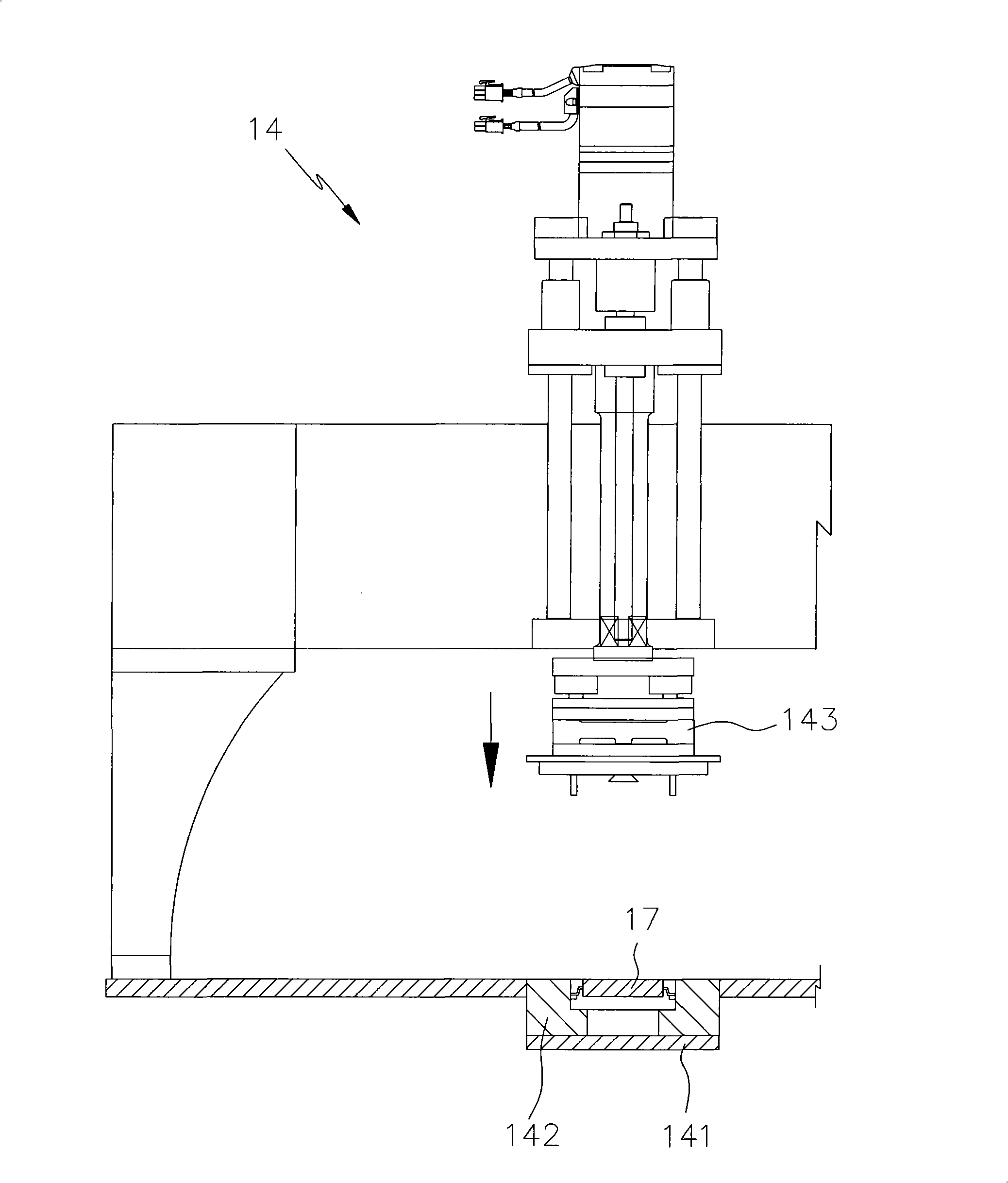

Temperature Control System for IC Tester

InactiveUS20130113509A1Easy to controlAvoid failureElectrical testingTemperature controlThermoelectric cooling

A temperature control system for IC tester, comprising: a test socket; a compressing device including a heat exchanger and a thermoelectric cooler (TEC); and a test head having a temperature sensor. The test head is configured at the front end of the compressing device such that, upon placing at least one device under test (DUT) onto the test socket, the test head coerces tightly one of the DUTs through downward pressure from the compressing device thereby allowing the temperature sensor to detect the surface temperature of the DUT to obtain a temperature signal, and then feed such a temperature signal back to a control processing unit for operations to generate a linear control signal thus that, through the control of the linear control signal, the heat absorption and heat discharge functions of the TEC are enabled to further control the temperature of the DUT within a determined range.

Owner:CHROMA ATE

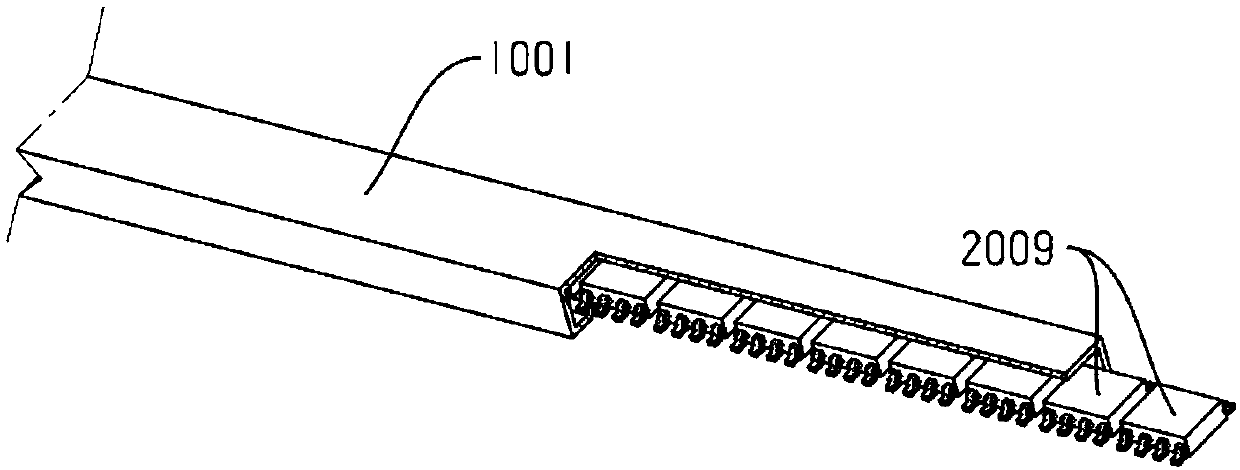

Memory body IC detecting and sorting machine

ActiveCN101342532AEasy to detectImprove efficiencyElectronic circuit testingSortingEngineeringService efficiency

The invention discloses a memory IC testing and classifying device, comprising a feeding box, an empty box, at least one receiving box and a transfer device arranged at the front end of the machine platform, and at least one testing device, a second transfer device and a removal receiving box arranged at the rear end of the machine platform, as well as a first material-moving device and a second material-moving device arranged among the feeding box, the receiving box and the testing box; the feeding box and the receiving box are used to hold the memory ICs to be tested / tested respectively; the testing device is a test circuit board provided with a plurality of test sheath seats; the first material-moving device transfers more than one memory IC to be tested in the feeding box to the firsttransferring device; the first transferring device is capable to preheat the held memory ICs to be tested, and make displacement movement to ensure the testing device to take materials at different positions. The invention is capable to transfer and test a plurality of memory ICs simultaneously, thereby, the testing capability is largely enhanced and the service efficiency of each device is improved effectively.

Owner:HON PRECISION INC

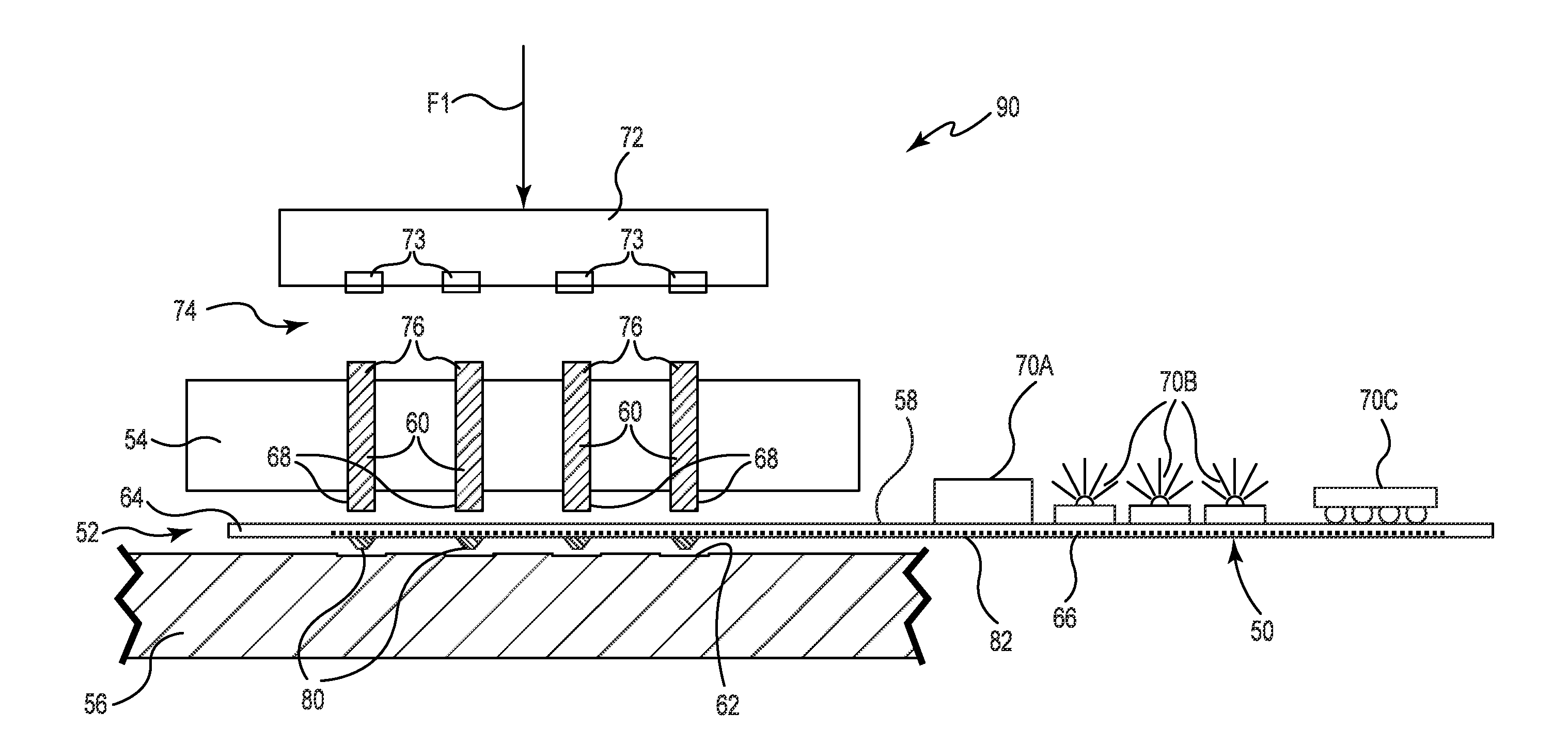

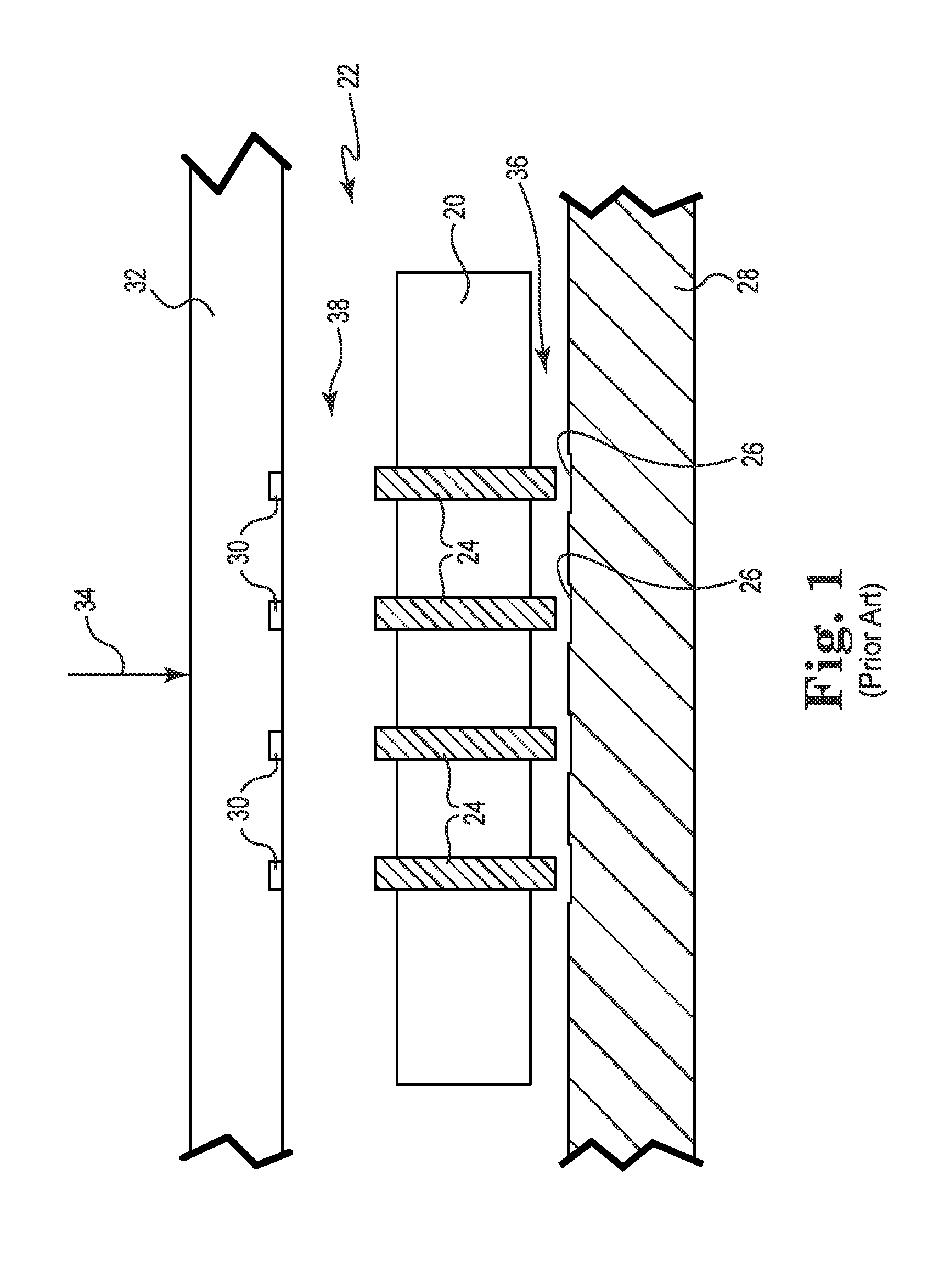

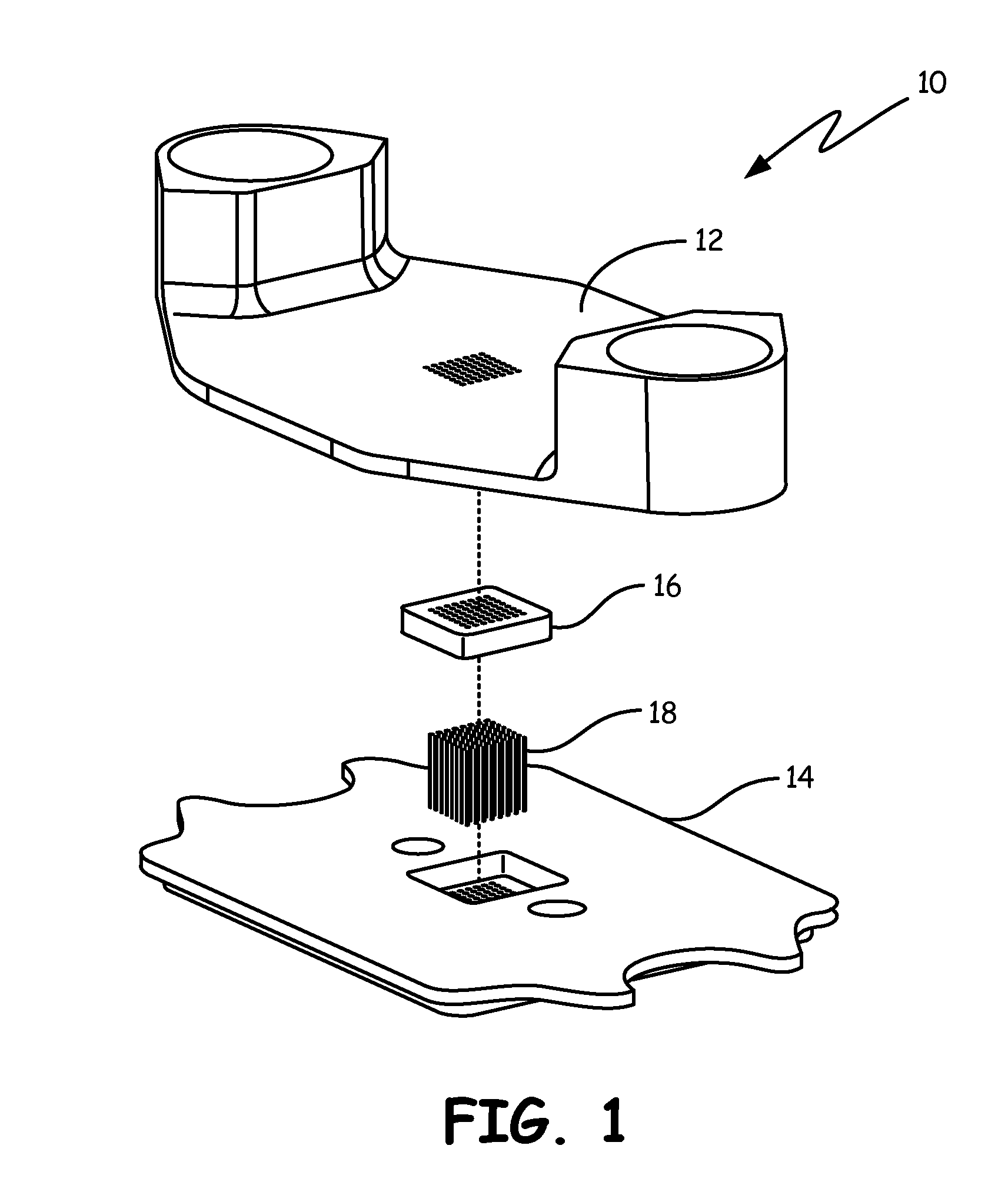

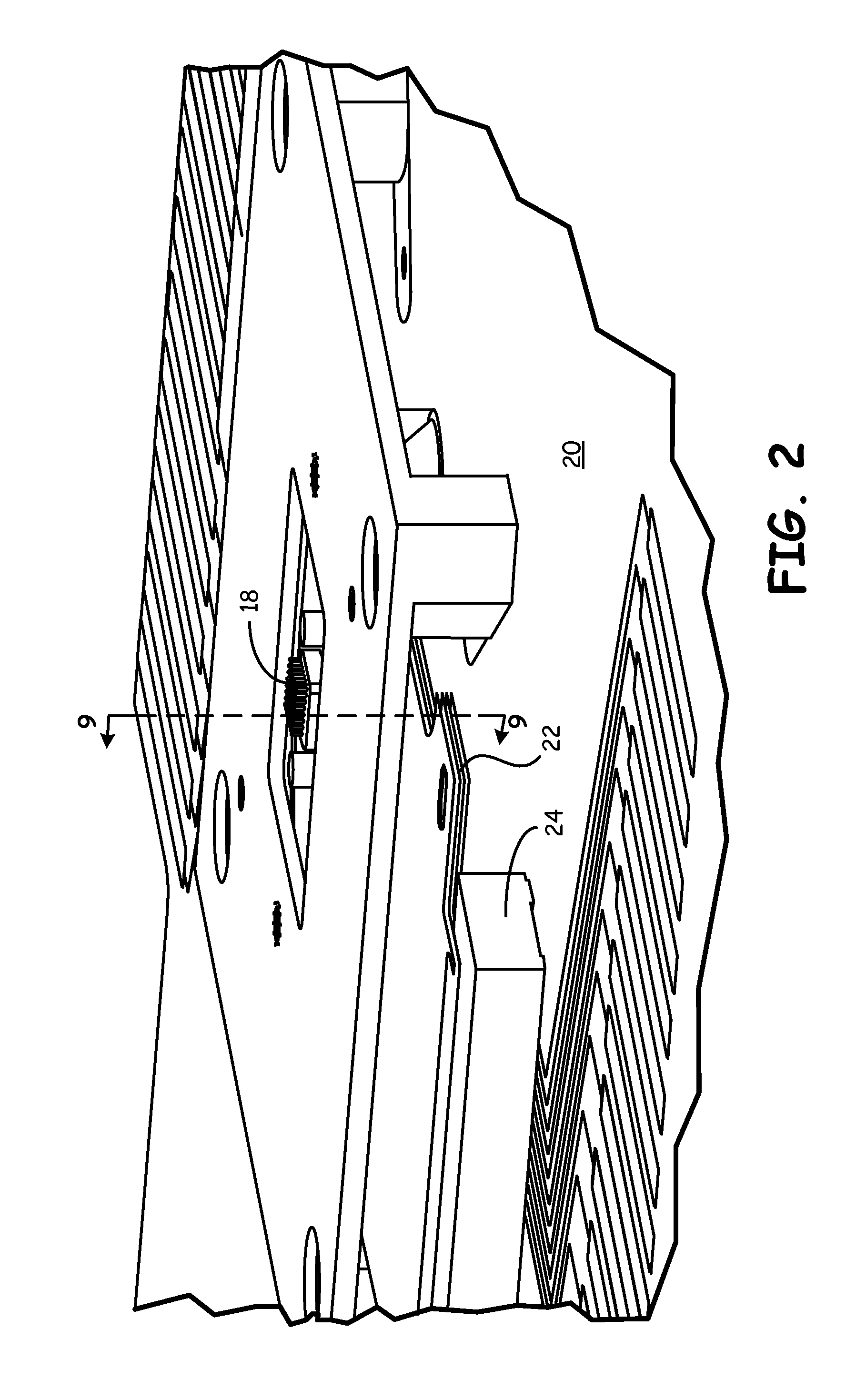

Testing apparatus and method for microcircuit and wafer level IC testing

ActiveUS20150015287A1Biasing forcePrinted circuit assemblingElectronic circuit testingElastomerProbe card

The test system provides an array of test probes having a cross beam. The probes pass through a first or upper probe guide retainer which has a plurality of slot sized to receive the probes in a way that they cannot rotate. The probes are biased upwardly through the retainer by an elastomeric block having a similar array of slots. The elastomer is then capped at its bottom by a second or lower retainer with like slots to form a sandwich with the elastomer therebetween. The bottom ends of the probes are group by probe height. A plurality of flex circuits at the different heights engage bottom probe ends at their respective height levels and take continue the circuits to a probe card where test signals originate.

Owner:JOHNSTECH INT

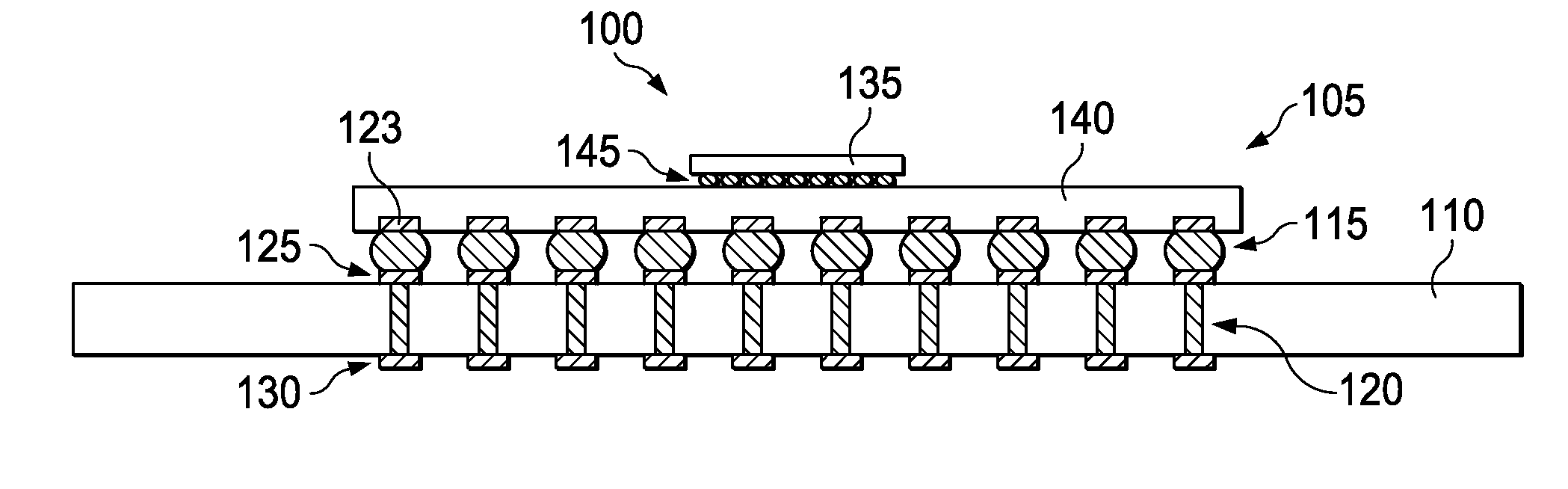

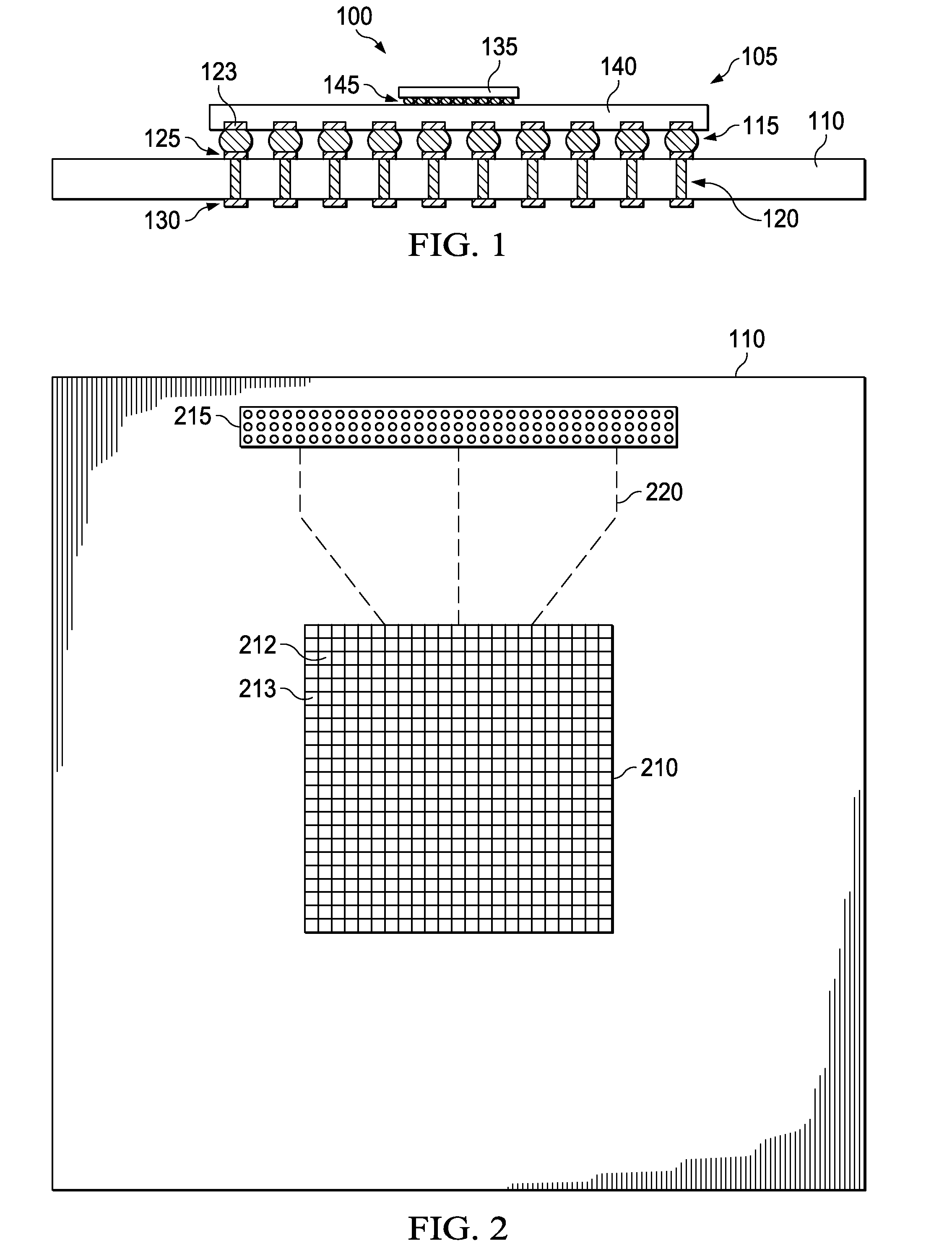

Method and apparatus for testing interconnection reliability of a ball grid array on a testing printed circuit board

ActiveUS20140111242A1Electrical measurement instrument detailsElectric connection testingSolder ballInterconnection

An apparatus for determining an electrical reliability of a ball grid array (BGA) assembly of an integrated circuit is presented. The assembly comprises a testing printed circuit board (PCB) having an integrated circuit (IC) test region located thereon. Vias extend through the testing PCB from a surface to an underside thereof within the IC test region. Each via has an IO pad or ground pad electrically connectable thereto. An IC package having an IC die connected thereto by solder bumps is connected to the IC test region by solder balls, such that each of the IO pads is electrically connectable to a respective pair of the solder balls and solder bumps by the vias. A method of testing interconnection reliability of the BGA using the apparatus is also presented.

Owner:NVIDIA CORP

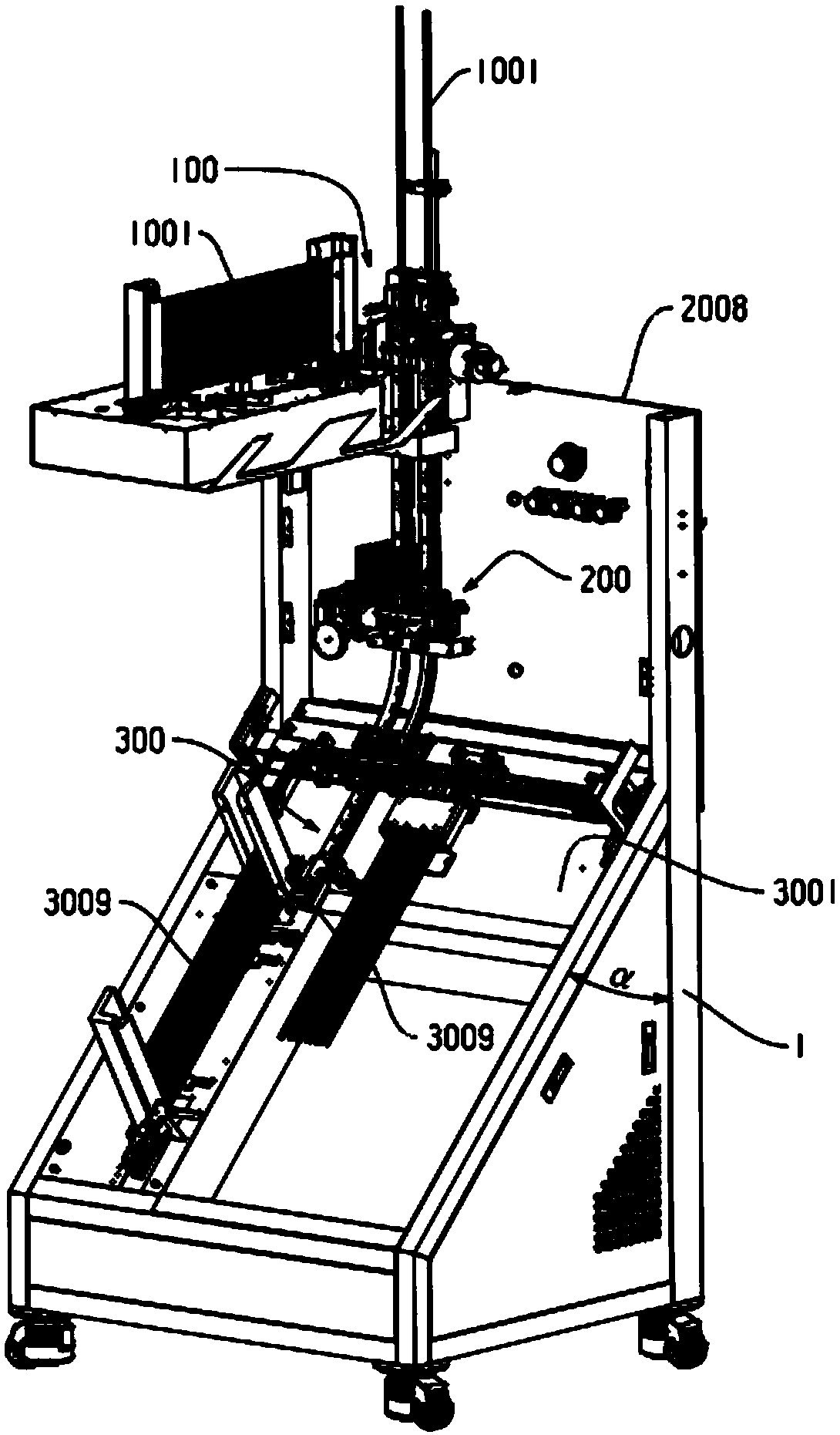

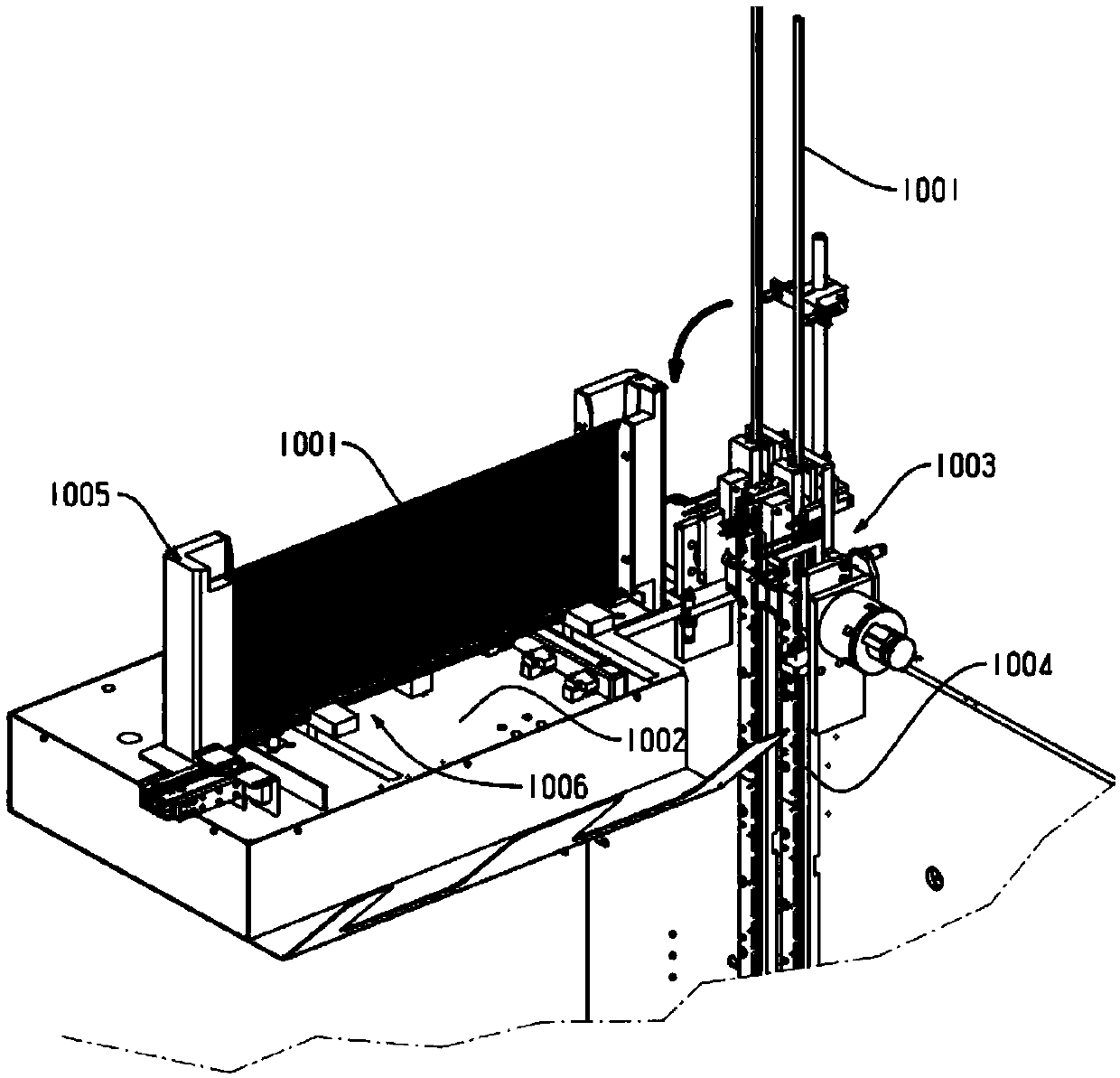

Automatic IC testing and sorting device

The invention discloses an automatic IC testing and sorting device. The device comprises a feeding device, a testing device and a sorting and storing device which are arranged on a machine frame; andthe machine frame comprises a first mounting plate and a second mounting plate, wherein the first mounting plate is vertically arranged, and the second mounting plate is connected with the bottom of the first mounting plate and is obliquely arranged. An IC material tube is clamped on the feeding device, IC chips which are not tested in the IC material tube are supplied to the testing device for testing through the feeding device, after the testing is finished, the chips are classified through the sorting and storing device and are stored in a plurality of empty material tubes. According to thedevice, a clamping mechanism with the IC material tube clamped is turned over, so that the IC material tube is changed into a vertical state, and the IC chips in the IC material tube slide out and get to a vertical material channel; the IC chips can be controlled by a blocking and pressing mechanism to be fed to the testing device one by one, testing chucks clamp the IC chips and push the IC chips to a testing PCB for testing, the IC chips are received through a material receiving table after the test is completed and are classified and placed to a first material storing mechanism or a second material storing mechanism, so that the speed of sorting and storing is increased, and the labor cost is saved.

Owner:昆山宇辰光通自动化科技有限公司

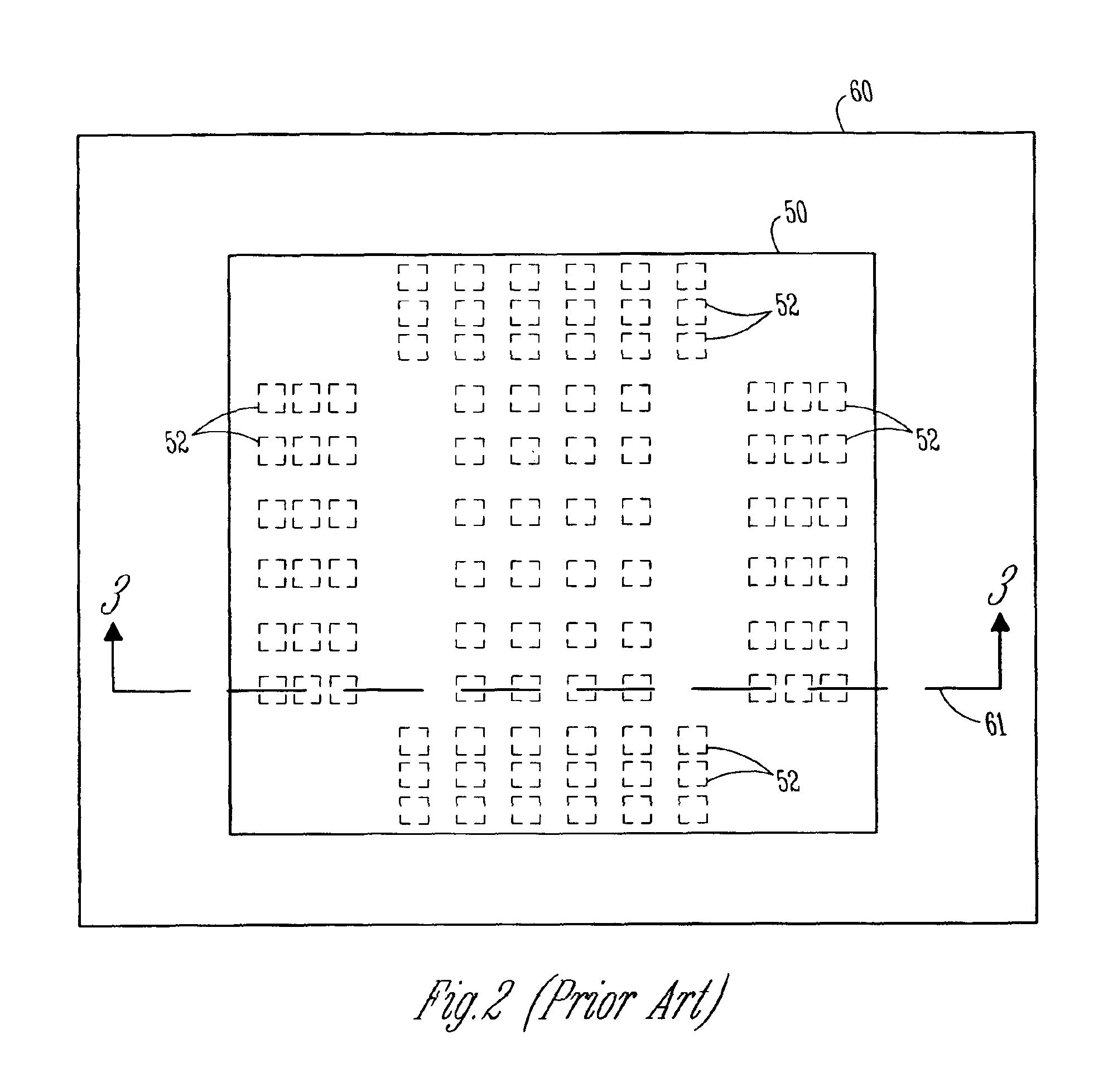

Semiconductor device testing apparatus and a test tray for use in the testing apparatus

InactiveUS6856128B2Shorten the timeIncrease profitSemiconductor/solid-state device testing/measurementElectronic circuit testingEngineeringSemiconductor

Owner:ADVANTEST CORP

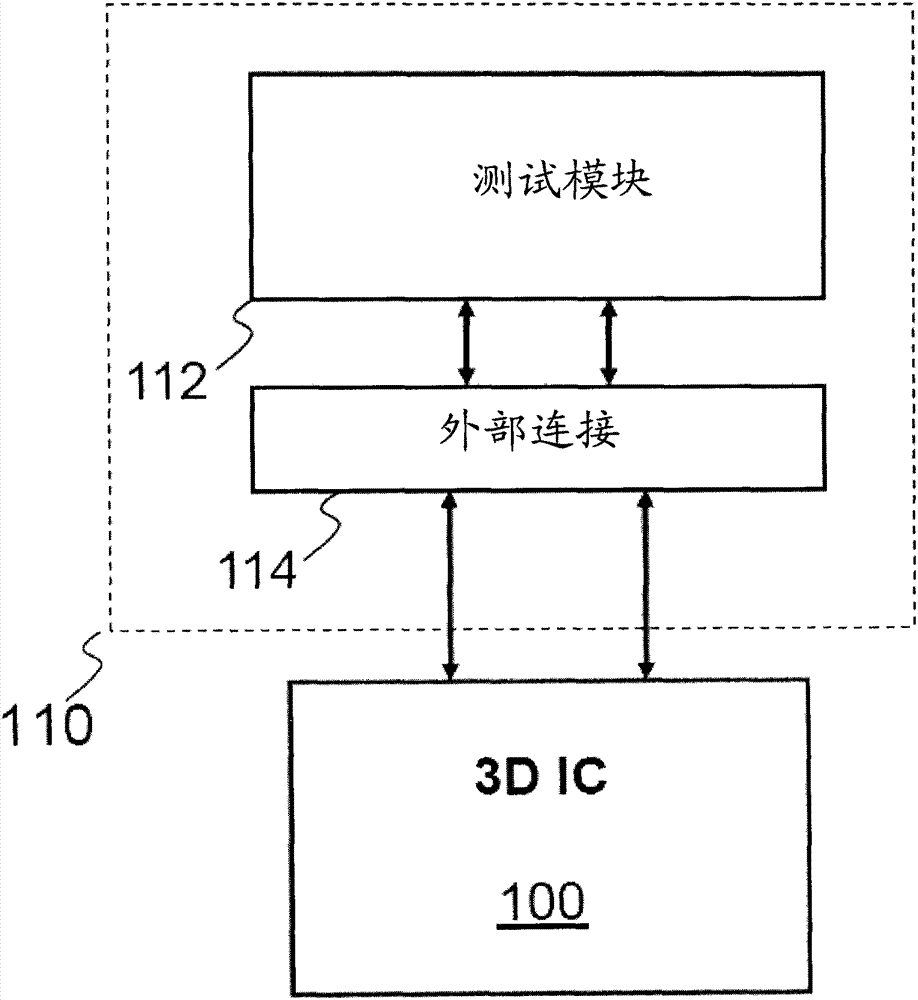

3D IC testing apparatus

ActiveCN102778646ASemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsElectricityInterposer

A three dimensional (3D) integrated circuit (IC) testing apparatus comprises a plurality of connection devices. When a device under test (DUT) (such as an interposer or a 3D IC) formed by a plurality of 3D dies operates in a testing mode, the 3D IC testing apparatus is coupled to the DUT via a variety of interface channels (such as probes). The connection devices and a variety of through silicon vias (TSVs) in the DUT form a TSV chain so that electrical characteristics of the variety of TSVs can be tested all at once.

Owner:TAIWAN SEMICON MFG CO LTD

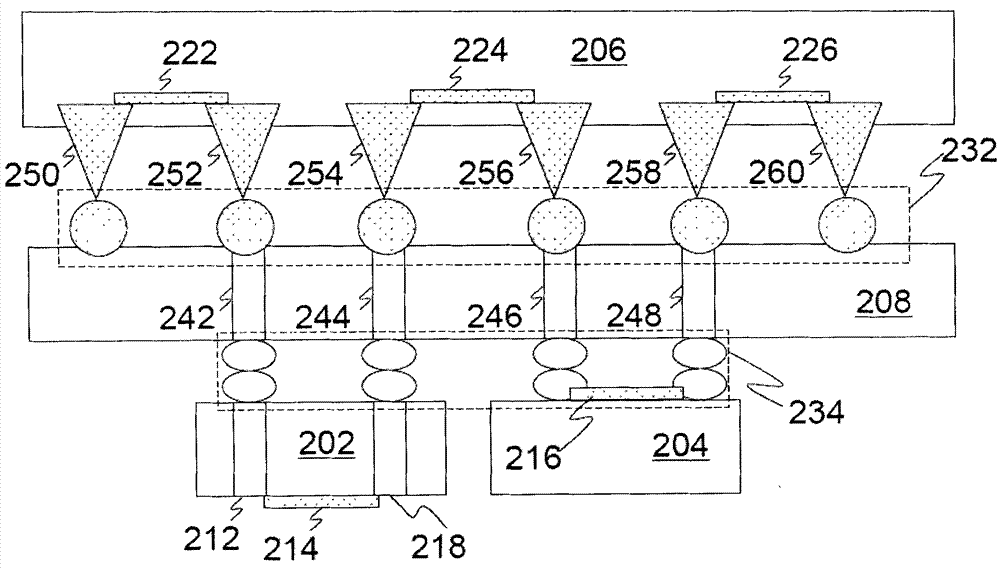

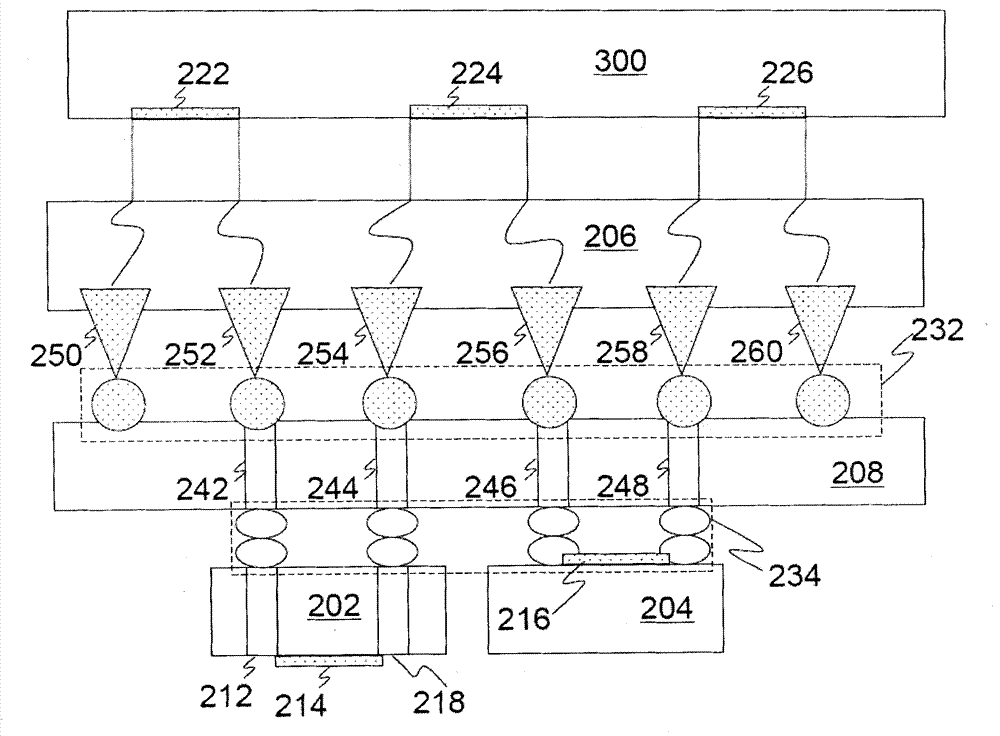

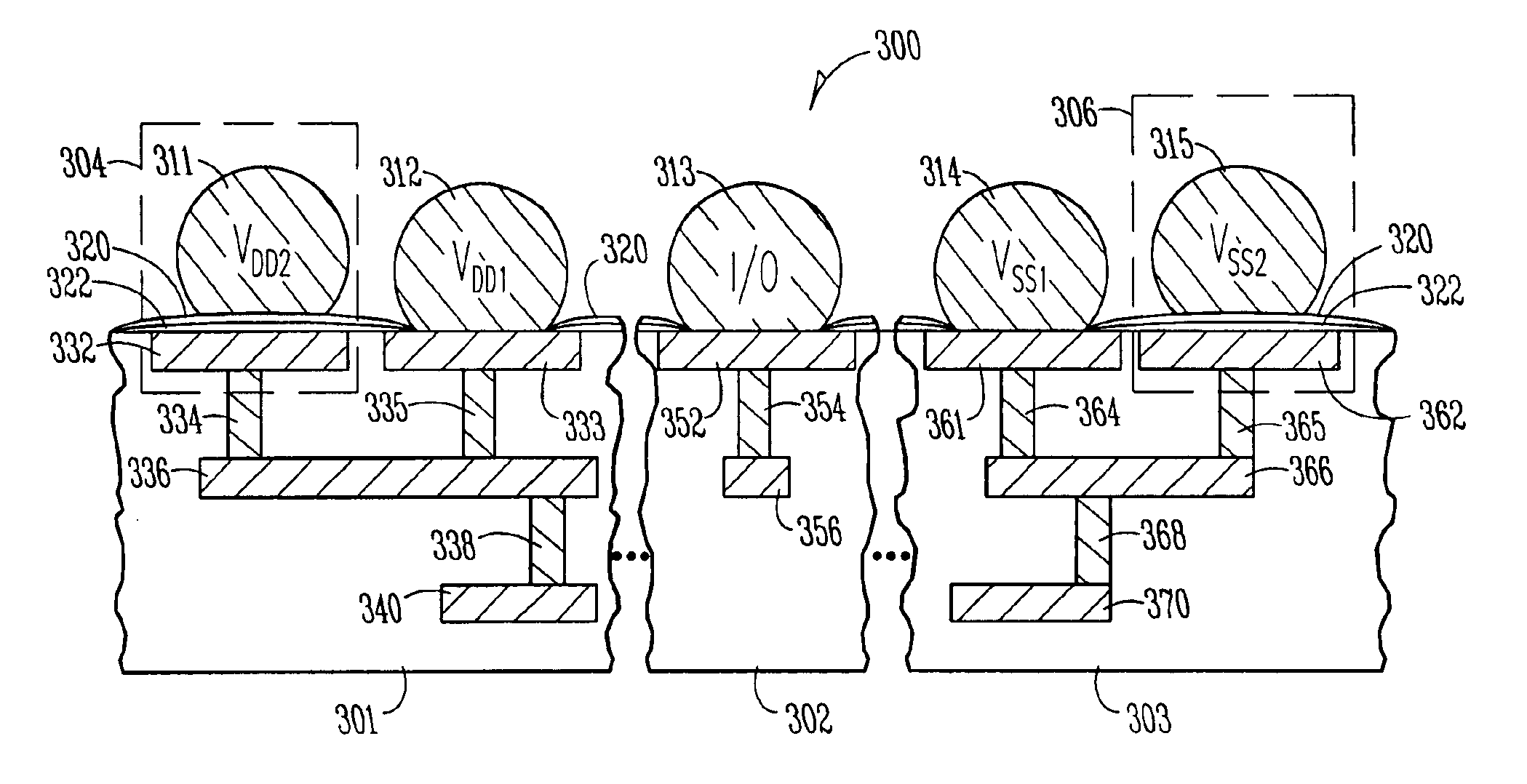

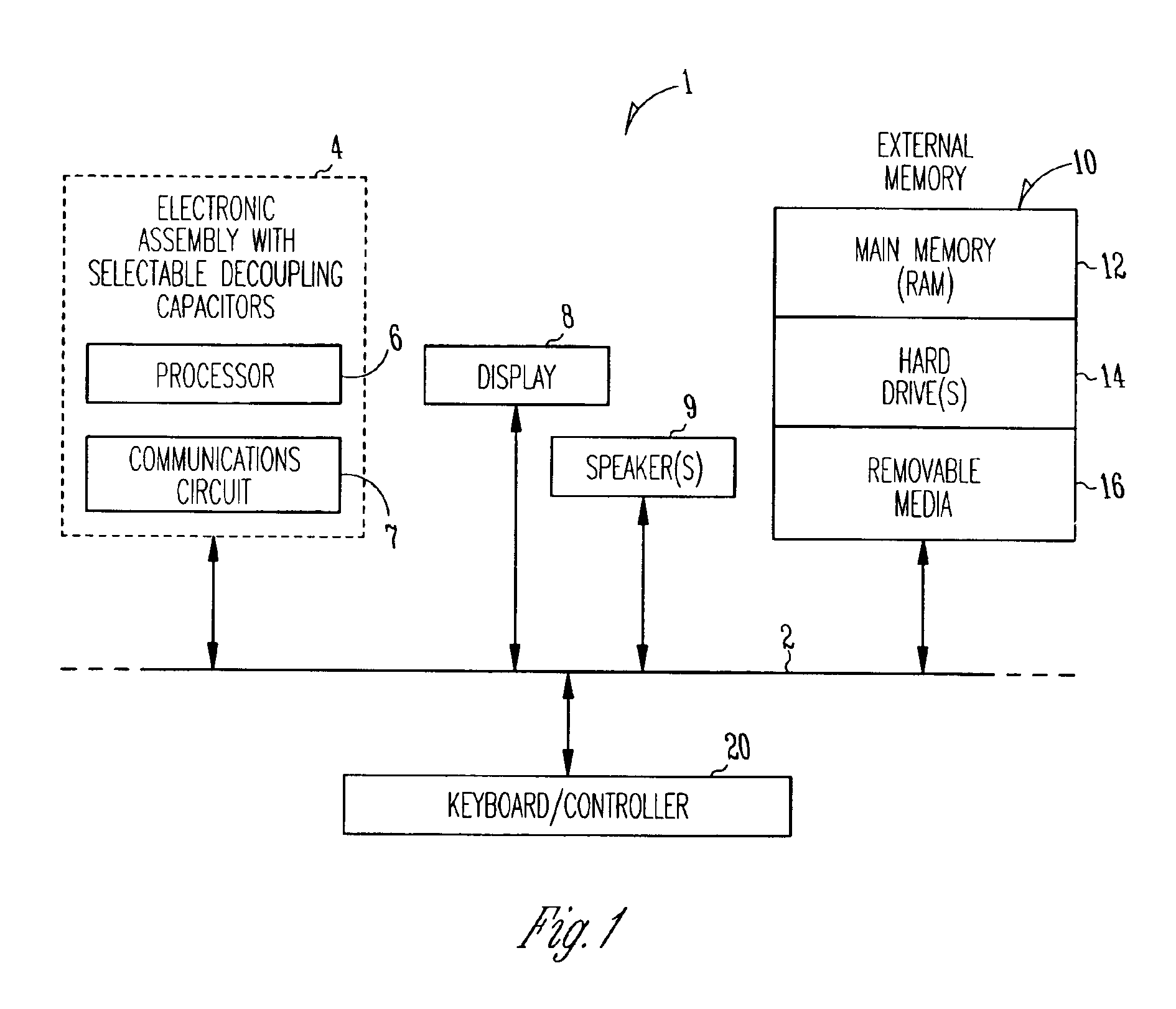

Selectable decoupling capacitors for integrated circuit and methods of use

InactiveUS6937458B2Fixed capacitor electrodesFixed capacitor dielectricElectronic systemsControl signal

Selectable capacitors are used to modify performance characteristics of functional circuit elements of an integrated circuit (IC). In one embodiment, the decoupling capacitors are implemented as additional or alternative mounting pads on a surface of the IC. At least one selectable capacitor is provided for each IC circuit element, such as a logic network, whose operational characteristic(s) is predicted to be and is actually identified as sub-optimal through IC testing, particularly following a process change, a mask shrink, operation of the IC at higher clock frequency, or the like. Expensive redesign is avoided by selectively coupling capacitors into the IC circuit element as needed, under control of selector logic that is responsive to control signals. Methods of operation, as well as application of the apparatus to an electronic assembly and an electronic system, are also described.

Owner:INTEL CORP

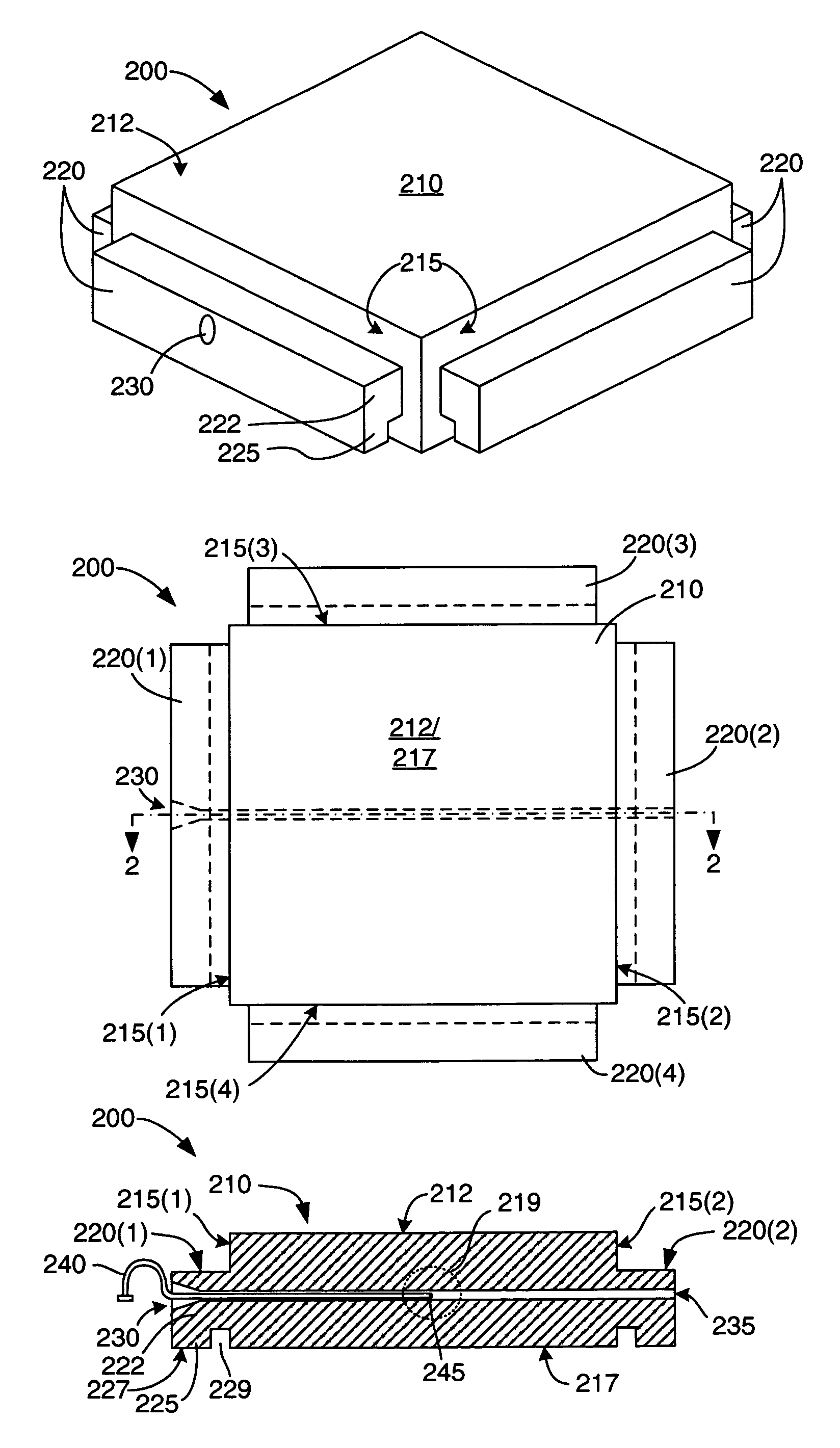

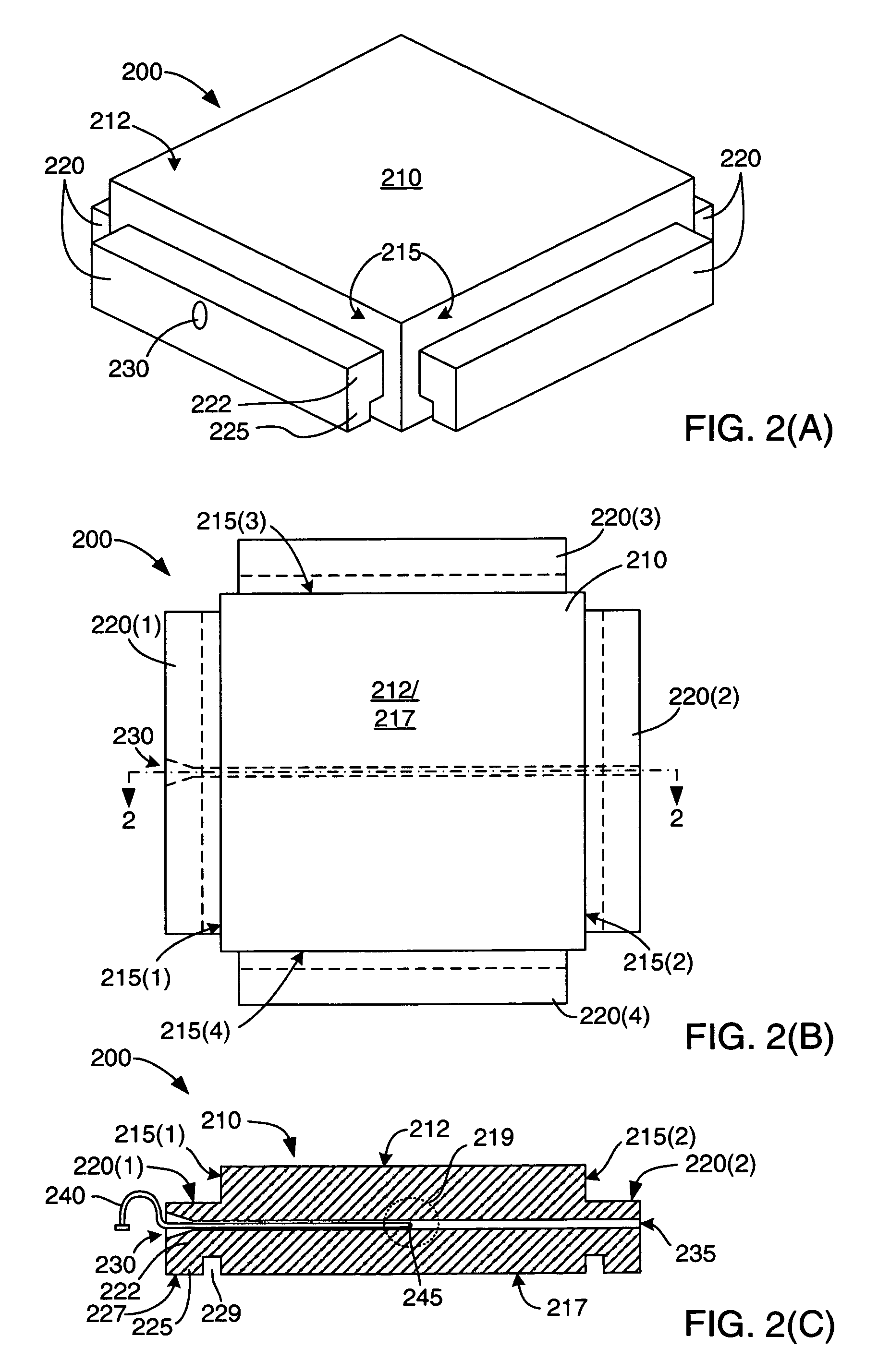

Method and apparatus for verifying temperature during integrated circuit thermal testing

ActiveUS6956390B1Accurate estimateAccurate predictionMeasurement instrument housingIndividual semiconductor device testingContact padConfirmation test

An test block includes a box-like body and four rails extending from side edges of the body. During thermal testing, the test block is mounted between a test head and a test socket such that the rails provide a thermal path between the test block body and contact pads formed on the test socket. In this manner the rails emulate the thermal path formed by the metal leads extending from a conventional Quad Flat Pack Integrated Circuit (QFP IC), thereby reliably duplicating the actual thermal path of the QFP IC. The test block is mounted on the test system and its temperature is measured before and after testing QFP IC devices. Confirming that the test block is within test temperature specifications before and after the QFP-IC test procedure provides a highly reliable verification that the QFP-IC's actual test temperature is within the test temperature specifications.

Owner:XILINX INC

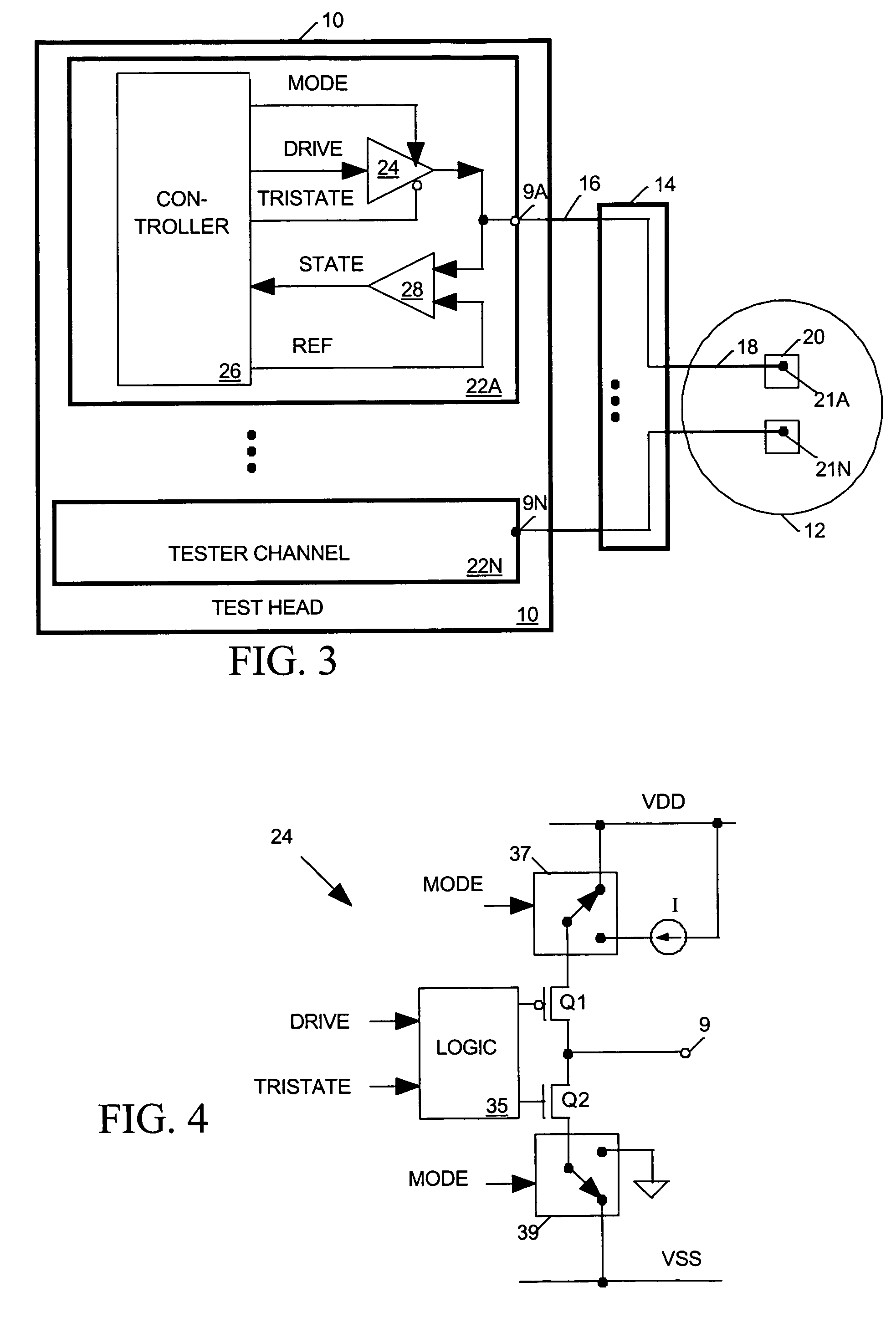

System for measuring signal path resistance for an integrated circuit tester interconnect structure

InactiveUS7109736B2Digital circuit testingResistance/reactance/impedenceElectrical resistance and conductanceElectrical conductor

Resistances of signal paths within a interconnect structure for linking input / output (I / O) ports of an integrated circuit (IC) tester to test points of an IC are measured by the IC tester itself. To do so the interconnect structure is used to link the tester's I / O ports to a similar arrangement of test points linked to one another through conductors. Drivers within the tester, which normally transmit digital test signals to IC test points via the I / O ports when the IC is under test, are modified so that they may also either transmit a constant current through the I / O ports or link the I / O ports to ground or other reference potential. The tester then transmits known currents though the signal paths interconnecting the tester's I / O ports. Existing comparators within the tester normally used to monitor the state of an IC's digital output signals are employed to measure voltage drops between the I / O ports, thereby to provide data from which resistance of signal paths within the interconnect structure may be computed.

Owner:FORMFACTOR INC

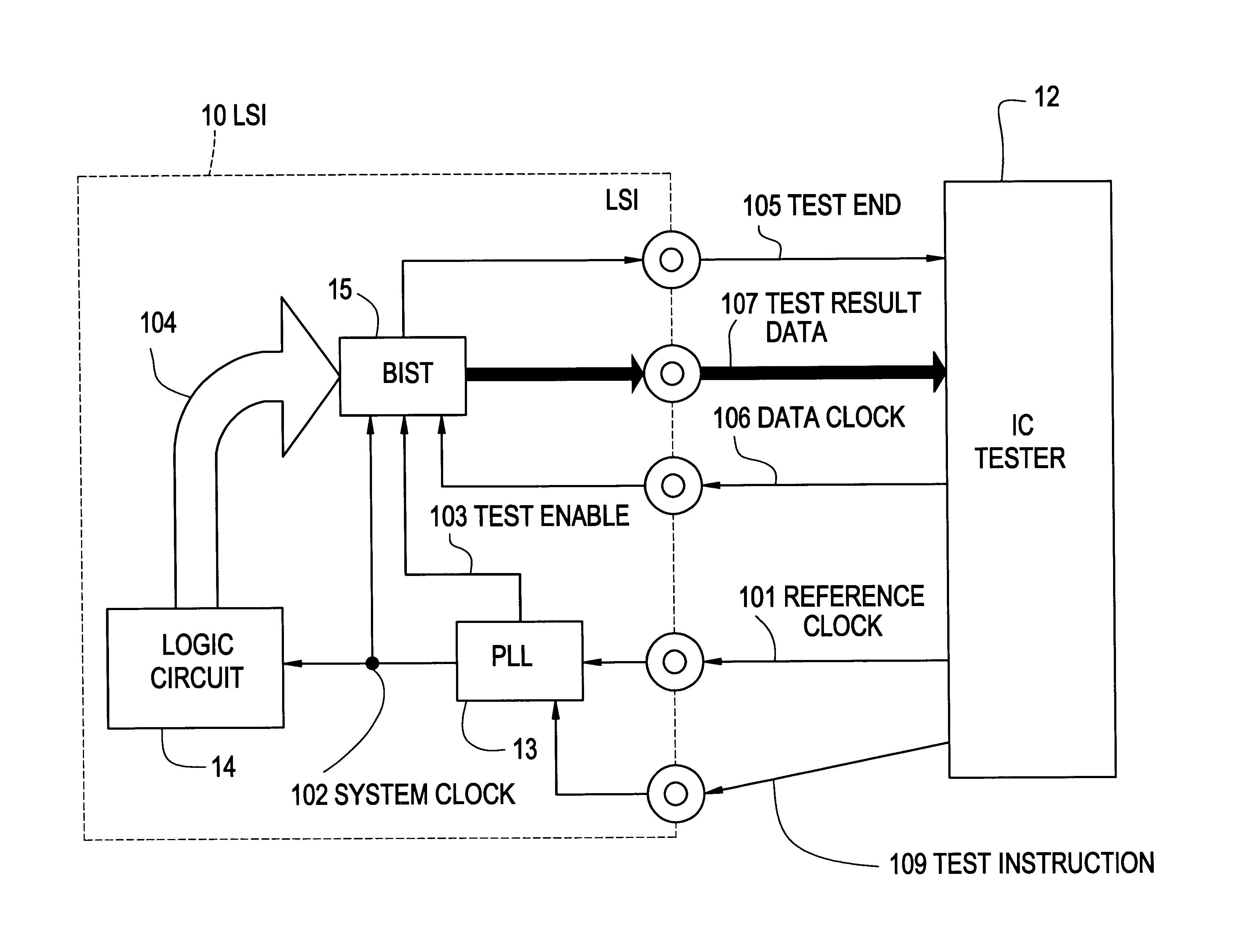

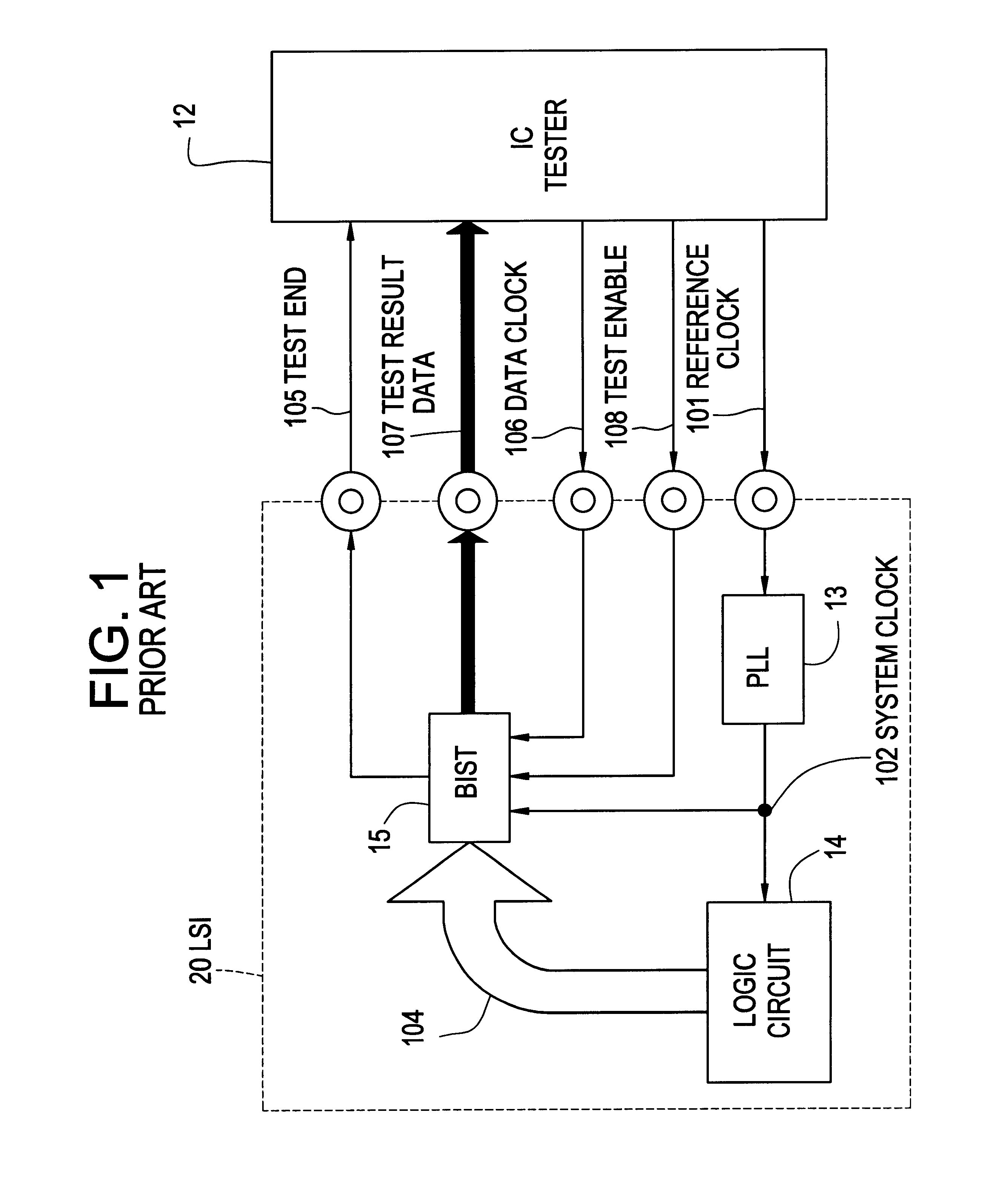

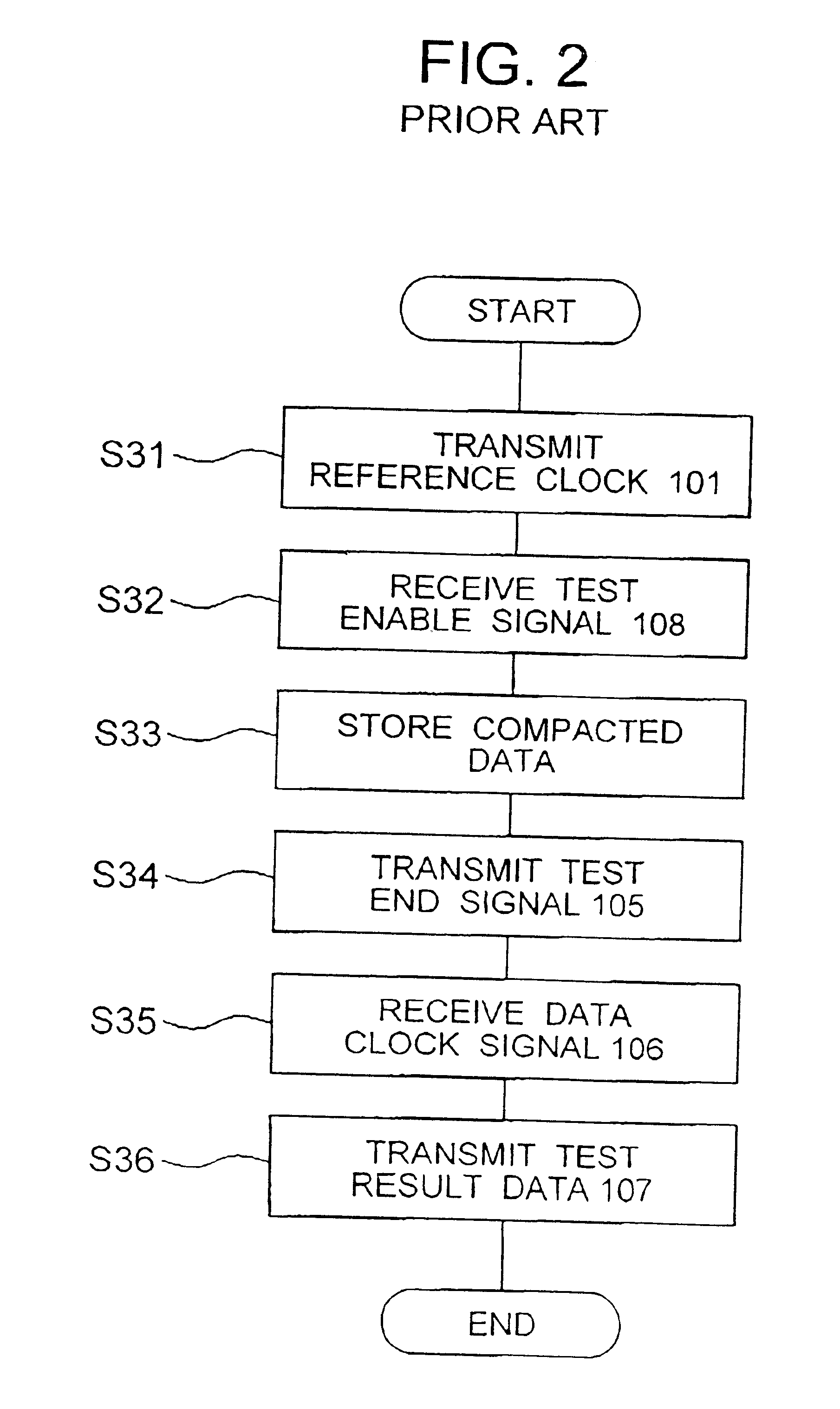

LSI having a built-in self-test circuit

InactiveUS6687866B2Pulse automatic controlElectronic circuit testingBuilt-in self-testLogic circuitry

Owner:NEC ELECTRONICS CORP

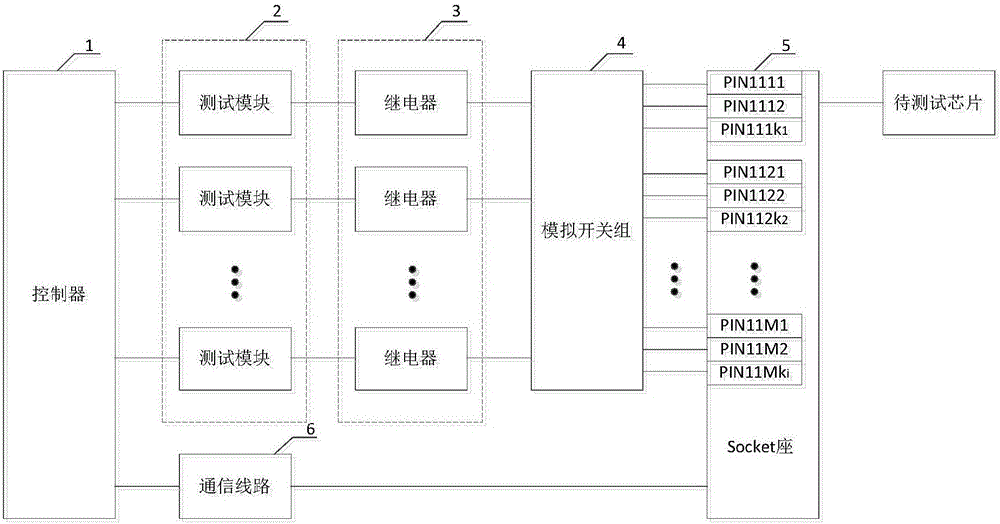

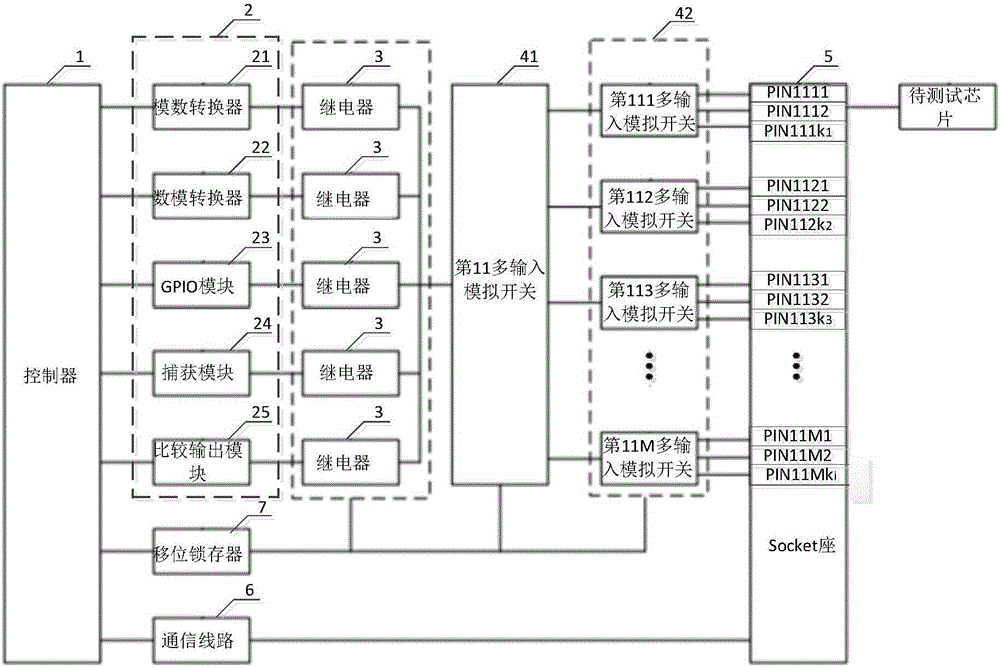

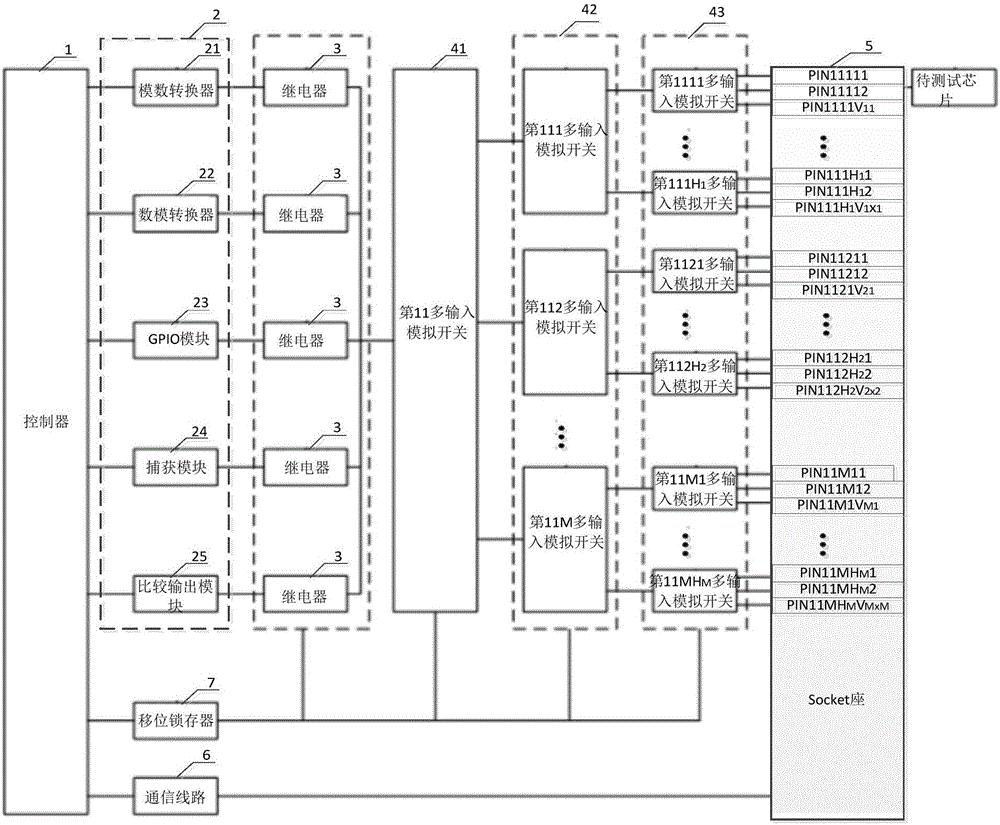

IC (integrated circuit) testing device and method

The invention discloses an IC (integrated circuit) testing device and method. The device comprises a controller, a socket, N testing modules, N relays, an analog switch group and a communication circuit, a second end of the analog switch group is connected with the socket, a control end of the analog switch group is connected with the controller, L-level multi-input analog switches are cascaded to form the analog switch group, the analog switch group is used for selecting corresponding pins of a chip to be tested to connect with corresponding testing modules according to control of the controller, a first end of the communication circuit is connected with the controller, the other end of the communication circuit is connected with the socket, and the communication circuit is used for establishing communication between the controller and the socket. According to the testing device, the analog switch group formed by cascade of the L-level multi-input analog switches is arranged between the N testing modules and the socket for placing chips to be tested, pins of the chips to be tested cannot be directly with the controller when the chips to be tested are tested, a plurality of controller are omitted, controller resources are greatly saved, cost of the testing device is reduced, and structures of the testing device are simplified.

Owner:HANGZHOU VANGO TECH