Patents

Literature

546 results about "Circuit delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method, system, and program product for computing a yield gradient from statistical timing

InactiveUS7480880B2Geometric CADComputation using non-denominational number representationCircuit delayComputer science

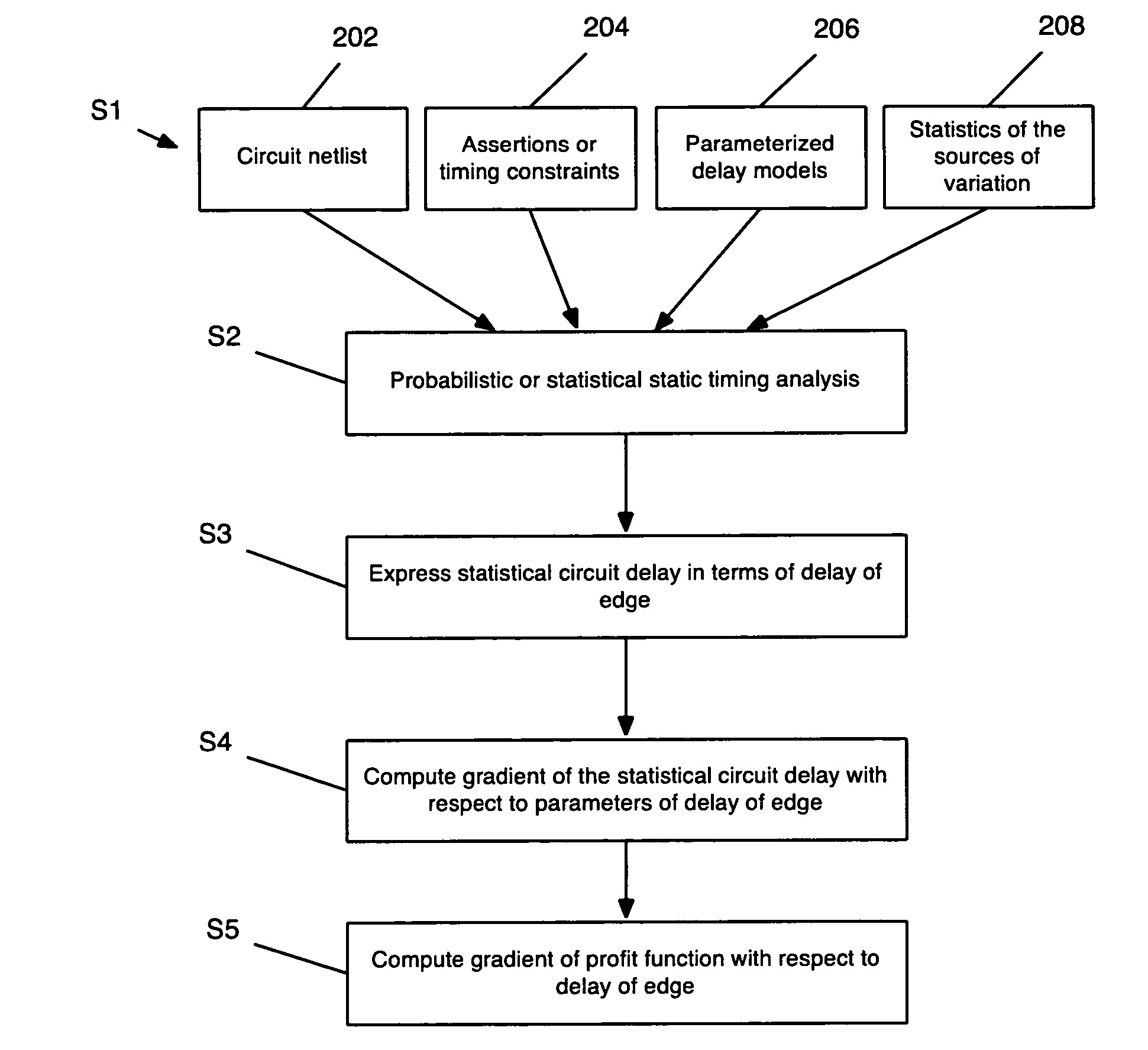

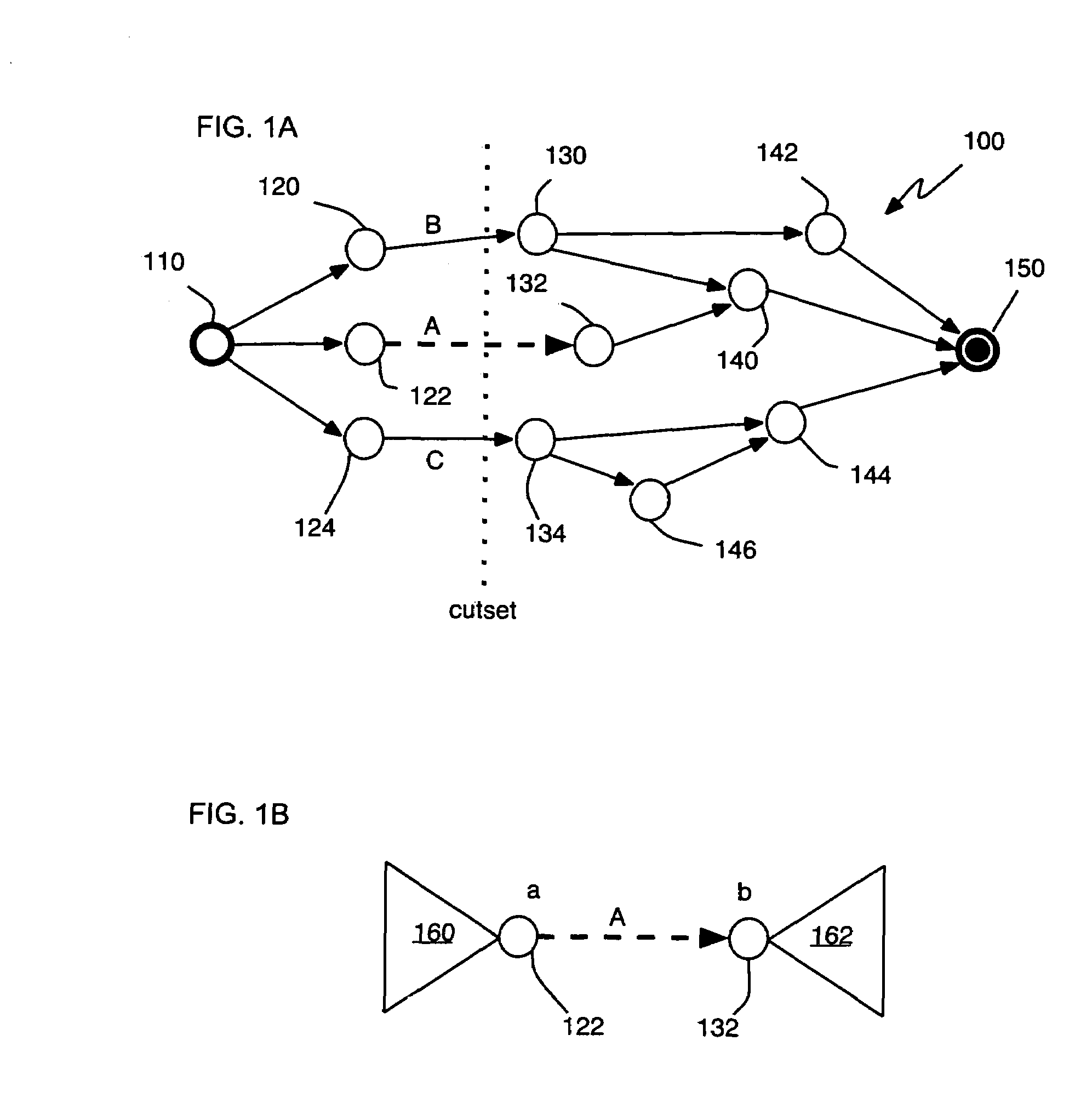

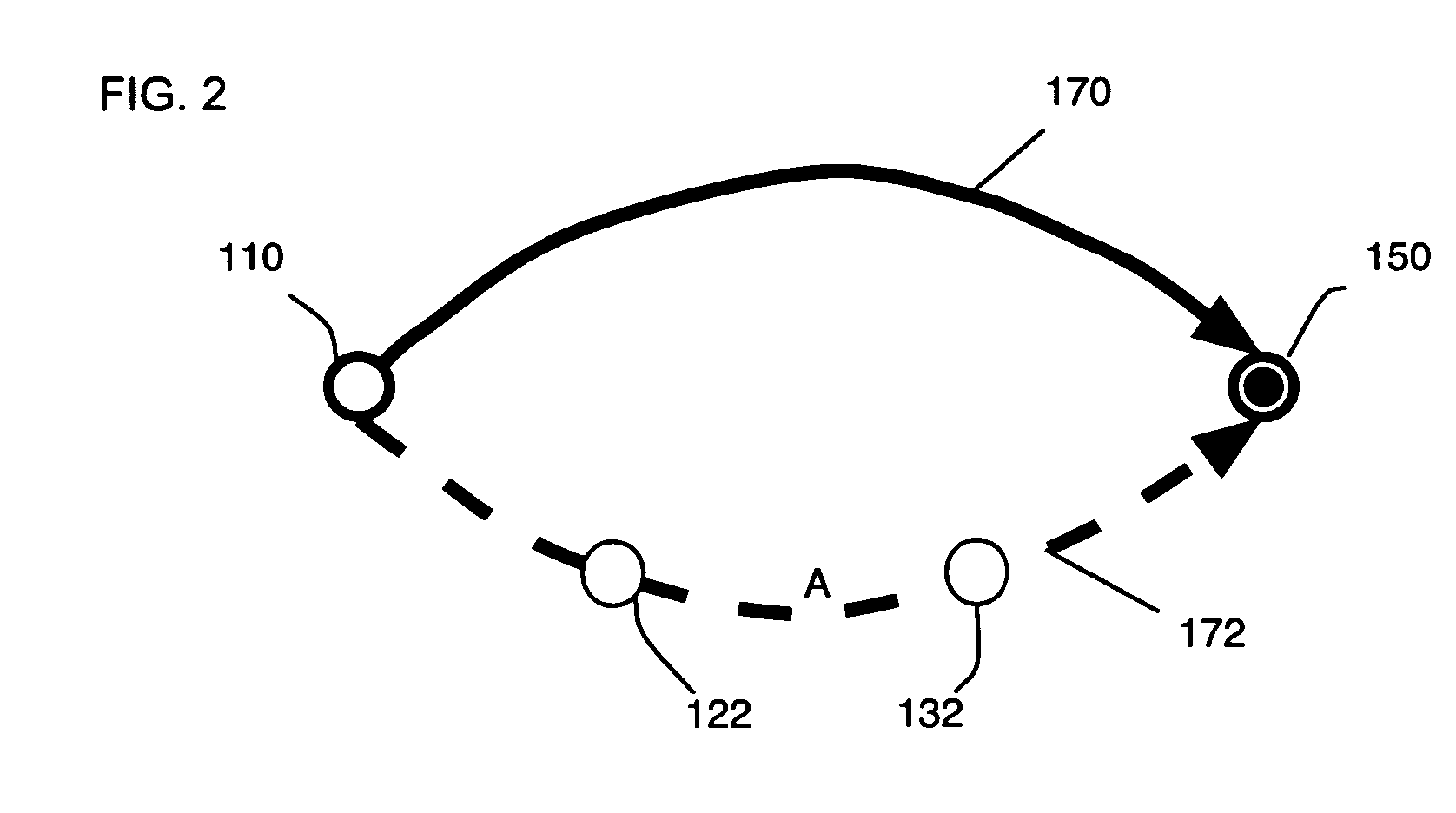

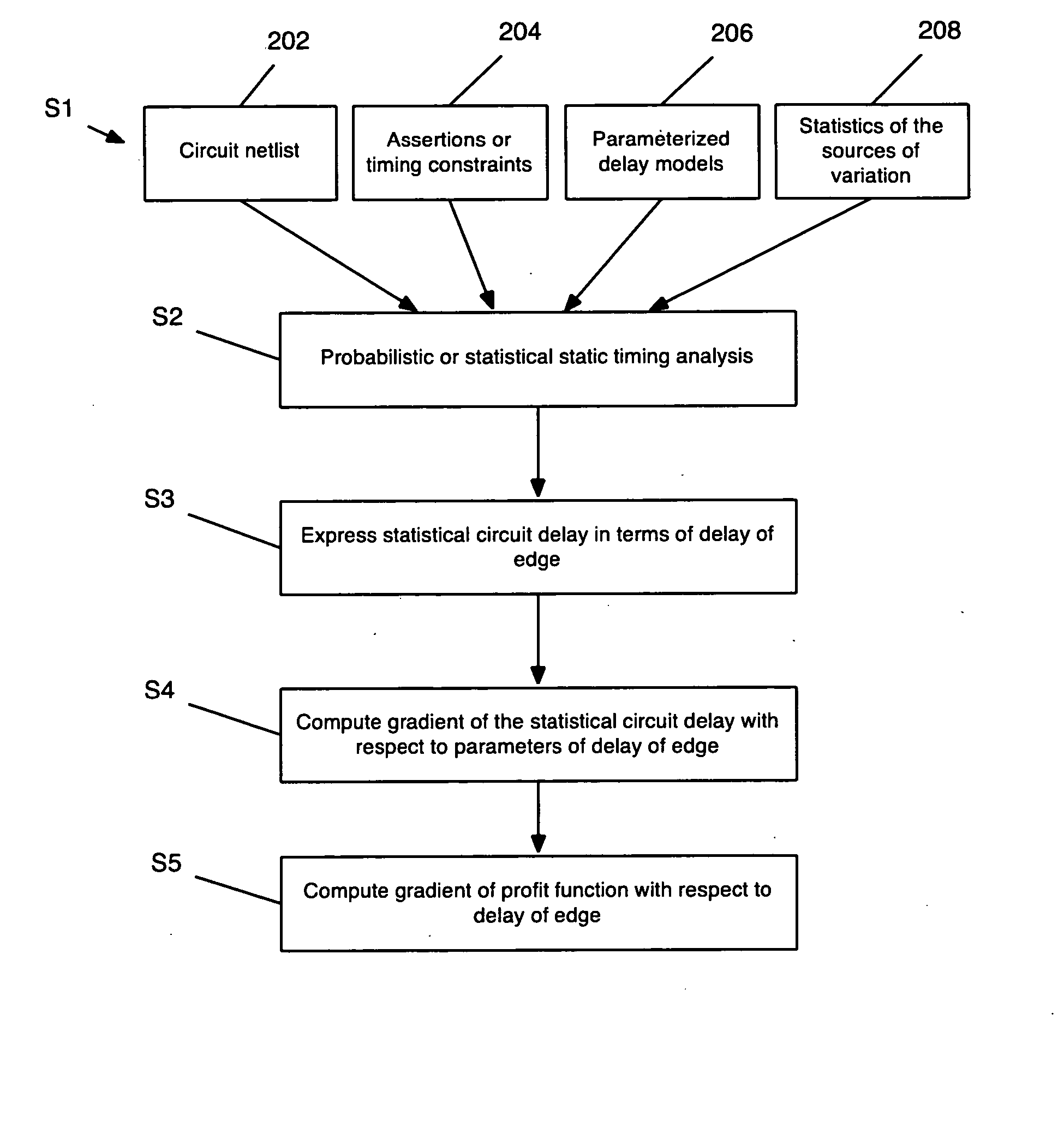

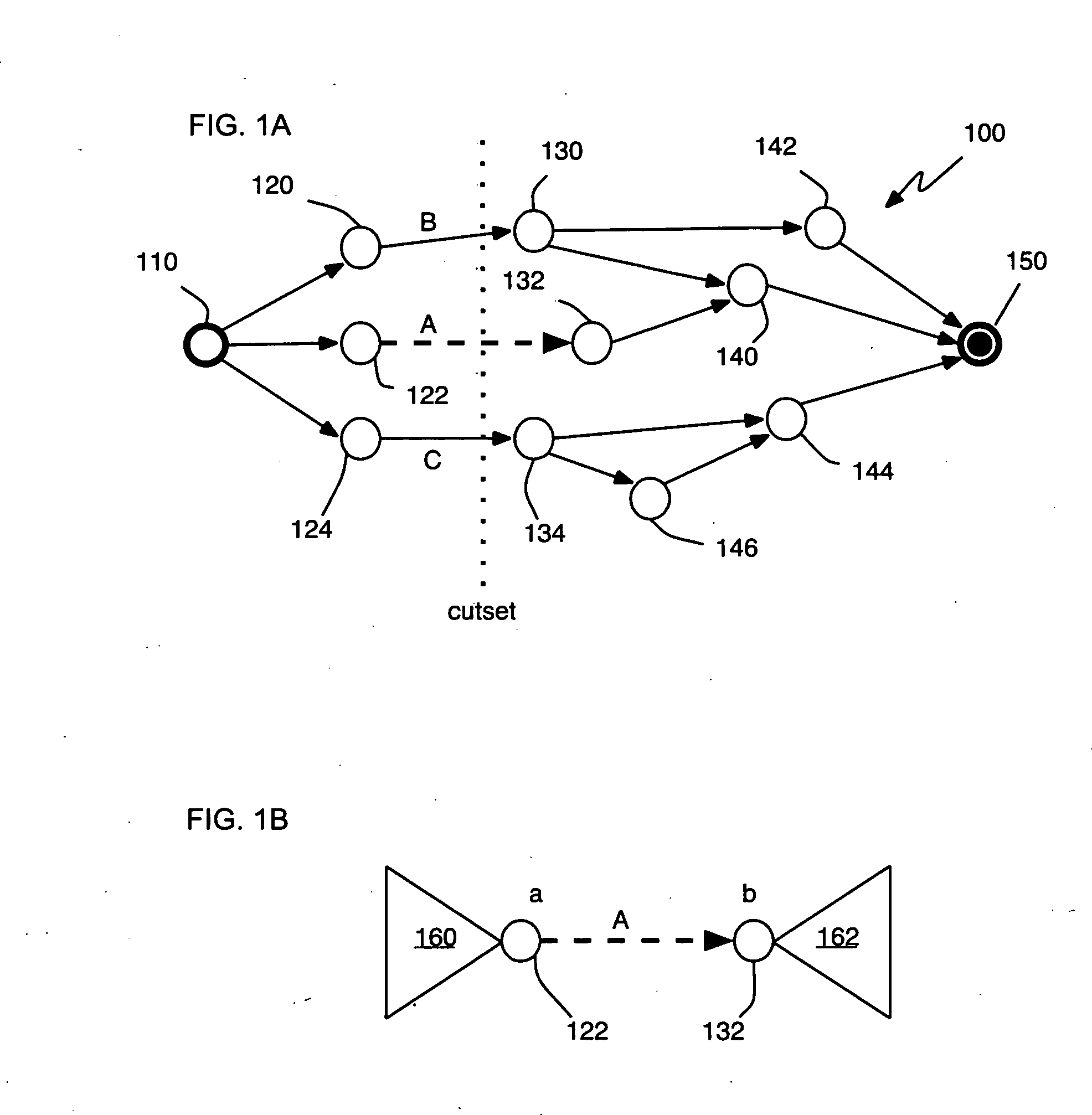

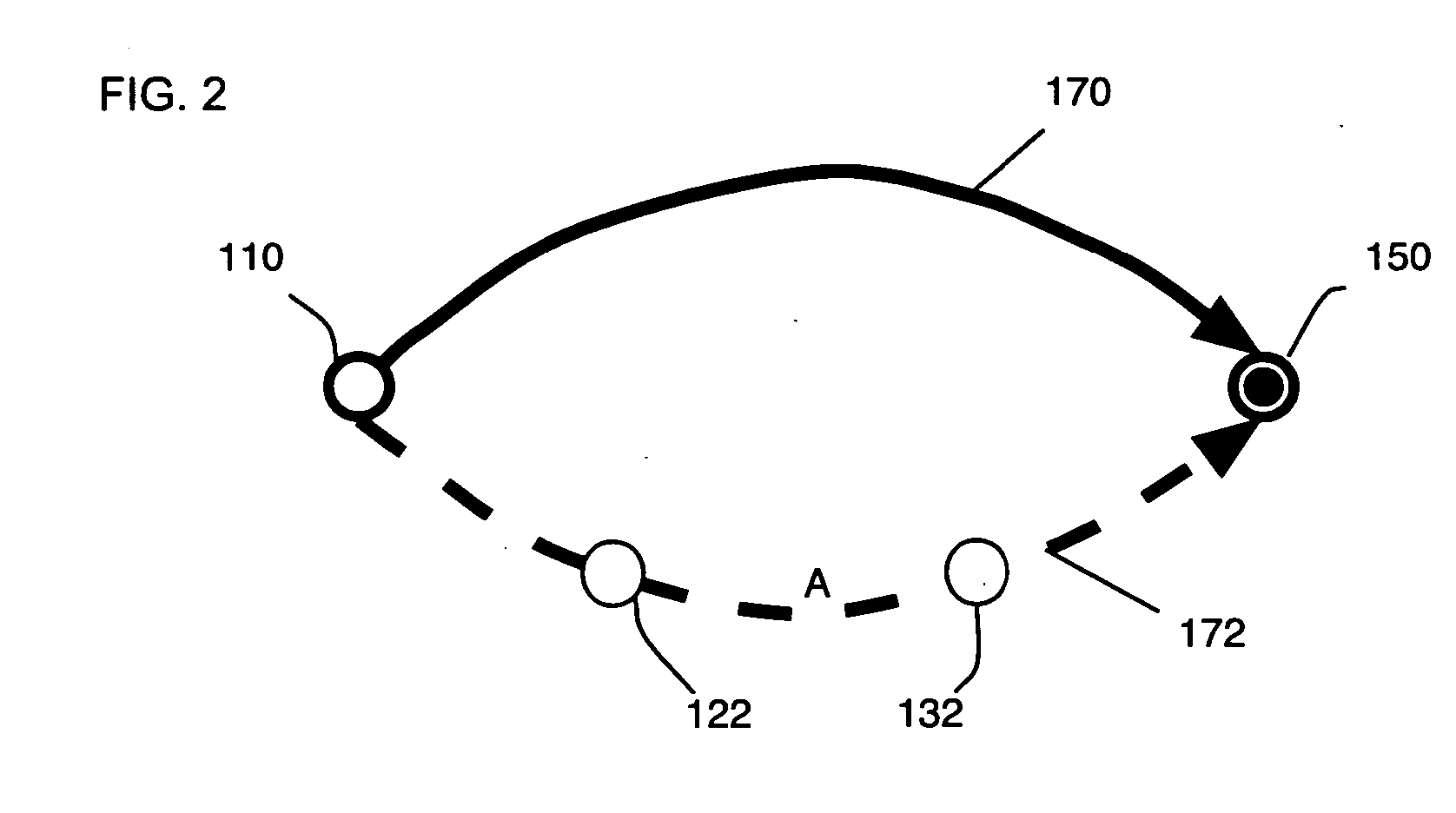

The invention provides a method, system, and program product for determining a gradient of a parametric yield of an integrated circuit with respect to parameters of a delay of an edge of a timing graph of the circuit. A first aspect of the invention provides a method for determining a gradient of a parametric yield of an integrated circuit with respect to parameters of a delay of an edge of a timing graph of the circuit, the method comprising: conducting a statistical timing analysis; expressing a statistical circuit delay in terms of a delay of the edge; and computing a gradient of the statistical circuit delay with respect to parameters of the delay of the edge.

Owner:GLOBALFOUNDRIES INC

Method, system, and program product for computing a yield gradient from statistical timing

The invention provides a method, system, and program product for determining a gradient of a parametric yield of an integrated circuit with respect to parameters of a delay of an edge of a timing graph of the circuit. A first aspect of the invention provides a method for determining a gradient of a parametric yield of an integrated circuit with respect to parameters of a delay of an edge of a timing graph of the circuit, the method comprising: conducting a statistical timing analysis; expressing a statistical circuit delay in terms of a delay of the edge; and computing a gradient of the statistical circuit delay with respect to parameters of the delay of the edge.

Owner:GLOBALFOUNDRIES INC

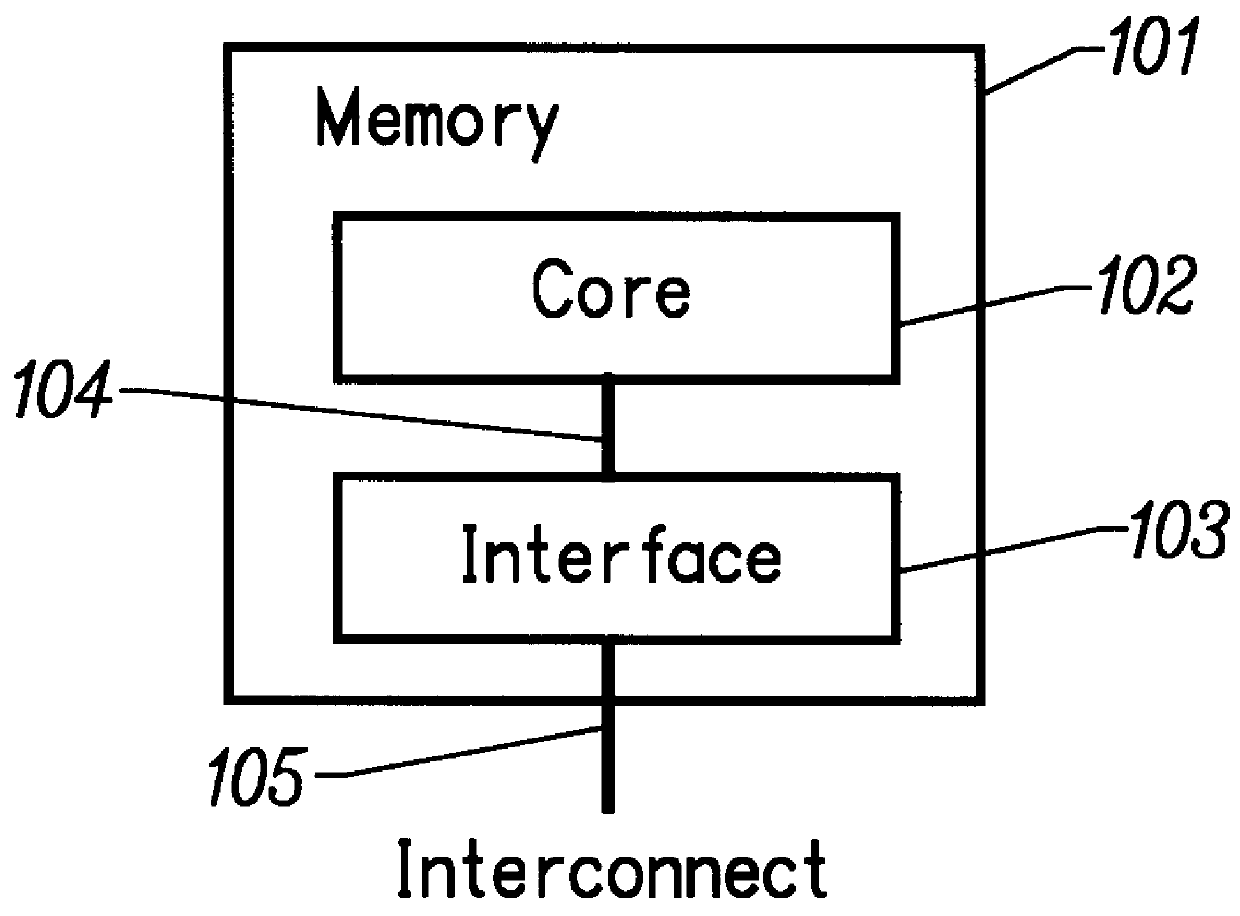

High performance cost optimized memory with delayed memory writes

A memory device includes an interconnect with control pins and bidirectional data pins. A memory core stores data. A memory interface circuit is connected to the interconnect and the memory core. The memory interface circuit includes a delay circuit to establish a write delay during a memory core write transaction such that the memory core write transaction has a processing time that is substantially equivalent to a memory core read transaction. The delay circuit delays the memory core write transaction for a time corresponding to the time required for signals to travel on the interconnect.

Owner:RAMBUS INC +1

Disk drive including a delay circuit to provide a delayed reset signal

InactiveUS7907364B2Driving/moving recording headsRecord information storageDisk controllerCircuit delay

A disk drive including a delay circuit to provide a delayed reset signal is disclosed. The disk drive includes a head to perform write and read operations to and from a disk and a disk controller that is coupled to the head to control the write and read operations performed by the head. The disk drive further includes: a power loss detection circuit to detect a power loss and to generate a reset signal in response to the power loss; a reset power line coupled to the disk controller and the power loss detection circuit to provide a non-delayed reset signal to the disk controller; and a delay circuit coupled to the reset power line wherein the delay circuit delays the reset signal to provide a delayed reset signal.

Owner:WESTERN DIGITAL TECH INC

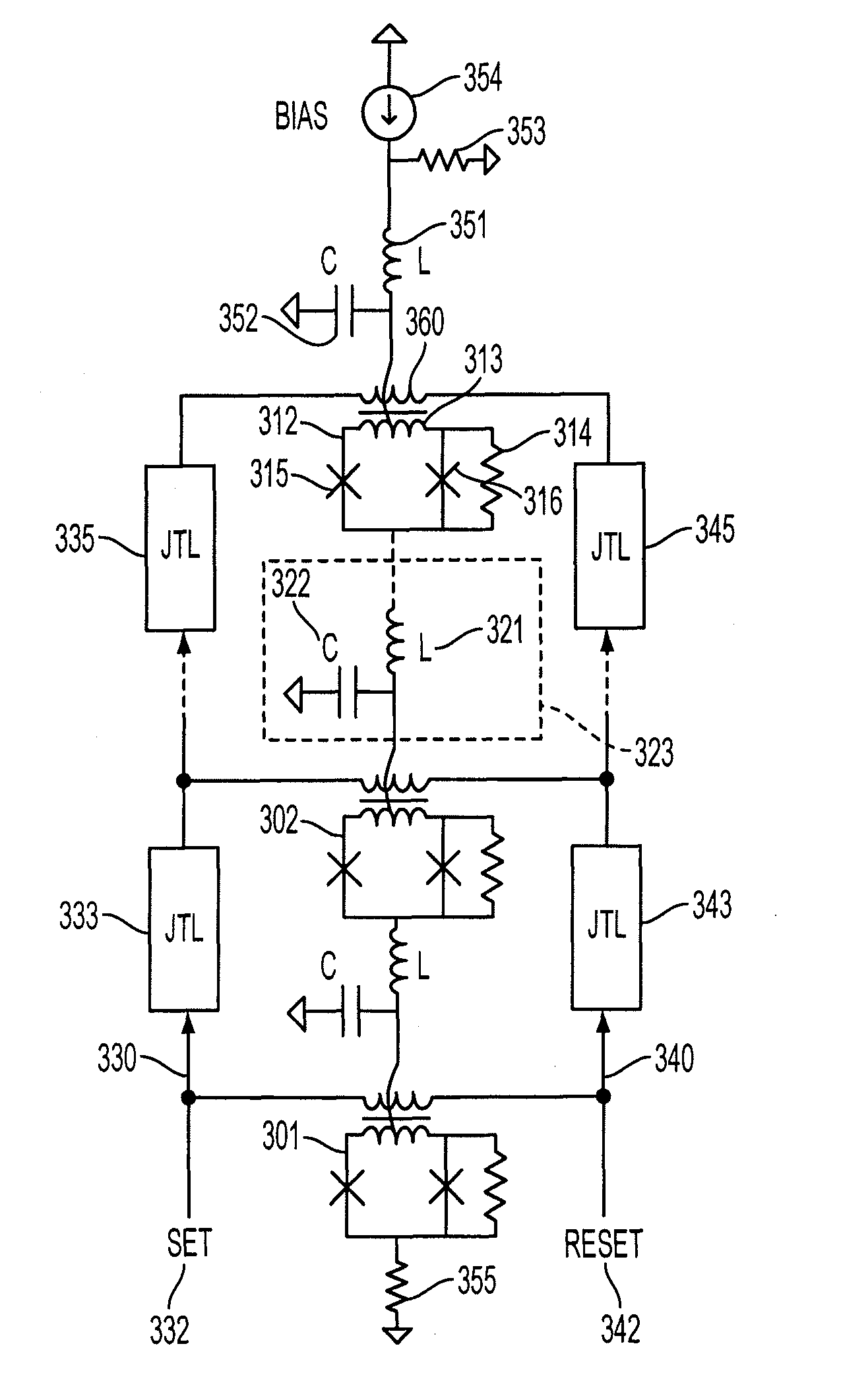

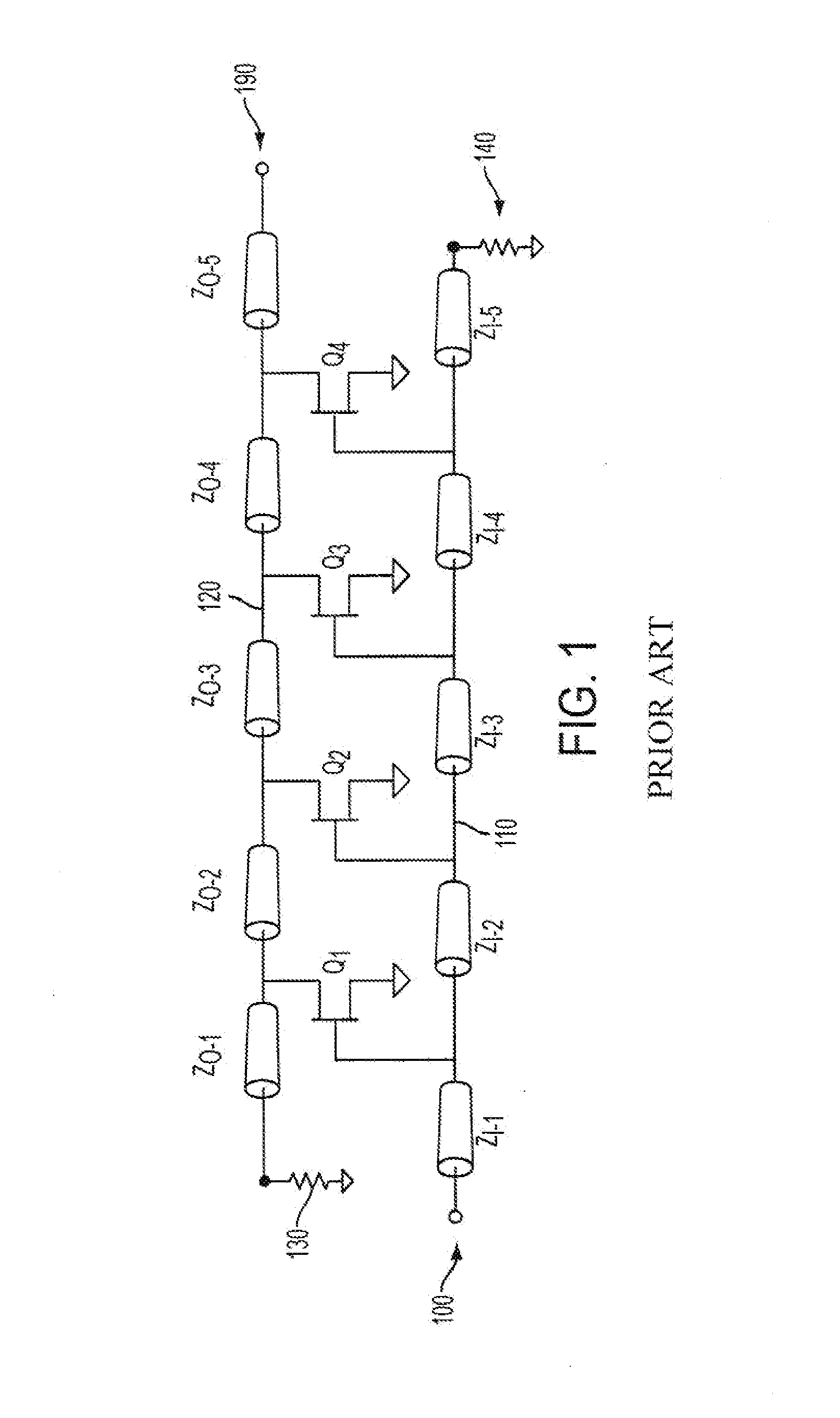

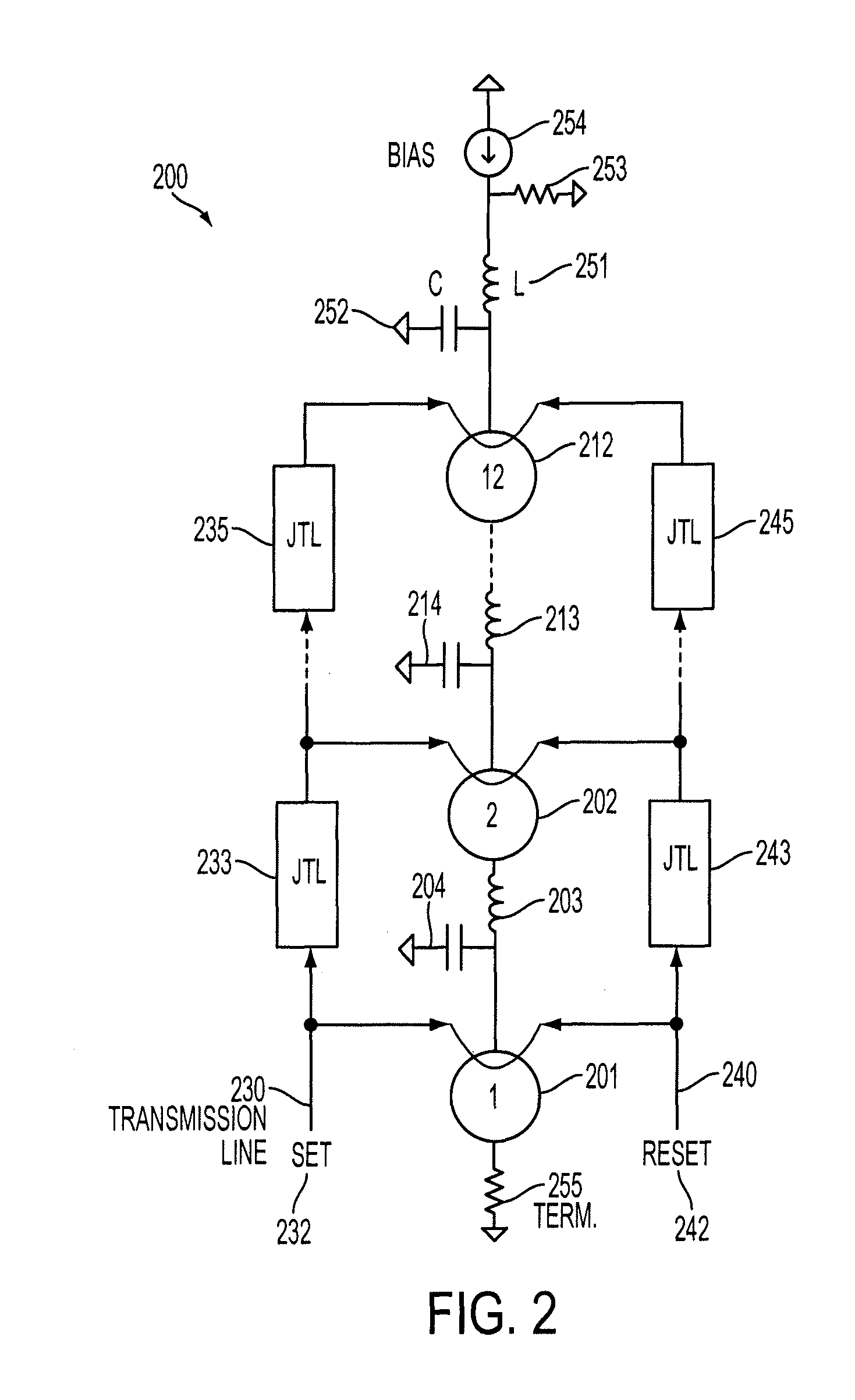

Method and apparatus for Josephson distributed output amplifier

The disclosure generally relates to a method and apparatus for providing high-speed, low signal power amplification. In an exemplary embodiment, the disclosure relates to a method for providing a wideband amplification of a signal by forming a first transmission line in parallel with a second transmission line, each of the first transmission line and the second transmission line having a plurality of superconducting transmission elements, each transmission line having a transmission line delay; interposing a plurality of amplification stages between the first transmission line and the second transmission line, each amplification stage having an resonant circuit with a resonant circuit delay; and substantially matching the resonant circuit delay for at least one of the plurality of amplification stages with the transmission line delay of at least one of the superconducting transmission lines.

Owner:NORTHROP GRUMMAN SYST CORP

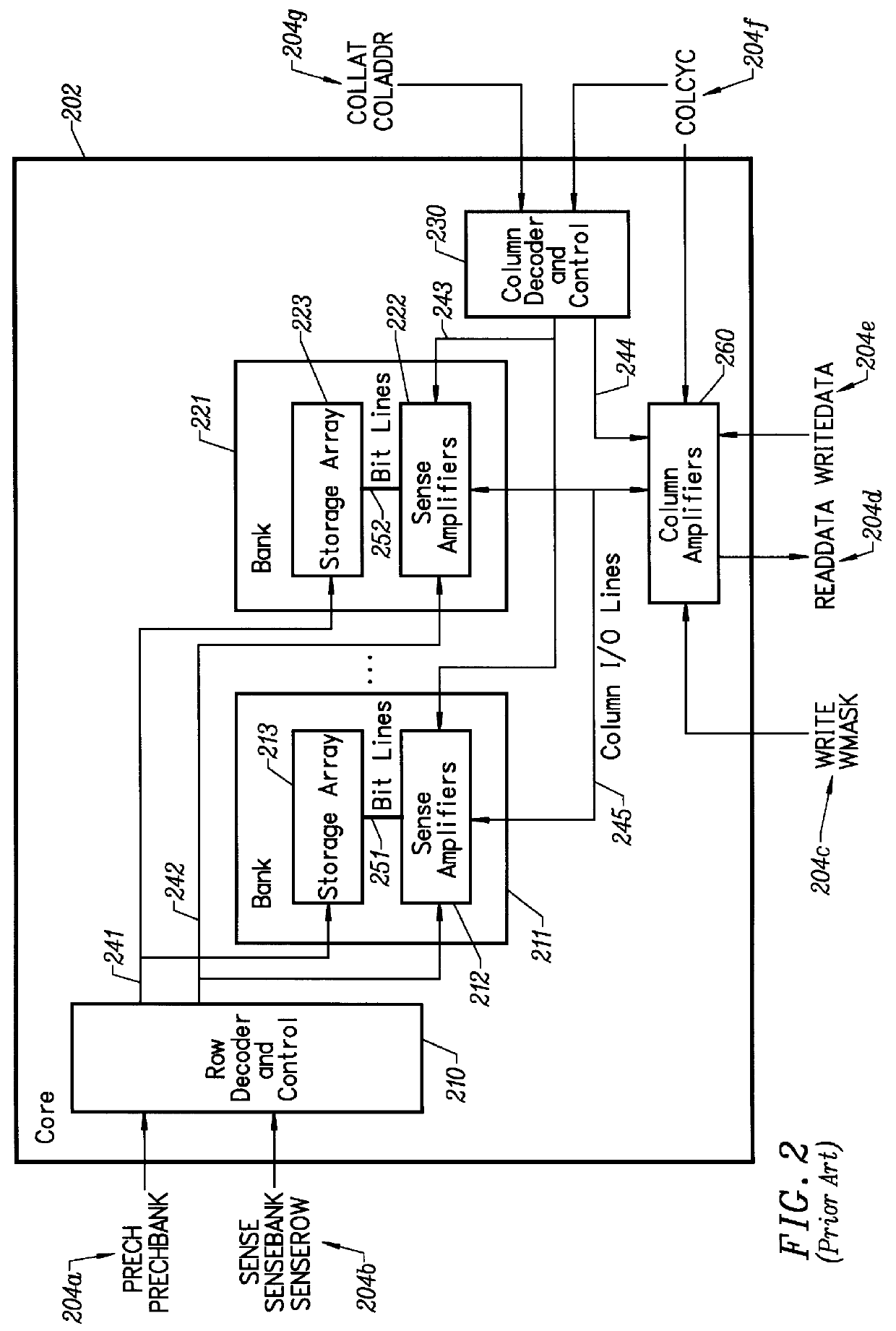

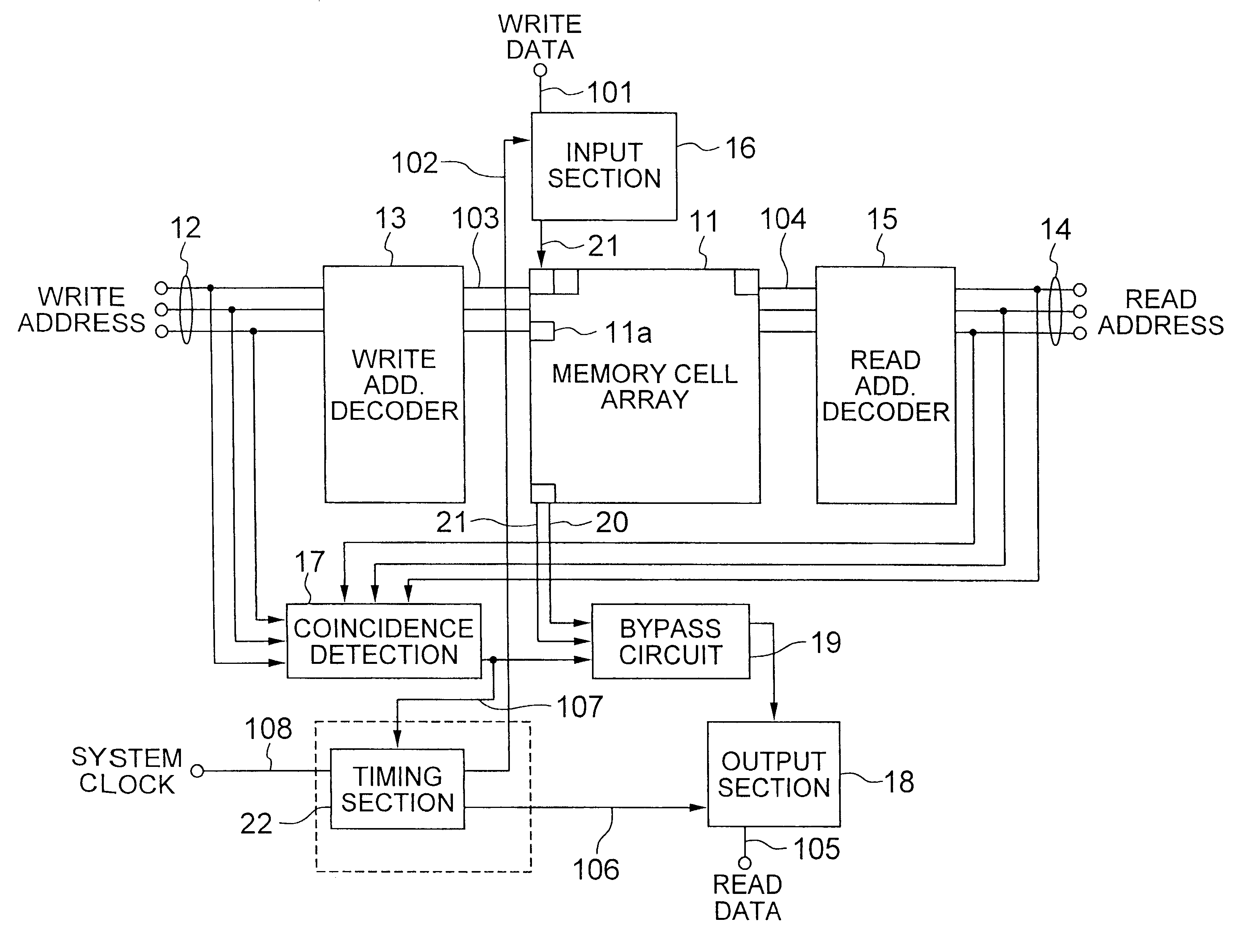

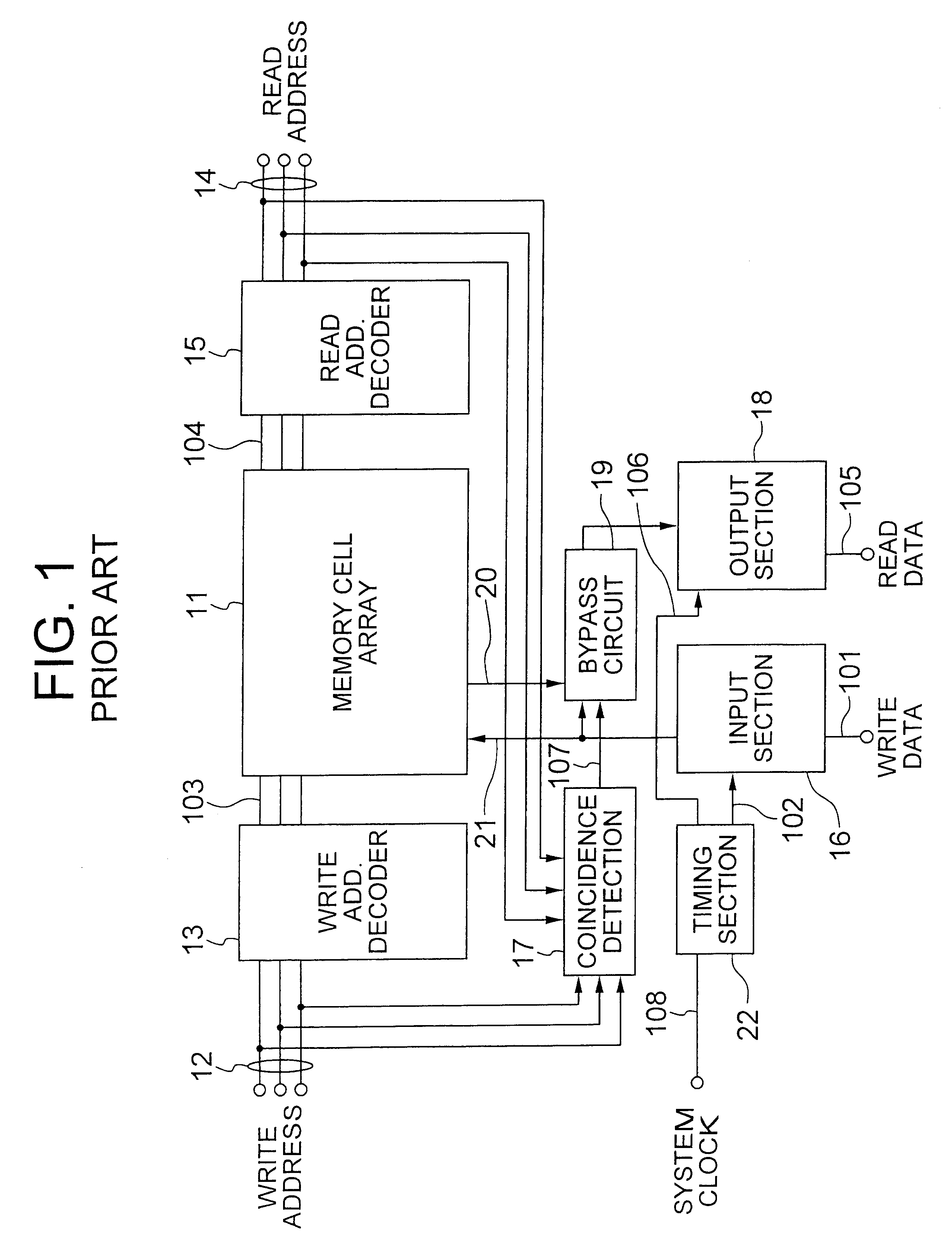

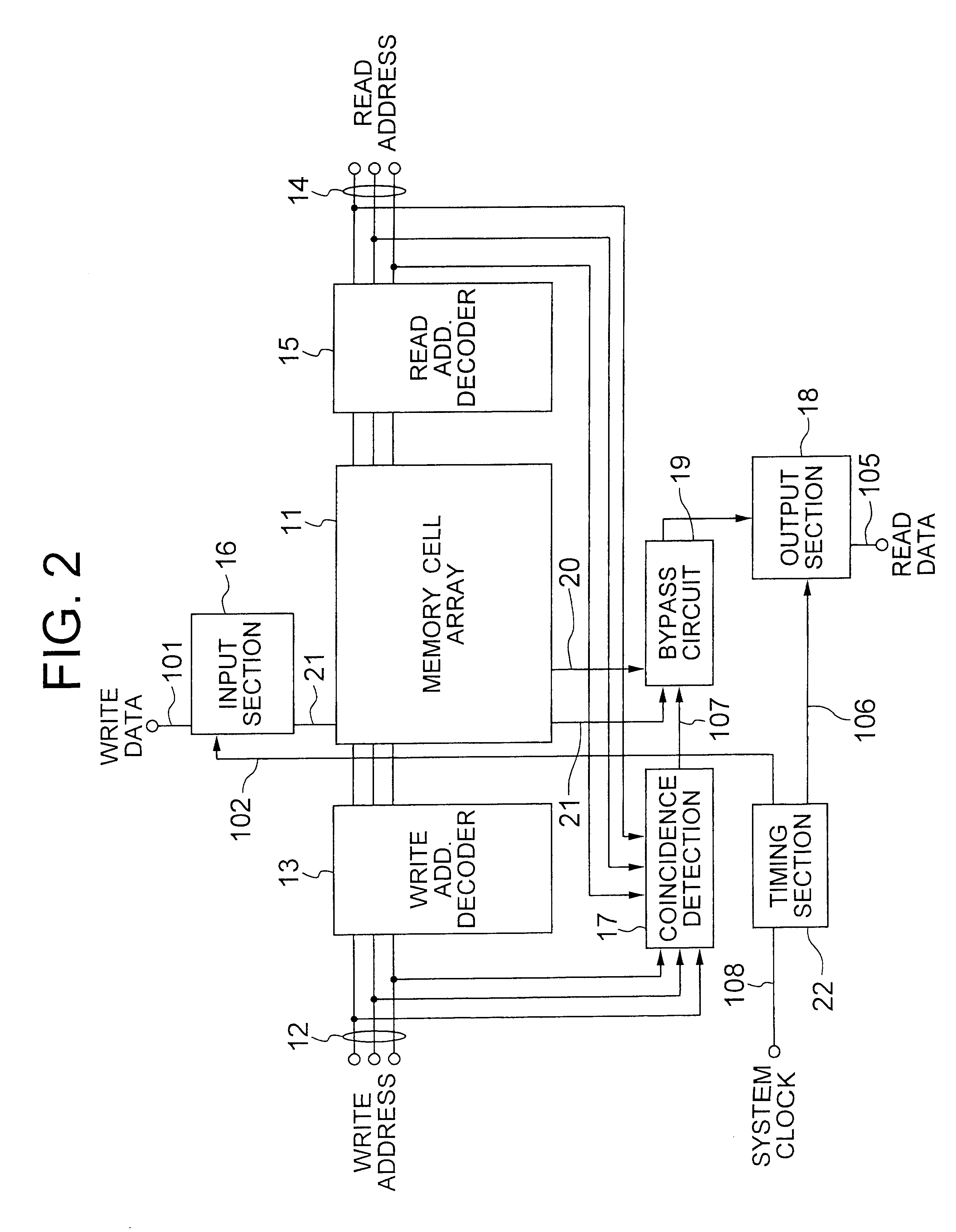

Multiple-port semiconductor memory device

A dual-port SRAM operates for read and write operations in a single clock cycle. The SRAM has a comparator for comparing the read address and the write address to detect a coincidence therebetween. A bypass circuit bypasses the write data as a read data upon detection of a coincidence, whereas a timing circuit delays the write control signal with respect to the read control signal upon detection of no coincidence. The timing control between the read operation and the write operation reduces signal interference between the write data and the read data and enables a higher speed operation of the computer system.

Owner:RENESAS ELECTRONICS CORP

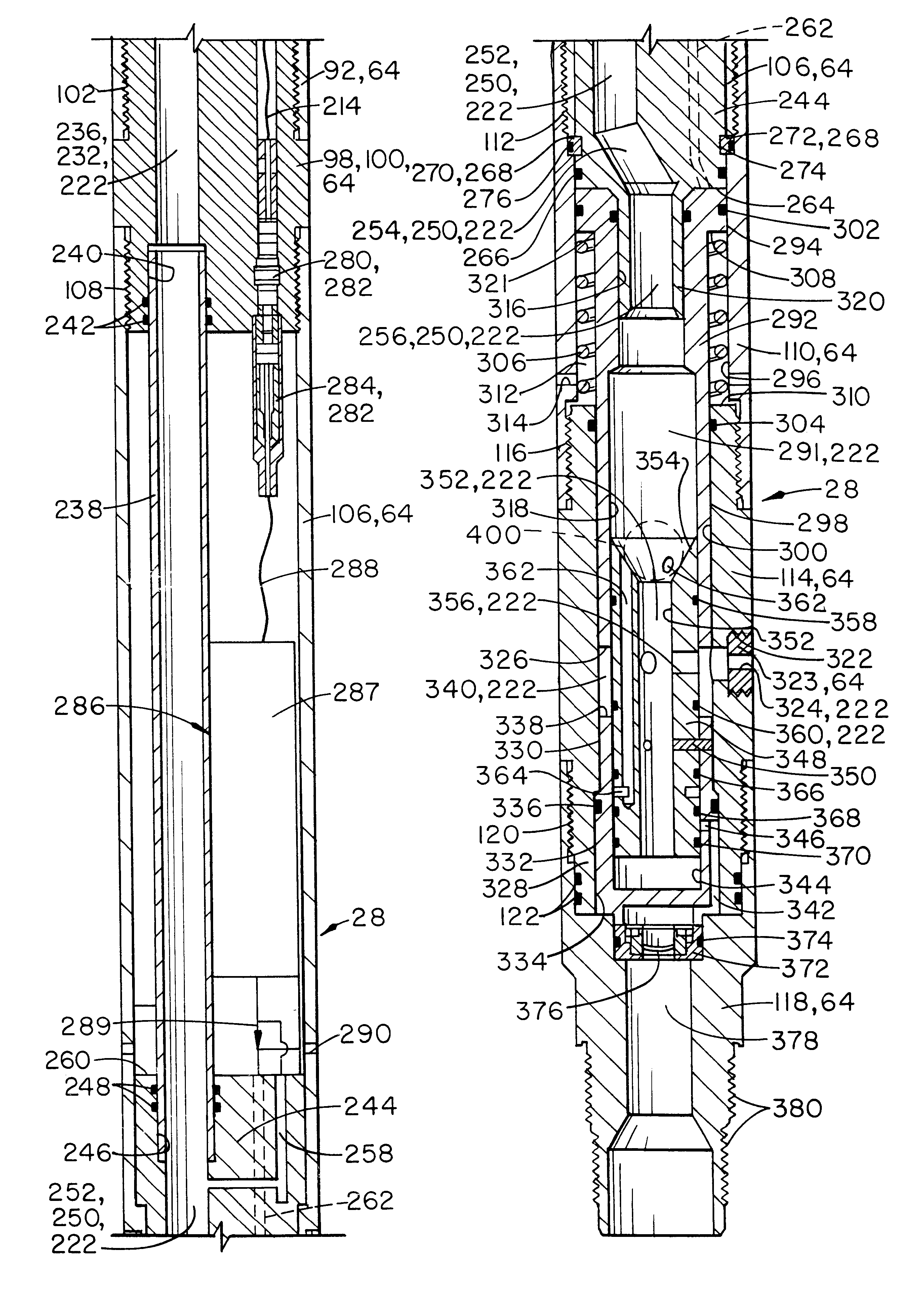

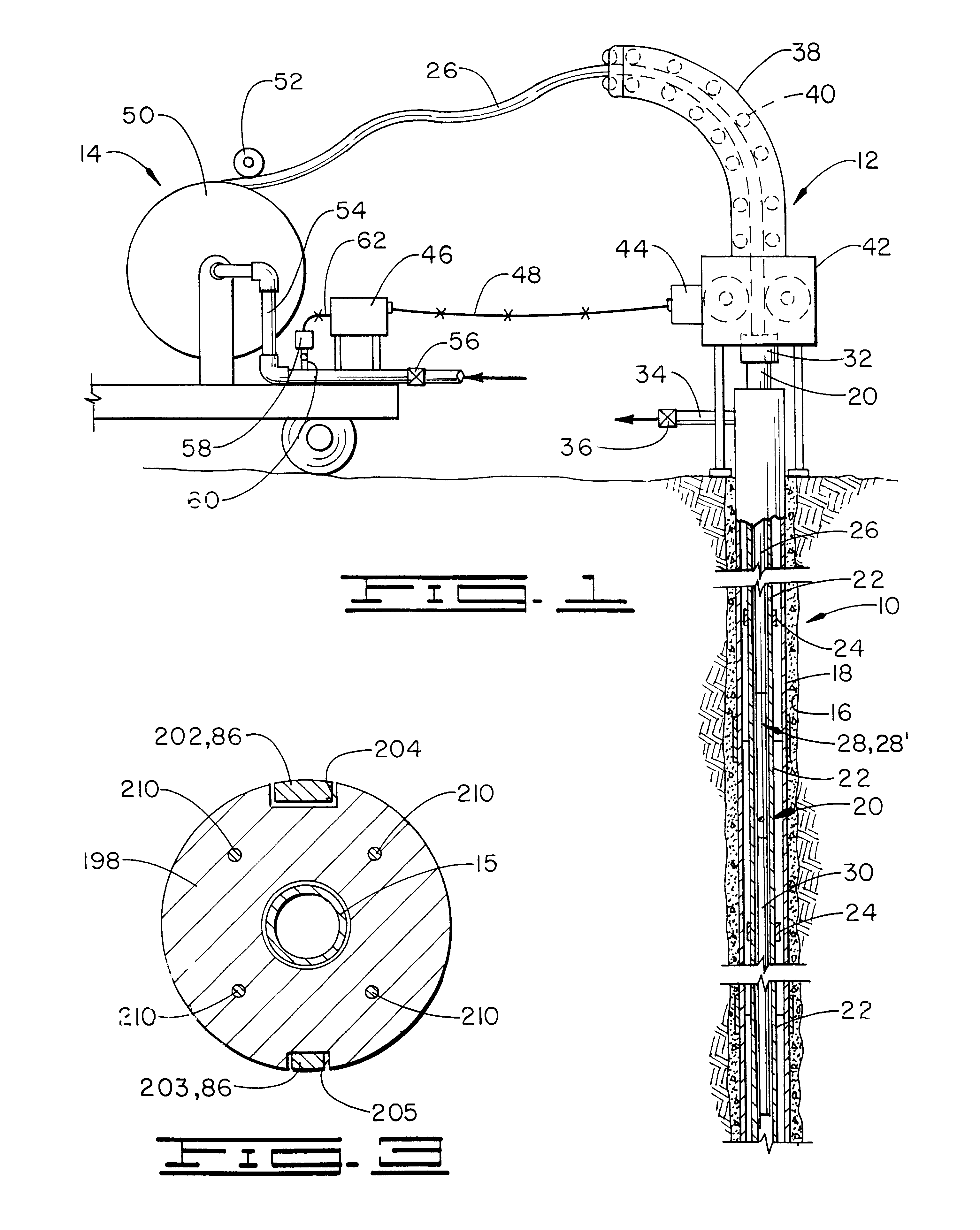

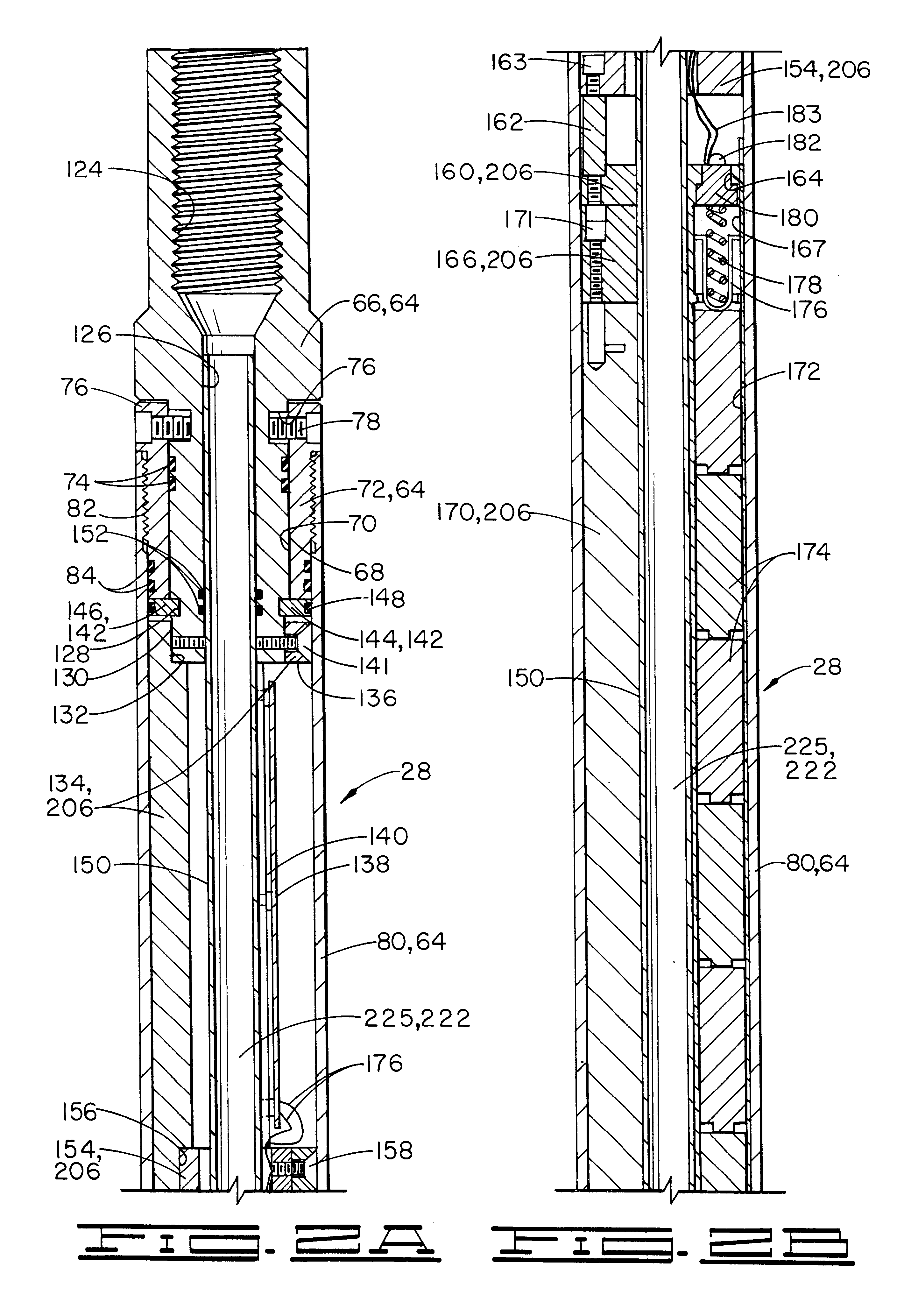

Wireless coiled tubing joint locator

A wireless coiled tubing joint locator for locating joints or collars in a production tubing string. An electromagnetic coil assembly or giant magnetoresistive digital field sensor senses the increased mass of a pipe joint, and provides a signal to an electric circuit which generates a signal received by a pilot solenoid valve. The solenoid valve momentarily opens a pilot passageway which activates a piston to close a circulation port in the joint locator, resulting in an increase in a surface pressure reading observable by the operator. In one embodiment, a rupture disk is provided so that pressure cannot be applied to any downhole tool below the joint locator prematurely. A seat sleeve prevents premature communication of fluid to the rupture disk but can be opened by dropping a ball into the joint locator. A second embodiment may be used for either logging or washing operations or both. The electronic circuit can provide a selected one of a plurality of time delays. A fixed test period in the circuit delays activation of the time delay so that the joint locator may be tested before it is run into the well. The electric circuit and power supply are provided in a removable case.

Owner:HALLIBURTON ENERGY SERVICES INC

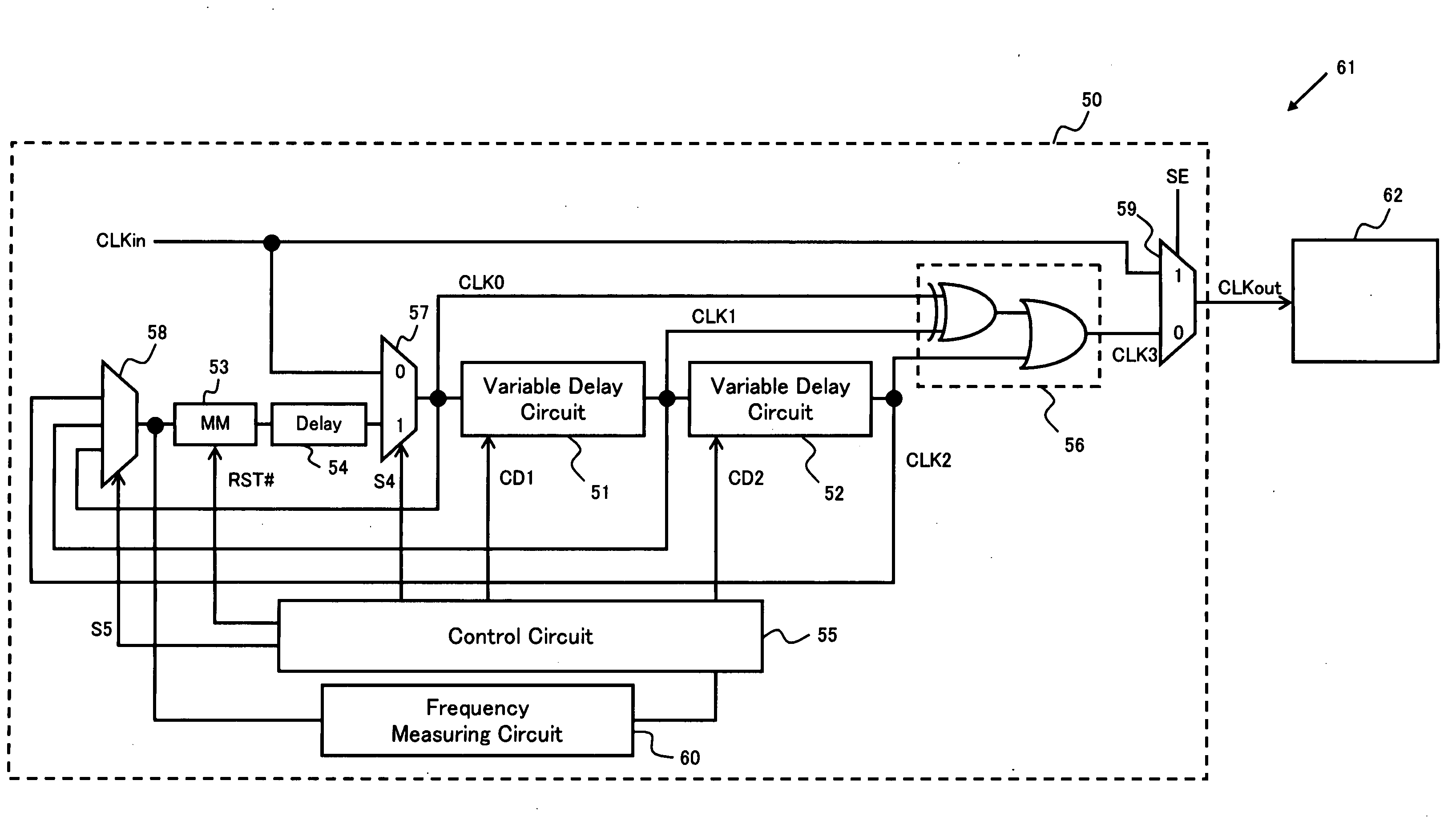

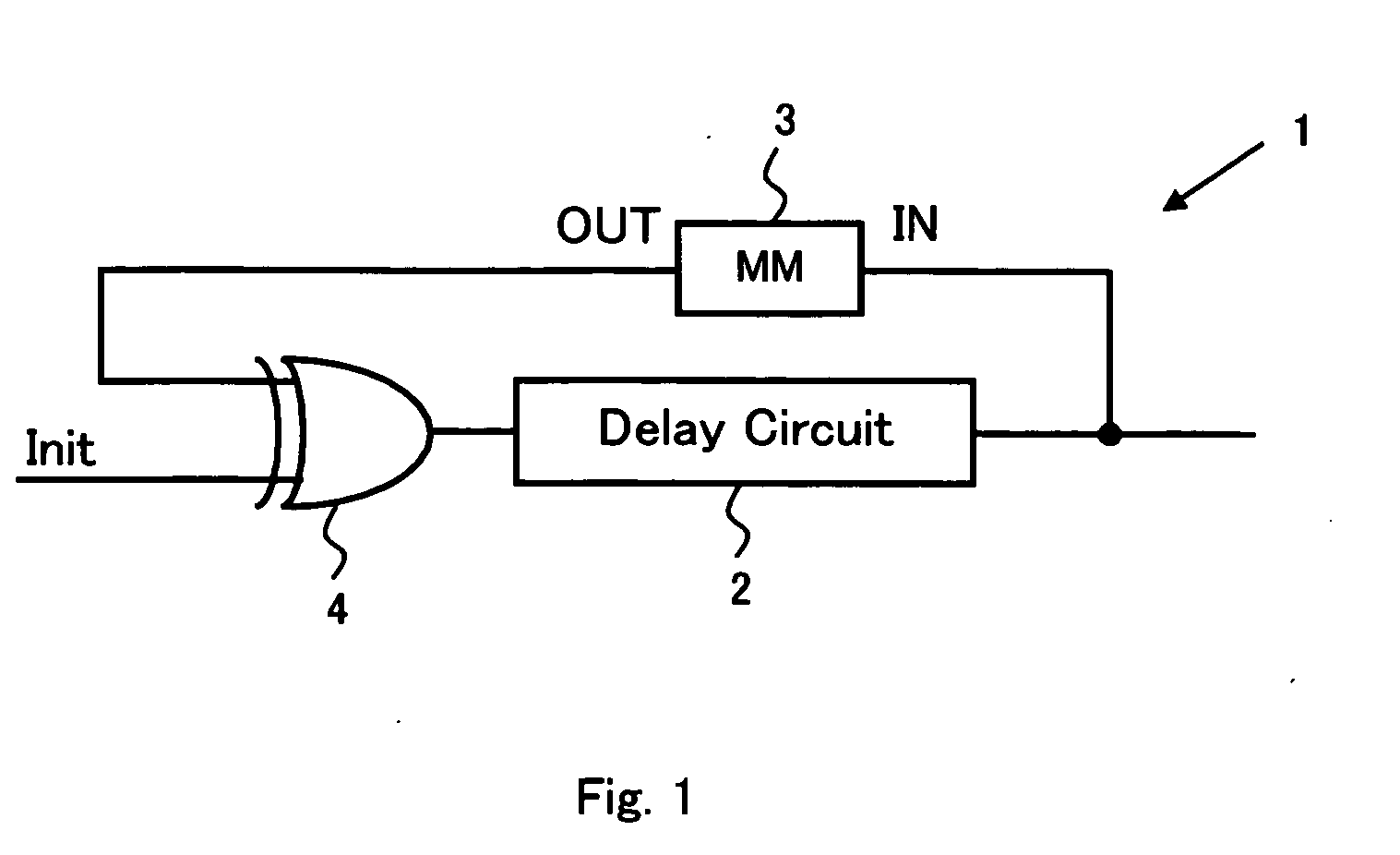

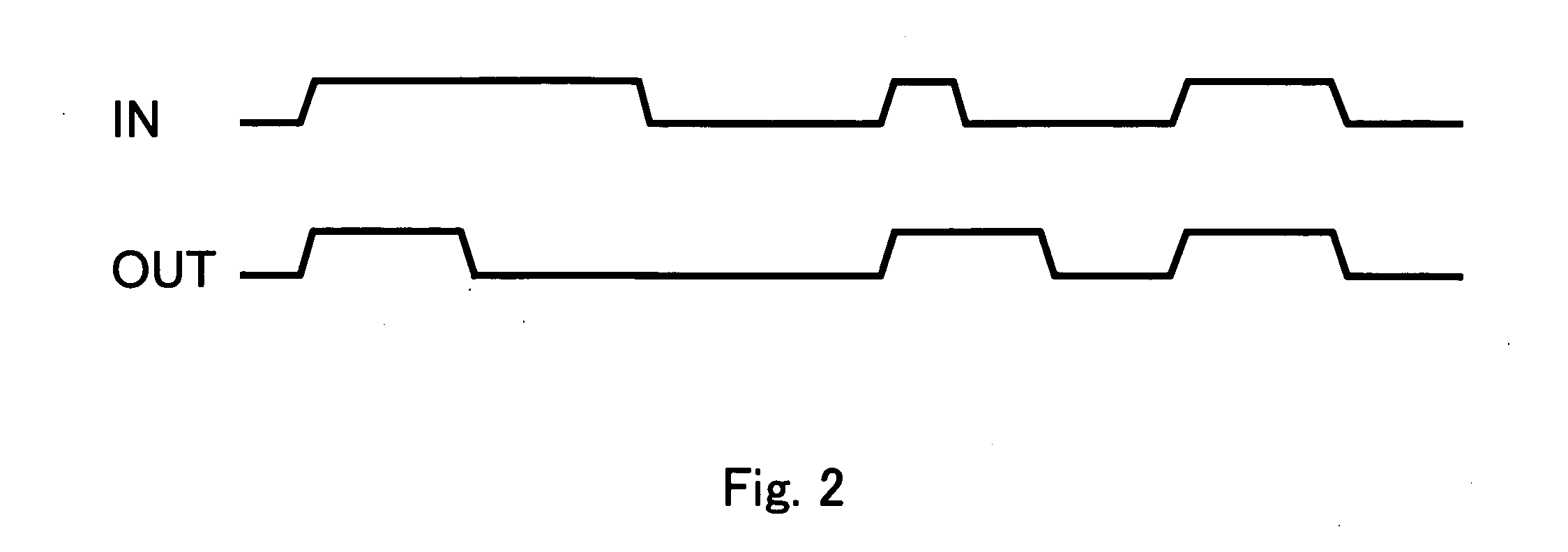

Ring Oscillation Circuit, Delay Time Measuring Circuit, Testing Circuit, Clock Generating Circuit, Image Sensor, Pulse Generating Circuit, Semiconductor Integrated Circuit, and Testing Method Thereof

InactiveUS20090051396A1Stably continueEasy to operateNoise figure or signal-to-noise ratio measurementPulse automatic controlImage sensorPositive feedback

A ring oscillation circuit, which can operate the ring oscillation due to a positive feedback stably and continuously, is provided and it is applied to an accurate measurement of delay time and a measurement of timing accuracy in a jitter of a clock signal or the like with a high accuracy. A ring oscillation circuit comprises a delay circuit and a monostable multivibrator. An output of the delay circuit is connected to an input of the monostable multivibrator, an output of the monostable multivibrator is connected to an input of the delay circuit, and the delay circuit and the monostable multivibrator configure a positive feedback loop. An oscillation starting circuit for starting oscillation upon receipt of an input of a trigger pulse for triggering oscillation is provided on the positive feedback loop, or in the inside of the delay circuit or the monostable multivibrator.

Owner:SHARP KK

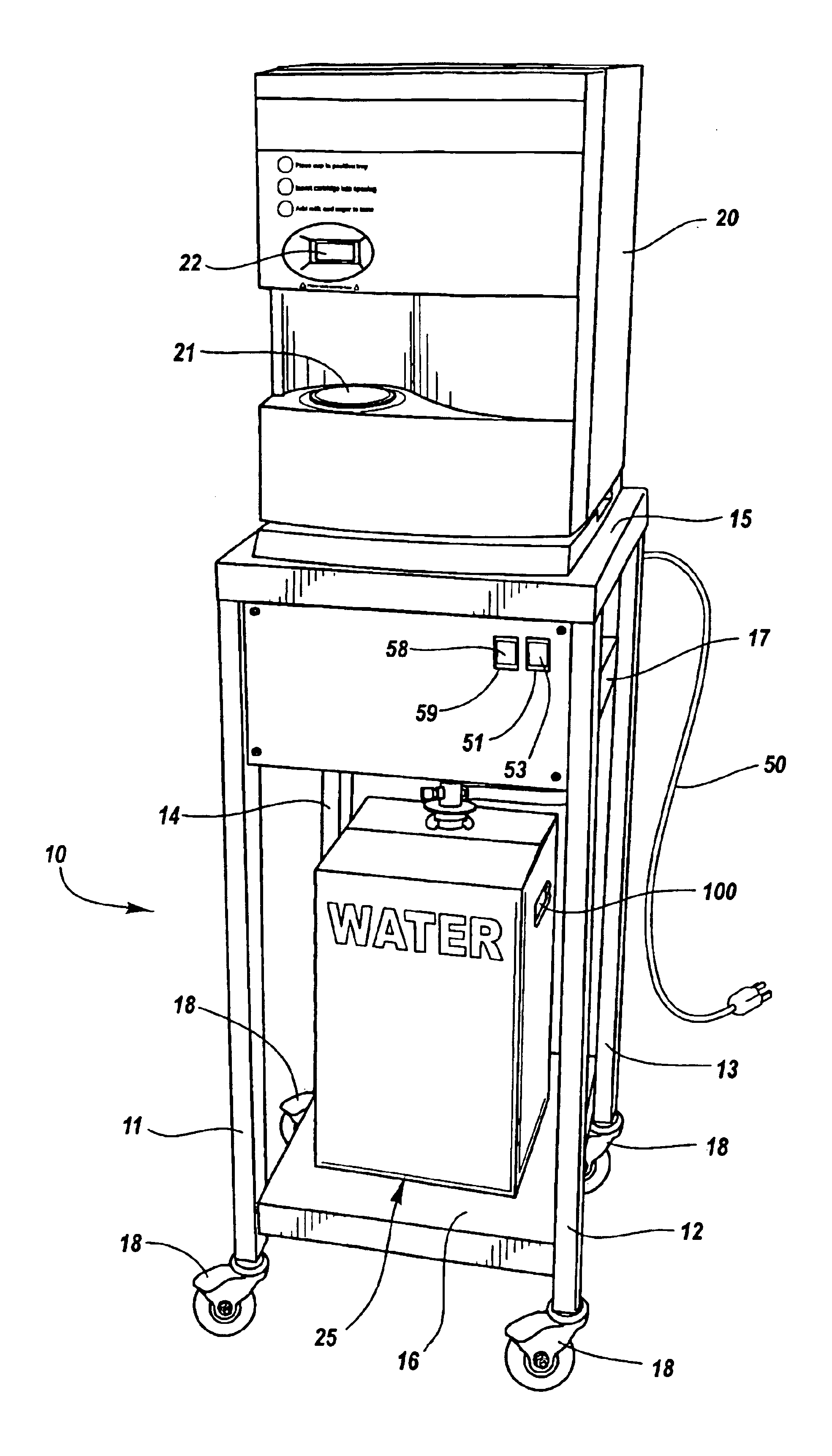

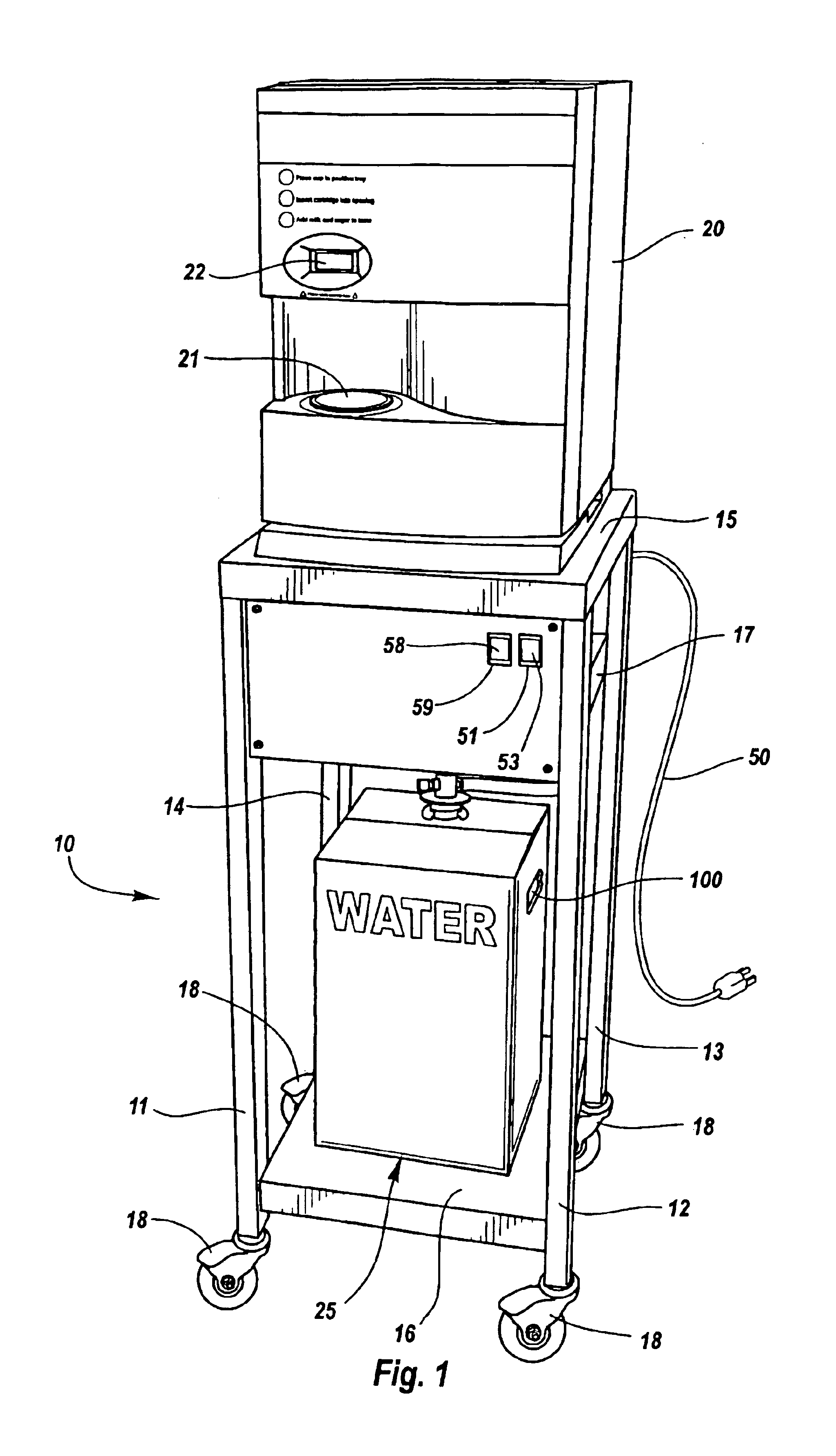

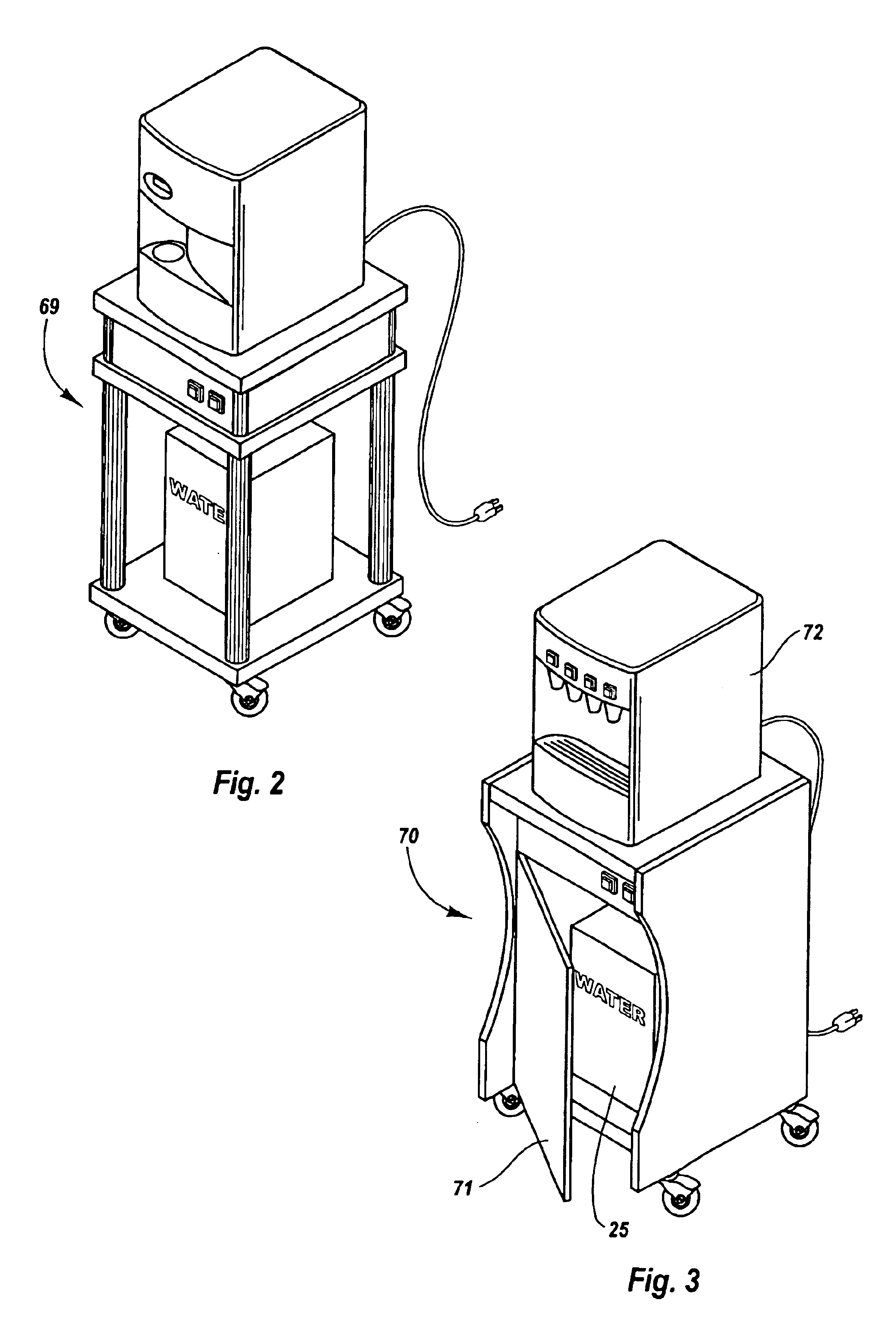

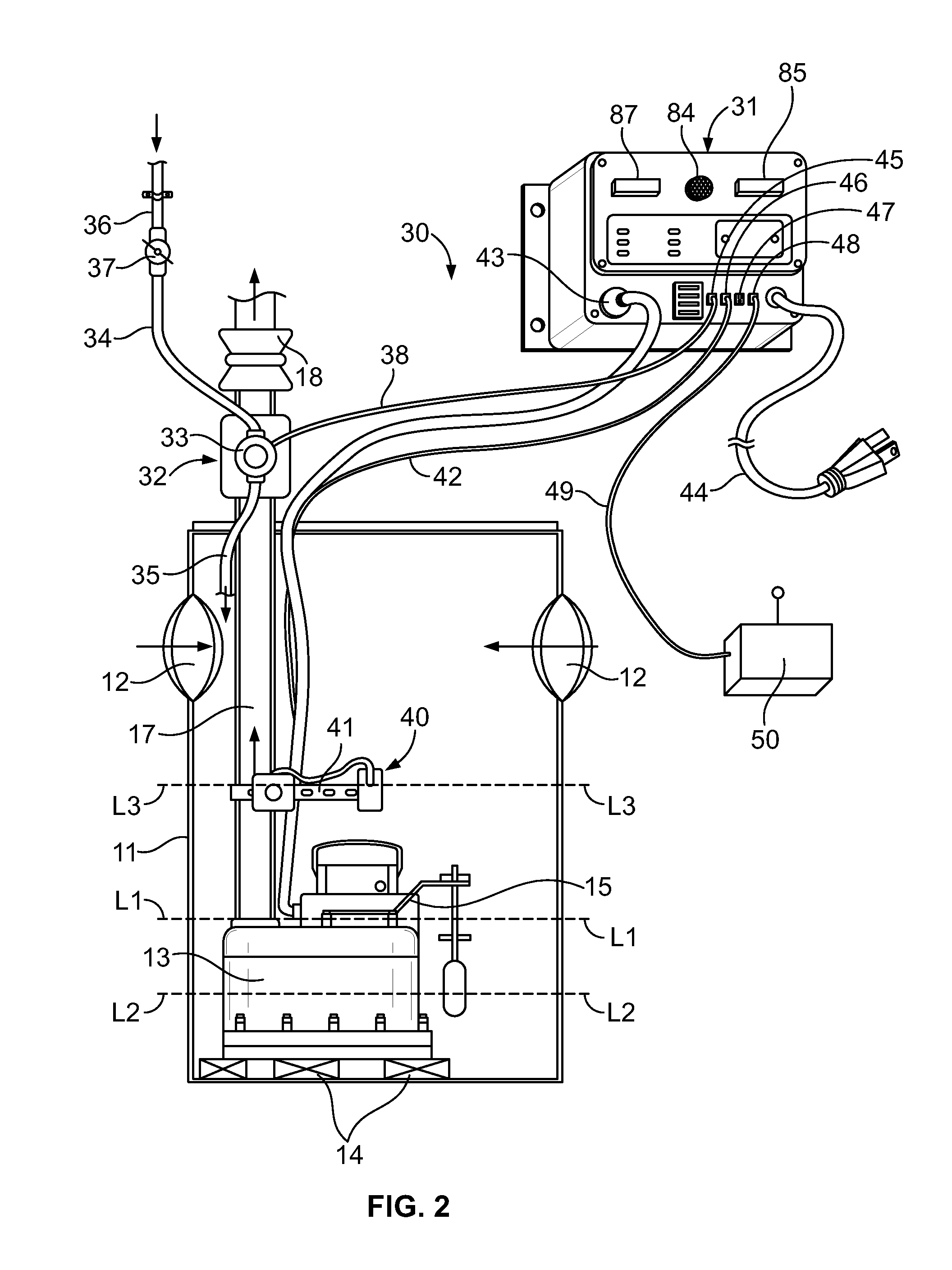

Drink dispensing cart and water packaging and supply system

InactiveUS6926170B2Eliminate storageEliminate needTank vehiclesLiquid transferring devicesLine tubingTime delays

A drink dispensing cart includes a drink dispensing machine that is normally plumbed directly into a municipal water pipe at a fixed location. The cart includes a container of water, preferably a disposable container of water such as a bag-in-box container of water, and a pump to pump water from the container of water to the drink dispensing machine. A controller controls operation of the pump to operate the pump only when water is needed by the drink dispensing machine and to provide an indication when the container of water is empty and needs changing. A pressure sensor in an outlet line extending between the pump and drink dispensing machine senses when water is needed by the dispenser and a pressure sensor in an inlet line extending between the pump and the container of water senses when the container of water is empty and needs replacing. A time delay circuit delays start of operation of the pump when water is needed by the drink dispenser to avoid pulsing of the pump. The bag-in-box container of water is sized for efficient packing and shipping.

Owner:GROESBECK R CLAY

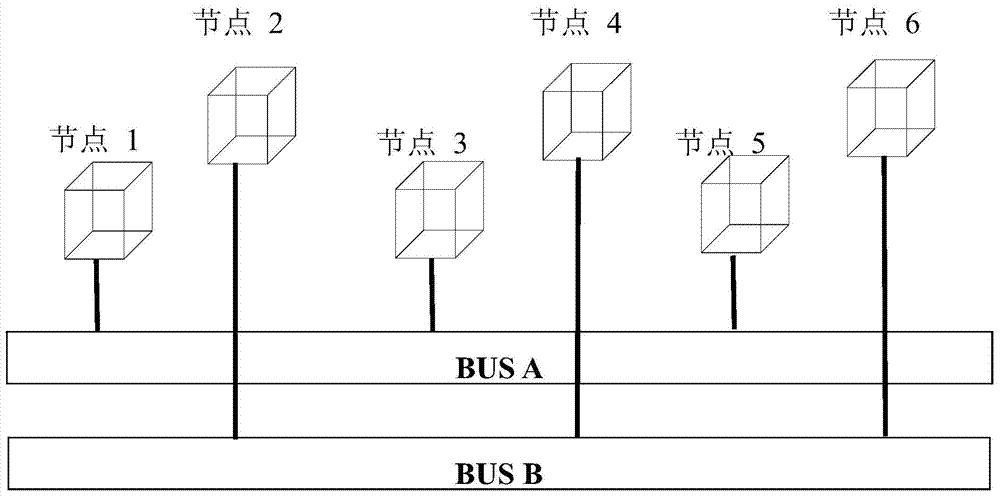

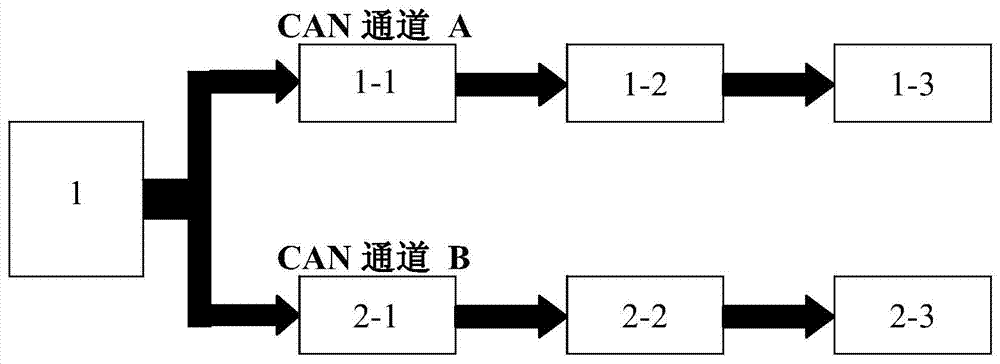

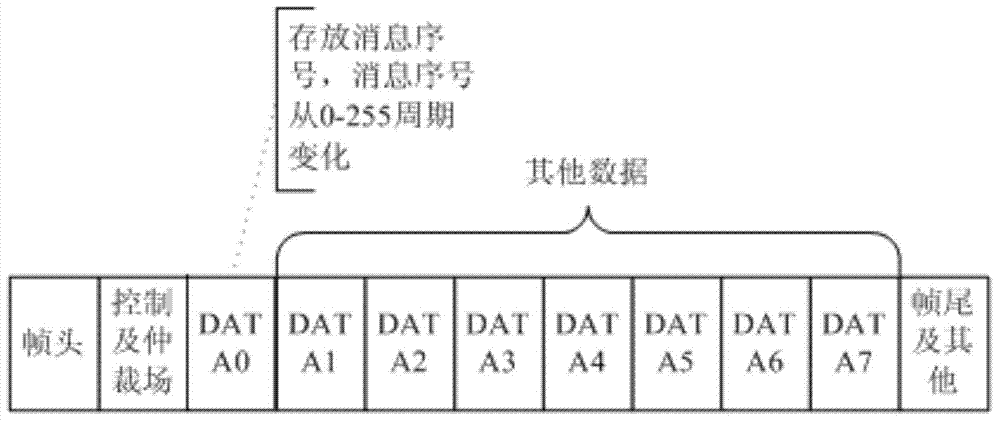

Dual-redundancy CAN bus data receiving and processing method

The invention provides a dual-redundancy CAN bus data receiving and processing method which aims to solve the problem the existing technique can not simply and effectively solve the problem that two channels receive repeated data. The method comprises the steps of (1) sending data composed of data frames on a first channel and a second channel of a dual-redundancy CAN bus at the same time, (2) receiving the data of the first channel of the dual-redundancy CAN bus and the data of the second channel of the dual-redundancy CAN bus, (3) judging whether repeated data distinguishing needs to be carried out on the data frames of the data received from the two channels, (4) directly using the data with repeated data distinguishing not needed, distinguishing the data frames with repeated data distinguishing needed, using unrepeated data in the data frames treated with distinguishing, and discarding the repeated data. According to the dual-redundancy CAN bus data receiving and processing method, influence of software delay and circuit delay on dual-redundancy CAN bus data receiving is avoided with simple methods.

Owner:BEIJING INST OF SPACE LAUNCH TECH +1

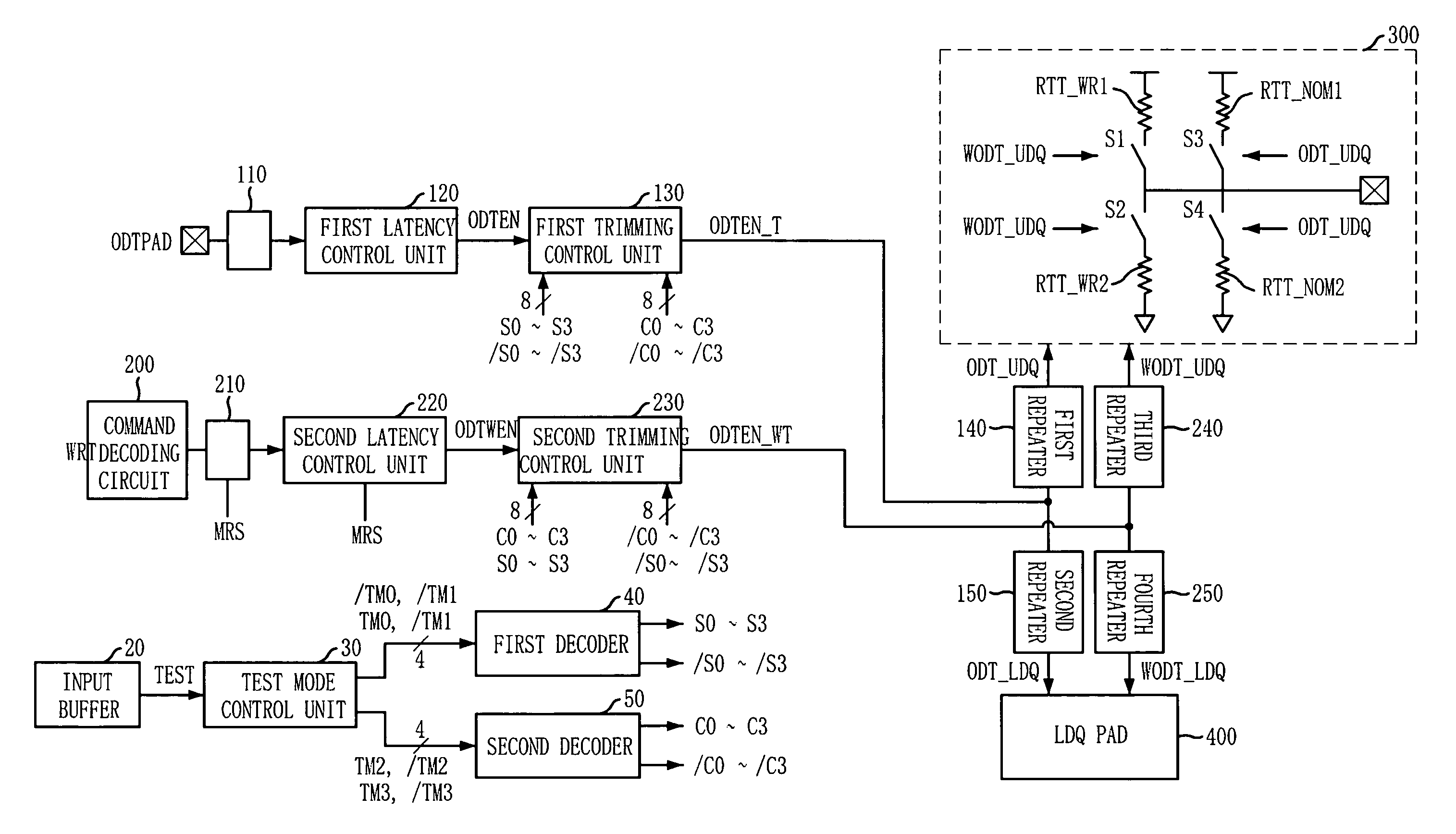

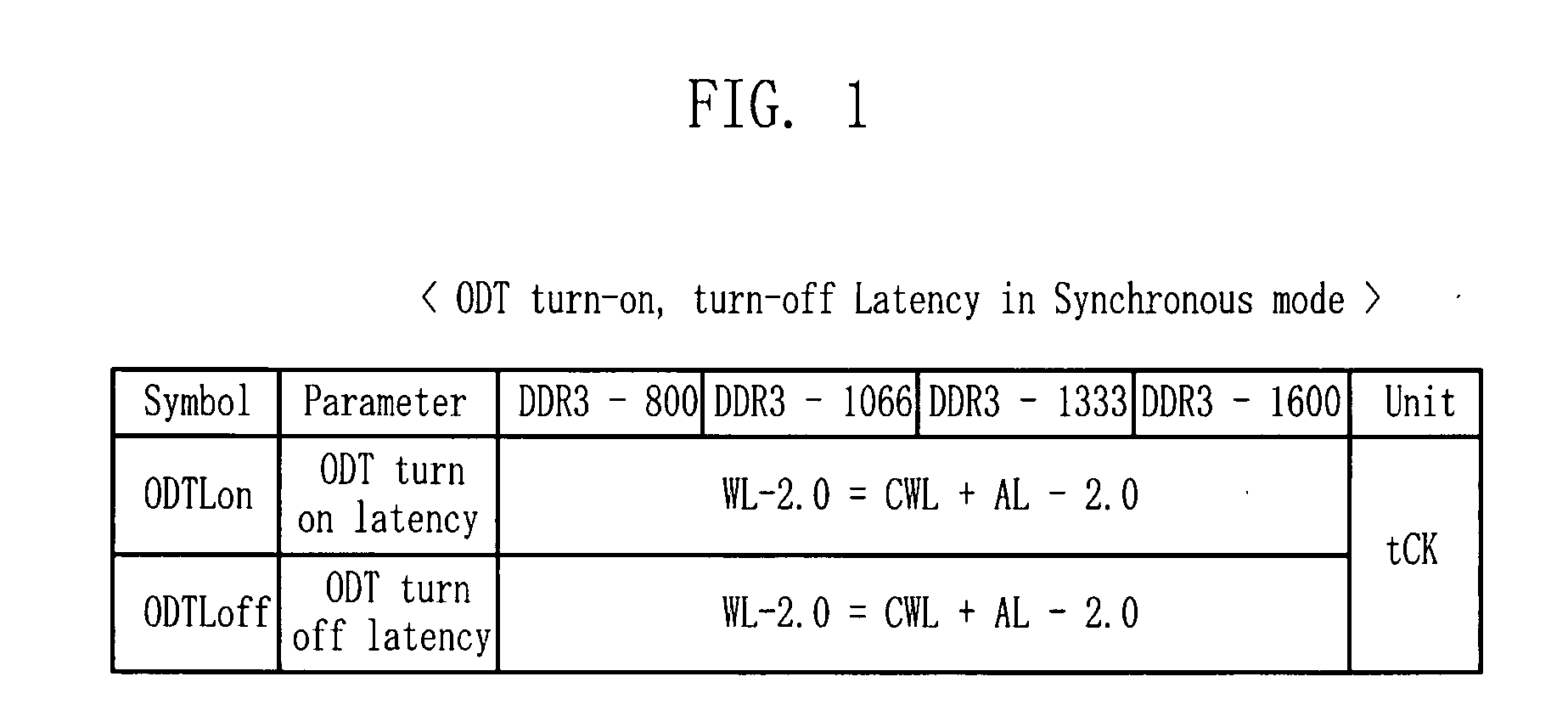

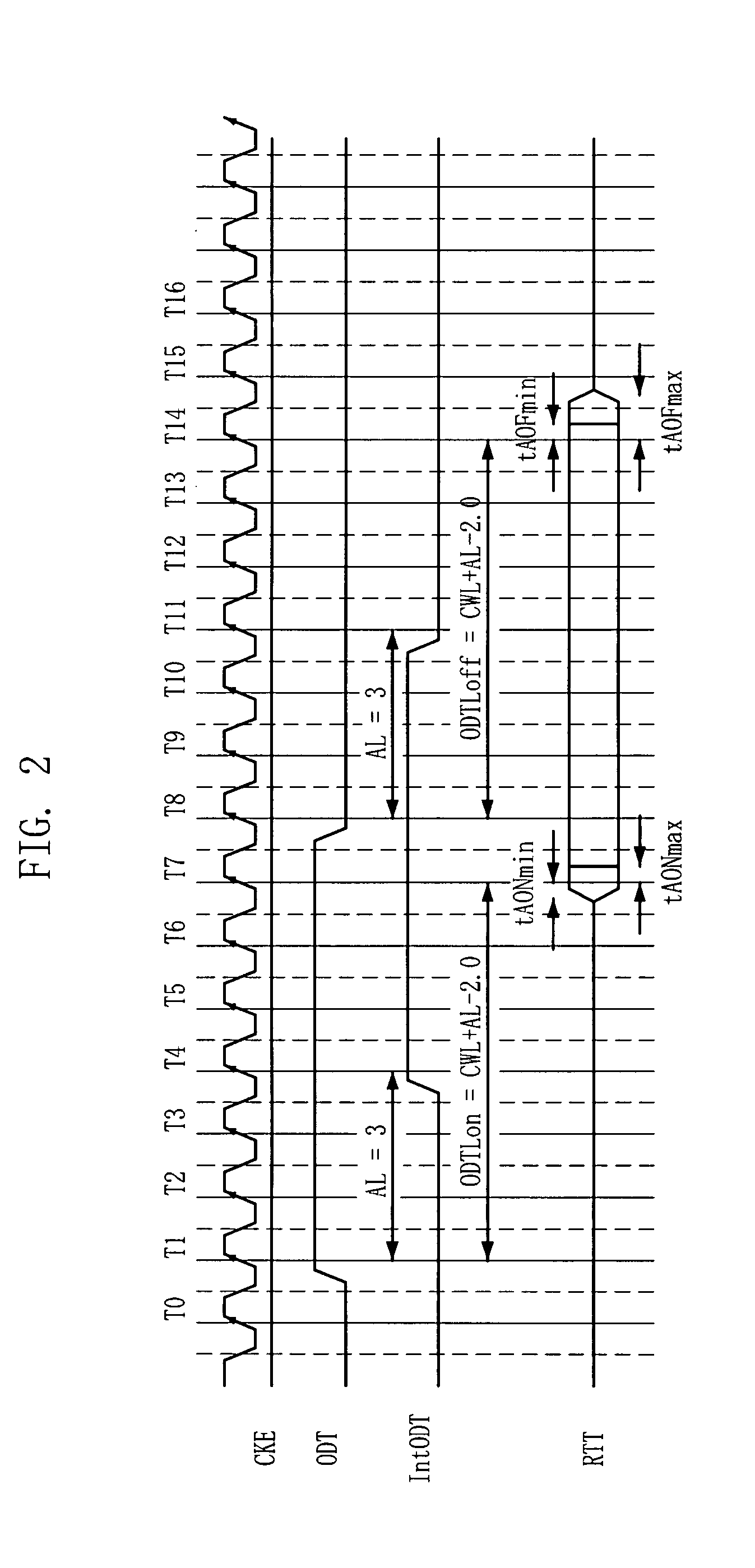

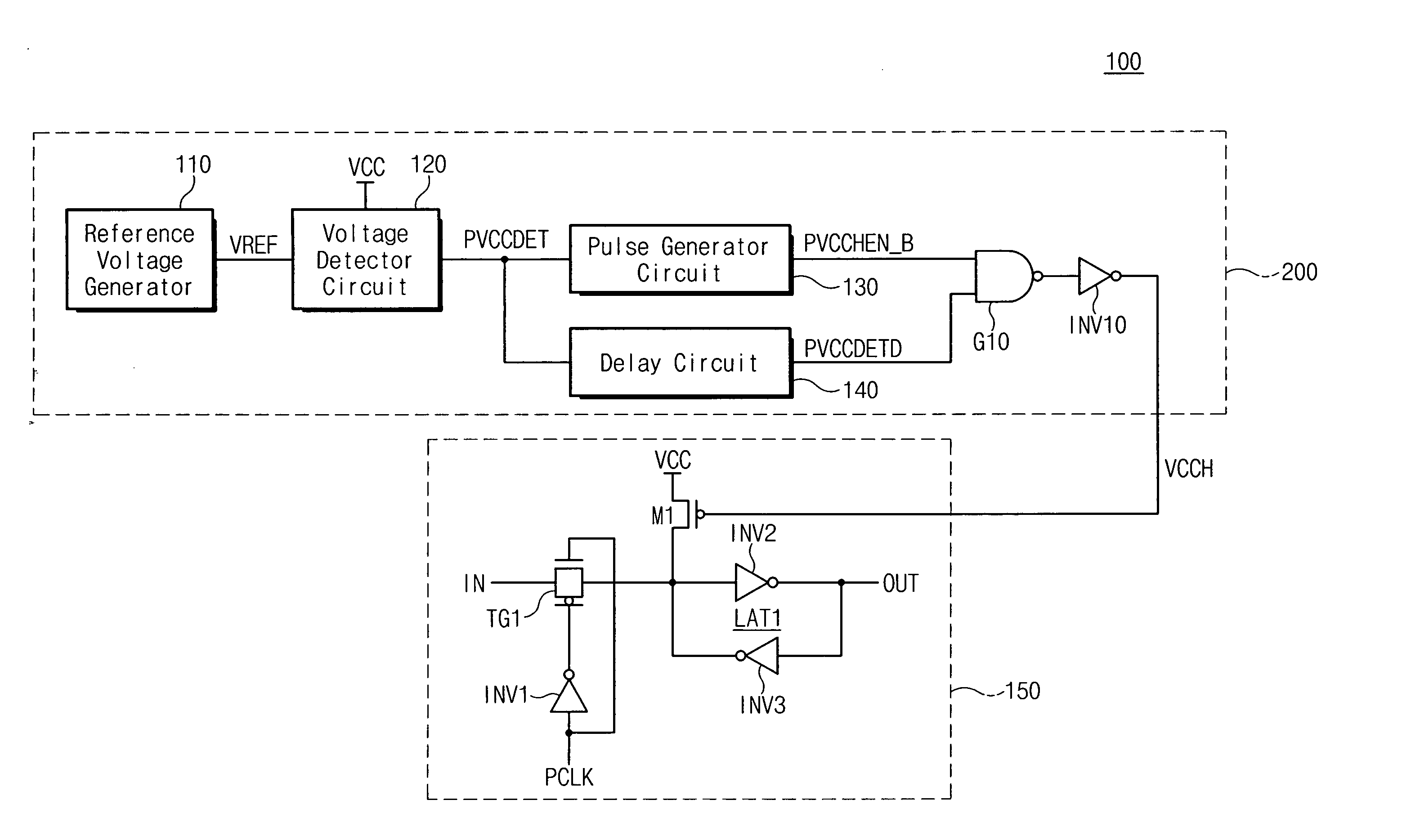

Semiconductor memory device with ability to effectively adjust operation time for on-die termination

ActiveUS20080164904A1Effectively adjust operation timeInput/output impedence modificationReliability increasing modificationsControl signalEngineering

A semiconductor memory device is effectively able to adjust operation time for on-die termination (ODT). The semiconductor memory device includes a latency control unit, a control signal generating unit, a trimming control unit, and a termination circuit. The latency control unit produces an ODT driving enable signal by delaying an ODT operation signal from an external circuit during a predetermined latency. The control signal generating unit produces control signals to control a change of waveform of the ODT driving enable signal. The trimming control unit changes the waveform of the ODT driving enable signal in response to the control signals, thereby outputting a ODT driving signal. The termination circuit connects a termination resistance to an impedance adjusting node in response to the ODT driving signal.

Owner:SK HYNIX INC

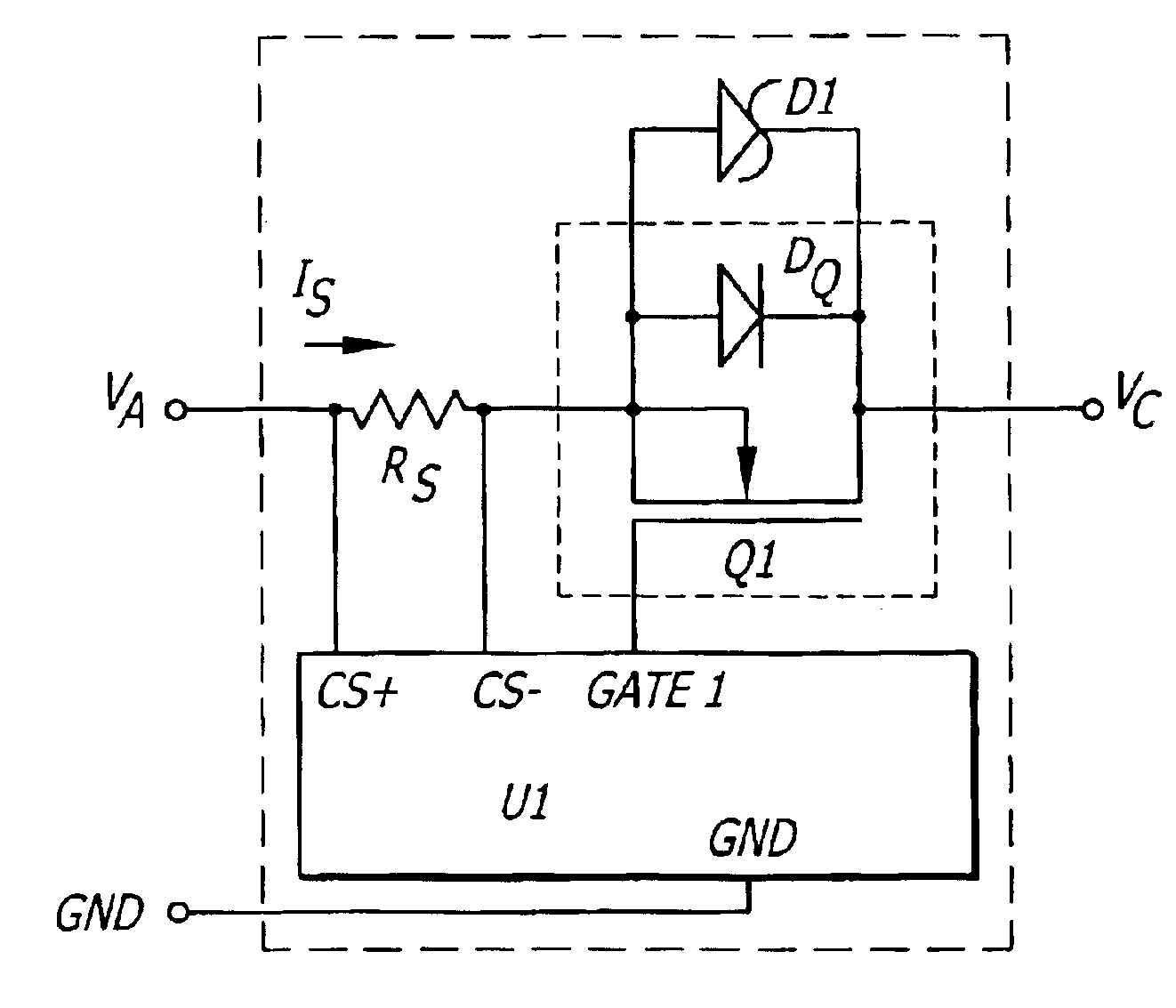

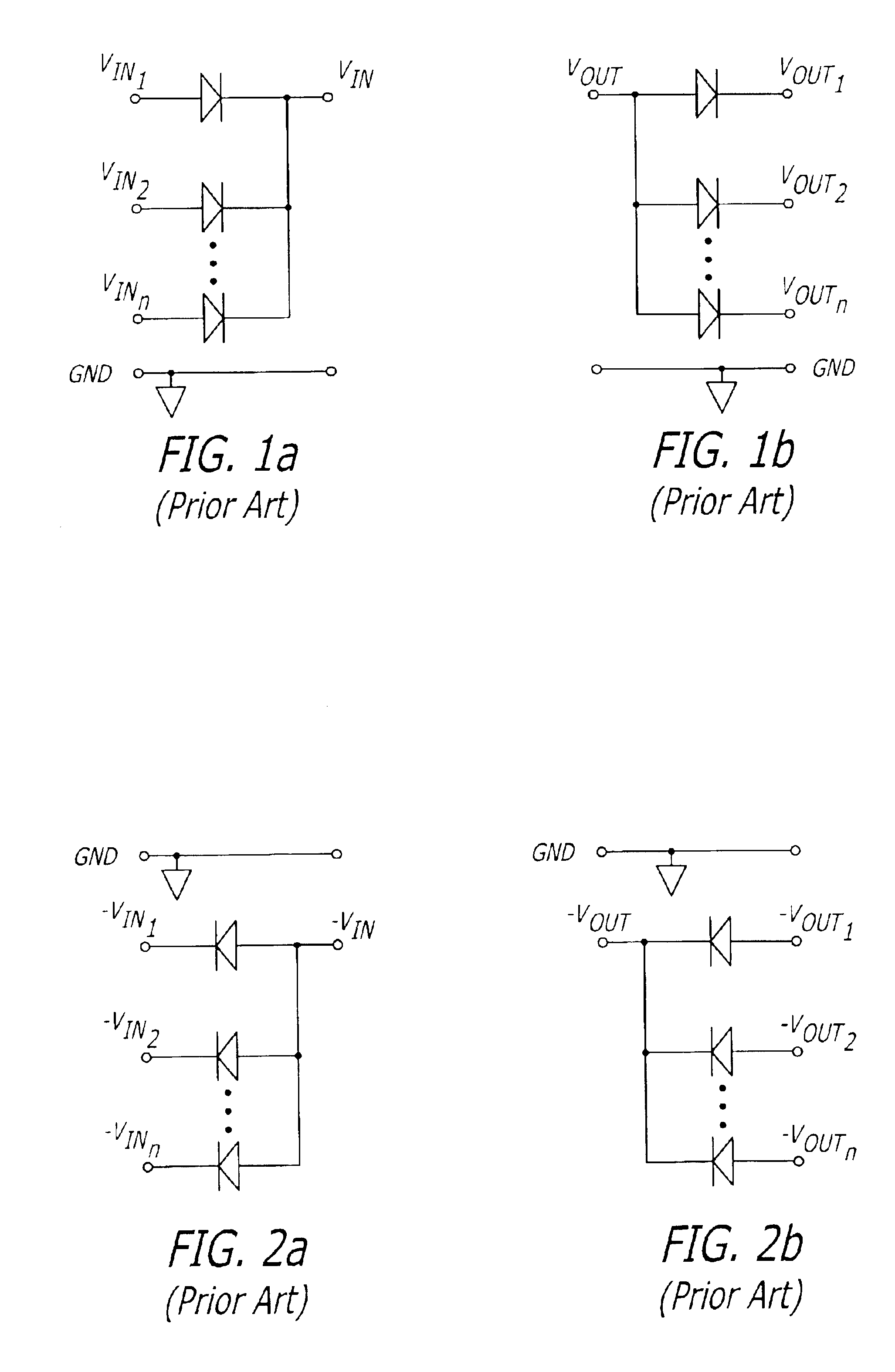

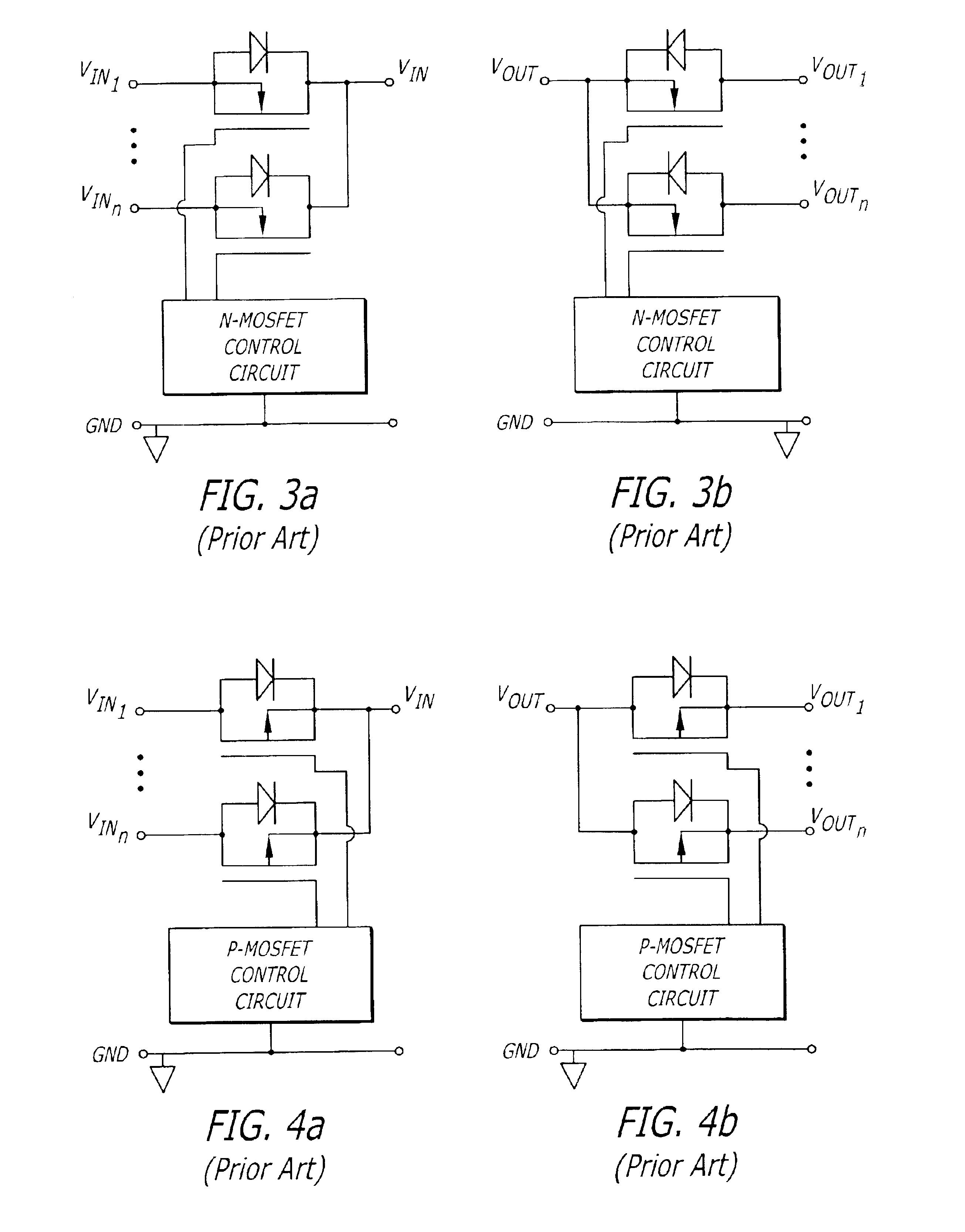

Low voltage or'ing circuits and methods with zero recovery time

Low voltage drop ORing circuits with zero recovery time and reverse current protection. In use, a MOSFET is coupled between a power supply and a load in a multiple power supply, single load system, or between a power supply and a load in a single power supply, multiple load system, or in both locations in multiple power supply, multiple load systems. A controller senses the current through the MOSFET, and turns the MOSFET off when the current falls below a predetermined threshold current. This allows time for circuit delays and the discharge of the gate of the MOSFET to turn the MOSFET off before the current through the MOSFET car reverse. Turn-on of the MOSFET when the current exceeds the threshold may be purposely slowed to avoid current spikes. Addition of another MOSFET controlled by the controller adds a hot swap capability and the control of the VC slew rate. Various other features and embodiments are disclosed, including various current sensing techniques and circuits using transistors other than MOSFETs.

Owner:MAXIM INTEGRATED PROD INC

Low-voltage IC test for defect screening

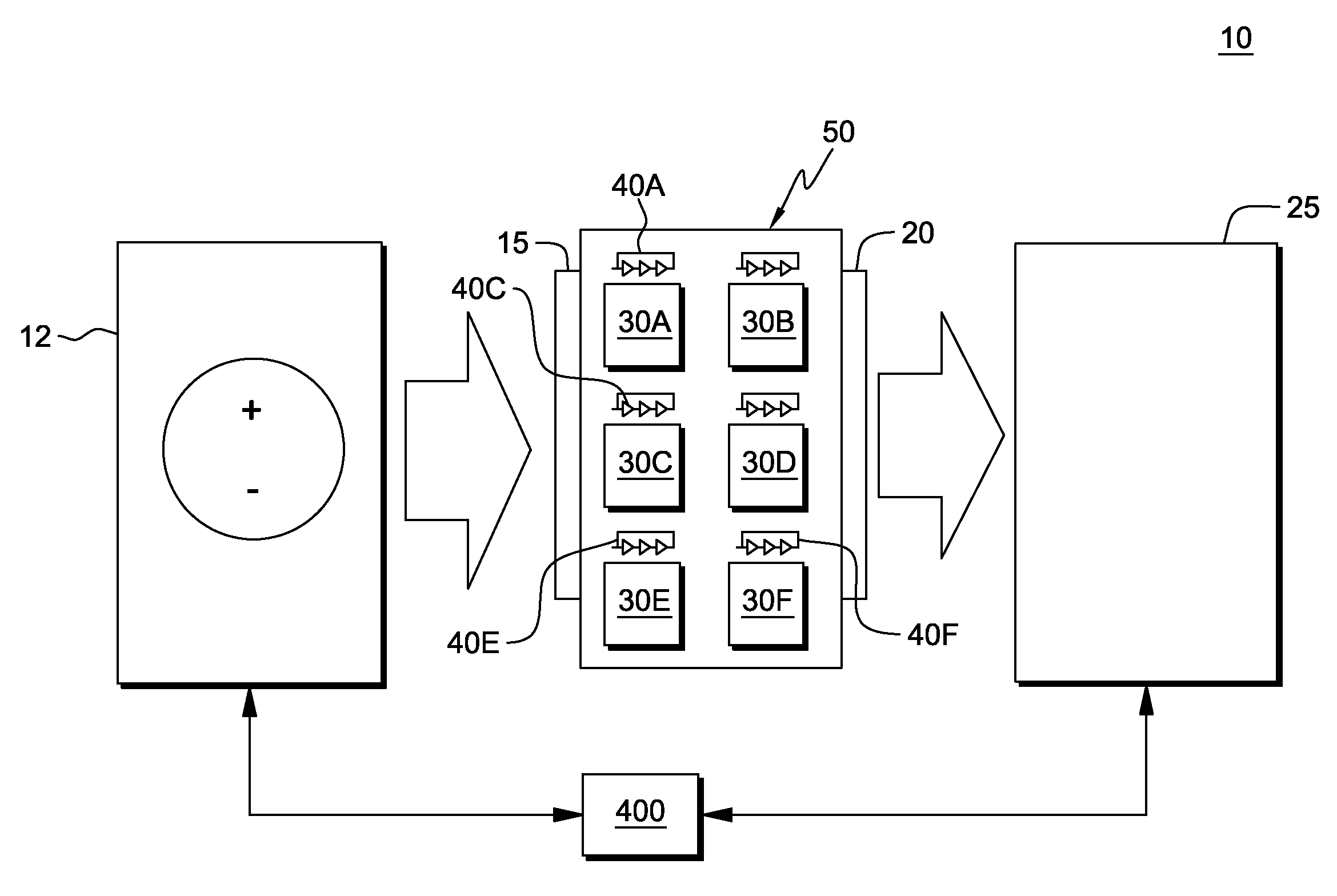

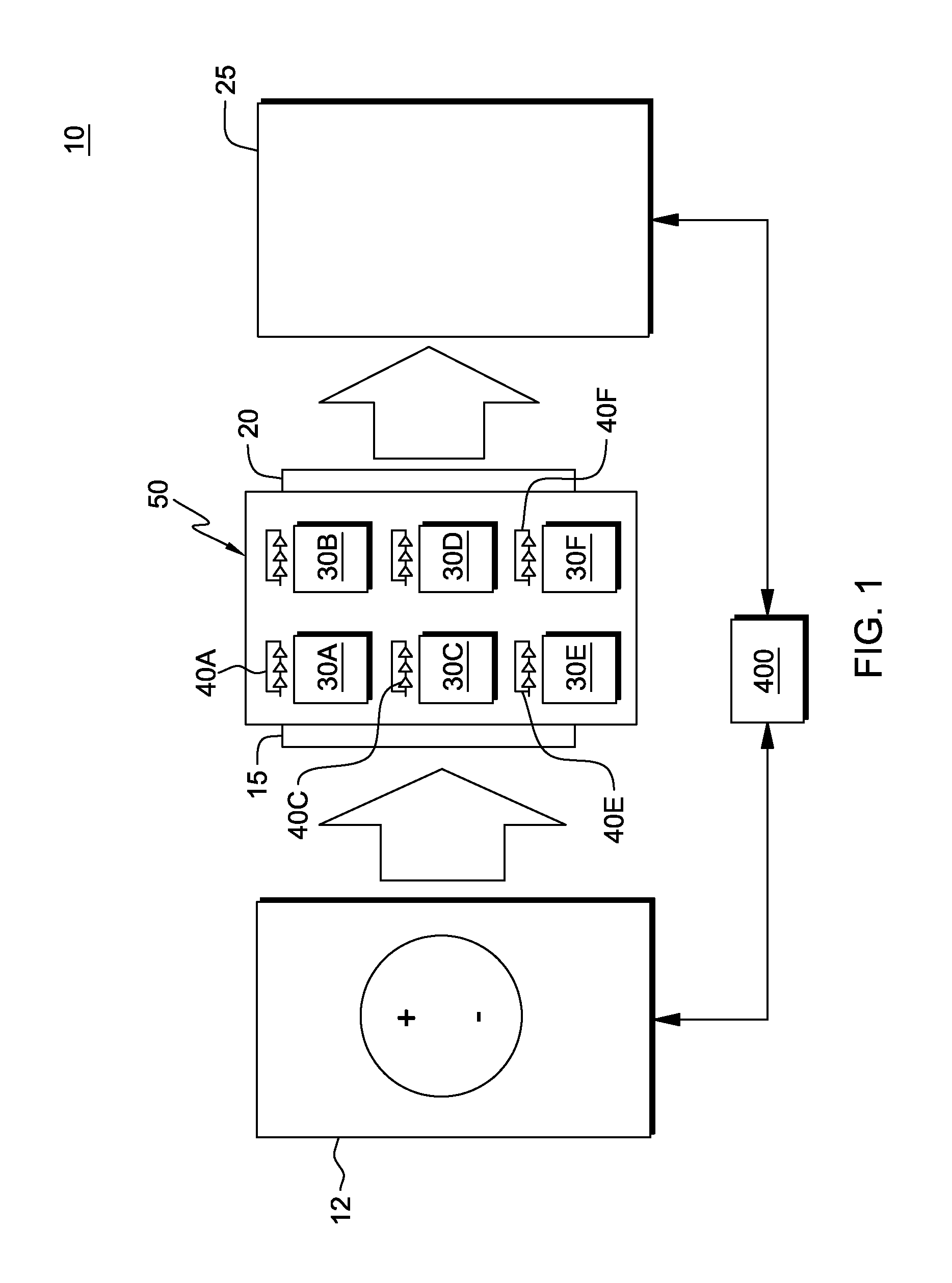

InactiveUS20140184262A1Strong signalDetection moreElectronic circuit testingSolid-state devicesTest flowLow voltage

System and method using low voltage current measurements to measure voltage network currents in an integrated circuit (IC). In one aspect, a low voltage current leakage test is applied voltage networks for the IC or microchip via one or more IC chip connectors. One or multiple specifications are developed based on chip's circuit delay wherein a chip is aborted or sorted into a lesser reliability sort depending whether the chip fails specification. Alternately, a low voltage current leakage test begins an integrated circuit test flow. Then there is run a high voltage stress, and a second low voltage current leakage test is thereafter added. Then, there is compared the second low voltage test to the first low V test, and if the measured current is less on second test, this is indicative of a defect present which may result in either a scrap or downgrade reliability of chip.

Owner:ALSEPHINA INNOVATIONS INC

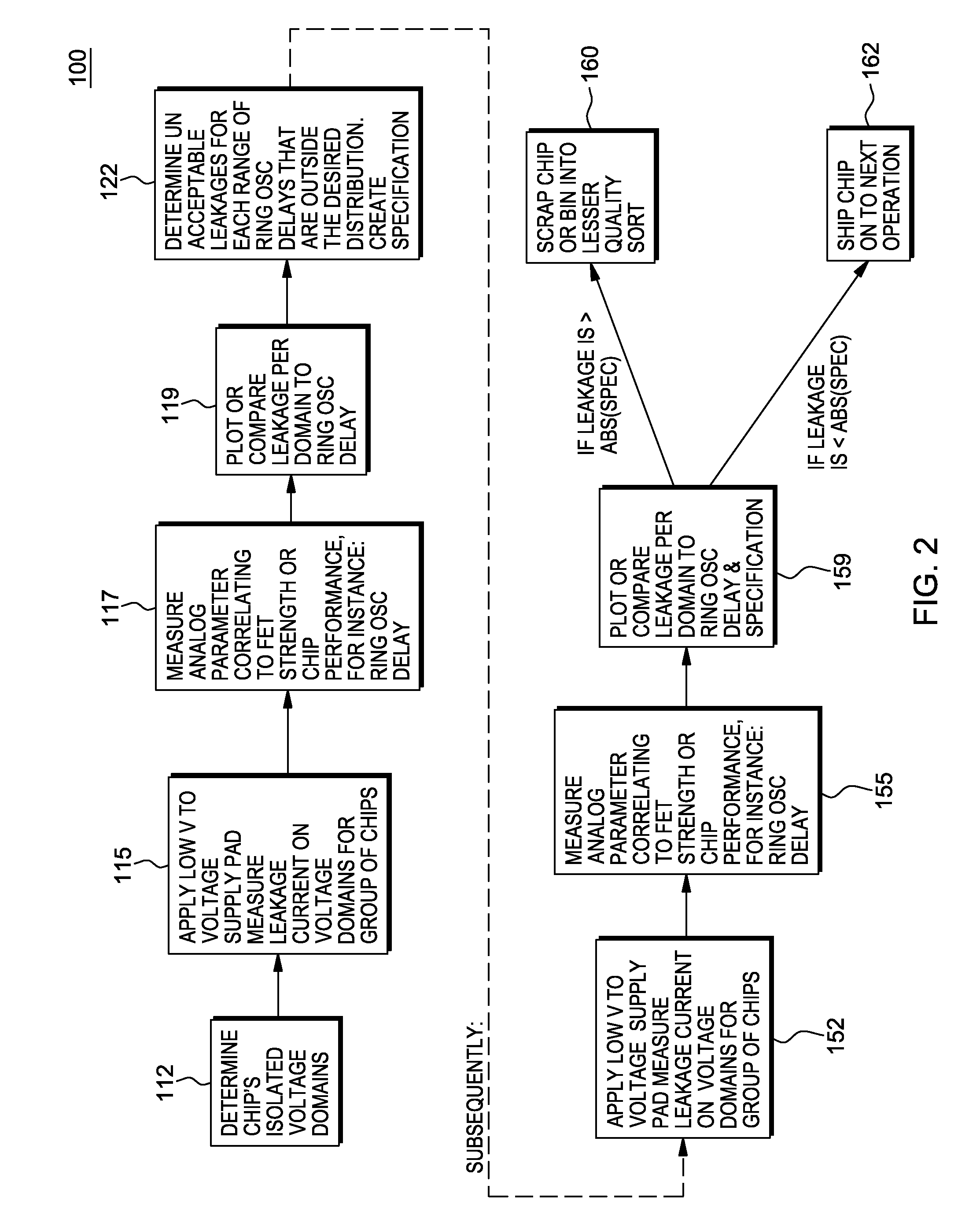

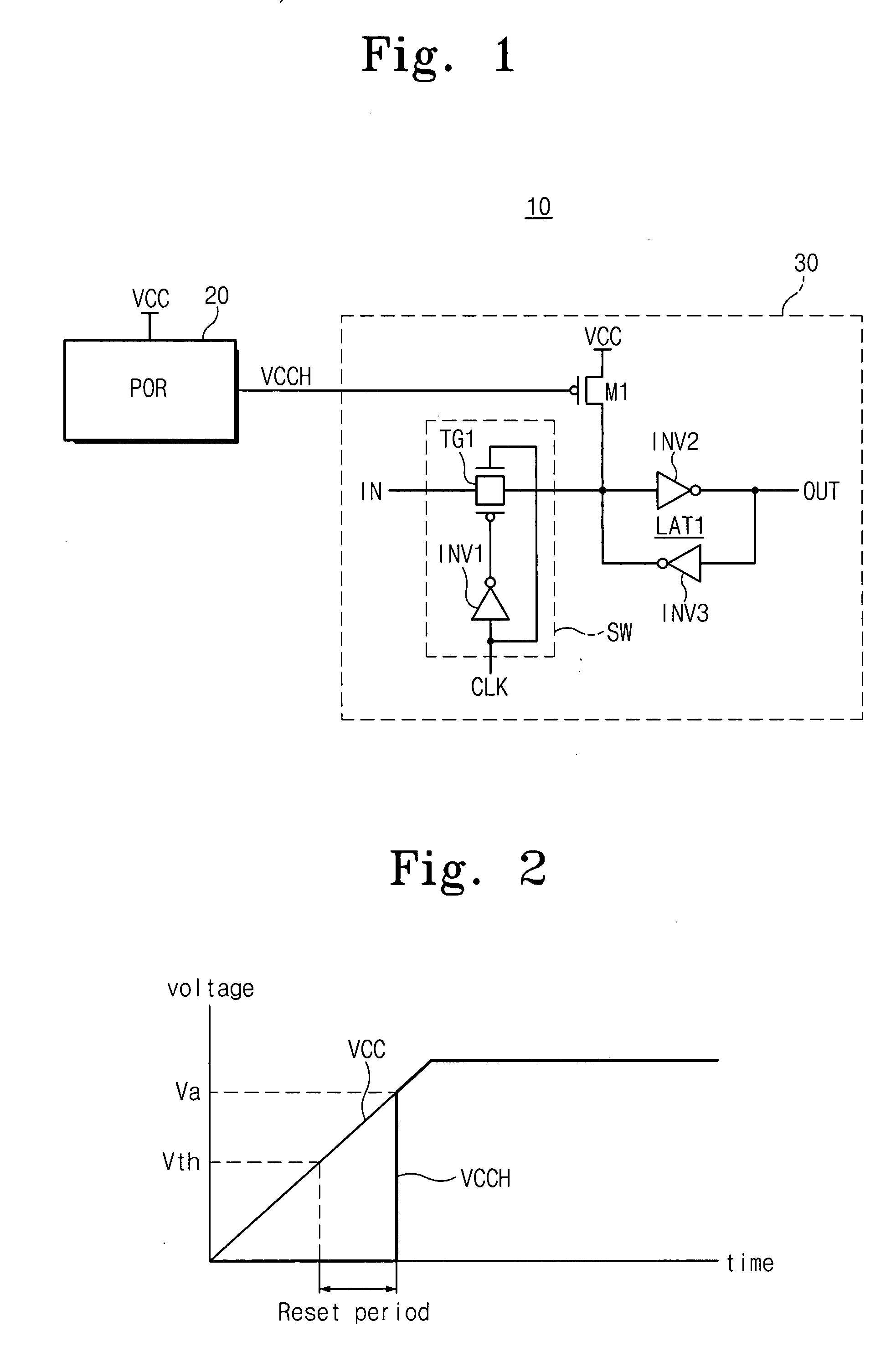

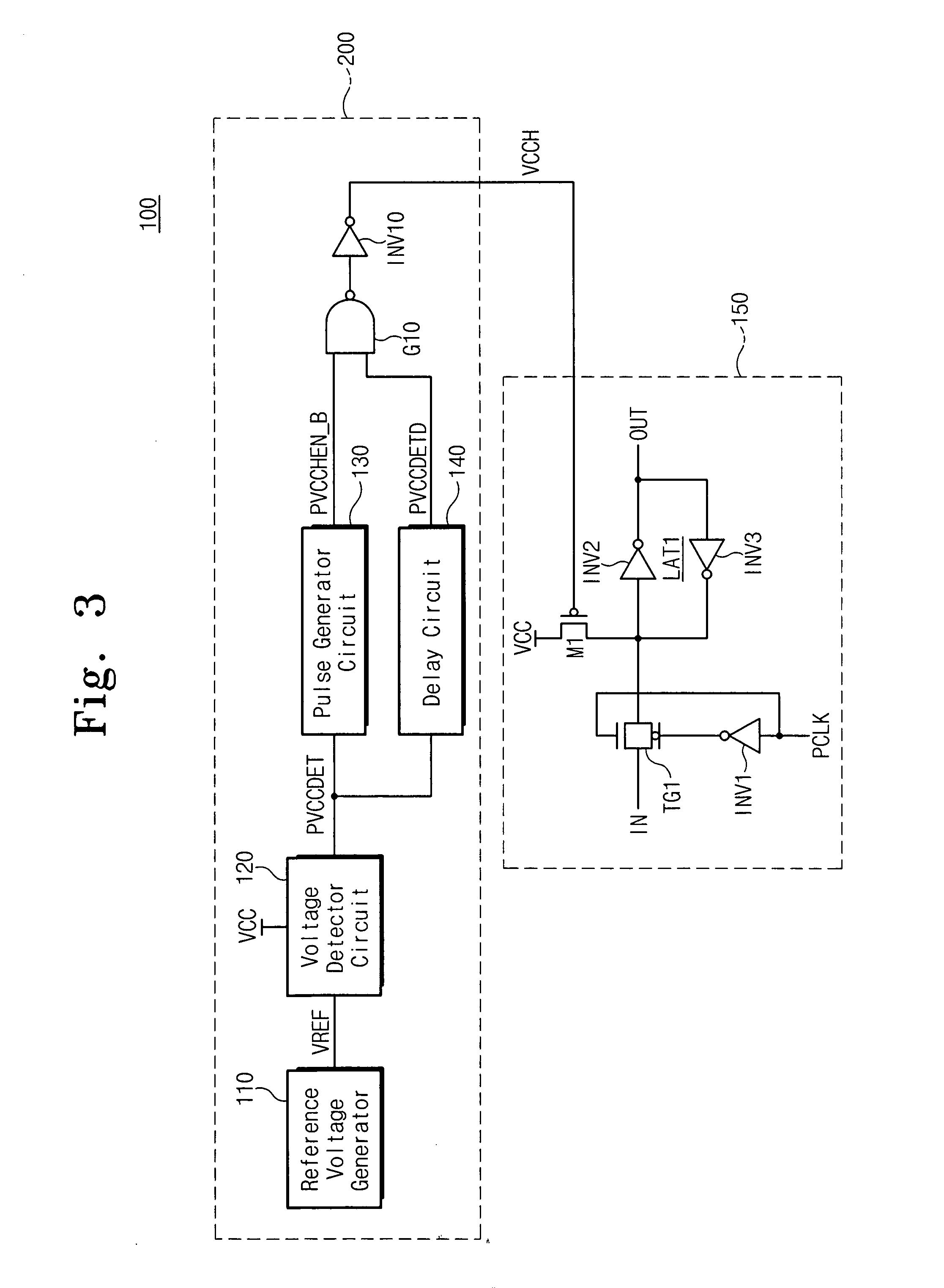

Power-on reset circuit, semiconductor integrated circuit device including the same and method for generating a power-on reset signal

A semiconductor integrated circuit may include an internal circuit, and a power-on reset circuit for generating a power-on reset signal to initialize the internal circuit at a power-on. At the power-on, the power-on reset circuit delays a transition of the power-on reset signal from a first level to a second level until a given time duration after the power supply voltage reaches a detection voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

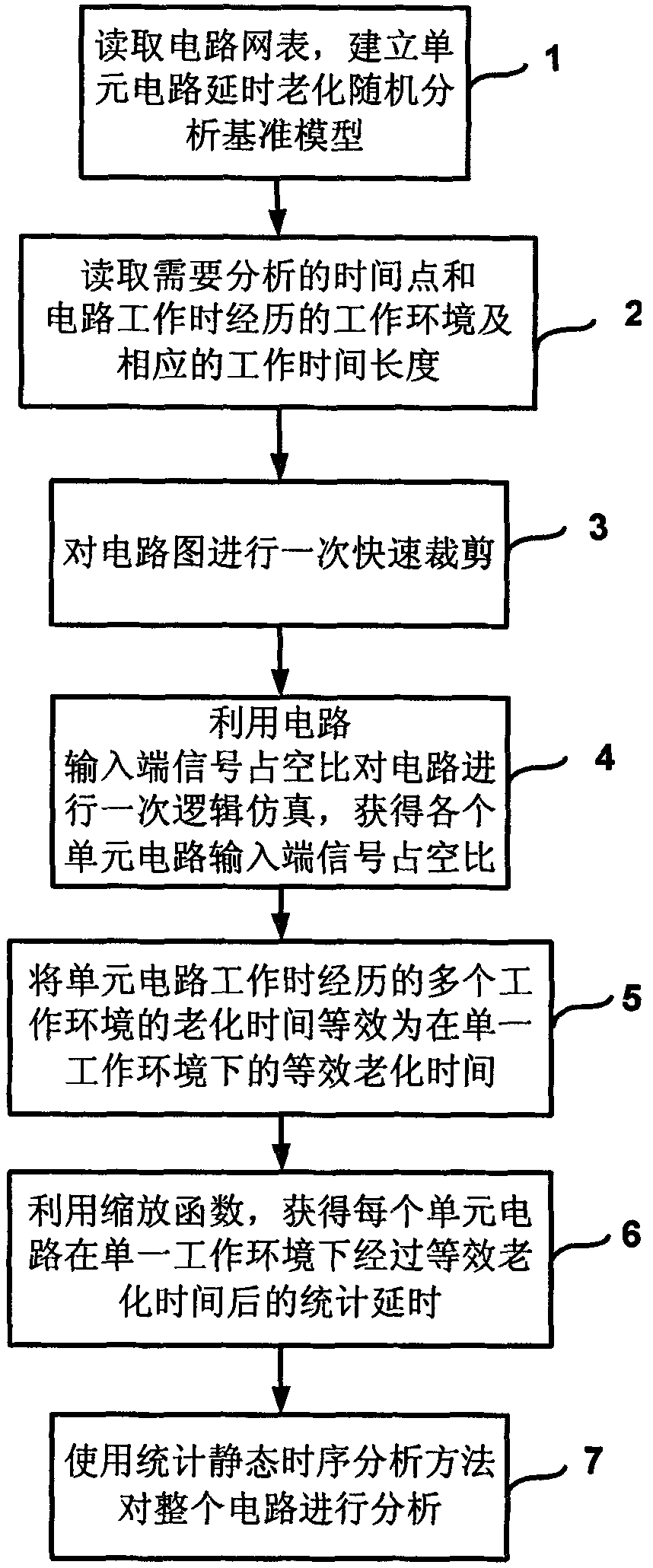

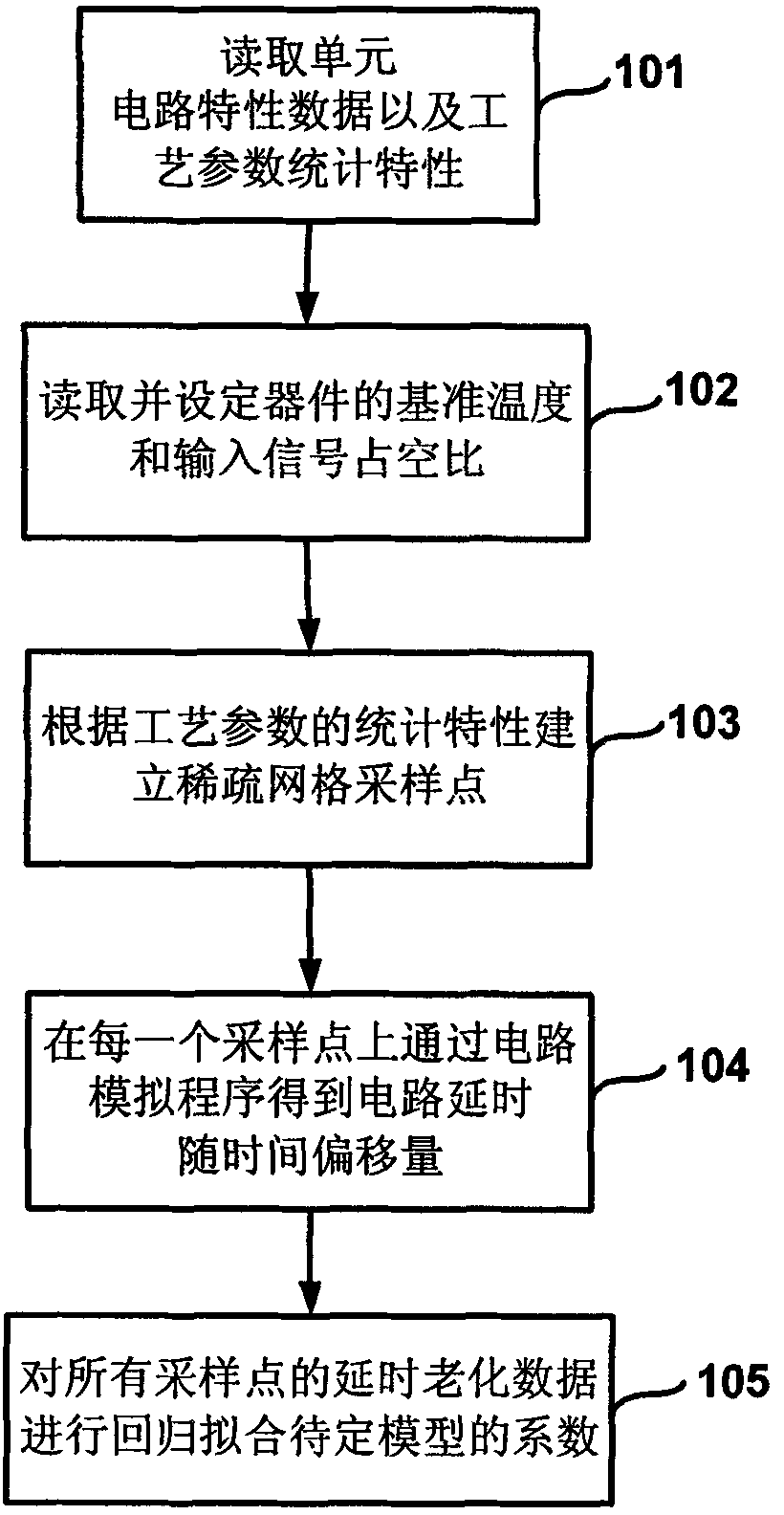

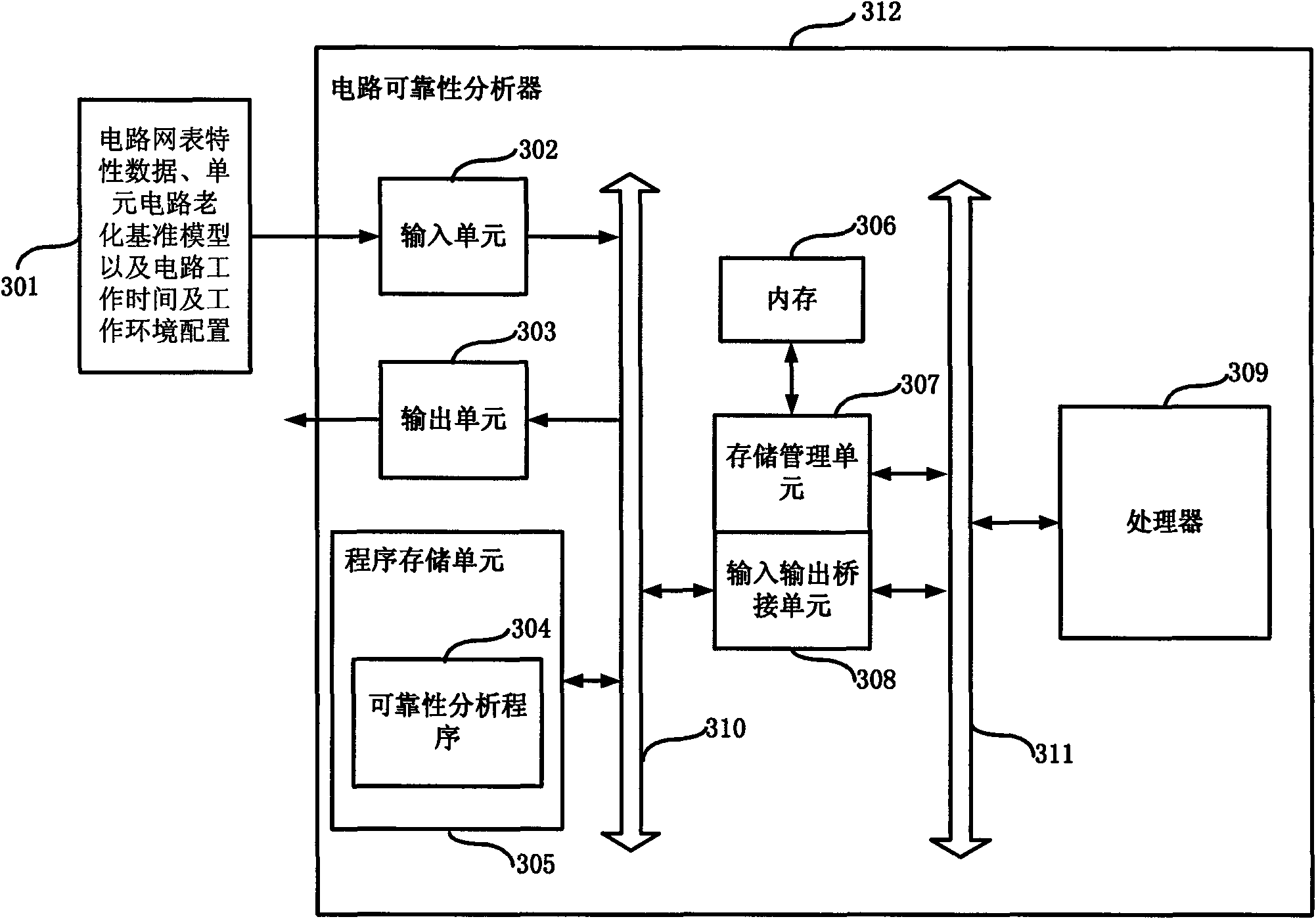

Method and device for analyzing reliability of integrated circuit

ActiveCN101964003AMeet analysis needsExtension of timeSpecial data processing applicationsProcess deviationsCircuit delay

The invention relates to a method and a device for analyzing the reliability of an integrated circuit. In the analytical method, a unit circuit delayed aging stochastic analysis reference model in consideration with both negative bias temperature instability (NBTI) effect and process parameter perturbation is established, a scaling function and an equivalent aging time concept are provided to solve the delayed statistical distribution of a unit circuit under the actual work environment quickly from the reference model, and the pre-clipping process of the circuit is provided to reduce the complexity of reliable analysis. The device of the invention comprises an input unit, an output unit, a program storage unit, an external bus, a memory, a storage administration unit, an input / output bridging unit, a system bus and a processor. In the method and the device, the effect of the process parameter perturbation, the NBTI effect and the work environment of the circuit on reliability are considered simultaneously, and the complexity of the reliable analysis can be reduced effectively by utilizing the scaling function, equivalent aging time and the pre-clipping technology so as to realize the quick analysis on the reliability of super-large-scale integrated circuits in consideration with process deviation.

Owner:FUDAN UNIV

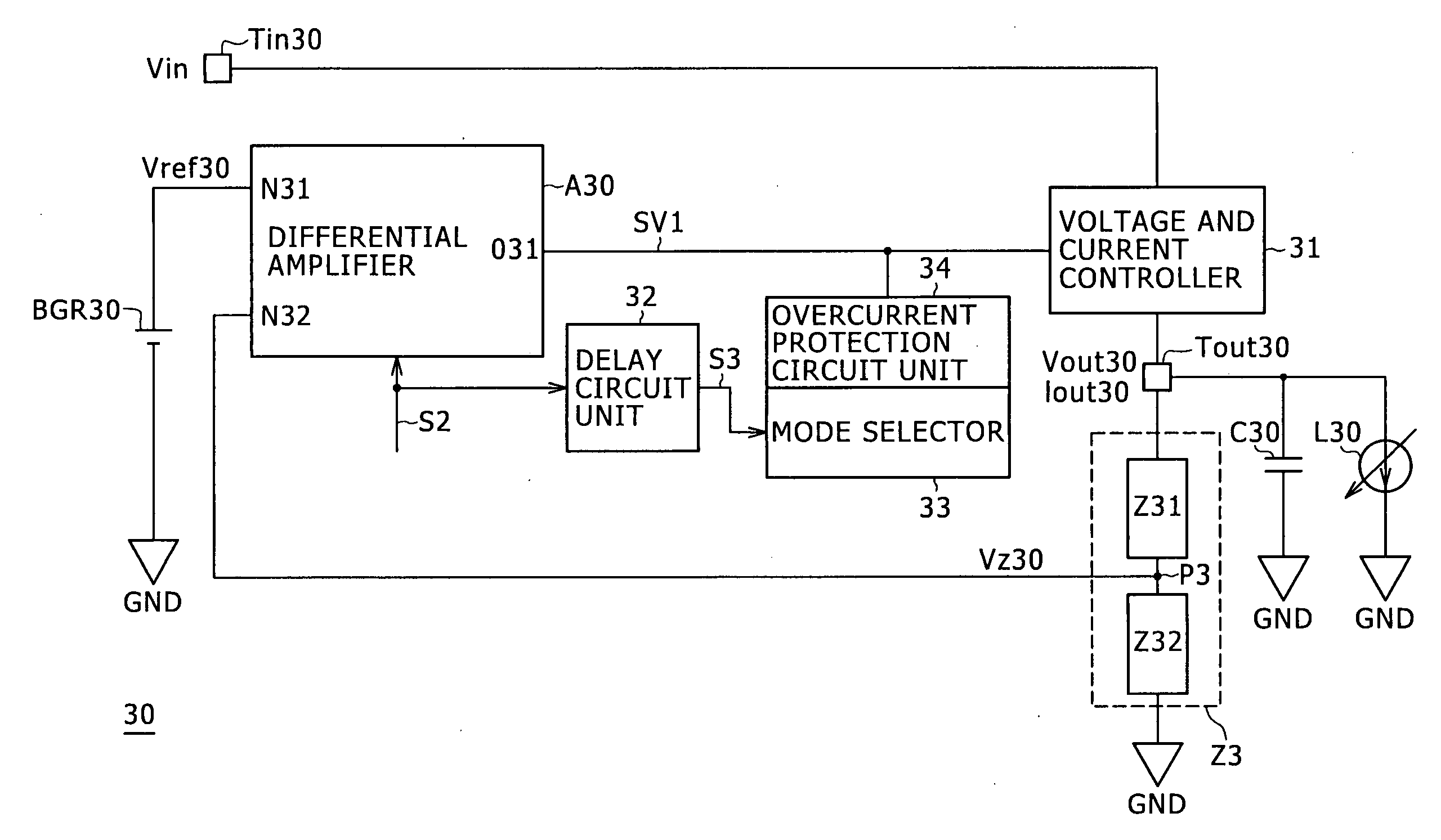

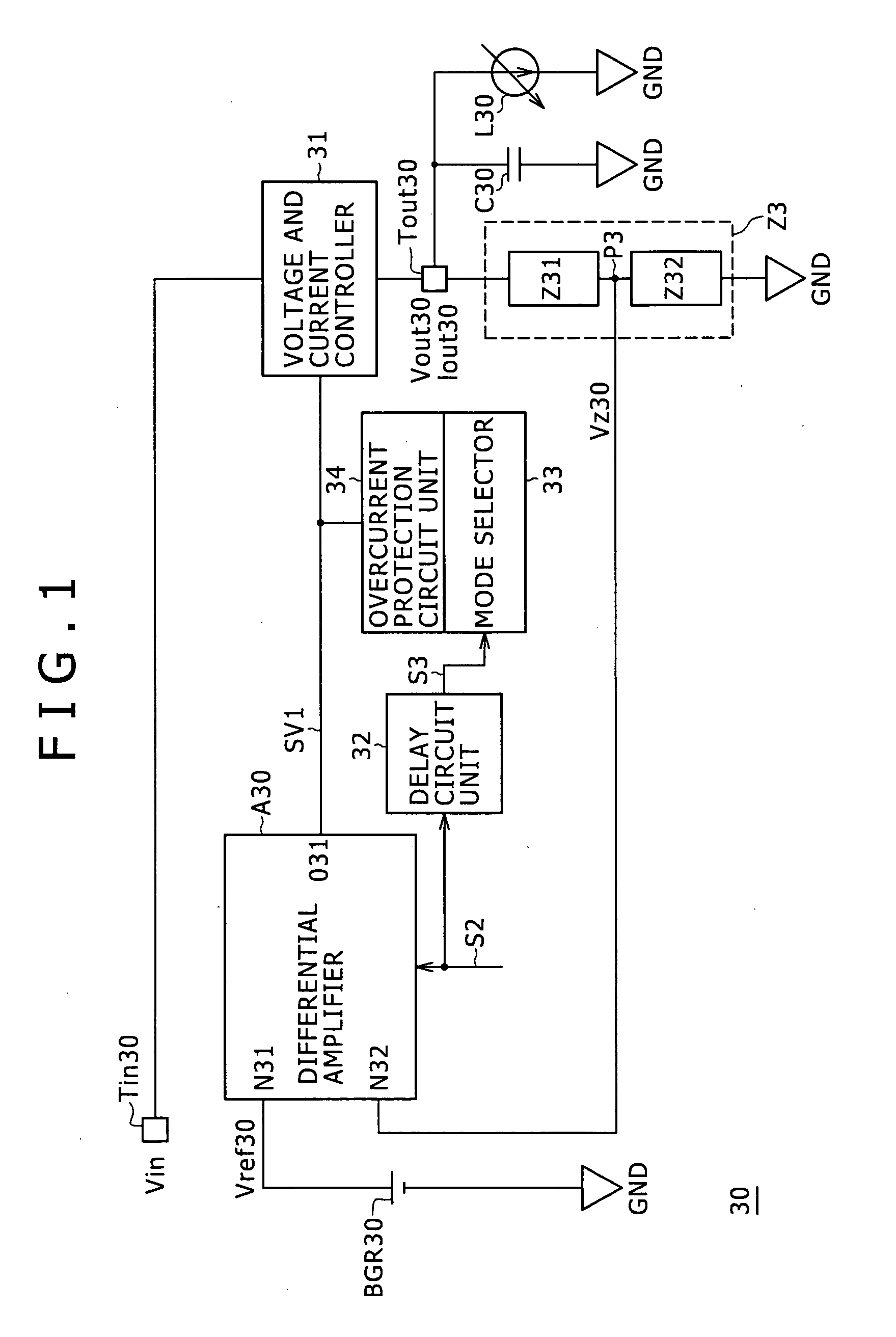

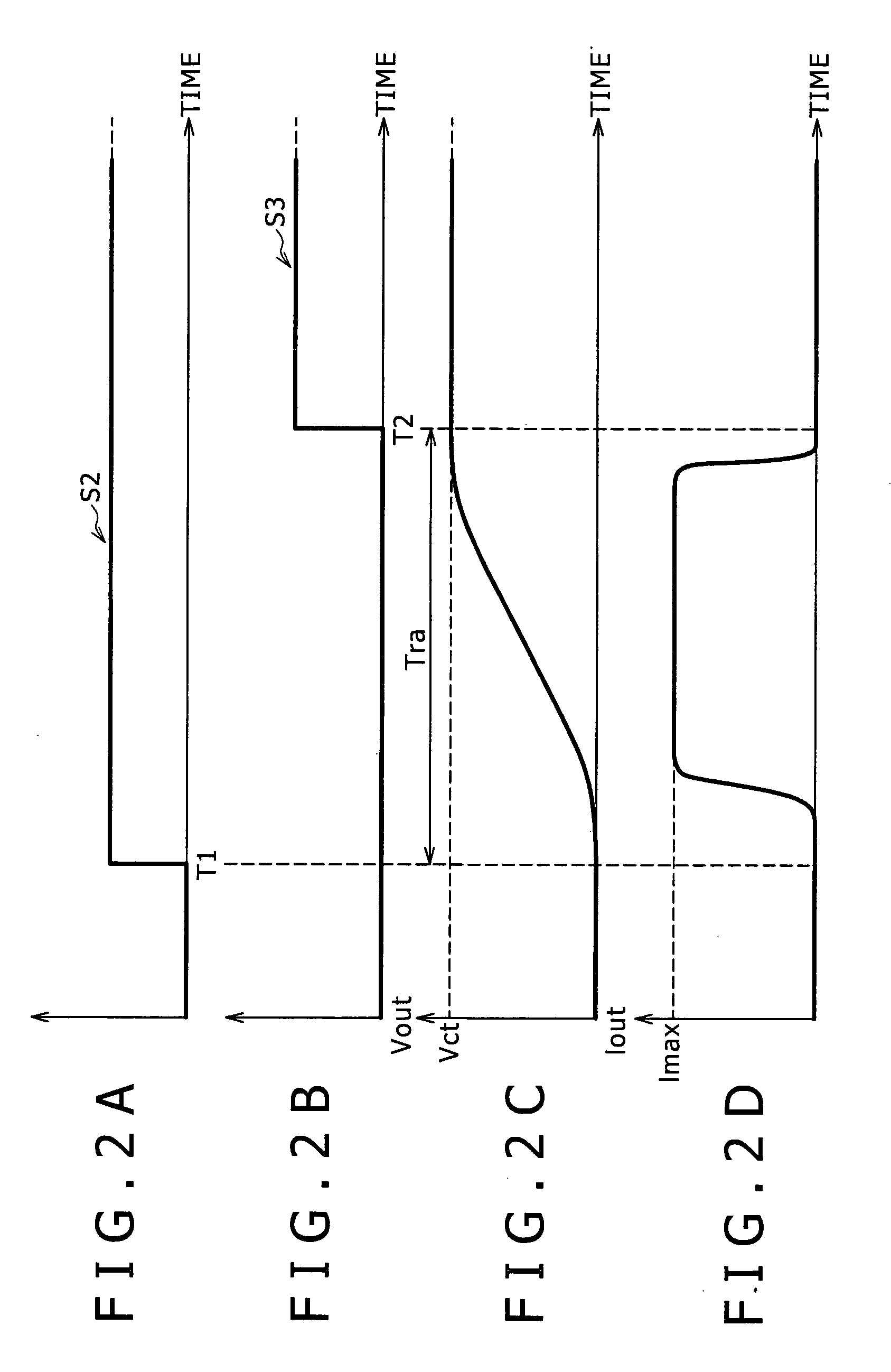

Voltage regulator

InactiveUS20060113978A1Reduce the valueProtect the loadElectric variable regulationCapacitanceStart time

In a voltage regulator according to an embodiment of the present invention, a delay circuit delays an enable signal by a delay time or less, the delay time corresponding to a certain time from a start of charging of the output capacitor to a completion of the charging of the output capacitor, and sends the delayed enable signal as a delayed signal to a mode selector. An overcurrent protection circuit unit operates according to a constant current type drooping characteristic from a time point of input of the enable signal. The overcurrent protection circuit unit operates according to a current limiting characteristic that can lower an output current below an upper limit value after a time point of input of the delayed signal. Thereby the output current having the upper limit value is prevented from continuing to flow after a time point of completion of charging of the output capacitor at the latest. The voltage regulator according to the embodiment of the present invention can protect the regulator itself and a load without lengthening a starting time.

Owner:SONY CORP

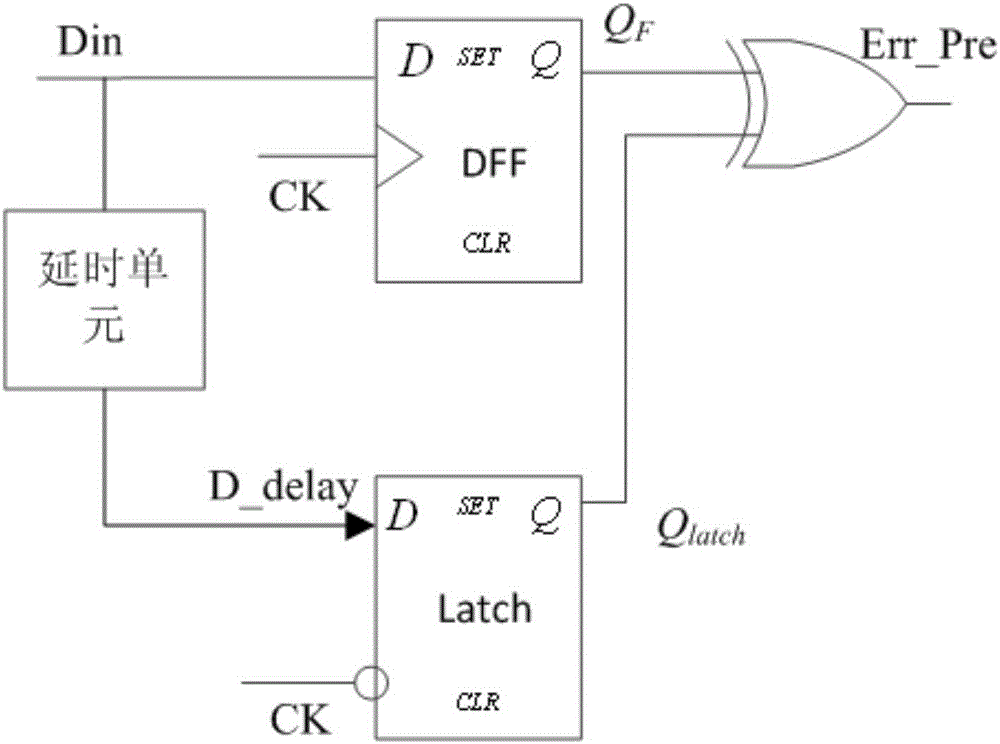

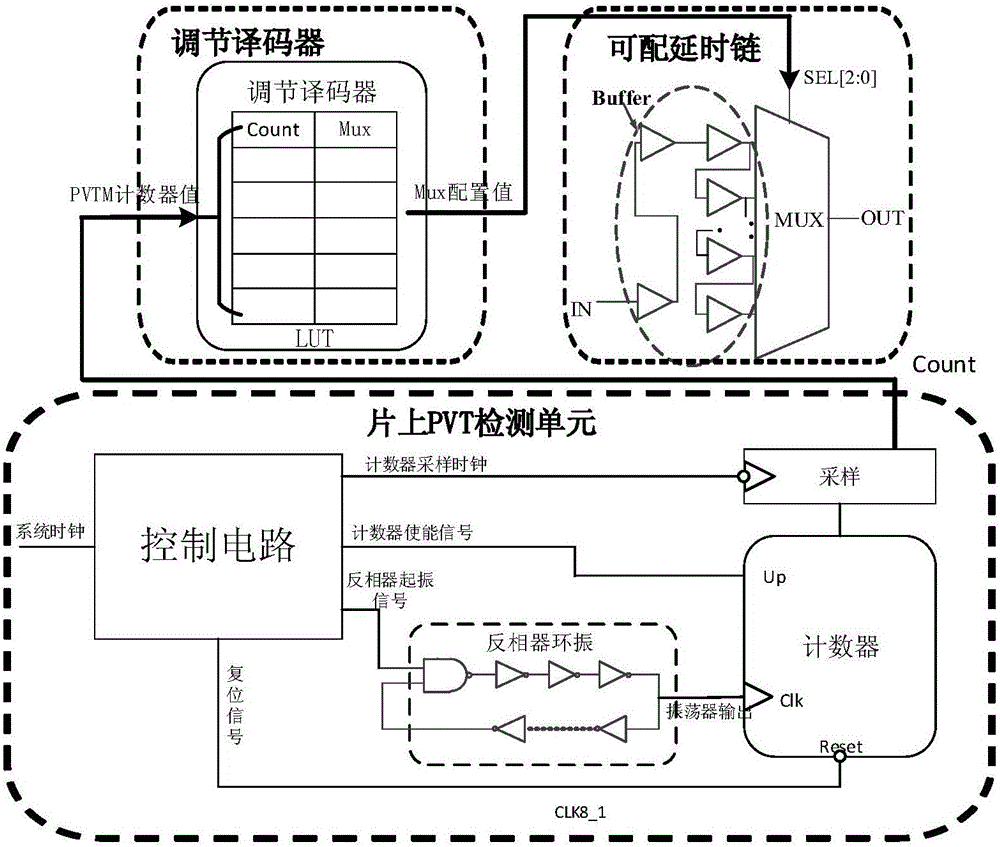

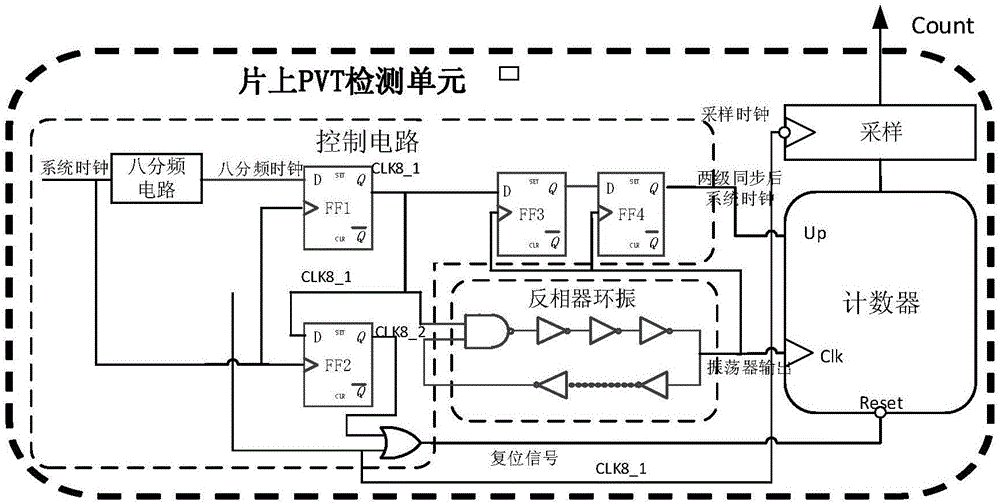

Online monitoring unit oriented to ultrawide voltage and monitoring window self-adaptive adjusting system

ActiveCN105159374AReduce power consumptionAccurately capture timing violationsElectric variable regulationCircuit delayCell design

The invention discloses an online monitoring unit oriented to ultrawide voltage and a monitoring window self-adaptive adjusting system. Based on a traditional prediction type online time sequence monitoring unit, the online monitoring unit with an adjustable monitoring window is designed so as to adapt to the change of circuit delay at ultrawide voltage within a larger range. The invention further discloses the adjusting system, with the self-adaptive adjusting function, of the monitoring window. The window value can be adjusted in a self-adaptive mode within the ultrawide voltage range according to the monitored PVT (Process-Voltage-Temperature) state of a circuit, and therefore the reserved time sequence margin in traditional design can be fully reduced, and power consumption of the circuit is effectively reduced.

Owner:南京集成电路设计服务产业创新中心有限公司

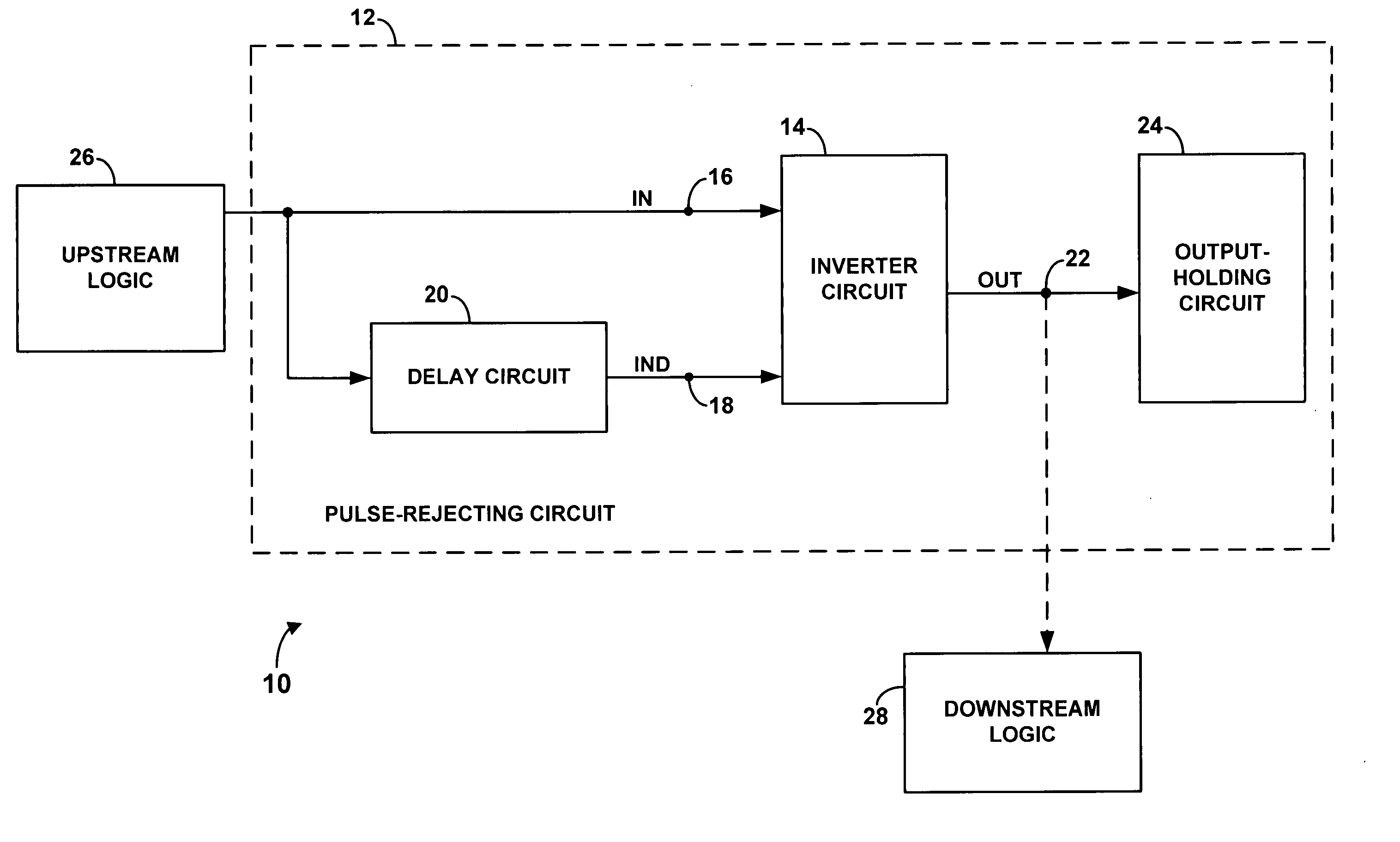

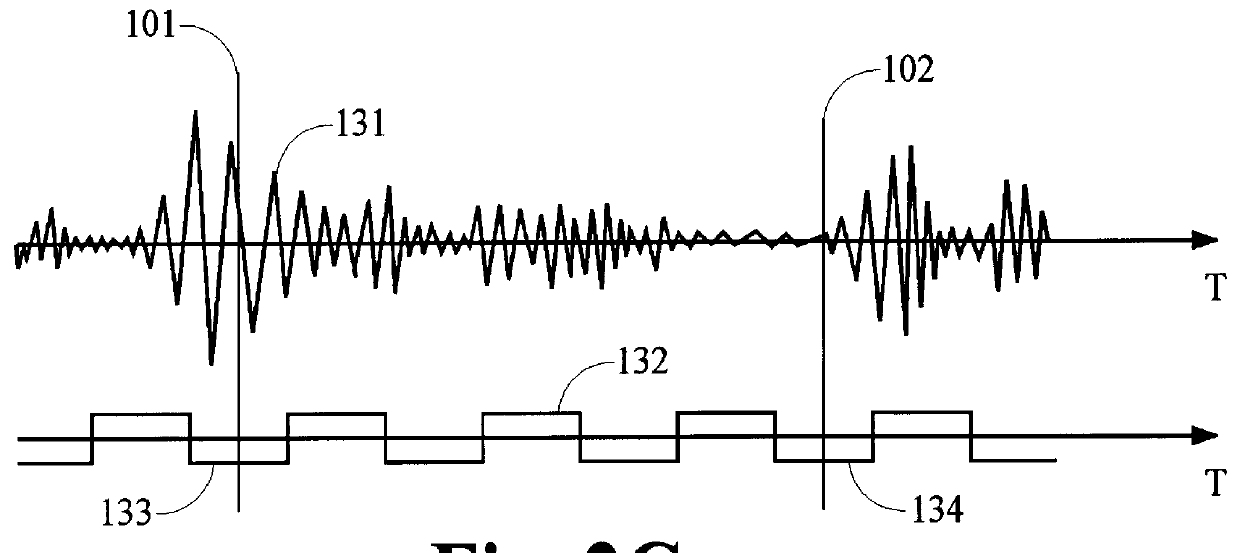

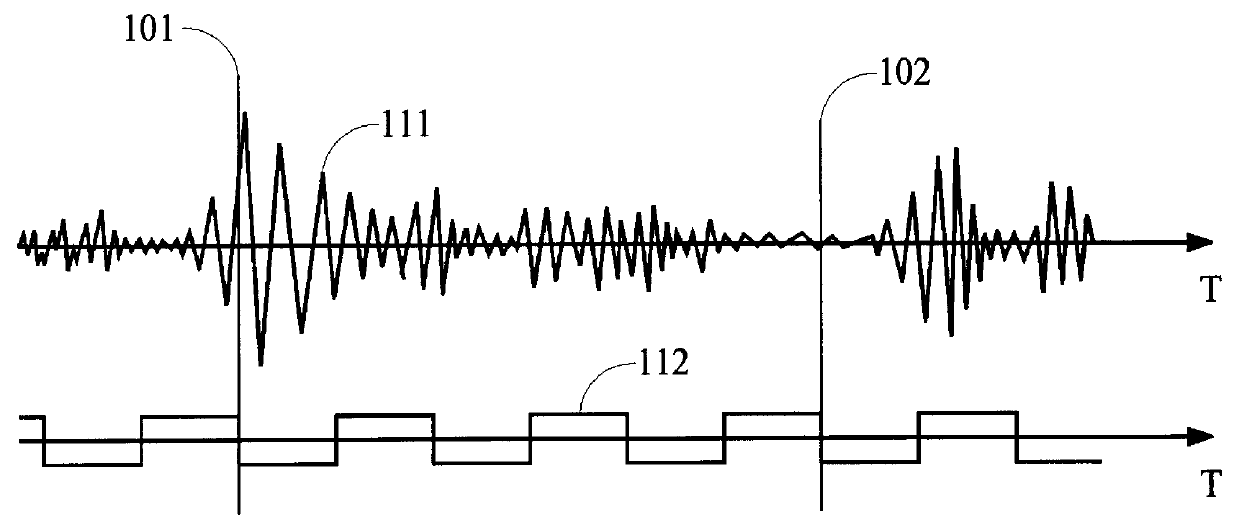

Pulse-rejecting circuit for suppressing single-event transients

InactiveUS20060119410A1Prevented from appearingPulse automatic controlPulse shapingTime delaysEngineering

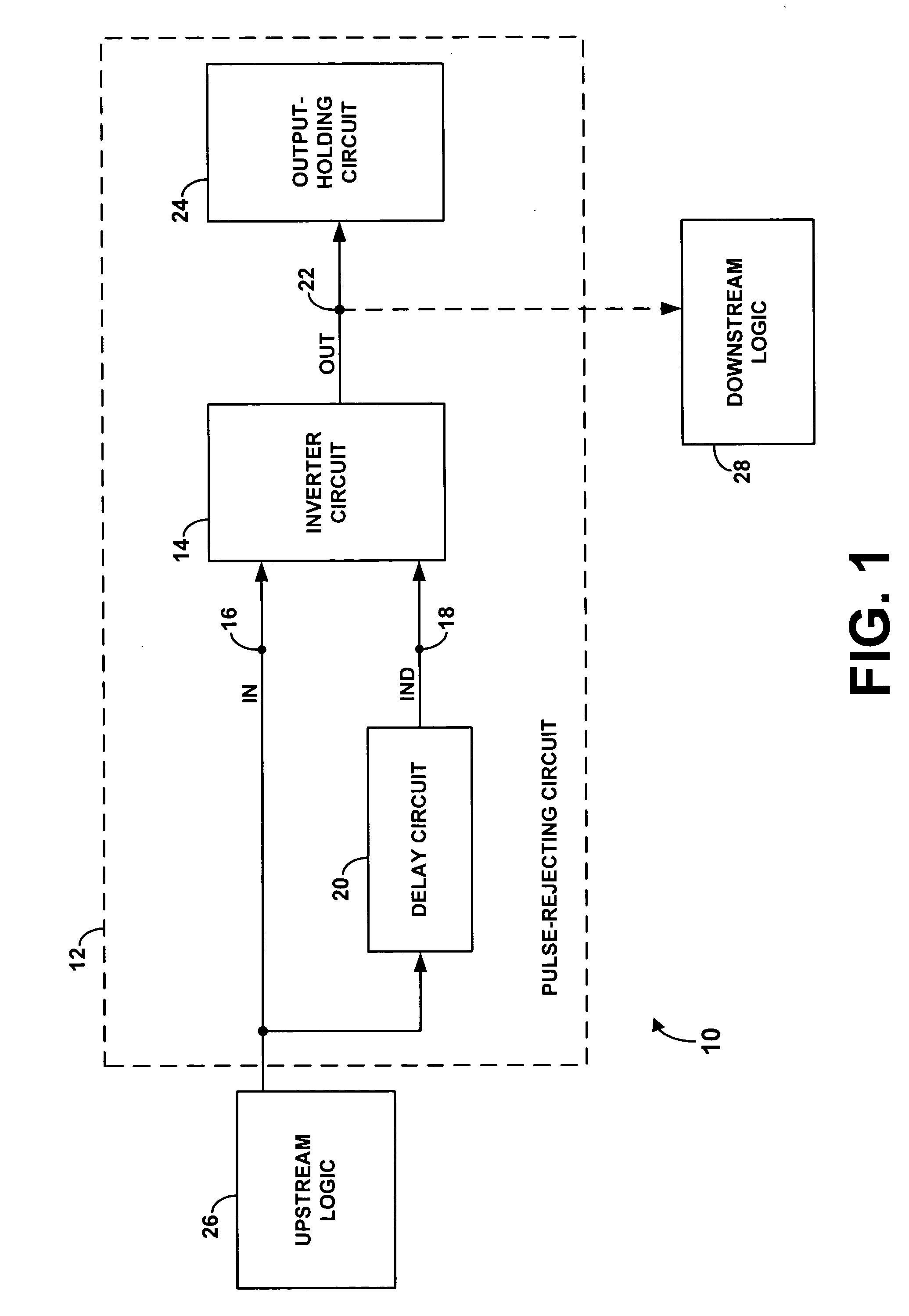

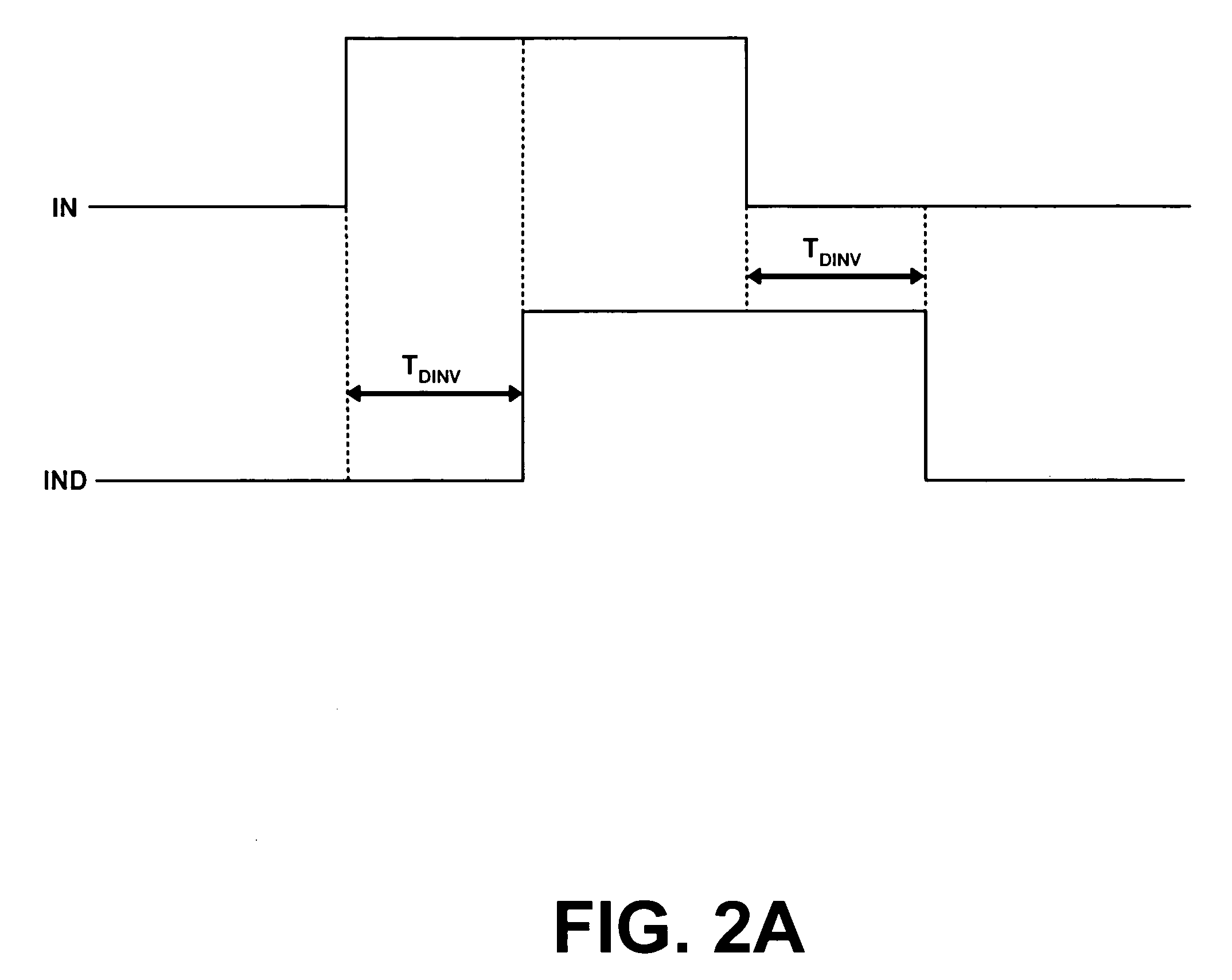

A circuit for rejecting single-event transients (SETs) from logic signals is provided. The circuit includes a delay circuit, an inverter circuit, and an output-holding circuit. The delay circuit receives an input signal and delays the input signal to produce a time-delayed version of the input signal. The input signal and the time-delayed version of the input signal are fed into the inverter circuit that propagates a corresponding output signal only when the input signal and the time-delayed version of the input signal have the same logic level. If the input signal or the time-delayed version of the input signal transitions such that both input signals presented to the inverter circuit have opposite logic levels, the output-holding circuit maintains the output signal in its previous state.

Owner:HONEYWELL INT INC

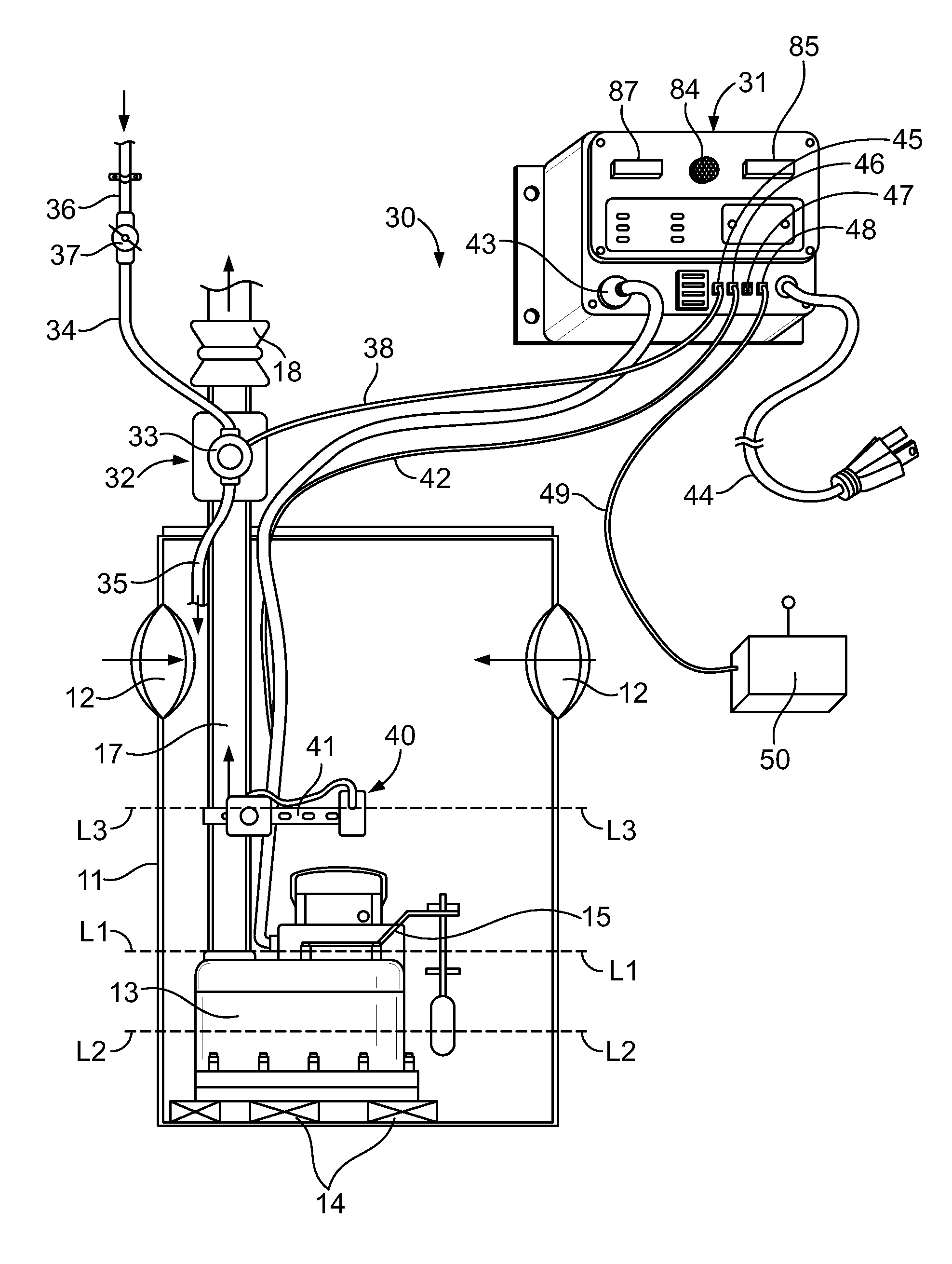

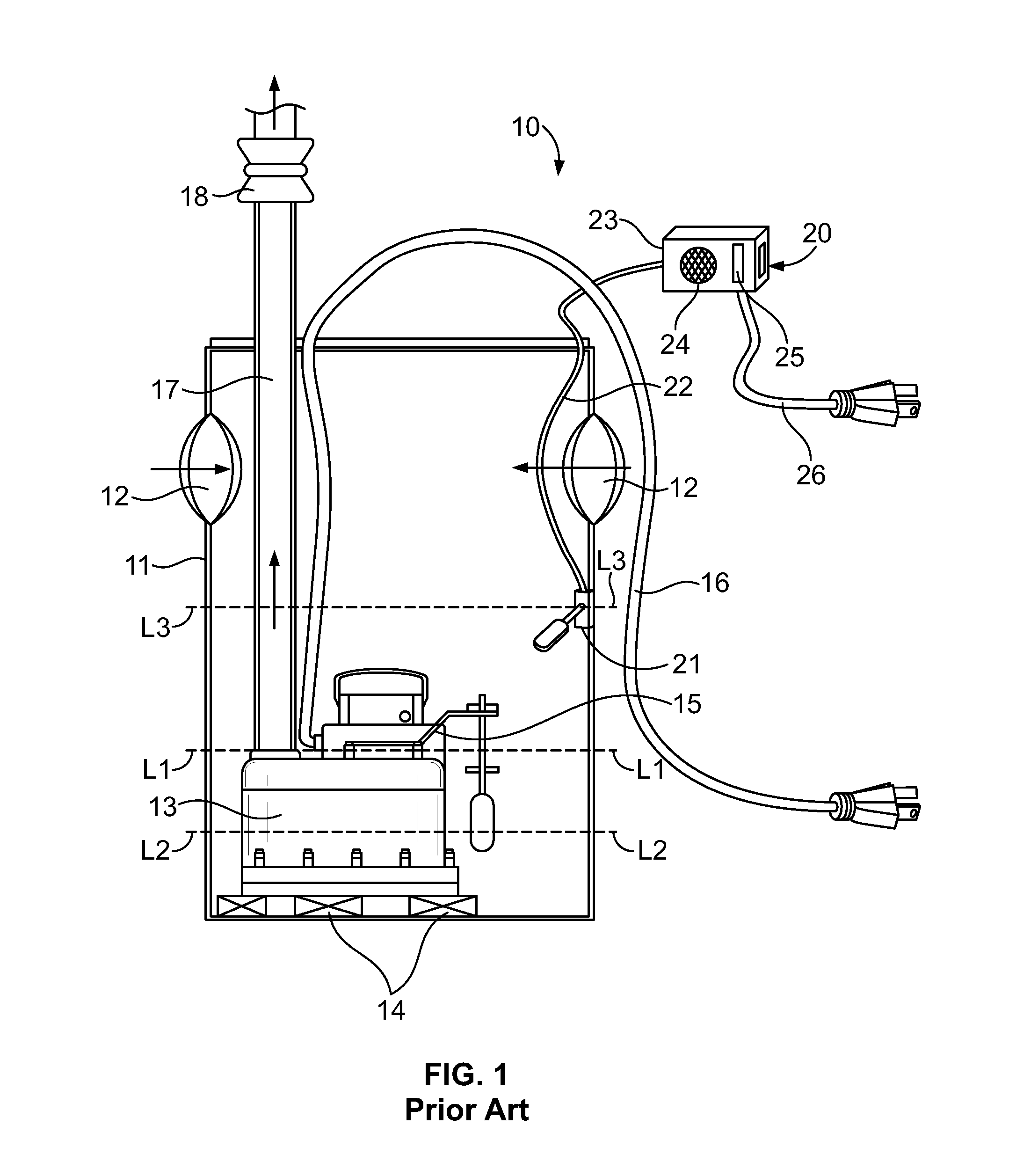

Test and monitoring system for a sump pump installation having a self-monitoring liquid level sensing module

A liquid level sensing module for sensing a high liquid level in a sump container rising comprises a first liquid-actuated switch which provides a first output signal upon the liquid level reaching a first level, and a second liquid-actuated switch which provides a second output signal upon the liquid level reaching a second level above the first. A delay circuit delays the first output signal by a period if time sufficient for the liquid to rise from the first switch level to the second switch level to produce a delayed output signal. An alarm circuit produces a fault signal indicating a switch module fault upon the occurrence of the second output signal. An alarm circuit produces a fault signal upon the occurrence of the second output signal in the absence of the first output signal, or upon the occurrence of the delayed output signal in the absence of the second output signal, and the occurrence of either the delayed output signal or the second output signal, producing an alarm signal indicative of the pump failing to function.

Owner:SCHWEITZER ENGINEERING LABORATORIES

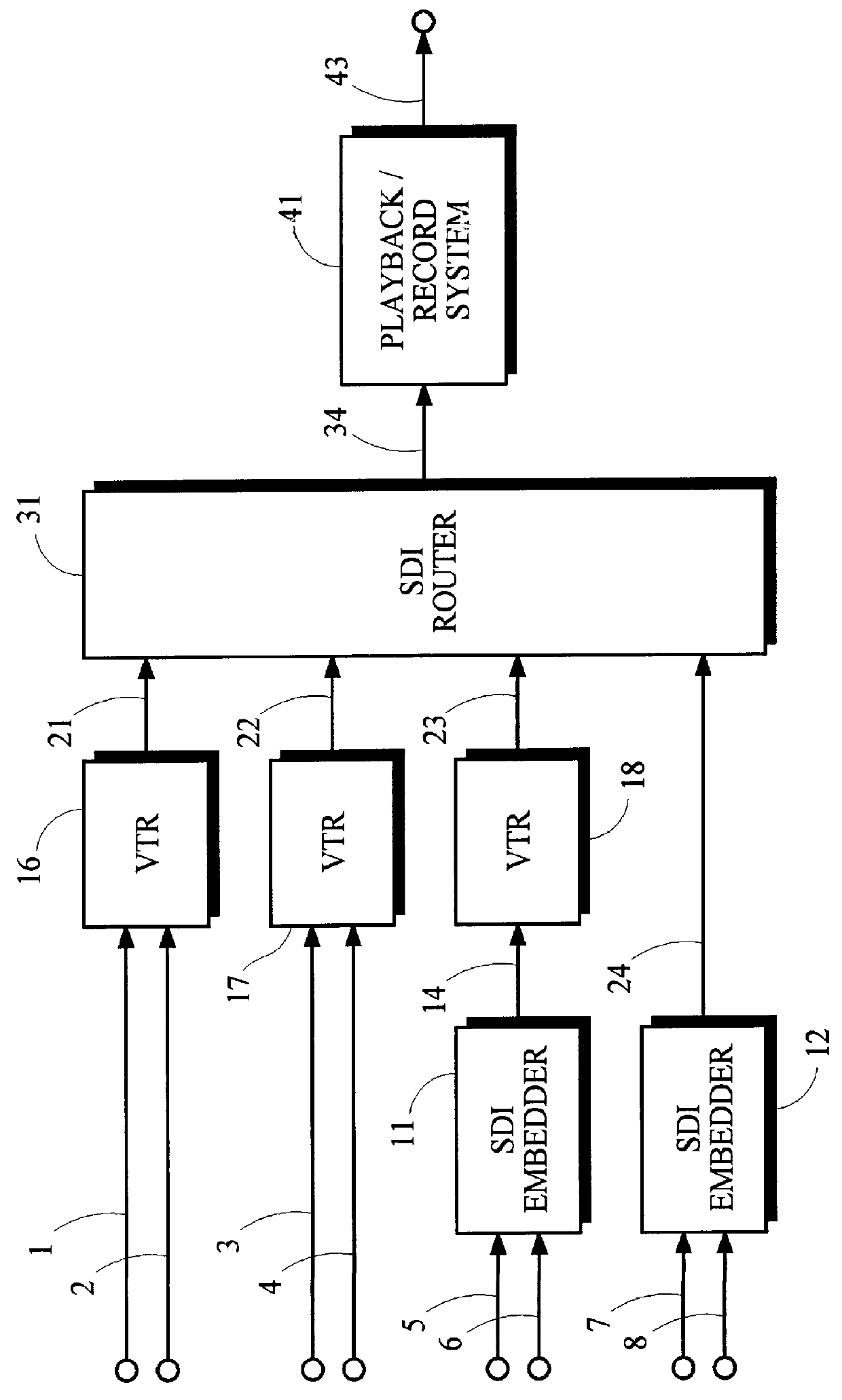

Using time-aligned blocks of encoded audio in video/audio applications to facilitate audio switching

InactiveUS6085163AAvoid problemsPulse modulation television signal transmissionSpeech analysisCircuit delayAudio frequency

An audio signal processor forms gaps or guard bands in sequences of blocks conveying encoded audio information and time aligns the guard bands with video information. The guard bands are formed to allow for variations in processing or circuit delays so that the routing or switching of different streams of video information with embedded audio information does not result in a loss of any encoded audio blocks.

Owner:DOLBY LAB LICENSING CORP

Method and apparatus for compensating for thermal drift in a logic circuit

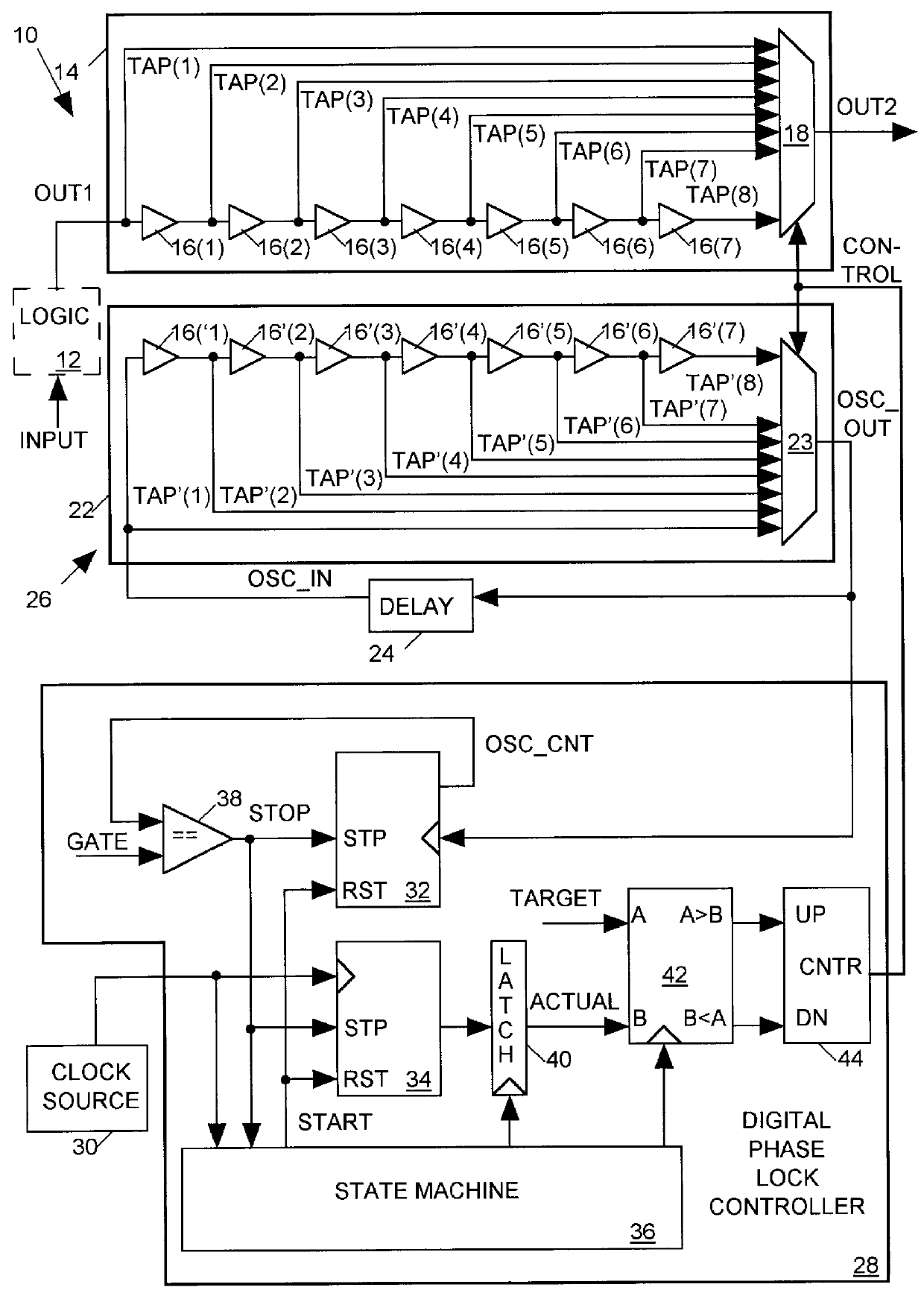

A system for compensating for thermal drift of an output signal (OUT1) produced by a logic circuit in response to an input CLOCK signal after a temperature dependent delay includes a variable delay circuit, an oscillator and a digital phase lock controller. The delay circuit delays the OUT1signal to produce a compensated output signal (OUT2) with a variable delay controlled by input CONTROL data. The oscillator generates an output signal (OSC-OUT) having a period also controlled by the input CONTROL data which is substantially proportional to the sum of the temperature dependent delay of the logic circuit and the delay of the variable delay circuit. The digital phase lock controller continually monitors the period of the OSC-OUT signal and adjusts the CONTROL data so that the period of the OSC-OUT signal remains substantially constant. This ensures that the delay between the CLOCK signal and OUT2 remains constant despite temperature dependent variations in the delay of the logic circuit.

Owner:CREDENCE SYSTEMS

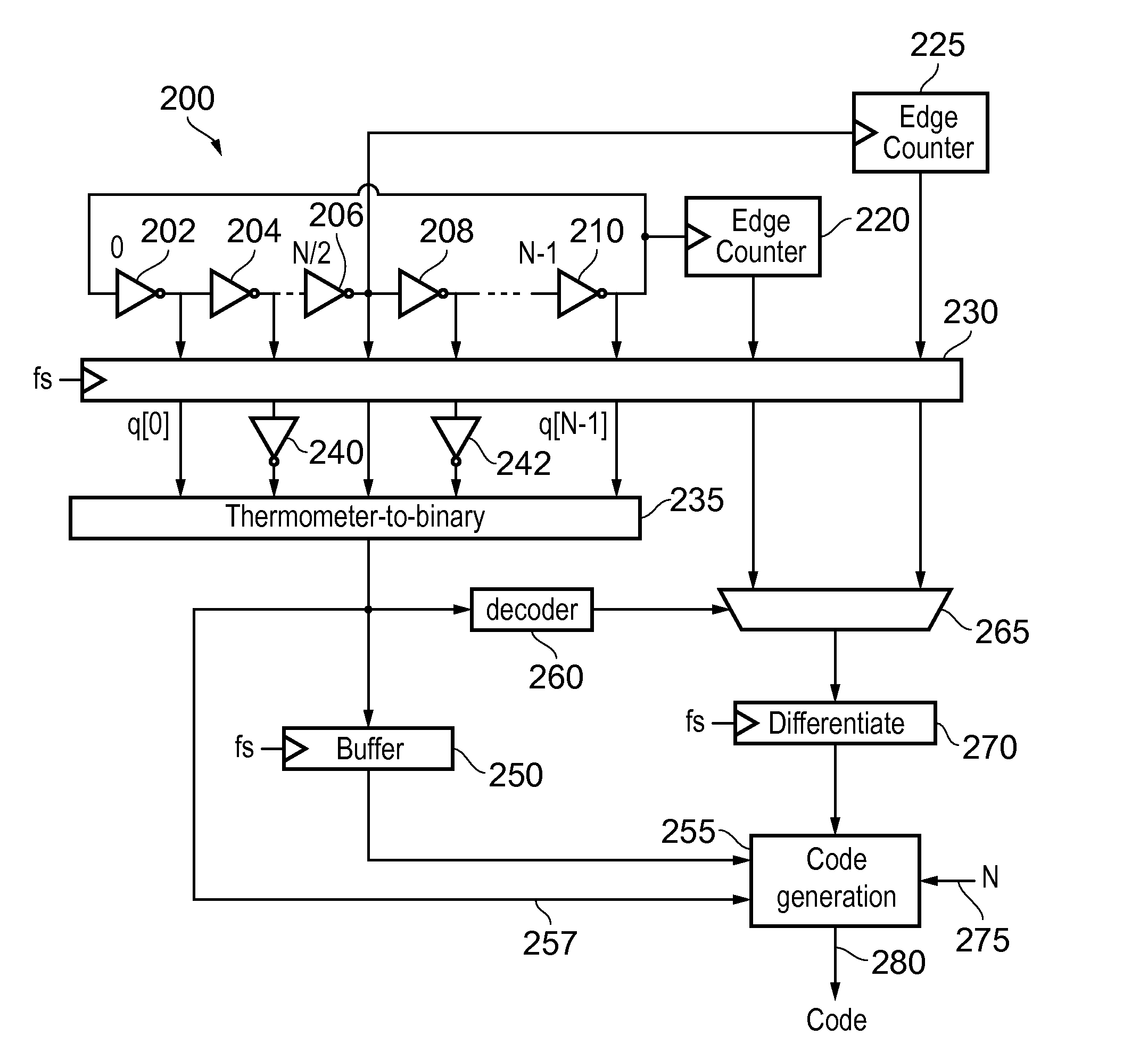

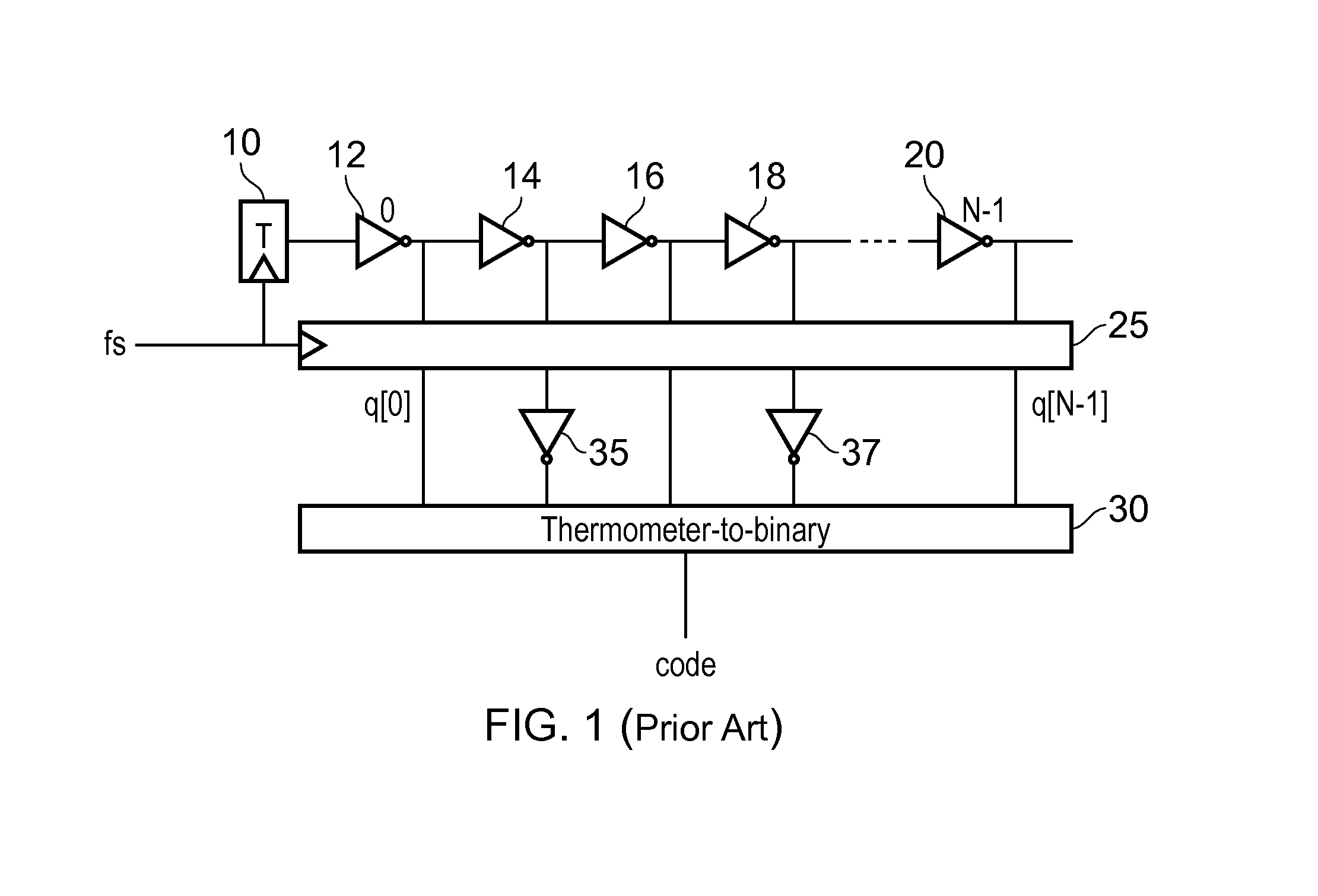

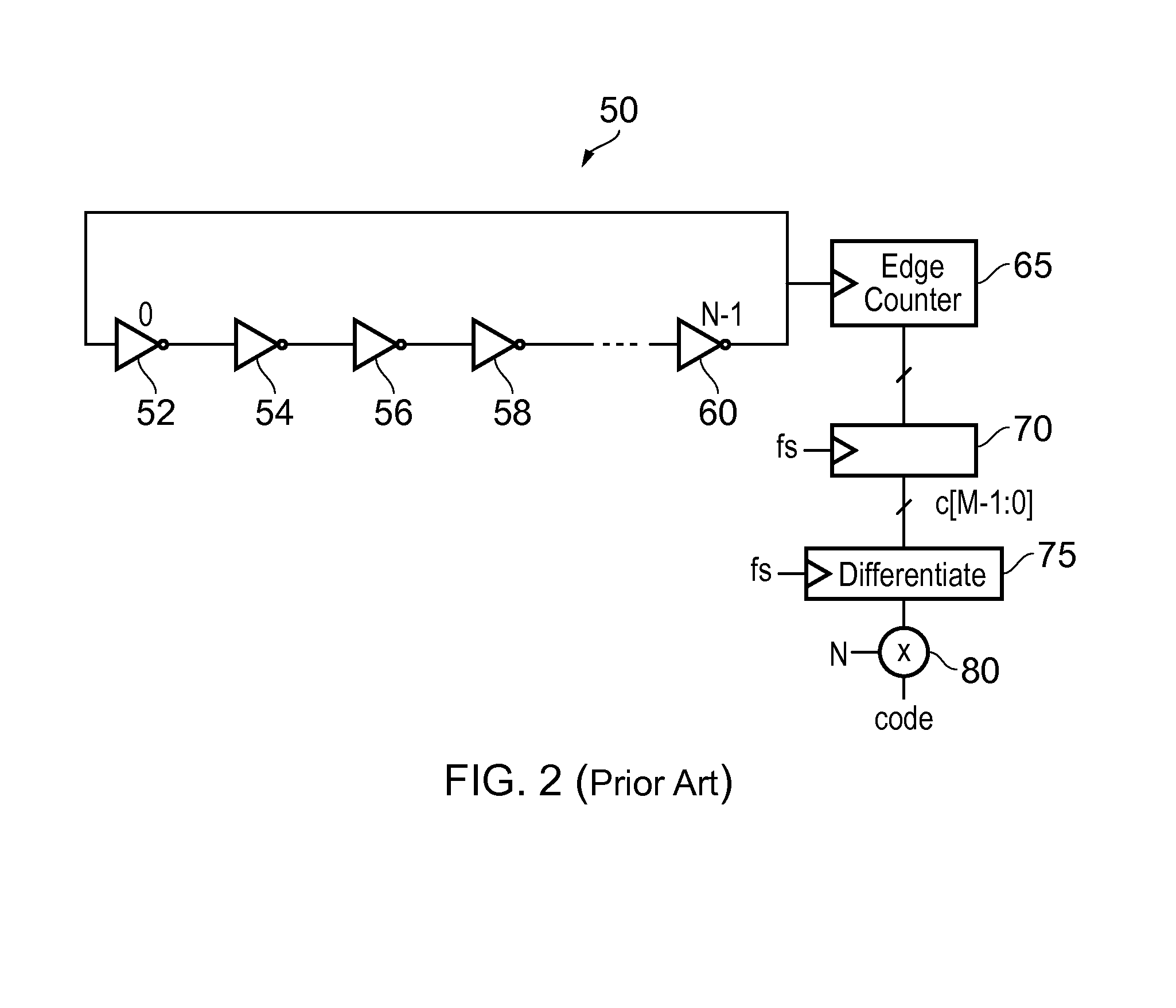

Circuit delay monitoring apparatus and method

ActiveUS20150137864A1Improve the level ofEnsure consistencyPulse automatic controlPulse manipulationTime segmentCircuit delay

A circuit delay monitoring apparatus has a ring oscillator with a plurality of delay elements, a signal transition being propagated through the delay elements of the ring oscillator, and a plurality N of sampling points being distributed around the ring oscillator. Selection circuitry selects, in dependence on the indication of the current location of the signal transition generated by the fine sampling circuitry, one of the M transition counter circuits whose associated location is greater than said predetermined amount from the current location of the signal transition. Output generation circuitry then generates a count indication for a reference time period dependent on a sampled count value of the transition counter circuit selected by the selection circuitry, the indication of the current location of the signal transition within the ring oscillator, and reference count data relating to the start of the reference time period.

Owner:ARM LTD

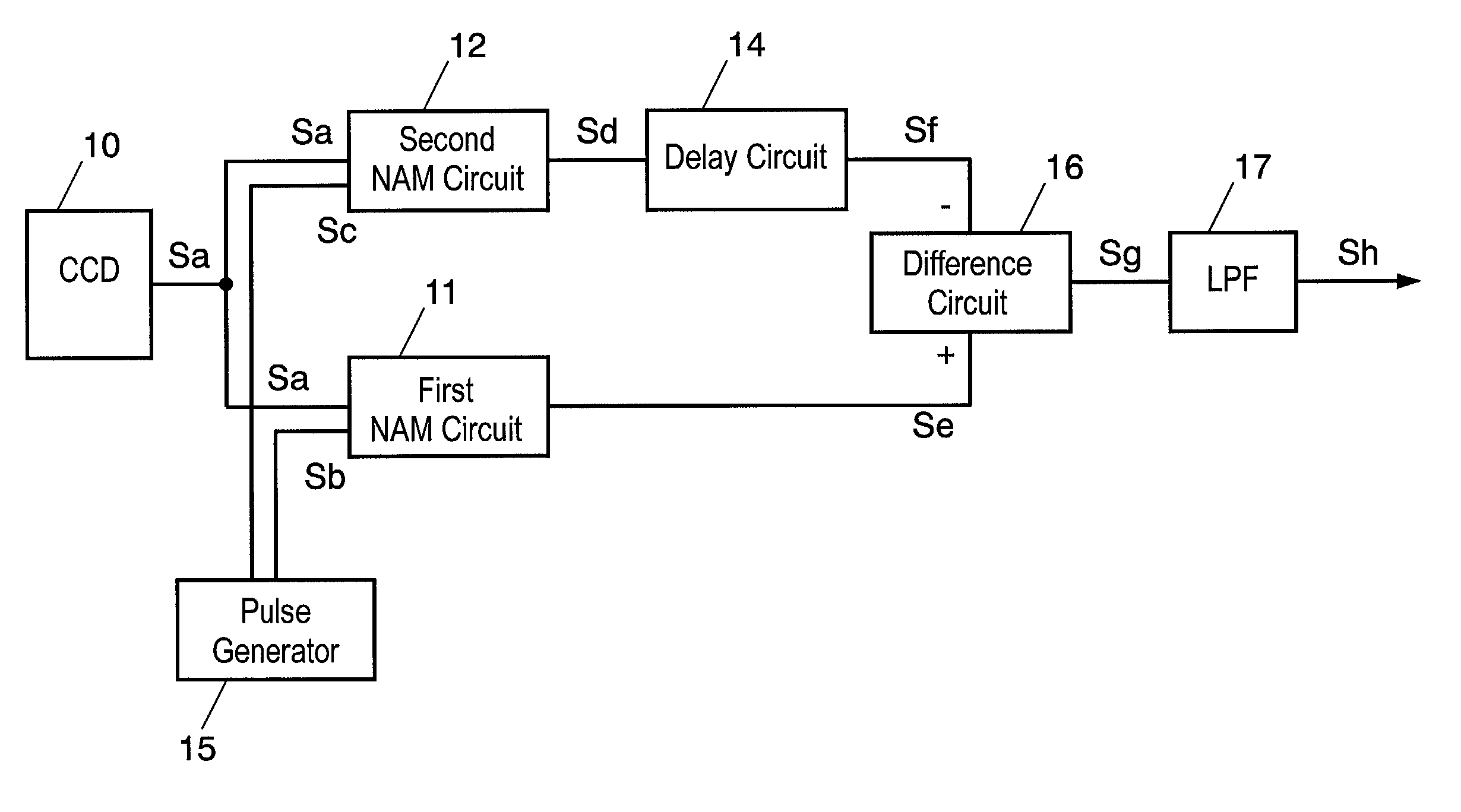

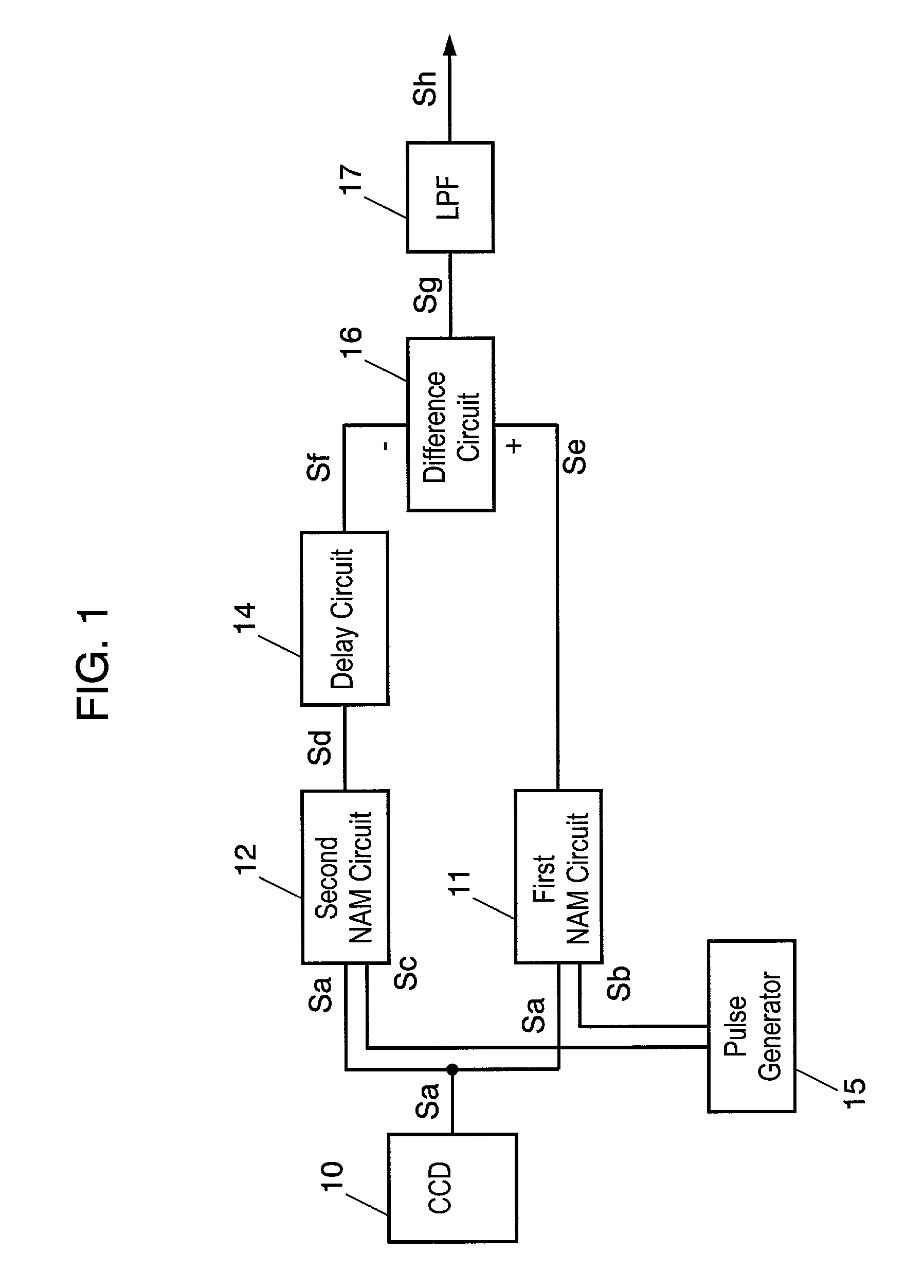

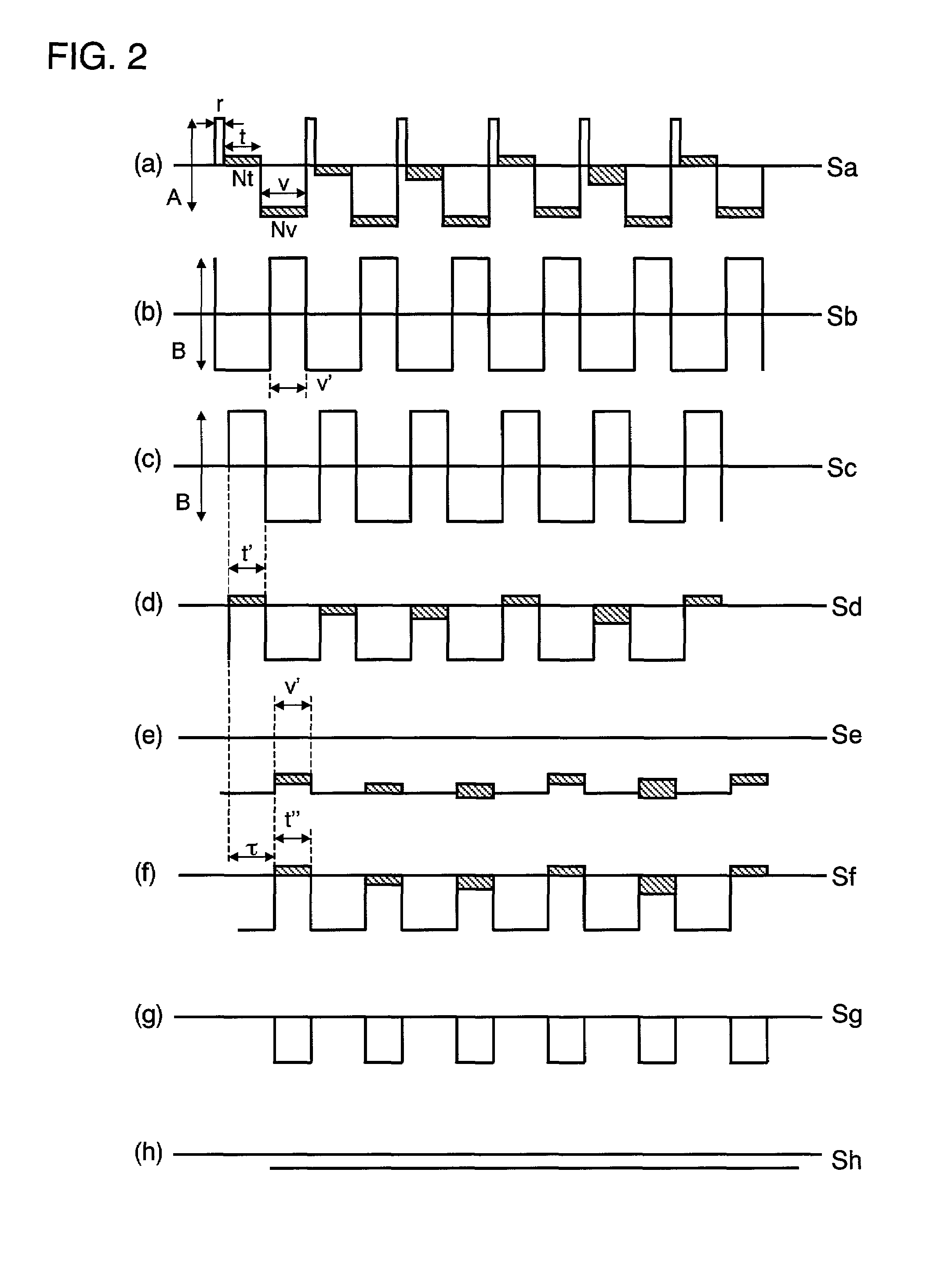

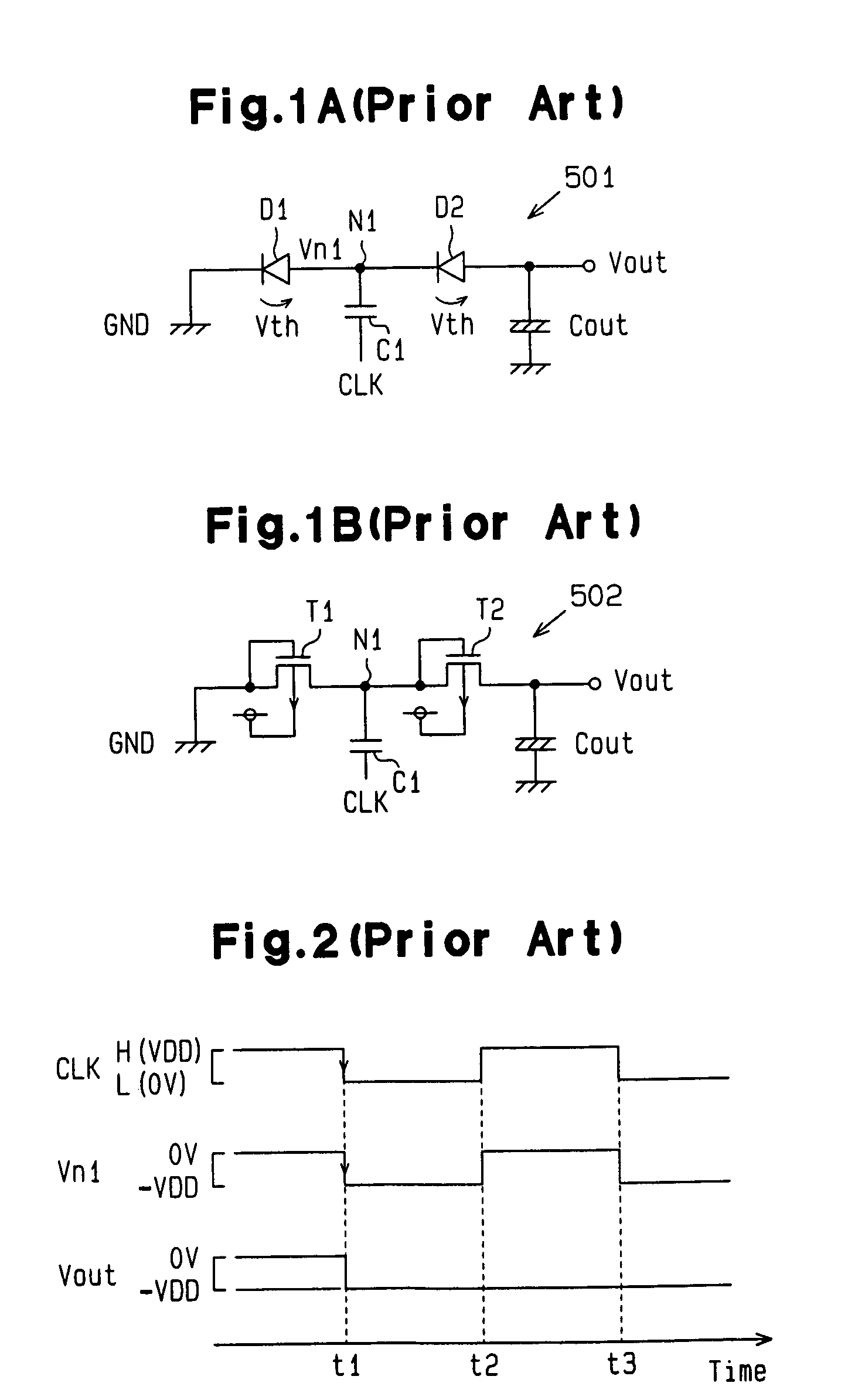

Noise reduction circuit for CCD output signal

ActiveUS6940547B1Reduce noise outputNarrow dynamic rangeTelevision system detailsTelevision system scanning detailsImage resolutionCircuit delay

A noise reduction circuit with high noise reduction effect and low power consumption for a high resolution charge coupled device (CCD) as well as for a usual resolution CCD is provided. A delay circuit delays an CCD output signal, and a pulse generator outputs a pulse signal having the same period that the CCD output signal has. A part of period during which the pulse signal is at a high level overlaps with a signal-level period oh the CCD output signal. A first non-additive mixing (NAM) circuit selects and output a lower level signal between the CCD output signal and the pulse signal. A second NAM circuit selects and outputs a lower level signal between the output signal from the delay circuit and the pulse signal. A difference circuit calculates difference between an output signal of the first NAM circuit and an output signal of the second NAM circuit. A delay time of the delay circuit is set so that a feedthrough-level period of an output signal of the delay circuit overlaps with a signal-level period of the CCD output signal.

Owner:PANASONIC CORP

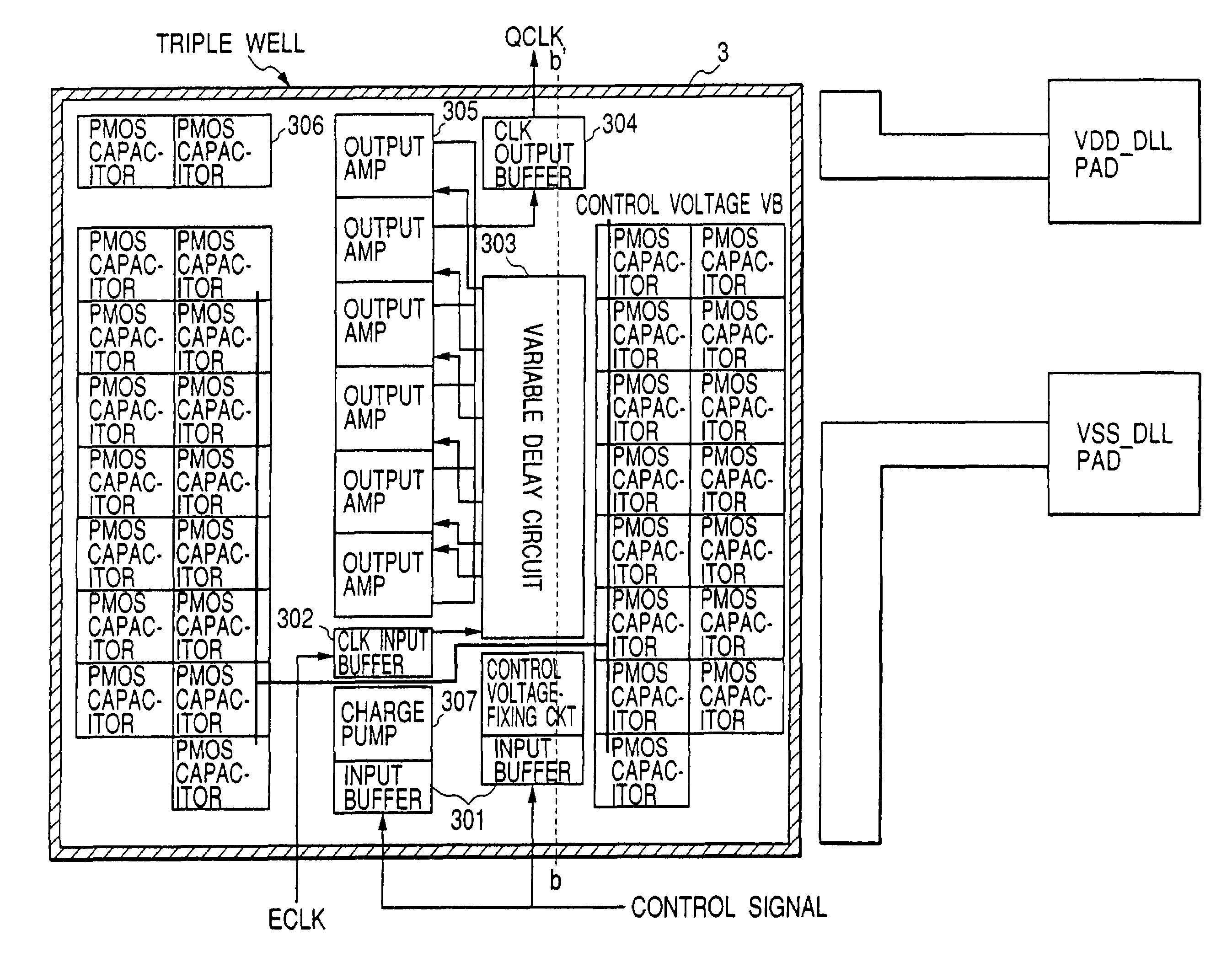

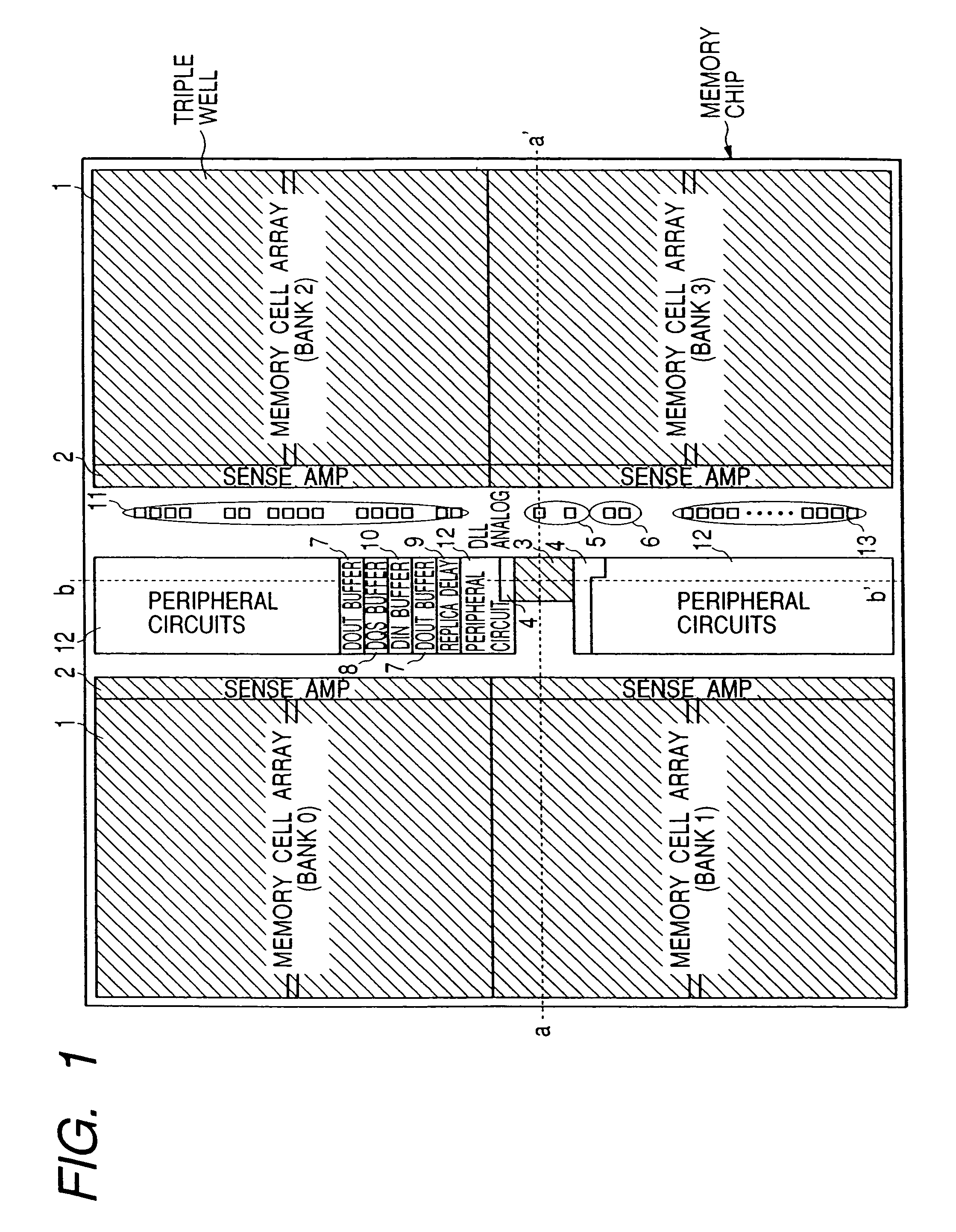

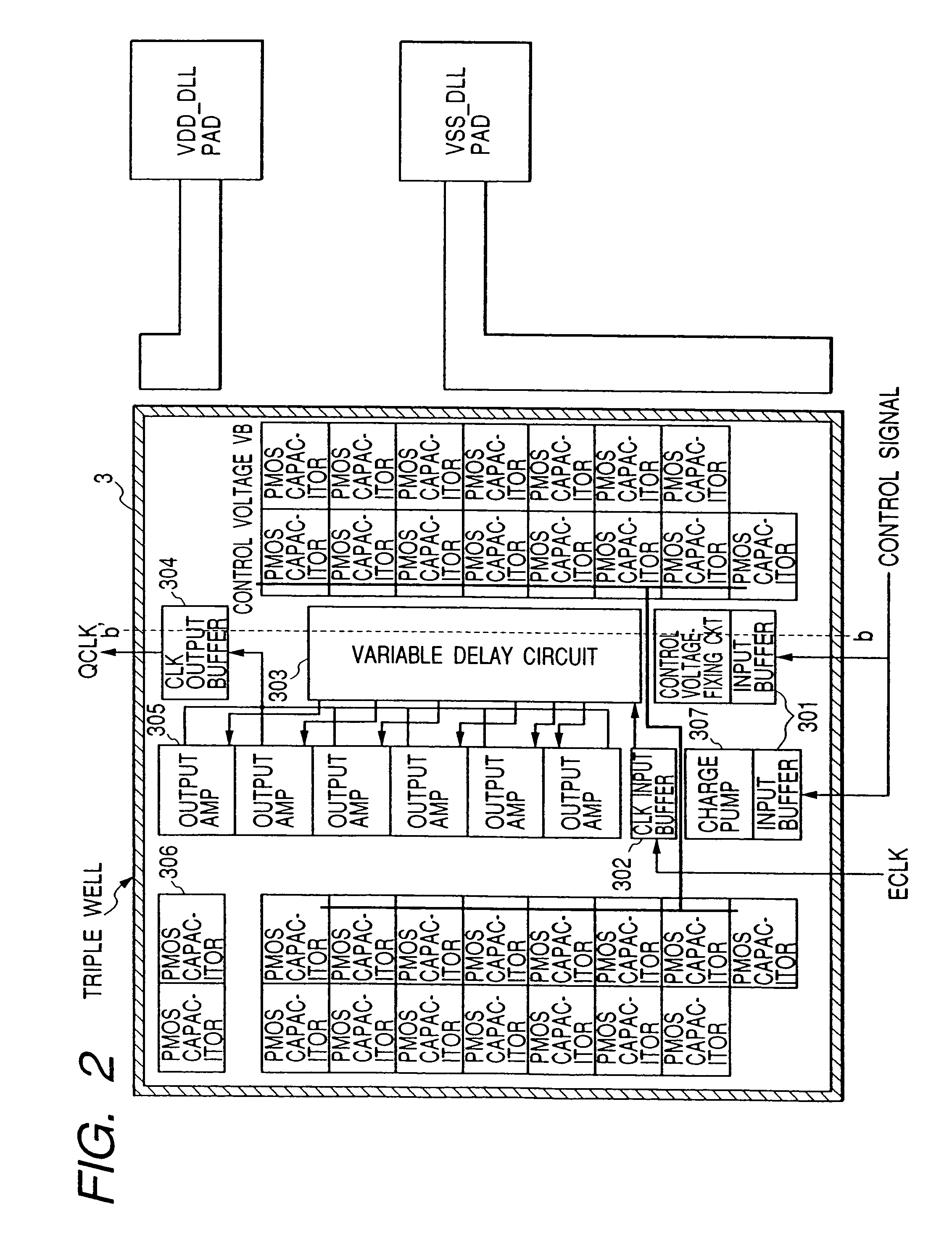

Semiconductor integrated circuit device

InactiveUS7072242B2Solve high precisionShort lock-in cycleTransistorPulse automatic controlComparators circuitsCircuit delay

A clock-generating circuit for forming internal clock signals by comparing a signal obtained by delaying, through a variable delay circuit, an input clock signal input through an external terminal with the input clock signal through a phase comparator circuit, and so controlling the delay time of the variable delay circuit that they are brought into agreement with each other, wherein the clock-generating circuit and an internal circuit to be operated by the clock signals formed thereby are formed on a common semiconductor substrate, and an element-forming region in which the clock-generating circuit is formed is electrically isolated from an element-forming region in which the digital circuit is constituted on the semiconductor substrate relying upon the element-isolation technology. The power-source passages, too, are formed independently of other digital circuits.

Owner:RENESAS ELECTRONICS CORP

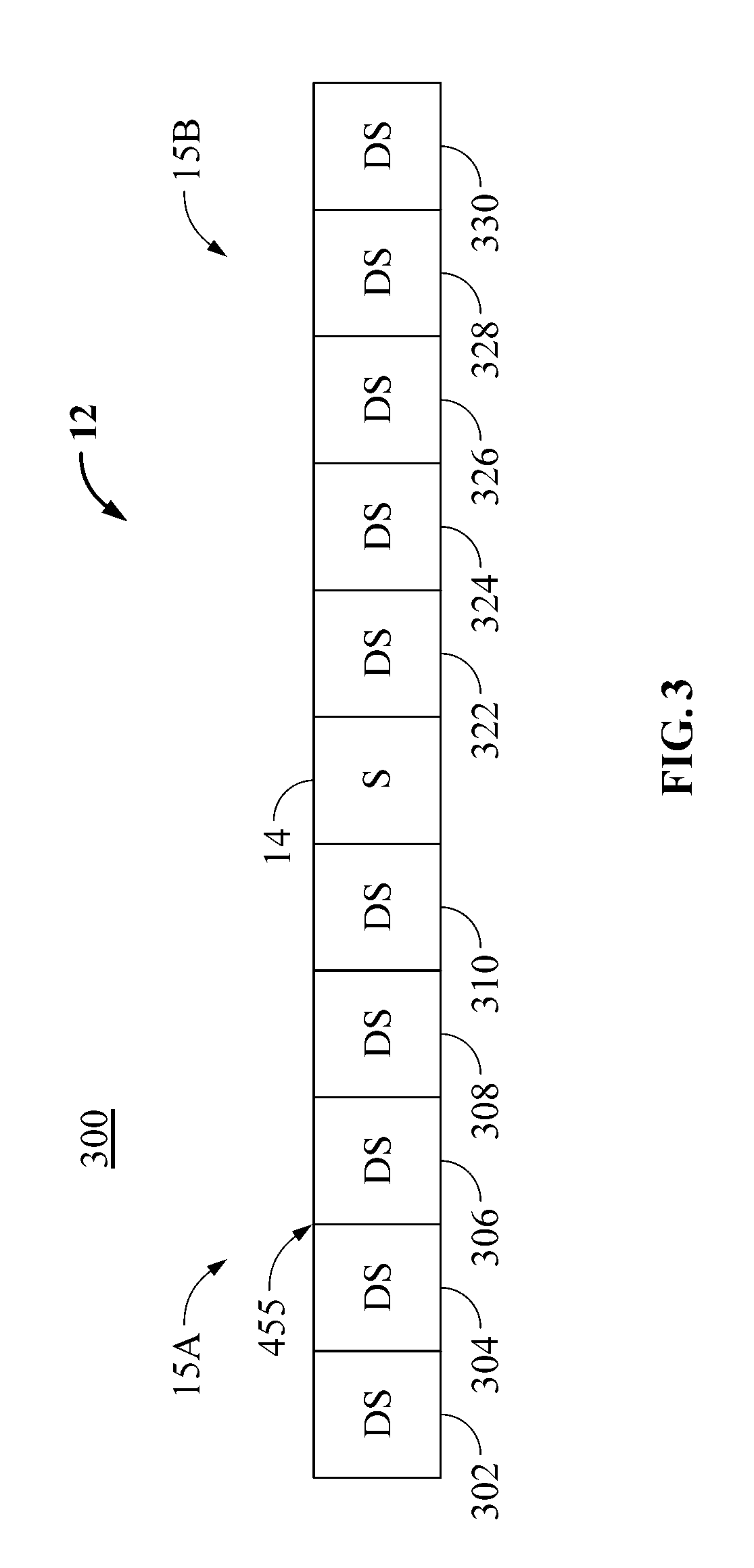

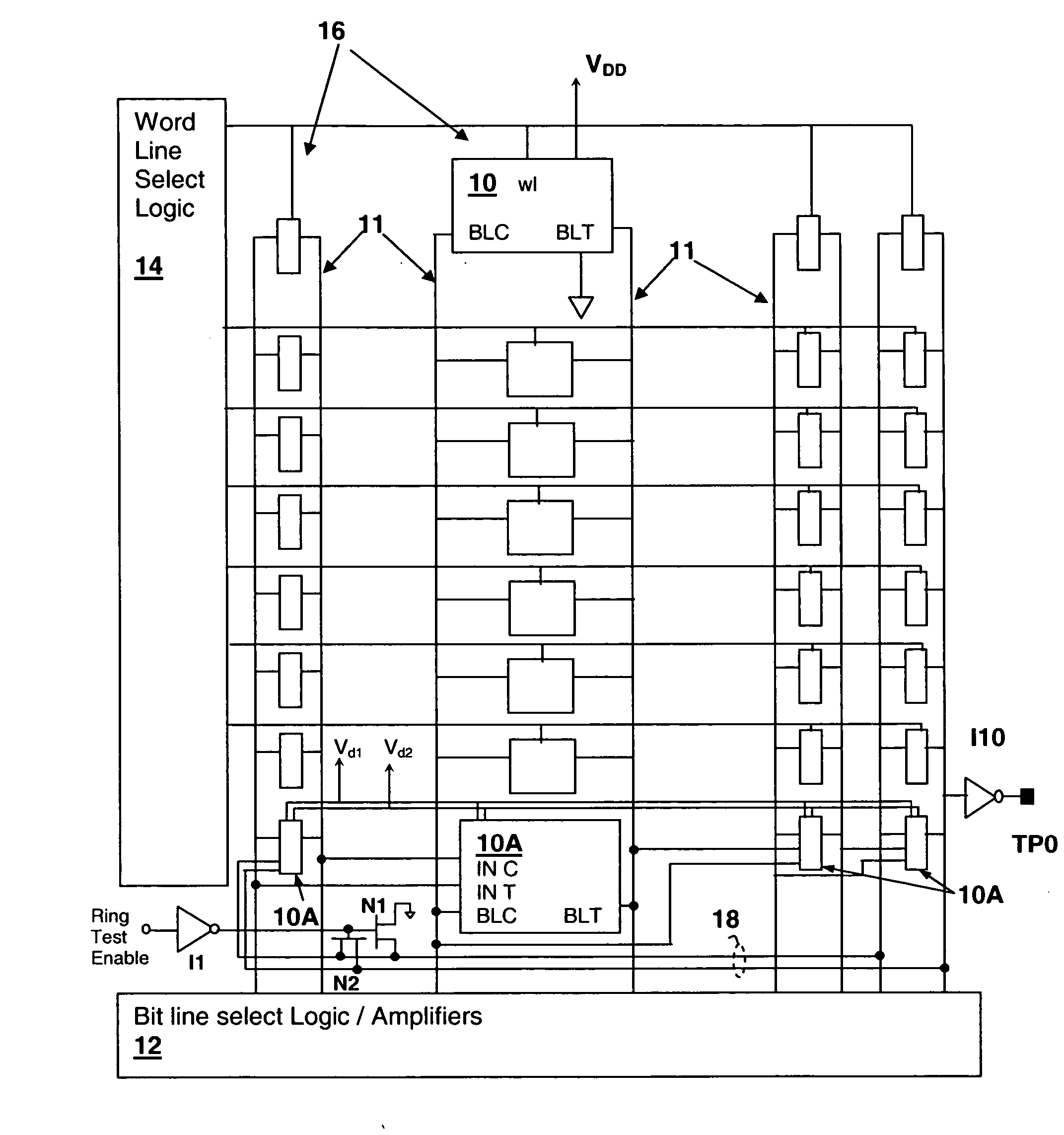

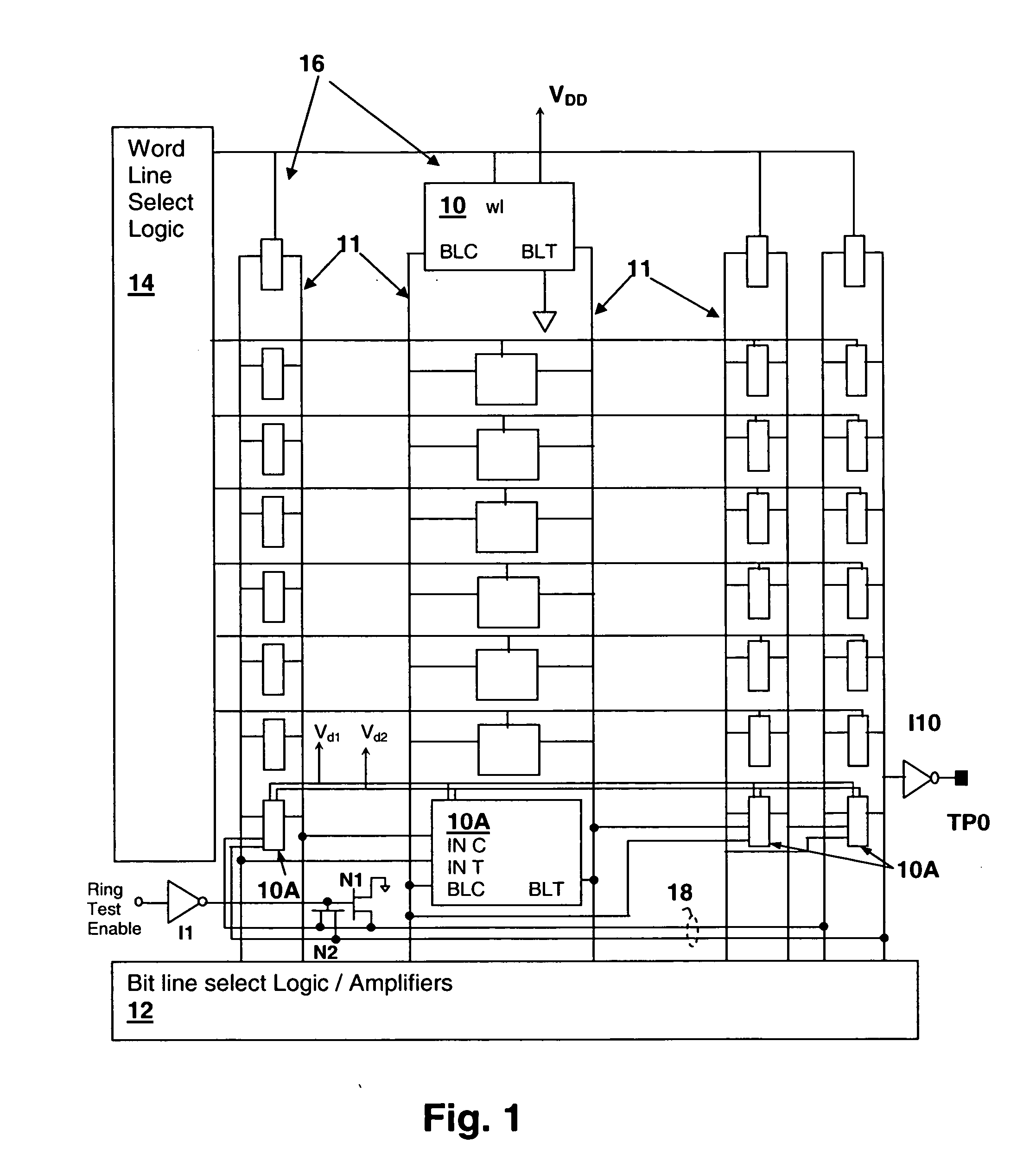

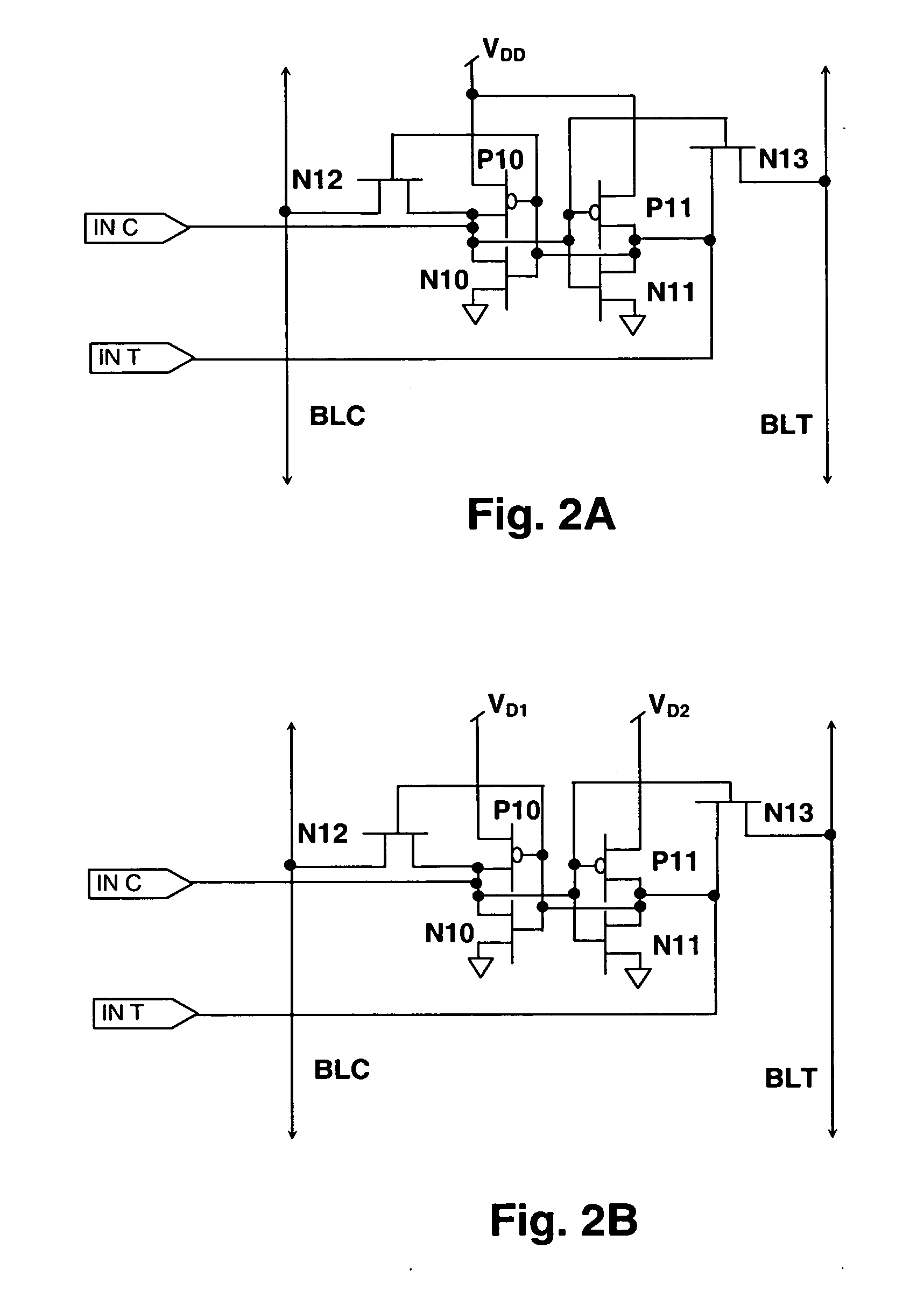

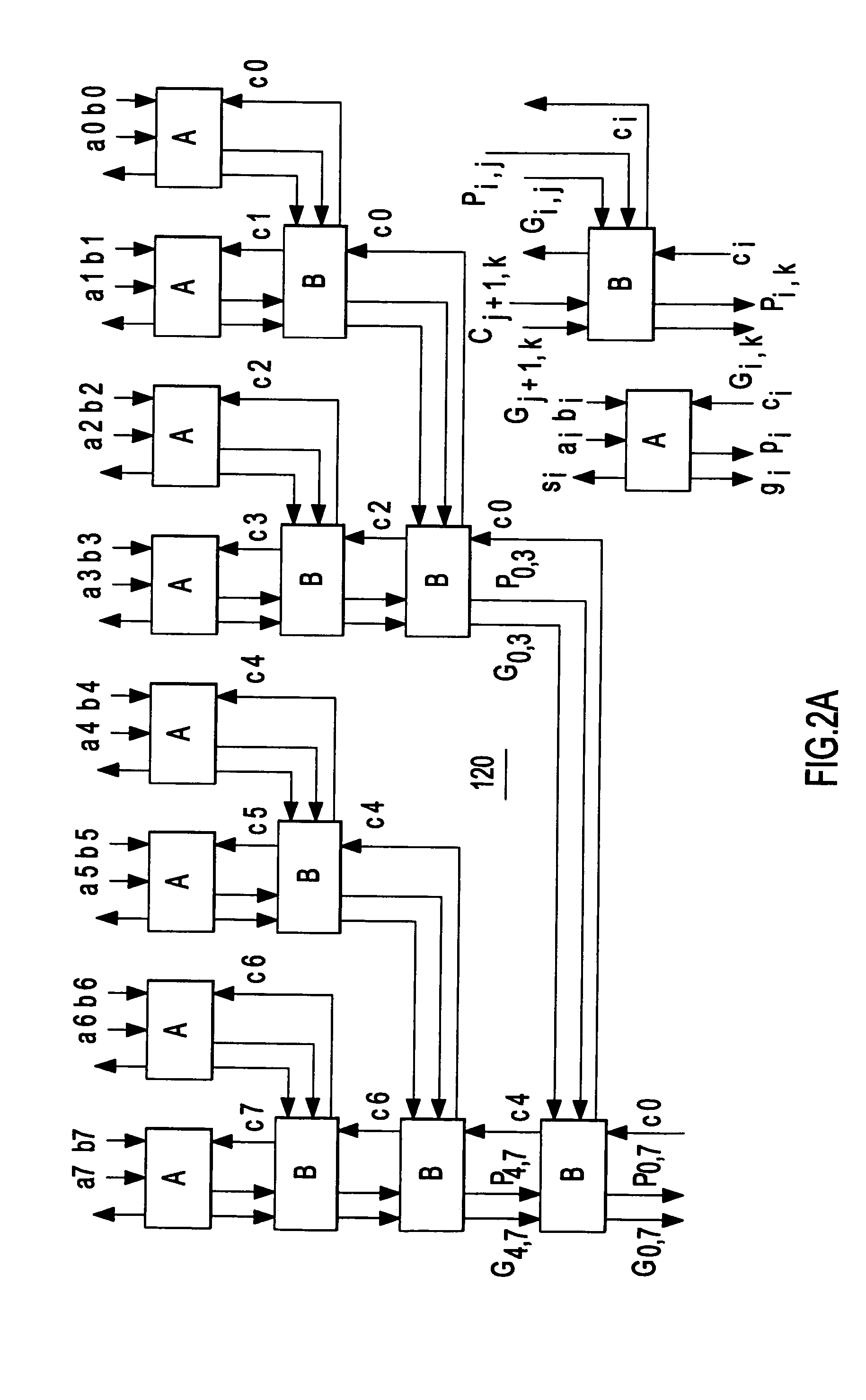

Ring oscillator row circuit for evaluating memory cell performance

A ring oscillator row circuit for evaluating memory cell performance provides for circuit delay and performance measurements in an actual memory circuit environment. A ring oscillator is implemented with a row of memory cells and has outputs connected to one or more bitlines along with other memory cells that are substantially identical to the ring oscillator cells. Logic may be included for providing a fully functional memory array, so that the cells other than the ring oscillator cells can be used for storage when the ring oscillator row wordlines are disabled. One or both power supply rails of individual cross-coupled inverter stages forming static memory cells used in the ring oscillator circuit may be isolated from each other in order to introduce a voltage asymmetry so that circuit asymmetry effects on delay can be evaluated.

Owner:MARVELL ASIA PTE LTD

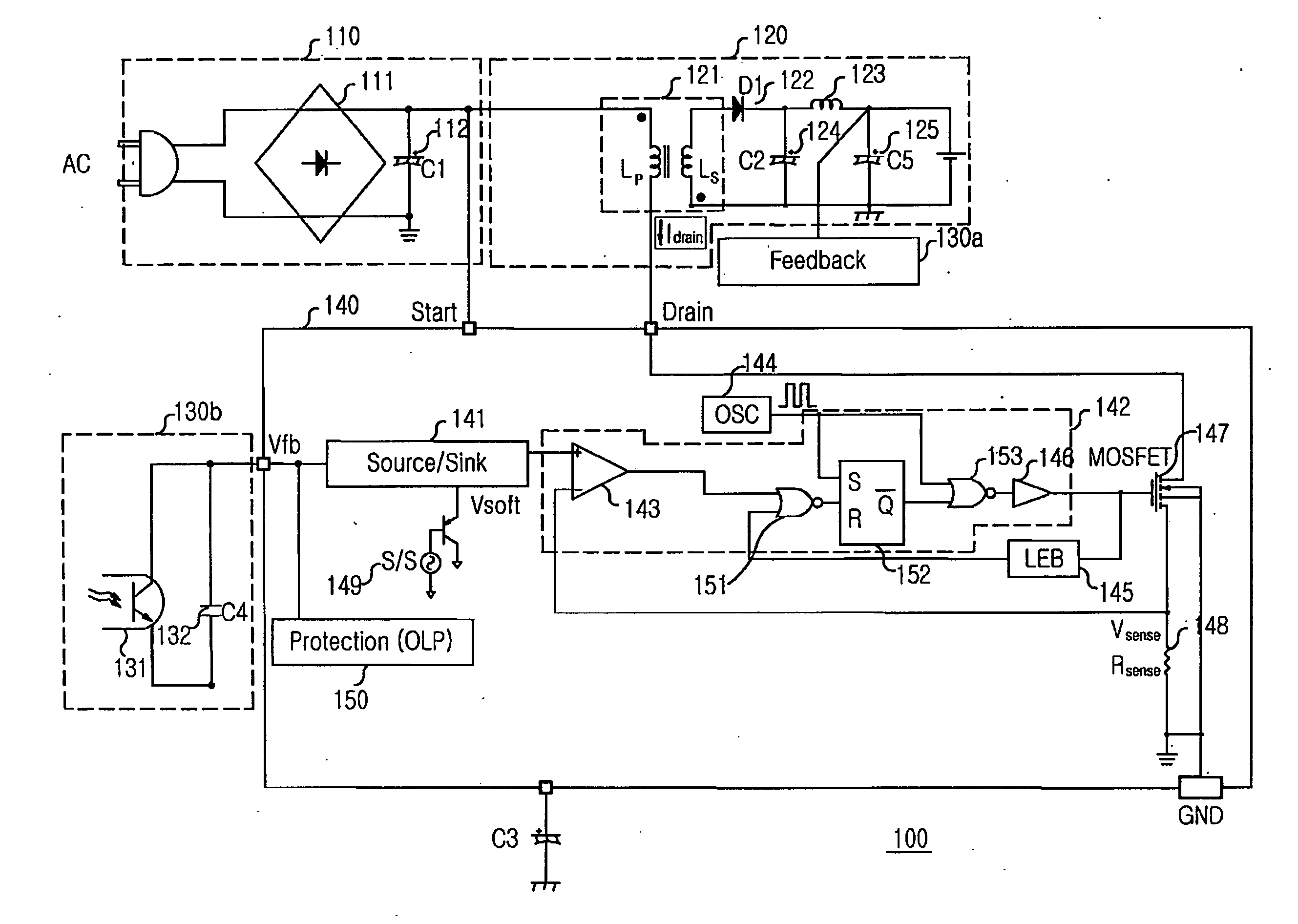

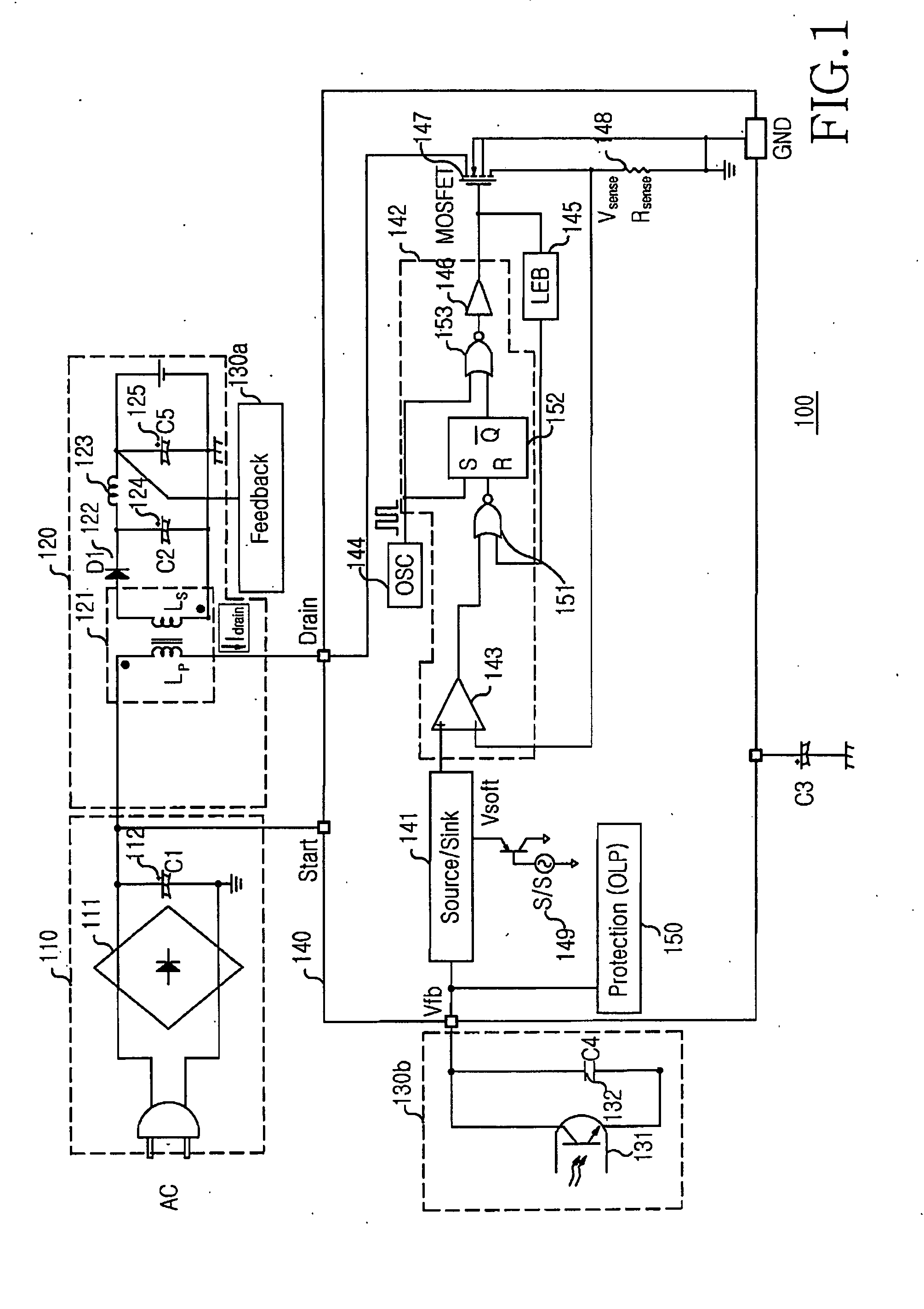

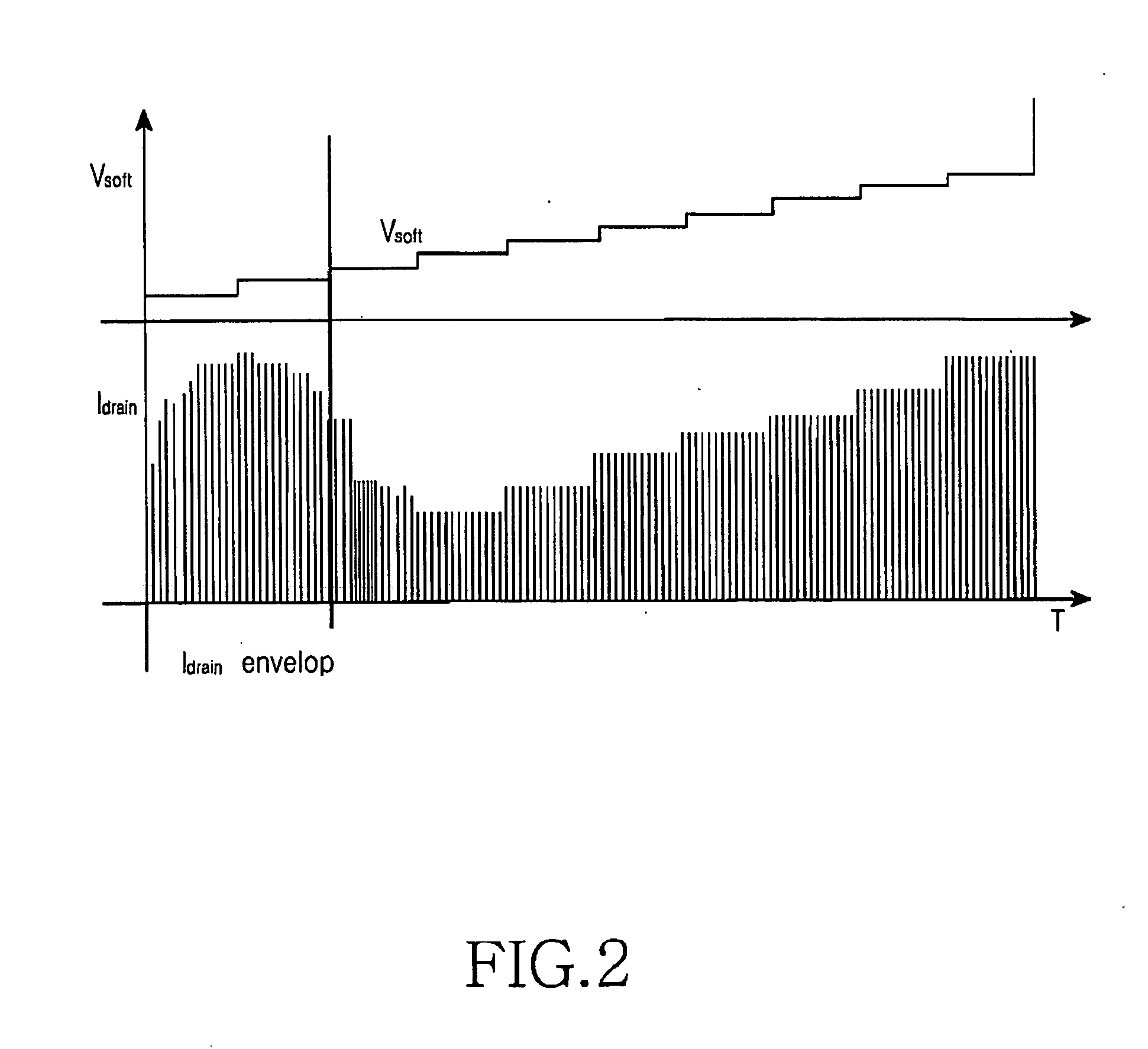

Current controlled switching mode power supply

ActiveUS20070132438A1Increase the output voltageInhibit currentDc-dc conversionElectric variable regulationLeading edgeDriving current

A current controlled switching mode power supply is provided. A turn on / off time of a switching device is adjusted by controlling a leading edge blanking (LEB) time and an external drive current of the switching device by means of a switching controller, thus capable of preventing a switching current from being excessive due to a delay of a turn-off time of the switching device, which is caused by a circuit delay during a soft start of the switching mode power supply. Also, it is possible to prevent a switching current from being excessive due to a failure of accurately controlling a turn-off time of the switching device because of a delay caused when an output voltage (a voltage at a secondary winding of a transformer) of the switching mode power supply is designed to have a high voltage.

Owner:SEMICON COMPONENTS IND LLC

Method of reducing the propagation delay and process and temperature effects on a buffer

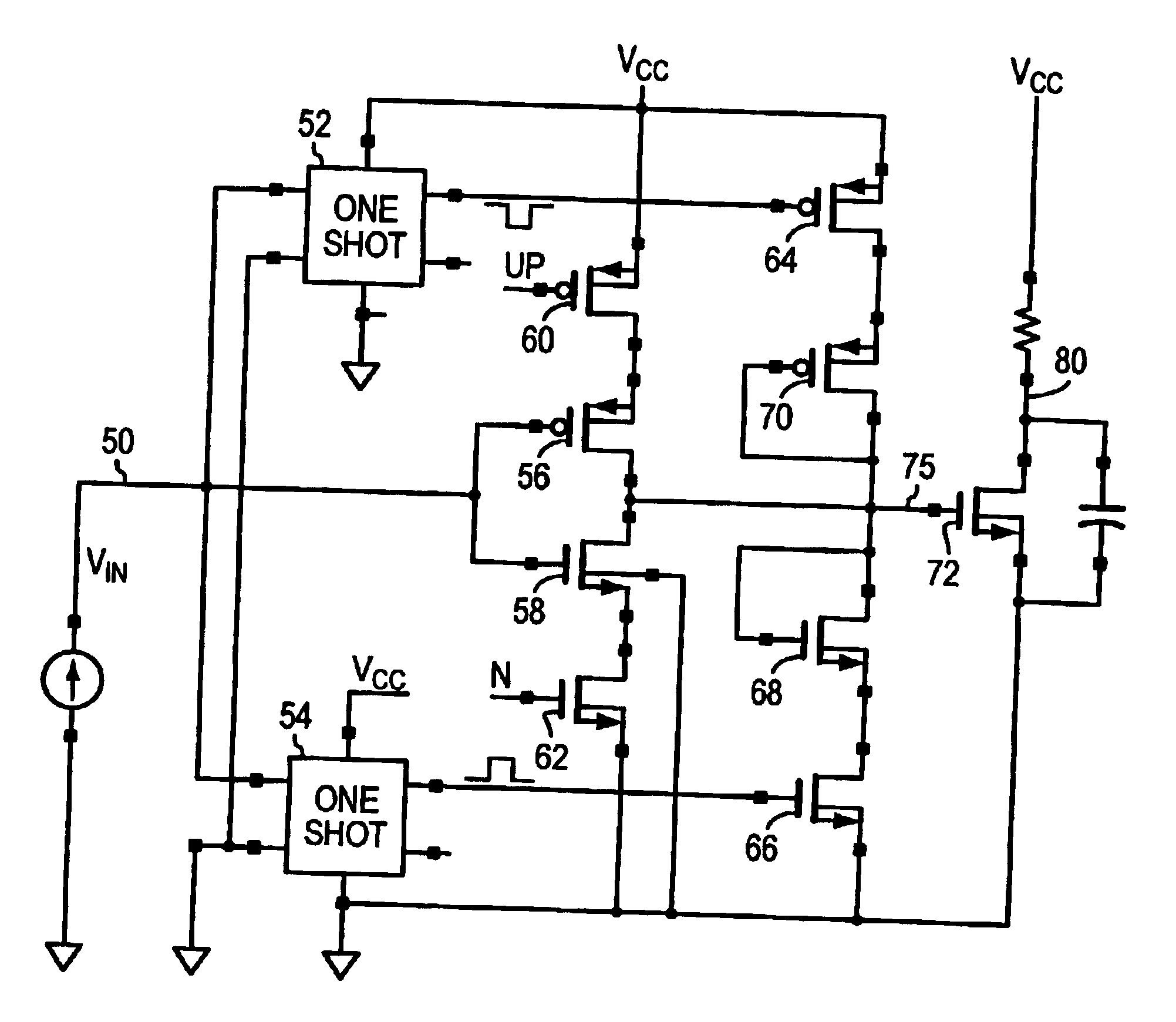

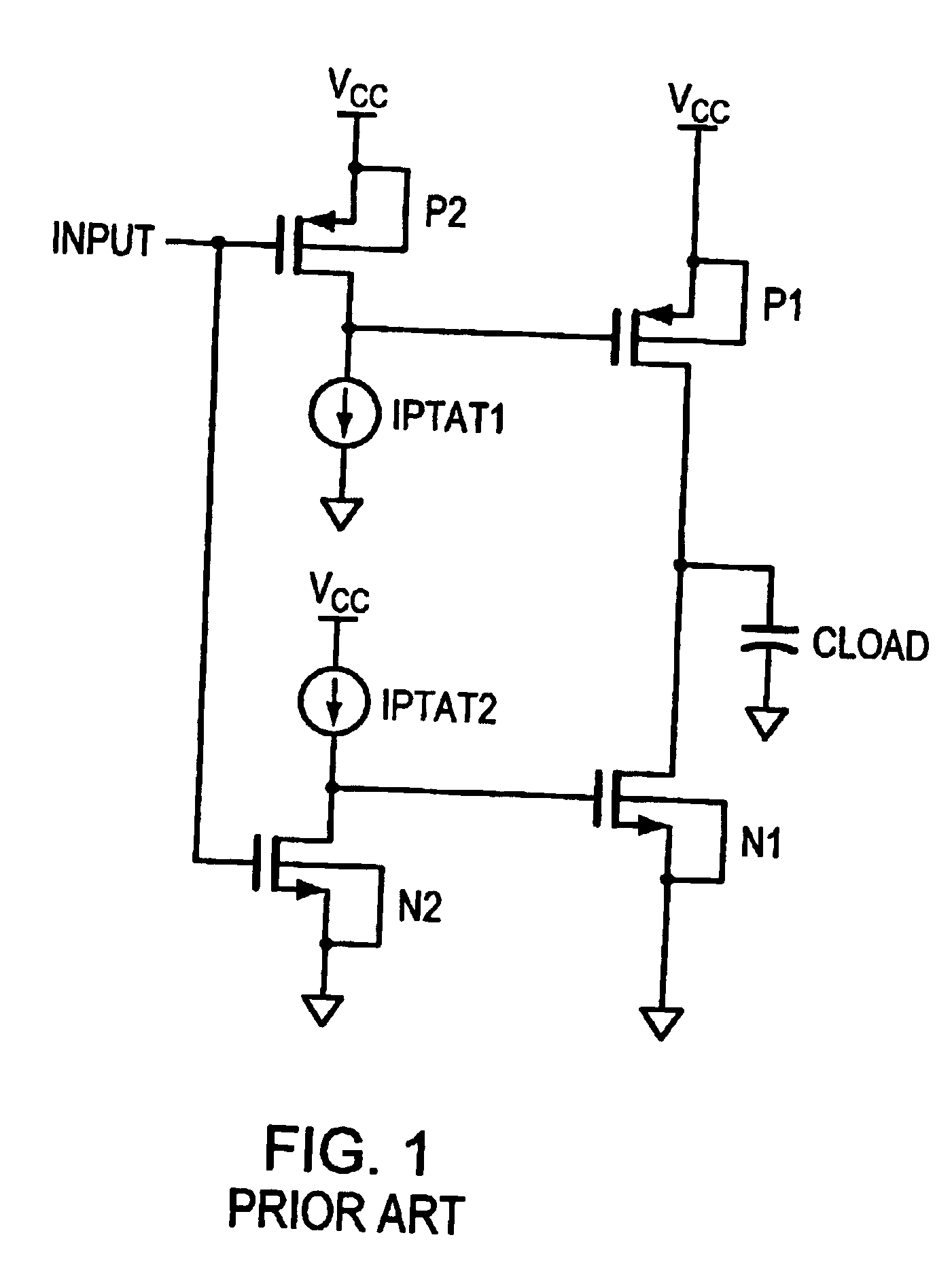

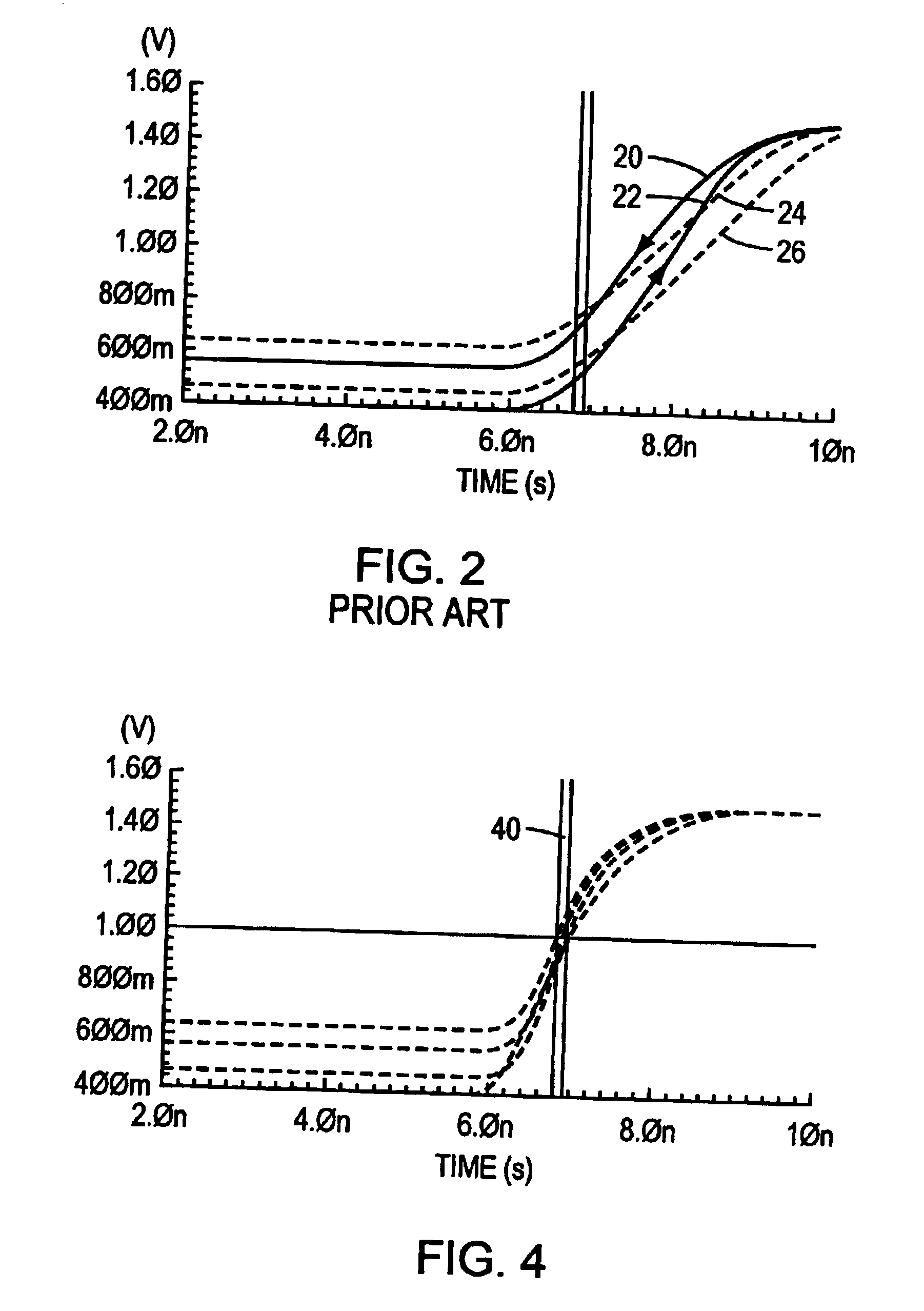

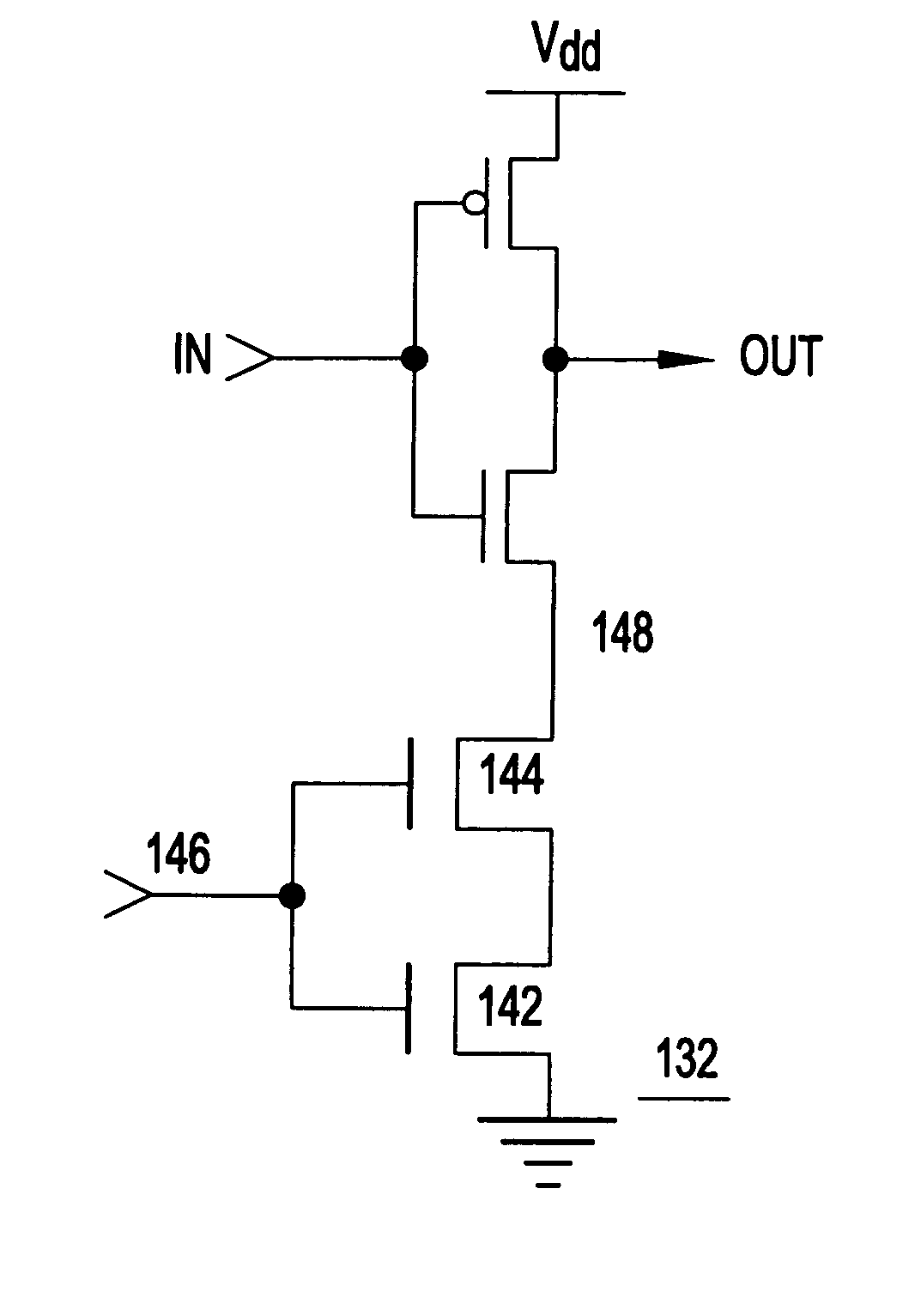

InactiveUS6756826B1Easy to processPresent inventionElectronic switchingElectric pulse generatorPropagation delayMOSFET

A buffer circuit with slow output edges is described. Pulsed higher value currents are driven from one shot timing circuits to inject a pulse of current into the control gate of the buffer's output MOSFET to speed up the beginning of the turning on or the turning off of the output MOSFT. When the beginning and turning on and off is reached lower value current sources continue to drive the gate of the output MOSFET. In one embodiment, one shots are triggered from the rising and falling edges of the input signal. The effect of the higher value current pulses is to reduce the circuit delay through the buffer. Also, the pulse width can be designed as temperature sensitive, and supply voltage sensitive so as to maintain the buffer circuit delay as substantially constant as temperature, supply voltage and process variation occur.

Owner:SEMICON COMPONENTS IND LLC

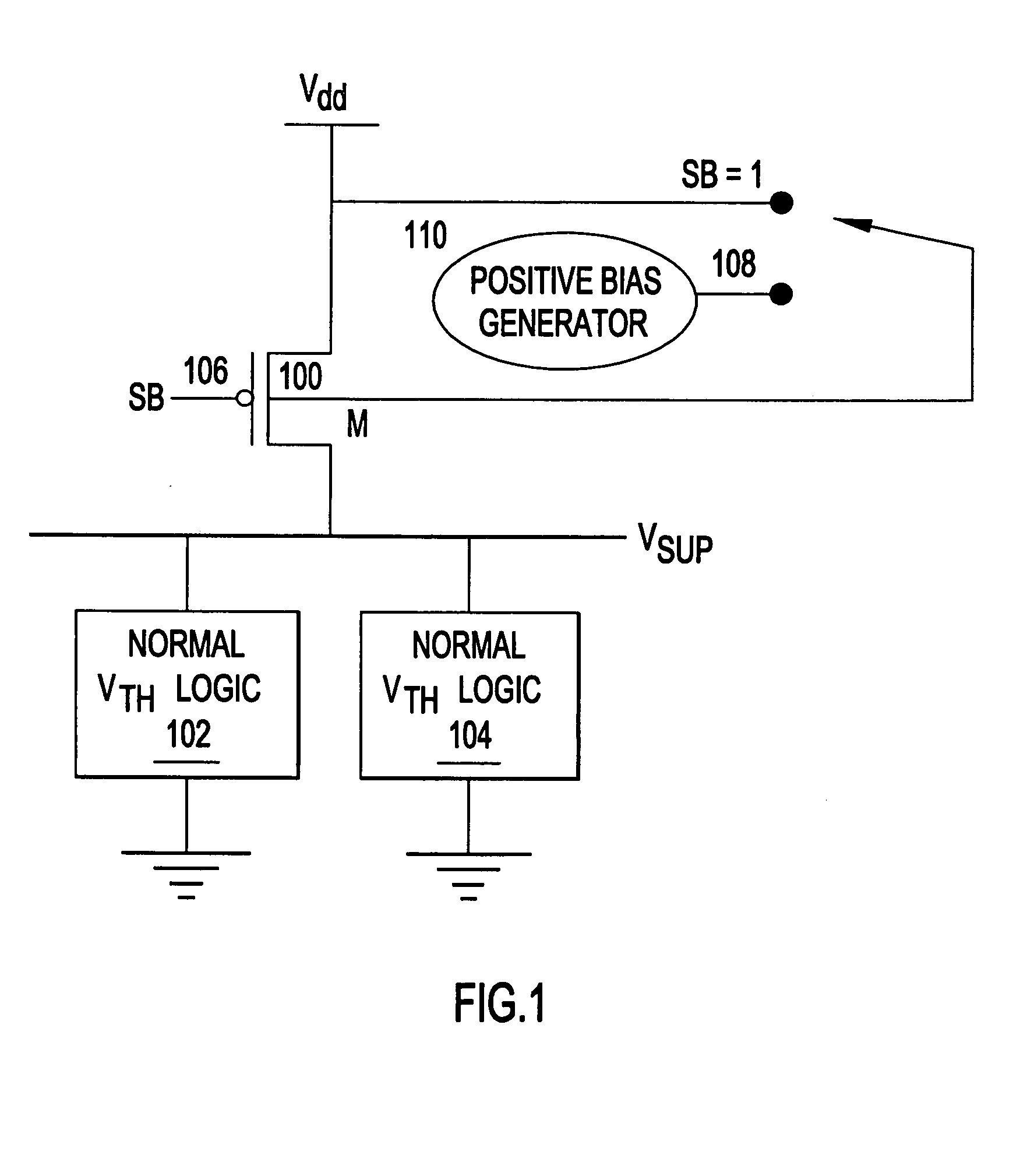

Method of reducing leakage current in sub one volt SOI circuits

ActiveUS20050040881A1Reduced subthreshold leakageReduce leakageReliability increasing modificationsPower reduction by control/clock signalCapacitanceElectrical resistance and conductance

A multi-threshold integrated circuit (IC) with reduced subthreshold leakage and method of reducing leakage. Selectable supply switching devices (NFETs and / or PFETS) between a logic circuit and supply connections (Vdd and Ground) for the circuit have higher thresholds than normal circuit devices. Some devices may have thresholds lowered when the supply switching devices are on. Header / footer devices with further higher threshold voltages and widths may be used to further increase off resistance and maintain / reduce on resistance. Alternatively, high threshold devices may be stacked to further reduce leakage to a point achieved for an even higher threshold. Intermediate supply connects at the devices may have decoupling capacitance and devices may be tapered for optimum stack height and an optimum taper ratio to minimize circuit leakage and circuit delay.

Owner:GLOBALFOUNDRIES US INC

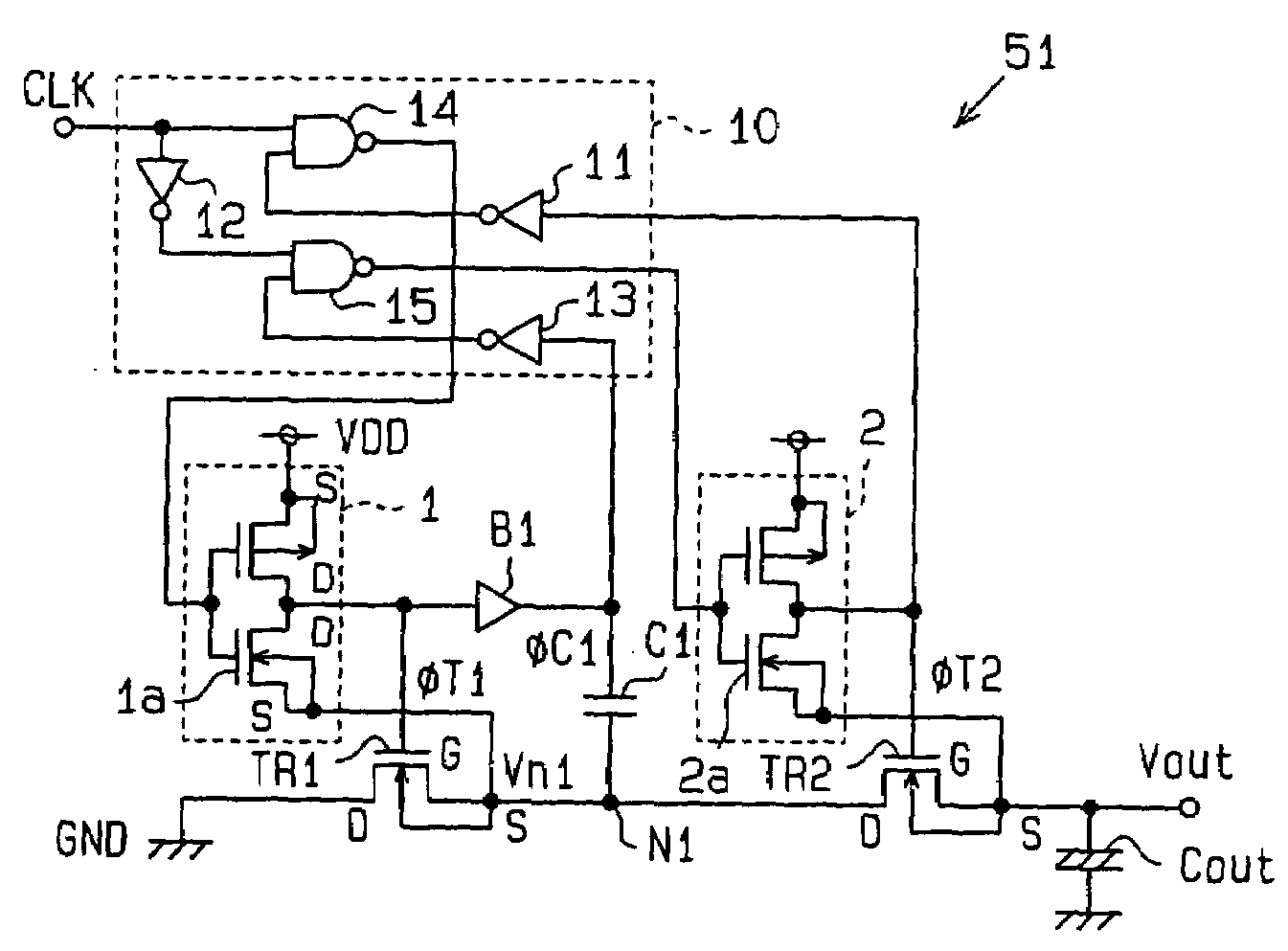

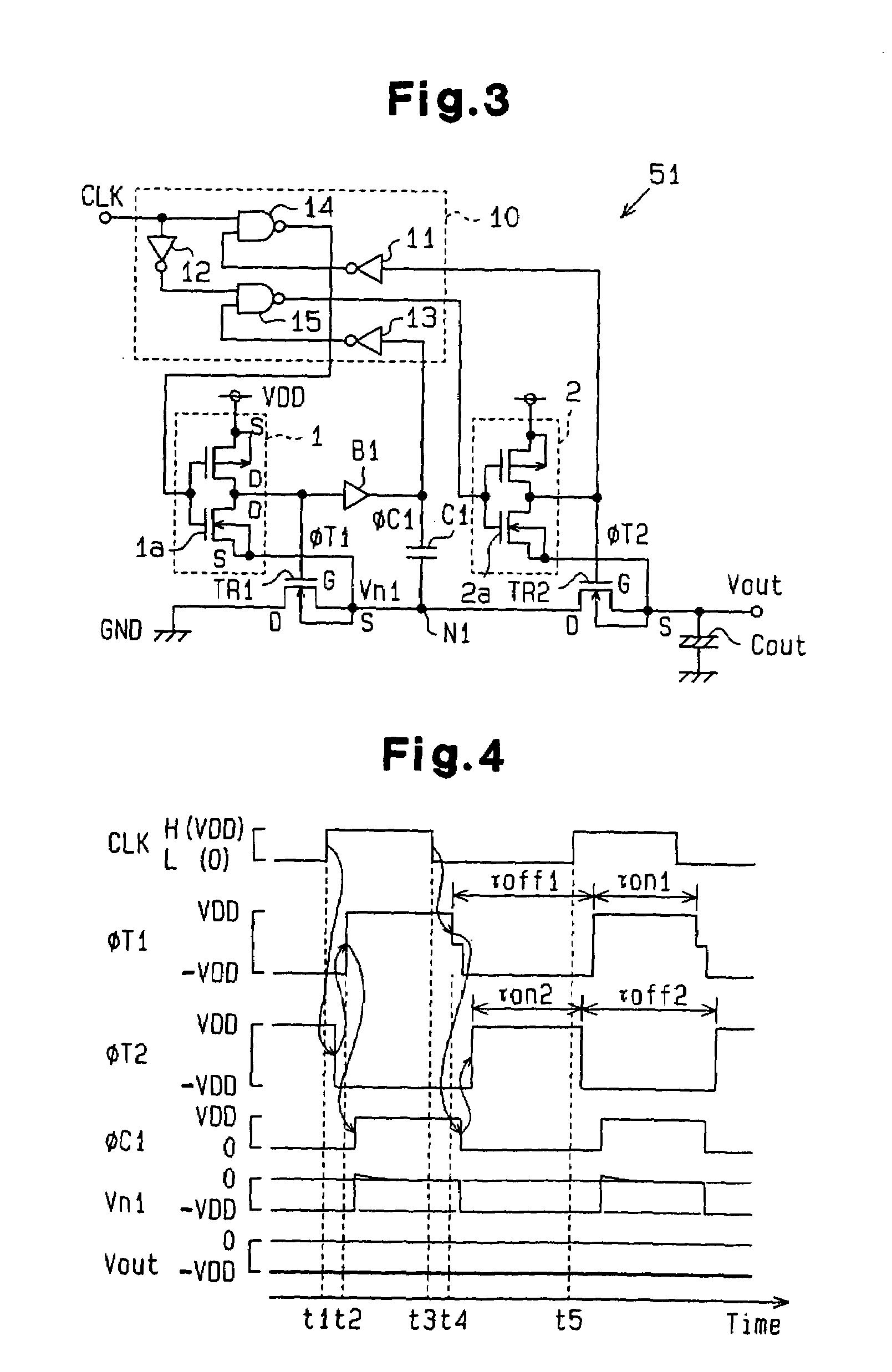

Charge pump circuit

InactiveUS6970035B2Improve voltage conversion efficiencyImprove reliabilityApparatus without intermediate ac conversionStatic storageCircuit delayCapacitor

A charge pump circuit for converting an input voltage to a predetermined voltage. The charge pump circuit includes switching transistors, which are connected in series between an output terminal and reference potential terminal of the charge pump circuit, and a capacitor connected to a node between the first and second transistors. The switching transistors include a first transistor connected to the reference potential terminal and a second transistor connected to the first transistor. The capacitor has a first terminal connected to a node between the transistors and a second terminal connected to a delay circuit. The delay circuit is connected between the second terminal of the capacitor and a control terminal of the first transistor. The delay circuit delays a clock signal received by the control terminal by a predetermined time and provides the delayed first clock signal to the second terminal of the capacitor.

Owner:SEMICON COMPONENTS IND LLC

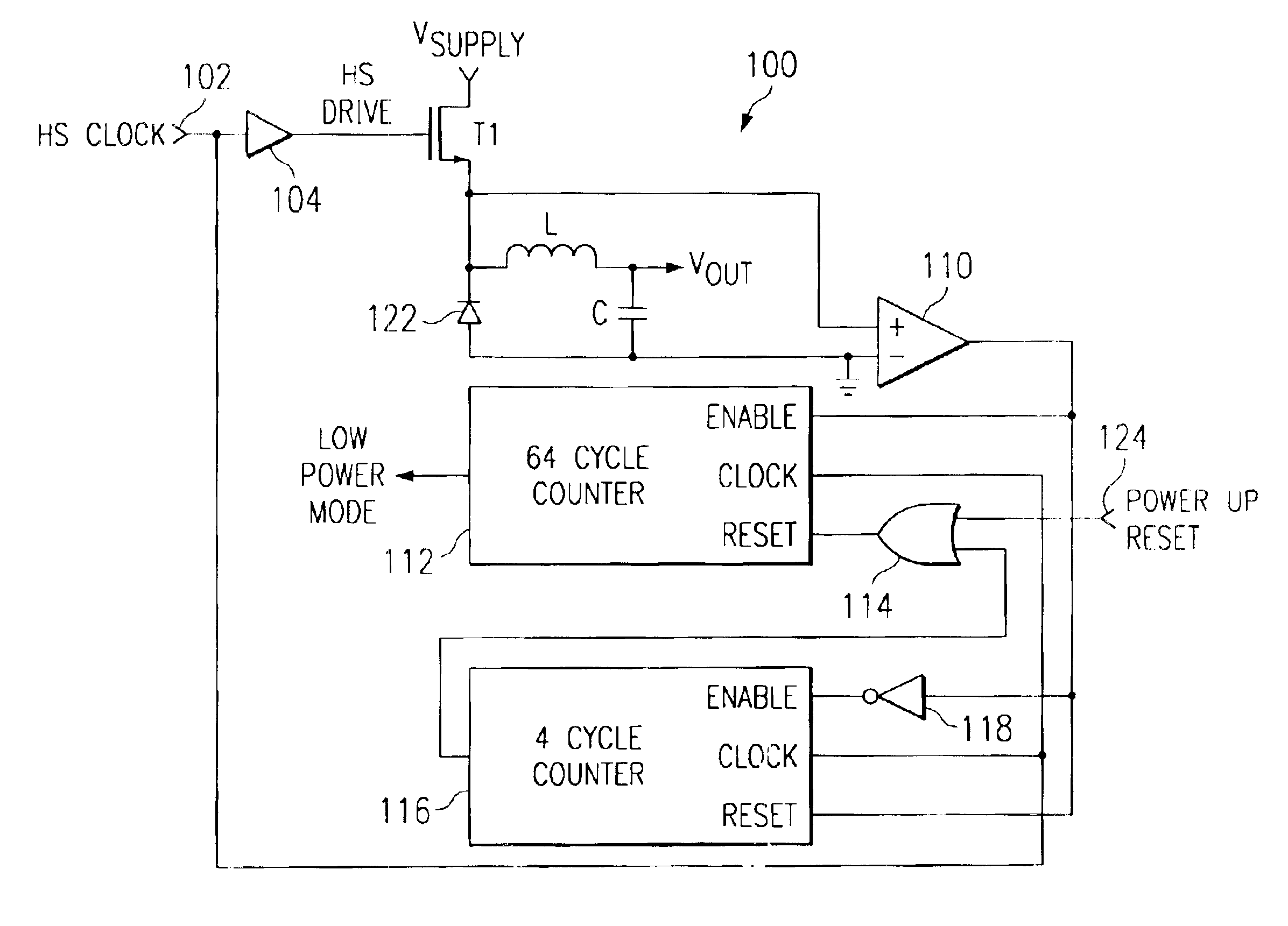

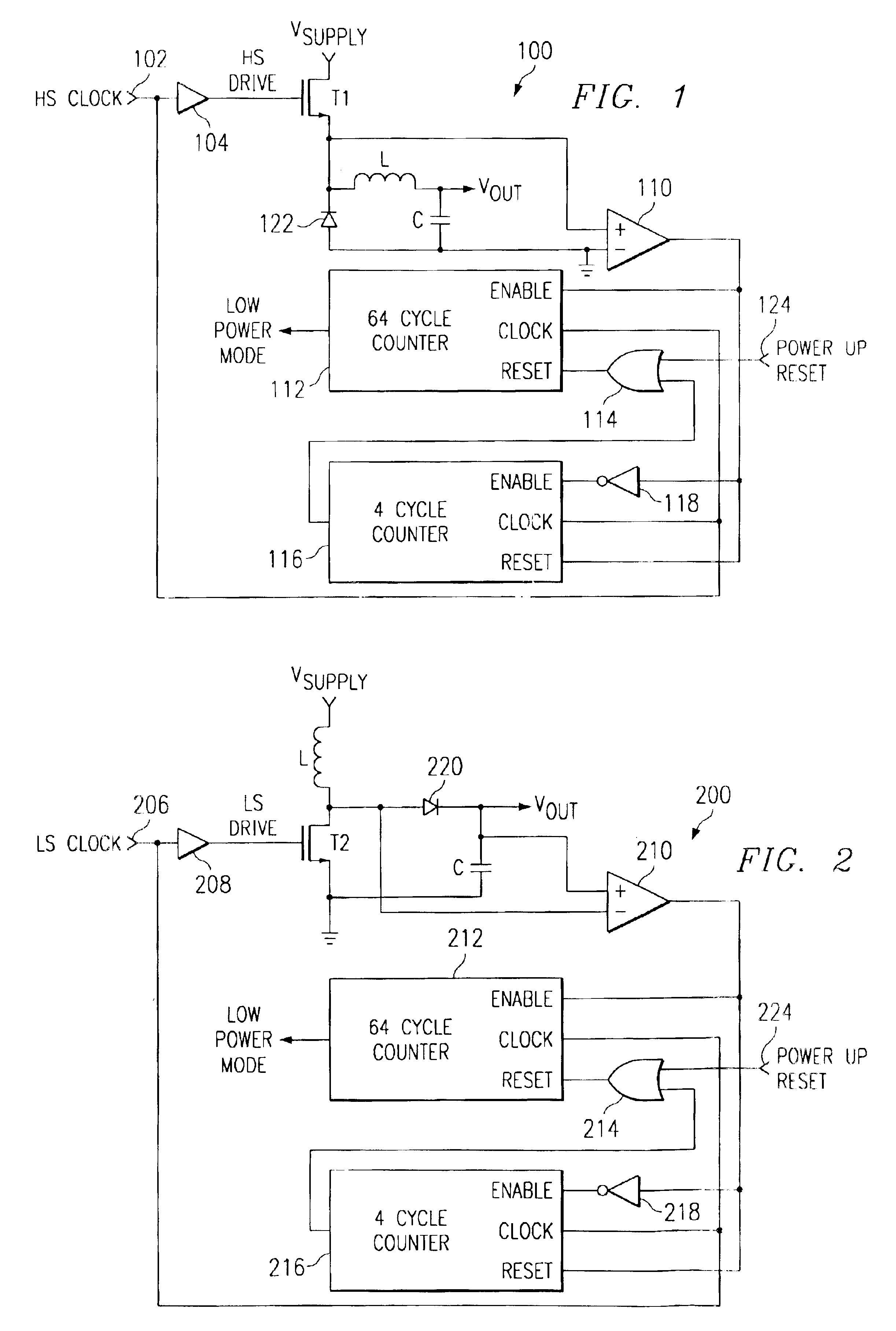

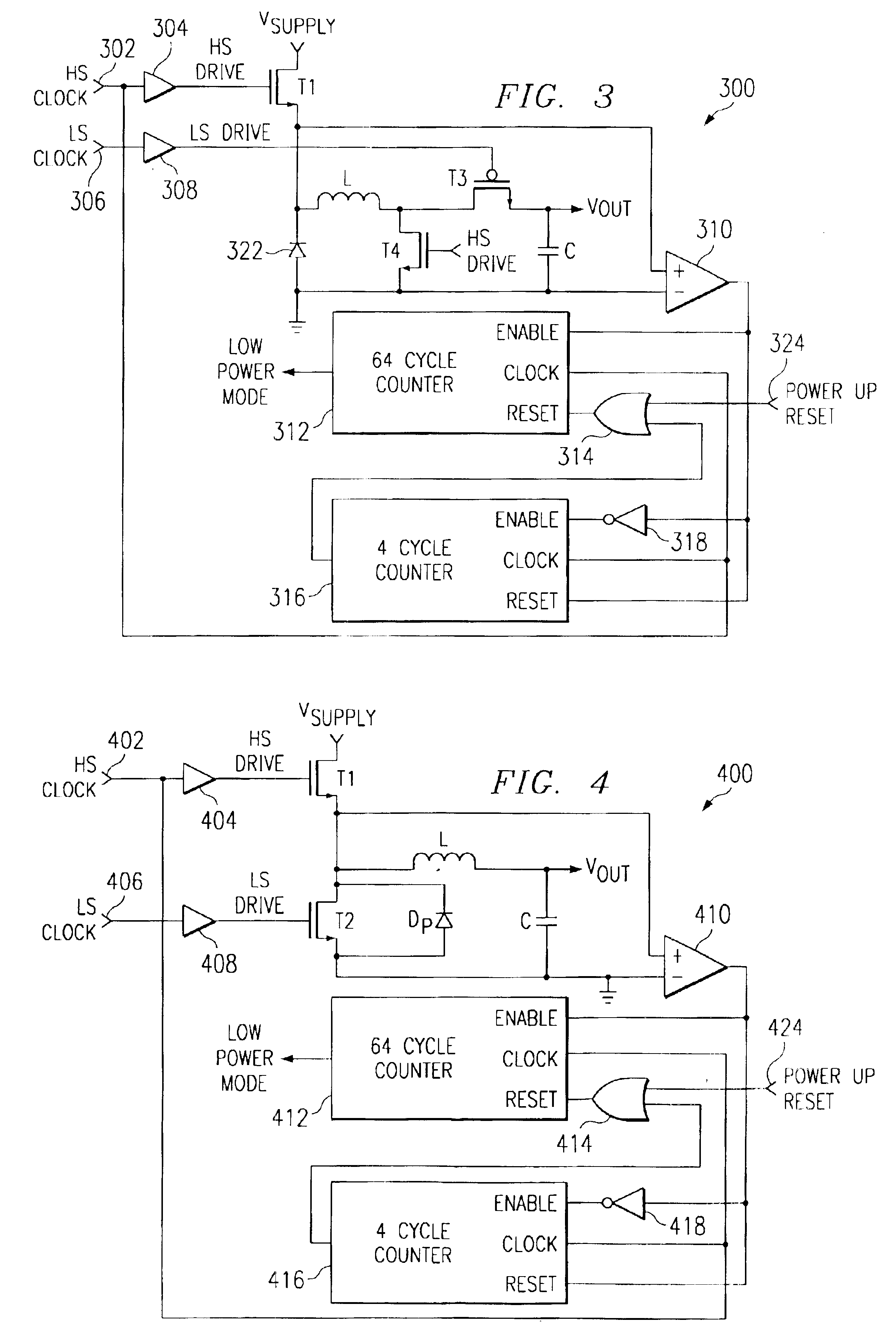

Low power mode detection circuit for a DC/DC converter

InactiveUS6859020B2Efficient power electronics conversionApparatus without intermediate ac conversionControl signalCircuit delay

A DC / DC converter has a semiconductor switch coupled to an inductor, a capacitor and a rectifier. A comparator is coupled to across the rectifier to detect a polarity reversal during the second portion of converter operation to place the converter in a low power mode if the voltage across the rectifier is of an appropriate polarity for reverse current flow. The rectifier may be a synchronous rectifier transistor and the voltage converter placed in a low power mode when the polarity across the synchronous rectifier indicates that reverse current flow is possible. A timing circuit delays the generation of the control signal to place the converter in a low power mode until the steady state current is below a predetermined threshold for a predetermined amount of time. The synchronous rectifier may be turned OFF when the current through the converter falls below another predetermined threshold value and the voltage across the synchronous rectifier will become the voltage across the parasitic diode of the FET synchronous rectifier.

Owner:TEXAS INSTR INC