Patents

Literature

1243 results about "Power-on reset" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A power-on reset (PoR) generator is a microcontroller or microprocessor peripheral that generates a reset signal when power is applied to the device. It ensures that the device starts operating in a known state.

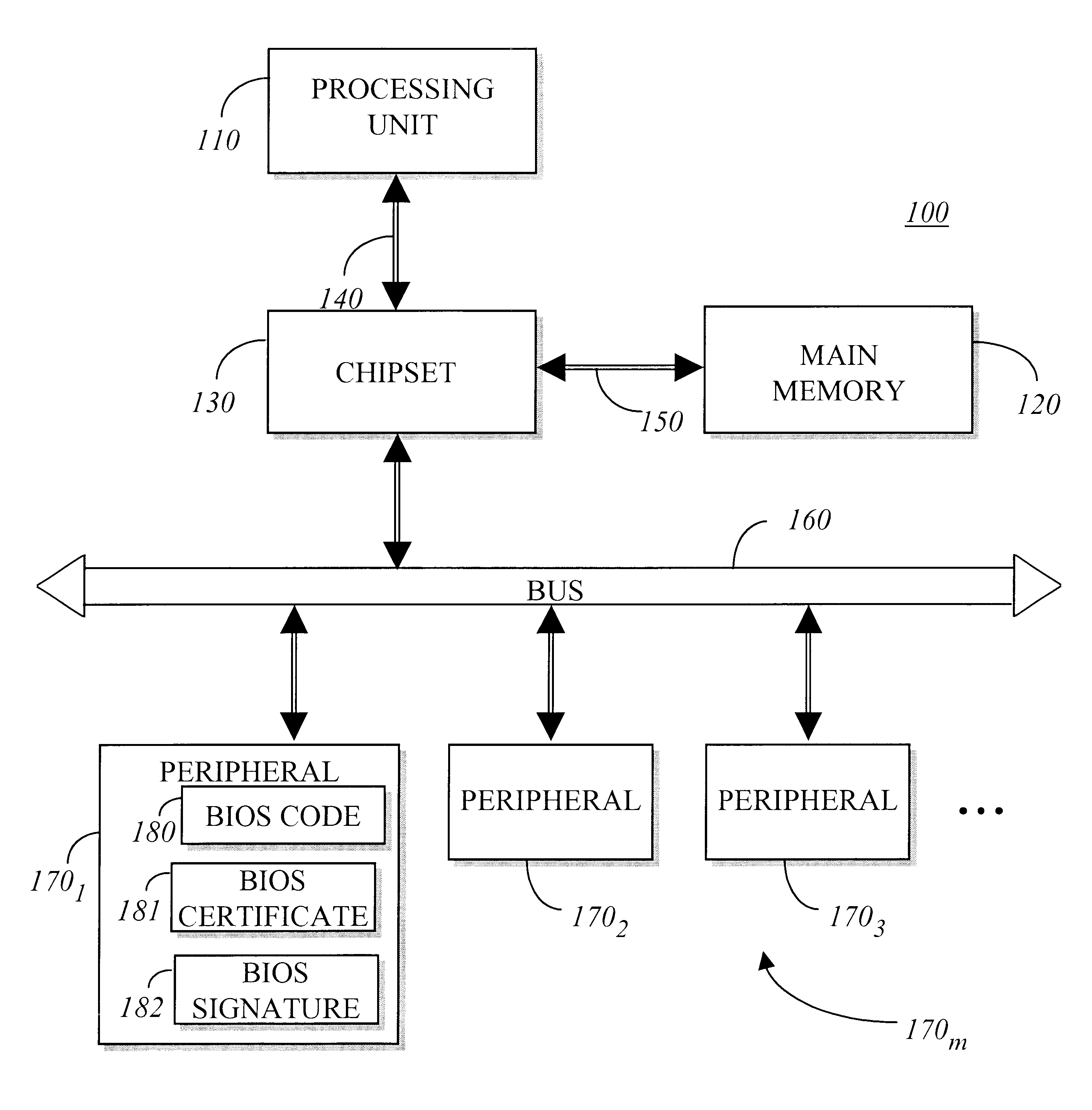

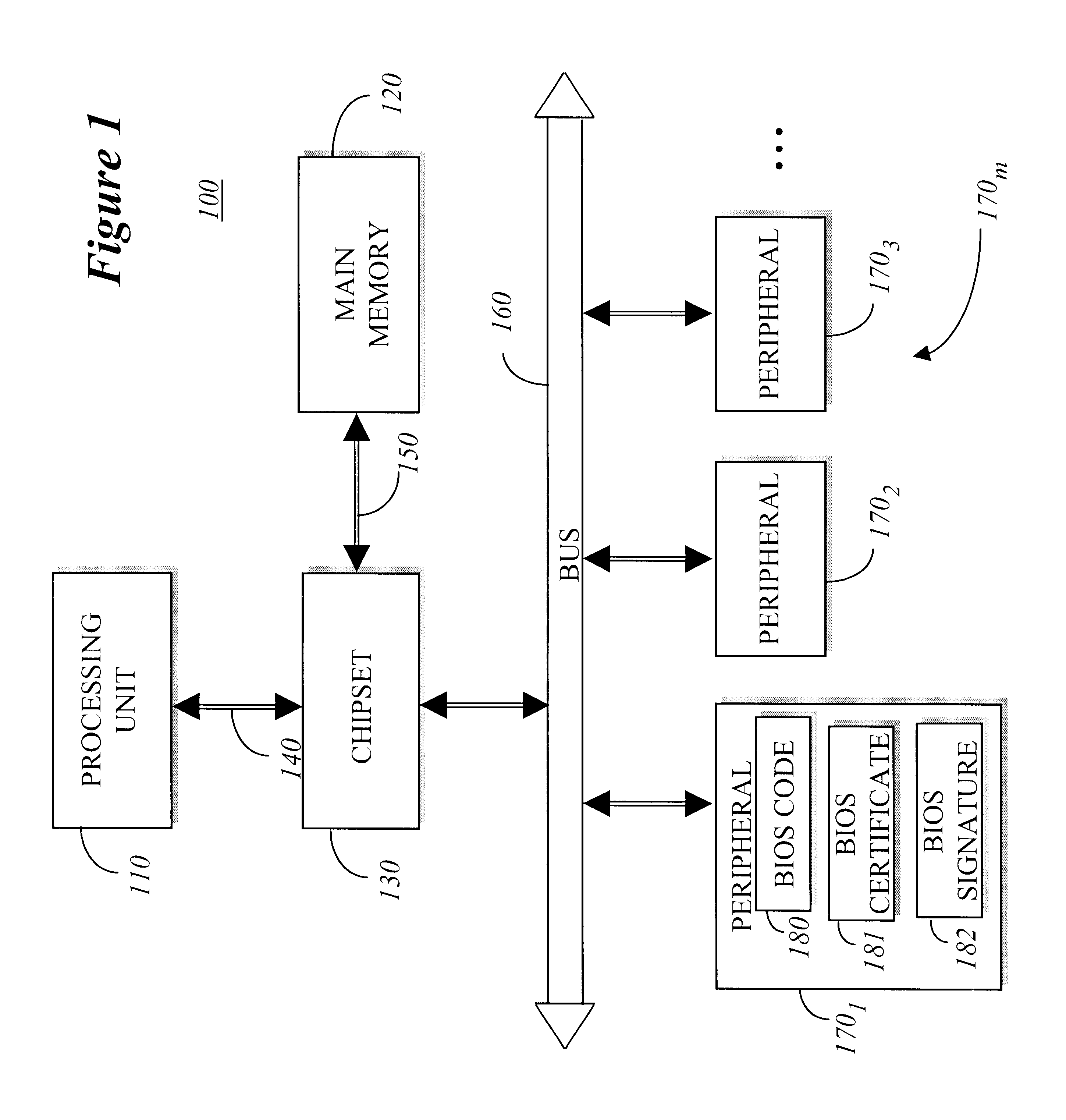

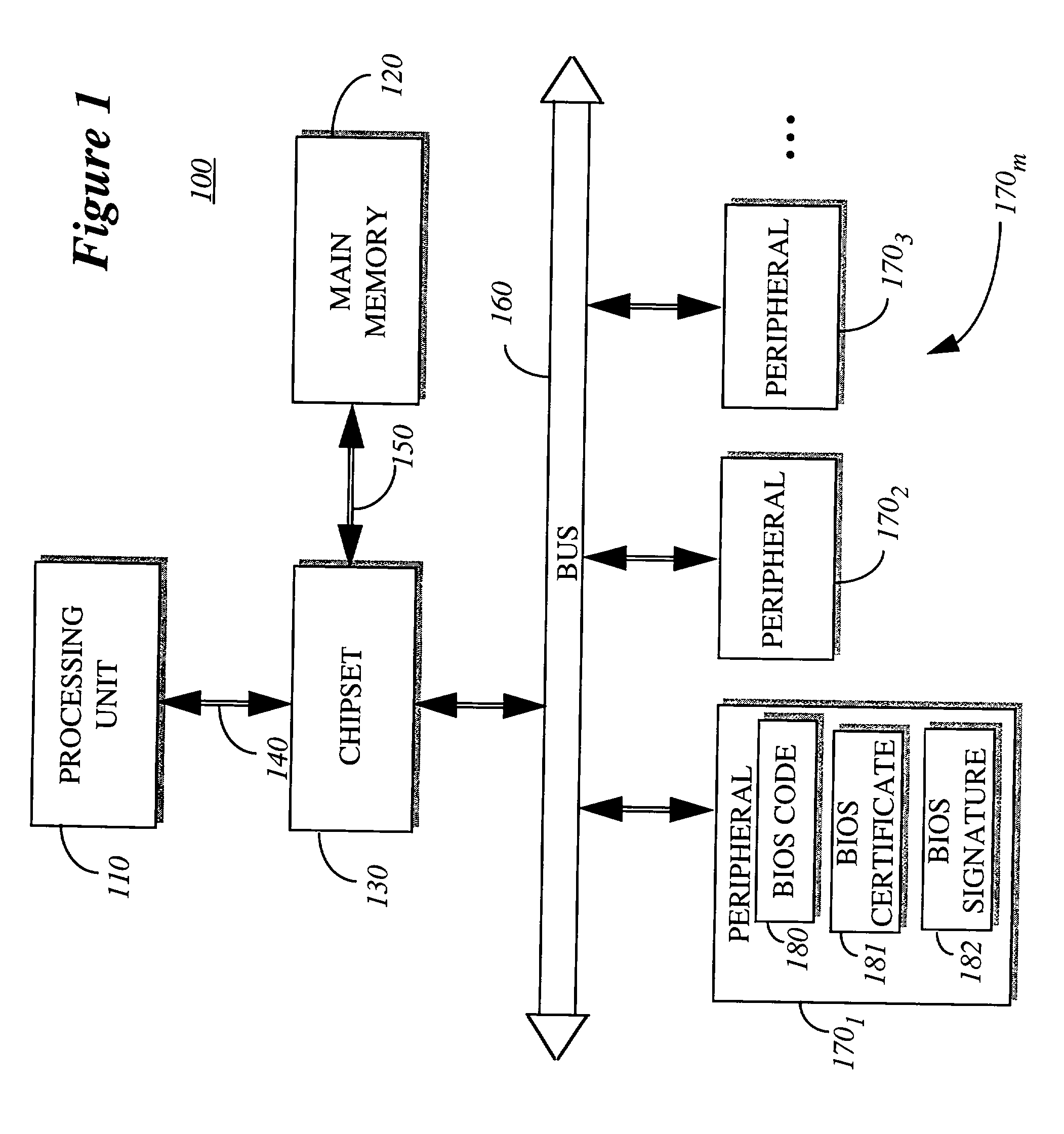

Method for BIOS authentication prior to BIOS execution

InactiveUS6401208B2User identity/authority verificationUnauthorized memory use protectionPower-on resetBIOS

Owner:INTEL CORP

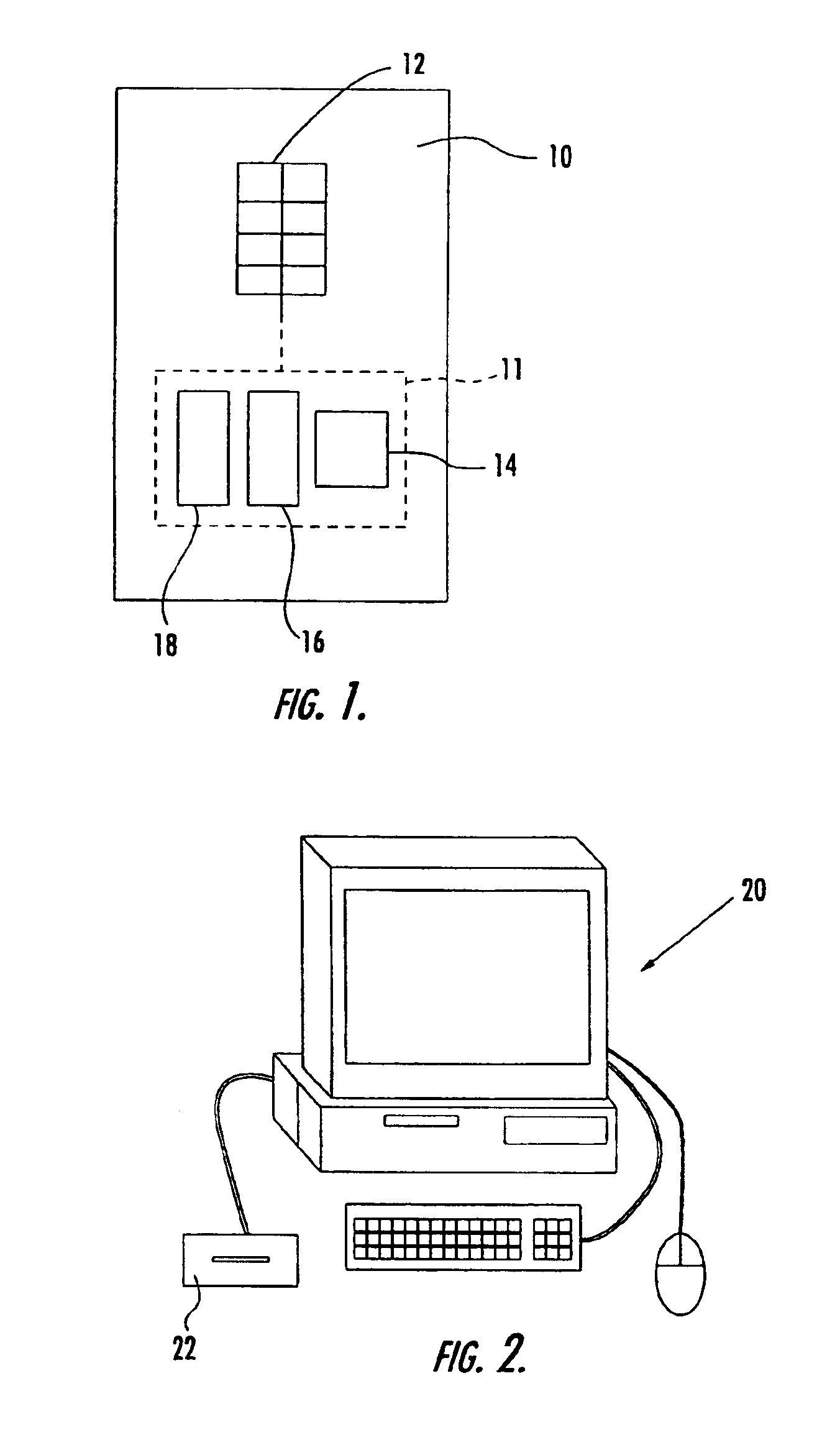

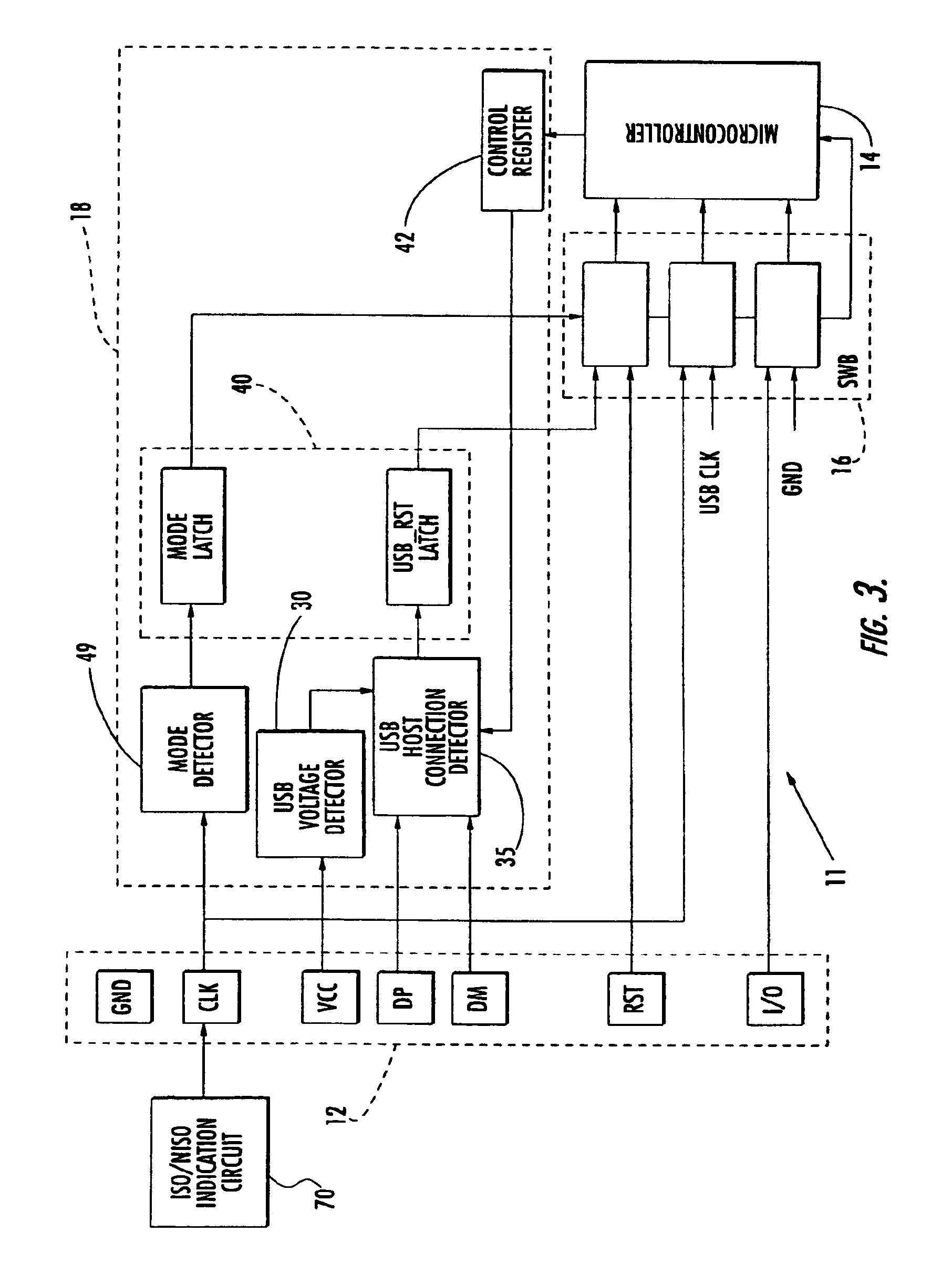

Multi-mode smart card, system and associated methods

InactiveUS6883715B1Co-operative working arrangementsSensing record carriersPower-on resetElectricity

A multi-mode IC is provided for operating in a first mode such as an ISO mode in accordance with International Standards Organization 7816 (ISO 7816) protocol, and a second, non-ISO mode, such as a USB mode in accordance with Universal Serial Bus (USB) protocol. The multi-mode IC is preferably in a smart card and includes a microprocessor and an external interface. The external interface comprises a voltage supply pad, a ground pad, a first set of pads for the first mode, and 2 second set of pads for the second mode. The first set of pads preferably include a reset pad, a clock pad and an input / output pad in accordance with the ISO 7816 protocol, and may also include a variable supply voltage pad in accordance with the ISO 7816 protocol. The IC further includes a mode configuration circuit for detecting a mode condition on one pad of the first set of pads, and configuring the IC in the ISO mode or the non-ISO mode depending on the result. Once the IC is configured in a particular mode, it will operate in only that mode until the next power-on reset sequence.

Owner:STMICROELECTRONICS SRL +1

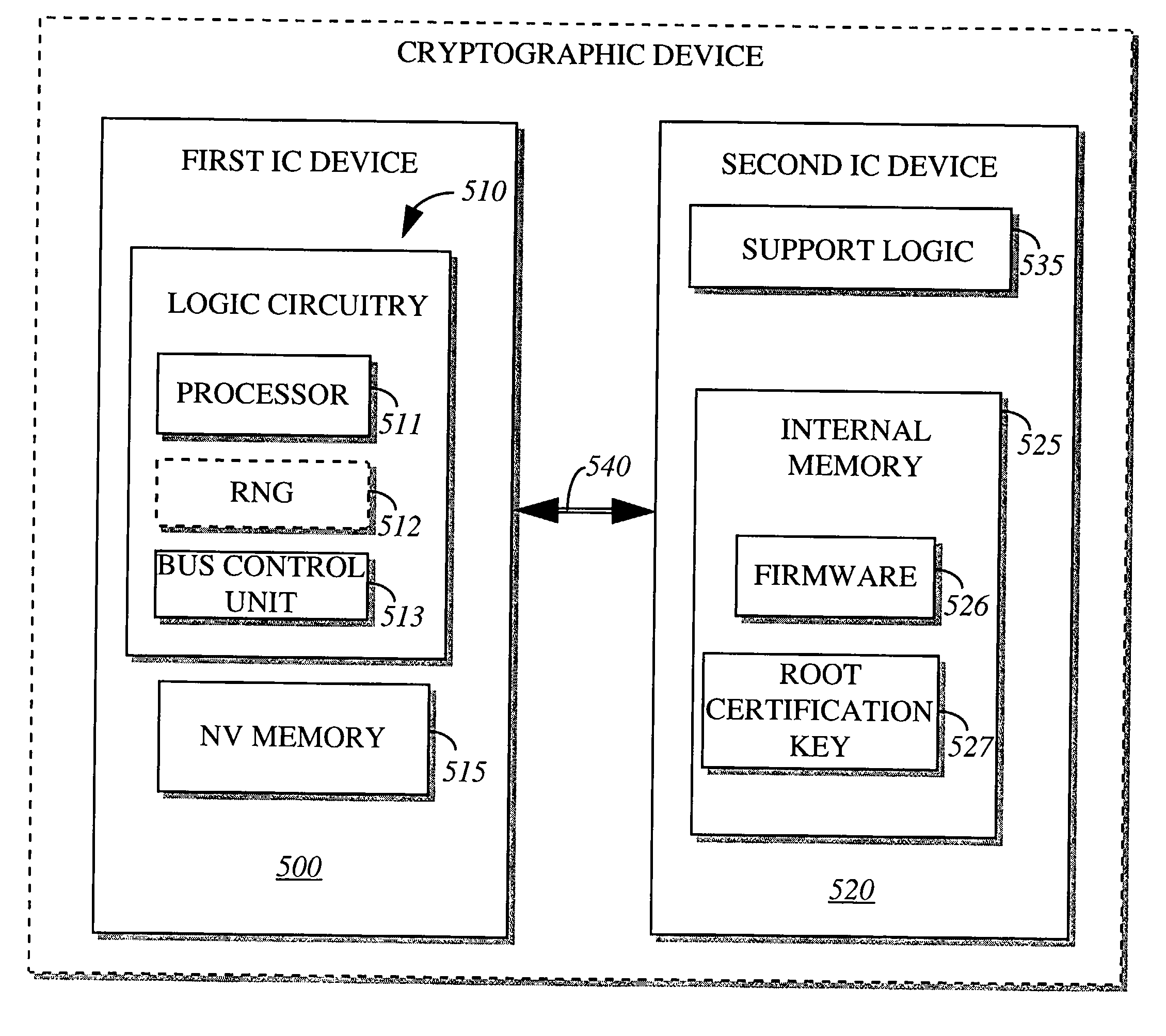

Method for BIOS authentication prior to BIOS execution

A cryptographic device is implemented in communication with a host processor to prevent the host processor from performing a standard boot-up procedure until a basic input output system (BIOS) code is authenticated. This is accomplished by a cryptographic device which is addressed by the host processor during execution of a first instruction following a power-up reset. The cryptographic device includes a first integrated circuit (IC) device and a second IC device. The first IC device includes a memory to contain firmware and a root certification key. The second IC device includes logic circuitry to execute a software code to authenticate the BIOS code before permitting execution of the BIOS code by the host processor.

Owner:INTEL CORP

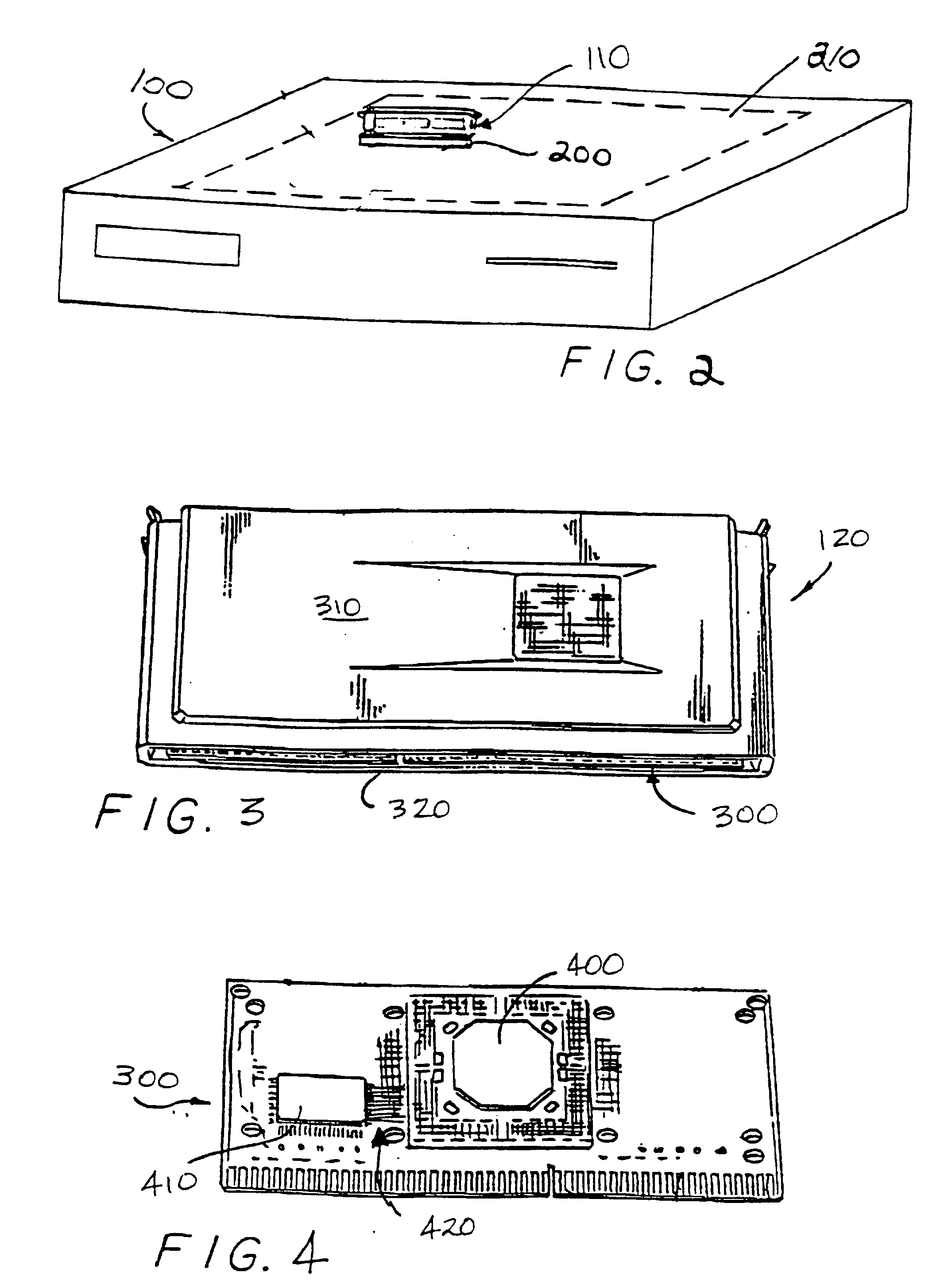

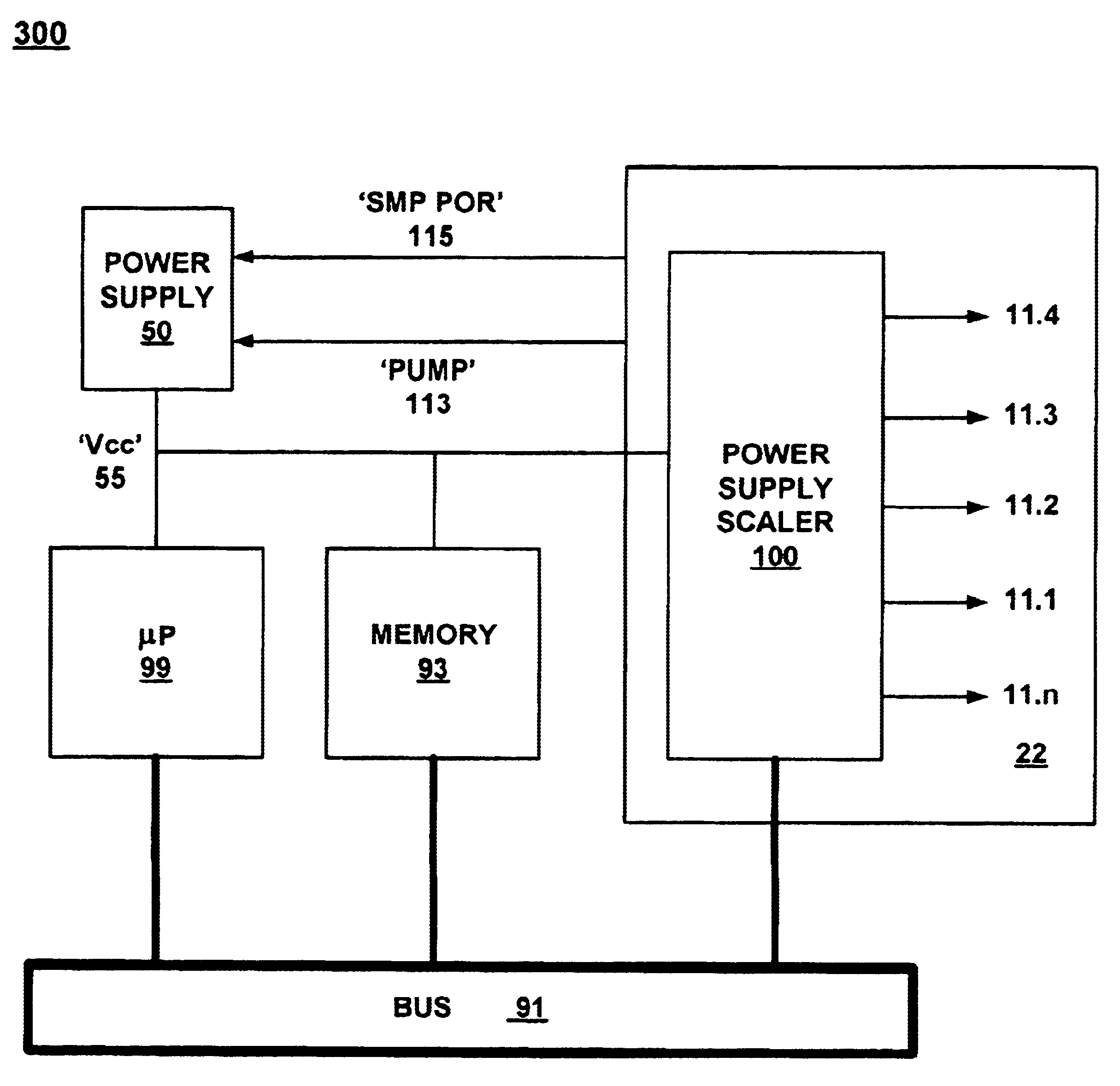

Method and system for interaction between a processor and a power on reset circuit to dynamically control power states in a microcontroller

InactiveUS6854067B1Optimize power stateEfficient workPulse automatic controlVolume/mass flow measurementPower-on resetMicrocontroller

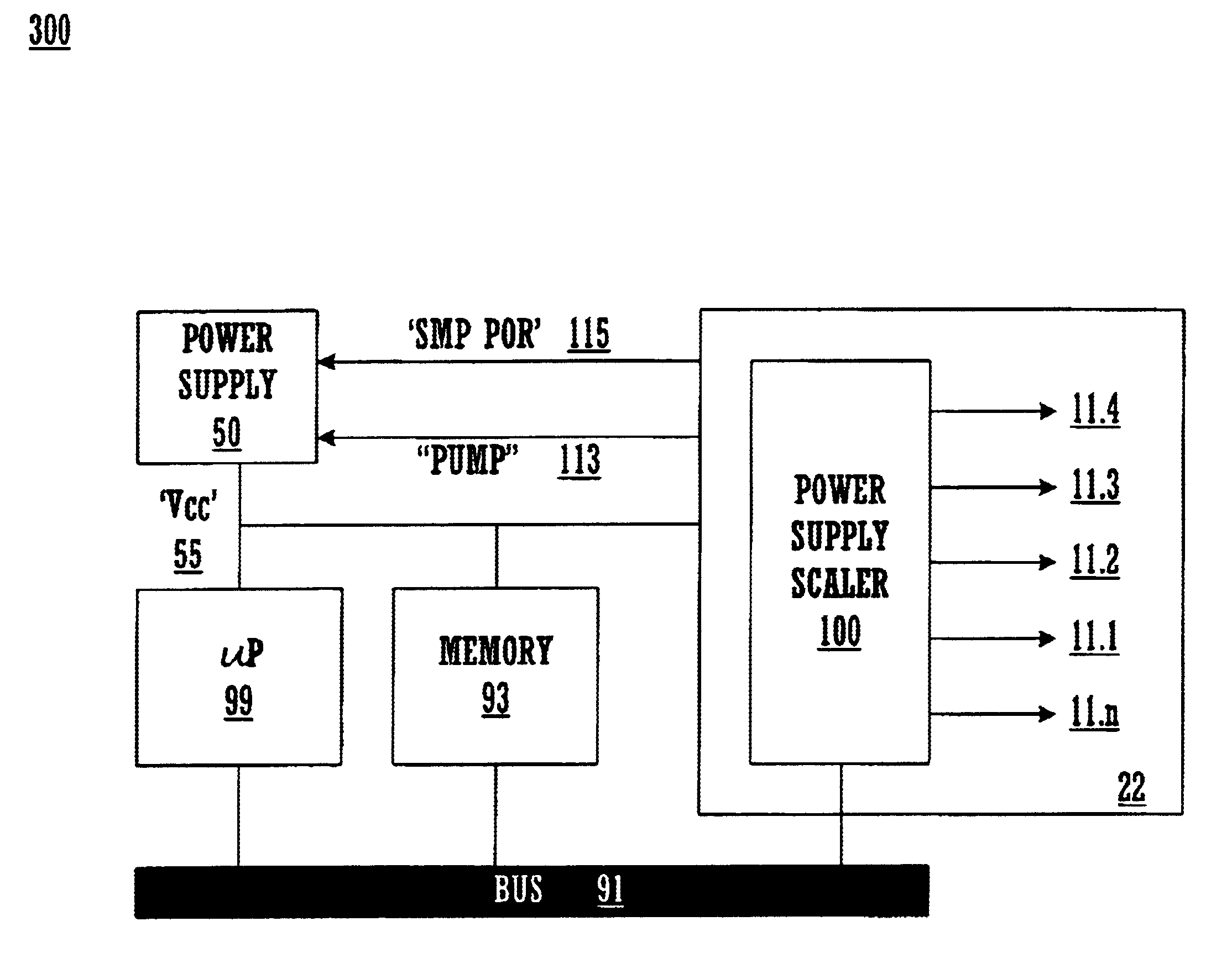

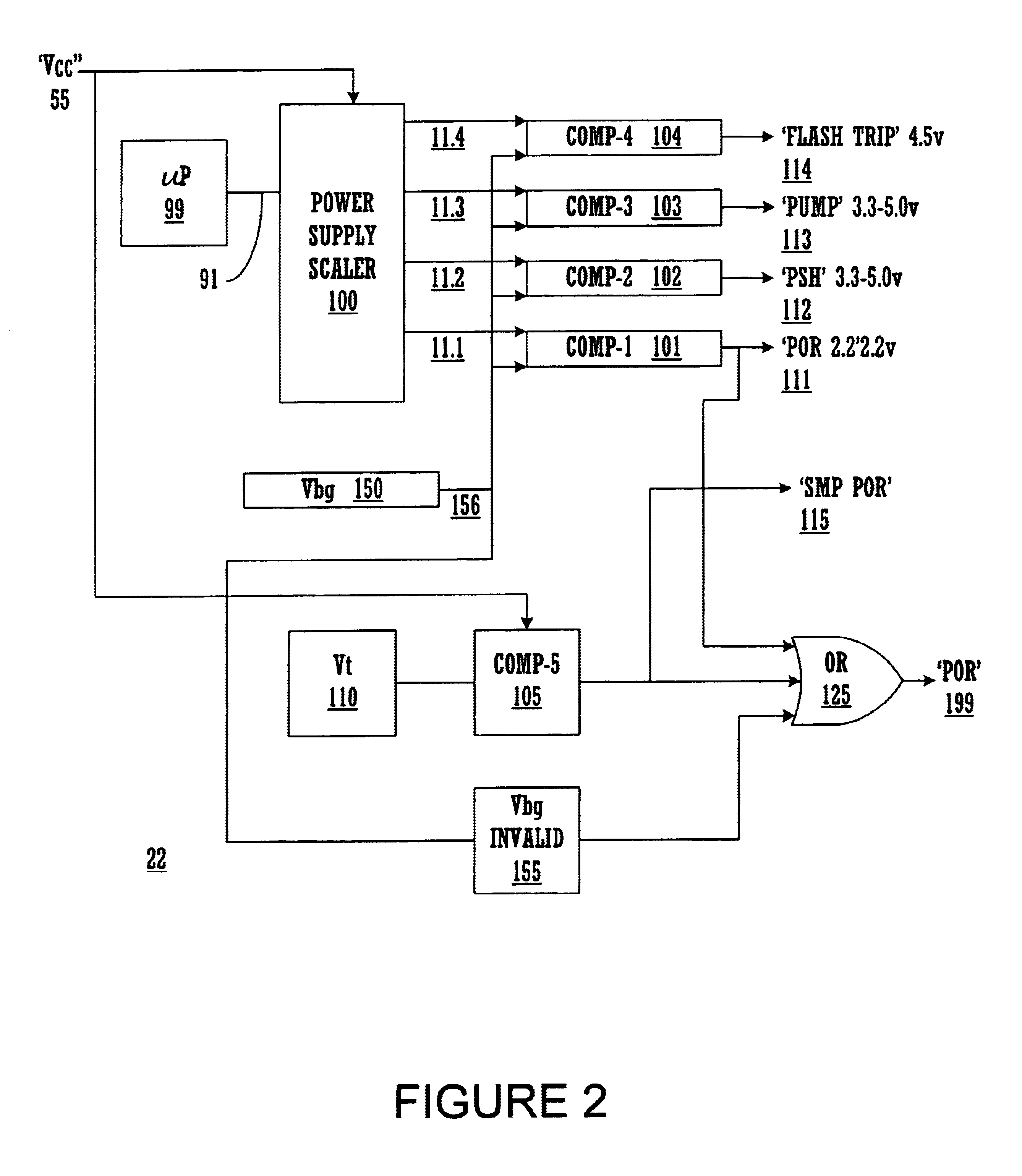

A method and system dynamically controlling microcontroller power. In one embodiment, the method and system configures a microcontroller power state, senses its condition, and determines its suitability status, communicates that status between a POR circuit and a processor, controls certain microcontroller functions accordingly, and dynamically programs power related functions. This is enabled, in one embodiment, by dynamic interaction between the POR circuit and the processor. Microcontroller power status is ascertained, and a corresponding optimal power state determined. Optimal values for programmable independent multiples of a supply voltage is programmatically calculated and set, dynamically adjusting microcontroller power states. In one embodiment, the optimal values are communicated to a scaler in the POR circuit by the processor, and registered within a multiplexer / register matrix within the scaler. The processor commands the matrix to change programmable independent multiples of supply voltage to correspond with the optimal values, and monitors corresponding action and power status.

Owner:HERITAGE IP LLC

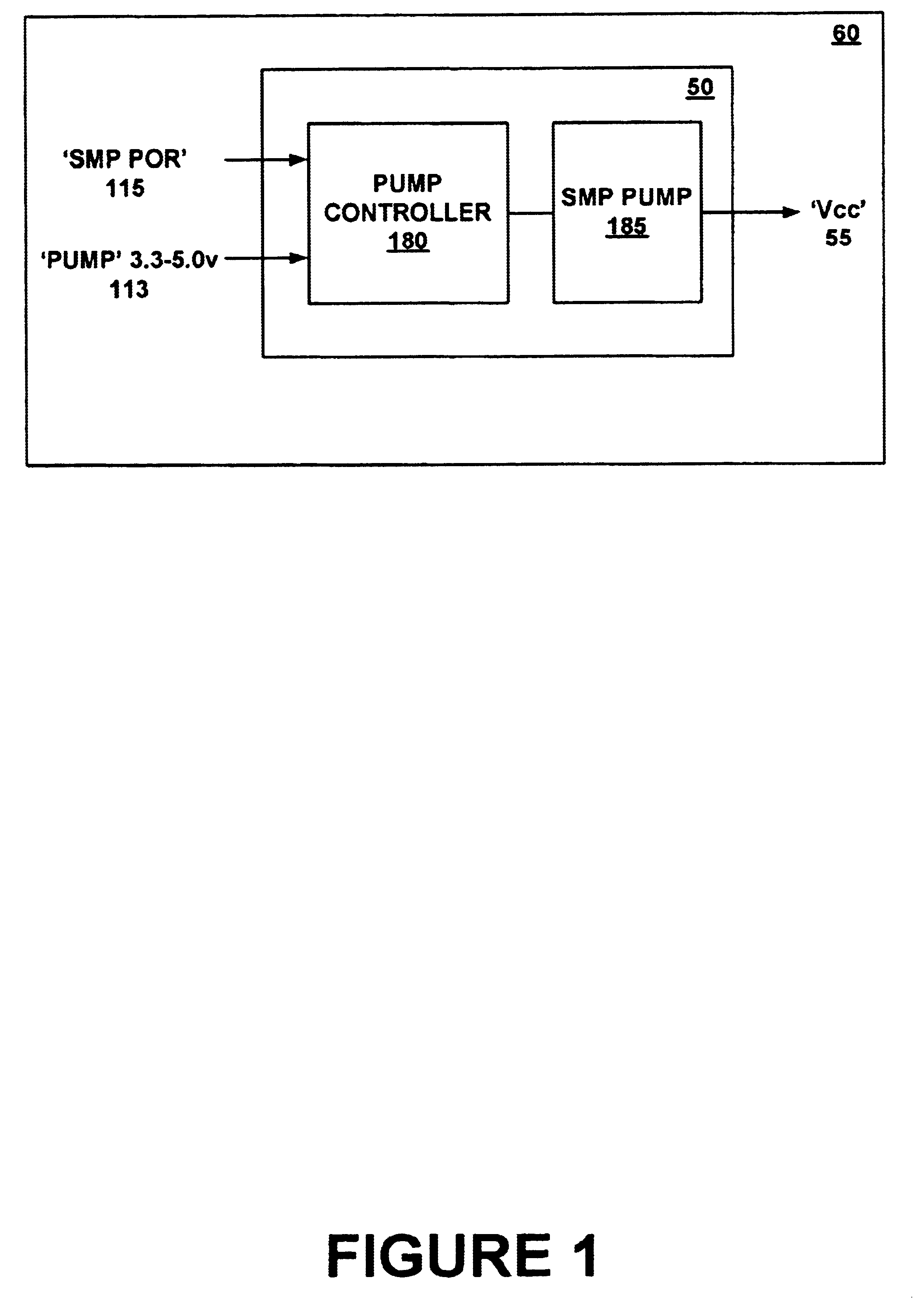

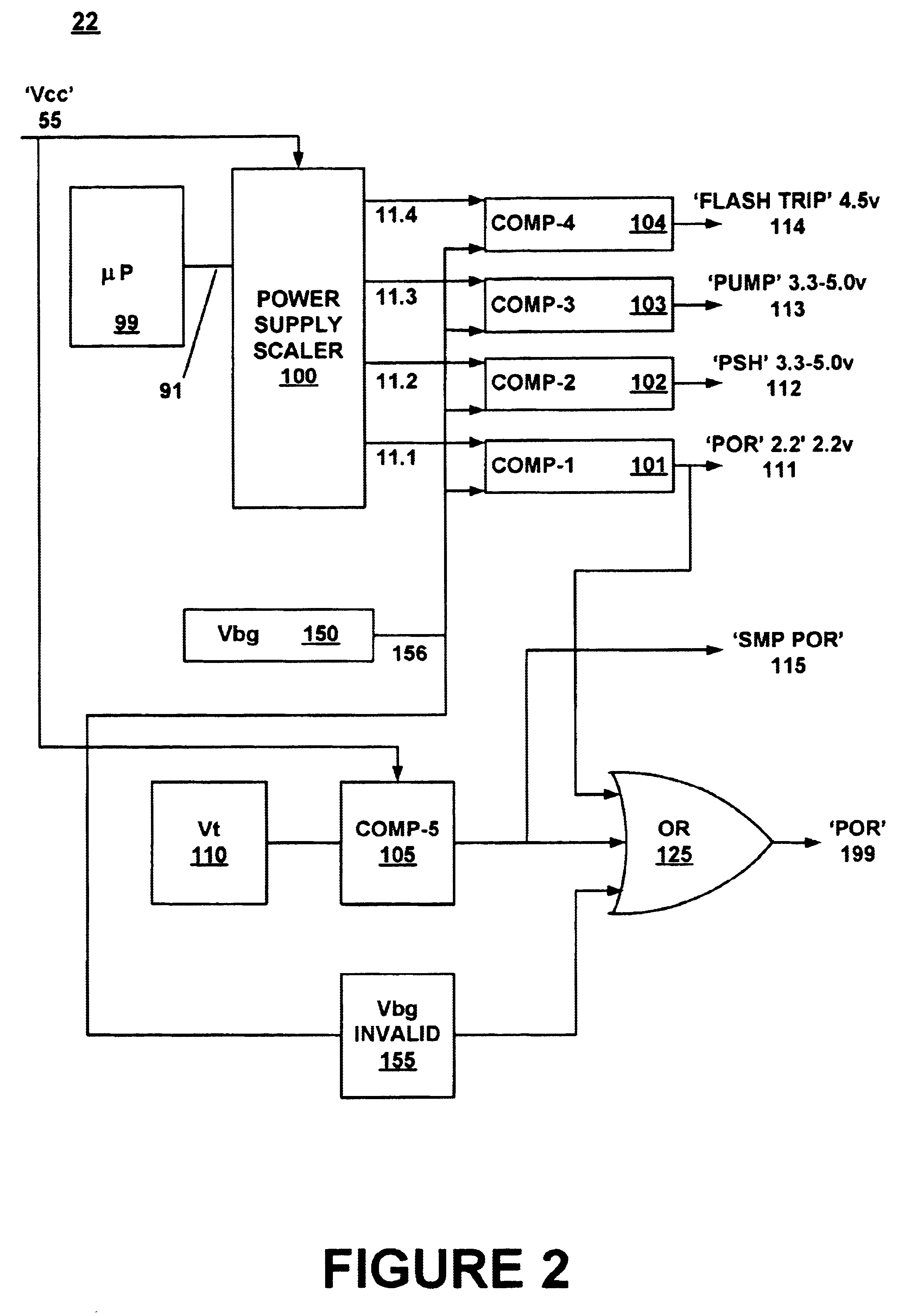

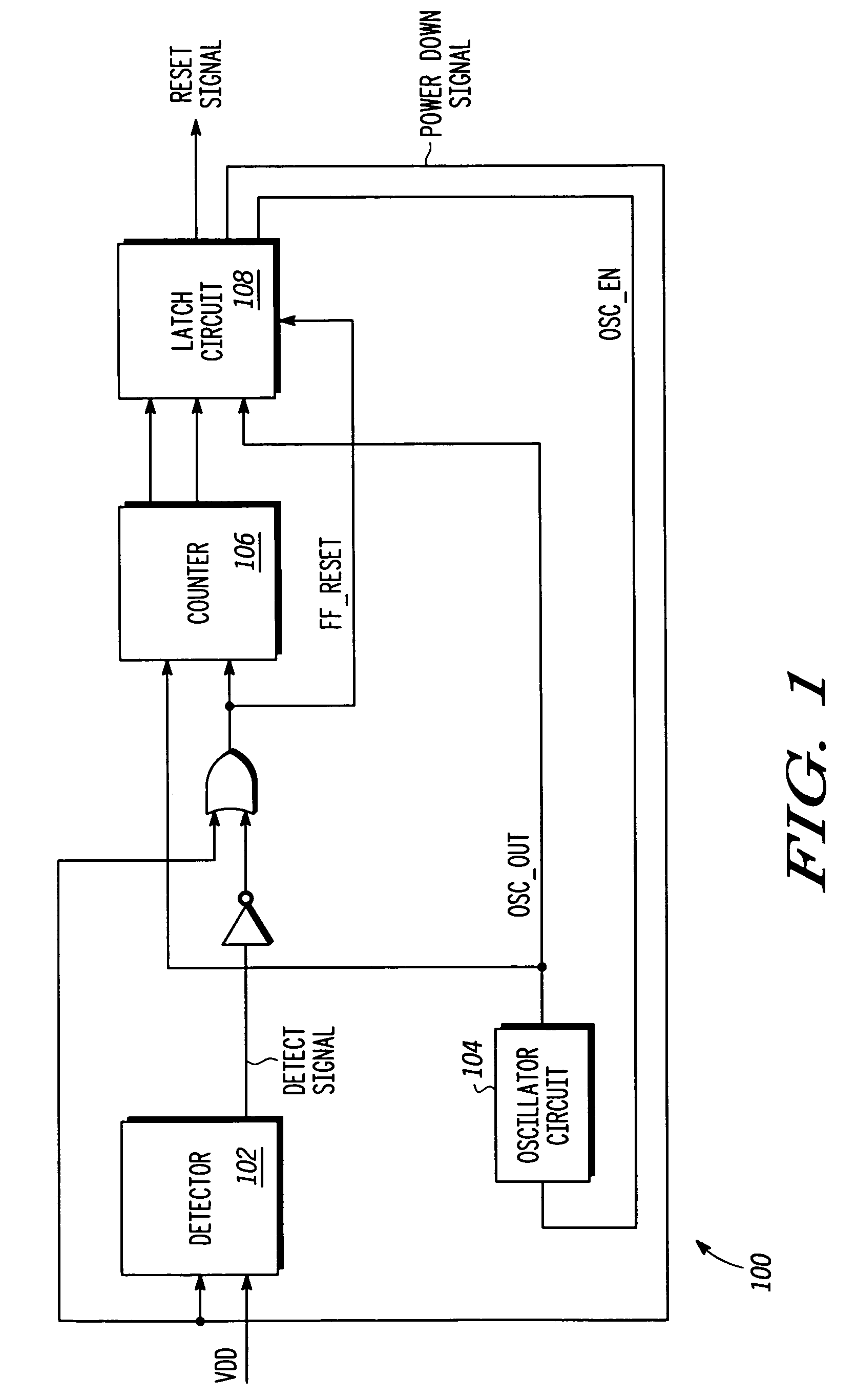

Power on reset circuit for a microcontroller

InactiveUS6868500B1Efficient workProvide functionalityPulse automatic controlVolume/mass flow measurementMicrocontrollerPower-on reset

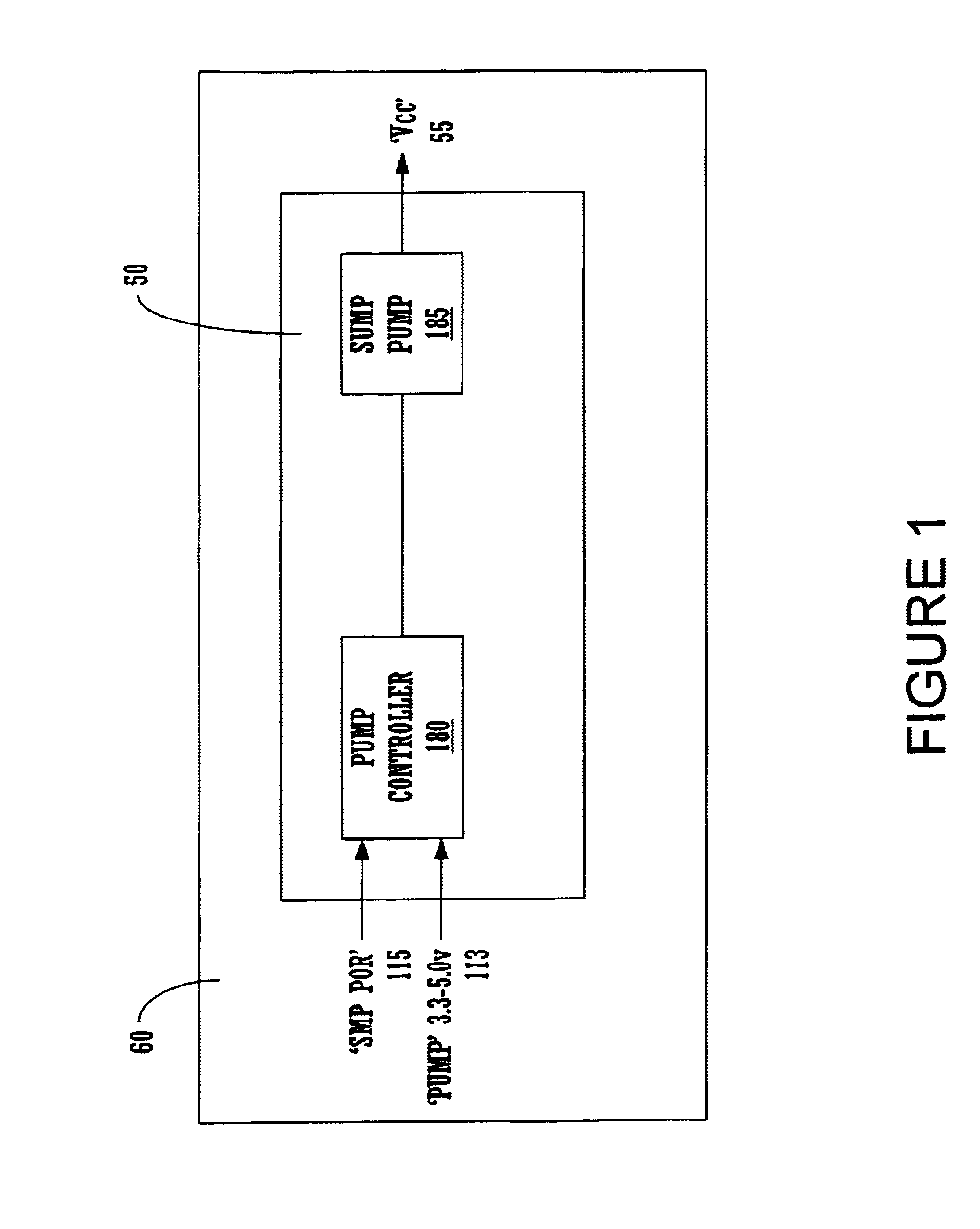

In accordance with one embodiment of the present invention, a circuit provides power stability functions for a microcontroller, during startup and normal operations performing power on reset functions and an array of power stability functions. The power on reset functions hold the microcontroller in a safe reset condition, reinforce the POR hold, and force its switch mode pump to drive up voltage provided to its common supply source. The power stability functions constitute a power on reset function, a power supply health, e.g., power state condition monitoring function, a control function for dynamically controlling the common supply source, and auxiliary functions, which may be protective of a flash memory. The power on reset function operates at a fixed and / or programmably changeable voltage levels. In one embodiment, the POR circuit is interconnected with a processor through a bus, enabling programmatic processor control of microcontroller power through interaction with the POR circuitry.

Owner:MONTEREY RES LLC

Method for initializing an electronic device using a dual-state power-on-reset circuit

InactiveUS6141764AMinimum power consumptionPulse automatic controlVolume/mass flow measurementPower-on resetElectricity

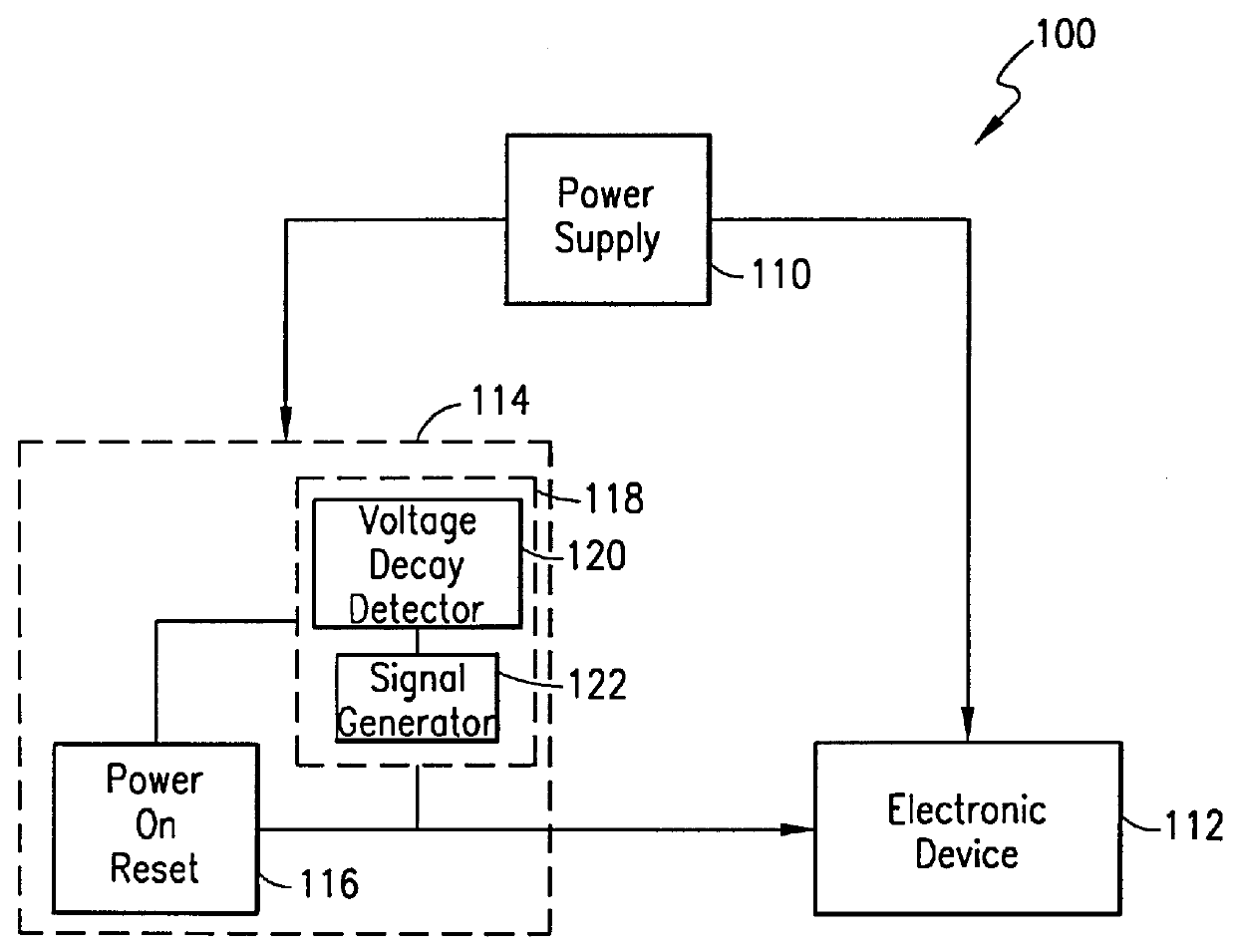

An initializer that responds to change in a power supply potential level, for generating an initialize signal to initialize a circuit to a select state, the initializer includes a power-on reset circuit that switches between an active and a powered-down state, and is for generating the initialize signal. The initializer also includes a wake-up circuit that monitors the power supply potential level and switches the power-on reset circuit from the powered-down state to the active state when selected change in the power supply potential level occurs.

Owner:MAXIM INTEGRATED PROD INC

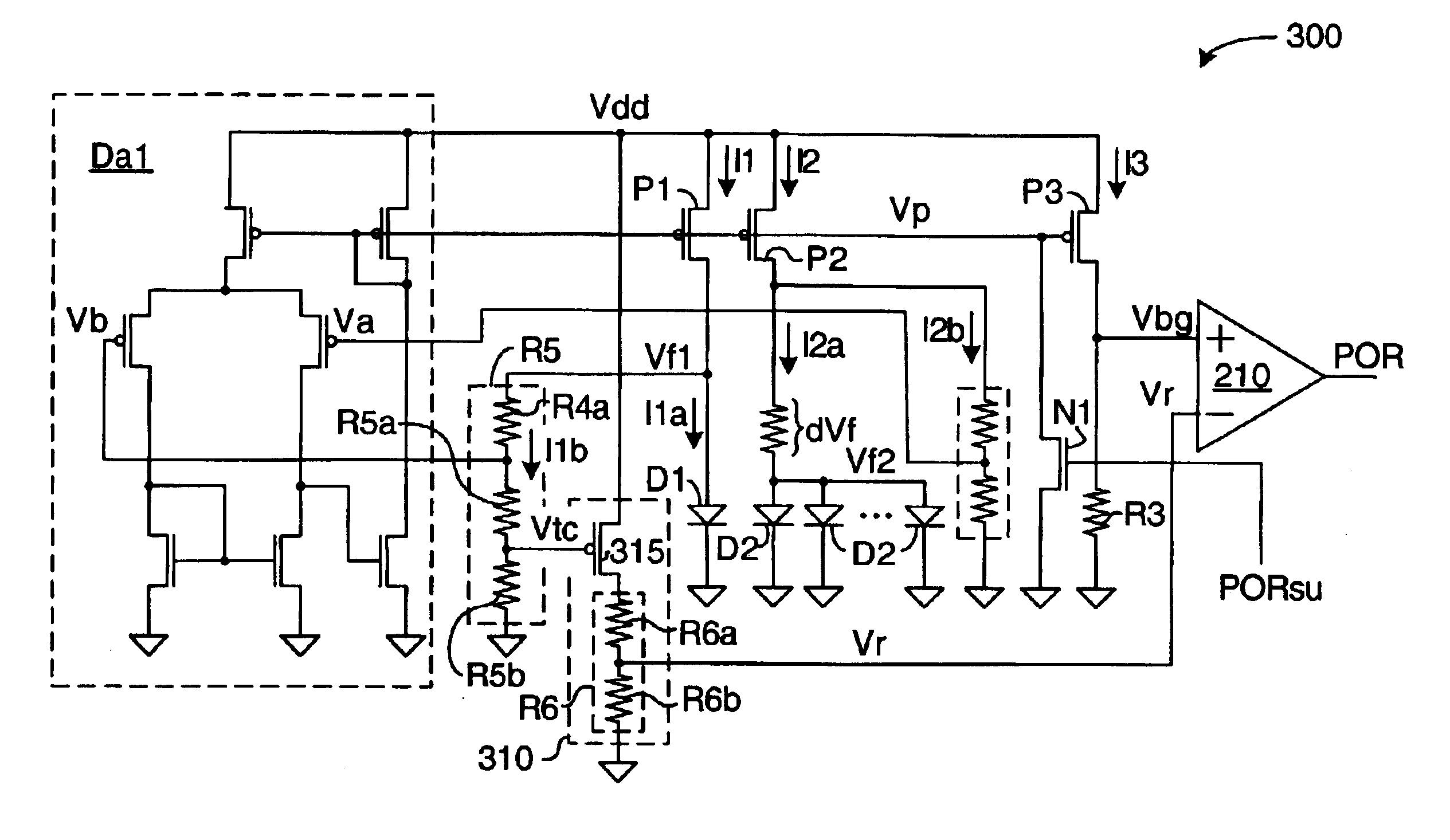

Power-on-reset circuit with temperature compensation

Described are power-on reset methods and circuits for resetting and subsequently enabling integrated circuits in response to applied power. A POR circuit in accordance with one embodiment is capable of operating at exceptionally low temperatures and supply voltages, and is relatively tolerant to process variations. The POR circuit compares a band-gap reference signal to a temperature-compensated reference signal that varies in inverse proportion to temperature. The temperature-compensated reference signal extends the useful temperature range of the POR circuit.

Owner:XILINX INC

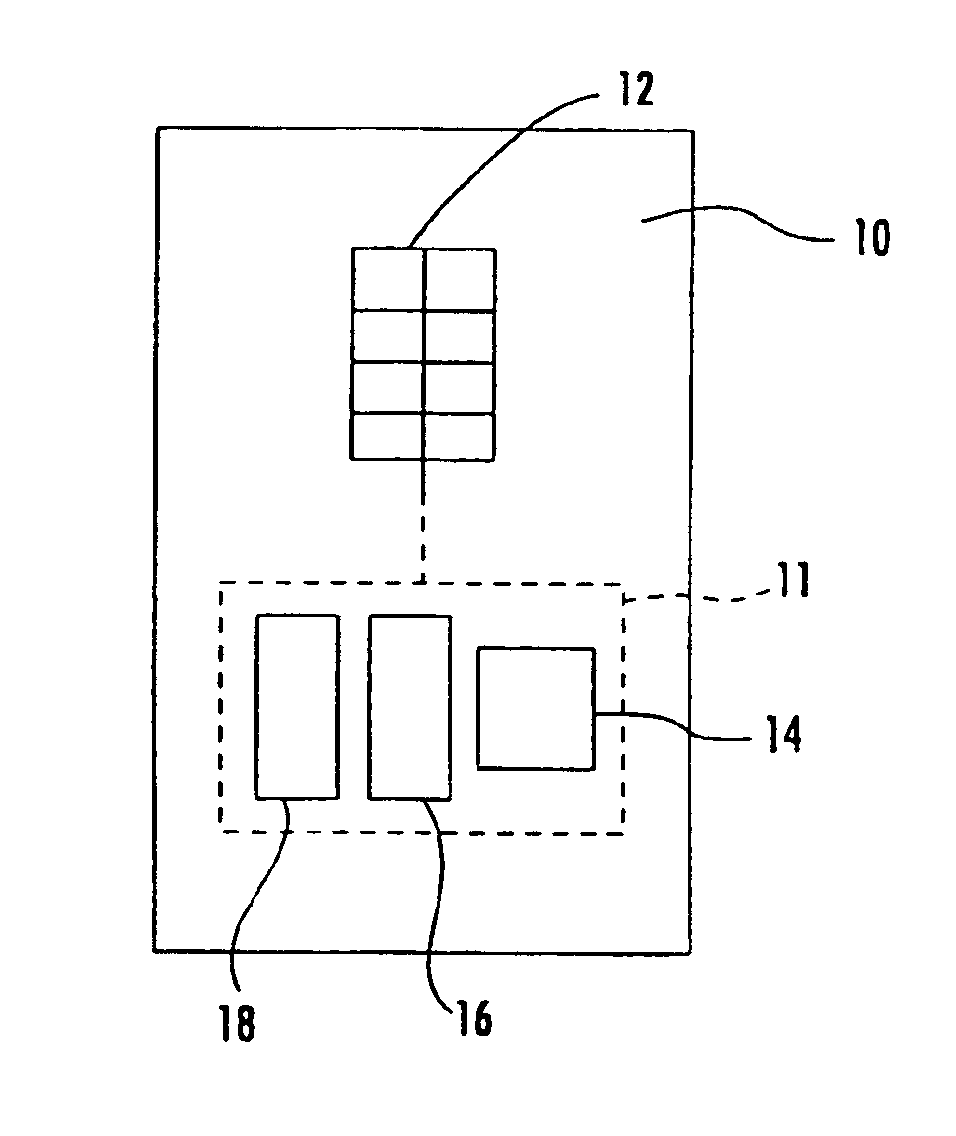

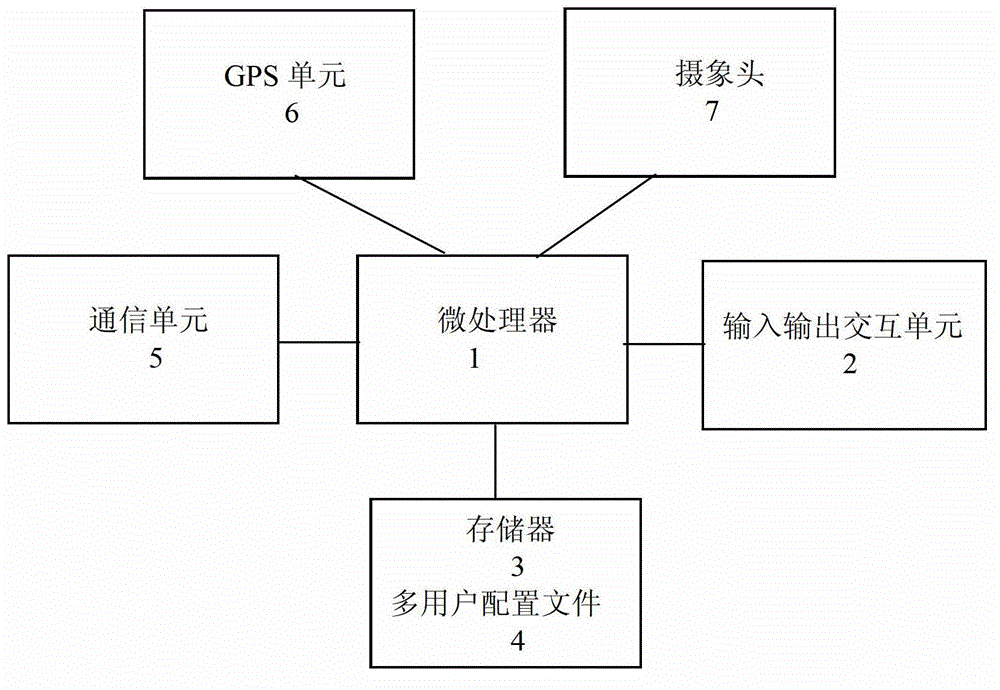

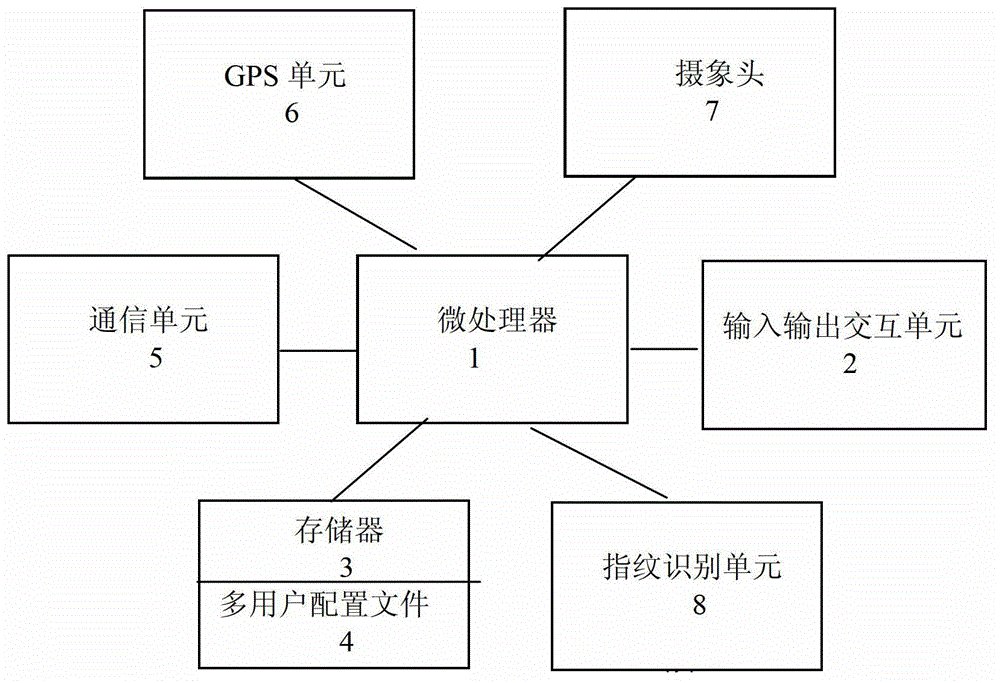

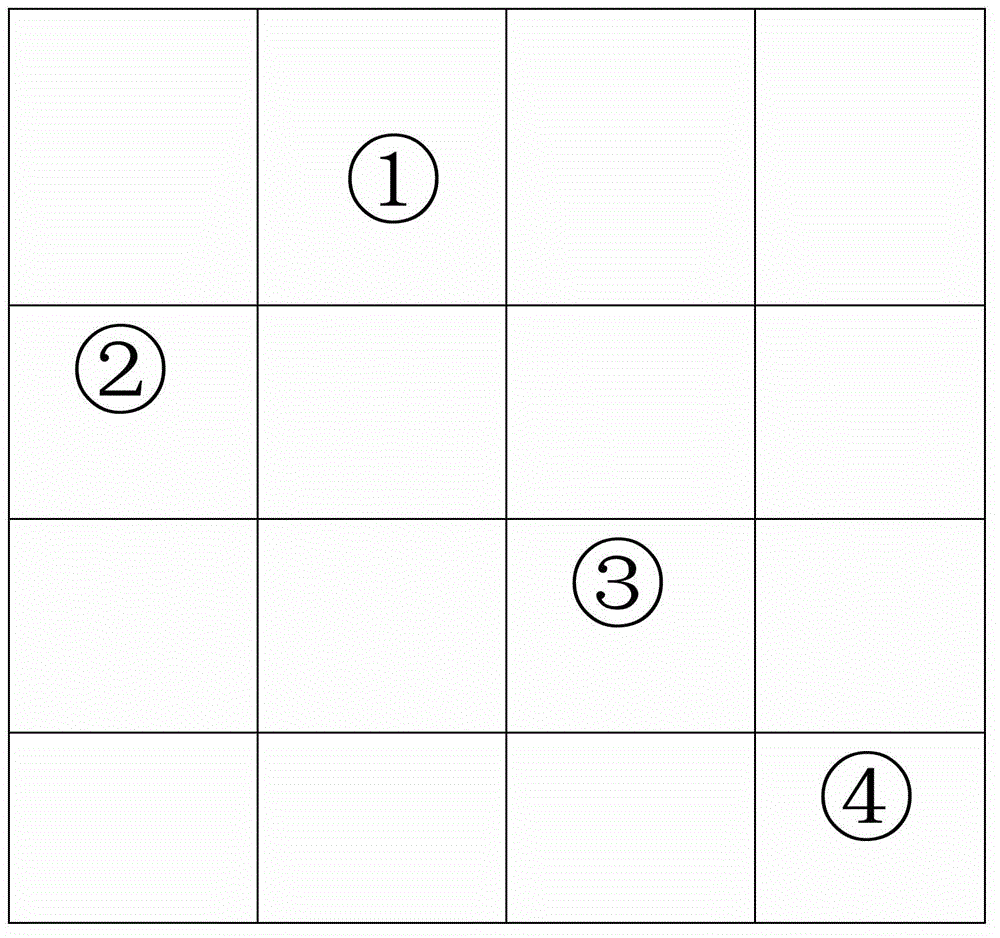

Intelligent multi-user mobile phone and logging method thereof

InactiveCN102917348APrevent leakageSatisfy securityEnergy efficient ICTSecurity arrangementPower-on resetAddress book

The invention discloses a multi-user mobile phone logging method and an intelligent mobile phone employing the same. The method adopts a multi-user configuration file (4) in which parameters configured for each user include a user name, a login user name, a login password and an exclusive file folder. Following steps in the method are carried out during power-on reset of the intelligent mobile phone: S1) inputting the login password; S2) carrying out a step S3) if the login password is consistent with a login password on a user log sheet, or returning to the step S2) or enabling the mobile phone to execute a safety alarm step; and S3) loading an exclusive address book file, an exclusive call log file, an exclusive short message file, an exclusive application program and an exclusive data file in the exclusive file folder under a current user name in the multi-user configuration file (4) from a memory device (3).By adopting the method and the mobile phone, the mobile phone can be used under different user names, non-shared data and programs among users can be segregated from each other, therefore the security and the operating requirements on special occasions are met, and energy consumption is reduced.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

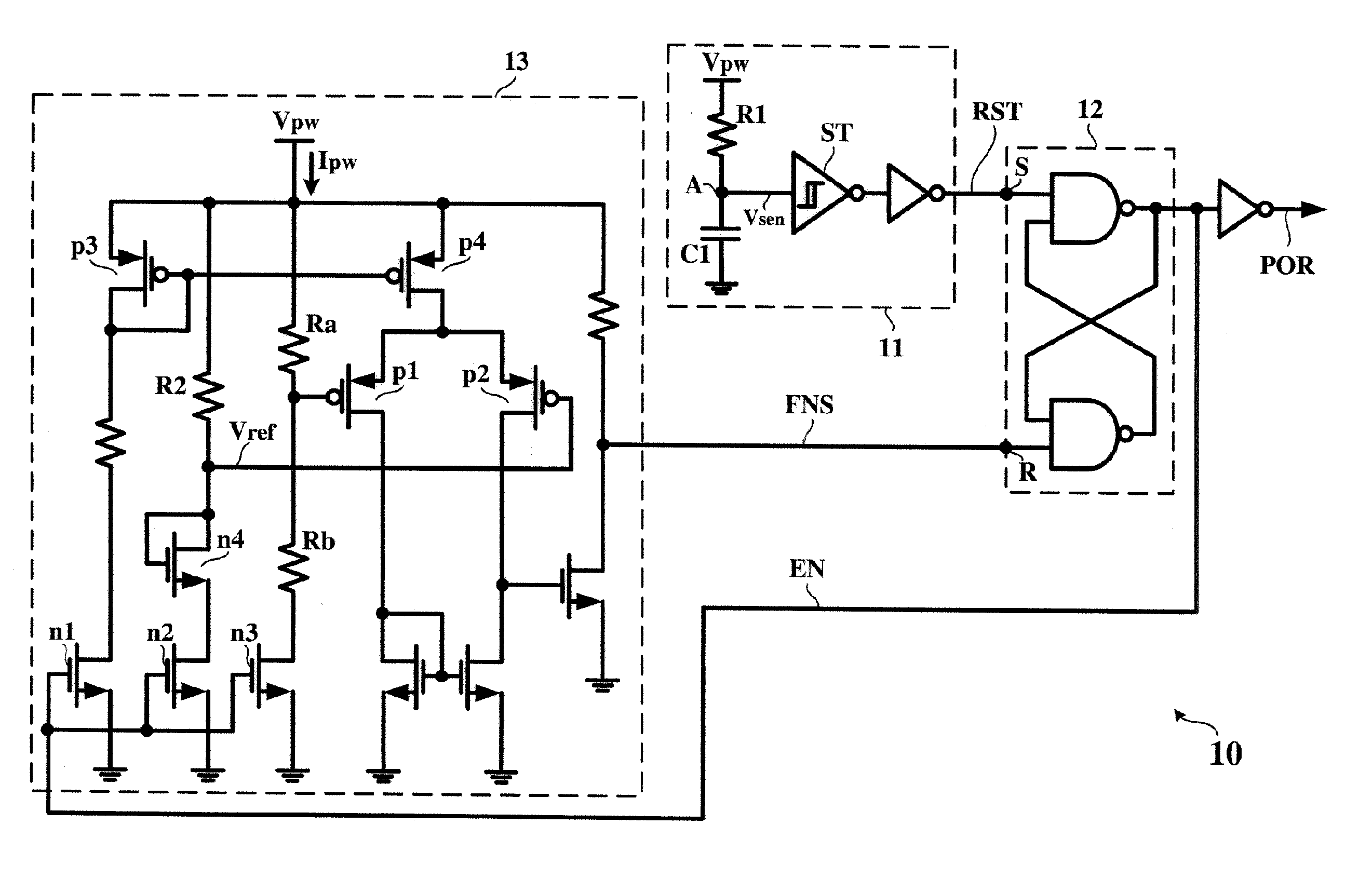

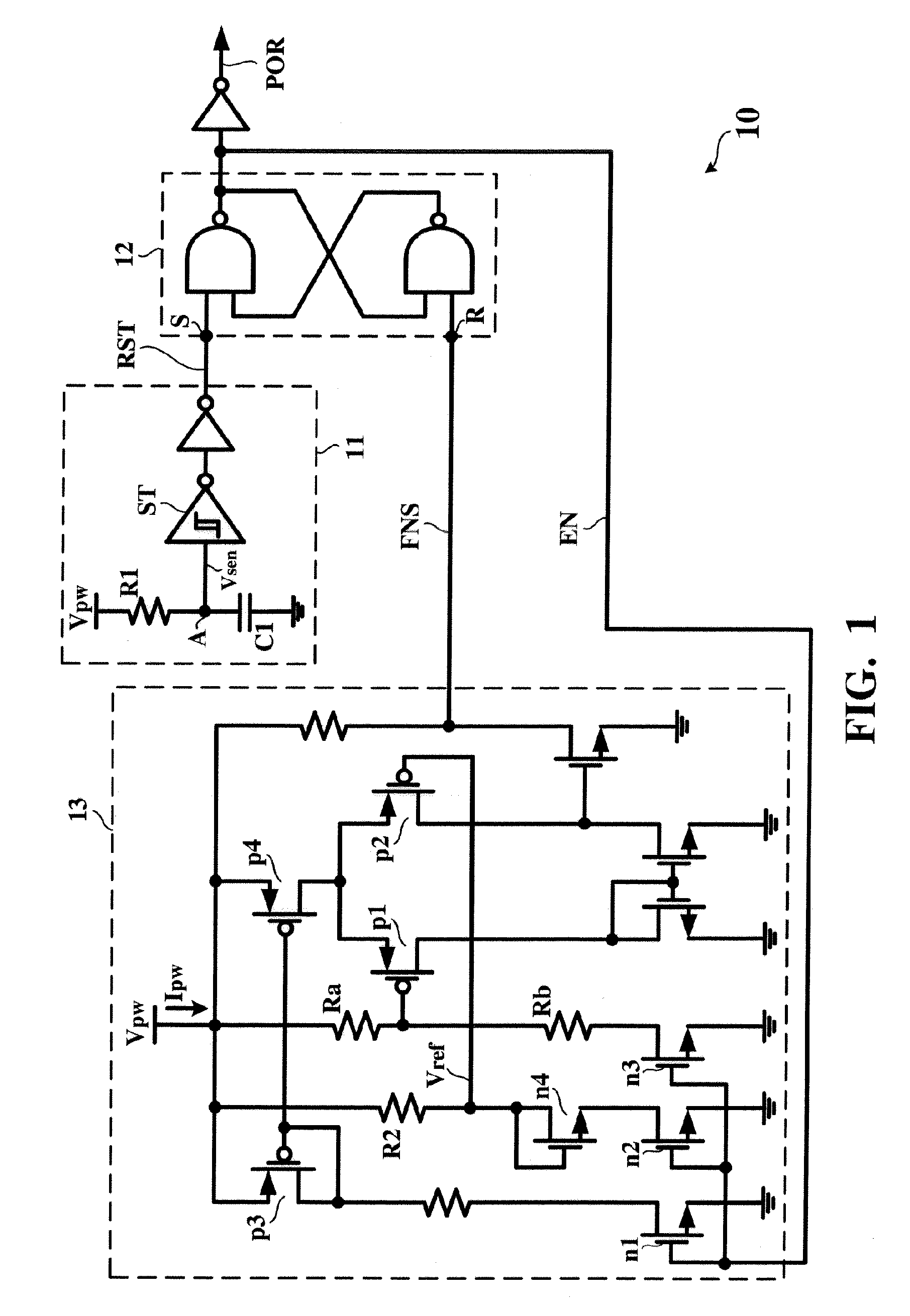

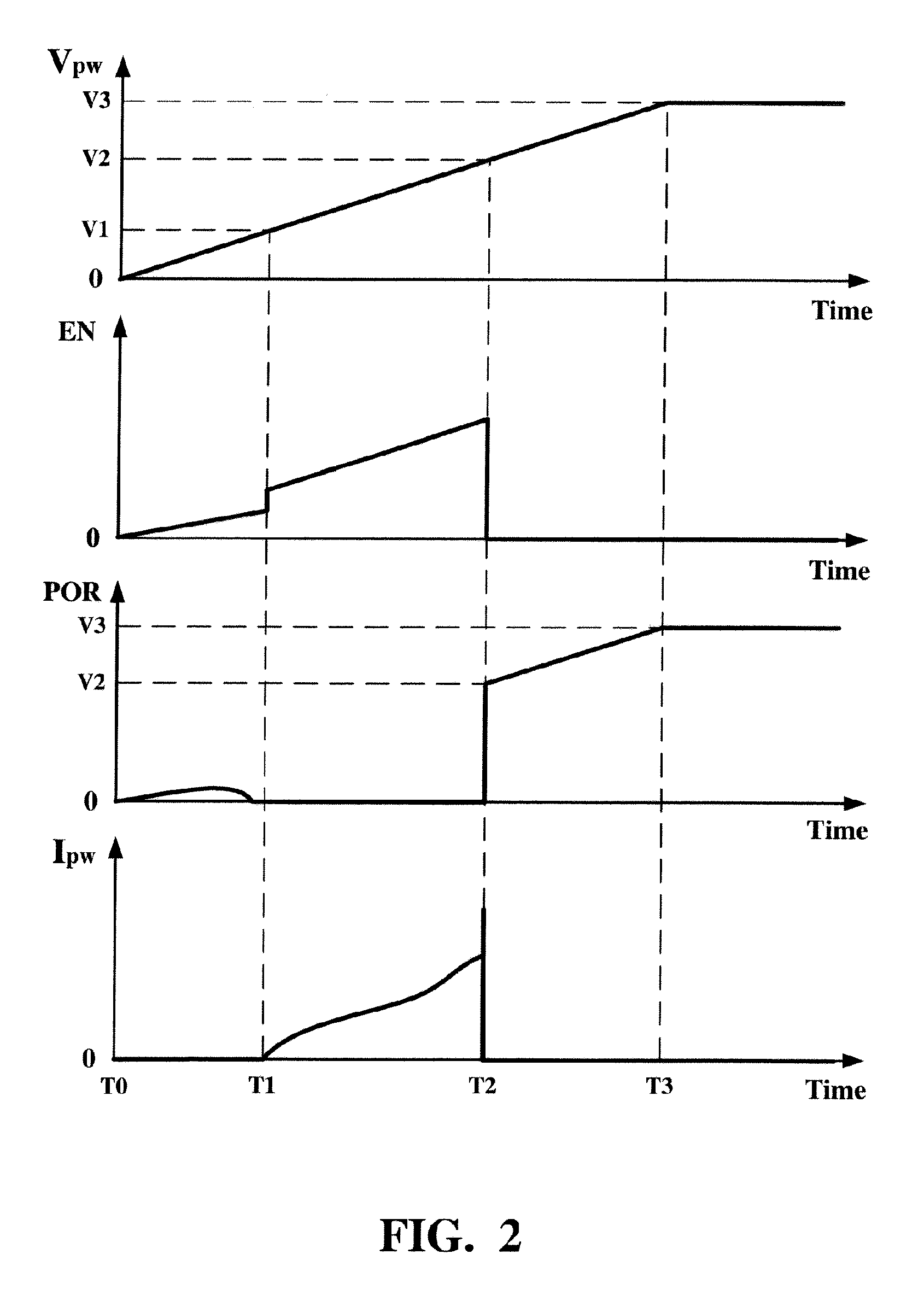

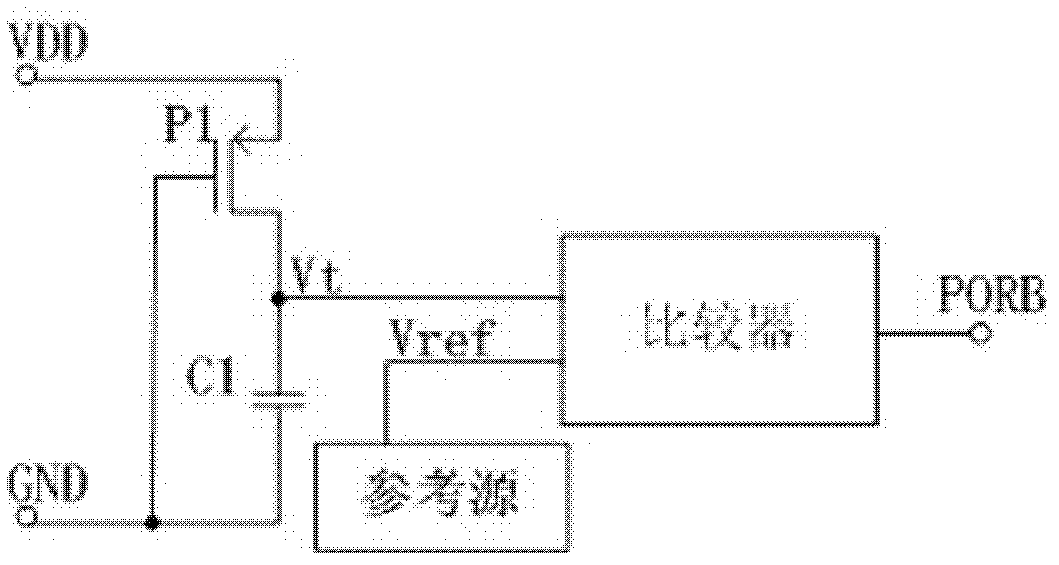

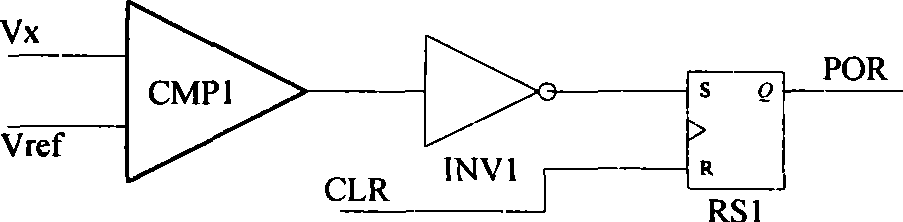

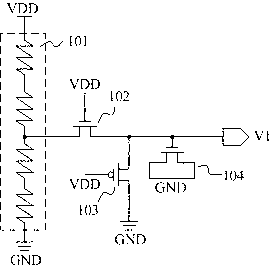

Power-on reset circuit

InactiveUS20070001721A1Accurately adjusting reset finishing voltageAccurately setting and adjusting reset finishing voltagePulse automatic controlElectronic switchingPower-on resetElectricity

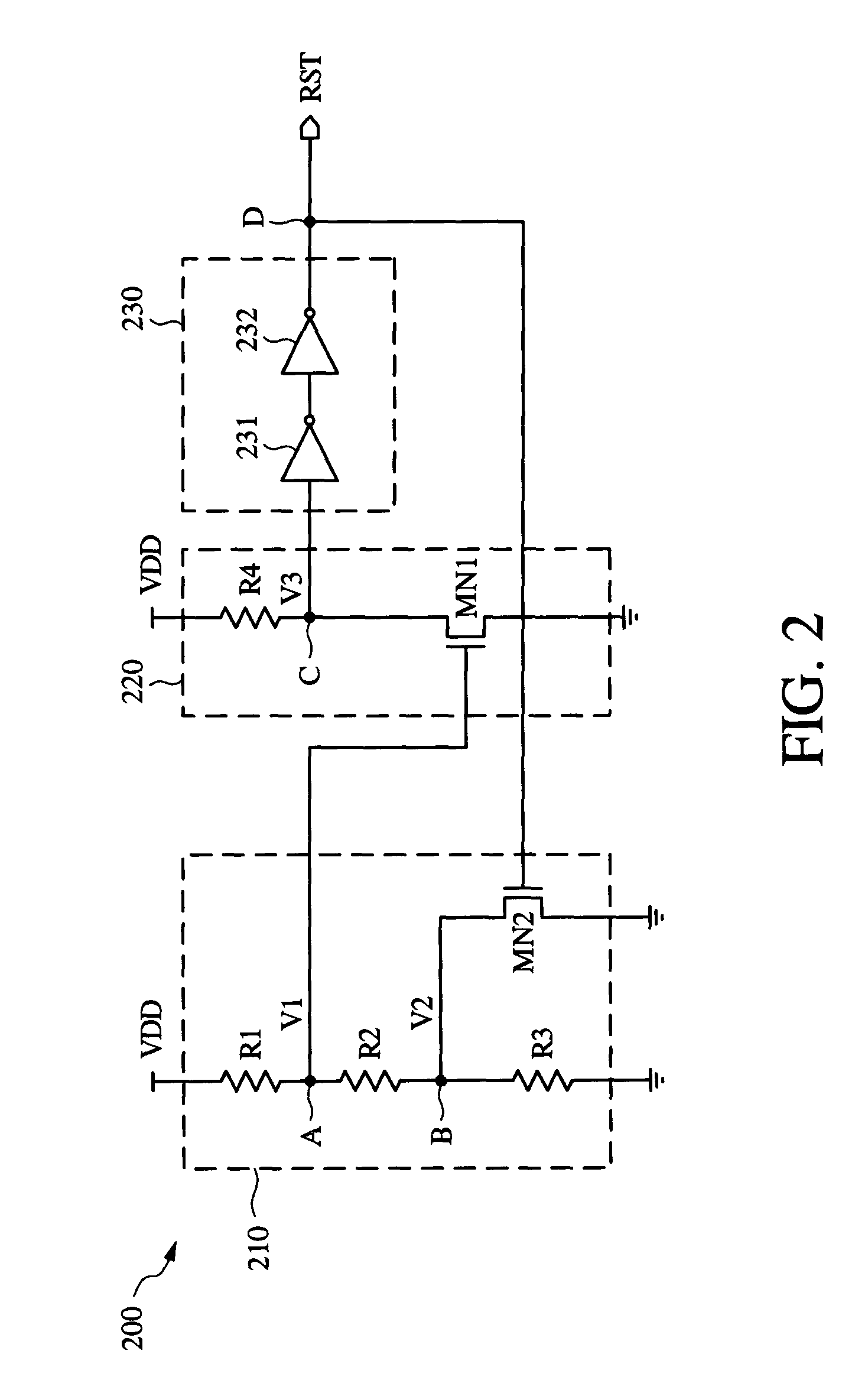

A power-on reset circuit has a reset starting circuit, a reset finishing circuit, and a latch circuit. The reset starting circuit generates a reset starting signal in response to a power voltage. When the power voltage reaches a predetermined reset finishing voltage, the reset finishing circuit generates a reset finishing signal. The latch circuit generates a power-on reset signal having a first state and a second state. In response to the reset starting signal, the latch circuit causes the power-on reset signal to transition to the first state. In response to the reset finishing signal, the latch circuit causes the power-on reset signal to transition to the second state.

Owner:AIMTRON TECH CORP

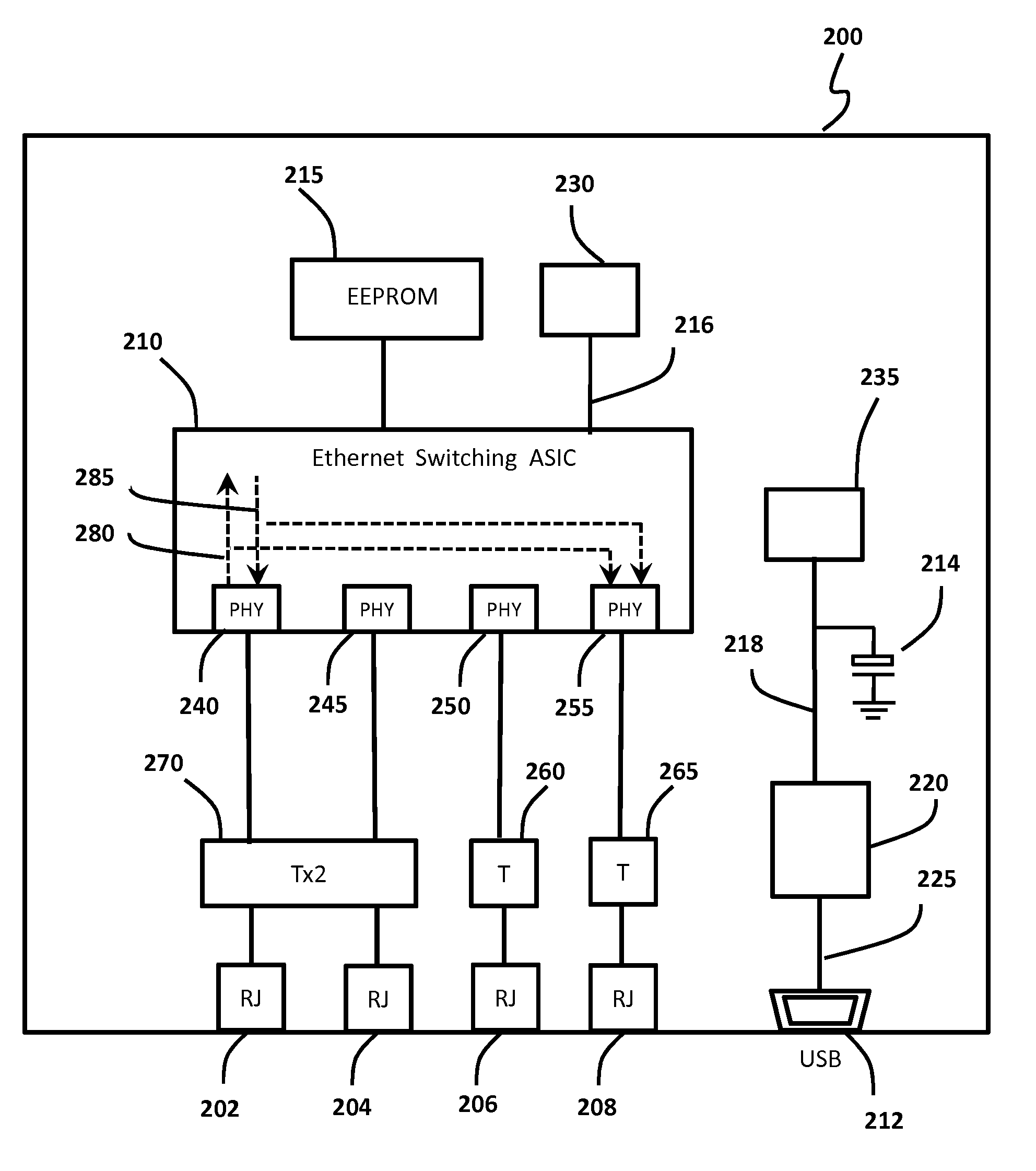

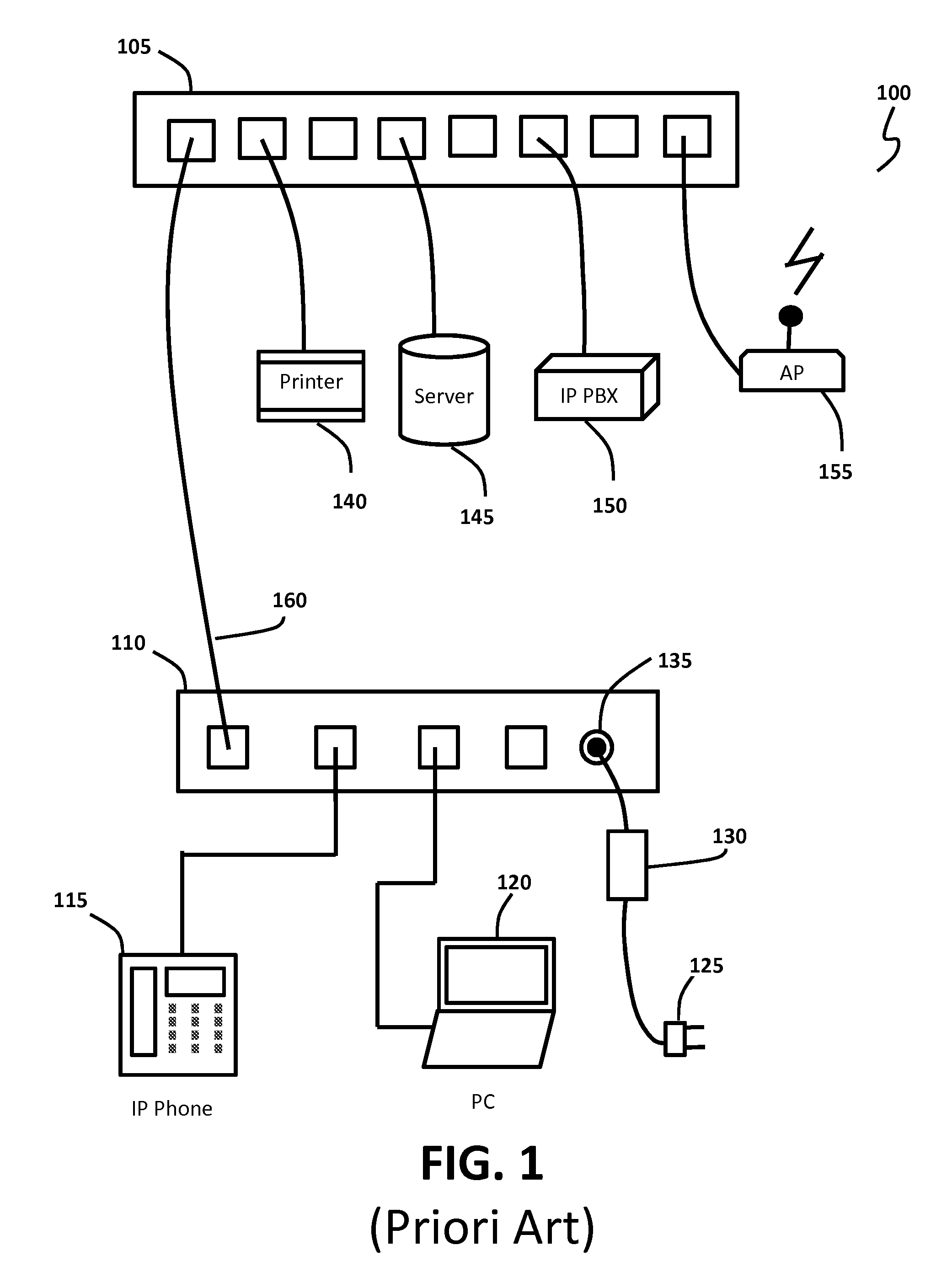

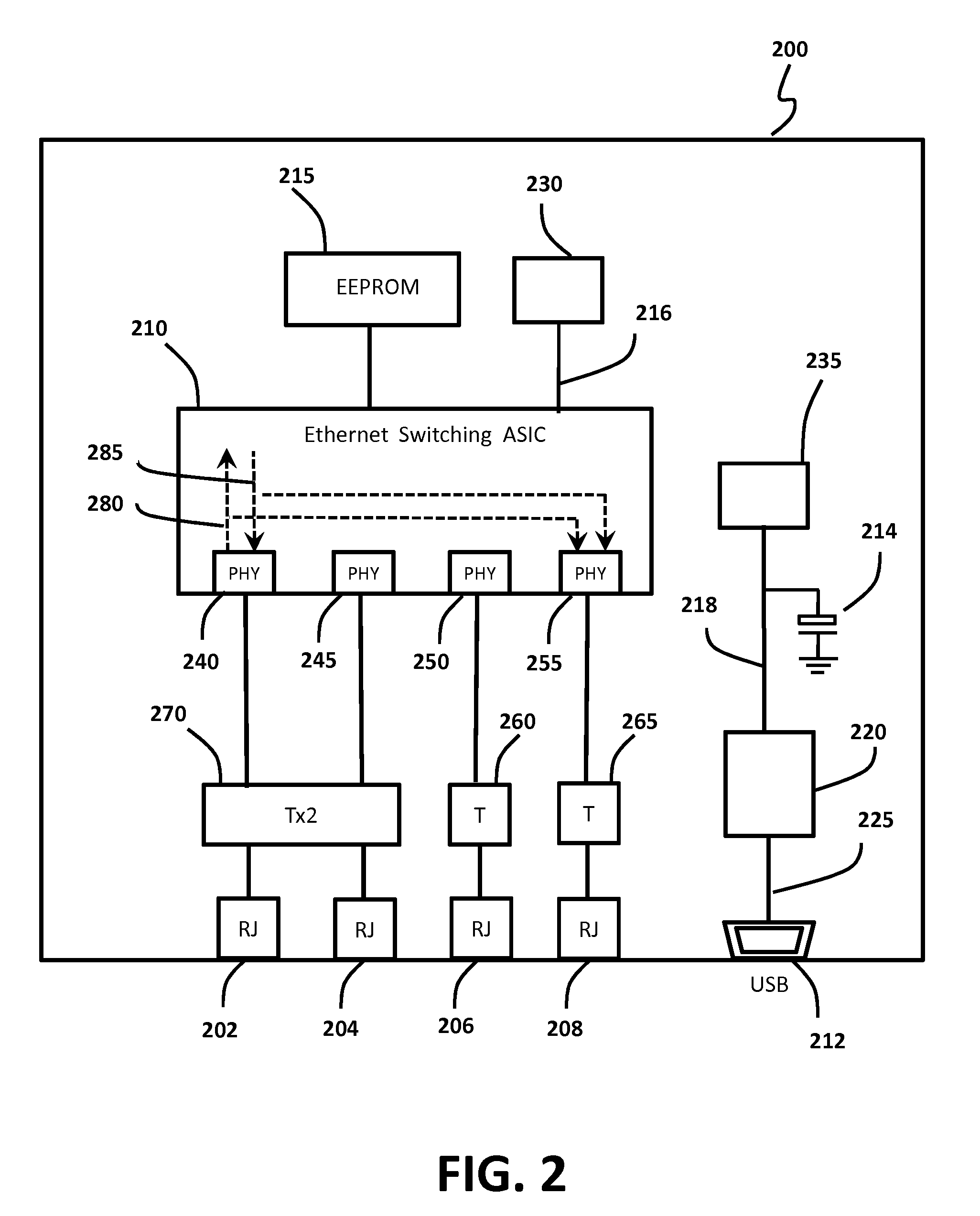

Ethernet Switch and System

An Ethernet switch includes a plurality of network ports, wherein visibility of data packets traffic is configured by loading port-mirroring related configuration data from a configuration memory device into the Ethernet switch upon power-on reset. As a result, no manual configuration by a user is required, and the hardware cost of the Ethernet switch is reduced. The Ethernet switch is further configured to enable pass-through of Power over Ethernet (PoE) inline power between two selected network ports. A USB connector is further included and adapted for the Ethernet switch to receive input power from a USB port of a USB host device and for the Ethernet switch to send and receive data packets to and from the USB host device.

Owner:HE ZIQIANG

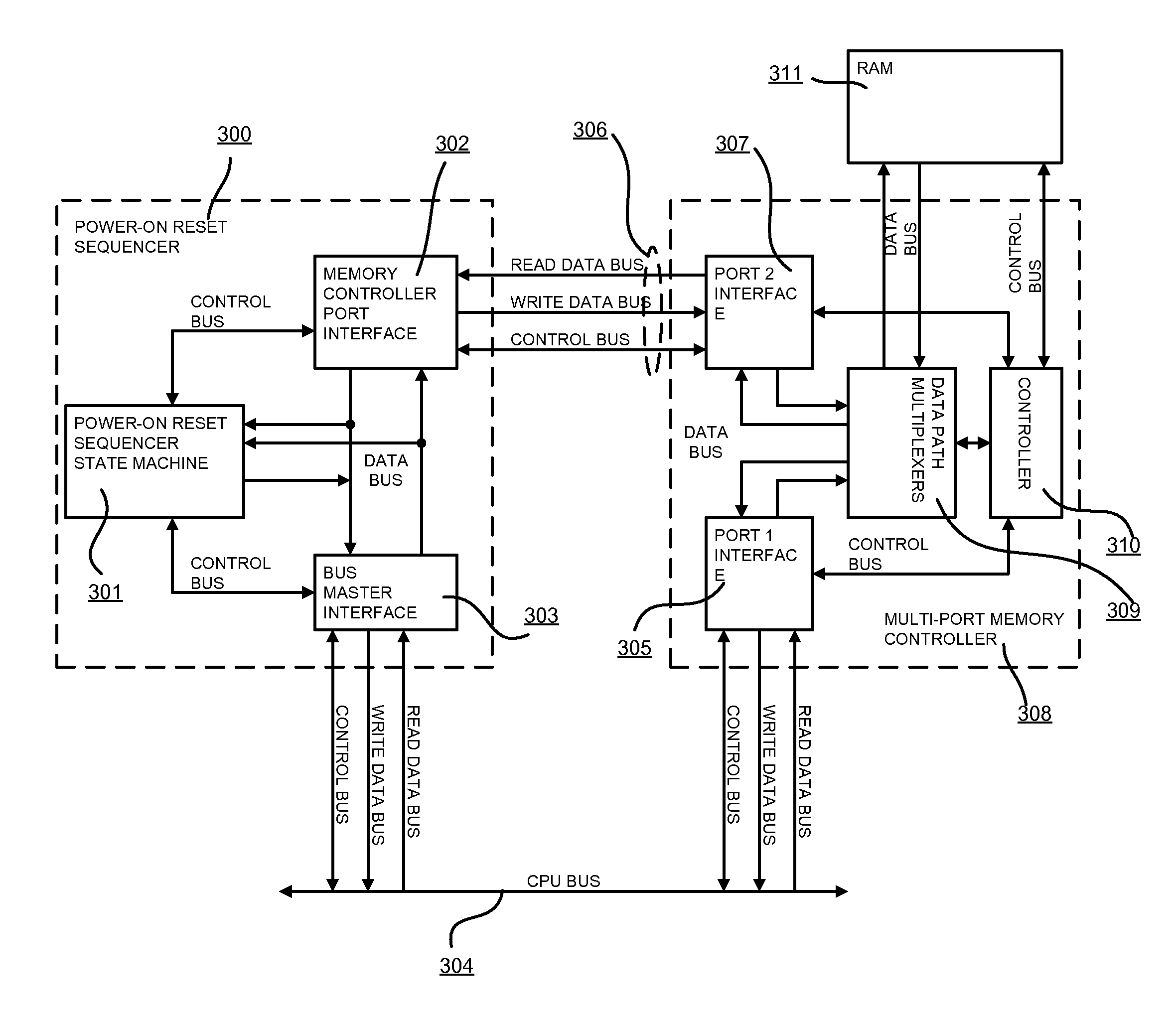

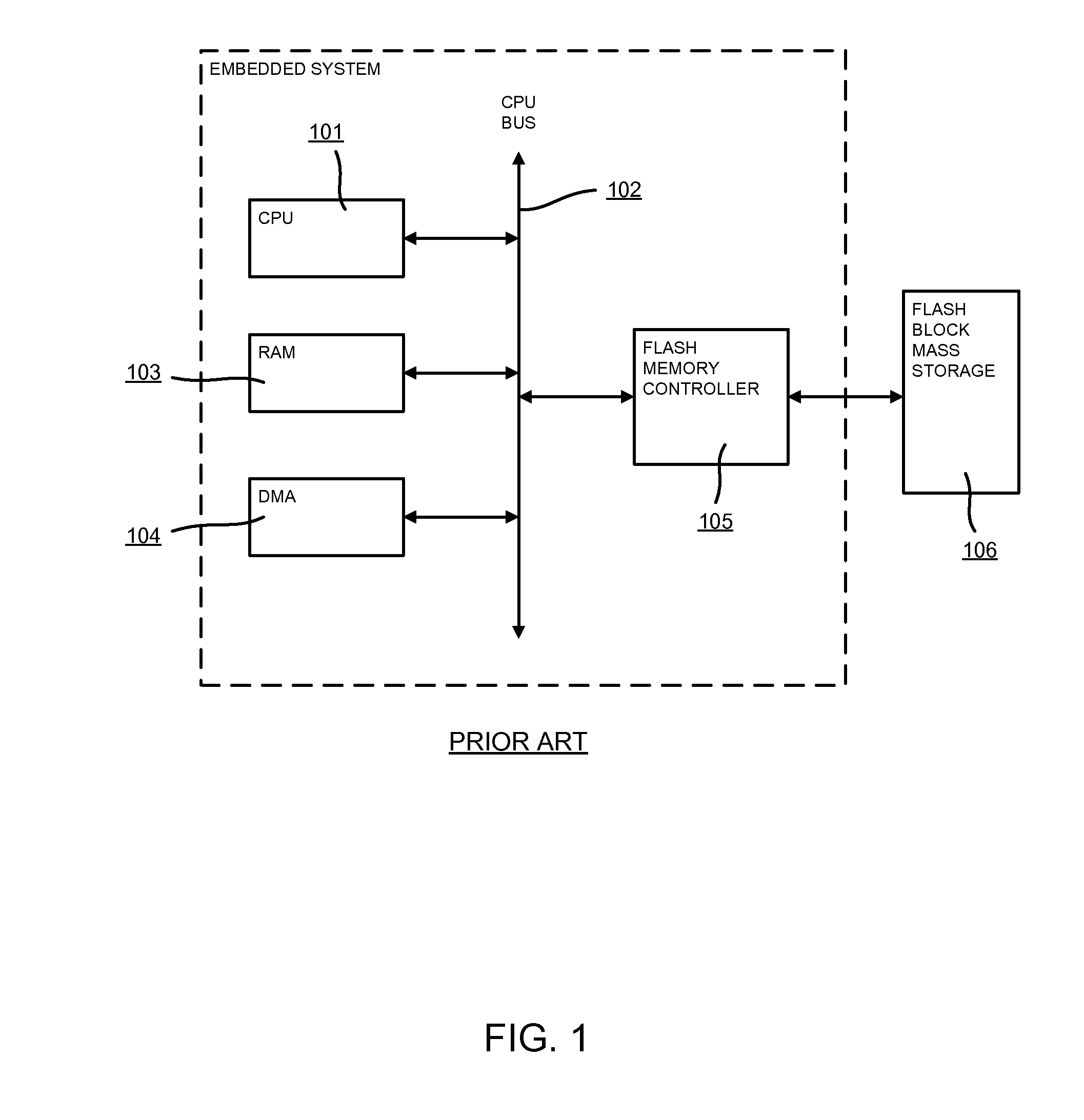

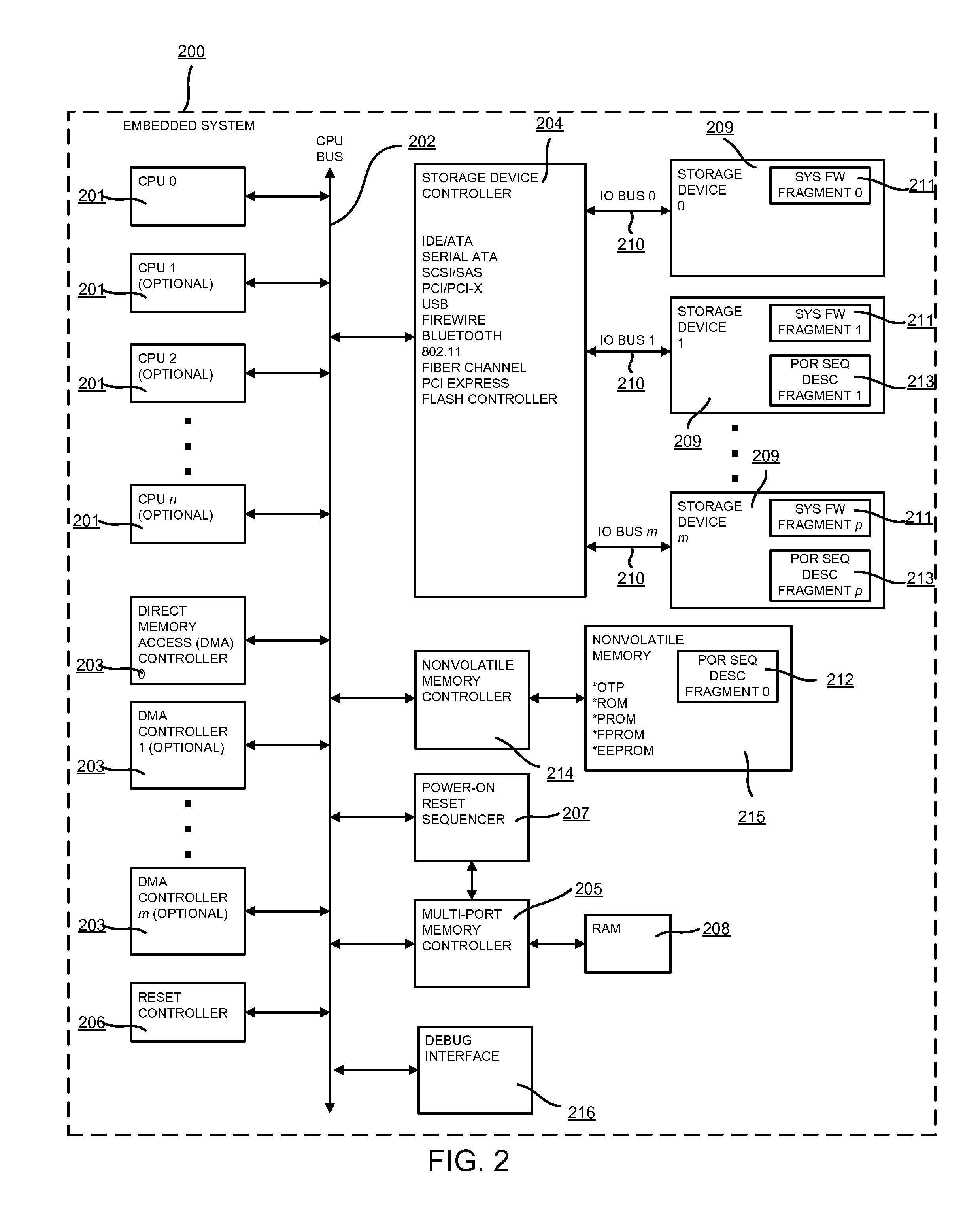

Embedded system boot from a storage device

ActiveUS20140331034A1Small sizeMinimal amountDigital computer detailsData resettingPower-on resetElectricity

A mechanism of booting up a system directly from a storage device and a means of initializing an embedded system prior to activating a CPU is presented. The said system is comprised of one or more CPUs, a reset controller, a storage device controller, one or more direct memory access controllers, a RAM and its controller, a ROM and its controller, a debug interface and a power-on reset (POR) sequencer. The POR sequencer controls the overall boot process of the embedded system. Said sequencer uses descriptors (POR Sequencer descriptors) which are used to update the configuration registers of the system and to enable CPU-independent data transfers with the use of DMA controllers.Using a minimal amount of non-volatile memory for booting up a system brings down costs associated with increased silicon real estate area and power consumption. Capability of pre-initializing the system even before a CPU is brought out of reset provides flexibility and system robustness. Through the use of the Power-On Reset Sequencer module, integrity of program code and user data used in the boot up process can be verified thus providing a resilient boot up sequence.

Owner:BITMICRO LLC

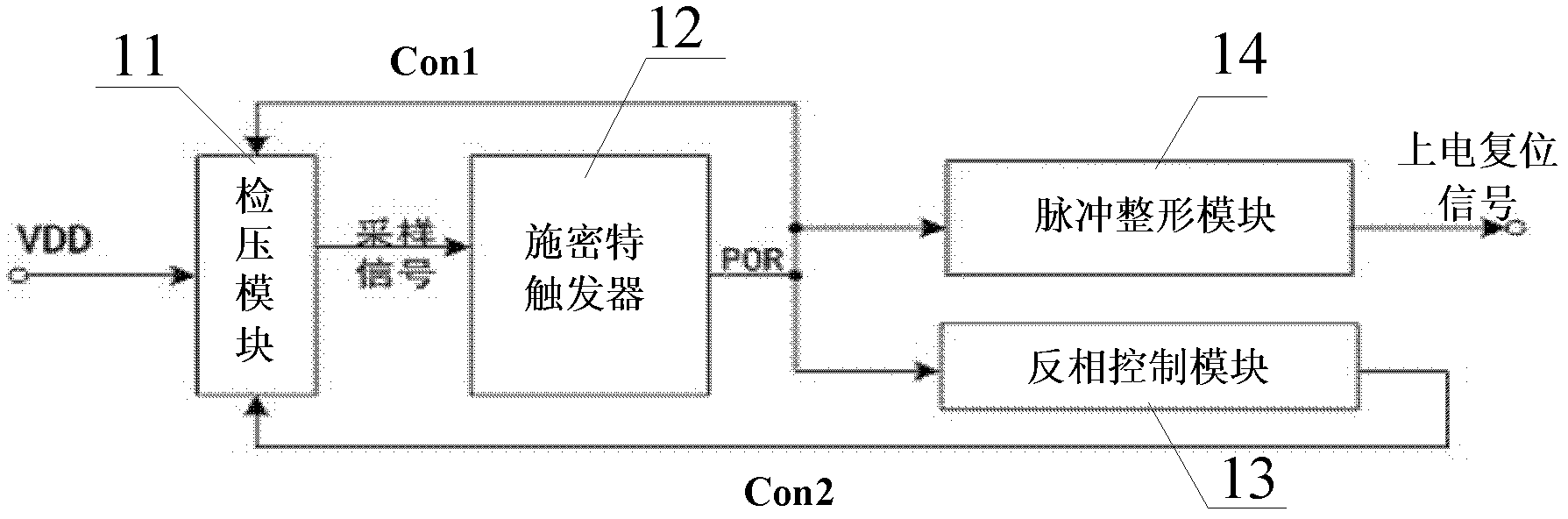

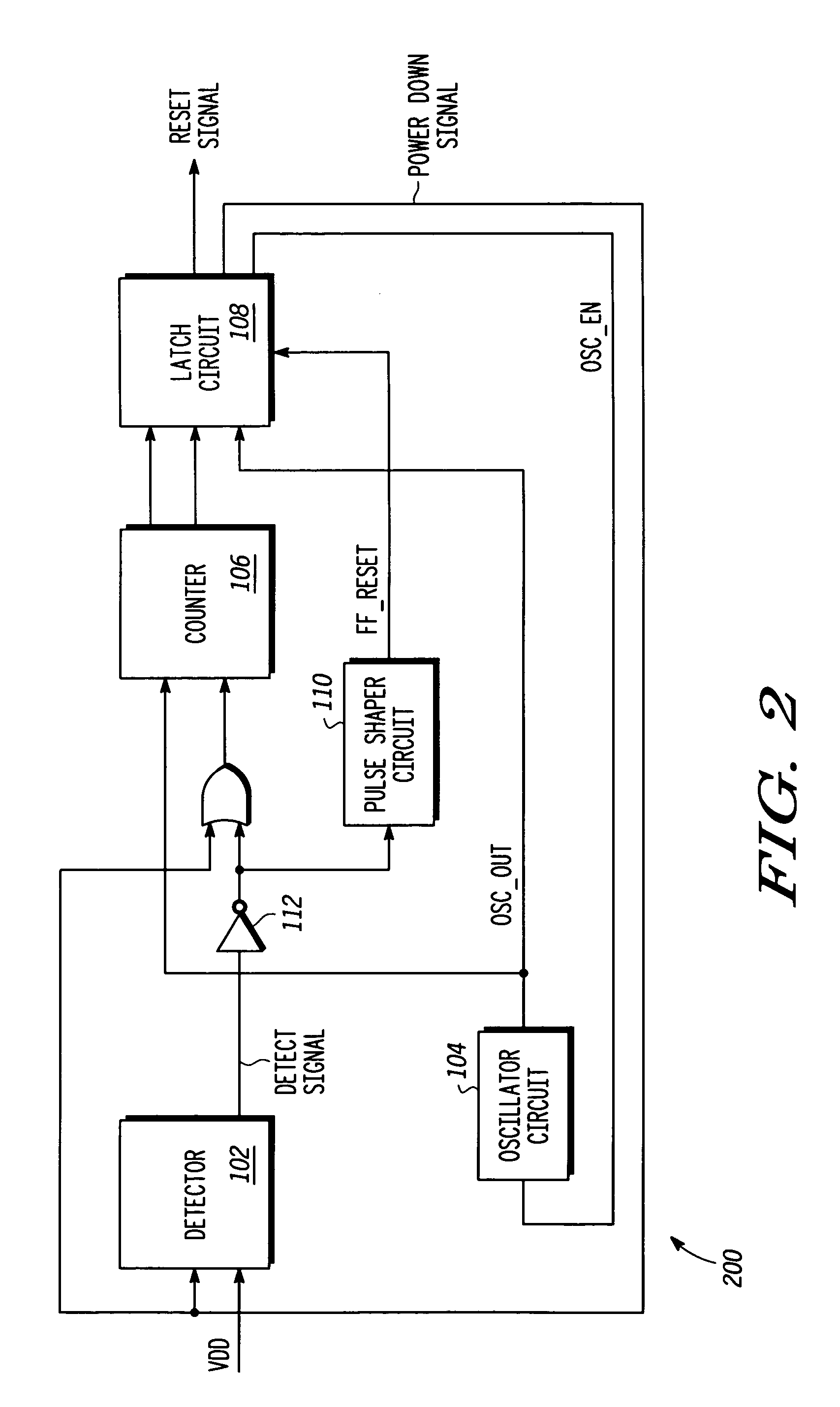

Power on reset circuit

ActiveCN102403988AImprove stabilityWith static zero power designElectronic switchingPower-on resetElectricity

The invention provides a power on reset circuit, comprising a voltage detecting module, a Schmitt trigger, a phase inversion control module and a pulse shaping circuit, wherein, in a power on progress of a power supply, the voltage detecting module detects voltage change of the power supply and outputs a sampling signal; the sampling signal enters the Schmitt trigger and outputs a step signal; onone hand, the step signal is output to the voltage detecting module for controlling rapid effusion of the voltage detecting module so as to lower the sampling signal; on the other hand, the phase of the step signal is inverted through the phase inversion control module and then the step signal is used for controlling switching effusion of the voltage detecting module; at last, the step signal is delayed and treated through XOR operation by the pulse shaping module, and then a power on reset signal is output. Design of the power on reset circuit provided by the invention is simple in structure; by utilizing delaying characteristics of two paths of feedback control signals and the Schmitt trigger, the power on reset circuit has very high stability and good anti-noise performance; and, afterpower on is finished, static power consumption of the power on reset circuit is very low.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

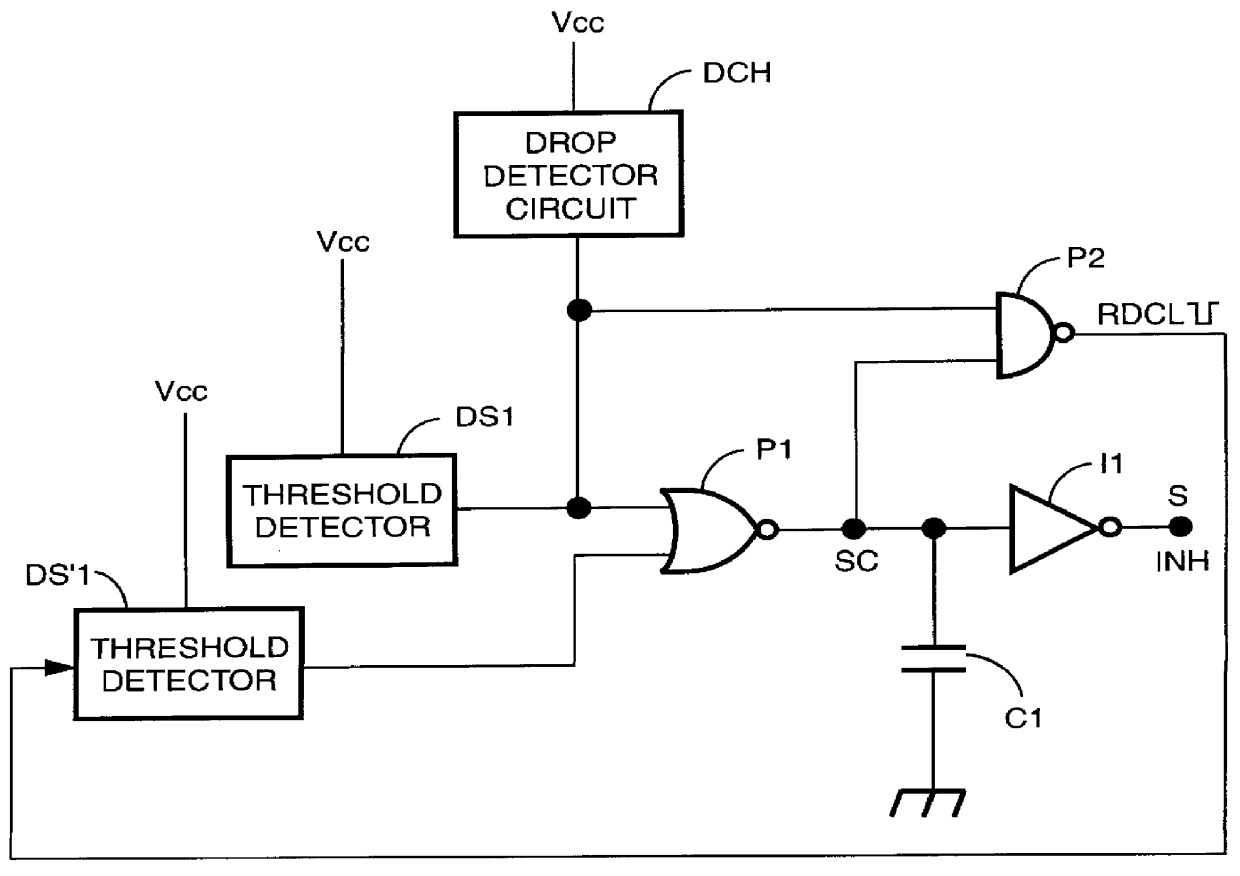

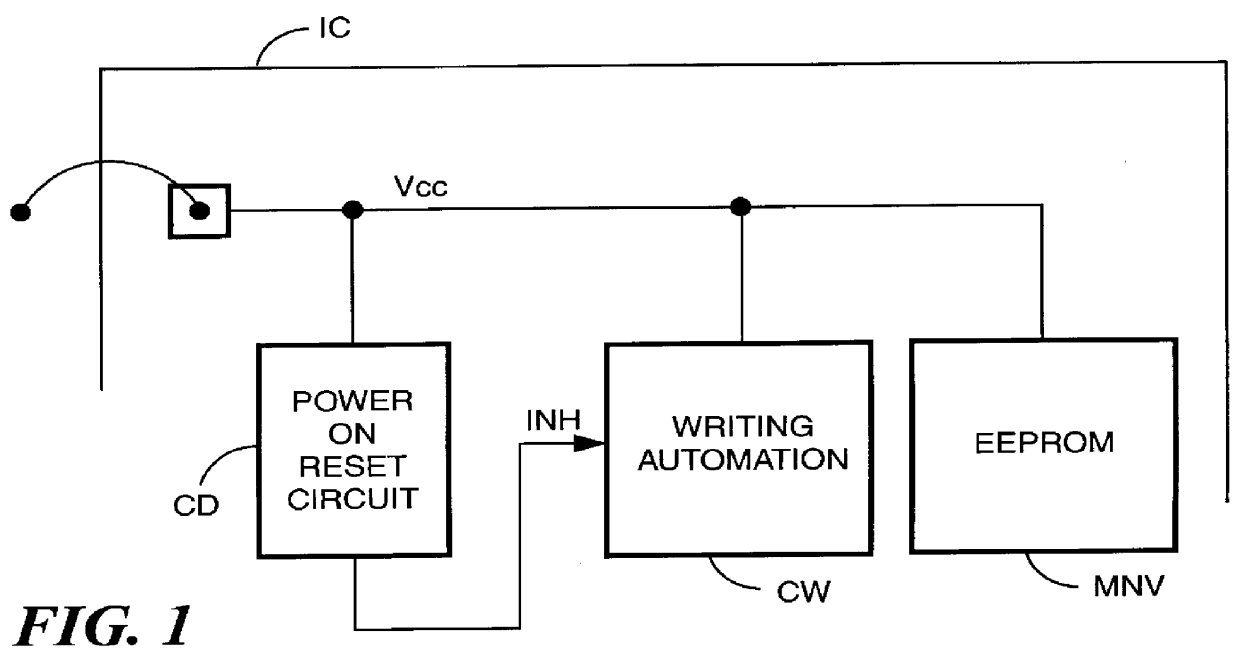

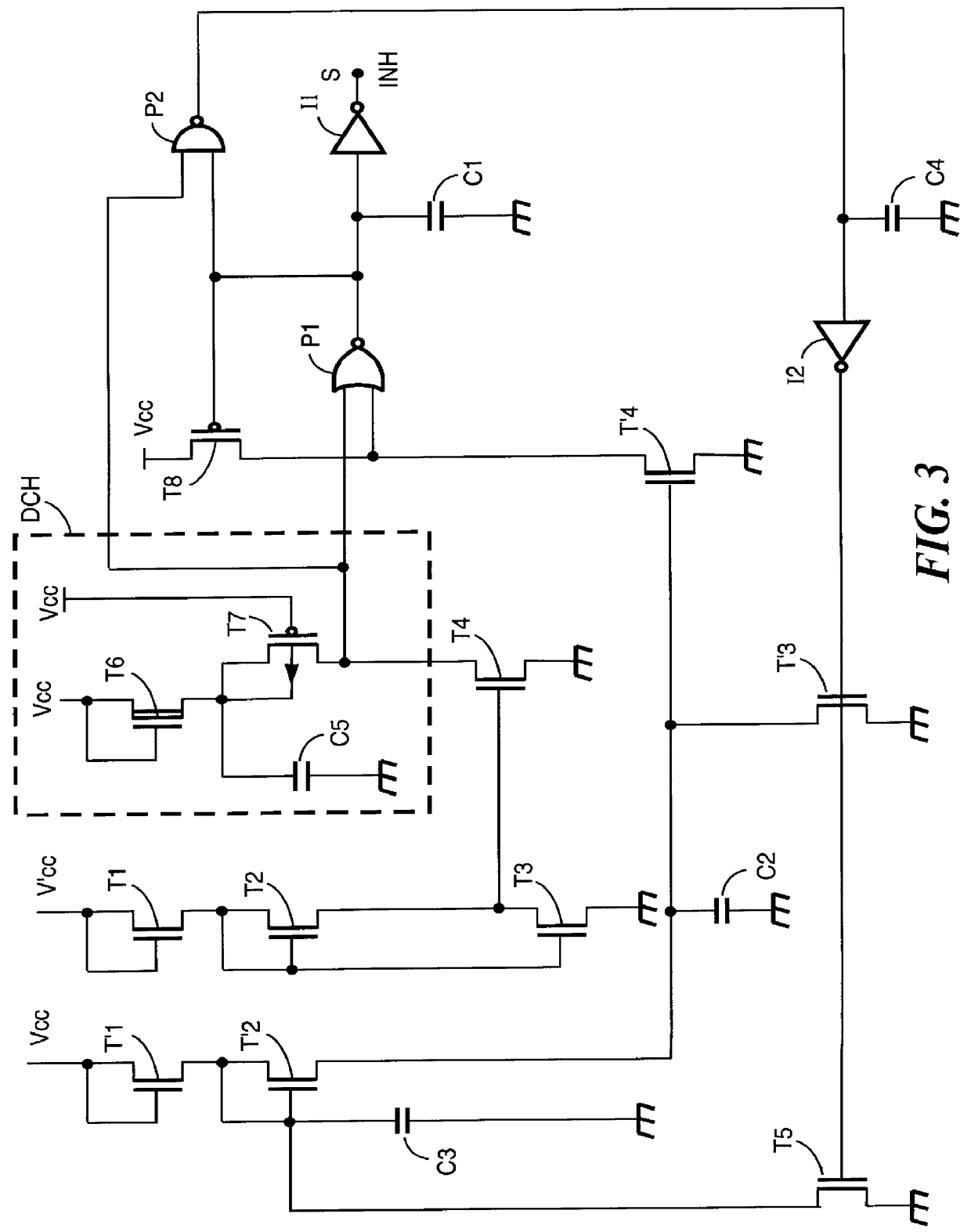

Power-on-reset circuit providing protection against power supply interruptions

The disclosure relates to integrated circuits and, more particularly, to a power-on-reset circuit. The proposed circuit produces an inhibition signal when the power is turned on, this signal being interrupted after the supply voltage Vcc has reached a first threshold (VS1) (VS1). Furthermore, the circuit has means to re-trigger the inhibition signal when the supply voltage drops by a certain value, in doing so even if the supply voltage remains above the first threshold. The reliability of the integrated circuit is improved. The disclosed circuit is particularly applicable to the inhibition of the writing circuit of an EEPROM memory.

Owner:STMICROELECTRONICS SRL

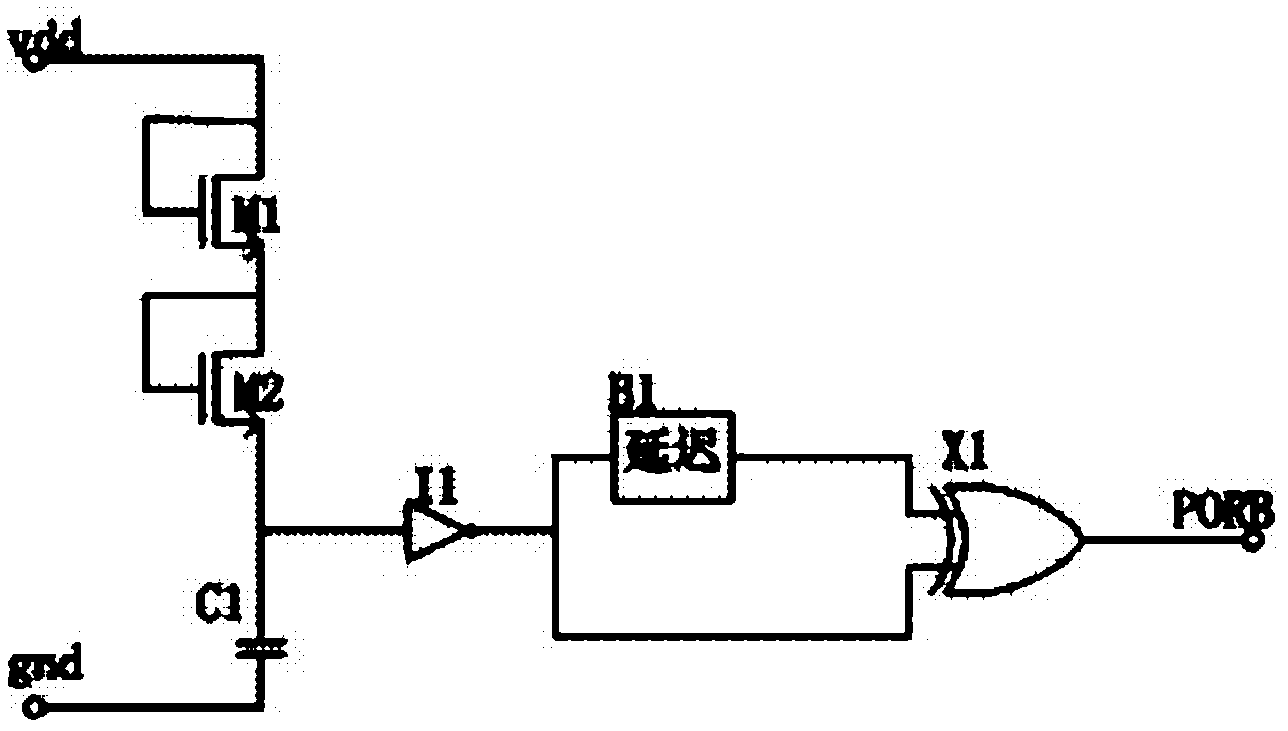

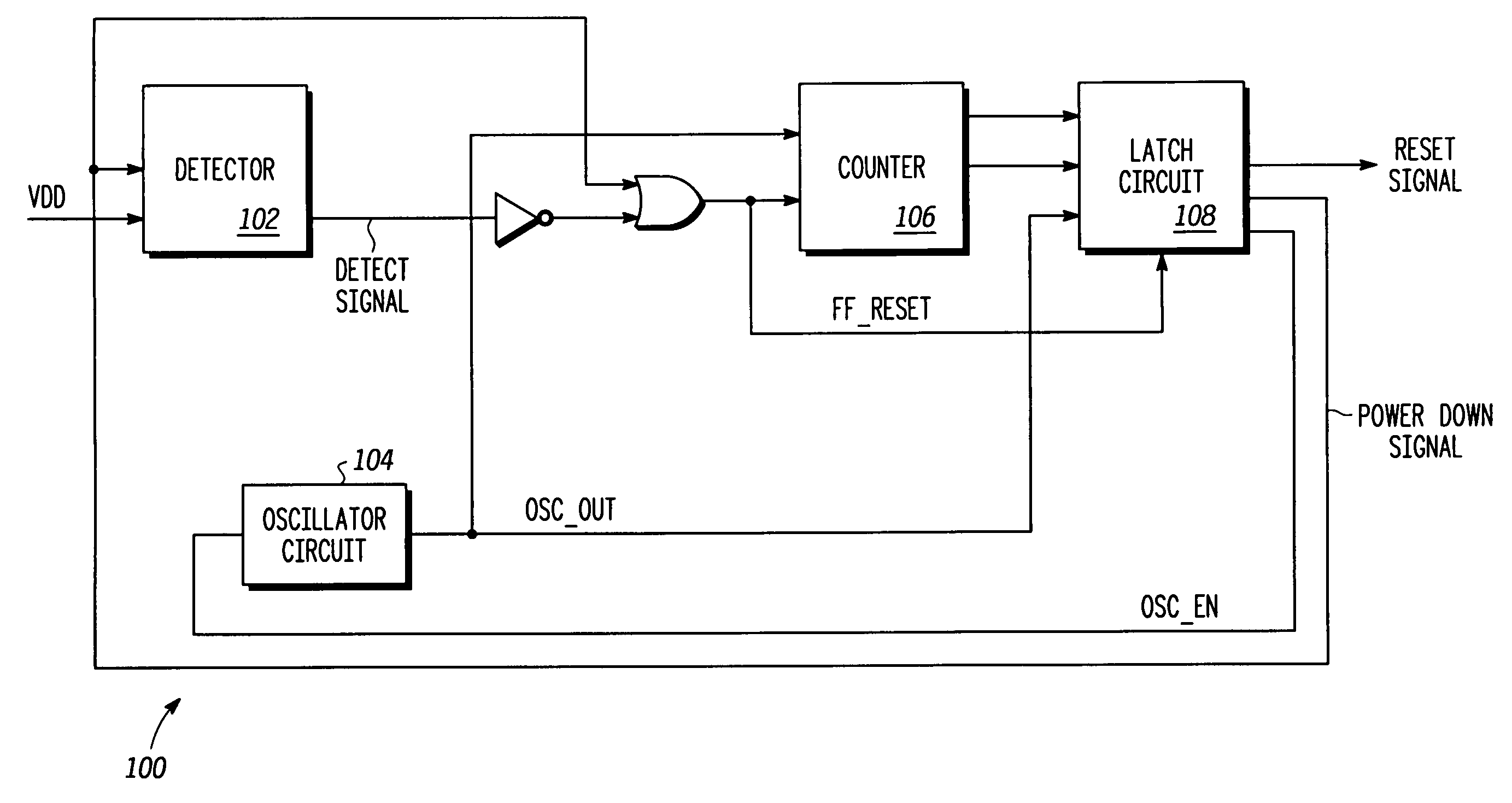

Power on reset circuit

A power on reset (POR) circuit for providing a reset pulse signal to a chip when power supply voltage, VDD, ramps up so that the chip always starts in a known state. The POR circuit generates the reset pulse as soon as VDD exceeds an assertion voltage. The assertion voltage is independent of the ramp rate of VDD. The POR circuit is shut off as soon as the reset signal is generated, thereby drawing zero steady state current from VDD. The re-arm time for the POR circuit is very small. The POR circuit does not reset the chip when there is a dynamic change in VDD.

Owner:SK HYNIX INC

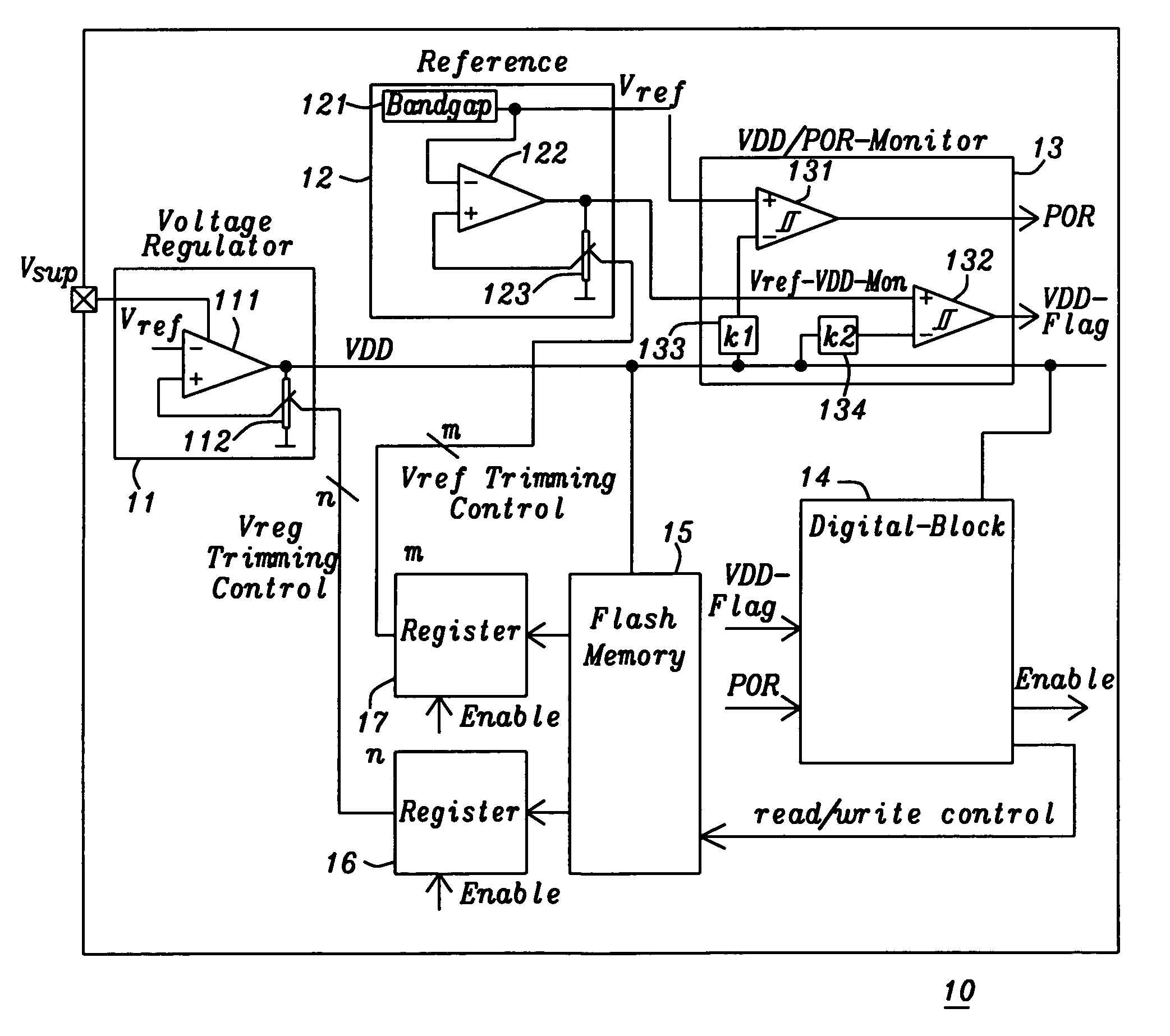

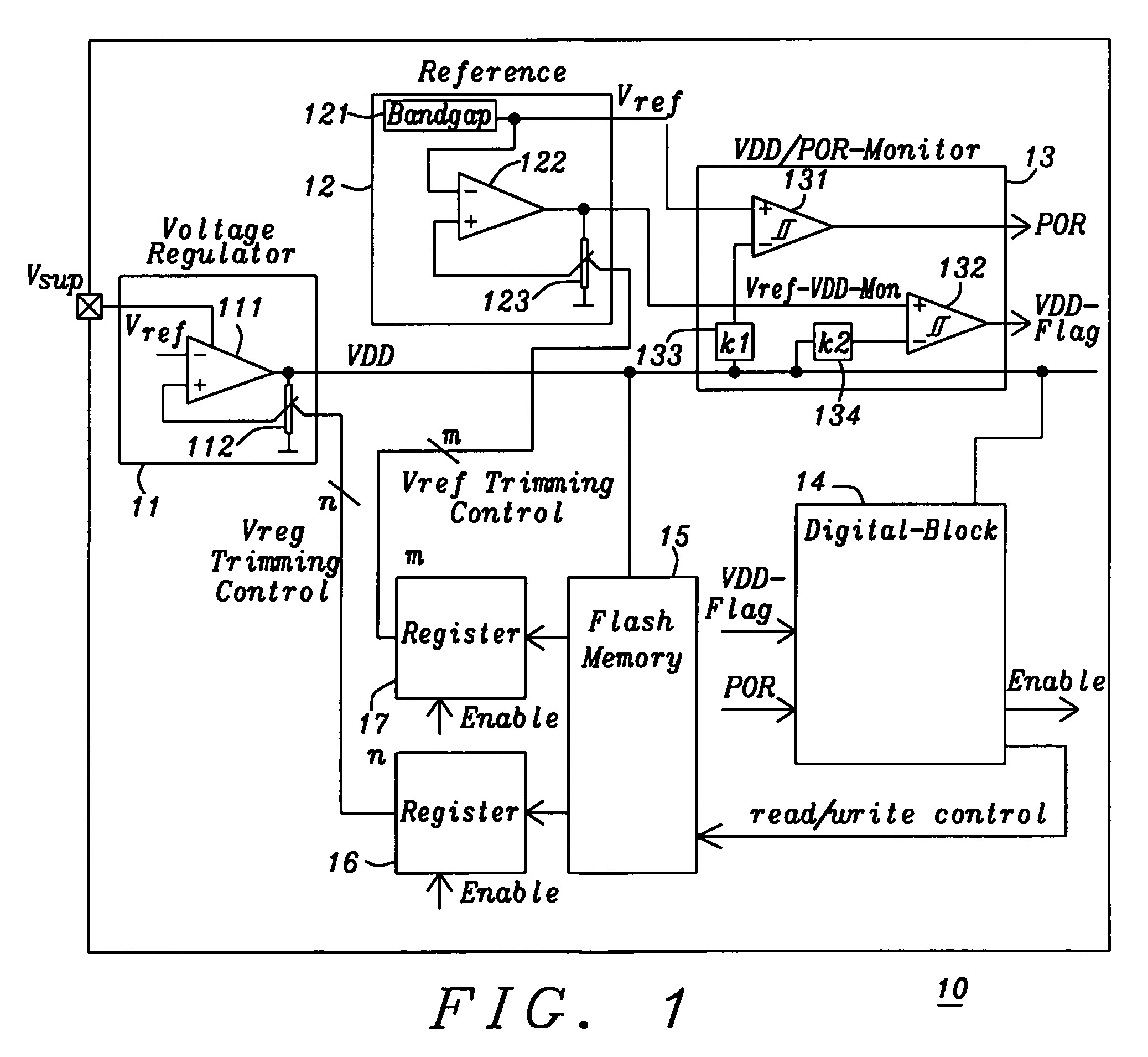

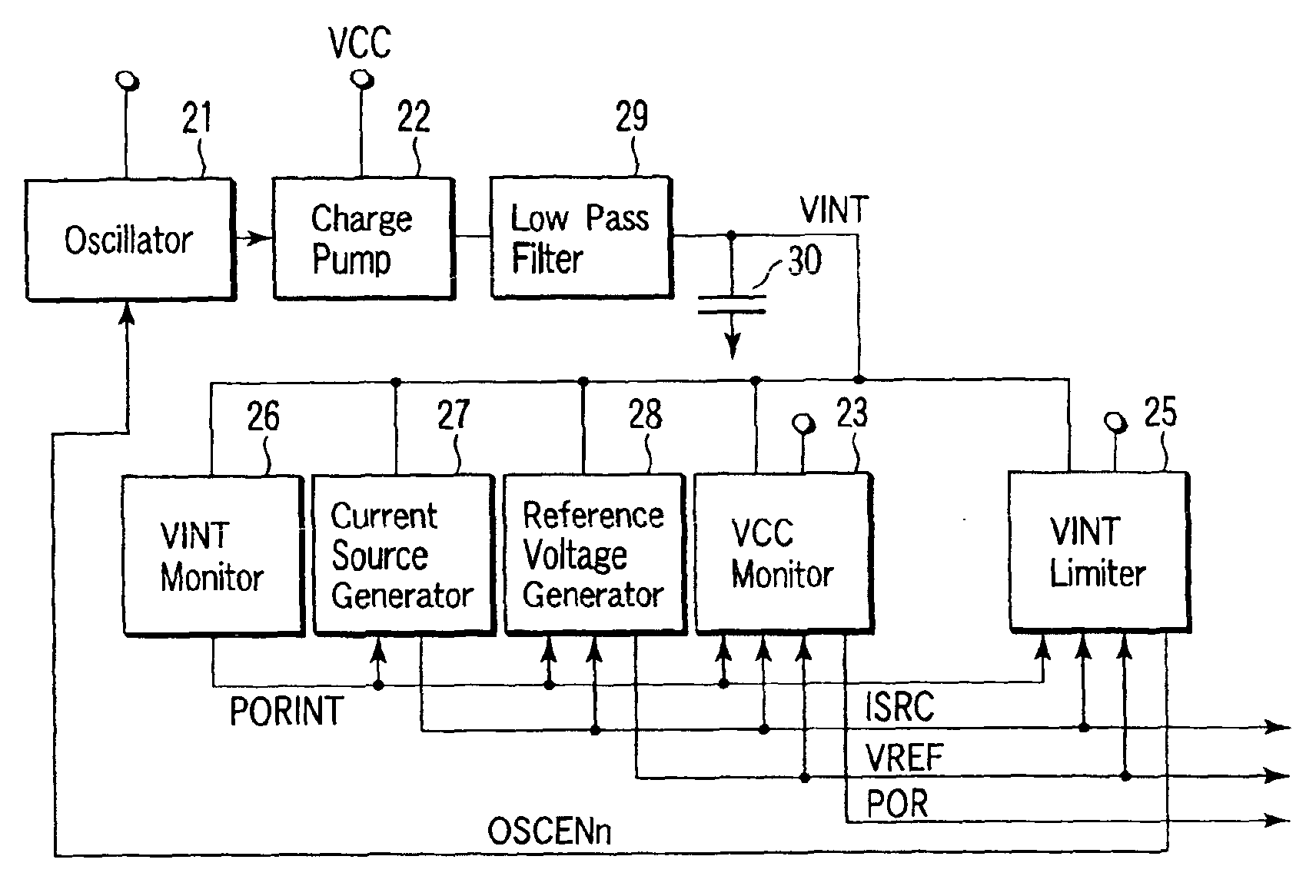

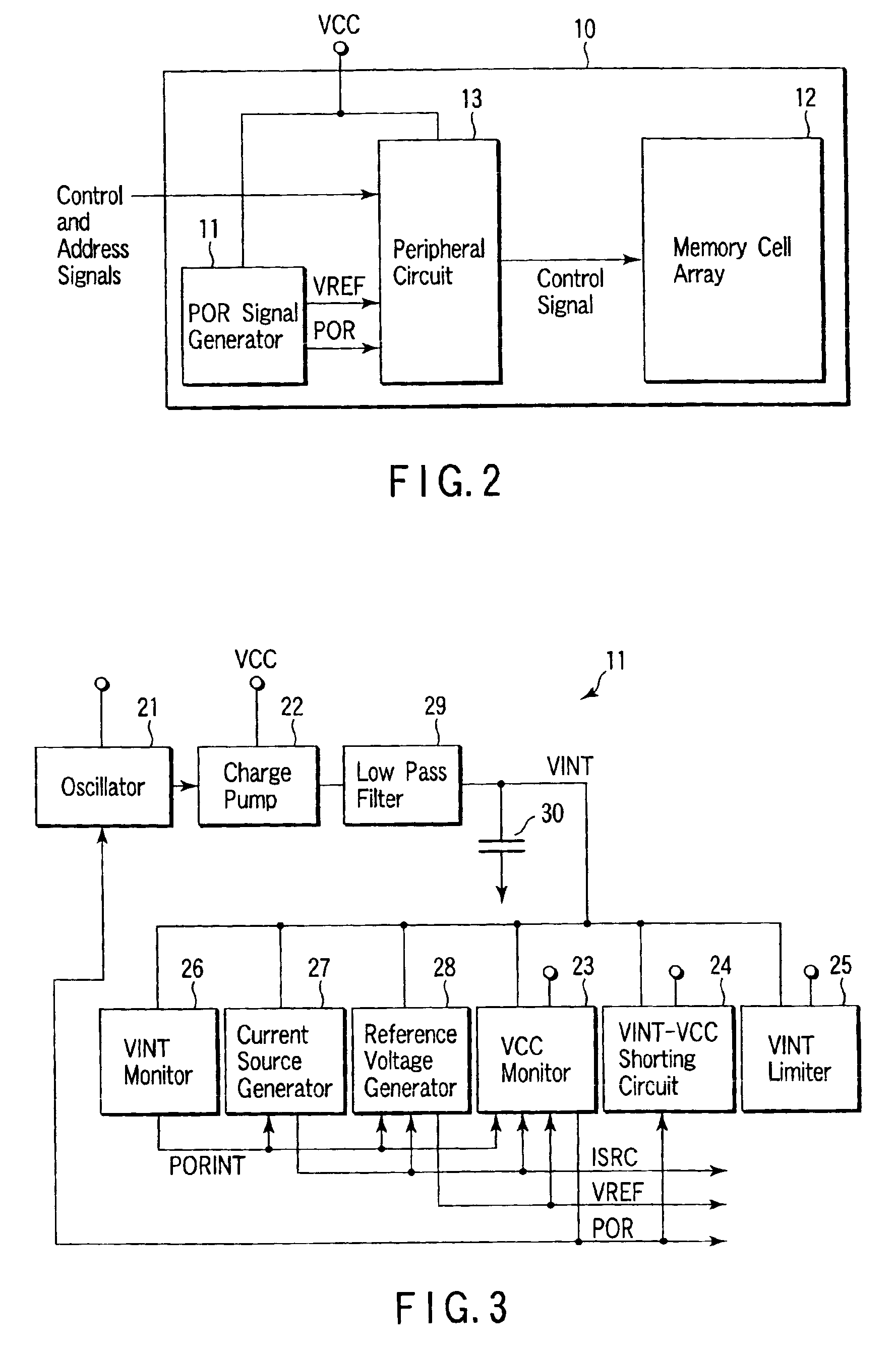

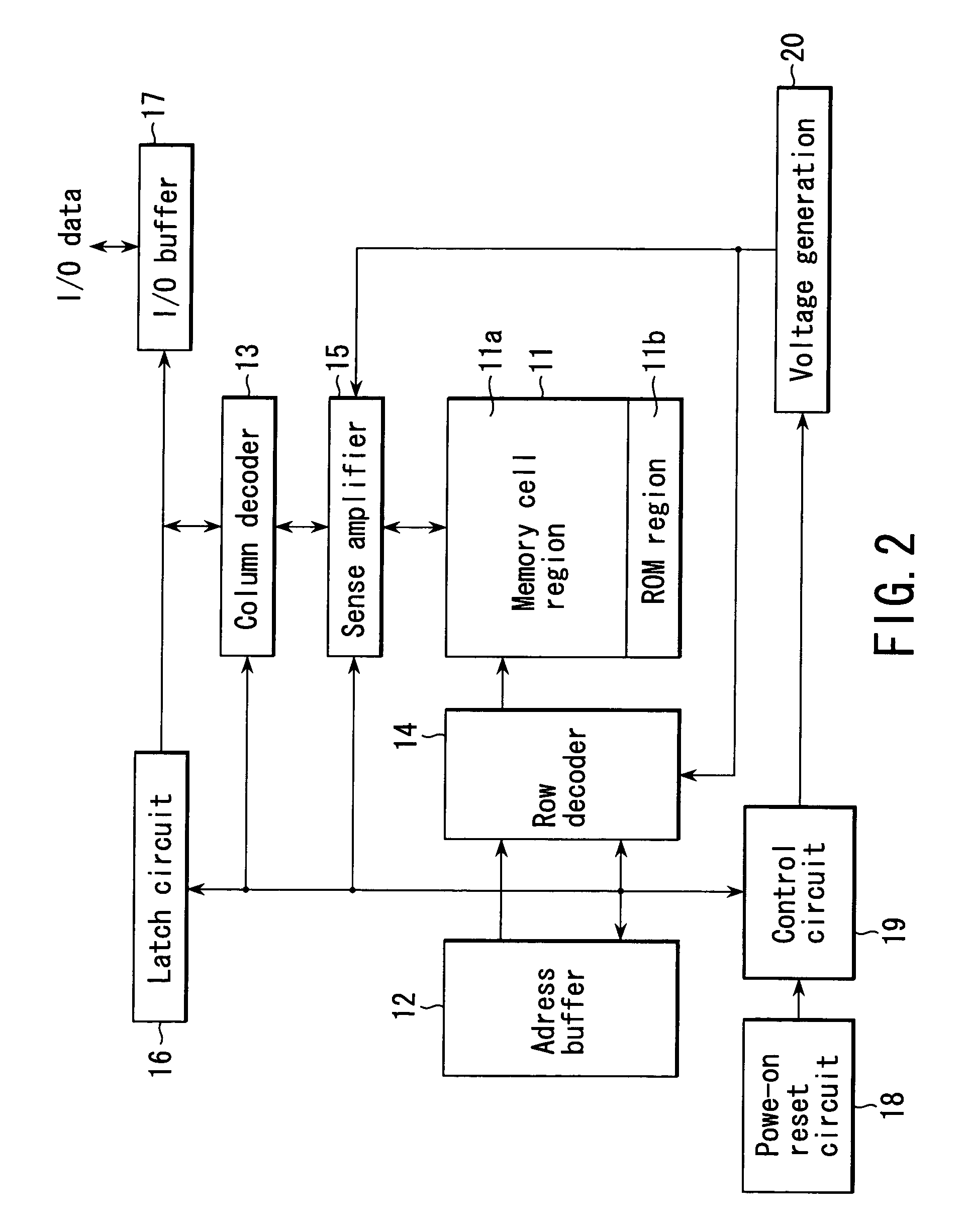

Accurate power supply system for flash-memory including on-chip supply voltage regulator, reference voltage generation, power-on reset, and supply voltage monitor

ActiveUS7200066B2Prevent and reduce self-power-up sequencing and instabilityRead-only memoriesDigital storagePower-on resetControl signal

The supply voltage of an on-chip flash memory is regulated with two feedback loops. One loop comprises the flash memory, a register, and a voltage regulator with bandgap reference to regulate the supply voltage. The other loop comprises the flash memory, another register, an amplifier with bandgap reference, and comparators to monitor the supply voltage and adjust the threshold of the signals which control the operation of the flash memory and registers. The calibration data controls variable resistive means in the feedback paths of the voltage regulator and in the calibration of the threshold values of the control signals. Calibration data is held in the registers when the supply voltage is out-of-range to prevent self-start up.

Owner:DIALOG SEMICONDUCTOR GMBH

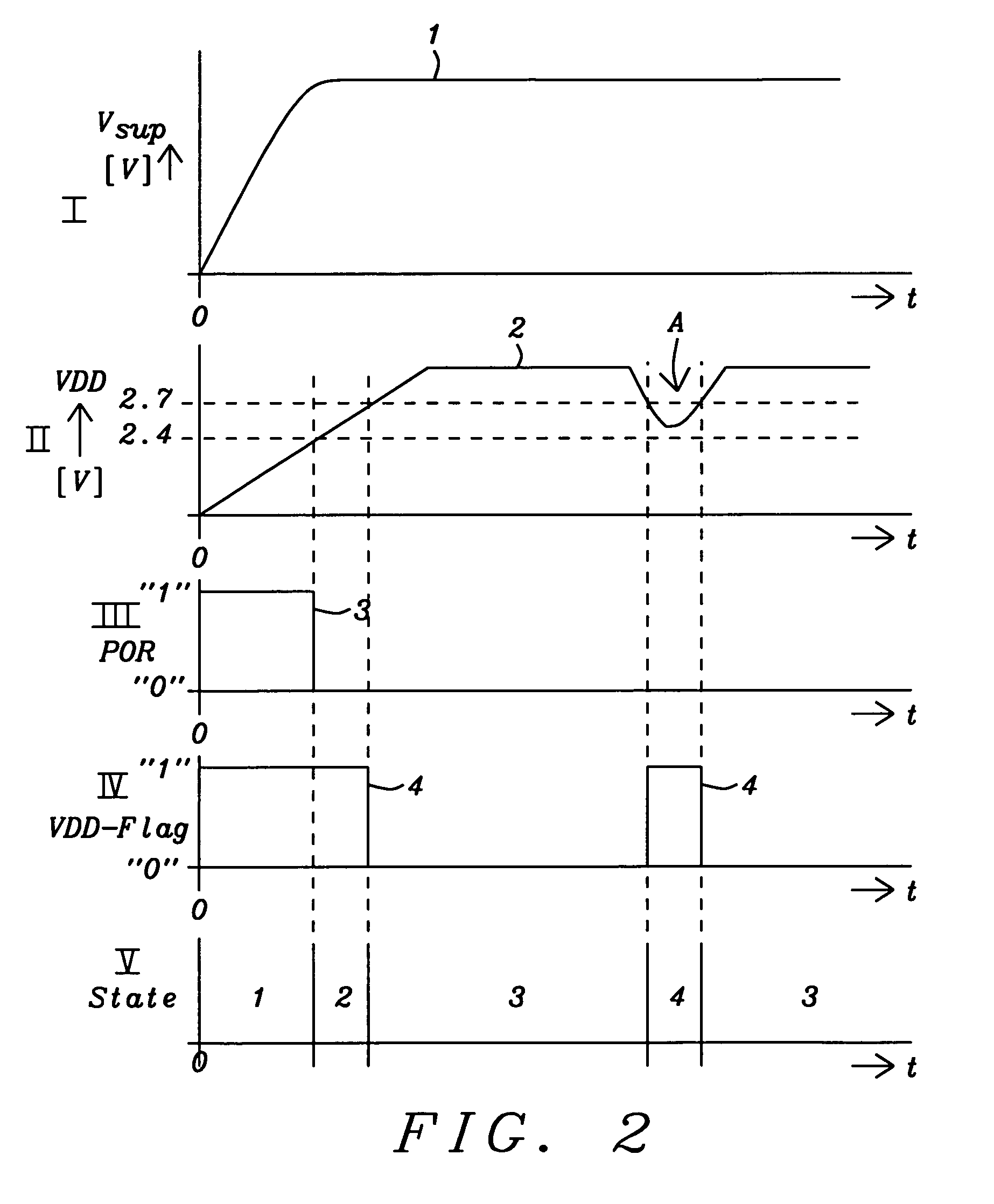

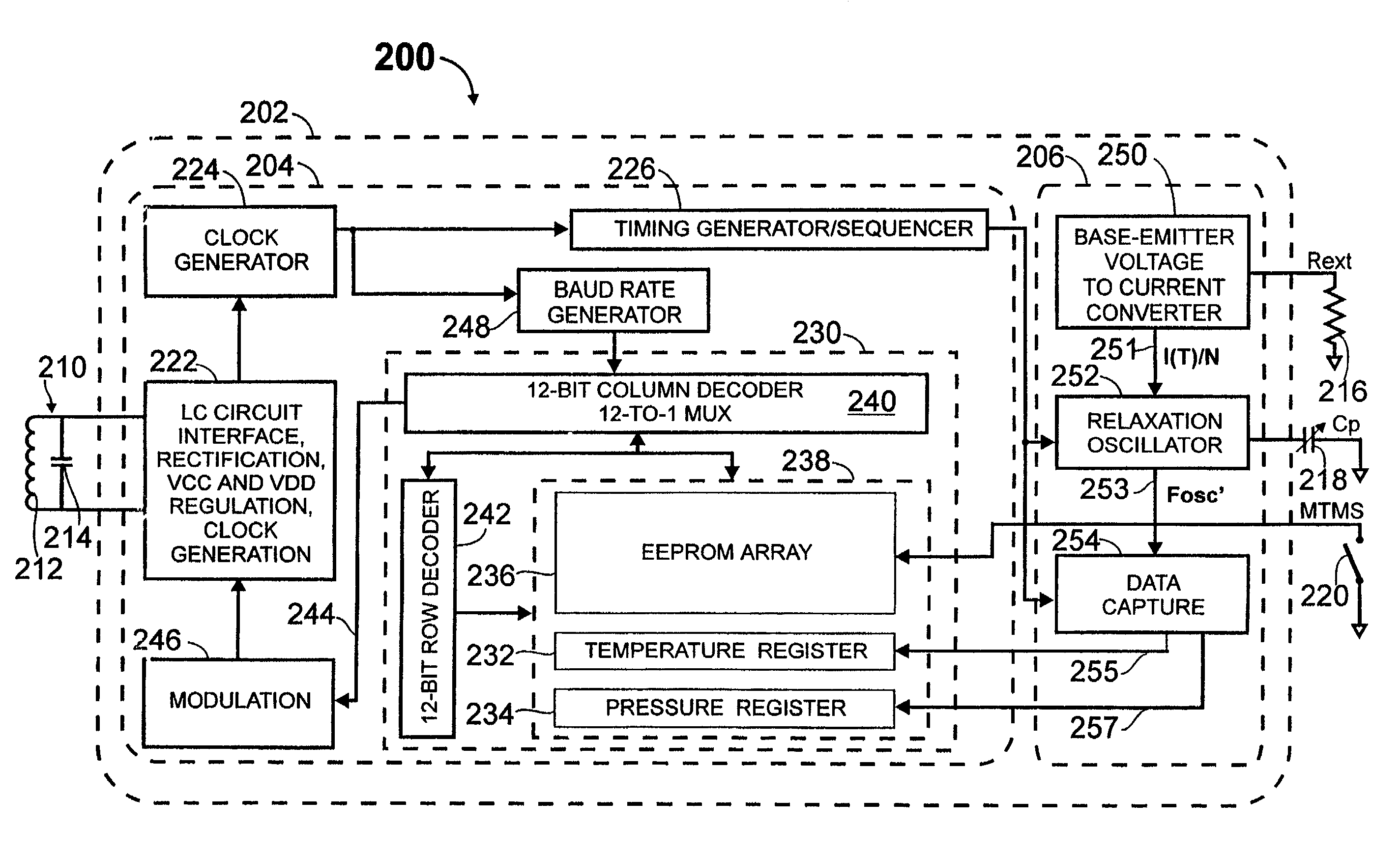

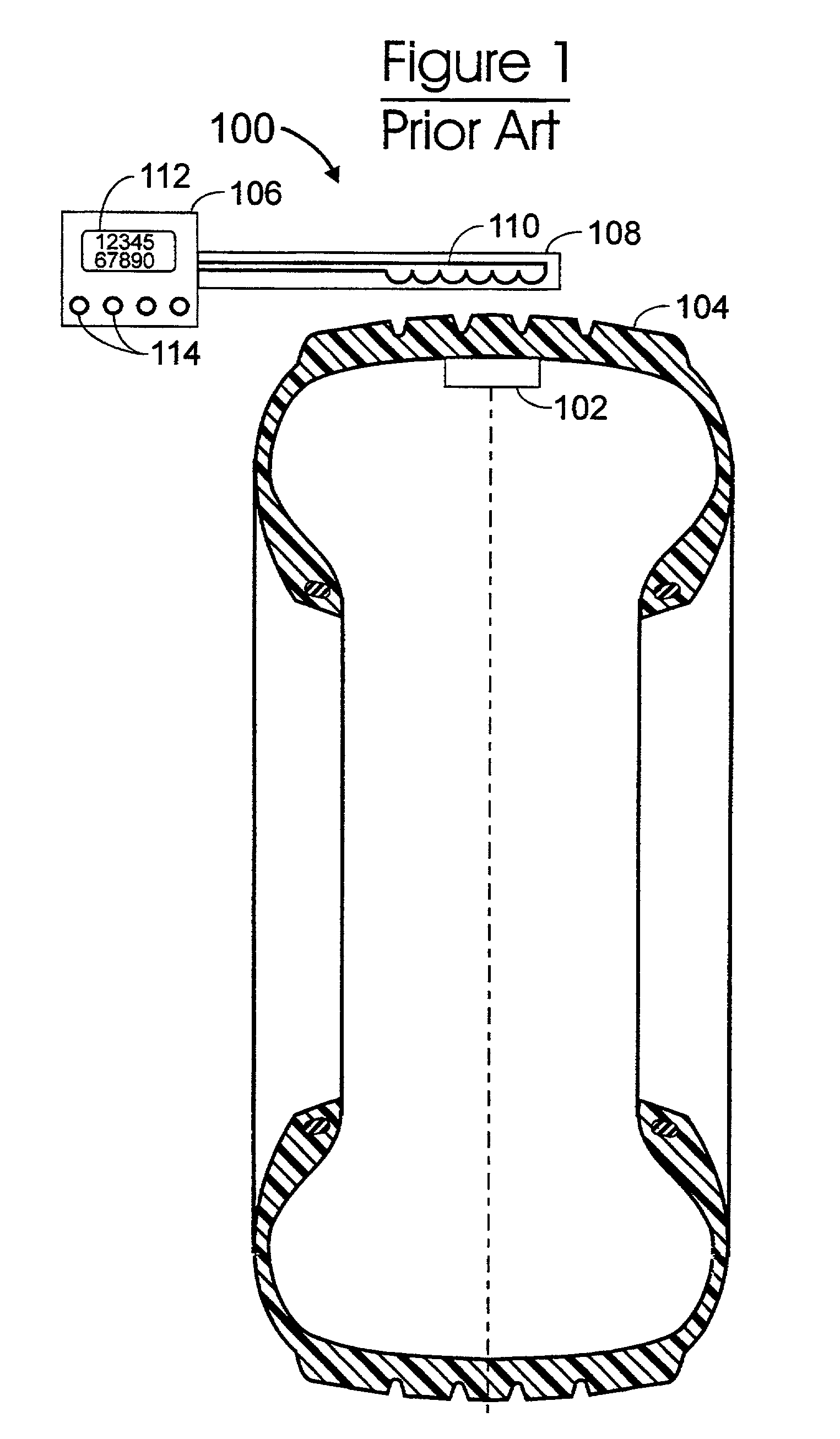

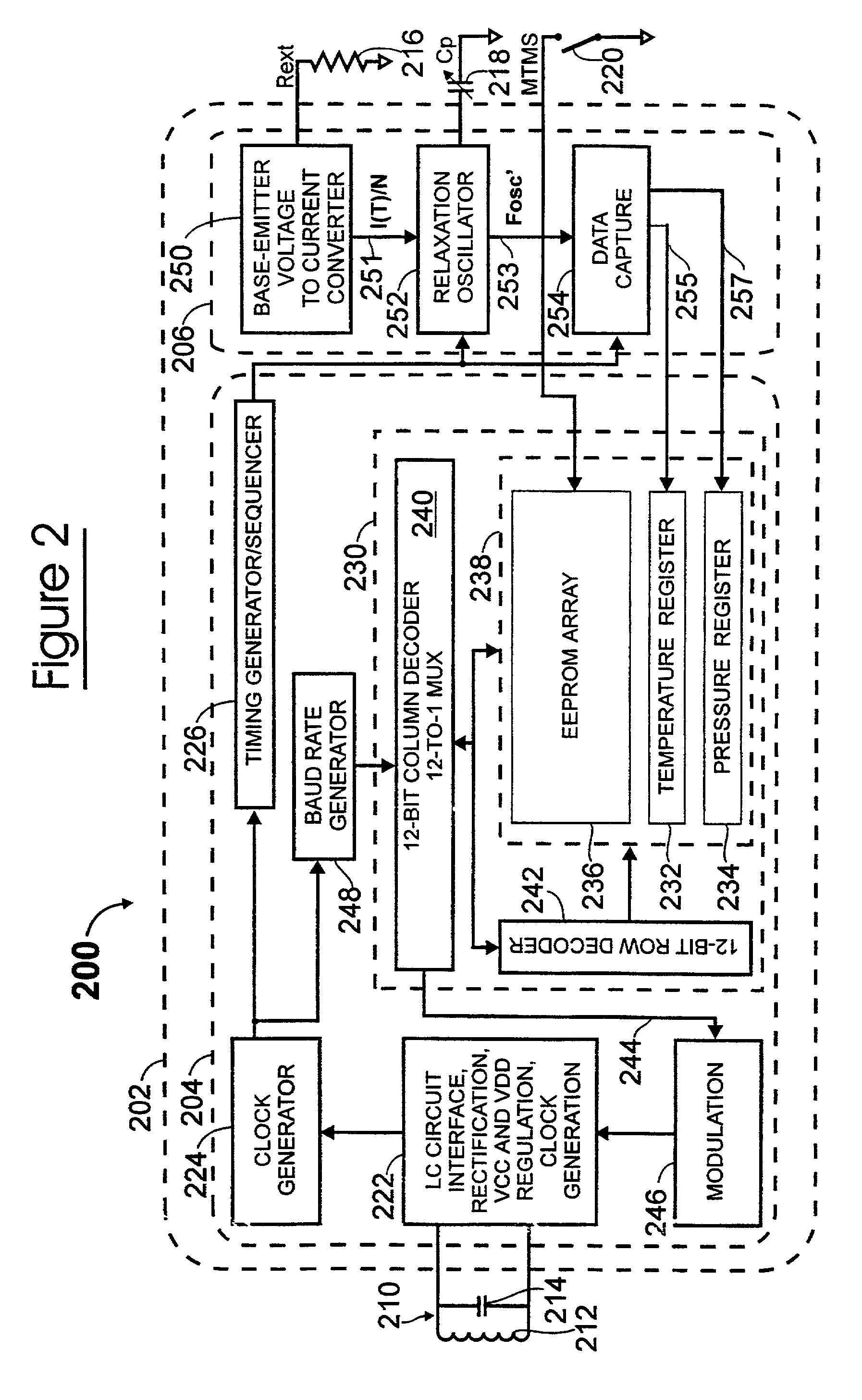

Power-on reset for transponder

InactiveUS6980084B1Easy to calculateElectric signal transmission systemsElectric controllersElectricityPower-on reset

A power-on reset for a transponder (102, 200, 400) capable of measuring one or more parameters (e.g., temperature, pressure) in an object (e.g., a tire, 104) and transmitting a data stream (FIGS. 3C, 4B) to an external reader / interrogator (106). The transponder typically operates in a passive mode, deriving its power (Vxx, Vcc, Vdd) from an RF interrogation signal received by an antenna system (210, 410), but can also operate in a battery-powered active mode. The transponder includes memory (238, 438) for storing measurements, calibration data, programmable trim settings (436b), transponder ID and the like. A power-on reset circuit (600) prevents operation of the transponder until it is stable, and starts transmission of the data stream at a first bit of the data stream, in order to ensure a first-pass transmission of a complete data stream. It also prevents modulation of the antenna system for data stream transmission if the power levels are too low for stable transponder operation during modulation.

Owner:THE GOODYEAR TIRE & RUBBER CO

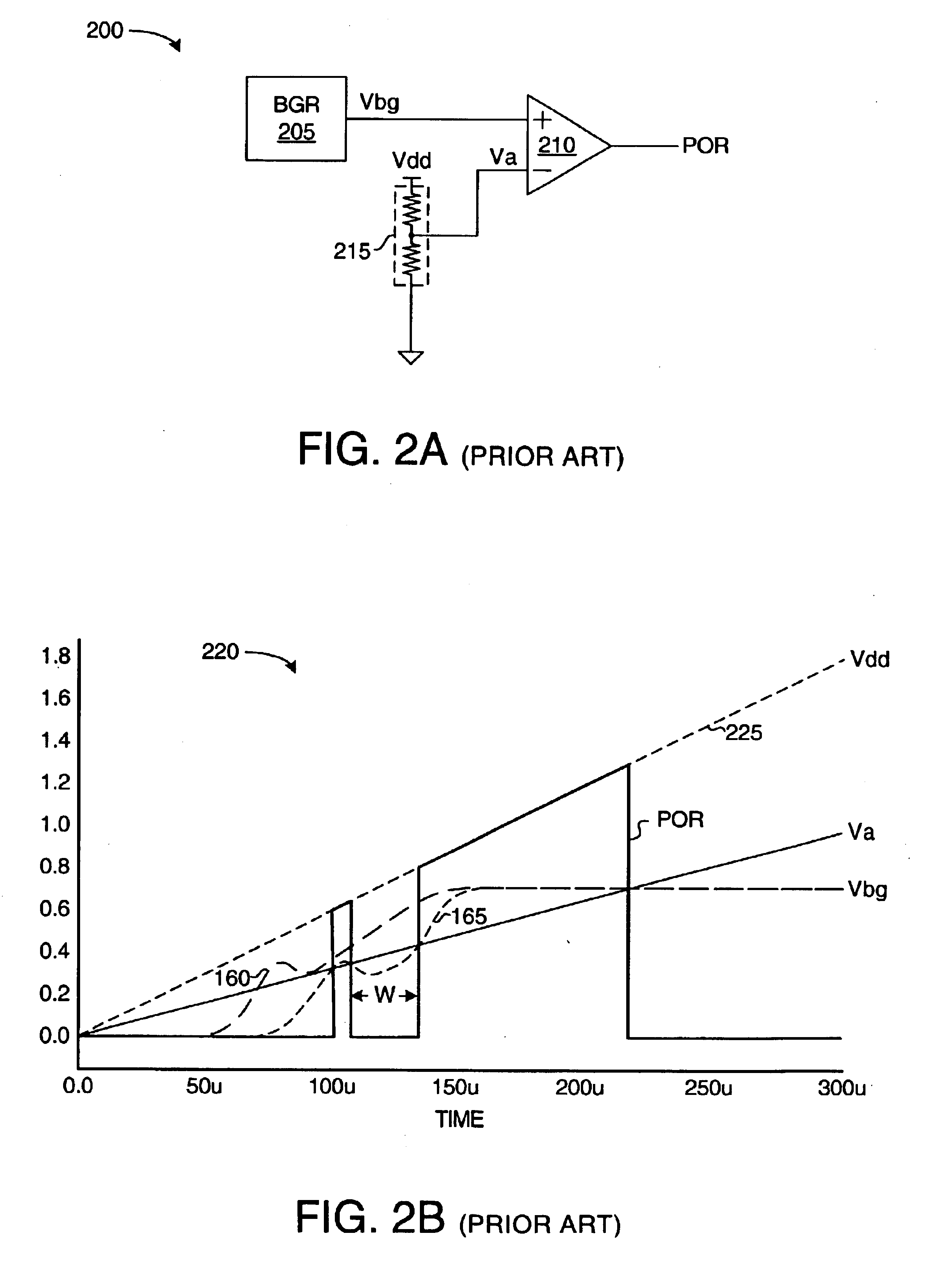

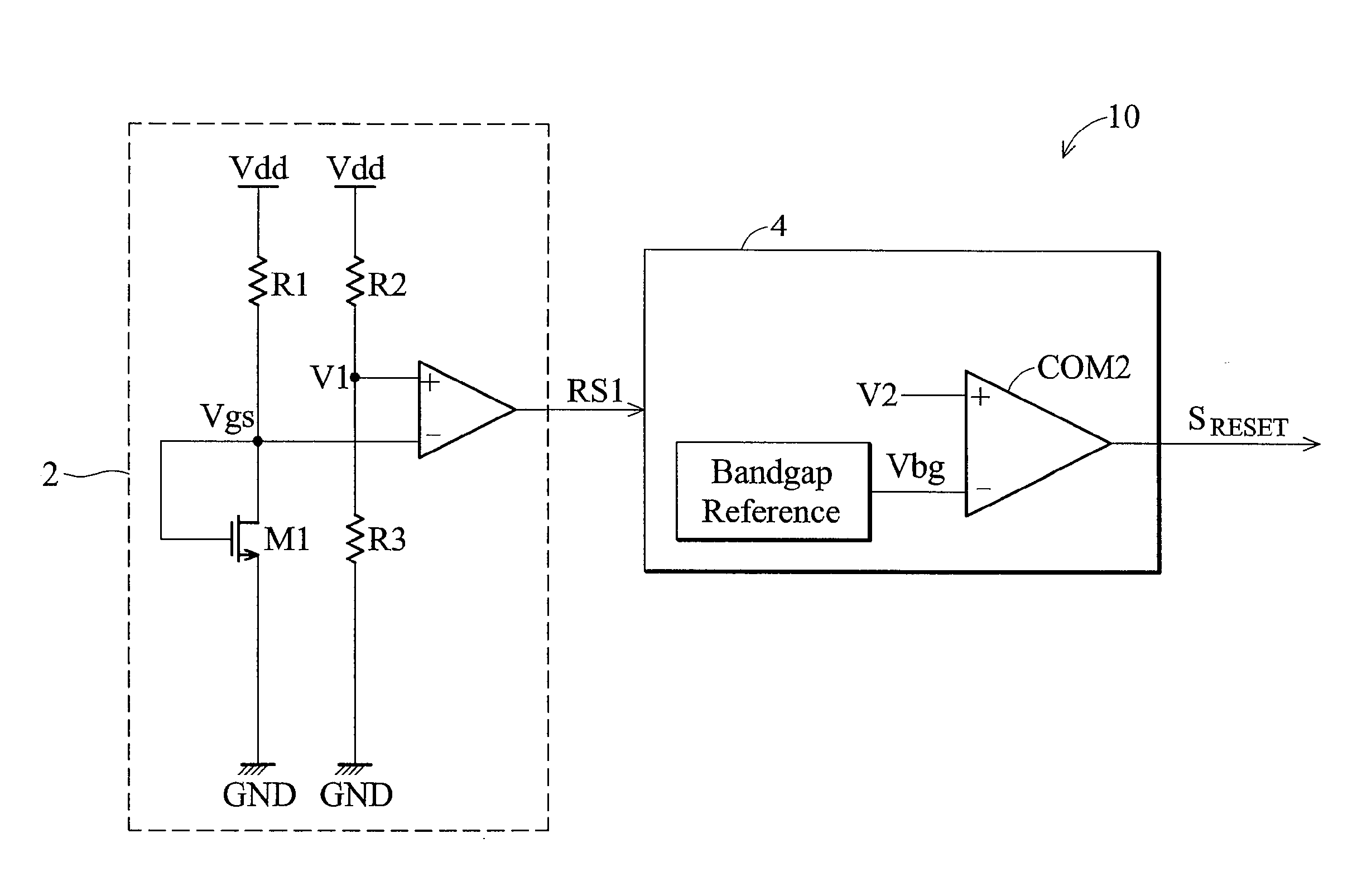

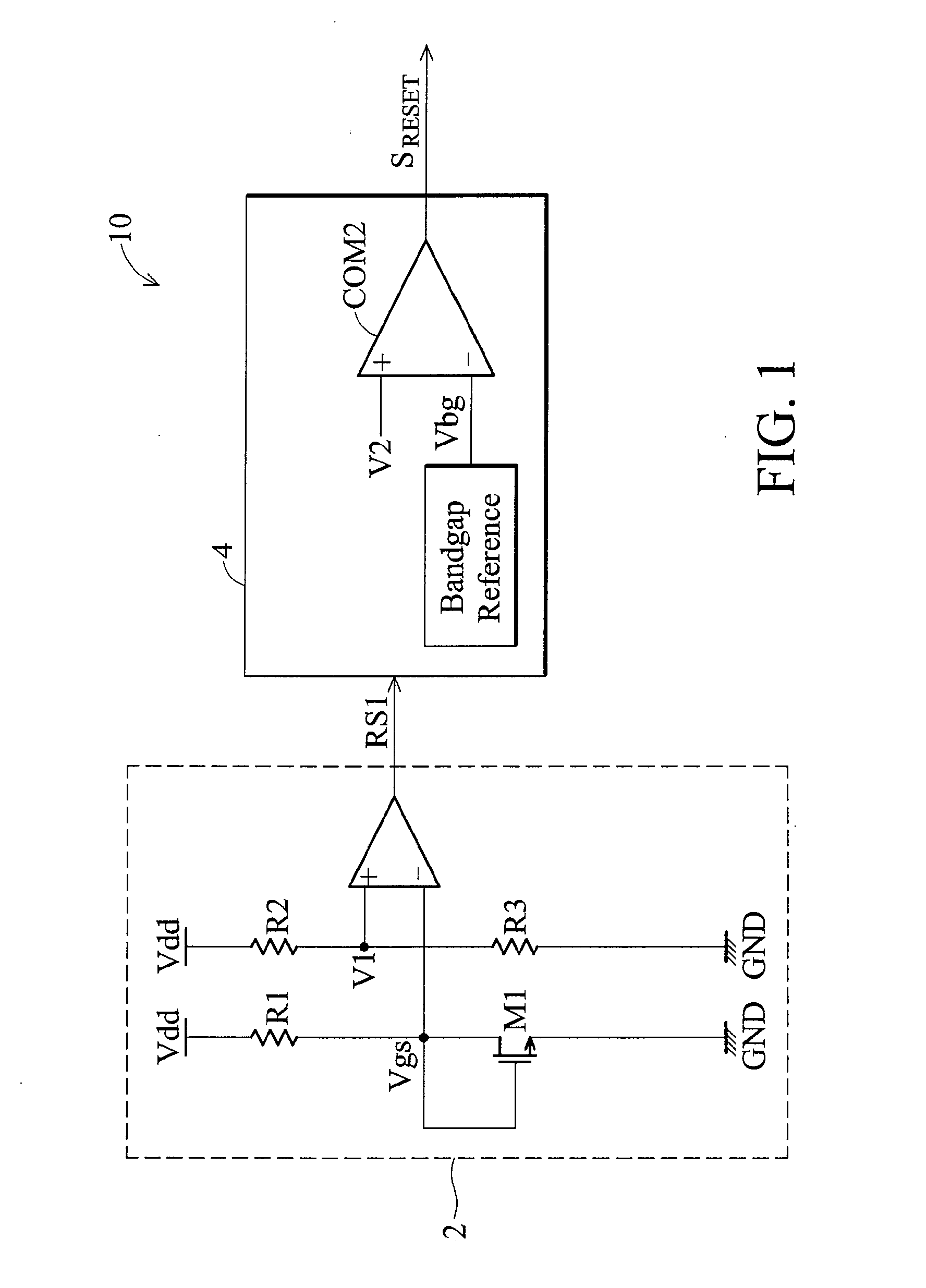

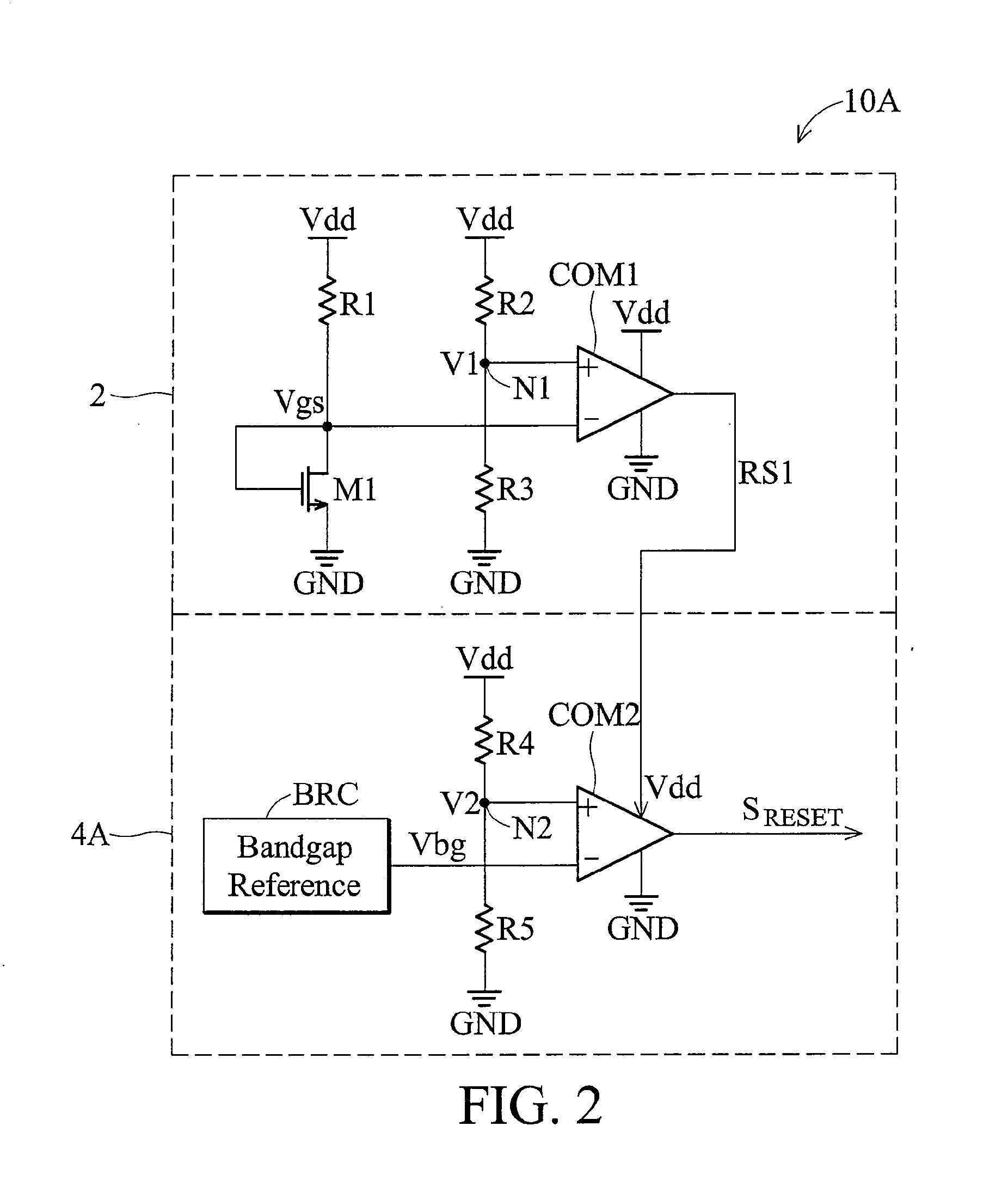

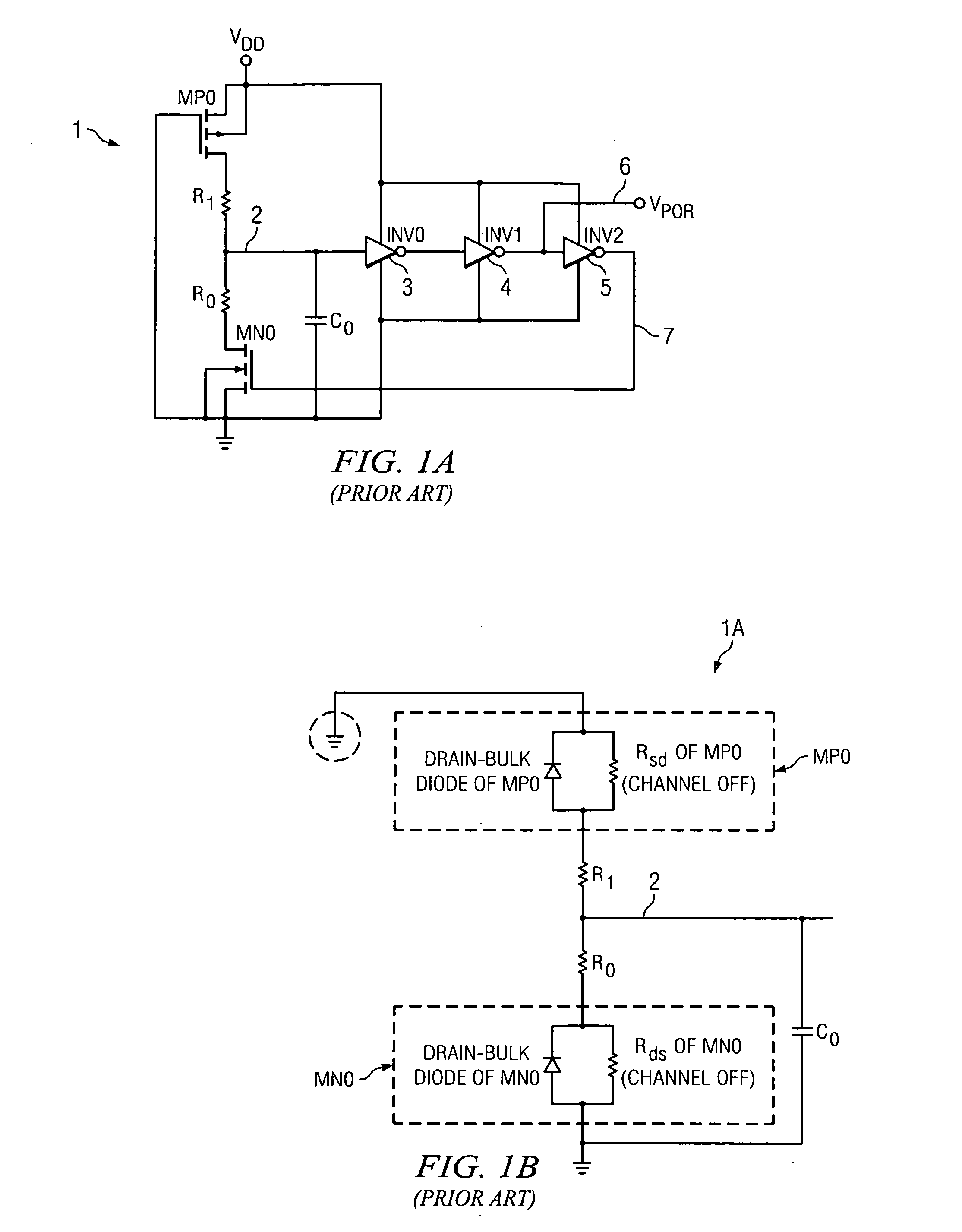

Power-on reset circuits

Power-on reset circuits are disclosed. A first reset circuit includes a first comparator to output a system reset signal, and a second reset circuit outputs a first reset signal to control operations of the first comparator, such that the first reset circuit outputs the system reset signal when a first voltage is less than a first reference voltage.

Owner:MEDIATEK INC

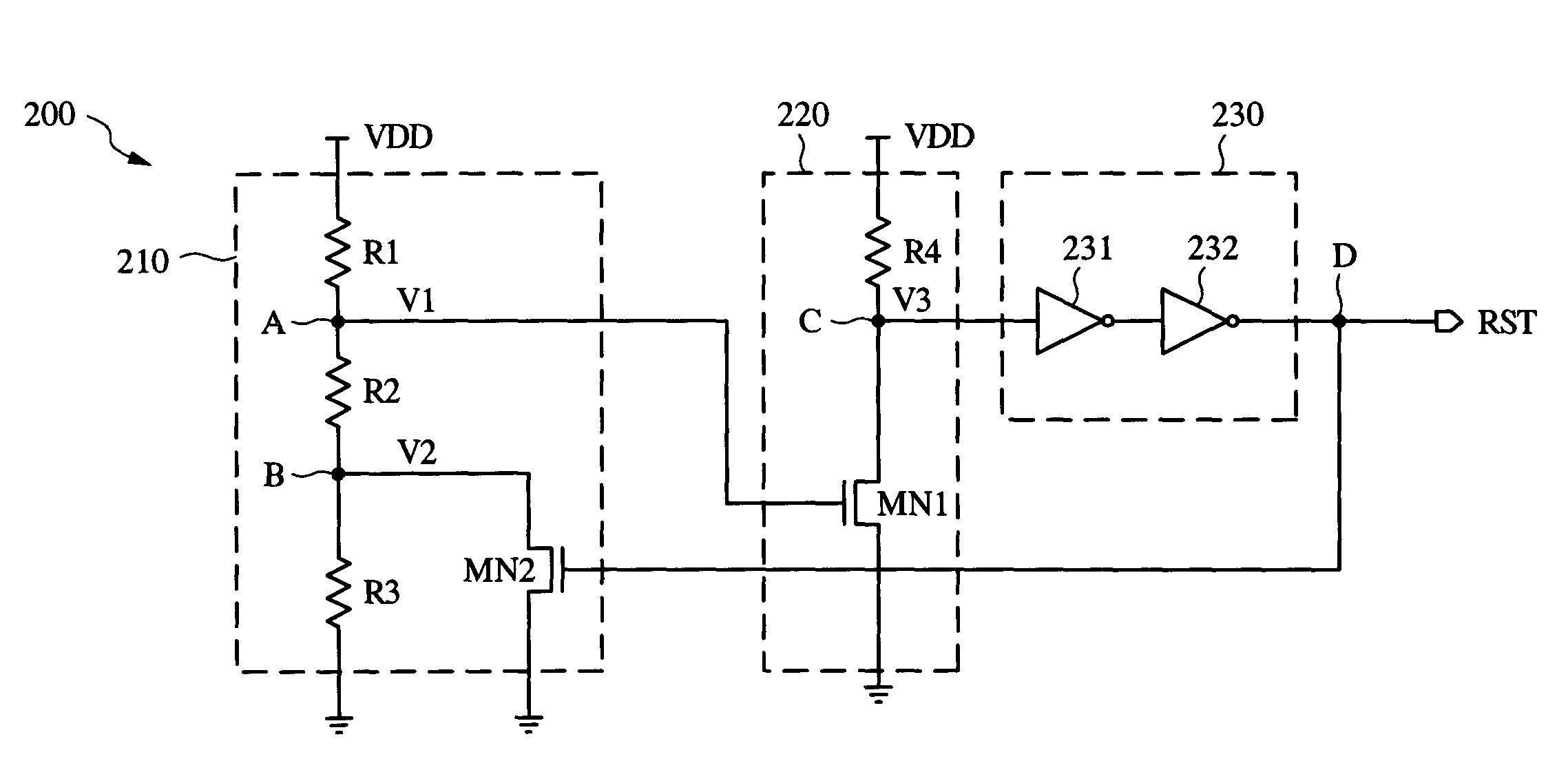

CMOS power on reset circuit

ActiveUS7161396B1Less sensitiveCreates hysteresisPulse automatic controlElectronic switchingPower-on resetCMOS

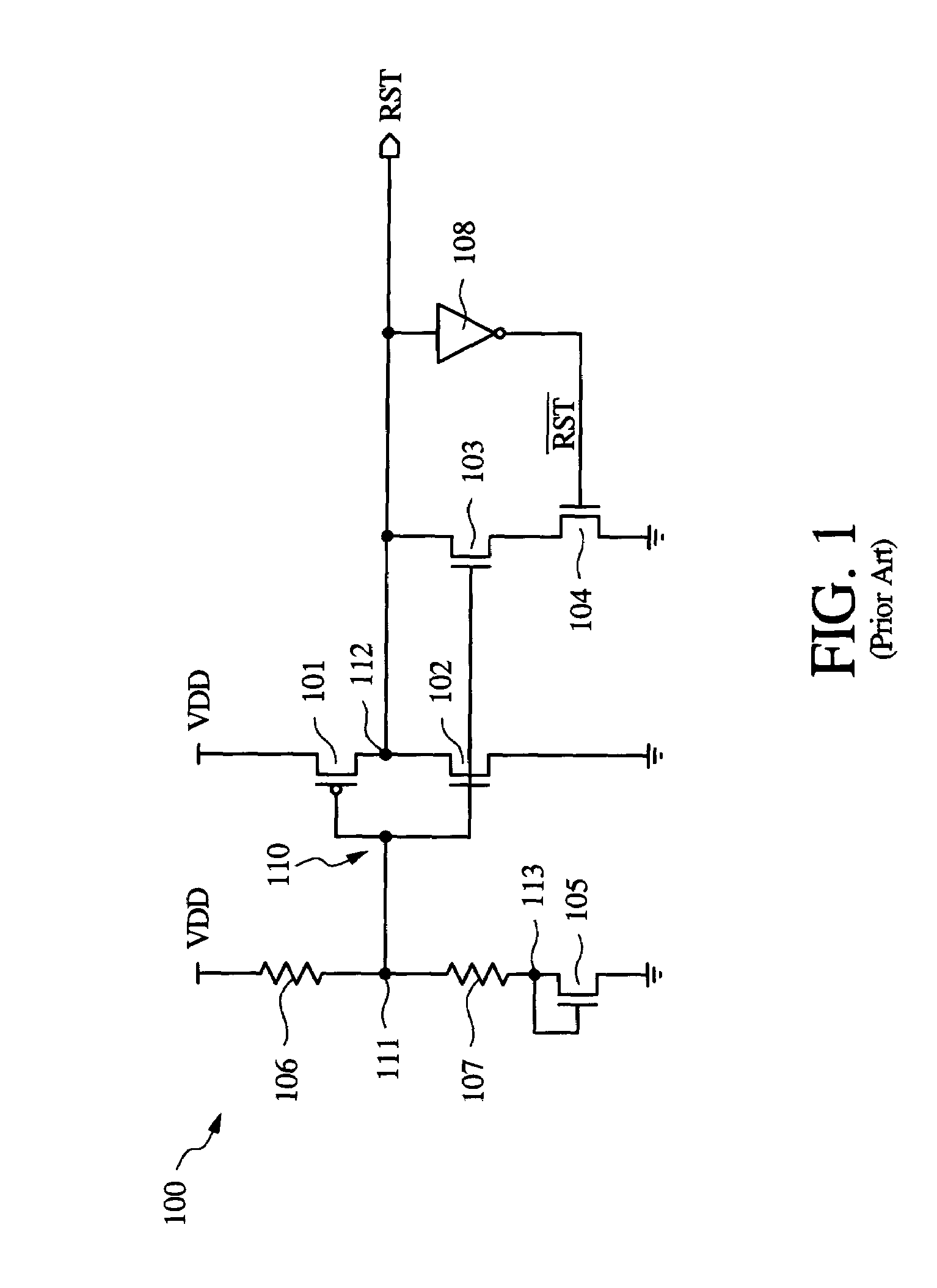

A power-on reset circuit for generating a reset signal for an associated IC device includes a pull-up resistor connected between a supply voltage and a tracking node, a pull-down transistor connected between the tracking node and ground potential, and a voltage divider circuit connected between the supply voltage and ground potential. The voltage divider circuit has a first ratioed voltage node coupled to the gate of the pull-down transistor. For some embodiments, the voltage divider circuit includes a first resistor connected between the voltage supply and the first ratioed voltage node, a second resistor connected between the first ratioed voltage node and a second ratioed voltage node, a third resistor connected between the second ratioed voltage node and ground potential, and a shunt transistor connected between the second ratioed voltage node and ground potential has a gate responsive to the reset signal.

Owner:XILINX INC

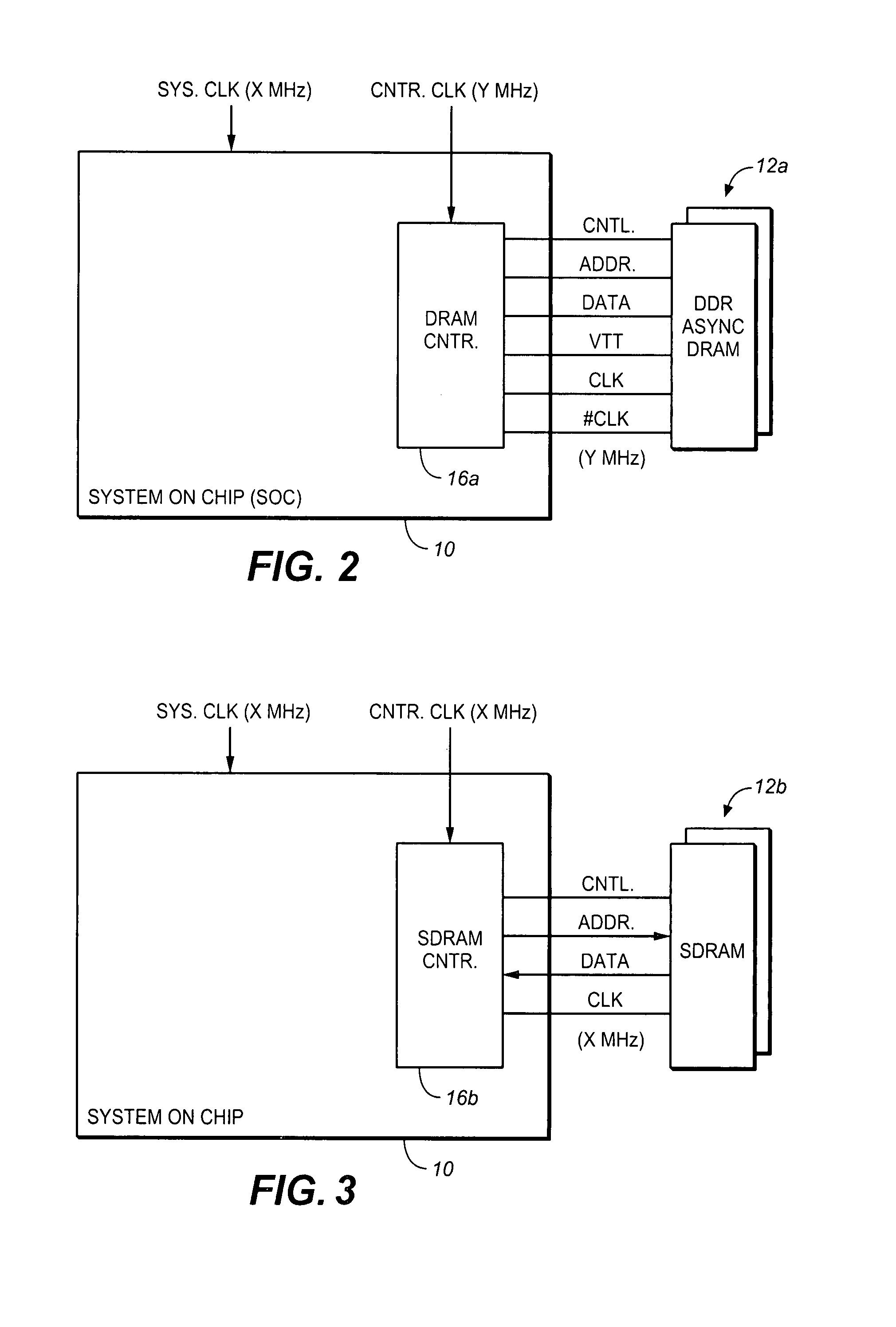

Low power memory controller that is adaptable to either double data rate DRAM or single data rate synchronous DRAM circuits

ActiveUS7243254B1Data transfer rateLess costlyGenerating/distributing signalsMemory systemsPower-on resetElectricity

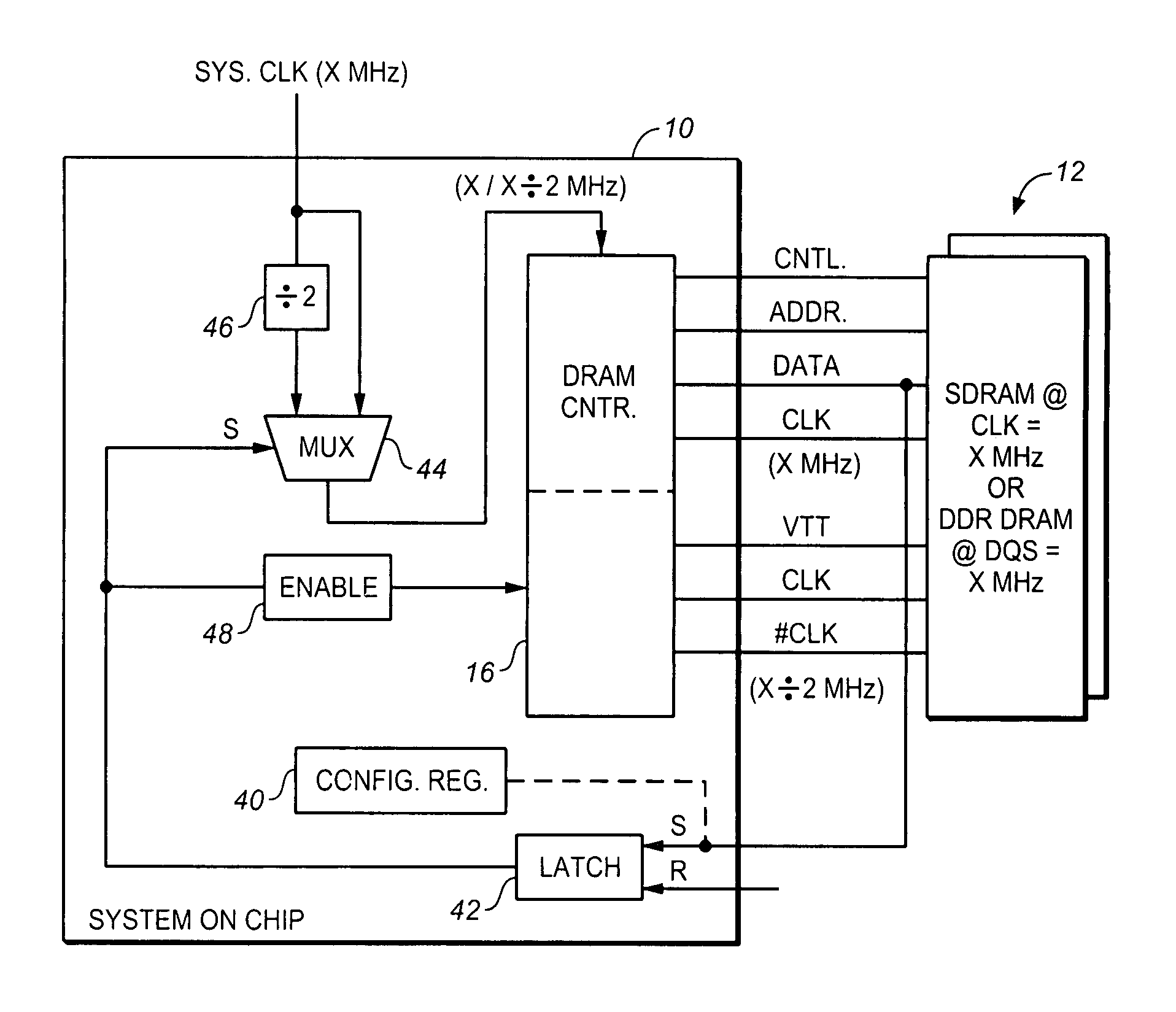

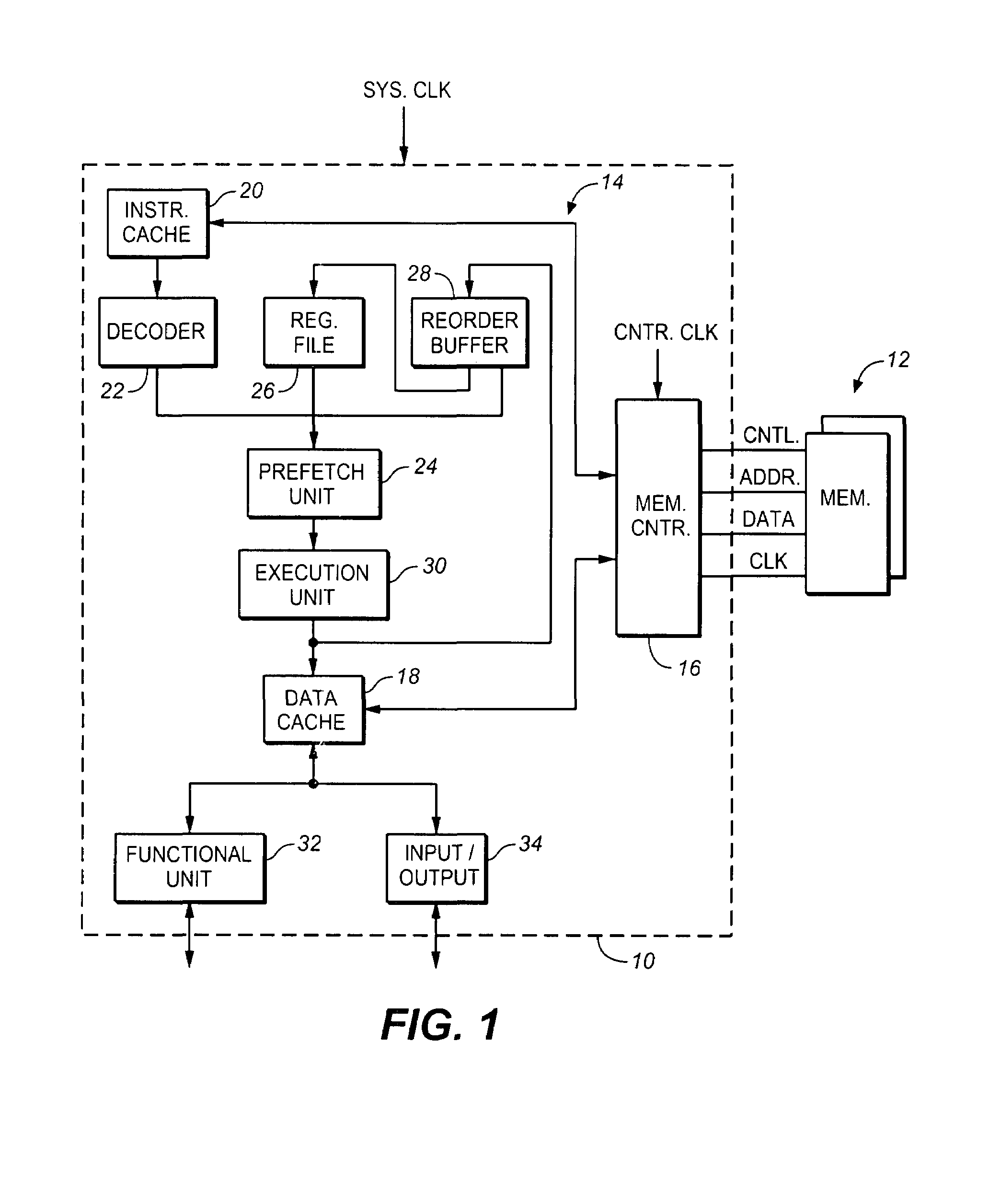

A memory controller is provided and a method for transferring data between the memory controller and a memory device. The memory controller can be implemented on an integrated circuit that also contains an execution unit. The execution unit can be clocked at a first clock rate, whereas the memory controller can be selectively clocked at either the first clock rate or a second clock rate that is approximately one-half frequency of the first clock rate. By clocking the memory controller at either the first clock rate or the second clock rate, the memory controller can accommodate different types of semiconductor memory. For example, the memory controller can control single data rate (SDR) DRAM memory if it is clocked at a first clock rate. Conversely, the memory controller can control double data rate (DDR) DRAM memory if it is clocked at approximately one-half the first clock rate. By selectively clocking the memory controller at different clocking rates, the memory controller need not be modified in hardware, yet can accommodate different memory devices by allowing a user to simply plug one type of memory into a receptacle rather than another depending on the cost constraints and user application. Therefore, the memory controller is adaptable during a power-on reset in which the computer system is initialized to automatically receive and control different types of memory selected by a user.

Owner:AVAGO TECH INT SALES PTE LTD

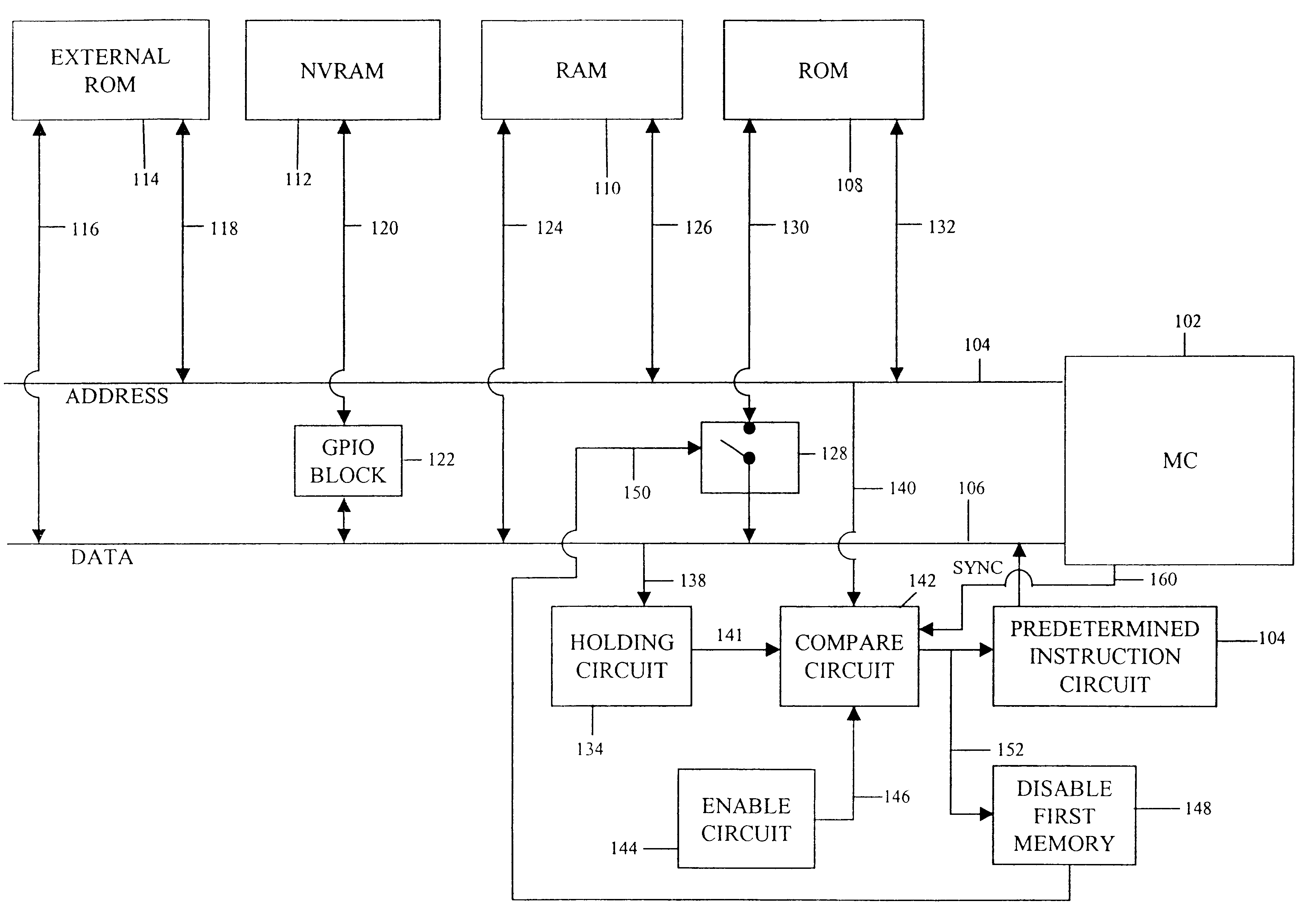

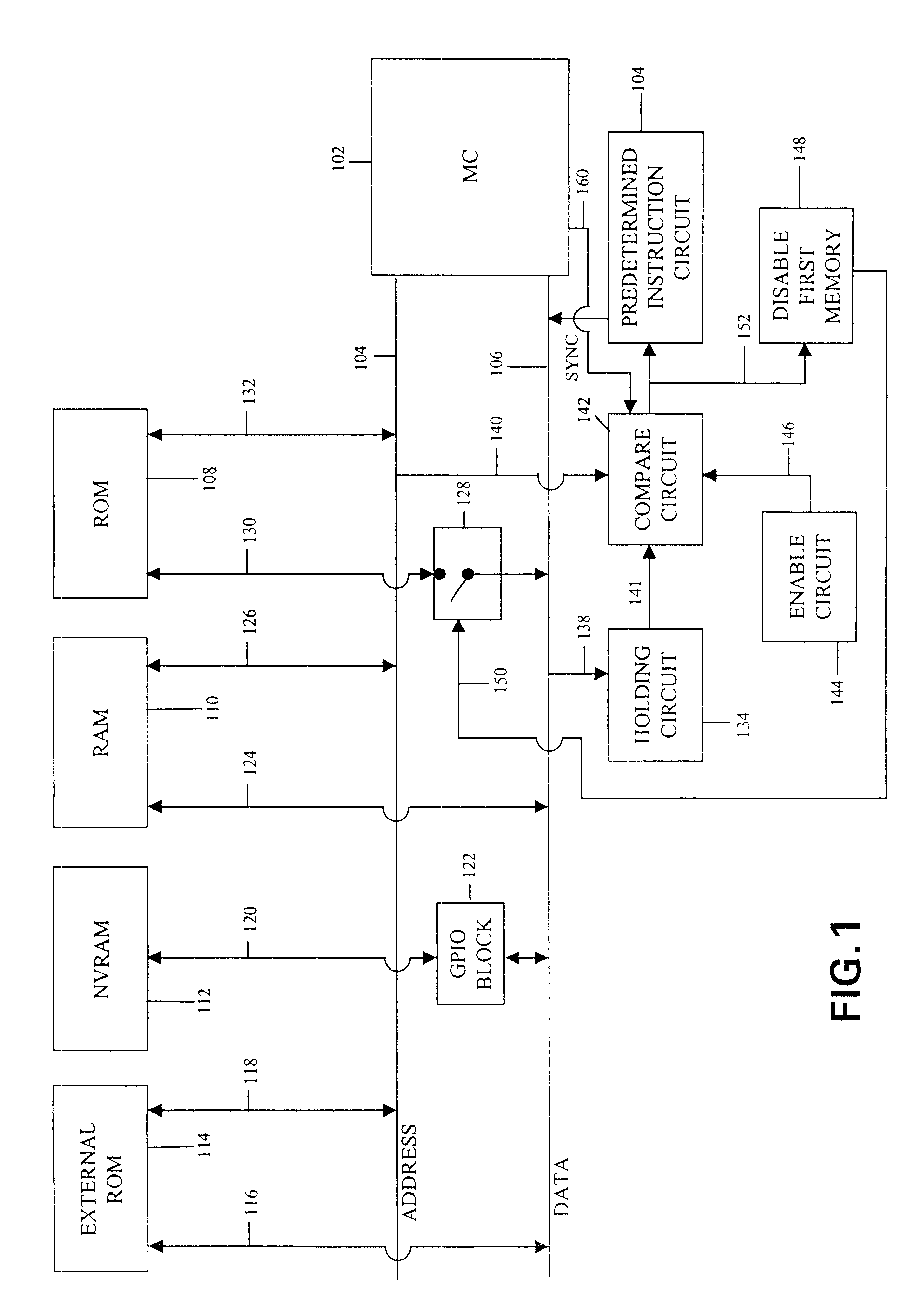

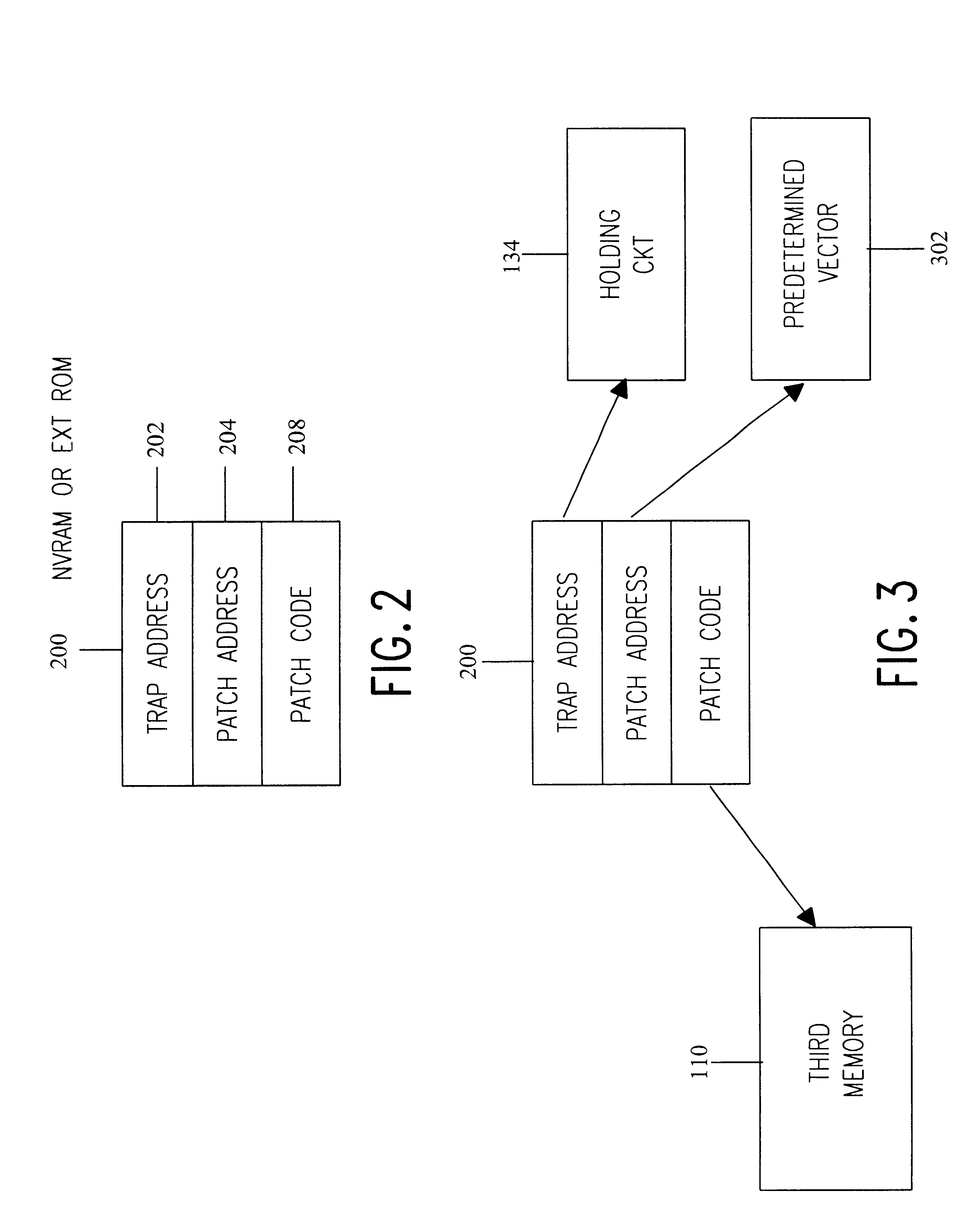

System and method for providing a trap and patch function to low power, cost conscious, and space constrained applications

InactiveUS6412081B1Less powerLess costEnergy efficient ICTProgram initiation/switchingPower-on resetElectricity

A system and method for providing a software trap and patch function to low power, cost conscious, and space constrained applications. When a programming error in a first memory is discovered, a data structure comprising a trap address, patch code, and patch address are stored in a second memory. A power-on-reset process detects the presence of the data structure, and in response thereto, enables the trap and patch function. In operation, upon the occurrence of a trap condition, the first memory is disconnected from the data bus and a predetermined instruction circuit is activated. Upon activation thereof, the predetermined instruction circuit, which comprises solely combinational circuitry, places the op code of the predetermined instruction on the data bus. In one embodiment, in which the predetermined instruction is a software interrupt instruction, a predetermined bit of the PSR is placed in a defined state responsive to the occurrence of a trap condition. Upon execution of the software interrupt instruction, the processor executes an interrupt request service routine. There, the predetermined bit of the PSR is examined to see if it is in the predefined state. If so, and the interrupt was caused by a trap condition in contrast to a software interrupt, the service routine causes the processor to execute the patch code in place of the error-containing code. If not, signifying a hardware interrupt, another service routine is executed.

Owner:SKYWORKS SOLUTIONS INC

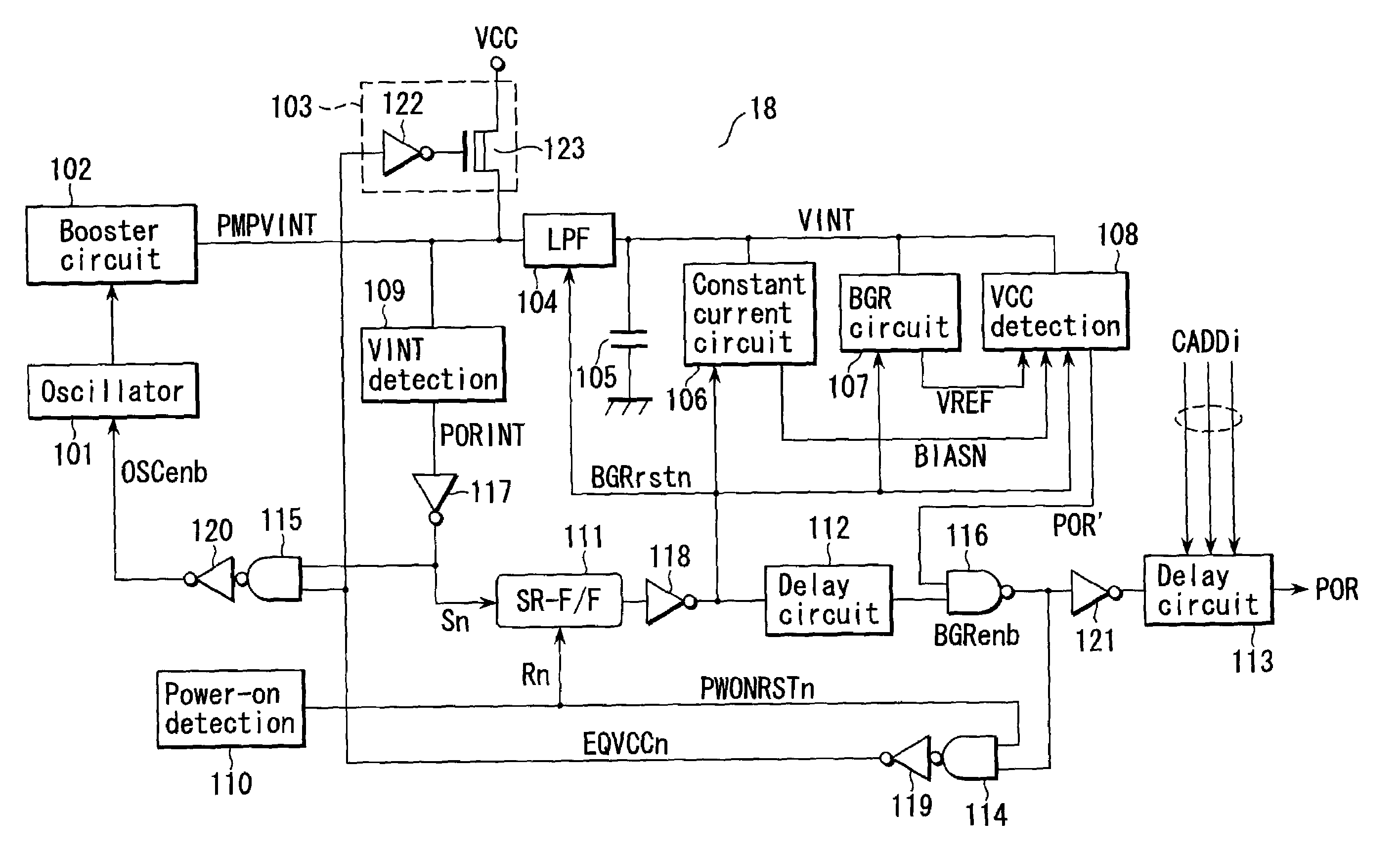

Semiconductor memory device having a power-on reset circuit

A semiconductor device includes an internal power supply terminal for supplying an internal power supply voltage, an oscillator generating a clock pulse when the internal power supply voltage becomes higher than a first voltage, a charge pump circuit charge pumping upon receiving the clock pulse, a reference voltage generator using the output voltage from the charge pump circuit as a power supply, and a voltage monitor which uses the output voltage from the charge pump circuit as a power supply, has a comparator for comparing a divided voltage of the internal power supply voltage with the reference voltage, and outputs a first signal of a first logic level as the power-on reset signal when the internal power supply voltage is higher than a second voltage. With this arrangement, a power-on reset circuit with little variation in power-on monitoring level can be provided.

Owner:TOSHIBA MEMORY CORP

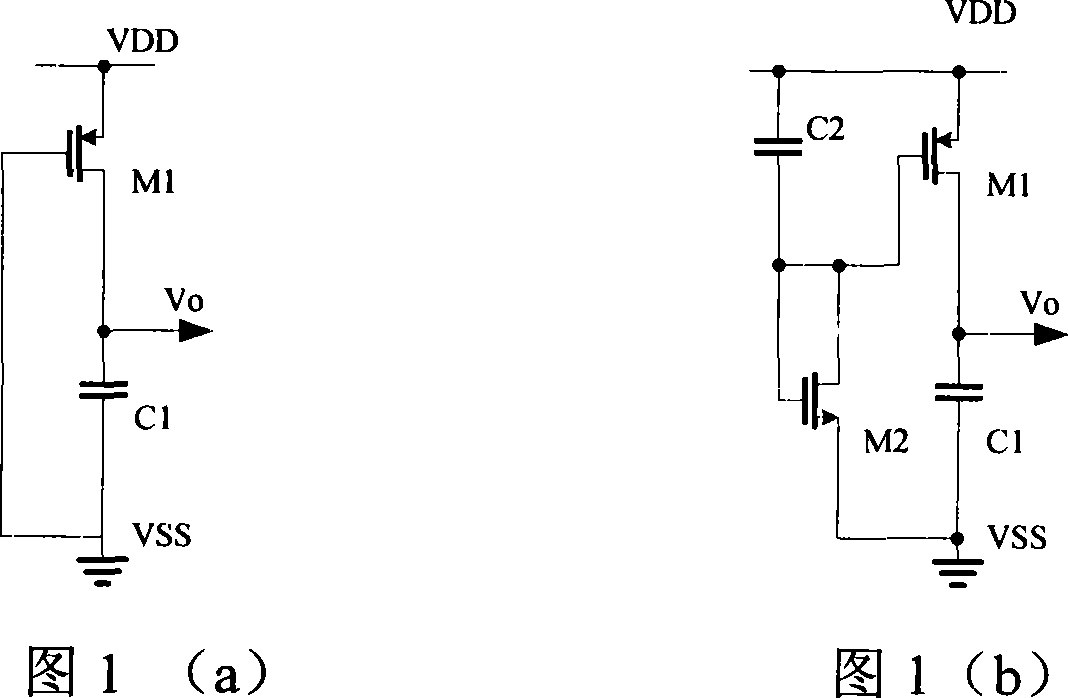

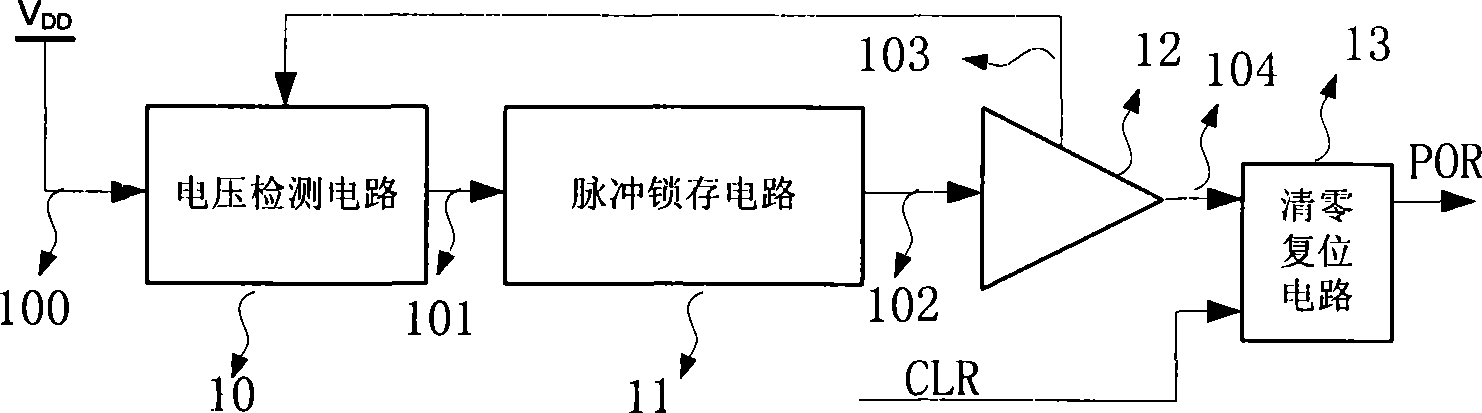

Static zero-consumption power-on resetting circuit

The invention discloses a static zero-consumption power-on reset circuit which comprises a voltage detecting circuit, an impulse latch circuit, an output buffer circuit, and a zero clearing reset circuit. Wherein one input end of the voltage detecting circuit is connected to a power supply, the other end thereof is connected to an enable control output end of the output buffer circuit; an output end of the voltage detecting circuit is connected to an input end of the impulse latch circuit; an output end of the impulse latch circuit is connected to an input end of the output buffer circuit; an enable control output end of the voltage detecting circuit and an input end of the zero clearing reset circuit are respectively connected with an output end of the output buffer circuit; and an input end of zero clearing reset circuit receives an external zero clearing reset signal, and an output end thereof outputs an electrifying reset signal. The invention has a simple and novel structure, needs no external RC element, the occupied area of a chip is small, static consumption is nearly zero, and the invention can be applied to the SoC chip with low consumption.

Owner:HUAZHONG UNIV OF SCI & TECH

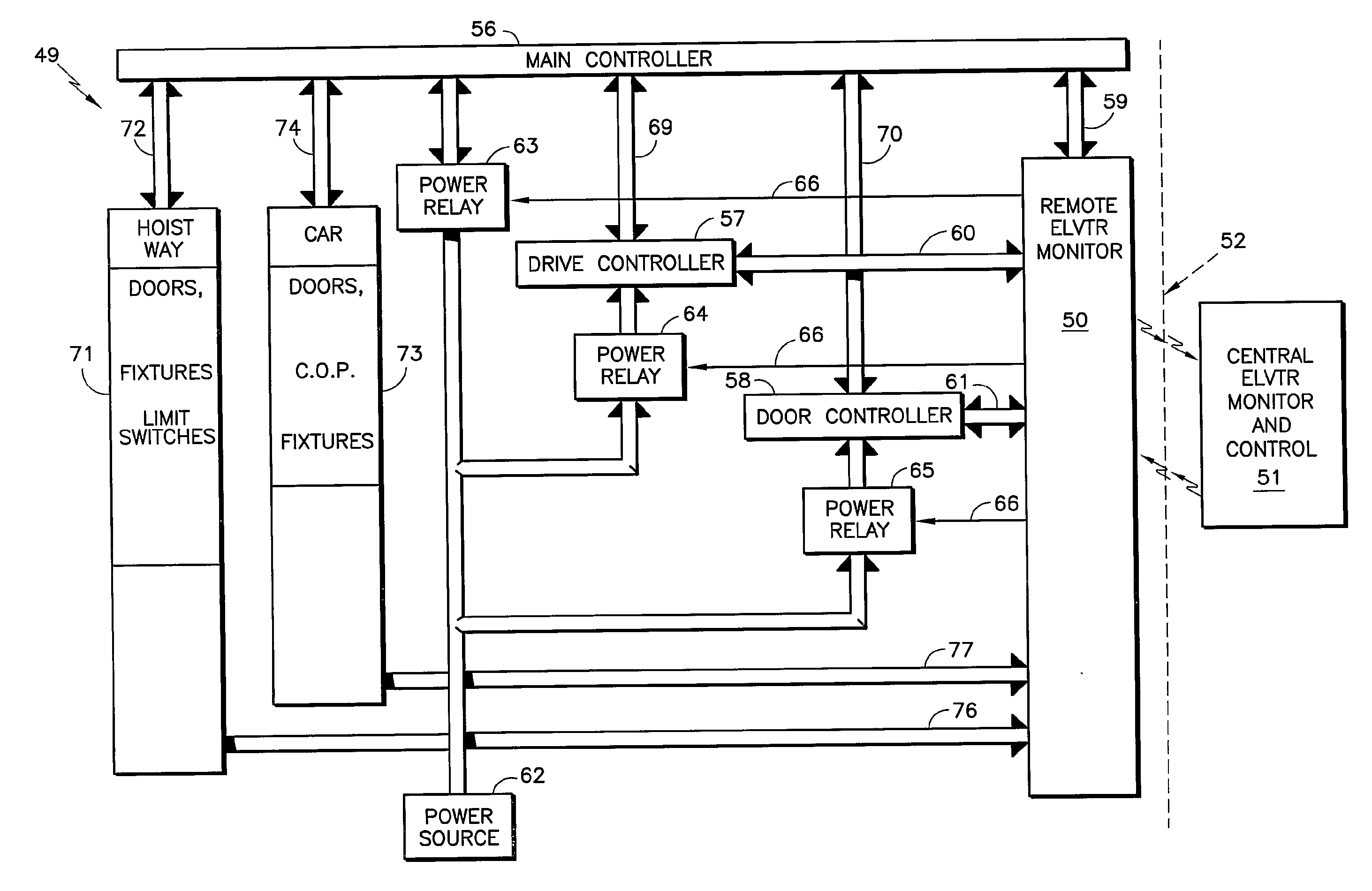

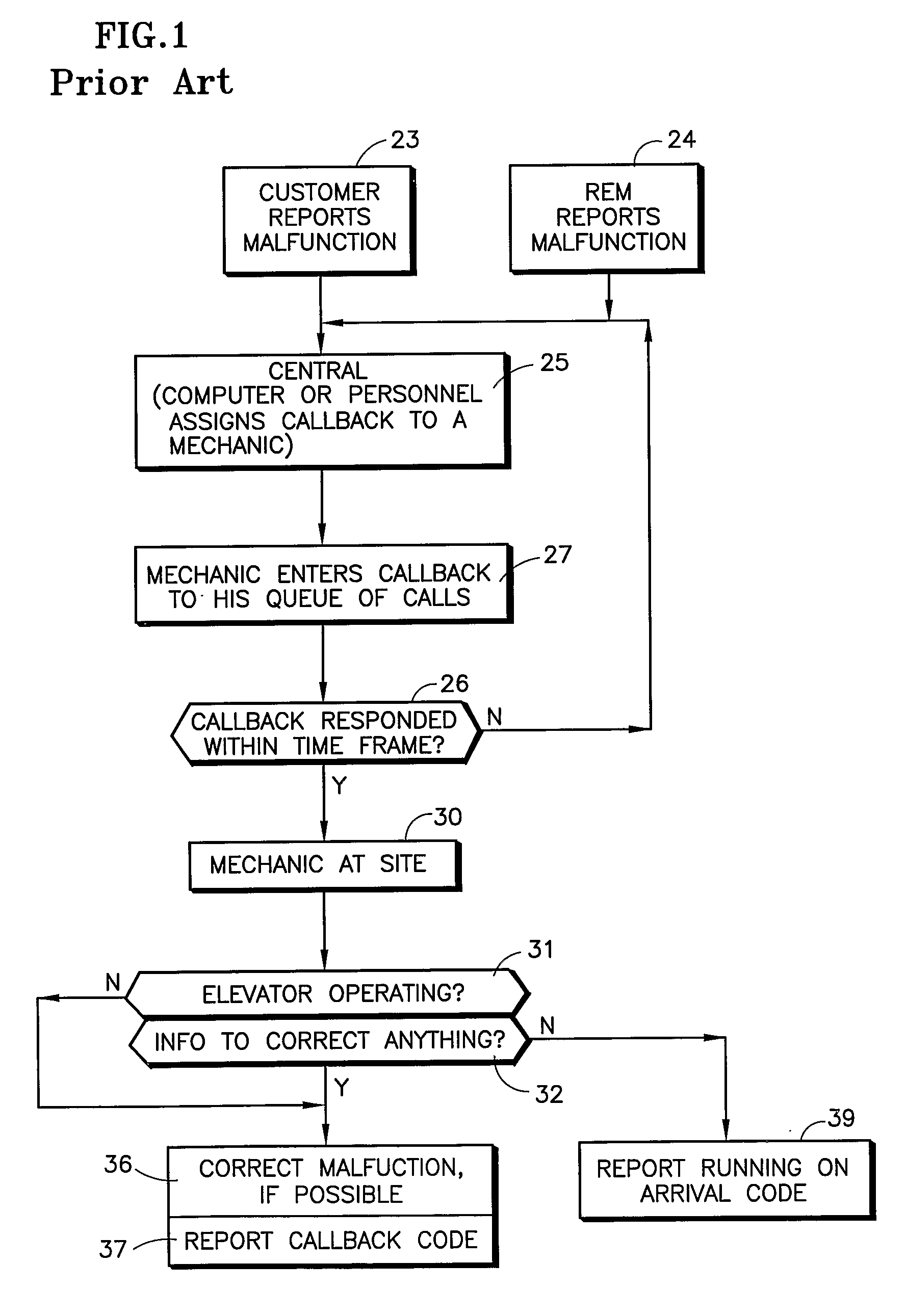

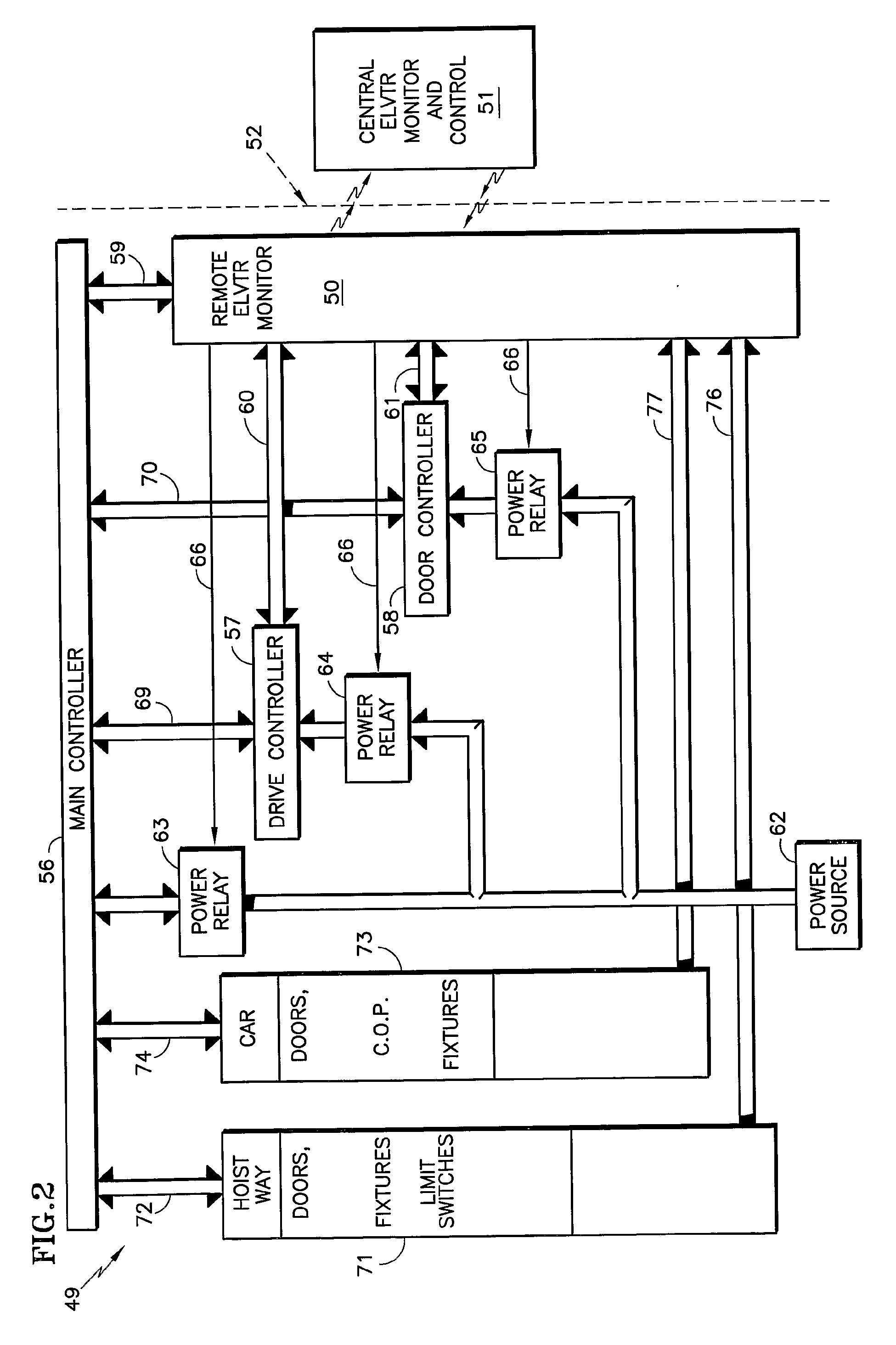

Remotely Performed and/or Assisted Restoration of Elevator Service

ActiveUS20090218178A1Avoiding unnecessary service callReduce in quantityComputer controlElevatorsPower-on resetStation

An elevator (49) includes remote elevator monitoring equipment (50) (REM) connected by a communication linkage (52) to a central elevator monitoring and control station (51). Main, drive, and door controllers (56-58) are interconnected (5961) with the REM. Power-on-reset (POR) of controllers is caused internally (150) or by remotely-operable relays (63-65). An elevator expert at the remote station may order a POR (108), disable components (120), try various fixes (124), and / or order maintenance (115, 135) with instructions. In another embodiment, the controller (56a, 56b) includes elevator diagnostics (150) which can recognize an elevator malfunction and either cause a relay (63) to interrupt power for an interval or cause a reboot.

Owner:OTIS ELEVATOR CO

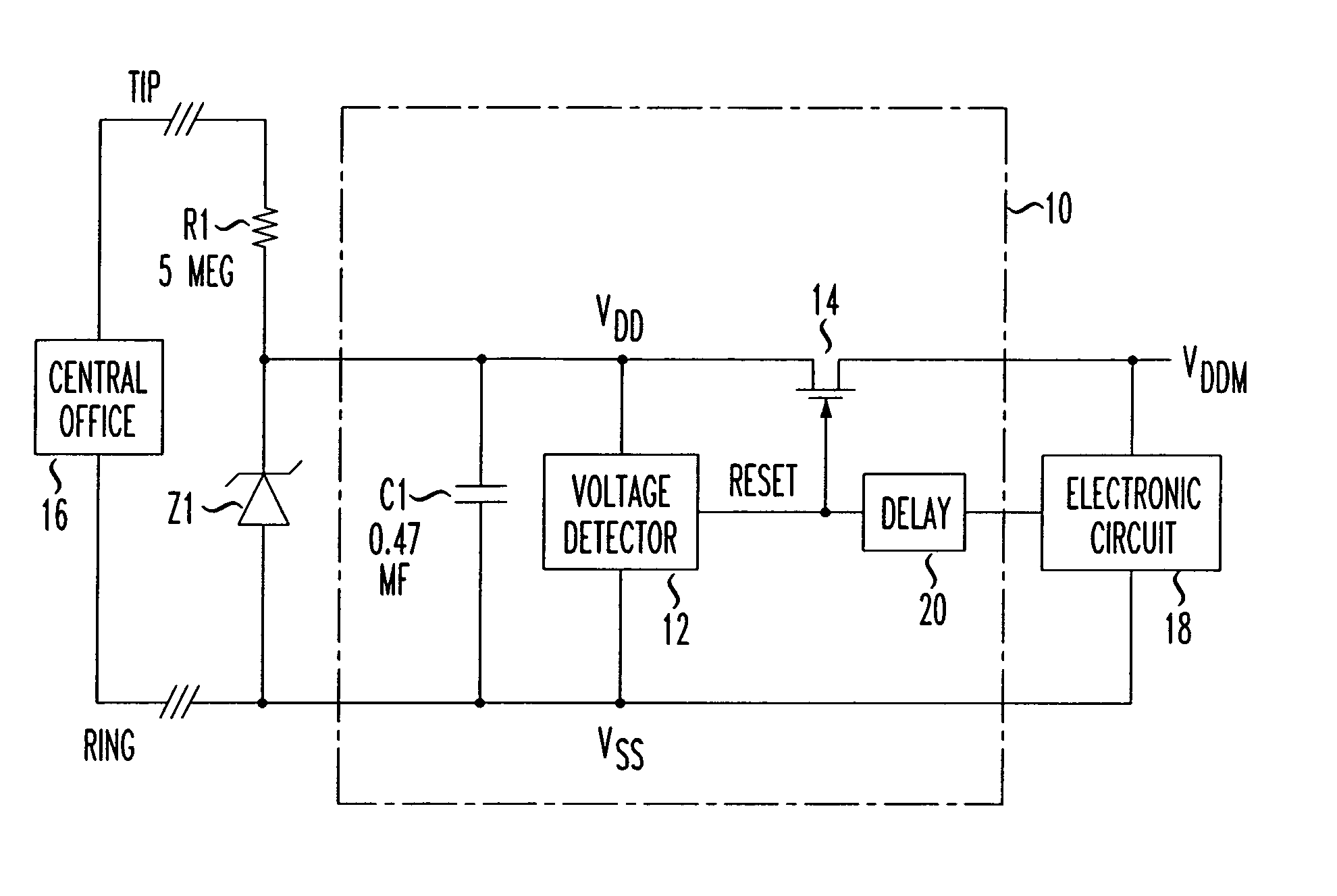

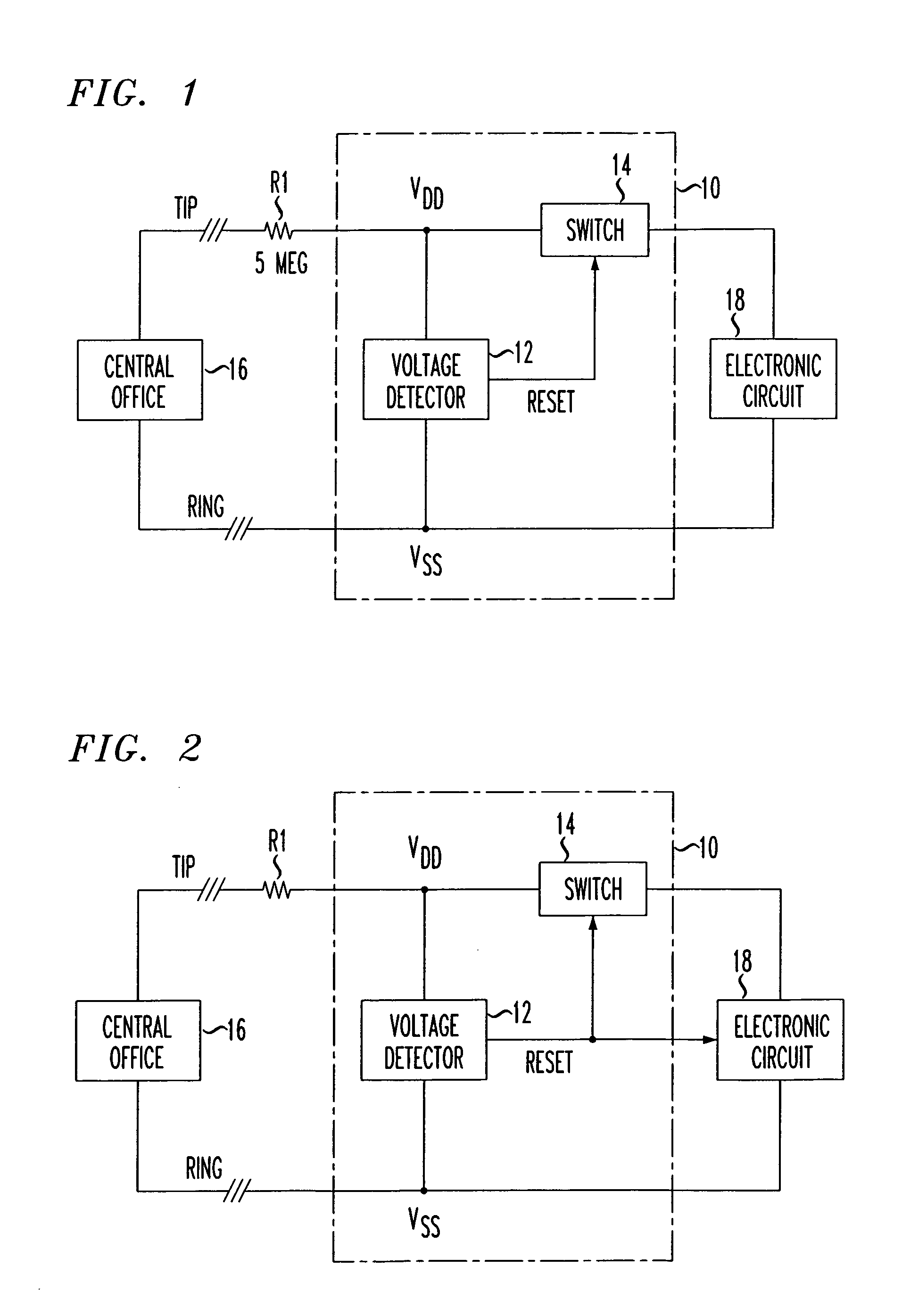

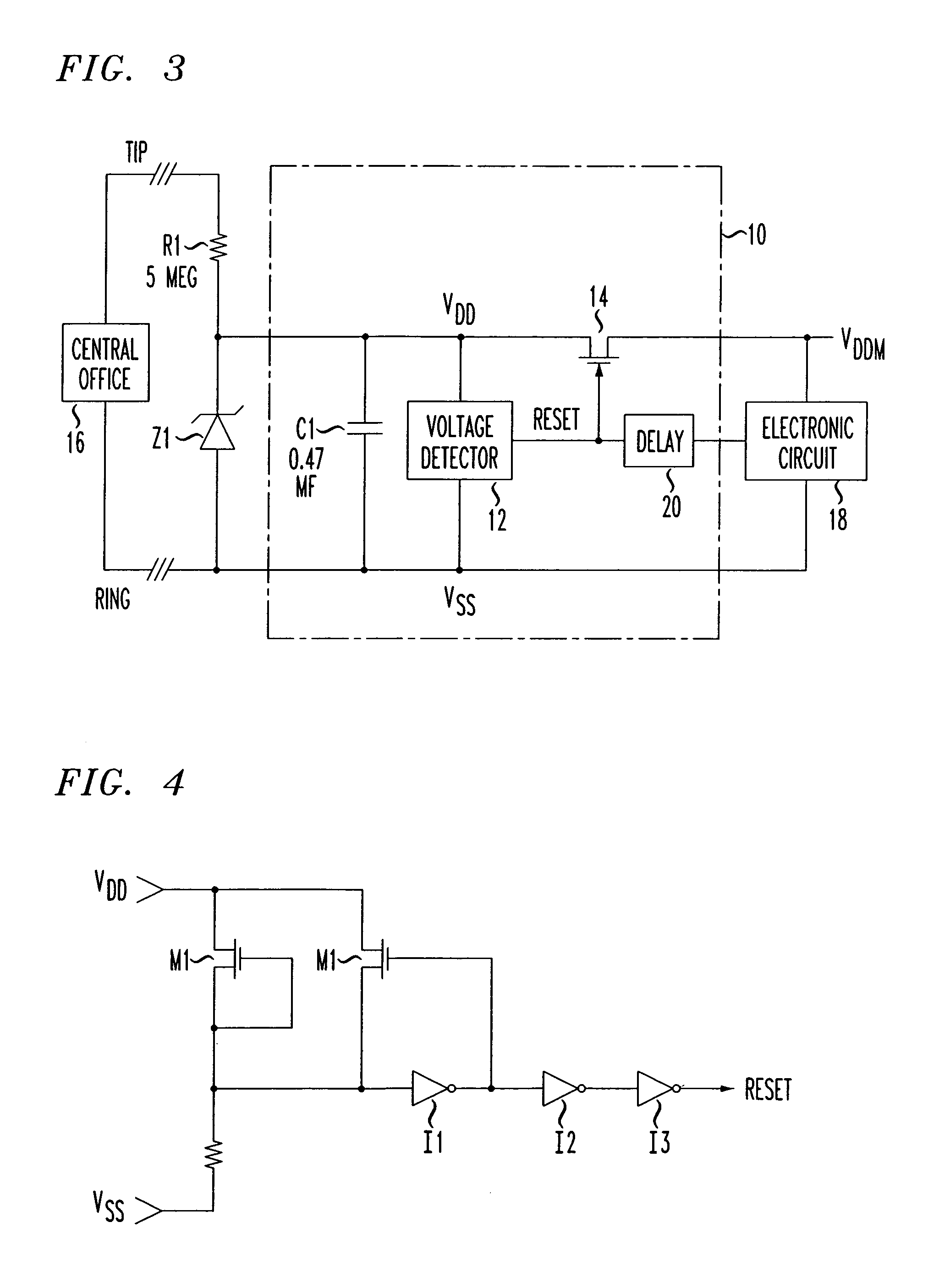

Power up reset circuit for line powered circuit

InactiveUS7095848B1Two-way loud-speaking telephone systemsSubstations coupling interface circuitsPower-on resetElectricity

A system for powering up an electronic circuit with telephone line power such that the electronic circuit does not enter a lockup state. The system includes a voltage detector that measures the voltage across the telephone line and a switch coupled with the voltage detector. The voltage detector generates a Reset signal when the measured voltage exceeds a selected voltage level, and the switch applies power to the electronic circuit in response to the generated Reset signal.

Owner:LUCENT TECH INC +1

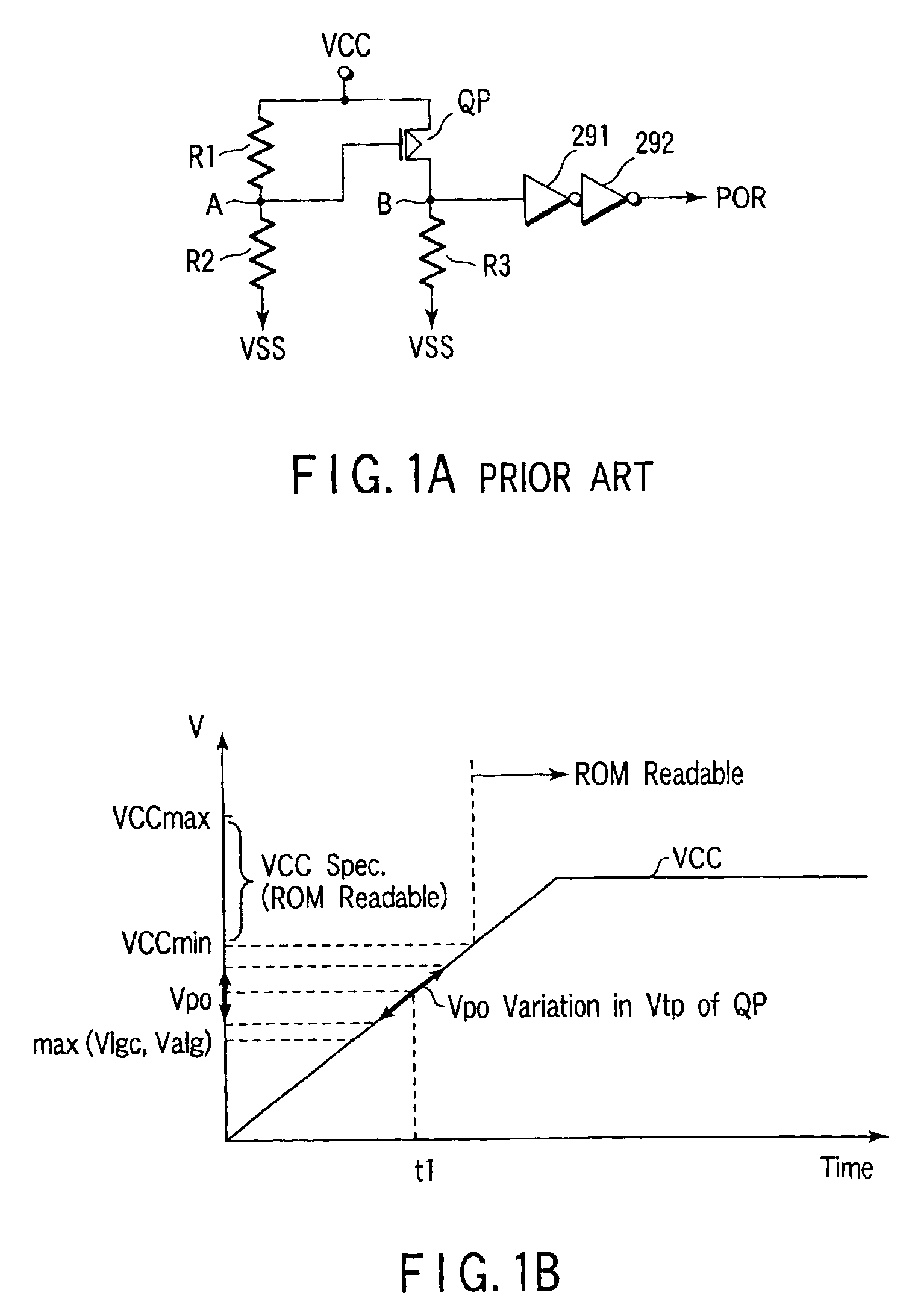

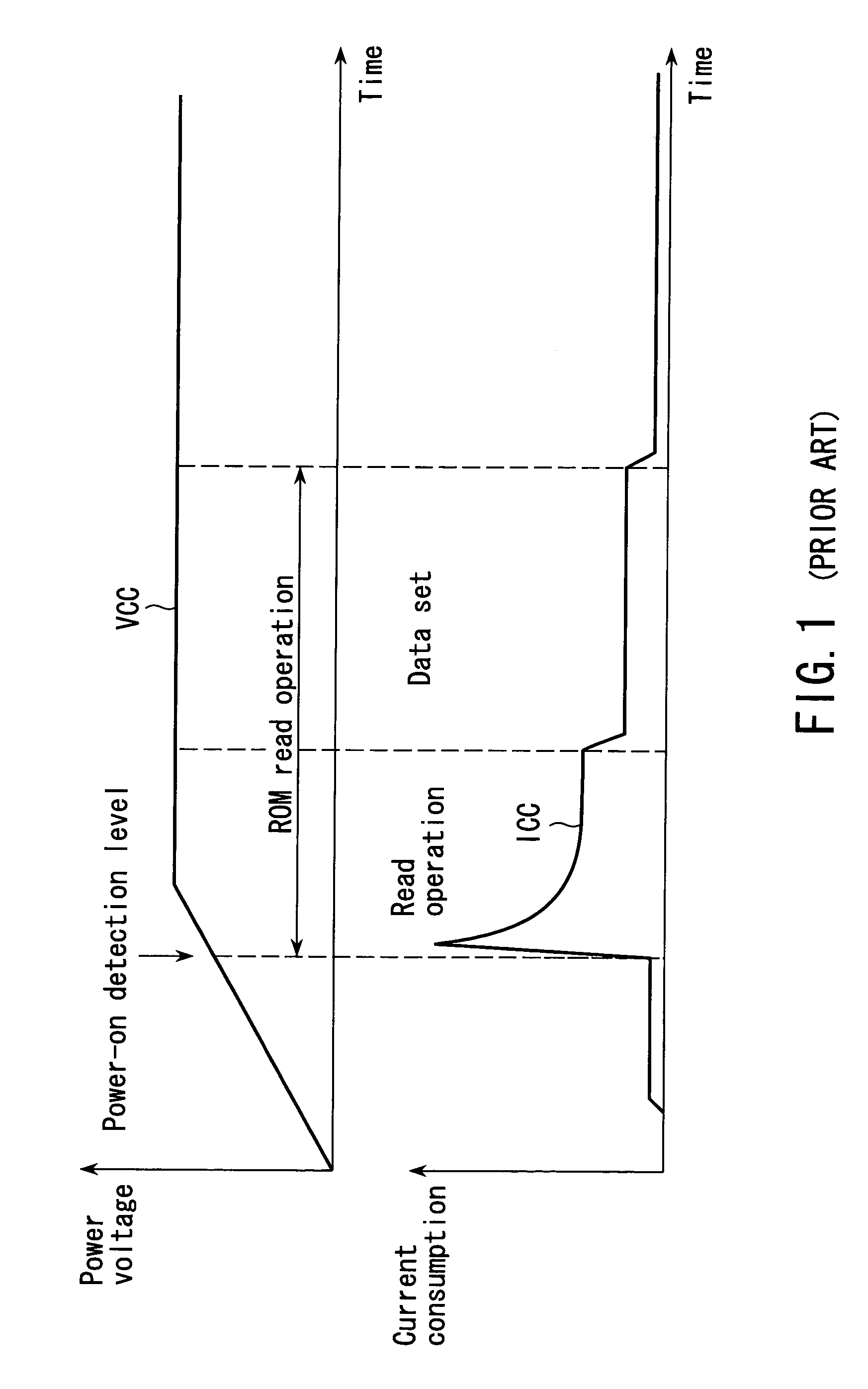

Non-volatile semiconductor storage device performing ROM read operation upon power-on

A power-on reset circuit has a power-on level detecting circuit which detects a power voltage to output a power-on reset signal and a delay circuit which delays the power-on reset signal output by the power-on level detecting circuit. Two chip address specifying pads are connected to the delay circuit. Delay time in the delay time is controlled according to a chip address supplied to these two pads.

Owner:KIOXIA CORP

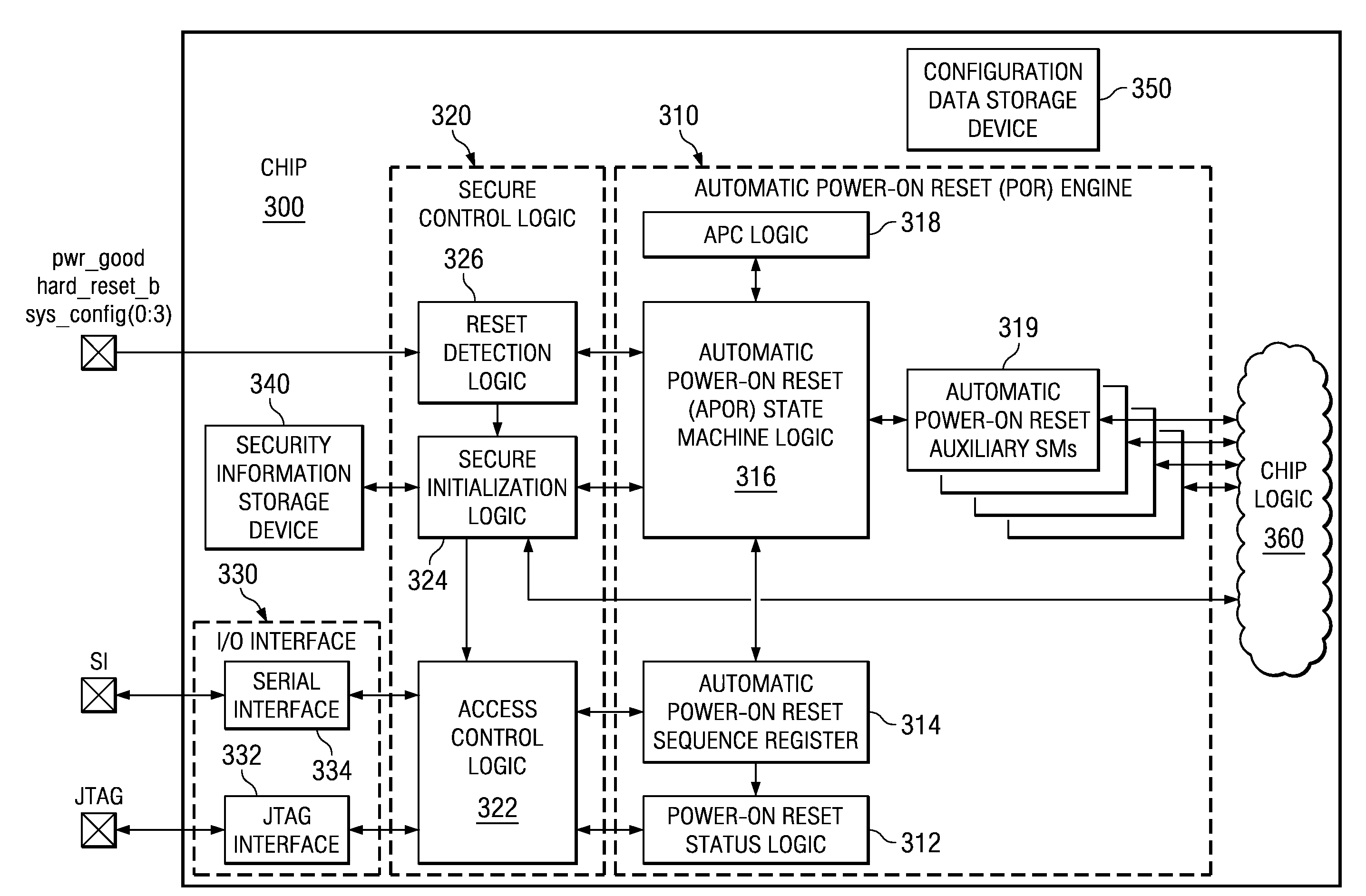

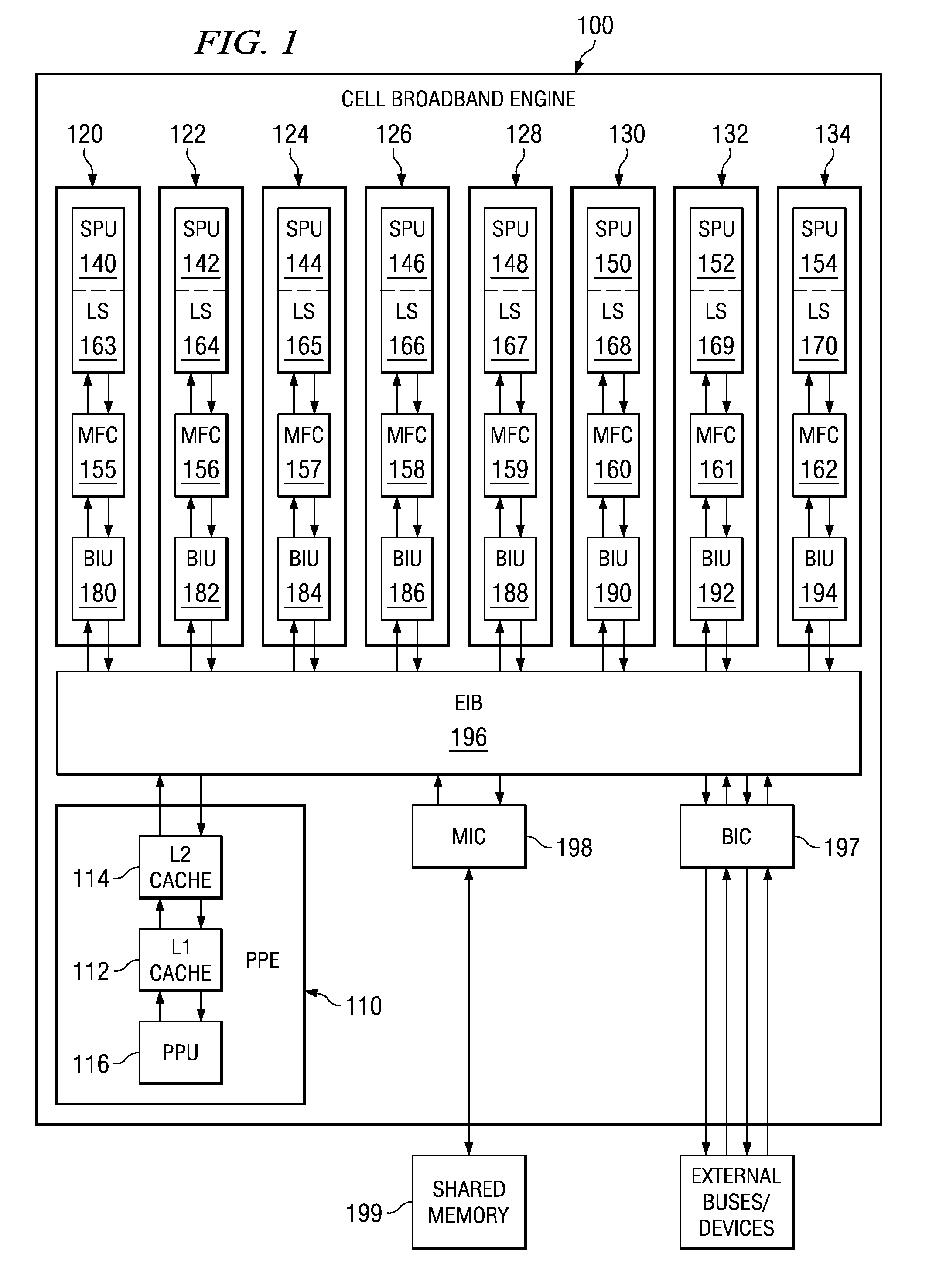

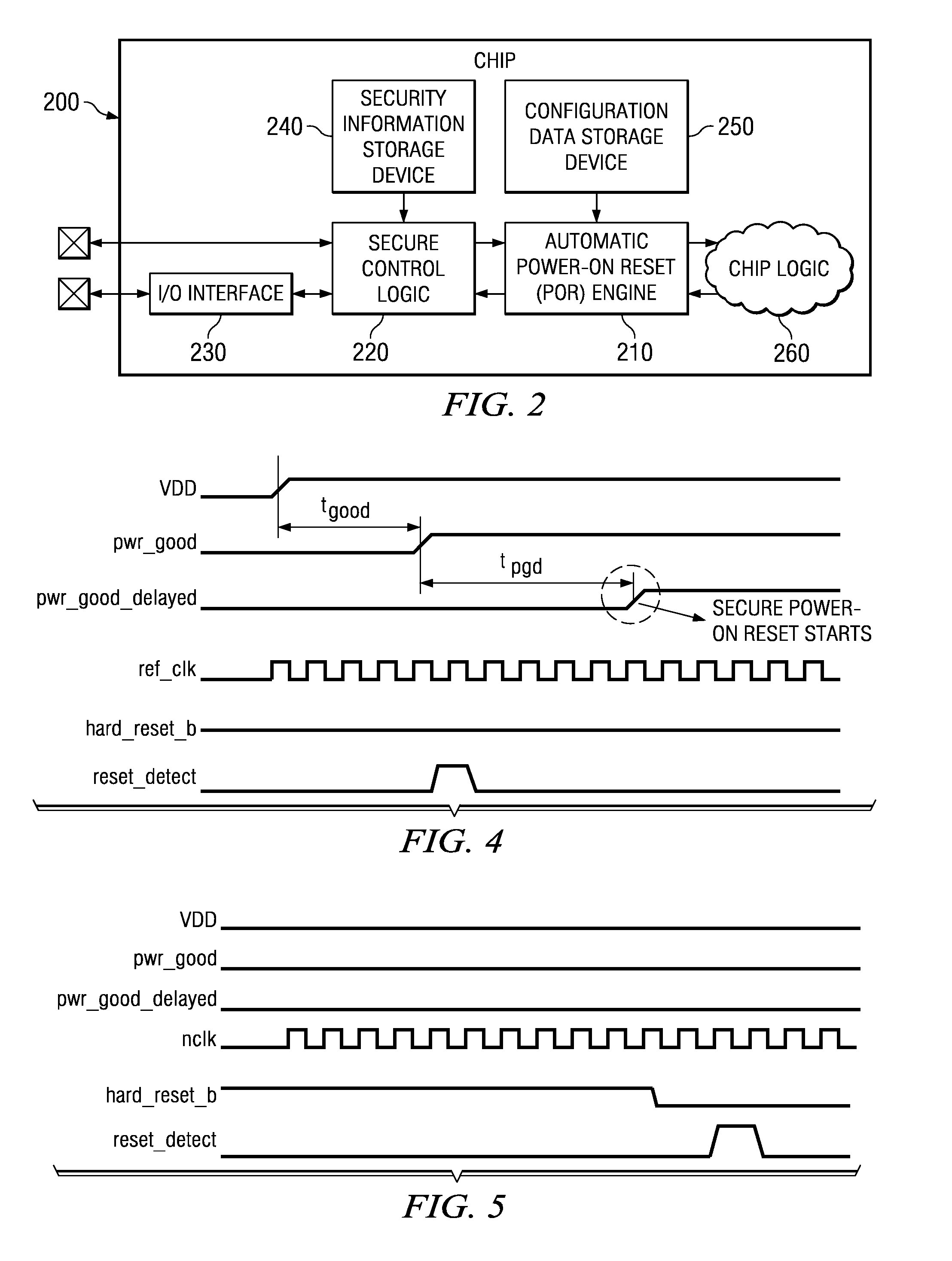

Secure power-on reset engine

InactiveUS20090055637A1Filter access to chip resourcesPulse automatic controlError detection/correctionPower-on resetThird party

A secure Power-on Reset (POR) engine is provided, inside a processor chip, which guarantees a secure initialization of the chip to enable secure code execution. External access to chip resources is limited to a very few targeted settings that do not compromise the chip security. The POR engine comprises a small state machine that runs through a predefined sequence coded in persistent memory contained in the processor chip. The state machine initializes the chip and allows external access from an external processor to only some scan chains of the processor chip in order to configure interfaces, and the like, without compromising the chip security. The state machine also manages the encryption keys that are used to verify that the code, fetched by the processor to complete the initialization in software, is not modified by a third party.

Owner:IBM CORP

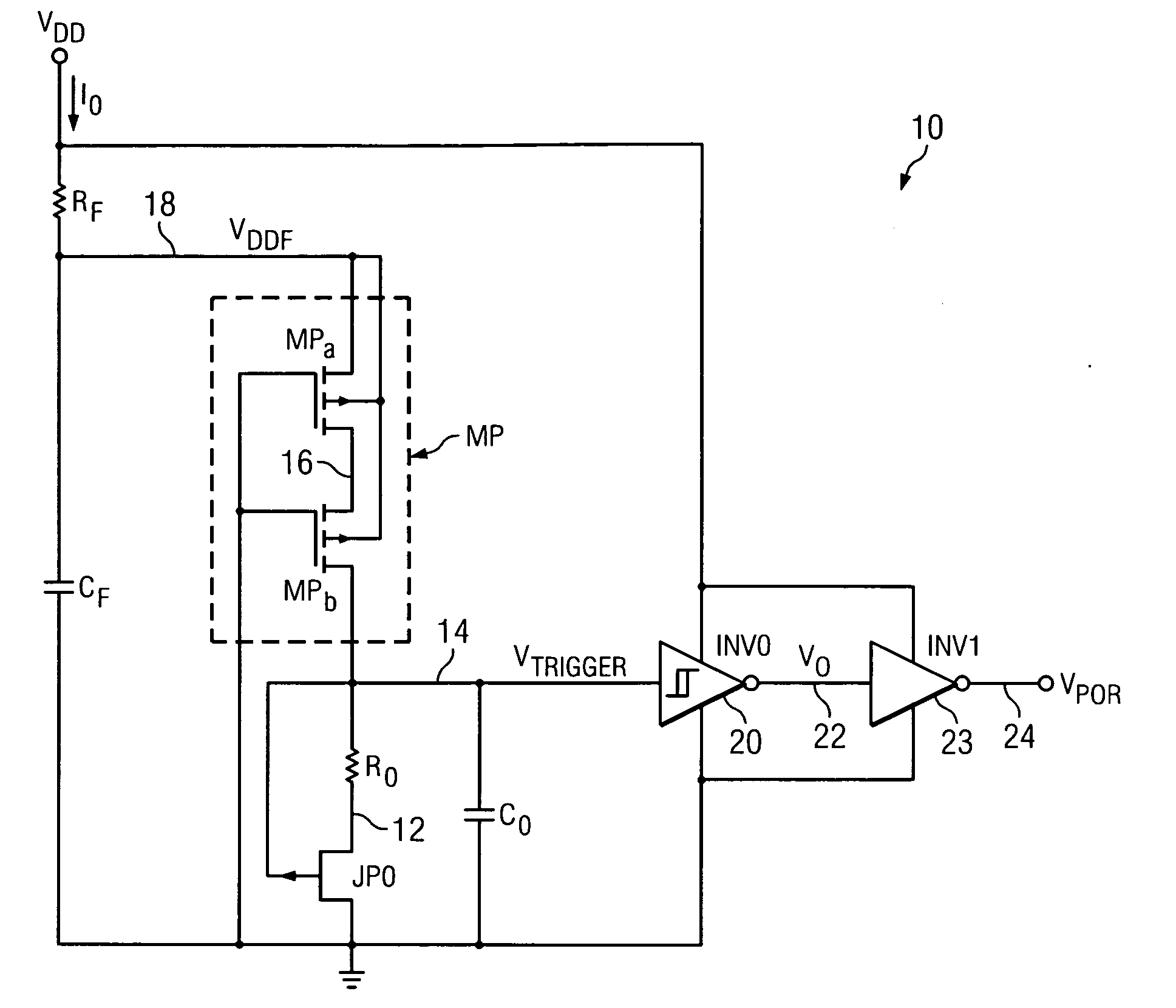

Low current power-on reset circuit and method

ActiveUS20110074470A1Easy dischargeDissipates very littlePulse automatic controlElectronic switchingElectricityPower-on reset

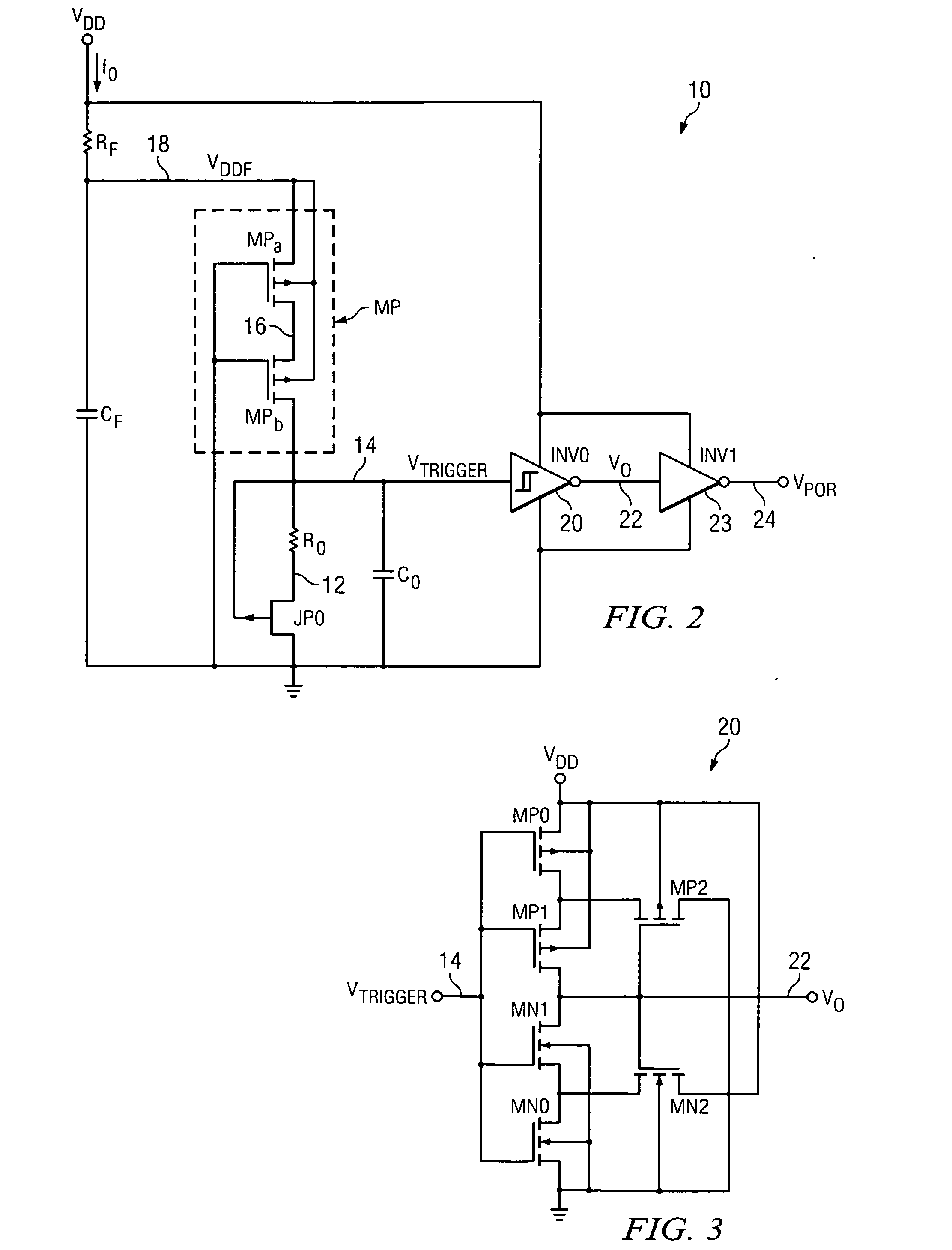

A power-on reset (POR) circuit includes a first transistor (MPa) having a source coupled to a first supply voltage (VDD) and a gate coupled to a second supply voltage (GND). A resistor (R0) has a first terminal coupled by a depletion mode transistor (JP0) to the second supply voltage and a second terminal coupled to a drain of the first transistor. A Schmitt trigger (20) has an input coupled to receive a first signal (VTRIGGER) on a conductor (14) coupled to the second terminal of the resistor and a terminal of a capacitor (C0), for producing an output voltage (VO) representative of a power-on reset signal (VPOR) in response to an interruption of the first supply voltage (VDD).

Owner:TEXAS INSTR INC

Electronic device including motion sensitive power switching integrated circuit and related methods

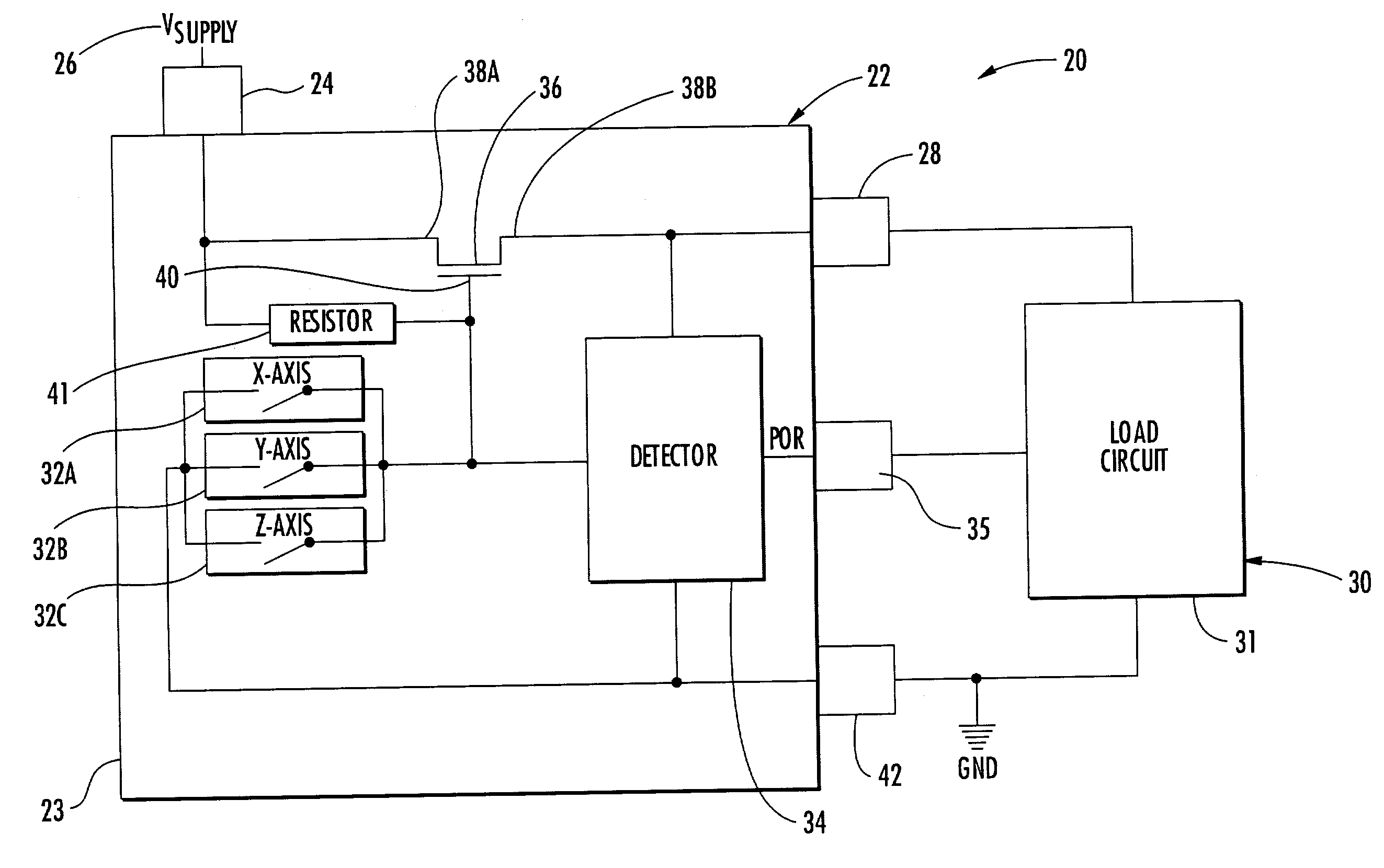

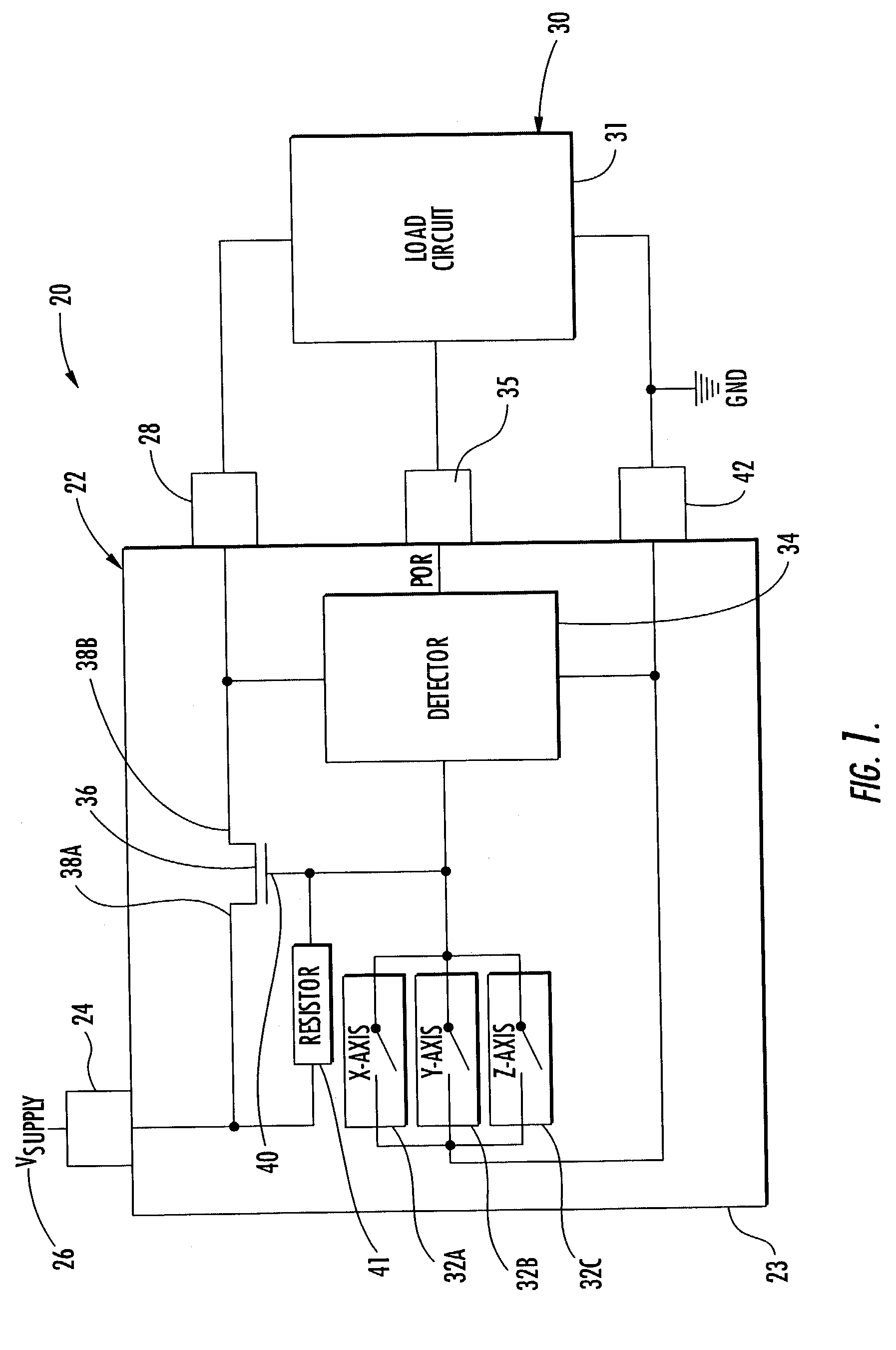

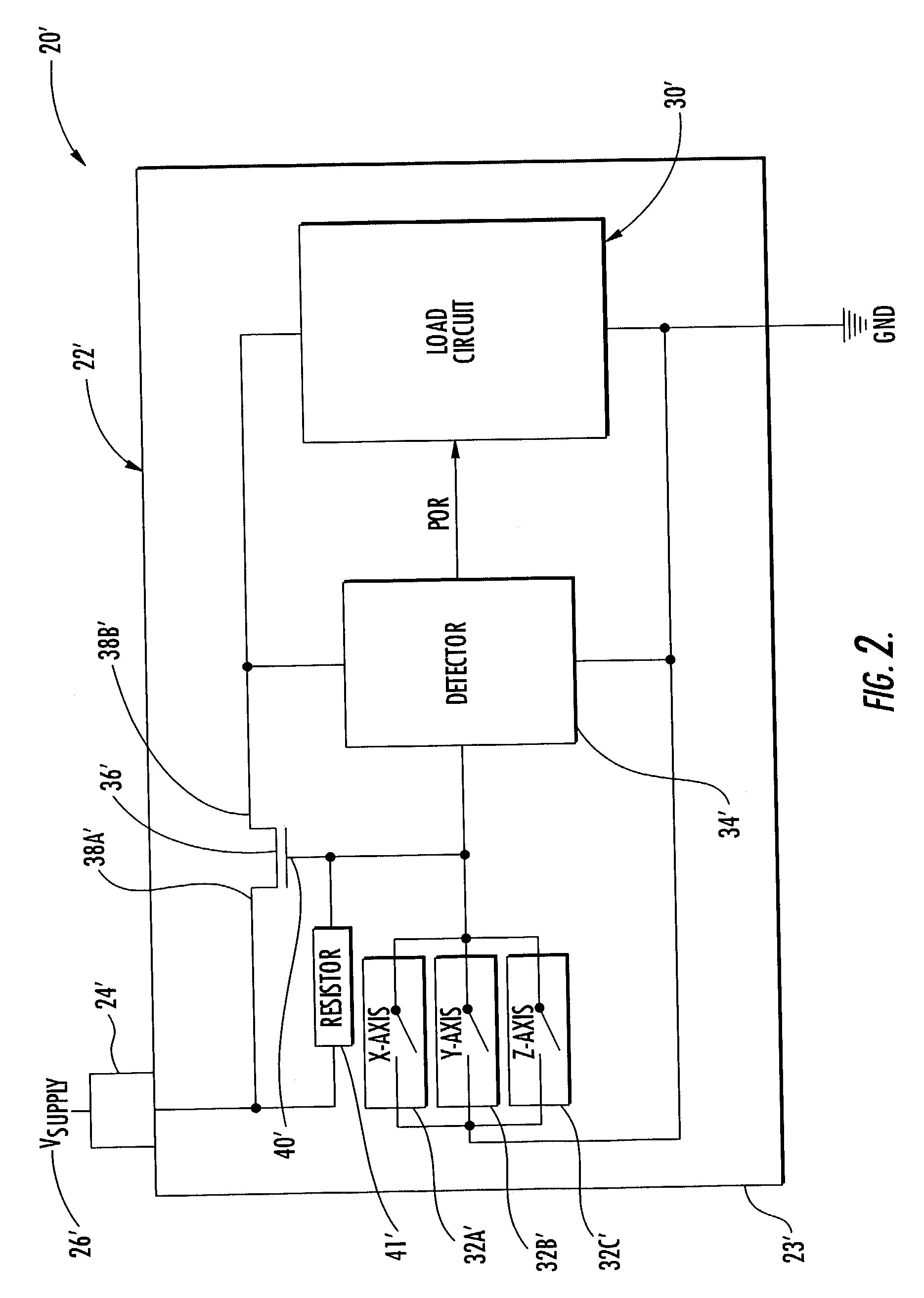

ActiveUS7084762B2Reduce power consumptionAcceleration measurement using interia forcesBurglar alarm by openingPower-on resetPower switching

An electronic device includes a motion sensitive power switching integrated circuit, which, in turn, includes a power switch connected between an input and an output, and a MEMS inertial sensing switch movable from a first position to a second position based upon motion thereof. The motion sensitive power switching integrated circuit also includes a detector operating the power switch to supply power to the output from the input based upon the MEMS inertial sensing switch moving from the first position to the second position. The first and second positions may be, respectively, a normally open position and a closed position. The device may be unpowered until the MEMS inertial sensing switch moves from the open to the closed position. The detector may generate a power on reset (POR) signal based upon the MEMS inertial sensing switch moving from the open to the closed position.

Owner:STMICROELECTRONICS SRL

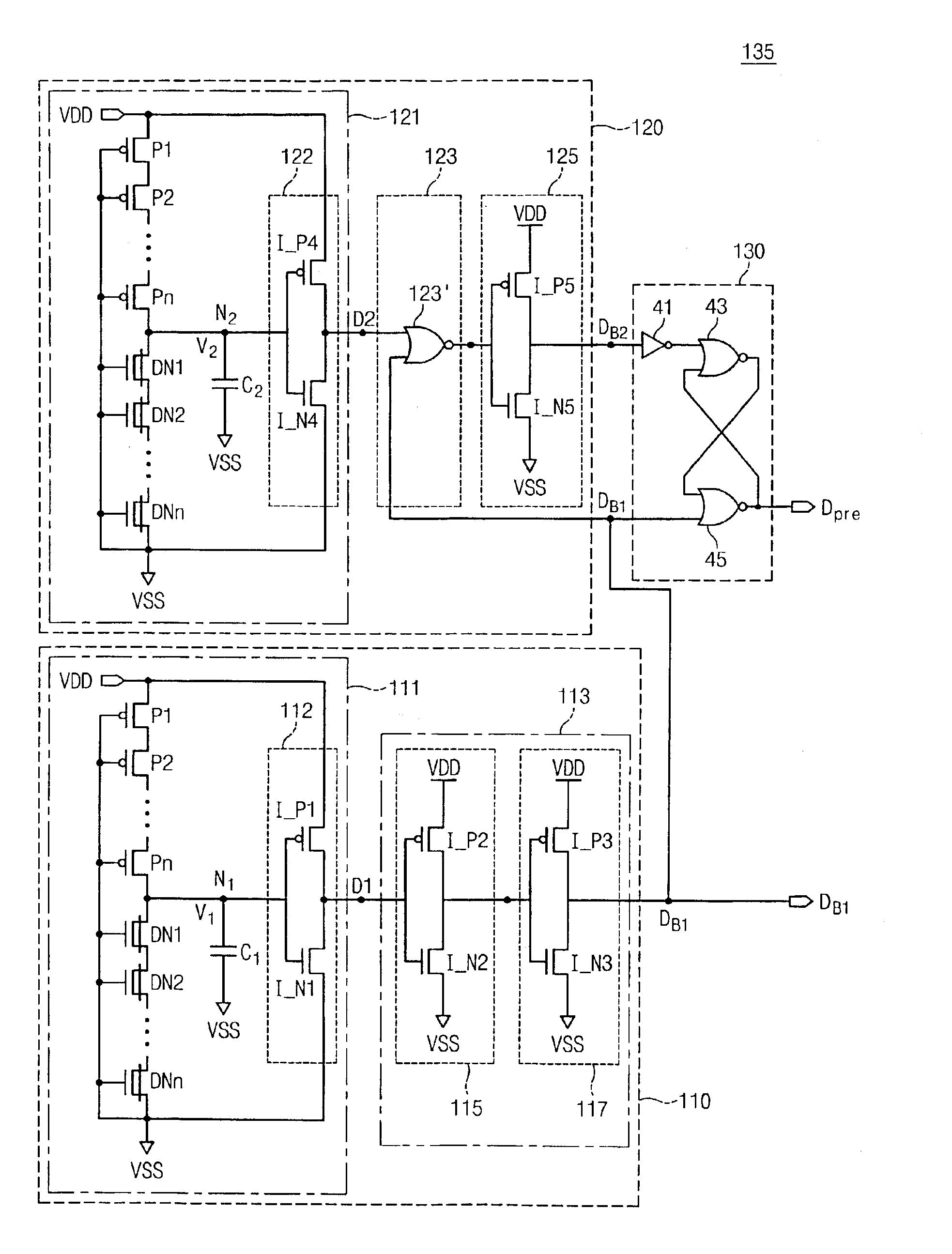

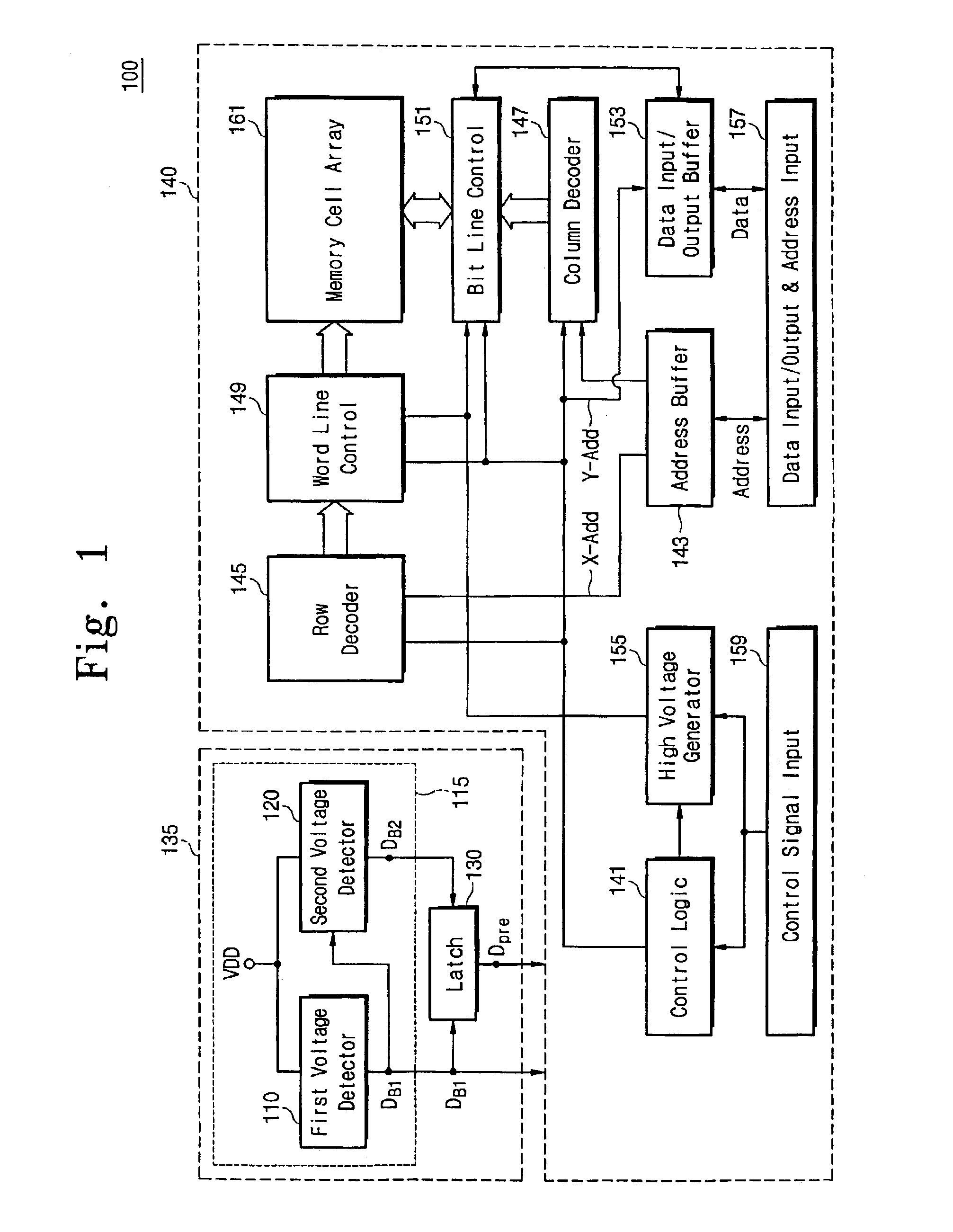

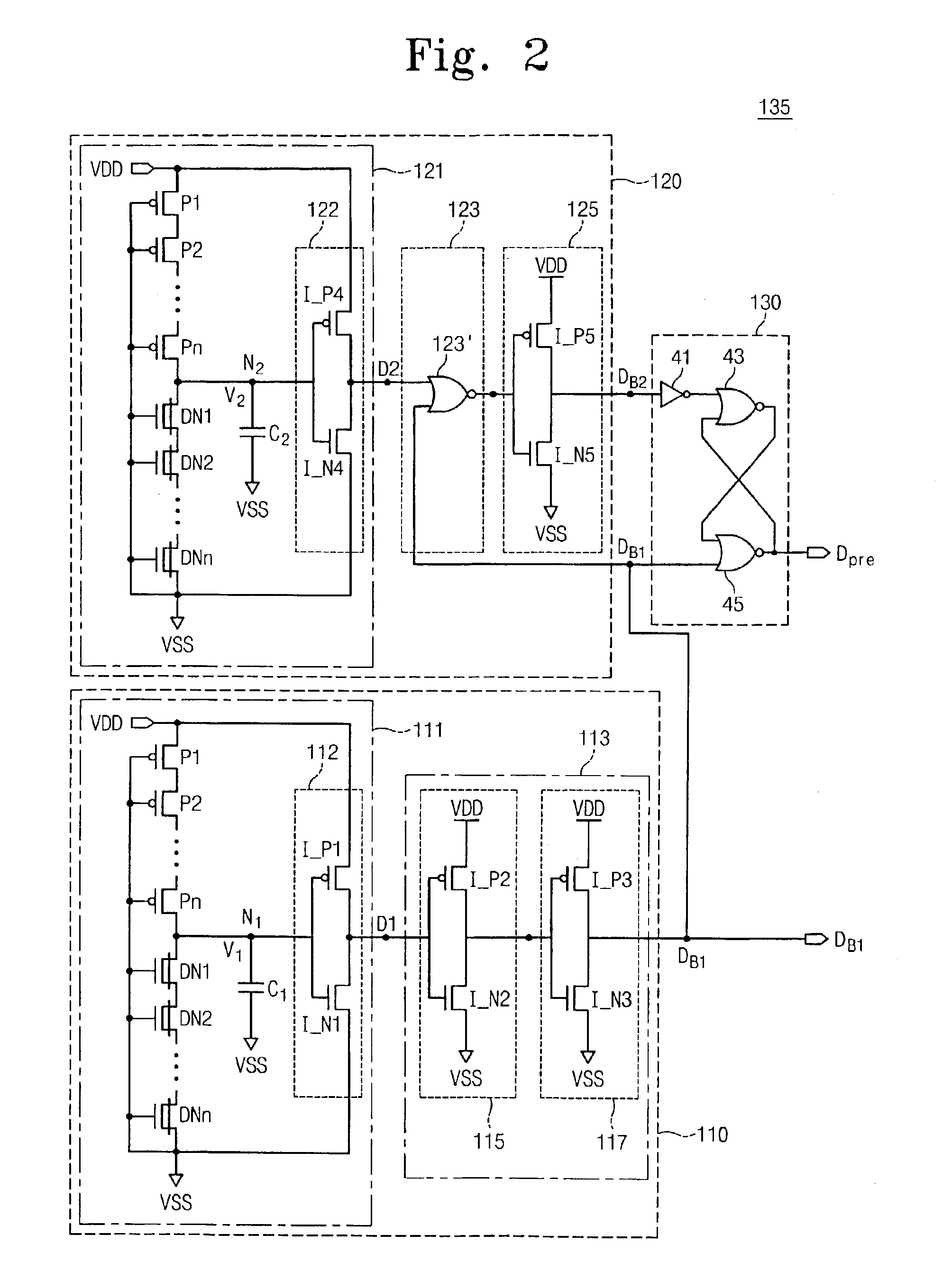

Power detecting circuit and method for stable power-on reading of flash memory device using the same

InactiveUS6882570B2Stable power-on reading methodImprove noise immunityVolume/mass flow measurementRead-only memoriesPower-on resetStable state

Embodiments of the invention provide a power-on reset function that establishes logic circuits in a memory chip at an initial stable state and a power-on read function that triggers a read operation of the memory chip. A first voltage detector output signal transitions when a power supply voltage reaches a first voltage, setting the logic circuits at the initial stable state. A second voltage detector output signal transitions when the power supply voltage reaches a second voltage, placing a latch in a set state that results in activation of a power-on read signal. A power-on read operation is carried out according to the activation of the power-on read signal. If the power supply voltage is not lowered below the first voltage, the second voltage detector output signal does not transition. Accordingly, embodiments are capable of preventing power-on read operations that are unnecessarily performed owing to power noise.

Owner:SAMSUNG ELECTRONICS CO LTD

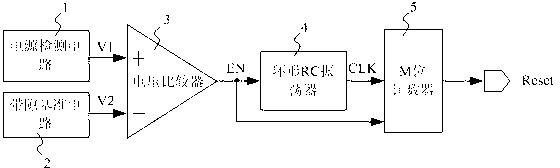

Automatic reset detection circuit for power up and power failure

ActiveCN103095265AAutomatically correct and fast outputEfficient outputElectronic switchingPower-on resetLow voltage

The invention discloses an automatic reset detection circuit for power up and power failure. The circuit comprises a power supply detection circuit (1), a band-gap reference circuit (2), a voltage comparator (3), a ring-shaped RC (remote control) oscillator (4) and an M-bit counter (5), wherein the power supply detection circuit (1) is used for detecting change of power supply voltage, when the power supply voltage is higher than preset threshold voltage, the voltage comparator (3) outputs a high voltage level, the ring-shaped RC oscillator (4) and the M-bit counter (5) begin to work, after 2M periods, an output Reset signal is changed to the high voltage level, and the power up reset detection is completed; when the power supply voltage is lower than the preset threshold voltage, the voltage comparator (3) outputs a low voltage level, the ring-shaped RC oscillator (4) and the M-bit counter (5) stop working, the output Reset signal is changed to the low voltage level, and the power failure reset detection is completed. The automatic reset detection circuit is simple in structure and easy to implement, and further has the power up and power failure reset detection functions simultaneously.

Owner:CHANGSHA JINGJIA MICROELECTRONICS