Patents

Literature

182 results about "Interrupt request" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In a computer, an interrupt request (or IRQ) is a hardware signal sent to the processor that temporarily stops a running program and allows a special program, an interrupt handler, to run instead. Hardware interrupts are used to handle events such as receiving data from a modem or network card, key presses, or mouse movements.

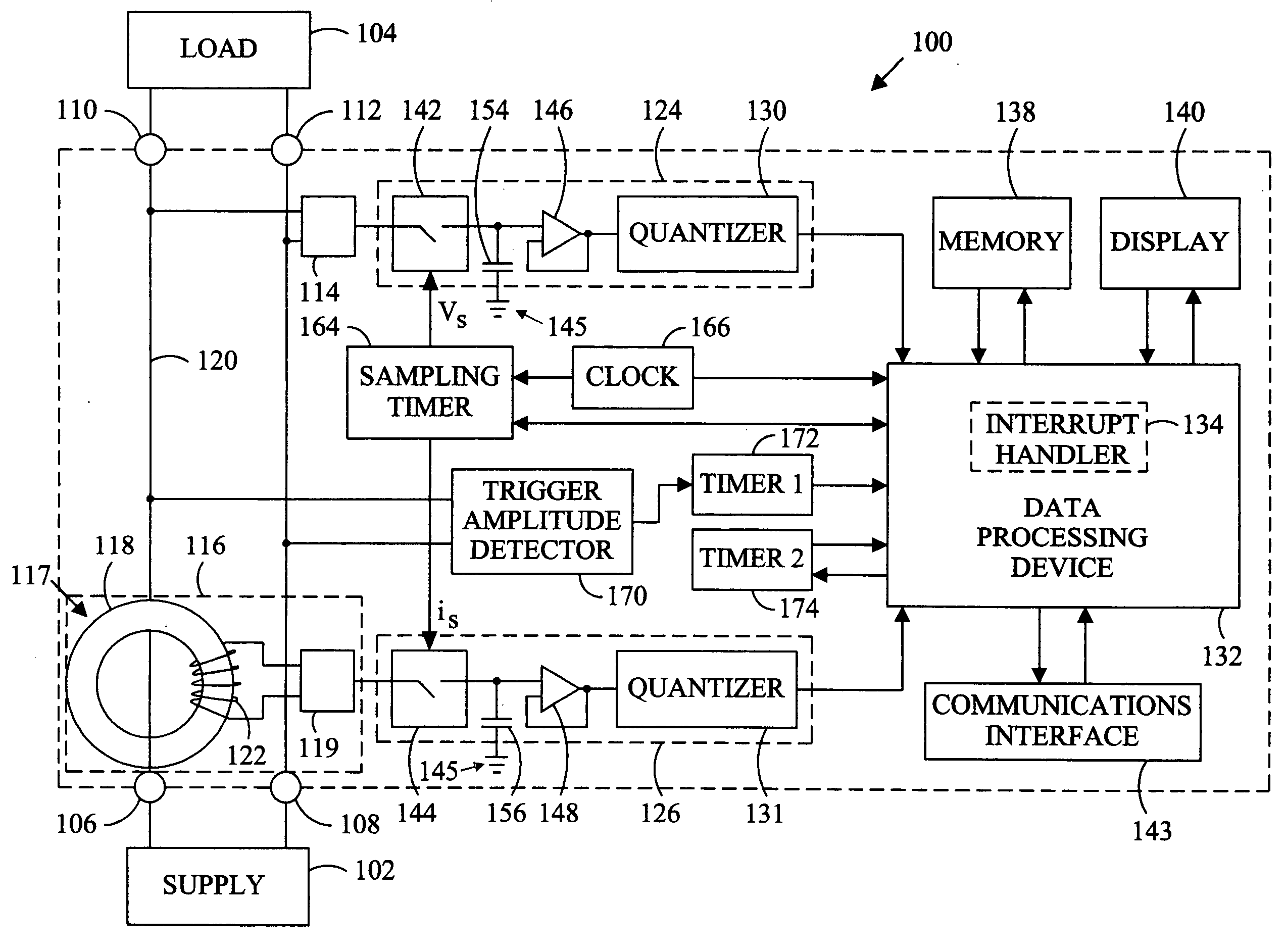

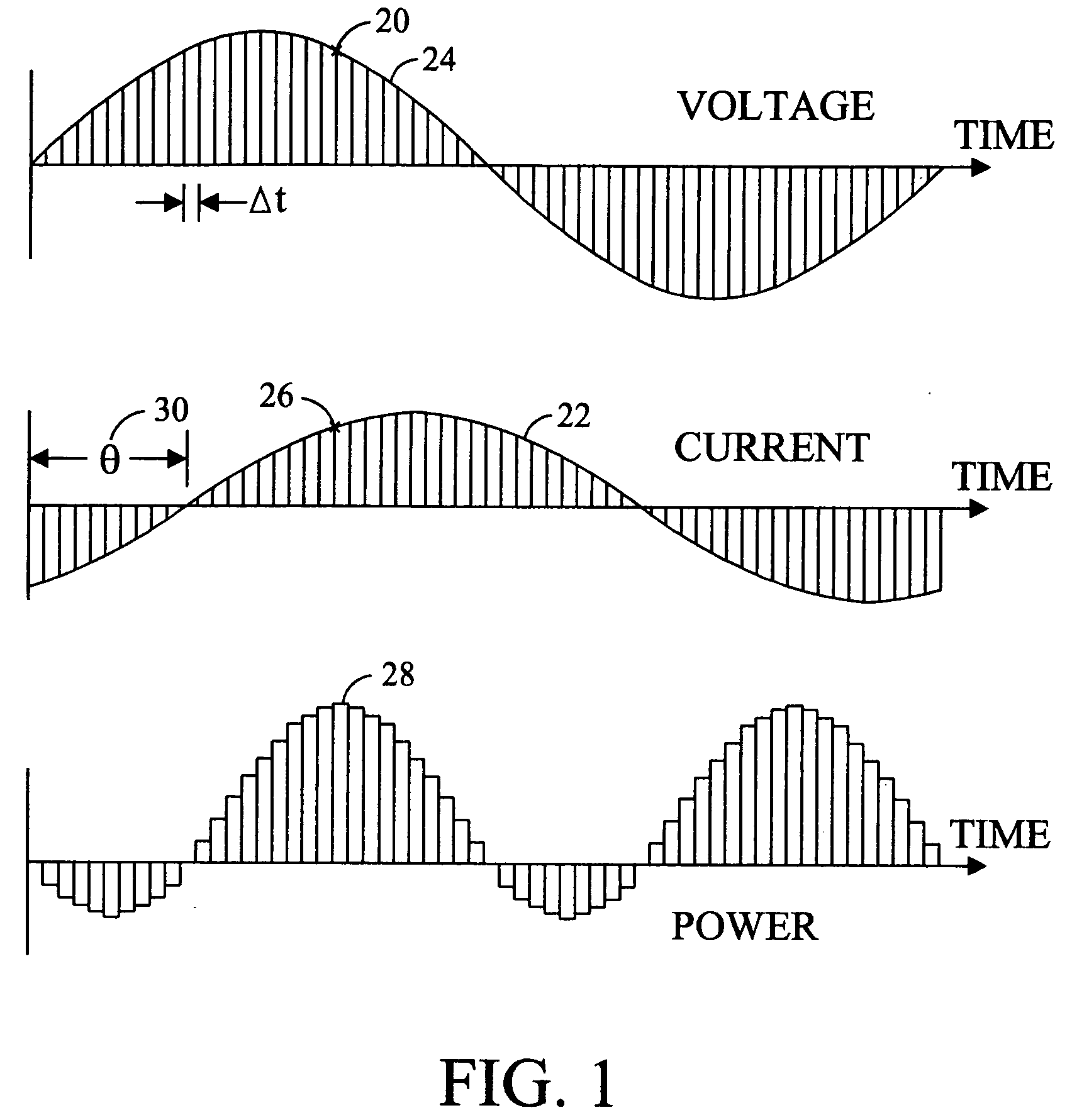

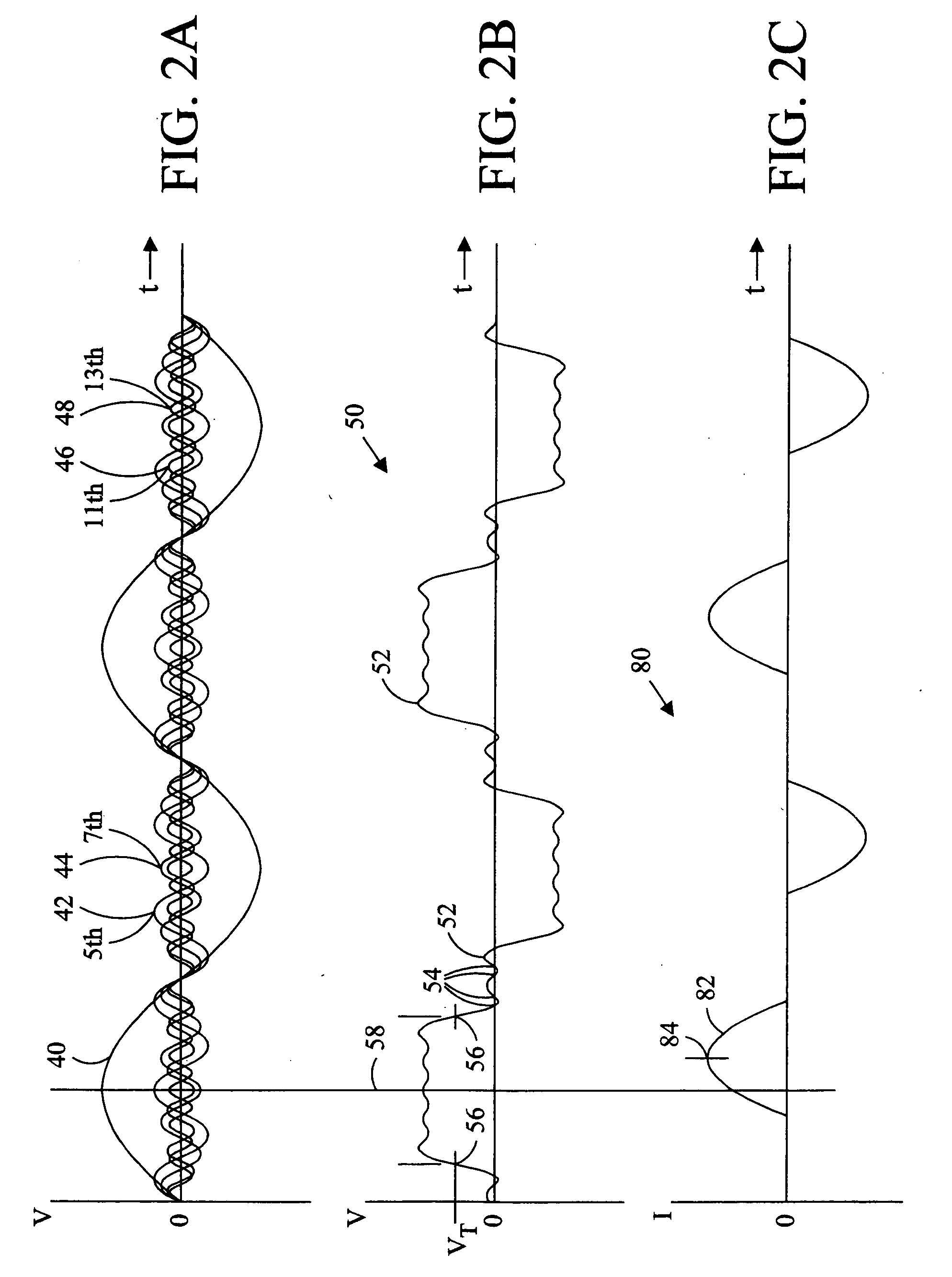

Power meter

The computational resources of a digital power meter can be reduced by utilizing an interrupt requested in anticipation of interrupt latency to perform real-time tasks, an approximation of a root mean square load current at an earlier time to compensate for a phase shift between the load current and the current transducer output, and an amplitude that is neither zero nor maximum to distinguish the cycles of a harmonically distorted waveform.

Owner:VERIS INDS

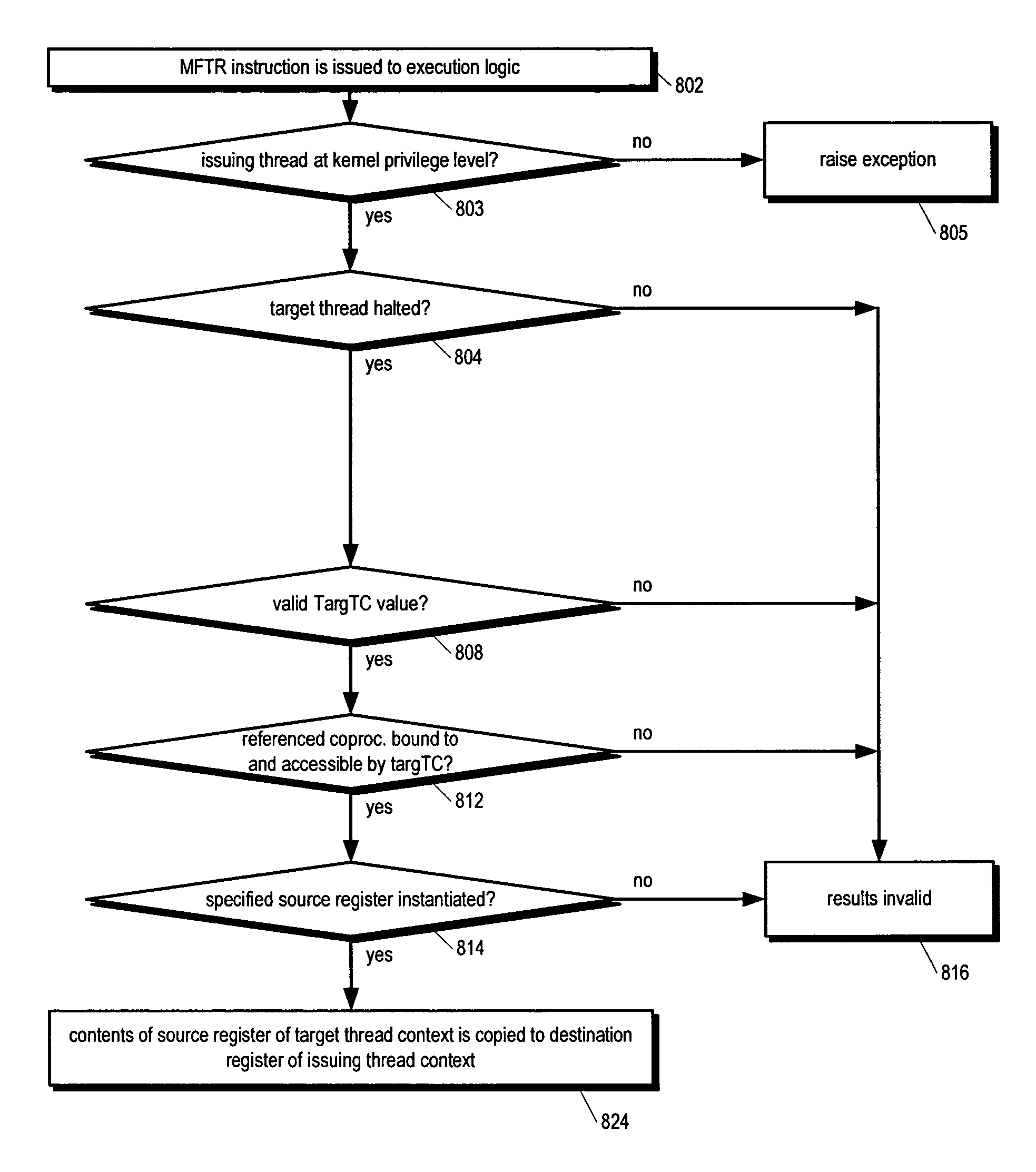

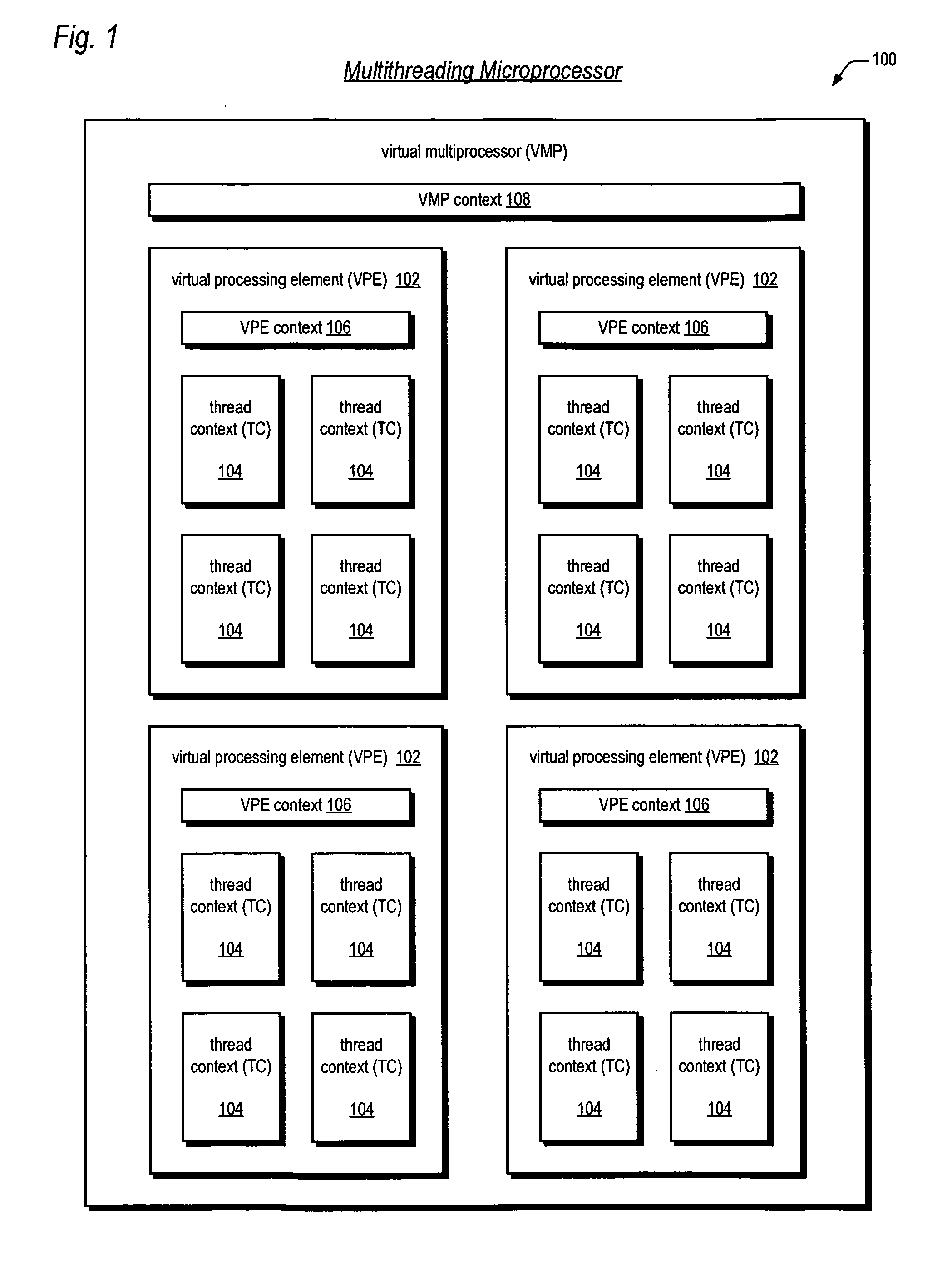

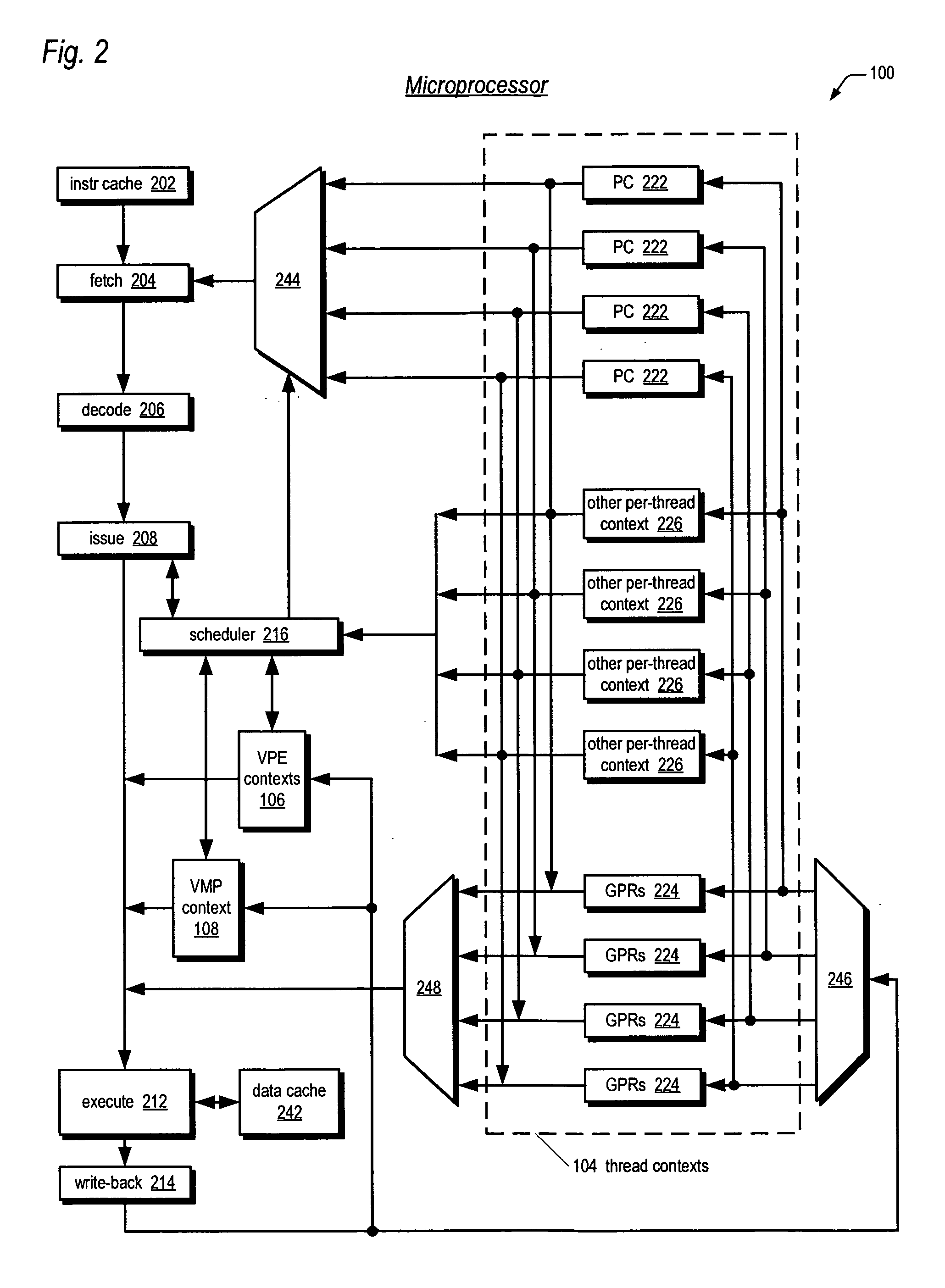

Symmetric multiprocessor operating system for execution on non-independent lightweight thread context

ActiveUS20060190945A1Lightweight in of chip area and power consumptionHighly scalableEnergy efficient ICTMultiprogramming arrangementsNon specificSymmetric multiprocessing

A multiprocessing system is disclosed. The system includes a multithreading microprocessor, including a plurality of thread contexts (TCs), each comprising a first control indicator for controlling whether the TC is exempt from servicing interrupt requests to an exception domain for the plurality of TCs, and a virtual processing element (VPE), comprising the exception domain, configured to receive the interrupt requests, wherein the interrupt requests are non-specific to the plurality of TCs, wherein the VPE is configured to select a non-exempt one of the plurality of TCs to service each of the interrupt requests, the VPE further comprising a second control indicator for controlling whether the VPE is enabled to select one of the plurality of TCs to service the interrupt requests. The system also includes a multiprocessor operating system (OS), configured to initially set the second control indicator to enable the VPE to service the interrupts, and further configured to schedule execution of threads on the plurality of TCs, wherein each of the threads is configured to individually disable itself from servicing the interrupts by setting the first control indicator, rather than by clearing the second control indicator.

Owner:MIPS TECH INC

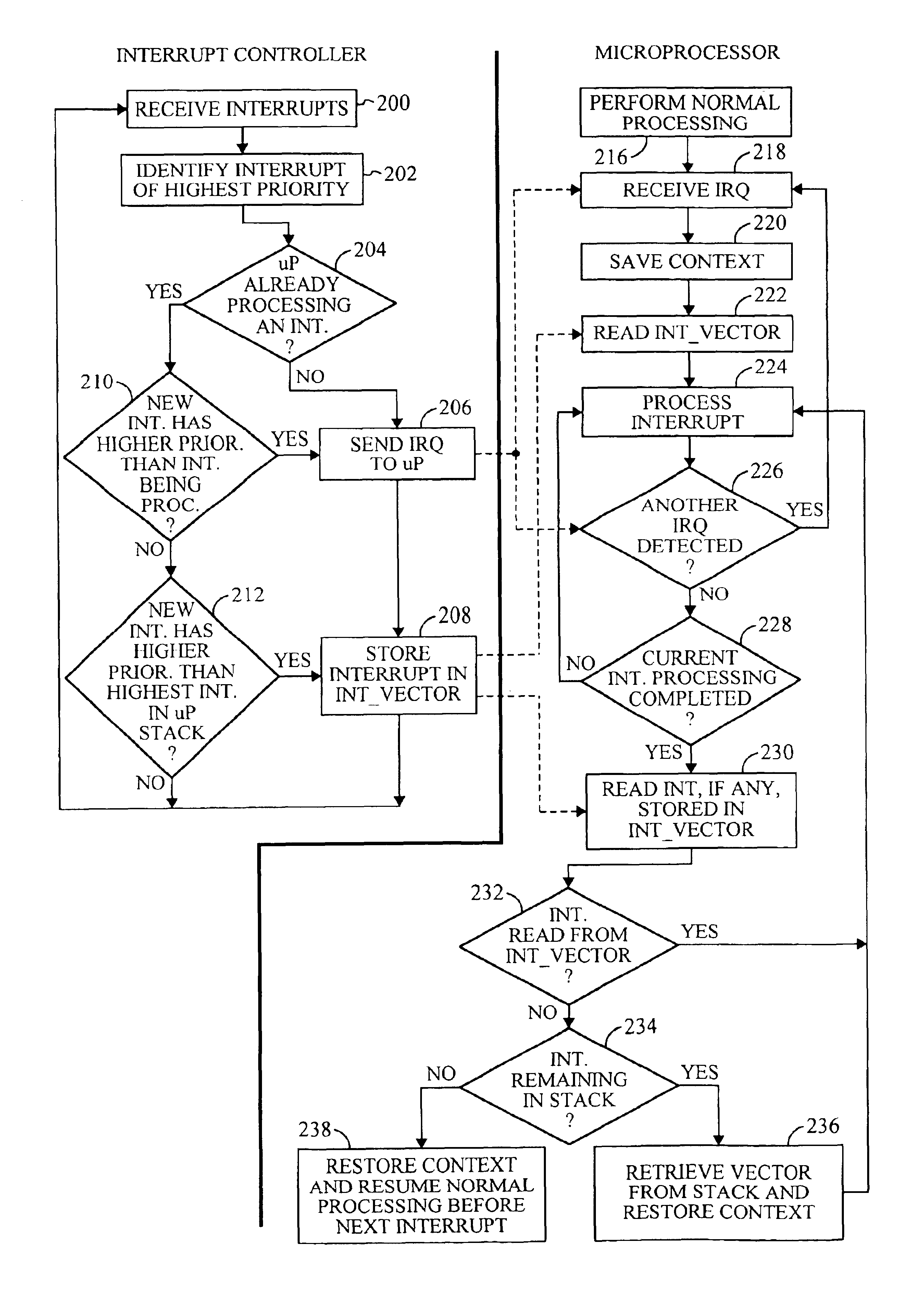

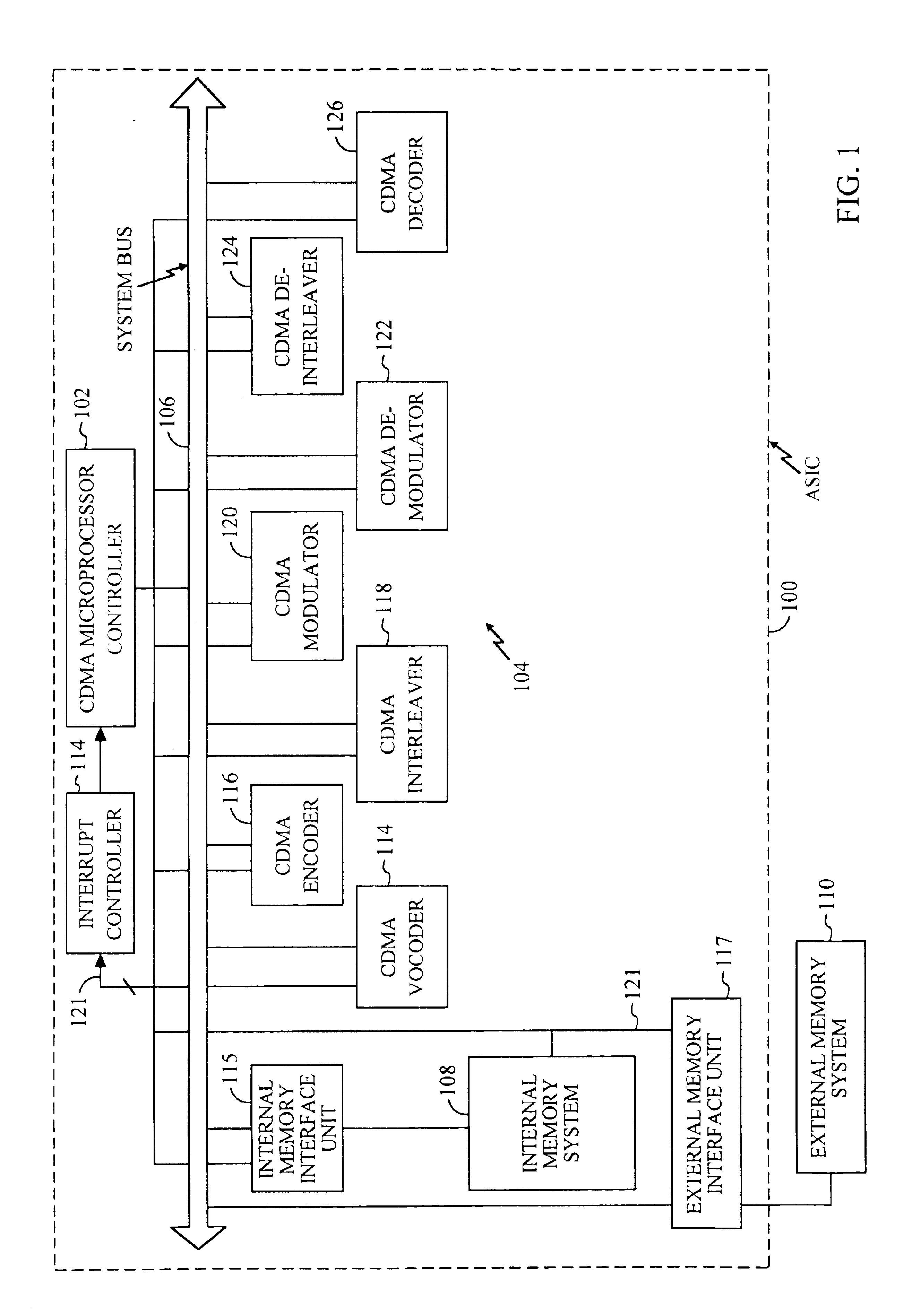

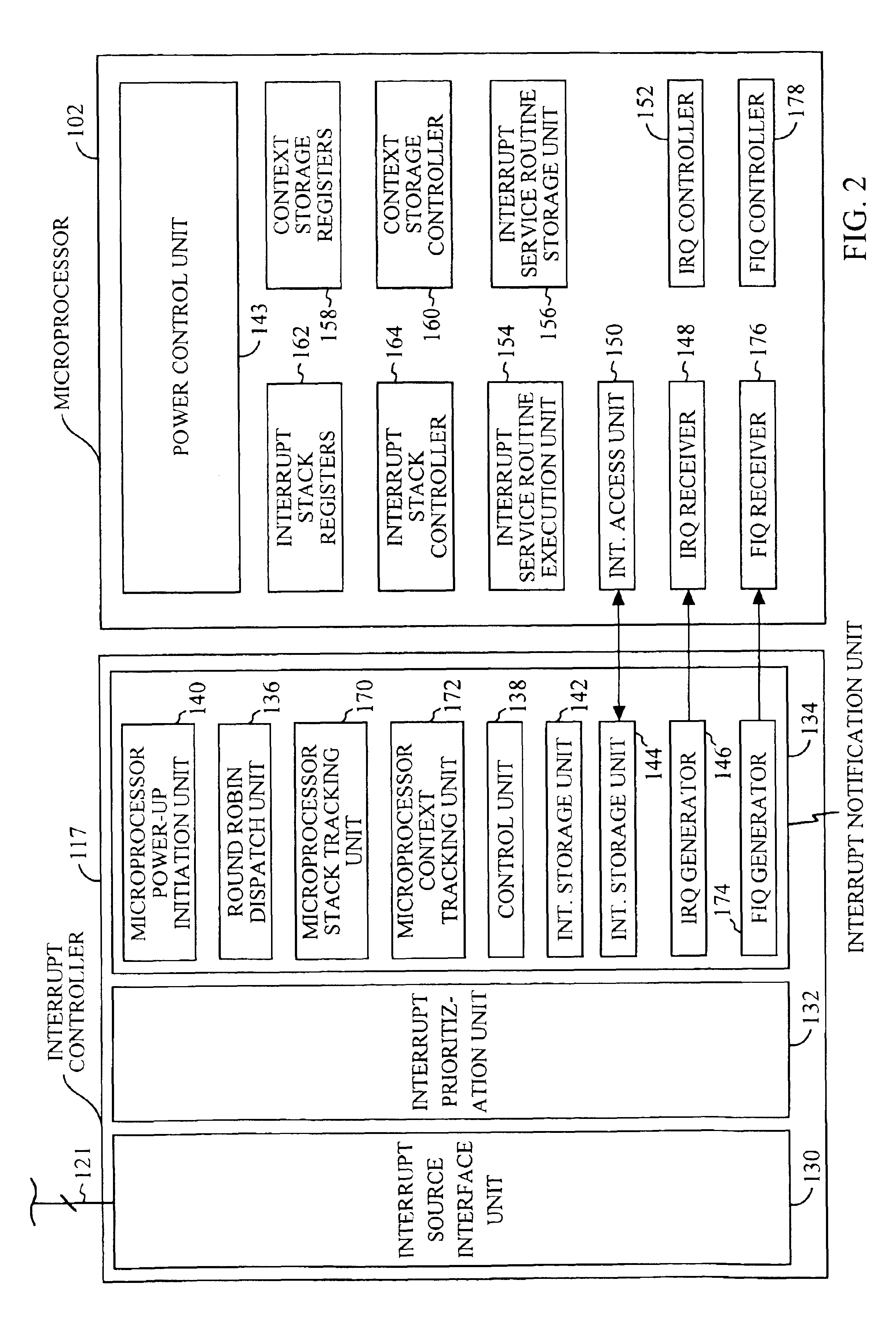

Mobile communication device having a prioritized interrupt controller

InactiveUS6807595B2Energy efficient ICTEnergy efficient computingProgrammable Interrupt ControllerComputer science

A microprocessor system having an interrupt controller is provided for use in a mobile communications device. Peripheral processing units generate interrupt requests for sending to the microprocessor. The microprocessor has components for responding to interrupt requests by interrupting current processing and performing an interrupt service routine associated with the interrupt request. The interrupt controller receives interrupt requests directed to the microprocessor from the peripheral processing units and for prioritizes the interrupt requests on behalf of the microprocessor. By providing an interrupt controller for prioritizing interrupt requests on behalf of the microprocessor, the microprocessor therefore need not devote significant internal resources to prioritizing the interrupt request signals.

Owner:QUALCOMM INC

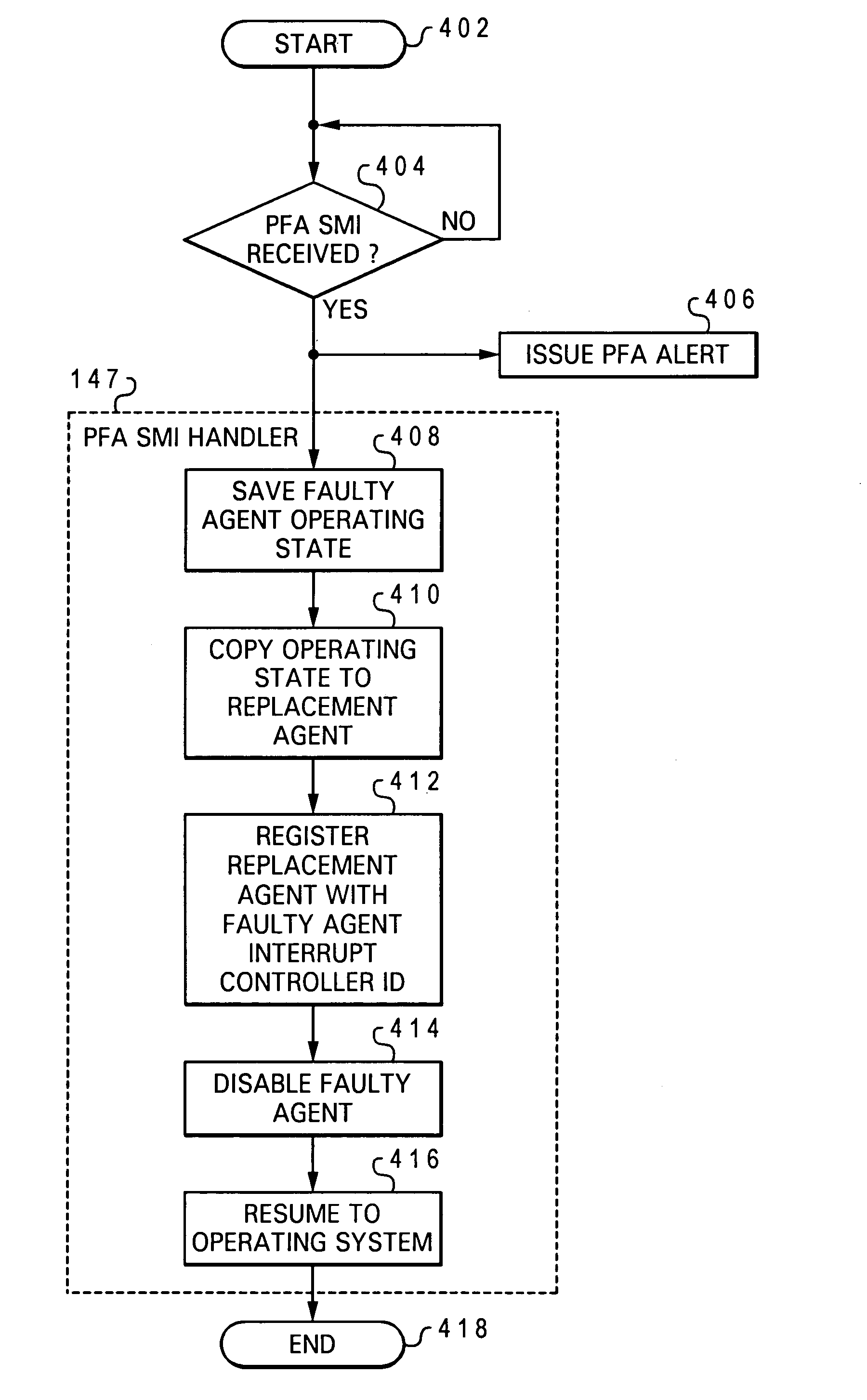

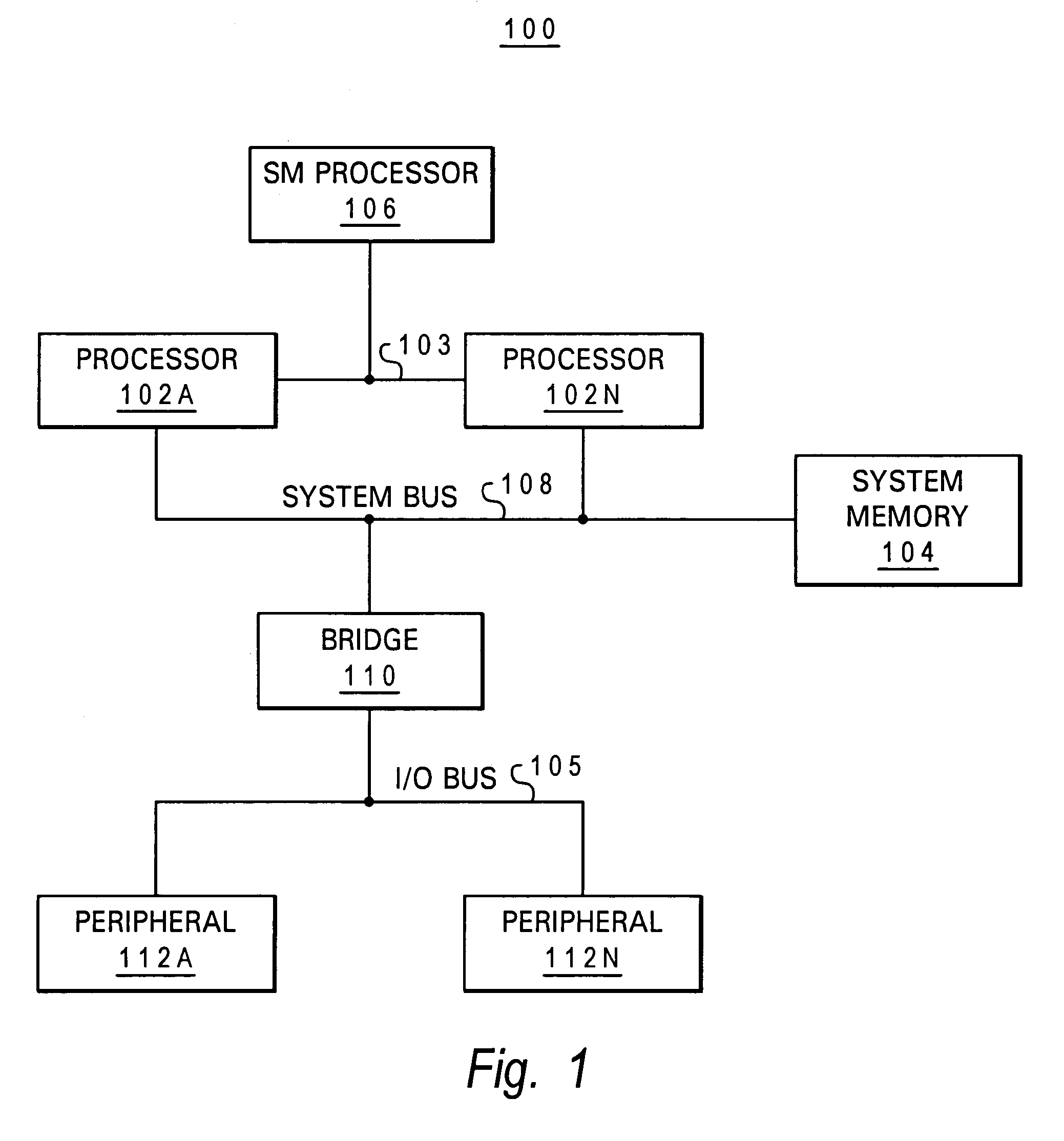

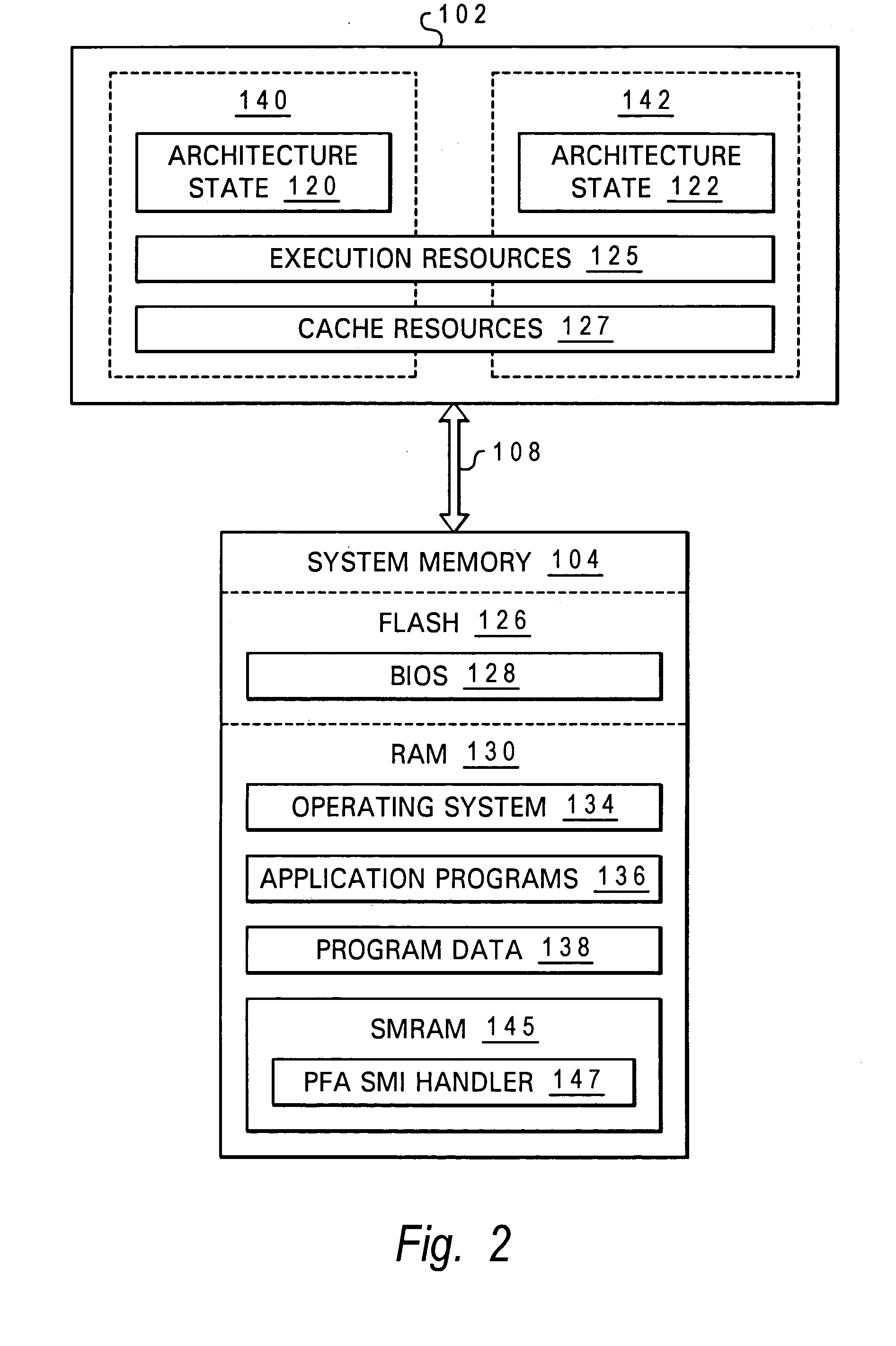

System and method for predictive processor failure recovery

A system, method, and computer program product for reporting and recovering from an internal processor error in a multiprocessor system supporting system management mode. In accordance with the method of the present invention one or more replacement agents are allocated such as during system startup within the multiprocessor system. Machine specific error-reporting registers are monitored for one or more active processor agents during system operation. In response to detecting a faulty agent via the monitoring, a system management interrupt (SMI) request is issued to one or both the faulty agent and a selected replacement agent. In response to receiving the SMI request, the operating state of the faulty agent is copied to the selected replacement agent in system management mode. Operating system processing is then resumed using the replacement agent.

Owner:LENOVO GLOBAL TECH INT LTD

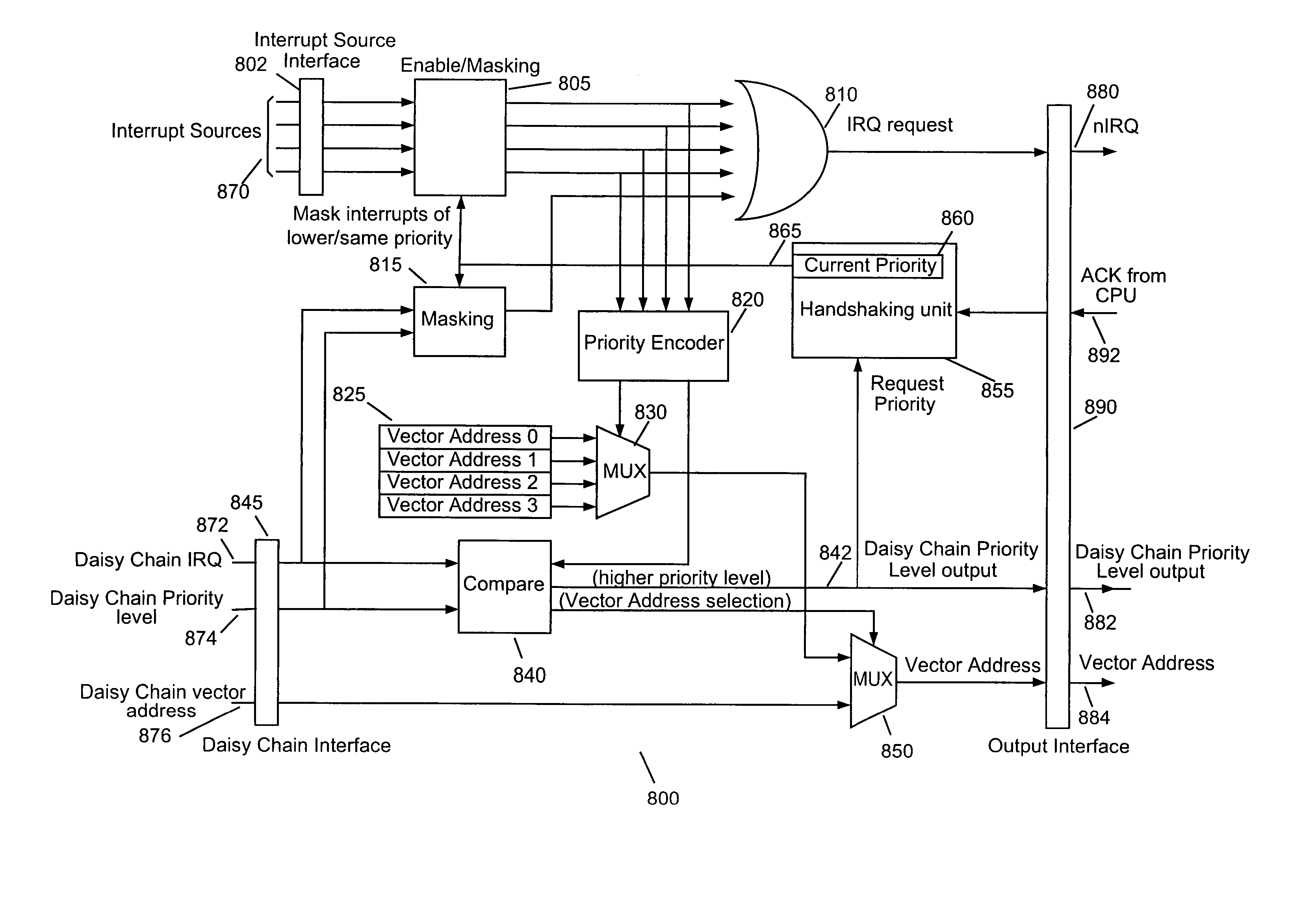

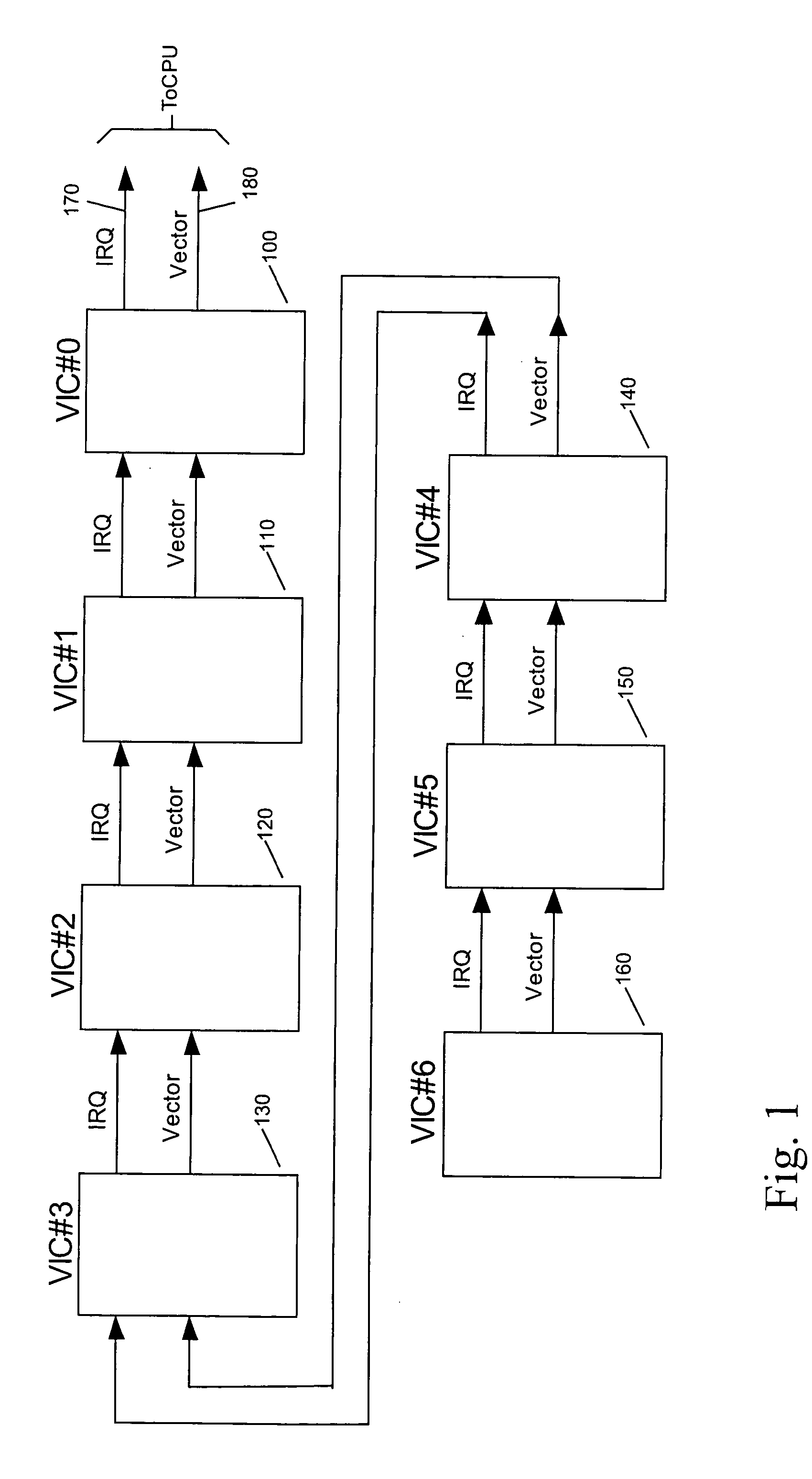

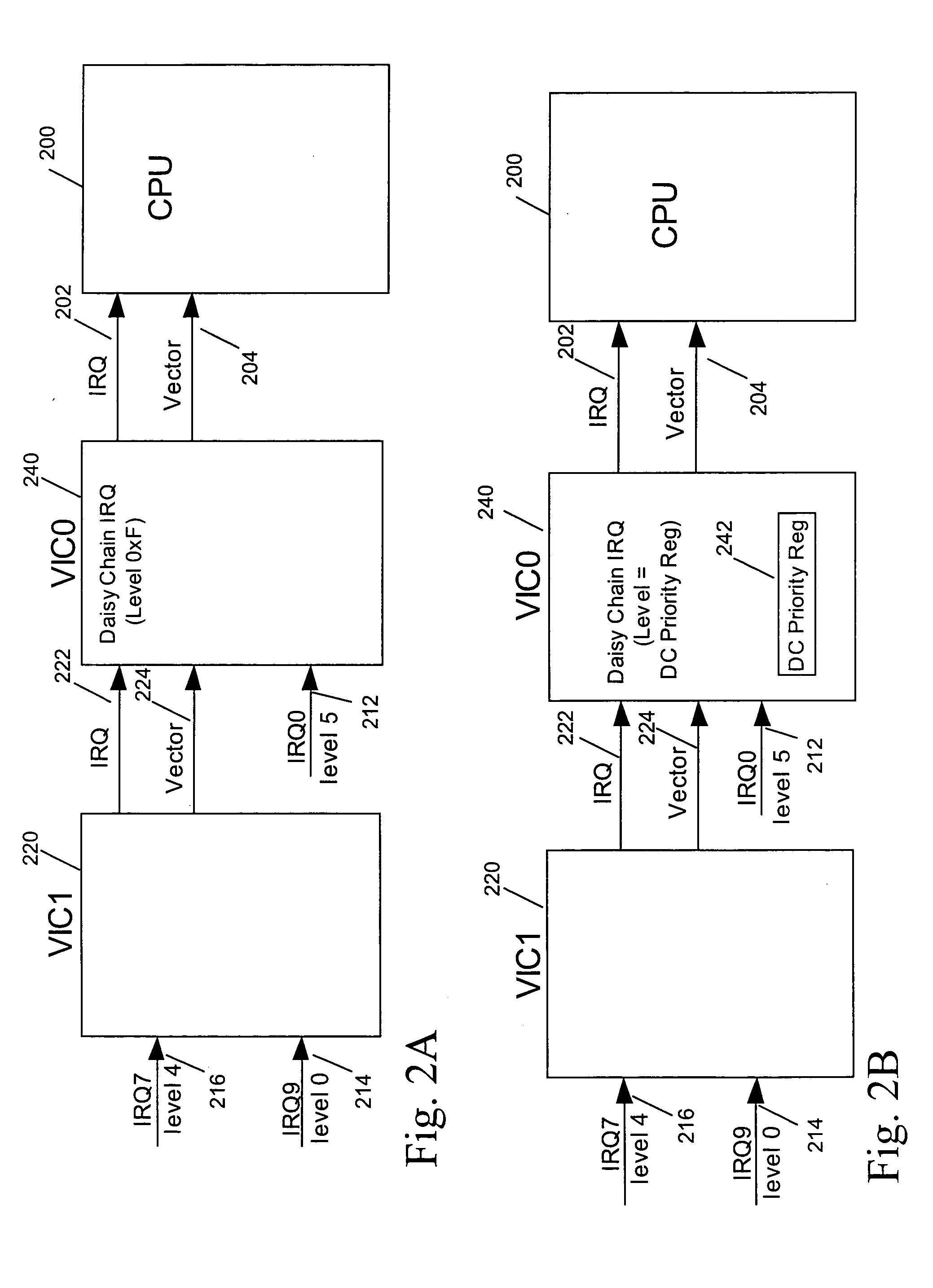

Interrupt controller and interrupt controlling method for prioritizing interrupt requests generated by a plurality of interrupt sources

An interrupt controller and interrupt controlling method are provided for prioritizing interrupt requests generated by a plurality of interrupt sources. The interrupt controller comprises an interrupt source interface operable to receive interrupt requests generated by a first plurality of interrupt sources, and a daisy chain interface operable to receive a daisy chain interrupt request output by a further interrupt controller based on a second plurality of interrupt requests generated by a second plurality of interrupt sources. The daisy chain interface includes a priority input operable to receive a daisy chain priority signal indicating a priority associated with the daisy chain interrupt request. Prioritization logic is operable to receive the daisy chain priority signal and to apply predetermined prioritisation criteria to determine the highest priority interrupt request selected from the daisy chain interrupt request and the interrupt request generated by the first plurality of interrupt sources. An output interface is operable to output the highest priority interrupt request, the output interface including a priority output operable to provide an output priority signal indicating a priority associated with the highest priority interrupt request.

Owner:ARM LTD

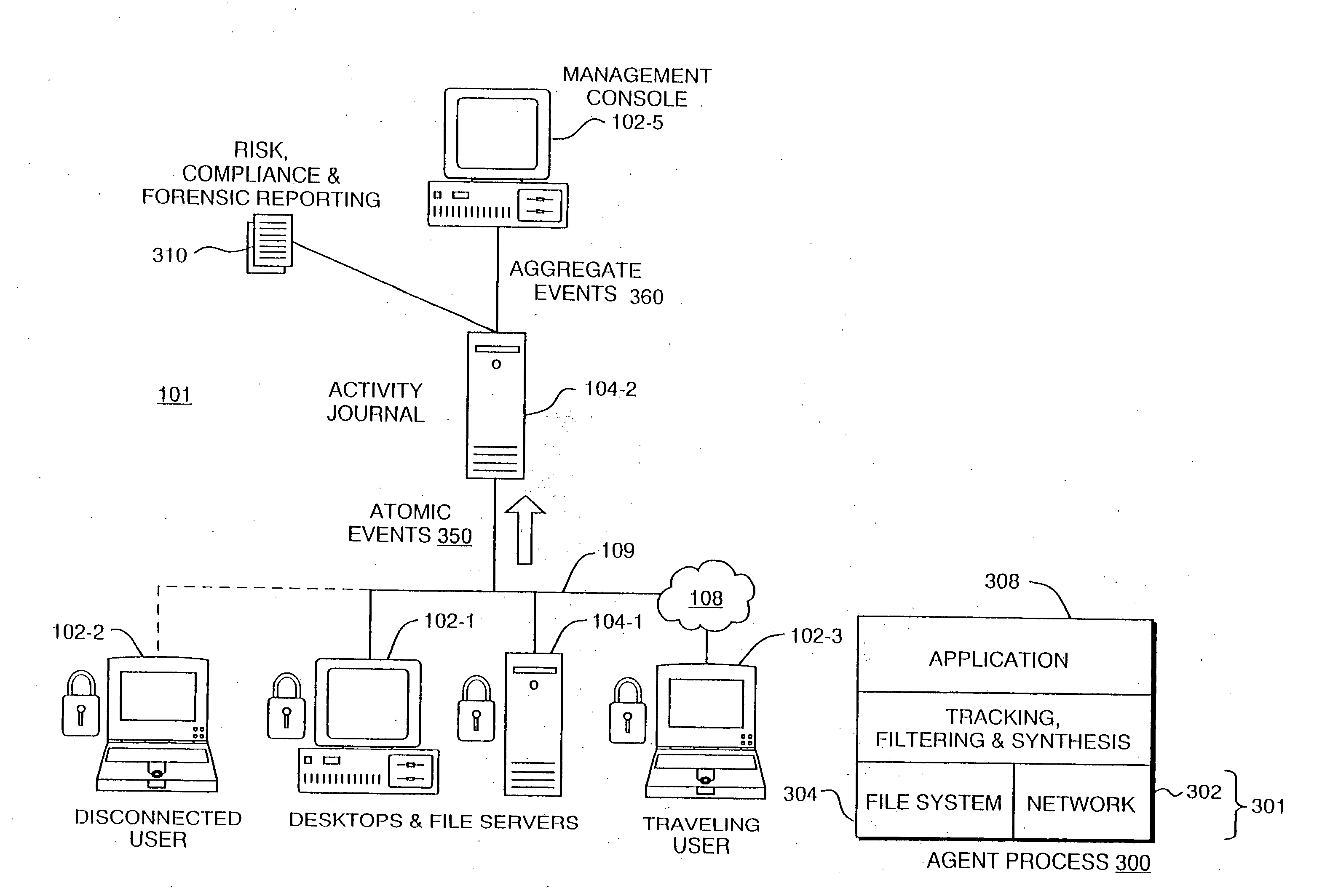

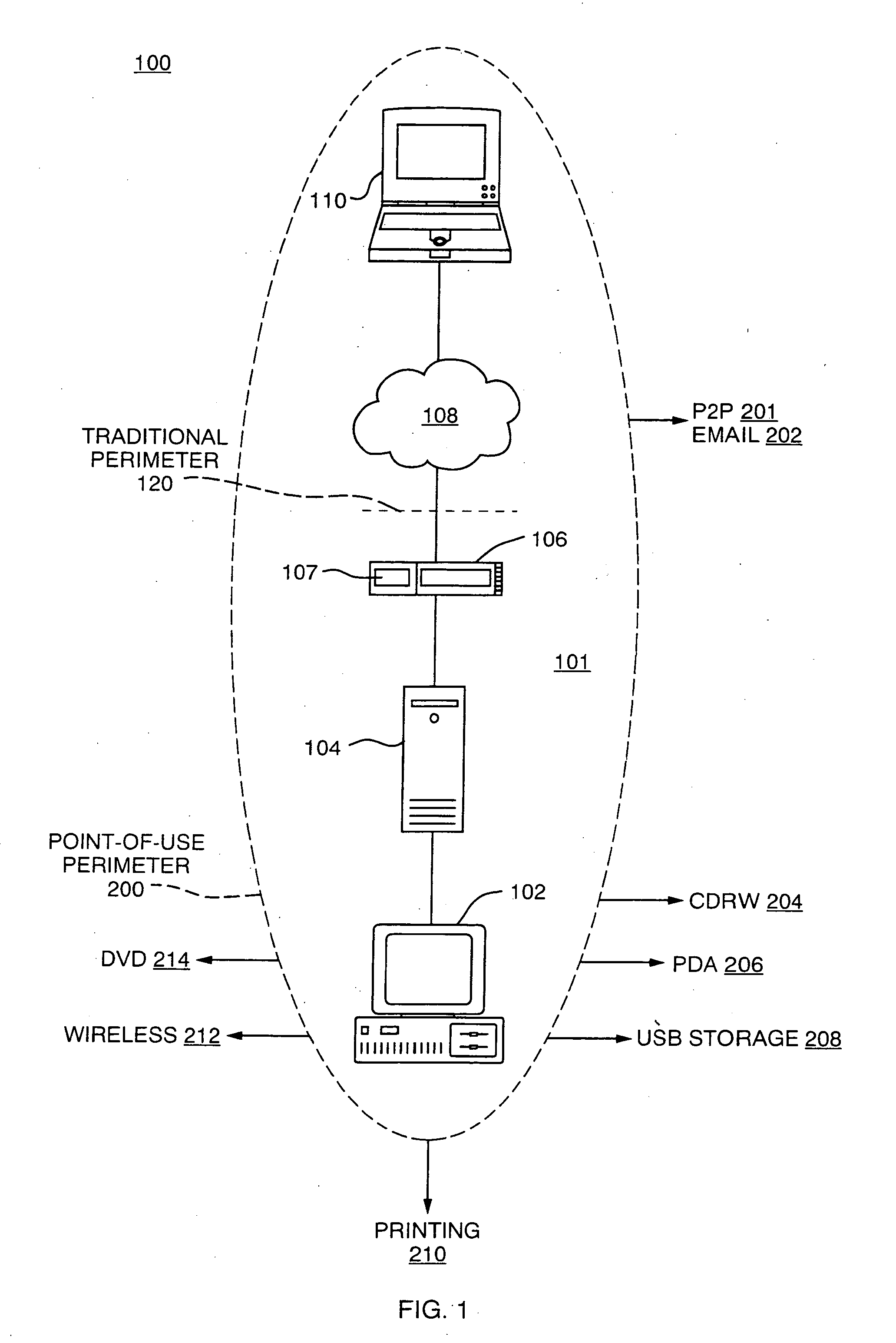

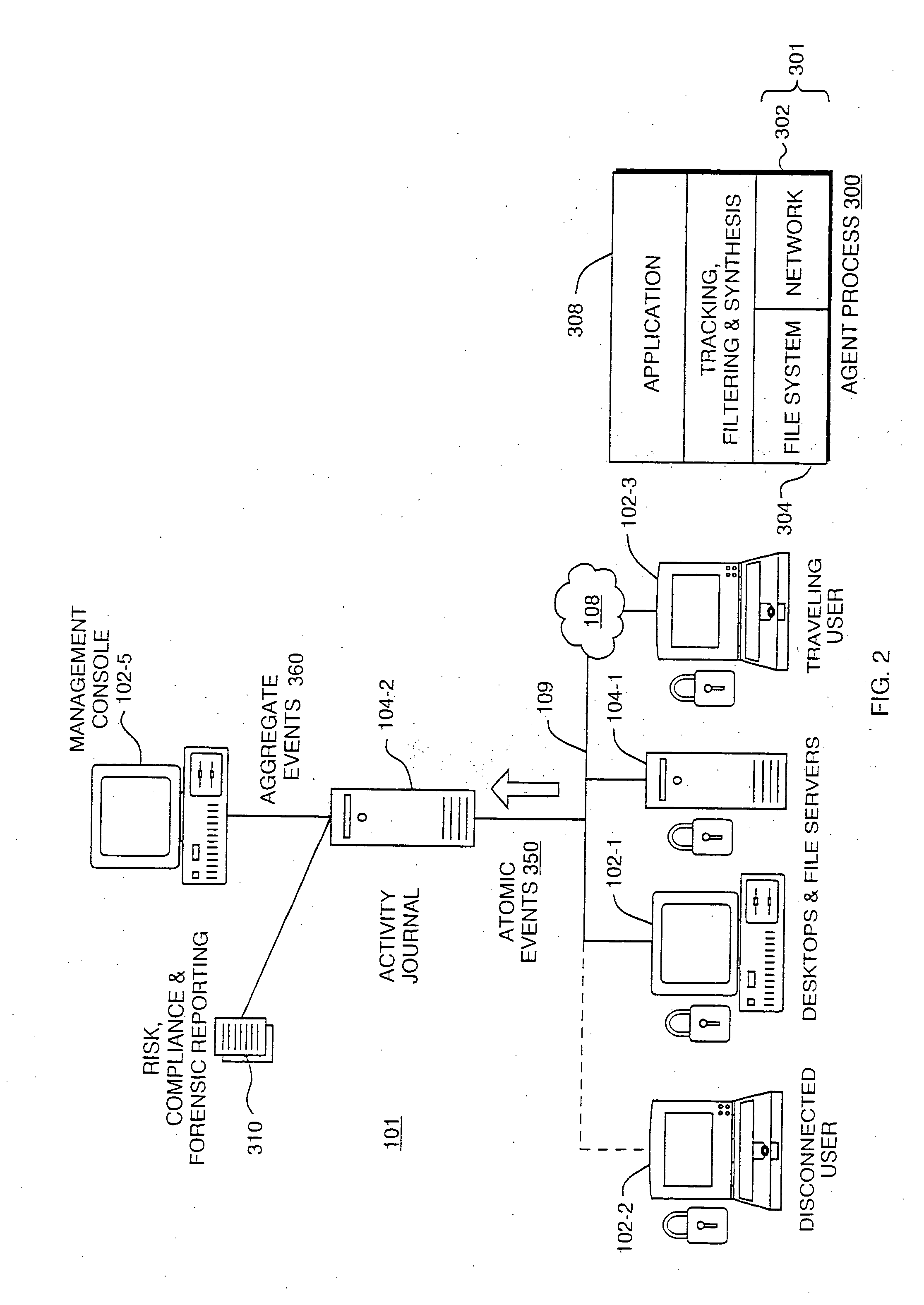

Digital asset usage accountability via event journaling

InactiveUS20090198765A1High frequencyDigital data processing detailsAnalogue secracy/subscription systemsOperational systemData file

A technique for establishing a perimeter of accountability for usage of digital assets such as data files. The accountability model not only tracks authorized users' access to files, but monitors passage of such files to uncontrollable removable storage media or through network connections and the like which may indicate possible abuse of access. In accordance with a preferred embodiment, an autonomous independent agent process running at a point of use, such as in the background of a client operating system kernel, interrupts requests for access to resources. The agent process senses low level system events, filters, aggregates them, and makes reports to a journaling server. The journaling server analyzes sequences of low level events to detect when aggregate events of interest occur, such as “FileEdit”, network file transfers and the like. Reports can be generated to provide an understanding of how digital assets have been accessed, used or communicated by individuals in an enterprise.

Owner:DIGITAL GUARDIAN LLC

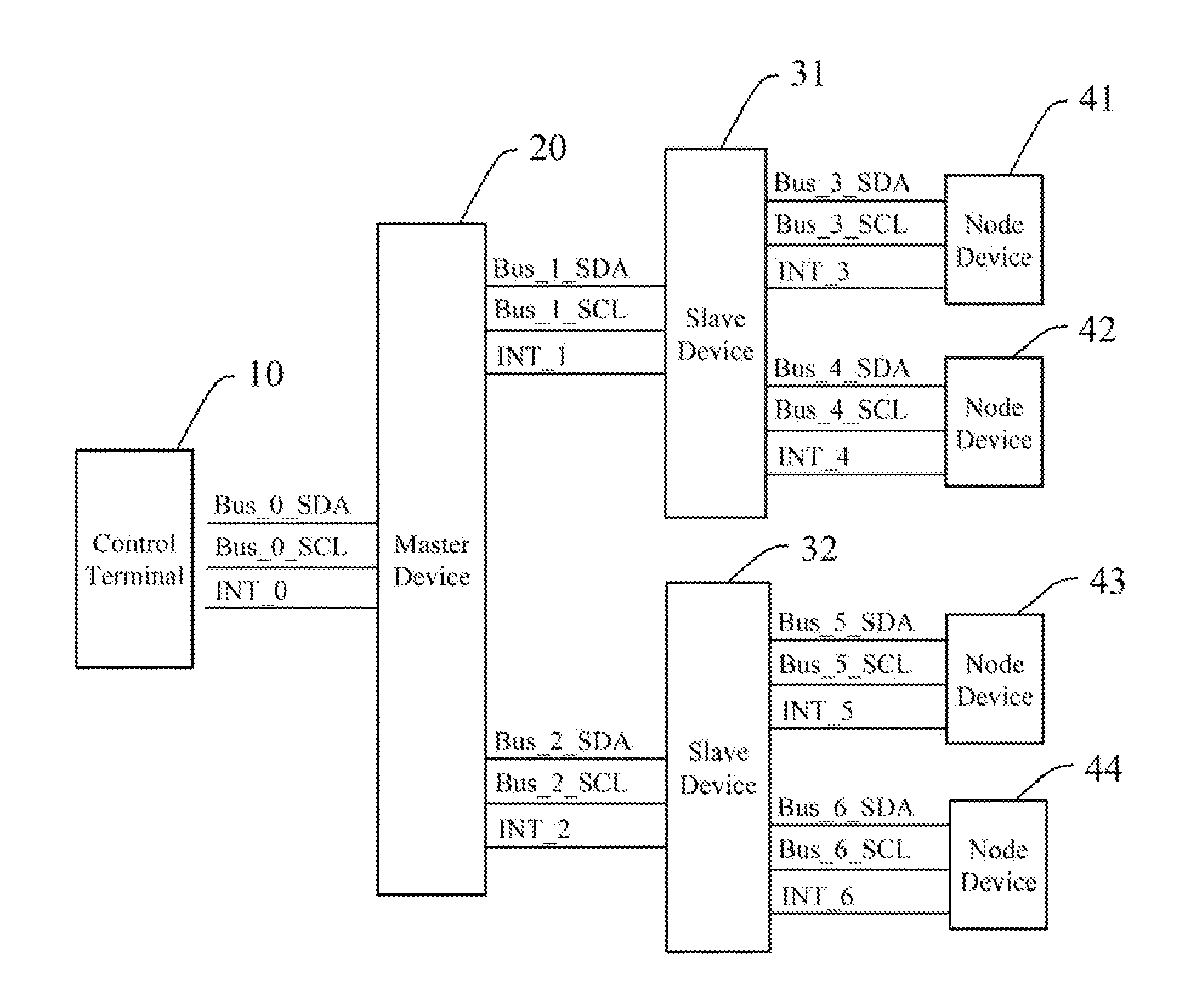

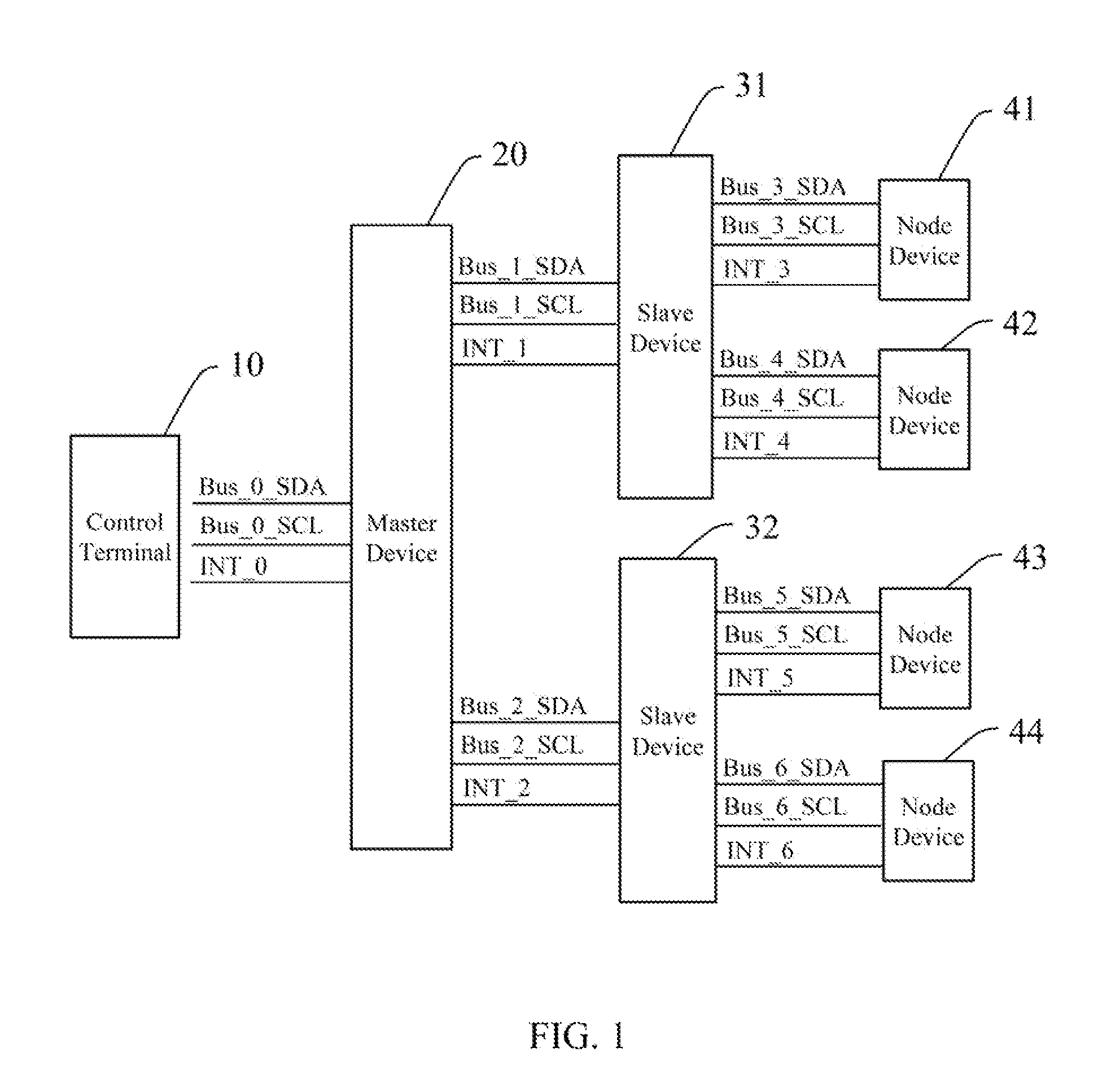

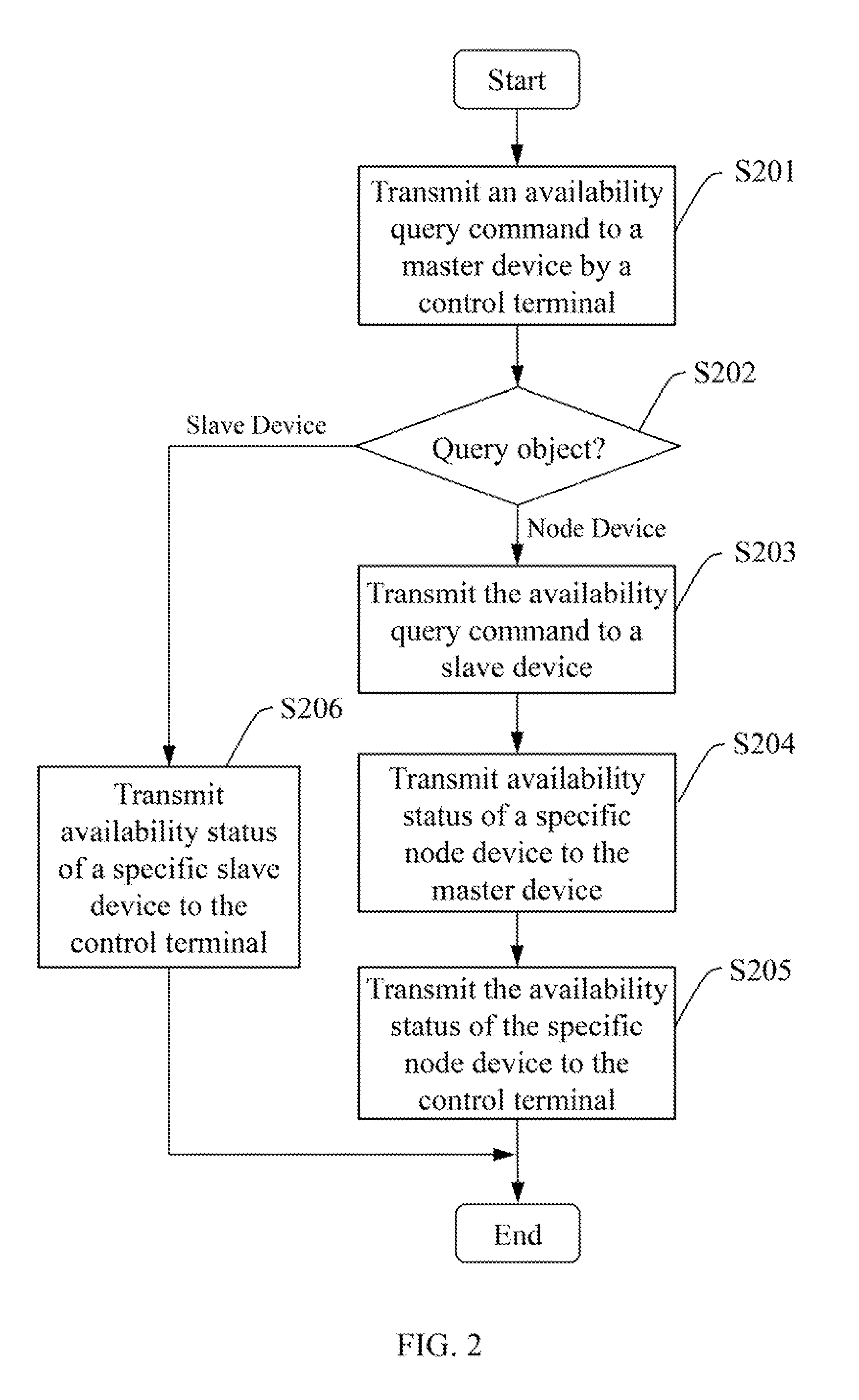

I2c bus structure and device availability query method

An Inter-Integrated Circuit (I2C) bus structure includes a master device and a slave device. The slave device is connected to the master device via an I2C bus and an interrupt line. When the master device receives an interrupt request from the slave device via the interrupt line, the master device determines that the slave device is available. When the master device has not received any interrupt request from the slave device via the interrupt line for a time period, the master device determines that the slave device is not available. A device availability query method is also provided.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

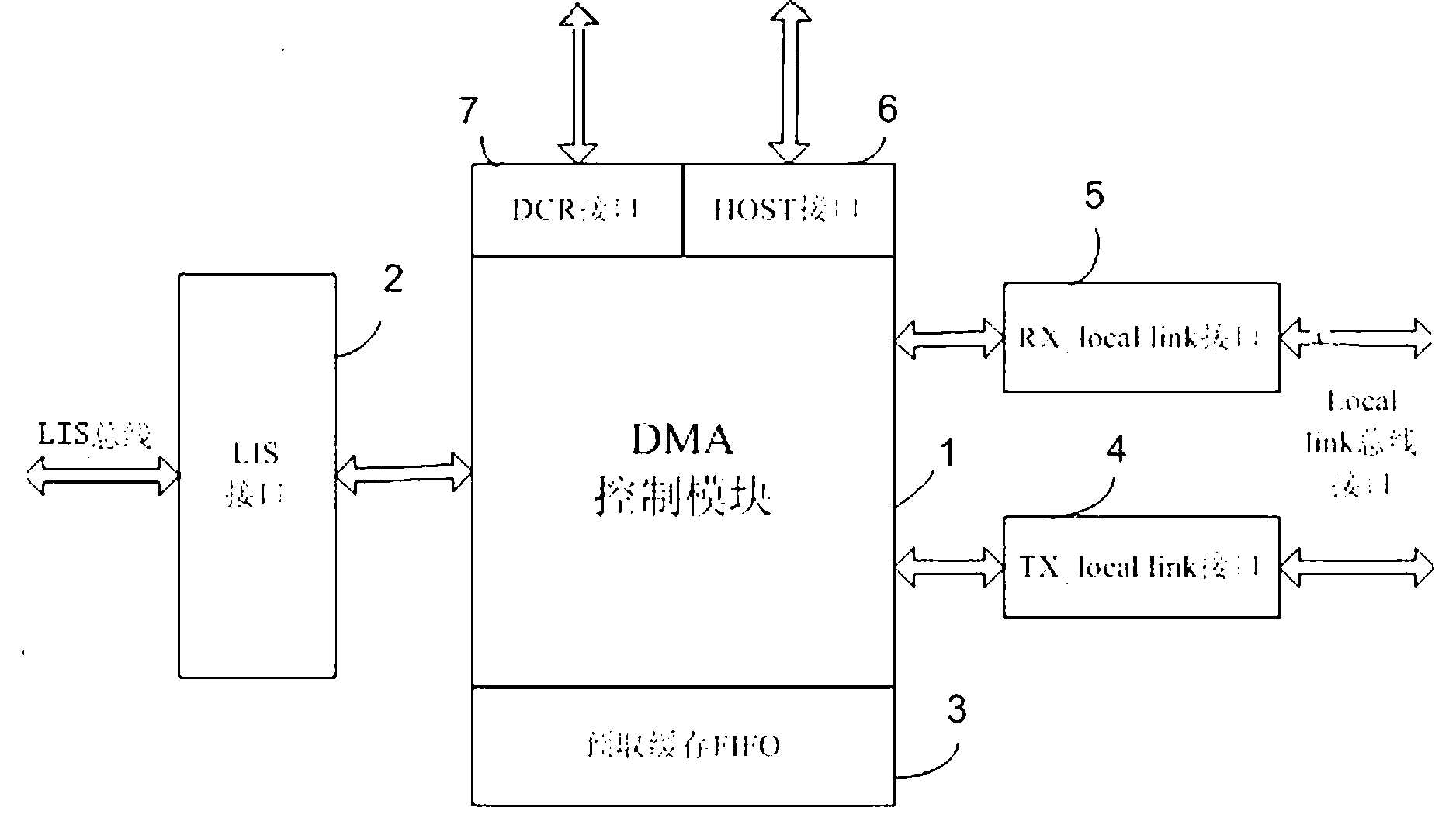

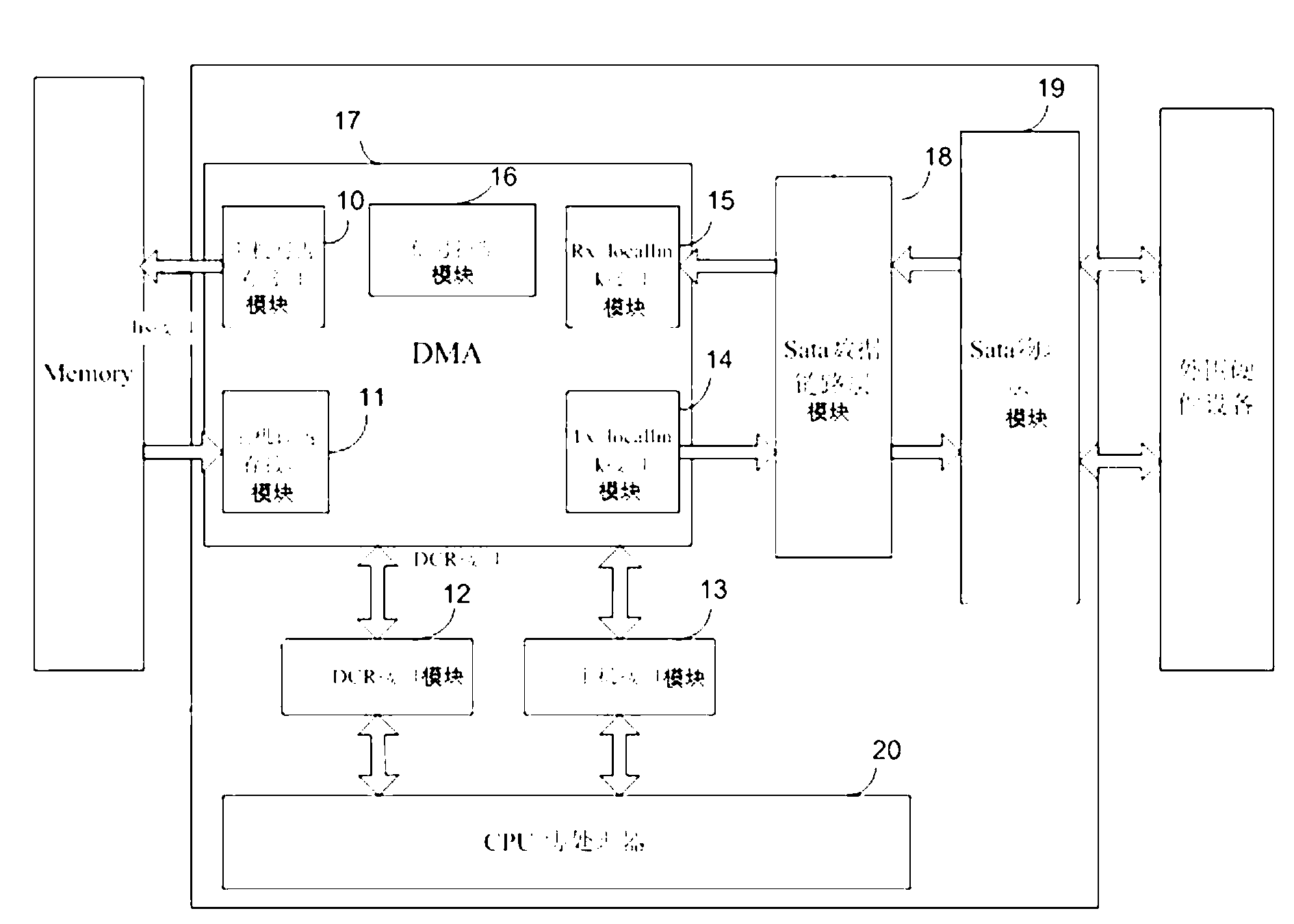

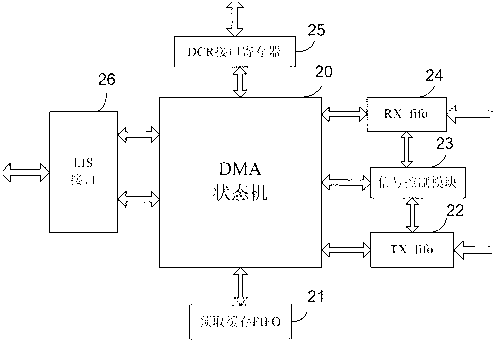

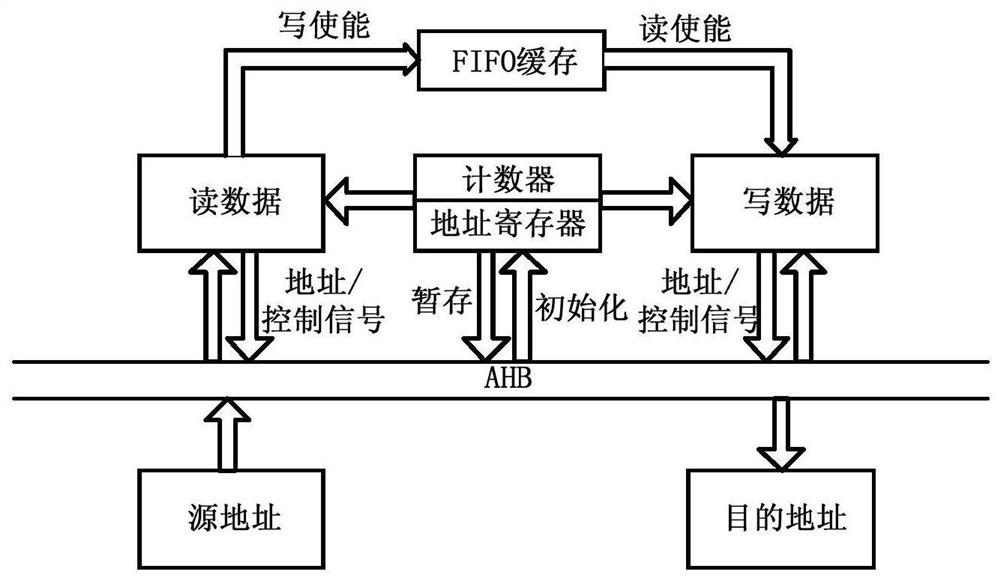

DMA (Direct Memory Access) address couple pre-reading method based on SATA (Serial Advanced Technology Attachment) controller

ActiveCN102937939AImprove data transfer efficiencyPerformance to improve data transfer efficiencyElectric digital data processingDirect memory accessNetwork packet

The invention discloses a DMA (Direct Memory Access) address couple pre-reading method based on an SATA (Serial Advanced Technology Attachment) controller. A pre-reading cache FIFO (First In, First Out) module is called by hardware logic, wherein the cache FIFO module caches address and length (address couple) pre-operated by the DMA. When the DMA transmits data, a CPU (Central Processing Unit) processes an interrupt request of the DMA, judges data interaction information of a transmission layer, analyzes the address couple information of DMA operation from a data packet, and issues the address couple information of the data to the hardware cache FIFO module by a DCR (Device Control Register) bus. As long as the hardware cache FIFO module is null, the CPU will issue the address couple information to the hardware cache FIFO. When the DMA transmits data, the address couple information is directly red from the hardware cache FIFO, so that the time that the DMA reads the address couple information from a memory to transmit data is saved, the time of waiting the CPU to operate the request of the DMA is not needed, the data transmission efficiency of the DMA is improved while the CUP operation IO (Input-Output) efficiency is improved.

Owner:无锡北方数据计算股份有限公司

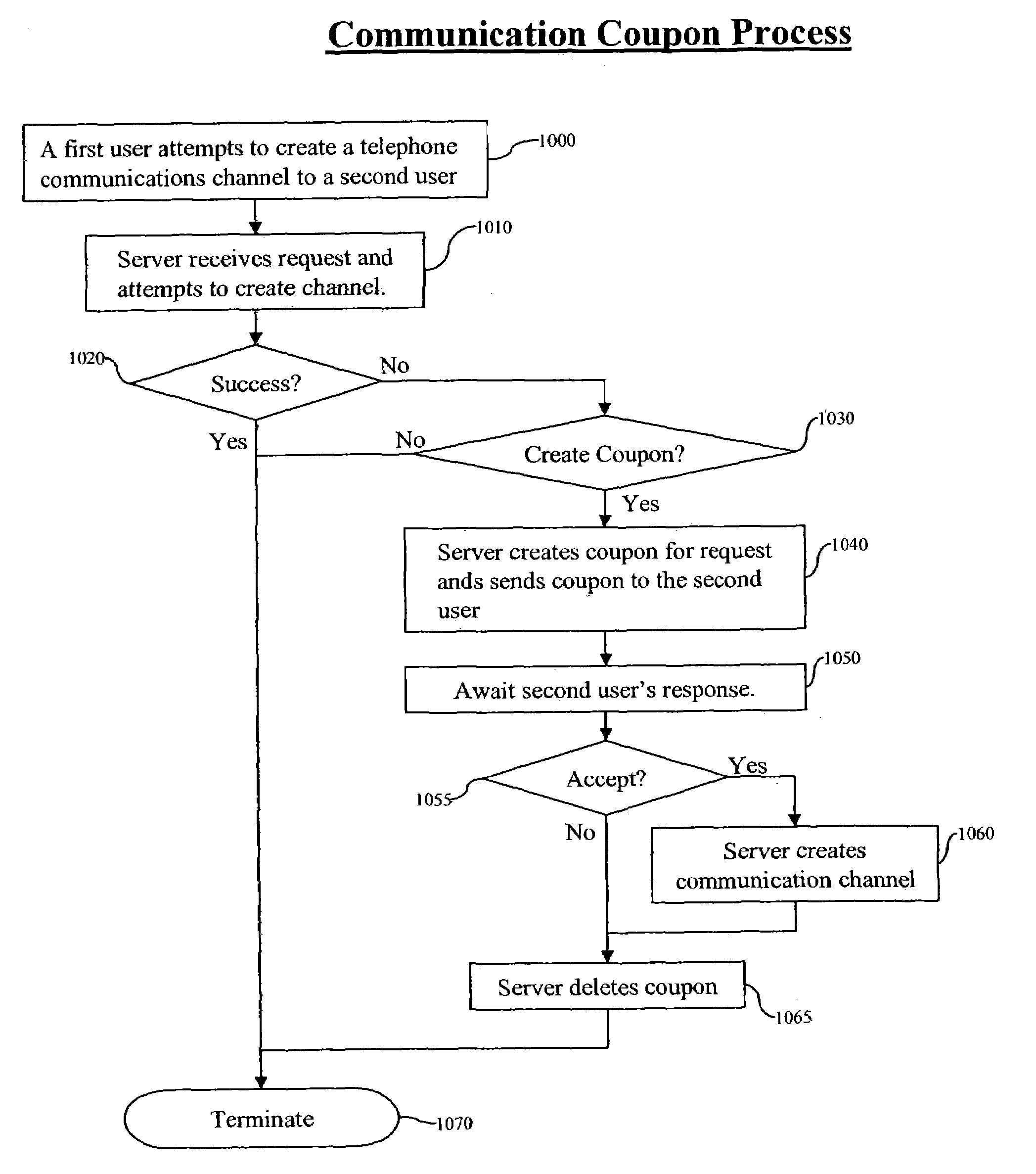

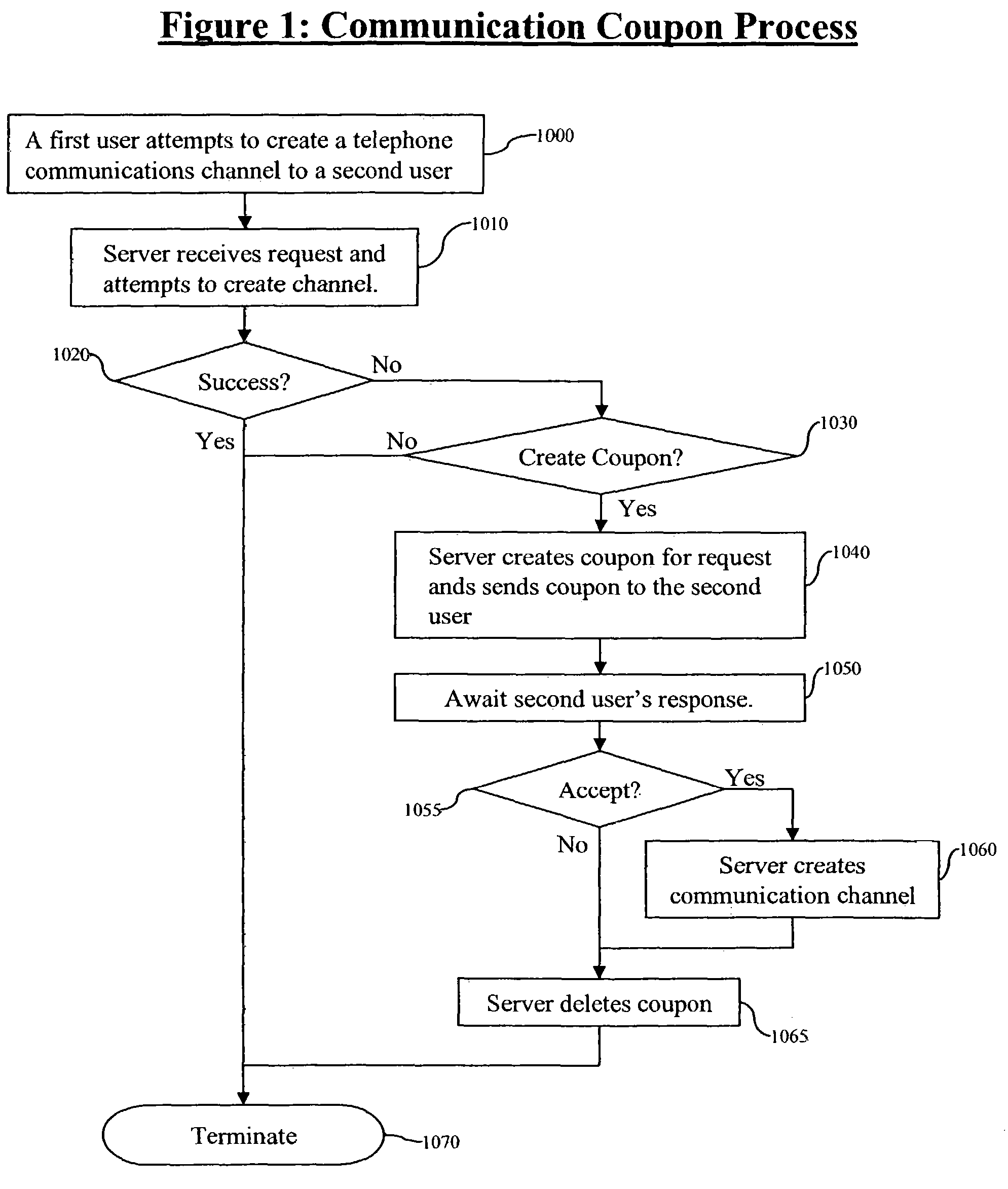

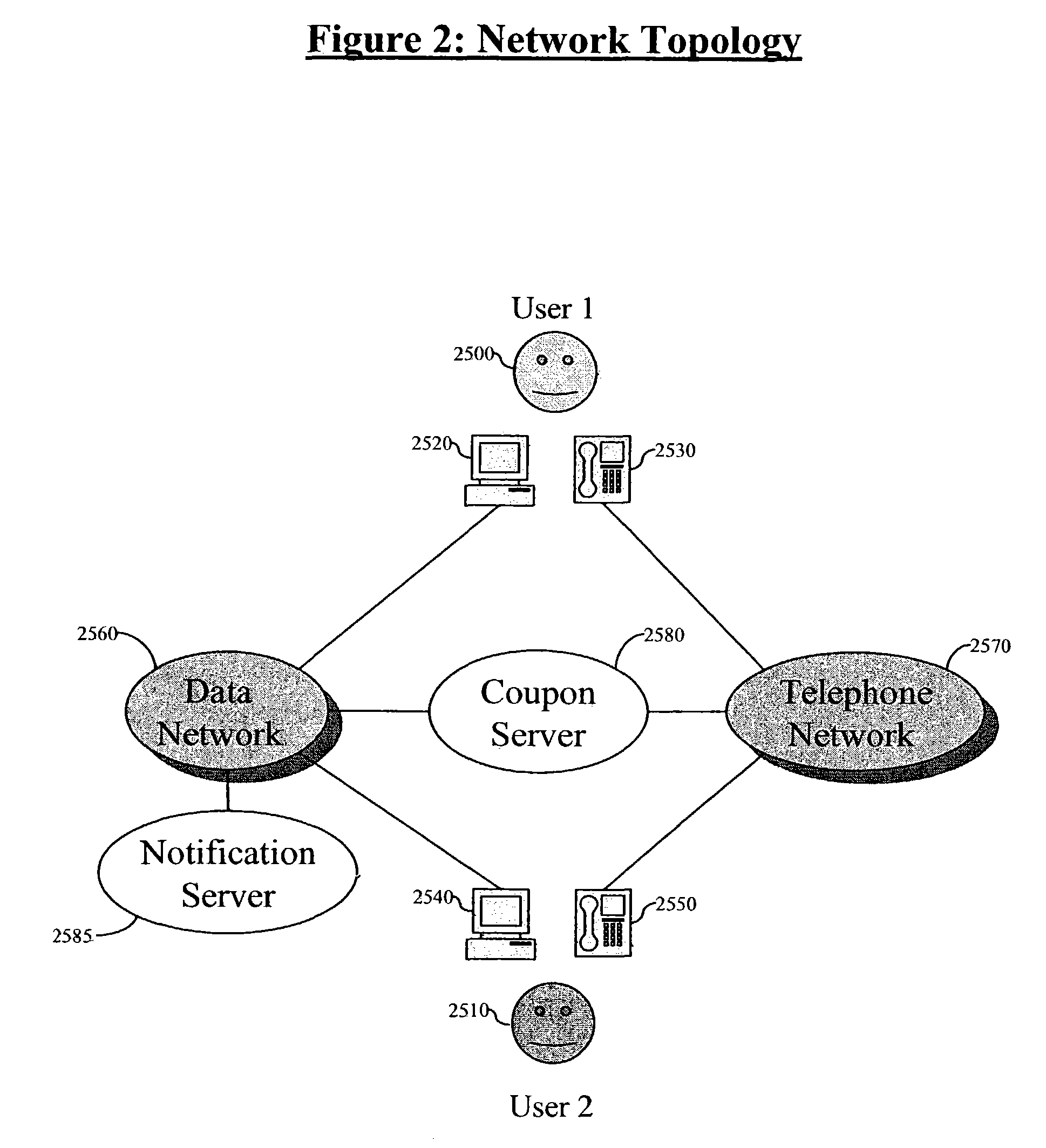

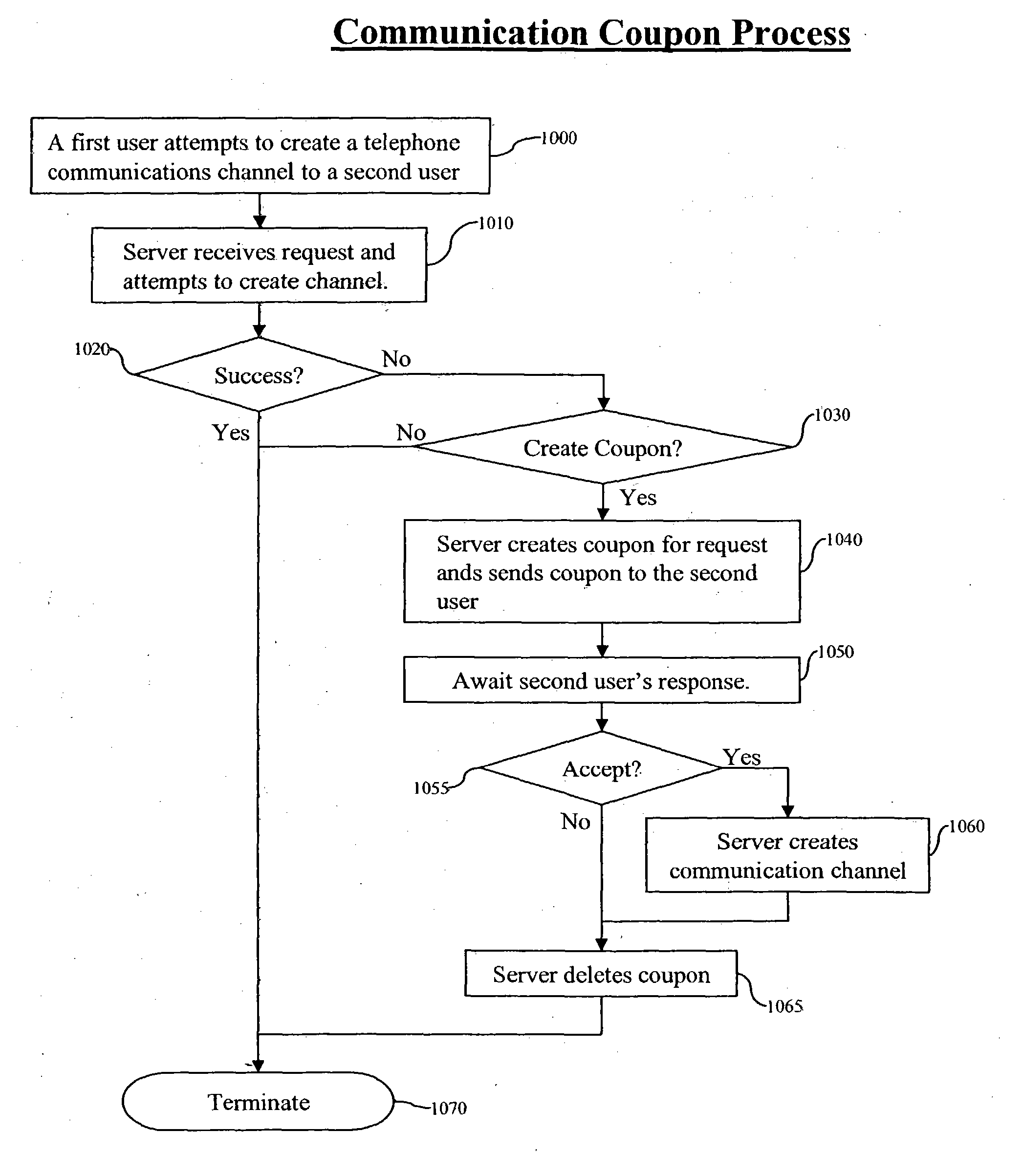

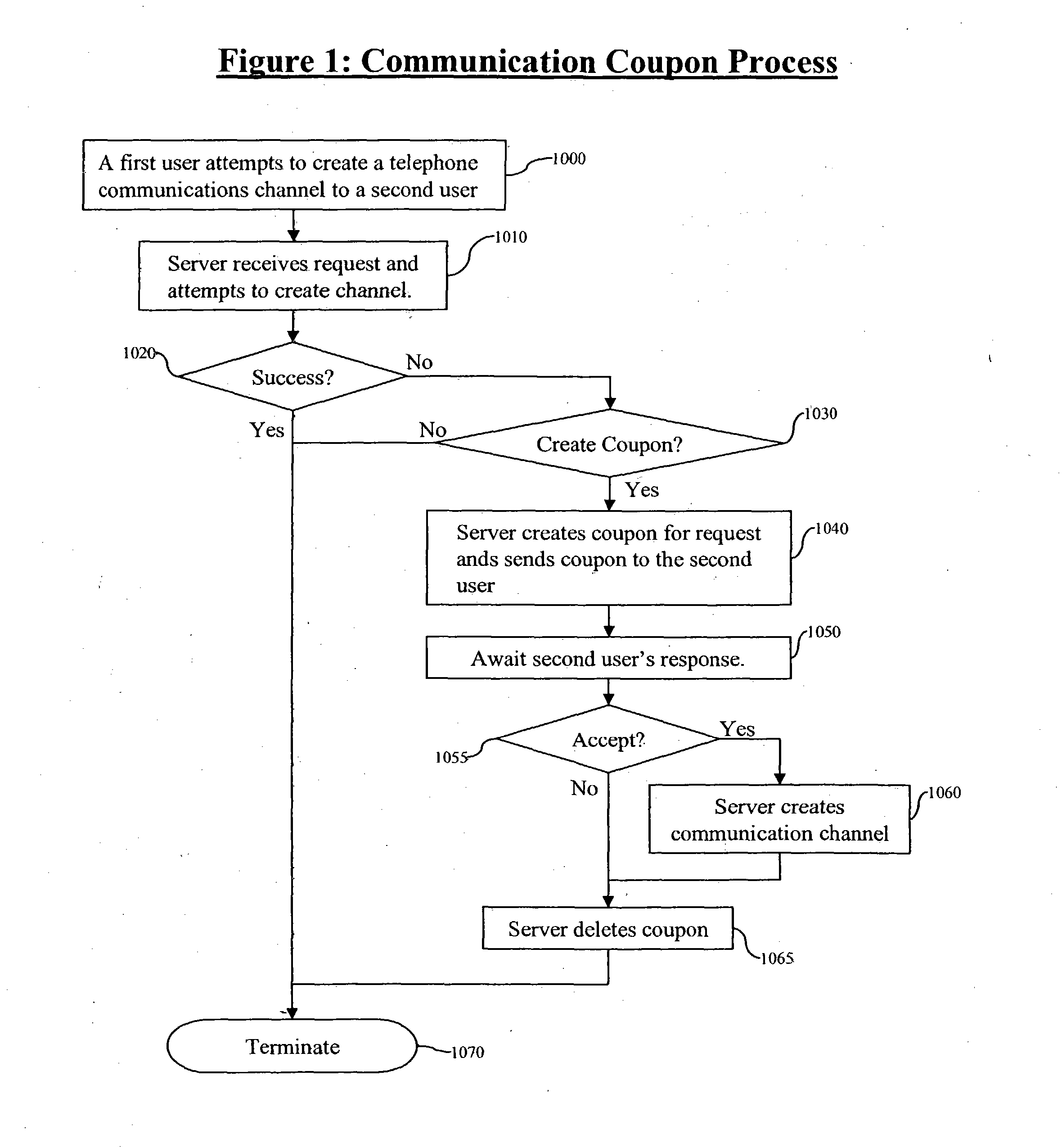

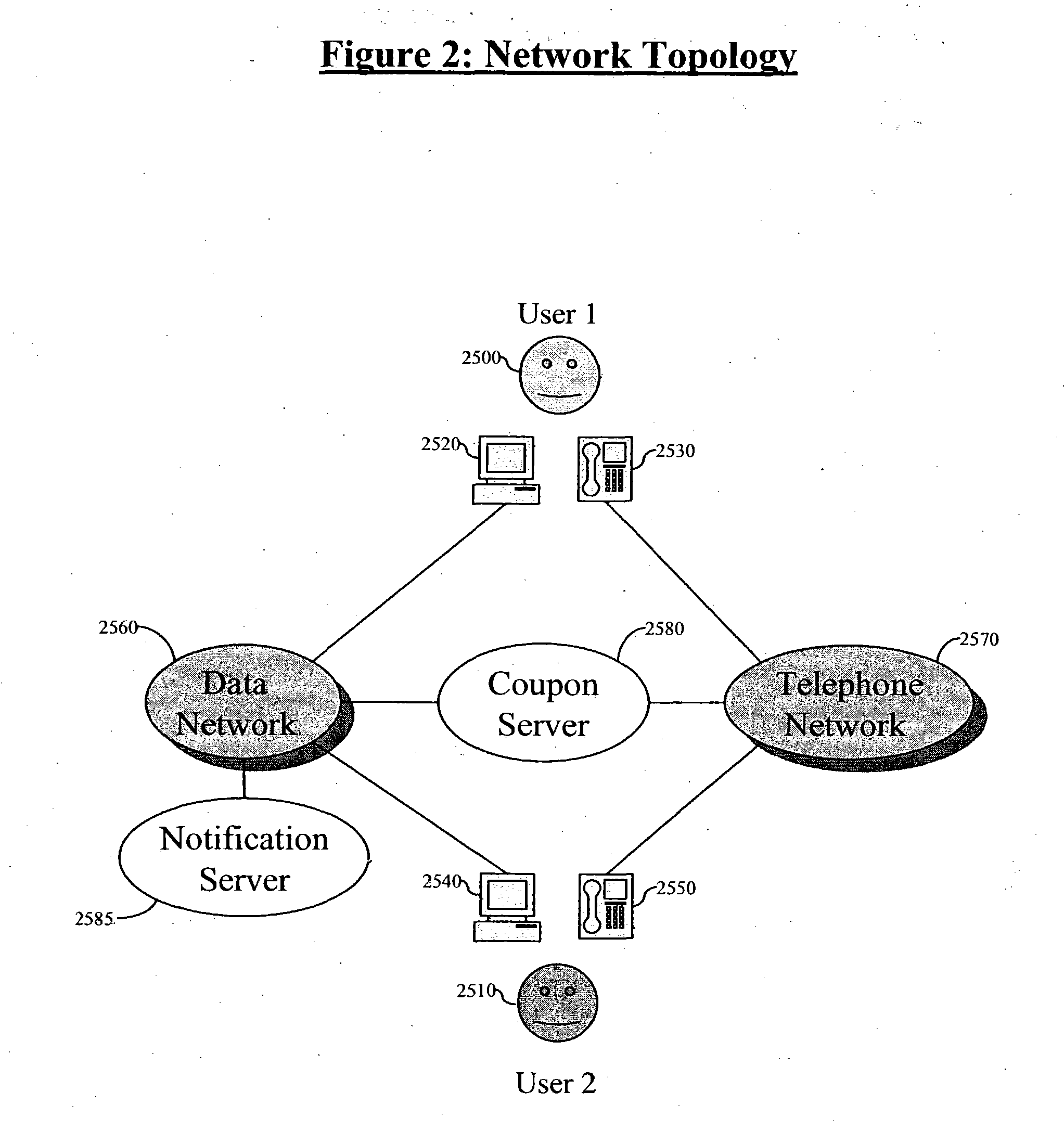

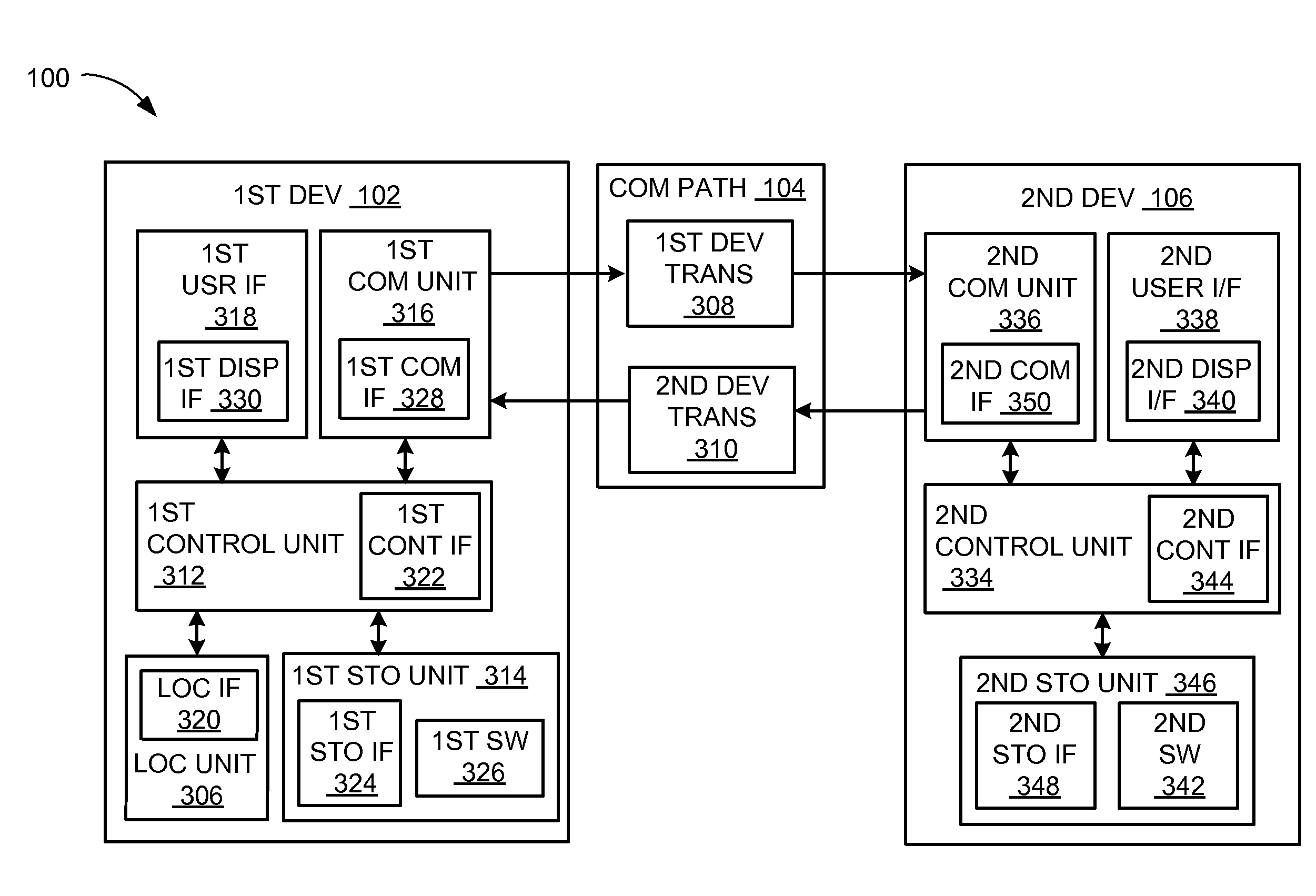

Communication capability coupons

InactiveUS7424537B2Telephone data network interconnectionsSpecial service for subscribersServer applianceNetwork on

A system and method for establishing communications between first and second parties. In one embodiment, a request initiated by a first party is generated for establishing a communications channel over a first communications network between the first and second parties. An intermediary server device interrupts receipt of the request and attempts to generate the channel. If unsuccessful in the attempt, the server device translates the request into a data network object, which is passed to the second party via a second communications network. The network object enables a second party to communicate acceptance for establishing communication with the first party over the first communications network. The second party invokes the network object upon receipt thereof or at a future time for initiating creation of a communications channel between the first and second parties. Alternately, the first party may establish the network object in the form of a coupon for communication directly to a second party without a first prior attempt to create the channel.

Owner:DAEDALUS BLUE LLC

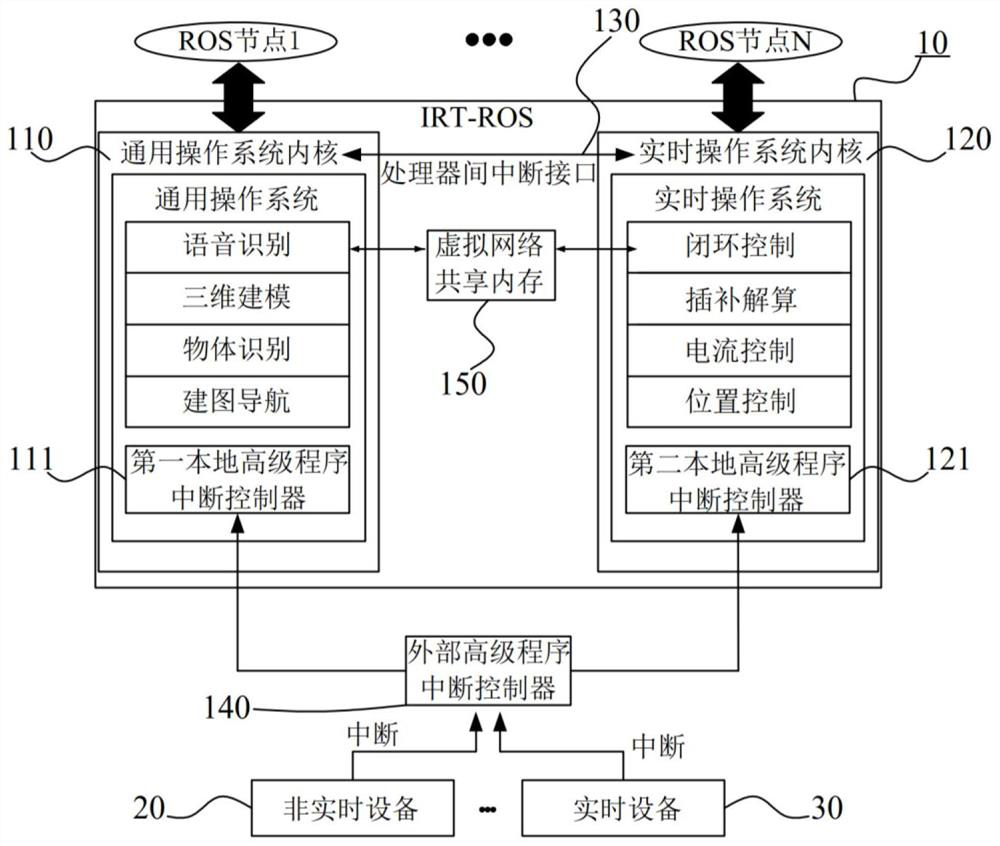

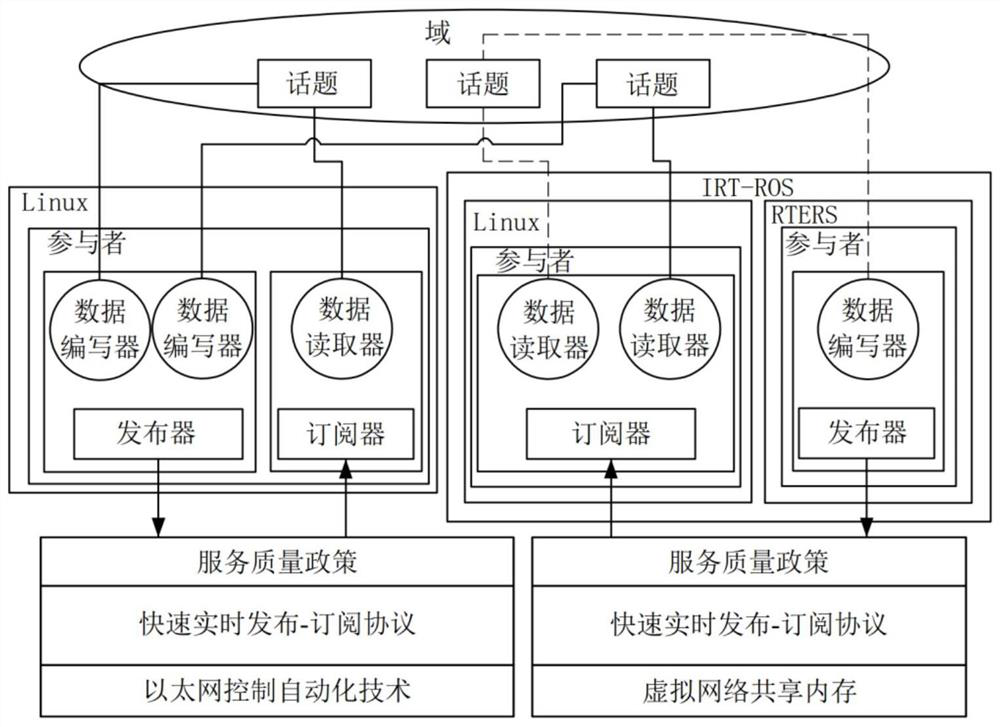

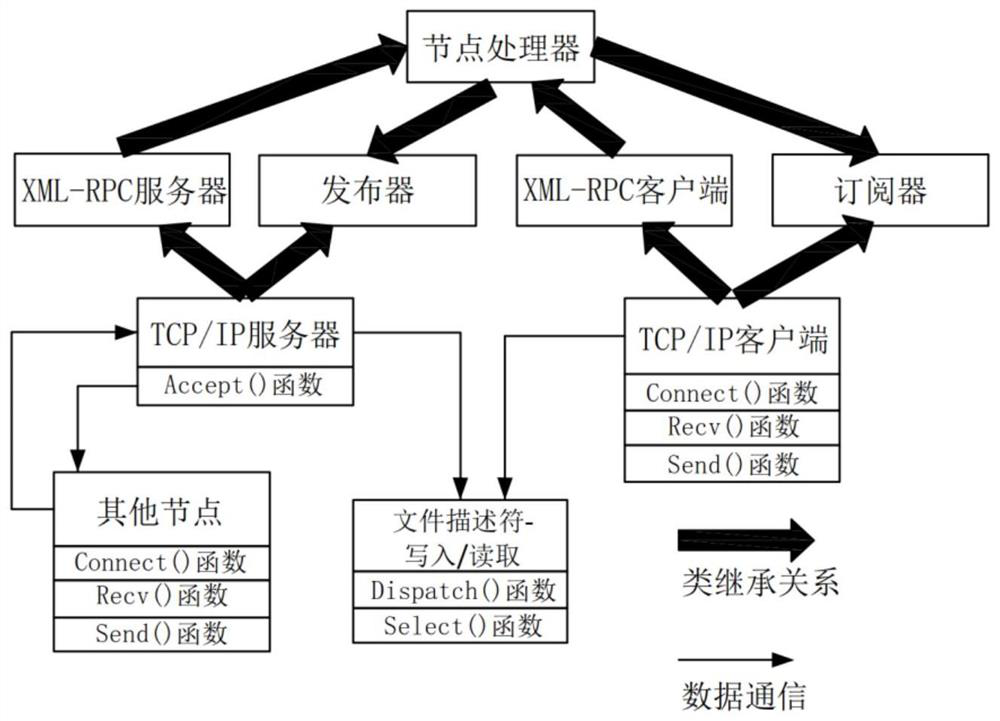

Intelligence real-time robot operating system structure and operating method thereof

ActiveCN111745651AReduce workloadProgramme-controlled manipulatorProgram initiation/switchingControl engineeringWorkload

Owner:HEFEI HRG XUANYUAN INTELLIGENT TECH CO LTD

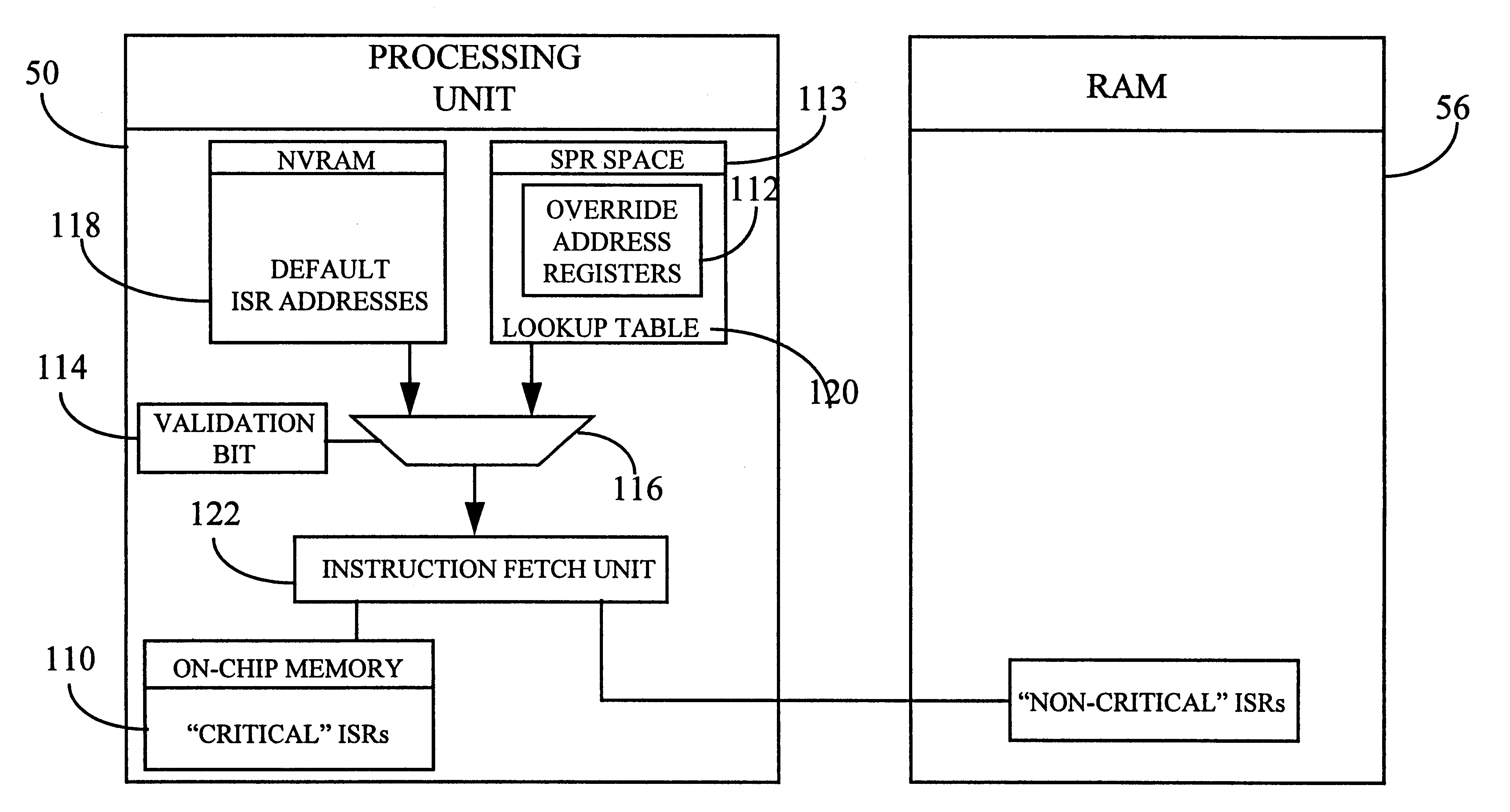

Exceptions and interrupts with dynamic priority and vector routing

InactiveUS6601122B1Increase flexibilityLower latencyProgram initiation/switchingInput/output processes for data processingOperating systemComputerized system

A method of handling an interrupt request in a computer system by programmably setting an override address associated with a specific interrupt service routine, and servicing an interrupt request based on the override address, which is different from a power-on default address associated with the same interrupt service routine. The method may determine whether the interrupt service routine is critical and, if so, set the override address to a physical location in the on-chip memory of the processing unit, instead of in the off-chip memory (RAM). Override address registers are accessed via the special purpose registers of the processing unit. A validation bit may be turned on in response to the setting of the override address, with both the default address and the override address being provided as separate inputs to a multiplexing device controlled by the validation bit. The override address is forwarded from the multiplexing device to an instruction fetch unit whenever the validation bit has been set. The result is decreased latency associated with interrupt handling, and increased flexibility in user definition of critical versus non-critical interrupts.

Owner:IBM CORP

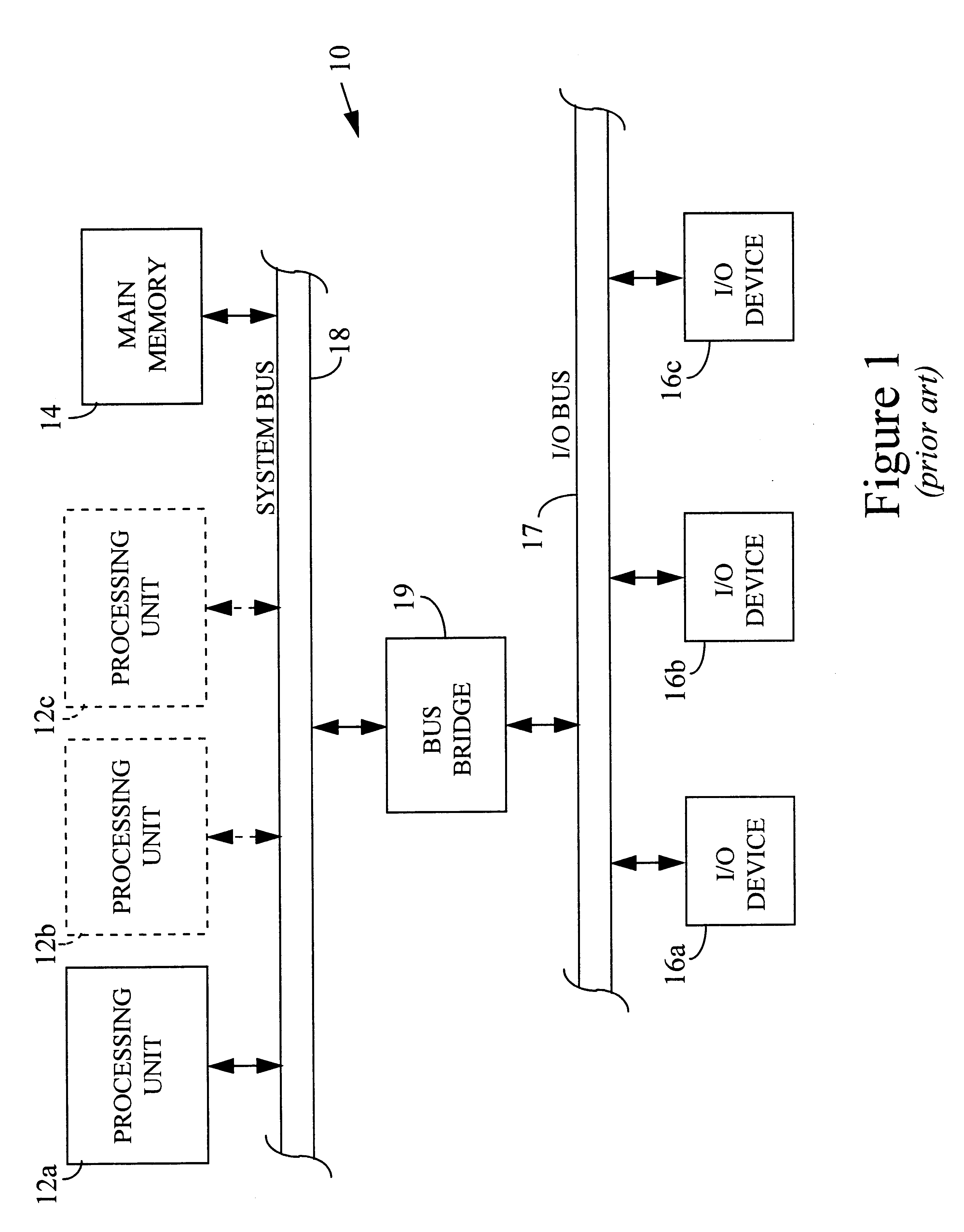

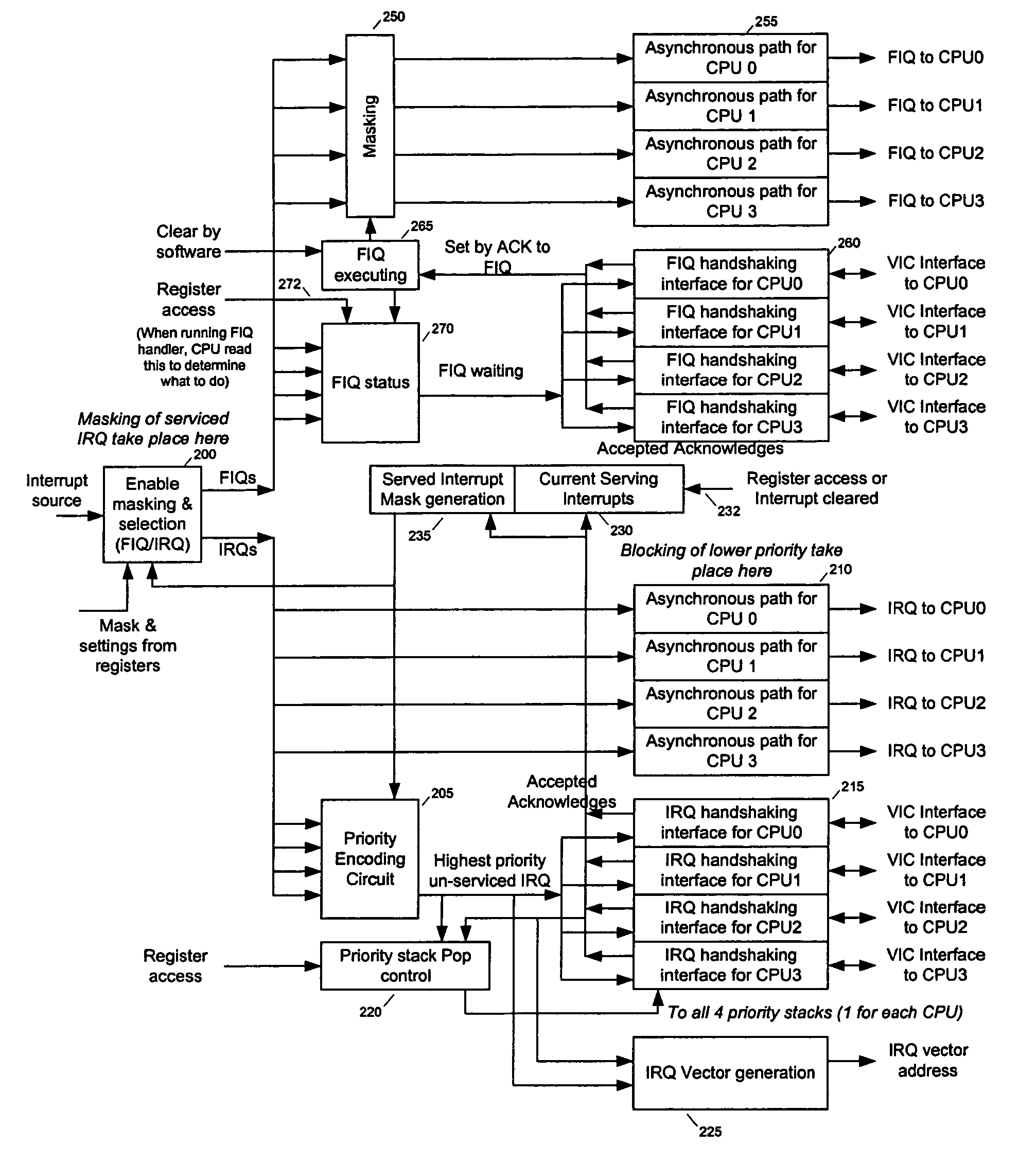

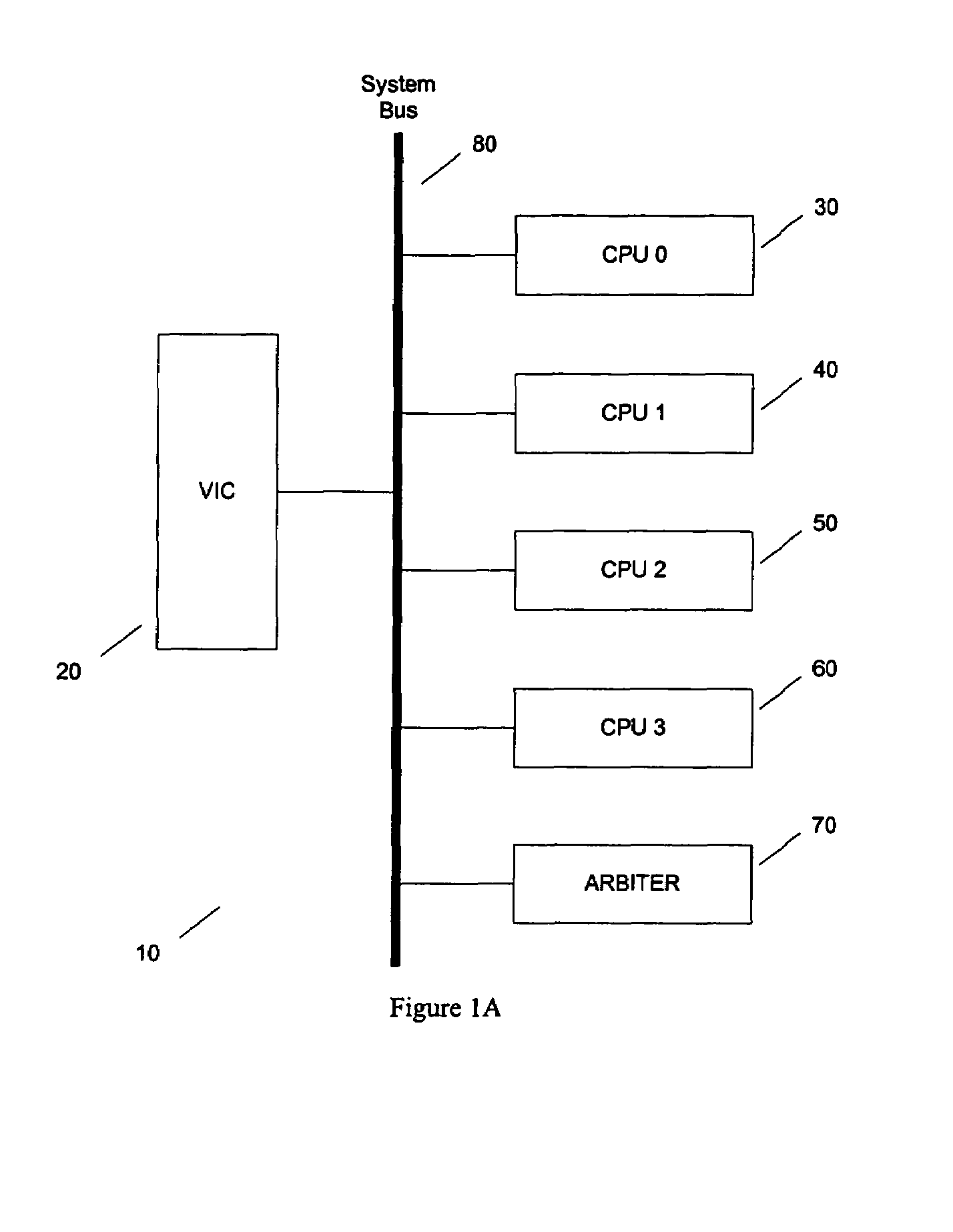

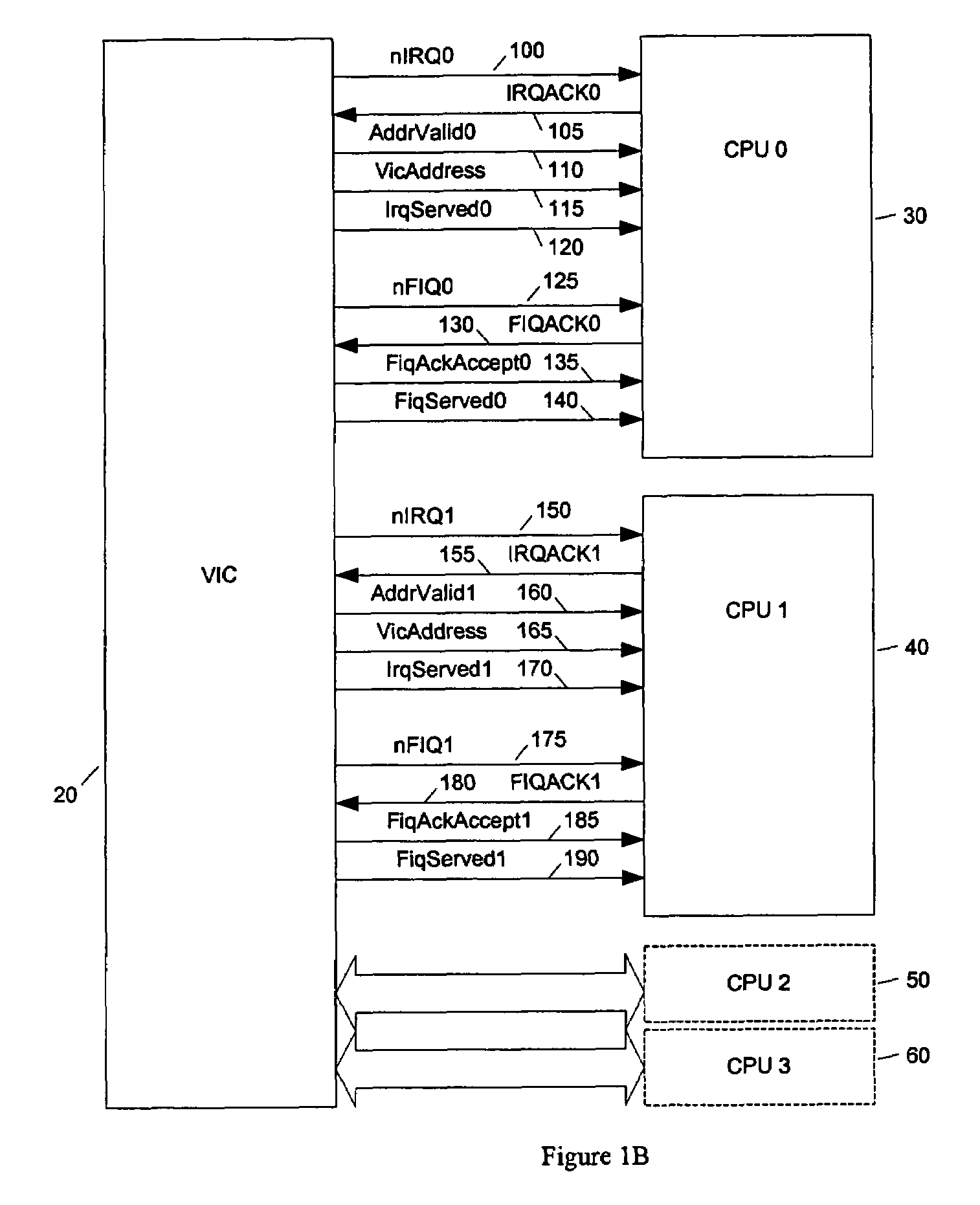

Handling interrupts in a system having multiple data processing units

ActiveUS7350005B2Increase speedAvoid the needGeneral purpose stored program computerInput/output processes for data processingEmbedded systemReceipt

An interrupt controller is provided for processing interrupt requests in a system having a plurality of data processing units operable to service those interrupt requests, each interrupt request having an associated priority level. The interrupt controller comprises request logic operable to receive an indication of unserviced interrupt requests, to apply predetermined criteria to determine which of said plurality of data processing units are candidate data processing units for servicing at least one of said unserviced interrupt requests, and to issue a request signal to each said candidate data processing unit. Priority encoding logic is operable to determine a highest priority unserviced interrupt request based on the associated priority levels of the unserviced interrupt requests. Further, handshake logic is operable to receive acknowledgement signals associated with said candidate data processing units replying to said request signals issued by the request logic, upon receipt of a first acknowledgement signal, the handshake logic being operable to allocate to the candidate data processing unit associated with that first acknowledgement signal the highest priority unserviced interrupt request as indicated by the priority encoding logic. By this approach, the highest priority unserviced interrupt request will be allocated to the data processing unit whose associated acknowledgement signal is first received by the handshake logic, and hence this increases the speed with which that highest priority interrupt request is serviced.

Owner:ARM LTD

Wireless access point and method for operating the same

InactiveUS20070019574A1Reduce throughputReduce transmission efficiencyRadio transmissionWireless communicationProcessing elementRF module

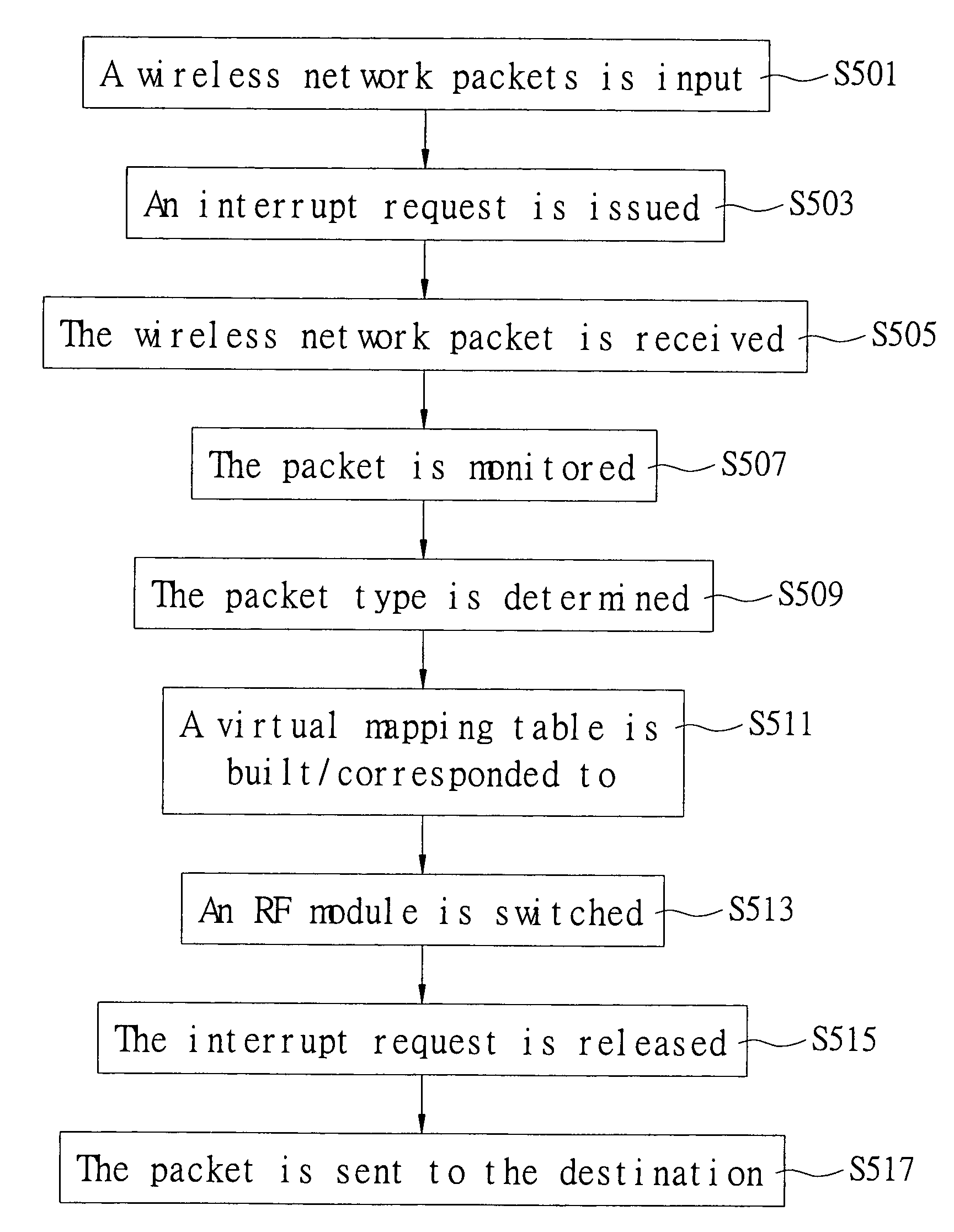

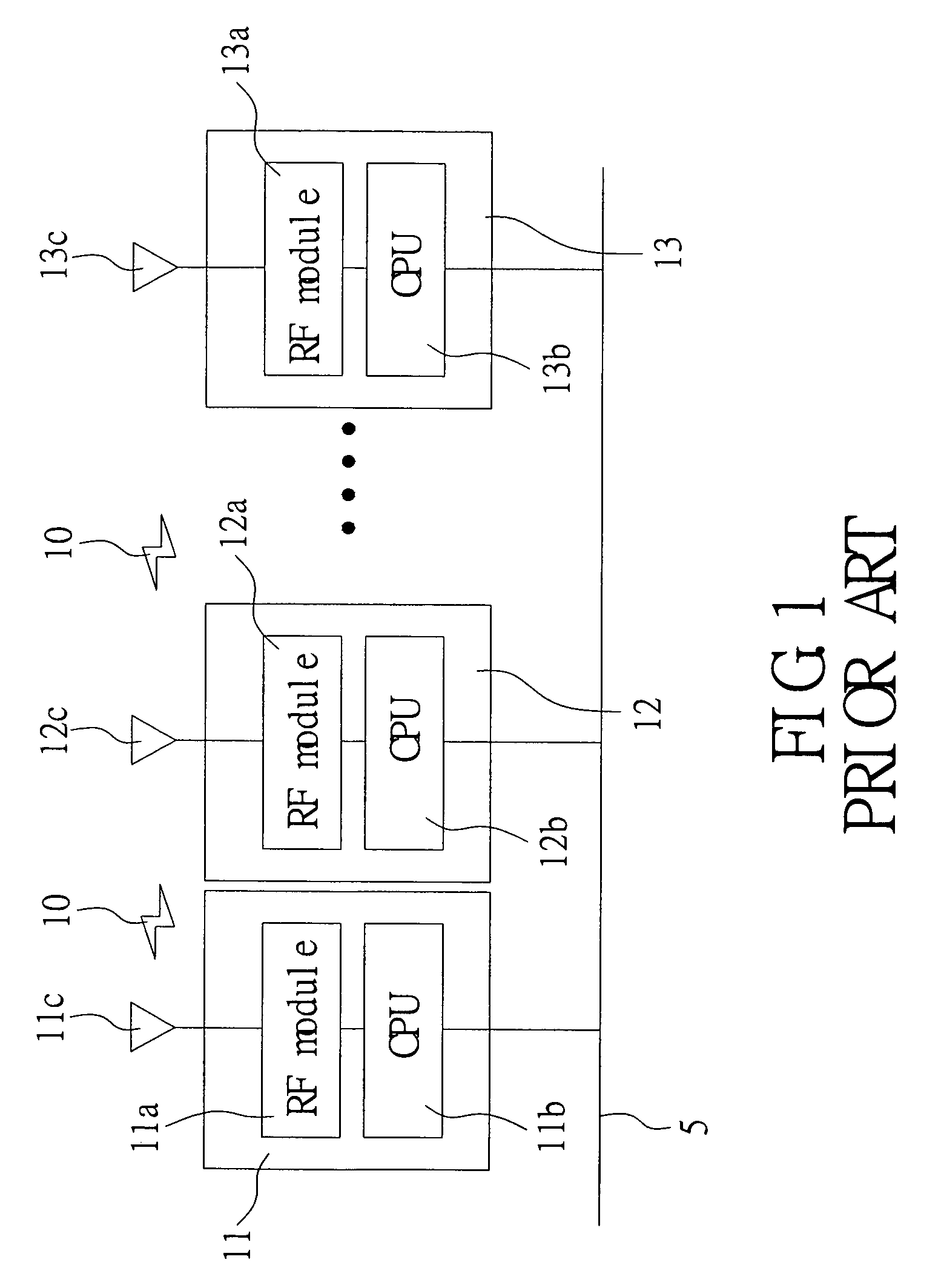

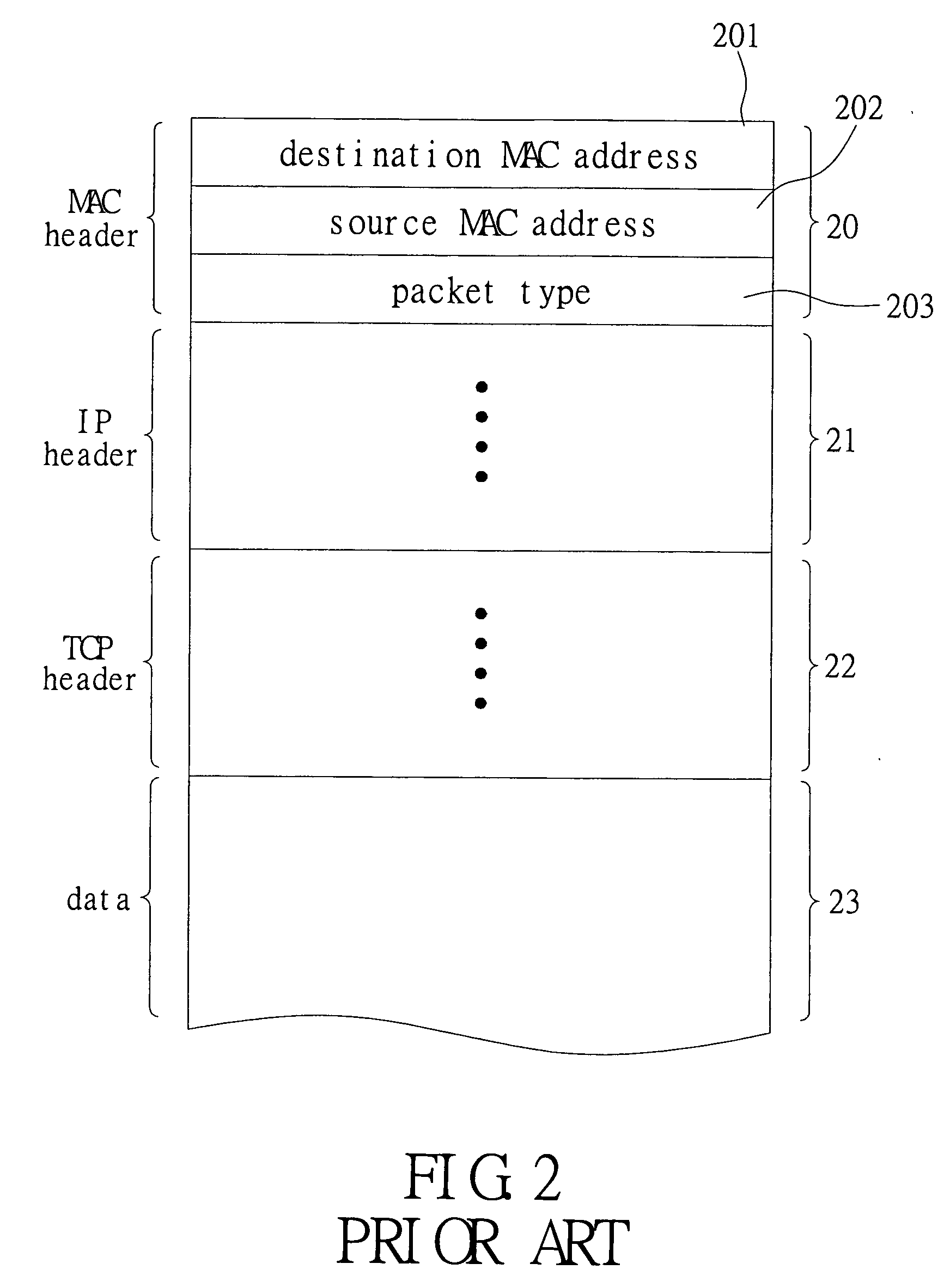

A wireless access point and a method for operating the same are proposed, in which a virtual bridging control module carried out by software is used to bridge a plurality of RF modules, and a virtual mapping table is used to record information of incoming and outgoing transmission packets, thereby establish ingg a seamless sequential wireless network environment. The throughput won't drop when hopping transmission is performed between each access point. The method comprises the steps of: inputting a wireless network packet; issuing an interrupt request to a processing unit; receiving the packet by using an RF module; monitoring the packet by using a virtual bridging control module; determining the type of the packet; establishing a virtual mapping table; switching the packet to another RF module; and finally sending the packet to the destination.

Owner:APHELION USA

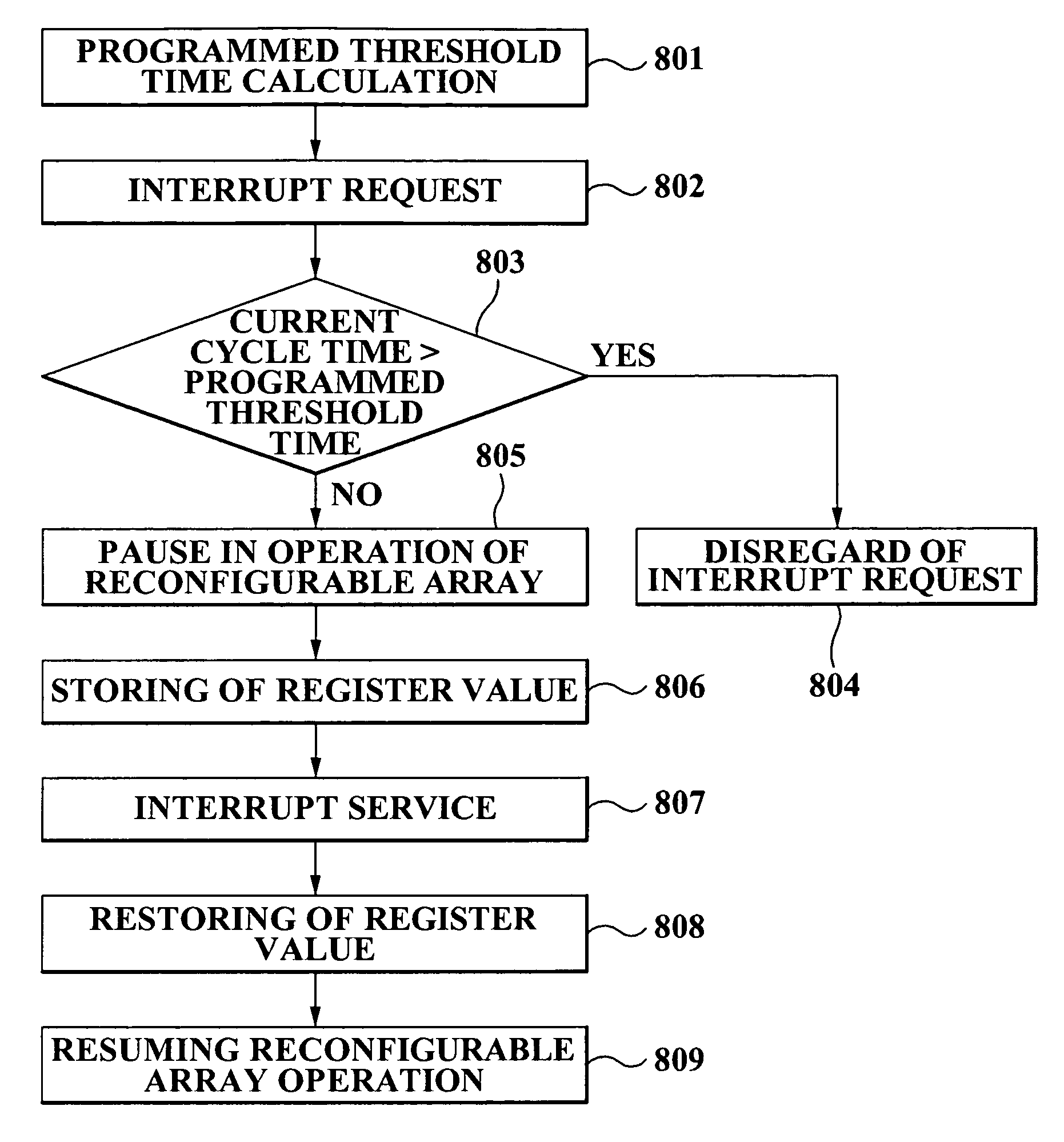

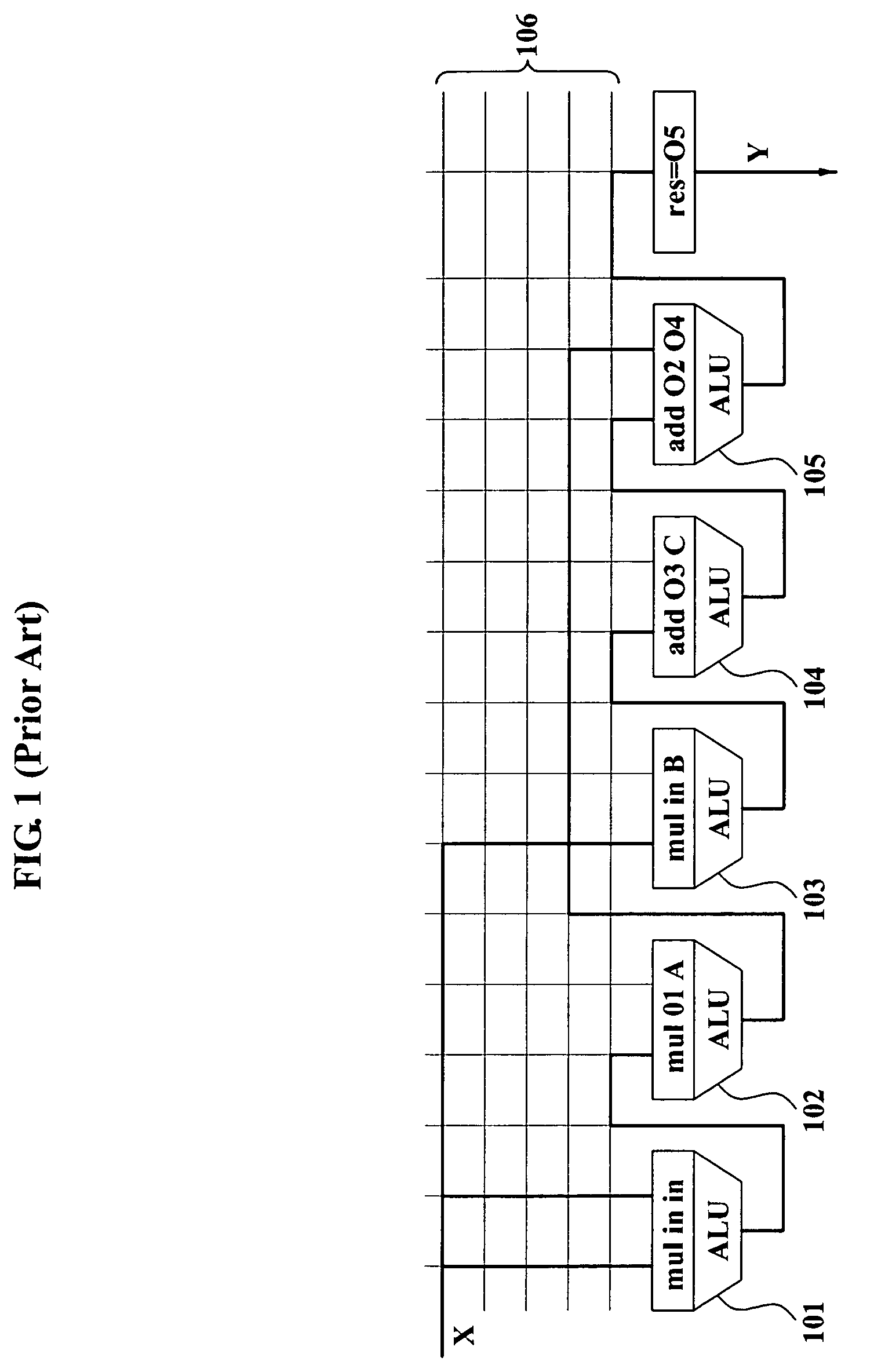

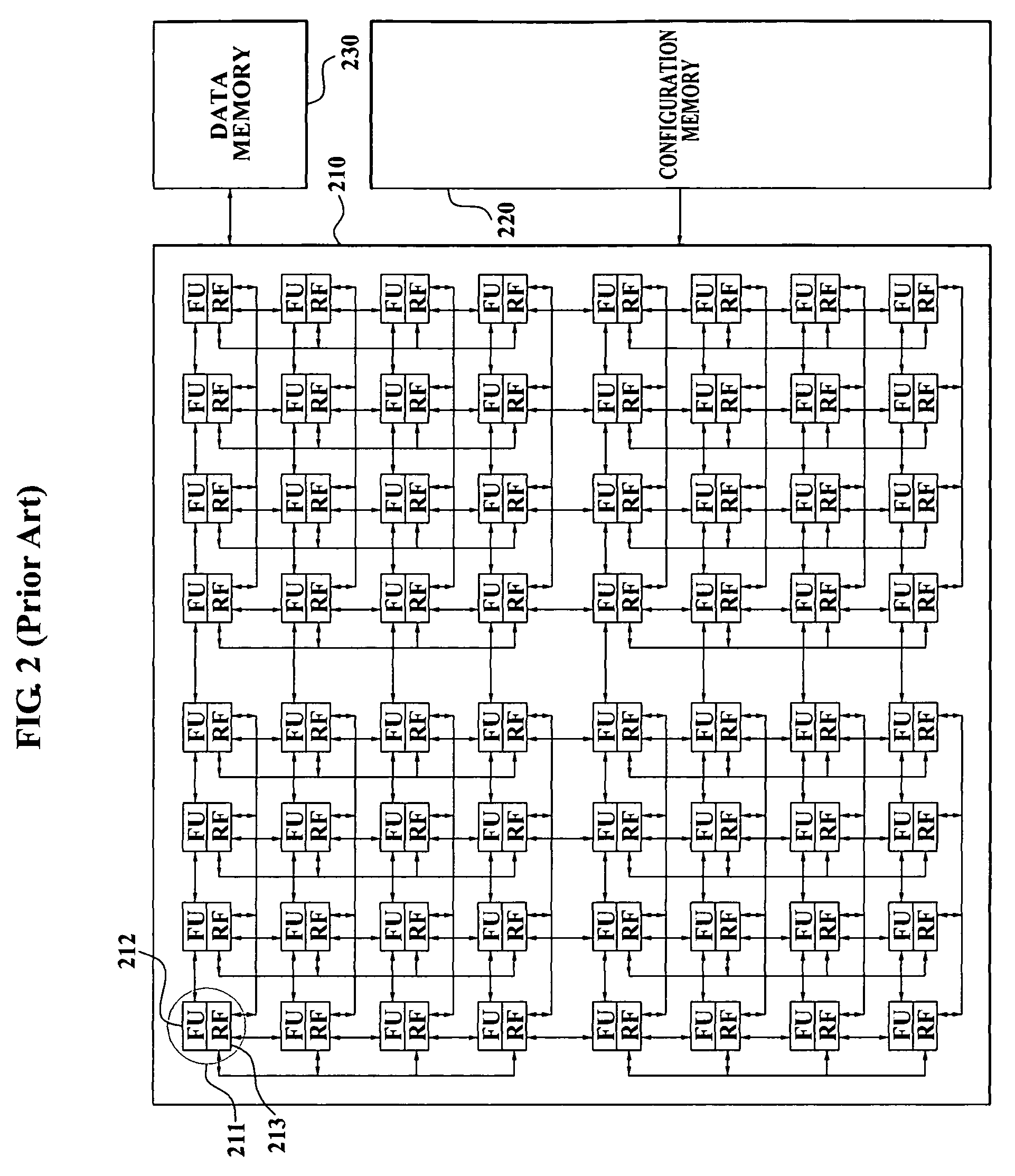

Method, medium, and apparatus with interrupt handling in a reconfigurable array

ActiveUS7836291B2Easy to handleMinimize overheadTextile treatment machine partsDigital computer detailsReconfigurable antennaProcessor register

Owner:SAMSUNG ELECTRONICS CO LTD

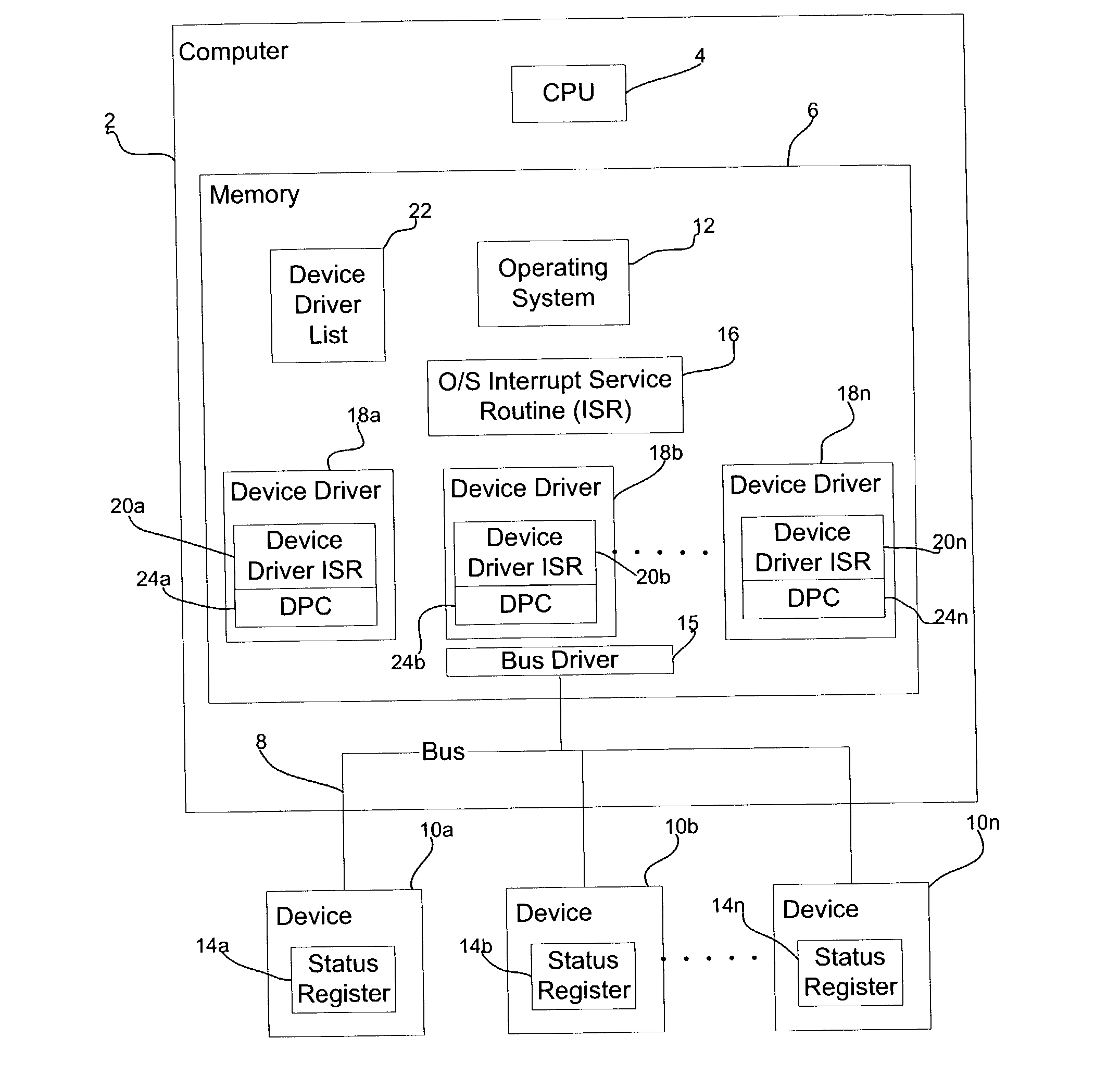

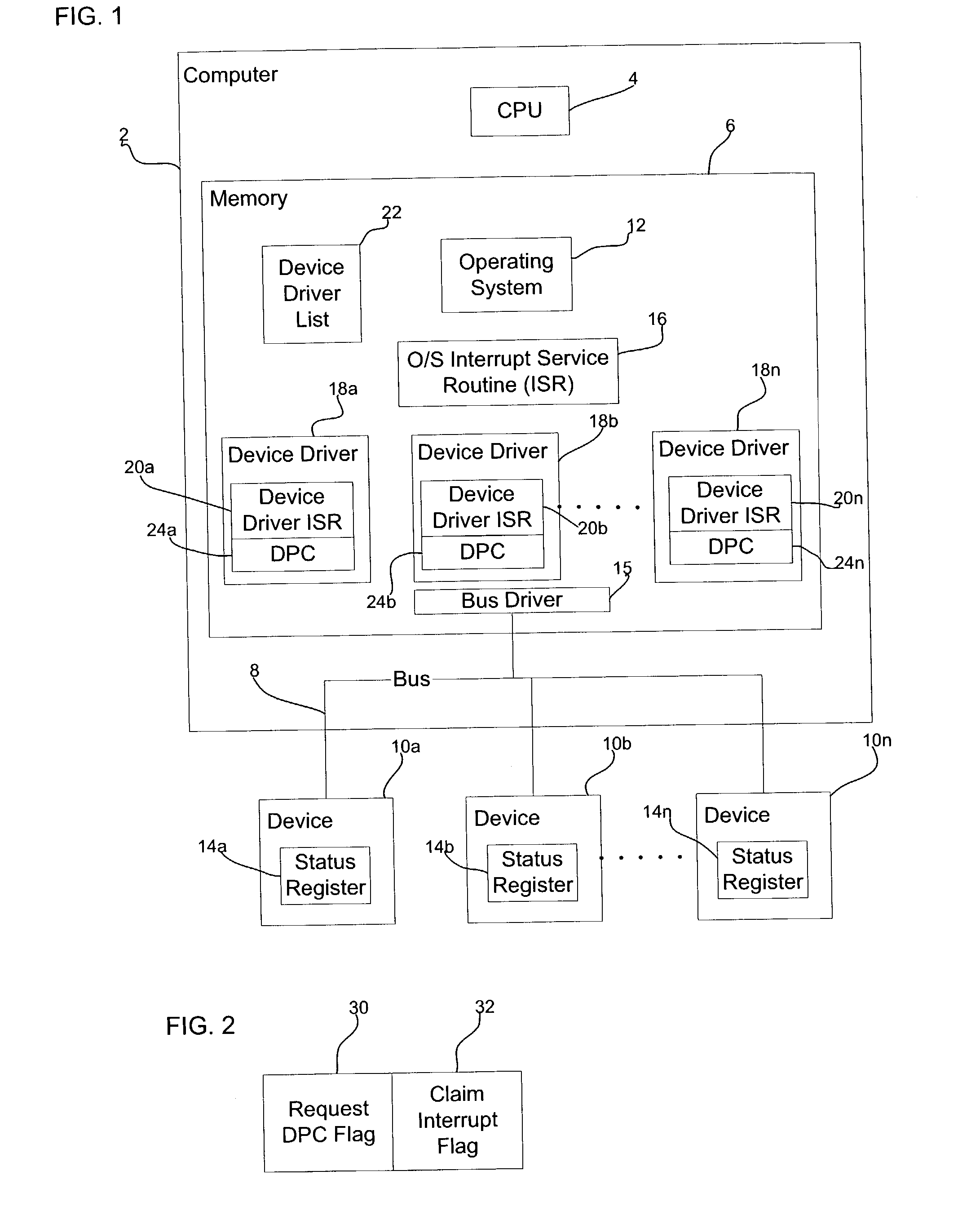

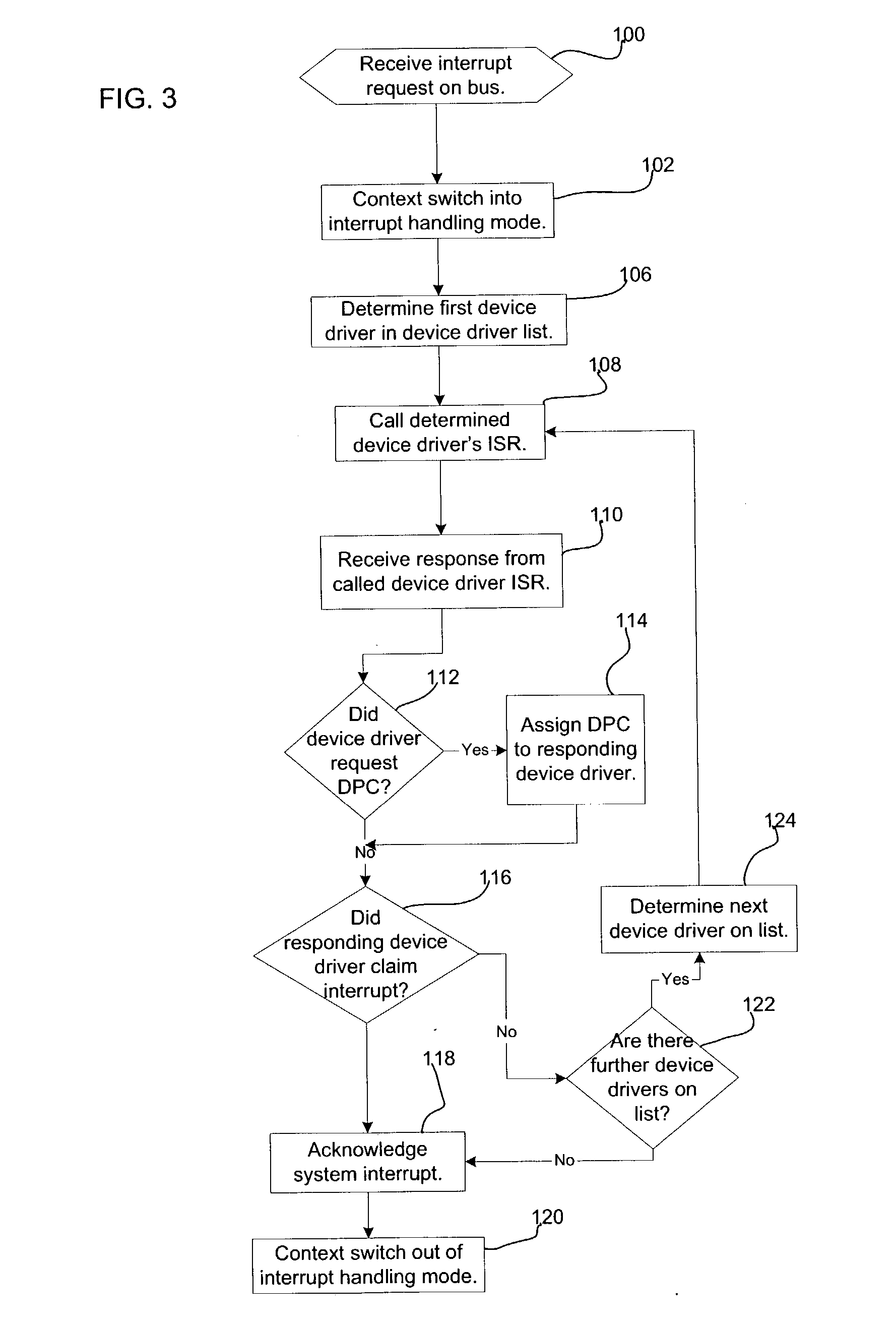

Method, system, and program for handling interrupt requests

InactiveUS20040122997A1Input/output processes for data processingData conversionOperating systemComputer engineering

Provided are a method, system, and program for handling interrupts. A request is received as to whether a device transmitted an interrupt and a determination is made as to whether the device transmitted the interrupt. If the device transmitted the interrupt, then indication is made that the device did not transmit the interrupt and work from the device related to the interrupt is processed.

Owner:INTEL CORP

Communication capability coupons

InactiveUS20050021664A1Telephone data network interconnectionsSpecial service for subscribersServer applianceCommunication channel

A system and method for establishing communications between first and second parties. In one embodiment, a request initiated by a first party is generated for establishing a communications channel over a first communications network between the first and second parties. An intermediary server device interrupts receipt of the request and attempts to generate the channel. If unsuccessful in the attempt, the server device translates the request into a data network object, which is passed to the second party via a second communications network. The network object enables a second party to communicate acceptance for establishing communication with the first party over the first communications network. The second party invokes the network object upon receipt thereof or at a future time for initiating creation of a communications channel between the first and second parties. Alternately, the first party may establish the network object in the form of a coupon for communication directly to a second party without a first prior attempt to create the channel.

Owner:DAEDALUS BLUE LLC

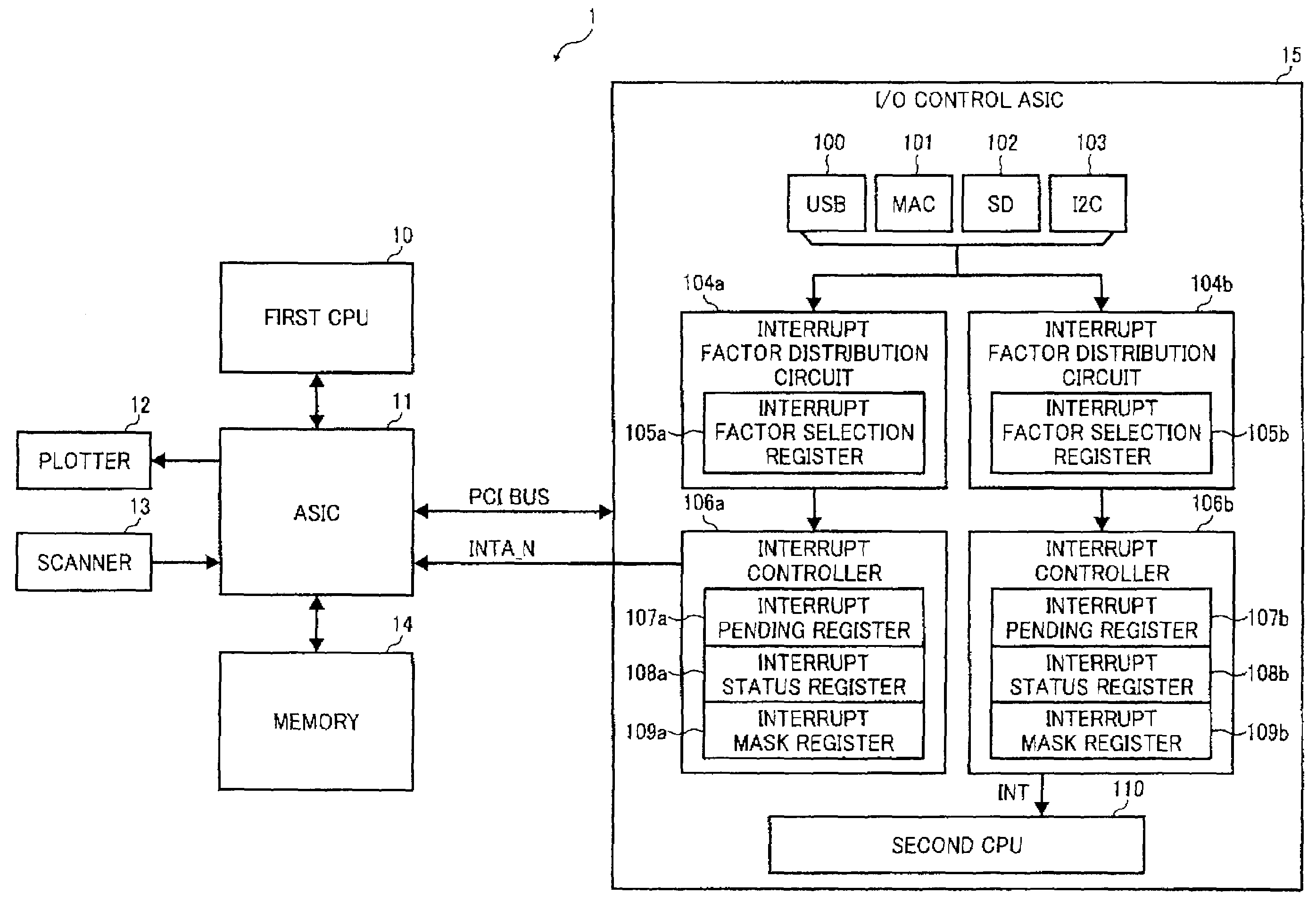

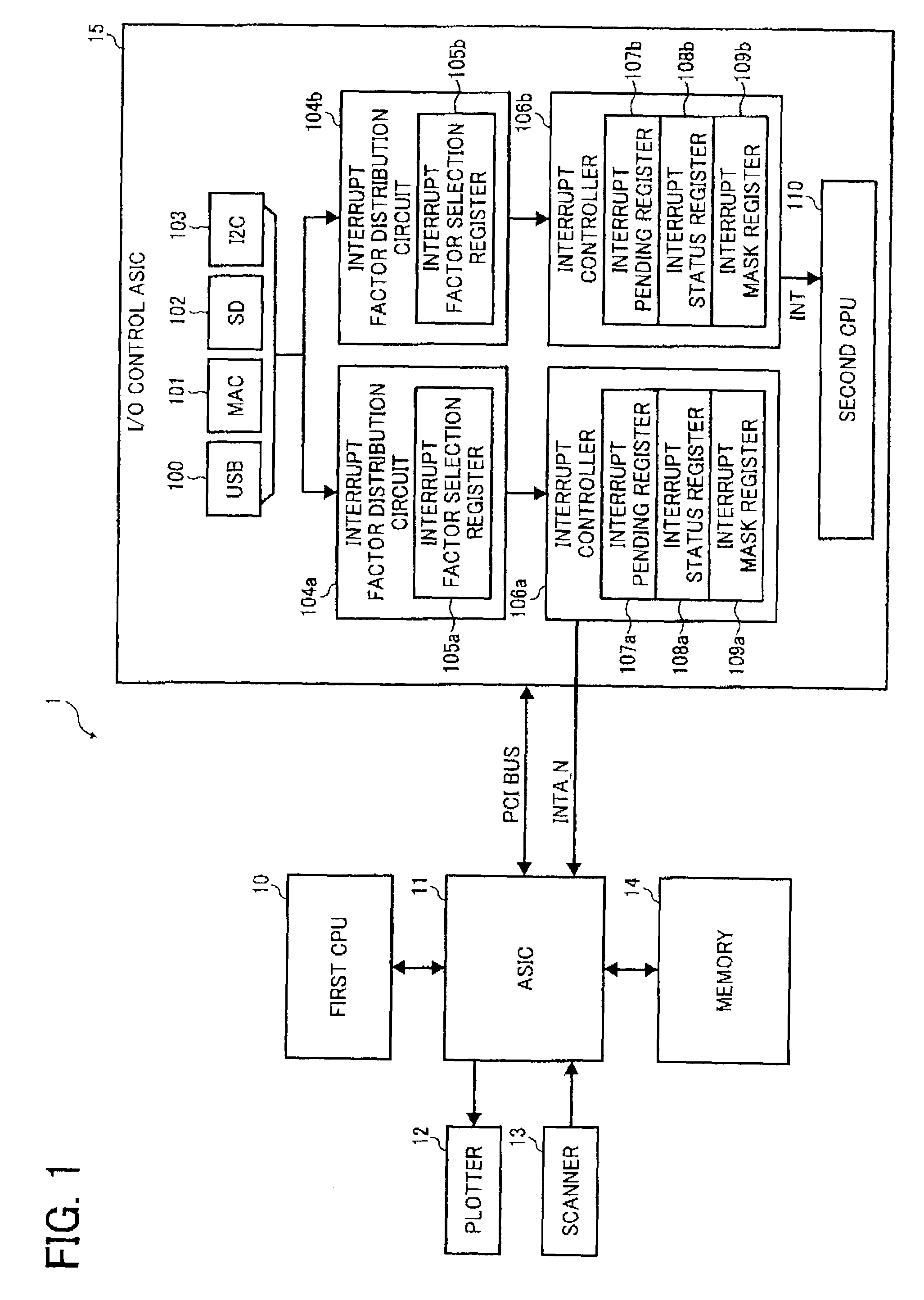

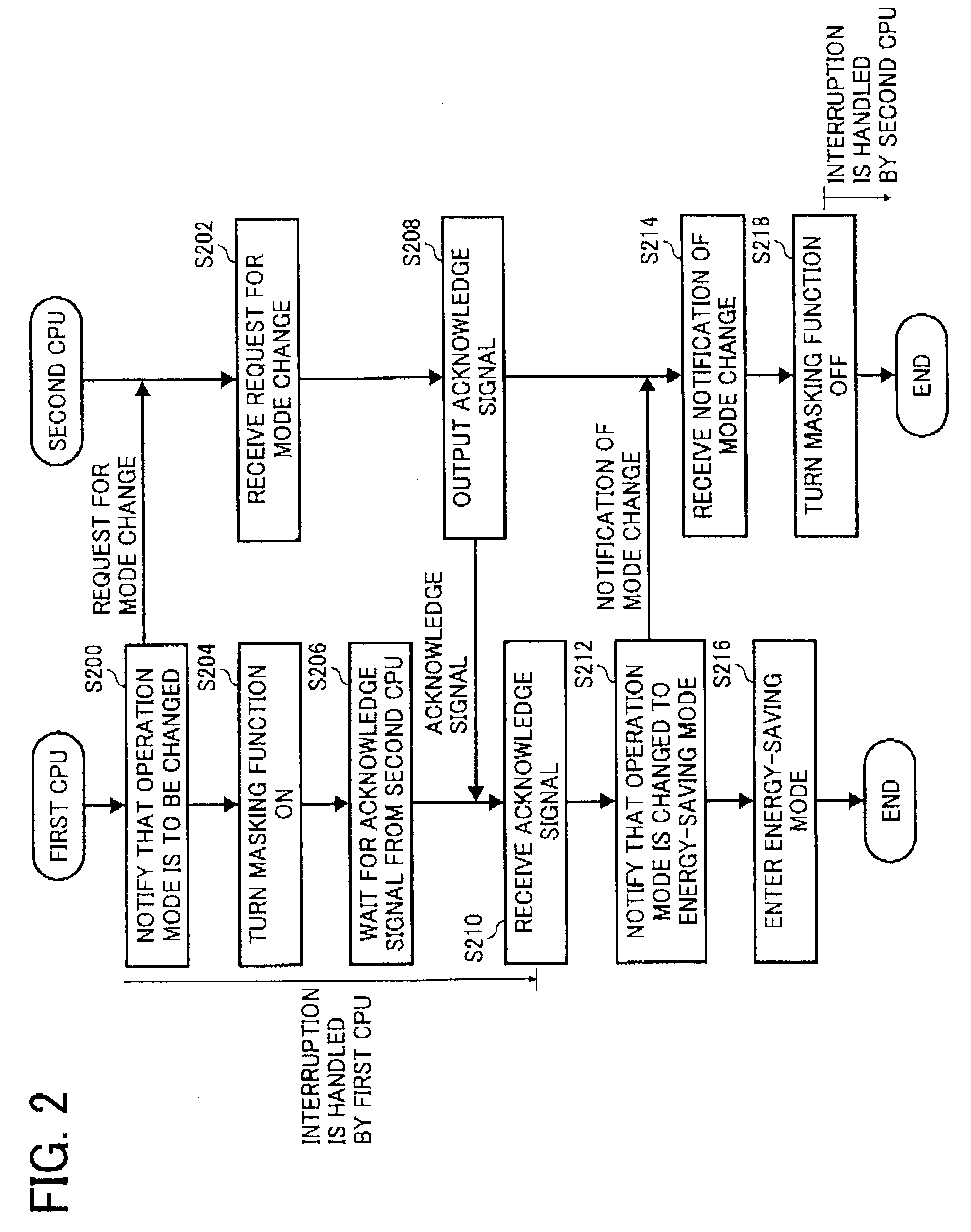

Image processing device, image processing method, and recording medium

ActiveUS20090240966A1Smoothly handling interruptPower supply for data processingImaging processingOperation mode

An image processing device including a first control unit to control a normal operating mode during which image processing is performed, a second control unit to control an energy-saving mode during which power consumption is lower than during the normal operating mode, an interrupt request receiver connected to an external device to receive an interrupt request from the external device, interrupt factor distributors to distribute the interrupt request received by the interrupt request receiver based on whether or not the interrupt request includes a predetermined interrupt factor, interrupt request notification units to notify the second control unit as well as the first control unit of the interrupt request in accordance with distribution results from the interrupt factor distributors, and job adjustors to control transfer of a job between the first control unit and the second control unit based on notification from the interrupt request notification units.

Owner:RICOH KK

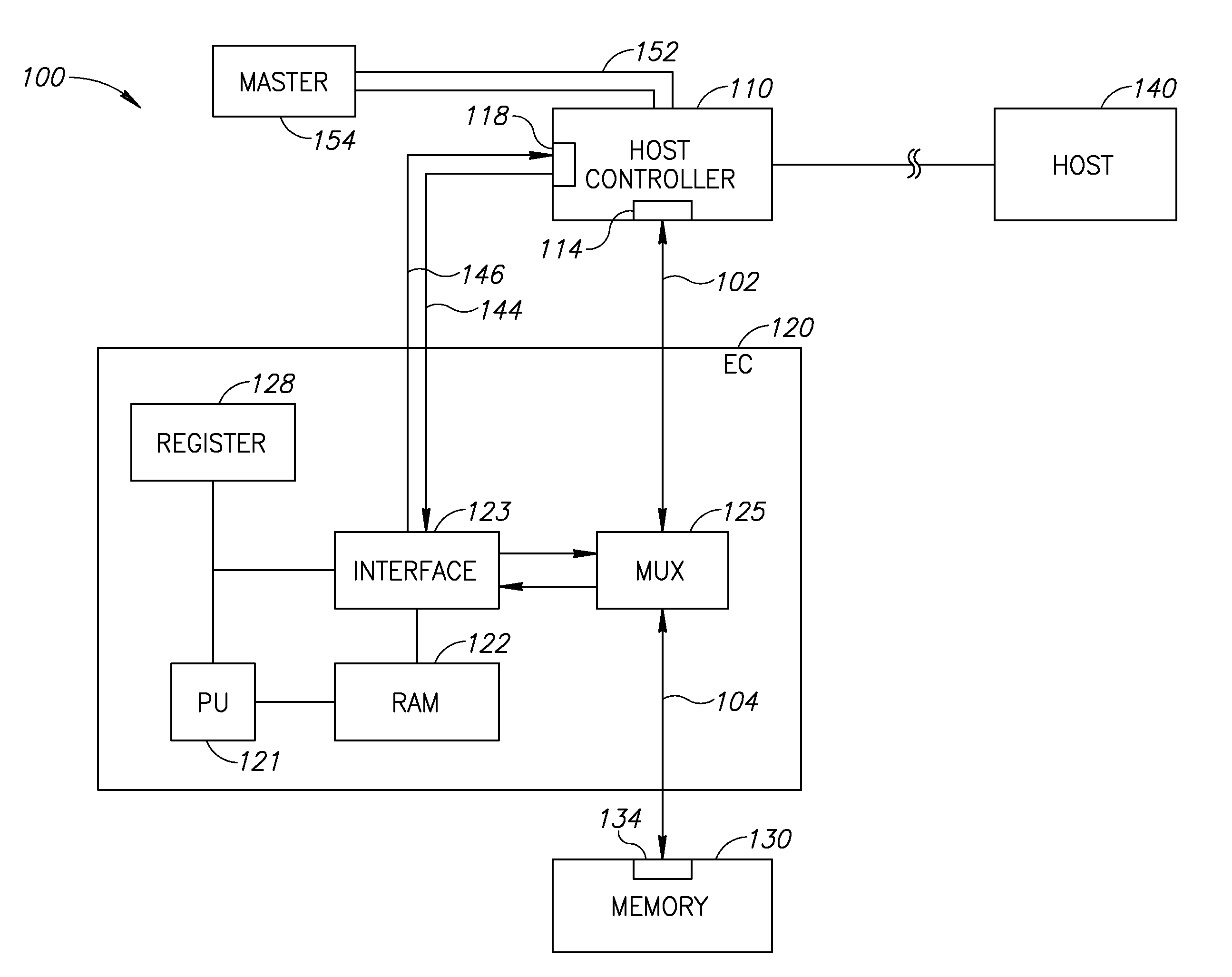

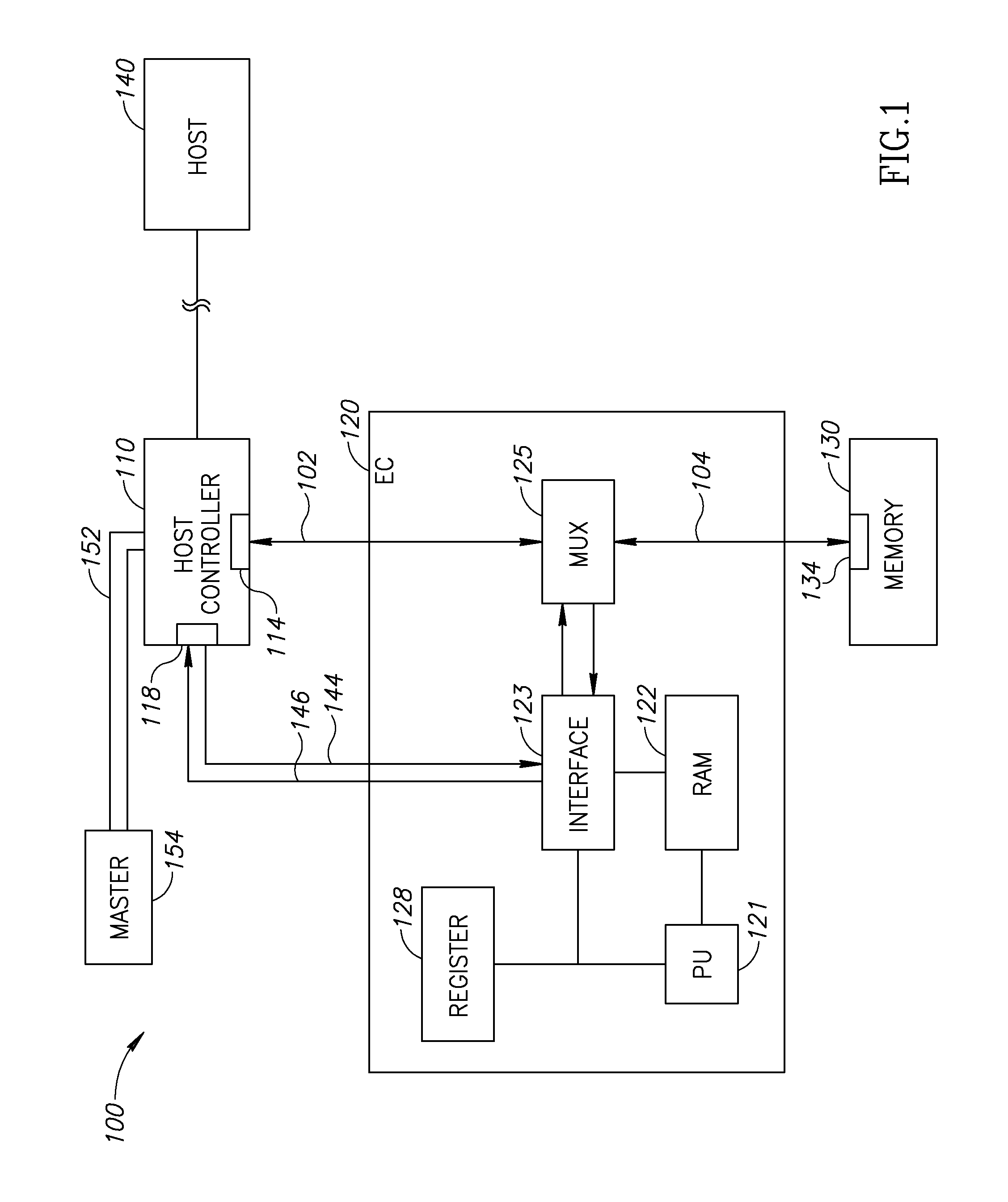

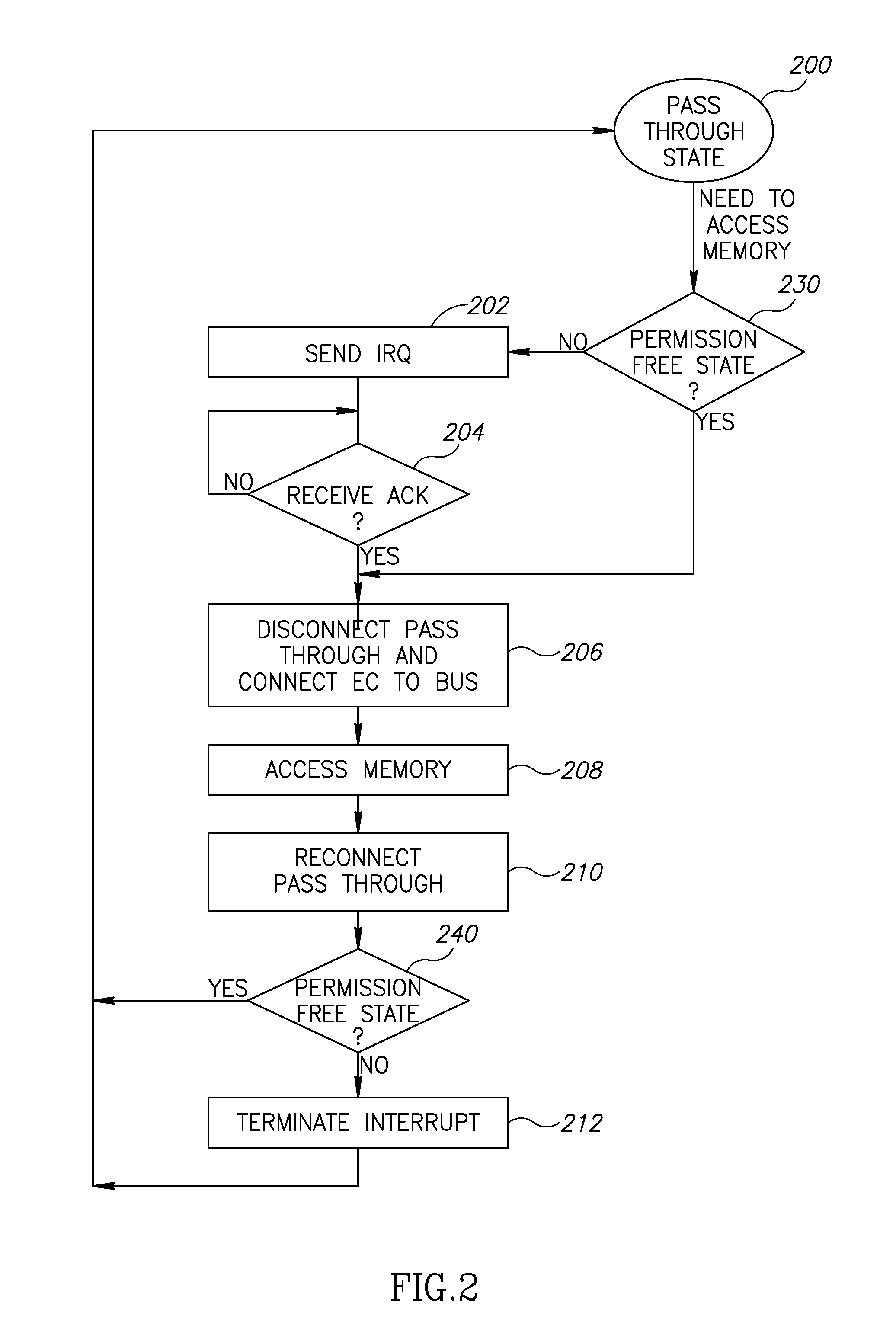

Handshake Free Sharing in a Computer Architecture

ActiveUS20090043916A1Input/output processes for data processingData conversionMemory interfaceOperating system

A system arrangement including a memory unit having a memory interface in accordance with a handshake-free protocol between the memory and an accessing master, a bus connected to the memory unit and first and second masters. The first master operative to access the memory unit through the bus and the memory interface and operative to perform interrupts following reception of an interrupt request through an interrupt interface. The second master operative to access the memory unit through the bus and memory interface. The second master being configured to transfer an interrupt request to the first processor before accessing the memory unit.

Owner:WINBOND ELECTRONICS CORP

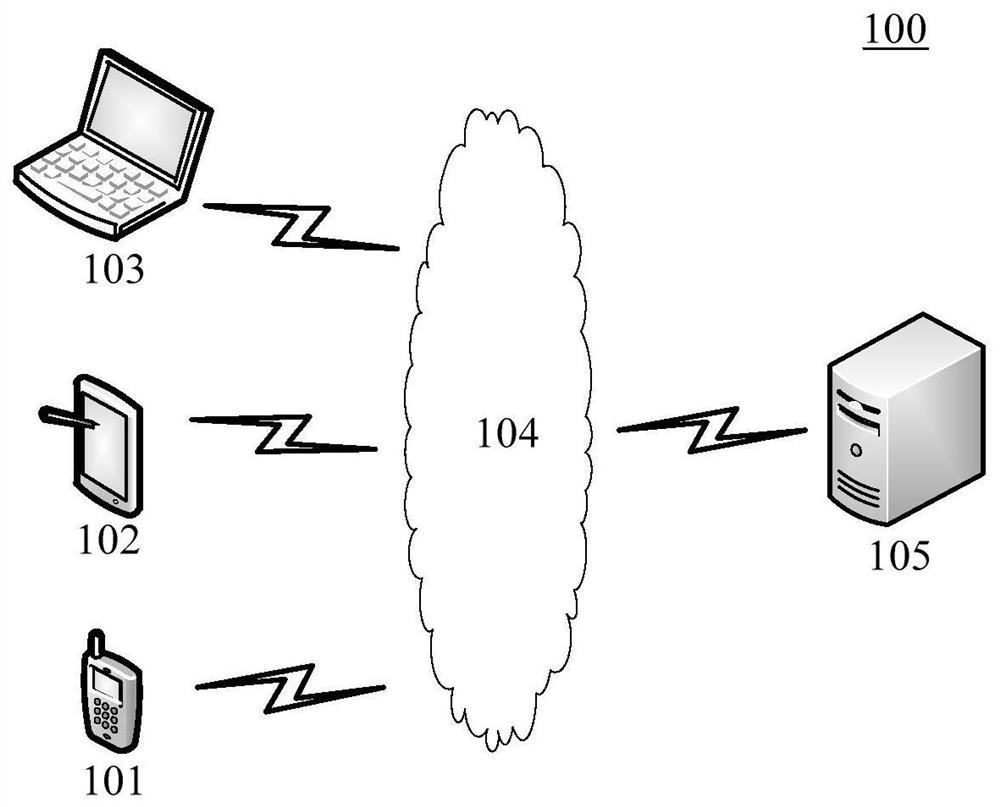

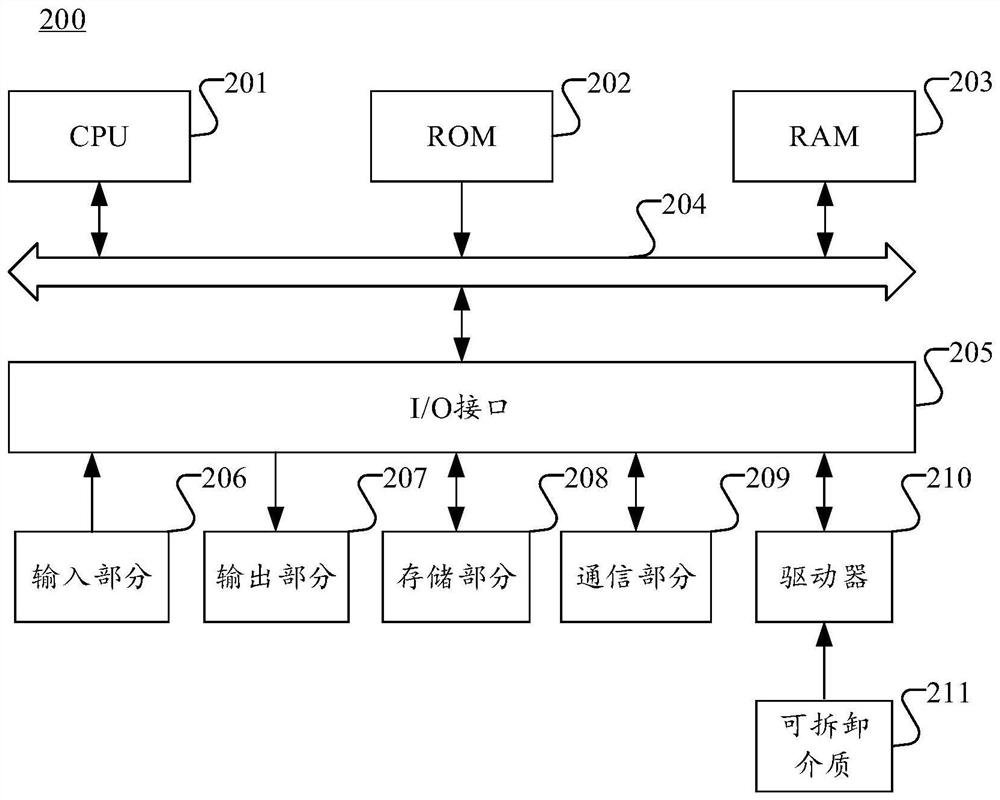

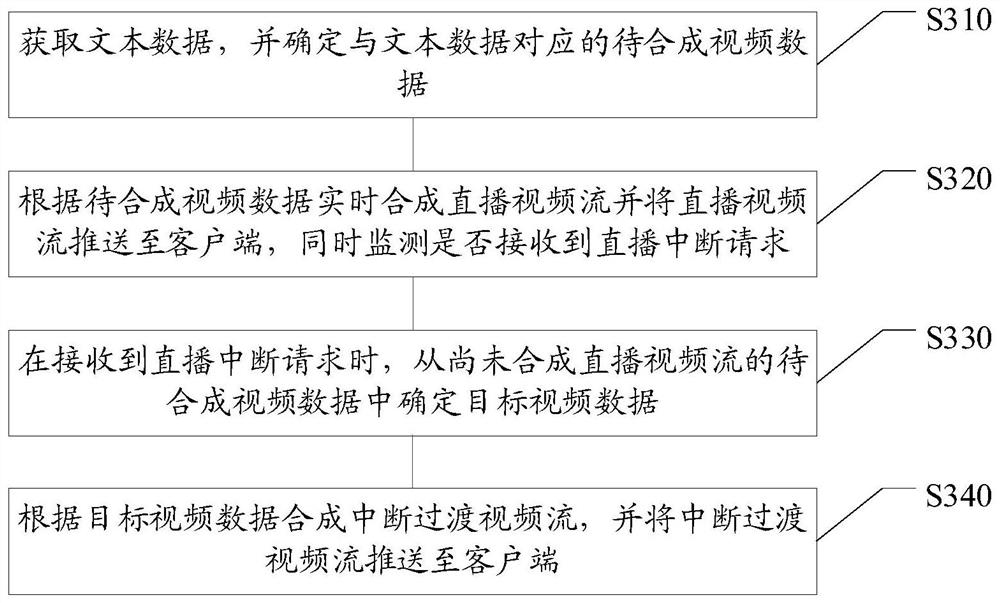

Virtual video live broadcast processing method and device, storage medium and electronic equipment

ActiveCN112543342AImprove smooth performanceAvoid CatonSelective content distributionSpeech synthesisEquipment computersLive video

The invention provides a virtual video live broadcast processing method and device, electronic equipment and a computer readable storage medium. The invention relates to the technical field of virtualvideo live broadcast. The virtual video live broadcast processing method comprises the steps of obtaining text data, and determining to-be-synthesized video data corresponding to the text data; synthesizing a live broadcast video stream in real time according to the to-be-synthesized video data, pushing the live broadcast video stream to the client, and monitoring whether a live broadcast interruption request is received or not; when a live broadcast interruption request is received, determining target video data from the to-be-synthesized video data of the live broadcast video stream which is not synthesized yet; and synthesizing an interrupt transition video stream according to the target video data, and pushing the interrupt transition video stream to the client. According to the method and the device, the smooth transition process of the current video action and the next video action can be realized without influencing the real-time performance of the live video under the condition that the live video is interrupted in the virtual video live broadcast process.

Owner:TENCENT TECH (SHENZHEN) CO LTD

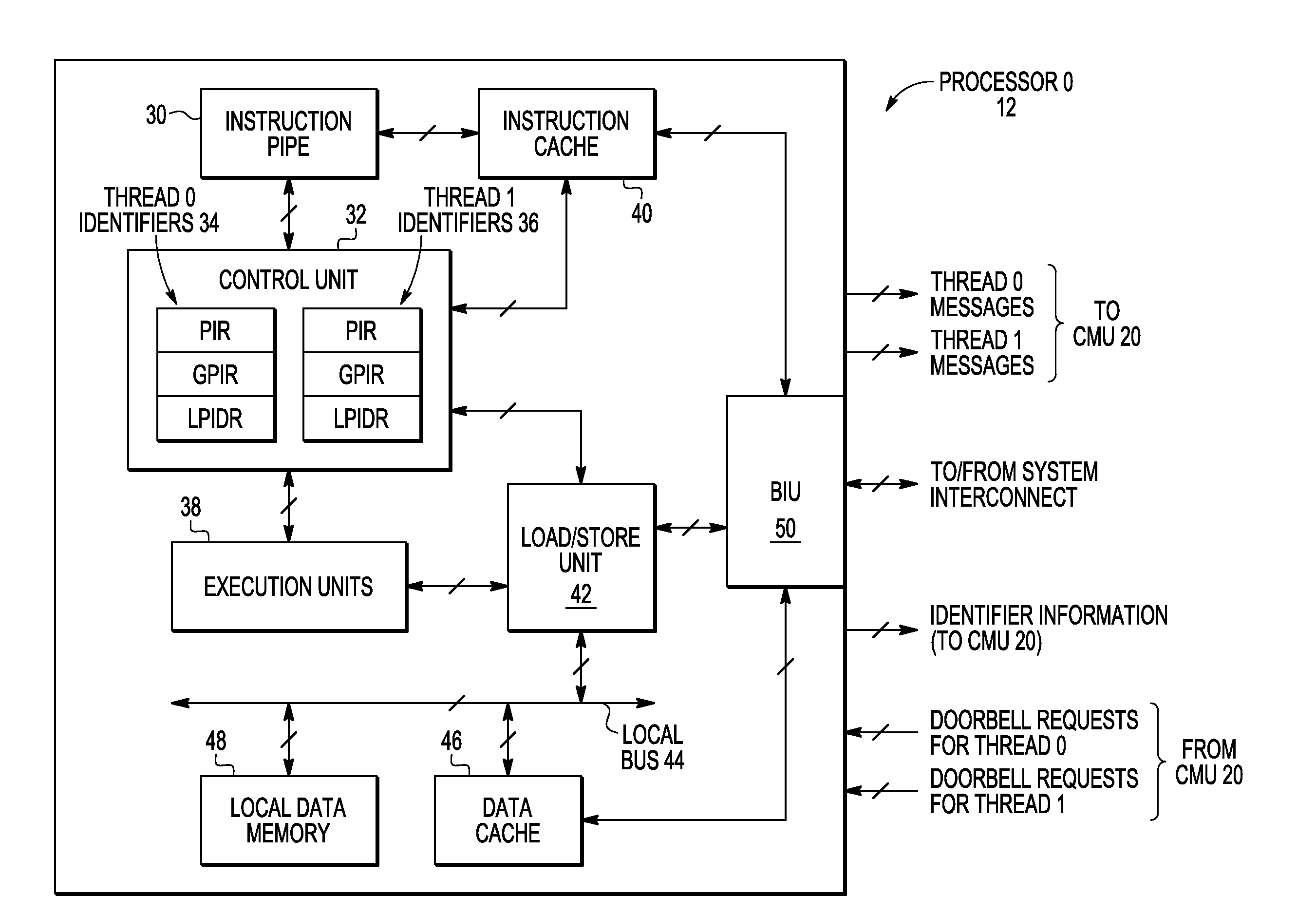

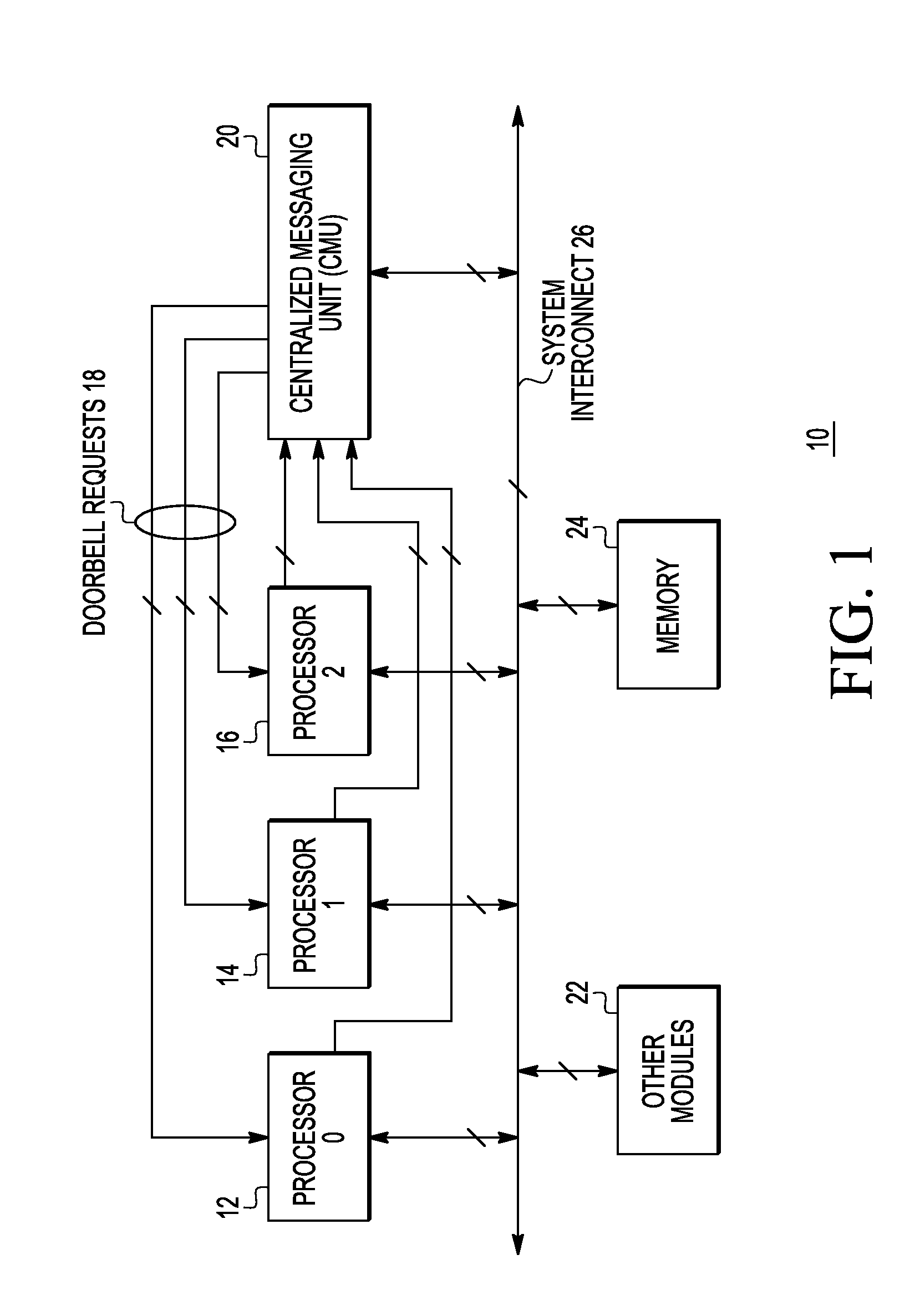

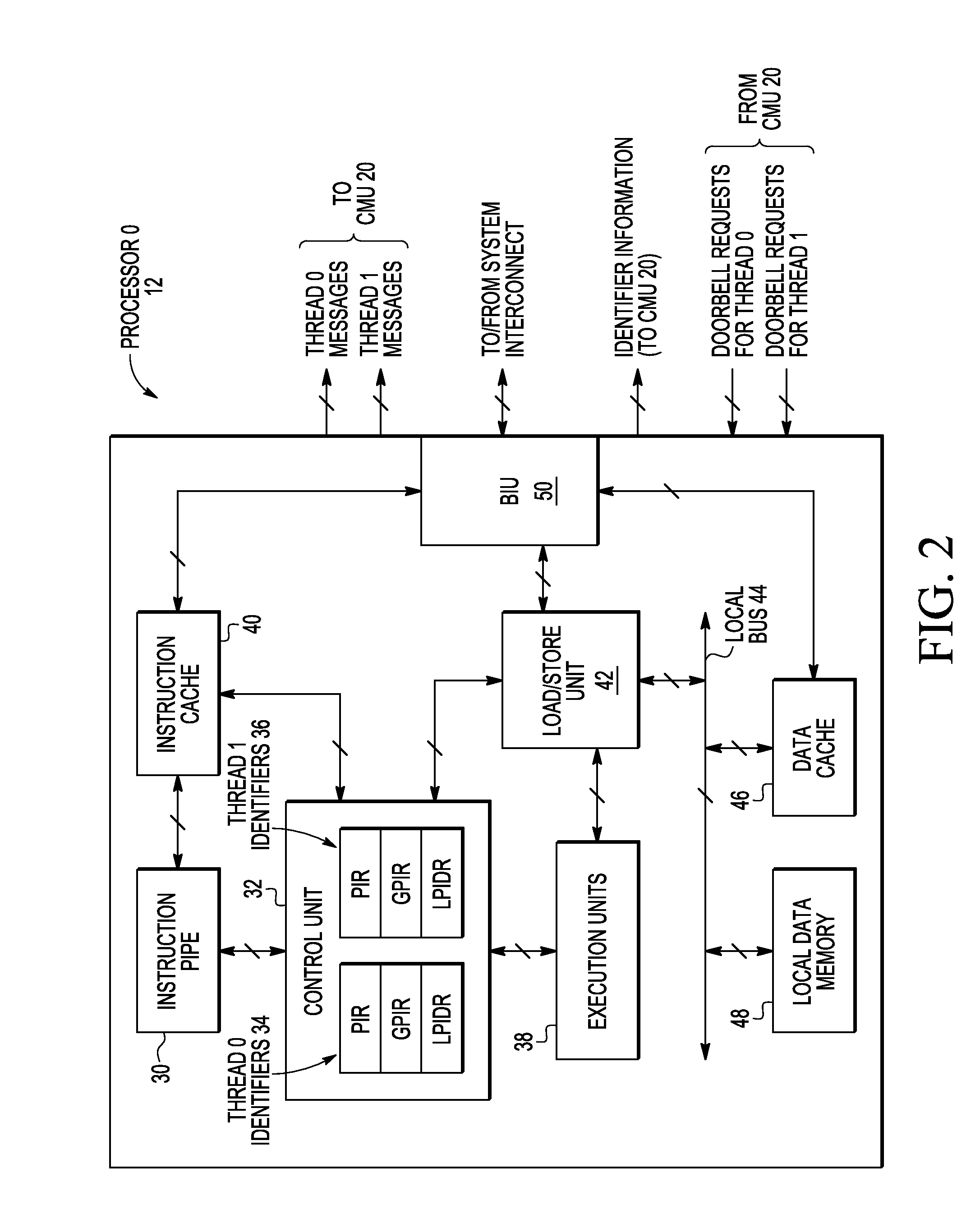

Message filtering in a data processing system

A data processing system includes a plurality of processors, each processor configured to execute instructions, including a message send instruction, and a message filtering unit. The message filtering system is configured to receive messages from one or more of the plurality of processors in response to execution of message send instructions, each message indicating a message type and a message payload. The message filtering unit is configured to determined, for each received message, a recipient processor indicated by the message payload. The message filtering system is further configured to, in response to receiving, within a predetermined interval of time, at least two messages having a same recipient processor and indicating a same message type, delivering a single interrupt request indicated by the same message type to the same recipient processor, wherein the single interrupt request is representative of the at least two messages.

Owner:NXP USA INC

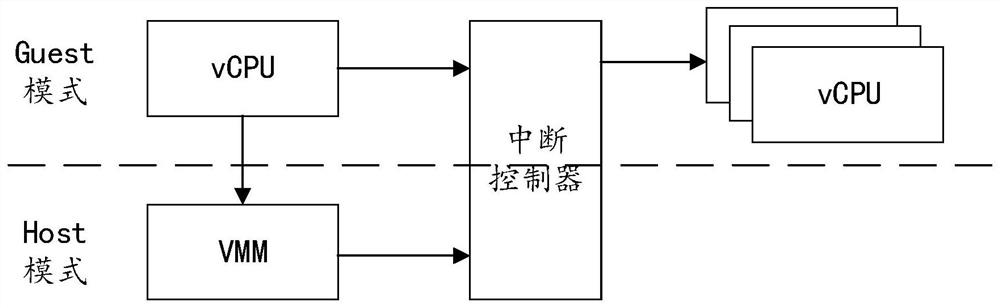

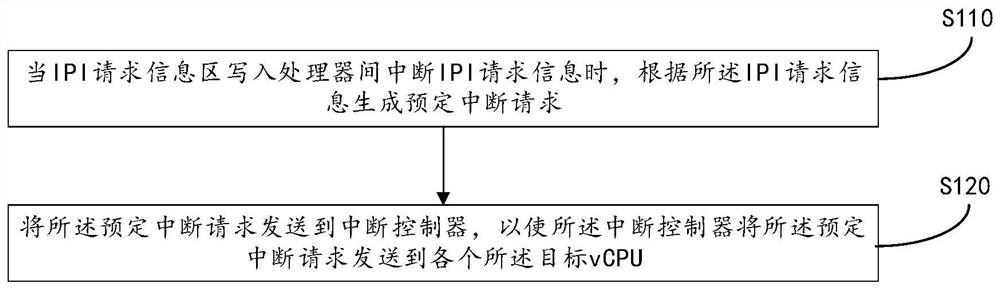

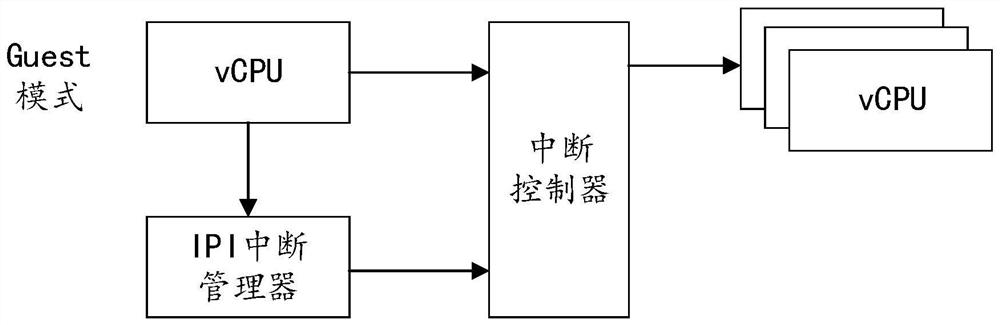

Interrupt processing method, interrupt manager, electronic equipment and computer readable medium

PendingCN112783600AImprove operational efficiencyReduce performance lossSoftware simulation/interpretation/emulationSoftware engineeringPhysical address

The invention provides an interrupt processing method. The method comprises the steps: when IPI request information is written into an IPI request information area among processors, generating a predetermined interrupt request according to the IPI request information, wherein the IPI request information carries an identifier of at least one target virtual central processing unit vCPU, the storage space of a current IPI interrupt manager comprises at least one IPI request information area, the IPI request information area corresponds to a virtual machine, and the physical address of the IPI request information area is mapped to the corresponding virtual machine through memory mapping input and output (MMIO); and sending the predetermined interrupt request to an interrupt controller, and enabling the interrupt controller to send the predetermined interrupt request to each target vCPU. The invention further provides the interrupt processing method, the IPI interrupt manager, electronic equipment and a computer readable medium.

Owner:ZTE CORP

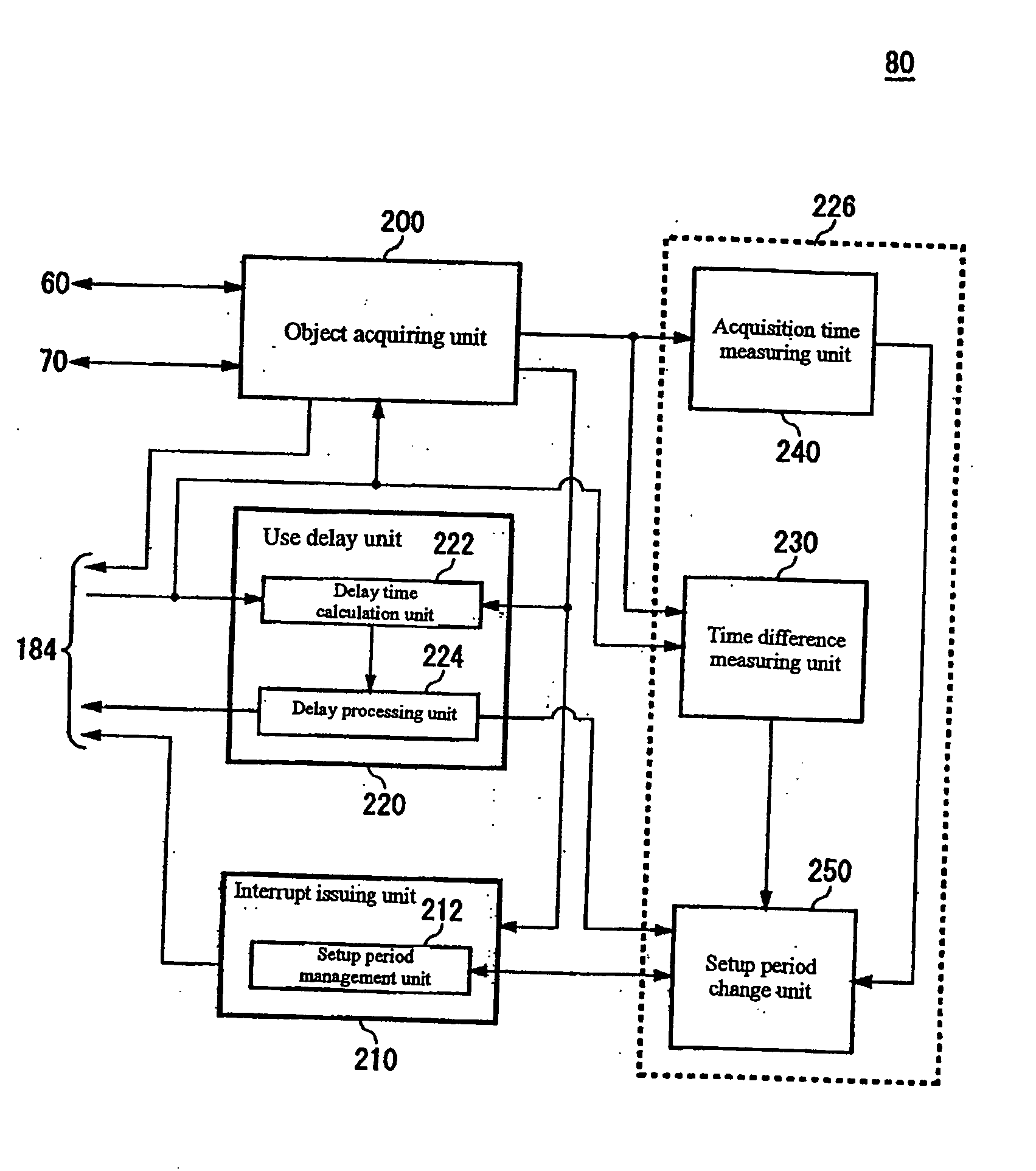

Method for data protection for removable recording medium

ActiveUS20040225789A1Delay minimizationProgram initiation/switchingInput/output processes for data processingProcessing elementRecord

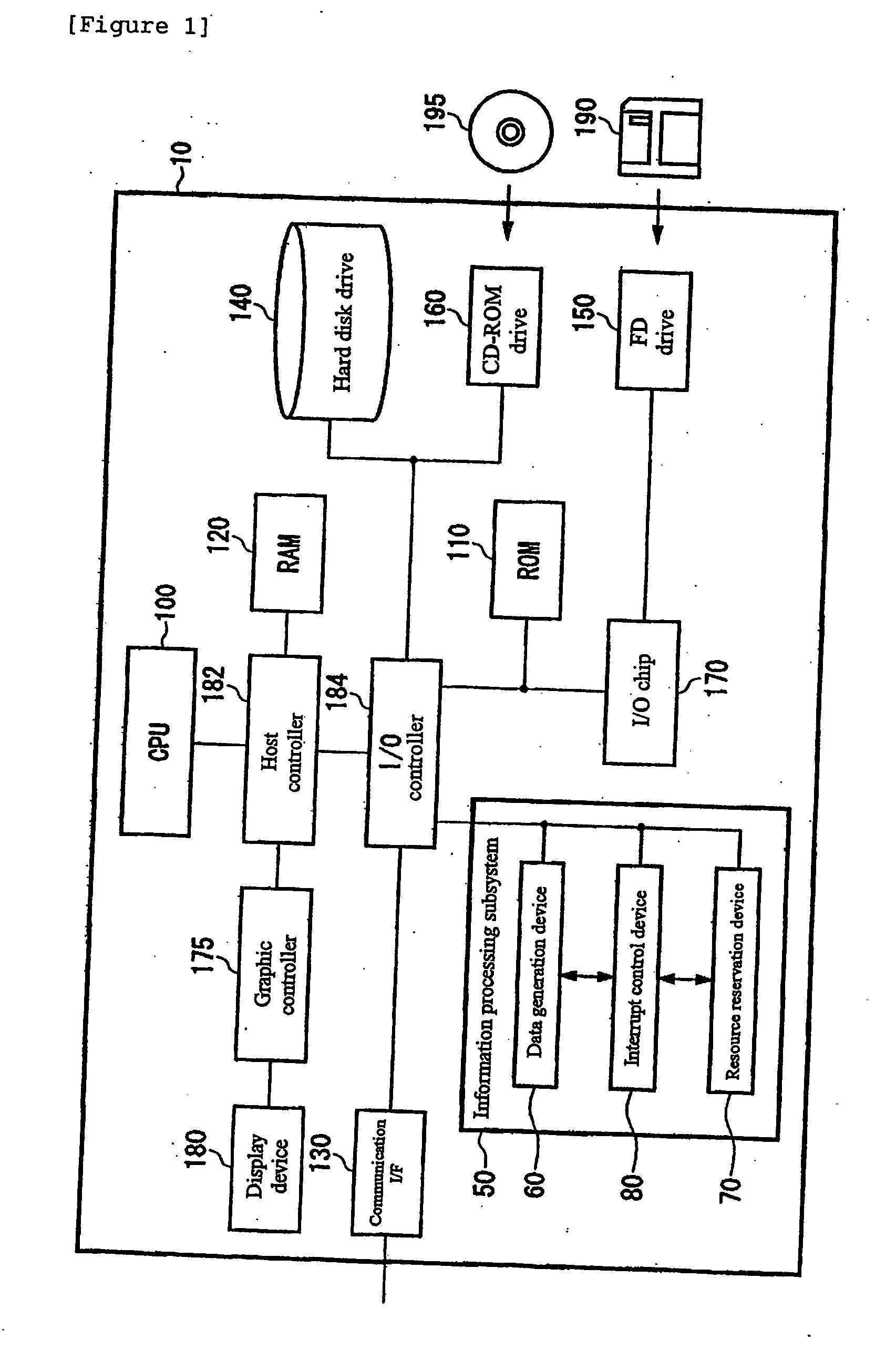

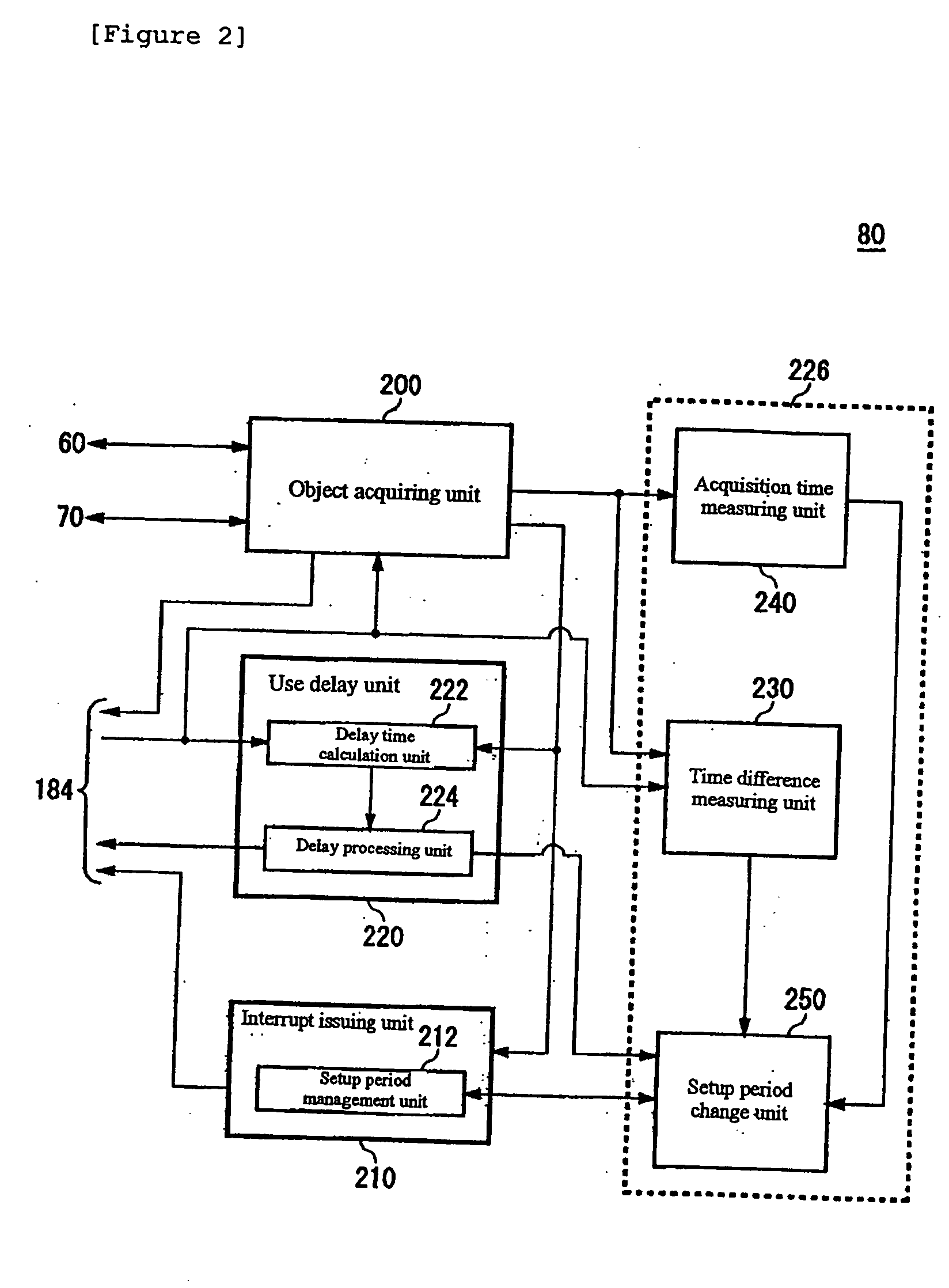

An interrupt control device for issuing interrupts to a central processing unit (CPU) includes an object acquiring unit for acquiring data or resource(s) for use by the CPU and an interrupt issuing unit for issuing interrupts to the CPU. The interrupt issuing unit issues each interrupt to the CPU before the object acquiring unit actually acquires the data or the resource, but the interrupt indicates that the data or the resource is available. The interrupt control device further includes a use delay unit for delaying the use of the data or resource by the CPU unit until the object acquiring unit acquires the data or the resource if the CPU which has received the interrupt requests the use of the data or the resource before the object acquiring unit acquires the data or the resource. By adjusting the exact timing of the issuance of the interrupt according to the actual delays experienced by the CPU, the overall delays associated with interrupt handling are minimized.

Owner:PULSE LINK INC +1

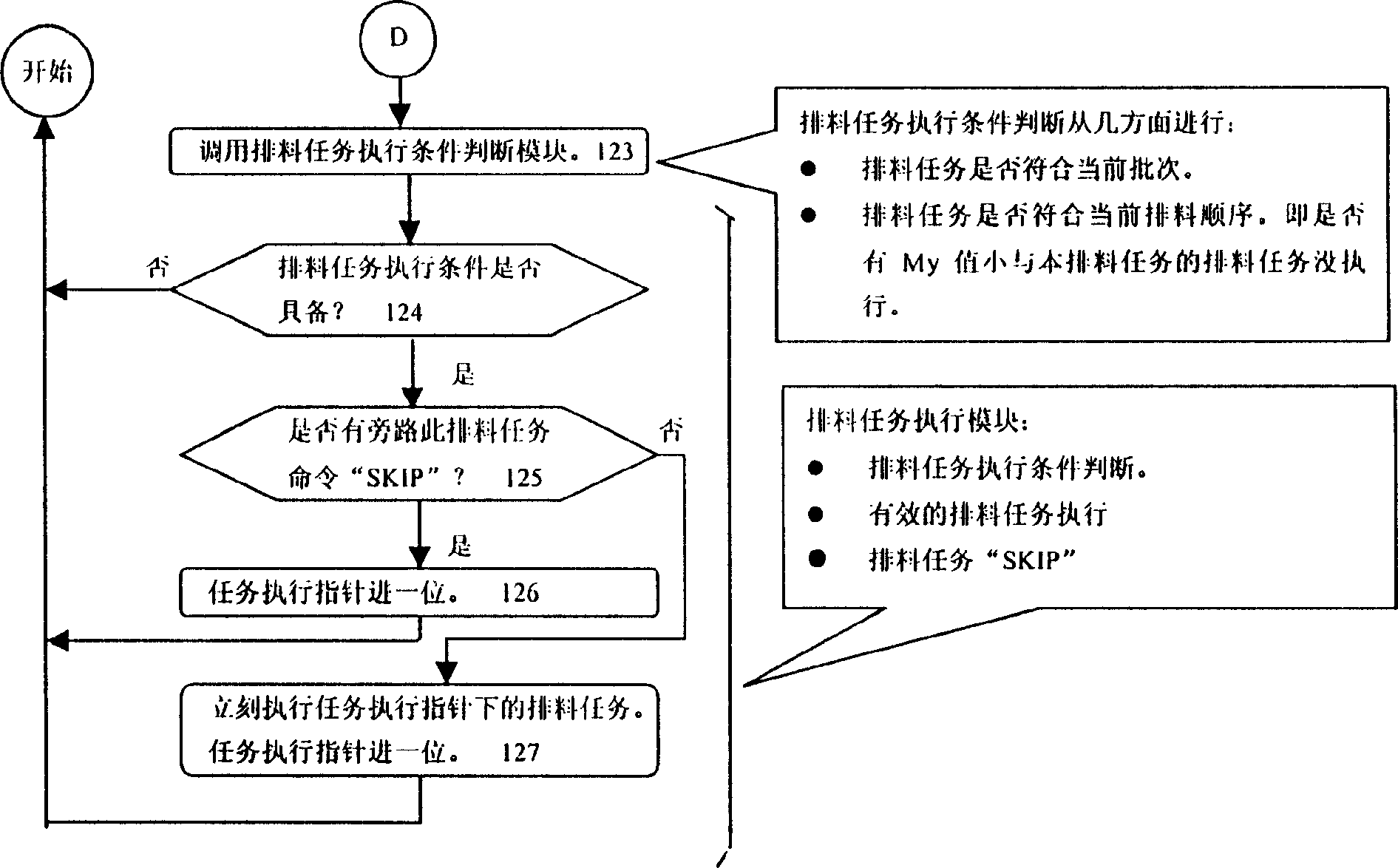

Control method based on task queue

ActiveCN1673917ASolve the lack of spaceCompiled language enoughDigital computer detailsTotal factory controlControl systemModularity

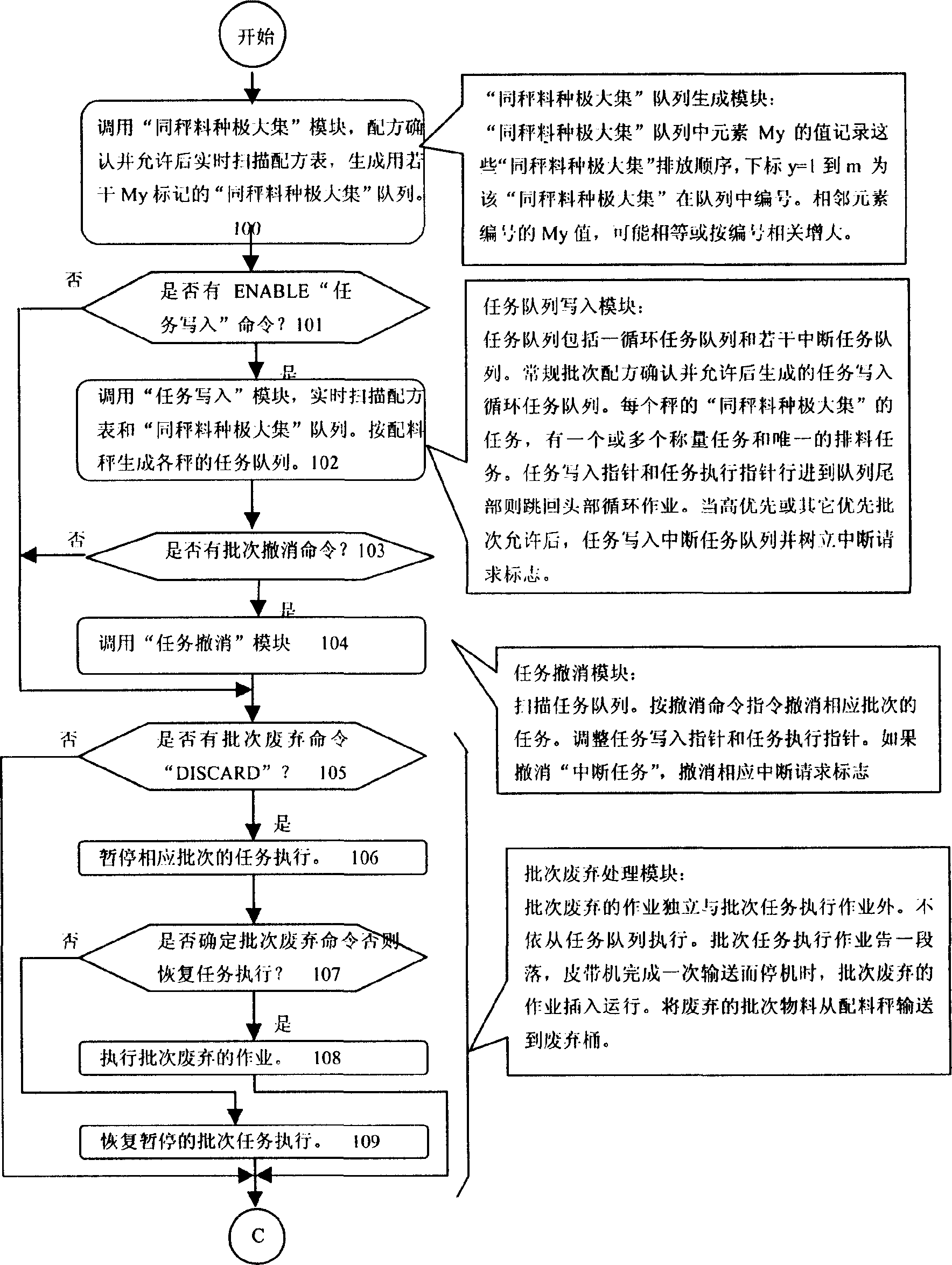

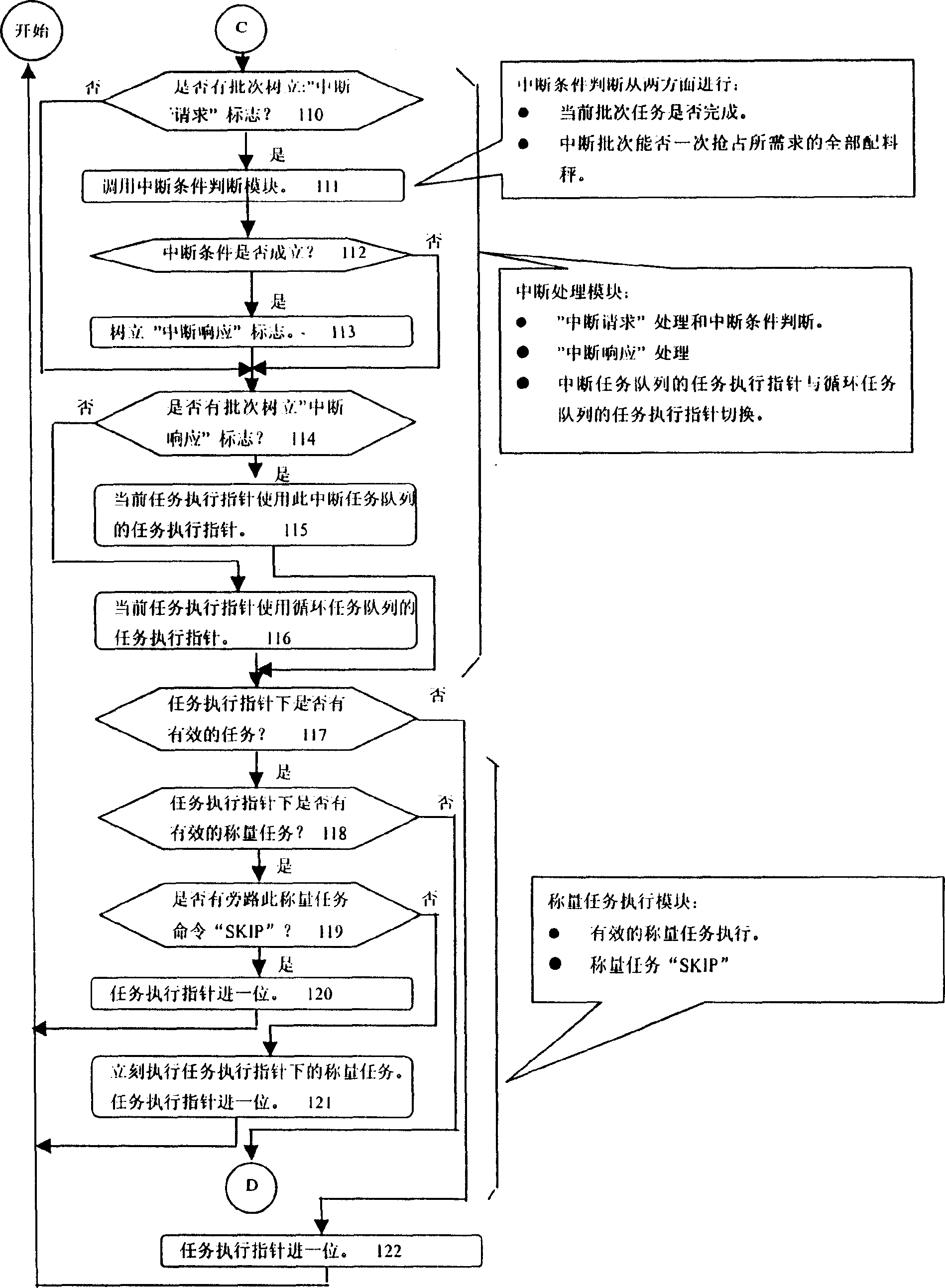

The control process based on task queue includes the following steps: the step of creating 'maximum same-weighing unit material variety set' queue including confirming recipe and scanning recipe list to create several My labeled 'maximum same-weighing unit material variety set'; the step of writing in task queue to establish for each material compounding weighing unit one circulating task queue and several interruption task queues controlled with separate task writing in pointer and task executing pointer; the step of interruption processing to write the task to the interruption task queue and create interruption request label; and the step of processing task to write different kinds of task to the queue. The present invention simplifies complicated technological process via writing task queue and control system configuration.

Owner:SHANGHAI BAOSIGHT SOFTWARE CO LTD

System, method and computer program product for providing a programmable quiesce filtering register

InactiveUS20120144154A1Memory adressing/allocation/relocationMicro-instruction address formationTranslation lookaside bufferMode switch

Storing translation lookaside buffer (TLB) entries are in a TLB1 at the processor. The TLB1 includes entries associated with main storage accesses of programs executing in a guest mode in a current zone and entries associated with main storage accesses of firmware executing in a host mode. A quiesce interruption request is received at the processor that includes a requesting zone indicator. The processor is either executing in the host mode and has no zone or in the guest mode with the current zone. The requesting zone indicator and the contents of a programmable filtering register that indicates exceptions to filtering performed by the processor is used to determine if filtering should be performed. The quiesce interruption request may be filtered based on the requesting zone indicator even after the mode switches from the guest mode to the host mode.

Owner:INT BUSINESS MASCH CORP

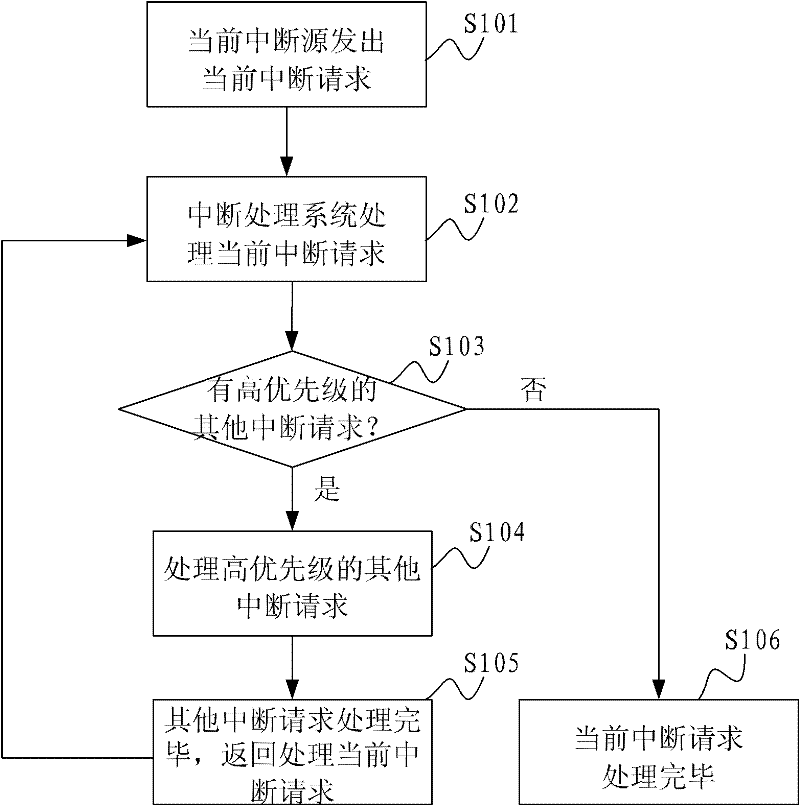

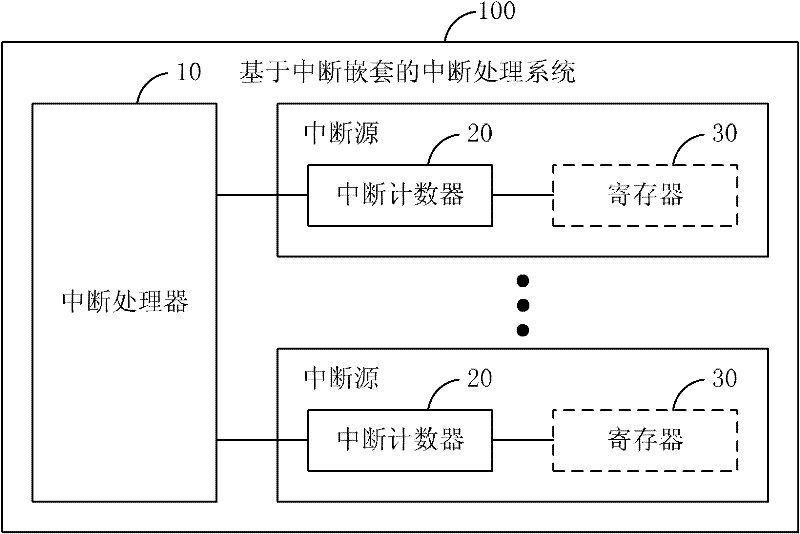

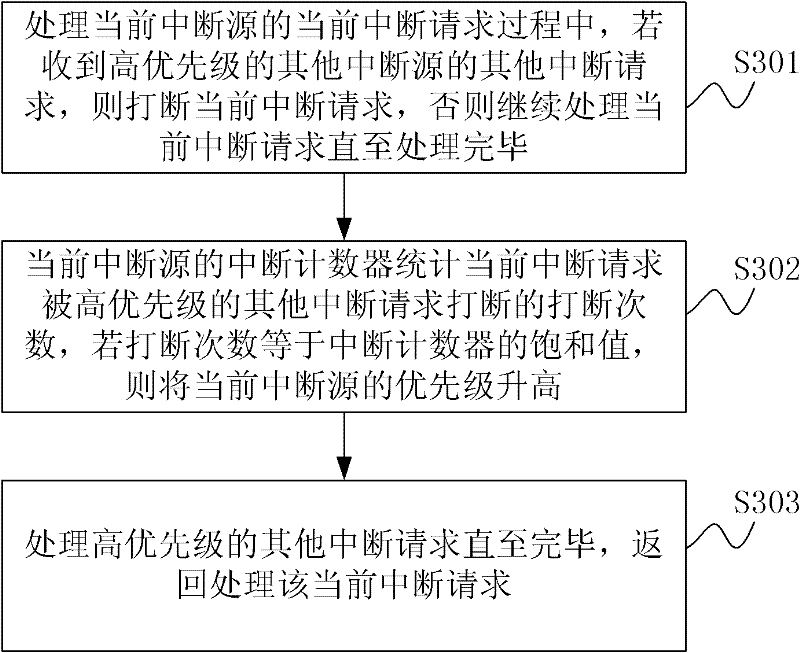

Interrupt processing method and system based on interrupt nesting

InactiveCN102262566AImprove interrupt handling efficiencyRaise priorityProgram initiation/switchingEmbedded systemLower priority

The invention discloses an interrupt processing method and system based on interrupt nesting. Interrupt sources of various priorities are respectively provided with interrupt counters, and each of the interrupt counters is provided with a saturation value. The interrupt processing method includes: processing the current interrupt During the current interrupt request process of the source, if other interrupt requests from other high-priority interrupt sources are received, the current interrupt request will be interrupted, otherwise the current interrupt request will continue to be processed until the processing is completed; The interrupt counter counts the number of times the current interrupt request is interrupted by the other high-priority interrupt requests, and if the number of interruptions is equal to the saturation value of the interrupt counter, the current interrupt source The priority is increased; the other interrupt requests with high priority are processed until the end, and the current interrupt request is returned to be processed. Thereby, the present invention solves the problem that the low-priority interrupt request cannot be processed for a long time, and improves the interrupt processing efficiency.

Owner:RAMAXEL TECH SHENZHEN

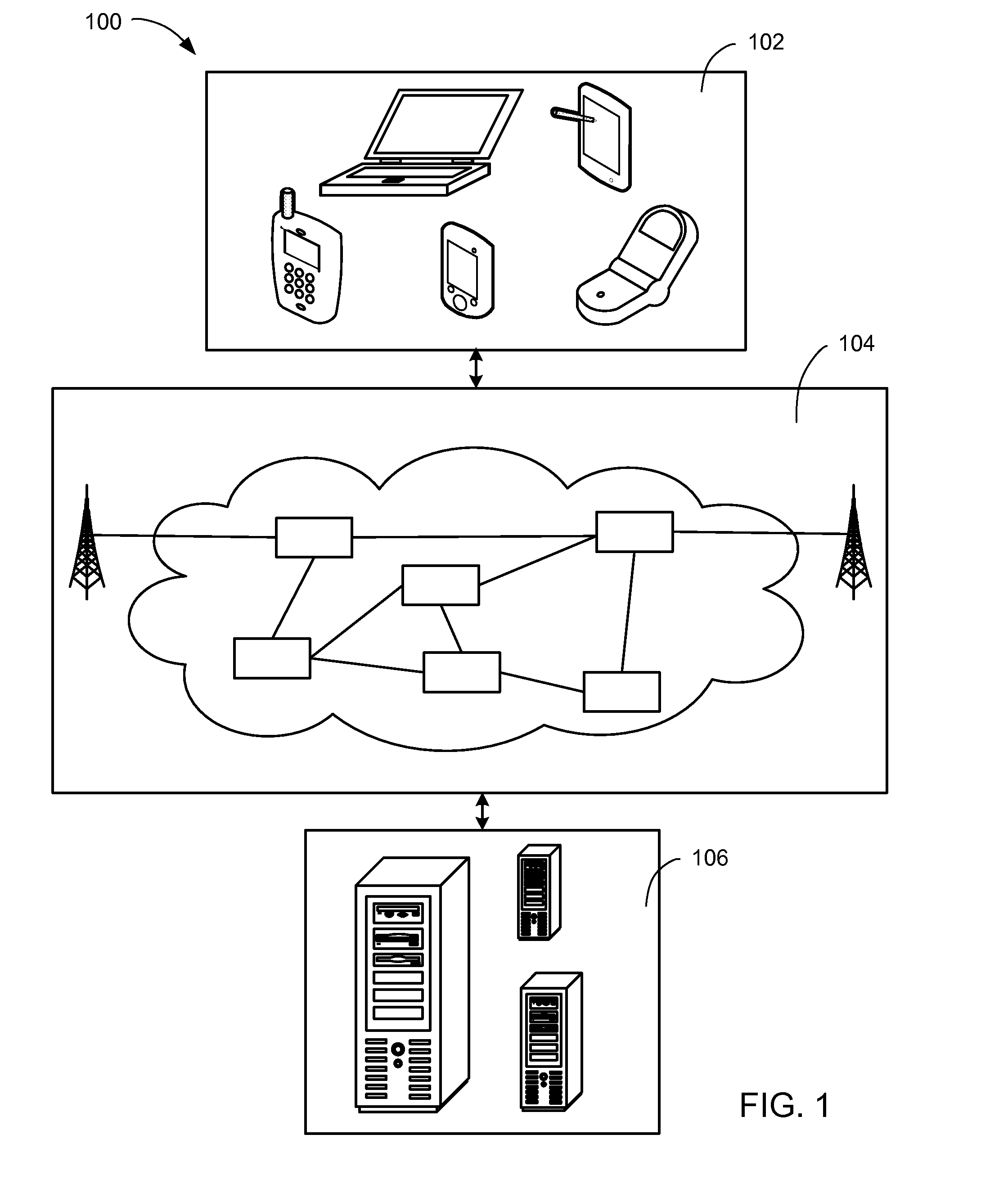

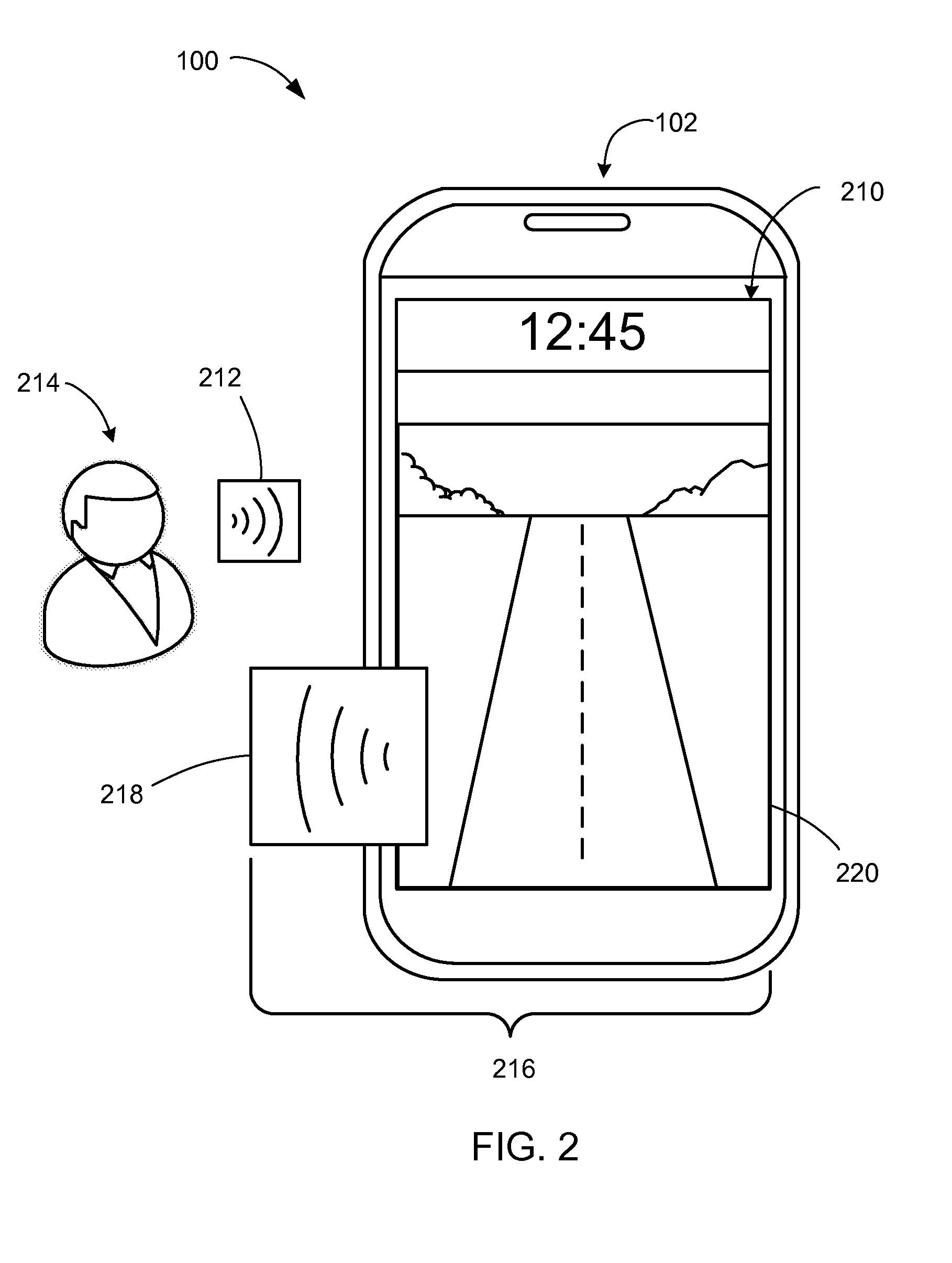

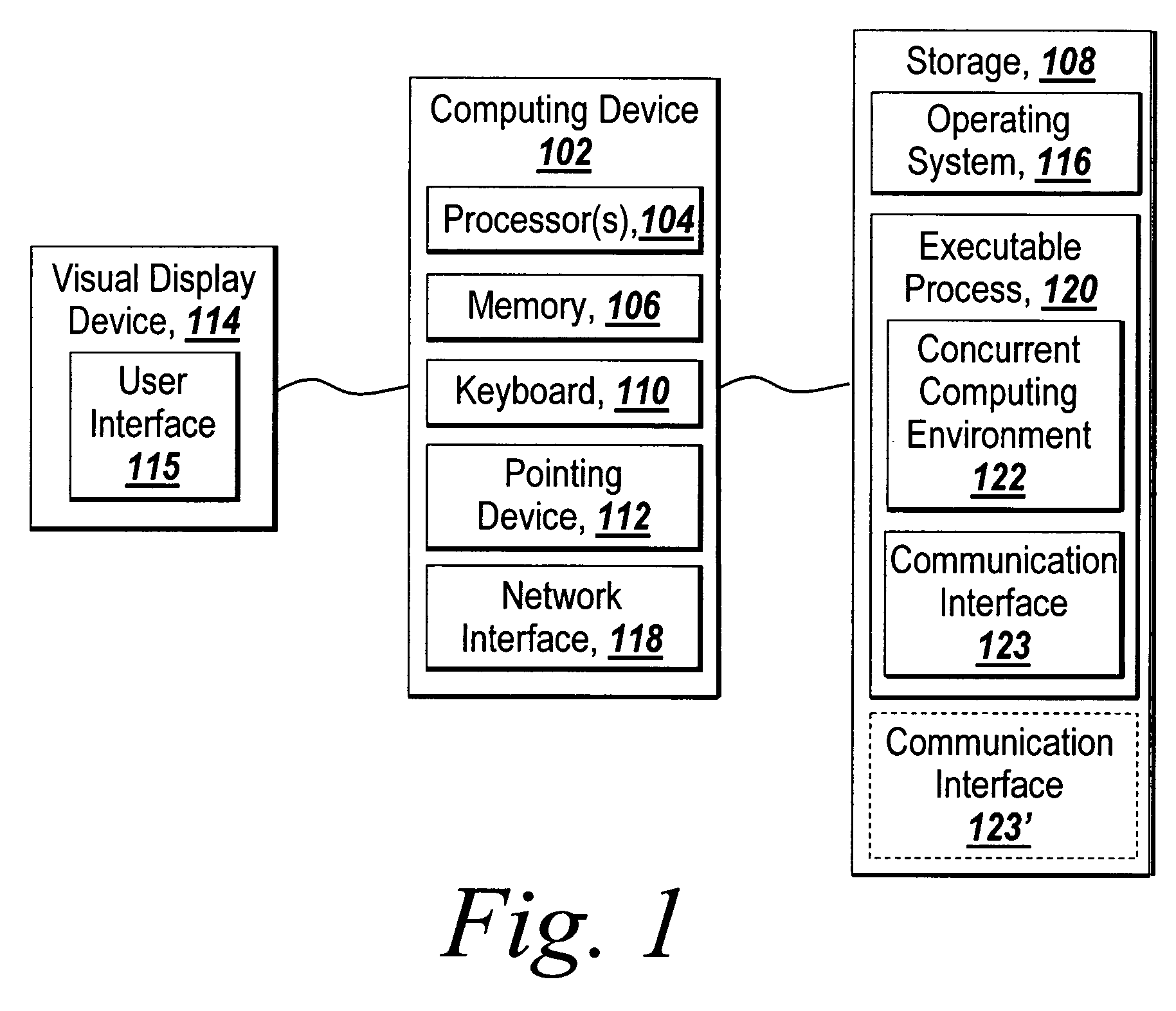

Computing system with multimodal interaction mechanism and method of operation thereof

ActiveUS20140195700A1Program controlInput/output processes for data processingMultimodal interactionComputing systems

A method of operation of a computing system includes: receiving a interrupt request for an interrupt task request; determining a request intent, with a control unit, from the interrupt request; generating a system notification for the interrupt task request based on the request intent; and determining a presentation order of the system notification relative to an existing system notification based on a notification priority associated with the interrupt task request.

Owner:TELENAV

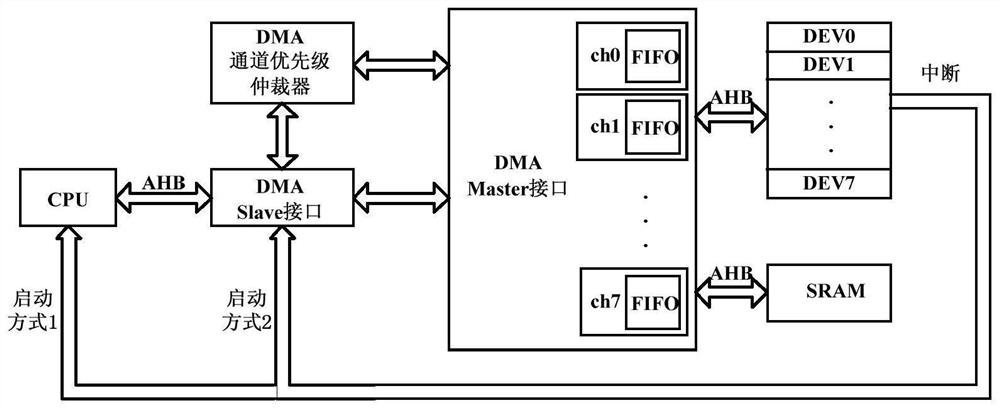

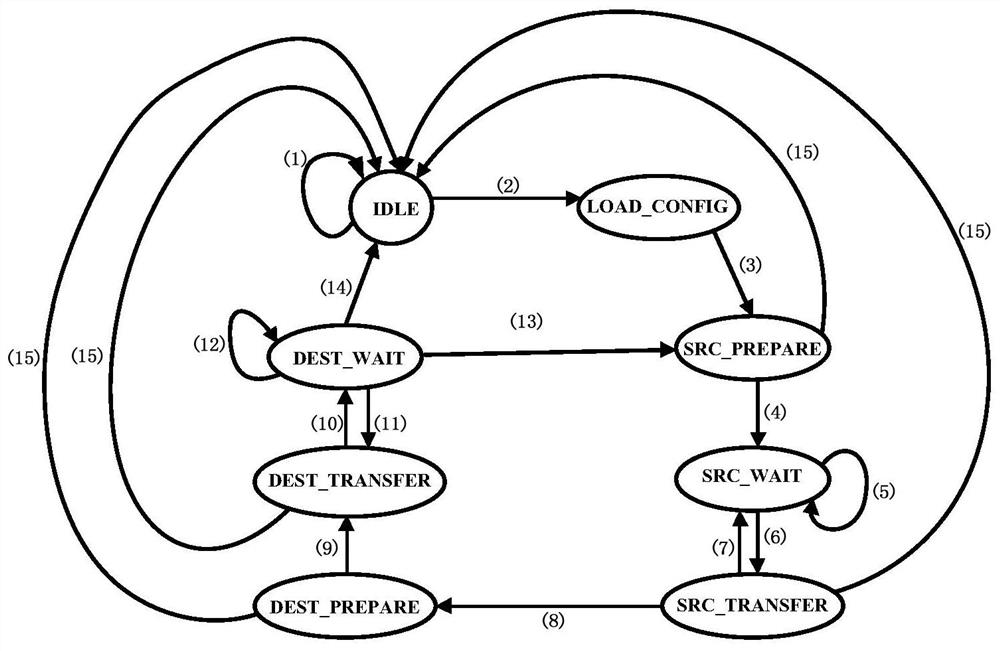

Multi-mode DMA data transmission system

ActiveCN113468084AFlexible and efficient data transfer allocation channelsImprove transmission efficiencyElectric digital data processingEnergy efficient computingControl dataData transmission systems

The invention discloses a multi-mode DMA data transmission system. The peripheral sends interruption request DMA transmission to the microprocessor or directly sends interruption to the DMA controller to request transmission; according to the two modes, channels of the DMA controller are divided into hardware handshake starting channels and software request starting channels; the channel allocation efficiency is improved in a pre-configuration and flexible replacement mode; a DMA channel FIFO threshold register is configured, an FIFO threshold of a working channel is pre-configured according to application requirements, threshold full interruption of the channel FIFO is obtained, and the data transmission rhythm is flexibly controlled; in order to improve the working efficiency of the system, a channel arbitration mode is provided, and a group of current state temporary storage registers and load_agin marks are used for setting a waiting stack, so that the transmission of a high-priority channel can be carried out without waiting for the completion of the transmission of the current channel.

Owner:BEIJING MXTRONICS CORP +1

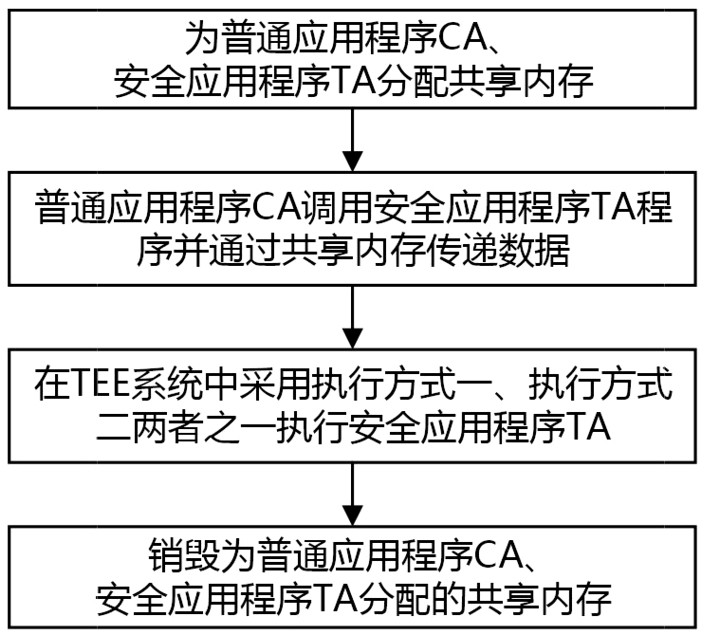

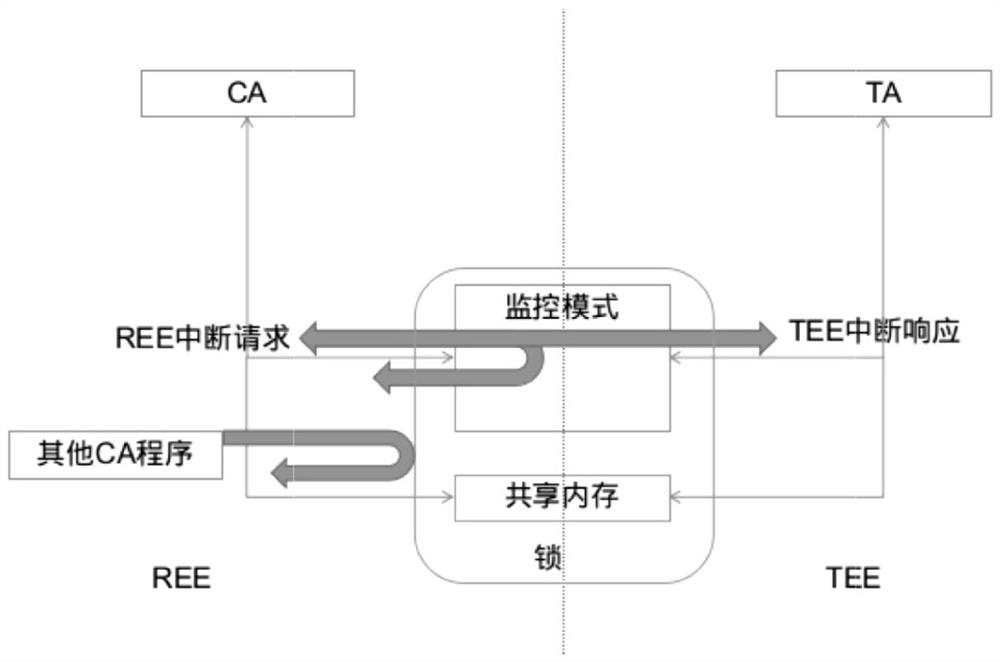

Communication optimization method and system on computing platform with TEE extension

PendingCN111859395AMeet needsSolve \"starve to death\"Interprogram communicationPlatform integrity maintainanceCommunications securityComputer architecture

The invention discloses a communication optimization method and system on a computing platform with TEE extension. The communication optimization method comprises the following steps: allocating a shared memory to a common application program CA and a secure application program TA; enabling the common application program CA to call the security application program TA and transmit data through theshared memory; executing the security application program TA in one of an execution mode I and an execution mode II in the TEE system; and destroying the shared memory allocated to the common application program CA and the security application program TA. An execution mode I and an execution mode II provide two TEE calling interfaces; the REE interrupt request is shielded or not shielded through selection; the two switching modes are achieved, various functions of the trusted execution environment can be met, according to actual needs, in the program execution process, the communication efficiency is comprehensively considered and improved, the communication safety and diversified communication requirements are met, and the problems of starvation of REE application programs, unreasonable shared memory allocation and the like are further solved.

Owner:NAT UNIV OF DEFENSE TECH

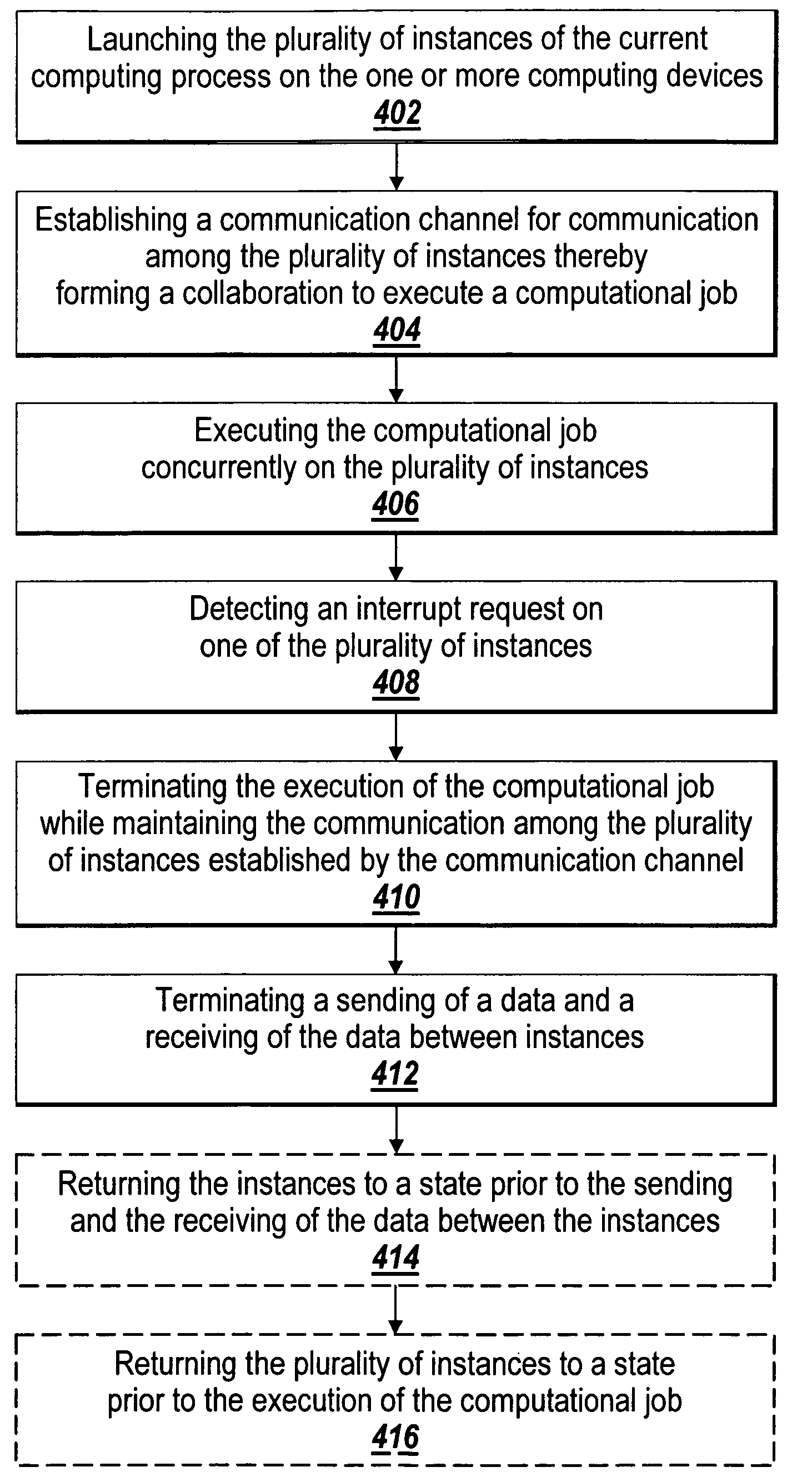

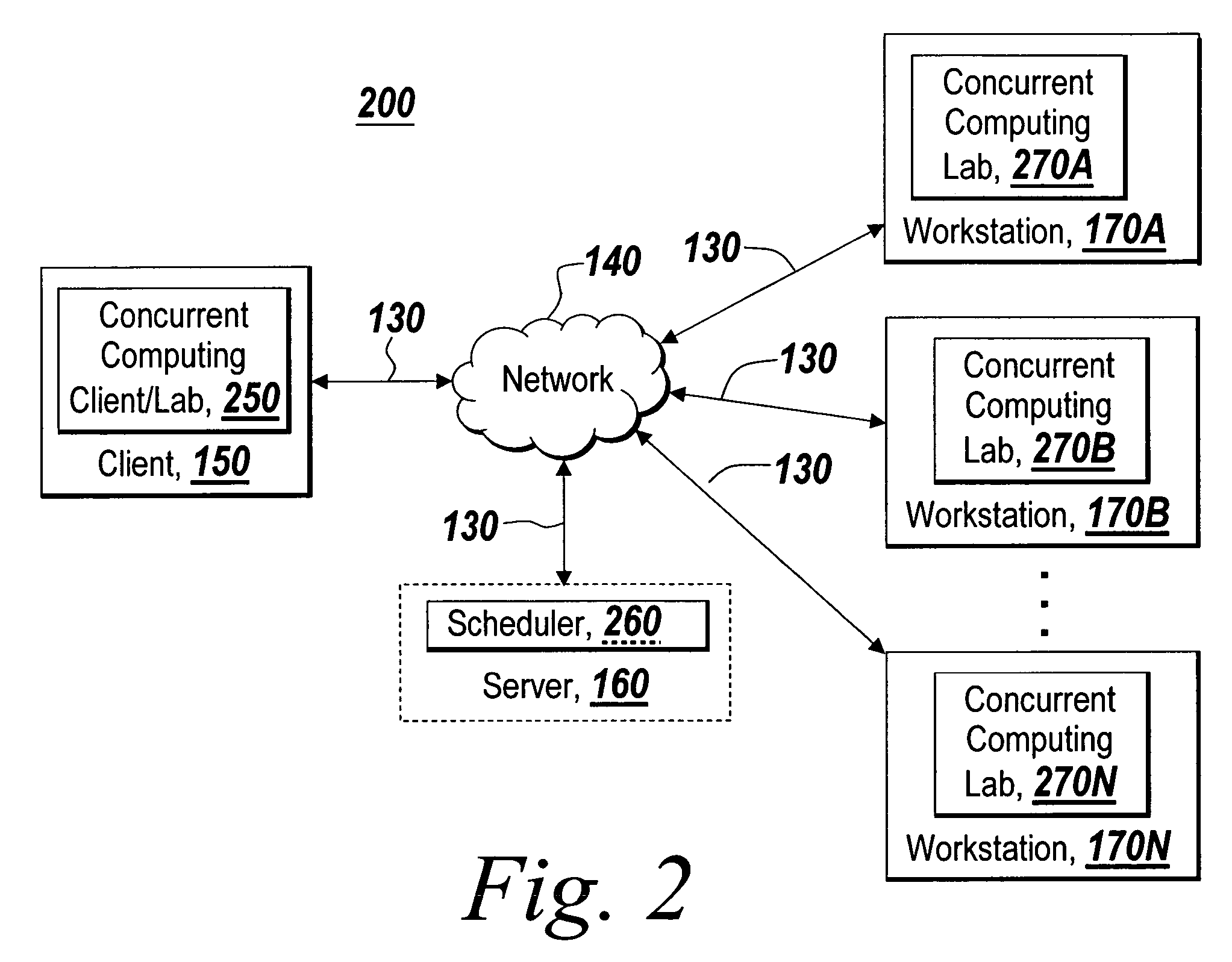

Exception handling in a concurrent computing process

ActiveUS8156493B2Error preventionFrequency-division multiplex detailsConcurrent computingProcess (computing)

The present invention provides a method and system for exception handling in an executable process executing in a concurrent computing environment. The present invention allows a user to interrupt the executable process at any stage of the computation without disconnecting the communication channel among the instances of the executable process. Additionally, the present invention also allows interrupting the concurrent computing process at any stage when an error occurs in the executable process or the communication channel without terminating the communication among the instances of the executable process. Upon notification of an interrupt request, each of the instances of the executable process in the concurrent computing environment flushes any pending incoming messages to return itself to a previous known state while maintaining the communication channel between the instances of the executable process.

Owner:THE MATHWORKS INC

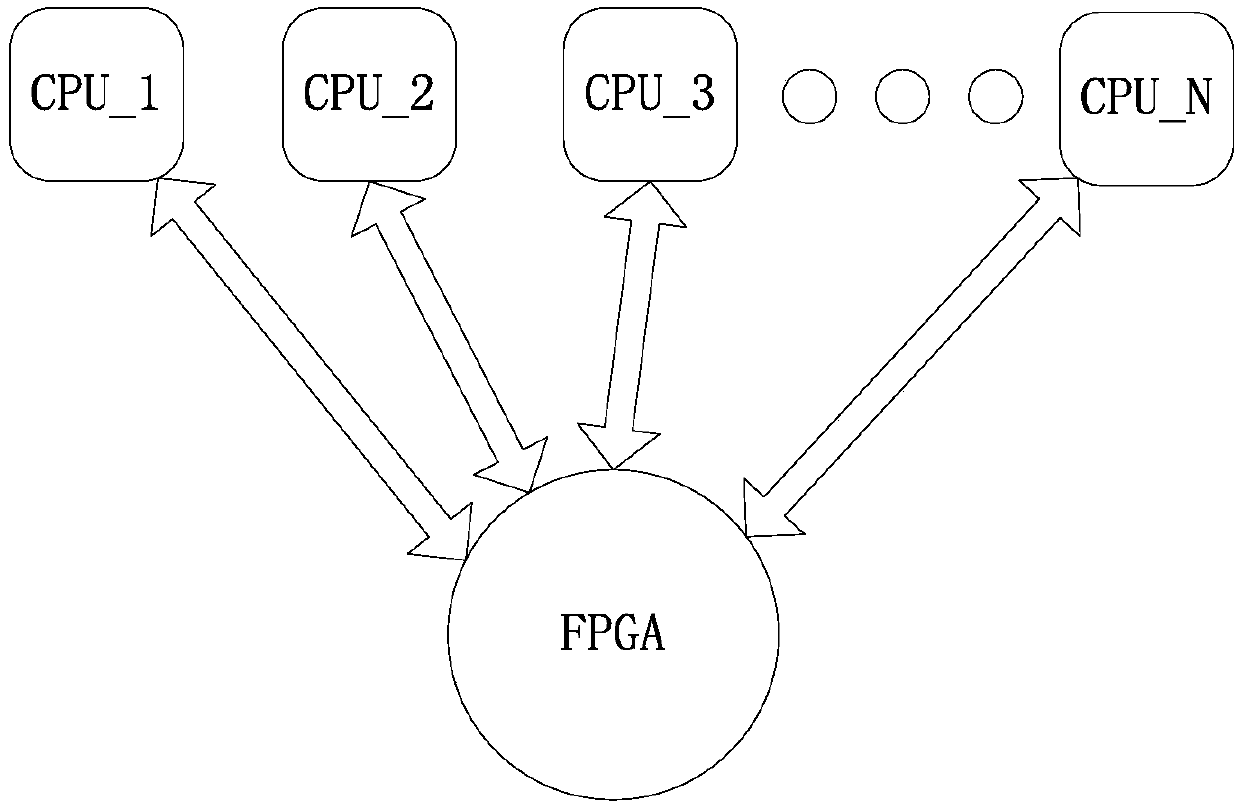

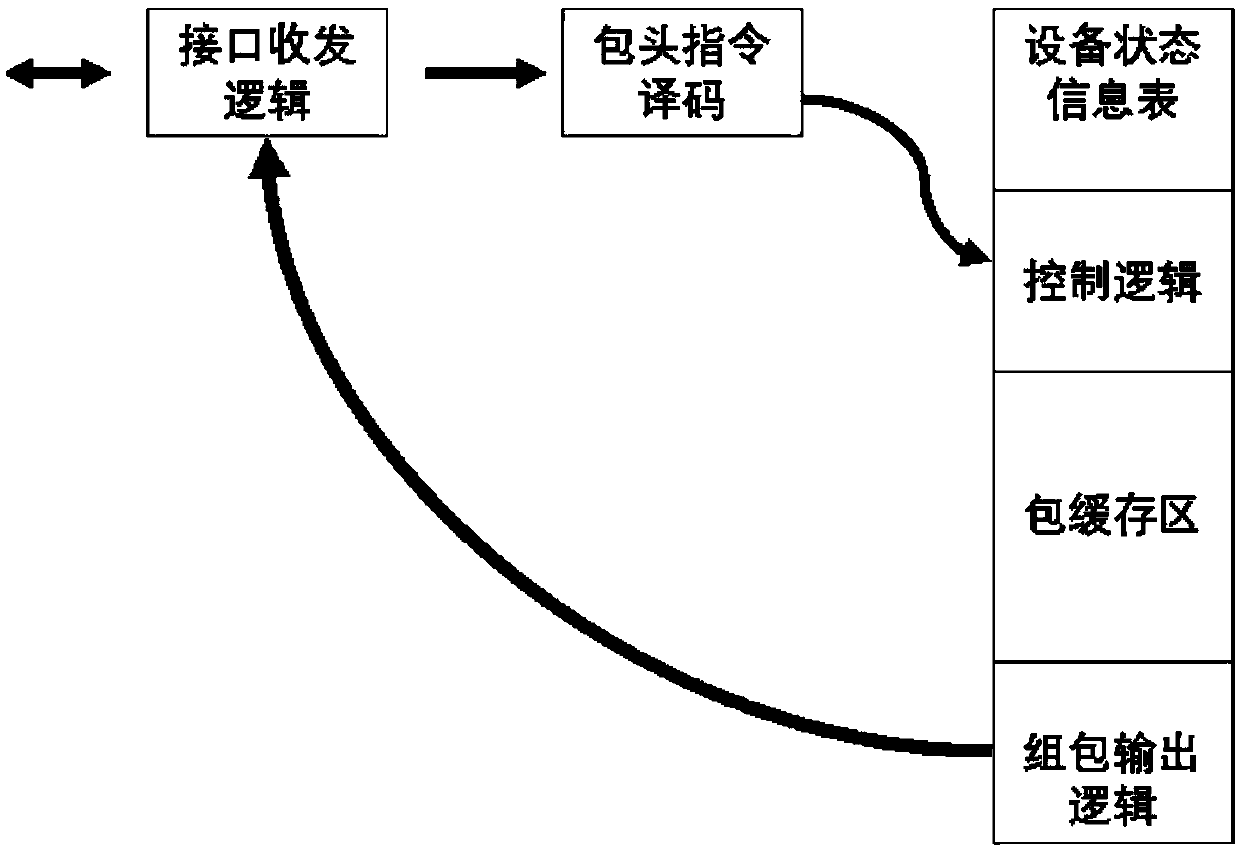

Multi-party central processing unit communication architecture based on field-programmable gate array control

InactiveCN111190840AImprove compatibilityScalable Communication ArchitectureElectric digital data processingData packComputer architecture

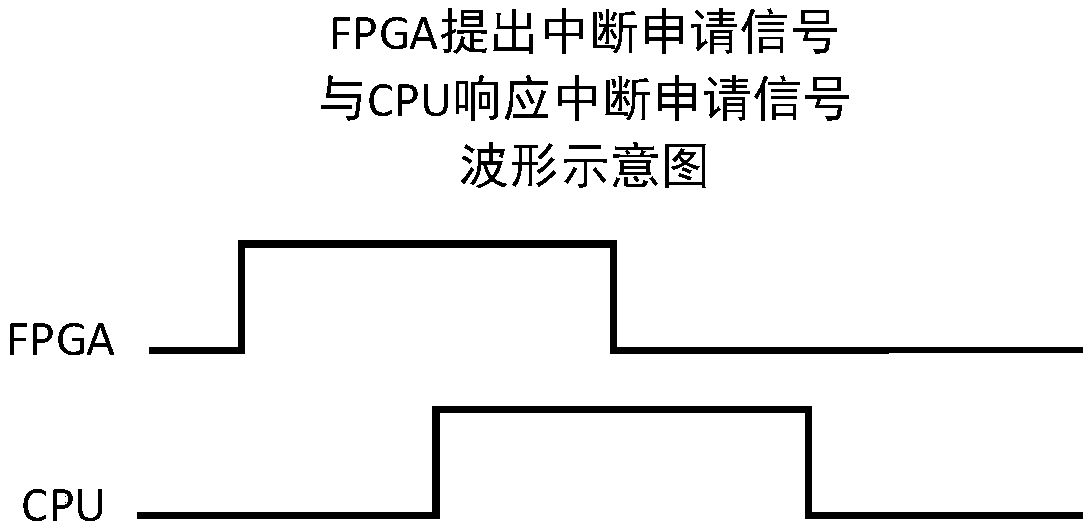

The invention provides a multi-party central processing unit communication architecture based on field-programmable gate array control, which is characterized in that data forwarding communication iscarried out among a plurality of CPU chips through the control of FPGA chips, and the FPGA chips are used for scheduling data streams of all parties. When the CPU _ A needs to send data to the CPU _ B, the data packet is firstly sent to the FPGA chip in a special format; the FPGA analyzes and caches the data packet and notifies the CPU _ B to prepare to receive data in an interrupt mode, and afterthe CPU _ B reads the data from a buffer area of the FPGA, communication between CPUs is completed once. The FPGA chip receives an instruction issued by the CPU chip at any time through the high-speed data transceiving port, and when the FPGA chip actively needs to communicate with the CPU chip, an interrupt request is sent to the CPU chip through the interrupt signal IO pin.

Owner:PEKING UNIV