Multi-party central processing unit communication architecture based on field-programmable gate array control

A central processing unit and gate array technology, applied in electrical digital data processing, instruments, etc., can solve the problems of high software programming pressure, long time, single transmission mode, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

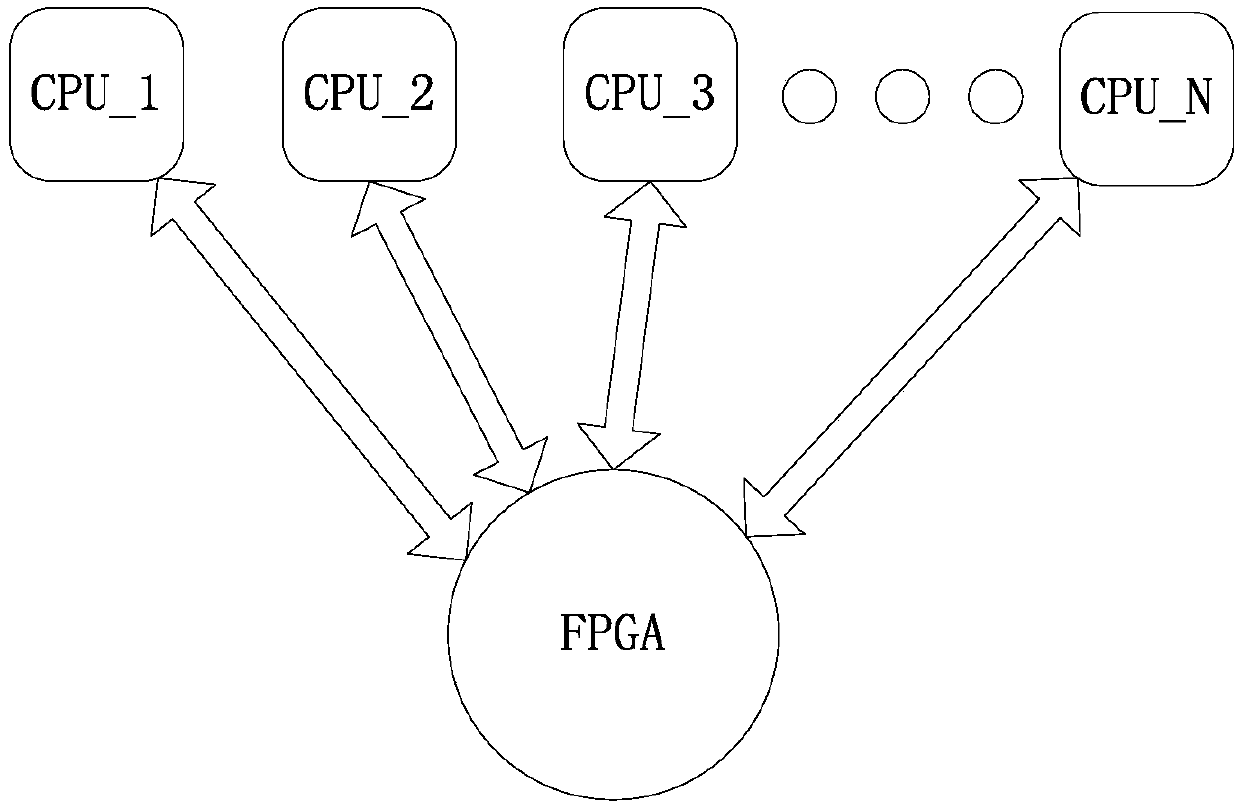

[0020] Communication Architecture: figure 1

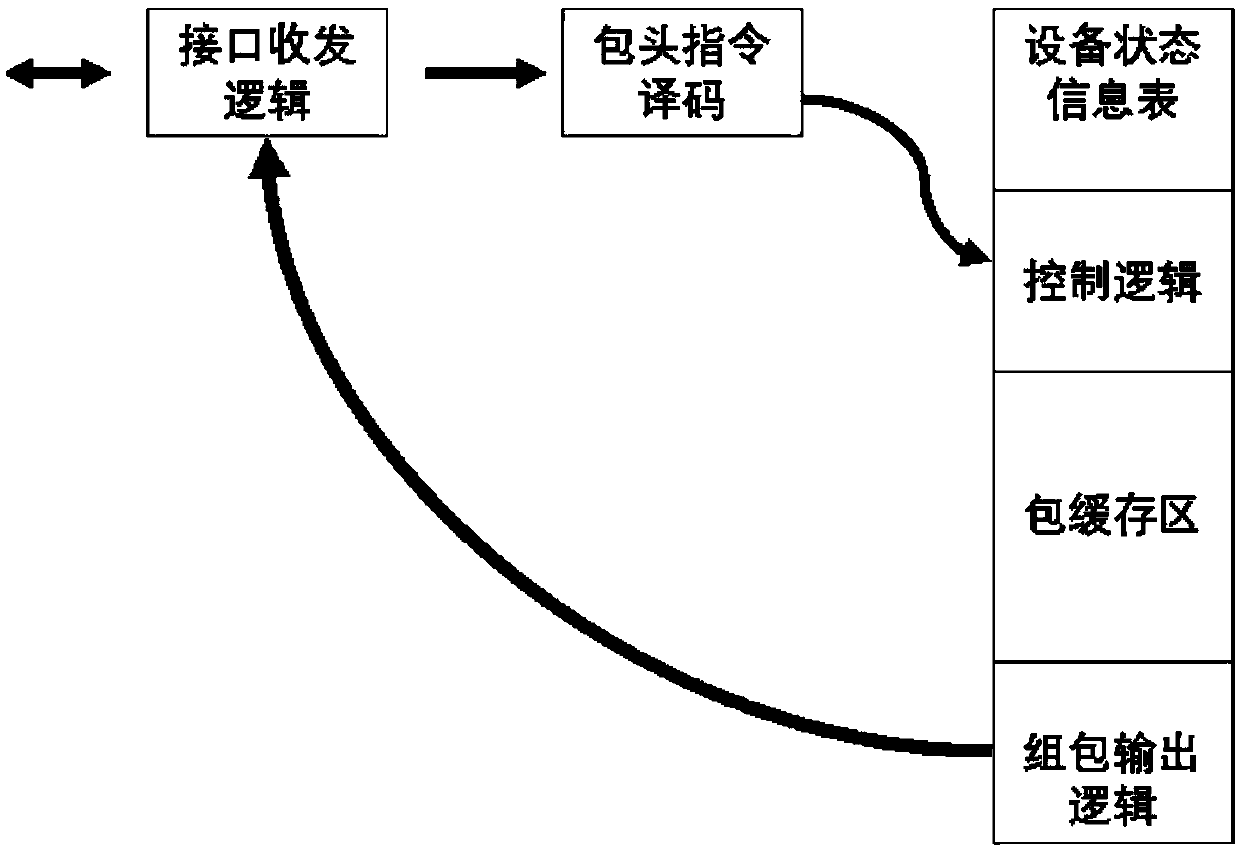

[0021] FPGA internal logic module: figure 2

[0022] Communication method:

[0023] 1. Communication between CPUs is controlled by FPGA.

[0024] 2. The CPU and the FPGA communicate through a high-speed transceiver port and an interrupt signal IO.

[0025] 3. The CPU can send various types of packets to the FPGA through the high-speed transceiver port at any time, and the FPGA side processes the received packets immediately.

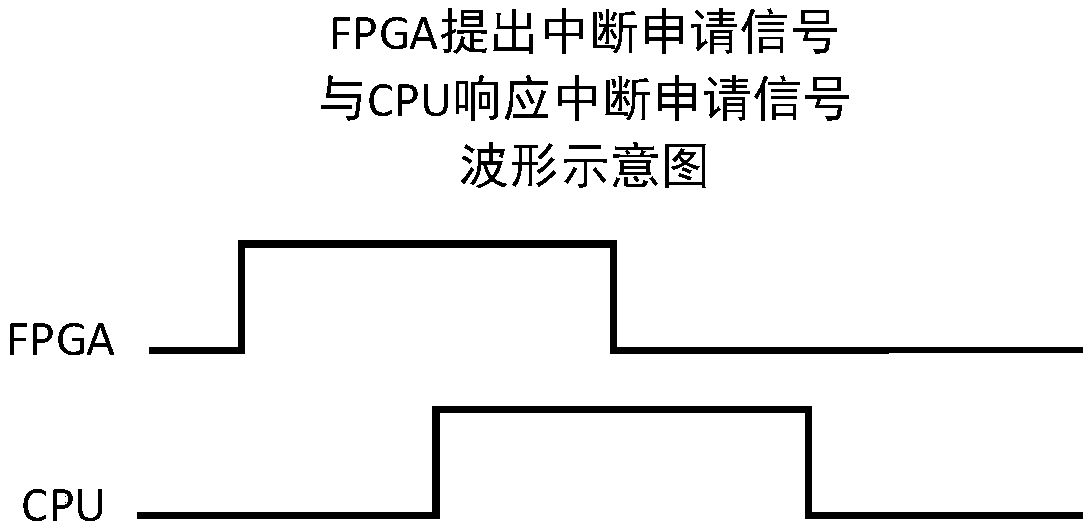

[0026] 4. In addition to the return packet required by the CPU, when the FPGA actively wants to send a packet to the CPU, it should first use the interrupt port to apply to the CPU side. The waveforms of interrupt request signal and response signal are as follows: image 3 shown. The FPGA then sends the packet to the CPU according to the required information carried in the packet responded by the CPU.

[0027] 5. There are only two cases where the FPGA actively sends packets to the CPU: 1) CPU status...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More