Patents

Literature

521 results about "Memory mapping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Physical Memory Forensics System and Method

ActiveUS20140032875A1Accurate reconstructionMemory adressing/allocation/relocationDigital data protectionMemory forensicsData pack

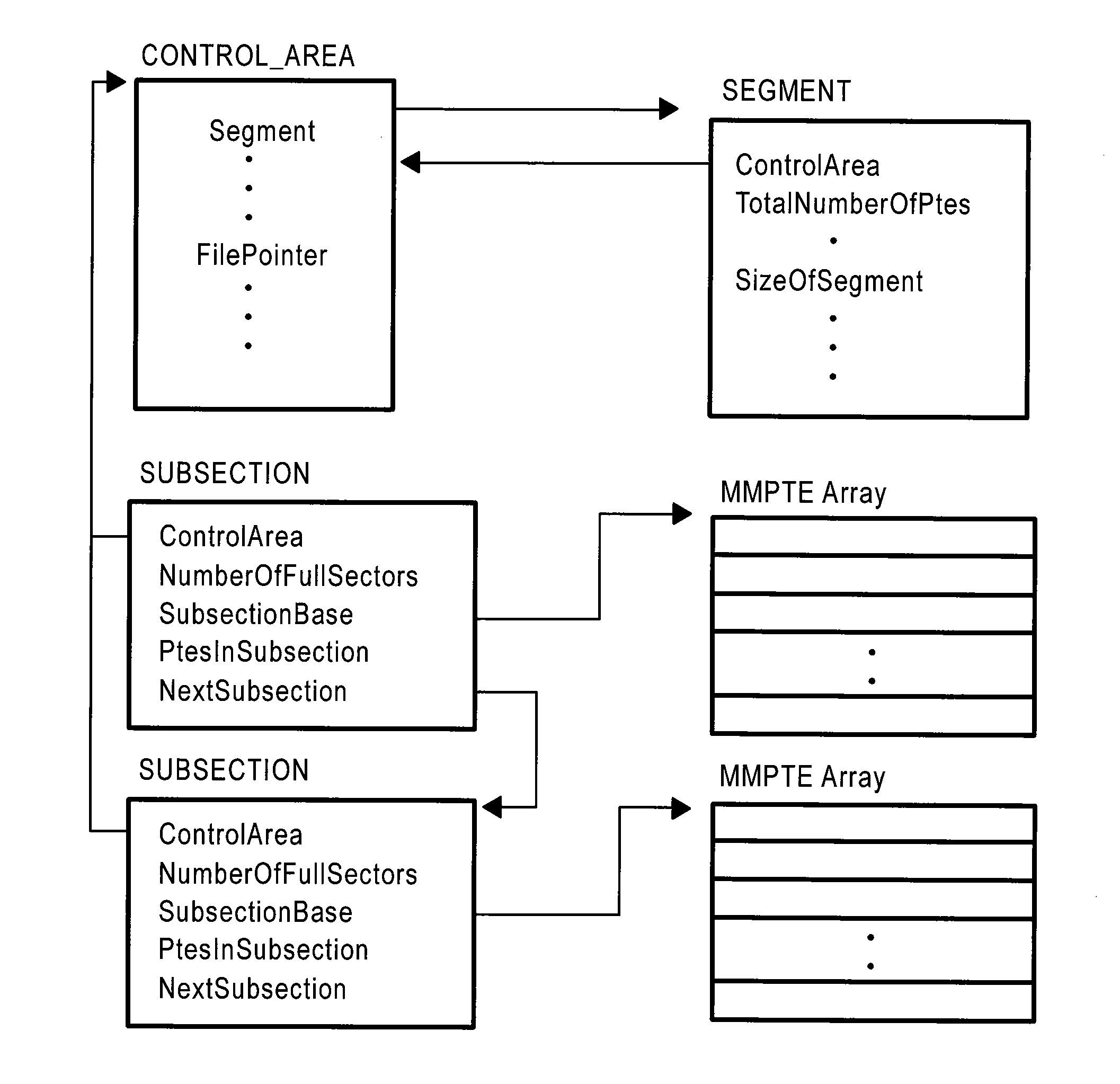

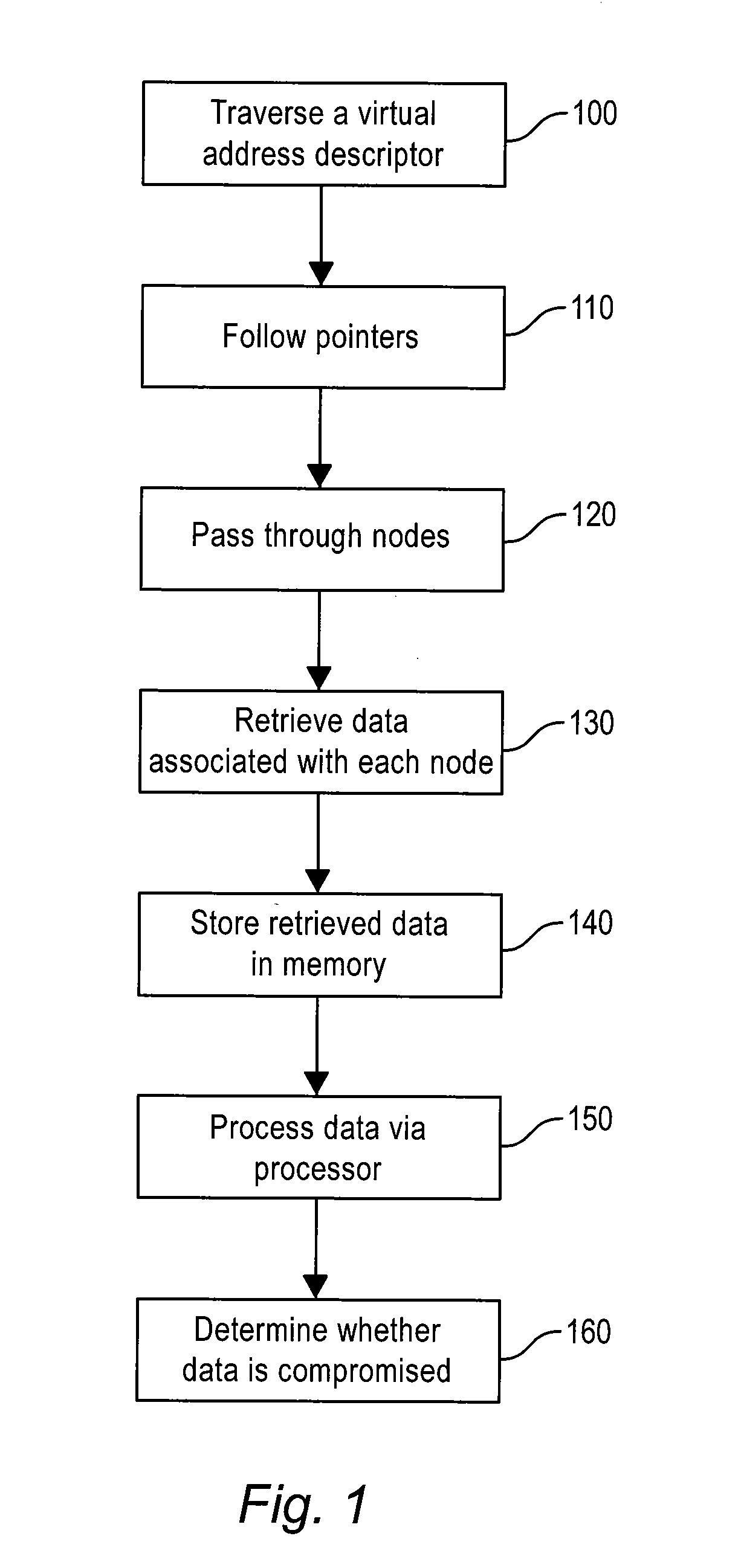

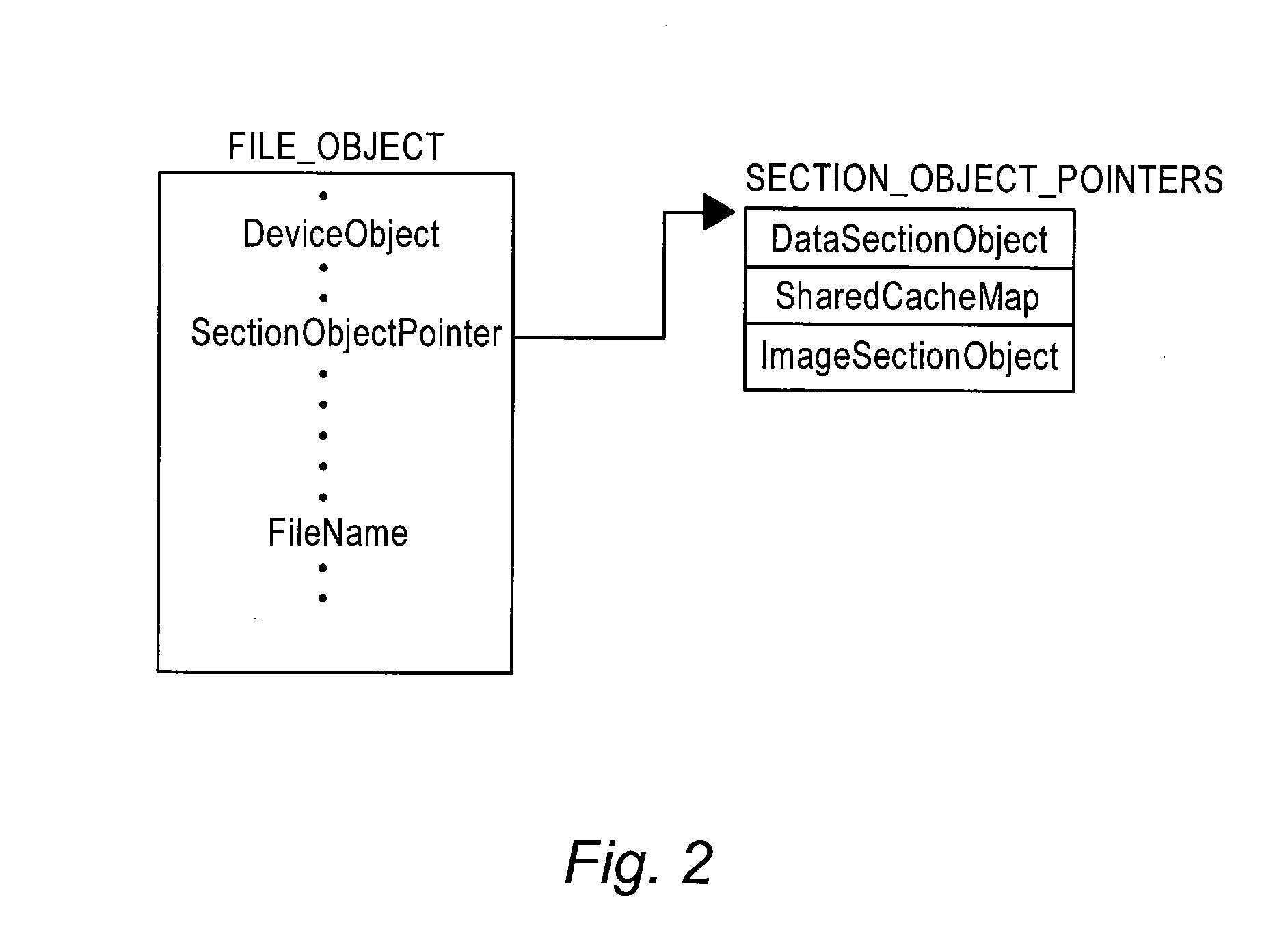

The method of the present inventive concept is configured to utilize Operating System data structures related to memory-mapped binaries to reconstruct processes. These structures provide a system configured to facilitate the acquisition of data that traditional memory analysis tools fail to identify, including by providing a system configured to traverse a virtual address descriptor, determine a pointer to a control area, traverse a PPTE array, copy binary data identified in the PPTE array, generate markers to determine whether the binary data is compromised, and utilize the binary data to reconstruct a process.

Owner:FIREEYE SECURITY HLDG US LLC

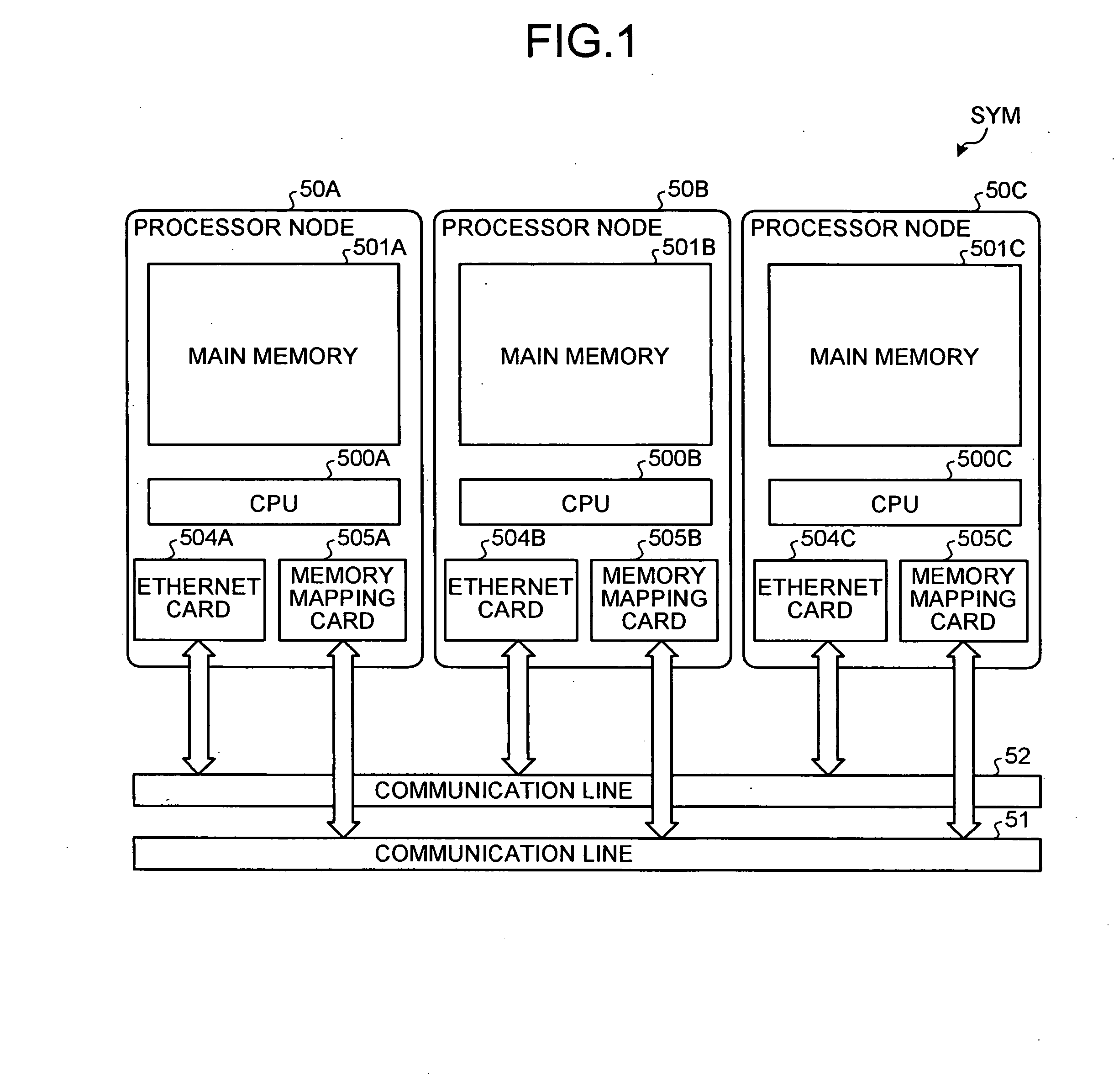

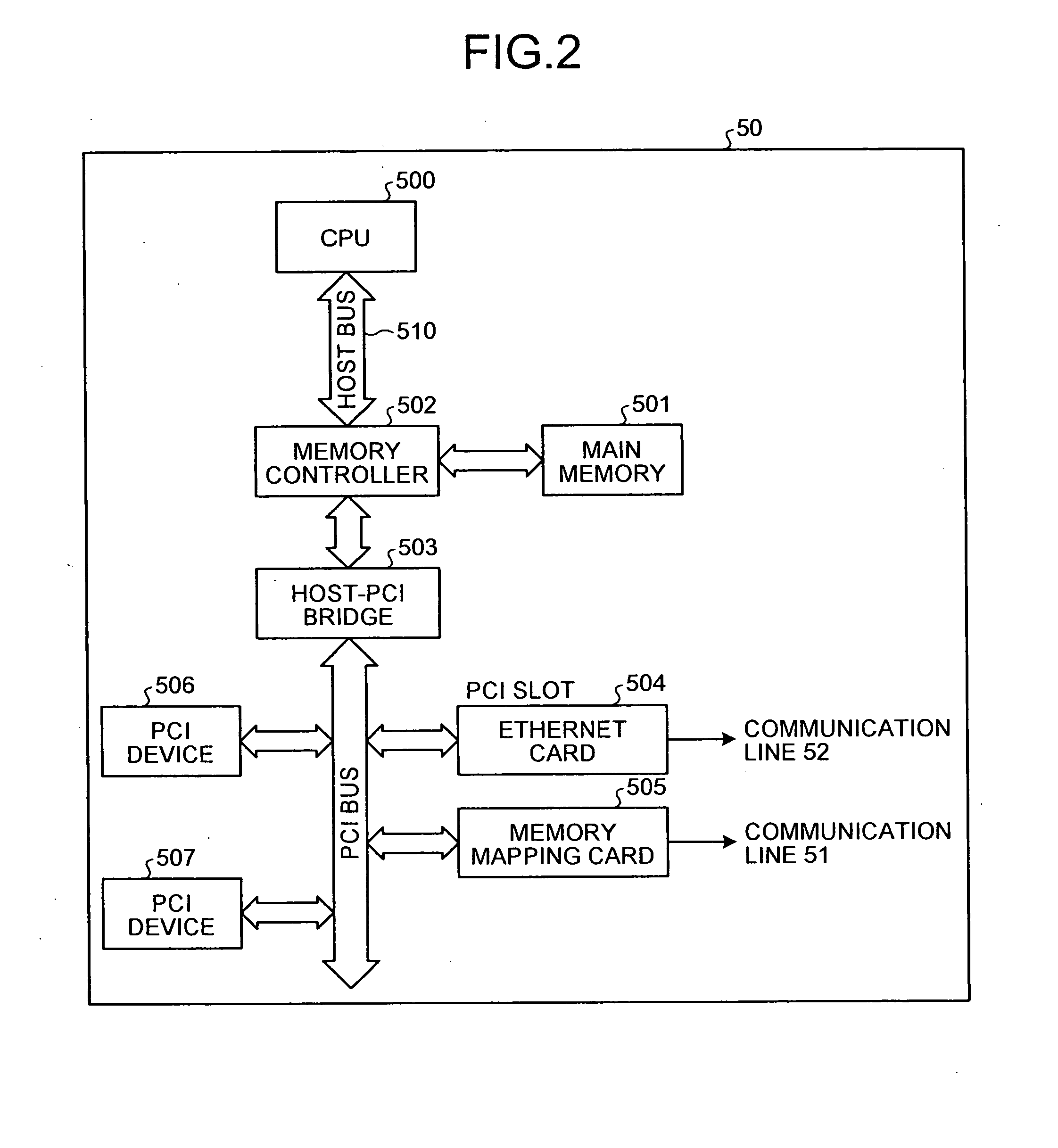

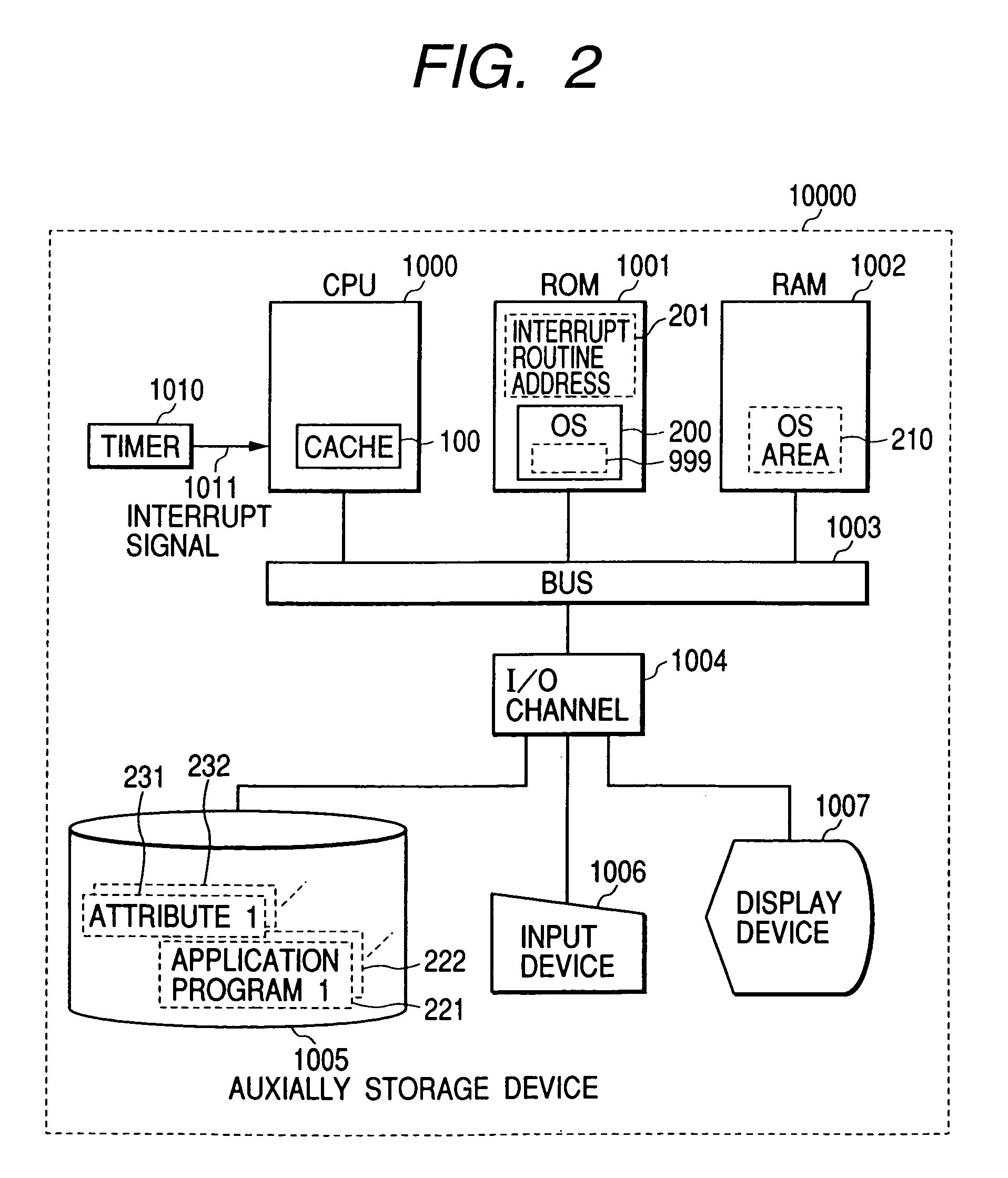

Multiprocessor system

InactiveUS20090077326A1Solve problemsMemory adressing/allocation/relocationGeneral purpose stored program computerCommunication unitManagement unit

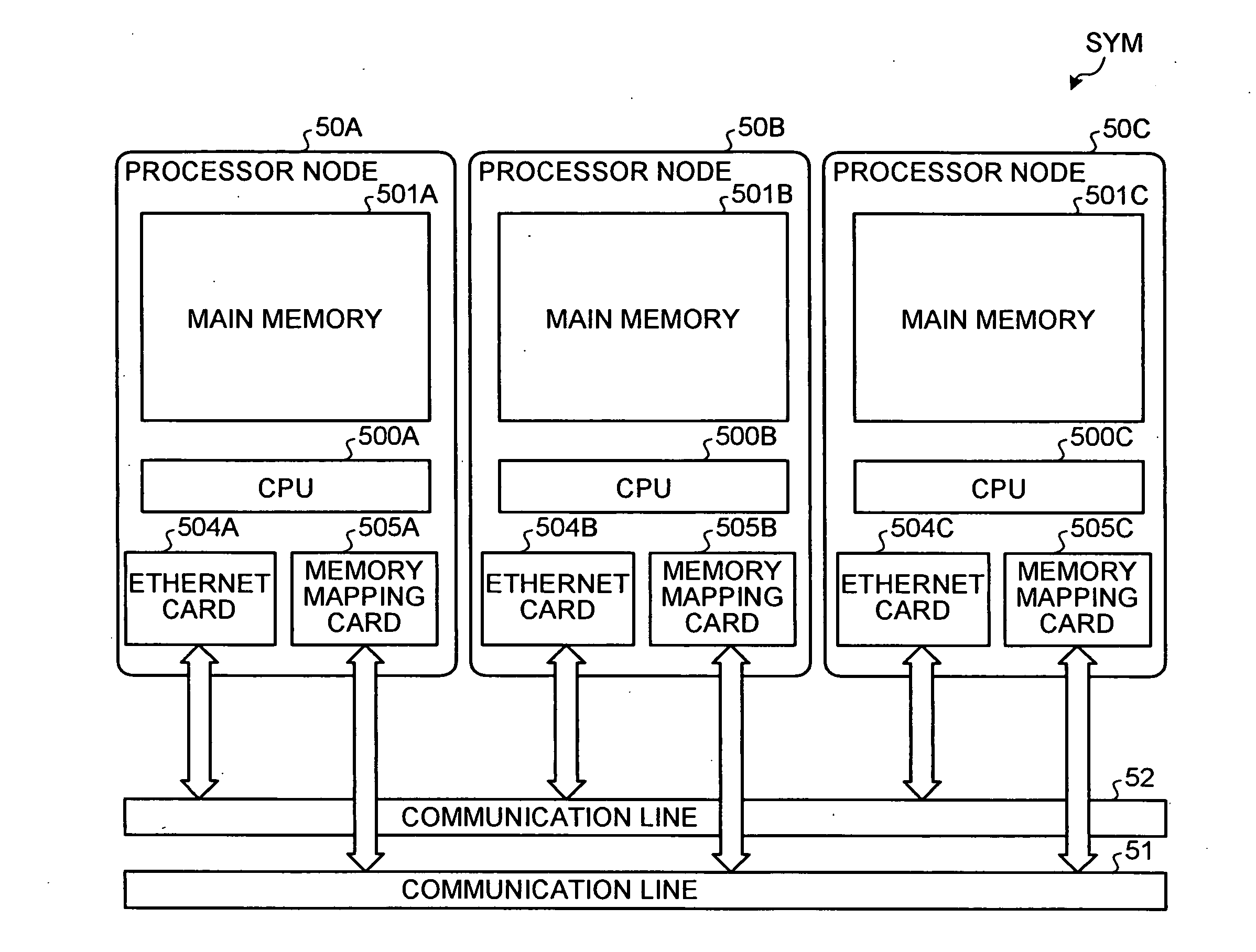

A memory mapping unit requests allocation of a remote memory to memory mapping units of other processor nodes via a second communication unit, and requests creation of a mapping connection to a memory-mapping managing unit of a first processor node via the second communication unit. The memory-mapping managing unit creates the mapping connection between a processor node and other processor nodes according to a connection creation request from the memory mapping unit, and then transmits a memory mapping instruction for instructing execution of a memory mapping to the memory mapping unit via a first communication unit of the first processor node.

Owner:RICOH KK

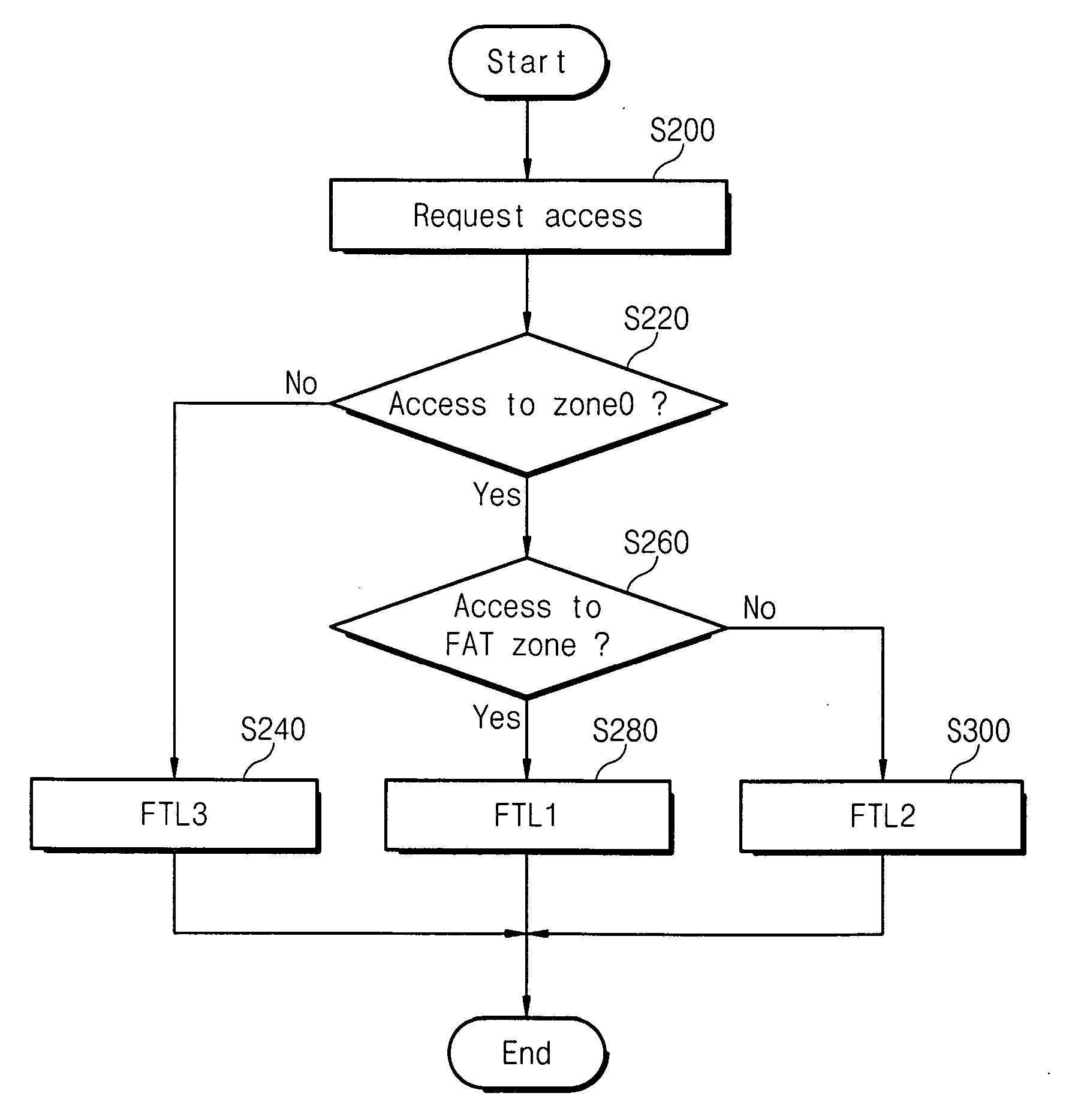

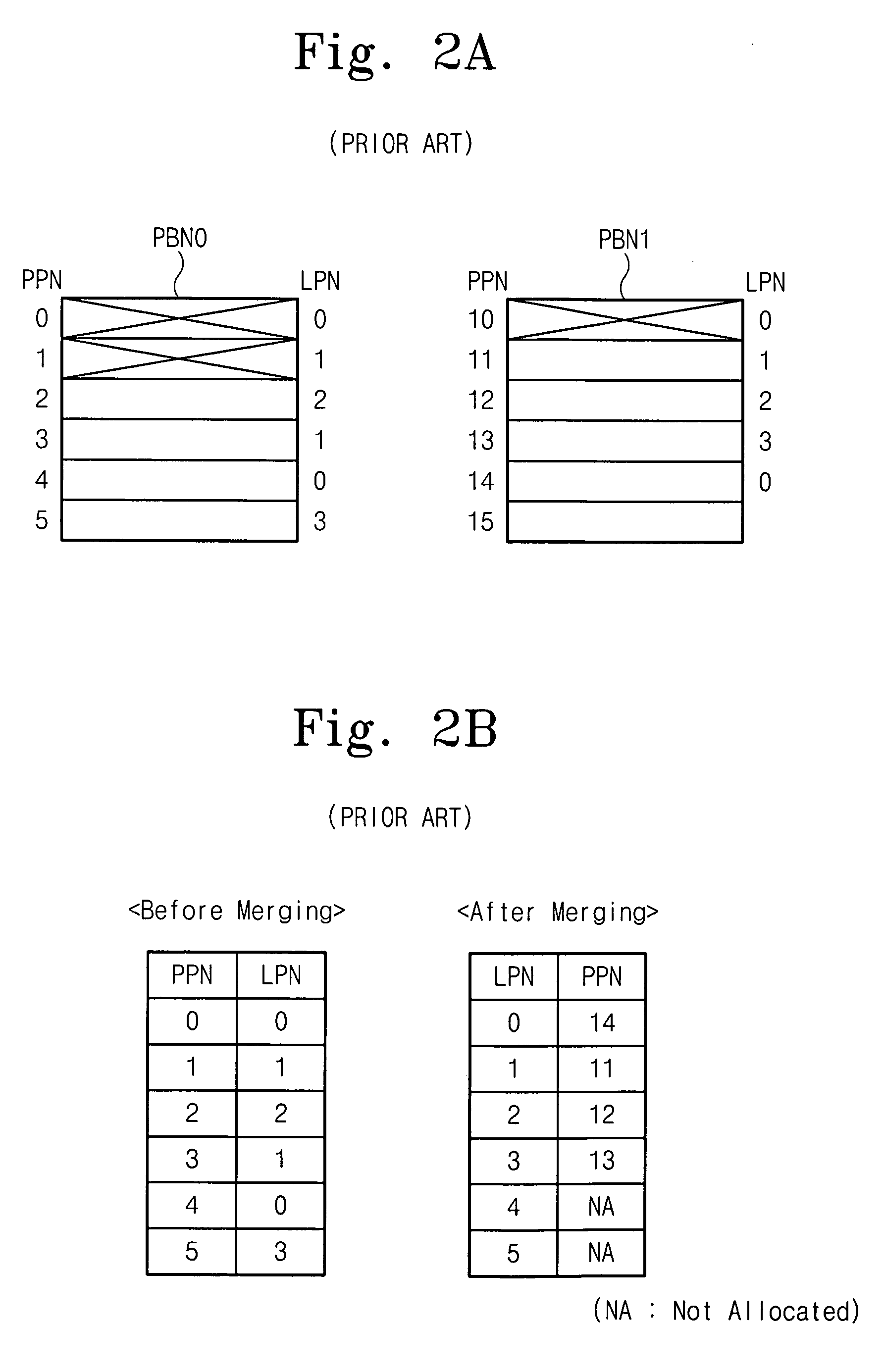

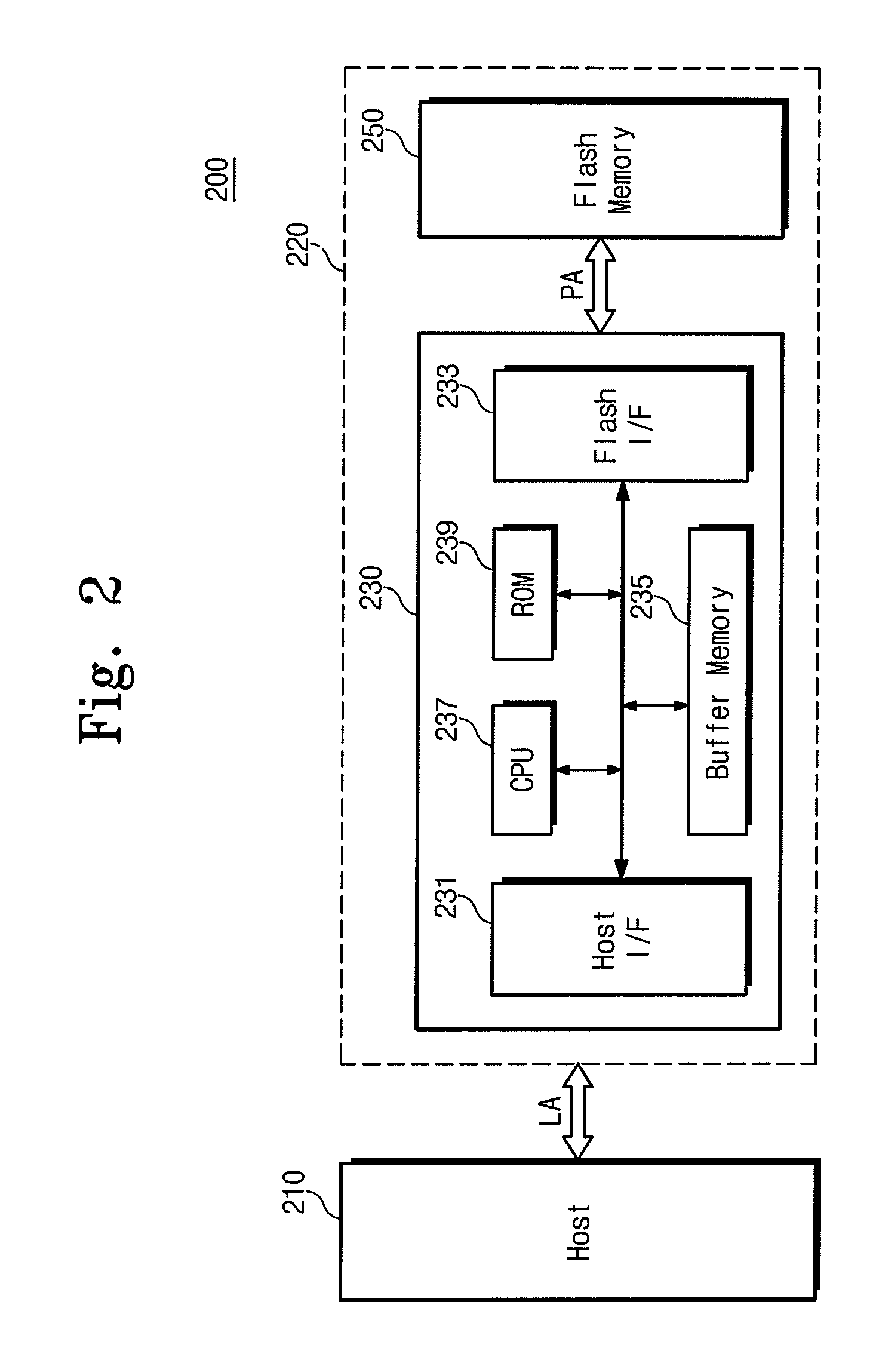

Flash memory control devices that support multiple memory mapping schemes and methods of operating same

ActiveUS20060179212A1Memory architecture accessing/allocationMemory systemsMemory mappingFlash memory

There is provided an apparatus for controlling a flash memory, which includes a memory for storing a plurality of flash translation layers; and a control block for, when an access is requested from outside, determining a pattern of the access, selecting one of the flash translation layers stored in the memory based on the determination result, and managing mapping data of the flash memory based on the selected flash translation layer.

Owner:SAMSUNG ELECTRONICS CO LTD

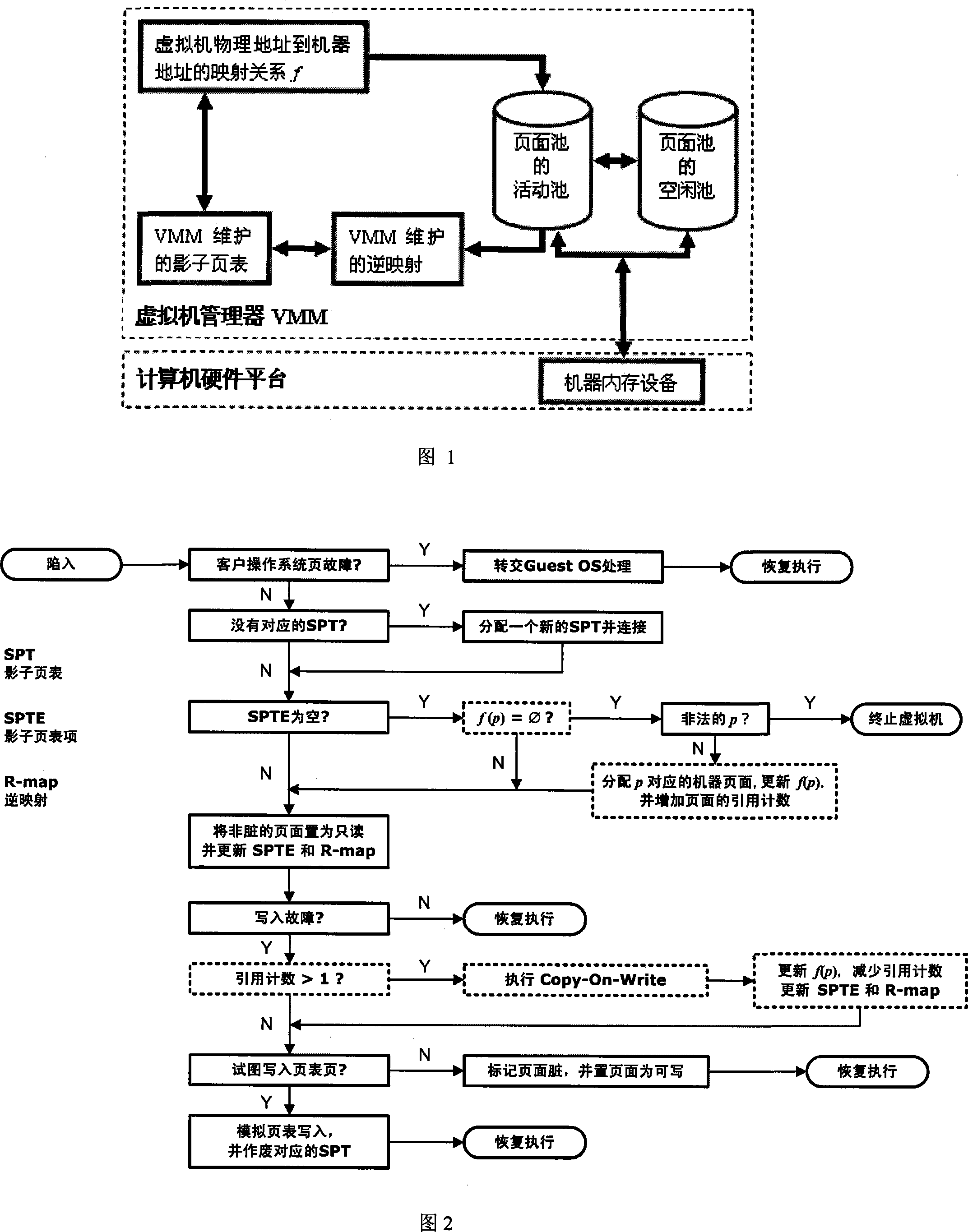

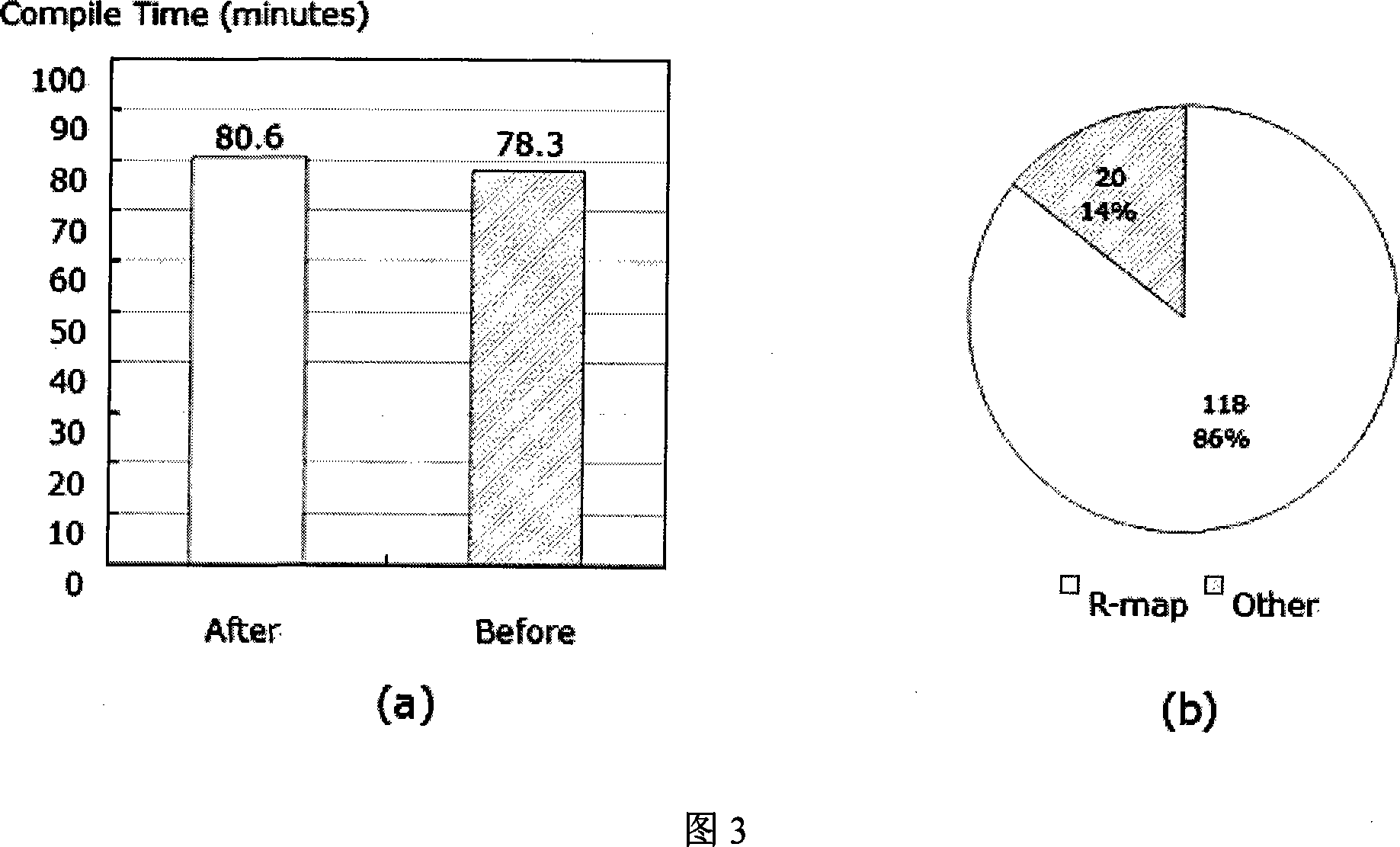

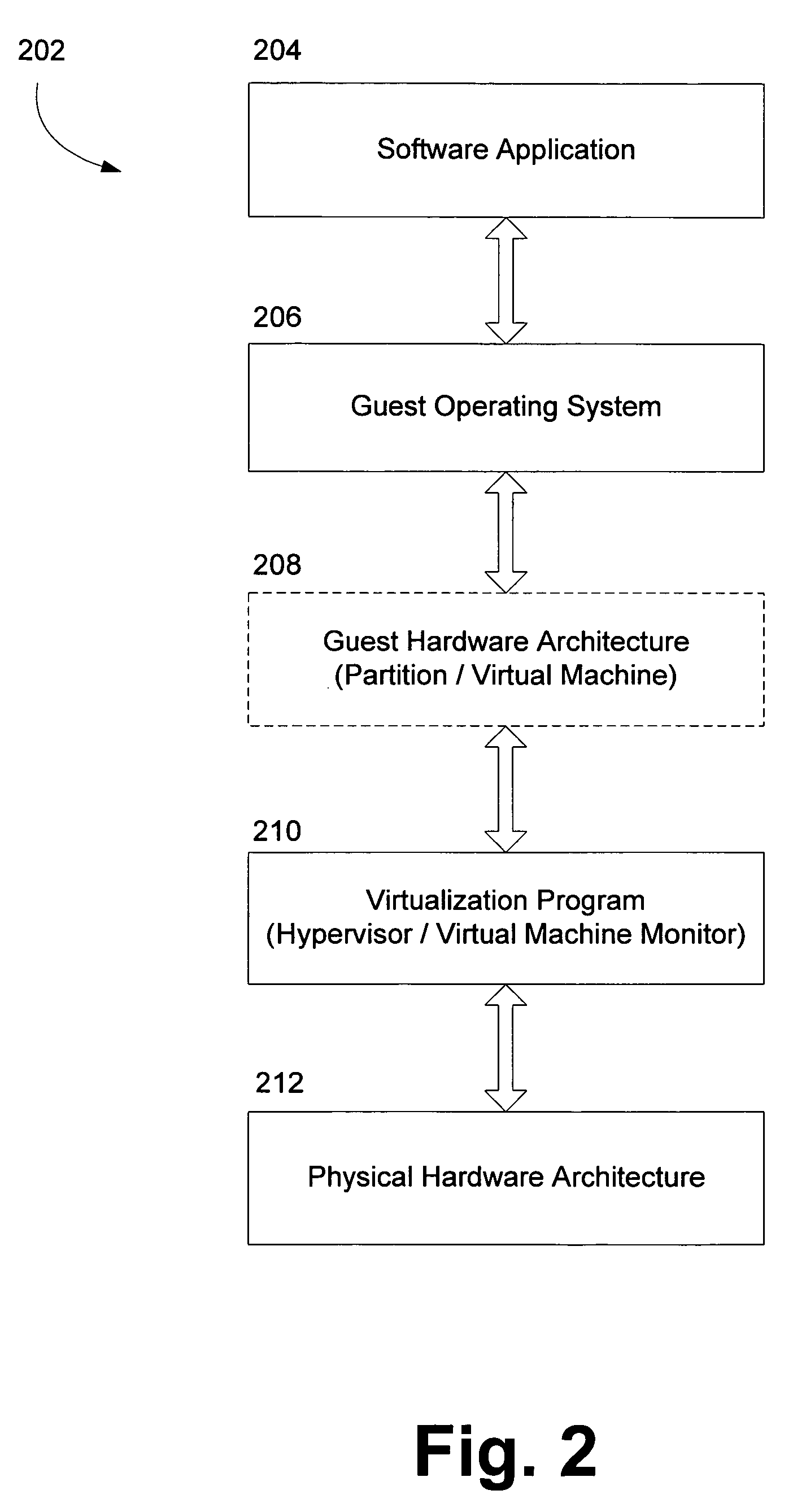

Dynamic EMS memory mappings method of virtual machine manager

InactiveCN101158924ARealize page fetching on demandImplement memory sharingMemory adressing/allocation/relocationSoftware simulation/interpretation/emulationDynamic managementMemory sharing

The invention discloses a dynamic memory mapping method of a virtual machine manager, the steps are that: separately establish a virtual machine page pool and a virtual machine manager page pool; when the virtual machine access is violated, the virtual machine manager dynamically establishes and updates the mapping relations f(p) form a physical memory collection P to a machine memory collection M in the virtual machine manager page pool; the inventive method can simultaneously support obtaining pages according to the requirements at upper layer, virtual storage, as well as memory shared functions, so as to make the virtual machine manager realize dynamic management and allocation of the virtual machine memory on the premise that the virtual machine manager sufficiently guarantees the virtual machine access memory performance.

Owner:PEKING UNIV

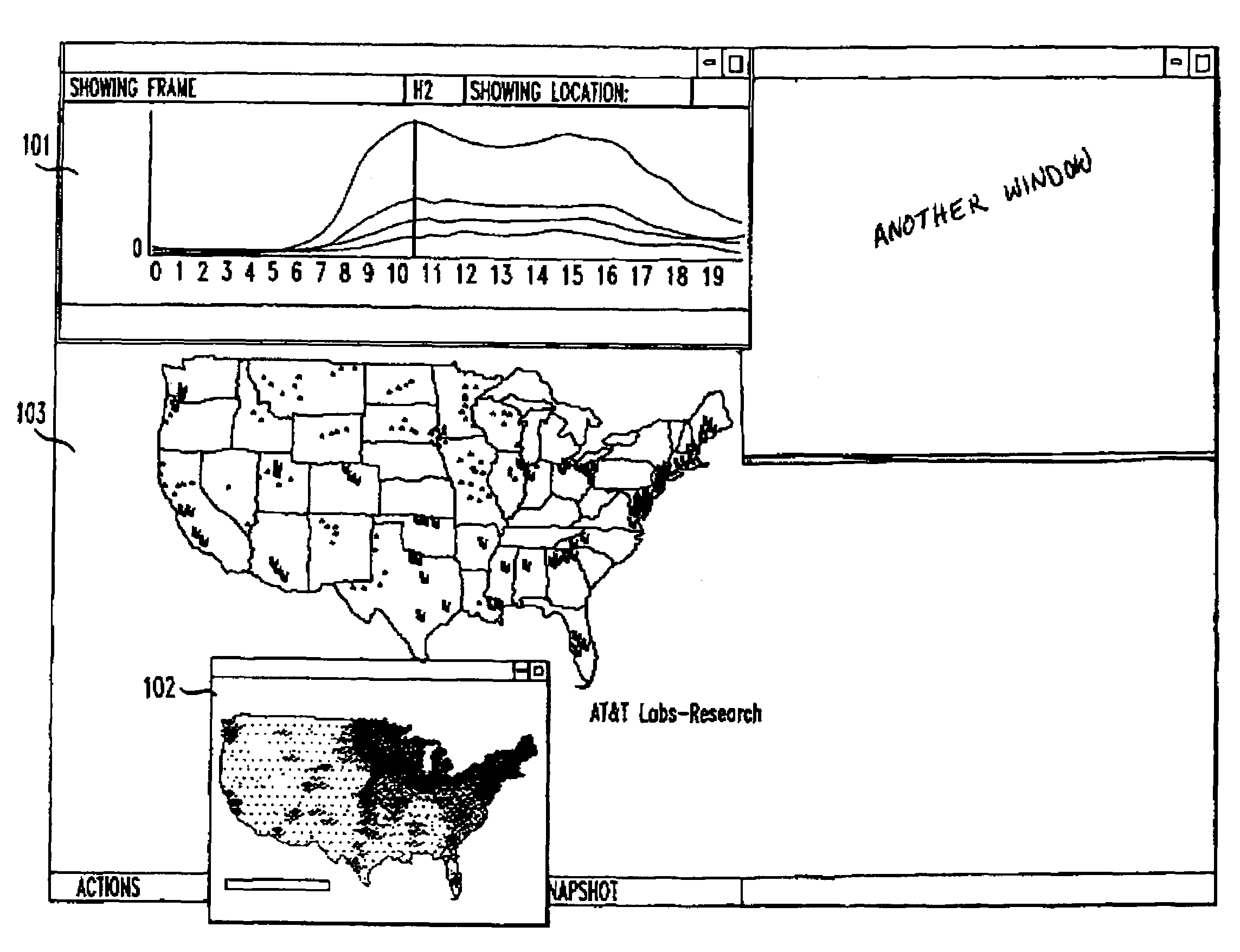

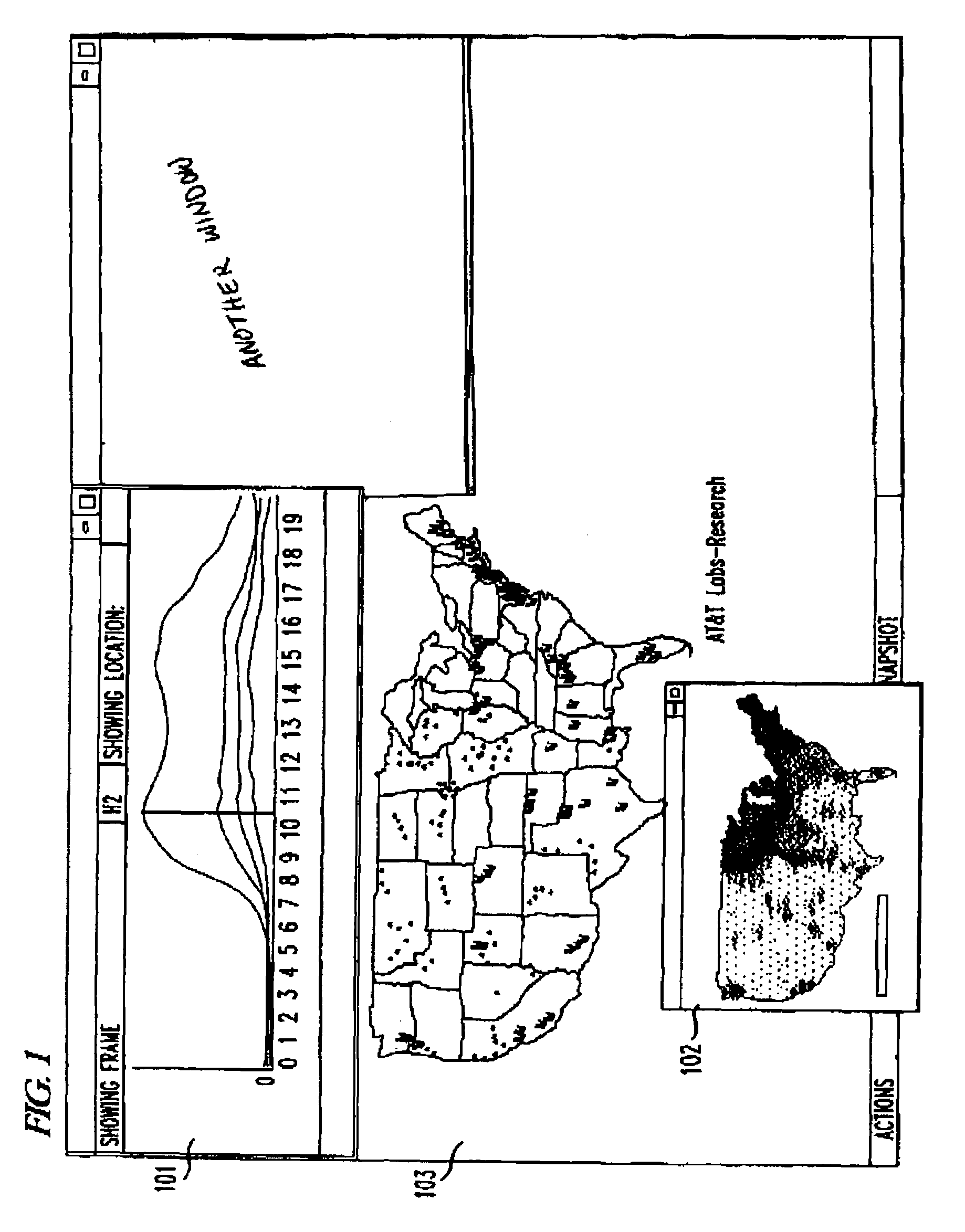

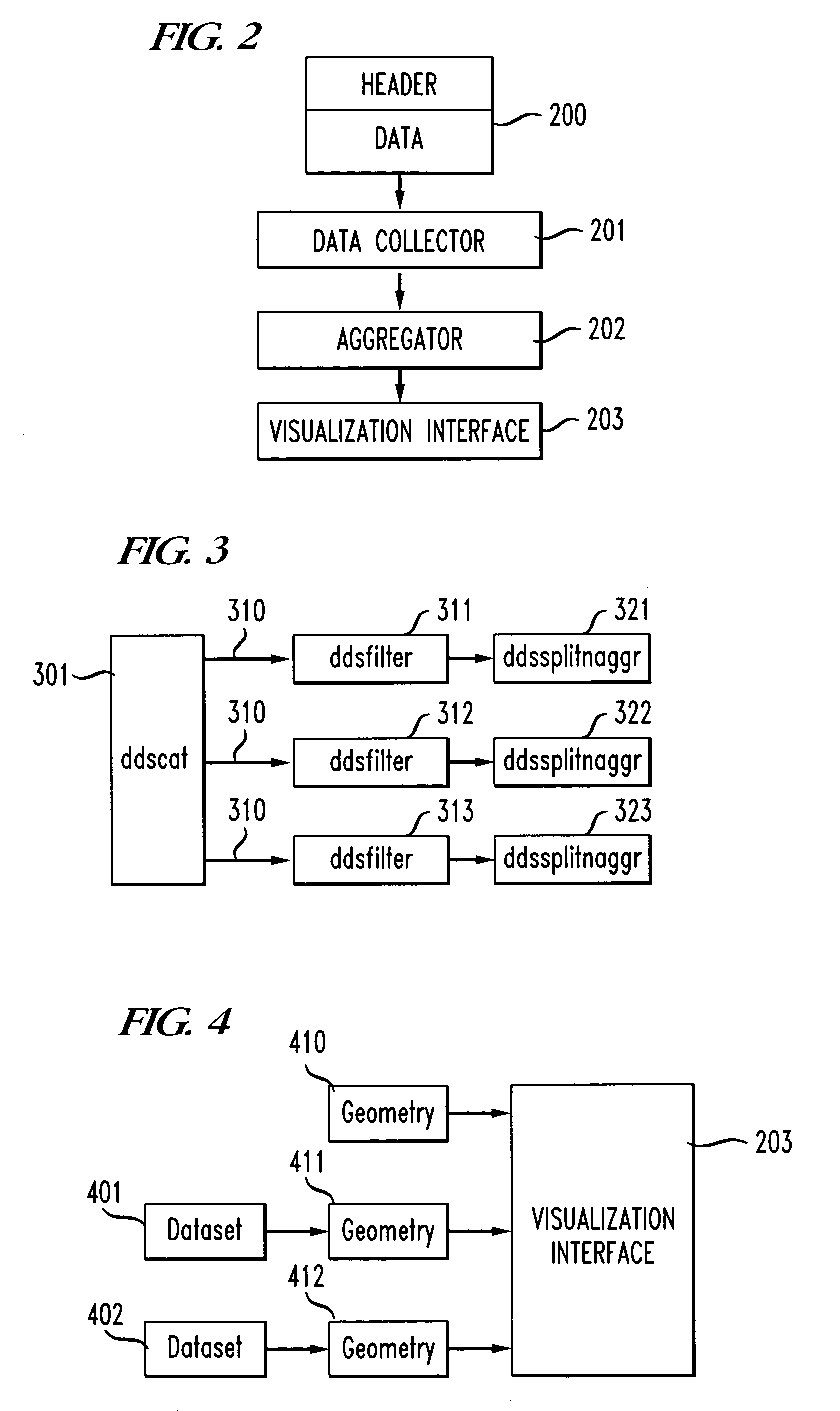

System and method for large-scale data visualization

ActiveUS7454439B1Minimize processing delayComprehensive supportDigital data processing detailsTransmissionData setData exploration

The present invention is directed to a new visualization platform for the interactive exploration of large datasets. The present invention integrates a collection of relevant visualization techniques to provide a new visual metaphor for viewing large datasets. It is capable of providing comprehensive support for data exploration, integrating large-scale data visualization with querying, browsing, and statistical evaluation. A variety of techniques are utilized to minimize processing delays and the use of system resources, including processing pipelines, direct IO, memory mapping, and dynamic linking of “on-the-fly” generated code.

Owner:AMERICAN TELEPHONE & TELEGRAPH CO

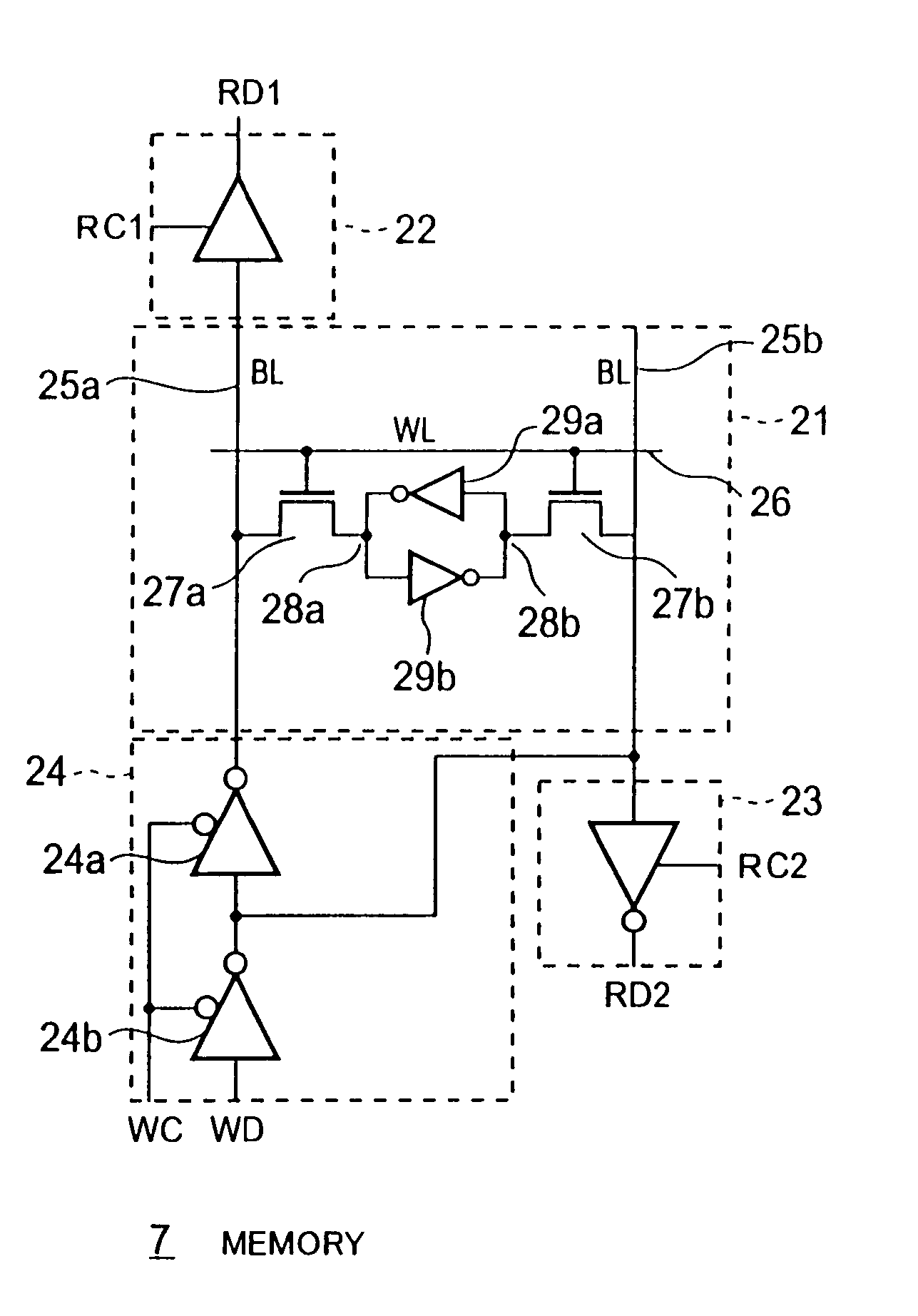

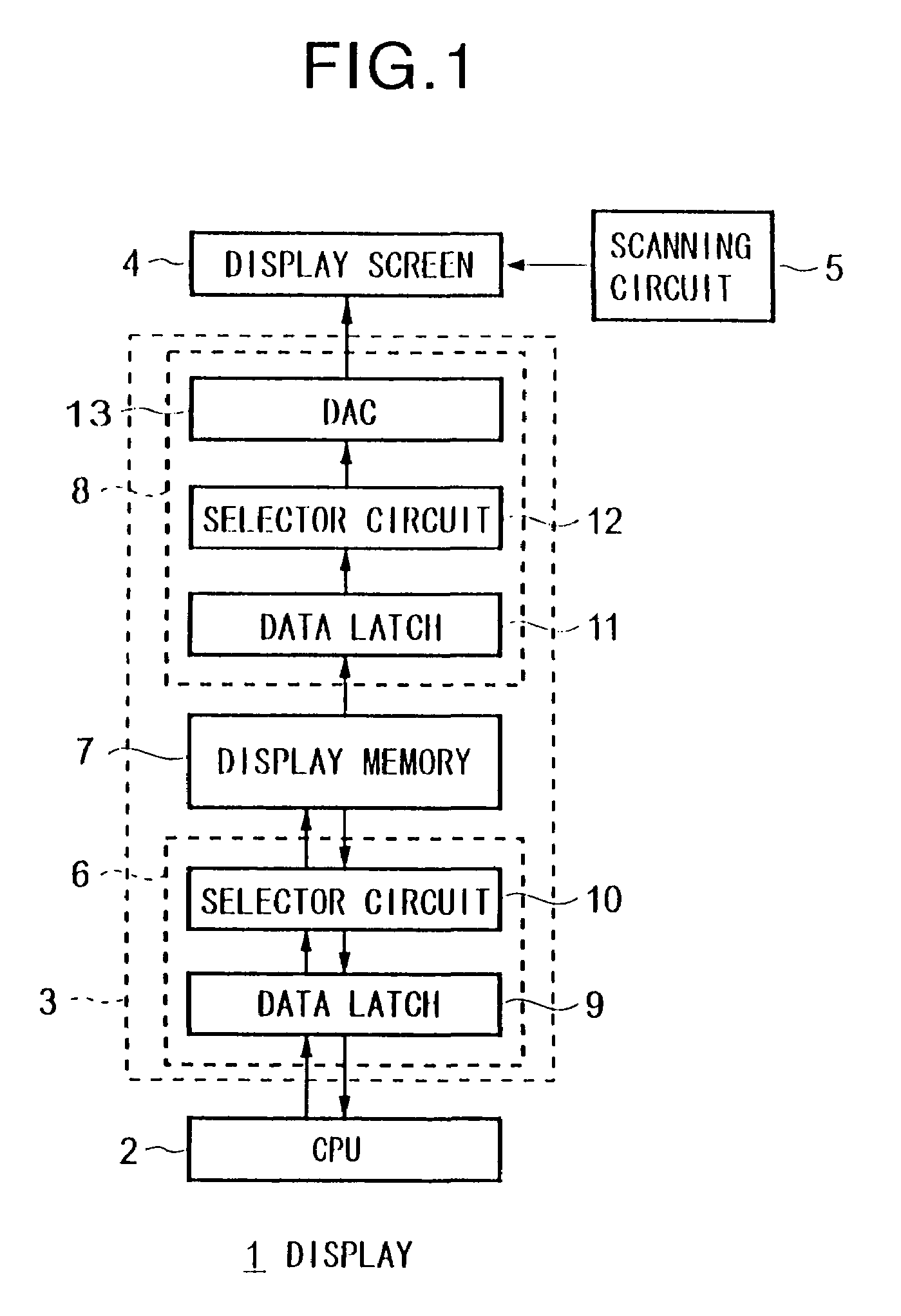

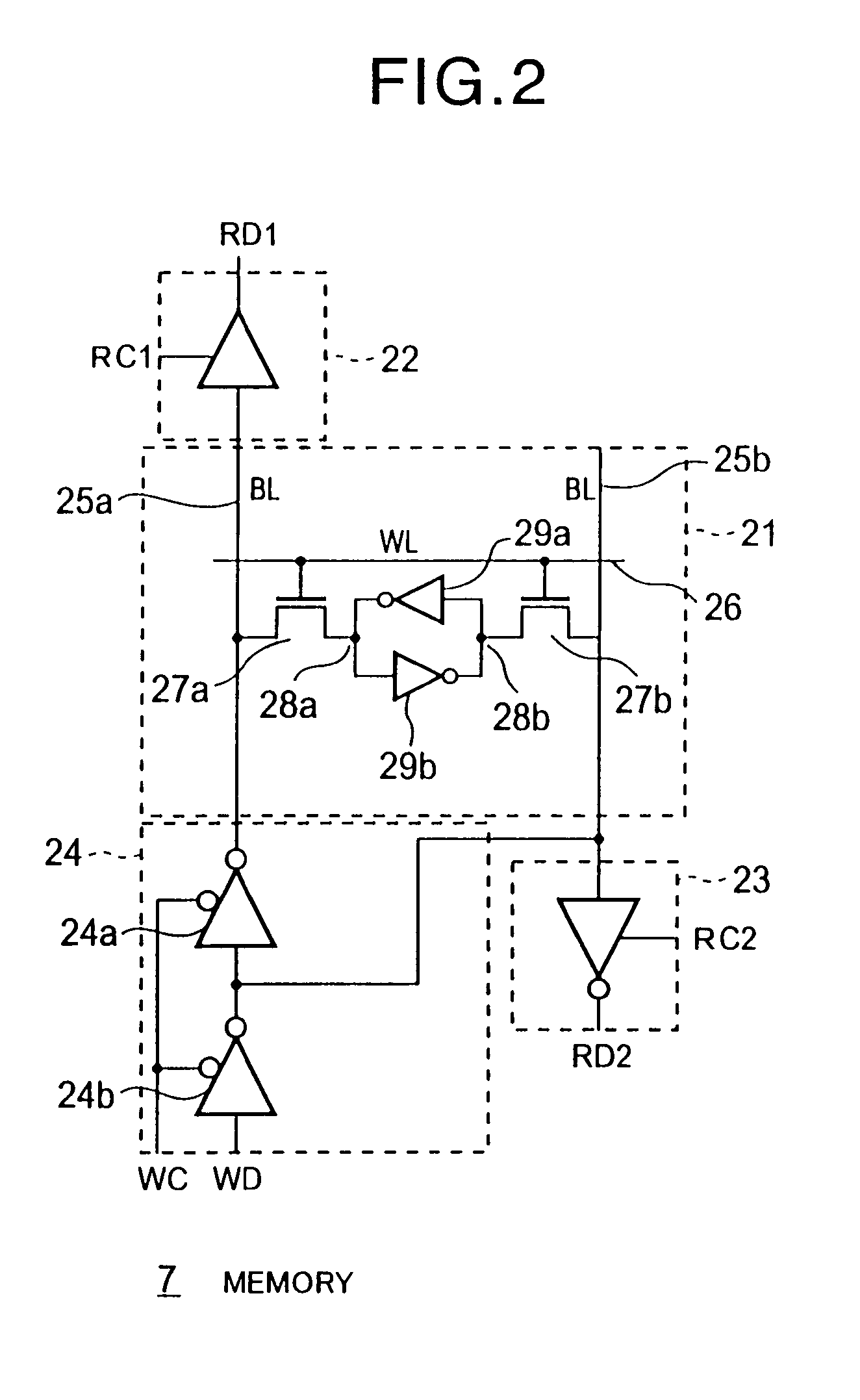

Display memory, driver circuit, display, and cellular information apparatus

InactiveUS7176864B2Reduce power consumptionIncrease speedCathode-ray tube indicatorsDigital storageBit lineDriver circuit

A display memory able to reduce power consumption, able to generate graphics at a high speed, and not needing memory mapping, a driver circuit, a display using the driver circuit, and a portable information apparatus, wherein a CPU read circuit is connected to one bit line of a display memory 7, a display read circuit is connected to the other bit line, a write circuit is connected to both bit lines, the CPU read circuit and write circuit are assigned to the access from the CPU, the display read circuit is assigned to the display screen display, and further the access from the CPU and the reading to the display screen are assigned to different two level periods of a clock signal of the memory and independently controlled. Further, a drive power supply of the display memory is divided and a drive power supply voltage is supplied to the display memory for every memory cell or for every plurality of memory cells.

Owner:SONY GRP CORP

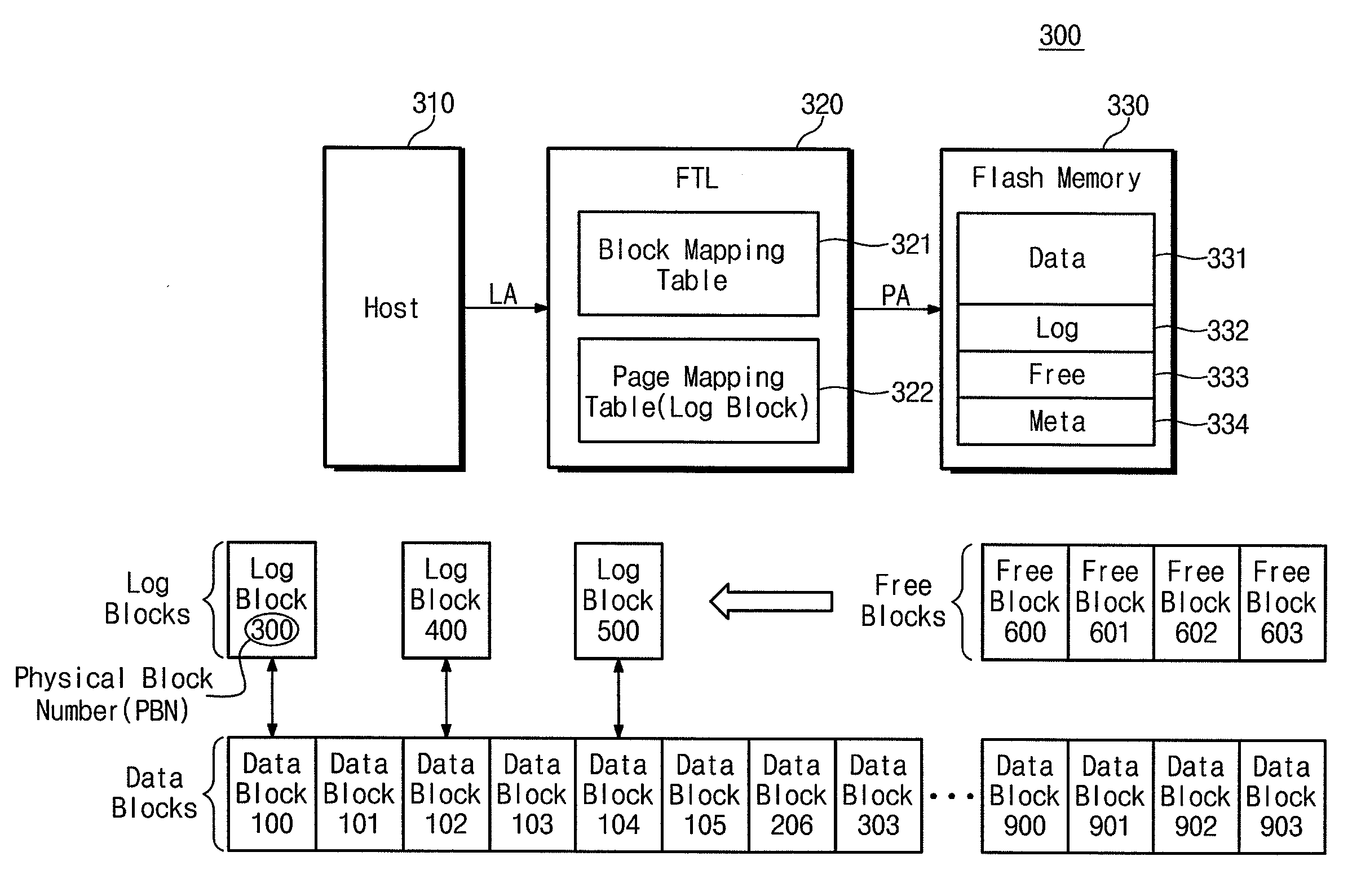

Memory mapping

InactiveUS20080189490A1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogic cellTerm memory

A system and method for memory mapping are provided, the system including a logical unit to physical unit map table, data unit groups in signal communication with the map table, and log unit groups, each associated with a corresponding one of the data unit groups, where updated data for any data unit within one of the data unit groups is stored in any log unit within the corresponding one of the log unit groups, and the method including receiving write data for a logical unit number from a host determining which of a plurality of data block groups comprises the logical unit number, and storing the write data in any unfilled log unit of a log block group corresponding to the determined data block group.

Owner:SAMSUNG ELECTRONICS CO LTD

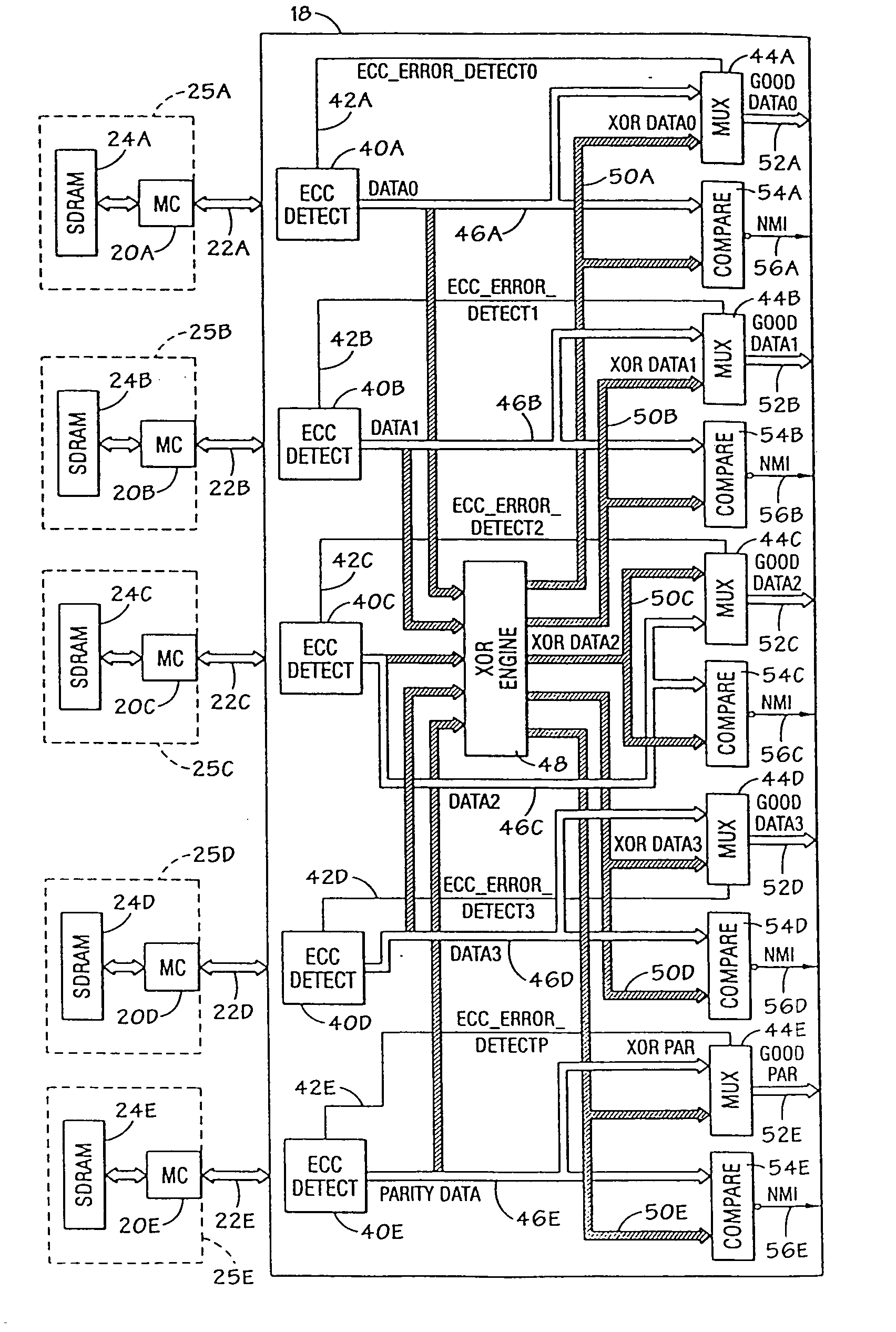

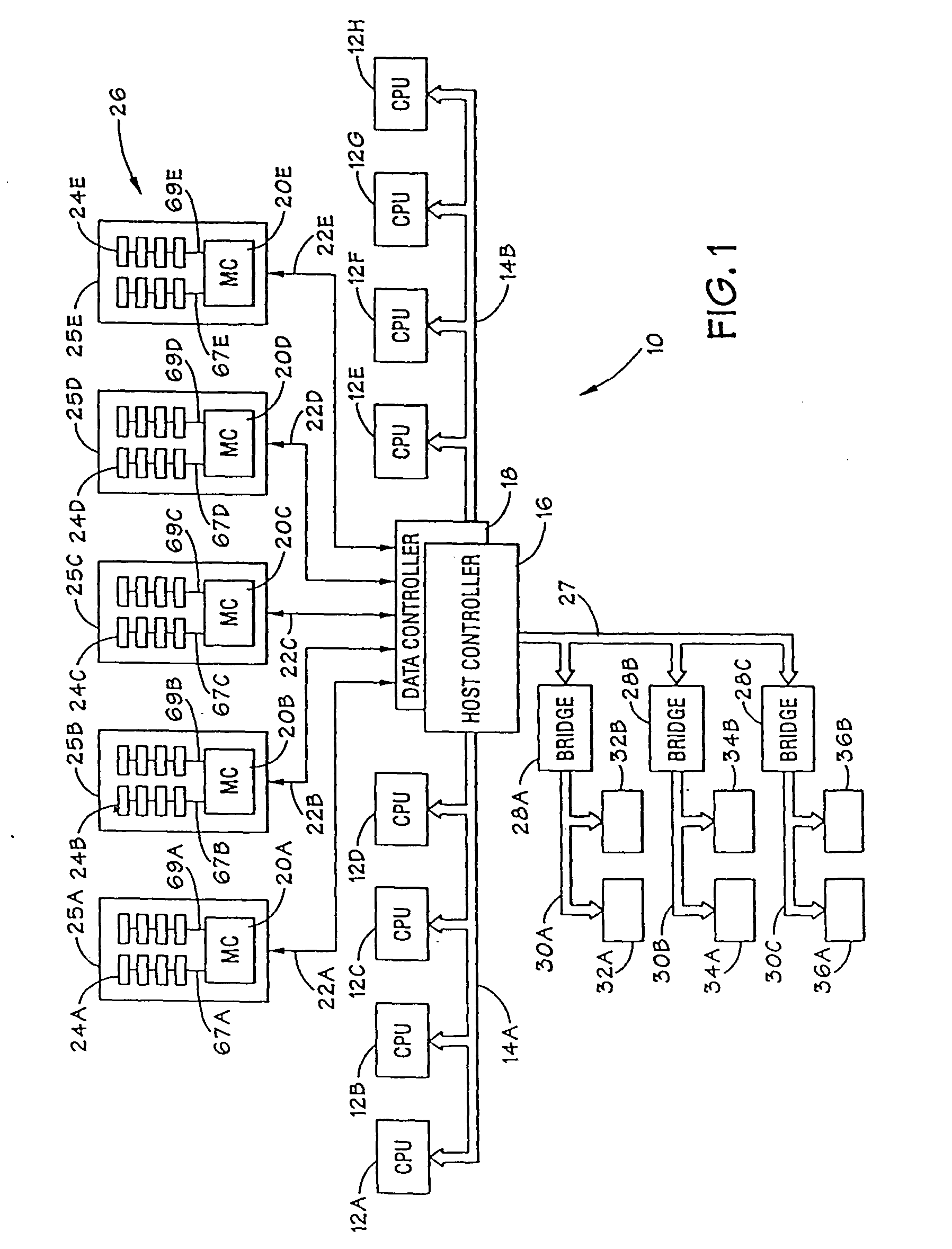

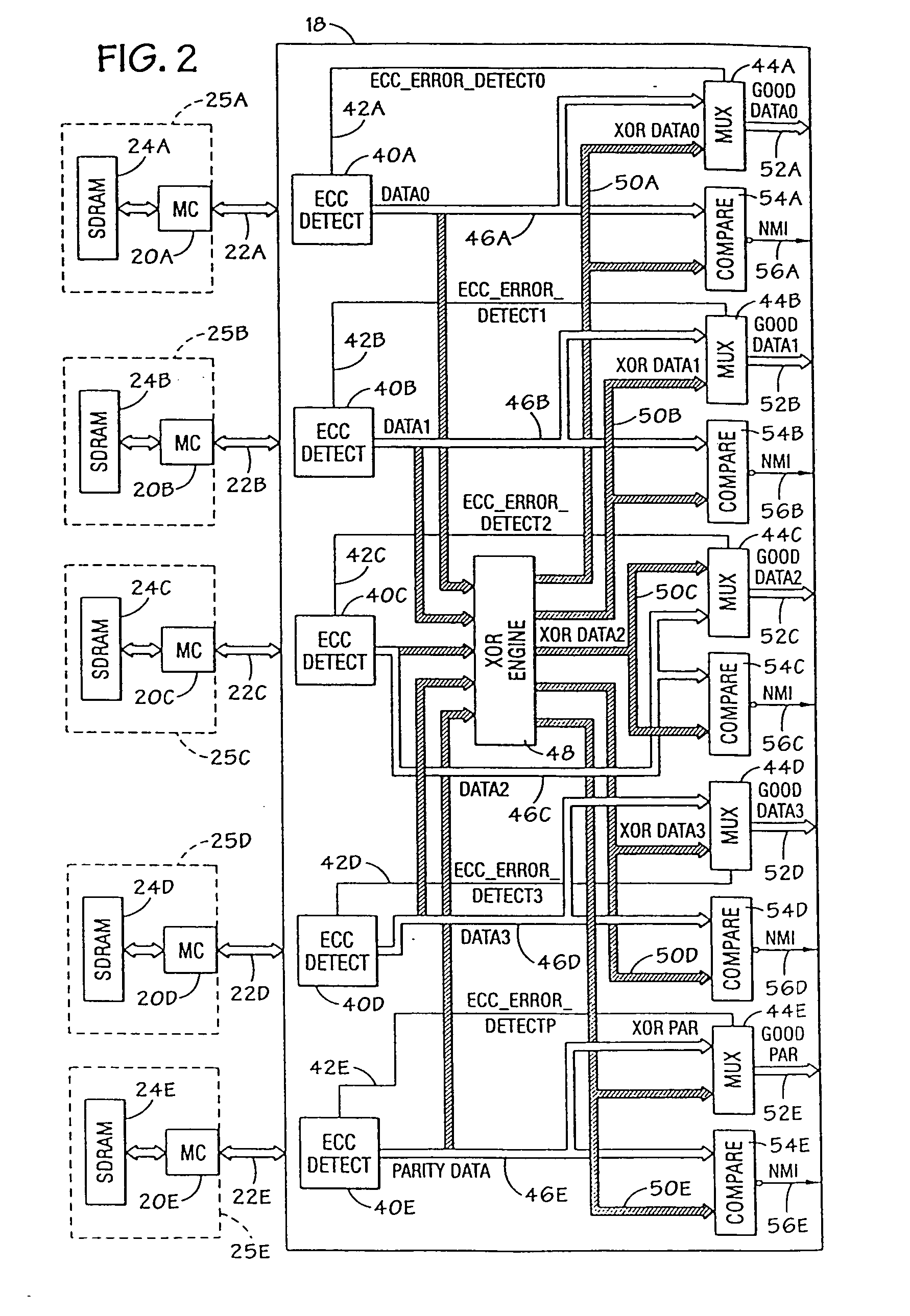

Memory latency and bandwidth optimizations

InactiveUS20040073767A1Memory adressing/allocation/relocationMicro-instruction address formationRAIDComputer architecture

Owner:HEWLETT PACKARD DEV CO LP

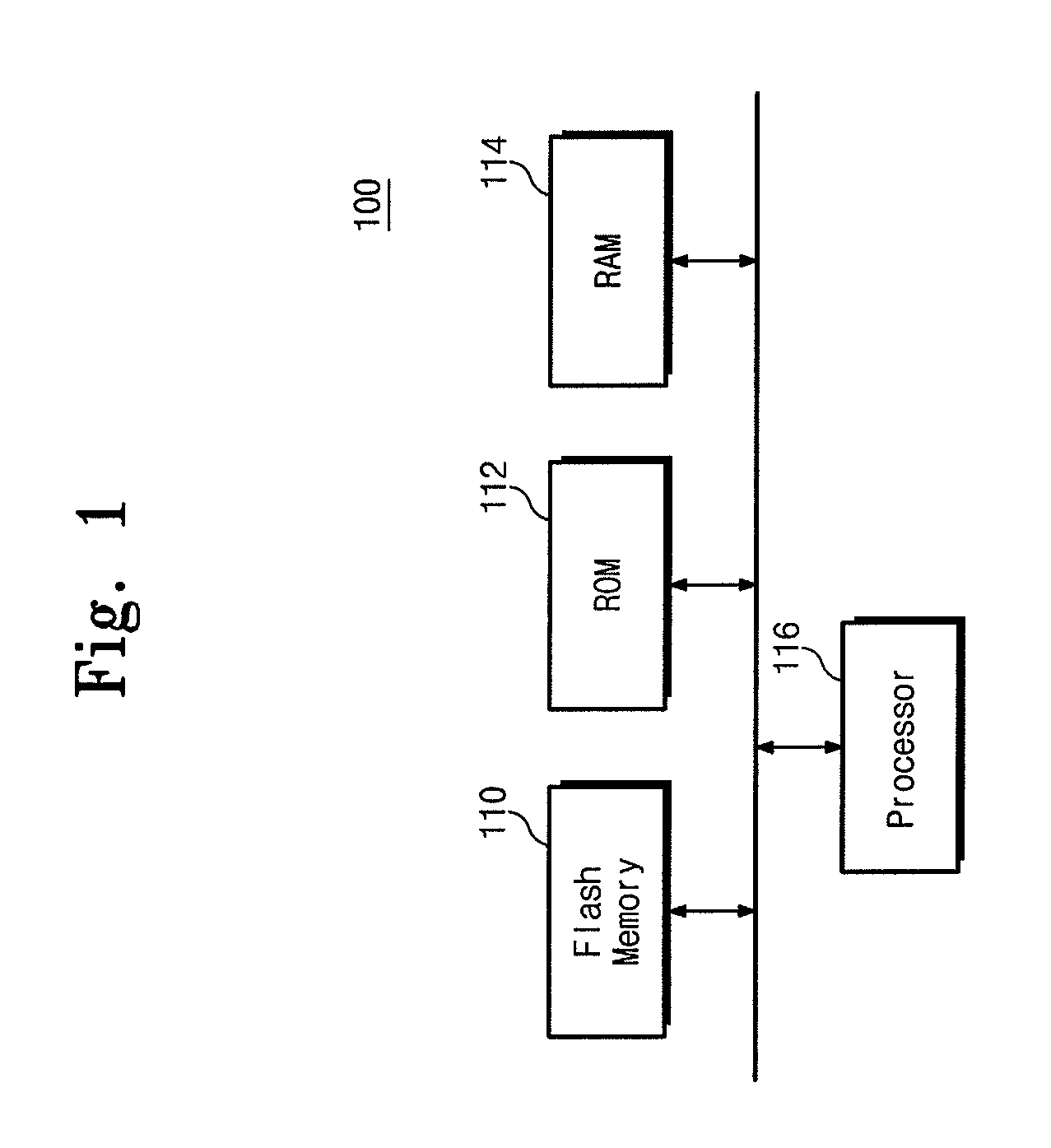

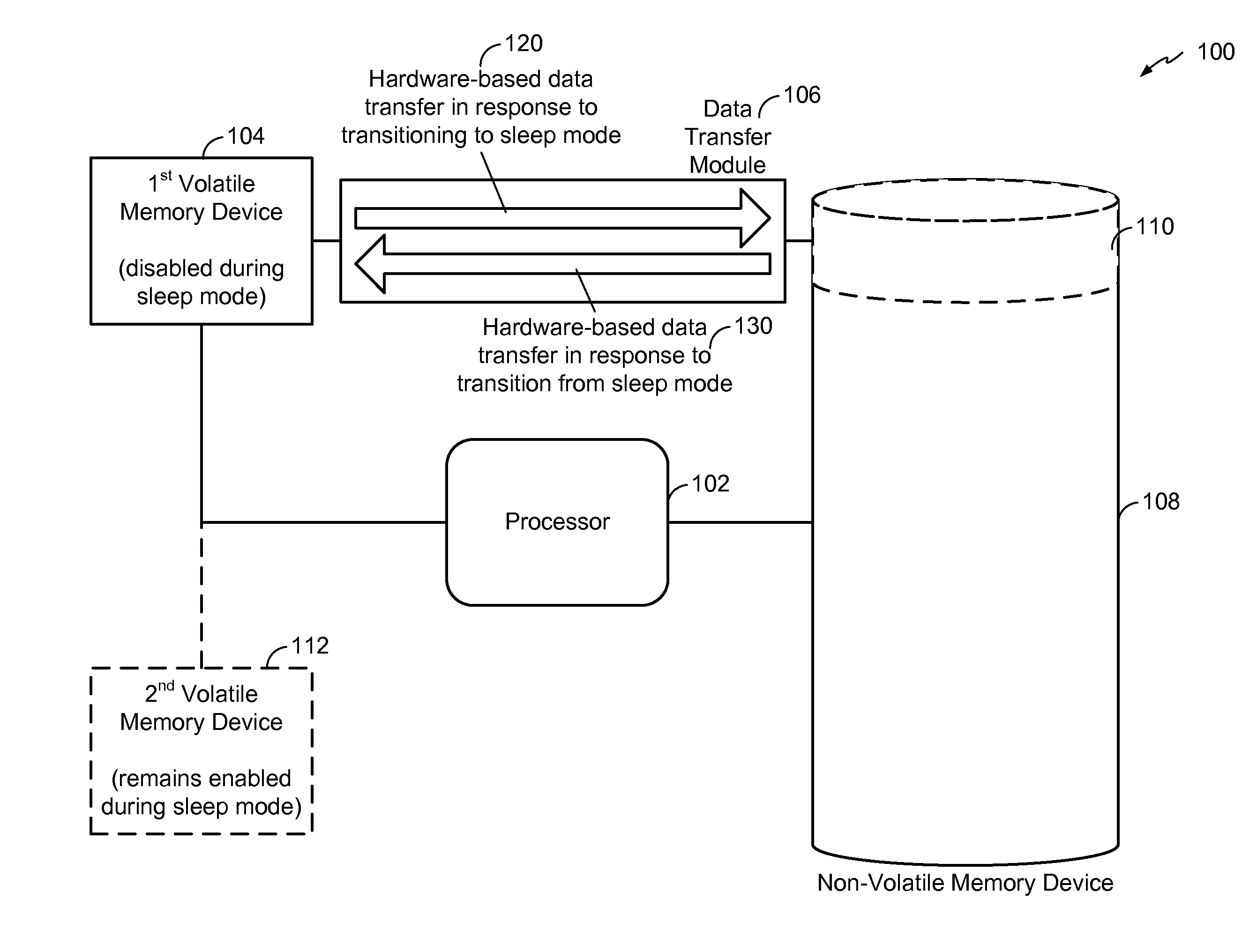

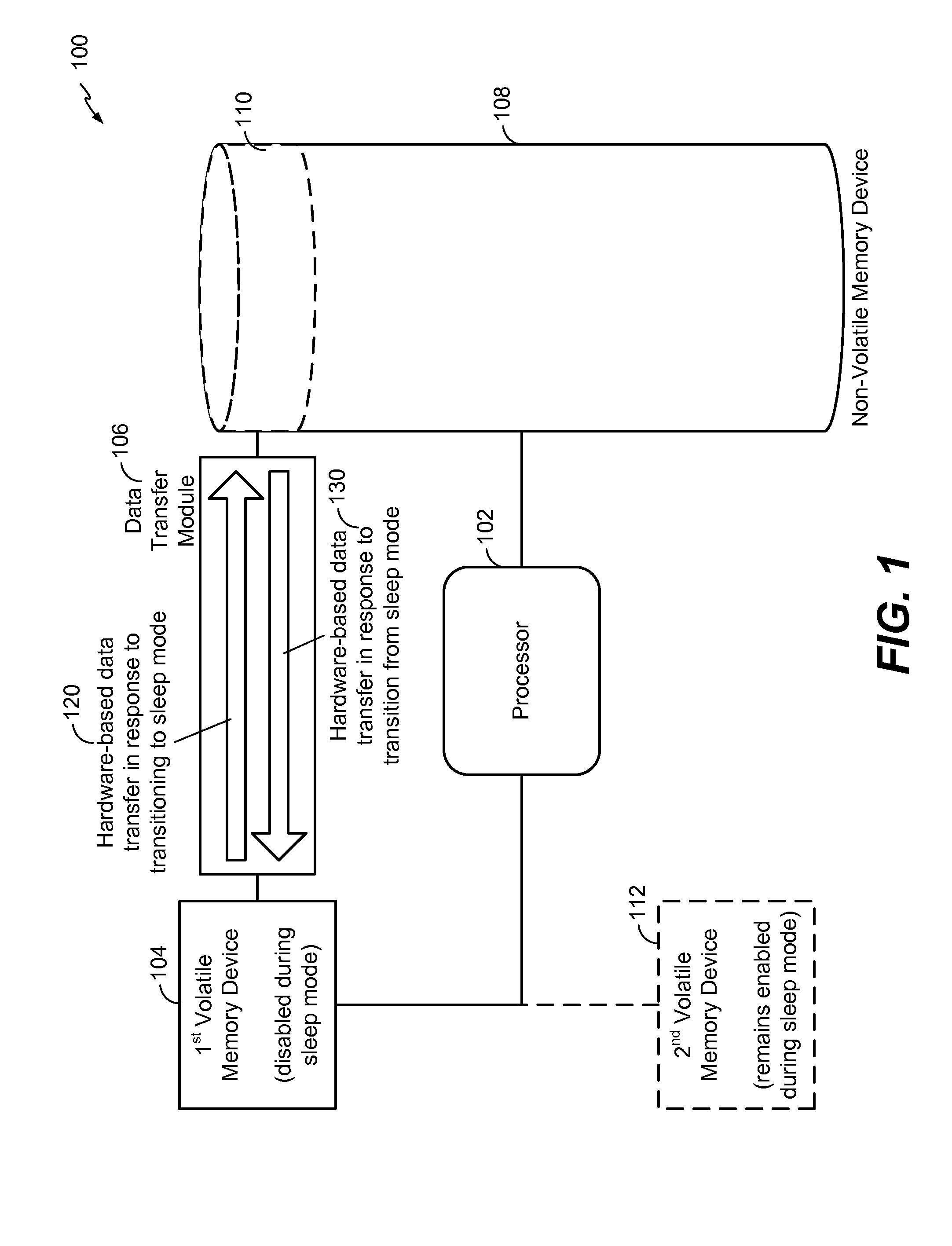

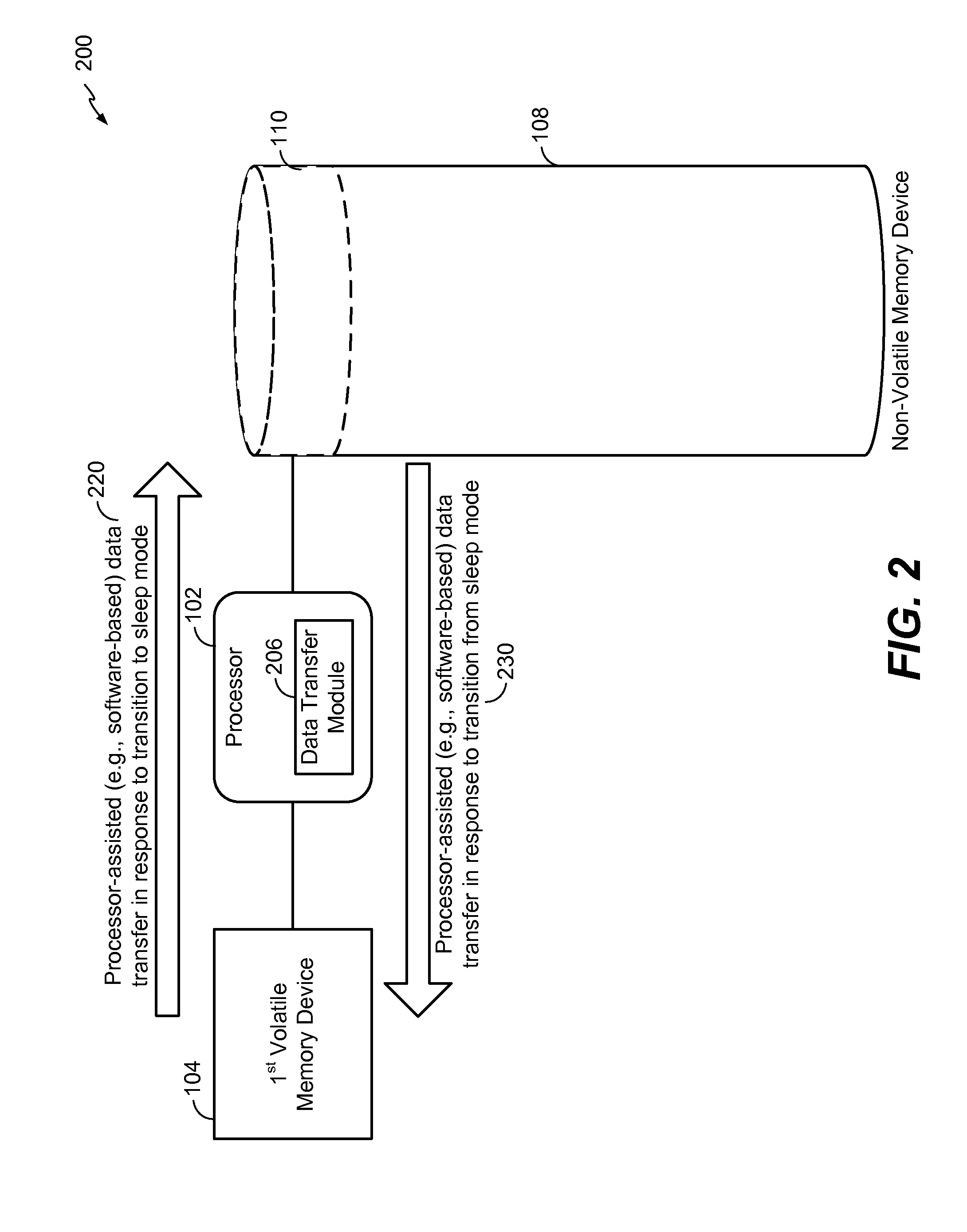

Reducing power consumption of volatile memory via use of non-volatile memory

ActiveUS20140181558A1Reduce performanceMemory adressing/allocation/relocationPower supply for data processingOperation modeComputer science

A method includes initiating a transition from an operating mode to a sleep mode at an electronic device that includes a volatile memory and a non-volatile memory. In response to the initiating, data is copied from the volatile memory to the non-volatile memory and a portion of the volatile memory is disabled. Another method includes determining that a low performance mode condition is satisfied at an electronic device that includes a volatile memory that stores a first copy of read-only data and a non-volatile memory that stores a second copy of the read-only data. A memory mapping of the read-only data is updated from the volatile memory to the non-volatile memory. A portion of the volatile memory that stores the first copy is disabled and access of the read-only data is directed to the non-volatile memory instead of the volatile memory.

Owner:QUALCOMM INC

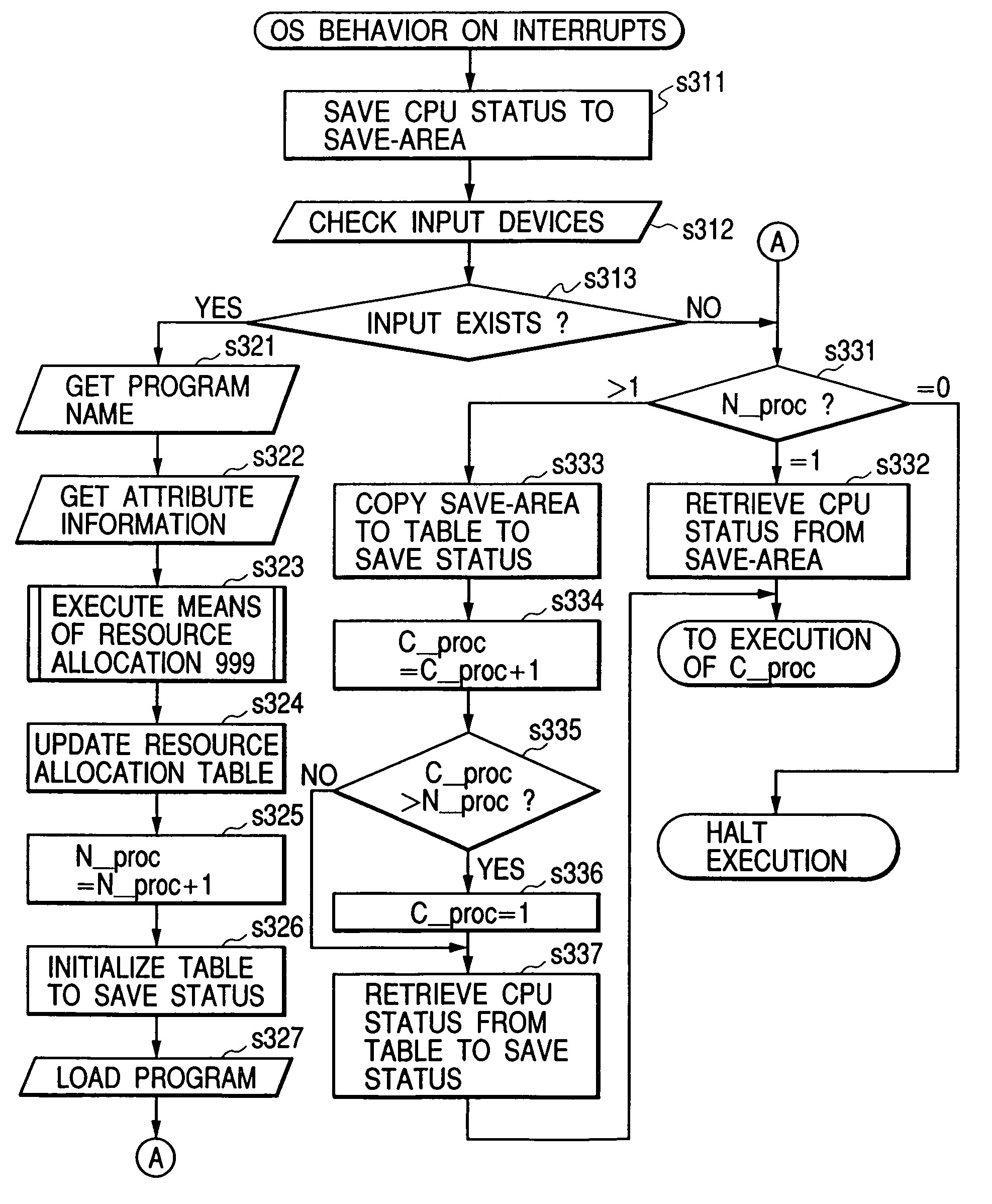

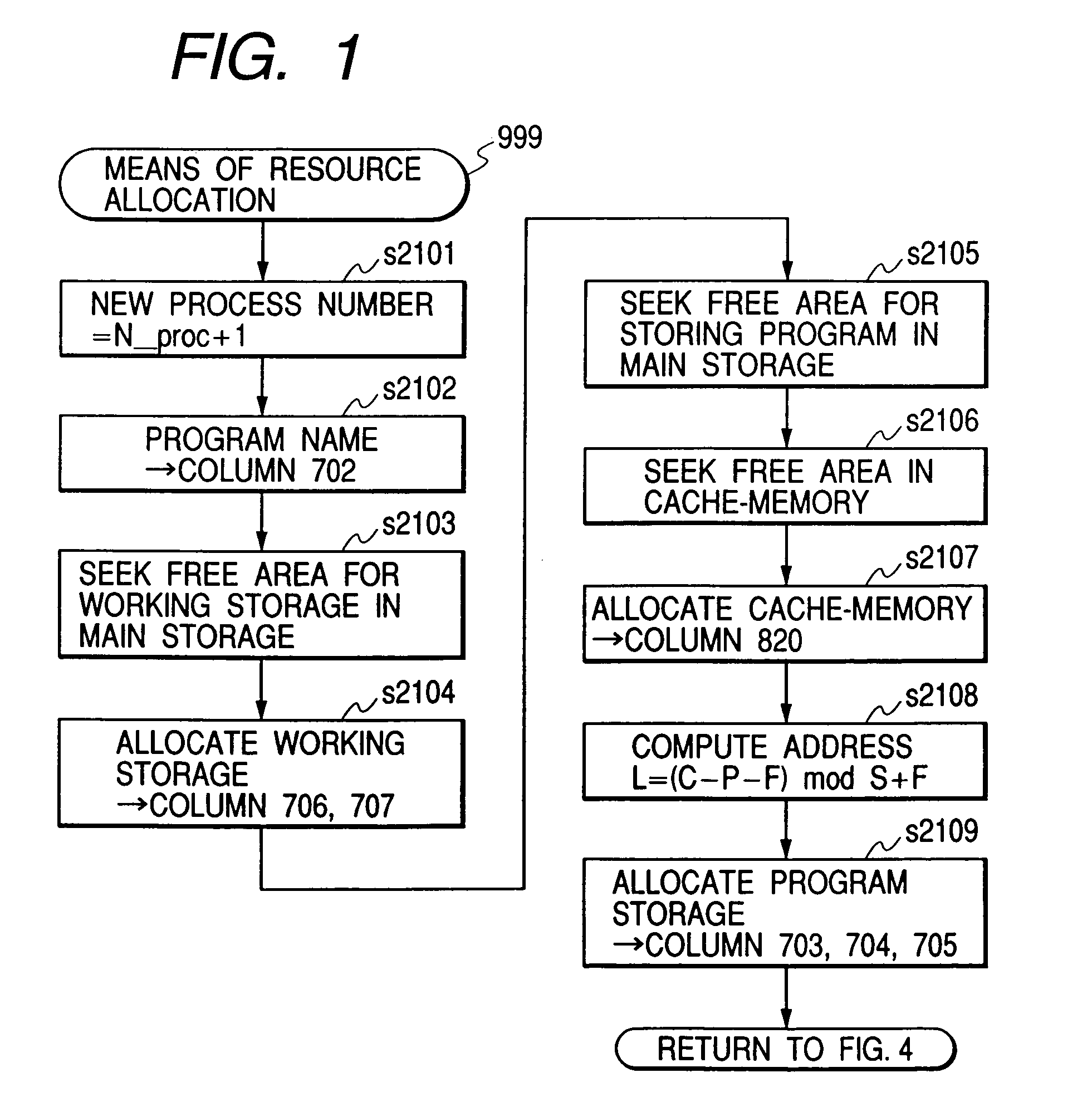

Cache memory allocation method

InactiveUS7000072B1Effective preventive measureAvoid bumpingMemory architecture accessing/allocationData processing applicationsDistribution methodComputerized system

To assure the multiprocessing performance of CPU on a microprocessor, the invention provides a method of memory mapping for multiple concurrent processes, thus minimizing cache thrashing. An OS maintains a management (mapping) table for controlling the cache occupancy status. When a process is activated, the OS receives from the process the positional information for a specific part (principal part) to be executed most frequently in the process and coordinates addressing of a storage area where the process is loaded by referring to the management table, ensuring that the cache address assigned for the principal part of the process differs from that for any other existing process. Taking cache memory capacity, configuration scheme, and process execution priority into account when executing the above coordination, a computer system is designed such that a highest priority process can have a first priority in using the cache.

Owner:HITACHI LTD

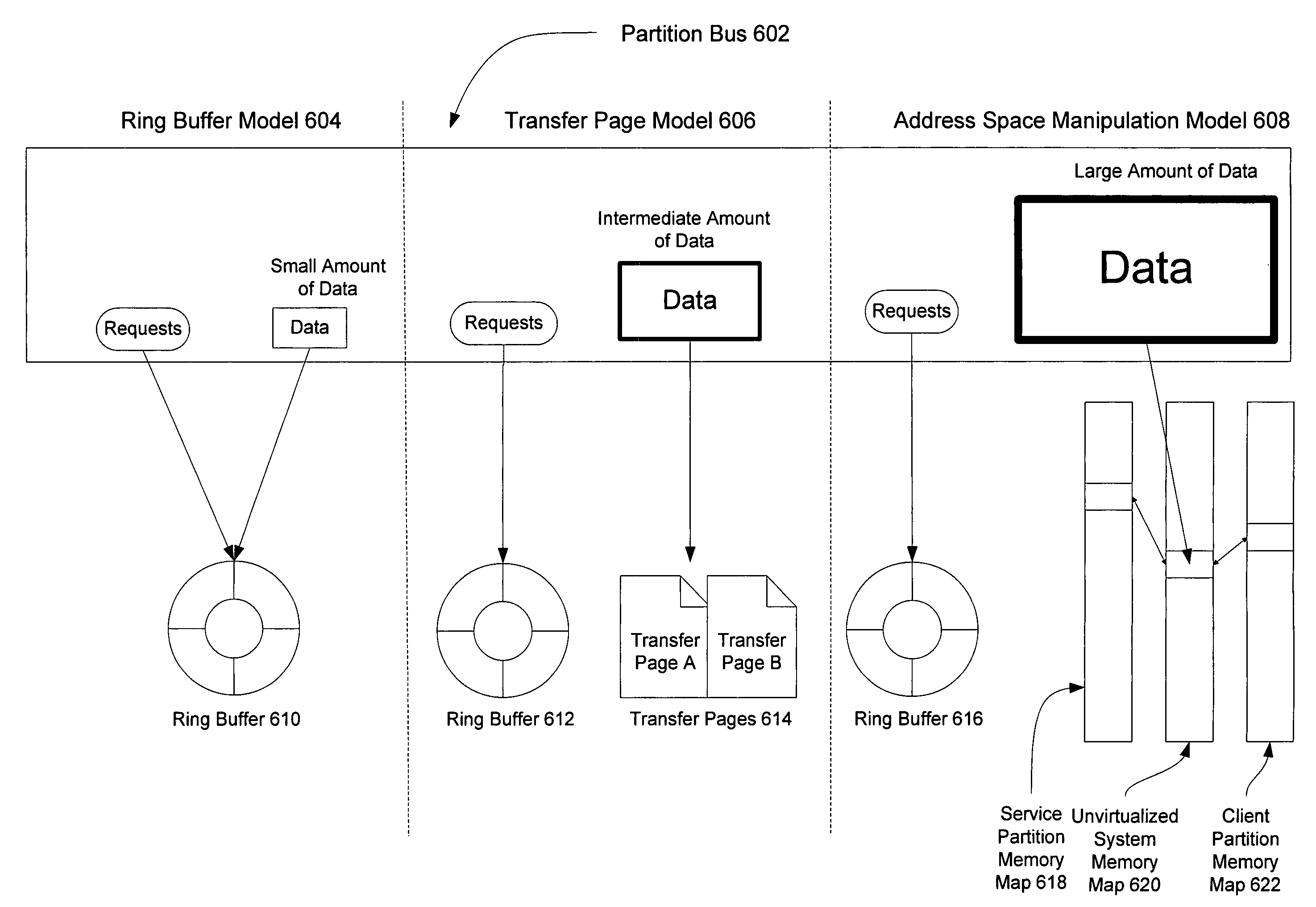

Partition bus

A method and system are provided for integrating partitions in a virtual machine environment. Specifically, a partition bus is provided, where the partition bus operatively connects partitions in such a way that it functions as a data transport mechanism allowing for data transfer and device sharing between partitions. The partition bus relies on virtualizing software in order to establish itself and to establish channels of communication between partitions and to inject interrupts to partitions where it is appropriate to do so. Furthermore, the partition bus employs such mechanisms ring buffers, transfer pages, and memory map changes to transfer information (requests and data). Furthermore, it uses policy agents to decide when information should be transferred or when devices should be shared among partitions. Lastly, it employs various mechanisms to ensure smooth integration between partitions, which includes remote services that have proxy devices and device versioning functionalities.

Owner:MICROSOFT TECH LICENSING LLC

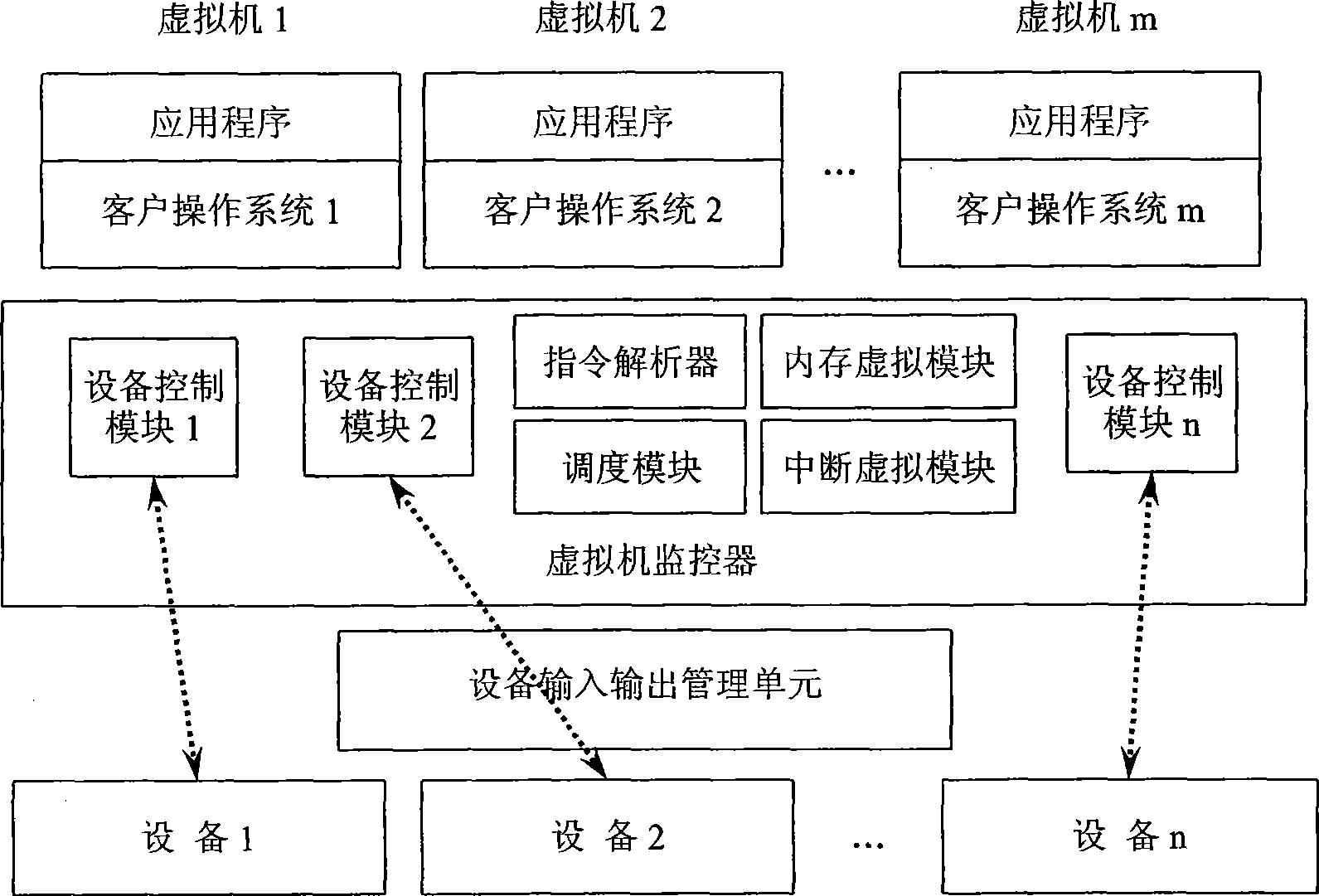

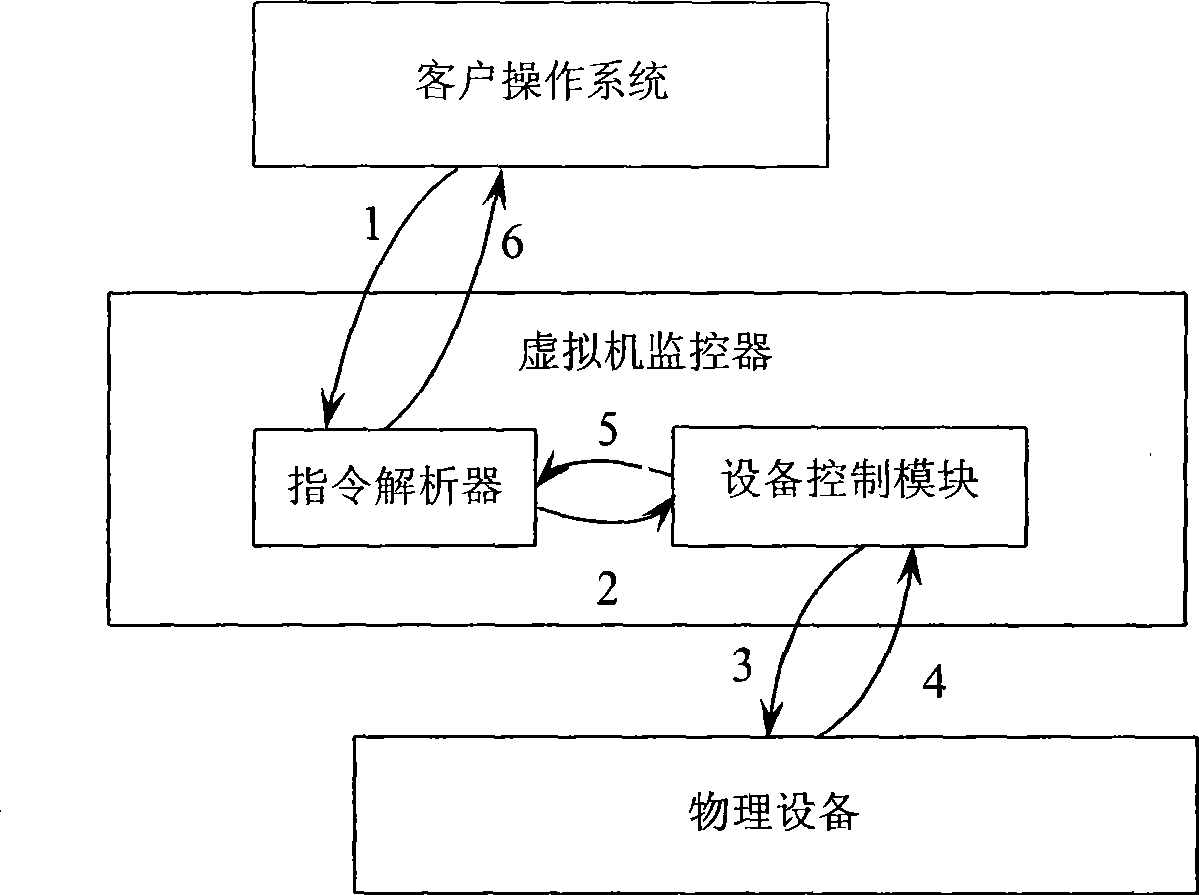

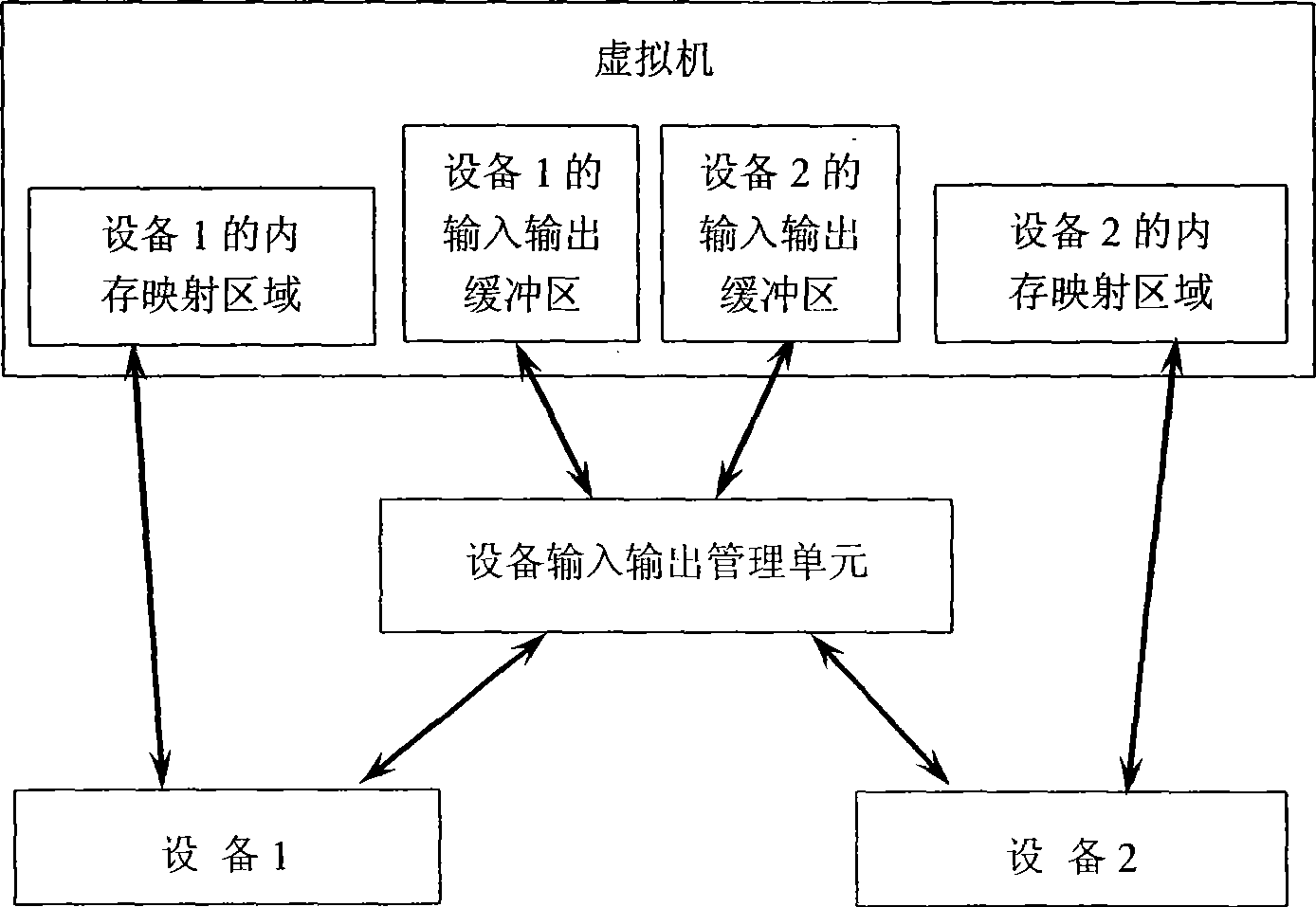

Virtual machine system based on the management technology of equipment access storage and equipment access control method thereof

InactiveCN101520738AReduce switching overheadImprove performanceSoftware simulation/interpretation/emulationOperational systemBottle neck

The invention provides a virtual machine system based on the management technology of equipment access storage and an equipment access control method thereof. The virtual machine system comprises a virtual machine monitor, an underlying hardware supporting the management technology of storage for equipment input and output, an equipment control module and a plurality of virtual machines; wherein the virtual machine monitor comprises a scheduling module which can schedule different virtual machines to run on a processor, a memory virtualization module used for completing memory management of the virtual system, an interrupt virtualization module, an instruction analyzer, a privilege calling interface used for providing services for privilege entity and a control module of a storage management unit of equipment input and output. In the virtual machine system, one equipment control module corresponds to physical equipment and is responsible for initiating privilege calling to the virtual machine monitor, receiving and executing an equipment port access instruction transmitted by the virtual machine monitor, detecting equipment state and hiding the virtualization equipment resources and the like. In the equipment access method provided by the invention, a client operating system in the virtual machine can access equipment data by a memory mapping mode; and the equipment utilizes the equipment access storage management technology to carry out direct storage access to virtual machine data. The virtual machine system and the equipment access control method lead the equipment performance to be improved greatly, relieve the system performance bottle-neck, and improve safety of equipment access control. The equipment access control method does not need to modify the client operating system, is easy to be realized and has wide application range.

Owner:黄歆媚

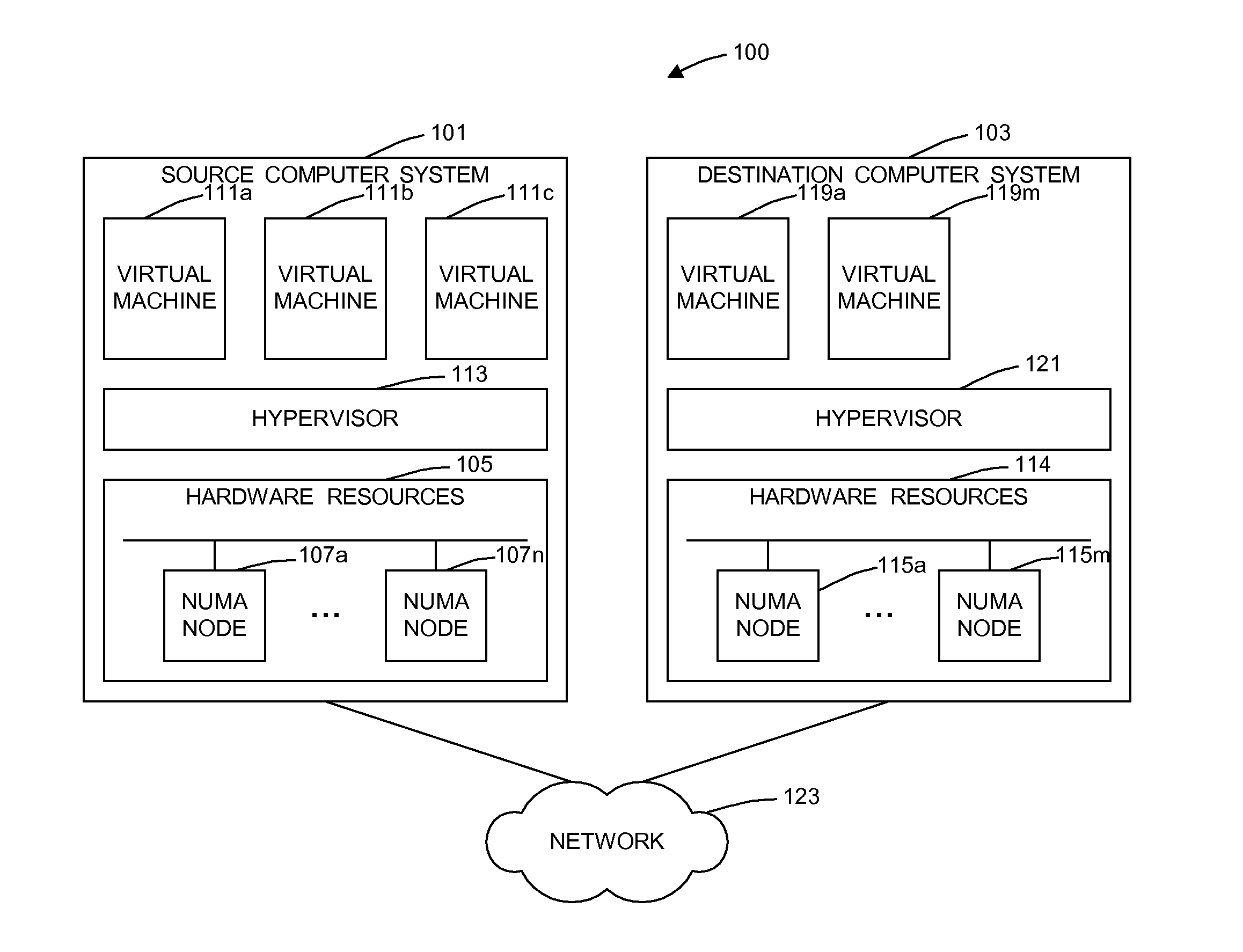

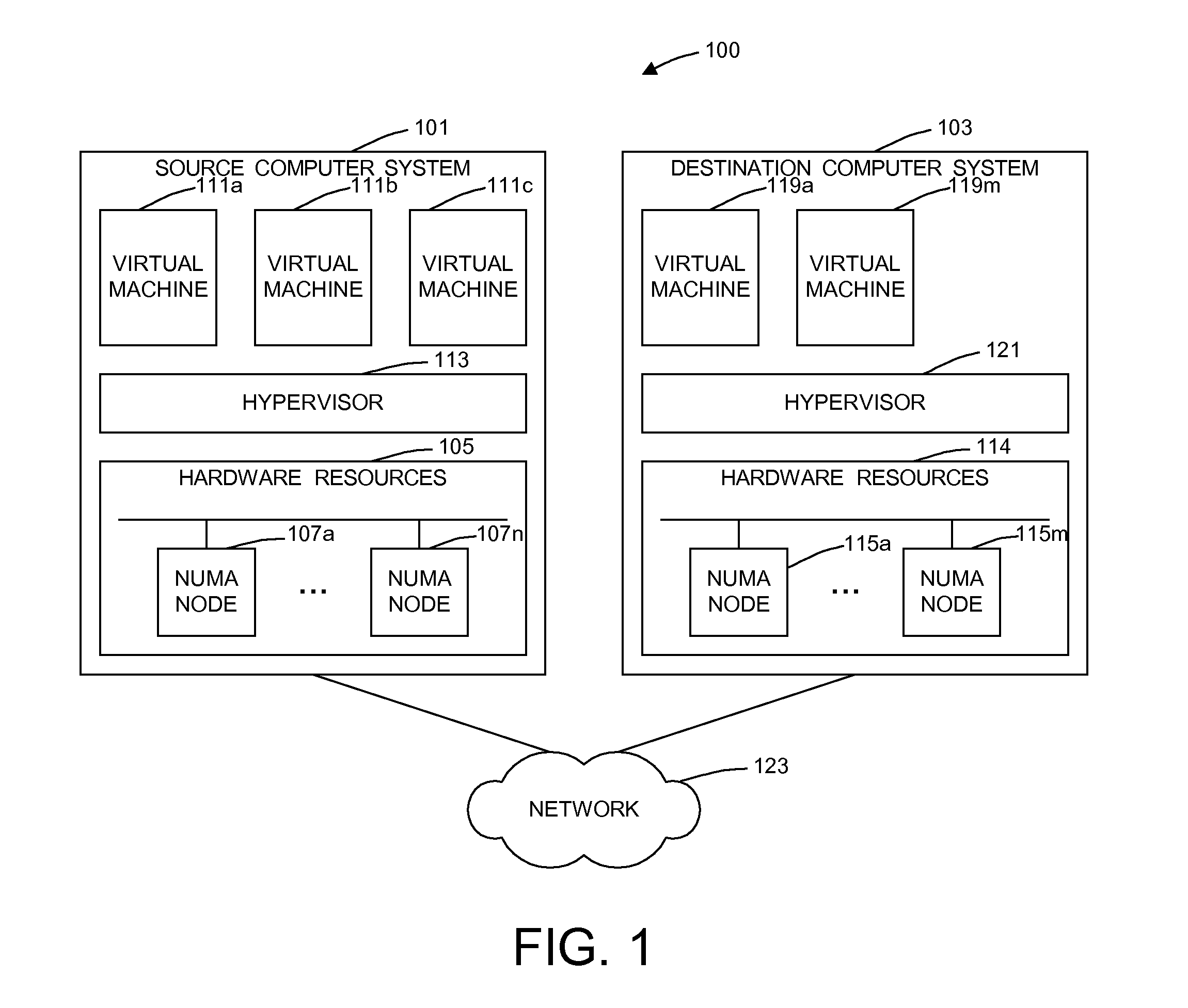

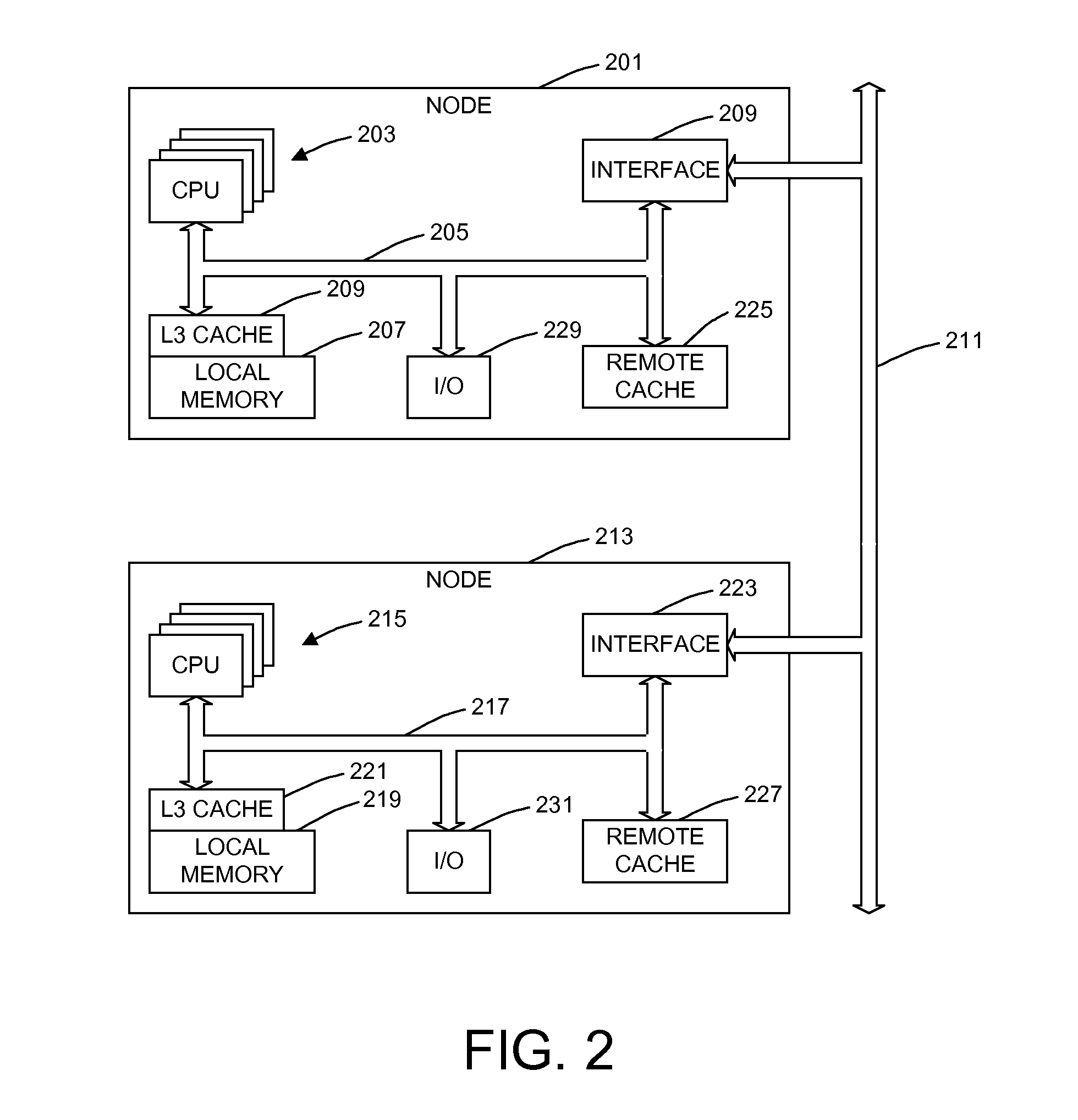

Dynamic memory affinity reallocation after partition migration

ActiveUS20120102258A1Memory adressing/allocation/relocationComputer security arrangementsProcessor nodeComputerized system

A method of dynamically reallocating memory affinity in a virtual machine after migrating the virtual machine from a source computer system to a destination computer system migrates processor states and resources used by the virtual machine from the source computer system to the destination computer system. The method maps memory of the virtual machine to processor nodes of the destination computer system. The method deletes memory mappings in processor hardware, such as translation lookaside buffers and effective-to-real address tables, for the virtual machine on the destination computer system. The method starts the virtual machine on the destination computer system in virtual real memory mode. A hypervisor running on the destination computer system receives a page fault and virtual address of a page for said virtual machine from a processor of the destination computer system and determines if the page is in local memory of the processor. If the hypervisor determines the page to be in the local memory of the processor, the hypervisor returning a physical address mapping for the page to the processor. If the hypervisor determines the page not to be in the local memory of the processor, the hypervisor moves the page to local memory of the processor and returns a physical address mapping for said page to the processor.

Owner:IBM CORP

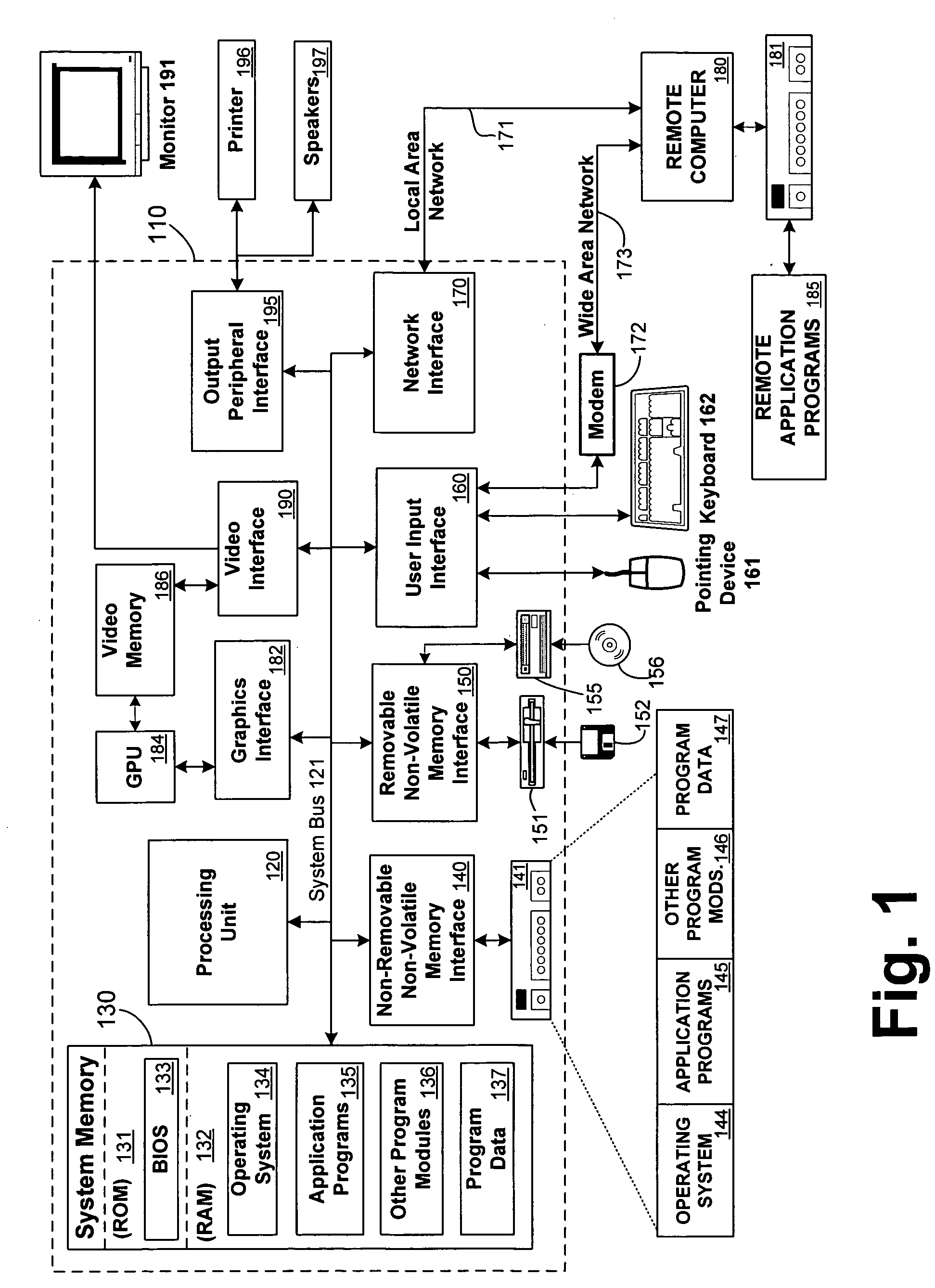

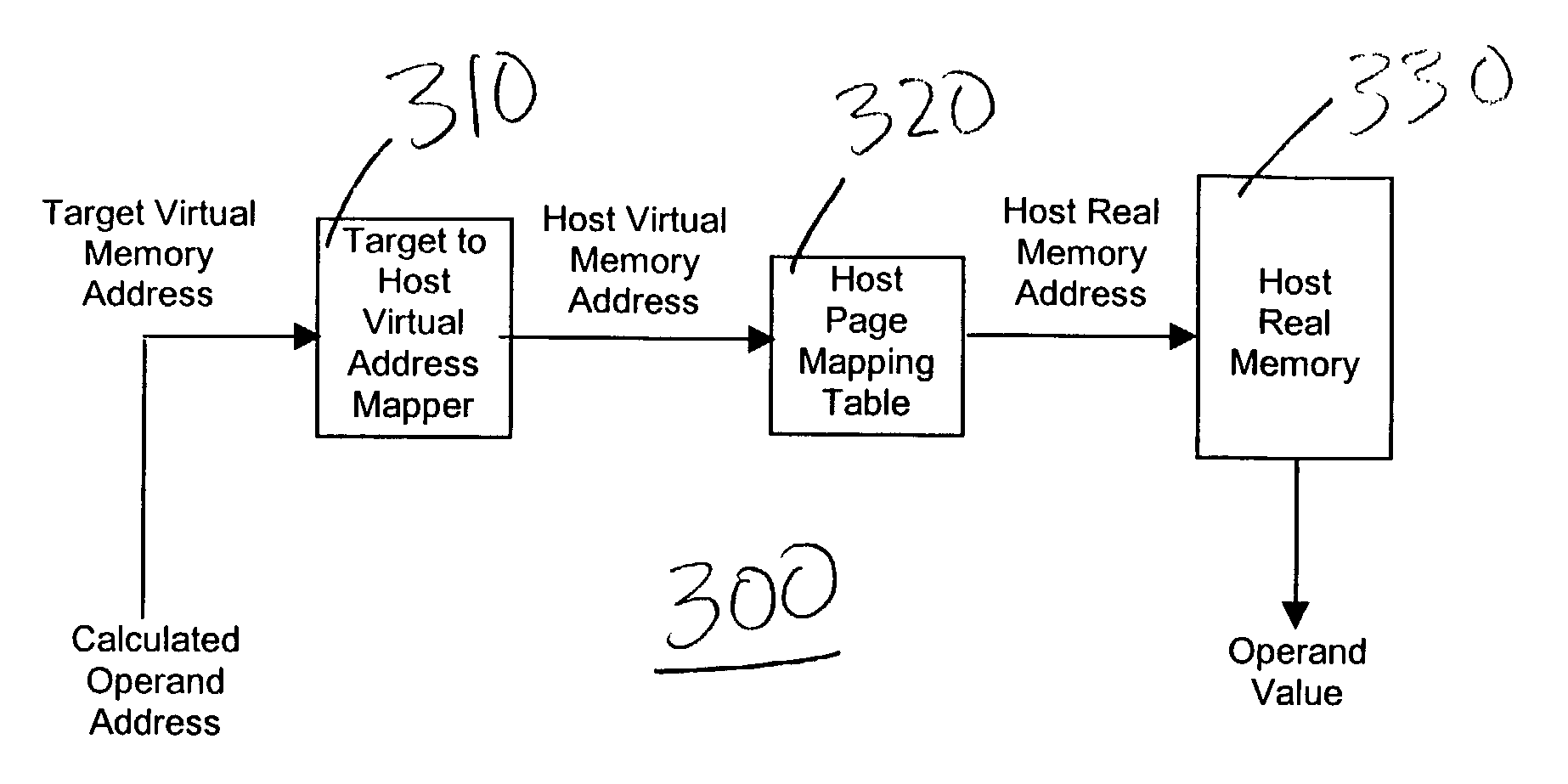

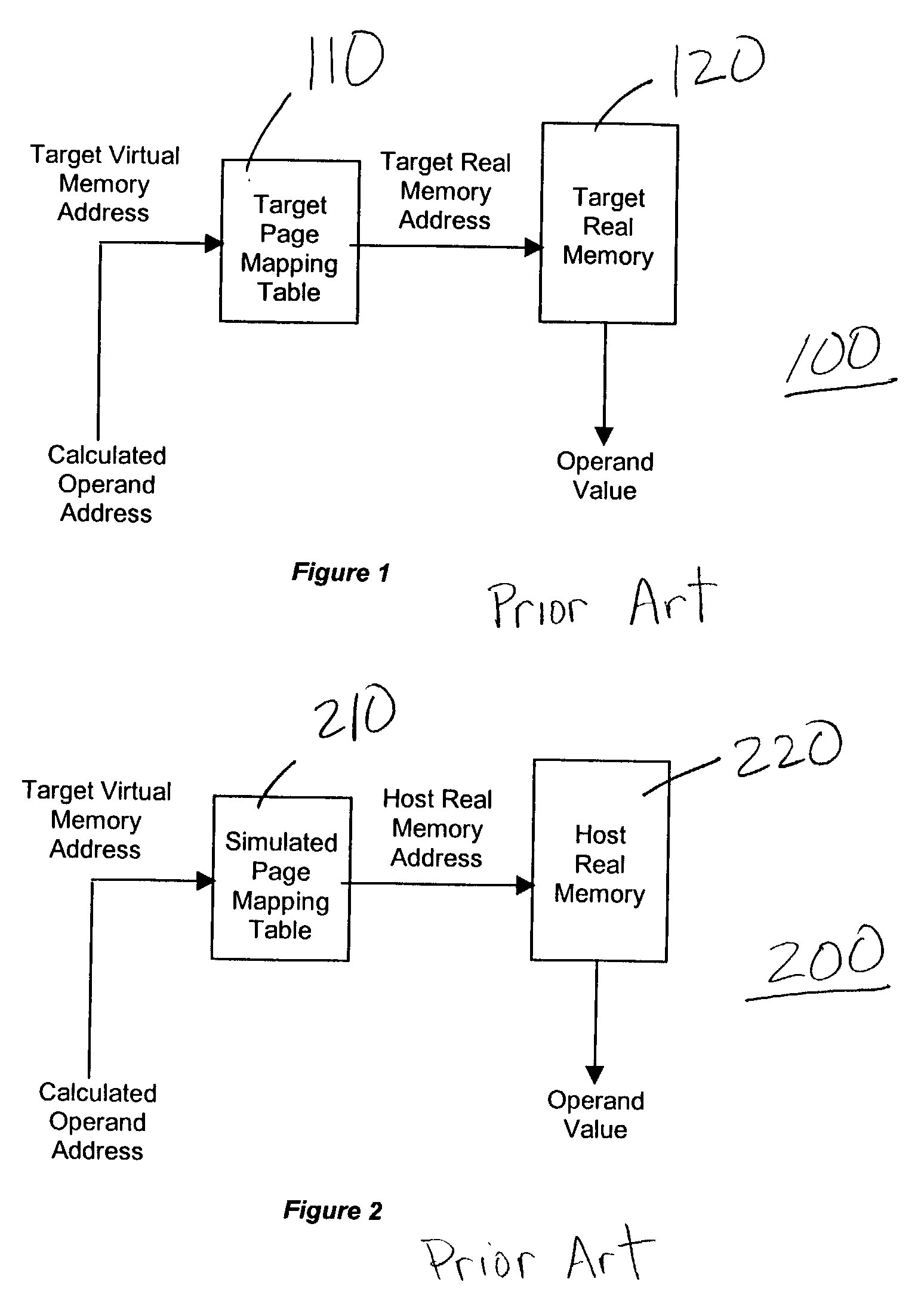

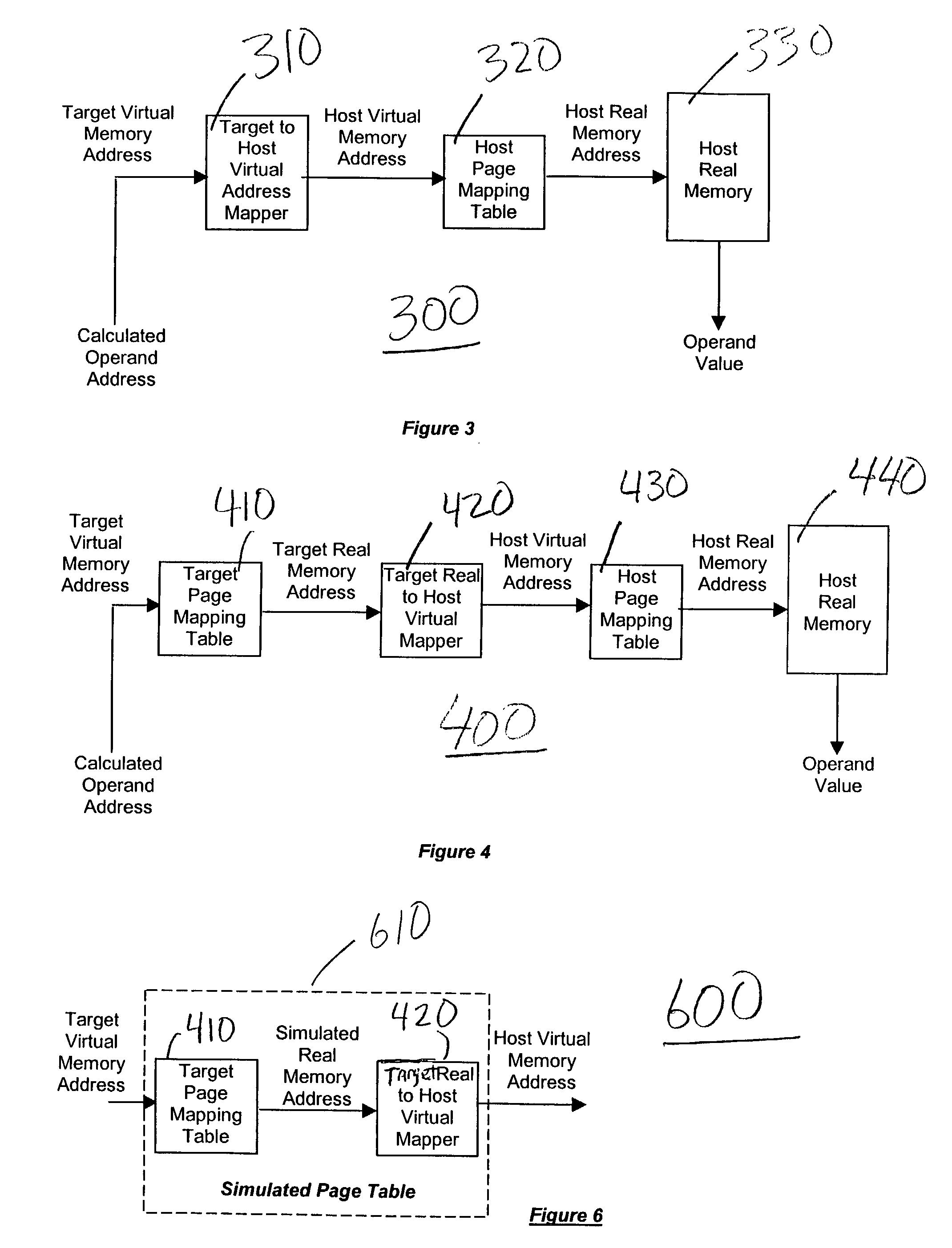

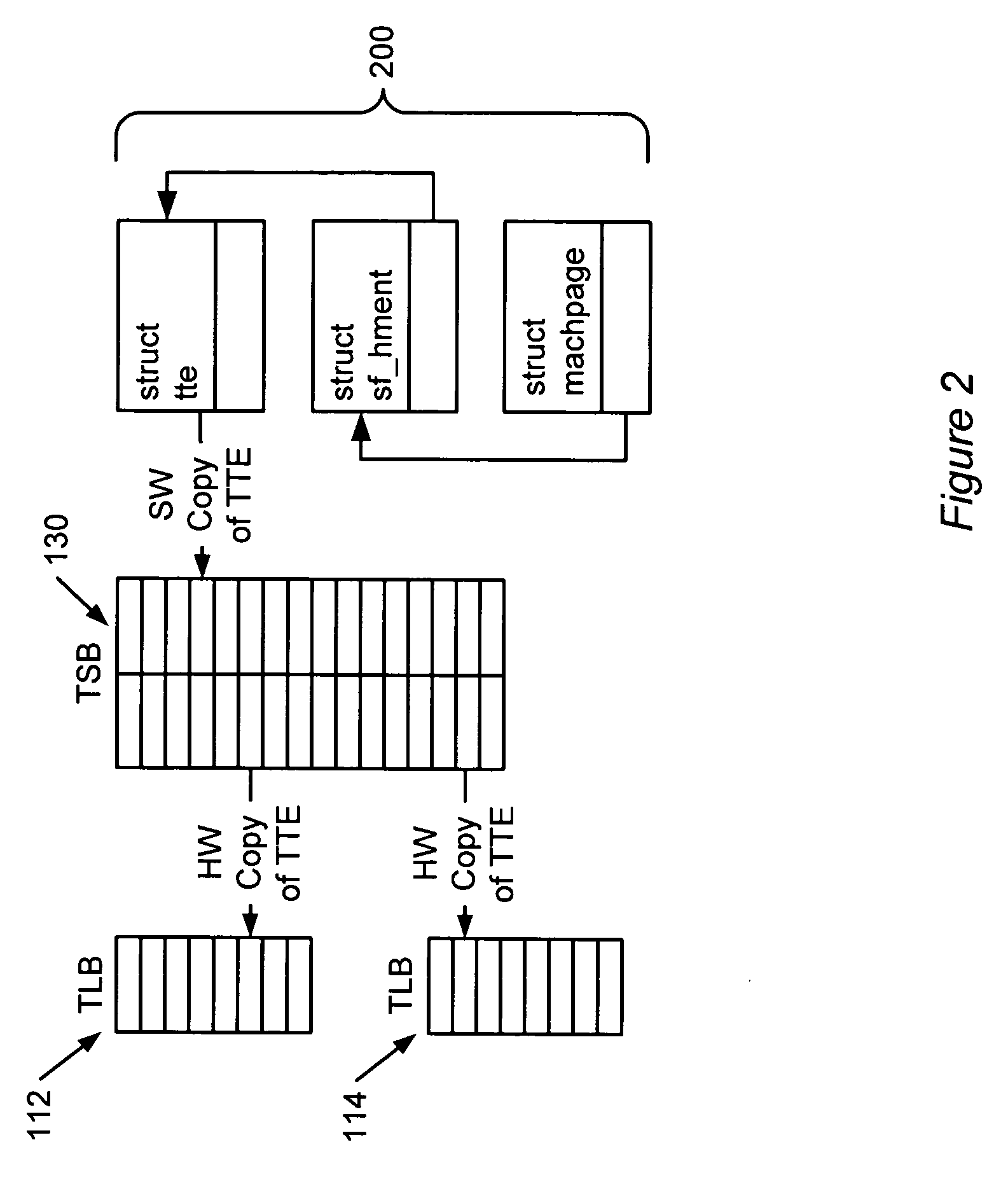

Method and system for efficient emulation of multiprocessor address translation on a multiprocessor host

ActiveUS20040054518A1Efficient mappingEfficiently maps the shared memoryError detection/correctionMemory adressing/allocation/relocationVirtual memoryMemory address

A method (and system) for emulating a target system's memory addressing using a virtual-to-real memory mapping mechanism of a host multiprocessor system's operating system, includes inputting a target virtual memory address into a simulated page table to obtain a host virtual memory address. The target system is oblivious to the software it is running on.

Owner:IBM CORP

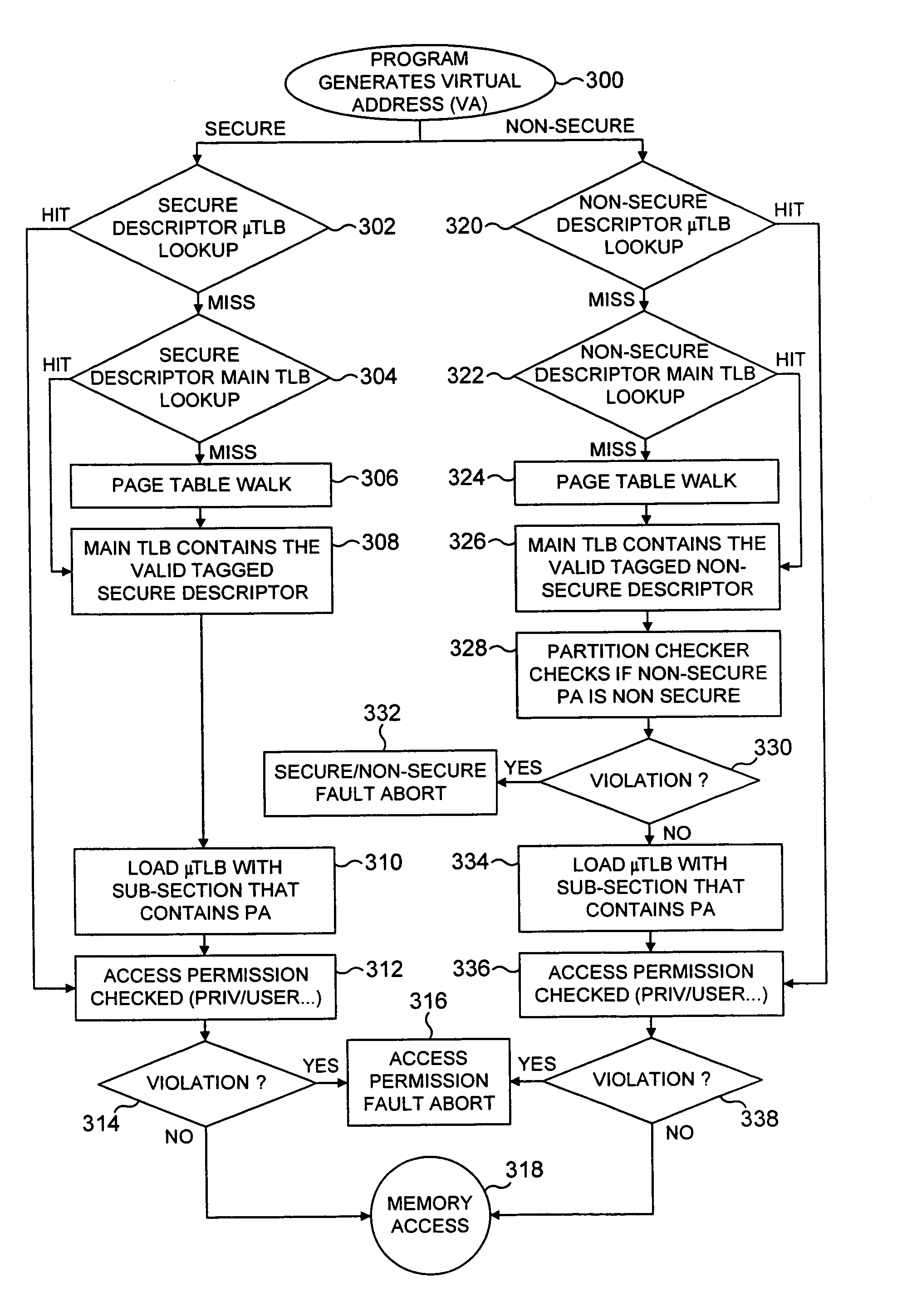

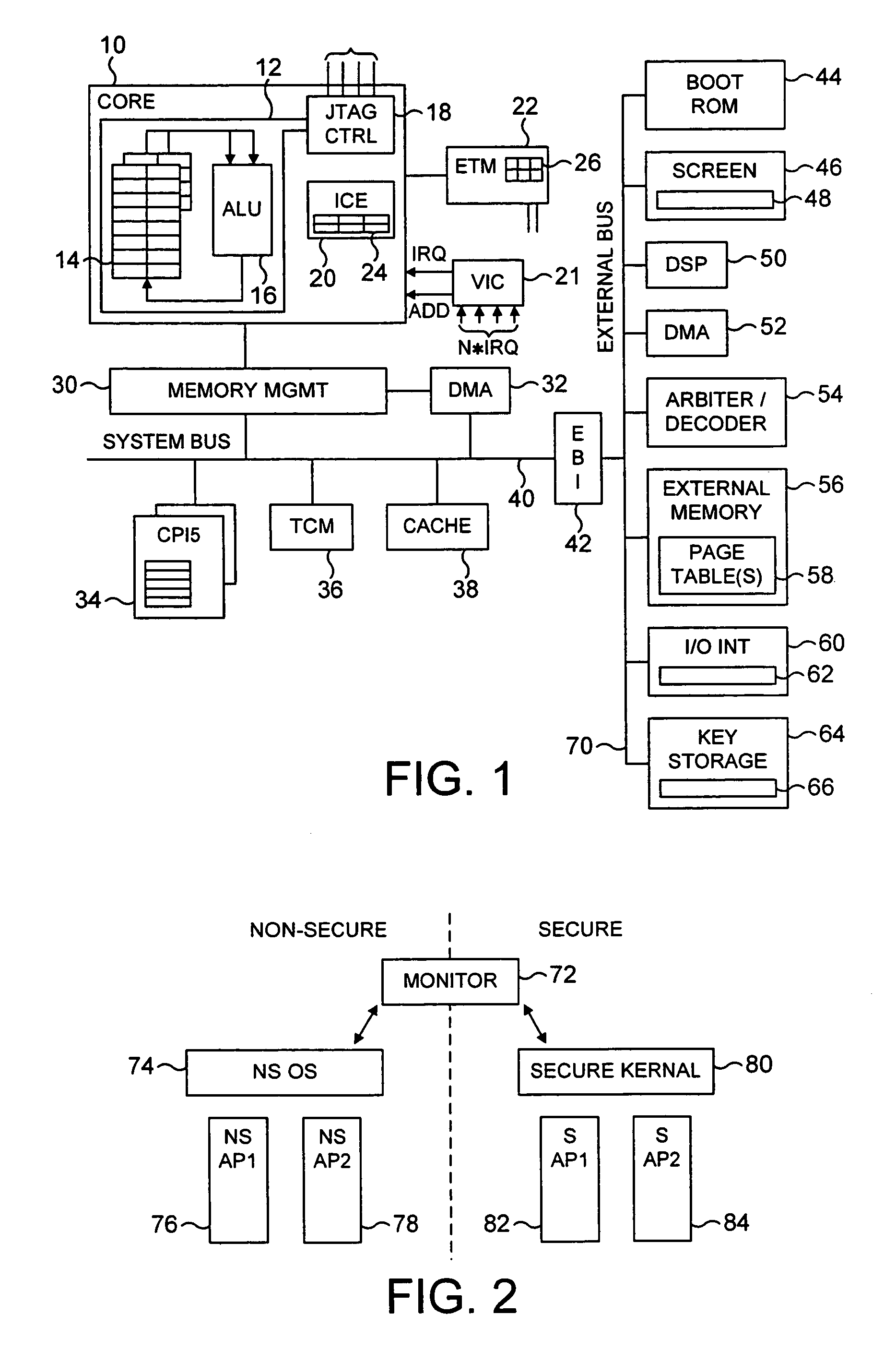

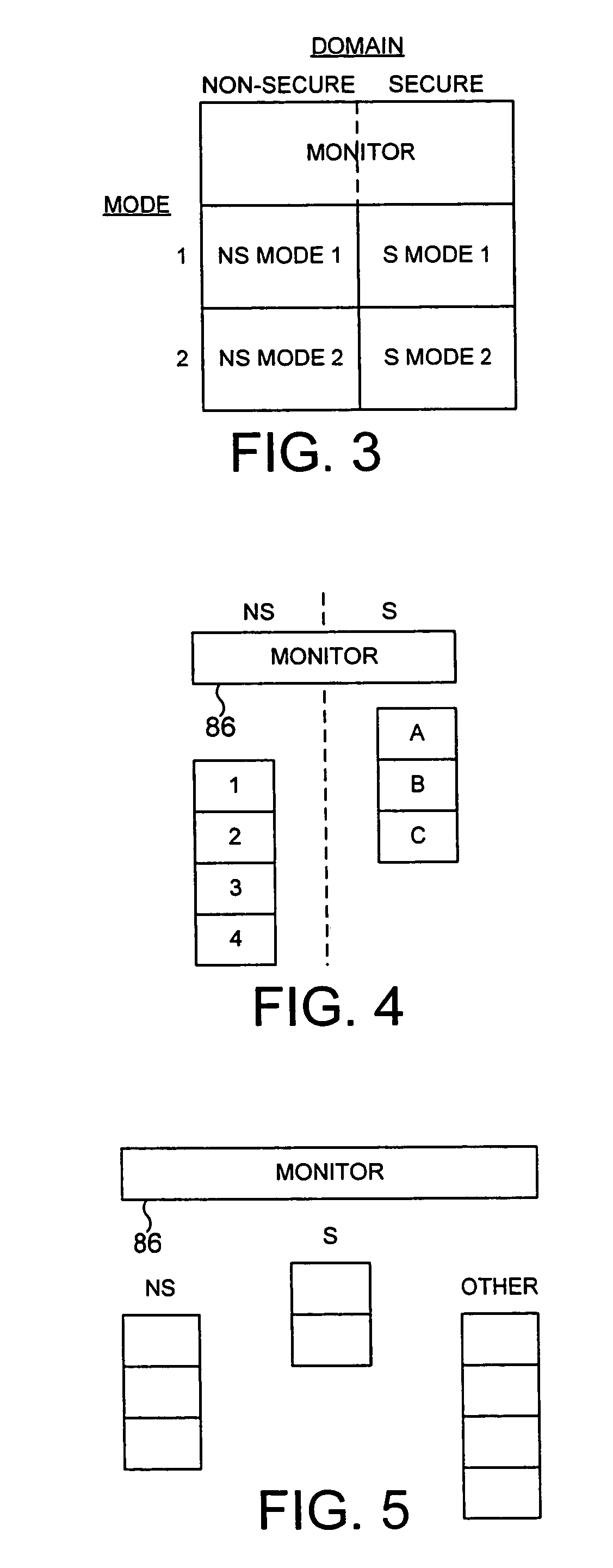

Virtual to physical memory address mapping within a system having a secure domain and a non-secure domain

ActiveUS7124274B2Reduce the possibilityImprove securityProgram initiation/switchingMemory adressing/allocation/relocationMemory addressProcessor register

An apparatus for processing data, the apparatus comprising: a processor operable in a plurality of modes and either a secure domain or a non-secure domain including at least one secure mode being a mode in the secure domain; and at least one non-secure mode being a mode in the non-secure domain. When the processor is executing a program in a secure mode, the program has access to secure data which is not accessible when the processor is operating in a non-secure mode. The processor further includes a non-secure translation table base address register and a secure translation table base address register operable in the non-secure and secure domain, respectively, to indicate a region of memory storing either non-secure or secure domain memory mapping data defining how virtual addresses are translated to physical addresses within either the non-secure or secure domain.

Owner:ARM LTD

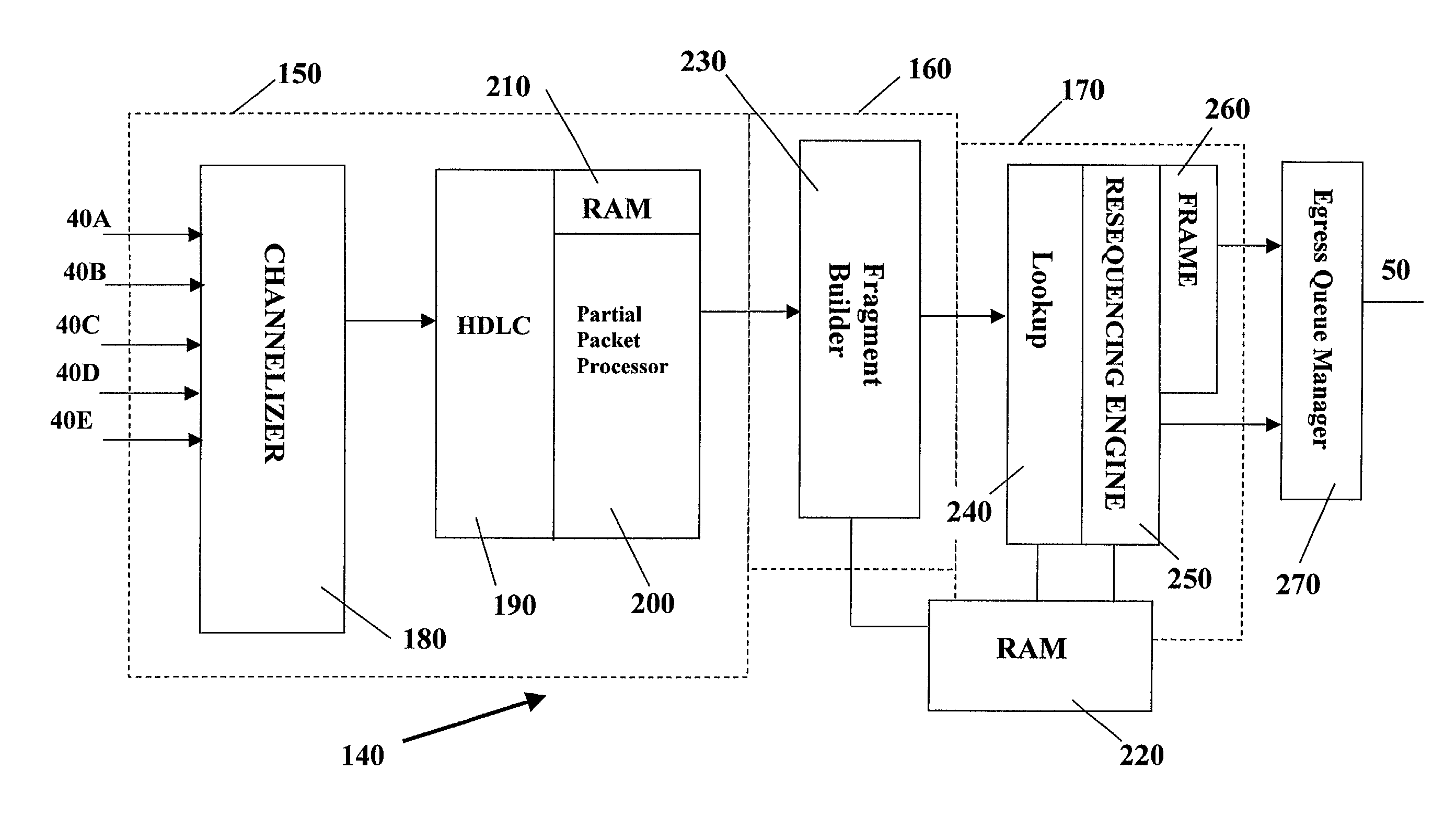

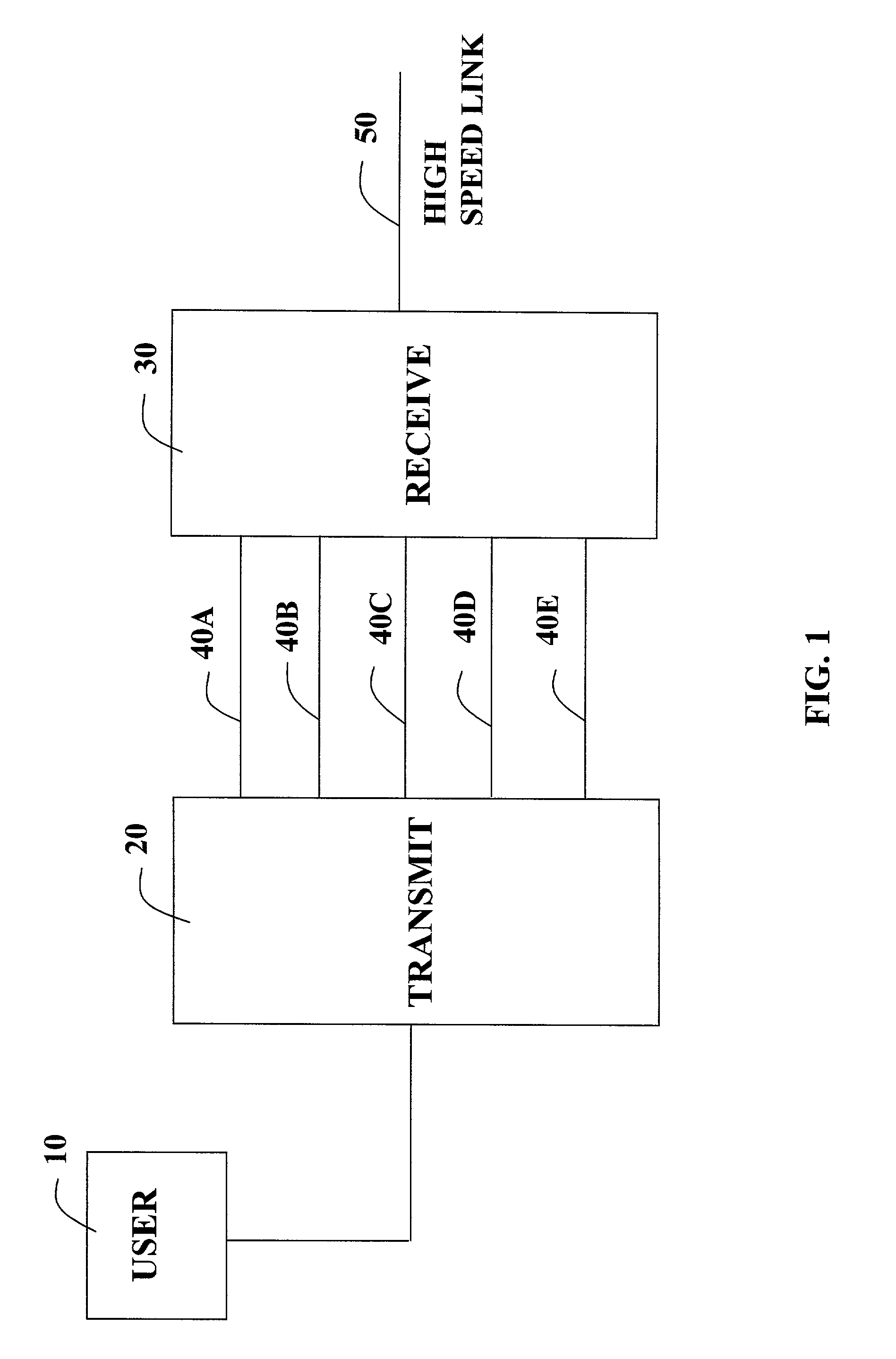

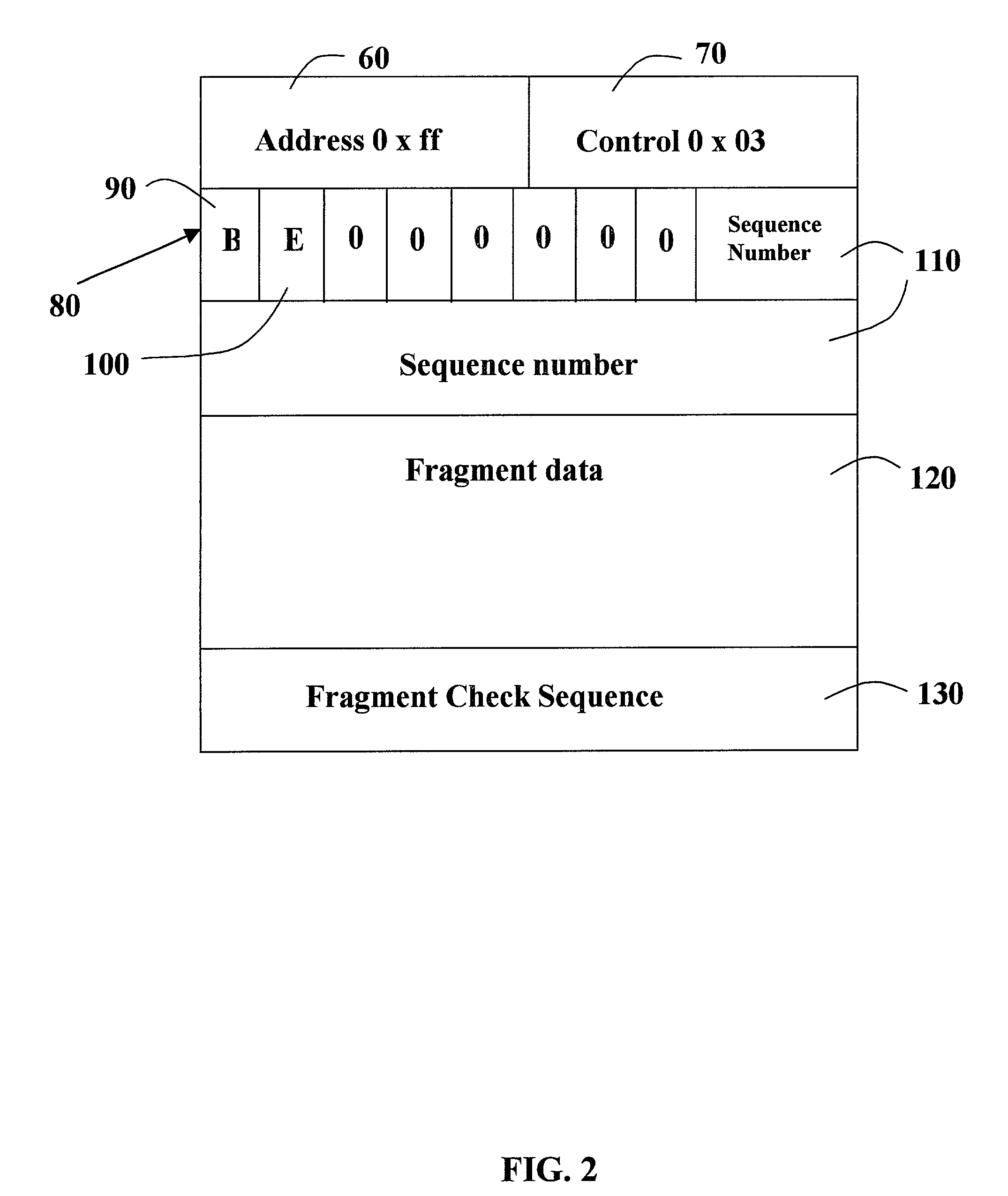

Reassembly engines for multilink applications

InactiveUS7027443B2Time-division multiplexData switching by path configurationNetwork packetMemory mapping

Methods, systems, and apparatus for processing packet fragments for reassembly into packets. Datastreams containing packet fragments are received and data corresponding to different channels are segregated. For each channel, data is then aggregated to recreate packet fragments. Once the fragments are recreated, they are, if required, resequenced using a two-tier memory mapping structure where only pointers, and not the fragments, are manipulated. After resequencing fragments to reassemble the packet, the reassembled packet is dispatched to its ultimate destination. The present invention also provides a method of load balancing between multiple links when packet fragments are transmitted from a fragmenting node through a multiple link bundle.

Owner:MICROSEMI STORAGE SOLUTIONS

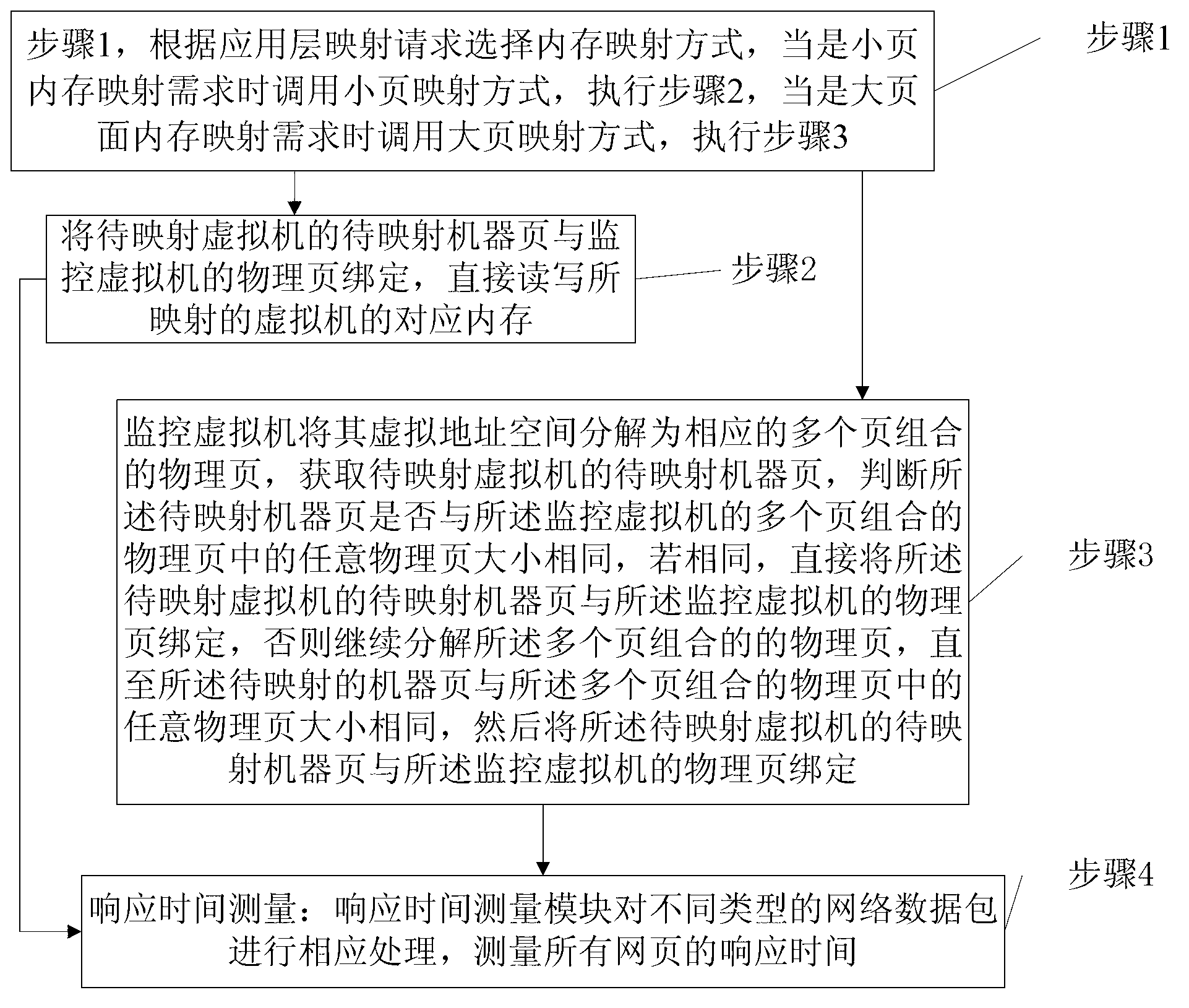

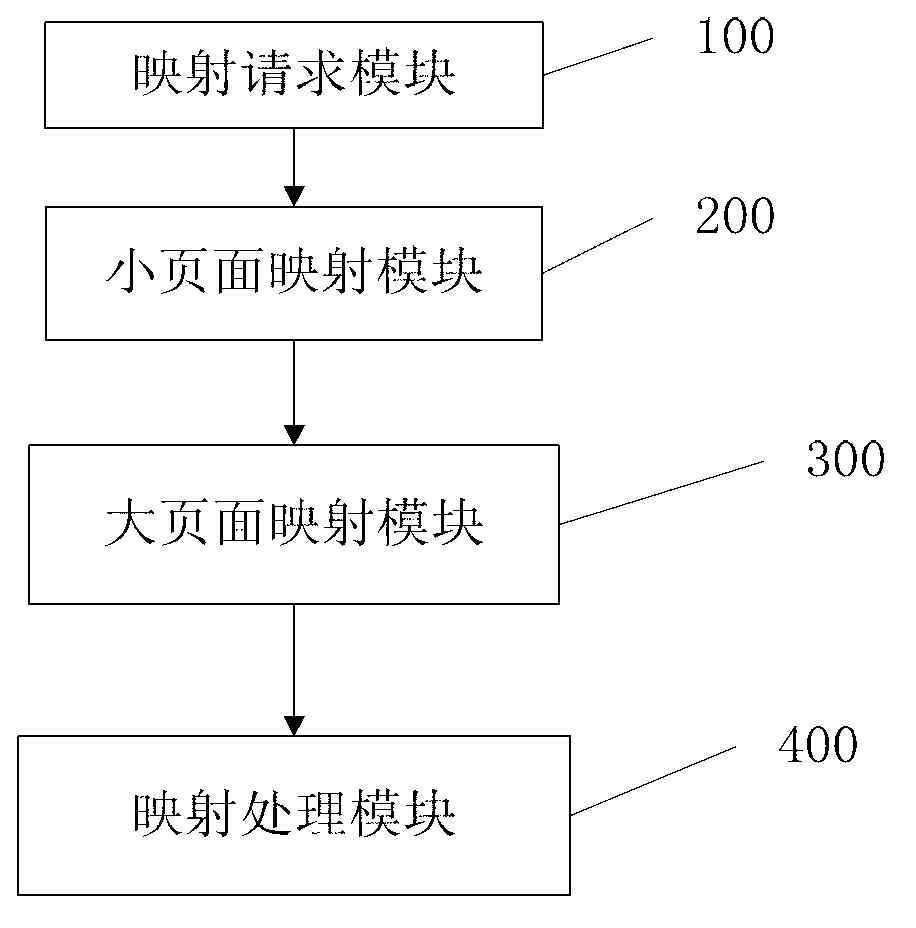

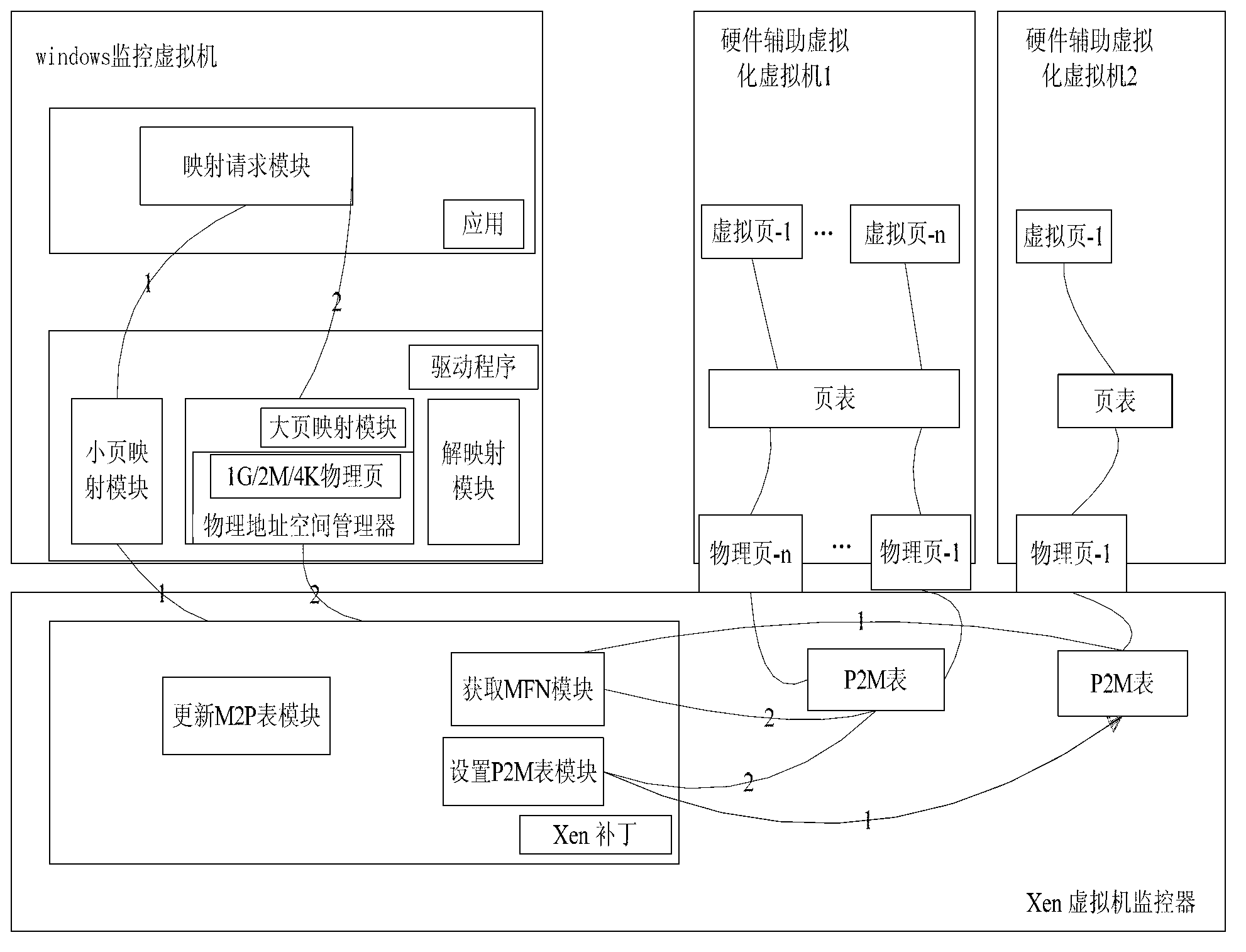

Virtual machine memory mapping method and system

InactiveCN103257929AAvoid visitingMeet the needs of specific applicationsMemory adressing/allocation/relocationSoftware simulation/interpretation/emulationProtocol ApplicationVirtual address space

The invention provides a virtual machine memory mapping method and a system, wherein the method comprises step 1 of selecting a memory mapping method according to an application layer mapping request, and executing step 2 or step 3; step 2 of binding machine pages to be mapped of a virtual machine to be mapped and physical pages of a monitoring virtual machine, directly reading and writing corresponding memory corresponding to the mapped virtual machine, and executing step 4; step 3 of enabling the monitoring virtual machine to decompose a virtual address space into corresponding physical pages combined by a plurality of pages after the monitoring virtual machine processes unused physical memory in the physical memory, obtaining the machine pages to be mapped of the virtual machine to be mapped, carrying out corresponding processing after judgment, then binding the physical pages of the monitoring virtual machine and the machine pages to be mapped of the virtual machine to be mapped, and executing step 4; step 4 of releasing the memory of the monitoring virtual machine corresponding to the mapping memory of the virtual machine to be mapped after mapping, setting a mapping list from the machine pages of the monitoring virtual machine to the physical pages, and setting a corresponding item to be an invalid machine page.

Owner:SHANGHAI YINGLIAN SOMATOSENSORY INTELLIGENT TECH CO LTD

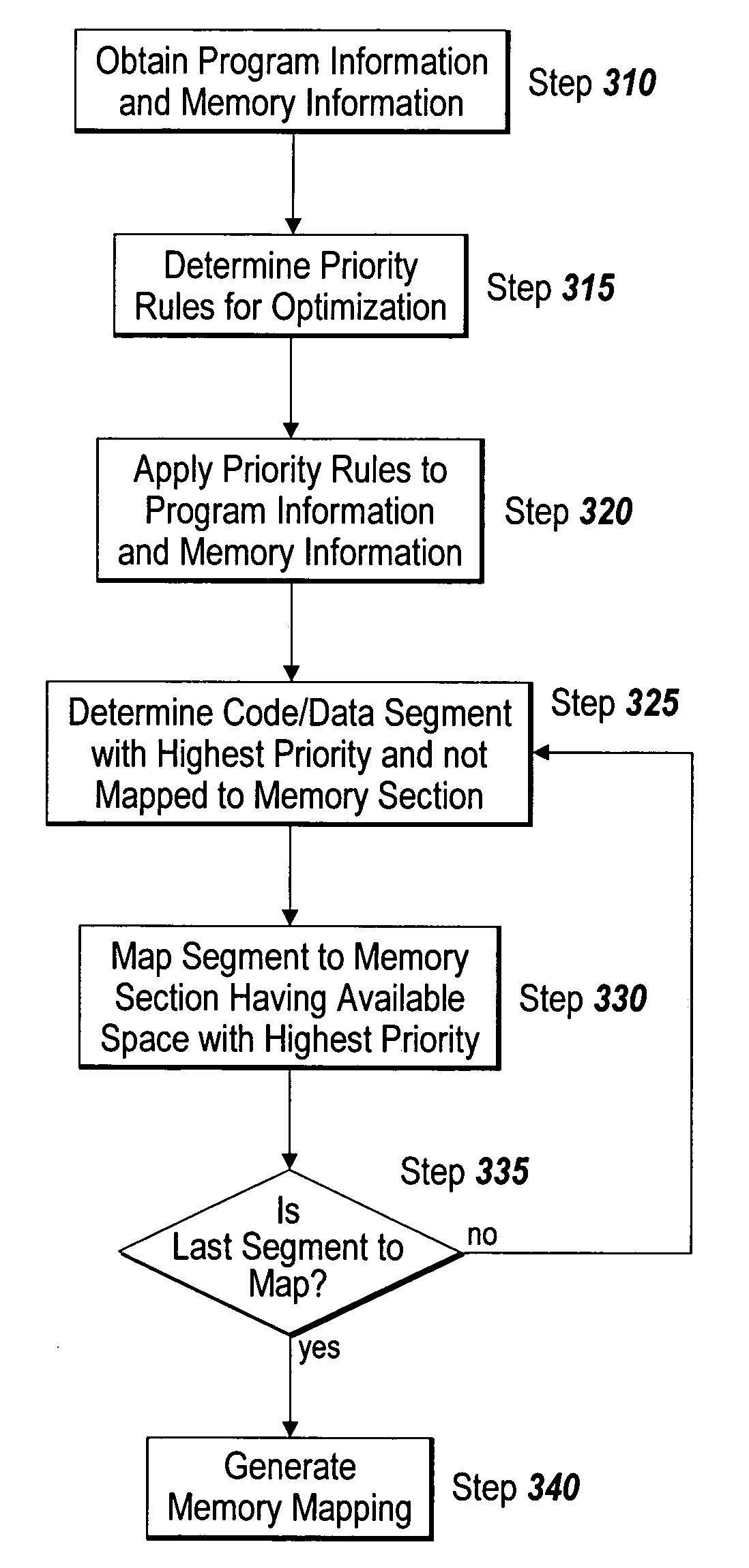

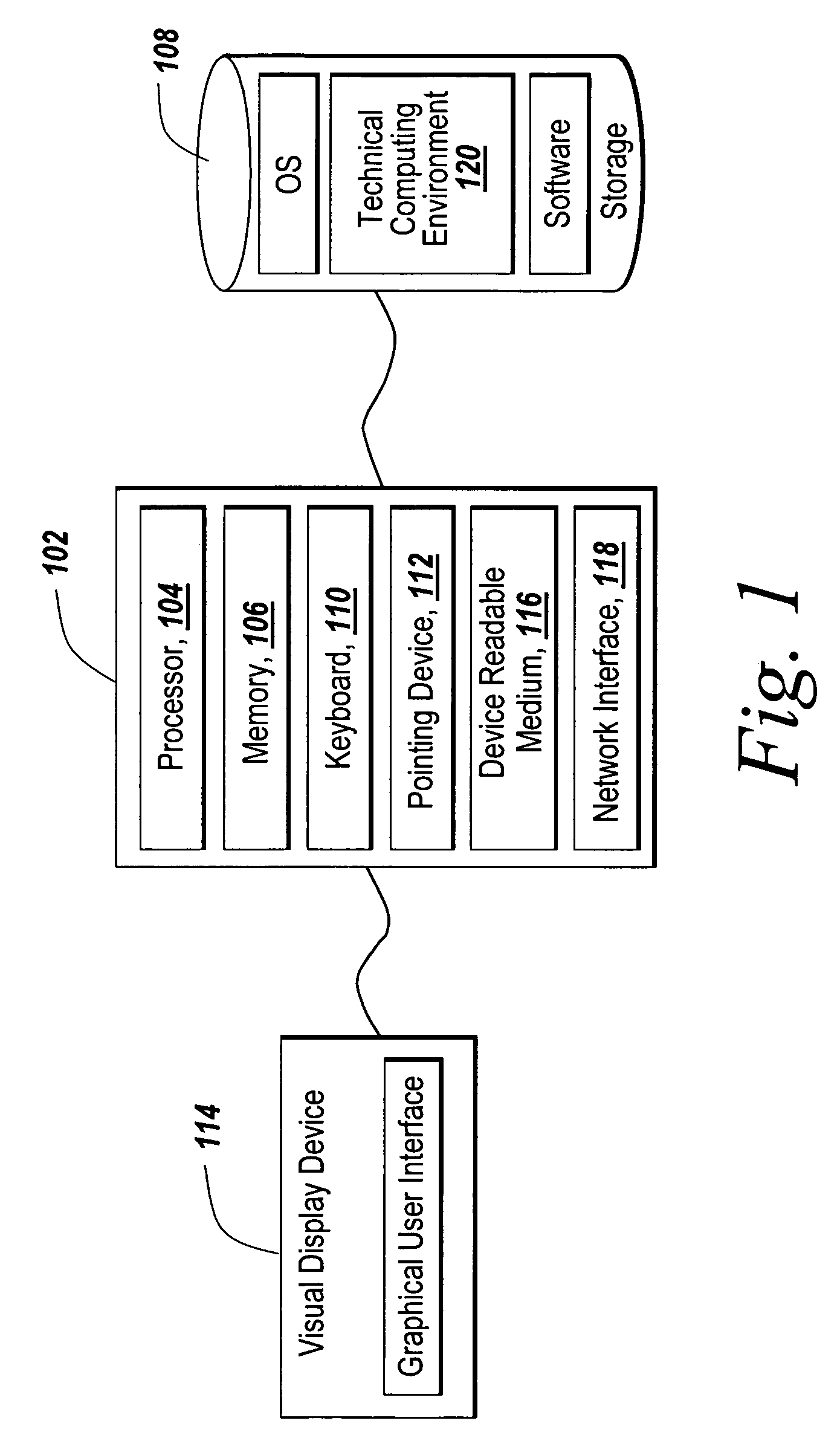

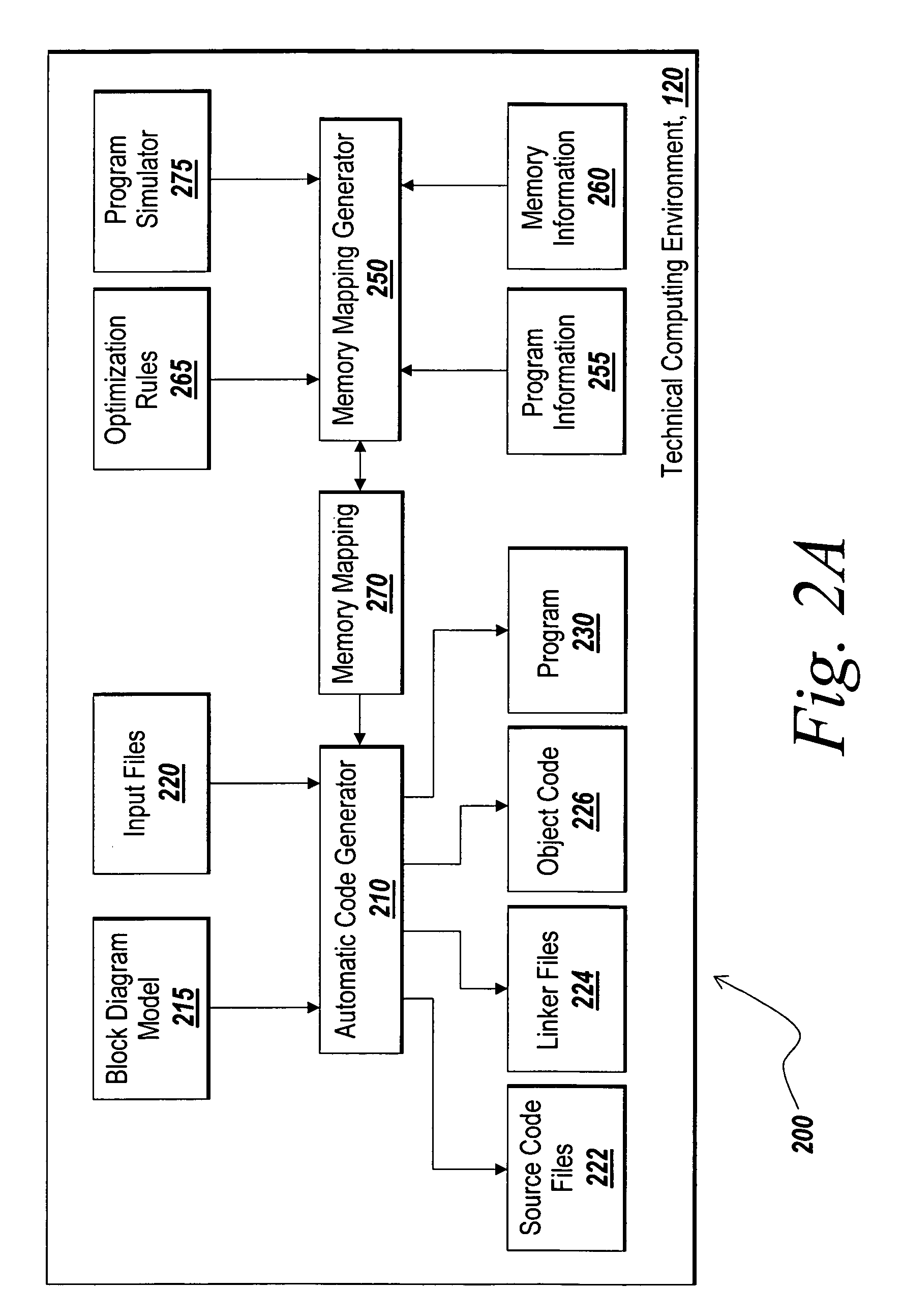

Memory mapping for single and multi-processing implementations of code generated from a block diagram model

ActiveUS7584465B1Improve programming performanceVisual/graphical programmingSpecific program execution arrangementsGraphicsModel method

Methods and systems are provided for automatically generating code from a graphical model representing a design to be implemented on components of a target computational hardware device. During the automatic code generating process, a memory mapping is automatically determined and generated to provide an optimization of execution of the program on the target device. The optimized memory mapping is incorporated into building the program executable from the automatically generated code of the graphical model.

Owner:THE MATHWORKS INC

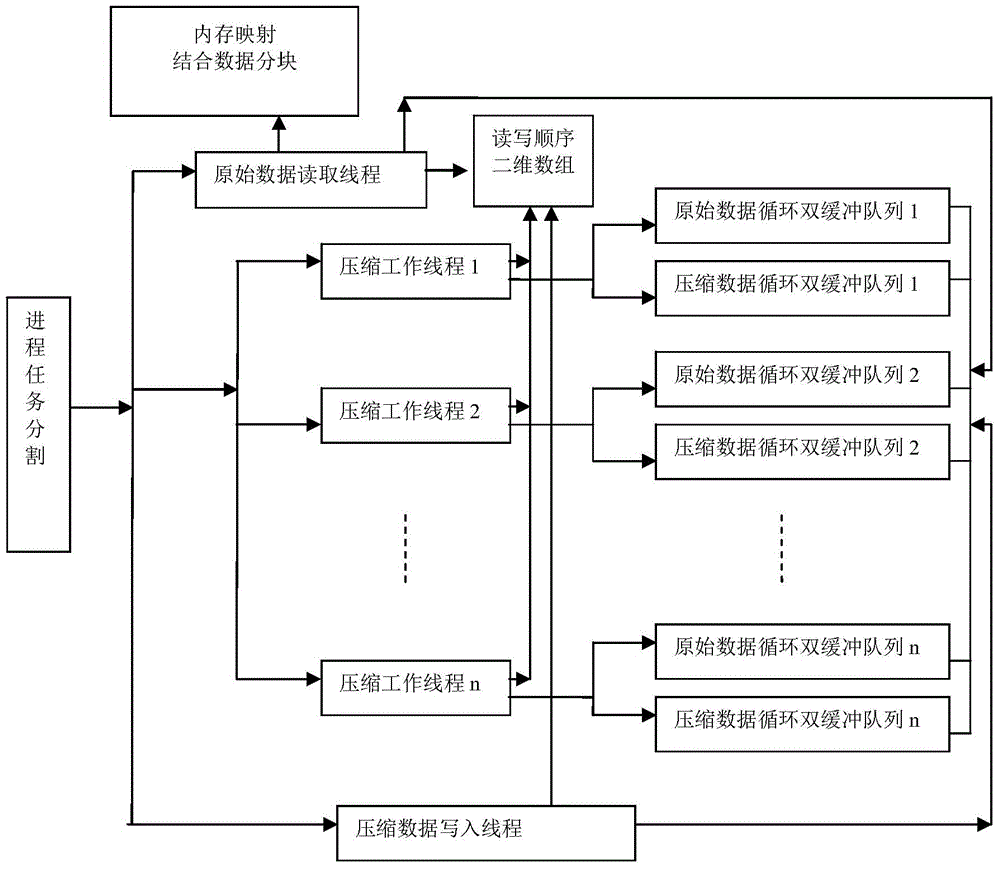

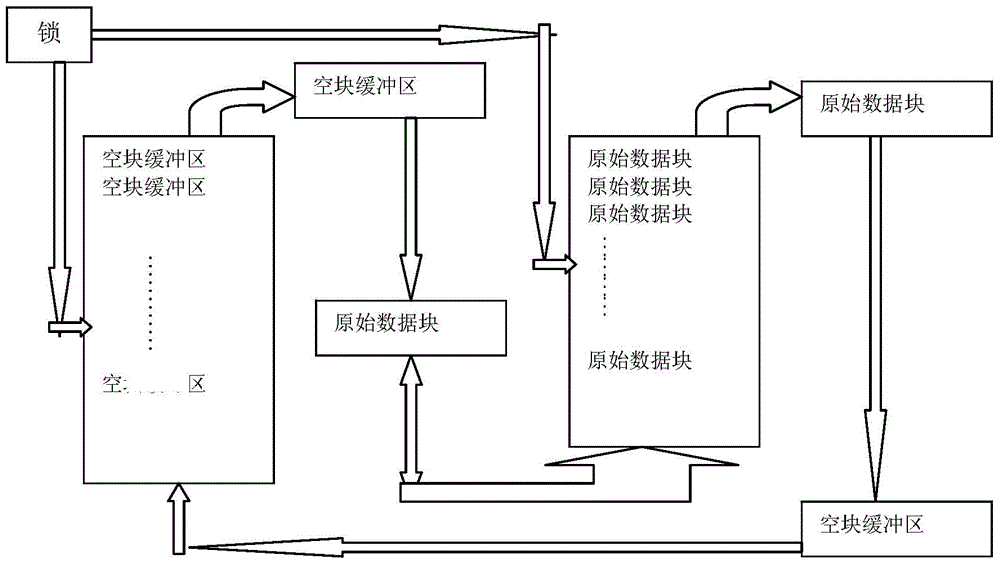

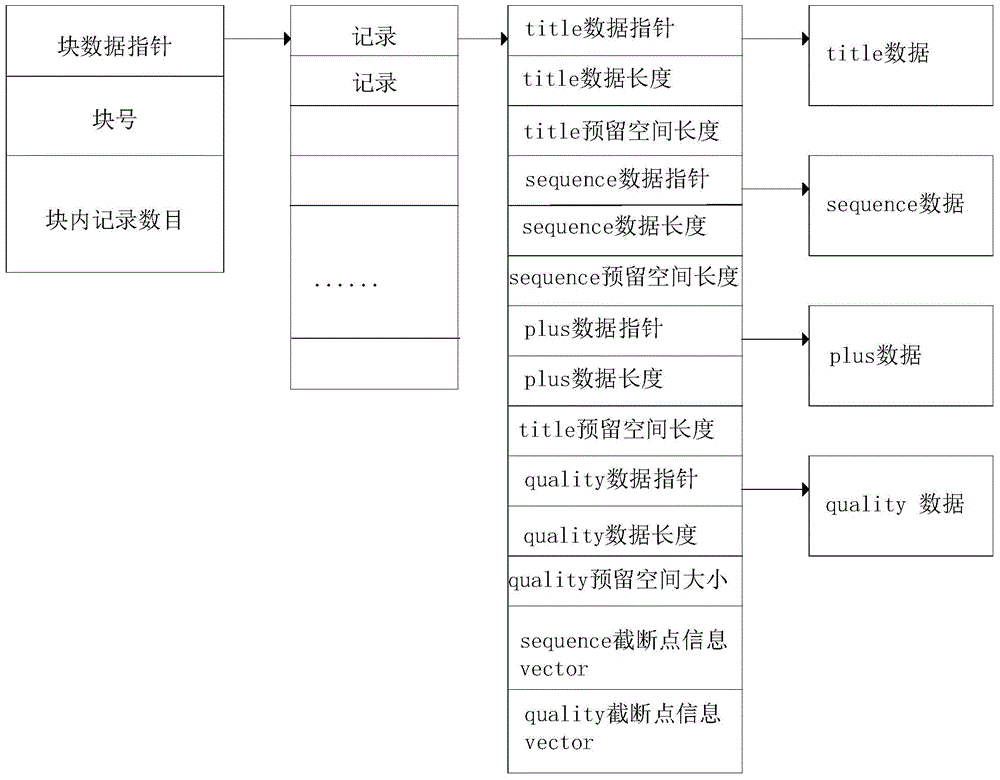

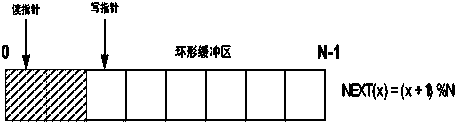

Method for realizing parallel compression and parallel decompression on FASTQ file containing DNA (deoxyribonucleic acid) sequence read data

InactiveCN103559020AAvoid restrictionsImprove flexibilityCode conversionConcurrent instruction executionParallel compressionPOSIX Threads

The invention discloses a method for realizing parallel compression and parallel decompression on an FASTQ file containing DNA (deoxyribonucleic acid) sequence read data. By aiming at the compression and the decompression of the FASTQ file containing the DNA sequence read data, by utilizing circular double buffering queues, circular double memory mapping and memory mapping and by combining the data segmentation processing technology, the multi-thread streamline parallel compression and parallel decompression technology, the read-write sequence two-dimensional array technology and the like, the parallel compression and the parallel decompression between multiple processes of the FASTQ file and between in-process multiple threads is realized. The parallel compression and parallel decompression can be realized based on MPI and OpenMP, and also can be realized based on the MPI and Pthread (POSIX thread). According to the method disclosed by the invention, by fully utilizing all computational nodes and the powerful computational capability of an intra-node multi-core CPU (central processing unit), constraints of resources, such as a processor, a memory and the like, on a serial compression and decompression program, can be released.

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI +1

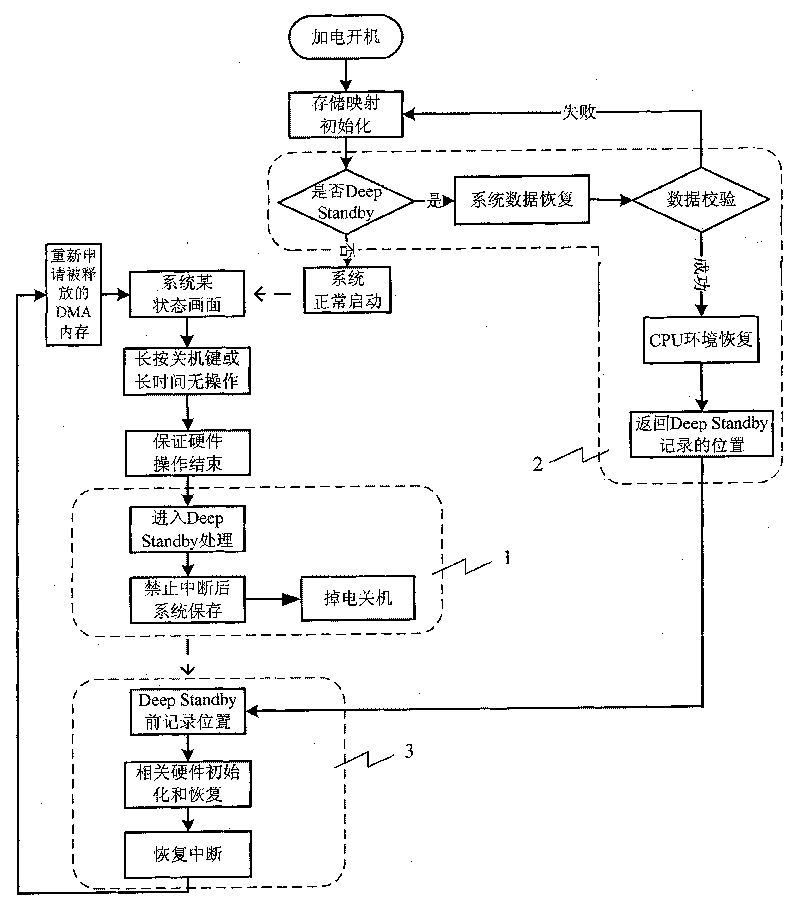

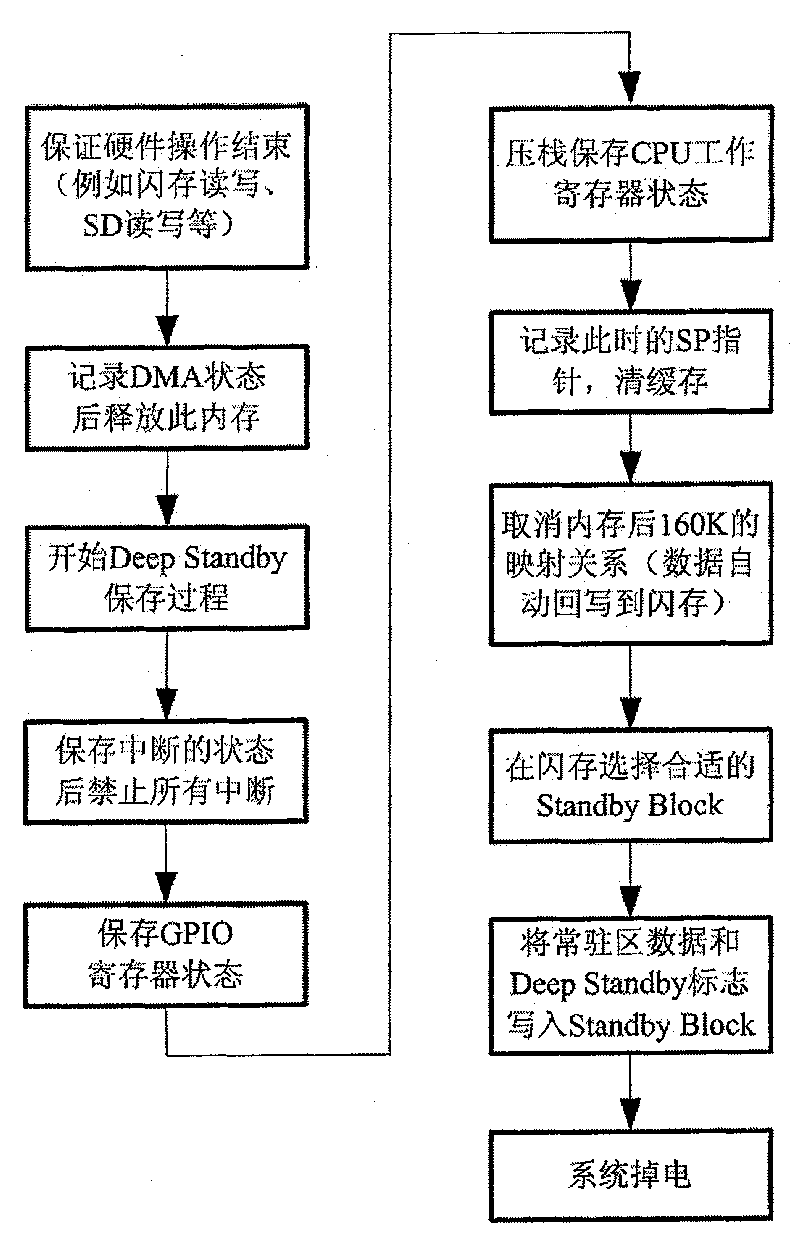

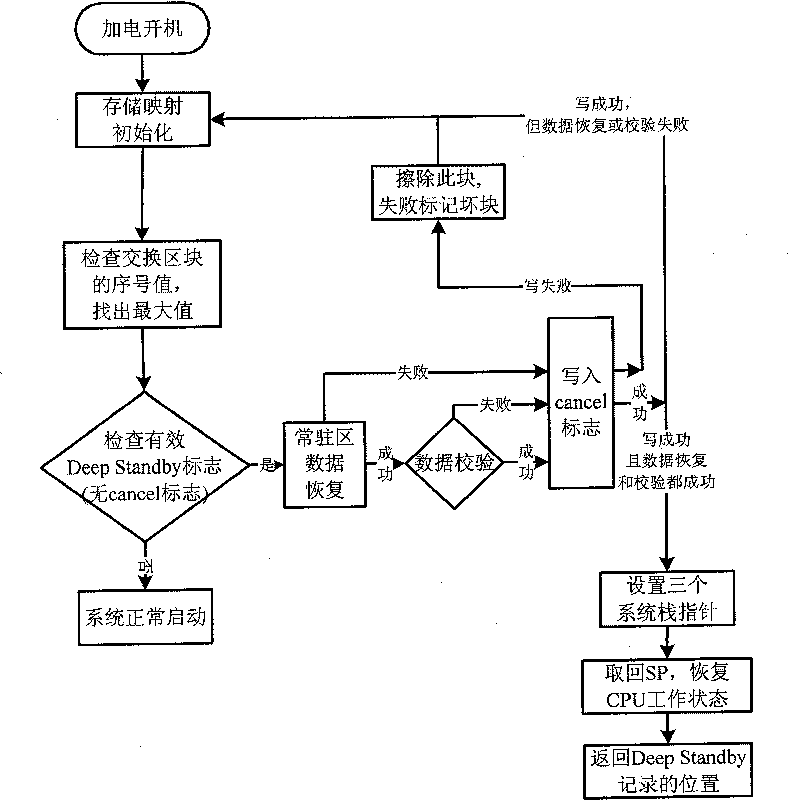

Deep-sleep method of embedded system

ActiveCN101710253AReduce standby power consumptionImprove boot speedEnergy efficient ICTPower supply for data processingElectricitySystem recovery

The invention provides a deep-sleep method of embedded system. The method mainly comprises the following processing steps: 1, in the system operating status, judging whether no operation is performed for long time to ensure that if so, the system preservation process is carried out after the hardware operation is ensured to be completed and then the system is closed to enter the deep-sleep mode, or receiving a system-closing signal; 2, starting the system, searching a deep-sleep block after the mapping and initializing of memory; after finding the effective deep-sleep sign, performing system data recovery process; and 3. after successfully recovering the system, performing the initializing of the related hardware, and returning to the state before the deep-sleep mode. By using the method of the invention, after the device is powered down or powered off and powered on again, the device can automatically return to the original interface to greatly reduce the power consumption of the stand-by system and save energy and electrical energy, thus prolonging the service time of the battery and ensuring the service life of the related hardware while largely increasing the startup speed of the system.

Owner:浙江金华凯宇电子科技有限公司

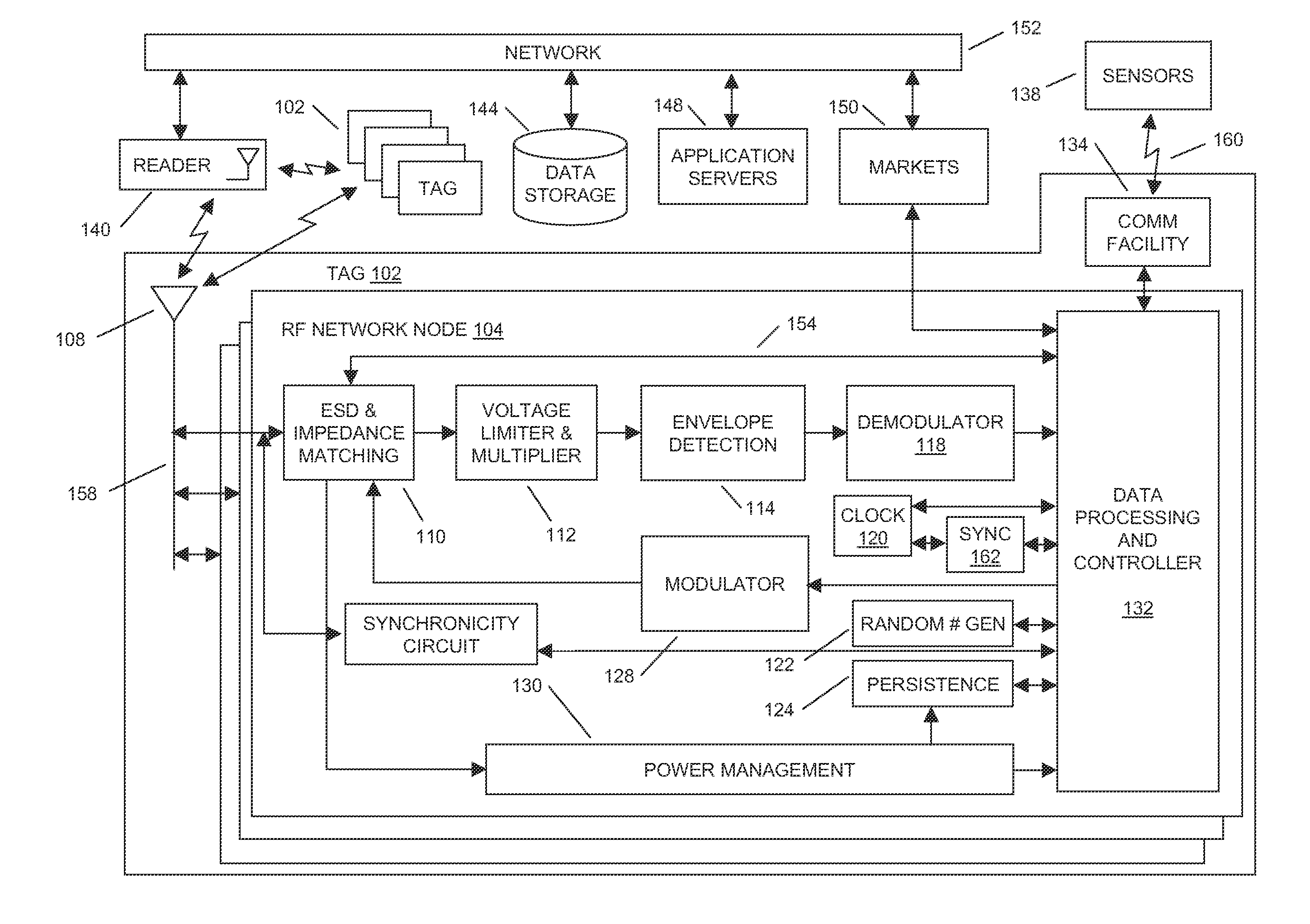

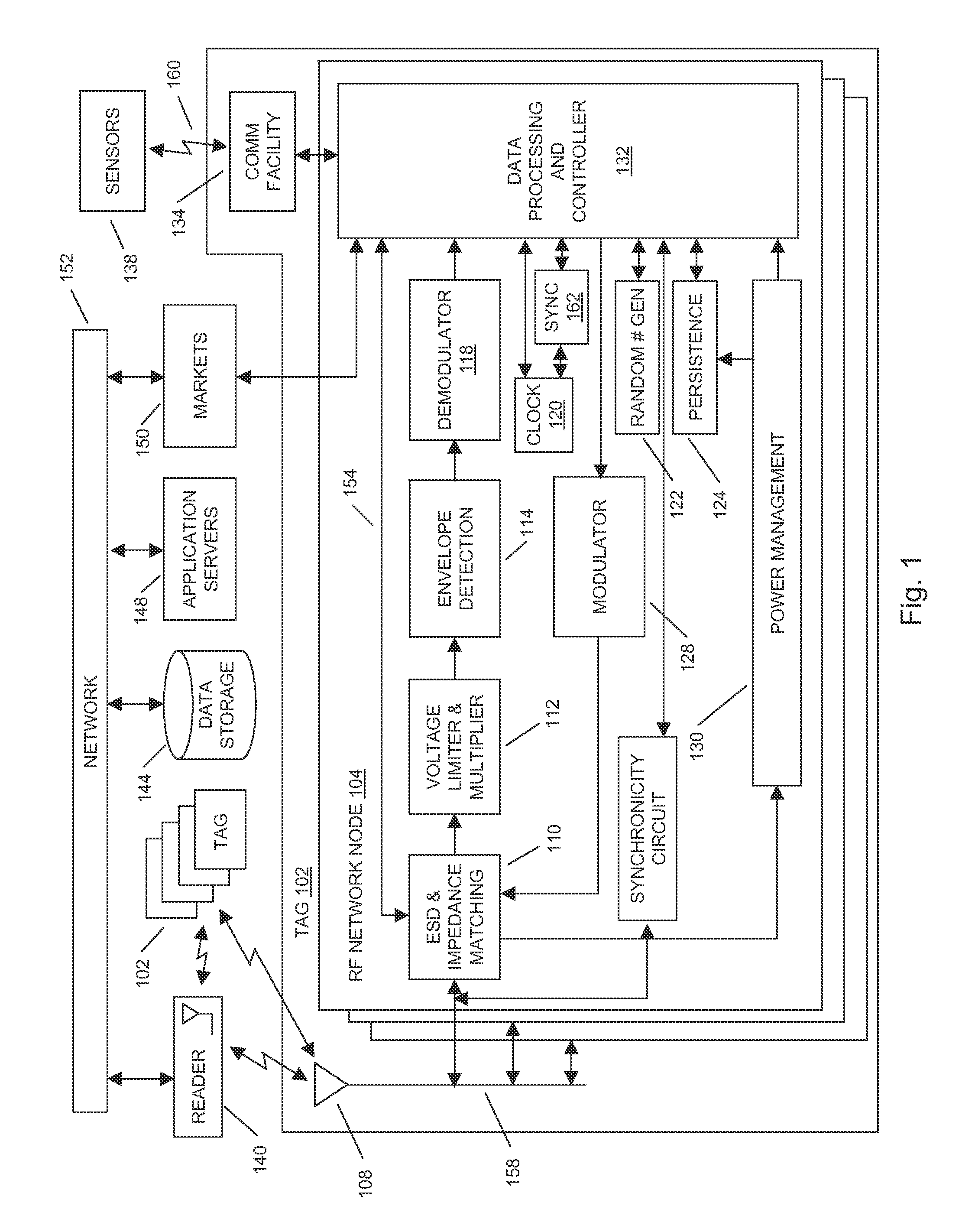

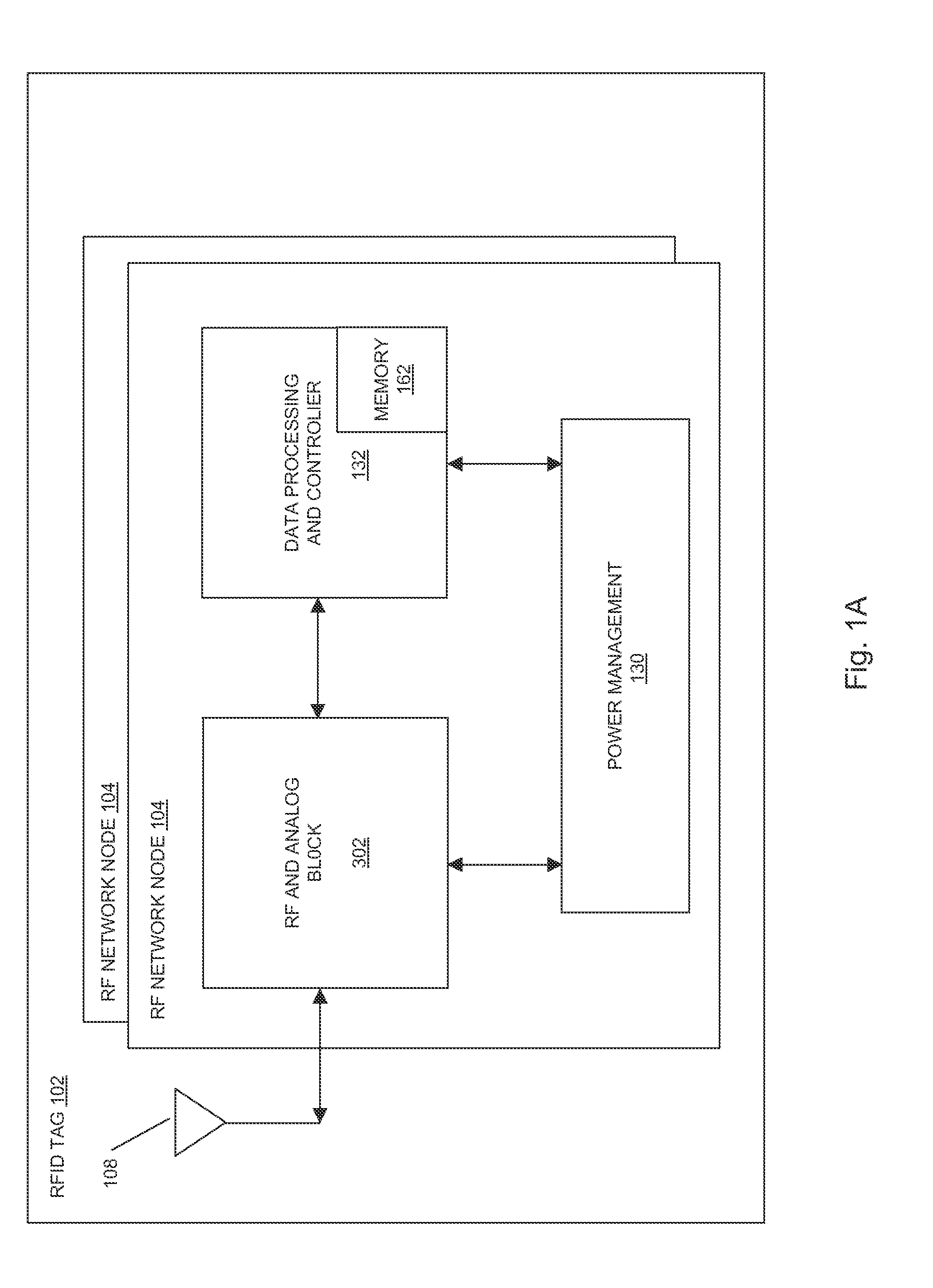

Method for memory mapping in a composite RFID tag facility

ActiveUS20120261479A1Electric signal transmission systemsCircuit arrangementsMemory addressAddress space

In embodiments of the present invention improved capabilities are described for a method of memory mapping disparate memories on a composite radio frequency identification (RFID) tag, where the RFID tag includes a plurality of individual RFID devices each having a memory store with a physical memory address range and mounted to a common substrate, where at least one of the individual RFID devices comprises memory configuration information, and where a memory addressing facility maps the physical memory address ranges of each of the individual RFID devices to a single logical addressing space and presents the address space as a single memory, where the memory addressing facility is included on a computing facility separate from the composite RFID tag.

Owner:TEGO INC

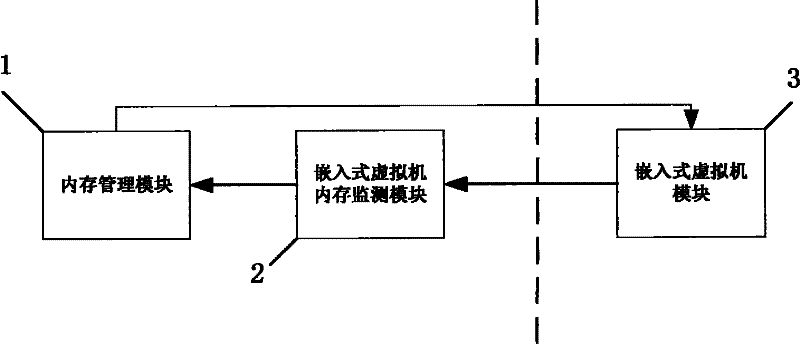

Method and system for dynamically distributing embedded virtual memory

InactiveCN102193814AEstablish a scheduling mechanismIncrease the monitoring mechanism of real-time memory pre-occupancyMemory adressing/allocation/relocationSoftware simulation/interpretation/emulationVirtual memoryVirtualization

The invention discloses a method and a system for dynamically distributing an embedded virtual memory. By the method for dynamically distributing the memory, memory resource waste due to the conventional embedded virtual fixed memory distribution can be avoided effectively. The system comprises a memory management module, an embedded virtual machine memory monitoring module and an embedded virtual machine module, wherein the virtual machine memory monitoring module is used for monitoring a real-time memory requirement condition of an embedded system in real time; the memory management module is used for initializing memory distribution, establishing an initialized memory mapping table and updating the memory distribution and the memory mapping table in real time according to a monitoring situation of the virtual machine memory monitoring module; and the embedded virtual machine module is used for generating an embedded hardware virtual environment and running an embedded operating system, and performing various embedded applications on the embedded operating system.

Owner:SHANGHAI BAIHAN NETWORK TECH

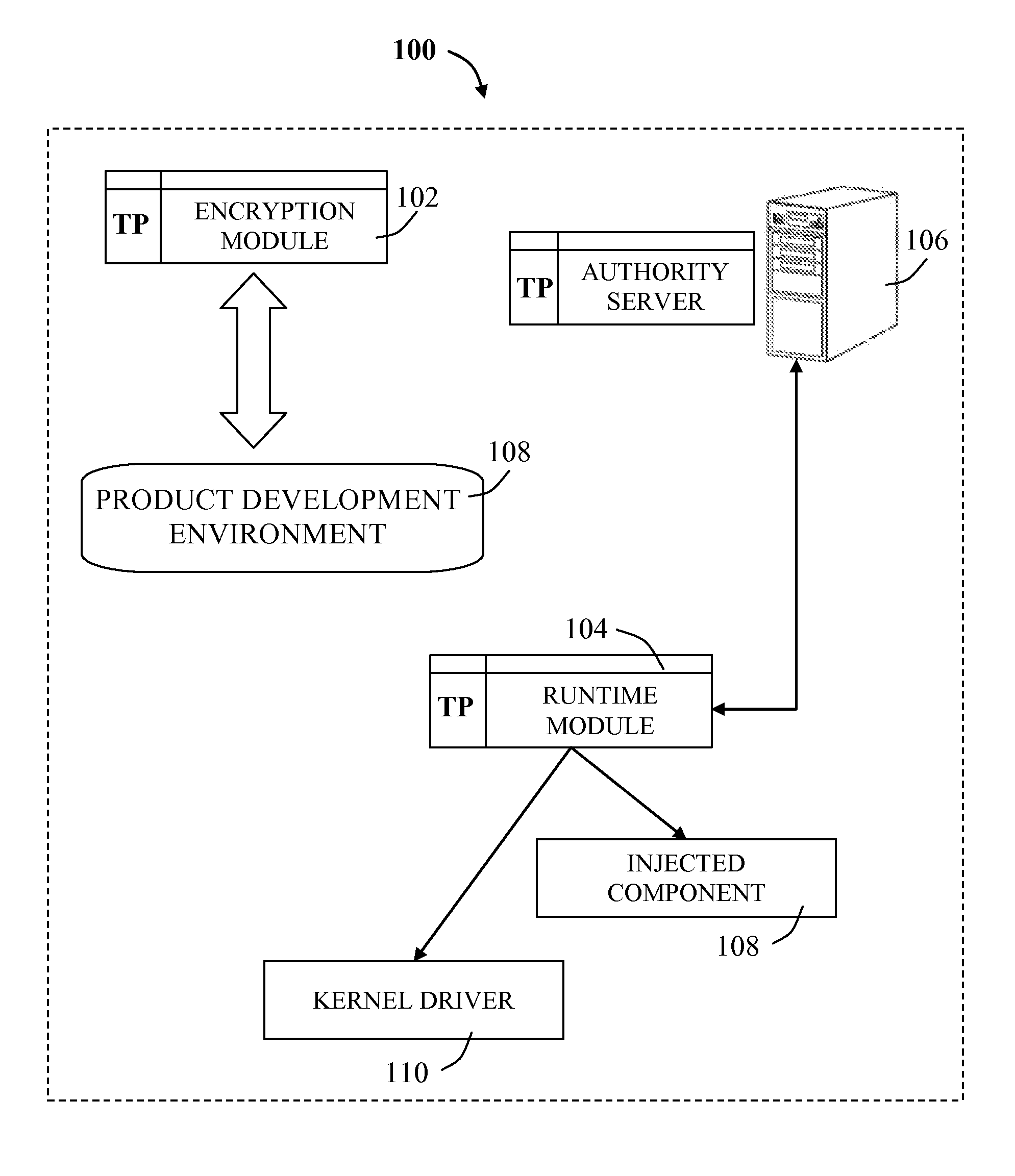

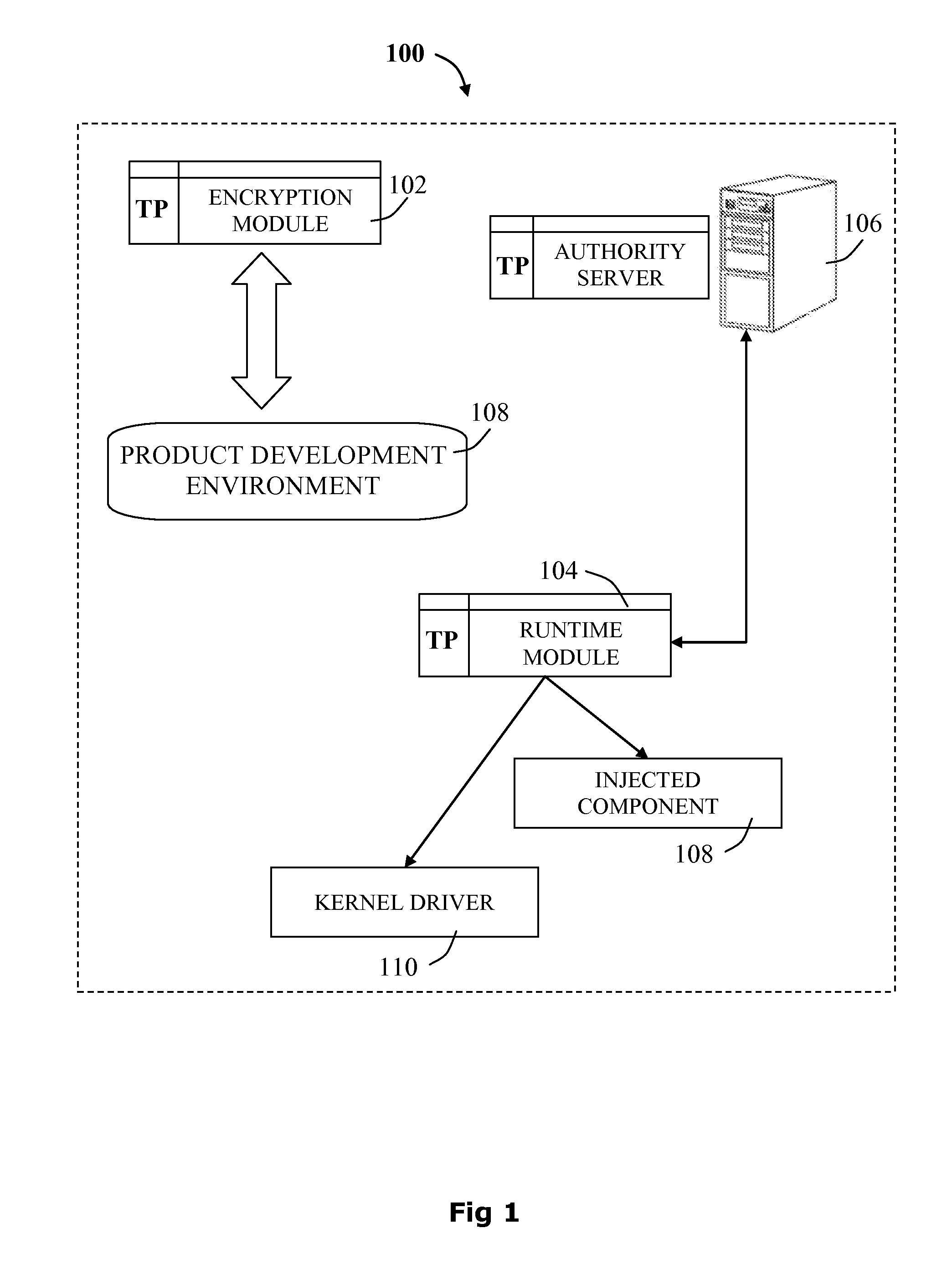

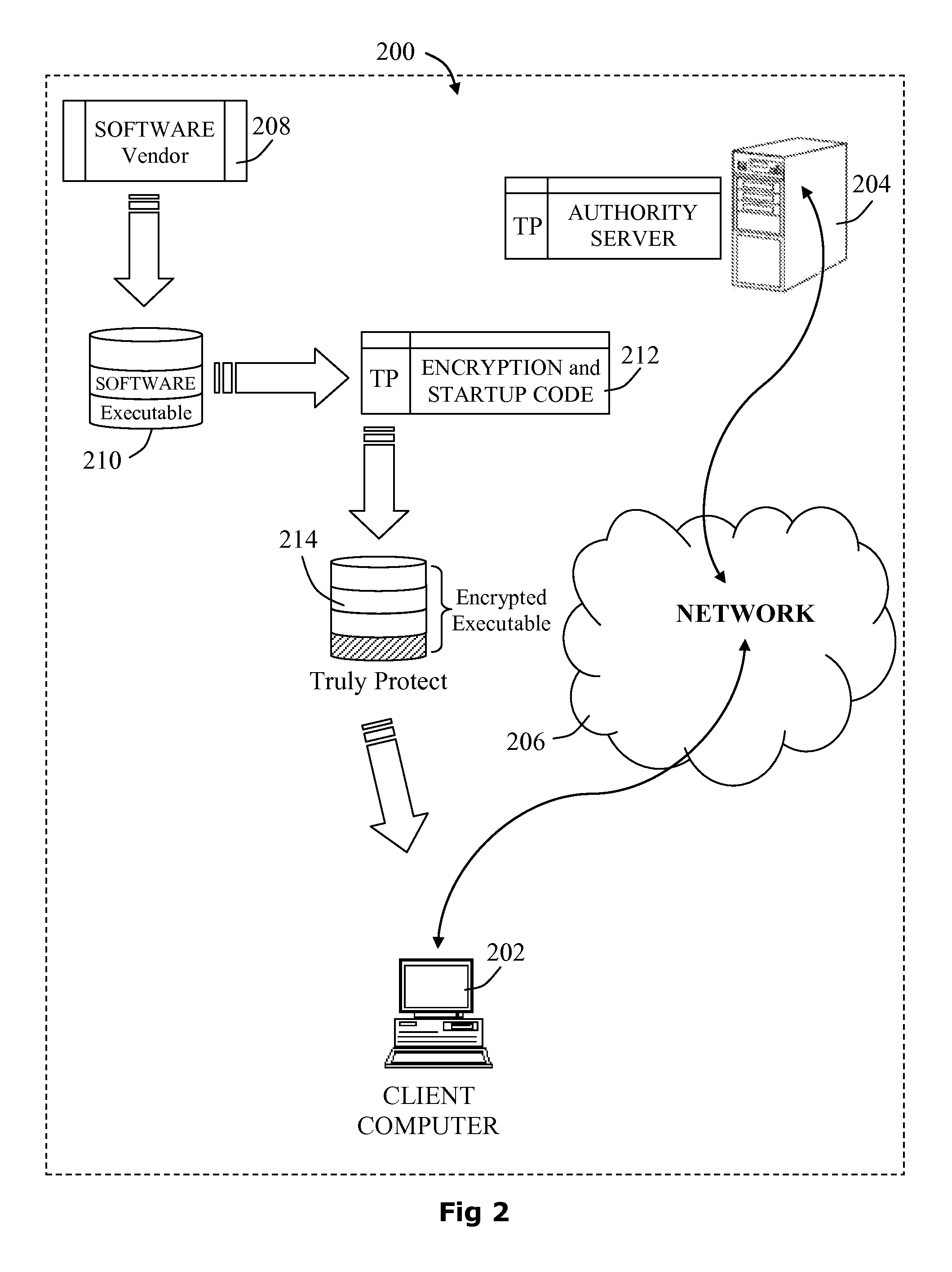

System and methods for CPU copy protection of a computing device

ActiveUS20150149732A1Avoiding evictionMemory architecture accessing/allocationMemory adressing/allocation/relocationOperabilityCopy protection

The present disclosure relates to techniques for system and methods for software-based management of protected data-blocks insertion into the memory cache mechanism of a computerized device. In particular the disclosure relates to preventing protected data blocks from being altered and evicted from the CPU cache coupled with buffered software execution. The technique is based upon identifying at least one conflicting data-block having a memory mapping indication to a designated memory cache-line and preventing the conflicting data-block from being cached. Functional characteristics of the software product of a vendor, such as gaming or video, may be partially encrypted to allow for protected and functional operability and avoid hacking and malicious usage of non-licensed user.

Owner:TRULY PROTECT

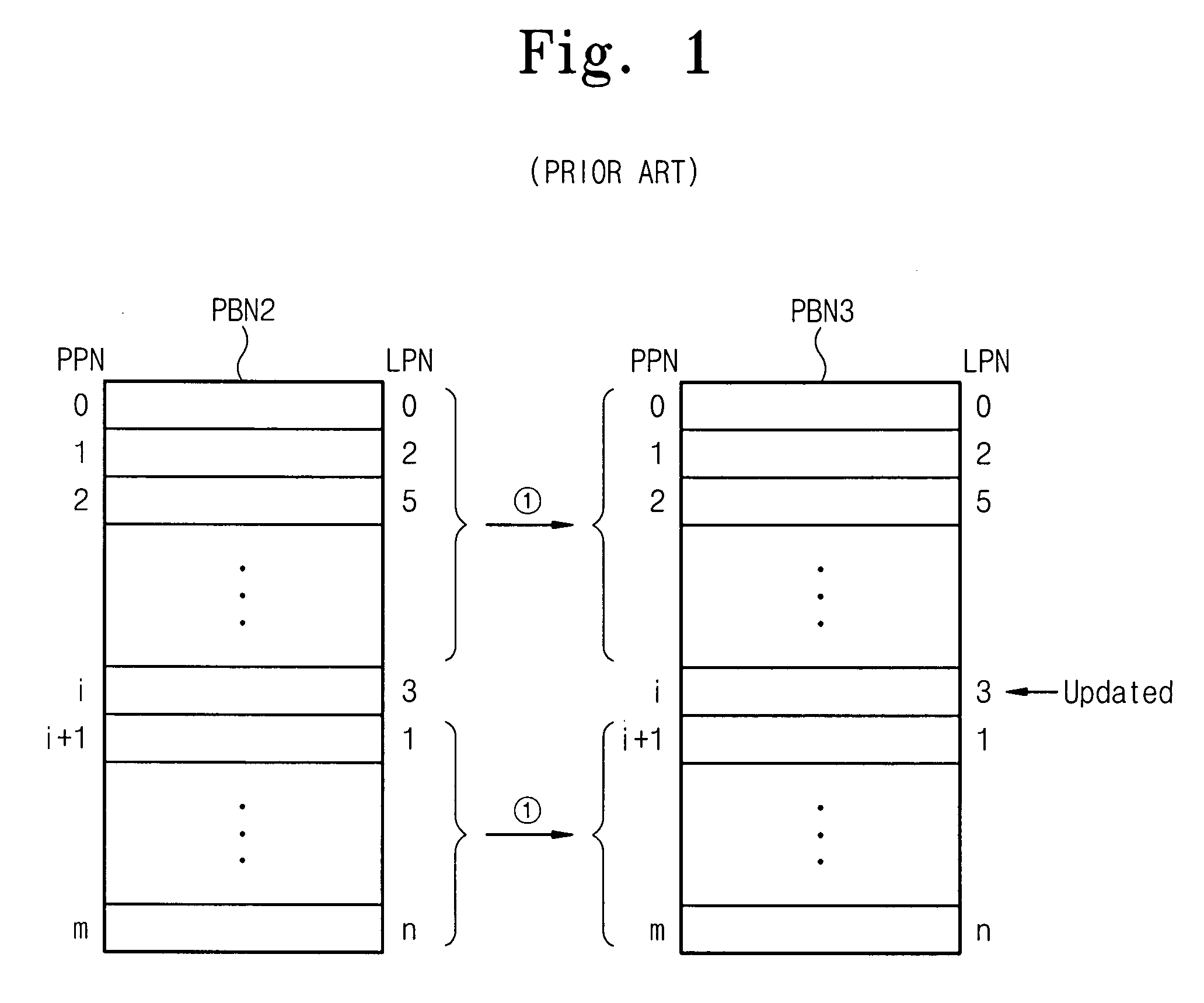

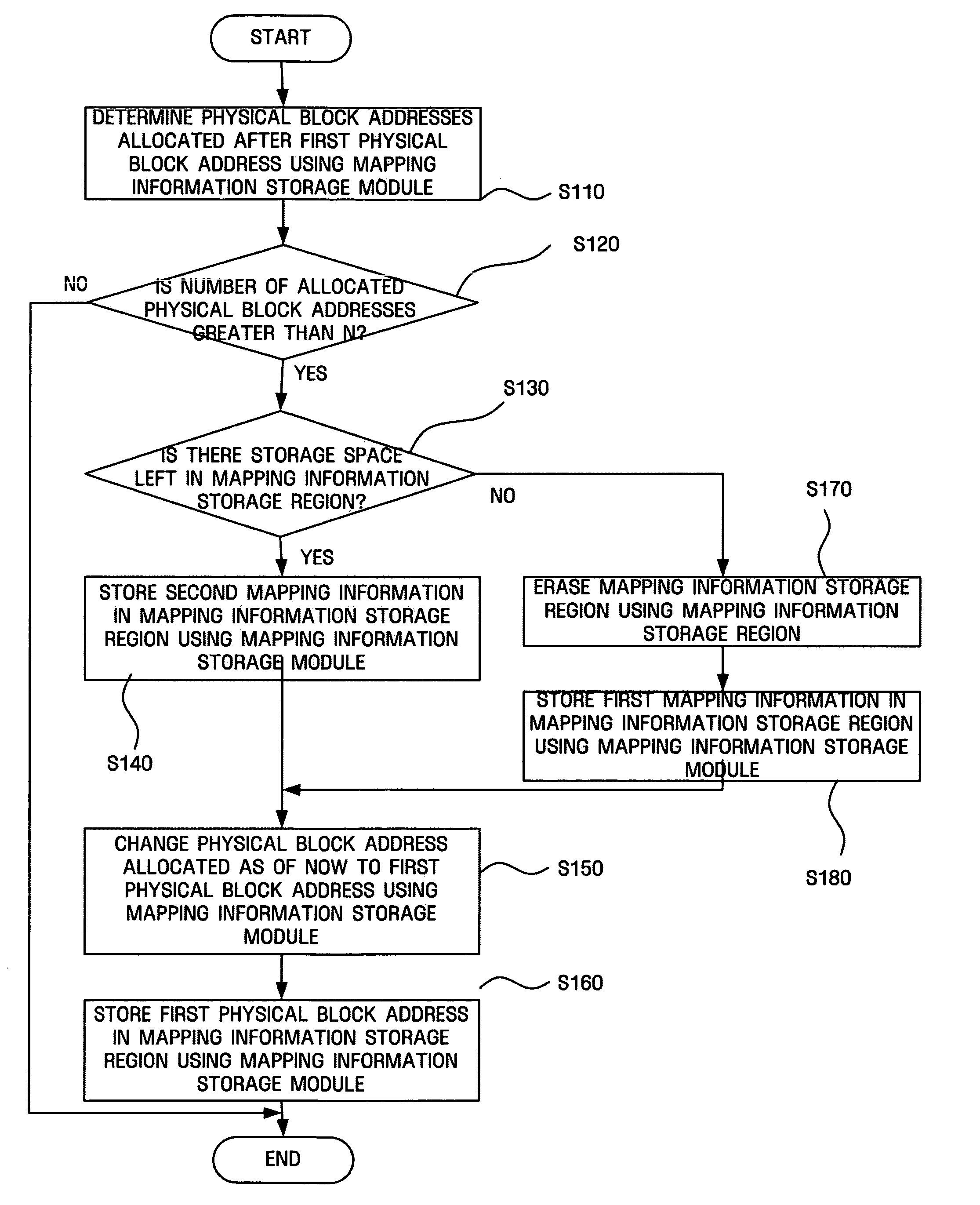

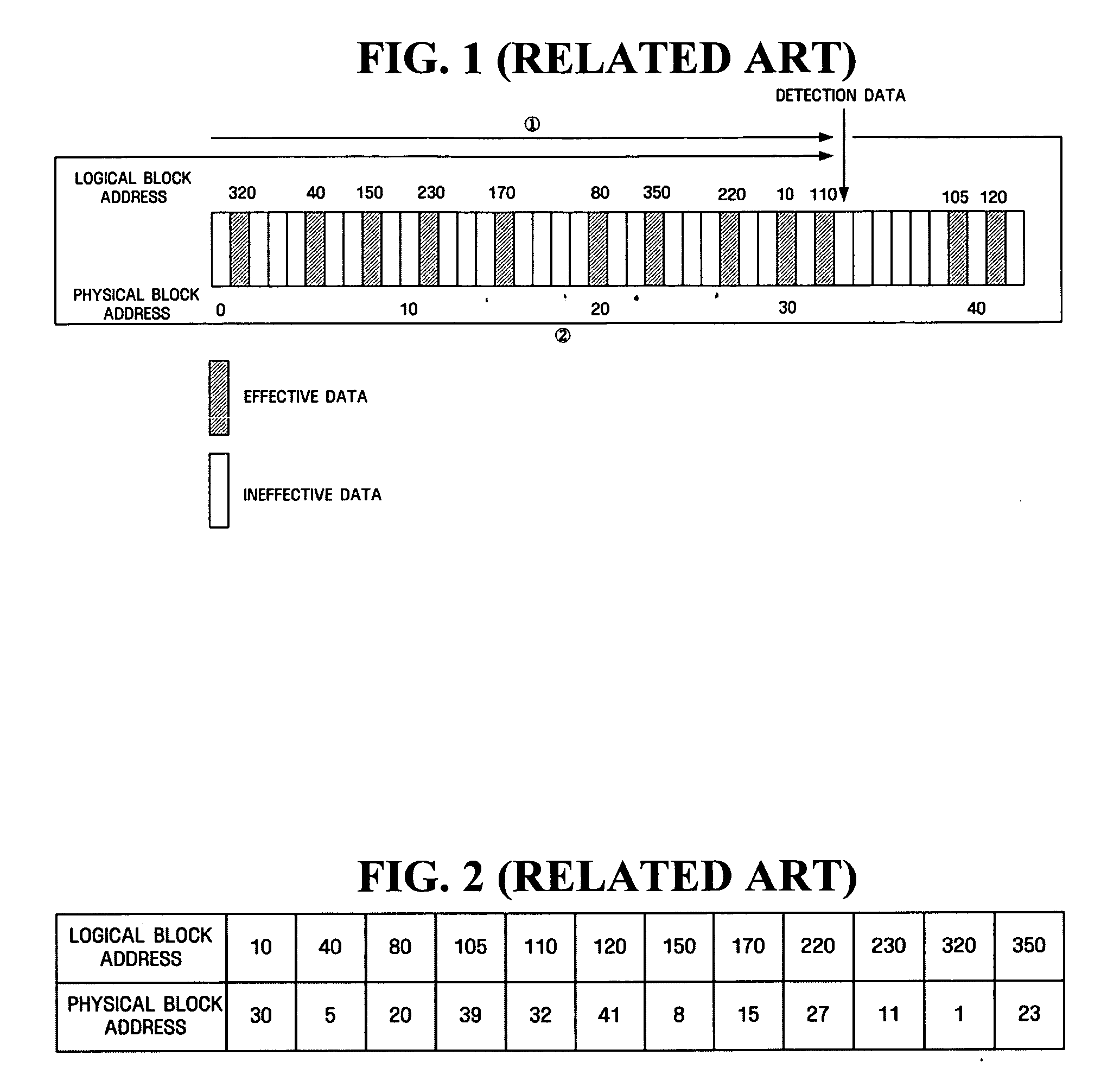

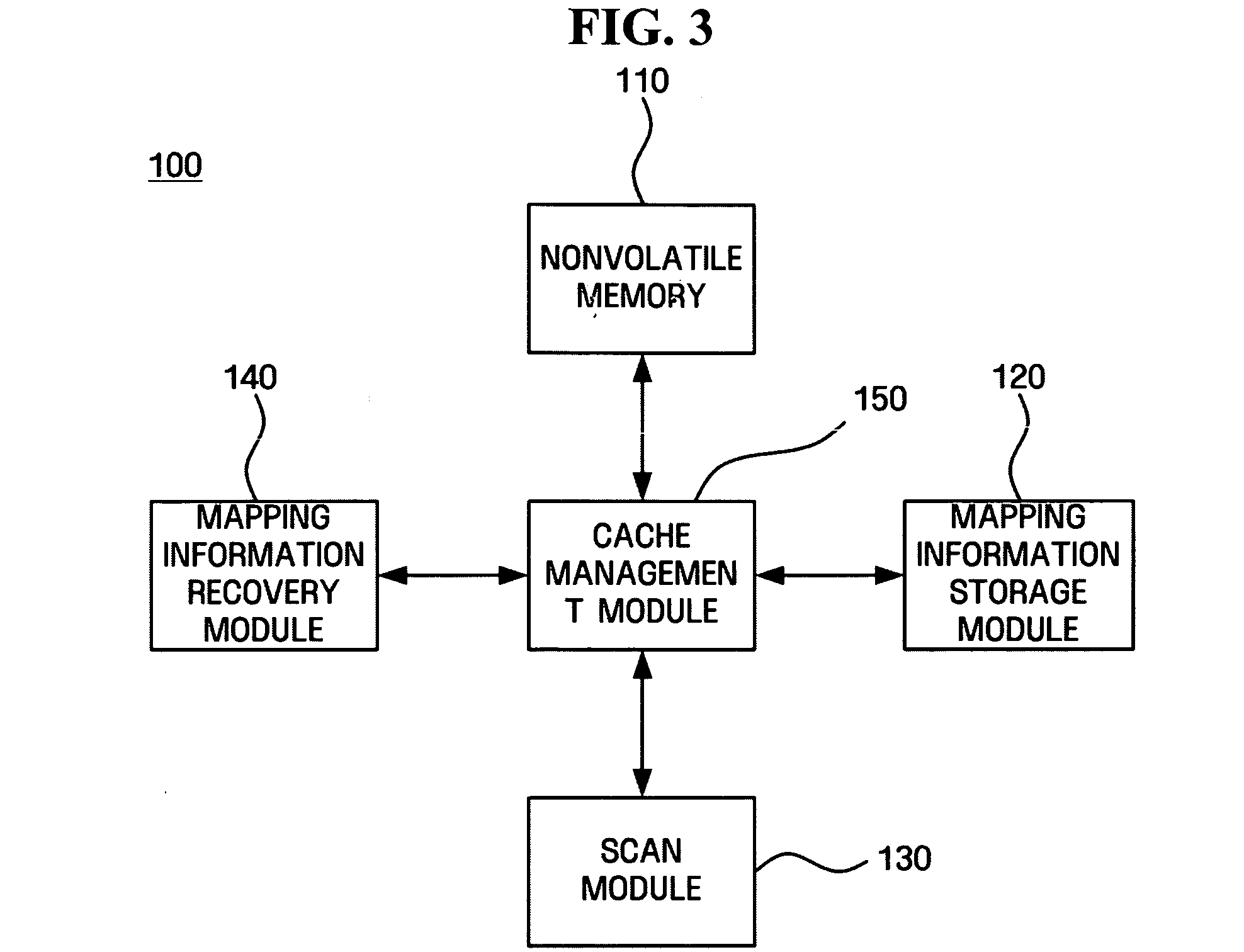

Storage apparatus using nonvolatile memory as cache and mapping information recovering method for the storage apparatus

ActiveUS20070204100A1Promote recoveryMemory architecture accessing/allocationError detection/correctionInformation recoveryOperating system

A storage apparatus using a nonvolatile memory as a cache and a mapping information recovering method for the storage apparatus are provided. The storage apparatus includes a mapping information storage module which stores in the nonvolatile memory mapping information of the nonvolatile memory and a first physical block address allocated when the mapping information is stored; a scan module which scans the first physical block address through a second physical block address allocated currently; and a mapping information recovery module which recovers the mapping information between the first physical block address and the second physical block address based on a result of the scan by the scan module.

Owner:SAMSUNG ELECTRONICS CO LTD

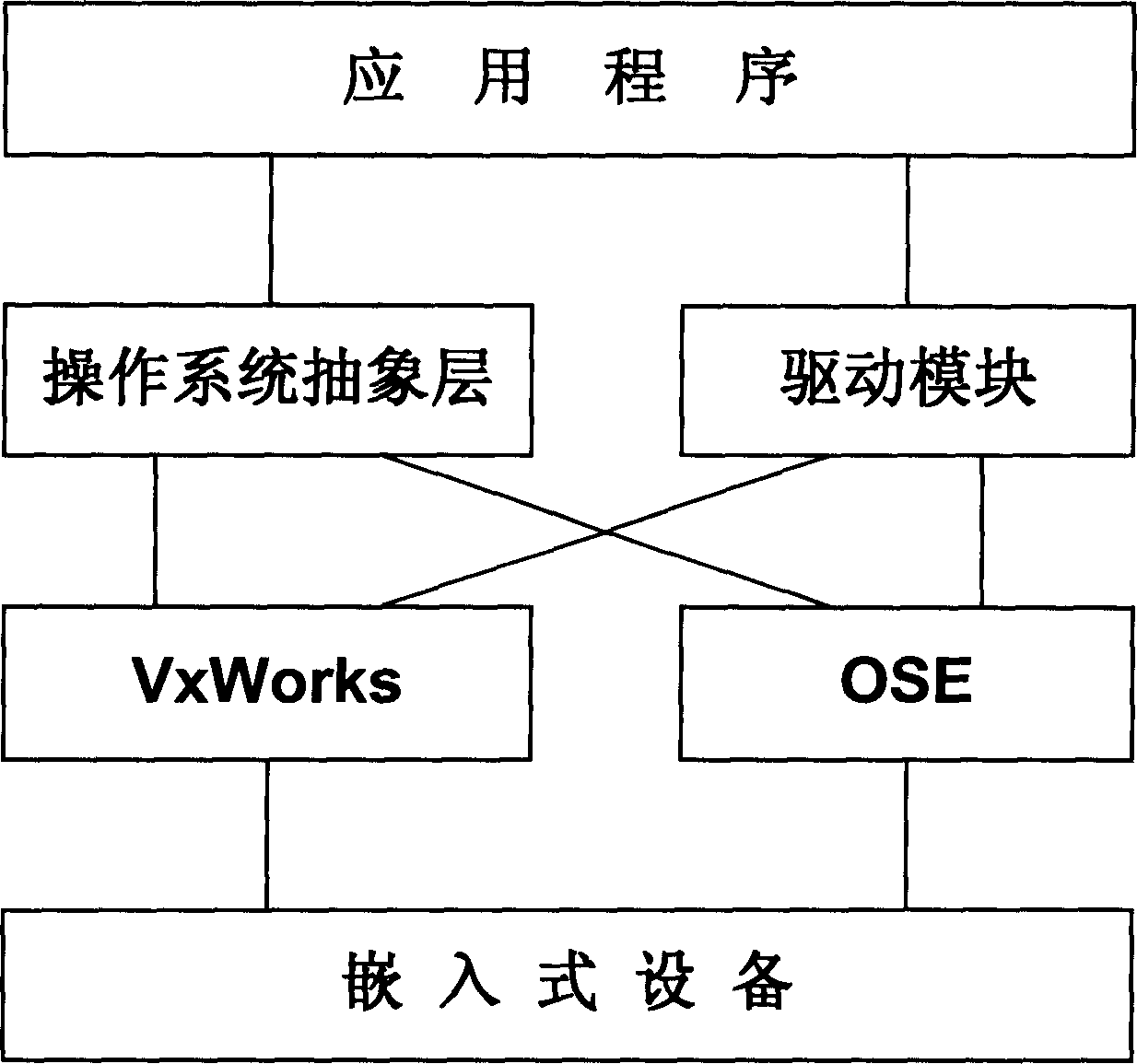

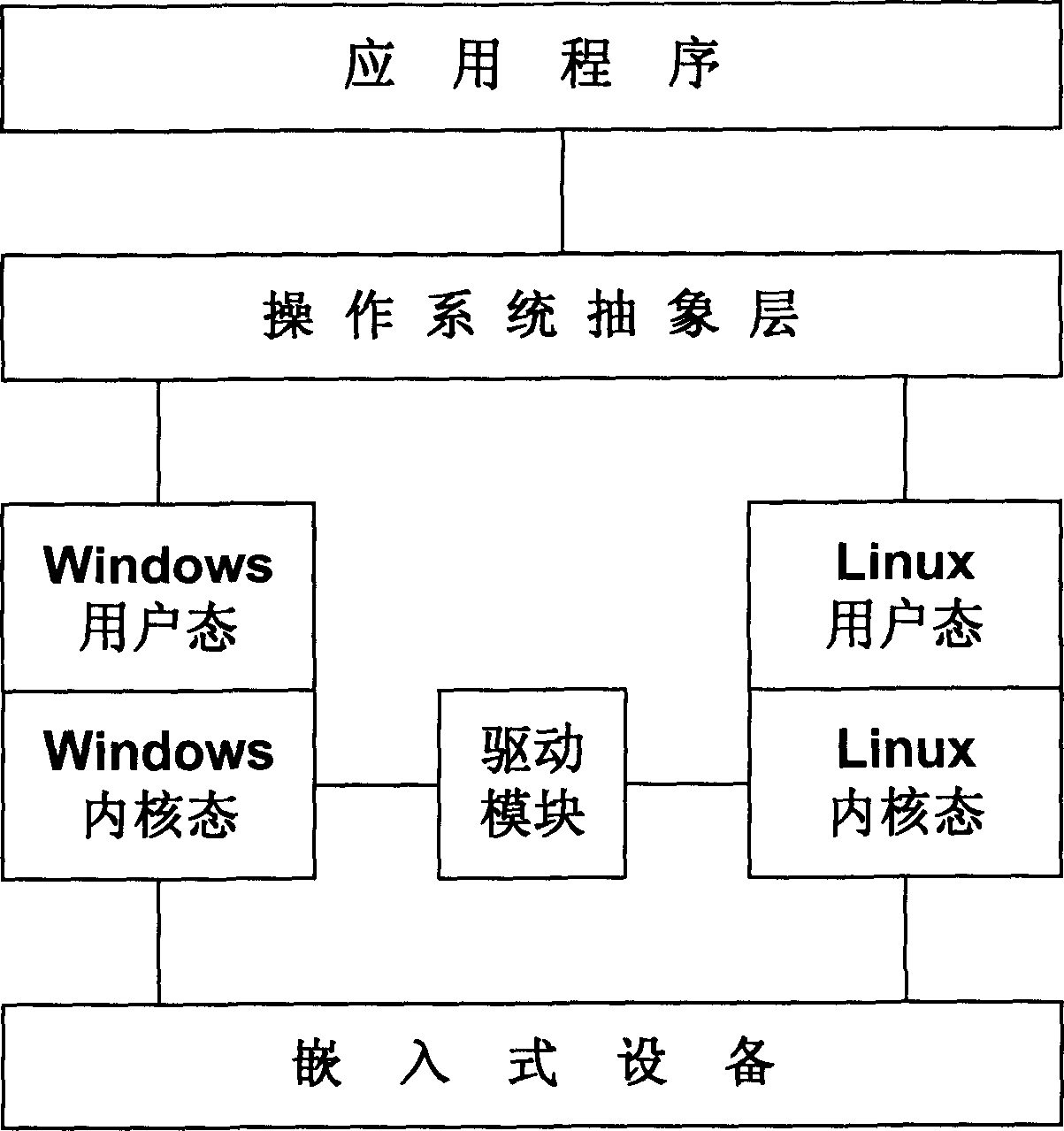

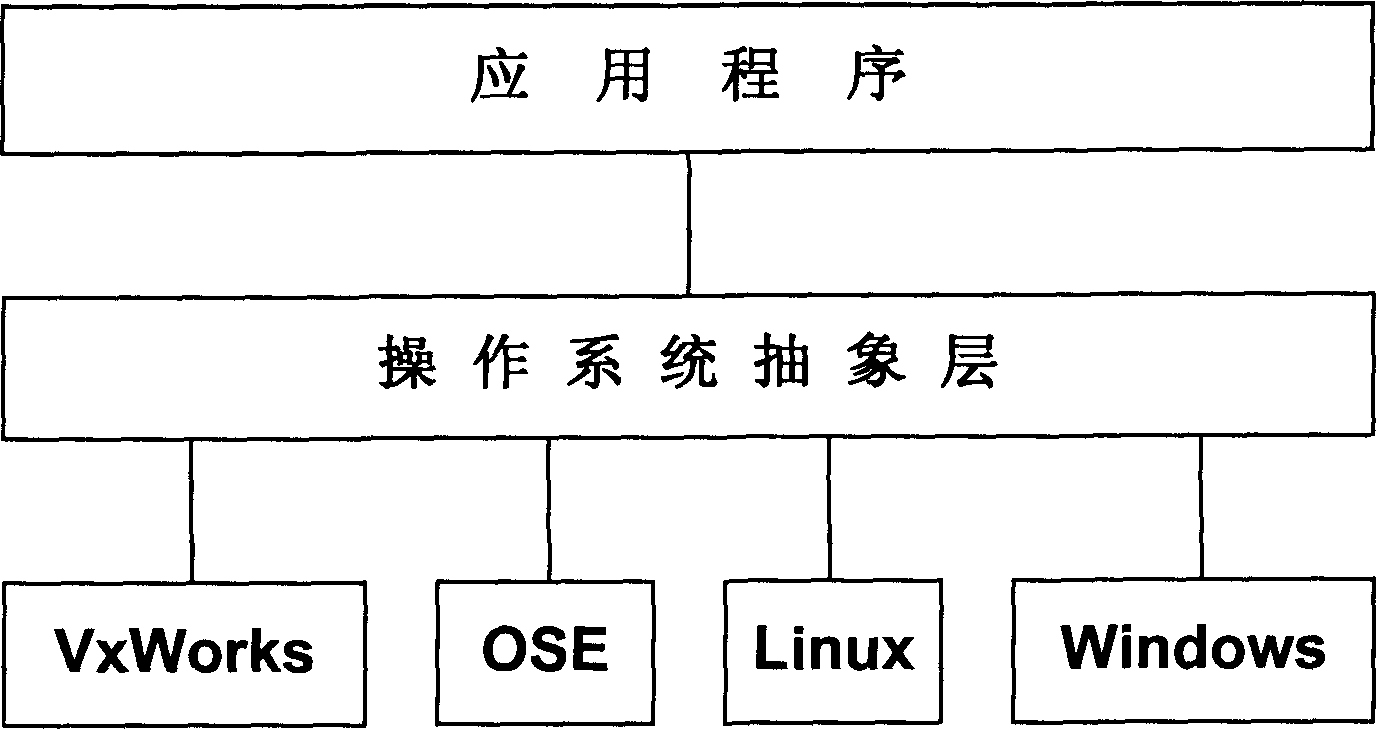

Drive method for embedded apparatus

ActiveCN1866202AReduce switching timesImprove operational efficiencySpecific program execution arrangementsInformation controlOperational system

The disclosed drive method for embedded device in protective-mode OS comprises: packing application program of different OS into uniform OS abstract interface function; registering the embedded device as OS-supported virtual device to build the mapping between virtual device kernel-state memory space and drive mode user-state memory space; calling the drive module and OS interface function by application program to interact with the embedded device for information control and / or data by memory mapping. This invention improves system running efficiency.

Owner:DATANG MOBILE COMM EQUIP CO LTD

Base station user plane data processing and optimizing method based on Linux system

ActiveCN103391256AReduce in quantityLower performance requirementsData switching networksEngineeringTerm memory

The invention provides a base station user plane data processing and optimizing method based on a Linux system. The method comprises the steps as follows: package classification is completed by using a package processing acceleration module; the interrupt of package reception is reduced in an intelligent switching manner for interrupt polls; memory copying is avoided by using a core space-user space memory mapping technology; and context switching between a core state and a user state is reduced by using a lock-free queue technology, so that the performance for processing base station user plane data is remarkably improved.

Owner:WUHAN POST & TELECOMM RES INST CO LTD

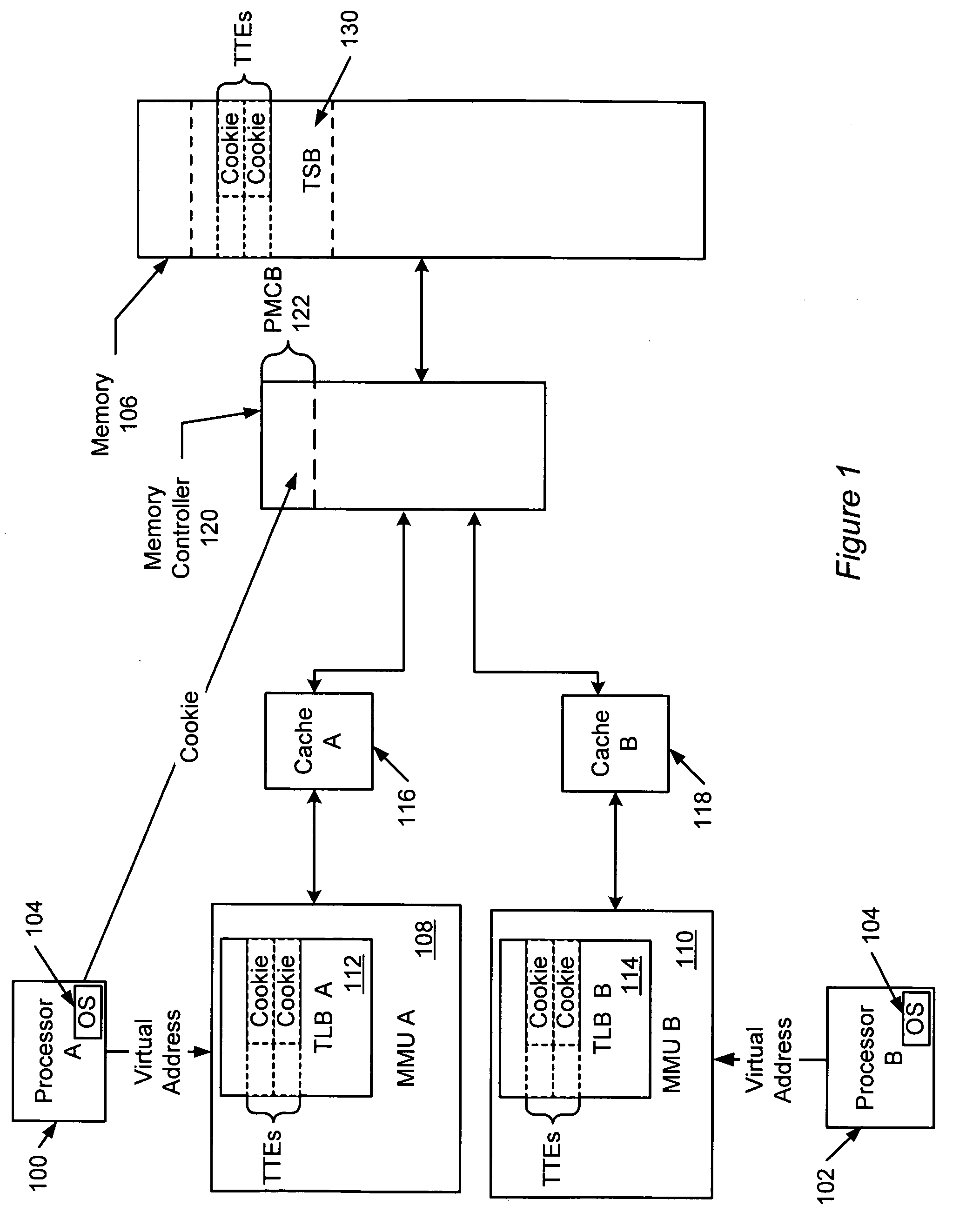

Page mapping cookies

ActiveUS7234038B1Memory architecture accessing/allocationMemory systemsVirtual memoryVirtual storage

A method for managing virtual memory including placing a first virtual memory page in a physical memory page to create a virtual-to-physical memory mapping, associating a first page mapping cookie value with the virtual-to-physical memory mapping, determining whether the virtual-to-physical memory mapping is valid using the first page mapping cookie value, and performing a memory operation addressing the first virtual memory page if the virtual-to-physical memory mapping is valid.

Owner:ORACLE INT CORP

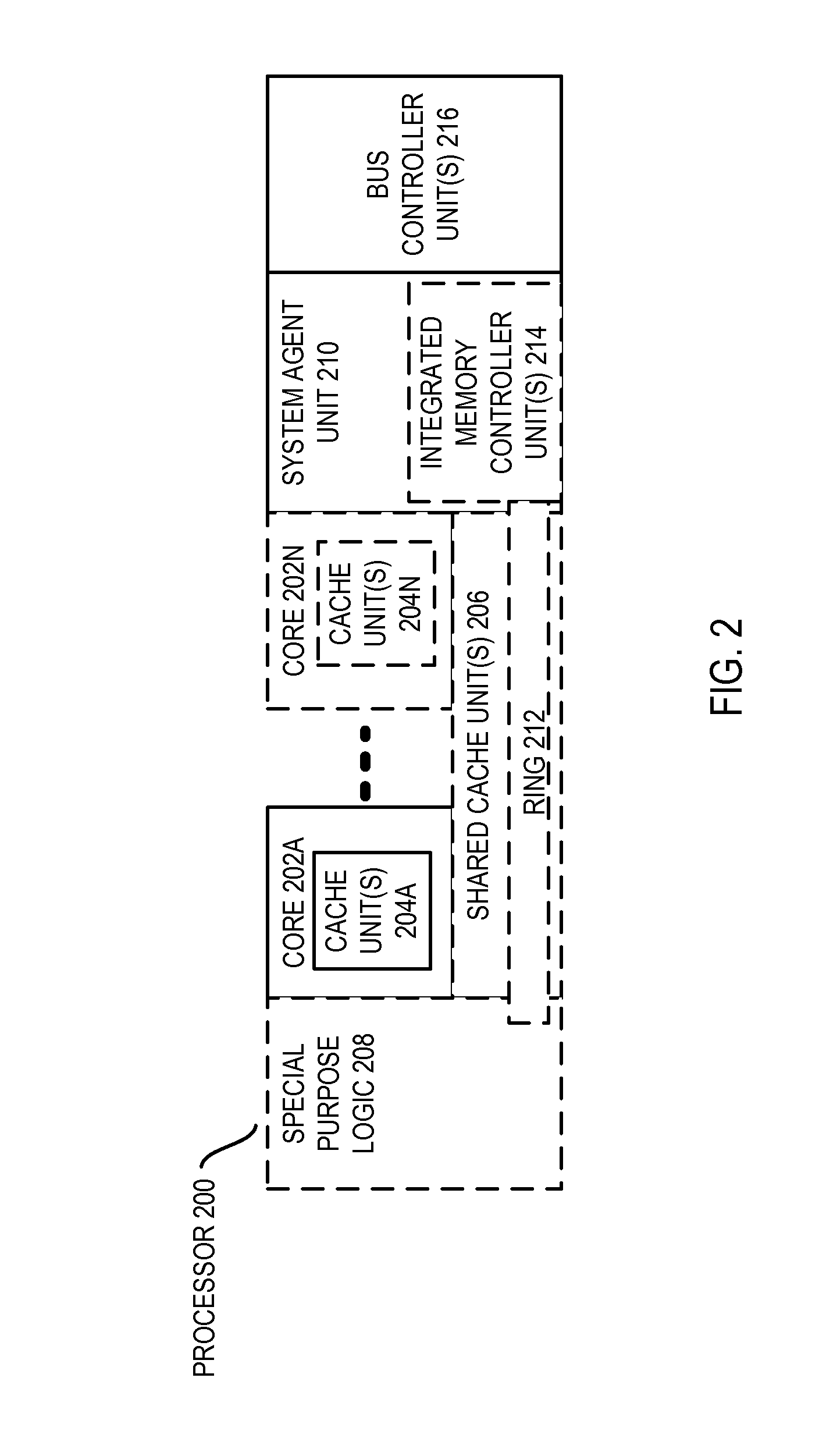

Method and apparatus for implementing a heterogeneous memory subsystem

ActiveUS20150278091A1Memory architecture accessing/allocationInput/output to record carriersParallel computingMemory mapping

An apparatus and method for implementing a heterogeneous memory subsystem is described. For example, one embodiment of a processor comprises: memory mapping logic to subdivide a system memory space into a plurality of memory chunks and to map the memory chunks across a first memory and a second memory, the first memory having a first set of memory access characteristics and the second memory having a second set of memory access characteristics different from the first set of memory access characteristics; and dynamic remapping logic to swap memory chunks between the first and second memories based, at least in part, on a detected frequency with which the memory chunks are accessed.

Owner:INTEL CORP

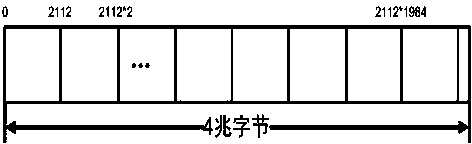

Large image real-time browsing method based on multi-core structure

InactiveCN101650820AImprove browsing efficiencyImprove reading efficiencyImage memory managementProcessor architectures/configurationParallel computingImage mode

The invention discloses a large image real-time browsing method based on a multi-core structure, comprising the following steps: (1) reading image data of appointed positions of a large image into a cache pool by a memory mapping technique; (2) displaying corresponding data blocks inside the cache pool in an image mode according to the appointment of a browser, wherein a displayed image area is acurrent browsing area, and reading and updating image data inside the cache pool when the browser selects an image area adjacent to the current browsing area to browse; and processing a plurality of threads by setting parallel working pipelines and utilizing a CPU multi-core technique when the image data of the current browsing area are displayed and the image data of the cache pool are read in the step (1) and the step (2). The large image real-time browsing method greatly enhances the browsing efficiency without any preprocessing operation by using the parallel working pipelines and being based on a predicted data processing technique.

Owner:ZHEJIANG UNIV

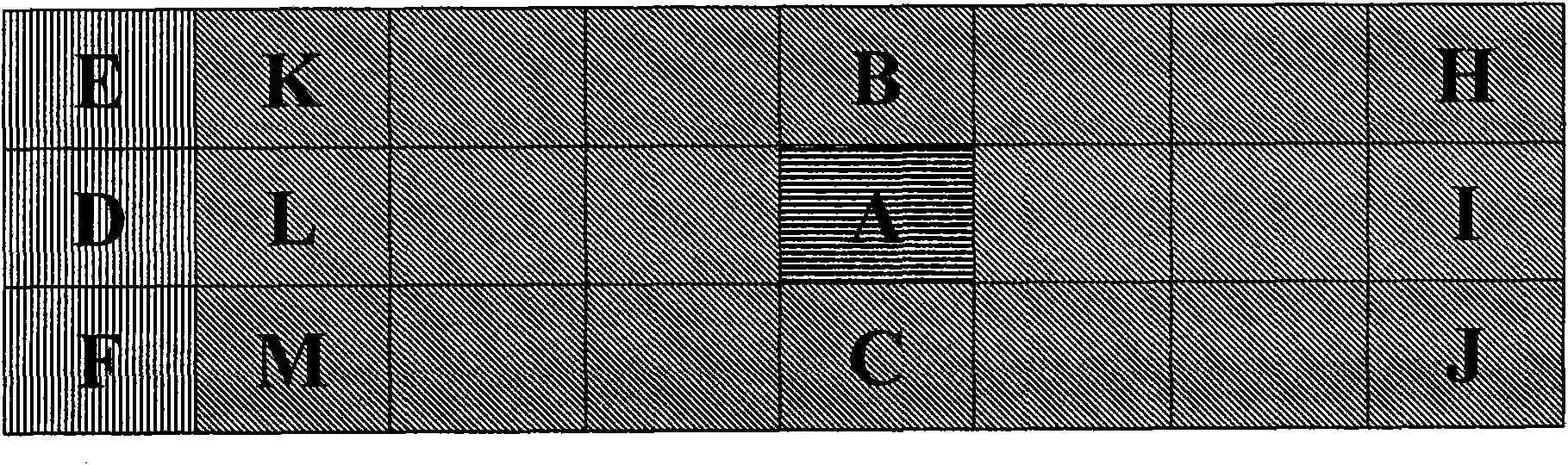

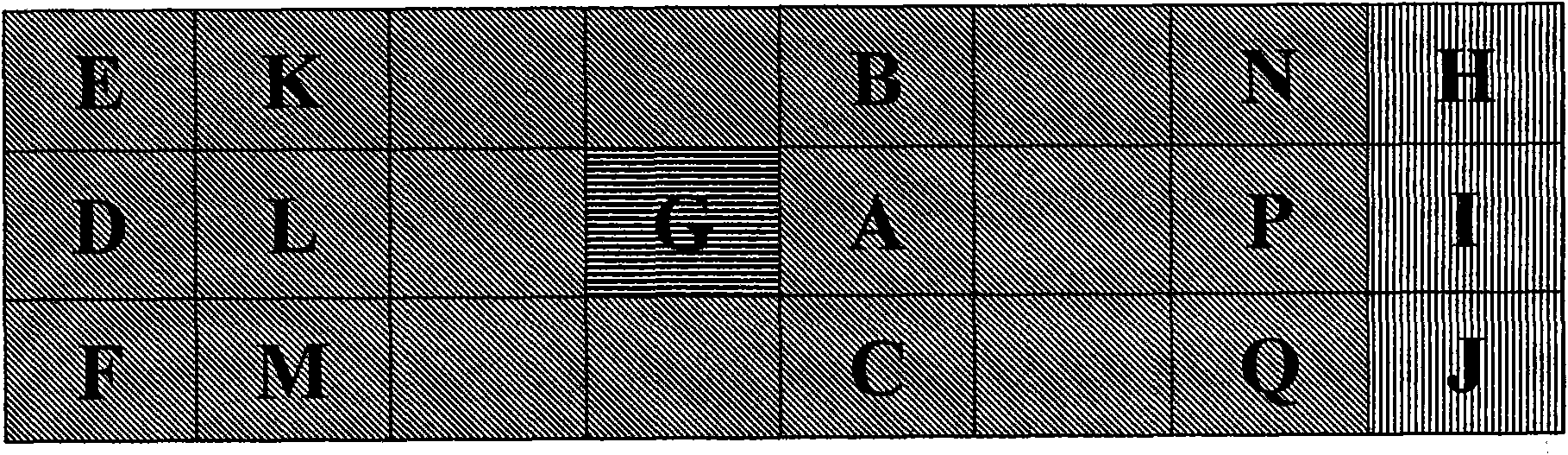

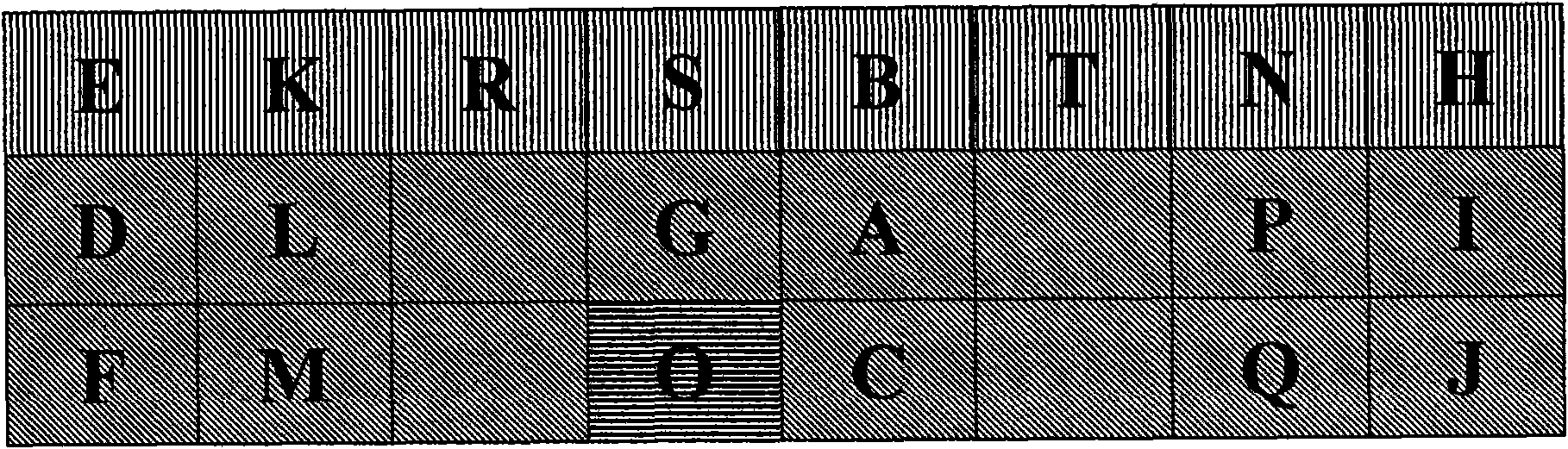

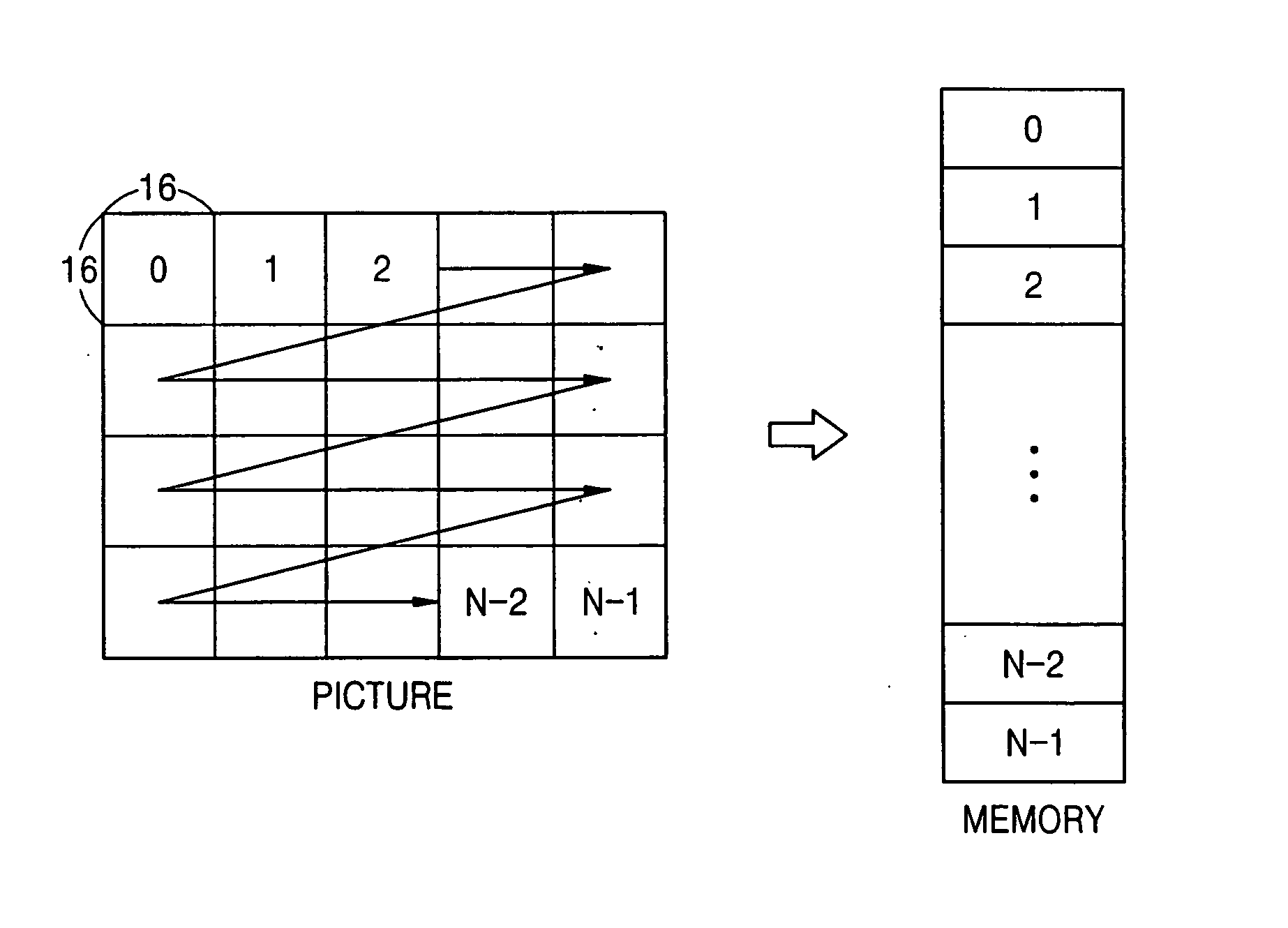

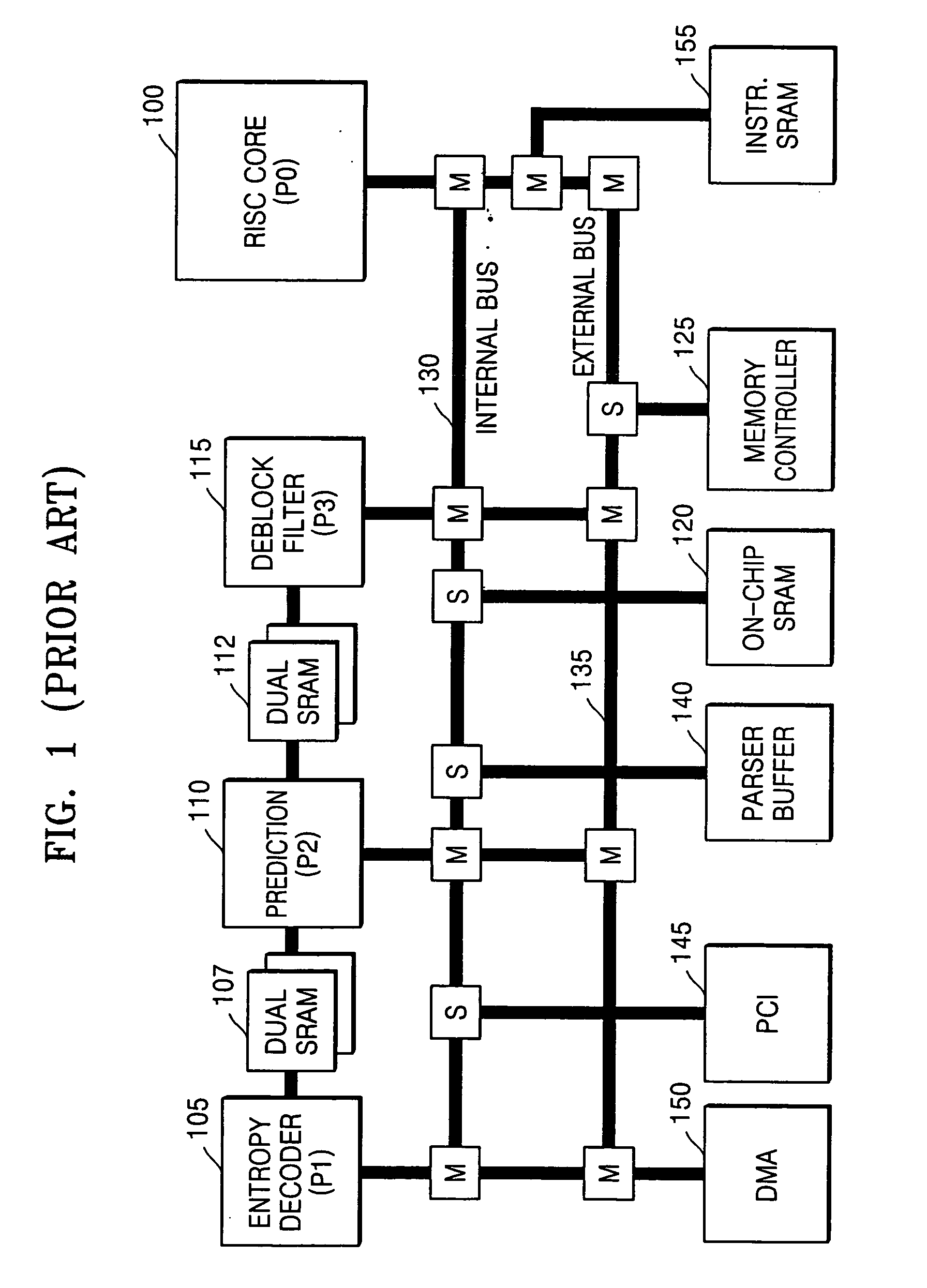

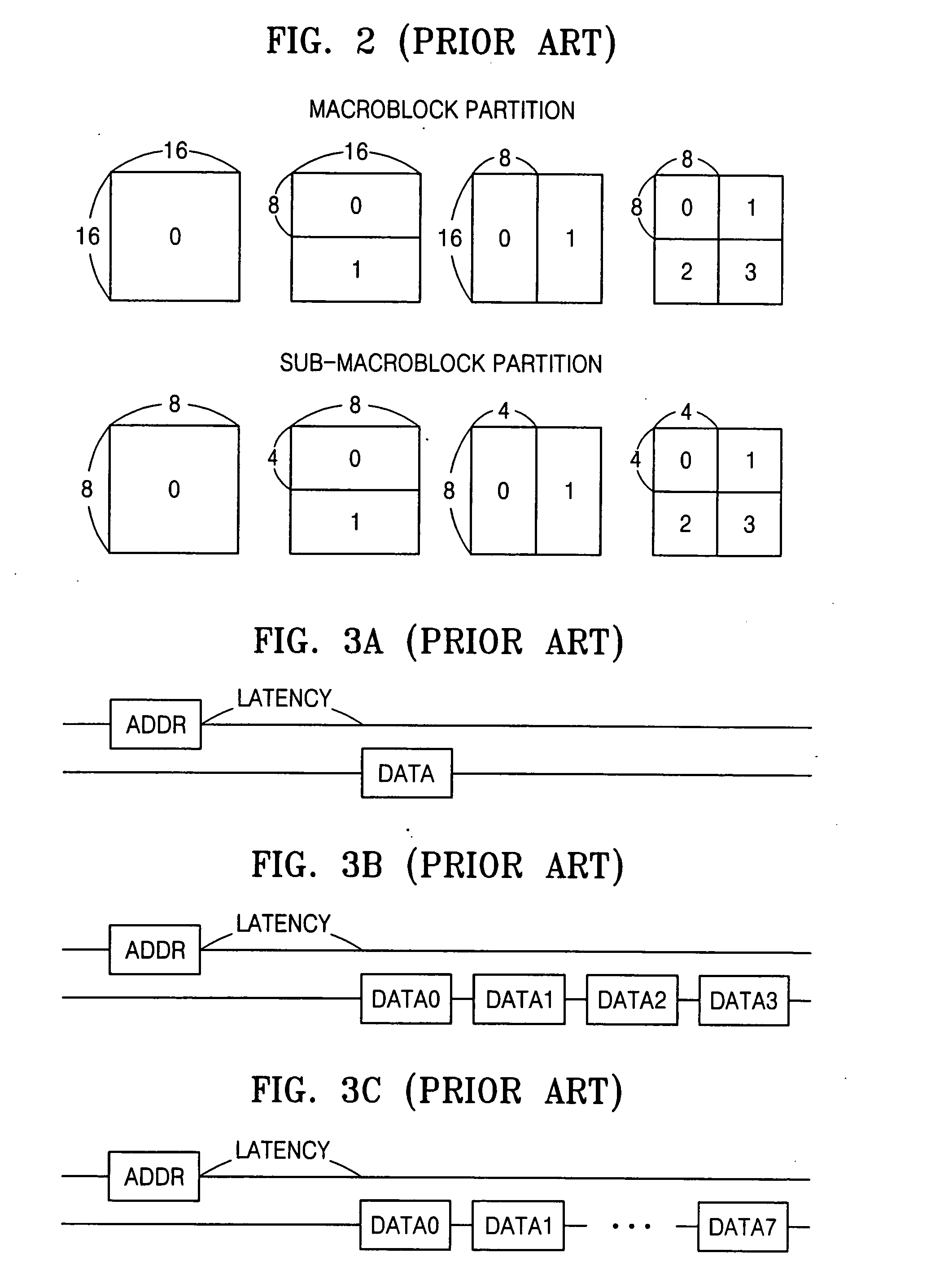

Memory mapping apparatus and method for video decoder/encoder

InactiveUS20060023792A1Reduce the number of cyclesColor television with pulse code modulationColor television with bandwidth reductionMemory bankParallel computing

A memory mapping apparatus and a method in a video decoder / encoder utilize a dividing unit, a storage unit and a memory allocation unit. The dividing unit divides picture data into macroblocks and divides each of the macroblocks, which are units of encoding, into partitions having a predetermined size. A storage unit comprises at least one memory bank which is independently accessible. A memory allocation unit allocates adjacent partitions to different memory banks. Accordingly, a total number of cycles necessary to read and write the picture data is reduced.

Owner:SAMSUNG ELECTRONICS CO LTD