Patents

Literature

260 results about "Programmable Interrupt Controller" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computing, a programmable interrupt controller (PIC) is a device that is used to combine several sources of interrupt onto one or more CPU lines, while allowing priority levels to be assigned to its interrupt outputs. When the device has multiple interrupt outputs to assert, it asserts them in the order of their relative priority. Common modes of a PIC include hard priorities, rotating priorities, and cascading priorities. PICs often allow the cascading of their outputs to inputs between each other.

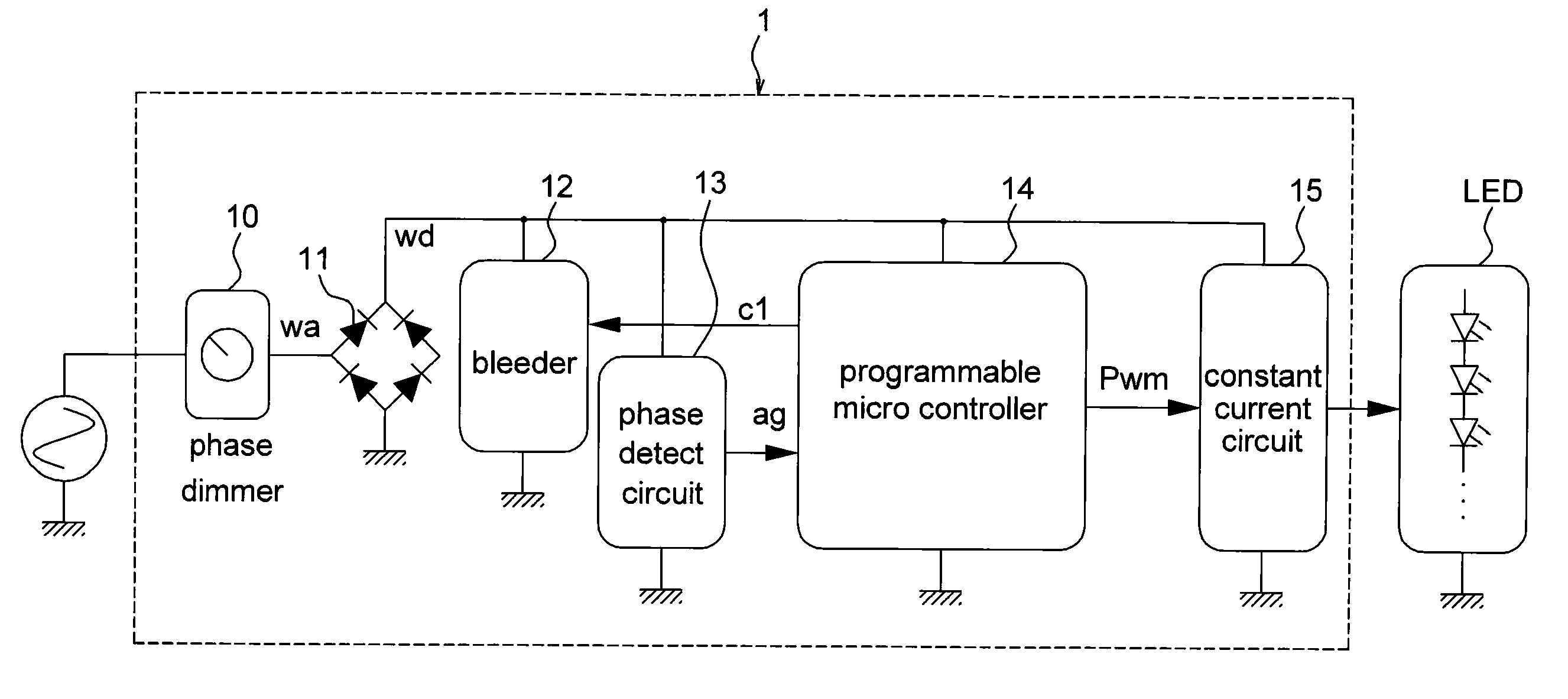

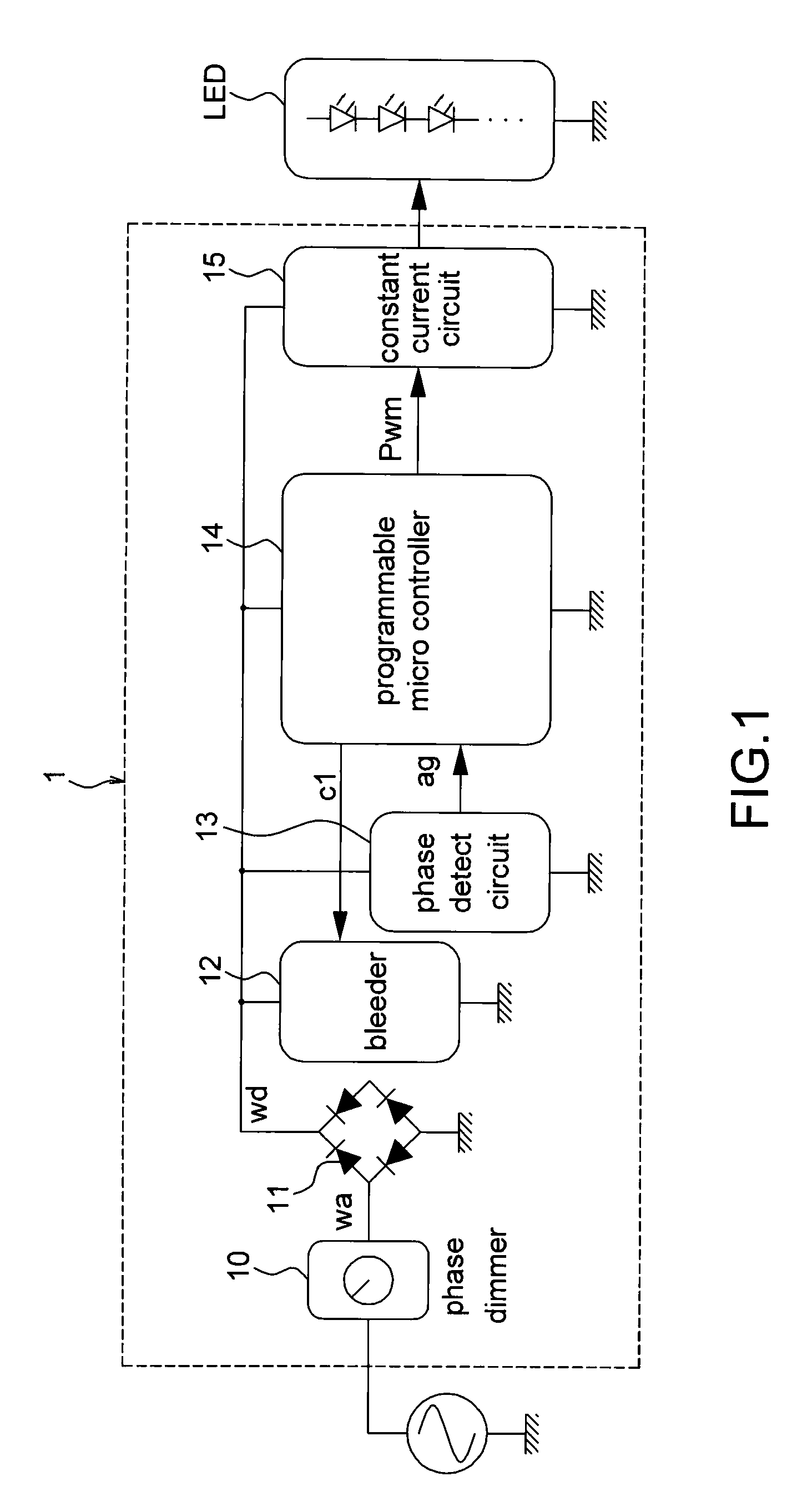

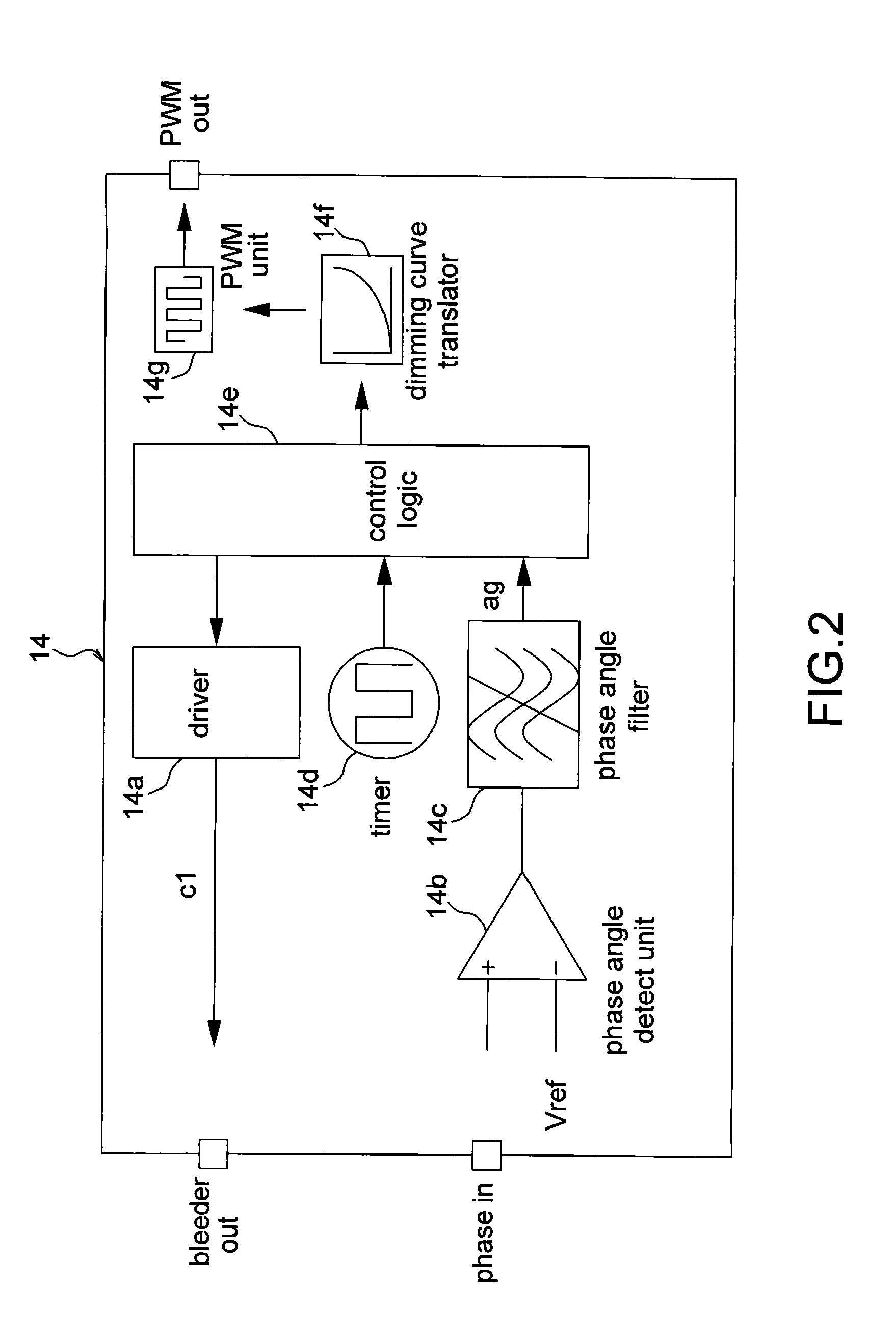

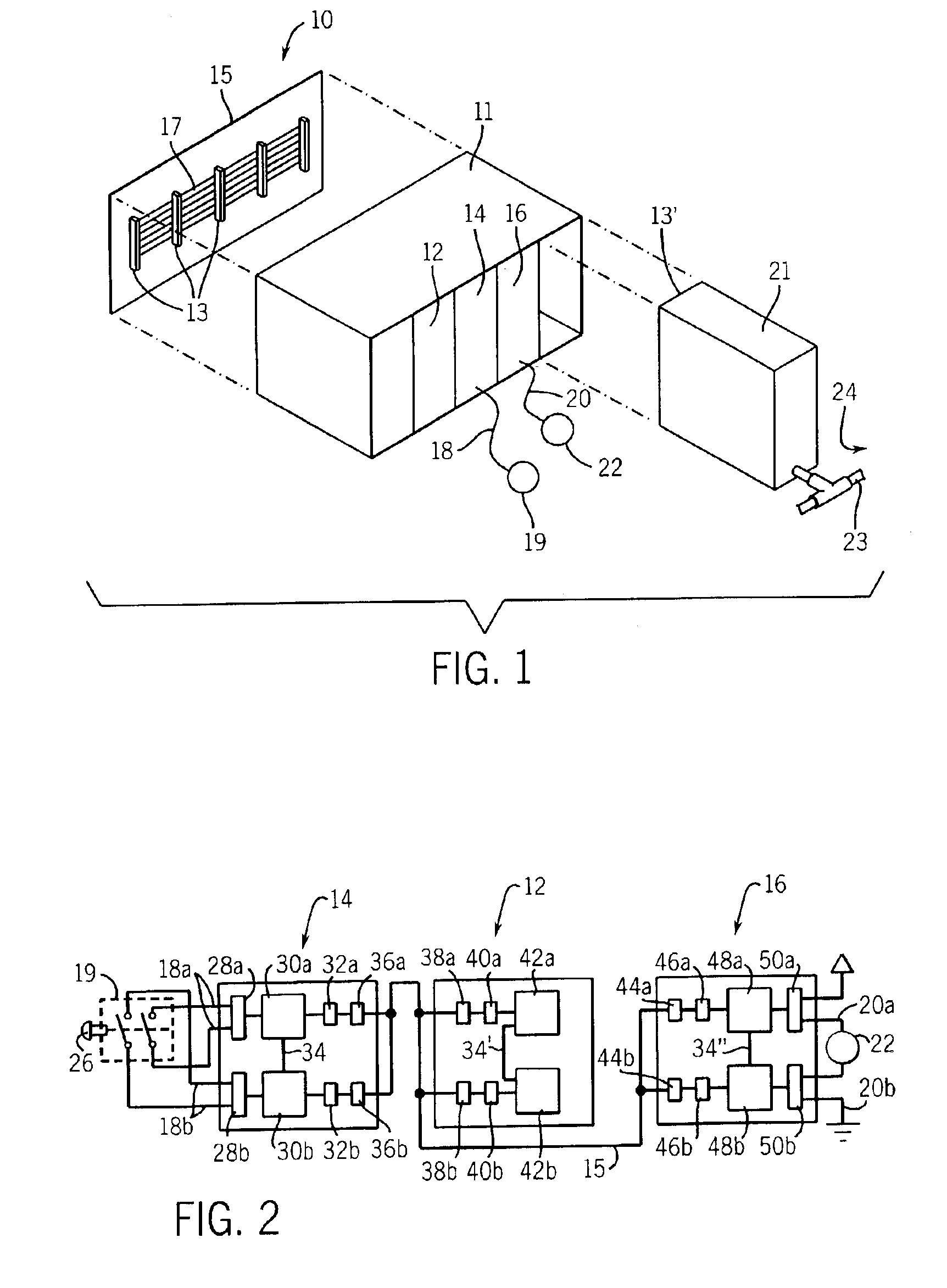

Dimmer circuit applicable for LED device and control method thereof

InactiveUS20110291583A1Improve efficiencyElectrical apparatusElectroluminescent light sourcesProgrammable logic controllerProgrammable Interrupt Controller

A dimmer circuit applicable for LED device and control method thereof is disclosed in the embodiments of the present invention. The dimmer circuit is applicable for controlling at least a LED device. The dimmer circuit includes a rectifier, a bleeder, a phase angle detect circuit, a constant current circuit and a programmable micro controller. The phase angle detect circuit couples to the programmable micro controller. The constant current circuit couples to the LED device The programmable micro controller generates a PWM signal according to the output signal of the phase angle detect circuit to adjust current of the constant current circuit.

Owner:UNITED POWER RES TECH CORP

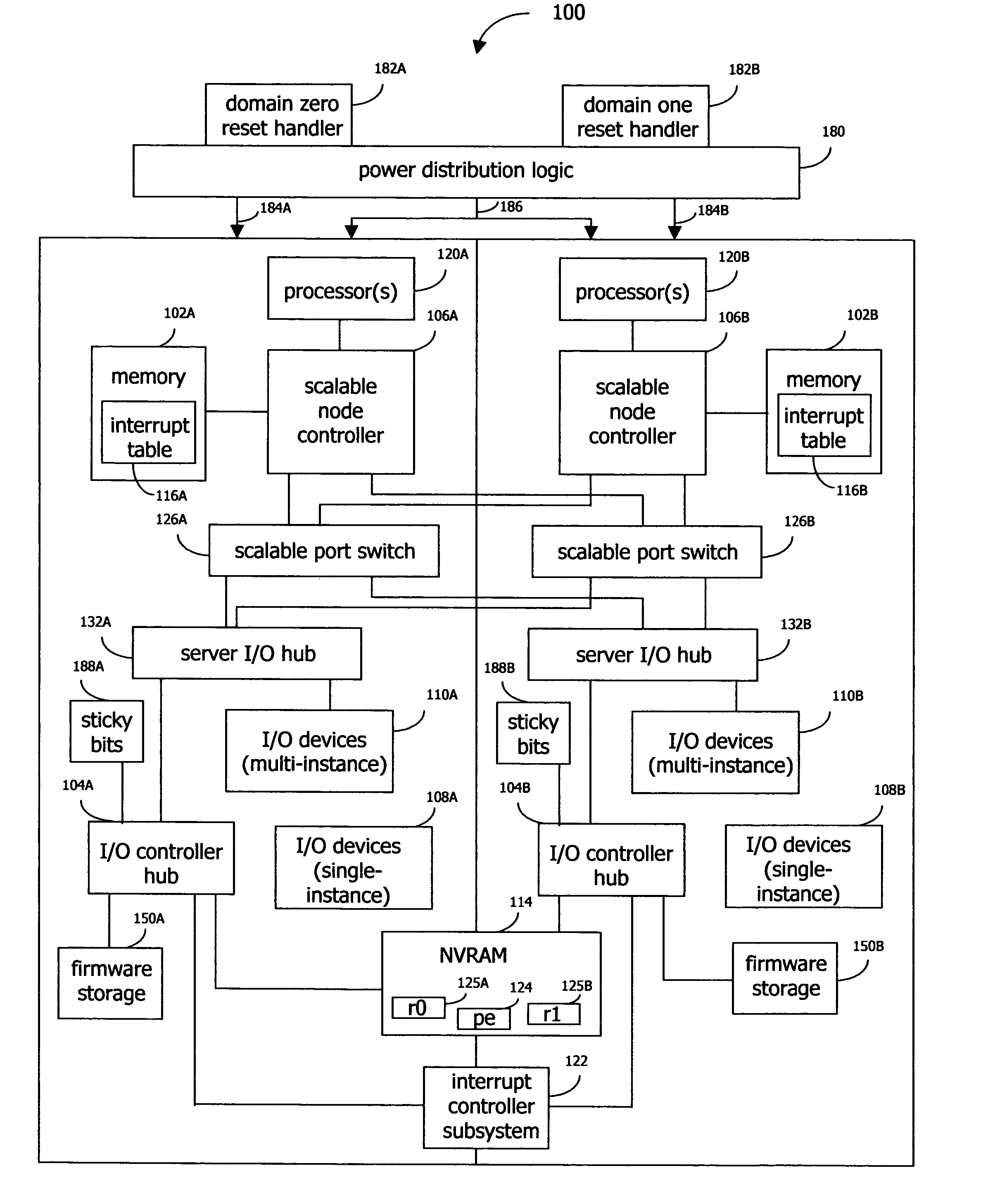

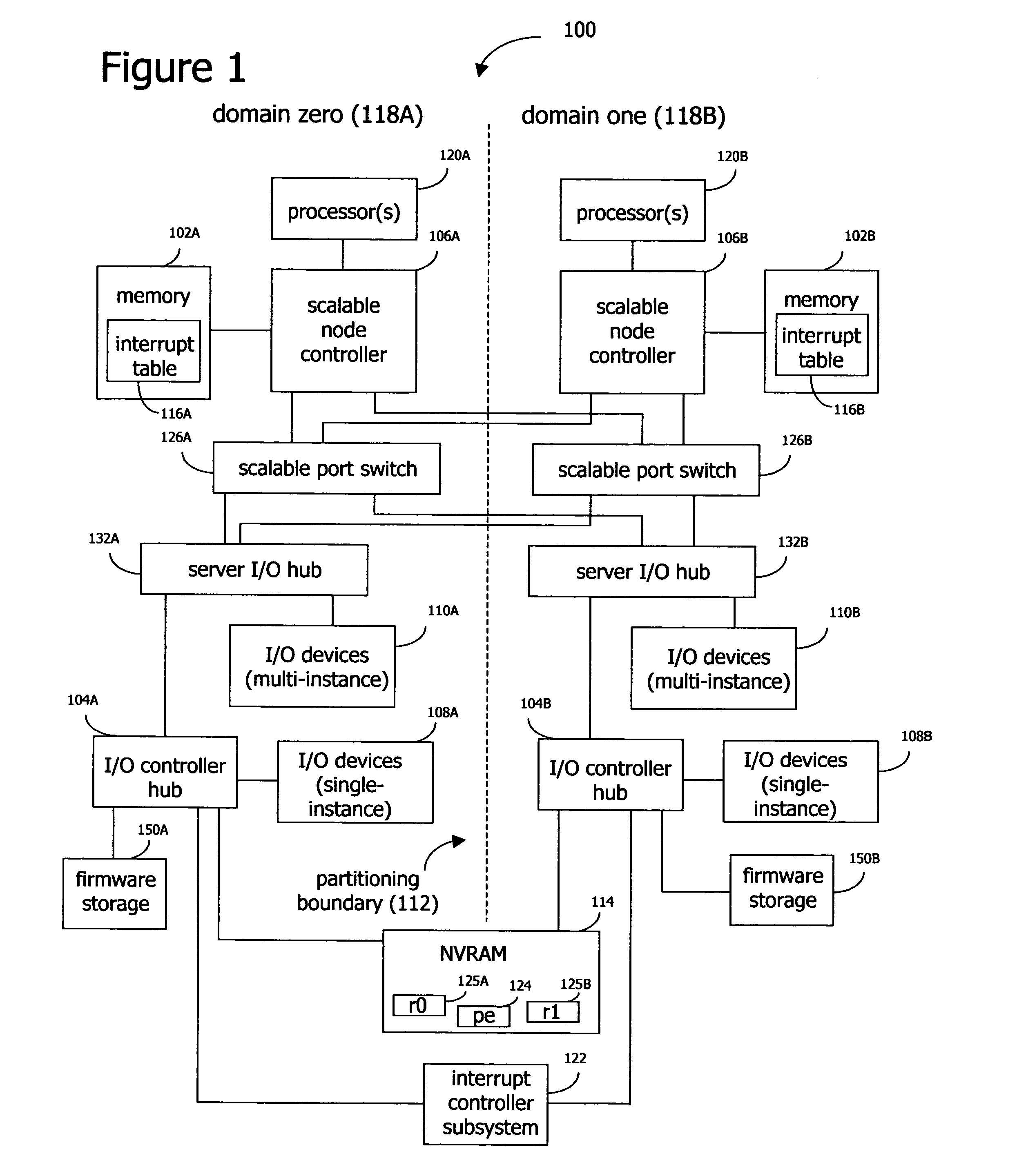

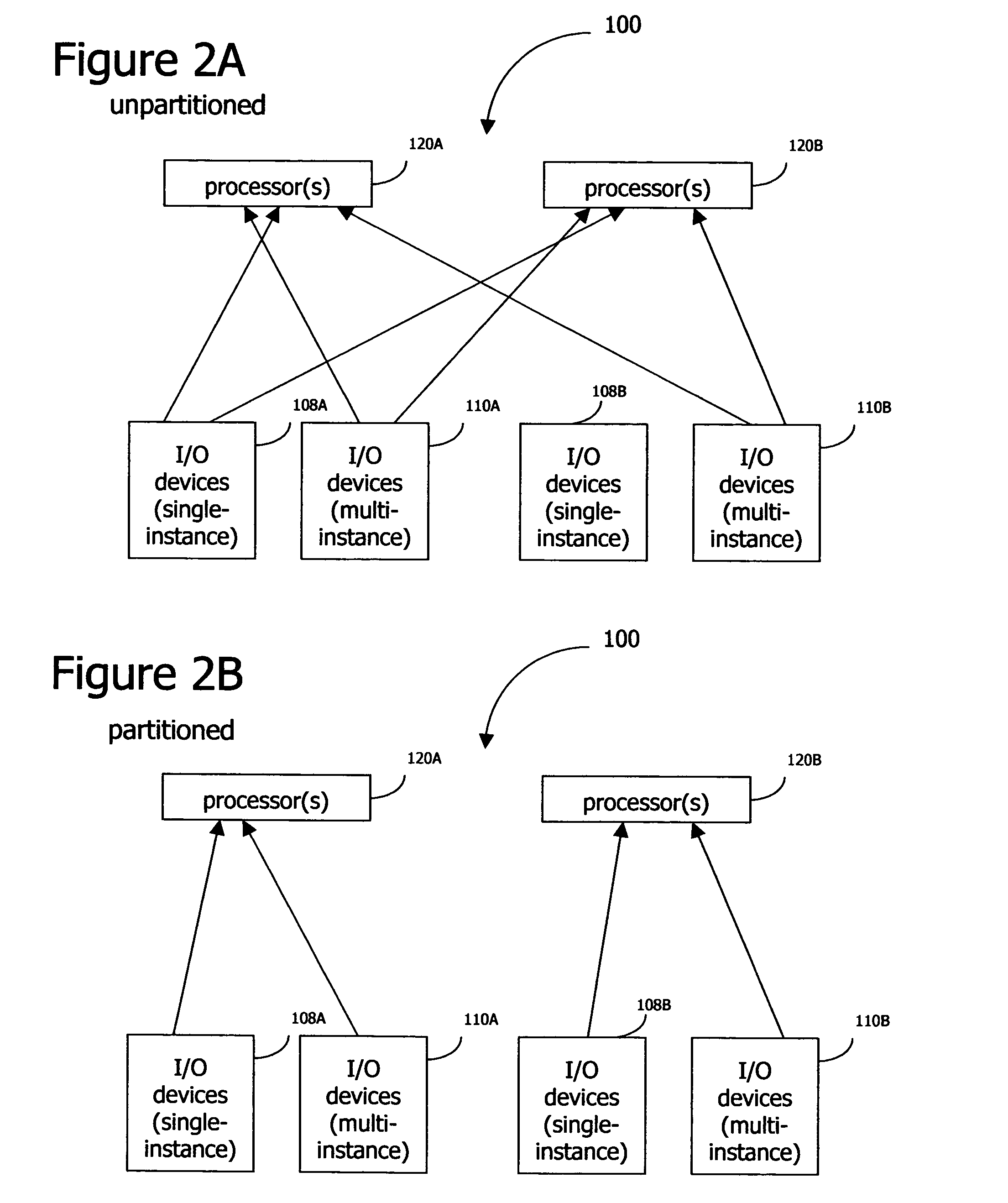

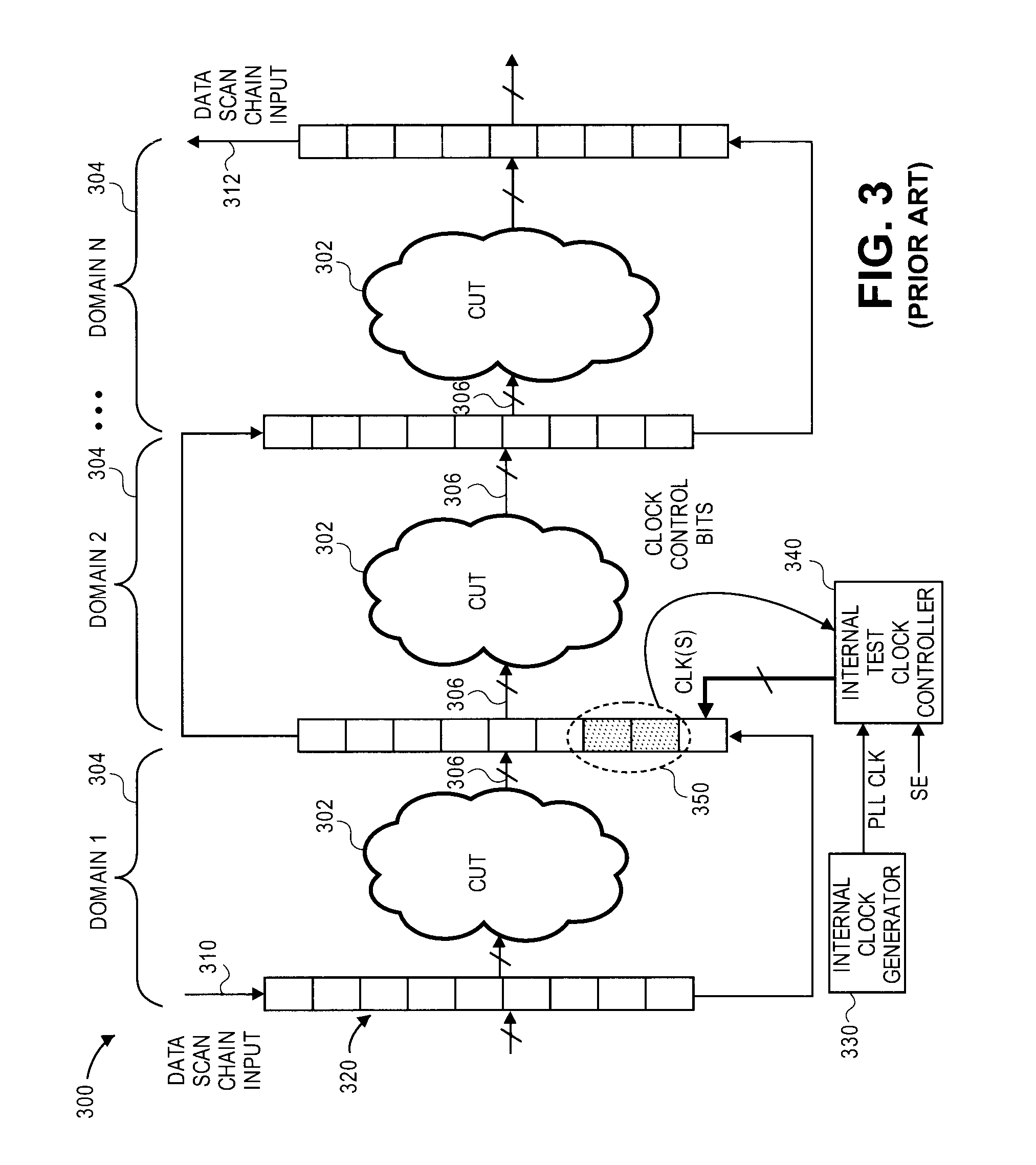

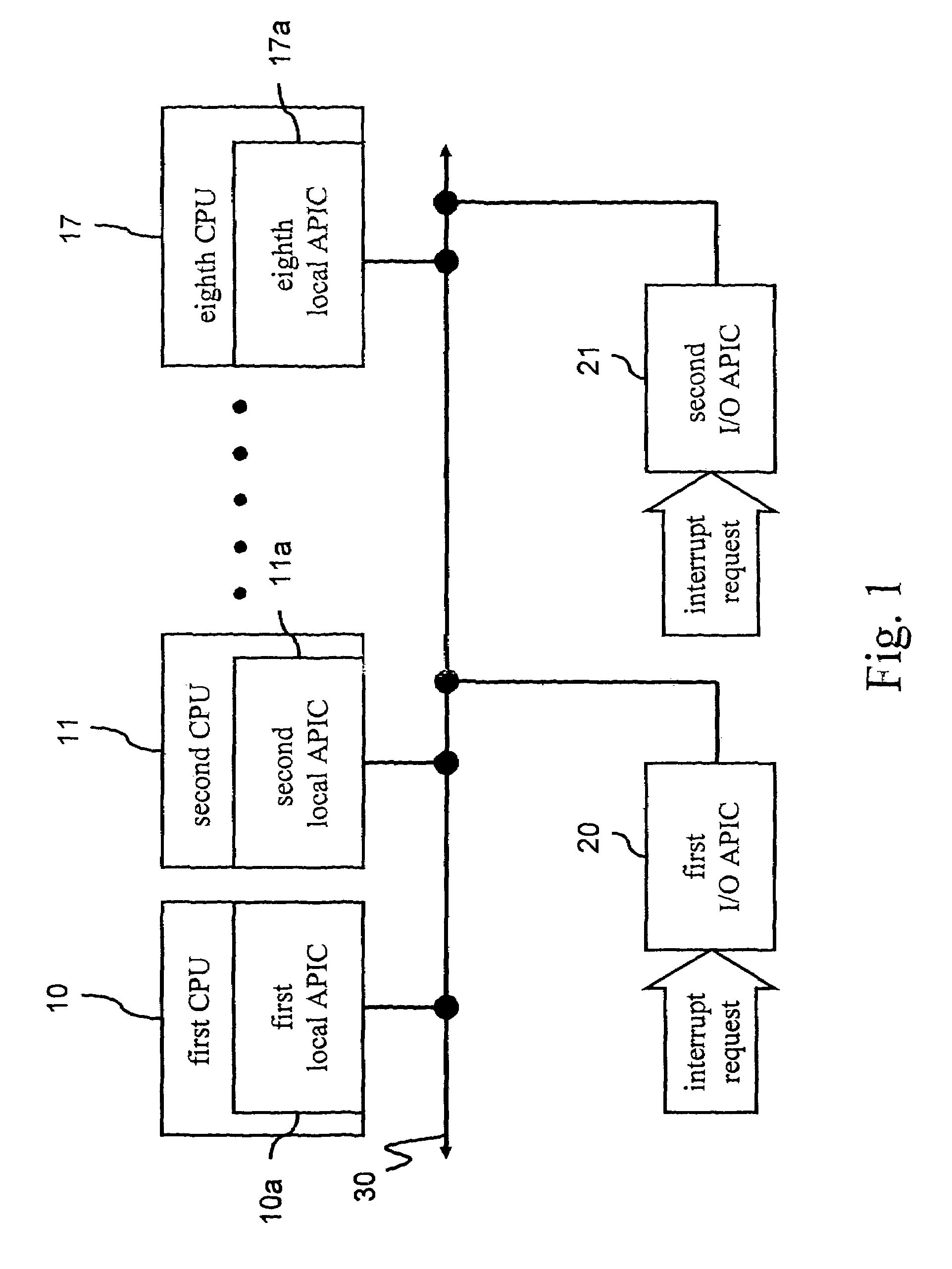

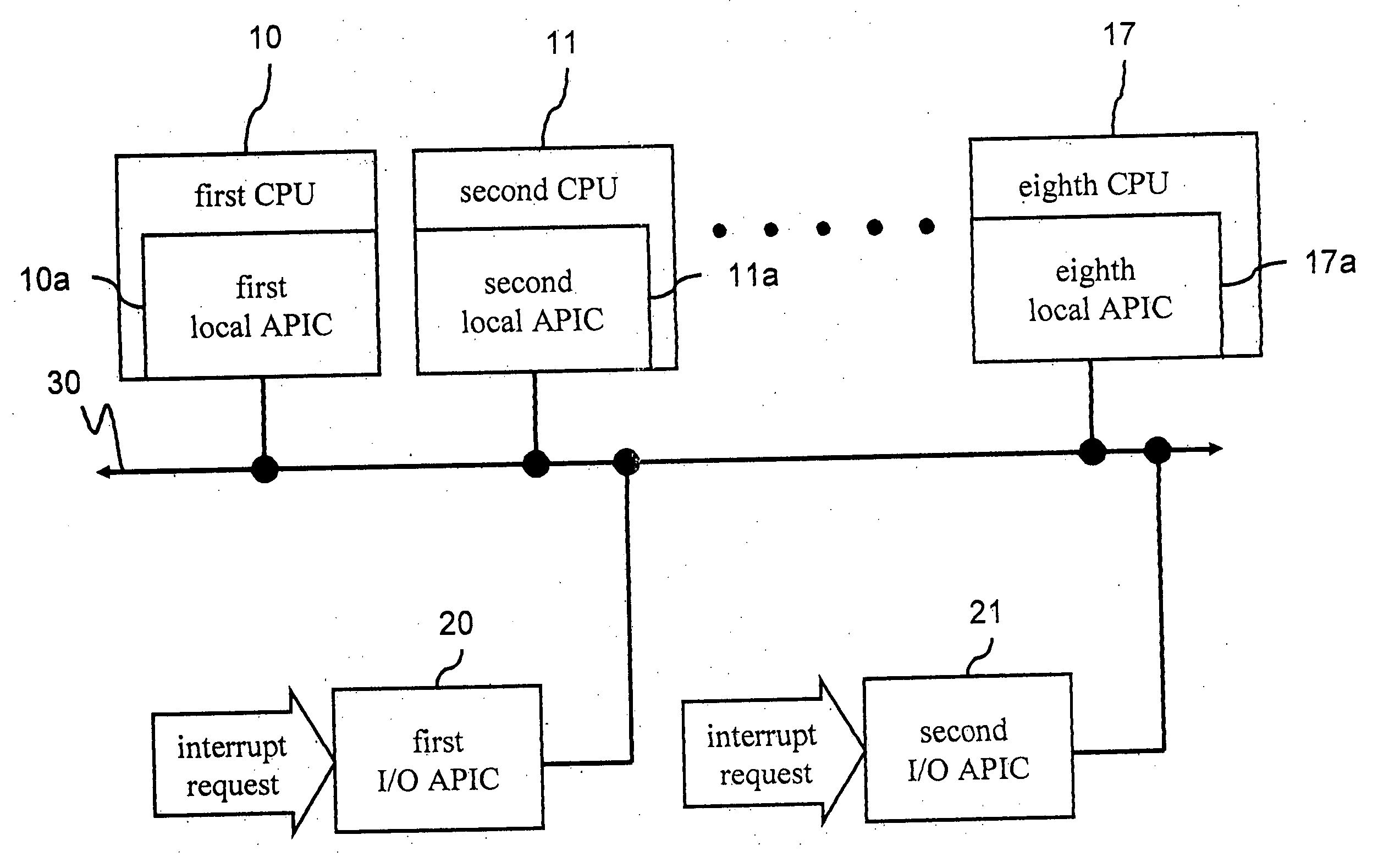

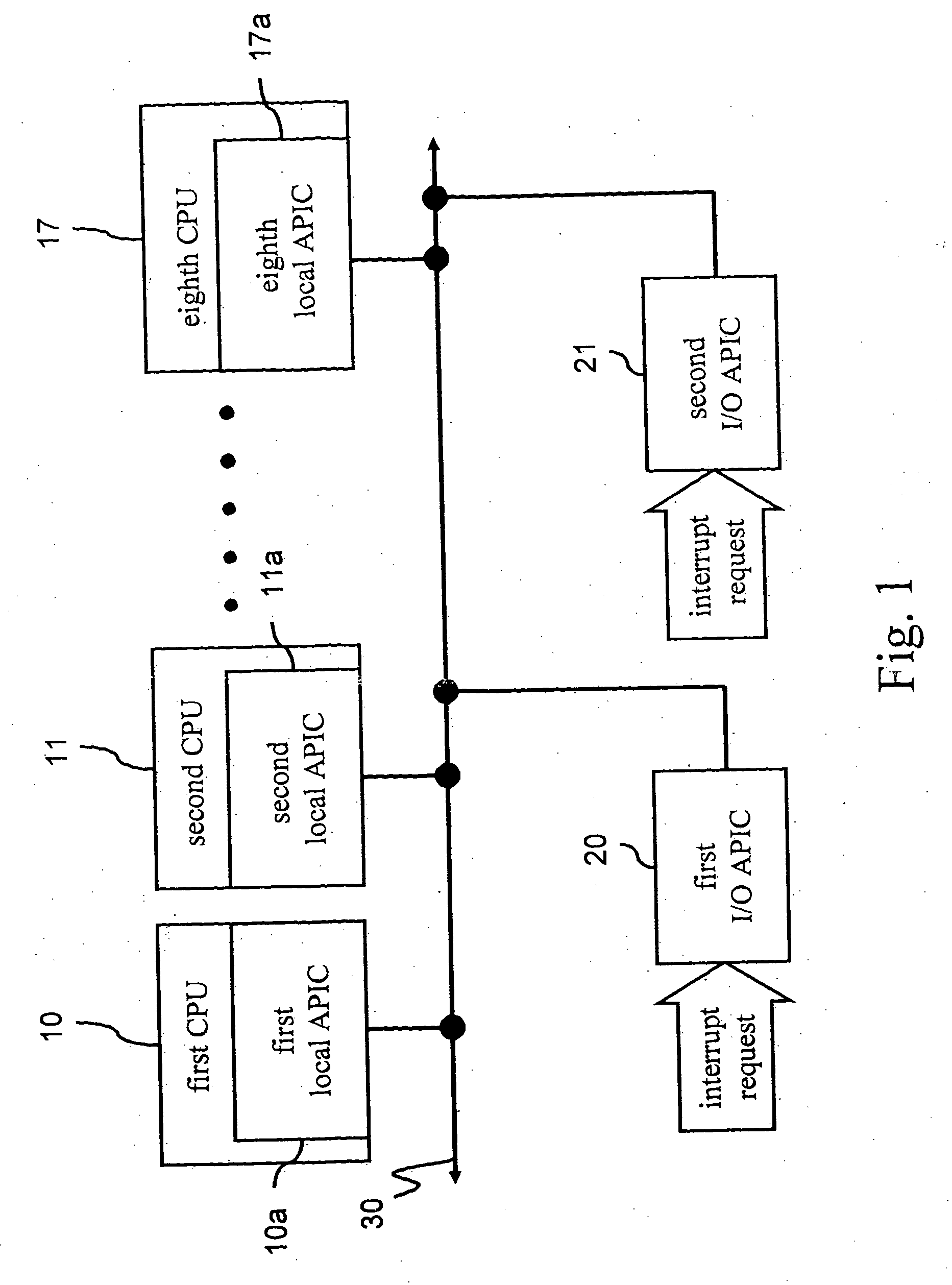

Partitionable multiprocessor system having programmable interrupt controllers

InactiveUS7162560B2General purpose stored program computerData resettingOperational systemMulti processor

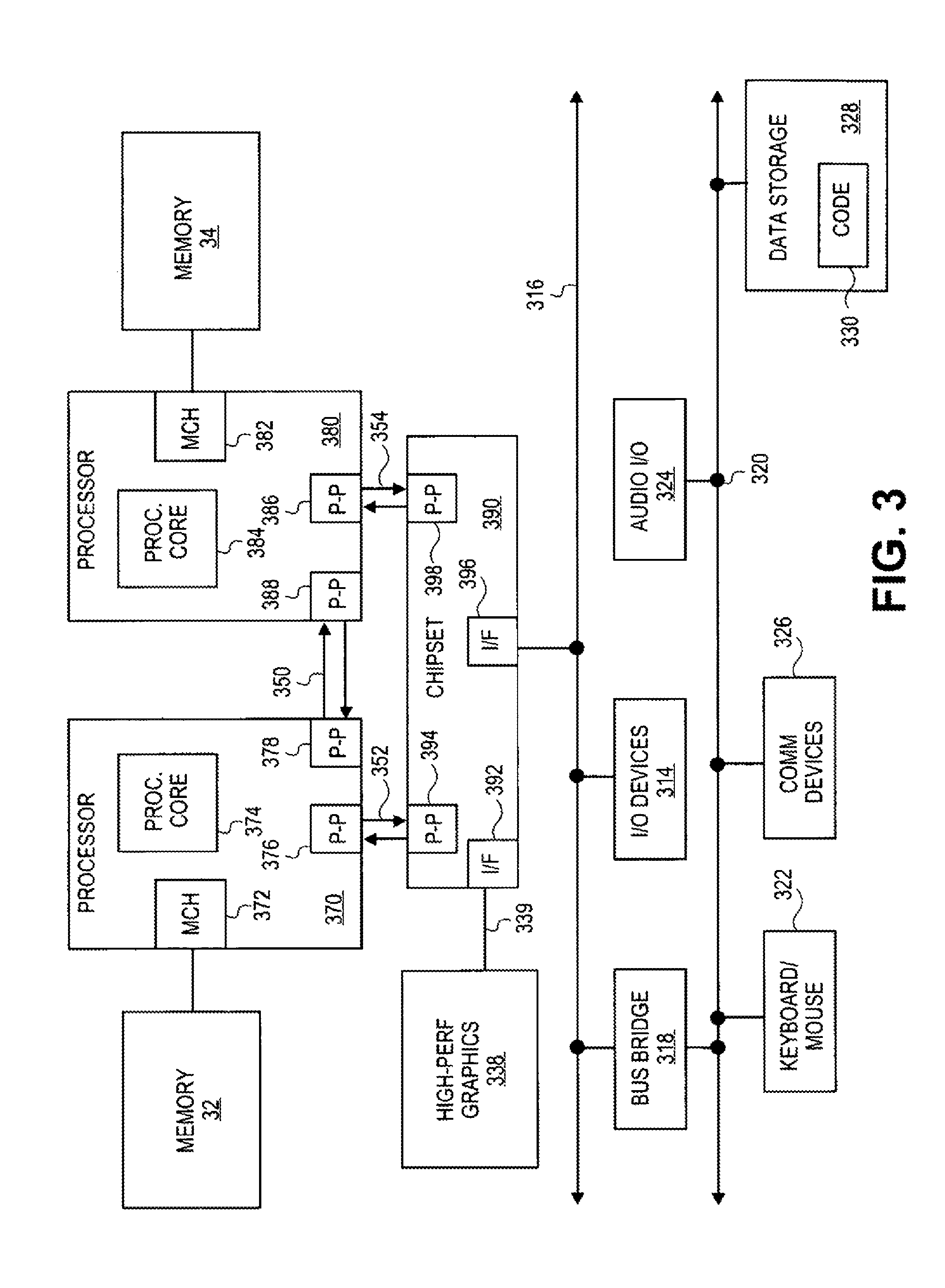

A system that may optionally be partitioned into multiple domains is disclosed. Each domain is capable of independently powering on, executing a firmware program, and loading an operating system, including a legacy operating system, as well as running an application program that is distinct from programs running on another domain. Interrupts, including boot interrupts, reset handlers, and inter-chassis communications are initialized differently, depending on whether the system is to be partitioned or not. The cost of redundant hardware and / or firmware is substantially avoided, yet the system fully supports multiple domains.

Owner:INTEL CORP

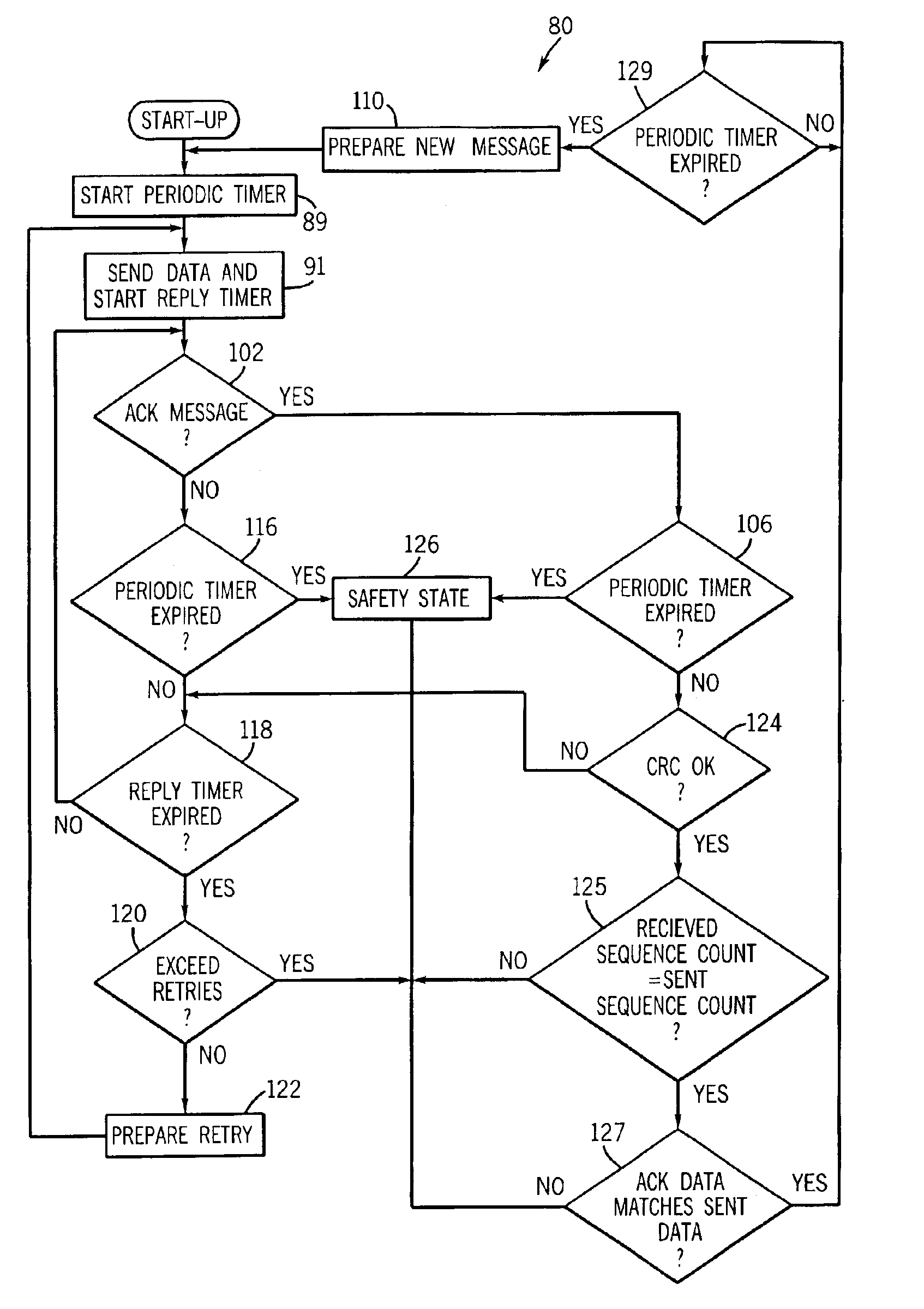

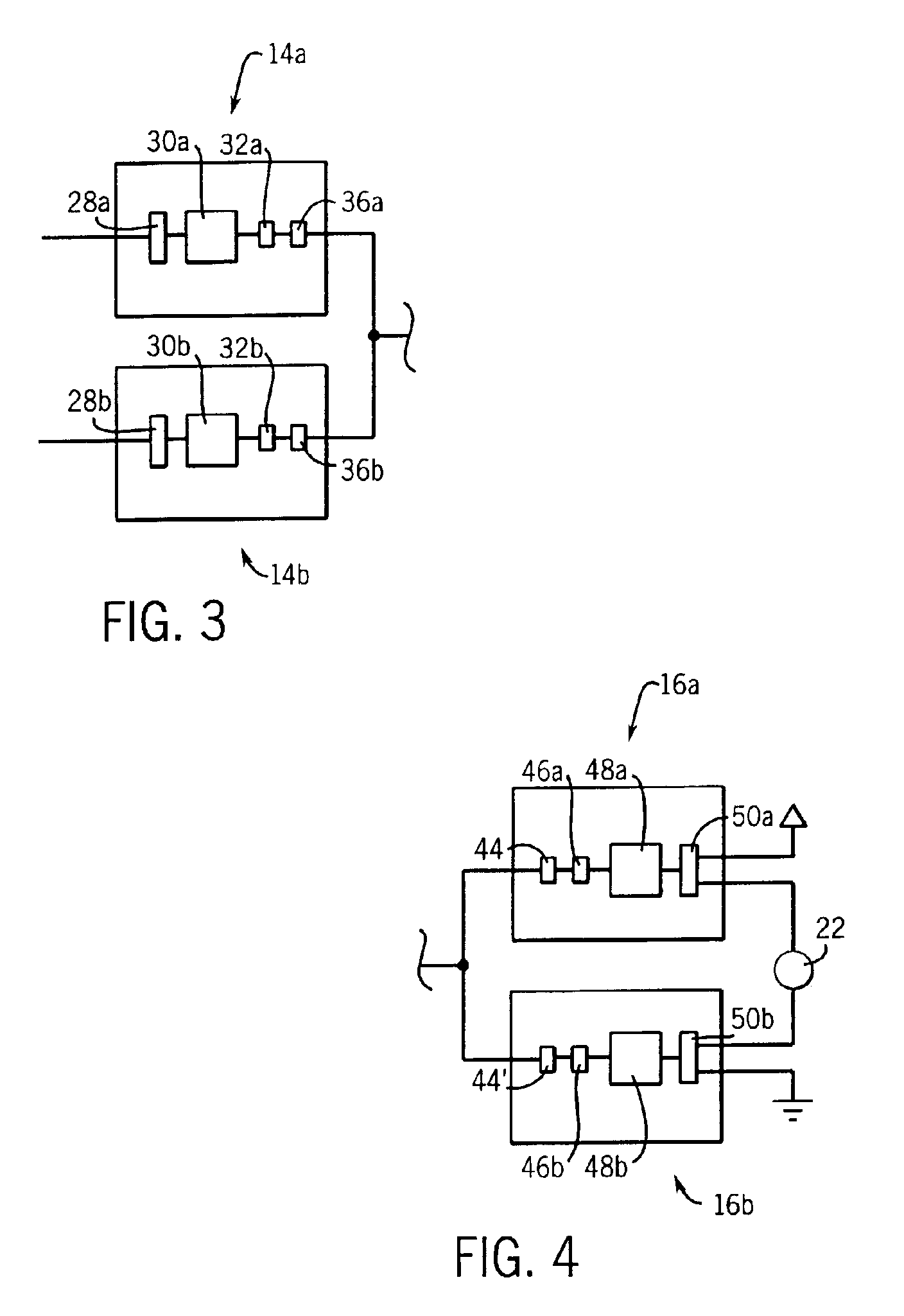

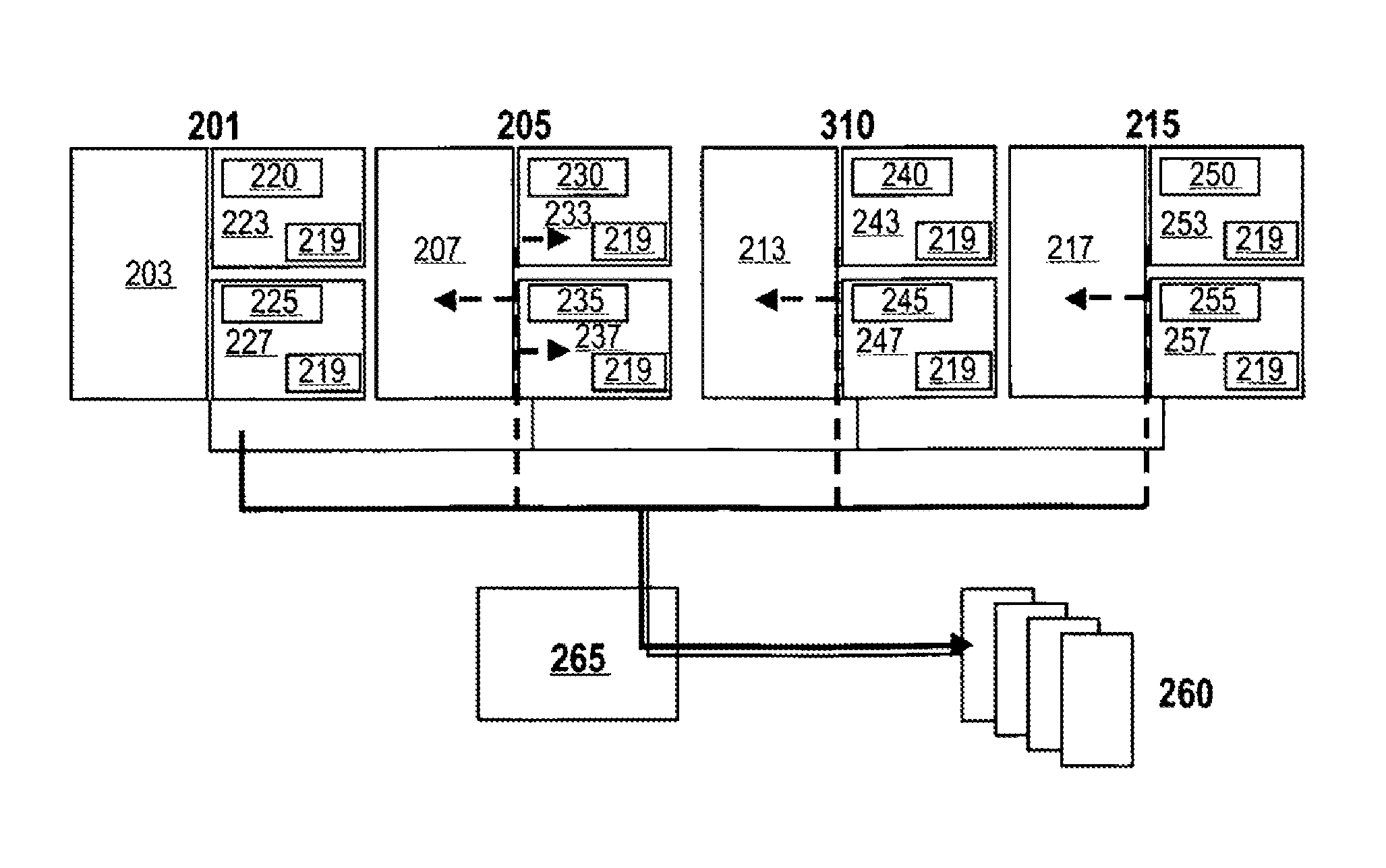

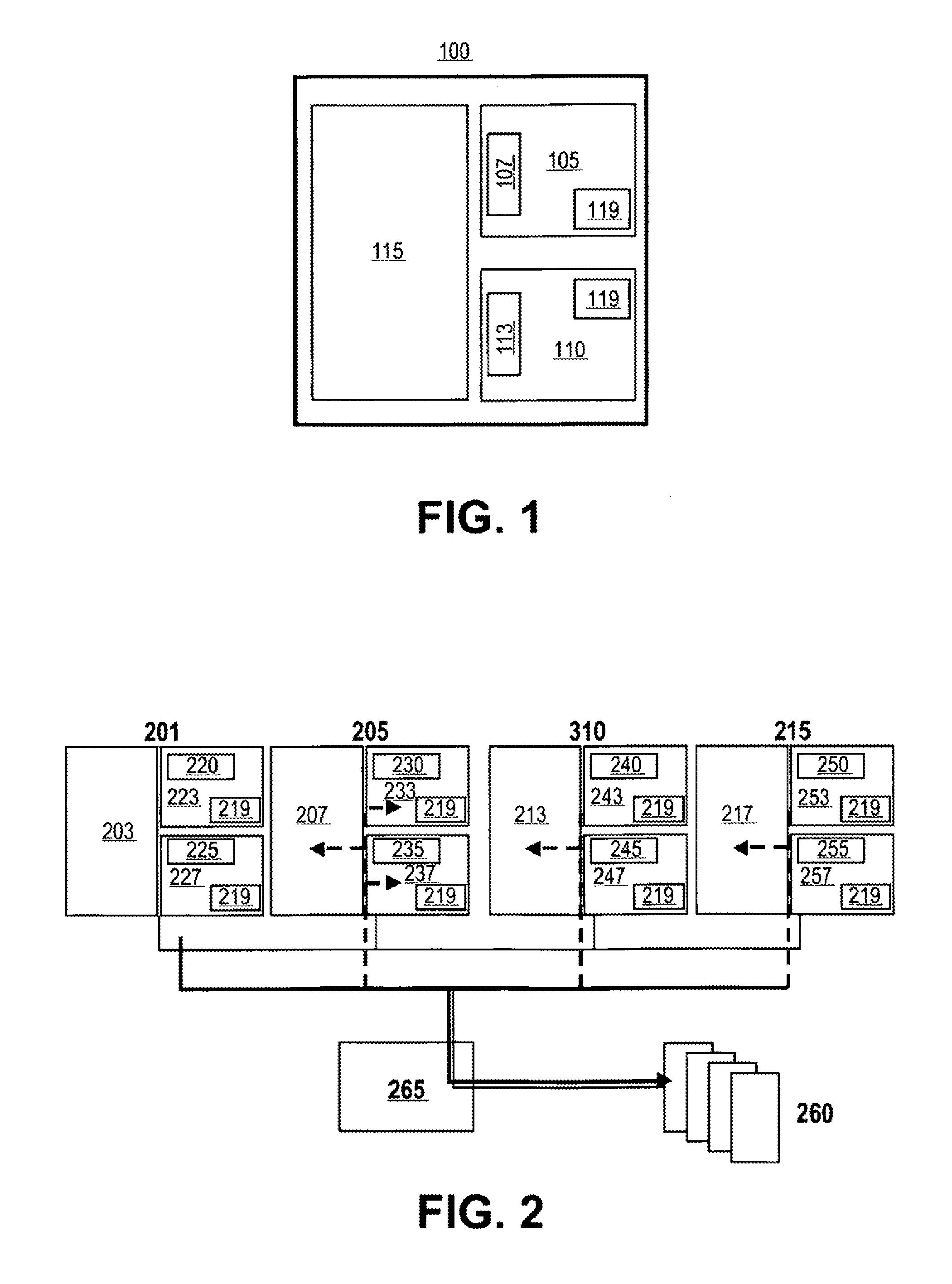

Safety communication on a single backplane

InactiveUS6909923B2Safety arrangmentsComputer controlProgrammable logic controllerProgrammable Interrupt Controller

Owner:ROCKWELL AUTOMATION TECH

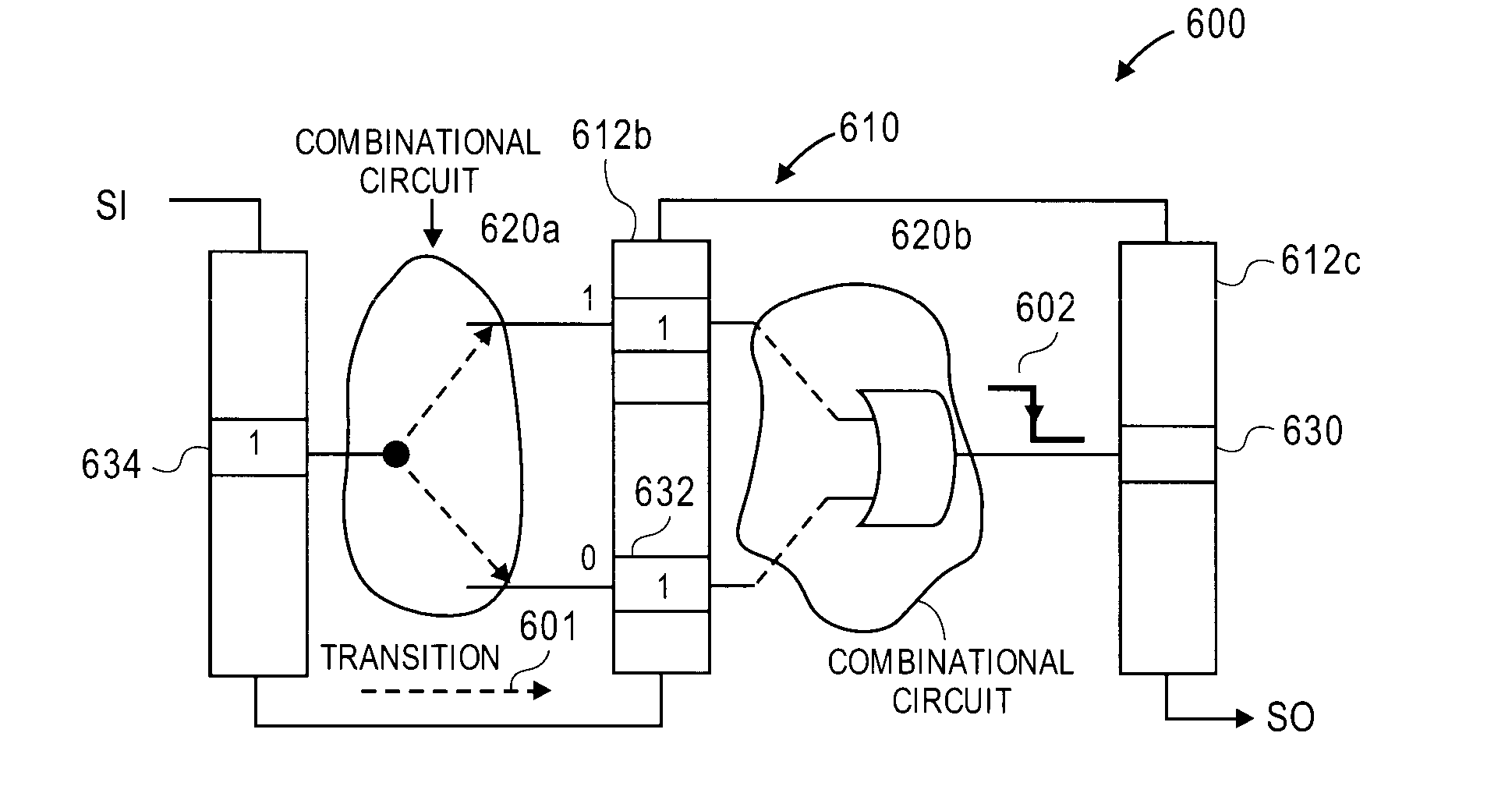

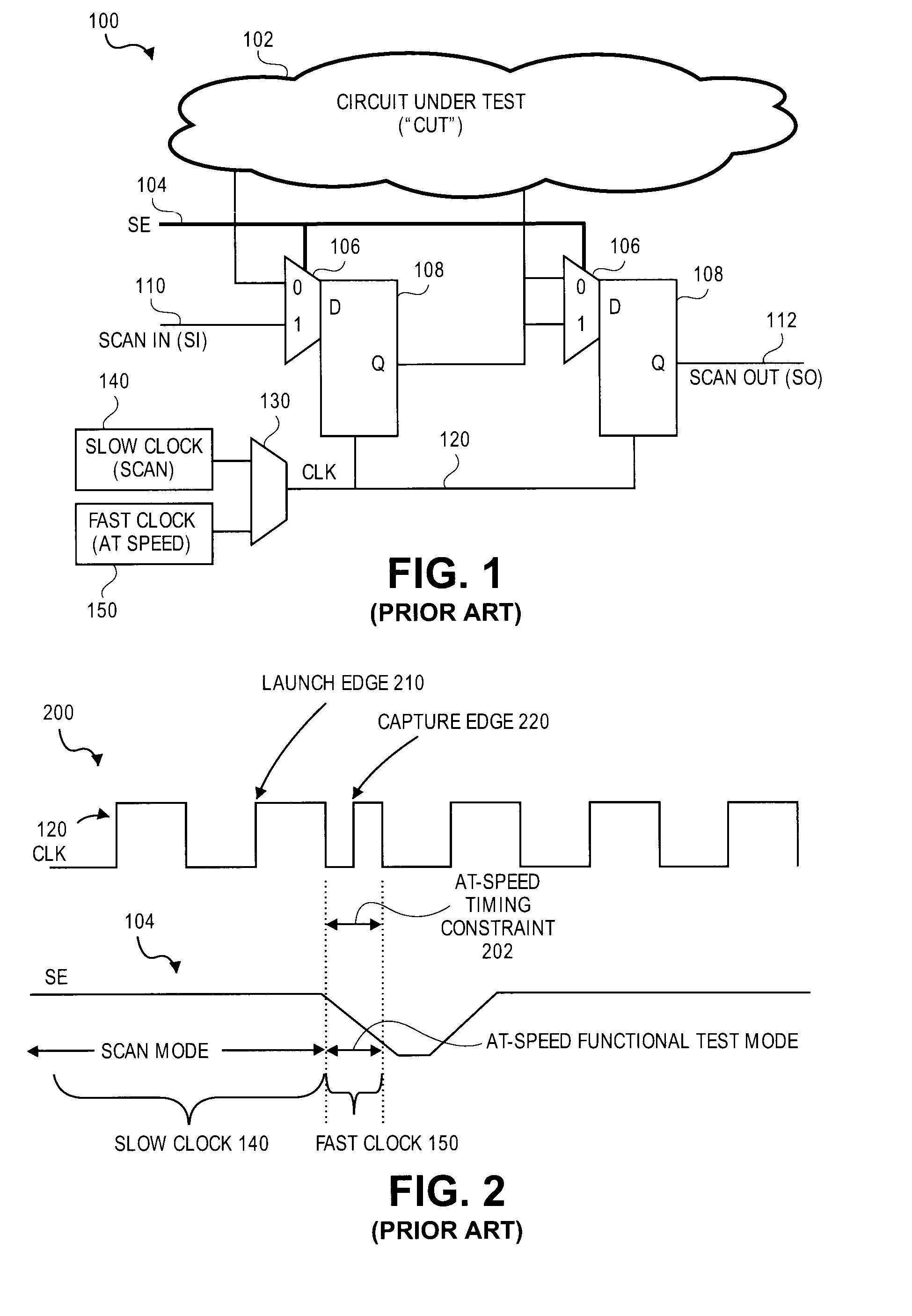

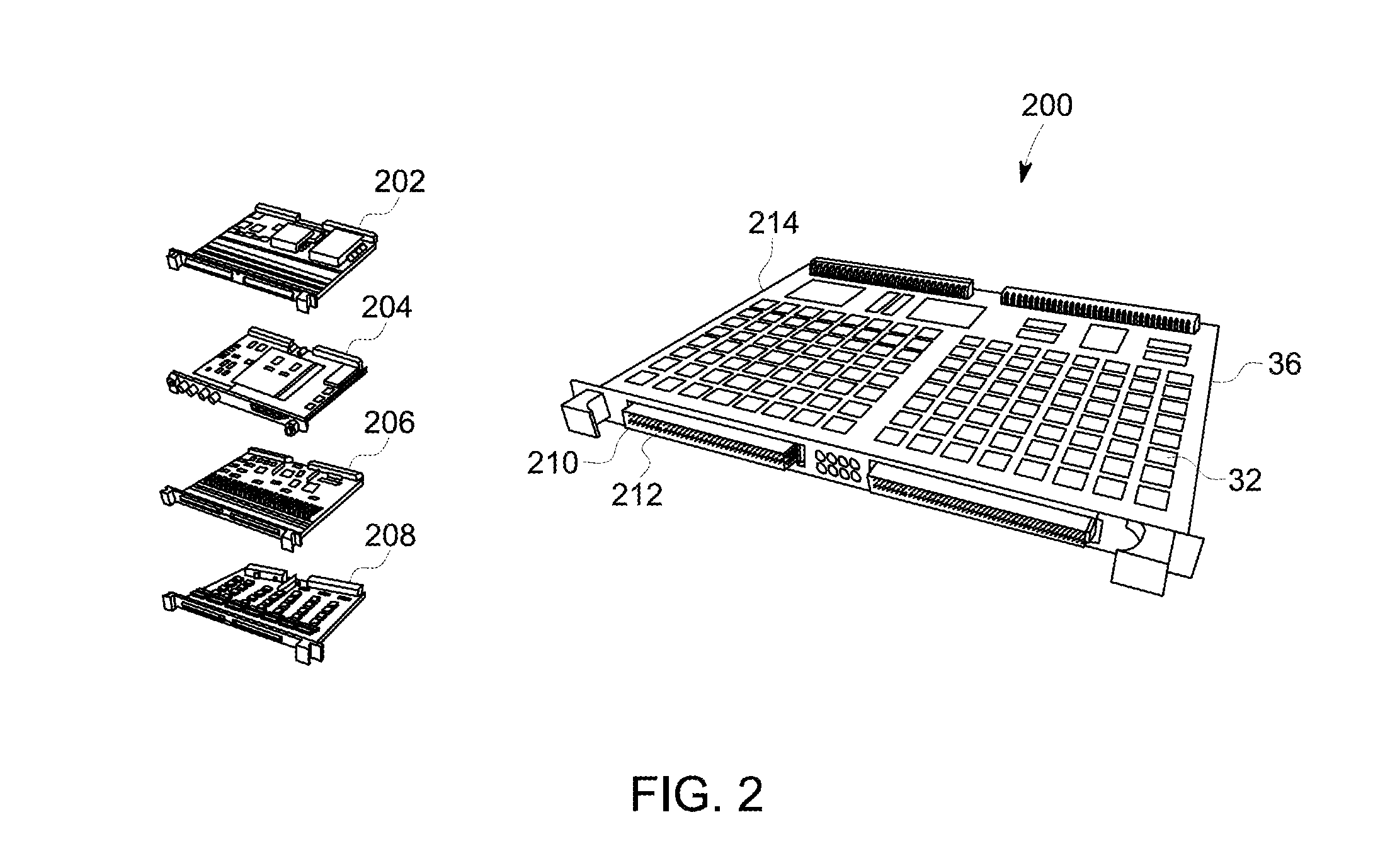

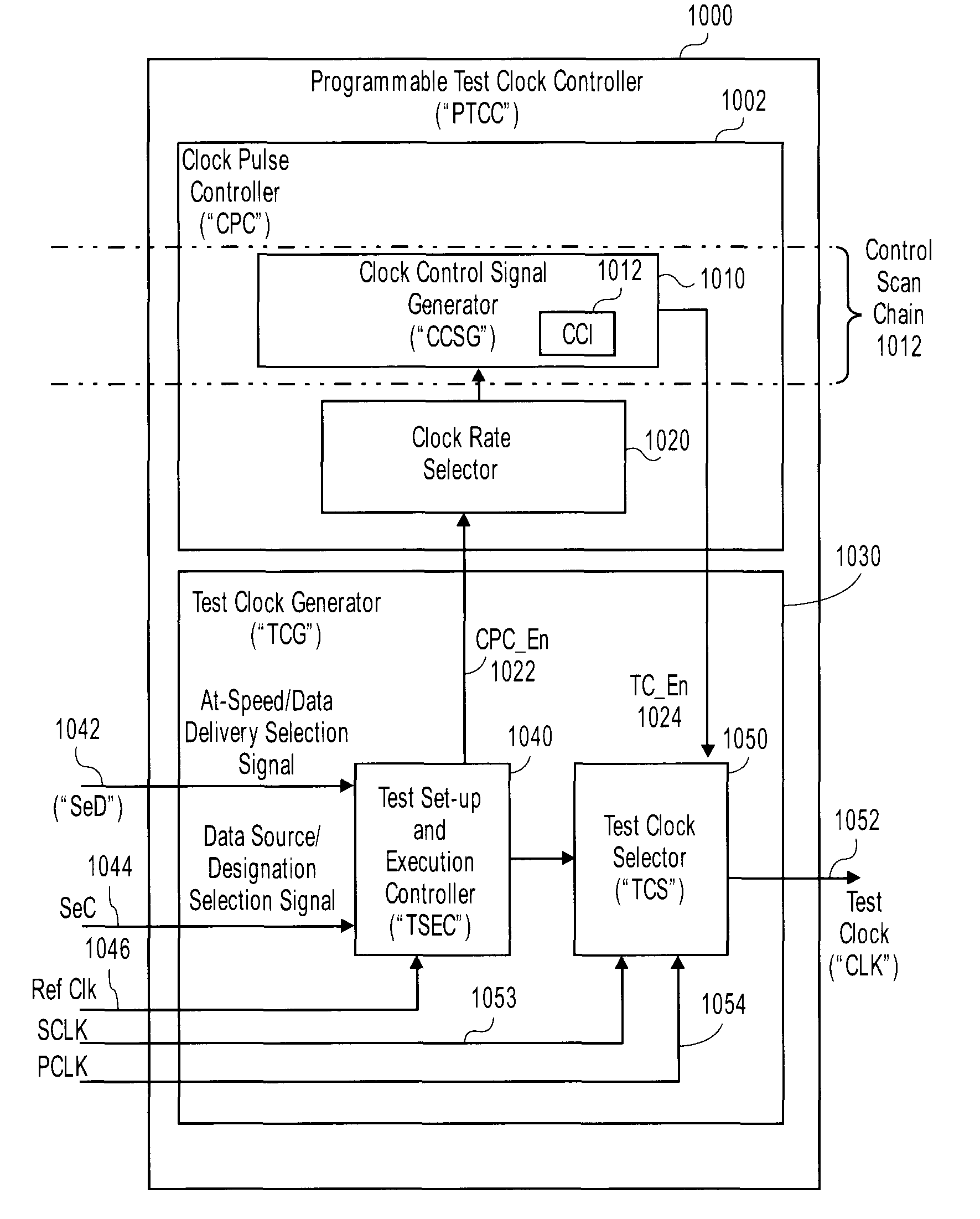

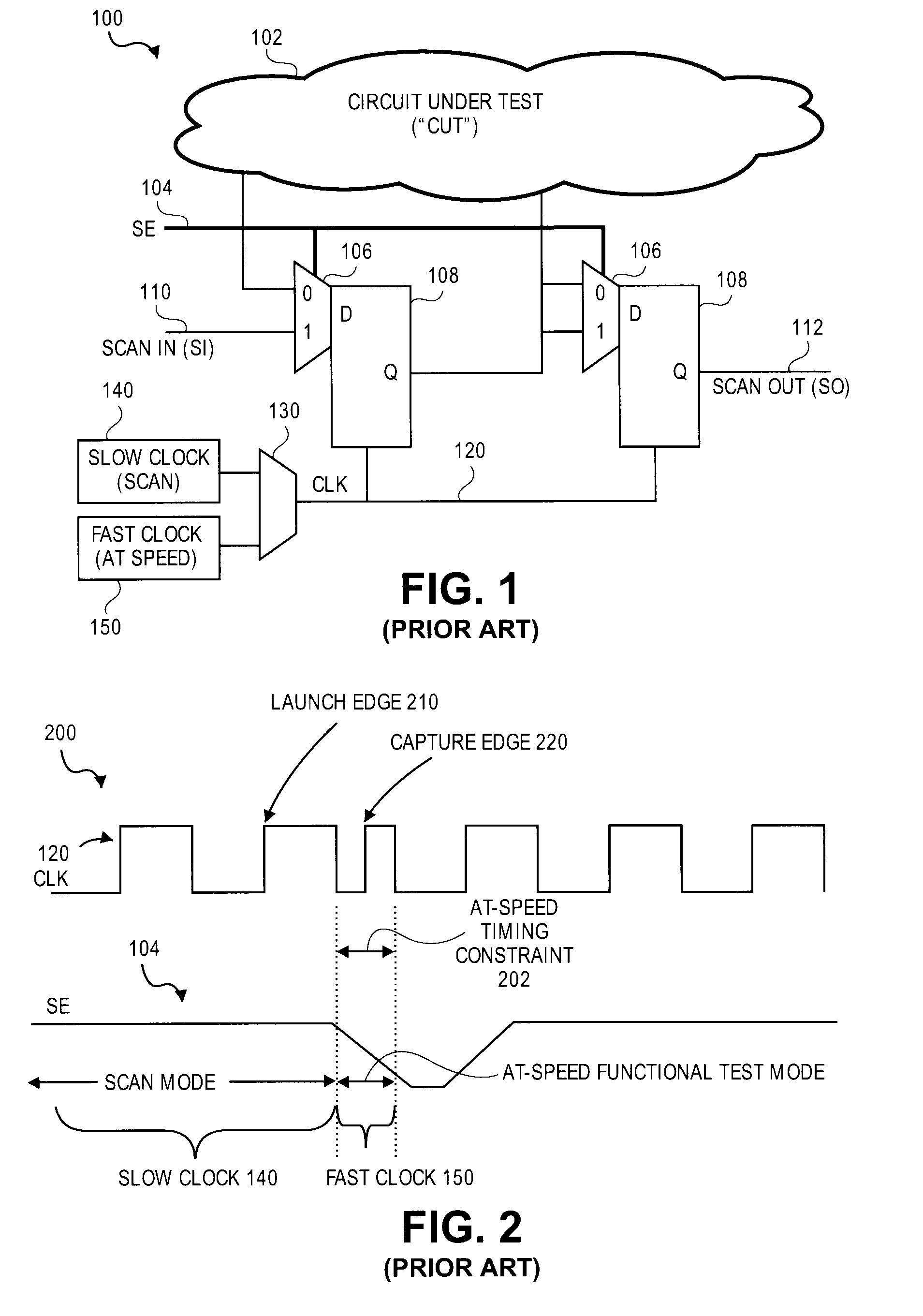

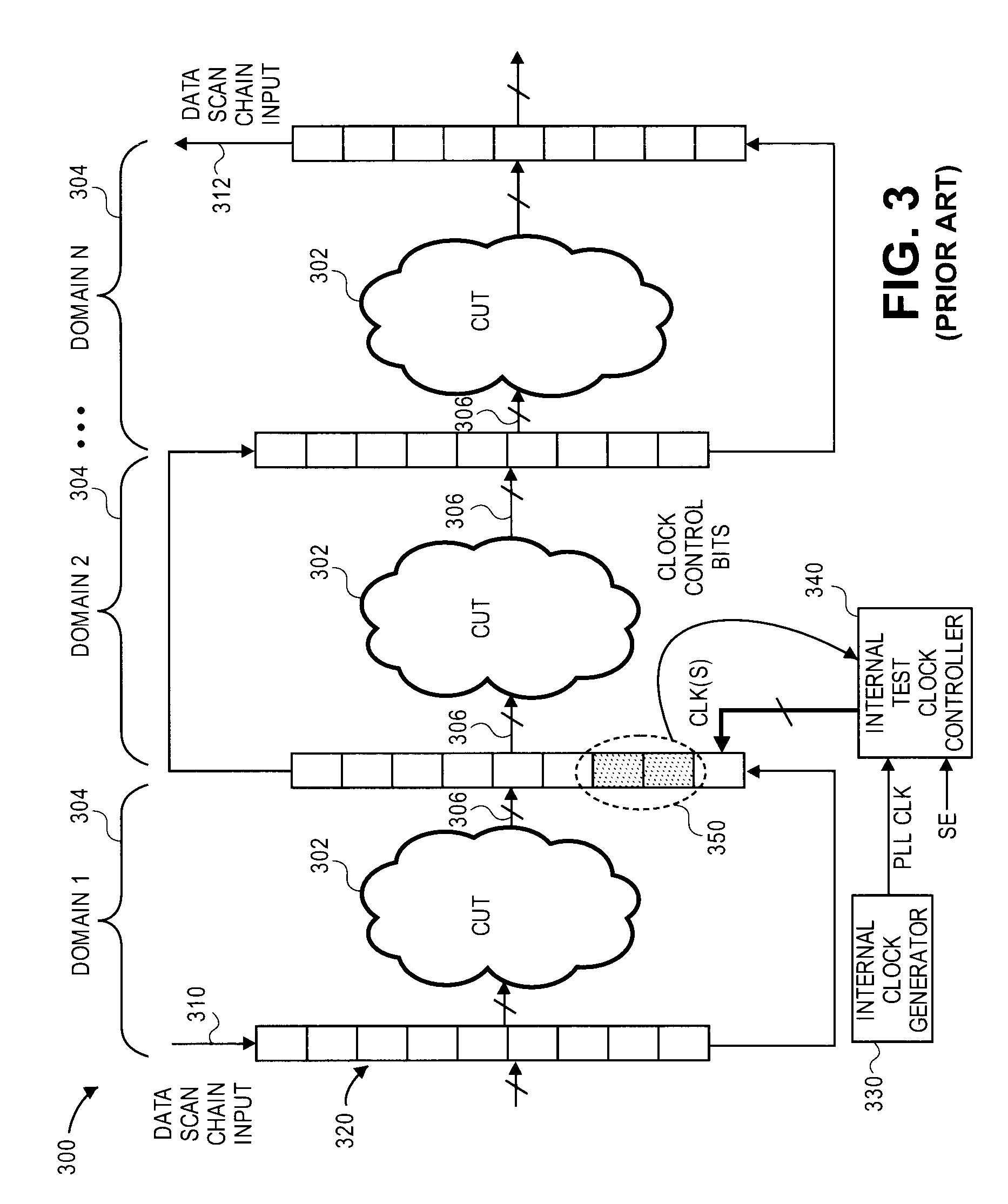

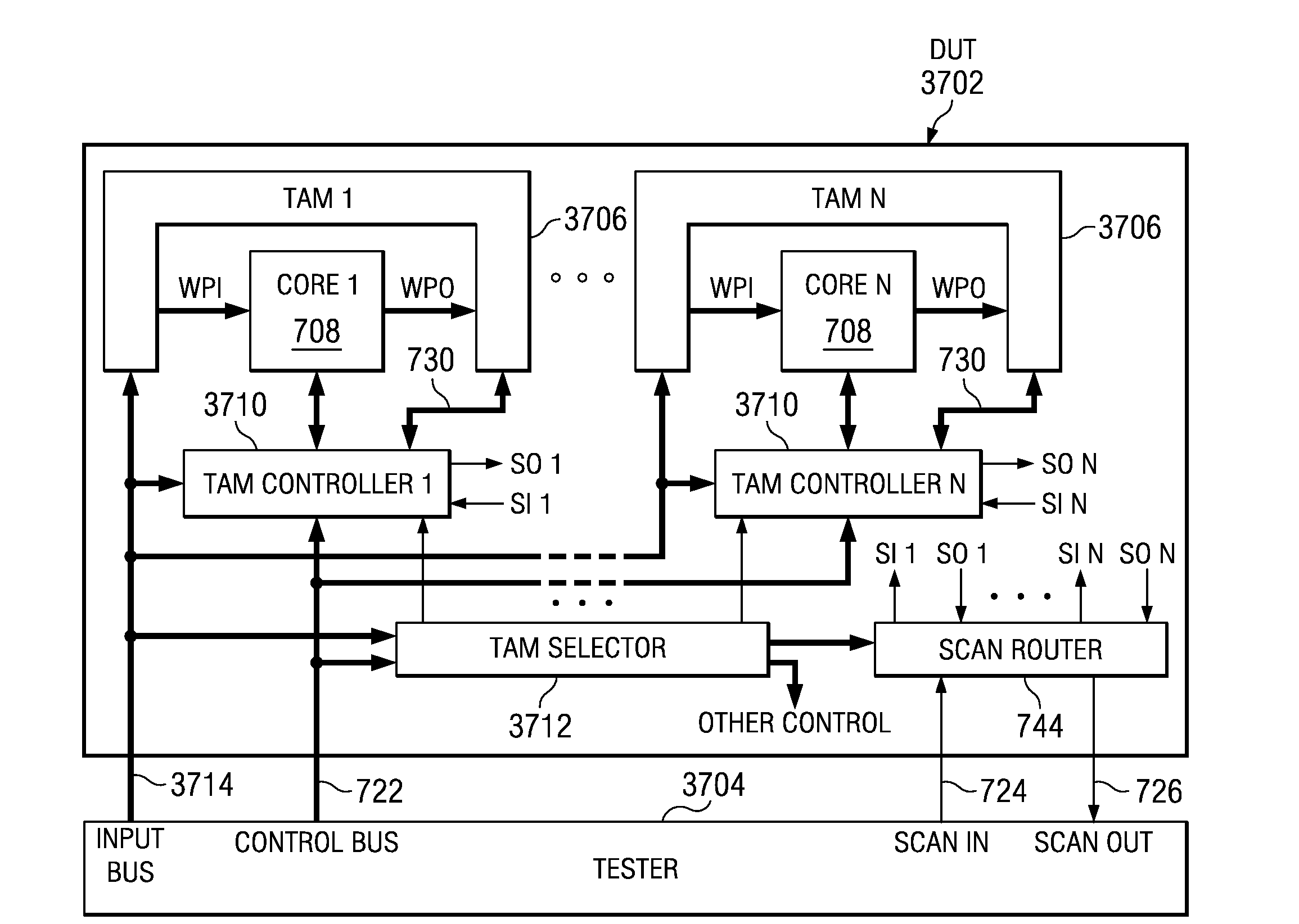

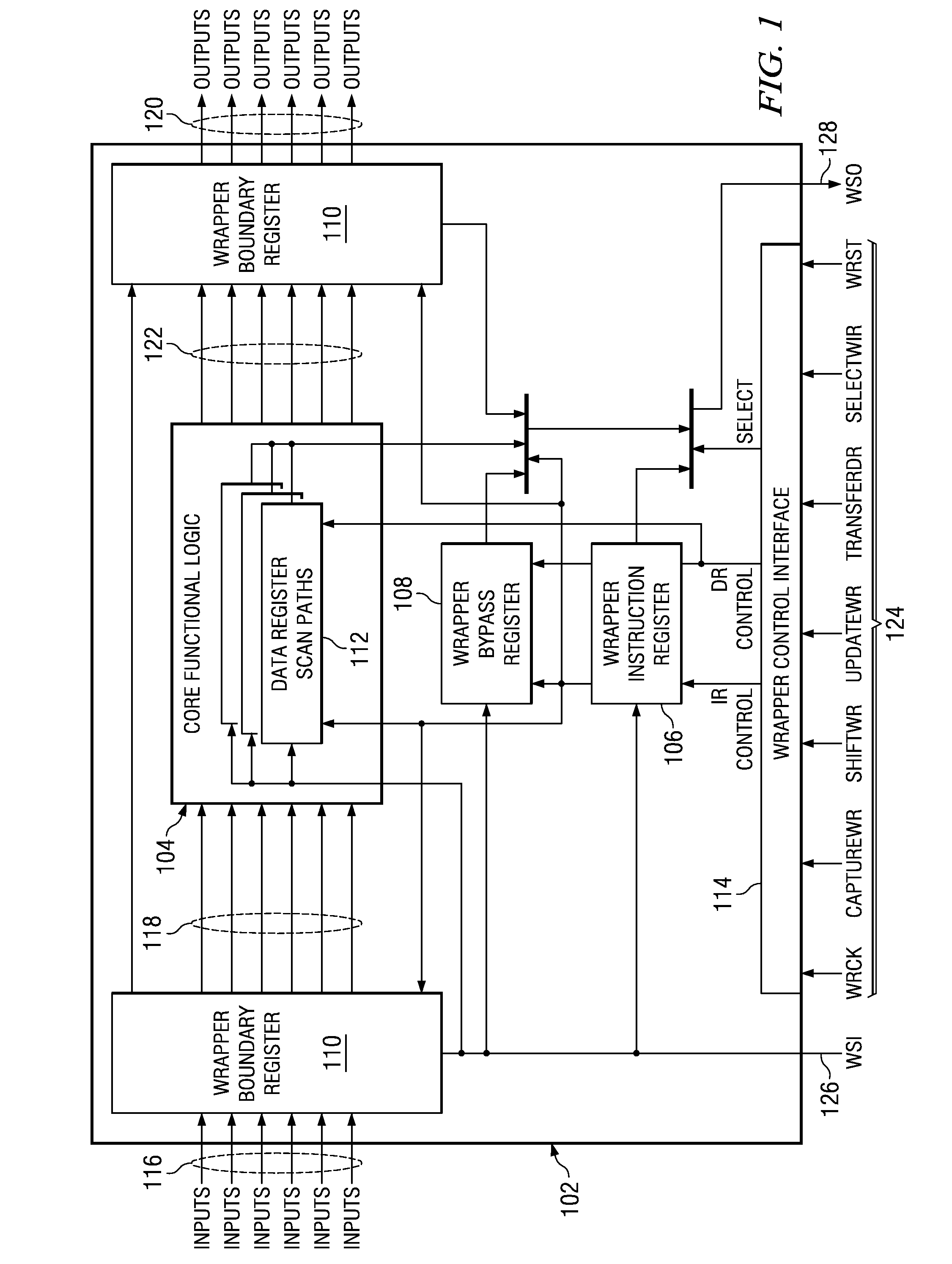

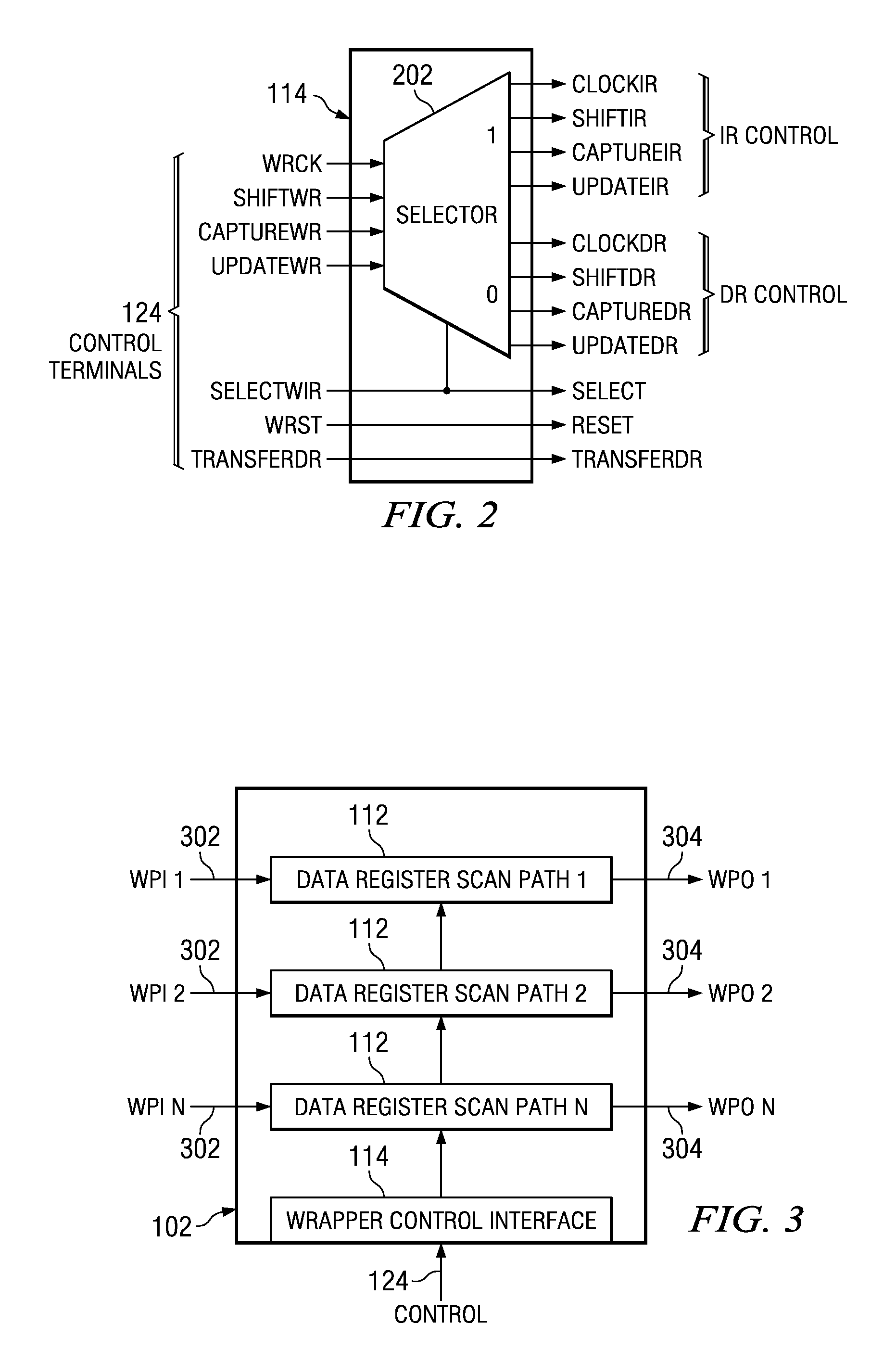

Test clock control structures to generate configurable test clocks for scan-based testing of electronic circuits using programmable test clock controllers

ActiveUS20080010573A1Reduce the number of timesLow costElectronic circuit testingFunctional testingControl layerProgrammable logic controller

Systems, structures and methods for generating a test clock for scan chains to implement scan-based testing of electronic circuits are disclosed. In one embodiment, a test clock control structure includes a programmable test clock controller. The programmable test clock controller includes a test clock generator for generating a configurable test clock. It also includes a scan layer interface to drive a scan chain portion with the configurable test clock, and a control layer interface configured to access control information for controlling the scan chain portion. In another embodiment, a method effectuates scan-based testing of circuits. The method includes performing at least one intra-domain test and performing at least one inter-domain test using implementing dynamic fault detection test patterns, which can include last-shift-launch test patterns and broadside test patterns.

Owner:LATTICE SEMICON CORP

Mobile communication device having a prioritized interrupt controller

InactiveUS6807595B2Energy efficient ICTEnergy efficient computingProgrammable Interrupt ControllerComputer science

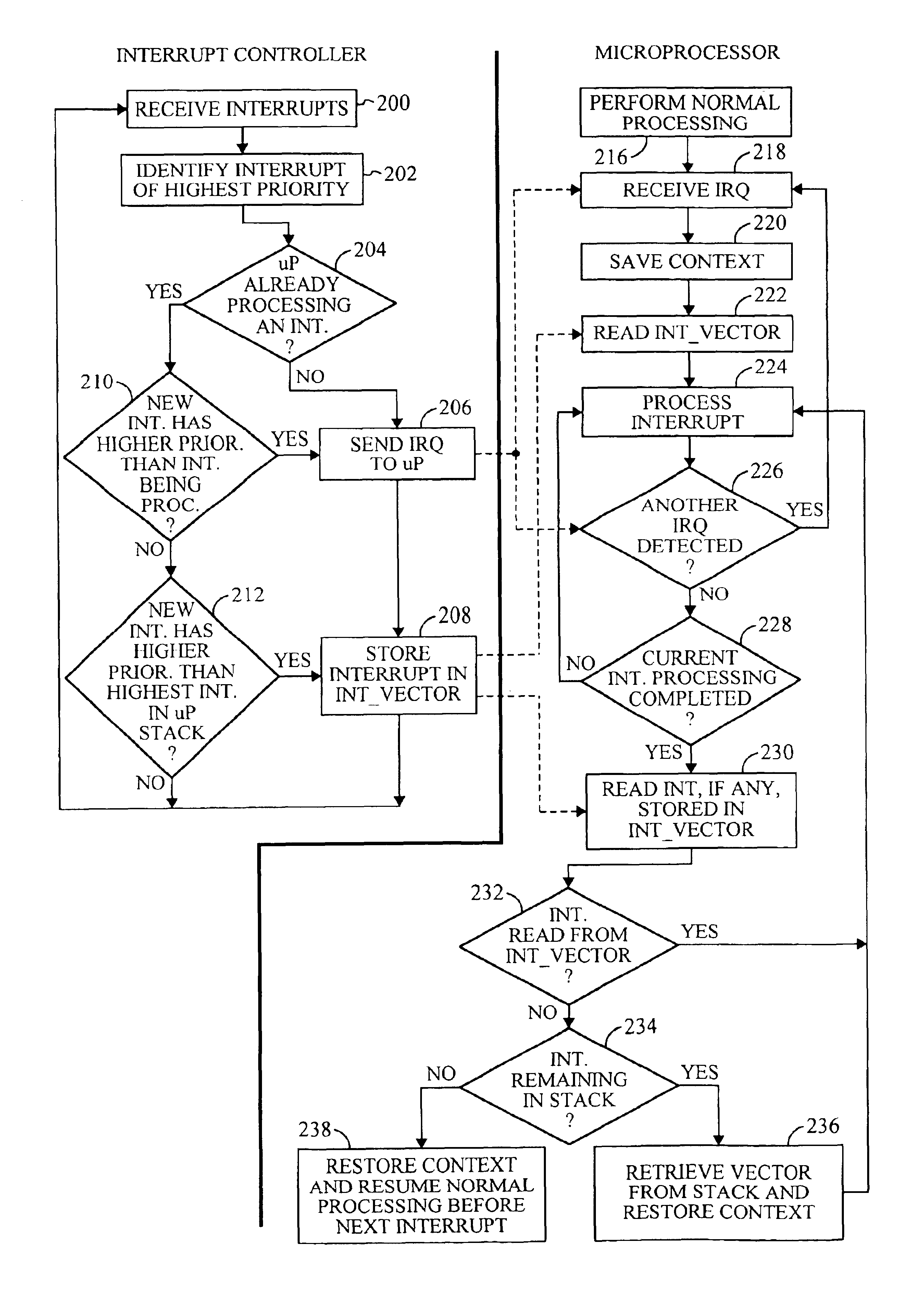

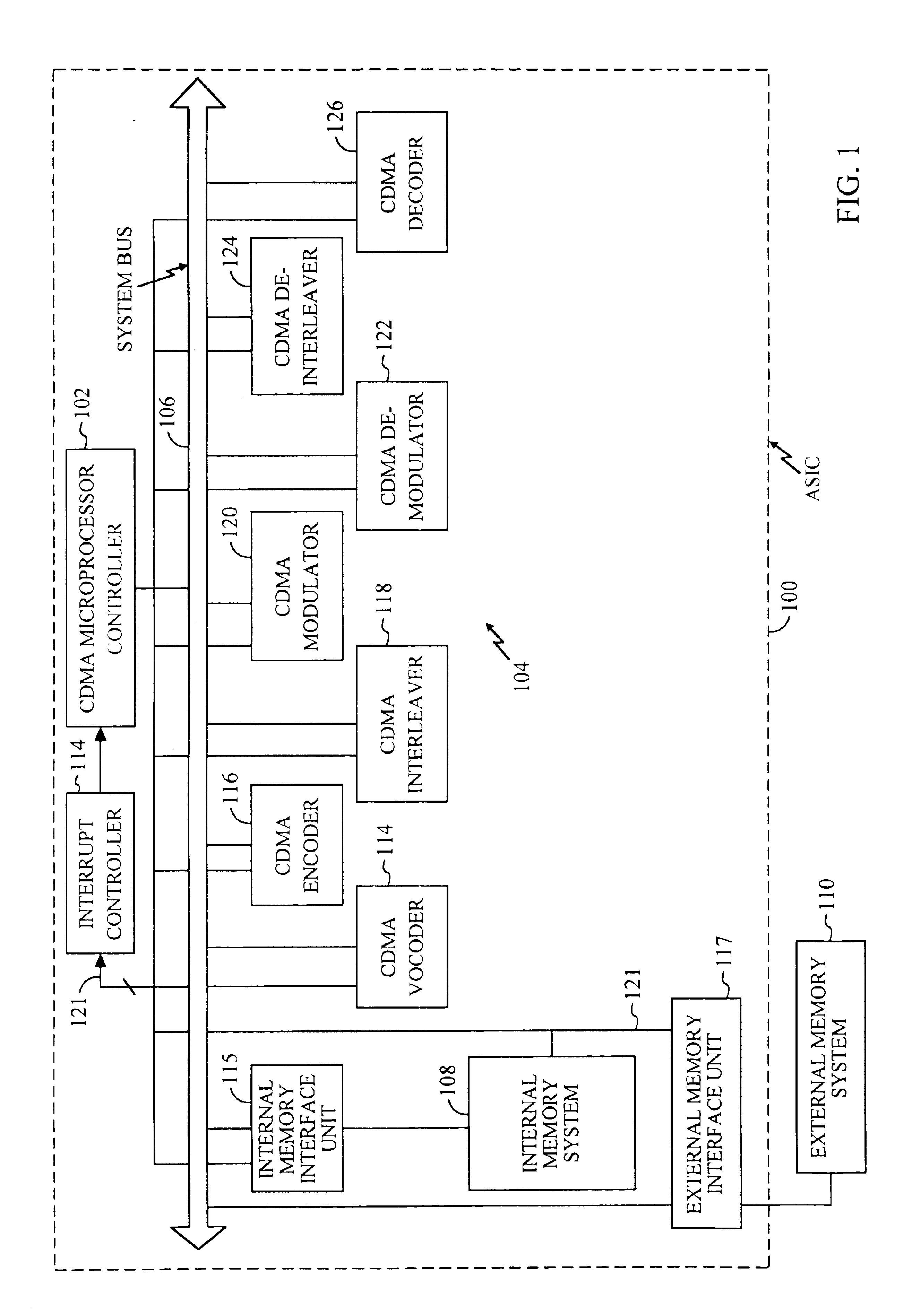

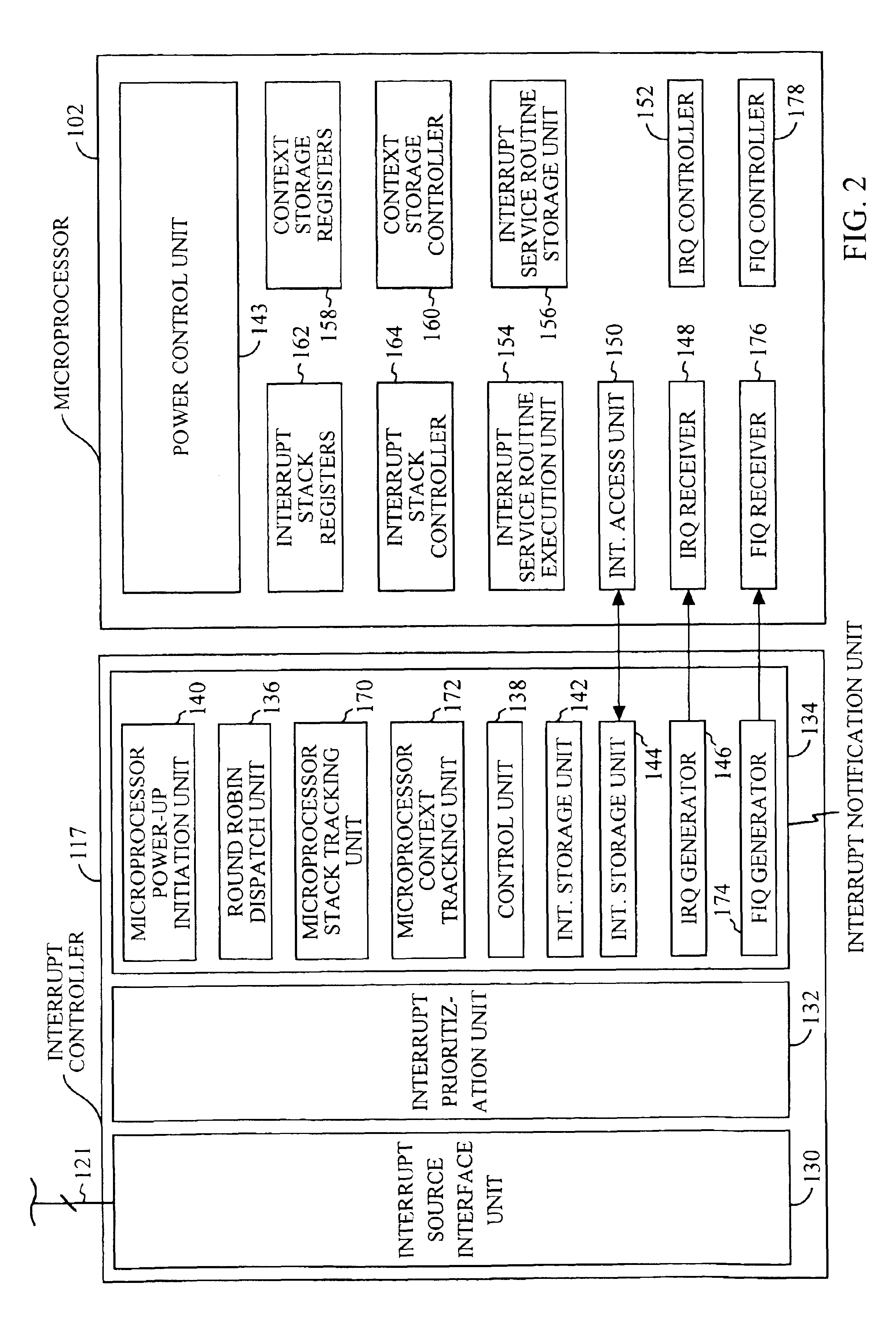

A microprocessor system having an interrupt controller is provided for use in a mobile communications device. Peripheral processing units generate interrupt requests for sending to the microprocessor. The microprocessor has components for responding to interrupt requests by interrupting current processing and performing an interrupt service routine associated with the interrupt request. The interrupt controller receives interrupt requests directed to the microprocessor from the peripheral processing units and for prioritizes the interrupt requests on behalf of the microprocessor. By providing an interrupt controller for prioritizing interrupt requests on behalf of the microprocessor, the microprocessor therefore need not devote significant internal resources to prioritizing the interrupt request signals.

Owner:QUALCOMM INC

Data modem

InactiveUS6839792B2Maximum flexibilityMinimal costTelephonic communicationGenerating/distributing signalsMass storageModem device

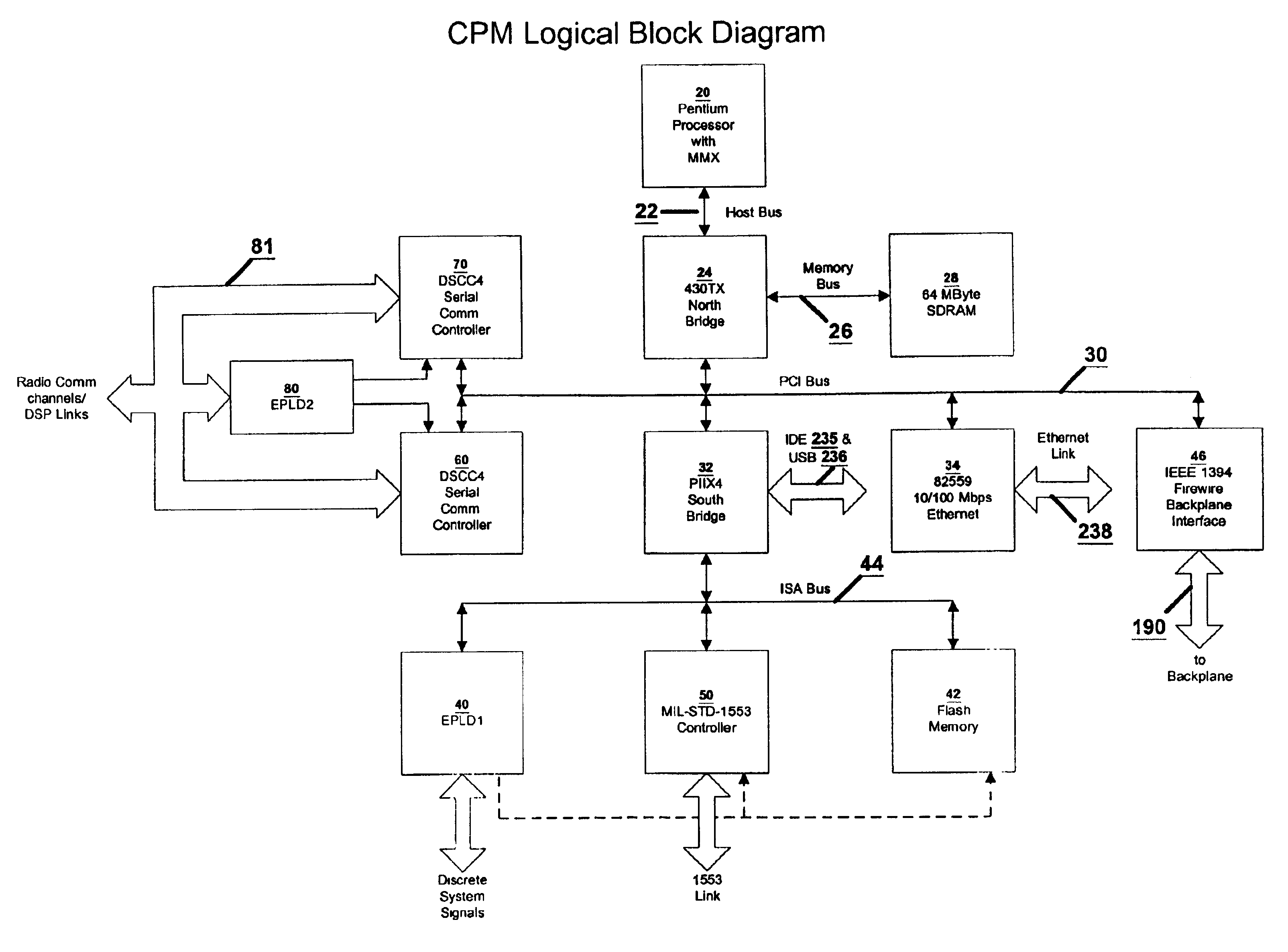

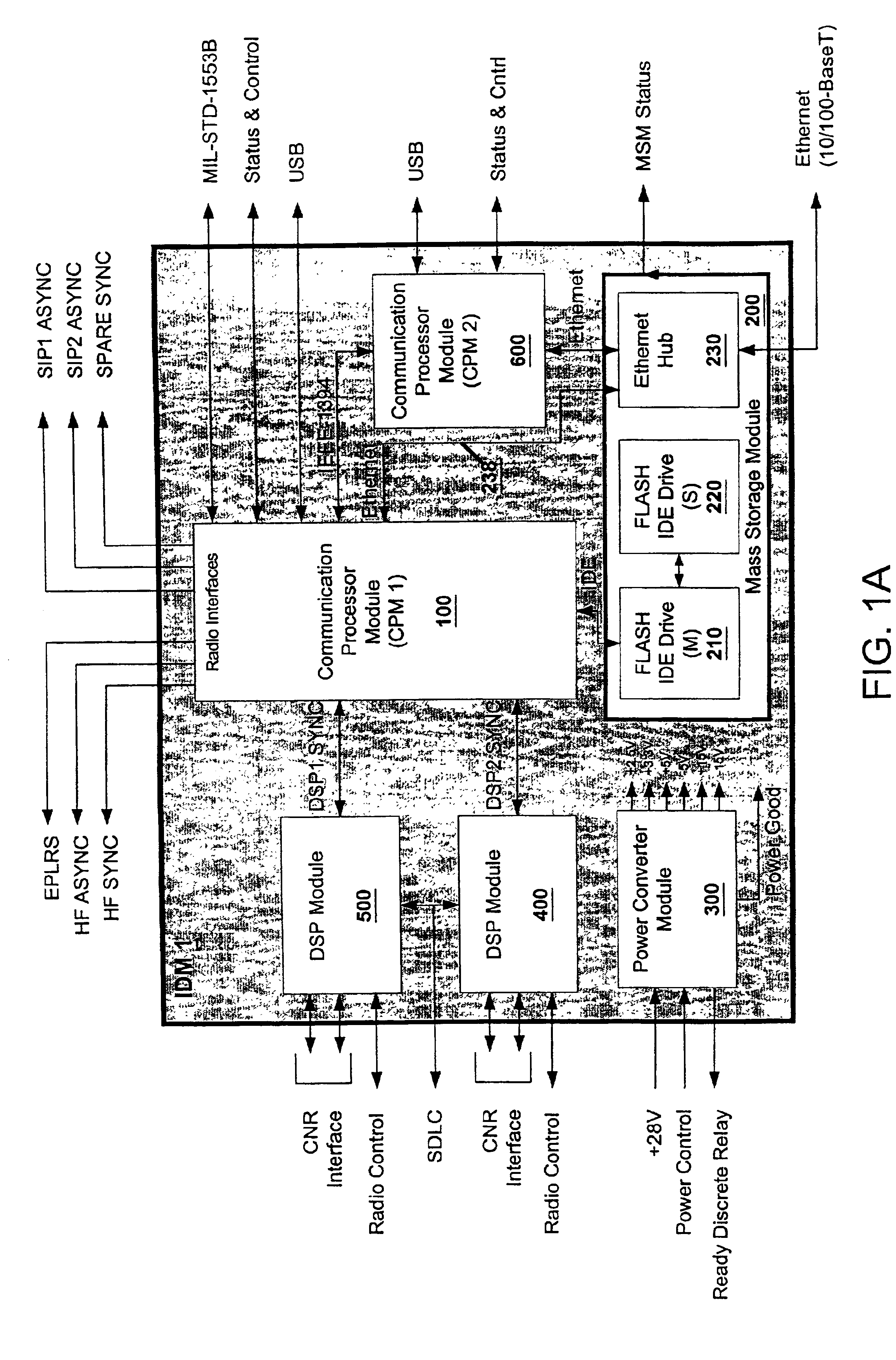

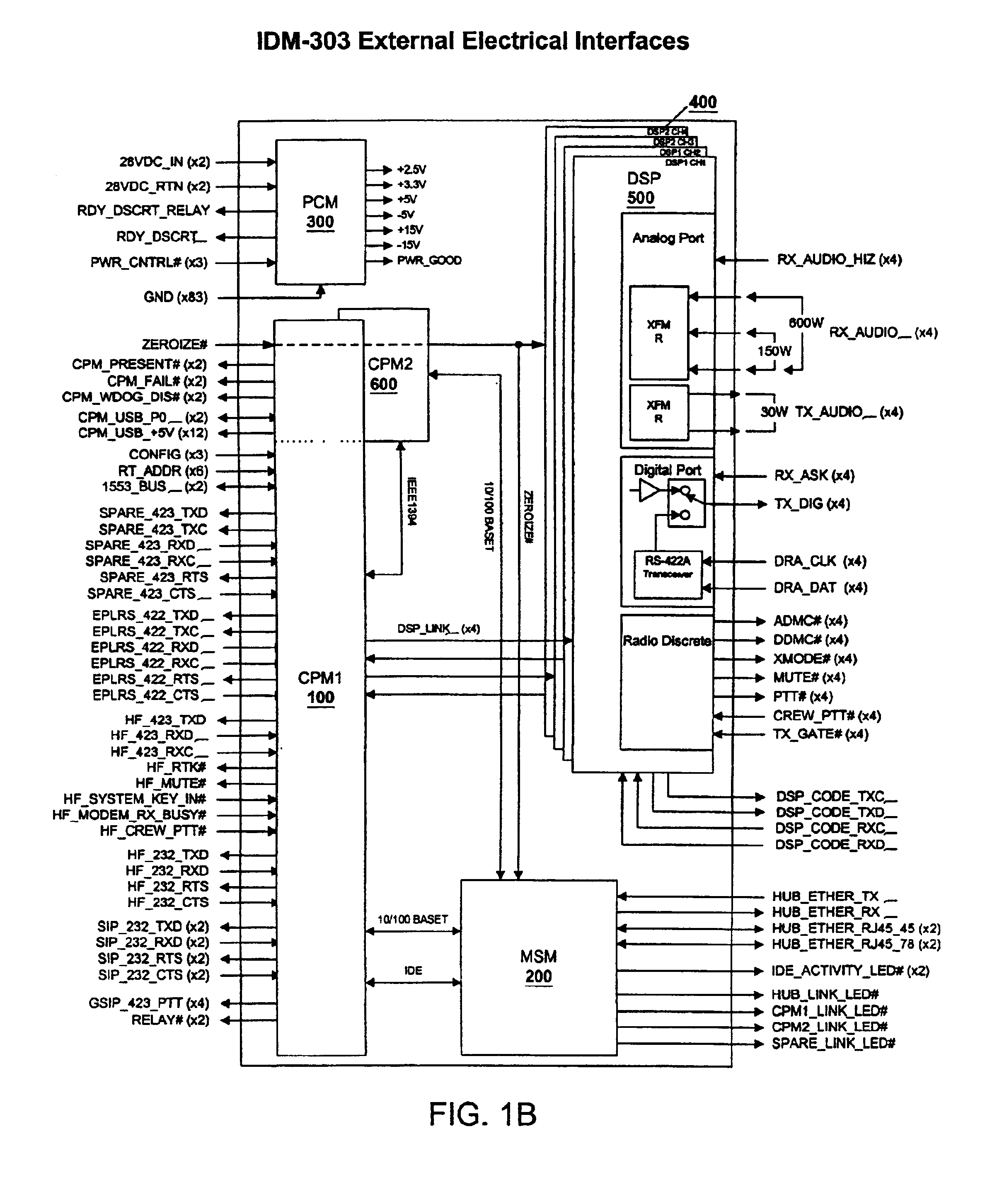

An improved data modem (IDM) and method includes a communication processor module, a mass storage module, a power converter module, and one or more DSP modules. The communication processor module utilizes commercial off-the-shelf components as well as programmable logic devices (EPLD), which are programmed to provide a watchdog timer, programmable interrupt controller, flash page addressing, ISA bus decoder and controller, and various circuits and logic.

Owner:ELBIT SYSTEMS OF AMERICA LLC

Input/output module for programmable logic controller based systems

ActiveUS20140047137A1Reducing number componentProgramme controlInput/output processes for data processingElectricityProgrammable logic controller

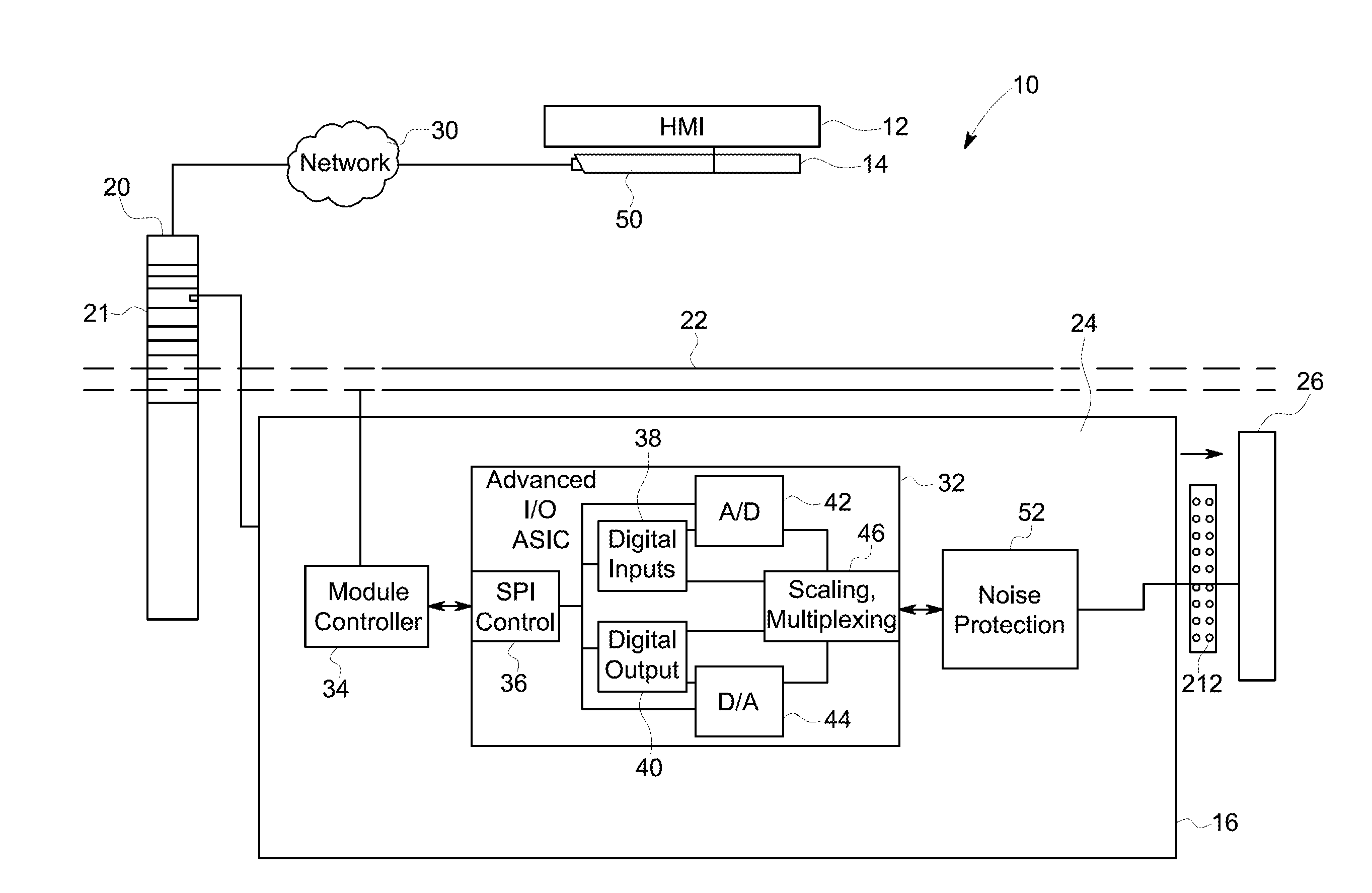

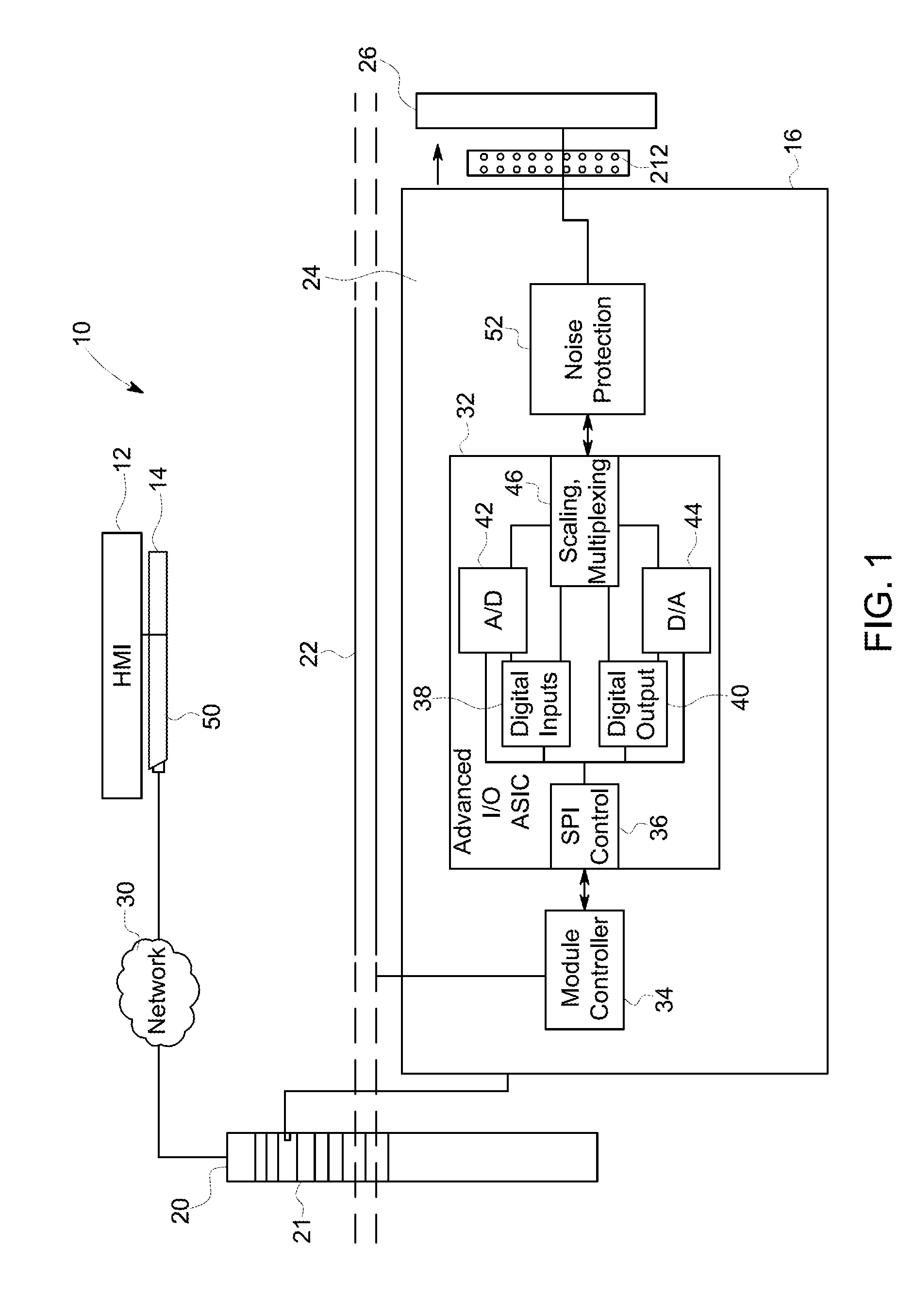

An input / output module for use in an industrial control system and connectable to a programmable logic controller (PLC), the input / output module having an interface configured for an electrical connection to the PLC, a plurality of pins configured for connection to one of a plurality of peripherals, an application specific integrated circuit (ASIC) disposed in the I / O module and electrically coupled to a system controller, the ASIC having a plurality of connection paths, each path being configured for a function, and a switch block configured to reassign a signal from a first connection path of the plurality of connection paths to a second connection path of the plurality of connection paths.

Owner:GE INTELLIGENT PLATFORMS LTD

Test clock control structures to generate configurable test clocks for scan-based testing of electronic circuits using programmable test clock controllers

ActiveUS7793179B2Easy to implementReduce loadElectronic circuit testingFunctional testingControl layerProgrammable logic controller

Systems, structures and methods for generating a test clock for scan chains to implement scan-based testing of electronic circuits are disclosed. In one embodiment, a test clock control structure includes a programmable test clock controller. The programmable test clock controller includes a test clock generator for generating a configurable test clock. It also includes a scan layer interface to drive a scan chain portion with the configurable test clock, and a control layer interface configured to access control information for controlling the scan chain portion. In another embodiment, a method effectuates scan-based testing of circuits. The method includes performing at least one intra-domain test and performing at least one inter-domain test using implementing dynamic fault detection test patterns, which can include last-shift-launch test patterns and broadside test patterns.

Owner:LATTICE SEMICON CORP

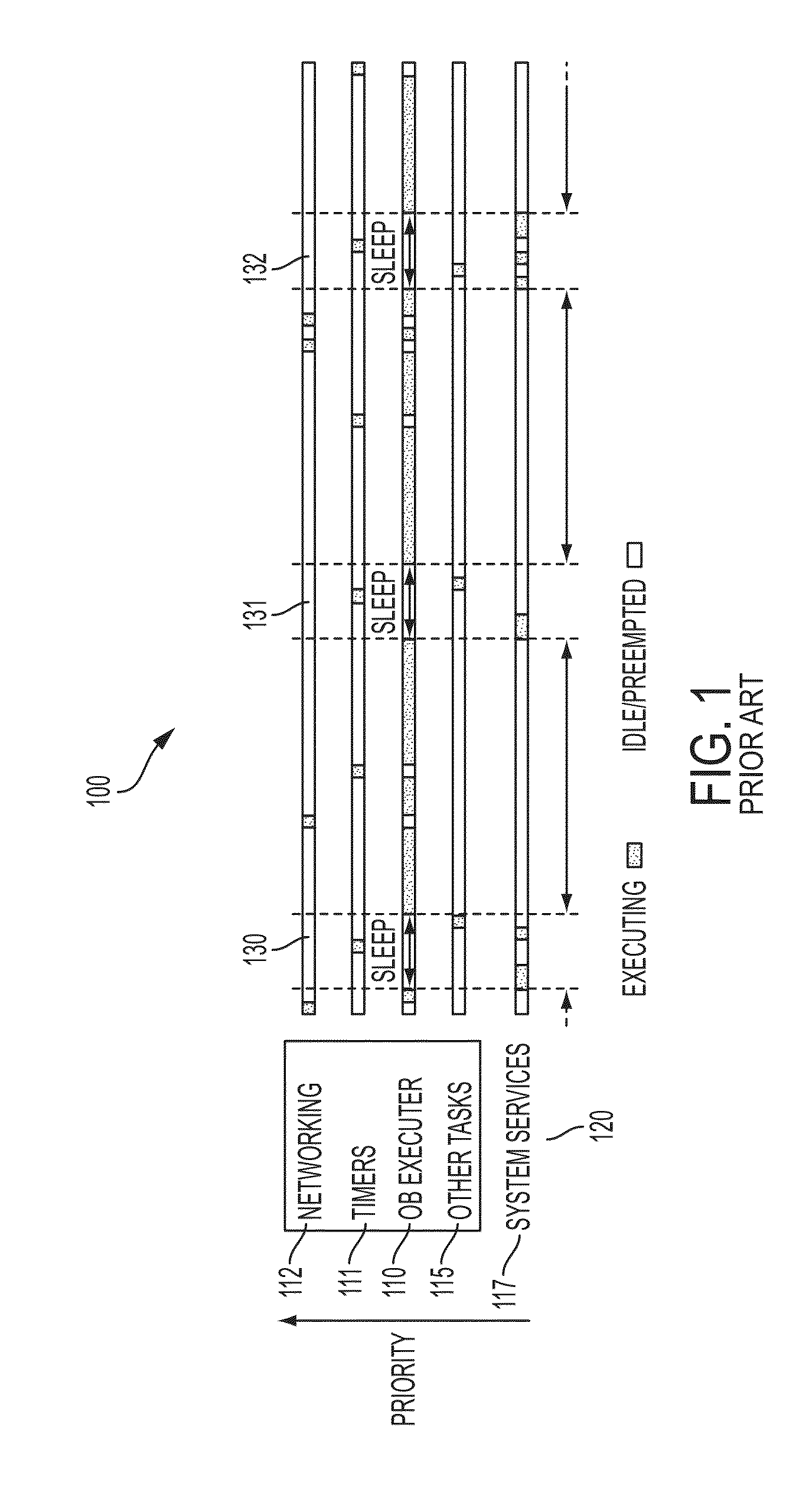

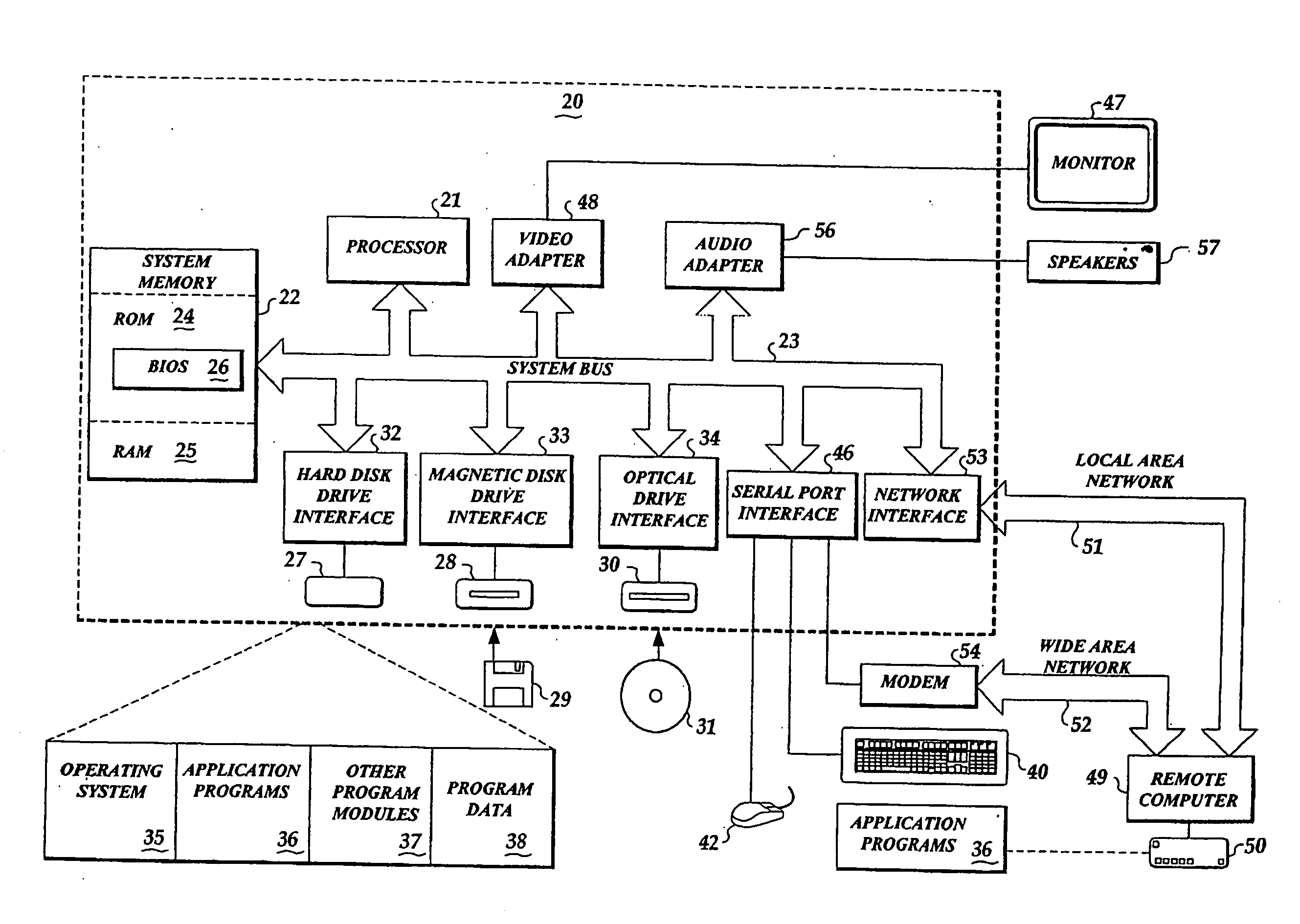

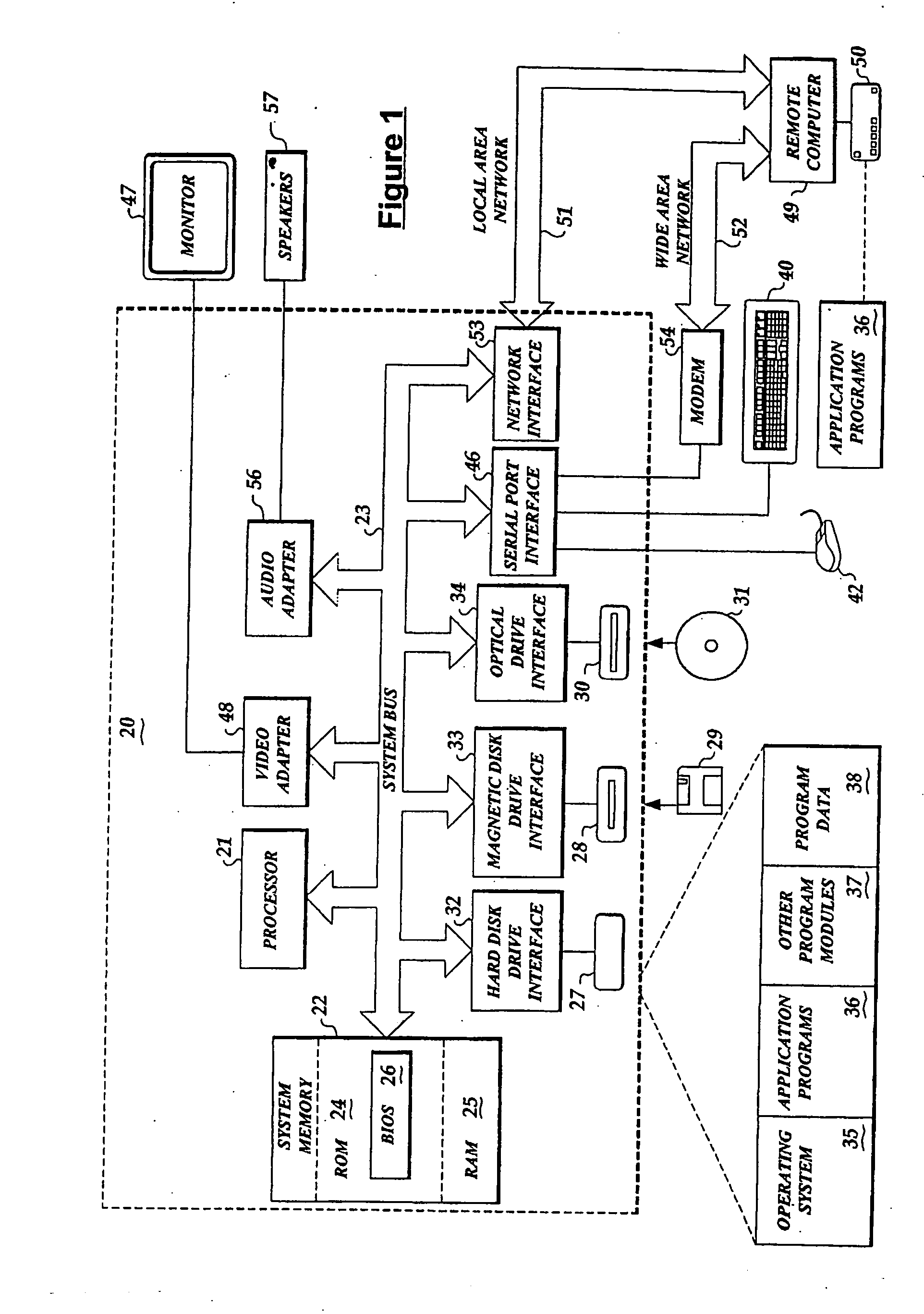

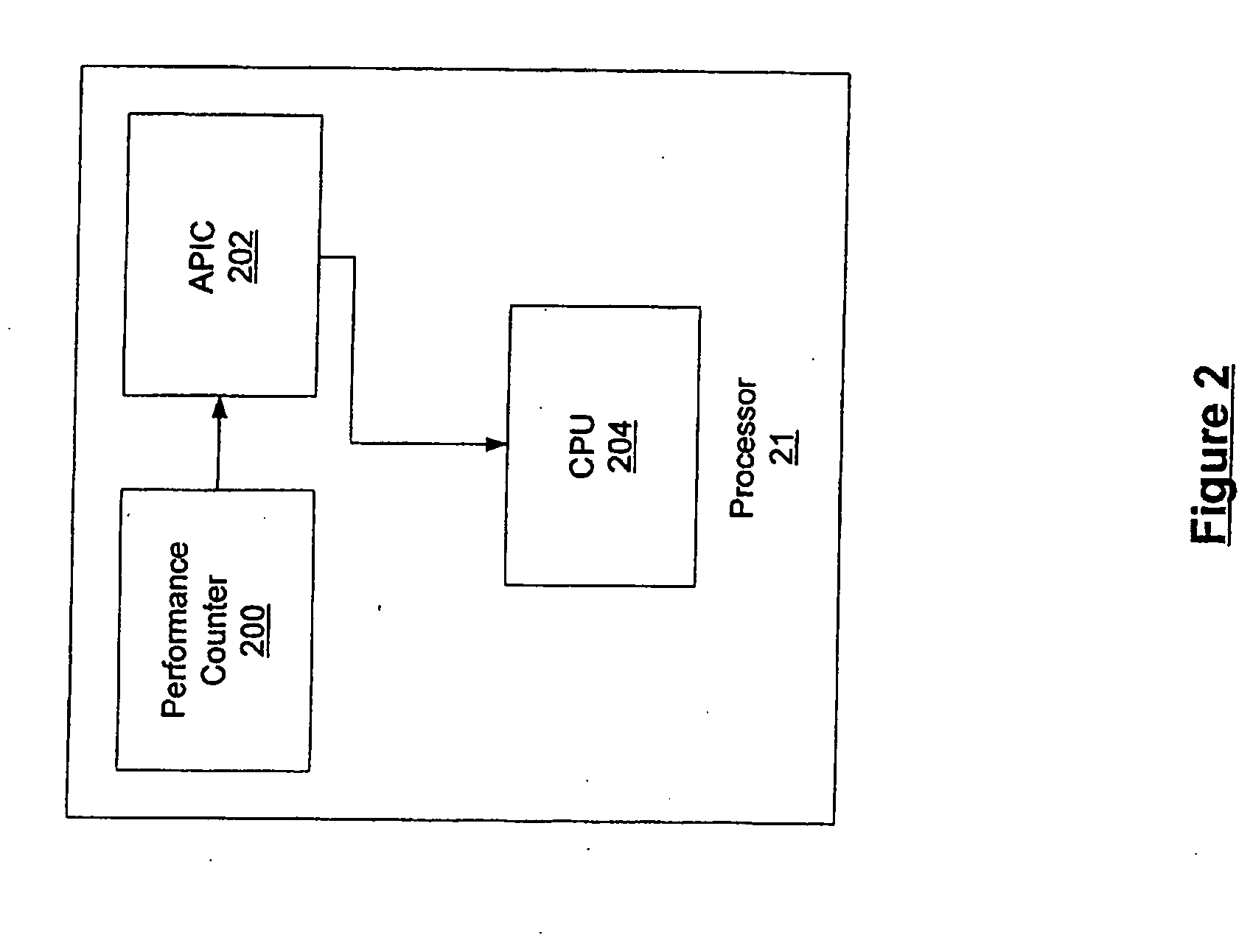

Method and system for real time scheduler

InactiveUS20050229179A1Facilitates real-time schedulingSpeed of execution of operatingProgram initiation/switchingResource allocationTime scheduleNon-maskable interrupt

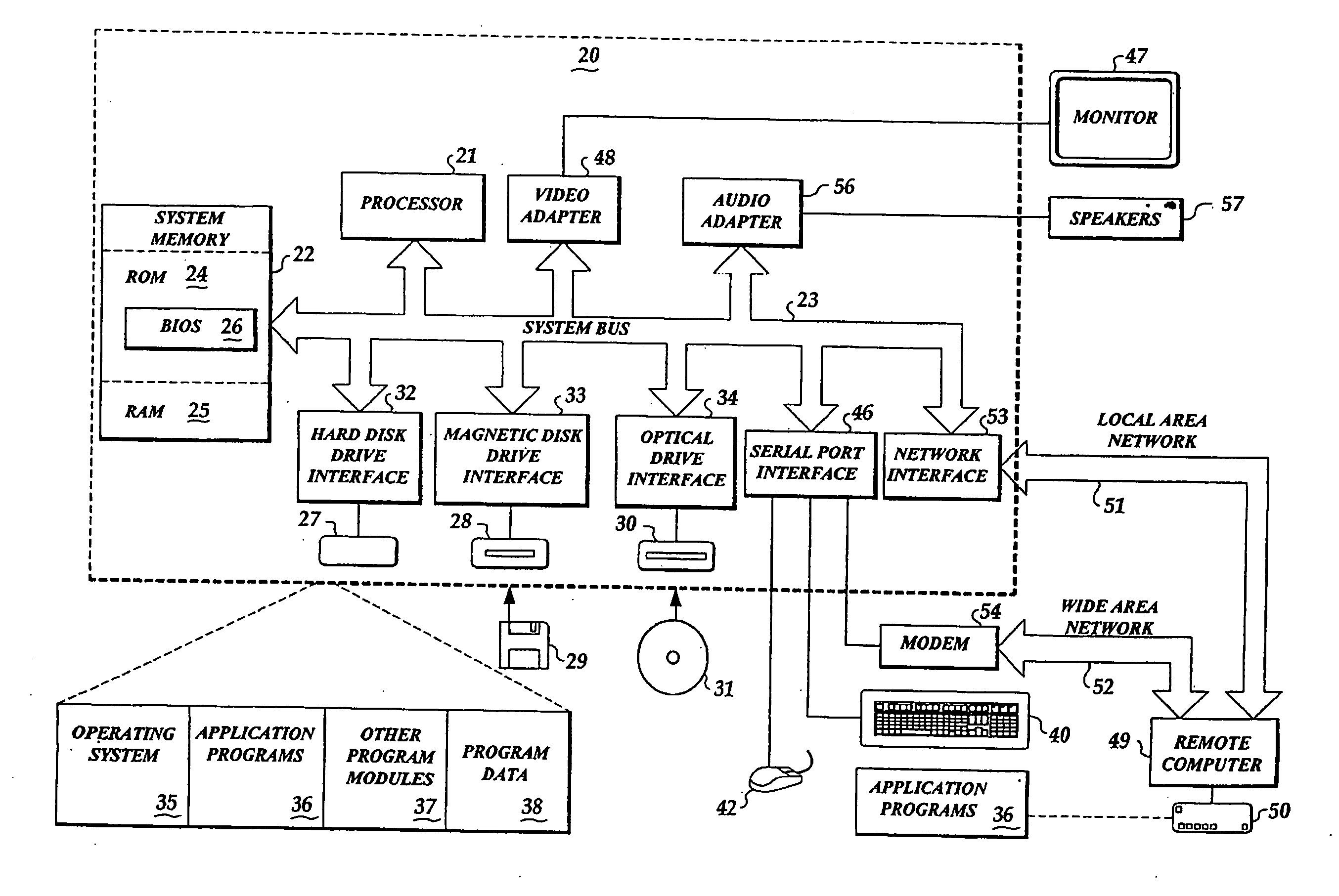

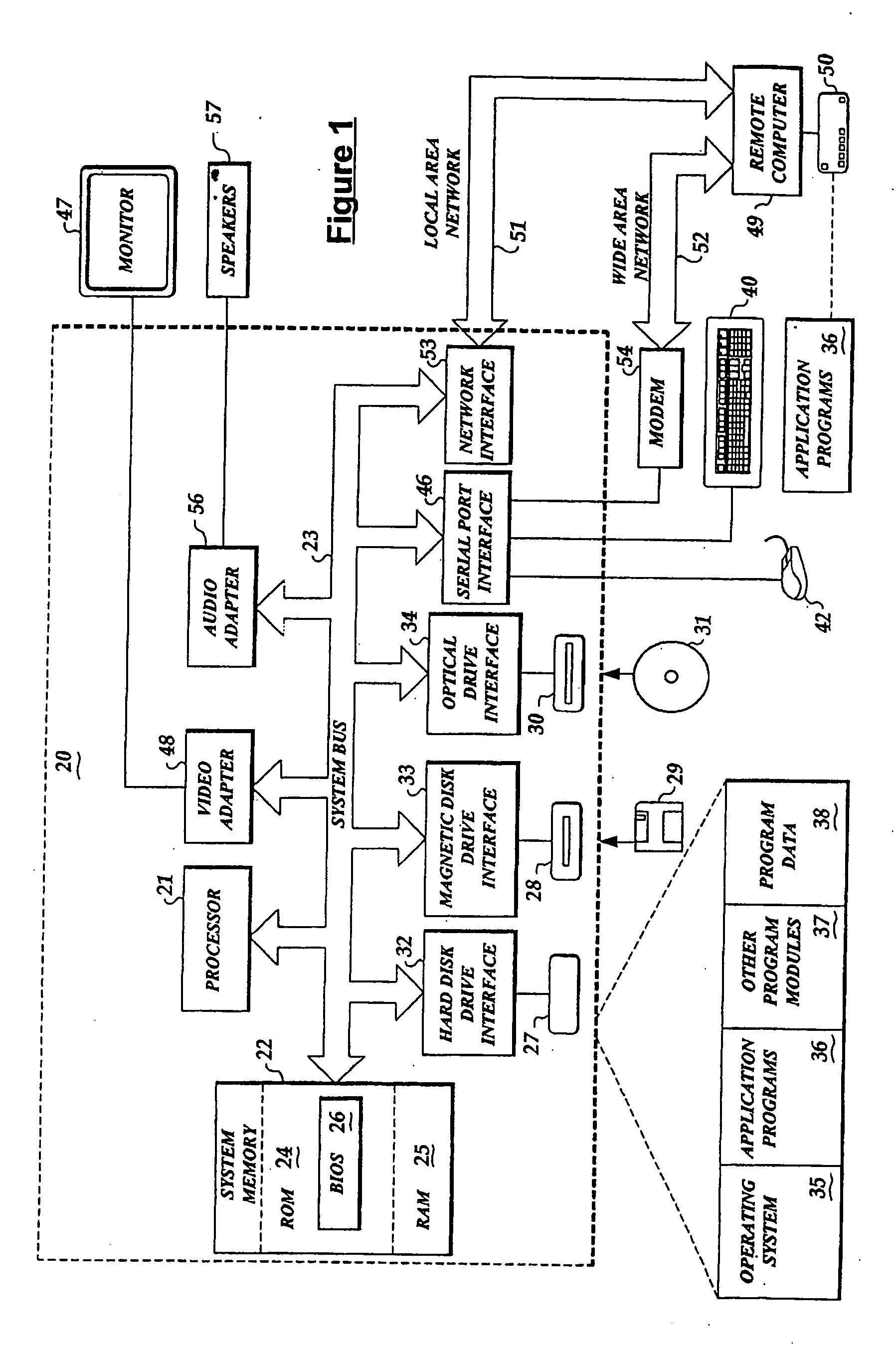

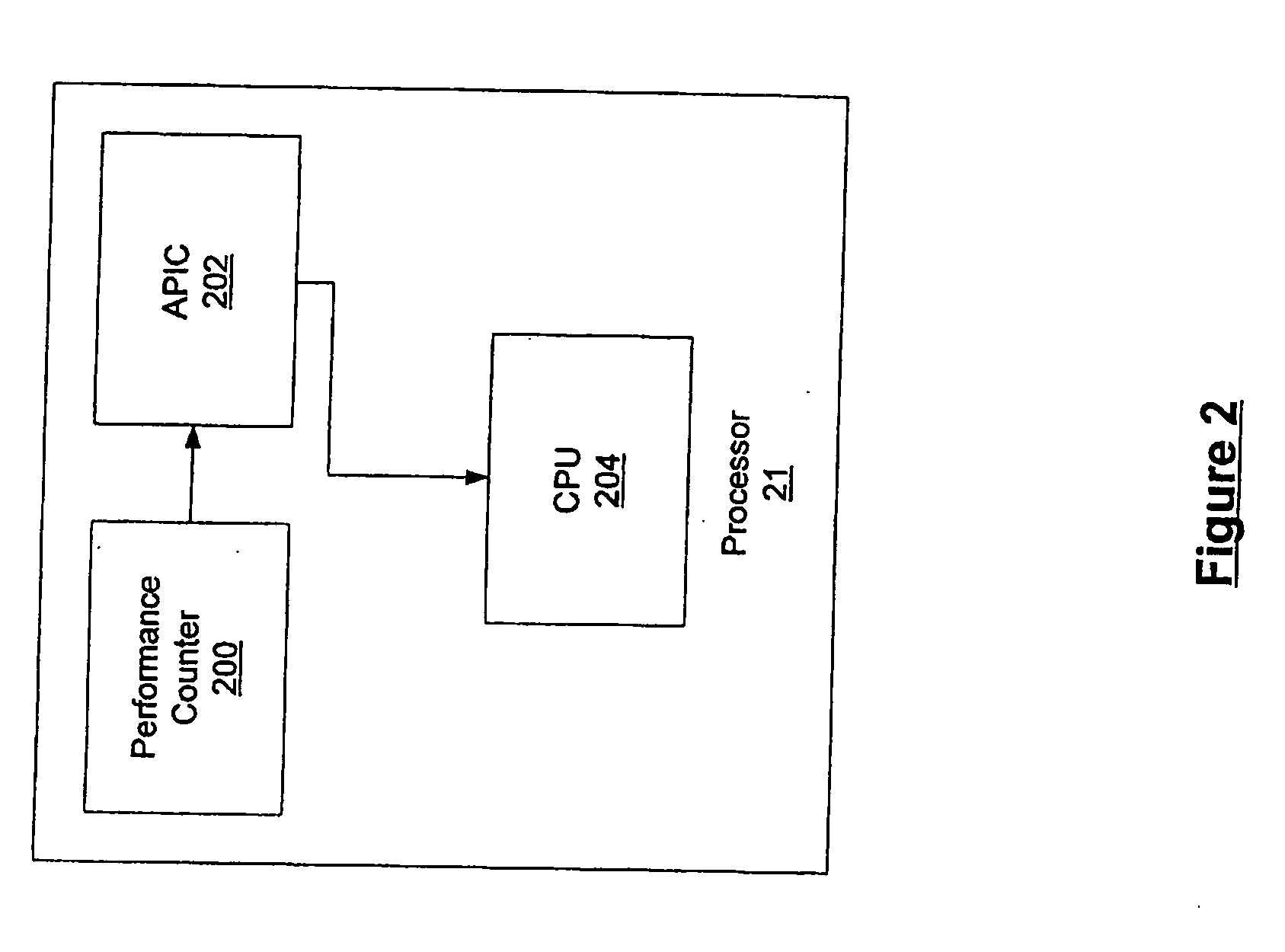

Methods and computer-executable components for real-time scheduling of CPU resources are disclosed. A performance counter determines when to allocate CPU resources to a thread. When it is time to allocate the CPU resources, the performance counter issues a maskable or non-maskable interrupt to an advanced programmable interrupt controller (APIC). The APIC then issues a maskable non-maskable interrupt to the CPU. In response to receiving the non-maskable interrupt, the CPU allocates resources to the thread. In addition, the disclosed methods and computer-executable components also: (a) allow scheduling of CPU resources such that real-time threads are guaranteed respective portions of time slots, (b) enable real-time scheduling on a non-real-time operating system, and (c) provide scheduling of CPU resources on a uni-processor machine such that at least first and second real-time threads dependent on one another are synchronized.

Owner:MICROSOFT TECH LICENSING LLC

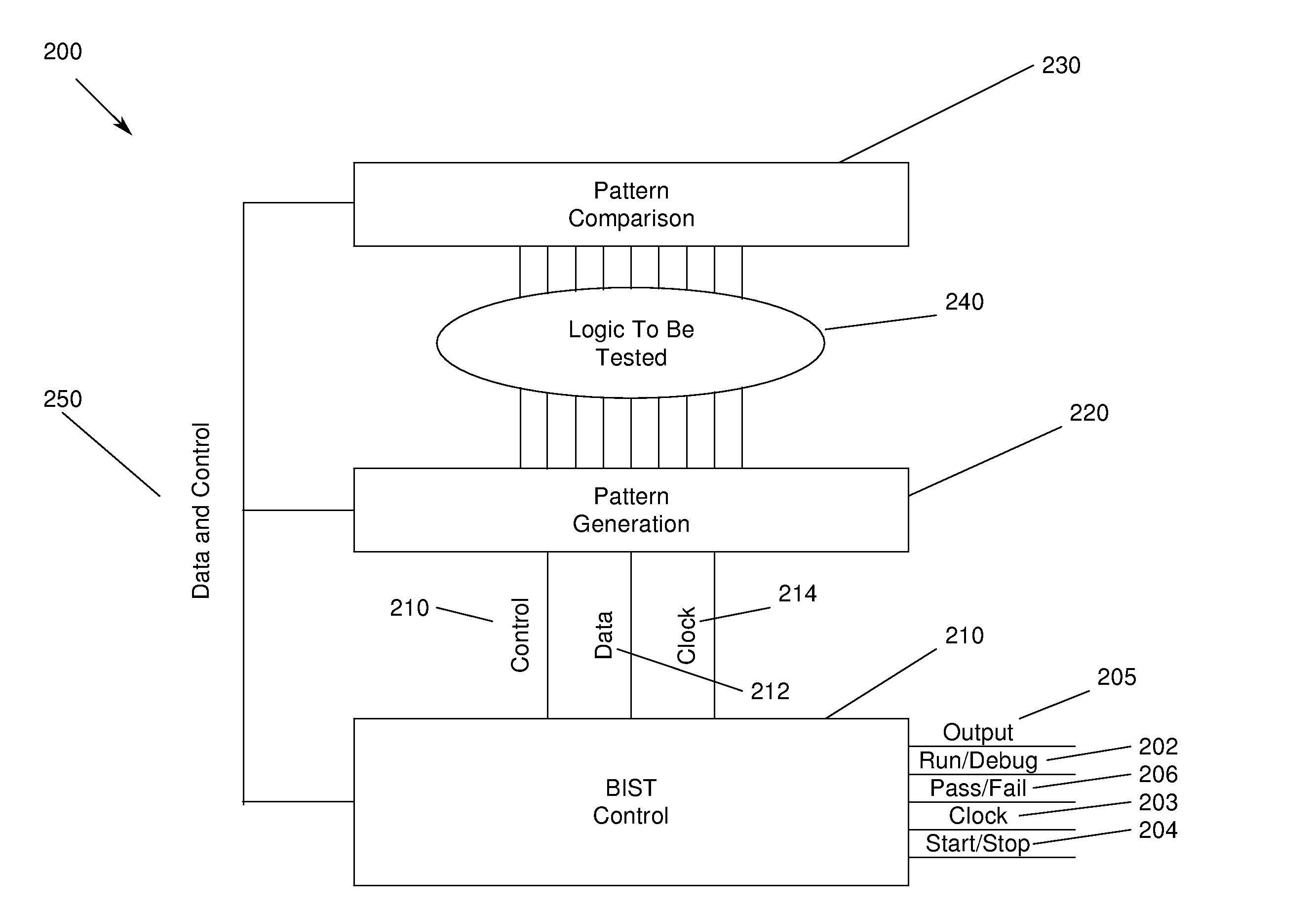

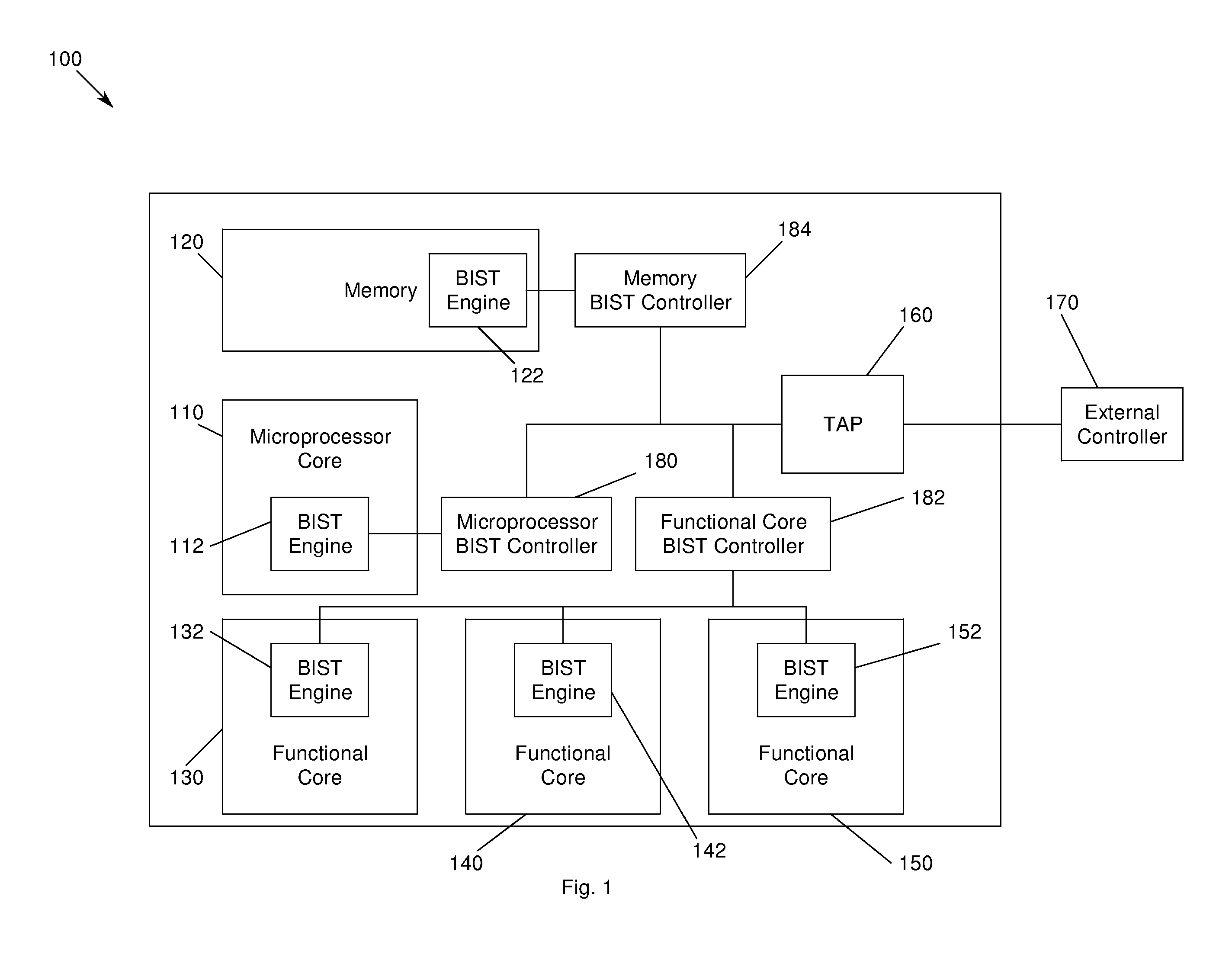

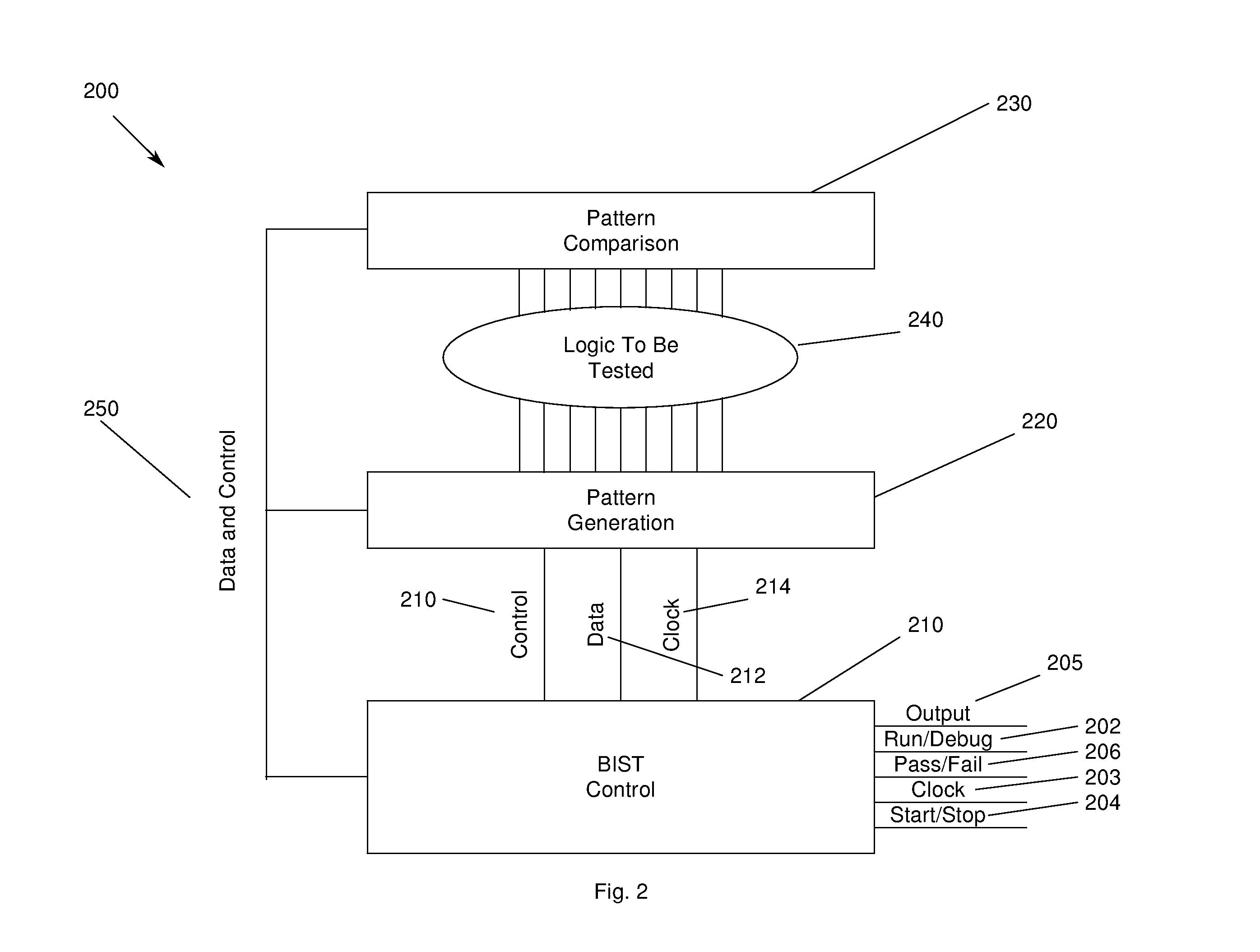

Method and apparatus for providing programmable control of built-in self test

InactiveUS20080016421A1Electronic circuit testingProgrammable Interrupt ControllerBuilt-in self-test

A method and apparatus provides programmable control of built-in self test. A programmable controller allows software selectively to run BIST on different ports of the complex circuit and examine the results. The programmable BIST controller is implemented to execute selected BIST operations, wherein software may choose to either enable or disable running of a particular BIST operation.

Owner:IBM CORP

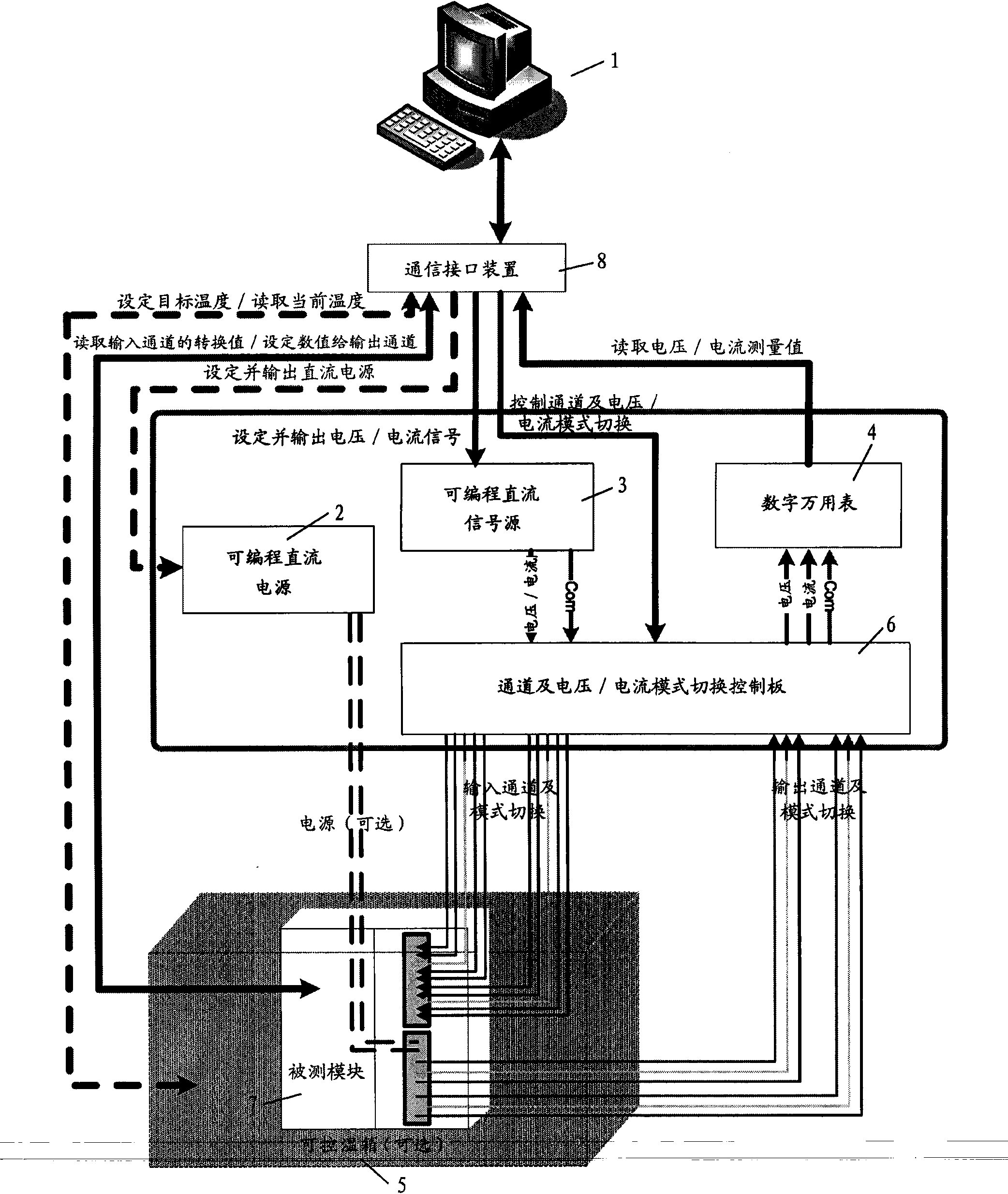

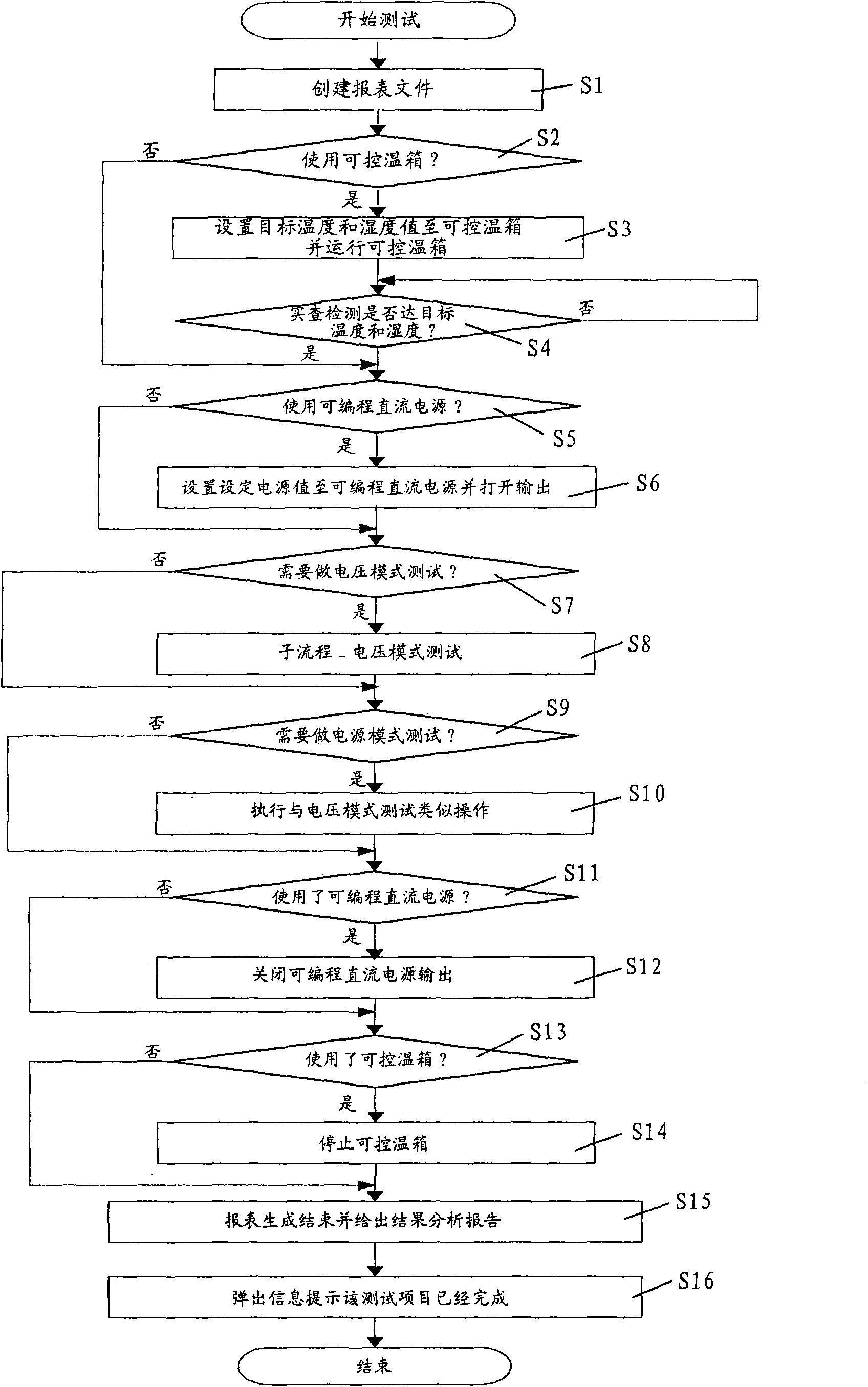

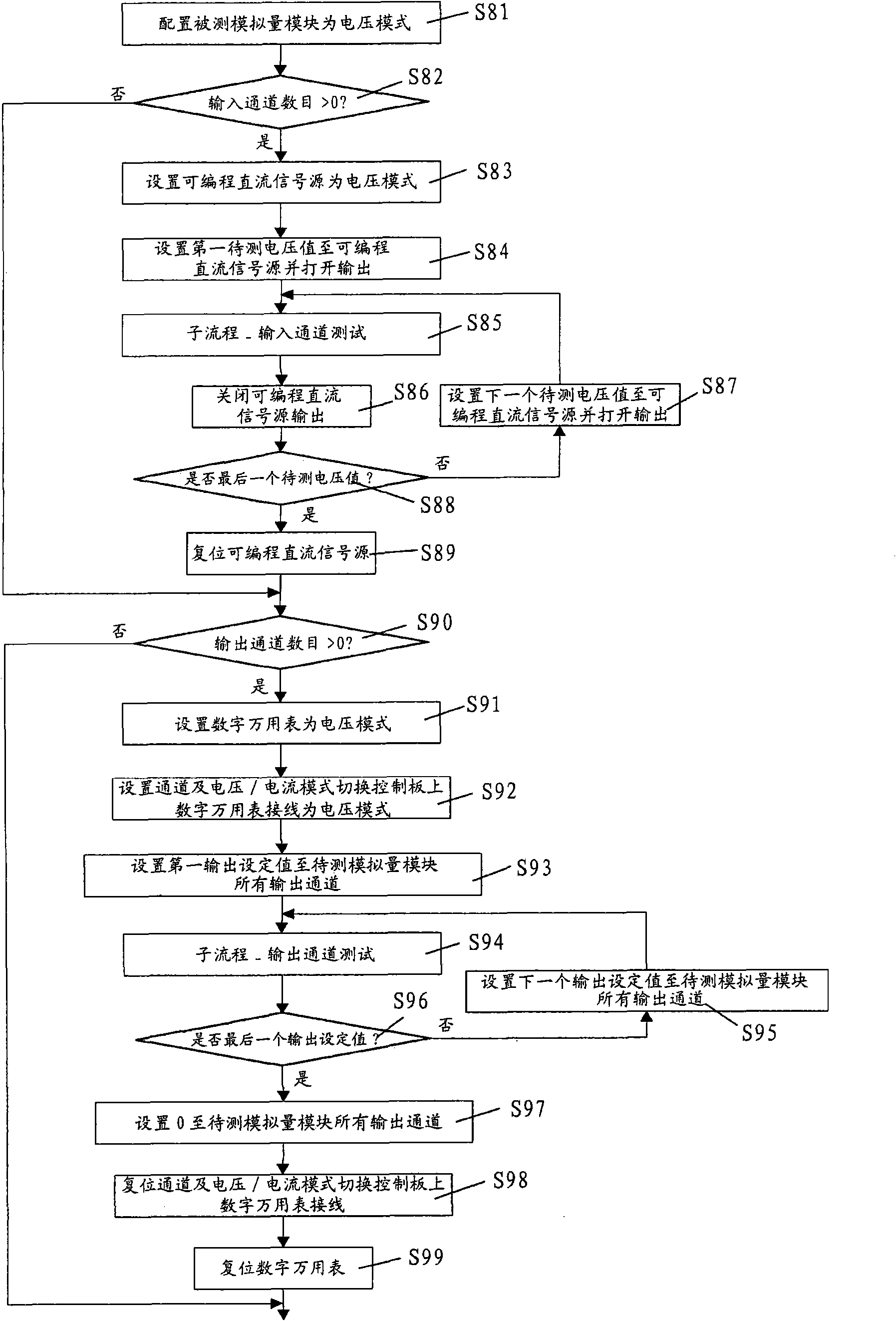

System and method for automatically testing analog module used for programmable logic controller (PLC)

InactiveCN101887111AImprove test efficiencyImprove accuracyElectrical measurementsProgrammable Interrupt ControllerCurrent mode

The invention discloses a system and a method for automatically testing an analog module with a settable input / output (I / O) channel in a programmable logic controller (PLC). The system comprises an upper control computer, a programmable direct current signal source, a digital multimeter, a channel and voltage / current mode switching control plate and a communication interface, wherein the upper control computer sets a testing parameter, issues an instruction to realize output or measurement, receives a test result and makes judgment according to the result; the programmable direct current signal source receives the instruction and the parameter to set the output as a voltage or current mode, sets and outputs a voltage / current signal to an input channel; the digital multimeter receives the instruction to set the measurement as the voltage or current mode, measures the voltage or current signal output by an output channel and returns a measured value to a computer; the channel and voltage / current mode switching control plate switches a test channel and a voltage / current connection mode according to the instruction; and the communication interface transmits the parameter, the instruction and the test result between each device and a tested model. A computer reads the conversion value of the voltage or current measured value of the input channel through the communication interface or transmits a set numerical value to the output channel to convert the set numerical value into a voltage or a current.

Owner:SCHNEIDER ELECTRIC IND SAS

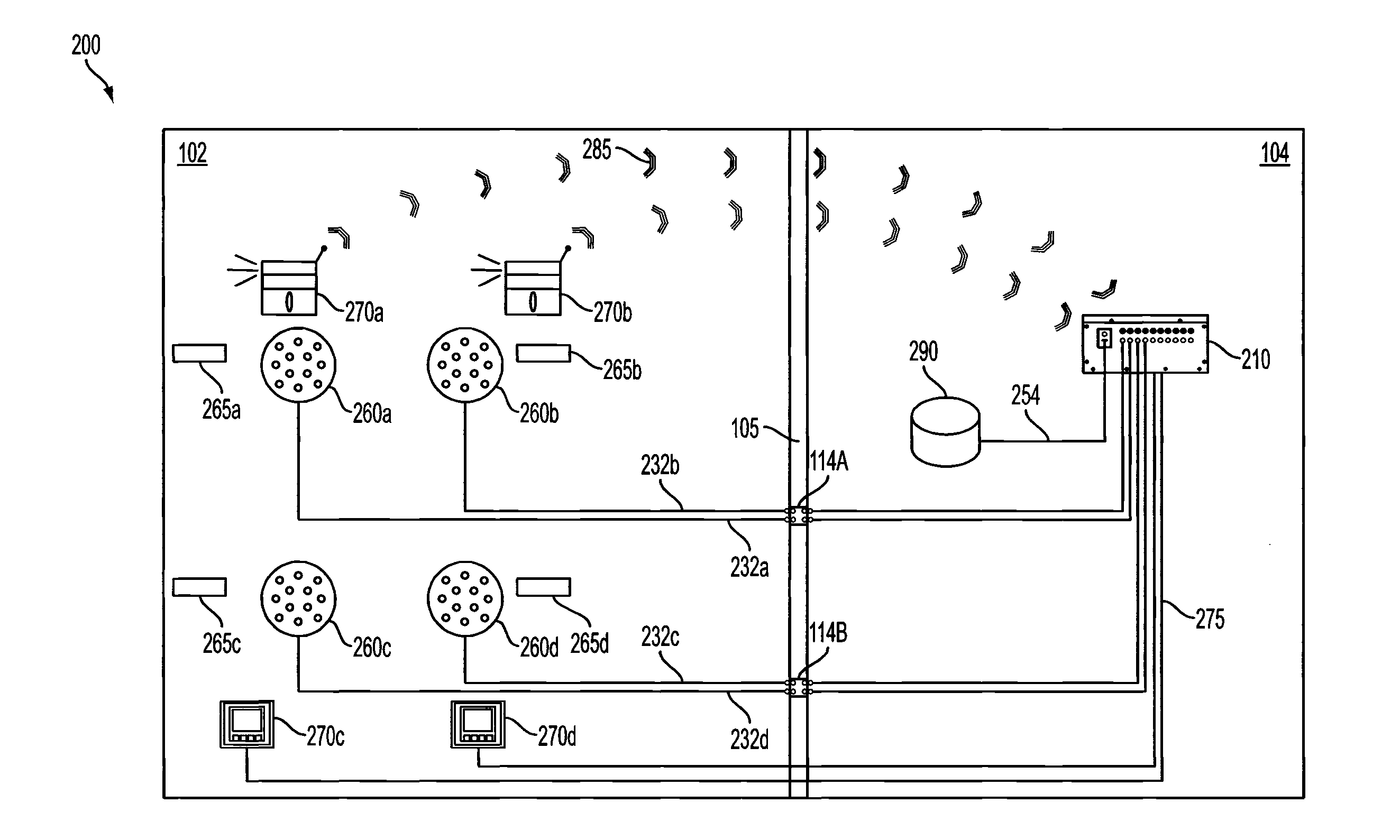

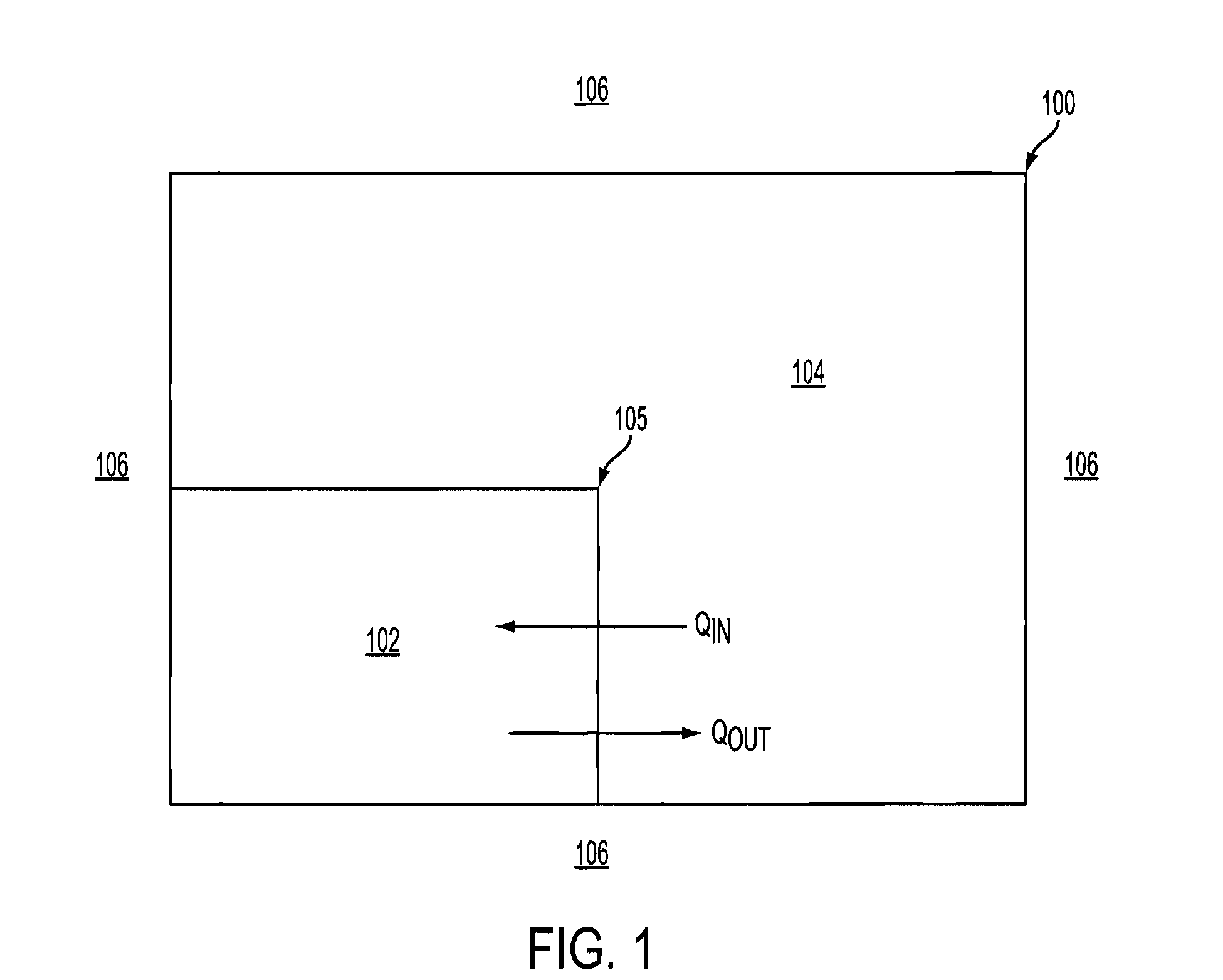

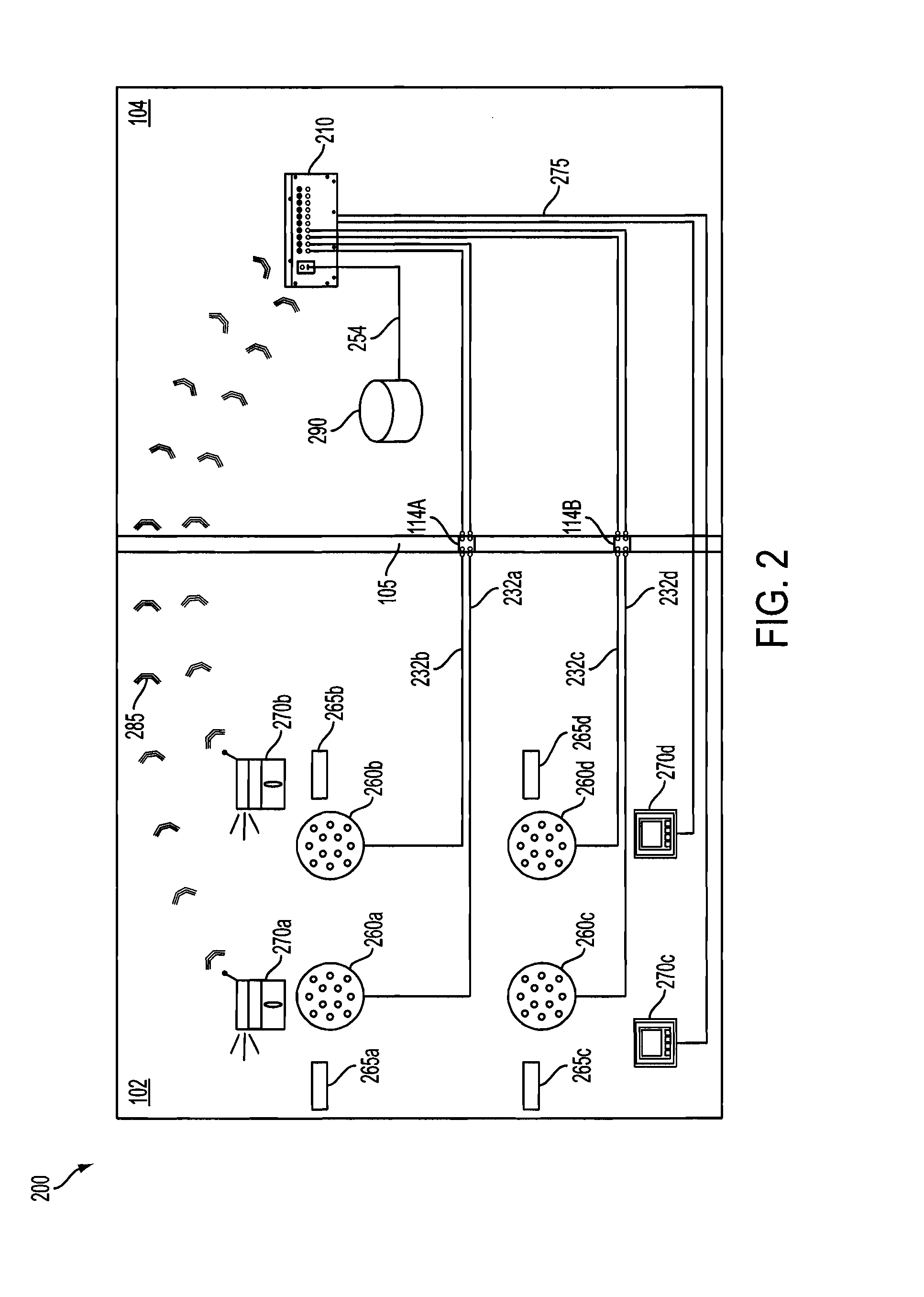

Programmable logic controller-based control center and user interface for air sampling in controlled environments

ActiveUS20140132415A1Simple configurationIncrease flexibilitySamplingElectric controllersHuman–machine interfaceProgrammable logic controller

In accordance with an aspect of the present invention there is provided a system for sampling air at multiple locations in a controlled environment. The system includes one or more air sampling devices configured to monitor and test a volume of air within a controlled environment. A control center including a programmable logic controller (PLC) is configured to monitor and control the one or more air sampling devices. One or more touch panel displays are connected to the control center and provide a human-computer interface between the control center and users.

Owner:VALTEK ASSOC INC

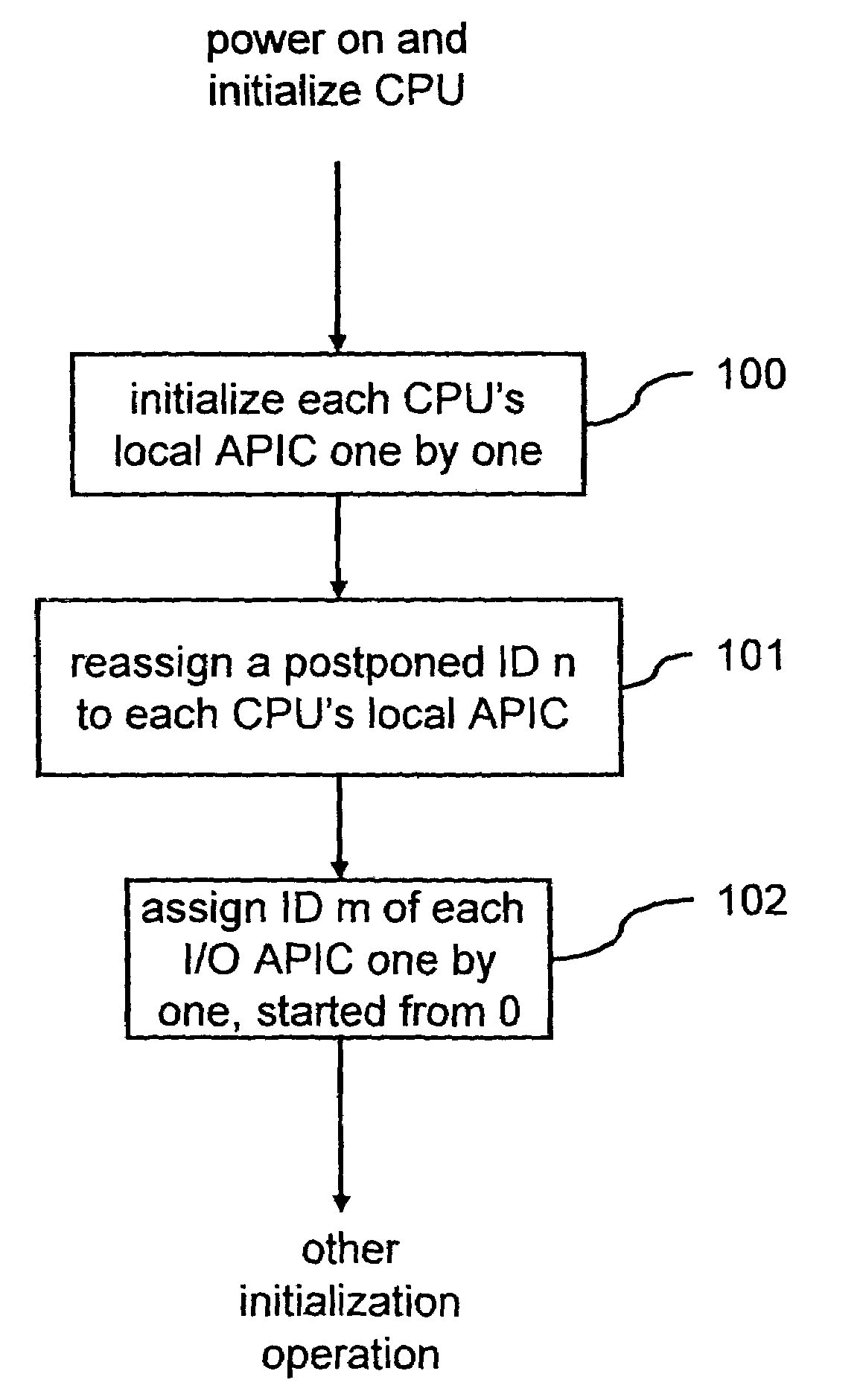

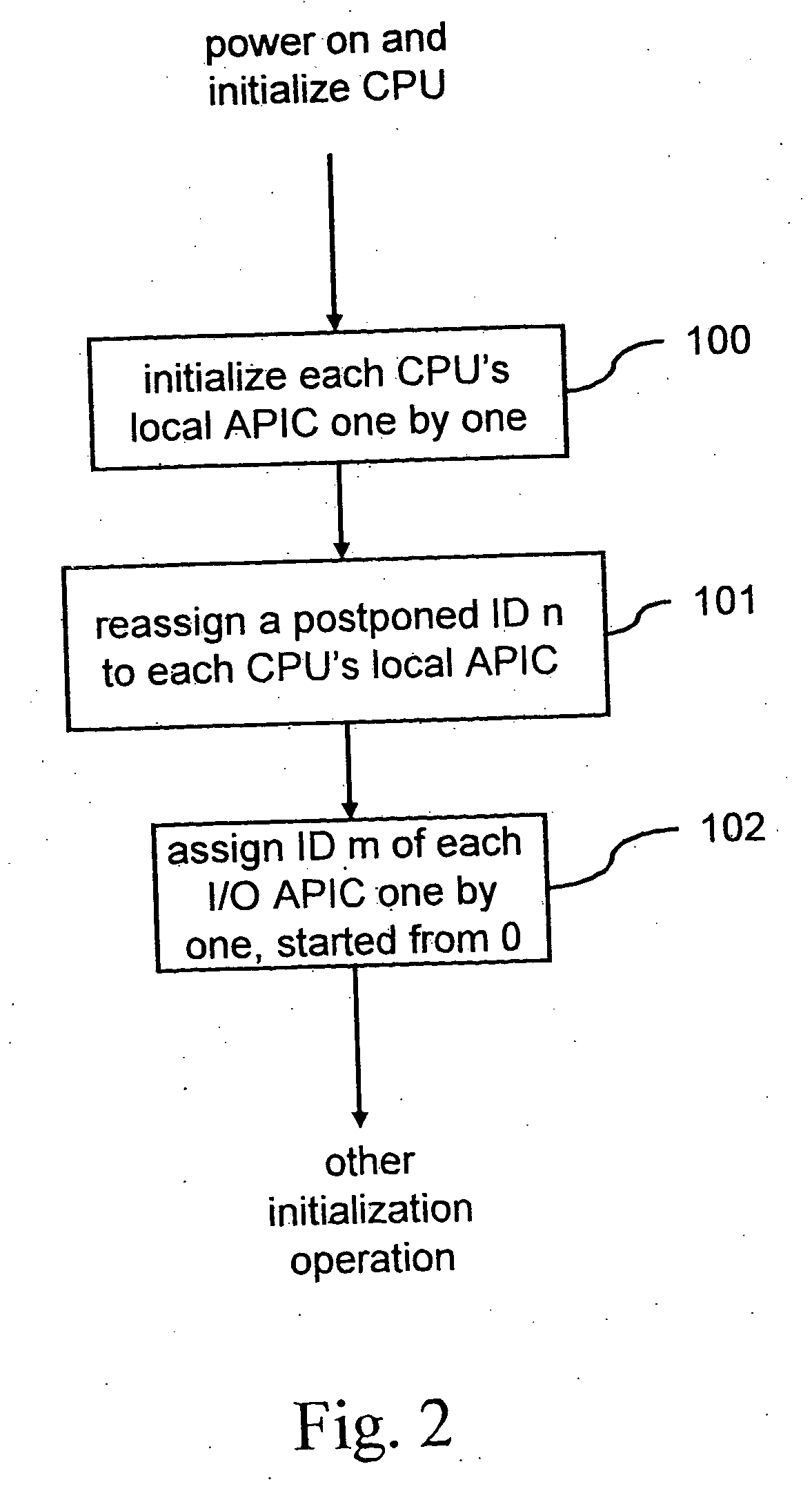

ID configuration method for advanced programmable interrupt controller

ActiveUS7363394B2Improve stabilityDigital computer detailsProgram controlMulti processorProgrammable Interrupt Controller

An advanced programmable interrupt controller (APIC) identification (ID) configuration method is applied to a multiprocessor computer system. The method assigns a postponed ID to each CPU's APIC IDs respectively during the initialization. Plural reserved IDs are assigned to the I / O APICs. A multiprocessor configuration table in a basic input output system (BIOS) will be updated with renewed ID configuration, to avoid an ID conflict when processing the interrupt request from the peripheral devices and raise the stability of the multiprocessor computer system.

Owner:MITAC INT CORP

TAM controller for plural test access mechanisms

ActiveUS7519884B2Efficient testingSimplifies testerElectronic circuit testingComputer hardwareProgrammable logic controller

Owner:TEXAS INSTR INC

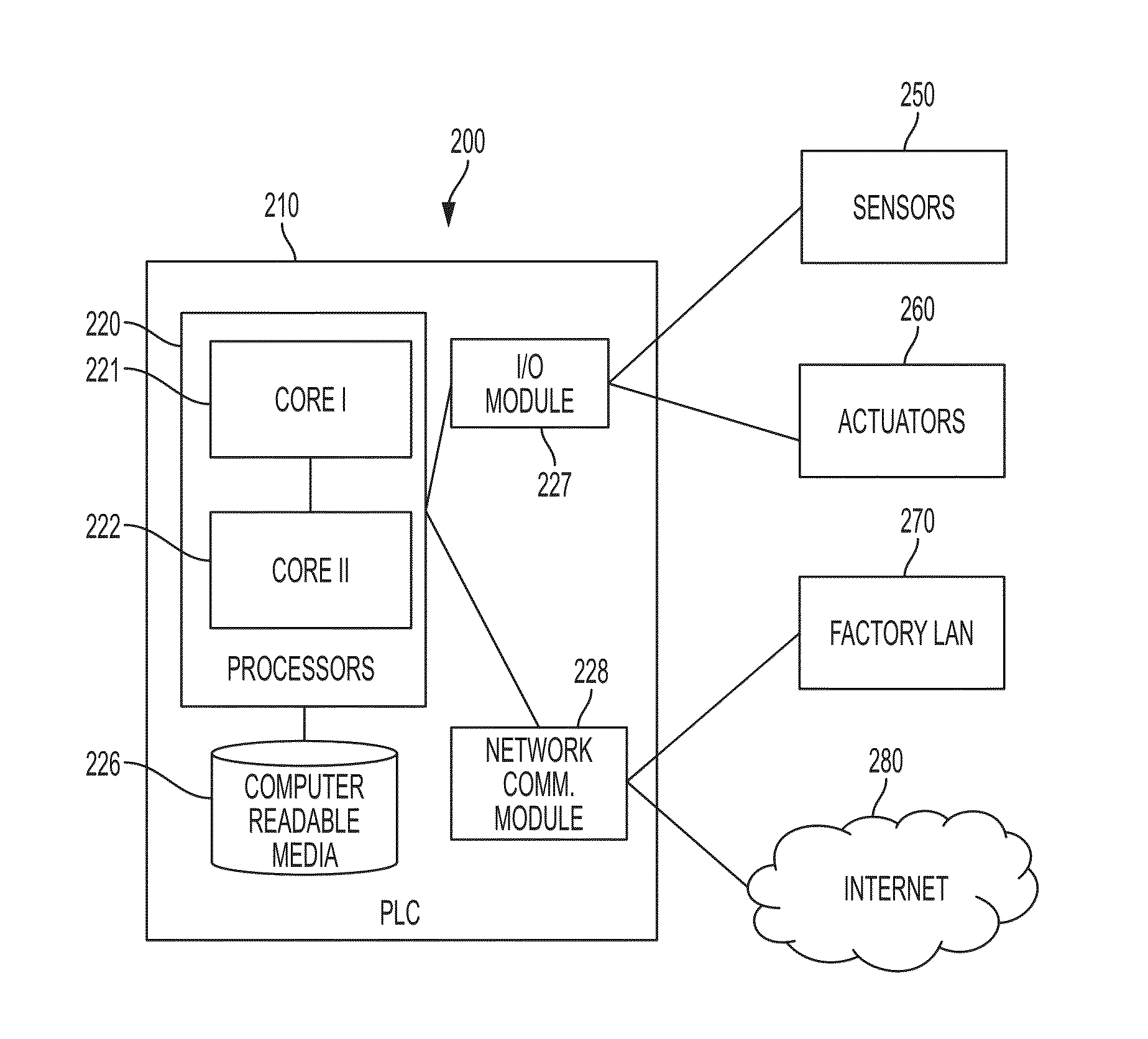

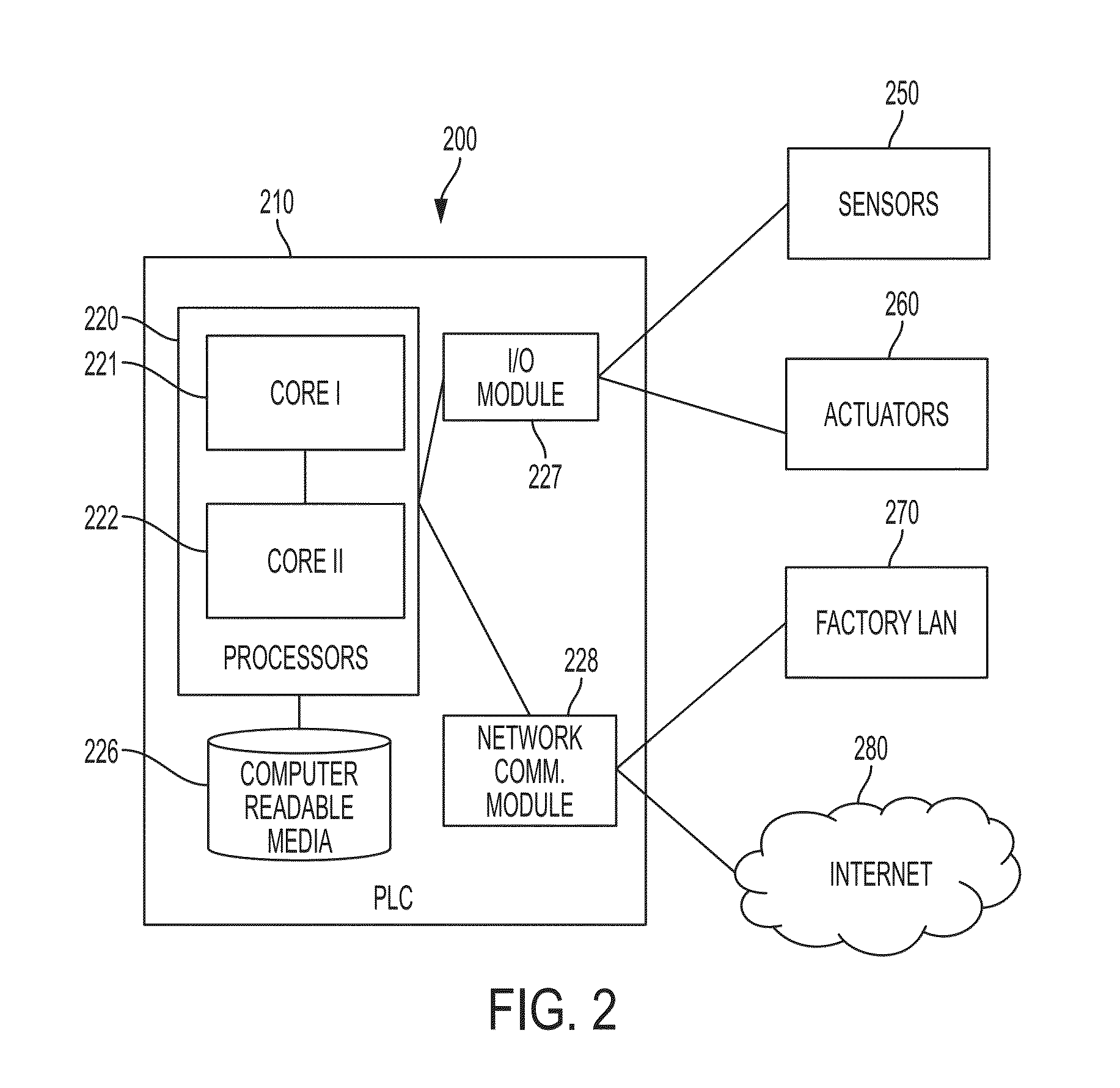

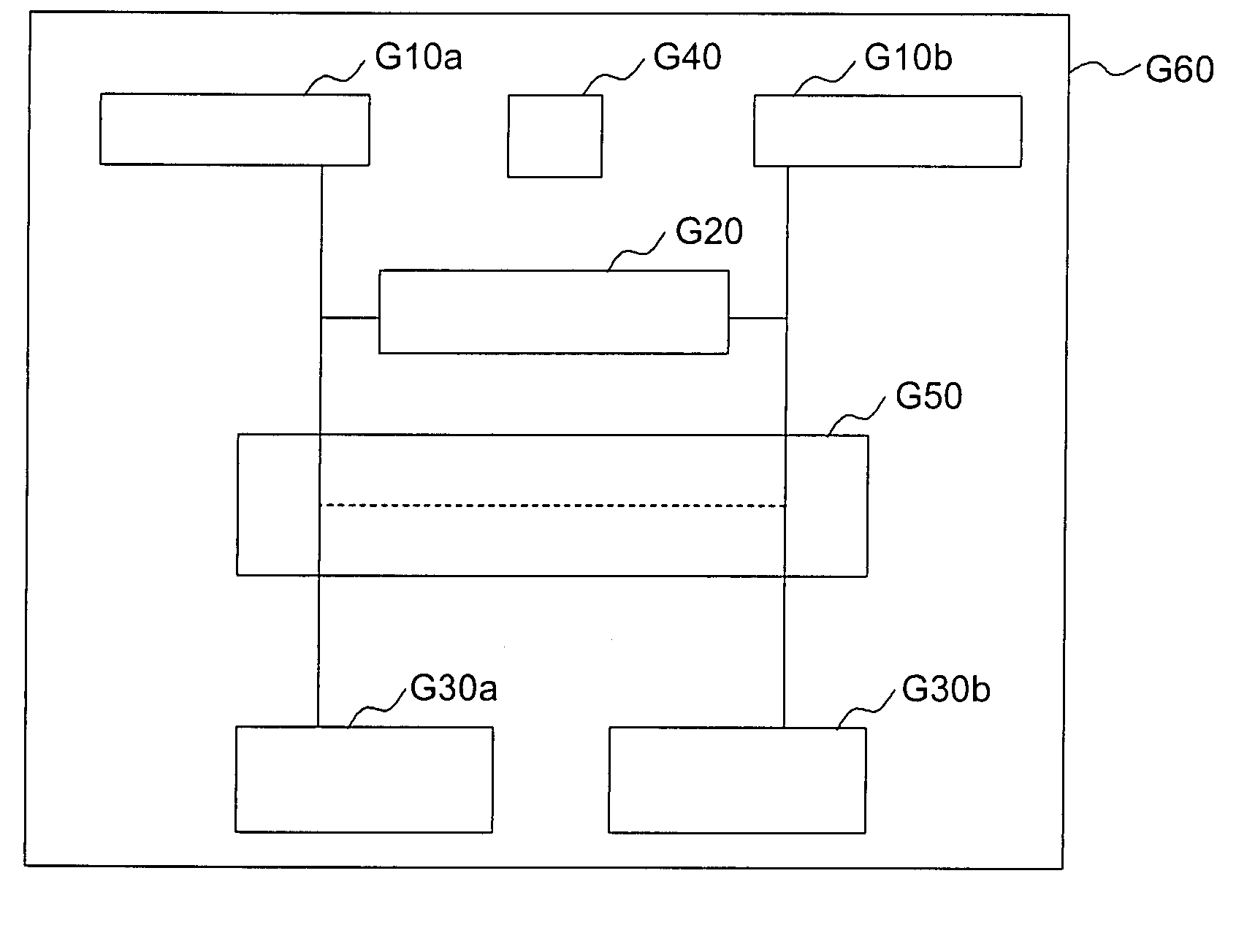

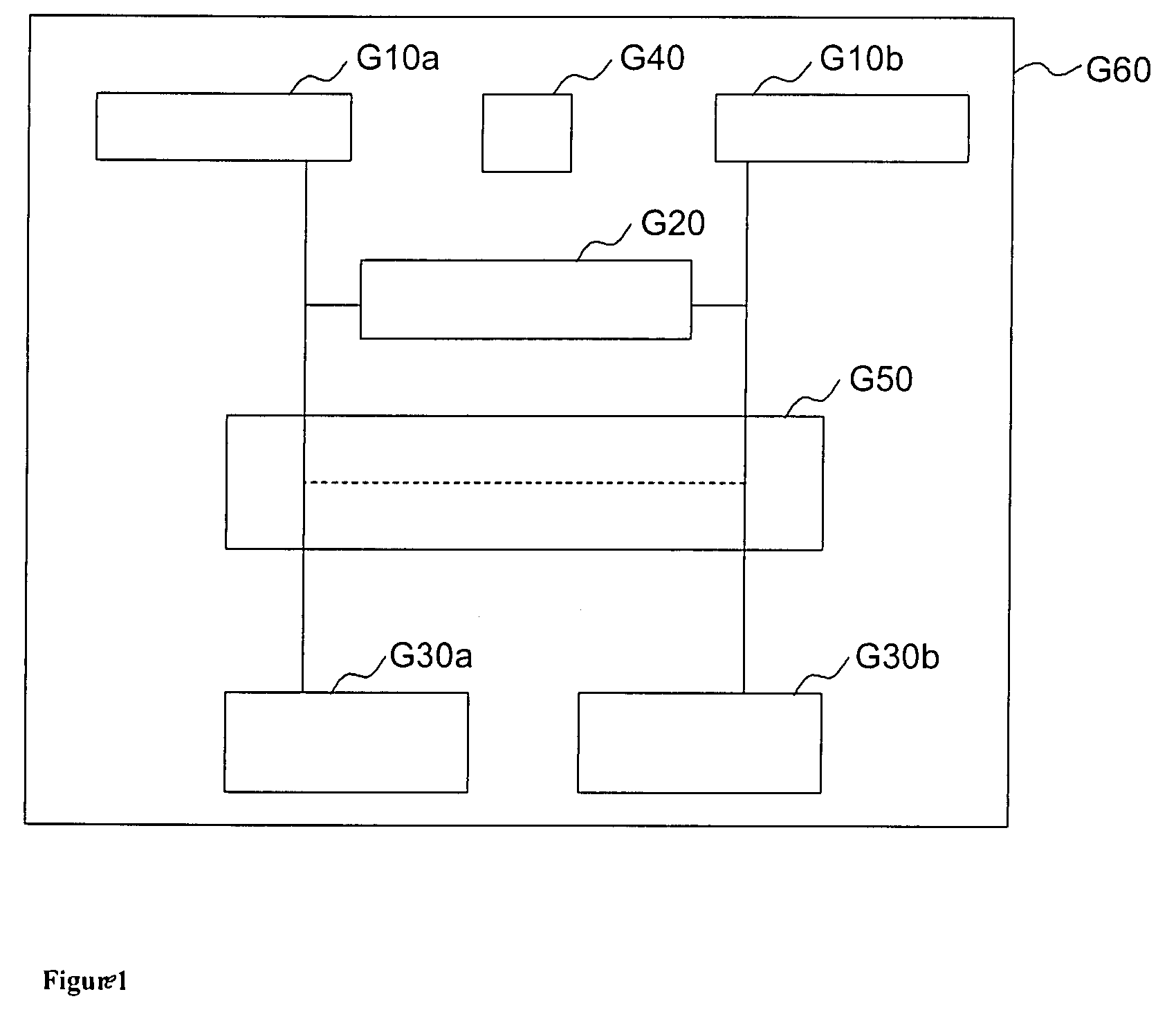

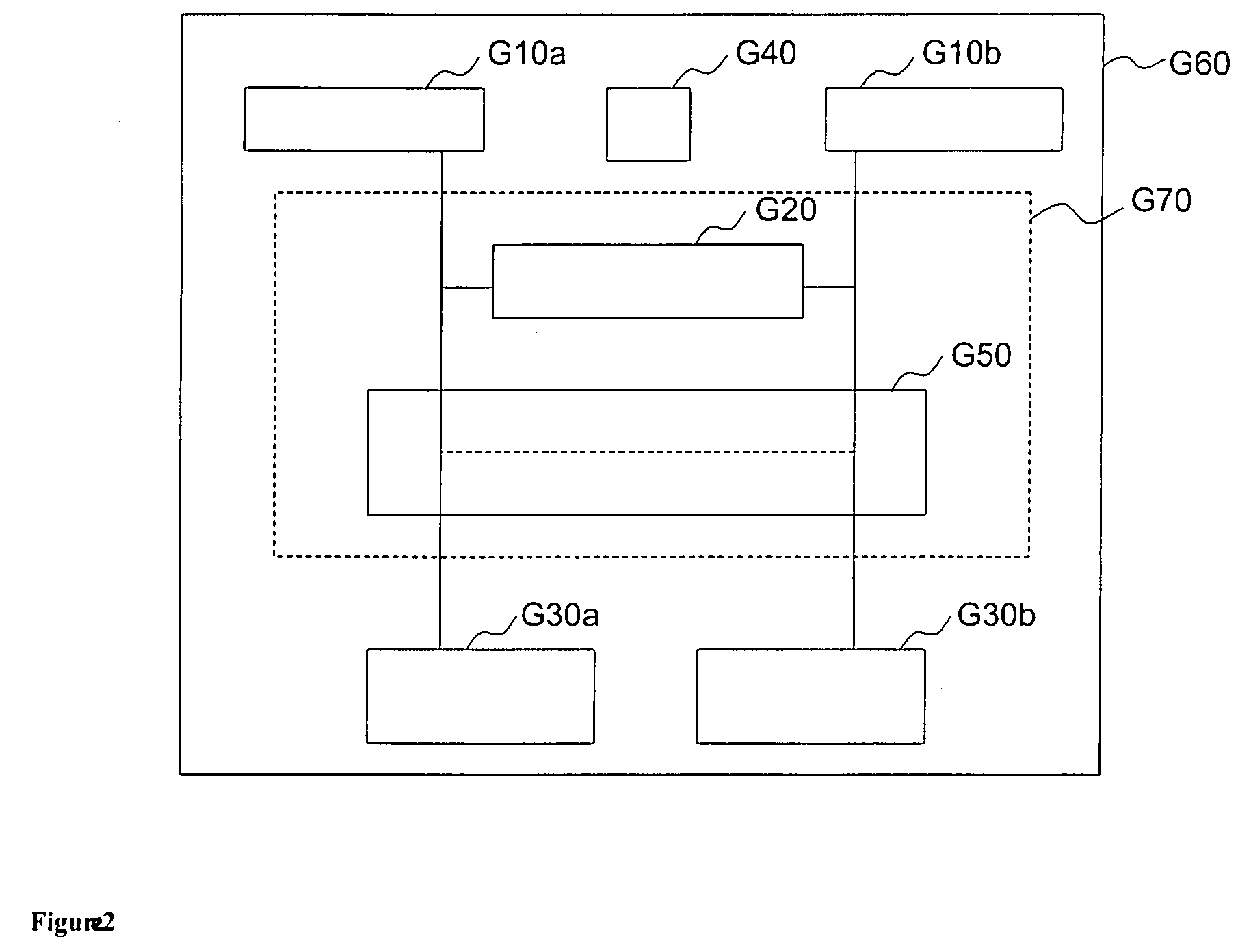

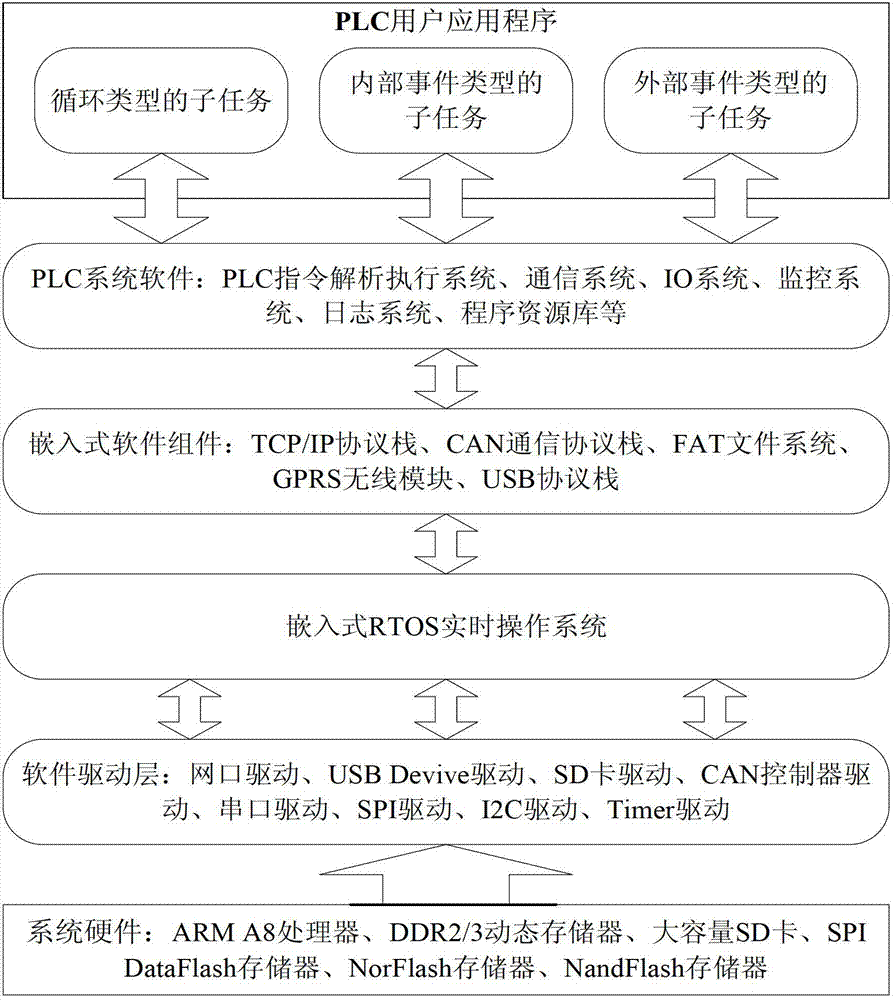

System and method of multi-core based software execution for programmable logic controllers

InactiveUS20160091882A1Computer controlSimulator controlProgrammable logic controllerProgrammable Interrupt Controller

Real-time programmable logic controller software is executed on a multicore processor system. An organizational block executer is executed on a first core, and system service functions associated with the programmable logic controller software are executed on the second core. The organizational block executer includes I / O scanning and logic solving in a single-threaded execution. Core-switch operations may be cyclically performed to move execution of the organizational block executer from the first core to the second core and back to the first core.

Owner:SIEMENS CORP

ID configuration method for advanced programmable interrupt controller

ActiveUS20070067521A1Improve stabilityDigital computer detailsProgram controlMulti processorProgrammable Interrupt Controller

An advanced programmable interrupt controller (APIC) identification (ID) configuration method is applied to a multiprocessor computer system. The method assigns a postponed ID to each CPU's APIC IDs respectively during the initialization. Plural reserved IDs are assigned to the I / O APICs. A multiprocessor configuration table in a basic input output system (BIOS) will be updated with renewed ID configuration, to avoid an ID conflict when processing the interrupt request from the peripheral devices and raise the stability of the multiprocessor computer system.

Owner:MITAC INT CORP

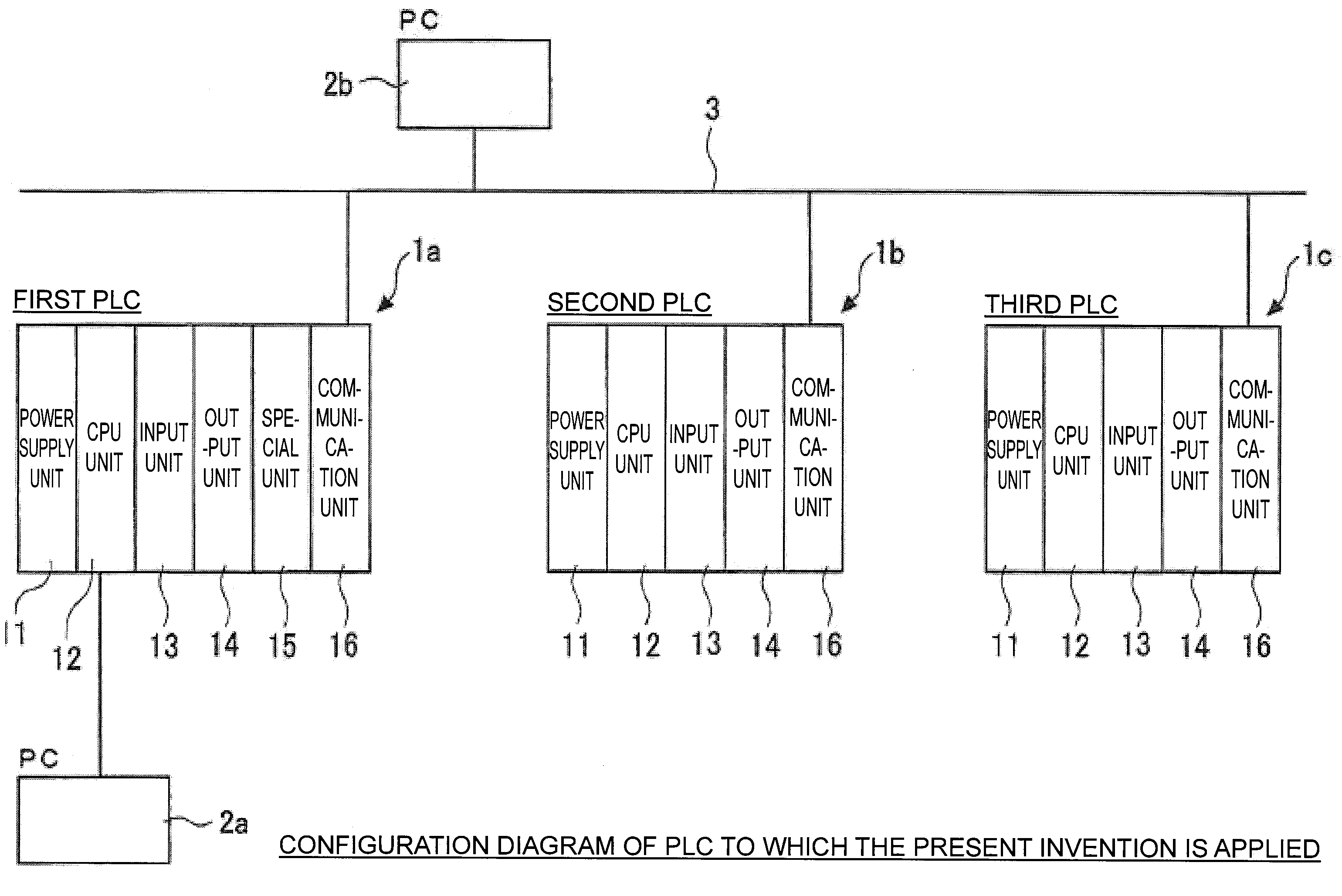

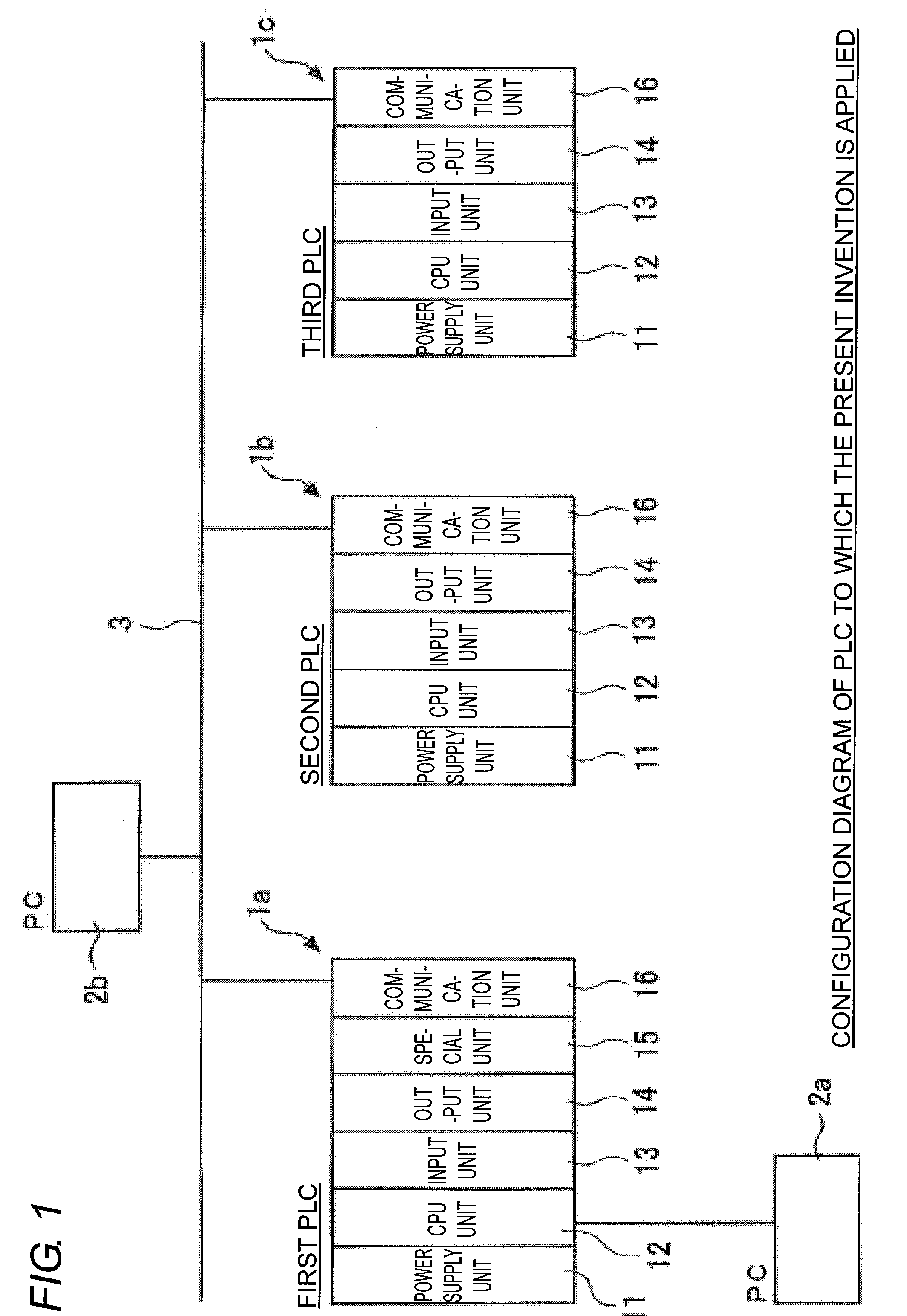

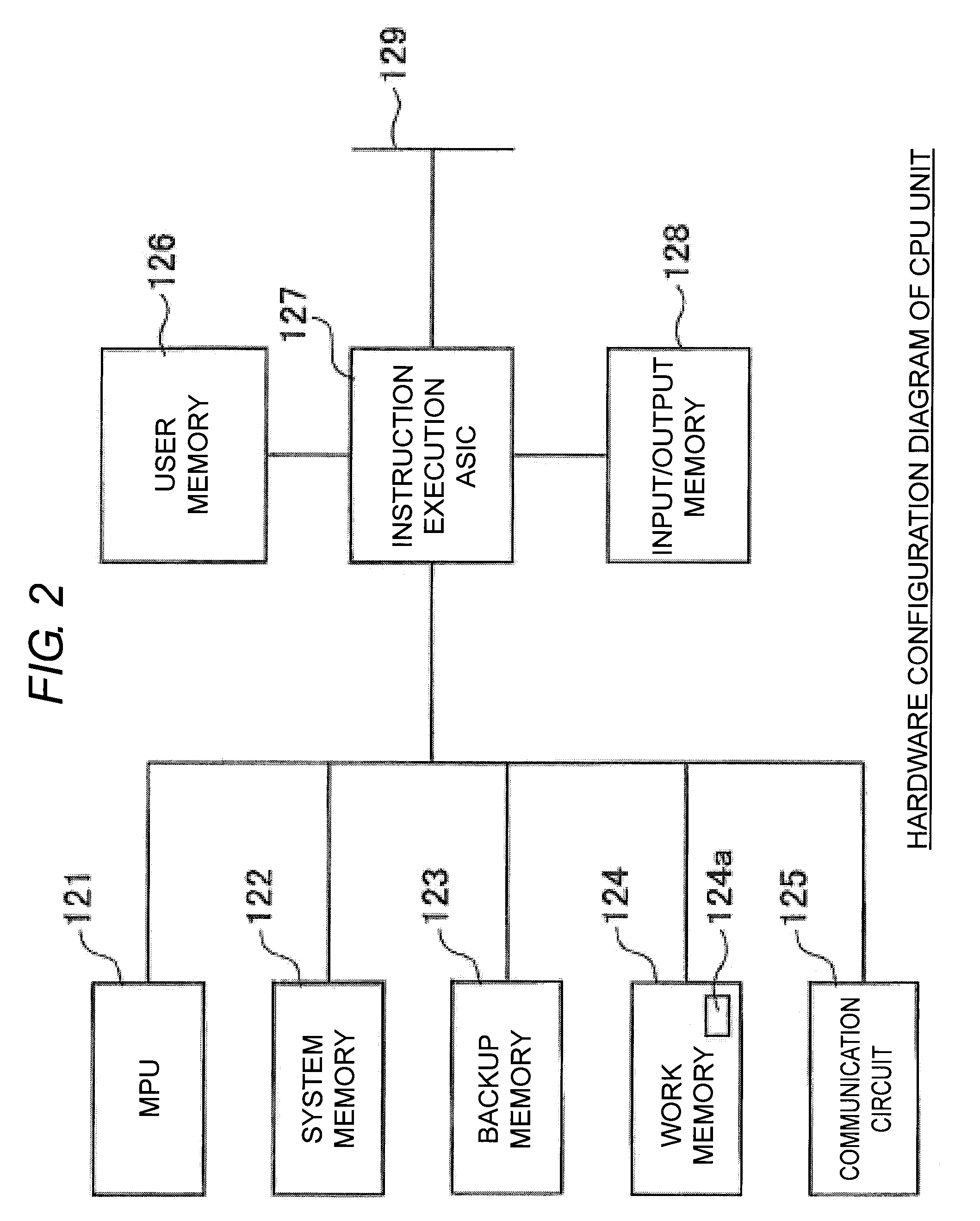

Programmable controller

ActiveUS20100174387A1Increase speedImprove throughputComputer controlSimulator controlProgrammable logic controllerProgrammable Interrupt Controller

The value of fixed cycle time is adjusted to an optimum value in a short period of time. In a second operational mode (MON) of a PLC, a series of a plurality of system processes are repeatedly performed with a change to a user program in a peripheral service process being allowed. A change to fixed cycle time to be compared with actual cycle time is prohibited in a first operational mode (RUN) but is allowed in the second operational mode (MON) and a non-operational mode (PRG).

Owner:ORMON CORP

Technique for communicating interrupts in a computer system

InactiveUS9043521B2Electric digital data processingProgrammable Interrupt ControllerComputerized system

A technique to enable efficient interrupt communication within a computer system. In one embodiment, an advanced programmable interrupt controller (APIC) is interfaced via a set of bits within an APIC interface register using various interface instructions or operations, without using memory-mapped input / output (MMIO).

Owner:INTEL CORP

Method and device for switching over in a computer system having at least two execution units

InactiveUS7669079B2Program control using stored programsError detection/correctionProgrammable Interrupt ControllerComputerized system

A device and method for switching over in a computer system having at least two execution units are provided, in which switchover units are included which are designed in such a way that they switch between at least two operating modes, a first operating mode corresponding to a comparison mode and a second operating mode corresponding to a performance mode. A programmable interrupt controller is assigned to each execution unit, and a storage element is included, in which information is stored that describes at least parts of a configuration of at least one of these interrupt controllers.

Owner:ROBERT BOSCH GMBH

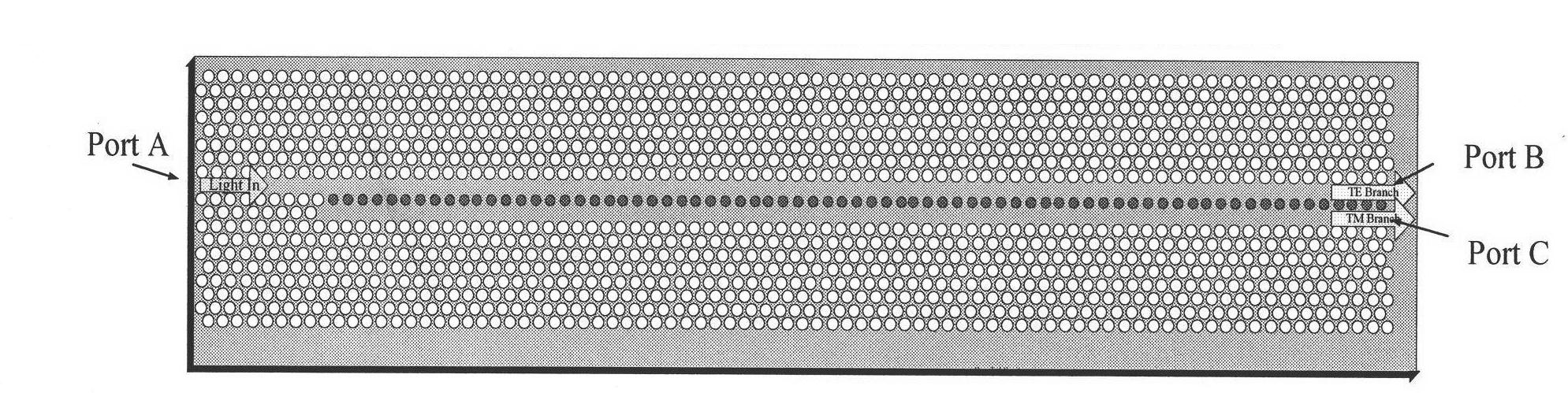

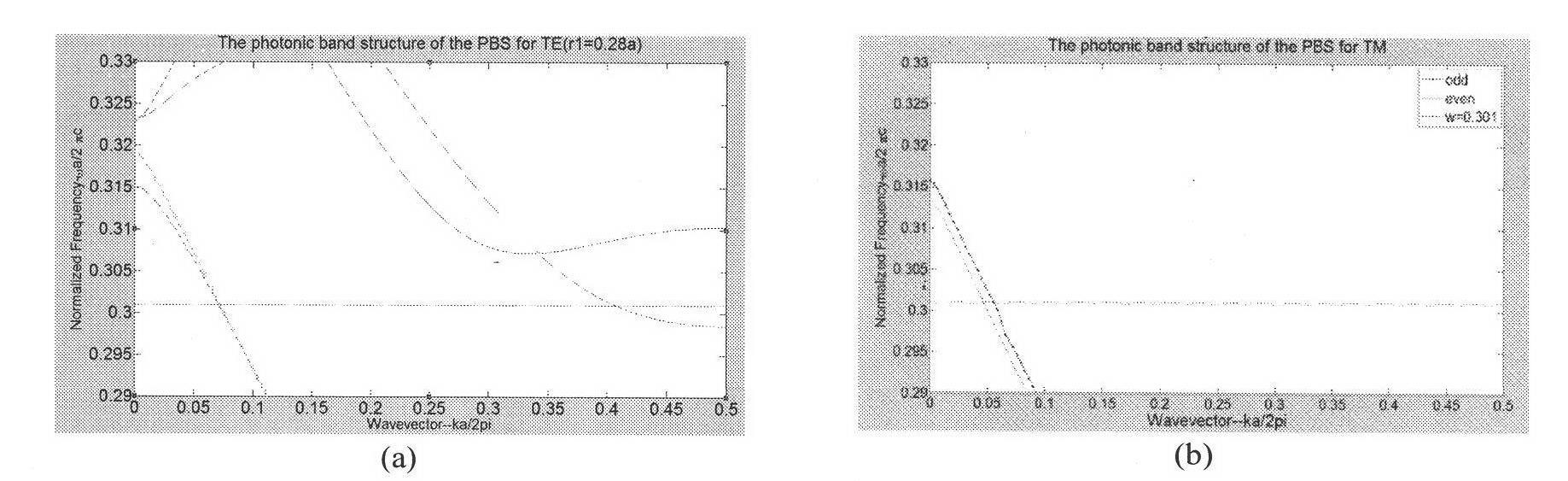

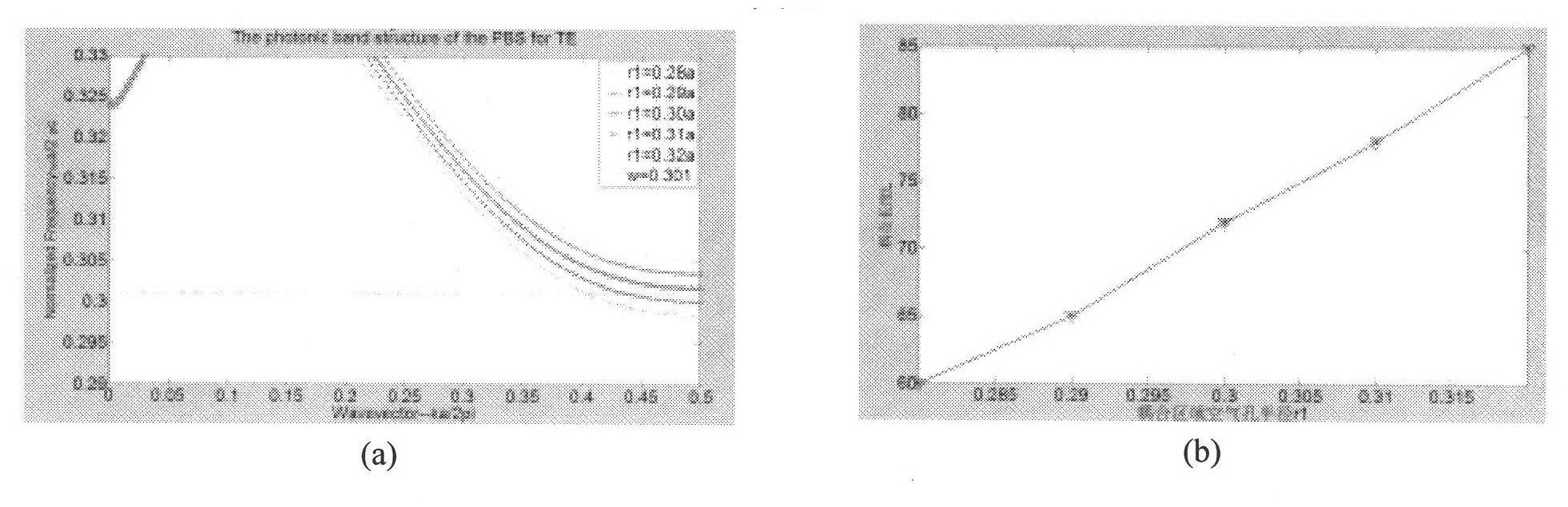

Method for realizing integration of polarizing beam splitter and slow light device by using bend waveguide

InactiveCN102200613AGood beam splitting performanceChange working frequency bandCoupling light guidesManufacturing technologyBeam splitter

The invention relates to a method for realizing integration of a polarizing beam splitter and a slow light device by using a bend waveguide, belonging to the technical field of micro optical integration. In the invention, the polarizing beam splitter and a coupled-cavity waveguide slow light device are integrated on the same flat plate by using the bend waveguide with two turn angles of 60 degrees for the first time. In the invention, a flat-plate structure based on a two-dimensional photonic crystal is designed; and the structure of the device is designed in such a way that each module of an integrated device works at the same frequency, thus high efficient coupling between the polarizing beam splitter and the bend waveguide as well as the slow light device is realized. The basic structure of the flat-plate structure is a photonic crystal GaAlAs (Gallium-Aluminum-Arsenic) flat-plate structure based on an air-vent triangular lattice, which is much closer to a traditional widely-applied photonic crystal manufacturing technology based on SOI (Silicon-On-Insulator) and has the characteristic of very good realizability. In addition, the polarizing beam splitter and the coupled-cavity waveguide slow light device are connected with each other by using the bend waveguide in the design of the scheme so as to provide a new method for realizing the micro PIC (Programmable Interrupt Controller).

Owner:BEIJING UNIV OF POSTS & TELECOMM

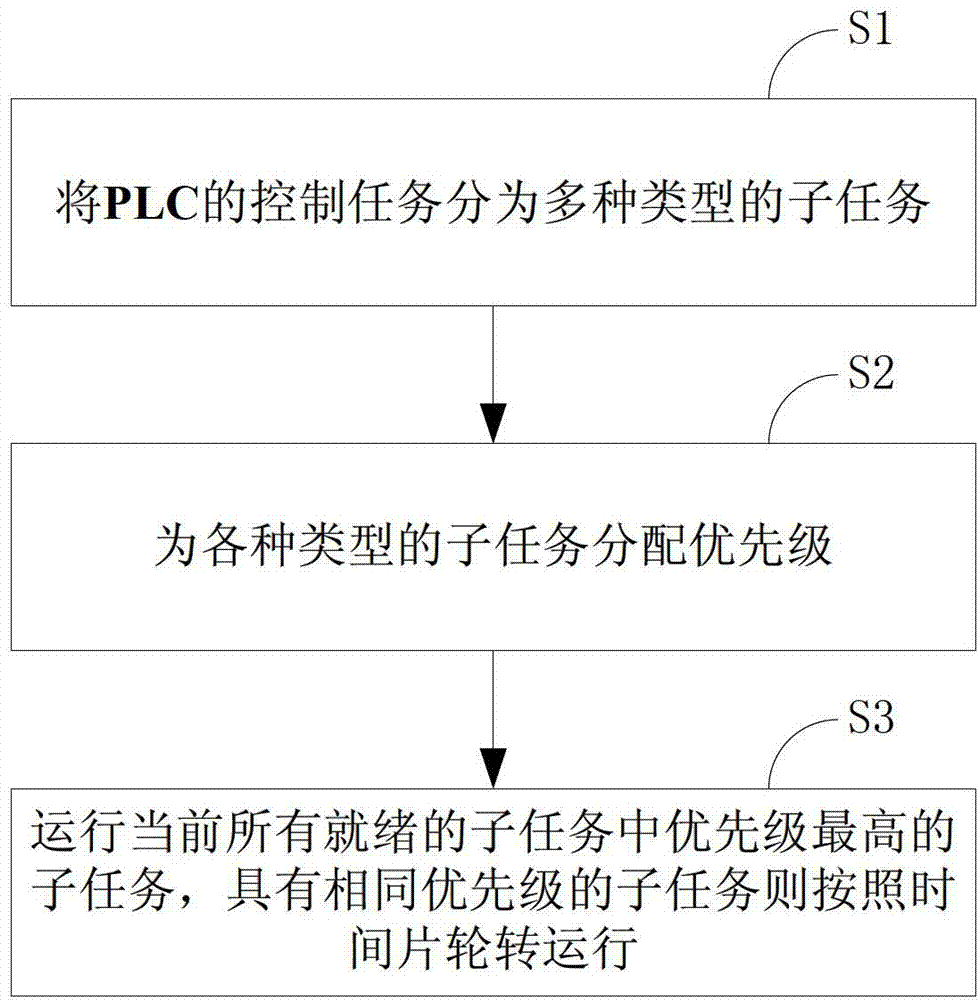

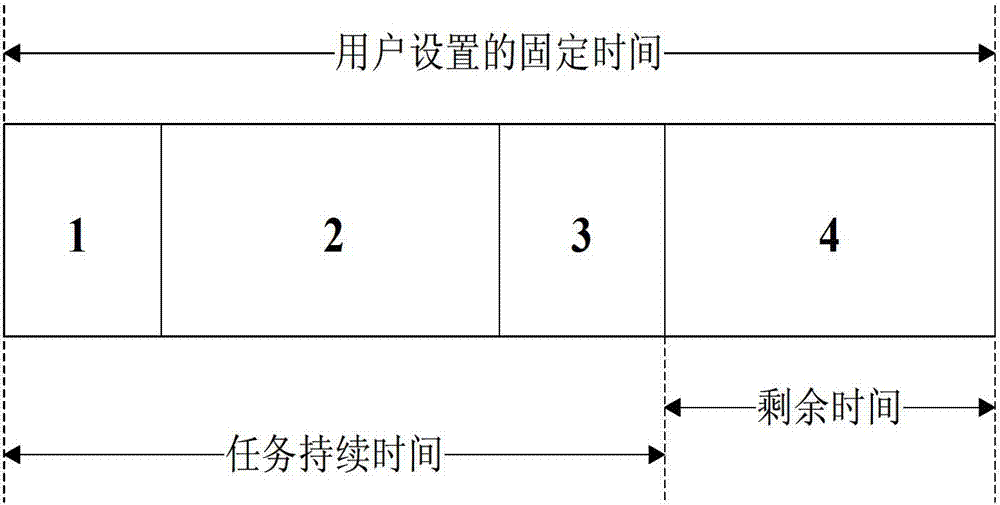

Multitask control method and multitask control device of PLC (programmable logic controller)

InactiveCN103399798AFunctional division is clearRealize time-sharing multitasking controlProgram initiation/switchingResource allocationControl systemProgrammable logic controller

The invention discloses a multitask control method and a multitask control system of a PLC (programmable logic controller). The system comprises a classifying unit, a priority distribution unit and an execution unit. The method includes S1, dividing a control task of the PLC into various types of sub-tasks, S2, distributing priorities to the various types of sub-tasks, S3, under scheduling of a real-time operating system, operating the sub-tasks with the highest priorities in all current ready sub-tasks, and operating the sub-tasks with the same priorities in a rotation manner according to time slices. The control task of a PLC control system is divided into multiple sub-tasks which operate under the scheduling of an RTOS (real-time operating system) in a coordinated manner, so that time-sharing multitask control is realized, and real-time performance, system efficiency, convenience in programming and the like are greatly improved as compared with those of conventional single-task PLCs.

Owner:SHENZHEN HUICHUAN CONTROL TECH +2

Method and system for real time scheduler

InactiveUS20050229178A1Facilitates real-time schedulingSpeed of execution of operatingProgram initiation/switchingResource allocationTime scheduleNon-maskable interrupt

Methods and computer-executable components for real-time scheduling of CPU resources are disclosed. A performance counter determines when to allocate CPU resources to a thread. When it is time to allocate the CPU resources, the performance counter issues a maskable or non-maskable interrupt to an advanced programmable interrupt controller (APIC). The APIC then issues a maskable non-maskable interrupt to the CPU. In response to receiving the non-maskable interrupt, the CPU allocates resources to the thread. In addition, the disclosed methods and computer-executable components also: (a) allow scheduling of CPU resources such that real-time threads are guaranteed respective portions of time slots, (b) enable real-time scheduling on a non-real-time operating system, and (c) provide scheduling of CPU resources on a uni-processor machine such that at least first and second real-time threads dependent on one another are synchronized.

Owner:MICROSOFT TECH LICENSING LLC

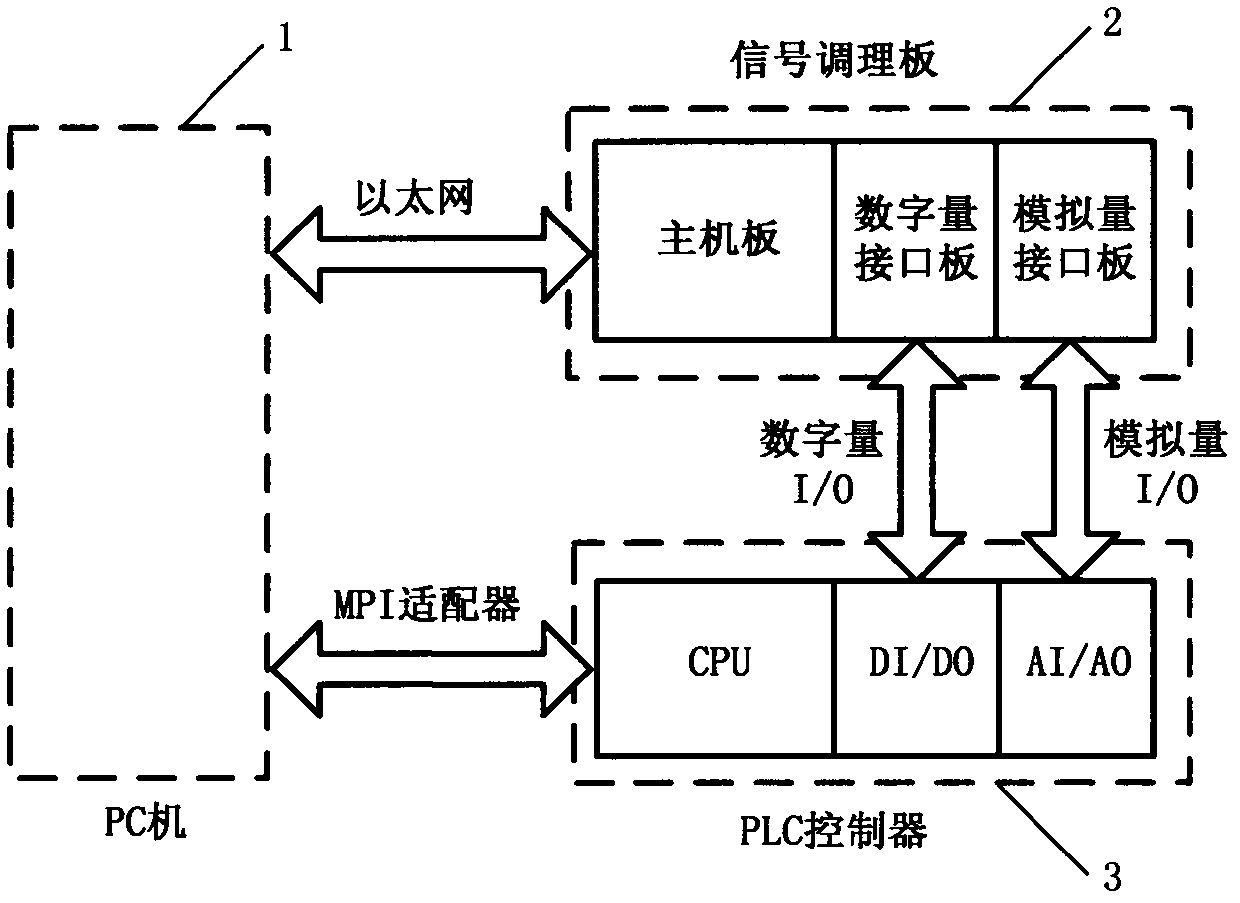

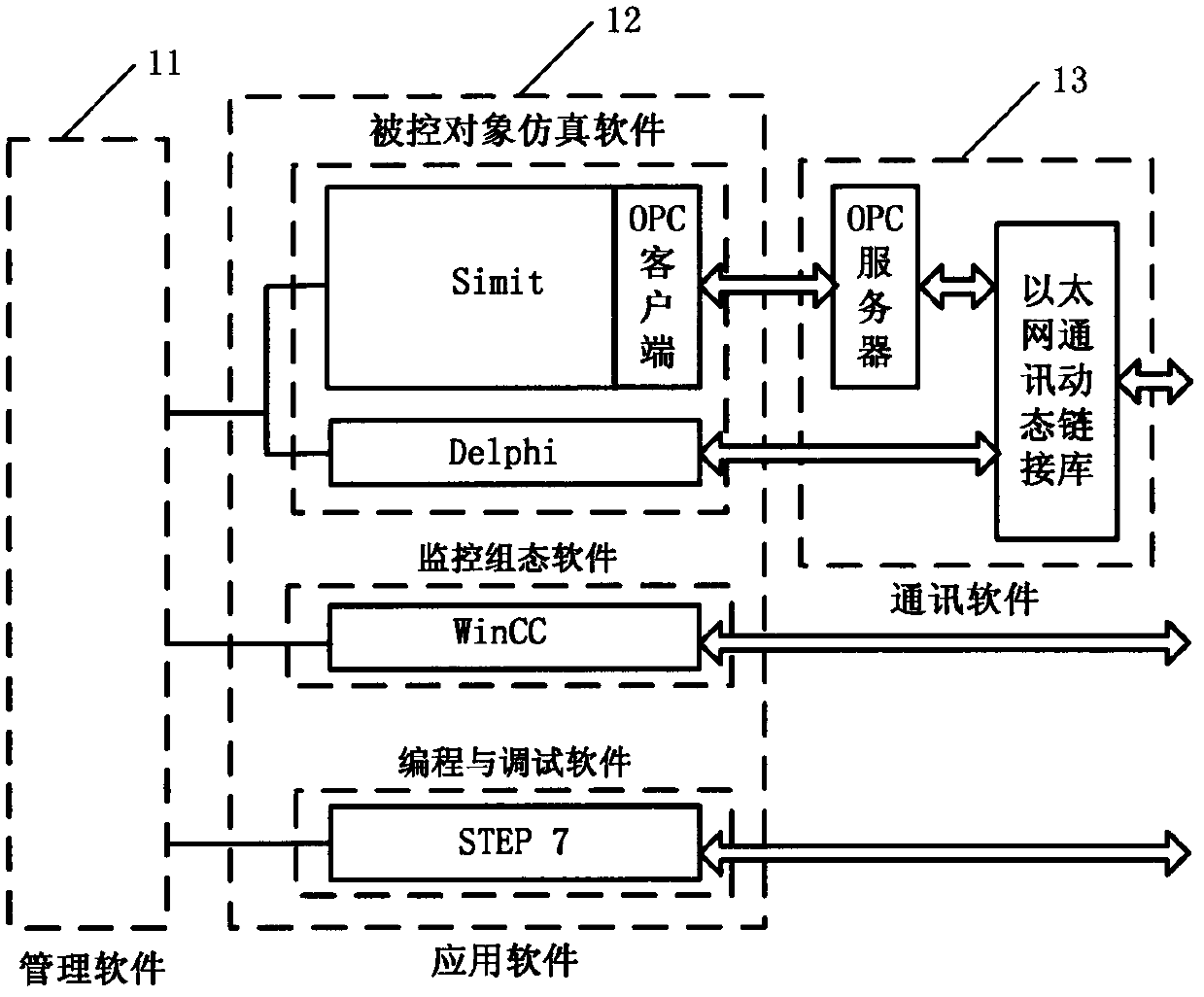

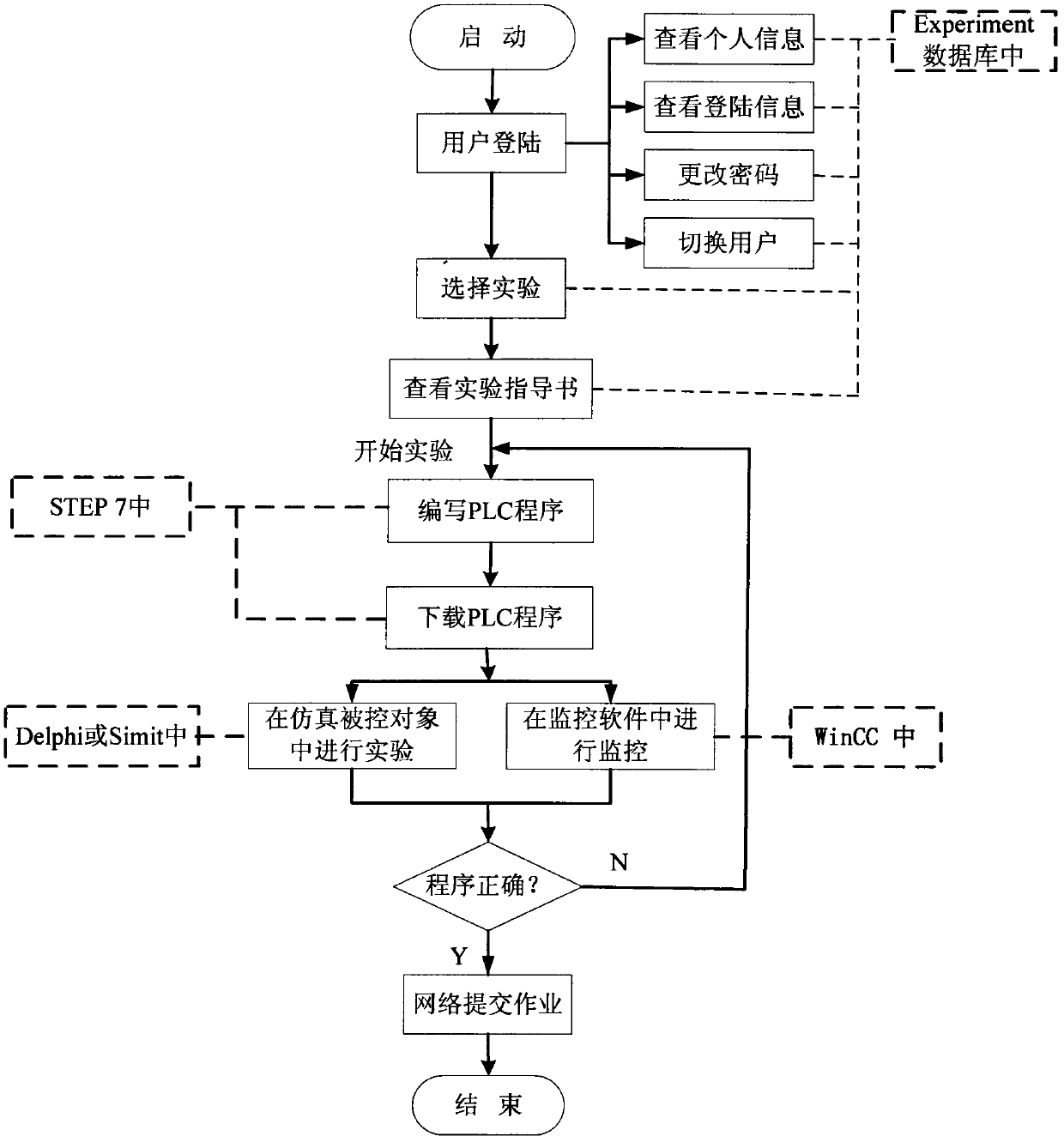

Programmable logic controller (PLC) experimental system

InactiveCN102608946ALow priceProgramme control in sequence/logic controllersAutomatic controlProgrammable Interrupt Controller

The invention belongs to the technical field of automatic control and electronics, and discloses a programmable logic controller (PLC) experimental system, which comprises three parts of a PC (personal computer) (1), a signal conditioning board (2), a PLC controller (3), wherein the signal conditioning board comprises a mainboard (21), a digital quantity interface board (22) and an analog quantity interface board (23); the PLC controller comprises a central processing unit (CPU) (31), a digital input / output data input (DI) / data output (DO) (32) and an analog input / output (AI / AO) (33). The PC is communicated with the signal conditioning board through an Ethernet; the PC is communicated with the PLC controller through a multi-point interface (MPI) adapter; and the signal conditioning board is communicated with the input (I) / output (O) port of the PLC. The software resource of the PC is substituted for a controlled object in a PLC control system, the lack of the number and the types of the controlled object of a real object in the experiment is made up, and the price of the experimental system is maintained low.

Owner:CHANGSHU RES INSTITUE OF NANJING UNIV OF SCI & TECH

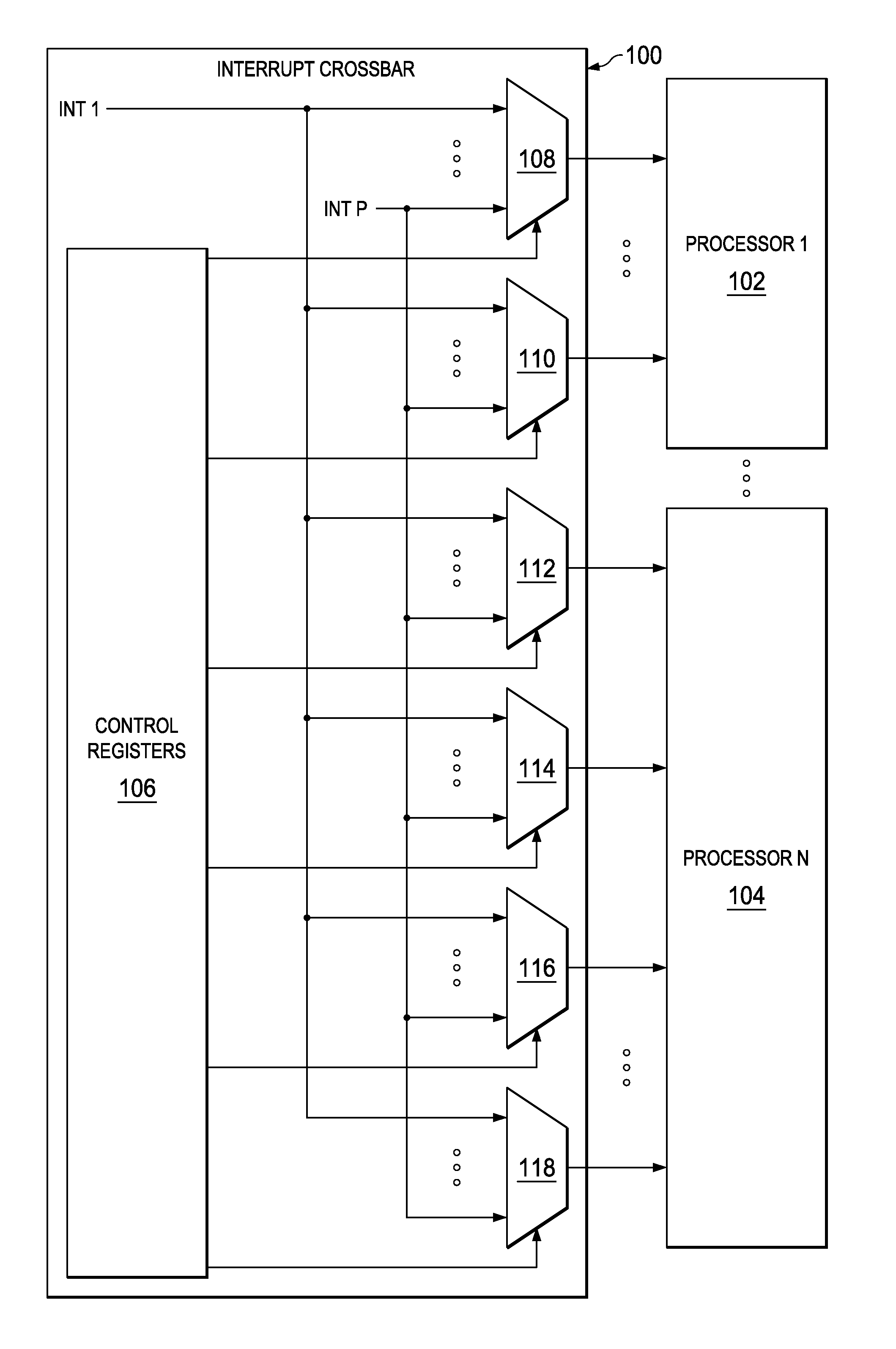

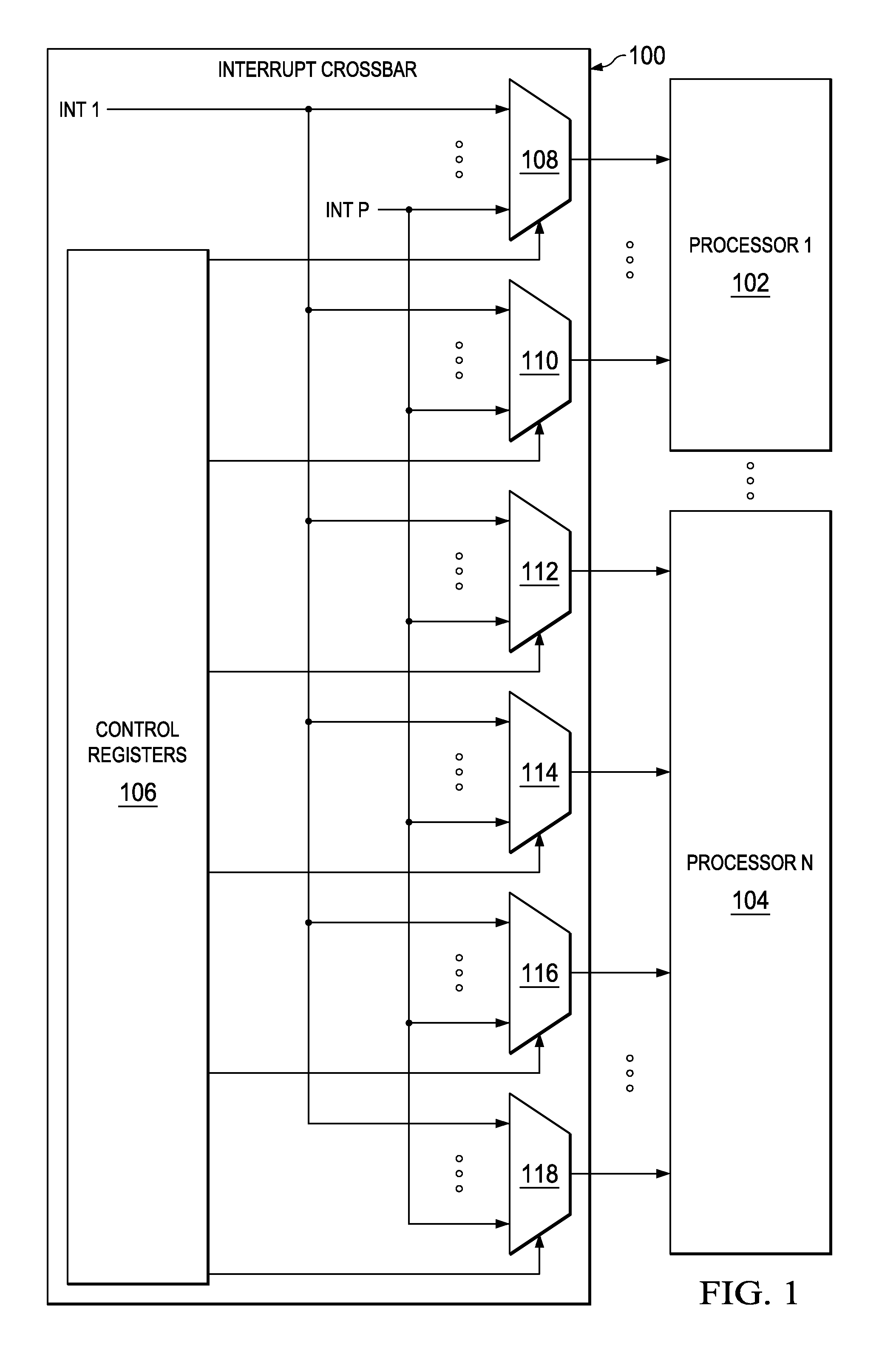

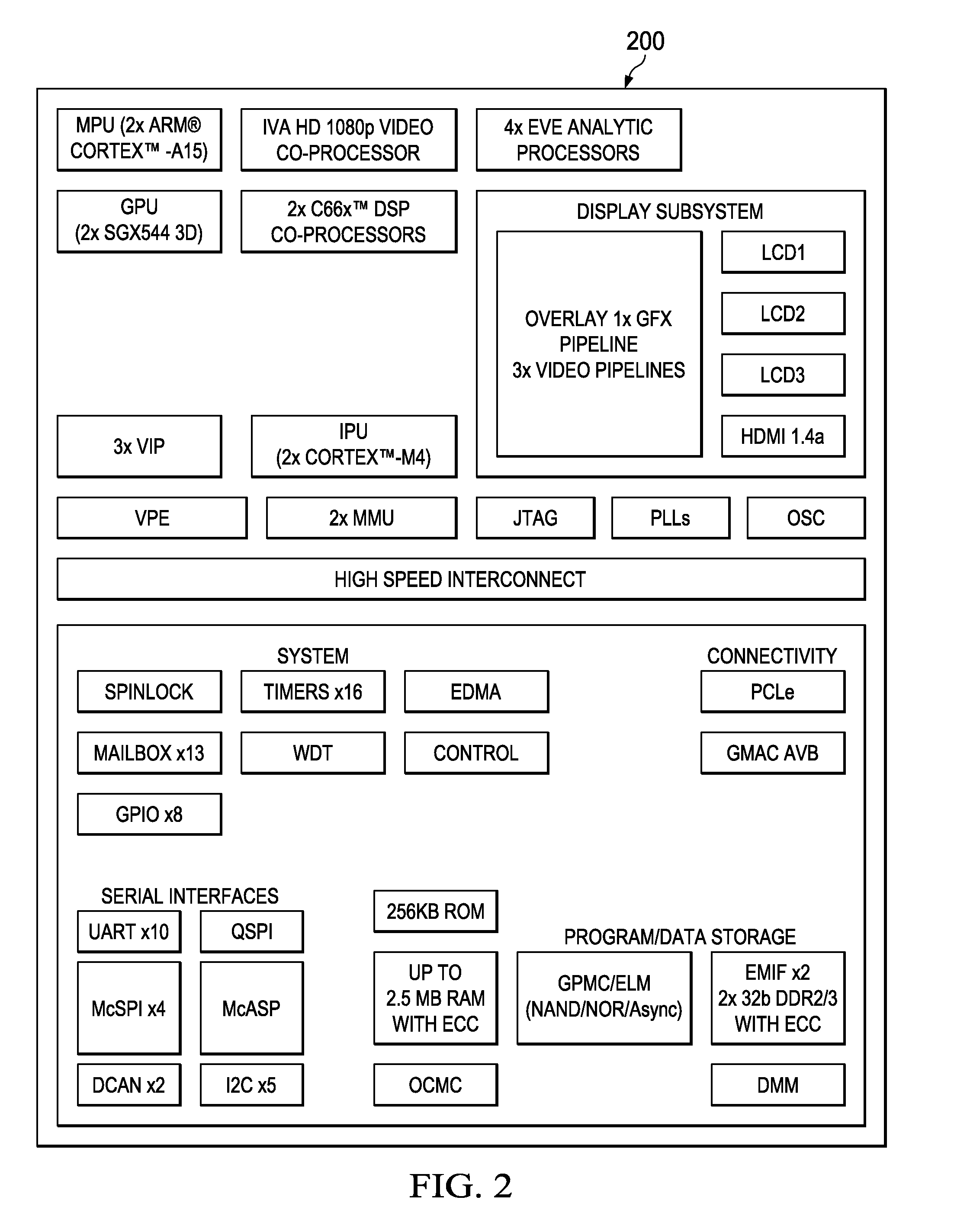

Programmable Interrupt Routing in Multiprocessor Devices

A multiprocessor device is provided that includes a plurality of processors in which each processor of the plurality of processors includes an interrupt controller, and a symmetric interrupt crossbar having a plurality of interrupt inputs in which each interrupt input that is not reserved is coupled to a respective interrupt output of an interrupt source of a plurality of interrupt sources, and a plurality of interrupt outputs in which each interrupt output is coupled to a respective interrupt input of an interrupt controller of one of the plurality of processors, in which the symmetric interrupt crossbar is programmable to map an interrupt signal from any interrupt source of the plurality of interrupt sources coupled to the symmetric interrupt crossbar to any interrupt input of any interrupt controller coupled to the symmetric interrupt crossbar.

Owner:TEXAS INSTR INC

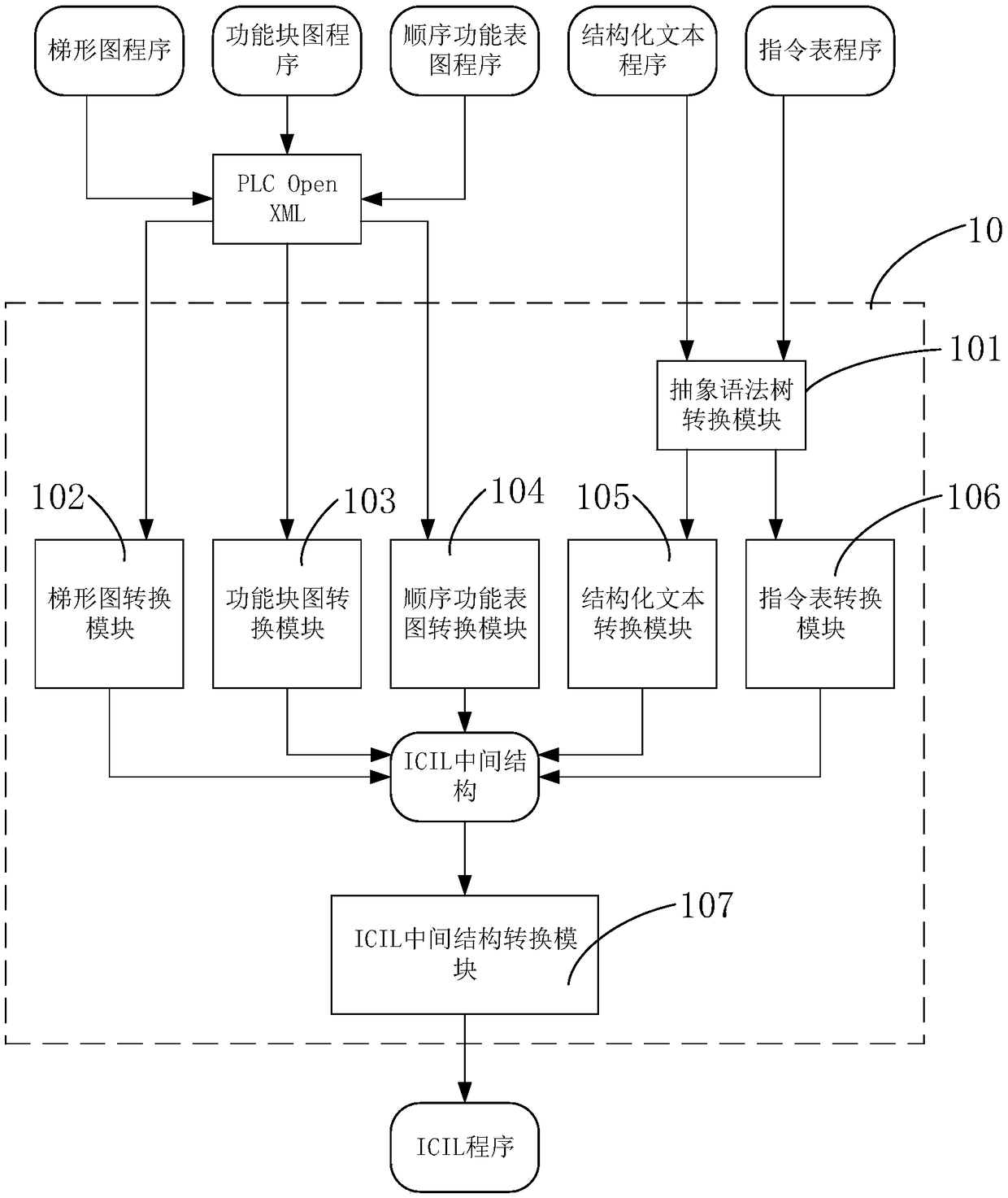

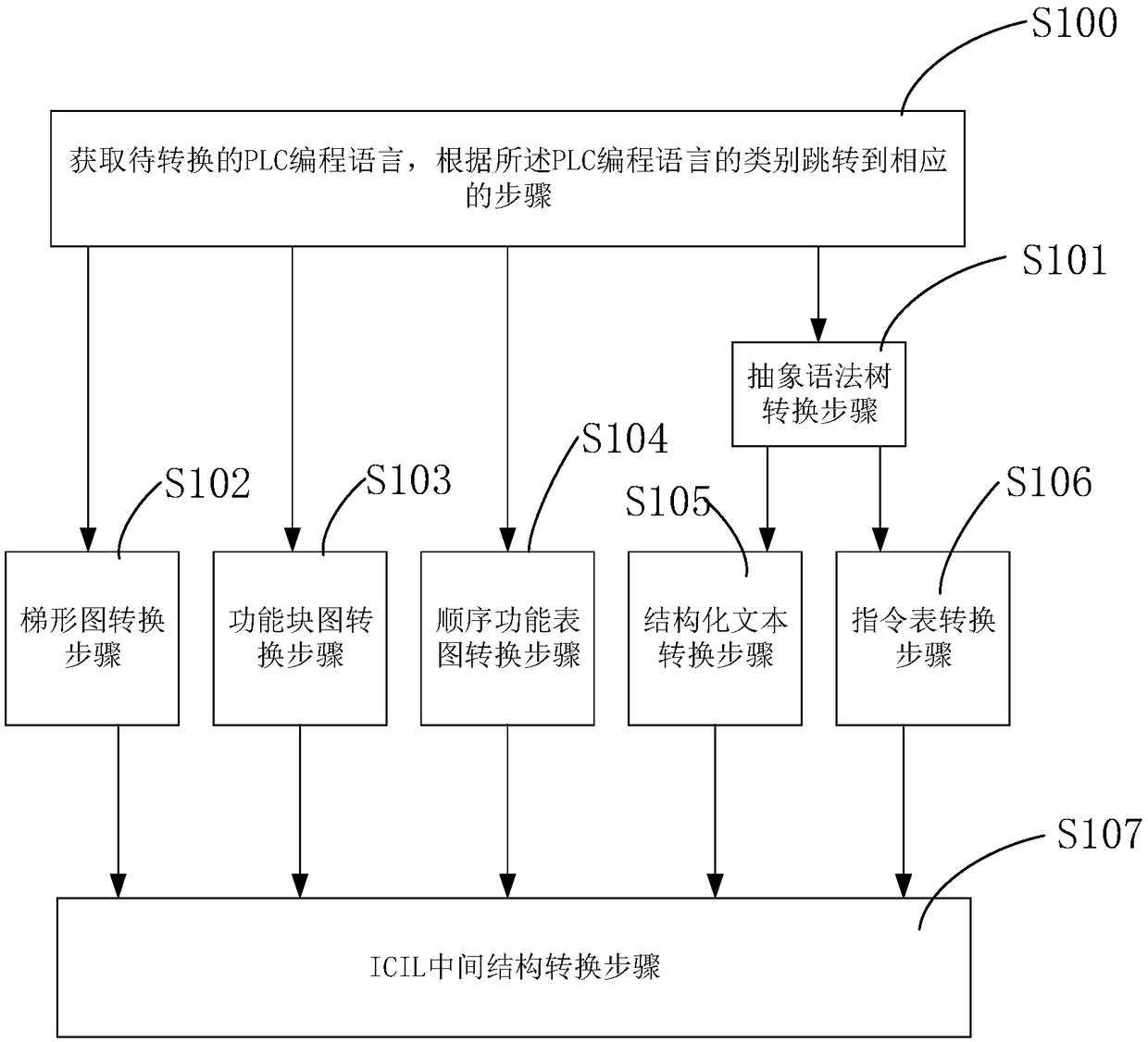

Programming language conversion system of programmable logic controller

ActiveCN109143952AAchieve unified conversionUnified conversion is beneficial toProgramme control in sequence/logic controllersProgrammable Interrupt ControllerIntermediate structure

The invention provides a programming language conversion system of a programmable logic controller. The programming language conversion system comprises an abstract syntax tree conversion module, a ladder diagram conversion module, a function block diagram conversion module, a sequence function table-diagram conversion module, a structured text conversion module, an instruction table conversion module, and an ICIL intermediate structure conversion module. With the programming language conversion system, unified conversion of the IEC 61131-3 language is realized; a phenomenon that a corresponding transplanting code is compiled for each kind of PLC language during the process of development and transplantation of PLC products of different manufacturers is avoided; and the intermediate-language-based formal modeling, analysis and verification work can be carried out deeply.

Owner:上海丰蕾信息科技有限公司

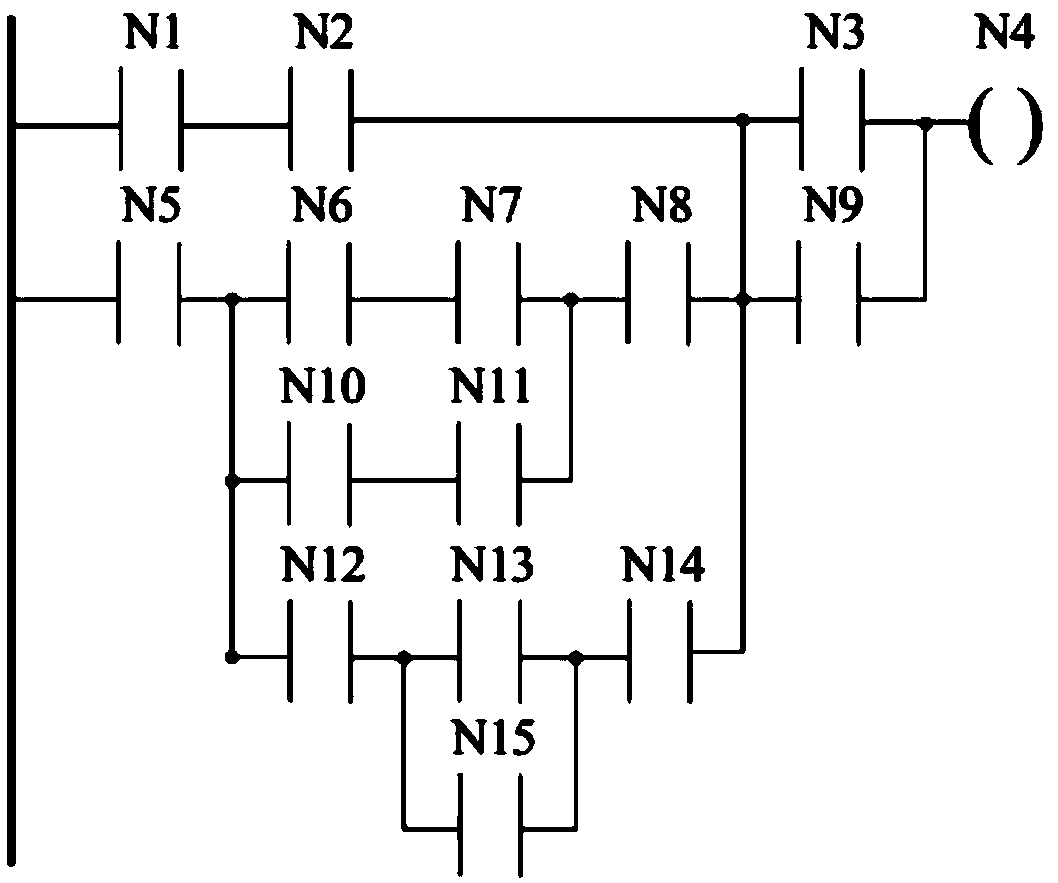

Method for detecting whether race condition exists in PLC (programmable logic controller) ladder diagram program or not

ActiveCN103019233AImprove efficiencyMeet the standard of automationElectric testing/monitoringProgramme control in sequence/logic controllersProgrammable logic controllerReachability

The invention provides a method for detecting whether a race condition exists in a PLC (programmable logic controller) ladder diagram program or not. Whether the race condition exists in a program to be detected or not is determined by computing a reachability graph of a common Petri network, so that detection can be completed at a time, and a programmer can directly discover connotative logical errors in the program from the reachability graph clearly and visually. Besides, each detection step can be completed by the computer, so that the method is more outstanding in efficiency, and automation standards are reached.

Owner:HUAQIAO UNIVERSITY

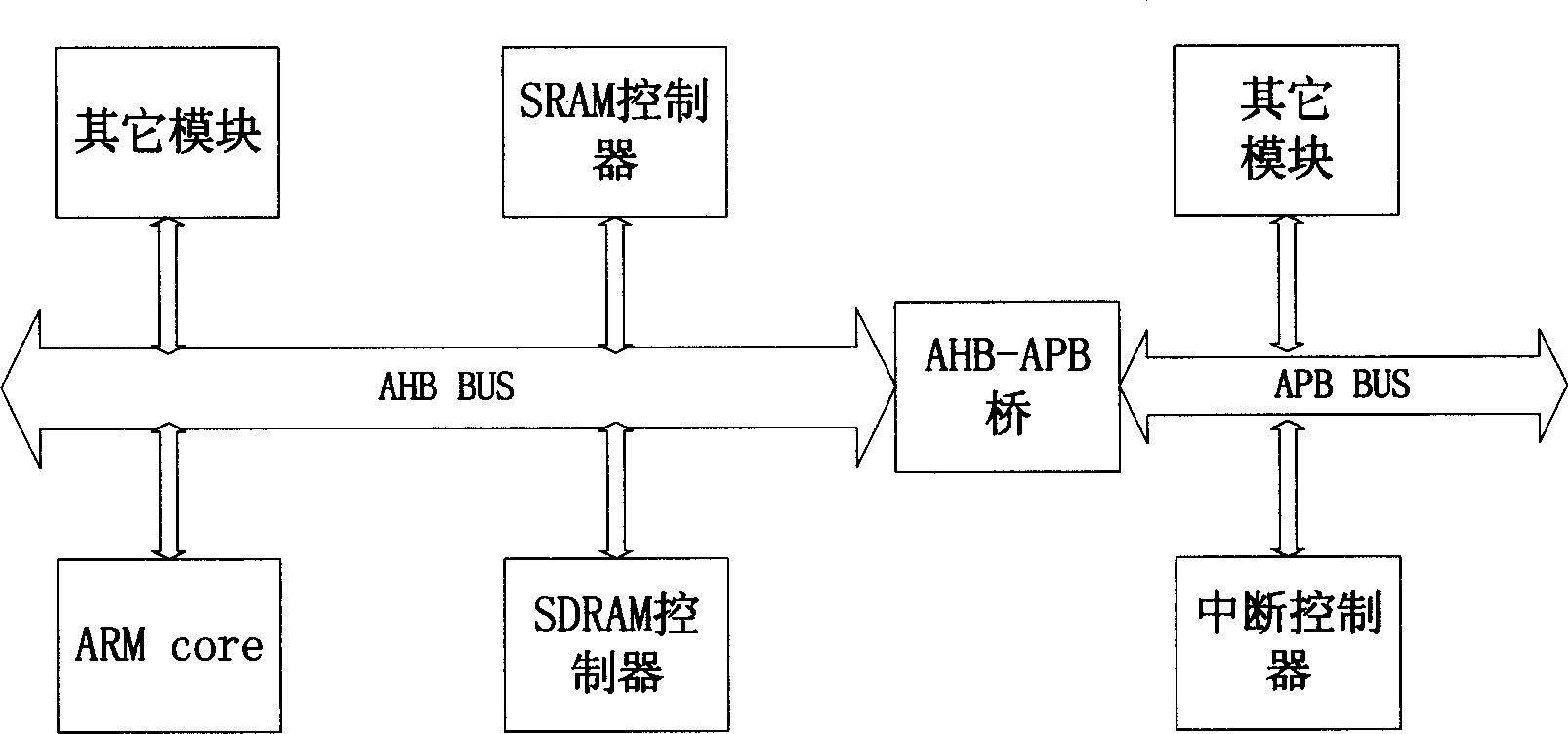

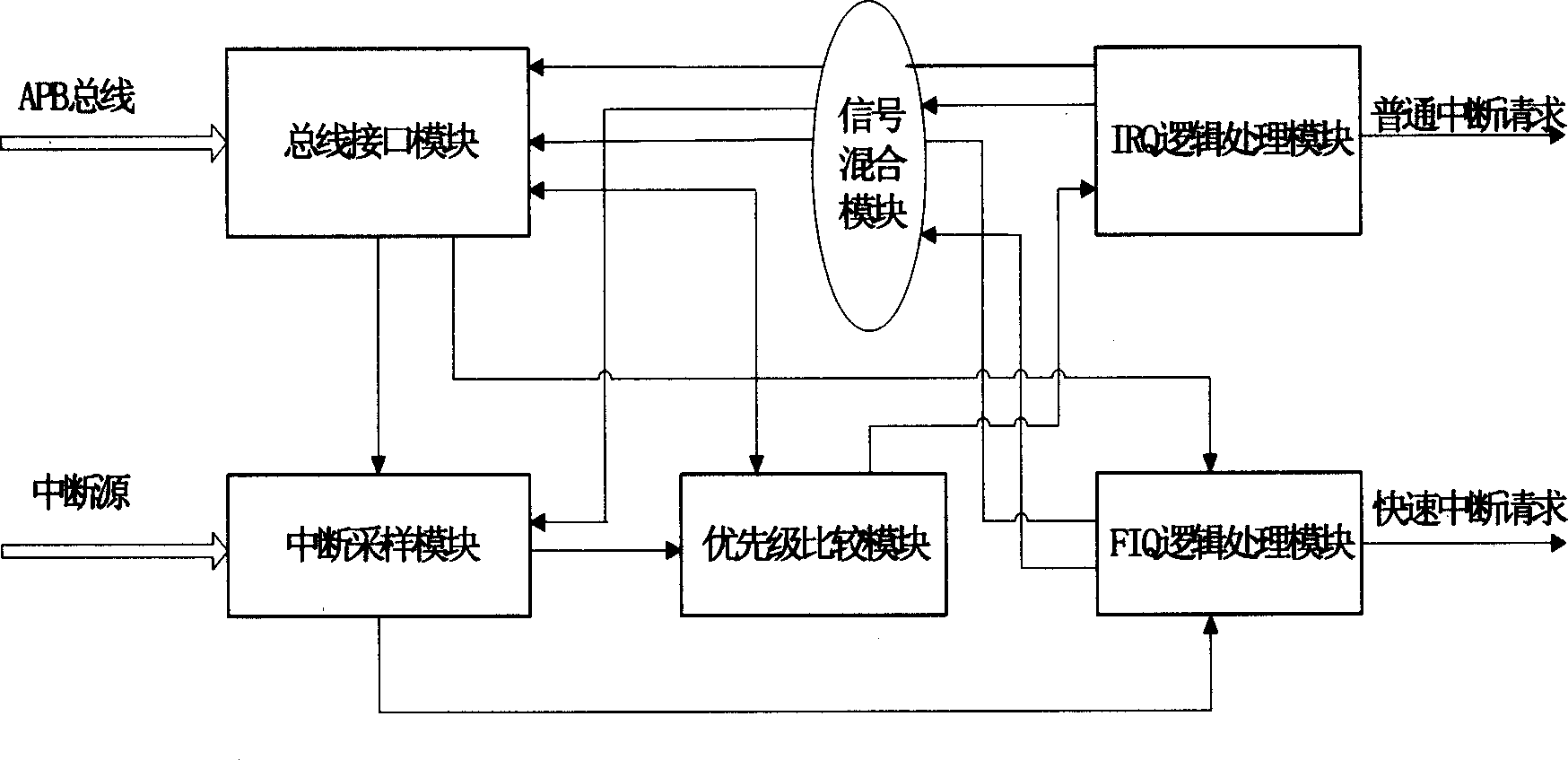

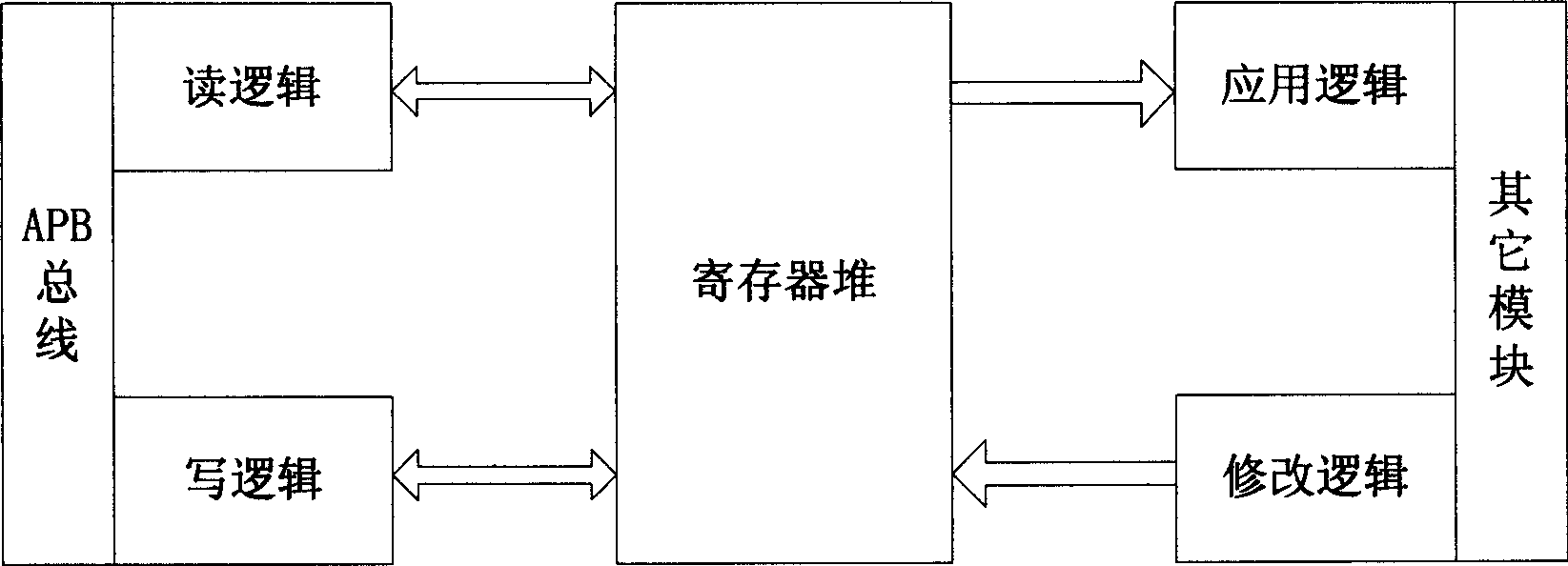

Programmable interrupt controller

InactiveCN1547082AFlexible configurationProgramme control in sequence/logic controllersProgrammable logic controllerProgrammable Interrupt Controller

The invention is a kind of programmable interrupt controller, which refers to a kind of interrupt controller which can select the interrupt with the highest priority from the primary device interrupt, the salve device interrupt, the soft interrupt and the outer interrupt, and sends out interrupt application to the processor core (ARM core). The device includes a bus interface model, an interrupt sampling model, an iRQ (normal interrupt quest) logic processing model, a FIQ (fast interrupt quest) logic processing model, priority comparing model and signal blending model. The controller can solve the problem that the function is single, the configuration is inflexible, and the repeatability is bad in the current technology.

Owner:SANECHIPS TECH CO LTD

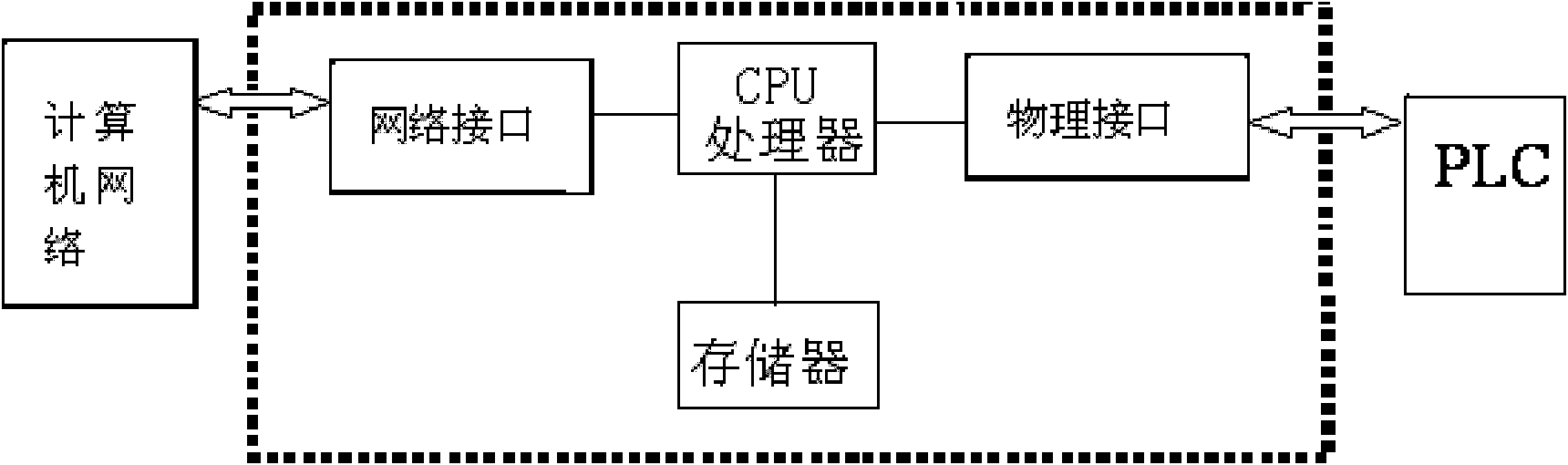

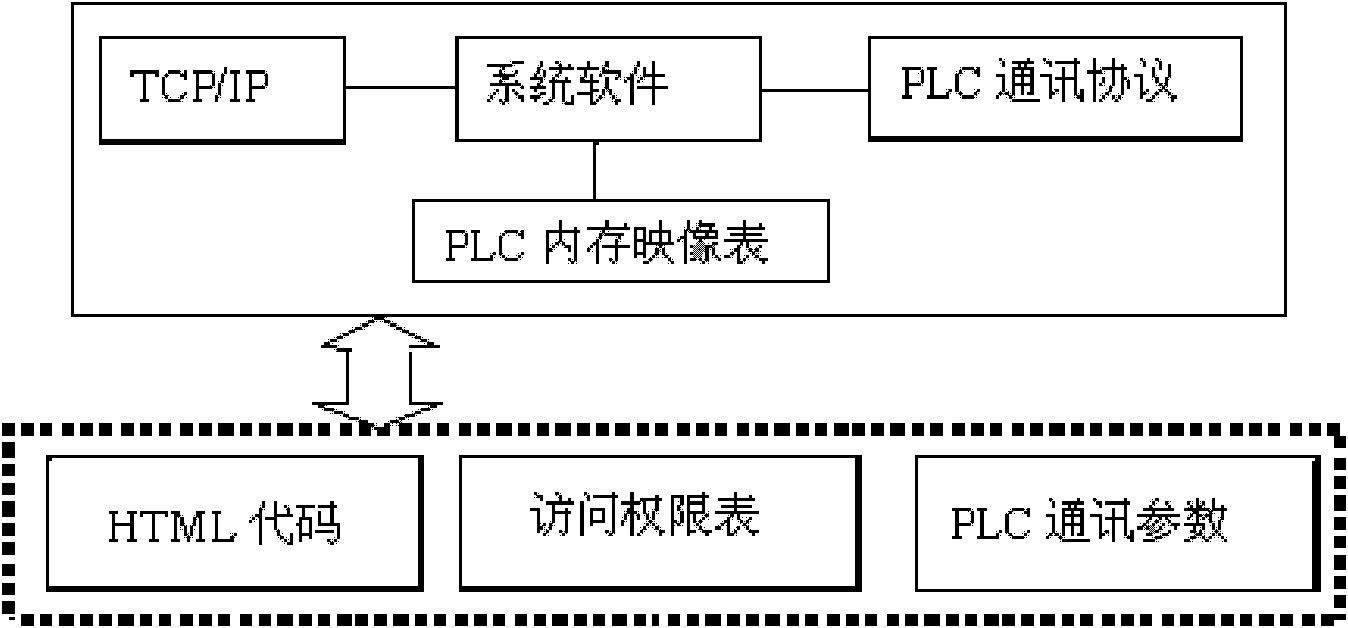

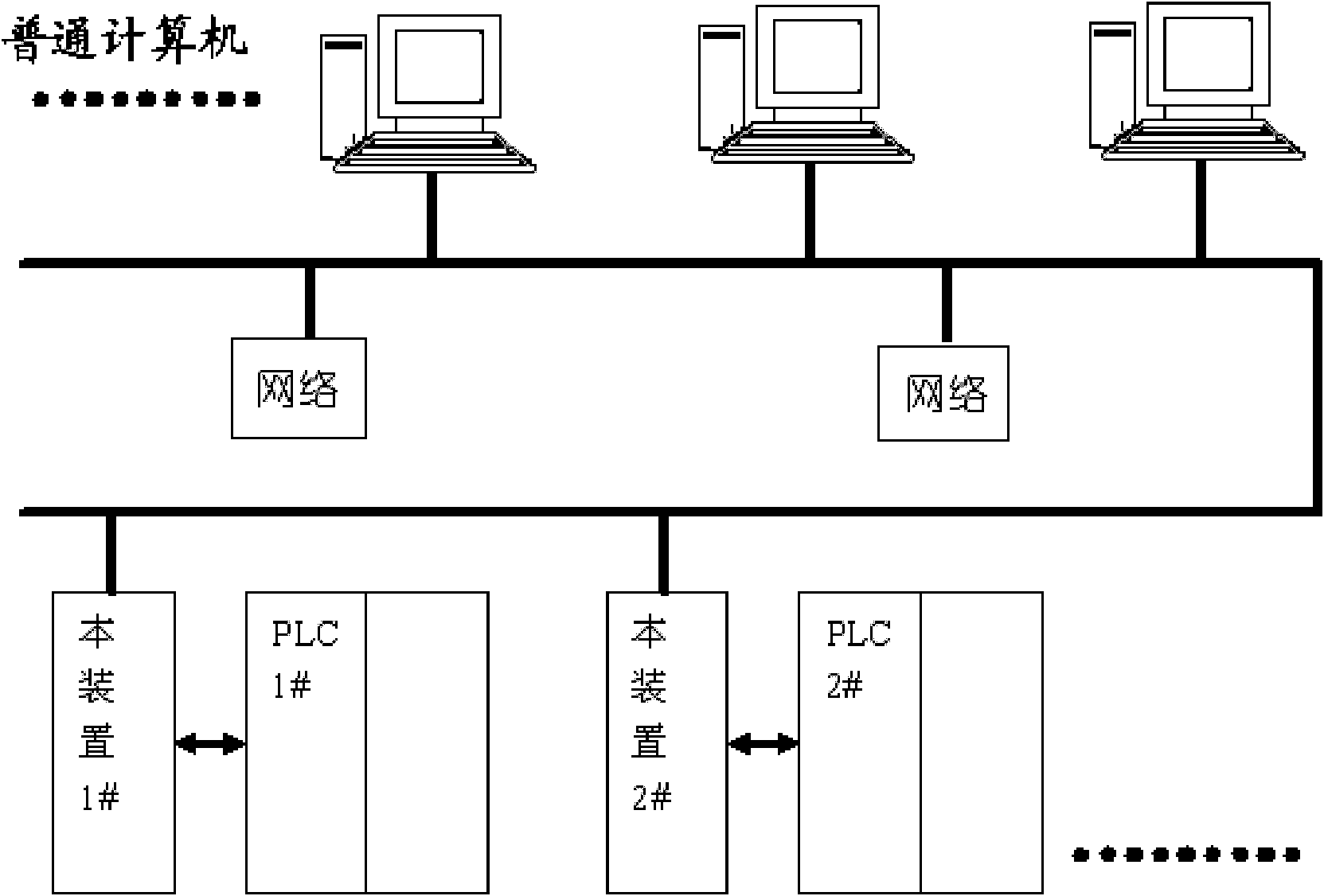

Information publish device of production line equipment controlled by programmable logic controller (PLC) based on hypertext markup language (HTML)

ActiveCN102081393ARealize remote monitoringAchieve interventionTotal factory controlProgramme total factory controlProgrammable Interrupt ControllerComputer access

The invention provides an information publish device of production line equipment controlled by a programmable logic controller (PLC) based on a hypertext markup language (HTML). The device provided by the invention is characterized in that a central processing unit (CPU) is adopted as control part; the CPU is connected with a memorizer; the CPU is connected with a computer network interface; the CPU is connected with the physical interface of the PLC for the production line equipment; the memorizer comprises a network interface zone and a user zone; the network interface zone comprises a communication protocol and a memory mapping list, a transmission control protocol / internet protocol (TCP / IP) module and system software, wherein the communication protocol and the memory mapping list access to the PLC of the production line equipment; and the user zone comprises an HTML code module, an access authority list and a PLC communication parameter module. An HTML webpage is adopted to store a man-machine interaction interface containing PLC data, so that a computer in networks can perform access so as to realize human-machine interaction by means of webpage operations. Based on the communication protocol of the PLC and the memory data structure of the PLC, the system software calls subfunctions in accordance with the memory mapping list so as to obtain or modify the memory data of the PLC, and results are stored in the mapping list. The corresponding data in the memory mapping list is embedded into a webpage which is complied by means of HTML codes so as to form an integrated human-machine interaction interface.

Owner:DONGFENG AUTOMOBILE COMPANY

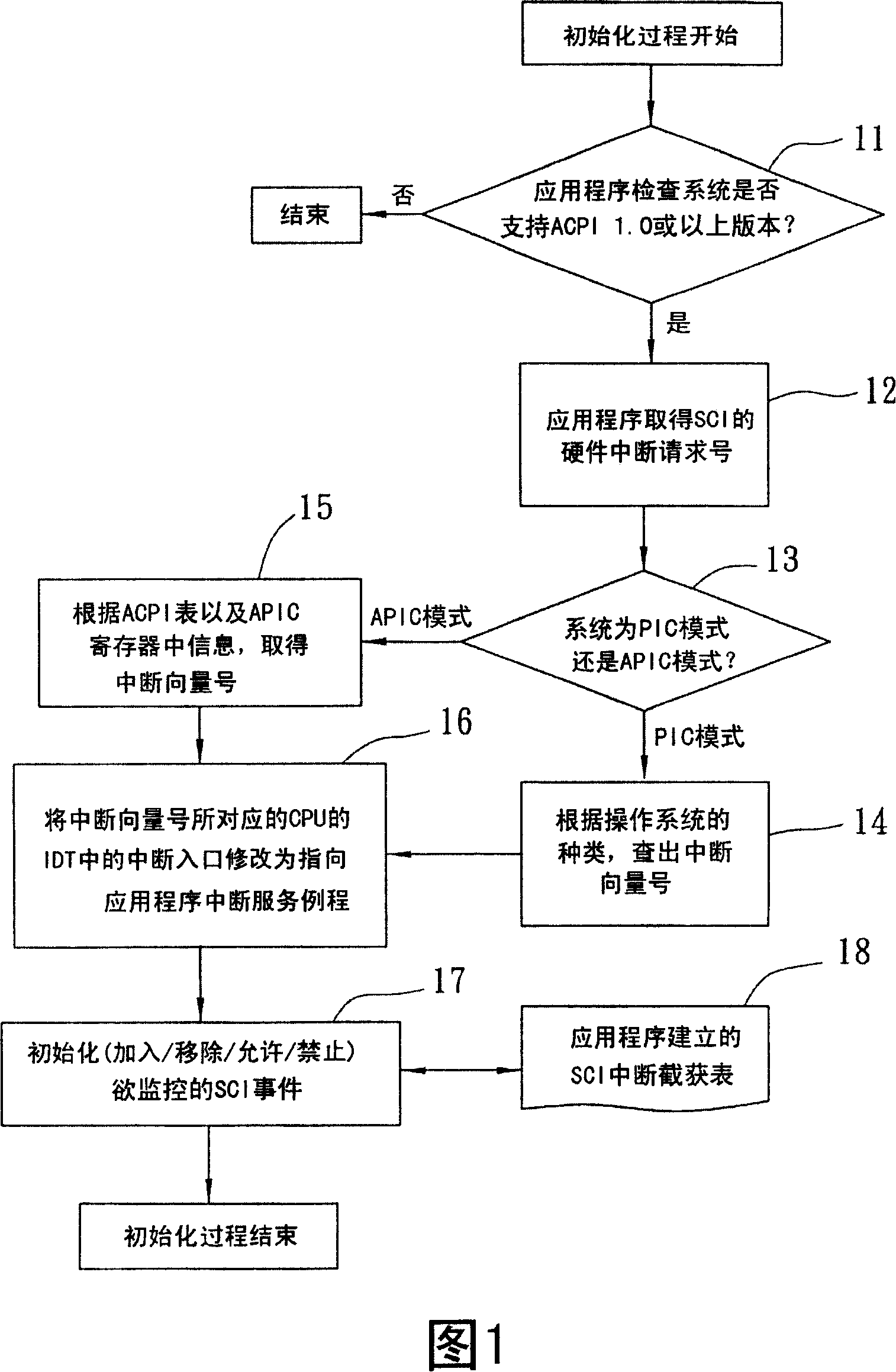

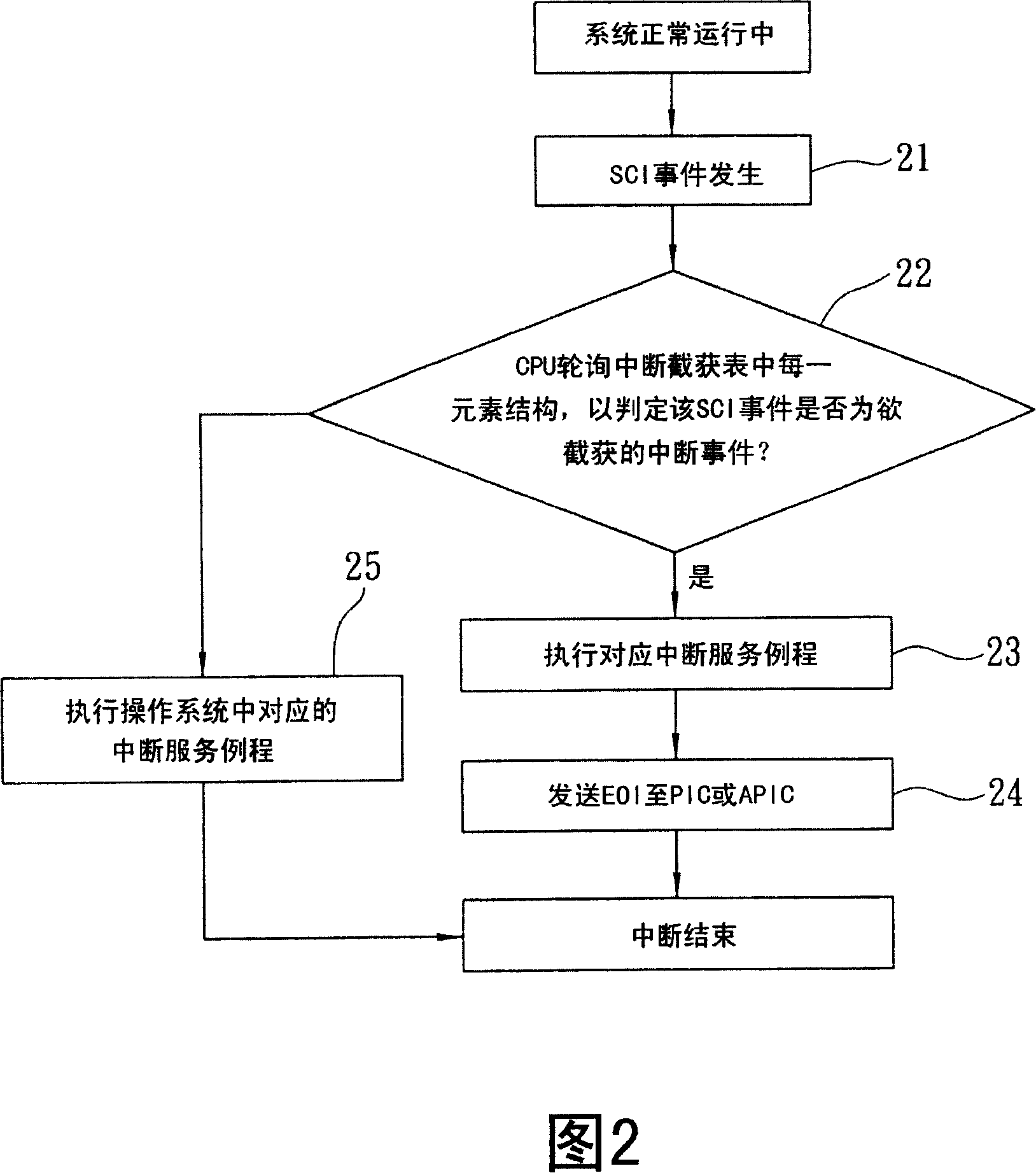

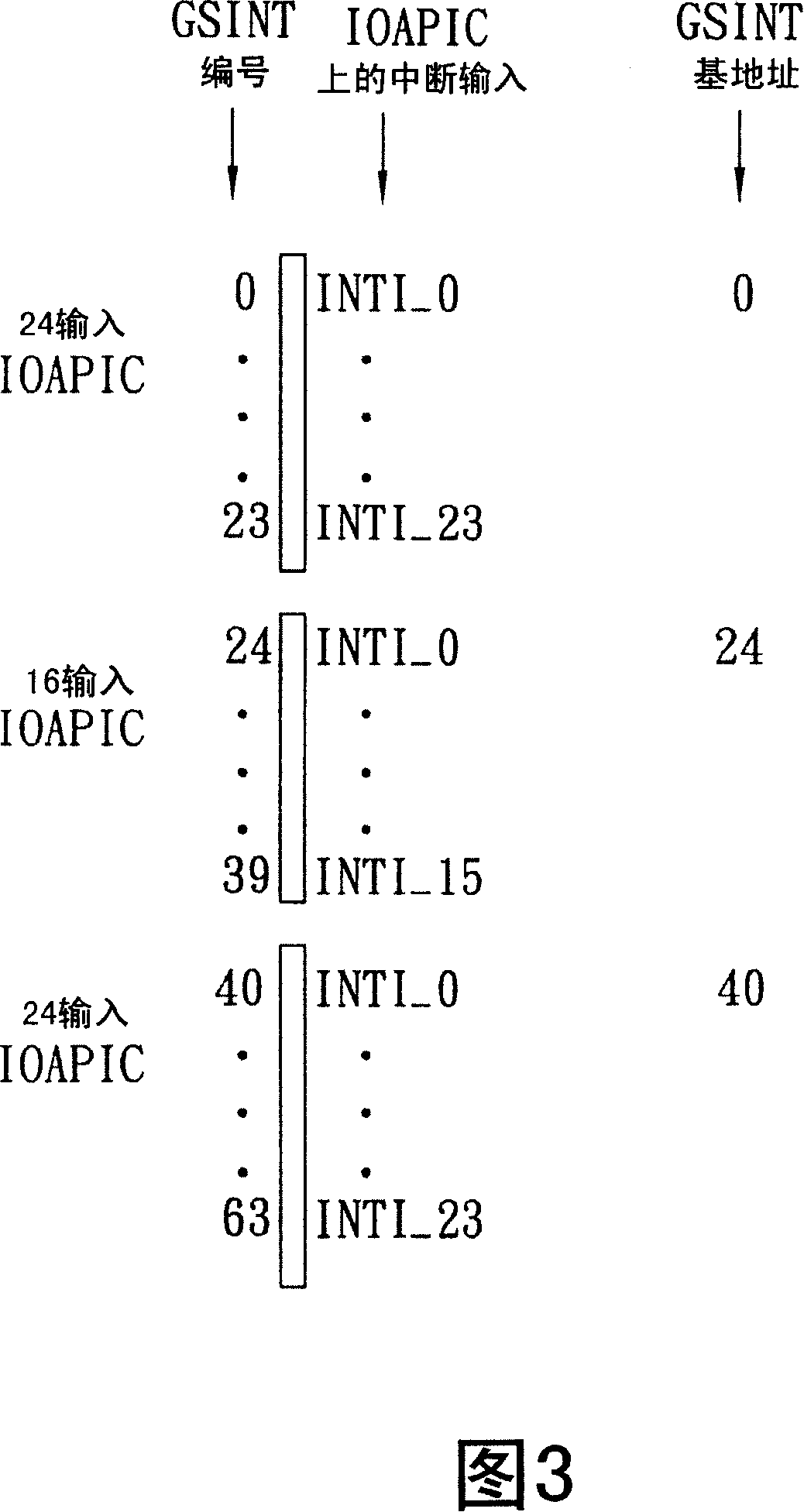

Application program intercept and capture and monitoring system control break method

A control interruption method for application program interception and monitoring systems, comprises: A hardware interruption request number of a system control interruption that is taken by an application program from a Basic Input and Output System (BIOS); an interruption vector number that corresponds with the hardware interruption request number, and acquired by the application program in a corresponding way according to that the interruption mode is a programmable interruption controller mode, or an advanced programmable interruption controller mode; a plurality of interruption service program examples that modify interruption entrance in an interruption description symbol list in a Central Process Unit (CPU) corresponds with interruption vector number, into pointing to application programs; as well as a plurality of interruption events corresponding with initialization information that is pre-established according to an interruption and interception list in the application program, and initialization hardware interruption request number.

Owner:UNIVERSAL SCI IND CO LTD

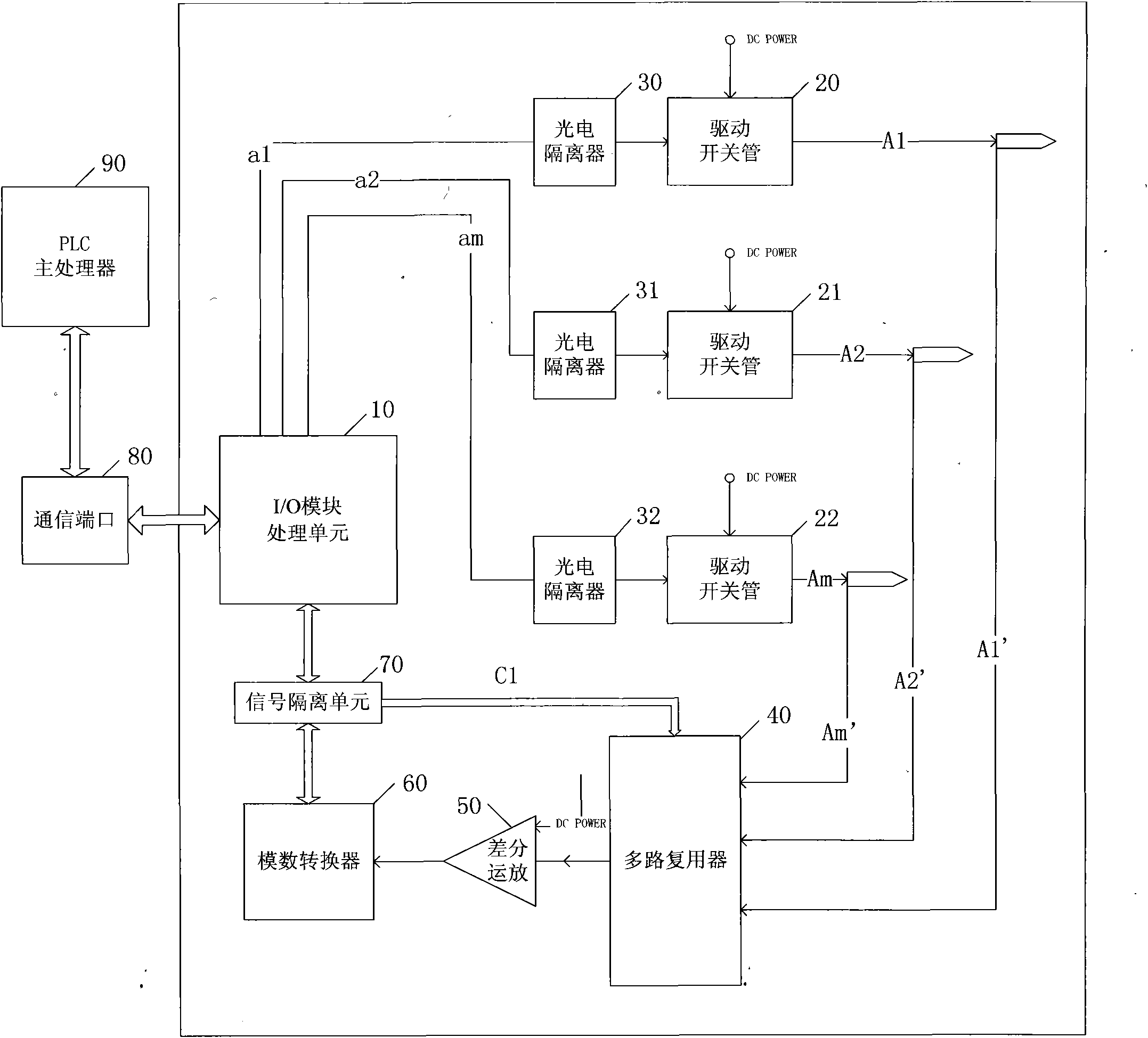

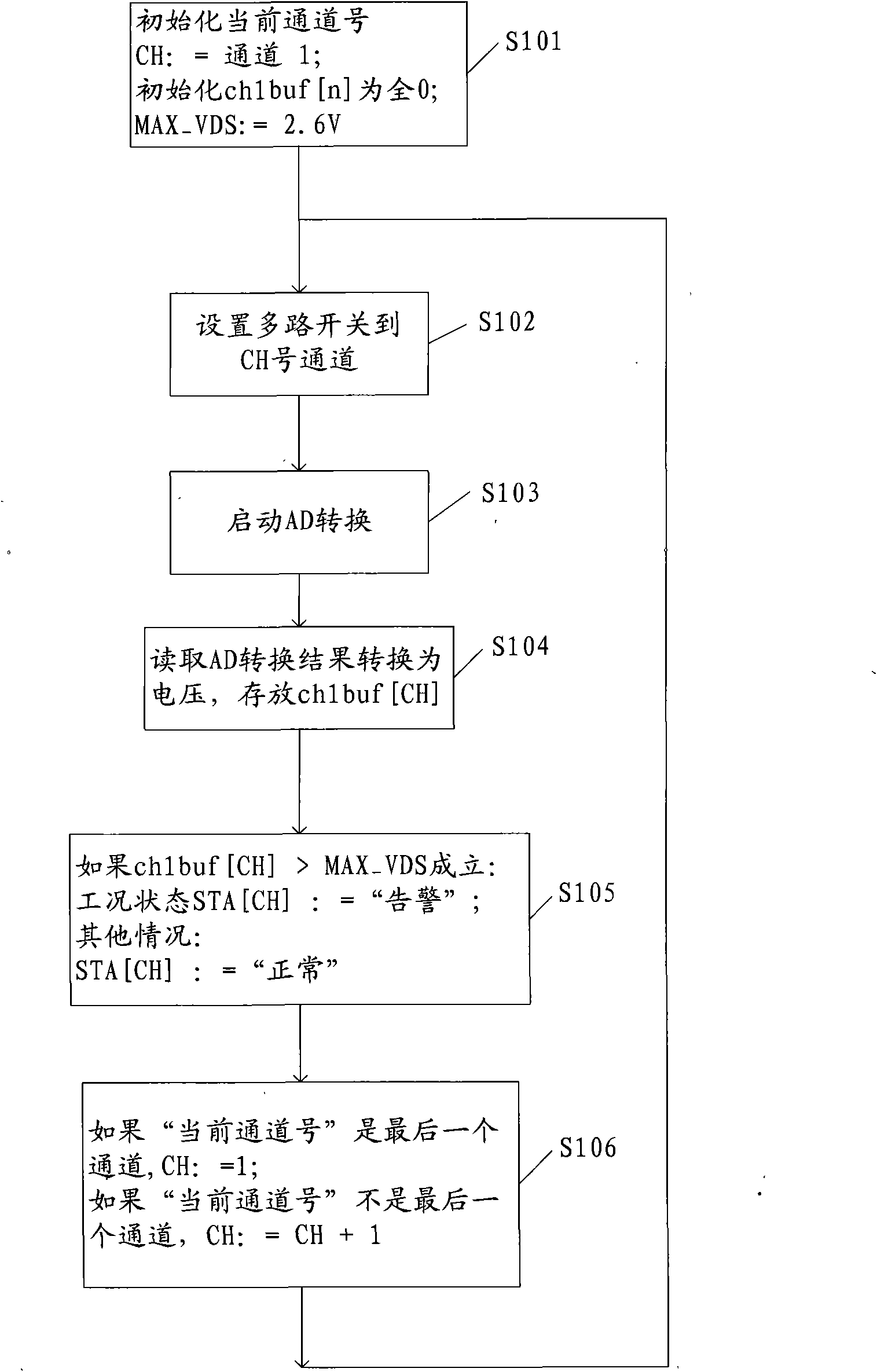

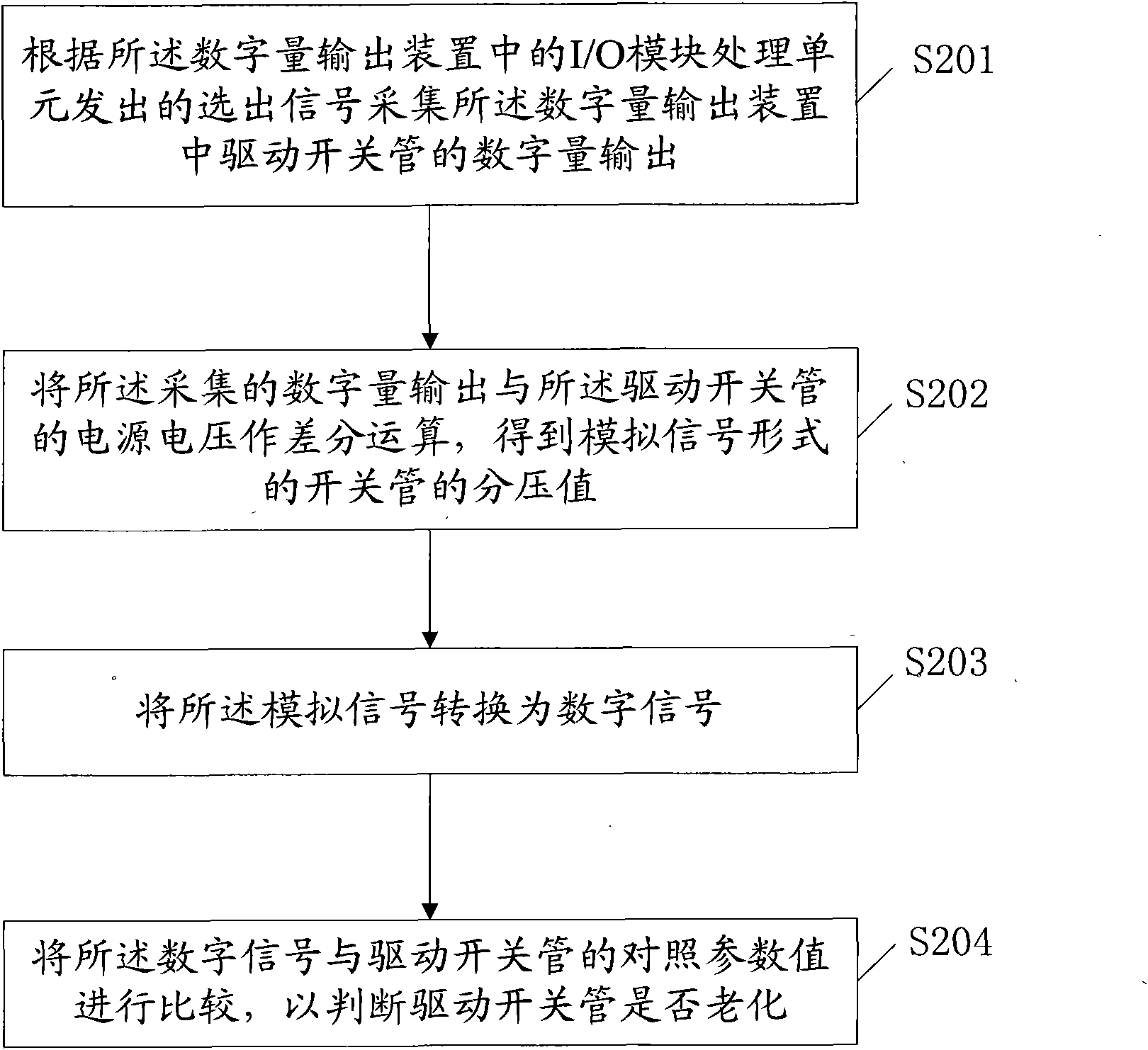

Digital quantity output device of programmable logic controller and self-checking method

ActiveCN102315844AKnowing the Recession in AdvanceDetecting faulty computer hardwareElectronic switchingElectricityProgrammable logic controller

The invention provides a self-checking method for a digital quantity output device of a programmable logic controller, and the method comprises the following steps: collecting the digital quantity output when a driving switching tube is in a turn-on state / off state in the digital quantity output device according to a selected signal transmitted by an I / O (input / output) module processing unit in the digital quantity output device; carrying out a differential operation to the collected digital quantity output and the supply voltage of the driving switching tube to obtain a simulation signal forrepresenting the turn-on voltage drop / electricity leakage judgment parameter of the driving switching tube; converting the simulation signal into a digital signal; and comparing the digital signal with the turn-on voltage drop parameter value of the driving switching tube / the voltage value which is the same to the power supply of the driving switching tube, thereby judging whether the driving switching tube is aged or not. Correspondingly, the embodiment of the invention also provides a digital quantity output device of a programmable logic controller. According to the digital quantity outputdevice provided by the invention, the recession conditions of the driving switching tube can be known in advance, and users can perform equipment maintenance before cataleptic failures.

Owner:深圳市合信自动化技术有限公司