Patents

Literature

137 results about "Race condition" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A race condition or race hazard is the condition of an electronics, software, or other system where the system's substantive behavior is dependent on the sequence or timing of other uncontrollable events. It becomes a bug when one or more of the possible behaviors is undesirable.

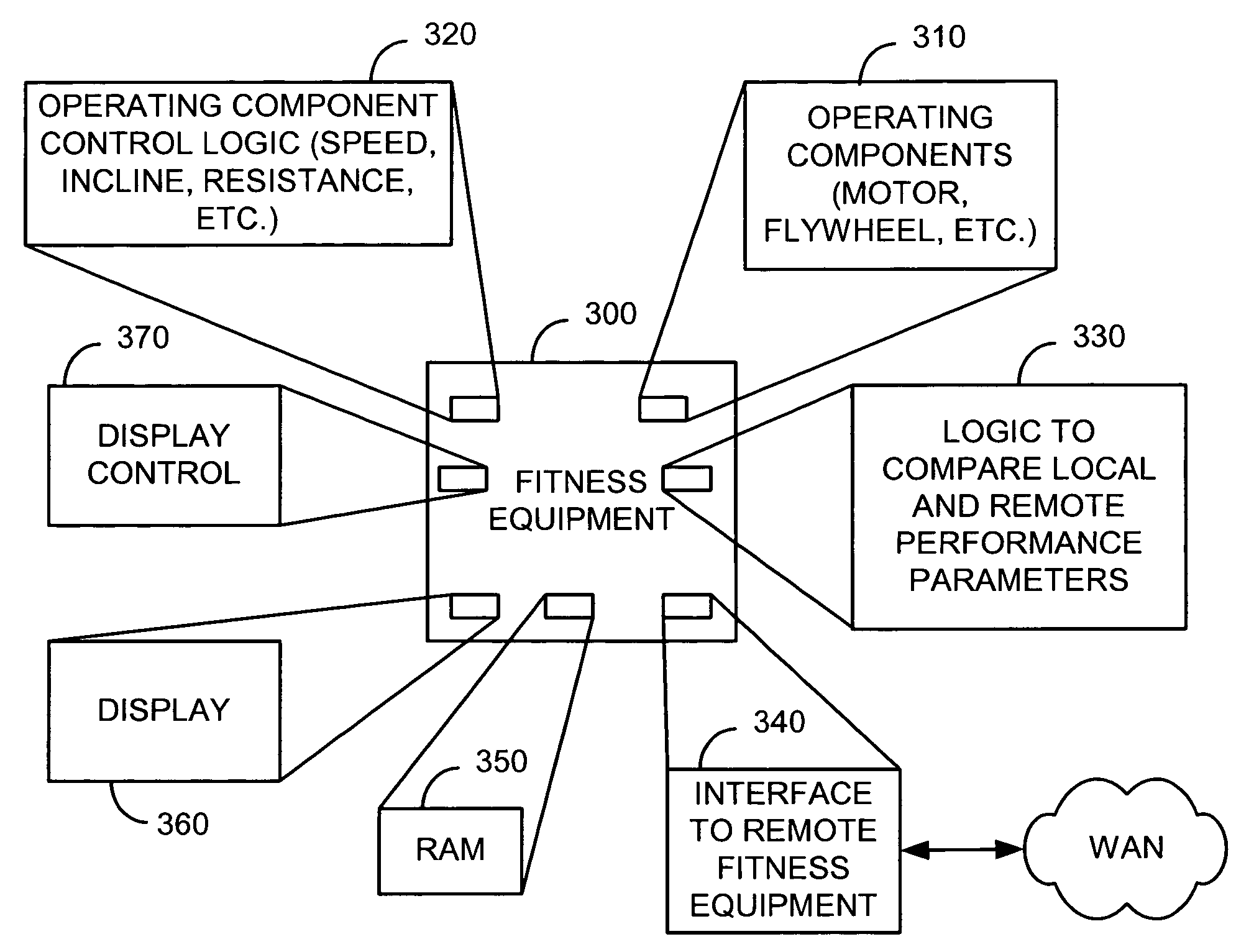

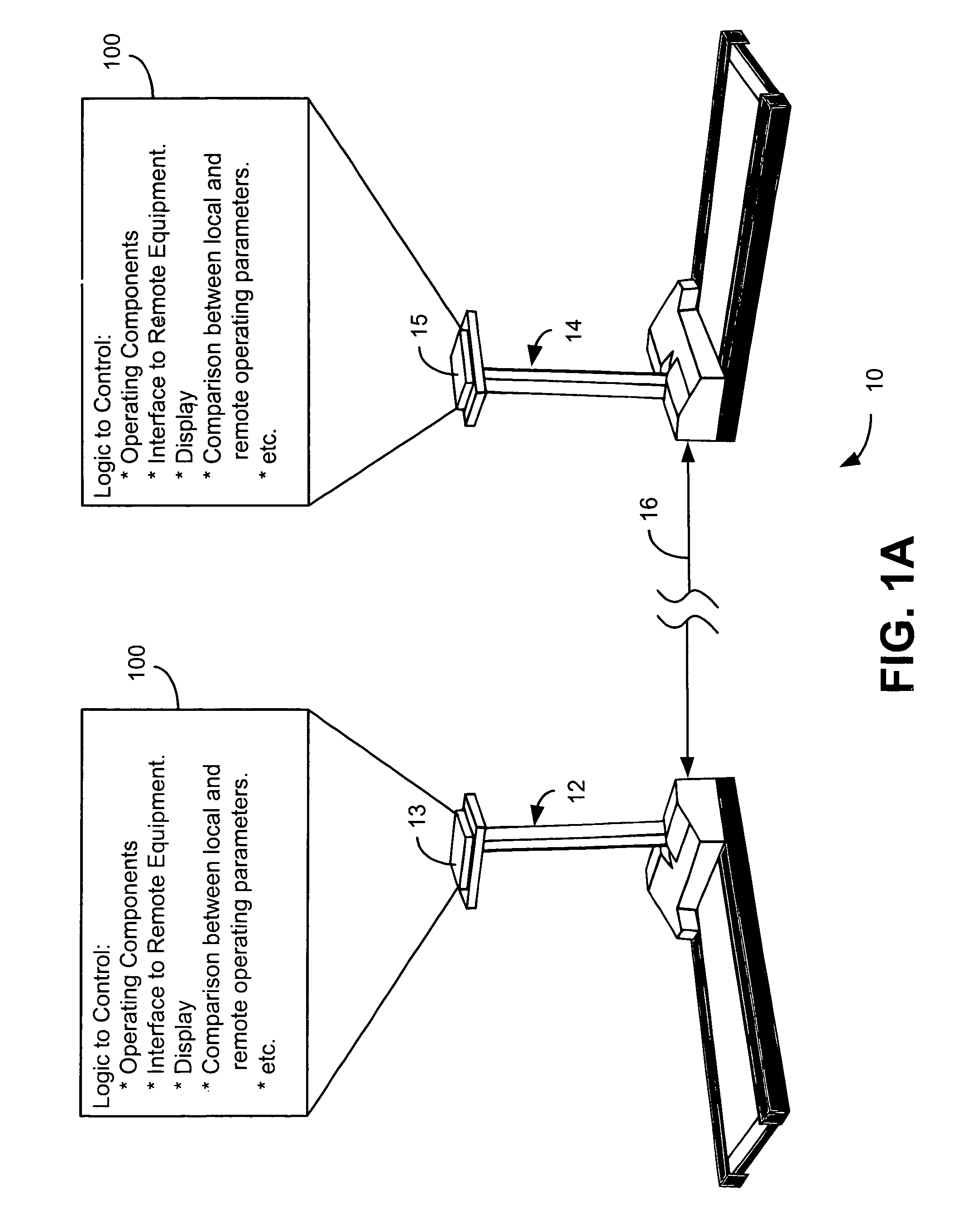

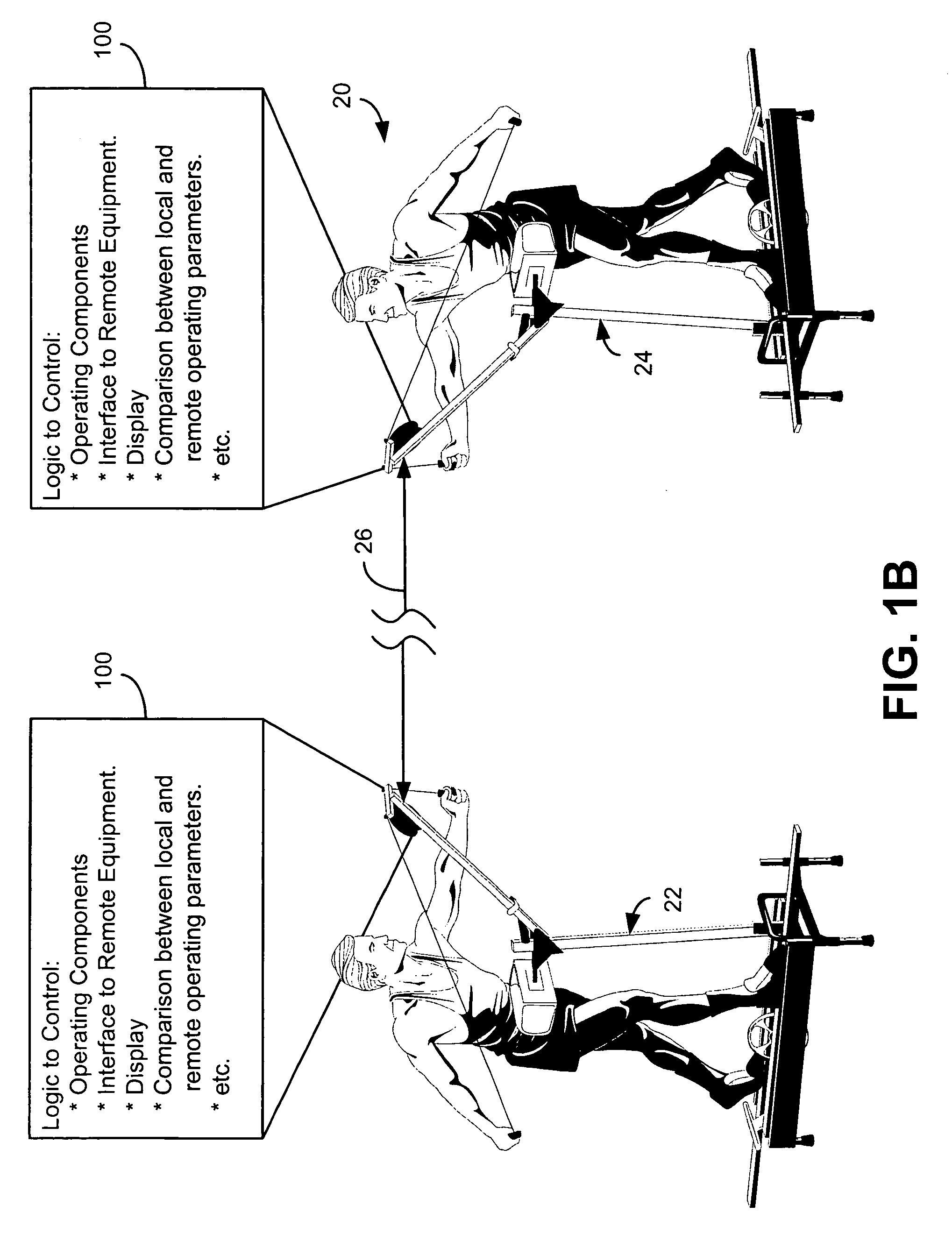

Interactive fitness equipment

InactiveUS6902513B1Therapy exerciseInput/output processes for data processingCommunication interfaceSimulation

The present invention is generally directed to a computerized fitness equipment that is designed to simulate, emulate, or implement actual race conditions with other users. An exemplar fitness equipment includes at least one operating component and sensors to monitor performance parameters of the at least one operating component (such as speed of movement). A display is also provided, along with logic to provide a visual display of a user's performance (as measured through the first performance parameters). In one embodiment, a communication interface is provided to communicate the first performance parameters to at least one remote, similarly-configured, fitness equipment. Performance parameters from the remote fitness equipment are also received through the communication interface. The fitness equipment includes logic to compare the first performance parameters with performance parameters received from remote fitness equipment and display the results in a comparative fashion to the user.

Owner:VR OPTICS LLC

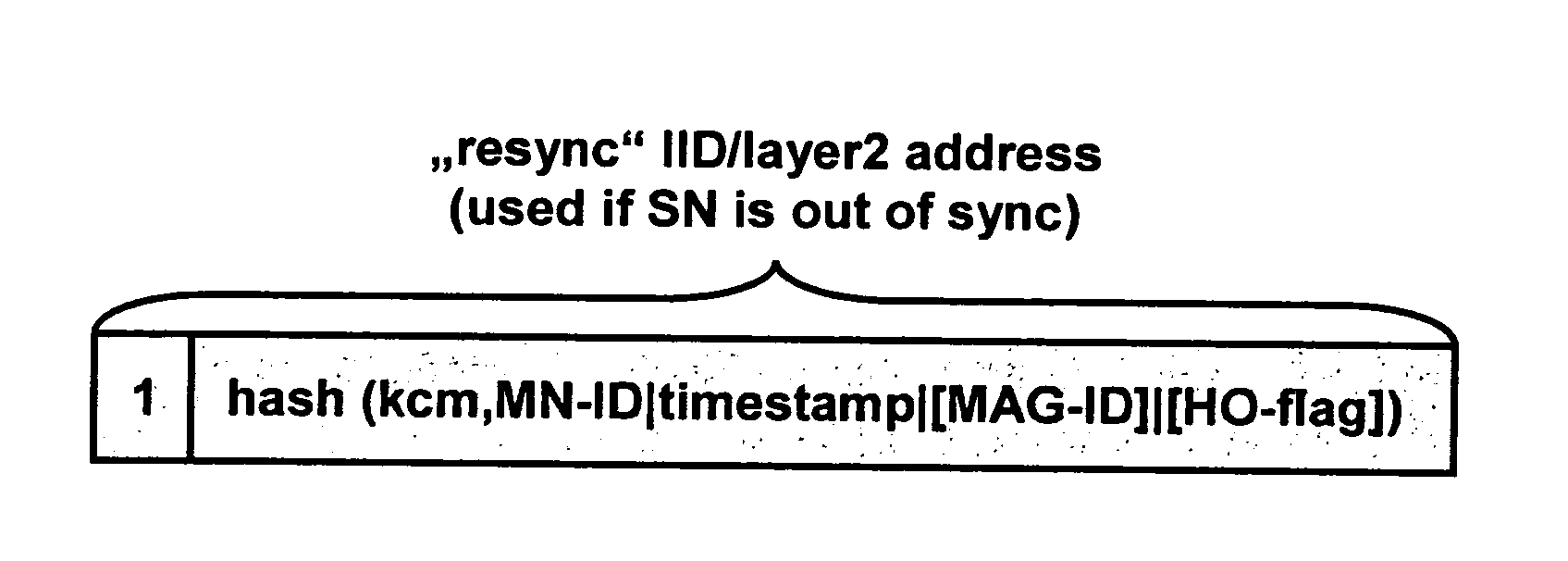

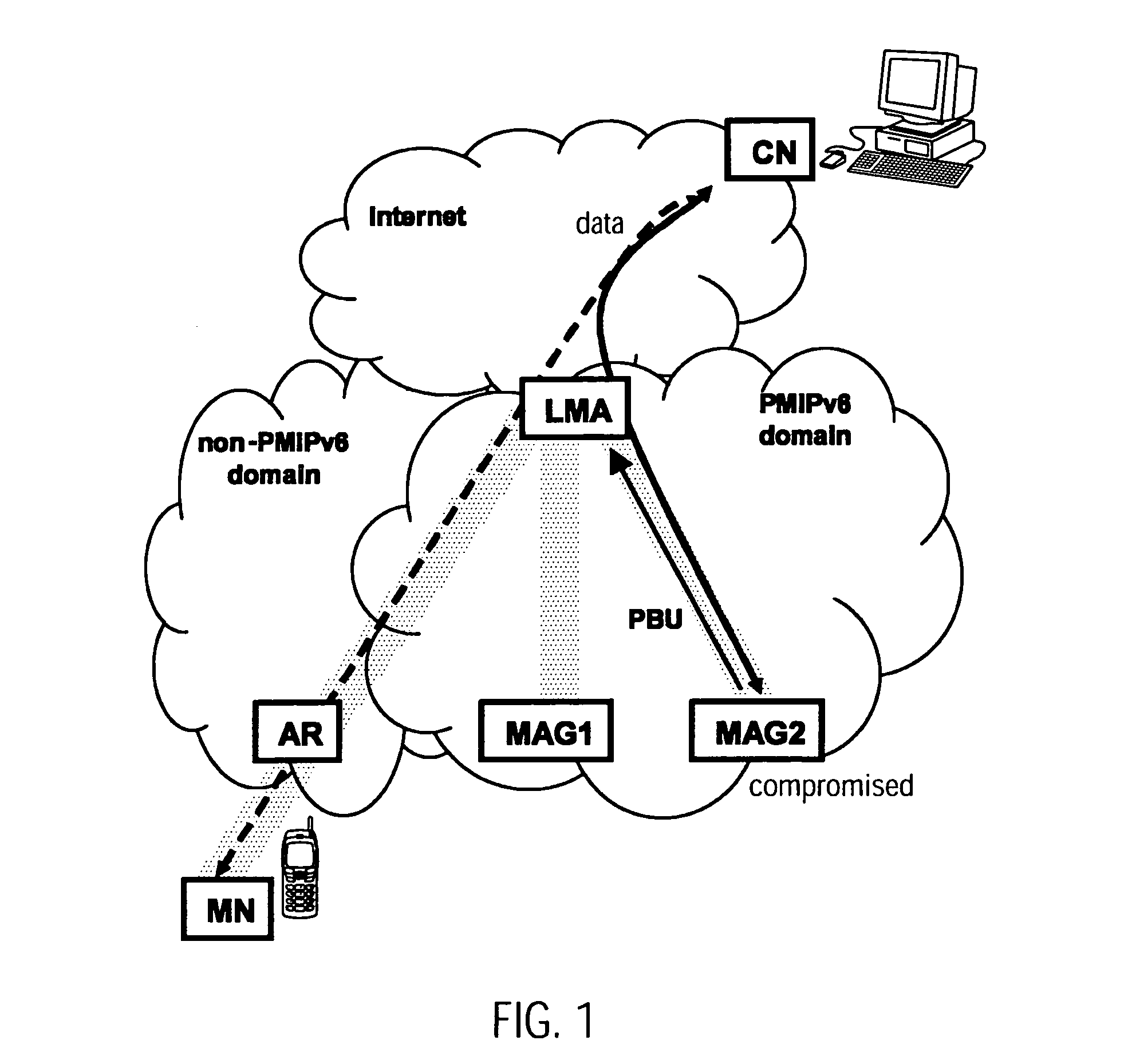

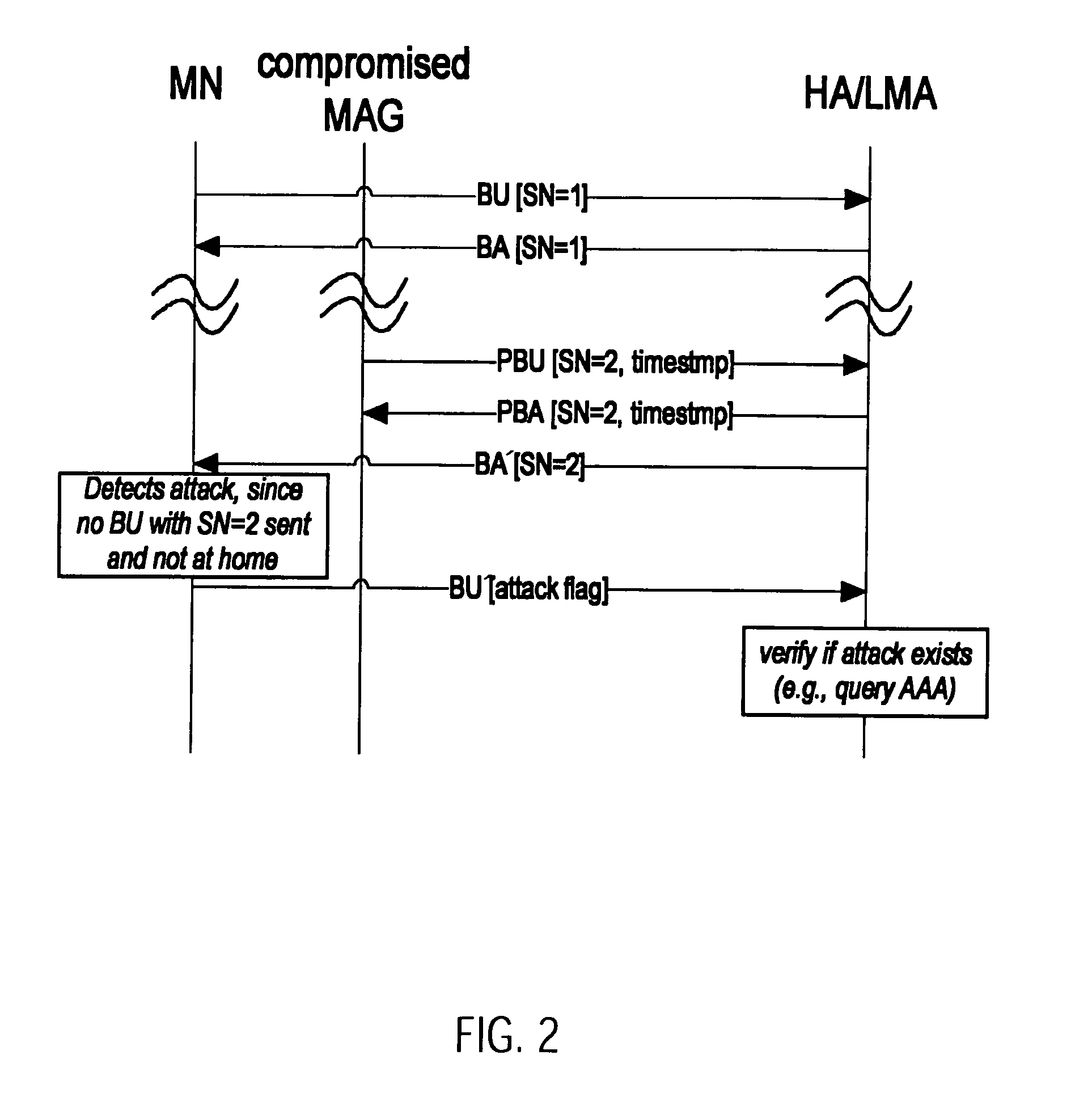

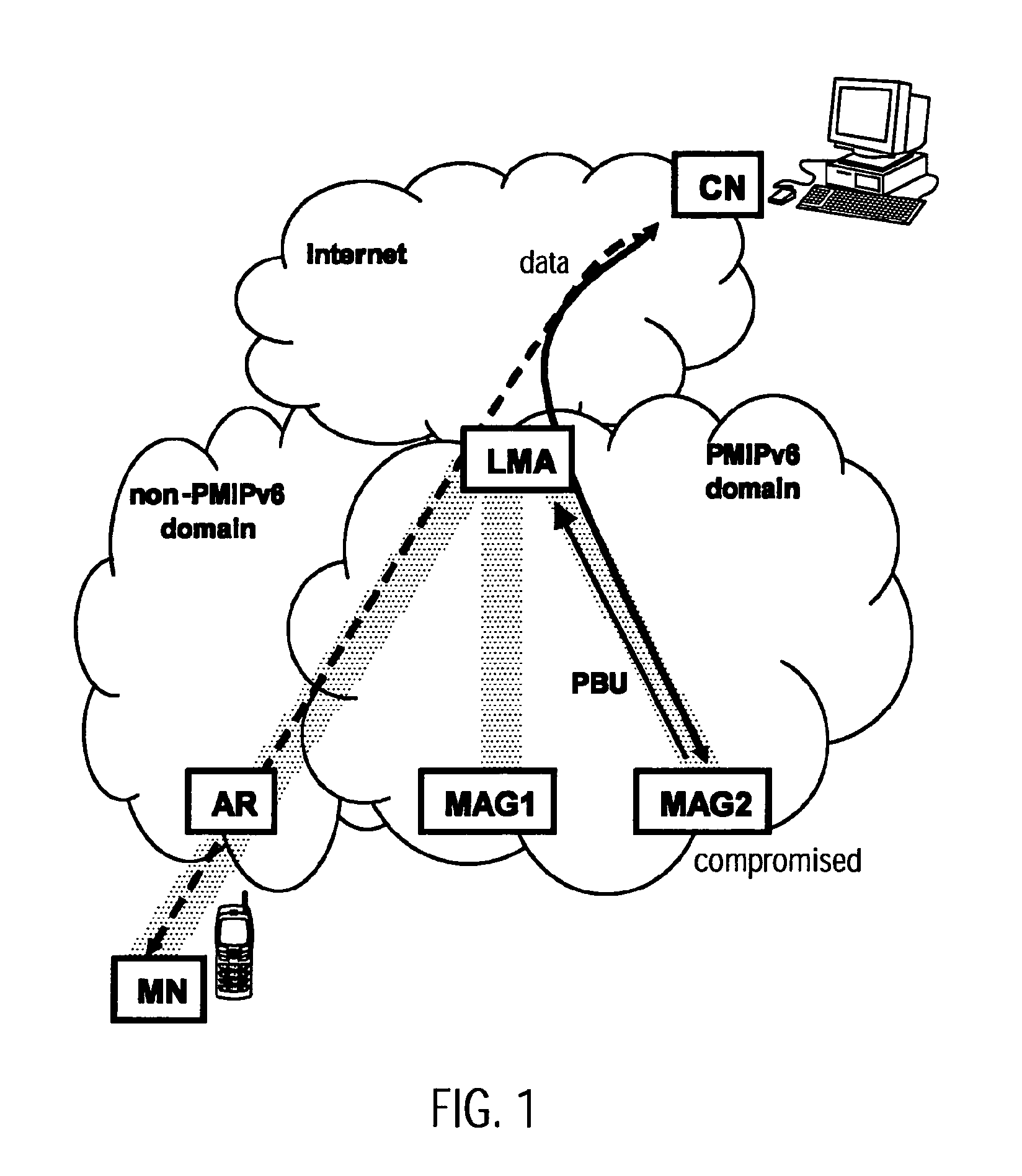

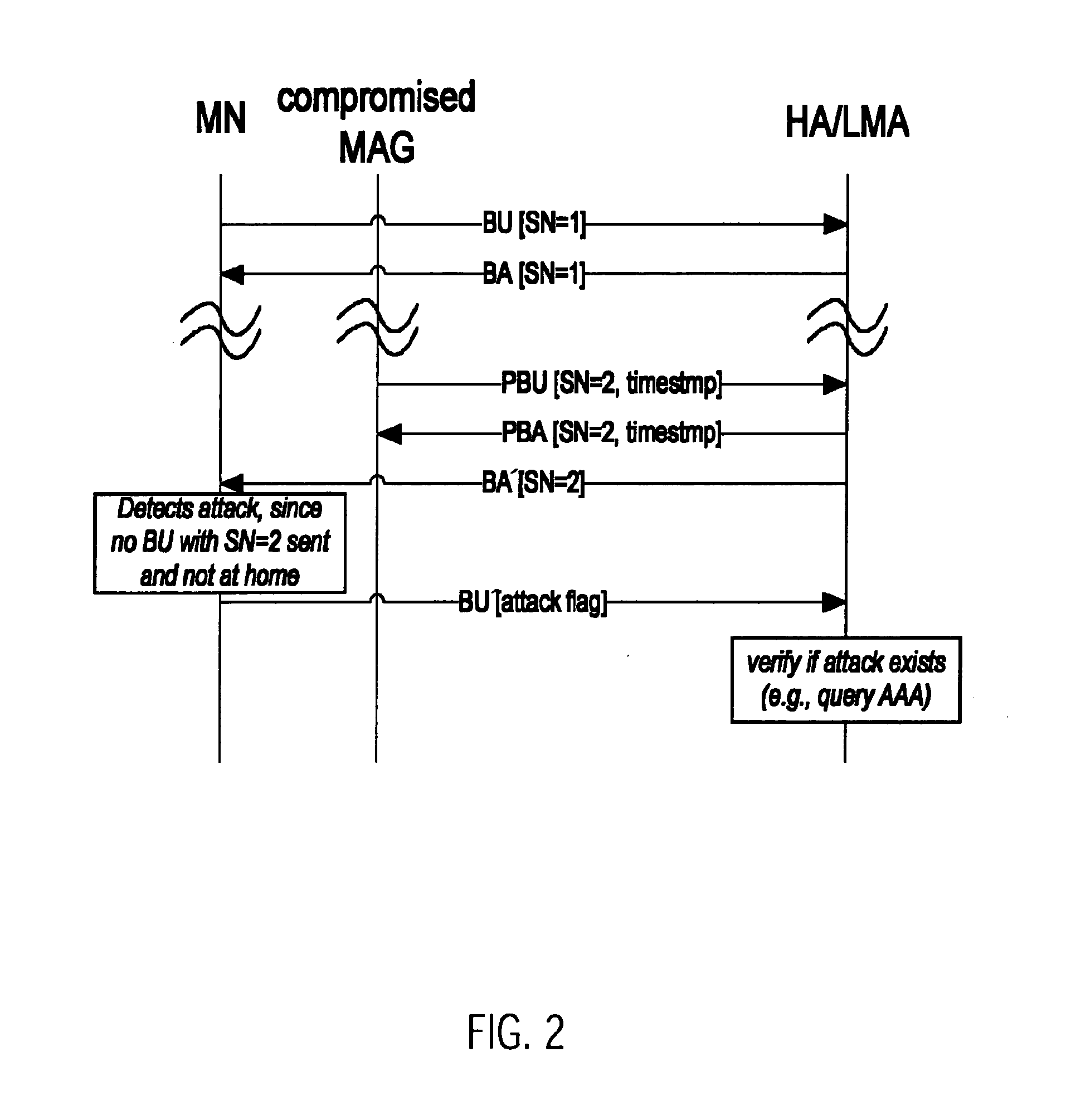

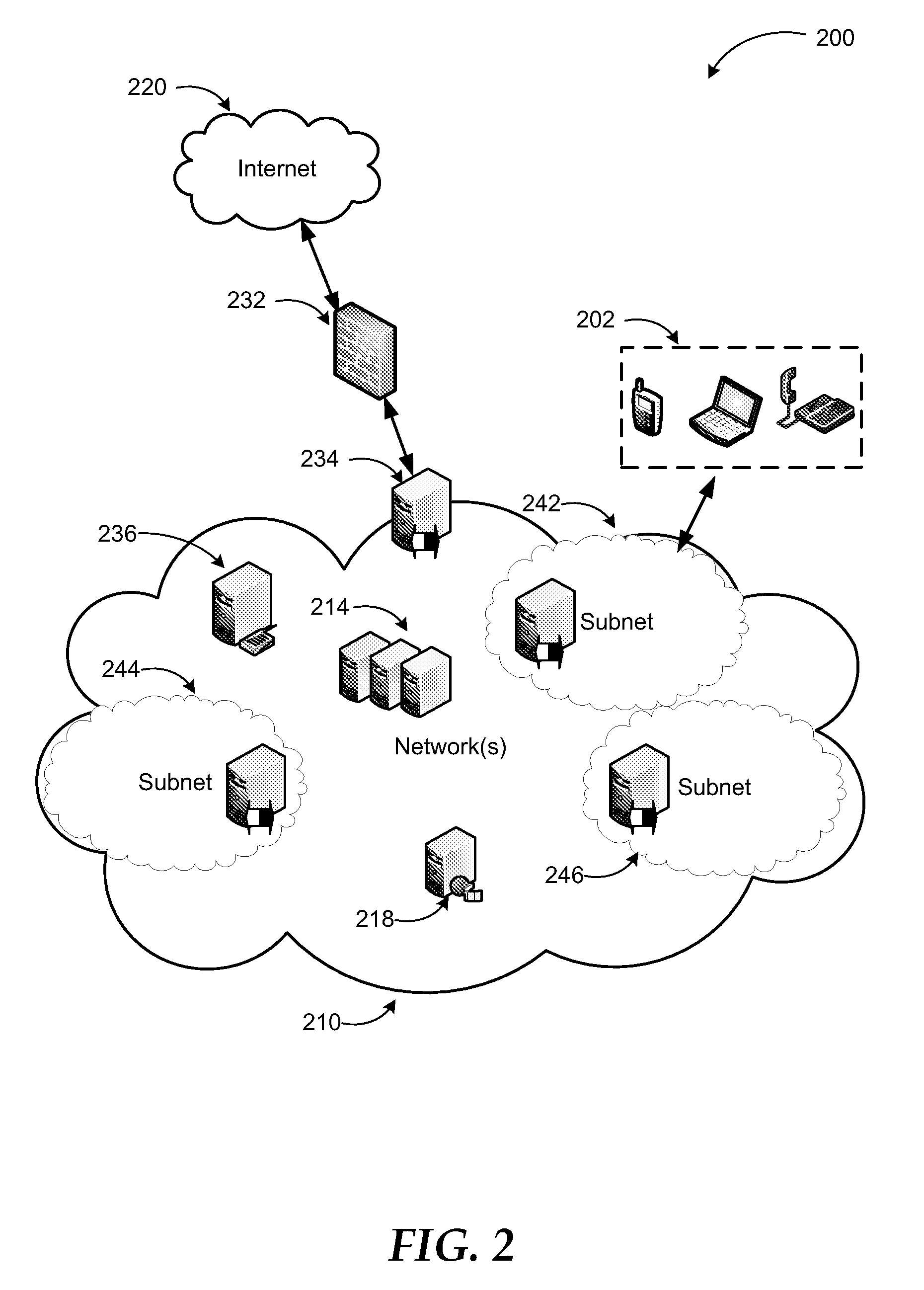

Methods in Mixed Network and Host-Based Mobility Management

InactiveUS20100313024A1Increases handover delayReduce switching delayKey distribution for secure communicationUser identity/authority verificationMix networkMobility management

A first aspect of the invention relates to a method for verifying an attachment of a mobile node to a network element in a network. A second aspect of the invention relates to a method to be implemented in a mobility anchor node, which detects whether a race condition between registration messages occurs and resolves the most recent location of a mobile node. A third aspect of the invention relates to a method for detecting whether a binding cache entry for a mobile at a correspondent node has been spoofed and to a method for registering a care-of address of a mobile node at a correspondent node. A fourth aspect of the invention relates to a method for providing from a mobile node to a local mobility anchor information on an attachment of a mobile node to a network element.

Owner:PANASONIC CORP

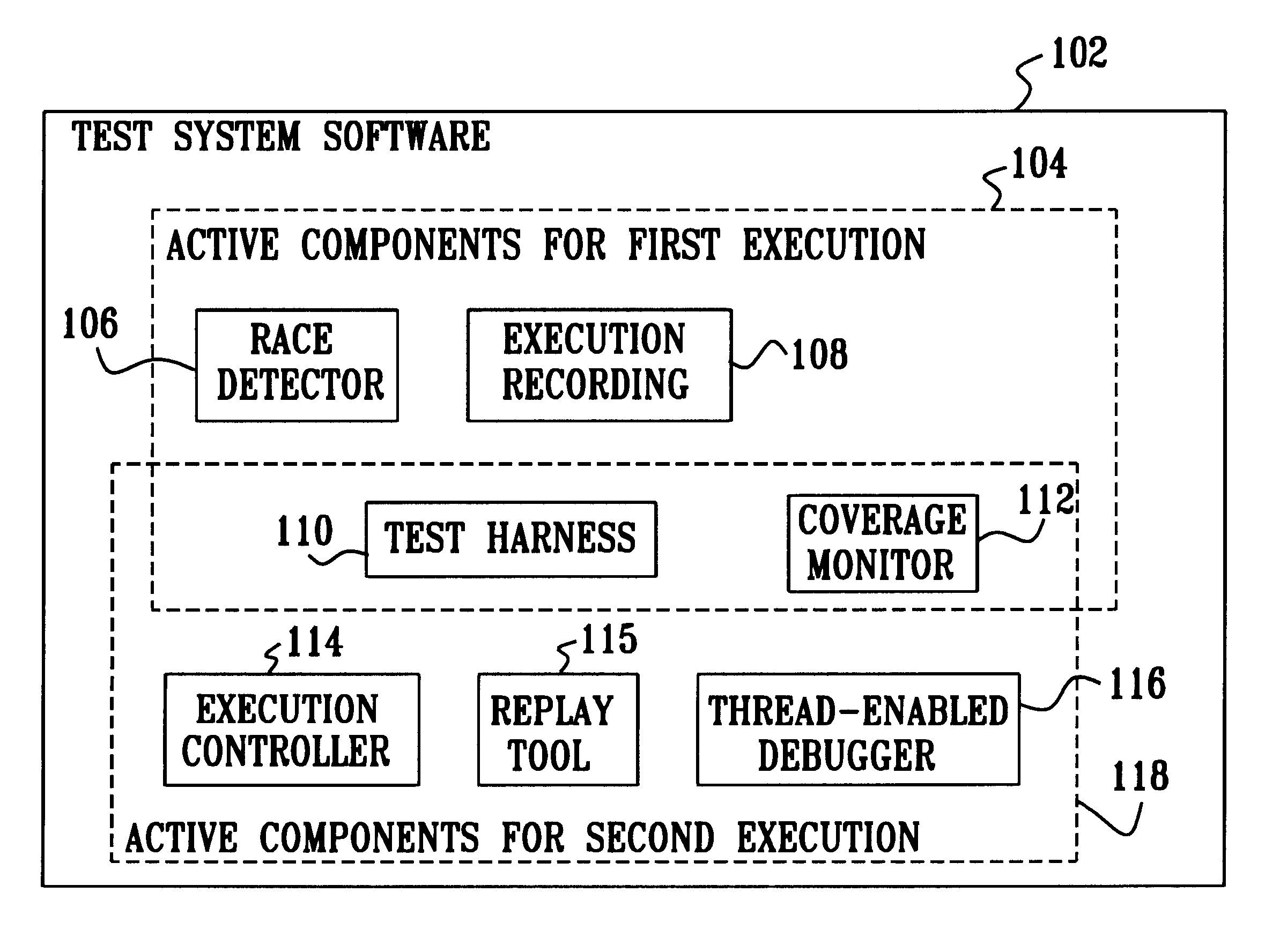

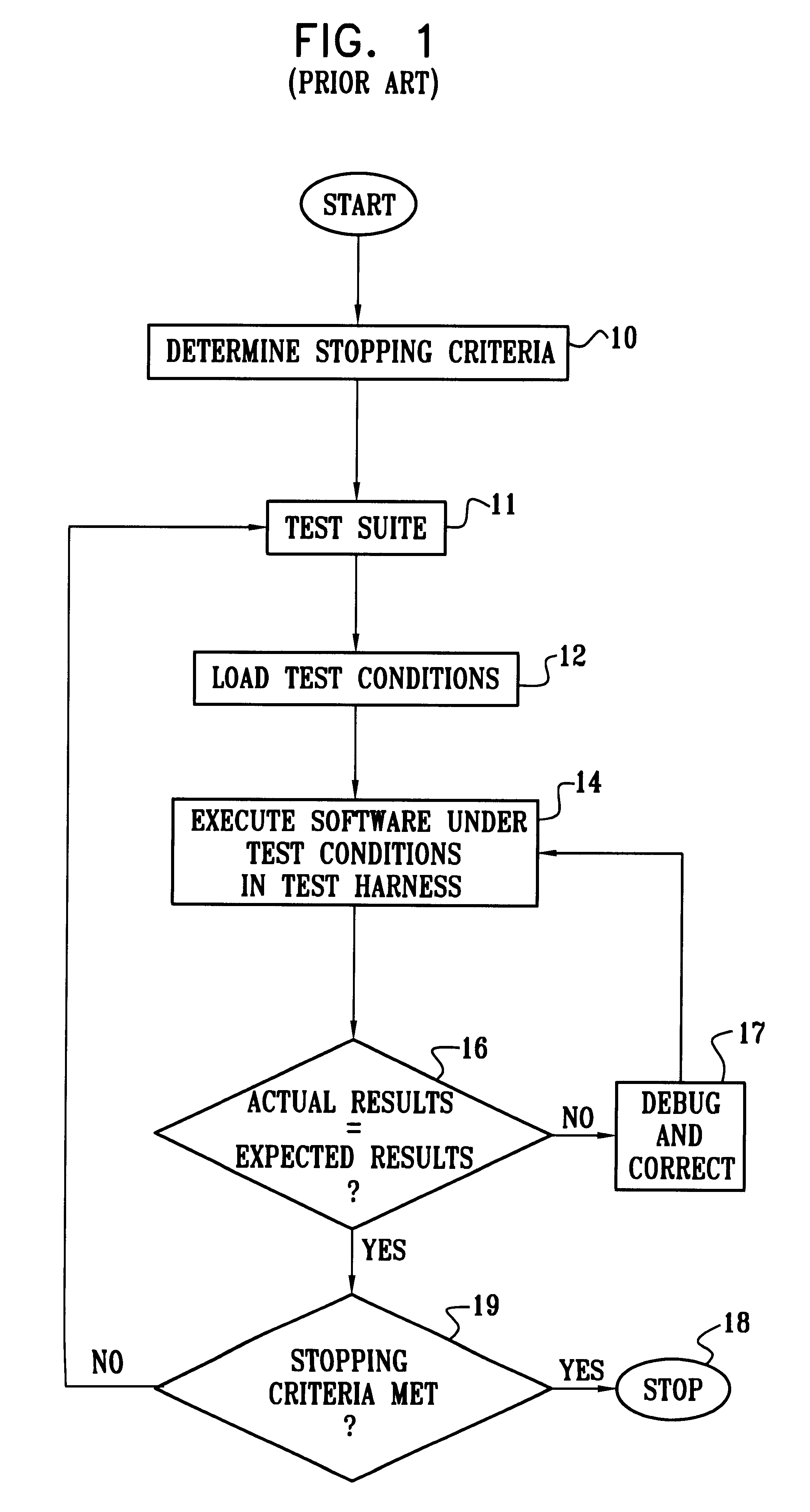

Race detection for parallel software

ActiveUS6851075B2Reduce effortImprove reliabilityError preventionSoftware testing/debuggingRace conditionParallel software

A method for race detection in parallel software, including performing an execution of software under test (SUT), the SUT having an expected outcome. The method further includes detecting a race condition in the SUT responsive to a first interleaving generated during the execution, replaying the first interleaving to a start-point of the race condition, and imposing a second interleaving at the start-point of the race condition. The method also includes determining a second-execution outcome of the SUT responsive to the second interleaving, and comparing the expected outcome with the second-execution outcome.

Owner:IBM CORP

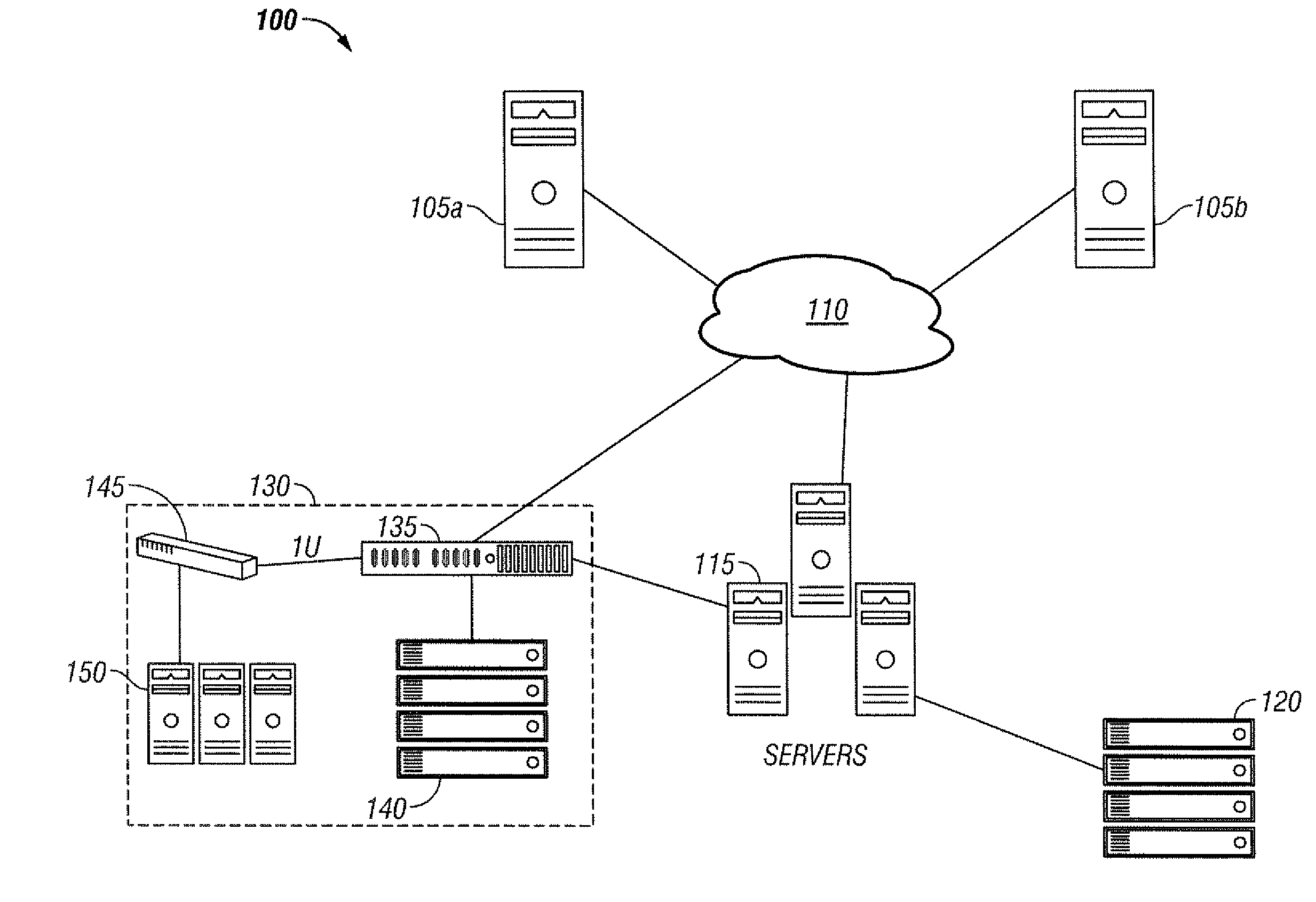

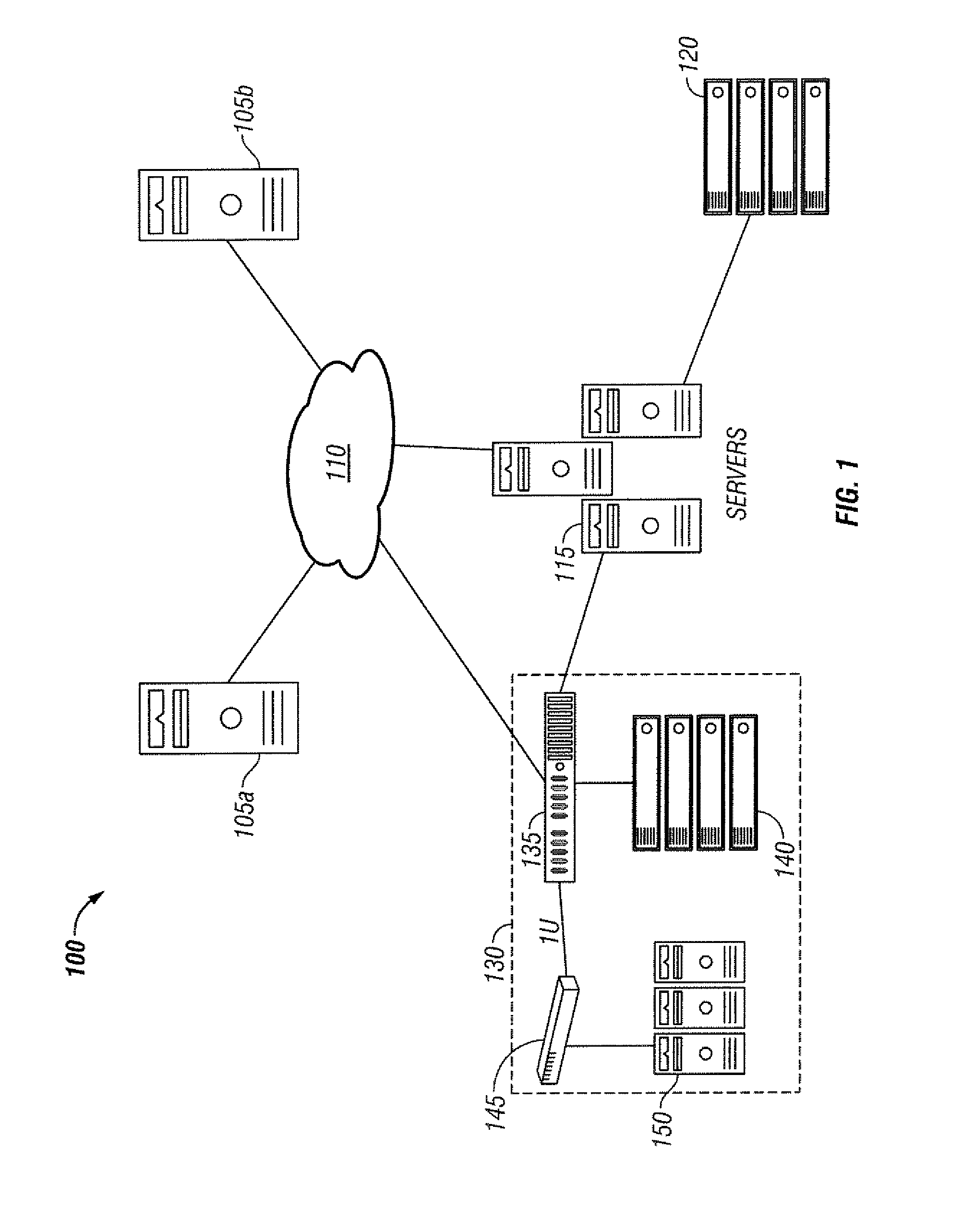

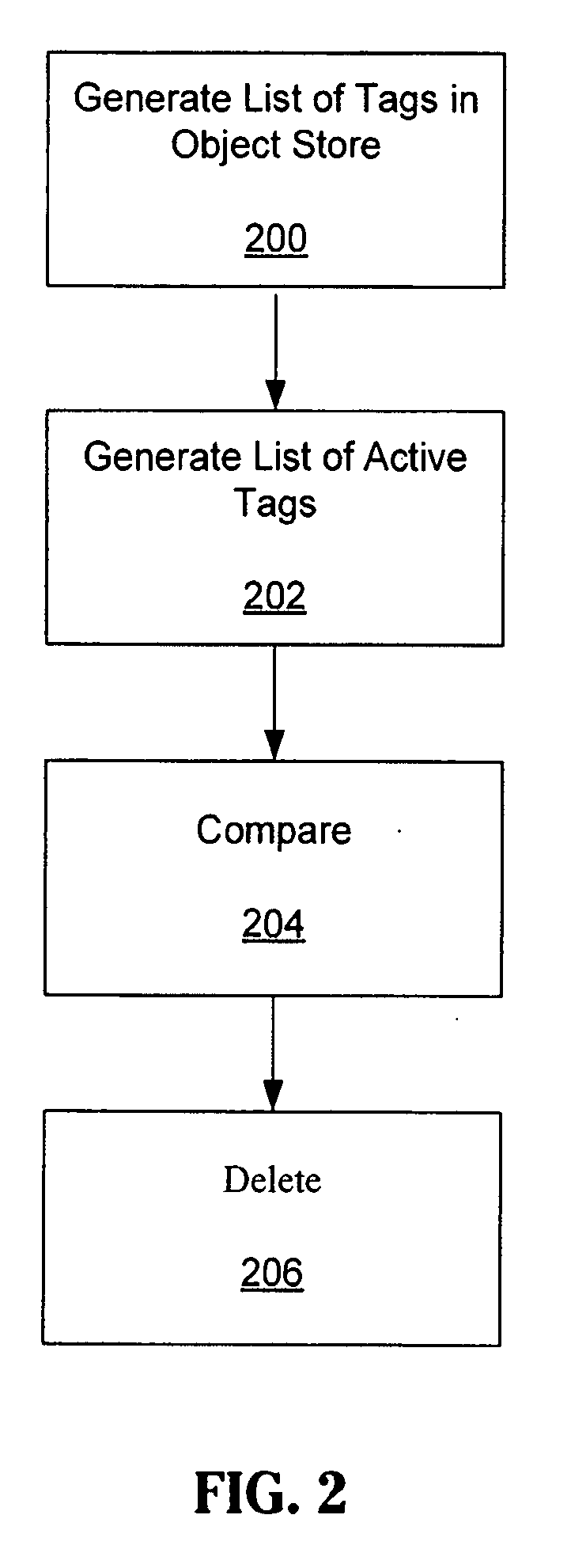

Methods and systems for space management in data de-duplication

ActiveUS20090259701A1Digital data information retrievalError detection/correctionObject storeSpace management

The present invention is directed toward methods and systems for data de-duplication. More particularly, in various embodiments, the present invention provides systems and methods for data de-duplication that may utilize storage reclamation. In various embodiments, data de-duplication may be performed using data storage reclamation by reconciling a list of all active tags against a list of all tags present within the object store itself. Any tags found to be in the object store that have no corresponding active usage may then be deleted. In some embodiments additional steps may be taken to avoid race conditions in deleting tags that are needed by incoming data. In some embodiments the object store may request the lists. In other embodiments, a runtime list, in which each new tag is entered as they are returned from the object store. In another embodiment the object store may maintain this list directly.

Owner:QUANTUM CORP

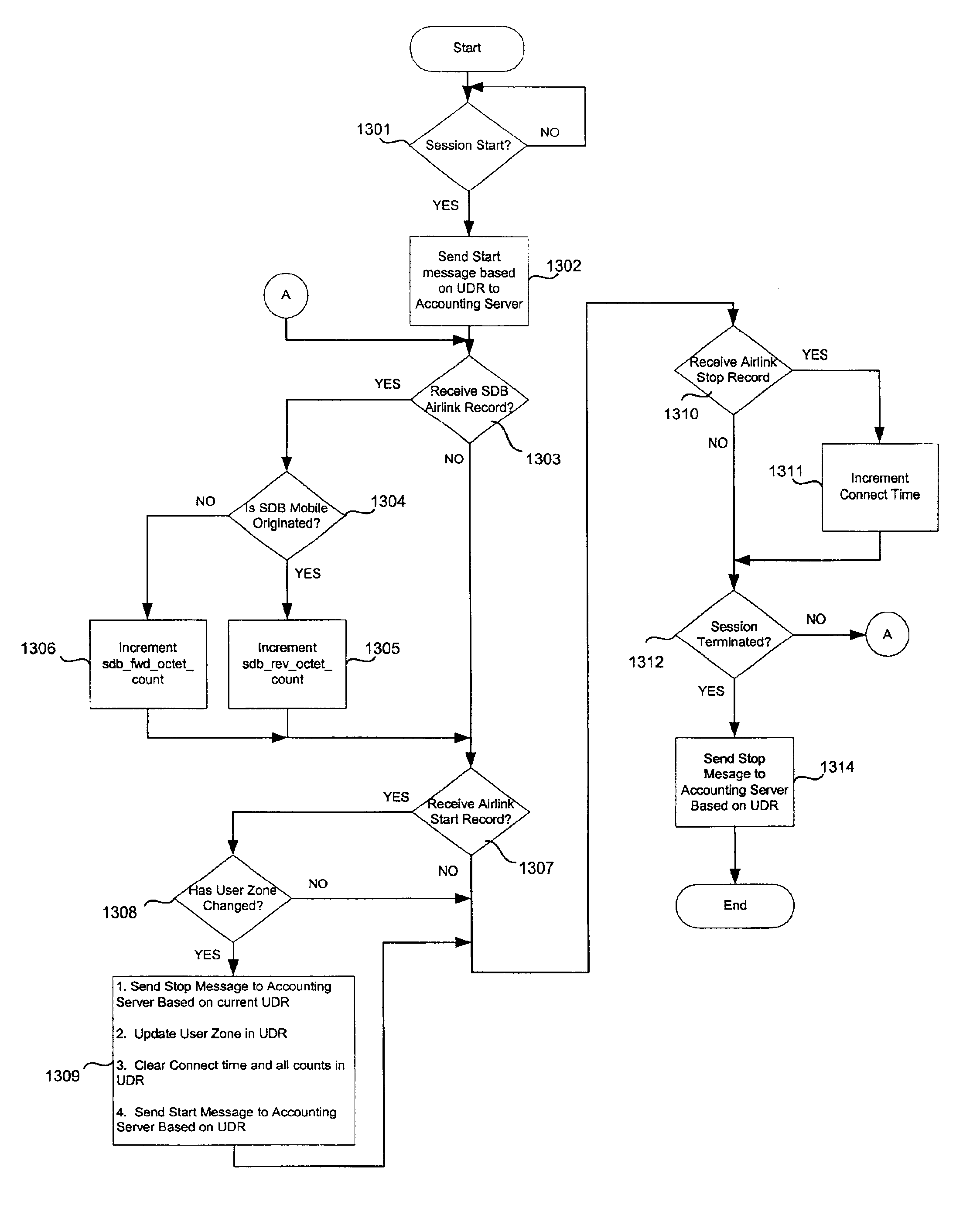

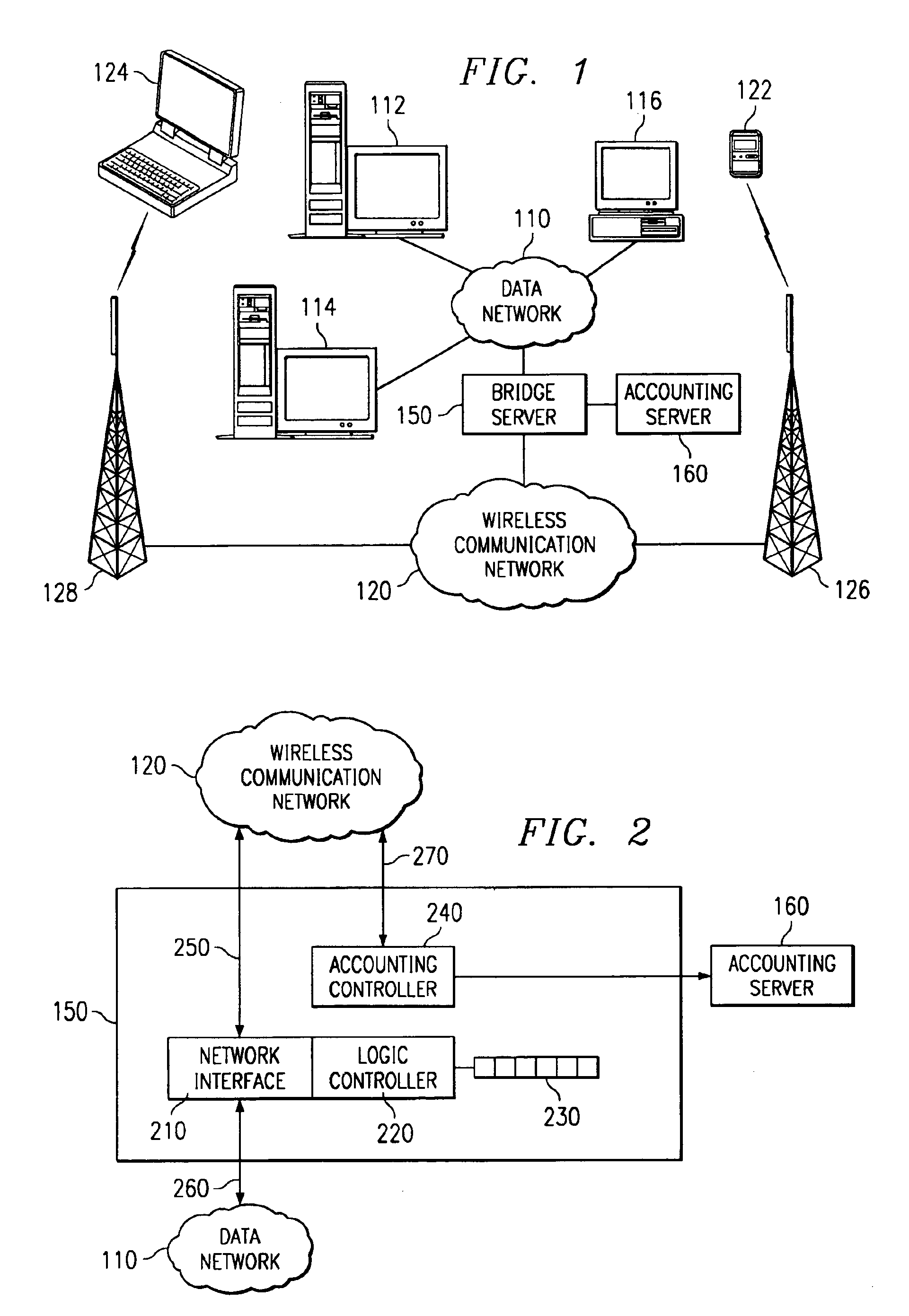

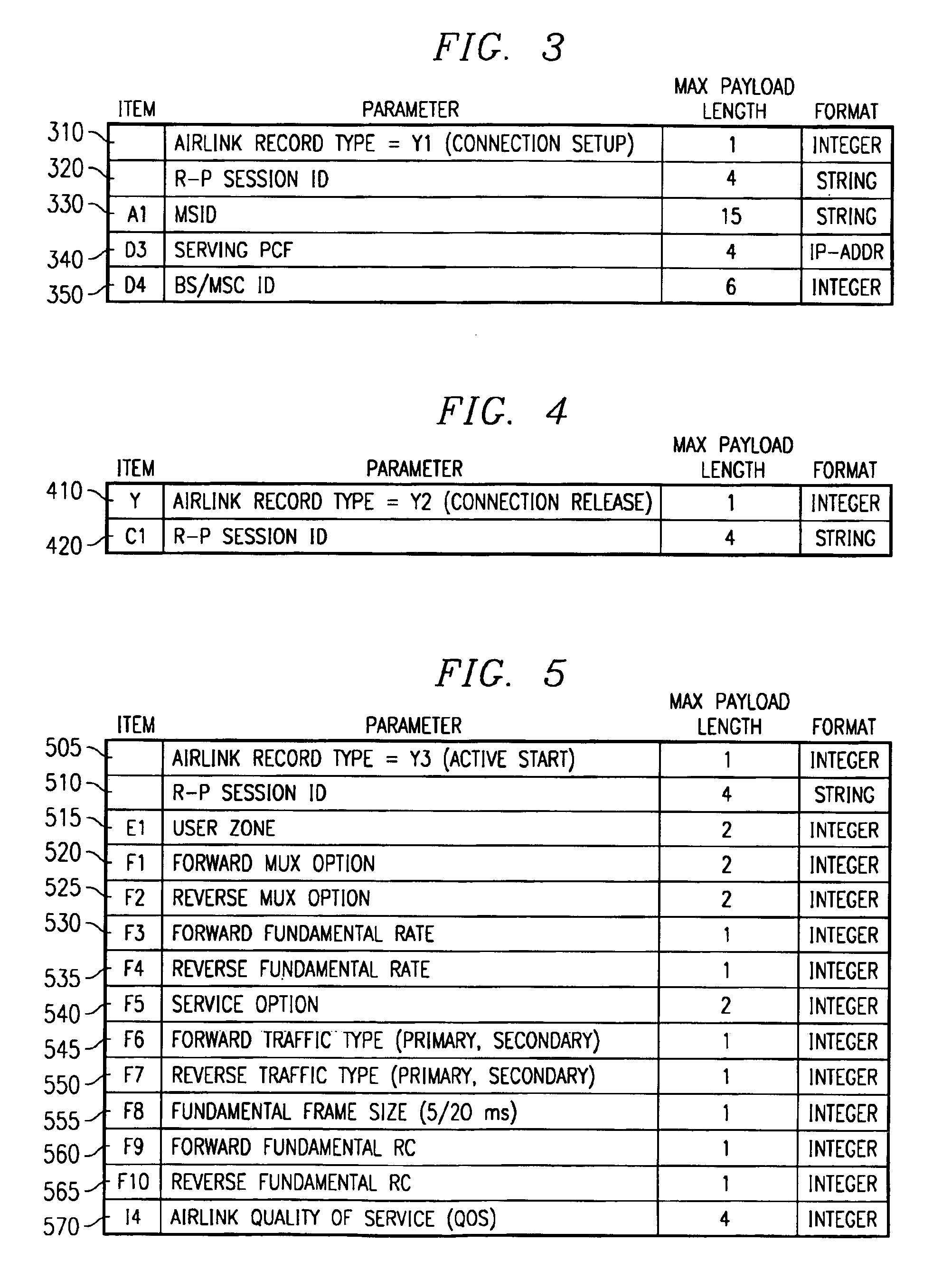

Method and apparatus for merging accounting records to minimize overhead

InactiveUS6853630B1Minimize overheadReduce in quantityAccounting/billing servicesTelephonic communicationBurst transmissionData transmission

A method and apparatus for merging accounting records to minimize overhead is provided. The method and apparatus accumulate accounting information for data transmissions between a wireless communication device and a host on a data network. The method and apparatus are capable of accumulating accounting information for short data bursts and for active traffic channel transmissions such that an accounting messages is sent to an accounting server only when transitions from short data burst transmission or active traffic channel transmission to another state are encountered. Thus, accounting information for a plurality of sequential short data bursts and / or active traffic channel transmissions are accumulated. This reduces the number of accounting messages sent to an accounting server and eliminates race conditions that may be encountered by sequential short data bursts.

Owner:RPX CLEARINGHOUSE

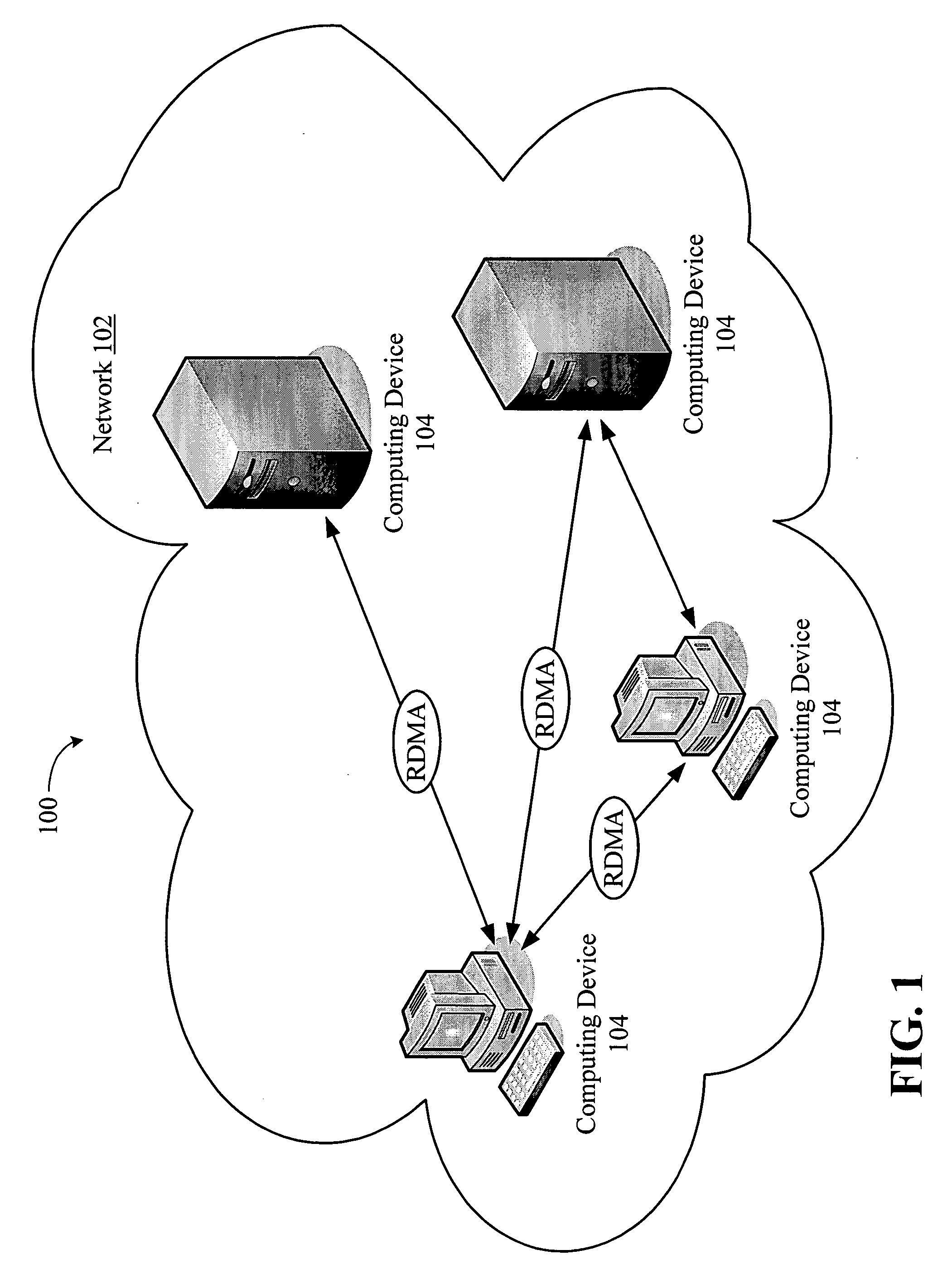

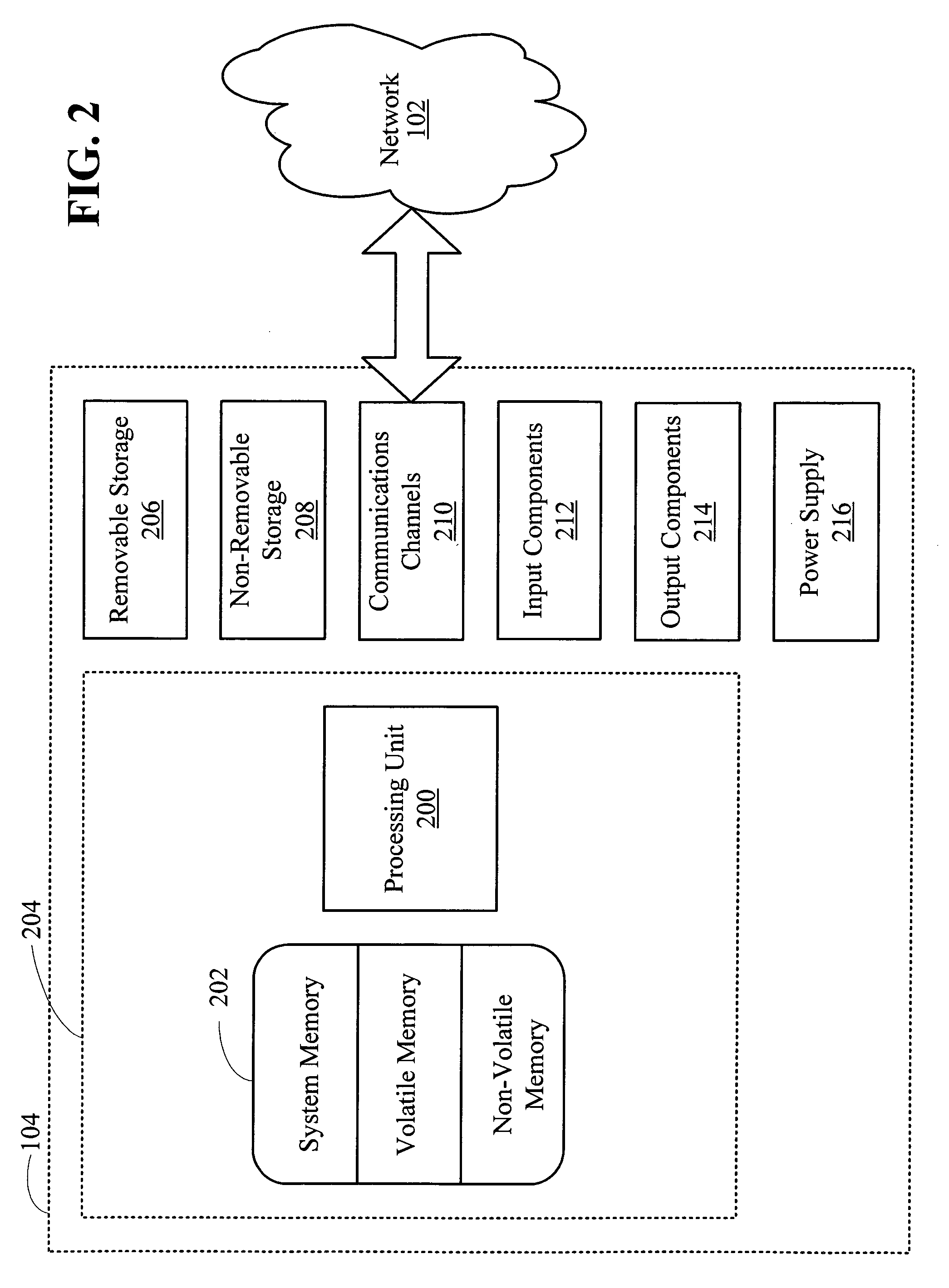

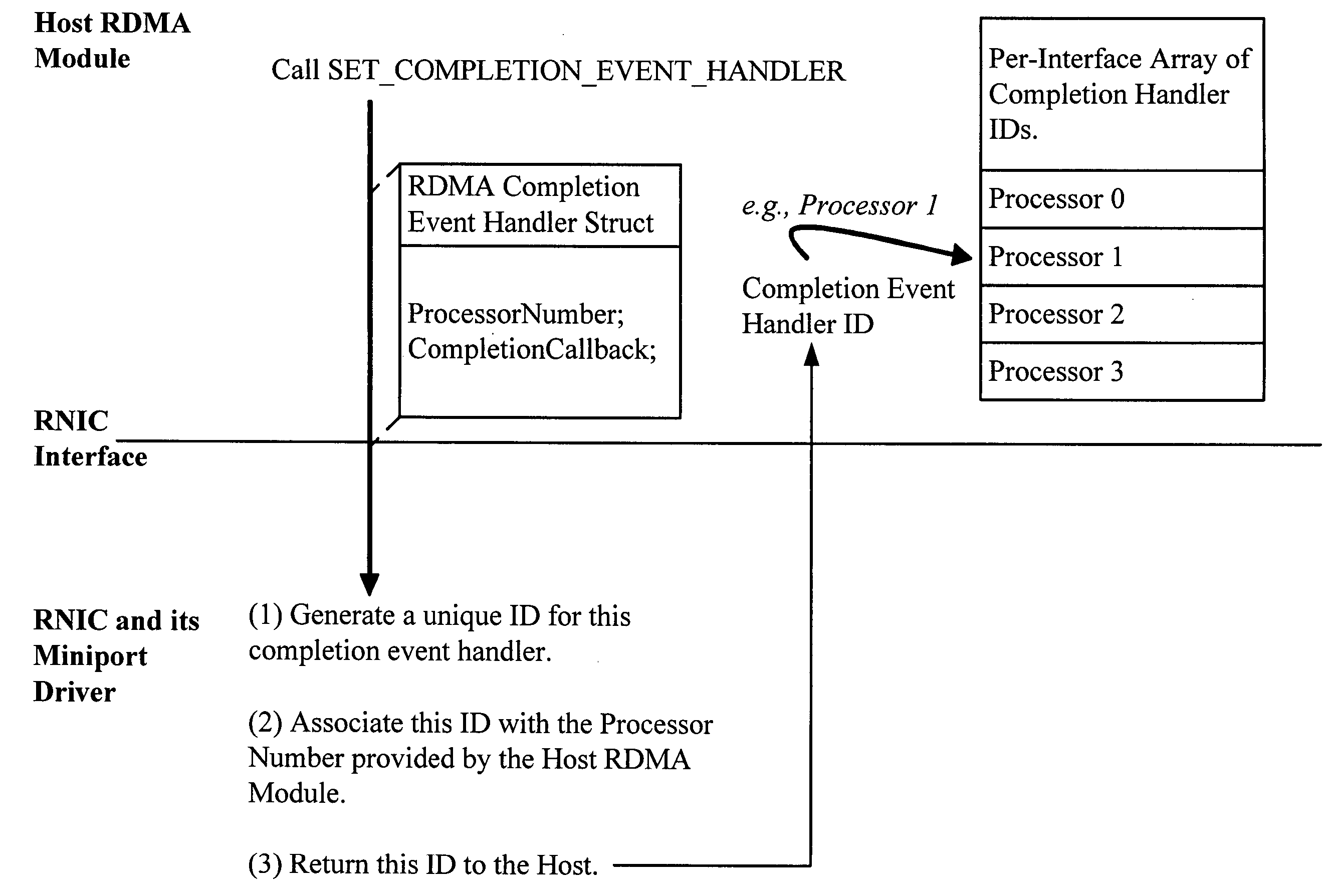

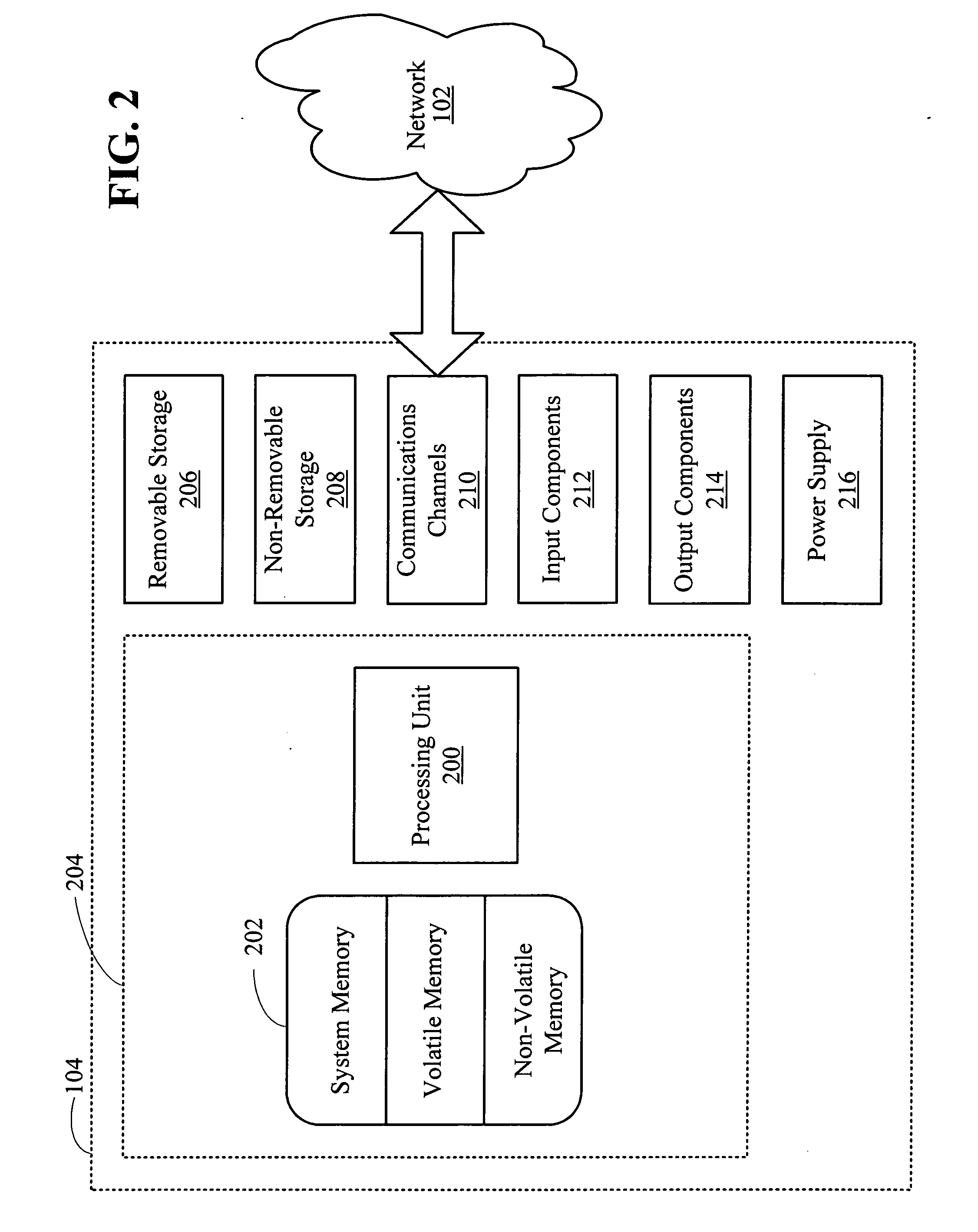

Method and system for parallelizing completion event processing

InactiveUS20060259661A1Efficient processingEliminate processing bottlenecksDigital computer detailsComputer security arrangementsMulti processorSemantics

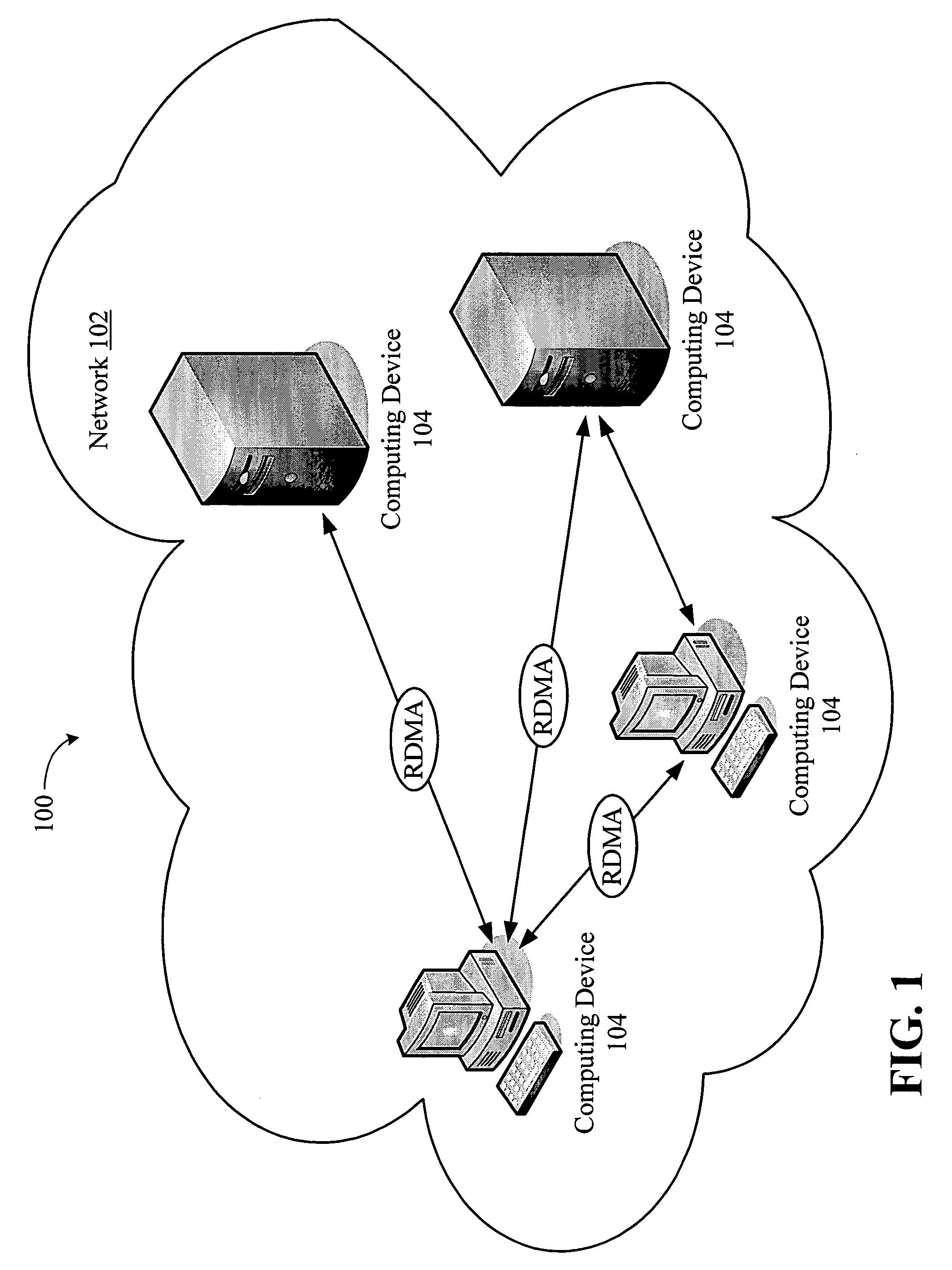

Disclosed are methods for handling RDMA connections carried over packet stream connections. In one aspect, I / O completion events are distributed among a number of processors in a multi-processor computing device, eliminating processing bottlenecks. For each processor that will accept I / O completion events, at least one completion queue is created. When an I / O completion event is received on one of the completion queues, the processor associated with that queue processes the event. In a second aspect, semantics of the interactions among a packet stream handler, an RDMA layer, and an RNIC are defined to control RDMA closures and thus to avoid implementation errors. In a third aspect, semantics are defined for transferring an existing packet stream connection into RDMA mode while avoiding possible race conditions. The resulting RNIC architecture is simpler than is traditional because the RNIC never needs to process both streaming messages and RDMA-mode traffic at the same time.

Owner:MICROSOFT TECH LICENSING LLC

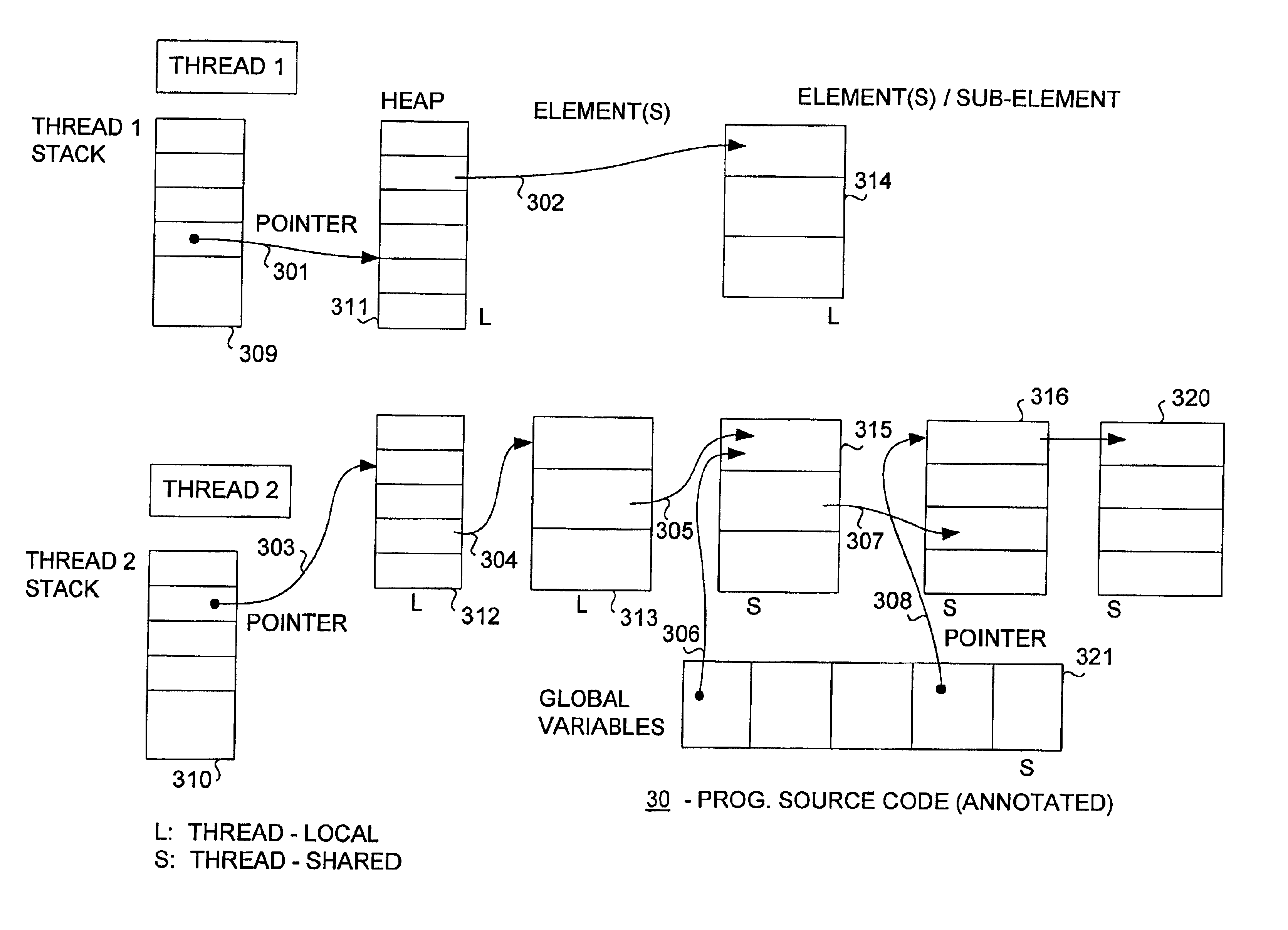

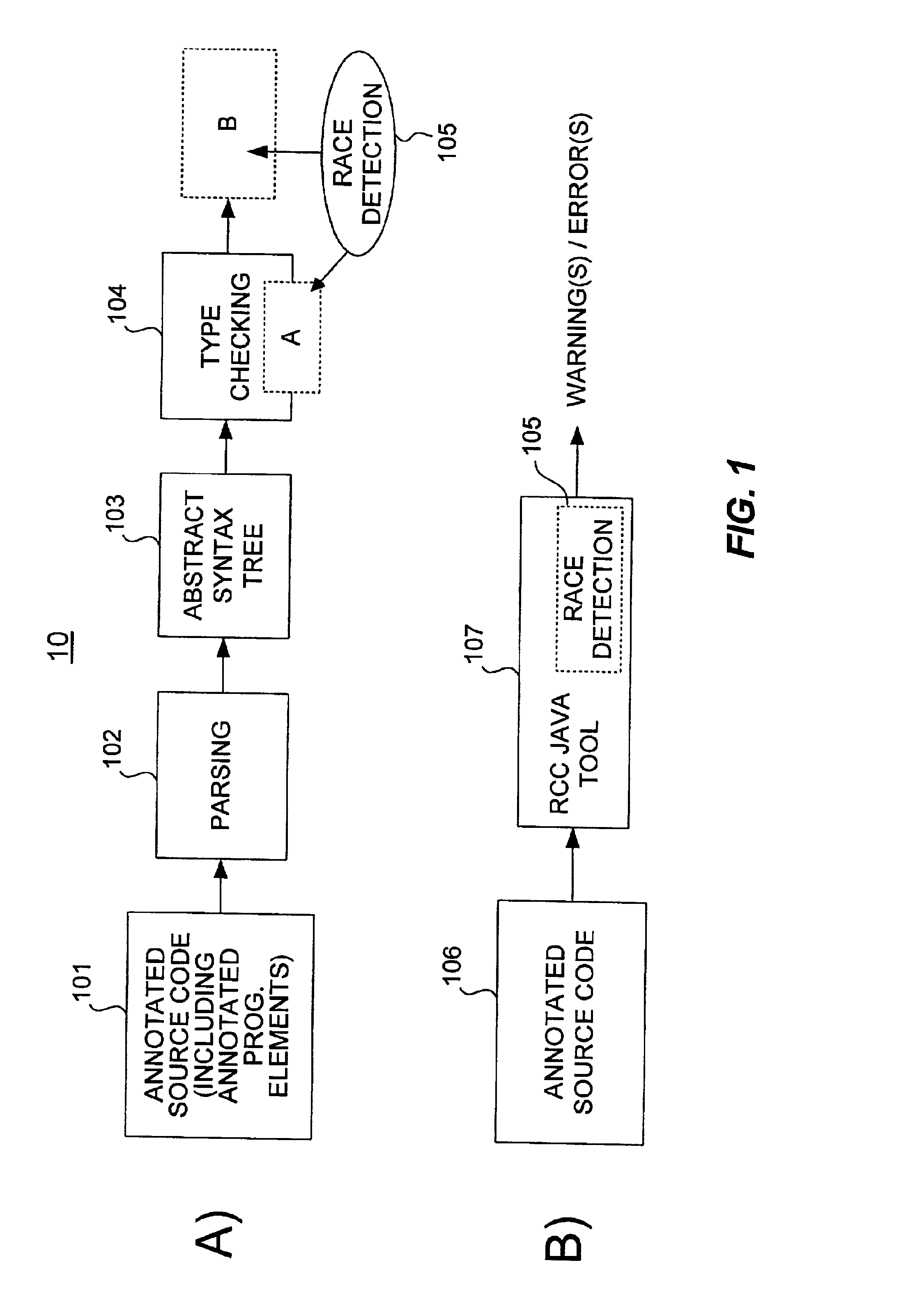

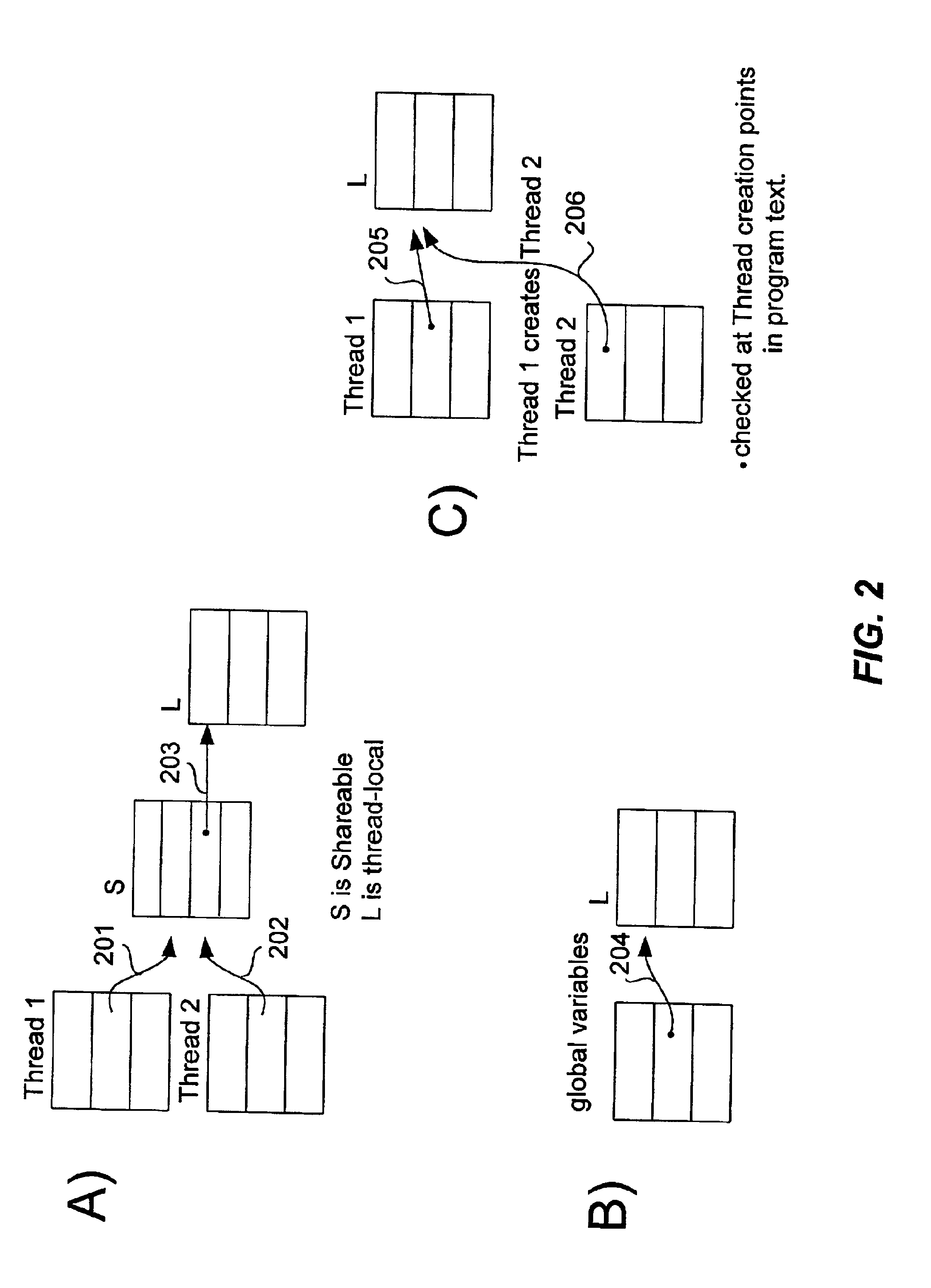

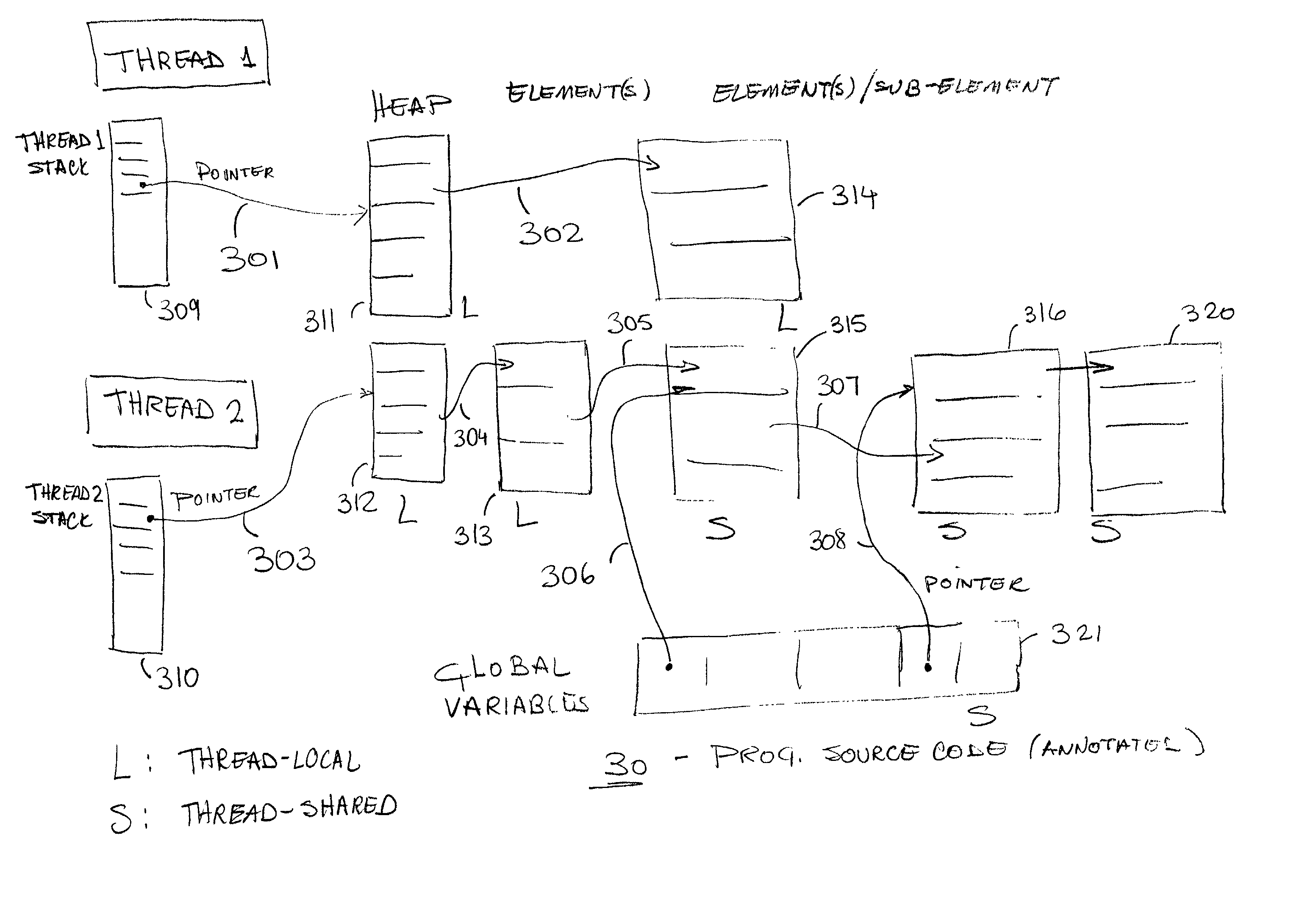

Method and apparatus for verifying data local to a single thread

InactiveUS6817009B2Ensuring validityAccurate checkError detection/correctionSoftware engineeringProgram analysisSource code

Concurrent program analysis is fashioned for detecting potential race conditions such as data races in computer programs. One feature of this analysis is verifying annotations of addressable resources in a program. Annotations are verified by checking if thread-local resources are indeed thread-local, and that thread-shared data spaces are not in fact thread-local. Another feature is detecting potential race conditions, such as data races, in the computer program. The computer program can spawn a plurality of threads that are capable of being executed concurrently. The source code of the computer program being analyzed includes an element annotated as either thread-local or thread-shared. The validity of the thread-local annotation is verified if the element is annotated in the computer program as thread-local, wherein an invalid thread-local annotation may cause a race condition.

Owner:VALTRUS INNOVATIONS LTD +1

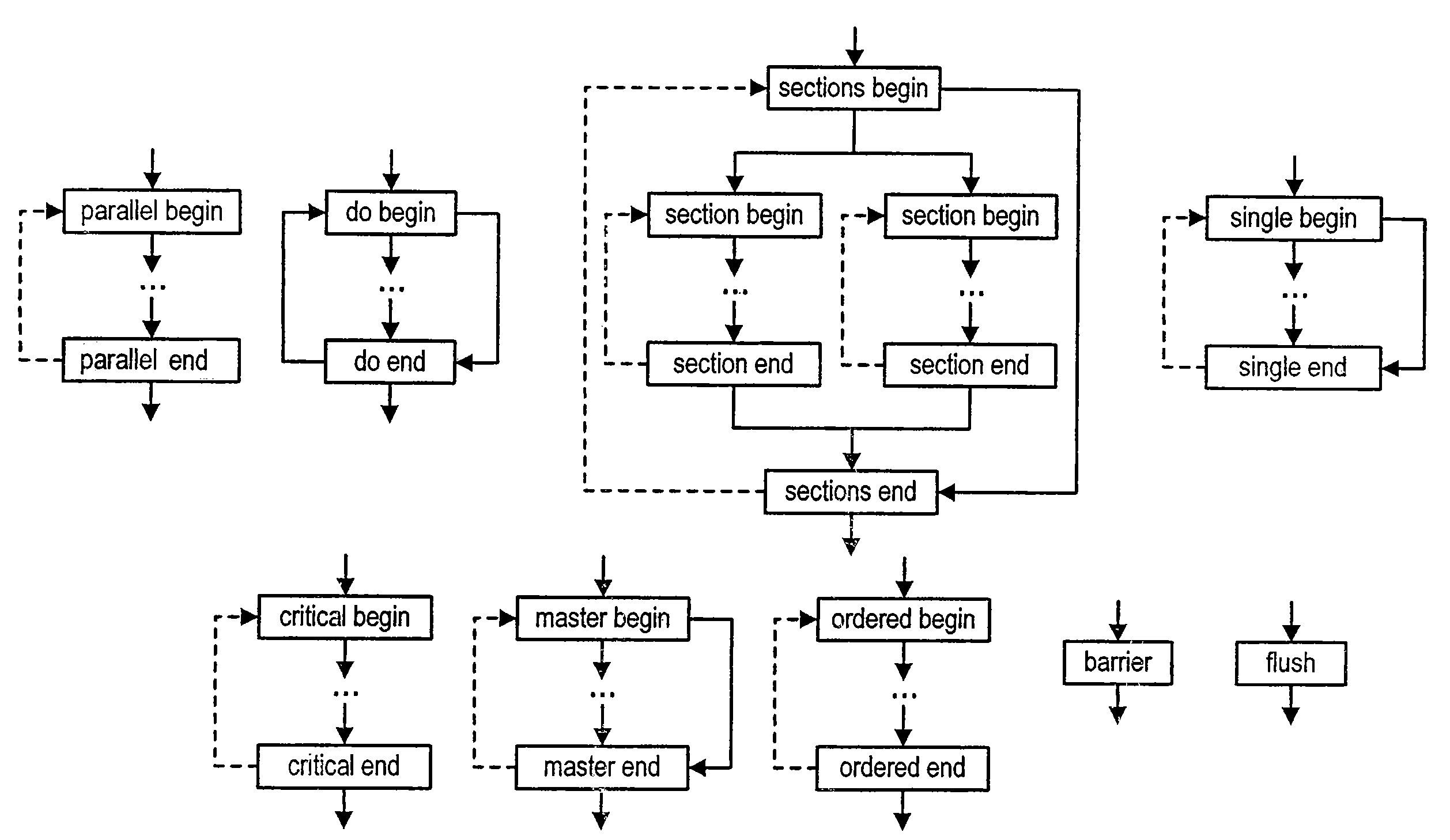

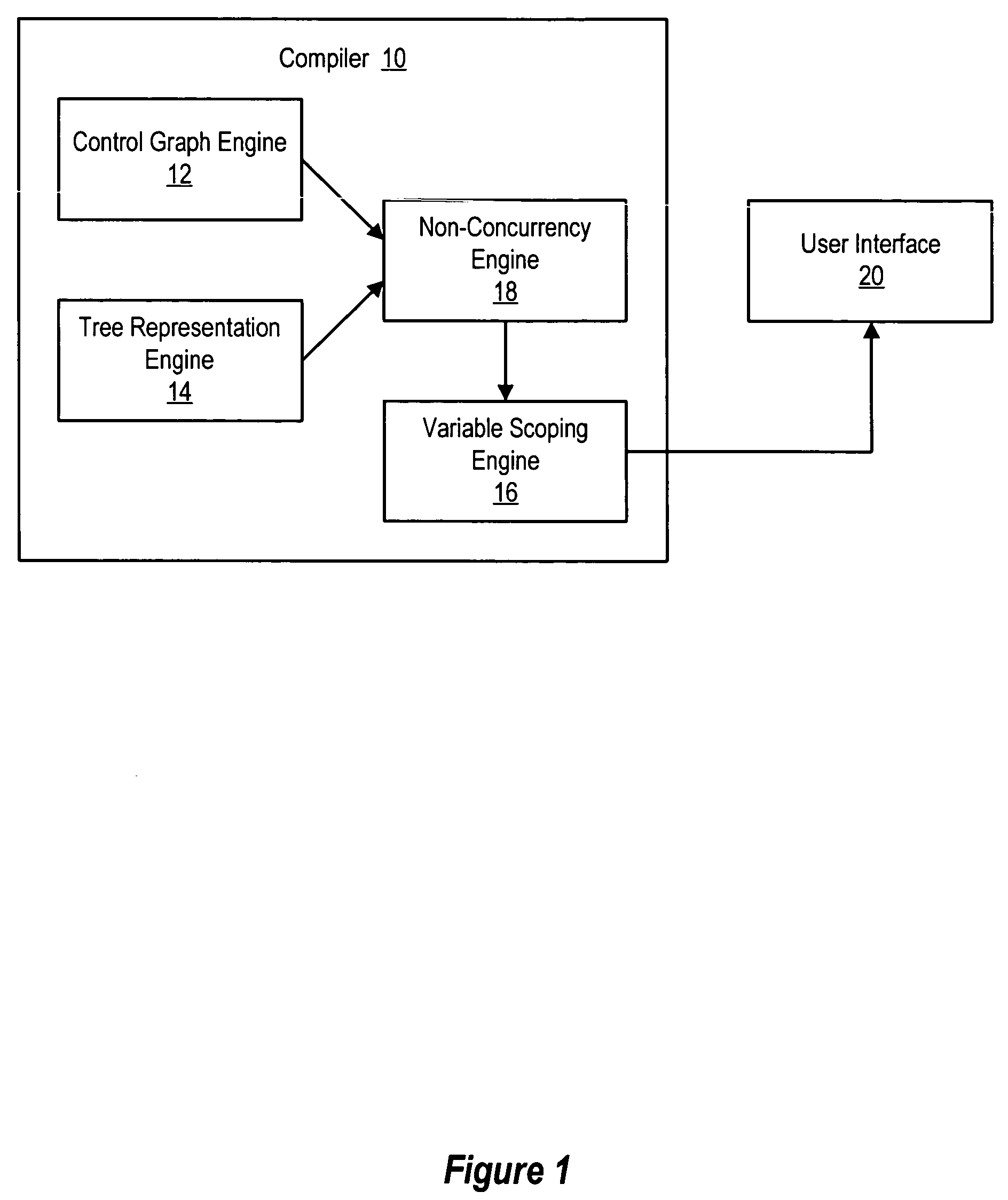

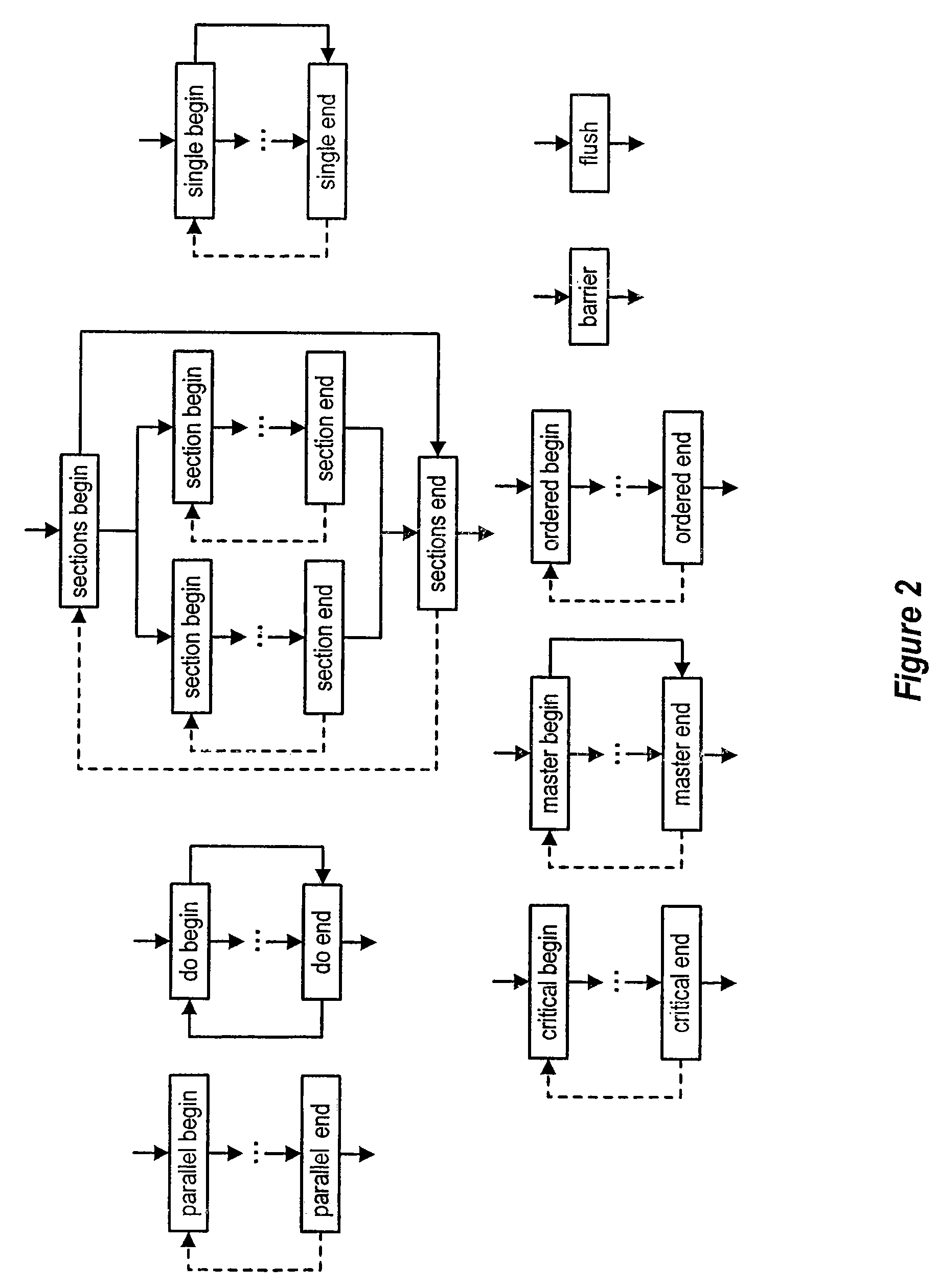

System and method for compile-time non-concurrency analysis

ActiveUS7673295B1Improve efficiencyReduce overheadSoftware engineeringError detection/correctionControl flowSemantics

Compile-time non-concurrency analysis of parallel programs improves execution efficiency by detecting possible data race conditions within program barriers. Subroutines are modeled with control flow graphs and region trees having plural nodes related by edges that represent the hierarchical loop structure and construct relationship of statements. Phase partitioning of the control flow graph allows analysis of statement relationships with programming semantics, such as those of the OpenMP language, that define permitted operations and execution orders.

Owner:ORACLE INT CORP

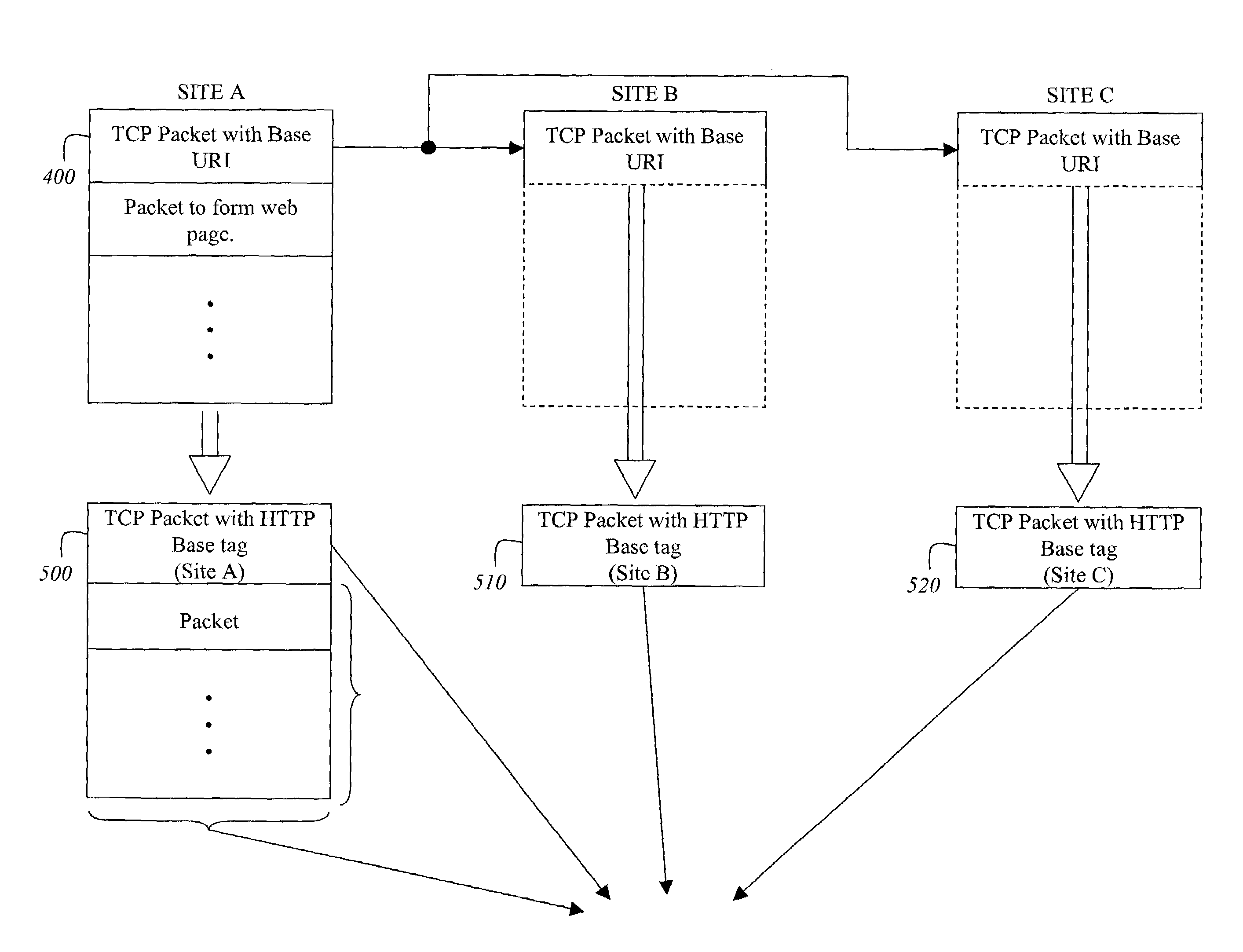

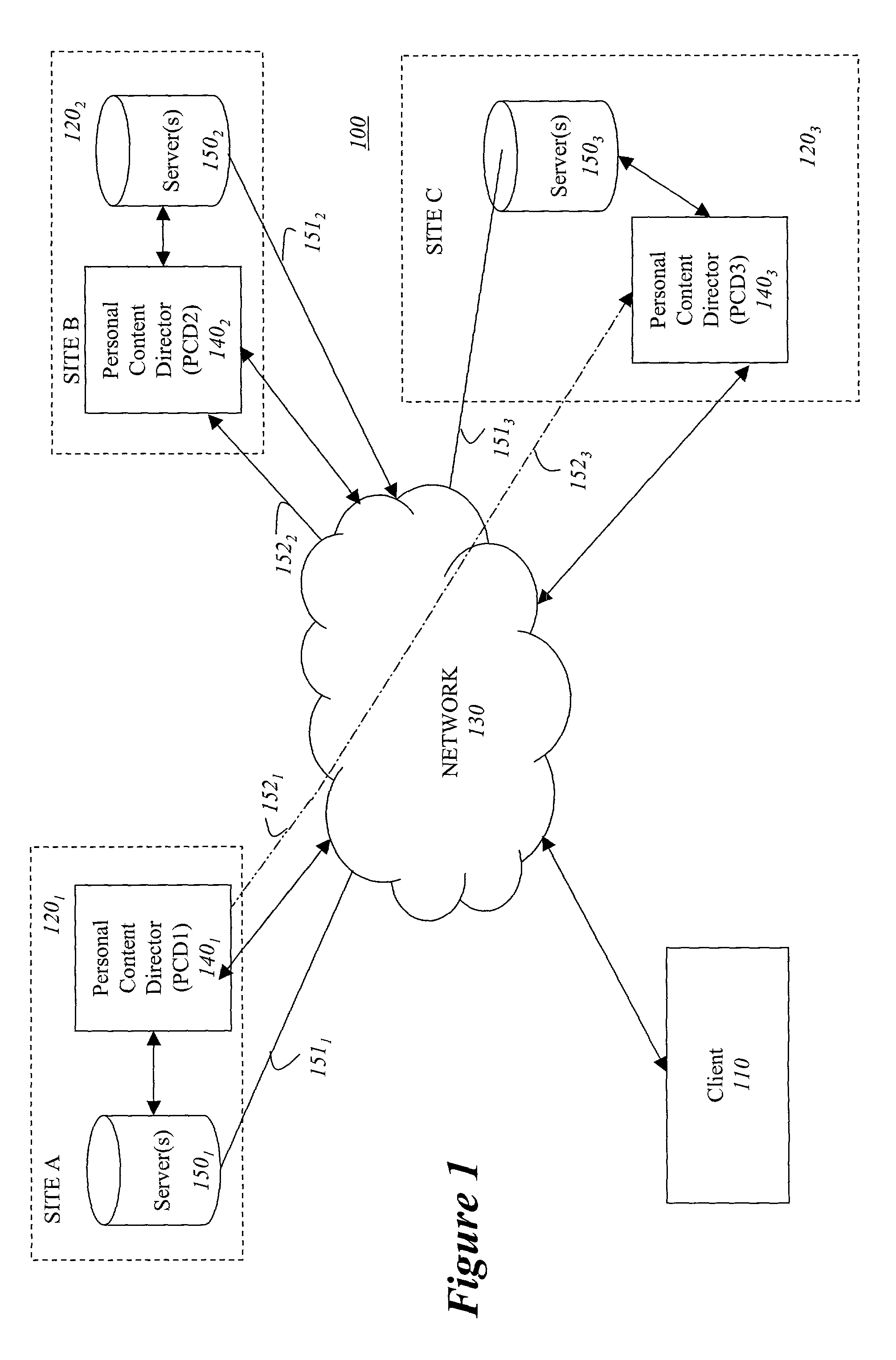

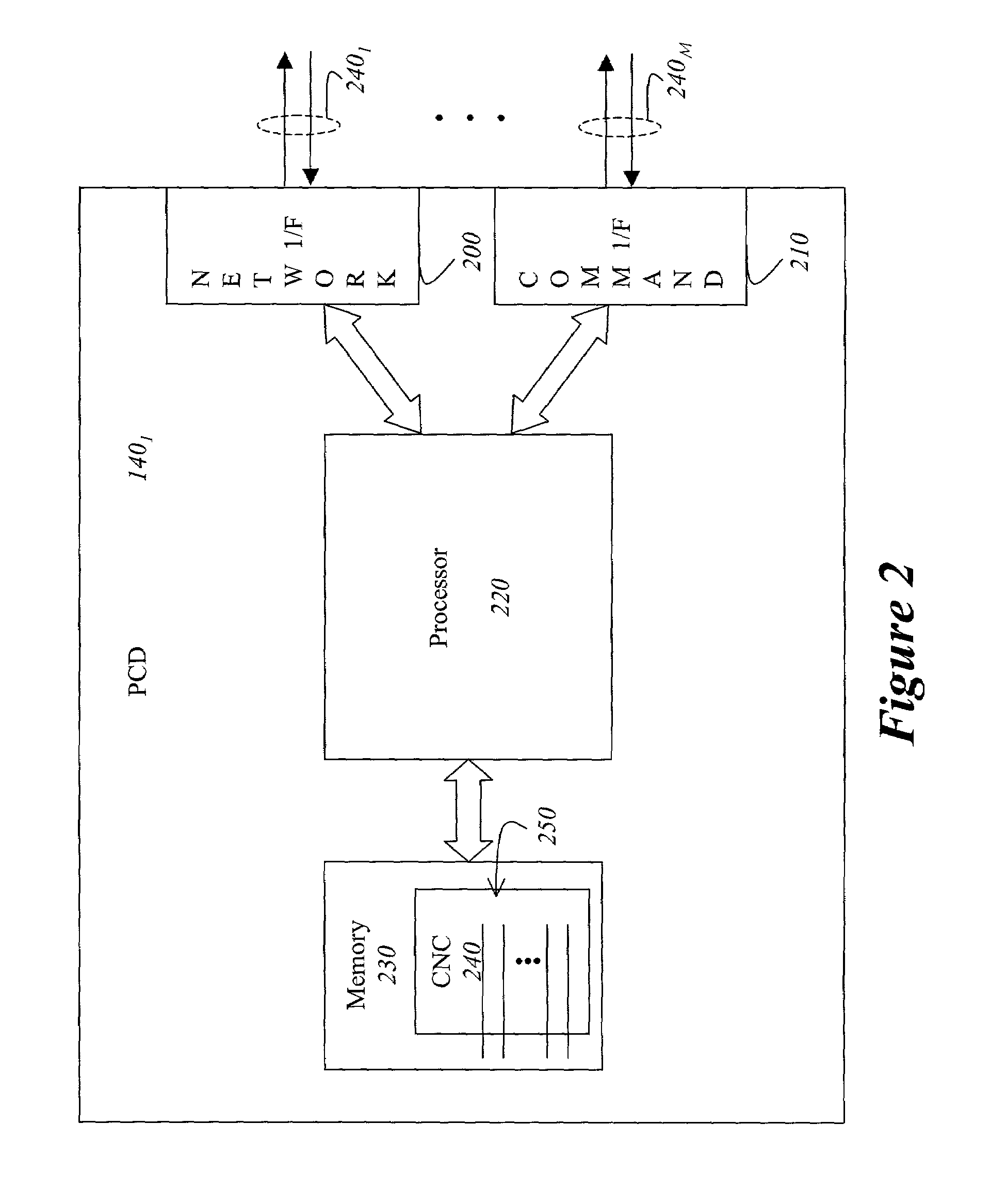

Method and apparatus for discovering client proximity using race type translations

ActiveUS7231458B2Optimize locationMultiple digital computer combinationsTransmissionWeb siteNetwork packet

A system and method for determining a chronometrically optimal web site location for access by a client based on proximity measurements on established connections that are a result of requests for actual content. In one embodiment, the technique involves a race condition between local domains each transmitting TCP packets loaded with a HyperText Markup Language (HTML) Base tag identifying that local domain. The earliest received TCP packet is incorporated into the TCP stream. In another embodiment, the technique involves a race condition between local domains each transmitting files having links to streaming media translated to point to its own local domain. The earliest received file is incorporated into the TCP stream while the others are discarded as TCP resends. In yet another embodiment, HTTP redirect operations are performed once for each grouping of links only the earliest redirect packet to reach the client is incorporated into the existing TCP stream.

Owner:RADWARE

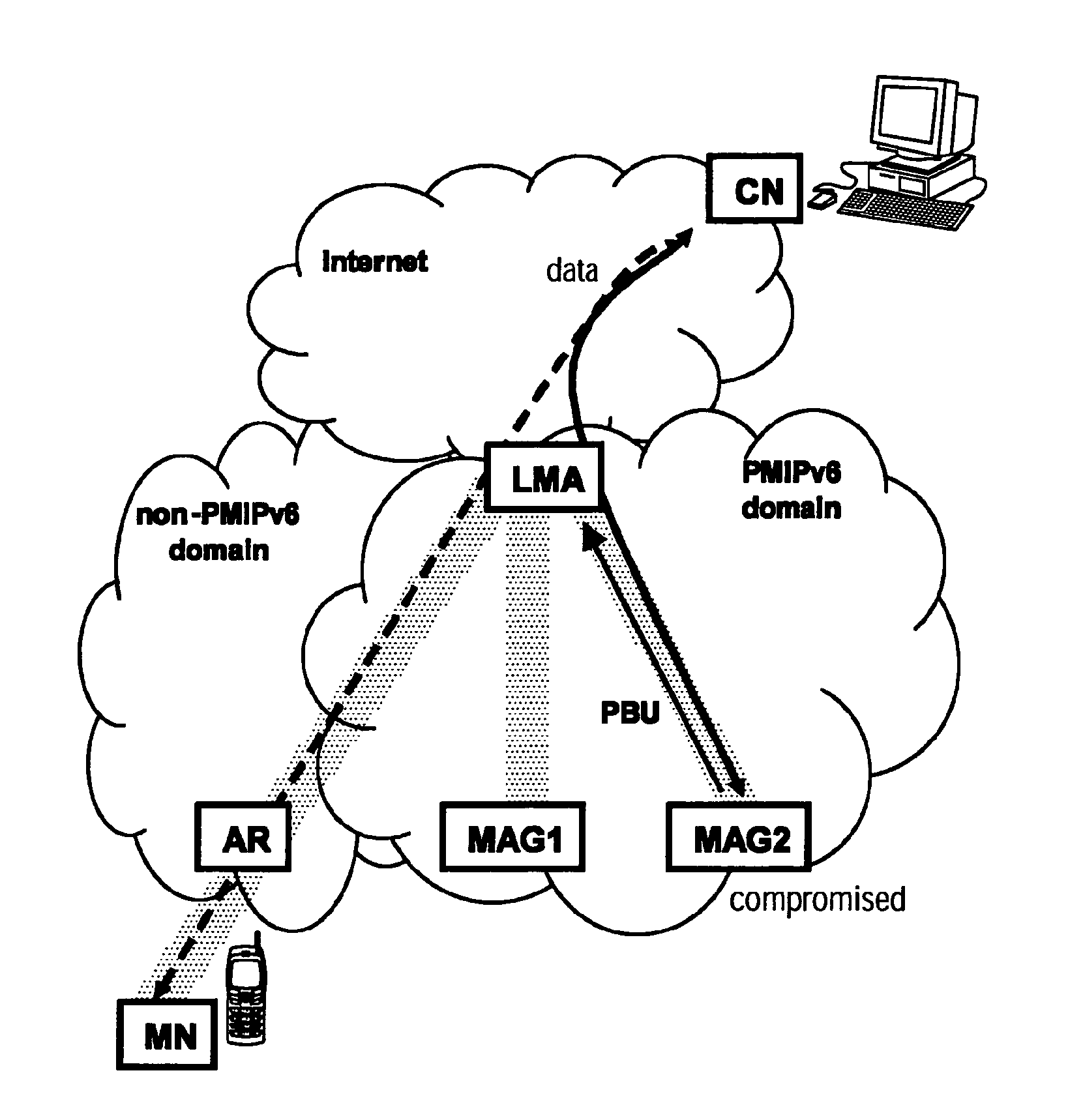

Methods in mixed network- and host-based mobility management

InactiveUS20100296481A1Increases handover delayReduce switching delayWireless network protocolsWireless commuication servicesMobility managementMobile device

A first aspect of the invention relates to a method for improving security at a local mobility anchor implementing both a network-based and a host-based mobility management scheme for managing the mobility of a mobile node. It suggests a method for verifying an attachment of a mobile node (MN) to a network element in a network. A second aspect of the invention relates to a method to be implemented in a mobility anchor node, which detects whether a race condition between registration messages occurs and resolves the most recent location of a mobile node. A third aspect of the invention relates to a method for detecting whether a binding cache entry for a mobile at a correspondent node has been spoofed and to a method for registering a care-of address of a mobile node at a correspondent node.

Owner:PANASONIC CORP

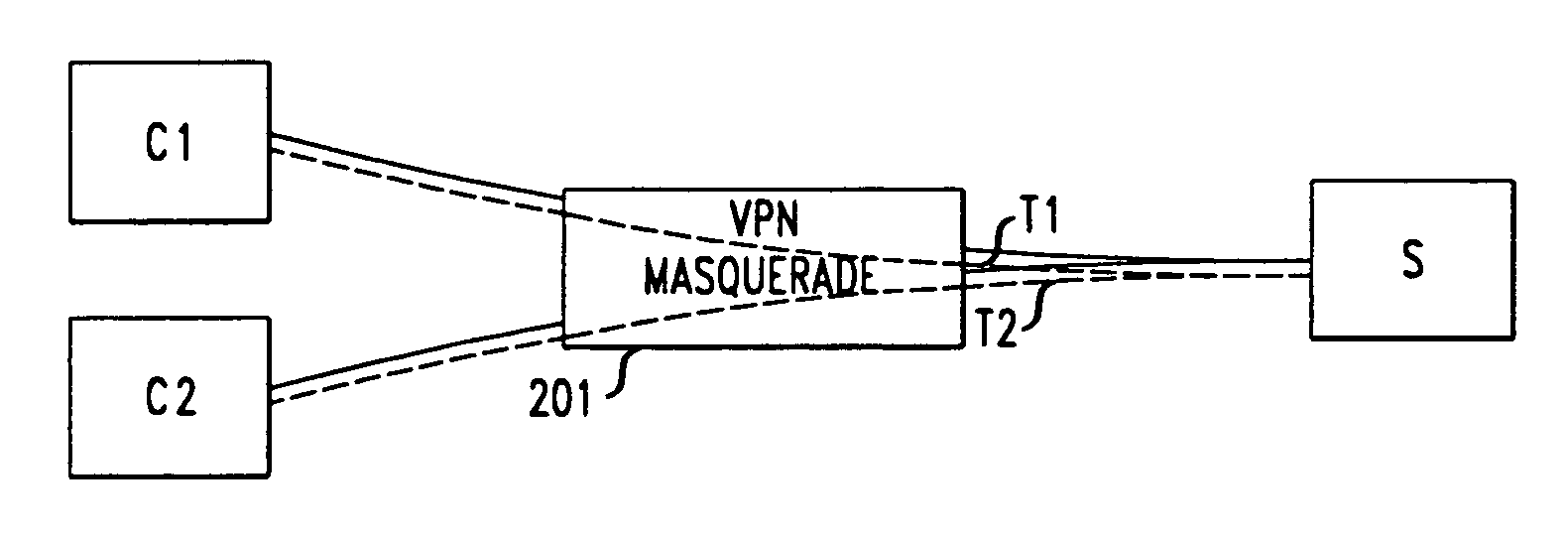

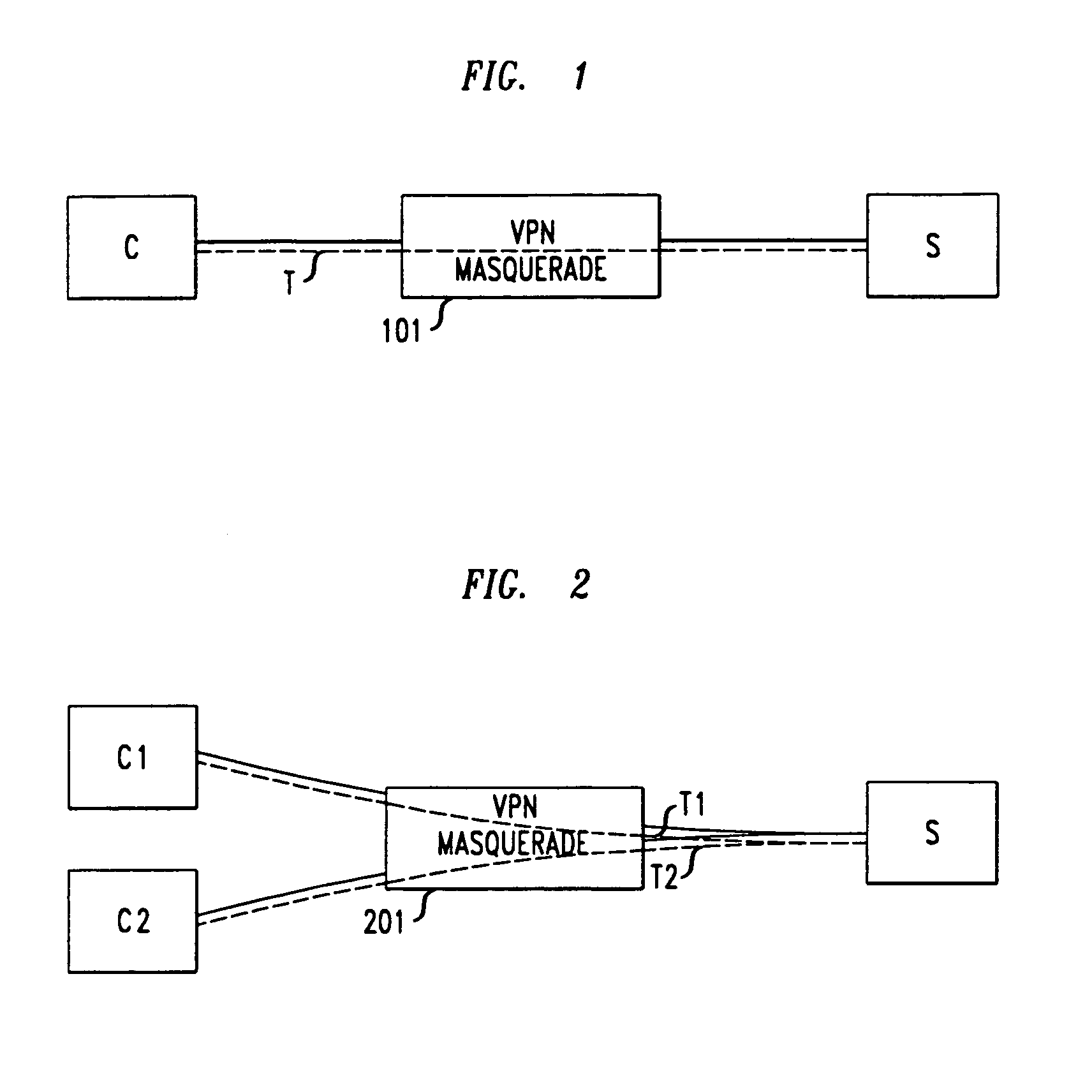

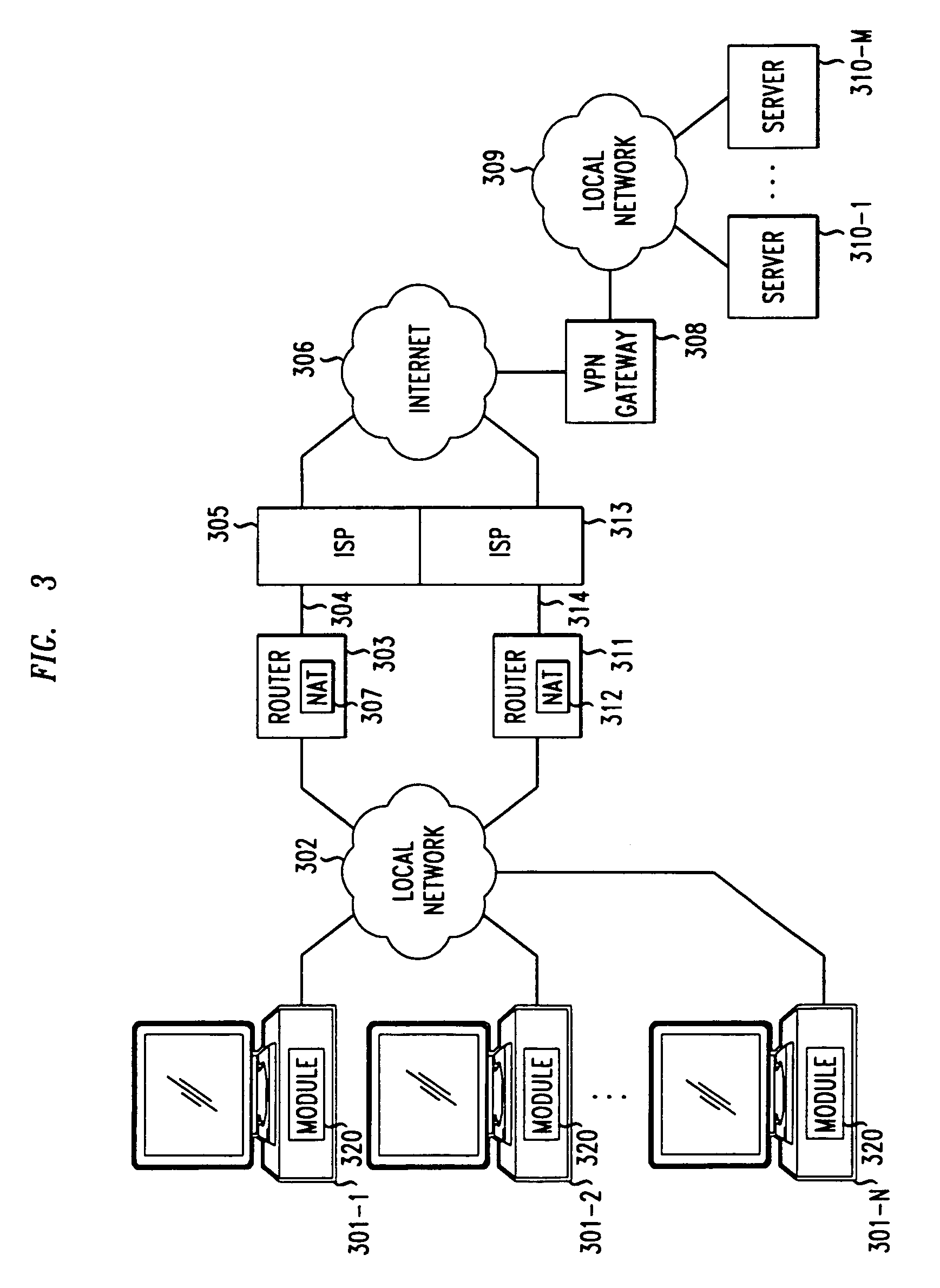

Method and apparatus for robust NAT interoperation with IPSEC'S IKE and ESP tunnel mode

InactiveUS7155740B2Solve the real problemDigital data processing detailsData switching by path configurationGNU/LinuxHeuristic

Linux's NAT (Network Address Translator) implementation, IP Masquerade, includes a VPN Masquerade feature that provides interoperation of NAT with IKE and ESP tunnel mode within the IPSec security protocol suite. VPN Masquerade uses heuristics to route packets from a server on the Internet to a client on a local network that shares access to the Internet with other clients over a common access link through a router running NAT. VPN Masquerade, however, is susceptible to crashes, collisions and race conditions that can disable IPSec communication. These are prevented, or recovery from such is automatically effected, by sending over a tunnel a control packet, a “ping”, from the client at one end of the tunnel to the server at the other end of the tunnel, and then waiting to send any packets other than a control packet over the tunnel until a responsive control packet is received from the server.

Owner:WSOU INVESTMENTS LLC +1

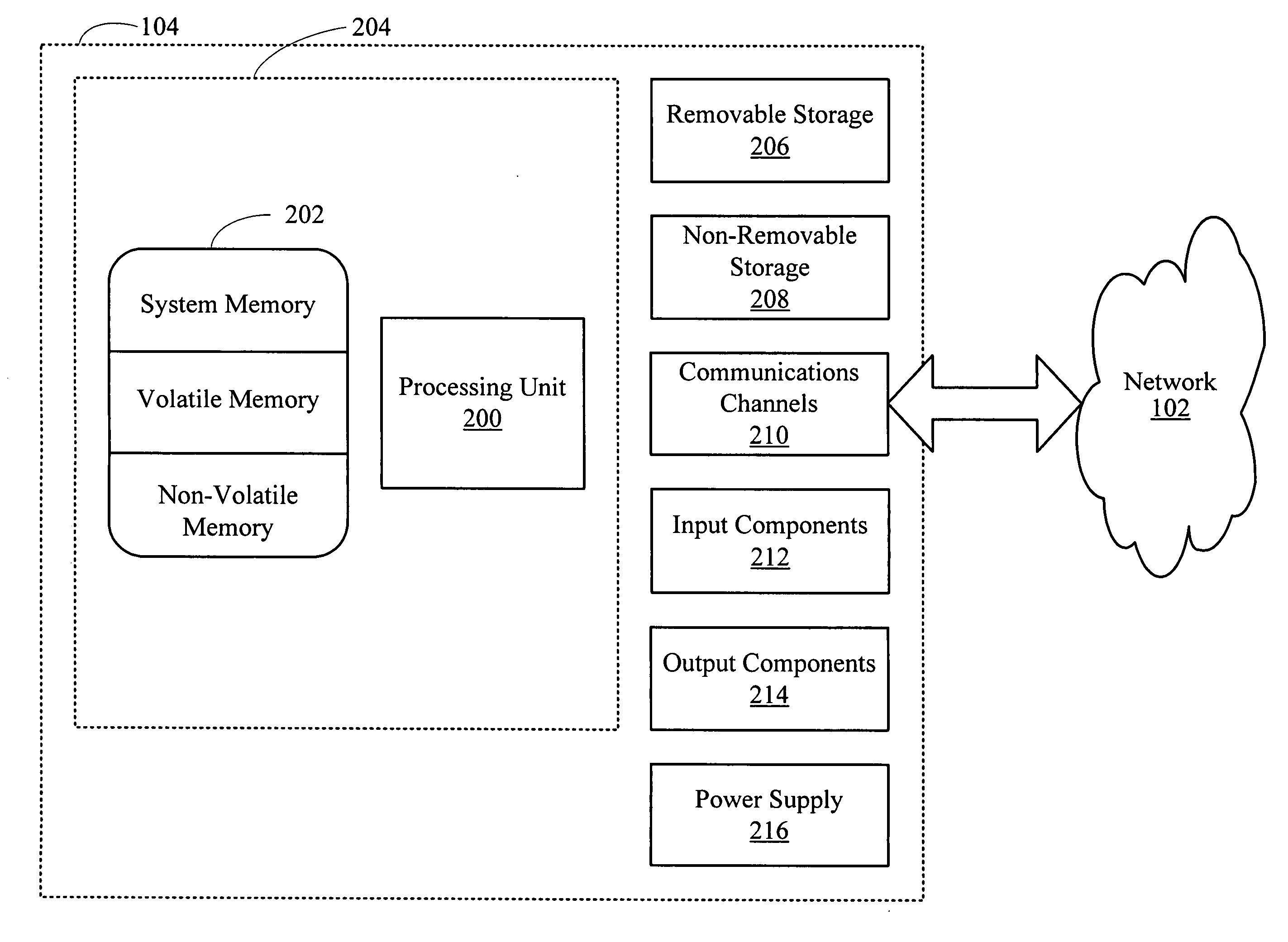

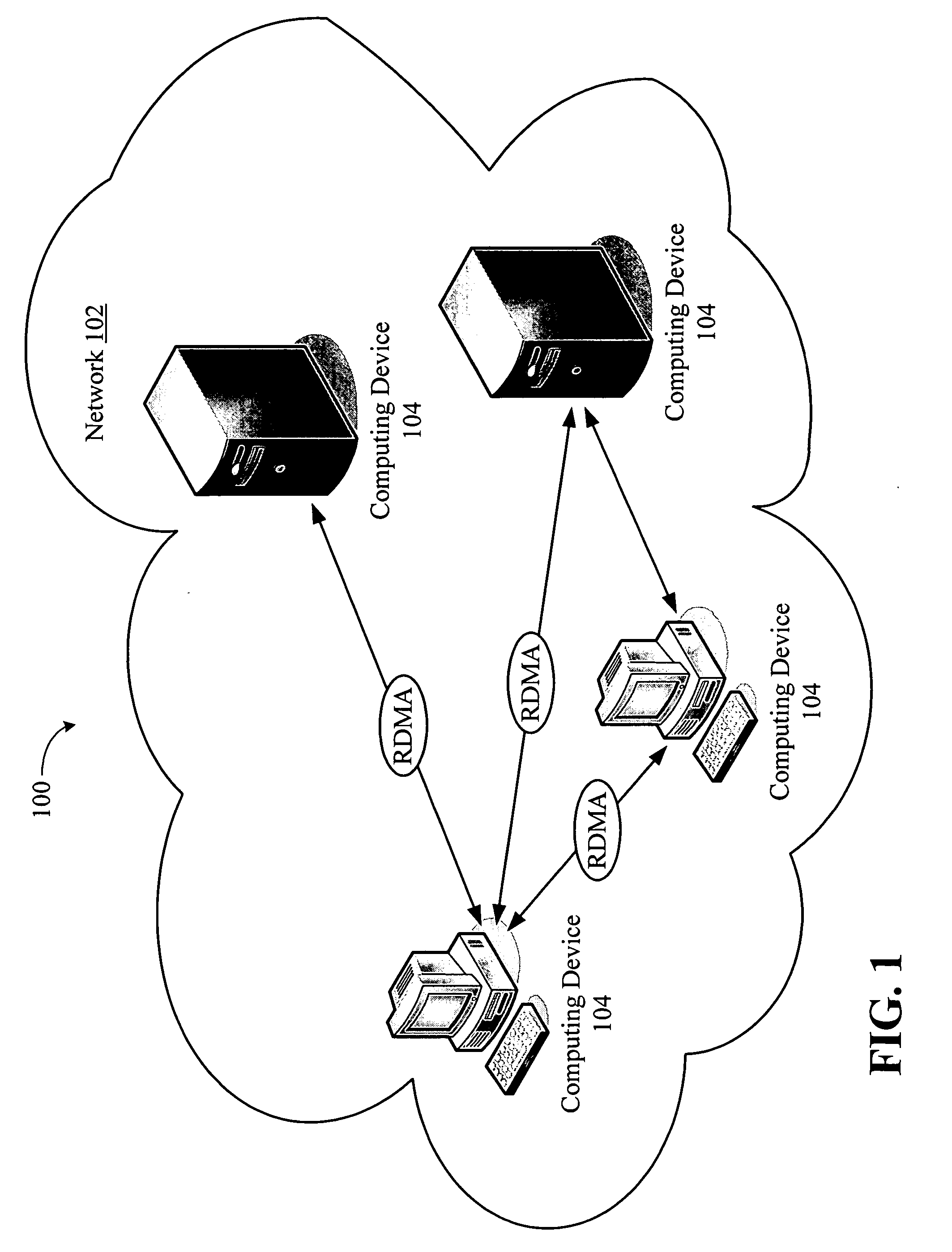

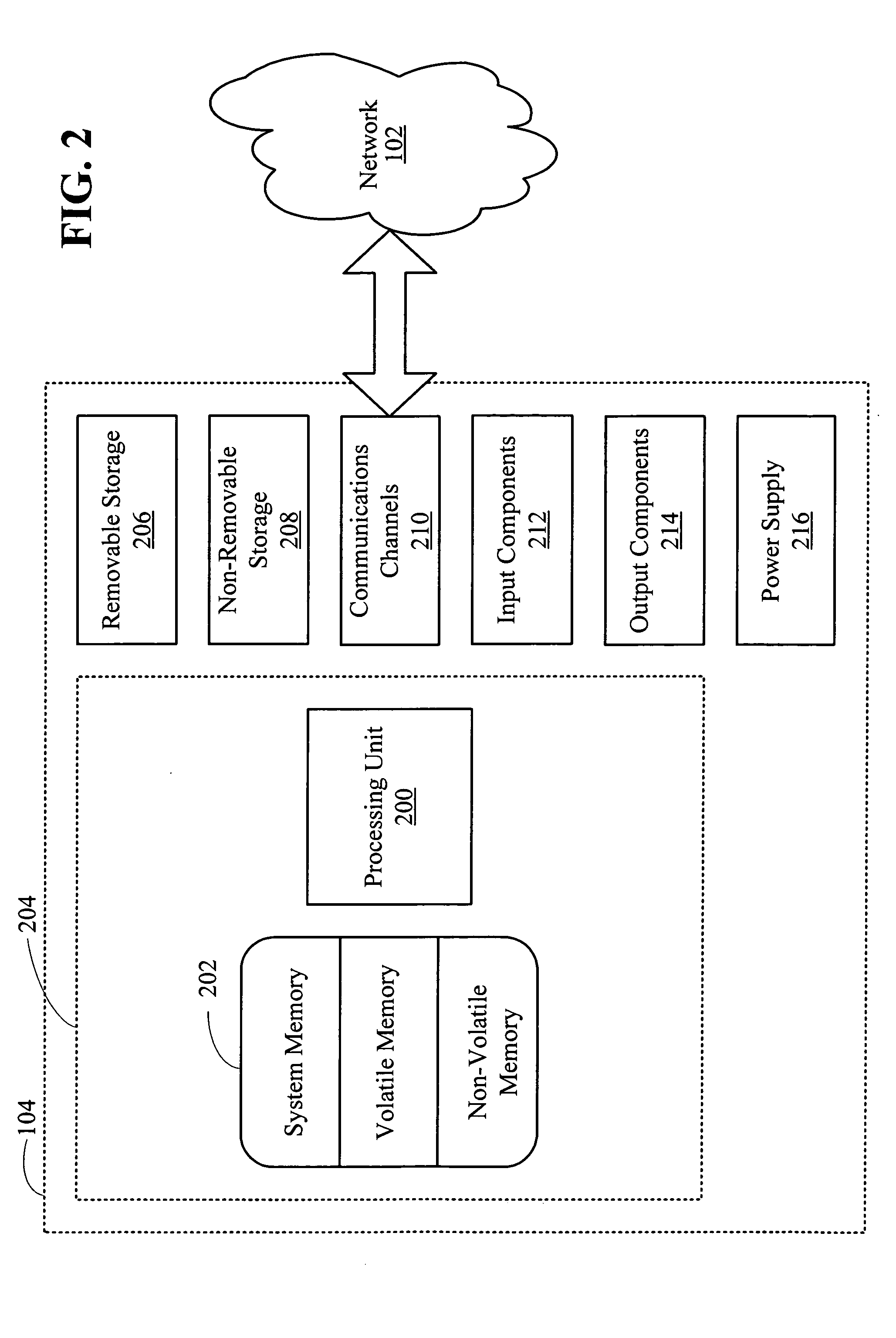

Method and system for transferring a packet stream to RDMA

InactiveUS20060256784A1Avoiding possible race conditionAvoid adjustmentMultiplex system selection arrangementsData switching by path configurationMulti processorSemantics

Disclosed are methods for handling RDMA connections carried over packet stream connections. In one aspect, I / O completion events are distributed among a number of processors in a multi-processor computing device, eliminating processing bottlenecks. For each processor that will accept I / O completion events, at least one completion queue is created. When an I / O completion event is received on one of the completion queues, the processor associated with that queue processes the event. In a second aspect, semantics of the interactions among a packet stream handler, an RDMA layer, and an RNIC are defined to control RDMA closures and thus to avoid implementation errors. In a third aspect, semantics are defined for transferring an existing packet stream connection into RDMA mode while avoiding possible race conditions. The resulting RNIC architecture is simpler than is traditional because the RNIC never needs to process both streaming messages and RDMA-mode traffic at the same time.

Owner:MICROSOFT TECH LICENSING LLC

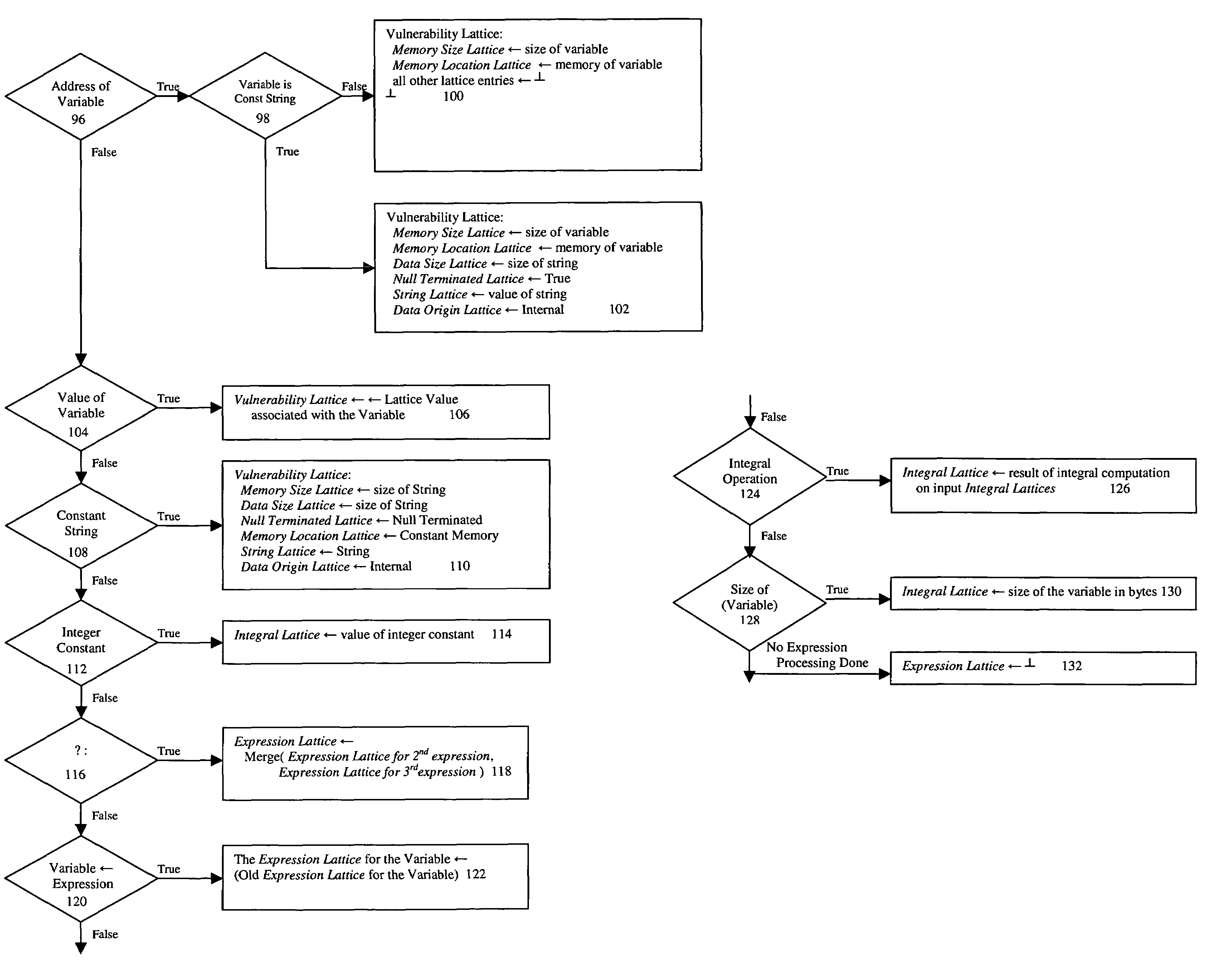

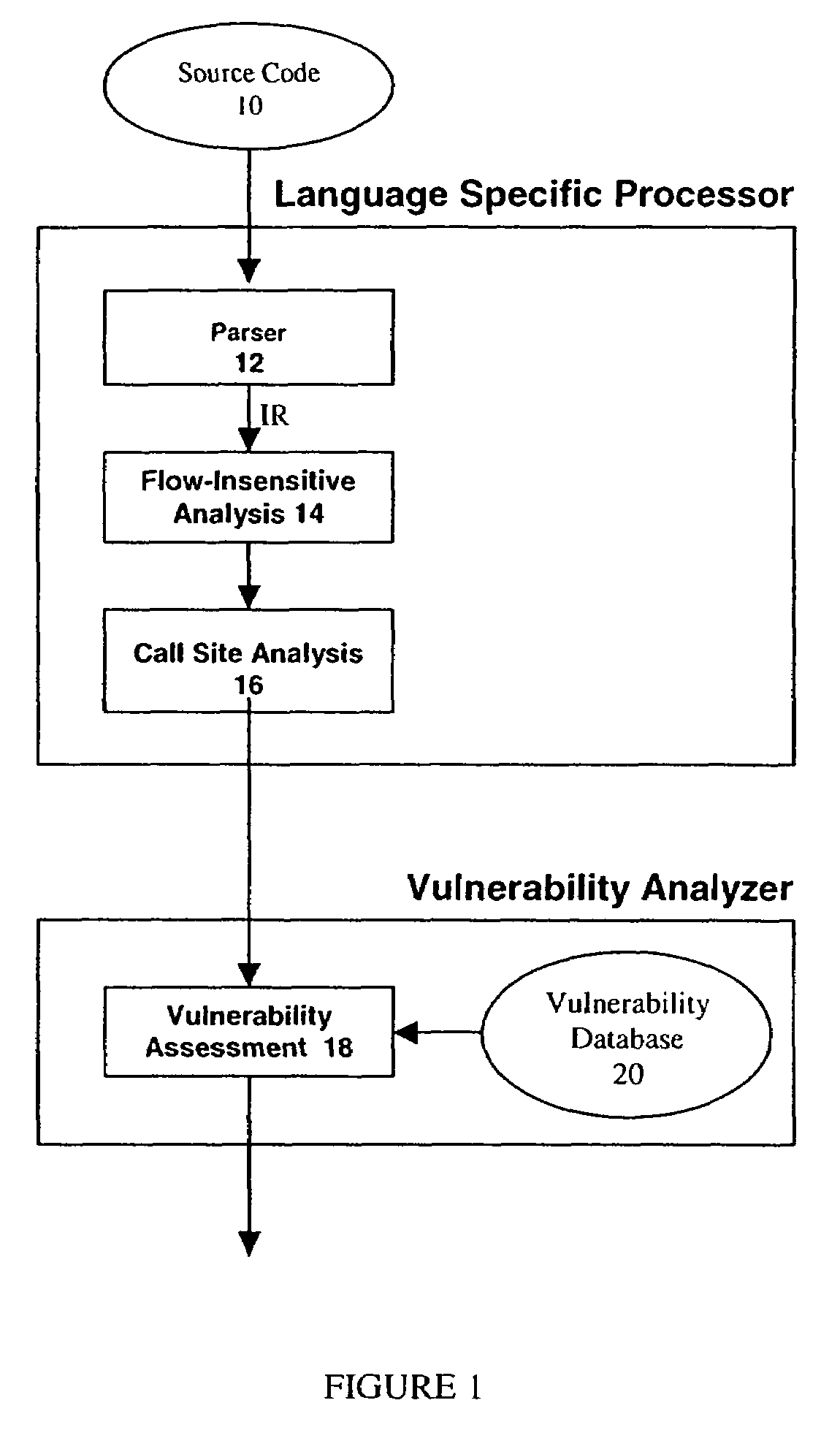

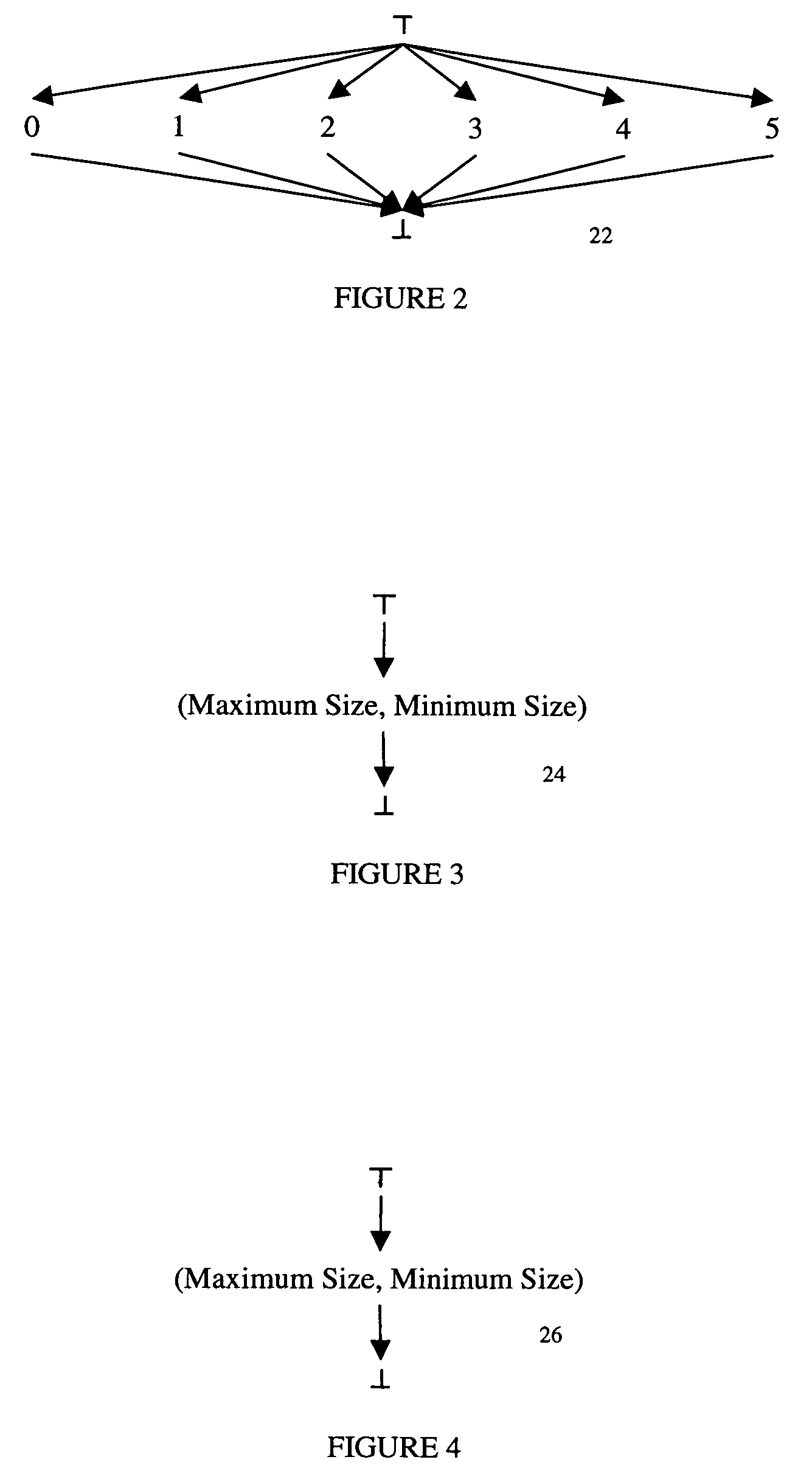

Method and system for detecting race condition vulnerabilities in source code

A method and system of detecting vulnerabilities in source code. Source code is parsed into an intermediate representation. Models are derived for the code and the models are then analyzed in conjunction with pre-specified rules about the routines to determine if the routines posses one or more of pre-selected vulnerabilities.

Owner:IBM CORP

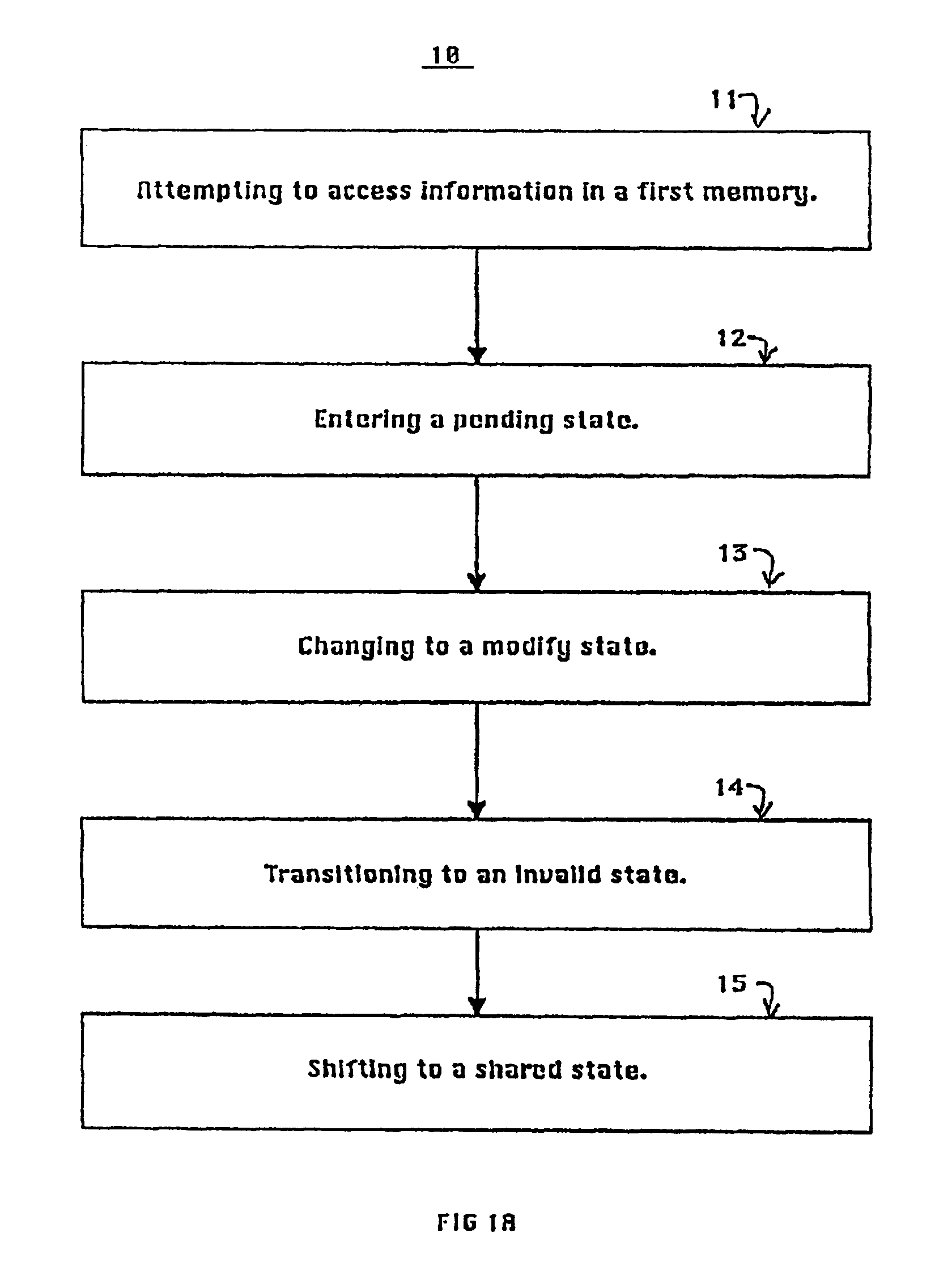

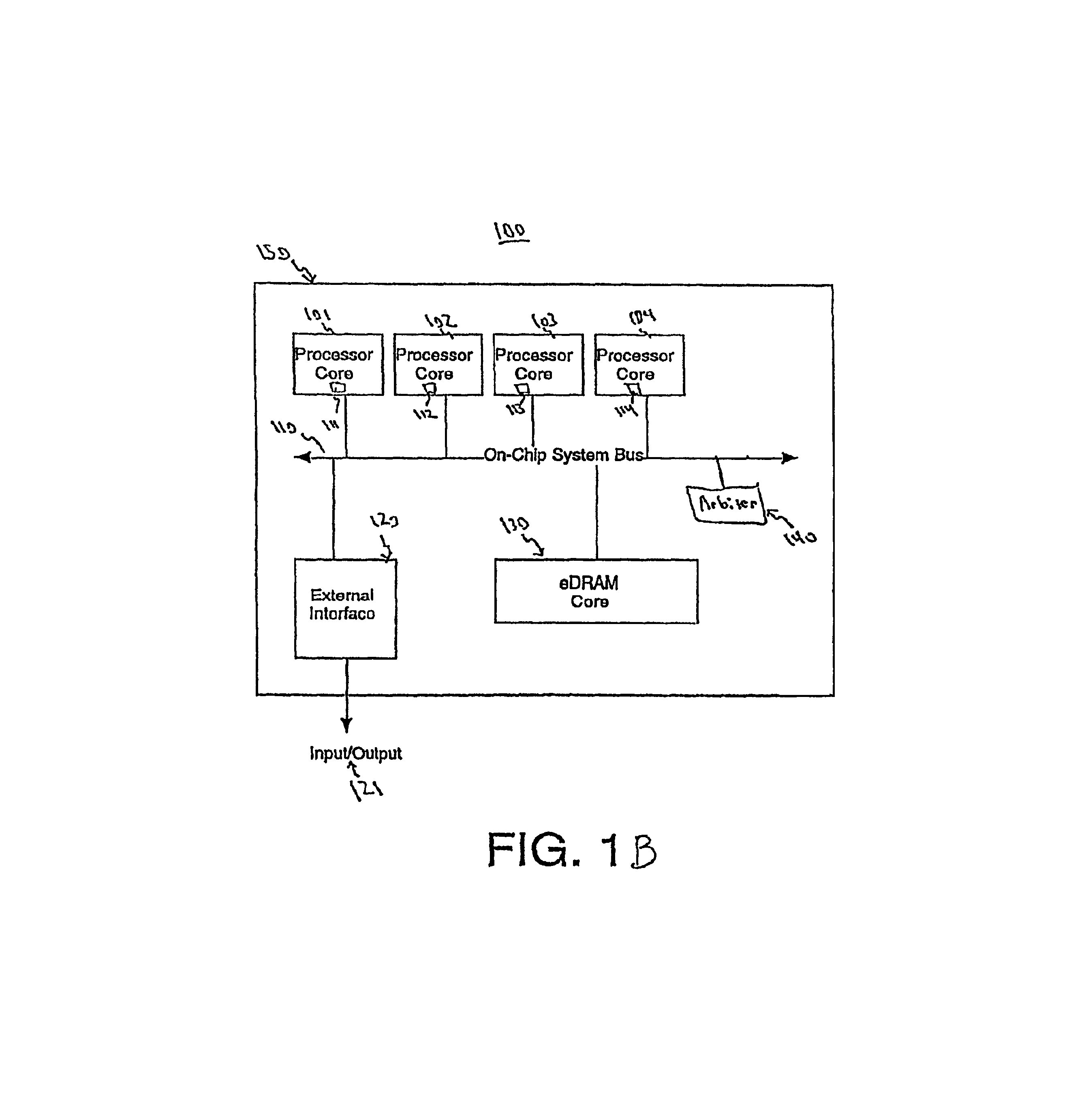

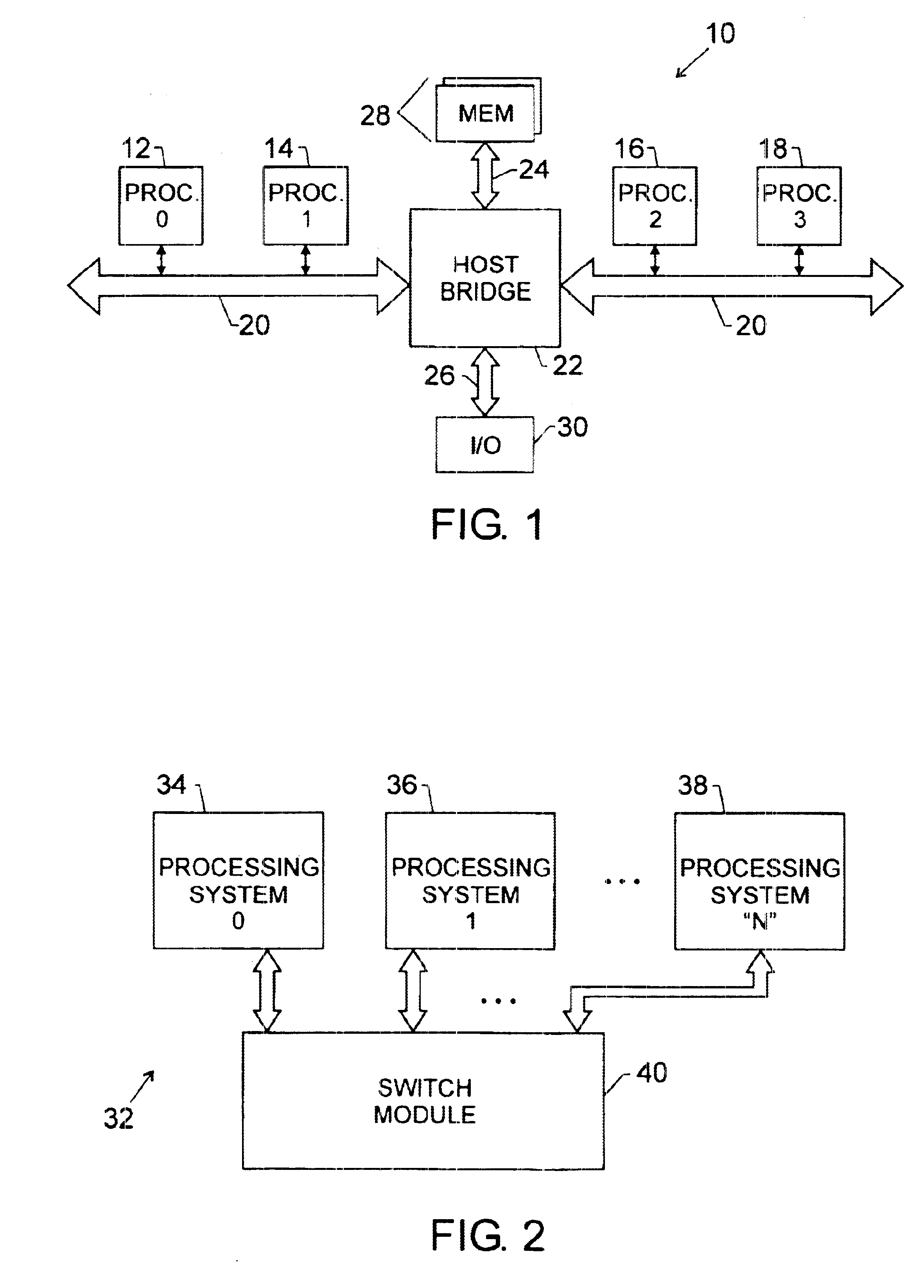

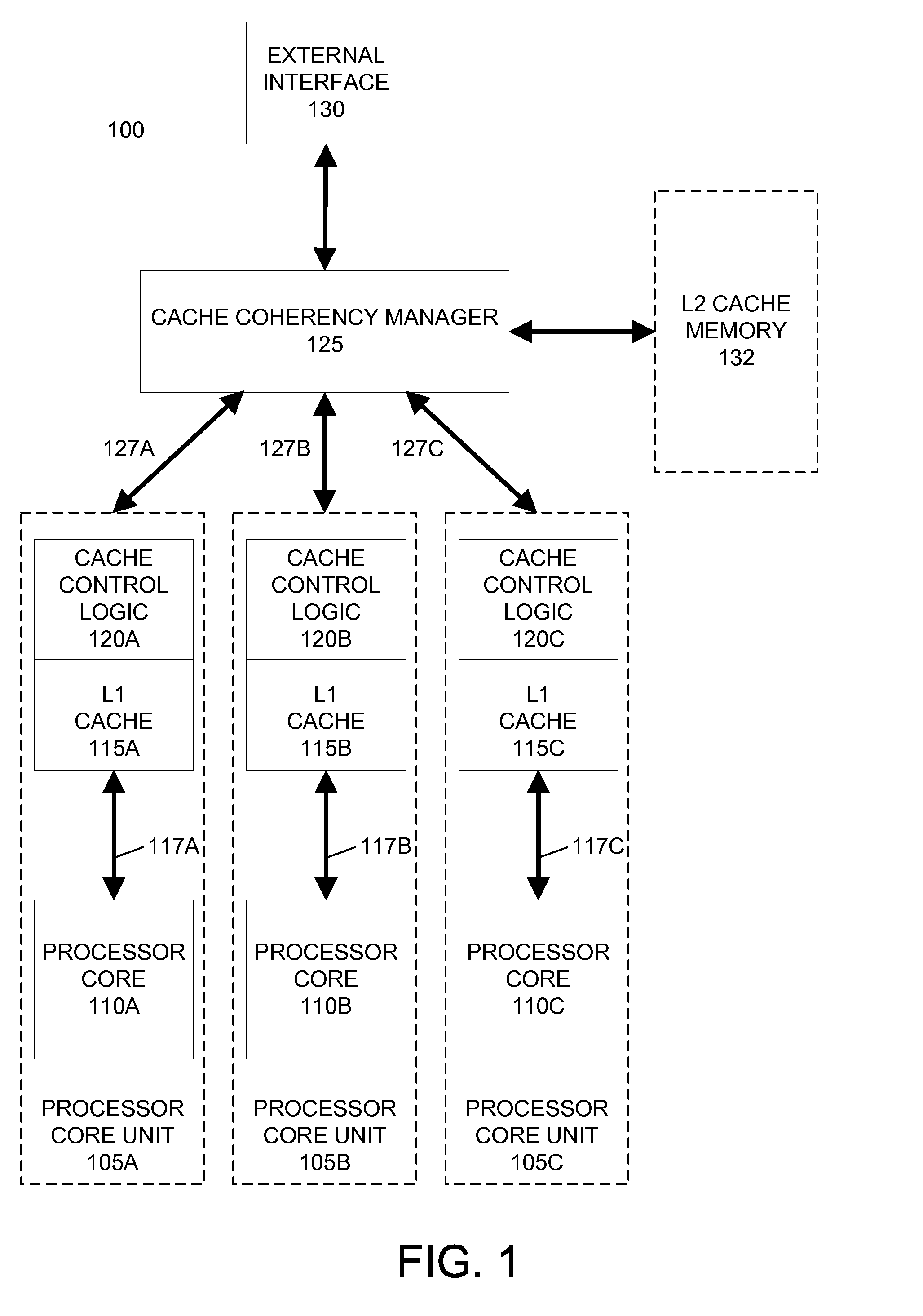

Streamlined cache coherency protocol system and method for a multiple processor single chip device

InactiveUS6918012B2Prevent race conditionAvoid accessMemory adressing/allocation/relocationUnauthorized memory use protectionMulti processorParallel computing

A streamlined cache coherency protocol system and method for a multiple processor single chip device. There are three primary memory unit (e.g., a cache line) states (modified, shared, and invalid) and three intermediate memory unit pending states. The pending states are used by the present invention to prevent race conditions that may develop during the completion of a transaction. The pending states “lock out” the memory unit (e.g., prevent access by other agents to a cache line) whose state is in transition between two primary states, thus ensuring coherency protocol correctness. Transitions between states are governed by a series of request and reply or acknowledgment messages. The memory unit is placed in a pending state while appropriate measures are taken to ensure access takes place at an appropriate time. For example, a modification occurs only when other agents can not access the particular memory unit (e.g., a cache line).

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

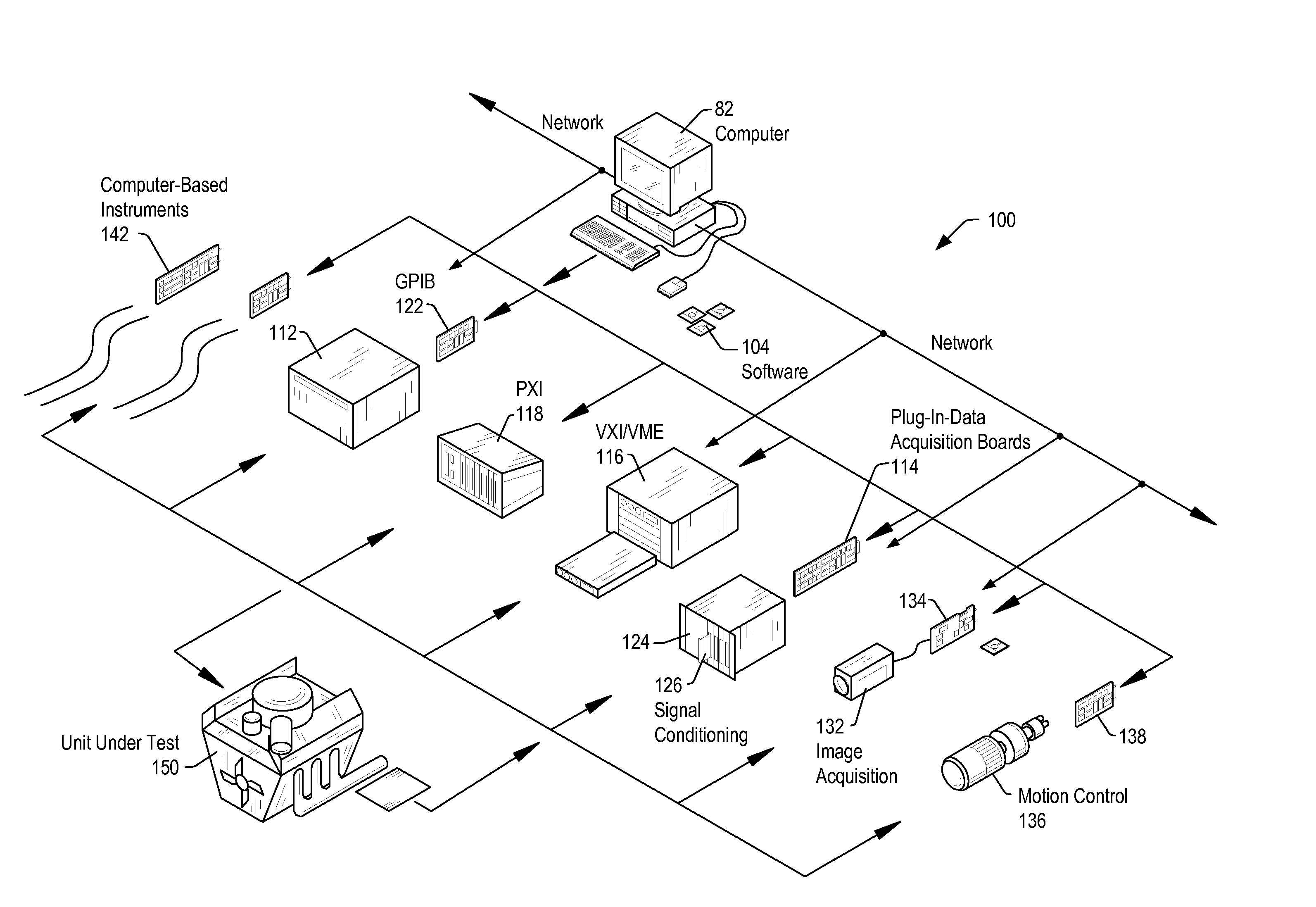

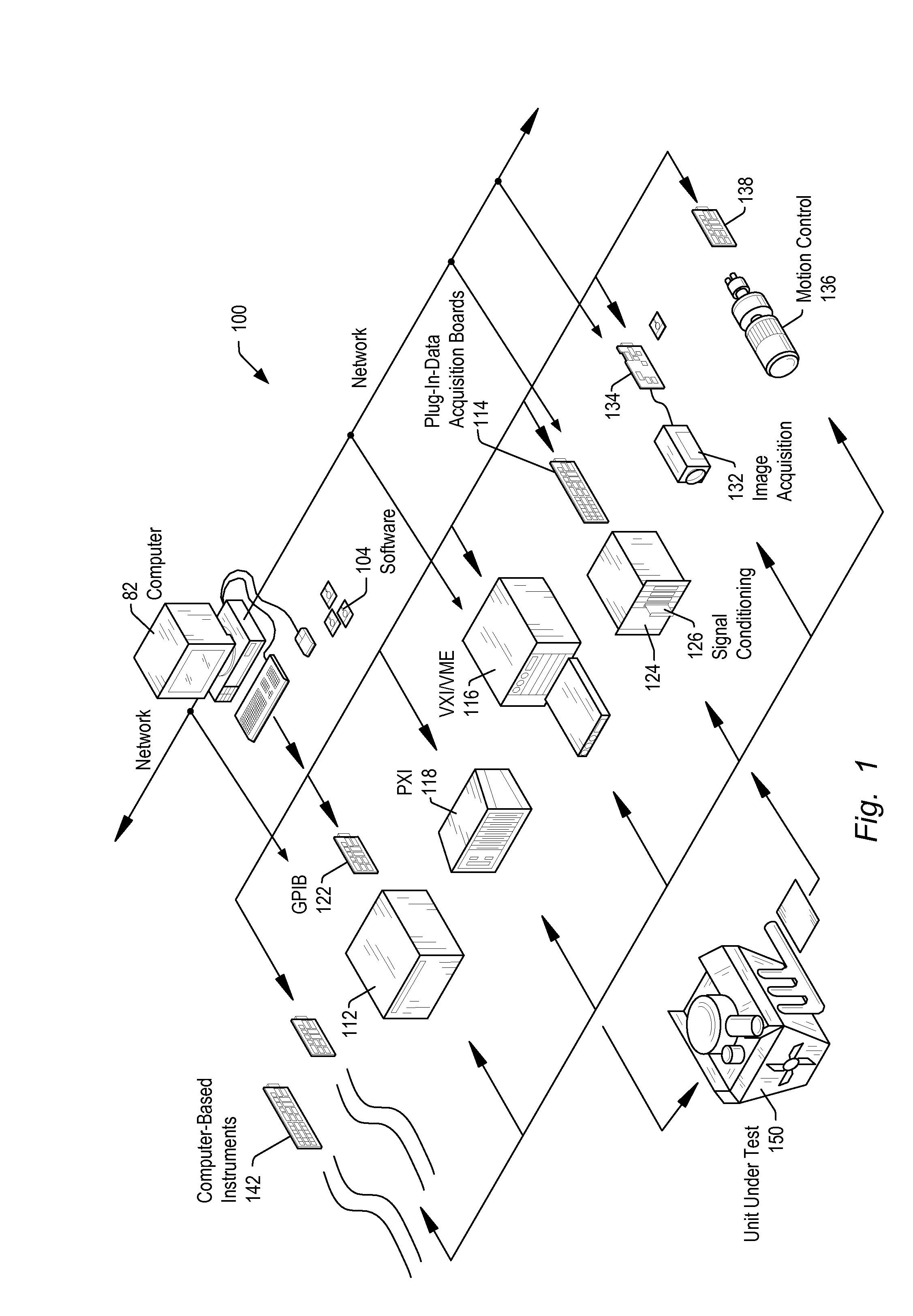

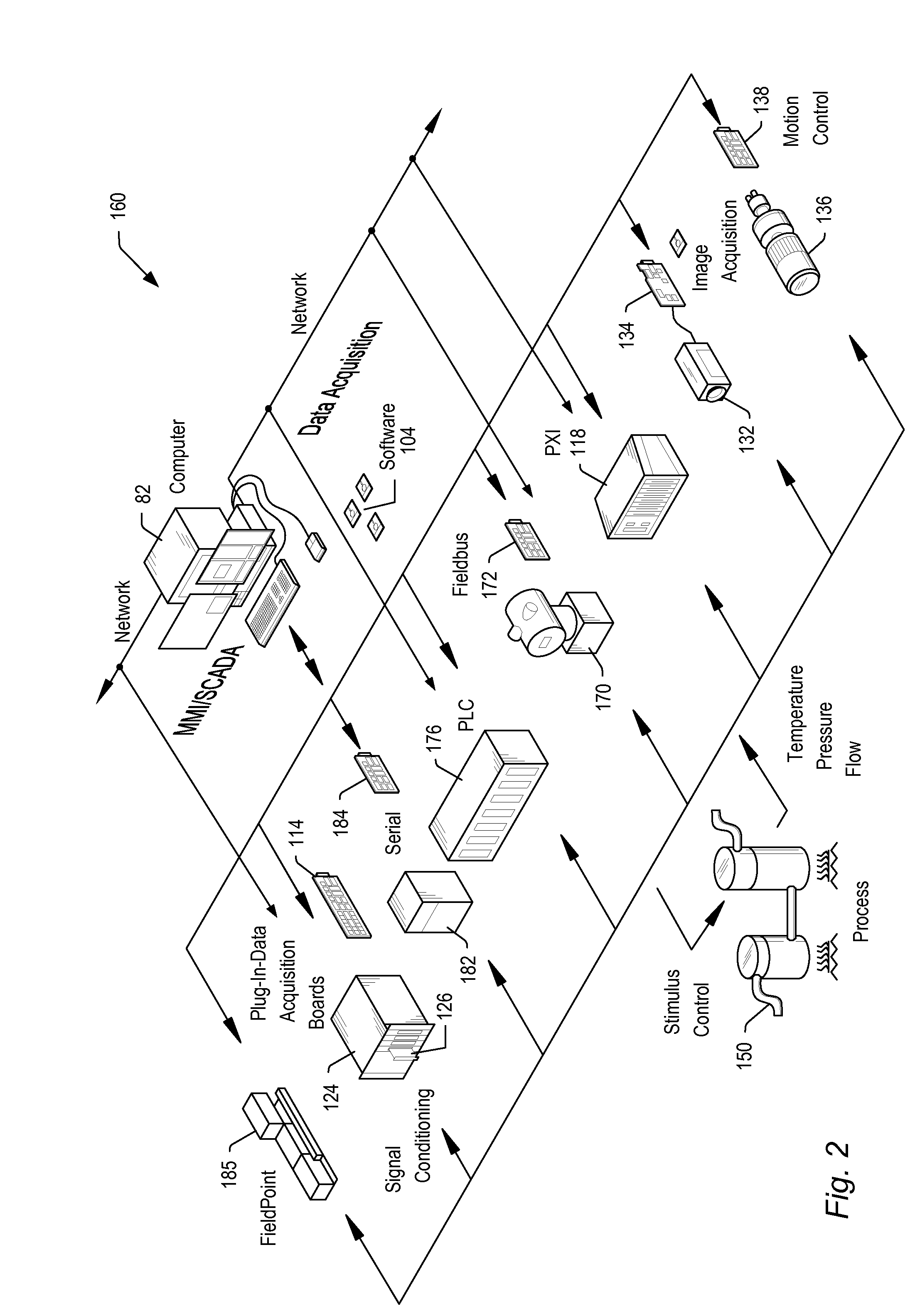

Methods for Data Acquisition Systems in Real Time Applications

ActiveUS20110029101A1Programme controlSampled-variable control systemsProgram instructionControl signal

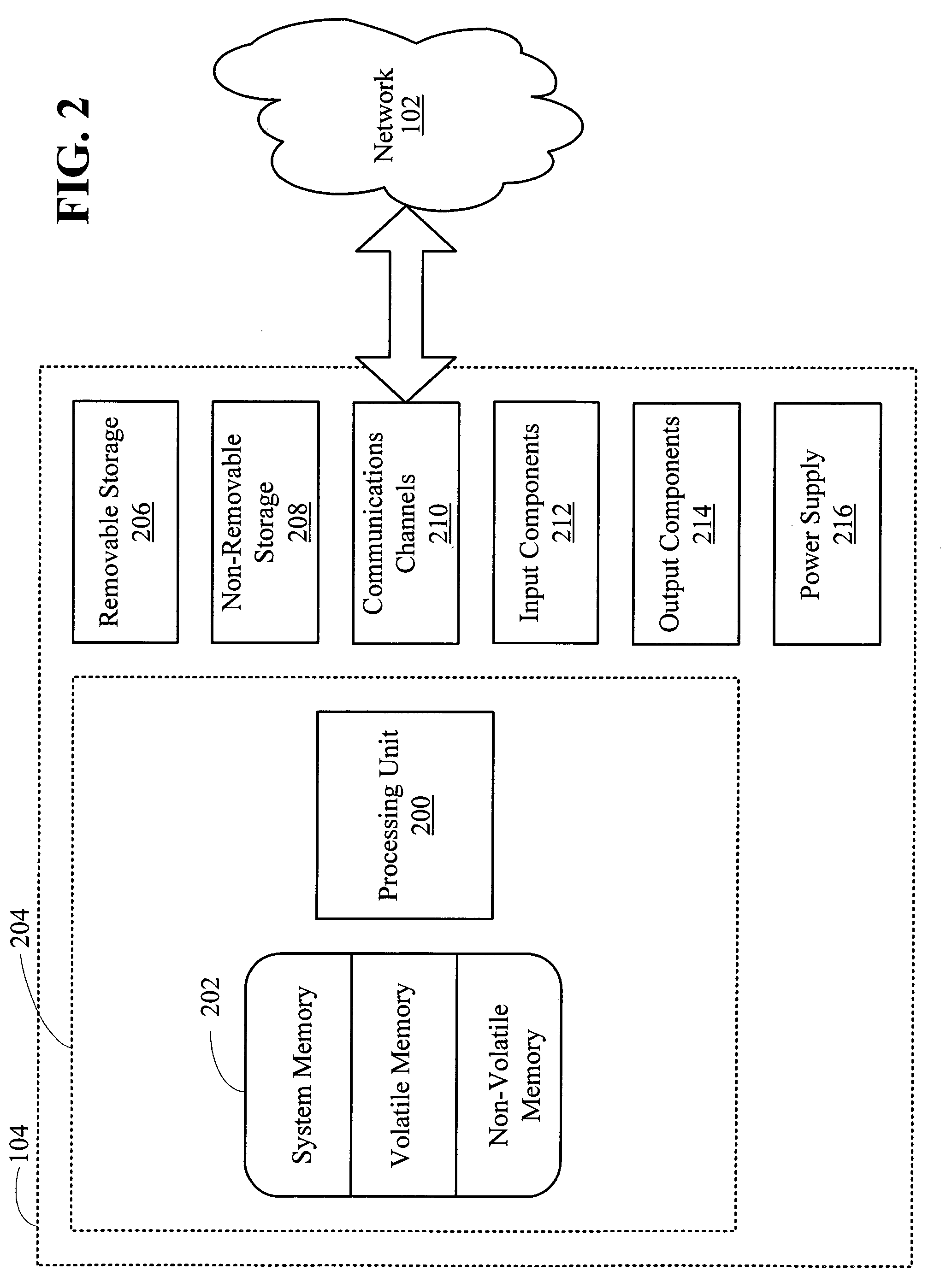

A system may include a processing unit executing program instructions (SW), a data acquisition (DAQ) hardware device for acquiring sample data and / or generating control signals, and host memory configured to store data samples and various data associated with the DAQ and processor operations. The DAQ device may push HW status information to host memory upon being triggered by predetermined events taking place in the DAQ device, e.g. timing events or interrupts, to avoid or reduce SW reads to the DAQ device. The DAQ device may update dedicated buffers in host memory with status data on any of these events. The status information pushed to memory may be read in a manner that allows detection of race conditions. Interrupts generated by the DAQ device may be similarly handled. Upon generating an interrupt, the DAQ device may gather information required to handle the interrupt, and push the information into system memory, along with information identifying the interrupt. SW may read system memory for this information, and handle the interrupts as required without having to query the DAQ device.

Owner:NATIONAL INSTRUMENTS

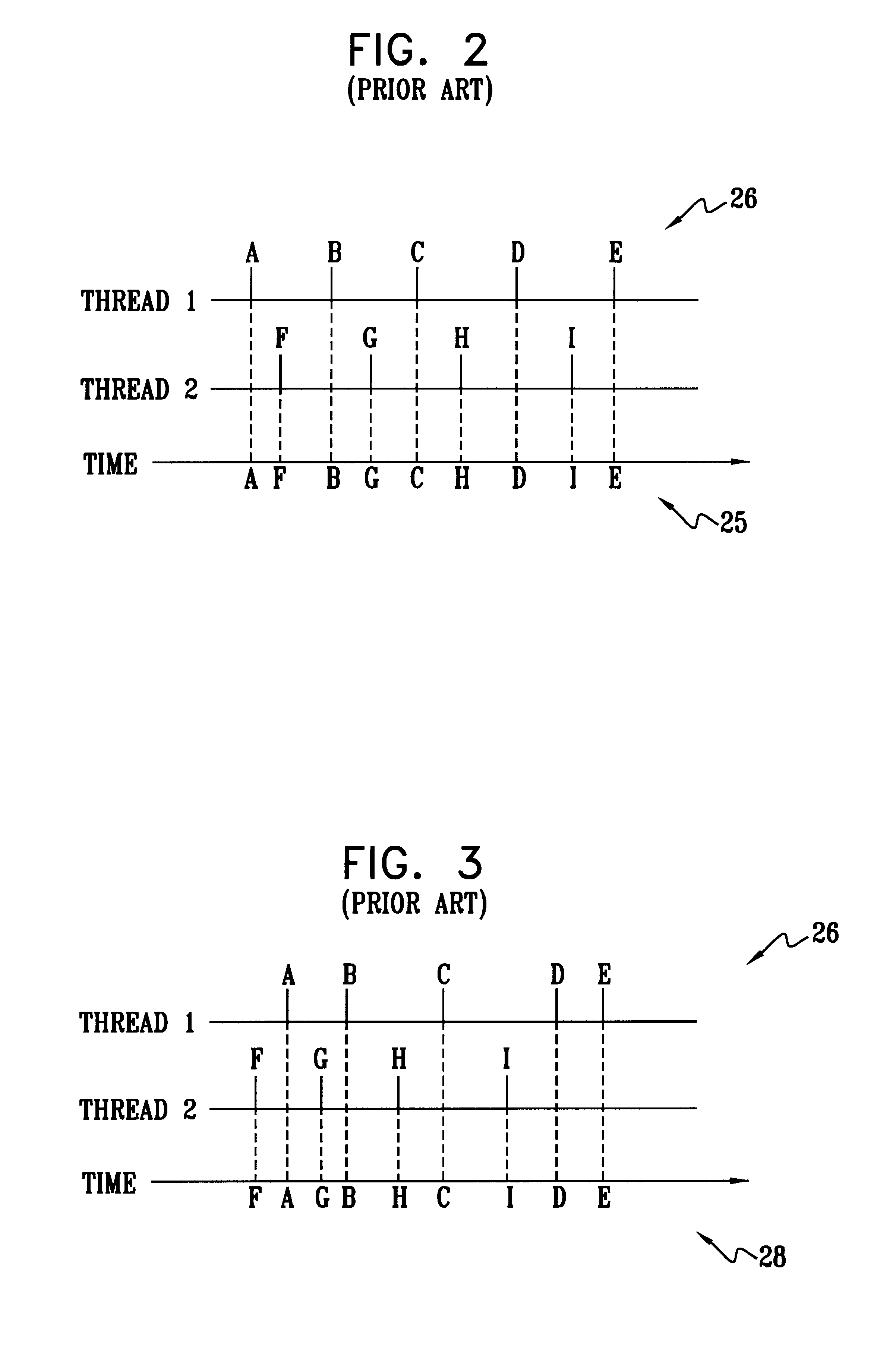

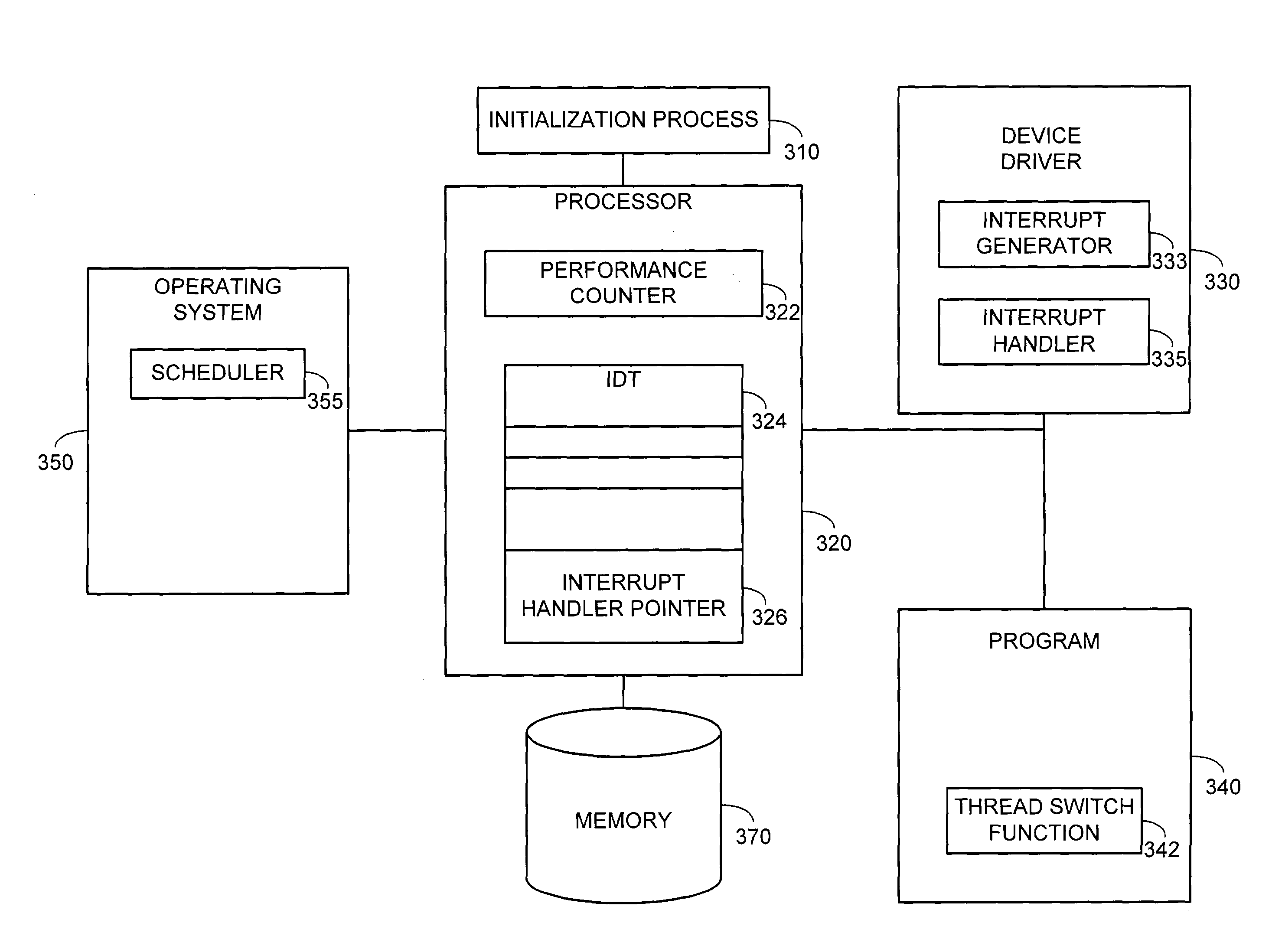

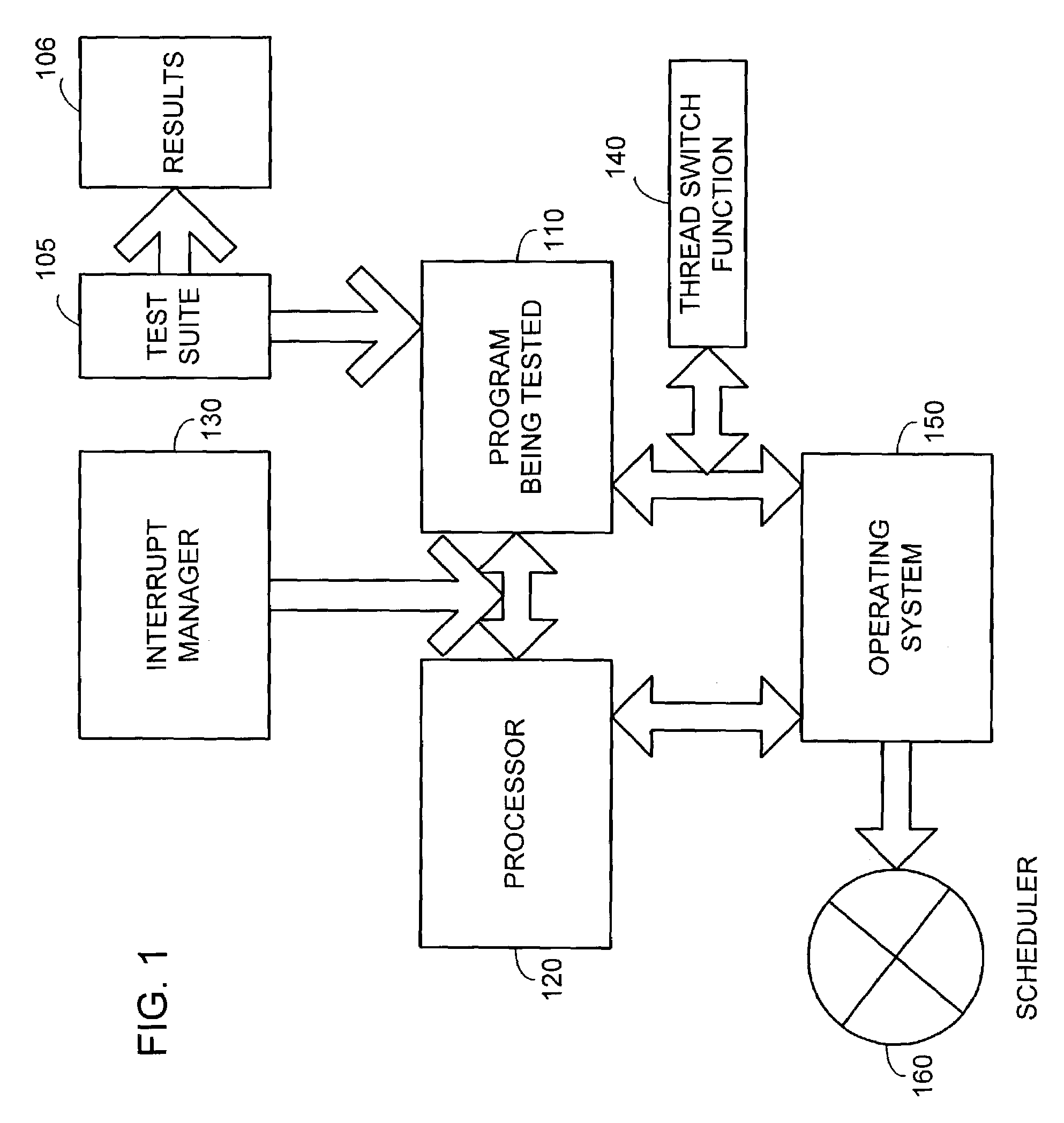

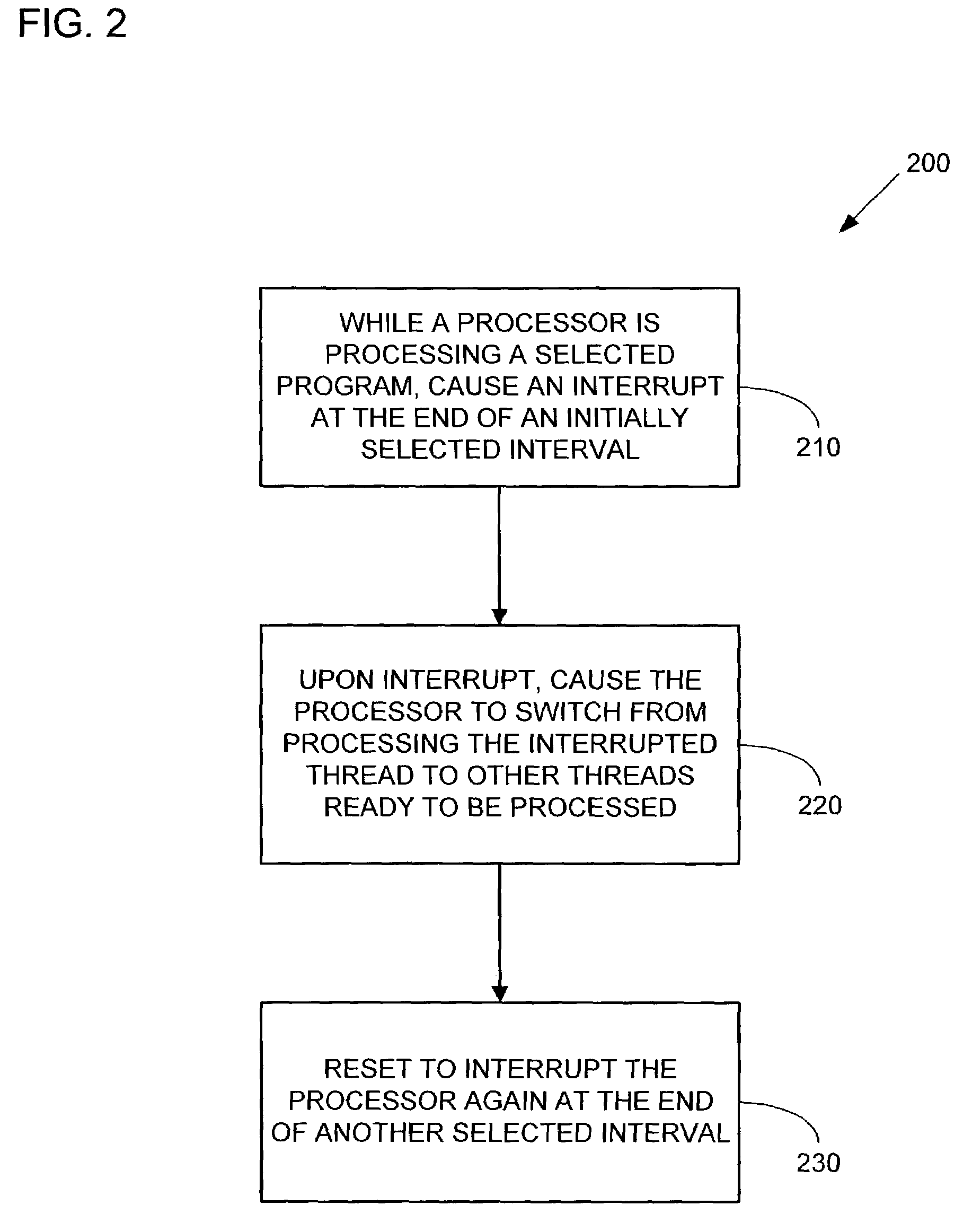

Tools and methods for discovering race condition errors

InactiveUS7174554B2Resistance/reactance/impedenceDigital computer detailsOperational systemUser input

Tools and methods are described herein for discovering race condition errors in a software program. The errors are discovered by deliberately causing a processor executing the test program to switch threads at intervals other than normally scheduled by an operating system. The thread switching is caused upon occurrence of selected events. The intervals may be selected automatically or with user input. Furthermore, thread switching may be caused during conditions more likely to cause race condition errors. For example, thread switches may be caused between threads that share control of a memory device or while the processor is executing instructions related to synchronization tools (e.g. locks, mutex, etc.).

Owner:MICROSOFT TECH LICENSING LLC

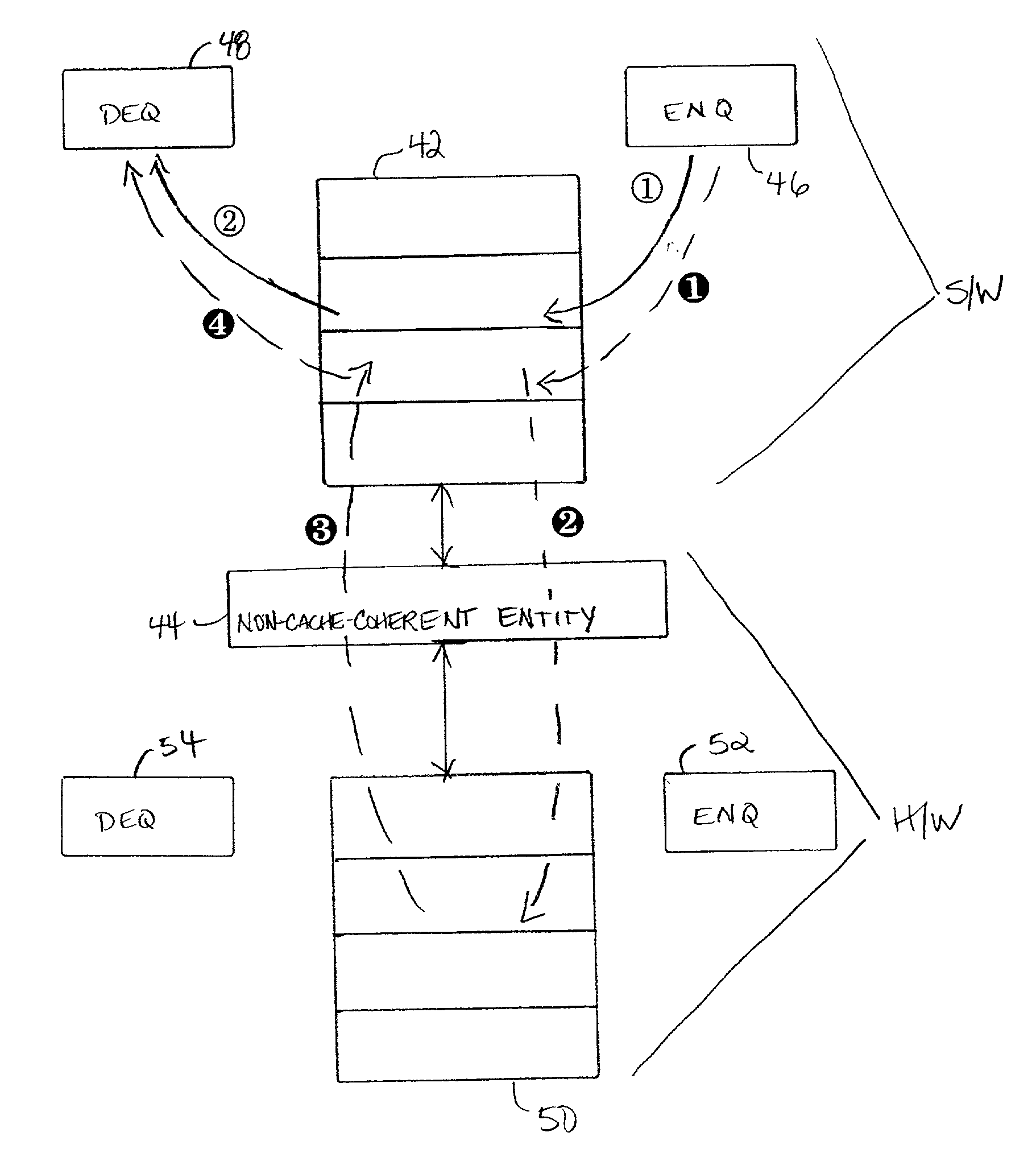

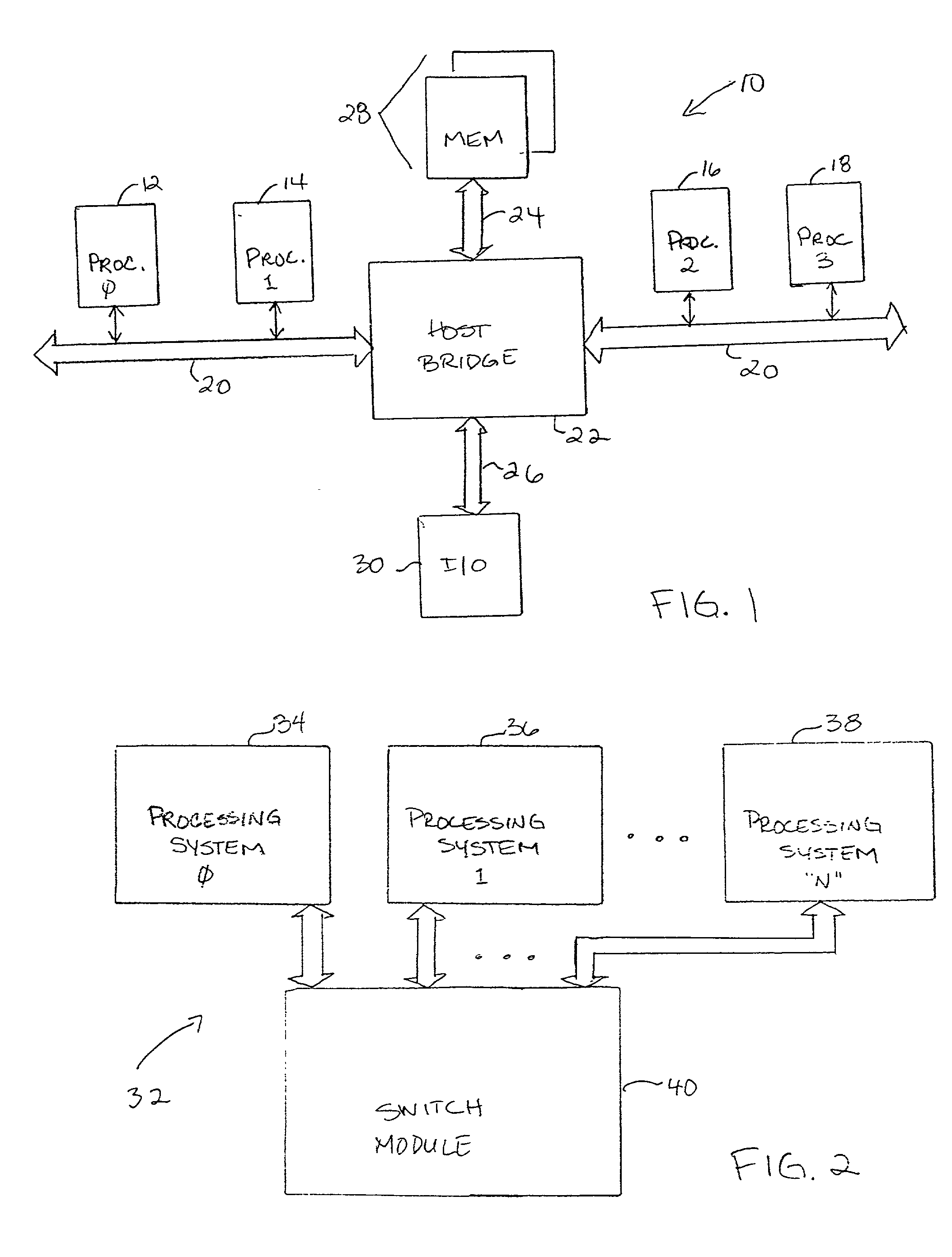

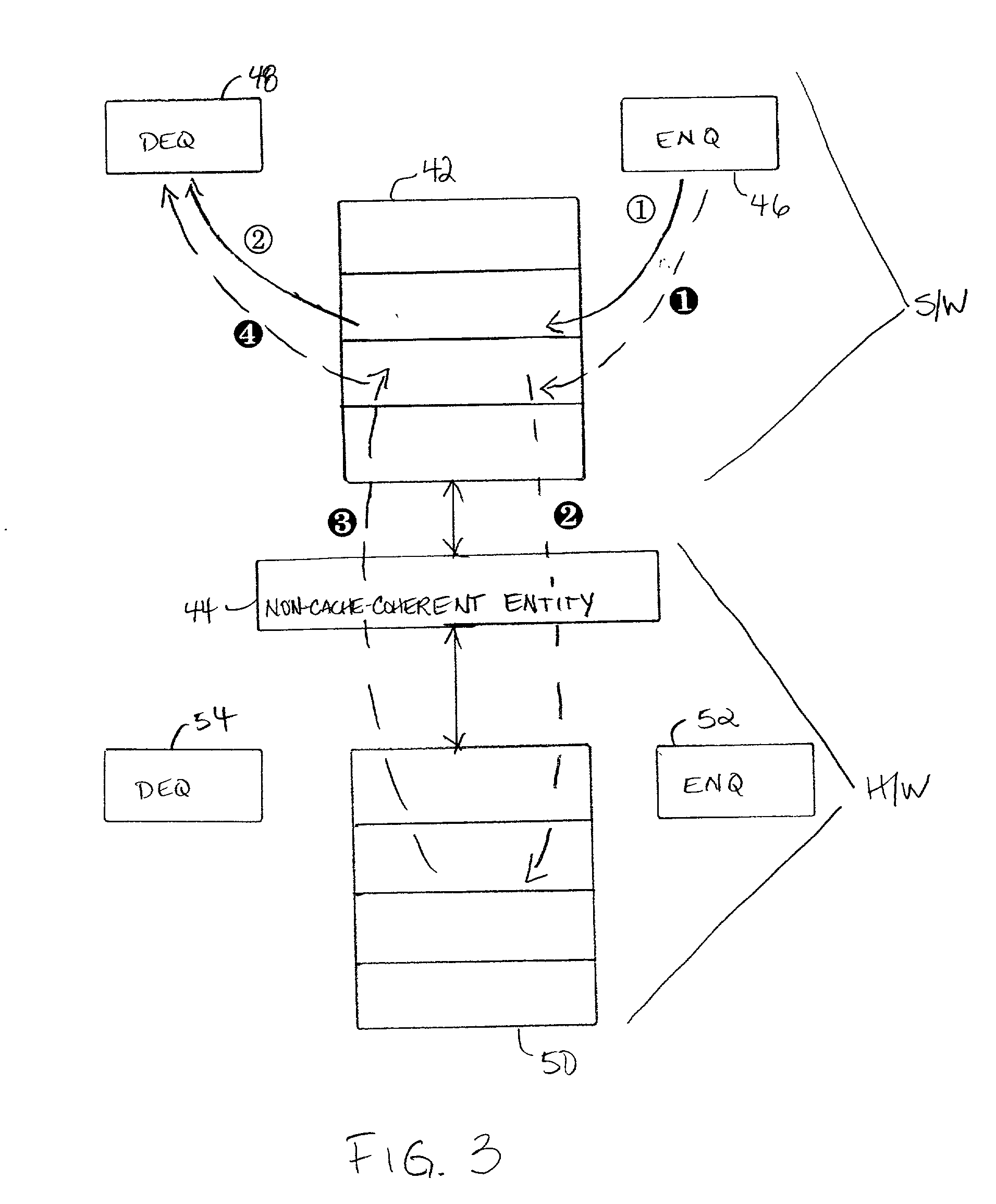

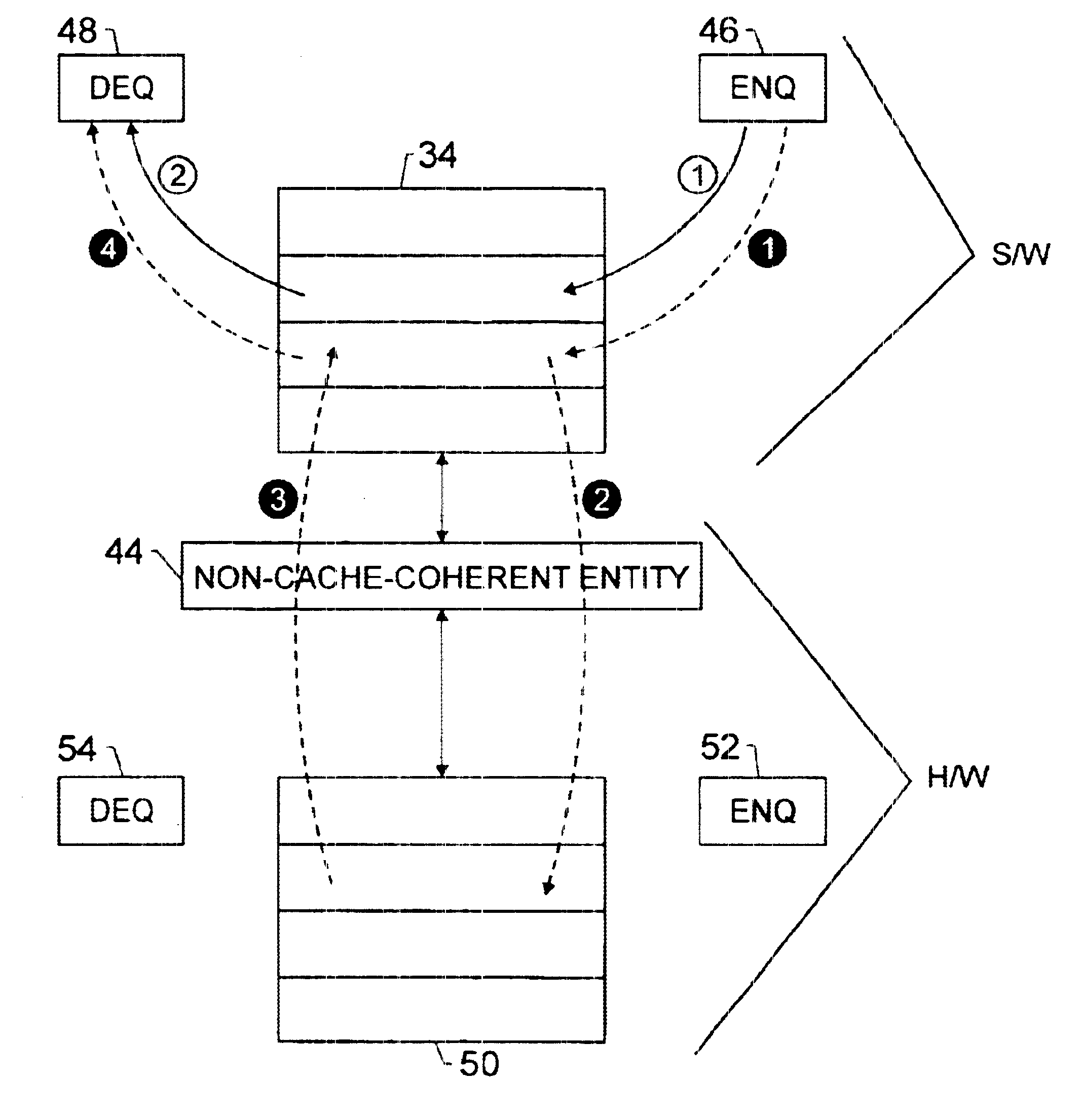

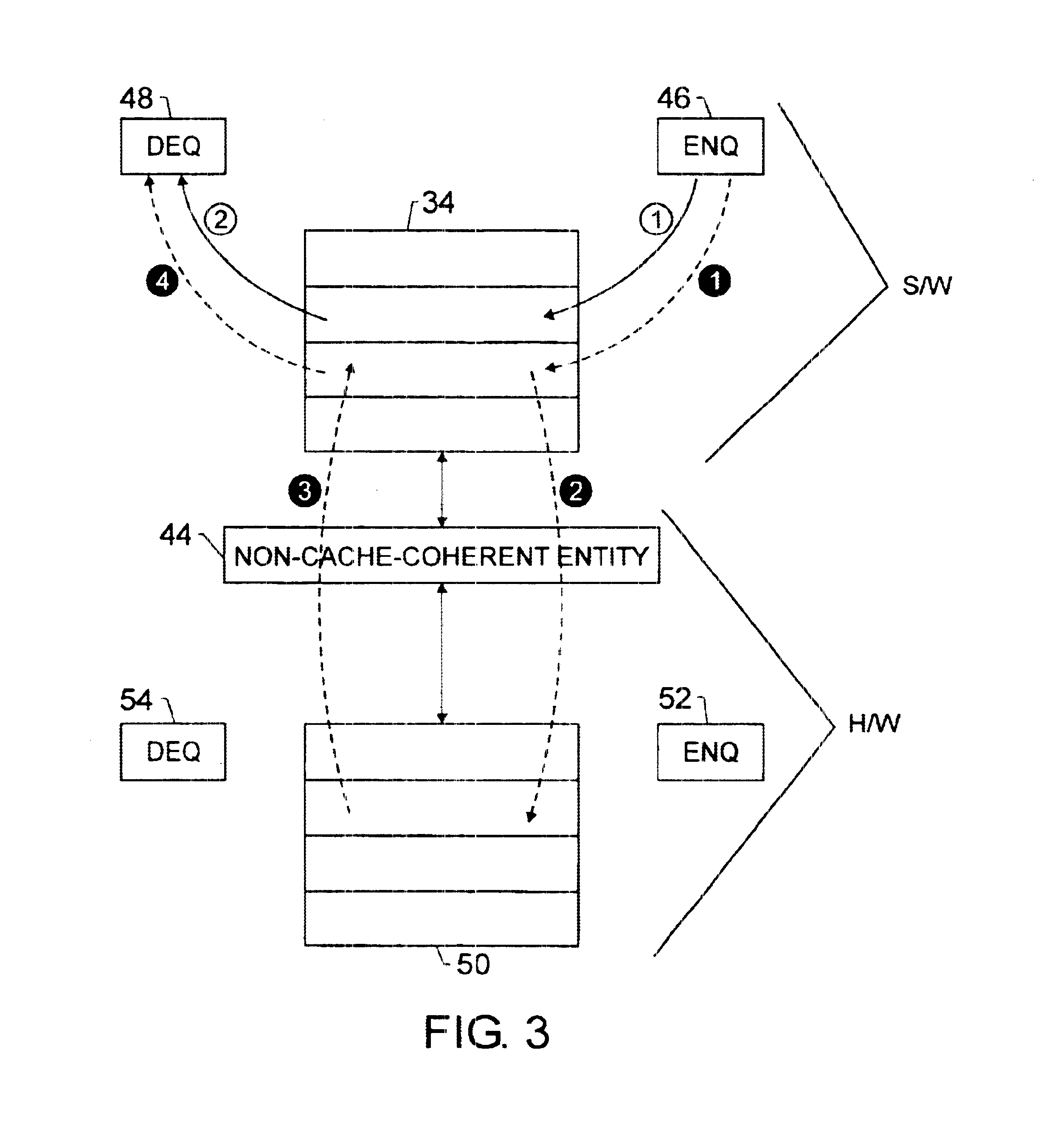

Concurrent non-blocking FIFO array

InactiveUS20030065892A1Memory systemsInput/output processes for data processingRace conditionDistributed computing

A technique for providing concurrent non-blocking access to a circular queue is provided. The concurrent non-blocking circular queue also may be configured such that cache-coherent requesters and a non-cache-coherent requester (e.g., software and hardware) both may concurrently access the queue. Further, the queue may be configured such that the probability of occurrence of the ABA race condition may be minimized.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Method and apparatus for verifying data local to a single thread

InactiveUS20020129306A1Ensuring validityValidity can be determinedError detection/correctionSoftware engineeringProgram analysisSource code

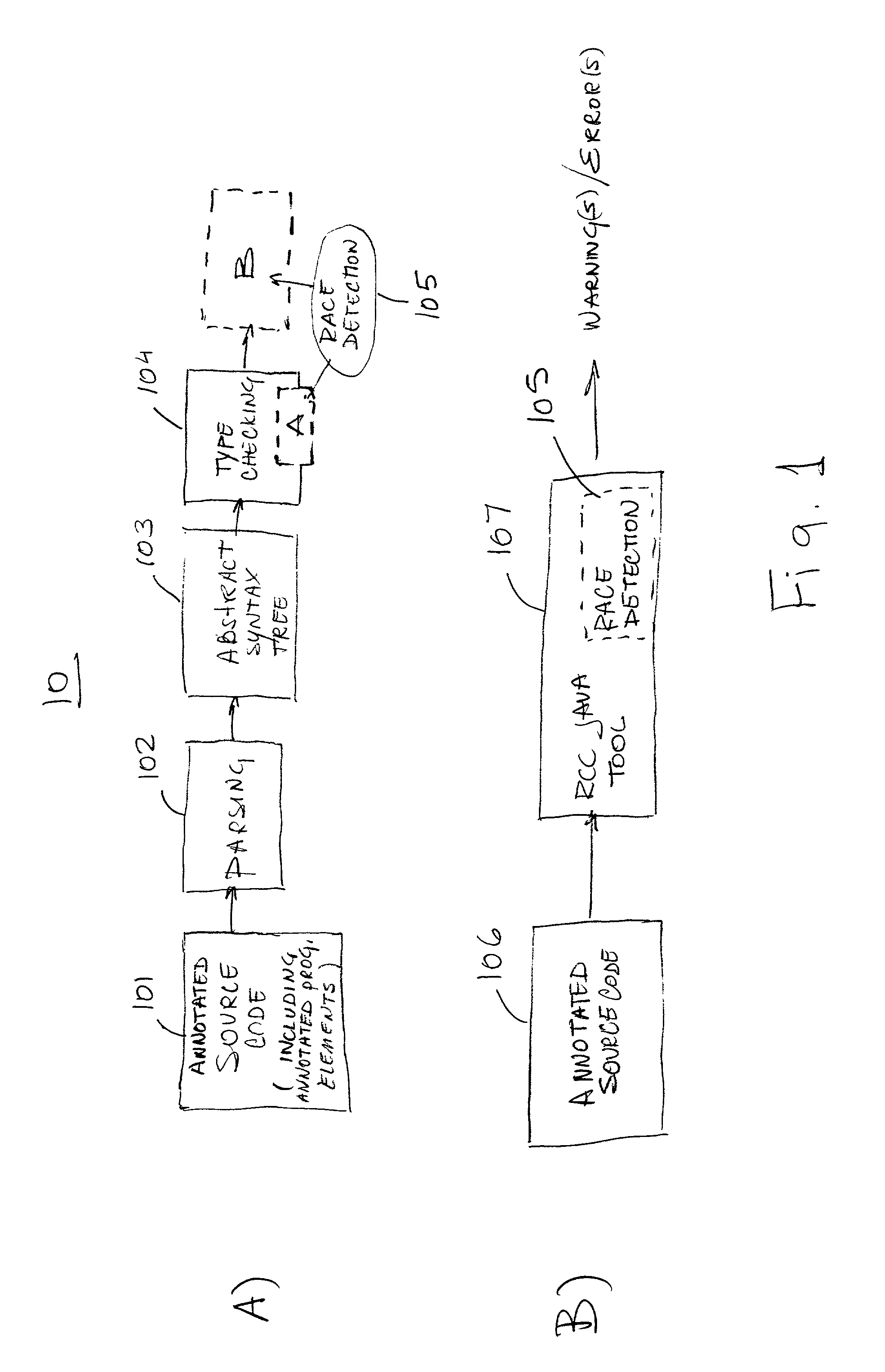

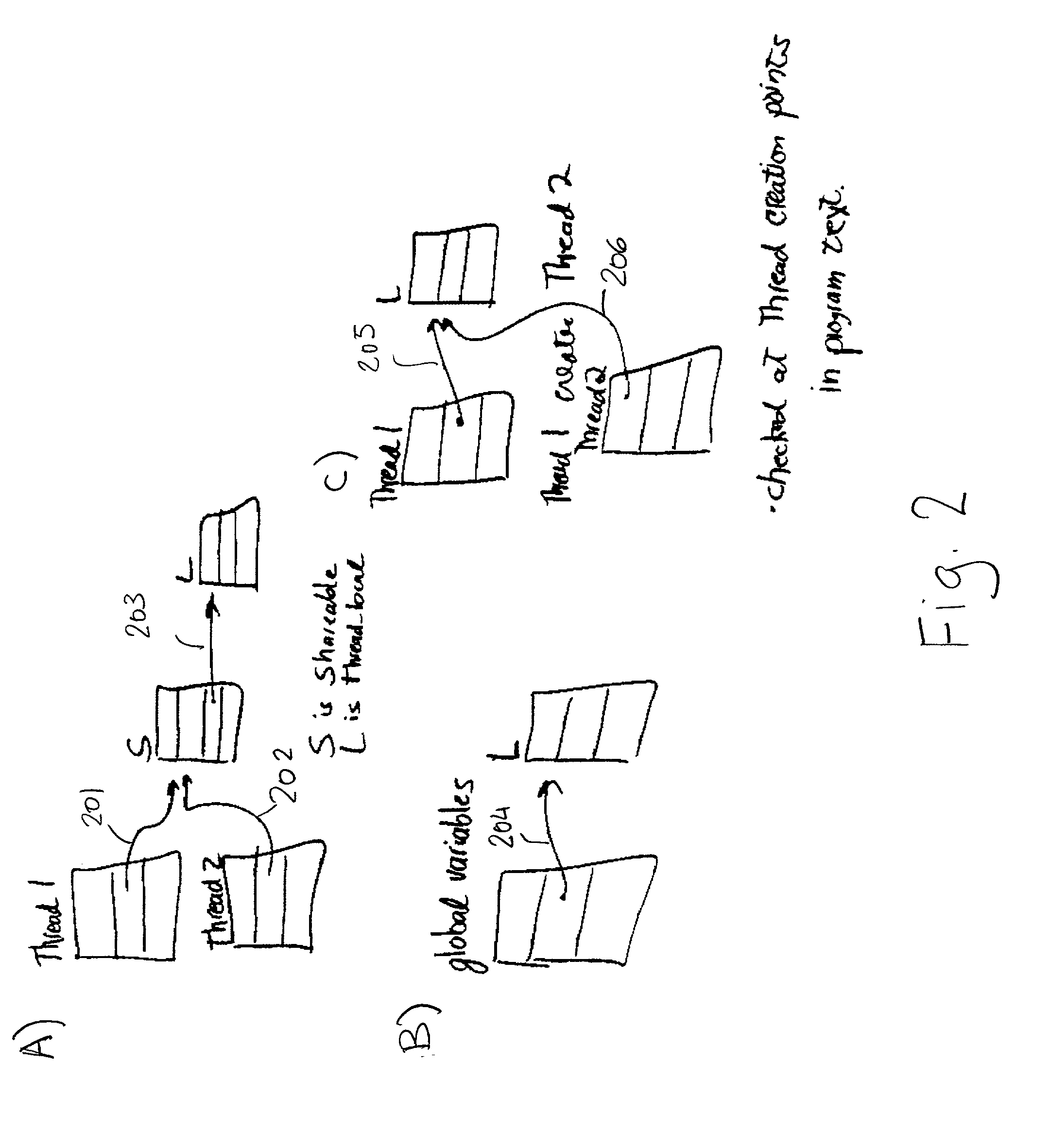

A method and apparatus are used in accordance with the present invention in concurrent program analysis for detecting potential race conditions such as data races in computer programs. A feature of the method and apparatus of the present invention is verifying annotations of addressable resources in a program. The present invention verifies annotations by checking if thread-local resources are indeed thread-local, and that thread-shared data spaces are not in fact thread-local. In accordance with the purpose of the invention, the method provides for detecting potential race conditions, such as data races, in a computer program. The computer program can spawn a plurality of threads that are capable of being executed concurrently. The method includes receiving a source code of the computer program. The source code includes an element annotated as either thread-local or thread-shared. The method also includes verifying the validity of the thread-local annotation if the element is annotated in the computer program as thread-local, wherein an invalid thread-local annotation may cause a race condition. The method can further include indicating a potential race condition if upon verifying the validity of the thread-local annotation it is determined that the element or a portion thereof is visible from more than one, rather than one and only one, of the plurality of threads. In further accordance with the purpose of the invention, the apparatus for concurrent program analysis includes means for receiving source code of the computer program. The source code includes an element annotated as either thread-local or thread-shared. The apparatus also includes means for type checking the source code; and means for thread-local checking located either inside or in series with the type checking means. The means for thread-local checking includes means for verifying the validity of the thread-local annotation if the element is annotated in the computer program as thread-local, where an invalid thread-local annotation may cause a race condition such as a data race. The apparatus can further include means for parsing the source code; and means for creating from the source code an abstract syntax tree. Accordingly, the present invention beneficially provides for a more effective concurrent program analysis.

Owner:VALTRUS INNOVATIONS LTD +1

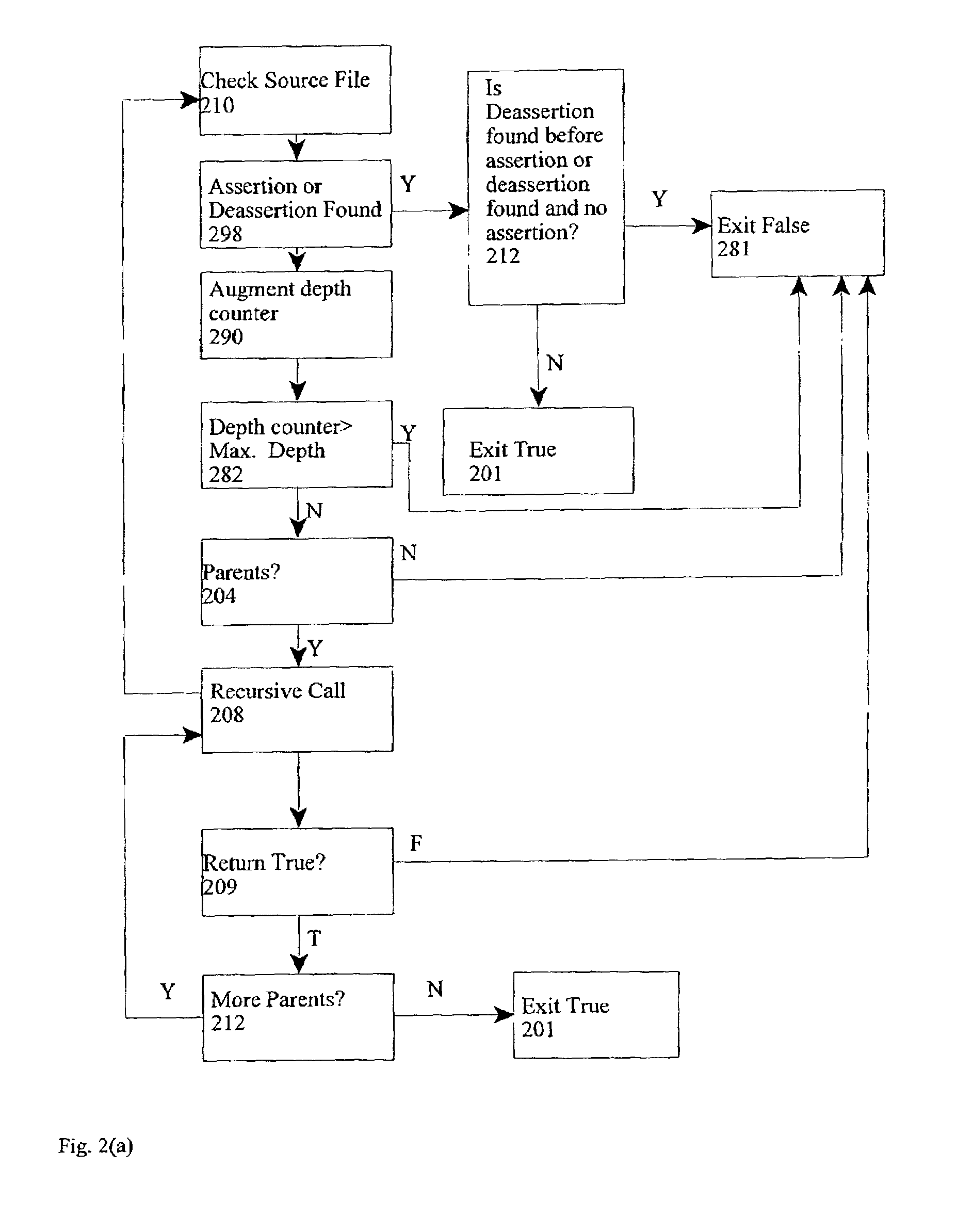

Automated tool for detection of potential race condition

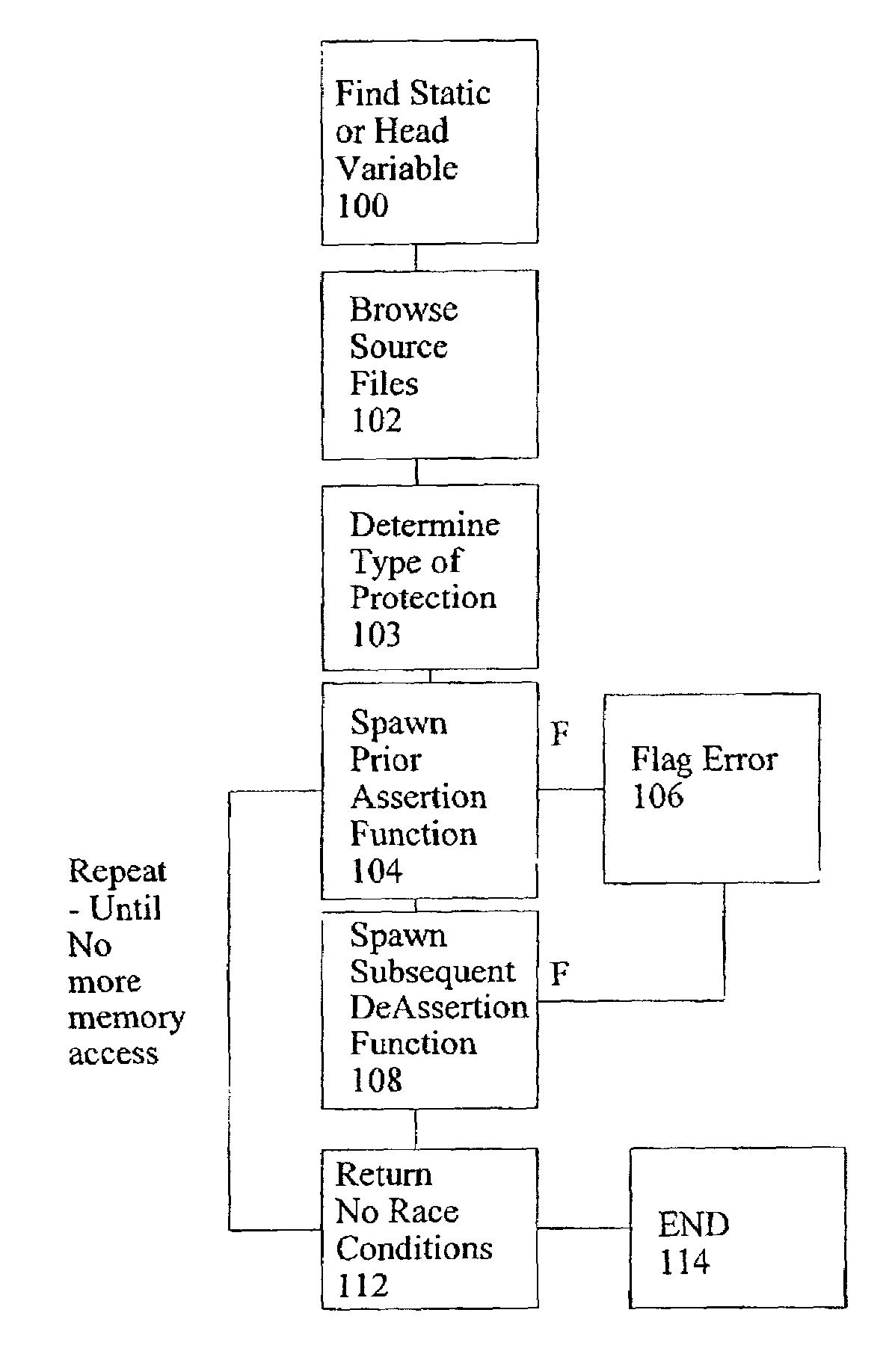

A method for detecting a potential race condition is provided comprising the steps of identifying a memory access in a source code segment, the source code segment being executable in any one of a plurality of execution threads; searching backward from the memory access through each of the plurality of threads for an assert protection declaration without any intervening deassert protection declaration, and identifying the potential race condition if the assert protection declaration without any intervening deassert protection declaration was not found in each of the plurality of threads; and searching forward from the memory access through each of the plurality of threads for the deassert protection declaration, and identifying the potential race condition if the deassert protection declaration was not found in each of the plurality of threads.

Owner:WIND RIVER SYSTEMS

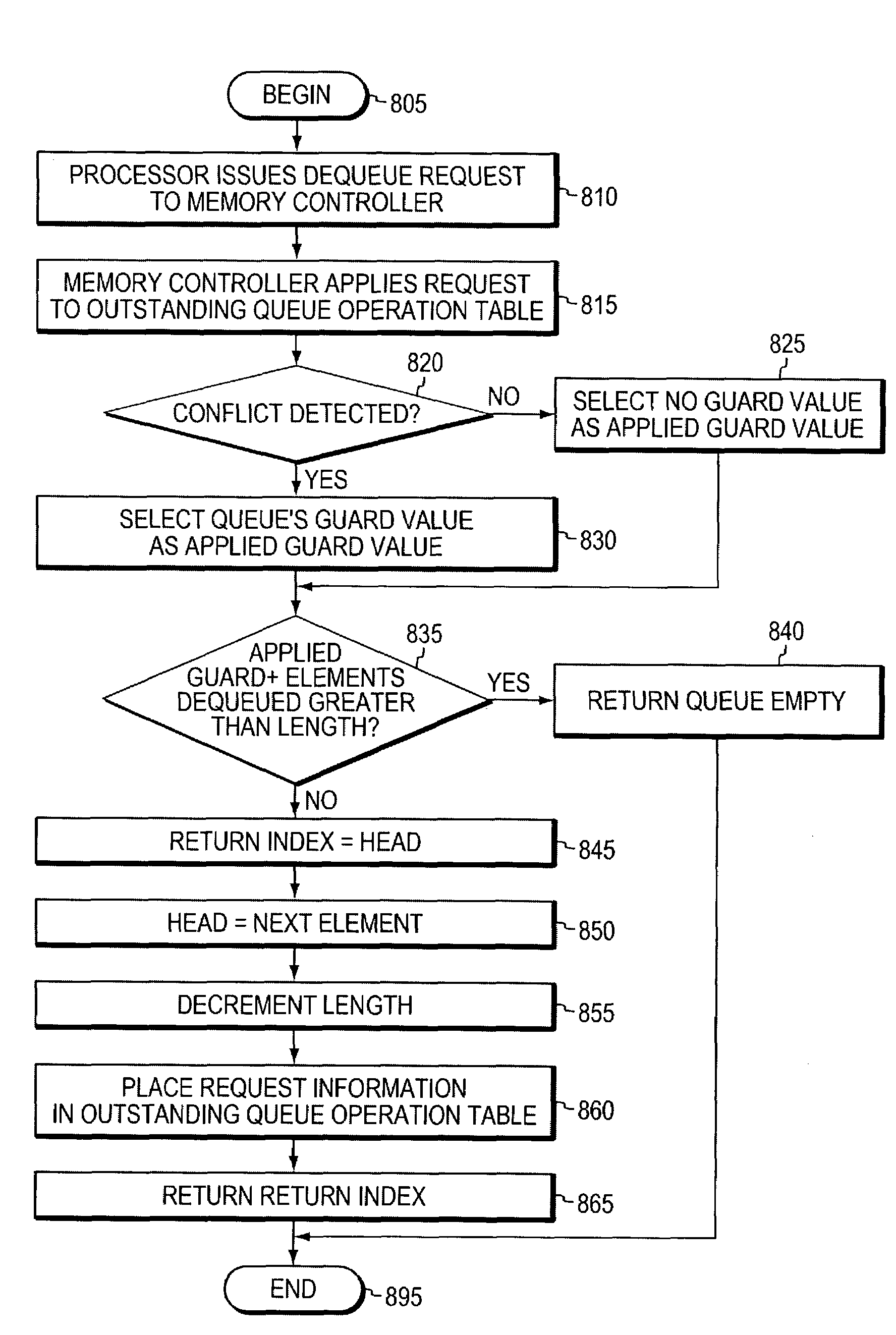

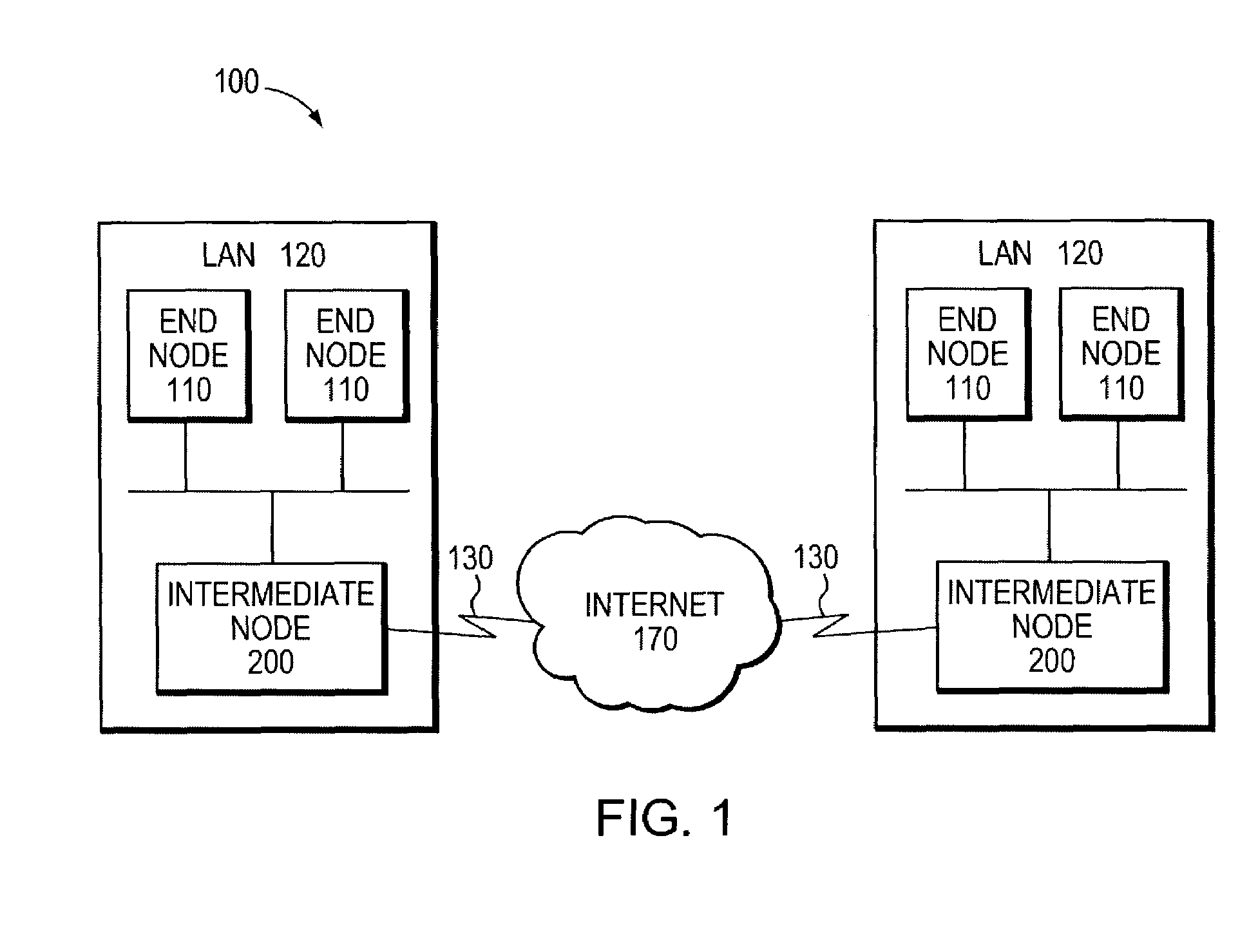

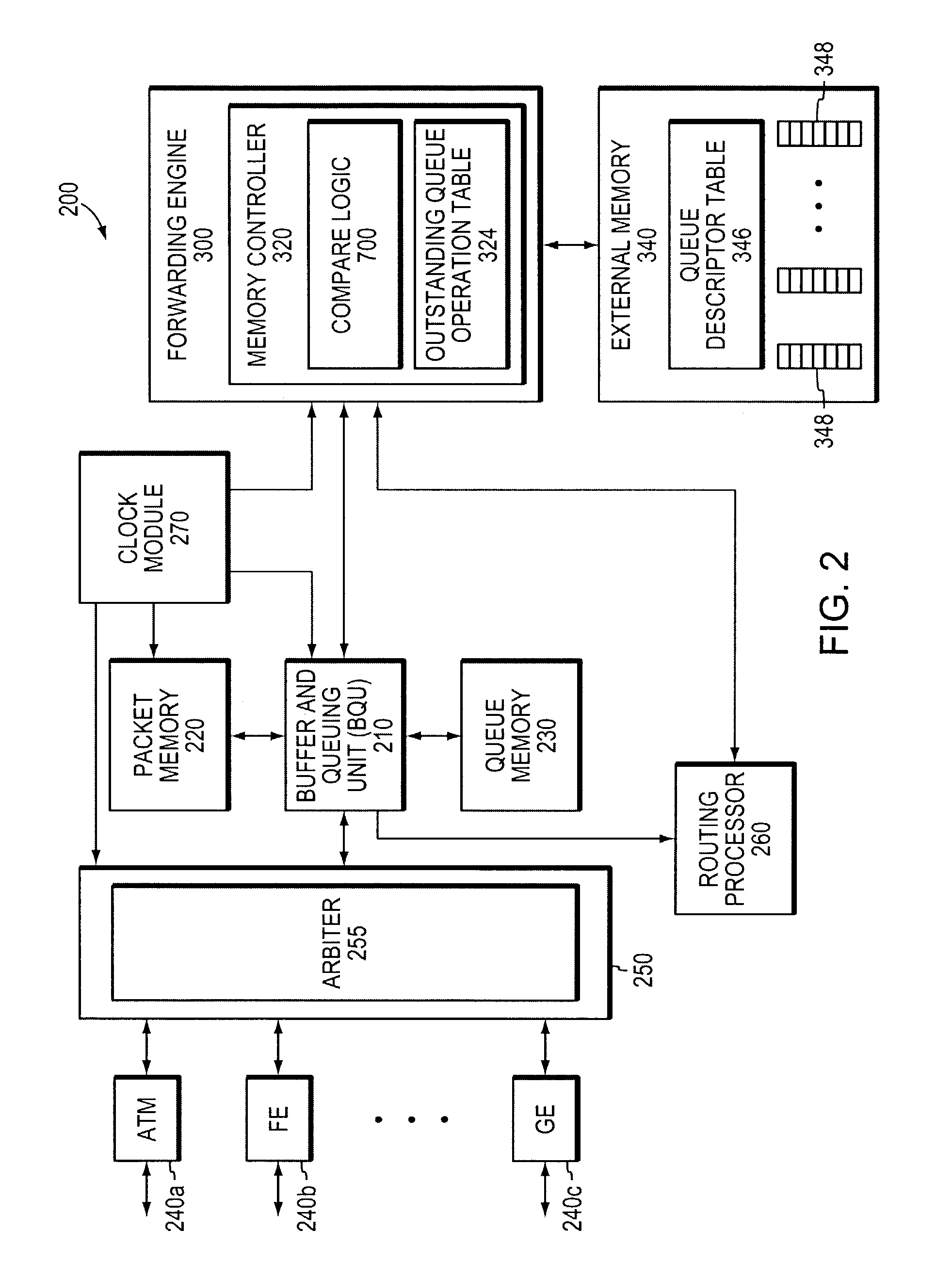

Memory controller that tracks queue operations to detect race conditions

InactiveUS7254687B1Technique is effectiveProgram controlMemory systemsMemory controllerShared resource

A technique for controlling access to resources that may be accessed by one or more entities in a system. According to the technique, an entity accesses a shared resource by issuing a request containing an identifier that identifies the resource and an operation that specifies an operation to be performed on the resource. The operation is compared with one or more outstanding operations associated with the shared resource to determine if the operation conflicts with one or more of the outstanding operations. If a conflict is detected, a guard value is applied to determine if a race condition could occur. If a race condition is detected, the operation is blocked; otherwise, the operation is allowed.

Owner:CISCO TECH INC

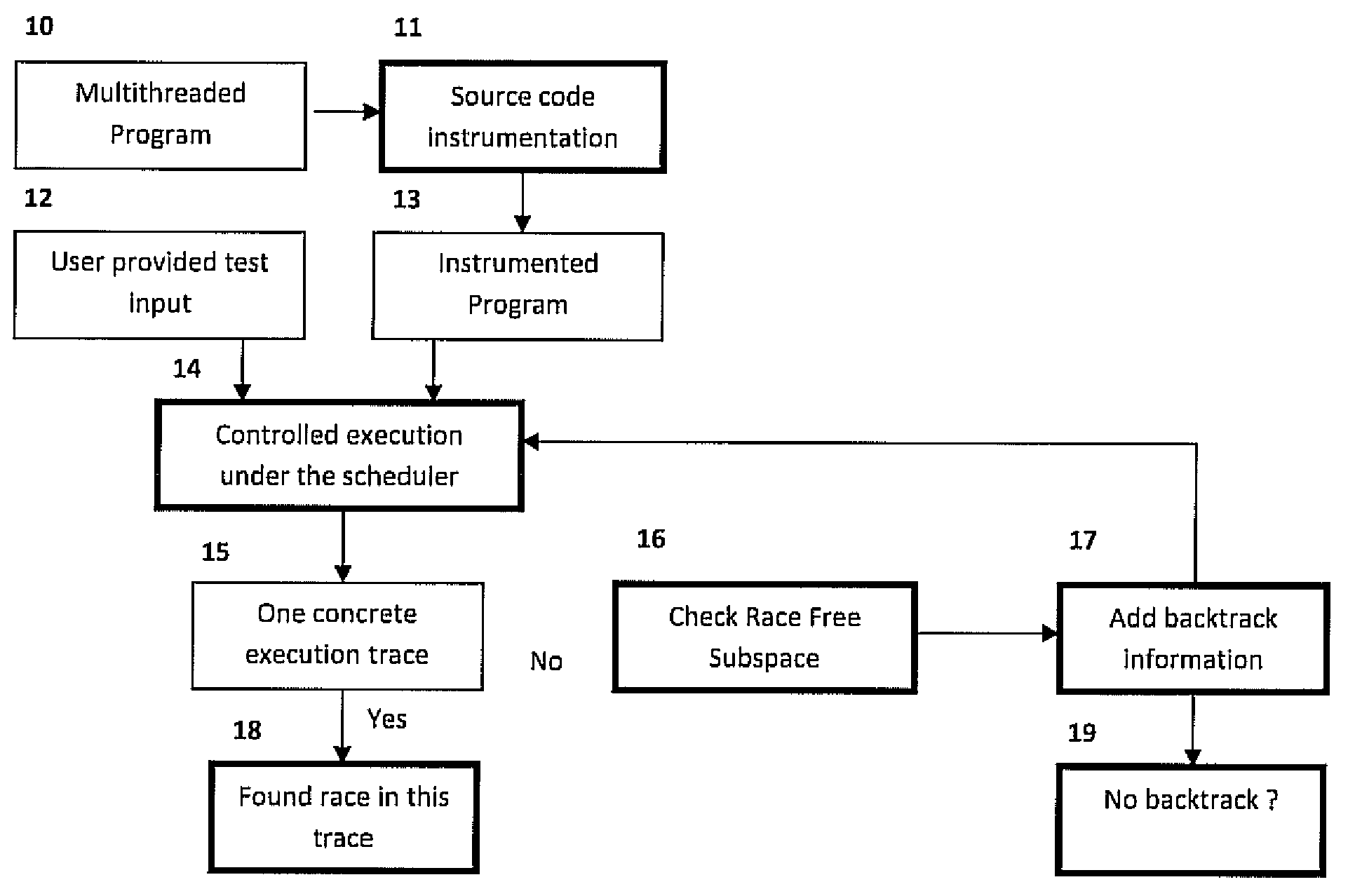

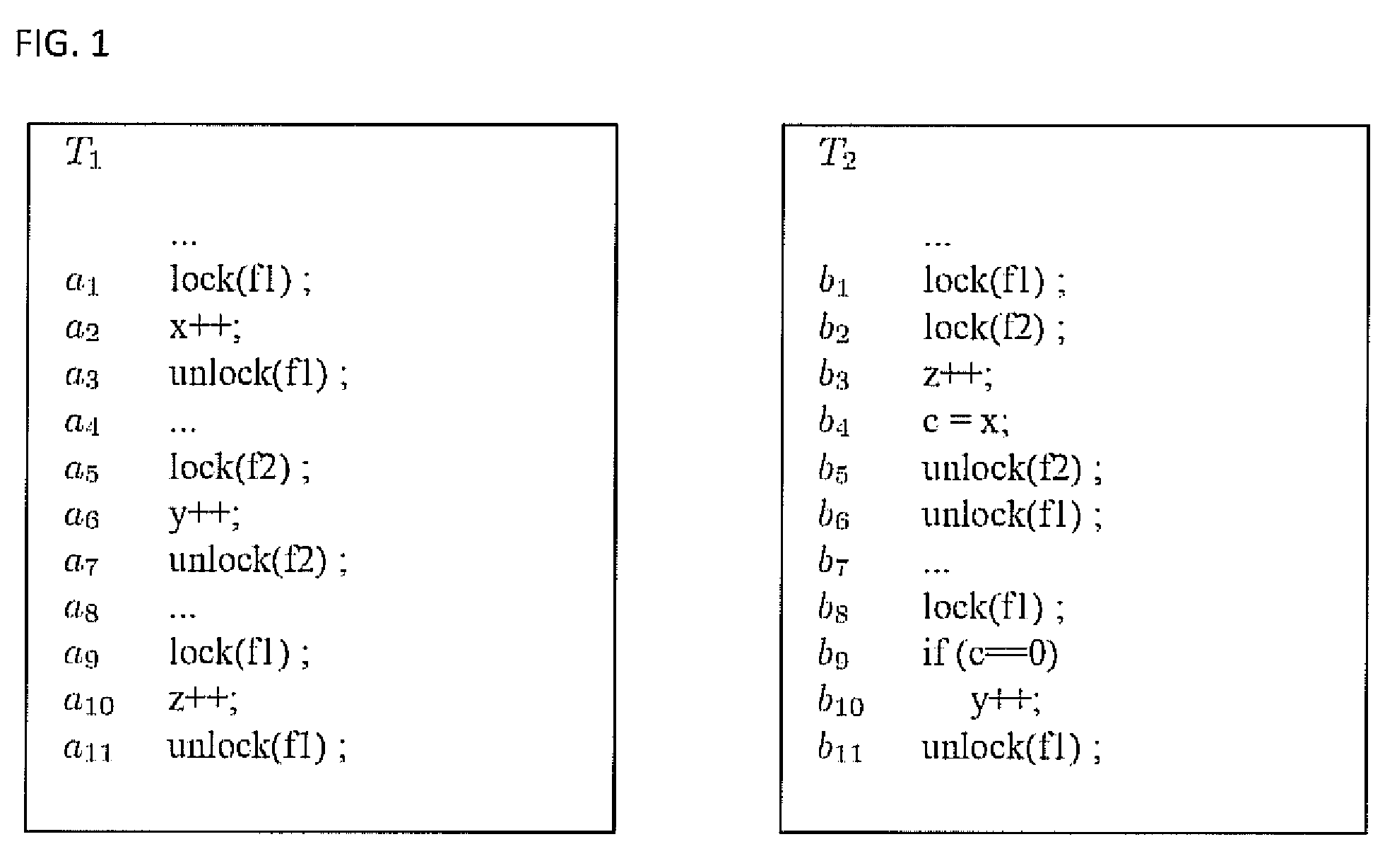

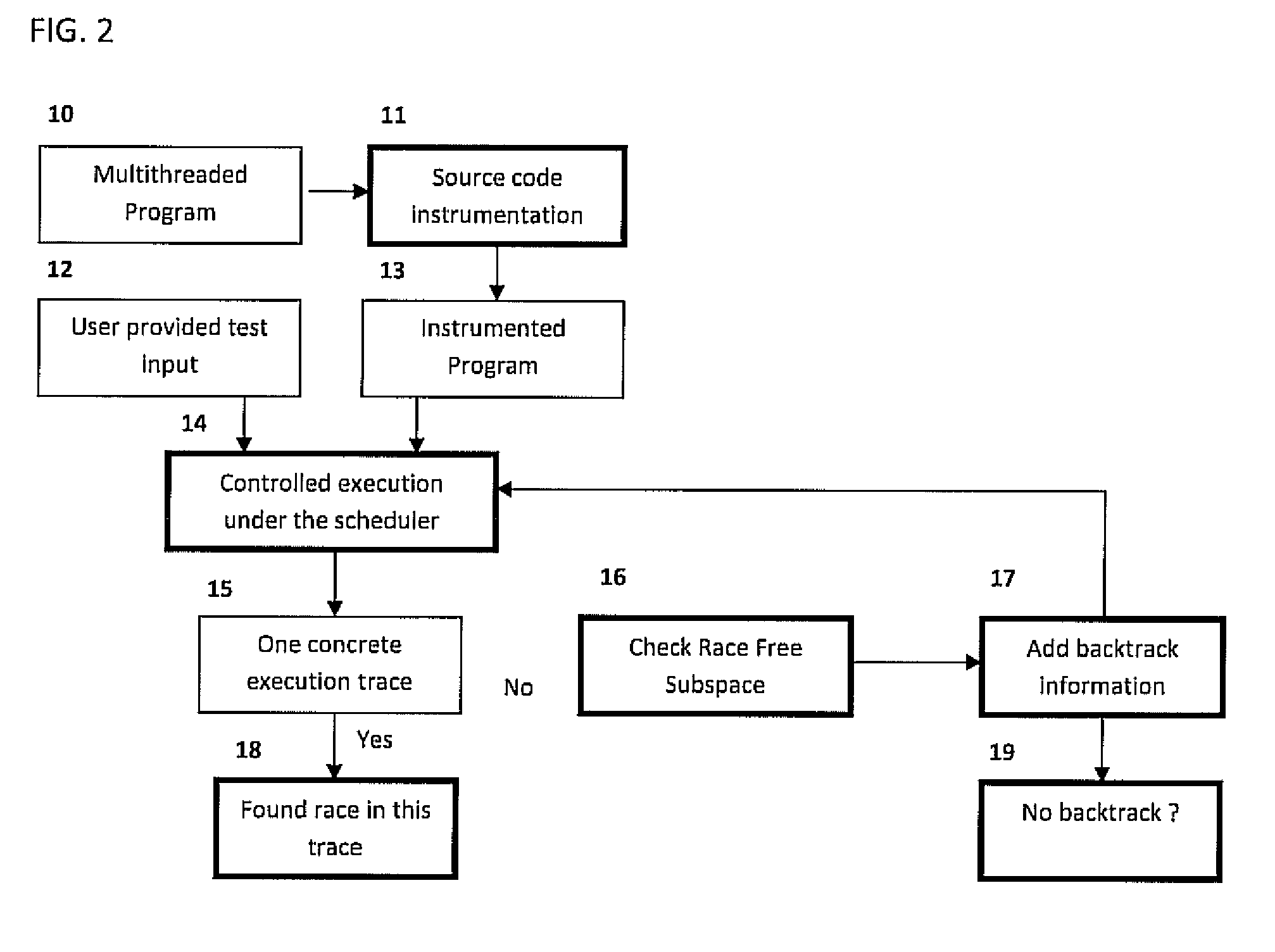

Dynamic model checking with property driven pruning to detect race conditions

ActiveUS20090282288A1Effective and practicalEasy to scaleFault responseProgram controlState dependentDynamic models

A system and method for dynamic data race detection for concurrent systems includes computing lockset information using a processor for different components of a concurrent system. A controlled execution of the system is performed where the controlled execution explores different interleavings of the concurrent components. The lockset information is used during the controlled execution to check whether a search subspace associated with a state in the execution is free of data races. A race-free search subspace is dynamically pruned to reduce resource usage.

Owner:NEC CORP

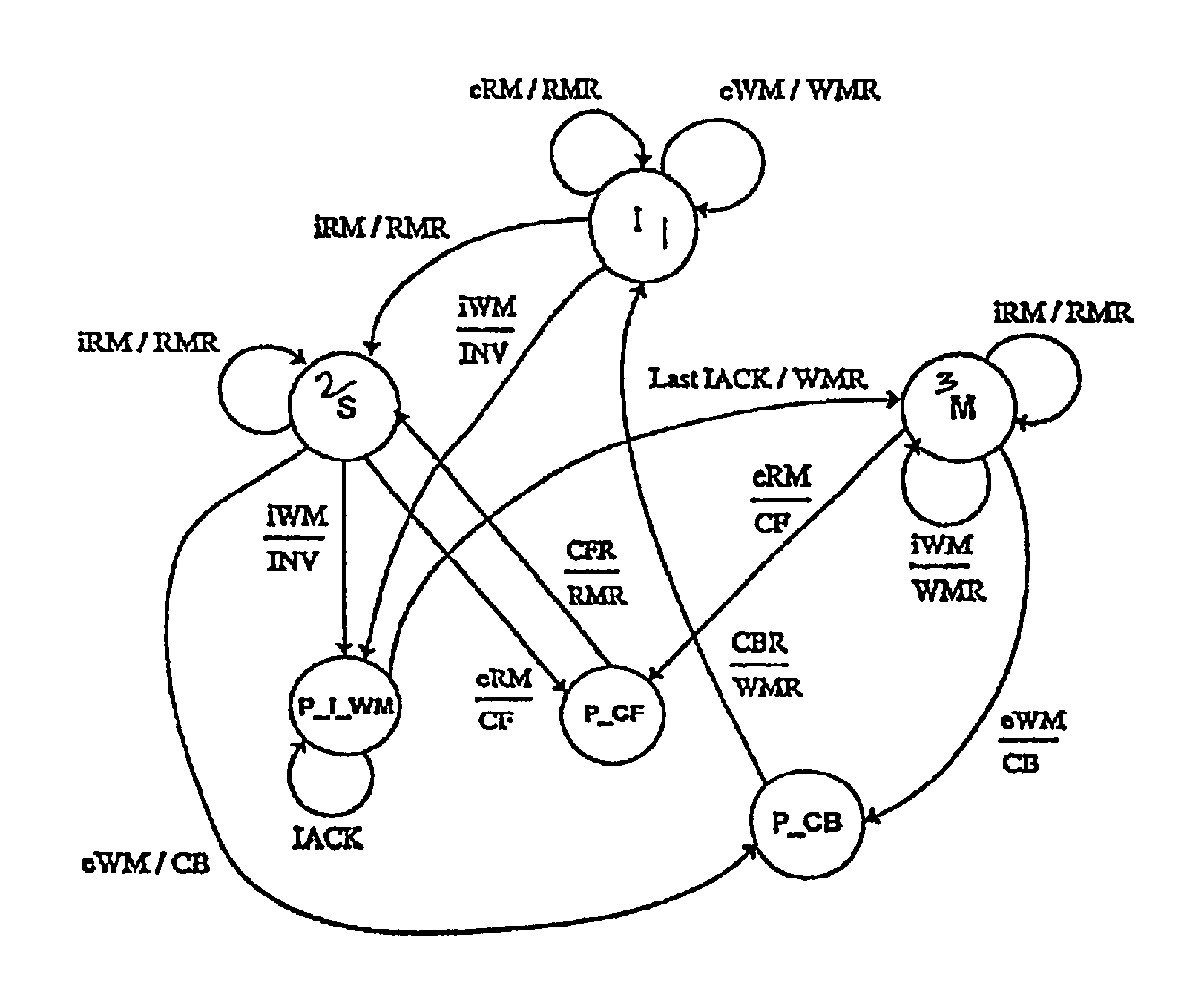

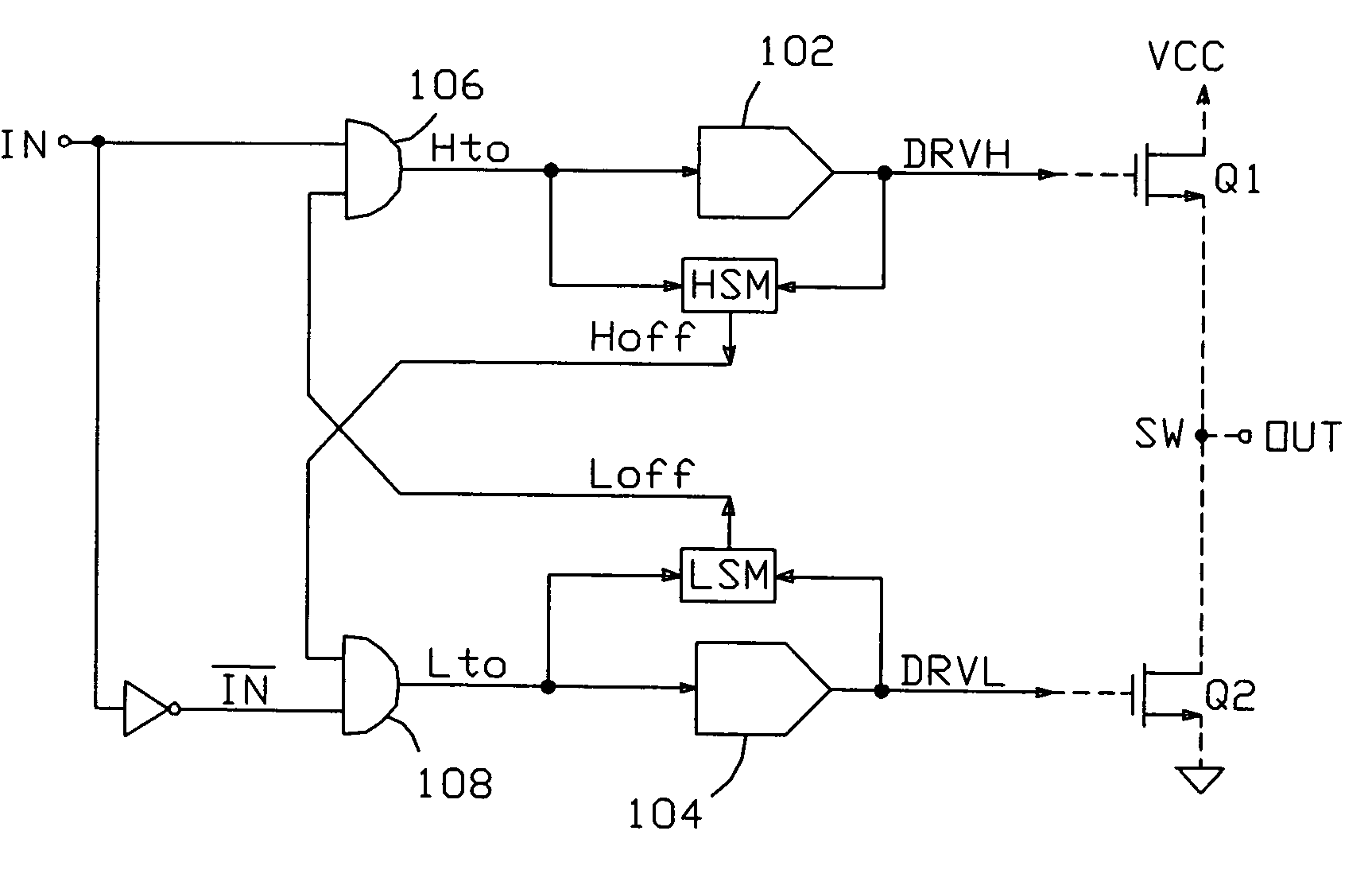

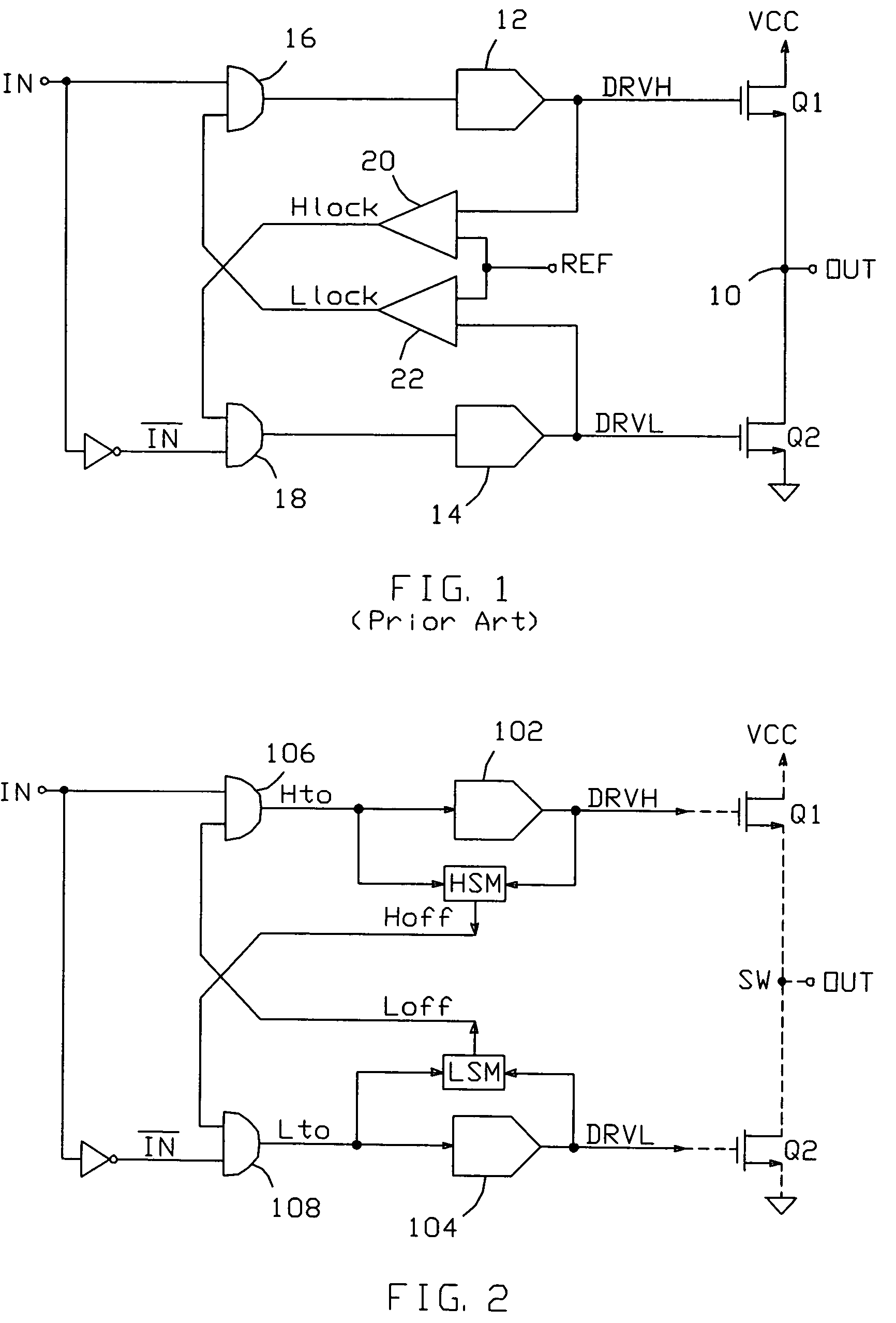

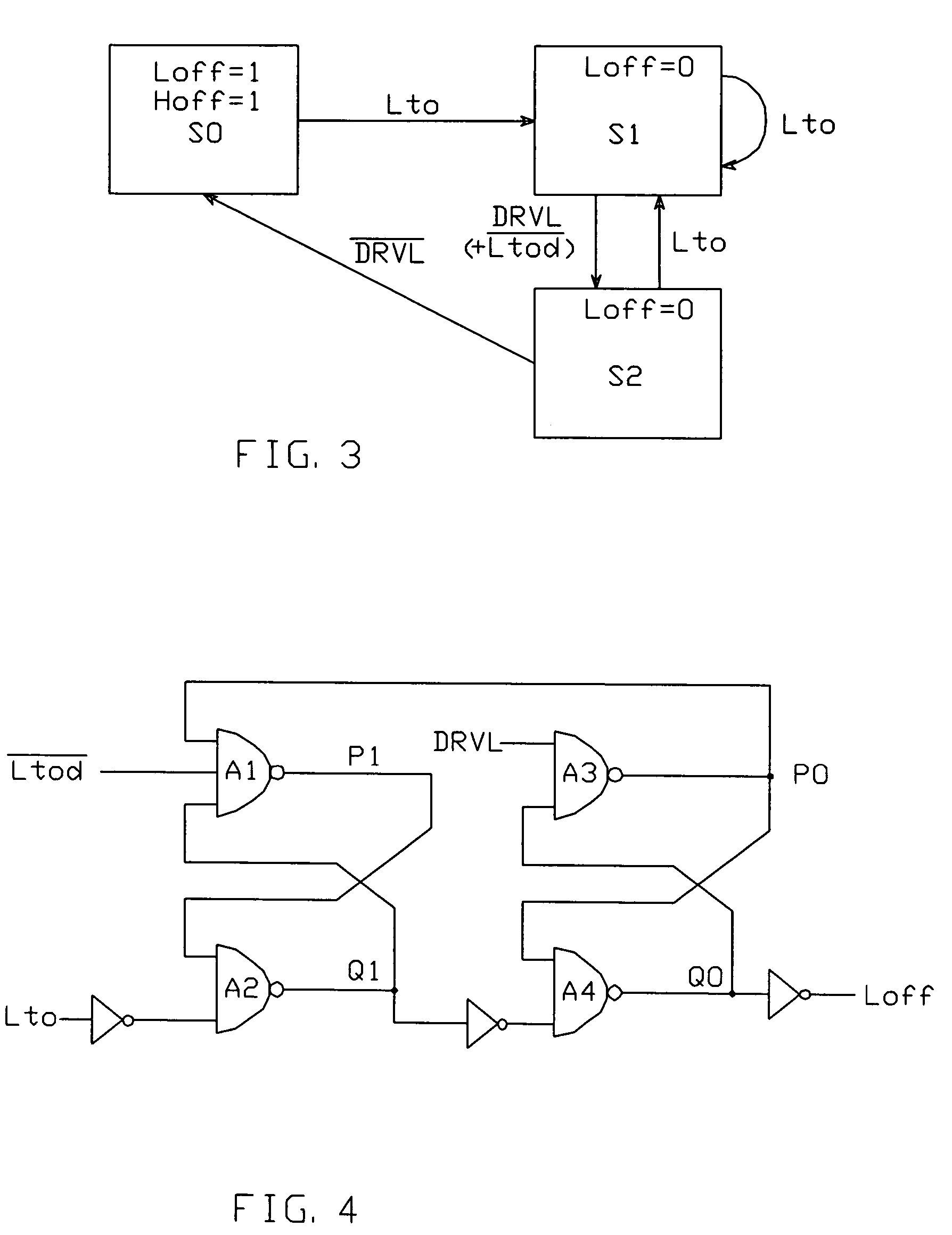

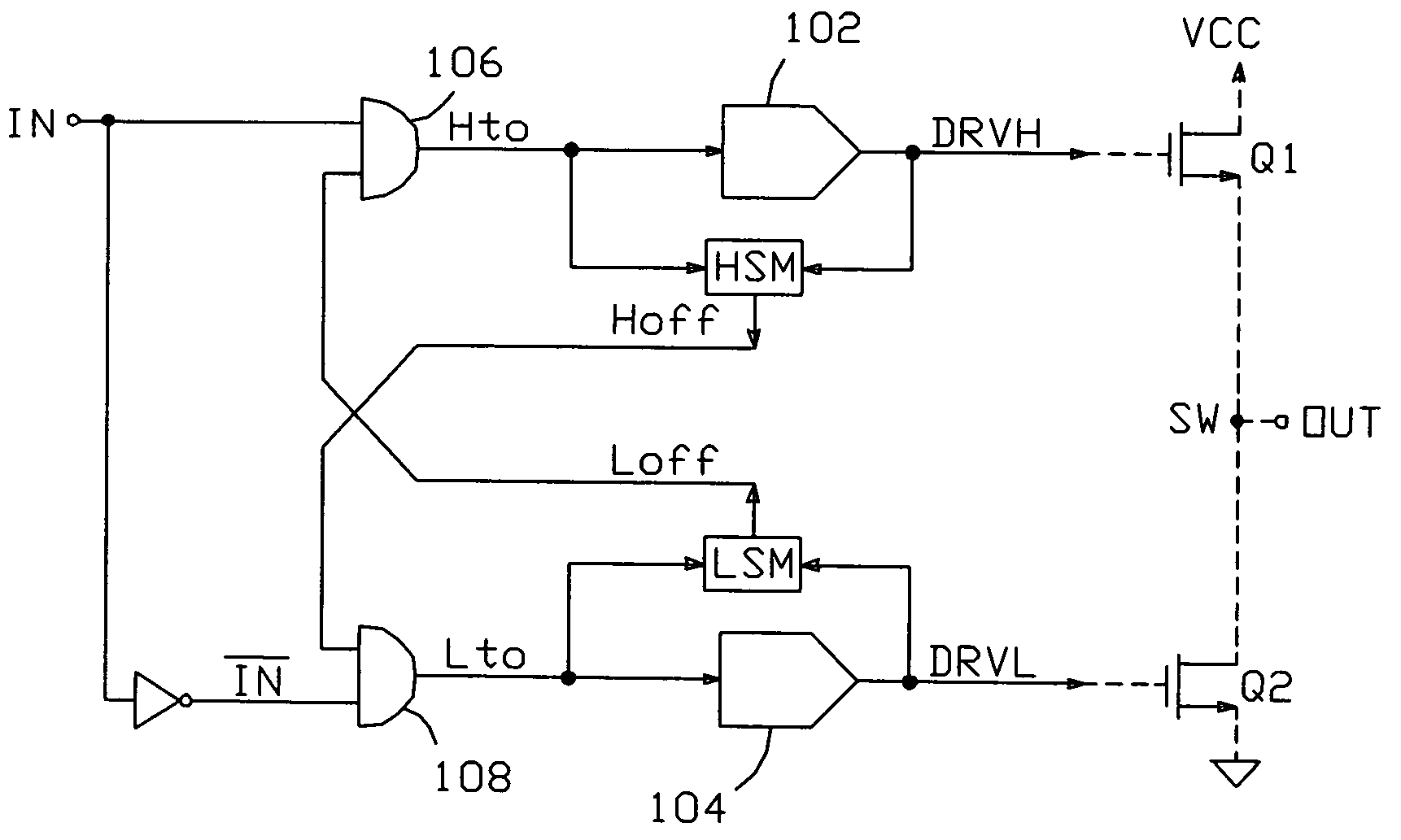

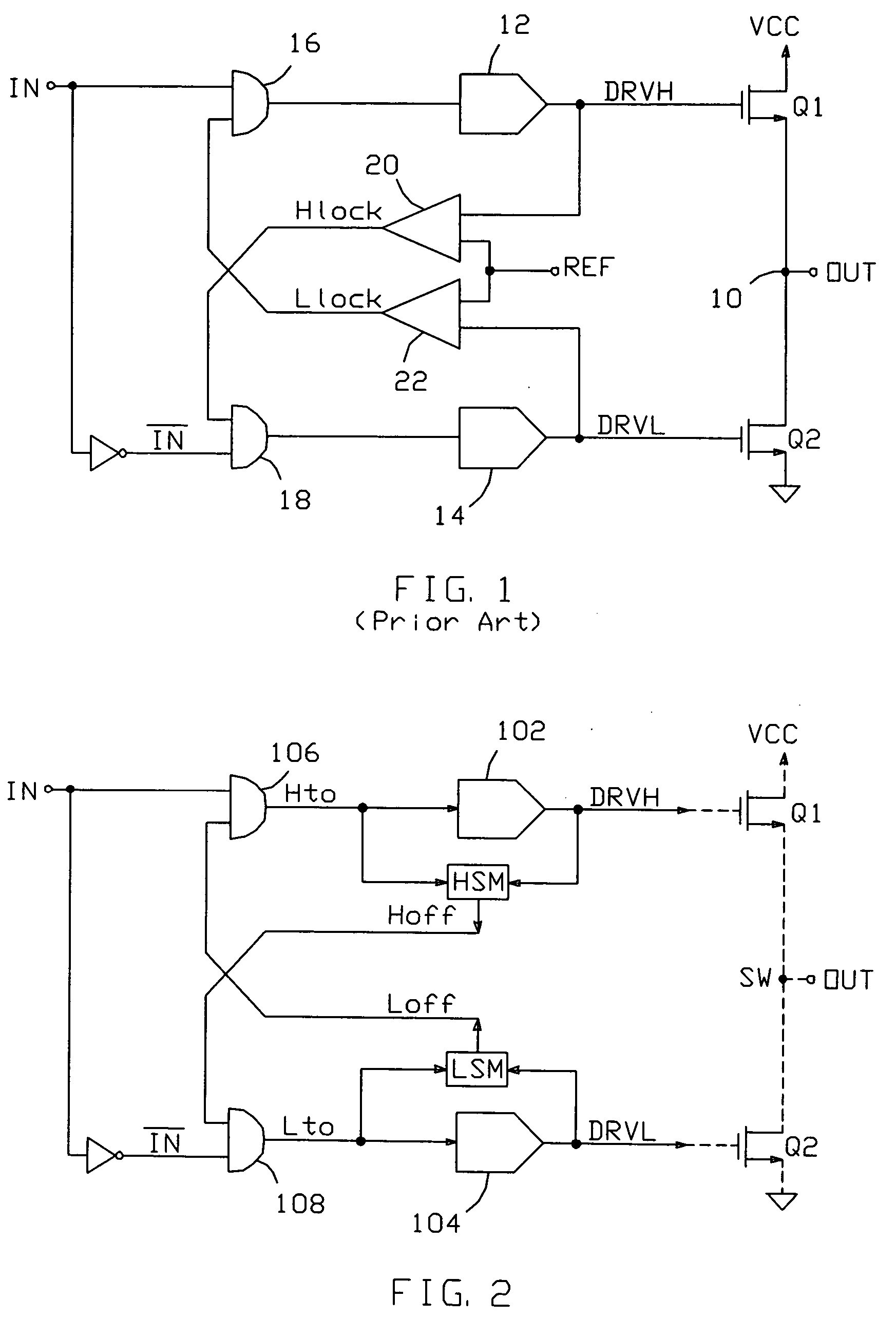

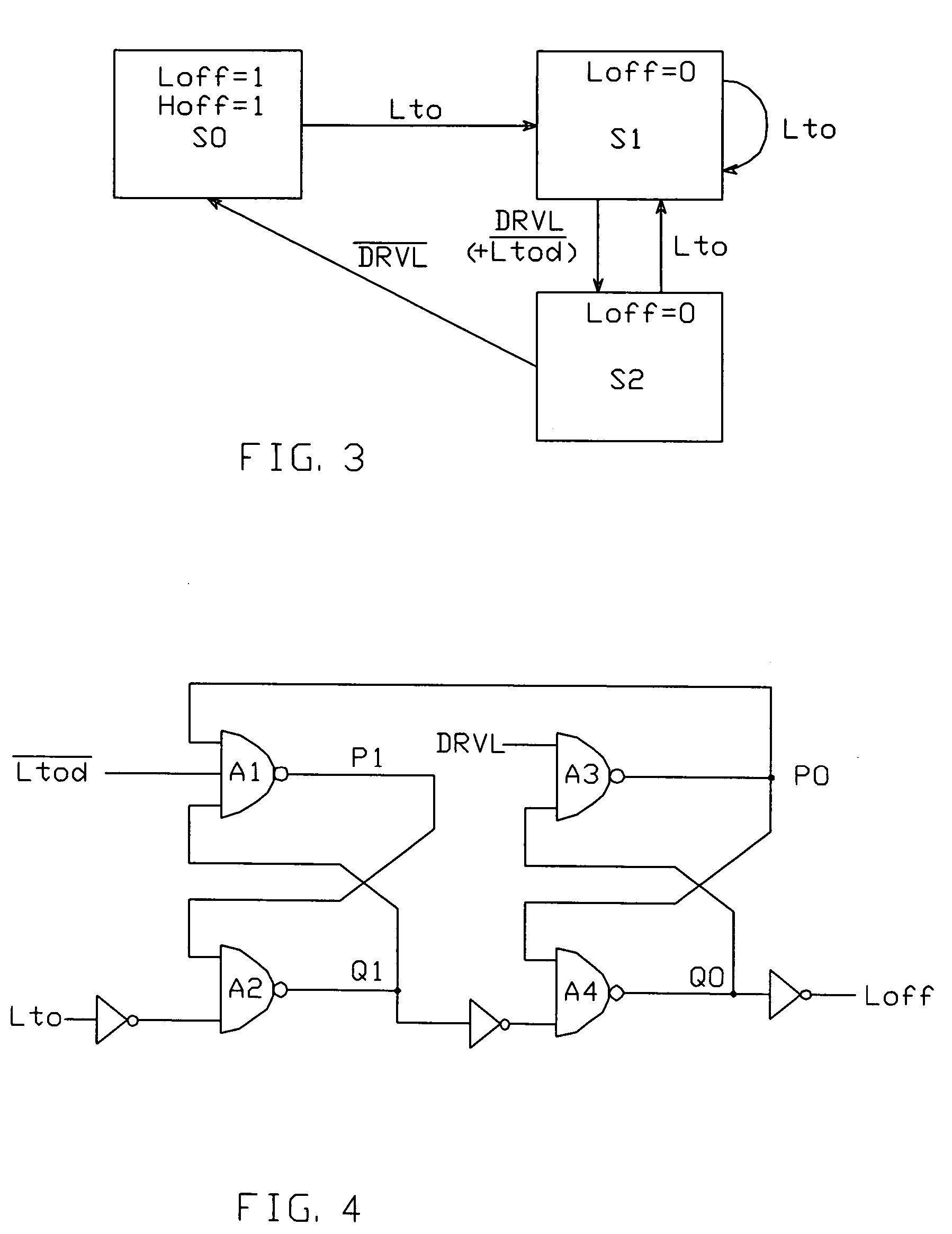

Anti-cross conduction drive control circuit and method

ActiveUS7187226B2Avoid it happening againPrevent cross-conductionTransistorReliability increasing modificationsMOSFETEngineering

An anti-cross conduction driver control circuit and method prevent the occurrence of race conditions and avoid cross-conduction between series-connected power devices, typically MOSFETs, controlled in accordance with the present invention. Individual state machines are connected across the inputs and outputs of each power device driver, and are arranged to accurately determine when the driver has completed a task requested of it. Each state machine produces a “lockout” signal based on driver status, which is used to inhibit the operation of the opposite driver under prescribed conditions, and to thereby prevent cross-conduction between the series-connected power devices.

Owner:ANALOG DEVICES INC

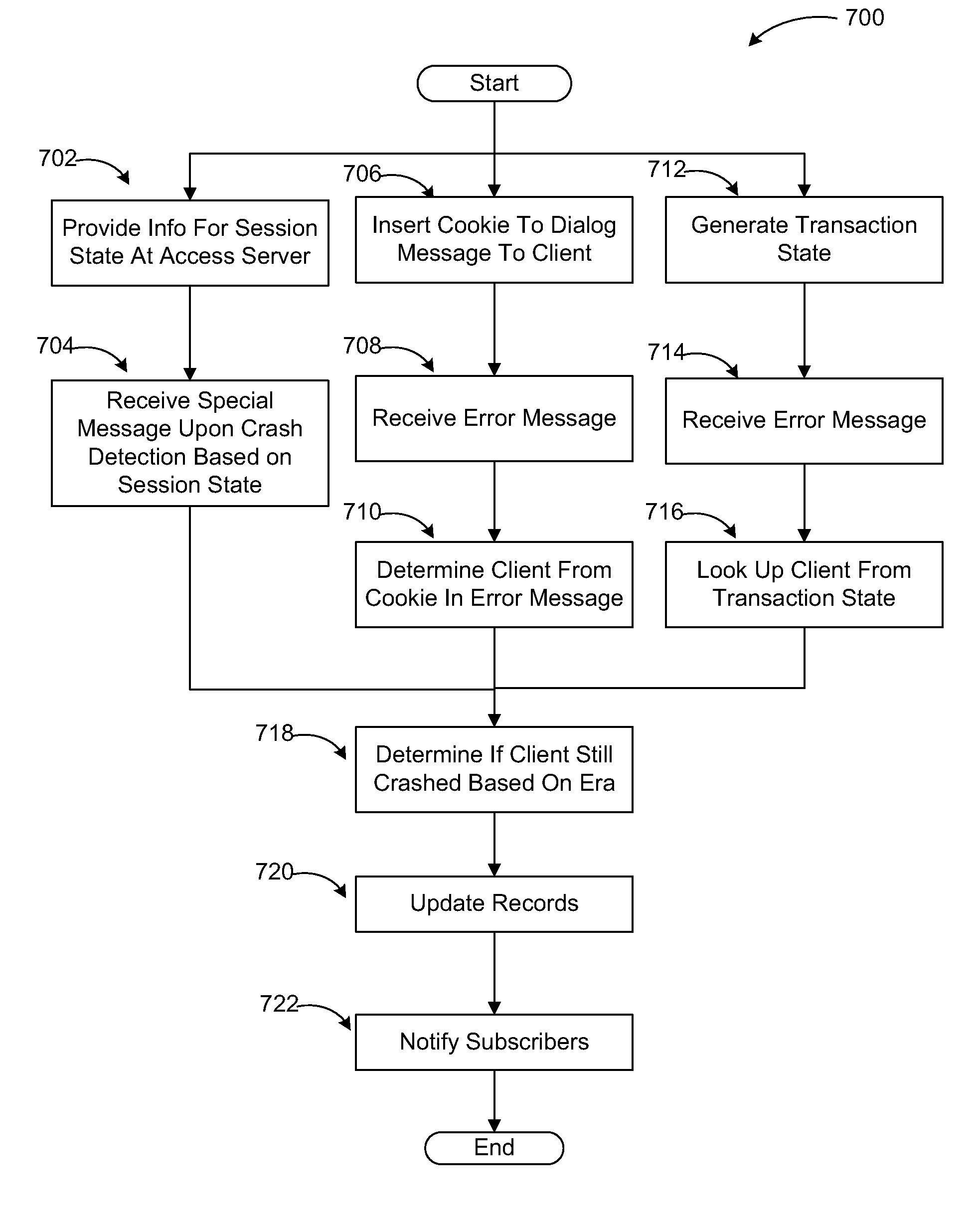

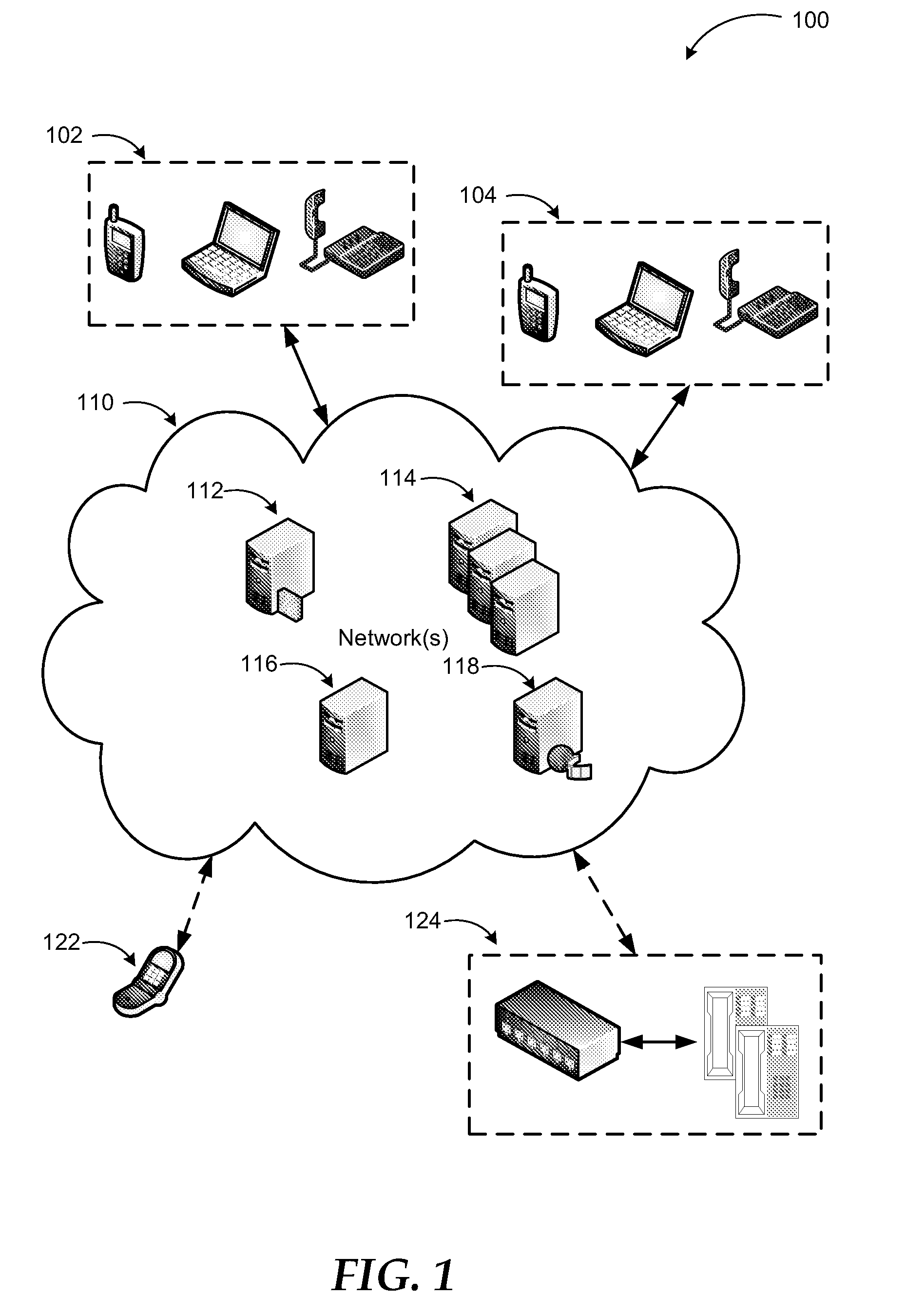

Enhanced presence routing and roster fidelity by proactive crashed endpoint detection

InactiveUS20090217109A1Avoid adjustmentFault responseAutomatic exchangesTimestampReal time communication systems

Endpoint crashes in a real time communication system are detected by a home server providing presence and other services to the endpoint upon receipt of an error message from an access server between the endpoint and the home server. The home server uses a cookie inserted into a dialog between itself and the endpoint identifying the endpoint, a session state created by the access server identifying the endpoint, or a transaction state maintained by the home server to look up the endpoint associated with the error message. Race conditions occurring when an endpoint crashes and recovers rapidly can be avoided employing a timestamp or sequence number incremented for each new endpoint registration and comparing a current timestamp or sequence number to the stored one before updating records at the home server. By notifying other subscribers about crashed endpoints, routing fidelity is enhanced.

Owner:MICROSOFT TECH LICENSING LLC

Concurrent non-blocking FIFO array

InactiveUS6697927B2Memory systemsInput/output processes for data processingRace conditionDistributed computing

A technique for providing concurrent non-blocking access to a circular queue is provided. The concurrent non-blocking circular queue also may be configured such that cache-coherent requesters and a non-cache-coherent requester (e.g., software and hardware) both may concurrently access the queue. Further, the queue may be configured such that the probability of occurrence of the ABA race condition may be minimized.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

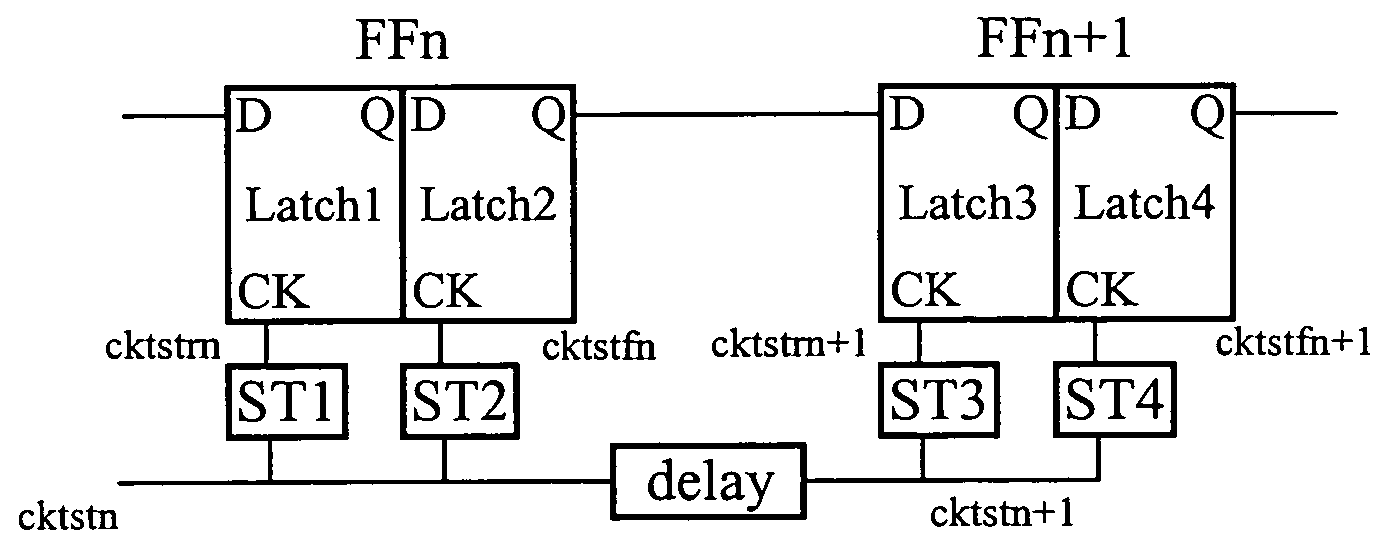

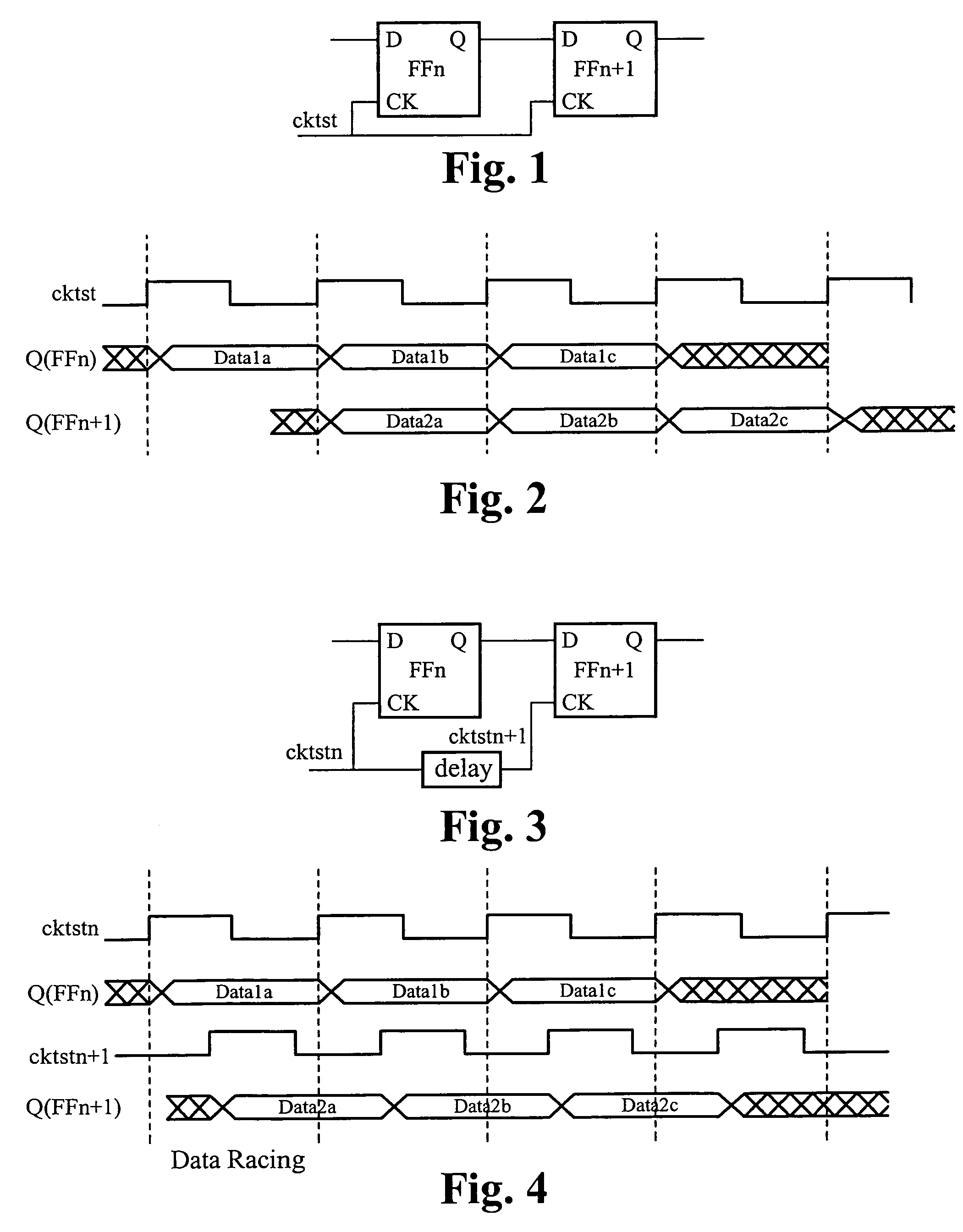

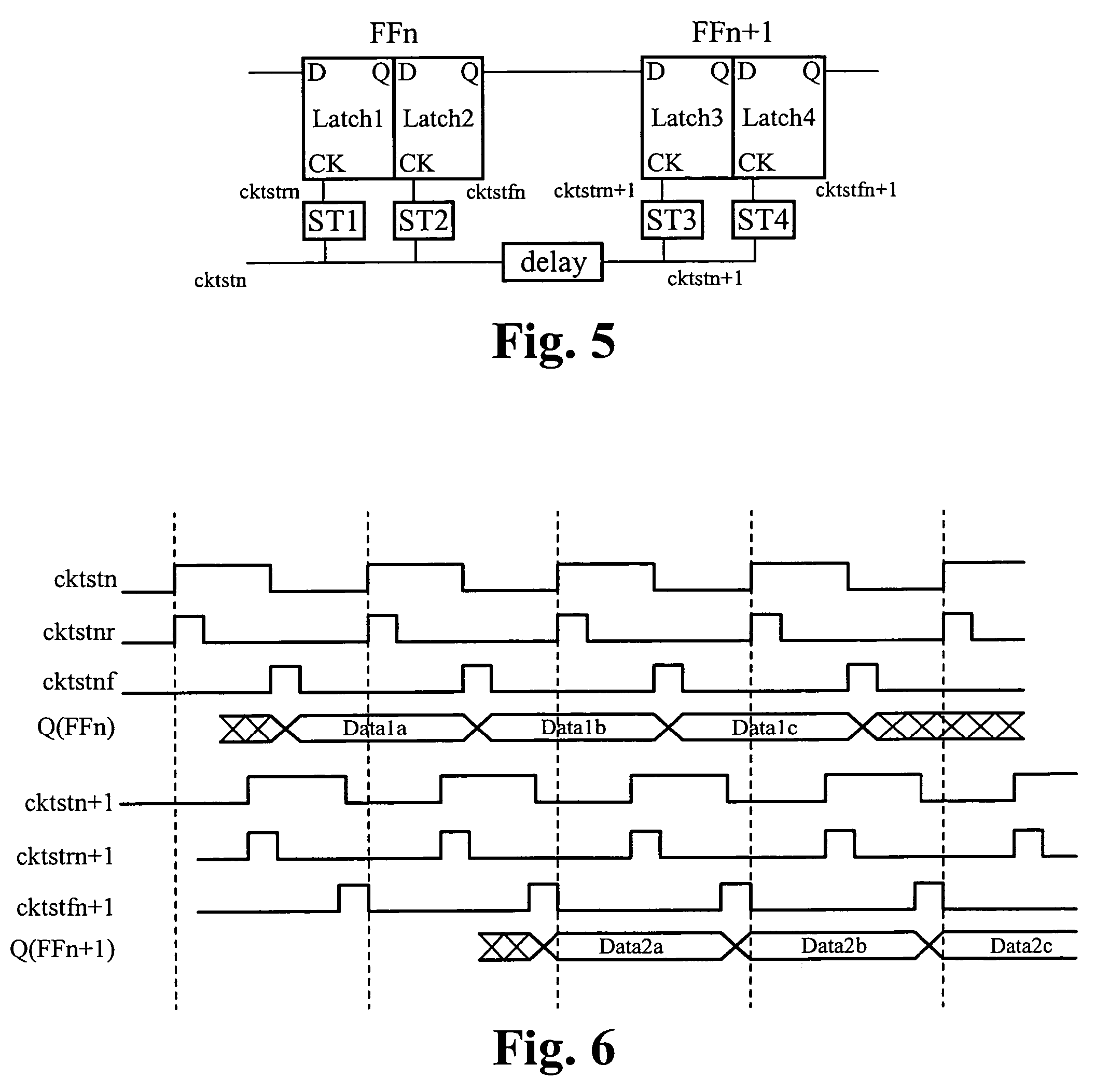

Shift registers free of timing race boundary scan registers with two-phase clock control

A chain of boundary scan registers is configured to use a two-phase clock signal to avoid data timing race conditions. The two-phase clock signal is generated according to a two-phase clock generator, which includes two self-timed clock pulse generators for each boundary scan register. The two-phase clock generator locally generates a self-timed clock pulse at the rising edge of a clock signal, which triggers a first stage of the boundary scan register. The two-phase clock generator also generates a self-timed clock pulse at the falling edge of the input clock signal, which triggers a second stage of the boundary scan register. The two-phase clock controlled boundary scan register includes two latches, each latch is triggered by one of the self-timed clock pulse generated locally from the rising and falling edge of the input clock signal.

Owner:GSI TECH

Method and system for parallelizing completion event processing

InactiveUS7761619B2Efficient processingEliminate processing bottlenecksDigital computer detailsComputer security arrangementsTraffic capacityComplex event processing

Disclosed are methods for handling RDMA connections carried over packet stream connections. In one aspect, I / O completion events are distributed among a number of processors in a multi-processor computing device, eliminating processing bottlenecks. For each processor that will accept I / O completion events, at least one completion queue is created. When an I / O completion event is received on one of the completion queues, the processor associated with that queue processes the event. In a second aspect, semantics of the interactions among a packet stream handler, an RDMA layer, and an RNIC are defined to control RDMA closures and thus to avoid implementation errors. In a third aspect, semantics are defined for transferring an existing packet stream connection into RDMA mode while avoiding possible race conditions. The resulting RNIC architecture is simpler than is traditional because the RNIC never needs to process both streaming messages and RDMA-mode traffic at the same time.

Owner:MICROSOFT TECH LICENSING LLC

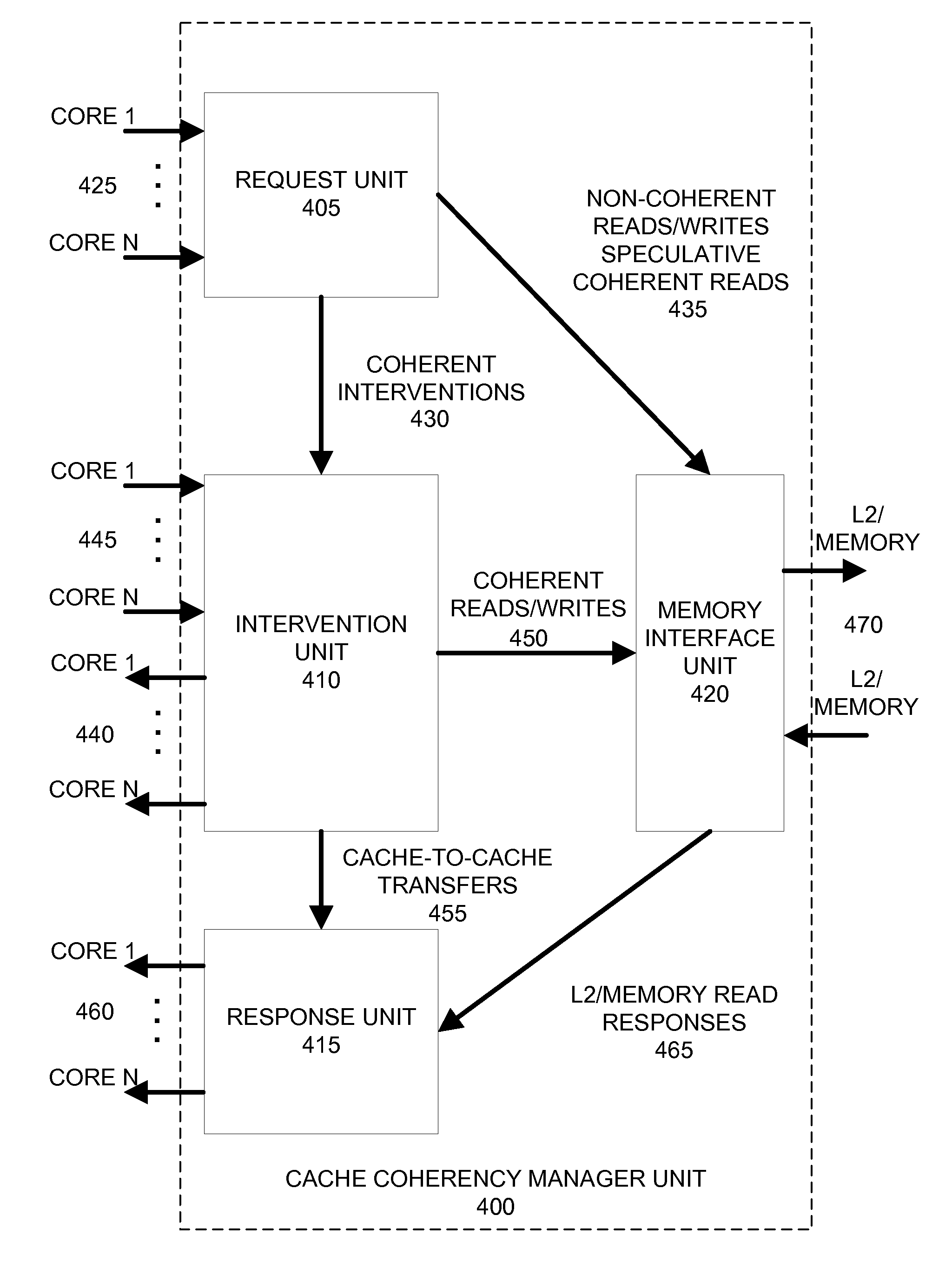

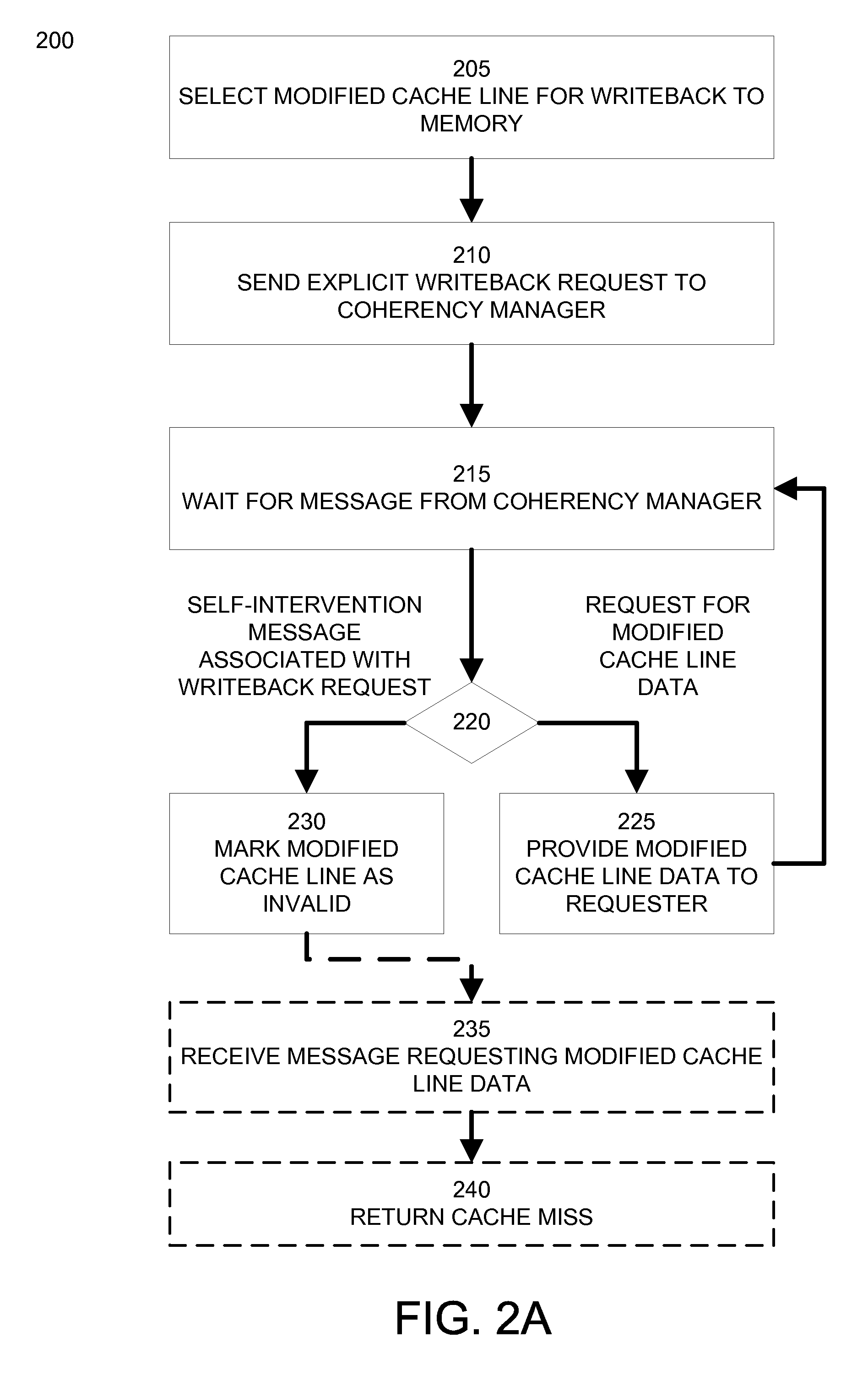

Preventing Writeback Race in Multiple Core Processors

ActiveUS20080320232A1Reduce complexityReduce overheadMemory adressing/allocation/relocationMulti-core processorRace condition

A processor prevents writeback race condition errors by maintaining responsibility for data until the writeback request is confirmed by an intervention message from a cache coherency manager. If a request for the same data arrives before the intervention message, the processor core unit provides the requested data and cancels the pending writeback request. The cache coherency data associated with cache lines indicates whether a request for data has been received prior to the intervention message associated with the writeback request. The cache coherency data of a cache line has a value of “modified” when the writeback request is initiated. When the intervention message associated with the writeback request is received, the cache lines's cache coherency data is examined. A change in the cache coherency data from the value of “modified” indicates that the request for data has been received prior to the intervention and the writeback request should be cancelled.

Owner:ARM FINANCE OVERSEAS LTD

Method and system for closing an RDMA connection

Disclosed are methods for handling RDMA connections carried over packet stream connections. In one aspect, I / O completion events are distributed among a number of processors in a multi-processor computing device, eliminating processing bottlenecks. For each processor that will accept I / O completion events, at least one completion queue is created. When an I / O completion event is received on one of the completion queues, the processor associated with that queue processes the event. In a second aspect, semantics of the interactions among a packet stream handler, an RDMA layer, and an RNIC are defined to control RDMA closures and thus to avoid implementation errors. In a third aspect, semantics are defined for transferring an existing packet stream connection into RDMA mode while avoiding possible race conditions. The resulting RNIC architecture is simpler than is traditional because the RNIC never needs to process both streaming messages and RDMA-mode traffic at the same time.

Owner:MICROSOFT TECH LICENSING LLC

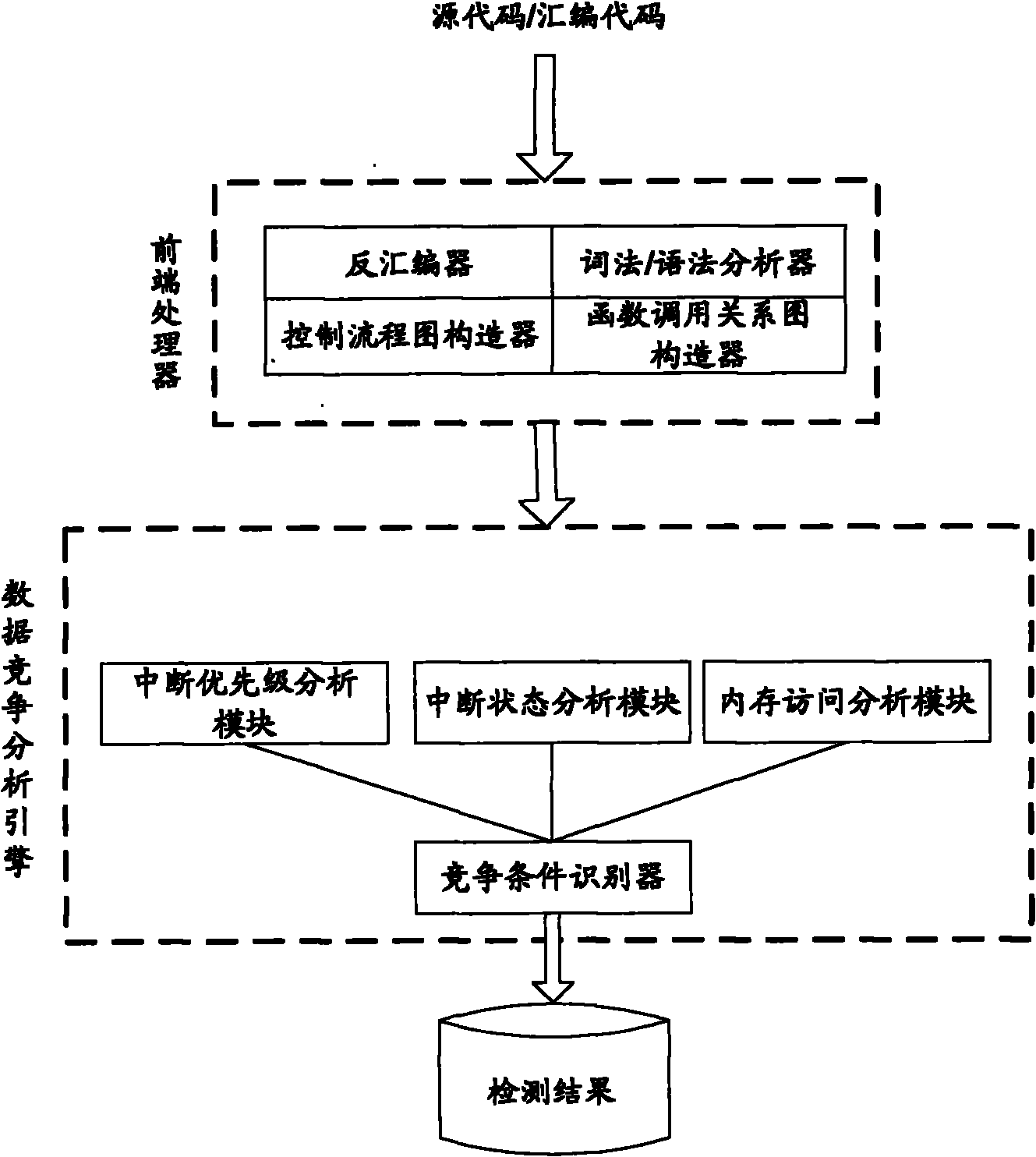

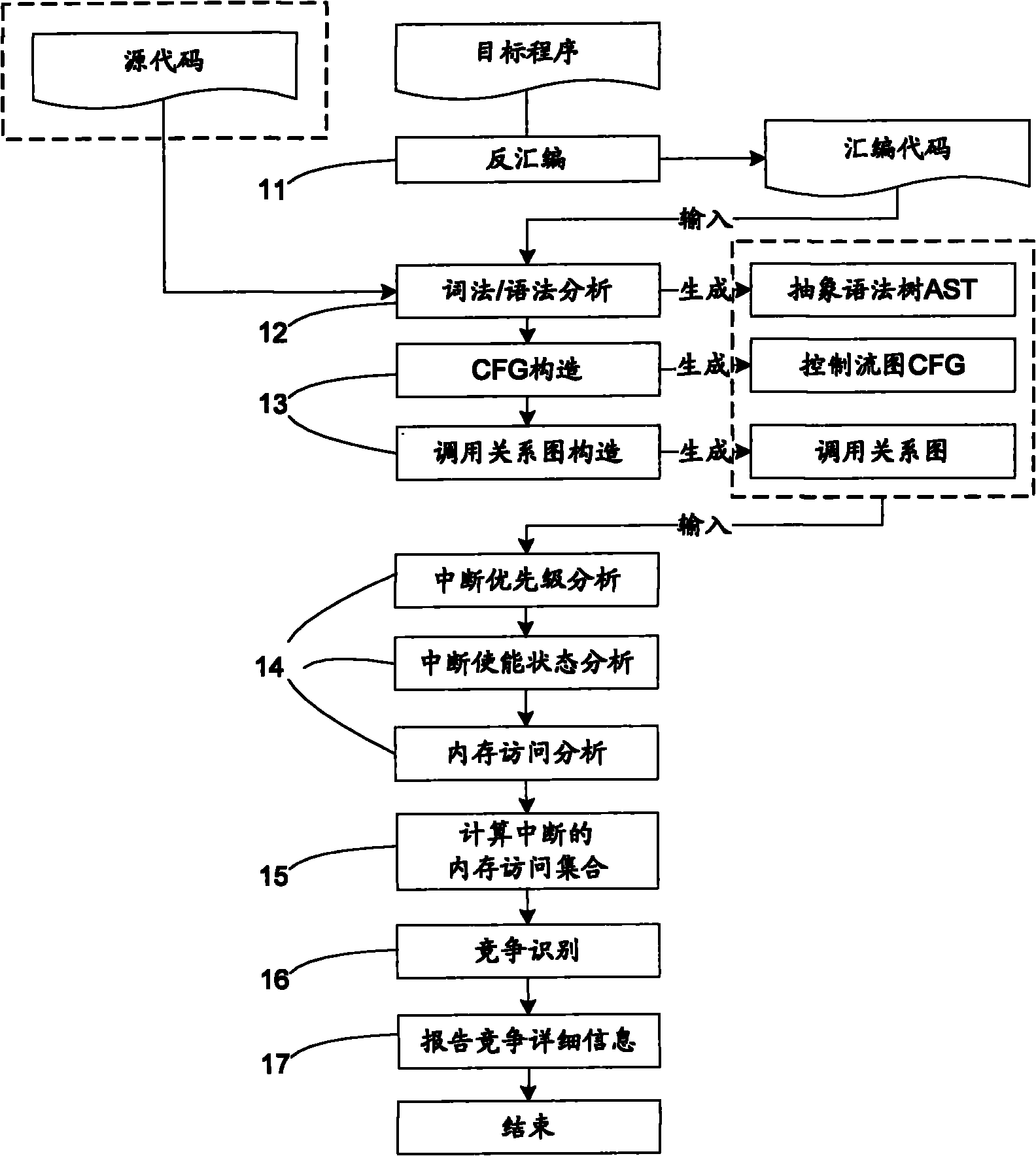

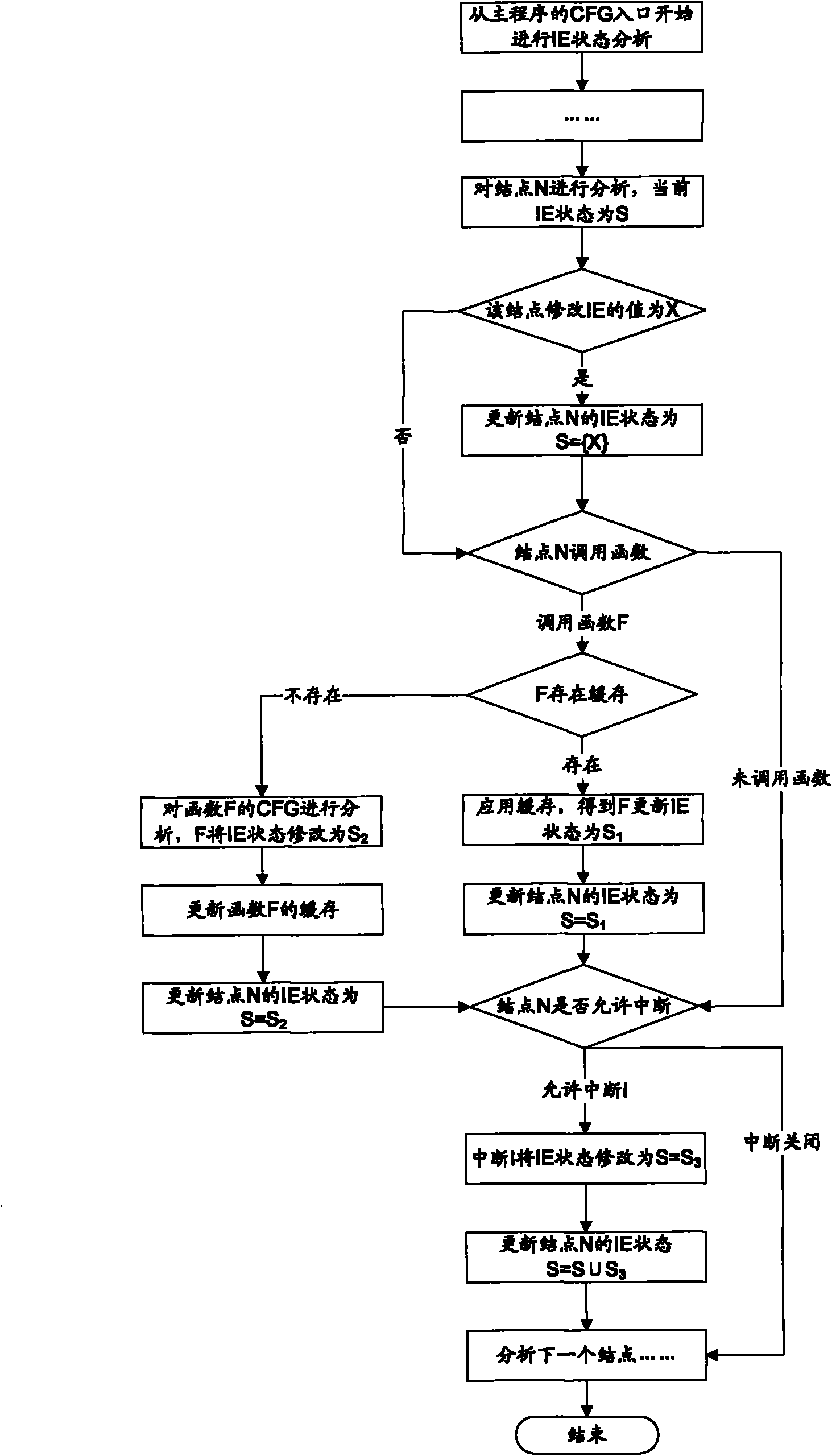

System for detecting interrupt-driven type program data competition

ActiveCN102063328AReduce false positivesHigh degree of automationMultiprogramming arrangementsSoftware developmentSyntax

The invention discloses a system for detecting interrupt-driven type program data competition, which comprises a front-end processor and a data race analysis engine, wherein the front-end processor comprises a disassembler, a morphology / syntax analyzer, a control flow graph constructor and a function call relation graph constructor, and the data race analysis engine comprises an interrupt priority analysis module, an interrupt state analysis module, a memory access analysis module and a race condition identifier. A static detection method is adopted in the invention, wherein a source code or assembly code is input; the detected program does not need to run; the method can be applied in the early stage of software development; the automaticity is high; and the interrupt enabled state is analyzed in iterative inter-process manner; through 'iteration', all the possible interrupt switching conditions can be extremely collected and the failed report of data race detection is reduced; and through 'inter-process', the function call and the influence of the interruption on the program state are regarded and the detection accuracy and the detection efficiency are increased.

Owner:BEIJING INST OF CONTROL ENG

Anti-cross conduction drive control circuit and method

ActiveUS20060001459A1Avoid it happening againPrevent cross-conductionTransistorReliability increasing modificationsMOSFETEngineering

An anti-cross conduction driver control circuit and method prevent the occurrence of race conditions and avoid cross-conduction between series-connected power devices, typically MOSFETs, controlled in accordance with the present invention. Individual state machines are connected across the inputs and outputs of each power device driver, and are arranged to accurately determine when the driver has completed a task requested of it. Each state machine produces a “lockout” signal based on driver status, which is used to inhibit the operation of the opposite driver under prescribed conditions, and to thereby prevent cross-conduction between the series-connected power devices.

Owner:ANALOG DEVICES INC