Patents

Literature

326 results about "Boundary scan" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

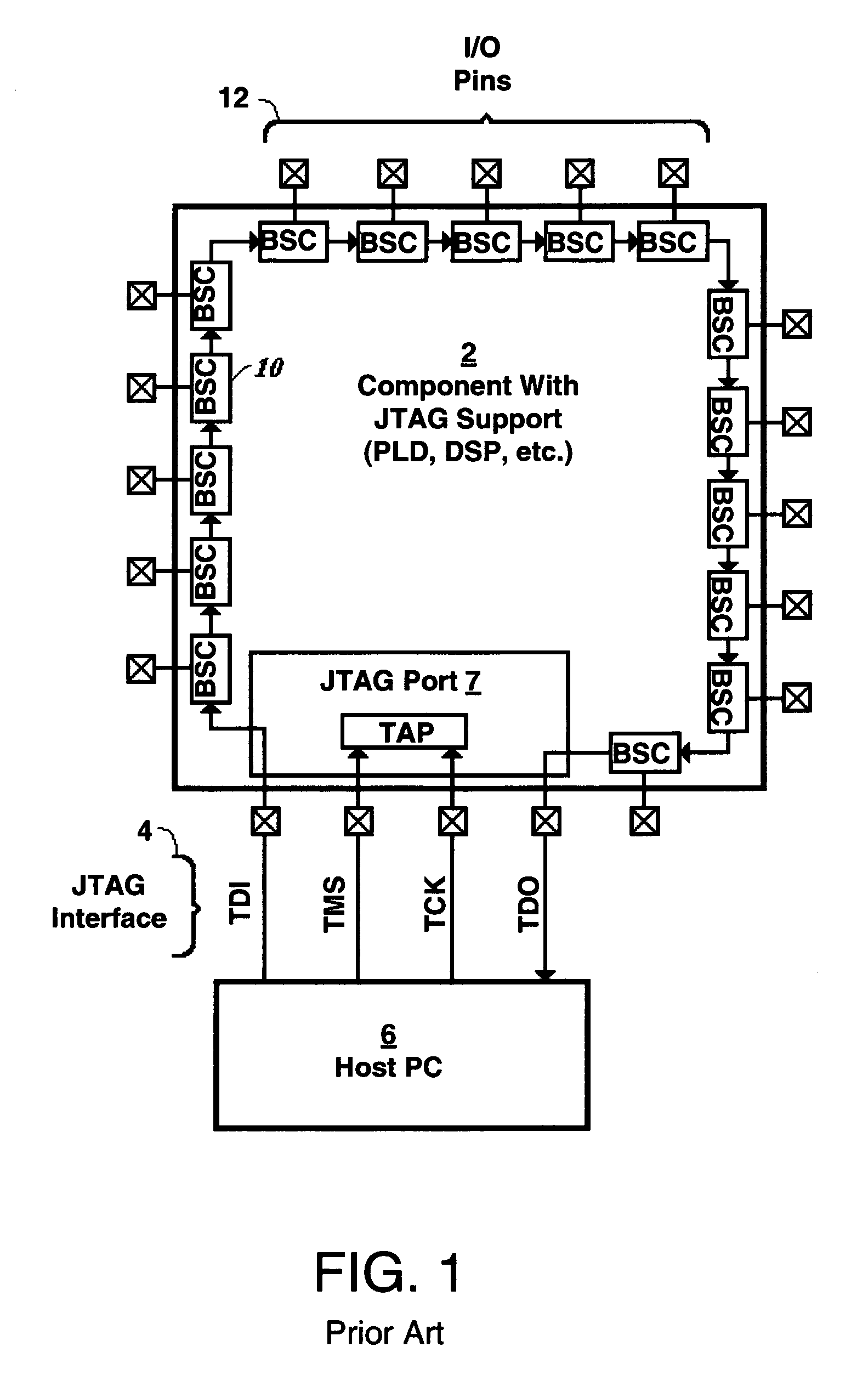

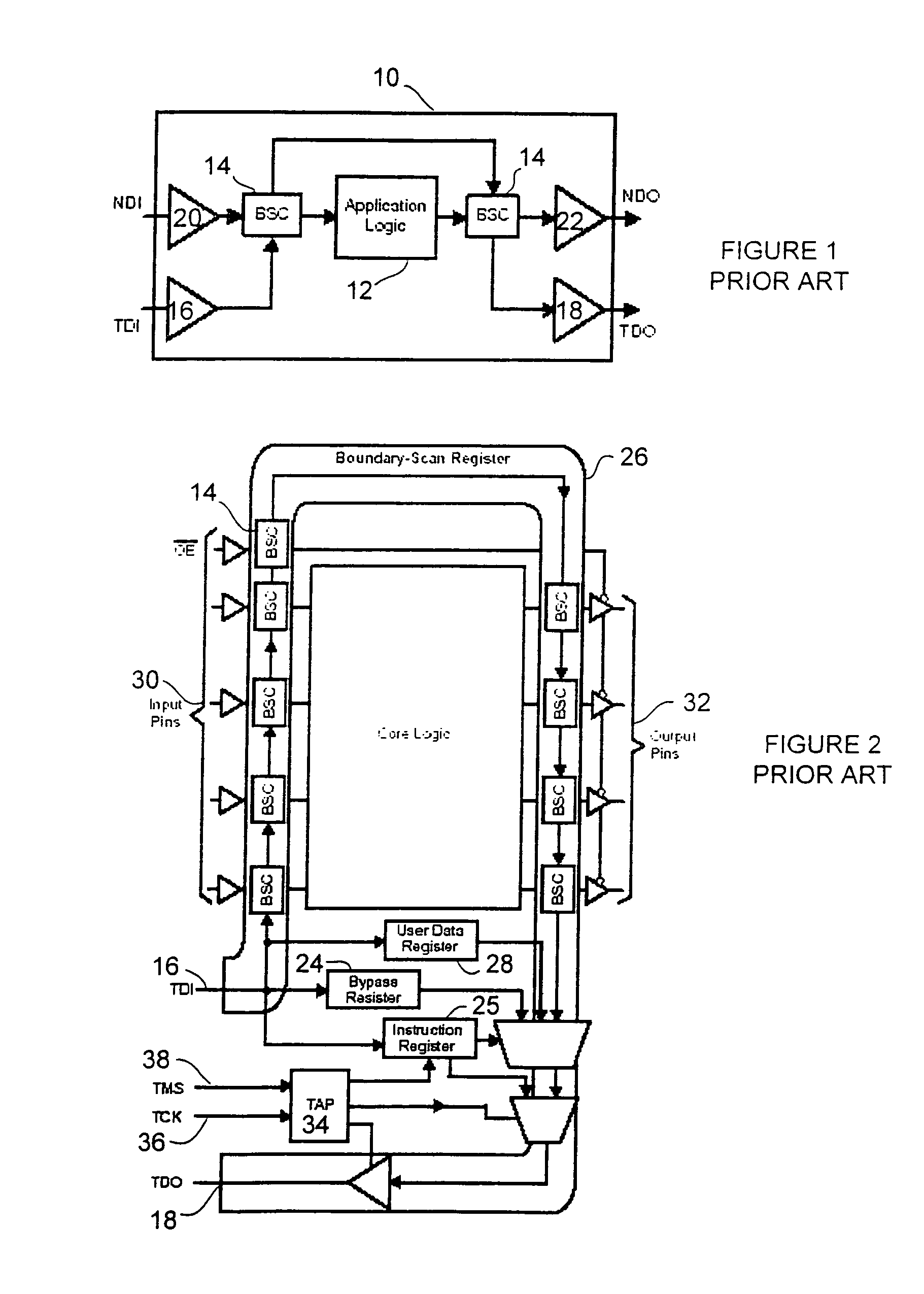

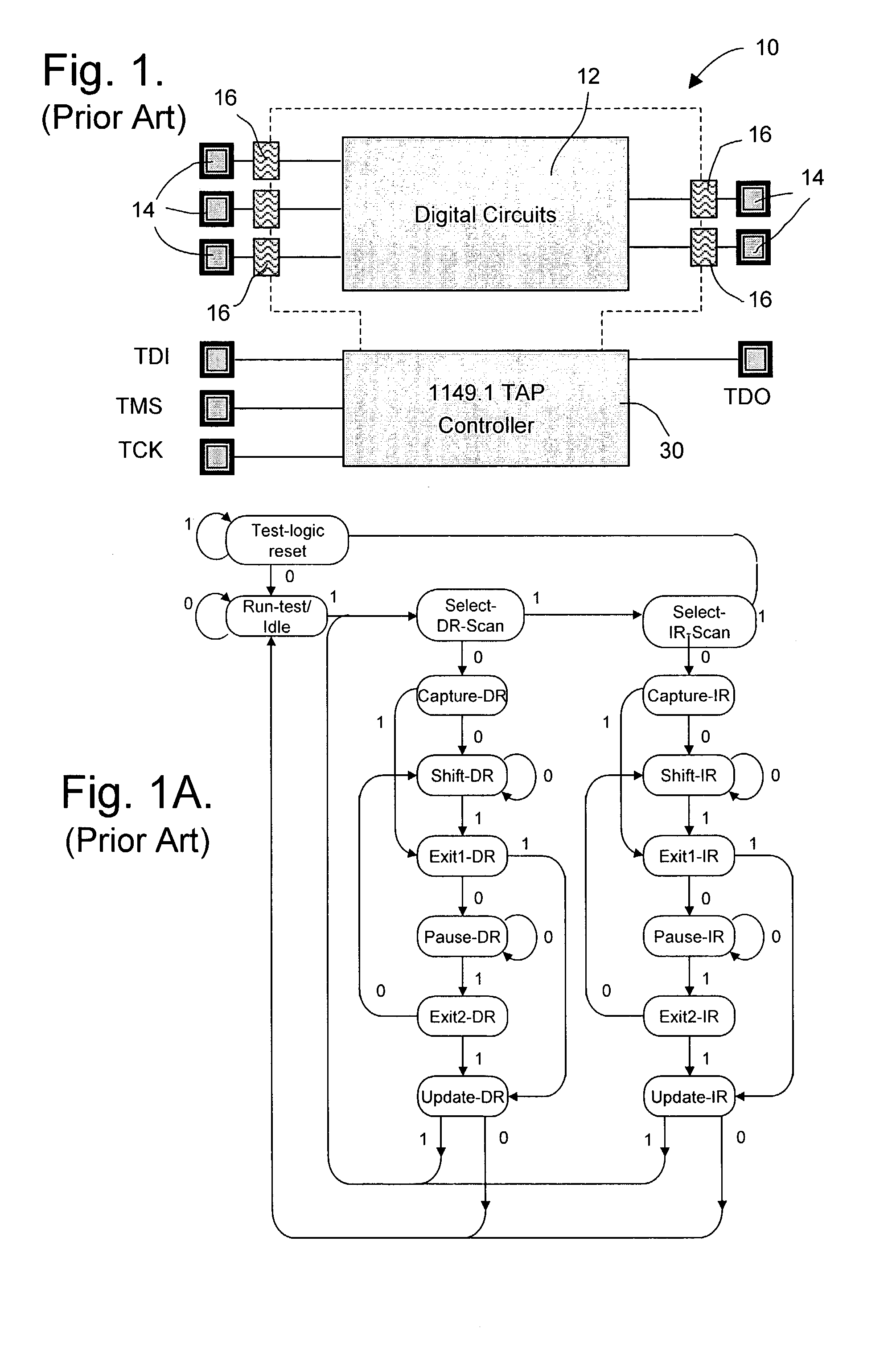

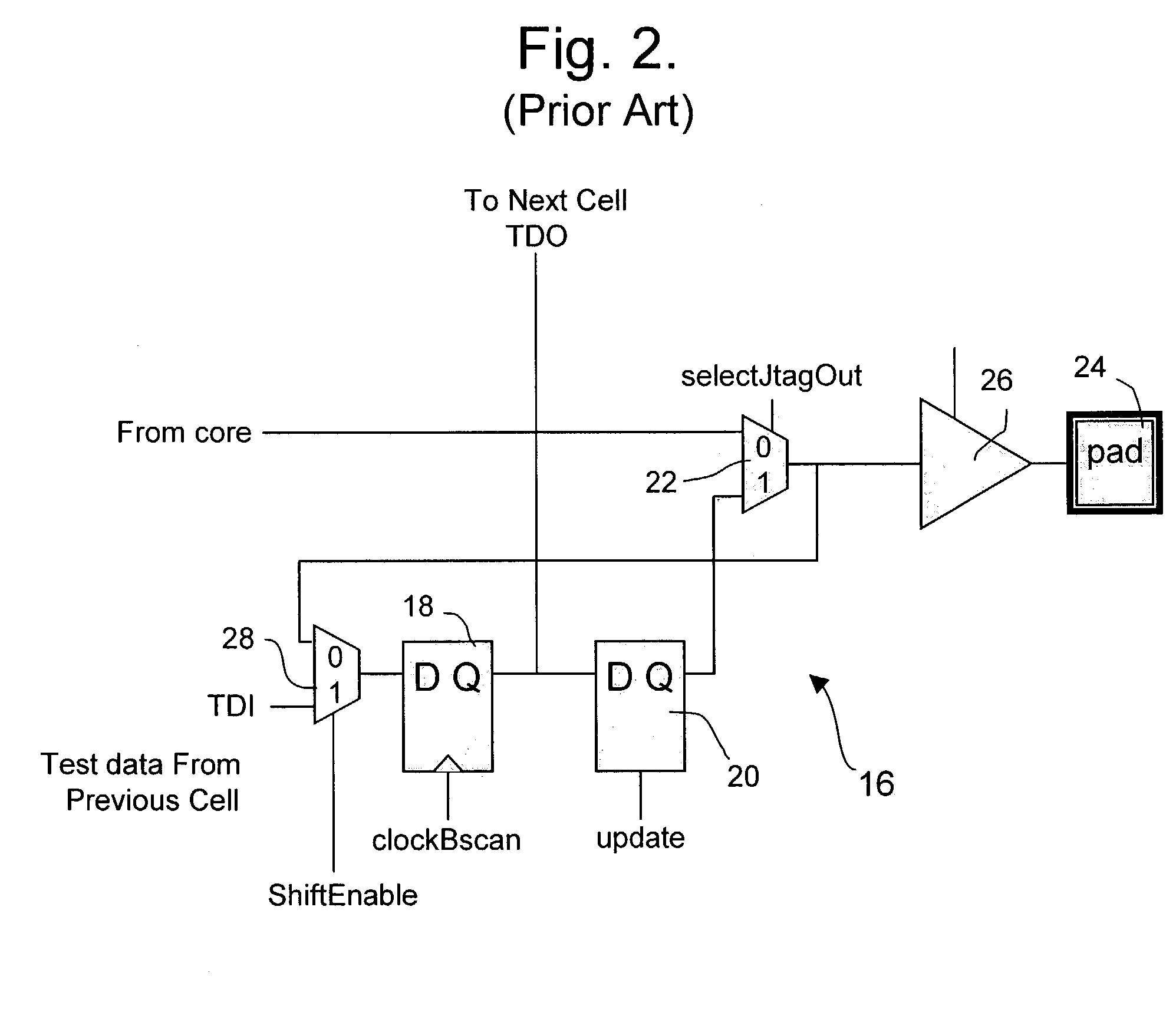

Boundary scan is a method for testing interconnects (wire lines) on printed circuit boards or sub-blocks inside an integrated circuit. Boundary scan is also widely used as a debugging method to watch integrated circuit pin states, measure voltage, or analyze sub-blocks inside an integrated circuit.

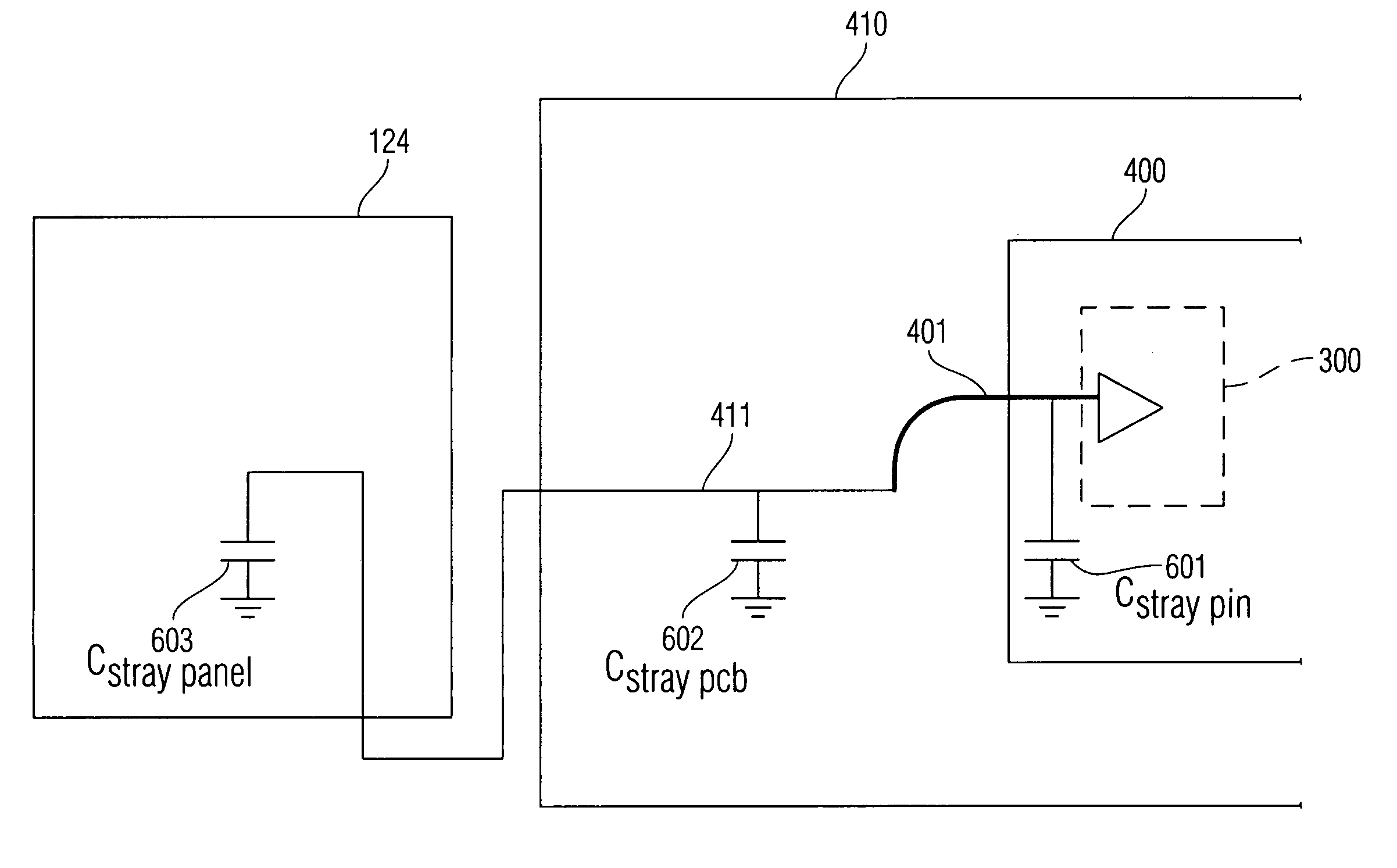

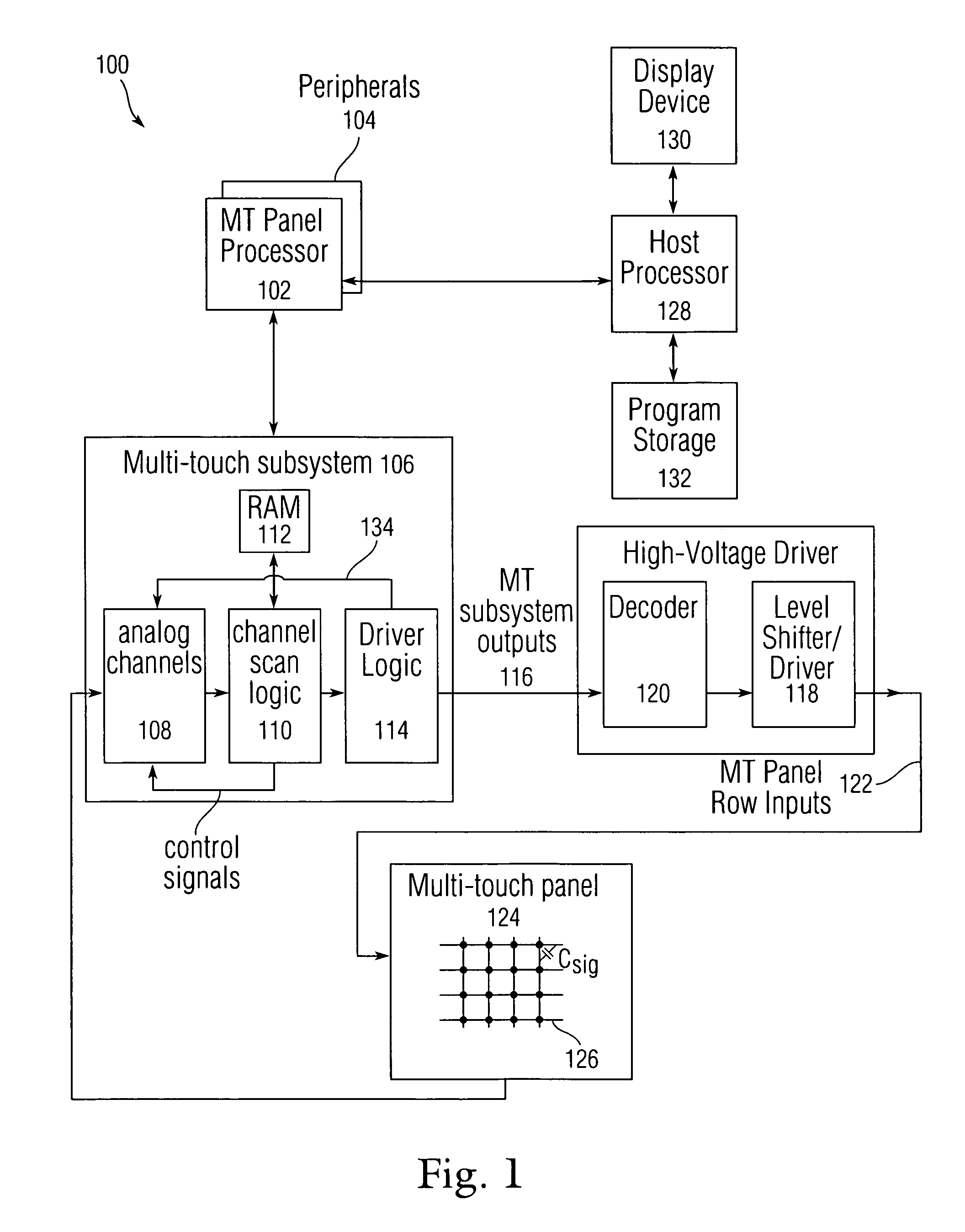

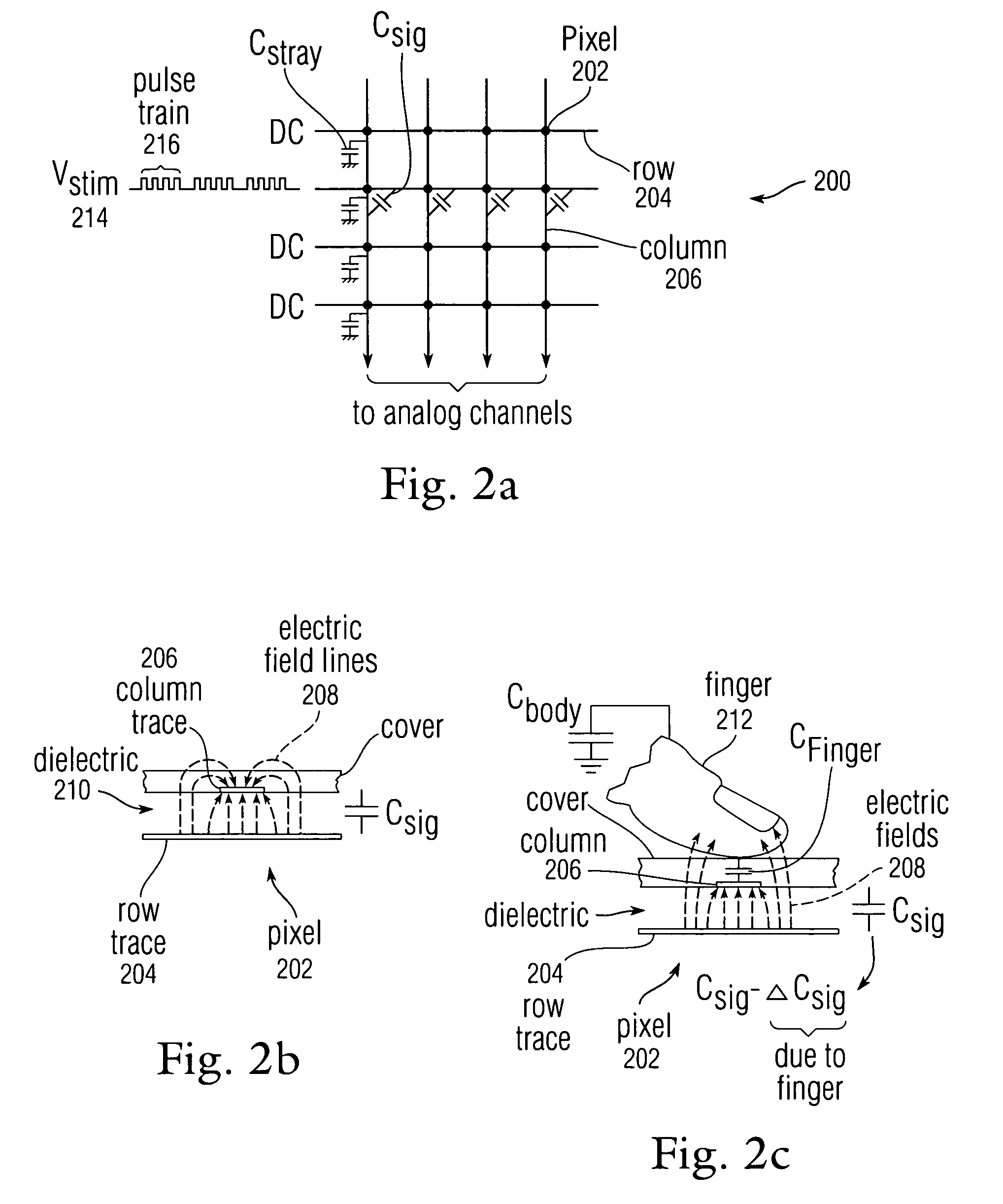

Analog boundary scanning based on stray capacitance

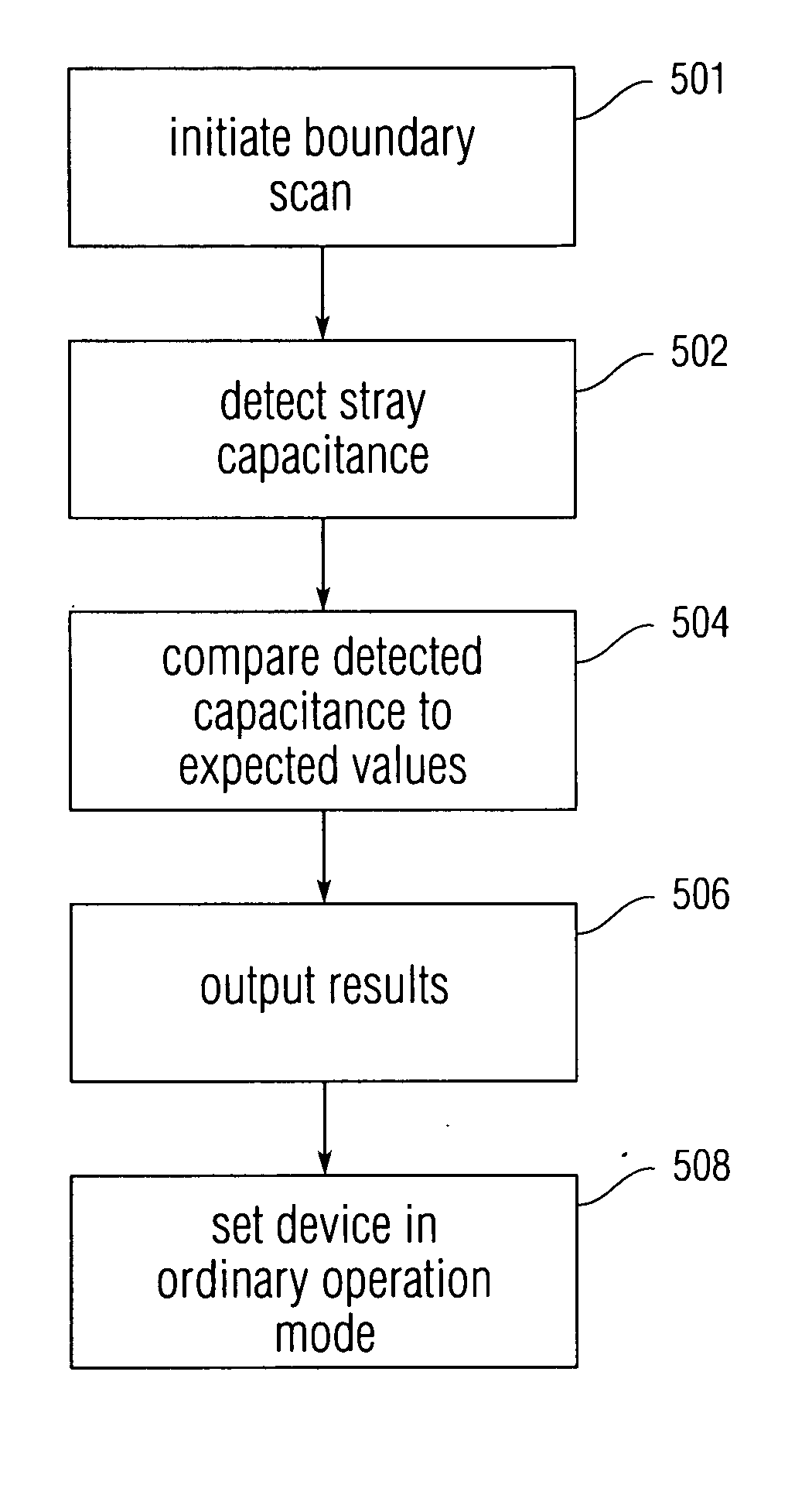

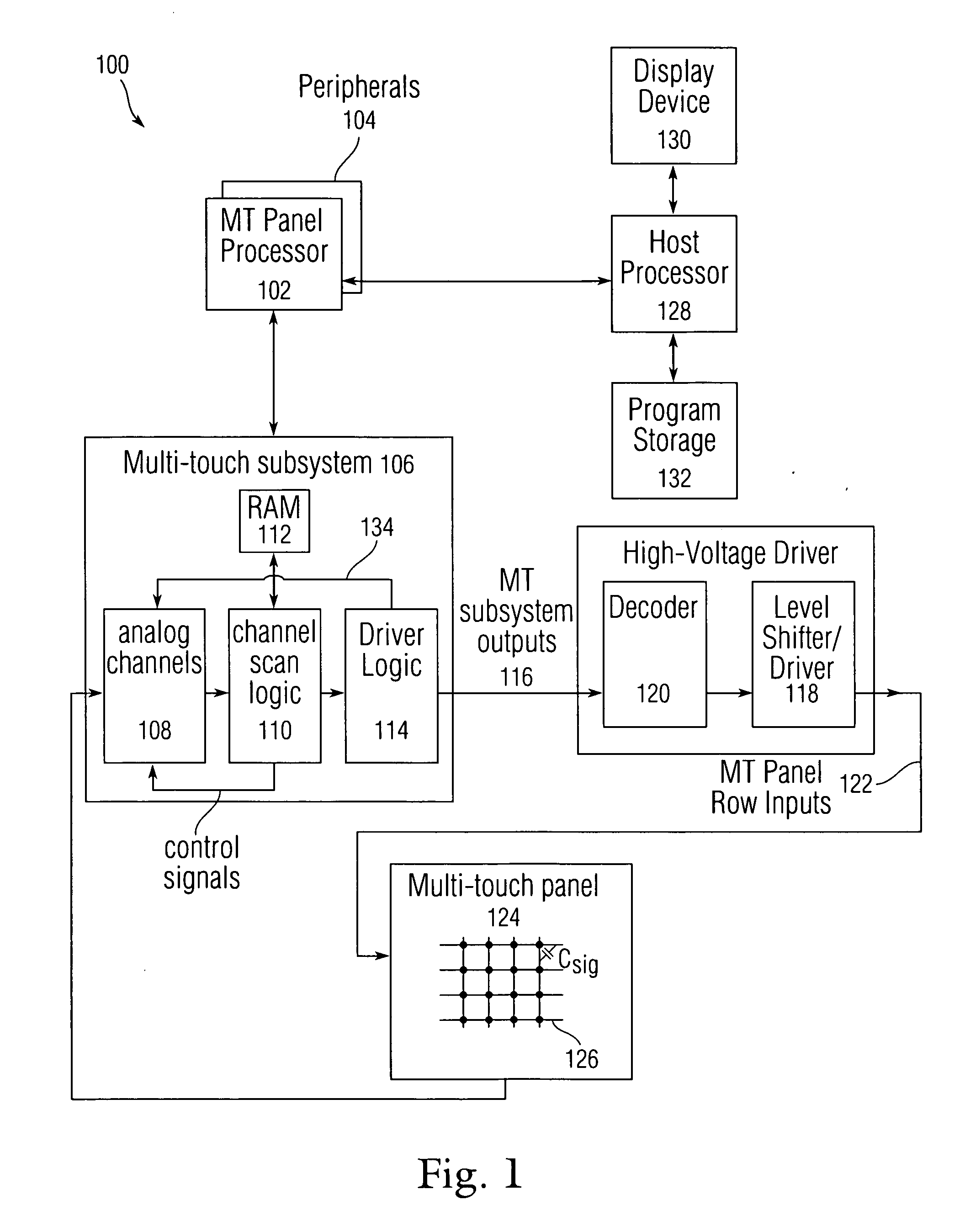

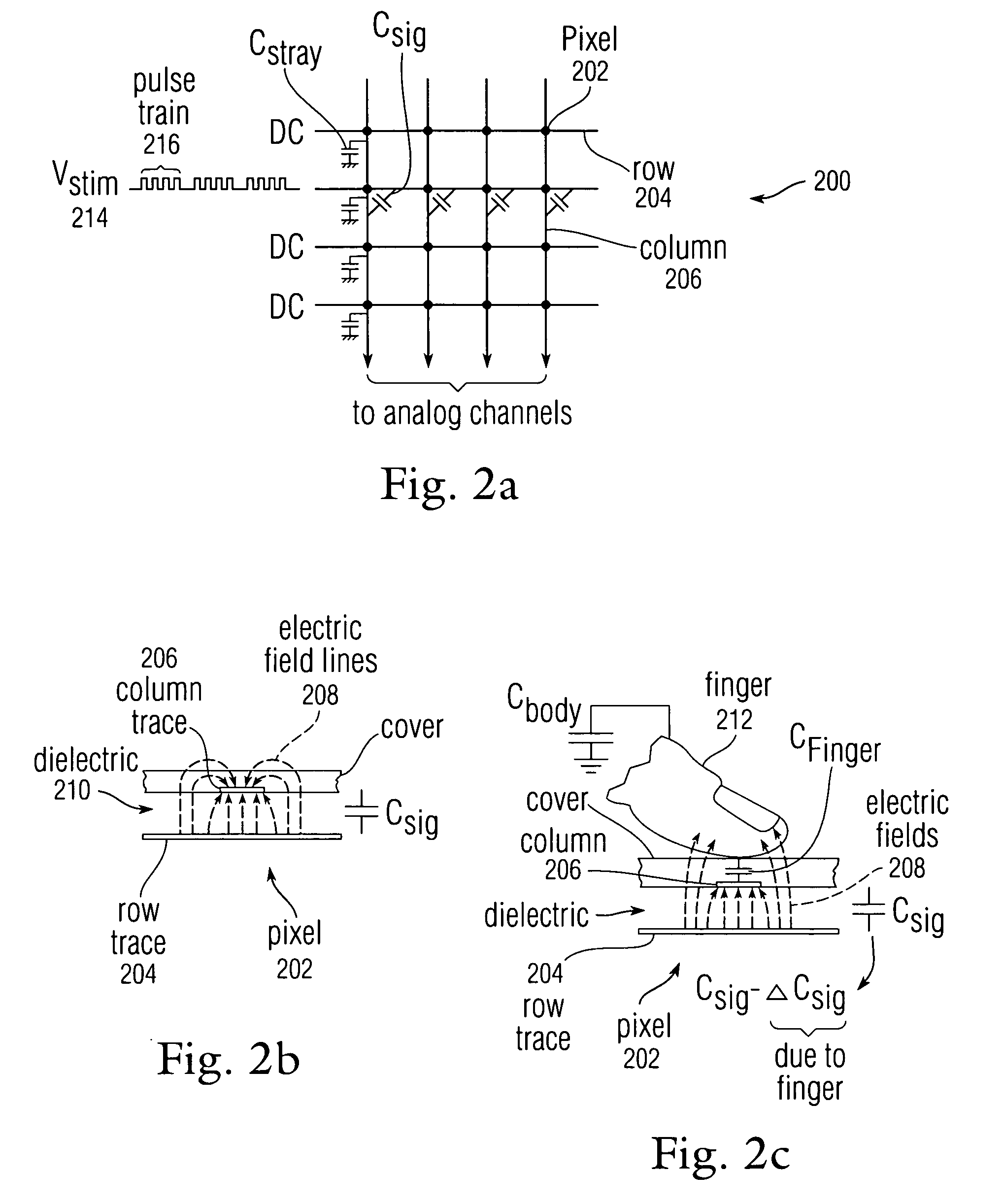

Embodiments of the present invention are directed to performing boundary scanning without using a pin which is exclusively dedicated for that purpose. The boundary scan can be performed by an integrated circuit by utilizing a pin which has an alternative use during ordinary operation of the integrated circuit and the device. This pin can be connected to an analog circuit configured to sense capacitance outside of the pin. The analog circuit may also have an alternative function in normal operation of the device. During a testing mode, the analog circuit can sense a stray capacitance present at the pin. The sensed capacitance can be compared to one or more stored expected capacitance values to determine an interconnection state of the system.

Owner:APPLE INC

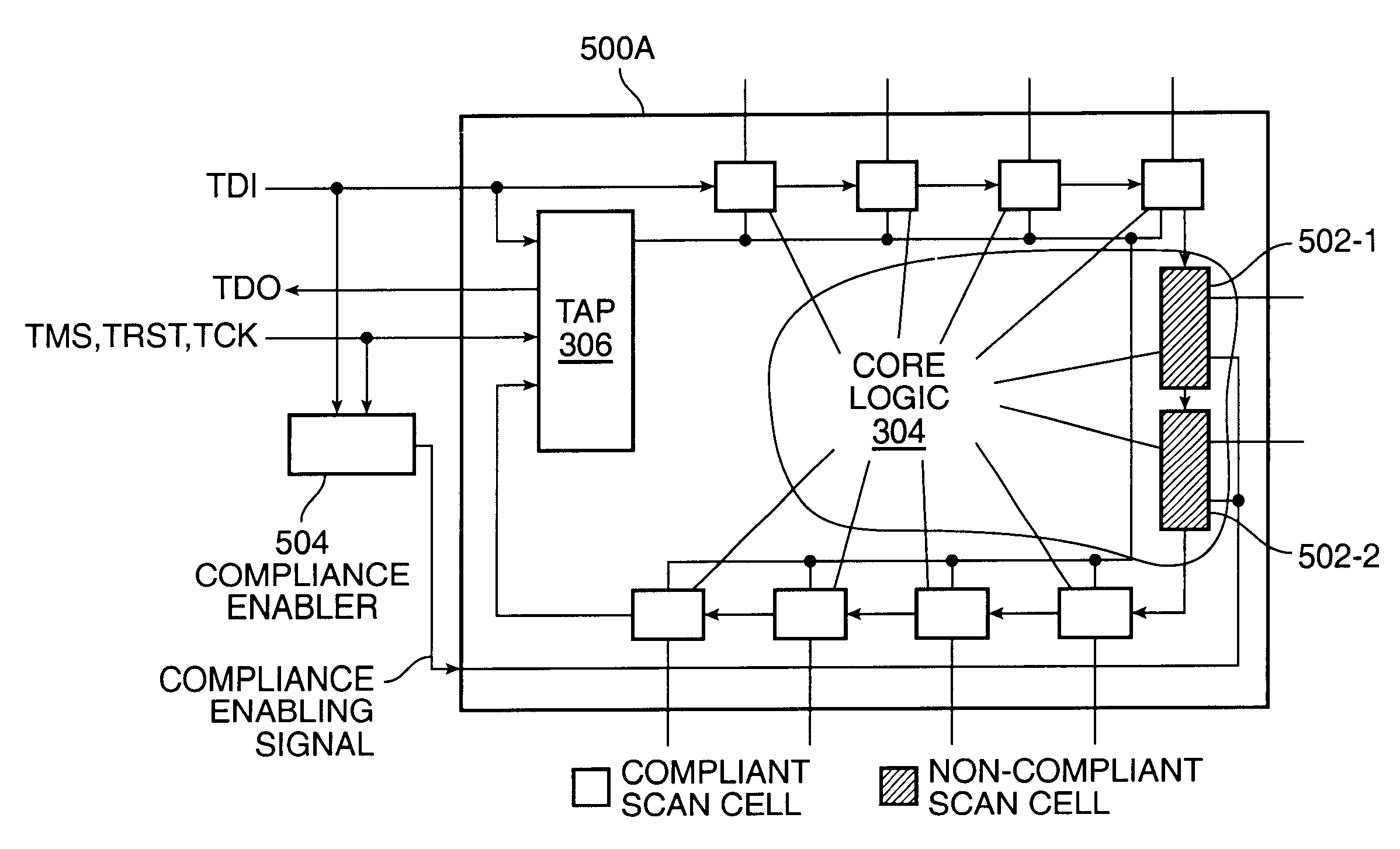

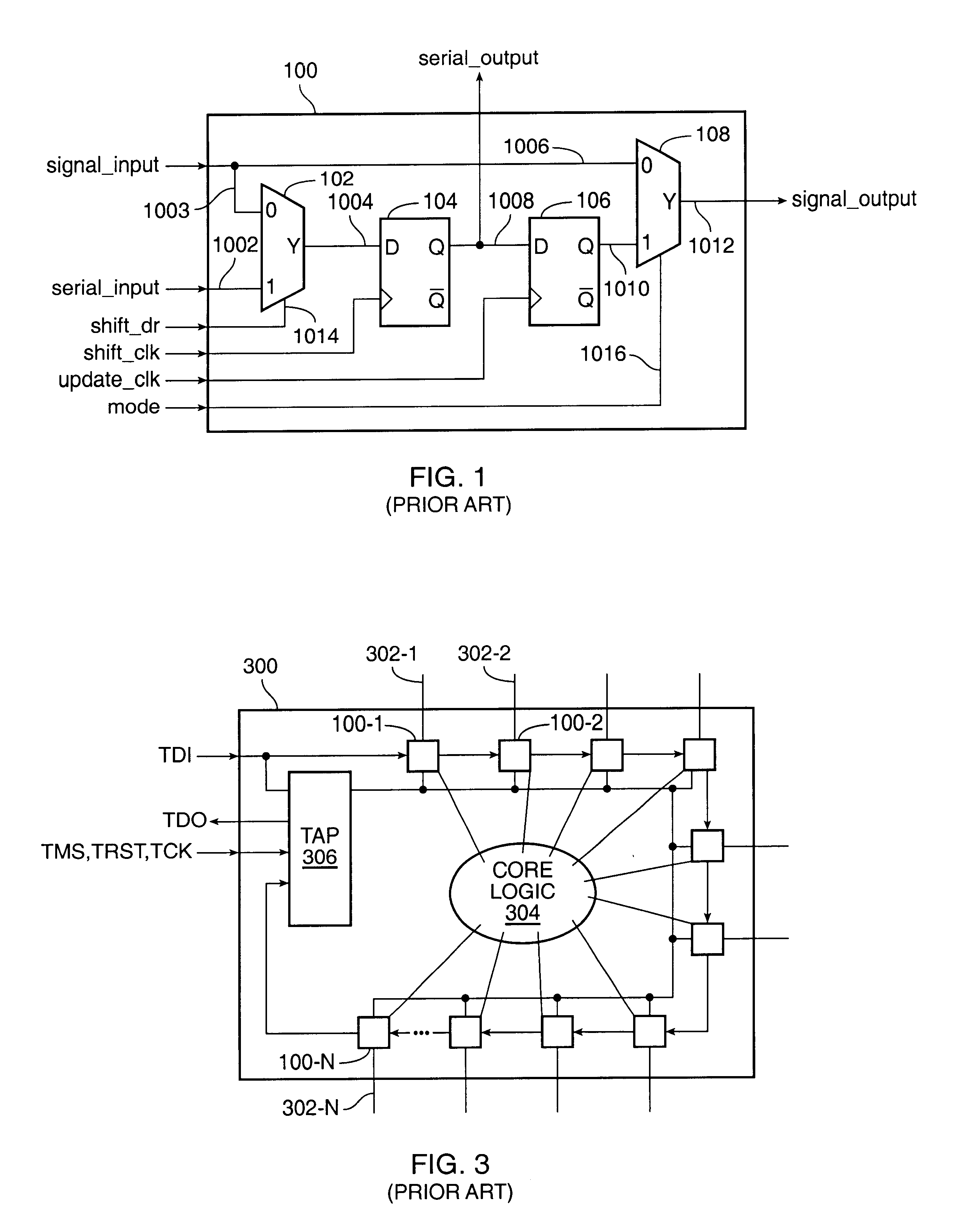

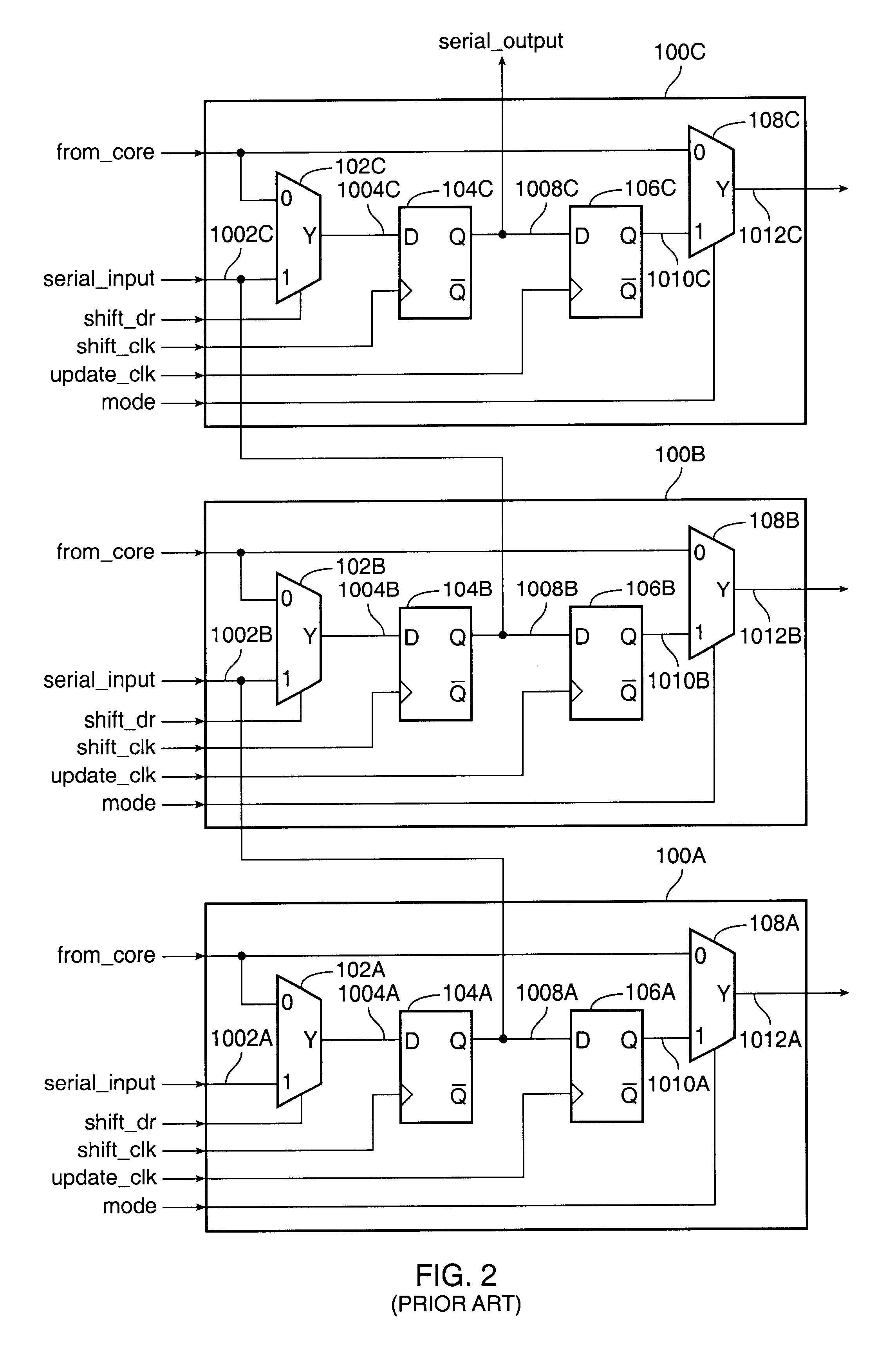

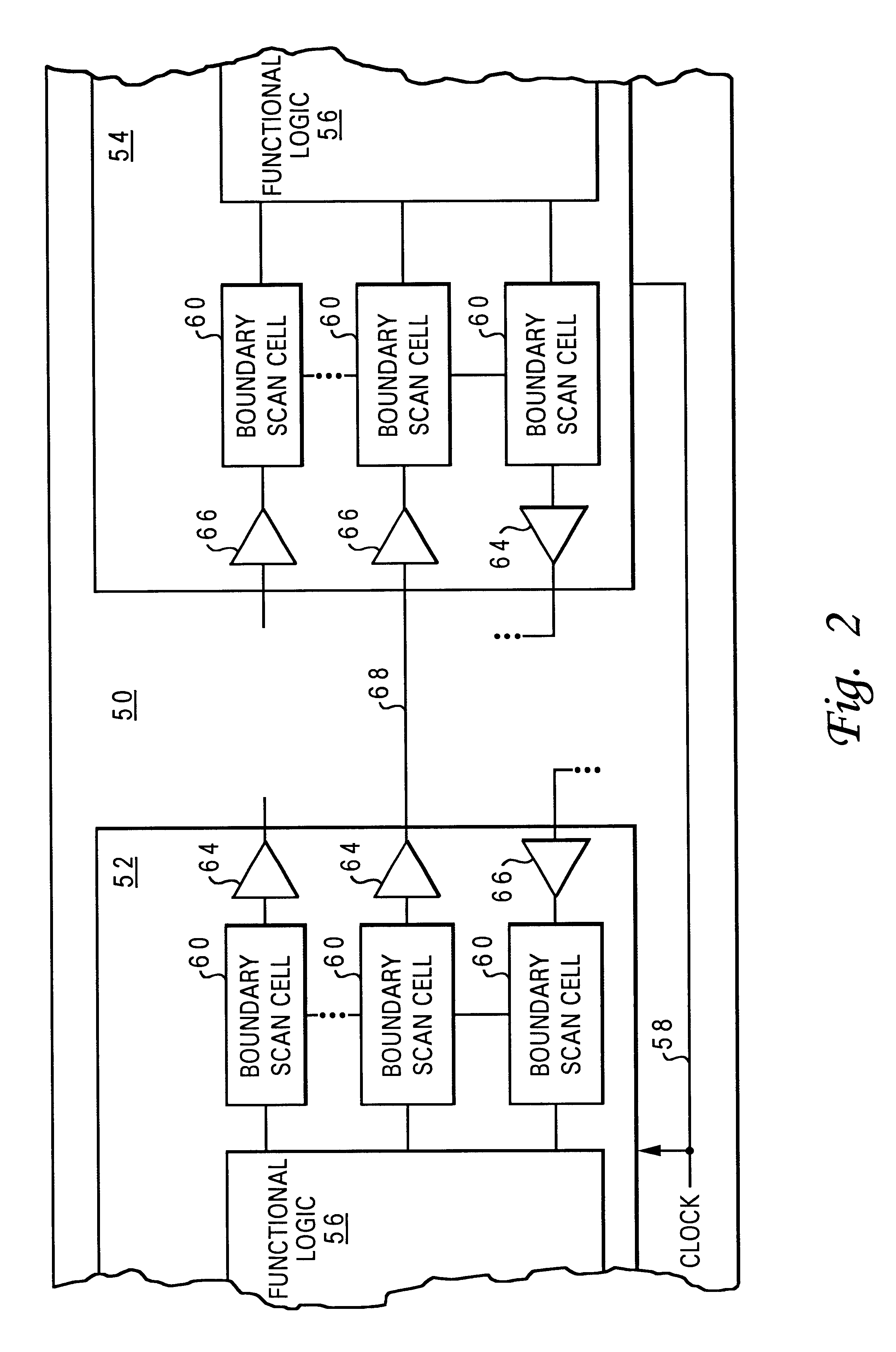

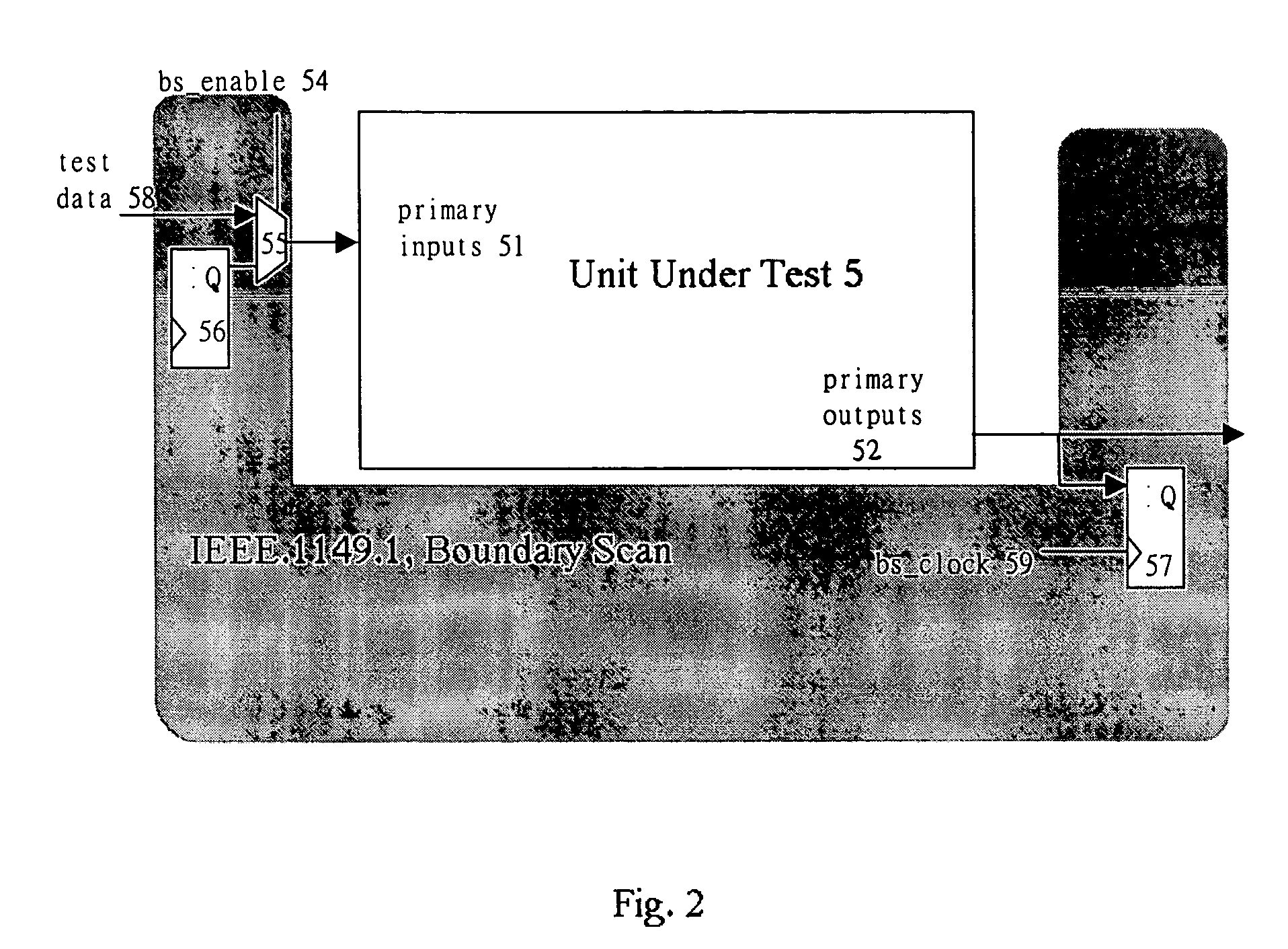

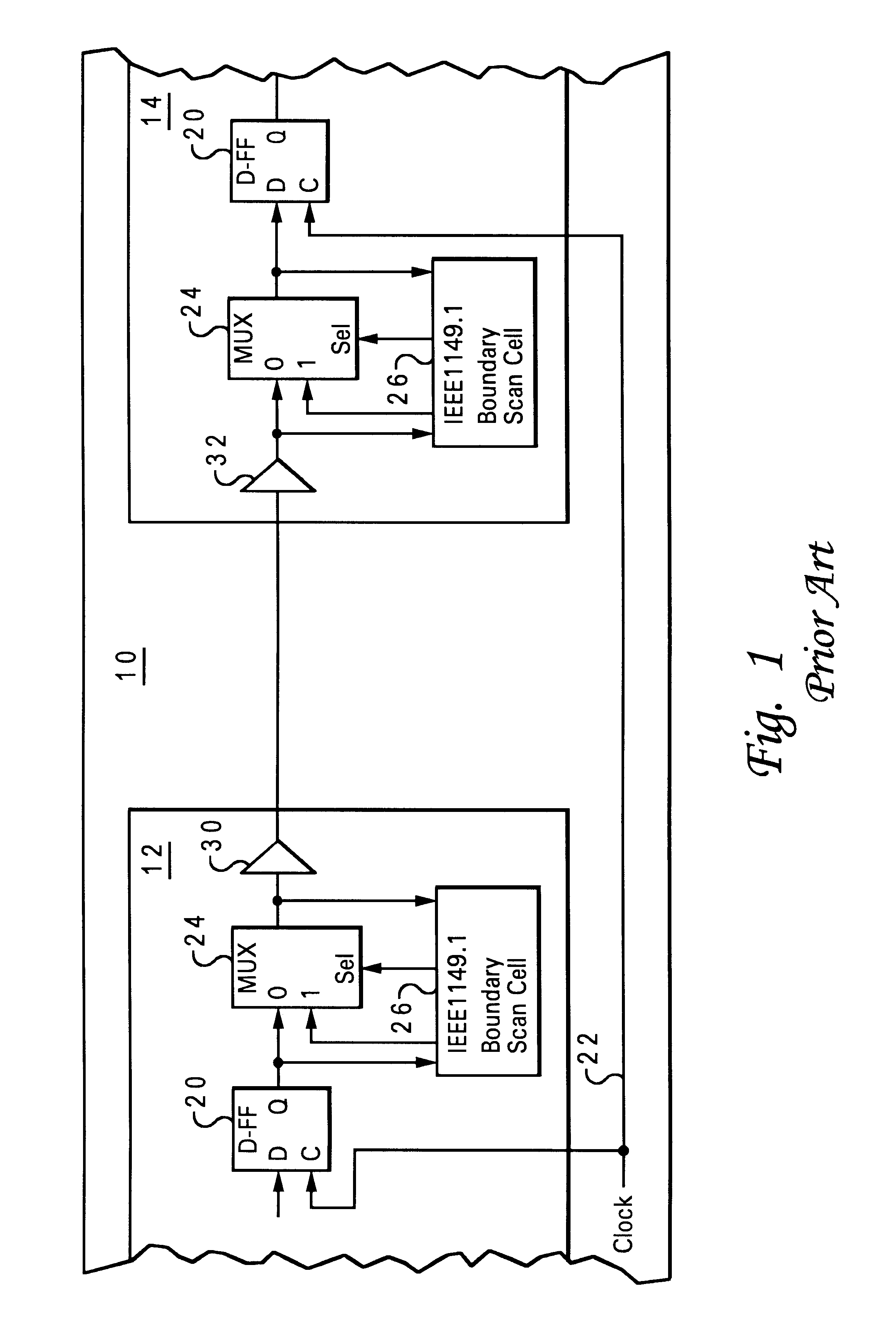

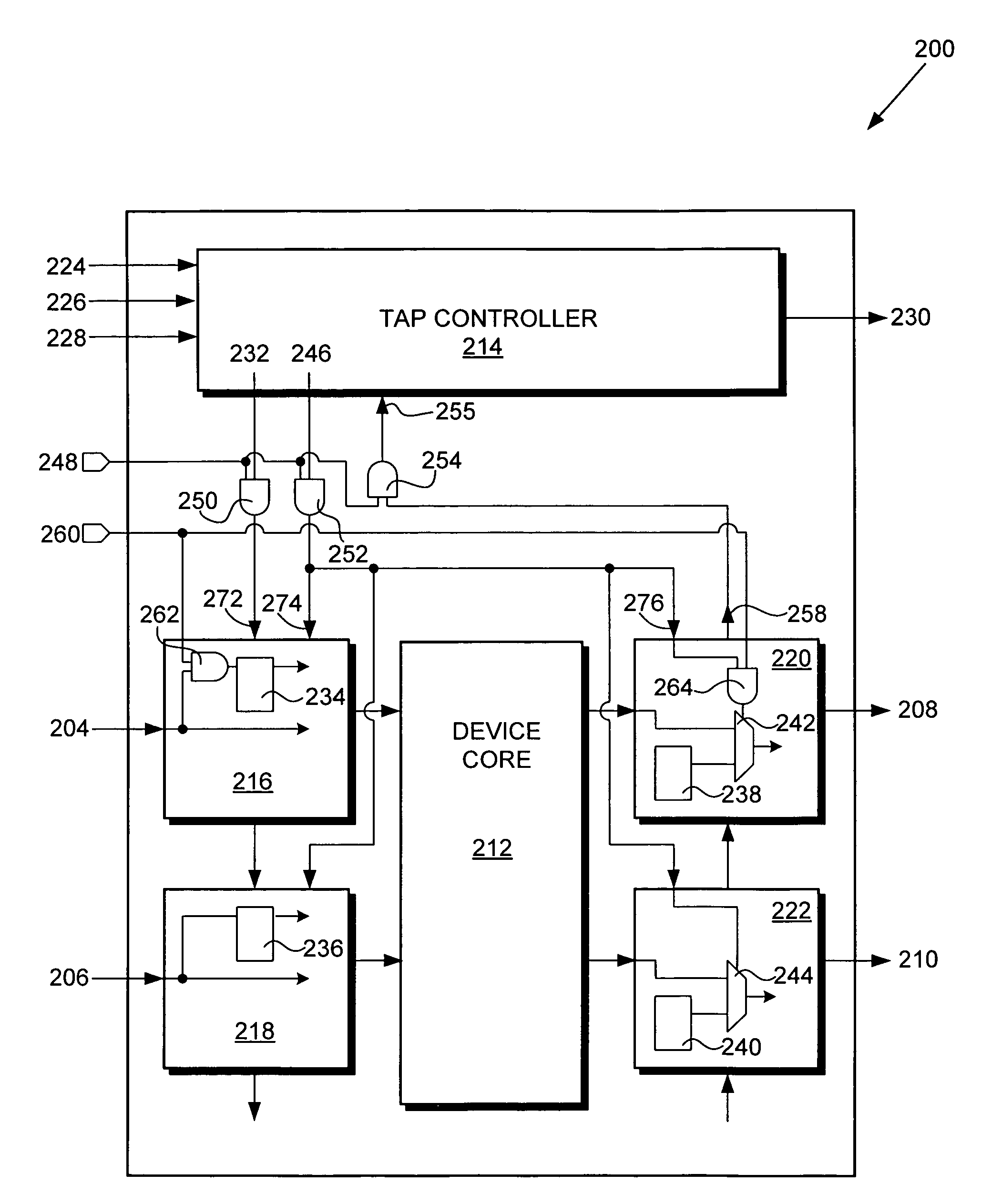

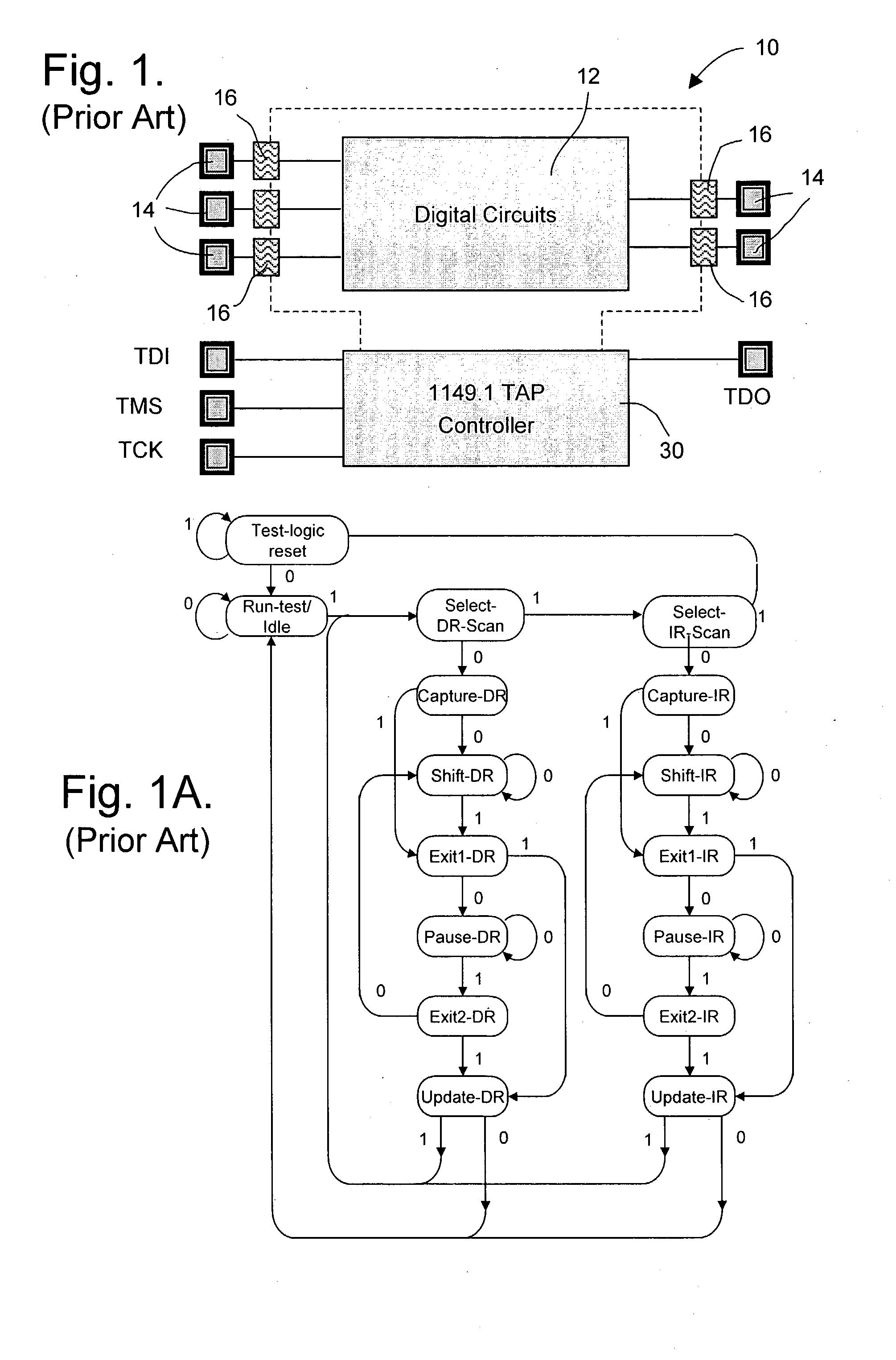

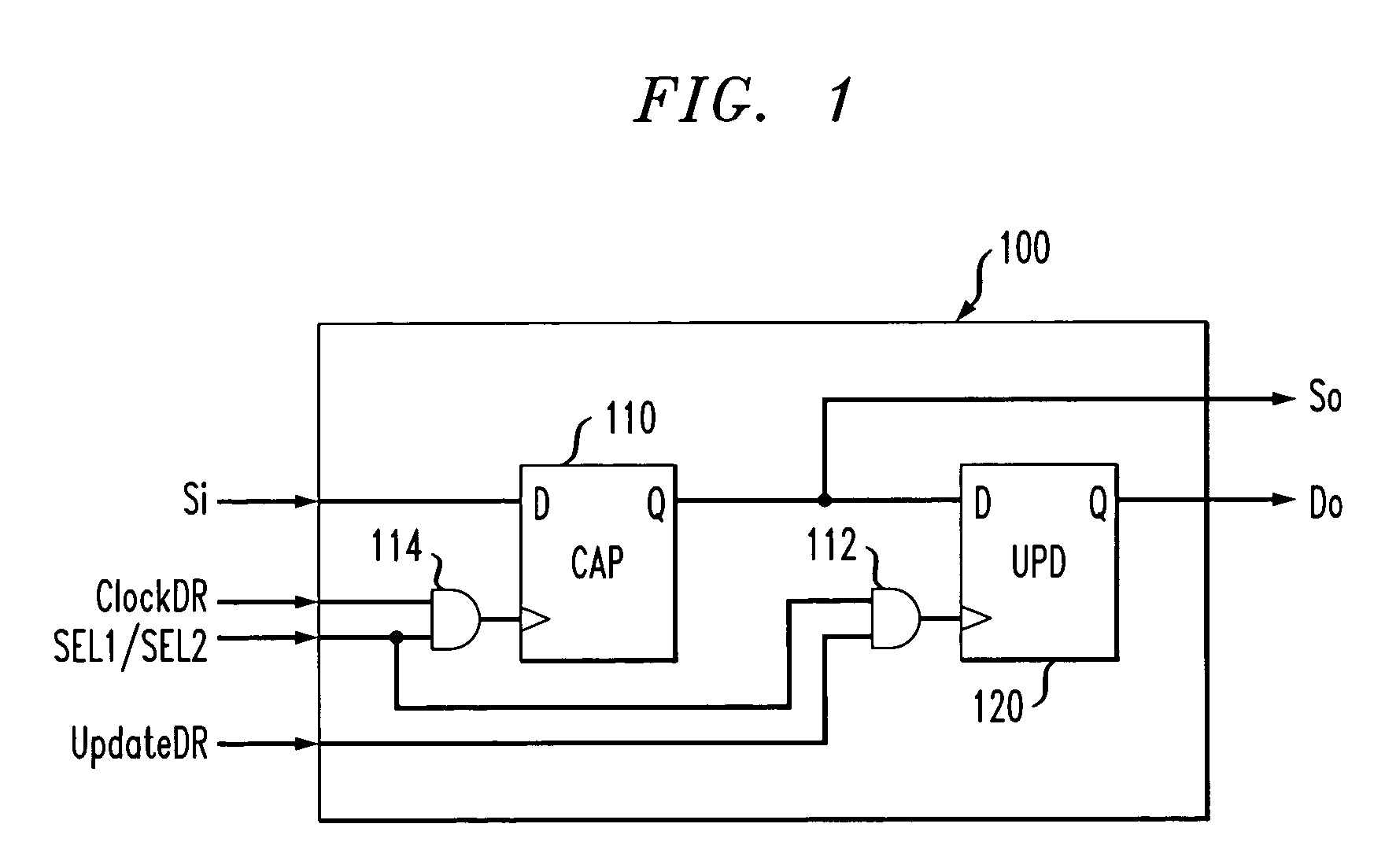

Mechanism for enabling compliance with the IEEE standard 1149.1 for boundary-scan designs and tests

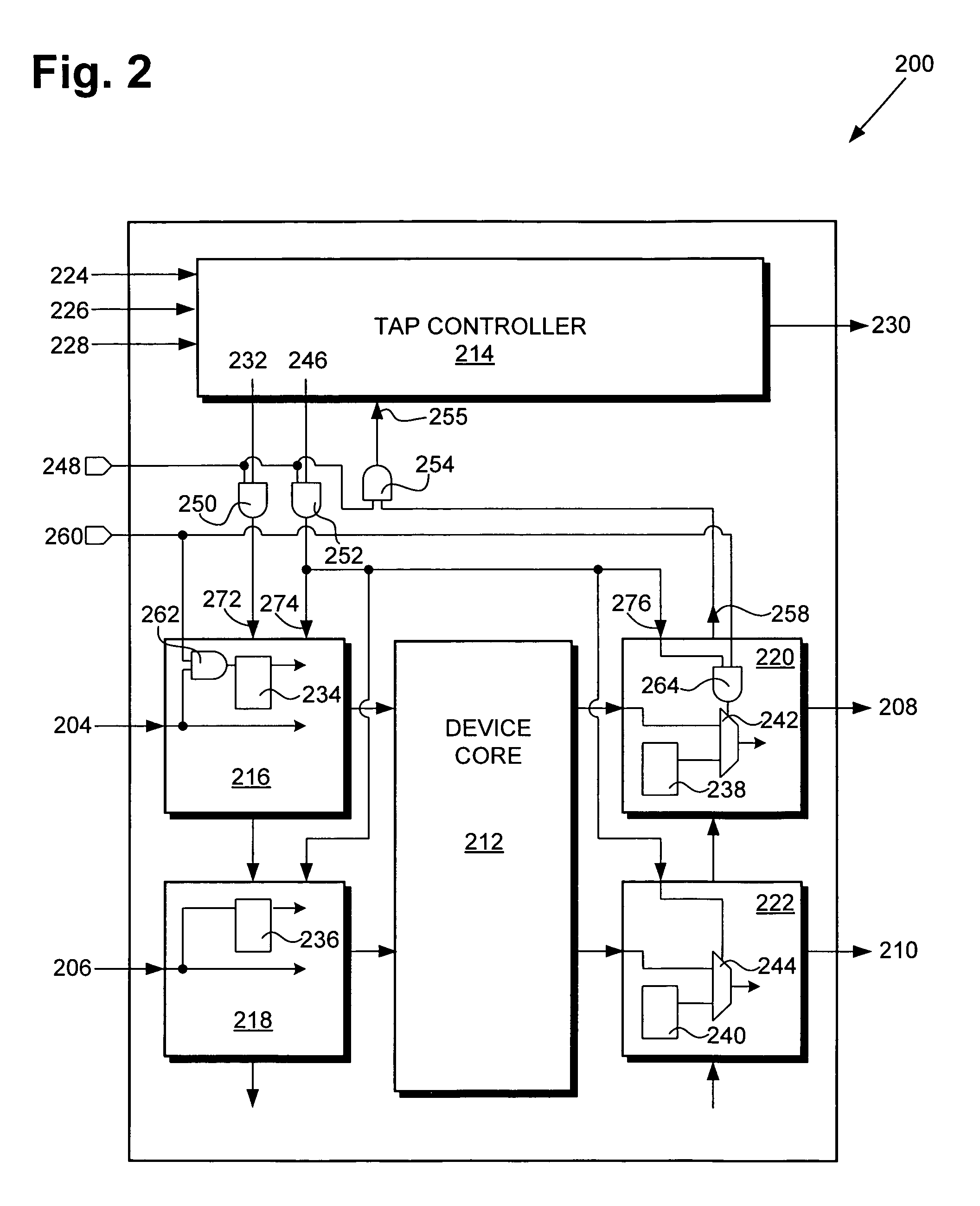

A mechanism for enabling compliance with the IEEE boundary-scan standard 1149.1 includes, in a first preferred embodiment, a compliance enabler working with non-compliant embedded boundary-scan cells to enable a Device Under Test (DUT) to function as an IEEE-standard-compliant part, thus allowing full utilization of existing test tool generation and operation of the IEEE standard. The enabler is preferably provided separately from boundary scan-cells embedded in core logic designs. The enabler includes a Test Access Port (TAP) controller and related decoding circuits to generate necessary compliance signals based on various conventional TAP controller variables and instruction functions. The embedded boundary-scan cells preferably include an internal scan cell architecture. In a second embodiment, a second enabler works with a TAP emulator to allow testing of TAP-less DUTs.

Owner:CISCO TECH INC

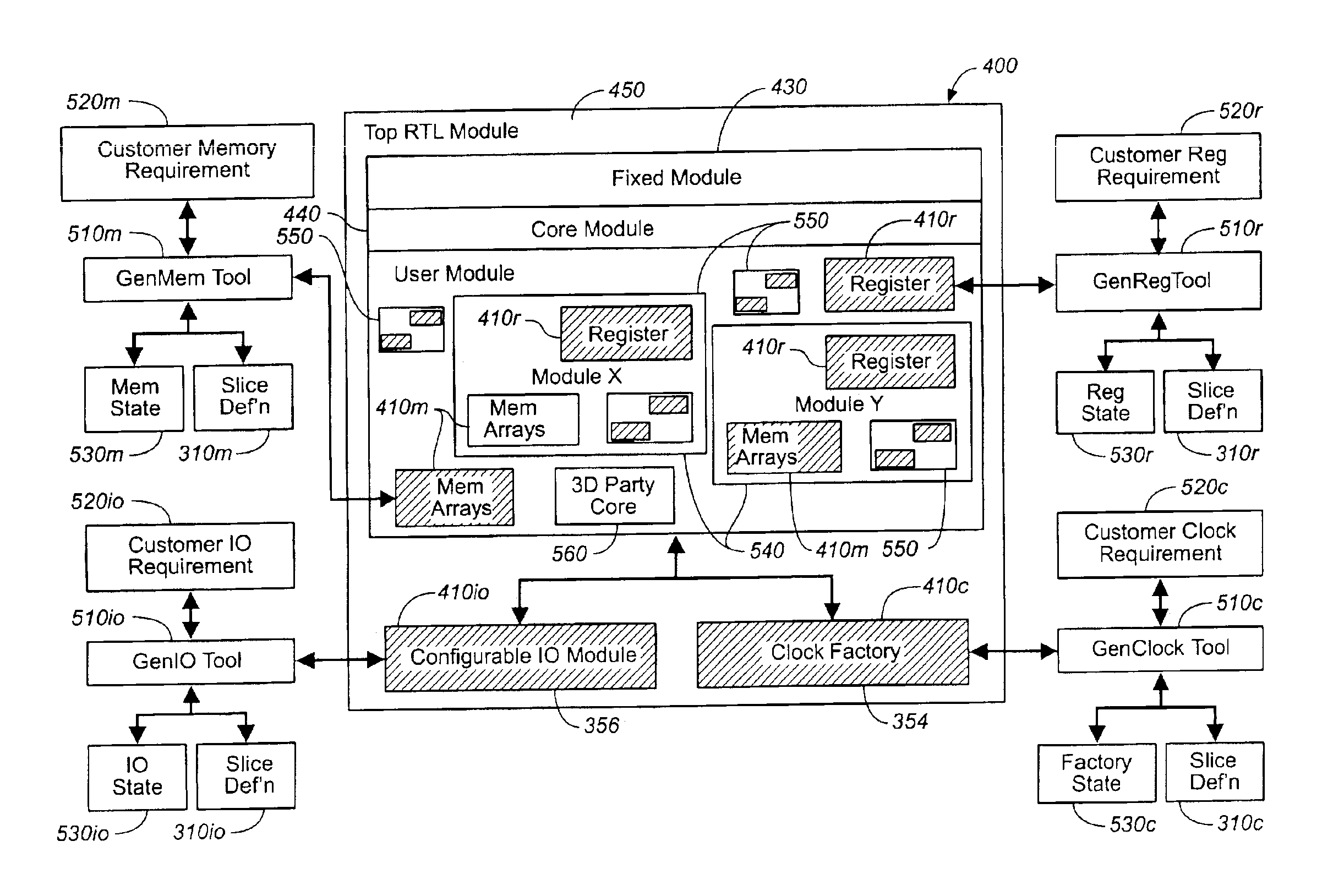

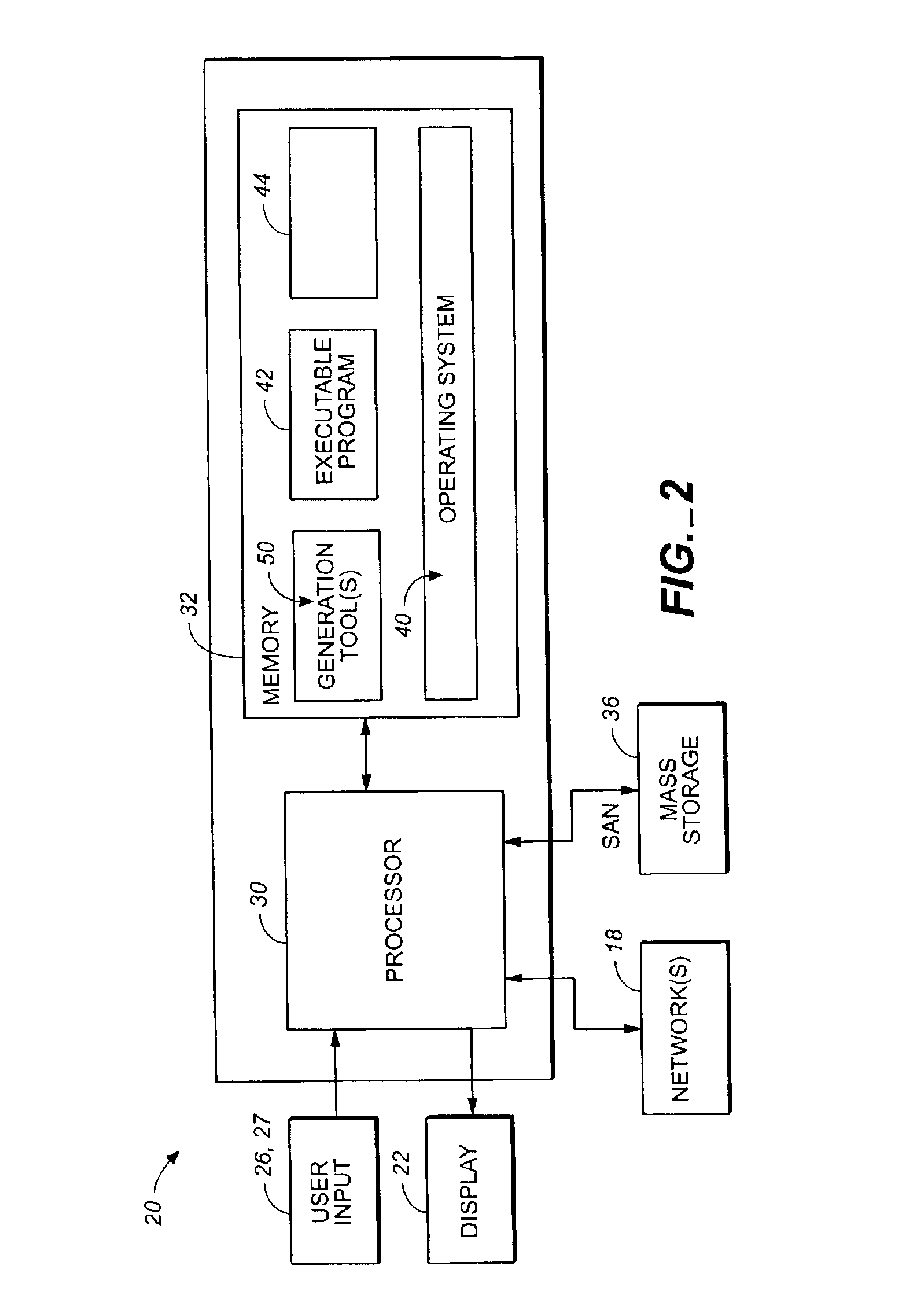

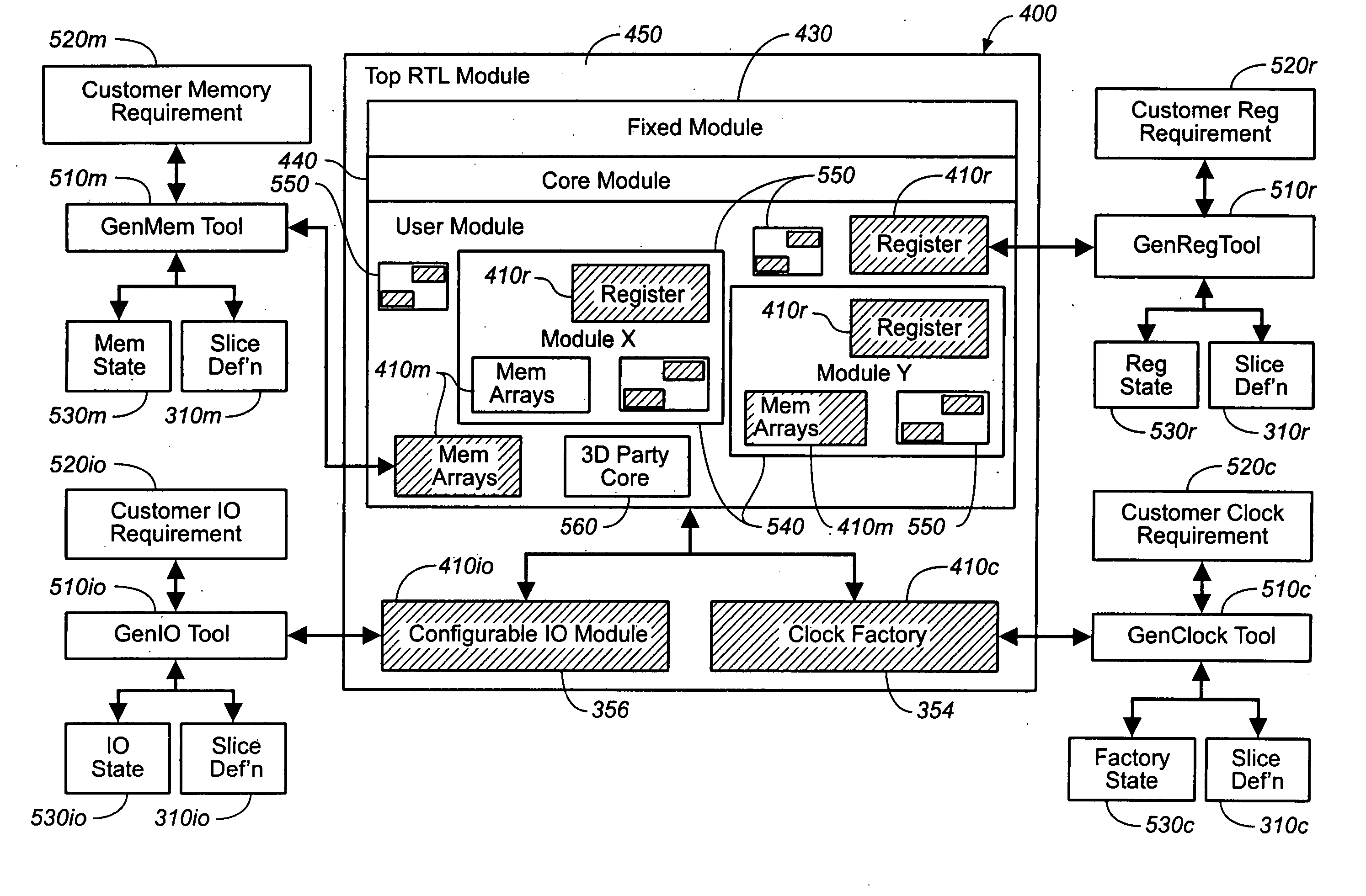

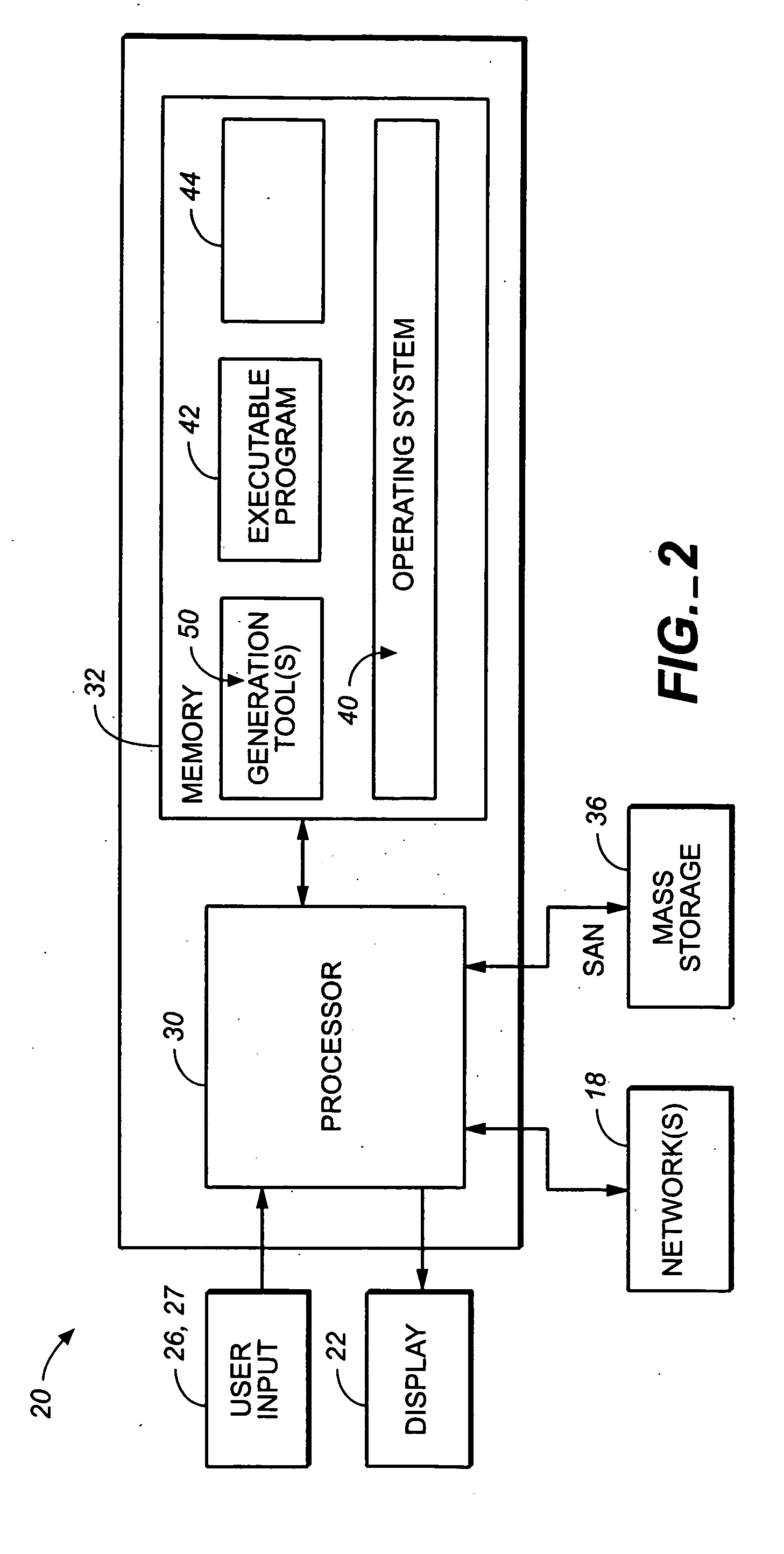

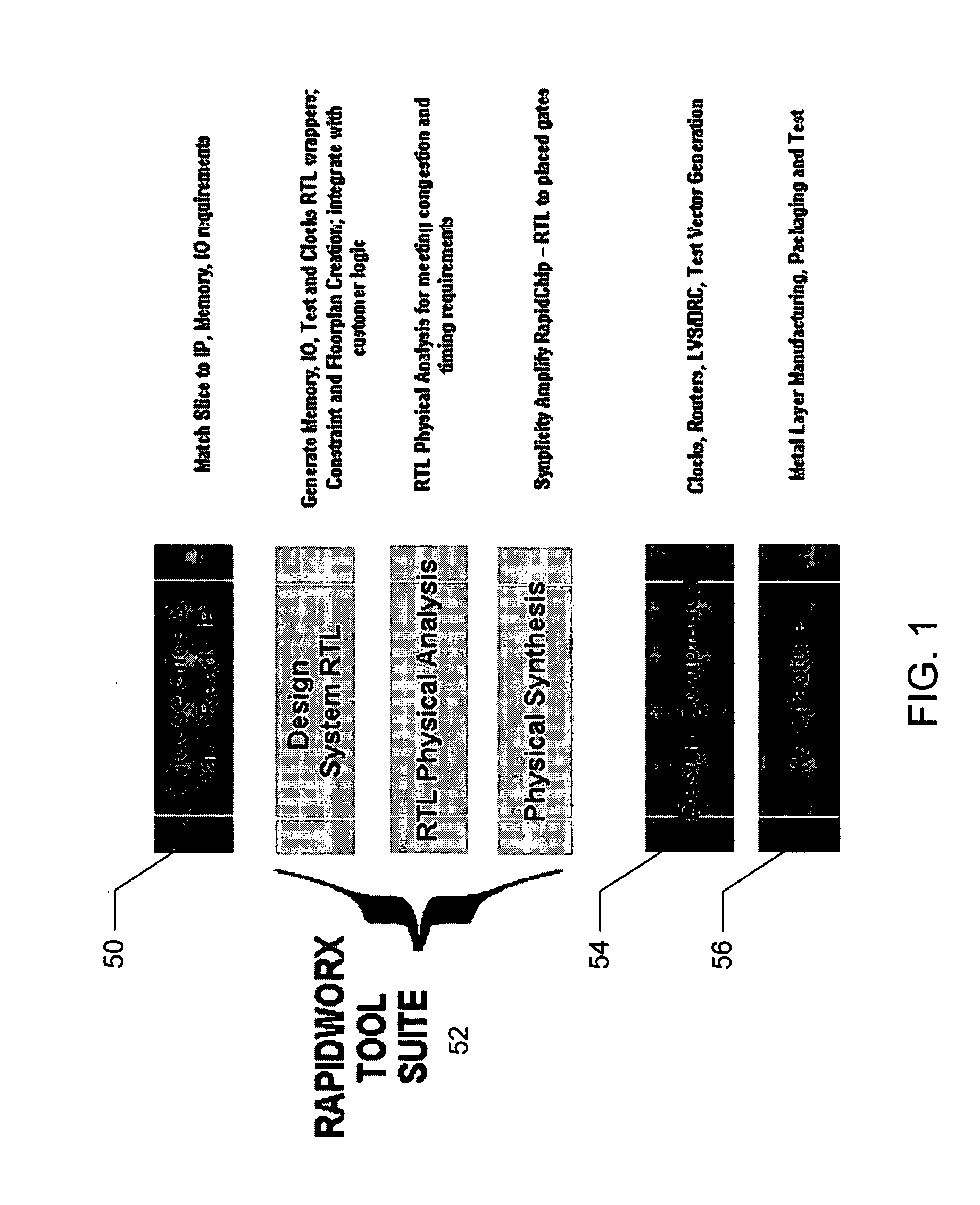

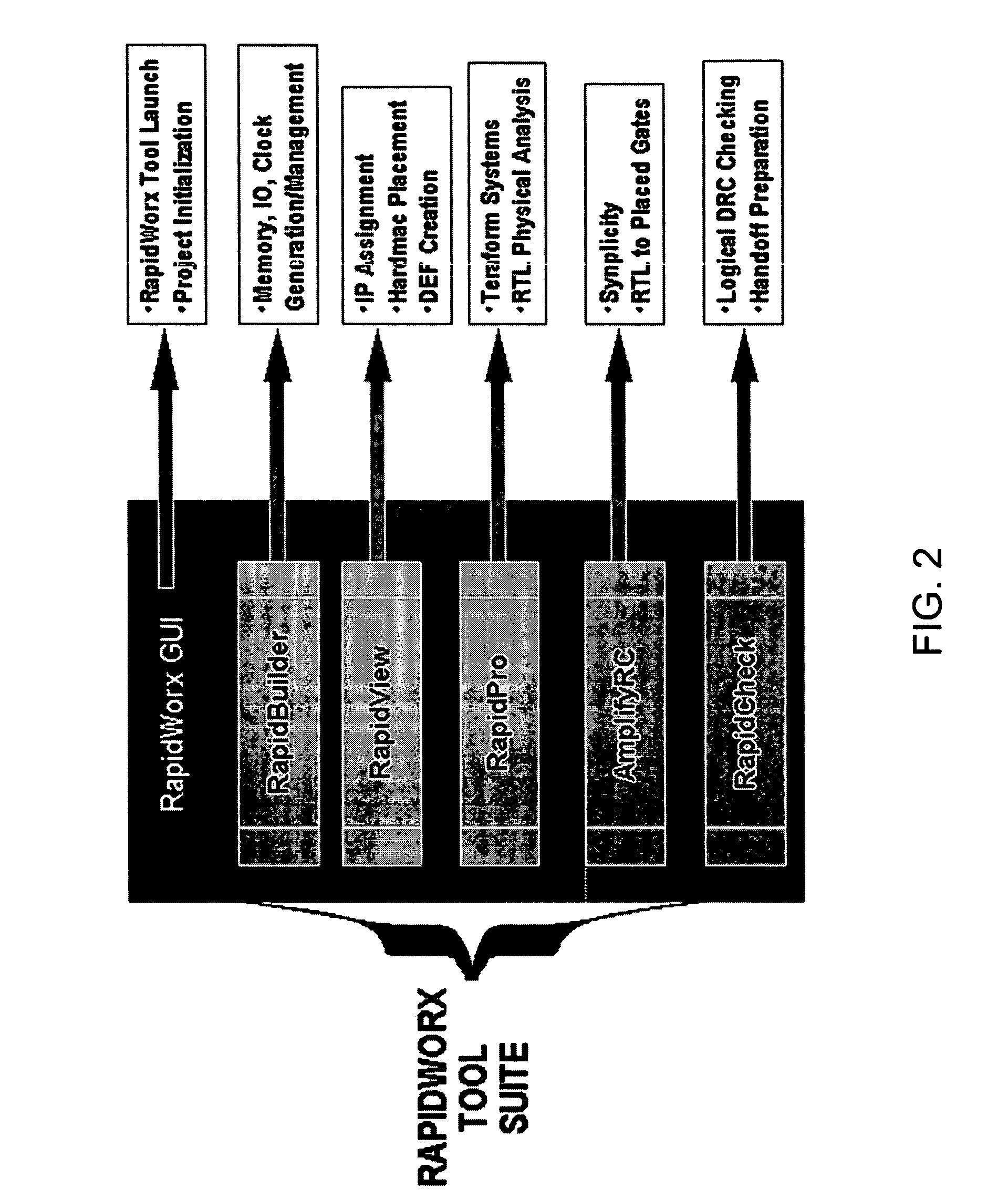

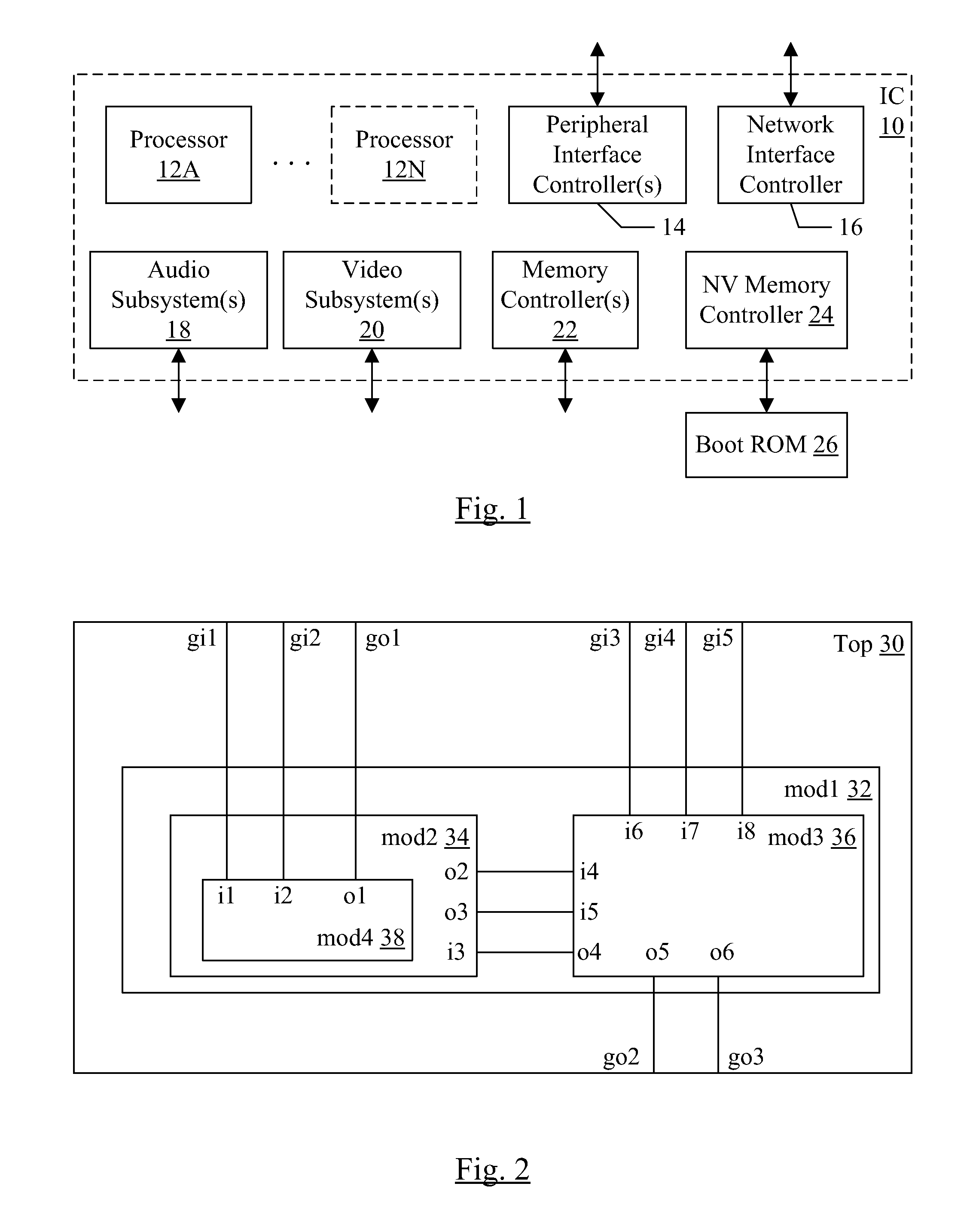

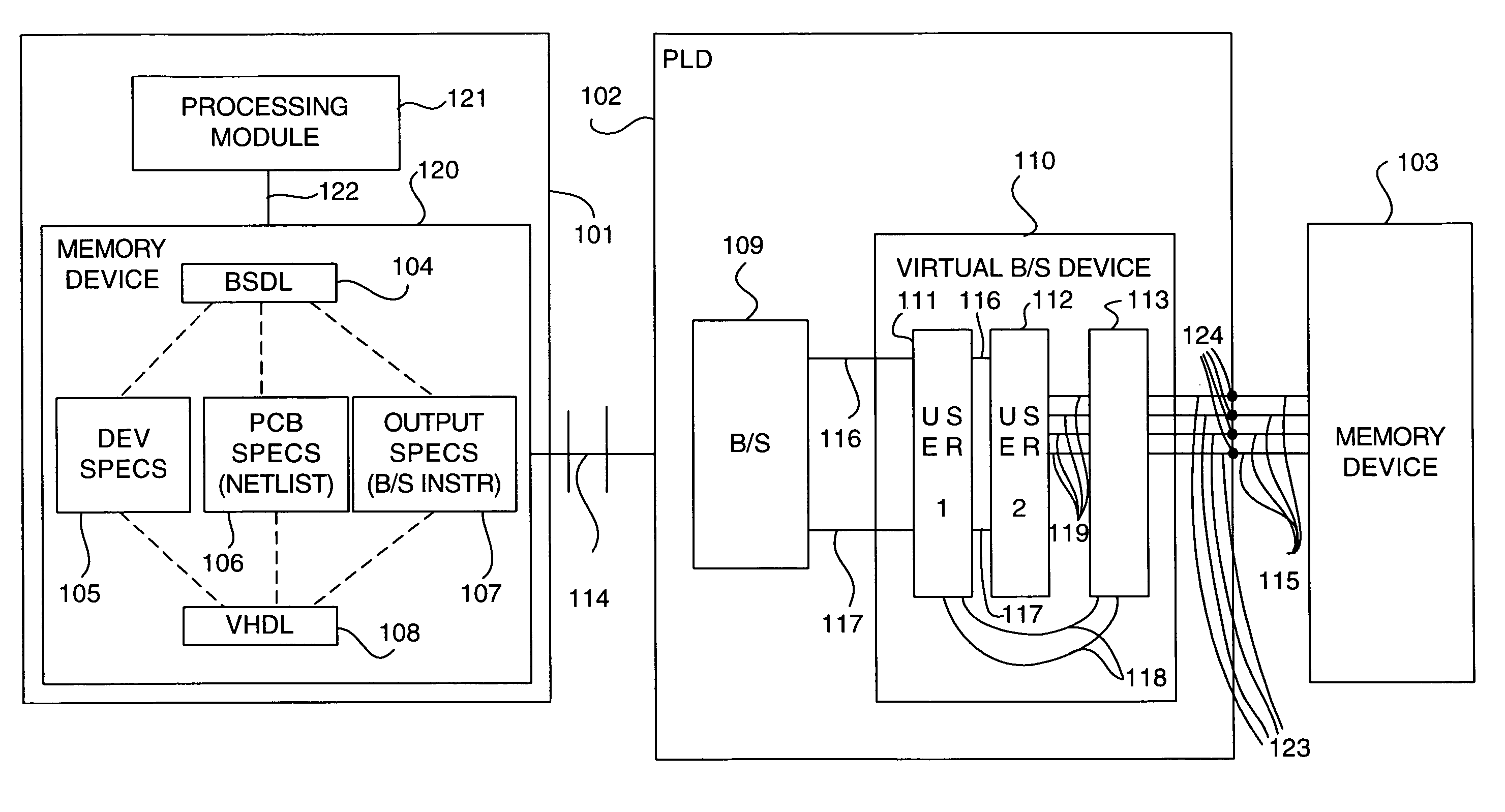

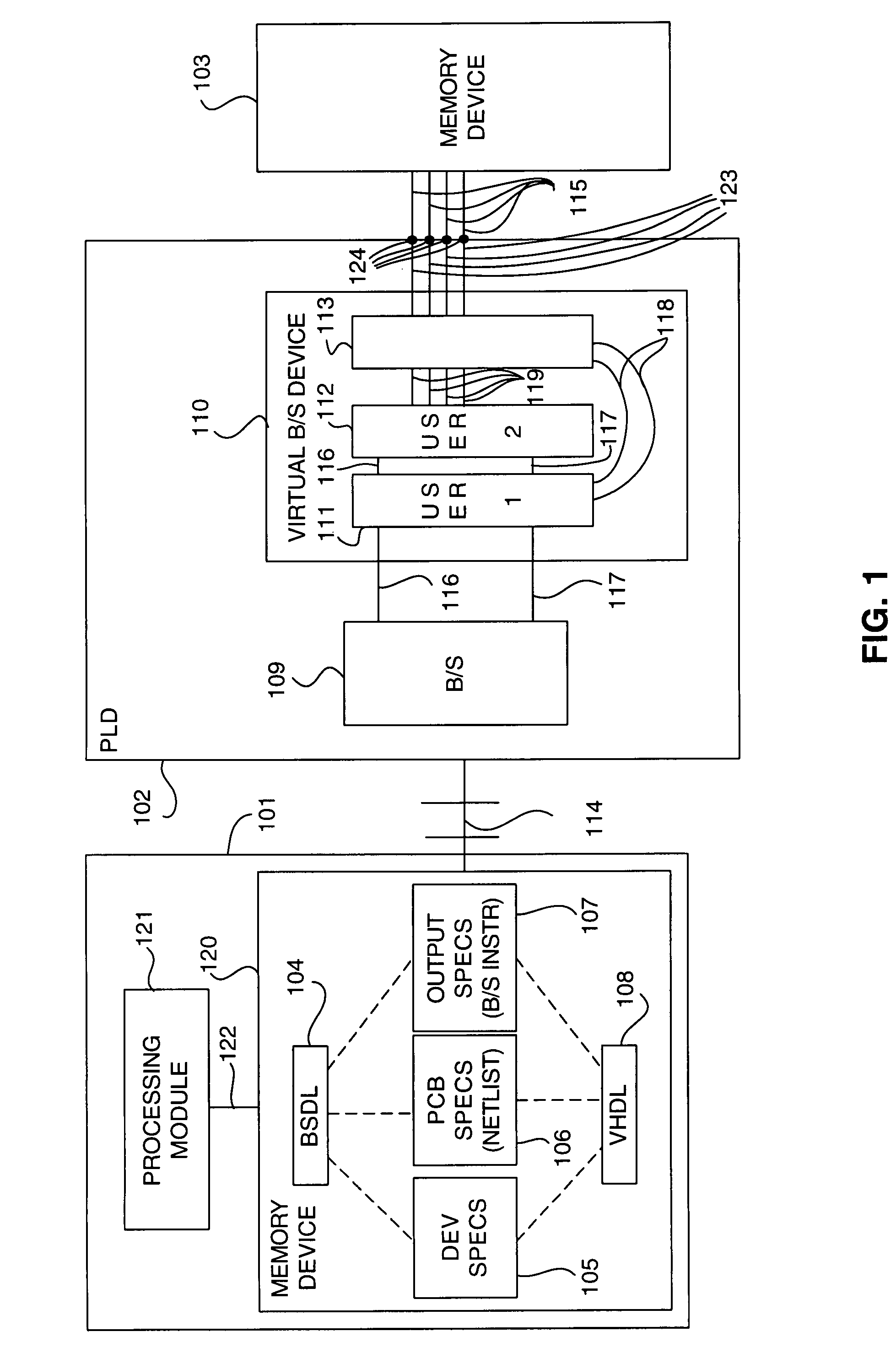

Simplified process to design integrated circuits

ActiveUS7055113B2Computer aided designSoftware simulation/interpretation/emulationCustomer requirementsFoundry

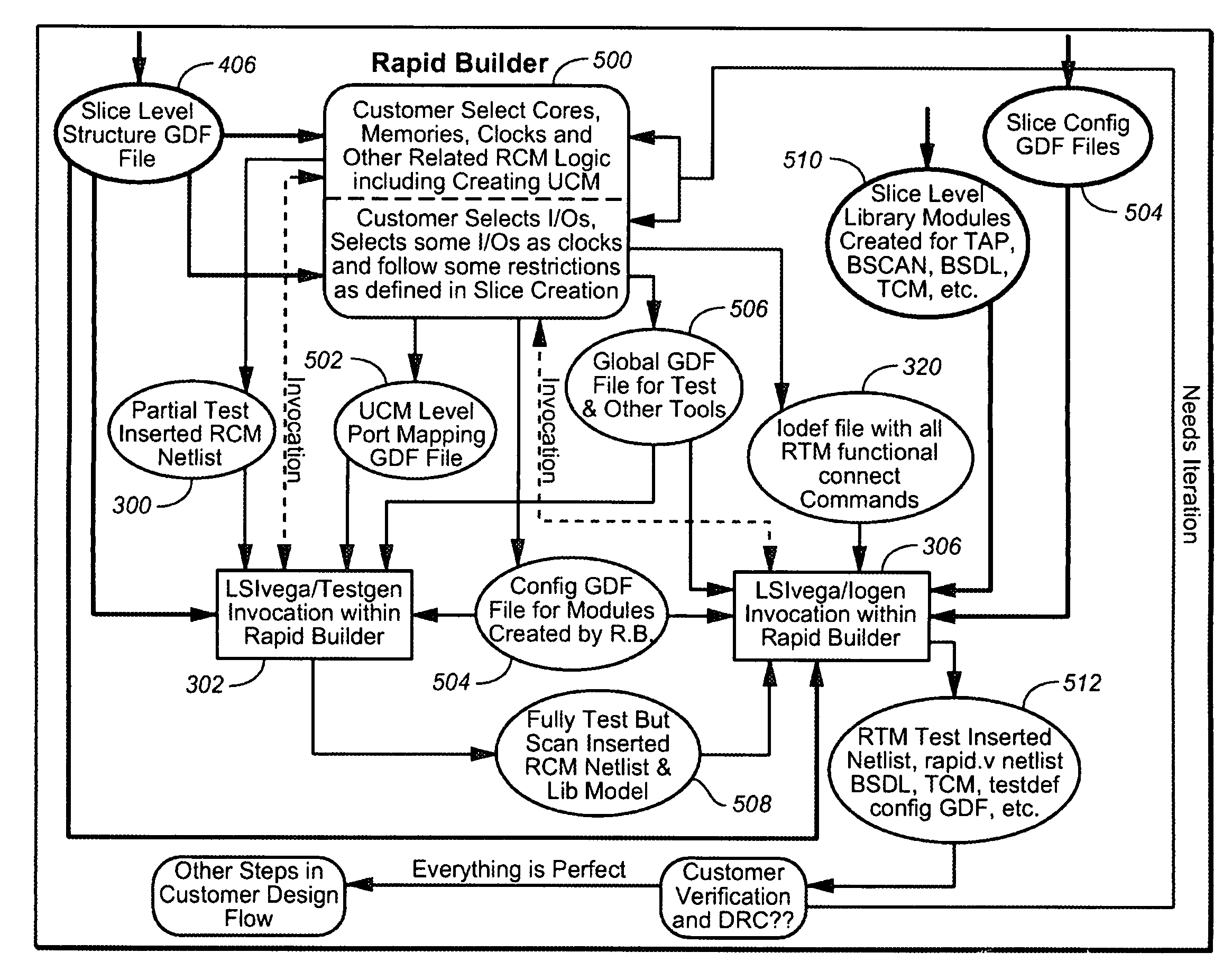

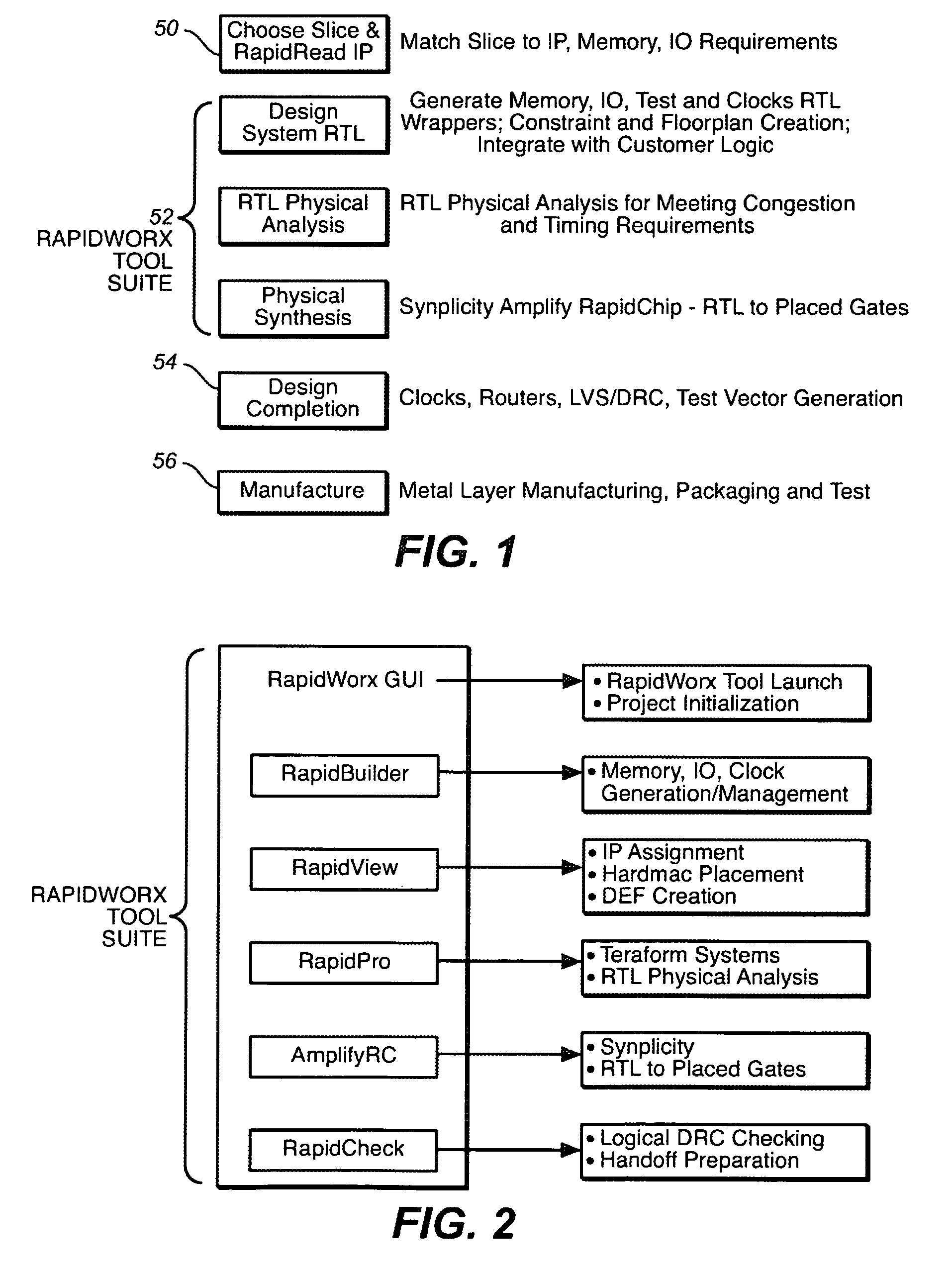

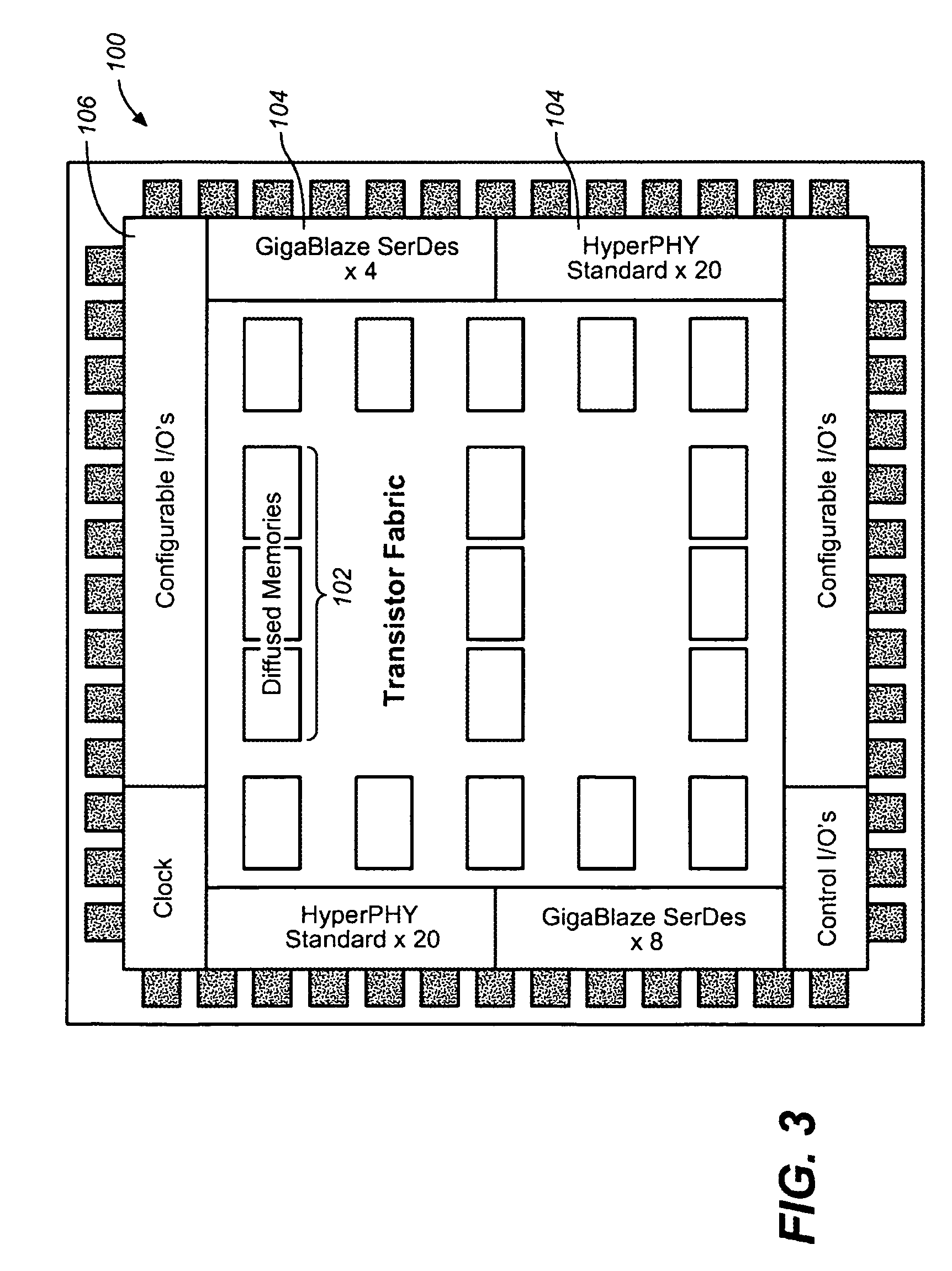

A set of tools is provided herein that produces useful, proven, and correct integrated semiconductor chips. Having as input either a customer's requirements for a chip, or a design specification for a partially manufactured semiconductor chip, the tools generate the RTL for control plane interconnect; memory composition, test, and manufacture; embedded logic analysis, trace interconnection, and utilization of spare resources on the chip; I / O qualification, JTAG, boundary scan, and SSO analysis; testable clock generation, control, and distribution; interconnection of all of the shared logic in a testable manner from a transistor fabric and / or configurable blocks in the slice. The input customer requirements are first conditioned by RTL analysis tools to quickly implement its logic. The slice definition and the RTL shell provides the correct logic for a set of logic interfaces for the design specification to connect. The tools share a common database so that logical interactions do not require multiple entries. The designs are qualified, tested, and verified by other tools. The tools further optimize the placement and timing of the blocks on the chip with respect to each other and with respect to placement on a board. The suite may be run as batch processes or can be driven interactively through a common graphical user interface. The tools also have an iterative mode and a global mode. In the iterative mode, one or more of the selected tools can generate the blocks or modify a design incrementally and then look at the consequences of the addition, or change. In the global mode, the semiconductor product is designed all at once in a batch process as above and then optimized altogether. This suite of generation tools generates design views including a qualified netlist for a foundry to manufacture.

Owner:BELL SEMICON LLC

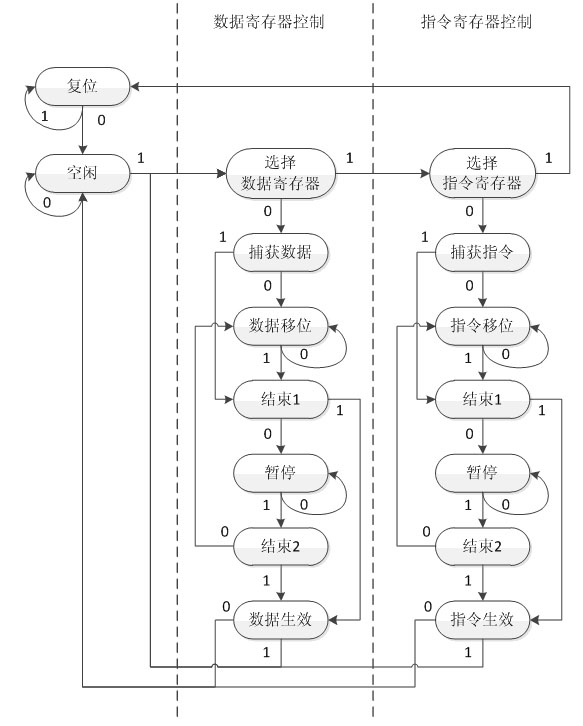

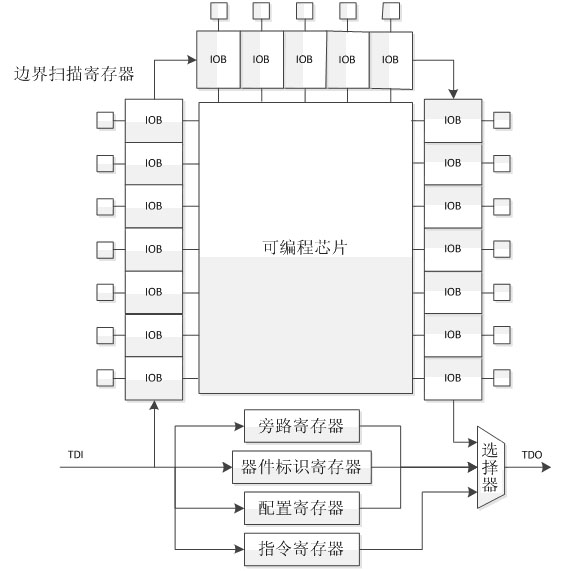

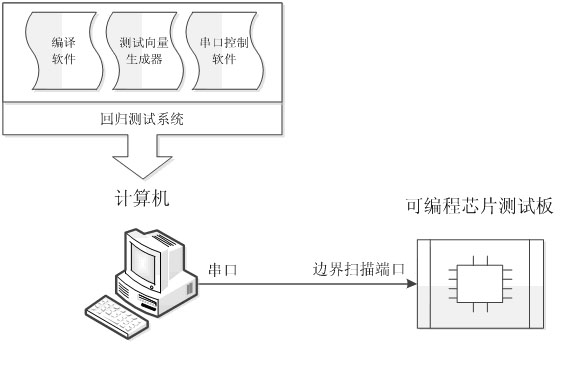

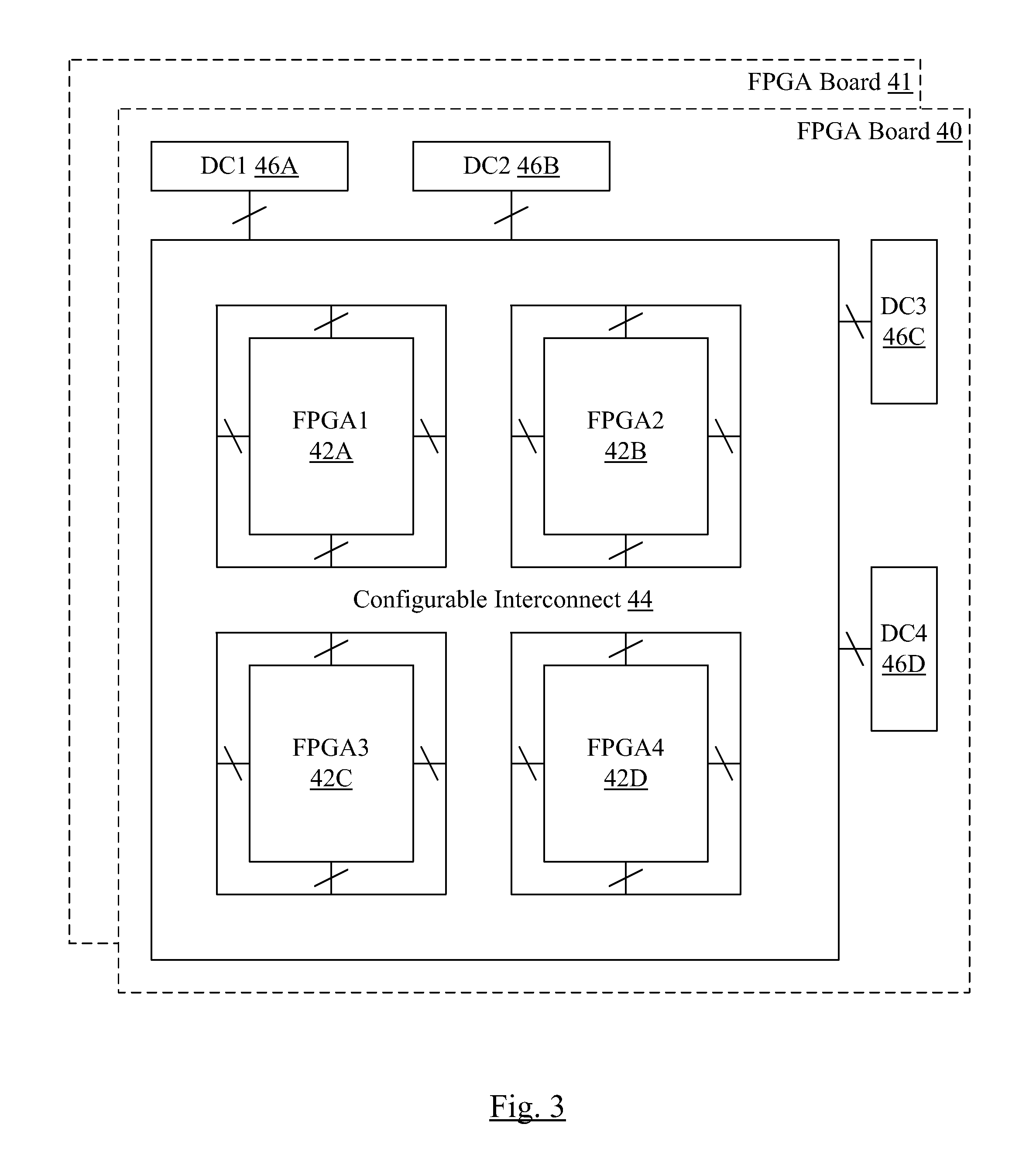

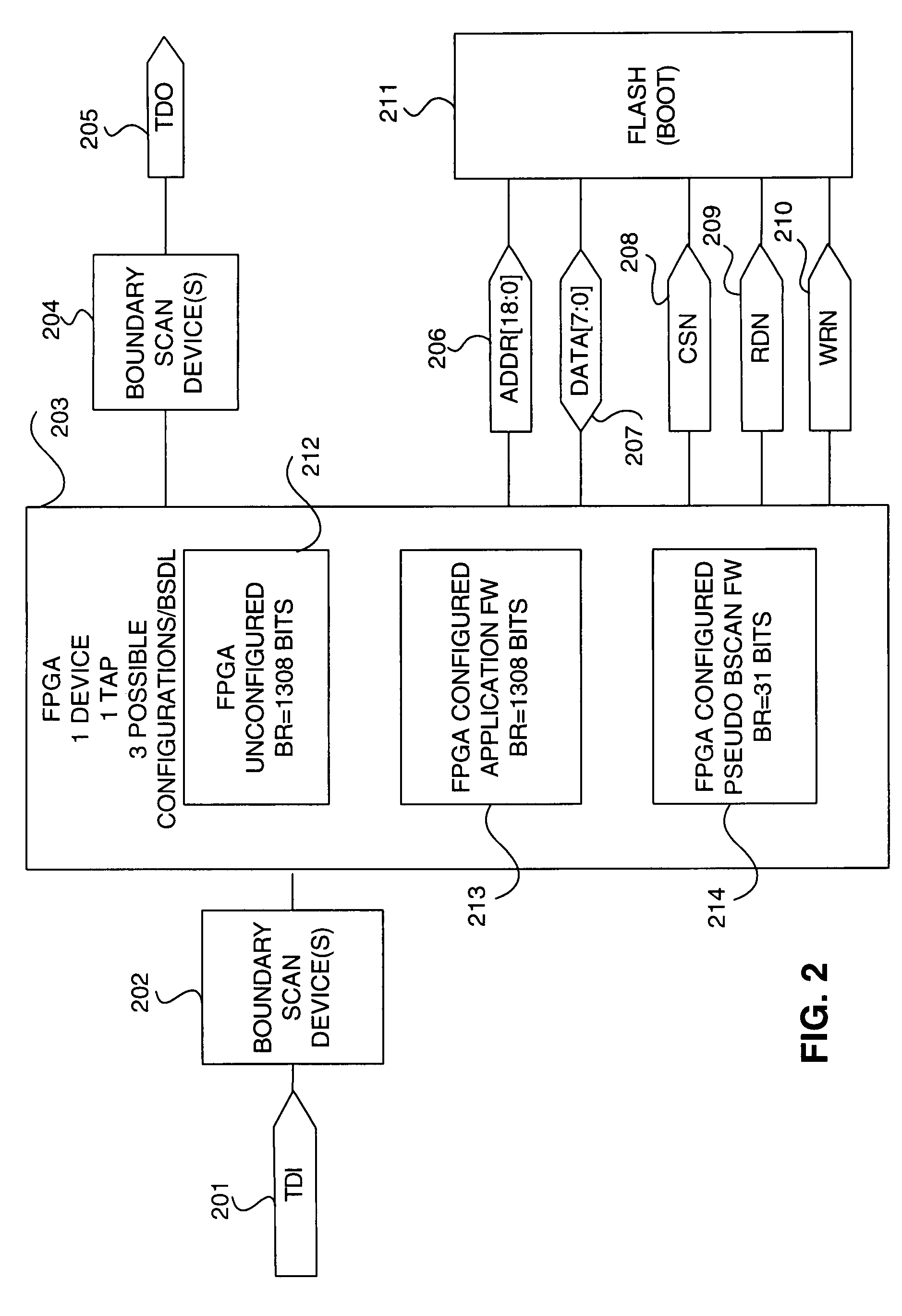

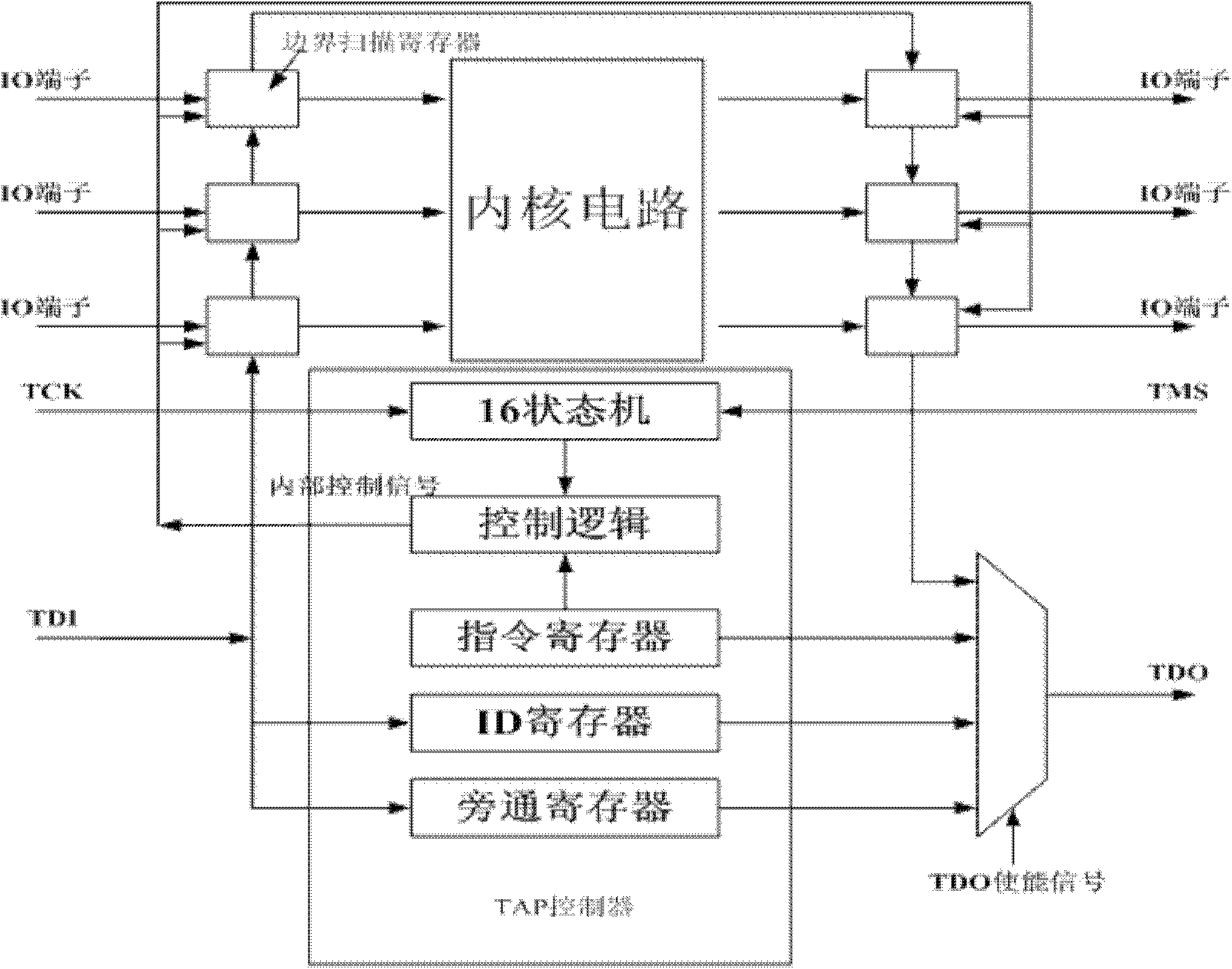

Automatic test system and method of programmable logic device on basis of boundary scan

The invention belongs to the field of electronic technology, in particular to an automatic test system and method of a programmable logic device on the basis of boundary scan. The test method comprises the following steps: generating a chip configuration file; downloading and configuring an FPGA (field programmable gate array) chip; generating and loading a test vector; comparing test results; building a corresponding test system; and completely realizing automation. In the invention, the test vector of an item to be tested is automatically generated by a user through software, and the on-line test of the hardware function of a user circuit is realized by combining JTAG (joint test action group) automatic downloading test software. Scripted test environment converts a series of complex manual test operation into full automatic software flow so as to greatly improve test speed and accuracy.

Owner:FUDAN UNIV

Suite of tools to design integrated circuits

InactiveUS20050240892A1Accelerate Design CycleI/O can be optimizedDetecting faulty computer hardwareComputer programmed simultaneously with data introductionFoundryCustomer requirements

A set of tools is provided herein that produces useful, proven, and correct integrated semiconductor chips. Having as input either a customer's requirements for a chip, or a design specification for a partially manufactured semiconductor chip, the tools generate the RTL for control plane interconnect; memory composition, test, and manufacture; embedded logic analysis, trace interconnection, and utilization of spare resources on the chip; I / O qualification, JTAG, boundary scan, and SSO analysis; testable clock generation, control, and distribution; interconnection of all of the shared logic in a testable manner from a transistor fabric and / or configurable blocks in the slice. The input customer requirements are first conditioned by RTL analysis tools to quickly implement its logic. The slice definition and the RTL shell provides the correct logic for a set of logic interfaces for the design specification to connect. The tools share a common database so that logical interactions do not require multiple entries. The designs are qualified, tested, and verified by other tools. The tools further optimize the placement and timing of the blocks on the chip with respect to each other and with respect to placement on a board. The suite may be run as batch processes or can be driven interactively through a common graphical user interface. The tools also have an iterative mode and a global mode. In the iterative mode, one or more of the selected tools can generate the blocks or modify a design incrementally and then look at the consequences of the addition, or change. In the global mode, the semiconductor product is designed all at once in a batch process as above and then optimized altogether. This suite of generation tools generates design views including a qualified netlist for a foundry to manufacture.

Owner:BELL SEMICON LLC

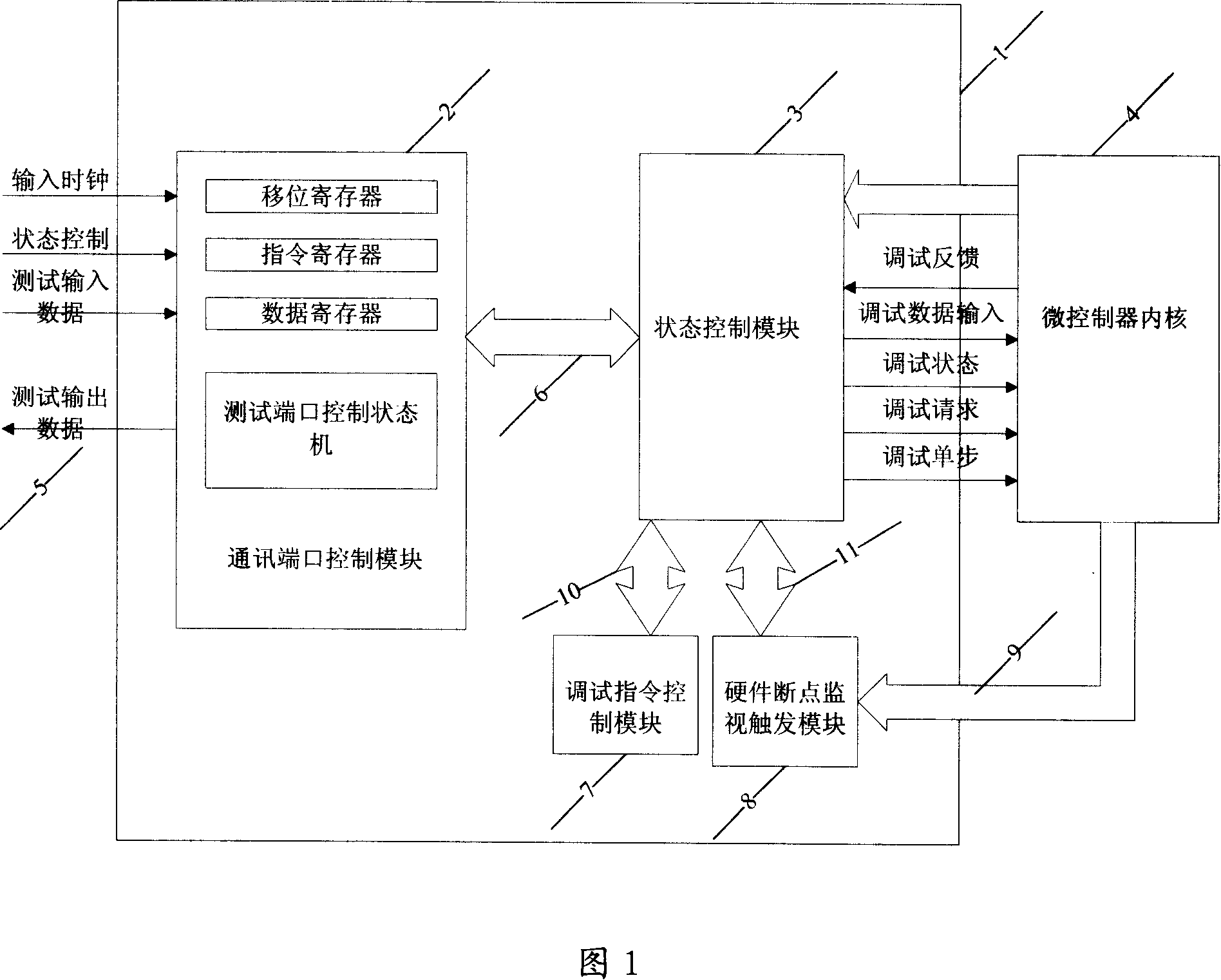

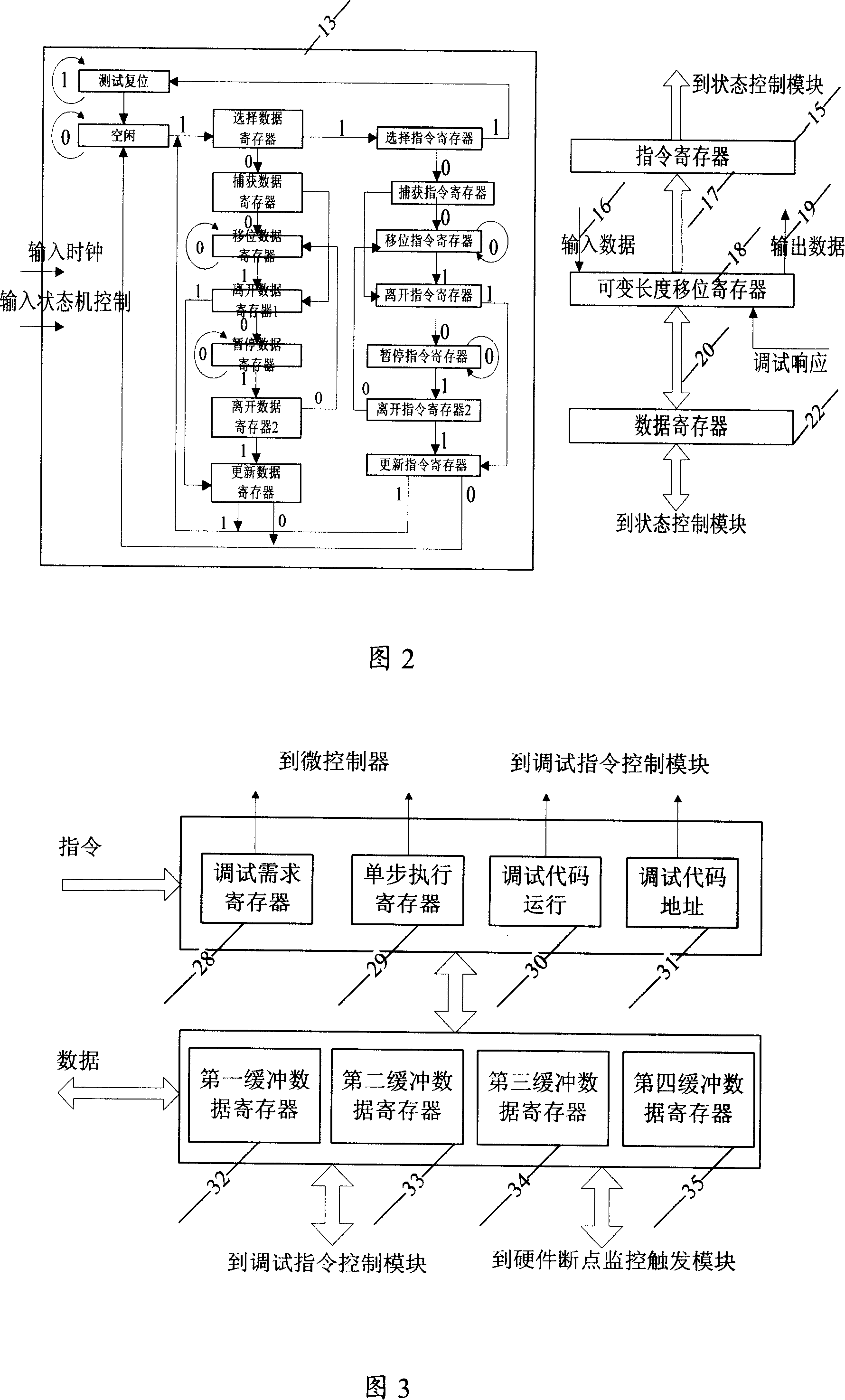

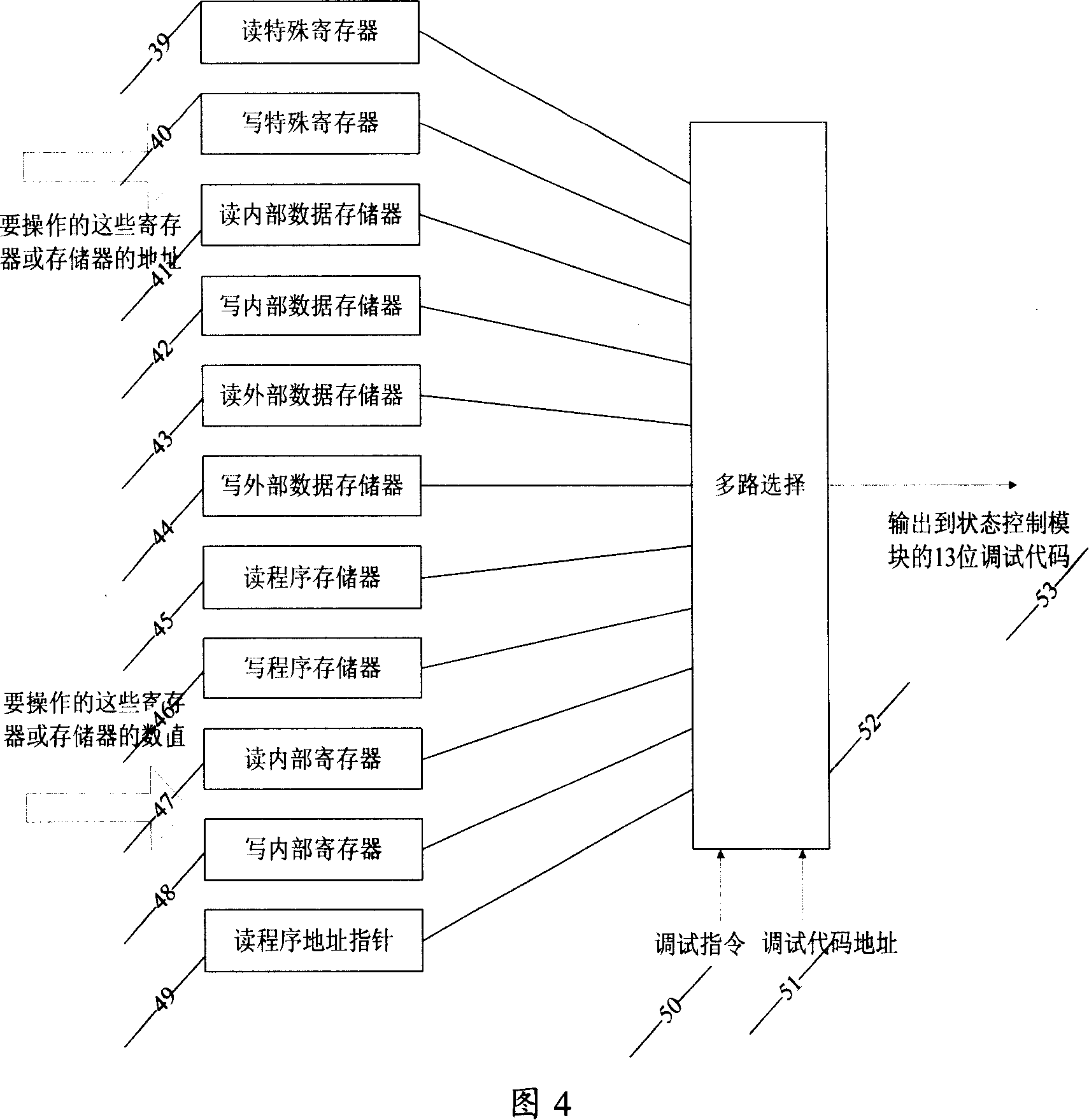

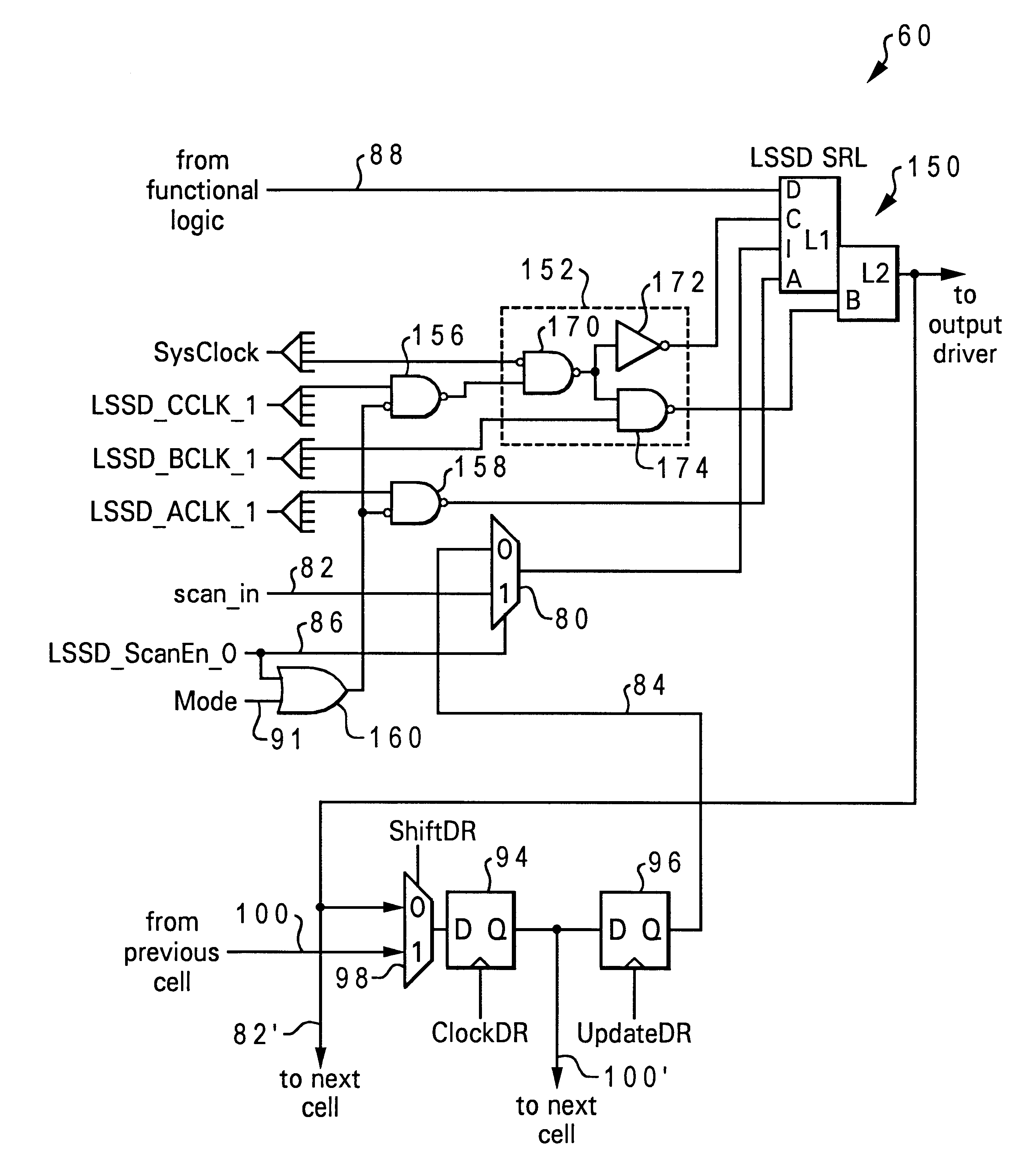

Microcontroller built-in type on-line simulation debugging system

InactiveCN101154183AImproved debugging capabilitiesRealize real-time monitoringSoftware testing/debuggingSpecific functionData memory

The invention provides a microcontroller flush bonding on-line simulation debugging system, comprising a communication port control module, a state control module, a debugging command control module and a hardware breakpoint monitoring trigger module; the modules are collected into a chip through a special debugging command transmitted by a mainboard to control the work of the whole on-line simulation debugging system; complex boundary scan to the inside of the chip through a standard test boundary scan can be finished; the microcontroller chip is controlled according to an outer command to be converted into a debugging mode from a normal mode; a program can be downloaded and numerated from any position in a memorizer of the microcontroller through the debugging communication interface of the mainboard to support the target system single-step debugging and support software breakpoints and hardware breakpoints; the contents of a specific function register, a data memorizer and a program memorizer of the inside of the chip are checked and altered real-time; address bus and data bus are monitored, and the functions of real-time logical tracing, etc. are realized. The invention is of clear and simple structure, high-efficient operating effect and precise real-time monitoring.

Owner:SHANGHAI EASTSOFT MICROELECTRONICS

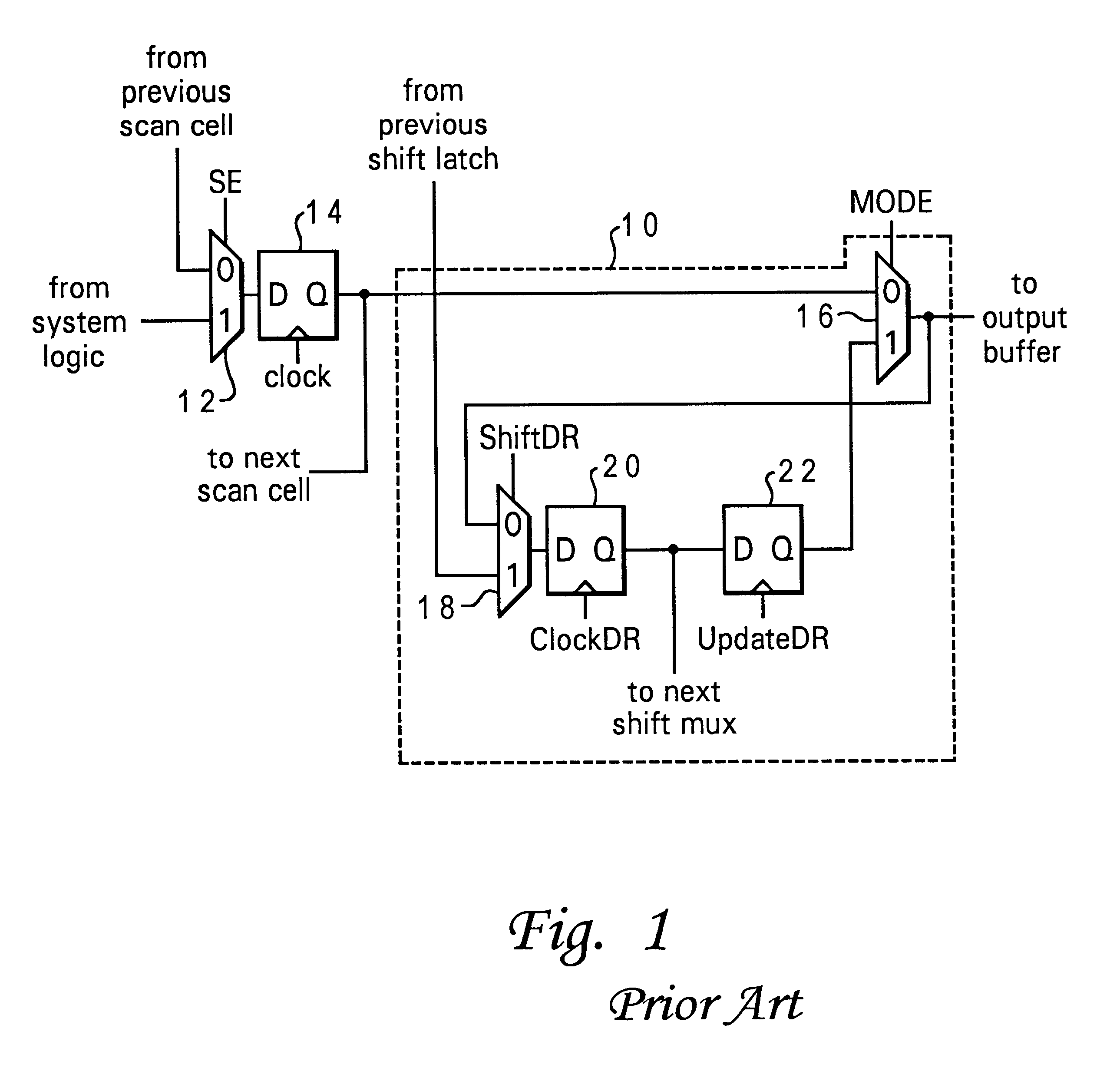

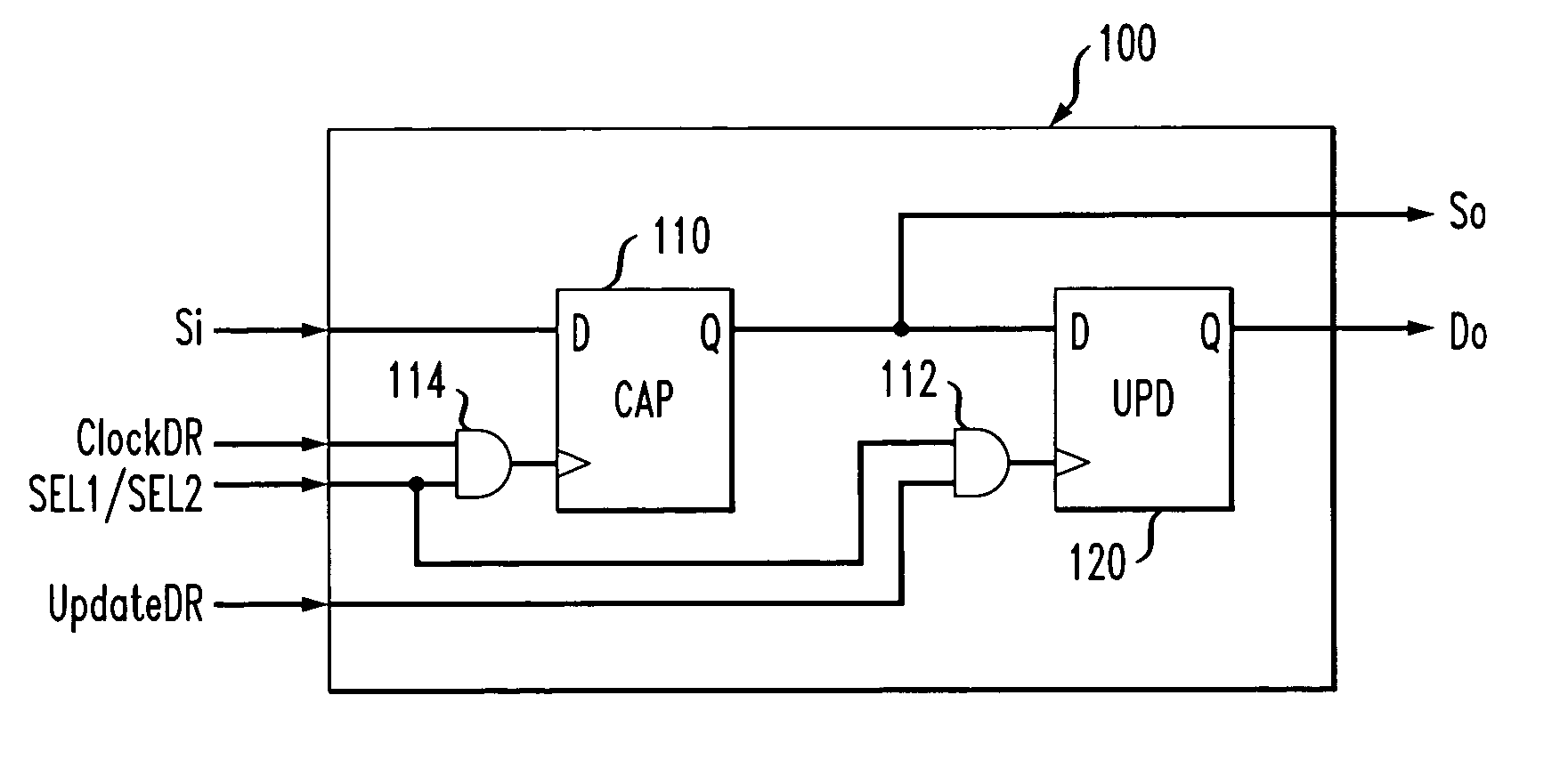

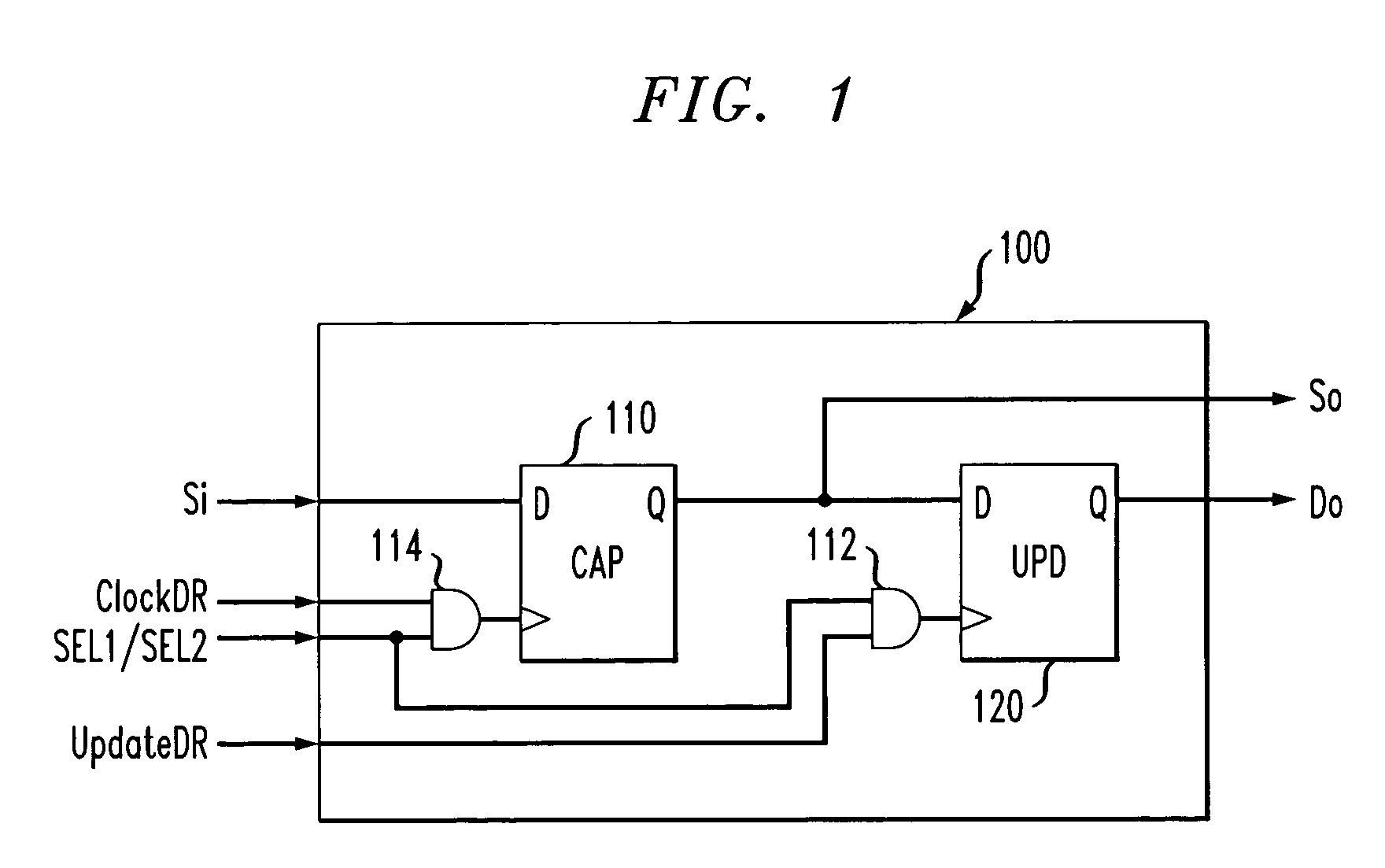

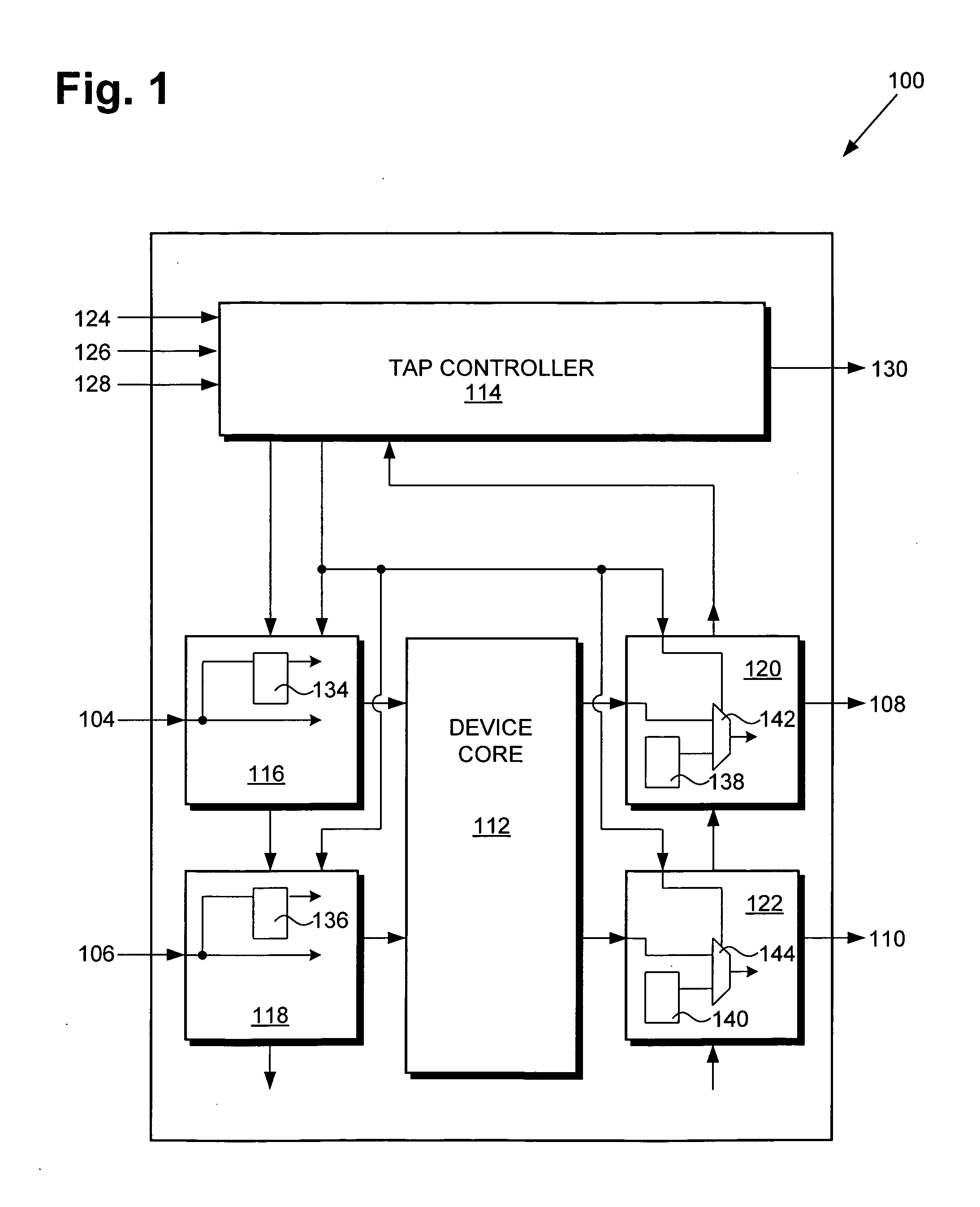

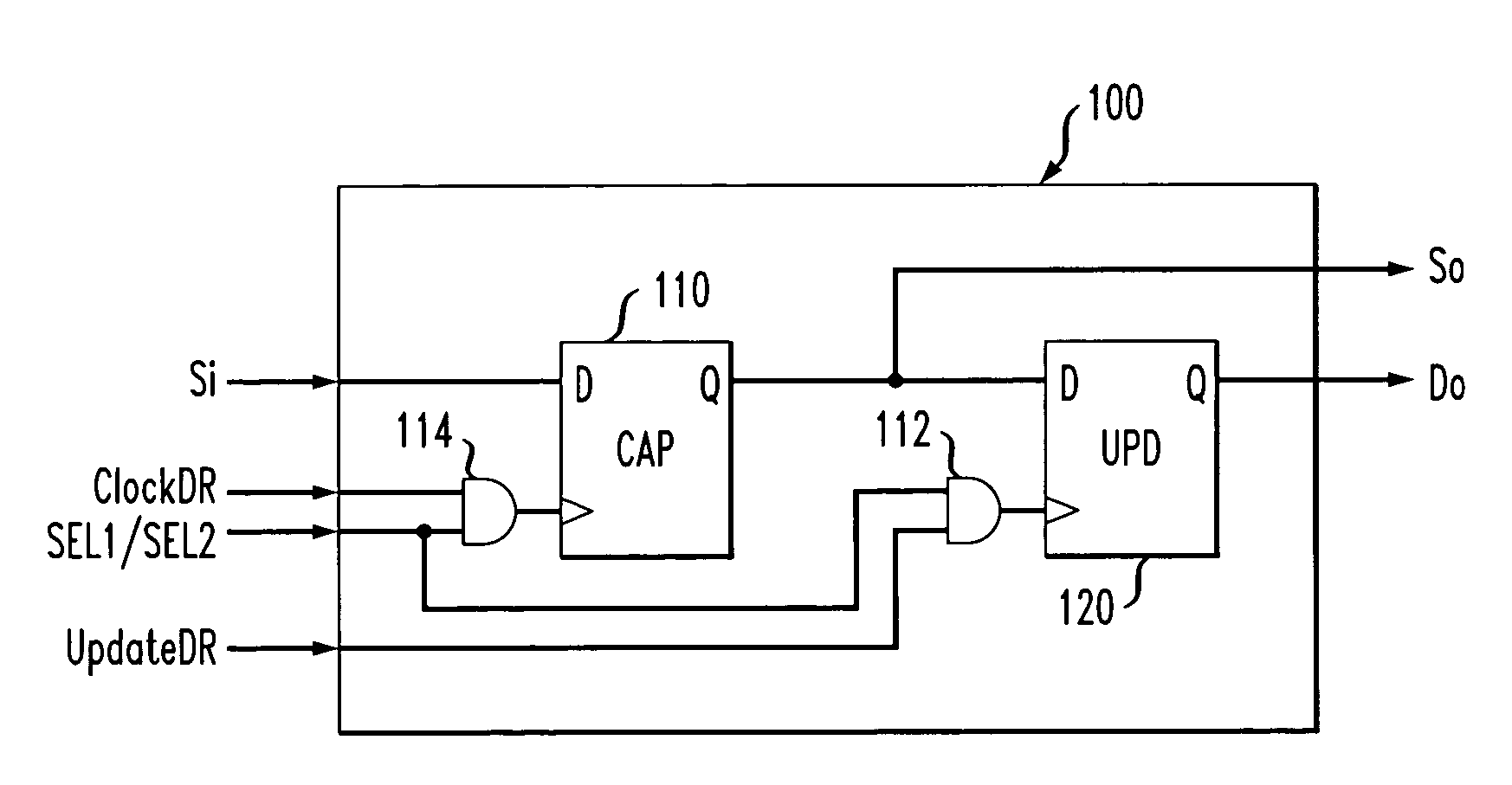

D flip-flop structure with flush path for high-speed boundary scan applications

A boundary scan cell includes a shift latch, an update latch and a flushable latch that each have at least a respective data input and at least a respective data output. The data output of the shift latch is coupled to the data input of the update latch. The boundary scan cell further includes control circuitry that controls operation of the flushable latch circuit. The control circuitry selects, as input data for the flushable latch, one of a functional logic signal and a boundary scan signal in response to a mode signal. If the mode signal indicates a test mode, the control circuitry selects the boundary scan signal as the input data and causes the flushable latch to flush through the input data to the data output of the flushable latch independent of a system clock signal. The boundary scan cell can be implemented as either an input or output cell and preferably is compliant with IEEE Std 1149.1.

Owner:GOOGLE LLC

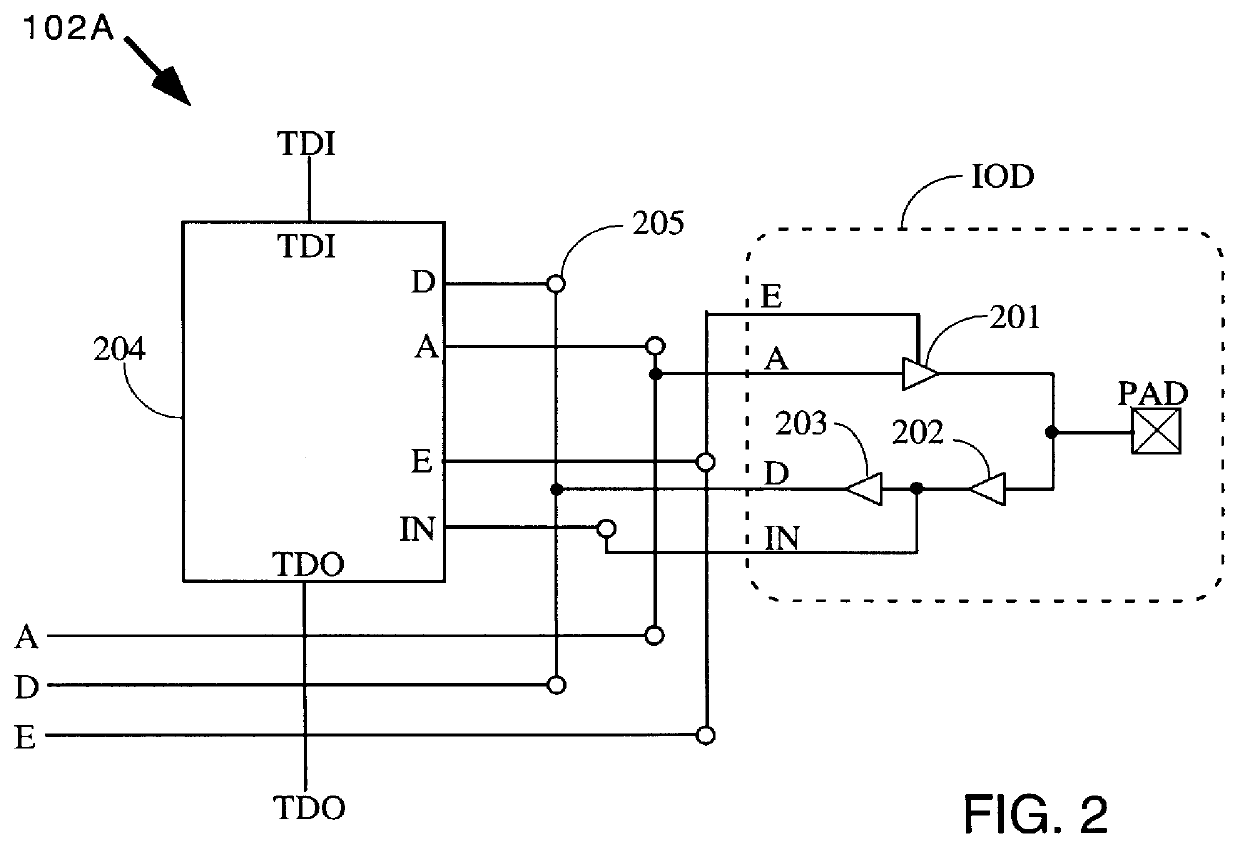

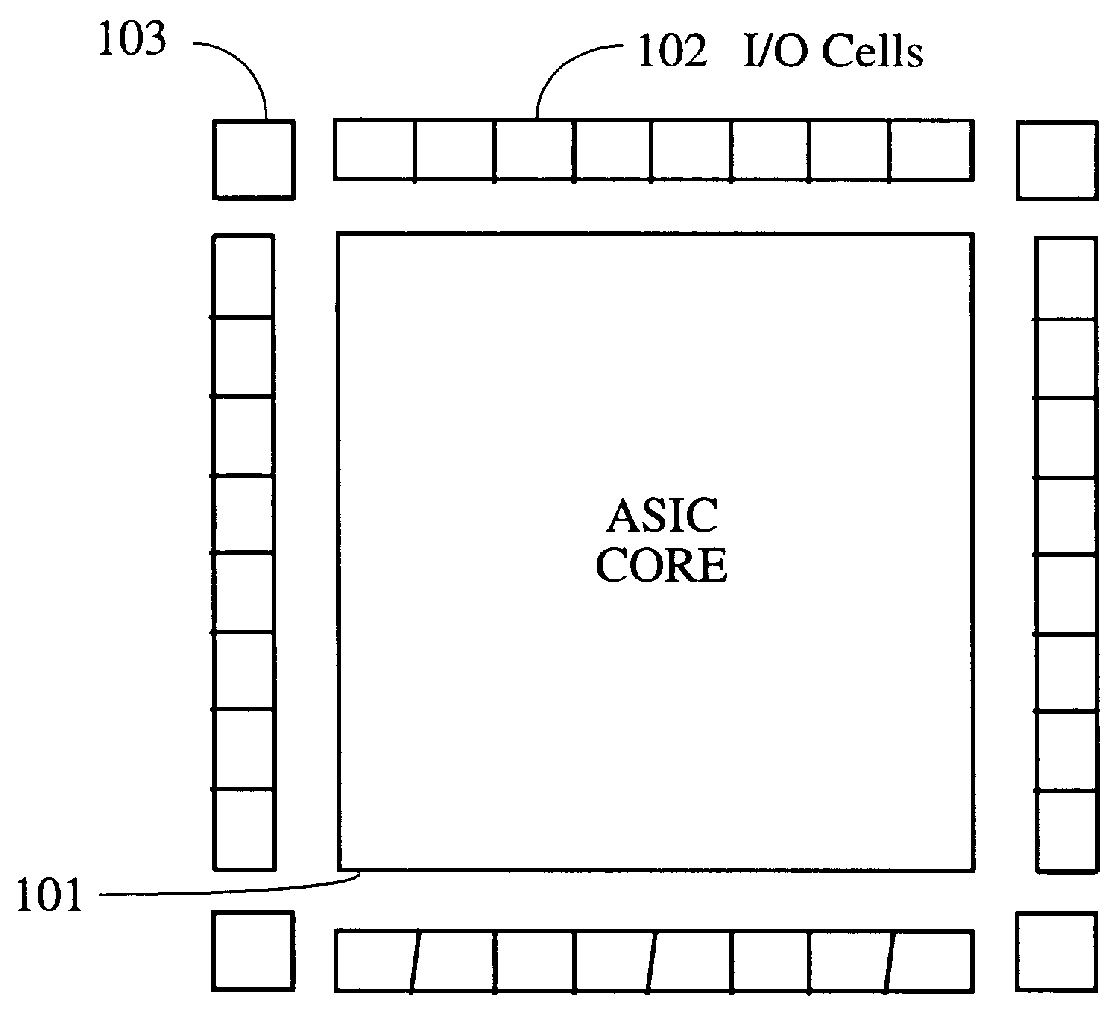

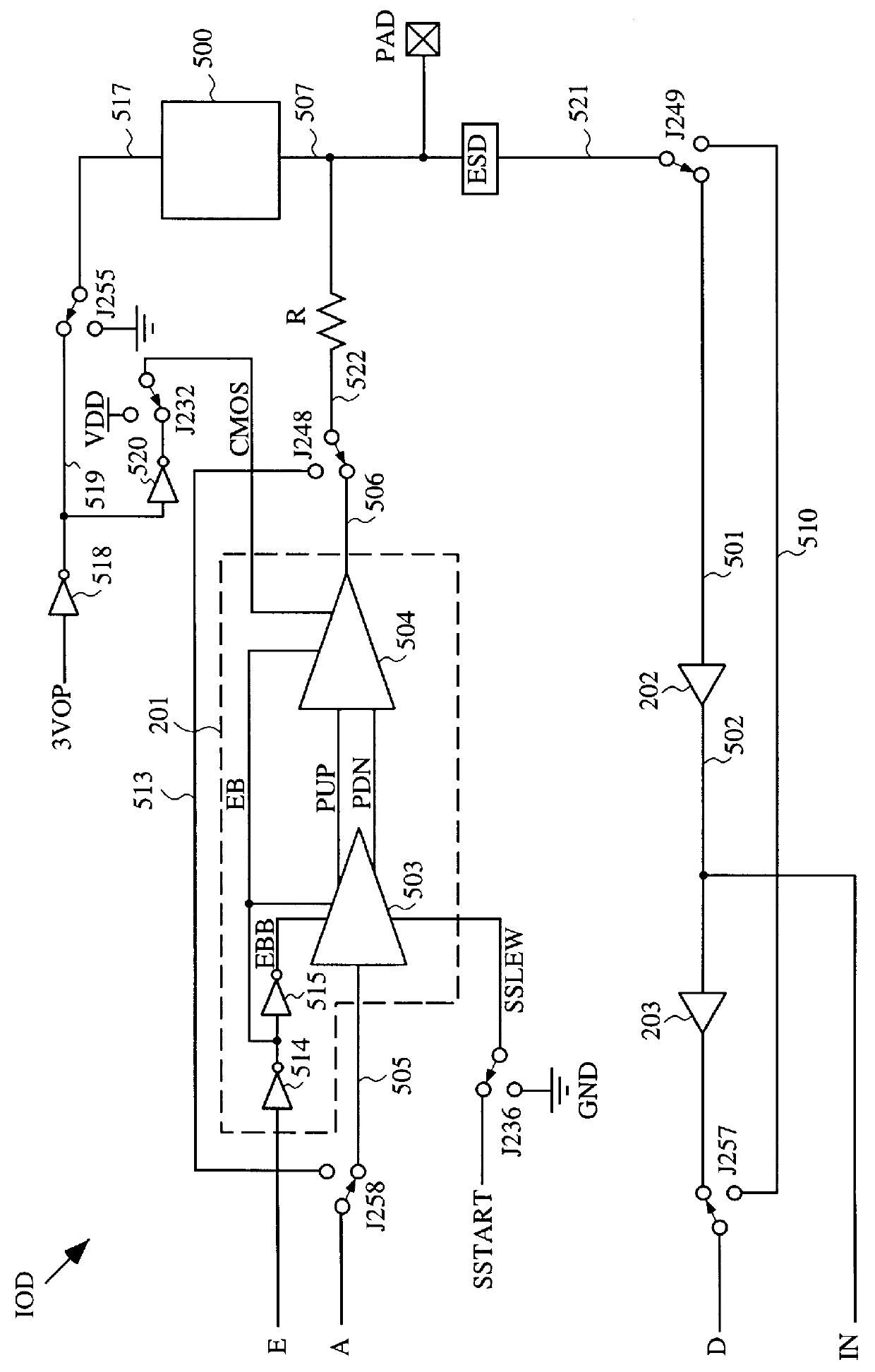

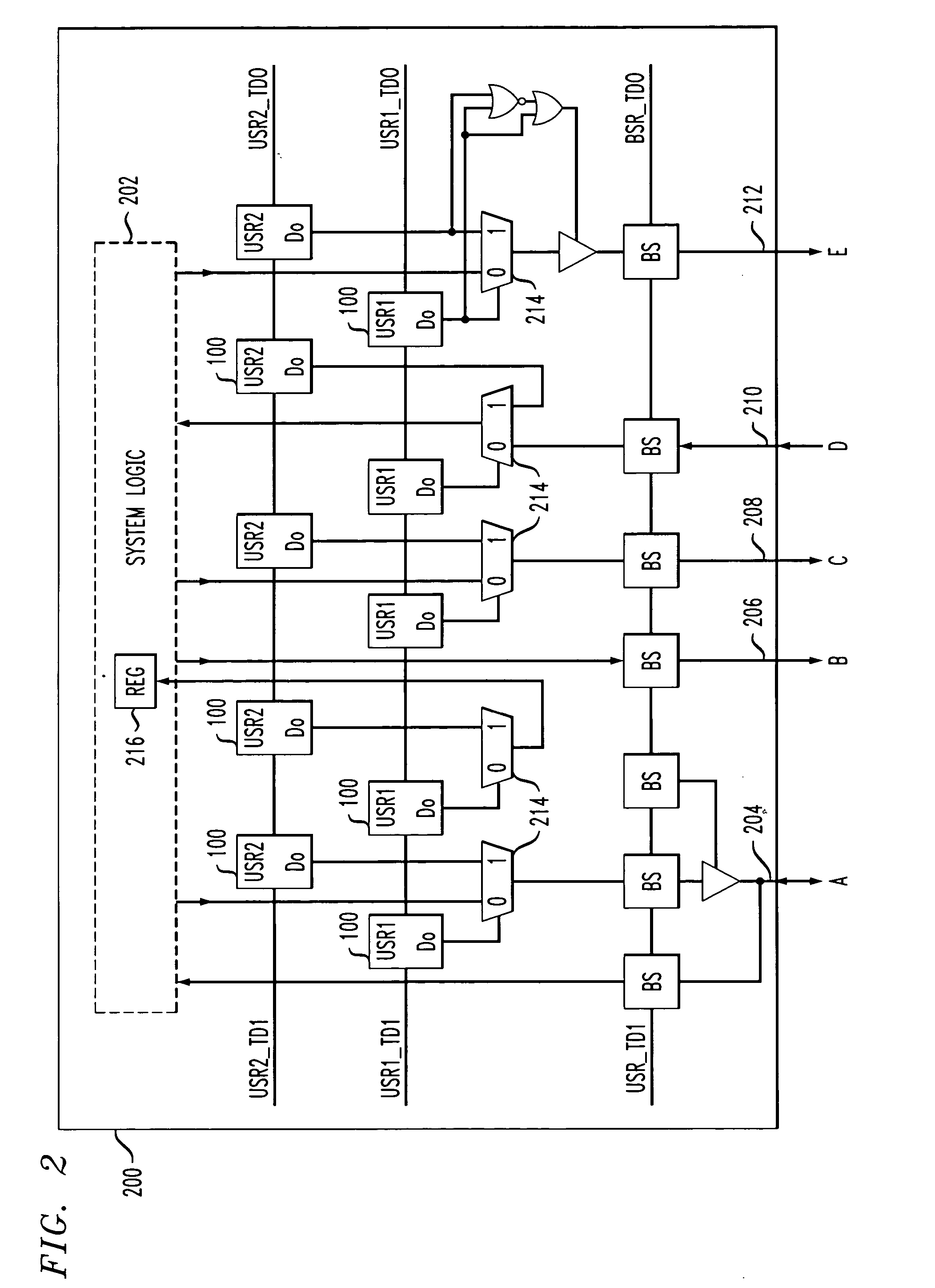

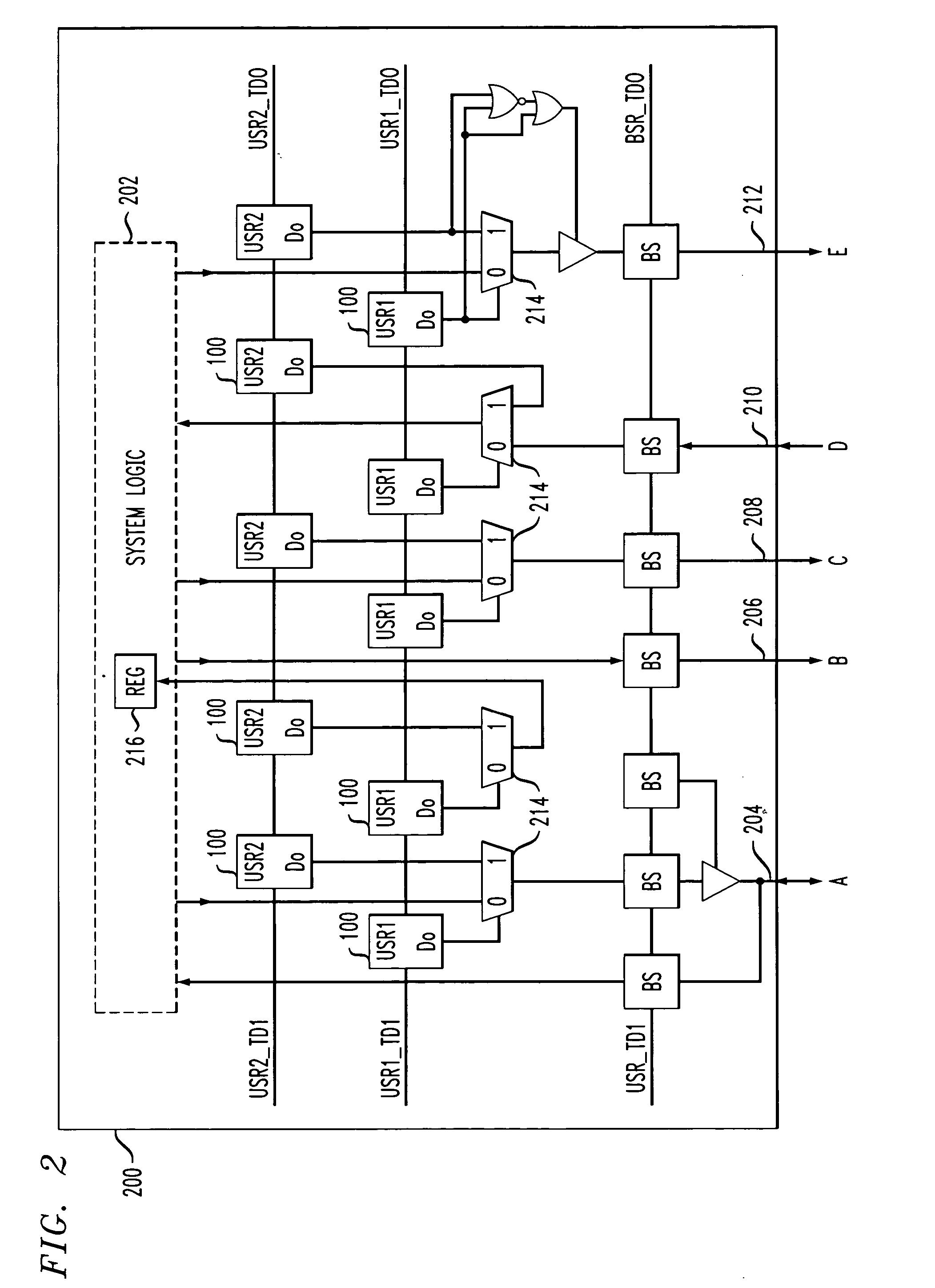

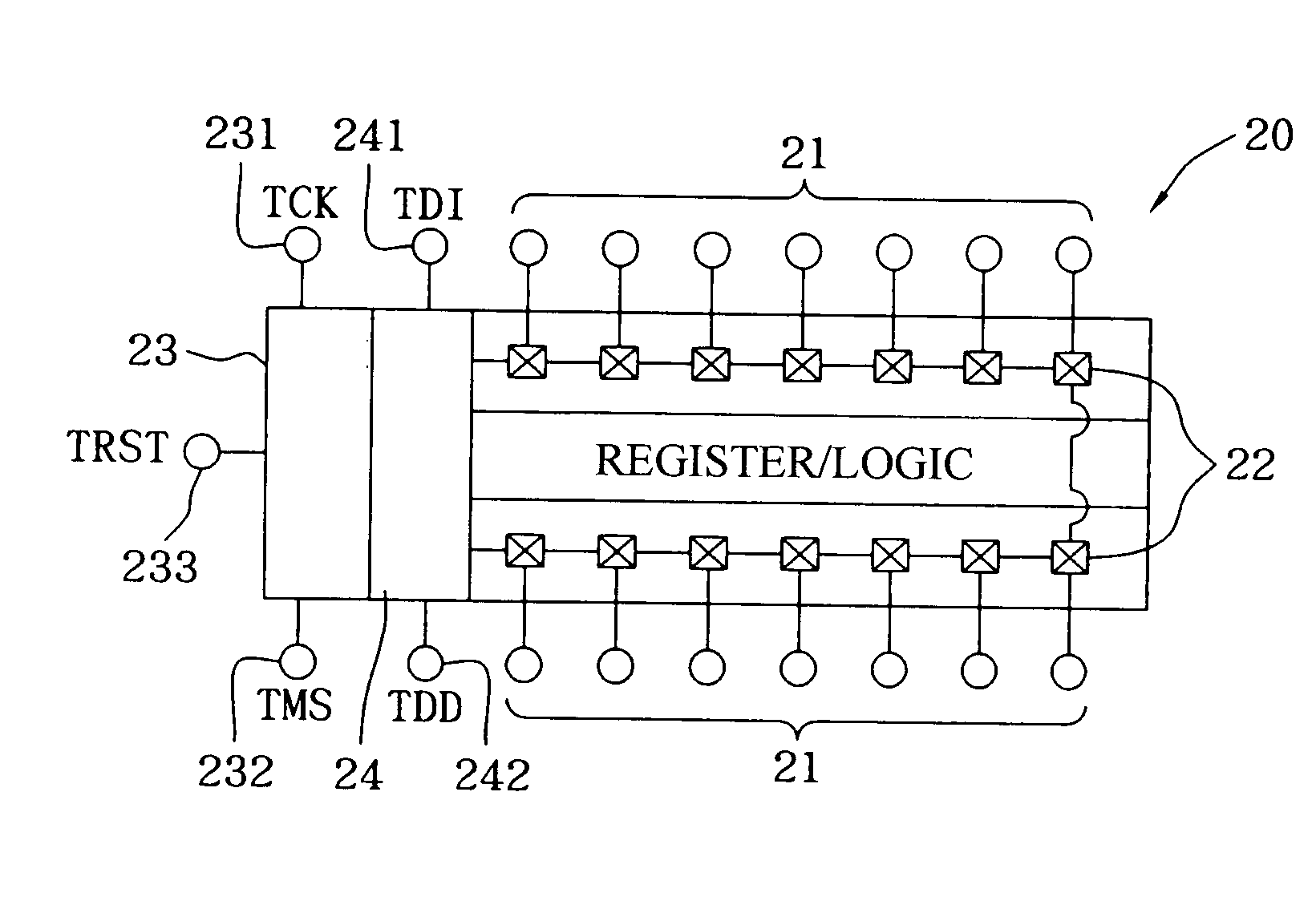

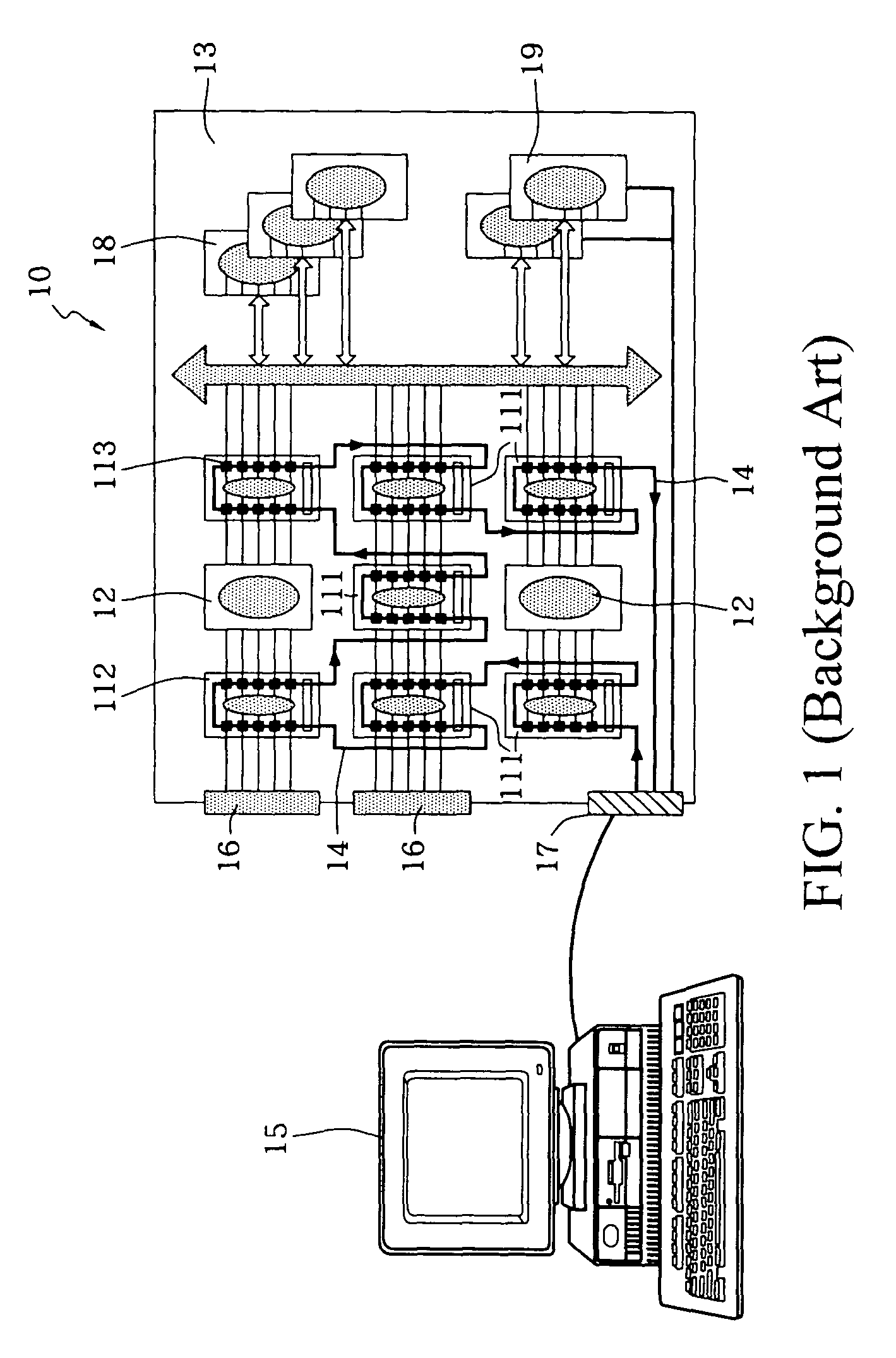

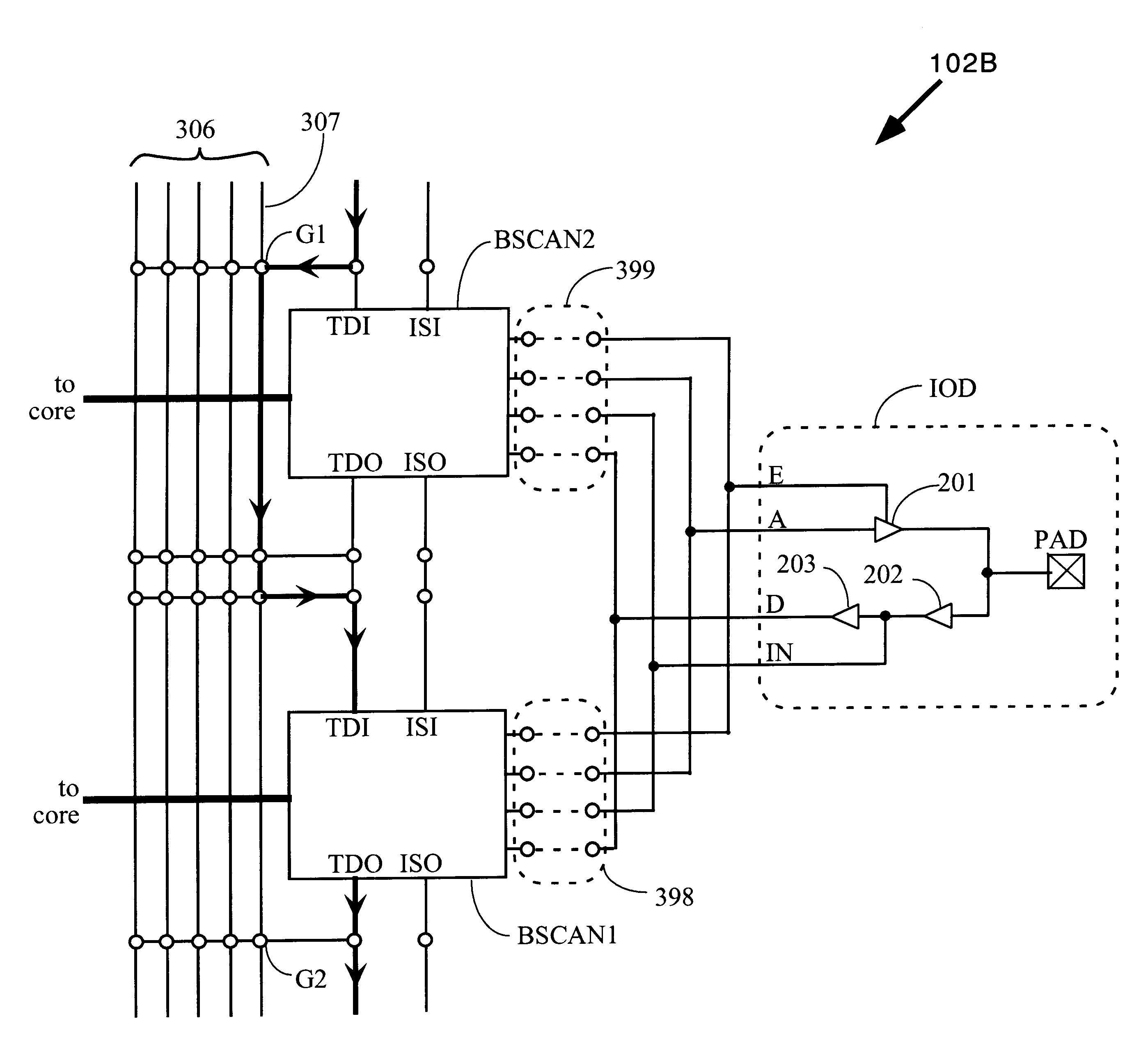

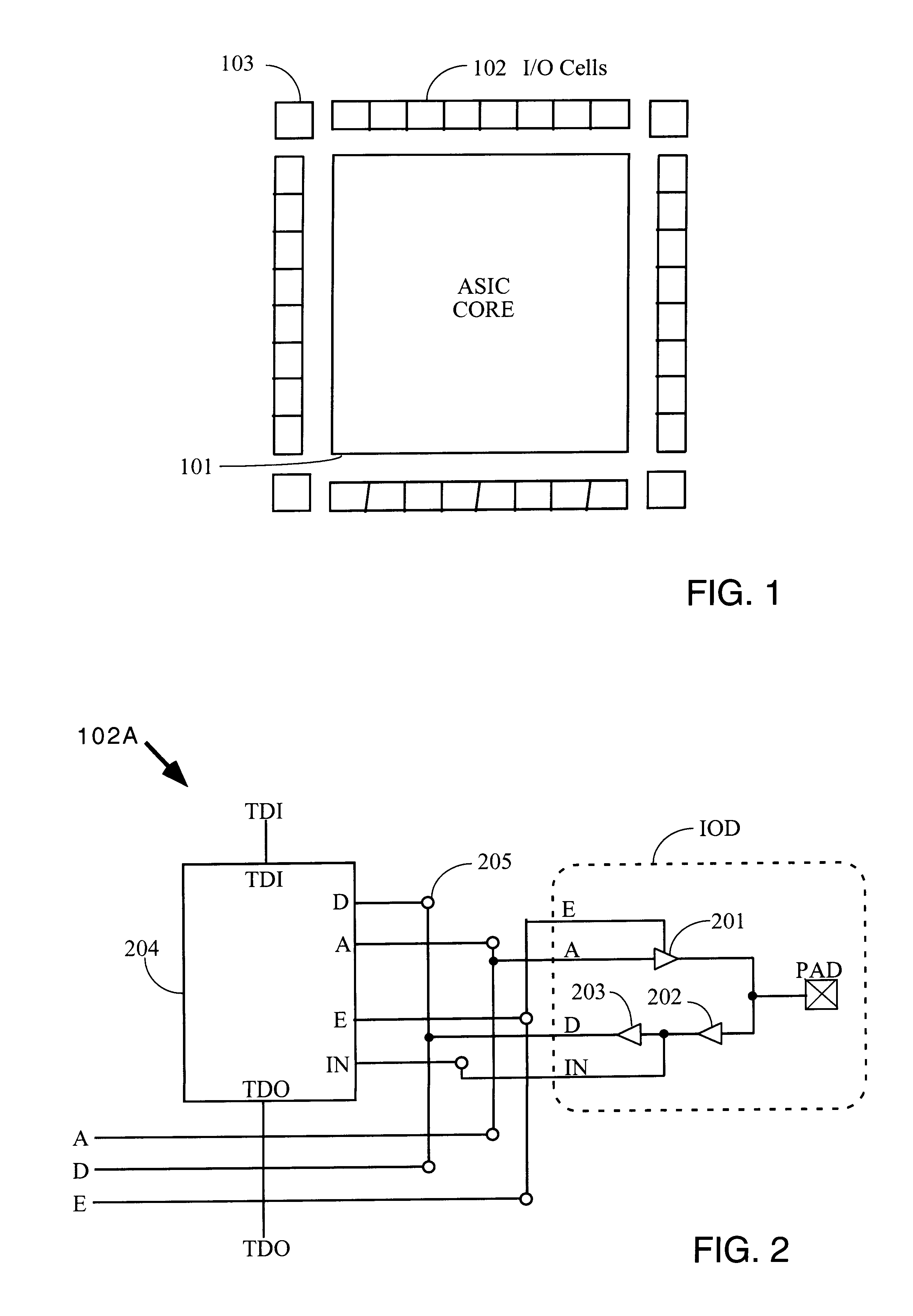

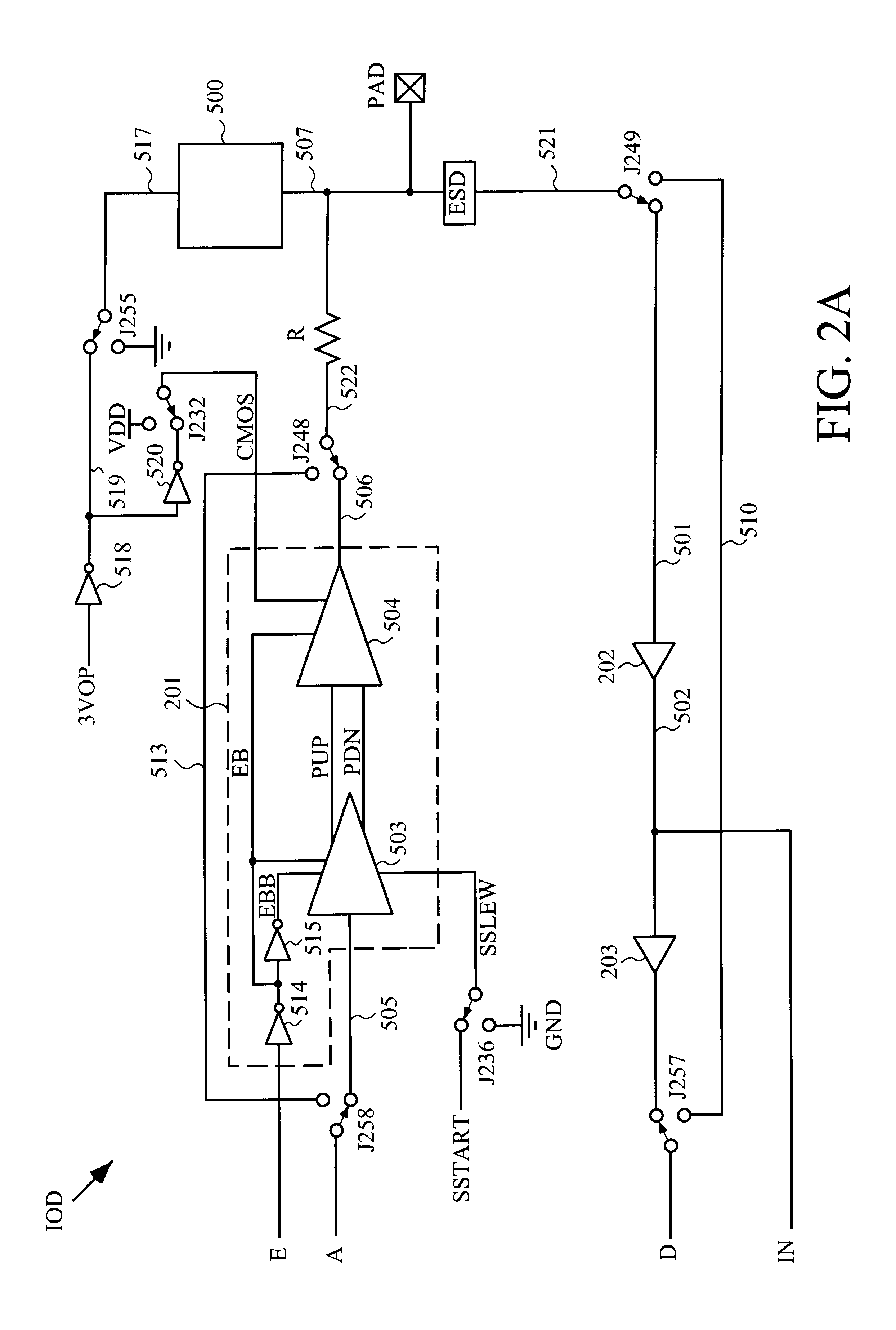

Programmable I/O cell with dual boundary scan

InactiveUS6071314ALow costReduce in quantityElectronic circuit testingSolid-state devicesBoundary scanData input

A mask programmable IC is provided that includes dedicated boundary scan logic in the I / O cells. Valuable core logic resources therefore need not be consumed to implement boundary scan logic. In one embodiment, one boundary scan cell is provided per I / O cell. Another embodiment provides great flexibility in emulating any of several FPGAs in any of several packages. In this embodiment, two boundary scan cells are provided for each I / O pad, each cell alone being capable of providing the boundary scan functions associated with one I / O pad. By selectively choosing which of the boundary scan cells are included in the boundary scan data chain, the order of the boundary scan chain of the emulated FPGA in any of two or more packages can be reproduced. Boundary scan behavior is therefore emulated as well as the programmable logic behavior of the FPGA. In one embodiment, additional programmable interconnect lines traversing each boundary scan cell are provided. Theses interconnect lines can be used to programmably connect the data output of a first cell to the data input of second cell which need not be adjacent to the first.

Owner:XILINX INC

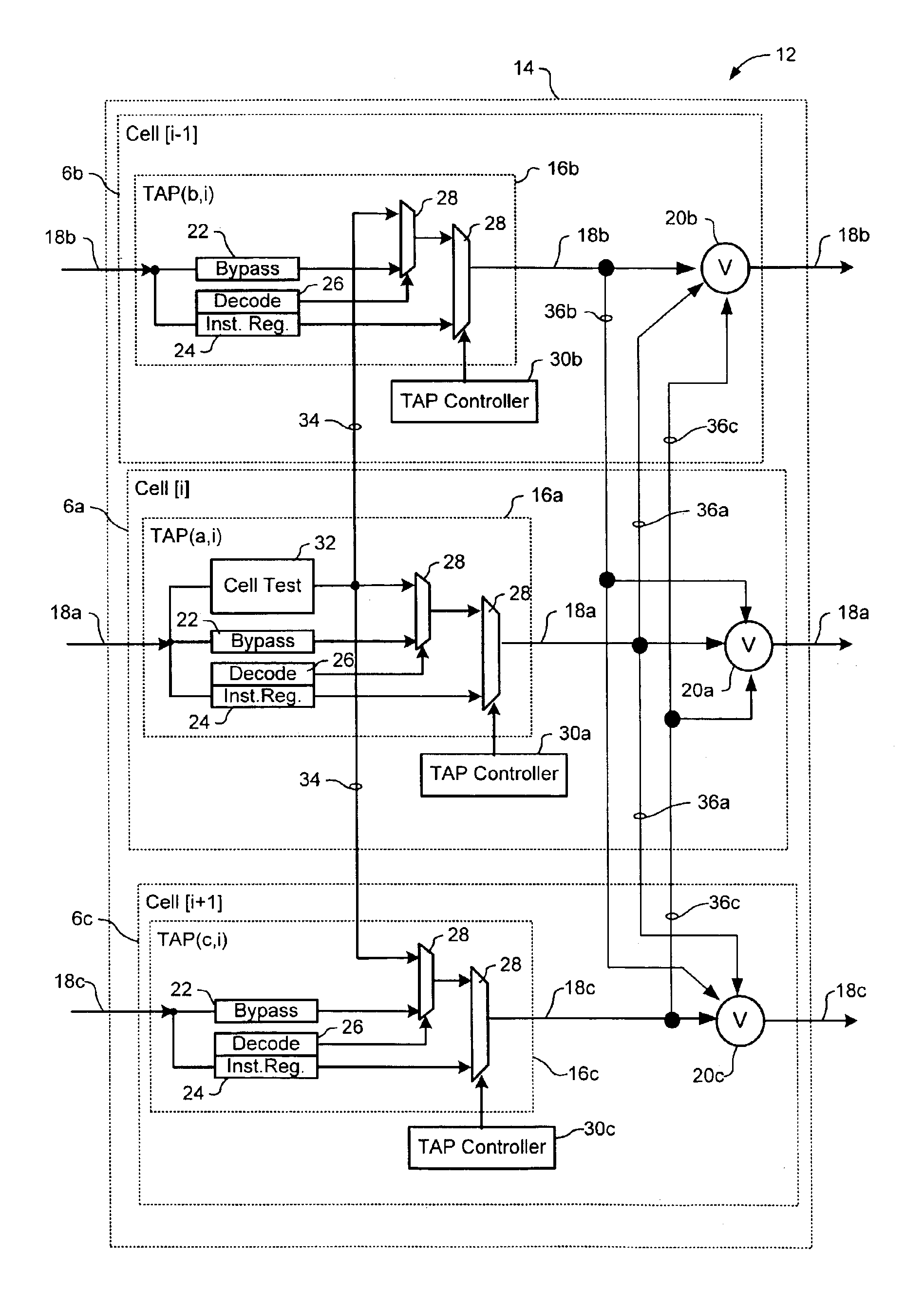

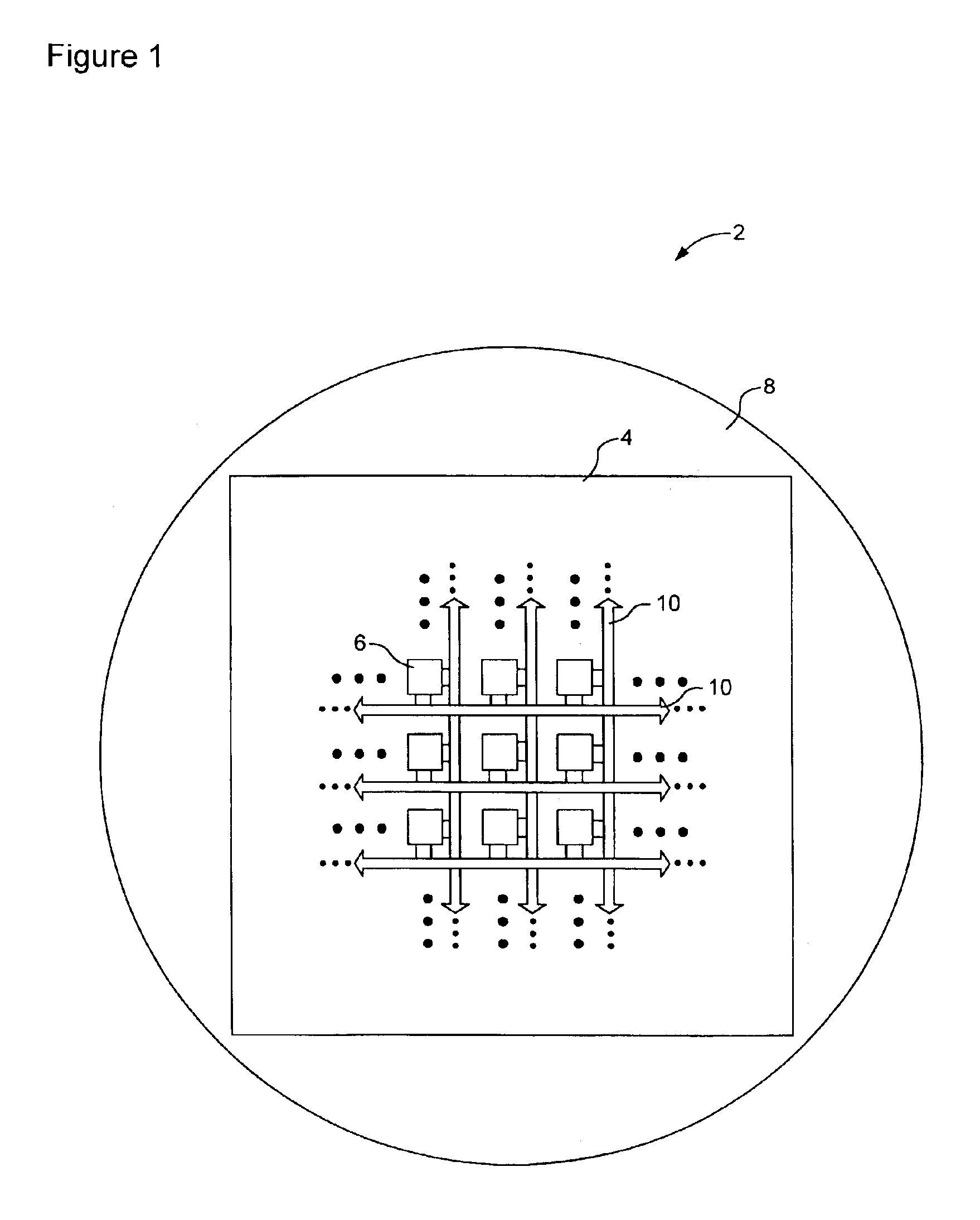

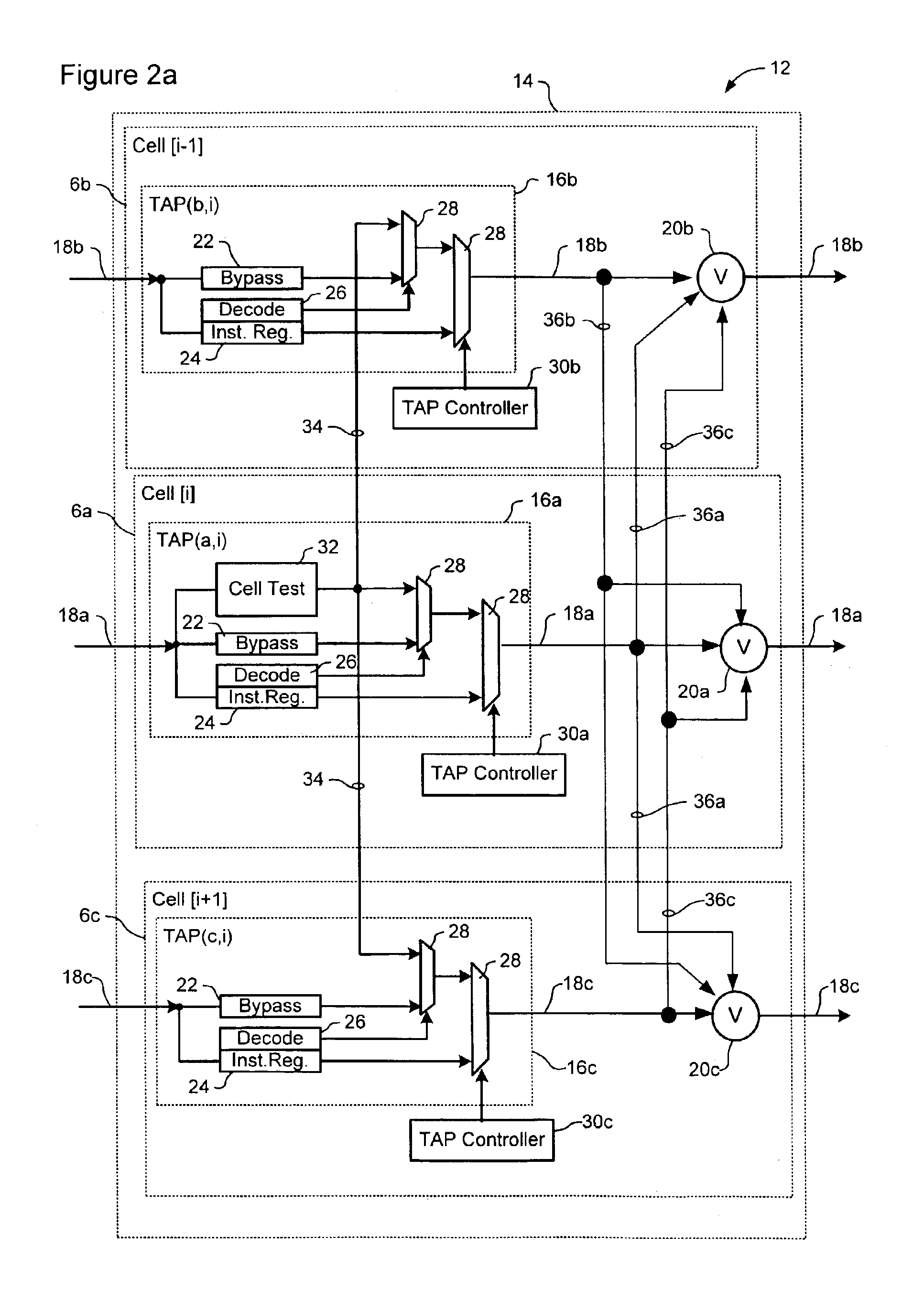

Fault tolerant scan chain for a parallel processing system

InactiveUS6928606B2Speed up preparationHighly robust fault tolerantElectronic circuit testingRedundant data error correctionVirtual cellControl signal

A highly robust fault tolerant scan chain is designed for scanning (and / or controlling a configuration of) a parallel processing system. The scan chain implements parallel redundant scan chains that follow physically diverse paths through the parallel processing system. For each IC under test, a set of redundant TAPs perform a boundary scan, and the test results are combined by voting. The TAPs of each set are physically diverse, in that they are physically located in separate power domains of the parallel processing system. As a result, the scan chain is robust to faults affecting power and / or control signal supply to any one power domain. Respective input and output dummy cells at opposite extreme ends of the scan chain provide a graceful separation and recombination of the redundant parallel scan chains, and so renders the architecture of the scan chain transparent to external boundary scan circuit elements.

Owner:NORMAN RICHARD S

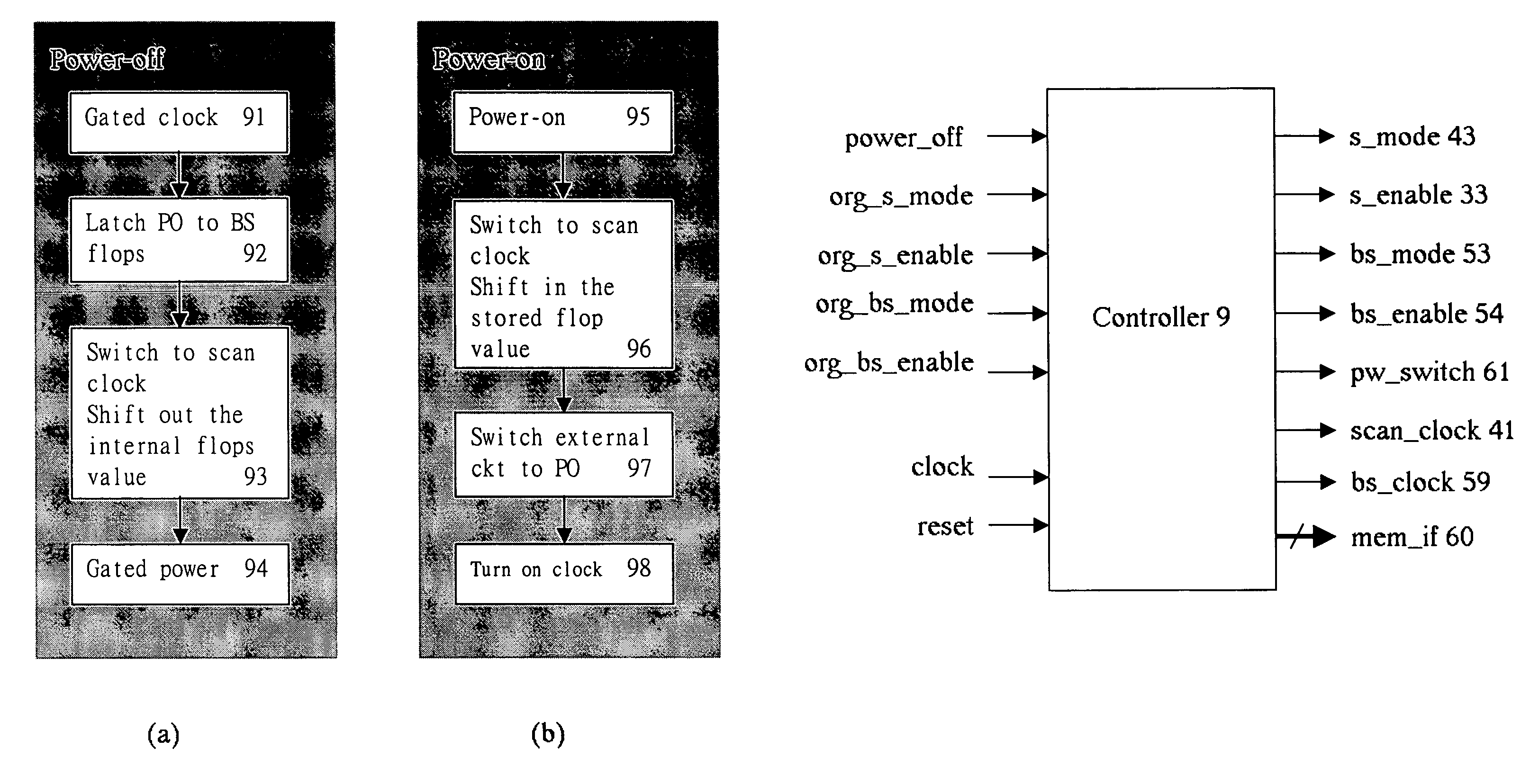

Method of using scan chains and boundary scan for power saving

InactiveUS7392447B2Reduce hardware overheadSave powerEnergy efficient ICTElectronic circuit testingInternal memoryExternal storage

Owner:PRINCETON TECH CORP

Fault injection method and system

InactiveUS20050050393A1Electronic circuit testingError detection/correctionProcessor registerComputer science

A method and system are disclosed for fault injection using Boundary Scan resources compliant with 1149.1, while operating in system mode. The system has two register circuits, one, for storing and updating fault selection data and another, for storing and updating fault injection values.

Owner:LUCENT TECH INC

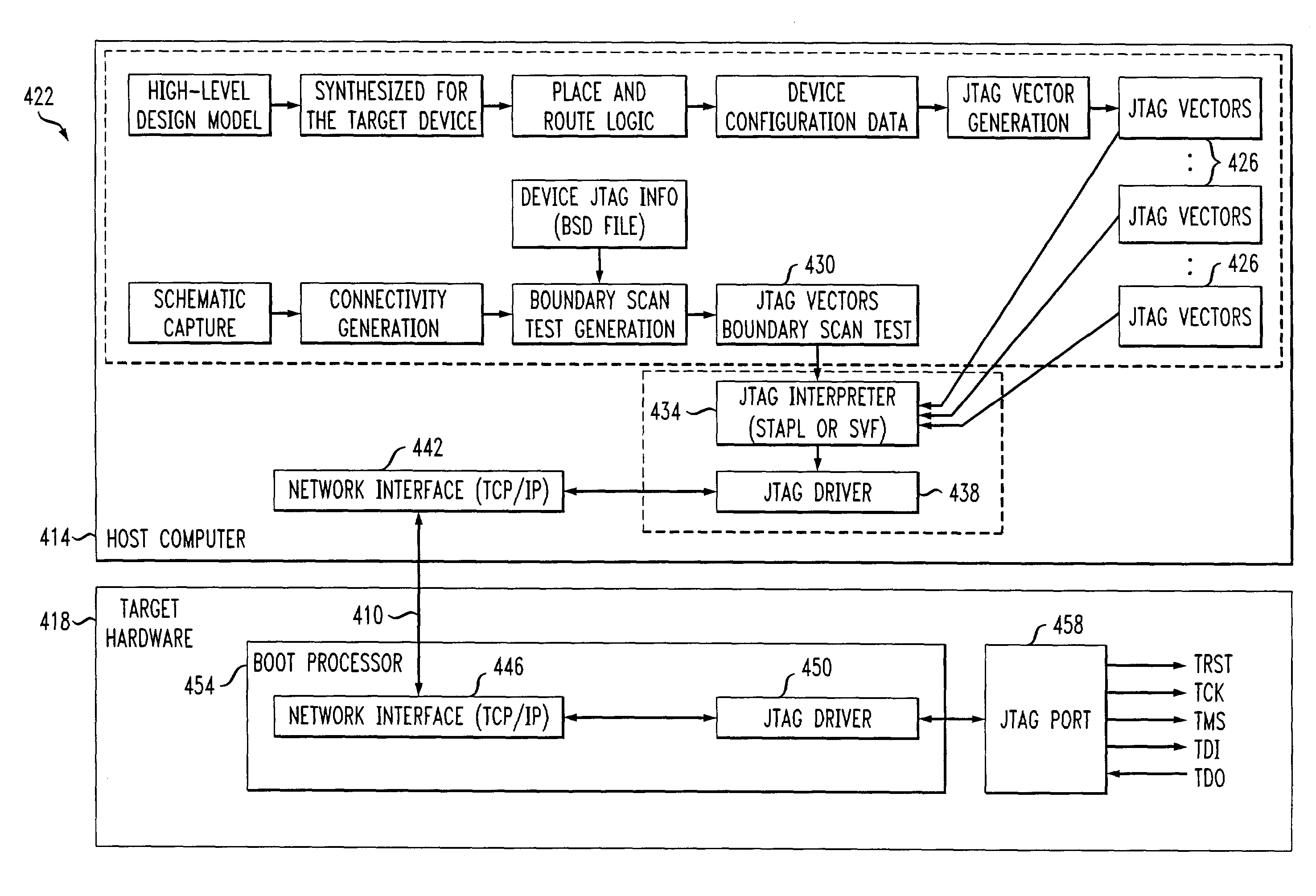

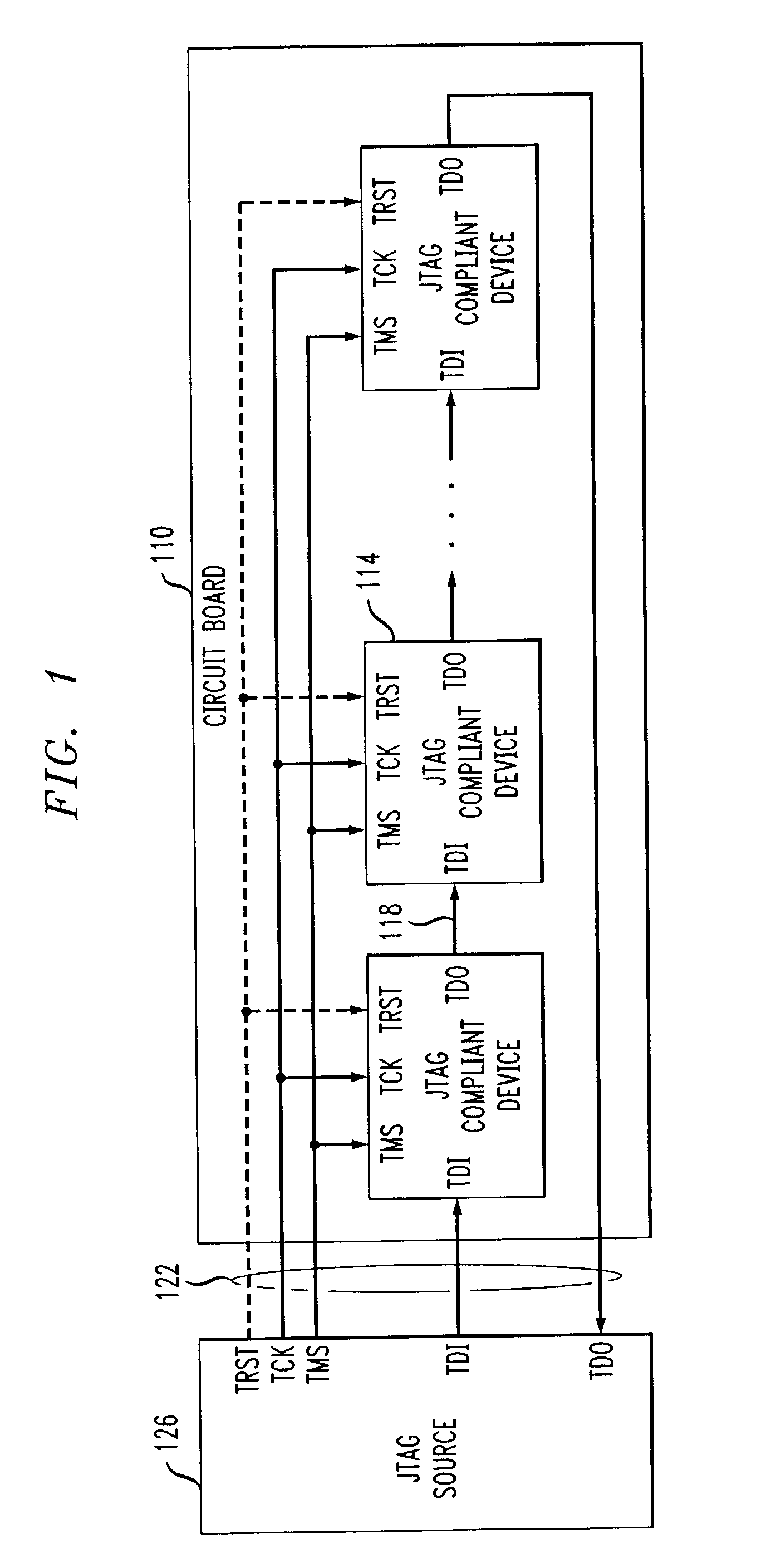

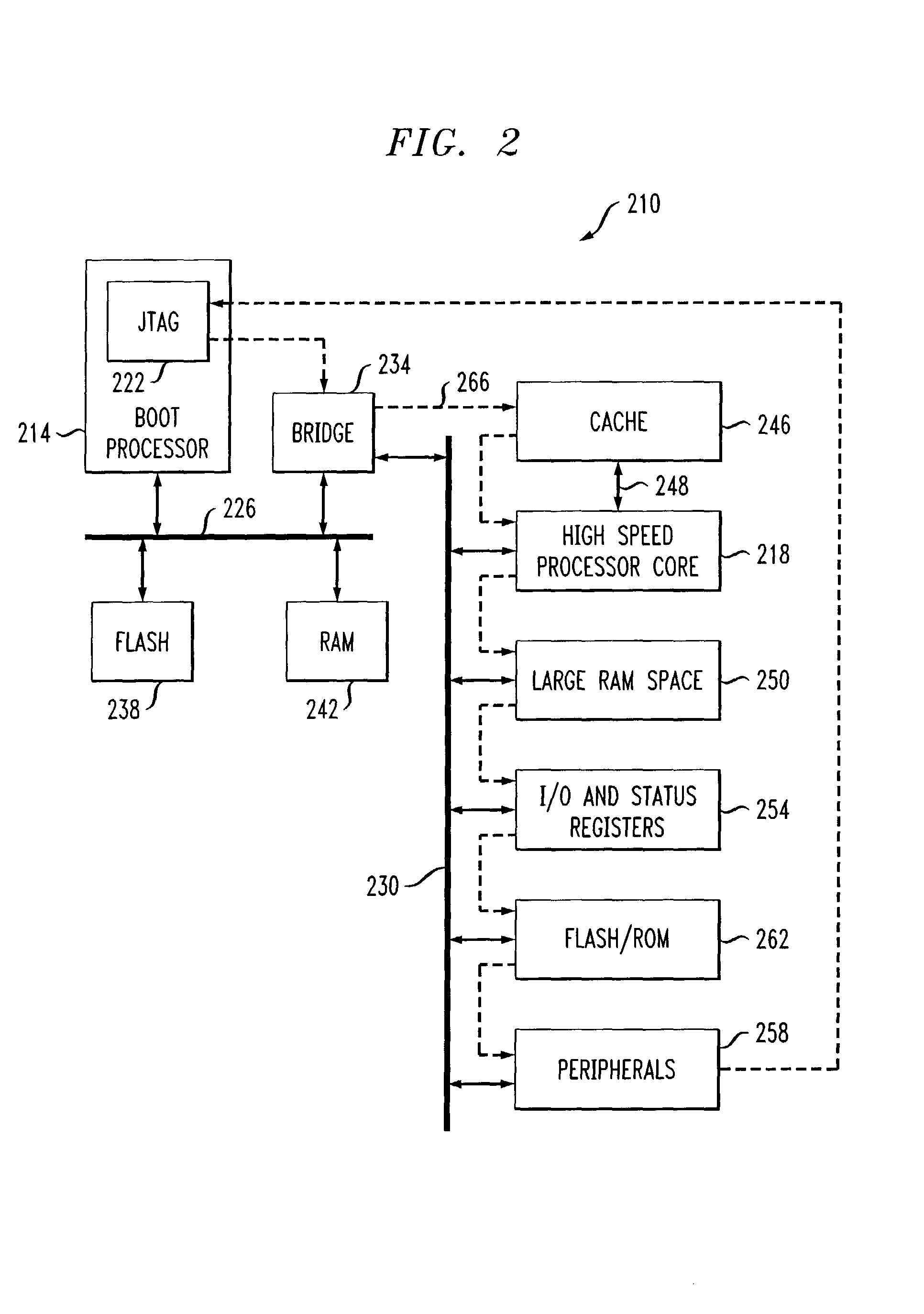

Methods and systems for remotely controlling a test access port of a target device

InactiveUS7017081B2Digital circuit testingDetecting faulty hardware by remote testNetwork linkJoint Test Action Group

JTAG operations are carried out remotely over a network interface. The host processor includes a JTAG interpreter and a host side JTAG driver. A target device includes a target side JTAG driver. The interpreter processes and translates JTAG design files. The host side JTAG driver generates messages for the target side JTAG driver based on the translation. The host JTAG driver delivers the messages to a host network interface. The host network interface is connected via a network link to a target network interface. The target network interface is connected to the target side JTAG driver. The target side JTAG driver communicates with a target boundary scan chain. The target side JTAG driver and host side JTAG driver communicate over the network link. Network overhead is reduced by buffering messages until a message requiring a return of test data is ready for transmission.

Owner:LUCENT TECH INC +1

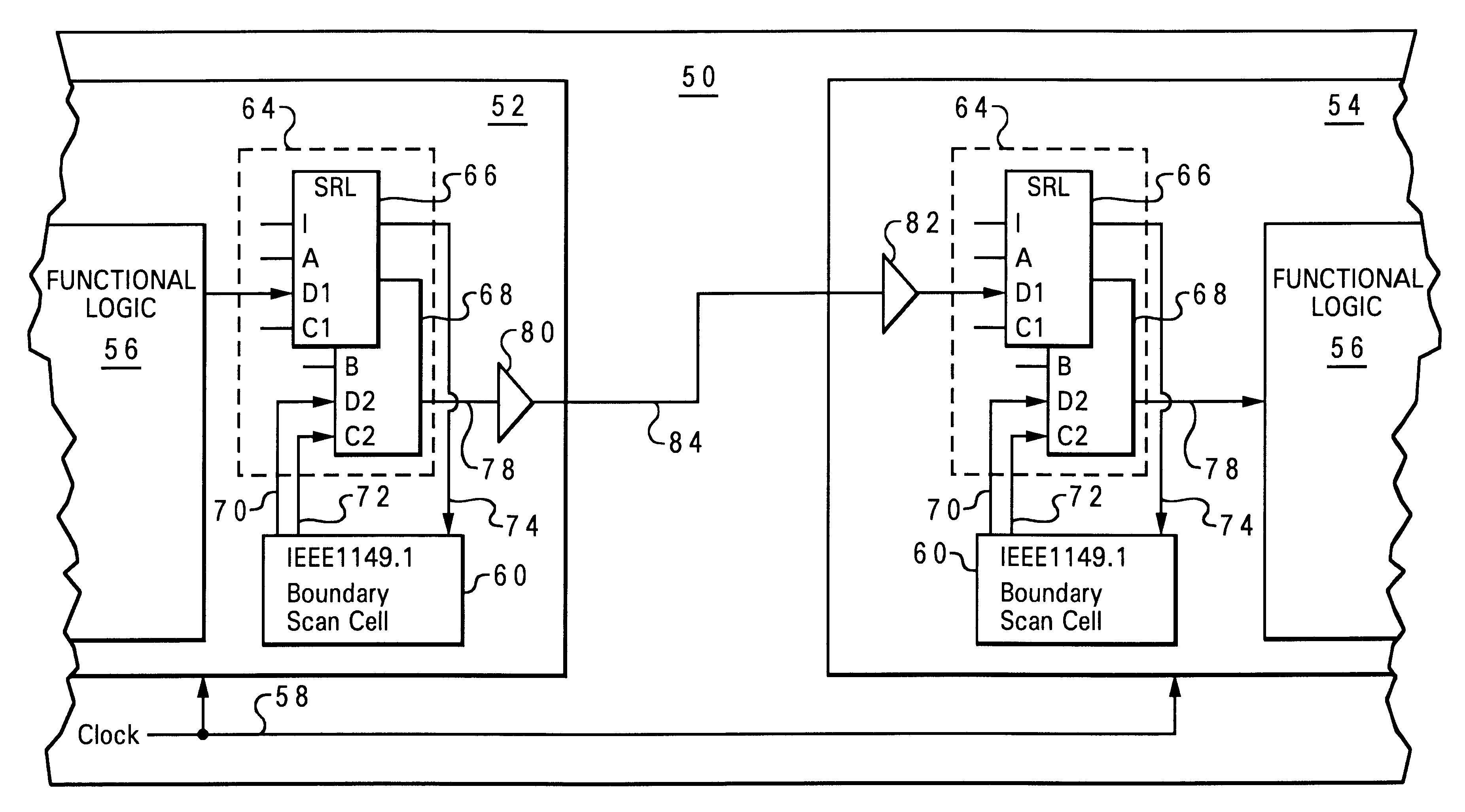

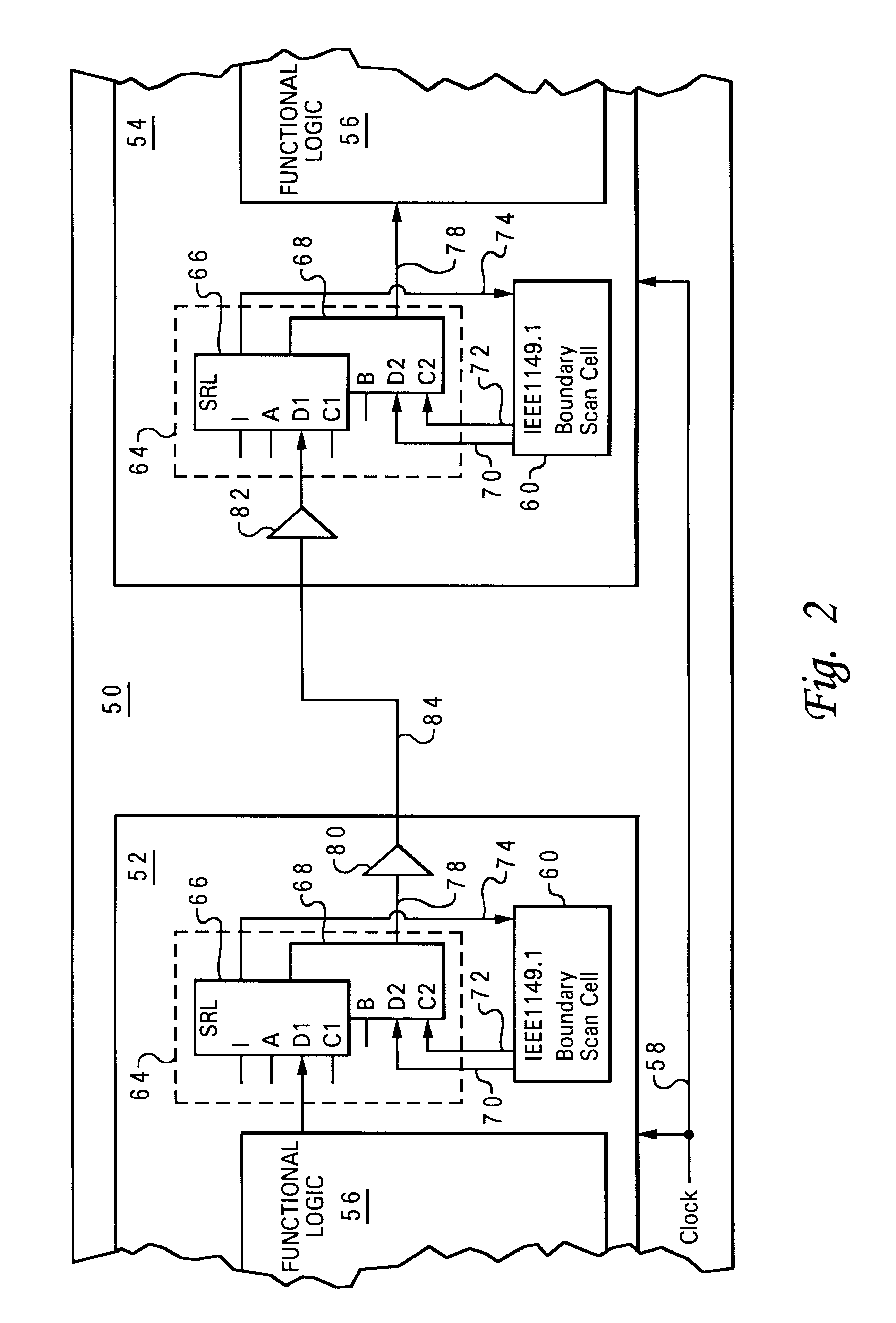

High-performance IEEE1149.1-compliant boundary scan cell

A circuit is disclosed that includes a latch circuit and boundary scan cell circuitry. The latch circuit includes a slave latch and a master latch having a data output. The slave latch includes at least a first data input connected to the data output of the master latch, a second data input, and a control input that receives a control signal that controls latching of data present at the second data input. The boundary scan cell circuitry is connected to the second data input and to the control input of the slave latch so that the boundary scan cell circuitry can supply the control signal and data to the slave latch. In one embodiment, the boundary scan cell circuitry is IEEE1149.1-compliant and the circuit further includes either an output driver coupled to the data output of the slave latch or an input receiver coupled to a data input of the master latch.

Owner:IBM CORP

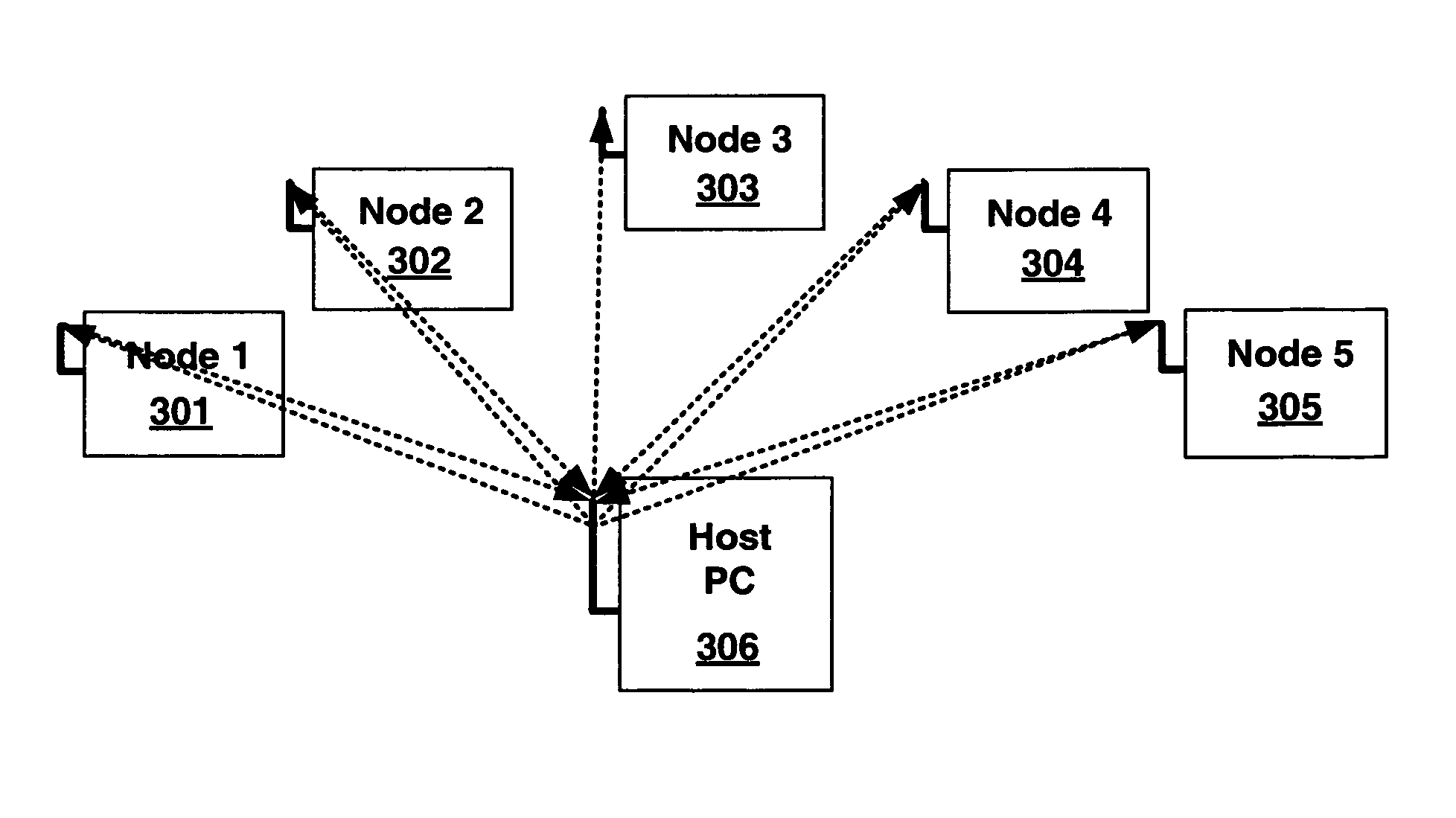

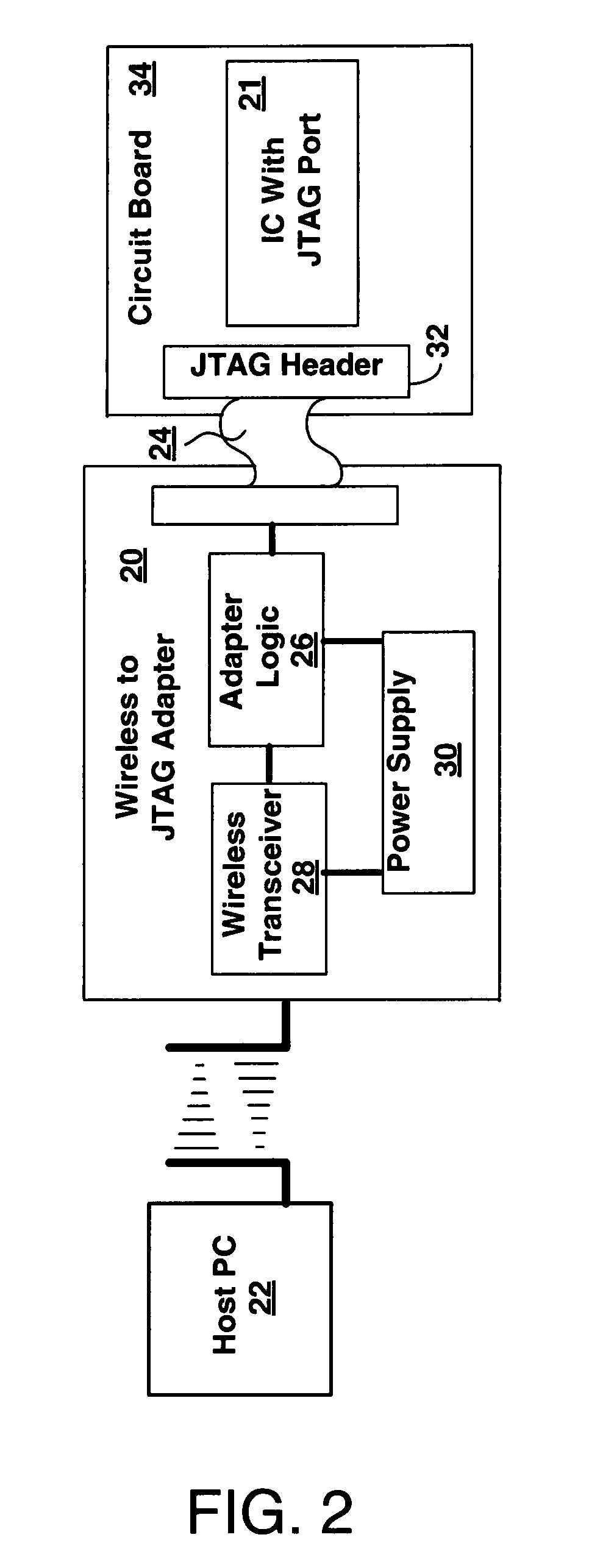

Wireless dynamic boundary-scan topologies for field

A programmable logic device (PLD) with a JTAG port, such as an FPGA, is provided with a wireless JTAG adapter to enable wireless communications. Multiple PLDs connected with wireless-to-JTAG adapters can be wirelessly linked in a network to form a large boundary-scan chain serial interface. To communicate with the PLDs having a wireless JTAG port, a host PC running application software is also equipped with a wireless transceiver.

Owner:XILINX INC

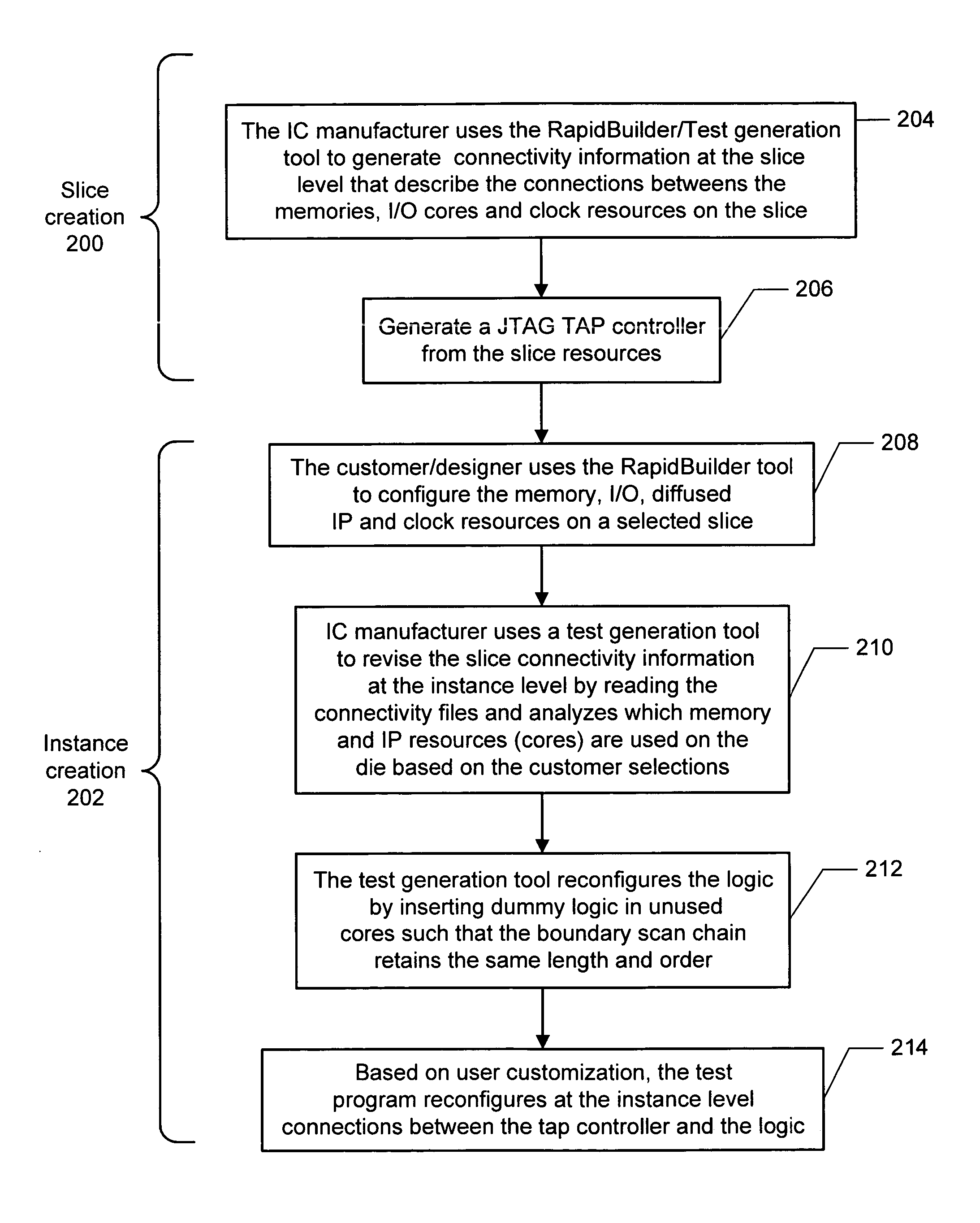

Handling of unused coreware with embedded boundary scan chains to avoid the need of a boundary scan synthesis tool during custom instance creation

ActiveUS20050262465A1Avoid the needCAD circuit designSpecial data processing applicationsComputer hardwareSoftware tool

A method and system is provided for handling unused structures in a slice during custom instance creation to avoid the need of a boundary scan synthesis tool, wherein the slice includes an embedded boundary scan chain having a particular length and order. Aspects of the present invention include using a software tool during slice creation to create at least one slice connectivity file. During instance creation, a customer designs a custom chip using the software tool by selecting which structures are to be use on the slice. The slice connectivity file is then reused for the instance by reading the connectivity file to determine which structures in the file are used and not used based on the customer's selections. Thereafter, the slice is reconfigured to include dummy logic in unused structures, such that the boundary scan chain retains the same length and order.

Owner:BELL SEMICON LLC

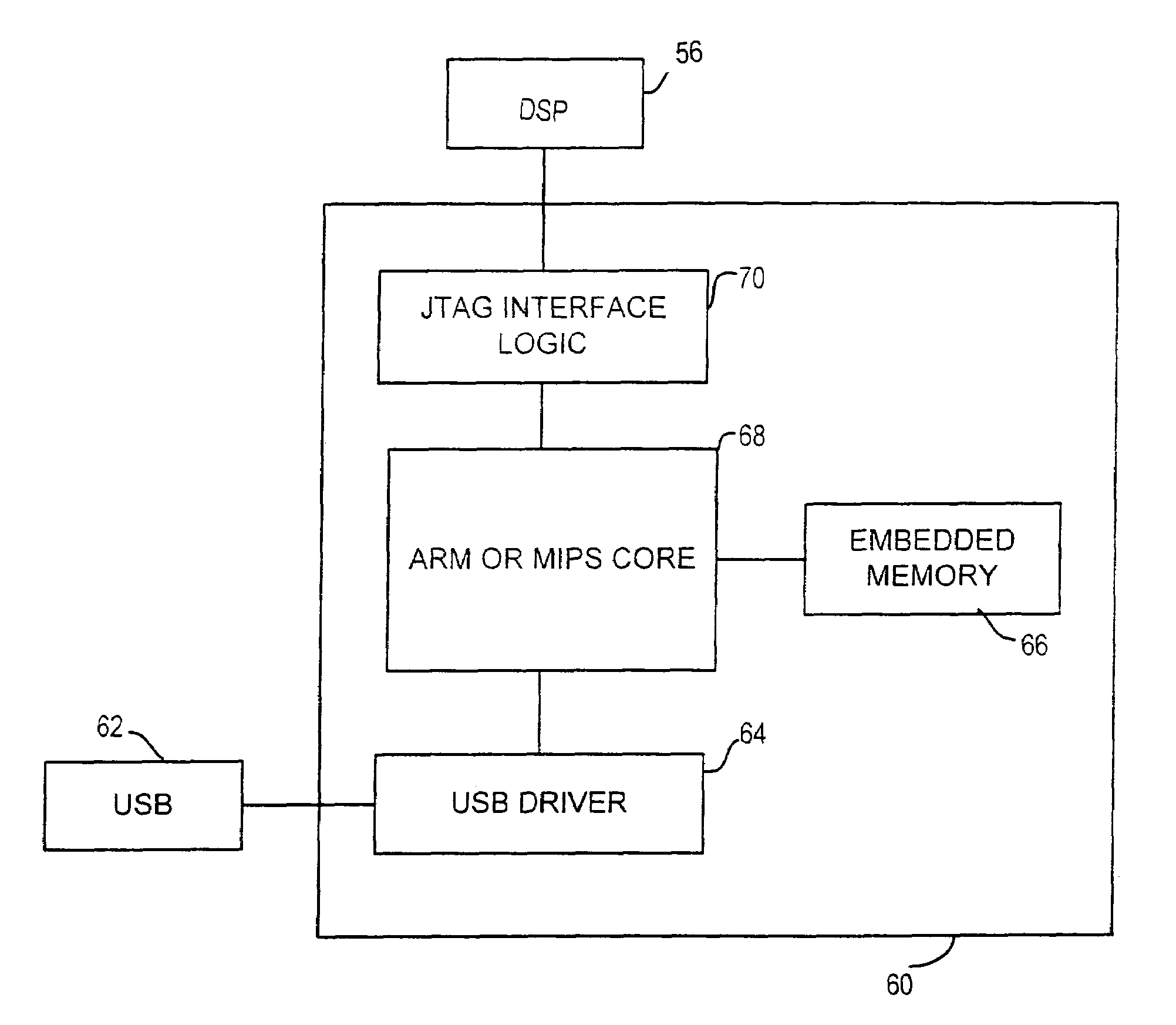

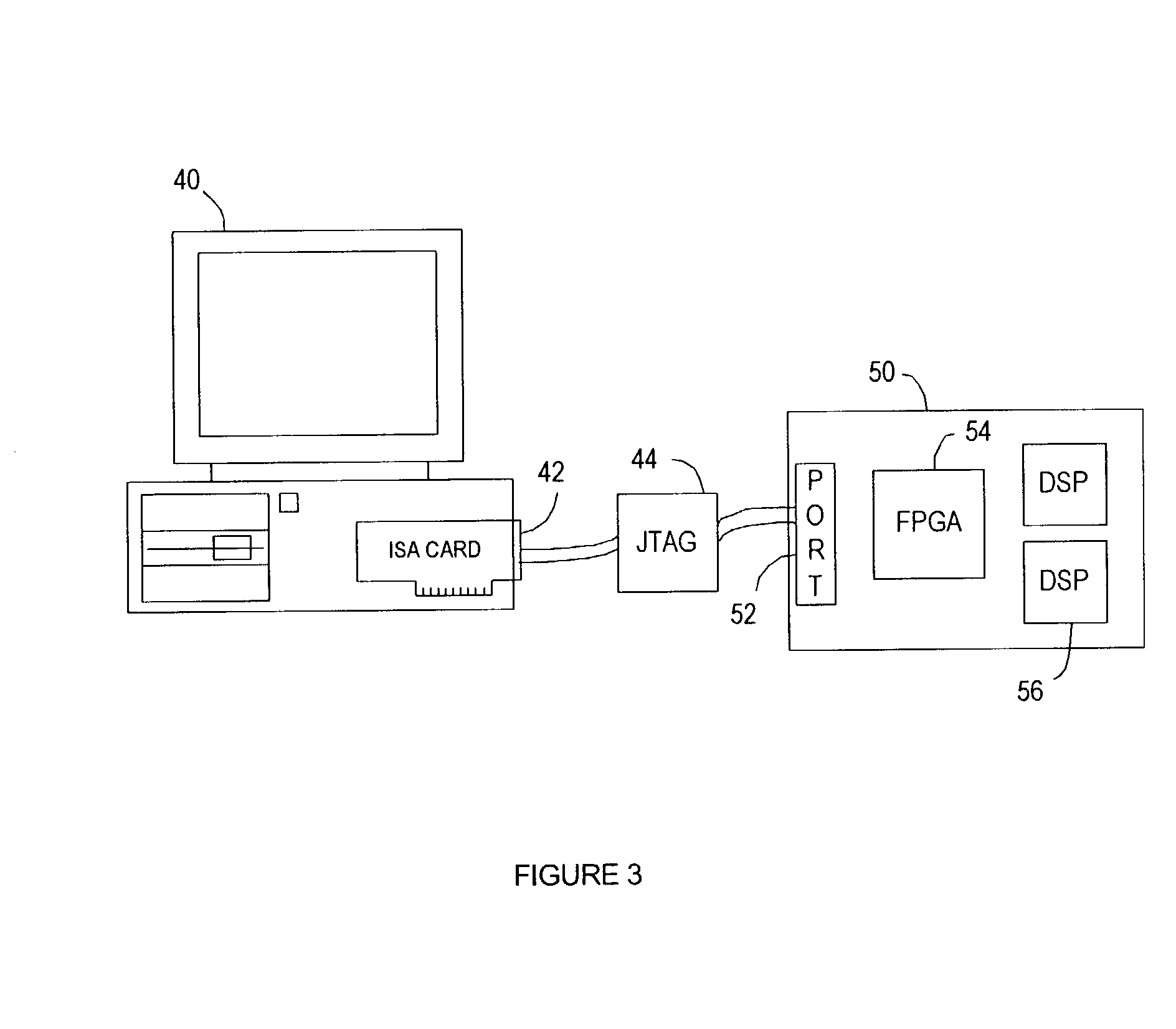

Embedding a JTAG host controller into an FPGA design

InactiveUS6983441B2Error preventionFrequency-division multiplex detailsJoint Test Action GroupEngineering

A method for embedding a Joint Test Action Group (JTAG) standard IEEE 1149.1 host controller into a field programmable gate array (FPGA) for platform development and DSP programming, and boundary scan of targeted hardware using JTAG commands and architecture is described. The FPGA-based JTAG host controller is bussed directly into the FPGA core, bypassing the board's JTAG communication port.

Owner:TELOGY NETWORKS

Handling of unused coreware with embedded boundary scan chains to avoid the need of a boundary scan synthesis tool during custom instance creation

ActiveUS7188330B2Avoid the needCAD circuit designSpecial data processing applicationsComputer hardwareComputer science

A method and system is provided for handling unused structures in a slice during custom instance creation to avoid the need of a boundary scan synthesis tool, wherein the slice includes an embedded boundary scan chain having a particular length and order. Aspects of the present invention include using a software tool during slice creation to create at least one slice connectivity file. During instance creation, a customer designs a custom chip using the software tool by selecting which structures are to be use on the slice. The slice connectivity file is then reused for the instance by reading the connectivity file to determine which structures in the file are used and not used based on the customer's selections. Thereafter, the slice is reconfigured to include dummy logic in unused structures, such that the boundary scan chain retains the same length and order.

Owner:BELL SEMICON LLC

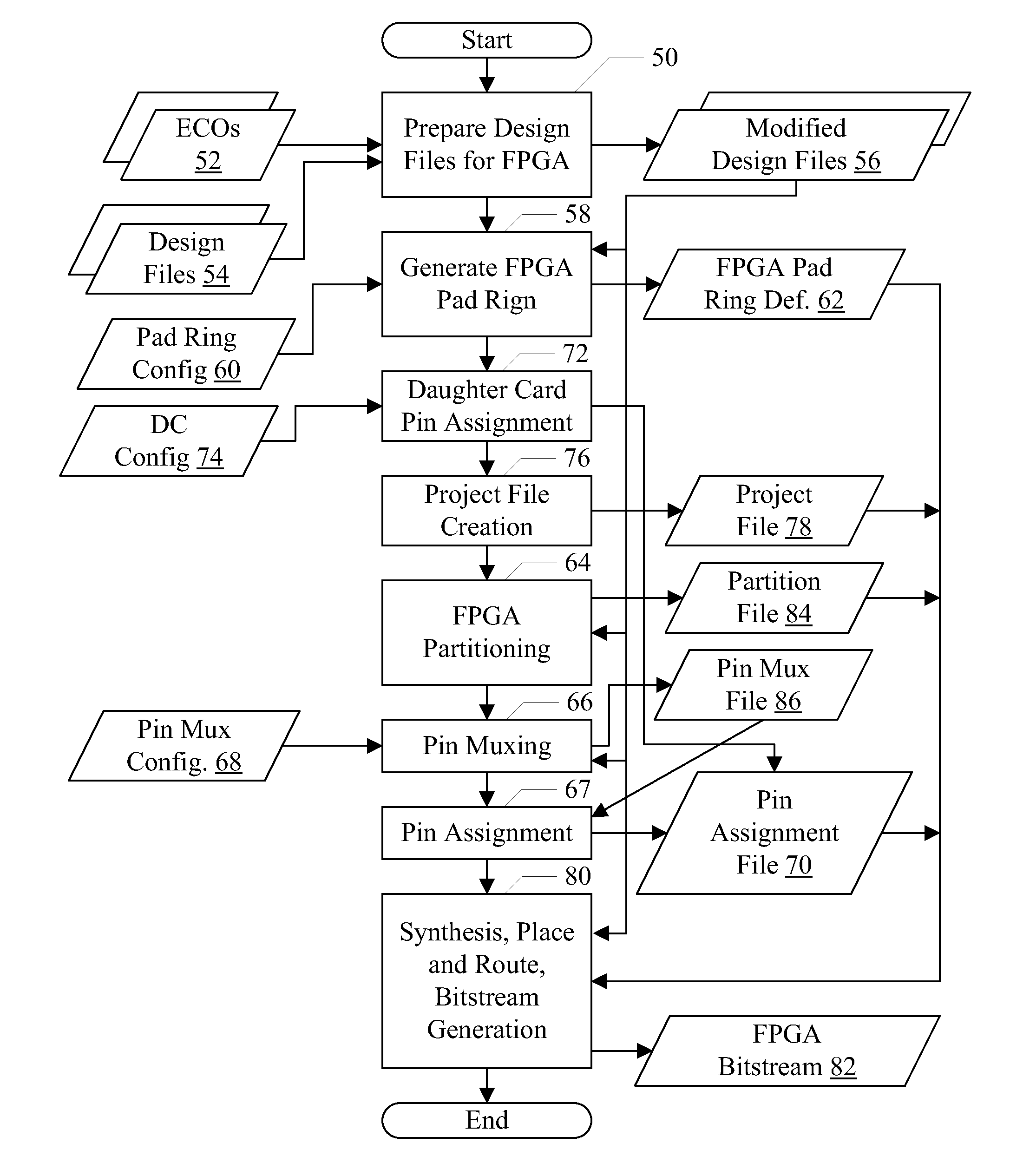

Automated Pad Ring Generation for Programmable Logic Device Implementation of Integrated Circuit Design

InactiveUS20110145778A1Detecting faulty computer hardwareCAD circuit designProgrammable logic deviceIntegrated circuit design

In an embodiment, a method to automatically generate a pad ring for a programmable logic device implementation of an integrated circuit is contemplated. The pad ring that will be used in the integrated circuit itself may include pad logic (e.g. to support boundary scan and other forms of testing), custom driver / receiver circuitry, etc. The pad ring in the programmable logic device, on the other hand, may be predetermined as part of the production of the programmable logic device. The generation may include removing the pad logic and other pad-related circuitry from one or more design files that represent the integrated circuit, as well as mapping the input, output, and input / output signals of the integrated circuit to the available programmable logic device pads.

Owner:APPLE INC

JTAG boundary scan compliant testing architecture with full and partial disable

A semiconductor device includes a JTAG boundary scan compliant testing architecture built into the semiconductor device, where the semiconductor device has a number of input points and output points. The JTAG boundary scan compliant testing architecture includes a TAP controller capable of receiving input test data, a test mode-select, and a test clock. In one embodiment, a full JTAG disable interface is utilized whereby the JTAG boundary scan compliant testing architecture allows an authorized user to prevent an unauthorized user from storing data into or reading data from input boundary scan registers and from reading data from output boundary scan registers. In another embodiment, a partial JTAG disable interface is utilized whereby an authorized user can prevent an unauthorized user from storing data into a pre-designated input boundary scan register, or from reading data from a pre-designated output boundary scan register.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

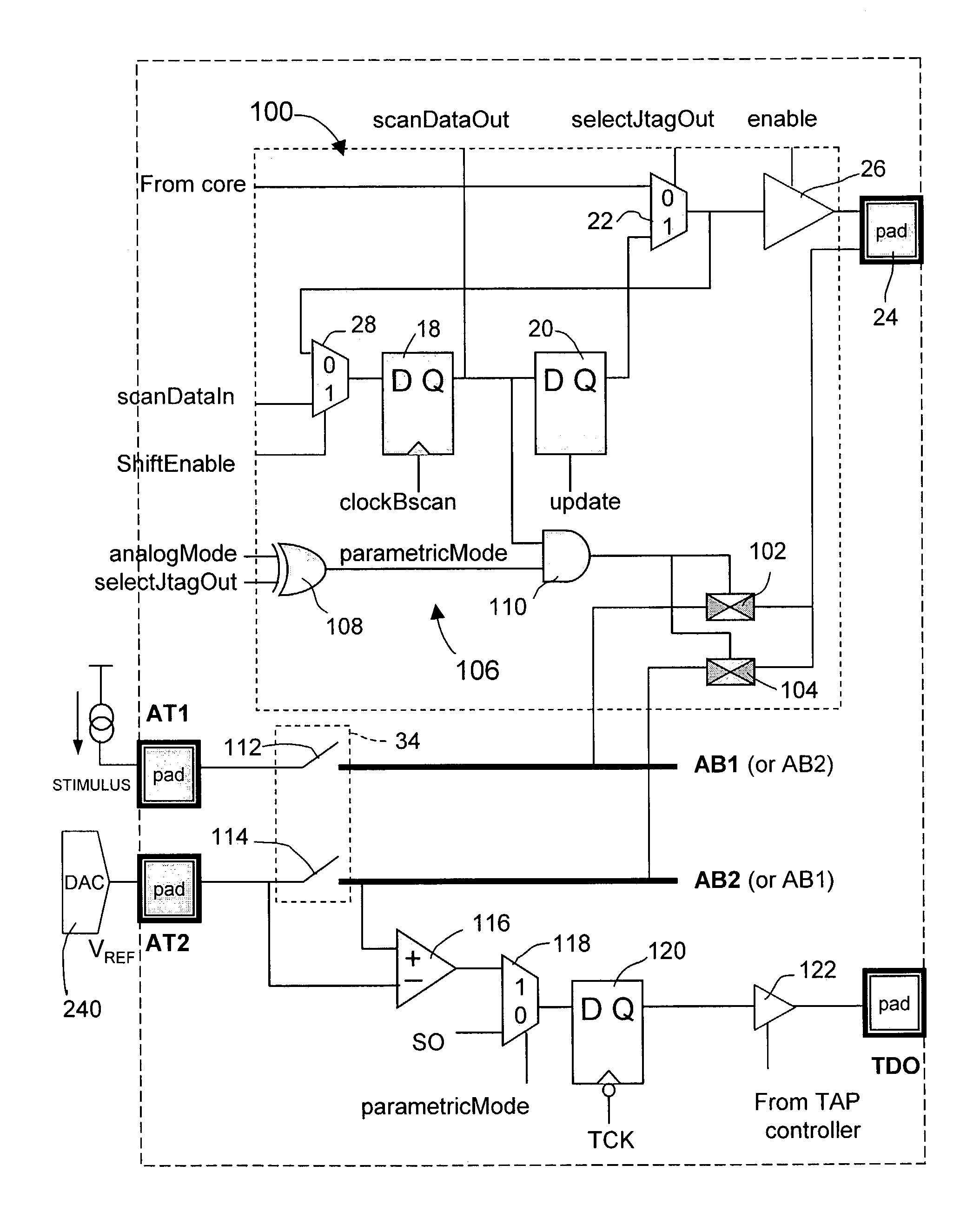

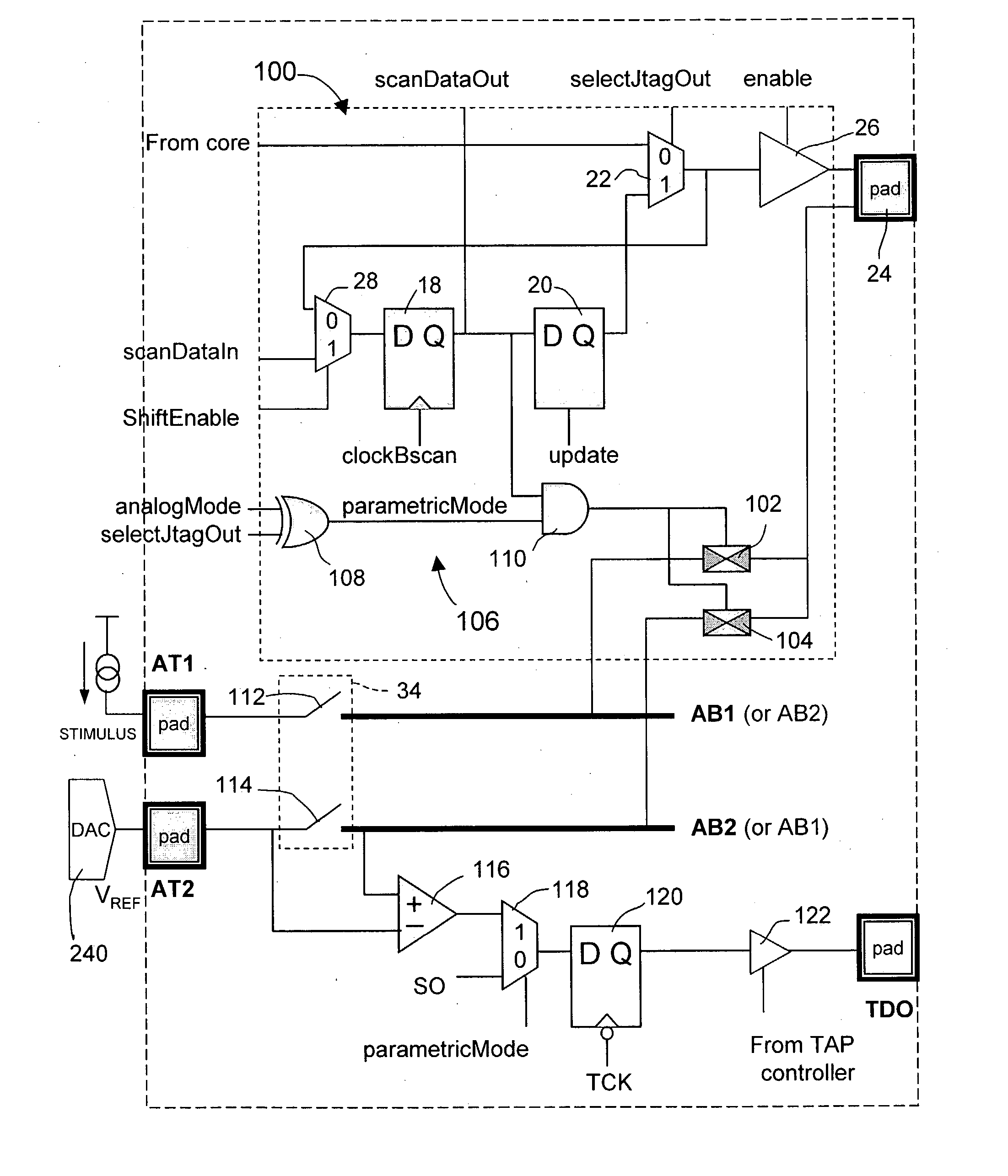

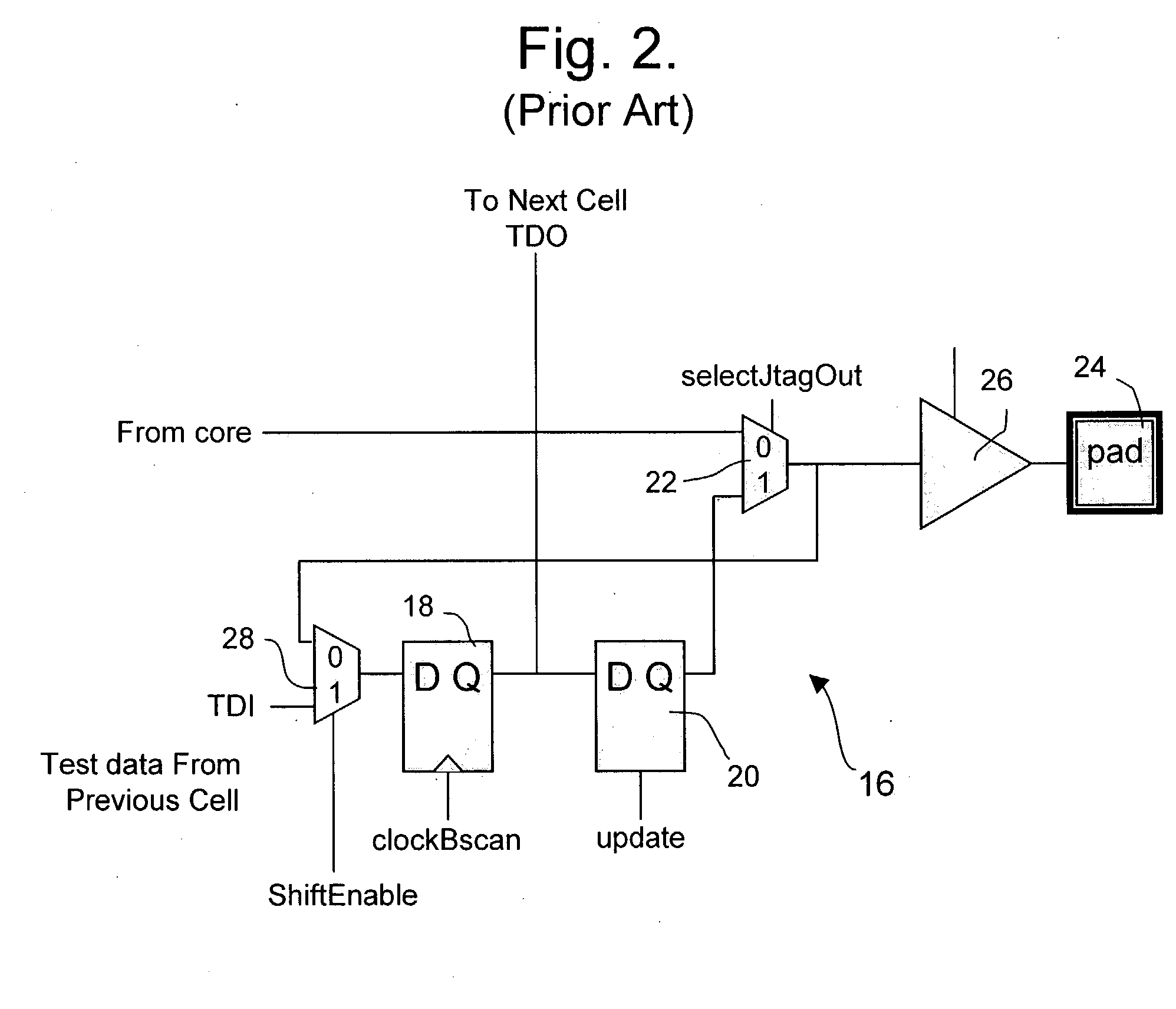

Circuit and method for adding parametric test capability to digital boundary scan

A boundary scan cell for use in a circuit having a boundary scan shift register (BSSR) having boundary scan cells associated with pins of the circuit, the cell having a single-bit shift register element and an associated update latch, comprises a logic circuit for controlling the logic state of an associated pin, analog switches connecting the associated pin to analog test buses, and logic circuitry for selectively configuring the cell in a parametric test mode in which the cell shift register element controls the analog switches, and in a digital test mode in which the cell shift register element controls the logic state of the associated pin.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

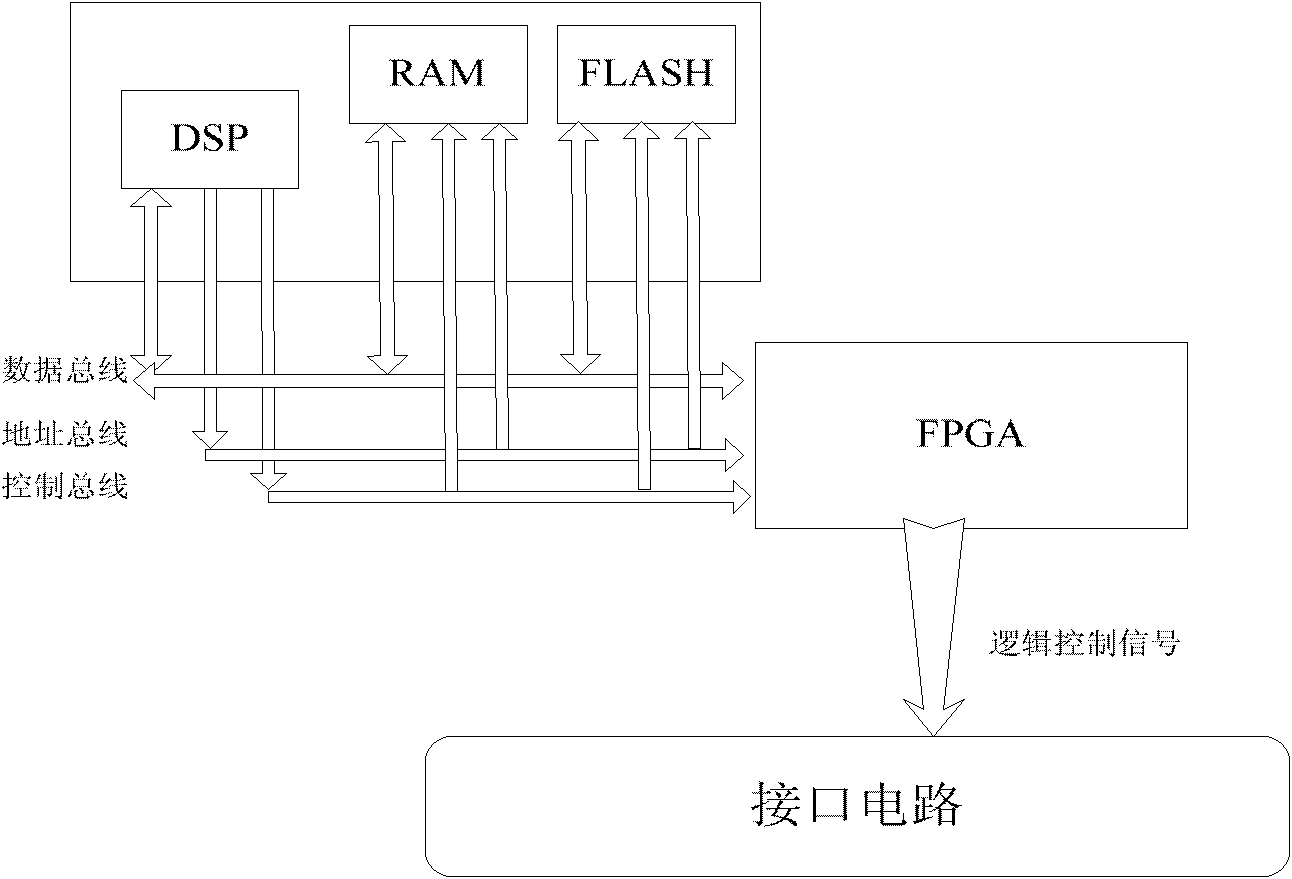

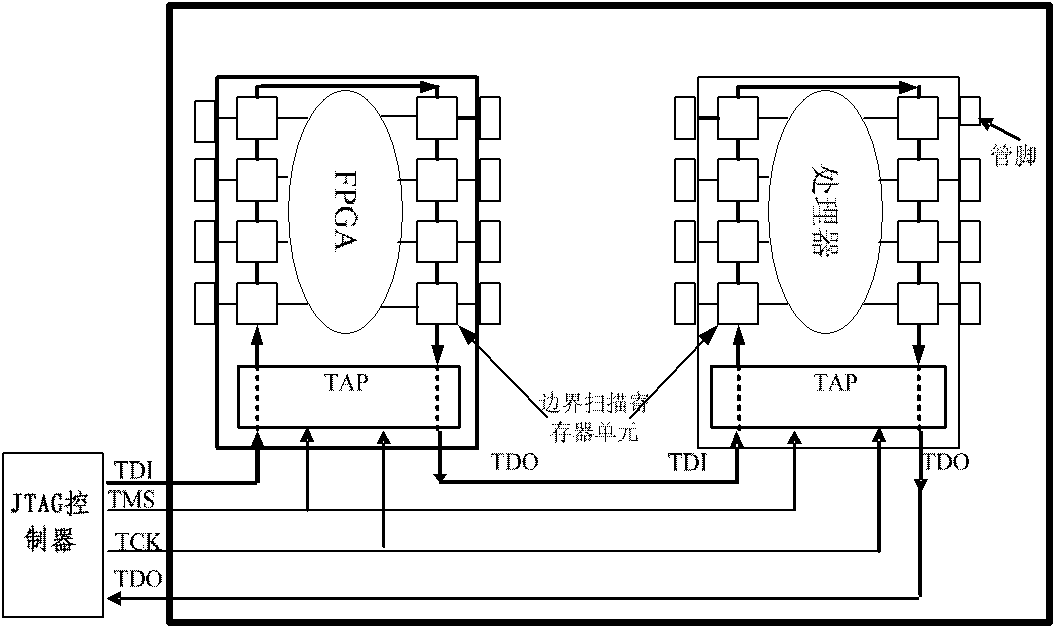

Fault injection system for embedded spaceborne computer and injection method thereof

ActiveCN102135920AAddress reliabilitySolve fault tolerance evaluationError detection/correctionFault coverageOperational system

The invention discloses a fault injection system for an embedded spaceborne computer and an injection method thereof, which are mainly used for software evaluation of the operation system of the spaceborne computer. The fault injection system for the embedded spaceborne computer comprises a Digital Signal Processor (DSP), a Random Access Memory (RAM), a FLASH, a Joint Test Action Group (JTAG) controller, and one or more Field Programmable Gate Arrays (FPGAs) (one of which is a fault injection FPGA) and an interface circuit, wherein the DSP processor and the fault injection FPGA are provided with boundary scanning units; the Test Compatibility Kit (TCK) and the Time-Multiplexed Switching (TMS) signal terminals of a chip are connected in parallel; the Total Domestic Output (TDO) signal terminal of a front-stage apparatus and the Transport Driver Interface (TDI) signal terminal of a rear-stage apparatus are connected in series to form a daisy chain. The device is simple and is capable ofshortening evaluation time and reducing evaluation cost; a signal level is directly controlled in the computer without special external instruments; signals needing to control influence can be flexibly selected to have a relatively large fault coverage rate; therefore, the reliability and the fault-tolerant capability of the embedded spaceborne computer can be more comprehensively verified.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

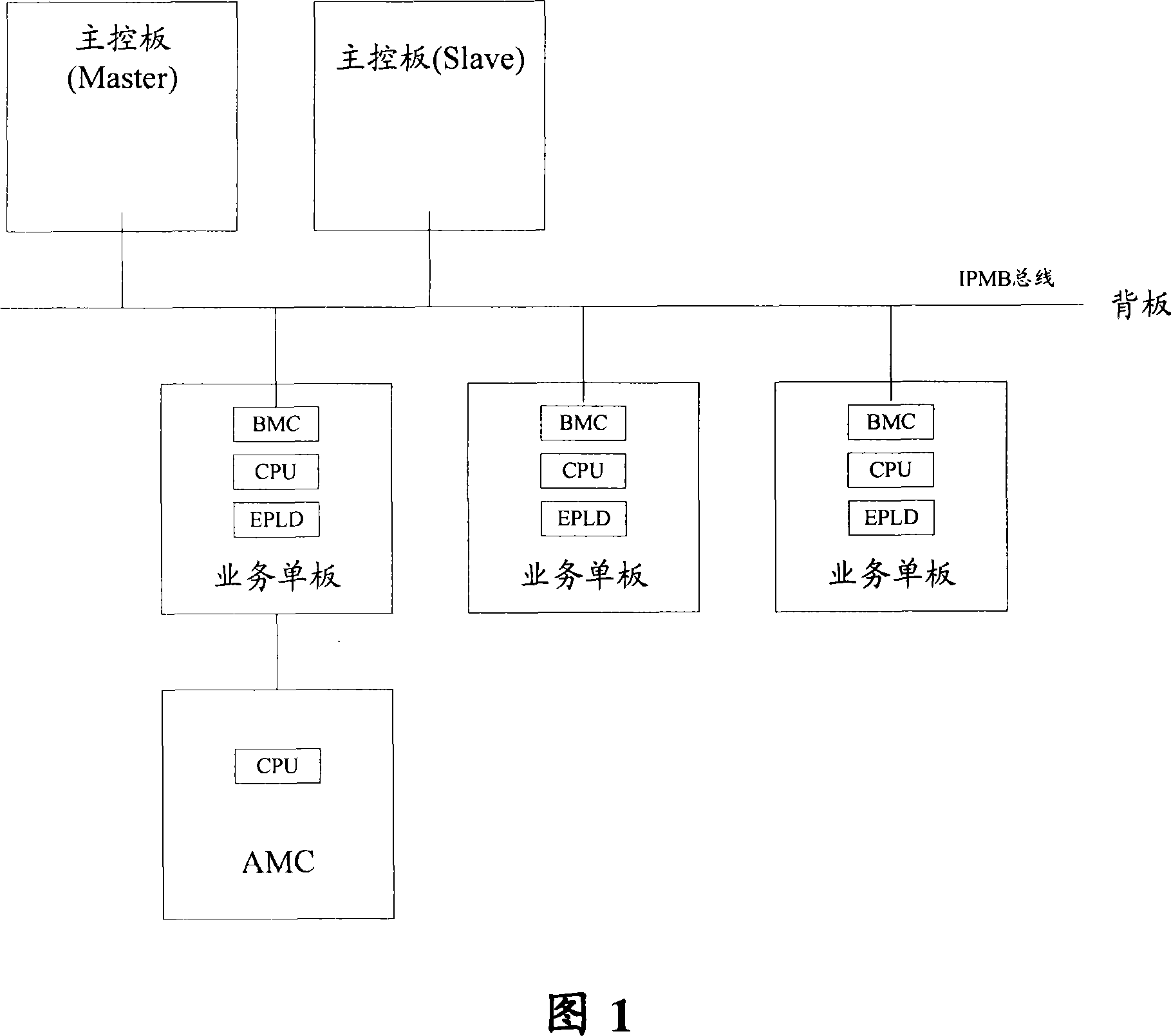

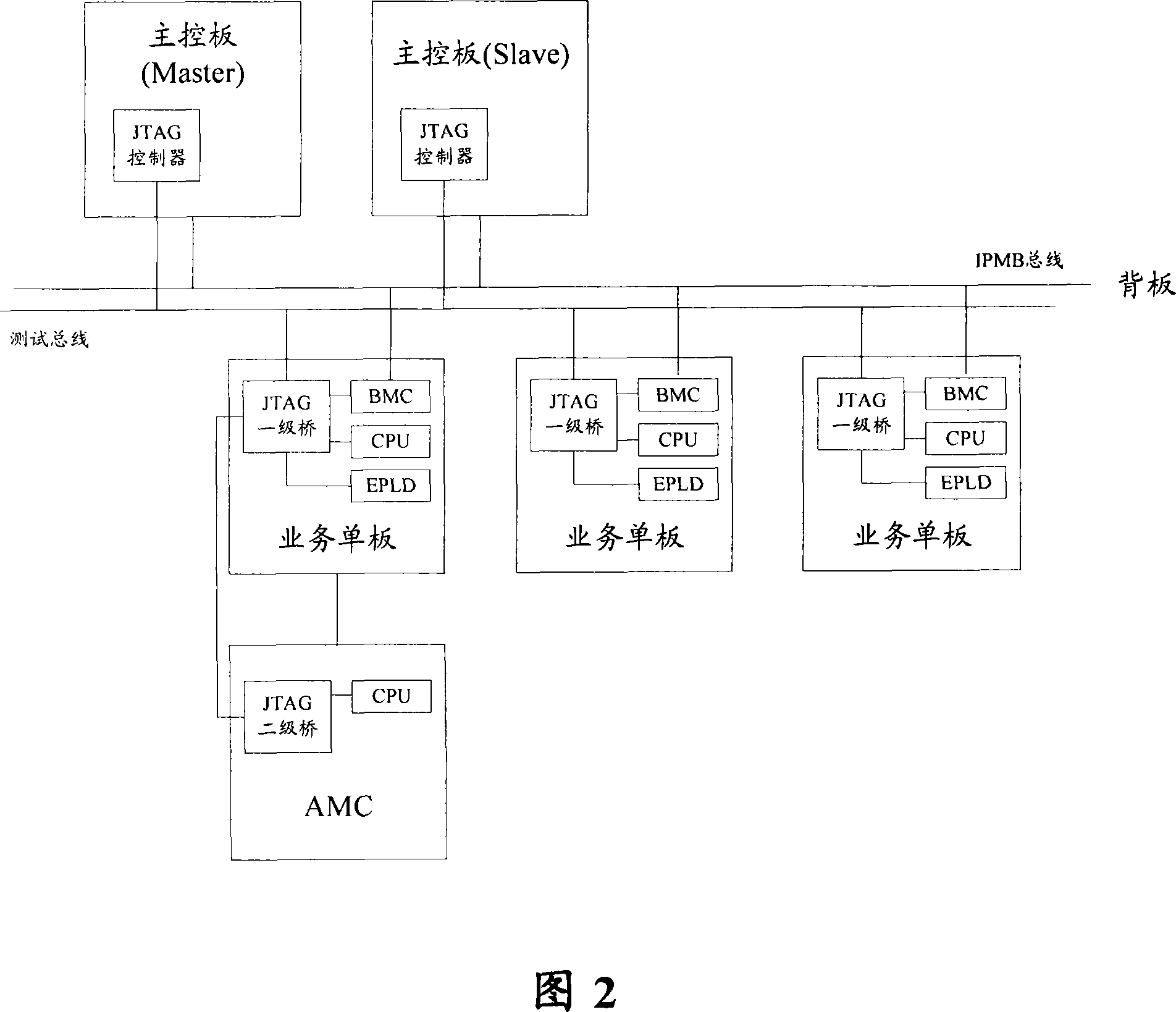

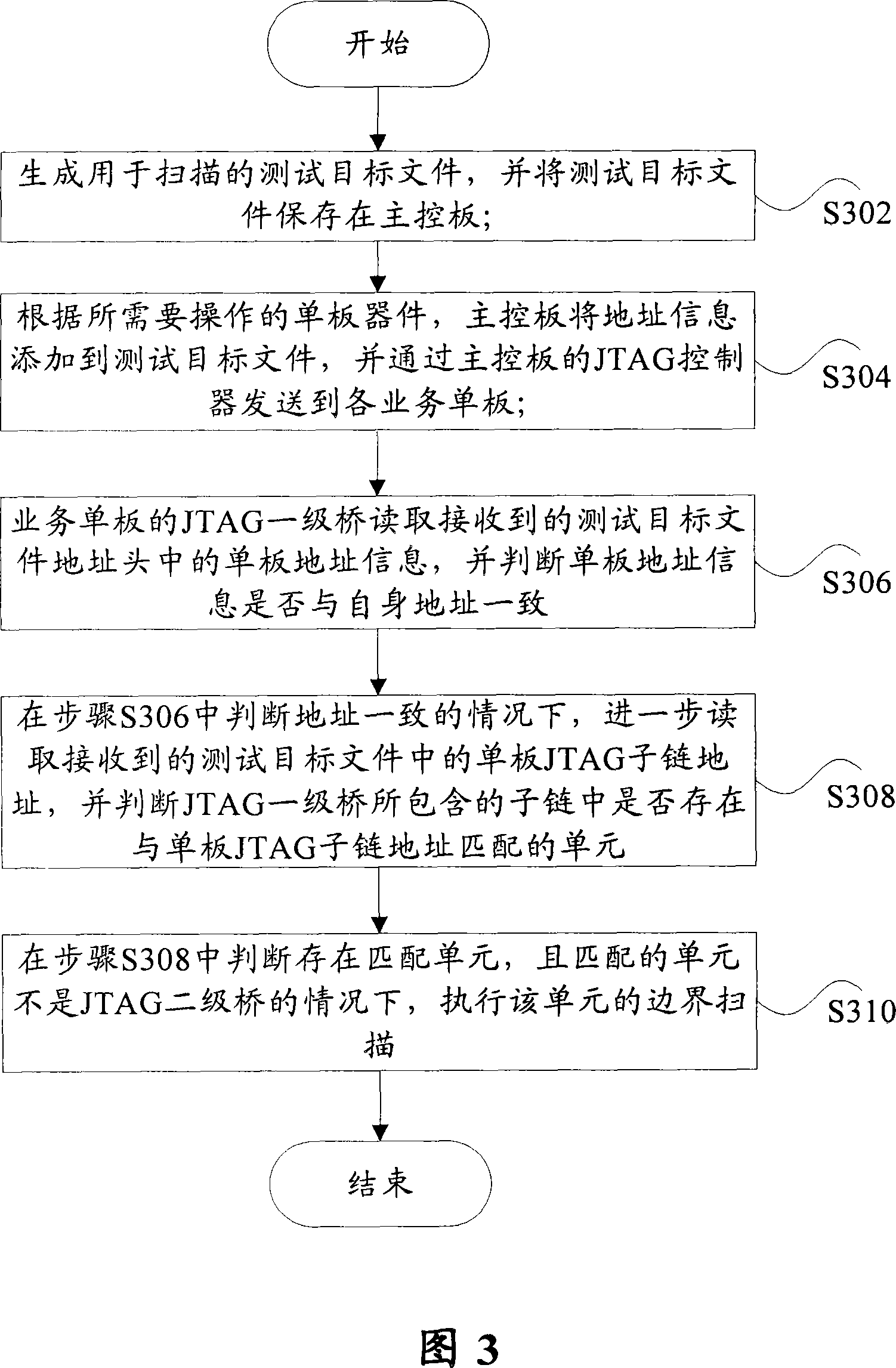

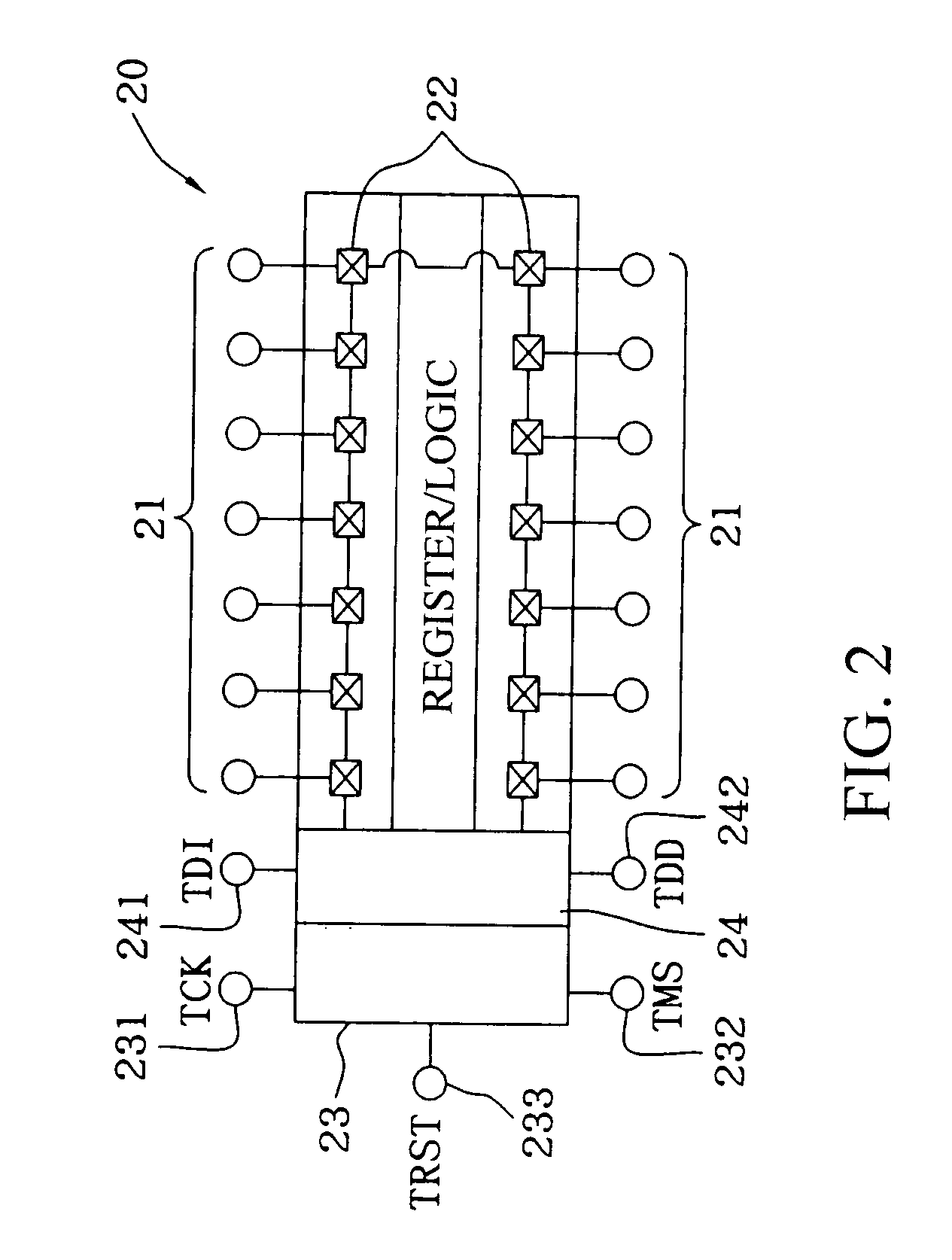

Border scanning system based on high-performance computer communication framework

InactiveCN101105782AHelp maintainSpeed up pin scanningDetecting faulty computer hardwarePerformance computingSingle plate

The invention provides a boundary scanning system and a method based on high-performance computing communication framework. The system comprises a main master board, a business single board, a backboard, and a senior interlayer card module, further a JTAG controller equipped on the main master board for transmitting control information to business single board; a JTAG Grade I bridge equipped on the business single board for connecting JTAG equipment on the business single board; and a JTAG Grade II bridge equipped on the senior interlayer card module for connecting JTAG equipment on the senior interlayer card module.

Owner:ZTE CORP

Circuit and method for adding parametric test capability to digital boundary scan

A boundary scan cell for use in a circuit having a boundary scan shift register (BSSR) having boundary scan cells associated with pins of the circuit, the cell having a single-bit shift register element and an associated update latch, comprises a logic circuit for controlling the logic state of an associated pin, analog switches connecting the associated pin to analog test buses, and logic circuitry for selectively configuring the cell in a parametric test mode in which the cell shift register element controls the analog switches, and in a digital test mode in which the cell shift register element controls the logic state of the associated pin.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

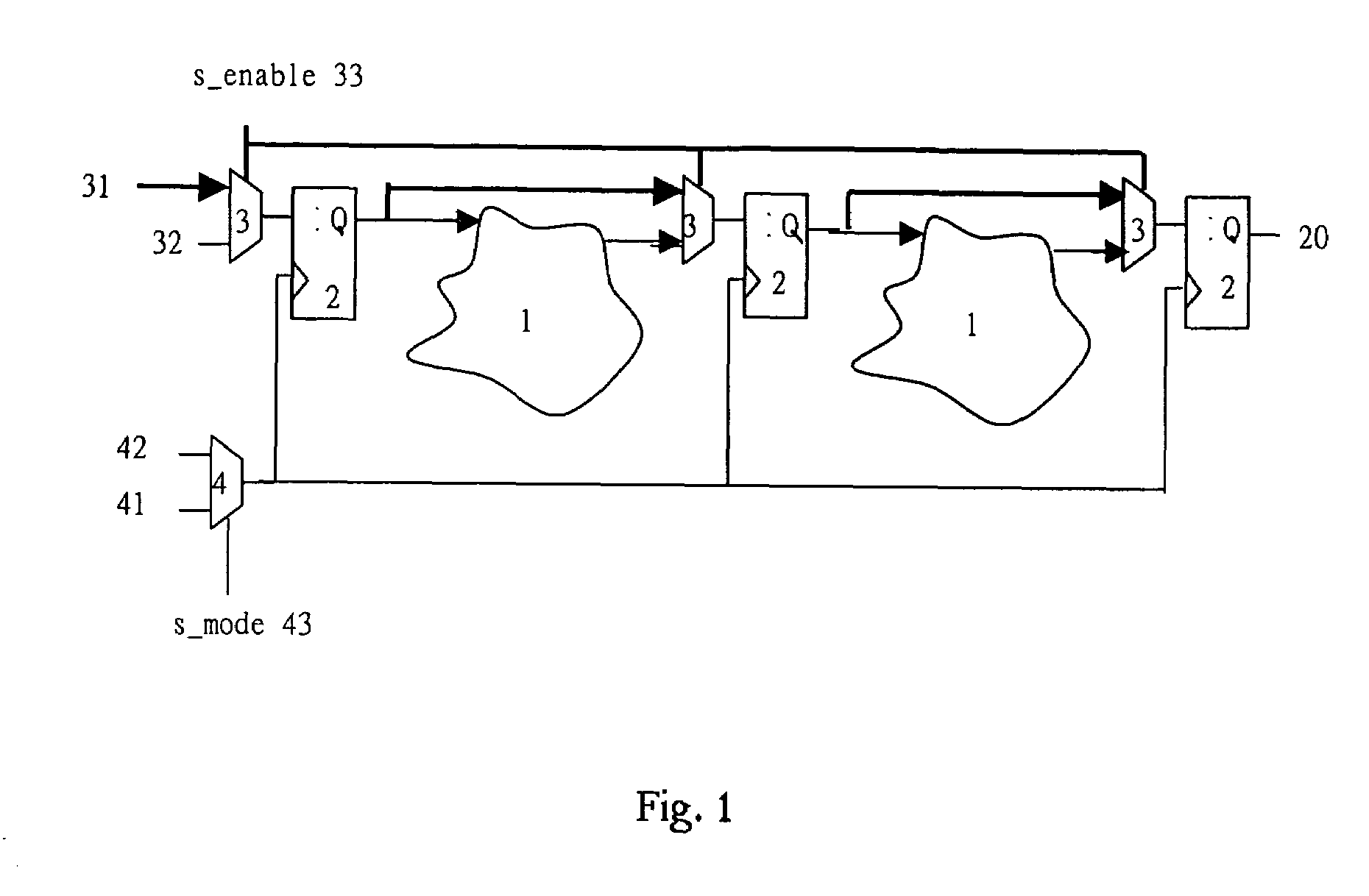

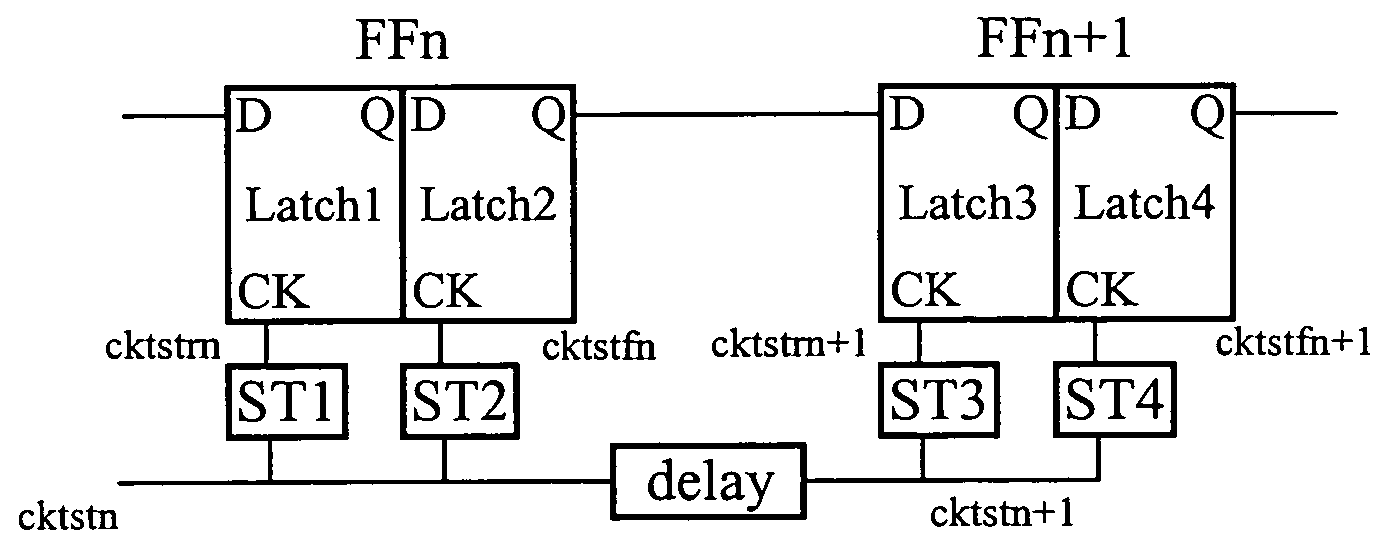

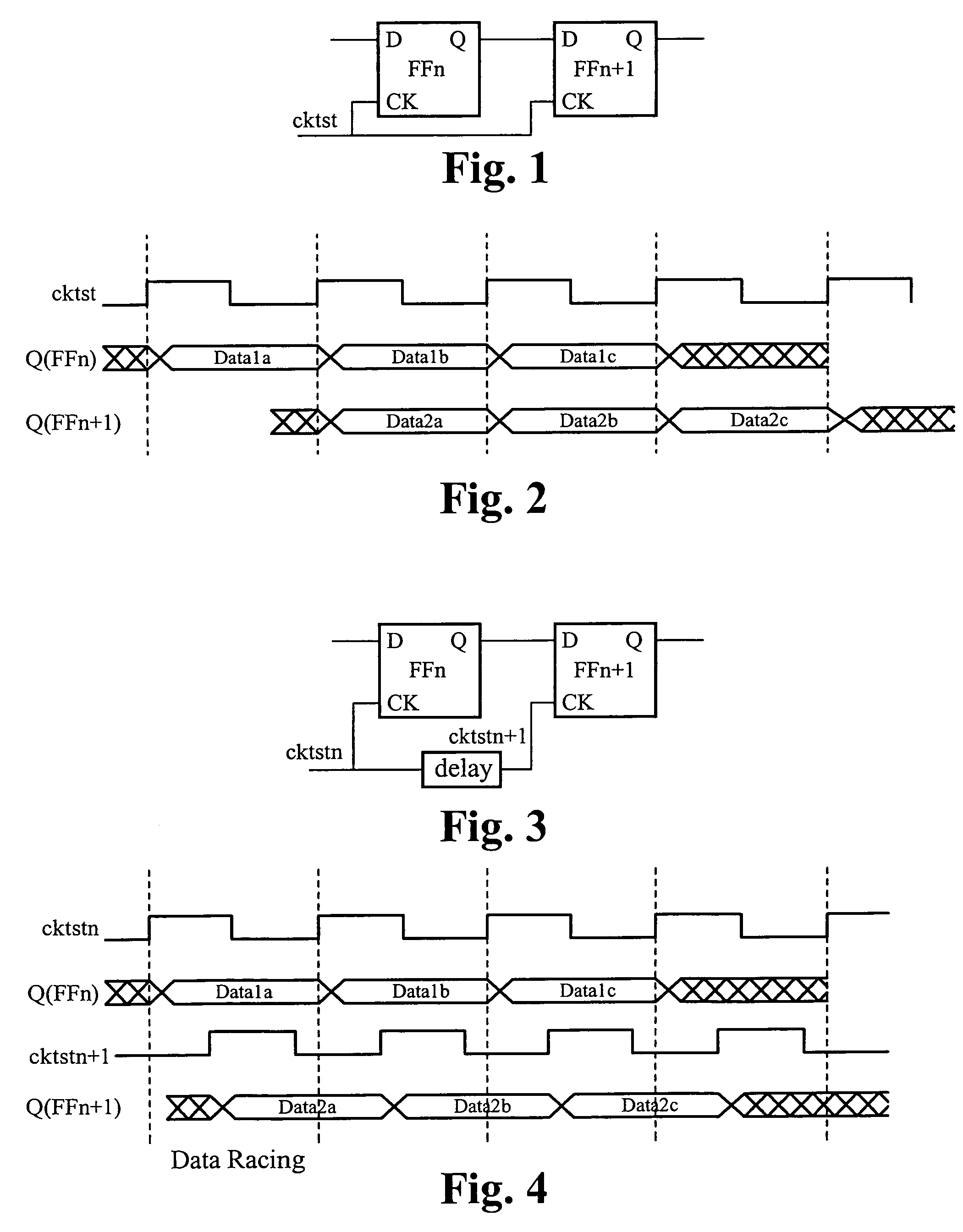

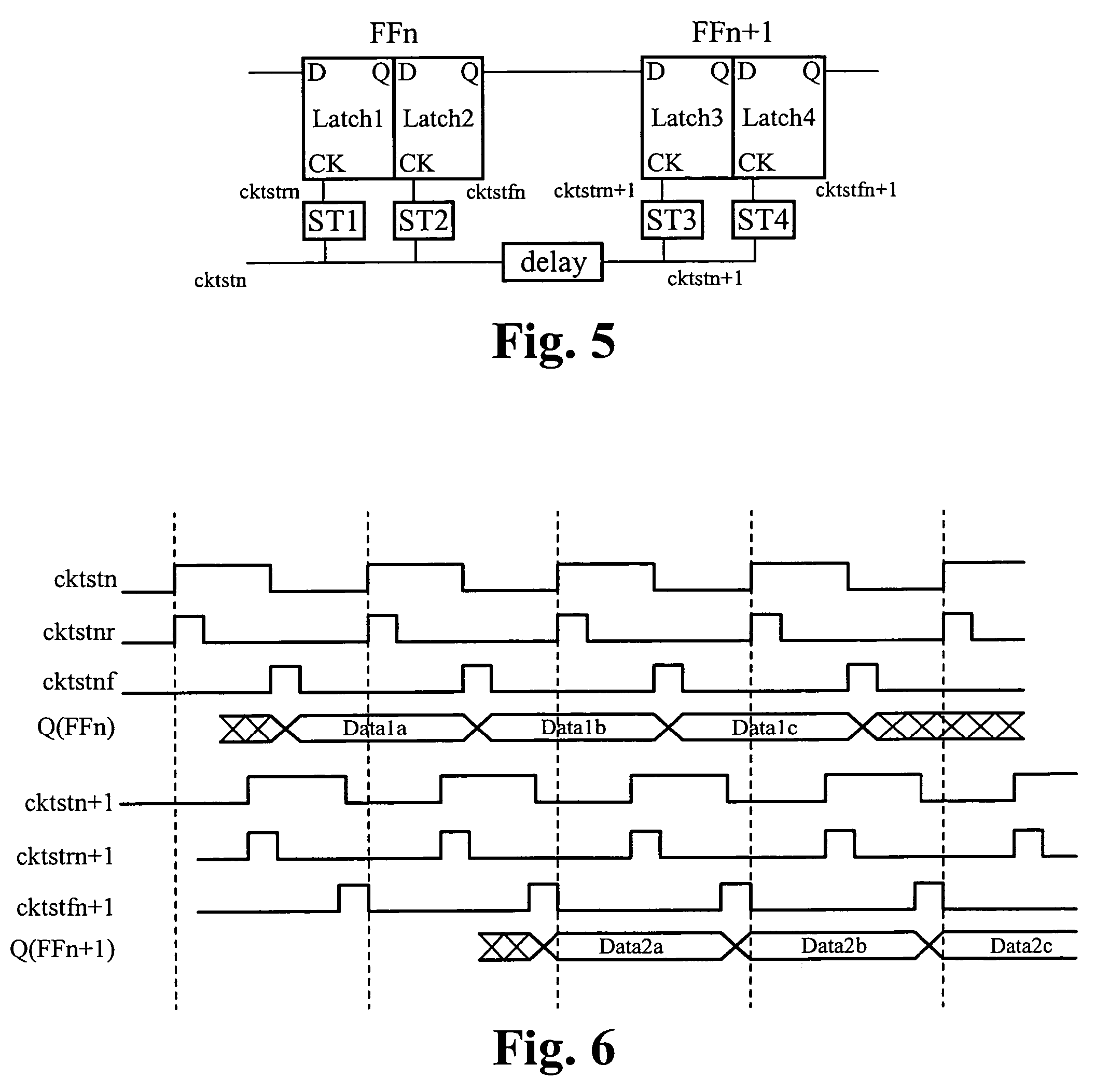

Shift registers free of timing race boundary scan registers with two-phase clock control

A chain of boundary scan registers is configured to use a two-phase clock signal to avoid data timing race conditions. The two-phase clock signal is generated according to a two-phase clock generator, which includes two self-timed clock pulse generators for each boundary scan register. The two-phase clock generator locally generates a self-timed clock pulse at the rising edge of a clock signal, which triggers a first stage of the boundary scan register. The two-phase clock generator also generates a self-timed clock pulse at the falling edge of the input clock signal, which triggers a second stage of the boundary scan register. The two-phase clock controlled boundary scan register includes two latches, each latch is triggered by one of the self-timed clock pulse generated locally from the rising and falling edge of the input clock signal.

Owner:GSI TECH

Fault injection method and system

InactiveUS7284159B2Electronic circuit testingError detection/correctionProcessor registerComputer science

A method and system are disclosed for fault injection using Boundary Scan resources compliant with 1149.1, while operating in system mode. The system has two register circuits, one, for storing and updating fault selection data and another, for storing and updating fault injection values.

Owner:LUCENT TECH INC

Analog boundary scanning based on stray capacitance

Embodiments of the present invention are directed to performing boundary scanning without using a pin which is exclusively dedicated for that purpose. The boundary scan can be performed by an integrated circuit by utilizing a pin which has an alternative use during ordinary operation of the integrated circuit and the device. This pin can be connected to an analog circuit configured to sense capacitance outside of the pin. The analog circuit may also have an alternative function in normal operation of the device. During a testing mode, the analog circuit can sense a stray capacitance present at the pin. The sensed capacitance can be compared to one or more stored expected capacitance values to determine an interconnection state of the system.

Owner:APPLE INC

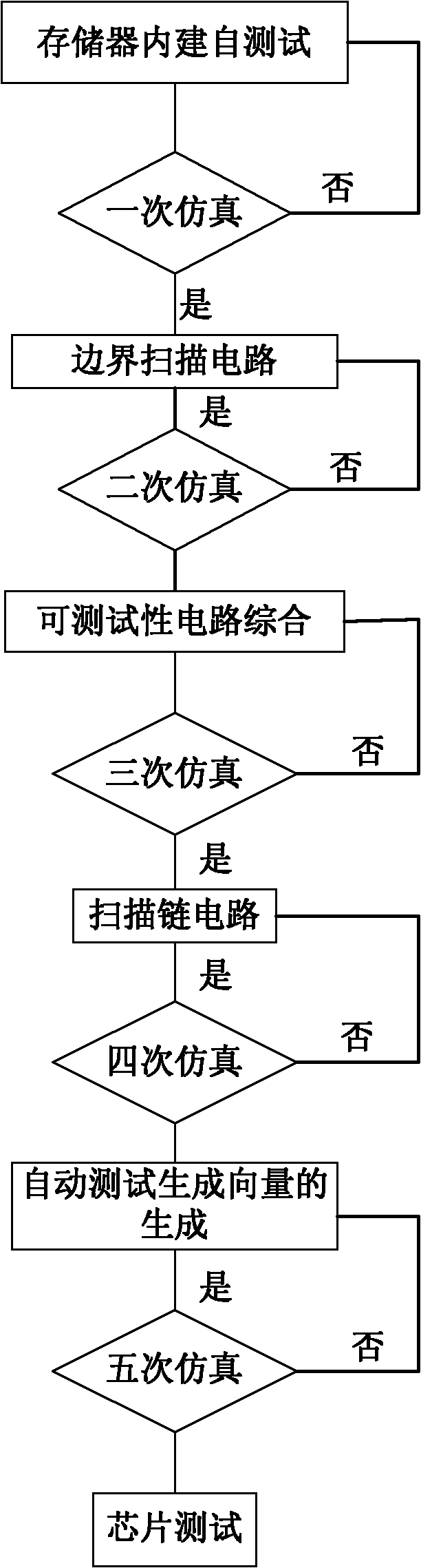

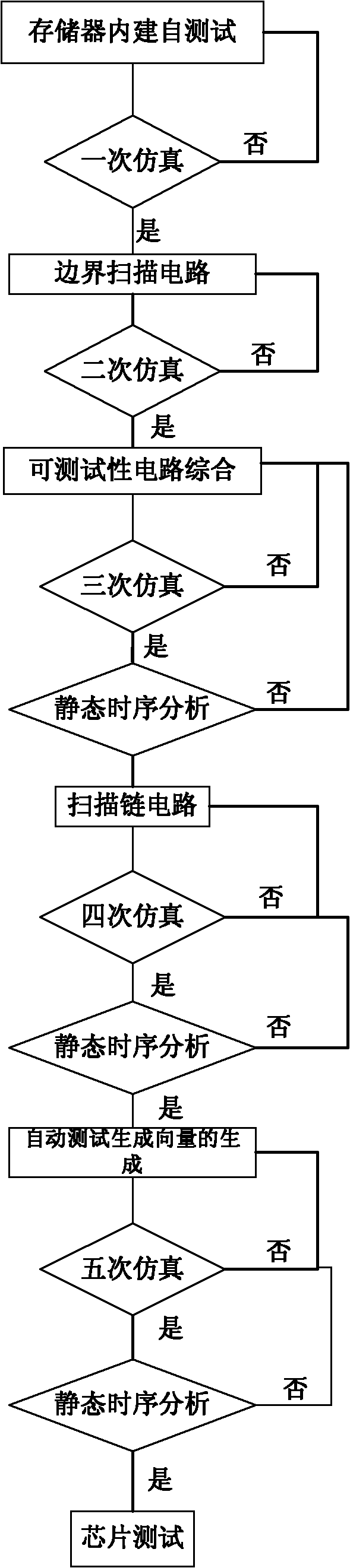

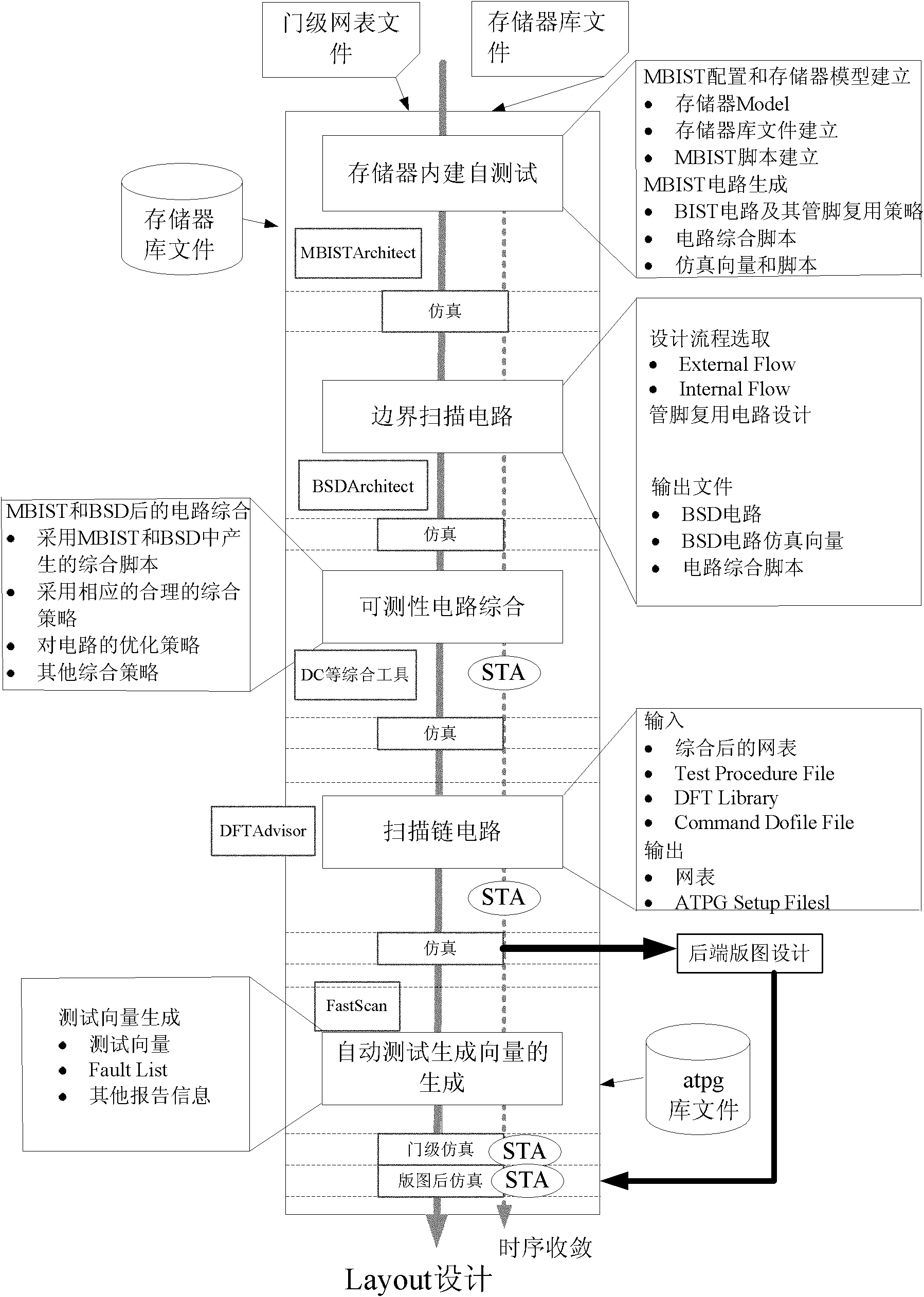

Method for designing testability of chip

ActiveCN102081689AHigh degree of automationSpecial data processing applicationsDesign for testingComputer architecture

The invention relates to a method for designing testability of a chip, which comprises the steps: (1) insertion of a built-in self test circuit of a memory; (2) insertion of a boundary scan circuit; (3) integration of a testability circuit; (4) insertion of a scan chain circuit; and (5) generation of automatic test generated vectors. In order to solve the technical problems that in the traditional chip design process, a set of complete and systematical method in test methods aiming at different test objects is not available, tools such as a DFT (diagnostic function test) tool, a logic synthesis tool, a circuit simulation tool and the like are not joined and the design program is complicated, the invention provides the process guarantee for automation of the DFT design and complete and systematical correctness of the DFT design.

Owner:西安翔腾微电子科技有限公司

Circuit board having boundary scan self-testing function

A circuit board with a boundary scan self-testing function comprises a substrate, a plurality of devices under test and an active testing device. The active testing device mounted the substrate can conduct circuit testing on the plurality of devices under test, and self-testing is allowed without employing any external testing equipment. The testing data of the active testing device is transmitted through a predetermined test route on the circuit board. Each of the devices under test is completely tested of all designated functions in either series connection or parallel connection with each other. The testing can help find out whether the devices have any defects.

Owner:LEADTEK

Programmable IC with gate array core and boundary scan capability

A mask programmable IC is provided that includes dedicated boundary scan logic in the I / O cells. Valuable core logic resources therefore need not be consumed to implement boundary scan logic. In one embodiment, one boundary scan cell is provided per I / O cell. Another embodiment provides great flexibility in emulating any of several FPGAs in any of several packages. In this embodiment, two boundary scan cells are provided for each I / O pad, each cell alone being capable of providing the boundary scan functions associated with one I / O pad. By selectively choosing which of the boundary scan cells are included in the boundary scan data chain, the order of the boundary scan chain of the emulated FPGA in any of two or more packages can be reproduced. Boundary scan behavior is therefore emulated as well as the programmable logic behavior of the FPGA. In one embodiment, additional programmable interconnect lines traversing each boundary scan cell are provided. These interconnect lines can be used to programmably connect the data output of a first cell to the data input of second cell which need not be adjacent to the first.

Owner:XILINX INC