Patents

Literature

2472 results about "Analogue electronics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Analogue electronics (American English: analog electronics) are electronic systems with a continuously variable signal, in contrast to digital electronics where signals usually take only two levels. The term "analogue" describes the proportional relationship between a signal and a voltage or current that represents the signal. The word analogue is derived from the Greek word ανάλογος (analogos) meaning "proportional".

Life sign detection and health state assessment system

InactiveUS20090131759A1Sufficient confidenceGuaranteed normal transmissionDiagnostic signal processingHealth-index calculationSign detectionEngineering

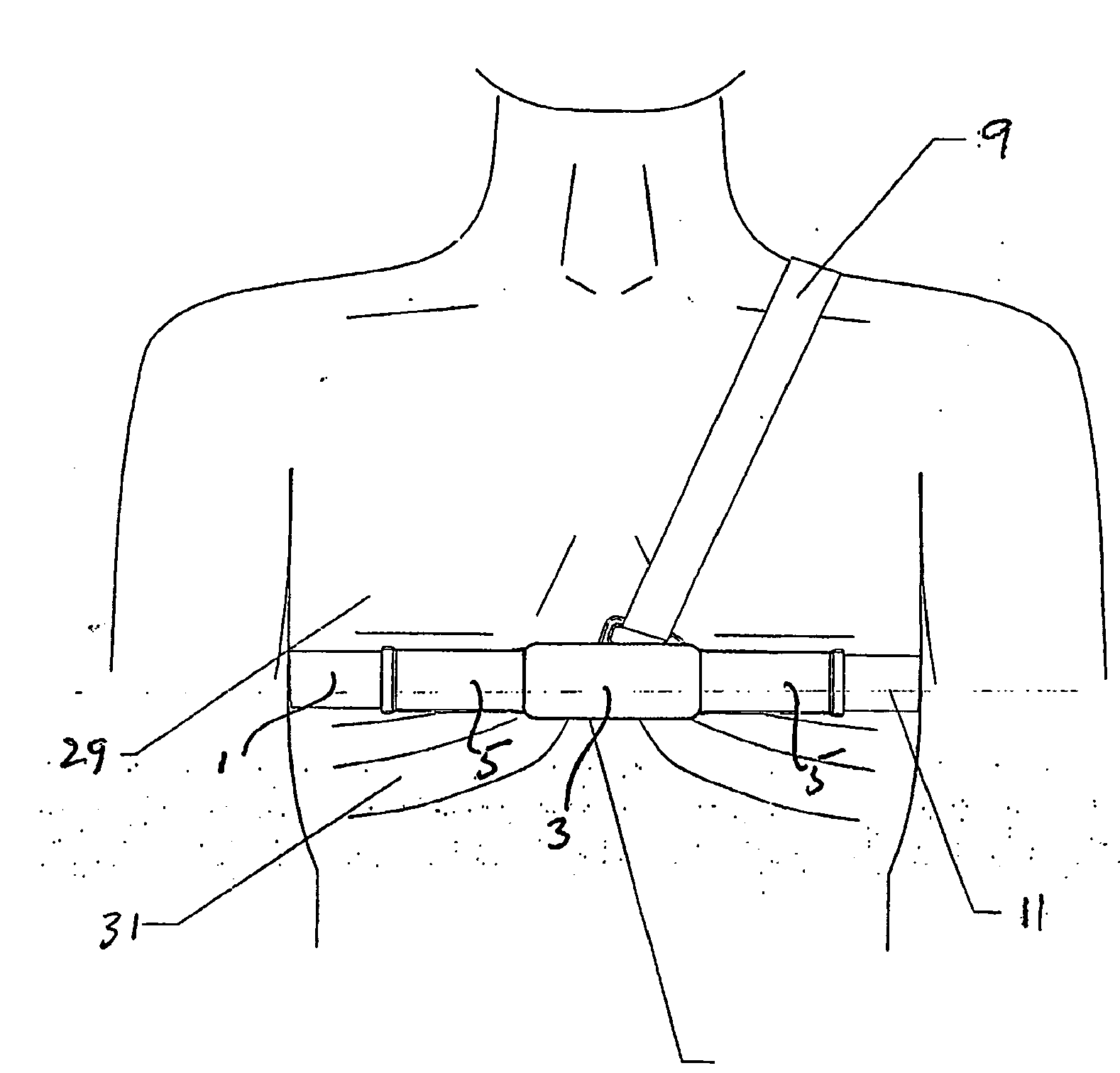

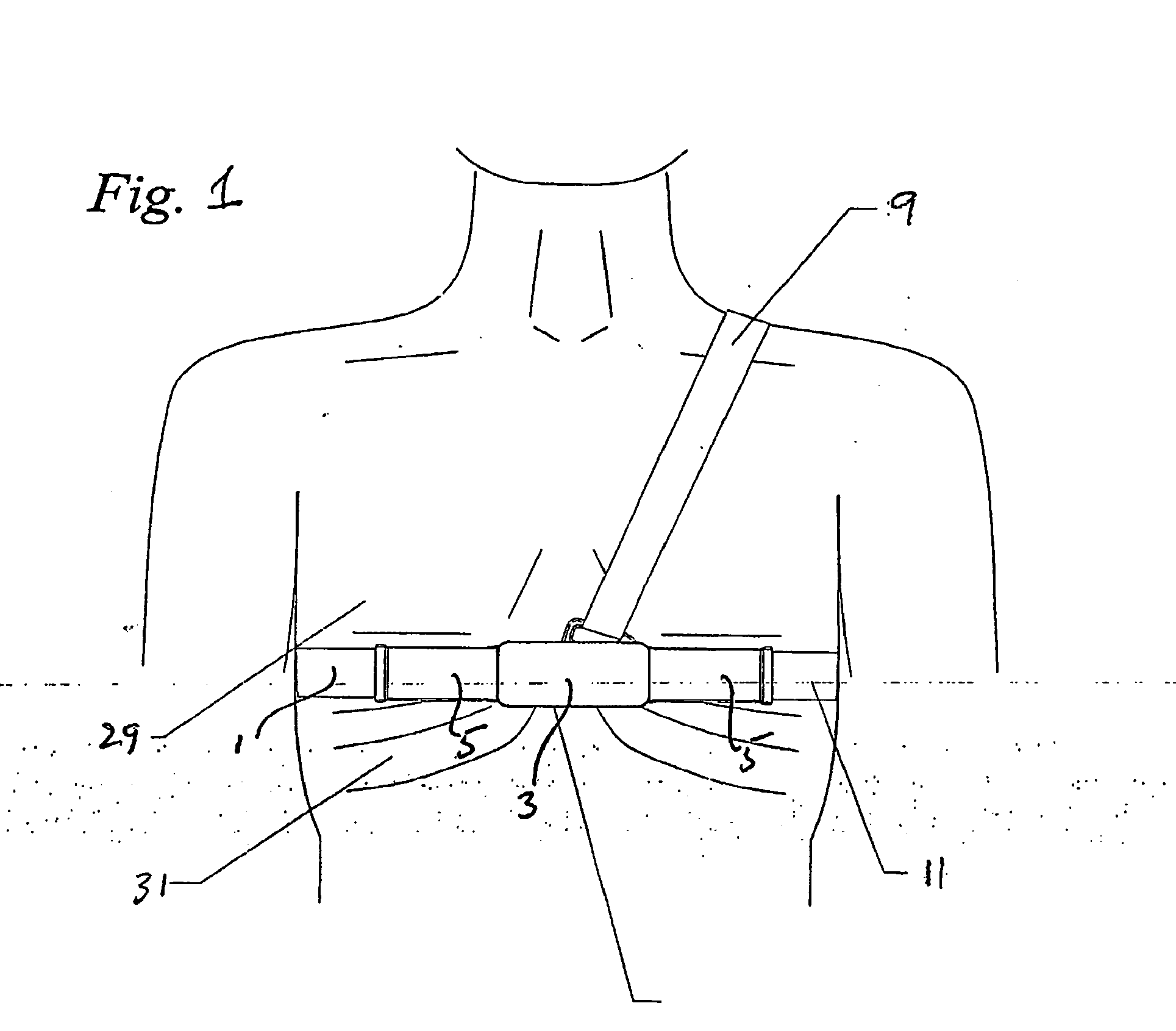

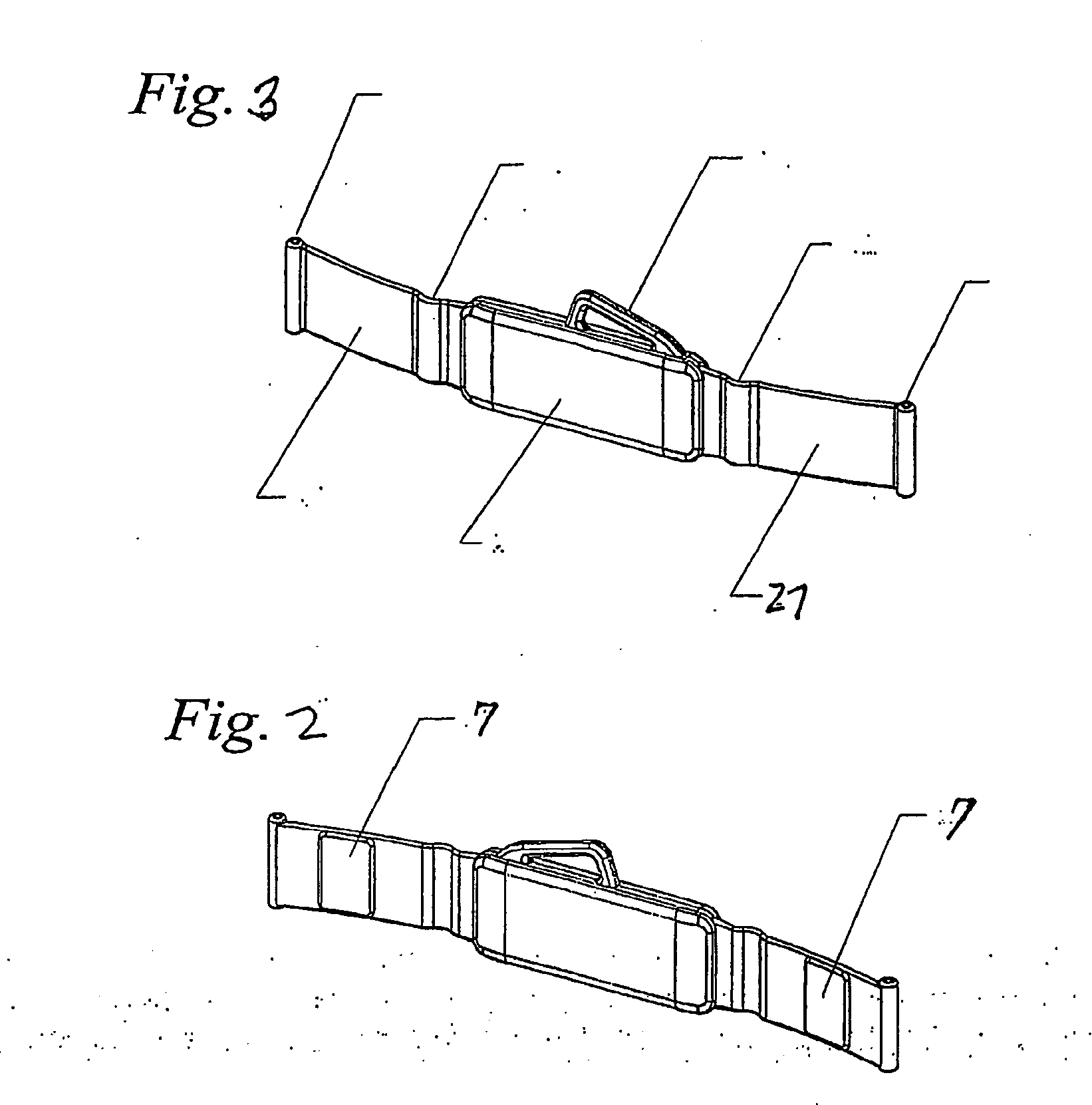

A wearable platform embodied in a belt or patch provides physiological monitoring of soldiers during field operations or trauma victims at accident sites and makes health state assessments. The platform includes sensors for heart rate, body motion, respiration rate and intensity, and temperature and further contains a microprocessor and short range transmitter. An analog circuit running an algorithm obtains the R-wave period from the EKG signal and produces electrical pulses with the period between pulses corresponding to the R-wave period. A rule based processing engine having an evaluation algorithm is capable of making a medical evaluation of subject condition and determines a confidence level for the evaluation. The rules are subject to variation depending upon the subject population. The information is communicated wirelessly to a local hub for relay to a remote monitor.

Owner:THE GENERAL HOSPITAL CORP

Adaptive programming method and apparatus for flash memory analog storage

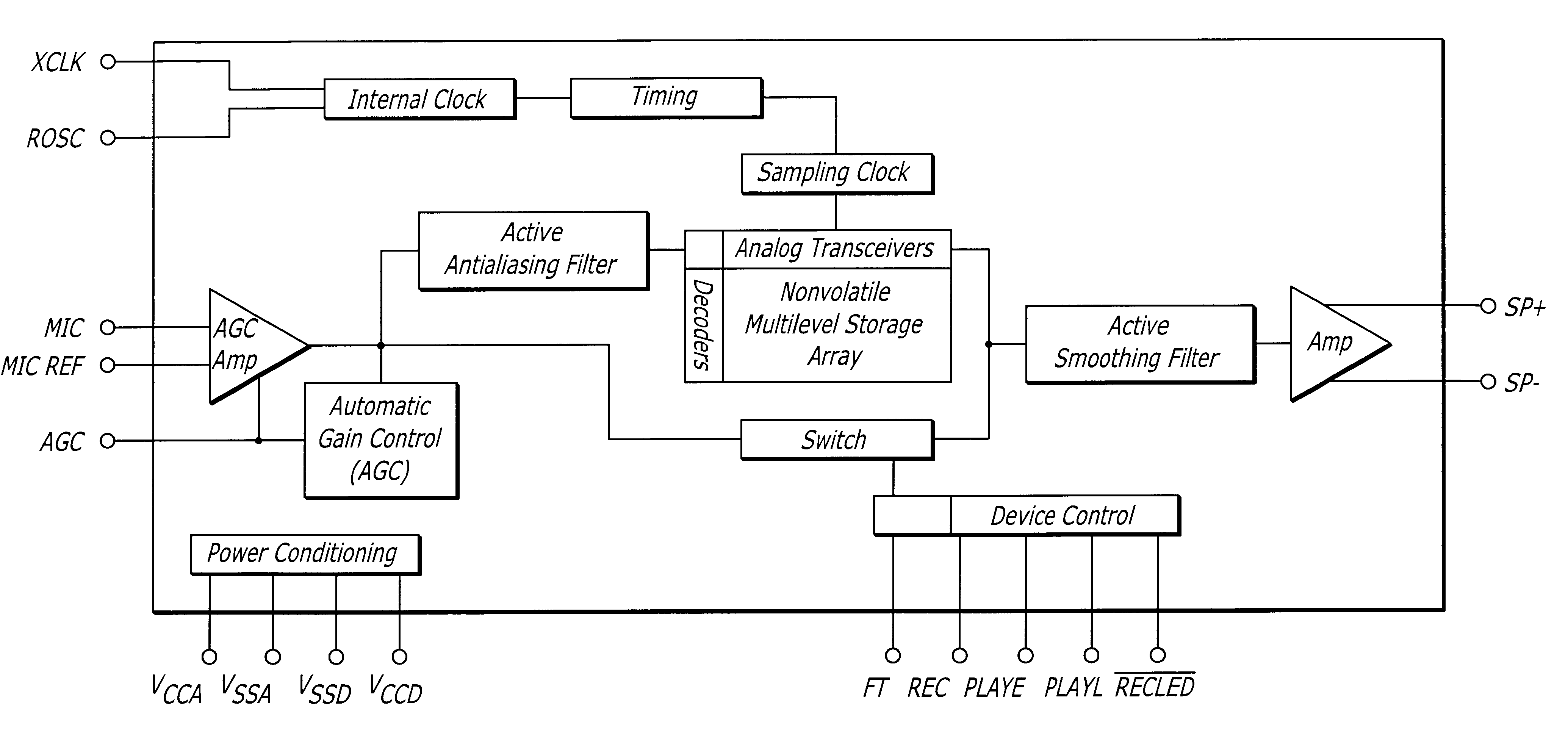

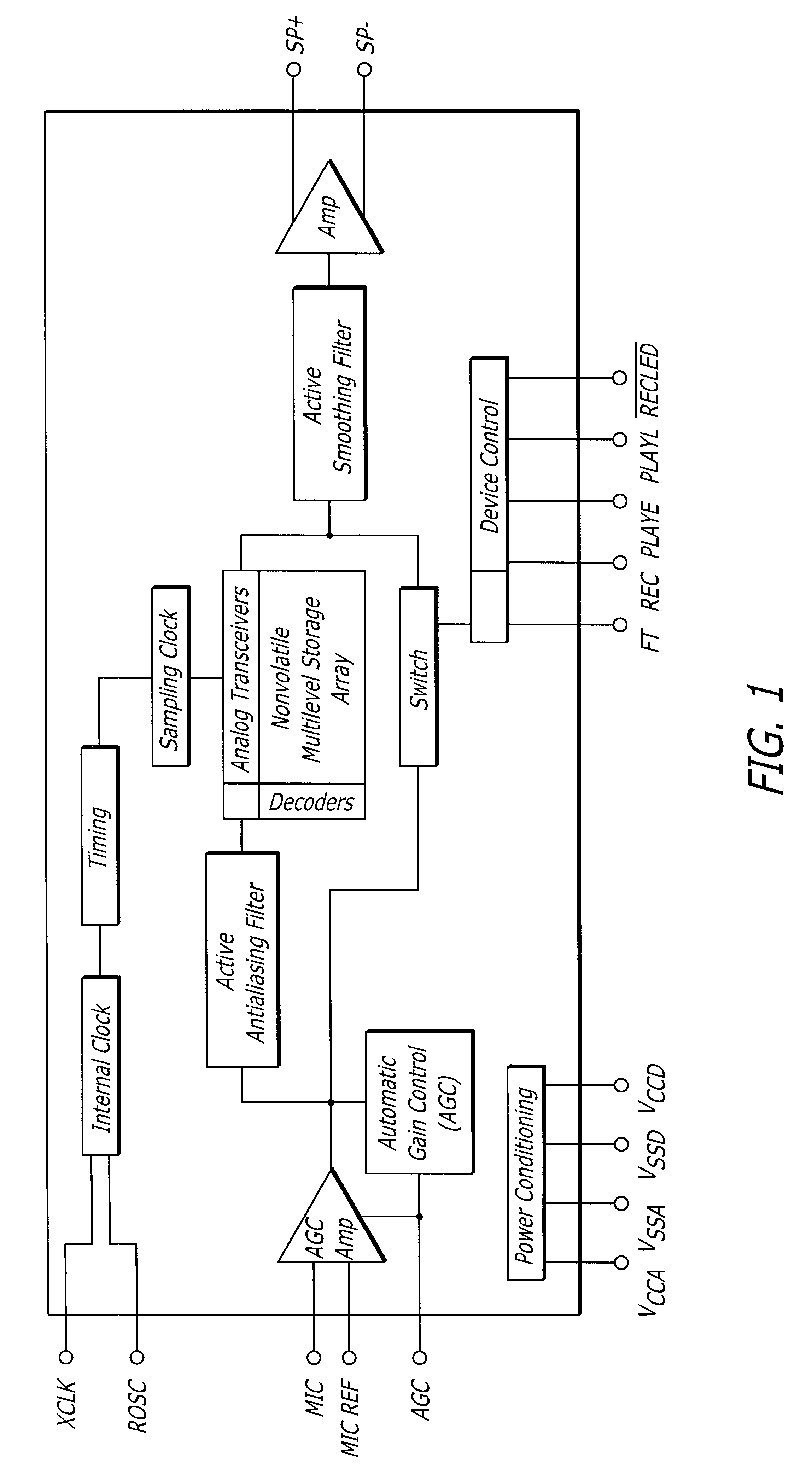

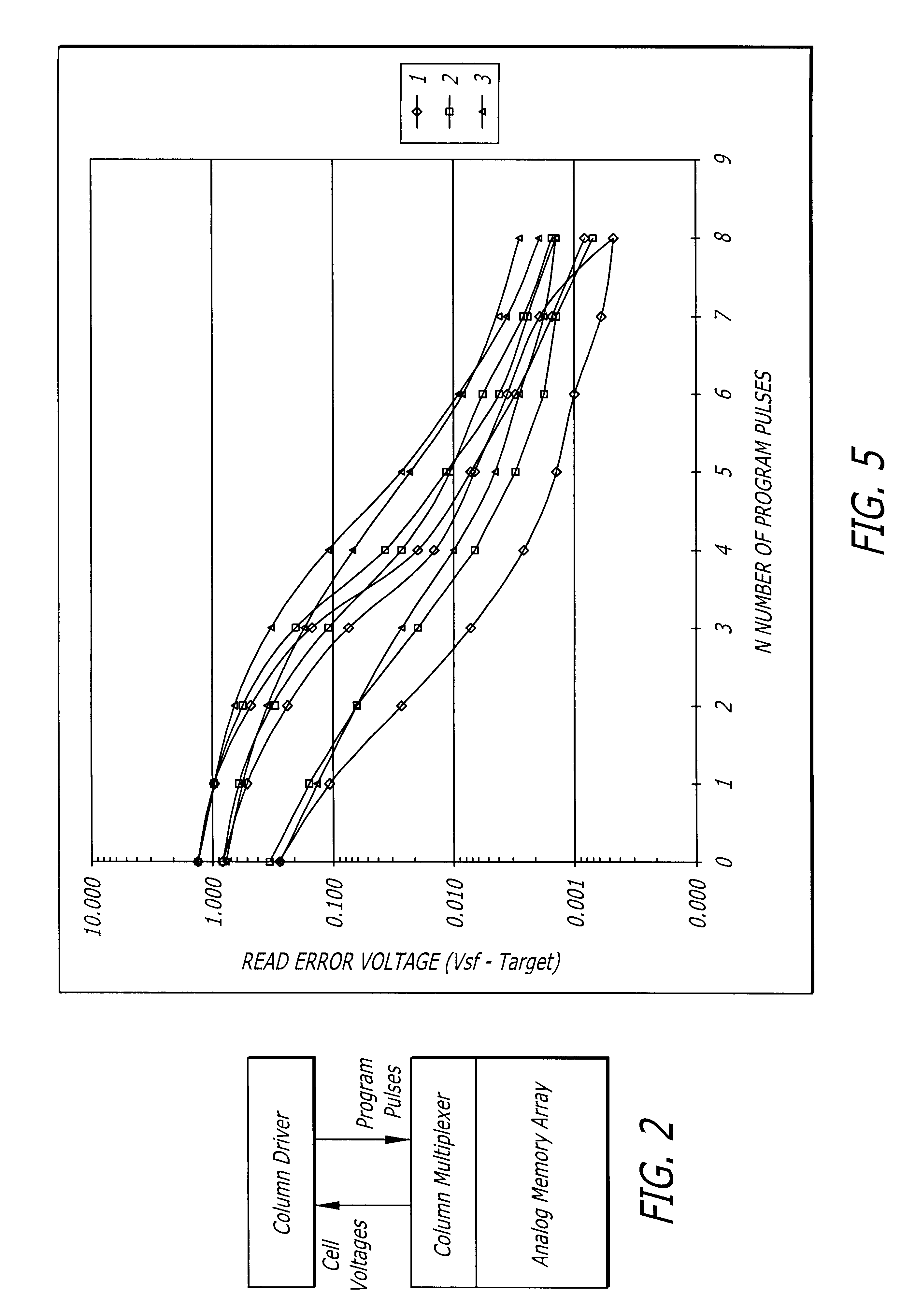

Adaptive programming method and apparatus for flash memory analog storage. The present invention method is to adjust the voltage of the programming pulse each time based on the result of the previous pulse. The expected change in the programmed value is compared to the measured change, and the difference used to improve the model of that cell after each programming pulse. The algorithm is "adaptive" because the voltage of each pulse is adapted to whatever the cell needs. If the cell is programming too slowly, the voltage is increased dramatically to make it faster. Conversely if the results show that a particular cell is programming too fast, the next voltage pulse is increased by only a small amount (or even decreased if necessary). Because the response of the cell is non-linear, a special analog circuit is used to calculate the optimum voltage for each pulse. As one alternative, a digital calculation may also be used to program the cells. Because of the programming speed of the exemplary method, a voice signal may be sampled and stored in flash memory one cell at a time. Variable programming parameters other than voltage may be used if desired.

Owner:WINBOND ELECTRONICS CORP

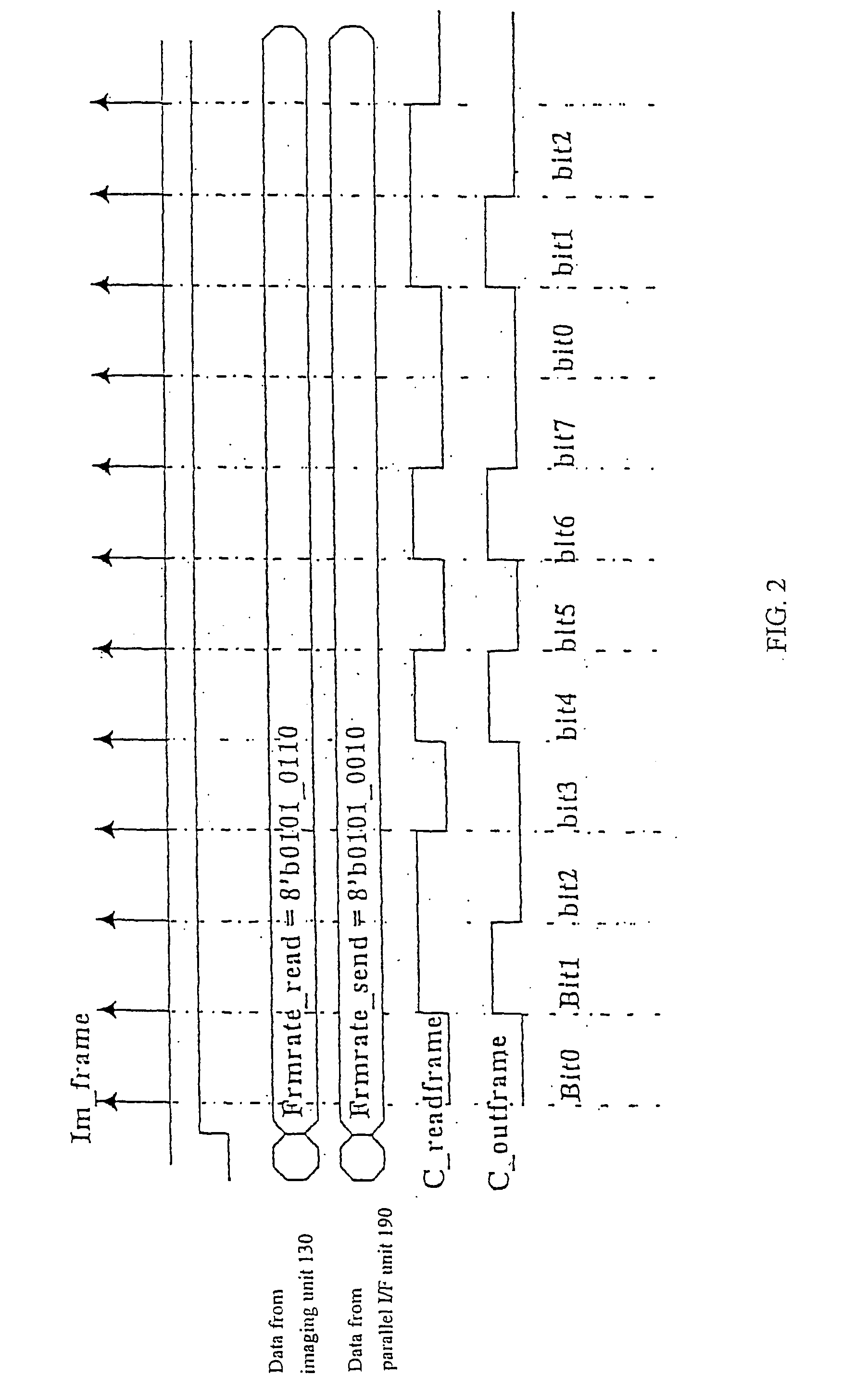

CMOS imager for cellular applications and methods of using such

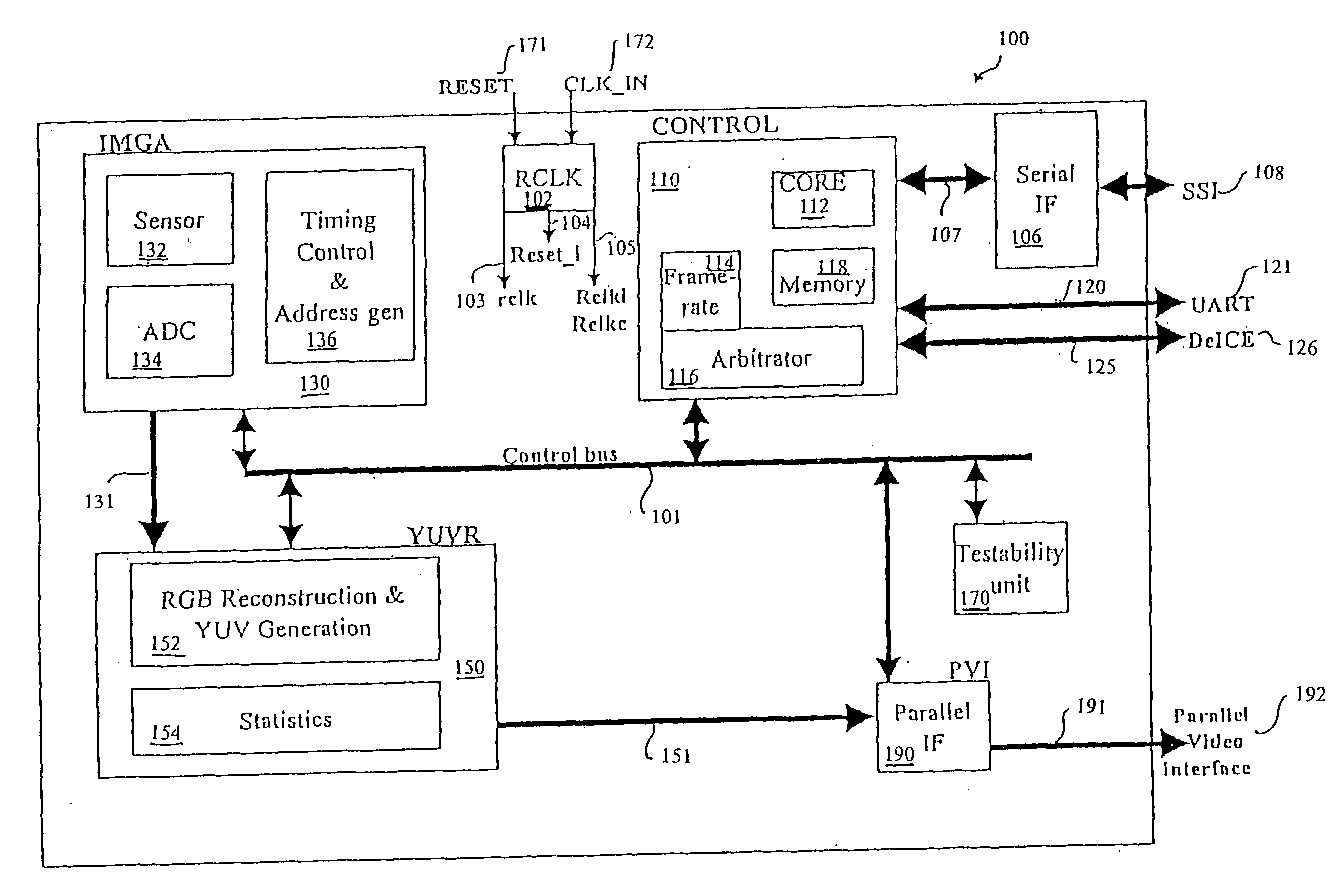

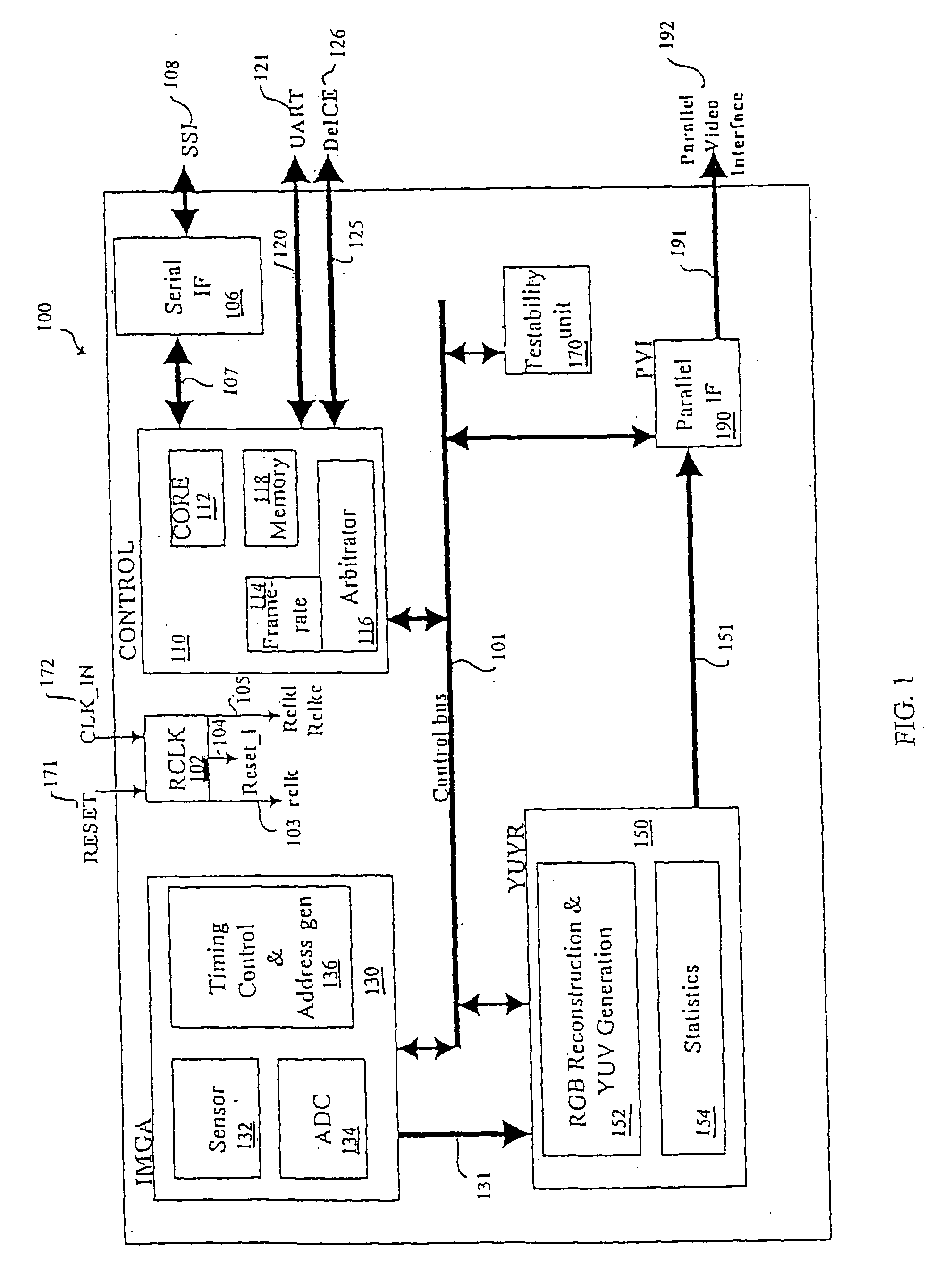

ActiveUS20050068436A1Reduce power consumptionMeet the noiseTelevision system detailsColor signal processing circuitsCMOSTransformation unit

Systems, methods and devices related to detecting and transmitting images. Imaging system and devices, as well as methods of using such that are provided herein include flicker detection and / or correction; and / or built-in self test (170) associated with various analog circuitry in the imaging devices; and / or power reduction ability; and / or pixels with charge evacuation functionality; and / or parallel to serial conversion (190) unit and associated serial output interface (106); and / or other advanced functionality.

Owner:TRANSCHIP ISRAEL

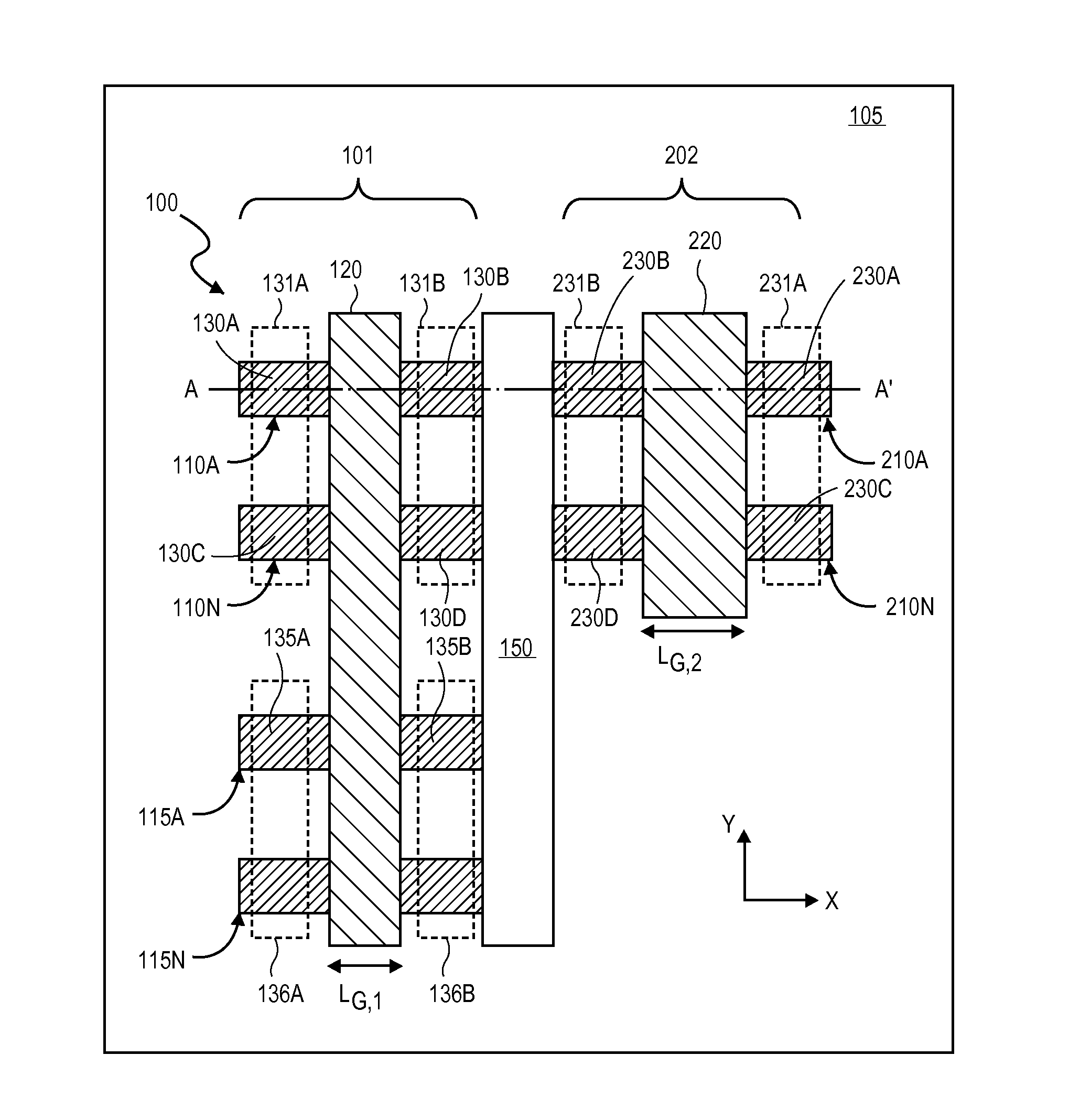

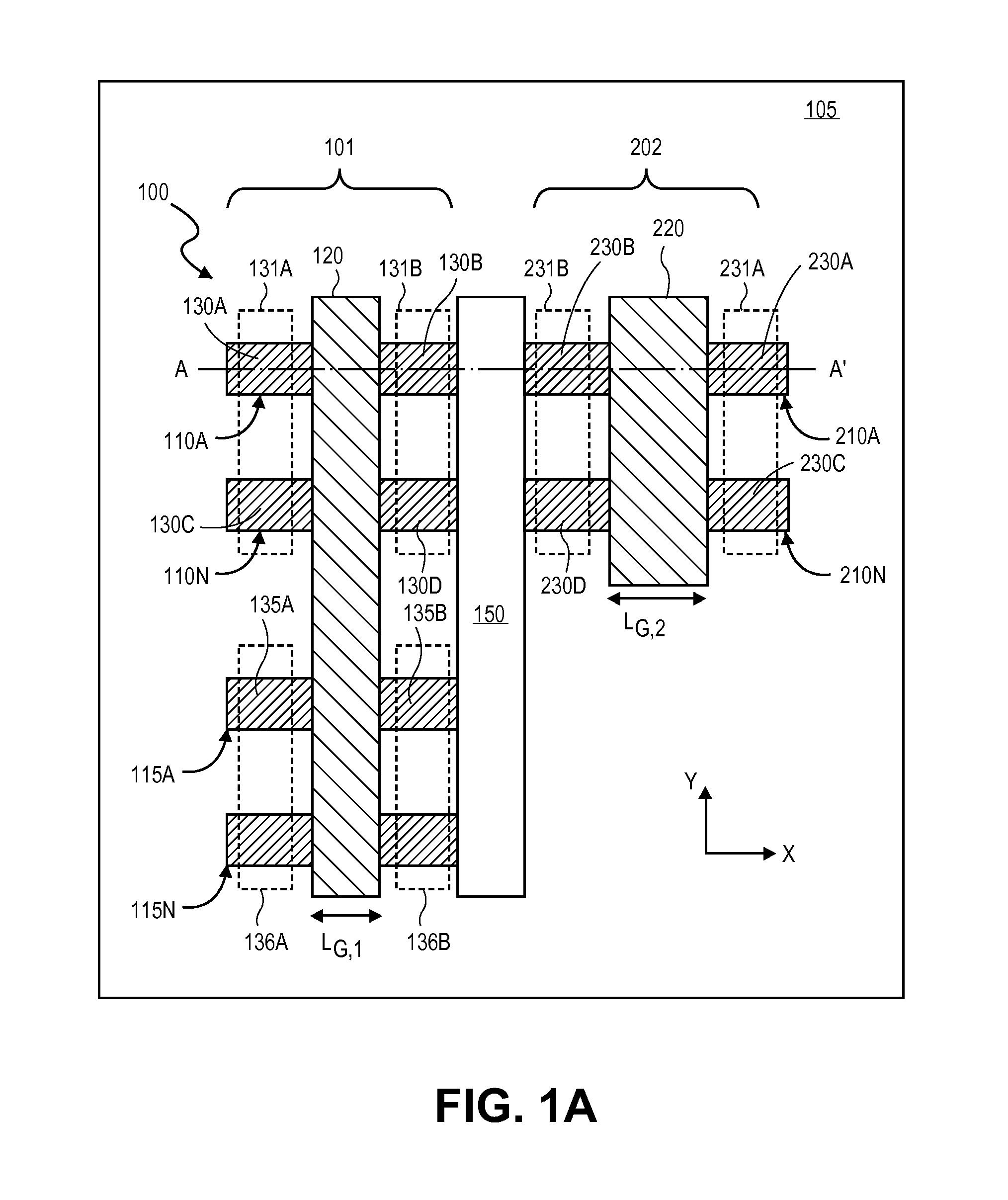

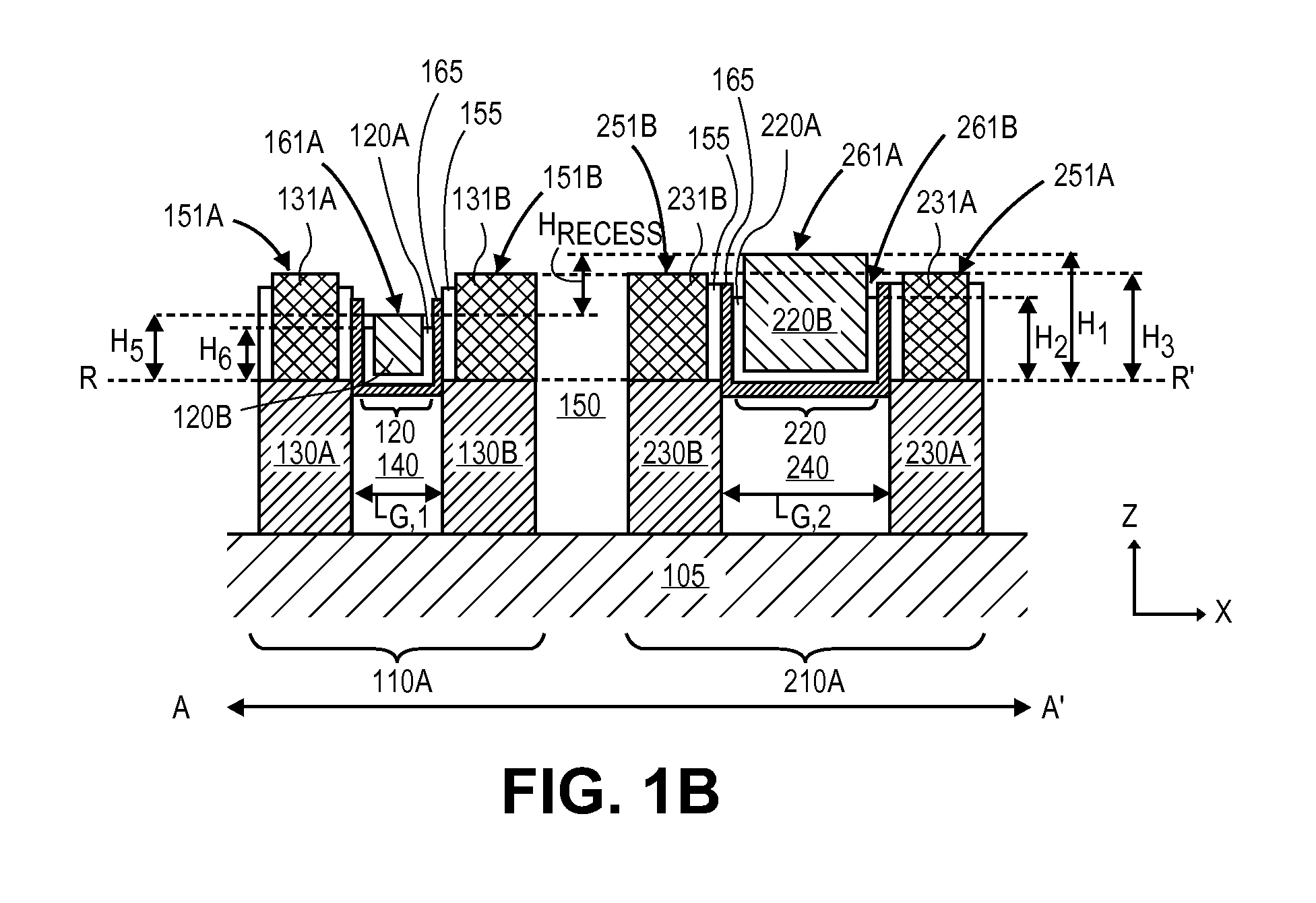

Integrated circuits with selective gate electrode recess

Integrated circuits including MOSFETs with selectively recessed gate electrodes. Transistors having recessed gate electrodes with reduced capacitive coupling area to adjacent source and drain contact metallization are provided alongside transistors with gate electrodes that are non-recessed and have greater z-height. In embodiments, analog circuits employ transistors with gate electrodes of a given z-height while logic gates employ transistors with recessed gate electrodes of lesser z-height. In embodiments, subsets of substantially planar gate electrodes are selectively etched back to differentiate a height of the gate electrode based on a given transistor's application within a circuit.

Owner:INTEL CORP

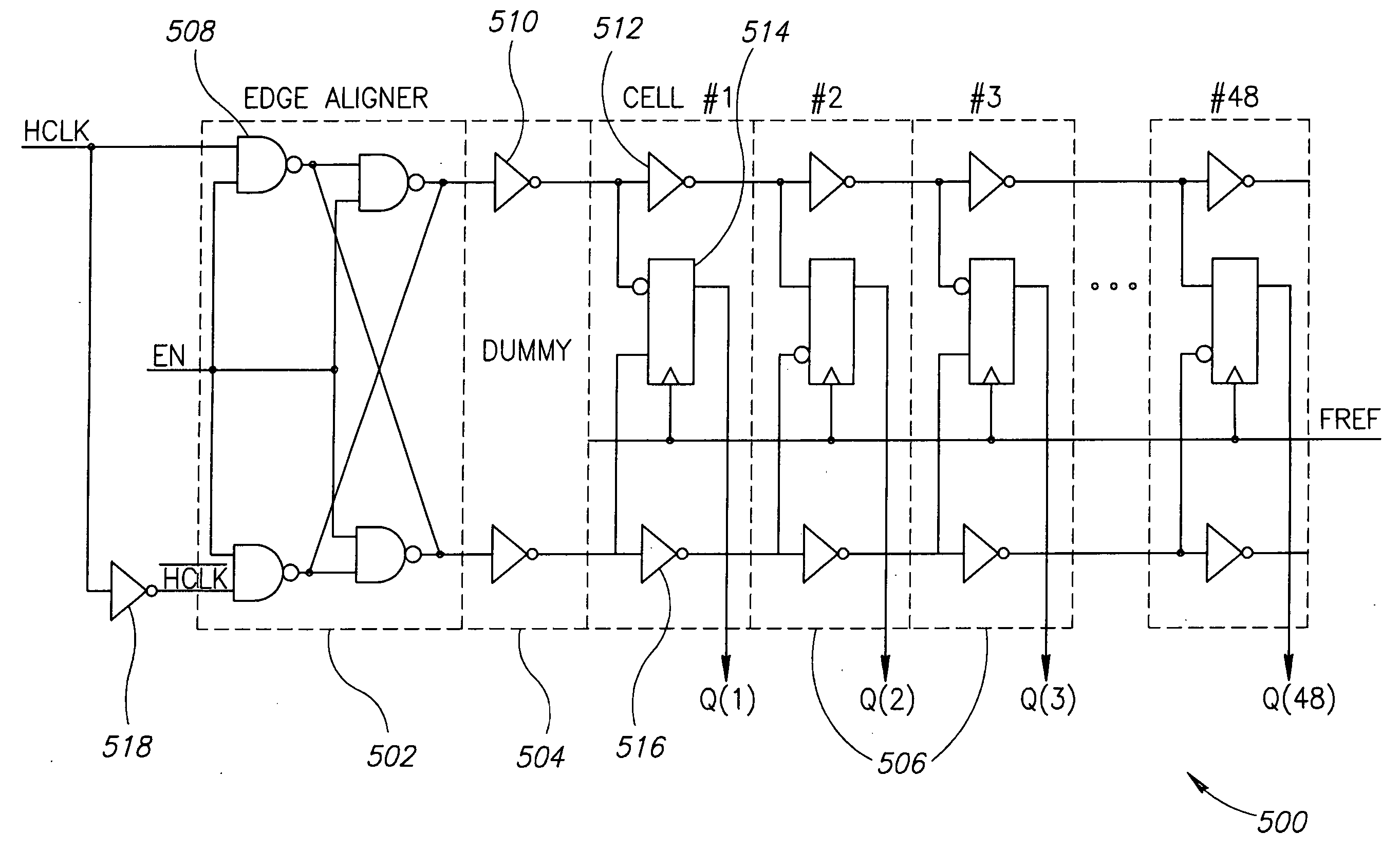

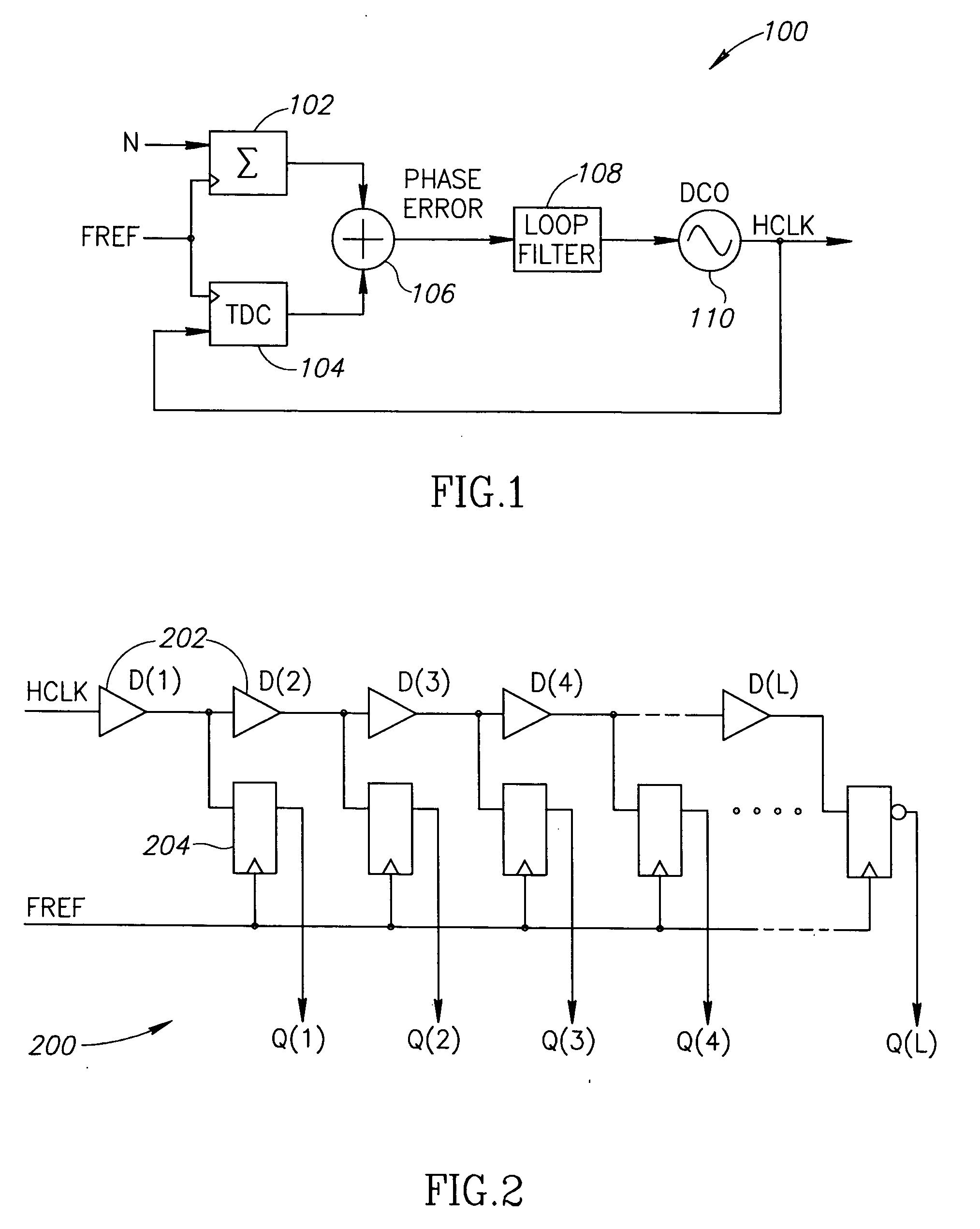

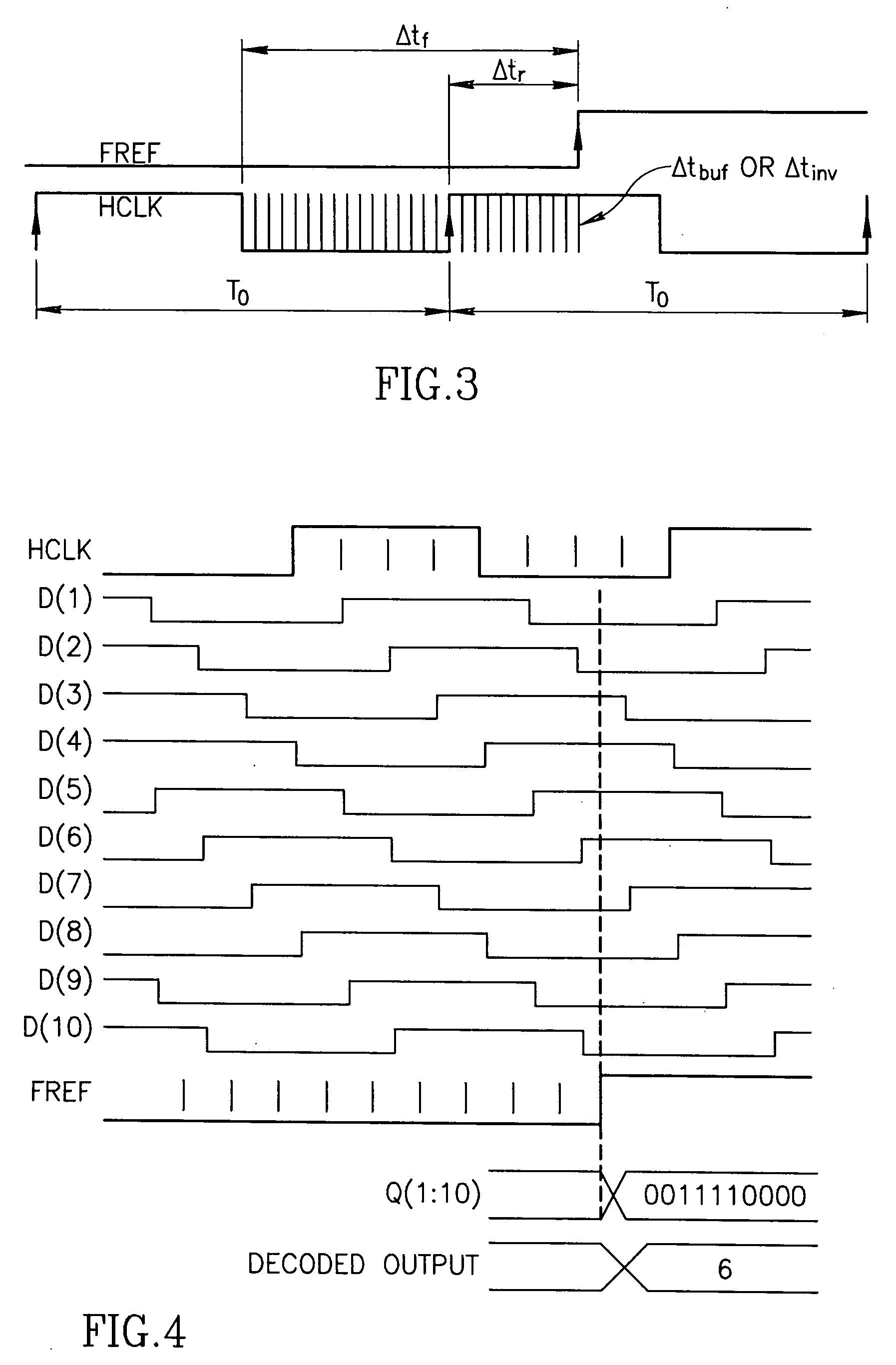

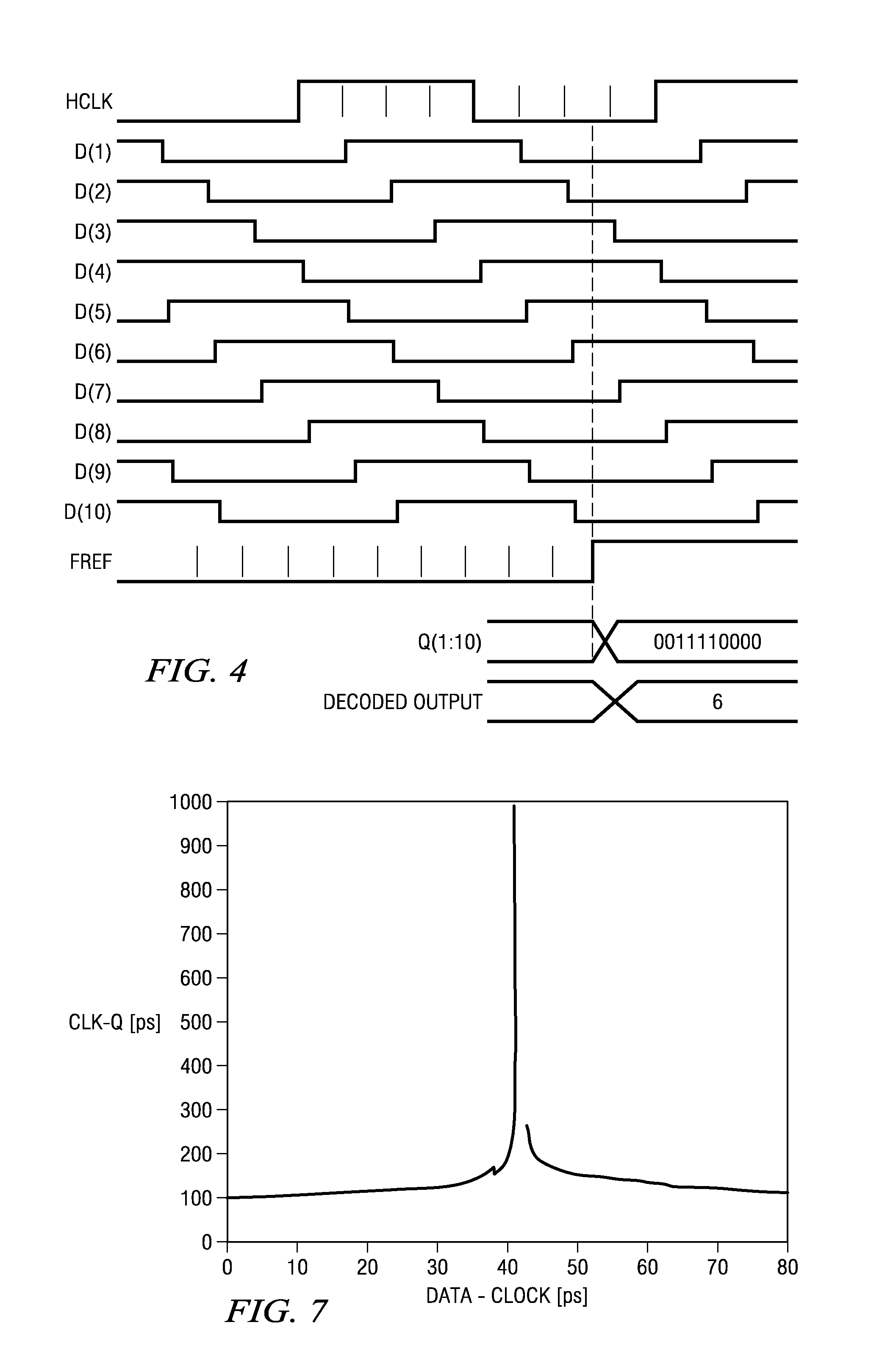

Circuit for high-resolution phase detection in a digital RF processor

ActiveUS20060103566A1Less sensitiveReduce power consumptionElectric signal transmission systemsPulse automatic controlEngineeringDigital converter

A novel time-to-digital converter (TDC) used as a phase / frequency detector and charge pump replacement in an all-digital PLL within a digital radio processor. The TDC core is based on a pseudo-differential digital architecture making it insensitive to NMOS and PMOS transistor mismatches. The time conversion resolution is equal to an inverter propagation delay, e.g., 20 ps, which is the finest logic-level regenerative timing in CMOS. The TDC is self calibrating with the estimation accuracy better than 1%. The TDC circuit can also serve as a CMOS process strength estimator for analog circuits in large SoC dies. The circuit also employs power management circuitry to reduce power consumption to a very low level.

Owner:TEXAS INSTR INC

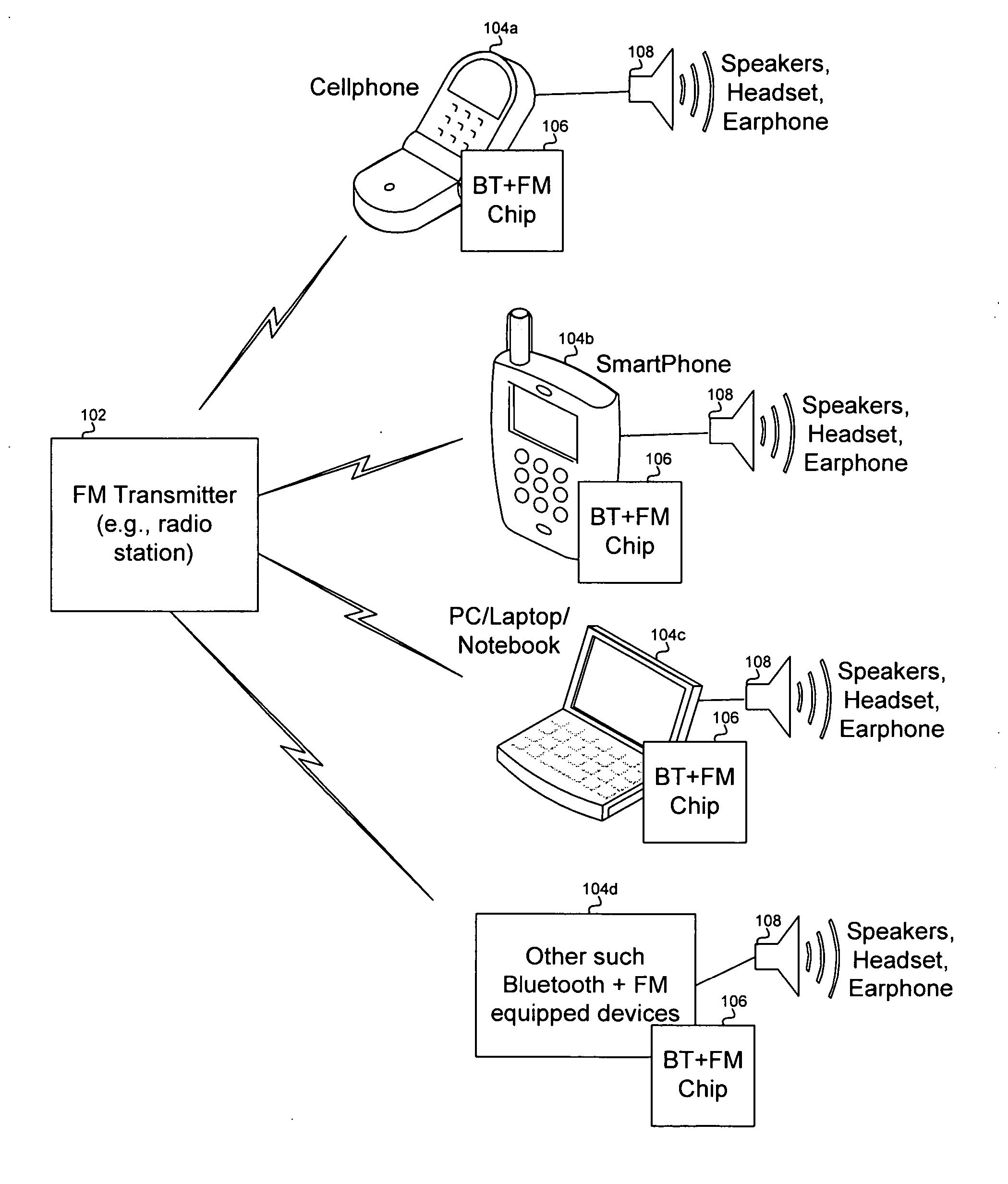

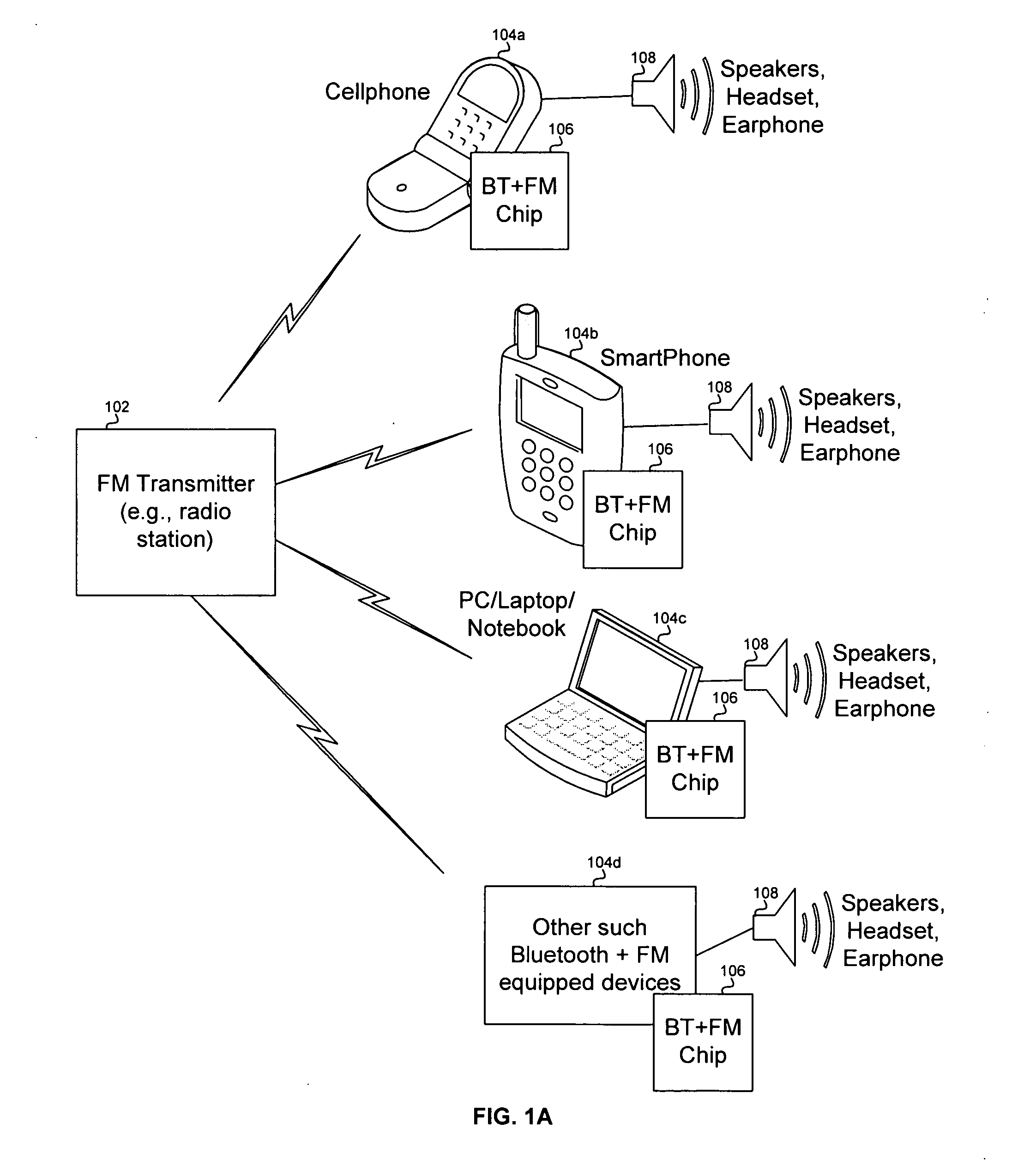

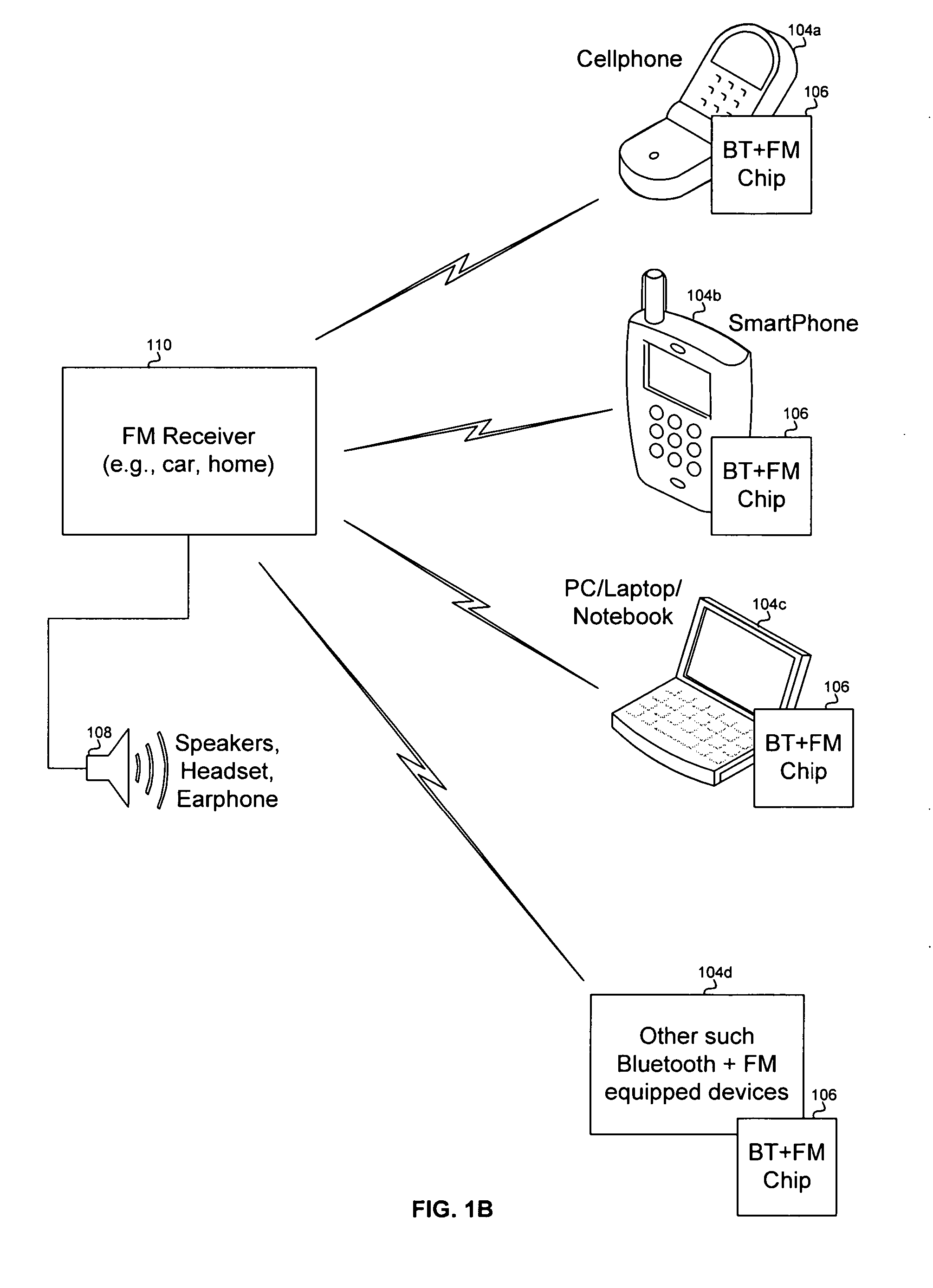

Method and system for a single chip integrated Bluetooth and FM transceiver and baseband processor

A method and system for a single chip integrated Bluetooth and FM transceiver and baseband processor are provided. The single chip may comprise a Bluetooth radio, an FM radio, a processor system, and a peripheral transport unit (PTU). FM data may be received and / or transmitted via the FM radio and Bluetooth data may be received and / or transmitted via the Bluetooth radio. The FM radio may receive radio data system (RDS) data. The PTU may support digital and analog interfaces. A processor in the processor system may time-multiplex processing of FM data and processing of Bluetooth data. The single chip may operate in an FM-only, a Bluetooth-only, and an FM-Bluetooth mode. The single chip may reduce power consumption by disabling portions of the Bluetooth radio during FM-only mode and / or disabling analog circuitry when performing digital processing. Communication between Bluetooth and FM channels may be enabled via the single chip.

Owner:NXP USA INC

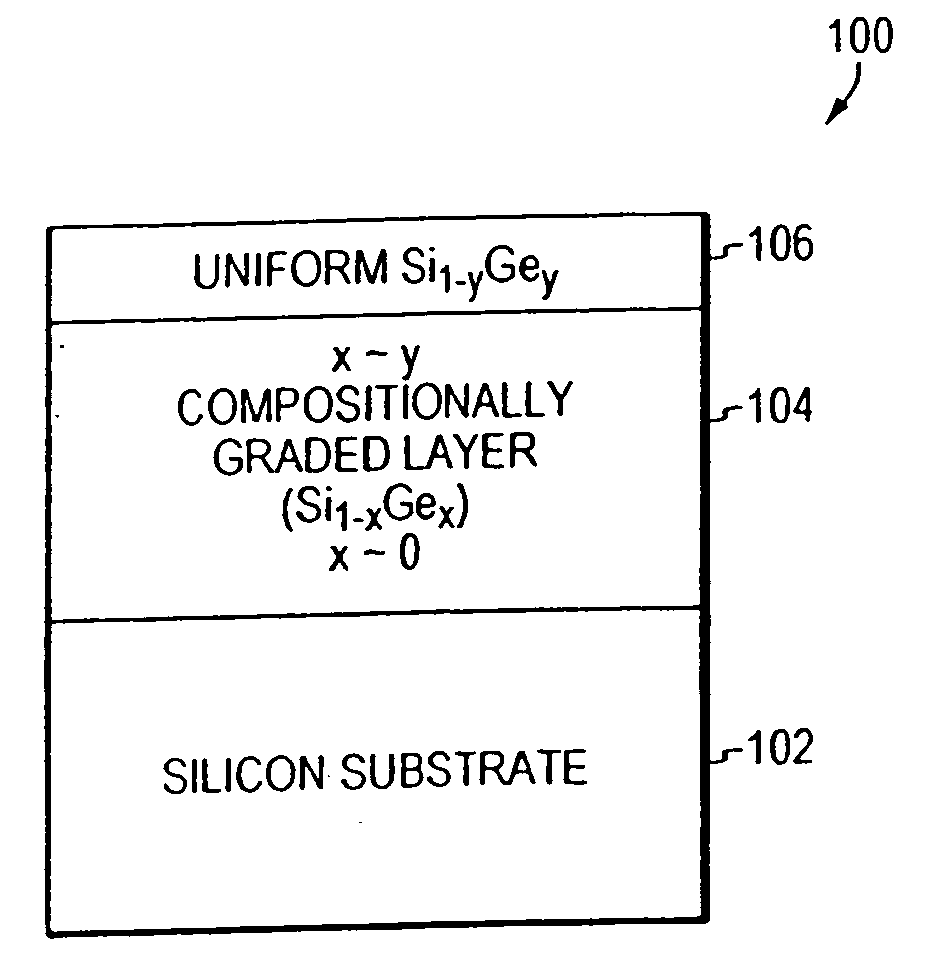

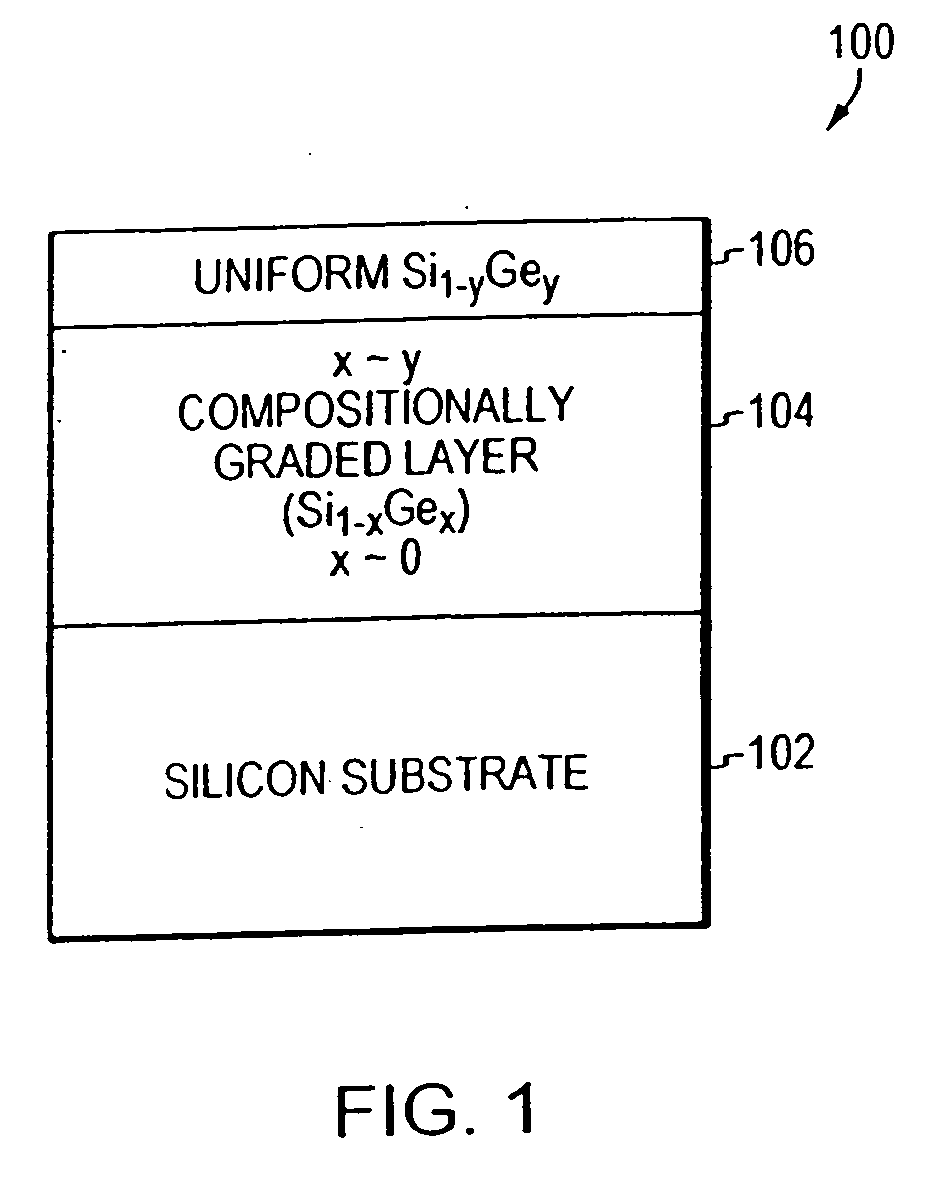

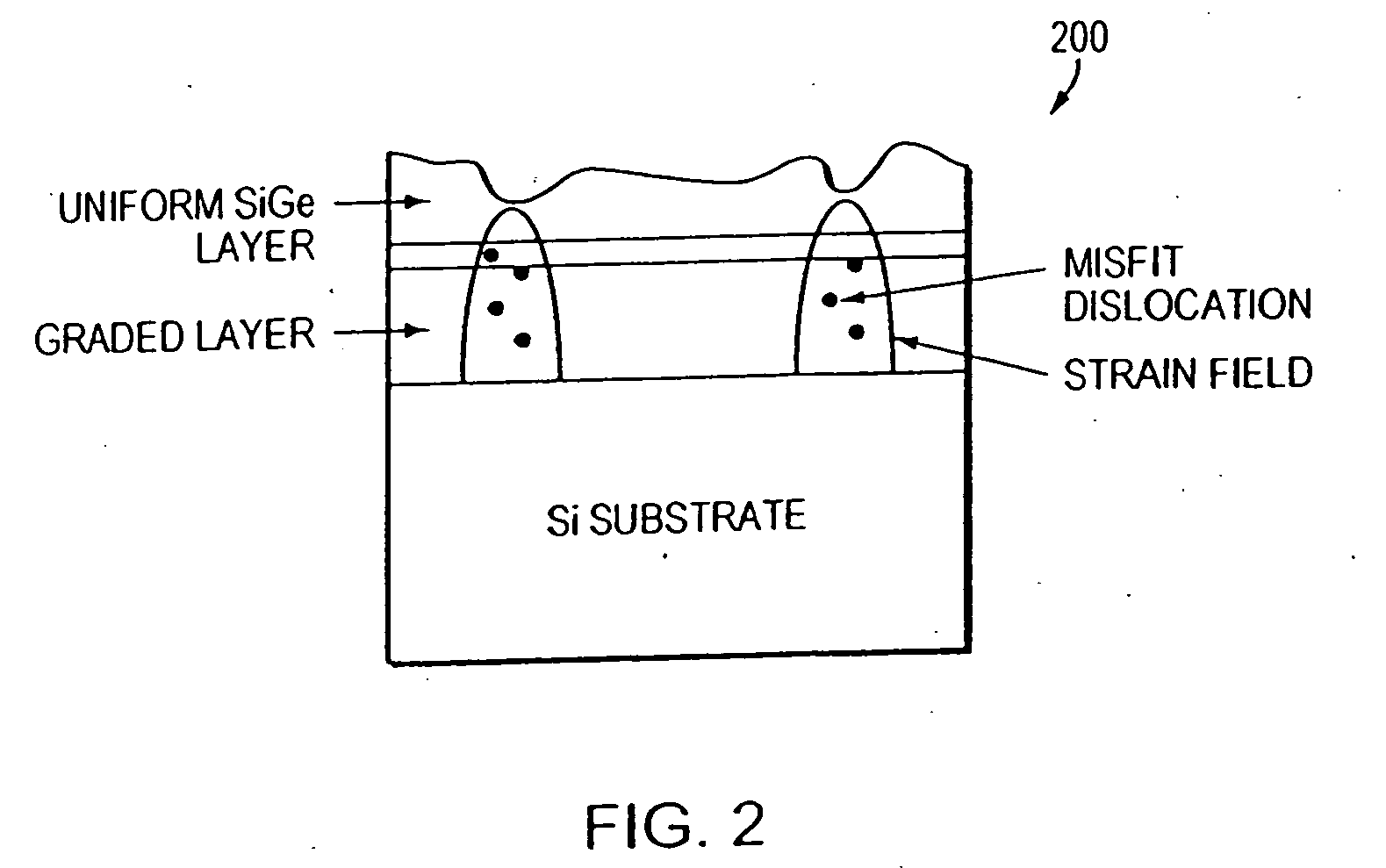

Relaxed SiGe platform for high speed CMOS electronics and high speed analog circuits

InactiveUS20050077511A1Minimal surface roughnessImprove featuresTransistorSemiconductor/solid-state device manufacturingMOSFETLithographic artist

Structures and methods for fabricating high speed digital, analog, and combined digital / analog systems using planarized relaxed SiGe as the materials platform. The relaxed SiGe allows for a plethora of strained Si layers that possess enhanced electronic properties. By allowing the MOSFET channel to be either at the surface or buried, one can create high-speed digital and / or analog circuits. The planarization before the device epitaxial layers are deposited ensures a flat surface for state-of-the-art lithography.

Owner:TAIWAN SEMICON MFG CO LTD

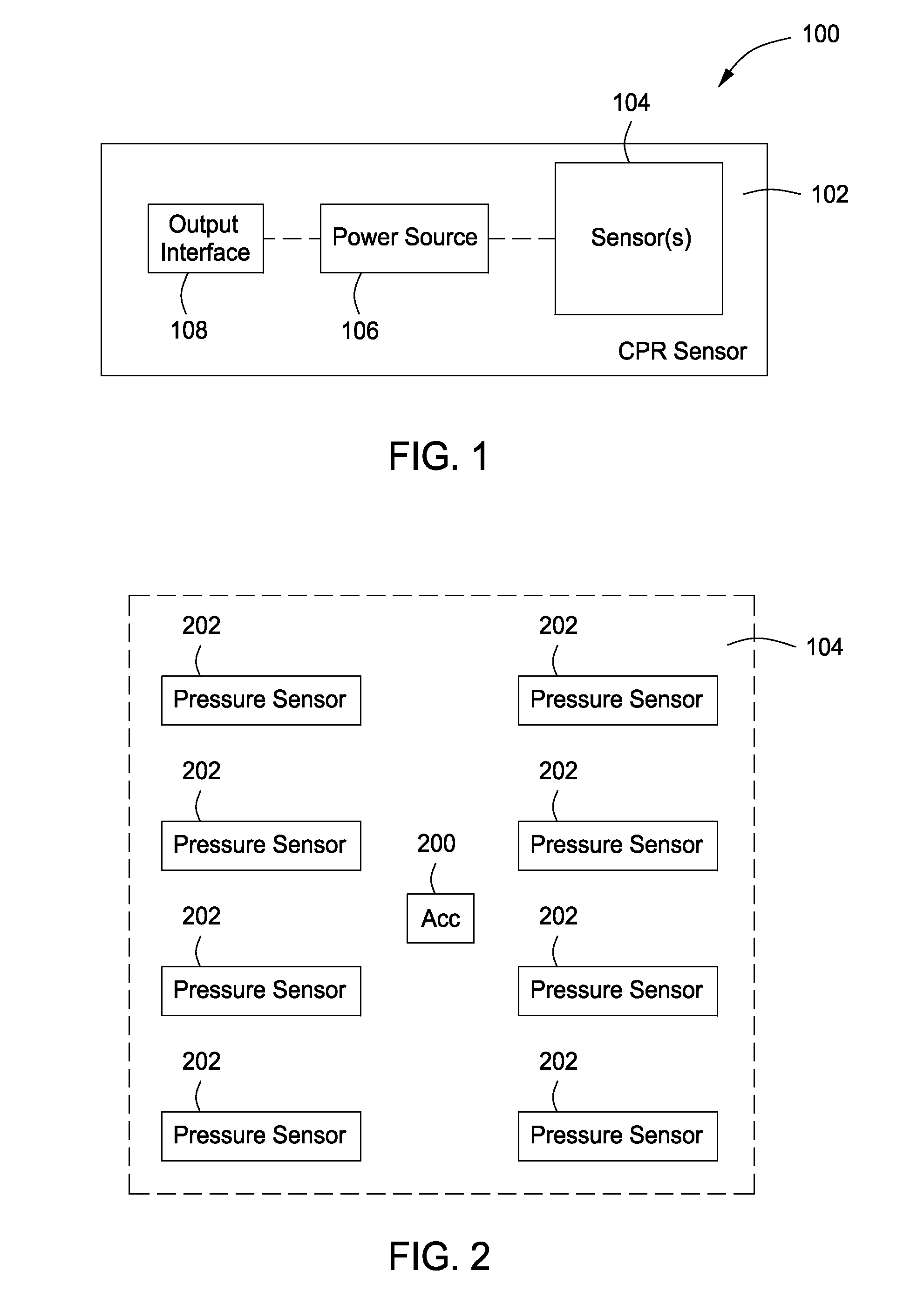

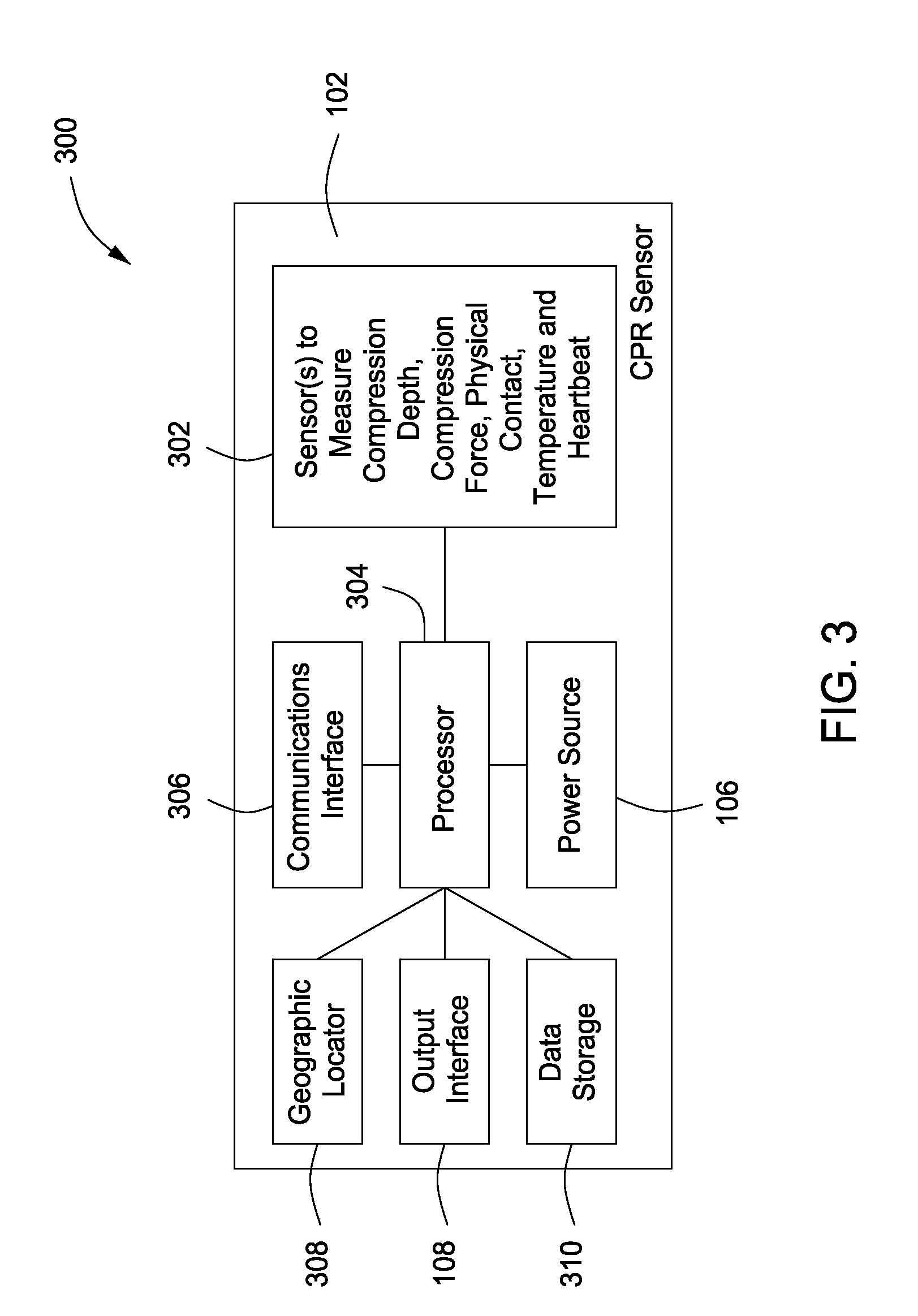

Cardiopulmonary Resuscitation Sensor

ActiveUS20080312565A1Readily availableEasily portableElectrotherapyAcceleration measurement using interia forcesSensor arrayCardiopulmonary resuscitation

The present invention provides a CPR sensor that includes a thin and substantially flat flexible substrate having one or more sensor arrays, a power source, an output interface and a processor or analog circuit, all of which are disposed on the substantially flat flexible substrate. The substrate can be any shape (e.g., rectangular, circular, a polygon, an irregular shape that is decorative) and made from a polymer, metal film or other suitable material. Note that the substrate can be rigid or semi-flexible instead of flexible. A protective layer may cover the sensor array, the power source, and the processor or analog circuit. Alternatively, a protective covering can be used to encapsulate the device. The one or more sensor arrays measure one or more of the following compressions characteristics: compression depth, compression force, compression frequency and compression acceleration.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST +1

Imaging device with multiple fields of view incorporating memory-based temperature compensation of an uncooled focal plane array

InactiveUS7235785B2Reduce the required powerUnanimous responseTelevision system detailsSolid-state devicesMultiplexingComputer module

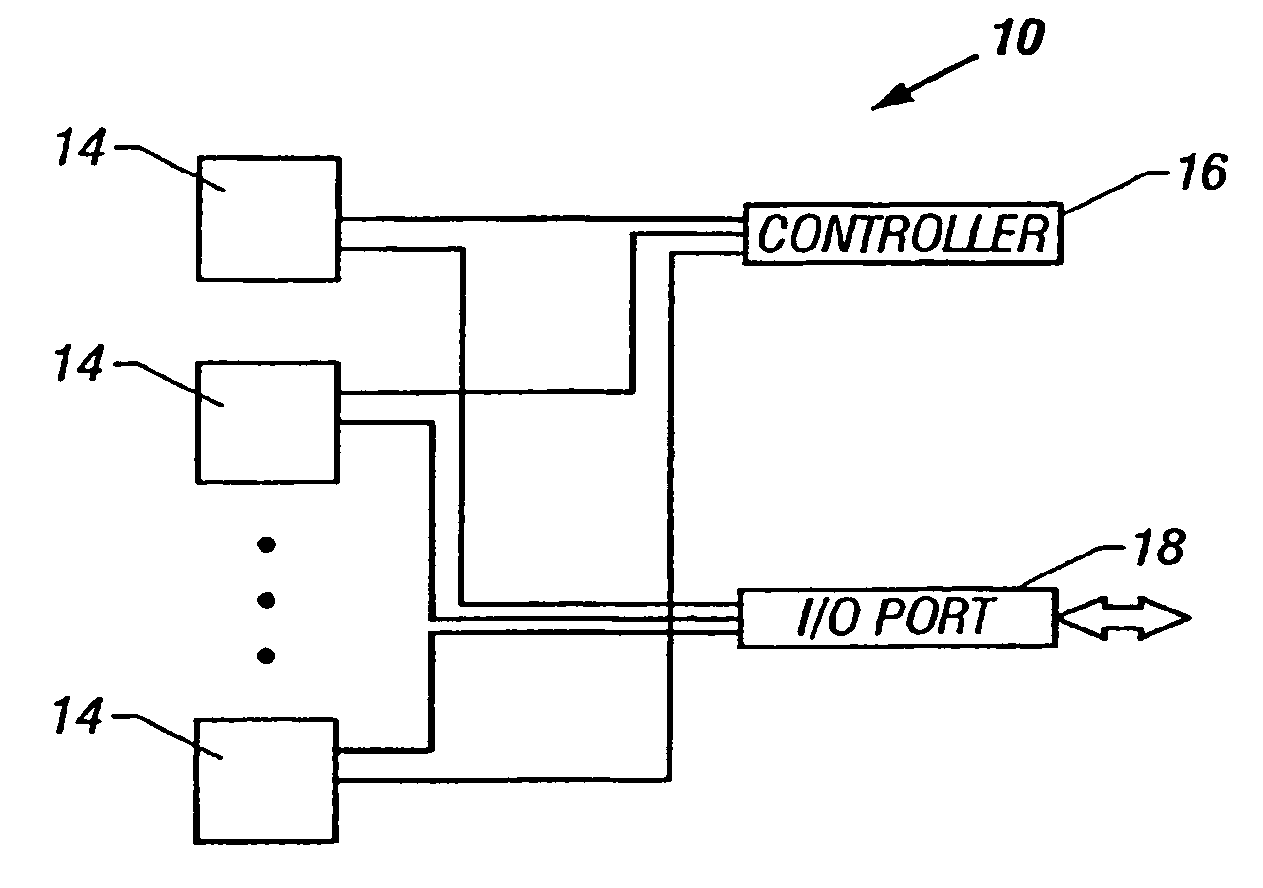

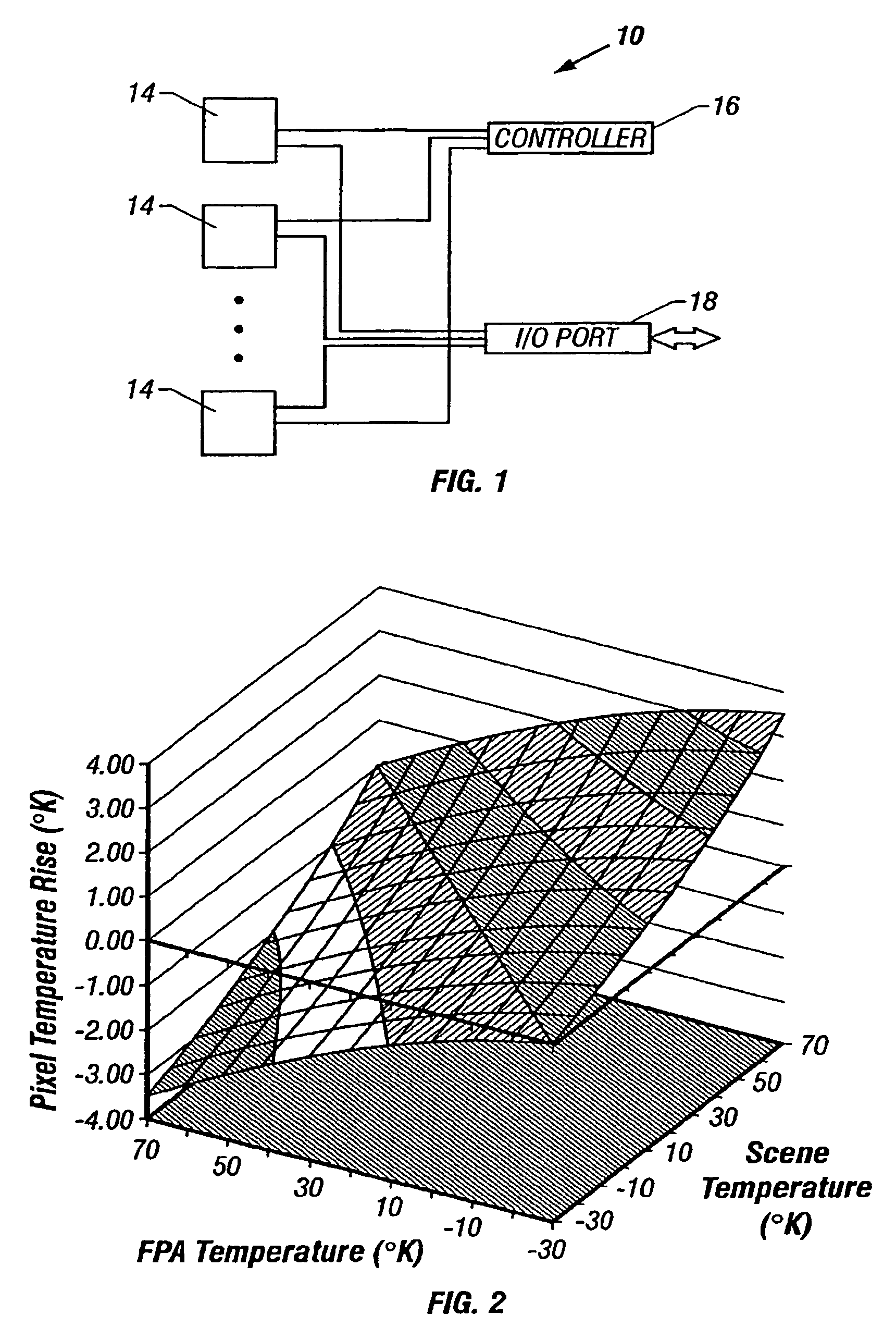

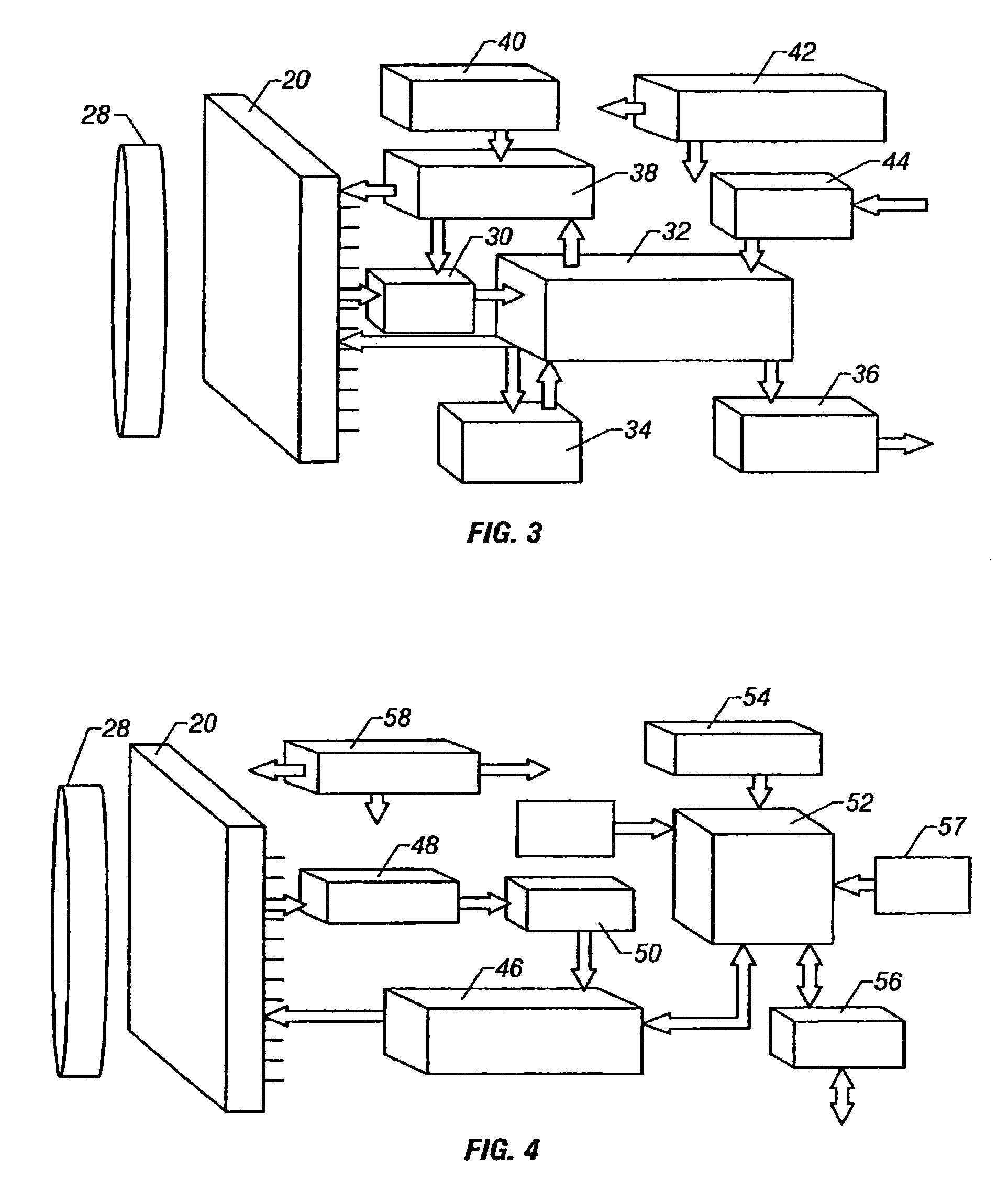

A plurality of temperature dependent focal plane arrays operate without a temperature stabilization cooler and / or heater over a wide range of ambient temperatures. Gain, offset and / or bias correction tables are provided in a flash memory in memory pages indexed by the measured temperature of the focal plane arrays. The memory stores a calibration database, which is accessed using a logic circuit which generates a memory page address from a digitized temperature measurement of each of the focal plane array. The calibration database is comprised of an array of bias, gain and offset values for each pixel in the focal plane array for each potential operating temperature over the entire range of potential operating temperatures. The bias, gain and offset data within the database are read out, converted to analog form, and used by analog circuits to correct the focal plane array response. The output of each of the FPAs is multiplexed to a shared processing module and calibration data for each of the FPAs is accessed from the shared processing module.

Owner:APROLASE DEV

Circuit for high-resolution phase detection in a digital RF processor

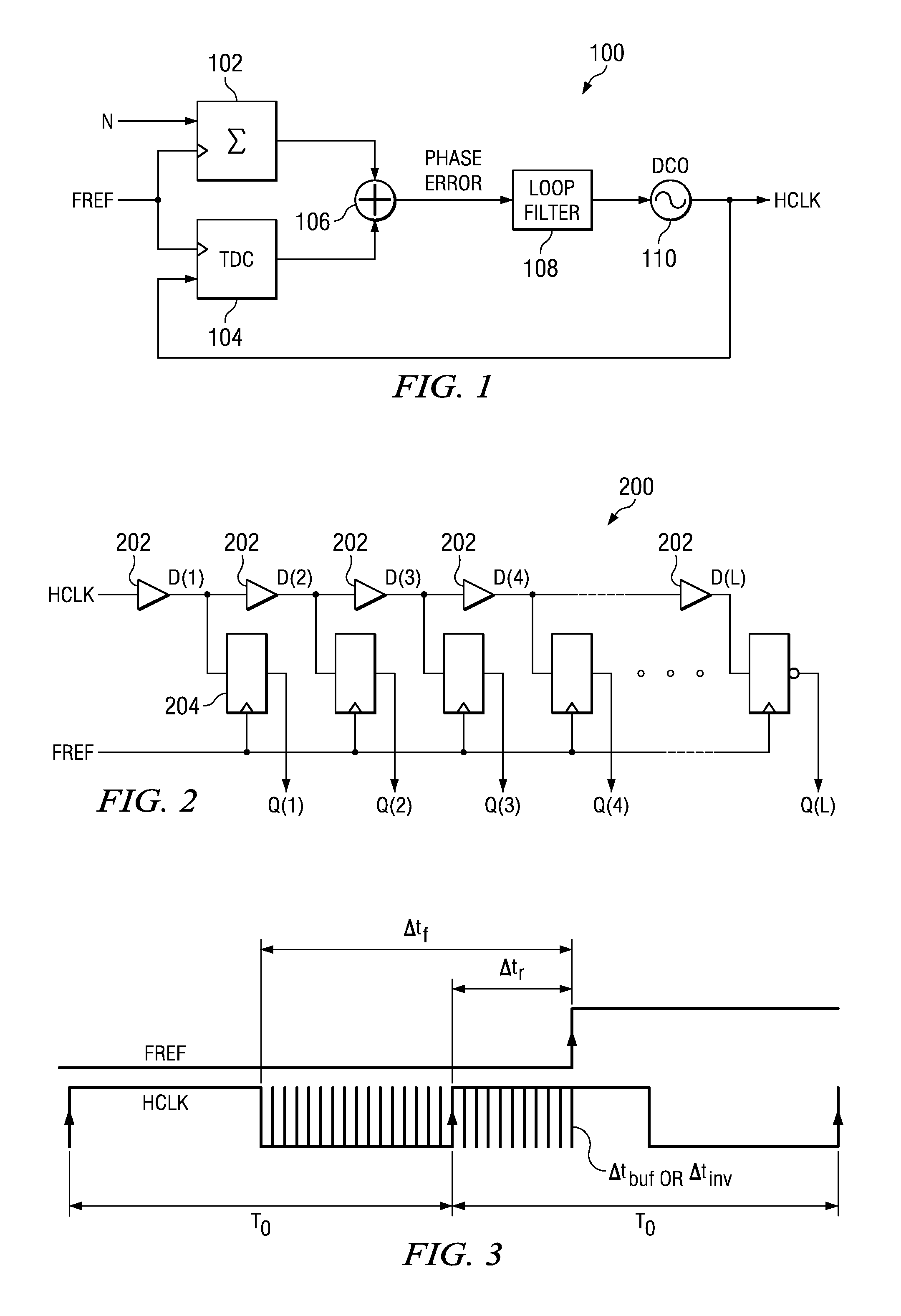

ActiveUS7205924B2Less sensitiveReduce power consumptionElectric signal transmission systemsModulated-carrier systemsDigital converterCmos process

A novel time-to-digital converter (TDC) used as a phase / frequency detector and charge pump replacement in an all-digital PLL within a digital radio processor. The TDC core is based on a pseudo-differential digital architecture making it insensitive to NMOS and PMOS transistor mismatches. The time conversion resolution is equal to an inverter propagation delay, e.g., 20 ps, which is the finest logic-level regenerative timing in CMOS. The TDC is self calibrating with the estimation accuracy better than 1%. The TDC circuit can also serve as a CMOS process strength estimator for analog circuits in large SoC dies. The circuit also employs power management circuitry to reduce power consumption to a very low level.

Owner:TEXAS INSTR INC

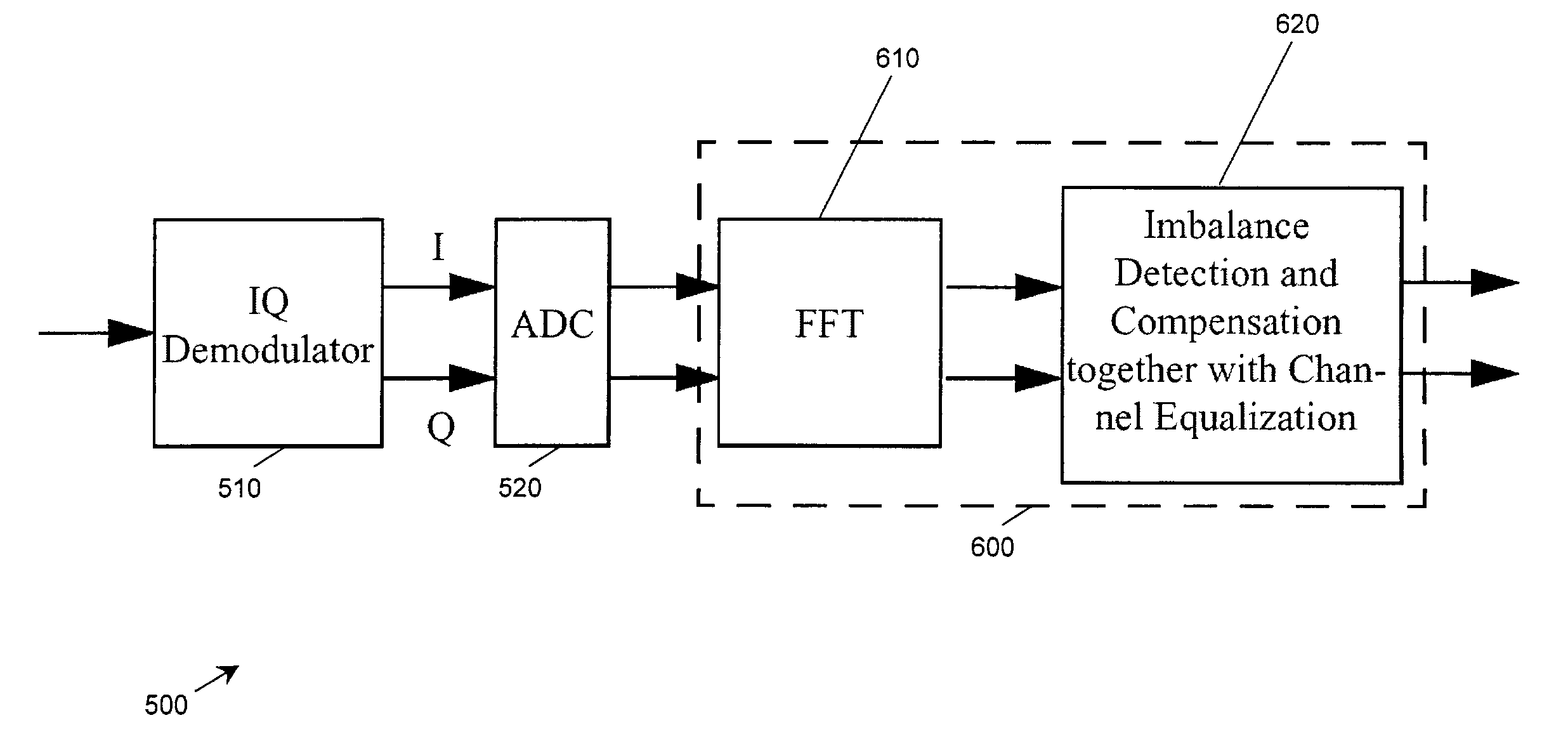

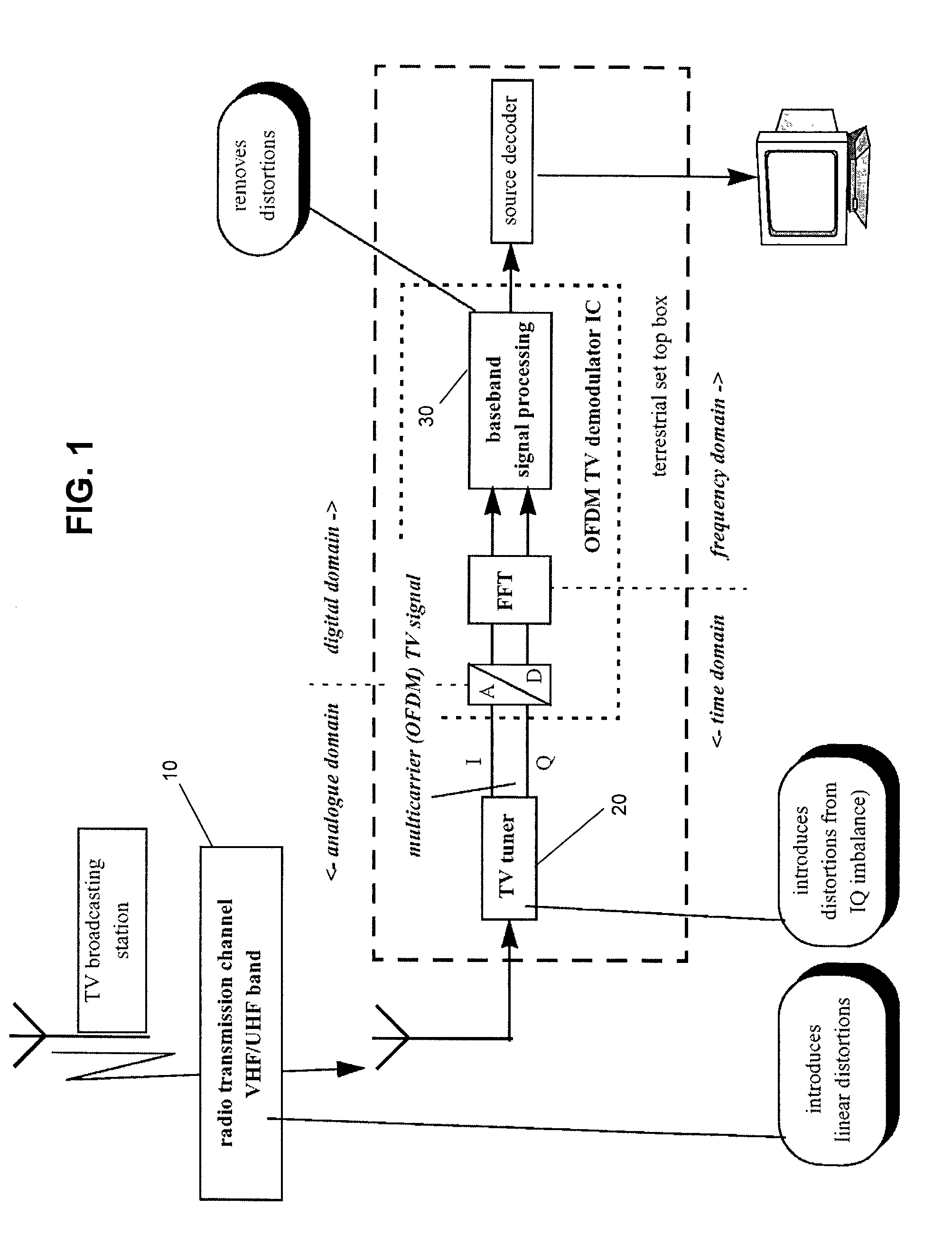

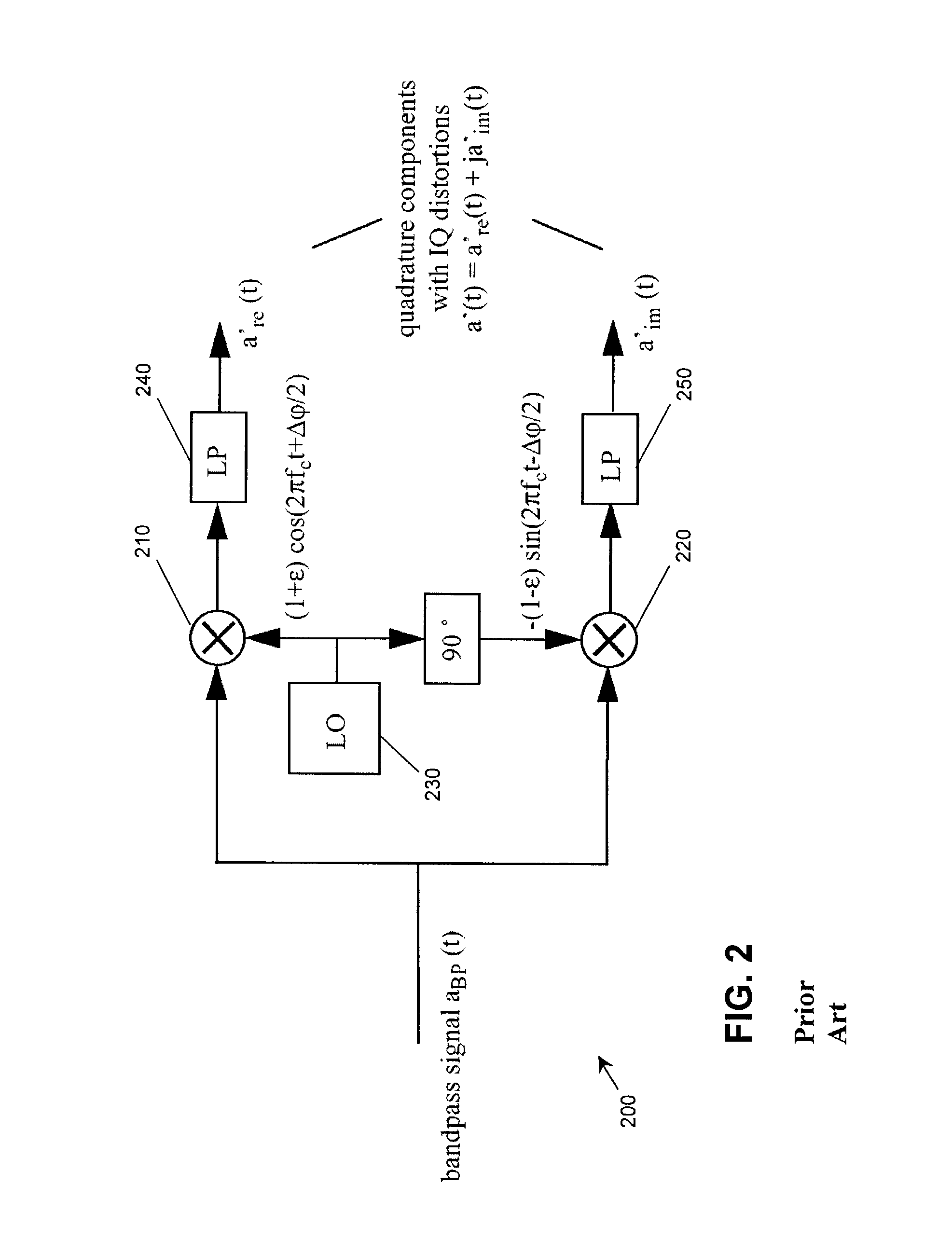

Arrangement and method for frequency domain compensation of OFDM signals with IQ imbalance

InactiveUS20030231726A1Multi-frequency code systemsTransmitter/receiver shaping networksDigital signal processingEqualization

An arrangement (600) and method for frequency domain compensation of OFDM signals with IQ imbalance by converting IQ signals to the frequency domain (610); and providing imbalance compensation and channel equalization means (620) and therewith, in the frequency domain, compensating for IQ imbalance in the IQ signals and providing channel equalization thereto. Adaptive equalization is used to adapt filter coefficients, allowing IQ imbalance compensation and channel equalization to be achieved simultaneously in a simple and elegant manner. This allows complexity in analog circuitry and associated costs to be reduced at the expense of additional digital signal processing, yielding an overall economic system solution. The invention can be easily applied to existing systems, such as the DVB-T standard, without requiring changes to installed broadcasting infrastructure in order use receivers incorporating the invention.

Owner:MOTOROLA INC

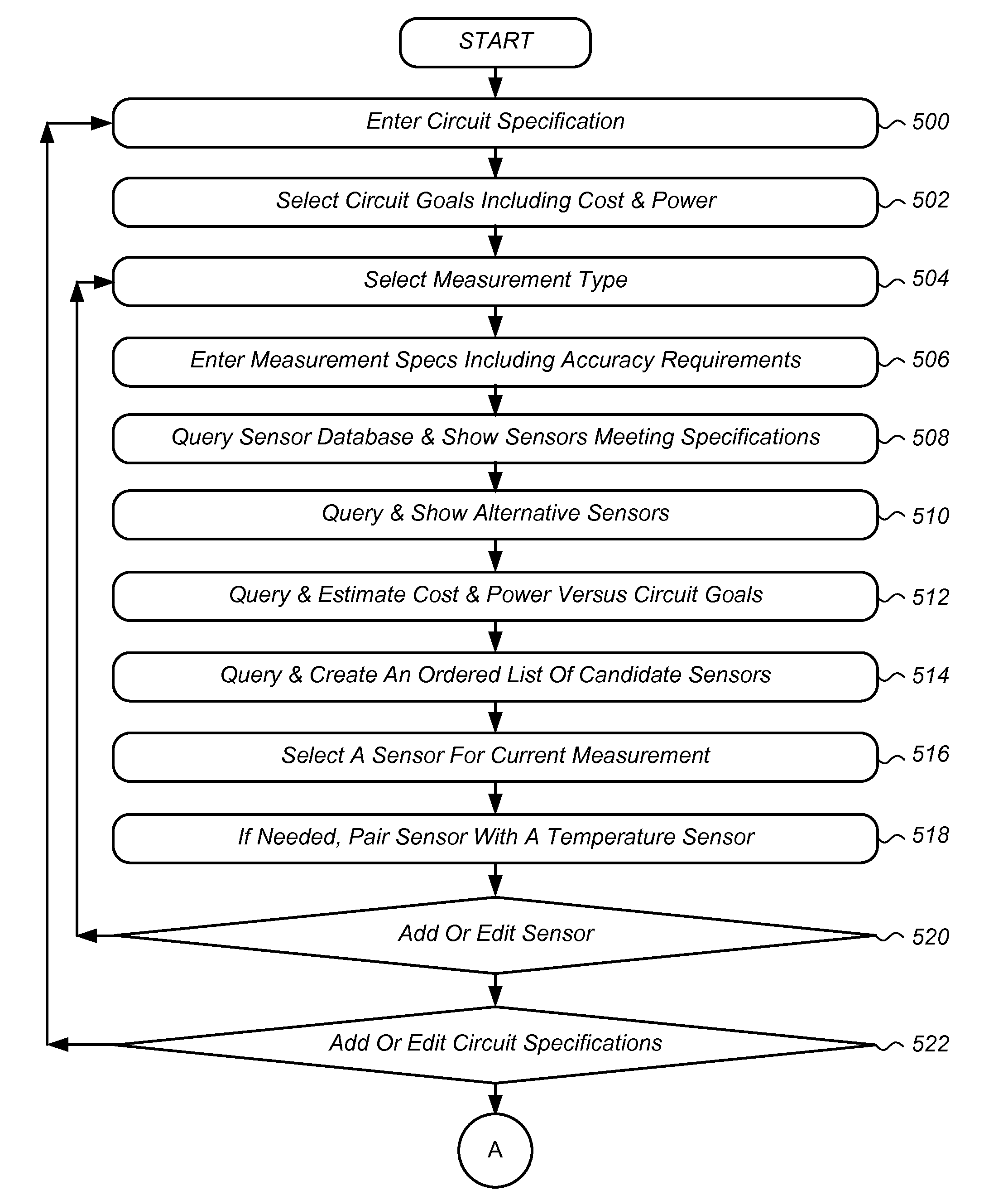

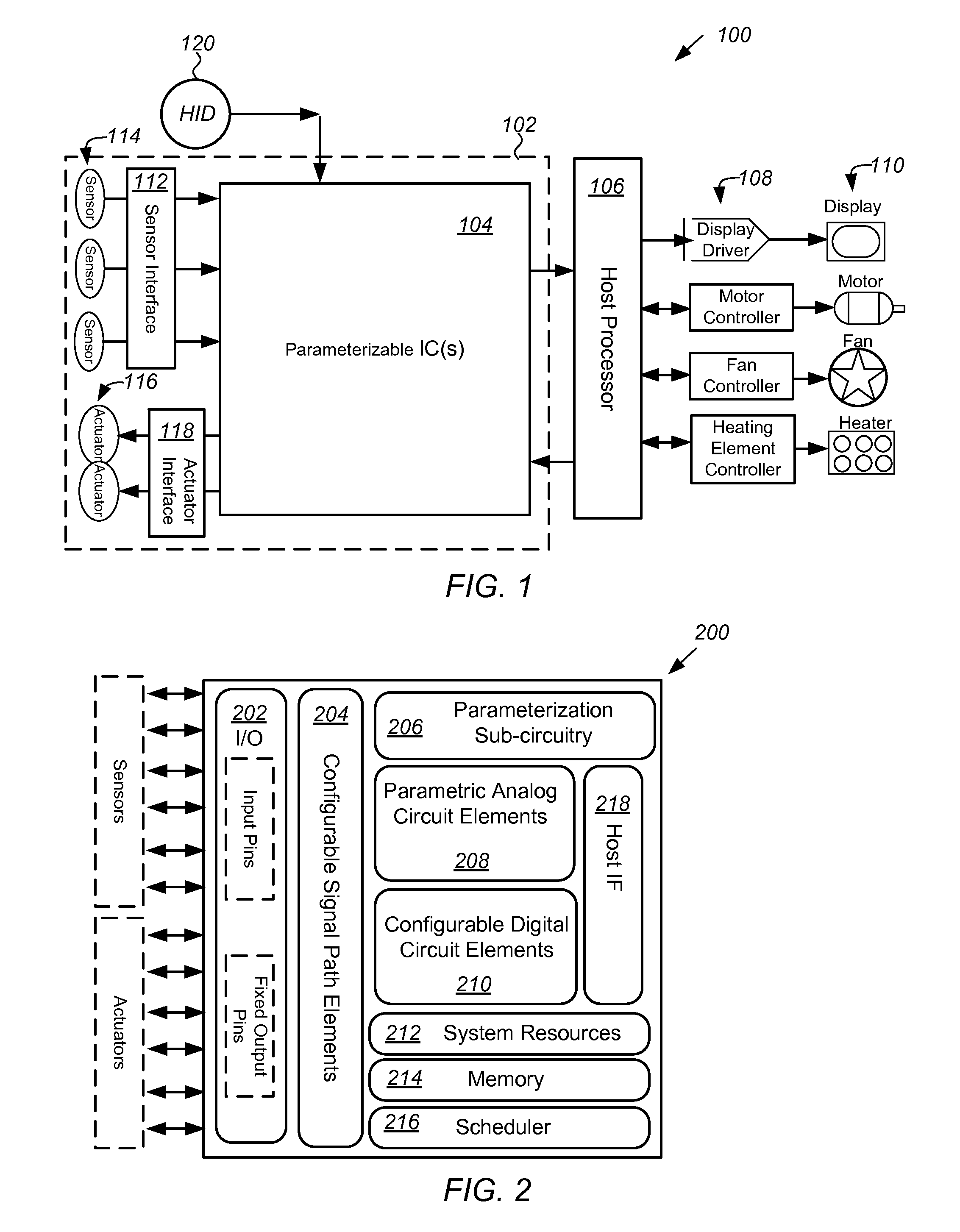

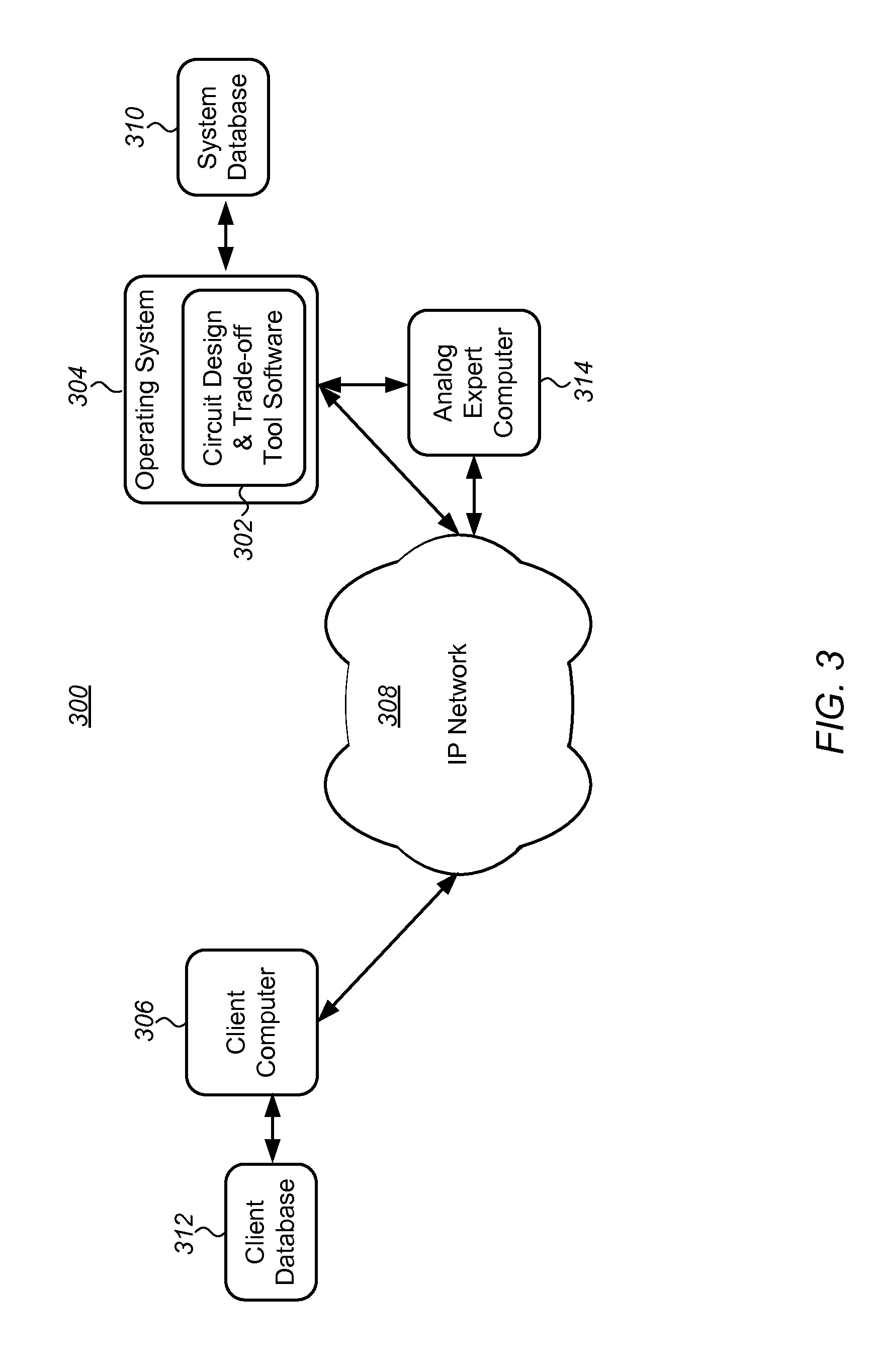

Implementing A Circuit Using An Integrated Circuit Including Parametric Analog Elements

ActiveUS20100306722A1CAD circuit designSoftware simulation/interpretation/emulationEngineeringClient machine

An environment and method are provided for designing and implementing a circuit comprising an integrated circuit (IC) including a number of parametric analog elements for which operating parameters can be set. Generally, the method comprises: specifying requirements for the circuit including physical properties to be sensed by the circuit and actions to be taken by the circuit; designing the circuit based on the specified requirements and resources available on the IC; and setting parameters of at least one of the parametric analog circuit elements of the IC based on the circuit design. In one embodiment, the specifying, designing, and setting parameters steps are performed using a computer executable code embodied in a computer readable medium on a server coupled to a client computer through an internet protocol network. Other embodiments are also provided.

Owner:CYPRESS SEMICON CORP

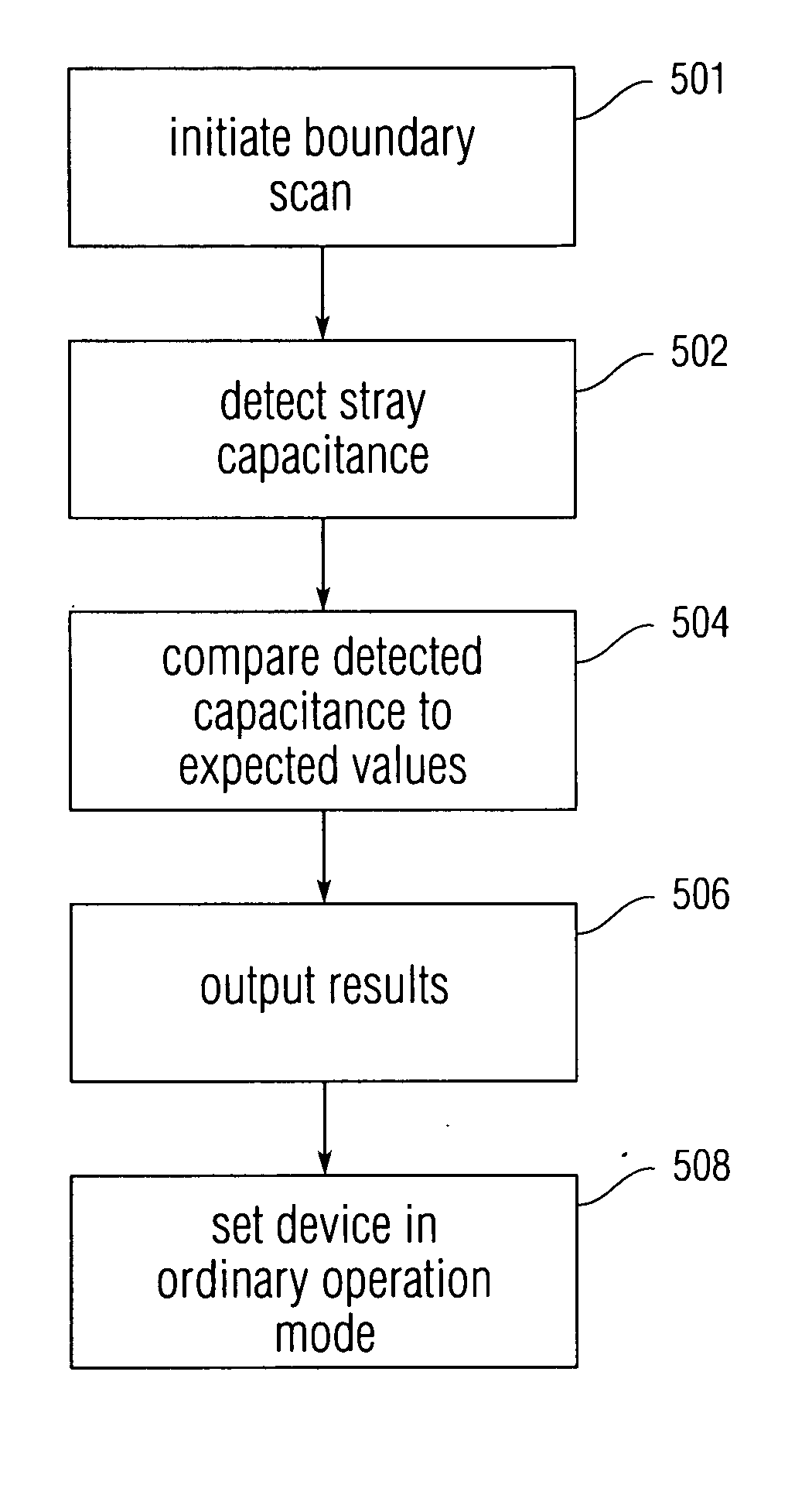

Analog boundary scanning based on stray capacitance

Embodiments of the present invention are directed to performing boundary scanning without using a pin which is exclusively dedicated for that purpose. The boundary scan can be performed by an integrated circuit by utilizing a pin which has an alternative use during ordinary operation of the integrated circuit and the device. This pin can be connected to an analog circuit configured to sense capacitance outside of the pin. The analog circuit may also have an alternative function in normal operation of the device. During a testing mode, the analog circuit can sense a stray capacitance present at the pin. The sensed capacitance can be compared to one or more stored expected capacitance values to determine an interconnection state of the system.

Owner:APPLE INC

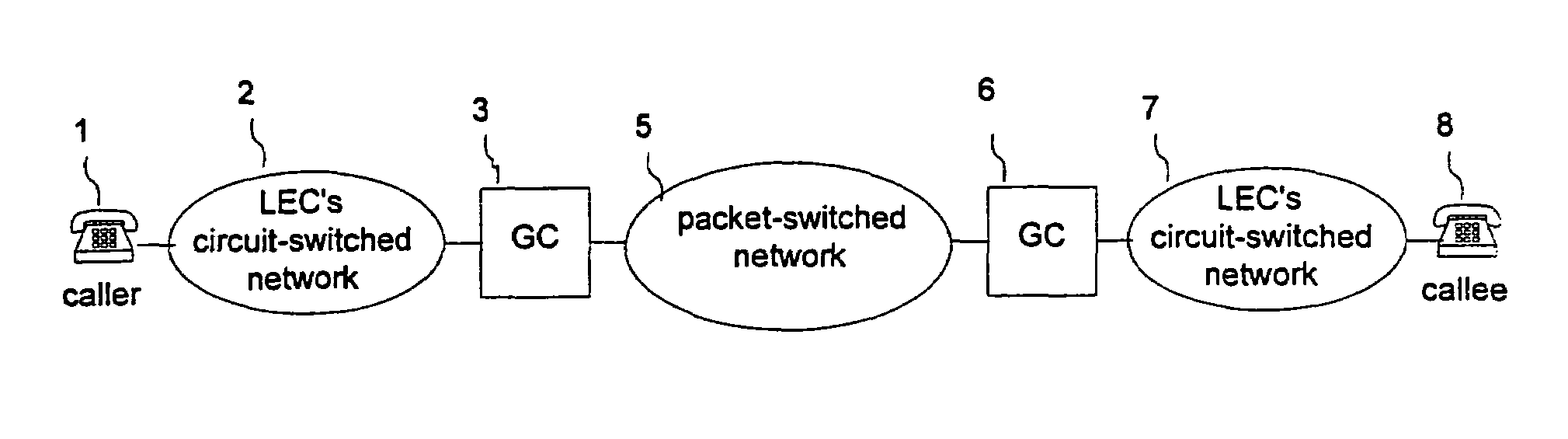

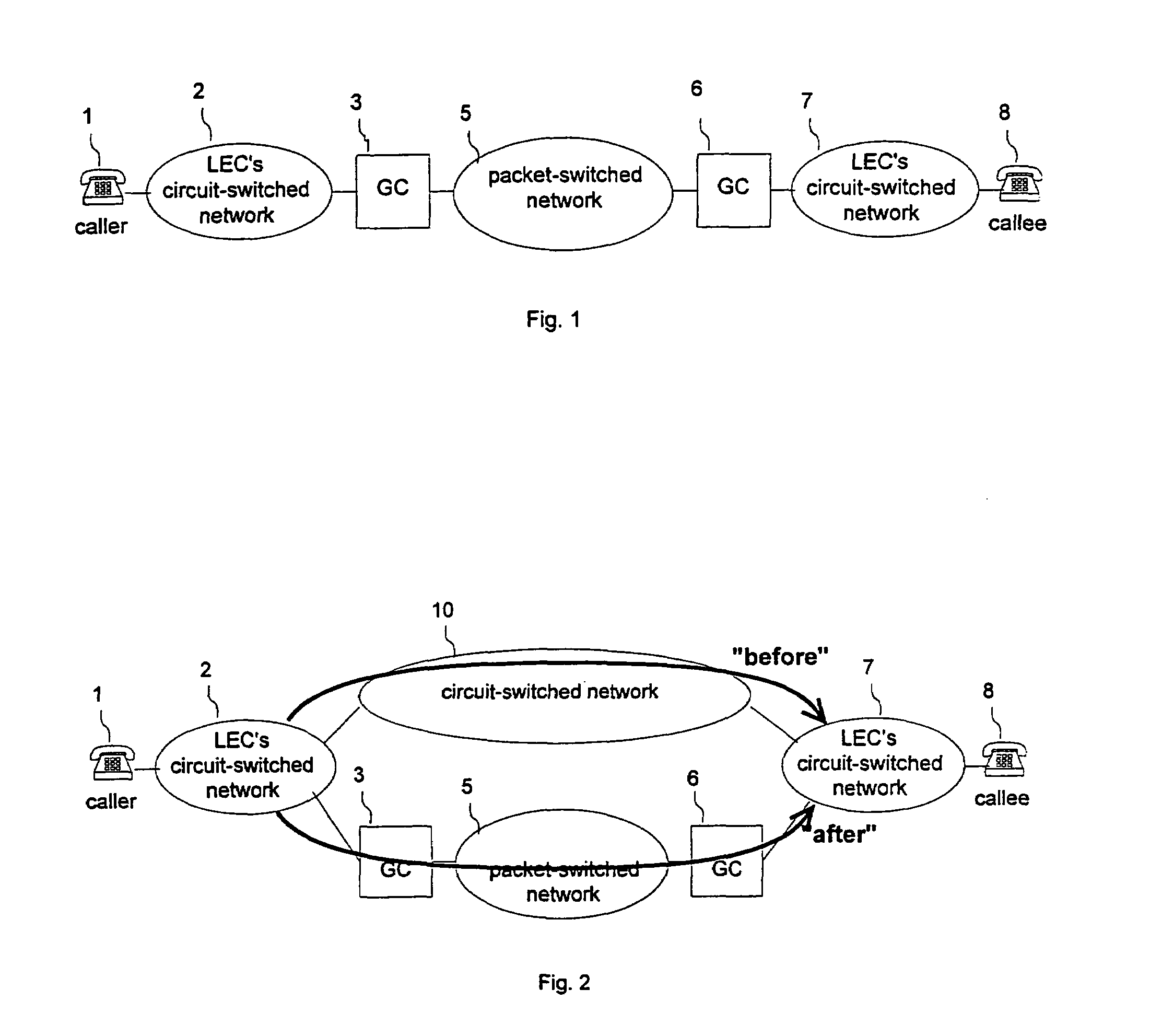

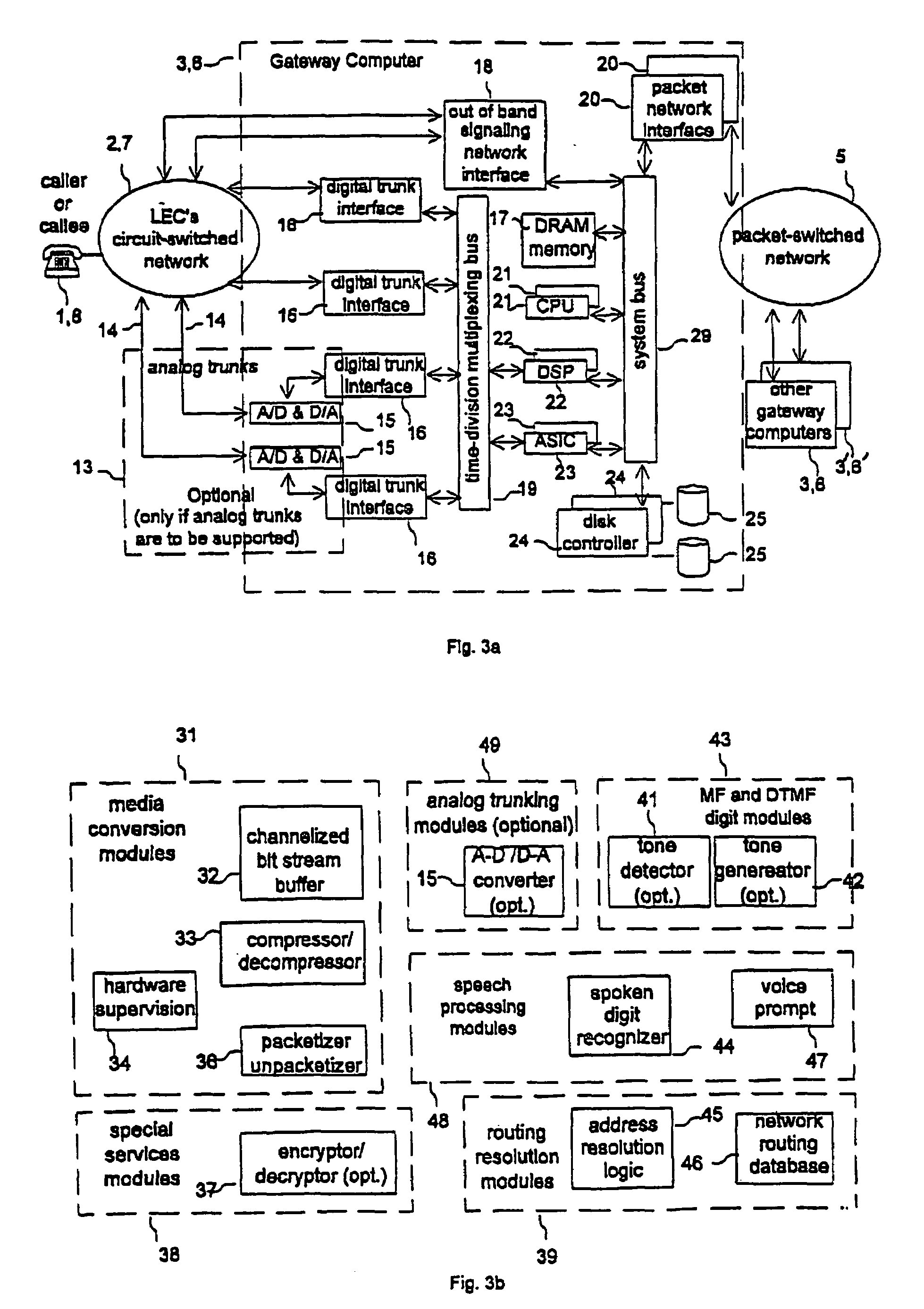

Hybrid packet-switched and circuit-switched telephony system

InactiveUS7336649B1Improve efficiencyImprove overall utilizationInterconnection arrangementsData switching by path configurationExchange networkSecure telephone

A hybrid telephony system with packet switching as well as circuit switching optimizes utilization of transport networks, and is accessible from any conventional telephone set. A call originating from a circuit-switched network is passed through a gateway computer to a backbone packet-switched network, and then through a second gateway computer to a second circuit-switched network where it terminates. The voice of both the originating party and the terminating party is converted to data packets by the near-end gateway computer and then converted back to voice by the far-end gateway computer. In an alternative scenario, the originating party uses a computer on the packet-switched network, which replaces the originating circuit-switched network and the originating computer. Powered by CPUs, DSPs, ASICs disks, telephony interfaces, and packet network interfaces, the gateway computers may have media conversion modules, speech processing modules and routing resolution modules, and are capable of translating telephony call signaling as well as voice between circuit-switched and packet-switched networks. Optionally, the gateway computers may also have analog trunking modules, MF and DTMF digit modules and special services modules, in order to support analog circuit-switched networks and secure telephone calls.

Owner:VERIZON PATENT & LICENSING INC

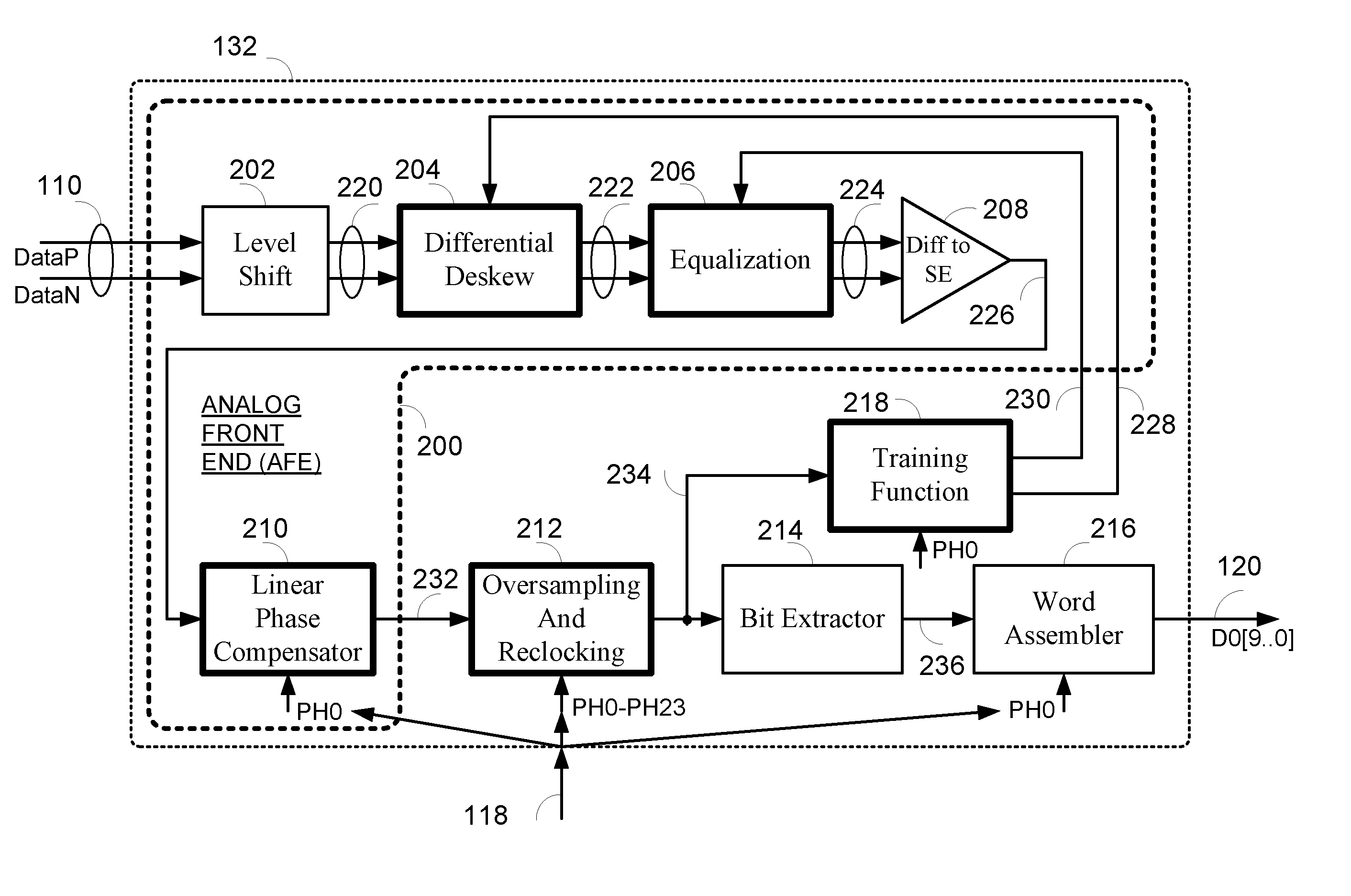

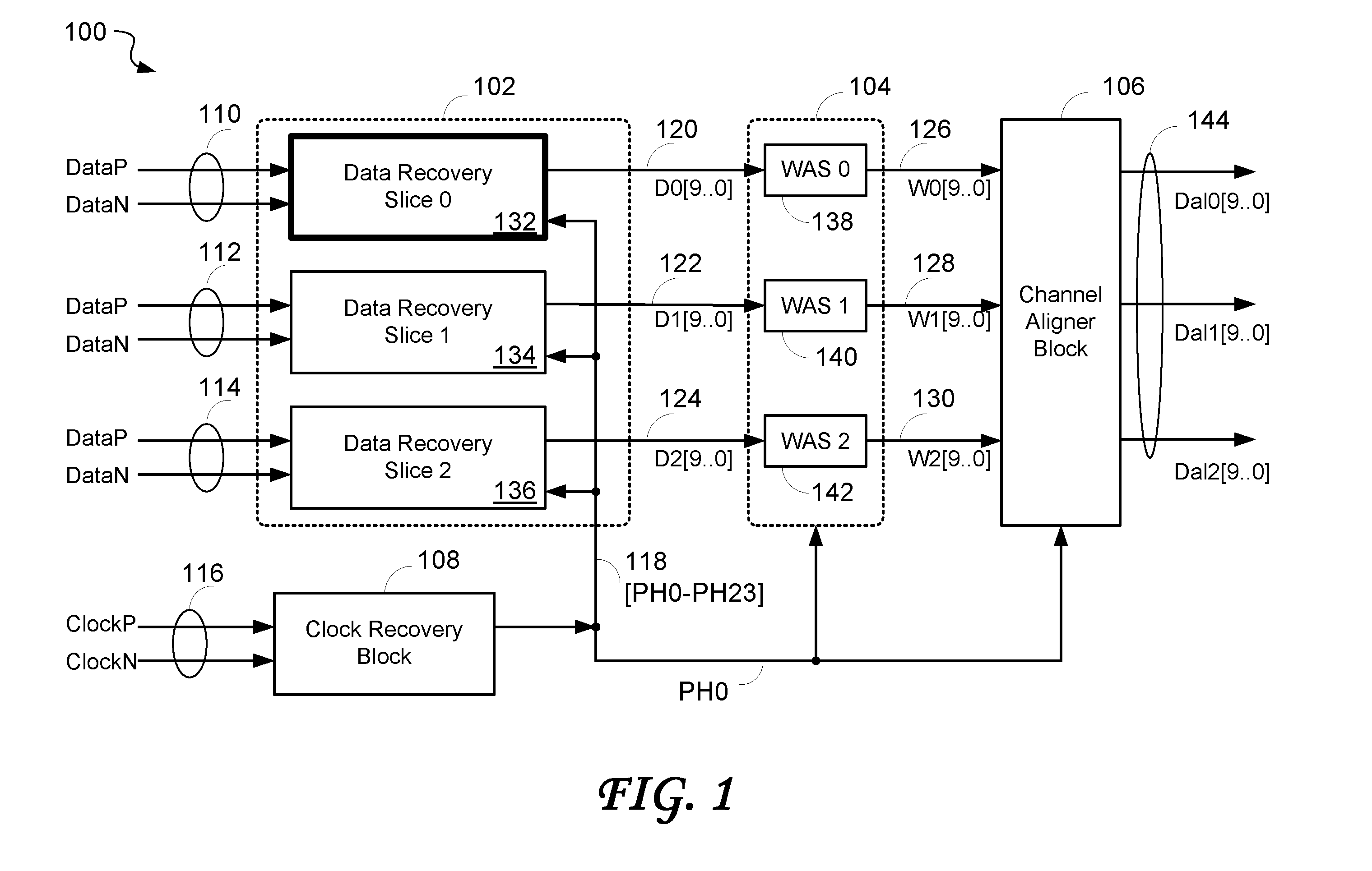

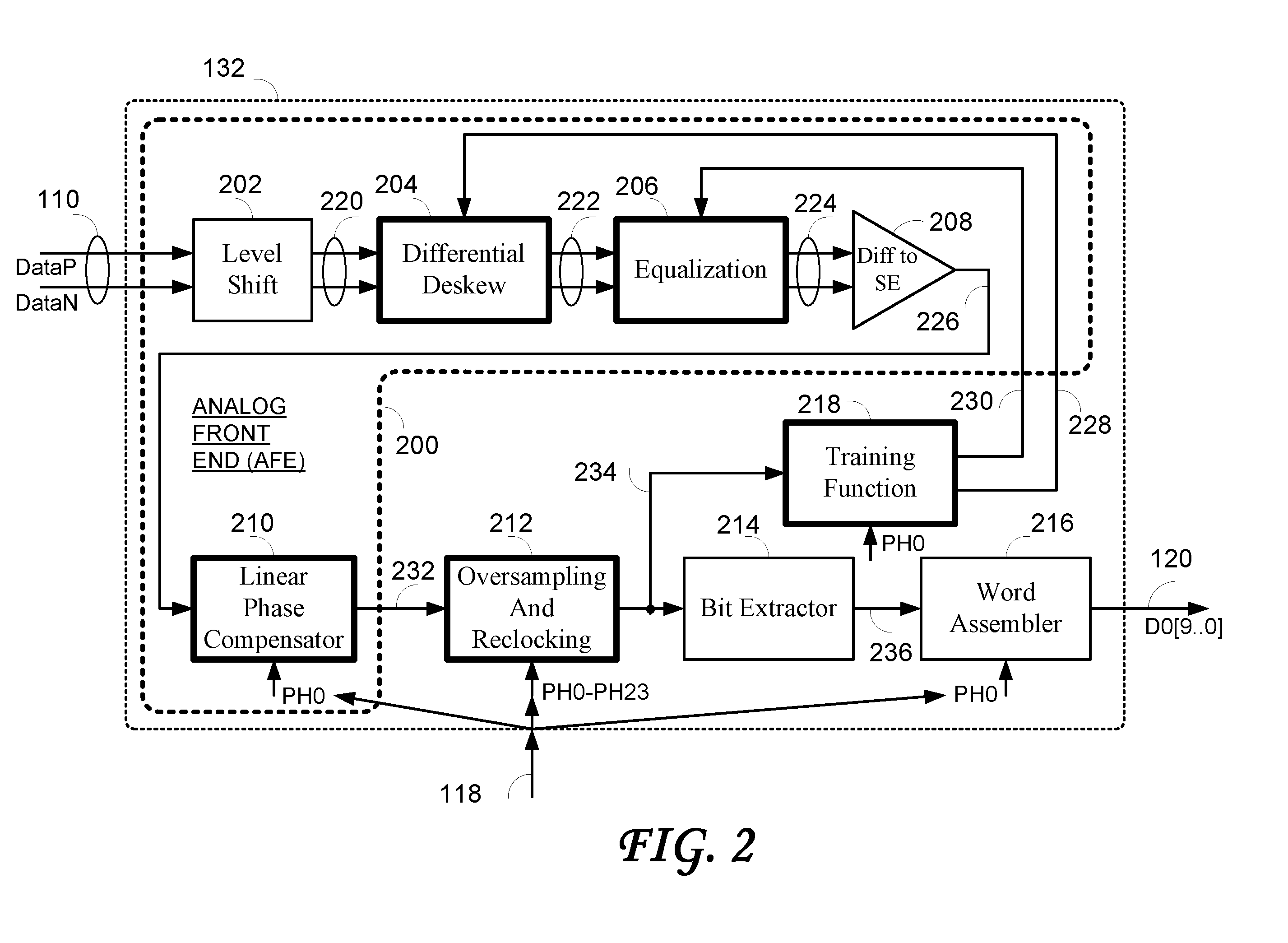

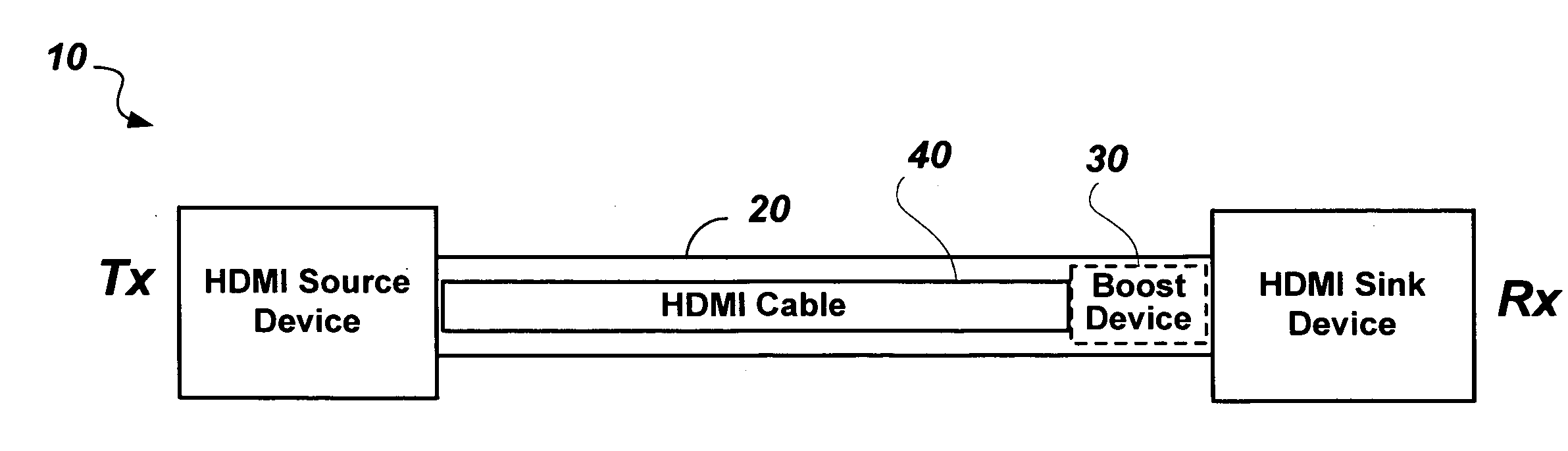

Data recovery system for source synchronous data channels

ActiveUS20070164802A1Easy Data RecoveryReduce distortion problemsModulated-carrier systemsPulse demodulator24-bitAnalog signal

A high-definition multimedia interface (HDMI) receiver recovers high speed encoded data which are transmitted differentially over data channels of a lossy cable, along with a clock. Inter symbol interference, high-frequency loss, skew between the clock and data channels, and differential skew within a differential signal are compensated by analog circuits which are automatically tuned for best performance by observing the quality of the recovered analog signal. Oversampling is used to provide a 24-bit digital representation of the analog signal for determining the quality of the signal. A corresponding method of deskewing a differential signal and a system and circuit therefor are also provided.

Owner:REDMERE TECH

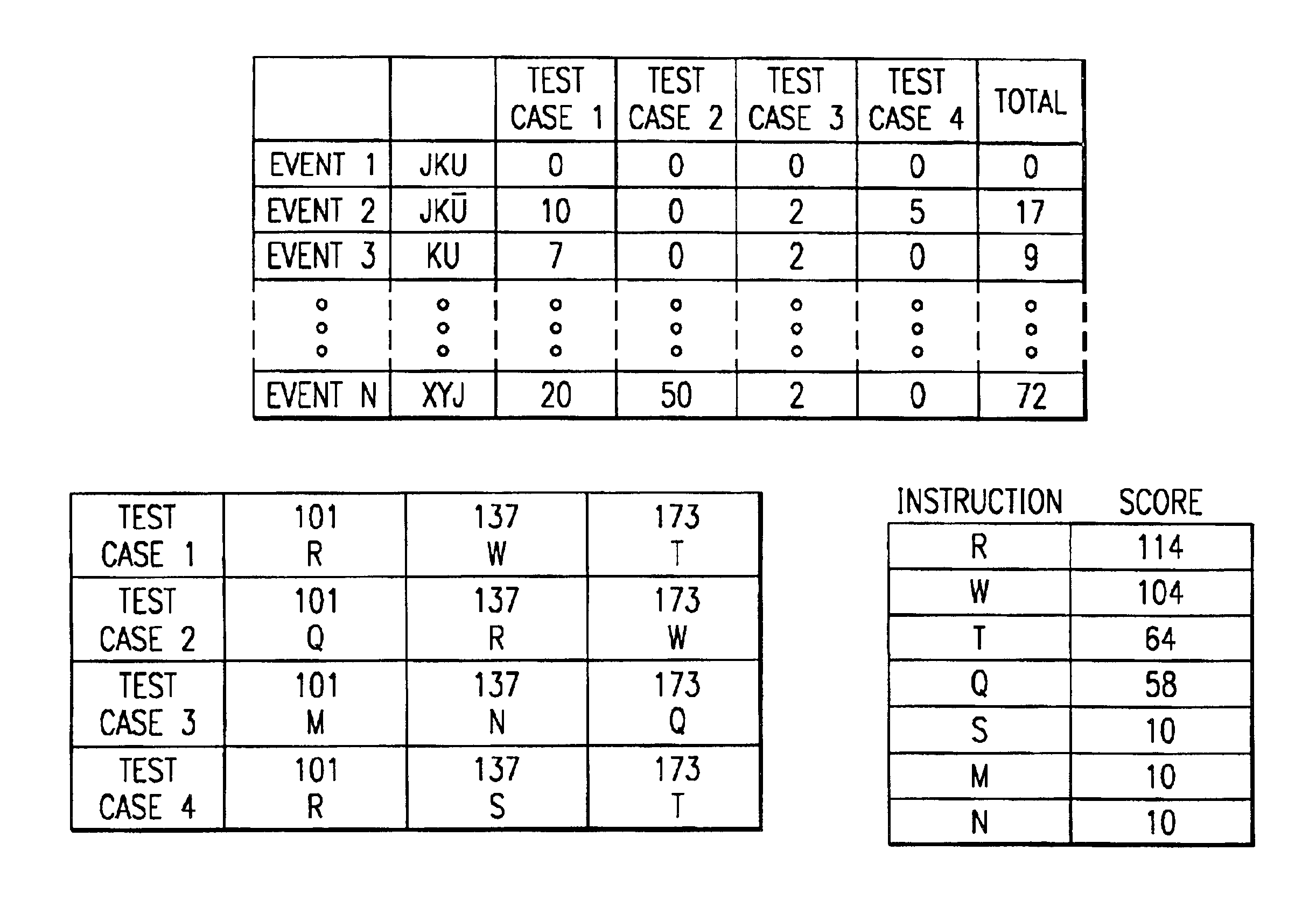

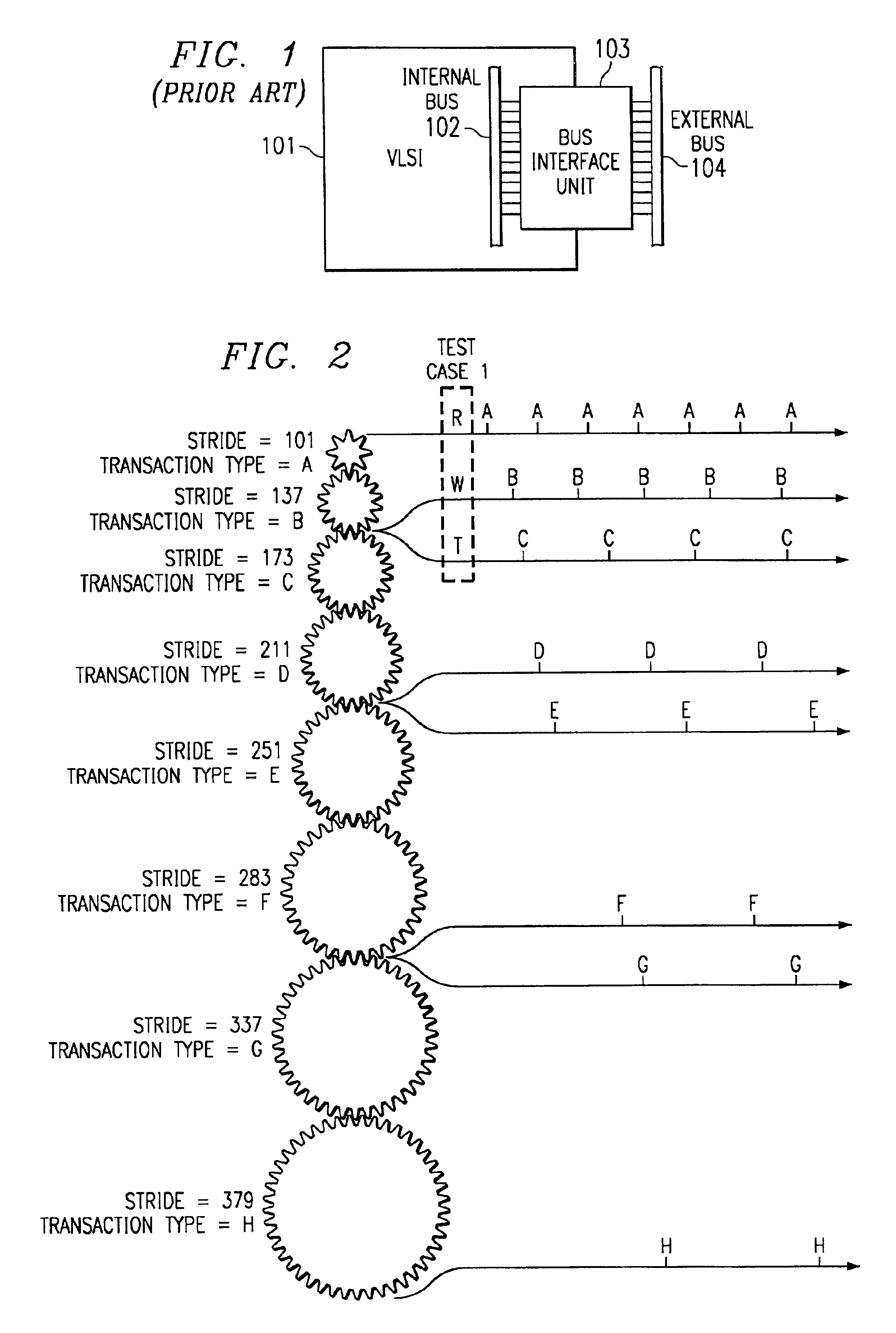

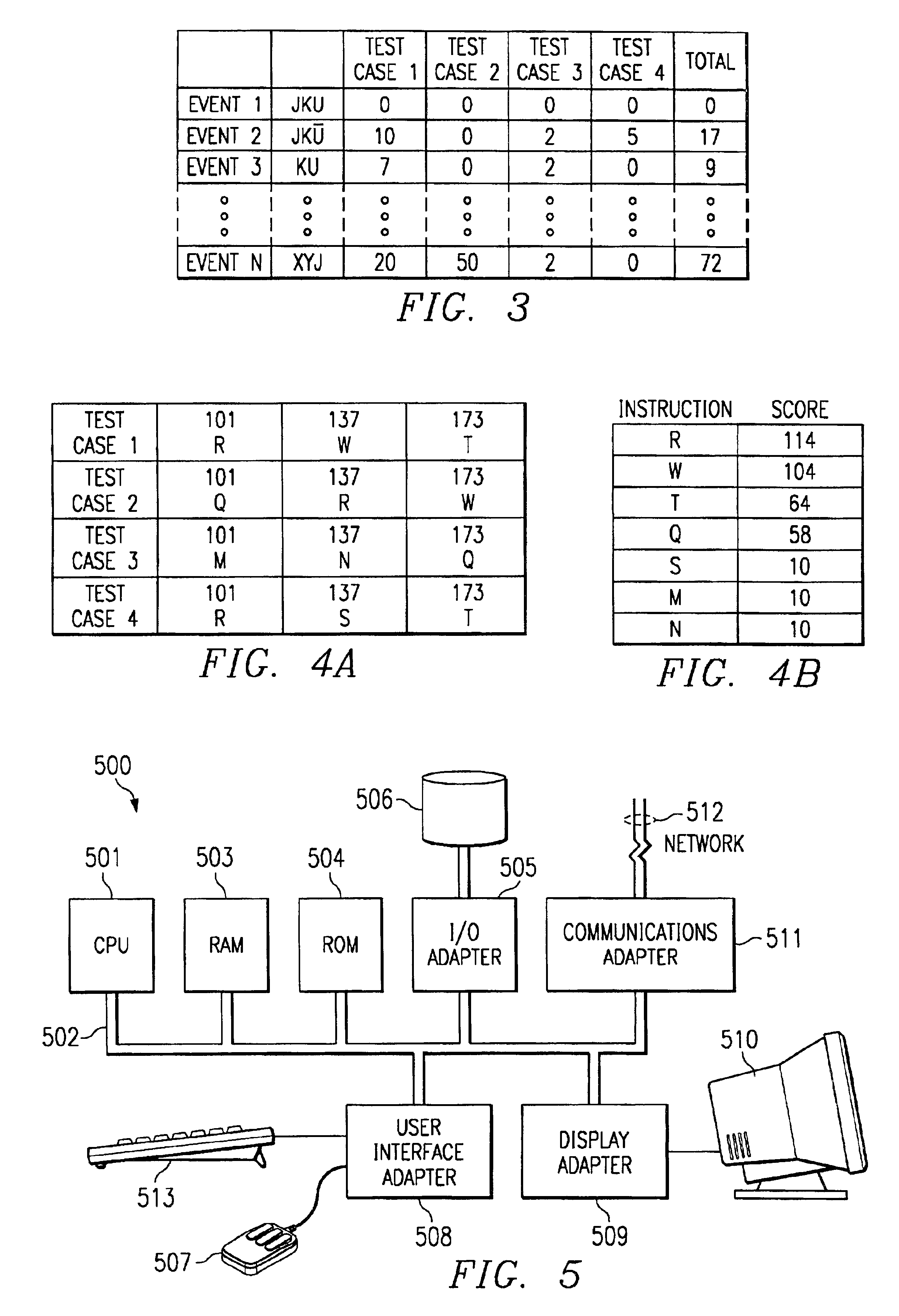

Method and apparatus for generating transaction-based stimulus for simulation of VLSI circuits using event coverage analysis

InactiveUS6859770B2Improve trustElectronic circuit testingAnalogue computers for electric apparatusSpecific testAlgorithm

The present invention applies genetic algorithmic generation of test cases the simulation of VLSI logic circuit blocks. The present invention generates a number of original test cases. This aggregate of solutions is provided to a circuit simulator. The results of the simulator are maintained in a matrix or table. The results detail the number of times that particular logic states or events associated with the VLSI block have been stimulated by particular test cases. The aggregate of solutions and the simulation results are then analyzed by the genetic algorithm. The genetic algorithm preferably identifies states associated with the circuit simulation that have not been produced by the original test cases. The genetic algorithm then combines characteristics of various test cases to generate new test cases. The new test cases are provided to the circuit simulator thereby providing a higher degree of confidence that the entire VLSI chip design has been simulated.

Owner:SAMSUNG ELECTRONICS CO LTD

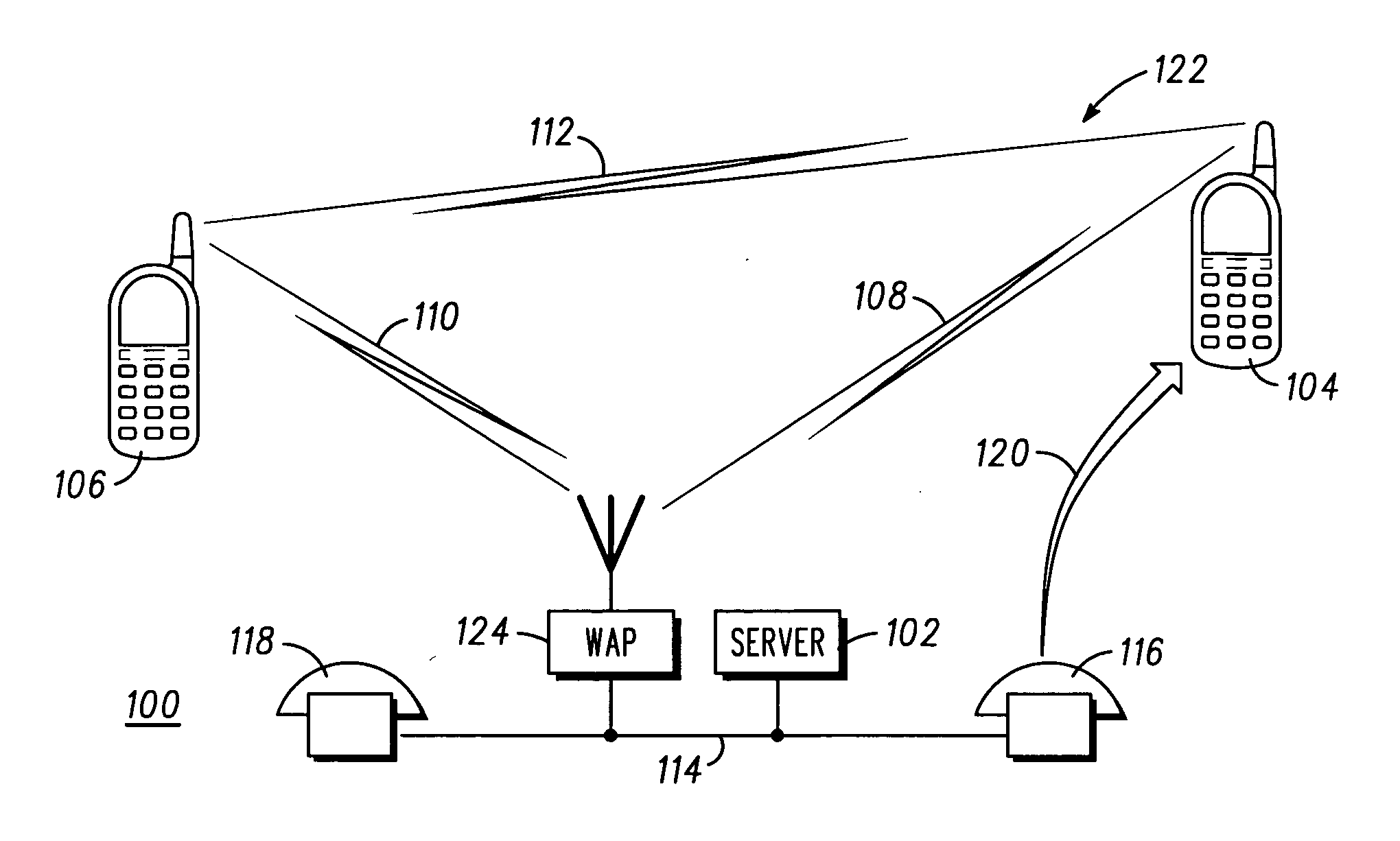

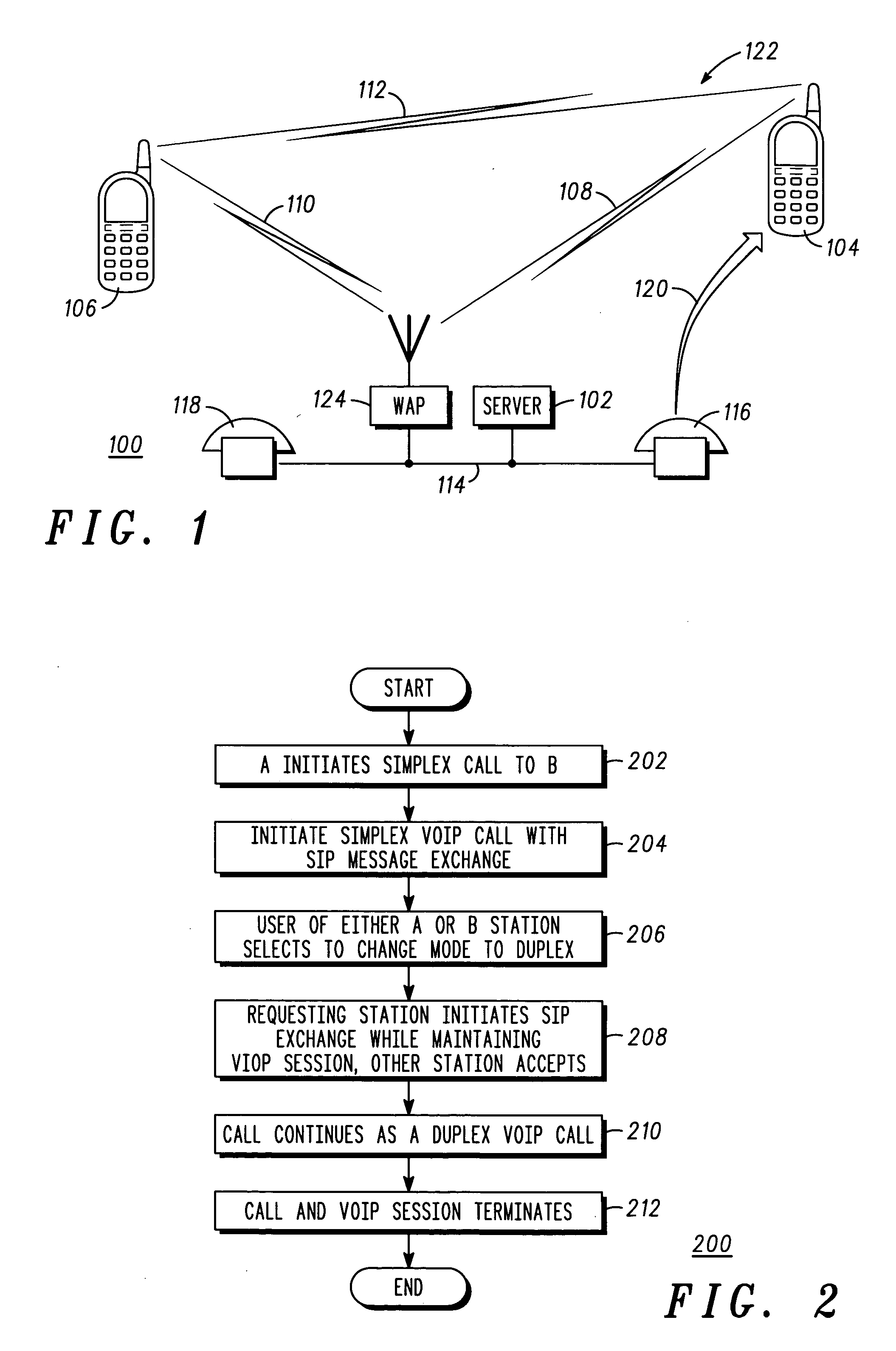

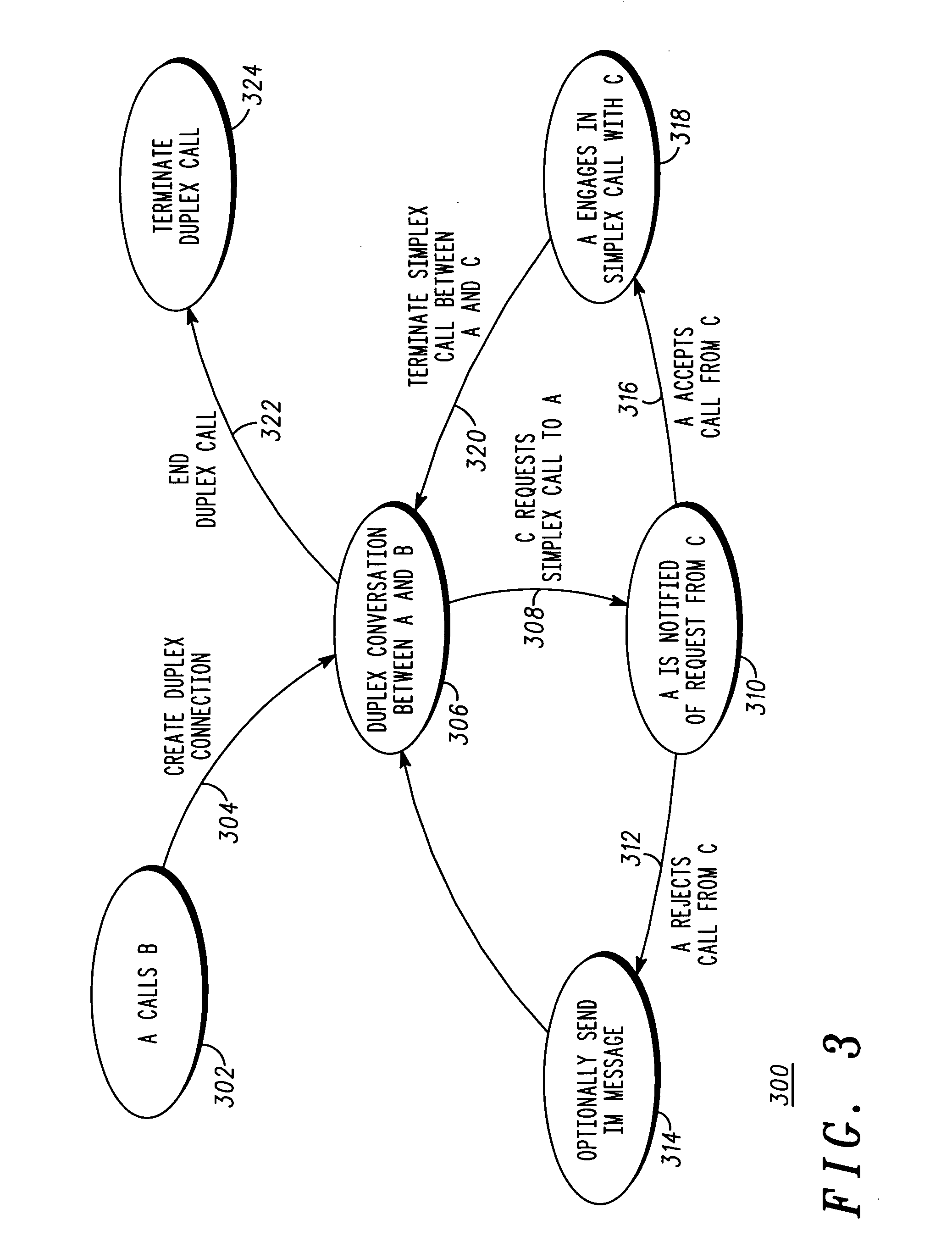

Mode shifting communications system and method

ActiveUS20050213518A1Two-way loud-speaking telephone systemsTransmission control/equalisingCommunications systemSpeech sound

A digital network based communications system that establishes communications sessions to communicate via a simulated circuit-switch environment. Exemplary embodiments communicate between a first communications station (104) and a second communications station (106) using Voice over Internet Protocol (VOIP) techniques. Calls are setup (700), maintained and torn down (800) using Session Initiation Protocol and Session Description Protocol messages. Call modes are able to be changed between duplex and simplex without disconnection. Duplex calls are also able to be interrupted with a request for a simplex call. A receiver (104) engaged in a duplex call can receive a request for a simplex call, accept the simplex call or send a response message, and then resume the duplex call, all while maintaining the duplex call data communications session.

Owner:GOOGLE TECH HLDG LLC

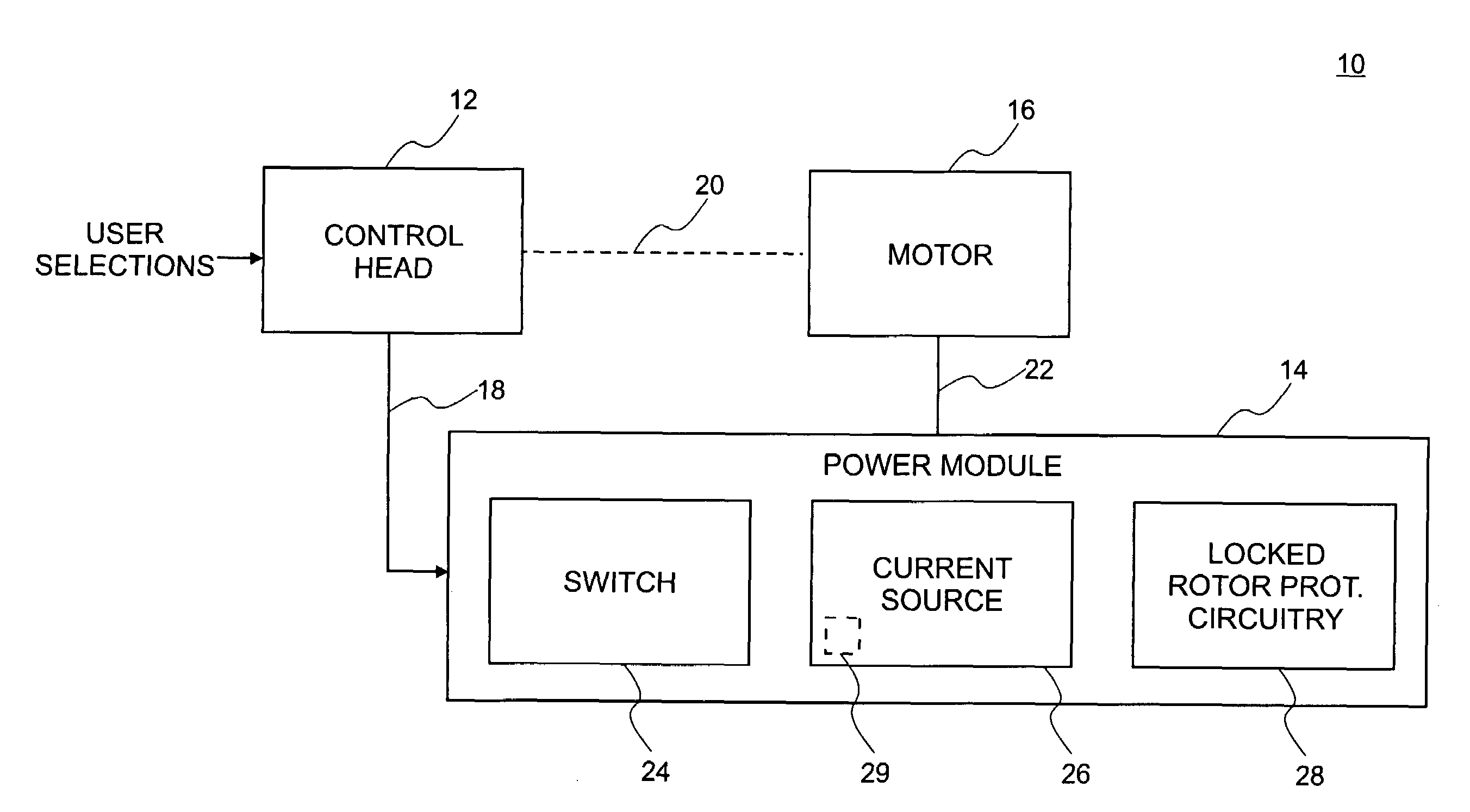

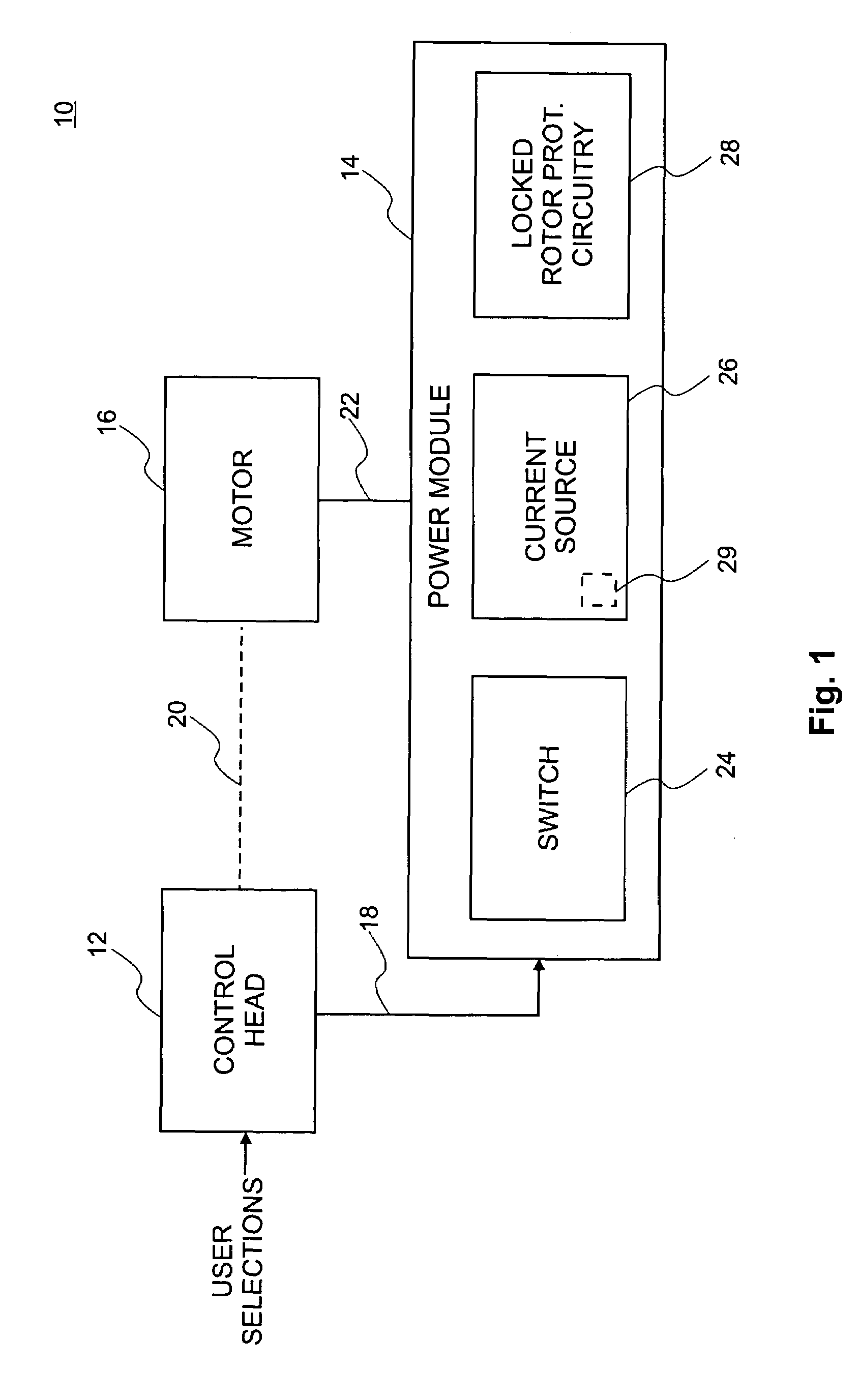

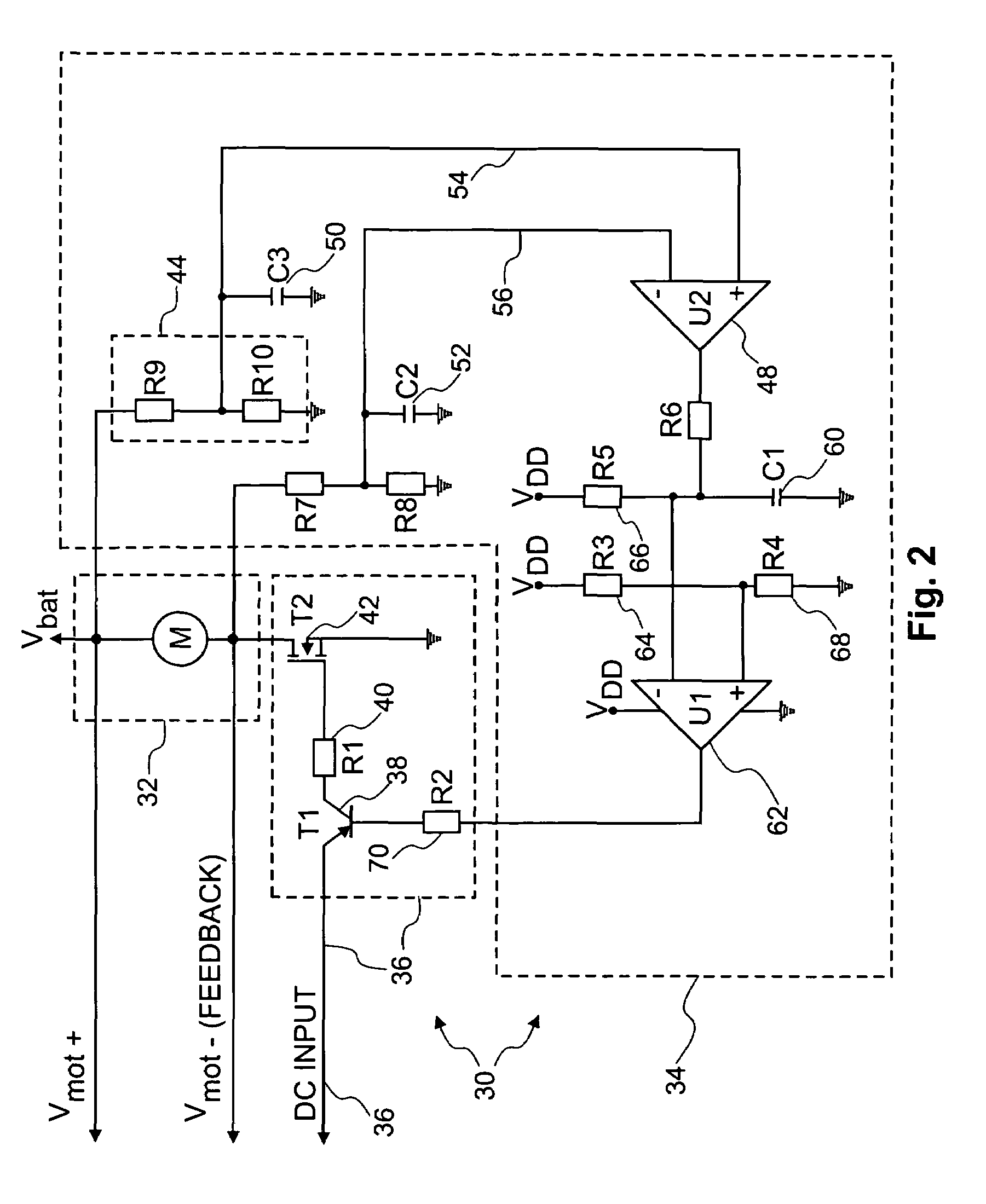

Auto-protected power modules and methods

InactiveUS7542251B2Improve performanceImprove simplicityElectric motor controlVehicle heating/cooling devicesPower controllerEngineering

A linear power controller system may be implemented that includes locked-rotor protection circuitry that is primarily assembled using analog circuit components. The locked rotor protection circuitry may be part of a power module in the system. The power module may be a switched power source that includes temperature circuit. A control loop may be established in the system to maintain the voltage across a motor that is driver by the power module. Circuitry for establishing a close loop with a motor may be positioned in a control head in the system or in a power module in the system. Temperature protection circuitry may be integrated into a current source in the power module to provide automatic thermal shutdown of the current source. The linear power module may specifically include analog circuitry that is arranged to establish a control loop with the motor.

Owner:CARTER GRP INC

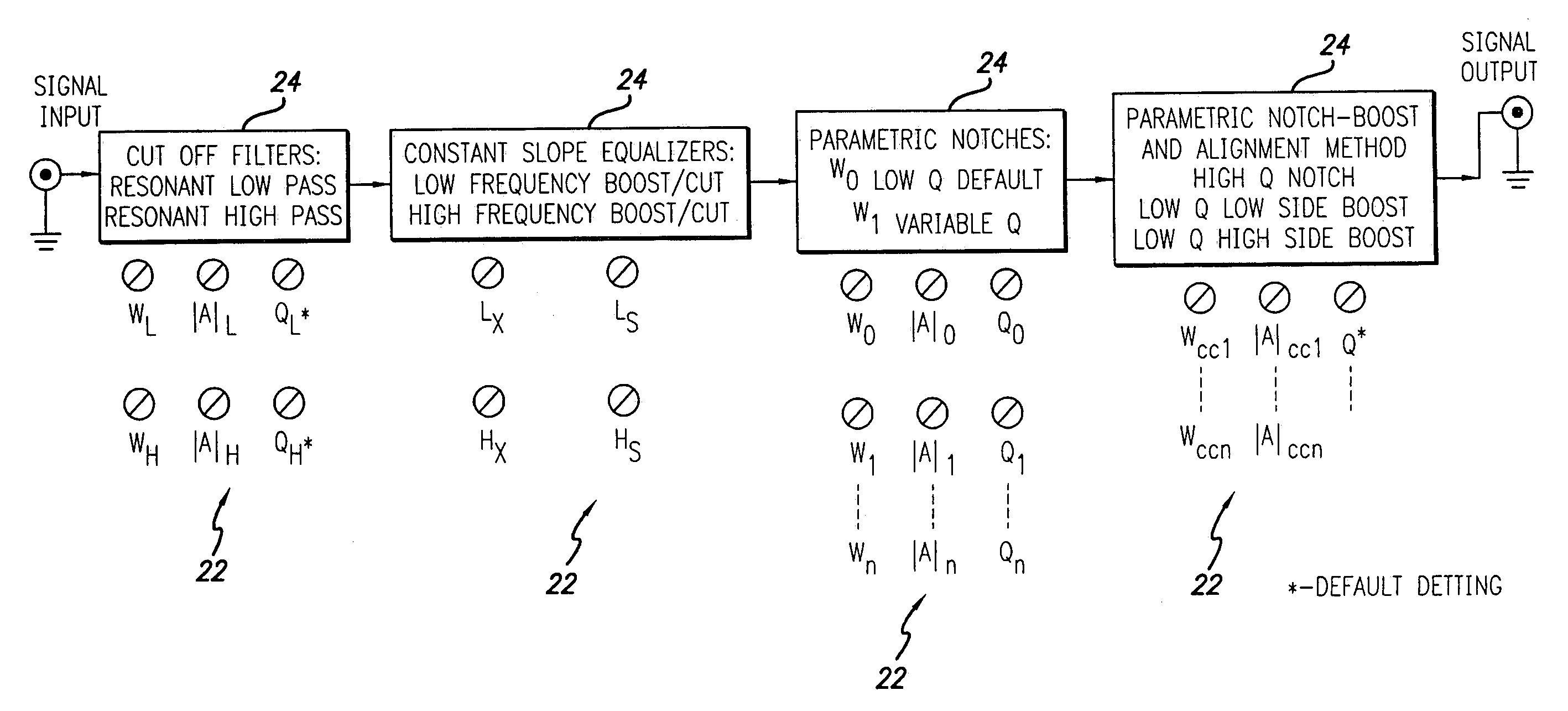

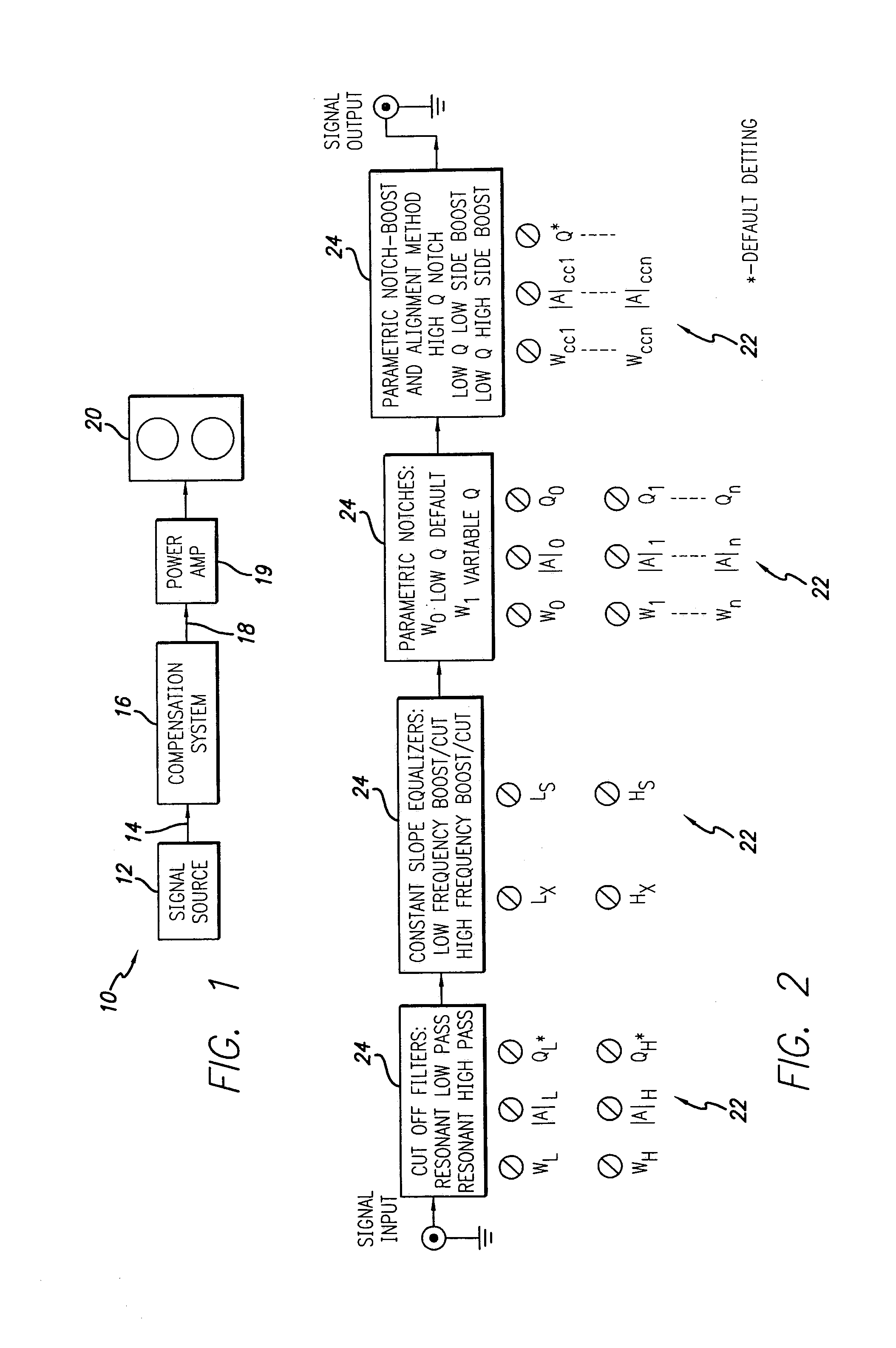

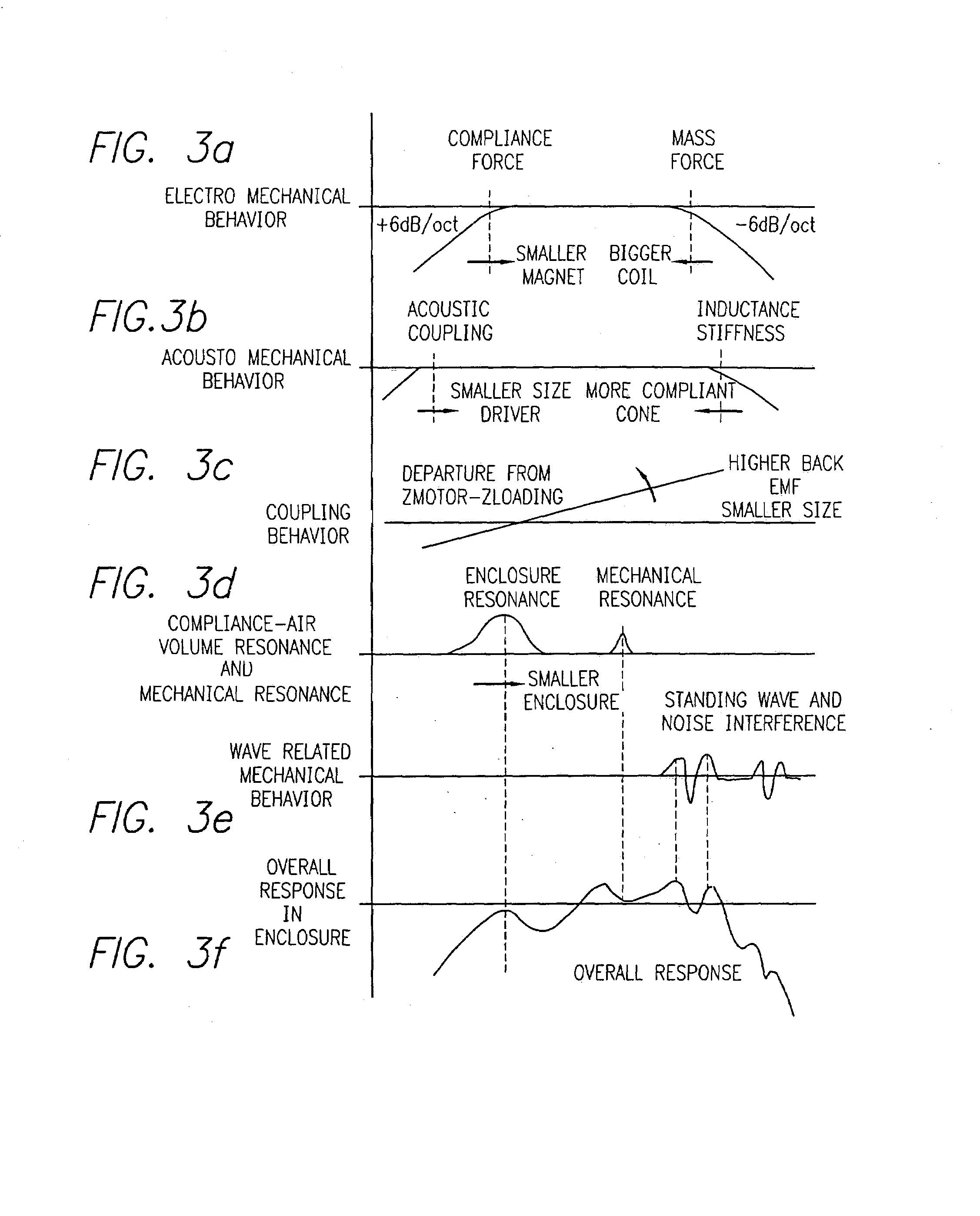

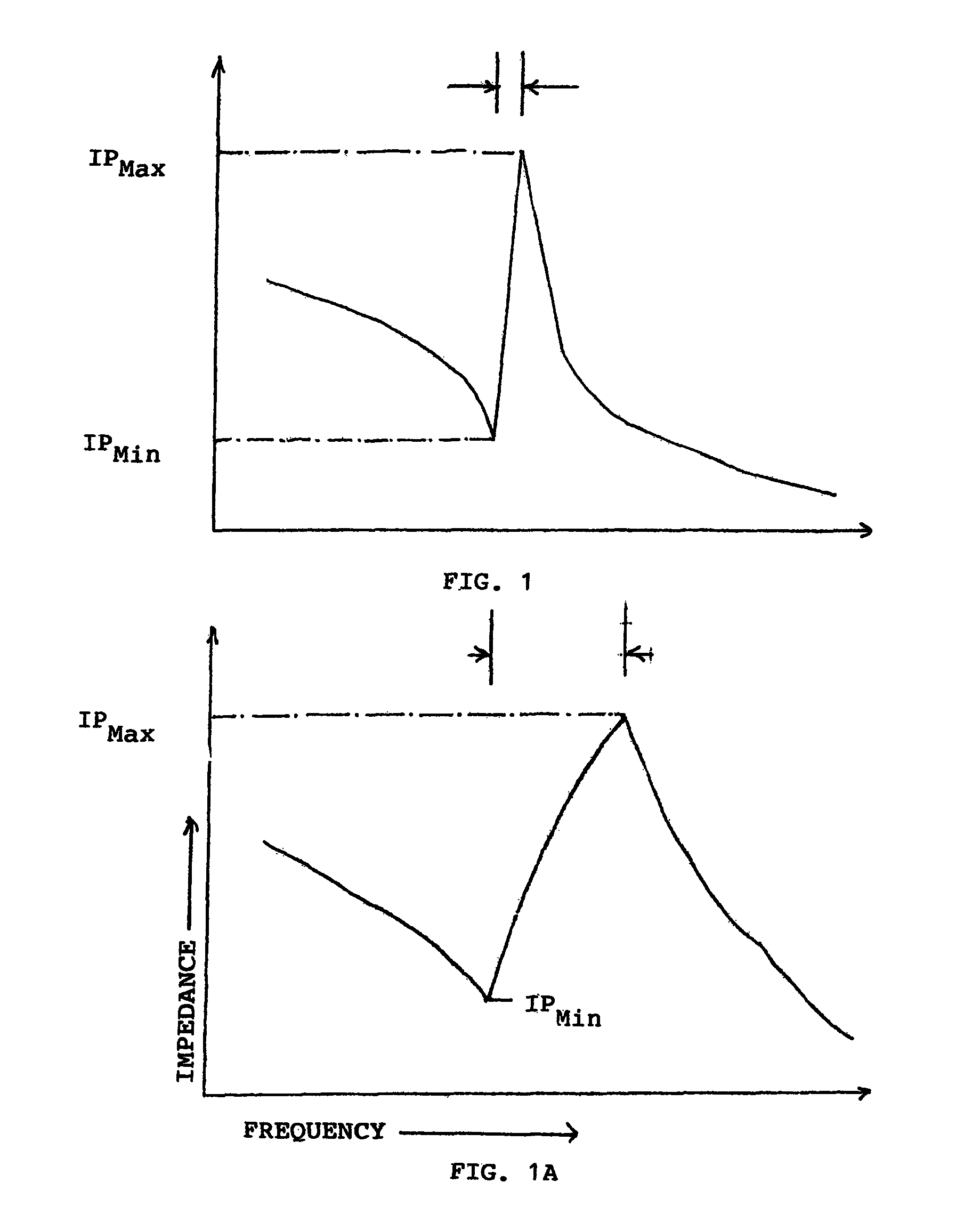

Compensation system and method for sound reproduction

InactiveUS7184556B1Reduce distortion problemsEnhance the imageGain controlDigital signal tone/bandwidth controlElectricityDigital signal processing

A sound compensation system alters an electrical audio signal for input to a sonic reproduction device having associated behavioral characteristics. The behavior characteristics of the device are defined by individual or groups of individual components of the sonic reproduction device and include mechanical, acoustic and electromagnetic behaviors. The model includes a plurality of filters that simulate at least one of the behavior characteristics of the sonic reproduction device. The filters are defined by digital signal processes or by analog circuits and are characterized by one or more of an associated frequency, time, phase and transient response. These responses combine to define an overall response for the model. The filters include adjustable parameters which are used to alter filter responses to produce responses that are conjugates to the responses of the unaltered filters and thus the sonic reproduction device. A controller modifies the parameters.

Owner:MICROSOFT TECH LICENSING LLC

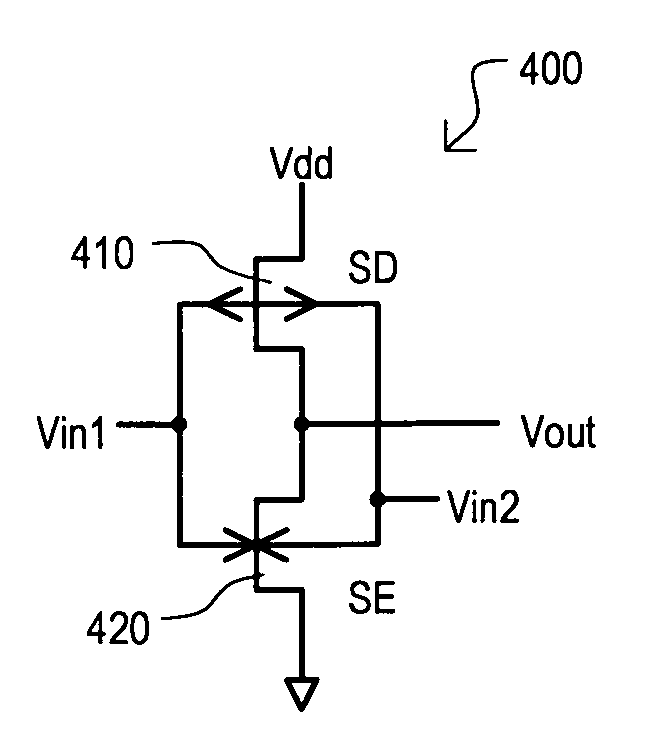

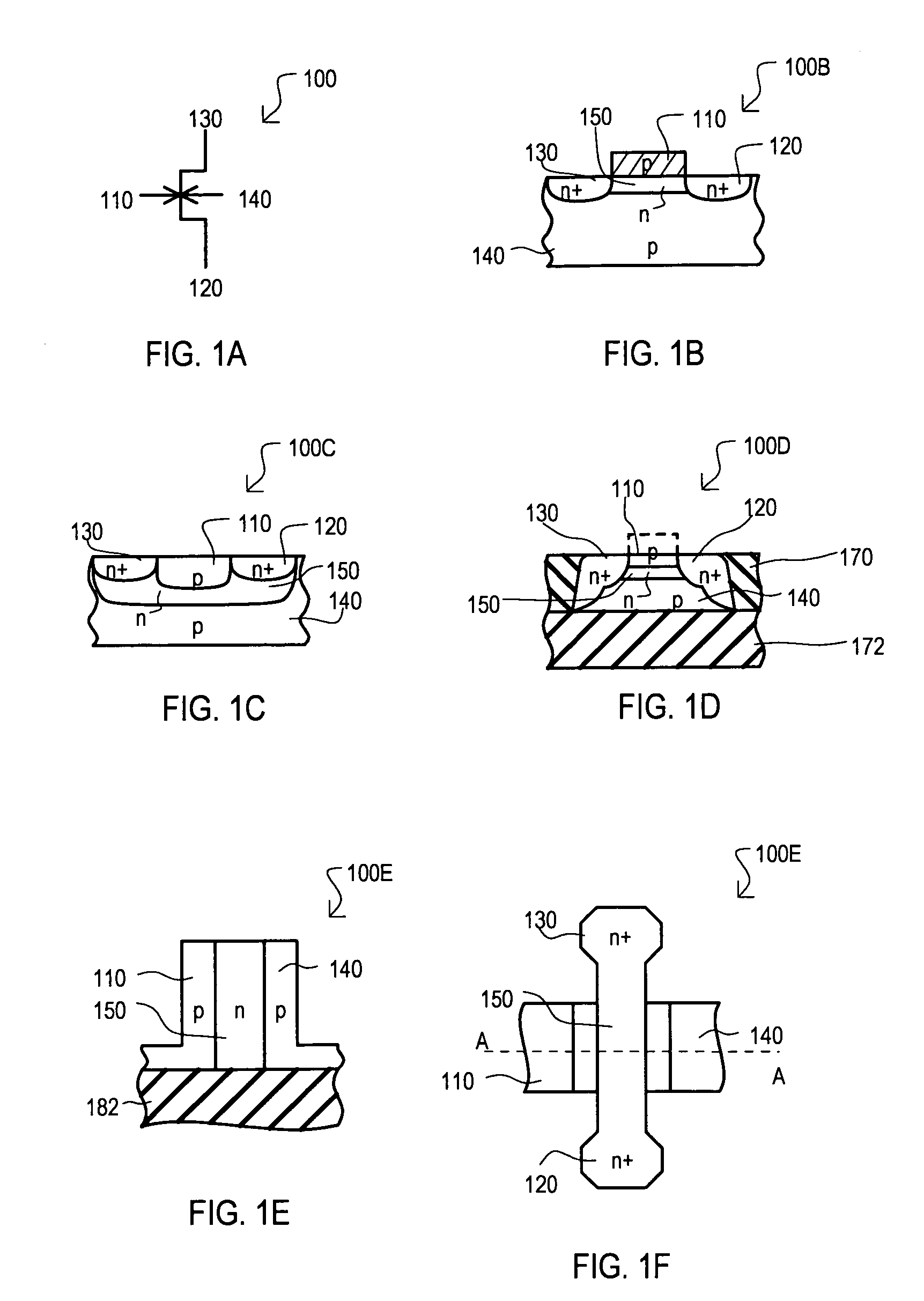

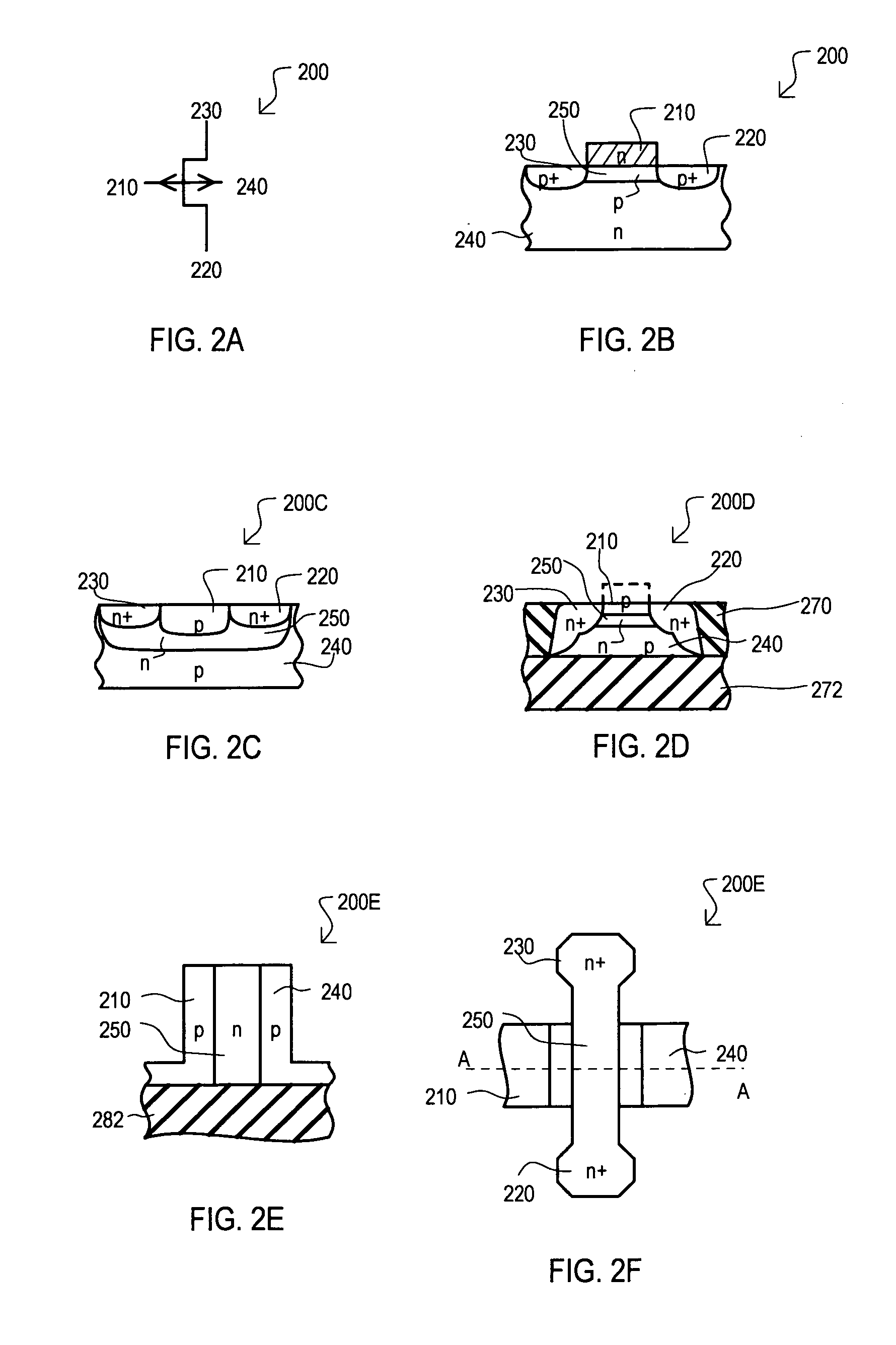

Circuit configurations having four terminal JFET devices

InactiveUS20070262793A1Logic circuits characterised by logic functionSolid-state devicesPhase detectorMultiplexer

Circuits using four terminal junction field effect transistors (JFETs) are disclosed. Such circuits can include various static and dynamic logic circuits, flip-flops, multiplexer, tri-state driver, phase detector, logic having variable speeds of operation, and / or analog circuit with such four terminal JFETs operating in a linear or nonlinear mode.

Owner:MIE FUJITSU SEMICON

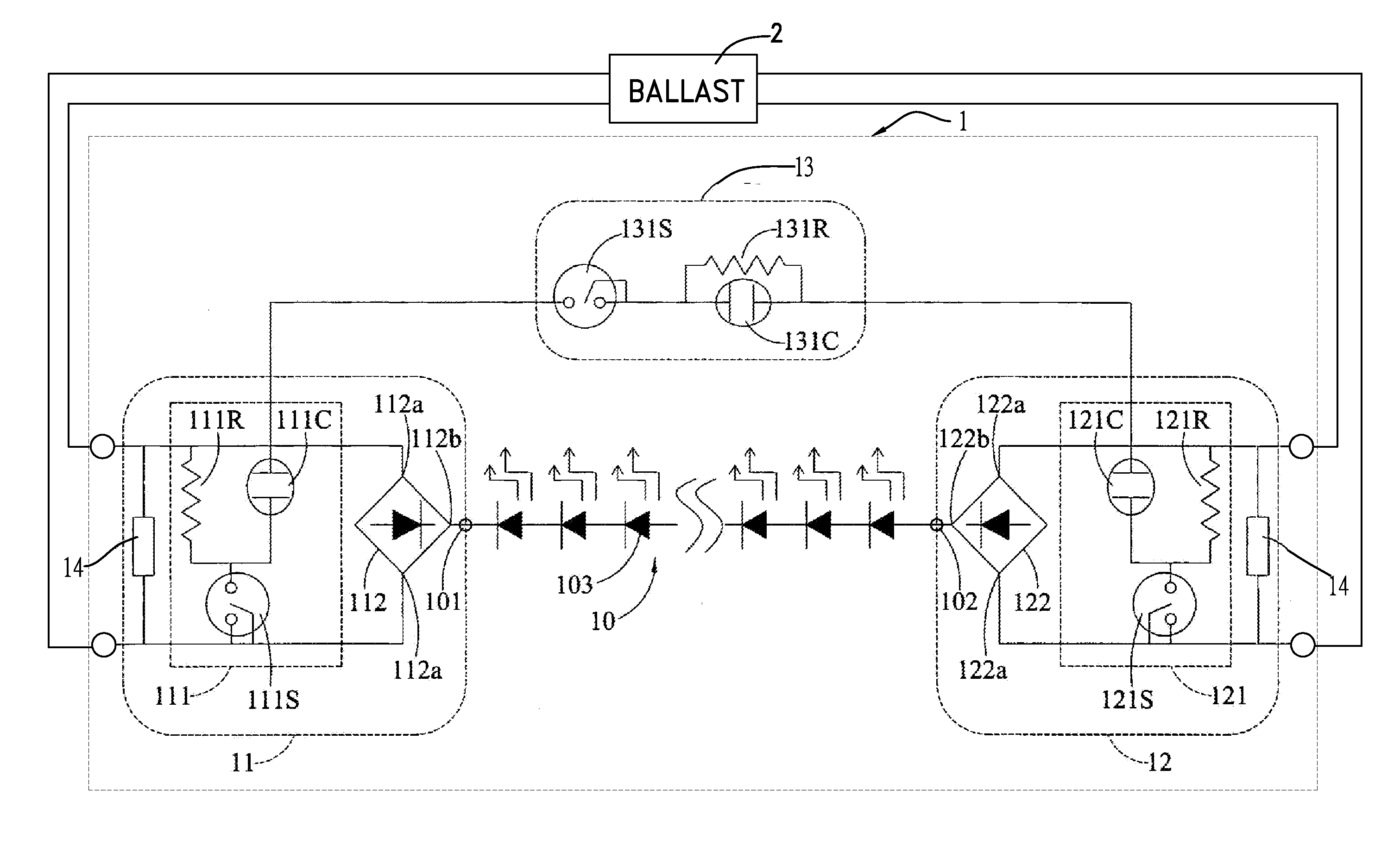

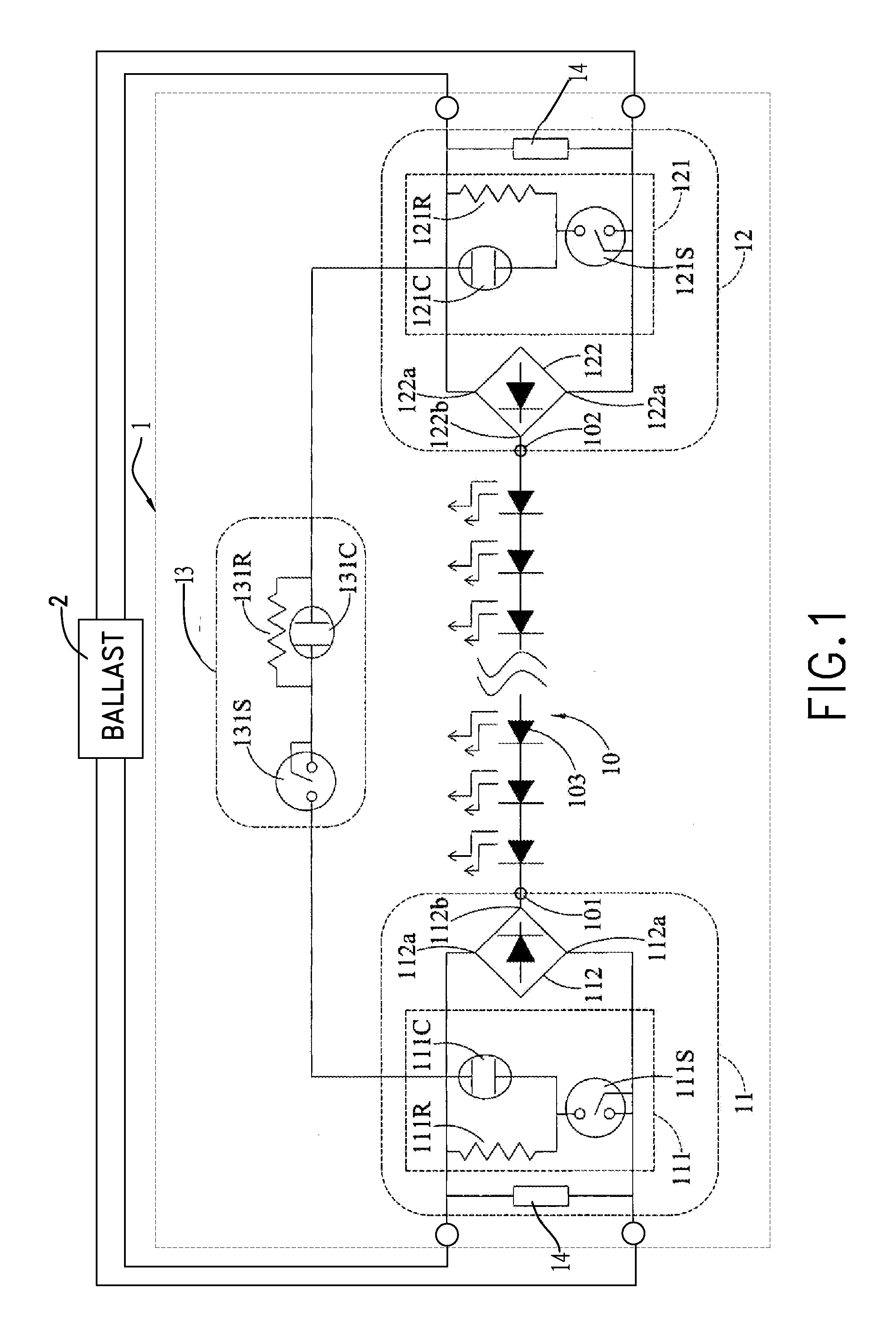

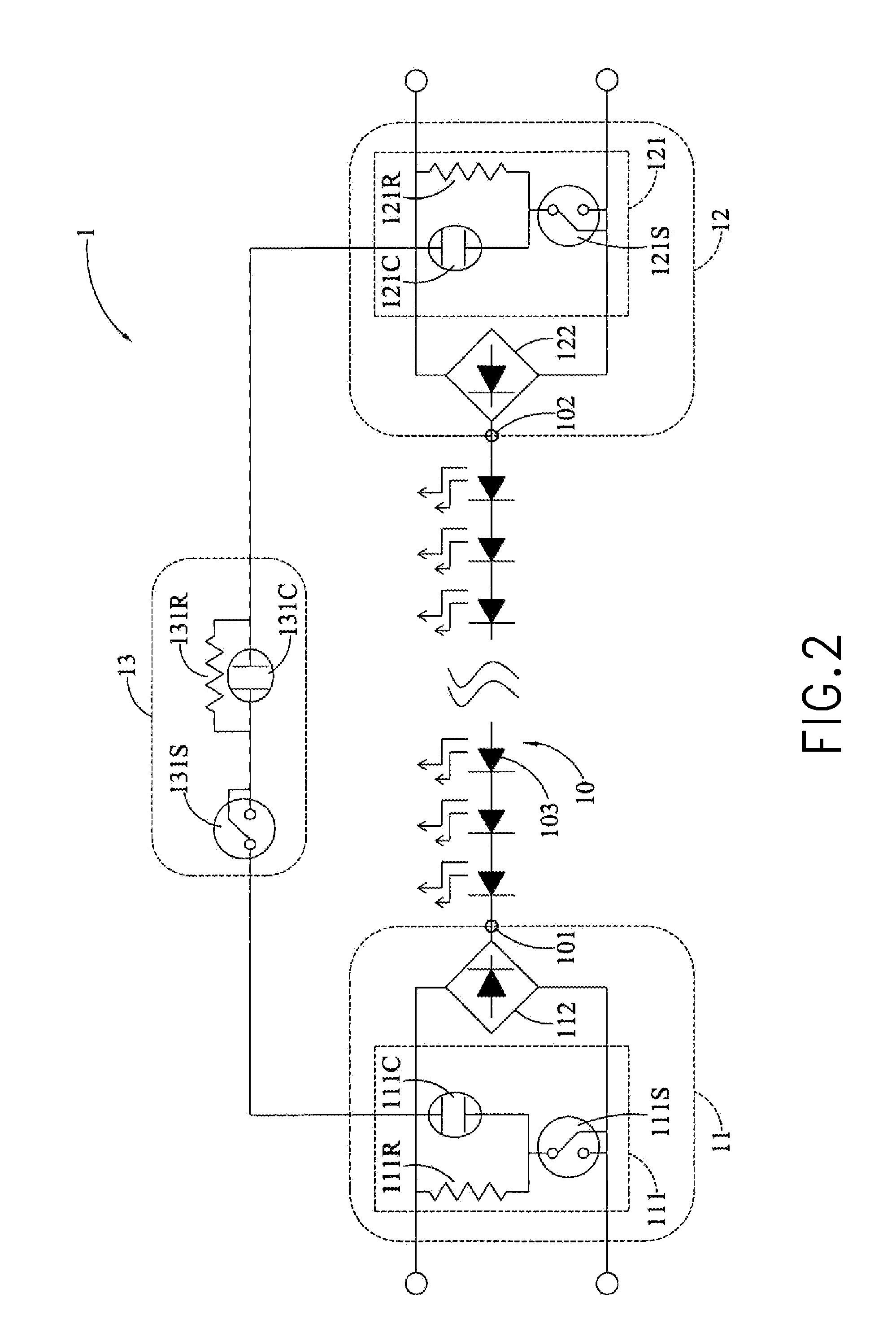

Light-emitting diode tube

InactiveUS20140225519A1Cost-effectiveElectrical apparatusElectroluminescent light sourcesHarmonicFluorescence

A light-emitting diode (LED) tube is applied to a lamp holder with a ballast, and has a lighting module, a first control module and a second control module connected to two ends of the lighting module, and a harmonic elimination module connected to the first and second control modules and parallelly connected to the lighting module. Each of the first control module and the second control module has a simulation circuit unit and a rectification unit. Each of the simulation circuit units and the harmonic elimination module has a switching element. The first and second control modules adjust electrical signals from the ballast, and the harmonic elimination module eliminates harmonic waves generated by the ballast so that the lighting module is compatible with the ballast and is lit. Accordingly, the LED tube can be directly mounted on a fluorescent lamp holder with the lamp holder intact.

Owner:POESEN ELECTRONICS

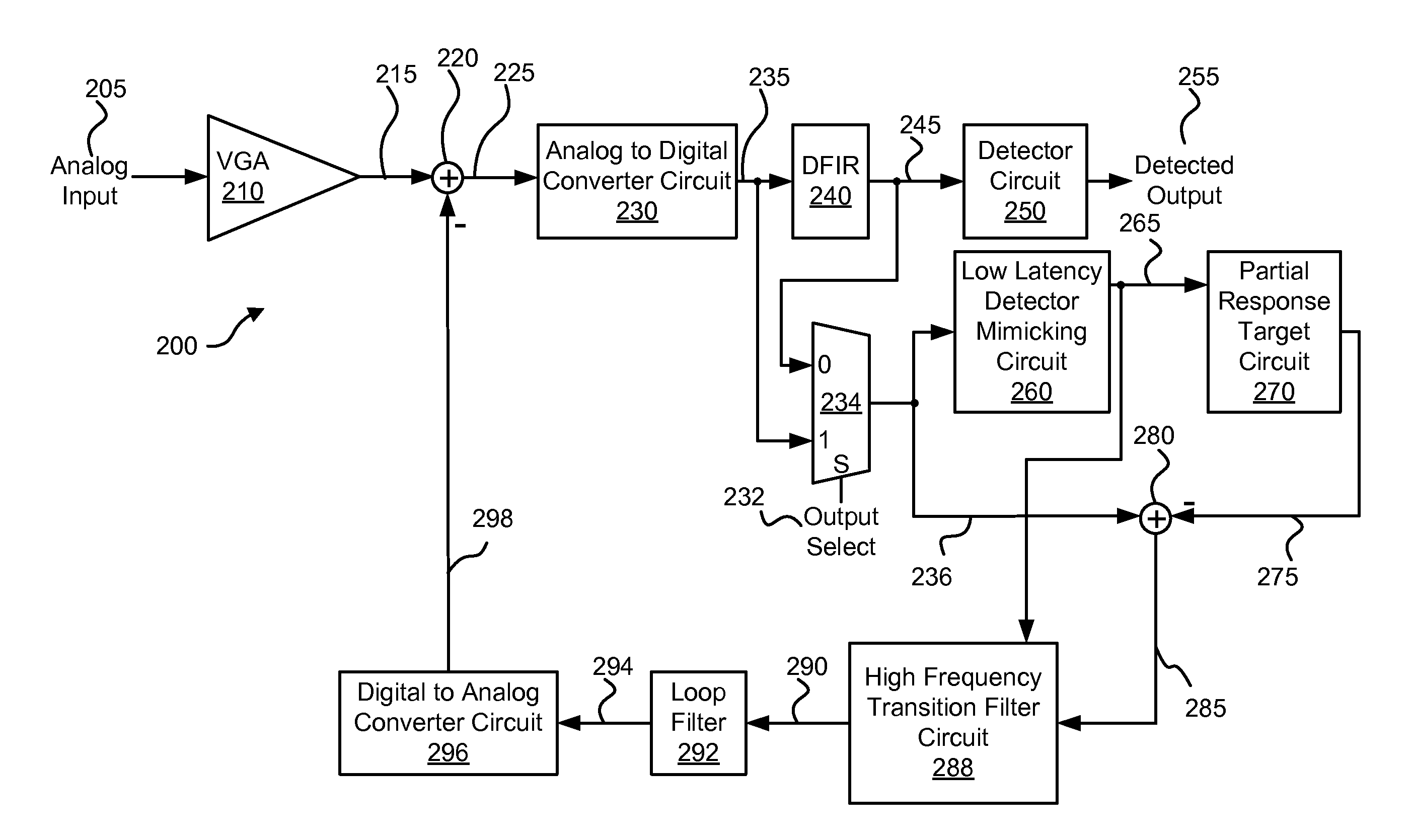

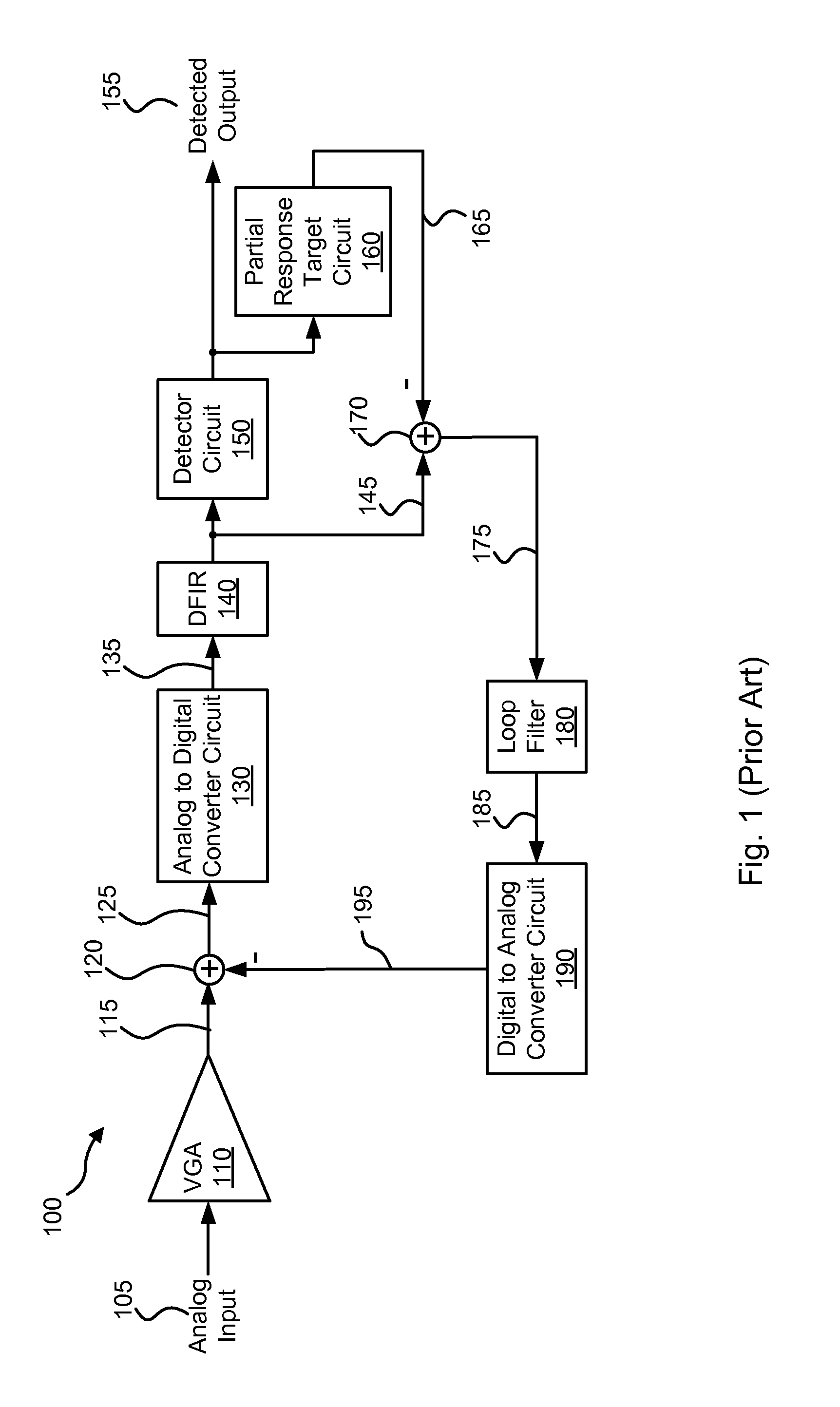

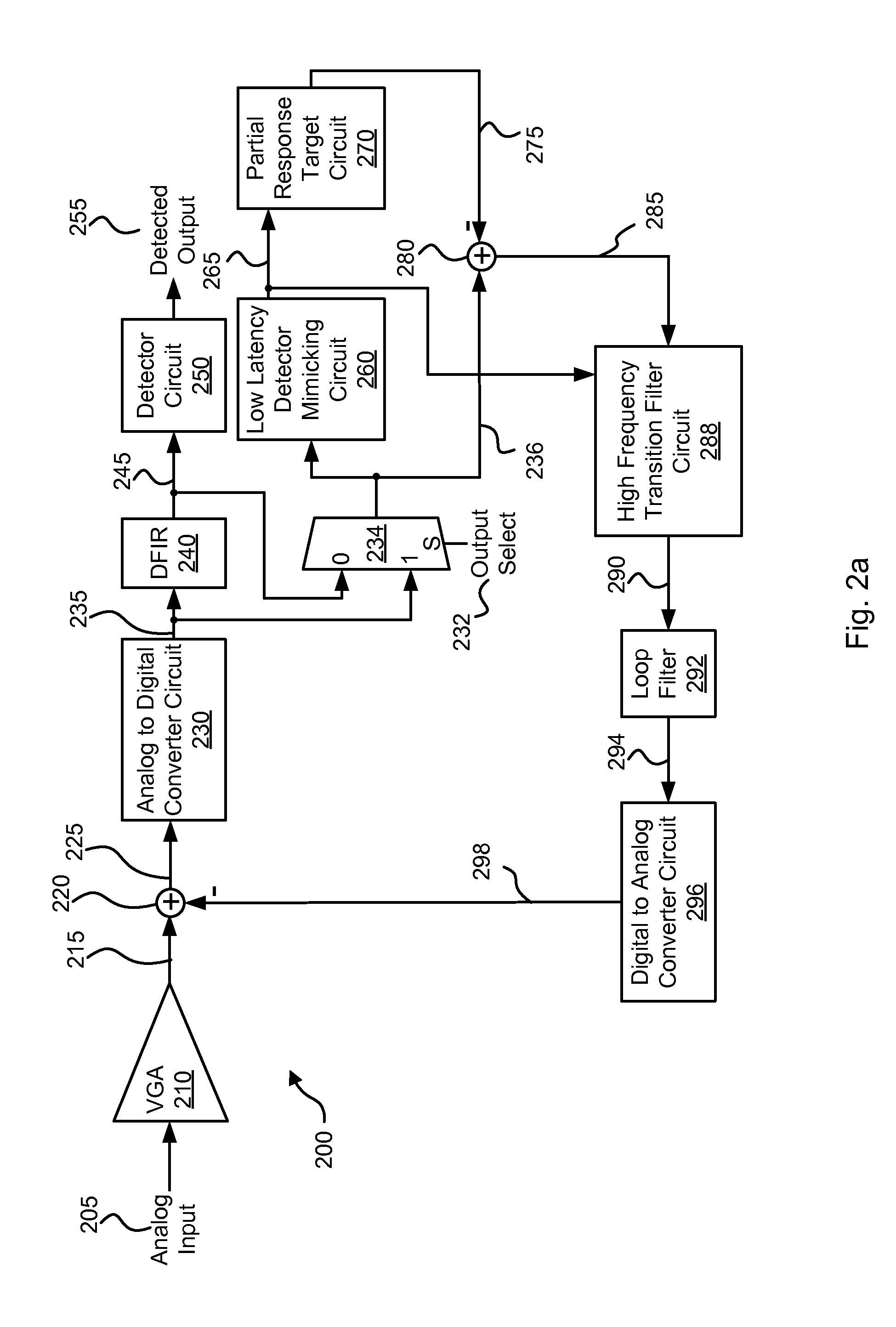

Systems and methods for low latency noise cancellation

ActiveUS8295001B2Reduce distractionsReduce the valueModification of read/write signalsRecord information storageDetector circuitsData simulation

Owner:AVAGO TECH INT SALES PTE LTD

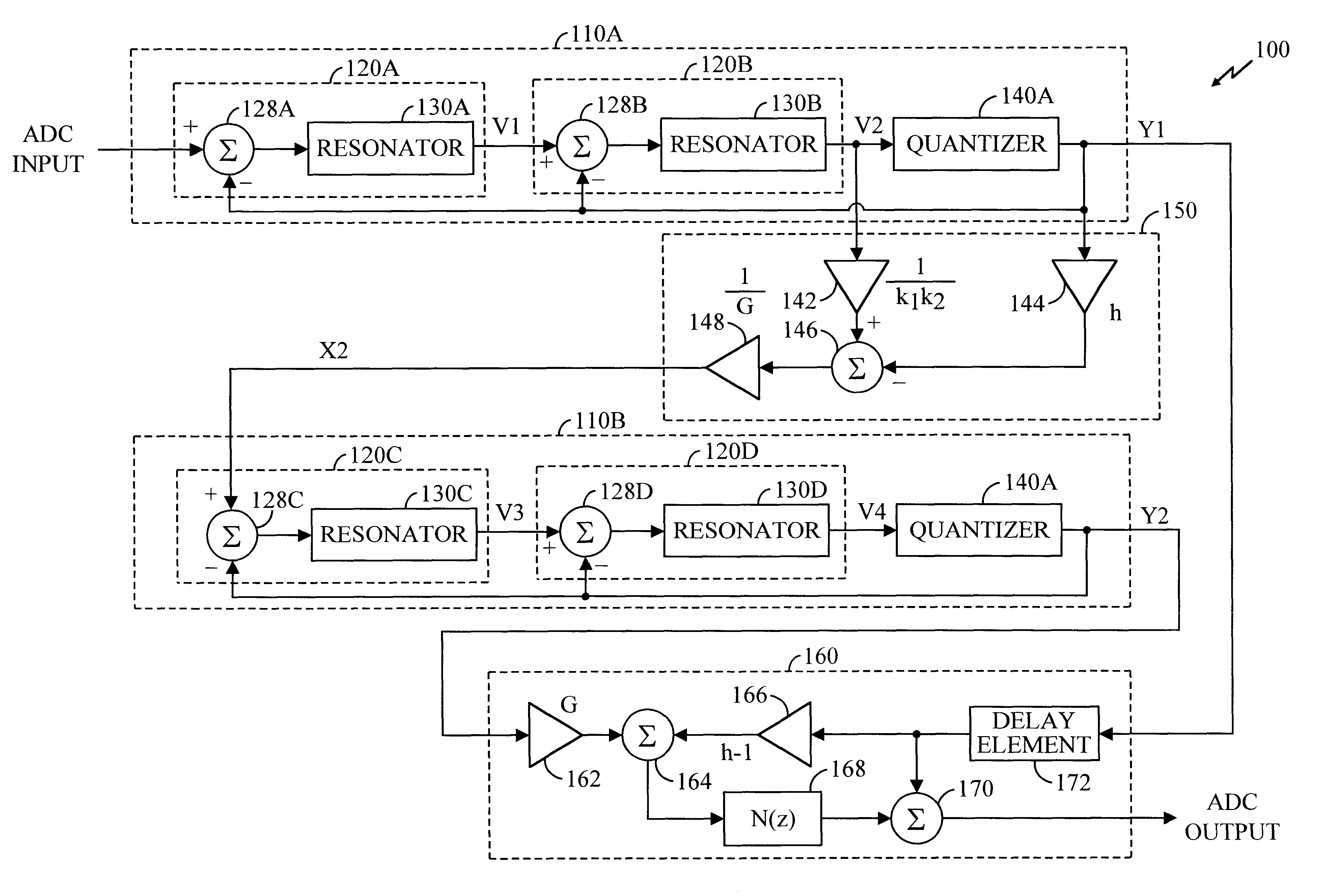

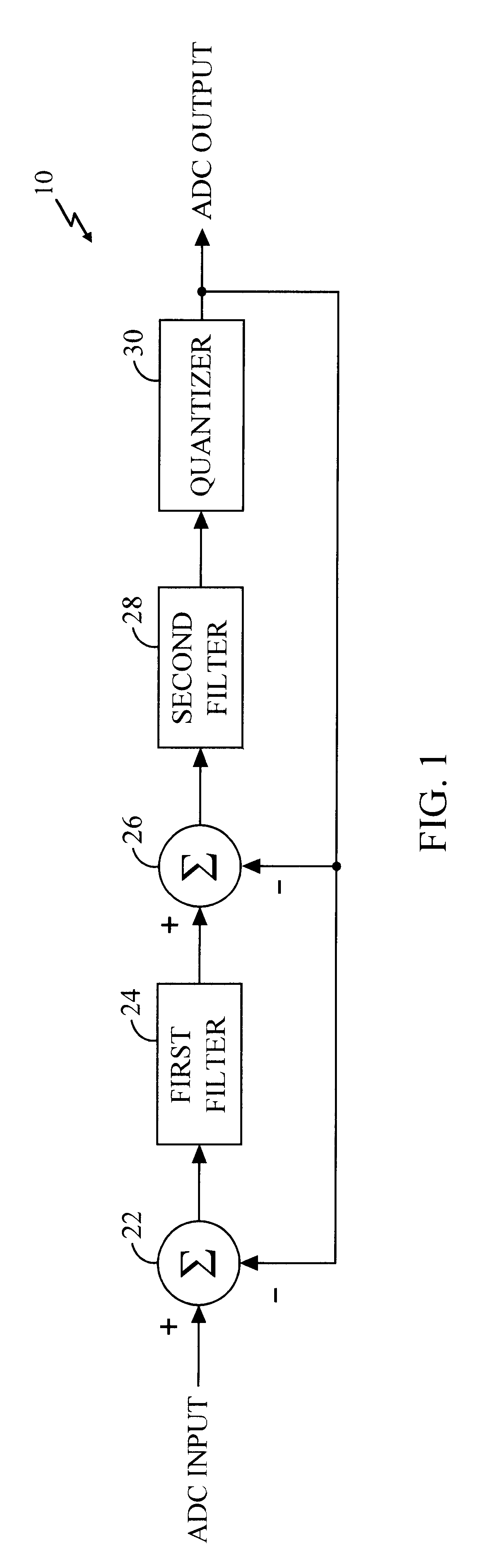

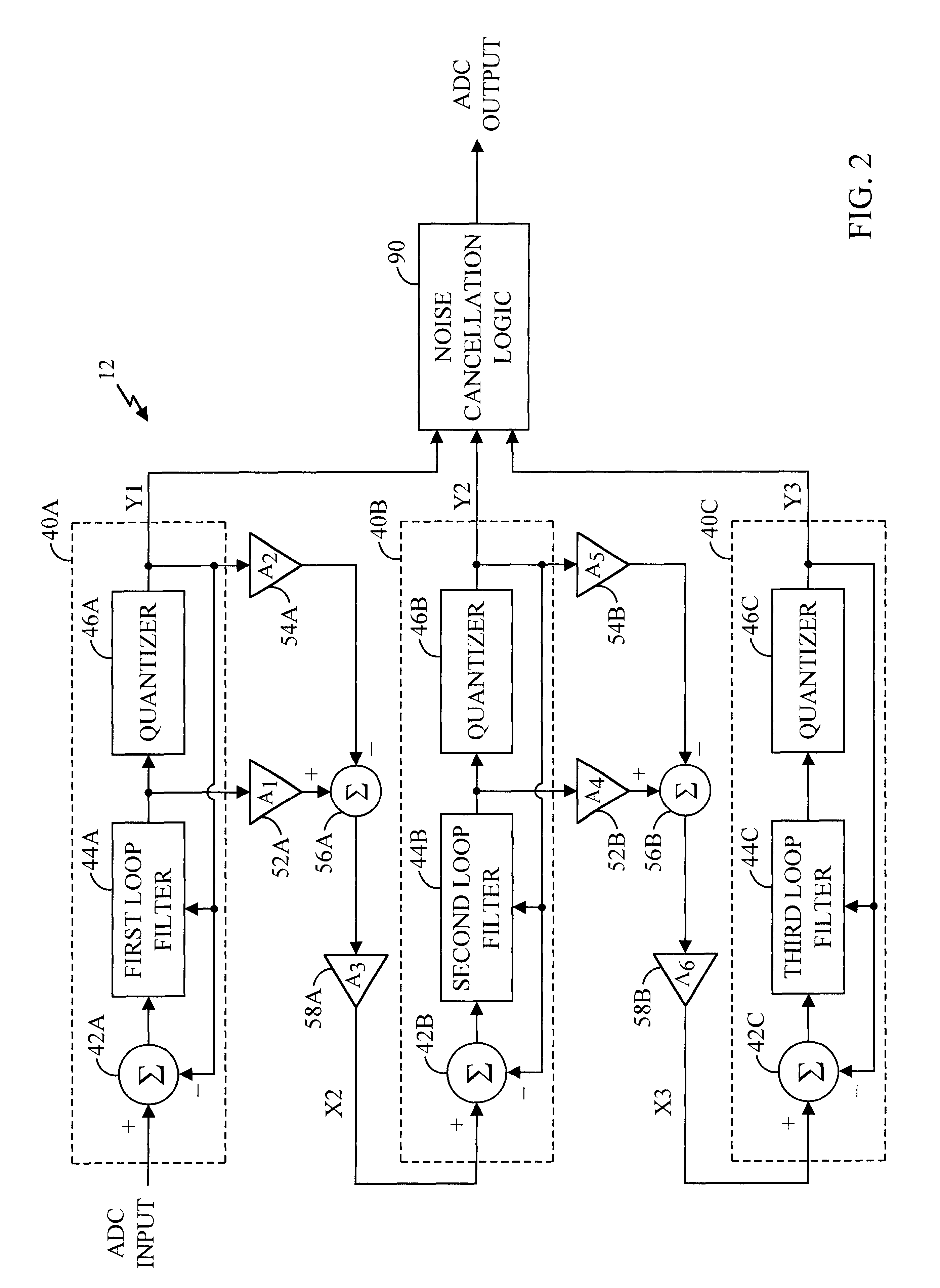

Multi-sampling SIGMA-DELTA analog-to-digital converter

A bandpass SIGMADELTA ADC utilizing either a single-loop or a MASH architecture wherein the resonators are implemented as either a delay cell resonator, a delay cell based resonator, a Forward-Euler resonator, a two-path interleaved resonator, or a four-path interleaved resonator. The resonator can be synthesized with analog circuit techniques such as active-RC, gm-C, MOSFET-C, switched capacitor, or switched current. The switched capacitor or switched current circuits can be designed using single-sampling, double-sampling, or multi-sampling circuits. The non-stringent requirement of a SIGMADELTA ADC using switched capacitor circuits allows the ADC to be implemented in a CMOS process to minimize cost and reduce power consumption. Double-sampling circuits provide improved matching and improved tolerance to sampling clock jitter. In particular, a bandpass MASH 4-4 SIGMADELTA ADC provides a simulated signal-to-noise ratio of 85 dB at an oversampling ratio of 32 for a CDMA application. The bandpass SIGMADELTA ADC can also be used in conjunction with undersampling to provide a frequency downconversion.

Owner:QUALCOMM INC

Body-worn sensor for characterizing patients with heart failure

ActiveUS20140187990A1Easy to coverSimple and low-costElectrocardiographySensorsA d converterEngineering

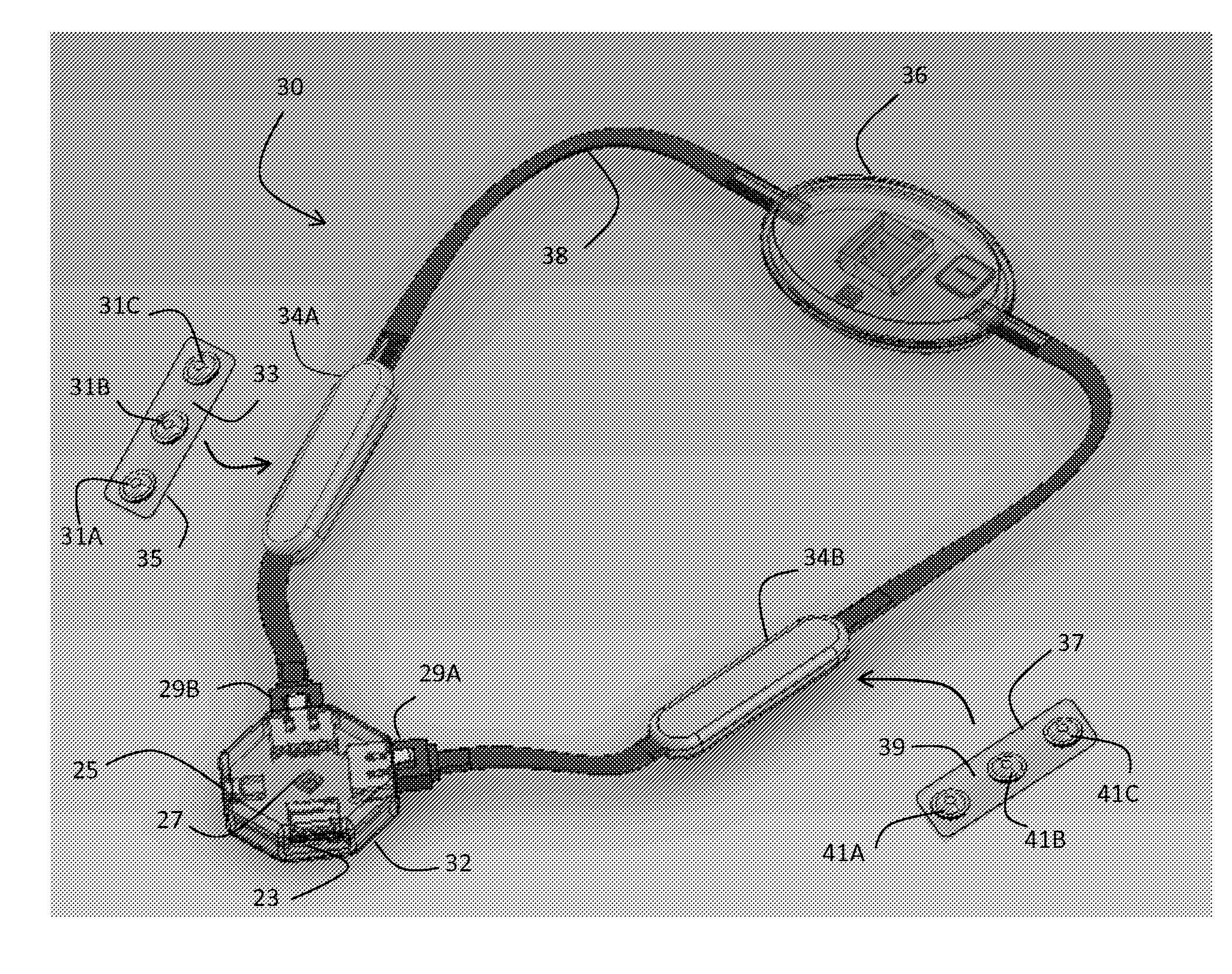

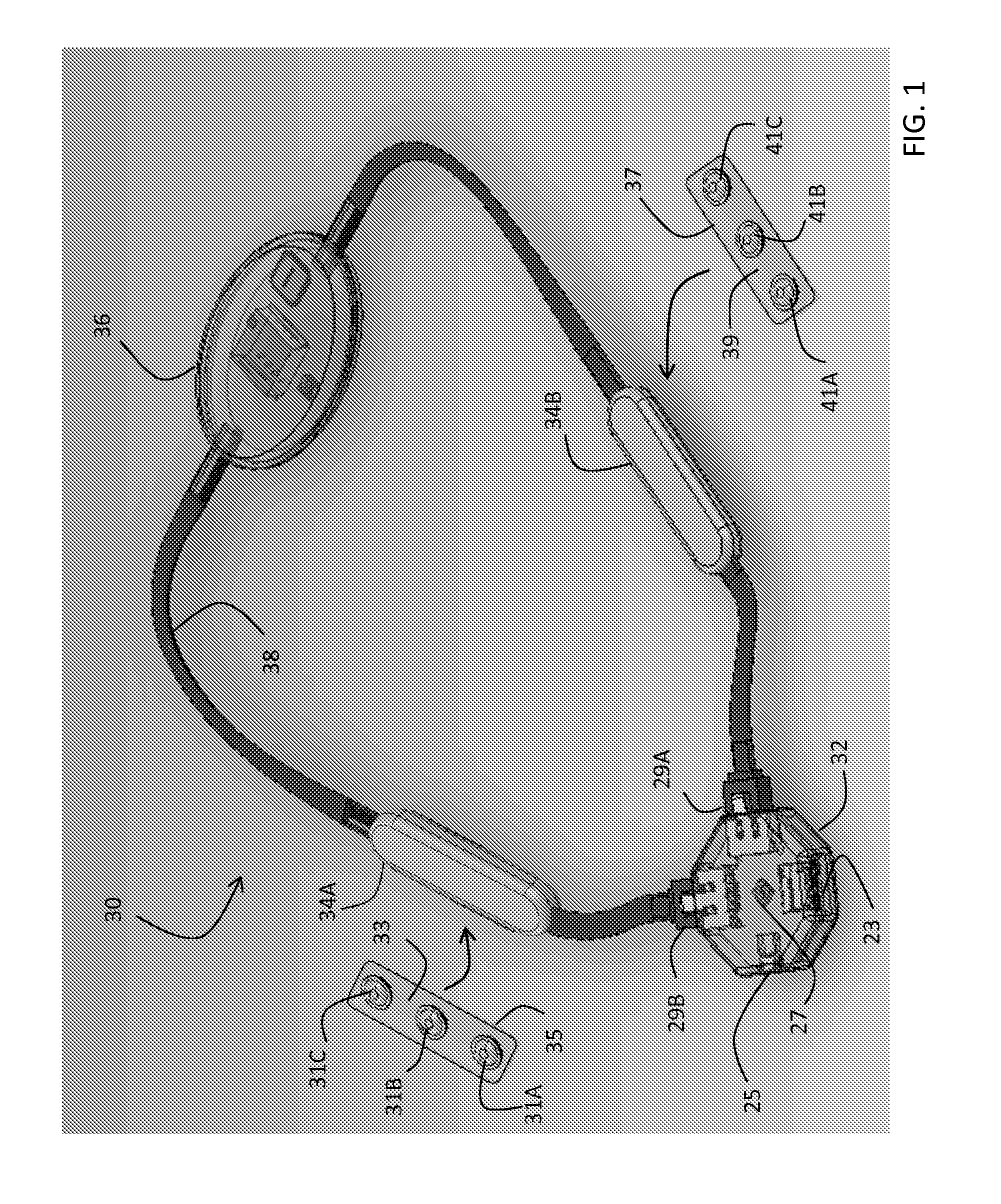

The invention provides a sensor for measuring both impedance and ECG waveforms that is configured to be worn around a patient's neck. The sensor features 1) an ECG system that includes an analog ECG circuit, in electrical contact with at least two ECG electrodes, that generates an analog ECG waveform; and 2) an impedance system that includes an analog impedance circuit, in electrical contact with at least two (and typically four) impedance electrodes, that generates an analog impedance waveform. Also included in the neck-worn system are a digital processing system featuring a microprocessor, and an analog-to-digital converter. During a measurement, the digital processing system receives and processes the analog ECG and impedance waveforms to measure physiological information from the patient. Finally, a cable that drapes around the patient's neck connects the ECG system, impedance system, and digital processing system.

Owner:BAXTER INT INC +1

Waveform generator for driving electromechanical device

ActiveUS9070856B1Small and inexpensiveReduce monetary roadblockMechanical vibrations separationPiezoelectric/electrostrictive device detailsConvertersHemt circuits

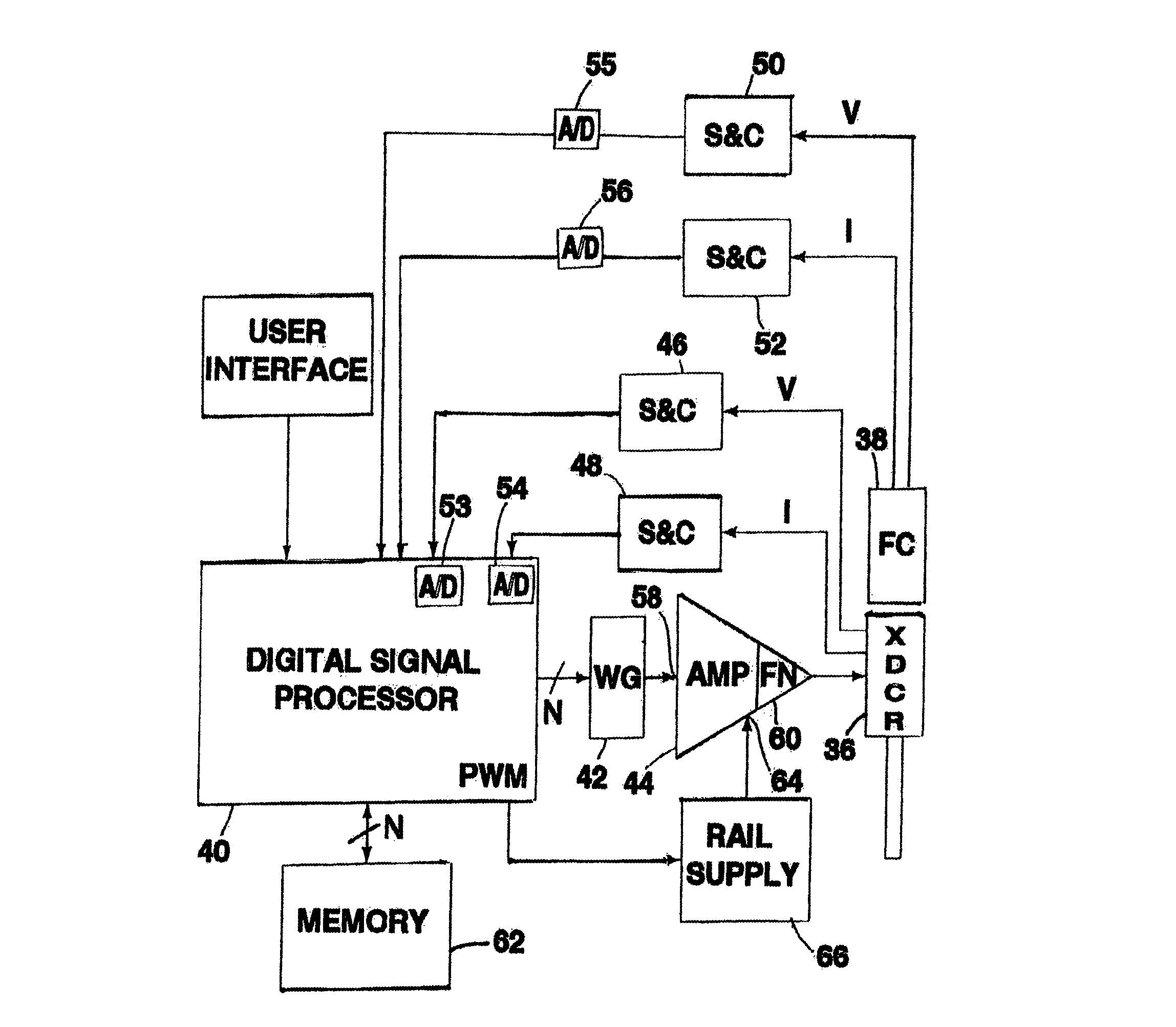

An electrical waveform generator for driving an electromechanical load includes a digital signal processor connected to a waveform generator component in turn connected to an amplifier section with a filter network, the latter being connected to sensing and conditioning circuit componentry that is in turn connected to analog-to-digital converter circuitry. A digital memory stores digitized voltage and current waveform information. The processor determines a phase difference between voltage and current waveforms, compares the determined phase difference to a phase difference command and generates a phase error or correction signal. The processor also generates an amplitude error signal for inducing the amplifier section to change its output amplitude to result in a predetermined amplitude error level for a respective one of the voltage and current waveforms.

Owner:MISONIX INC

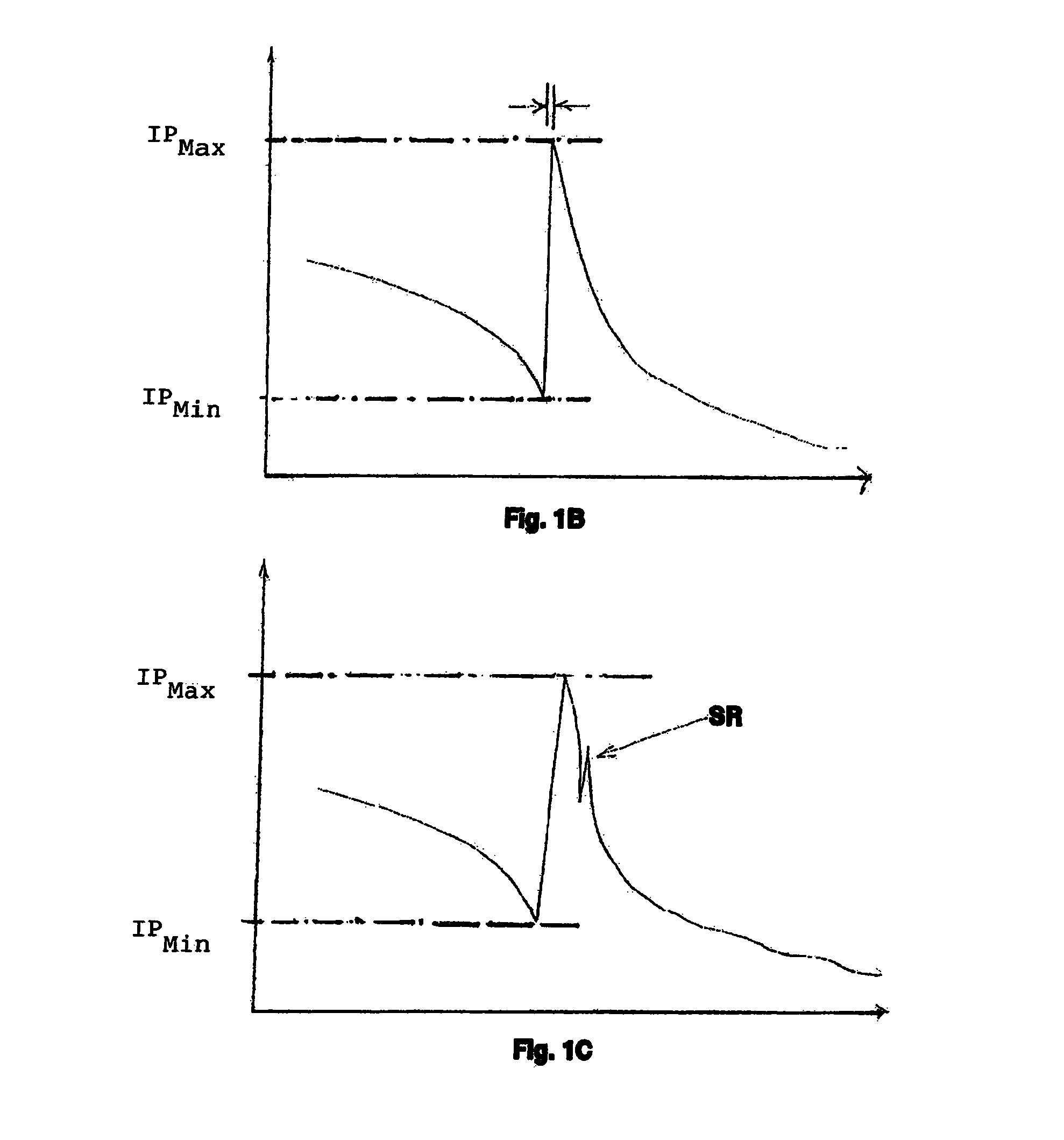

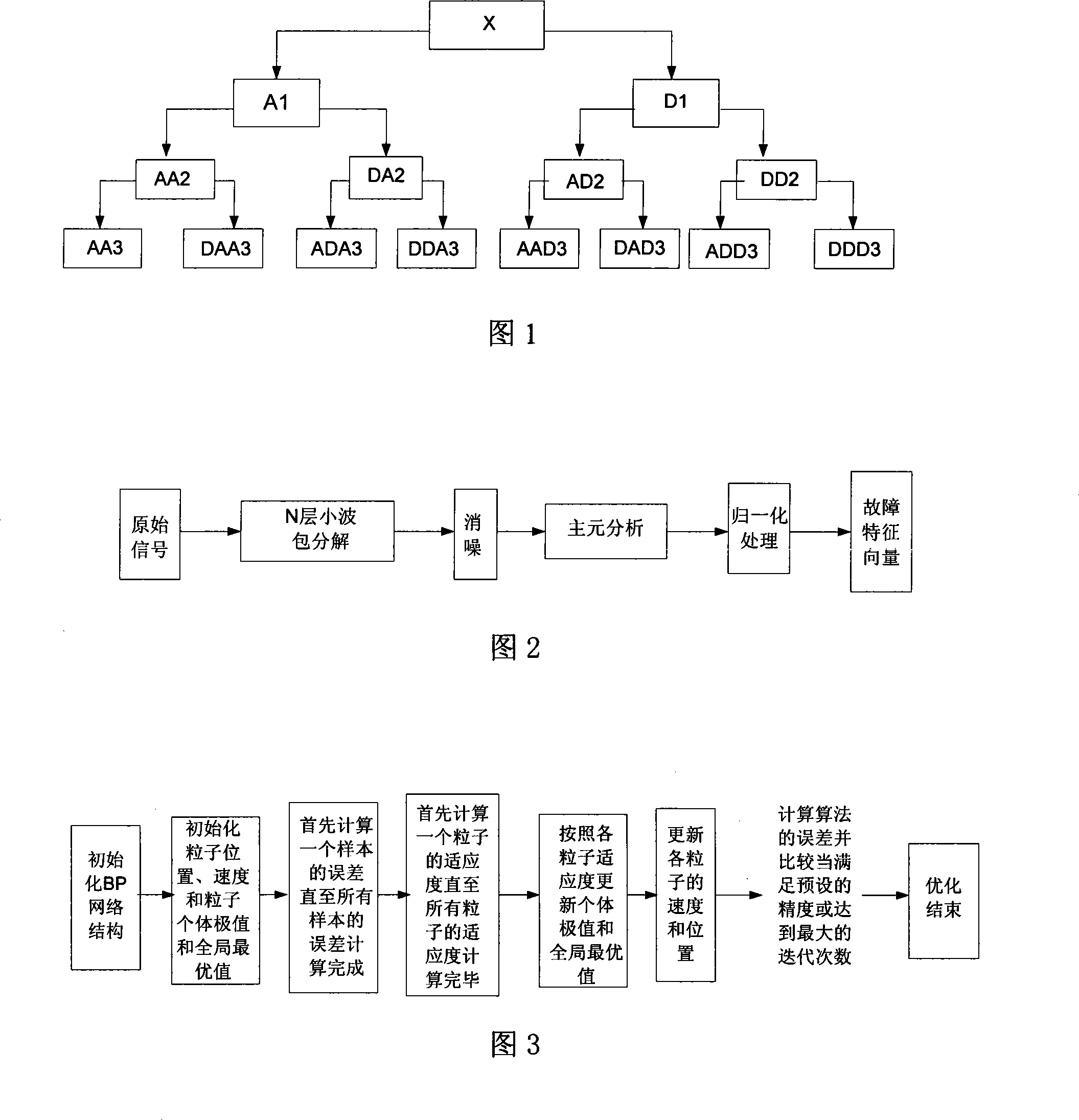

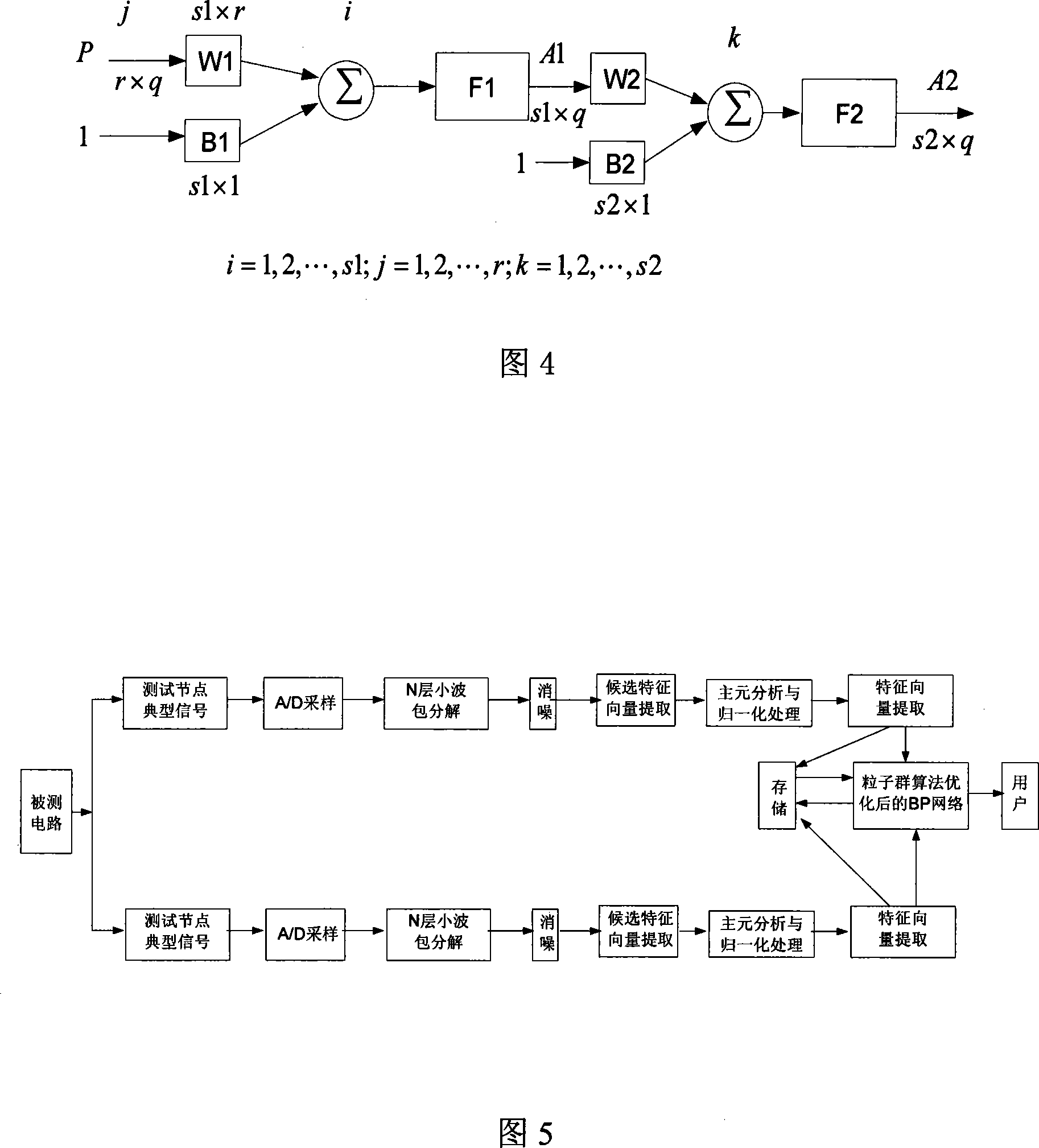

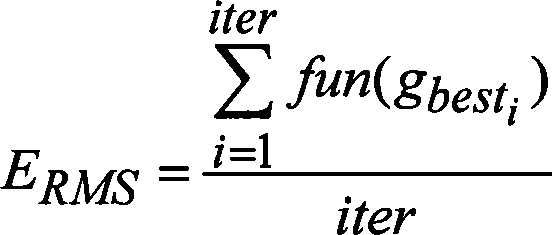

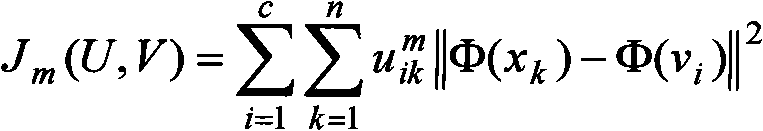

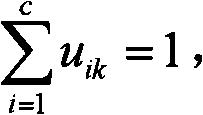

Analogue circuit fault diagnosis neural network method based on particle swarm algorithm

InactiveCN101221213AImplement extractionEliminate the effects ofElectronic circuit testingPhysical realisationNetwork ConvergencePrincipal component analysis

The invention discloses a neural network method for diagnosing analog circuit failures which is based on a particle swarm algorithm, and comprises the following steps: imposing an actuating signal to an analog circuit to be tested, measuring an actuating response signal in the testing nodes of the circuit, extracting the candidate signal of failure characteristics by implementing noise elimination and then wavelet packet transformation on the measured actuating response signal, extracting the failure characteristics information by further implementing orthogonal principal component analysis and normalization processing on the candidate signal of failure characteristics, and sending the failure characteristics information as samples to the neural network for implementing classification. The method adopts the particle swarm algorithm instead of a gradient descent method in traditional BP algorithms, thus leading the improved algorithm to be characterized in that the algorithm avoids the local minimum problem and has better generalization performance. The BP neural network method for diagnosing the analog circuit failures which is optimized on the basis of particle swarm can obviously reduce iteration times in the algorithm, improve the precision of network convergence, and improve diagnosis speed and precision.

Owner:HUNAN UNIV

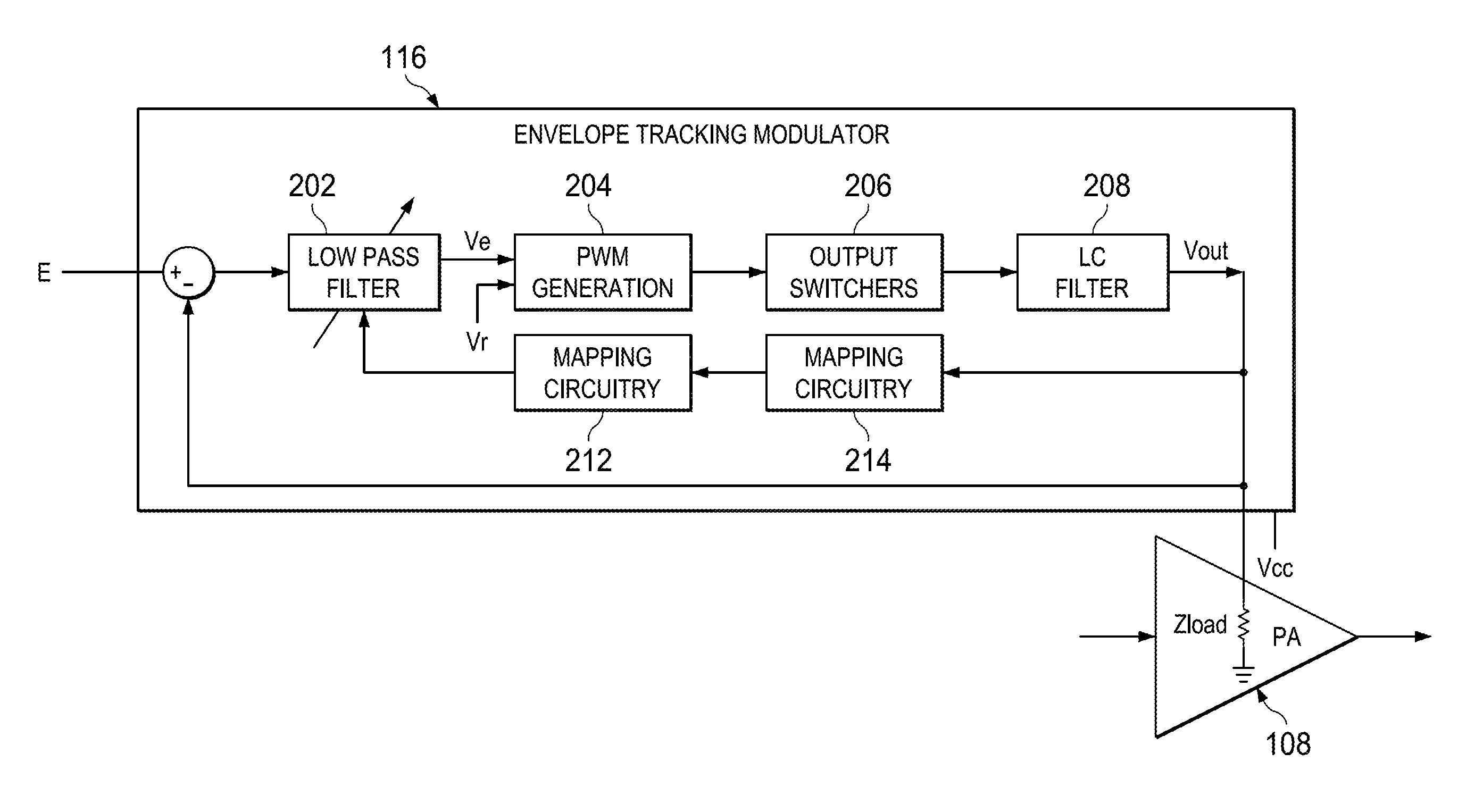

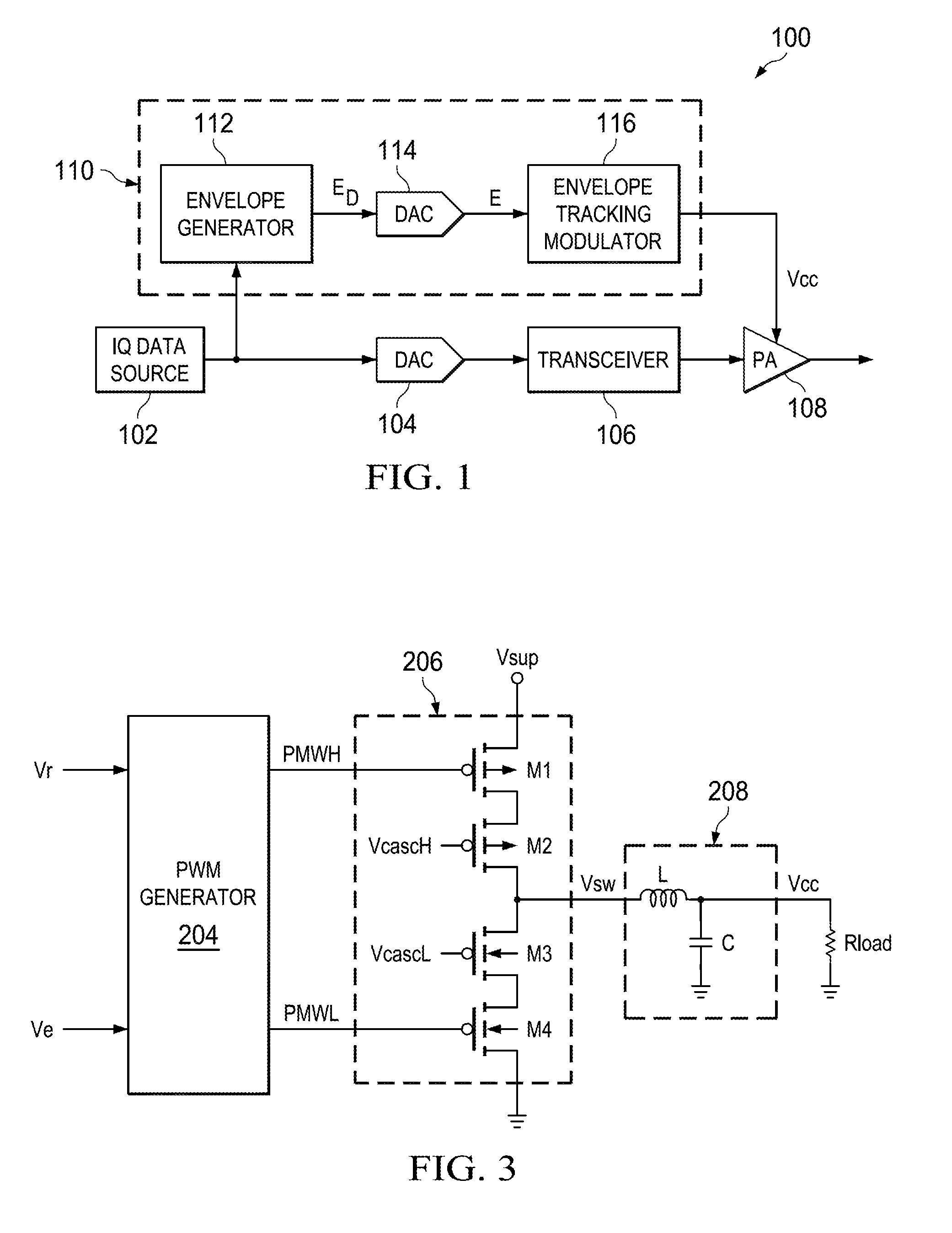

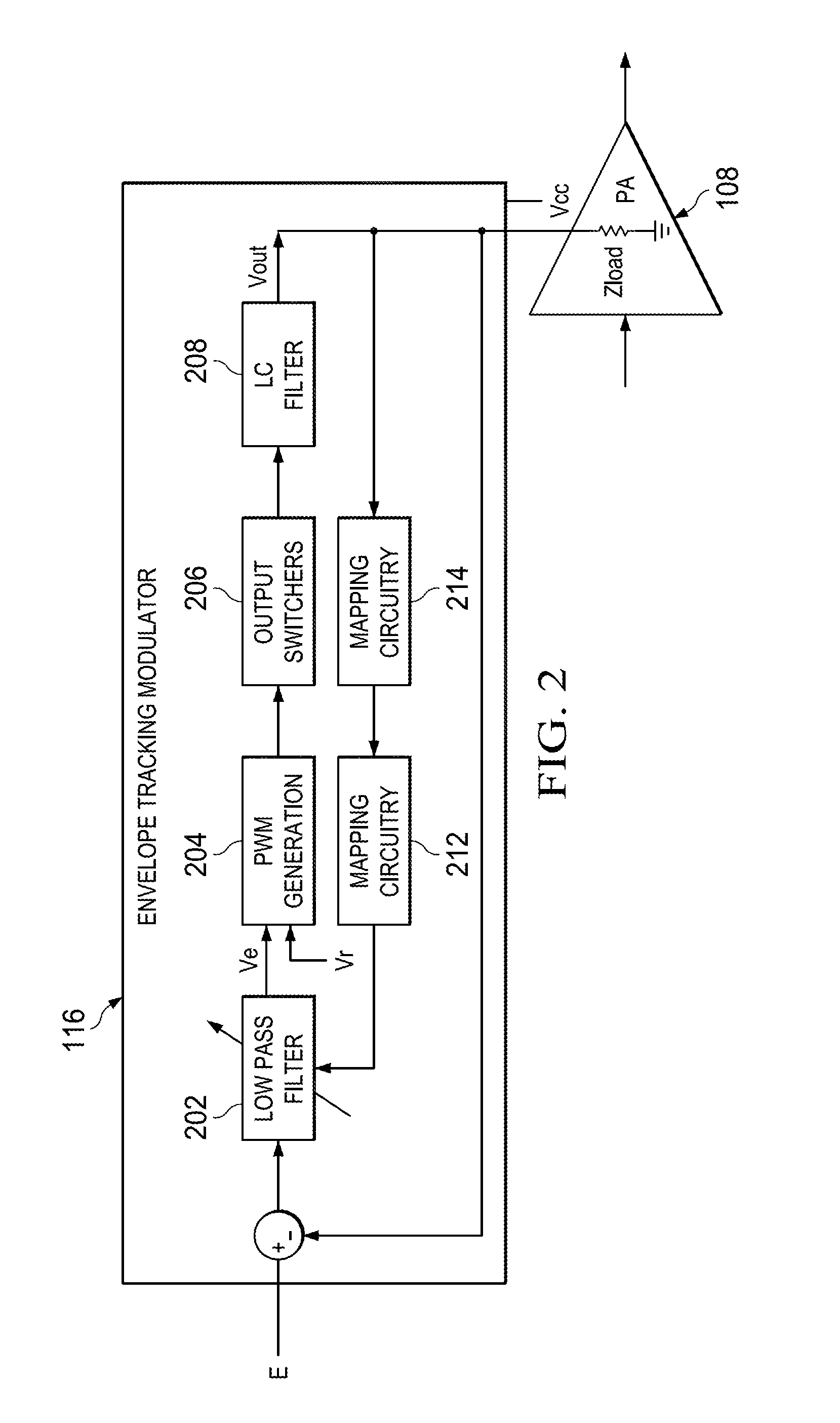

Envelope Tracking Apparatus and Method

ActiveUS20150236654A1Improved input-to-output frequency responseImprove system performanceHigh frequency amplifiersGain controlAudio power amplifierLow-pass filter

An apparatus comprises an amplifier having an input coupled to a radio frequency signal through a digital-to-analog circuit, an adaptive power supply having an output coupled to a bias voltage of the amplifier, wherein the output of the adaptive power supply is configured to have a shape similar to an envelope of the radio frequency signal and a feedback circuit comprising a sensing circuit and a mapping circuit, wherein the sensing circuit is configured to sense a current flowing from the adaptive power supply to the amplifier and sense the bias voltage of the amplifier, and wherein the mapping circuit is configured to sense the bias voltage of the amplifier, and wherein the mapping circuit is configured to generate a control signal for dynamically adjusting parameters of a low pass filter so as to stabilize the adaptive power supply.

Owner:FUTUREWEI TECH INC

Programmable cable with deskew and performance analysis circuits

ActiveUS20080106306A1Quality improvementBaseband system detailsPulse shapingDifferential signalingEngineering

An HDMI cable carries high speed encoded data which are transmitted differentially over data channels, along with a clock. High-frequency loss and differential skew within a differential signal may be compensated by analog circuits embedded in the cable. These embedded circuits are tuned at production for best performance by observing the quality of the recovered analog signal. The embedded circuits are powered by a combination of power sources, both carried within the cable, and harvested from the high-speed signals themselves.

Owner:REDMERE TECH

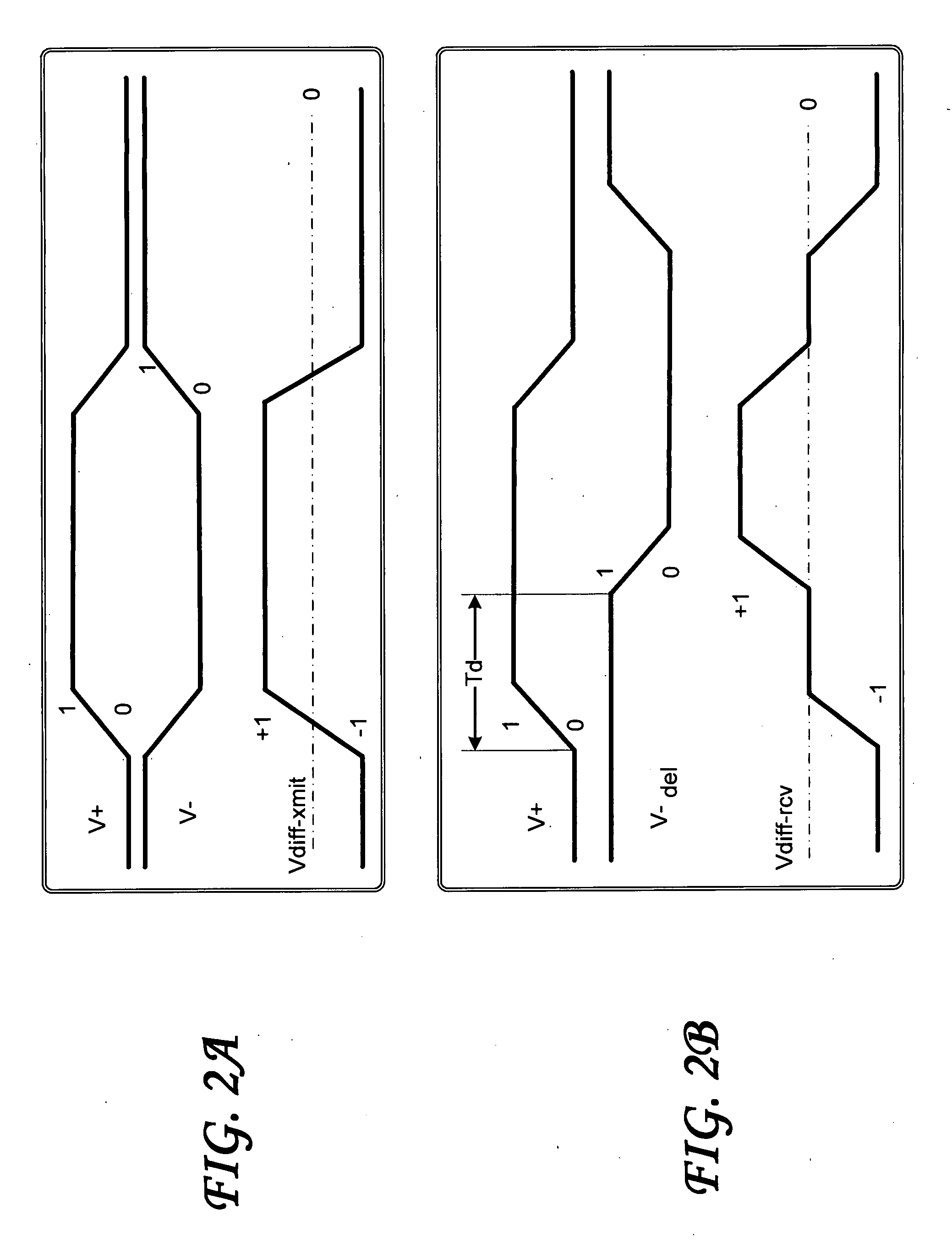

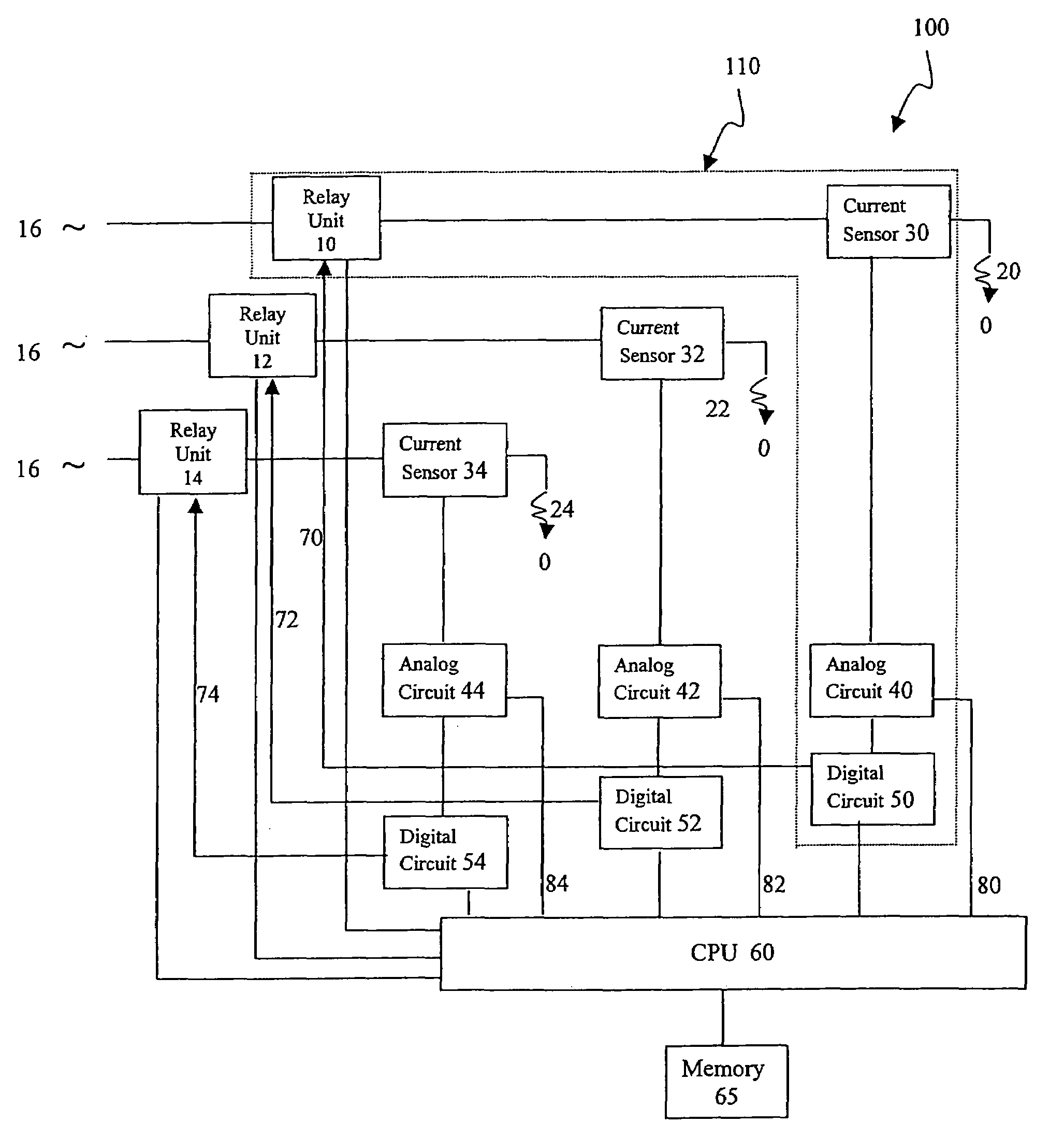

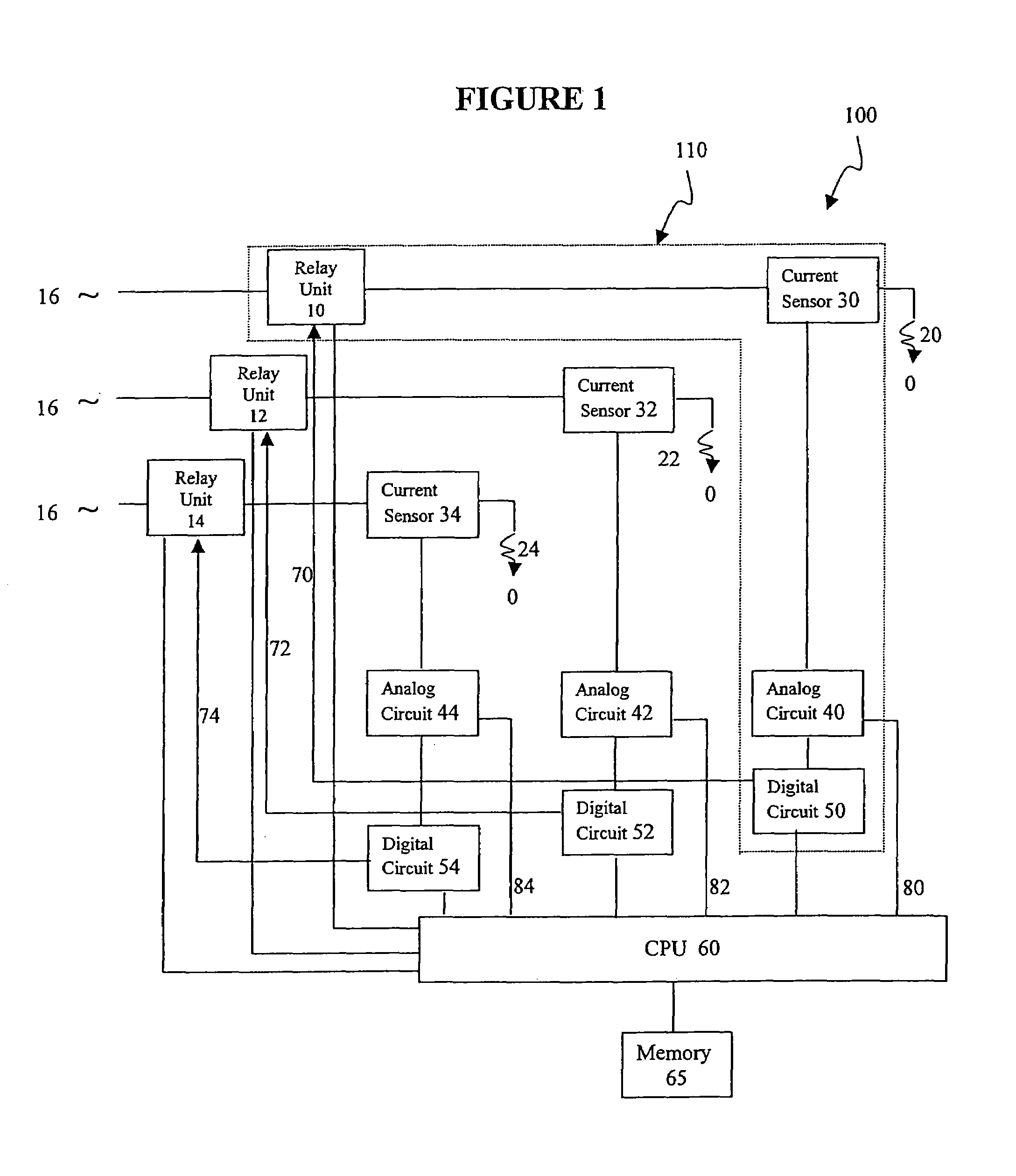

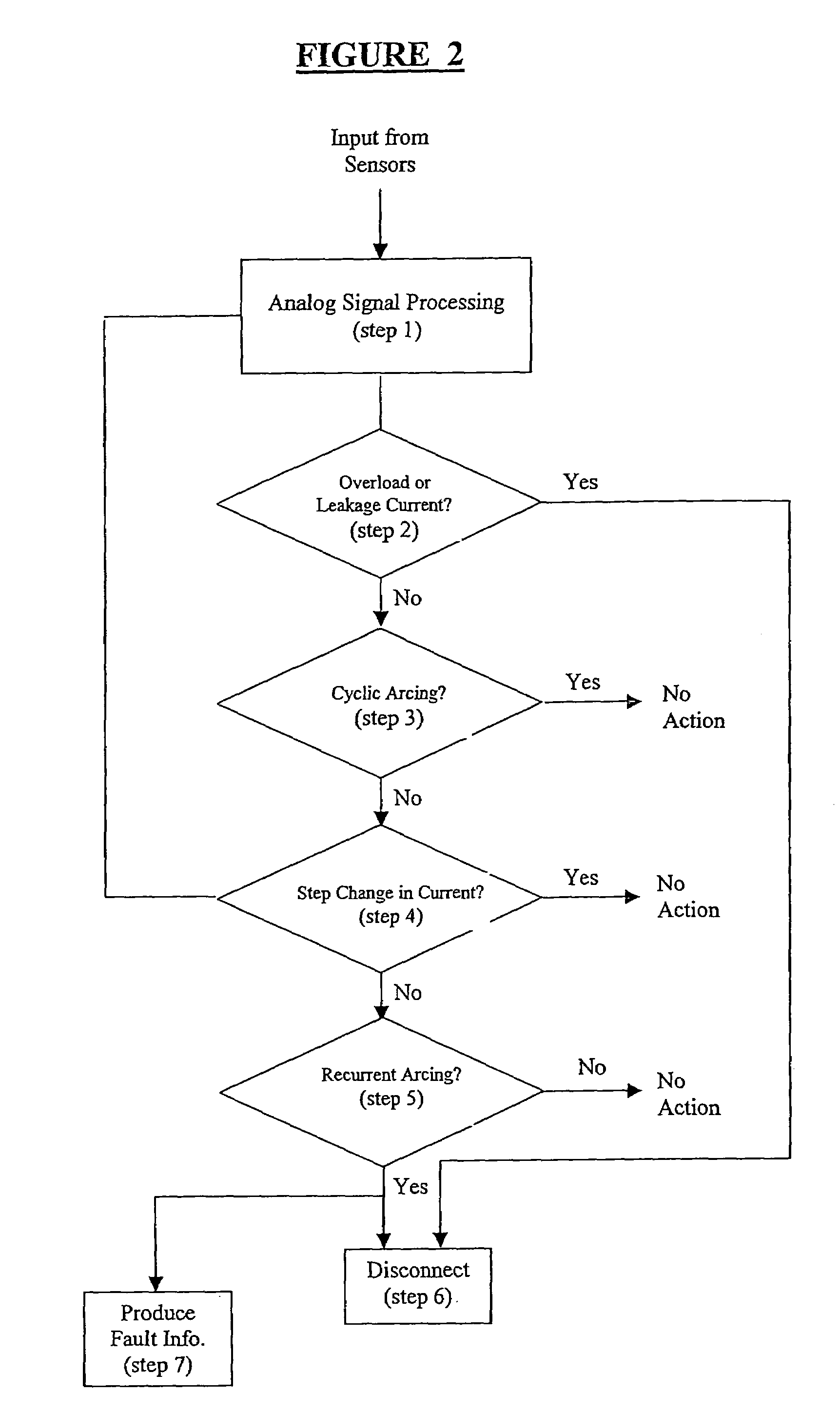

Computerized electricity system having an arc fault detecting sub-system

InactiveUS7282924B1Neutralize effectMechanical power/torque controlTesting dielectric strengthElectric power systemCurrent sensor

A computerized electricity system for connecting loads to a power source, including: (a) an arc fault detecting sub-system having at least one module including: (i) a relay unit, electrically associated with a particular load, for connecting and disconnecting to a power source; (ii) a current source for measuring a current being delivered from the power source to the load, to produce a current measurement; (iii) an analog circuit for receiving the current measurement from the current sensor, and for producing an analog signal based on the current measurement, and a second signal for indicating a potential arc fault event, and (iv) a digital circuit for receiving the second signal from the analog circuit and producing data, and (b) a processing unit connected to each module, so as to receive data corresponding to the analog signal, and the data from the digital circuit, the processing unit for identifying the arc faults, and wherein the processing unit is configured to command the relay unit to disconnect the current in response to identifying the arc faults, and wherein the processing unit is configured to provide this command only if several pre-determined conditions are met, (I) after detection of the potential arc fault event, the current measurement remains substantially unchanged, and (II) after a detection of at least one addition potential arc fault event, the arc fault events are found to be acyclic.

Owner:TARGET HI TECH ELECTRONICS

Analog circuit dynamic online failure diagnosing method based on GSD-SVDD

InactiveCN101907681AReflect the degree of separationHigh precisionAnalog circuit testingSpecial data processing applicationsClassification methodsDiagnostic system

The invention discloses an analog circuit dynamic online failure diagnosing method based on GSD-SVDD, belonging to the technical field of analog circuit failure diagnosis. In an offline test process, a KFCM algorithm is adopted to calculate a failure resolution value of each testable node and an optimal test node set is selected according to the failure resolution value. In an online diagnosis process, a failure diagnosis model is established by adopting an SVDD single classification approach based on a map spatial distance positive and negative sample weighting, test samples are diagnosed by a layered diagnosis method, and a failure class library and the diagnosis model are renewed dynamically. The method effectively reduces the drill and online diagnosis time of the diagnosis model, guarantees the real-time property of the online diagnosis and improves the precision of the failure diagnosis and can dynamically renew parameters of the diagnosis model so as to enable the a diagnosis system to have the self-adaption capability.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS