Patents

Literature

926 results about "Circuit Failure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Ideally contact resistance should be low and stable, however weak contact pressure, mechanical vibration, corrosion, and the formation of passivizing oxide layers and contacts can alter contact resistance significantly, leading to resistance heating and circuit failure.

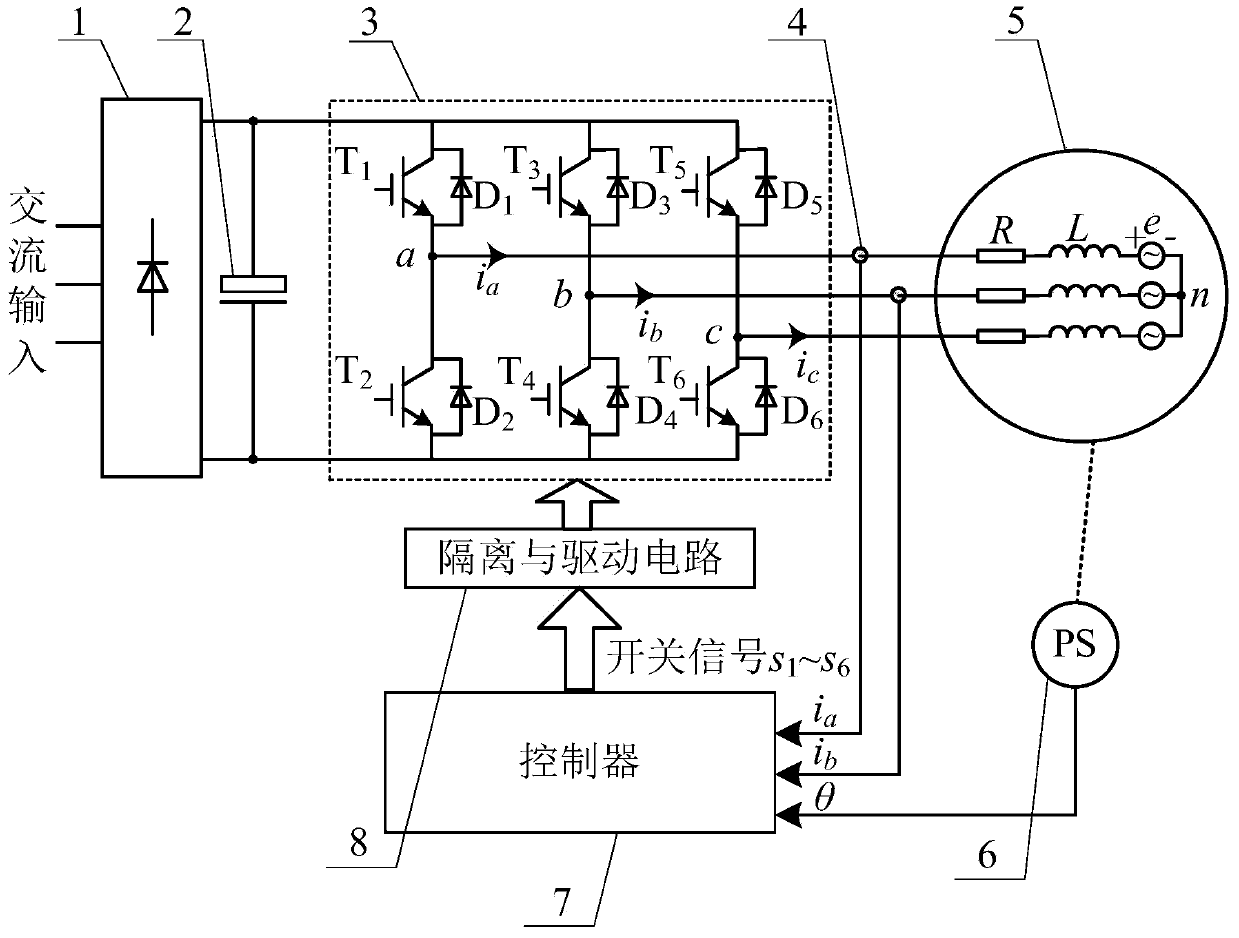

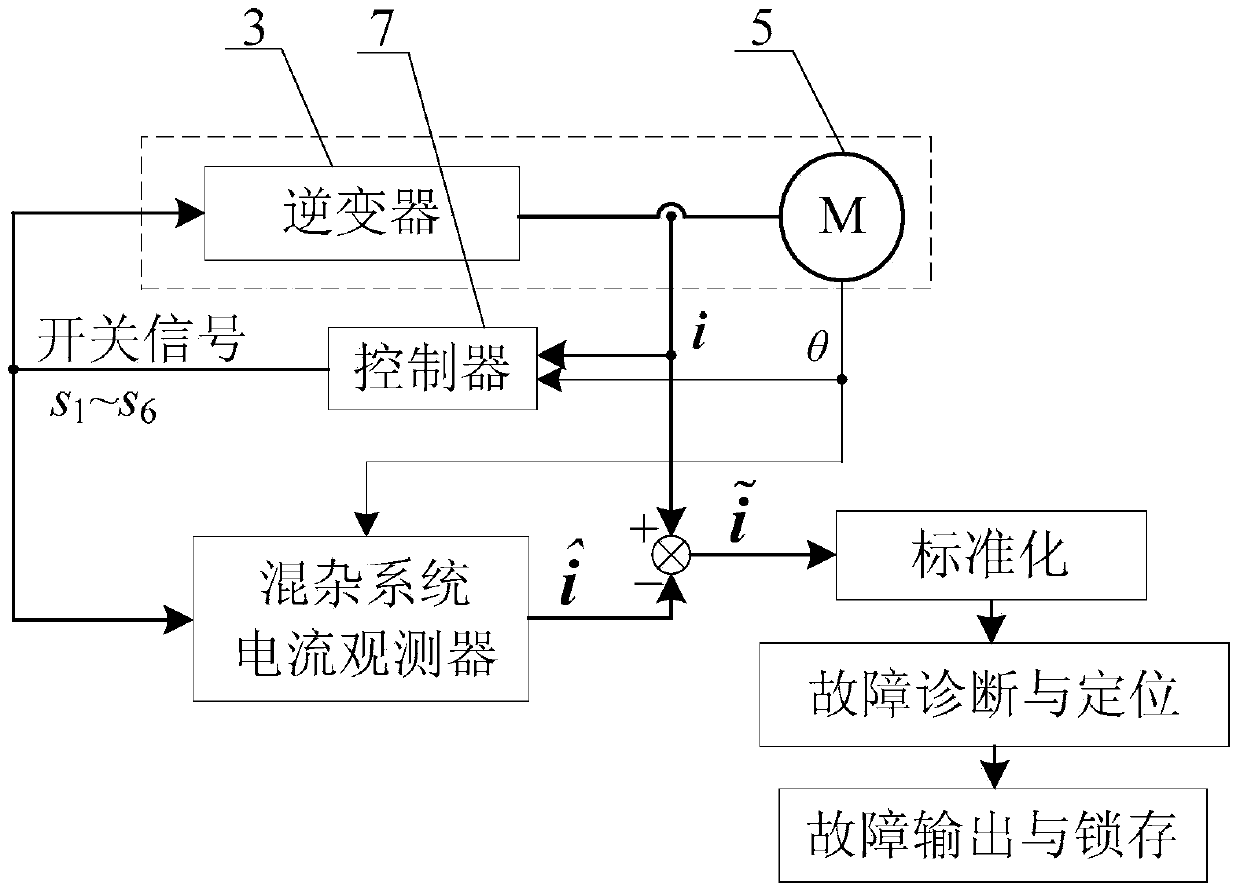

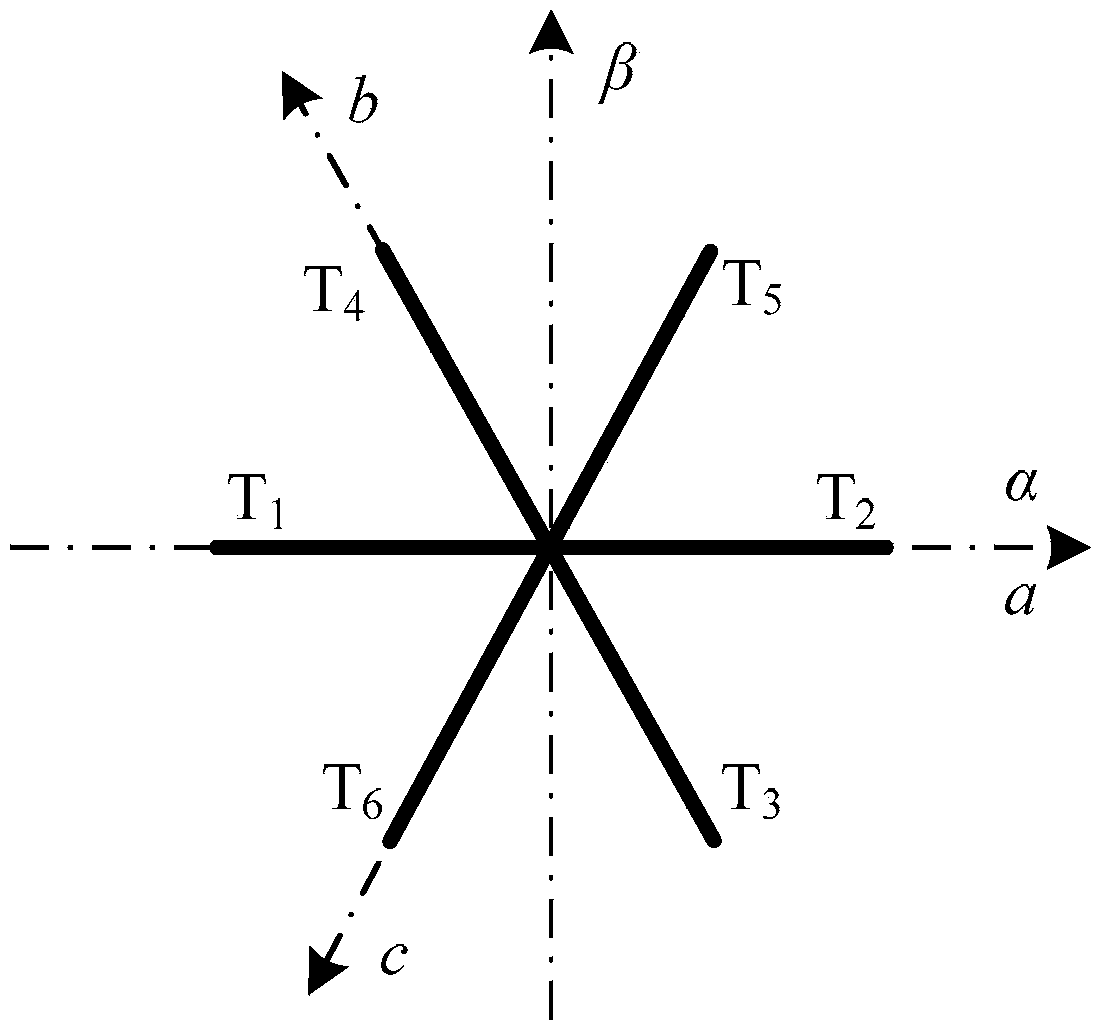

Current-magnitude-based open-circuit failure online-diagnosis method for power tube of inverter

InactiveCN103701394AImprove robustnessElectronic commutation motor controlVector control systemsObservational errorLoop control

The invention discloses a current-magnitude-based open-circuit failure online-diagnosis method for a power tube of an inverter, belongs to the field of motor control, and aims to solve the problem of poor robustness of a current-magnitude-based open-circuit failure diagnosis technology for the power tube of the inverter. The method comprises the following steps of establishing a current observer model of a permanent magnet synchronous motor driving system in a failure-free state, comparing an observed current value with detection current to obtain a three-phase current residual, converting the three-phase current residual to a two-phase coordinate system in a coordinate conversion way to obtain a current residual vector, standardizing the current residual vector, and diagnosing and positioning an open-circuit failure of the power tube of the inverter according to the amplitude and the phase of the standardized current residual vector. The current-magnitude-based open-circuit failure online-diagnosis method for the power tube of the inverter is free of influence of a system closed-loop control algorithm and insensitive to loads, and has higher robustness to parameter errors, measurement errors, system disturbance and the like.

Owner:HARBIN INST OF TECH

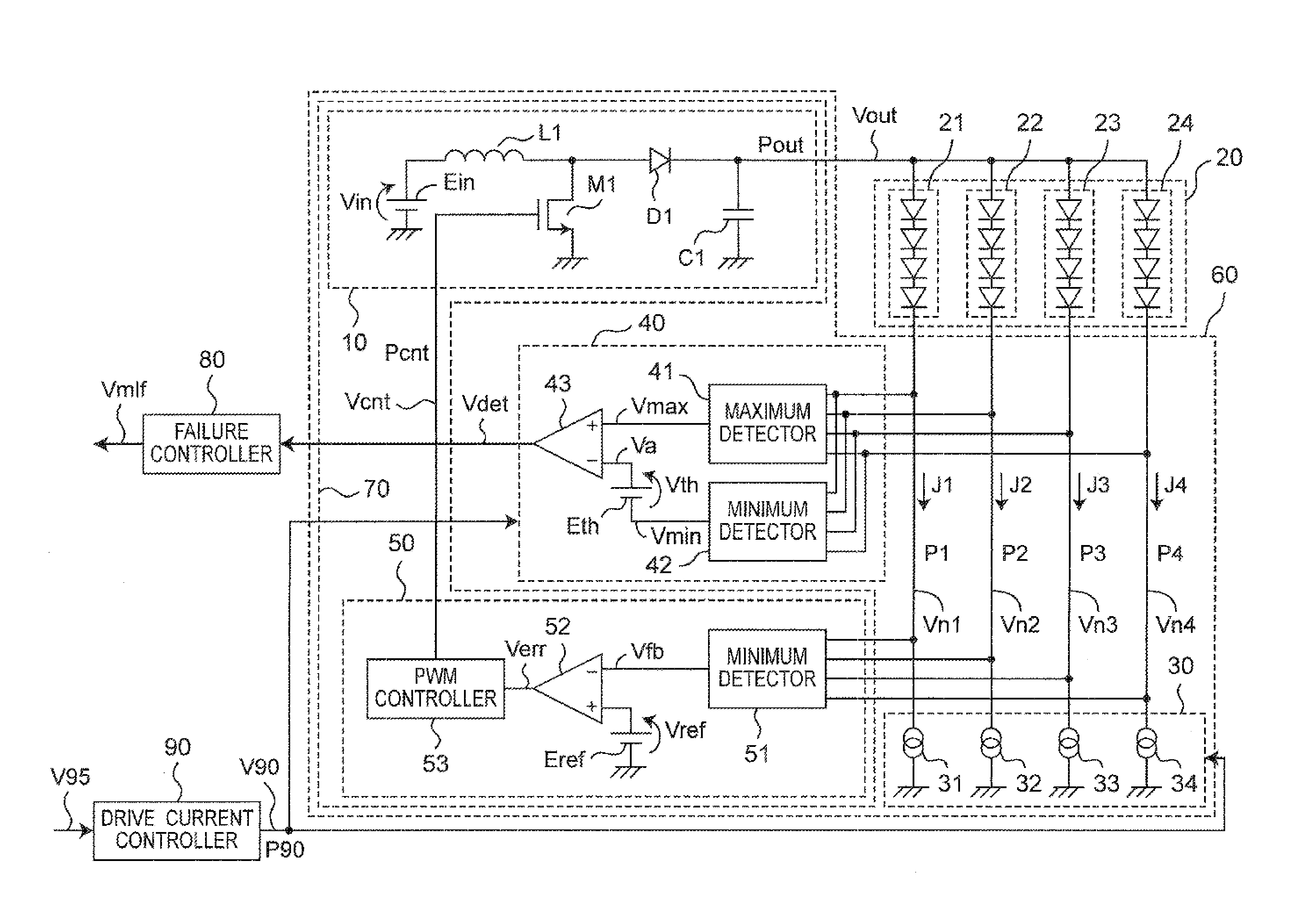

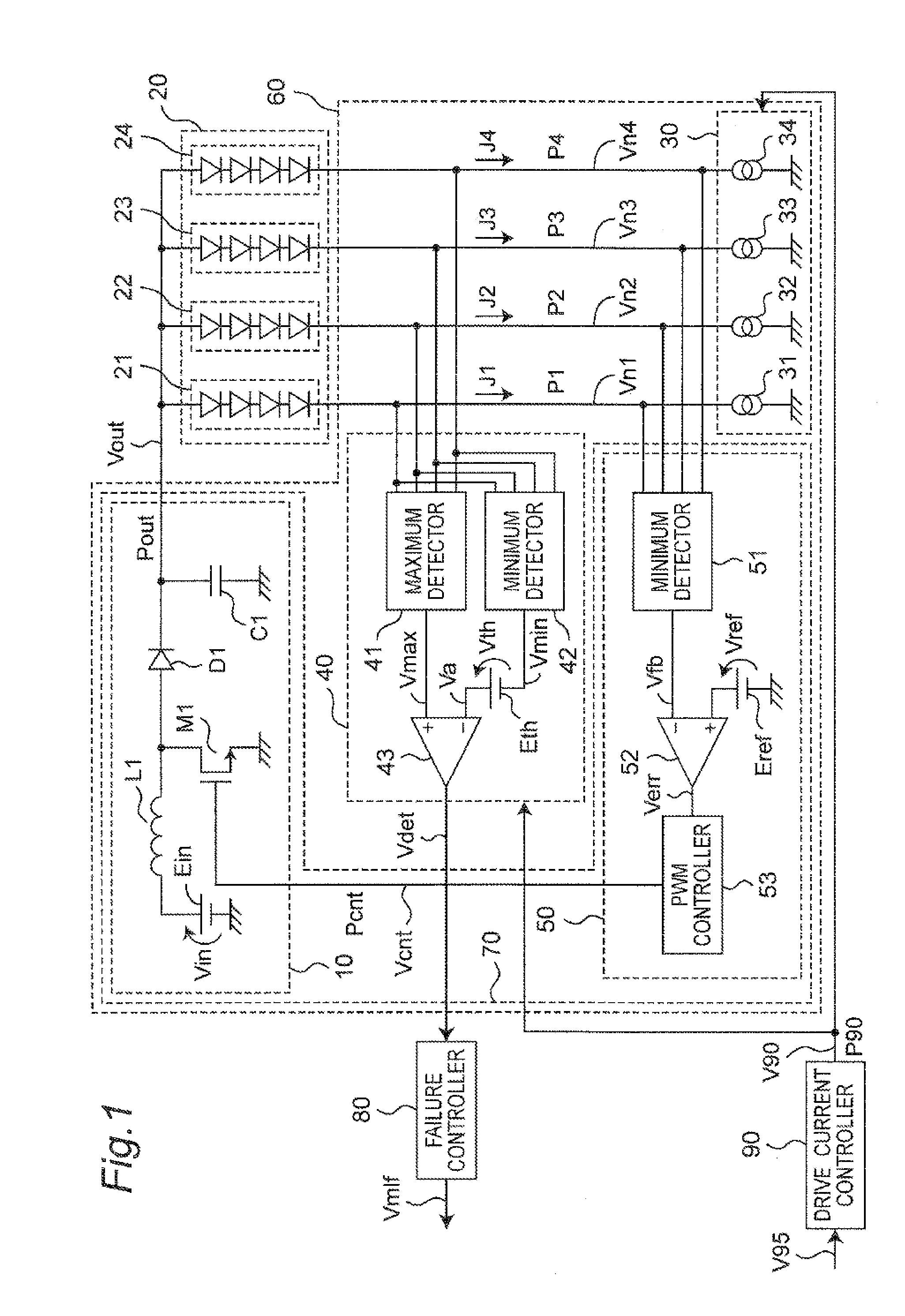

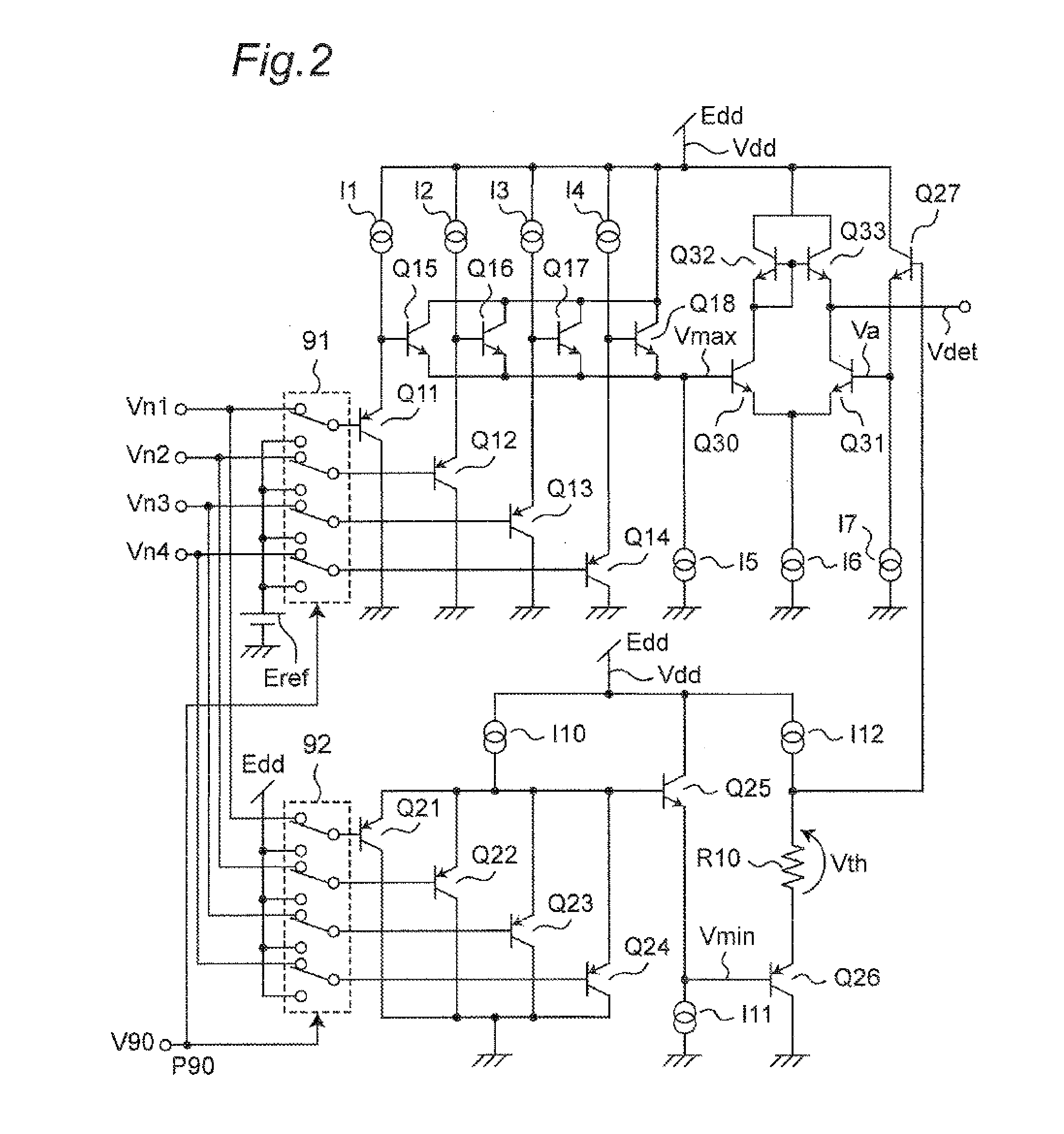

Light-emitting element driving device

ActiveUS20120074856A1Reduce stepsGuaranteed uptimeElectrical apparatusStatic indicating devicesVoltage referenceEngineering

Short circuit failures and open circuit failures of light-emitting elements used for the backlight in an LCD panel can be reliably and easily detected. The voltage at the node between each series-connected light-emitting element array and a drive circuit is detected as a monitored voltage. A maximum detector detects the highest and a minimum detector detects the lowest of these monitored voltages. Short circuit or open circuit failure of a light-emitting element is detected by comparing the voltage difference between the maximum detector output and the minimum detector output with a specific reference voltage.

Owner:PANASONIC CORP

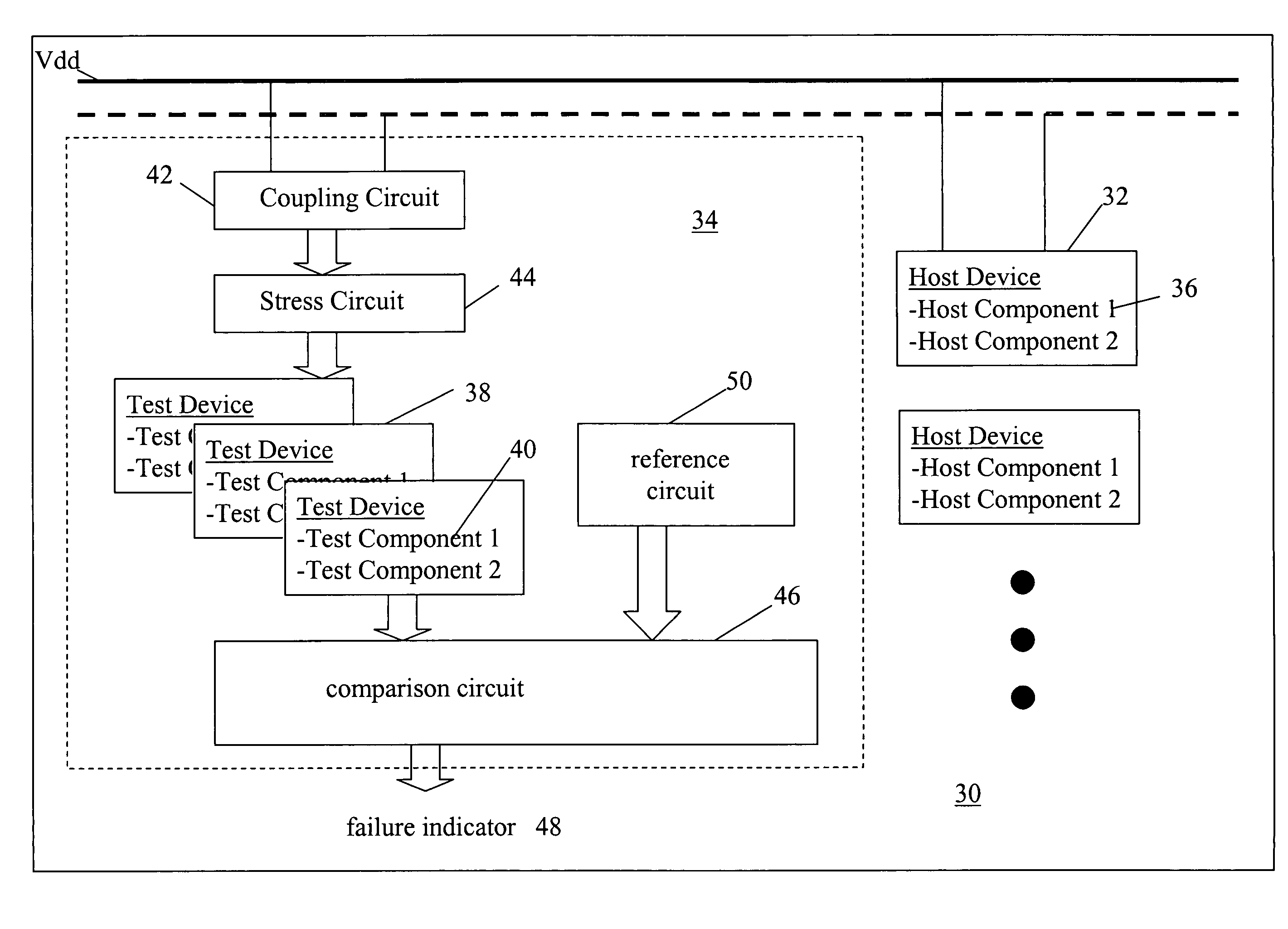

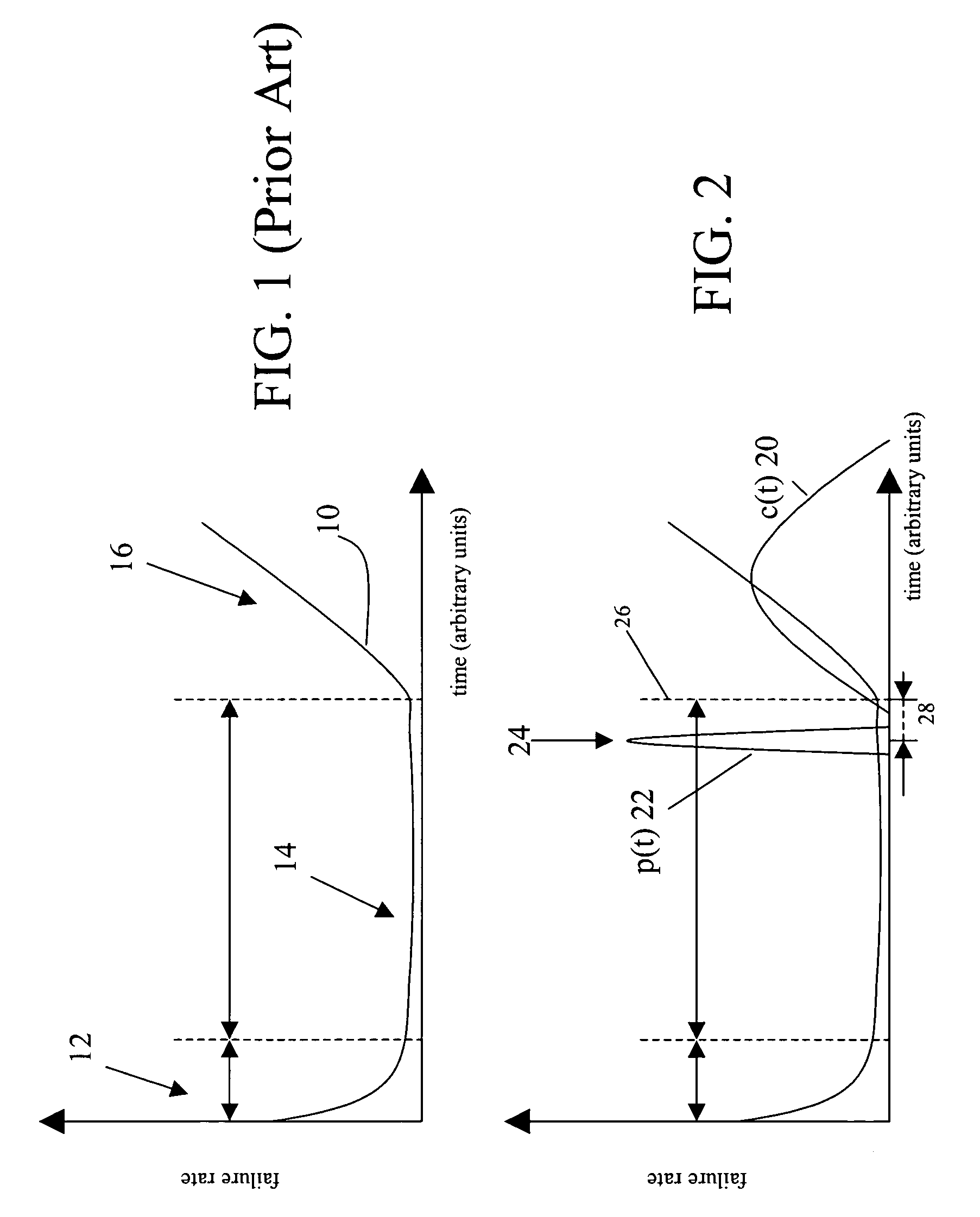

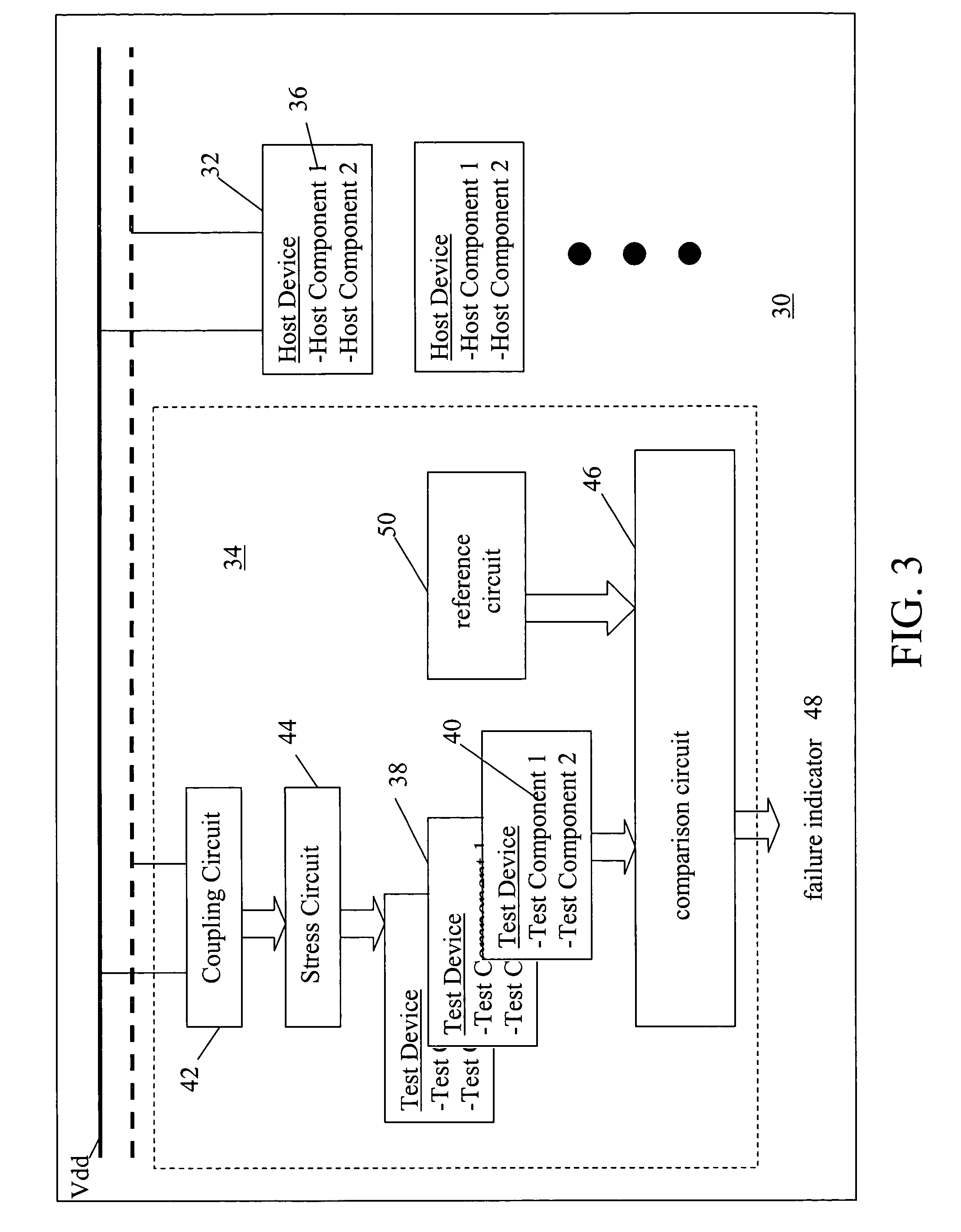

Prognostic cell for predicting failure of integrated circuits

InactiveUS7271608B1Improve deteriorationLow operating pressurePlug gaugesAlarmsRelative timesIntegrated circuit

A prognostic cell is used to predict impending failure of a useful circuit or circuits in a host IC. Increasing the stress on the prognostic cell relative to the useful circuit shifts the failure distribution of the cell along the time axis. The relative amount of time between the useful circuit failure and prognostic cell trigger point is the “prognostic distance”. The prognostic distance is controlled by designing in the excess stress applied in test device(s), by setting the threshold for triggering in the comparison circuit or by both. Prediction accuracy is enhanced by using multiple test devices to oversample the underlying failure distribution and triggering the failure indicator when a certain fraction fail.

Owner:RIDGETOP GROUP

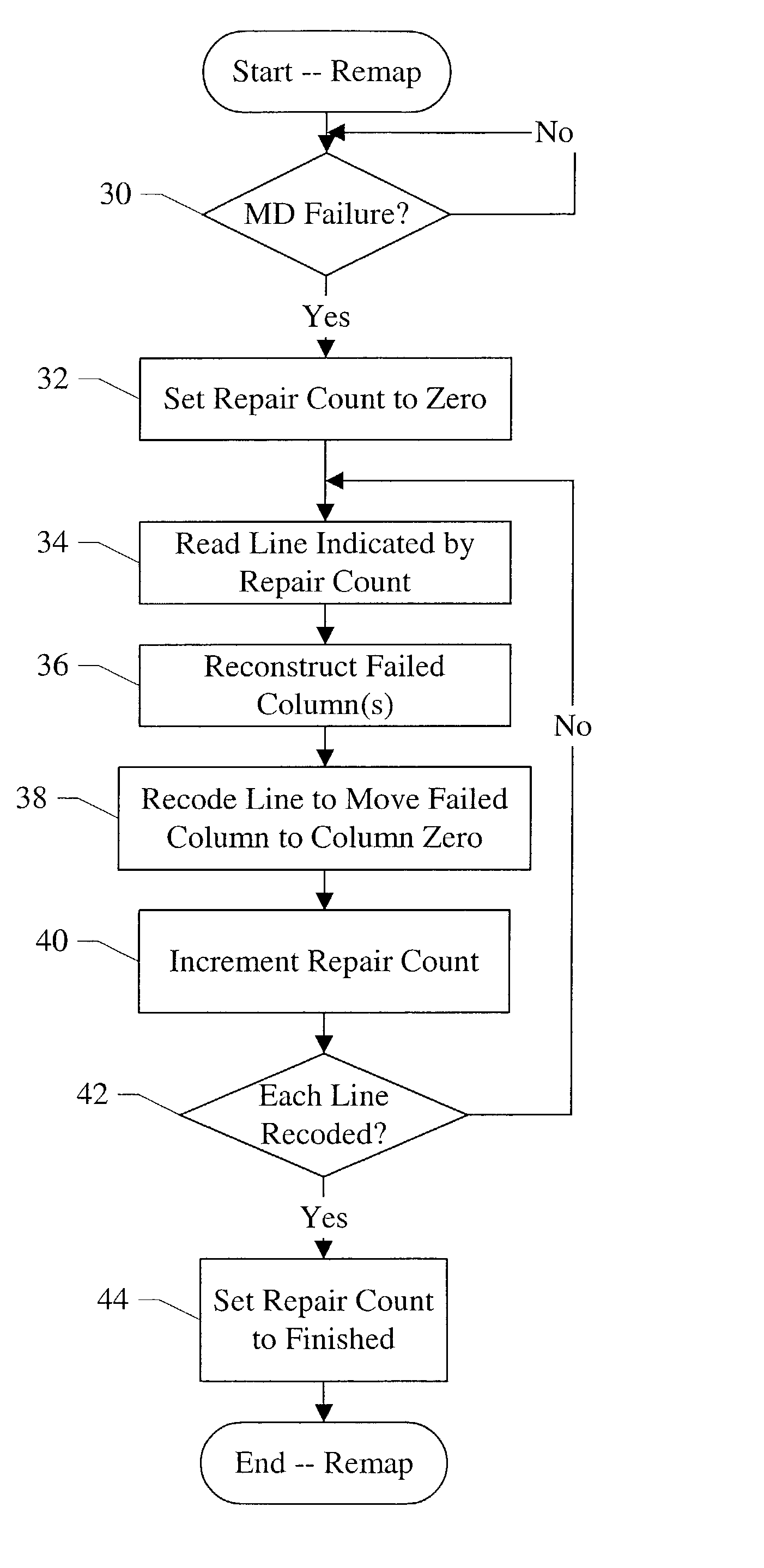

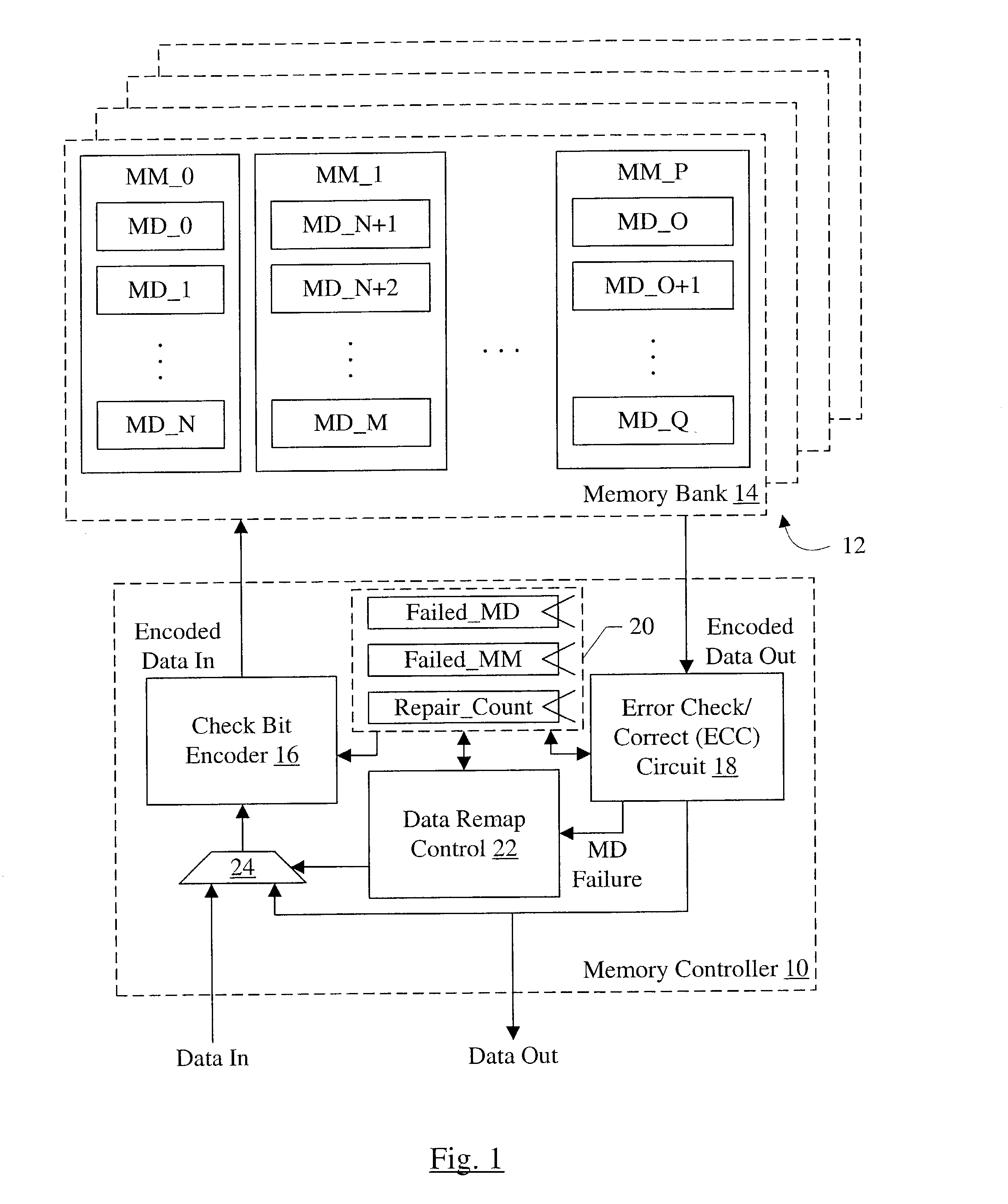

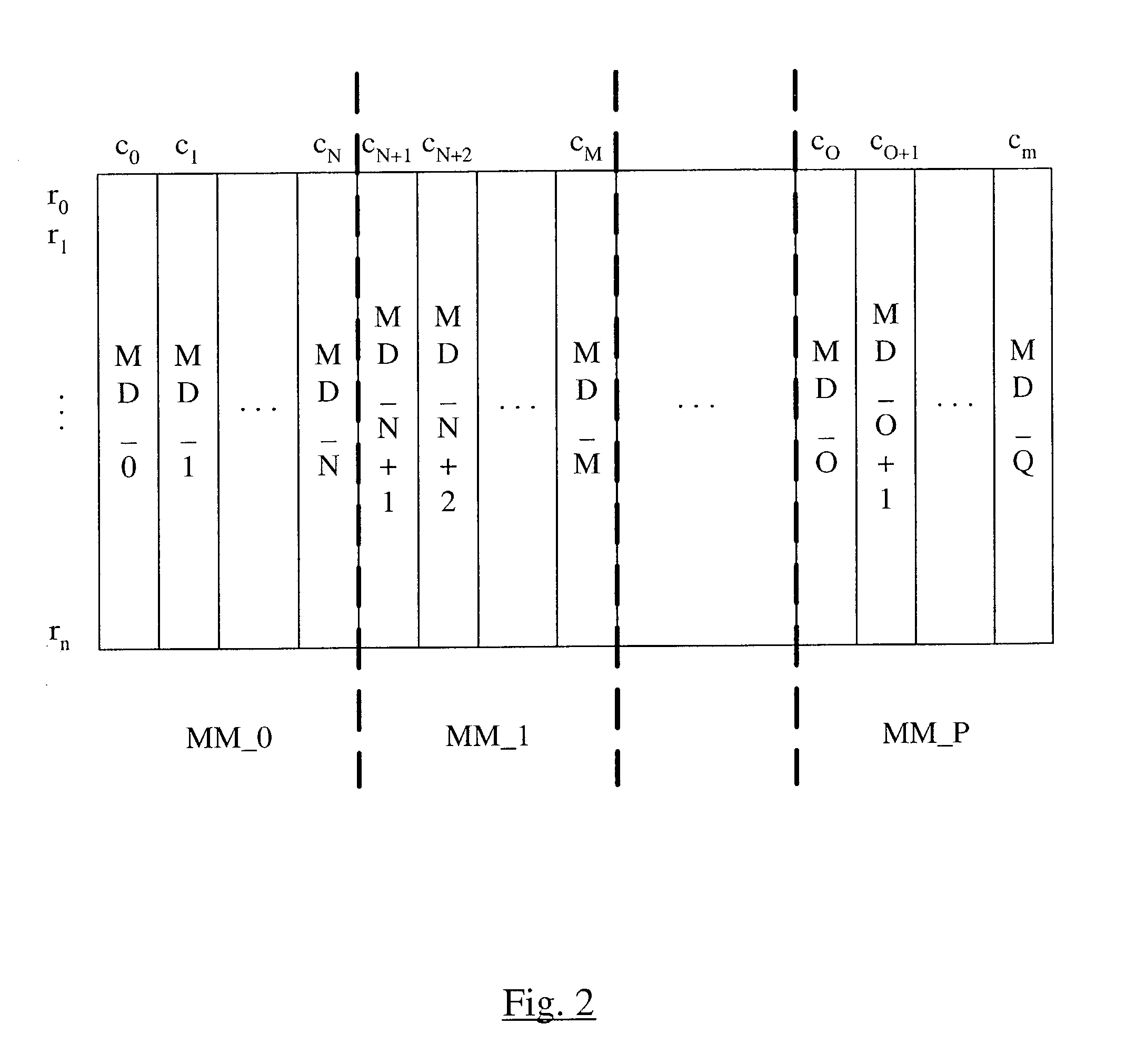

Error detection/correction code which detects and corrects memory module/transmitter circuit failure

A memory controller may include a check bit encoder circuit and a check / correct circuit. The check bit encoder circuit is coupled to receive a data block to be written to memory, where the memory includes a plurality of memory devices arranged on a plurality of memory modules. Each of the plurality of memory modules includes a plurality of the plurality of memory devices. The check bit encoder circuit is configured to encode the data block with a plurality of check bits to generate an encoded data block. The plurality of check bits are defined to provide at least detection of a failure of one of the plurality of memory modules. The check / correct circuit is coupled to receive the encoded data block from the memory, and is configured to detect the failure of one of the plurality of memory modules responsive to decoding the encoded data block.

Owner:ORACLE INT CORP

Stereoscopic vision based emergency treatment device and method for running vehicles

ActiveCN102390370AReduce speedAcoustic signal devicesAutomatic initiationsDriver/operatorVision based

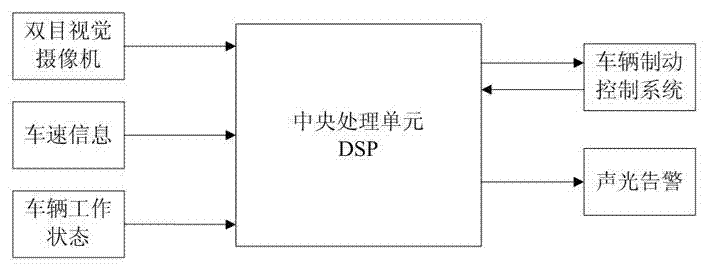

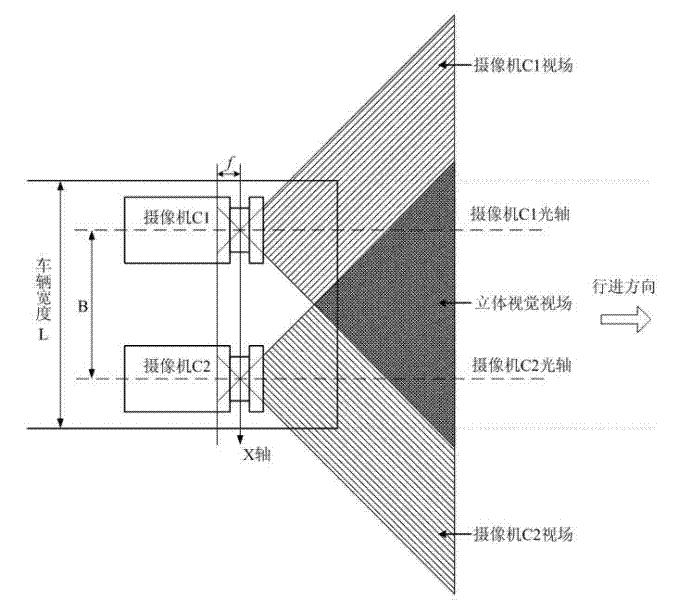

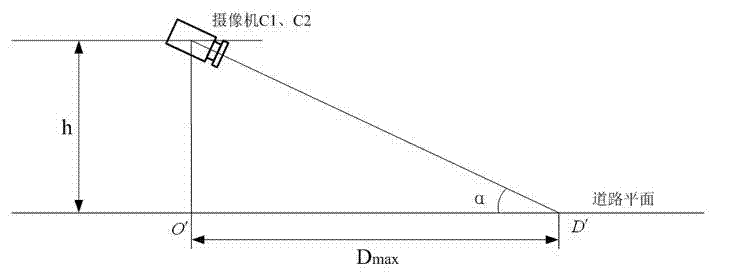

The invention relates to a stereoscopic vision based emergency treatment device and method for running vehicles, wherein the device comprises a binocular-vision image pick-up unit, an on-board bus interface, a central processing unit, a vehicle braking control system and an acousto-optic alarm circuit. The binocular-vision image pick-up unit is used for capturing an image of a road in front of a vehicle; the DSP (digital signal processor) based central processing unit is adopted for carrying out real-time quick calculation on a visual image so as to obtain a three-dimensional road scene, and compares the obtained three-dimensional road scene with a safe driving road model set up by a system so as to judge whether obstacles or dangers exist in the traveling direction of the vehicle; when adanger is found, the vehicle braking control system is started so as to reduce the speed of the vehicle and send an acousto-optic alarm to a driver; meanwhile, the central processing unit is connected with a vehicle sensor by an inter-vehicle bus so as to detect the state of the vehicle, and when the vehicle has mechanical or circuit faults, a braking system is started so as to reduce the speed of the vehicle and send an acousto-optic alarm. The device disclosed by the invention can be arranged on ordinary motor vehicles so as to avoid the occurrence of accidents or reduce the accident loss, thereby improving the driving safety performance.

Owner:HOHAI UNIV

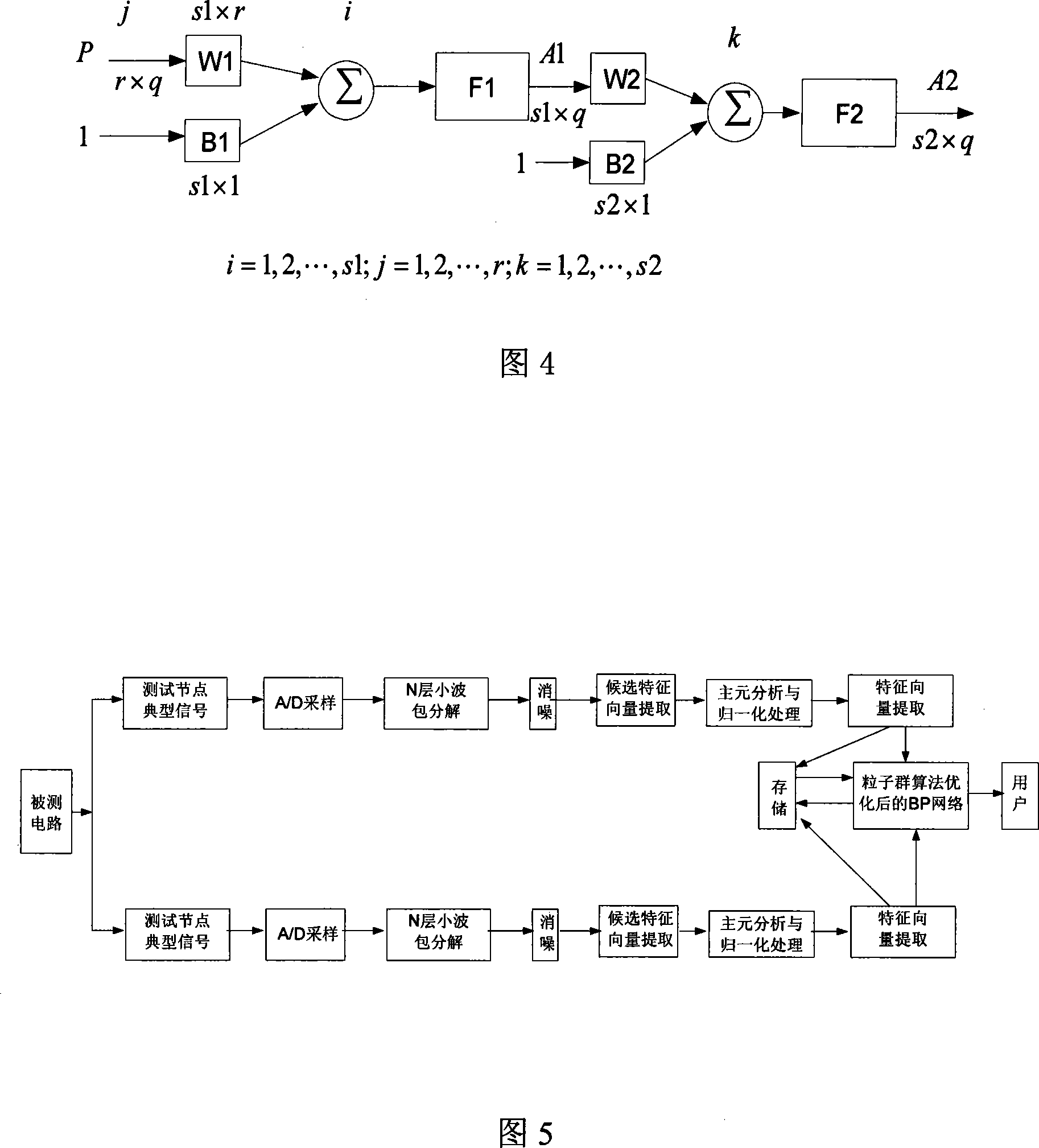

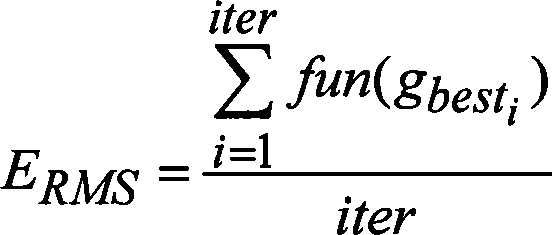

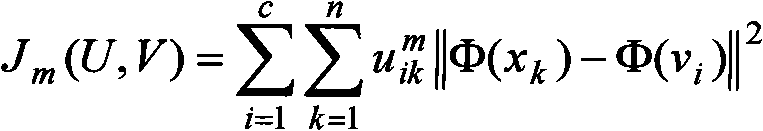

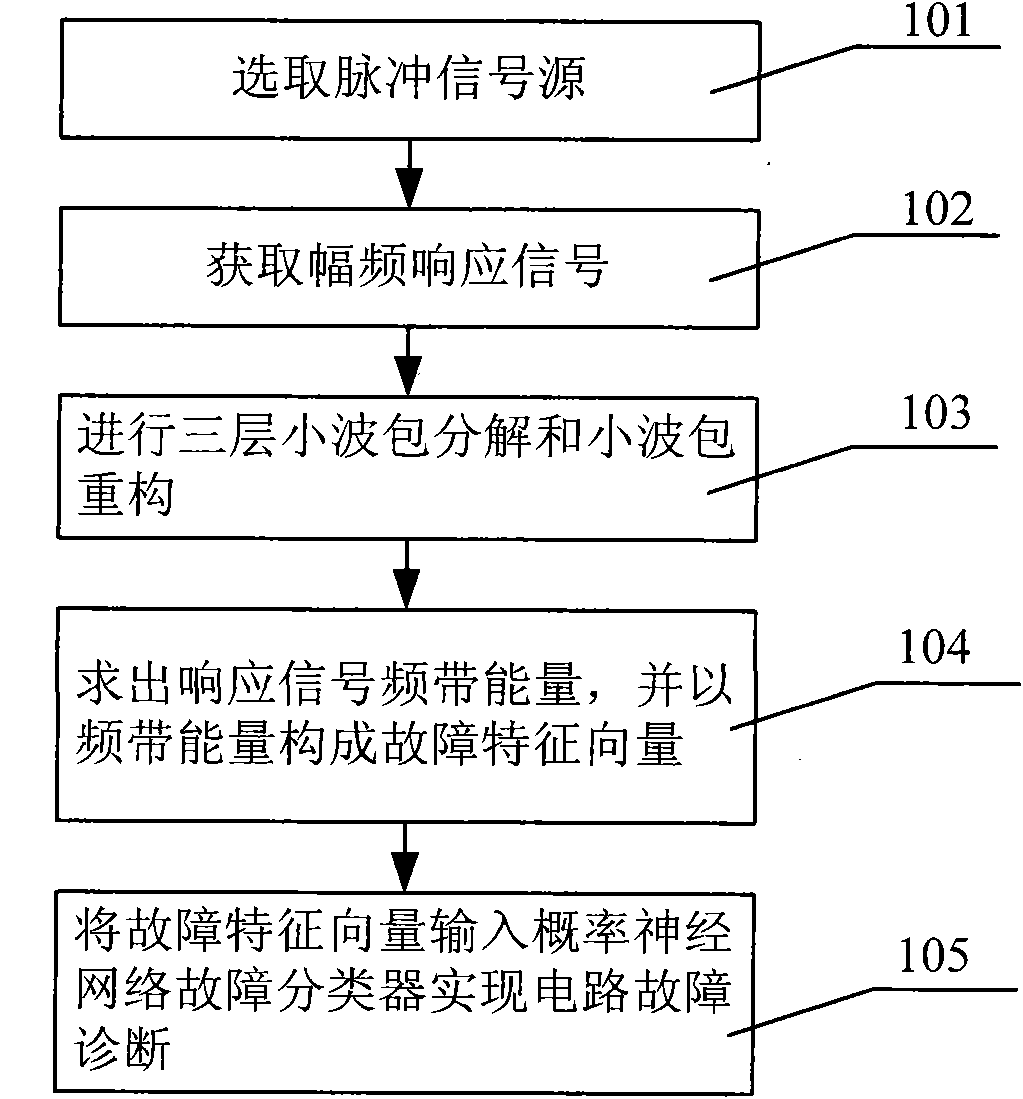

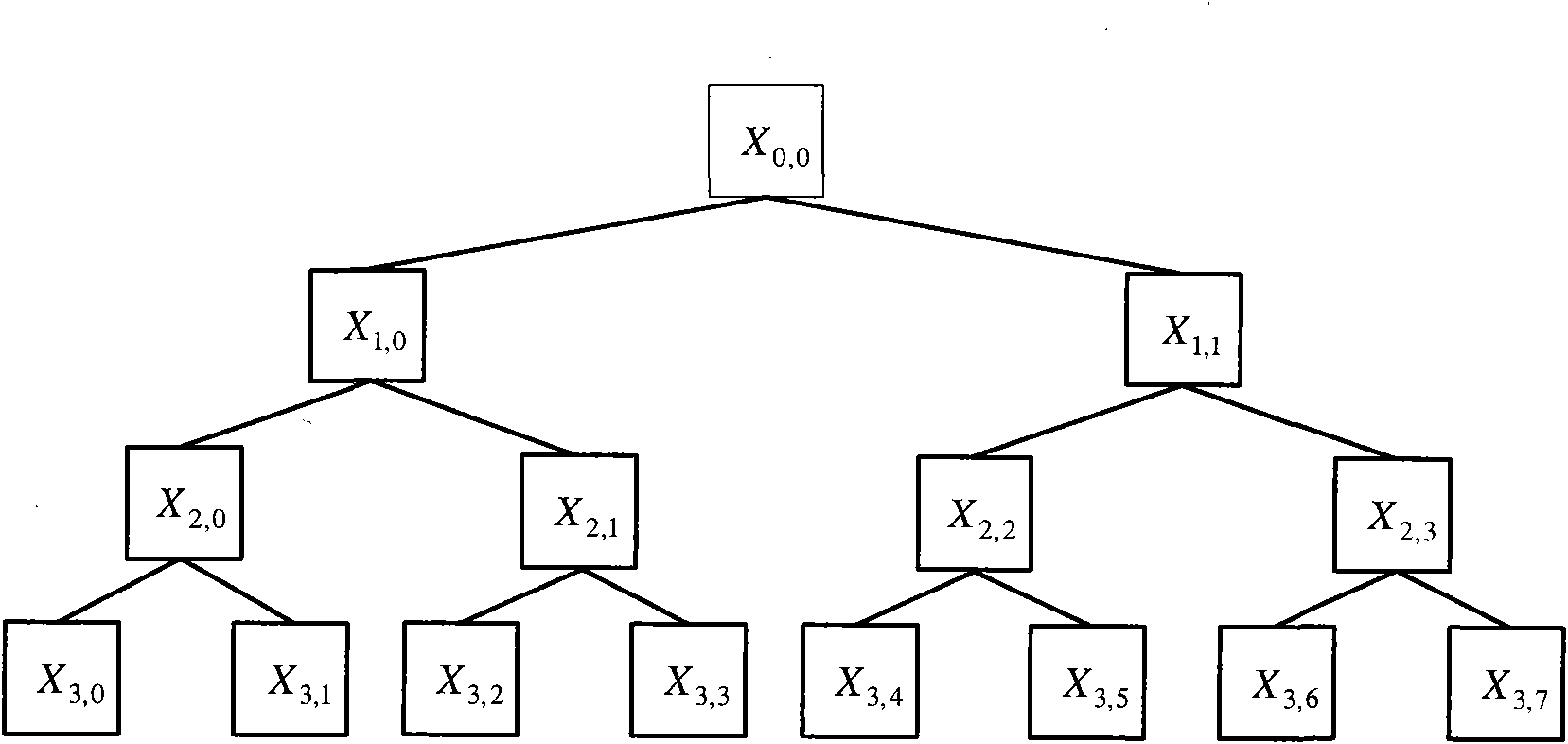

Analogue circuit fault diagnosis neural network method based on particle swarm algorithm

InactiveCN101221213AImplement extractionEliminate the effects ofElectronic circuit testingPhysical realisationNetwork ConvergencePrincipal component analysis

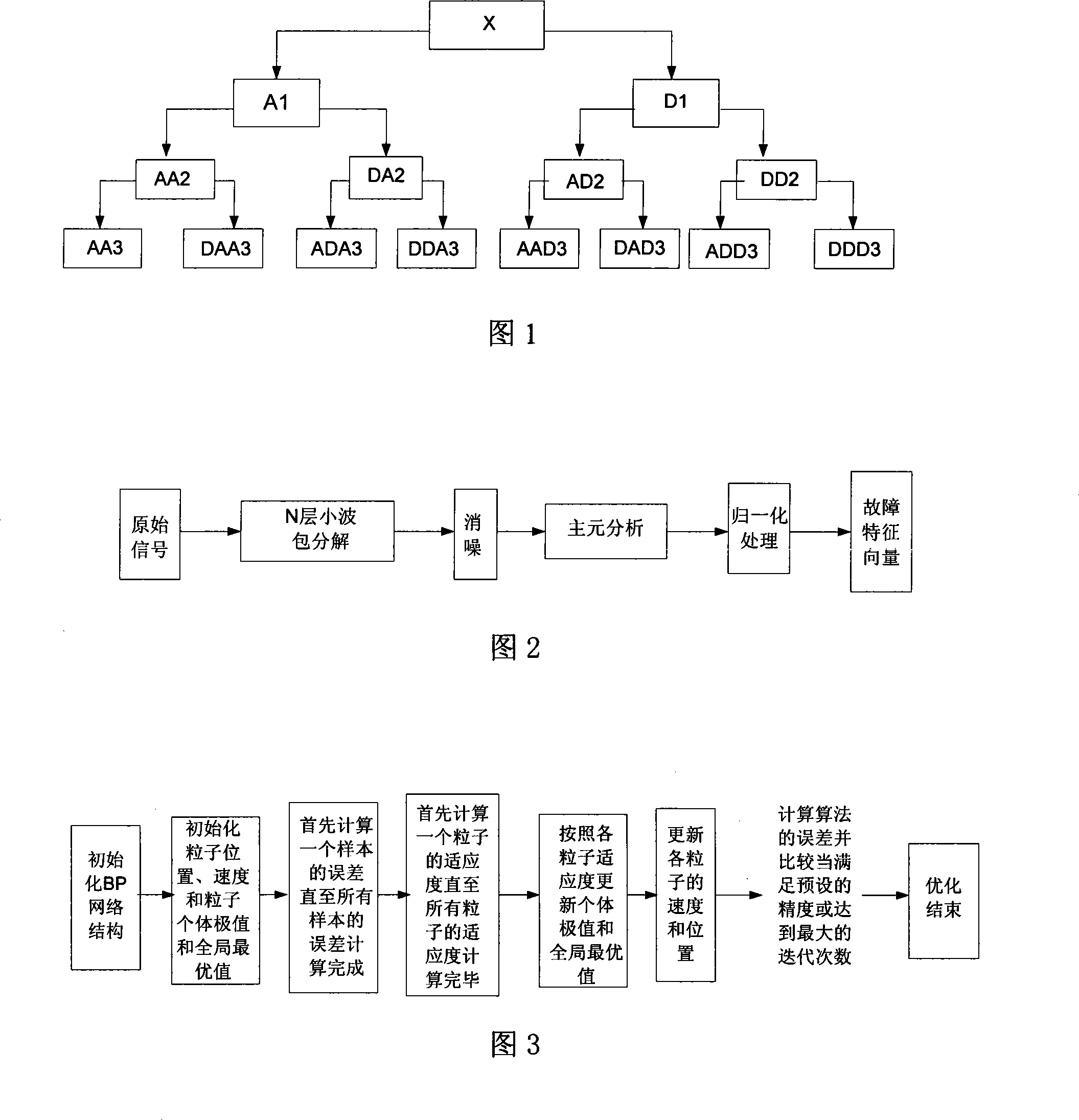

The invention discloses a neural network method for diagnosing analog circuit failures which is based on a particle swarm algorithm, and comprises the following steps: imposing an actuating signal to an analog circuit to be tested, measuring an actuating response signal in the testing nodes of the circuit, extracting the candidate signal of failure characteristics by implementing noise elimination and then wavelet packet transformation on the measured actuating response signal, extracting the failure characteristics information by further implementing orthogonal principal component analysis and normalization processing on the candidate signal of failure characteristics, and sending the failure characteristics information as samples to the neural network for implementing classification. The method adopts the particle swarm algorithm instead of a gradient descent method in traditional BP algorithms, thus leading the improved algorithm to be characterized in that the algorithm avoids the local minimum problem and has better generalization performance. The BP neural network method for diagnosing the analog circuit failures which is optimized on the basis of particle swarm can obviously reduce iteration times in the algorithm, improve the precision of network convergence, and improve diagnosis speed and precision.

Owner:HUNAN UNIV

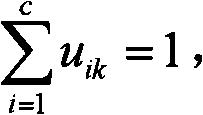

Analog circuit dynamic online failure diagnosing method based on GSD-SVDD

InactiveCN101907681AReflect the degree of separationHigh precisionAnalog circuit testingSpecial data processing applicationsClassification methodsDiagnostic system

The invention discloses an analog circuit dynamic online failure diagnosing method based on GSD-SVDD, belonging to the technical field of analog circuit failure diagnosis. In an offline test process, a KFCM algorithm is adopted to calculate a failure resolution value of each testable node and an optimal test node set is selected according to the failure resolution value. In an online diagnosis process, a failure diagnosis model is established by adopting an SVDD single classification approach based on a map spatial distance positive and negative sample weighting, test samples are diagnosed by a layered diagnosis method, and a failure class library and the diagnosis model are renewed dynamically. The method effectively reduces the drill and online diagnosis time of the diagnosis model, guarantees the real-time property of the online diagnosis and improves the precision of the failure diagnosis and can dynamically renew parameters of the diagnosis model so as to enable the a diagnosis system to have the self-adaption capability.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

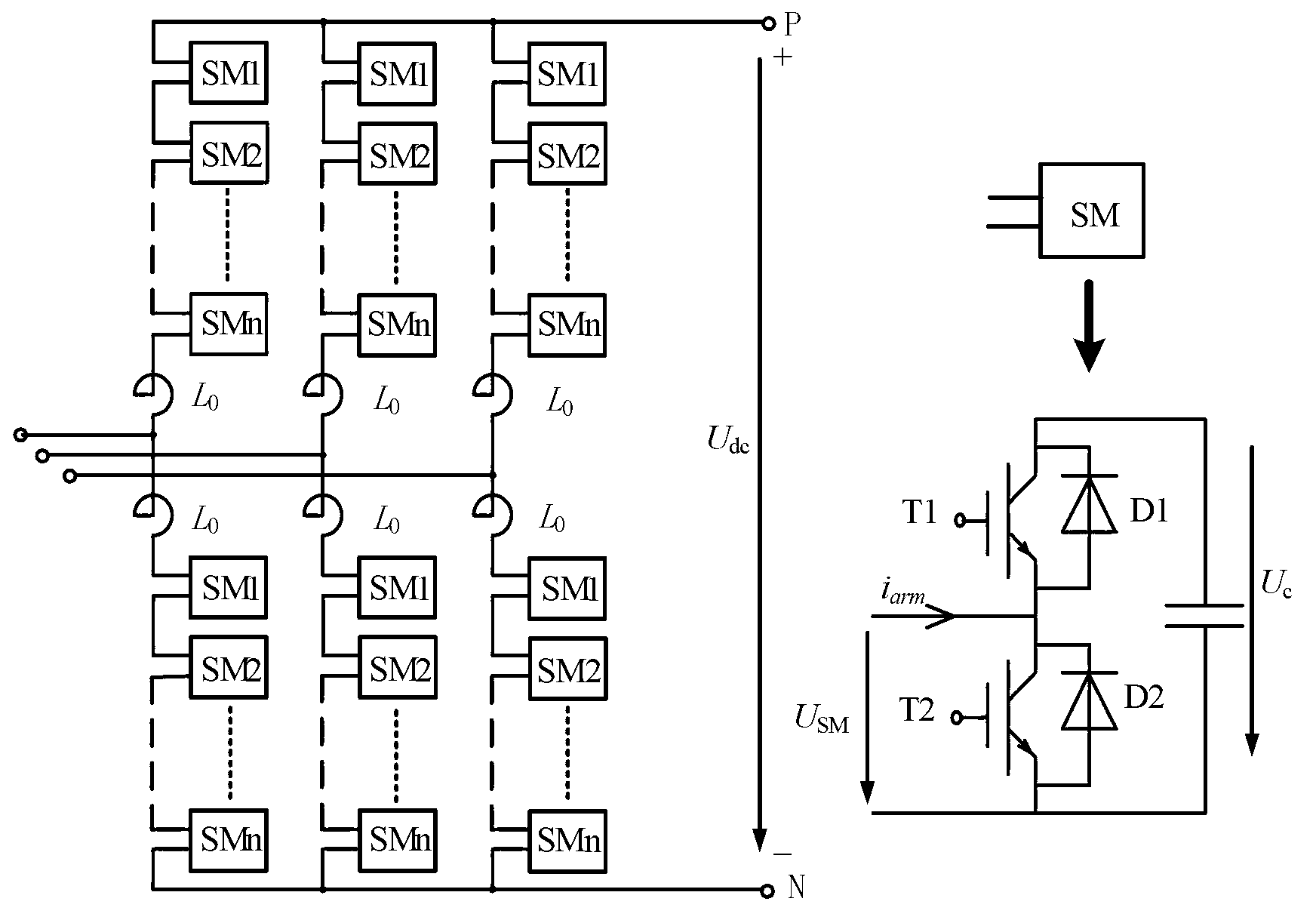

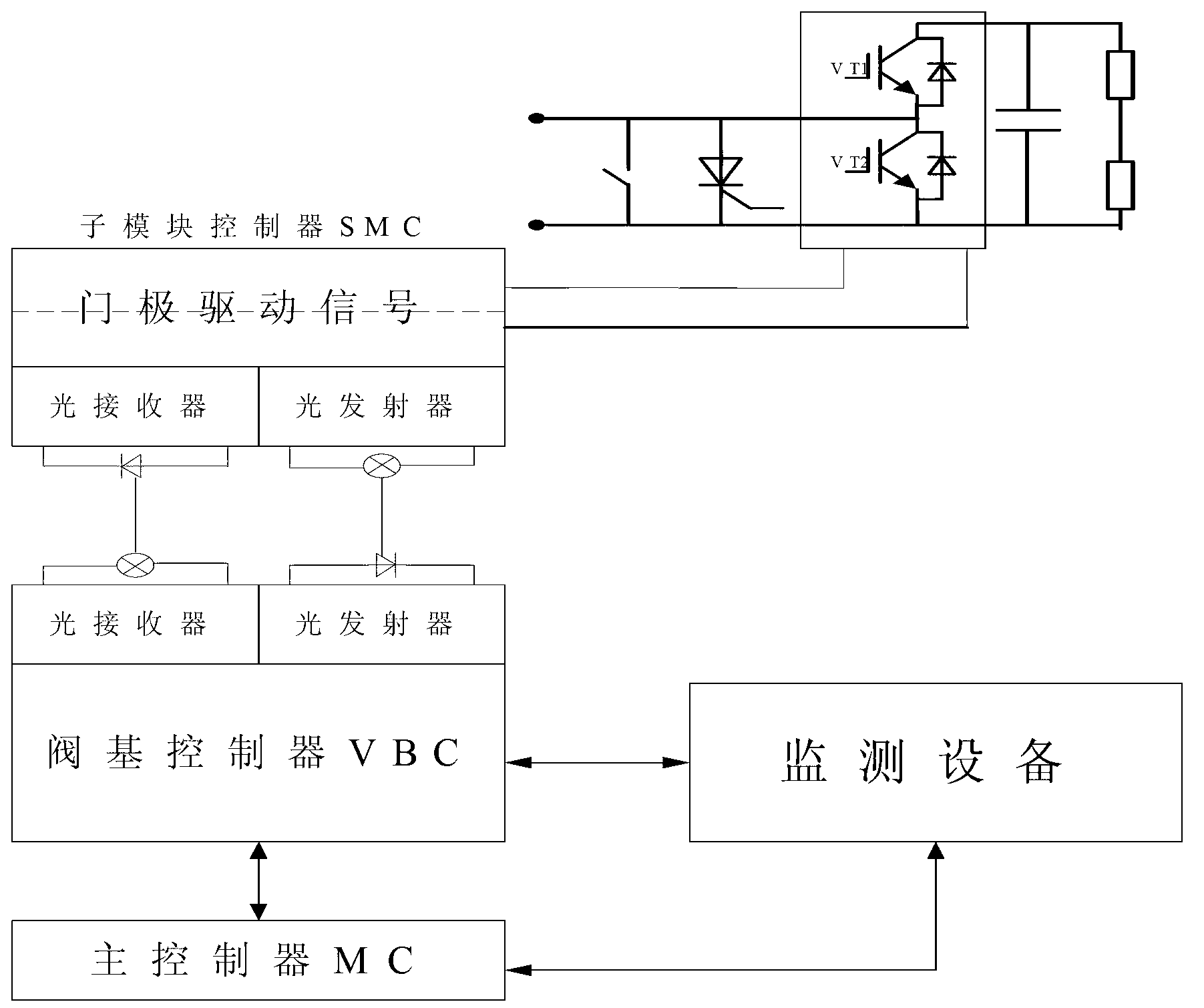

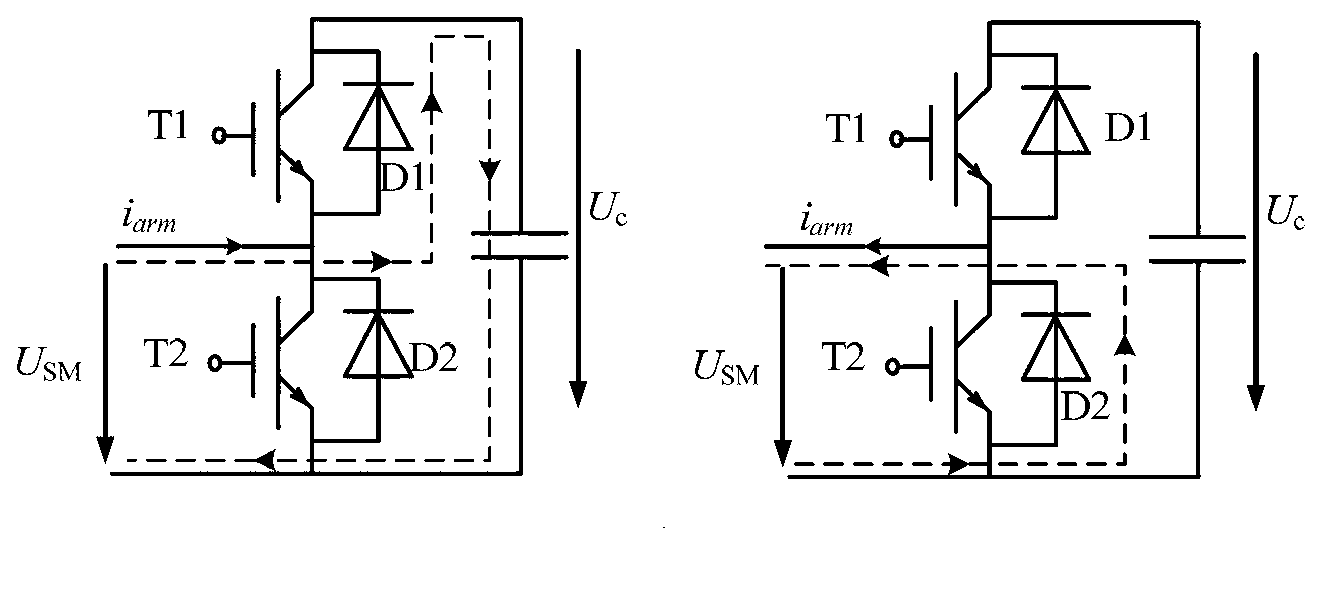

Sub-module fault diagnosis method of modular multilevel converter

InactiveCN103235219AEasy to implementQuick implementationAc-dc conversionElectrical testingFreewheelCapacitance

The invention discloses a sub-module fault diagnosis method of a modular multilevel converter in the technical field of power transmission and distribution. According to the technical scheme, the method includes: firstly, performing fault feature analysis aiming at typical faults of sub-modules; secondly, configuring an SFDU (sub-module fault diagnosis unit) in an SMC (sub-module controller), and combining provided sub-module fault diagnosis indexes by the aid of capacitor voltage, bridge arm current and trigger signals at the moment so as to achieve diagnosis of faults of sub-module IGBT (insulated gate bipolar translator) short circuit, IGBT open circuit, FWD (freewheel diode) short circuit, capacitor failure and the like; and finally, adopting an exclusive method in a VBC (valve base controller) to achieve diagnosis of faults of sub-module FWD open circuit, capacitor open circuit failure, connection line open circuit and the like. The method has the advantages that diagnosis of sub-module faults is achieved on the base of software, additional measuring points are not added to an original control protection system, and the method is easy to implement, has quick and efficient sub-module fault diagnosis capability, and has coordination with other protection settings.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

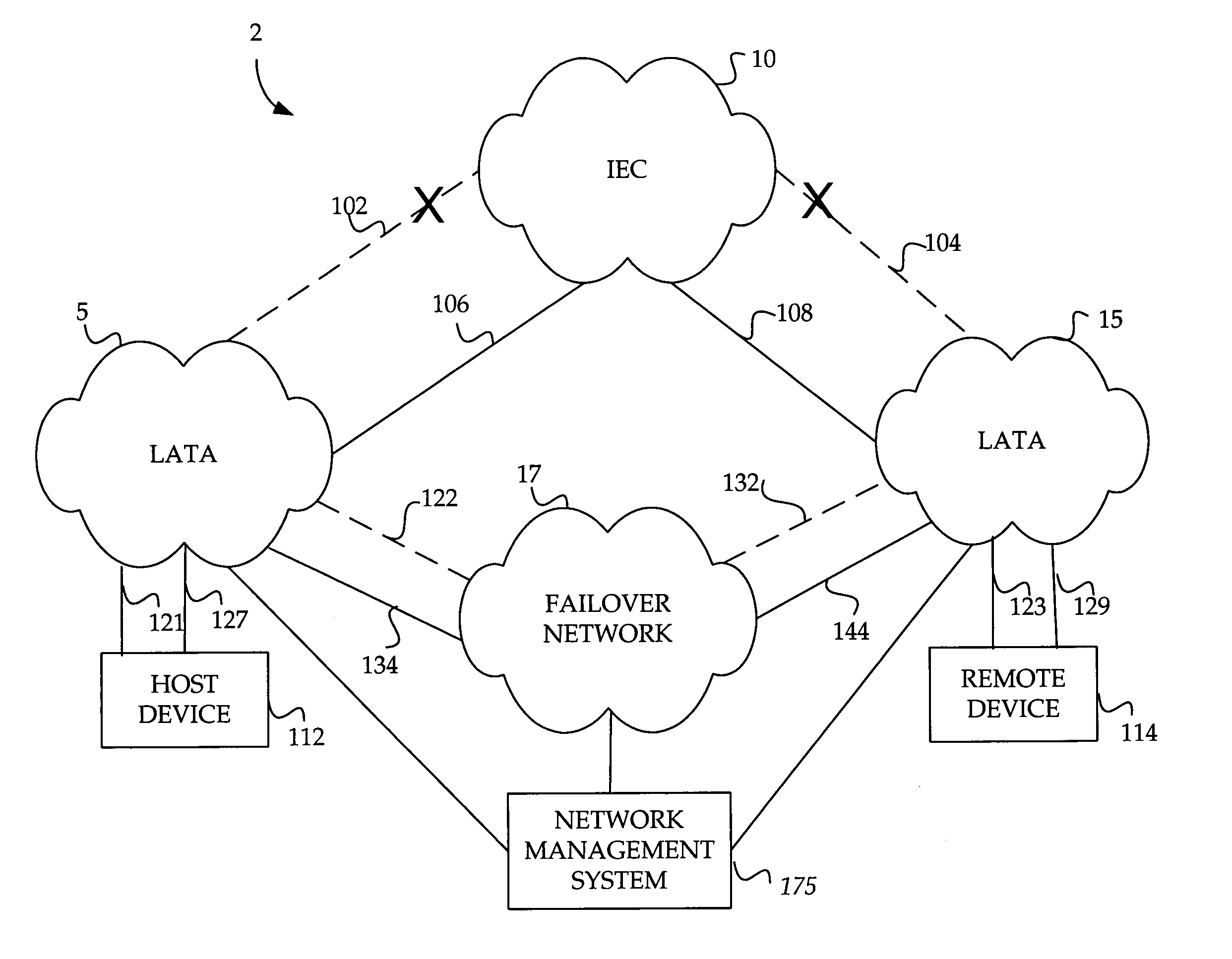

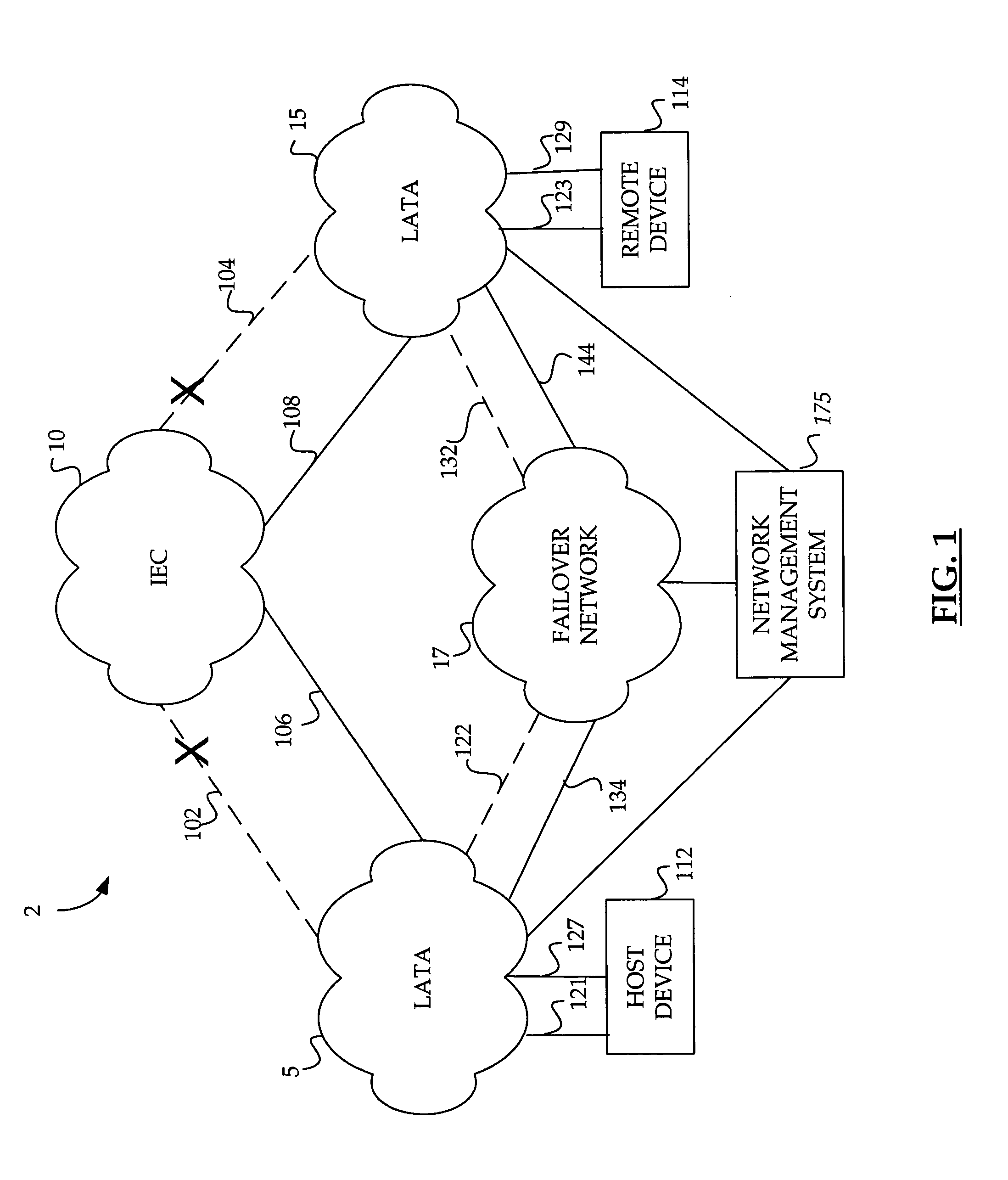

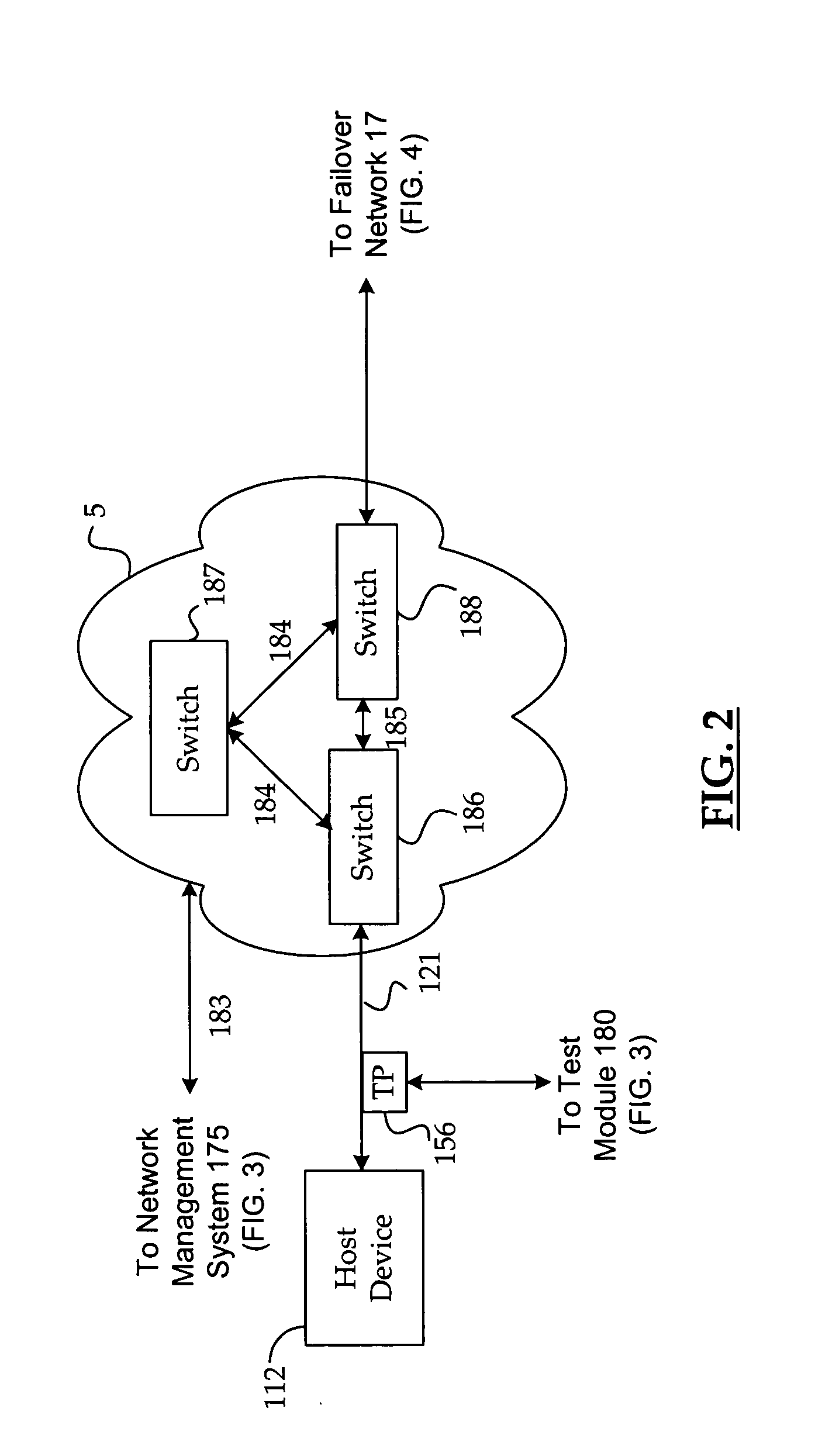

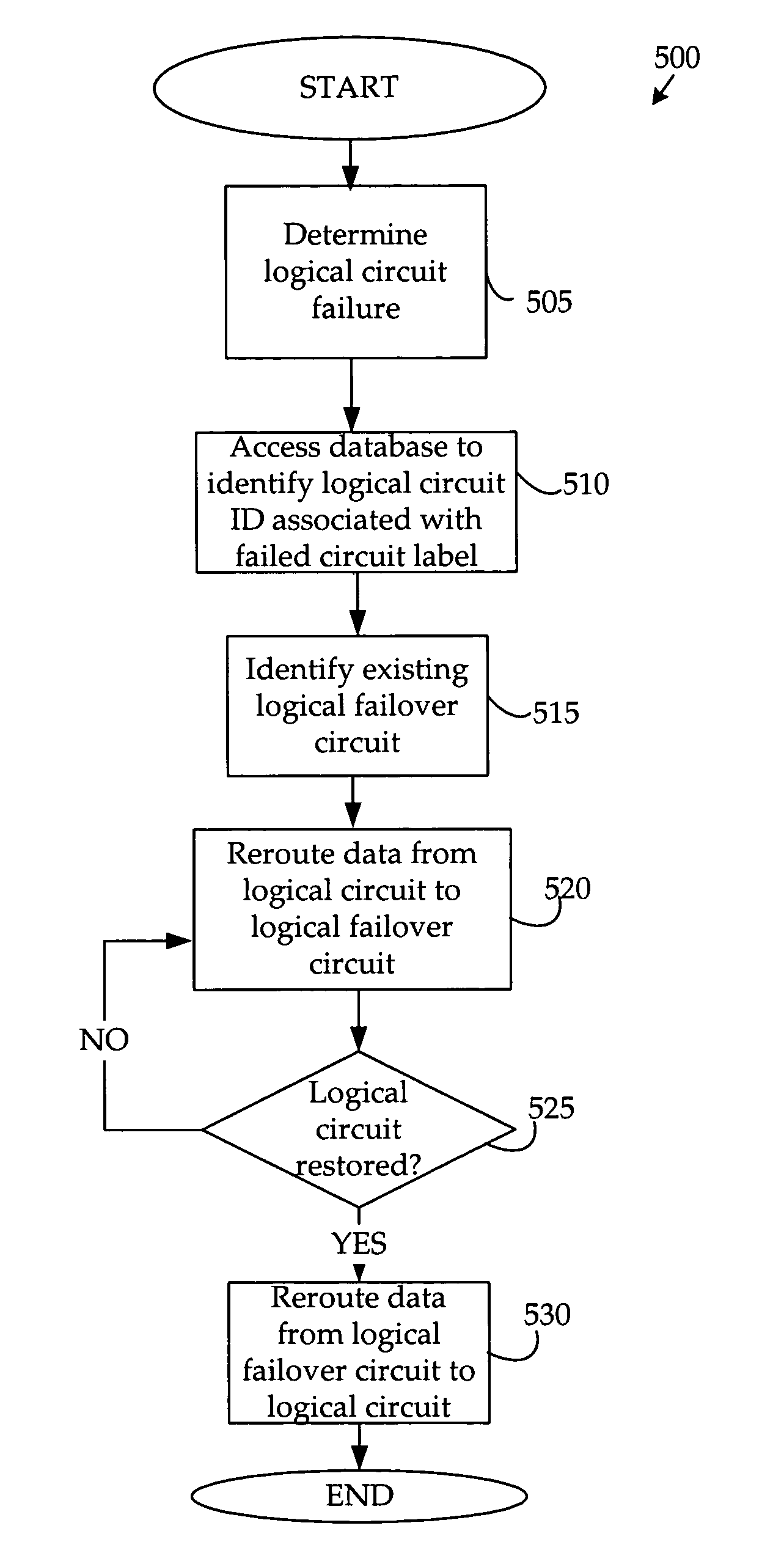

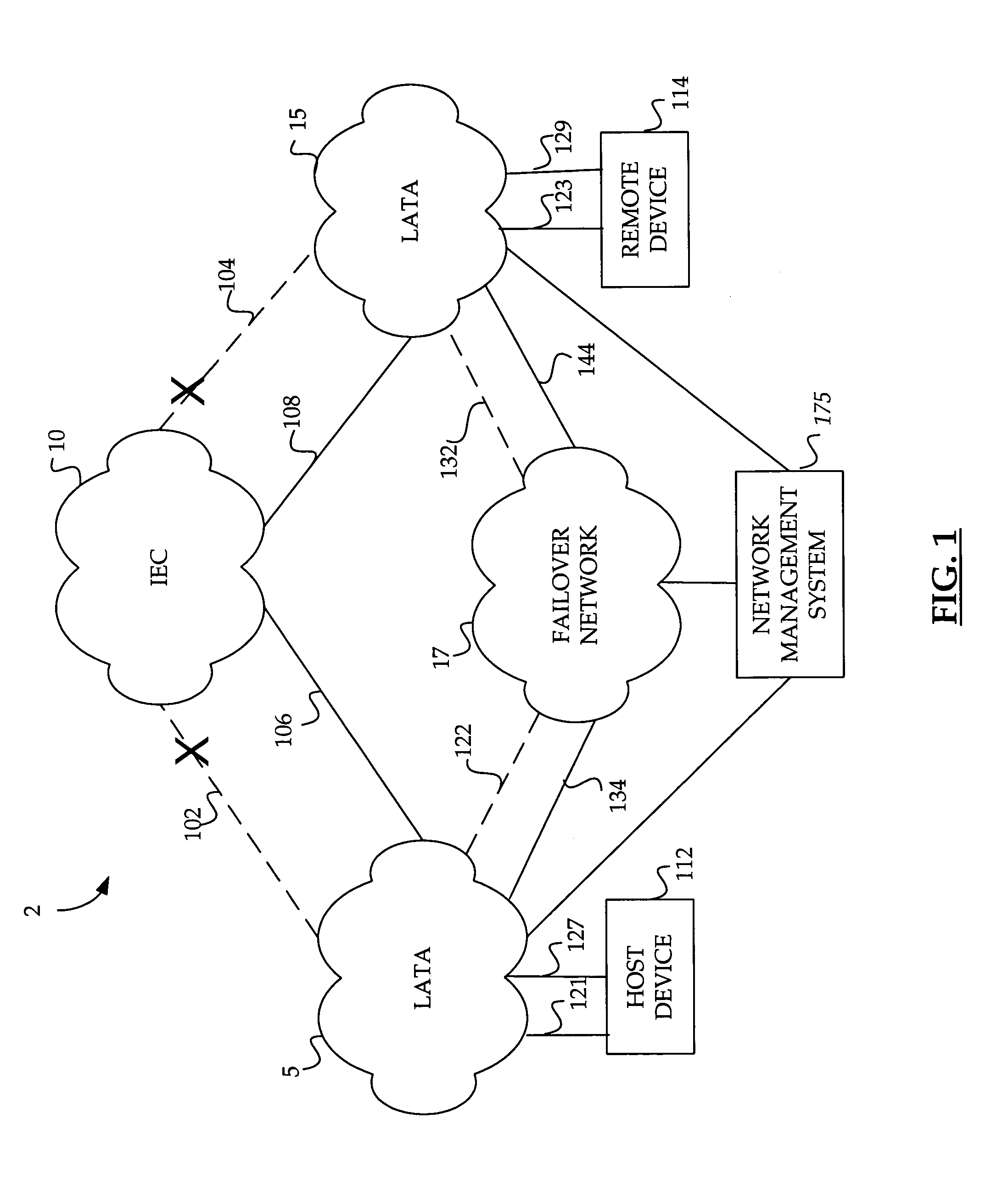

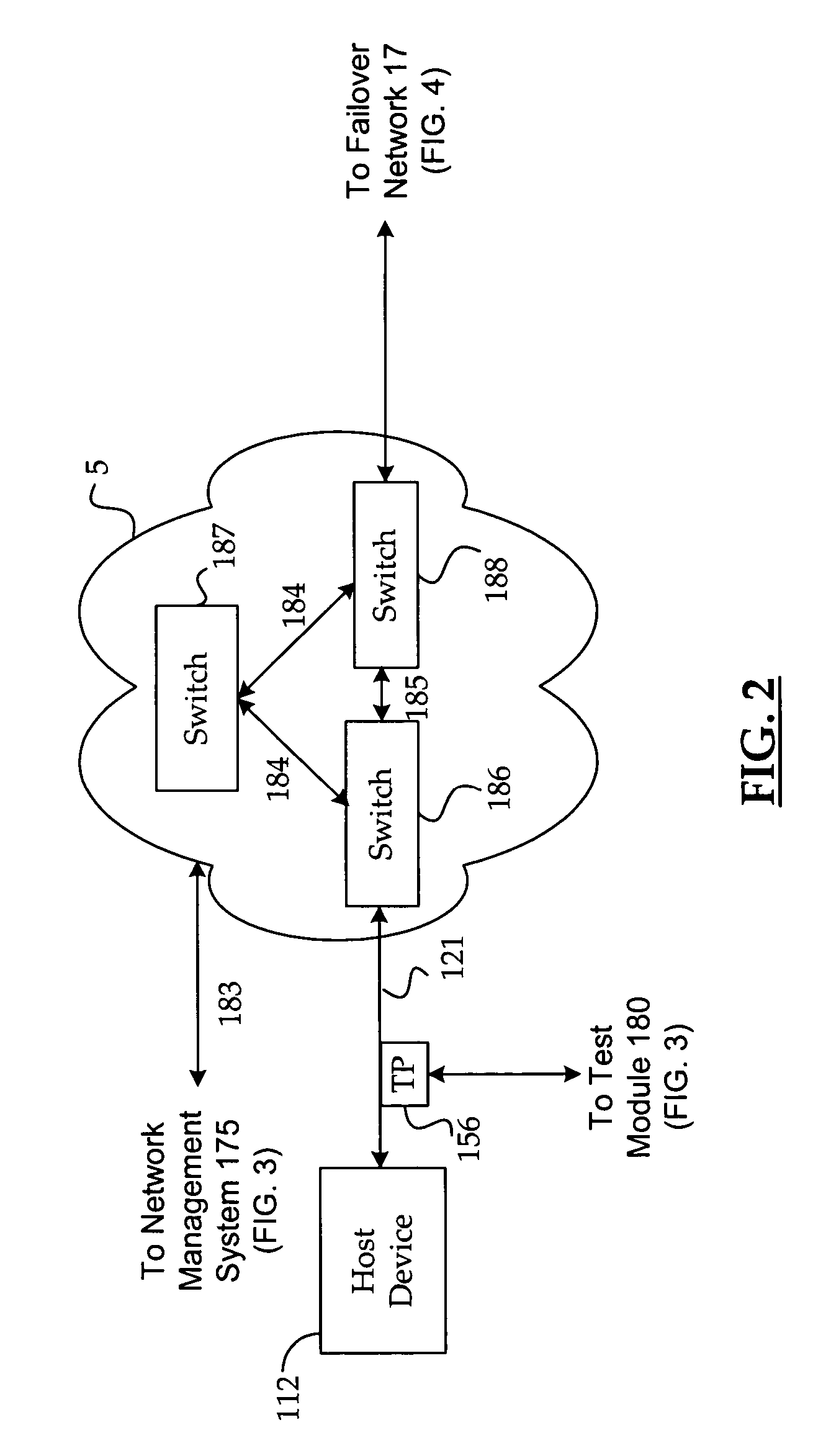

Method and system for automatically rerouting logical circuit data from a logical circuit failure to dedicated backup circuit in a data network

ActiveUS20050237925A1Minimizing lost dataError preventionTransmission systemsFailoverComputer architecture

A method and system are provided for automatically rerouting logical circuit data from a physical circuit failure in a data network. When a failure in a logical circuit is detected, a label or services name associated with the logical circuit is automatically associated with a logical circuit identifier utilized for identifying the logical circuit in the data network. Once the logical circuit is associated with the logical circuit identifier, the logical circuit data may be automatically rerouted to a “failover network,” thereby minimizing lost data until the failure in the logical circuit is resolved. The logical failover circuit may be an already existing logical circuit provisioned over a dedicated backup physical circuit in the data network.

Owner:AT&T INTPROP I L P

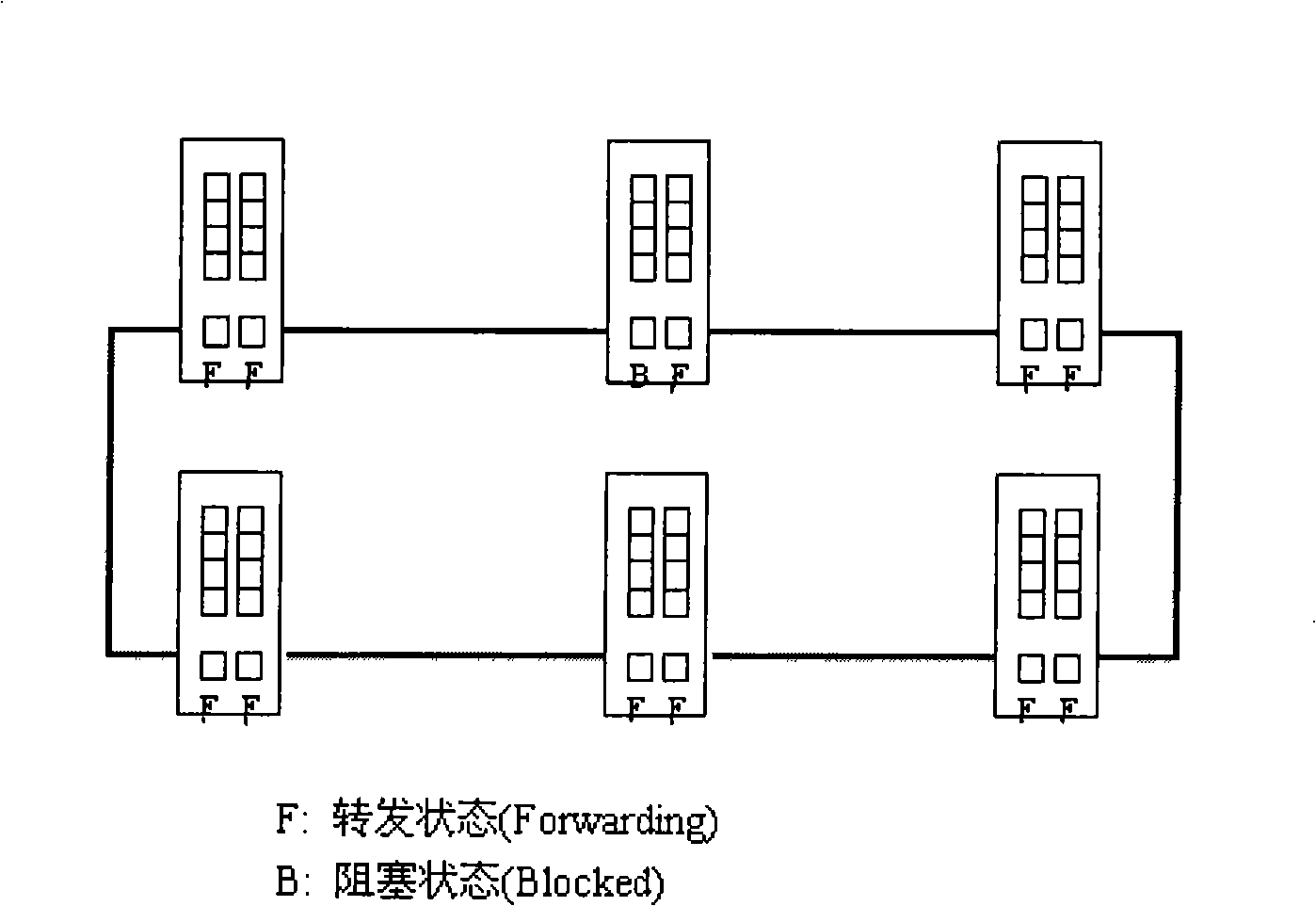

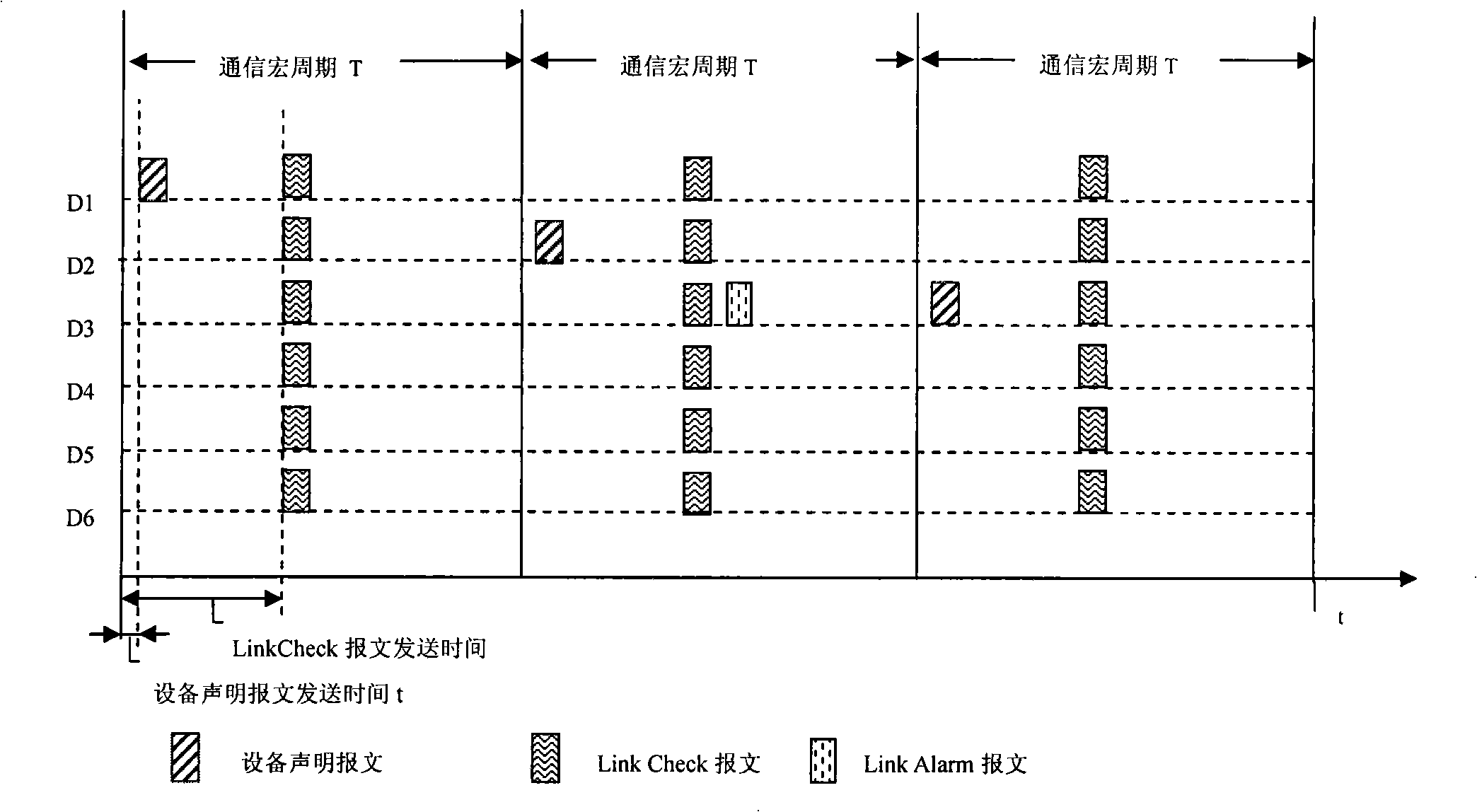

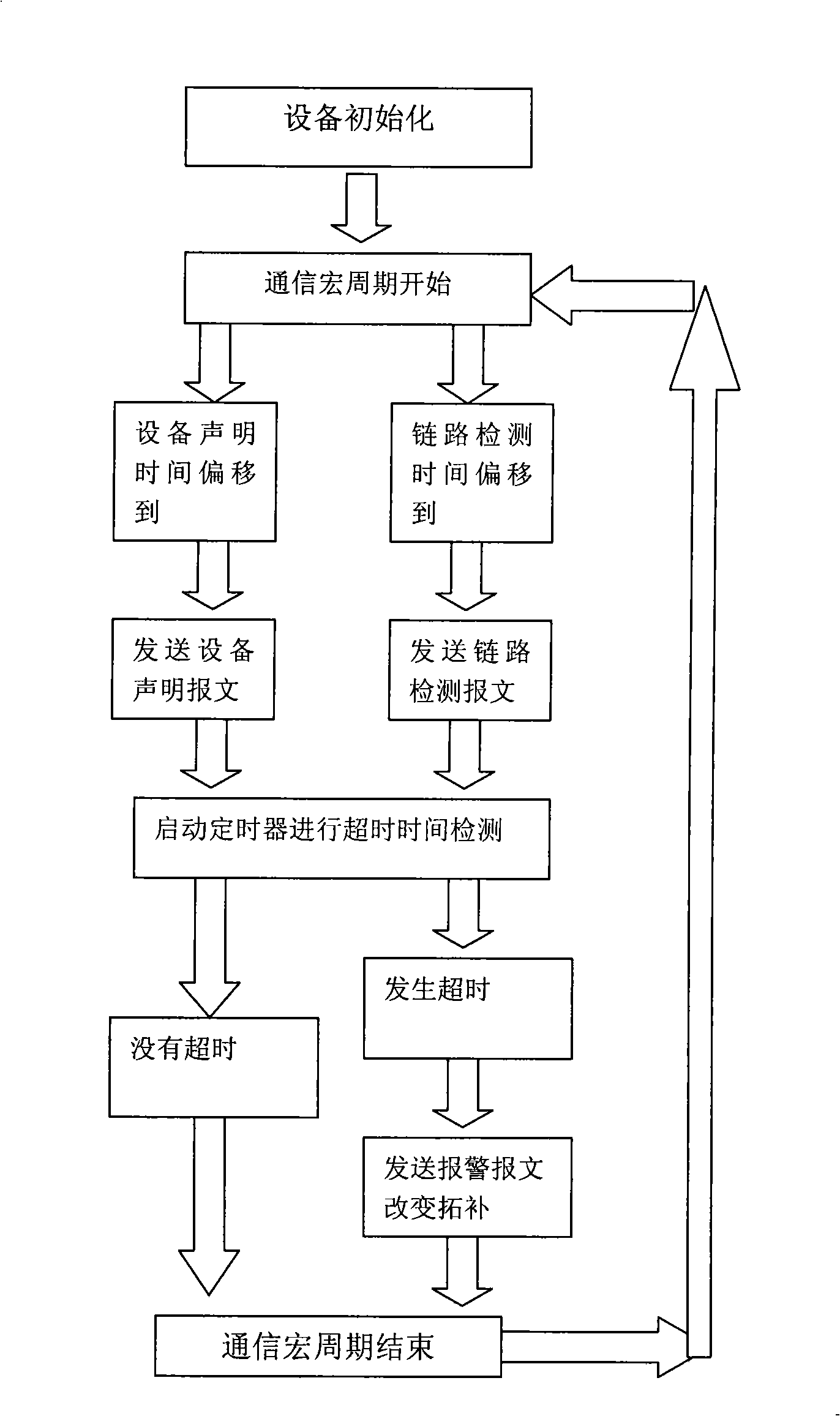

A method for realizing network recovery in loop network

ActiveCN101262401AGuaranteed to workGuaranteed Availability RequirementsData switching networksAlarm messageTelecommunications link

The invention discloses a method for recovering networks in a ring network. Ethernet switch equipment enters a communication status after an initial configuration and precise time synchronization based on an IEEE 1588 protocol. Each equipment according to the configuration of the network sends out time-sharing equipment statement messages and link circuit checking messages. The link circuit checking messages are sent by a multicast address in two ways; if a port of equipment receives no link checking messages of a connected port after the time out, then a network trouble can be determined and link circuit alarm messages are sent by the multicast address in two ways for alarming. The rest equipments in the ring network after receiving the link circuit alarm message, then empty an FDB list and utilize a backup link circuit to restart path learning. By adopting the method of the invention, any communication link circuit failure in the ring network can be quickly detected and correspondingly processed, thereby meeting the availability requirements of Ethernet communication by the industrial automatic field.

Owner:SHANGHAI AUTOMATION INSTRAION CO LTD

Method and system for automatically rerouting logical circuit data from a logical circuit failure to dedicated backup circuit in a data network

ActiveUS7466646B2Minimizing lost dataError preventionFrequency-division multiplex detailsFailoverComputer architecture

Owner:AT&T INTPROP I LP

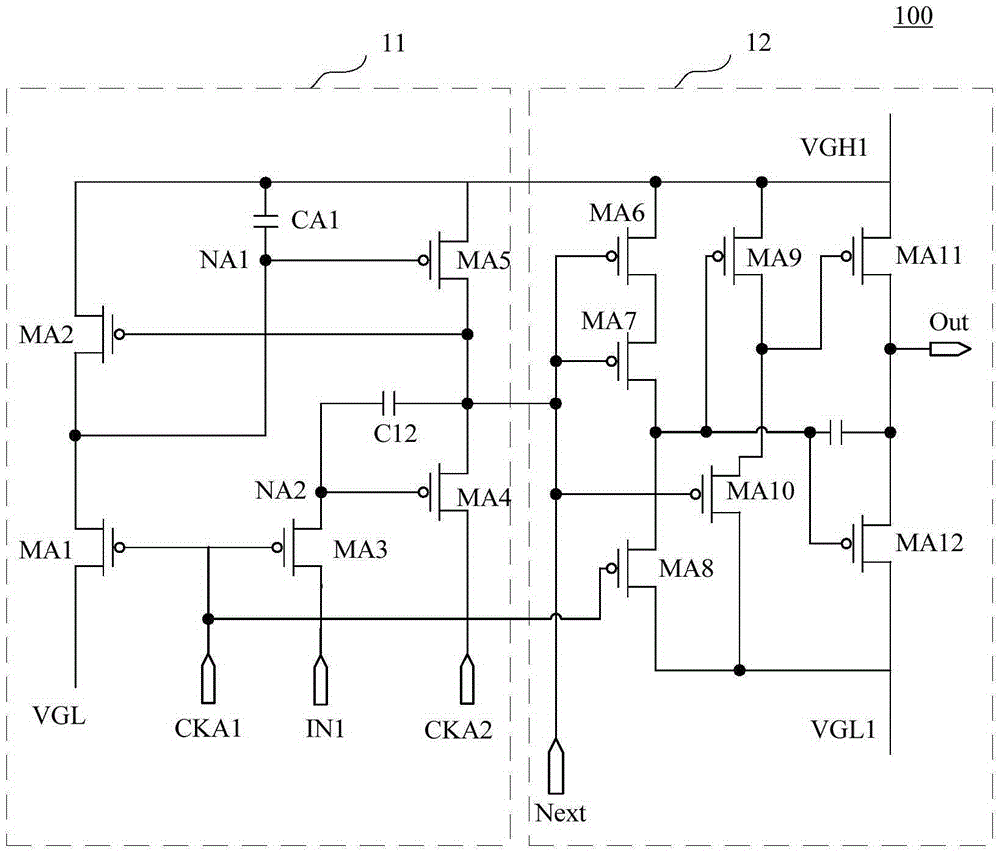

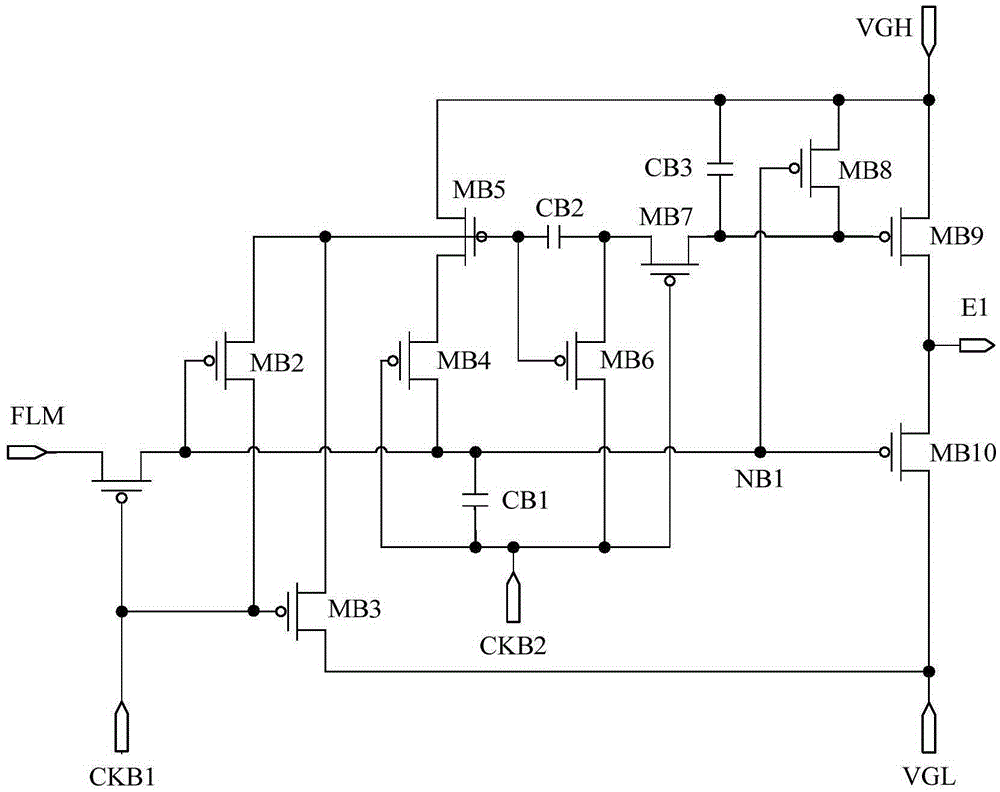

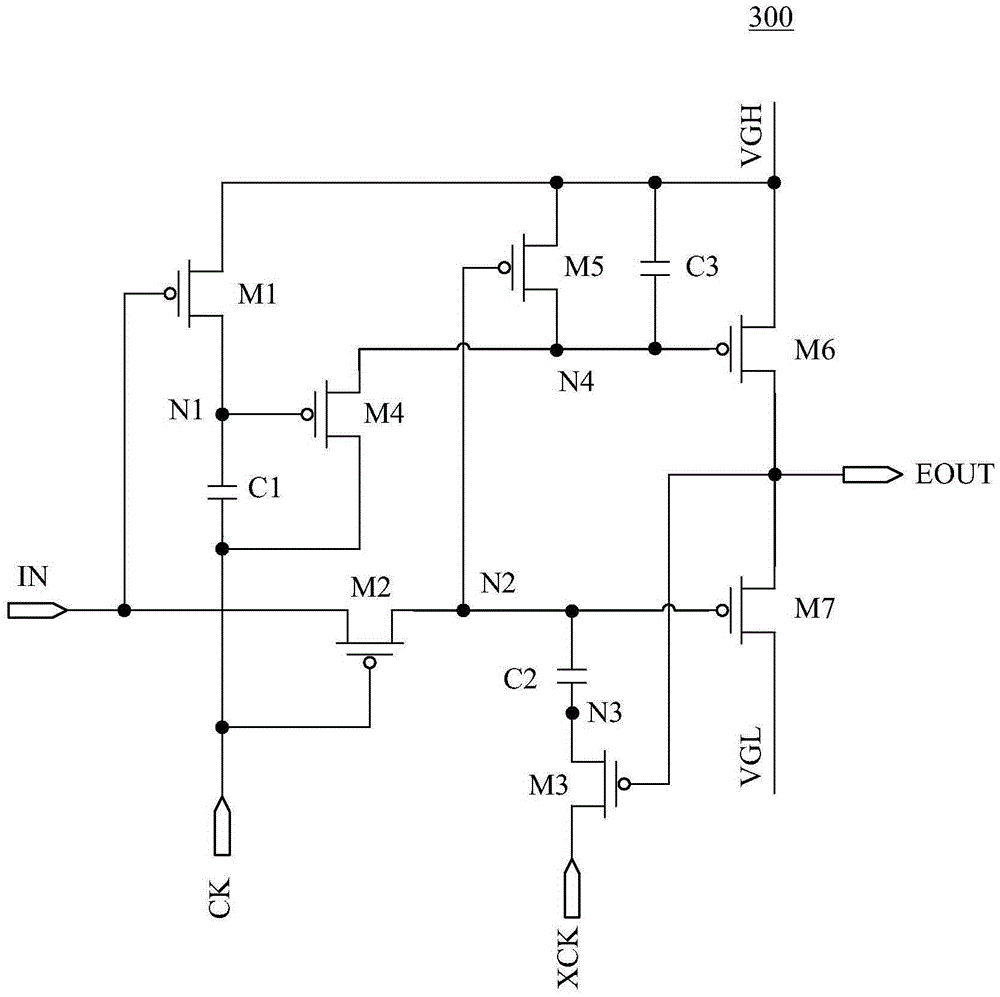

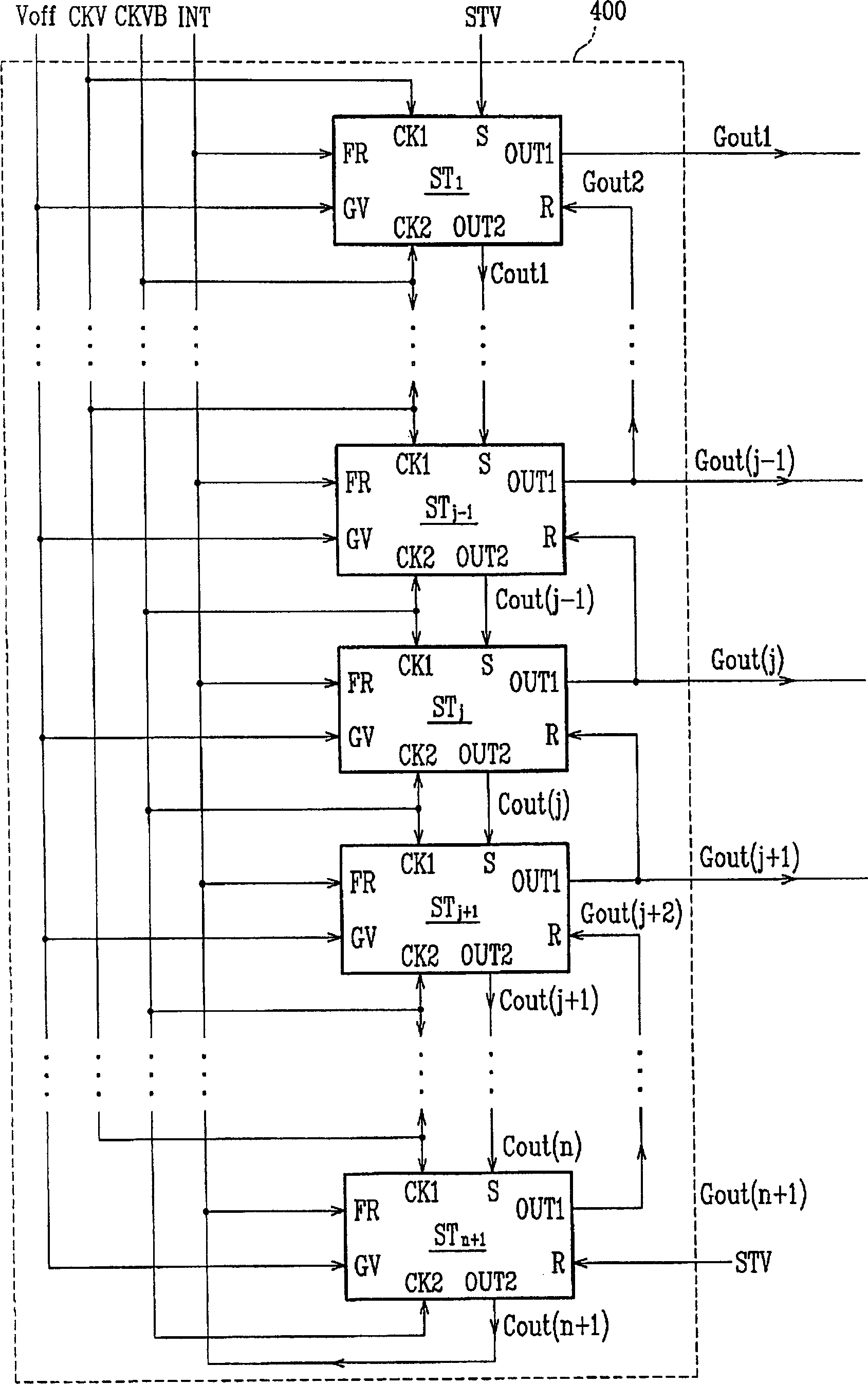

Shift registering unit, shift register, driving method of shift register and display device

ActiveCN105405383AReduce power consumptionAvoid failureStatic indicating devicesDigital storageShift registerDisplay device

The invention discloses a shift registering unit, a shift register, a driving method of the shift register and a display device. The shift registering unit comprises a first transistor, a second transistor, a third transistor, a fourth transistor, a fifth transistor, a sixth transistor, a seventh transistor, a first capacitor, a second capacitor, a third capacitor, an input signal end, a first clock signal end, a second clock signal end, a first voltage signal end, a second voltage signal end and a first output end. According to the invention, shift output of grid signals can be achieved via quite few transistors, power consumption of the shift register is reduced; a circuit failure caused by potential competence of nodes and threshold value drifting of the transistors can be avoided; and stability of circuit operation is enhanced.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD +1

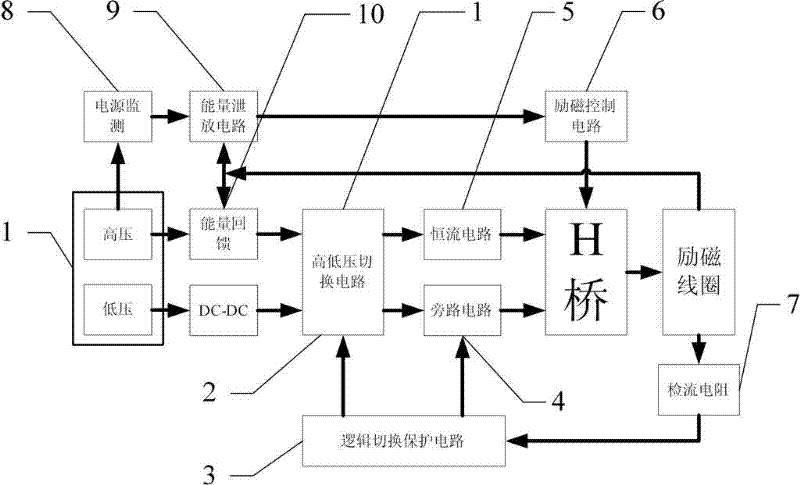

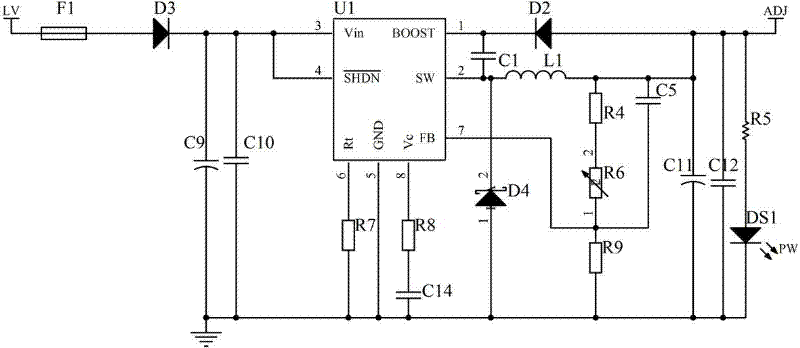

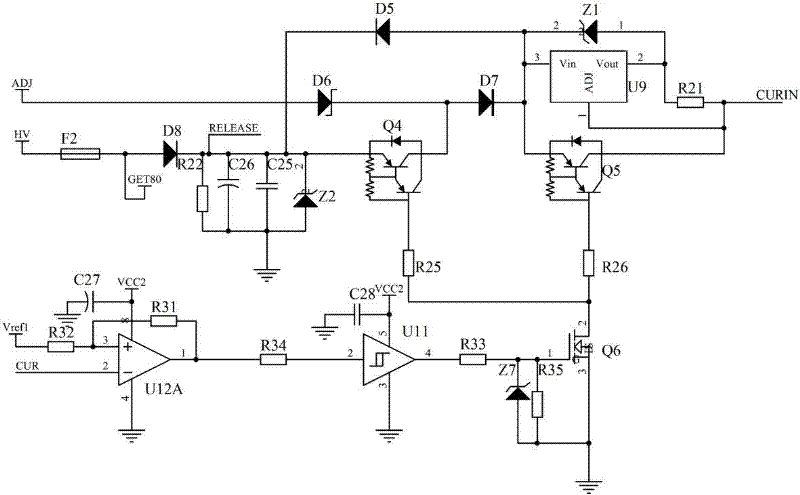

High/low voltage switching excitation system of electromagnetic flowmeter with bypass and energy feedback circuit

ActiveCN102393225AQuick responseImprove efficiencyVolume/mass flow measurementLow voltageEnergy leakage

The invention relates to a high / low voltage switching excitation system of an electromagnetic flowmeter with a bypass and an energy feedback circuit. The excitation system comprises an adjustable low voltage source circuit, a high / low voltage switching circuit, a constant-current circuit, a bypass circuit, an H-bridge excitation circuit, an excitation control circuit, a logic switching circuit, apower supply detection circuit, the energy feedback circuit and an energy leakage circuit. A practical excitation current detected on a current detecting resistor is compared with an excitation current threshold set in the logic switching circuit, thereby obtaining a control logic which is used for controlling the high / low voltage switching circuit and the bypass circuit, so as to select an excitation work voltage; introduction of the bypass circuit accelerates the response velocity of the excitation current in a coil obviously; the energy feedback circuit stores the energy fed back from an excitation coil; the power supply detection circuit, the energy leakage circuit and a switching protection circuit perform electrification, outage and error protection on the excitation system. The excitation system related to the invention improves the utilization rate of power supply, accelerates the response speed of excitation current, broadens the range of excitation frequency and provides circuit fault protection.

Owner:HEFEI UNIV OF TECH

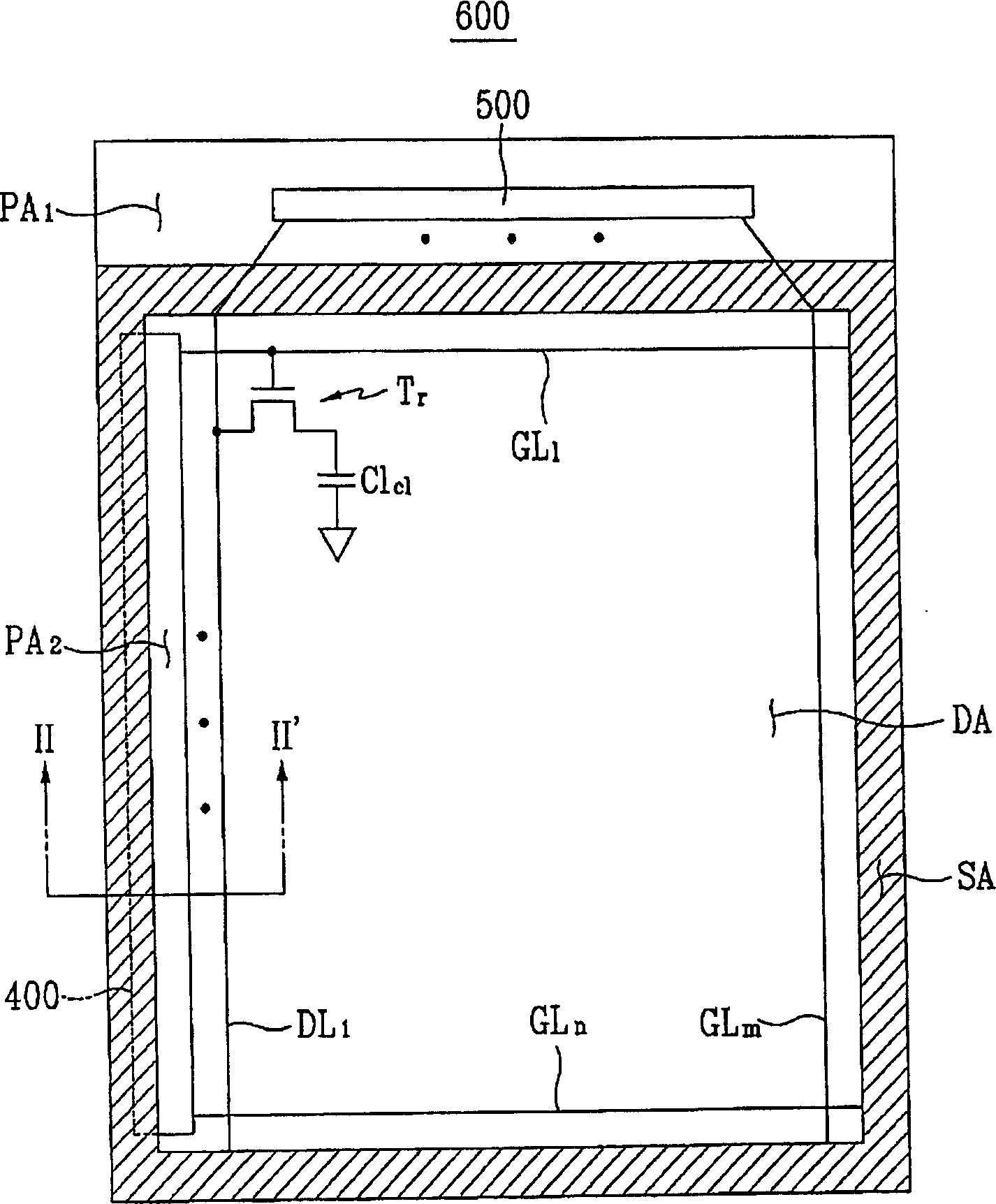

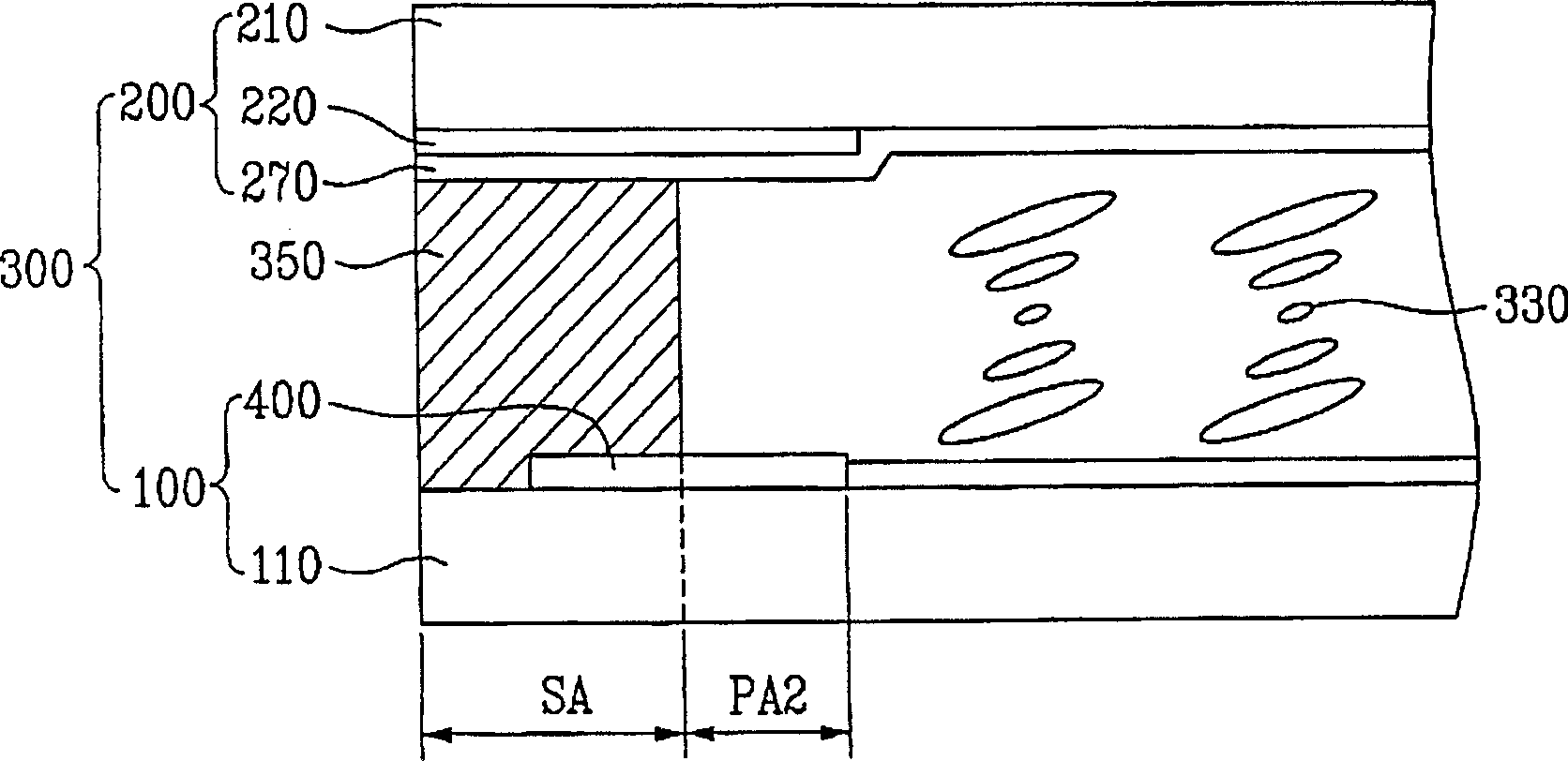

Thin film transistor array panel and display device including the same

ActiveCN1727972AComprehensive descriptionStatic indicating devicesNon-linear opticsTransistor arrayDriver circuit

The gate driving circuit of the thin film transistor array panel is formed on the same plane as the display area of the transistor array panel. The gate driving circuit includes a driving circuit and a signal line with a hole. Therefore, even if the light is irradiated from the thin film transistor array panel side, a sufficient amount of light can reach the phototypesetting sealant at least partially overlapping the gate driving circuit. The thin film transistor array panel and the opposing panel are assembled together air-tightly and moisture-tightly. As a result, the gate drive current can prevent corrosion caused by externally introduced moisture. It can also reduce gate drive circuit failures.

Owner:SAMSUNG DISPLAY CO LTD

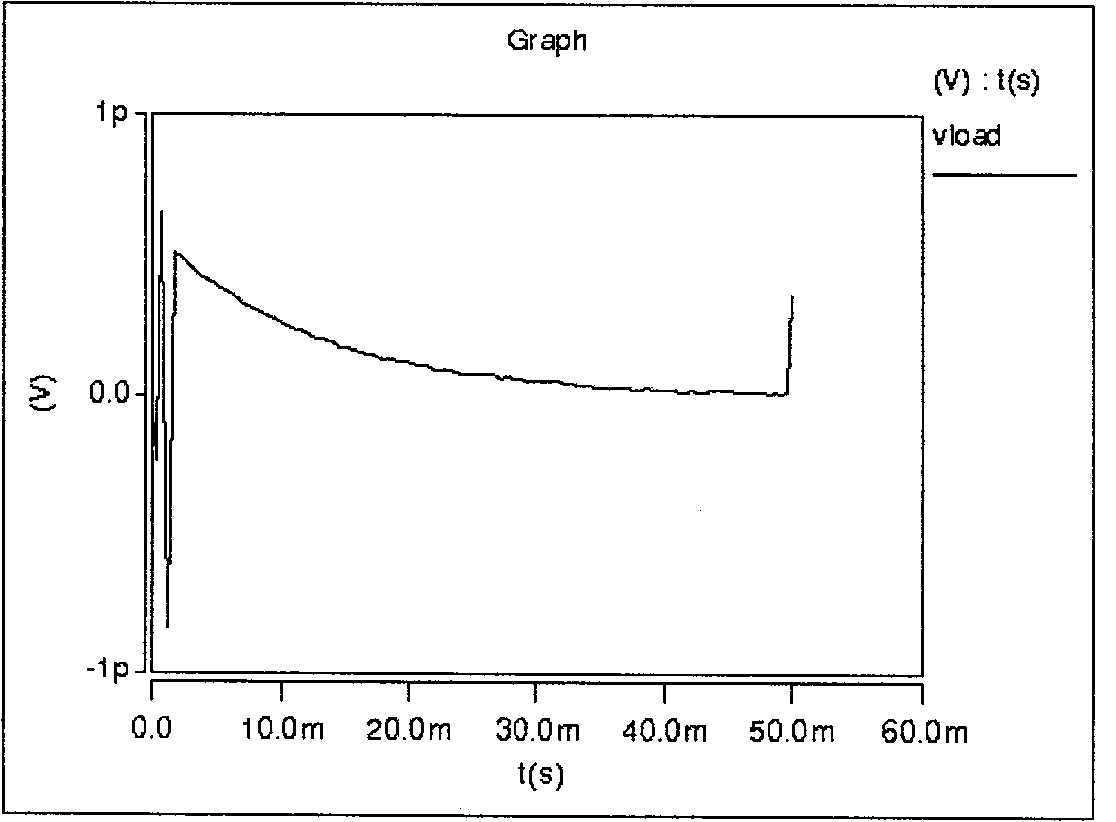

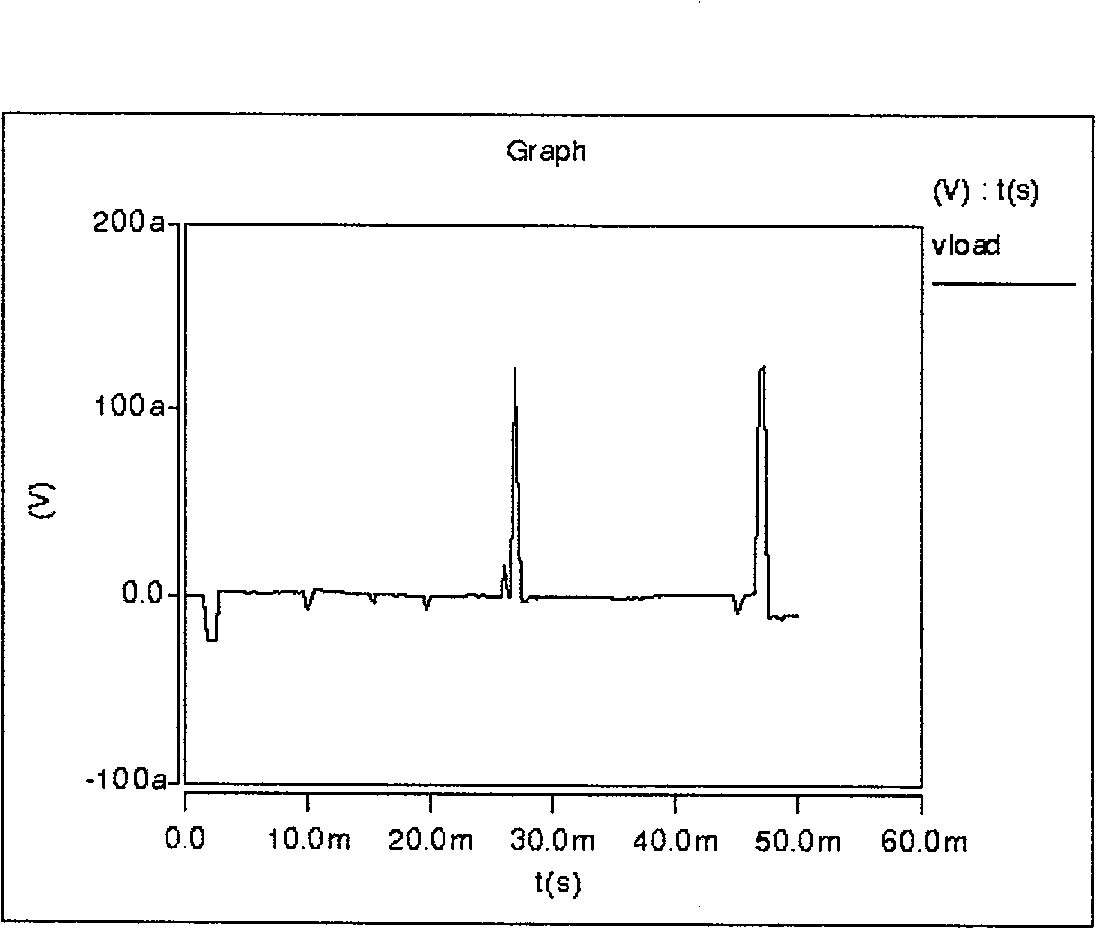

Saber-based circuit failure simulation analyzing method

ActiveCN102156760AImproving Failure Simulation EfficiencySpecial data processing applicationsModelSimHemt circuits

The invention provides a Saber-based circuit failure simulation analyzing method. The method is characterized by comprising the following steps: 1, performing Saber circuit function modeling and simulation; 2, determining the failure mode of a device to be simulated; 3, modeling the failure; 4, injecting the failure; 5, simulating a failed circuit to generate a failure simulation result; 6, setting a failure criterion; and 7, giving a failure analyzing result. Regarding the problem that the conventional circuit failure simulation can be only used for digital circuits, the method provides a practical failure simulation method based on the digital-analog hybrid simulation platform Saber. Furthermore, many failure simulation models which cannot be solved by predecessors are added, and 48 failure modes can be simulated. Realization of automatic failure injection greatly improves the failure simulation efficiency. The direct interface between Saber and failure simulation is broken through,and an effective signal failure determination method is provided.

Owner:苏州天航长鹰科技发展有限公司

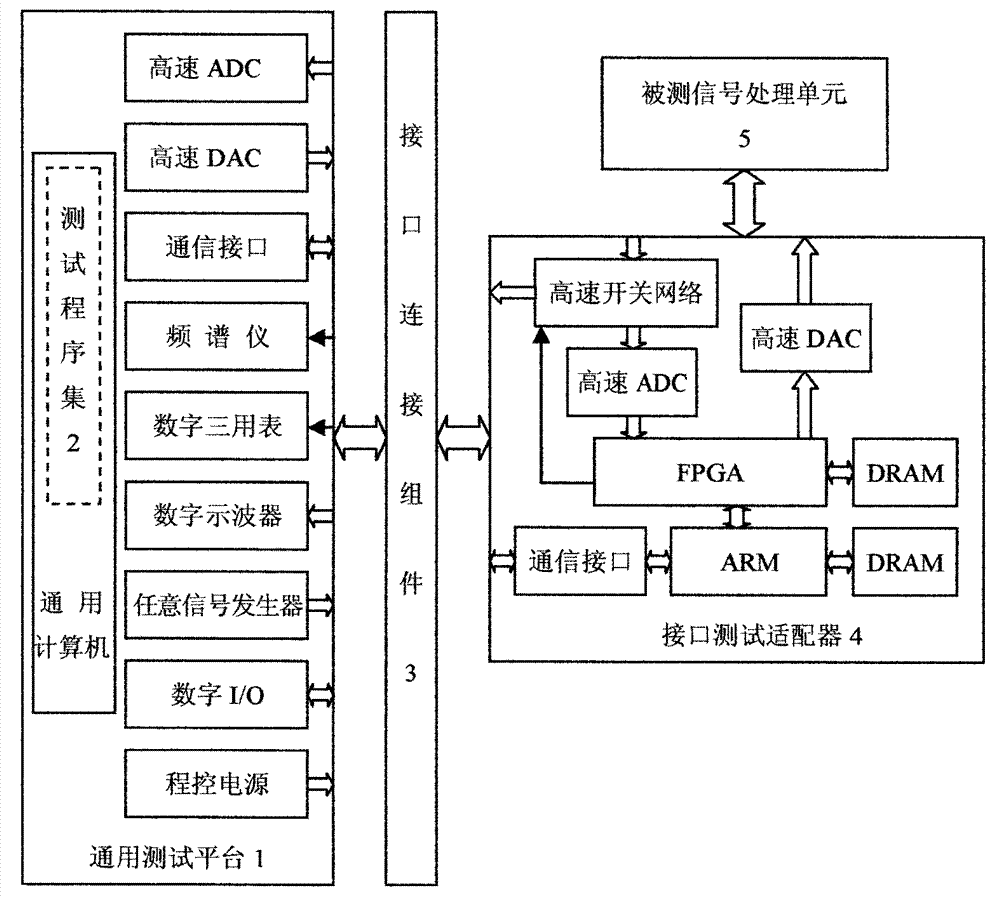

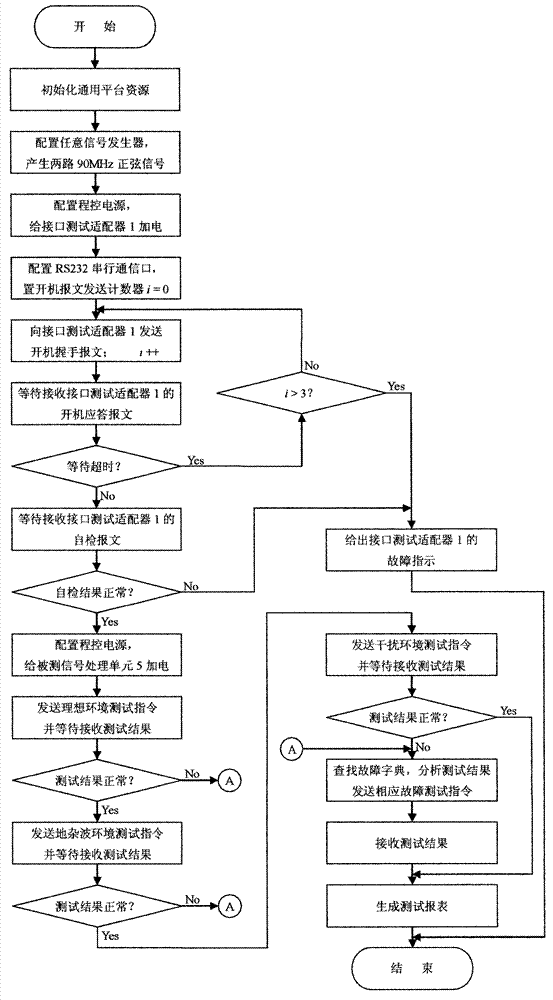

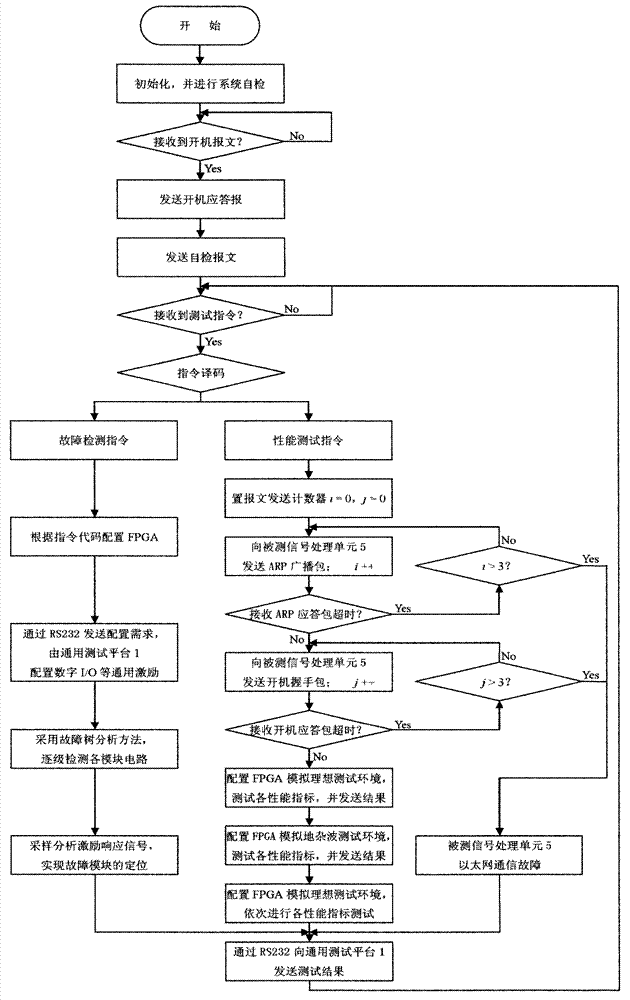

Radar signal unit performance test and fault diagnosis system based on general test platform

InactiveCN103713281AImprove general performanceStrong scalabilityWave based measurement systemsEngineeringTest platform

The invention relates to the technical field of radar circuit fault detection and diagnosis, specifically to a radar signal unit performance test and fault diagnosis system based on a general test platform. The system comprises a general test platform, a test procedure set, an interface connection module, an interface test adapter and a signal processing unit to be tested, the general test platform includes general test instruments and hardware resources including a test procedure set, a programmable power supply, a spectrometer, a signal generator, a digital oscilloscope, a digital triple-purpose meter, a digital I / O, a communication interface, a multichannel ADC and a multichannel DAC, and the test platform is connected with the interface test adapter through the interface connection module. By adoption of a system architecture of the general test platform plus the interface test adapter, the system has very strong universality and expandability, allows multiple equipment to share one test platform, and the interface test adapter adopts a hardware architecture of FPGA+ARM, and has very strong universality, expansibility and reconfigurability.

Owner:NAVAL UNIV OF ENG PLA

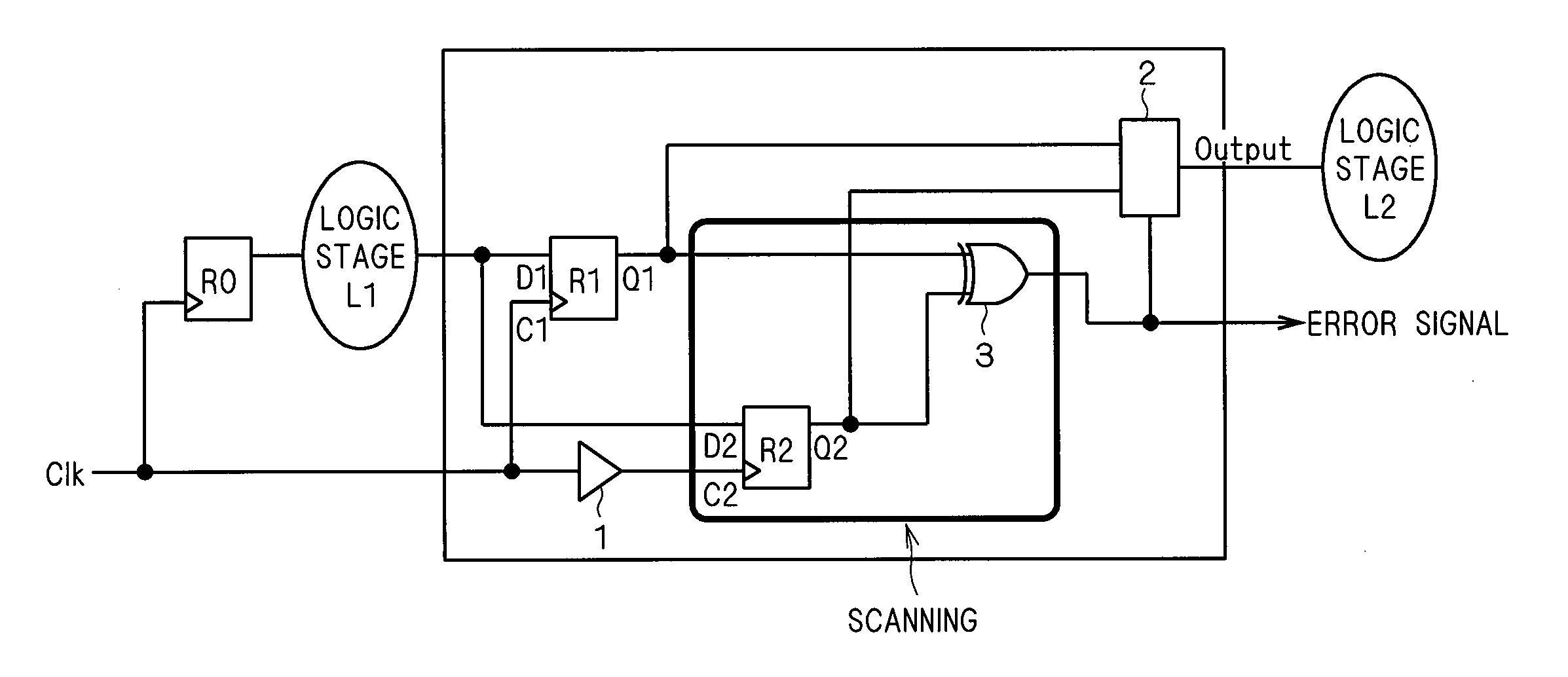

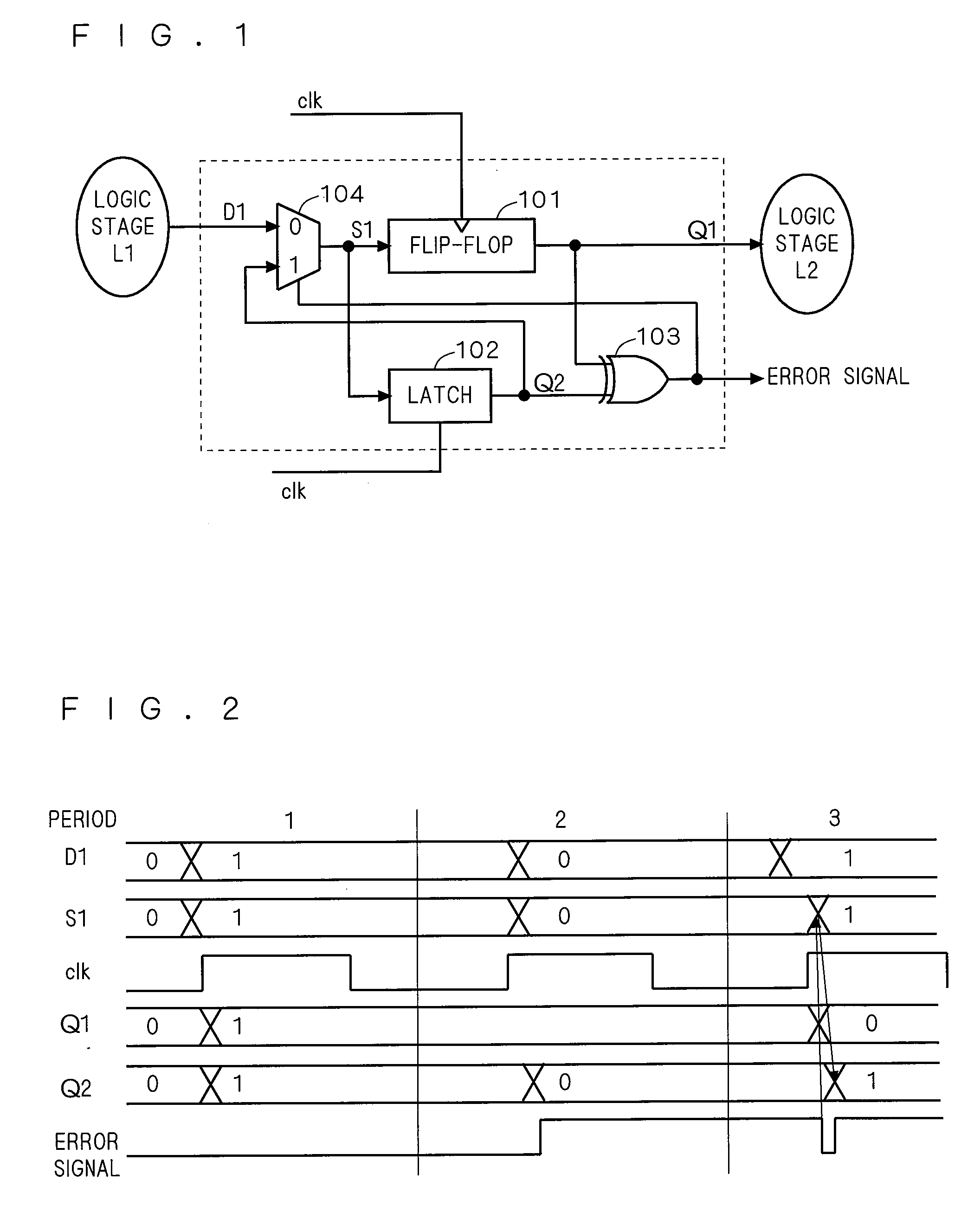

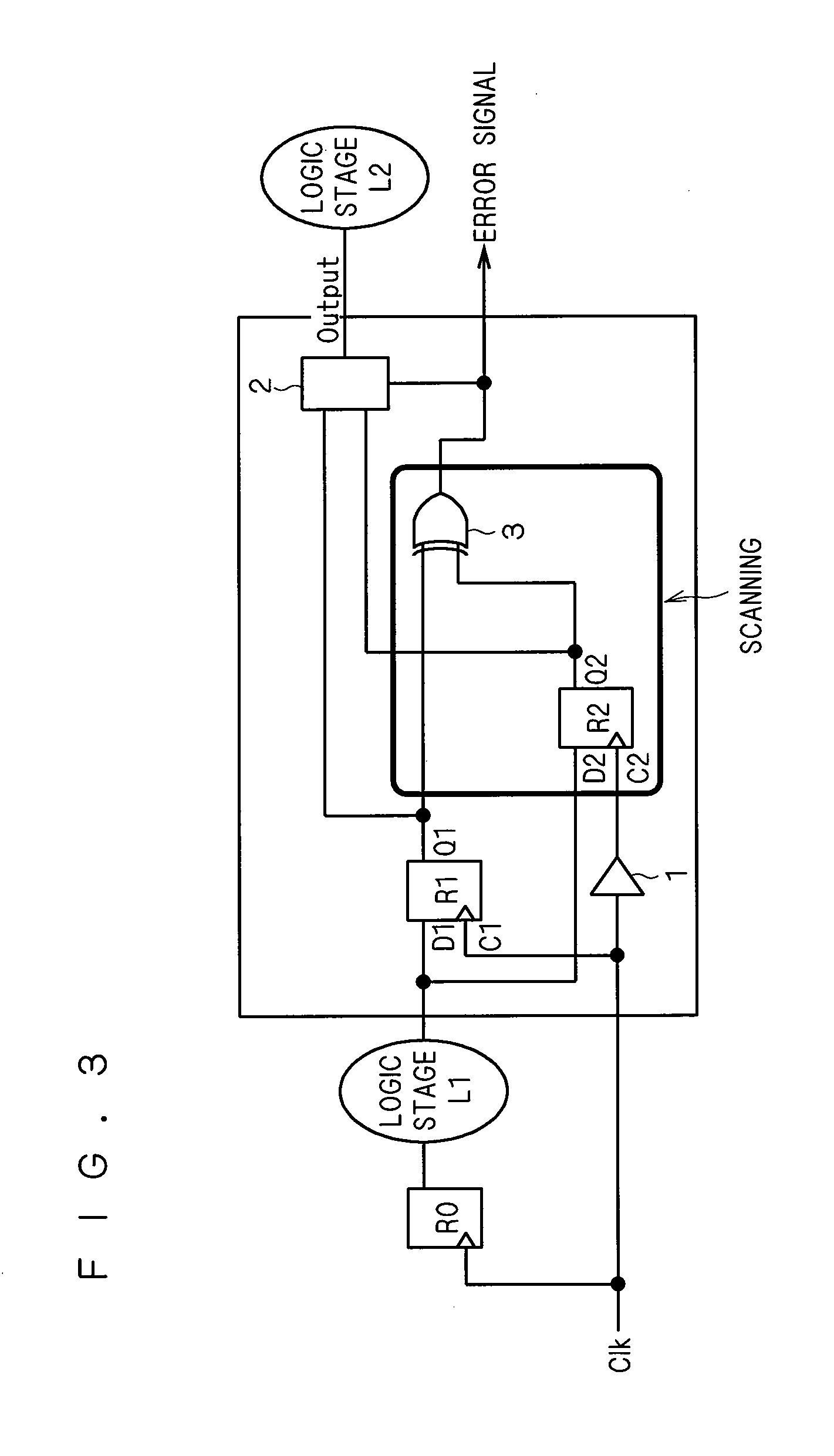

Semiconductor device

An object of the present invention is to provide a semiconductor device capable of recognizing circuit malfunction in an actual operation and of specifying a point of the circuit malfunction, and the semiconductor device, which does not induce the malfunction in the circuit of a subsequent stage when restoring the malfunction. The present invention is the semiconductor device provided with a plurality of logic circuits and a plurality of judging circuits for judging malfunction based on data from the logic circuits, wherein each of the judging circuits is provided with a first register, delay unit, a second register, a comparator and scanning unit, which makes the second register a shift register to allow to transmit an error signal held in the second register to the subsequent stage, while allowing the comparator to hold a comparison result.

Owner:RENESAS ELECTRONICS CORP

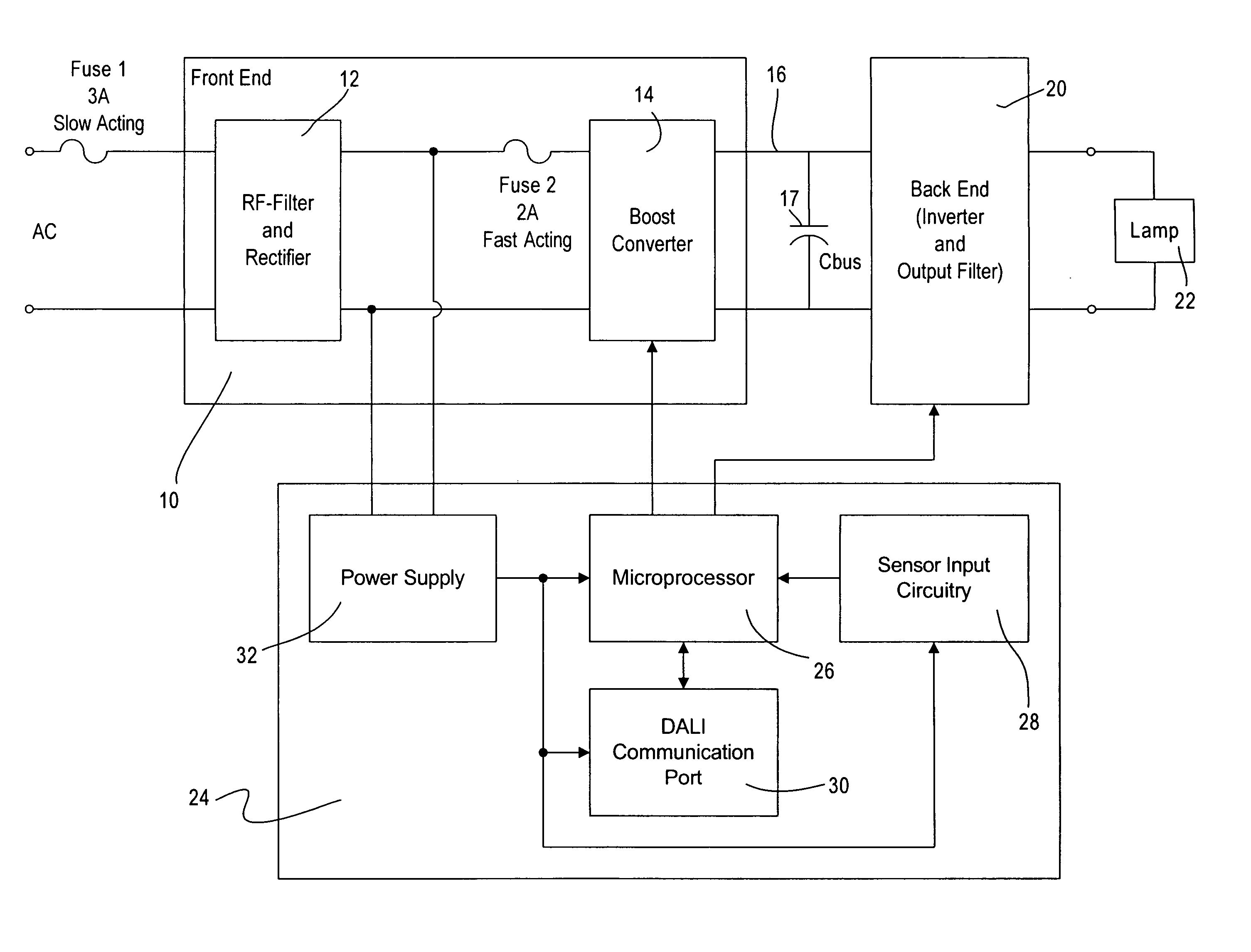

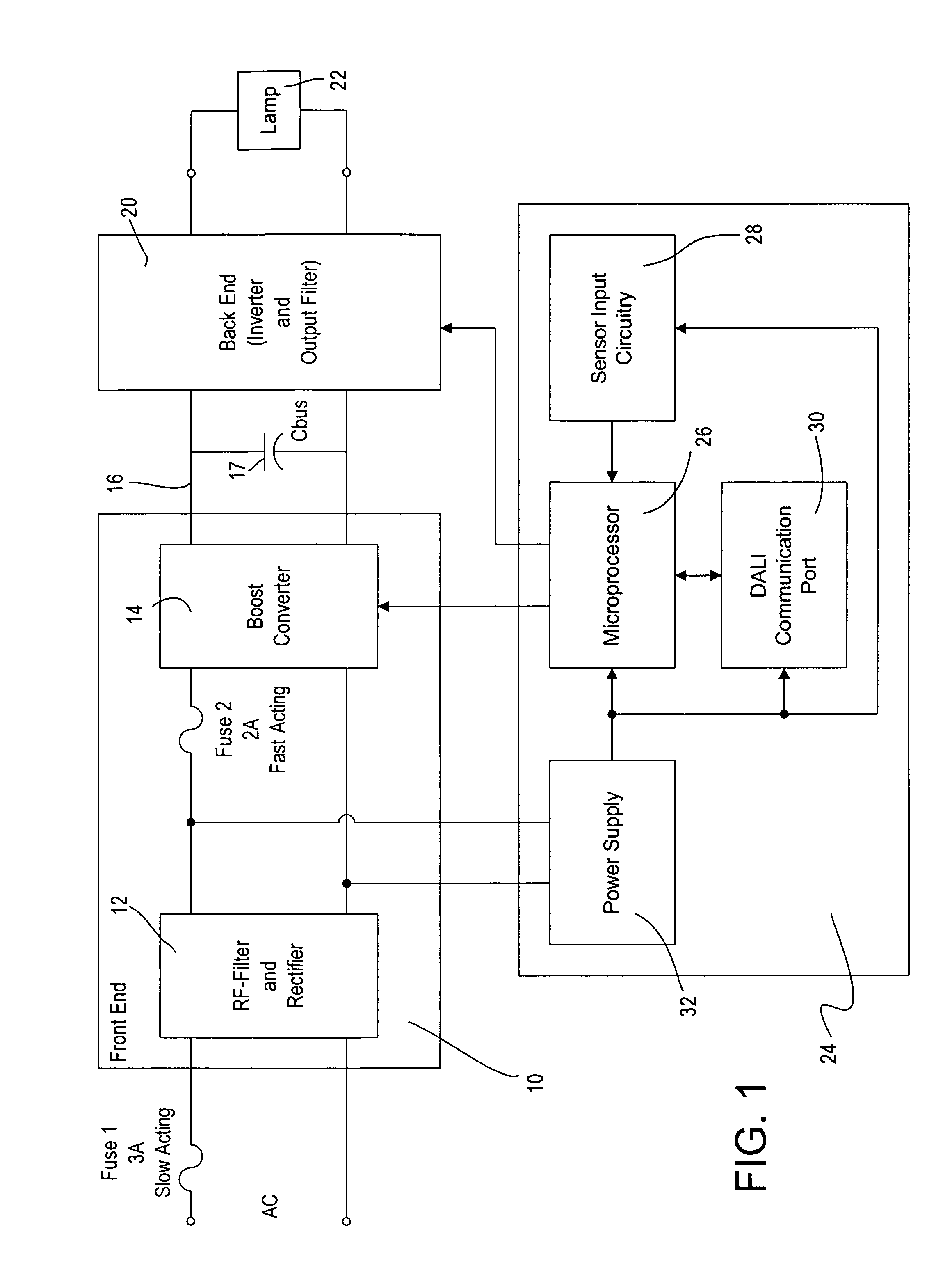

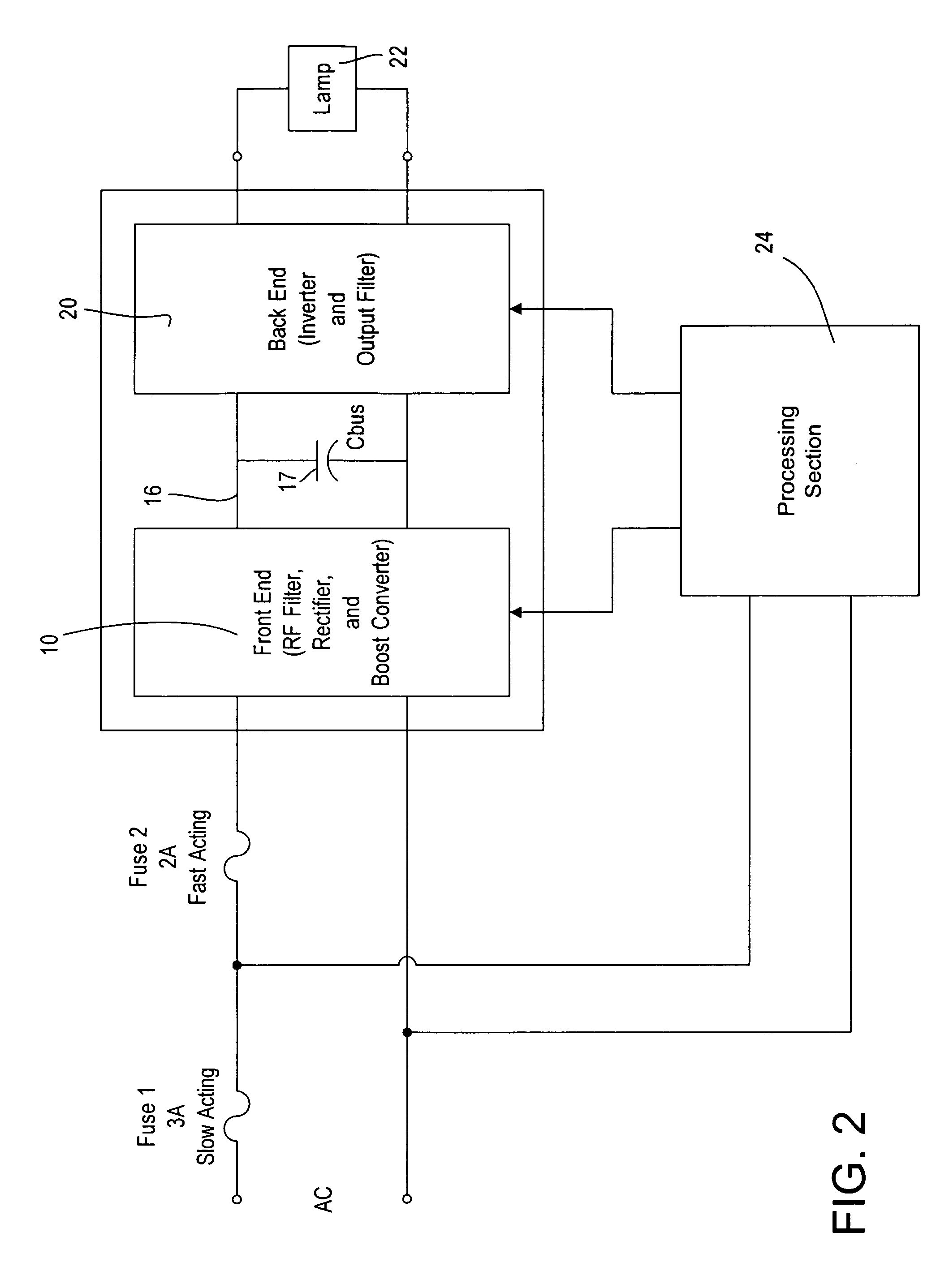

Ballast having multiple circuit failure protection and method for ballast circuit protection

InactiveUS7208887B2Electric light circuit arrangementElectric discharge lampsGas-discharge lampTelecommunications link

A ballast for a gas discharge lamp comprising a first circuit portion for providing power to a lighting load and a second circuit portion for processing data exchanged with a communication link, the first circuit portion receiving power from an AC main supply for conversion to a form suitable to supply power to the lamp, and the second circuit portion having a power supply supplied from the AC main supply, the power supply being coupled at the input of the AC main supply to the first circuit portion, further comprising a first protection circuit coupled in series with the AC main supply for protecting the first and second circuit portions in the event of an electrical circuit failure leading to an overcurrent condition, the power supply for the second circuit portion being coupled such that it is protected by the first protection circuit; further comprising a second protection circuit disposed in series with the first circuit portion and providing protection only in the event of electrical failure leading to an overcurrent condition in the first circuit portion; the second protection circuit adapted so that in the event of electrical failure in the first circuit portion, the second protection circuit will discontinue the supply of current to the first circuit portion, thereby preventing an overcurrent in the first protection circuit that would cause the first protection to interrupt current, and thereby allowing the first protection circuit to continue to supply electrical current to the second circuit portion.

Owner:LUTRON TECH CO LLC

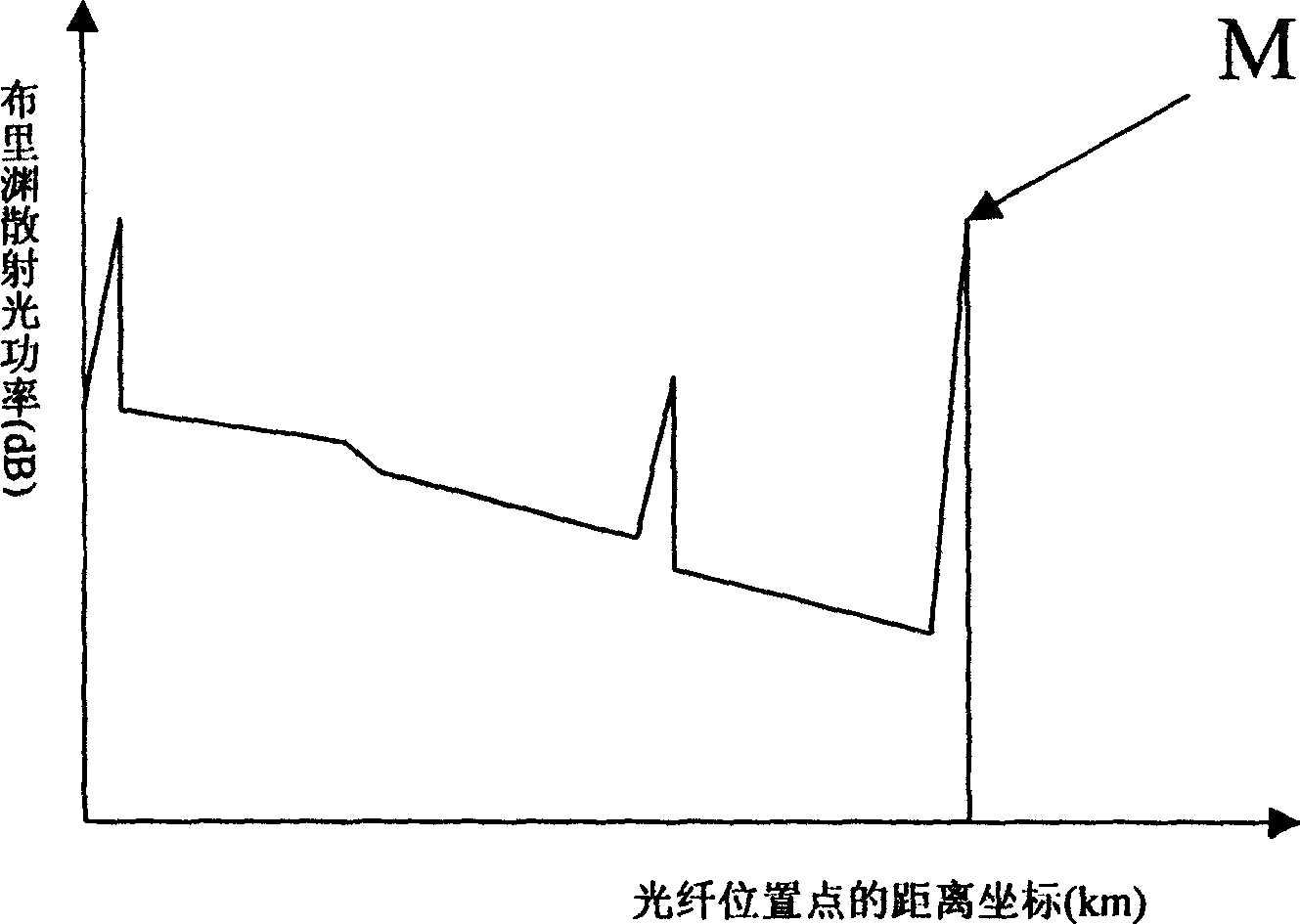

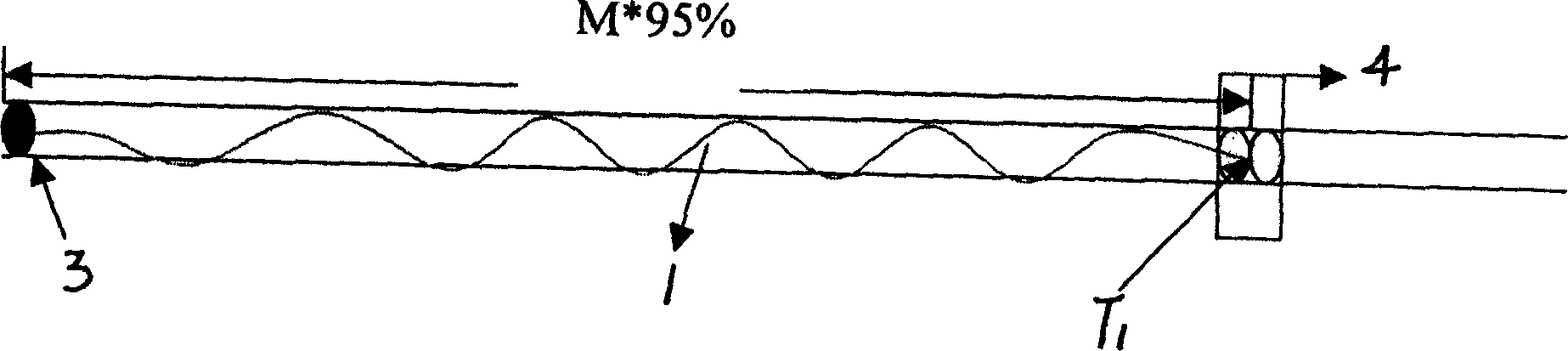

Optical cable circuit failure point precision locating method

InactiveCN1556384AImprove the efficiency of rushing throughReduce calculationTransmission monitoring/testing/fault-measurement systemsOptical apparatus testingAerial cableTime domain

Using Brillouin reflectance technique in optical time domain adopted in the invention picks up strain information carried by Brillouin frequency drift caused by change of position information and temperature change carried in power of reflected light. Using method of combining absolute positioning with relative positioning makes successive approximation till exact location is determined finally. Comparing with prior art, the invention has features of omitting tedious calculation and additional data log, shortening time for finding out fault point of optical cable line so as to save cost. The method is general suitable method for positioning fault point applicable to optical cable line in position fixing direct burying type, aerial cable or duct optical cable.

Owner:NANJING UNIV

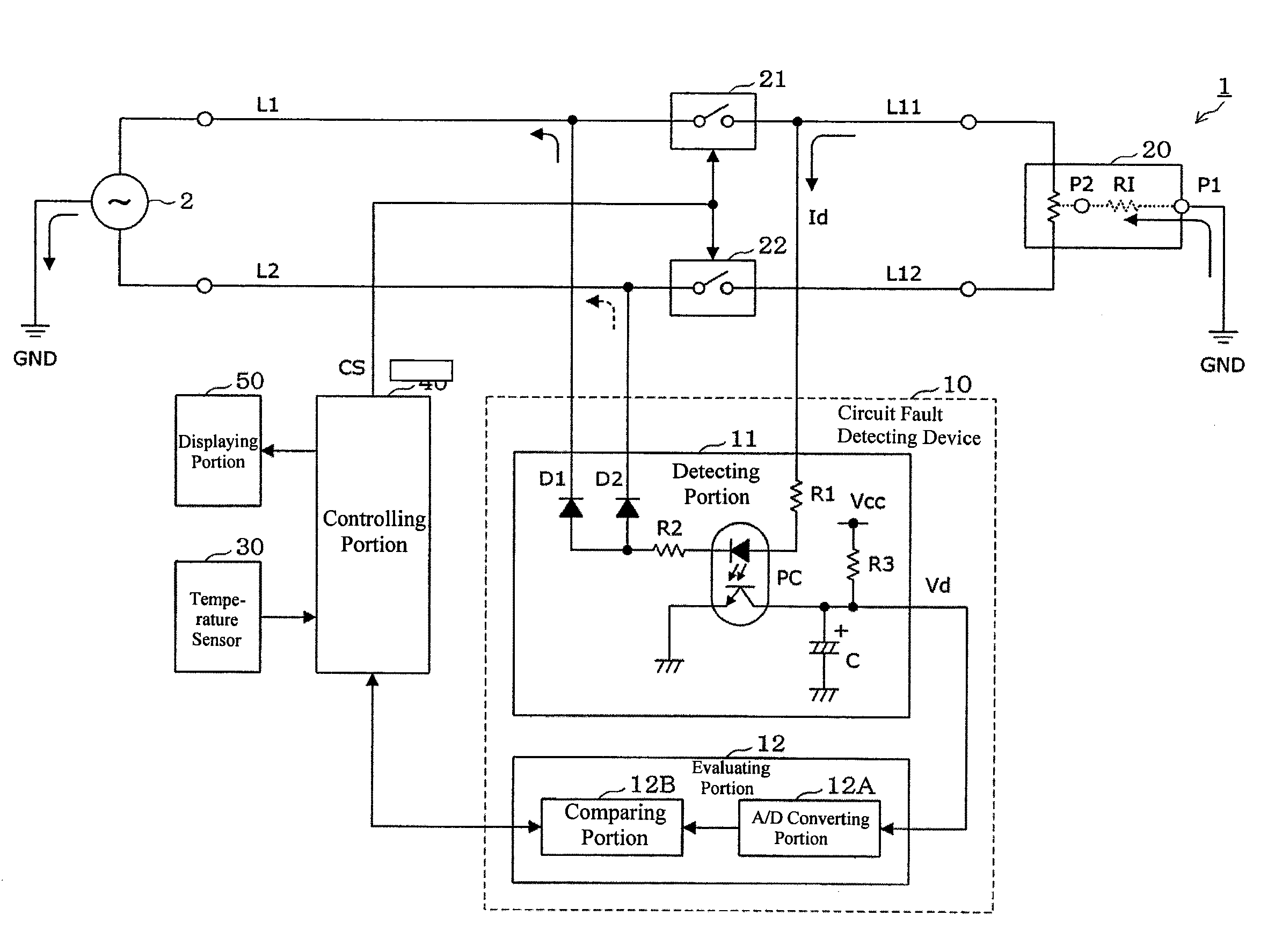

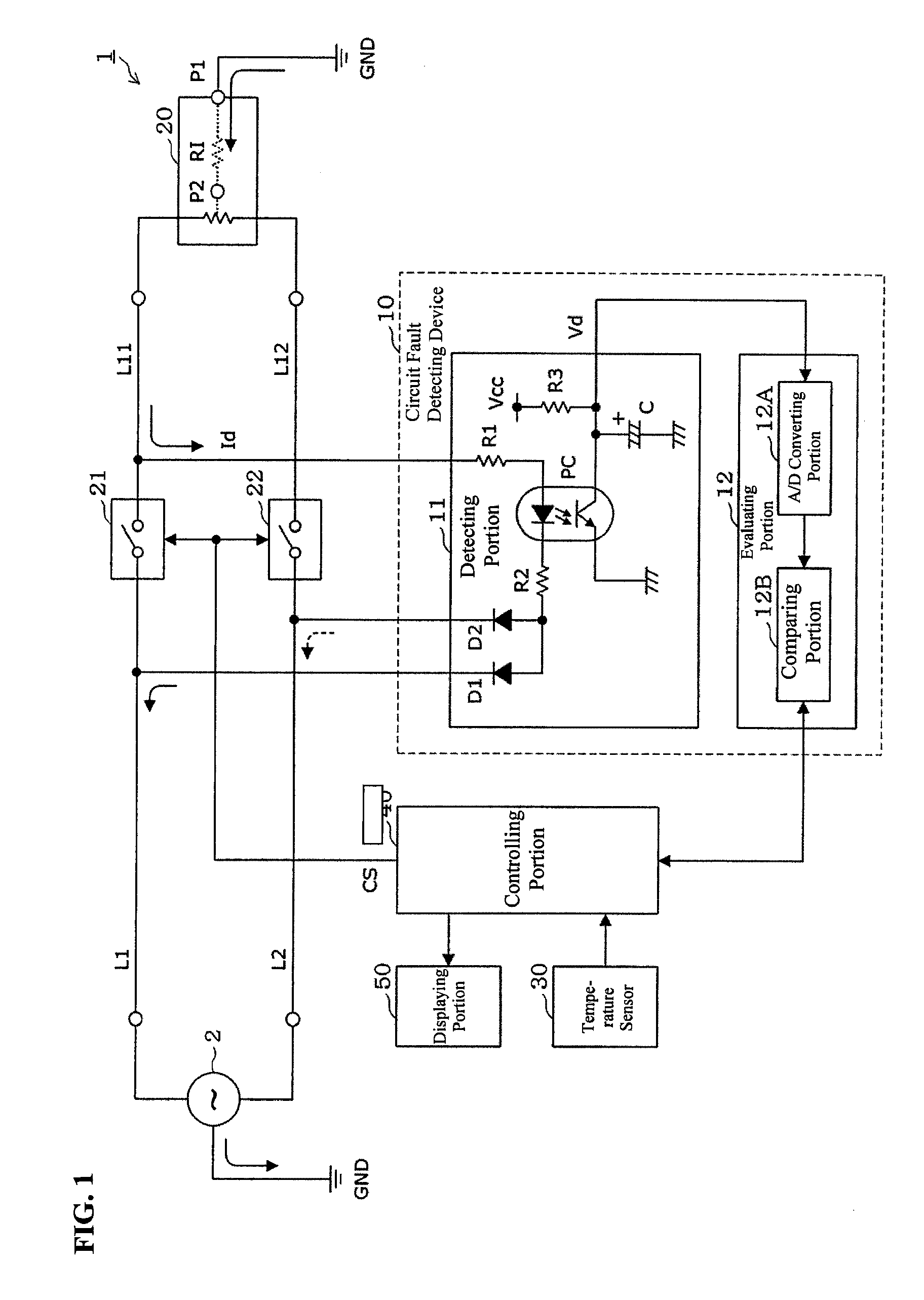

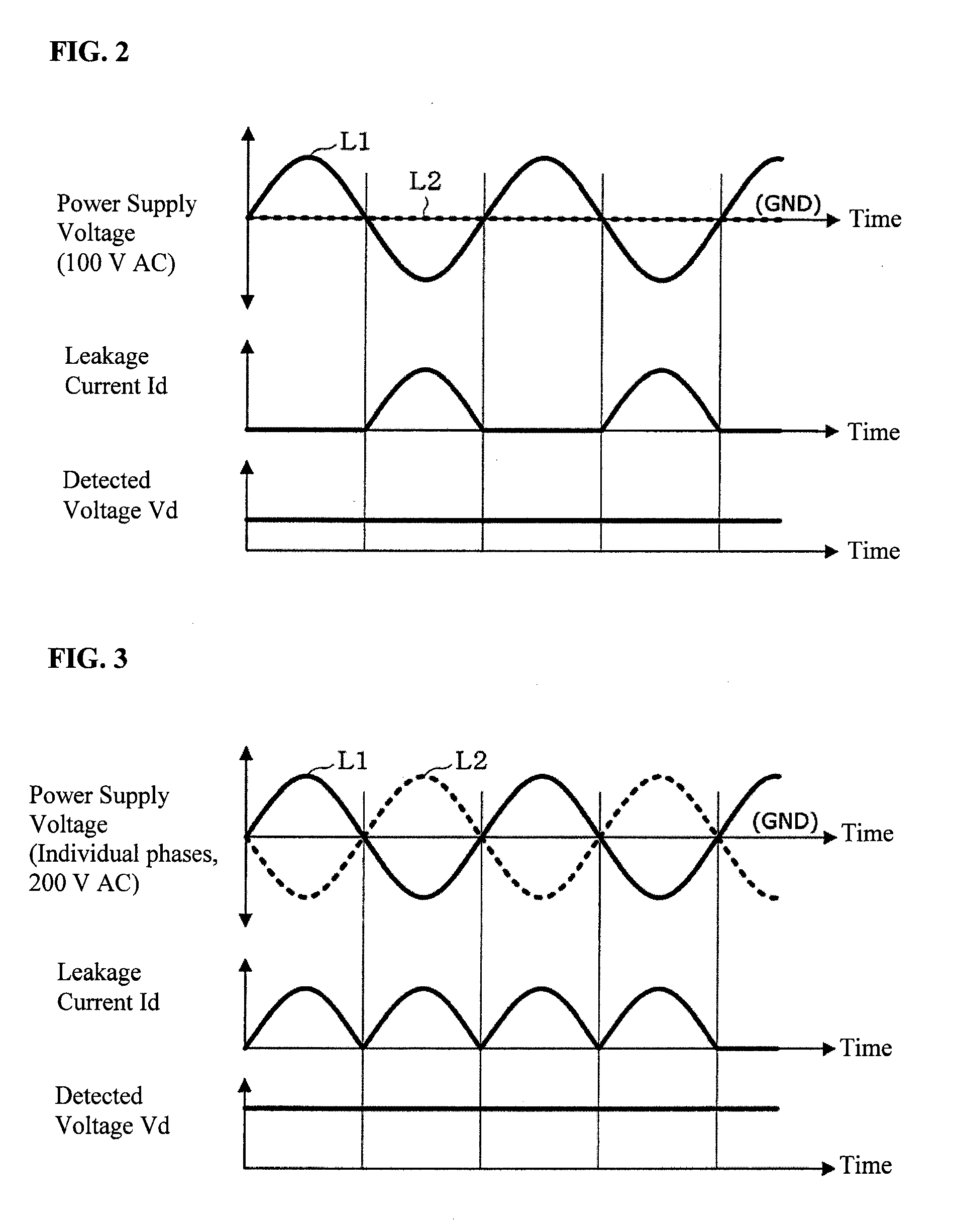

Circuit fault detecting device and method

InactiveUS20110163759A1Accurate detectionElectronic circuit testingLighting and heating apparatusLoad circuitEngineering

To detect accurately an insulation fault in a load circuit, Power supply lines and an electric heater (a load circuit) are connected by a detecting portion to detect a detected voltage (detected value) in accordance with the magnitude of a leakage current Id that flows through a ground between the power supply lines and the electric heater, and an evaluation as to whether or not there is a breakdown of insulation of the electric heater relative to the ground is performed by an evaluating portion based on the detected value obtained when the relay contact points are open.

Owner:YAMATAKE HONEYWELL CO LTD

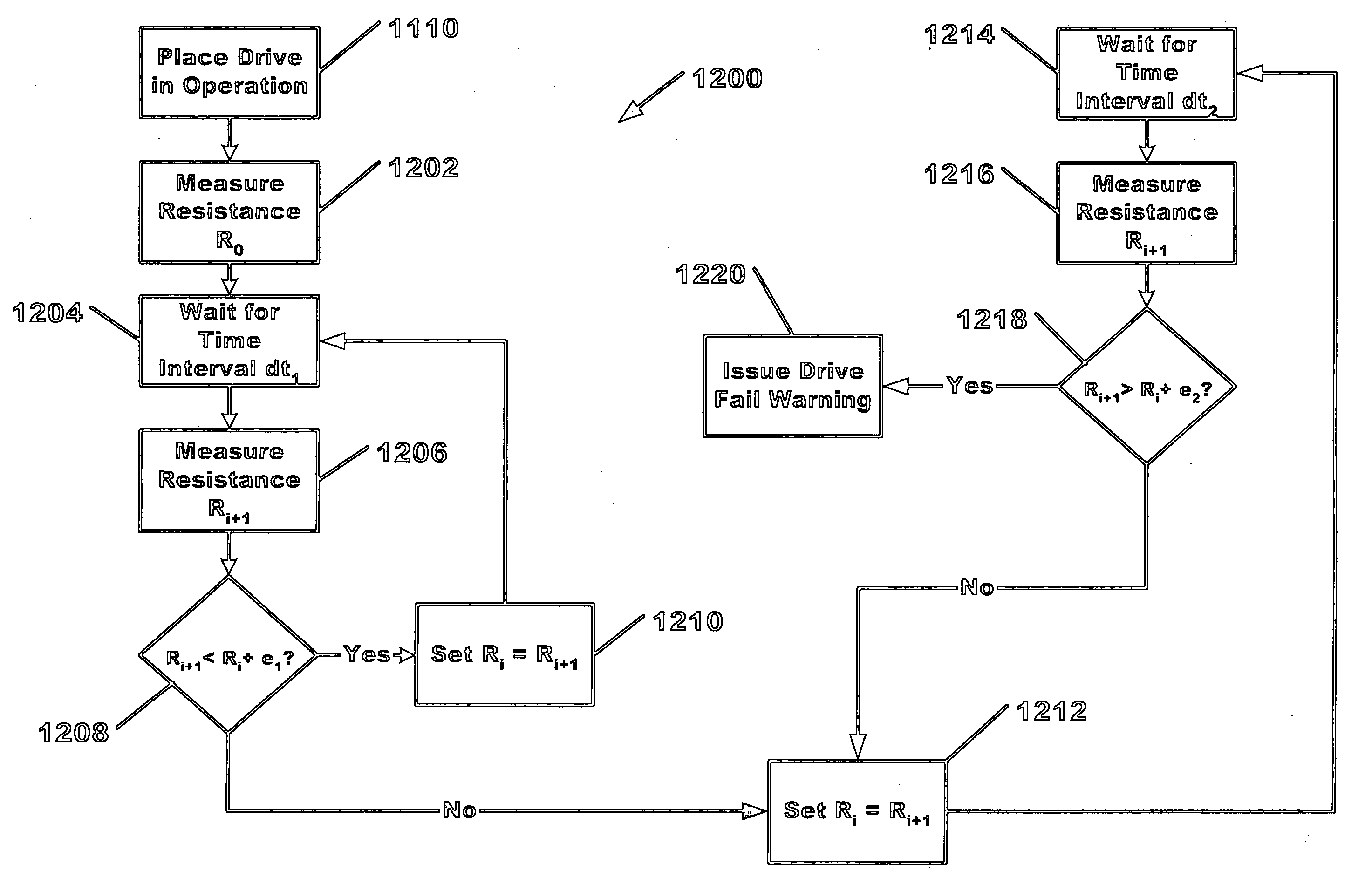

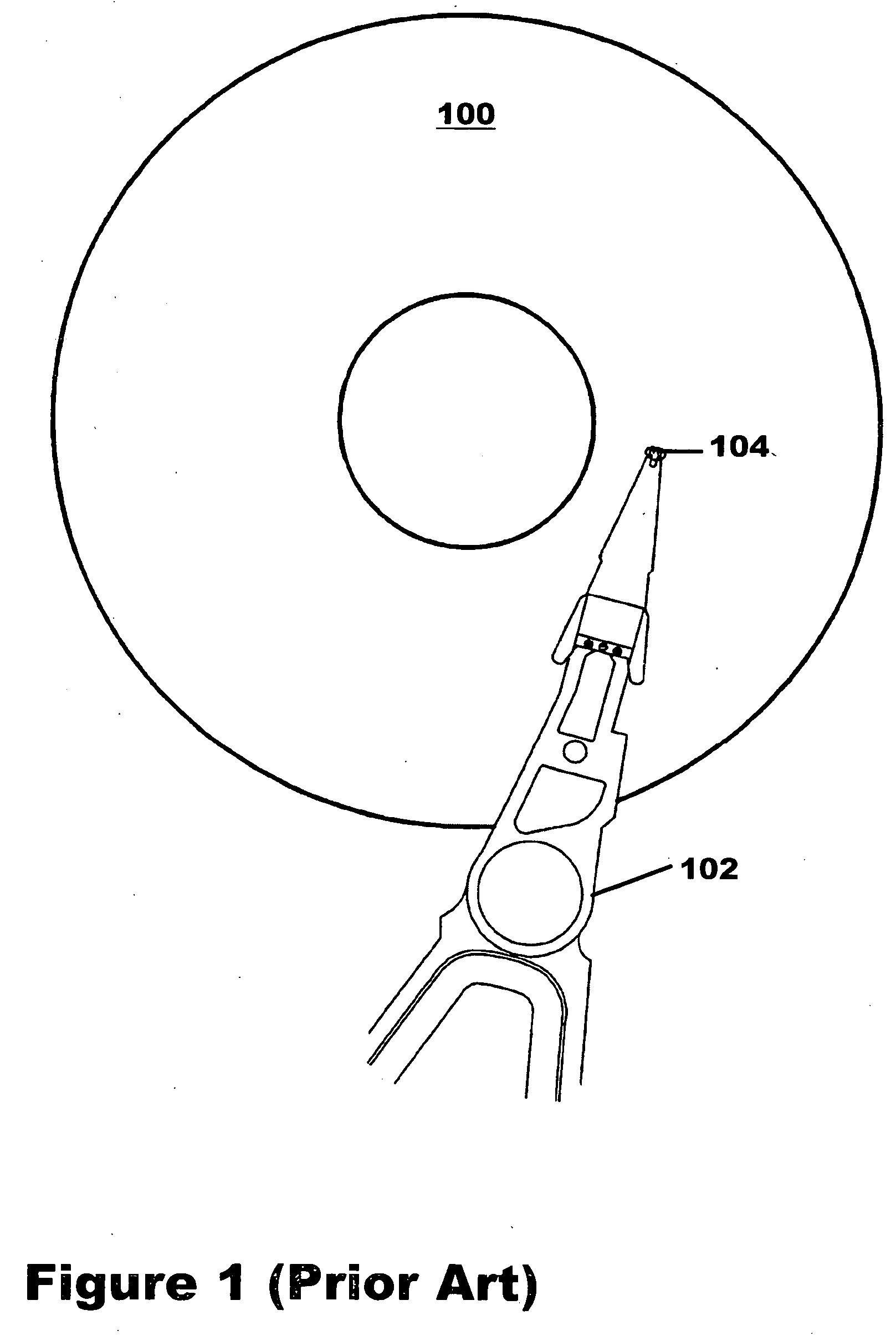

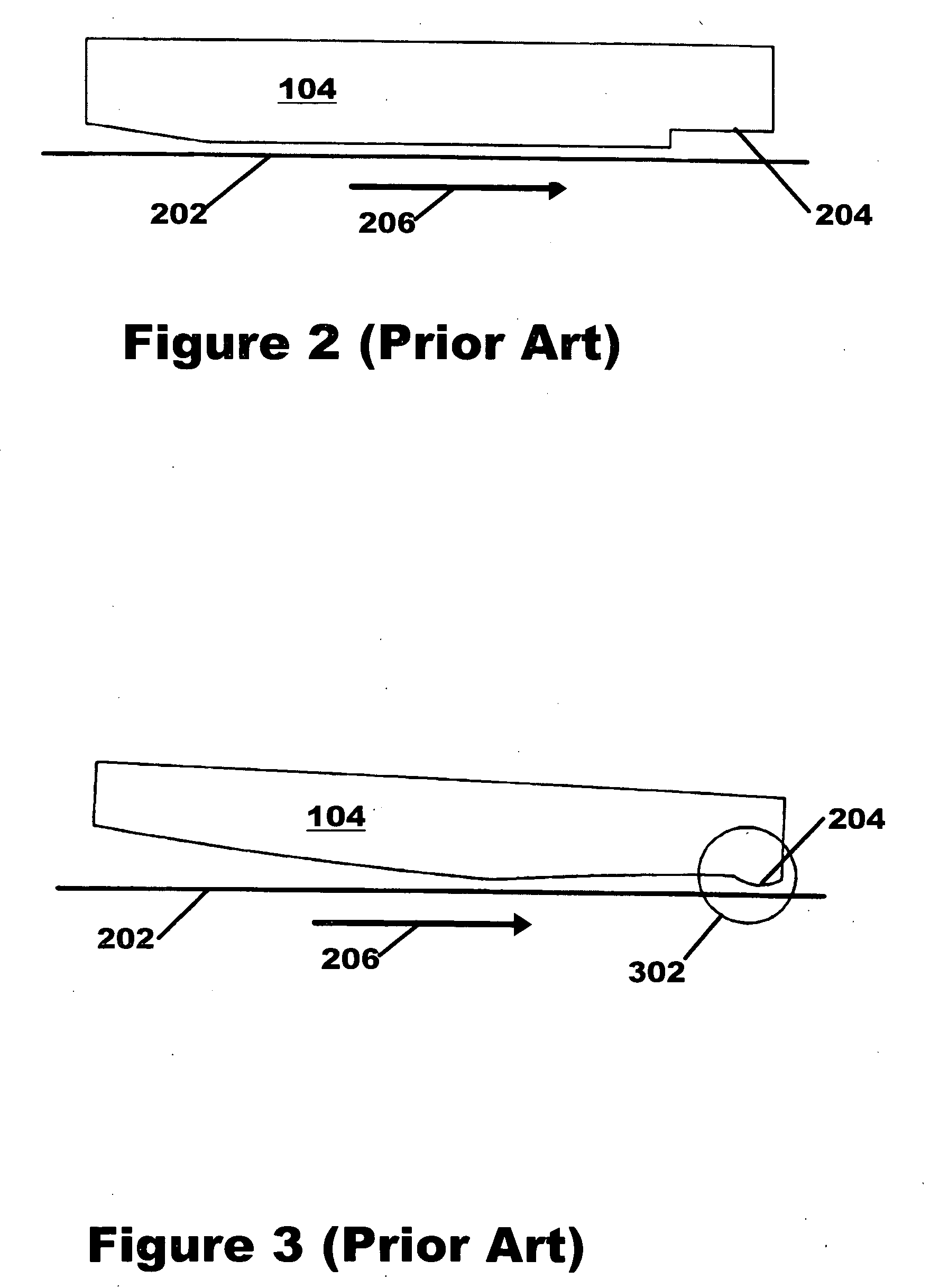

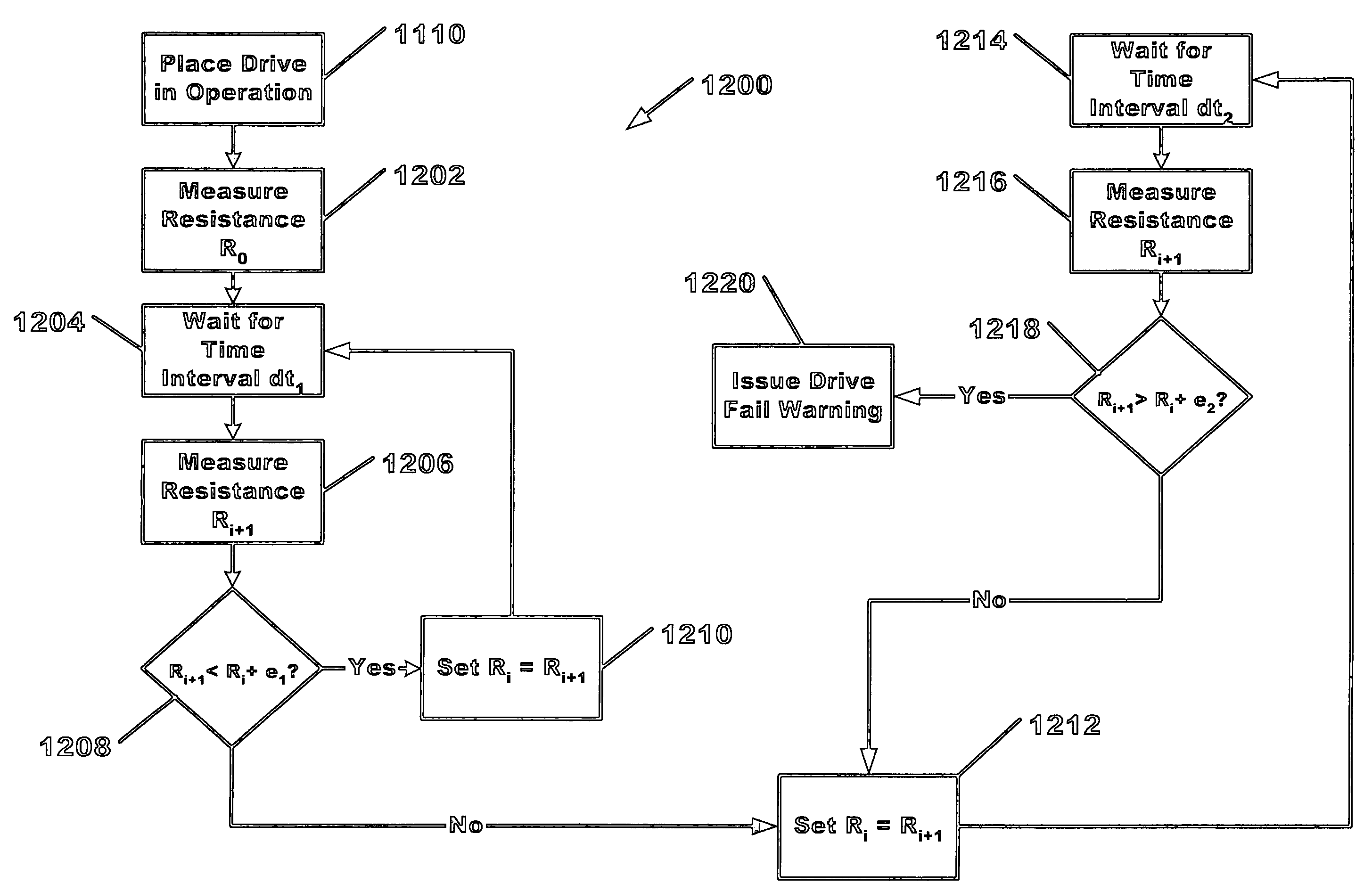

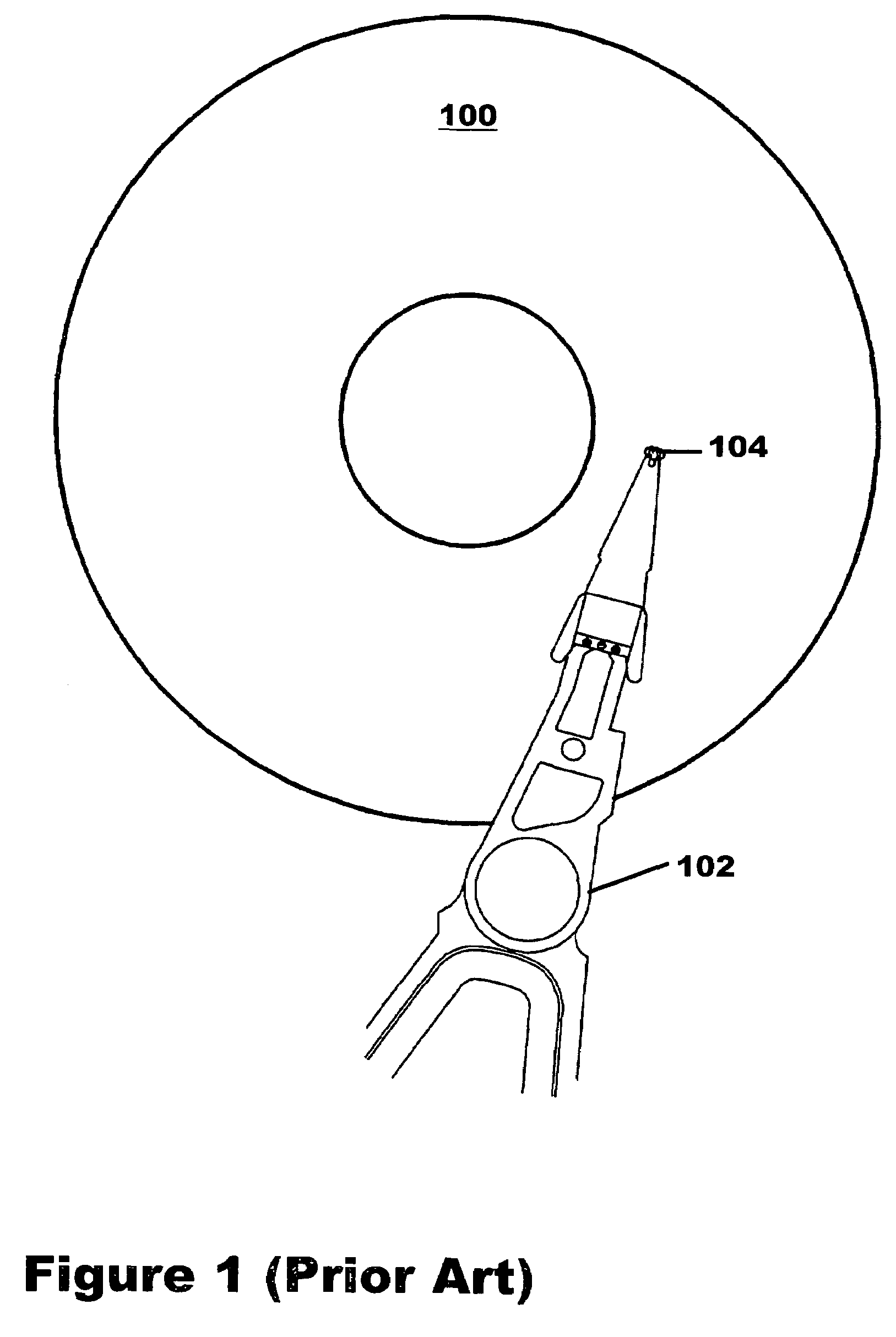

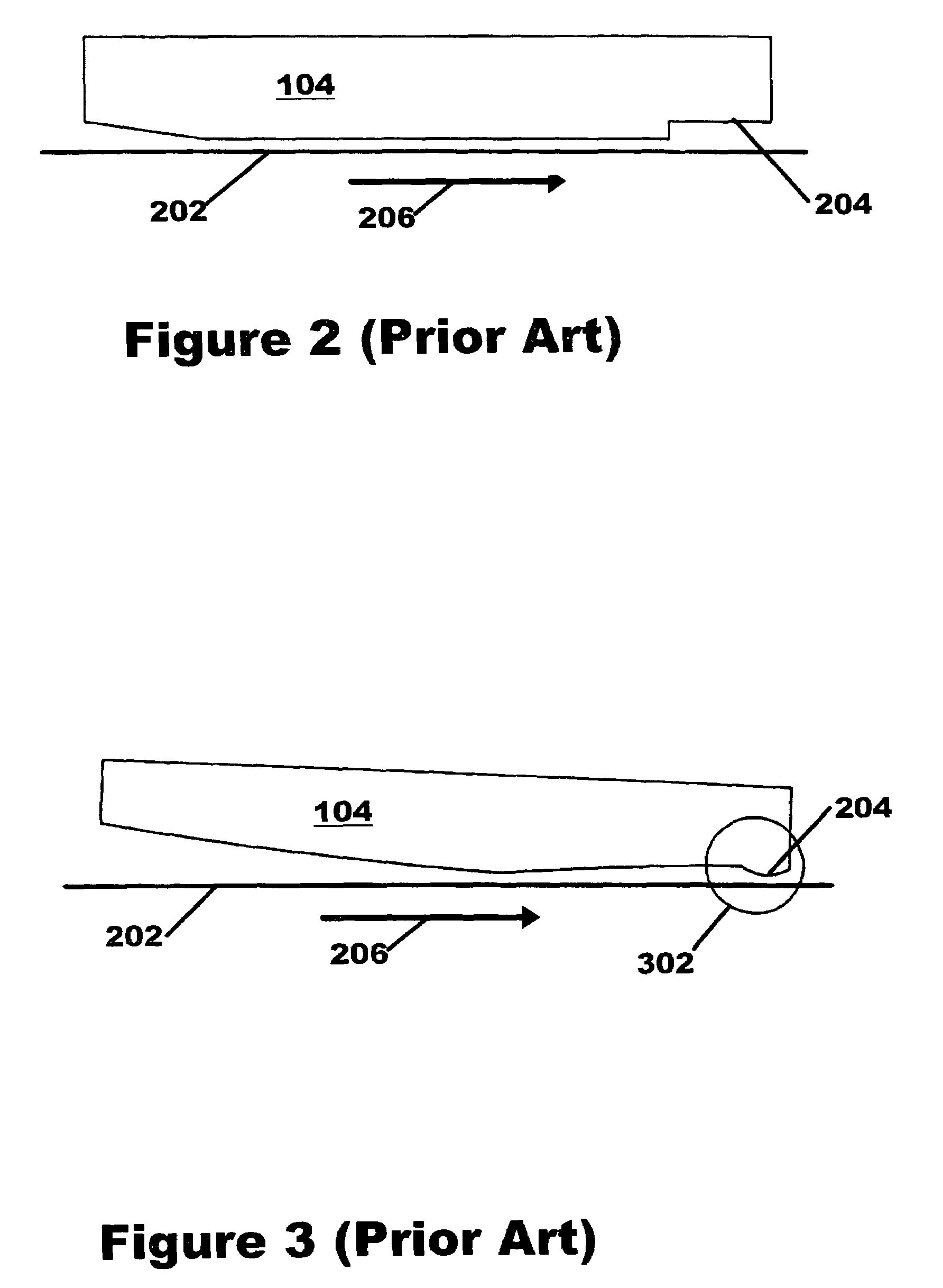

Predictive failure analysis of thermal flying height control system and method

InactiveUS20070014041A1Predict failureDriving/moving recording headsRecord information storageControl systemPredictive failure analysis

A method for predicting the failure of a data storage device having a slider heater is disclosed. For slider heaters exhibiting a decreasing resistance aging characteristic, a failure warning is produced when heater resistance suddenly increases 2 to 5%, or dR / dt changes sign from negative to positive. For slider heaters exhibiting an increasing resistance aging characteristic, a failure warning is produced when the heater resistance suddenly drops 2 to 5%, or dR / dt changes sign from positive to negative. Additionally, random changes in heater resistance exceeding nominal measurement error may also be utilized to produce a failure warning. This method provides advance warning of potential data read / write errors well before the open circuit failure of the slider heater occurs.

Owner:WESTERN DIGITAL TECH INC

Predictive failure analysis of thermal flying height control system and method

InactiveUS7336434B2Driving/moving recording headsRecord information storageObservational errorControl system

A method for predicting the failure of a data storage device having a slider heater is disclosed. For slider heaters exhibiting a decreasing resistance aging characteristic, a failure warning is produced when heater resistance suddenly increases 2 to 5%, or dR / dt changes sign from negative to positive. For slider heaters exhibiting an increasing resistance aging characteristic, a failure warning is produced when the heater resistance suddenly drops 2 to 5%, or dR / dt changes sign from positive to negative. Additionally, random changes in heater resistance exceeding nominal measurement error may also be utilized to produce a failure warning. This method provides advance warning of potential data read / write errors well before the open circuit failure of the slider heater occurs.

Owner:WESTERN DIGITAL TECH INC

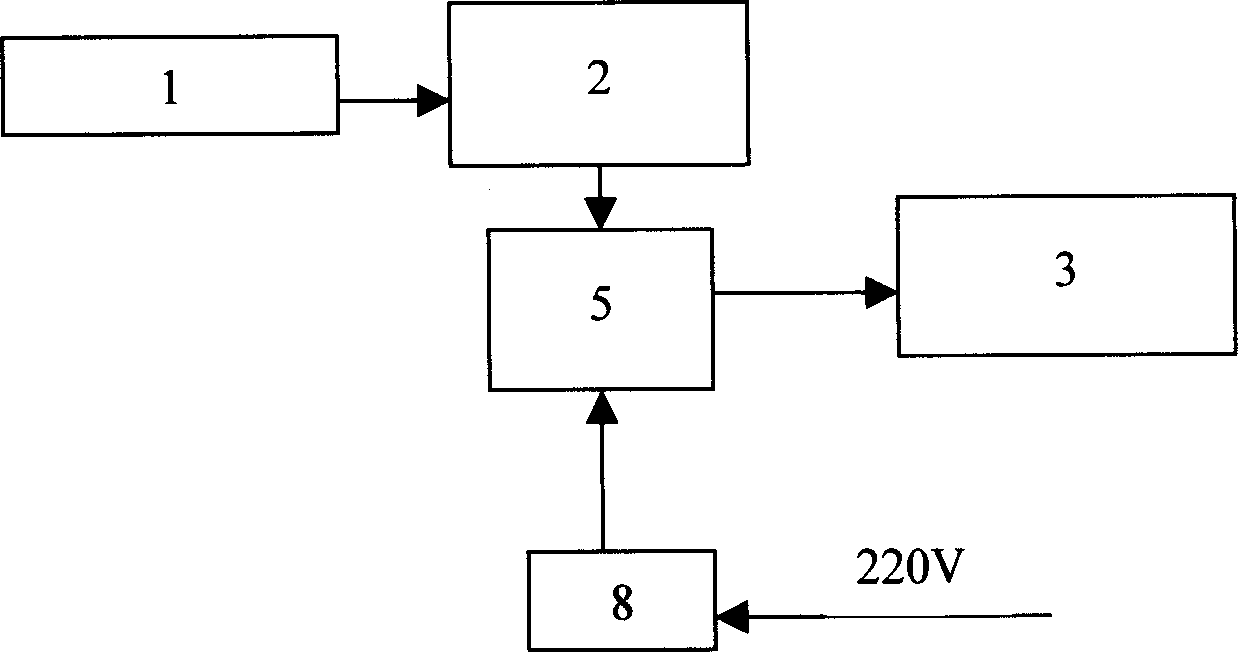

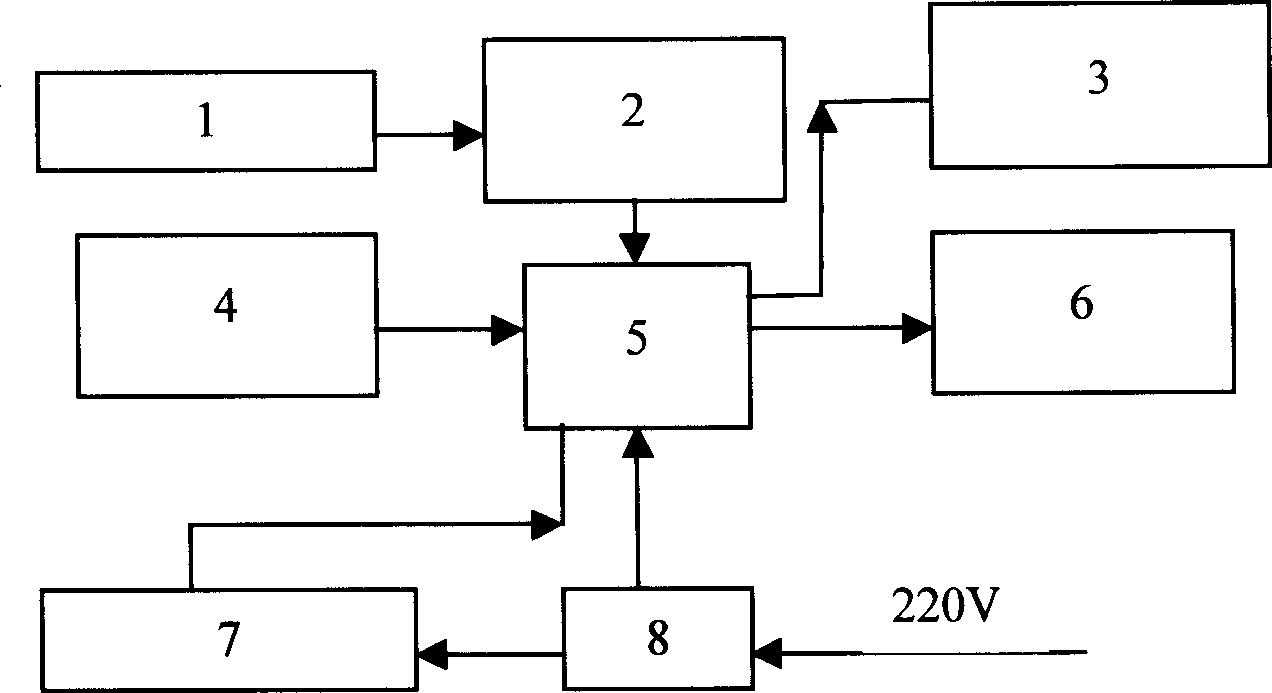

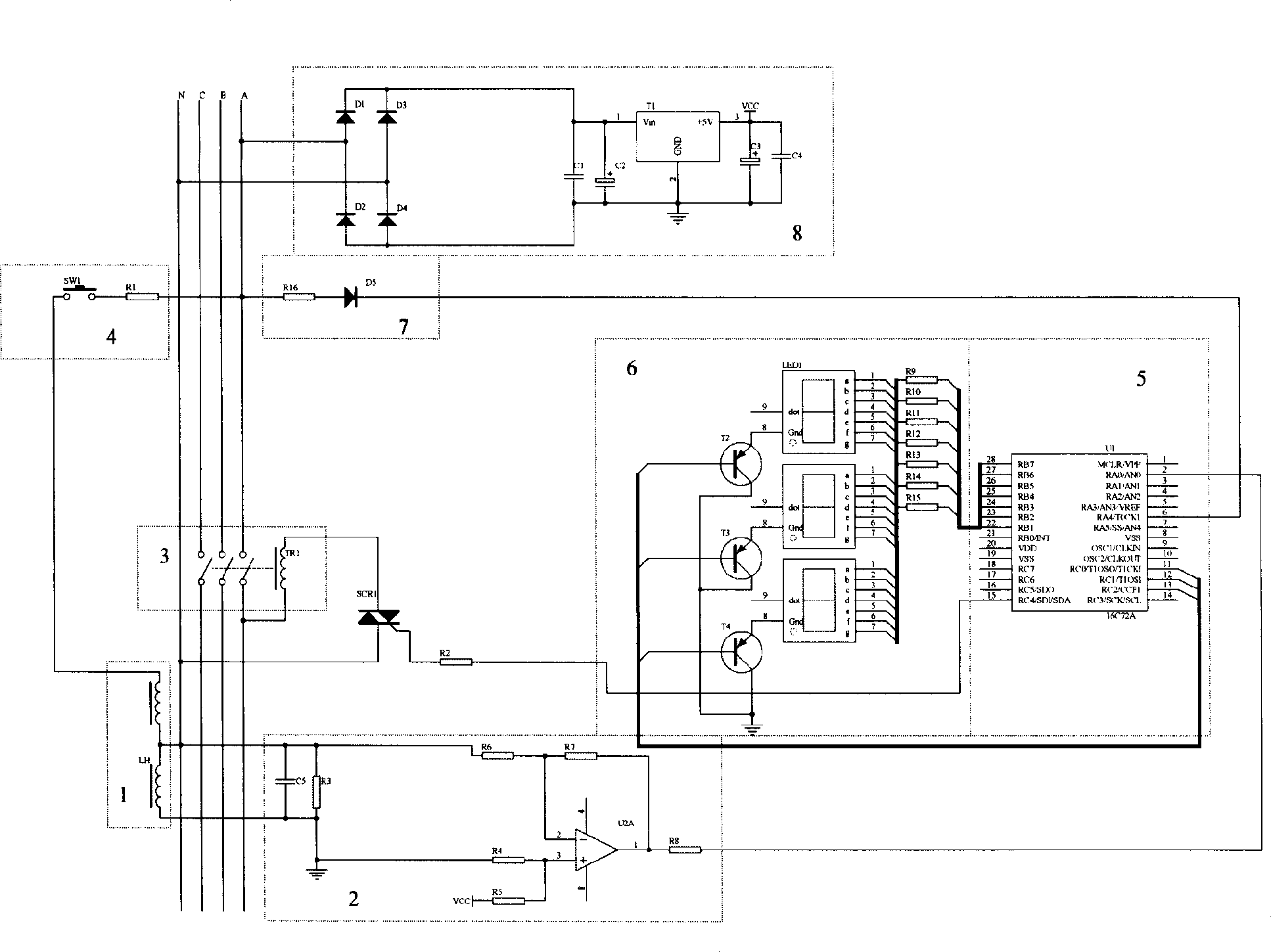

Automatic tracking protector for earth leakage and operation method thereof

InactiveCN1604418AImprove operating rateImplement automatic trackingEmergency protective arrangements for automatic disconnectionMicrocontrollerCurrent range

This invention relates to a drain self-tracing protector and its operation method, which comprises air breaker or relay, single machine, zero current mutual inductance, drain signal amplifying circuit and power, wherein the single comprises the following steps: first to initiate; second to measure the current range and phase angle; third to figure out drain changes; fourth to judge whether drain changes Is more than ten percent of drain action valve value; fifth to judge the sustain time of less than ten percent of drain action valve; sixth to change action valve. When the drain current amounts to or exceeds the drain action valve , the single machine sends out drain release order to trigger controllable silicon to activate the air breaker or relay to cut off the fault circuit to protect the fault drain.

Owner:HEBEI UNIV OF TECH

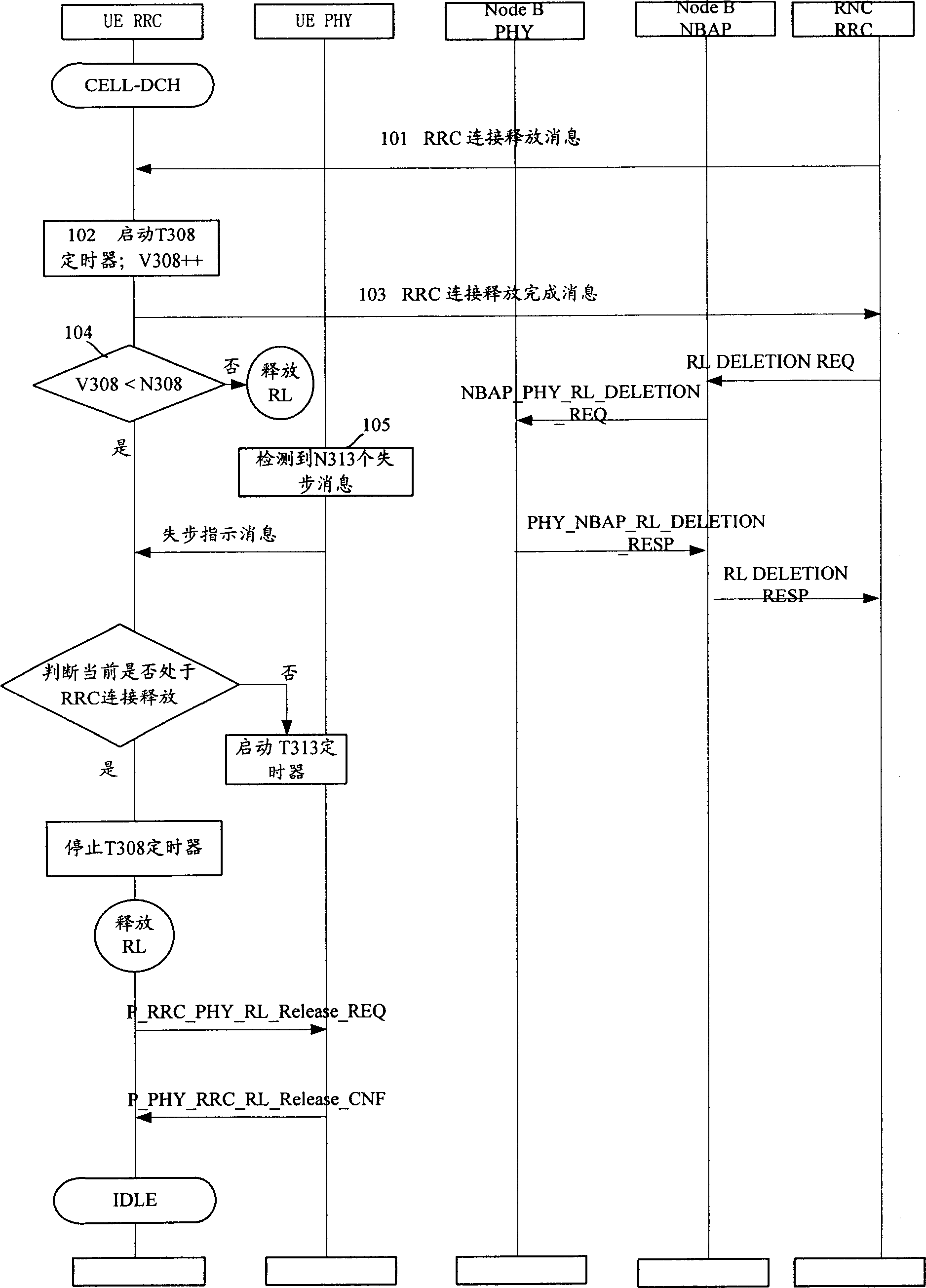

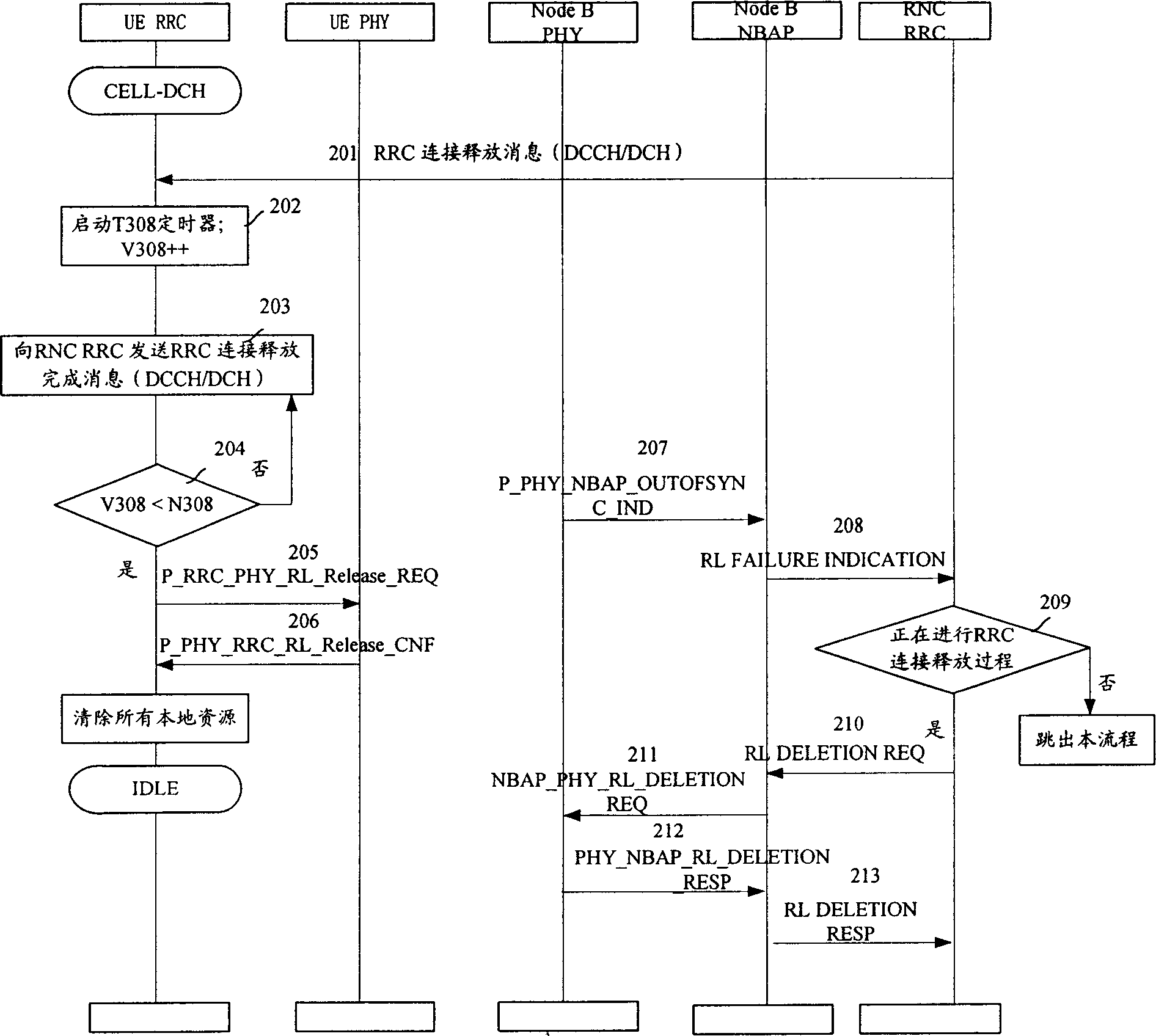

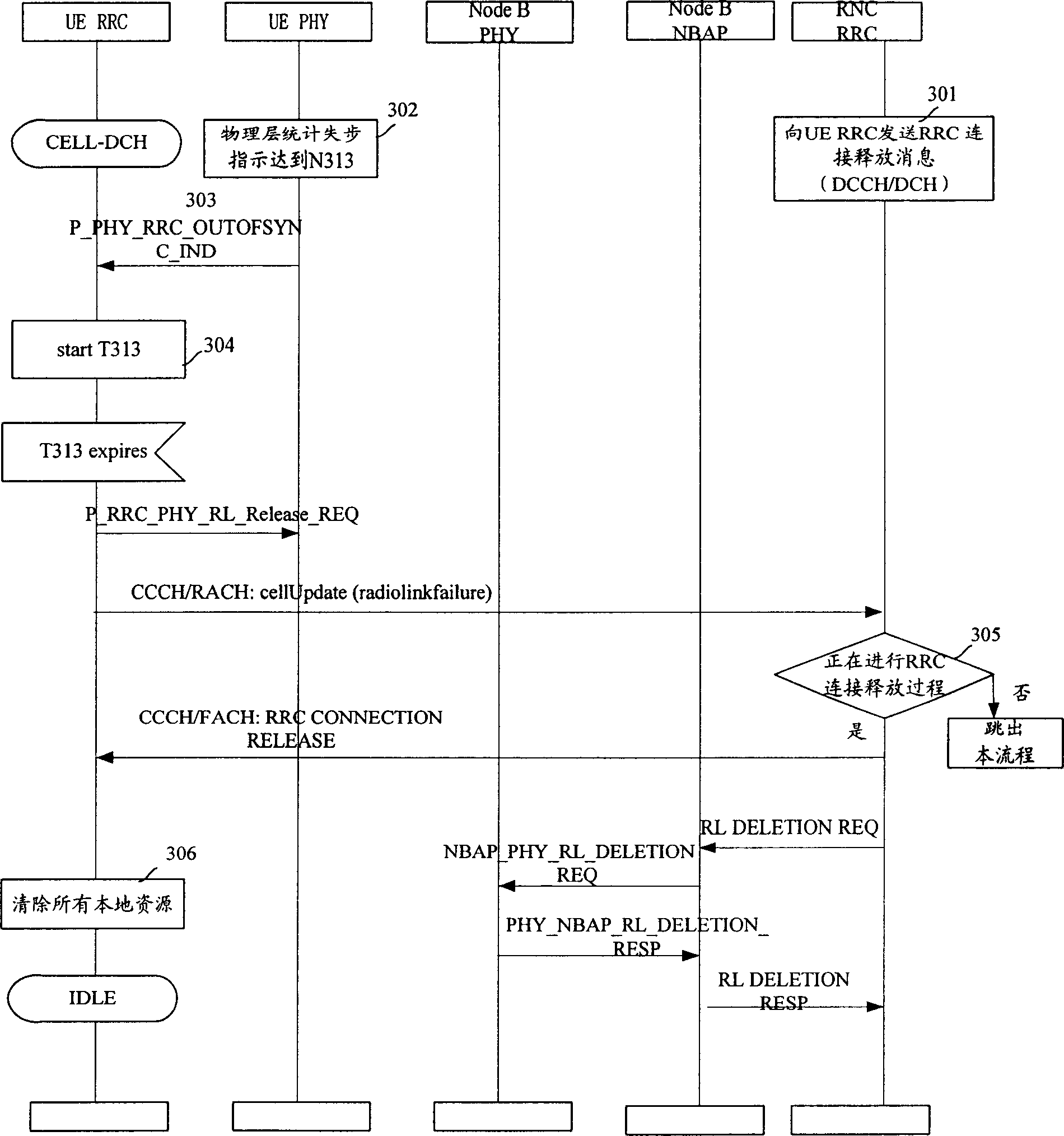

Method for deleting wireless link under out-of-step state

ActiveCN1867166AShorten the time intervalReduce signal interferenceConnection managementElectricityTelecommunications

The invention relates to a method for deleting the wireless chain circuit in out-of step condition, which comprises: when the user terminal (UE) receives the RRC connection release message sent from the network, and the responding to said RRC connection release message to the network, if the UE detects that it is out-of-step, directly releasing the chain circuit between it and network and deleting all local resource relative to said chain circuit; when the network UE sends RRC connection release message, and there is no RRC connection release complete message received in some time, responded by said UE, and if the network detects the chain circuit of said UE is out-of-step, directly releasing the network resource occupied by said chain circuit; when the network receives the region refresh message about RL chain circuit failure sent by UE at the second region, and assuring that said UE is in the RRC connection release process in the first region, the network uses the second region to send RRC connection release message to UE; and after said UE receives the RRC connection release message, it releases the chain circuit between it and networks, and deleting all local resource relative to the chain circuit. The invention can reduce the electricity consumption of terminal, and reduce the signal interference on other users.

Owner:DATANG MOBILE COMM EQUIP CO LTD

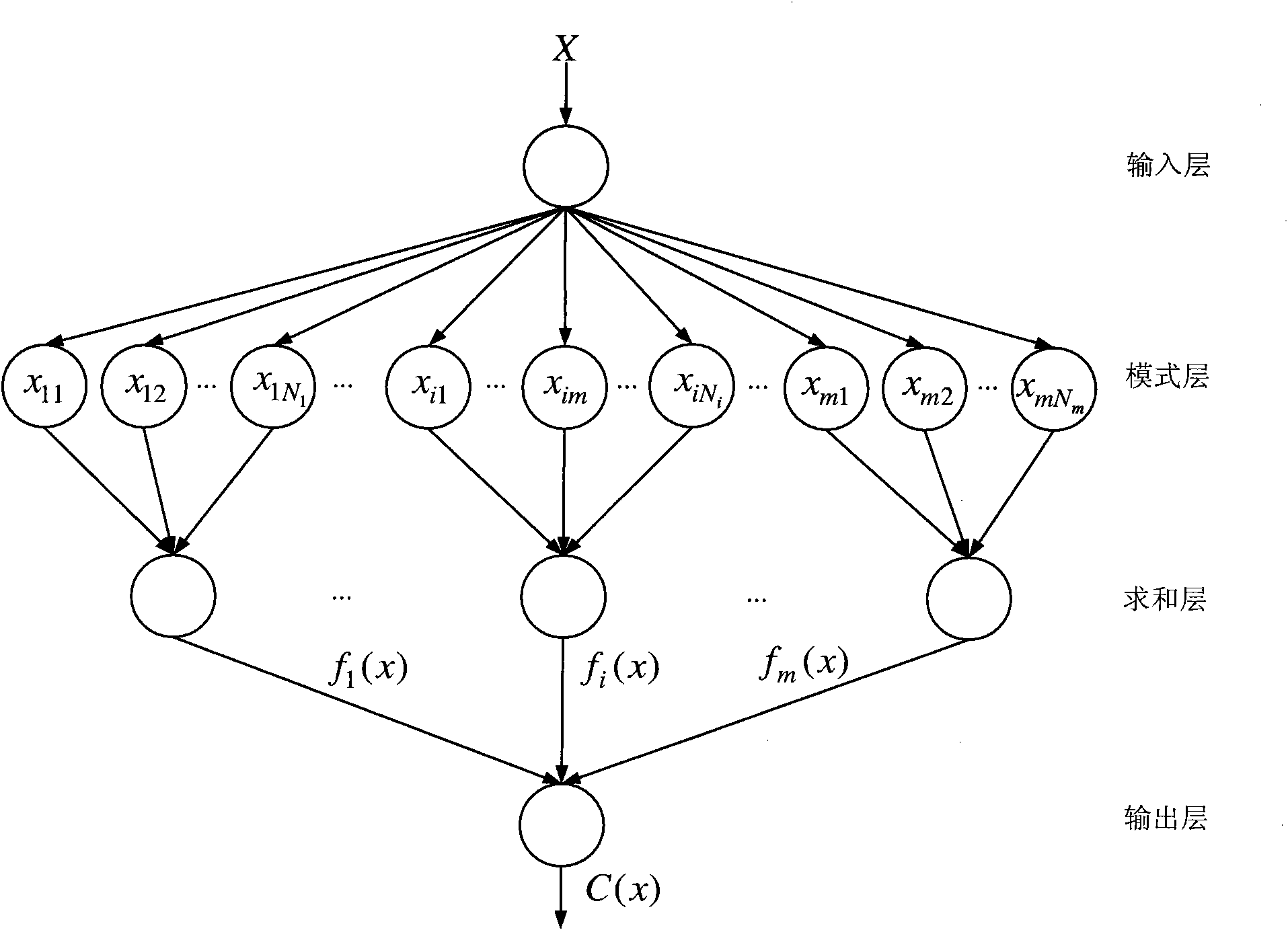

Probabilistic neural network-based tolerance-circuit fault diagnosis method

ActiveCN101819253AOvercome lossOvercoming structural complexityAnalog circuit testingBiological neural network modelsFault toleranceWavelet

Owner:HUNAN UNIV

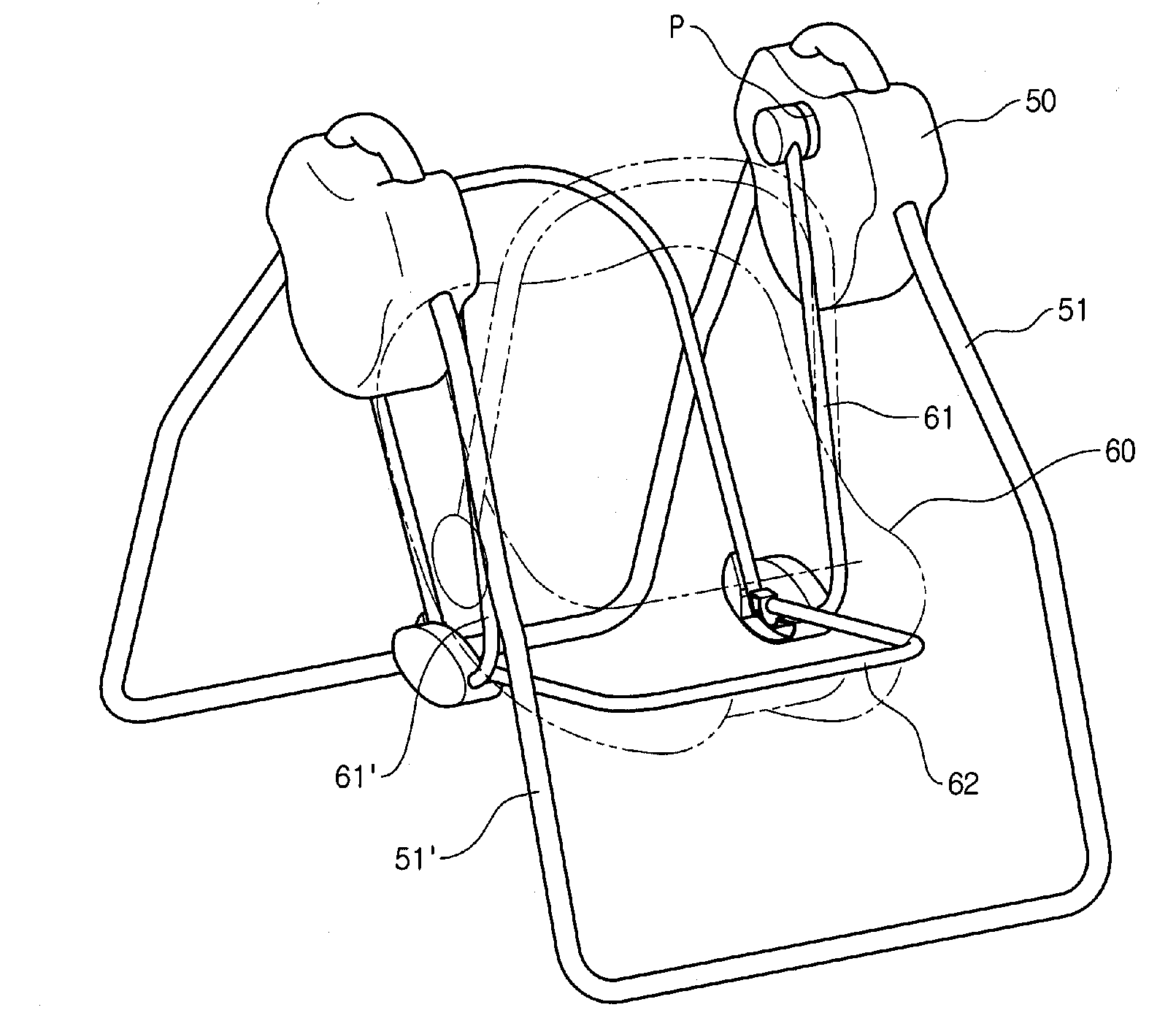

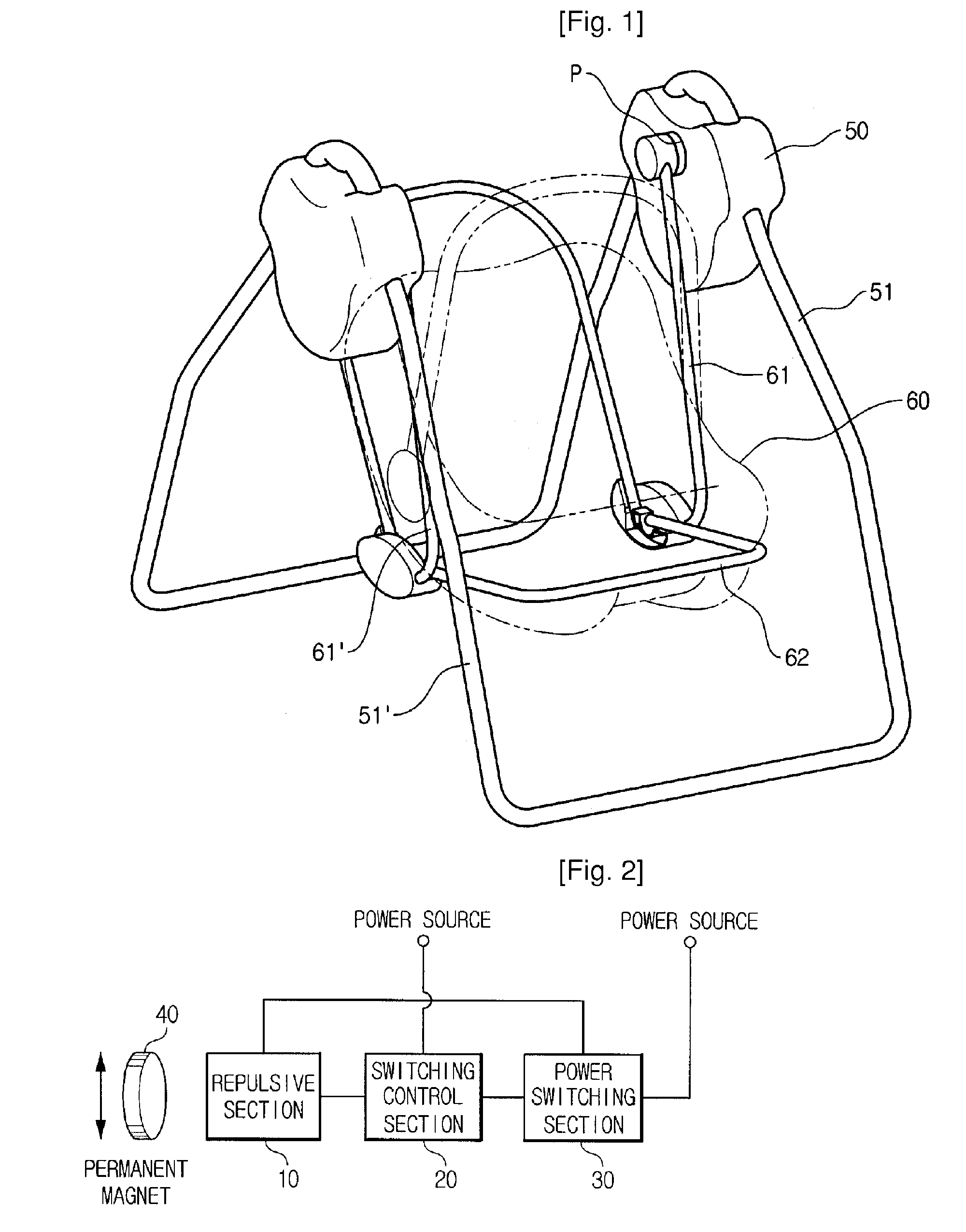

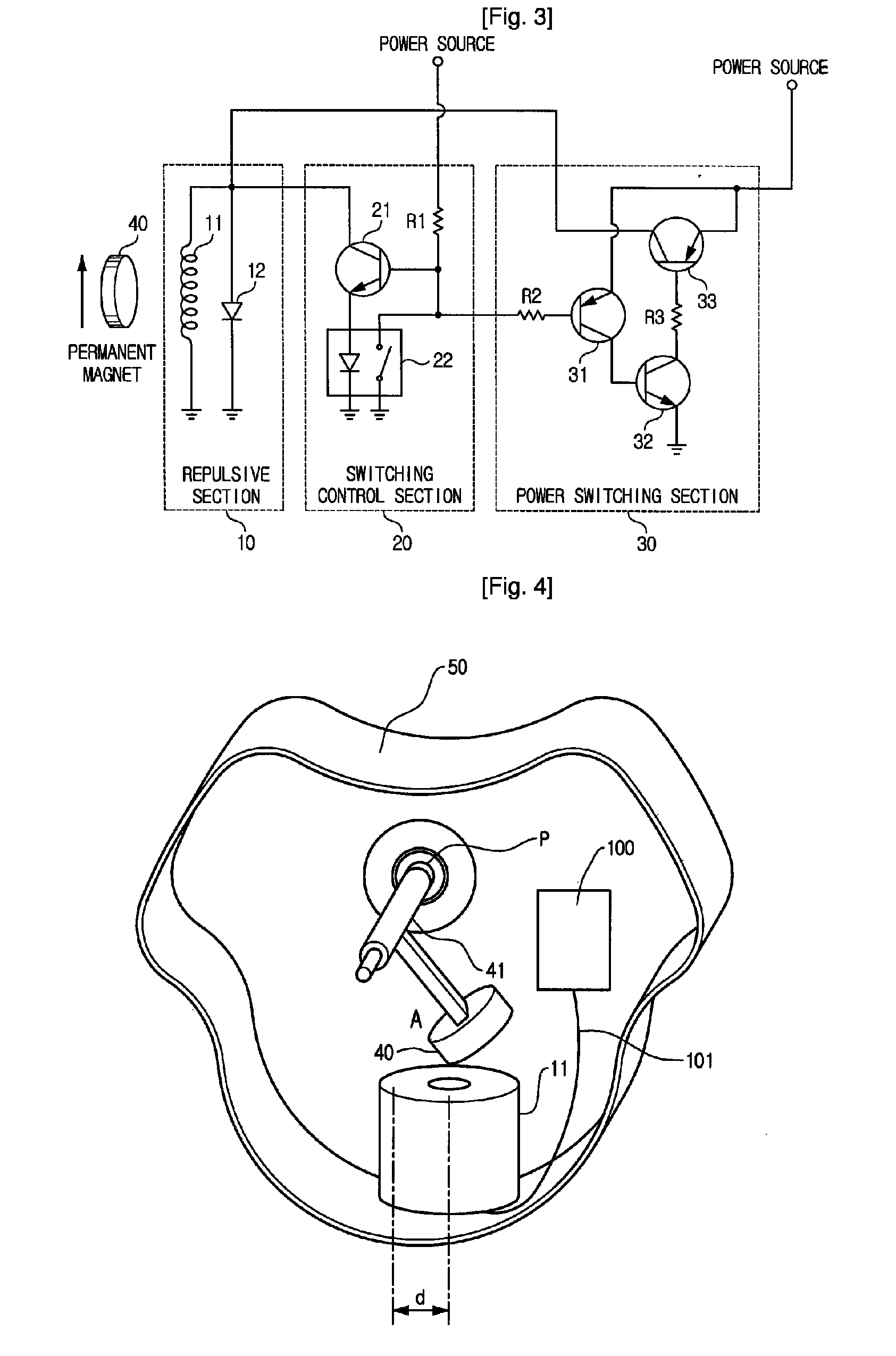

Swing device having circuit for generating repulsive force

A swing device has a support frame, a seat having a swing axis and swing back and forth about the swing axis while a bar thereof being hung on the support frame, and a repulsive circuit for repelling a permanent magnet installed on the swing axis. The repulsive circuit has a coil assembly instantly generating induced current when the permanent magnet passes by with a certain distance therebetween, and being supplied with power to become an electromagnet having the same polarity as the permanent magnet to instantly repel the permanent magnet, a first switching element for switching the induced current generated in the coil assembly, a second switching element switched on by the induced current switched from the first switching element to turn off the switching operation of the first switching element and to control a power switching operation at the same time, and a power switching unit for temporarily switching the power to the coil assembly according to the control of the power switching operation of the second switching element. According to the swing device, the construction of the circuit becomes simplified, manufacturing cost of products is reduced, and the possibility to cause the malfunction of the circuit is reduced.

Owner:KUKUTOYS

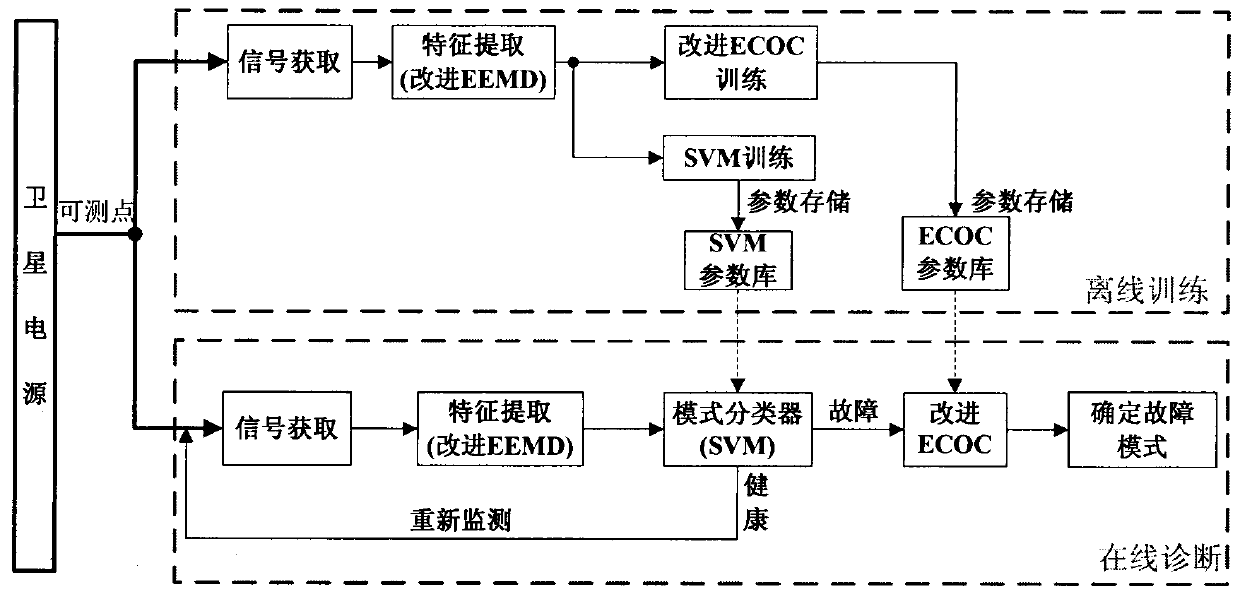

Satellite power supply system online fault diagnosis method

InactiveCN103995237AEfficient extractionImprove the accuracy of fault diagnosisPower supply testingNeural learning methodsSupport vector machineFeature extraction

The invention discloses a satellite power supply system online fault diagnosis method based on improved ensemble empirical mode decomposition (EEMD for short) and error correcting output codes-support vector machines (ECOC-SVM for short), and belongs to the field of circuit fault diagnosis. The method includes the following steps that first, a satellite power supply circuit to be tested is subjected to testability analysis, and testable points, fault levels, fault types and the number of faults are determined; second, off-line training is performed, and output signals of the circuit to be tested are collected in the testable points of the satellite power supply circuit; an improved EEMD method is adopted for performing fault characteristic extraction on collected circuit fault signals so that a sample can be formed and used for training the mode classifier SVM and the improved ECOC; third, on-line diagnosis is performed, the state of the circuit is judged through the trained mode classifier SVM, monitoring is performed again if the state of the circuit is healthy, diagnosis is performed through the improved ECOC if faults happen, and finally, the faults can be recognized and positioned.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

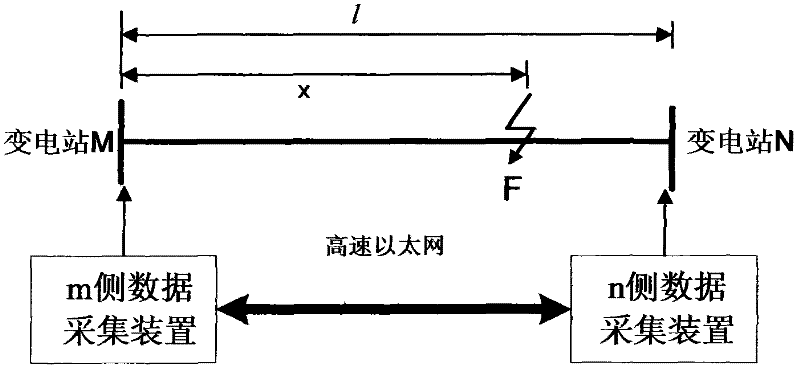

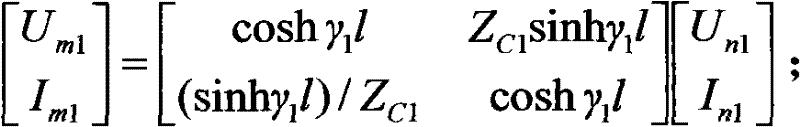

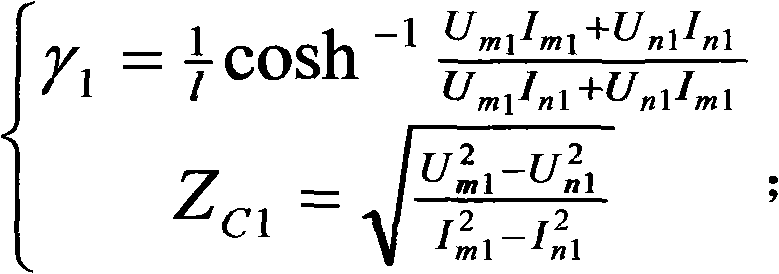

Method for measuring distance between two ends based on real-time circuit parameter measurement

The invention provides a method for measuring the distance between two ends based on real-time circuit parameter measurement. The method comprises the following steps: 1) when a power transmission circuit has a failure, a data collection device synchronously samples voltage and current signals of two ends of the circuit, and completes alignment of sampled data on two sides of the power transmission circuit; 2) the voltage and current values before the circuit has the failure are substituted into a parametric equation to acquire real-time circuit parameters; and 3) the real-time circuit parameters and the voltage and current values at the failure moment are substituted into a dual-end voltage linear distributional equation to acquire the distance from the transmission circuit failure pointto a reference point. By utilizing the method, the distance measurement accuracy is high, and is not influenced by the environment surrounding the circuit, weather and other factors, so that distancemeasurement errors caused by inaccurate circuit parameters are avoided. By searching the rule of voltage linear distributed equation, a dual-end distance measurement equation can be quickly solved with small calculated amount, and non-convergent result or false root which possibly exists in the conventional solving method cannot occur. In the method, the launched data collection device is utilized, but a new device is not required.

Owner:SHENZHEN SHUANGHE ELECTRIC CO LTD

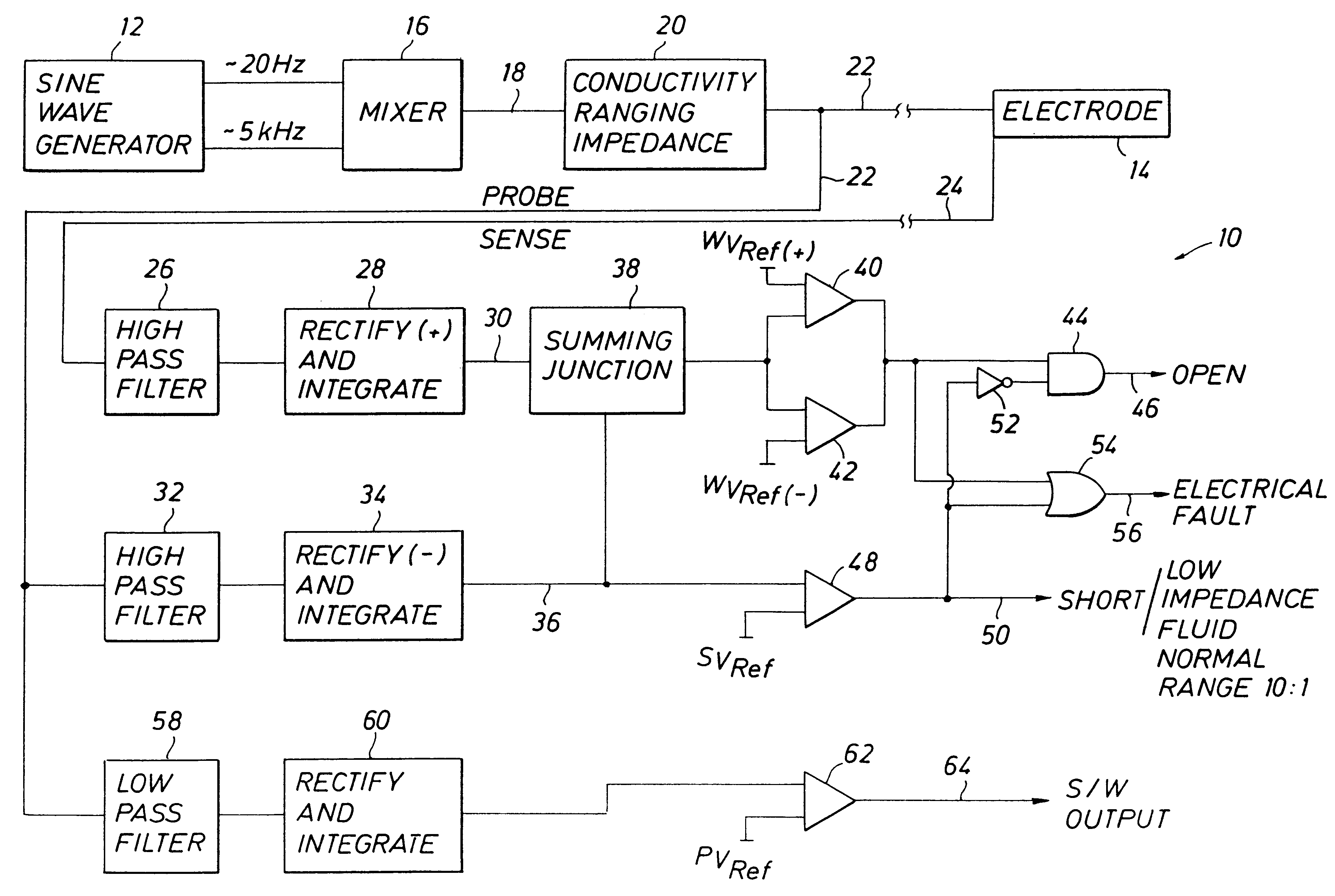

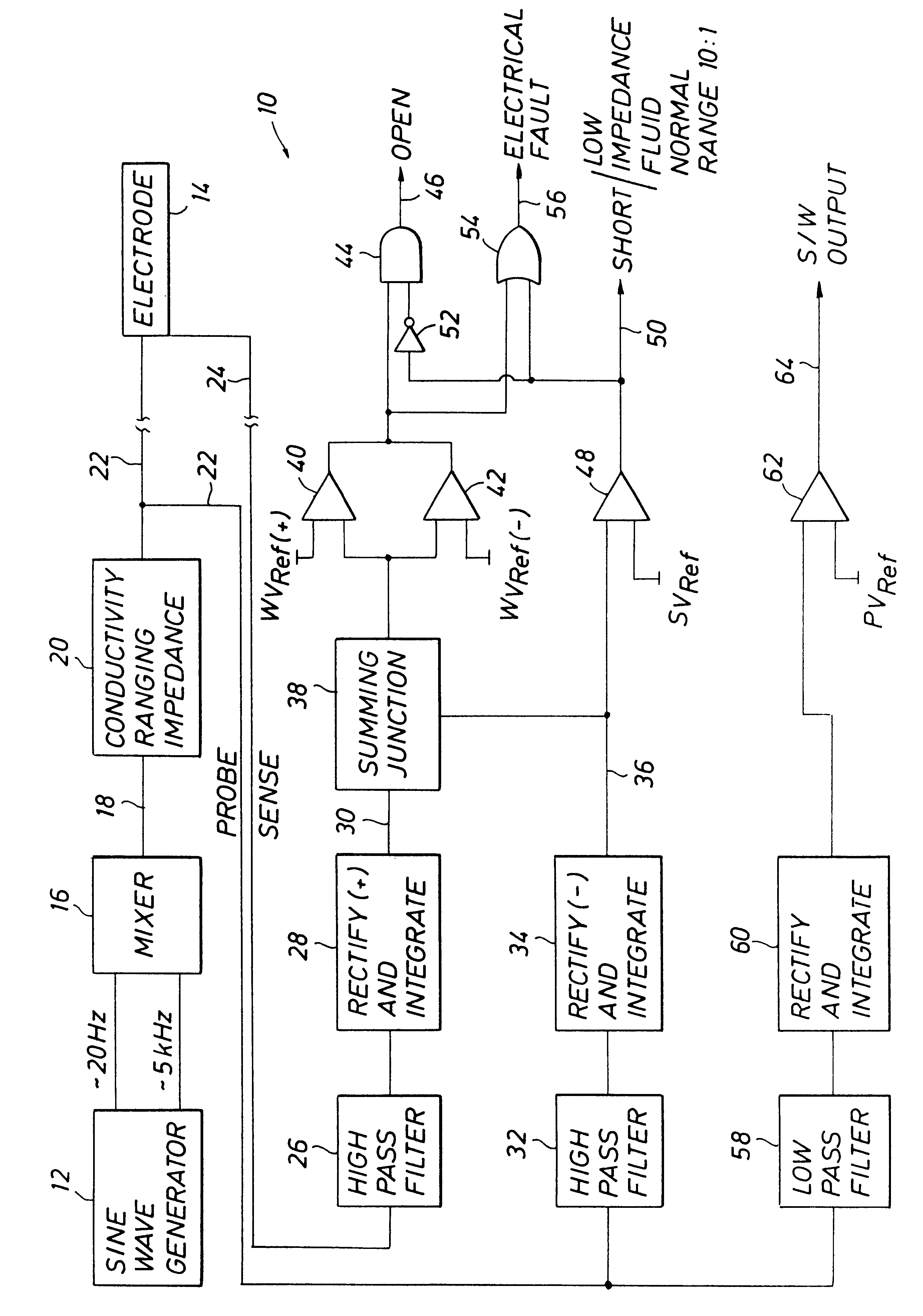

Method and apparatus for circuit fault detection with boiler water level detection system

InactiveUS6650128B2Rule out the possibilityTesting/calibration apparatusResistance/reactance/impedenceDual frequencyAc components

A fault detection circuit in a boiler-water level system includes a dual-frequency signal generator which develops two AC components with no associated DC component. The two frequencies are mixed and sent through an impedance matching circuit to match the impedance of the signal generating portion of the system with the impedance of the boiler water under measurement. The impedance-matched signal is then directed to two legs, one leg directed through one of a plurality of electrode probes and then to a first filter circuit, and the other leg is directed a second set of filters. In combination, the filters pass either the higher or the lower of the two frequencies to determine an open or short condition in the level sensing circuitry, as well as a steam vs. water condition.

Owner:TYCO VALVES & CONTROL INC

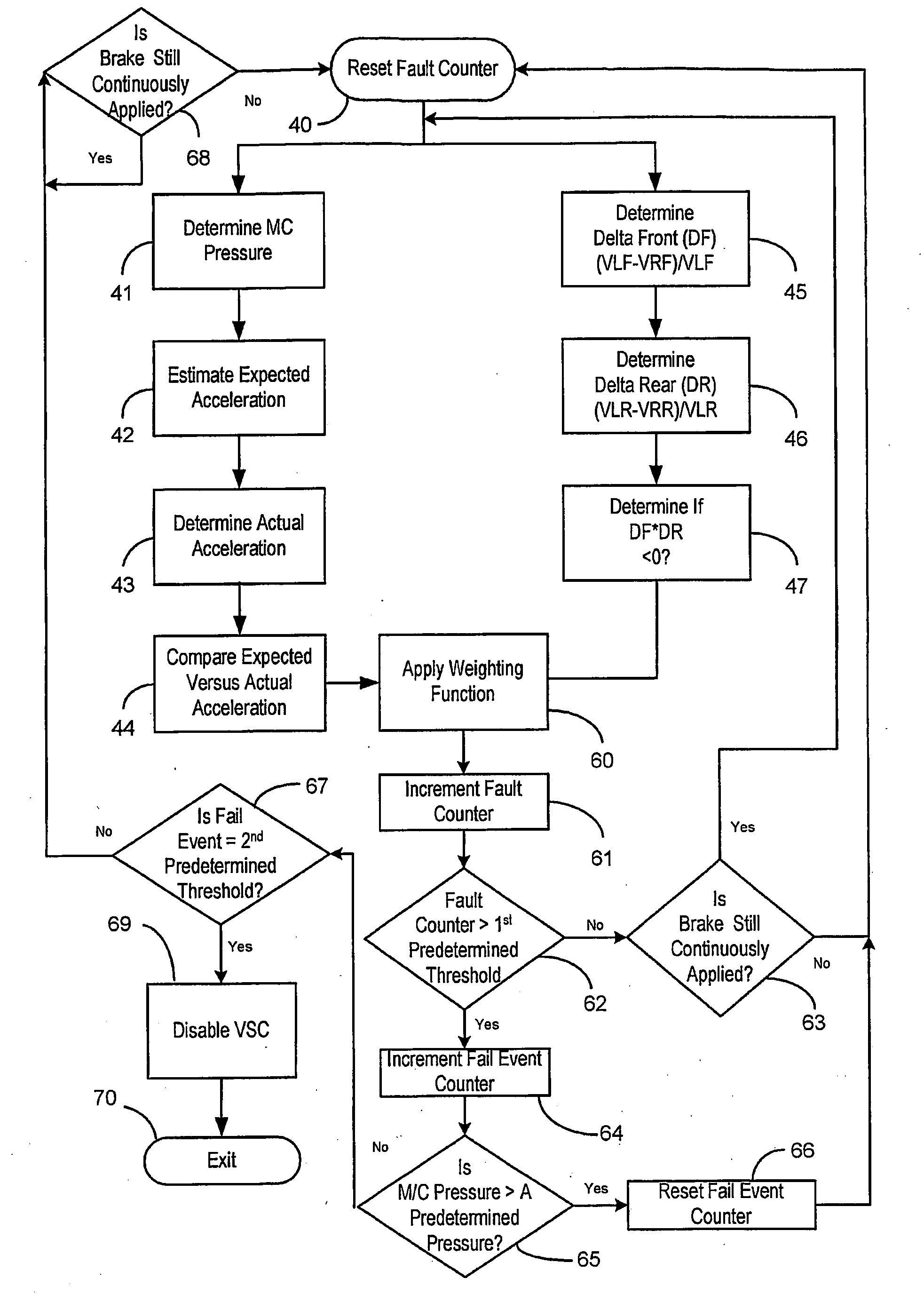

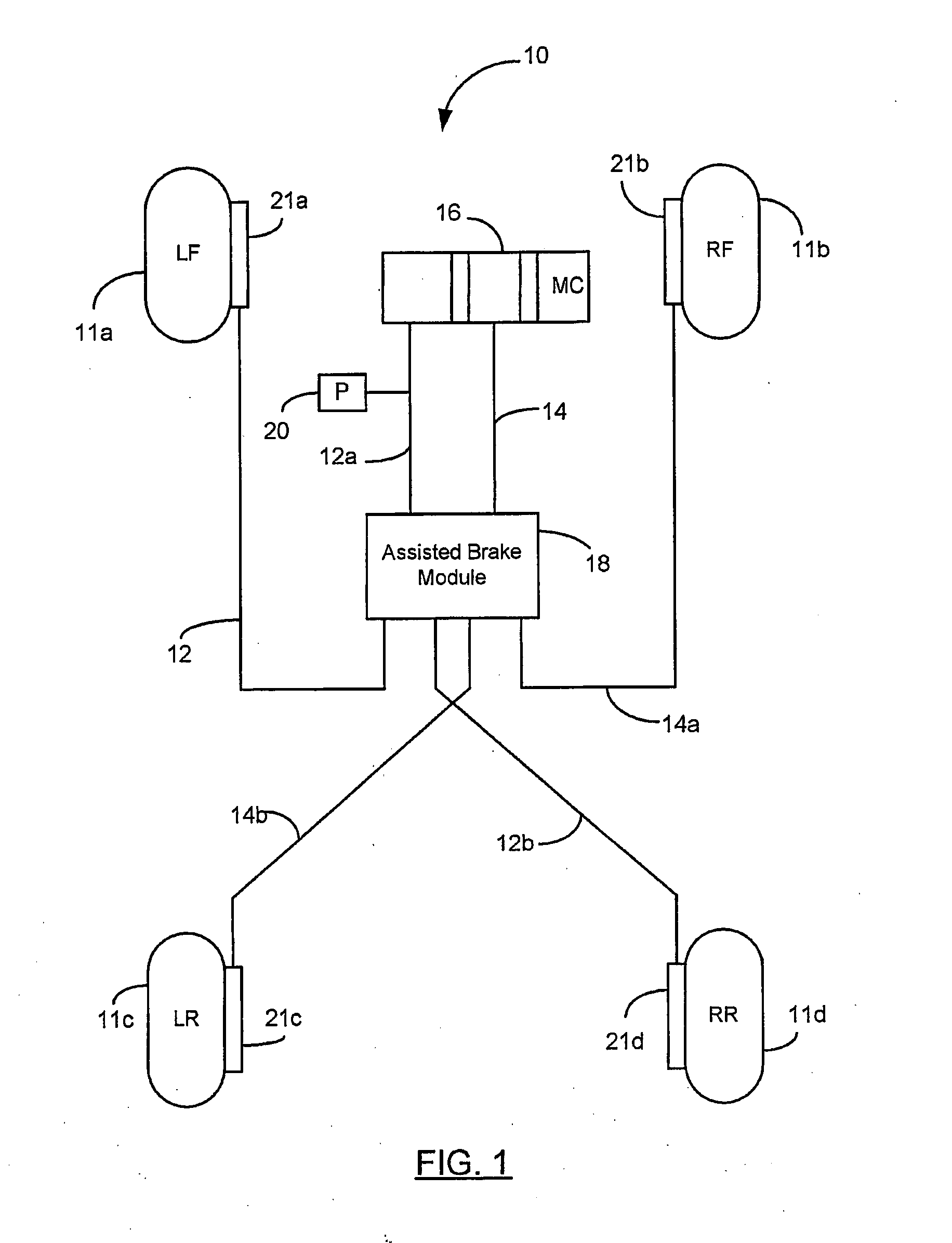

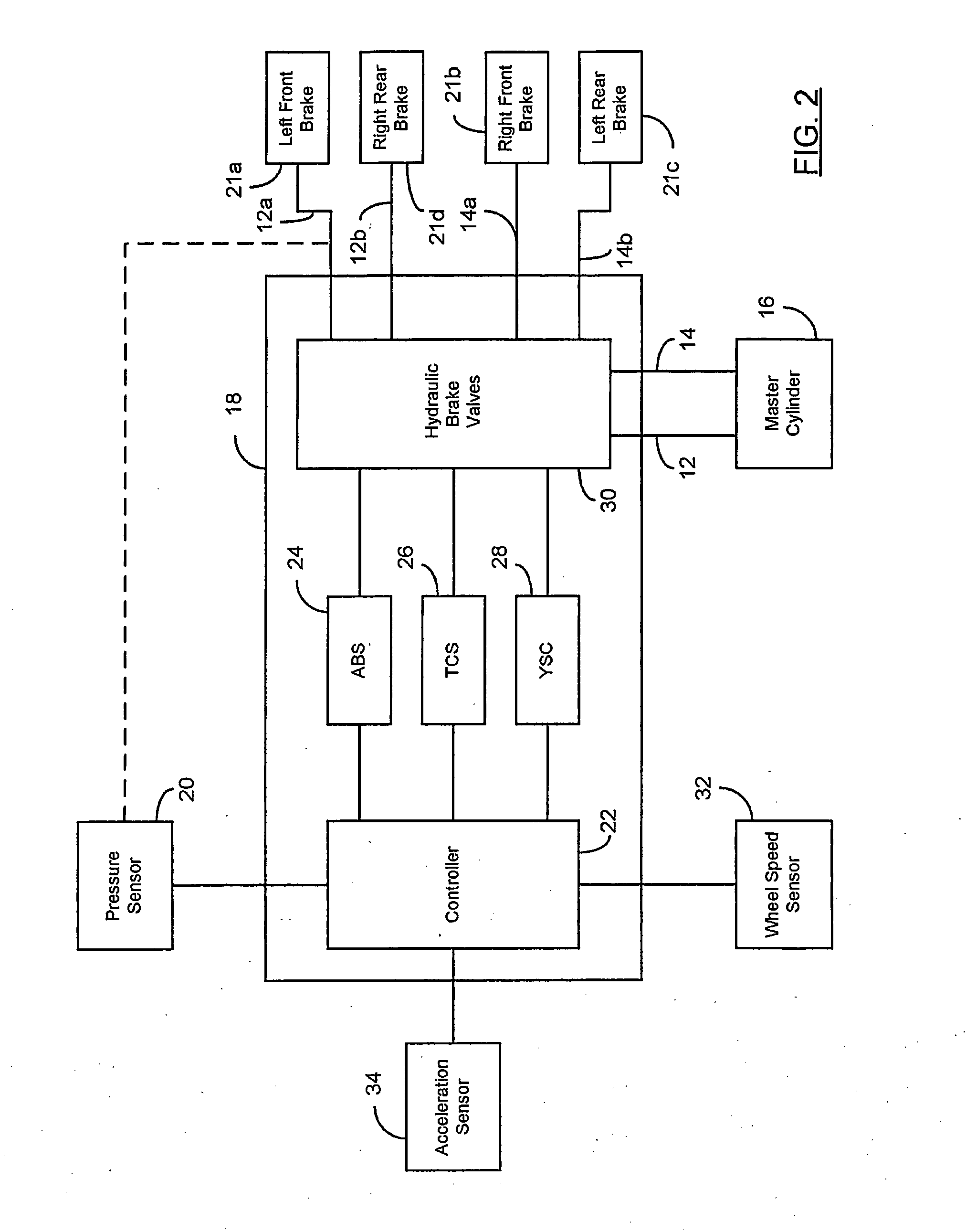

Method For Detecting Brake Circuit Failure

A method is provided for detecting a fault condition in a hydraulic brake system of a vehicle having a first hydraulic brake circuit and a second hydraulic brake circuit. A correlation ratio is determined between a measured pressure and the actual vehicle acceleration. A first wheel velocity differential is determined and a second wheel velocity differential is determined. A weighting value is selected in response to determining whether the correlation ratio is within the predetermined range and whether the first wheel velocity differential and the second wheel velocity differential are opposite signs. The selected weighting value is added to a fault counter. A determination is made whether the fault counter is equal to or greater than a predetermined threshold. A fault condition is detected in response to the fault counter greater than or equal to the first predetermined threshold.

Owner:KELSEY HAYES CO