Patents

Literature

451 results about "Testability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Testability, a property applying to an empirical hypothesis, involves two components: The logical property that is variously described as contingency, defeasibility, or falsifiability, which means that counterexamples to the hypothesis are logically possible. The practical feasibility of observing a reproducible series of such counterexamples if they do exist. In short, a hypothesis is testable if there is some real hope of deciding whether it is true or false of real experience. Upon this property of its constituent hypotheses rests the ability to decide whether a theory can be supported or falsified by the data of actual experience. If hypotheses are tested, initial results may also be labeled inconclusive.

Leadframe strip having enhanced testability

ActiveUS7008825B1Facilitate strip testingImprove design flexibilitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor packageTestability

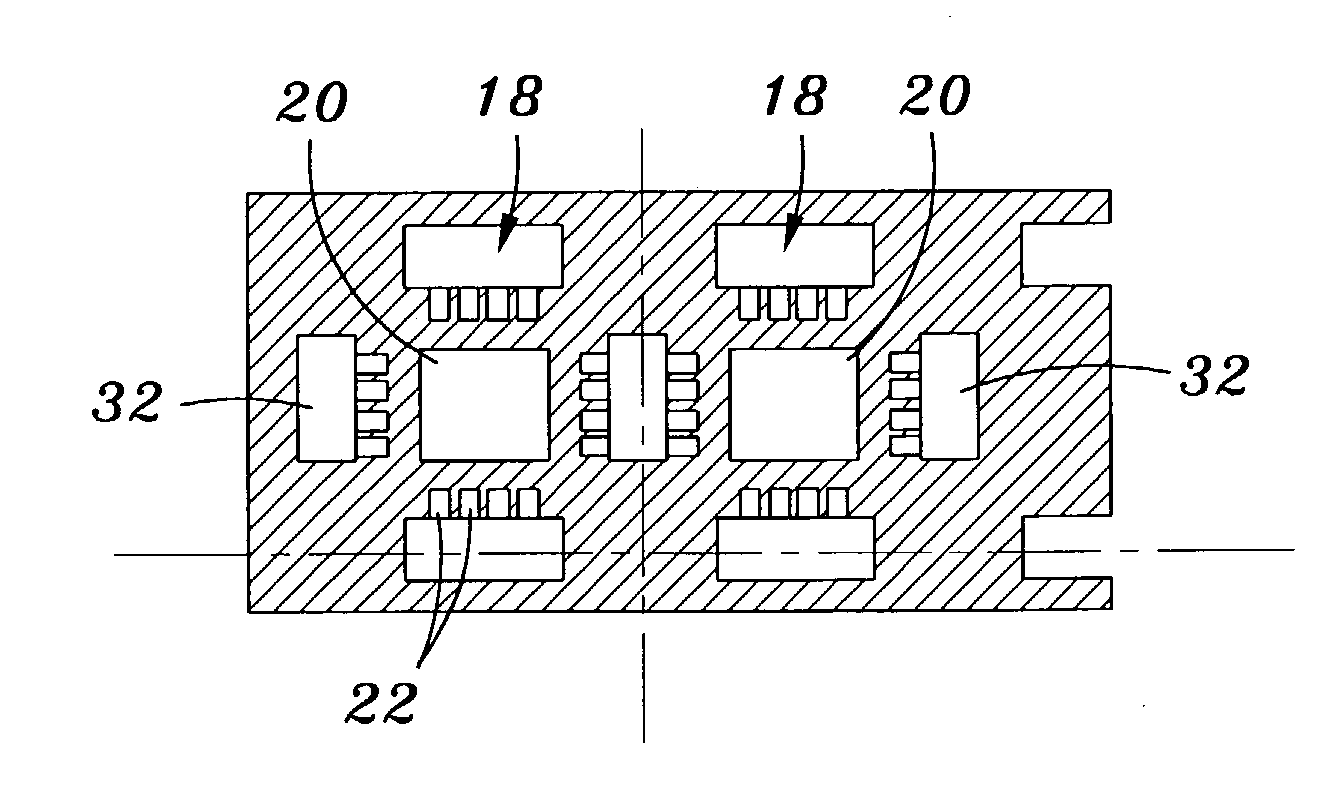

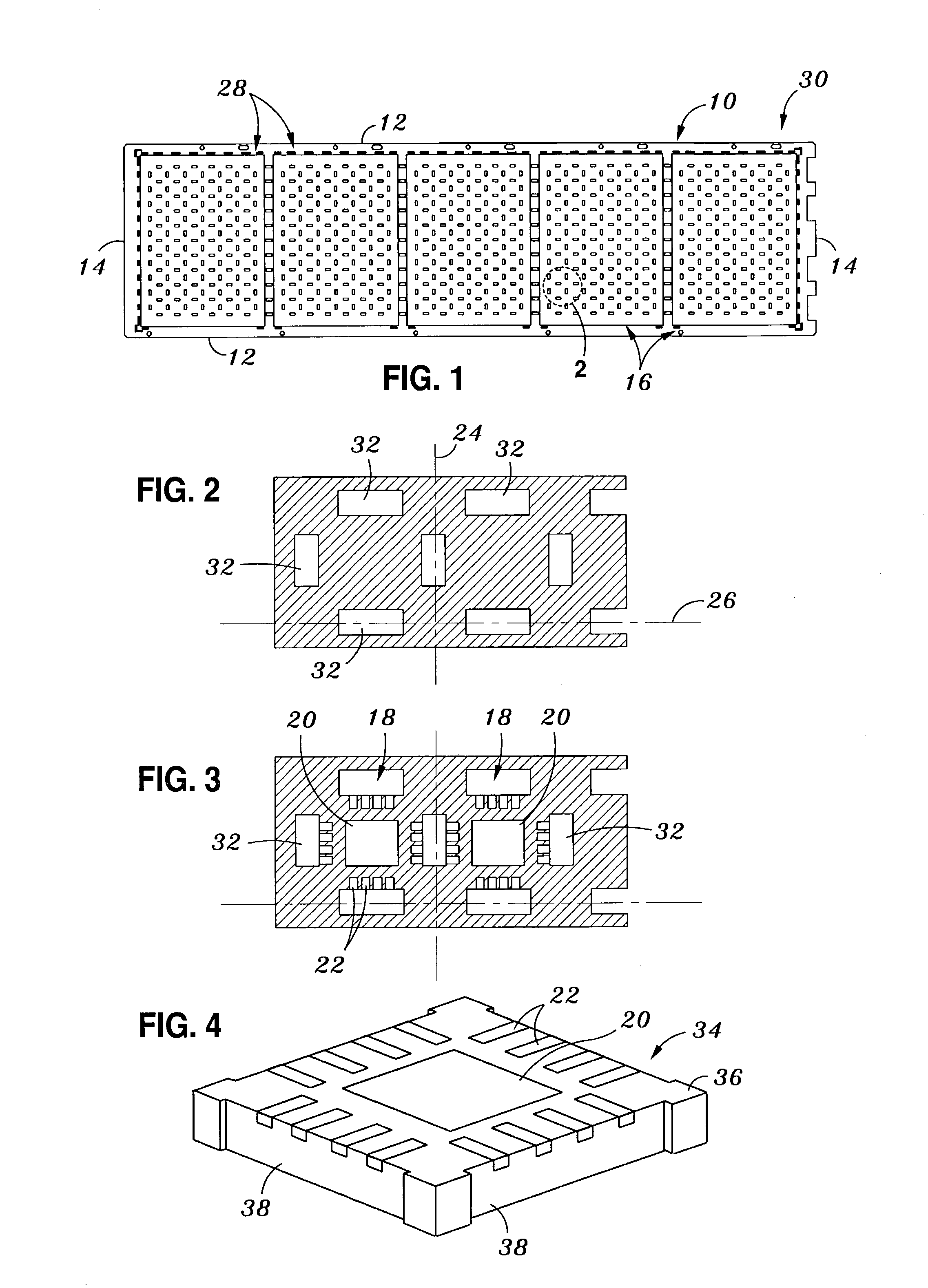

A method of fabricating a semiconductor package comprising the step of providing a leadframe strip which defines a strip plane and a multiplicity of leadframes. Each of the leadframes includes an outer frame defining a central opening and a die pad disposed within the central opening. Each leadframe further includes a plurality of leads which are attached to the outer frame and extend toward the die pad in spaced relation to each other. The outer frames are integrally connected to each other and collectively define connecting bars which extend in multiple rows and columns and define saw streets. Semiconductor dies are attached to respective ones of the die pads, with the semiconductor dies being mechanically and electrically connected to the leads of respective ones of the leadframes. Thereafter, an encapsulant material is applied to the leadframe strip to form at least one mold cap which at least partially encapsulates the leadframes, the semiconductor dies, and the conductive wires. The leadframe strip and the mold cap collectively define a package strip. Isolation cuts are formed through the package strip along at least some of the saw streets to effectively electrically isolate the leadframes from each other.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

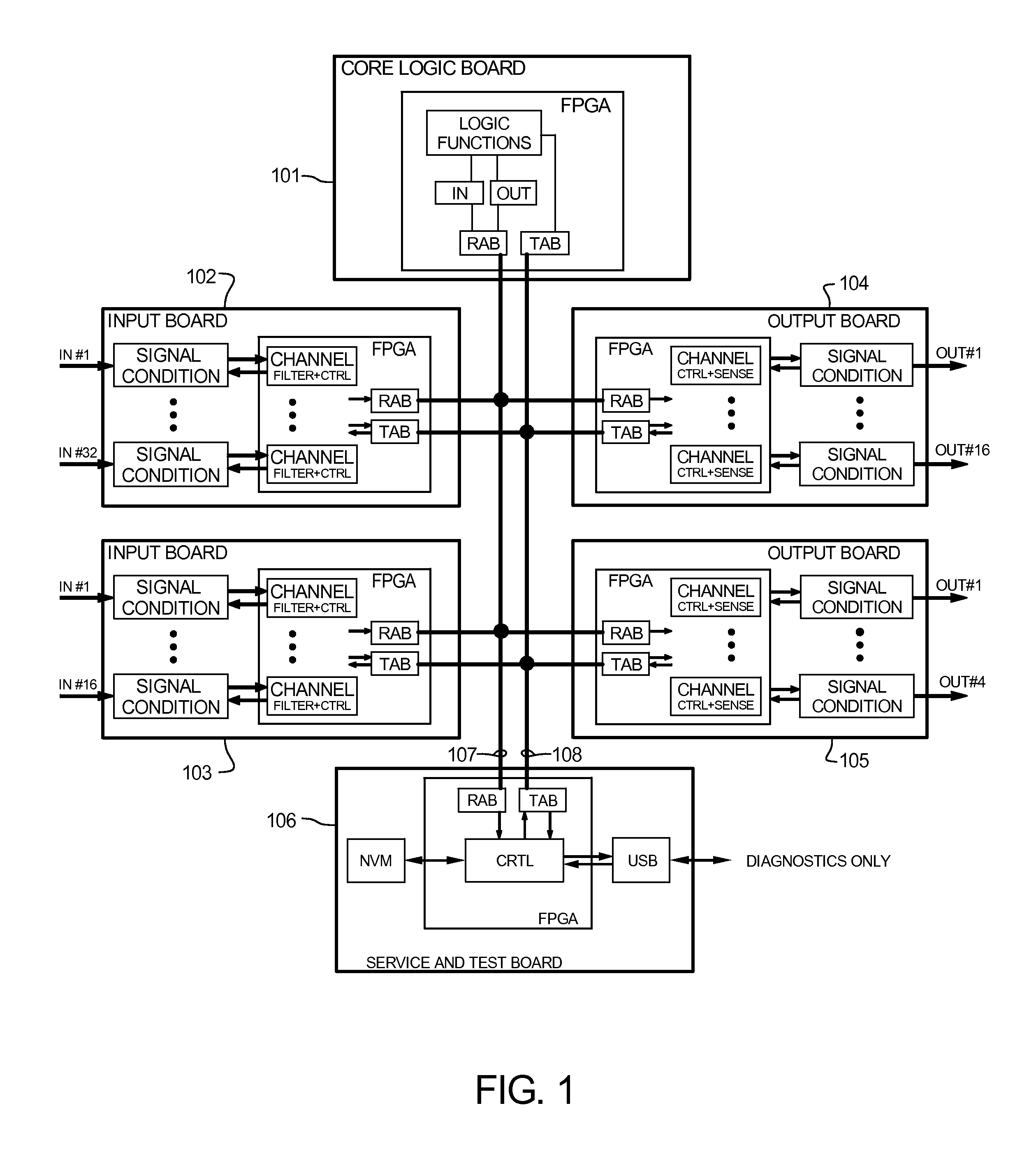

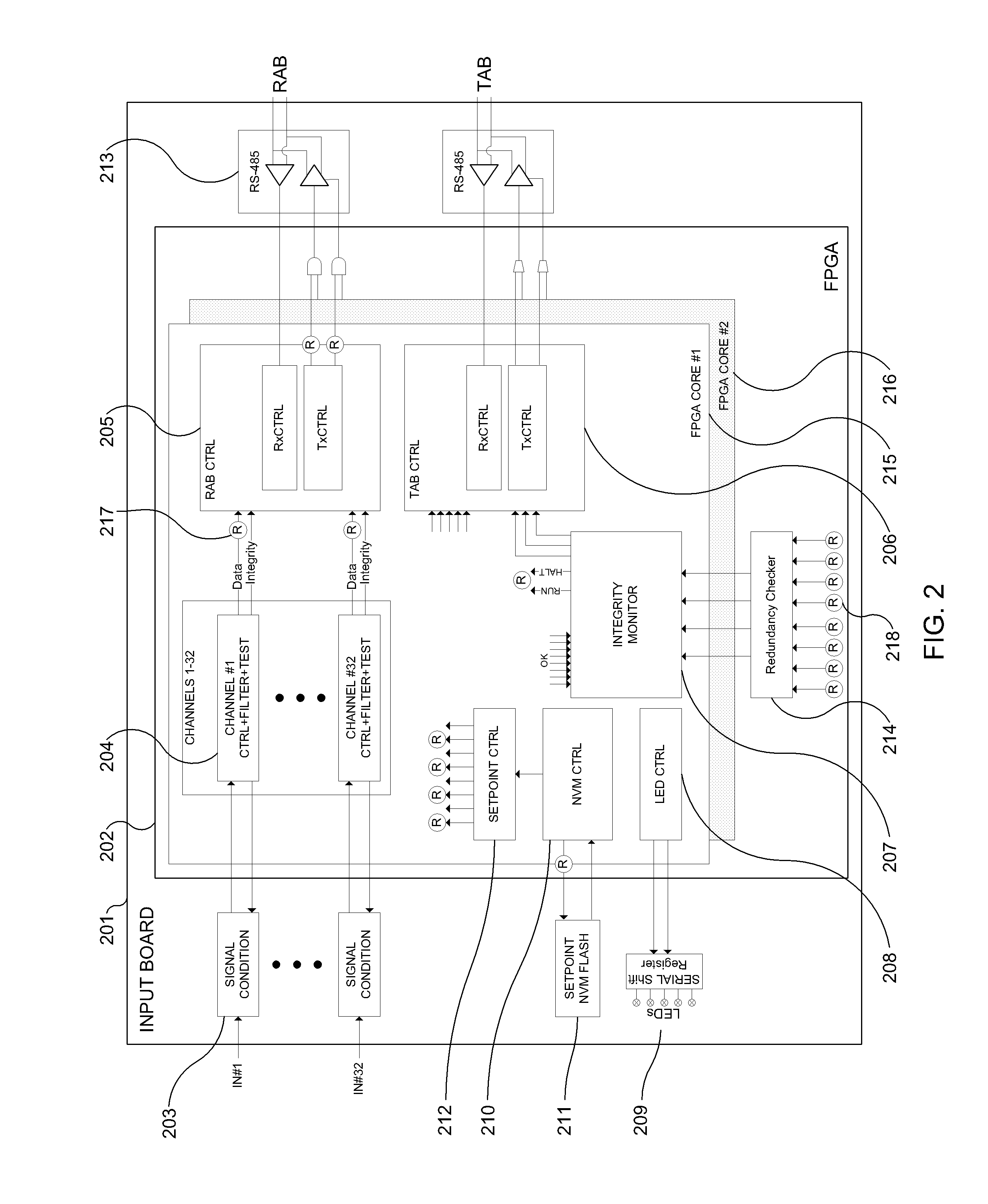

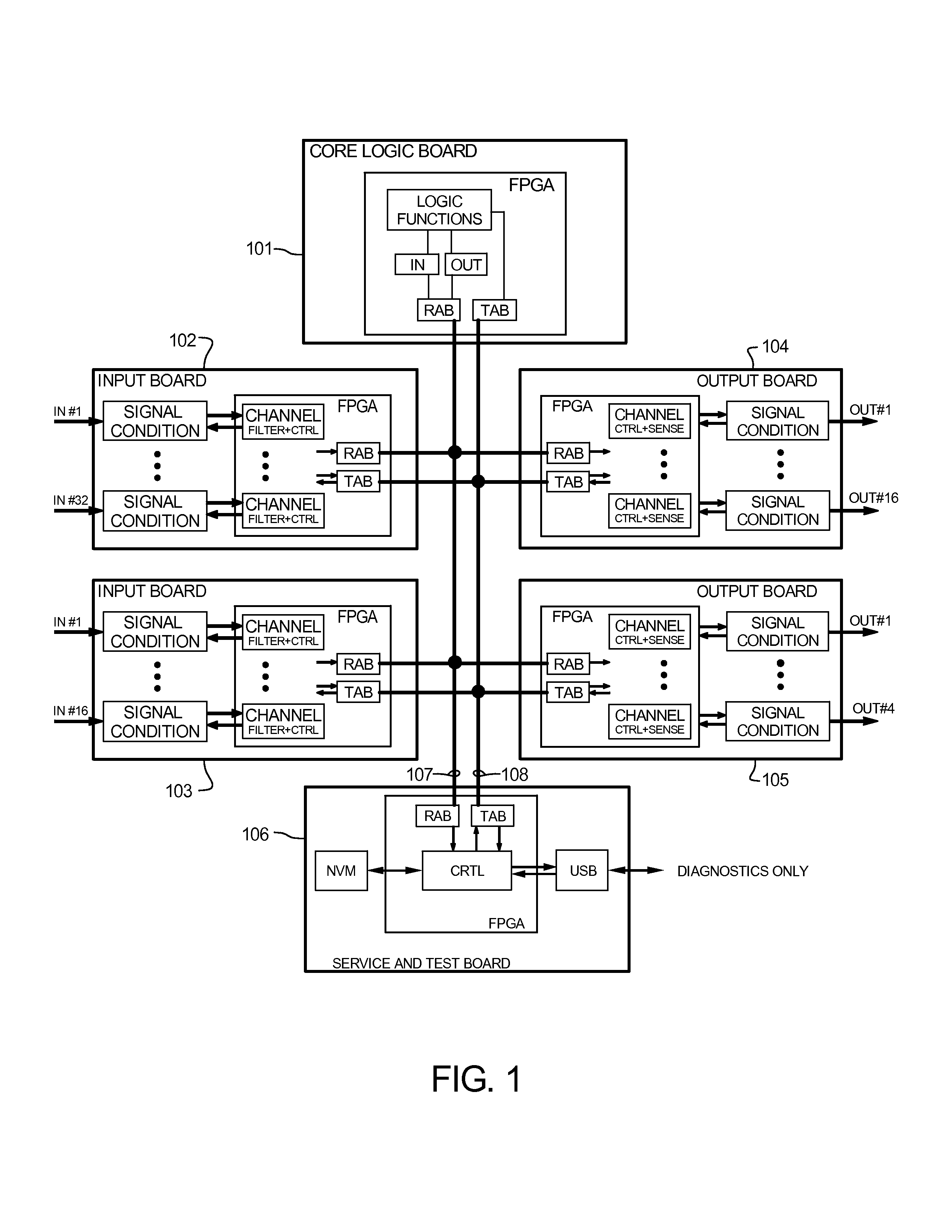

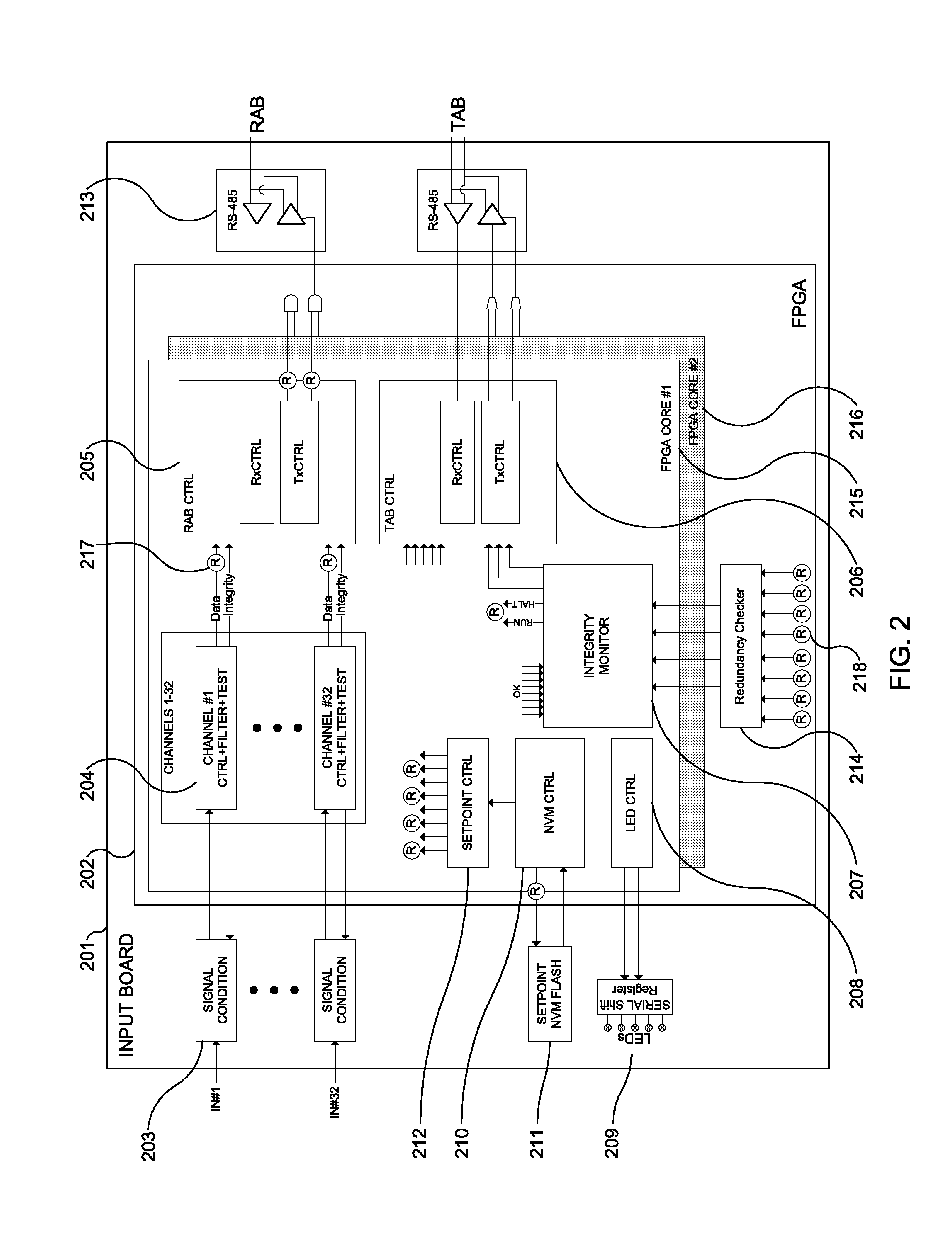

Advanced logic system

ActiveUS7870299B1Improve reliabilityImprove maintainabilityProgramme controlTesting/monitoring control systemsNuclear plantCommon mode failure

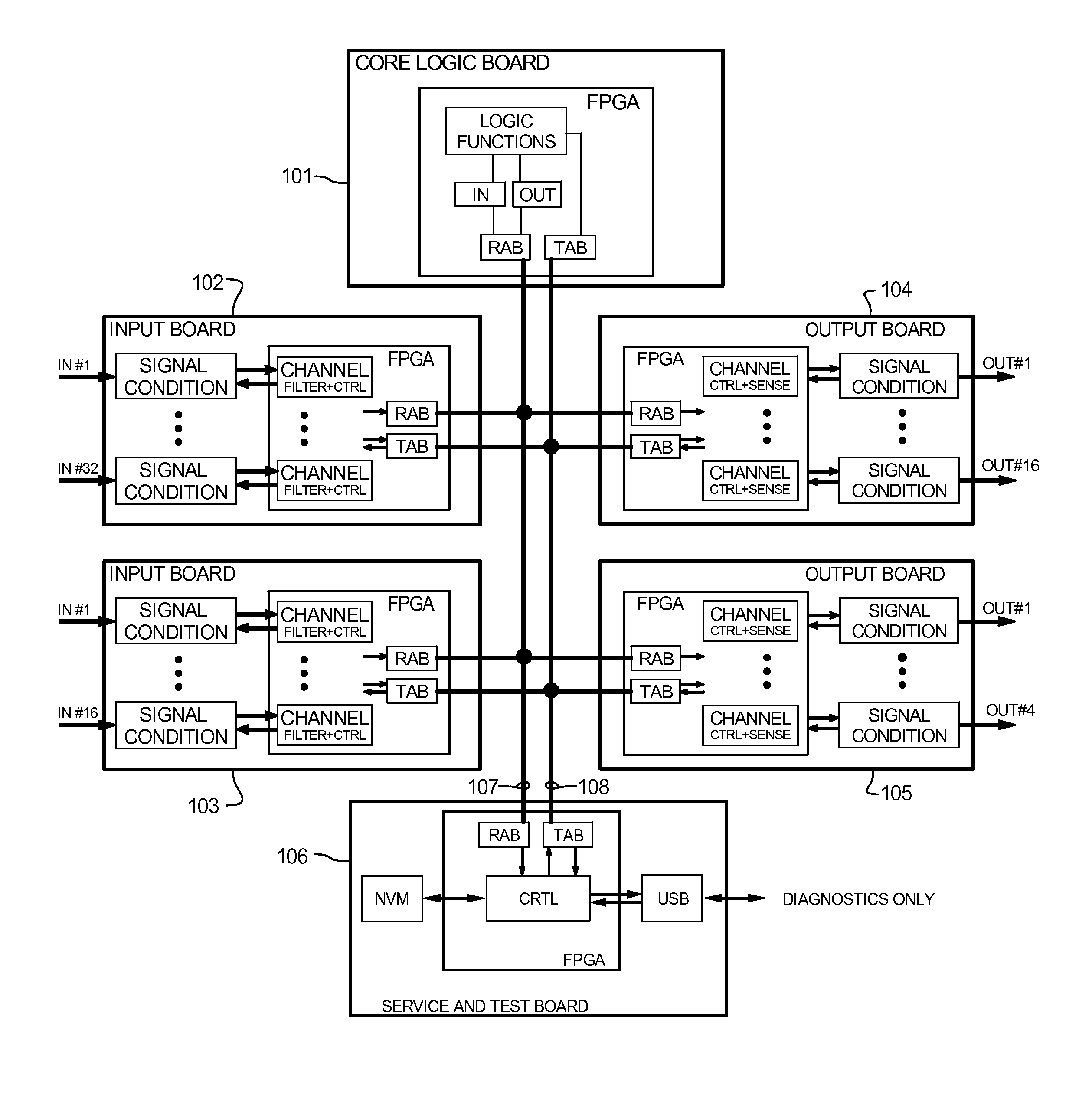

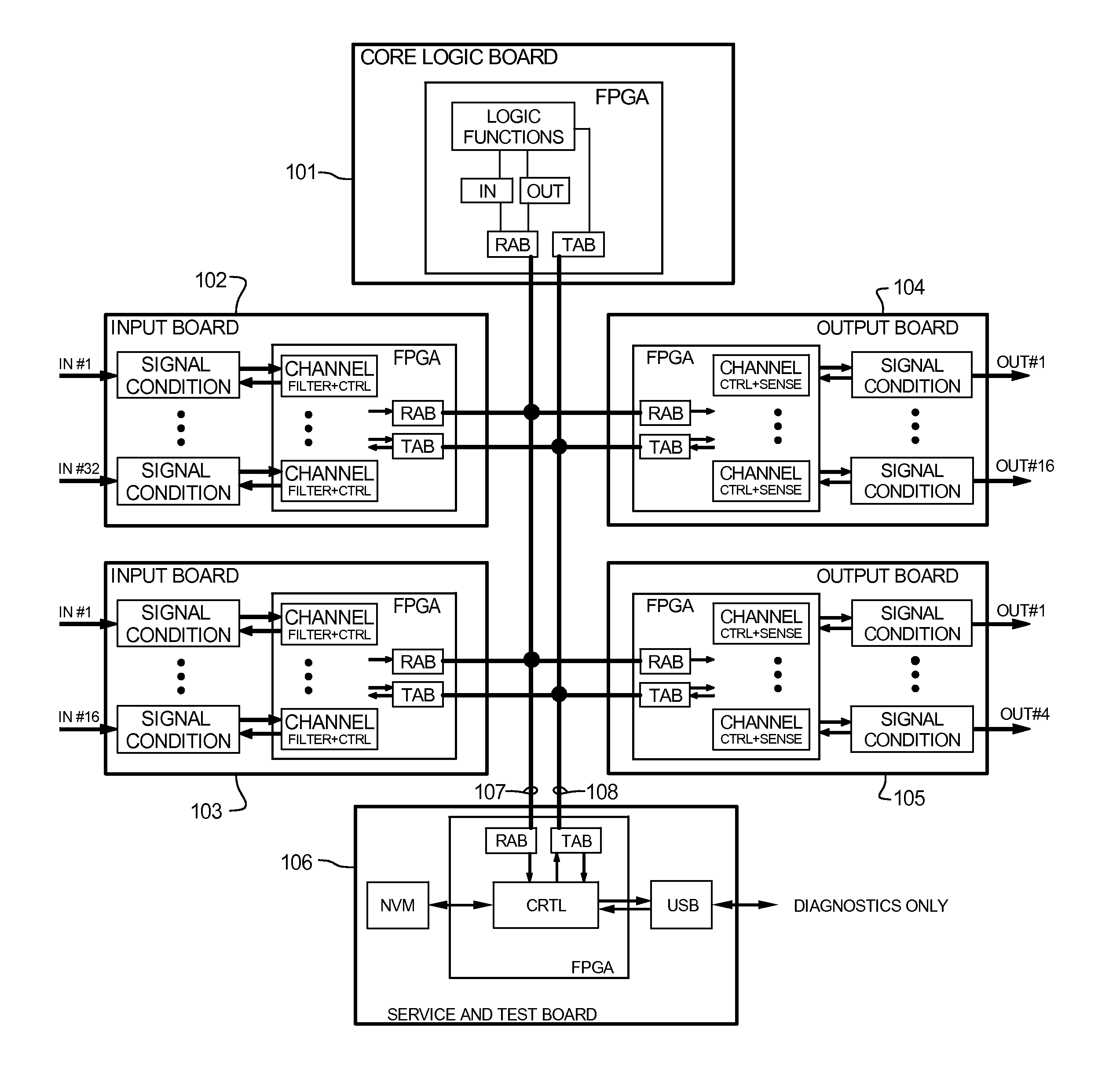

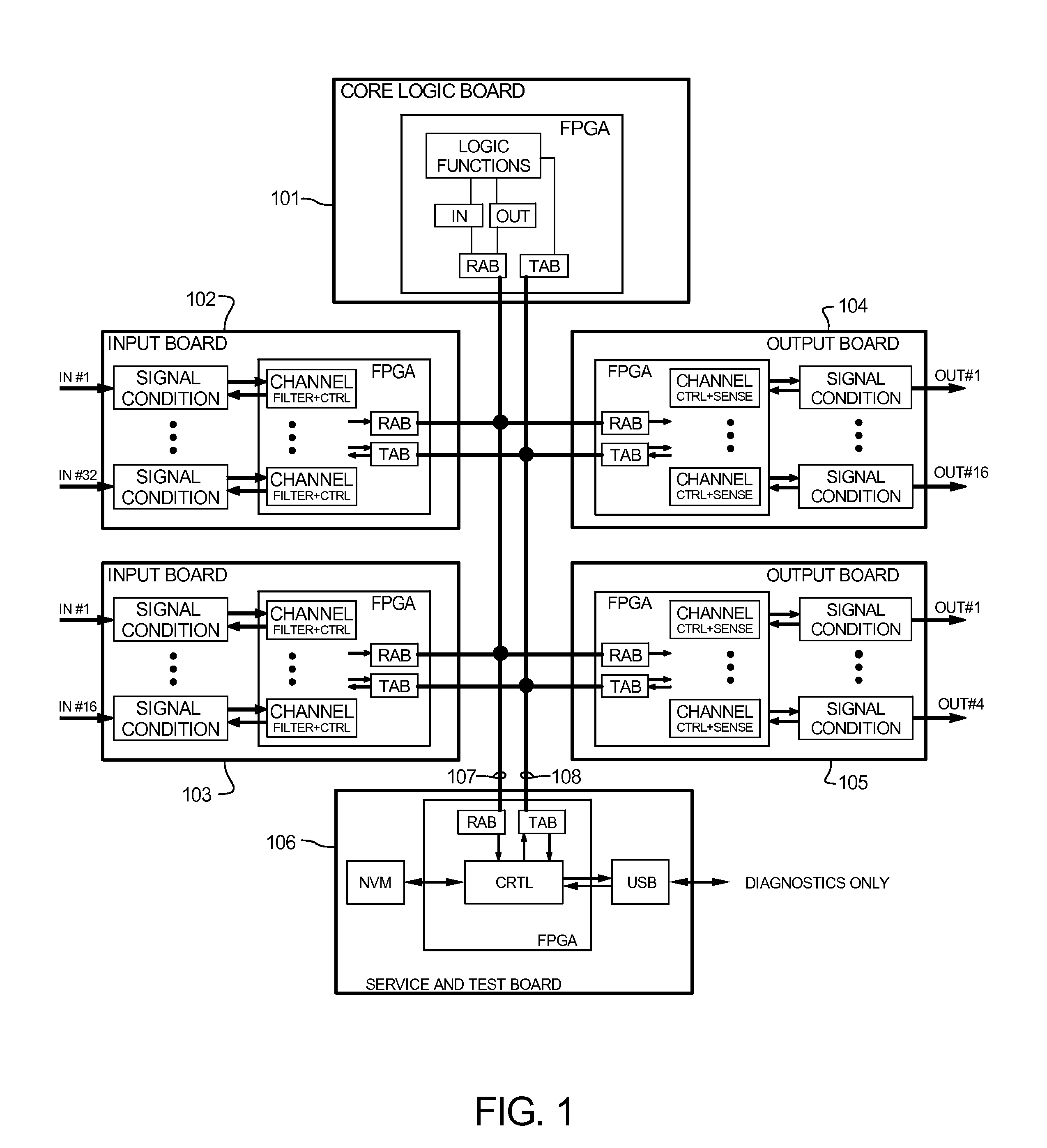

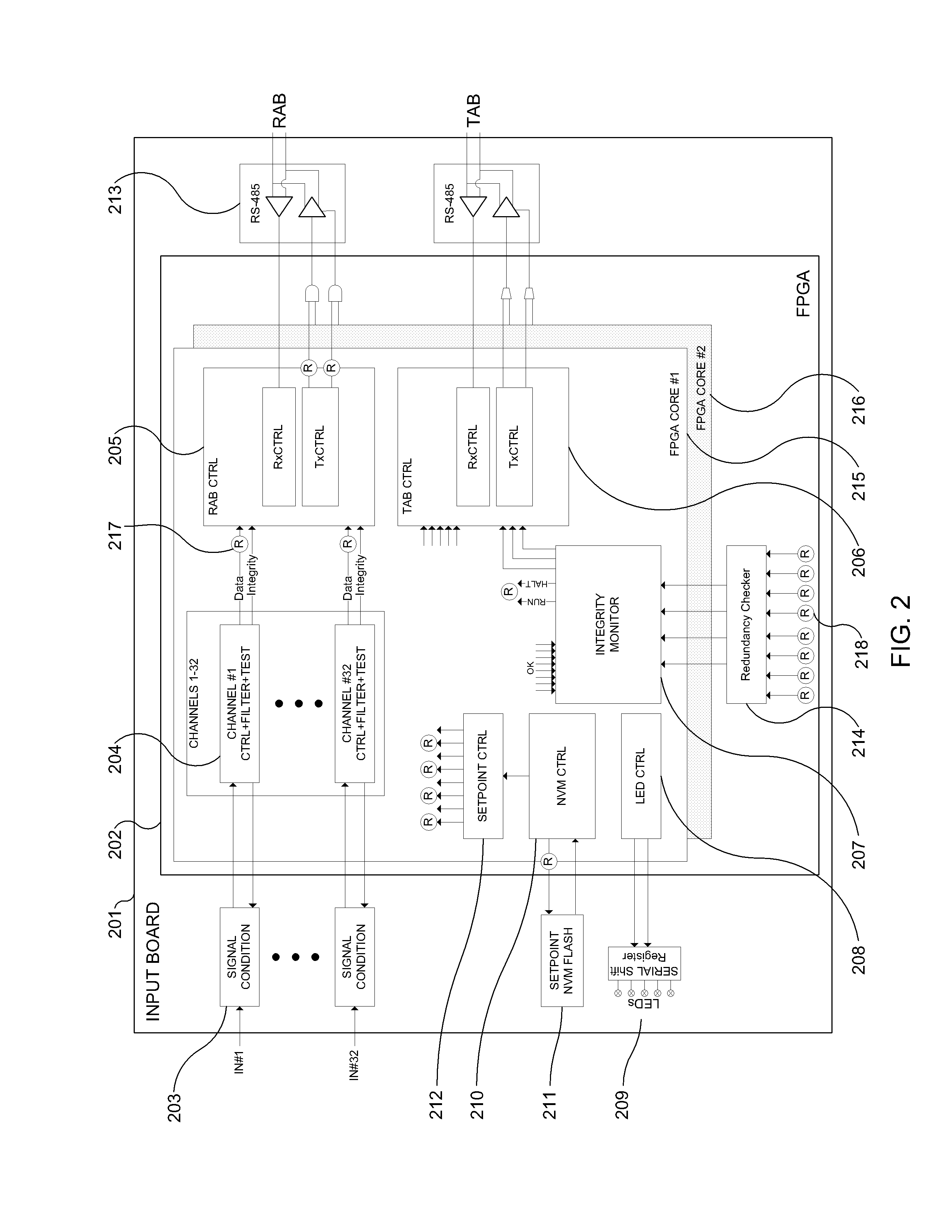

The Advanced Logic System (ALS) is a complete control system architecture, based on a hardware platform rather than a software-based microprocessor system. It is significantly different from other PLC-type control system architectures, by implementing a FPGA in the central control unit. Standard FPGA logic circuits are used rather than a software-based microprocessor which eliminate problems with software based microprocessor systems, such as software common-mode failures. It provides a highly reliable system suitable for safety critical control systems, including nuclear plant protection systems. The system samples process inputs, provides for digital bus communications, applies a control logic function, and provides for controlled outputs. The architecture incorporates advanced features such as diagnostics, testability, and redundancy on multiple levels. It additionally provides significant improvements in failure detection, isolation, and mitigation for the highest level of integrity and reliability.

Owner:WESTINGHOUSE ELECTRIC CORP

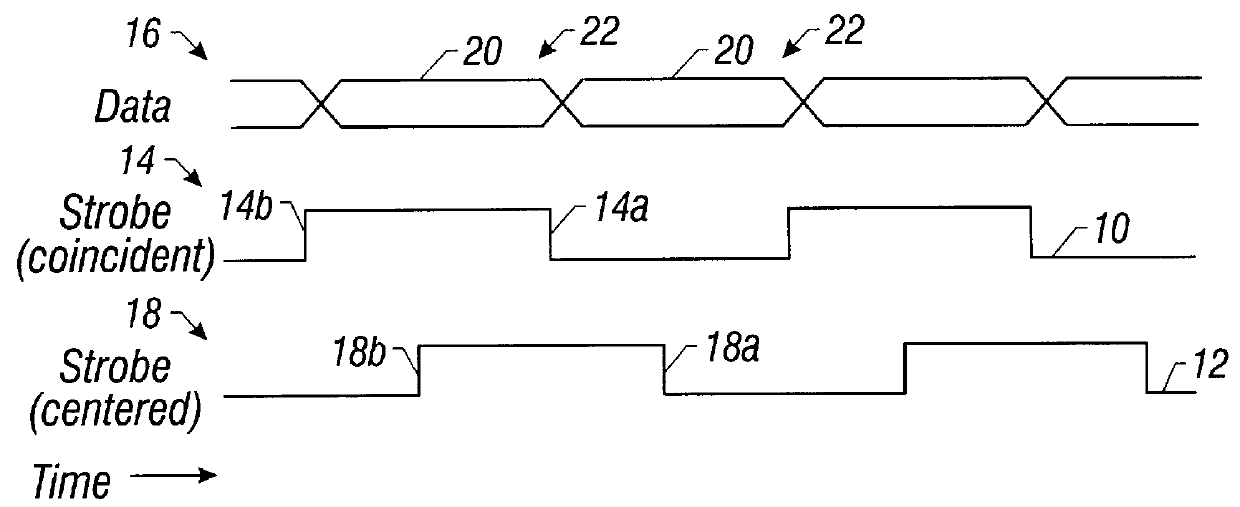

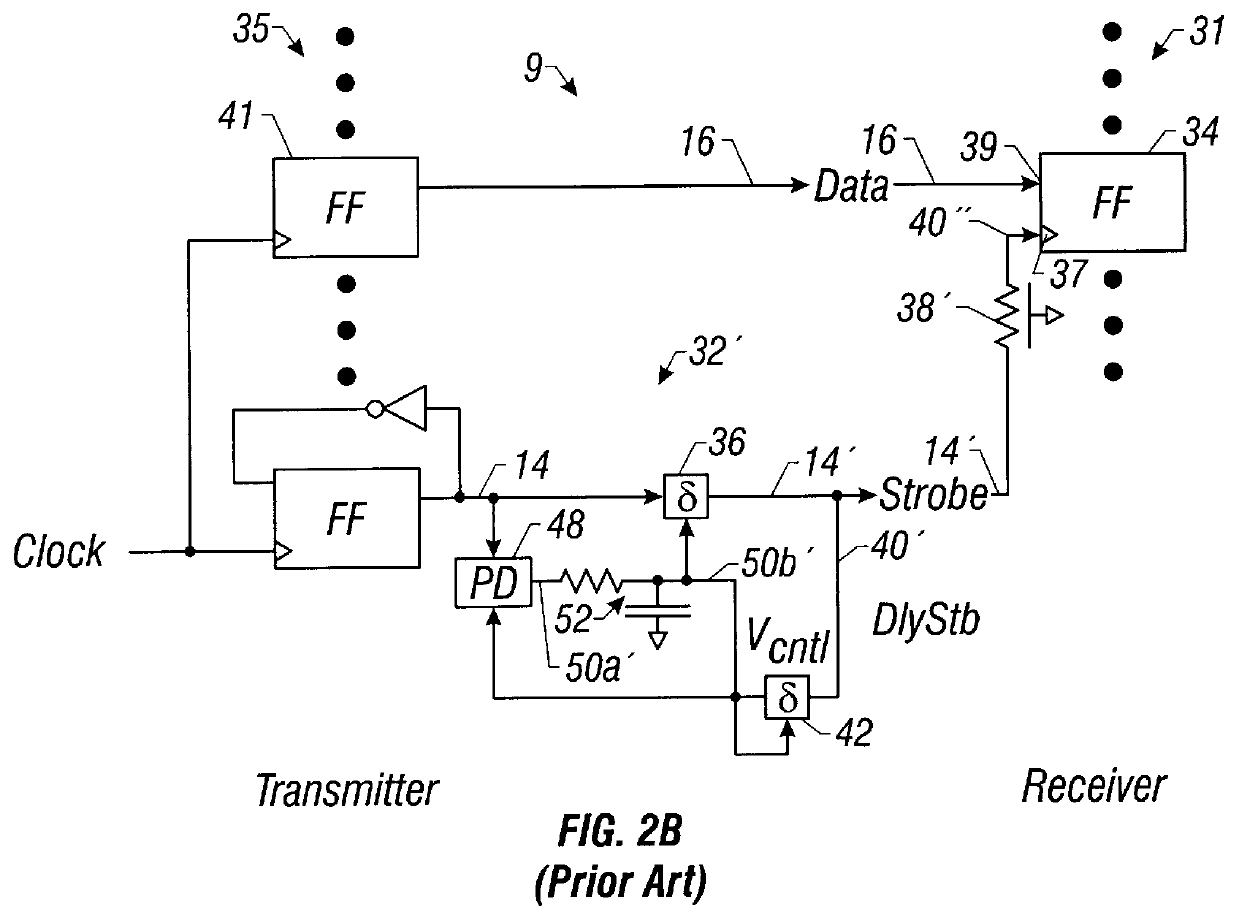

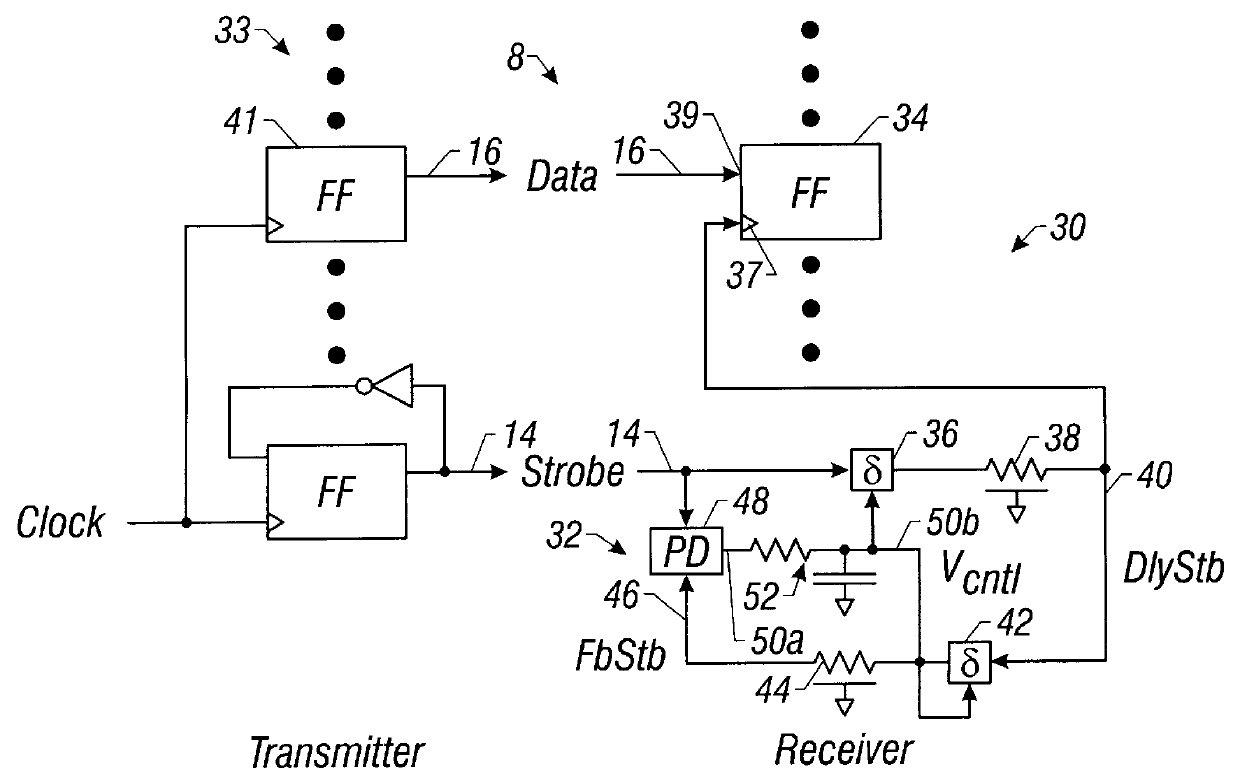

Timing control for input/output testability

InactiveUS6085345AMultiple input and output pulse circuitsPulse automatic controlPhase differenceDelay-locked loop

Circuitry added to chips that use source synchronous techniques reduces difficulties associated with testing the chips. The circuitry increases the ability to use source synchronous techniques for data transmission. The circuitry is implemented in a delayed-lock loop (DLL) in either a transmitter (driver) or a receiver. The DLL measures the phase difference between a strobe signal and a delayed strobe signal. The DLL can be externally controlled by a source selectable input which allows the delay of the delayed strobe signal to be varied to test Tsetup and Thold in the receiver without varying the timings of the strobe signal and the data signals supplied to the chips. A timing measurement circuit having the strobe signal, the delayed strobe signal, and reference signals as inputs may be used to calibrate the phase difference between the strobe signal and delayed strobe signal.

Owner:INTEL CORP

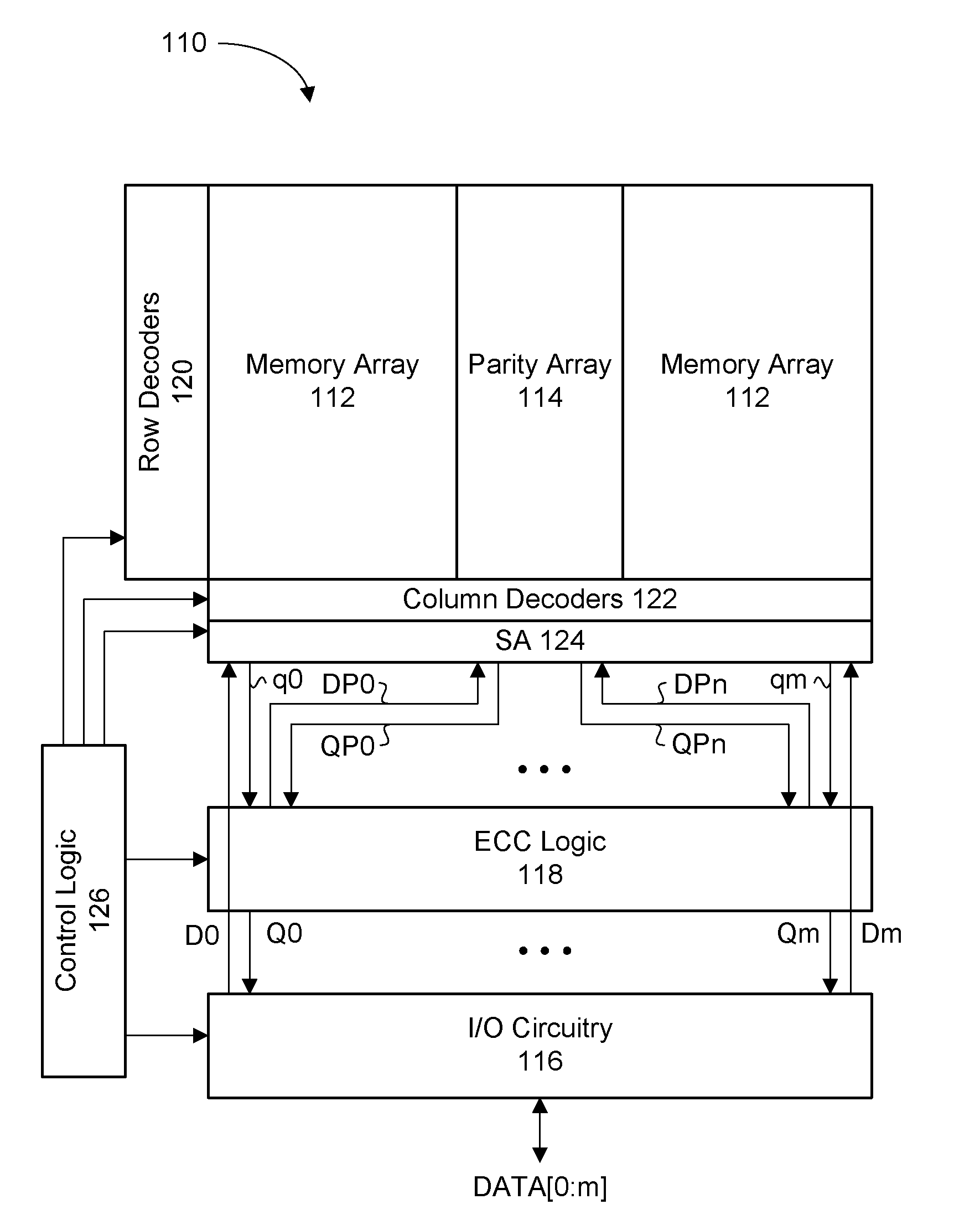

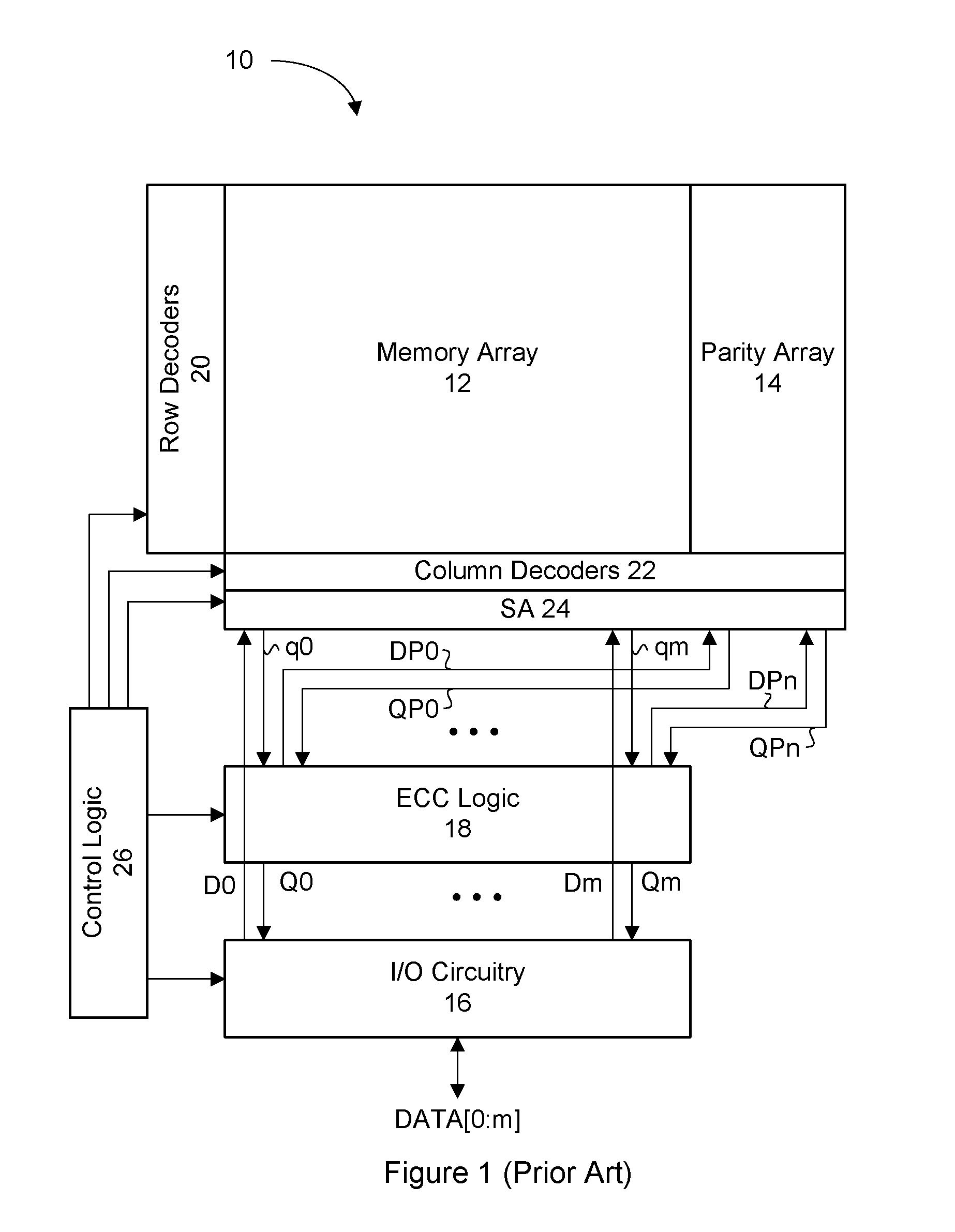

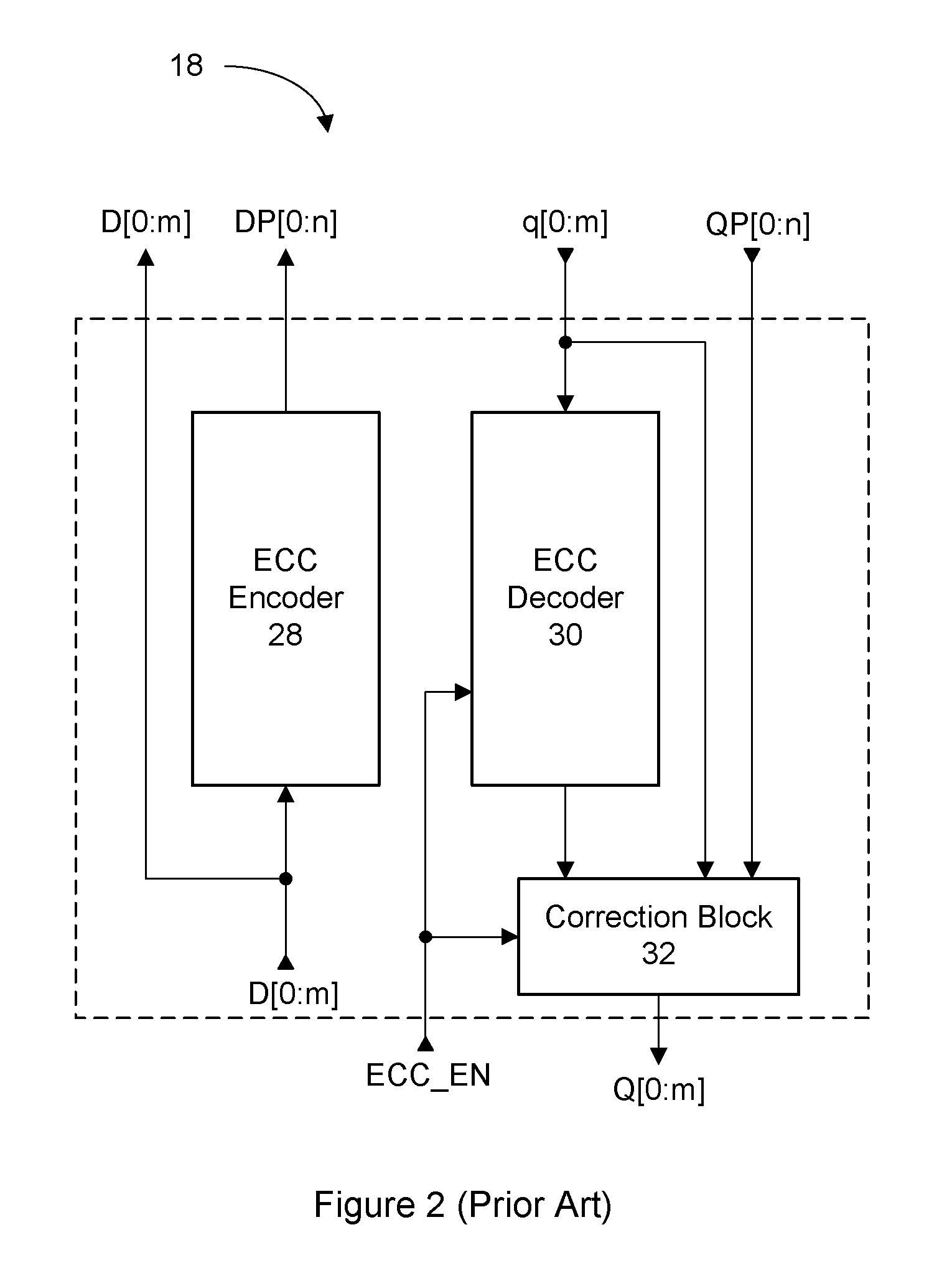

Ecc system for memory

ActiveUS20080016392A1Minimize wiring distanceDistance minimizationDigital storageRedundant hardware error correctionLogic circuitryCorrection code

An error correction code system for a memory for improving performance and testability. The parity columns of the memory array can be positioned centrally within the array to minimize routing distance to ECC logic circuitry. The parity columns can be grouped together or distributed throughout the array to optimize performance. A multiplexor circuit can be included for selectively coupling only the parity bits stored in the parity memory array to I / O circuitry. Therefore, the parity columns can be directly tested, and testing of the ECC logic circuitry is facilitated.

Owner:TAIWAN SEMICON MFG CO LTD

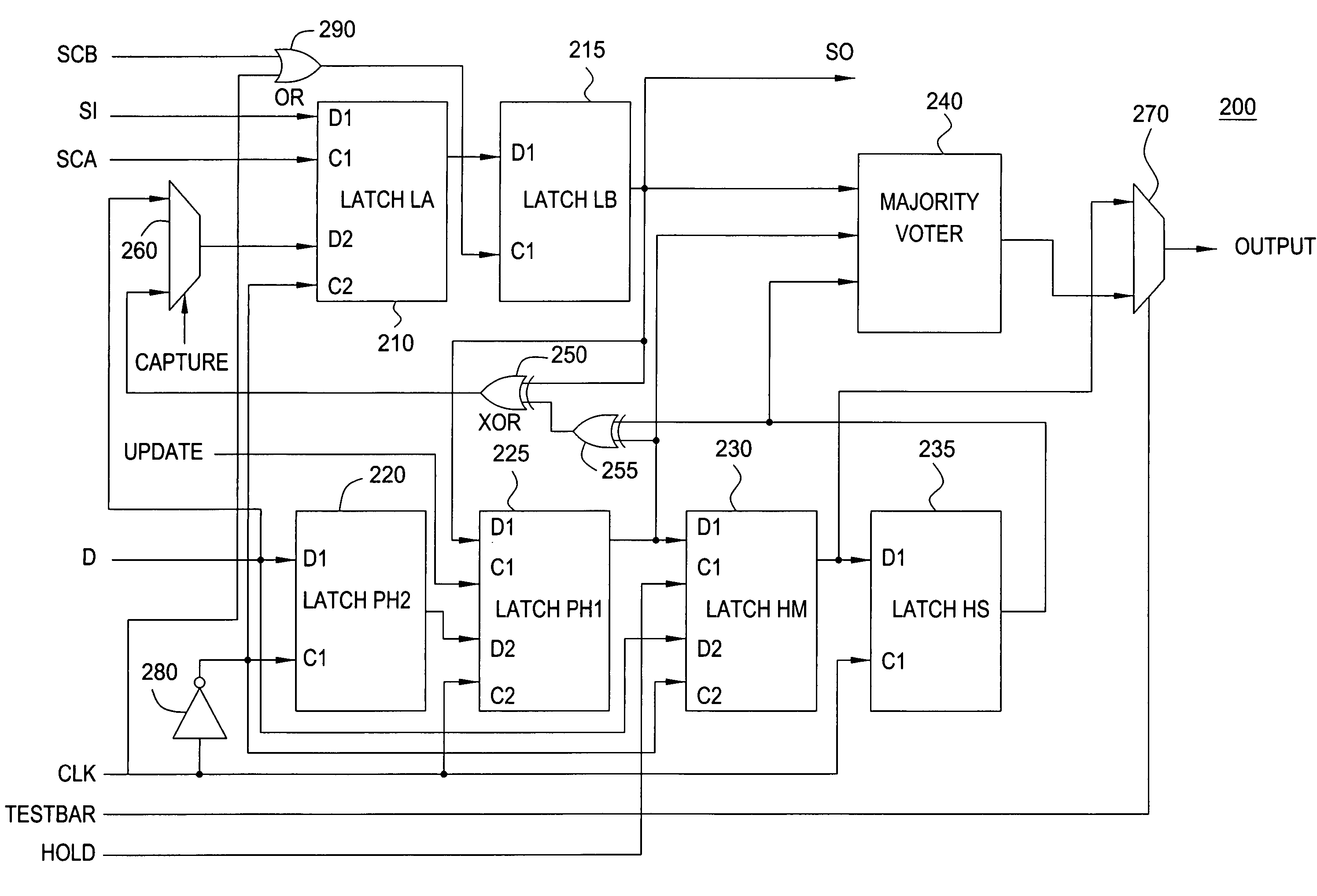

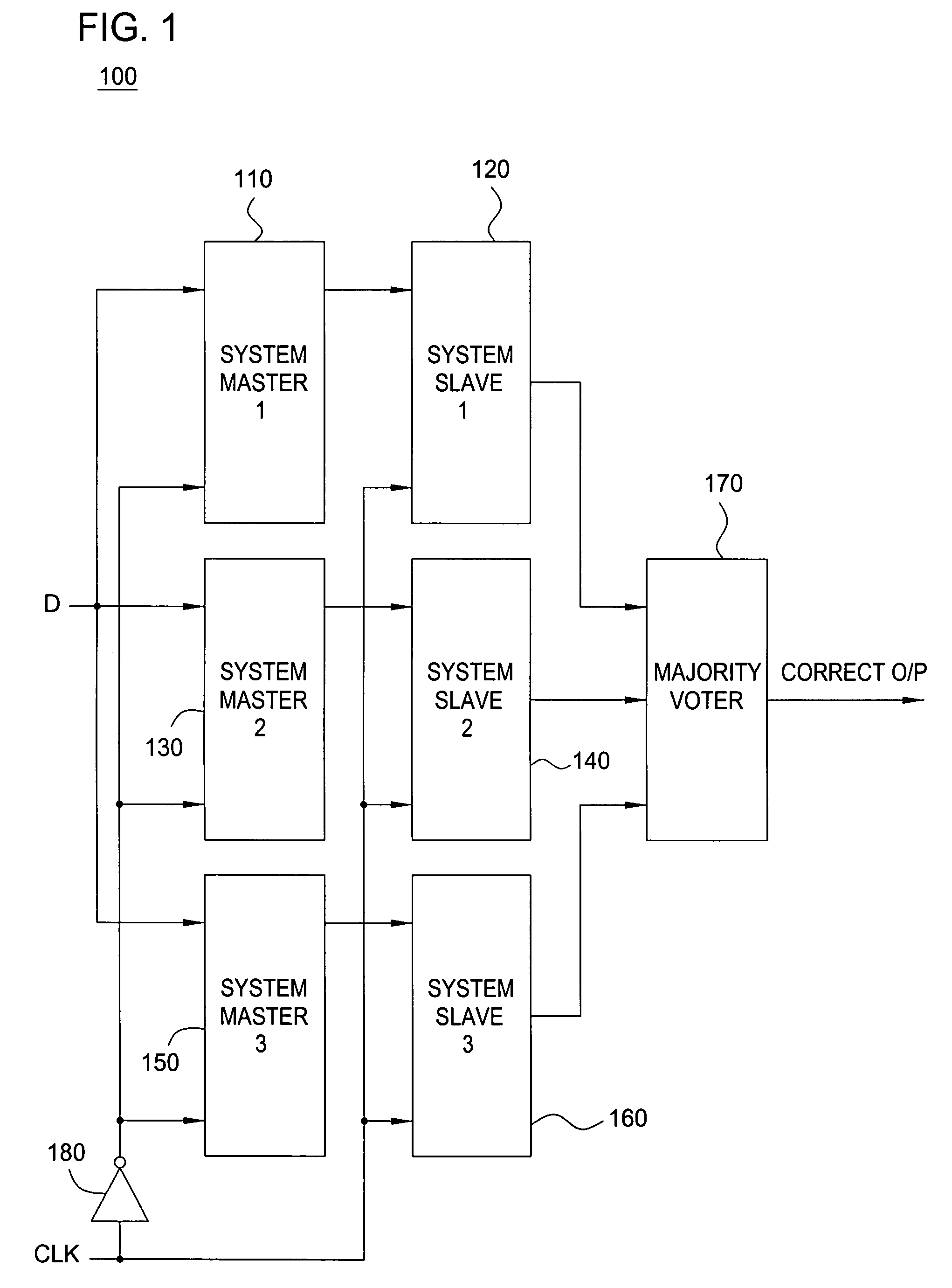

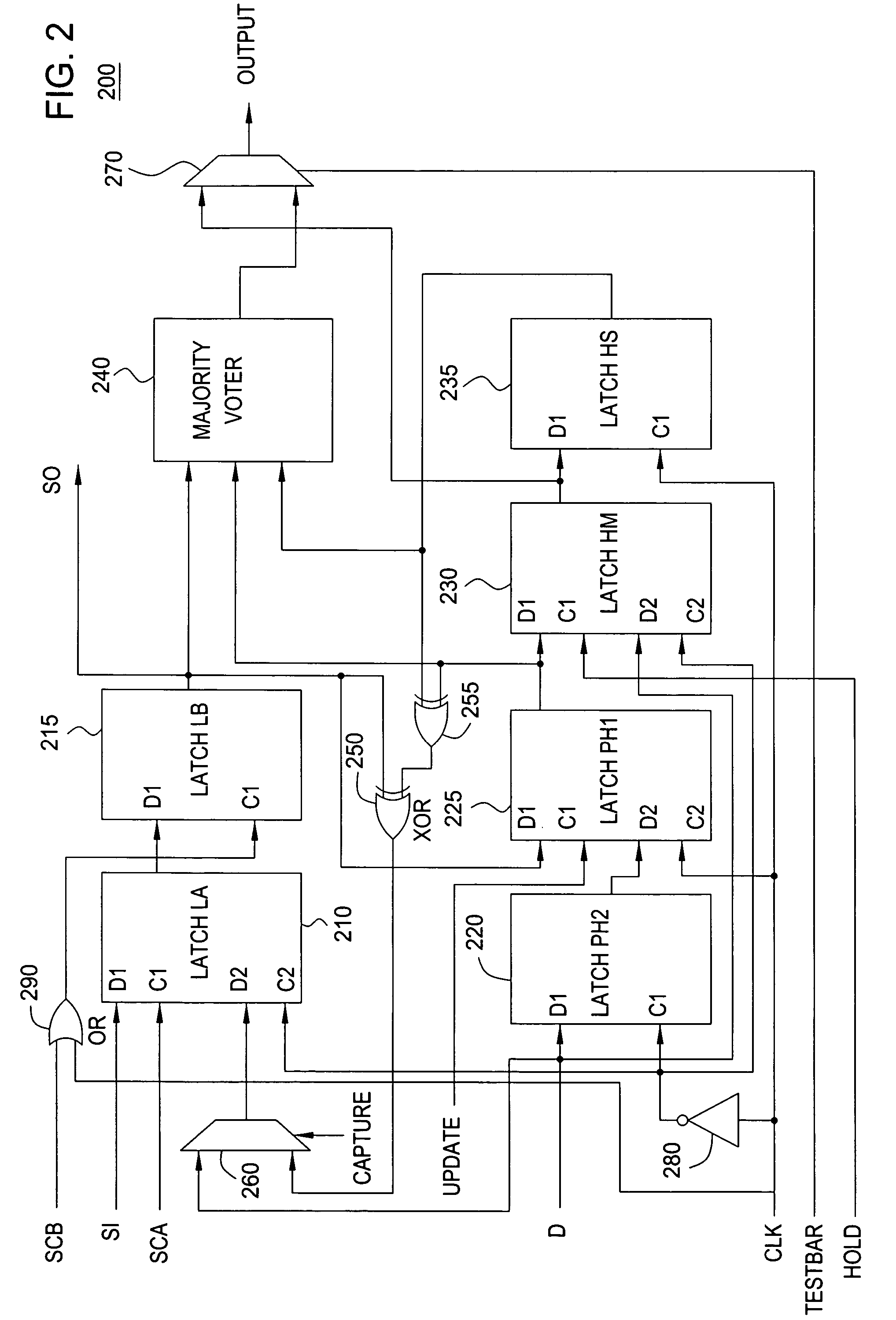

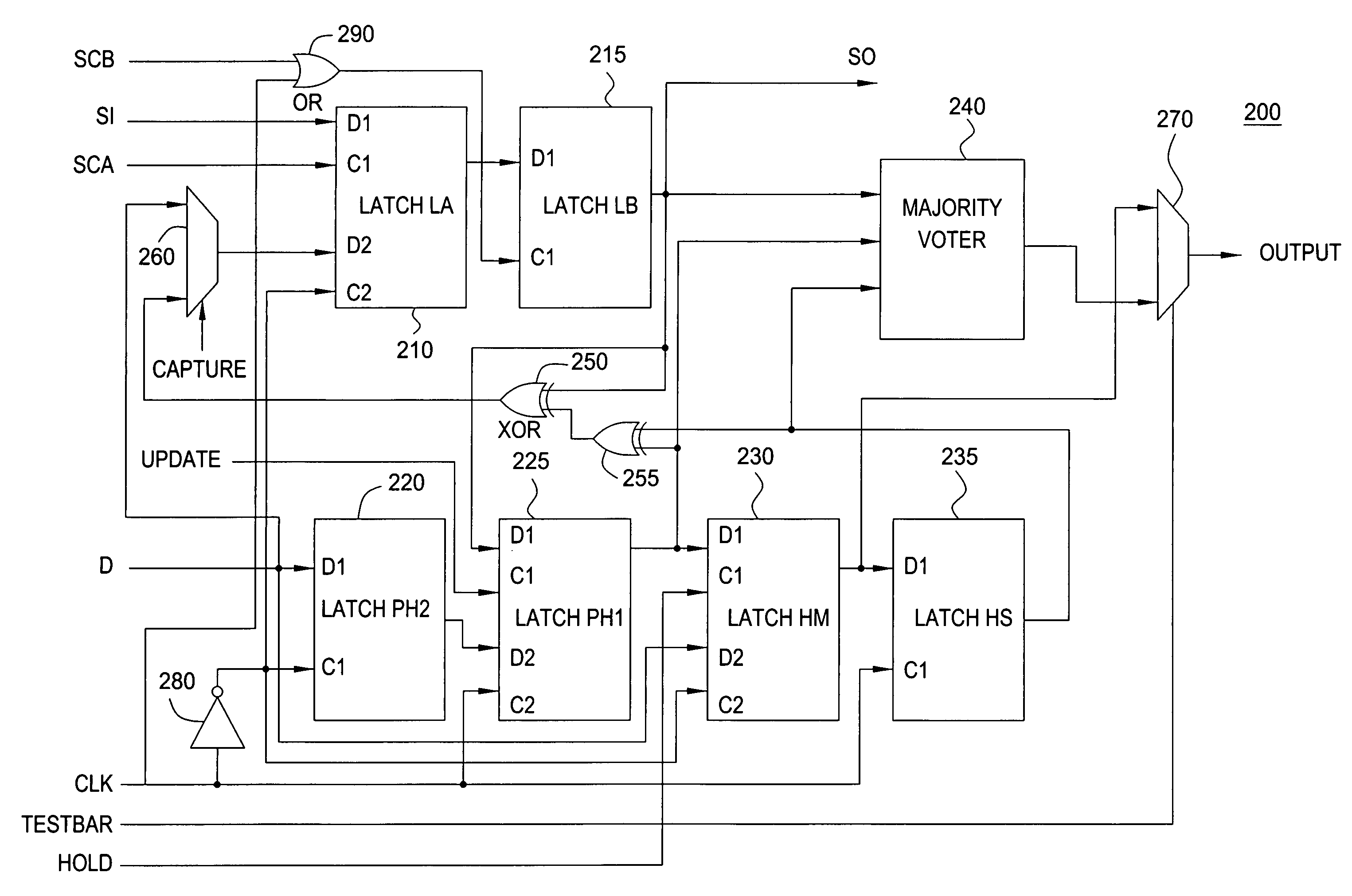

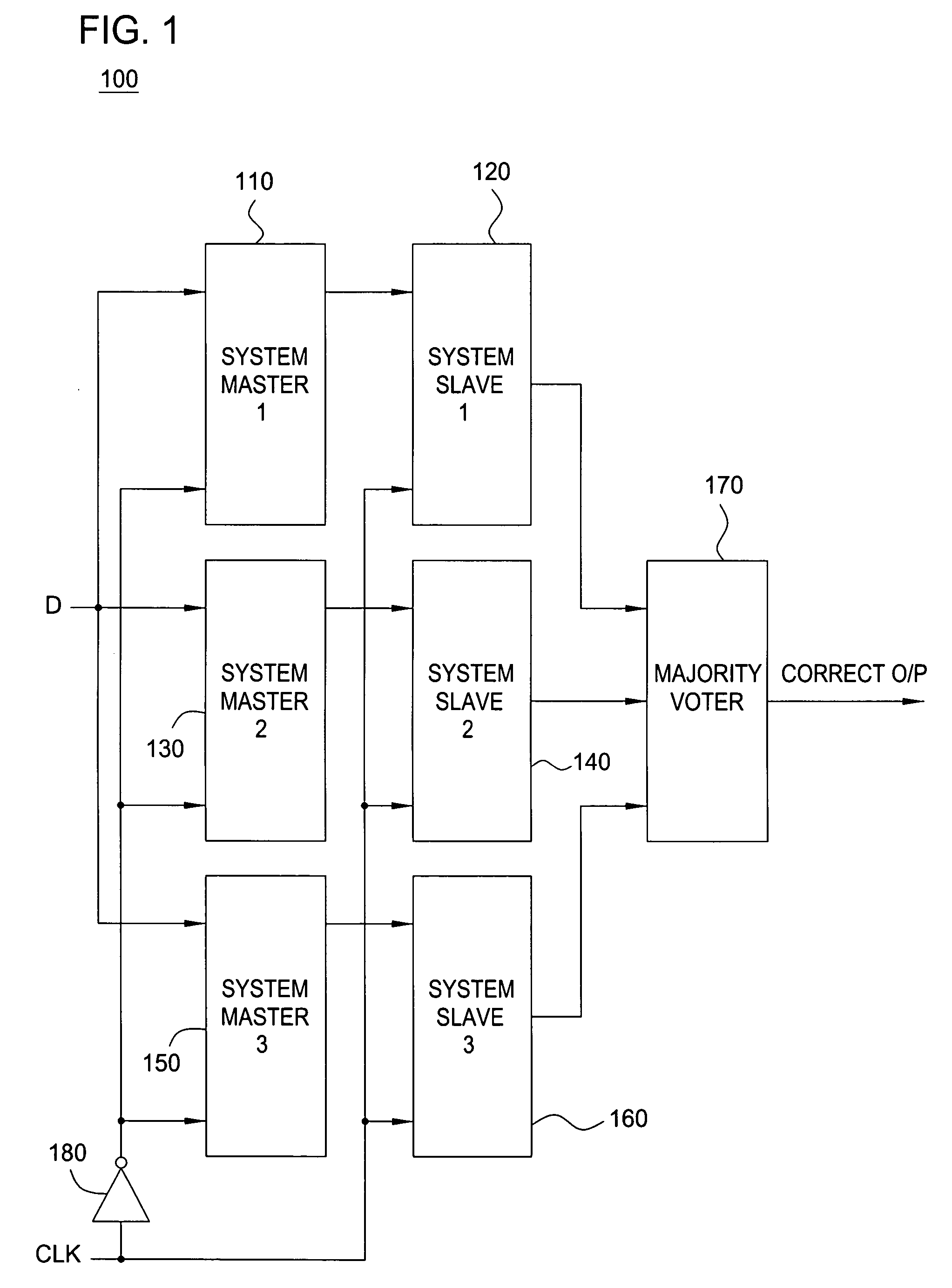

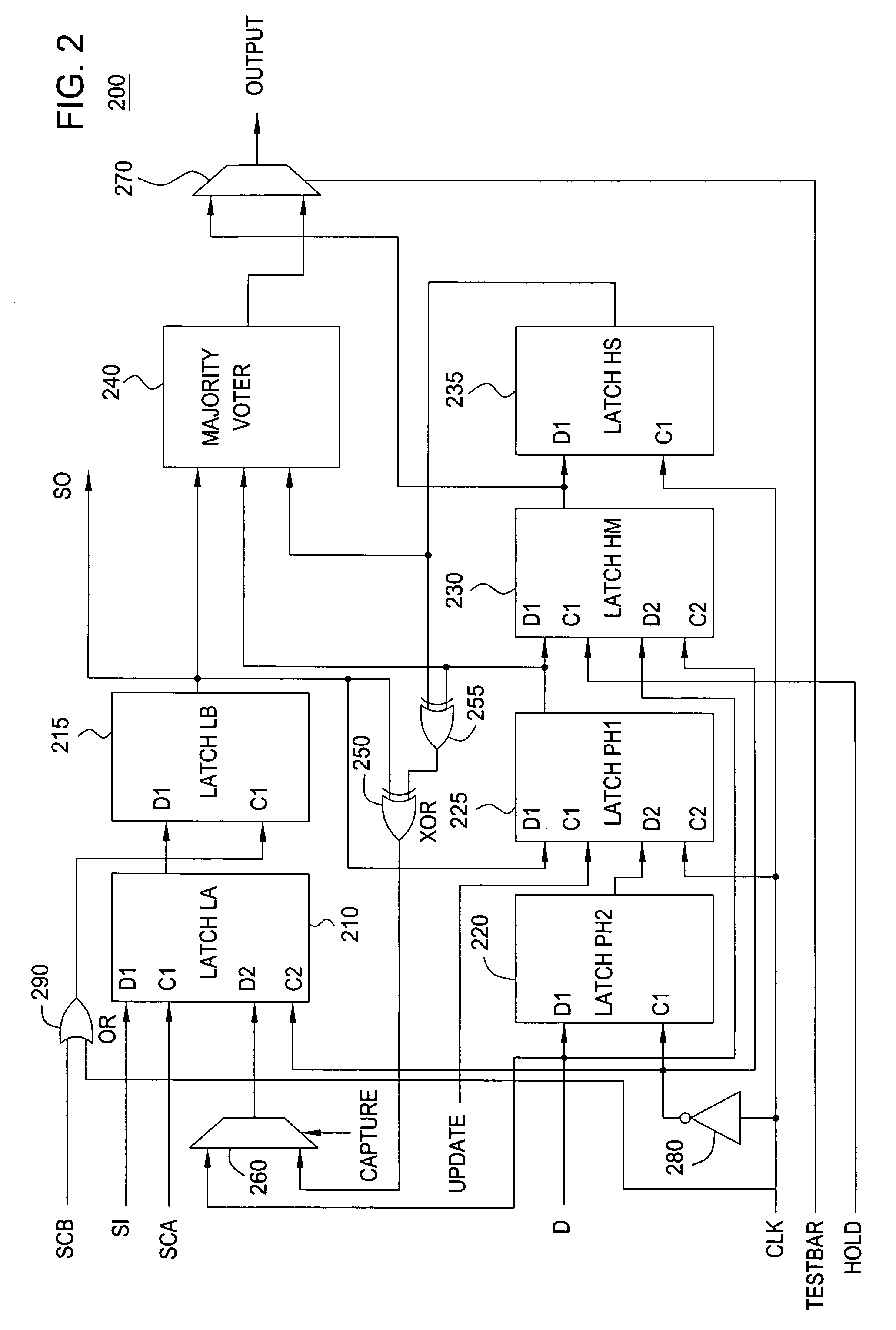

Soft error tolerant flip flops

ActiveUS7482831B2Reliability increasing modificationsElectric pulse generatorProcessor registerComputer science

A register designed to detect and correct soft errors in real time. A redundant latch is added to the existing structure of a flip flop and functional data is simultaneously registered at multiple latches. The content of these multiple latches are fed to a majority voting circuit. If the content of any of these latches is corrupted by soft error, it is filtered out through the majority voting circuit and correct data is passed out from the output of the flip flop. In one embodiment, this design operates as a simple scan flip flop or scan-hold flip flop, and is useful for system testability purposes.

Owner:RUTGERS THE STATE UNIV +1

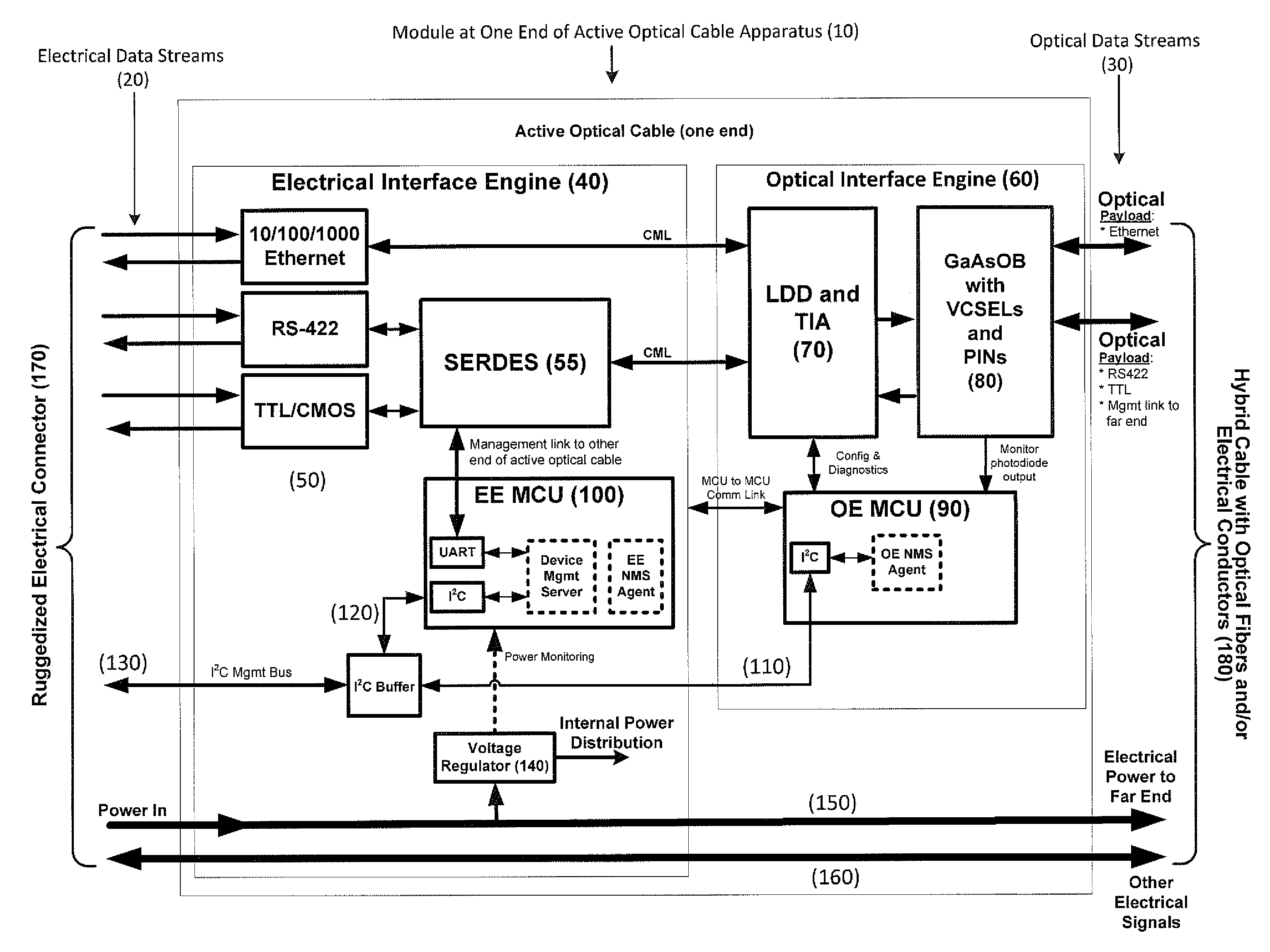

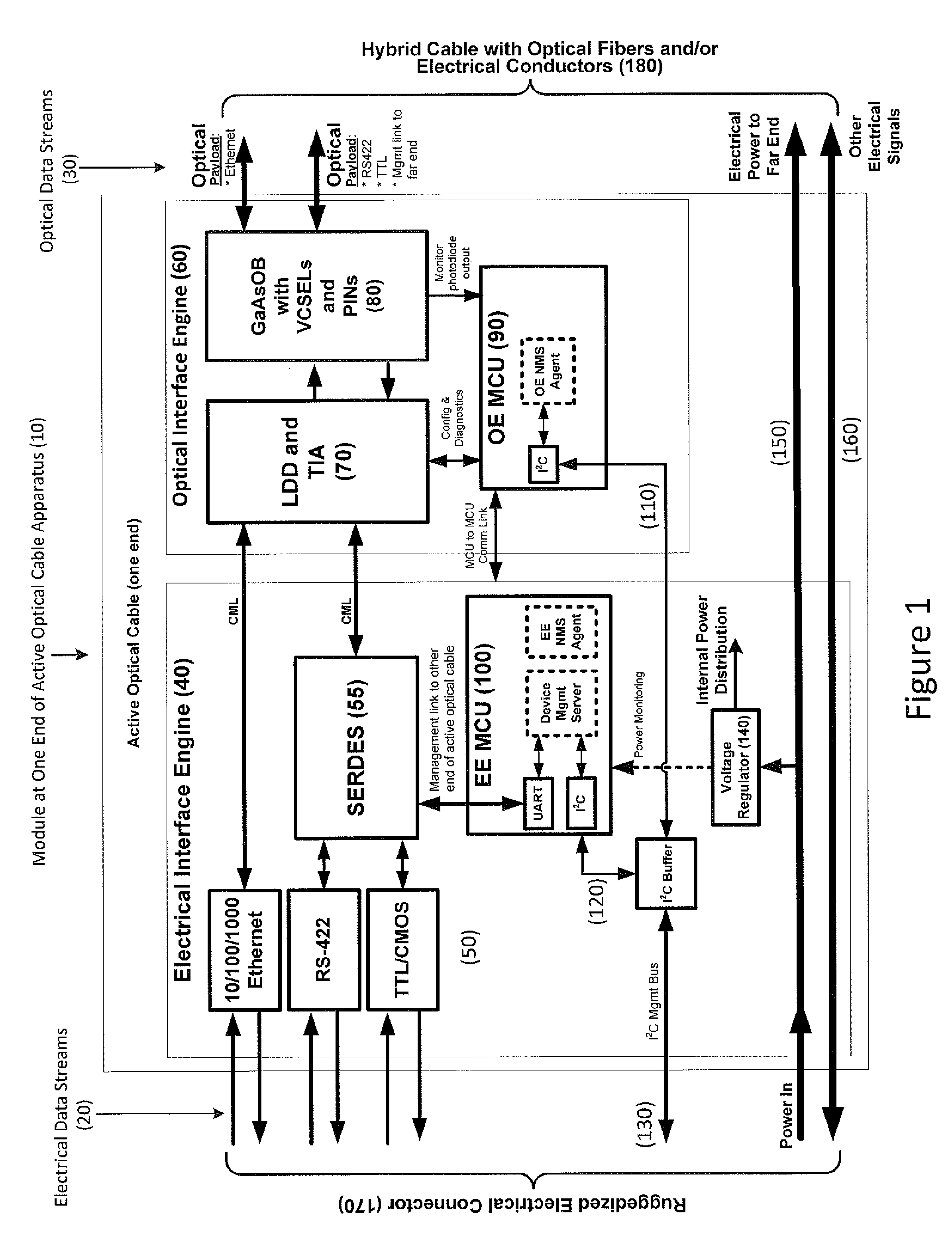

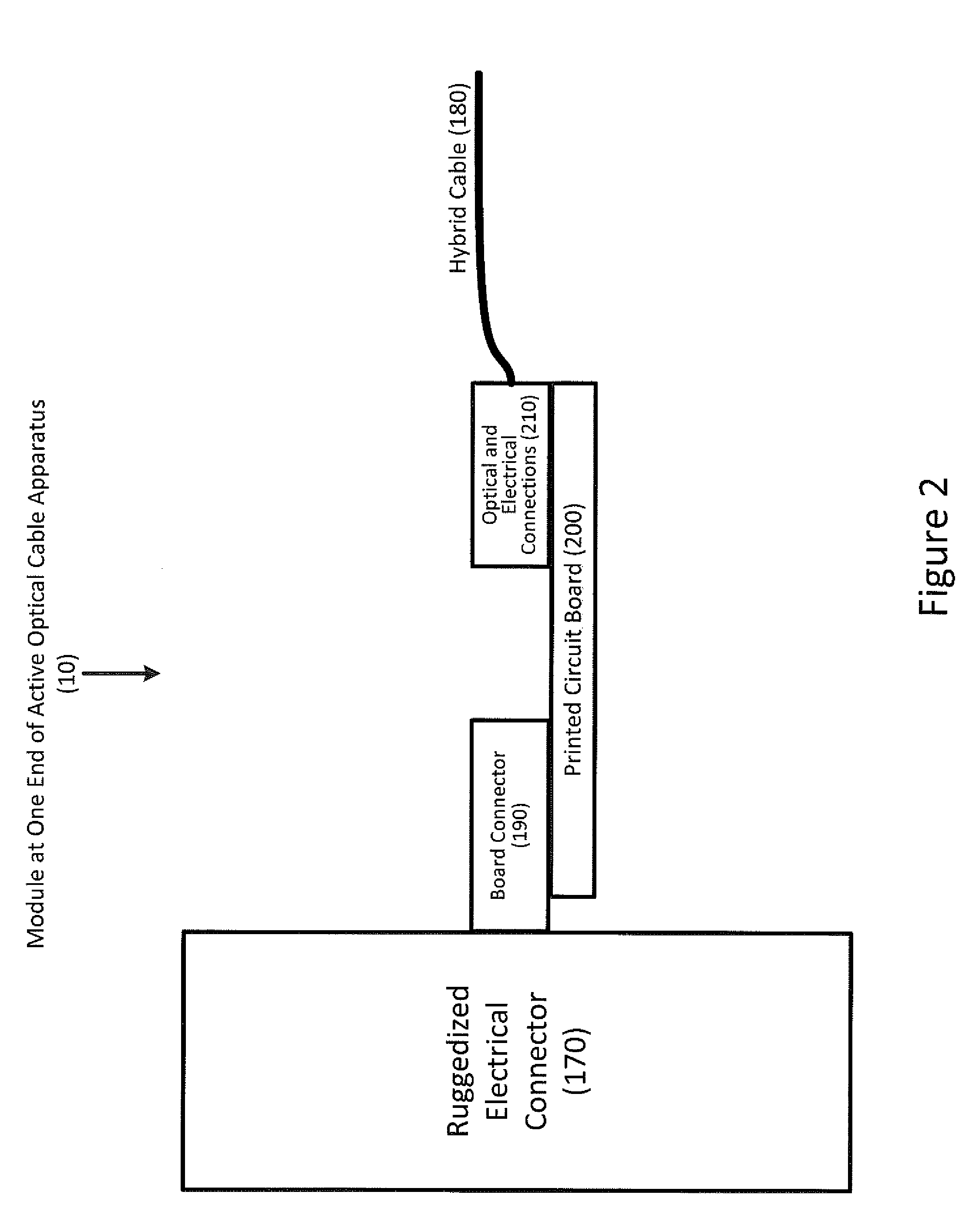

Apparatus for modular implementation of multi-function active optical cables

ActiveUS20140186023A1Protect connectionImprove linearityTransmission monitoringTransmission monitoring/testing/fault-measurement systemsLow noiseElectromagnetic pulse

Apparatus enabling modular implementation of active optical cable (AOC) with multiple integrated functions including: integration of different types of data on the AOC via media conversion; distribution of electrical power over the AOC; electrical multiplexing data channels for optical fibers; integration of voltage regulators enabling AOC operation at different supply voltages; integration of voltage regulators to provide stable, low noise power source; ruggedized, blind-mateable electrical connectors; integration of electronics and optoelectronics inside a connector backshell; implementation of health monitoring and test channel enabling monitoring, test, and control of both ends of the AOC and monitoring and control of upstream systems and components; and enabling a form, fit, function replacement of existing electrical cables to improve SWaP, electromagnetic interference resiliency, length-bandwidth product, electromagnetic pulse resistance, signal integrity, system reliability, testability and maintenance. AOCs are customized for different connectors, pin-outs, electrical data combinations, power distribution and power supplies with minimal redesign / requalification.

Owner:ZEPHYR PHOTONICS

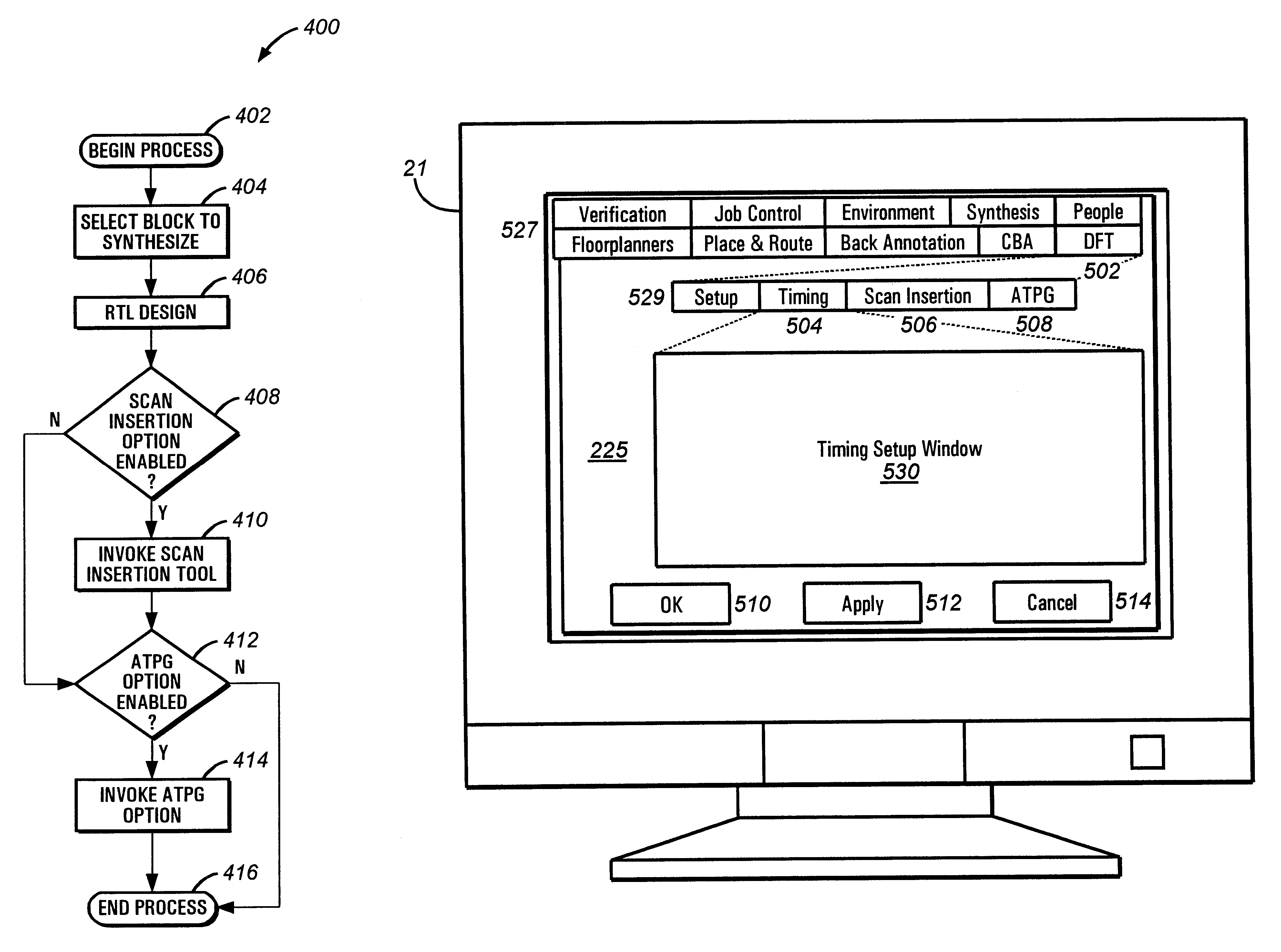

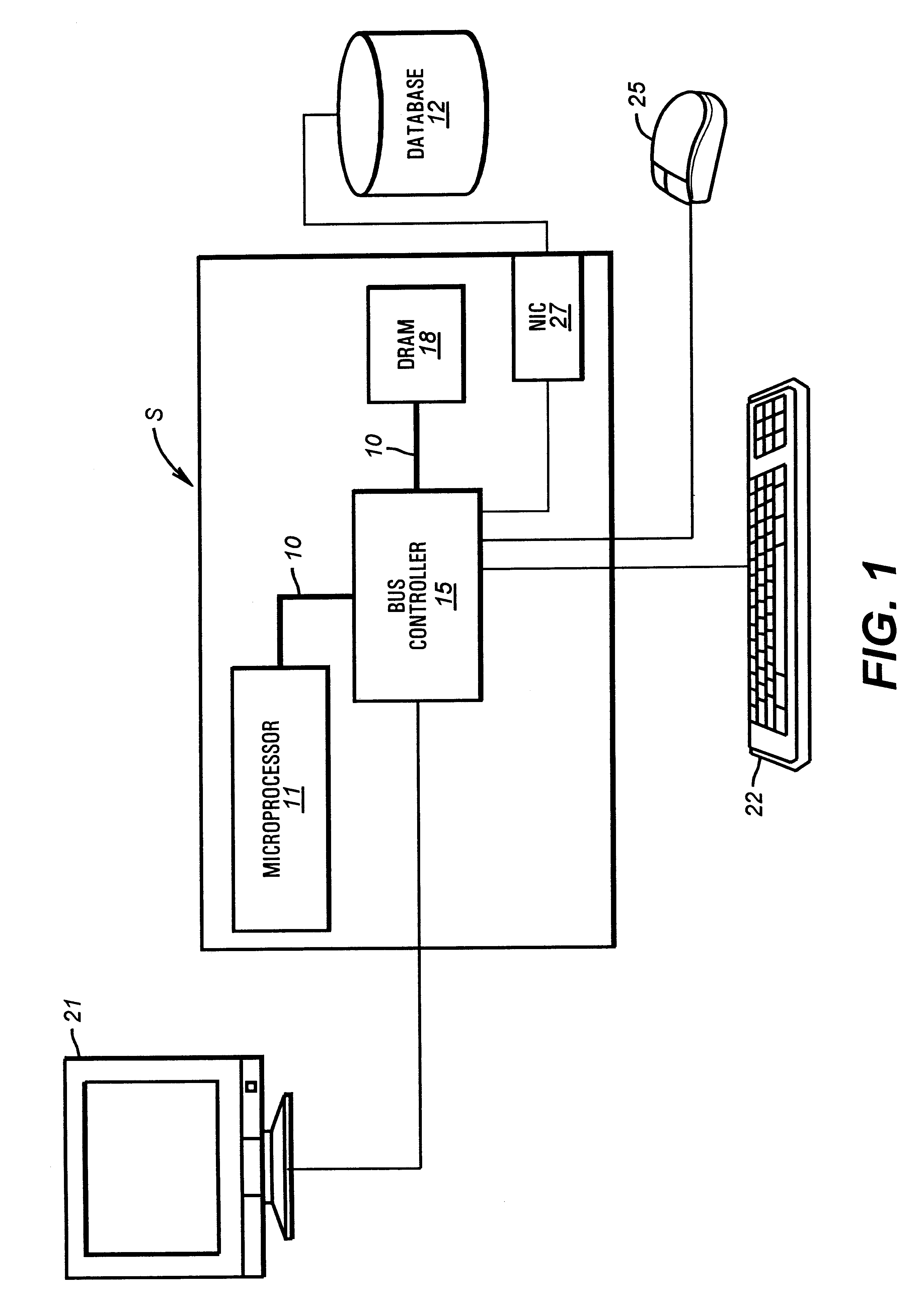

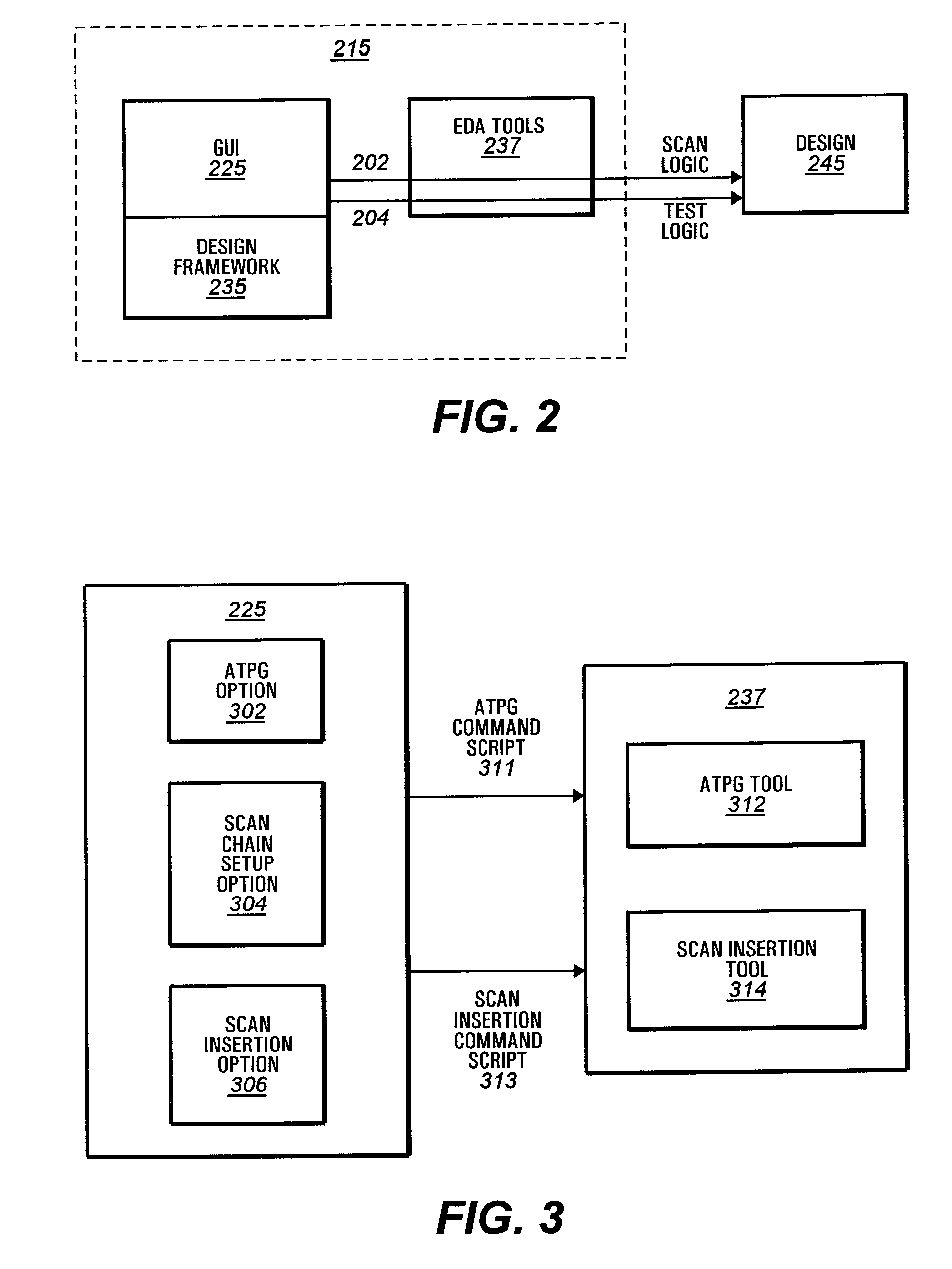

Graphical user interface for testability operation

InactiveUS6341361B1Accurate analysisQuickly and efficiently and accurately testabilityElectronic circuit testingFunctional testingFault coverageGraphics

A graphical user interface (GUI) provides a design engineer the capability of automatically inserting scan logic and test logic into a design. The graphical user interface includes a scan insertion option for a design engineer to invoke a scan insertion tool to check the design for testability. The graphical user interface also permits the design engineer to invoke a test generation tool such as an automatic test pattern generator (ATPG) tool to check the design for fault coverage. The graphical user interface, which can serve as a front end for a design framework, enables a design engineer to efficiently increase testability while still in a design phase.

Owner:ADVANCED MICRO DEVICES INC

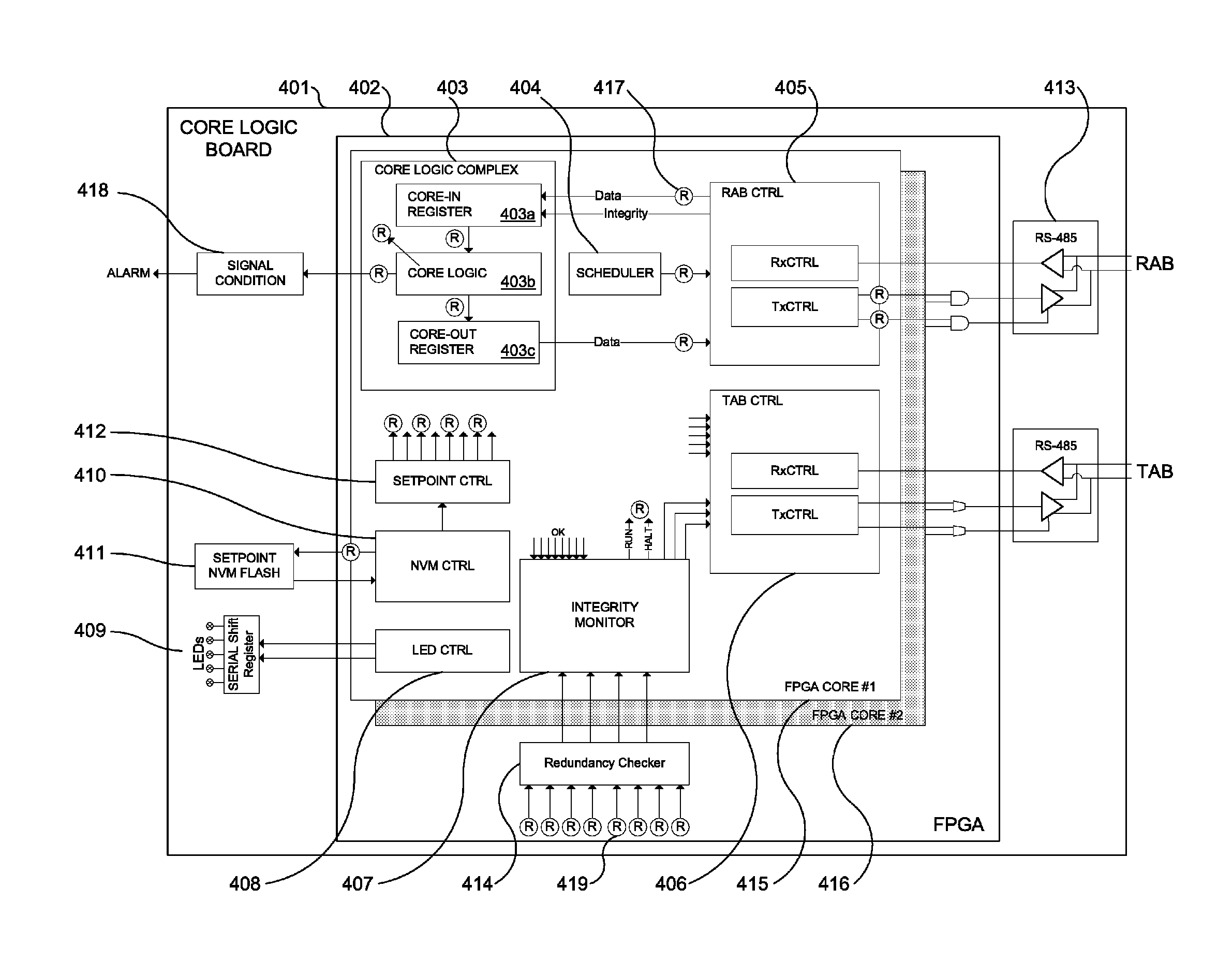

Advanced logic system diagnostics and monitoring

ActiveUS8554953B1Improve reliabilityImprove maintainabilityStethoscopeDiagnostic recording/measuringNuclear plantCommon mode failure

The Advanced Logic System (ALS) is a complete control system architecture, based on a hardware platform rather than a software-based microprocessor system. It is significantly different from other PLC-type control system architectures, by implementing a FPGA in the central control unit. Standard FPGA logic circuits are used rather than a software-based microprocessor which eliminate problems with software based microprocessor systems, such as software common-mode failures. It provides a highly reliable system suitable for safety critical control systems, including nuclear plant protection systems. The system samples process inputs, provides for digital bus communications, applies a control logic function, and provides for controlled outputs. The architecture incorporates advanced features such as diagnostics, testability, and redundancy on multiple levels. It additionally provides significant improvements in failure detection, isolation, and mitigation for the highest level of integrity and reliability.

Owner:WESTINGHOUSE ELECTRIC CORP

Advanced logic system

ActiveUS8156251B1Improve reliabilityImprove maintainabilityProgramme controlTesting/monitoring control systemsNuclear plantCommon mode failure

The Advanced Logic System (ALS) is a complete control system architecture, based on a hardware platform rather than a software-based microprocessor system. It is significantly different from other PLC-type control system architectures, by implementing a FPGA in the central control unit. Standard FPGA logic circuits are used rather than a software-based microprocessor which eliminate problems with software based microprocessor systems, such as software common-mode failures. It provides a highly reliable system suitable for safety critical control systems, including nuclear plant protection systems. The system samples process inputs, provides for digital bus communications, applies a control logic function, and provides for controlled outputs. The architecture incorporates advanced features such as diagnostics, testability, and redundancy on multiple levels. It additionally provides significant improvements in failure detection, isolation, and mitigation for the highest level of integrity and reliability.

Owner:WESTINGHOUSE ELECTRIC CORP

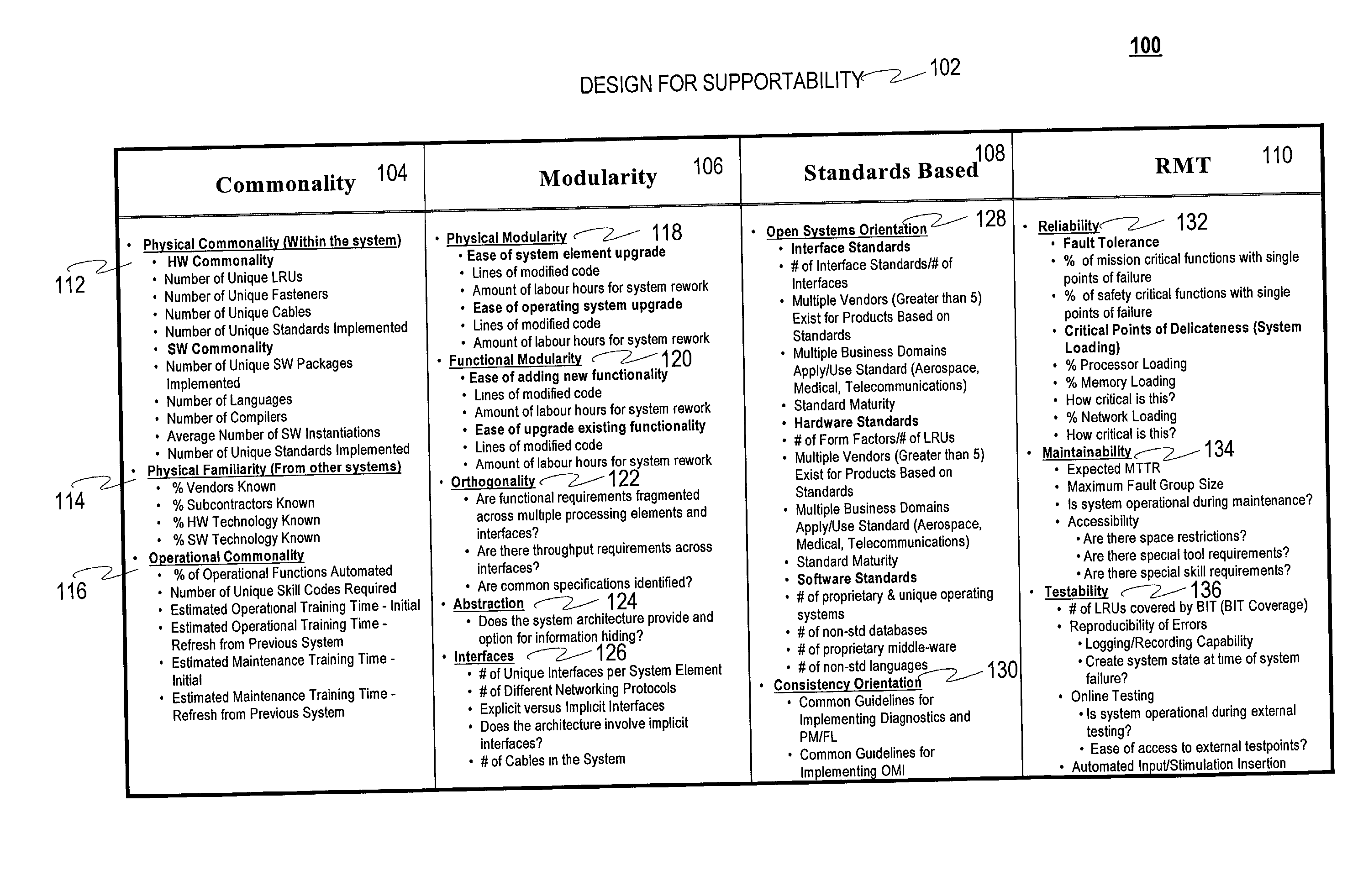

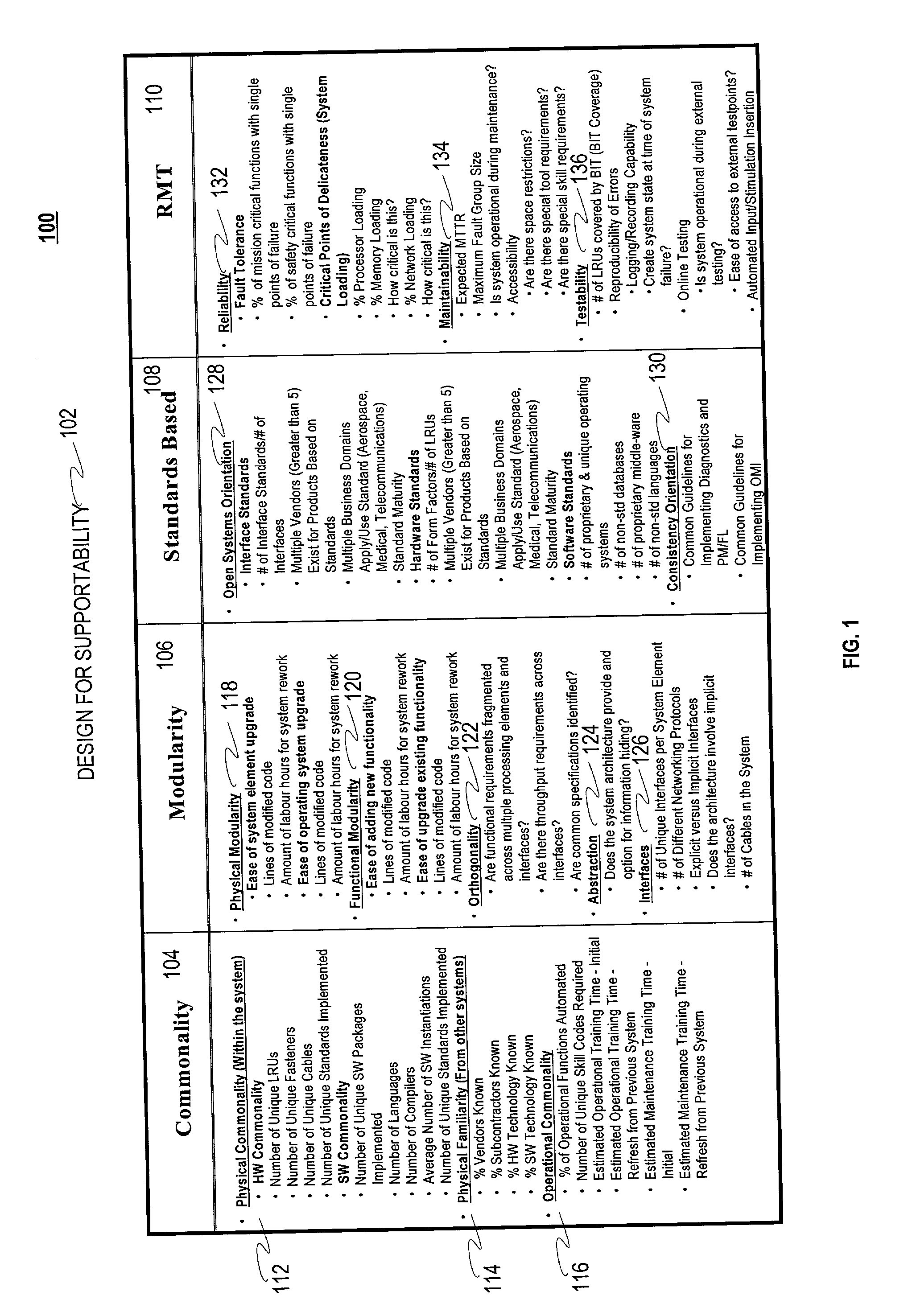

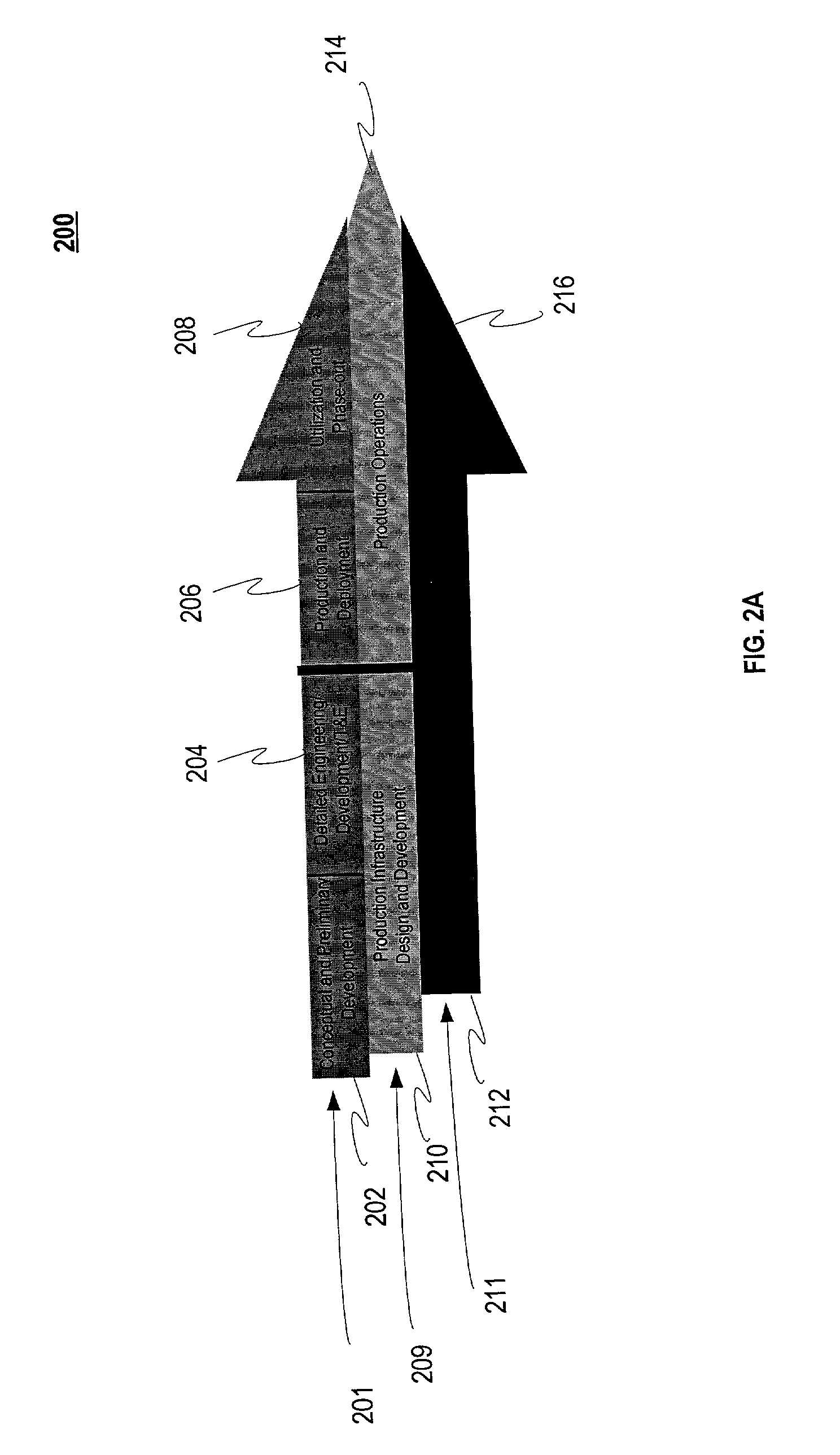

Supportability evaluation of system architectures

InactiveUS20020049571A1Office automationComputer aided designCustomer requirementsSystem architecture design

A system, method and computer program product is disclosed for evaluating system architectures from a long term sustainability perspective, sustainability in the presence of rapidly evolving information and networking technology, rapidly evolving customer requirements and expectations, and rapidly evolving standards and protocols. The multi-attribute architecture evaluation method can include specific architectural characteristics. At the top level the present invention can include four architectural characteristics or attributes: modularity, commonality, standards-based, and reliability / maintainability / testability (RMT). The attributes can be further classified into sub-attributes and metrics to facilitate the comparative evaluation of candidate system architectures. In an exemplary embodiment of the present invention a decision support system, method and CPP for evaluating supportability of alternative system architecture designs is disclosed including: an analytic hierarchy process (AHP) model including a plurality of attributes, wherein the plurality of attributes includes: a commonality attribute; a modularity sub-attribute; a standards based sub-attribute; and a RMT sub-attribute. The present invention in an exemplary implementation can be embedded within a commercially available AHP shell, to facilitate adaptation to specific domains.

Owner:LOCKHEED MARTIN NAVAL ELECTRONICS & SURVEILLANCE

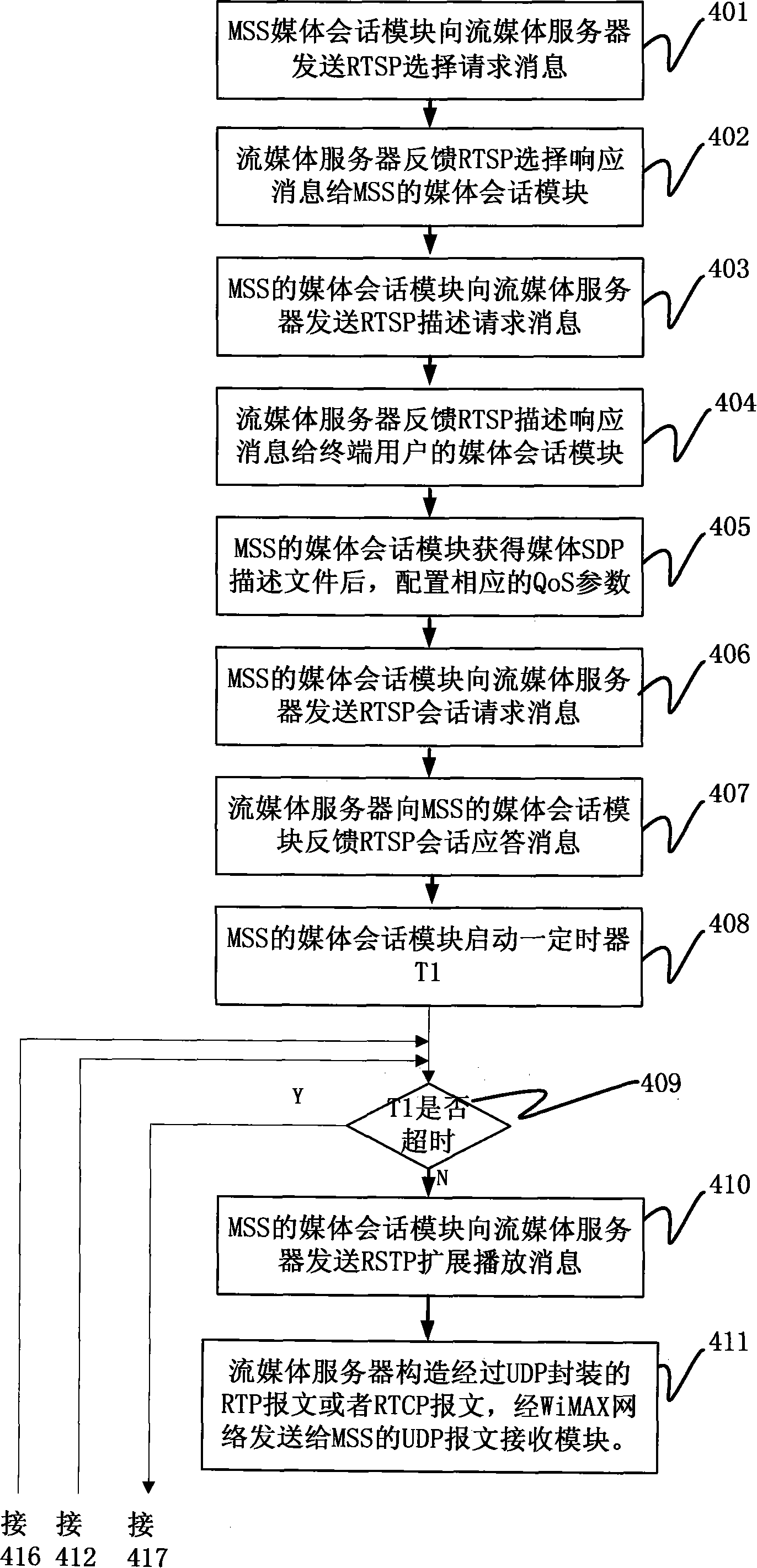

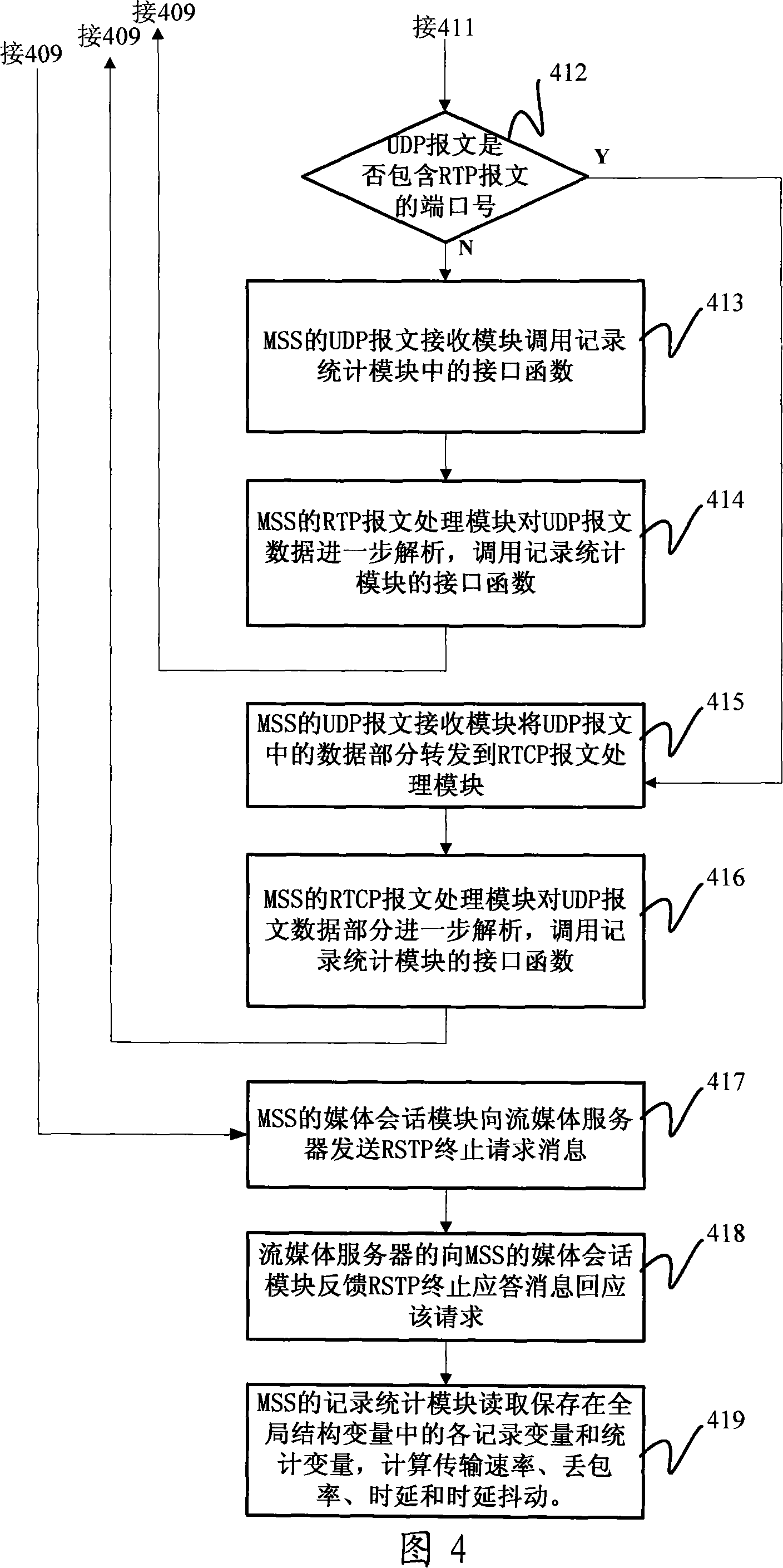

A terminal and method for testing real time service transmission performance of WiMAX network

InactiveCN101150763AImprove testabilityImprove analyzabilityError preventionNetwork topologiesNetwork connectionTime delays

The invention discloses a method for testing realtime service transmission performance of the WiMAX network, belongs to the wireless broadband access field. In the method, a mobile terminal establishes RTSP media session connection with a streaming media server; the streaming media server receives a session request according to the mobile terminal, determins corresponding coding speed, encapsulates realtime UDP messages, then sends to the mobile terminal through the WiMAX network, the mobile terminal analyzes received UDP messages; when the network connection is time-out, the mobile terminal stops the RTSP media session connection with the streaming media server, calculates performance indexes of the transmission rate, the packet loss rate, time delay and the time delay jitter according to the analysis result of the UDP messages. The invention also discoses a terminal for testing realtime service transmission performance of the WiMAX network. The invention acquires performance indexes such as the transmission rate, the packet loss rate, time delay and the time delay jitter, etc., under different Qos allocation, improves testability and analyzability.

Owner:ZTE CORP

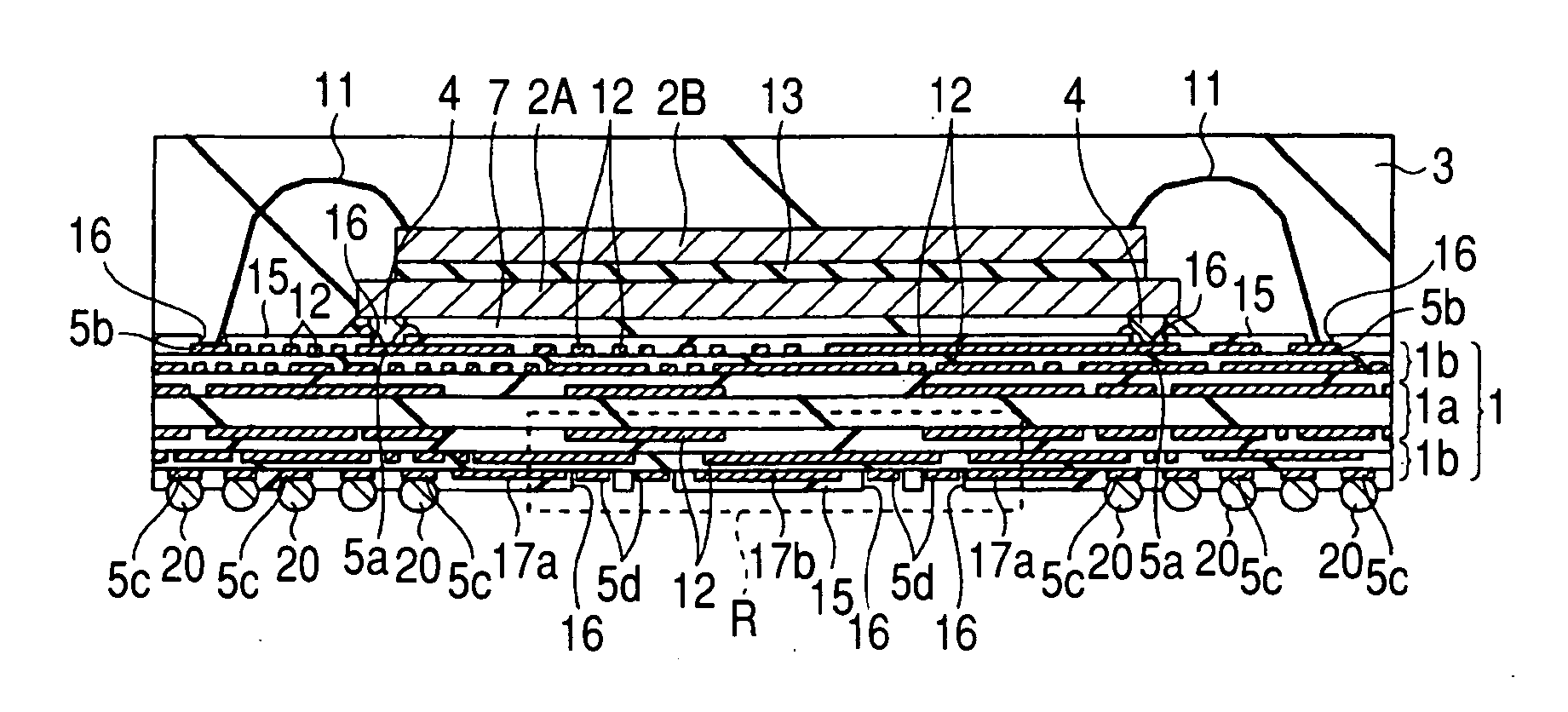

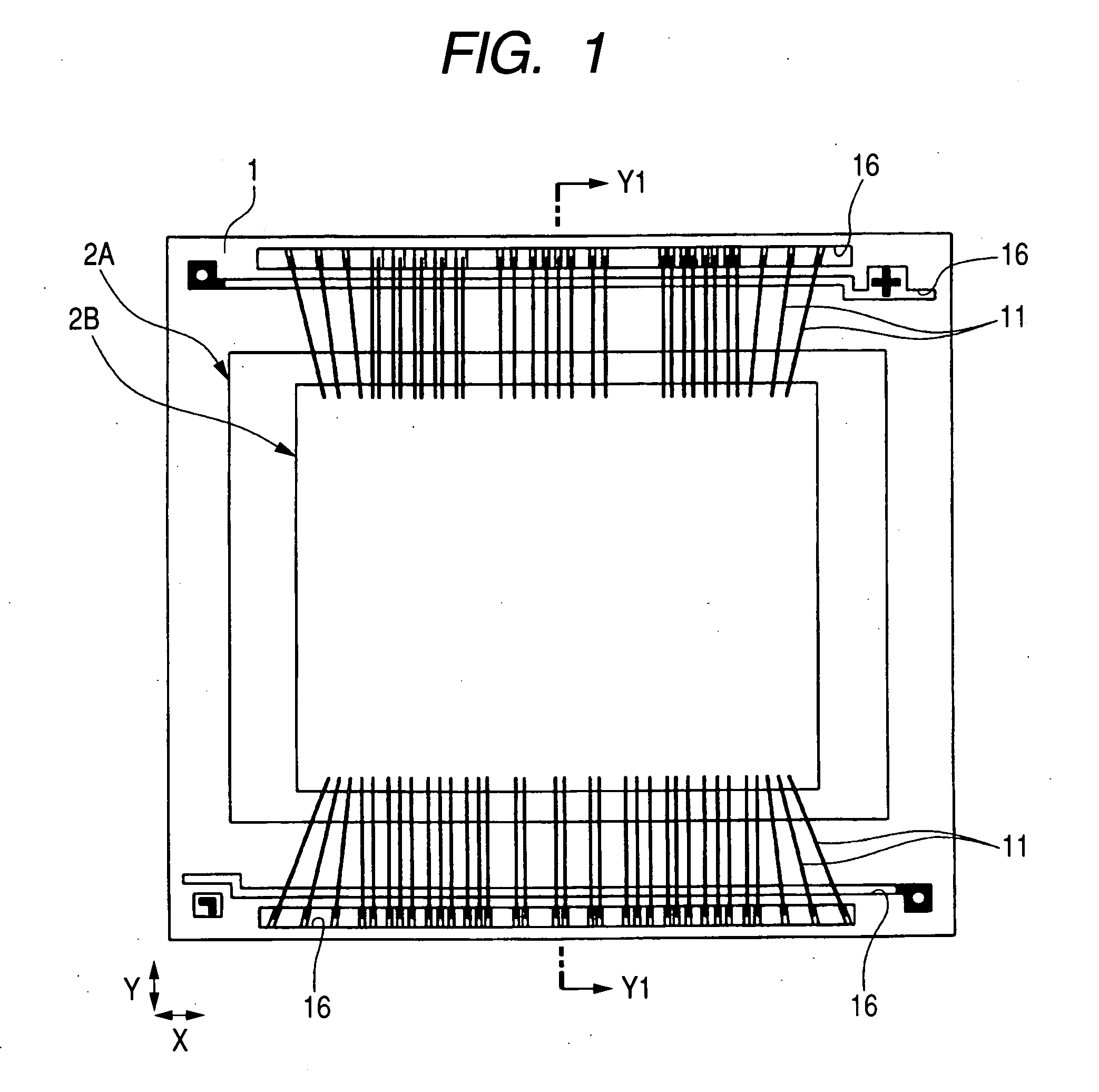

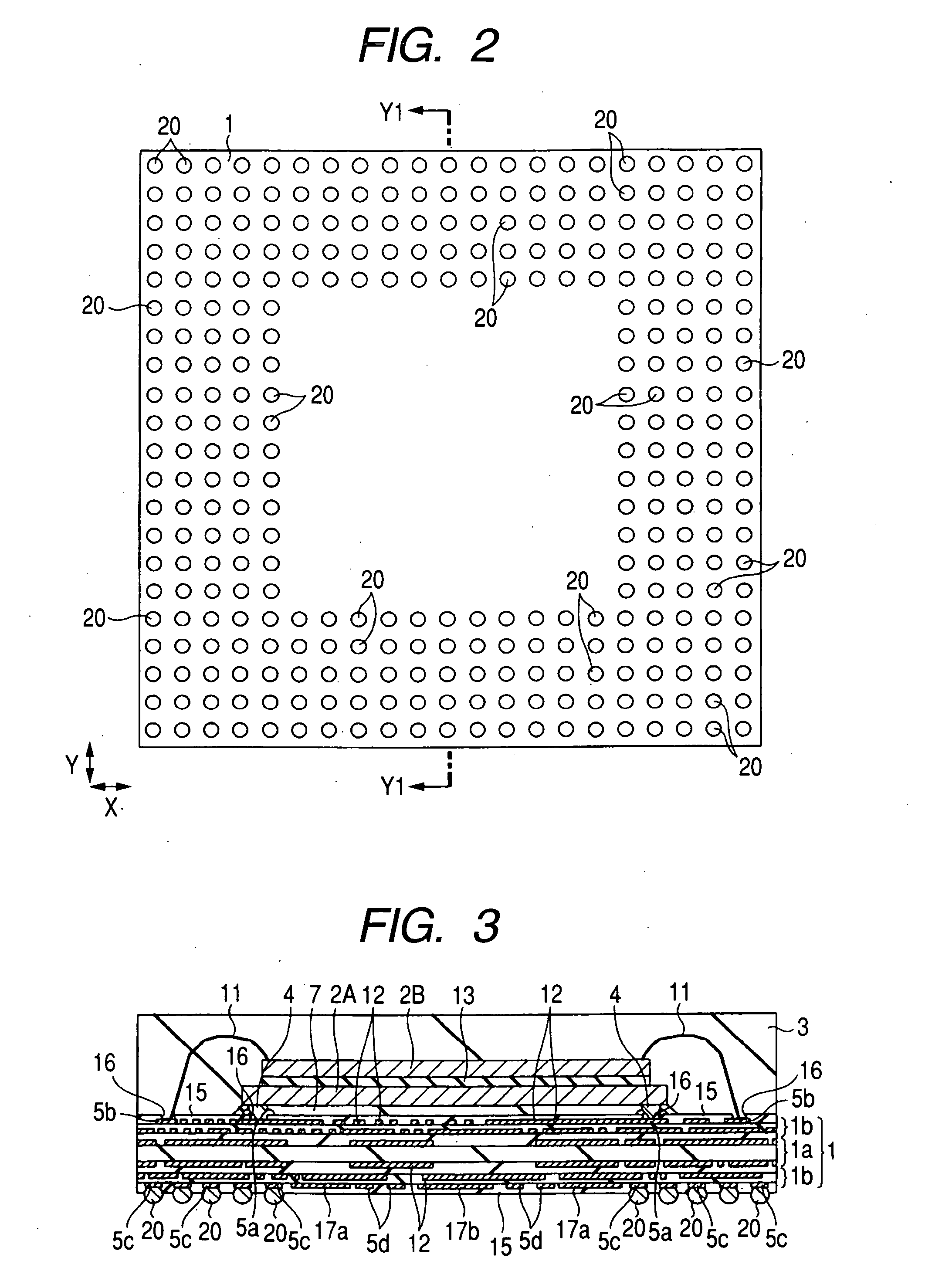

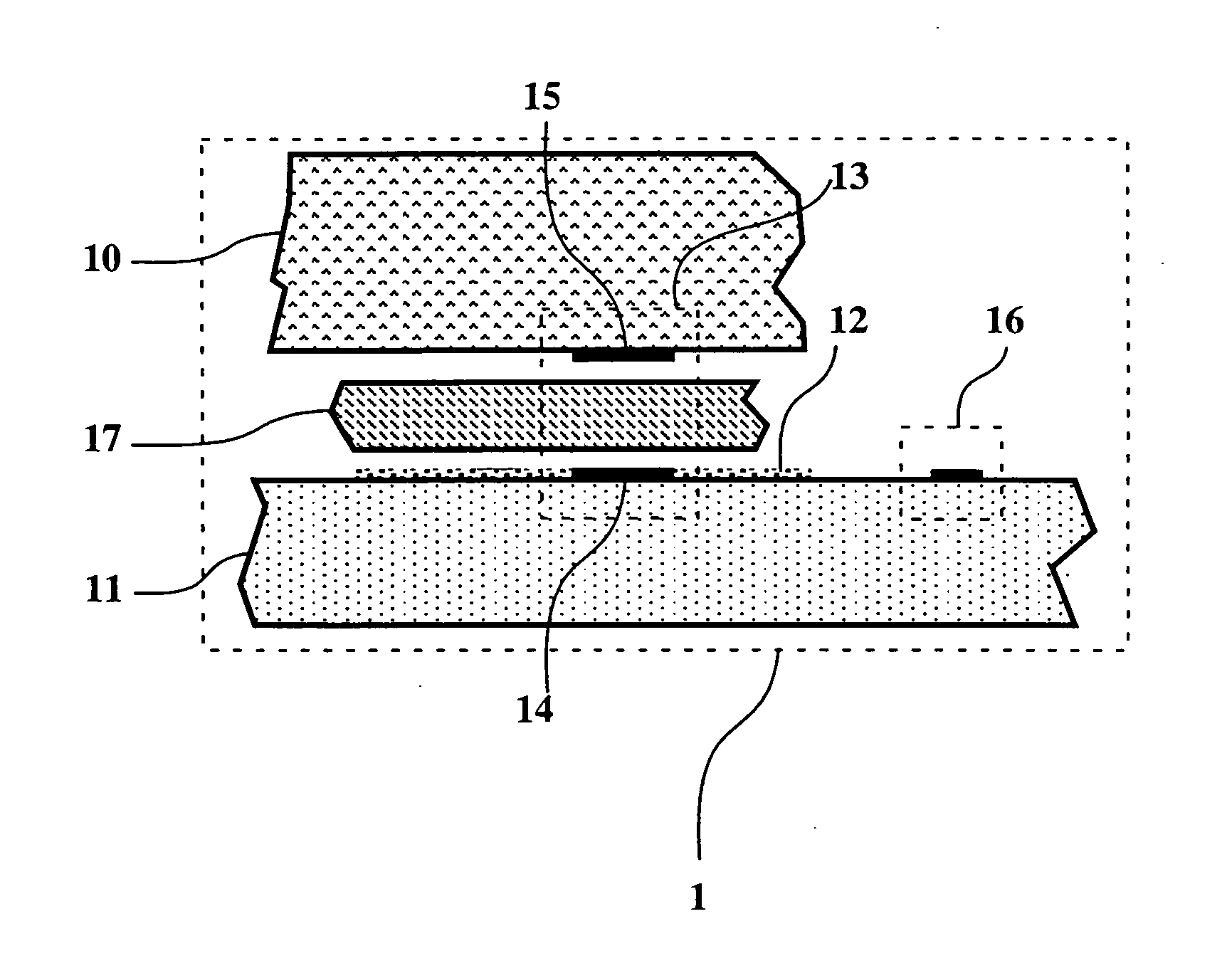

Semiconductor device

ActiveUS20060060959A1Reduce outline sizeSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor chipEngineering

There is disclosed a semiconductor device having first and second semiconductor chips. The first semiconductor chip has a memory circuit. The second semiconductor chip has a circuit controlling the memory circuit. The contour size of the semiconductor device is reduced down to a smaller size required by a client without impairing the testability of the first semiconductor chip having the memory circuit. The circuit controlling the memory circuit consists of an MPU. The memory circuit consists of an SDRAM. The two semiconductor chips are stacked on top of each other over the top surface of an interconnect substrate. The chips are sealed in a molding resin, thus forming an SiP (System-in-Package). First terminals electrically connected with the second chip are arranged as external terminals of the SiP on the outer periphery of the bottom surface of the interconnect substrate. Plural second electrodes electrically connected with interconnects, which electrically connect the two chips, are mounted as terminals for testing of the SDRAM. The second electrodes are located more inwardly than the innermost row of the first external electrodes on the bottom surface of the interconnect substrate.

Owner:RENESAS ELECTRONICS CORP

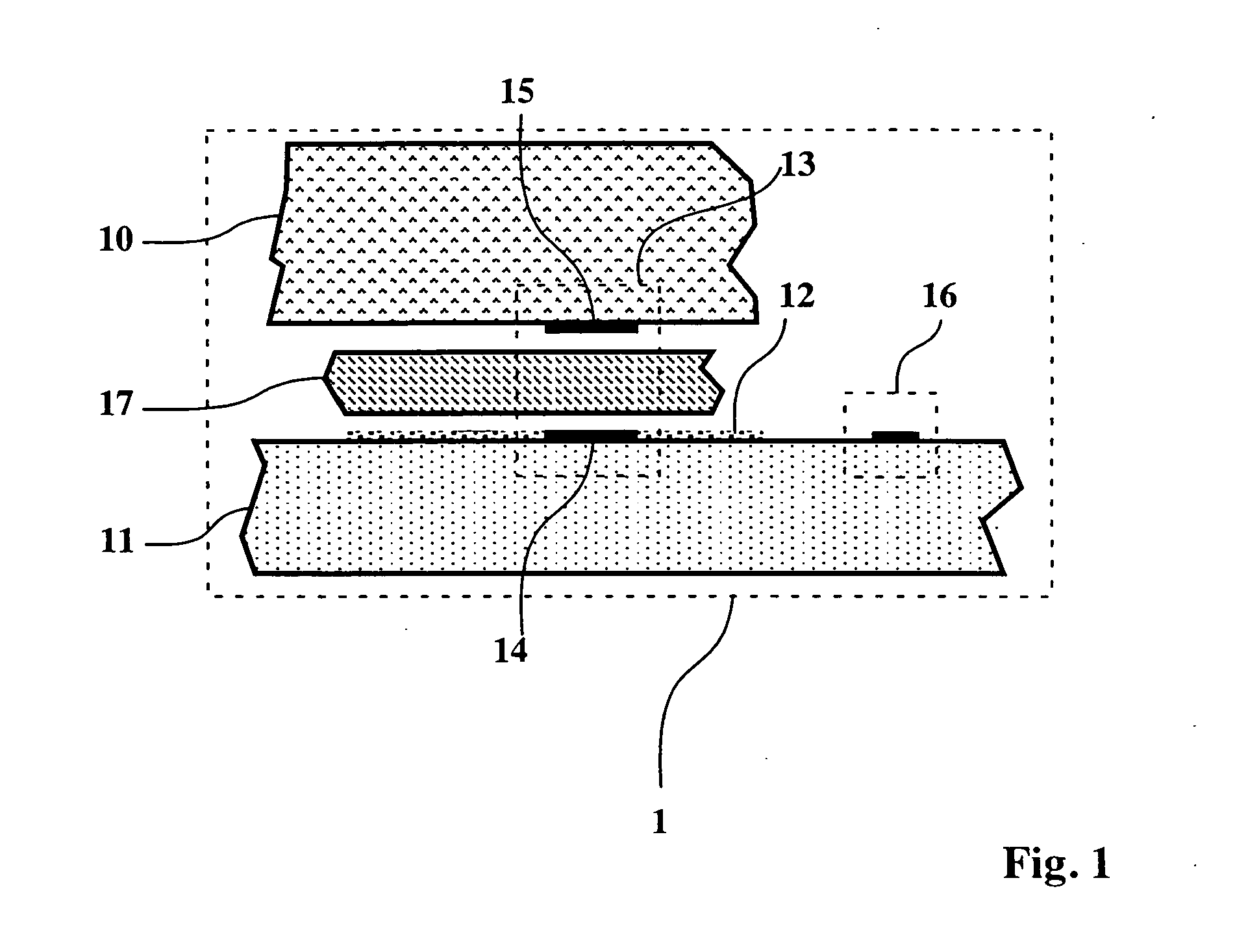

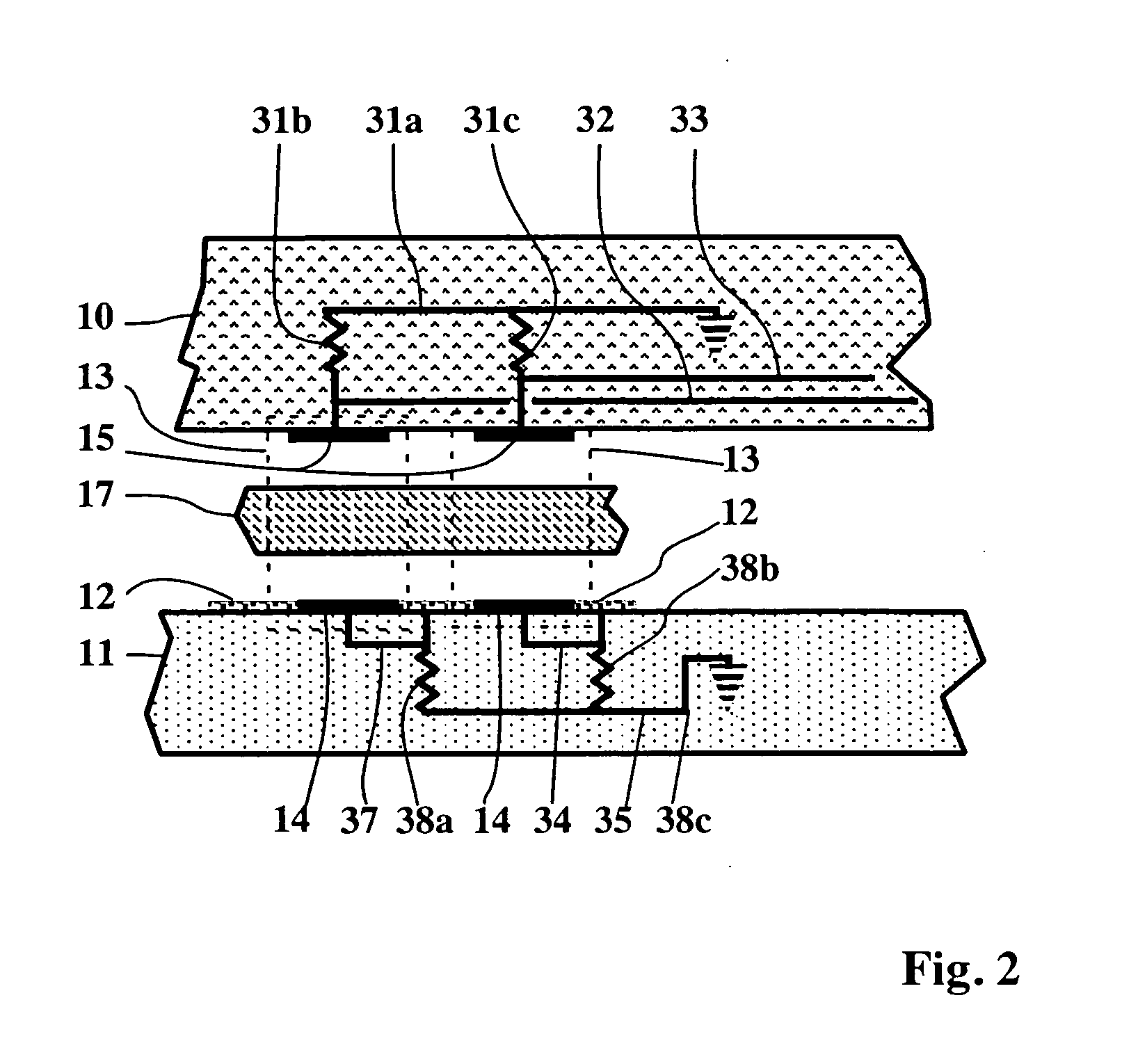

Method and apparatus for non-conductively interconnecting integrated circuits

InactiveUS20050002448A1Low costReduce turnaround timeMultiple-port networksSemiconductor/solid-state device testing/measurementElectronic systemsModularity

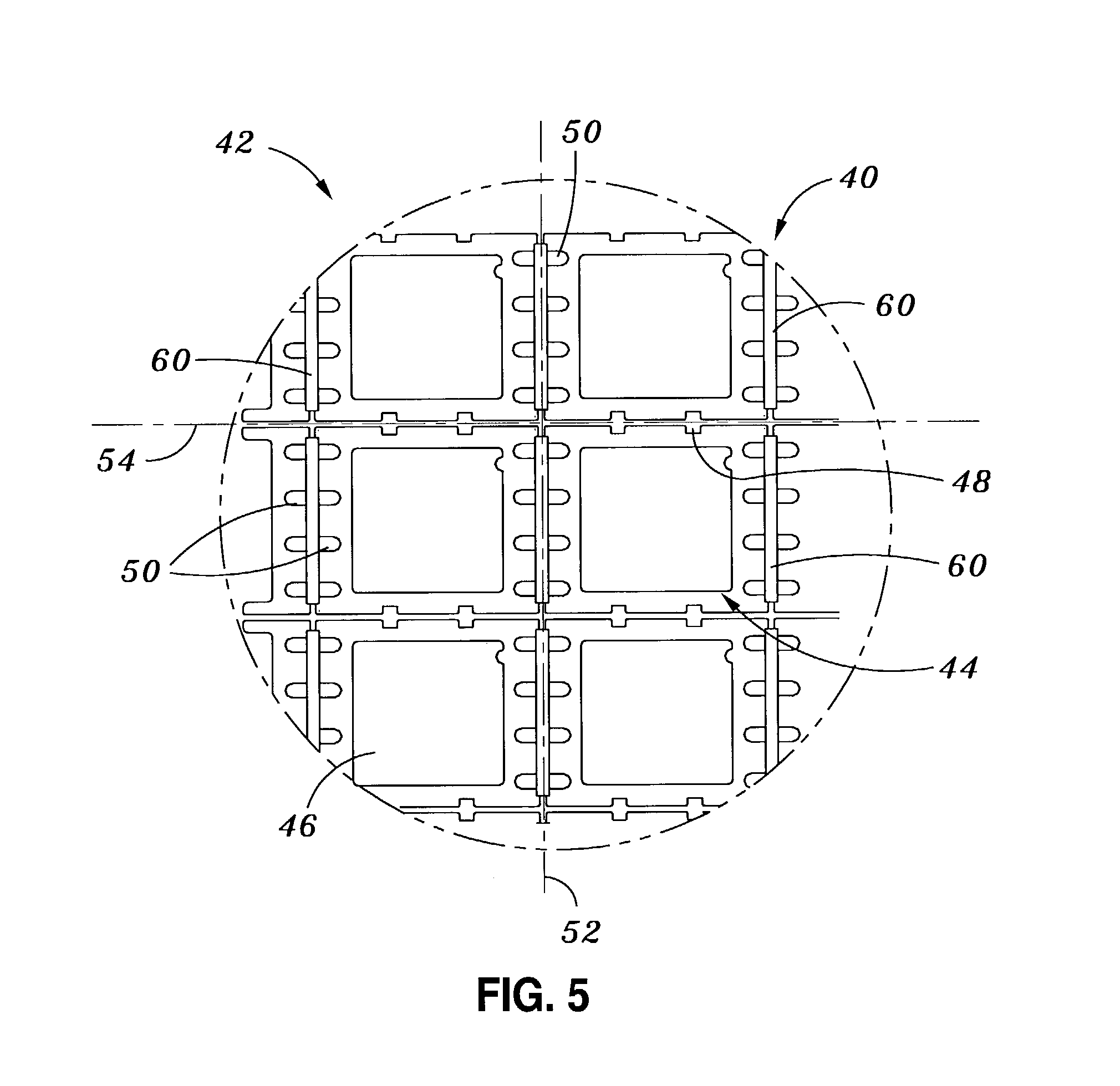

A method and apparatus for constructing, repairing and operating modular electronic systems utilizes peripheral half-capacitors (i.e., conductive plates on the outside of the modules) to communicate non-conductively between abutting modules. Such systems provide lower cost, improved testability / repairability and greater density than conventional modular packaging techniques, such as printed circuit boards and multi-chip modules. The non-conductive interconnection technique of the invention can be applied to all levels in the packaging hierarchy, from bare semiconductor dies to complete functional sub-units. Numerous exemplary systems and applications are described.

Owner:SUN MICROSYSTEMS INC

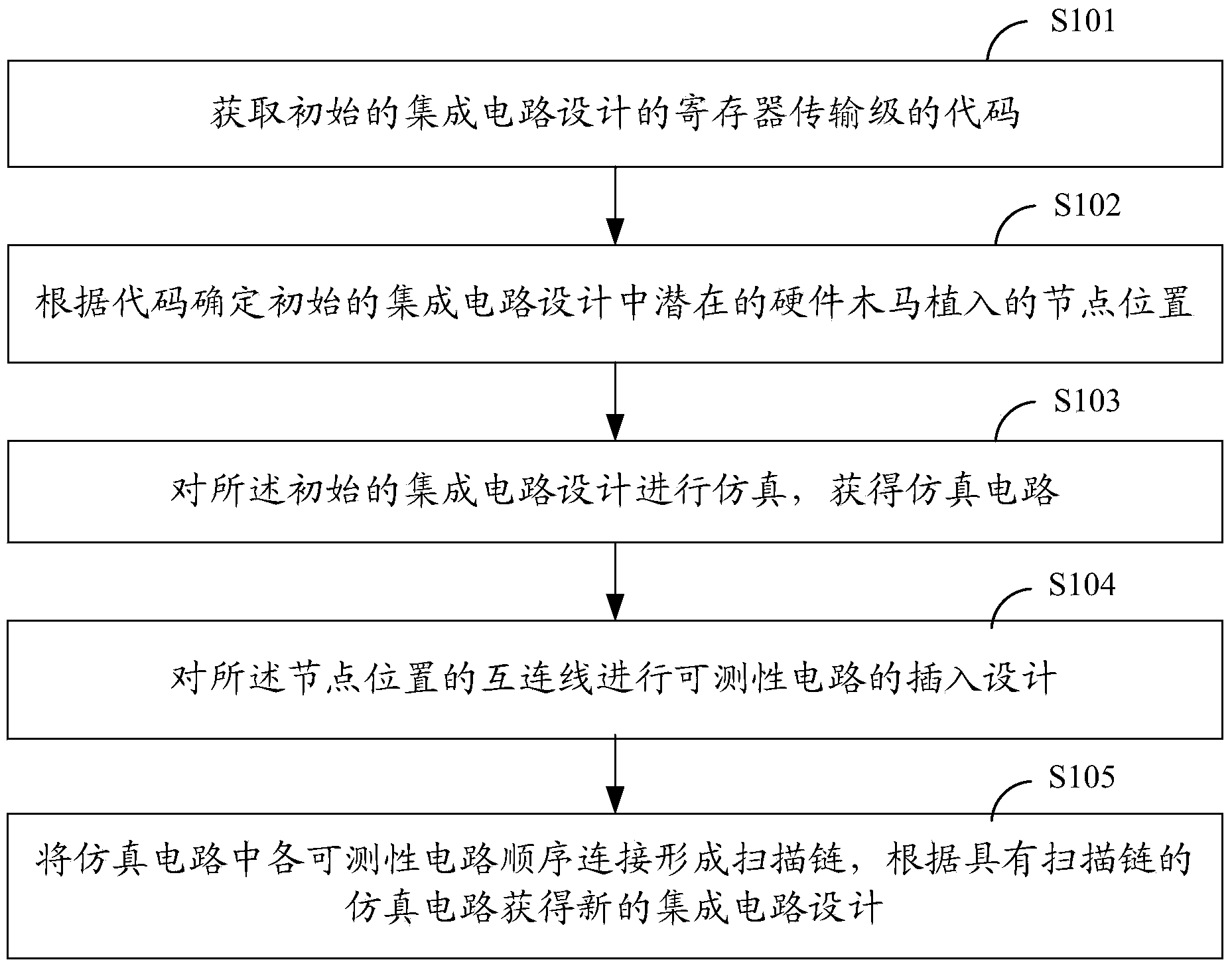

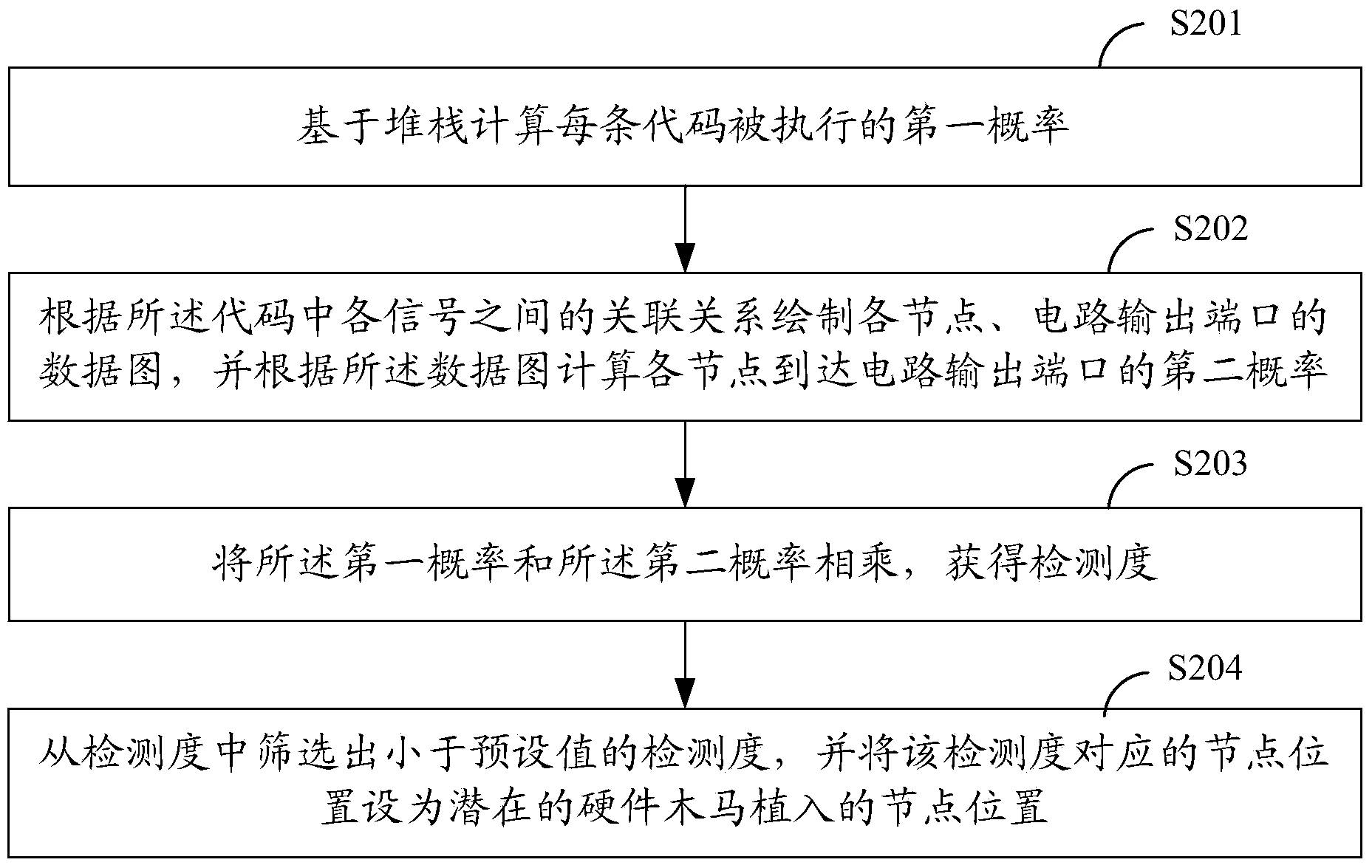

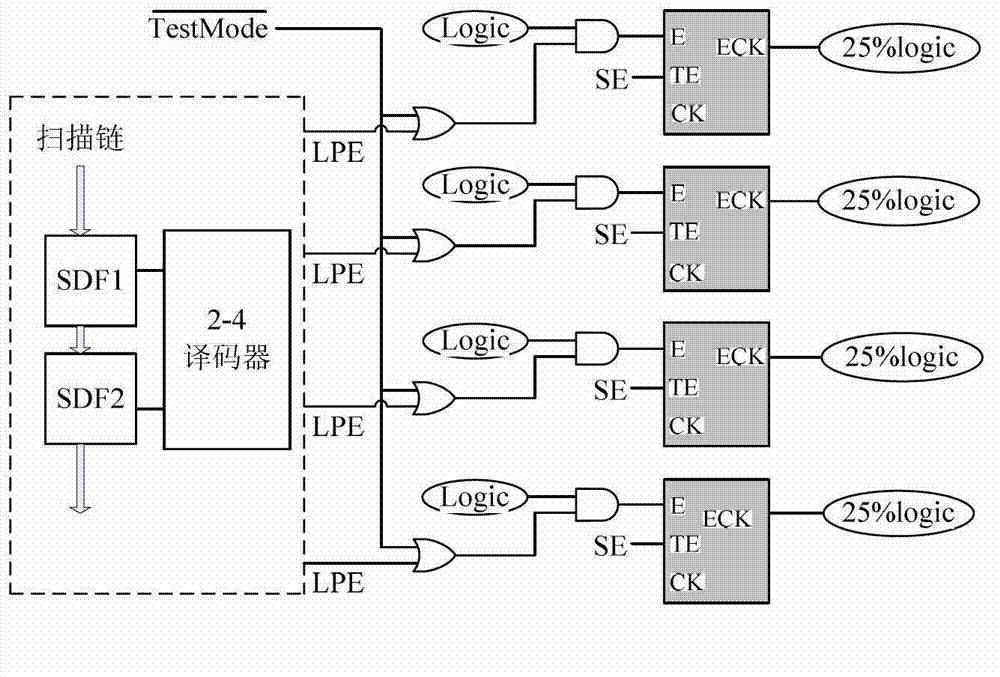

Design method of integrated circuit and hardware trojan detection method

ActiveCN104239616ALow costReduce overheadPlatform integrity maintainanceSpecial data processing applicationsHardware TrojanProcessor register

The invention relates to a design method of an integrated circuit and a hardware trojan detection method. The design method comprises the following steps of acquiring a code of a register transfer level of an initial integrated circuit design; confirming a node position embedded by a potential hardware Trojan in the initial integrated circuit design according to the code; simulating the initial integrated circuit design to obtain a simulating circuit; computing the logic value probability of an interconnection line of the node position in the simulating circuit, and carrying out insertion design of testability circuits on the interconnection line of the node position according to the logic value probability; sequentially connecting the testability circuits in the simulating circuit to form a scan chain, and acquiring a new integrated circuit design according to the simulating circuit with the scan chain, wherein the scan chain is used for detecting the position of the hardware trojan of the integrated circuit according to the input test signals and the output results. According to the integrated circuit designed by the scheme of the invention, the position of the hardware trojan can be found, and the cost is reduced.

Owner:FIFTH ELECTRONICS RES INST OF MINIST OF IND & INFORMATION TECH

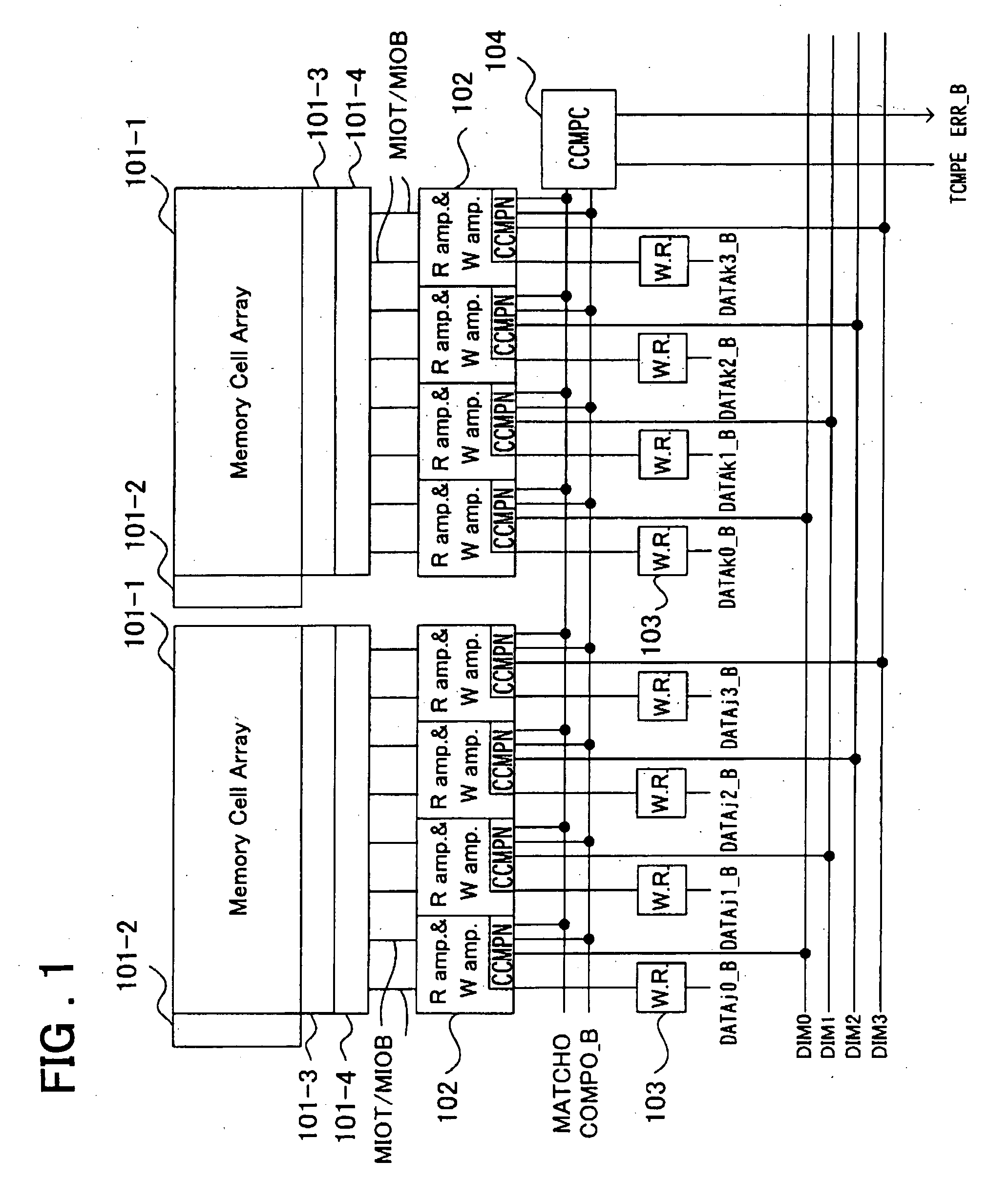

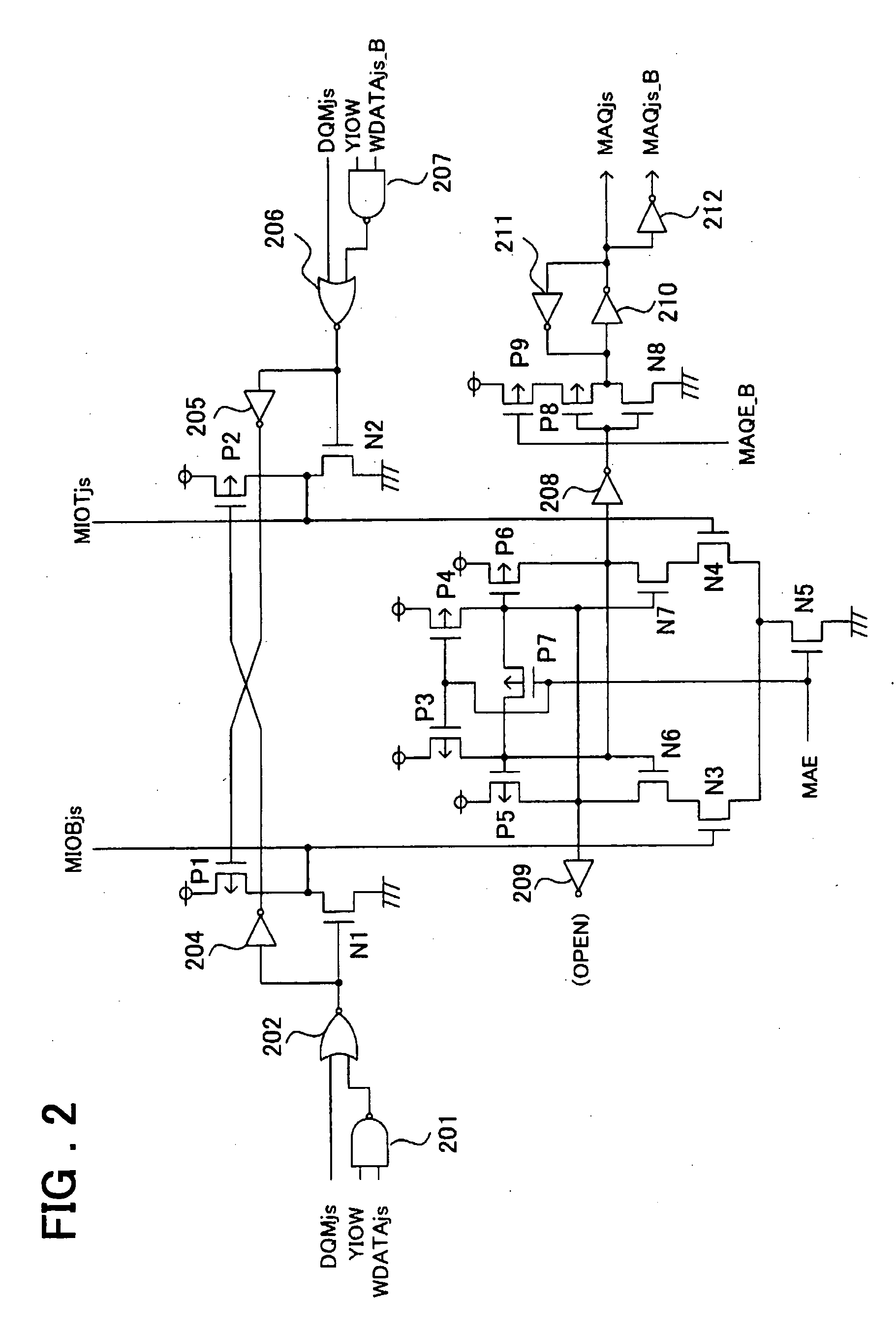

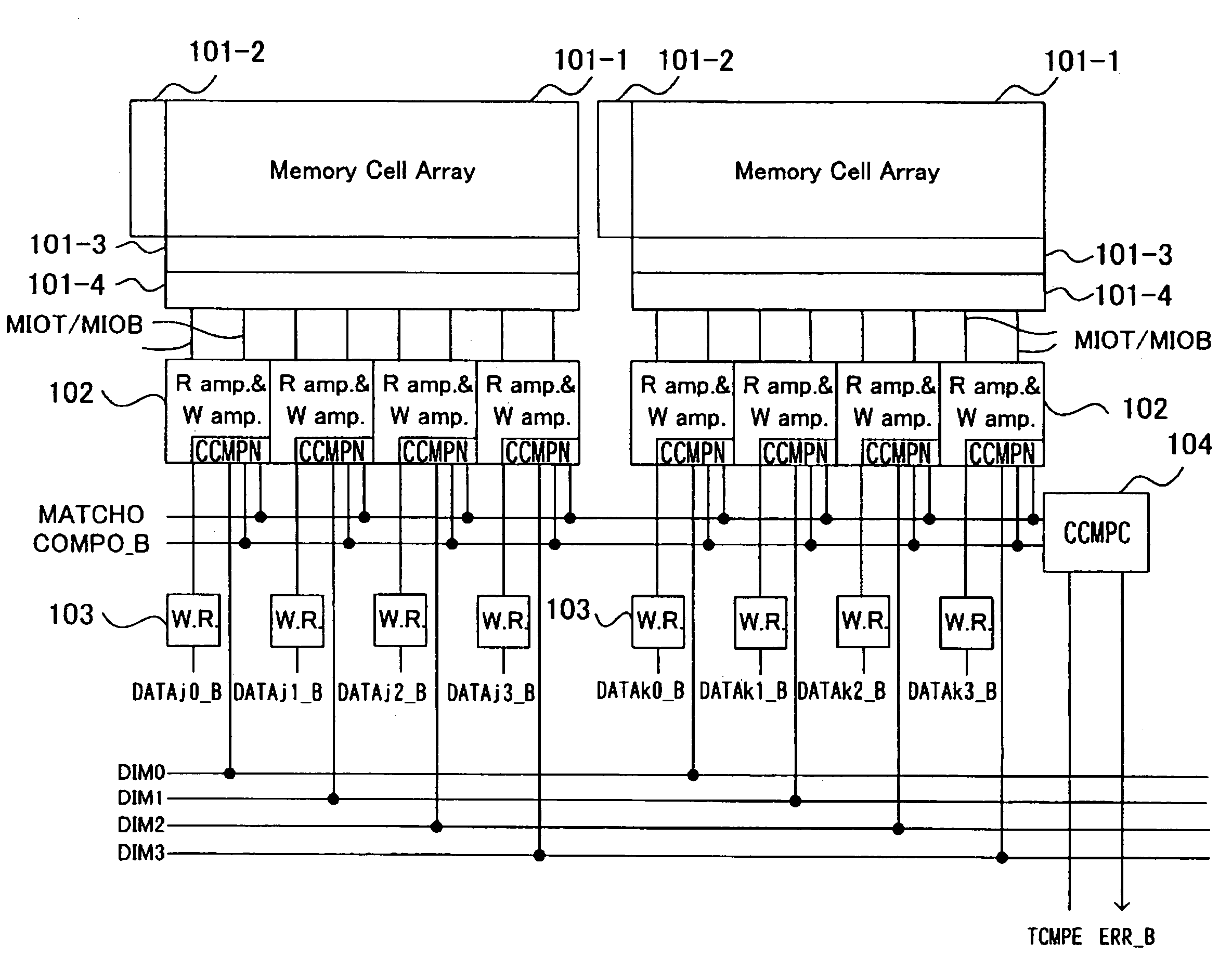

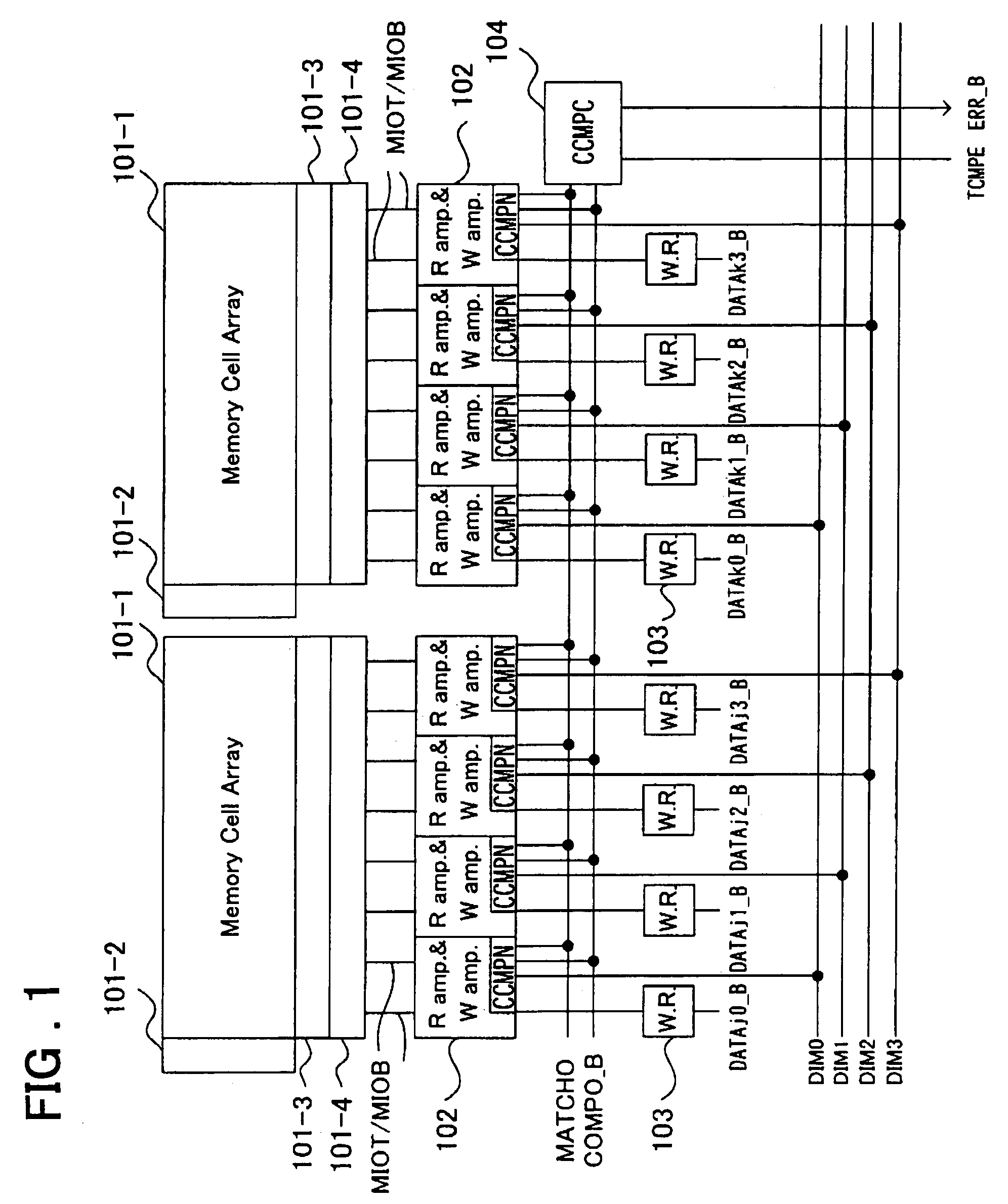

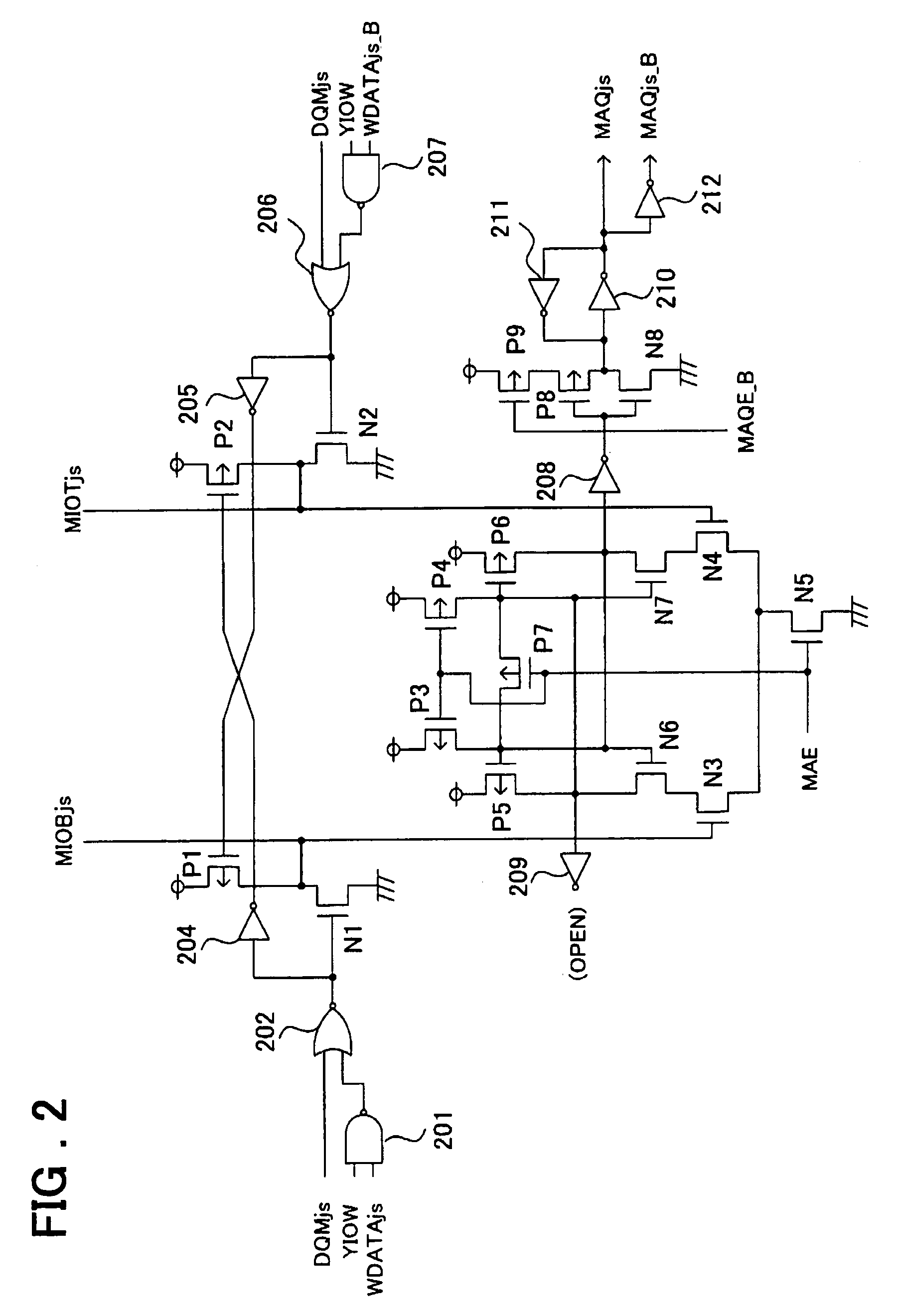

Semiconductor storage device

InactiveUS20040205429A1Improve testabilityFacilitate accommodationElectronic circuit testingDigital storageDecision circuitControl signal

A testing device for a semiconductor storage device which suppresses the increase in the circuit size, provides for facilitated accommodation to a test with frequent changes in the test pattern, and which improves testability of the semiconductor storage device. A plural number of holding circuits (103) are provided holding write data for memory cells of a memory cell array (101-1). The write data from the holding circuits (103) are written in the memory cells of the selected address. A plural number of comparators (CCMPN) are supplied with data read out from the memory cells and with data held by the holding circuits as expectation data to compare the readout data and the expectation data. The non-inverted value or the inverted value of the write data held by the holding circuits (103) is output as the write data to the memory cells and as expectation data to the comparators (CCMPN) depending on the value of the inversion control signal (DIM). A decision circuit (104) is provided which outputs an error flag based on a coincidence detection signal (MATCH0) coupled to the plural comparators.

Owner:LONGITUDE LICENSING LTD

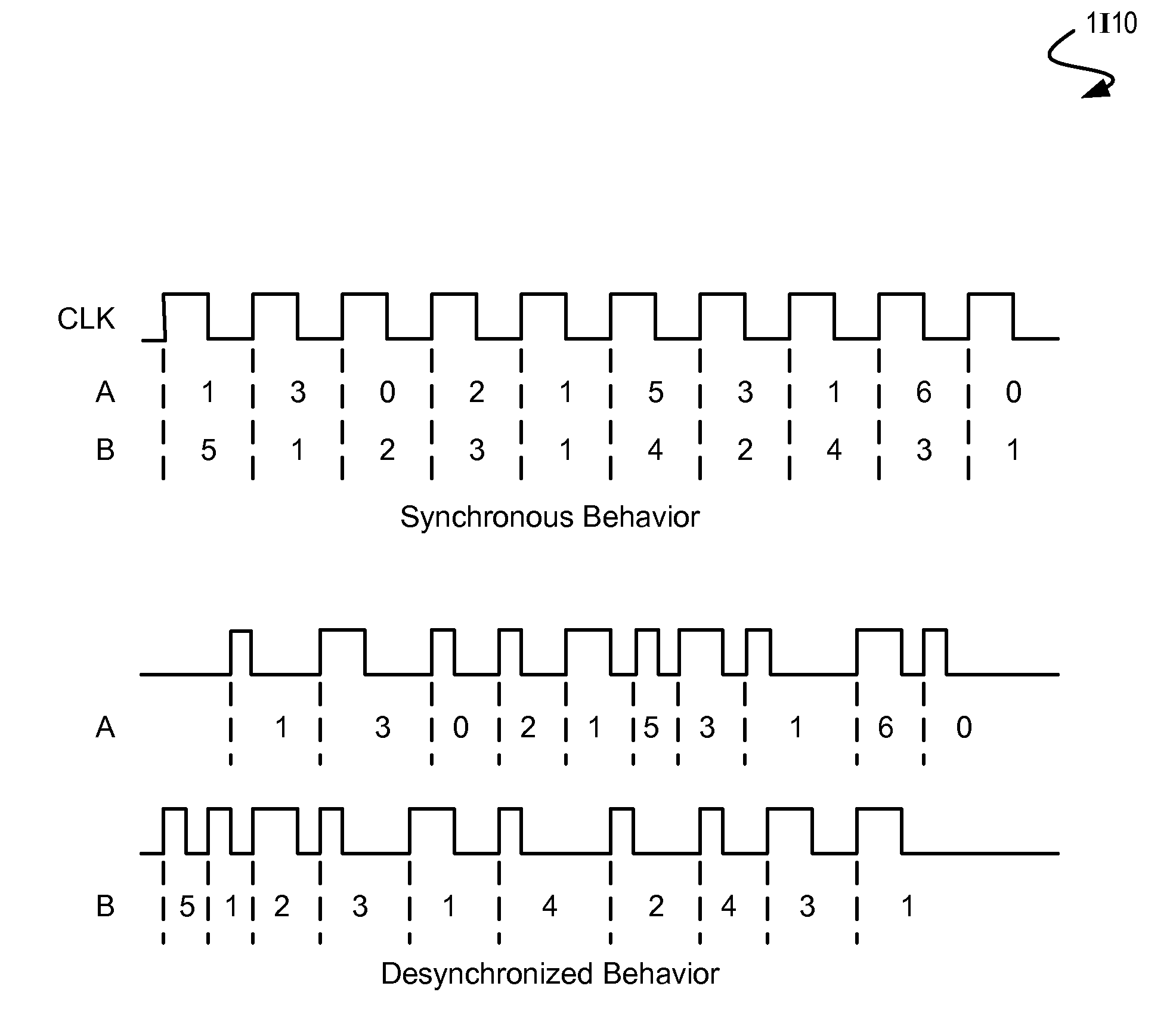

Variability-Aware Asynchronous Scheme for High-Performance Delay Matching

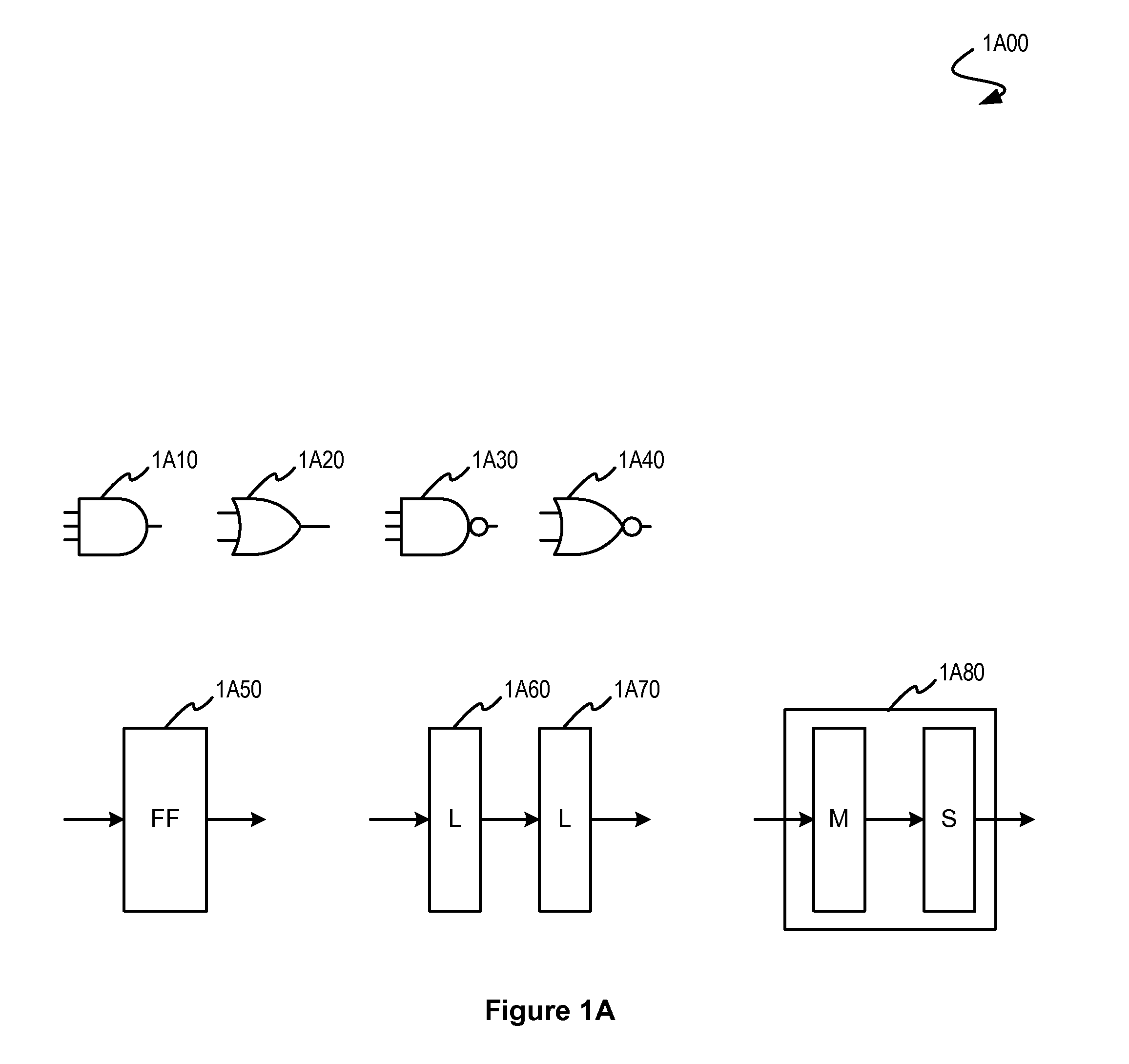

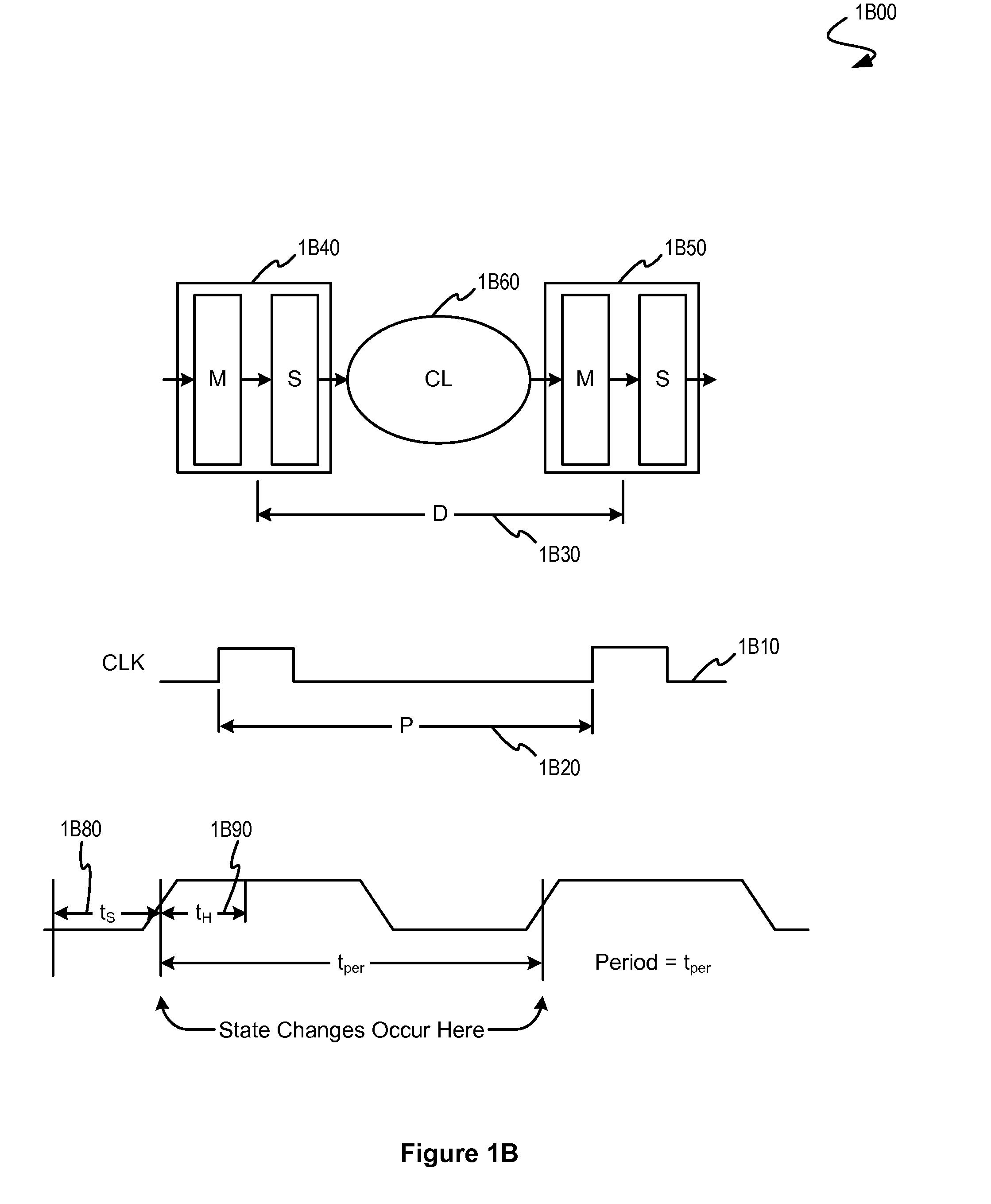

InactiveUS20090119631A1Logic circuits characterised by logic functionPulse automatic controlMathematical modelComputer science

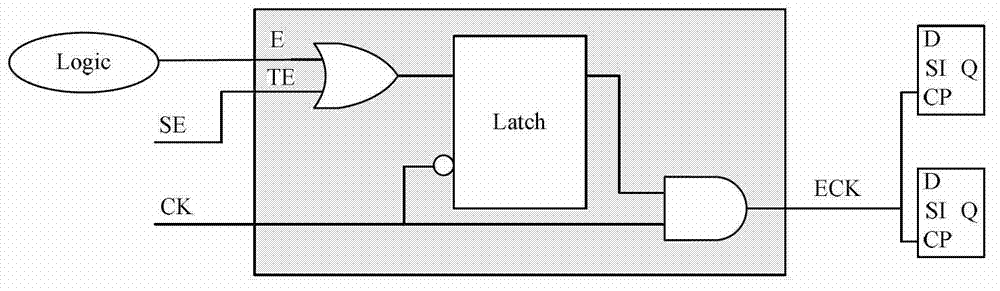

A system for automatically transforming a given synchronous circuit description into an equivalent and provably correct desynchronized circuit description. Included in the automated transformation are techniques for synthesizing a variability-aware controller using a two-phase protocol, techniques for synthesizing a variability-aware controller using gated clocks and testability circuits, techniques for synthesizing a variability-aware controller optimized for performance, techniques for initializing the synthesized controller, techniques for dynamically minimizing power requirements, and techniques for interfacing the desynchronized circuit with external synchronous circuits. Also disclosed are techniques for implementing a system for automatically transforming a synchronous circuit description into an equivalent and provably correct desynchronized circuit description within the context of an electronic design automation design flow. Exemplary circuits used in the application of the aforementioned techniques are provided. Application of mathematical models and techniques used for proving equivalence between the input description and the resulting desynchronized circuit are presented and explained.

Owner:CO INVERSION NEOTEC +1

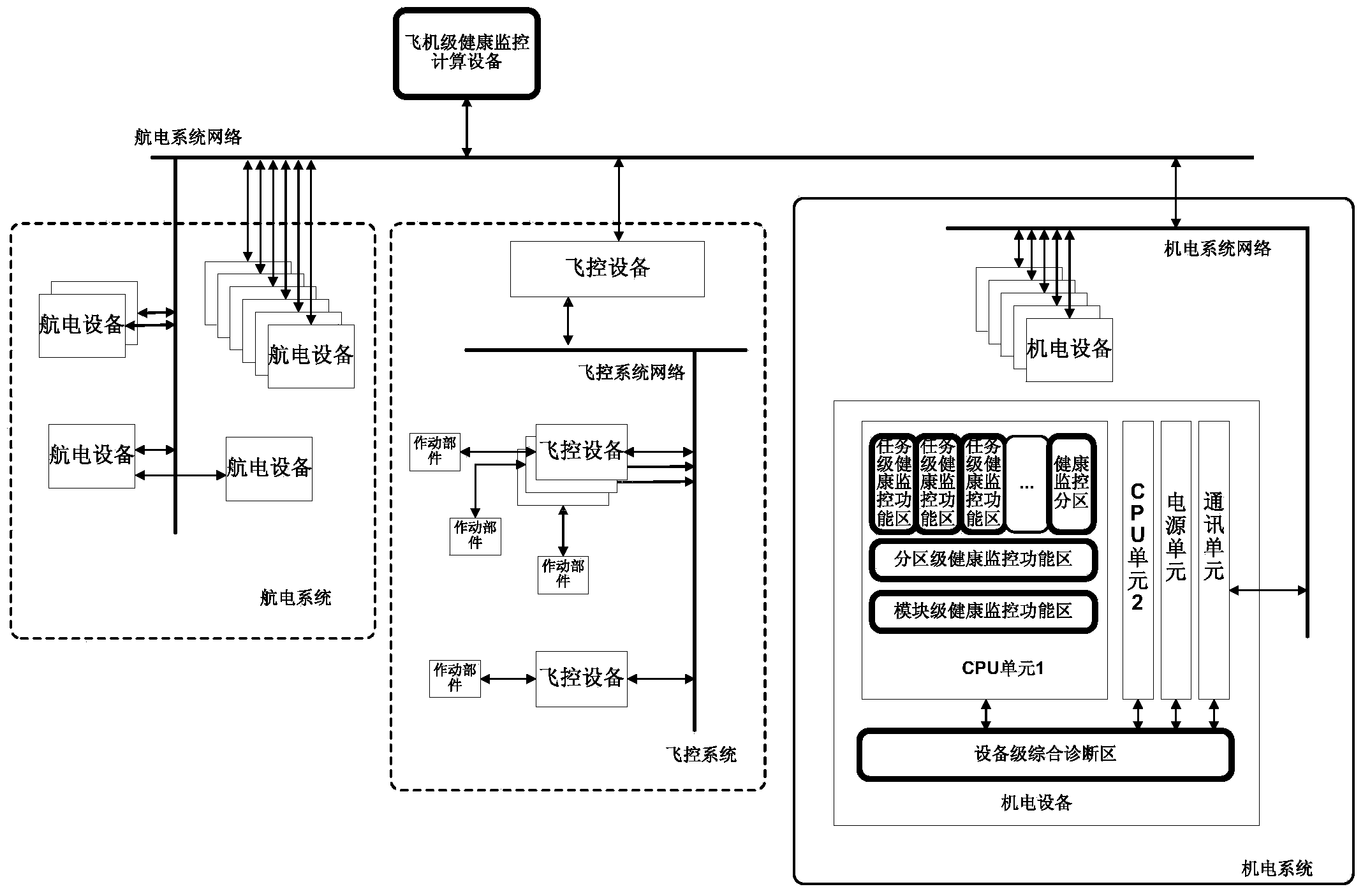

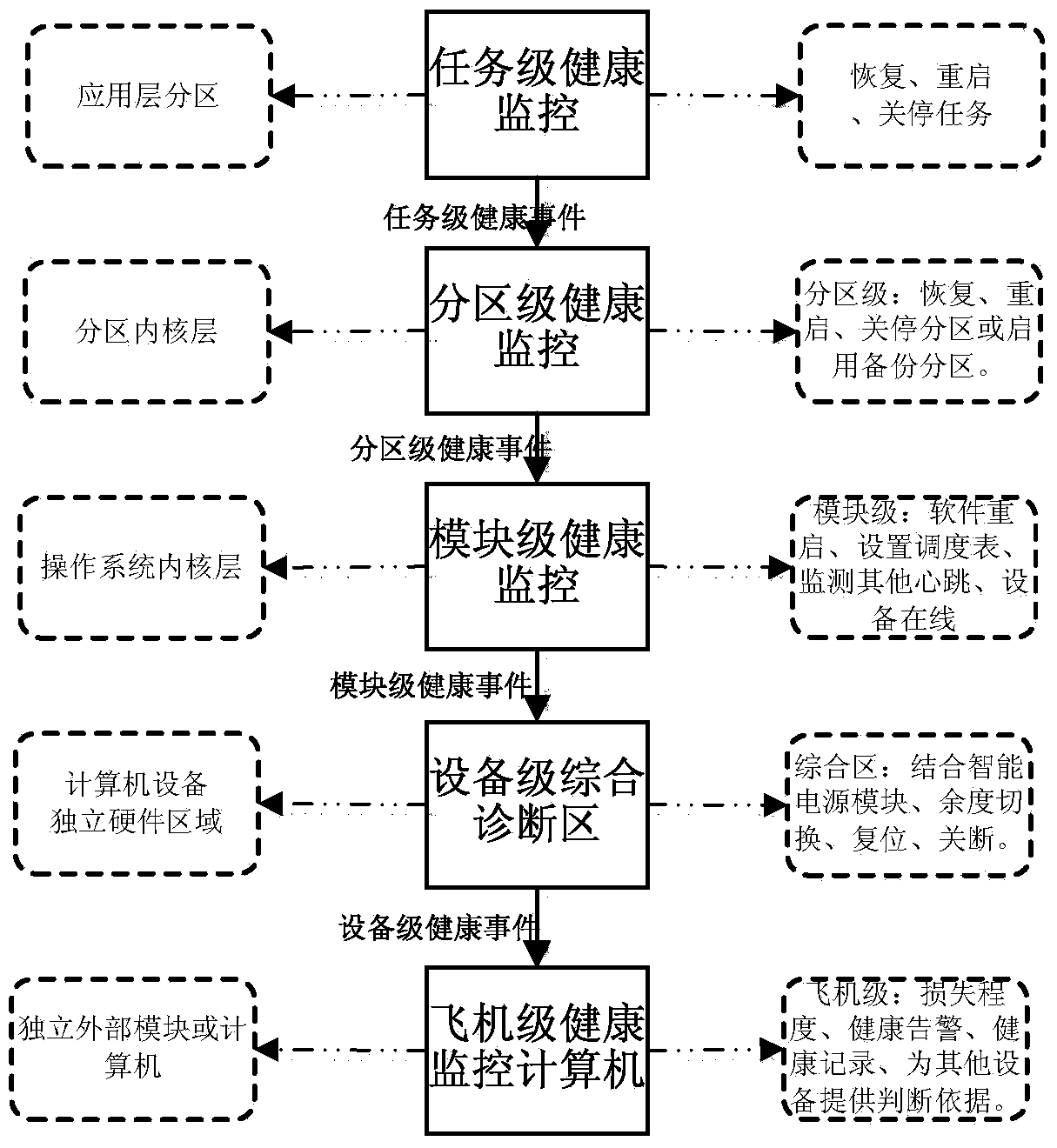

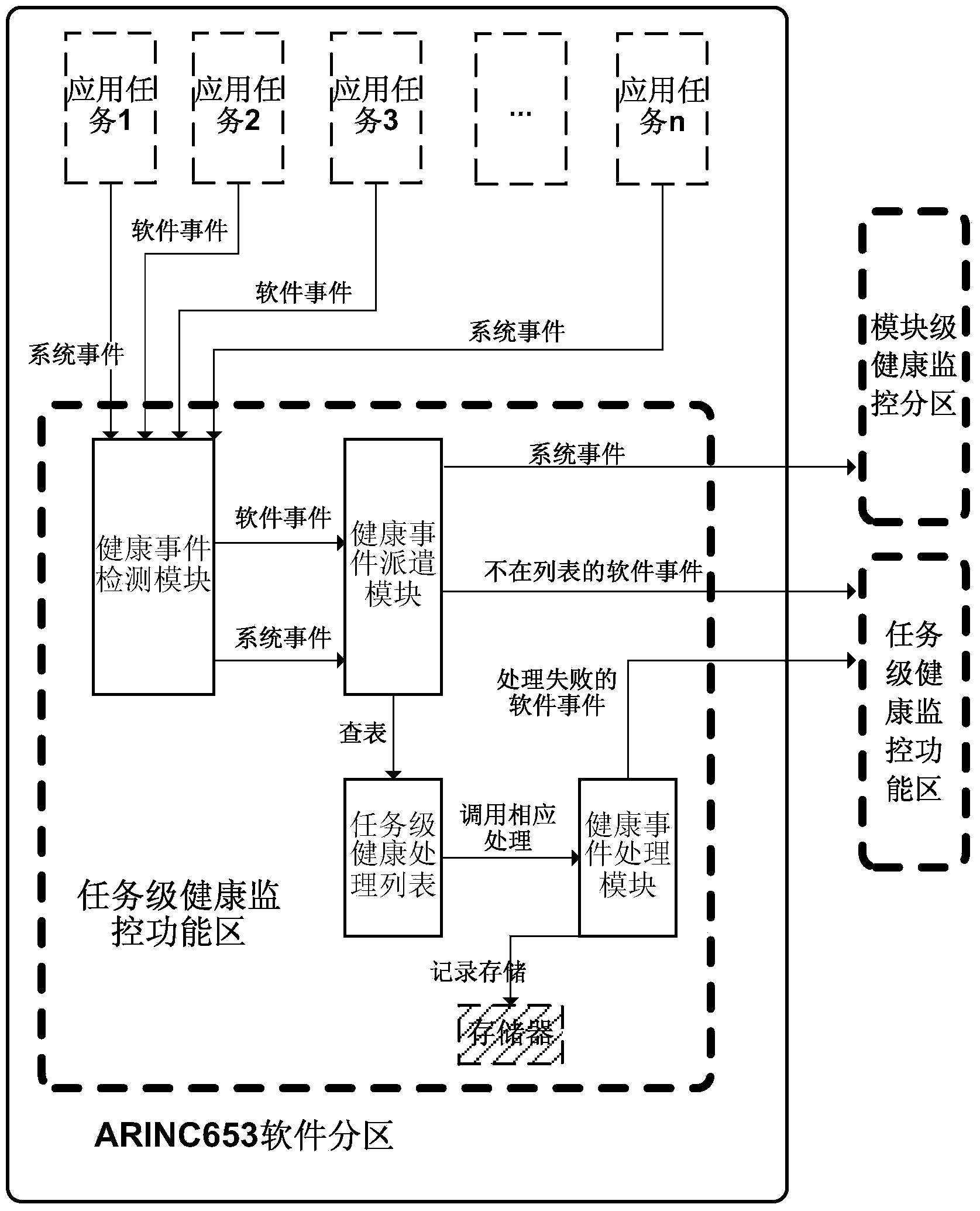

Health monitoring system of avionic electronic equipment based on ARINC653 standard

ActiveCN103544092AEnable on-board health managementEnsure safetyHardware monitoringOperational systemMonitoring system

The invention belongs to the aircraft avionics system technology and relates to a health monitoring system of avionic electronic equipment based on an ARINC653 standard. The health monitoring system adopts a mode of input step by step, diagnostic decision and stage treatment to process anomalous events, performs comprehensive diagnosis from a software task stage to an operation system and from an avionic electronic equipment layer to a full-aircraft system, and adopts a classification layered mode to assign fault events to processing steps of different stages according to a health monitoring stage, and processing permissions are enlarged step by step according to the health monitoring stage. By means of the mode of the stage treatment and report stage by stage, airborne health management of an aircraft is effectively achieved. Safety of fault processing is ensured through the processing permissions of different stages, and processing efficiency on the system fault events and sensing of the aircraft on the health states are improved by reporting the events stage by stage. Therefore, fault diagnosis recovery capability of the aircraft is effectively improved, and testability and safety of the aircraft are strengthened.

Owner:XIAN AIRCRAFT DESIGN INST OF AVIATION IND OF CHINA

Soft error tolerant flip flops

ActiveUS20070262787A1Reliability increasing modificationsElectric pulse generatorComputer scienceTestability

A register designed to detect and correct soft errors in real time. A redundant latch is added to the existing structure of a flip flop and functional data is simultaneously registered at multiple latches. The content of these multiple latches are fed to a majority voting circuit. If the content of any of these latches is corrupted by soft error, it is filtered out through the majority voting circuit and correct data is passed out from the output of the flip flop. In one embodiment, this design operates as a simple scan flip flop or scan-hold flip flop, and is useful for system testability purposes.

Owner:RUTGERS THE STATE UNIV +1

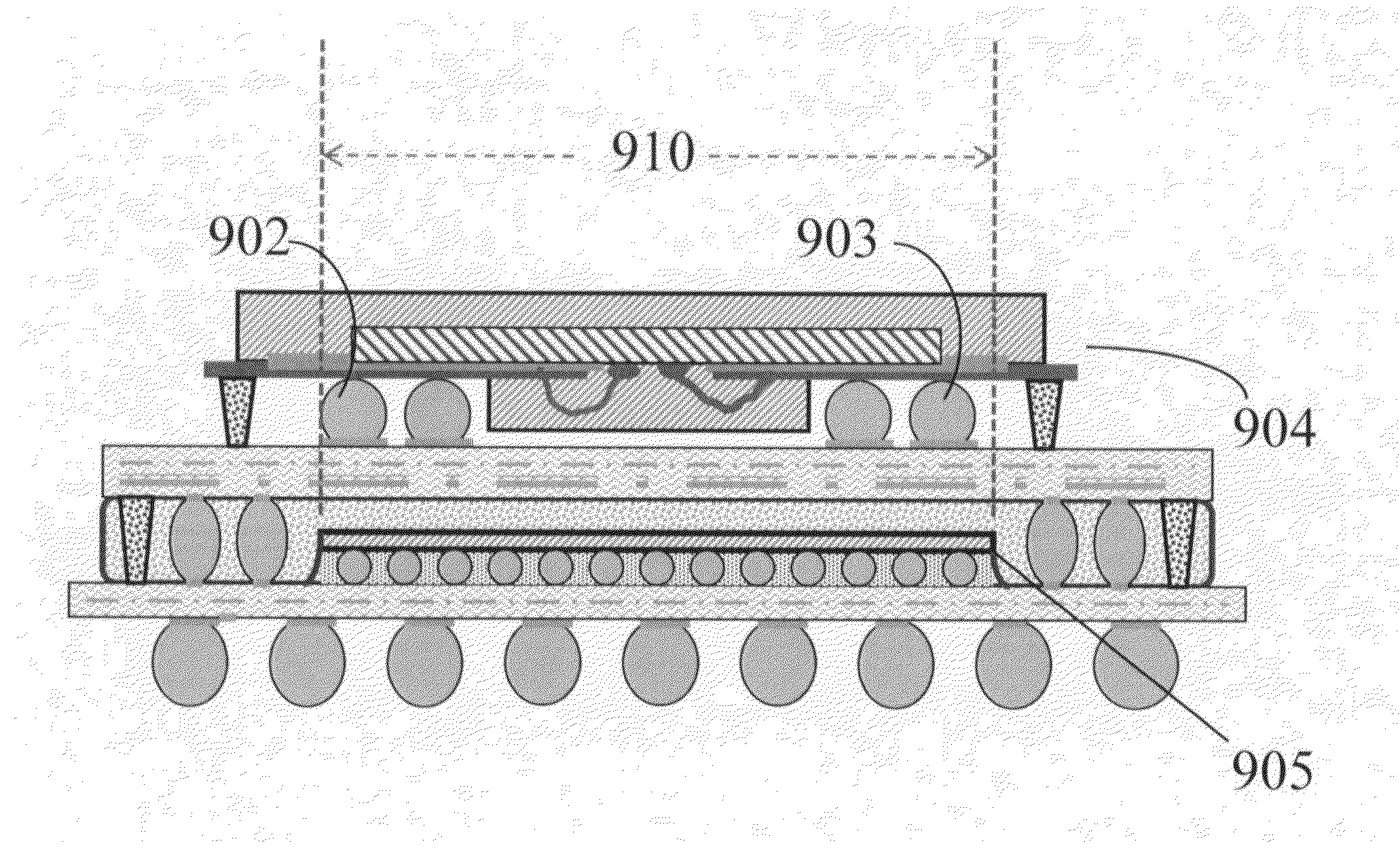

Package-to-package stacking by using interposer with traces, and or standoffs and solder balls

InactiveUS20120020040A1Easy to assembleOptimizationElectrically conductive connectionsSolid-state devicesContact padInterposer

The present invention discloses the structure and process for fabrication of an electronic package to contain and protect Package-to-Package (P2P) stacked module of integrated circuit (IC) chips. The process includes a step of providing an interposer that includes conductive traces interconnected between pre-designated contact pads disposed on a top and / or bottom surfaces for mounting at least a top or bottom packages of the IC chips with electric terminals contacting the contact pads disposed on the top and / or bottom surface of the interposer. Standoffs and passive components can also be added onto interposer in order to improve solder joints reliability, electrical performance and main board density at the same time. The inclusion of passive components on the interposer could enhance the electrical performance and the testability of the finished package stack.

Owner:LIN PAUL T +1

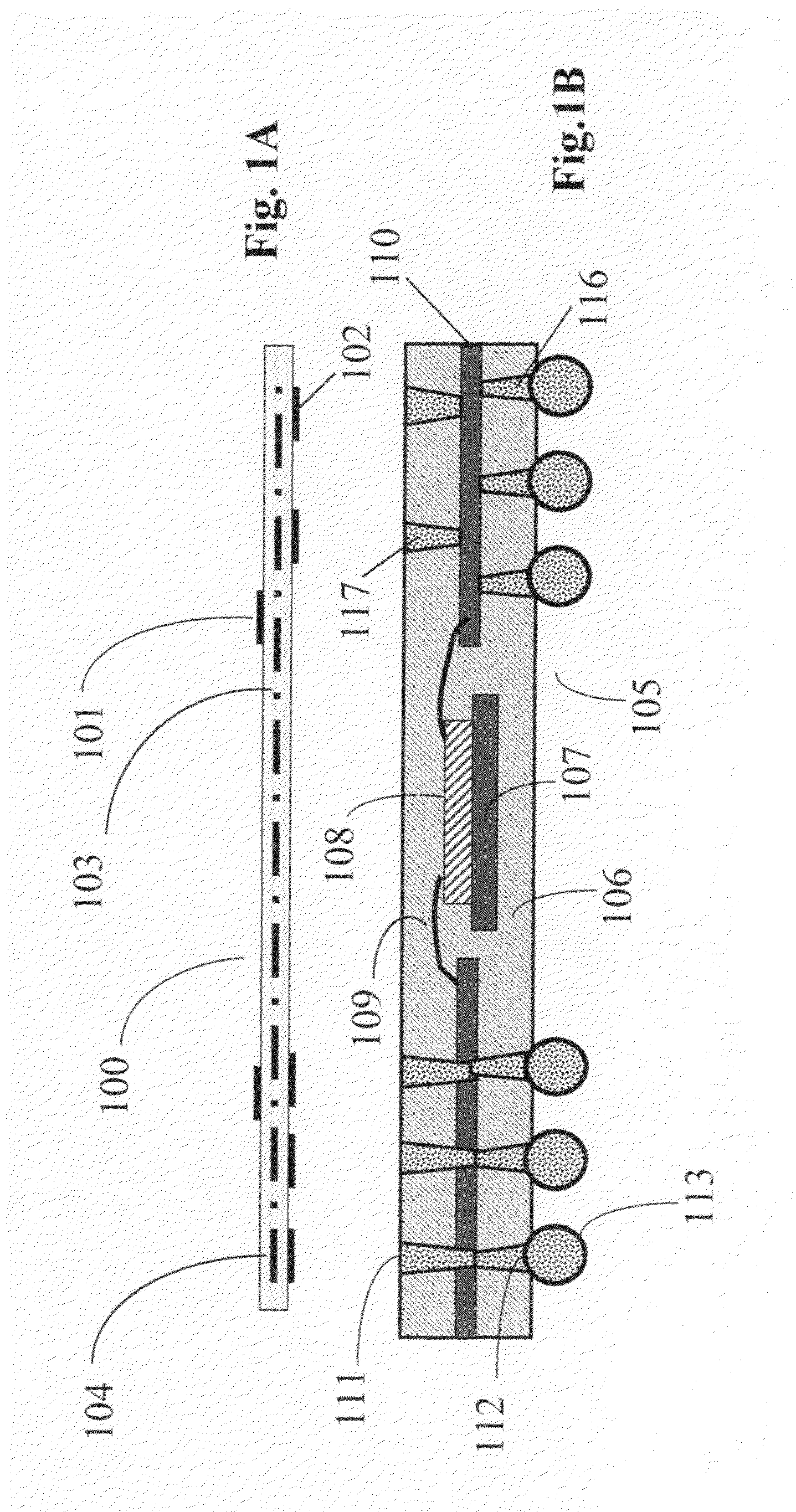

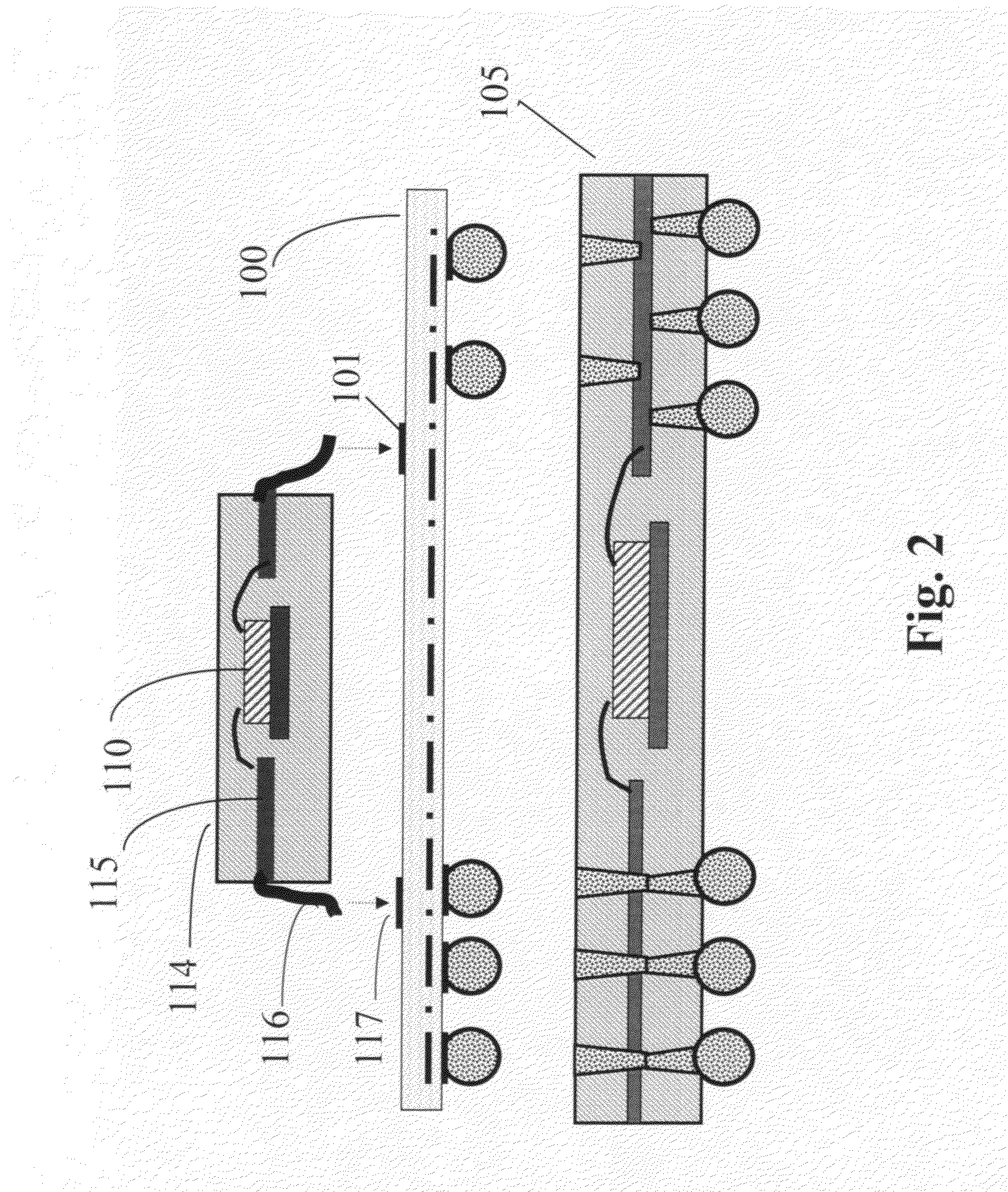

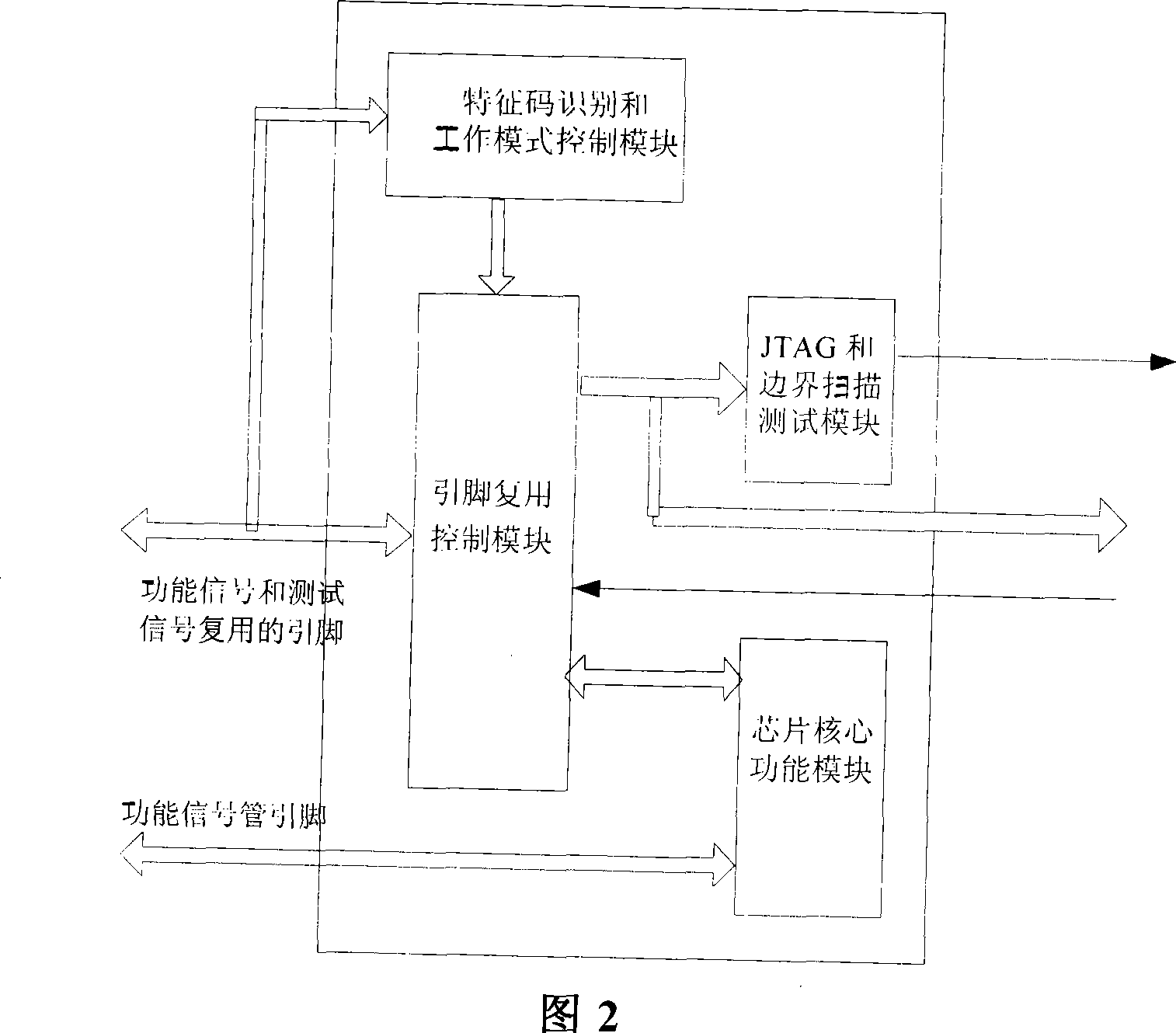

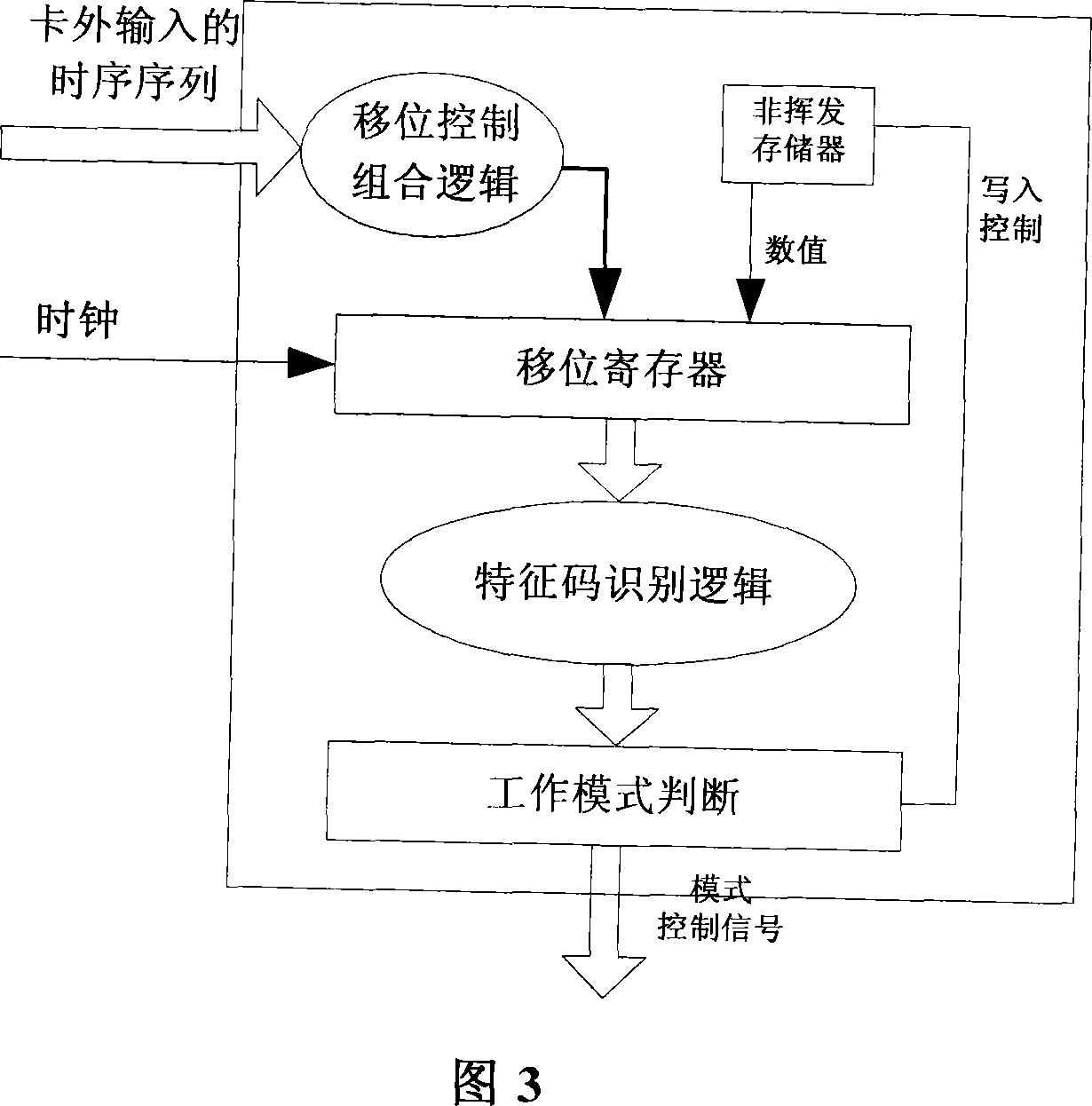

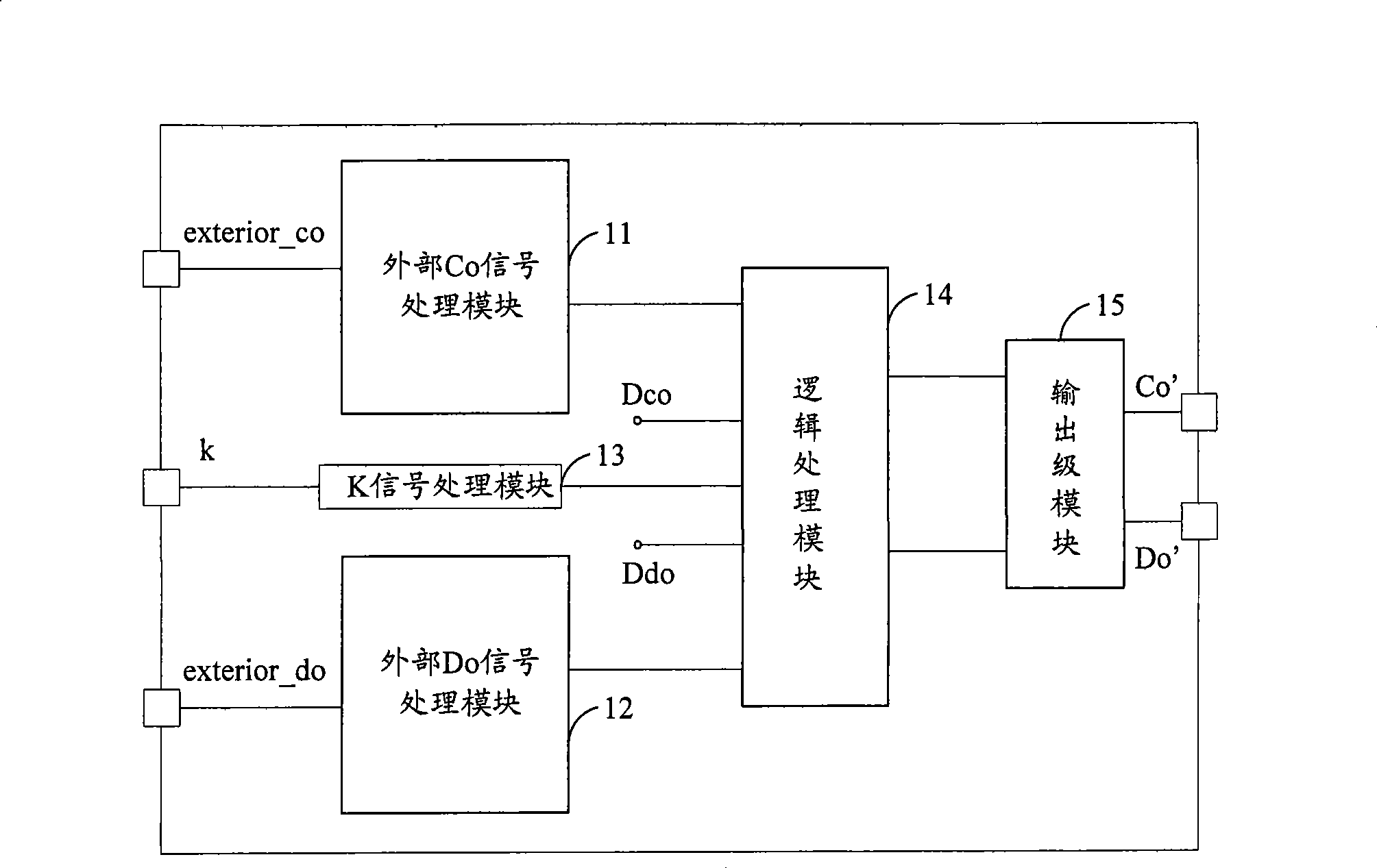

Border scanning test structure of multiple chip package internal connection and test method

ActiveCN101078746AConnected testingAvoid situations that mislead the chip into test modeSemiconductor/solid-state device testing/measurementIndividual semiconductor device testingElectricityEngineering

The invention relates to a boundary scanning testing structure connected with multiple-chip packaging body with finite pins in it and the testing method, belonging to IC chip design, chip testability design and chip packaging fields. A typical application is the modern new SIM card with large capacity constituted by multiple chips. The invention sets finite functional pins of packaging body as pins with boundary scanning function by a special logic sequence relationship when multiple-chip packaging body is tested and then by these pins boundary scanning test in packaging body can be carried out so as to achieve the test to inner connection relationship of packaging body. After test is done, by a special operation, the function of testing circuit is closed to avoid chip error action, which is not necessary in future. The invention realizes special power-on flow of chip, realization of a special circuit and corresponding structure adjustment of chip.

Owner:RDA MICROELECTRONICS SHANGHAICO LTD

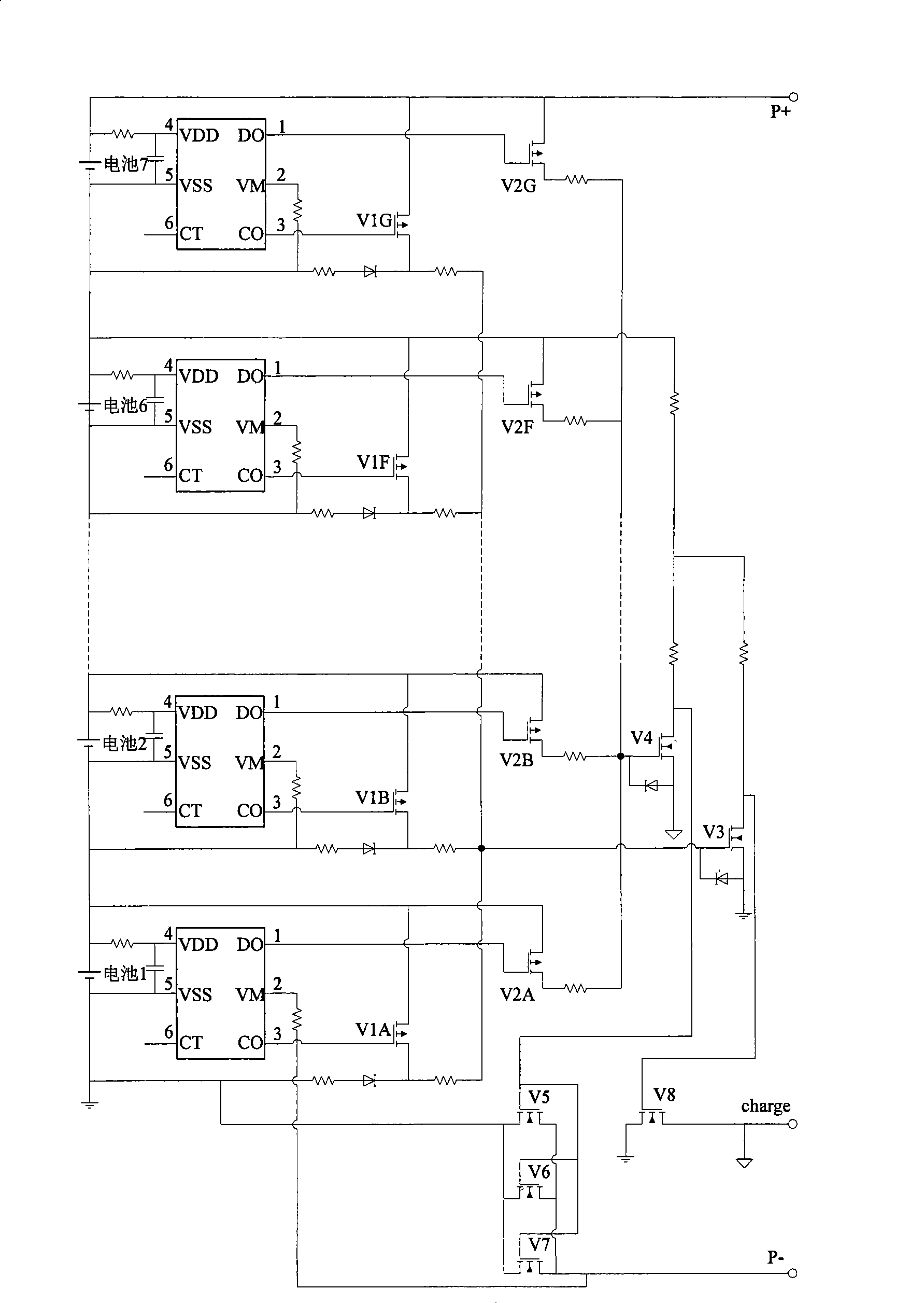

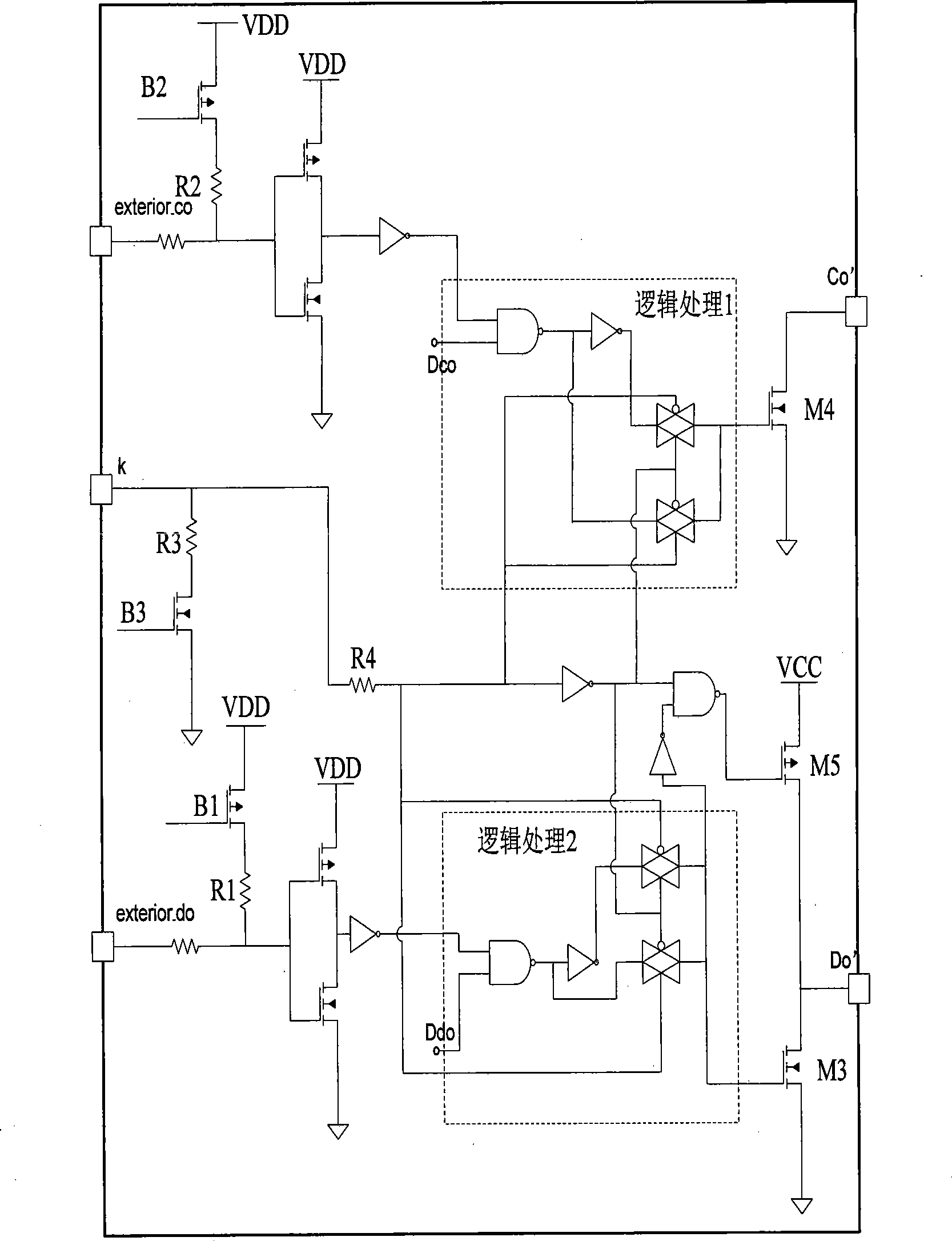

Protection circuit and method for multiple batteries

ActiveCN101399440ALow costImprove reliabilityCharge equalisation circuitEmergency protective circuit arrangementsComputer moduleCharge control

The invention is applicable to the field of battery protection, and provides a multiple-battery protection circuit and a method thereof. The multiple-battery protection circuit comprises one or a plurality of multiple-battery protection chips, and a charge control switch and a discharge control switch controlled by the multiple-battery protection chips, the multiple-battery protection chips comprise an application protection integrated circuit module for multiple battery packs in series and an expanding connection module, and the input end thereof is connected with the anode pole and the cathode pole of a corresponding single cell, the input end of the chips is connected with the anode and cathode of the corresponding single cell, and the output end thereof is respectively connected with an inner signal input end of the expanding connection module, the expanding signal input end of the expanding connection module is connected with the expanding signal output end of the expanding connection module of the adjacent multiple-battery protection chip, and the output end of the expanding connection module is respectively connected with the charge control switch and the discharge control switch. The multiple-battery protection circuit provided by the technical scheme of the invention can realize the protection of any batteries without any peripheral circuit, which reduces the cost, reduces the complexity of the circuit and improves the testability and the expandability of the circuit.

Owner:BYD SEMICON CO LTD

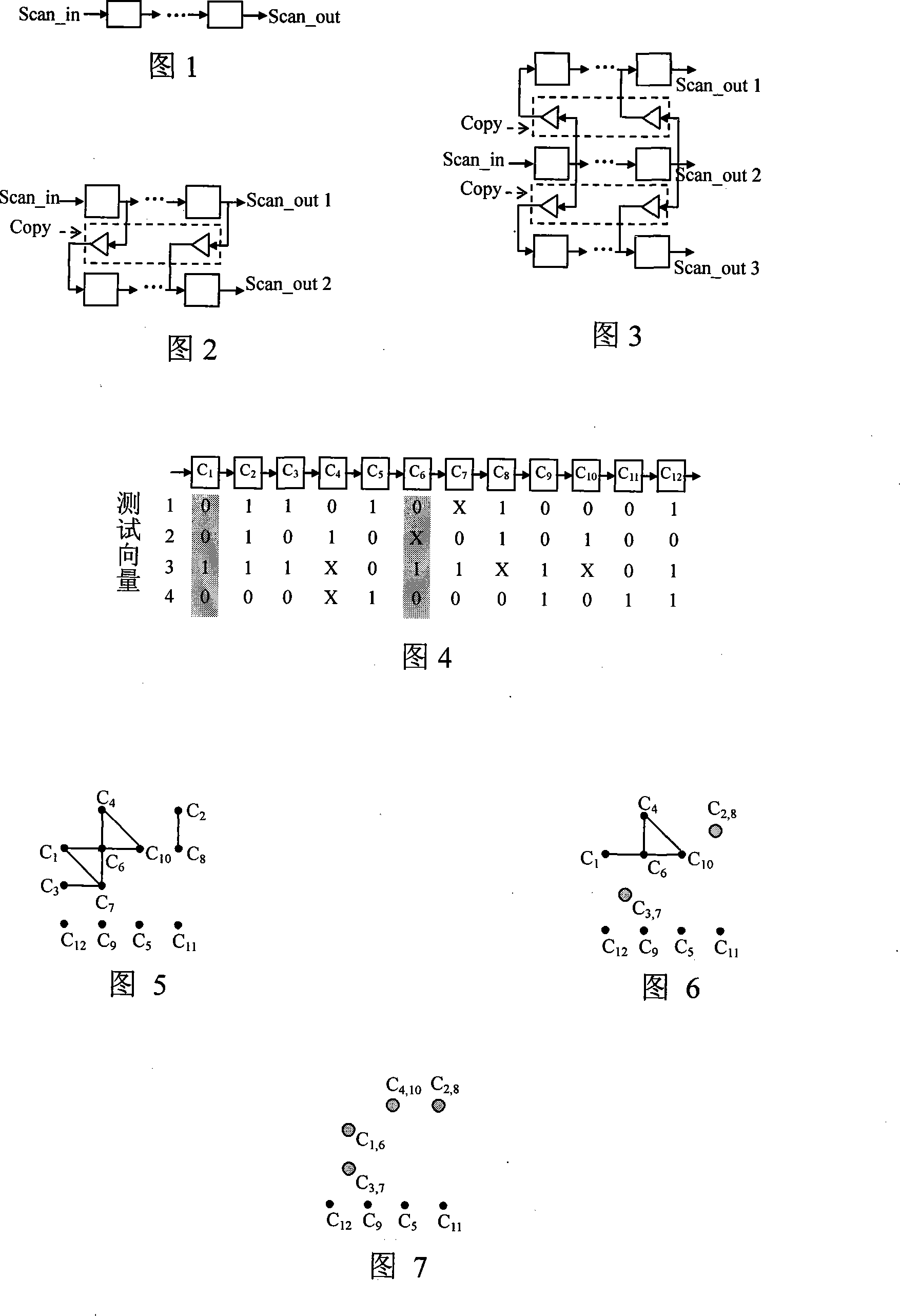

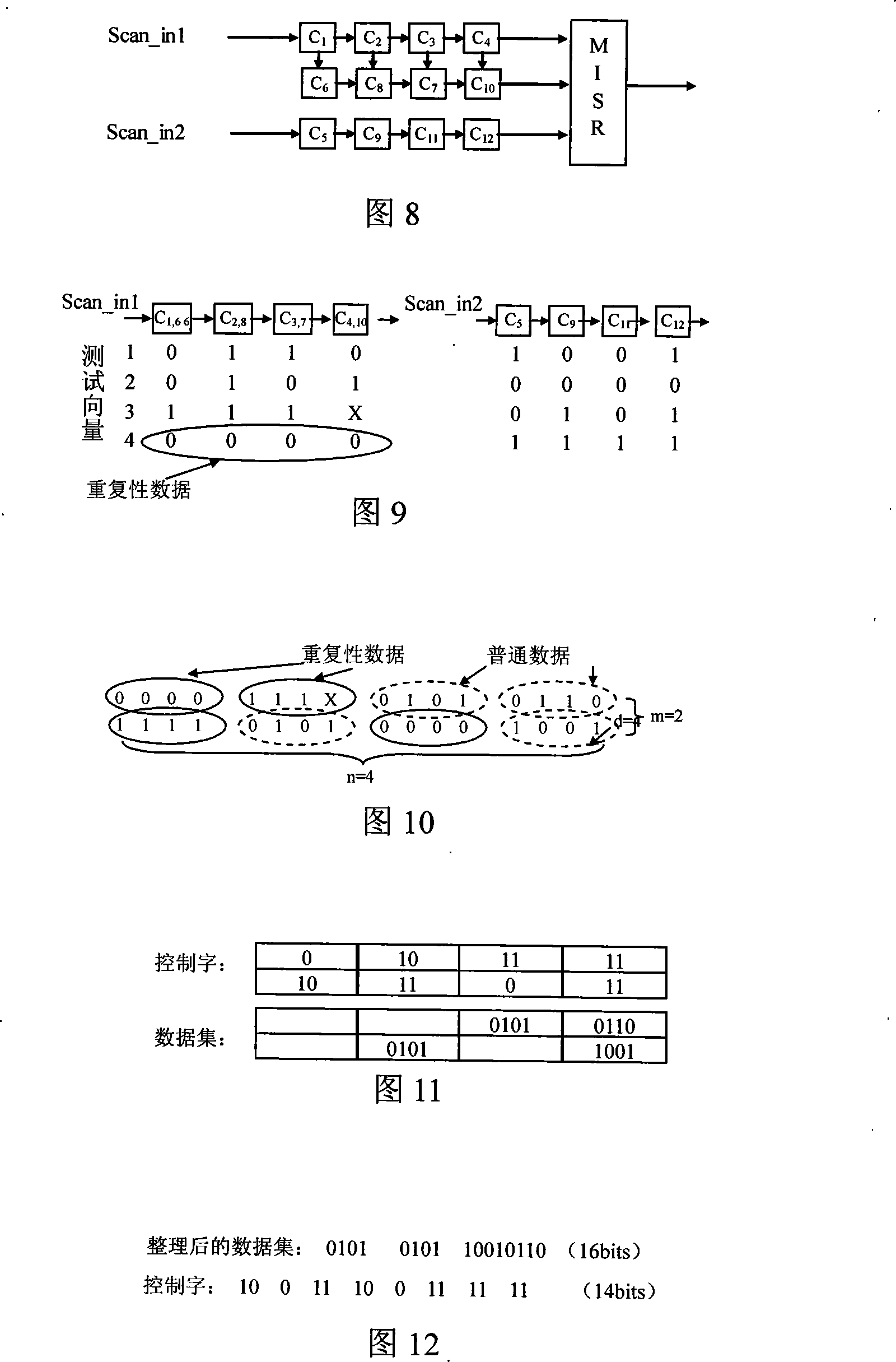

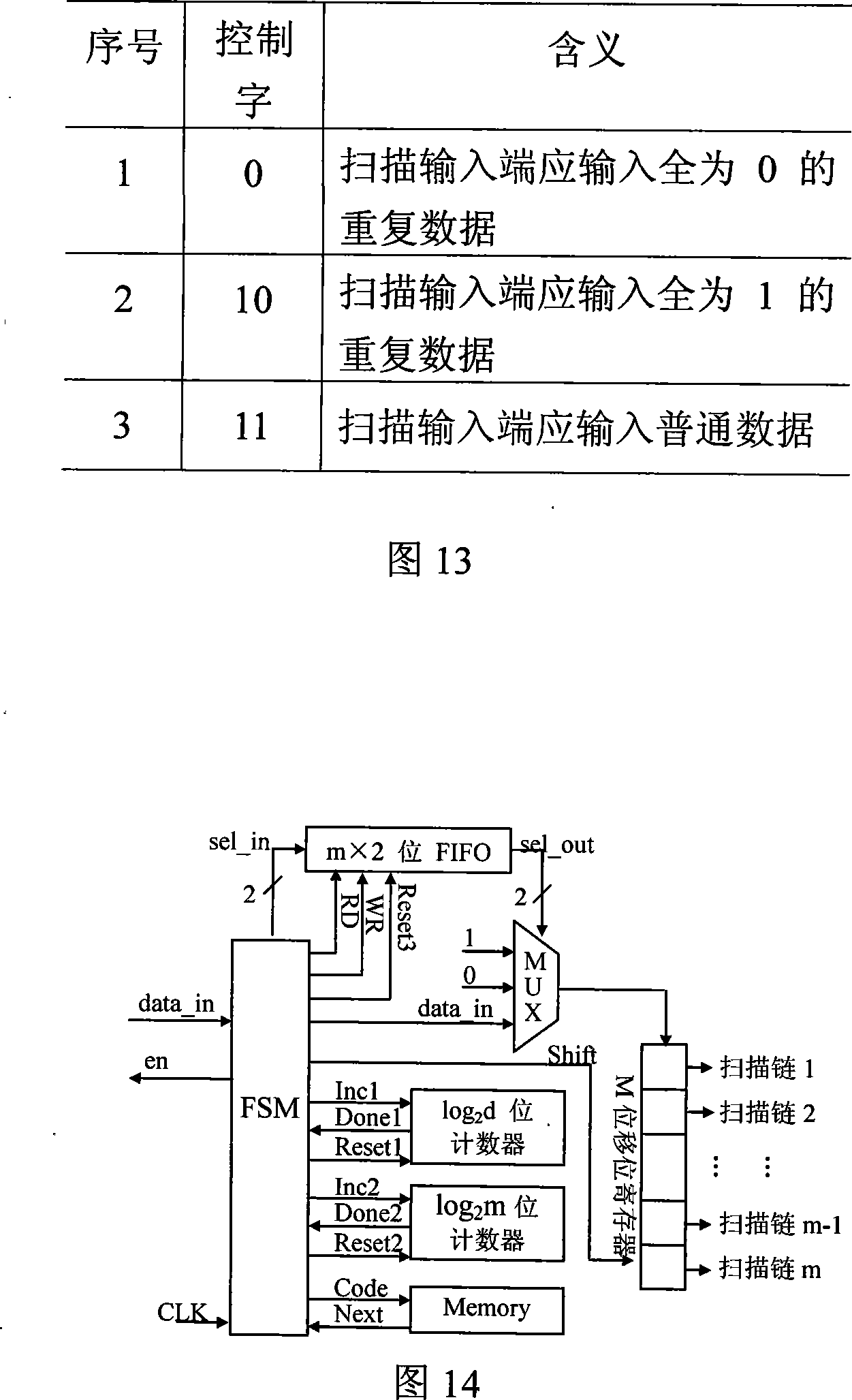

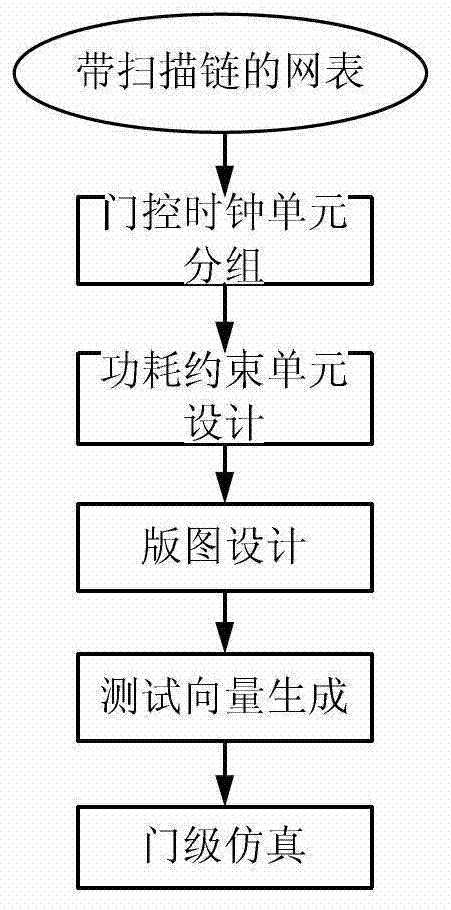

Large scale integrated circuit test data and method for testing power consumption cooperate optimization

InactiveCN101158706AReduce test power consumptionGuaranteed reliabilityElectronic circuit testingTest powerTest set

The invention relates to a method collaborating and optimizing the test data and the power consumption of testing large scale integrated circuits. The method relates to the technical field of the large scale integrated circuits and is proposed to resolve the problem that in the prior art of SOC test, no method is available to effectively reduce the test data and the power consumption of test at the same time. The method has the following steps: the compatibility of scanning units of the circuit is analyzed and accordingly the scanning units are classified into three categories; each category of scanning units are connected respectively, and a scanning chain with copying mechanism is built; a set of test vector is adjusted according to the new scanning chain structure; the test set is compressed by the method based on the compression of repeated data and a compressed test set TE is acquired. When in the testing process, the compressed data is fully recovered by a decompression circuit to be tested. The invention discloses a design method for the testability of integrated circuits, and reduces the power consumption of circuits in the testing process, thus ensuring the reliability and testability; furthermore, the invention can effectively reduce the quantity of test data, shorten the test process, and lessen the number of ATE channels.

Owner:HARBIN INST OF TECH

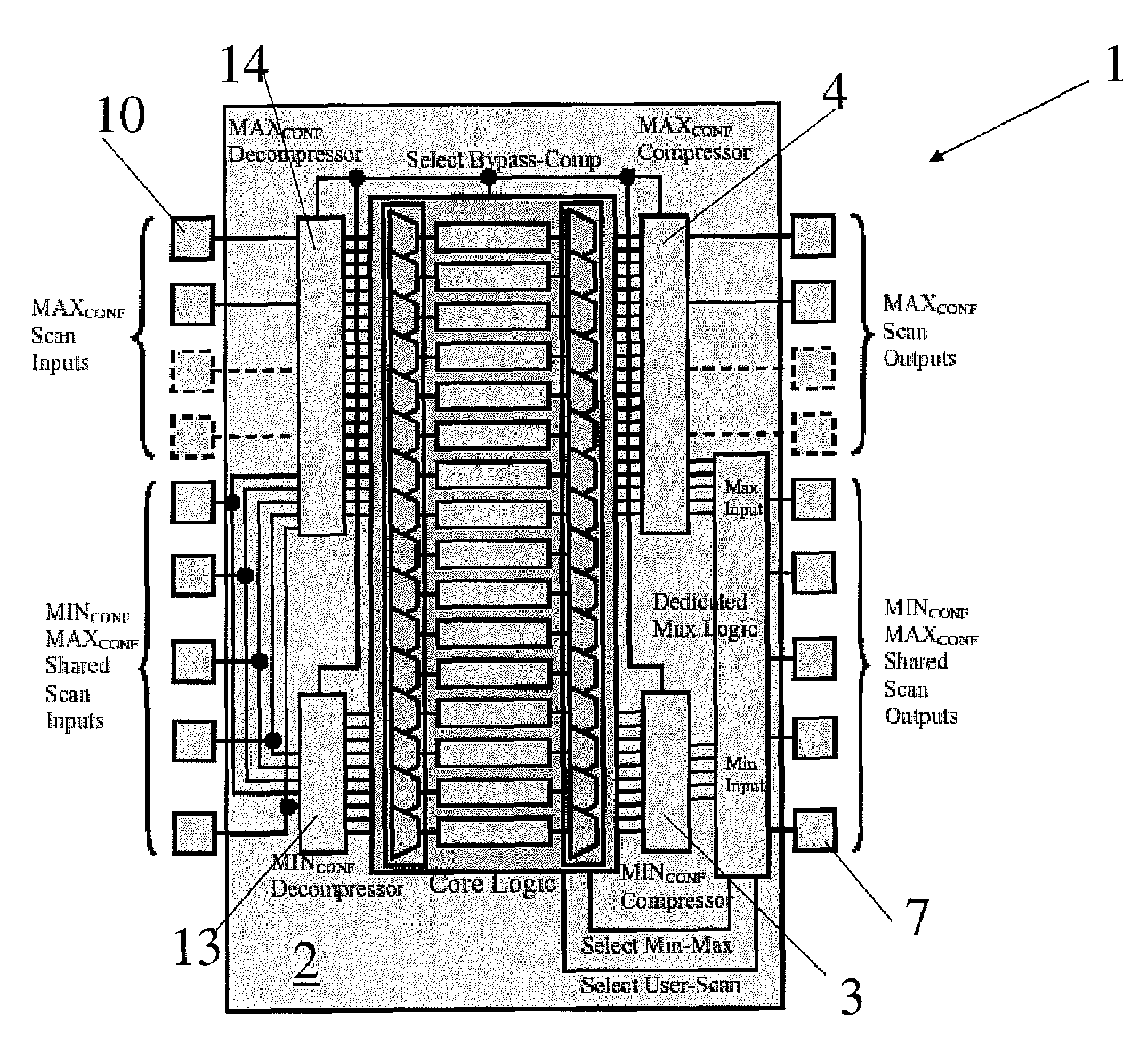

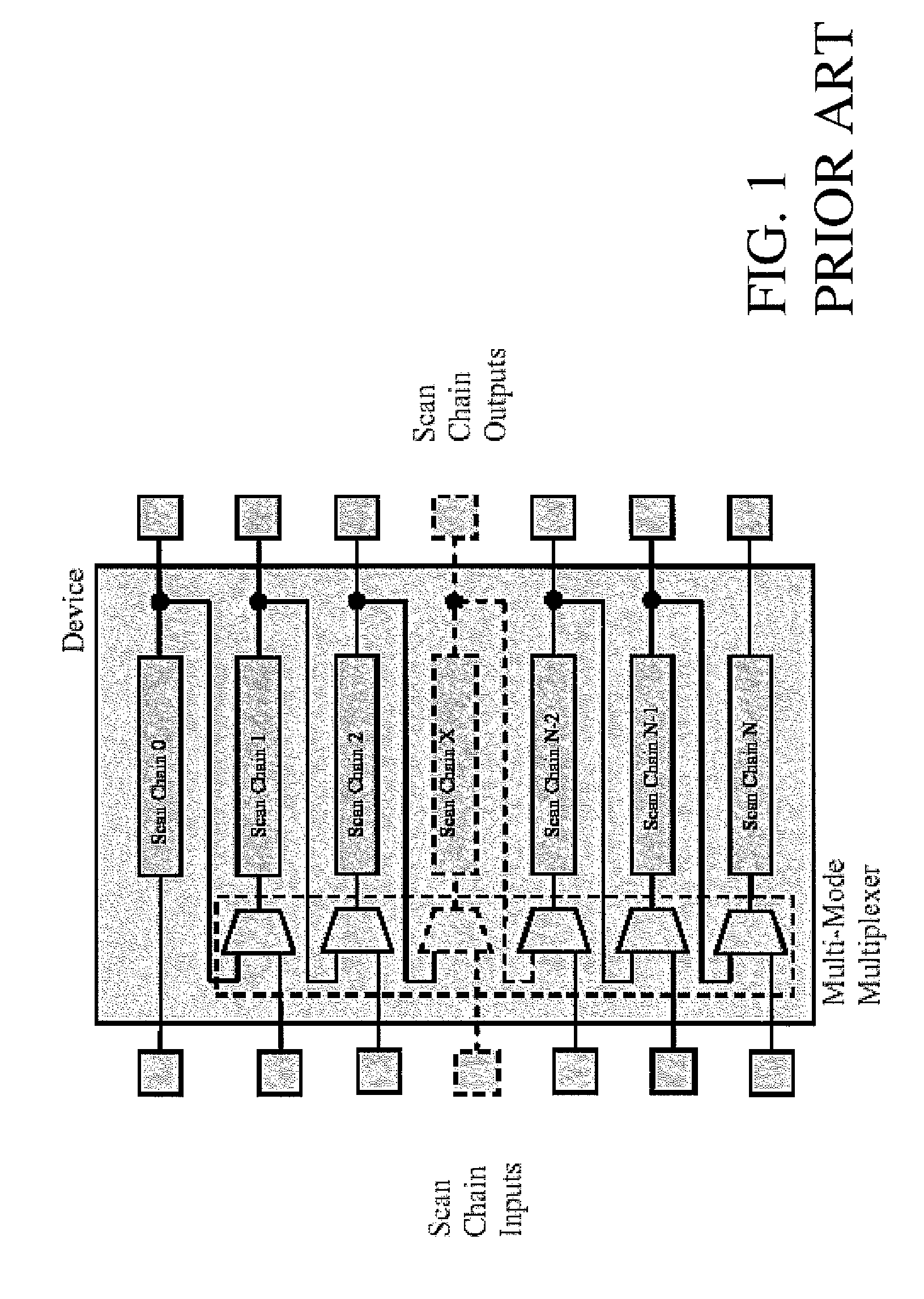

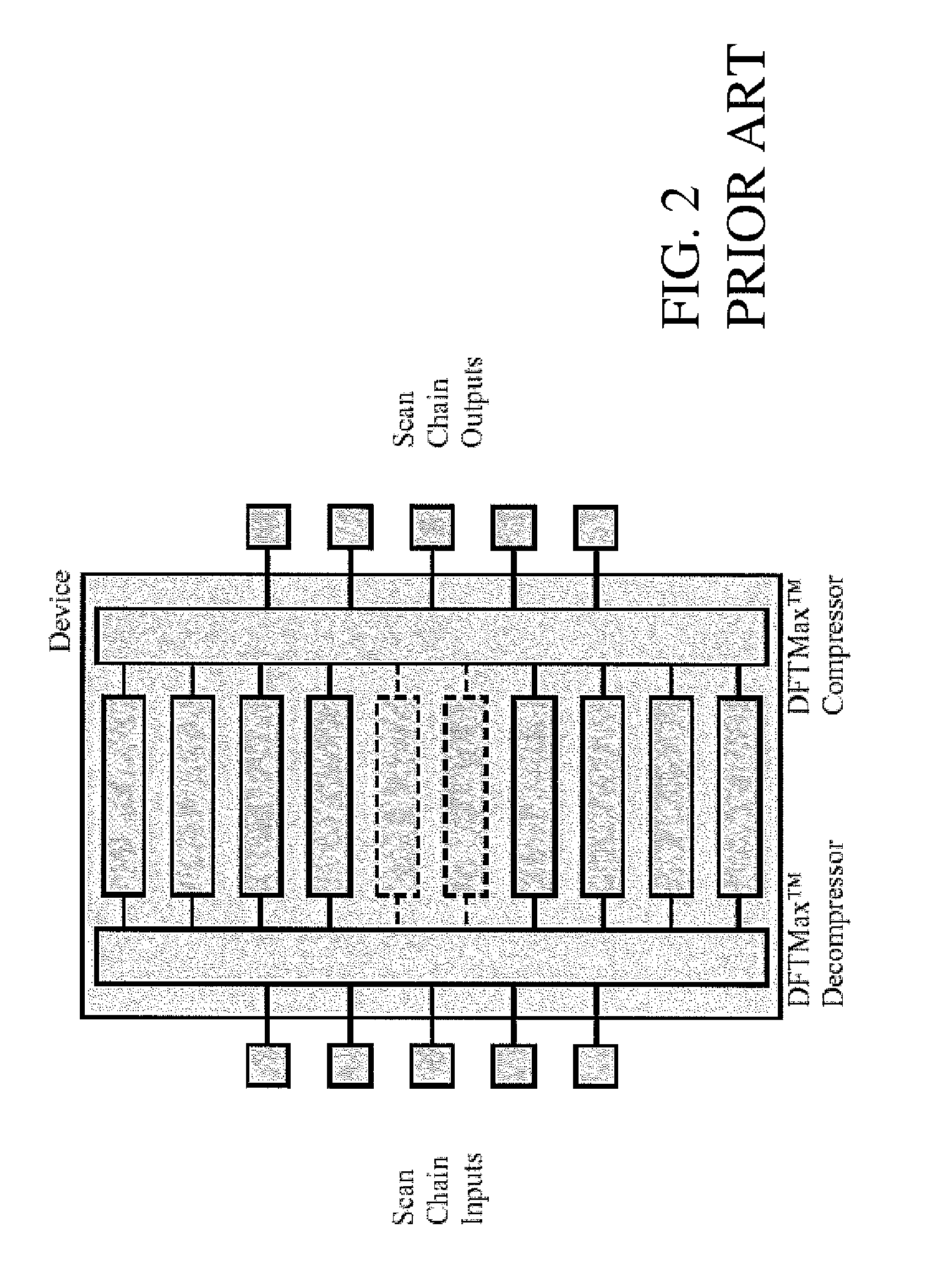

Scan compression architecture for a design for testability compiler used in system-on-chip software design tools

ActiveUS7702983B2Reduce testing costsImprove parallelismElectronic circuit testingComputer architectureSoftware design

A scan compression architecture for a design for a testability compiler used in system-on-chip software design tools includes a first scan architecture including a first scan compressor / decompressor configuration connected to a first predetermined set of pins, and a second scan architecture including a second scan compressor / decompressor configuration connected to a subset of the pins. The first scan architecture is selectively enabled for executing a scan test with a low time. The second scan architecture is for executing a scan test with high parallelism.

Owner:STMICROELECTRONICS SRL

Semiconductor storage device

InactiveUS7240253B2Avoid simple structuresImprove testabilityElectronic circuit testingDigital storageCircuit sizingControl signal

A testing device for a semiconductor storage device suppresses the increase in the circuit size, provides for facilitated accommodation to a test with frequent changes in the test pattern, and improves testability of the semiconductor storage device. A plurality of holding circuits are provided holding write data for memory cells of a memory cell array. (Original) The write data from the holding circuits are written in the memory cells of the selected address. A plurality of comparators are supplied with data read out from the memory cells and with data held by the holding circuits as expectation data to compare the readout data and the expectation data. The non-inverted or inverted value of the write data held by the holding circuits is output as the write data to the memory cells and as expectation data to the comparators depending on the value of the inversion control signal.

Owner:LONGITUDE LICENSING LTD

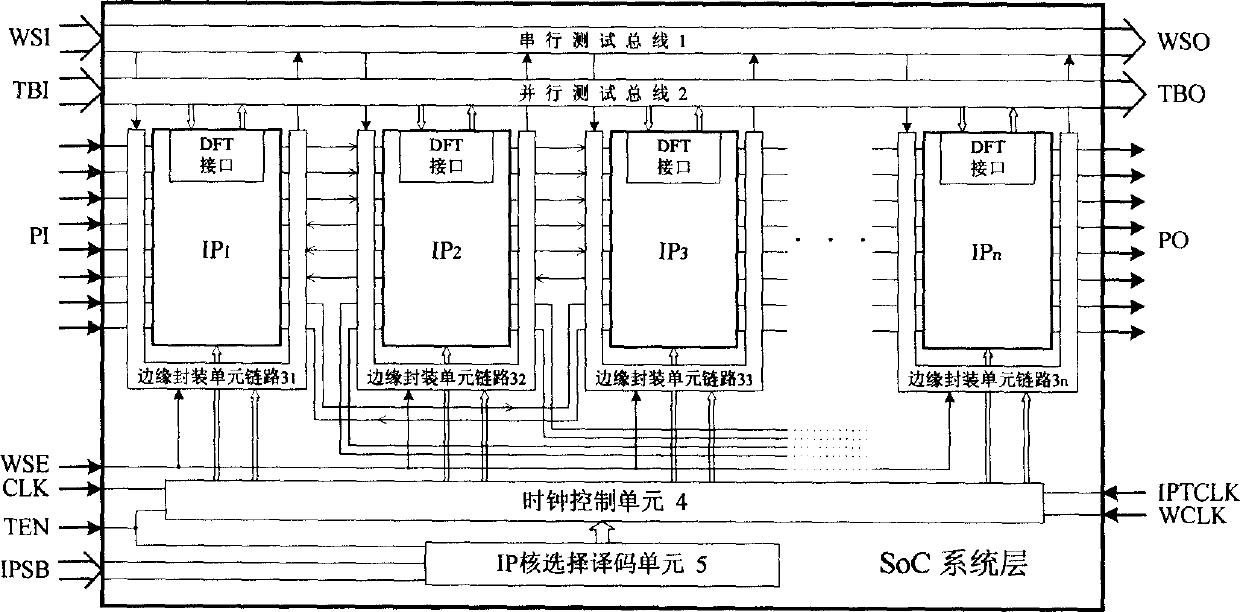

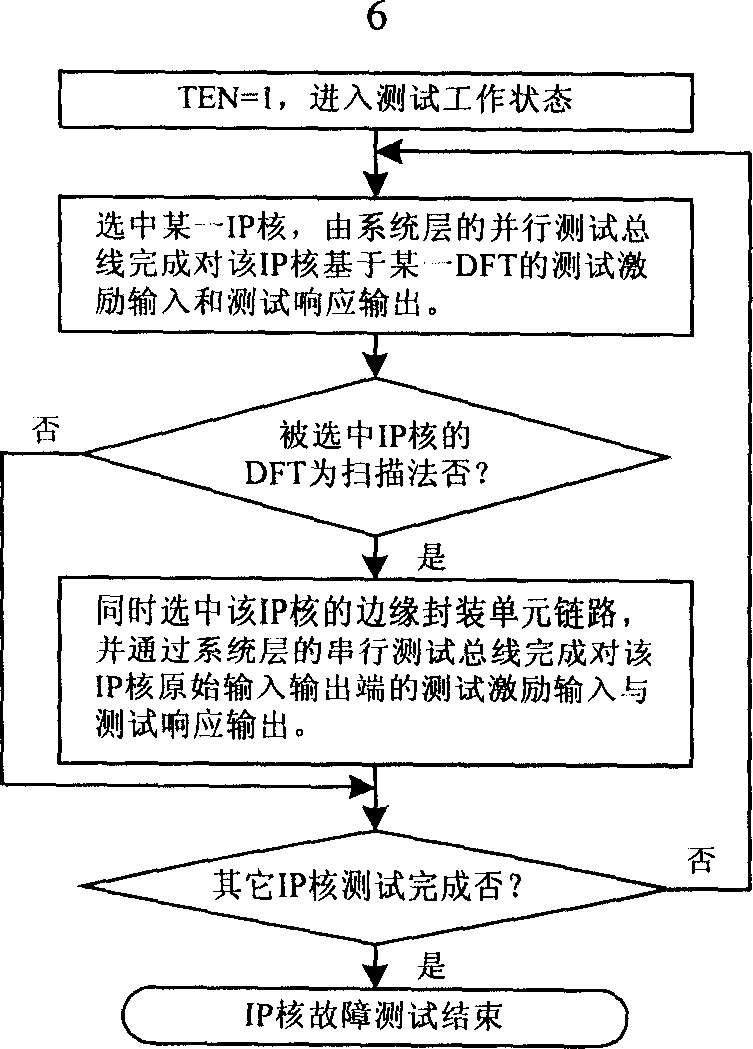

System and method for testing system fault on integrated circuit board

InactiveCN1734278ASimple structureImprove fault coverageElectronic circuit testingIntellectual propertyIntegrated circuit layout

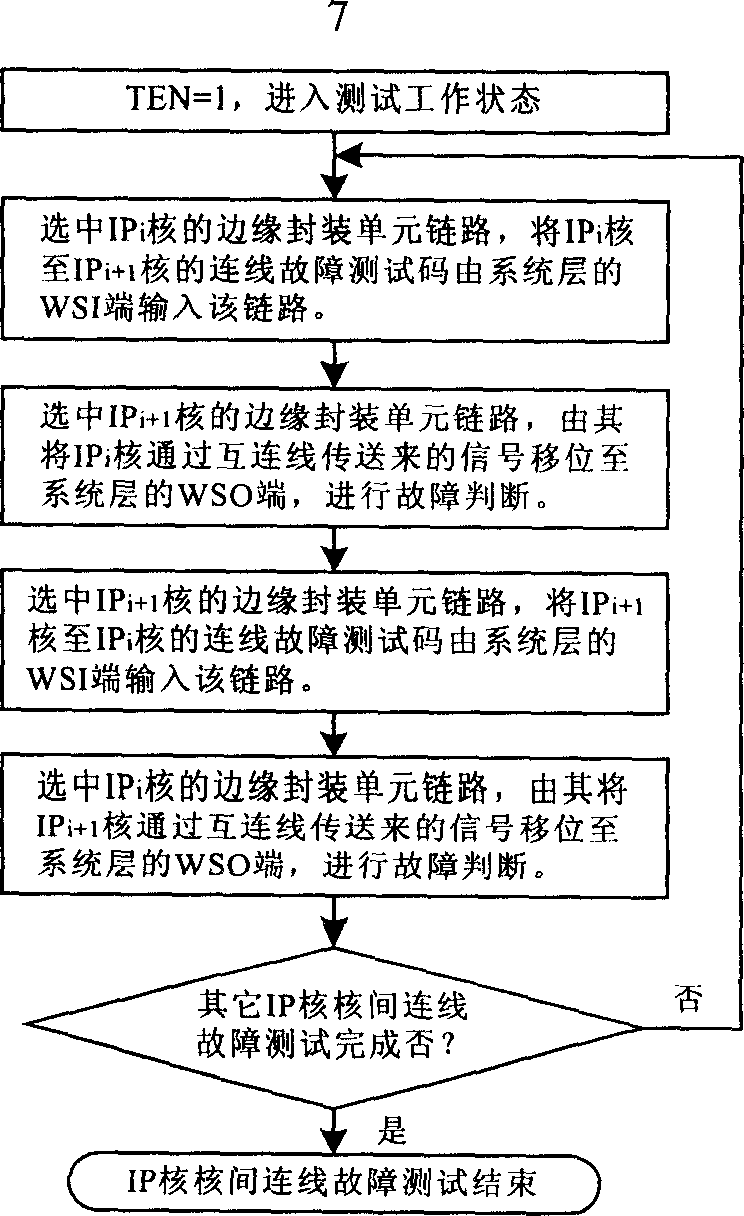

The invention relates to an accident detection system and method of SoC System on a chip, which comprises the following parts: strong detection circuit for complete integration chip; detection invitation mechanism whose circuit connects together with serial detection buses; parallel detection bus; IP (Intellectual Property) seed rim packaging chain circuit unit; clock controlling unit and IP seed selection decoding unit. The invitation detection mechanism consists of IP seed independent invitation detection mechanism and IP accident invitation detection mechanism between seeds. This invention adapts each present IP (DFT Design for Testability) method to detect circuit by system layer and IP seeds, which improves system accident percentage of coverage on the integration chip.

Owner:SHANGHAI UNIV +1

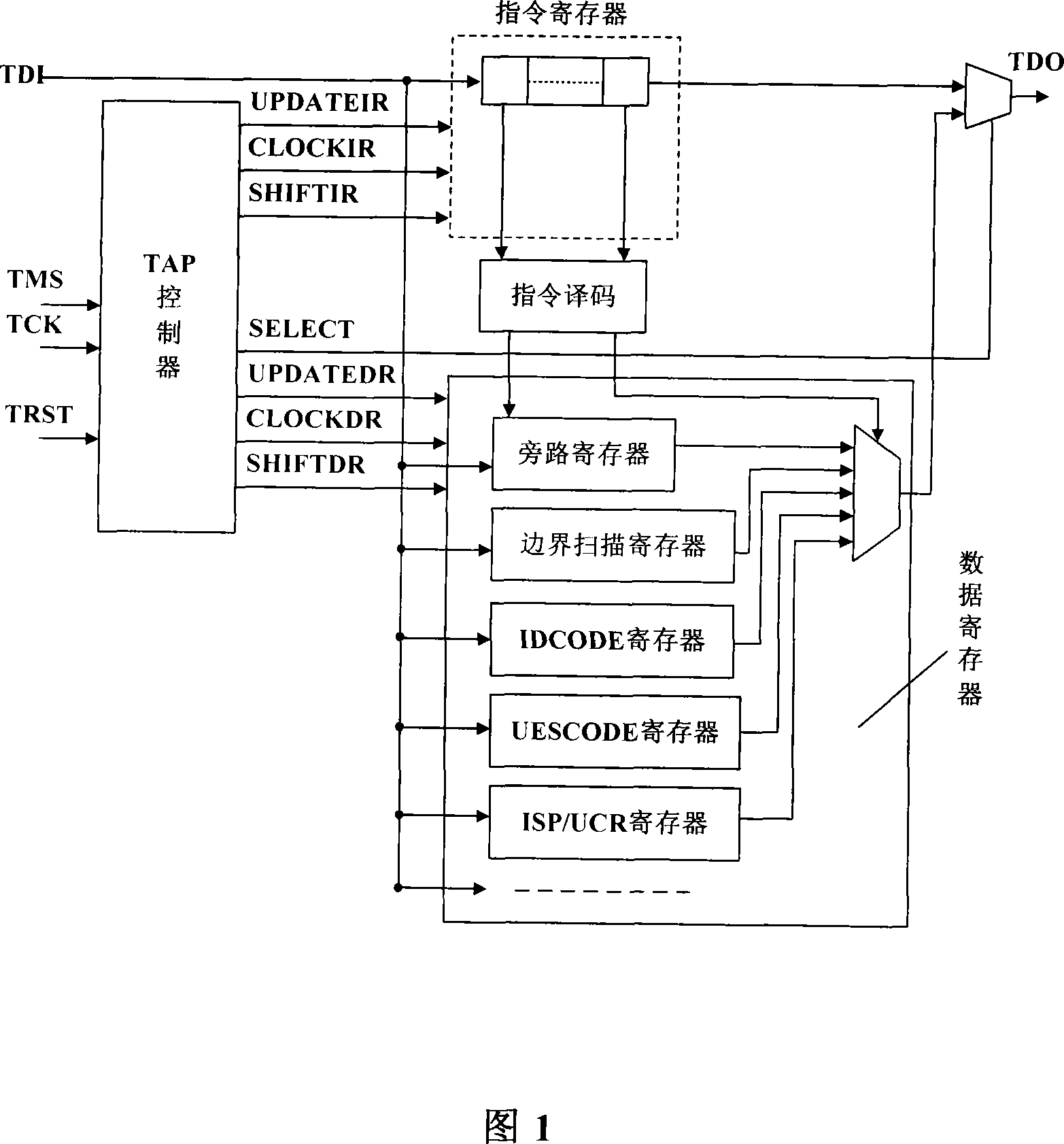

Method for designing testability of chip

ActiveCN102081689AHigh degree of automationSpecial data processing applicationsDesign for testingComputer architecture

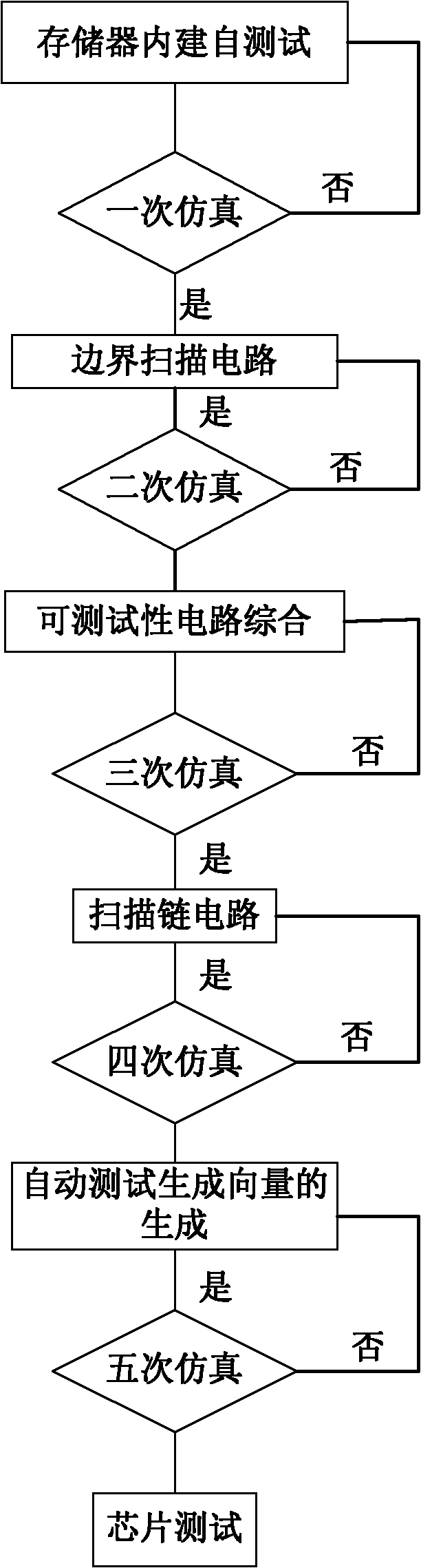

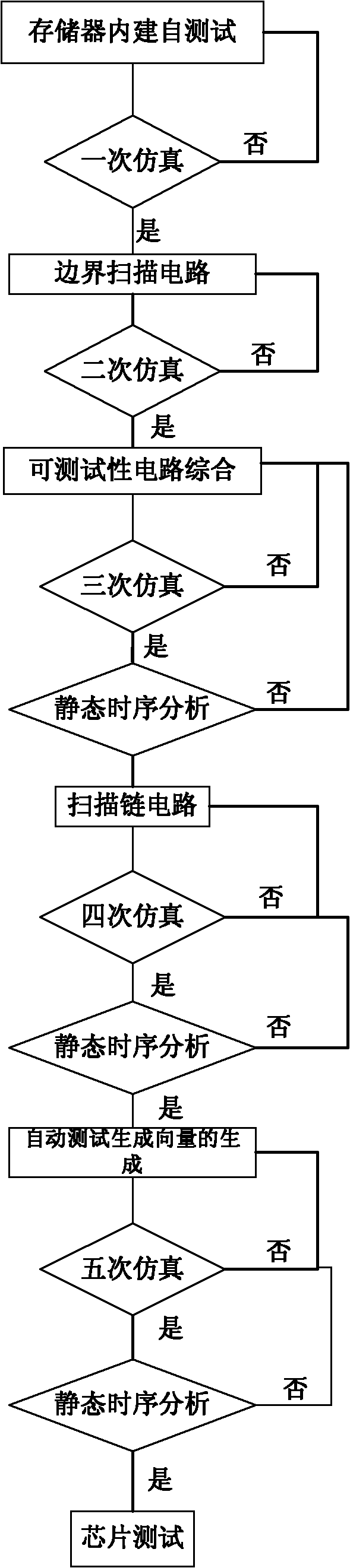

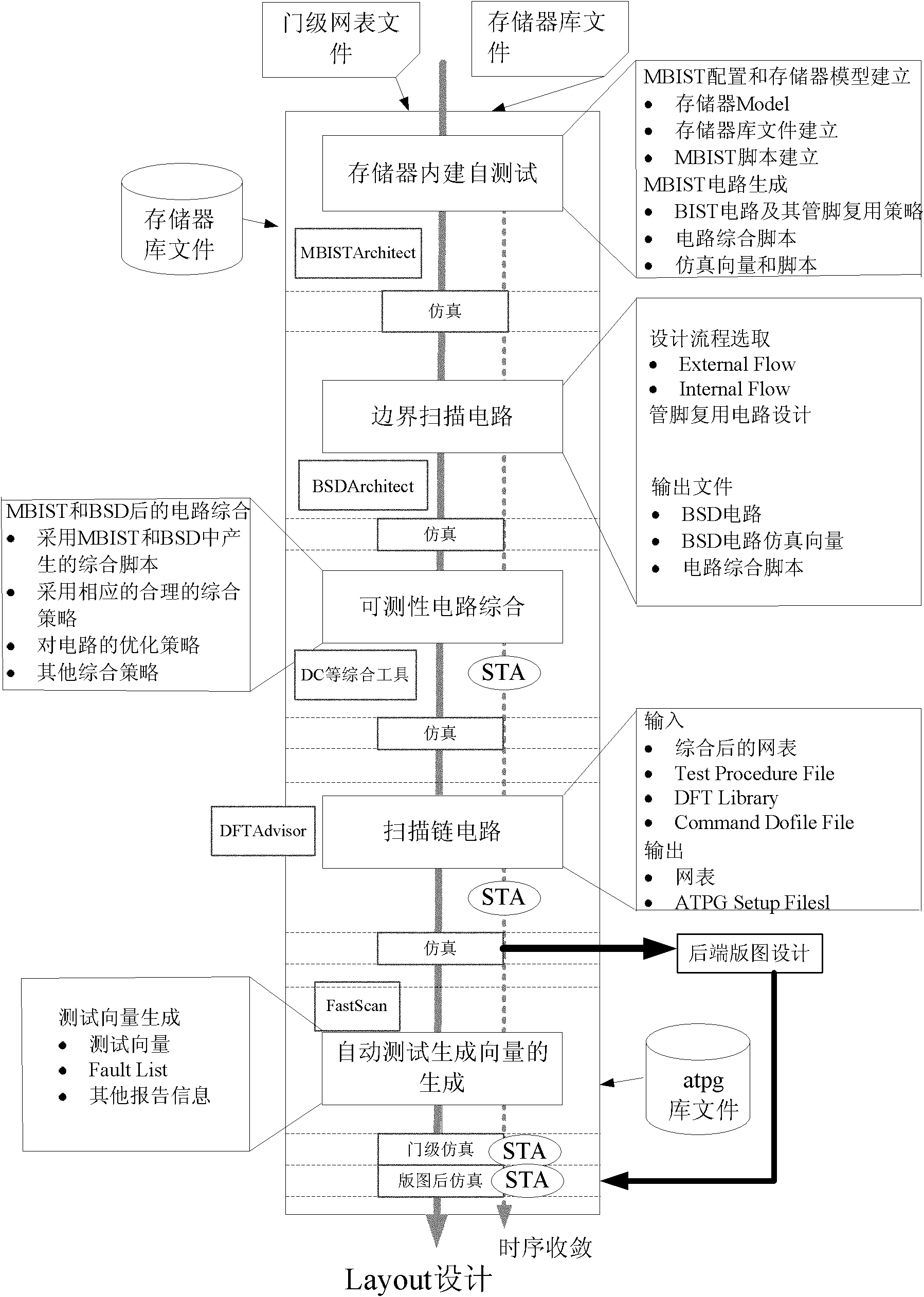

The invention relates to a method for designing testability of a chip, which comprises the steps: (1) insertion of a built-in self test circuit of a memory; (2) insertion of a boundary scan circuit; (3) integration of a testability circuit; (4) insertion of a scan chain circuit; and (5) generation of automatic test generated vectors. In order to solve the technical problems that in the traditional chip design process, a set of complete and systematical method in test methods aiming at different test objects is not available, tools such as a DFT (diagnostic function test) tool, a logic synthesis tool, a circuit simulation tool and the like are not joined and the design program is complicated, the invention provides the process guarantee for automation of the DFT design and complete and systematical correctness of the DFT design.

Owner:西安翔腾微电子科技有限公司

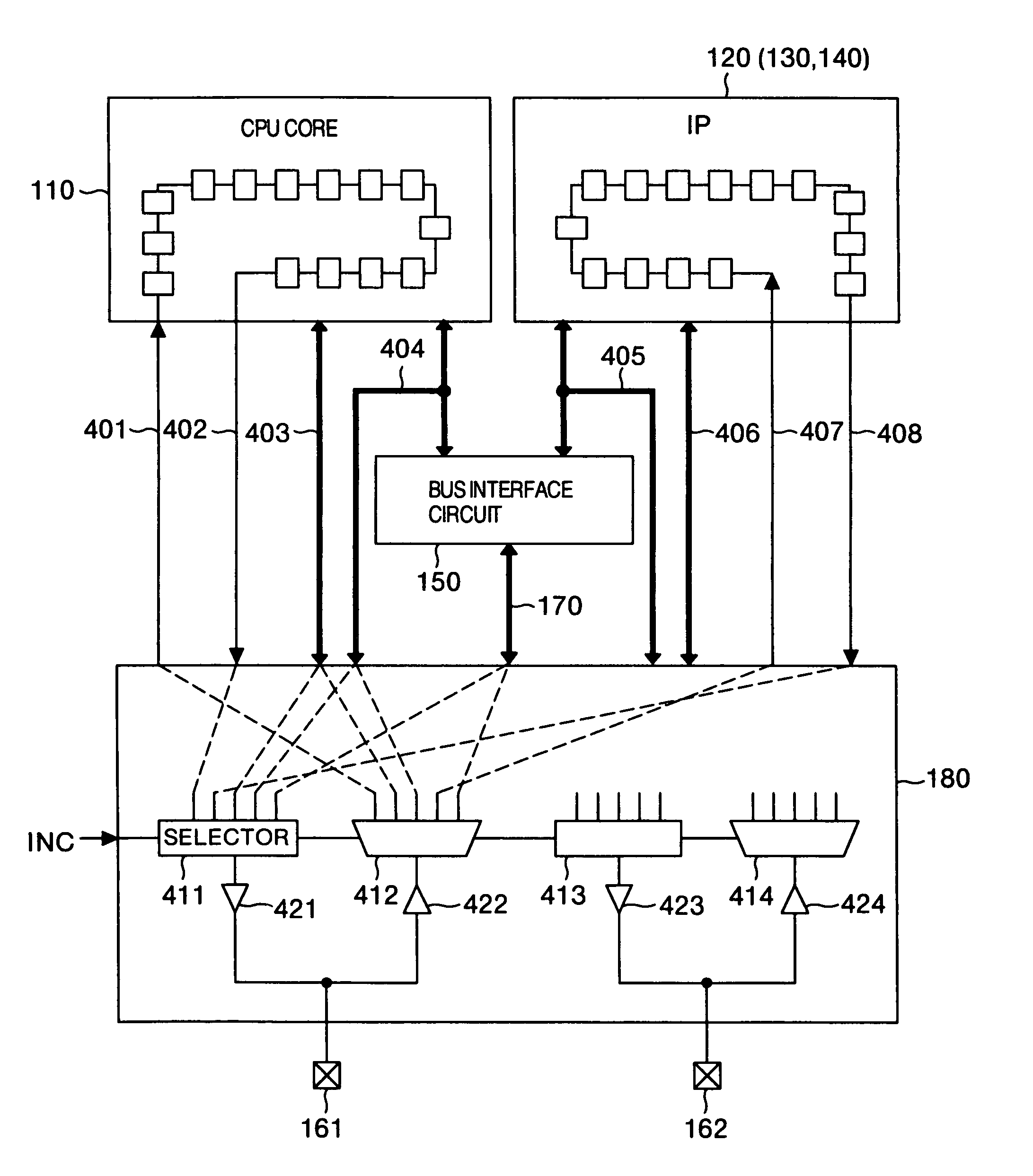

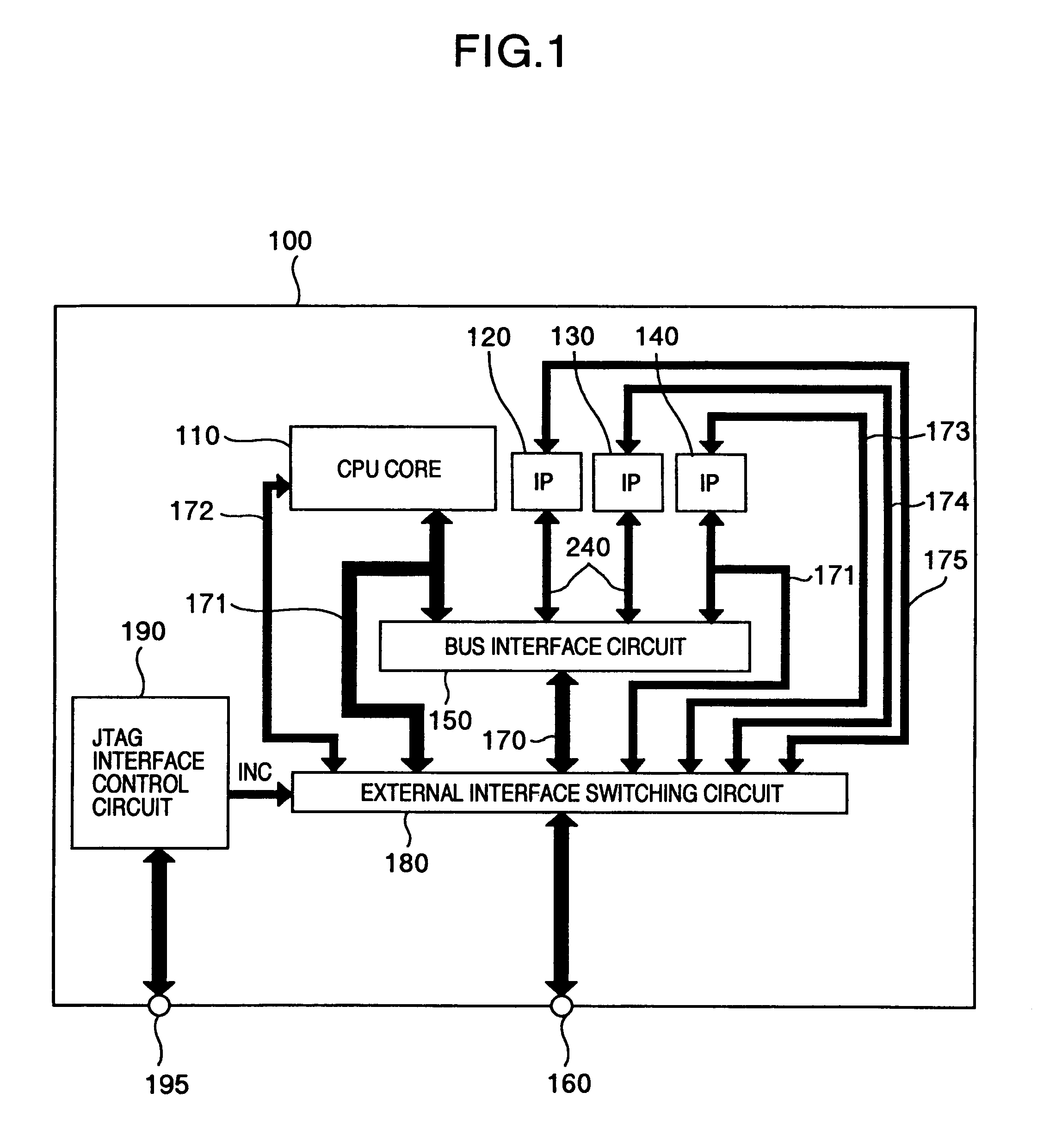

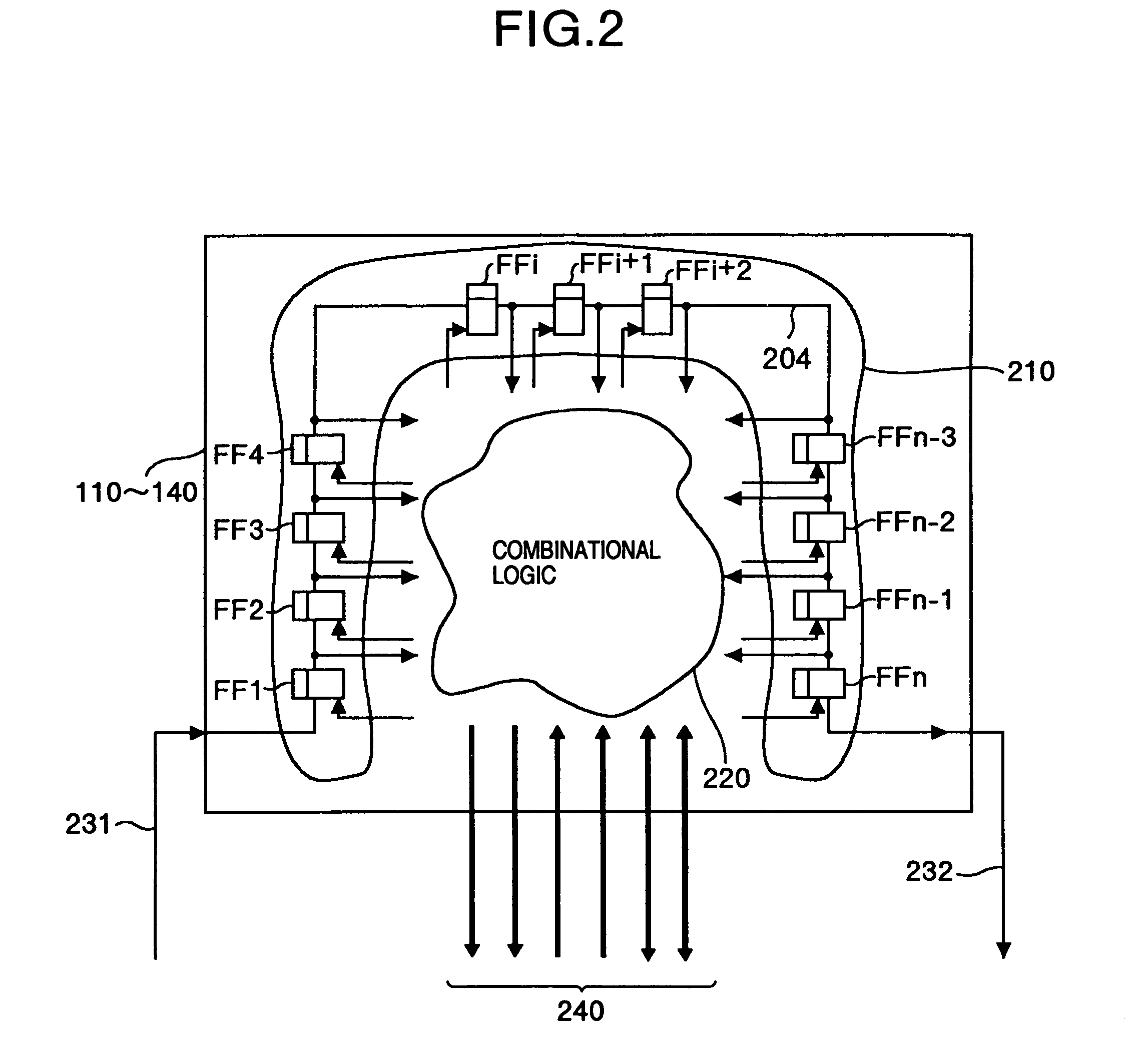

IC with internal interface switch for testability

InactiveUS7013415B1Shorten the development cycleIncrease flexibilityElectronic circuit testingError detection/correctionSemiconductor chipBus interface

A semiconductor integrated circuit which is provided with a shift scan path incorporated in each function module and a testing I / O terminal connected to a shift scan path and provided separately from a normal-operation-use I / O terminal, and which comprises, all formed on one semiconductor chip, a bus interface circuit for connecting normal-operation-use I / O terminals of a plurality of function modules to a bus, an external interface switching circuit which switches between the bus-side I / O terminal of the bus interface circuit and the testing I / O terminal of each function module for connection to an external terminal and an interface control circuit for switch-controlling the external interface switching circuit.

Owner:RENESAS ELECTRONICS CORP +1

Optimization method of capturing power consumption in scan test

InactiveCN103091620AReduce capture power consumptionElectronic circuit testingSpecial data processing applicationsTest designTest vector

The invention discloses an optimization method of capturing power consumption in a scan test. The optimization method of capturing power consumption in the scan test comprises the following steps: generating a netlist with a scan chain; grouping gating control clock units; designing a power constrain unit; combining with the generated netlist with the scan chain, conducting chip layout design which comprises a floorpan, a layout, a clock tree sythesis and wiring; reading a gate-level netlist with a scan structure, a process library, a timing sequence constrain file and a test protocol into an automatic test vector generating tool after the chip layout design is completed, conducting testability design rule checking, and generating a test vector; and conducting gate-level simulation to the test vector generated. By means of the optimization method of capturing the power consumption in the scan test, the capturing power consumption in a test process can be reduced significantly, the reduction of coverage or the sharp increase of the quantity of test vectors is not generated, changing of a test design process is needless, and realization is easy.

Owner:JIANGSU SEUIC TECH CO LTD

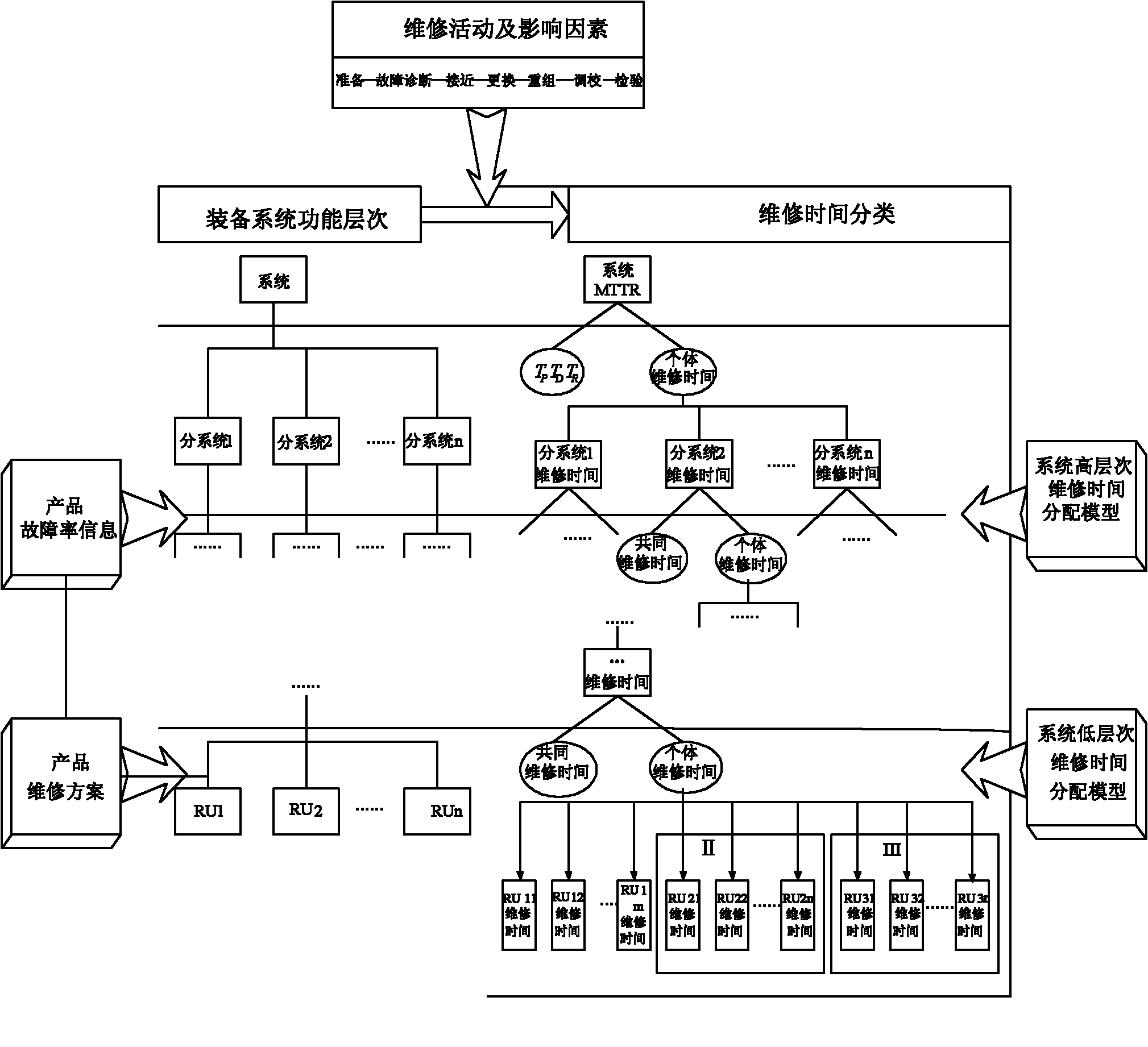

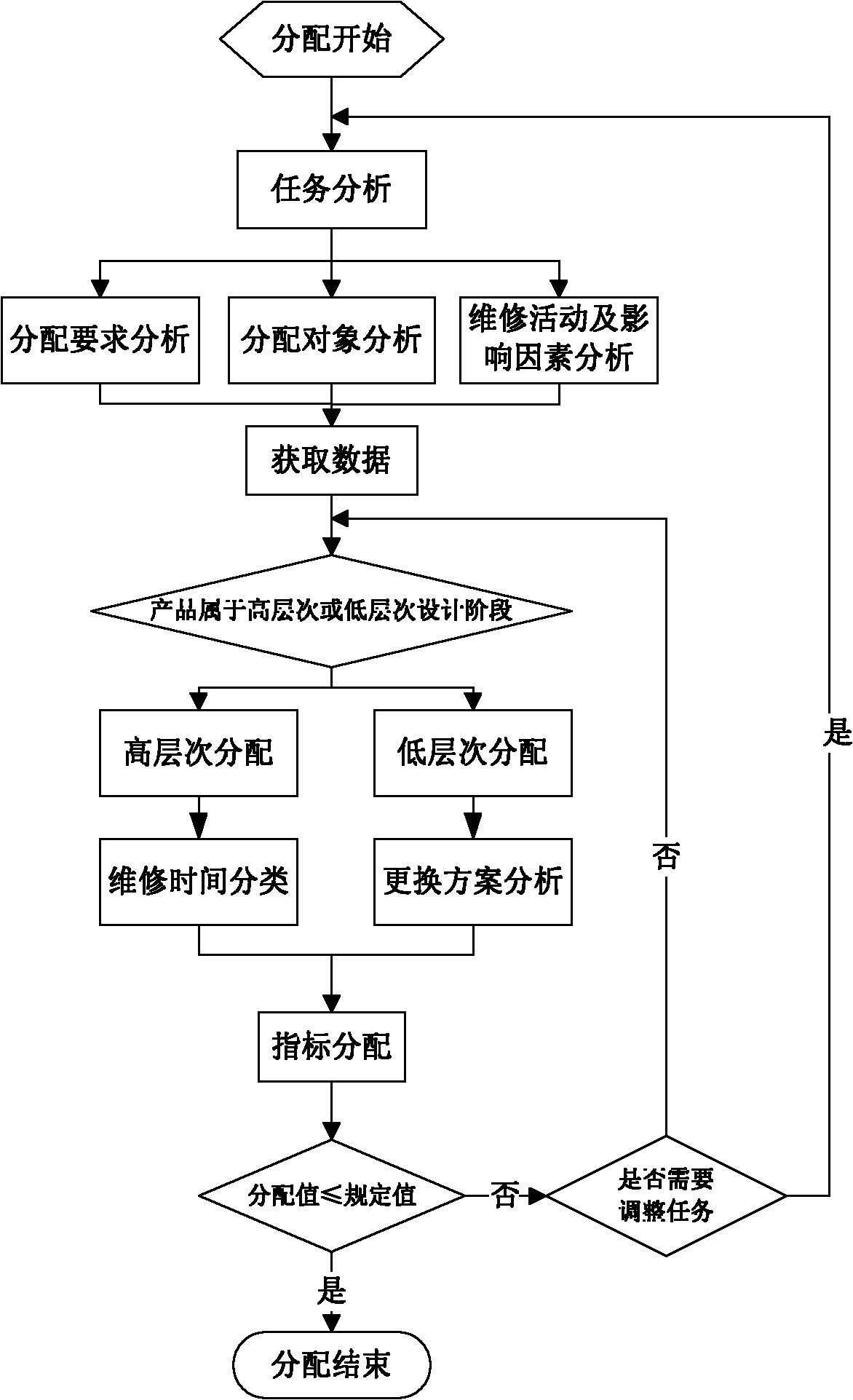

System maintenance time distribution method based on operation decomposition

InactiveCN102147889AClear time targetClear maintainability indicatorsInstrumentsTask analysisDecomposition

The invention relates to a system maintenance time distribution method based on operation decomposition, which comprises the following steps: 1. analyzing tasks, the step of analyzing the tasks comprises distribution request analysis, distribution object analysis, maintenance activity and influence factor analysis, wherein the distribution object analysis is mainly used for determining distributive system levels, functions and structural levels of all components of a device, and a product decomposed into the needed level by the system, namely, a replaceable unit, and mapping systemic functions and structural level diagrams; and the number of the levels is determined by complexity level of the device; 2. obtaining data, obtaining existing data of a distribution object required to be analyzed, namely, data of a similar product, fault frequency data, reachability data, testability data and the like; 3. selecting a distribution method, selecting high-level distribution or low-level distribution according to the stage of product design and the product level; 4. distributing indexes, distributing maintainability indexes of the given product to product units at all levels according to the selected method; 5. analyzing a result, judging whether a distribution result is in line with requirements and is feasible.

Owner:BEIHANG UNIV

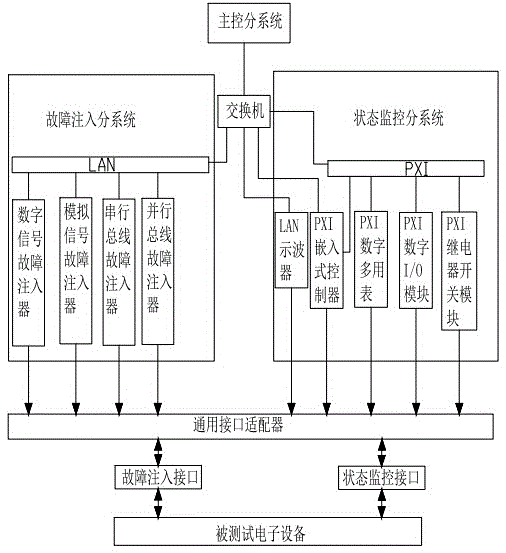

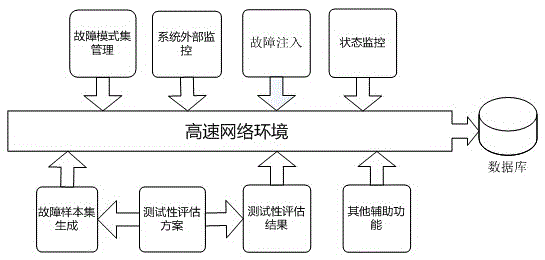

Universal system for electronic equipment testability validation and evaluation and testing method

The present invention discloses a universal system for electronic equipment testability validation and evaluation and a testing method, relating to the technical field of the monitoring device or method of electronic equipment. A master control subsystem is used for generating a fault signal and injecting the fault signal into a fault injection subsystem. A state monitoring sub system is used for collecting corresponding fault signal information according to a fault signal monitoring point set by a user, transmitting the information to the master control subsystem in real time and carrying out displaying. The fault injection subsystem is used for generating a corresponding fault signal according to the control command issued by the master control subsystem, coupling and transferring the generated fault signal and inputting the signal to tested electronic equipment through a universal adapter. According to the system, enough failure modes, testing resources and flexible software and hardware configurations are provided, and the various testability validation and evaluation tests of actual electronic equipment can be accurately supported.

Owner:NO 63908 TROOPS PLA