Patents

Literature

56 results about "Design for testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

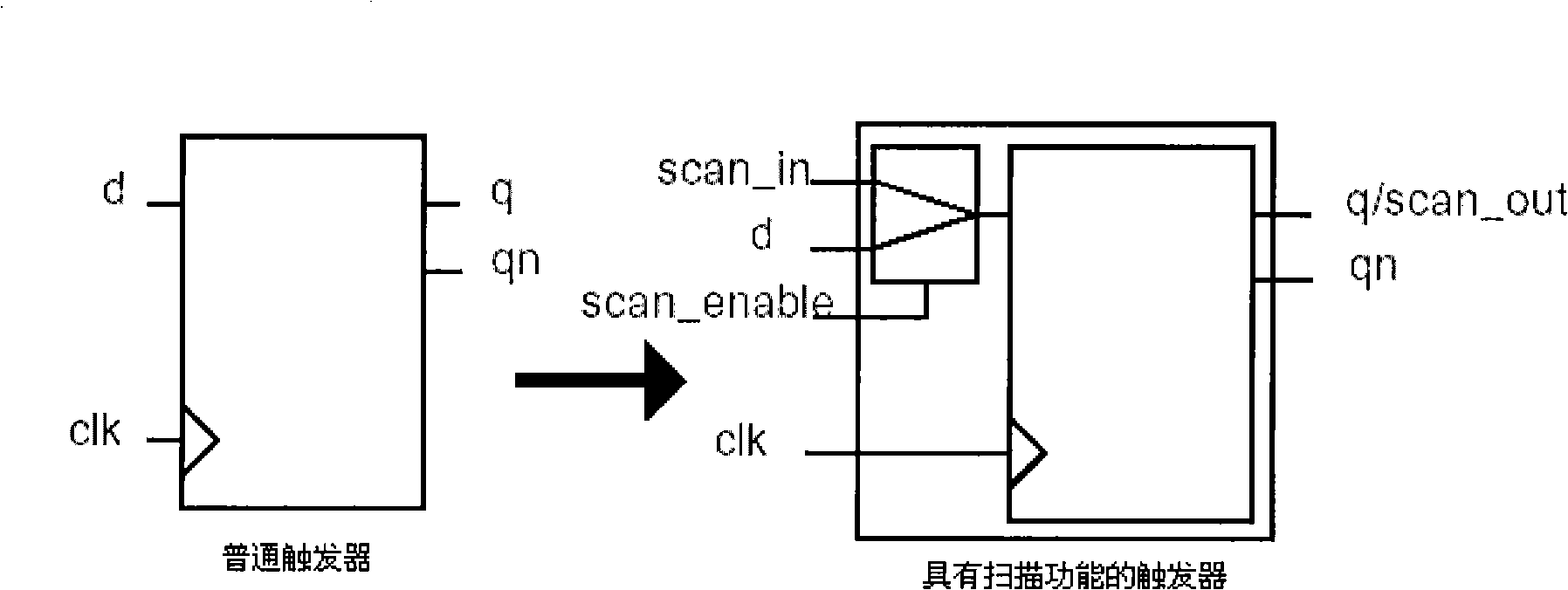

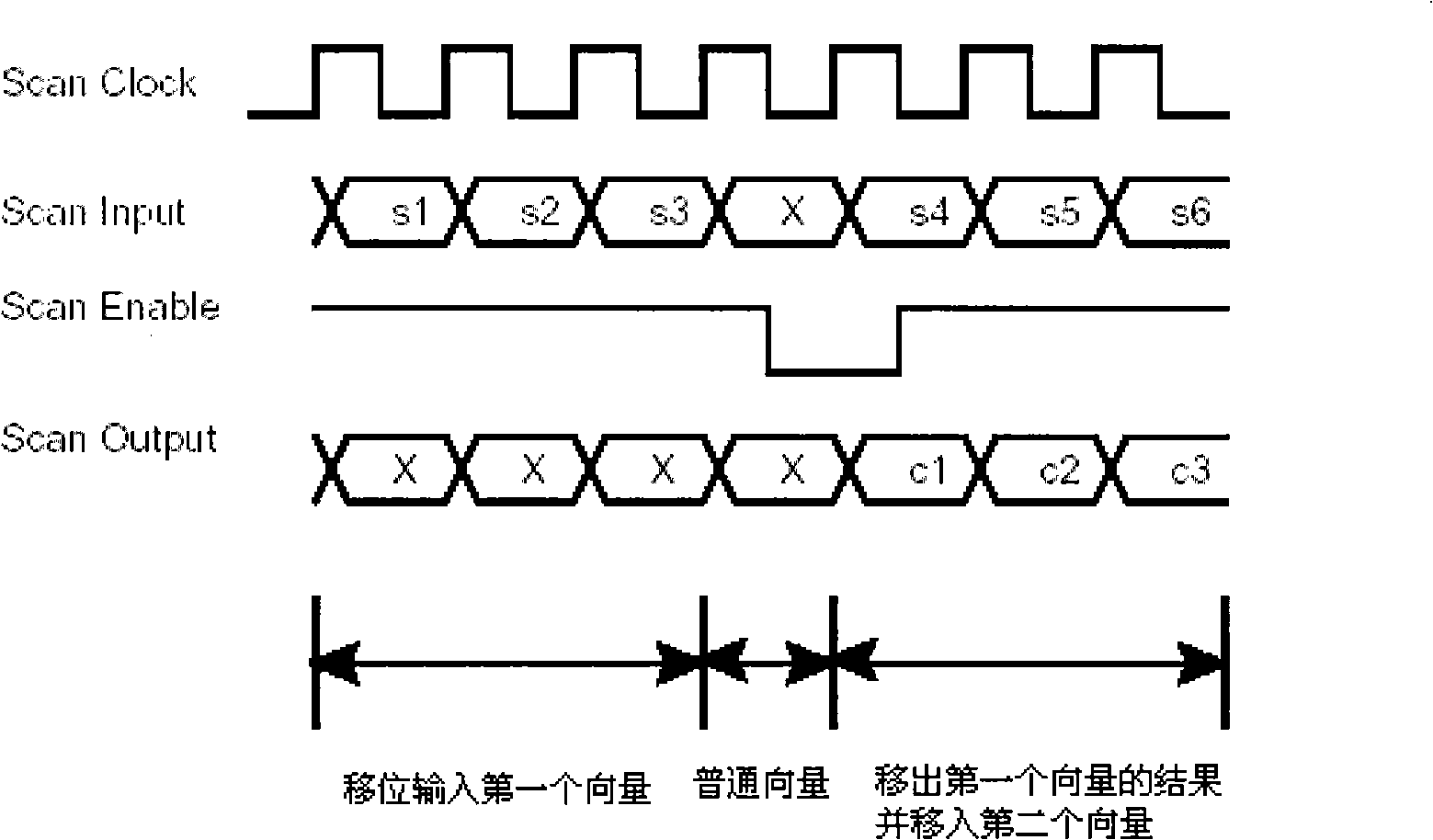

Design for testing or design for testability (DFT) consists of IC design techniques that add testability features to a hardware product design. The added features make it easier to develop and apply manufacturing tests to the designed hardware. The purpose of manufacturing tests is to validate that the product hardware contains no manufacturing defects that could adversely affect the product's correct functioning.

Method for designing testability of chip

ActiveCN102081689AHigh degree of automationSpecial data processing applicationsDesign for testingComputer architecture

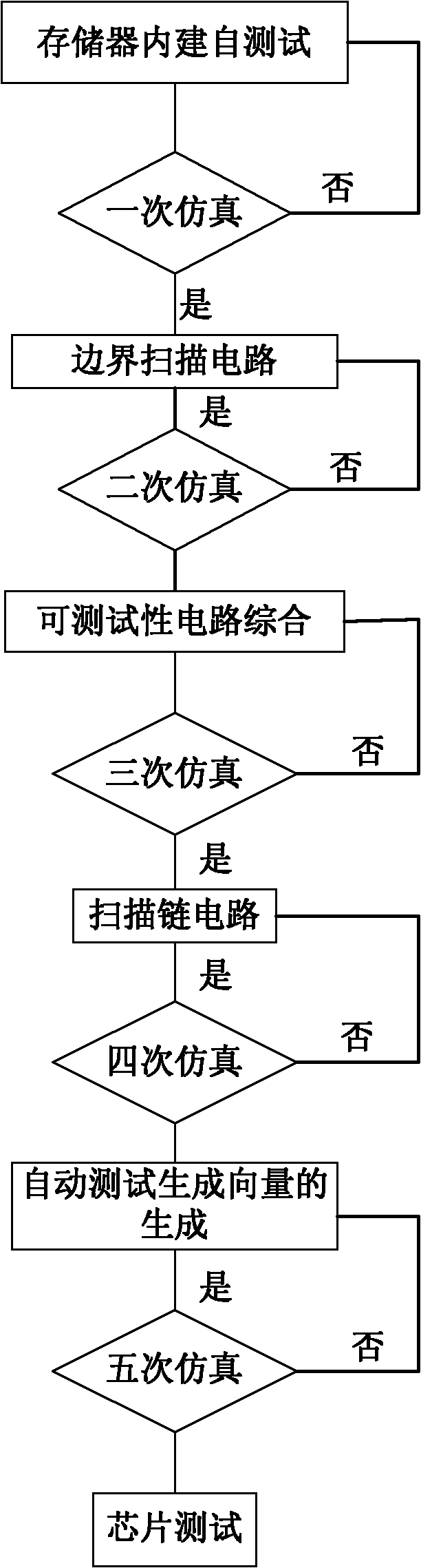

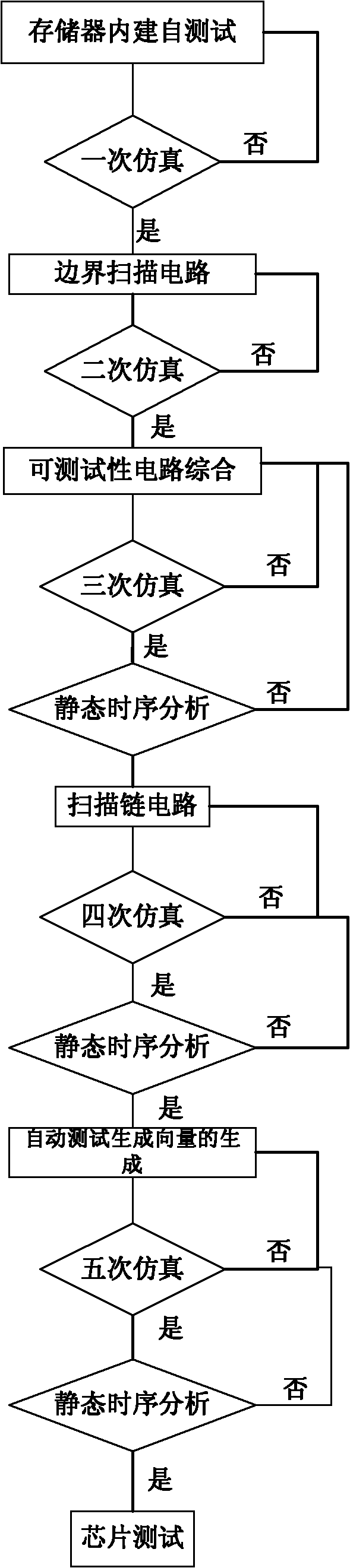

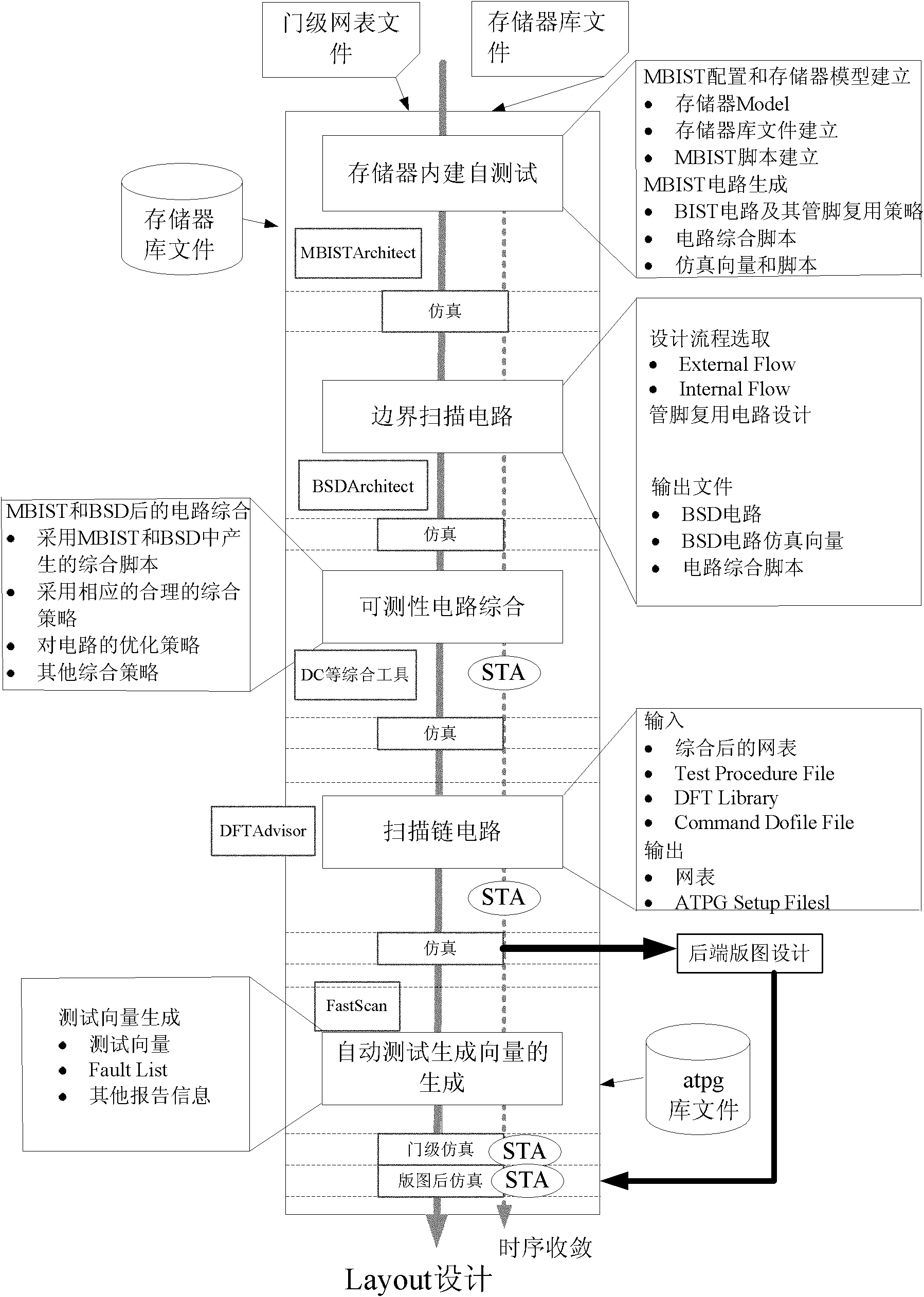

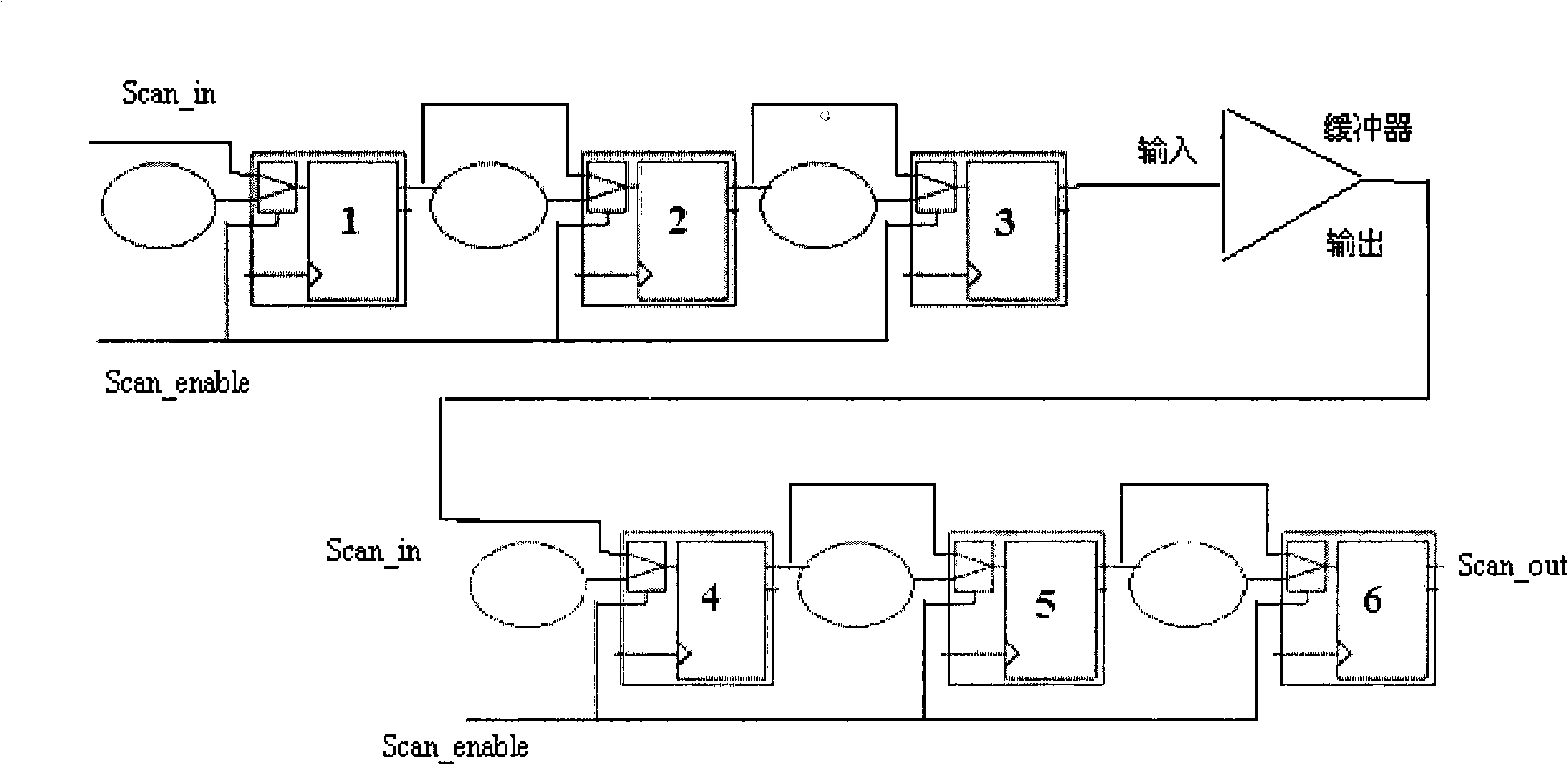

The invention relates to a method for designing testability of a chip, which comprises the steps: (1) insertion of a built-in self test circuit of a memory; (2) insertion of a boundary scan circuit; (3) integration of a testability circuit; (4) insertion of a scan chain circuit; and (5) generation of automatic test generated vectors. In order to solve the technical problems that in the traditional chip design process, a set of complete and systematical method in test methods aiming at different test objects is not available, tools such as a DFT (diagnostic function test) tool, a logic synthesis tool, a circuit simulation tool and the like are not joined and the design program is complicated, the invention provides the process guarantee for automation of the DFT design and complete and systematical correctness of the DFT design.

Owner:西安翔腾微电子科技有限公司

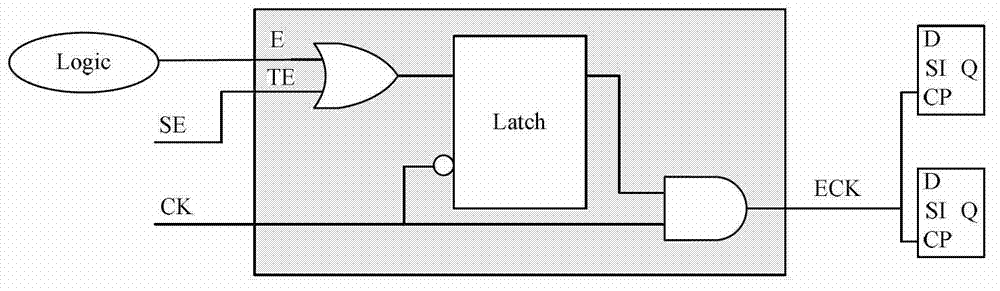

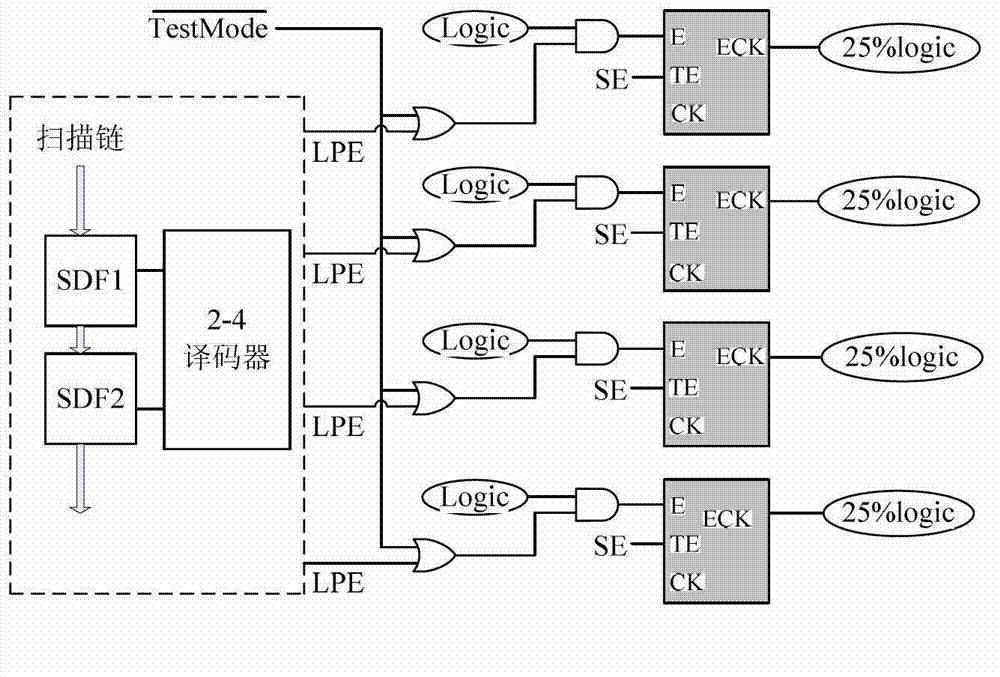

Optimization method of capturing power consumption in scan test

InactiveCN103091620AReduce capture power consumptionElectronic circuit testingSpecial data processing applicationsTest designTest vector

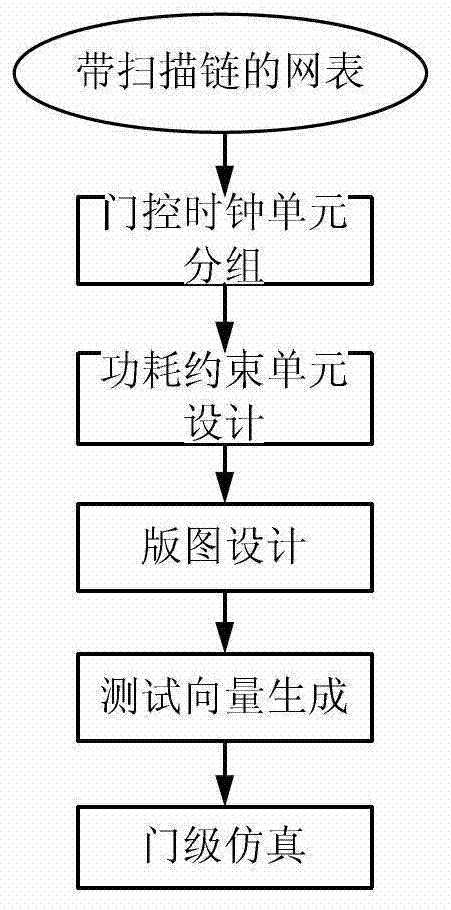

The invention discloses an optimization method of capturing power consumption in a scan test. The optimization method of capturing power consumption in the scan test comprises the following steps: generating a netlist with a scan chain; grouping gating control clock units; designing a power constrain unit; combining with the generated netlist with the scan chain, conducting chip layout design which comprises a floorpan, a layout, a clock tree sythesis and wiring; reading a gate-level netlist with a scan structure, a process library, a timing sequence constrain file and a test protocol into an automatic test vector generating tool after the chip layout design is completed, conducting testability design rule checking, and generating a test vector; and conducting gate-level simulation to the test vector generated. By means of the optimization method of capturing the power consumption in the scan test, the capturing power consumption in a test process can be reduced significantly, the reduction of coverage or the sharp increase of the quantity of test vectors is not generated, changing of a test design process is needless, and realization is easy.

Owner:JIANGSU SEUIC TECH CO LTD

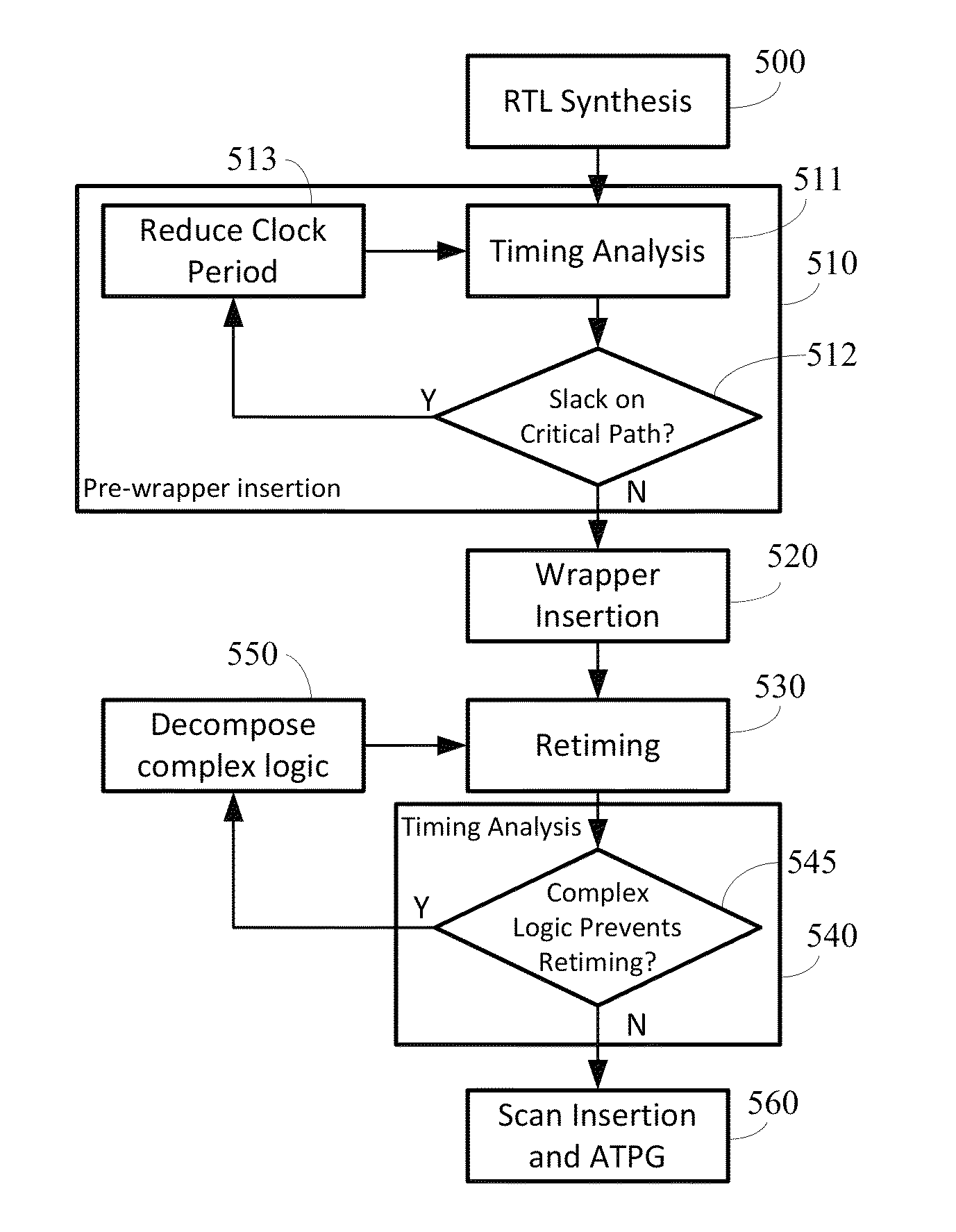

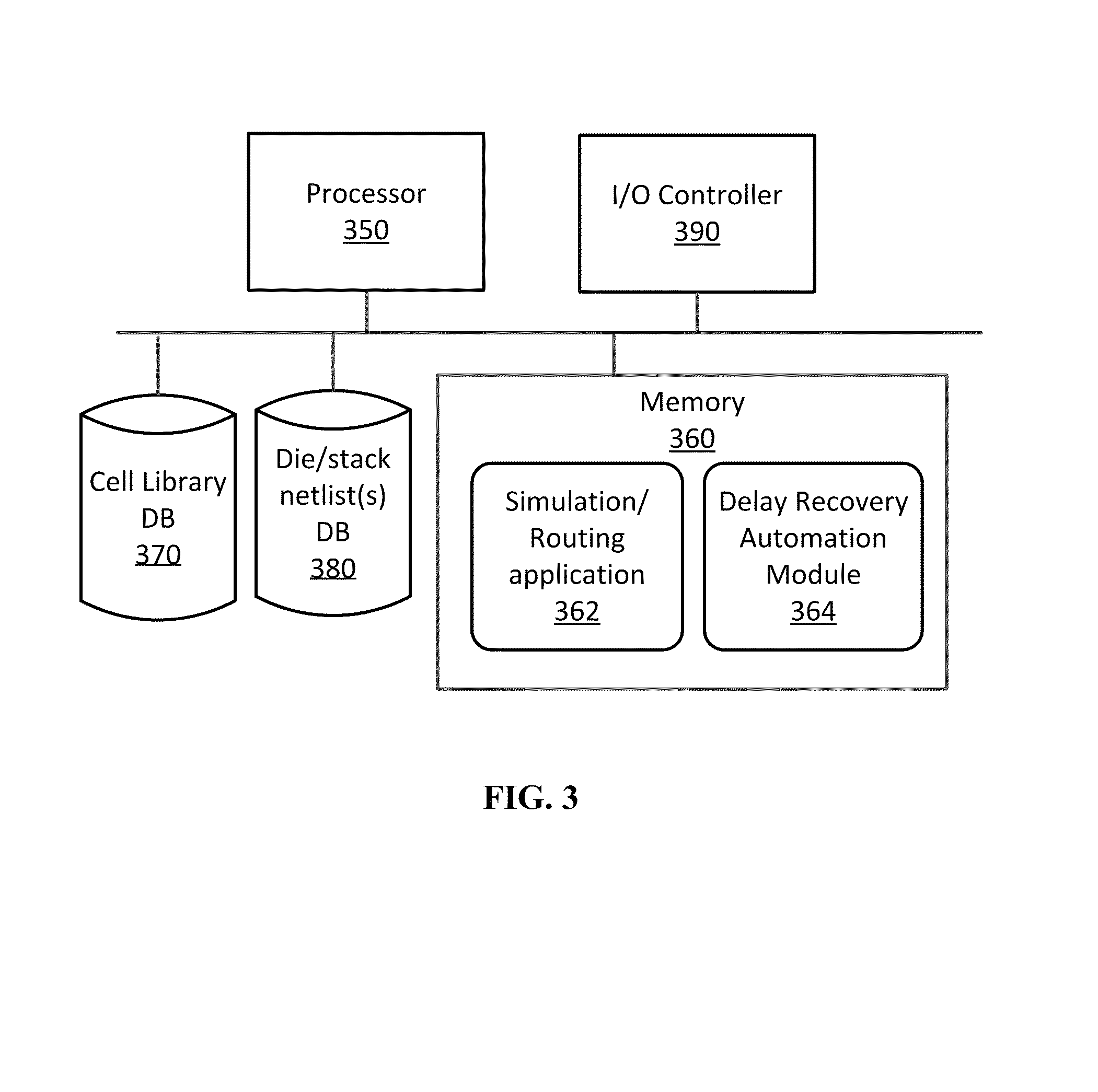

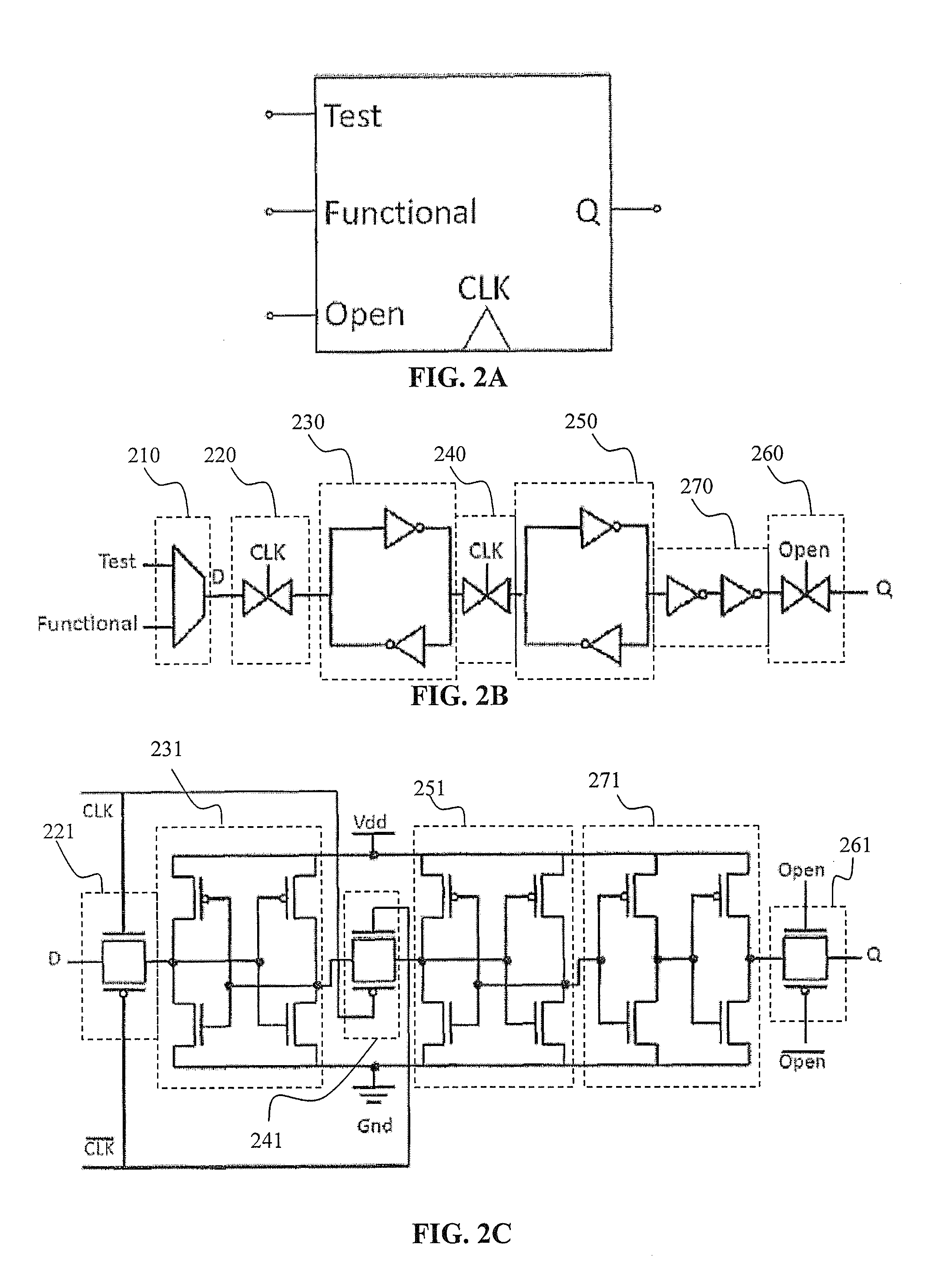

Retiming-based design flow for delay recovery on inter-die paths in 3D ICs

InactiveUS8832608B1Increase delayImprove latencyComputer aided designSpecial data processing applicationsDesign for testingDesign testing

A three dimensional (3D) stacked integrated circuit (IC) design-for-Testing (DfT) die-level wrapper boundary register having a bypass mode and design-level DfT delay recovery techniques are provided. Die wrappers that contain boundary registers at the interface between dies can be inserted into 3D ICs where the boundary registers include a gated scan flop with a bypass line passing the functional input to a through-silicon-via (TSV) in a manner avoiding the clocked stages of the gated scan flop during functional operation. A retiming process can be applied during design layout using a simulation / routing tool or standalone program to recover the additional delay added to the TSV paths by the DfT insertion. Retiming can be performed at both die and stack level, and in further embodiments, logic redistribution across adjacent dies of the stack can be performed for further delay optimization.

Owner:DUKE UNIV

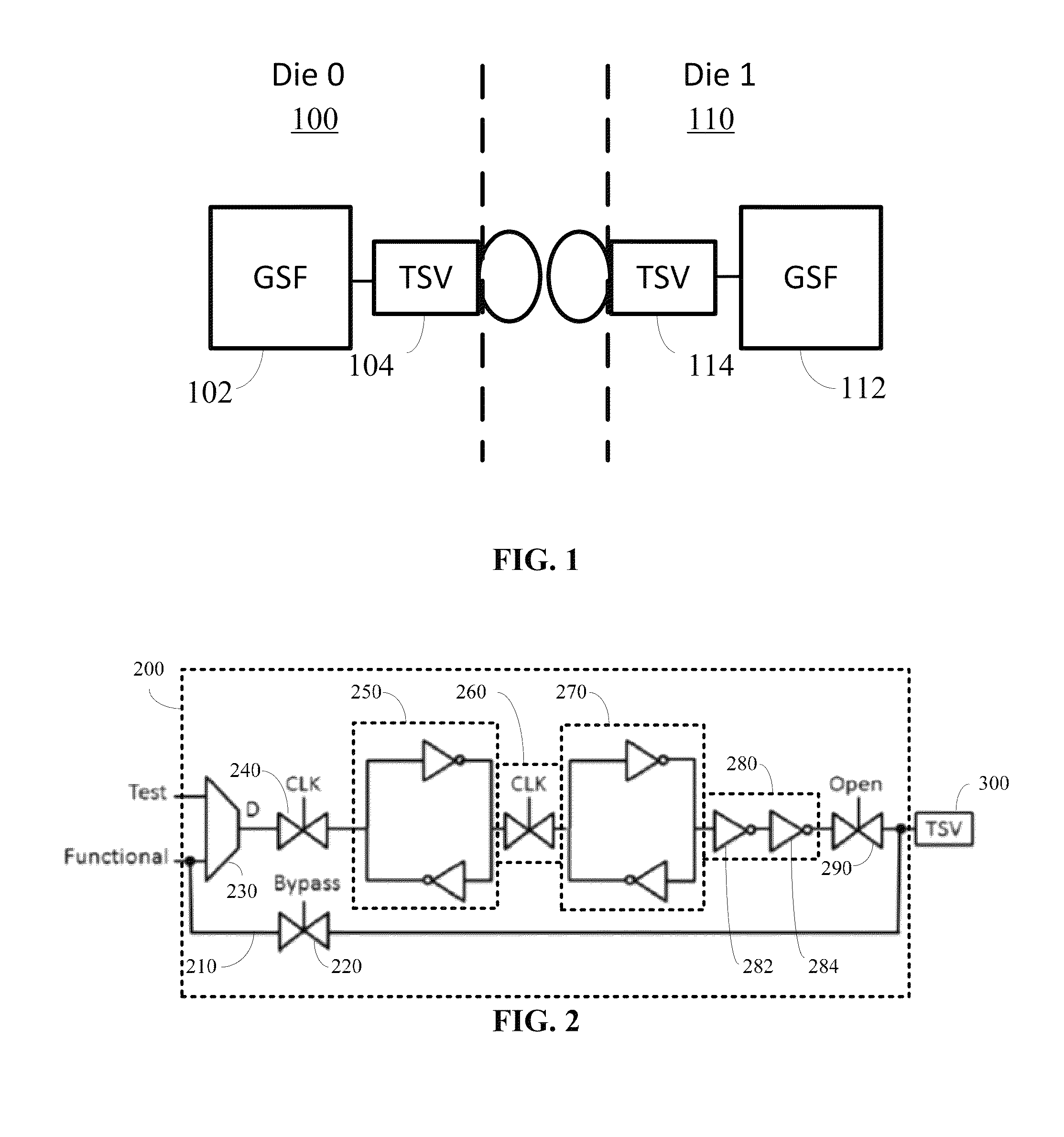

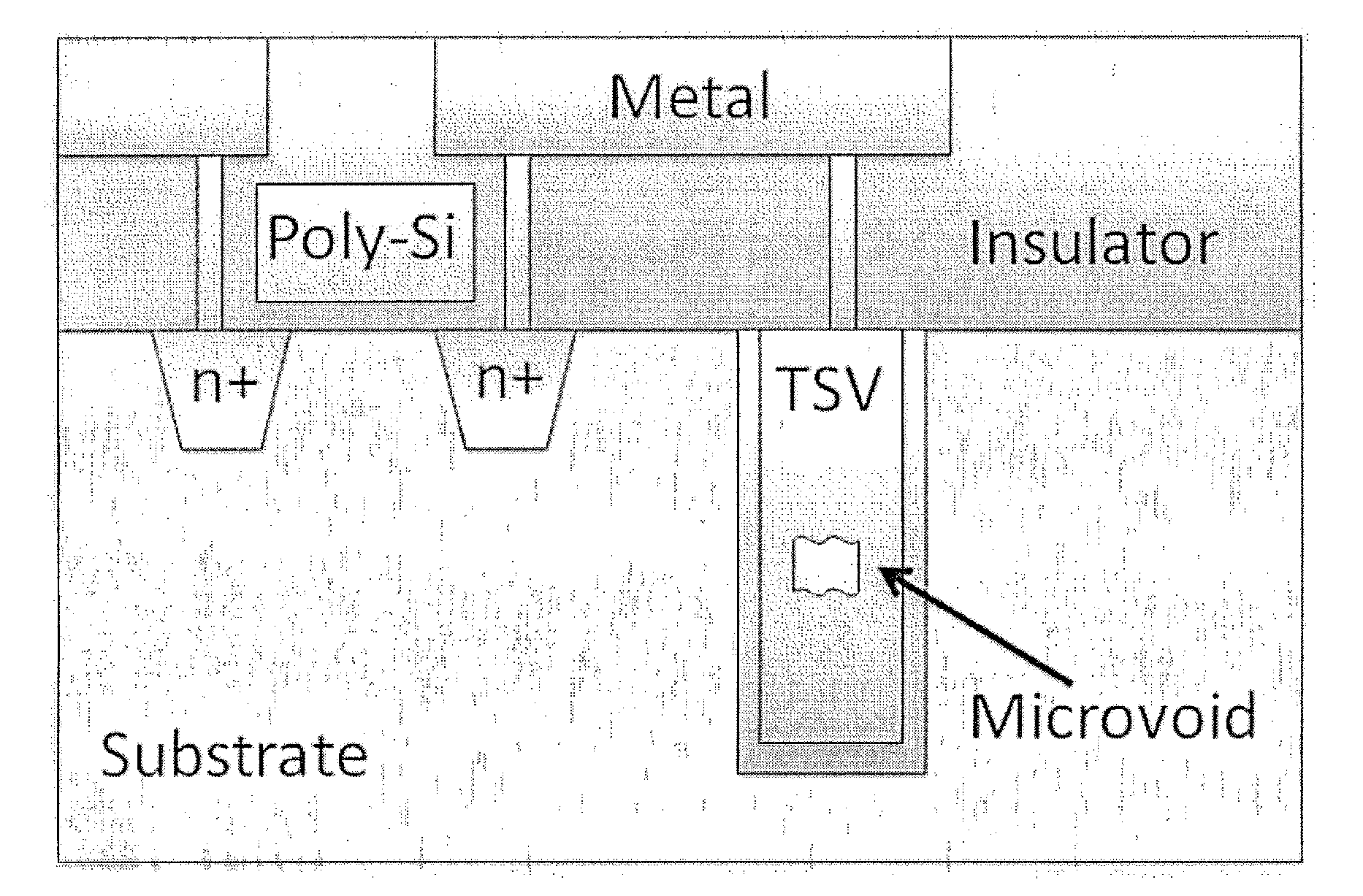

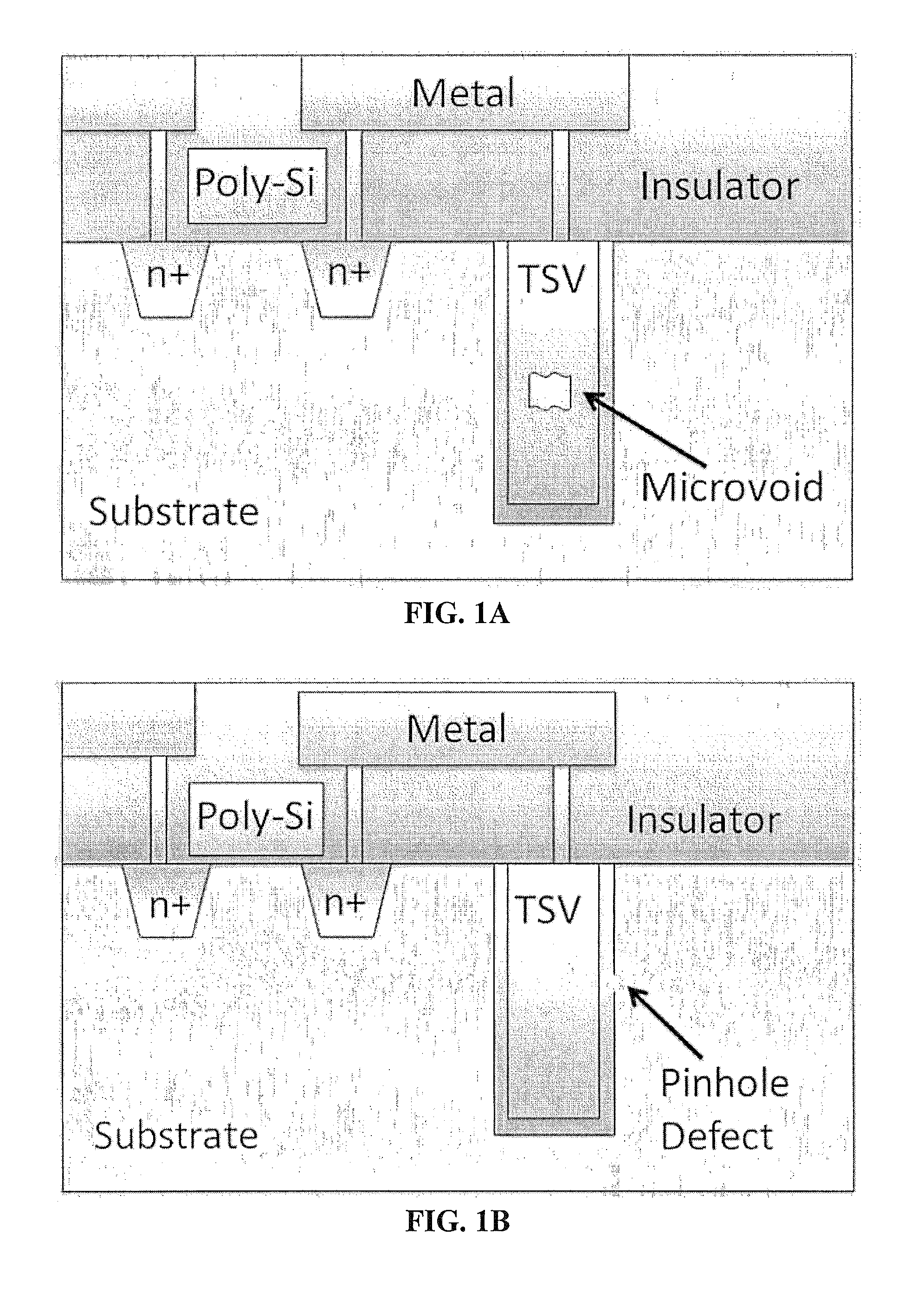

METHOD AND ARCHITECTURE FOR PRE-BOND PROBING OF TSVs IN 3D STACKED INTEGRATED CIRCUITS

ActiveUS20130006557A1Facilitate defect localizationPromote repairSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceCapacitanceDesign for testing

On-chip test architecture and design-for-testability methods for pre-bond testing of TSVs are provided. In accordance with certain embodiments of the invention, a die level wrapper is provided including gated scan flops connected to one end of each TSV. The gated scan flops include a scan flop structure and a gated output. The gated output is controlled by a signal to cause the output of the gated scan flop to either be in a “floated state” or take the value stored in the flip-flop portion of the gated scan flop. The gated output of the gated scan flop can be used to enable resistance and capacitance measurements of pre-bonded TSVs.

Owner:DUKE UNIV

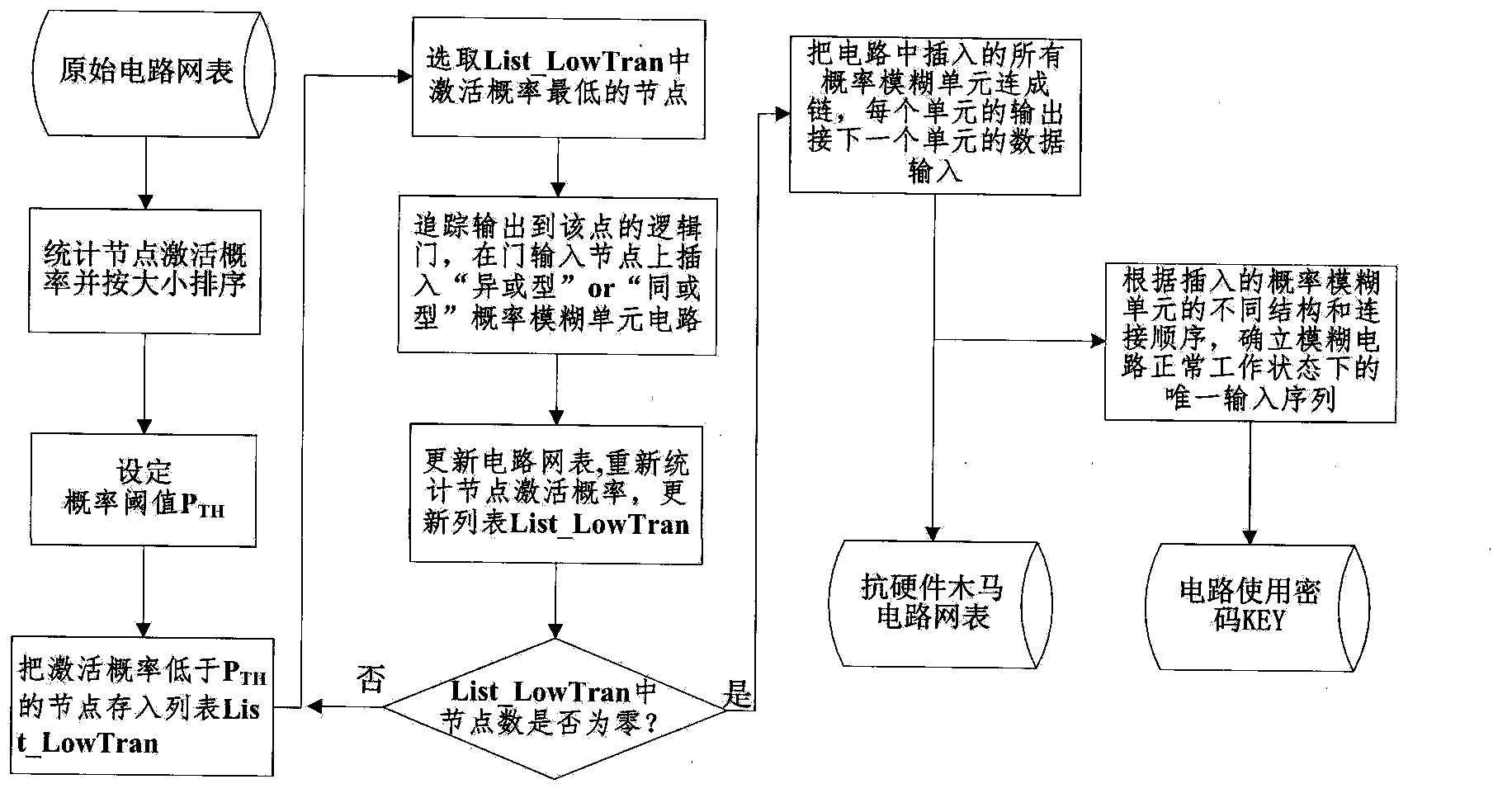

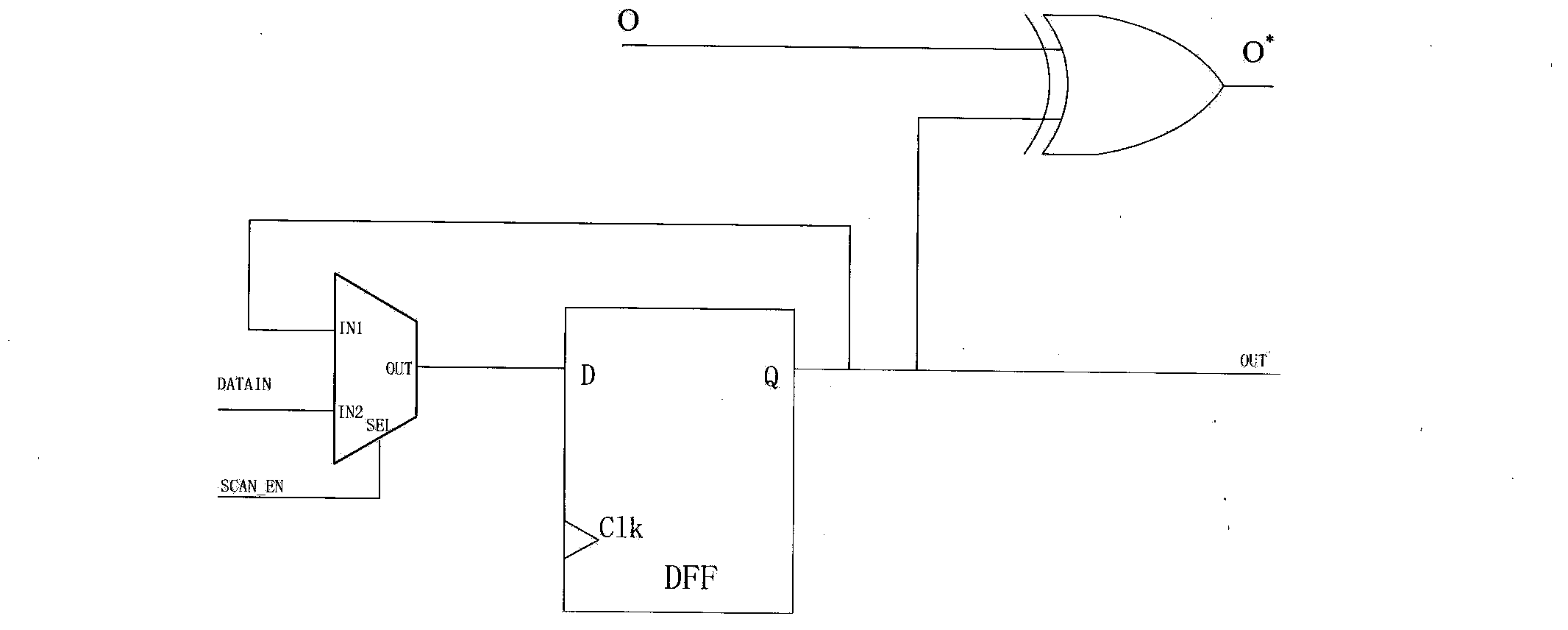

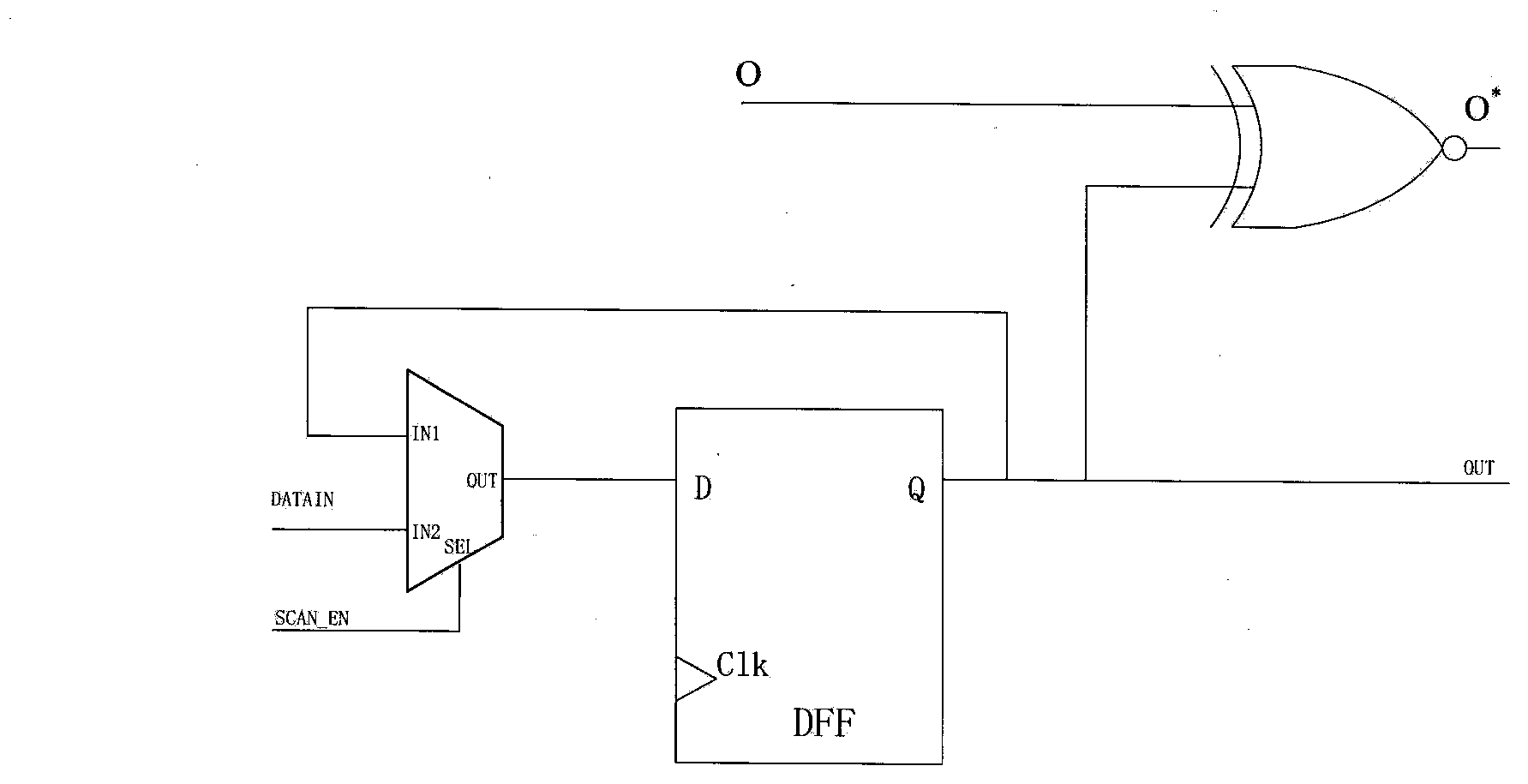

Hardware-Trojan-resisting circuit design method based on activation probability analysis

ActiveCN104101828AImprove the immunityIncreased protectionElectrical testingDesign for testingAlgorithm

The invention relates to the field of testability design of an integrated-circuit technology and discloses a hardware-Trojan-resisting circuit design method based on activation probability analysis. The method mainly includes two parts: a first part: circuit design of a probability fuzziness unit and a second part: an insertion algorithm of the probability fuzziness unit. Targeting at characteristics of high elusiveness and high perniciousness of hardware Trojans, through analysis of a circuit node activation probability, the method selects an appropriate node to insert the probability fuzziness unit circuit so that an attacker is incapable of correctly judging a signal jumping probability of nodes in the circuit and inserts hardware Trojans only based on the circuit which undergoes probability fuzziness. Compared with the prior art, the hardware-Trojan-resisting circuit design method based on activation probability analysis is capable of strengthening the hardware Trojan resisting capability of a design circuit so that implanted hardware Trojans are incapable of achieving a specific objective designed by an attacker and are easily detectable in a test period.

Owner:PEKING UNIV

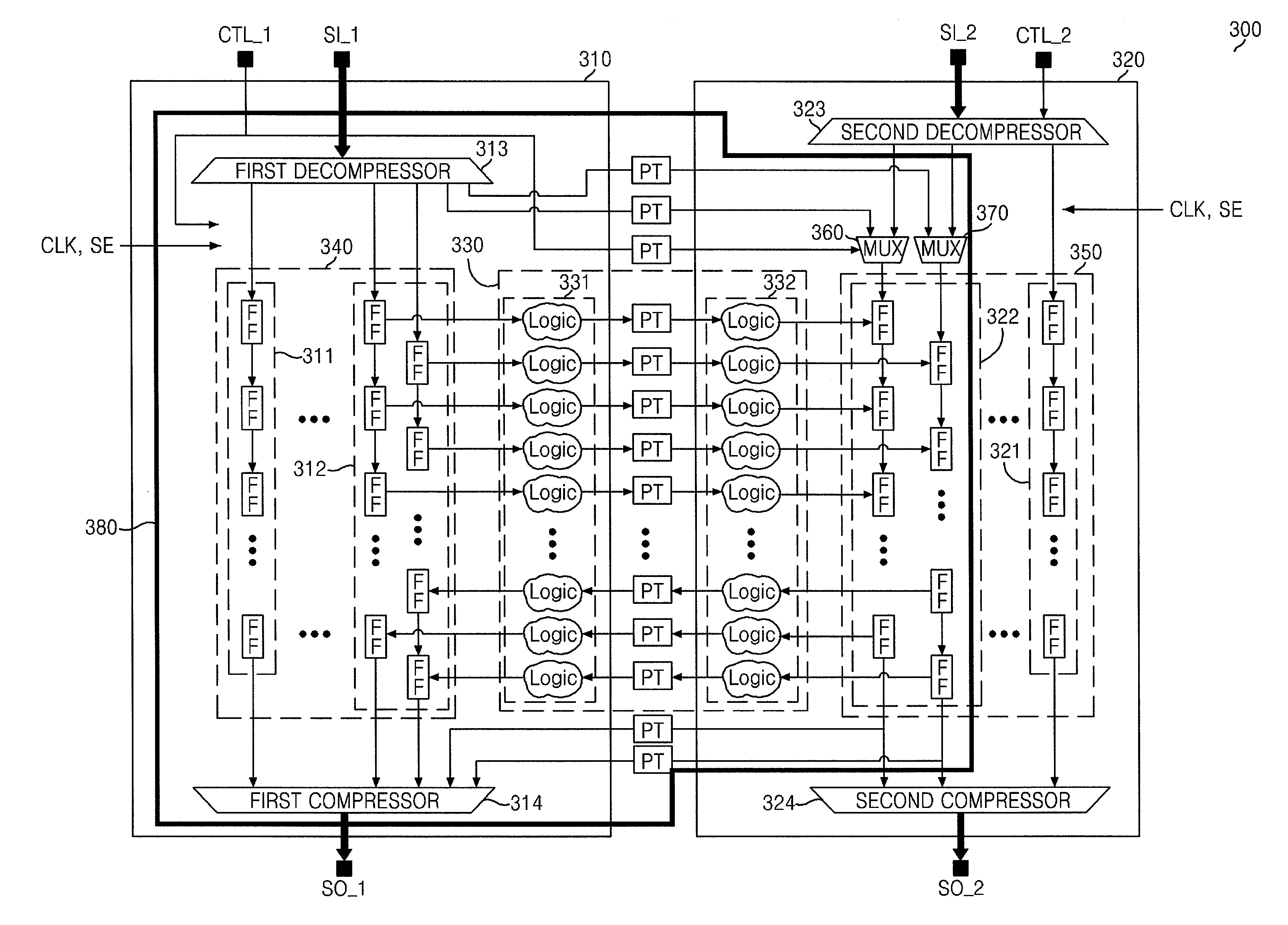

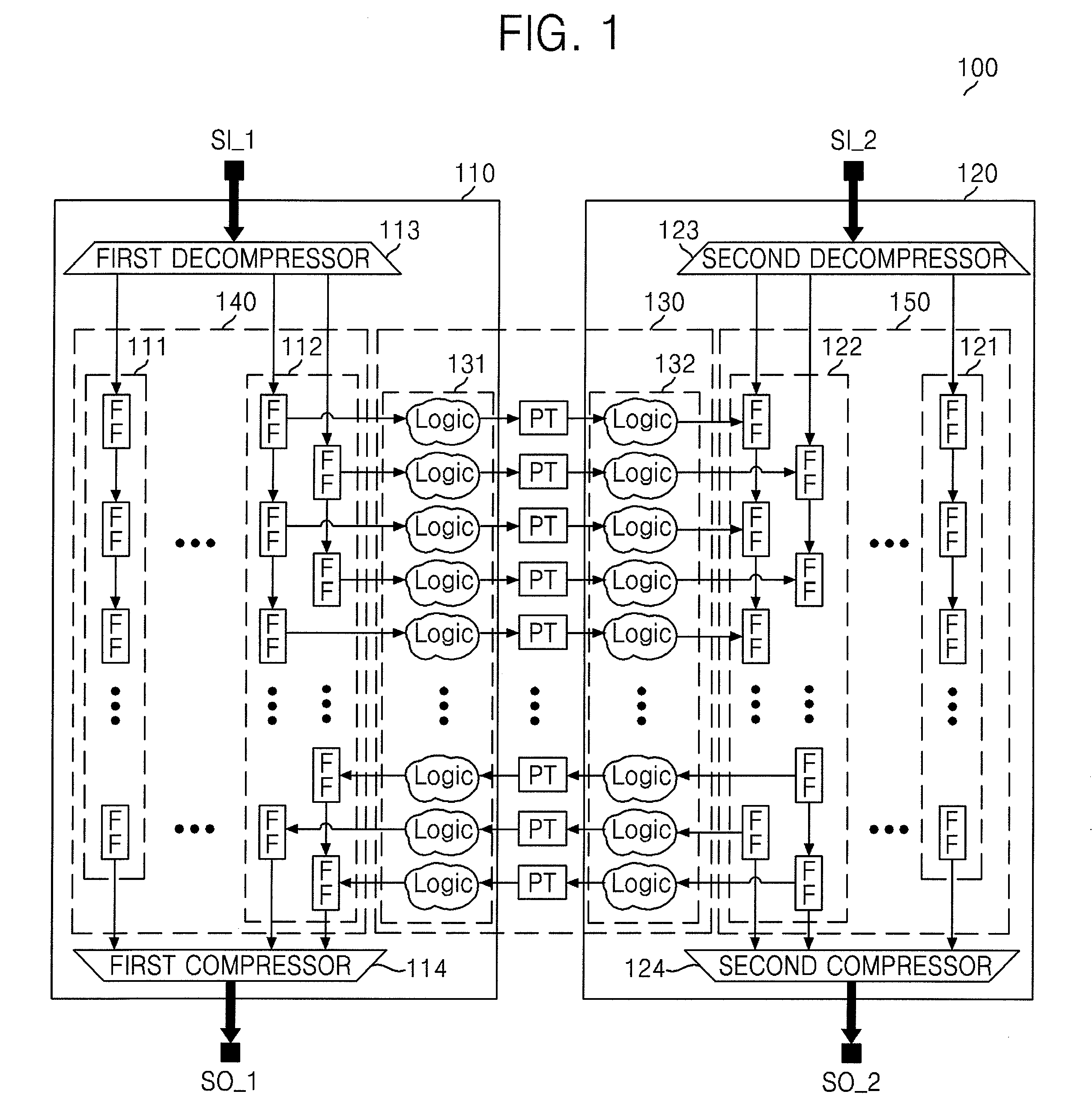

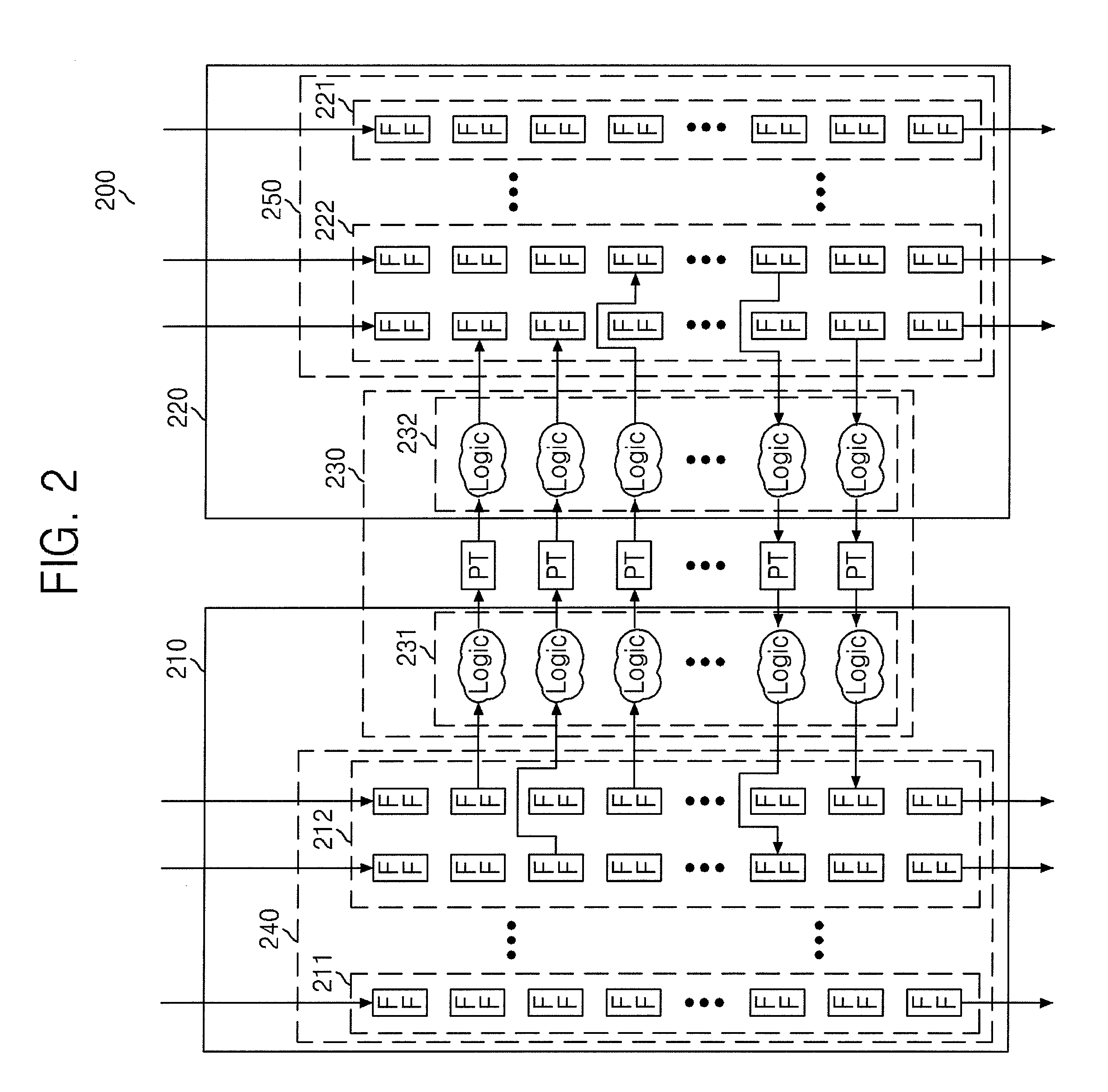

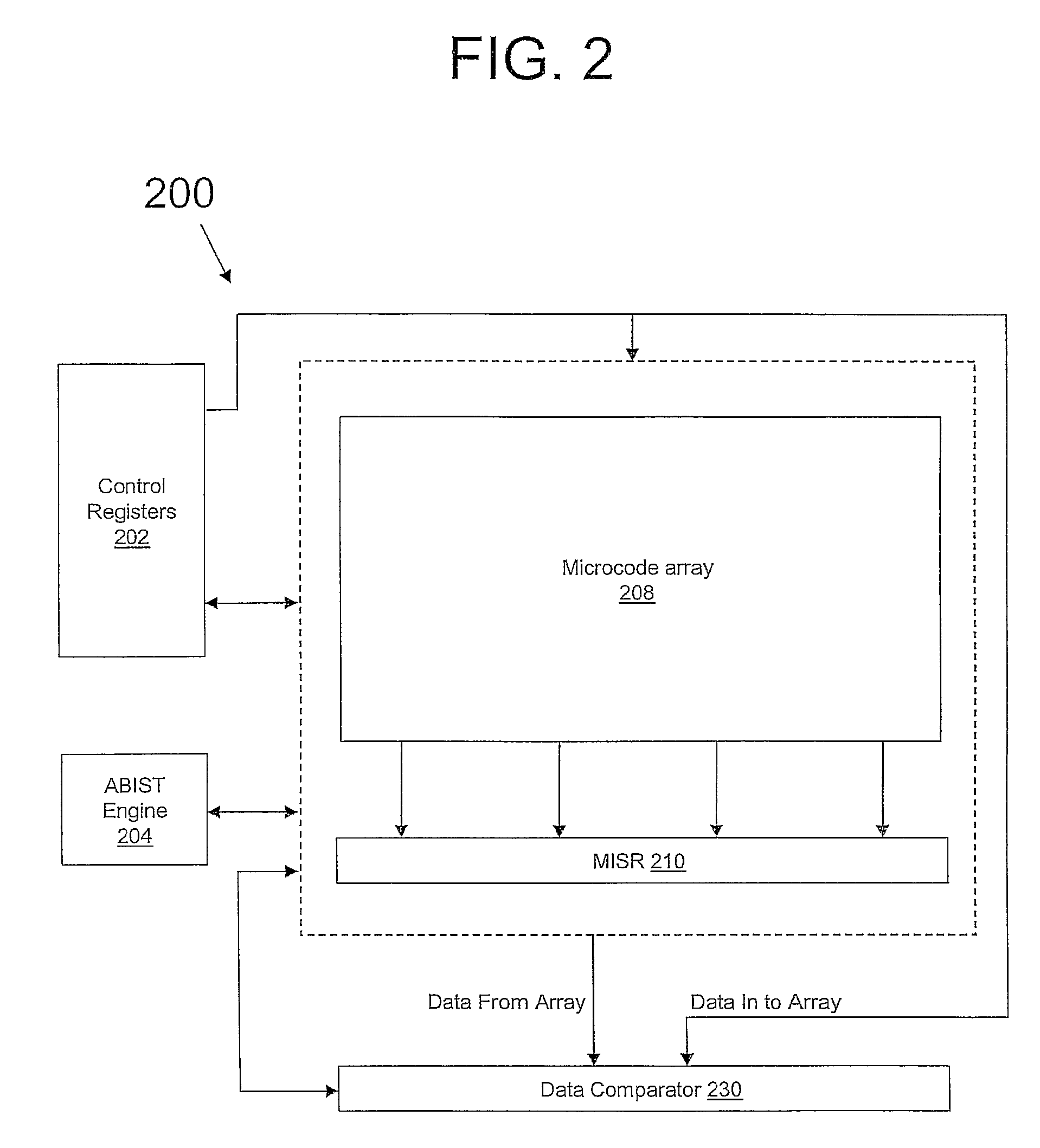

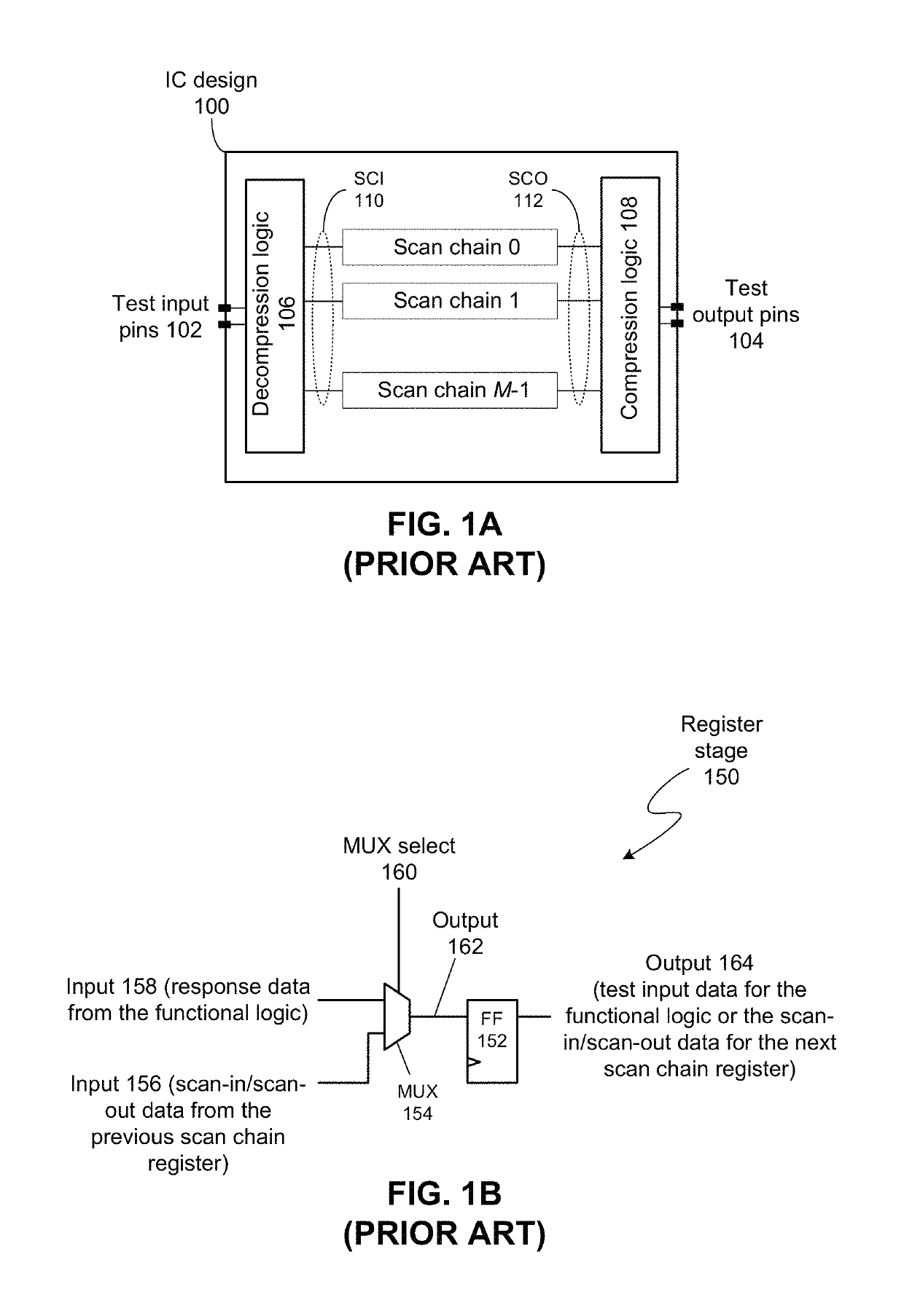

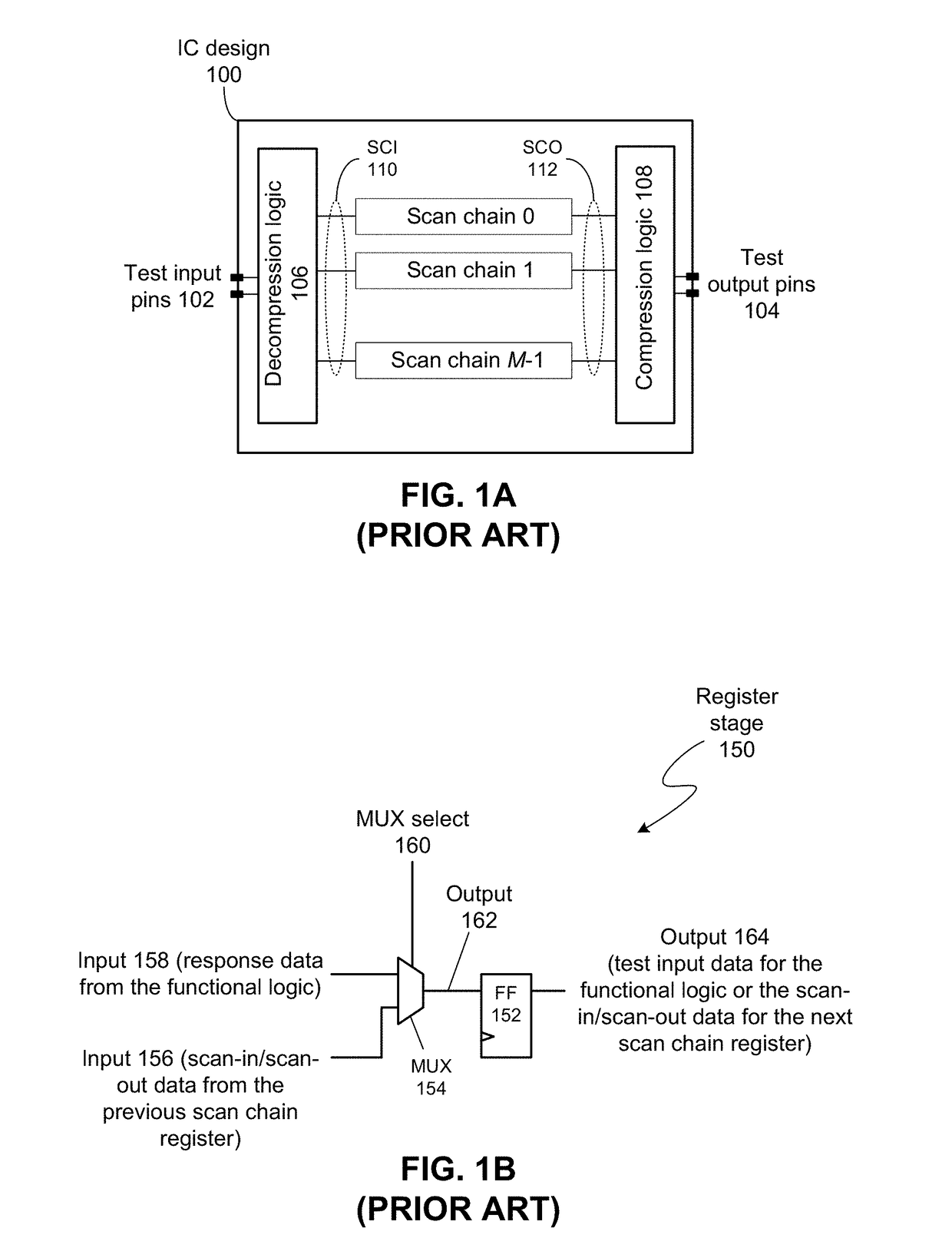

Integrated circuit for compression mode scan test

ActiveUS20110289369A1Electronic circuit testingLogical operation testingDesign for testingMultiplexer

An integrated circuit for performing a design for testability (DFT) scan test is provided. The integrated circuit includes at least one scan chain including a plurality of flip-flops, at least one interface scan chain including a plurality of flip-flops, a decompressor configured to be connected with an input terminal of the at least one interface scan chain and to decompress a first input signal and then transmit it to the at least one scan chain, a compressor configured to be connected with an output terminal of the at least one scan chain and to compress an output signal of the at least one scan chain, and at least one multiplexer configured to be connected with the decompressor and to selectively output an output signal of the decompressor or a second input signal in response to a control signal.

Owner:SAMSUNG ELECTRONICS CO LTD

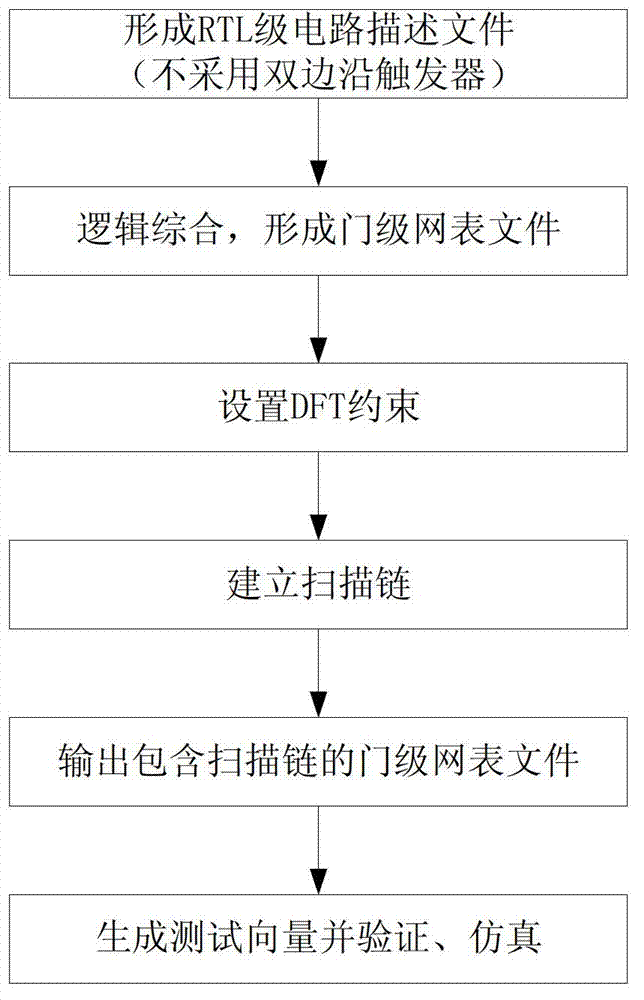

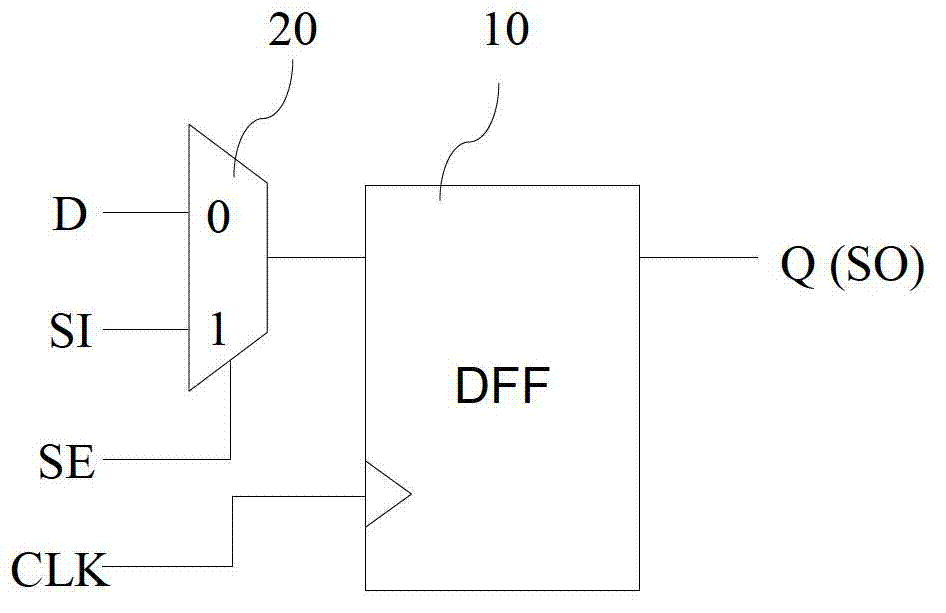

DFT (Design for Testability) method for double-edge trigger

ActiveCN102831272AImprove data processing capabilitiesPower consumption is halvedSpecial data processing applicationsDesign for testingAutomatic test equipment

The invention discloses a DFT (Design for Testability) method for a double-edge trigger, which comprises the following steps of: on the basis of the existing VLSI (Very Large Scale Integrated) DFT method designed by internal scan, using a double-edge scanning trigger to replace a single-edge scanning trigger in the gate-level netlist file with a built scan chain; adding a test clock circuit; simulating a test vector generated through the scan chain circuit of the single-edge scanning trigger by the scan chain circuit comprising the double-edge scanning trigger; and using the simulated test vector to test the scan chain circuit by an ATE (Automatic Test Equipment) device. In this way, the VLSI DFT method disclosed by the invention can be suitable for the circuit comprising the double-edge trigger and the circuit comprising the single-edge trigger, and further, the method is suitable for popularizing the double-edge trigger in the VLSI design and finally multiplying data handling capacity and reducing half of the power consumption of the integrated circuit.

Owner:RDA TECH

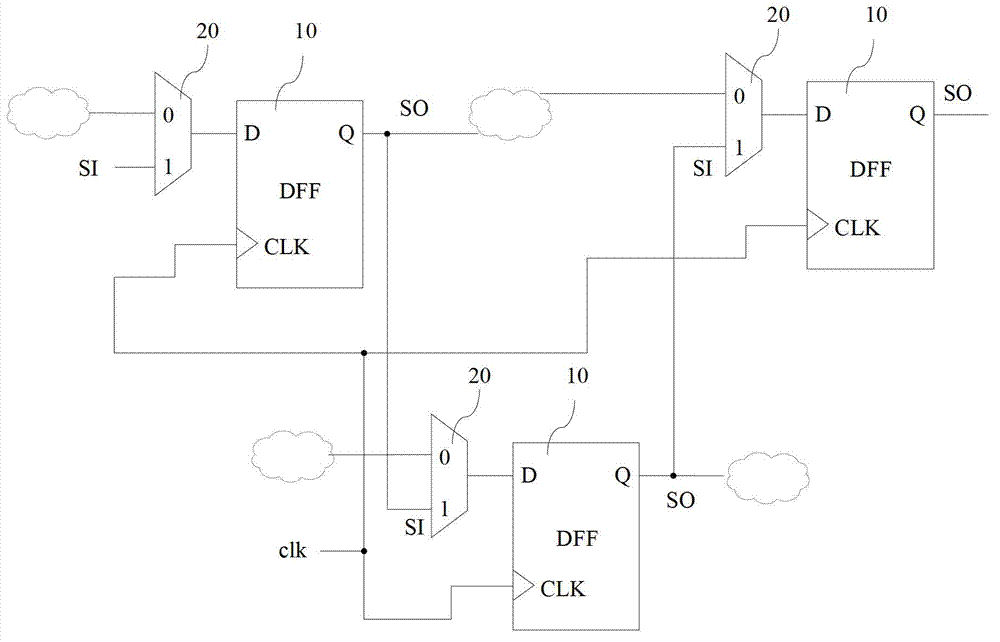

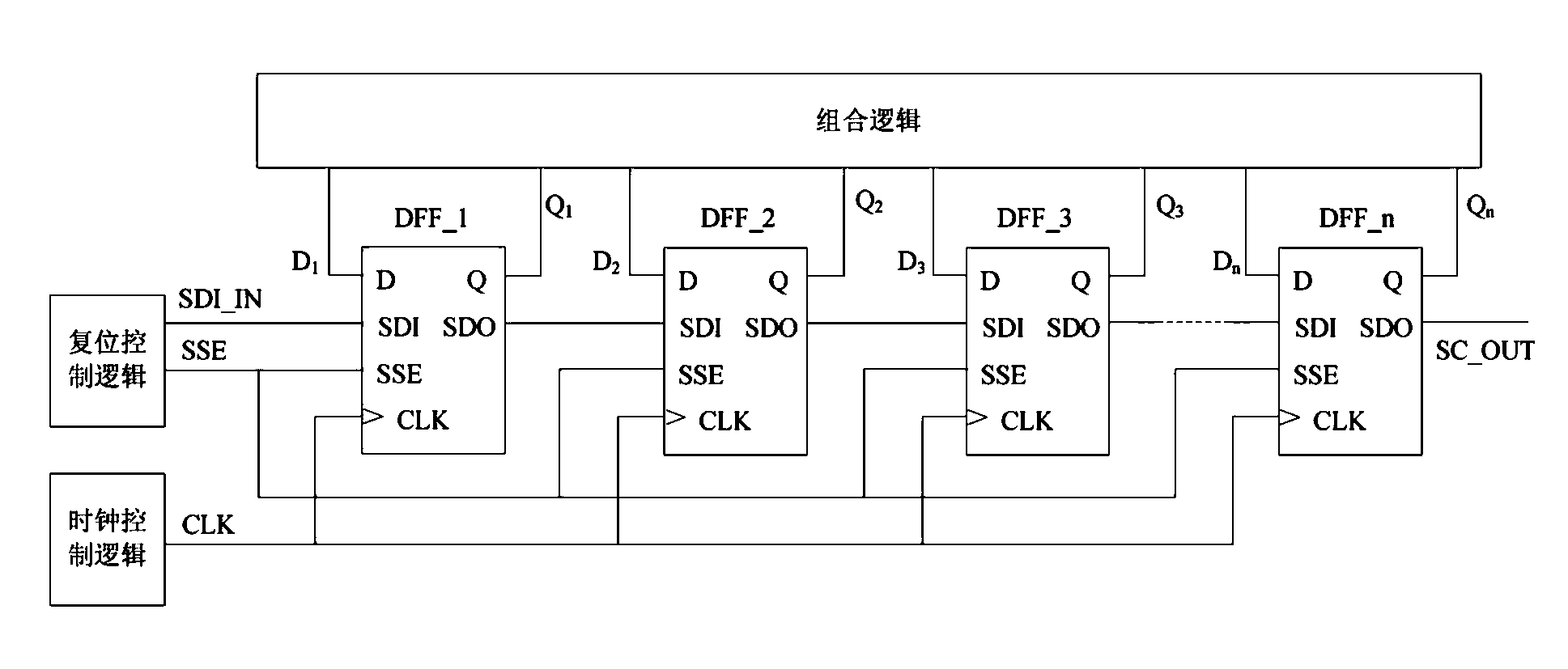

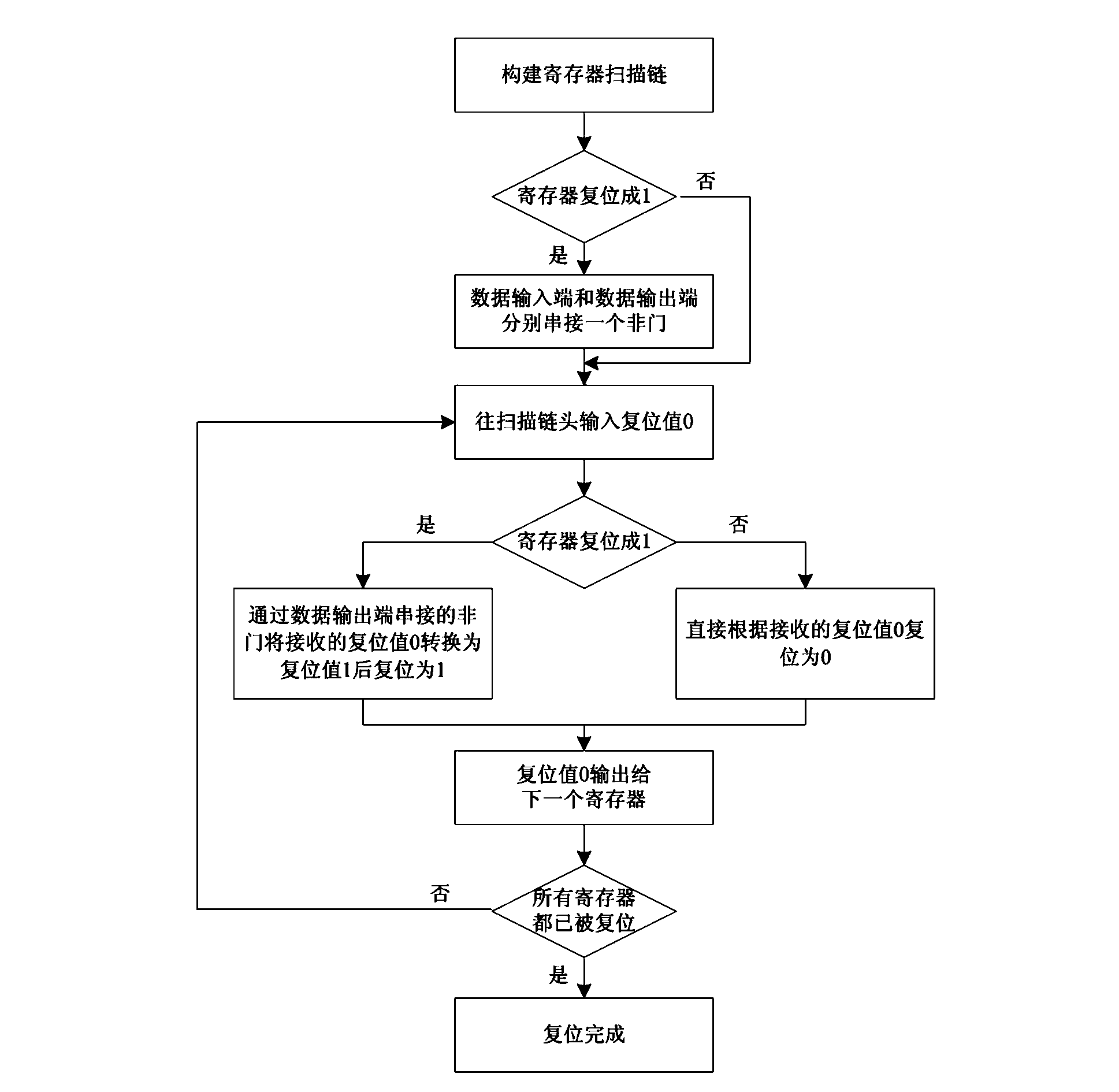

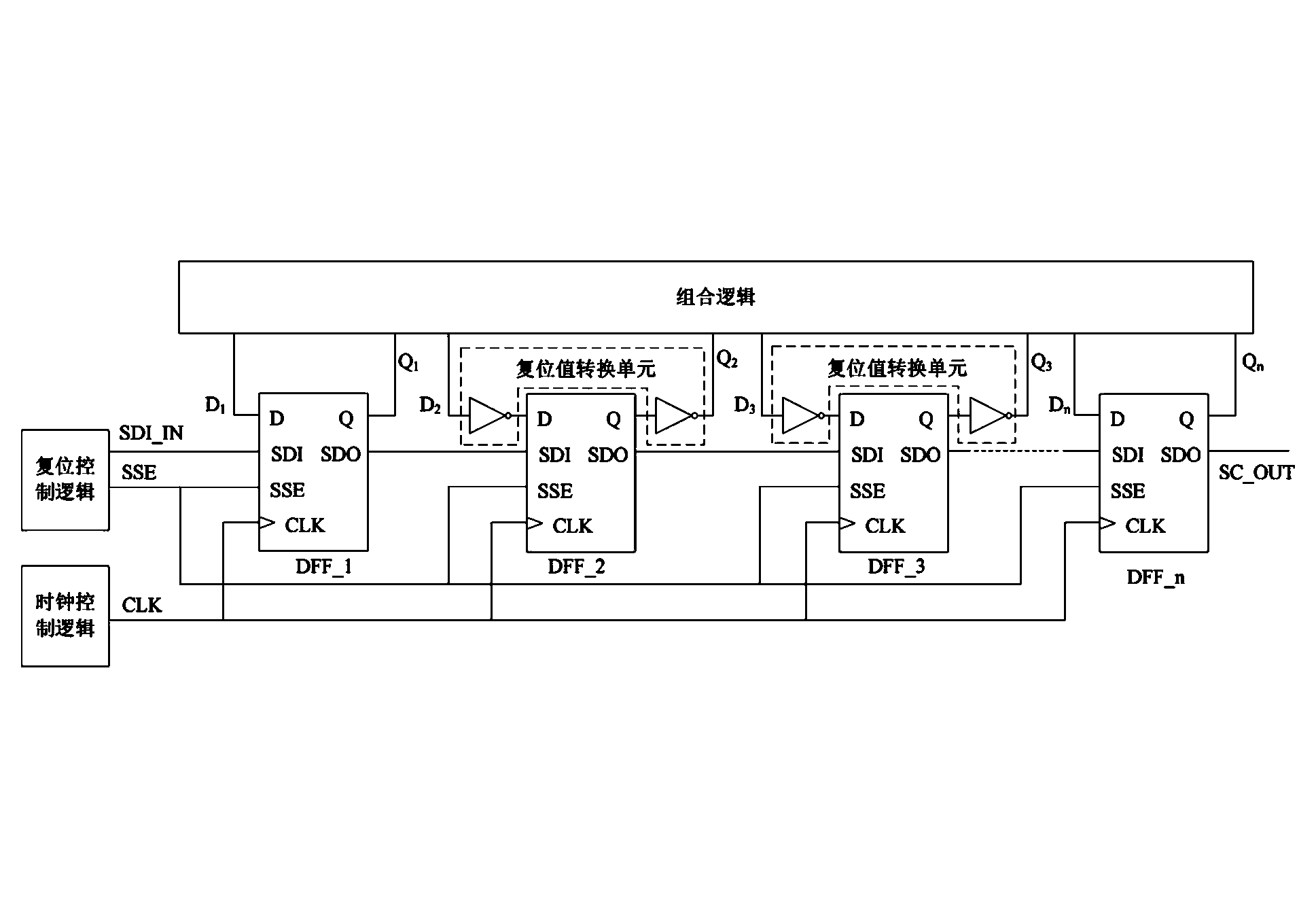

Register resetting method and device based on scanning mode

ActiveCN103023467ASimple designTransparency by design for testabilityElectronic switchingDesign for testingProcessor register

The invention discloses a register resetting method and device based on a scanning mode. The register resetting method comprises the following steps of: (1) constructing scan chains for all registers, respectively connecting data input ends and data output ends of the registers in the scan chains with a not gate, wherein the registers need to be reset to 1; and (2) continuously inputting a reset value 0 to the head of the scan chain. The register resetting device comprises a resetting control logic and a clock control logic which are respectively connected with each register; the register resetting device also comprises reset value converting units, the number of which is in one to one correspondence with the number of the registers needing to be reset to 1; each reset value converting unit comprises two not gates, wherein one of the not gates is connected with the data input end of the corresponding register in series, and the other not gate is connected with the data output end of the corresponding register in series. According to the register resetting method and device, the logic design can be simplified, the realization of resetting logic is transparent for testability design, and the workload of testability design can be reduced.

Owner:NAT UNIV OF DEFENSE TECH

Digital logic chip and method capable of testing design

The invention provides a digital logic chip and a method of design for testing, wherein, the method includes setting corresponding logic devices between each scanning trigger in the digital logic chip and each observing pin, by the observing pin, signal of each scanning trigger can be observed in different time; after the signal pass over the logic device, the observing result is compared with the forecasted observing result so as to determine whether the digital logic chip is normal or not. The digital logic chip of the invention and the method of design for testing can realize the observation of circuit scanning test by adopting few pins.

Owner:VIMICRO CORP

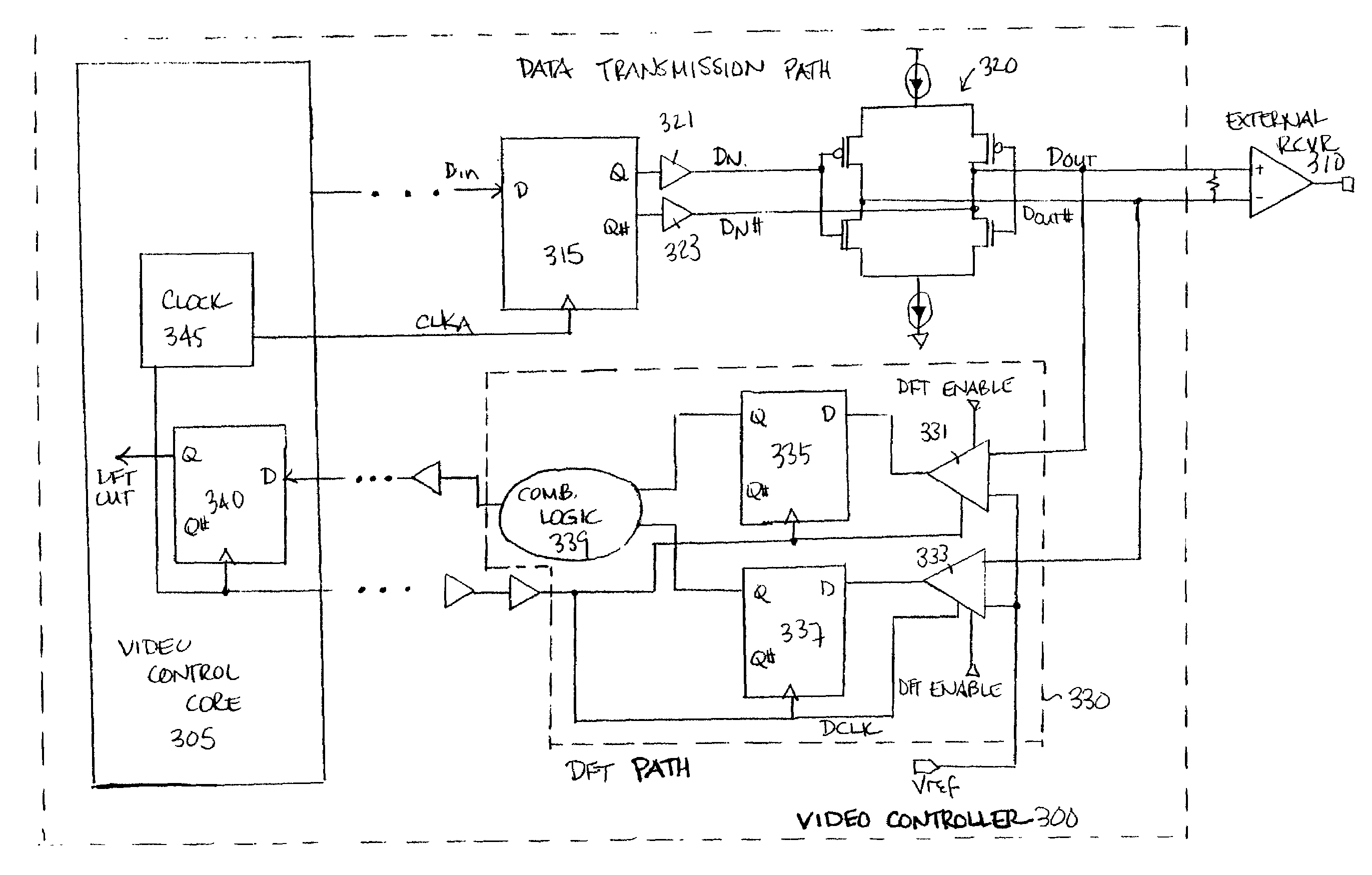

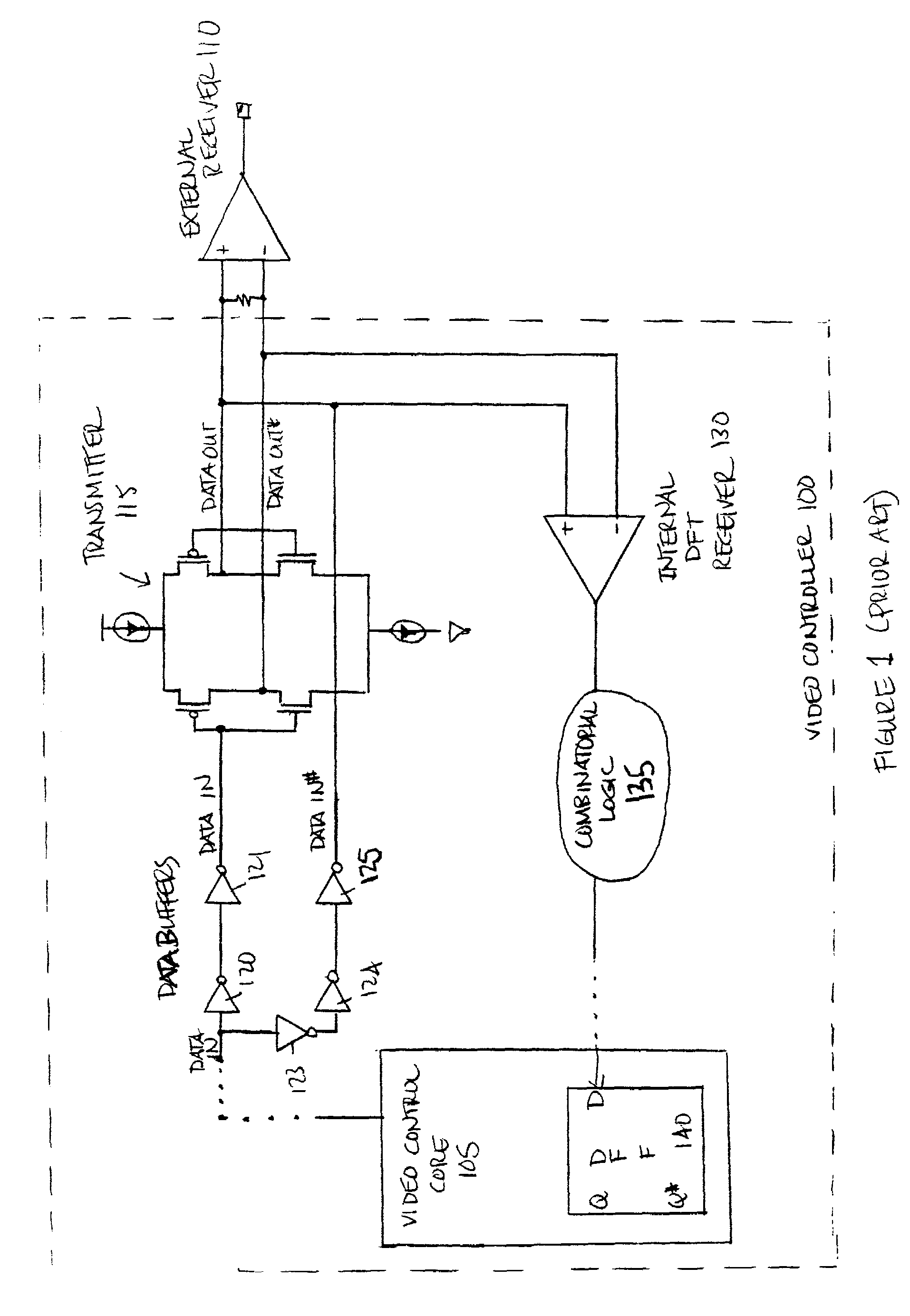

Method and apparatus for high frequency data transmission and testability in a low voltage, differential swing design

A high frequency data transmission circuit including design for testability (DFT) features. An integrated circuit includes core control logic to provide a data signal and output drive logic including a local data latch and a transmitter. The data latch receives the data signal and provides true and complementary forms of the data signal to the transmitter over symmetrical signal paths. The transmitter provides an output signal to an external receiver.

Owner:INTEL CORP

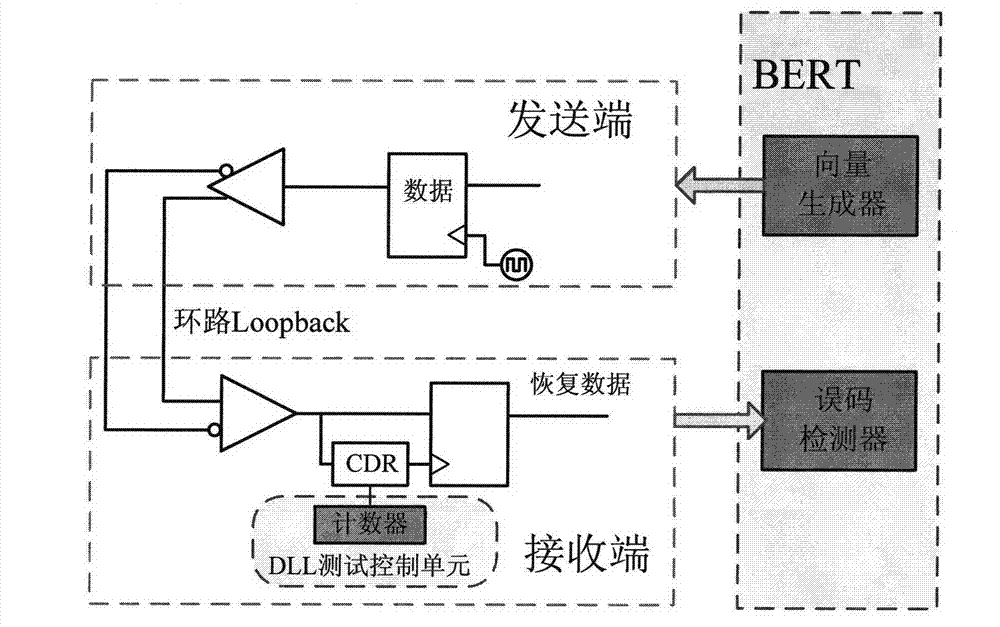

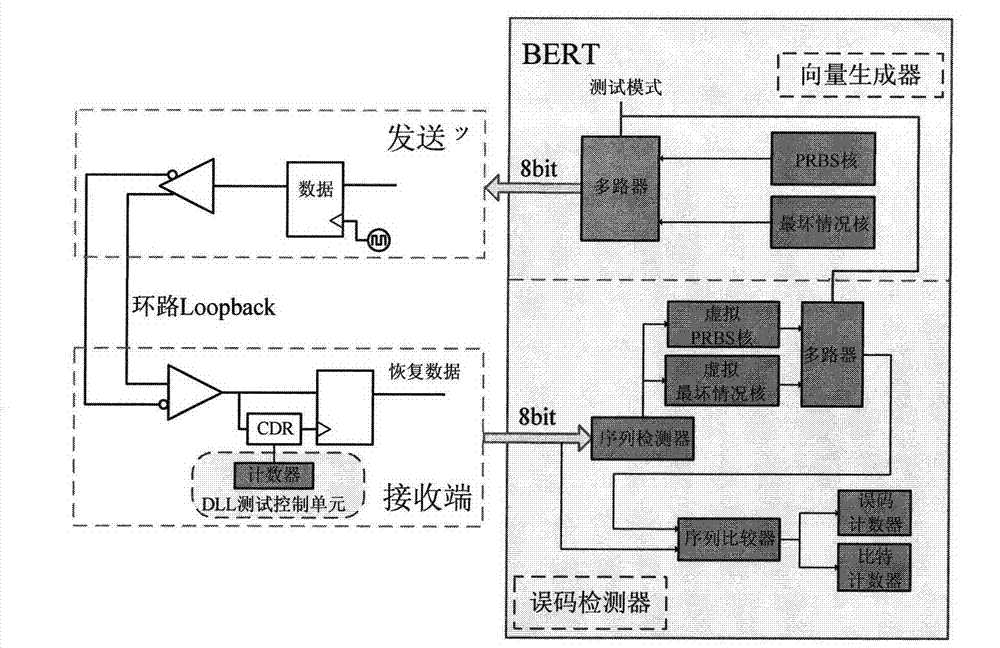

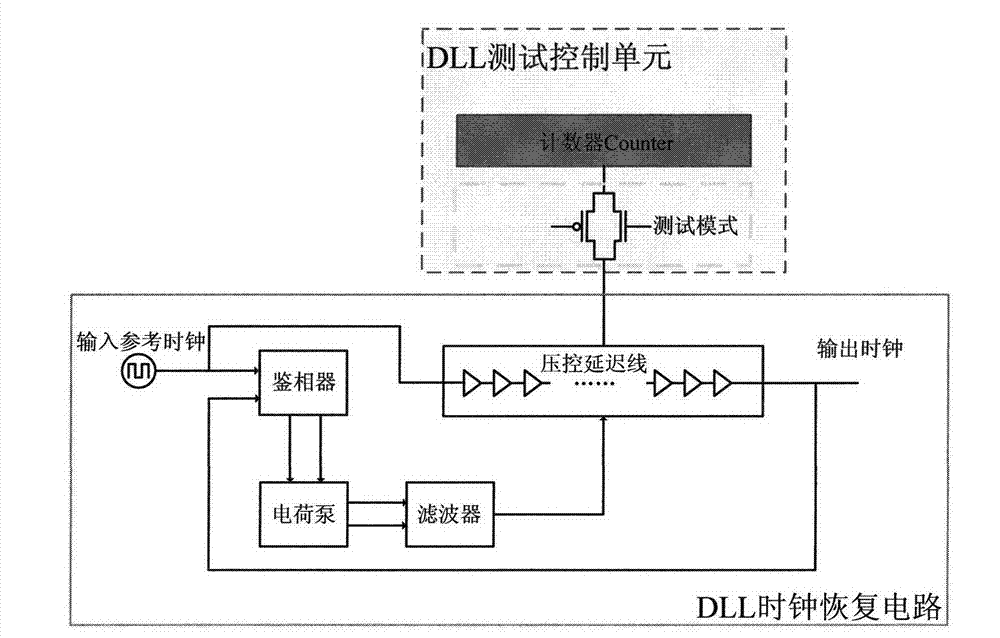

A method and a system for designing the testability of a high-speed serial IO interface based on DLL clock recovery

The invention discloses a method and a system for designing the testability of a high-speed serial IO interface based on DLL clock recovery. The idea of the method is that a DLL clock recovery may provide a group of clocks with different phases, that a control and selection signal of a DLL testing control unit is set, that a sampling point testing clock can be generated by using the group of clocks with different phases, that data is sampled at different positions of a UI, that a built-in BERT generates a test vector in order to perform detection and statistic on bit errors and test a bit error rate bathtub curve, and that then a jitter separation program fits random jitter and deterministic jitter according to a gating point and bit error rate information and estimates bit error rate. The method is also capable of testing parameters such as jitter tolerance, and sensitivity or the like and provides a condition for system-level testability. An internal clock is used as a testing clock so that high testing precision is guaranteed. A built-in testing circuit has a small scale and is easy to produce. A testing process does not relate to the use of ATE. Therefore, cost of testing the high-speed serial IO with a desk-type instrument can be effectively reduced and testing time is shortened.

Owner:PEKING UNIV

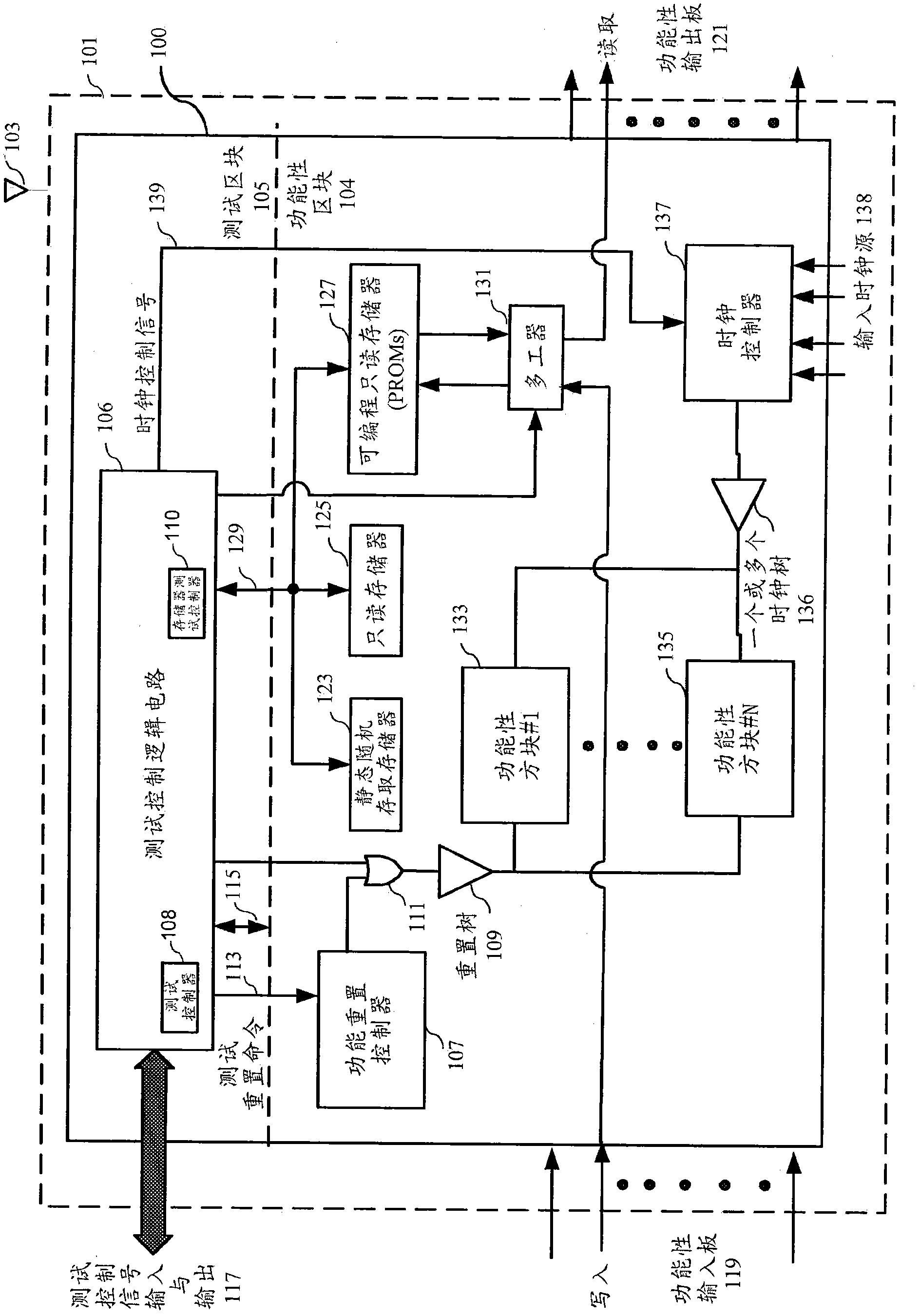

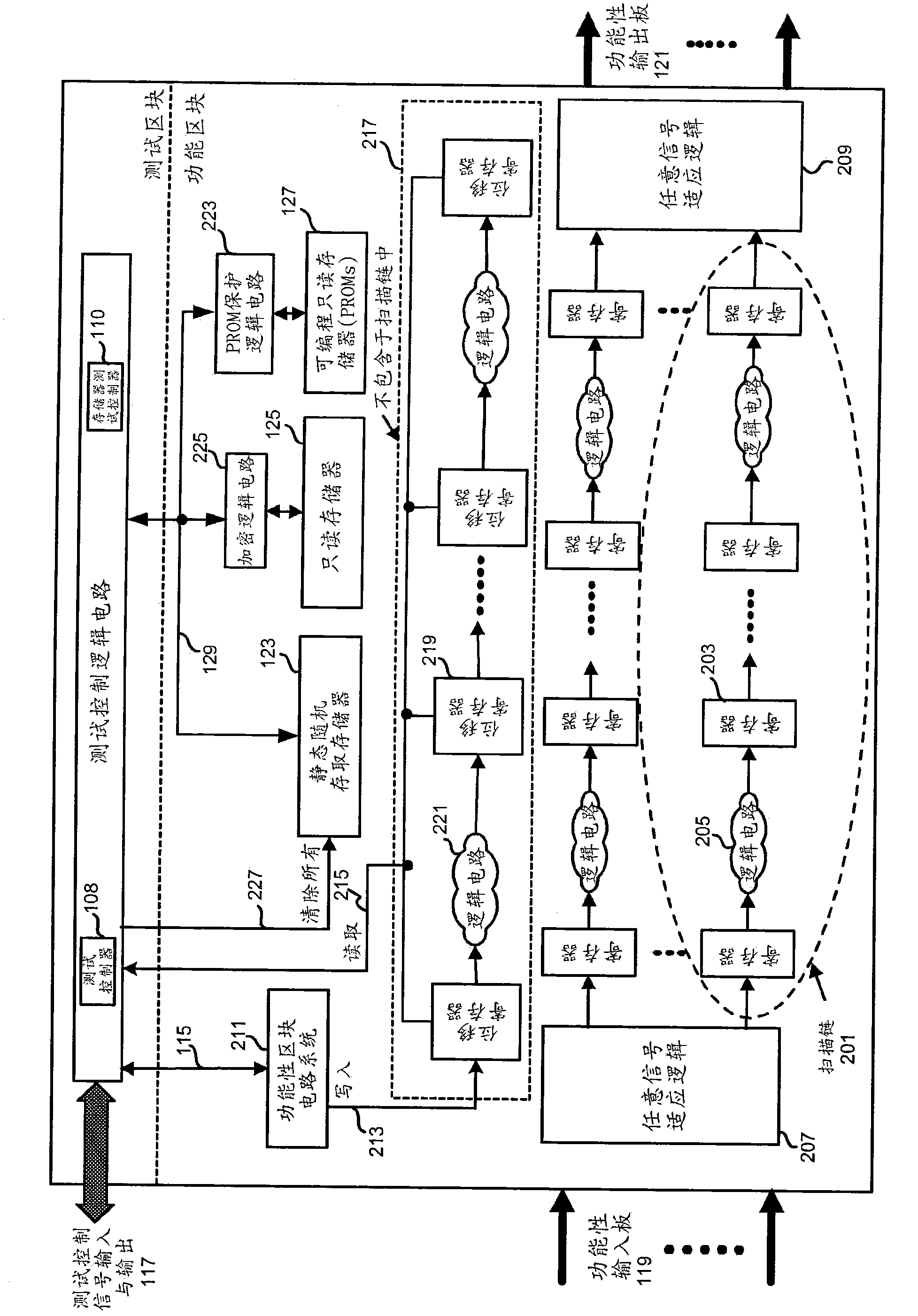

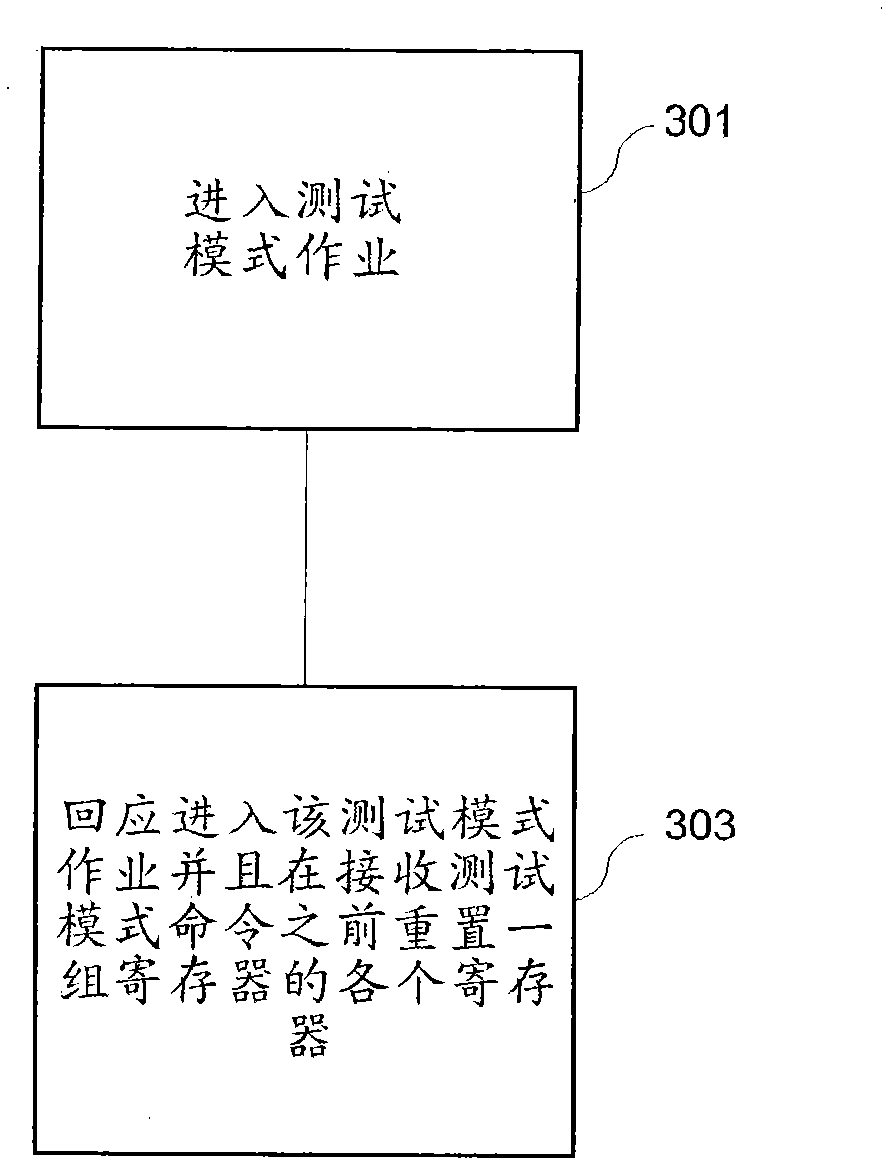

Method and apparatus for securing digital information on an integrated circuit during test operating modes

InactiveCN102066963AElectronic circuit testingDigital data protectionDesign for testingProcessor register

The embodiments protect an IC against Design-For-Test (DFT) or other test mode attack. Transitory secrets are secured whether stored in registers or latches, RAM, and / or permanent secrets stored in ROM and / or PROM. One embodiment for securing information on an IC includes entering a test mode and resetting each register in response to entering the test mode of operation and prior to receiving a test mode command. An integrated circuit embodiment includes a test control logic operative to configure the integrated circuit into a test mode and to control the integrated circuit while in the test mode, a set of registers, and a functional reset controller coupled to the test control logic and to the set of registers, operative to receive a reset command from the test control logic and provide the reset command to the set of registers in response to a command to enter the test mode.

Owner:ATI TECH INC

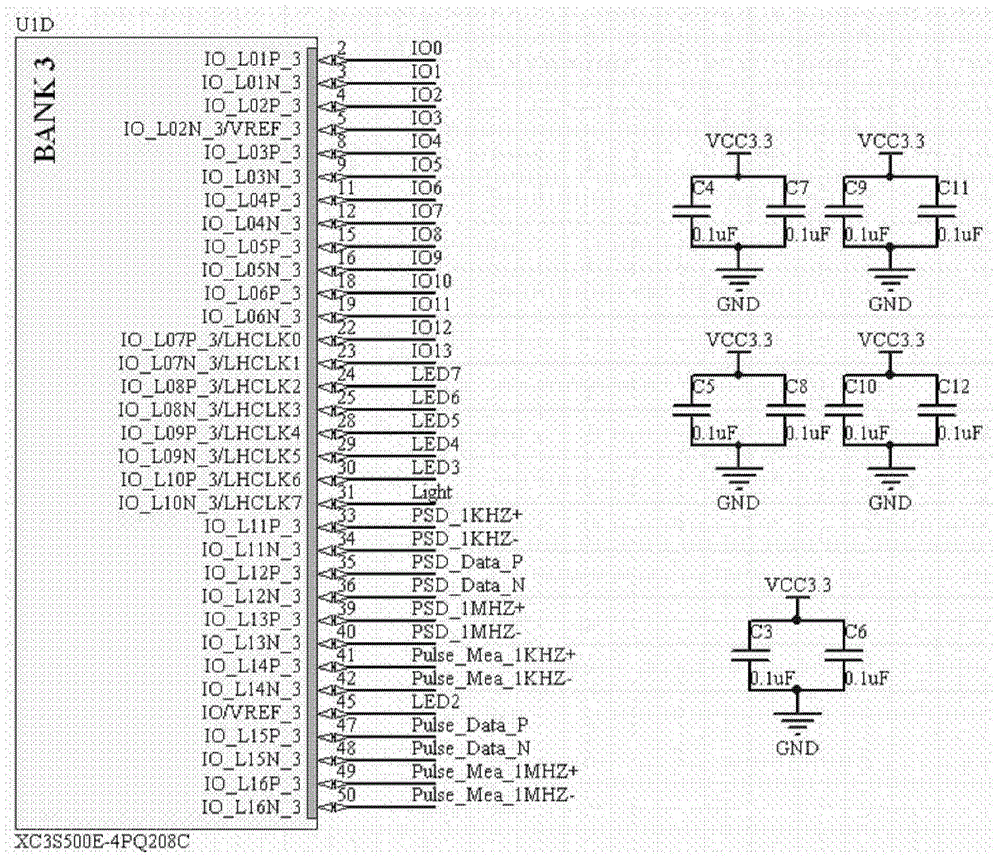

Synchronous data acquisition and communication circuit

ActiveCN104897056ARealize acquisitionRealize uploadUsing optical meansDesign for testingCommunication unit

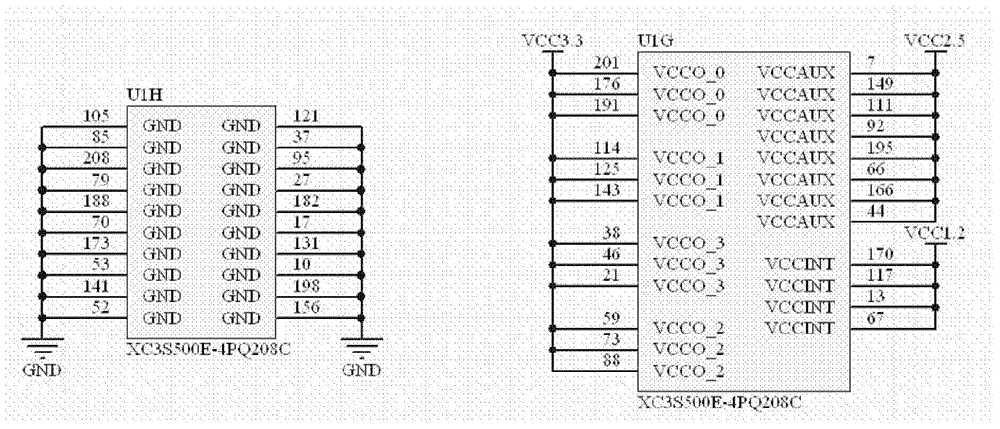

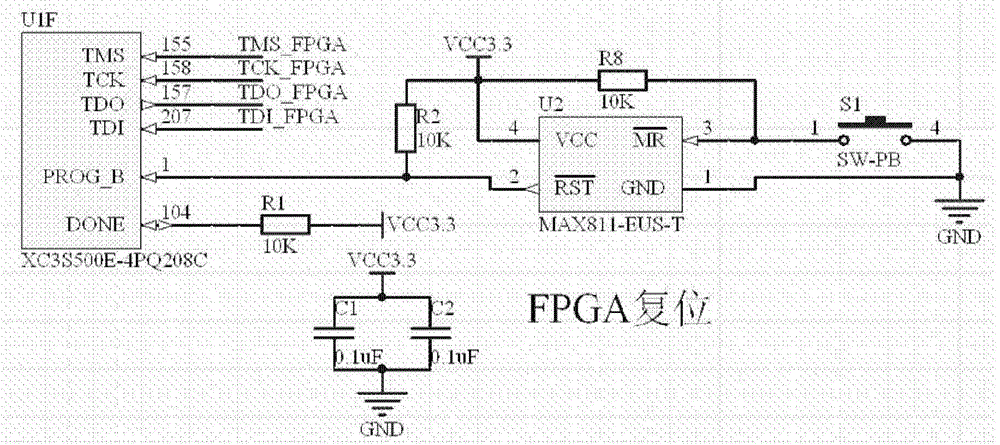

The invention discloses a synchronous data acquisition and communication circuit, which is realized through a programmable gate array and a matched circuit. The synchronous data acquisition and communication circuit is characterized in that the circuit uses an FPGA clock management module to generate a standard frequency, a differential synchronous signal is then obtained through frequency division, and the same differential synchronous signal source is adopted to trigger all synchronous units. In addition, the synchronous data acquisition and communication circuit introduces testability design and port expansion design through modular design. Compared with a former simple data acquisition or communication unit, acquisition and uploading of all data and complete functions can be realized. Due to the modular design idea, mutual influences can be reduced, diversity of module communication forms is enhanced, and due to the testability design idea, monitoring of working states of each module and the overall body can be enhanced, and the debugging efficiency and the troubleshooting efficiency are improved; and after all unused ports of the FPGA are expanded outwardly, unified management is realized, and function expansion is facilitated.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Virtual simulation test method

InactiveCN106570200AImprove reliabilityEasy to useSpecial data processing applicationsFailure detection and isolationLab test method

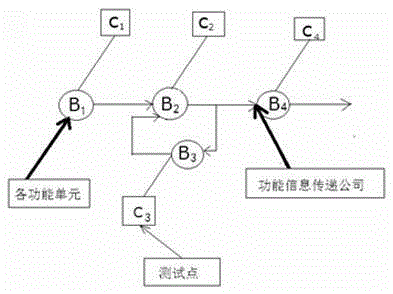

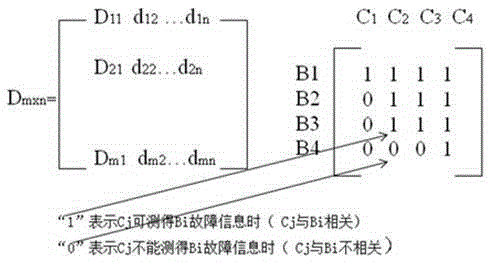

The invention provides a virtual simulation test method. The virtual simulation test method comprises constructing a test model and performing failure analysis on the constructed model. The virtual simulation test method is feasible and effective in the evaluation of modeling analysis of a product testability design, and can be used for evaluating the product testability design in related fields, so that the testability design is improved; the inherent testability of products is improved; and valuable suggestions are given to further failure diagnosis of equipment and optimization of an existing test method. Through implementation of the virtual simulation test method, the failure detection and isolation time can be shortened greatly, so that the maintenance time is shortened greatly; technical requirements on maintenance personnel are lowered; the task reliability is improved; the use efficiency of a system and the equipment is increased; and the cost in a life cycle is lowered. A failure detection rate (FDR) can be up to 95-98 percent; a failure isolation rate (FIR) can be up to 95-99 percent (isolation to a single LRU); and a false alarm rate (FAR) can be up to 1-5 percent.

Owner:南京赛宝工业技术研究院有限公司

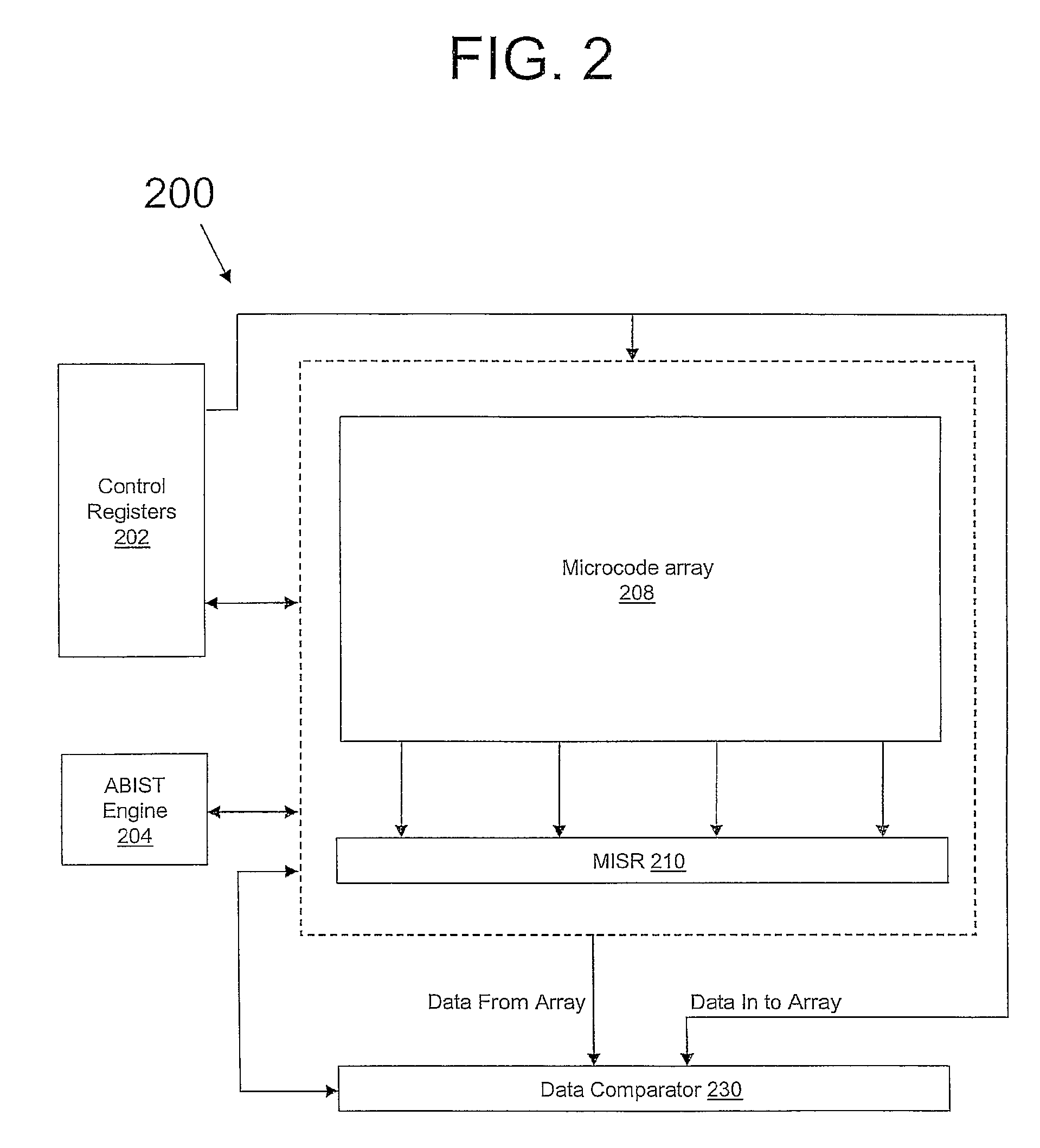

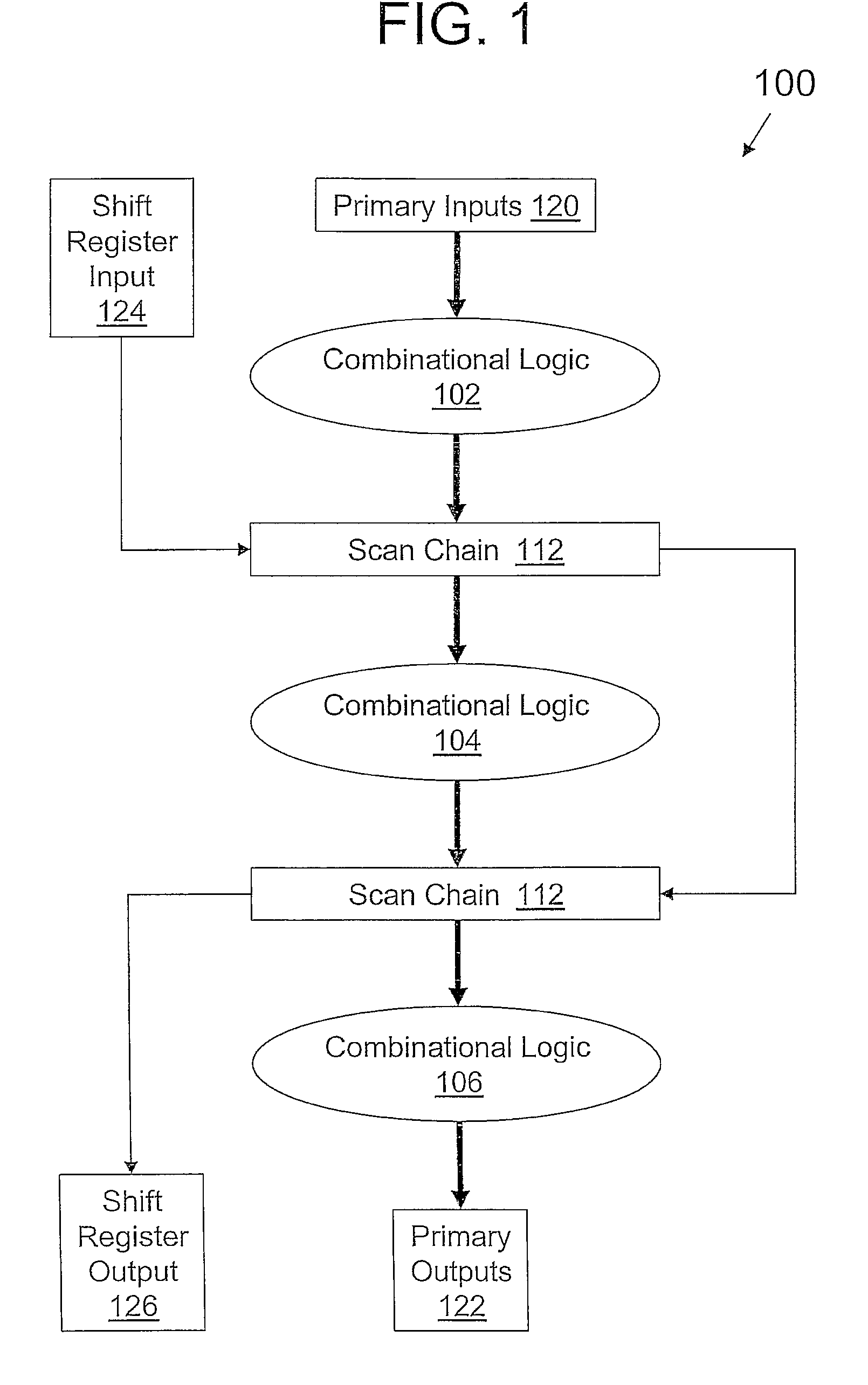

Verification of array built-in self-test (ABIST) design-for-test/design-for-diagnostics (dft/dfd)

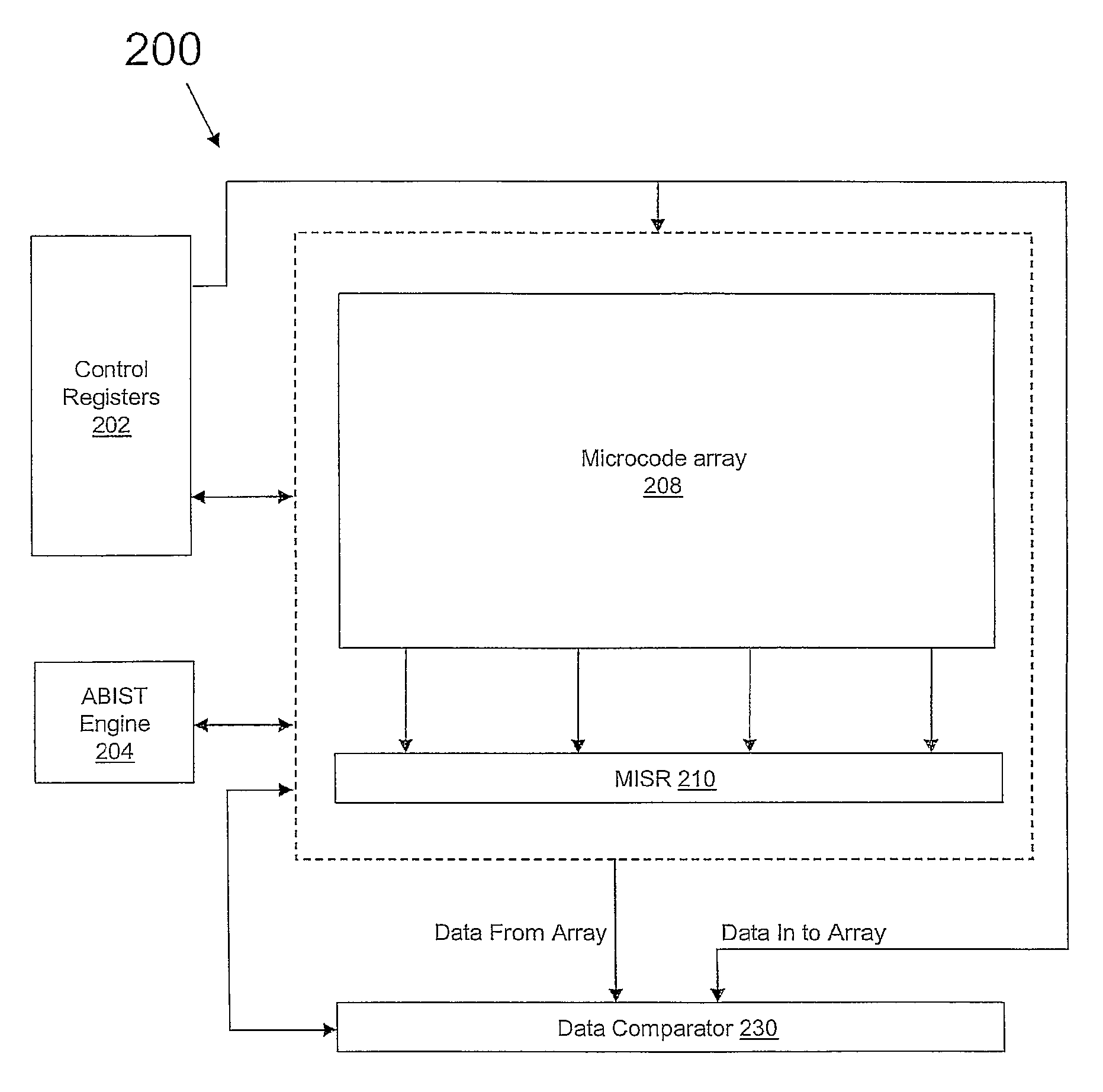

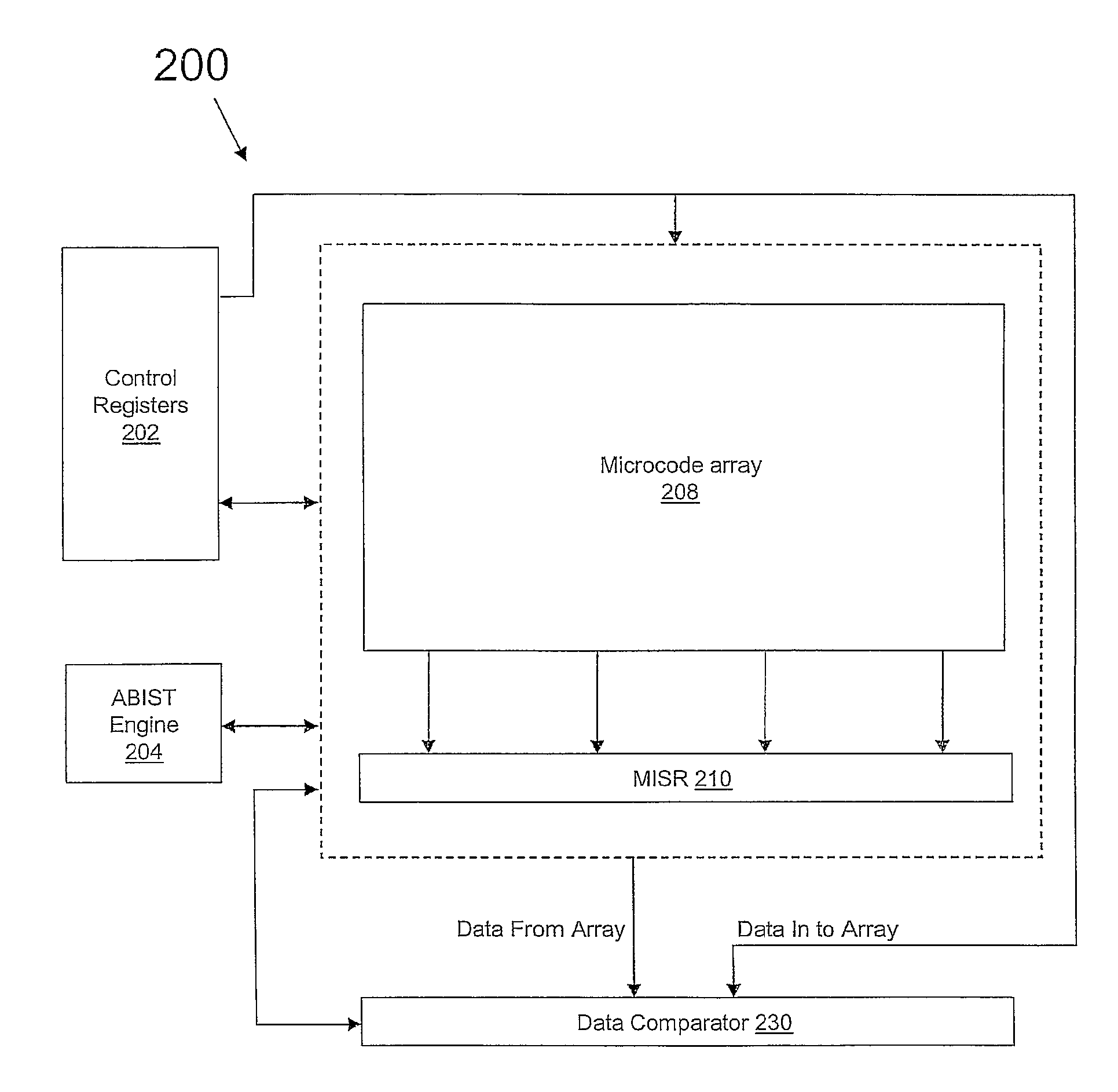

A method, system and computer program product for testing the Design-For-Testability / Design-For-Diagnostics (DFT / DFD) and supporting BIST functions of a custom microcode array. Upon completion of the LSSD Flush and Scan tests, the ABIST program is applied to target the logic associated direct current (DC) and alternating current (AC) faults of ABIST array Design-For-Testability / Design-For-Diagnostics DFT / DFD functions that support the microcode array. A LSSD test of the DFT functional combinational logic is performed by applying generated LSSD deterministic test patterns targeting the ABIST design-for-test faults to determine if the DFT supporting the microcode array is functioning correctly. Additional tests may be terminated upon resulting failure of the applied ABIST DFT circuitry surrounding the arrays.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

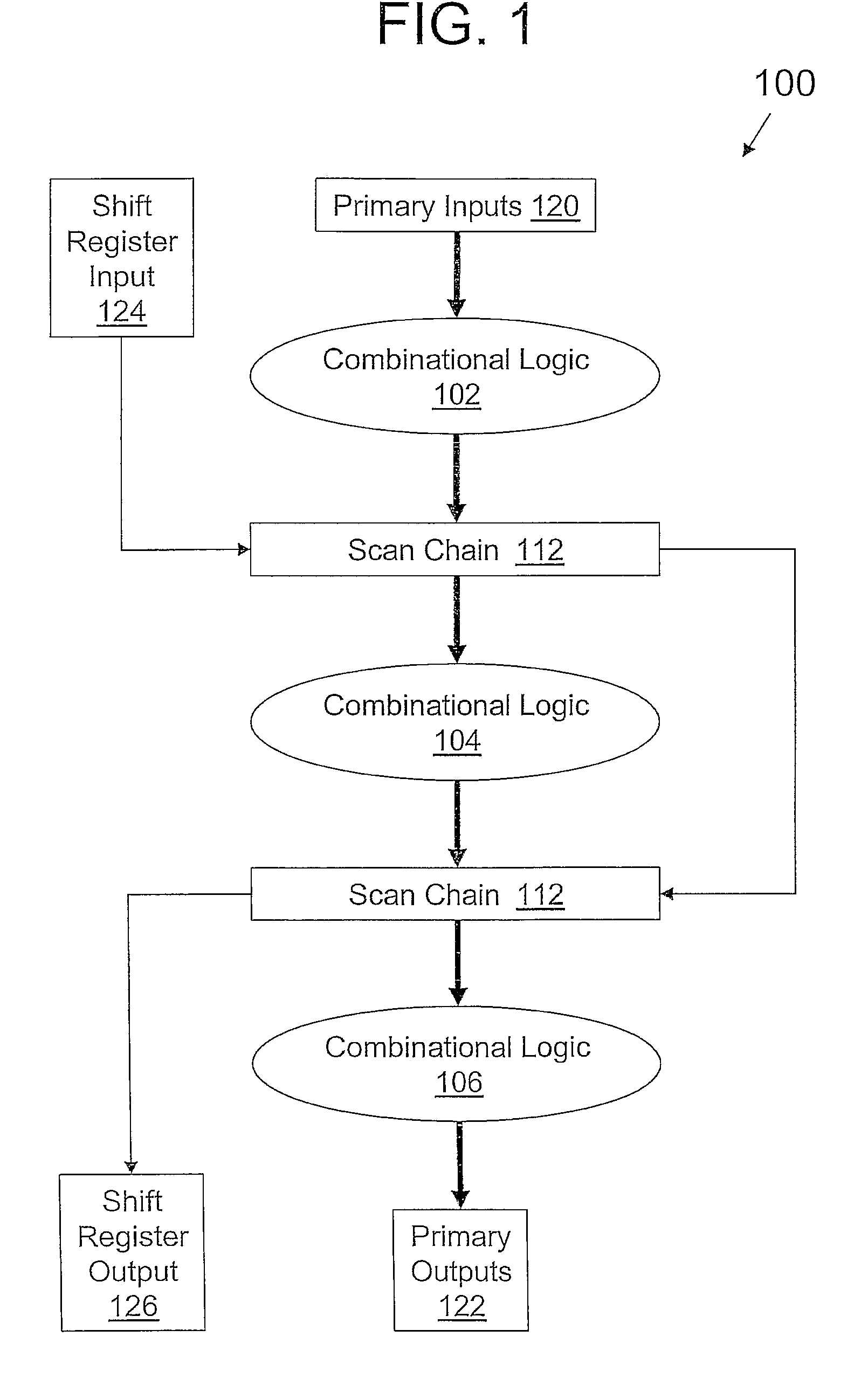

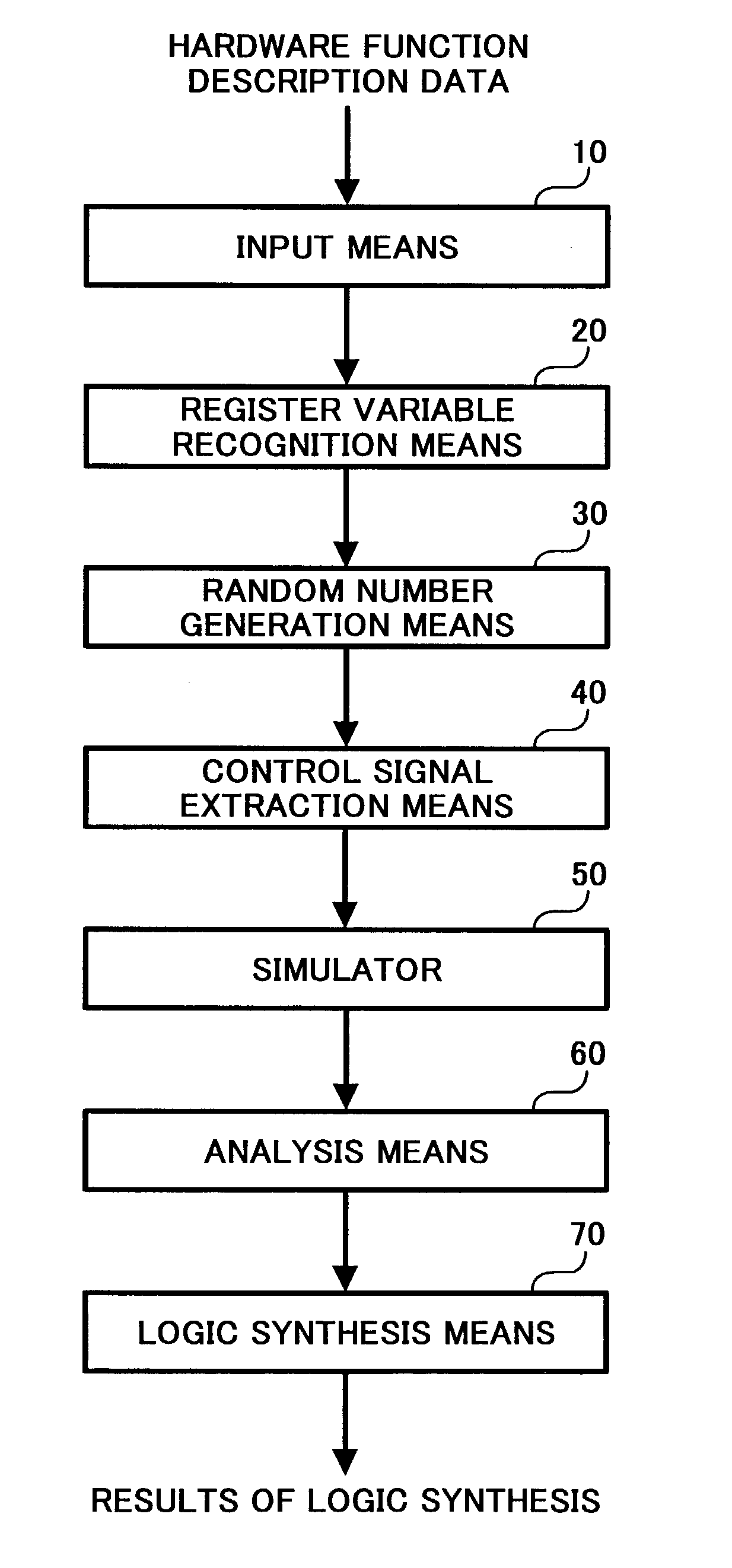

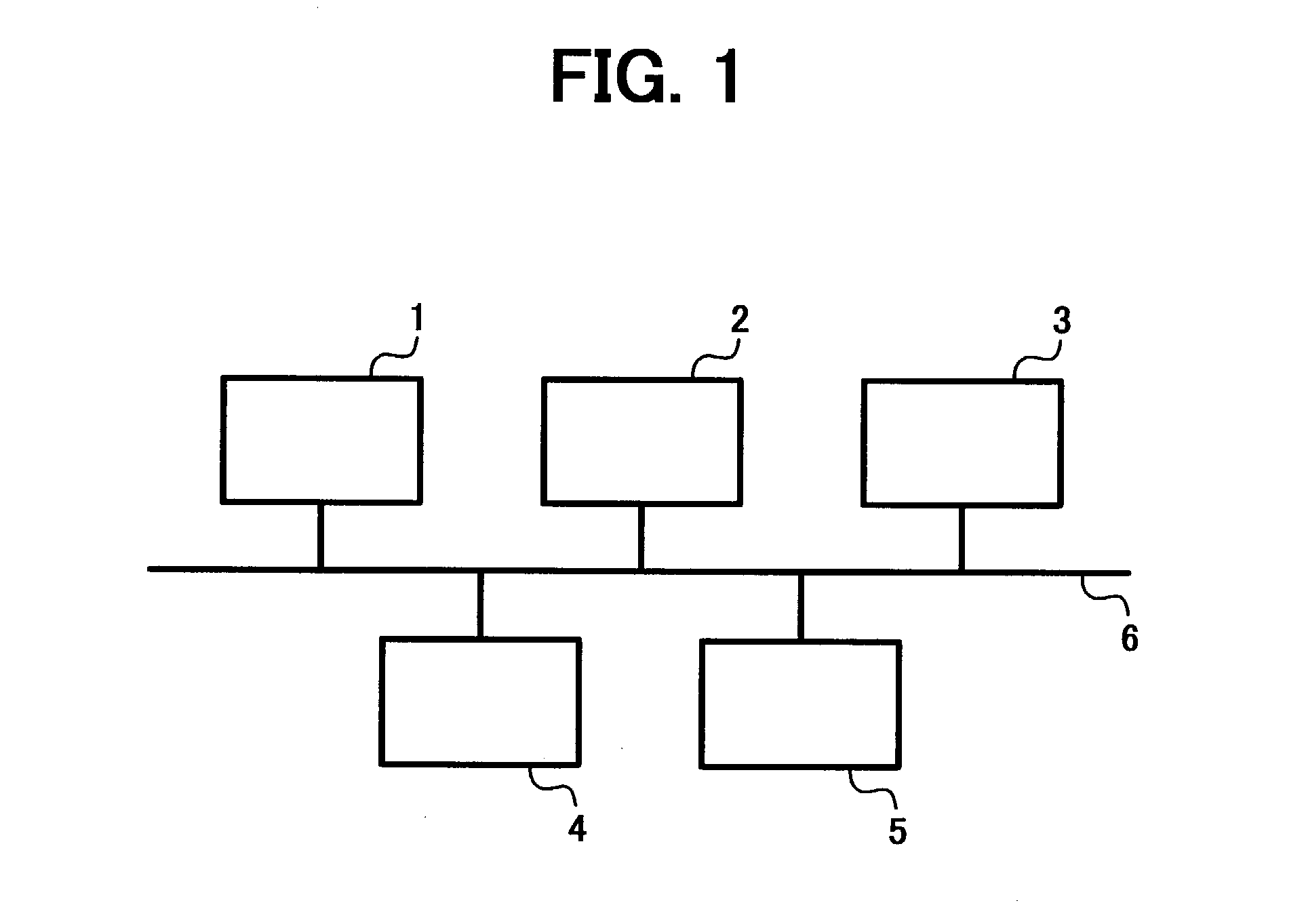

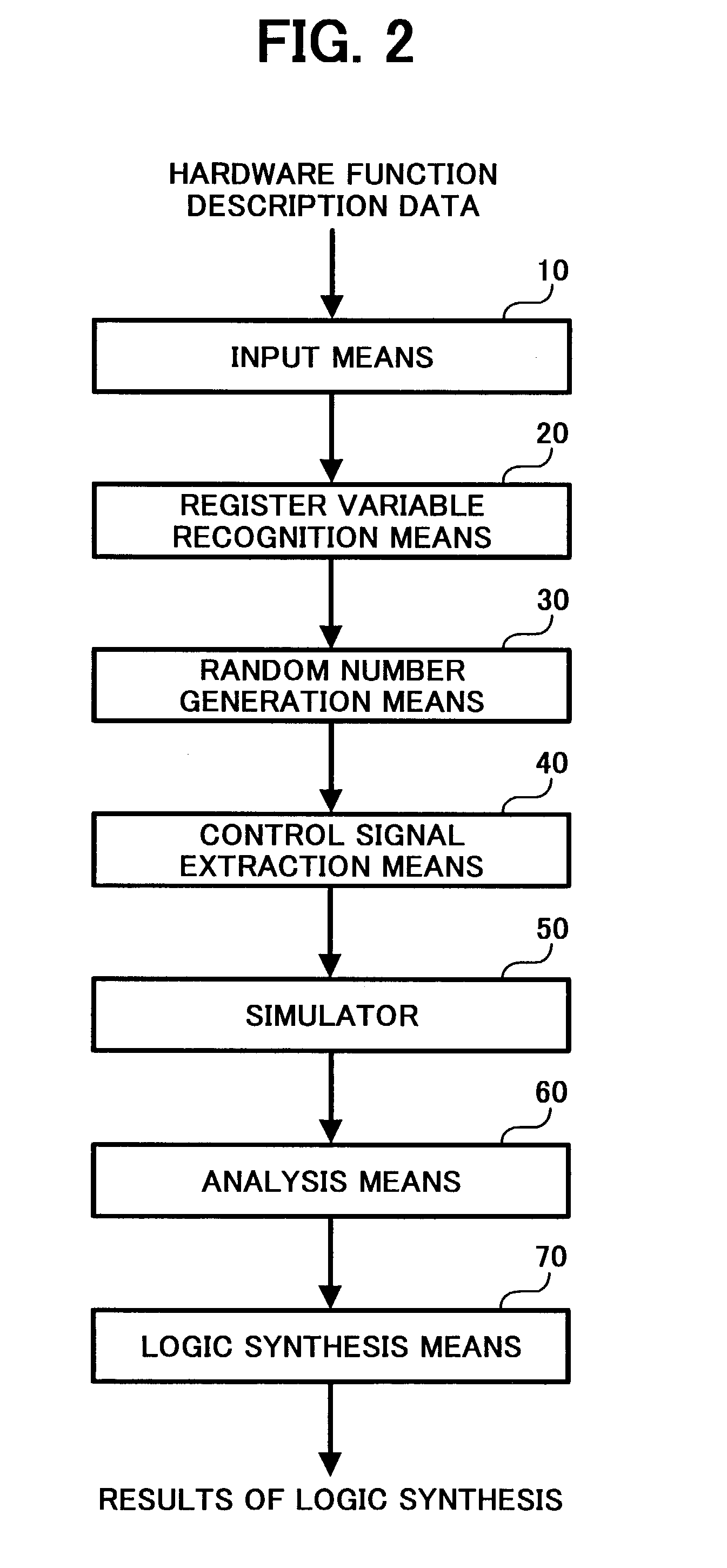

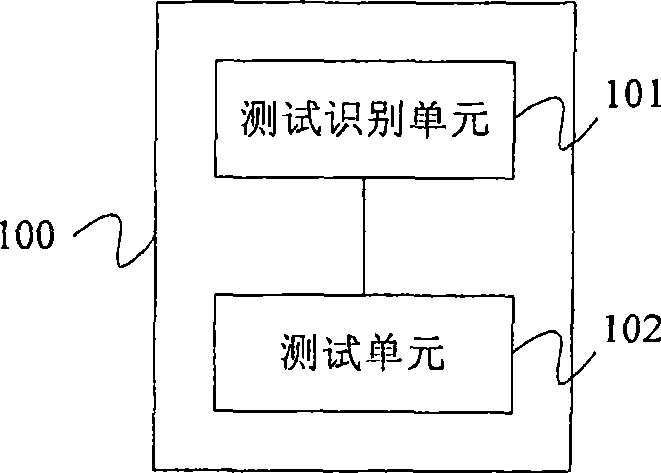

System and method of design for testability

InactiveUS7174530B2Eliminate disadvantagesReduce designSolid-state devicesDetecting faulty computer hardwareDesign for testingControl signal

A system and a method for implementing design for testability is disclosed, in that the method includes the steps of inputting function description data for defining hardware functions represented in the form independent of architecture; recognizing register variables inferable by memory elements, which are contained in the function description data; simulating events induced by affixing random numbers to the register variables; extracting control signals contained in the function description data as extracted control signals; analyzing the results of the simulation with respect to the extracted control signals; inserting test points for control signals having low toggle rates among the extracted control signals; and executing logic synthesis on the control signals having low toggle rates including the test points.

Owner:RICOH KK

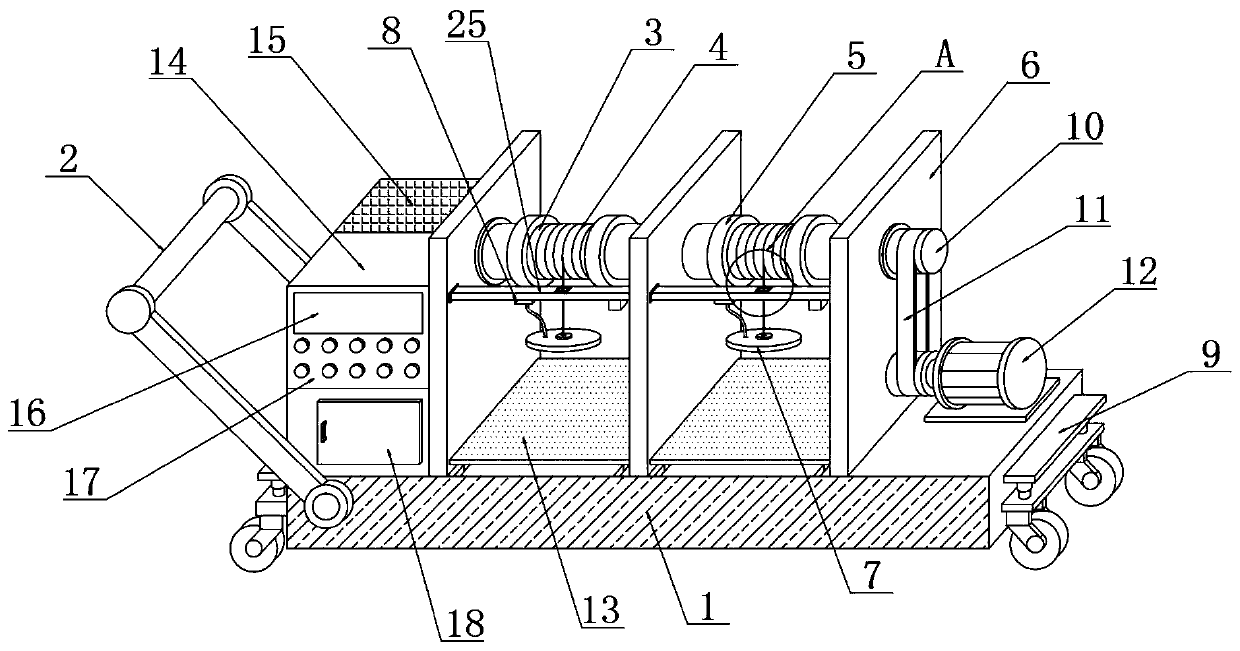

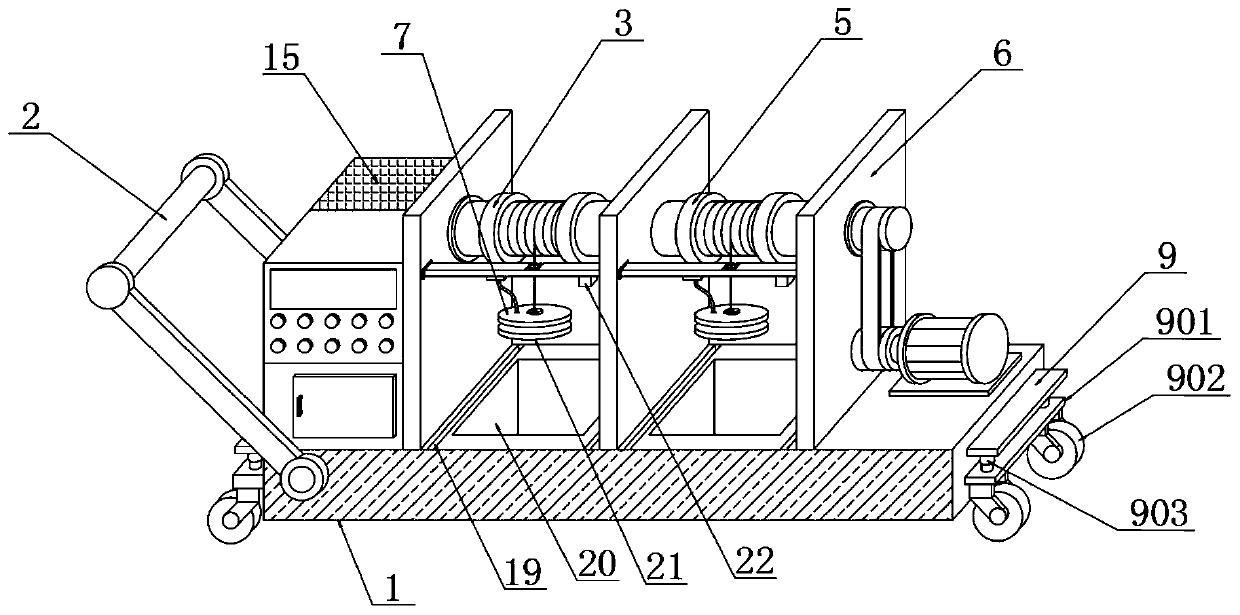

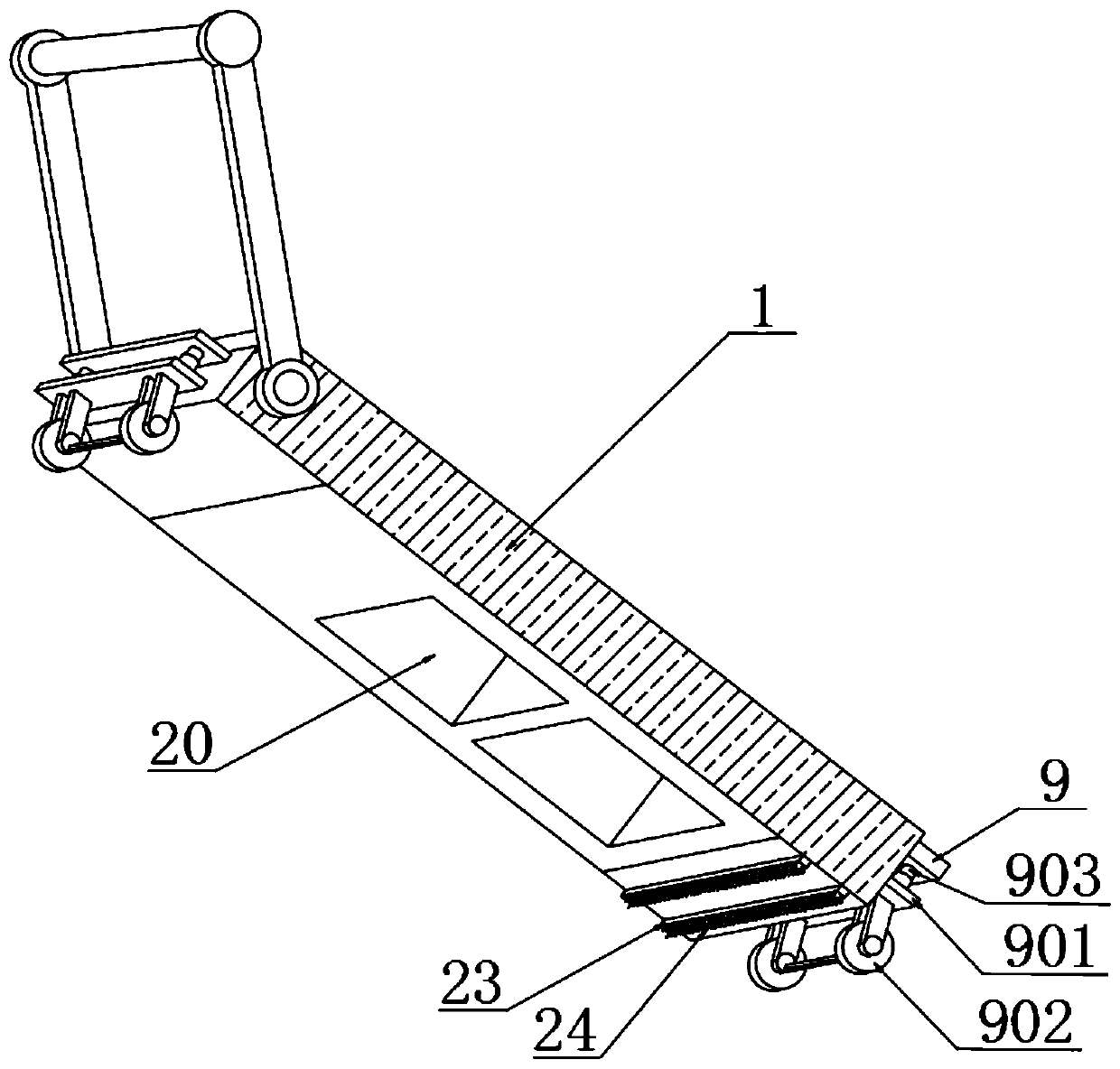

Impact toughness detecting device and detecting method for airport runway pavement structure

PendingCN109975139AEasy to wrapThe phenomenon of convenienceStrength propertiesDesign for testingRoad surface

The invention discloses an impact toughness detecting device and an impact toughness detecting method for an airport runway pavement structure, which relate to the technical field of airport runway pavement impact resistance detection. The impact toughness detecting device comprises a bottom plate, wherein a pushing hand for pushing the bottom plate is mounted on one side of the bottom plate, three side plates are mounted on the upper end of the bottom plate equidistantly, and the upper end of the bottom plate is provided with a servo motor at a position close to one side of the side plates. The impact toughness detecting device calculates impact forces to the airport runway pavement under different gravities by utilizing a gravitational potential energy formula can obtain different data for comparison under the conditions of different heights and gravities, adopts a double-row design for testing pavements the adjacent regions simultaneously, makes the operation more labor-saving by combining with the se of electromagnetic chucks, saves the trouble of manual calculation by comparing multiple sets of data and utilizing automatic calculation of the computer, is convenient to move, issuitable for testing multiple regions of the airport runway, saves time and labor, and is precise in detected data values.

Owner:ZHENGZHOU UNIVERSITY OF AERONAUTICS

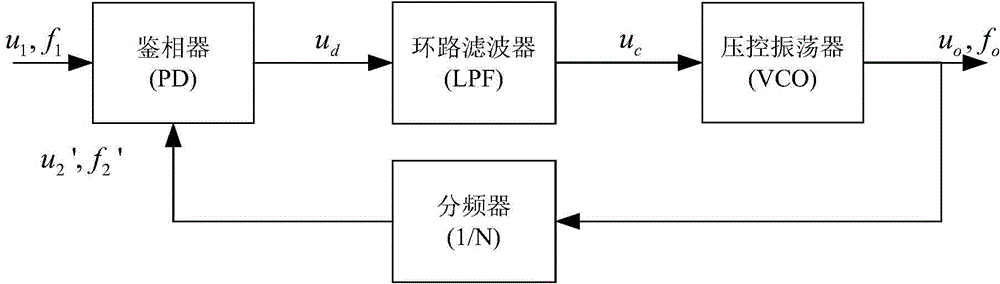

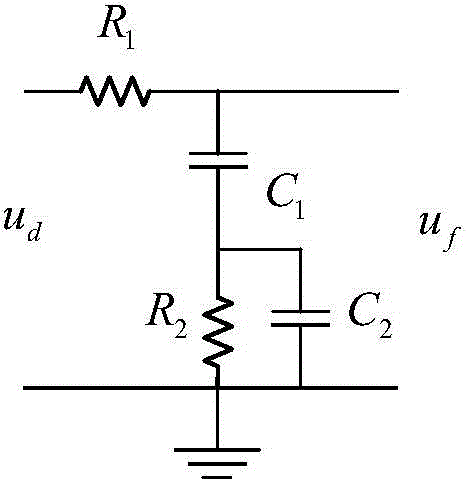

Embedded test method of phase-locked loop circuits

InactiveCN104569786AImplement fault diagnosisEasy to detectElectronic circuit testingDesign for testingPhase locked loop circuit

The invention provides an embedded test method of phase-locked loop circuits, which realizes the build-in self-test and fault diagnosis of a phase-locked loop, and increases the fault detection rate and the fault isolation rate of the phase-locked loop. The embedded test method comprises the following steps: step one, designing the testability of a phase-locked loop circuit; step two, verifying and evaluating testable points obtained in the step one, so as to obtain the fault detection rate and the fault isolation rate of a system; step three, designing hardware-testable points of each composition module of the phase-locked loop system, performing fault detection and isolation; step four, testing output frequency of the phase-locked loop, judging whether the phase-locked loop is in failure or not, if YES, controlling an analog switch to open the phase-locked loop, applying excitation to further testing each functional unit of the phase-locked loop, querying a fault dictionary, and displaying fault contents; otherwise, ending the test.

Owner:BEIJING AEROSPACE MEASUREMENT & CONTROL TECH

Verification of array built-in self-test (ABIST) design-for-test/design-for-diagnostics (DFT/DFD)

ActiveUS7921346B2Electronic circuit testingDetecting faulty computer hardwareTest designDesign for testing

A method, system and computer program product for testing the Design-For-Testability / Design-For-Diagnostics (DFT / DFD) and supporting BIST functions of a custom microcode array. Upon completion of the LSSD Flush and Scan tests, the ABIST program is applied to target the logic associated direct current (DC) and alternating current (AC) faults of ABIST array Design-For-Testability / Design-For-Diagnostics DFT / DFD functions that support the microcode array. A LSSD test of the DFT functional combinational logic is performed by applying generated LSSD deterministic test patterns targeting the ABIST design-for-test faults to determine if the DFT supporting the microcode array is functioning correctly. Additional tests may be terminated upon resulting failure of the applied ABIST DFT circuitry surrounding the arrays.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

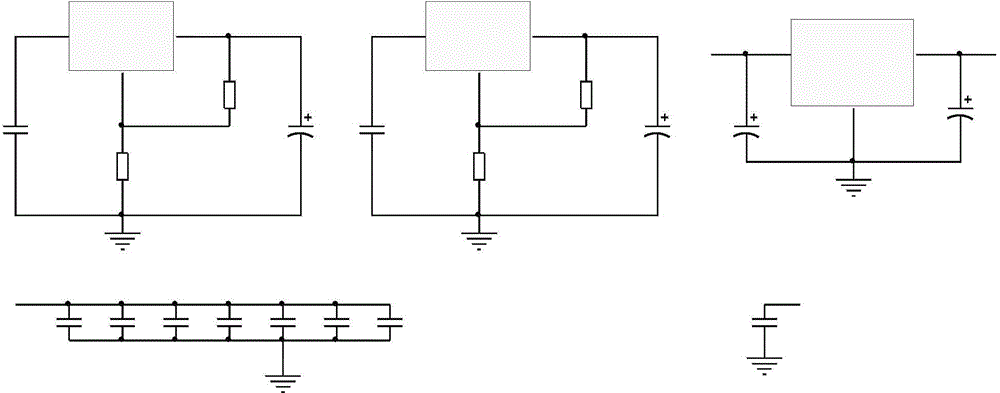

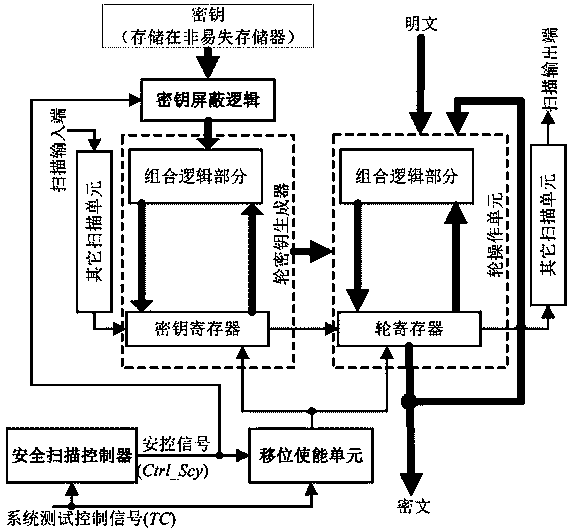

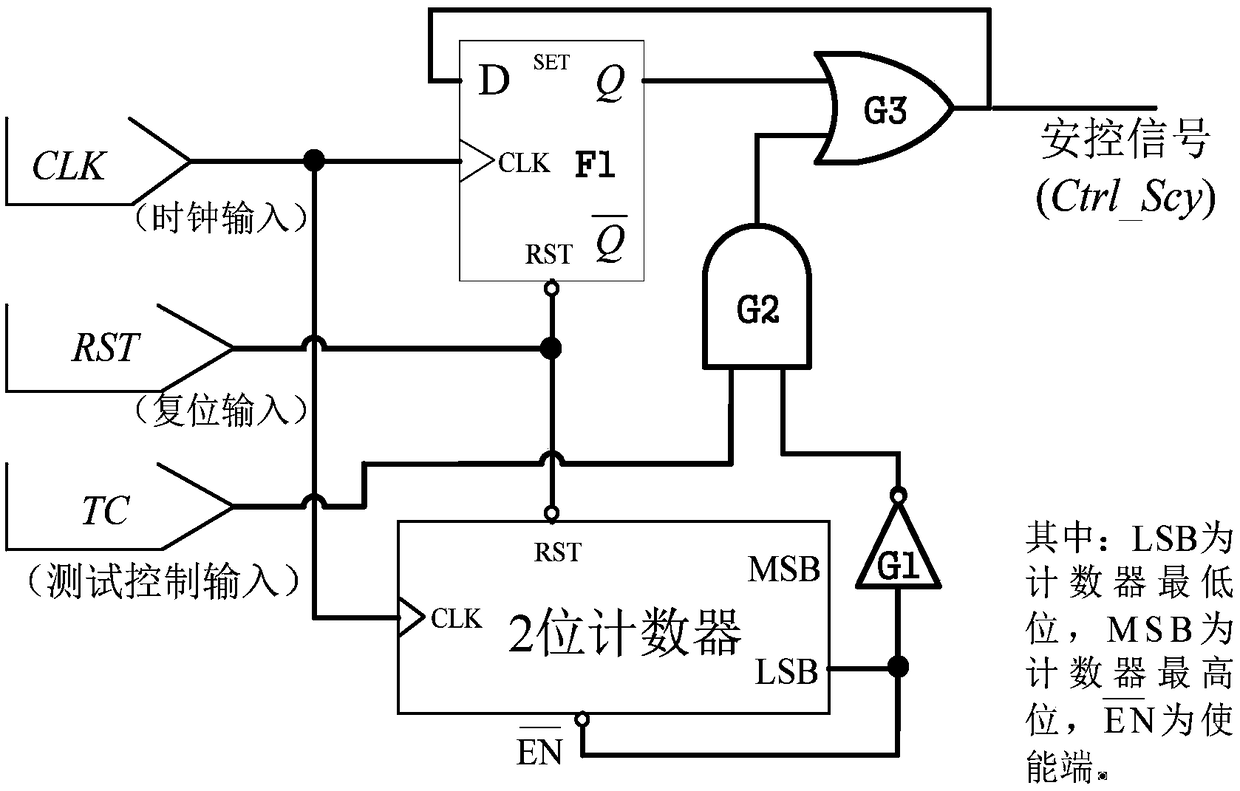

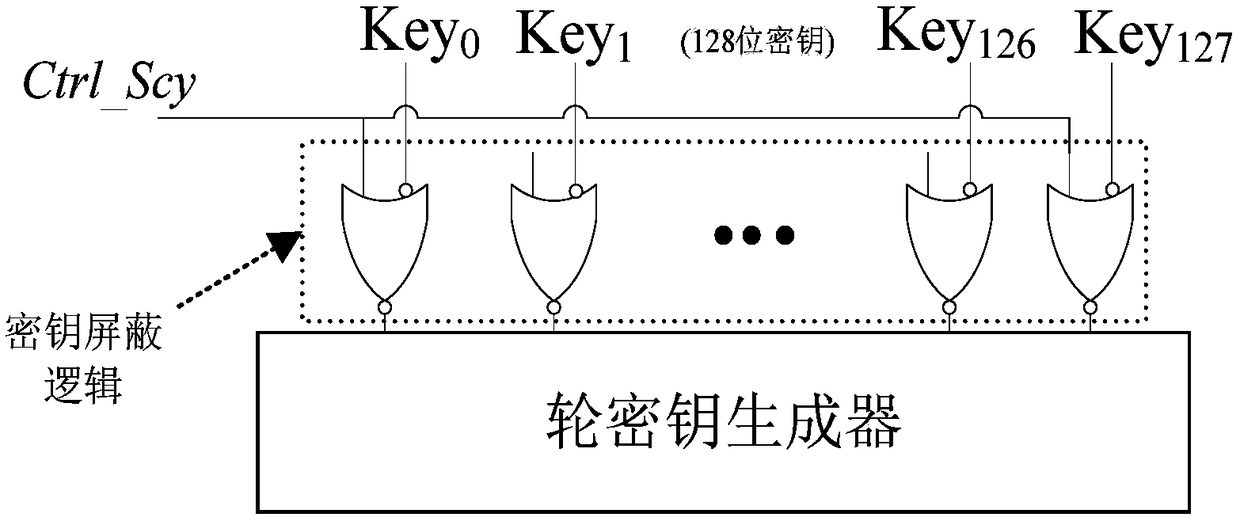

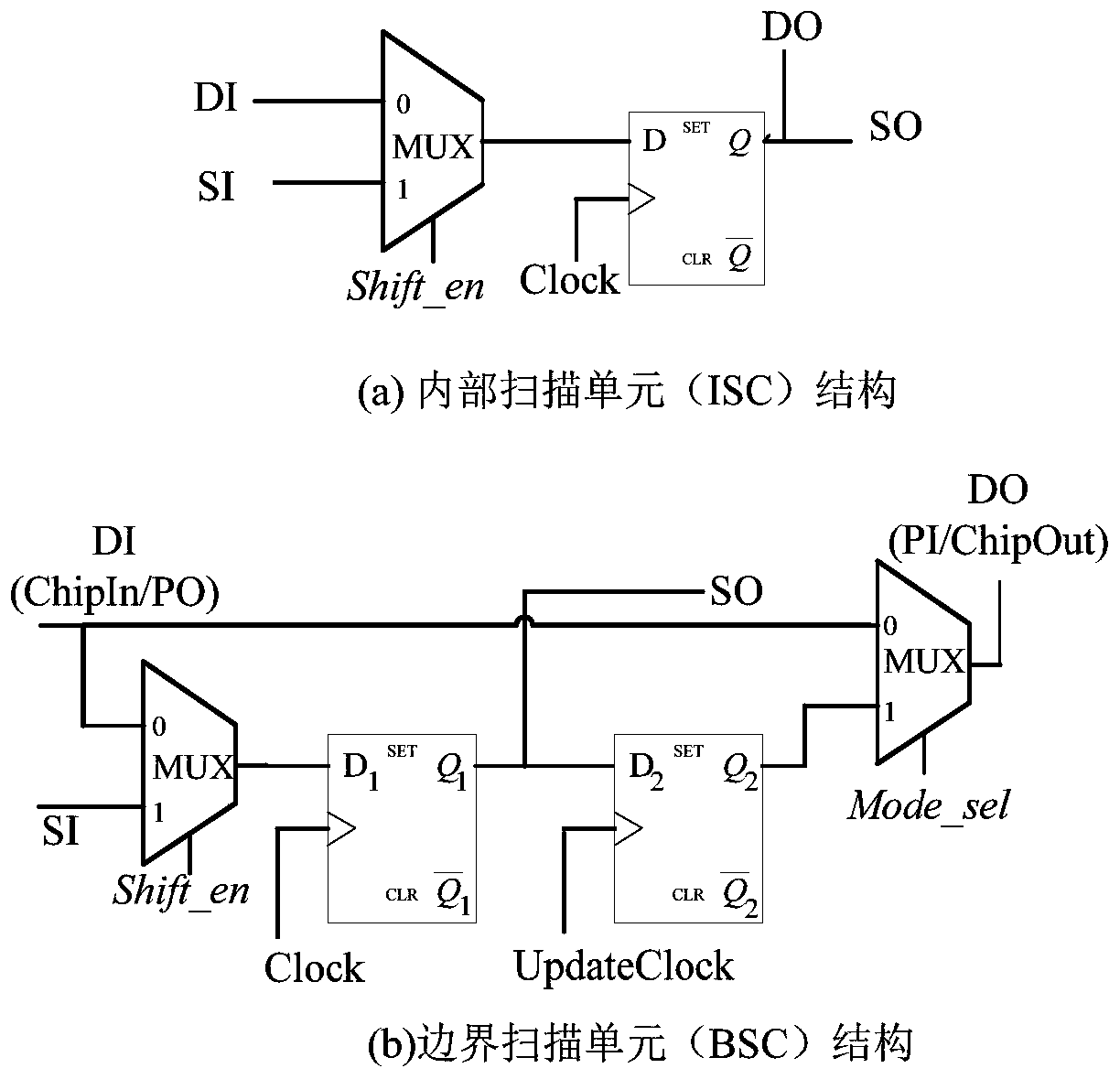

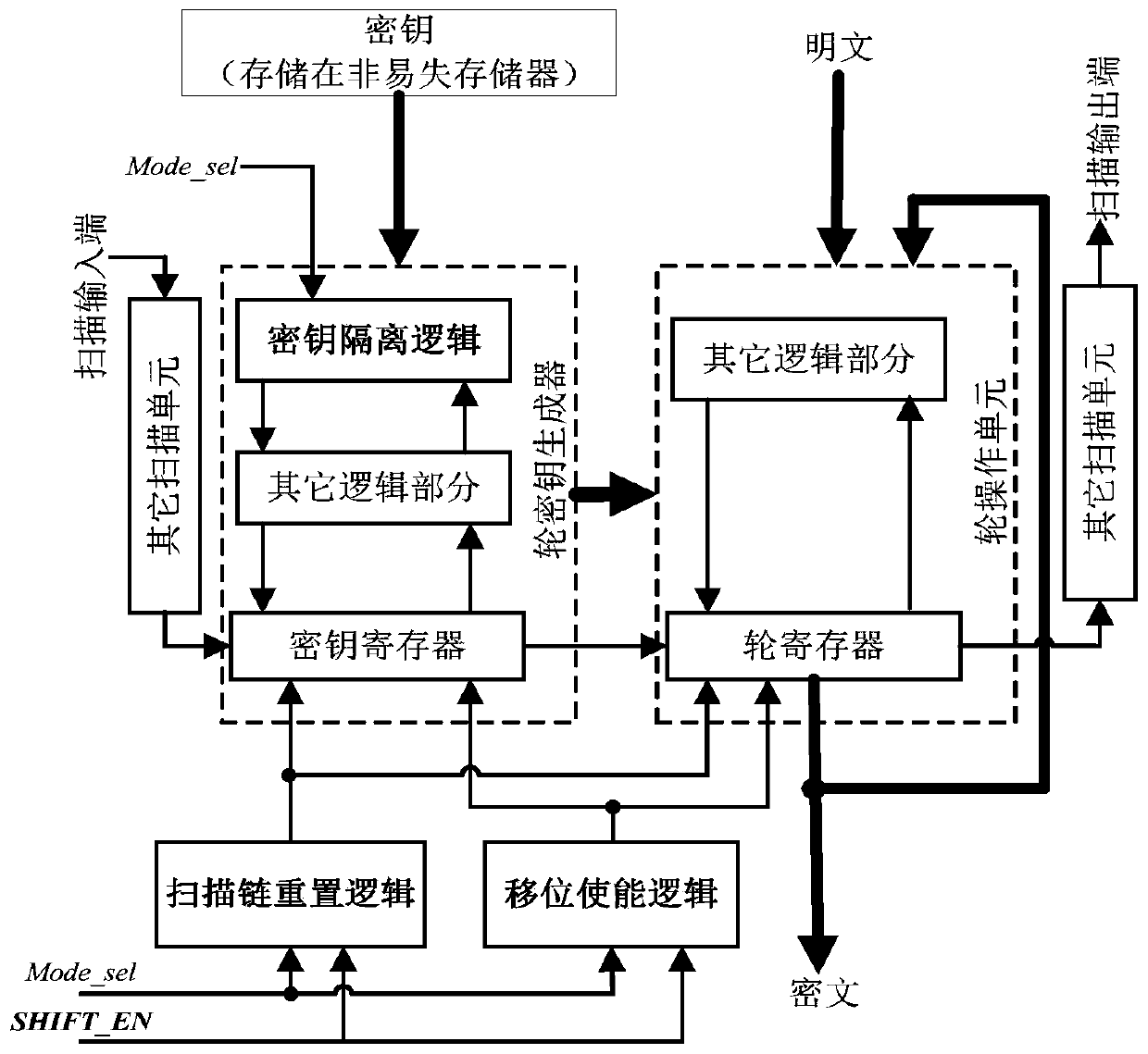

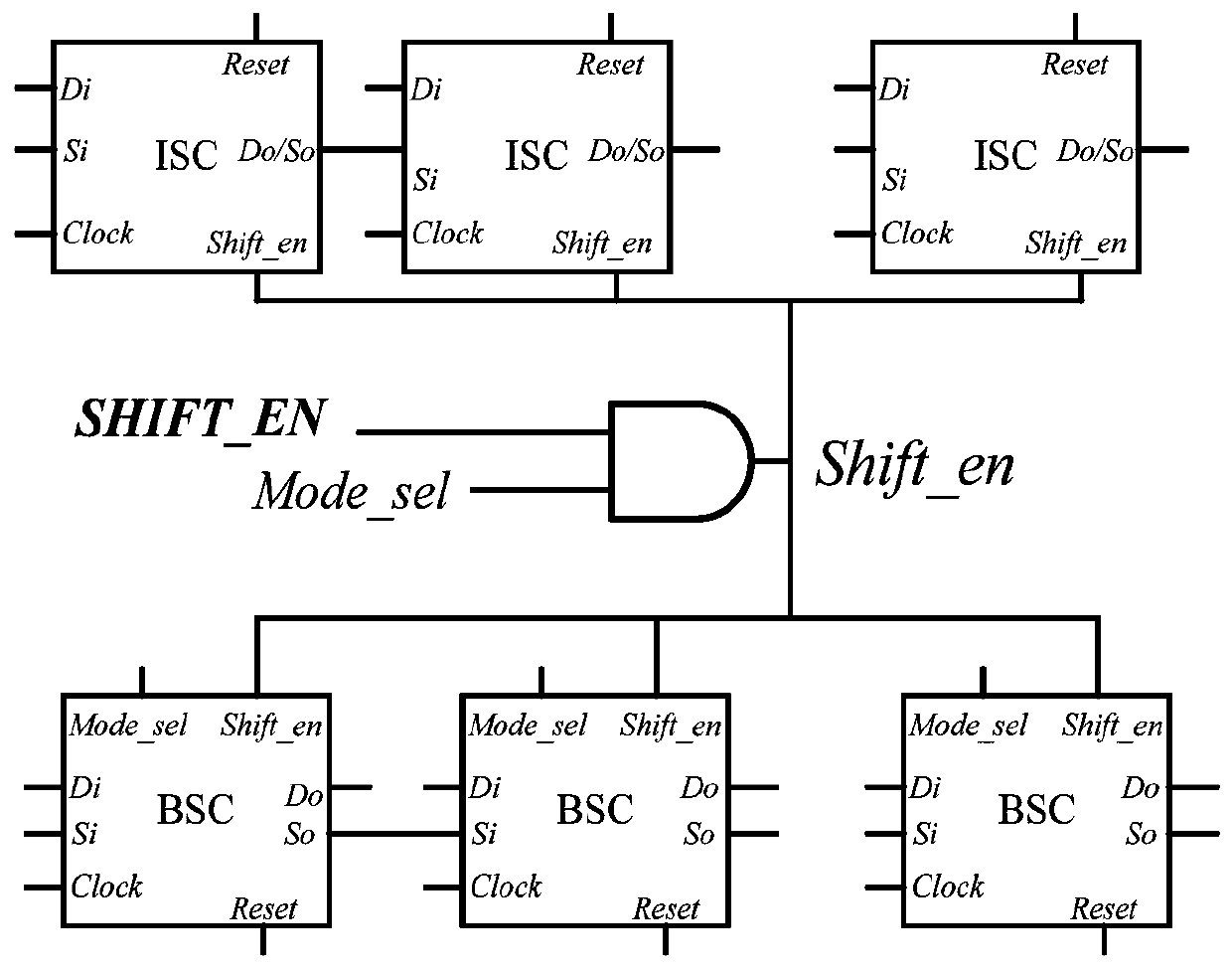

Secure testability design structure of encryption chip

The invention discloses a testability design structure for protecting an encryption chip from scanning attacks. The secure testability design structure of the encryption chip is introduced with key shielding logic, shift enabling logic and a secure scan controller based on the conventional scan design structure. If the encryption chip first enters the functional mode after power-on or reset, the key shielding logic allows the key to be loaded under the control of the security scan controller, while the shift enabling logic prevents the circuit from switching to the test mode, thereby avoidingthe leakage of the encrypted information. Conversely, if the encryption chip first enters the test mode after power-on or reset, the scan shift and the response capture can be performed normally underthe control of the security scan controller, while the key is isolated, thereby ensuring that the data removed from the scan chain is independent of the key. According to the secure testability design structure of encryption chip, by adding less hardware logic, all potential scan-based side channel attacks can be resisted while ensuring the circuit testability.

Owner:CHANGSHA UNIVERSITY OF SCIENCE AND TECHNOLOGY

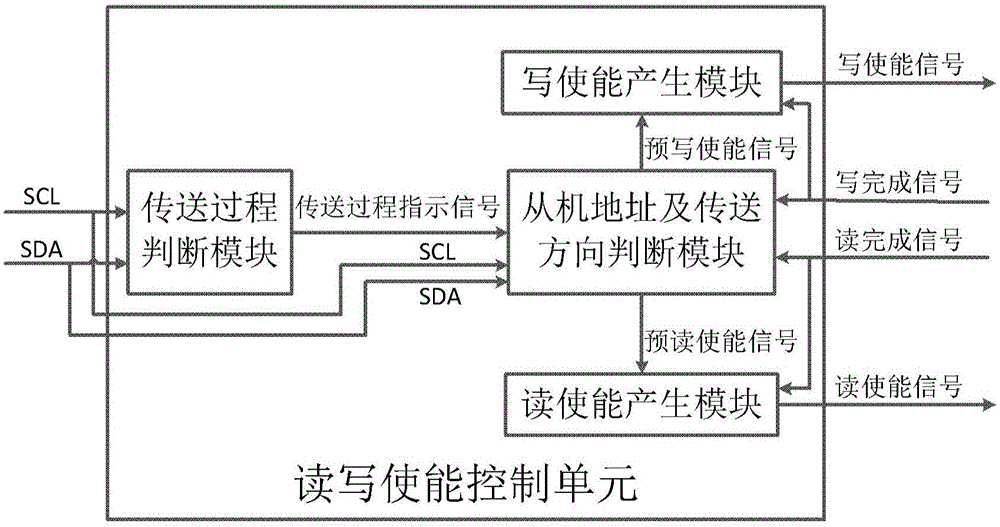

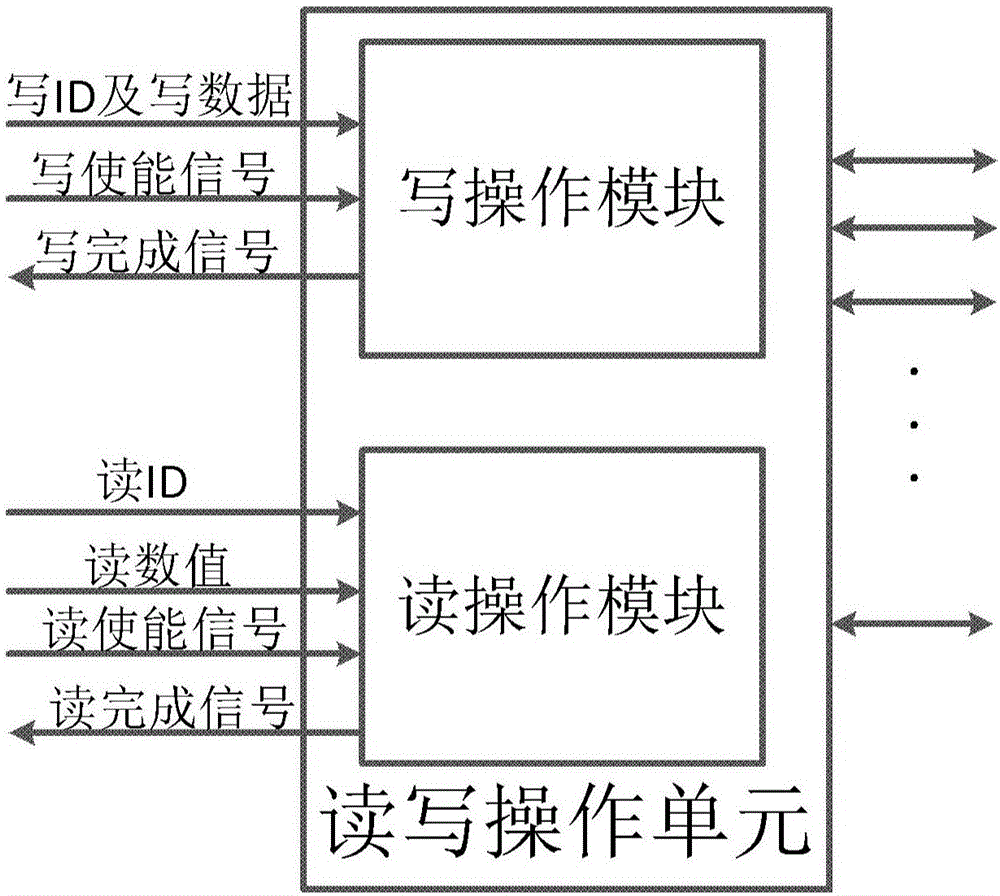

Apparatus and method of reading and writing internal register file through I2C interface

ActiveCN106649158ARead and write implementationImprove testabilityProgram controlDesign for testingProcessor register

The present invention relates to an apparatus and a method of reading and writing an internal register file through an I2C interface. The apparatus comprises an I2C host, an I2C slave, a read and write operation unit, and a read and write enabling control unit. The I2C host sends a signal to the I2C slave and the read and write enabling control unit and reads data in the I2C slave. The I2C slave comprises a first I2C read and write register, a second I2C read and write register and an I2C read-only register that are respectively used for storing write ID and write data and read ID and read data. The read and write operation unit is used for performing read and write operations on the internal register file. The read and write enabling control unit is used for generating a read and write enabling signal according to the signal sent by the I2C host and setting 1 for controlling the read and write operation unit. When a write enabling signal is 1, the write operation is performed, and when a read enabling signal is 1, the read operation is performed and read data is fed back to the I2C read-only register. According to the apparatus and method, extra external interface overhead and internal stored circuit consumption are not increased, further, read and write are performed on the internal register file of the chip, so that the apparatus and method are significant for testable designs.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

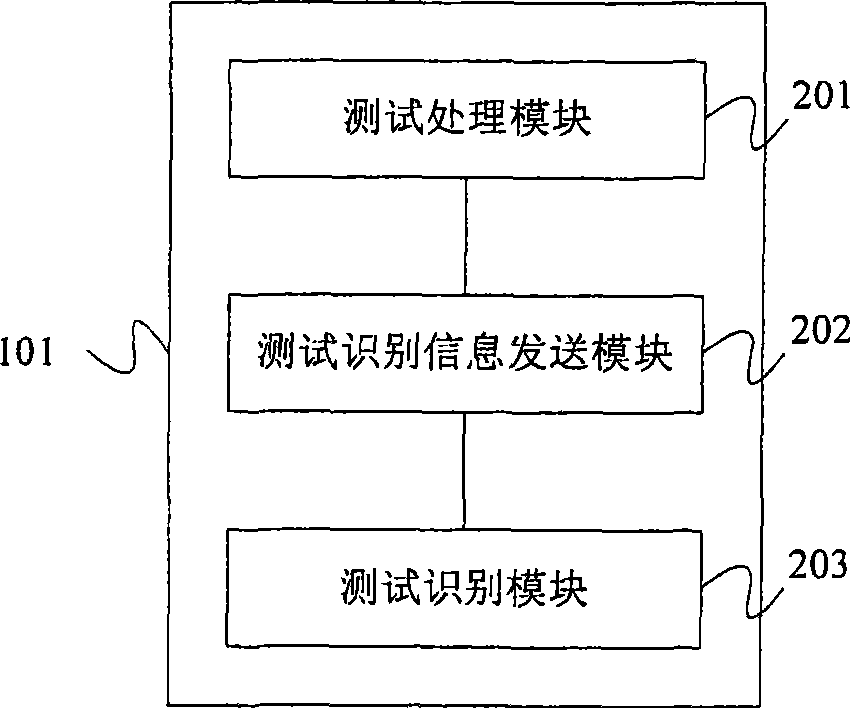

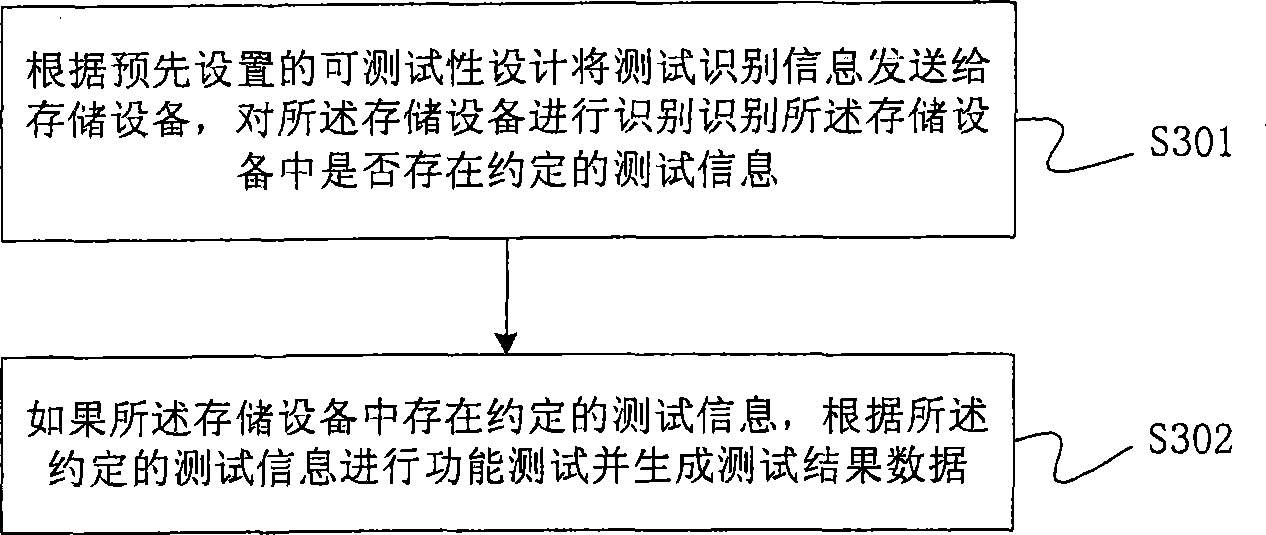

Functional test method, terminal device and system based on memory apparatus

ActiveCN101488984AReal-time communicationComprehensive functional coverageElectronic circuit testingSubstation equipmentDesign for testingFunctional testing

The invention provides a functional test method, terminal device and system based on storage device. The method comprises: sending test identifying information to the storage device according to predetermined design for testing, identifying whether there is promissory test information in the storage device; if so, processing functional test and generating test result data according to the promissory test information. The invention processes automated functional test for product by host computer interfaces of the storage device. A commissioning terminal can send test information to the storagedevice real-time to realize real-time communication of the commissioning terminal and the tested device. The invention is characterized in complete functional cover, good quality assurance, high testefficiency, low cost and convenient test operation.

Owner:HUAWEI DEVICE CO LTD

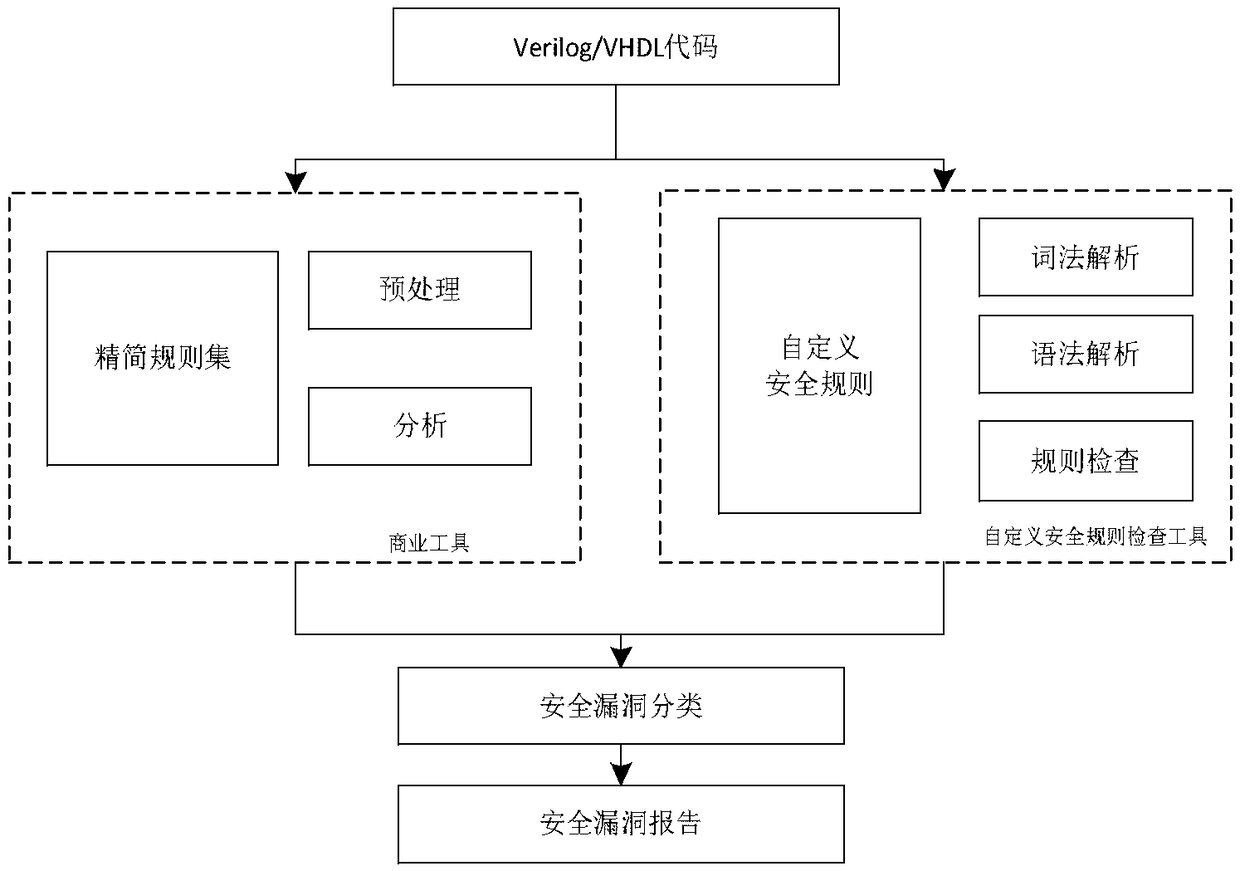

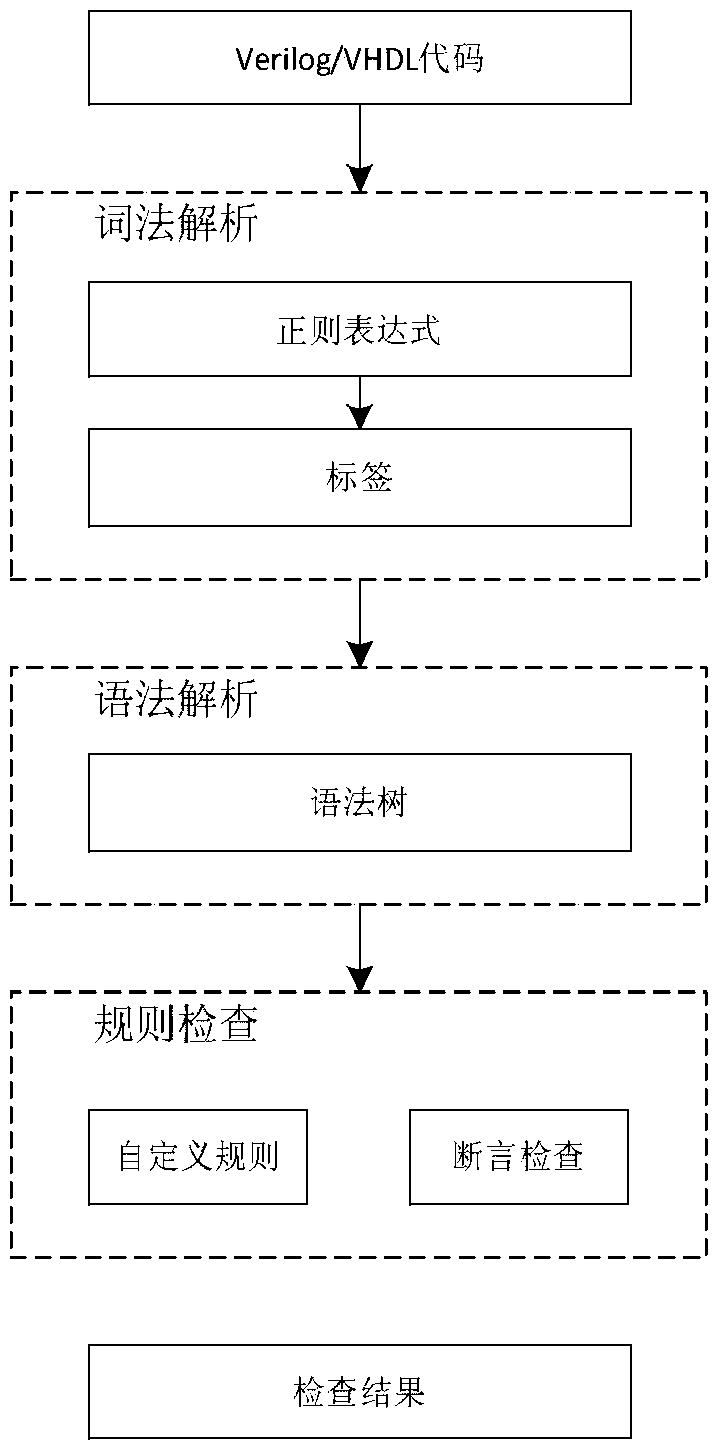

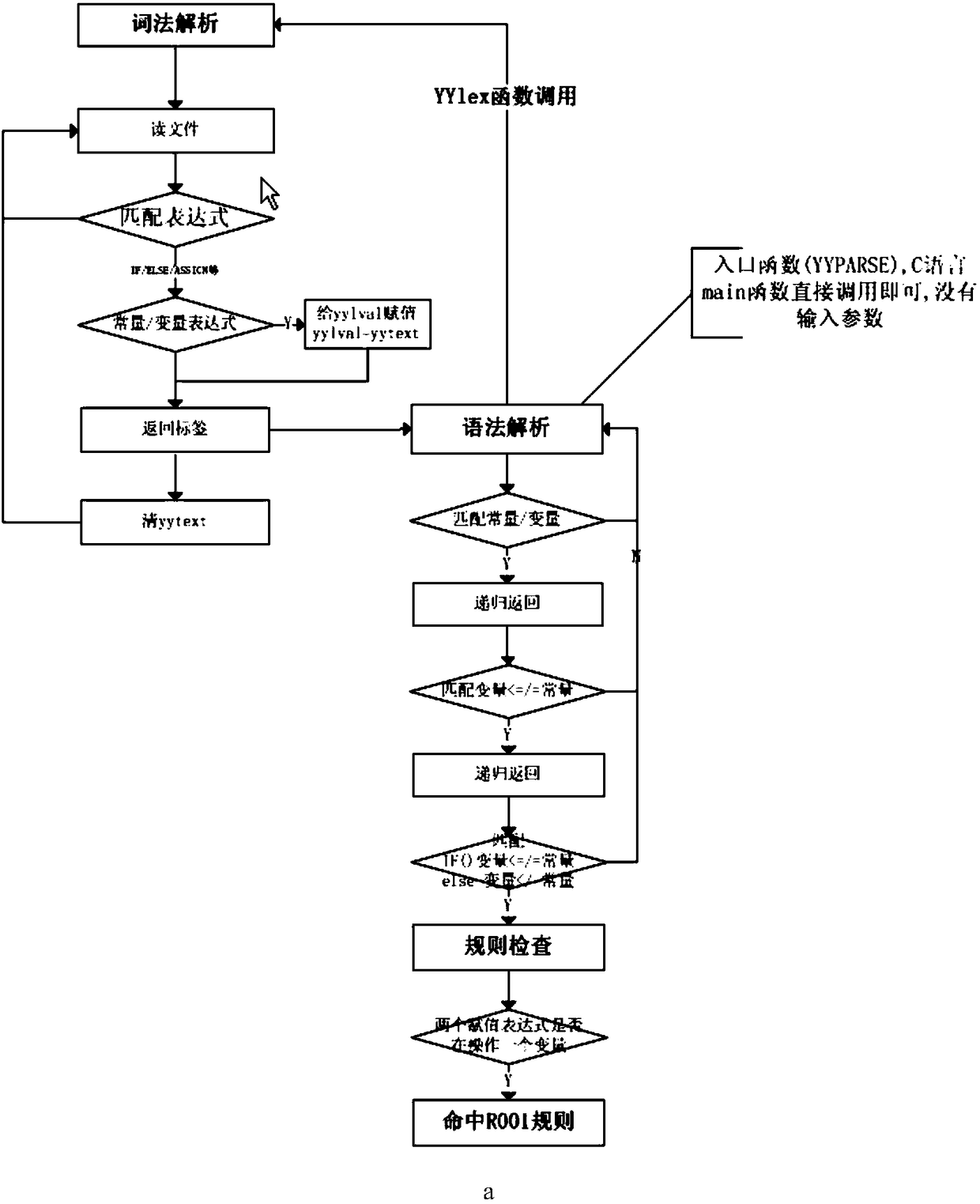

A FPGA/IP core logic code security rule detection method

ActiveCN109032934AQuality improvementReduce invalid strike rule termsSoftware testing/debuggingProgramming languageDesign for testing

The invention relates to a FPGA / IP core logic code security rule detection method, which relates to the technical field of FPGA / IP core verification. The invention adds and realizes FPGA state machinedeadlock, internal three-state and other rule clauses in the self-defined safety rule detection clauses according to the combination of the designed self-defined safety rule detection clauses and theexisting commercial clauses, and improves the quality of FPGA code. Deleting rules that are not applicable to the design for testability of FPGA, electrical characteristics detection, and so on, effectively reduces the invalid warning rules.

Owner:BEIJING INST OF COMP TECH & APPL

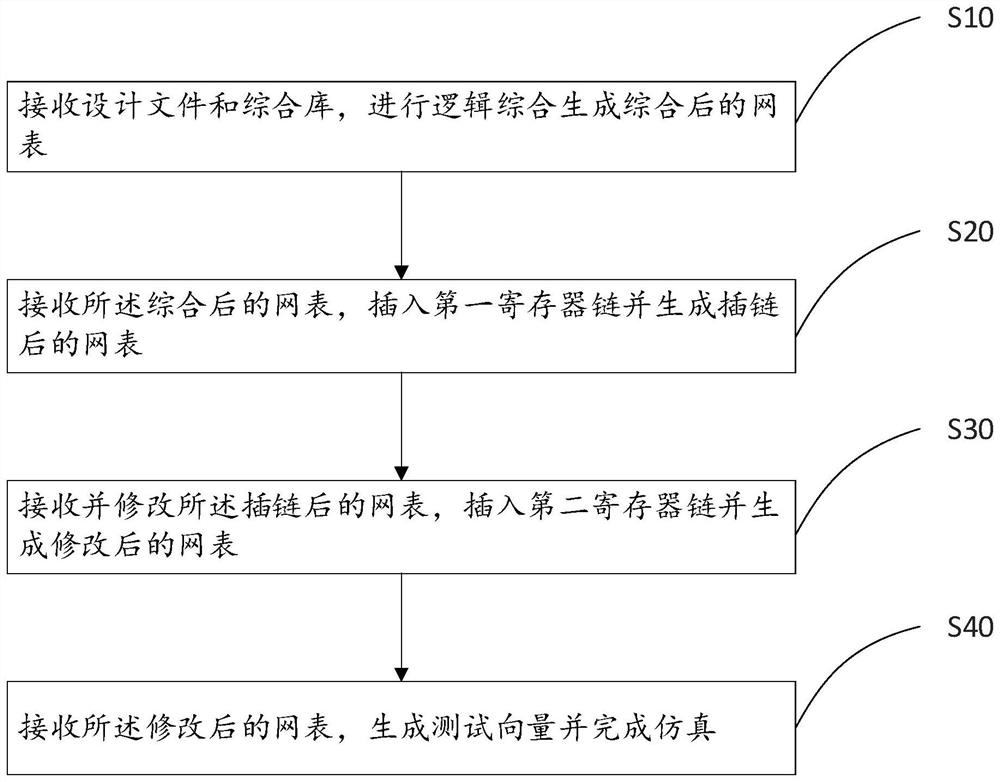

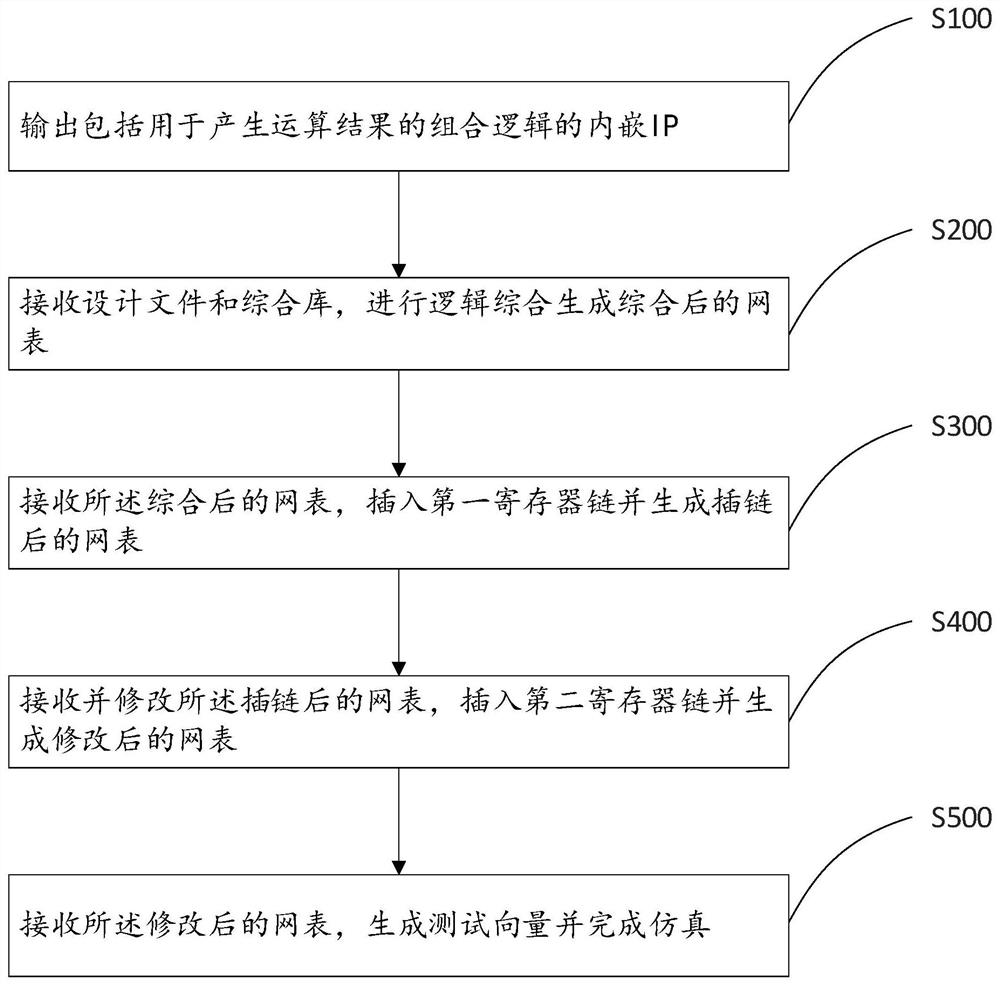

Testability design method for embedded IP of FPGA

ActiveCN112597723AImprove test coverageAvoid modificationCAD circuit designSpecial data processing applicationsComputer architectureDesign for testing

The invention provides a testability design method for an embedded IP of an FPGA, and the method comprises the steps: receiving a design file and a comprehensive library, and carrying out the logic synthesis to generate a synthesized netlist; receiving the integrated netlist, inserting a first register chain and generating a chain-inserted netlist; receiving and modifying the chain-inserted netlist, inserting a second register chain and generating a modified netlist; and receiving the modified netlist, generating a test vector and completing simulation. According to the testability design method, the input excitation of the embedded IP is changed by inserting the second register chain, so that the defects in the embedded IP can be detected through a DFT case; and the DFT test coverage rateof the embedded IP can be obviously improved on the premise that the circuit structure of the embedded IP is prevented from being greatly modified.

Owner:SHENZHEN PANGO MICROSYST CO LTD

Safe password chip testability design structure in boundary scanning design environment

PendingCN110020558ATest has no effectAvoid attackKey distribution for secure communicationEncryption apparatus with shift registers/memoriesDesign for testingPassword

The invention discloses a testability design structure for protecting an AES password chip from scanning attack in a boundary scanning design environment. According to the safe testability design structure, shift enable logic, scan chain mode switching reset logic and key isolation logic are introduced on the basis of a conventional boundary scan design structure. The shift enable logic is used for disabling a scanning shift operation in a functional mode; the scan chain mode switching reset logic enables the chip to execute a reset operation at first when switching from a function mode to a test mode, so that confidential information stored in the scan chain is protected; and the key isolation logic is used for isolating the encryption key in the test mode so as to prevent the attacker from obtaining the key information in the test mode. New input and output signals are not introduced, only little hardware expenditure is needed, the chip can be automatically protected, and all potential side channel attacks based on scanning can be resisted on the premise that the testability of the circuit is not damaged.

Owner:CHANGSHA UNIVERSITY OF SCIENCE AND TECHNOLOGY

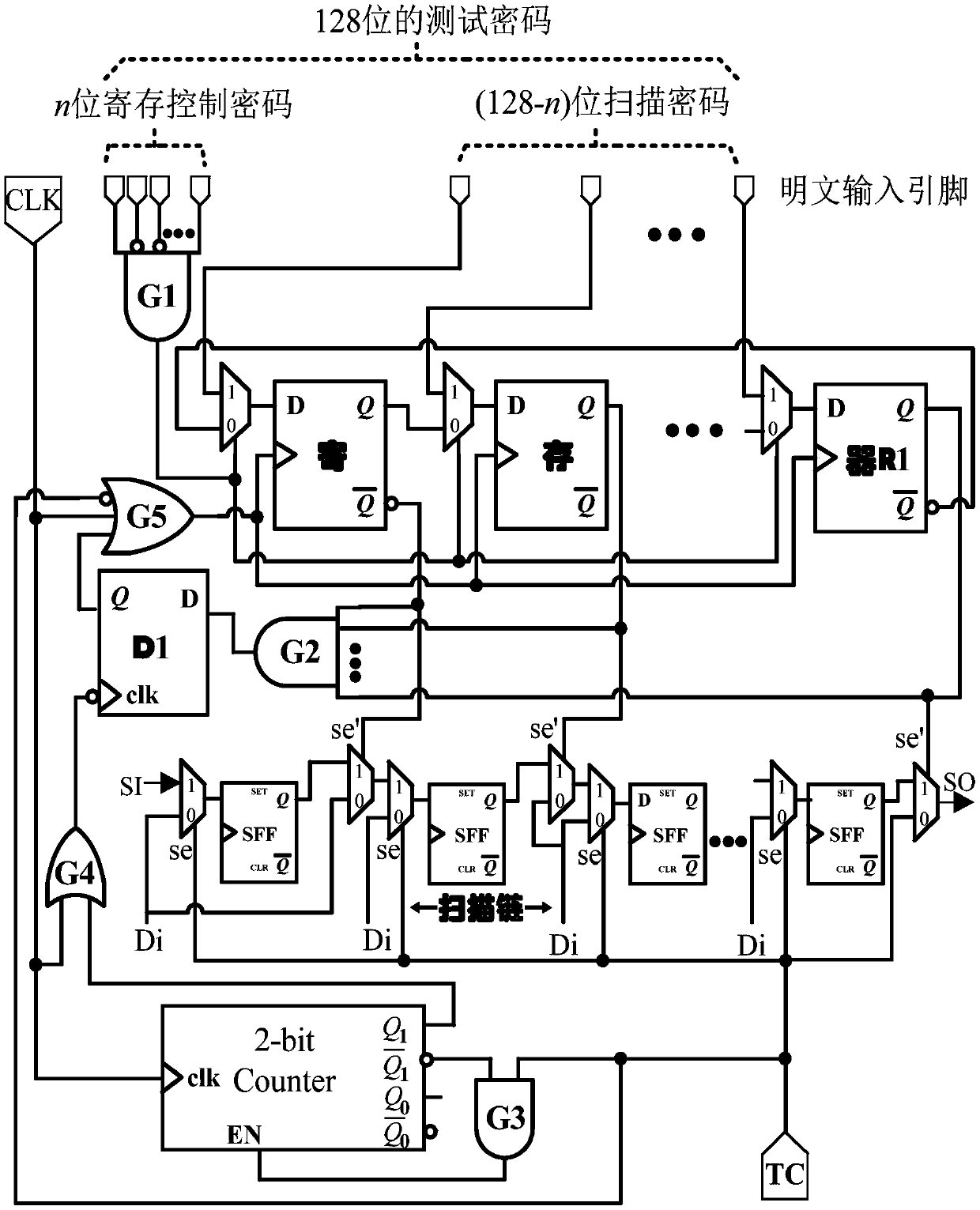

Encryption chip safety testing method based on scanning confusing

InactiveCN109633422ATest impactLow design impactElectrical testingDesign for testingProcessor register

The invention relates to a testable design structure based on scanning confusing and used for protecting an encryption chip against scanning attacks. Based on a conventional scanning design structure,a scanning password register and an associated logic are introduced into a secure testable design structure, and it is required that test passwords are firstly loaded from a chip input port during testing. Chip testing can be performed normally only after correct test passwords are loaded. If an attacker does not understand a correct test procedure and does not have the correct test passwords, the attacker cannot load the correct test passwords through the specific input port within the specified time, and therefore no value can be swept for a scanning chain under the 1-2-128 probability, thereal state of the scanning chain cannot be observed from the output end, and non-intrusive attacks based on scanning are virtually impossible. On the premises that the circuit performance and the testing quality are not influenced and the testing time is not added, existing non-intrusive attacks based on scanning can be resisted.

Owner:CHANGSHA UNIVERSITY OF SCIENCE AND TECHNOLOGY

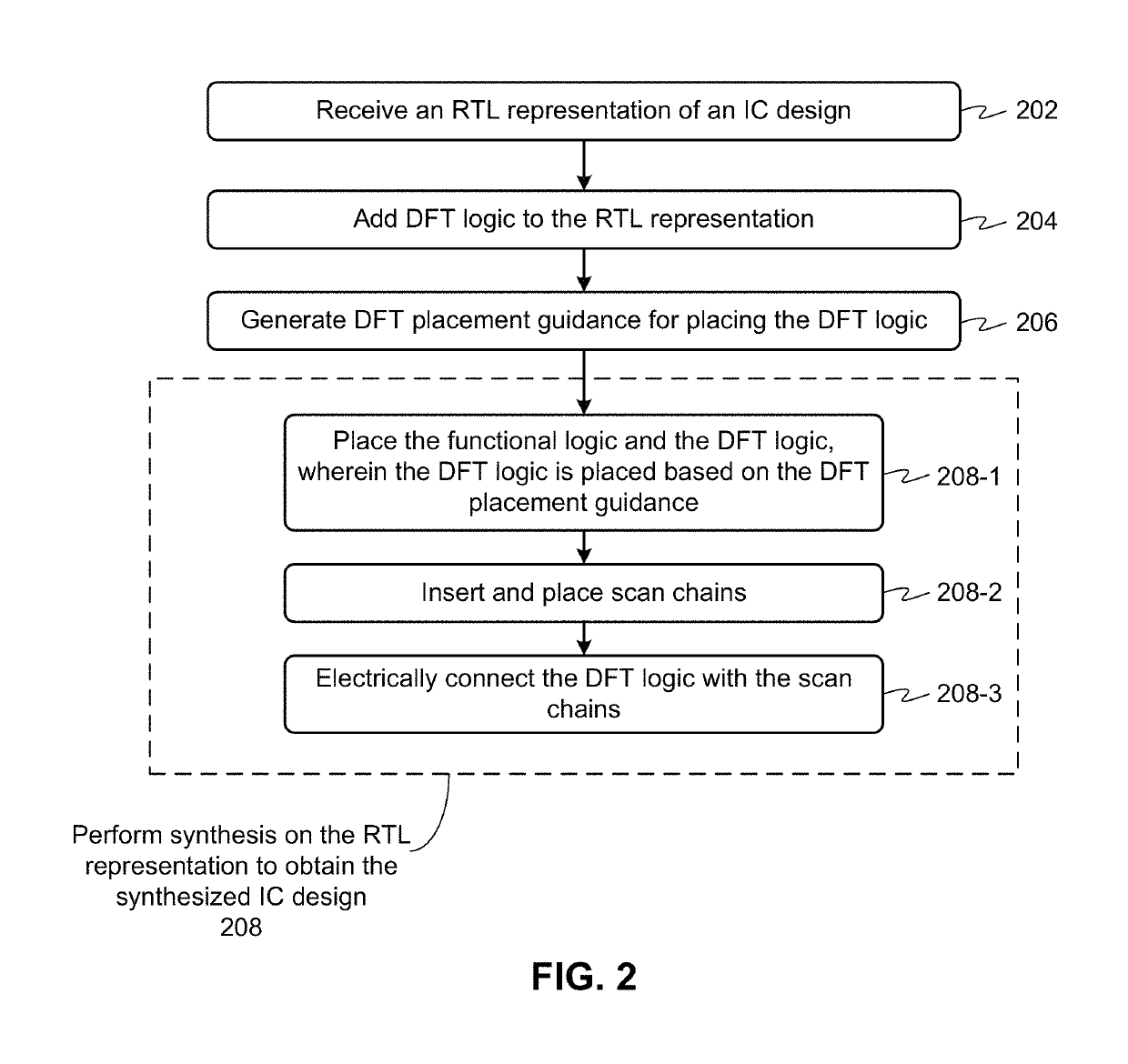

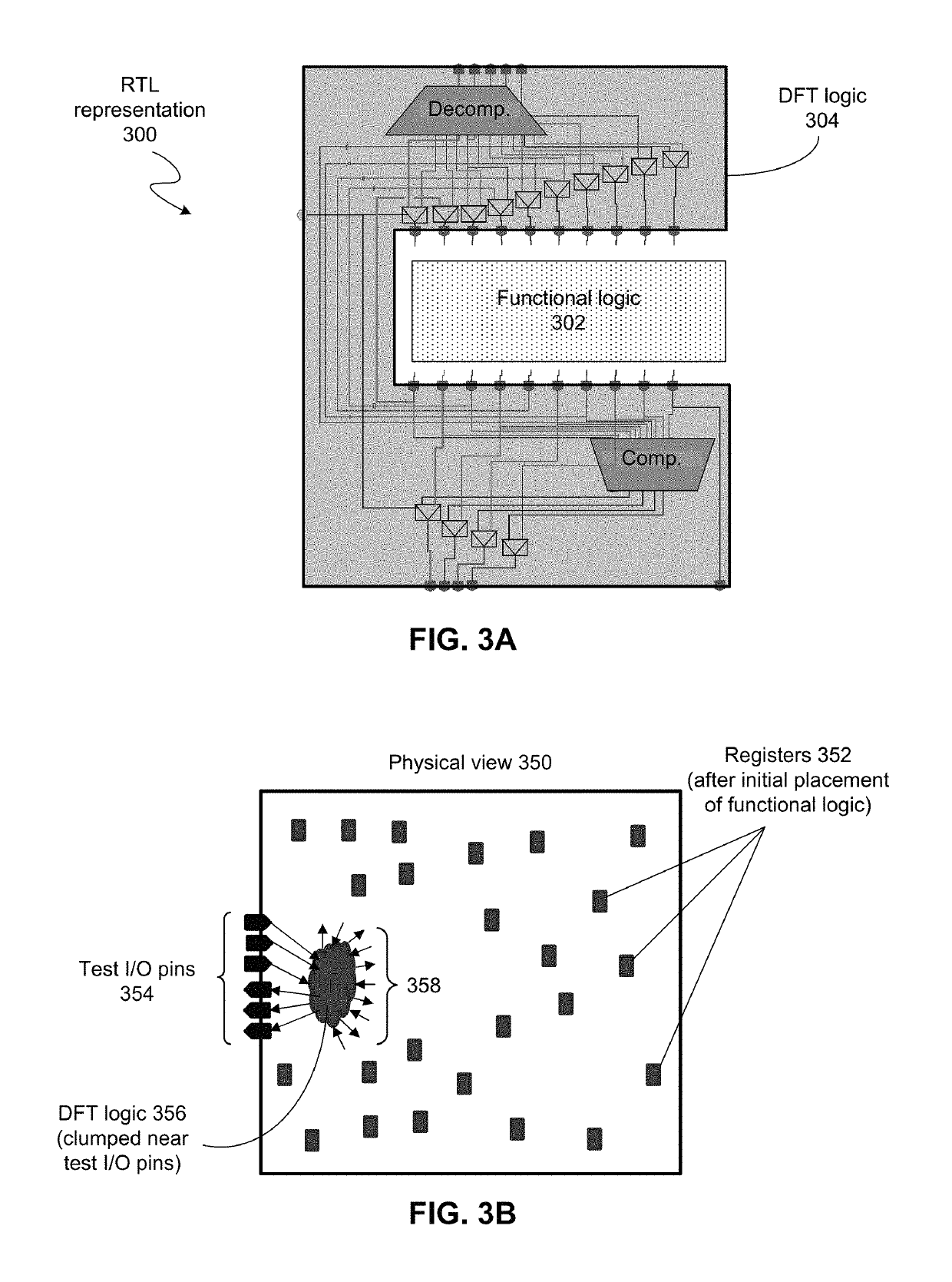

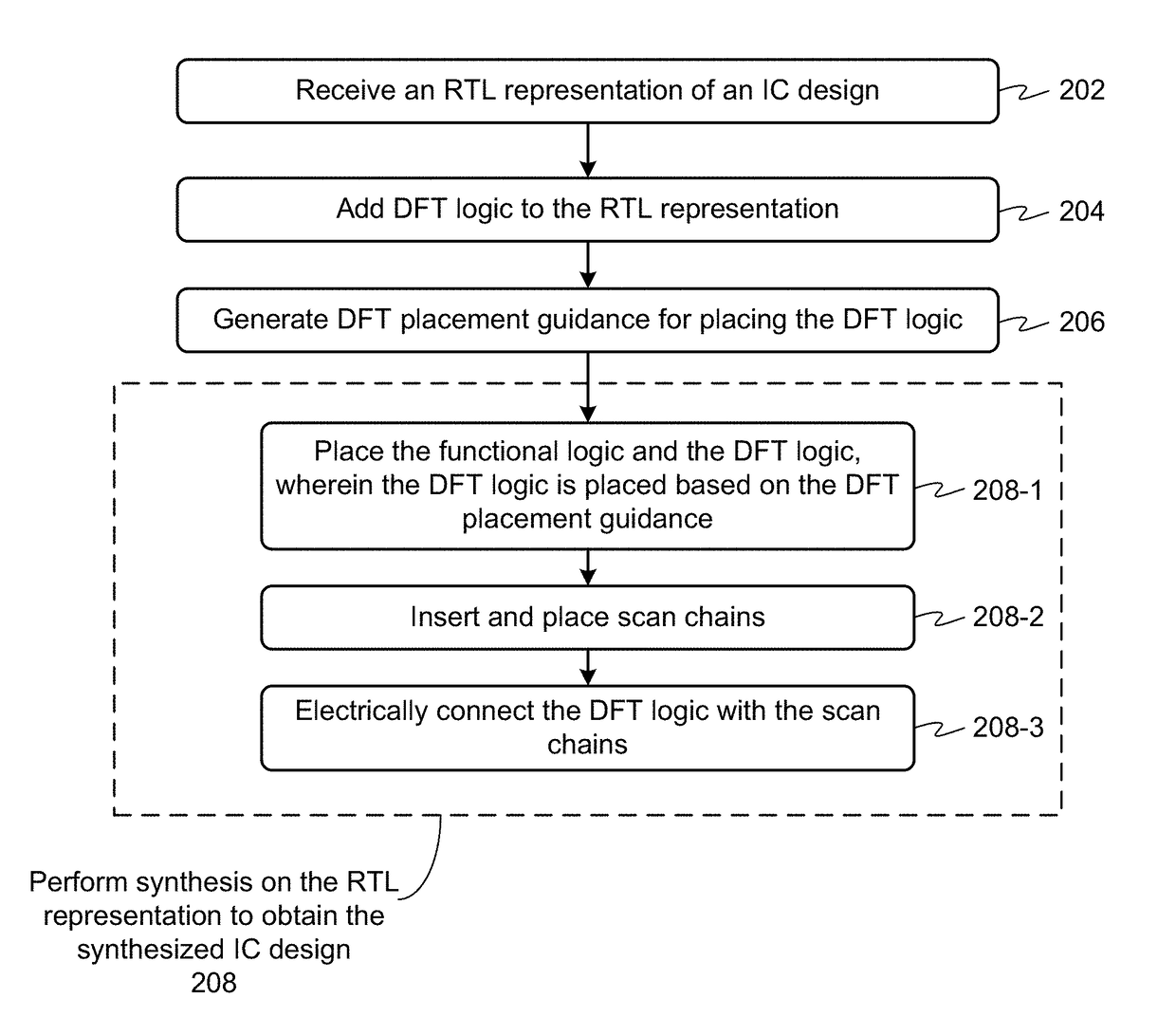

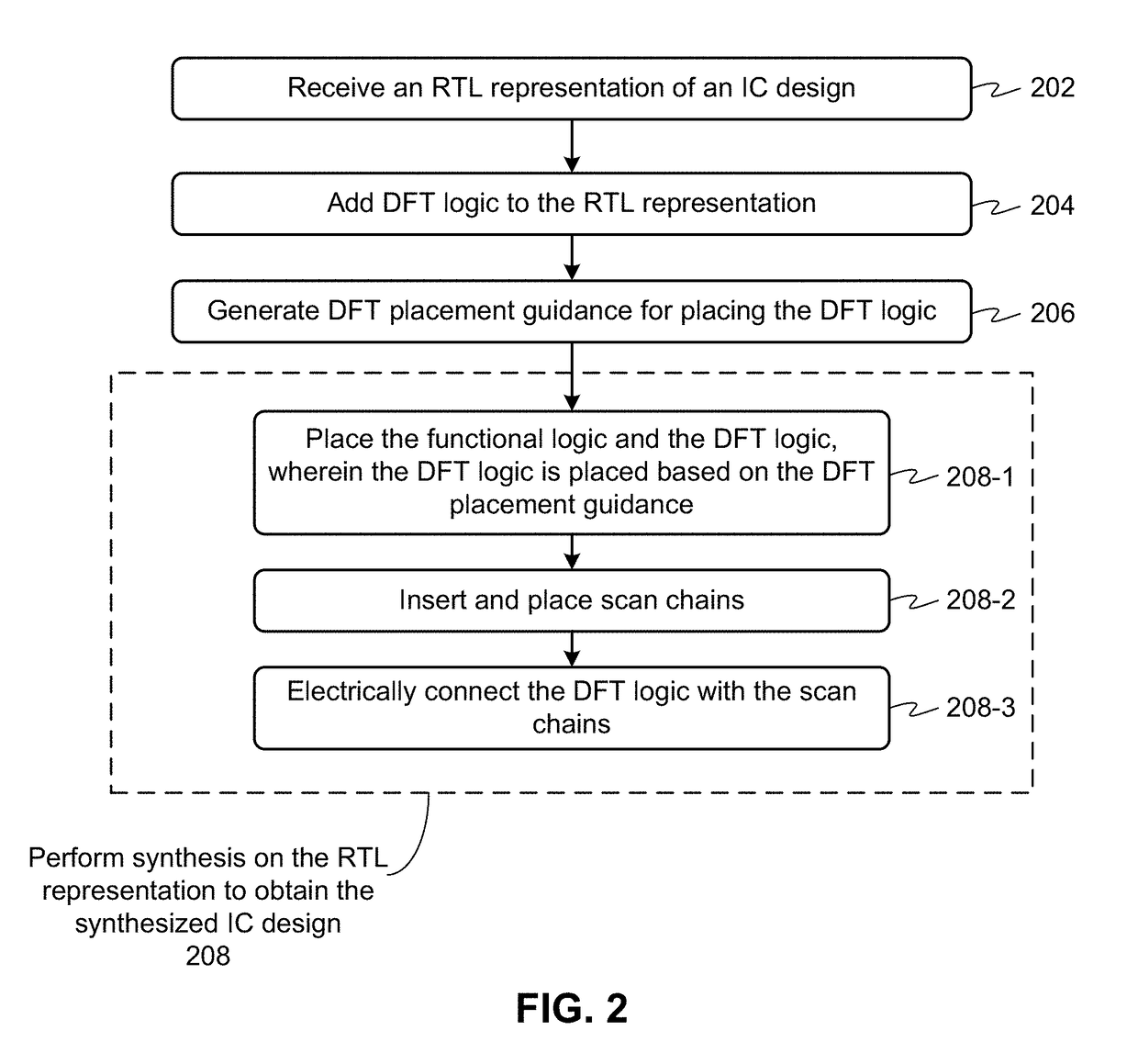

Design-for-testability (DFT) insertion at register-transfer-level (RTL)

ActiveUS10372858B2Faster runtimesBetter QoRComputer aided designSpecial data processing applicationsElectricityDesign for testing

Systems and techniques are described for producing a synthesized IC design that includes design-for-testability (DFT) circuitry. A register-transfer-level (RTL) representation of an IC design can be received, wherein the RTL representation includes functional logic. Next, DFT logic can be added to the RTL representation, and DFT placement guidance for placing the DFT logic can be generated. Synthesis can be performed on the RTL representation to obtain the synthesized IC design, wherein during synthesis, (1) the functional logic and the DFT logic can be placed, wherein the DFT logic is placed based on the DFT placement guidance, (2) scan chains can be inserted and placed, and (3) the DFT logic can be electrically connected with the scan chains.

Owner:SYNOPSYS INC

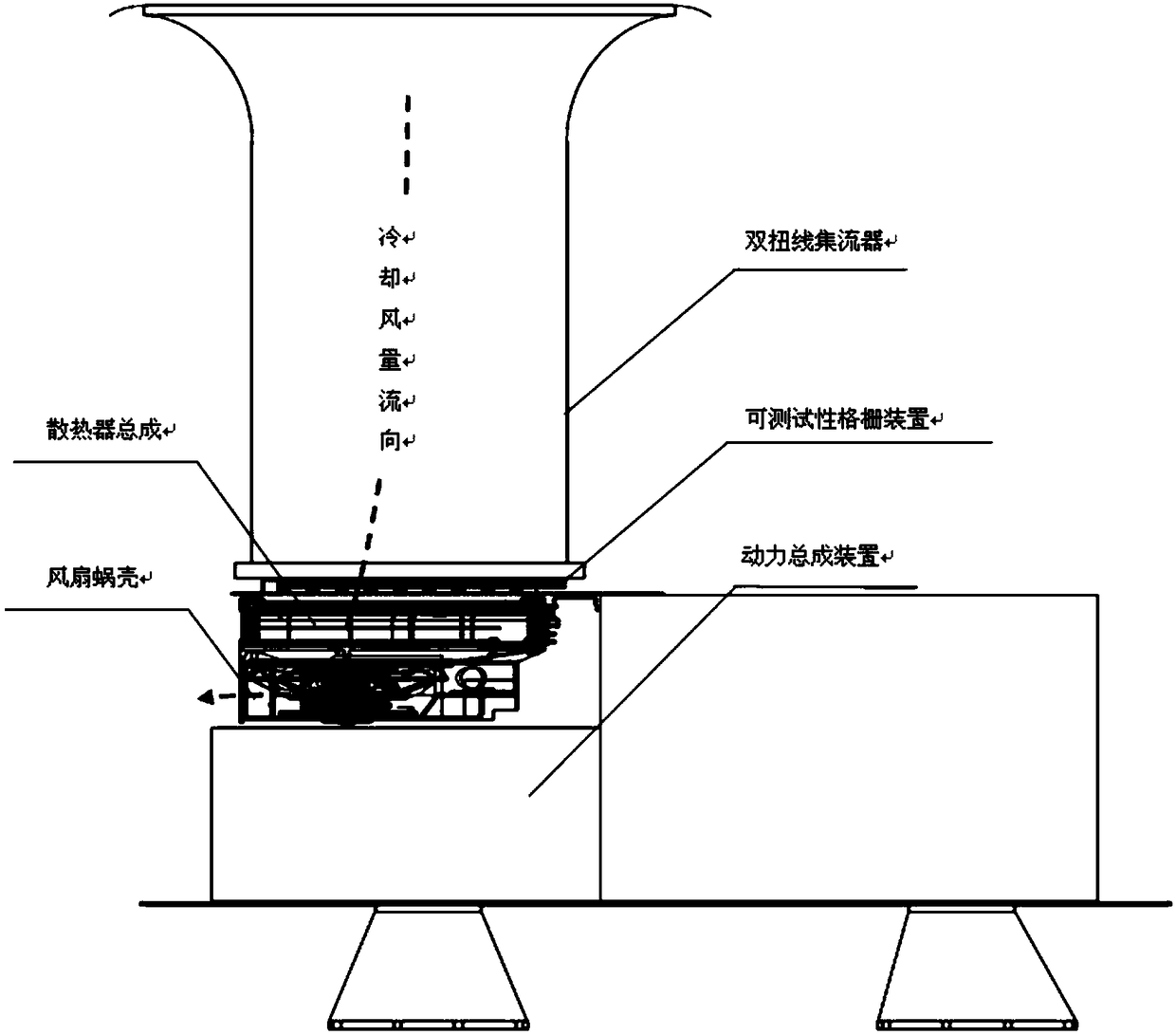

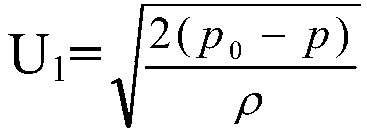

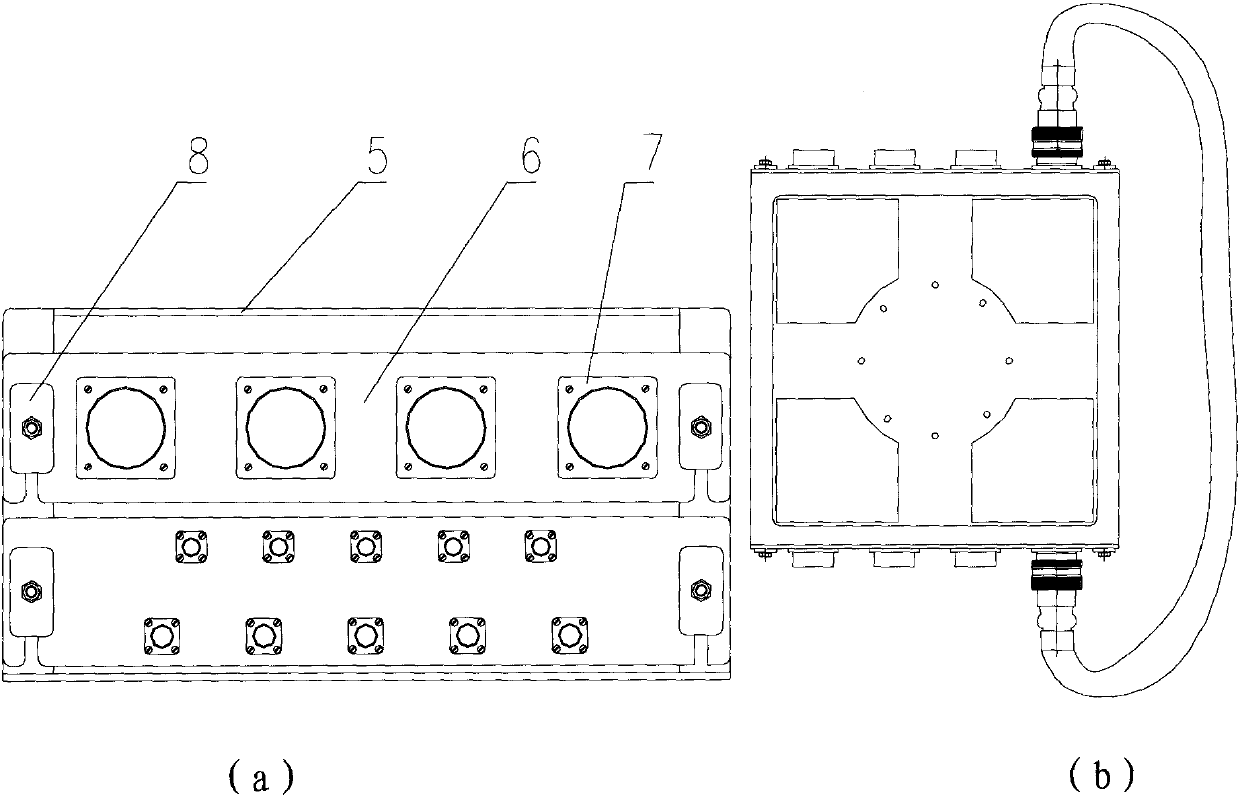

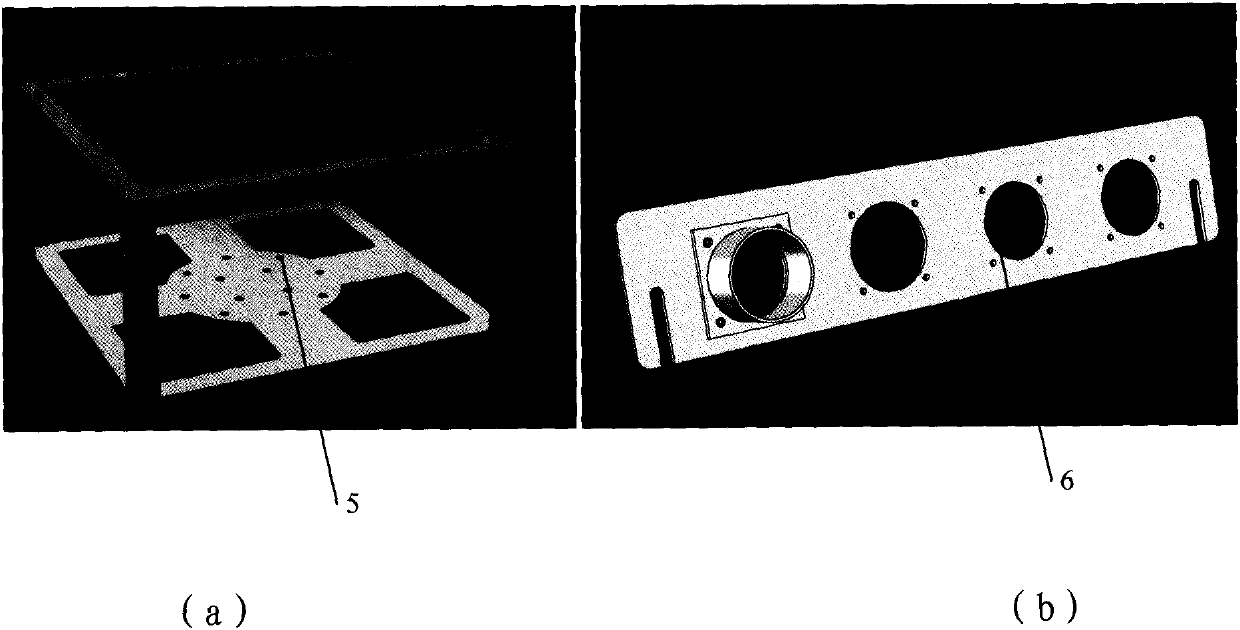

Special vehicle cooling air volume test device and method on basis of testable grating

The invention relates to a special vehicle cooling air volume test device and method on the basis of a testable grating and relates to the technical field of vehicle engineering. The special vehicle cooling air volume test device performs testable design on an air inlet grating of a vehicle, not only can test and obtain cooling air volume information of a vehicle, but also is integrated with the air inlet grating, does not adopt extra test equipment and does not influence an air inlet flow area of the vehicle.

Owner:CHINA NORTH VEHICLE RES INST

Tooling fixture for a vibration test bench

ActiveCN110972557BShorten the selection timeSolve the generality problemVibration testingDesign for testingTest bench

The invention discloses a tooling fixture for a vibration test bench, which belongs to the technical field of tooling design for testing and is suitable for clamping and fixing cables, boxes and cylindrical electrical components when performing vibration tests. It is composed of cable vibration tooling, box type and cylindrical type vibration tooling. The tooling fixture for the vibration test bench of the present invention has the advantages of simple structure, good manufacturability, flexible clamping and strong versatility, can clamp various test pieces at one time, and is economical and time-saving.

Owner:HUBEI JIANGSHAN HEAVY IND

Design-for-testability (DFT) insertion at register-transfer-level (RTL)

ActiveUS20180246996A1Faster runtimesBetter QoRComputer aided designSpecial data processing applicationsElectricityDesign for testing

Systems and techniques are described for producing a synthesized IC design that includes design-for-testability (DFT) circuitry. A register-transfer-level (RTL) representation of an IC design can be received, wherein the RTL representation includes functional logic. Next, DFT logic can be added to the RTL representation, and DFT placement guidance for placing the DFT logic can be generated. Synthesis can be performed on the RTL representation to obtain the synthesized IC design, wherein during synthesis, (1) the functional logic and the DFT logic can be placed, wherein the DFT logic is placed based on the DFT placement guidance, (2) scan chains can be inserted and placed, and (3) the DFT logic can be electrically connected with the scan chains.

Owner:SYNOPSYS INC