Method and apparatus for securing digital information on an integrated circuit during test operating modes

A test mode, integrated circuit technology, which is used in the field of ensuring digital information security and equipment on integrated circuits during the test operation mode, and can solve problems such as reducing the overall IC yield, unsupported, and impossible to accurately confirm registers.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

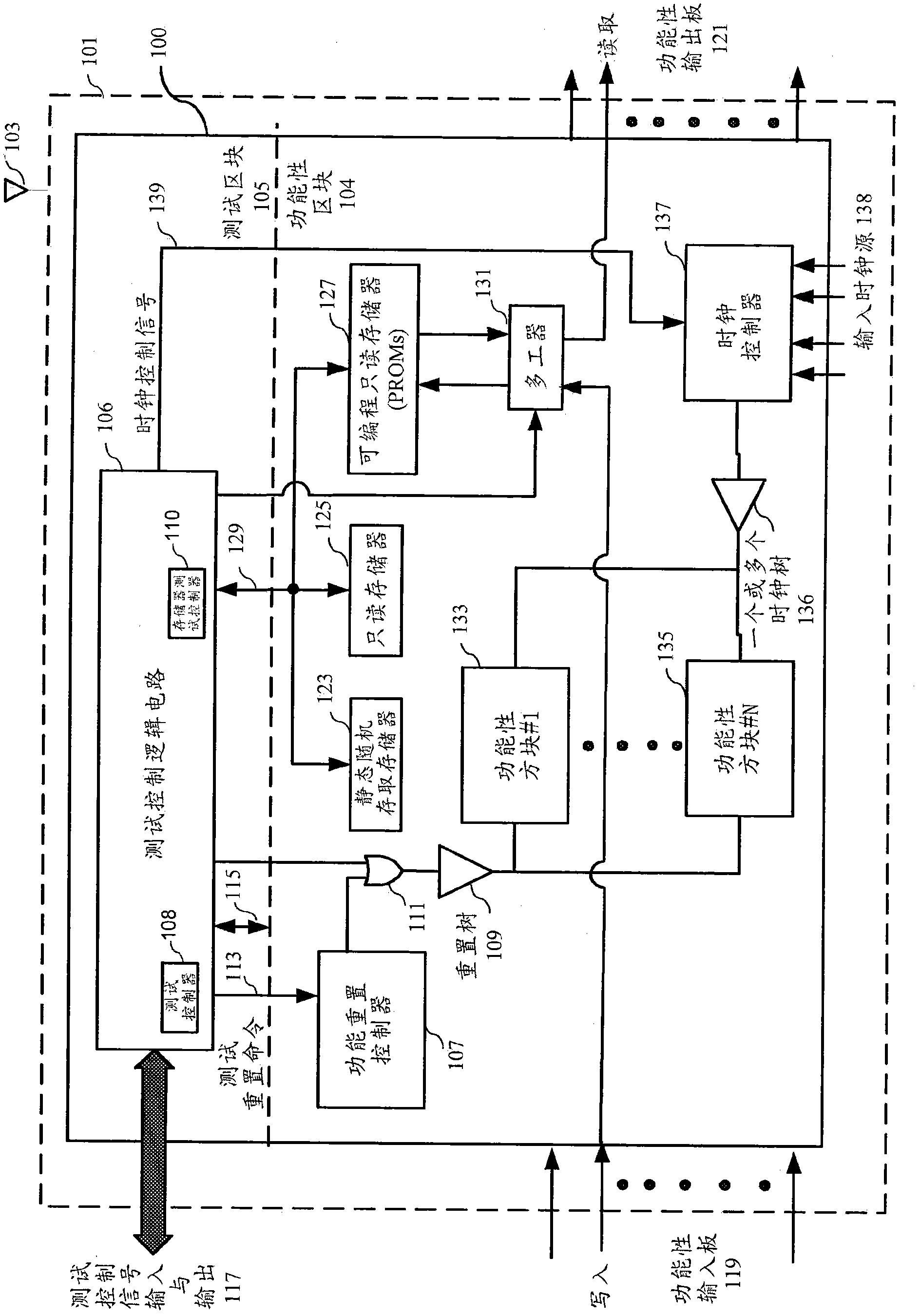

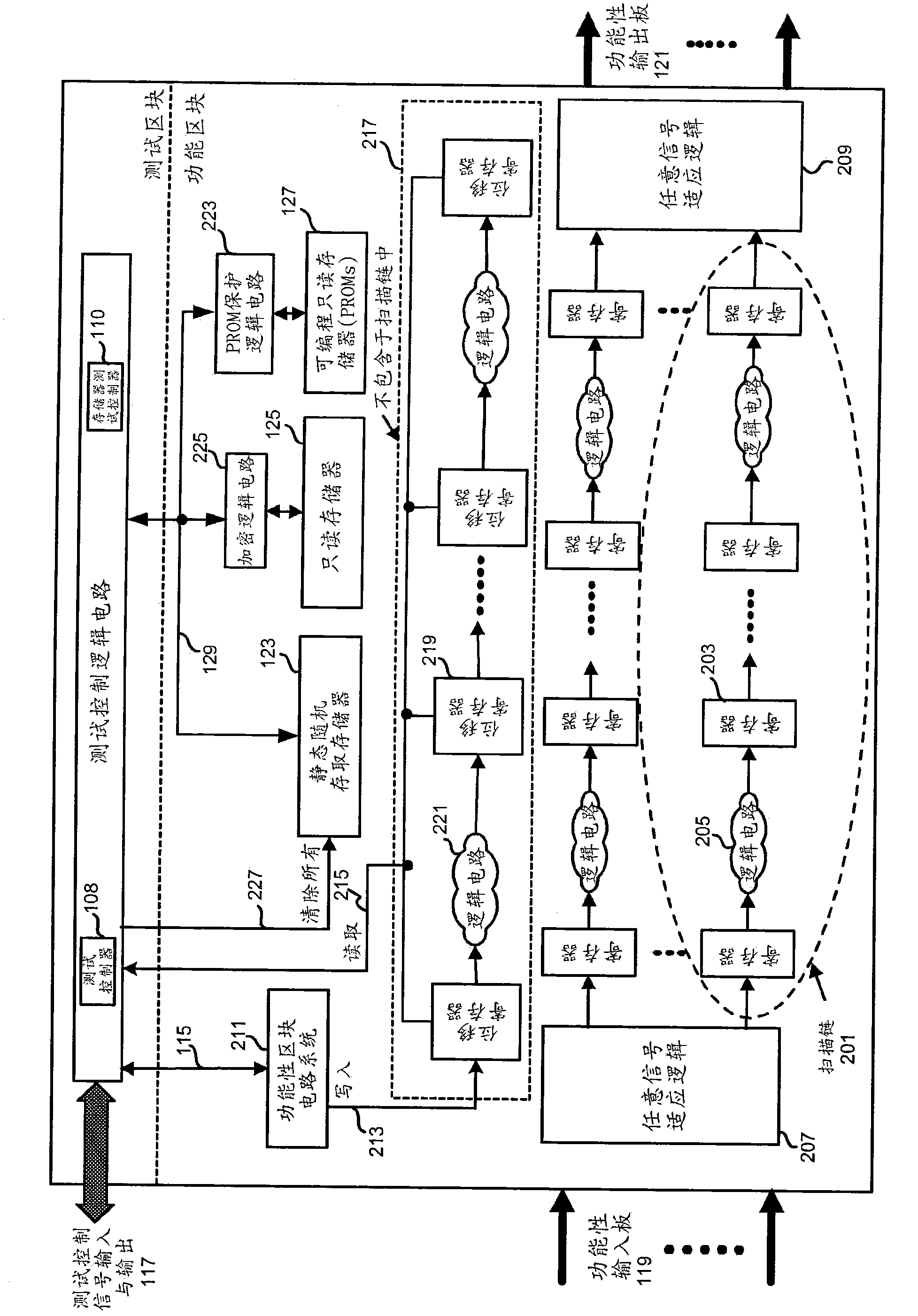

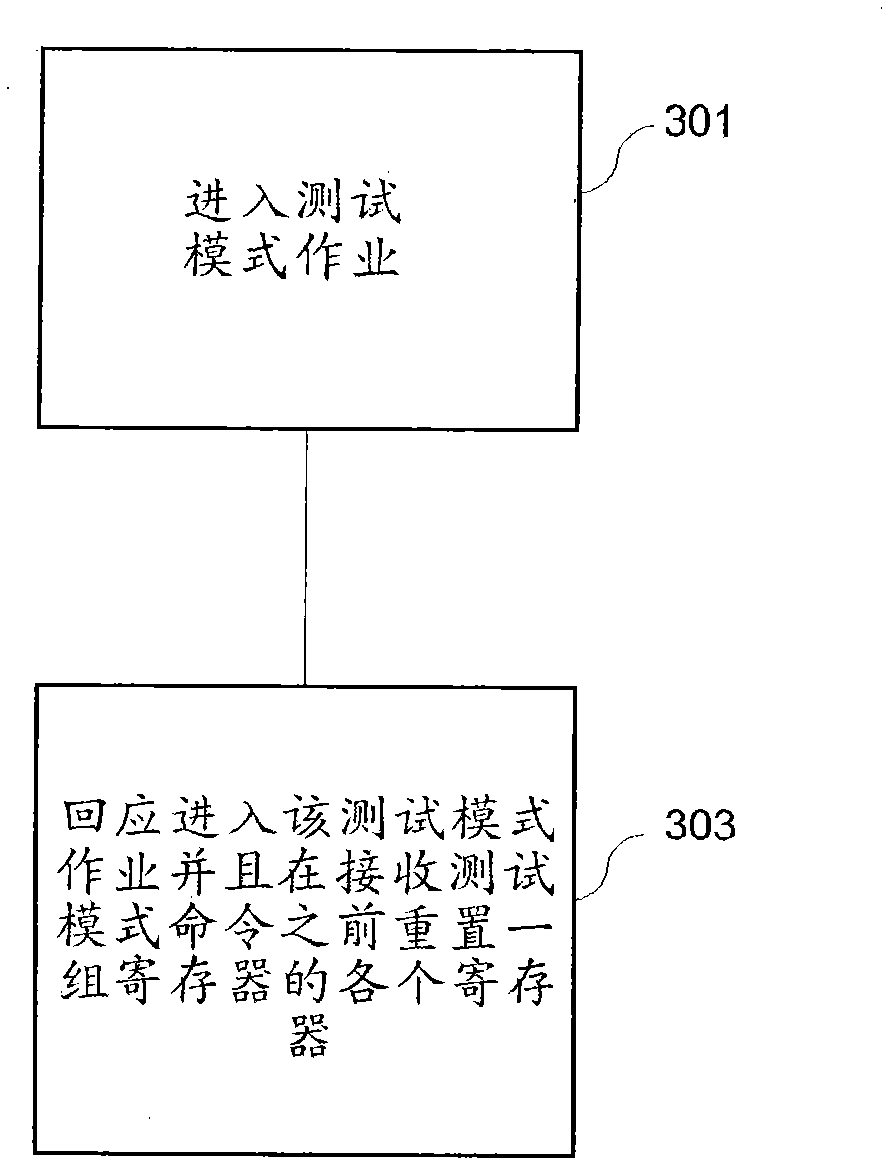

[0037] Referring now to the additional drawings, wherein like numerals represent like parts, FIG. 1 is a block diagram of an illustrative integrated circuit (IC) 100 in accordance with an embodiment. The IC 100 can be incorporated into an electronic device 101, and the electronic device 101 can be any suitable electronic device (such as a wireless communication device, a PDA, a tablet computer, a desktop computer, etc. that communicate via the antenna 103, but not limited thereto) . The circuit system inside the integrated circuit 100 can be classified into two logic blocks: a function block 104 and a test block 105 . The functional block 104 includes all the circuit systems and / or components required for the normal operation of the IC 100 , such as functional blocks 133 to 135 , and various memories. The functional blocks 133-135 may include various registers, flip-flops, latches, and / or logic gates required for the operation of the IC 100 . These memories may include rando...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More