Encryption chip safety testing method based on scanning confusing

A chip and security technology, which is applied in the field of security test structure, can solve the problem of not finding the patent invention of encryption chip security test method, and achieve the effect of high security performance, low area cost, and small area cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be described in detail below in conjunction with the accompanying drawings.

[0018] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

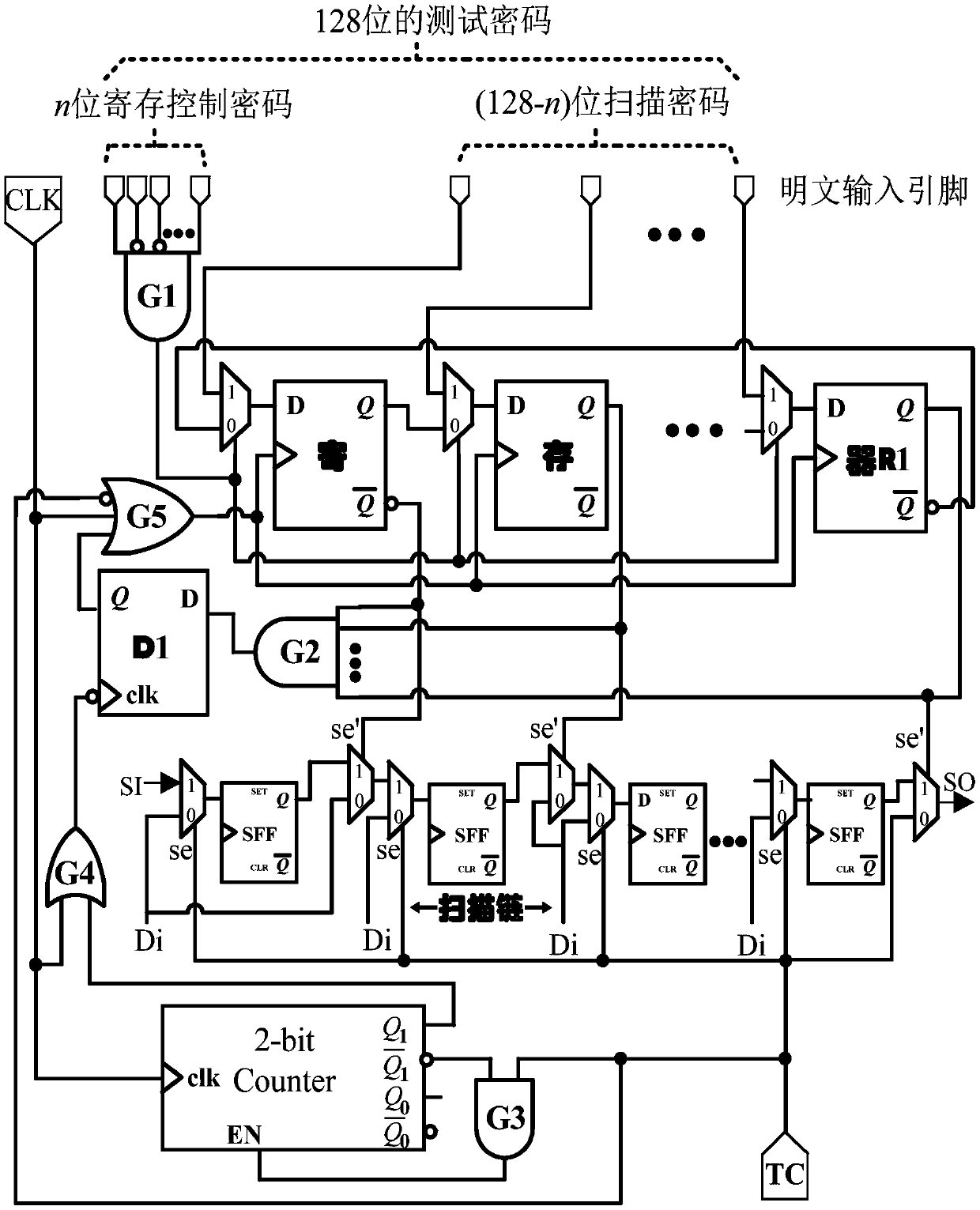

[0019] like figure 1 As shown, the security scanning scheme of the present invention can be added a shift register (R1), a 2-bit counter, a D flip-flop (D1) and a small number of logic gates (G1~G5) on the basis of the conventional scanning structure. to fulfill. For block-based encryption algorithms (such as AES encryption algorithm), its hardware implementation includes at least 128-bit plaintext input. When the chip enters the test mode for the first time after power-on or reset, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More