Patents

Literature

213results about How to "Small area overhead" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

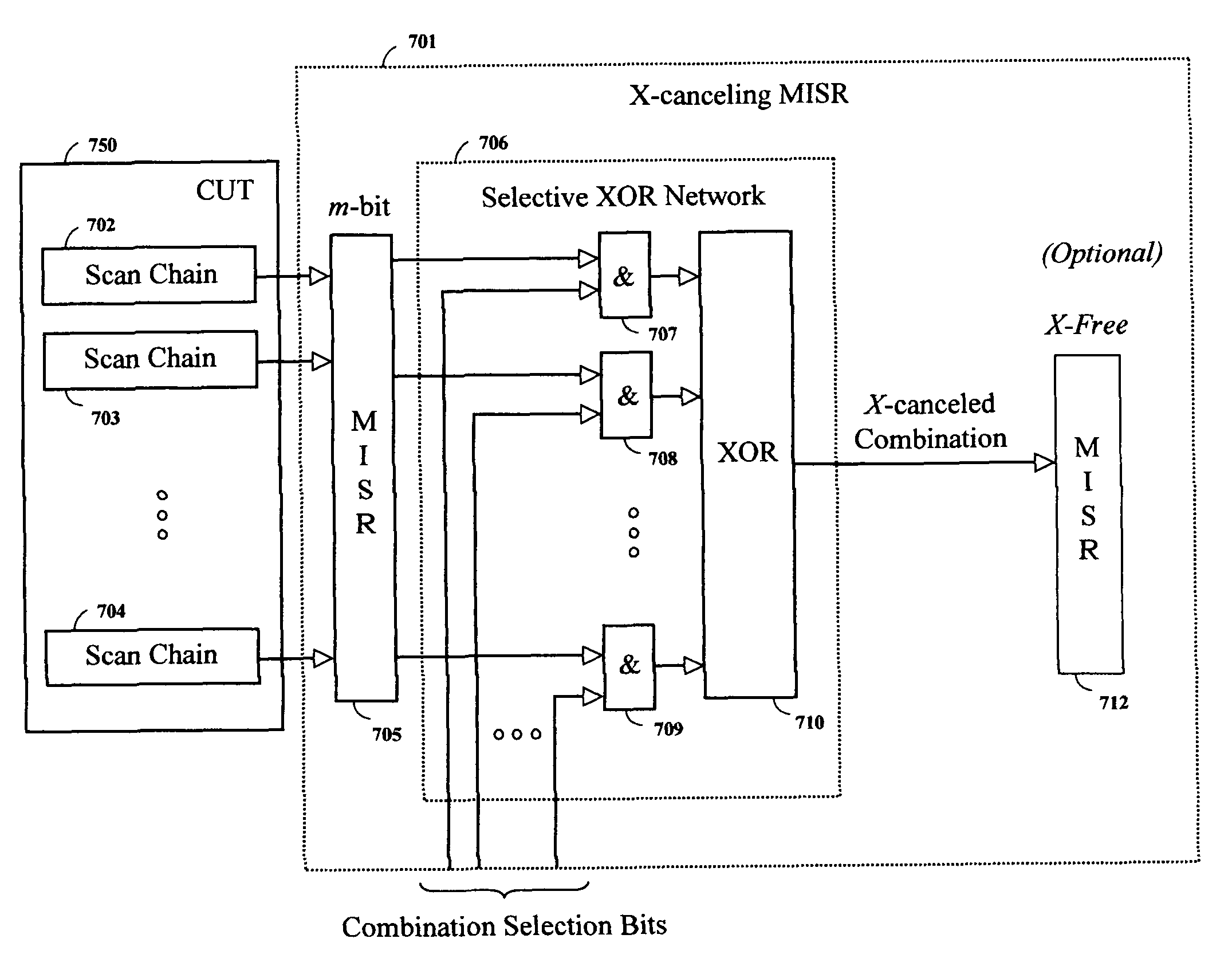

X-canceling multiple-input signature register (MISR) for compacting output responses with unknowns

InactiveUS7925947B1Small area overheadElectronic circuit testingLinear correlationProcessor register

A method and apparatus for compacting test responses containing unknown (X) values in a scan-based integrated circuit using an X-canceling multiple-input signature register (MISR) to produce a known (non-X) signature. The known (non-X) signature is obtained by selectively exclusive-ORing (XORing) together combinations of MISR bits which are linearly dependent in terms of the unknown (X) values using a selective XOR network.

Owner:SYNTEST TECH

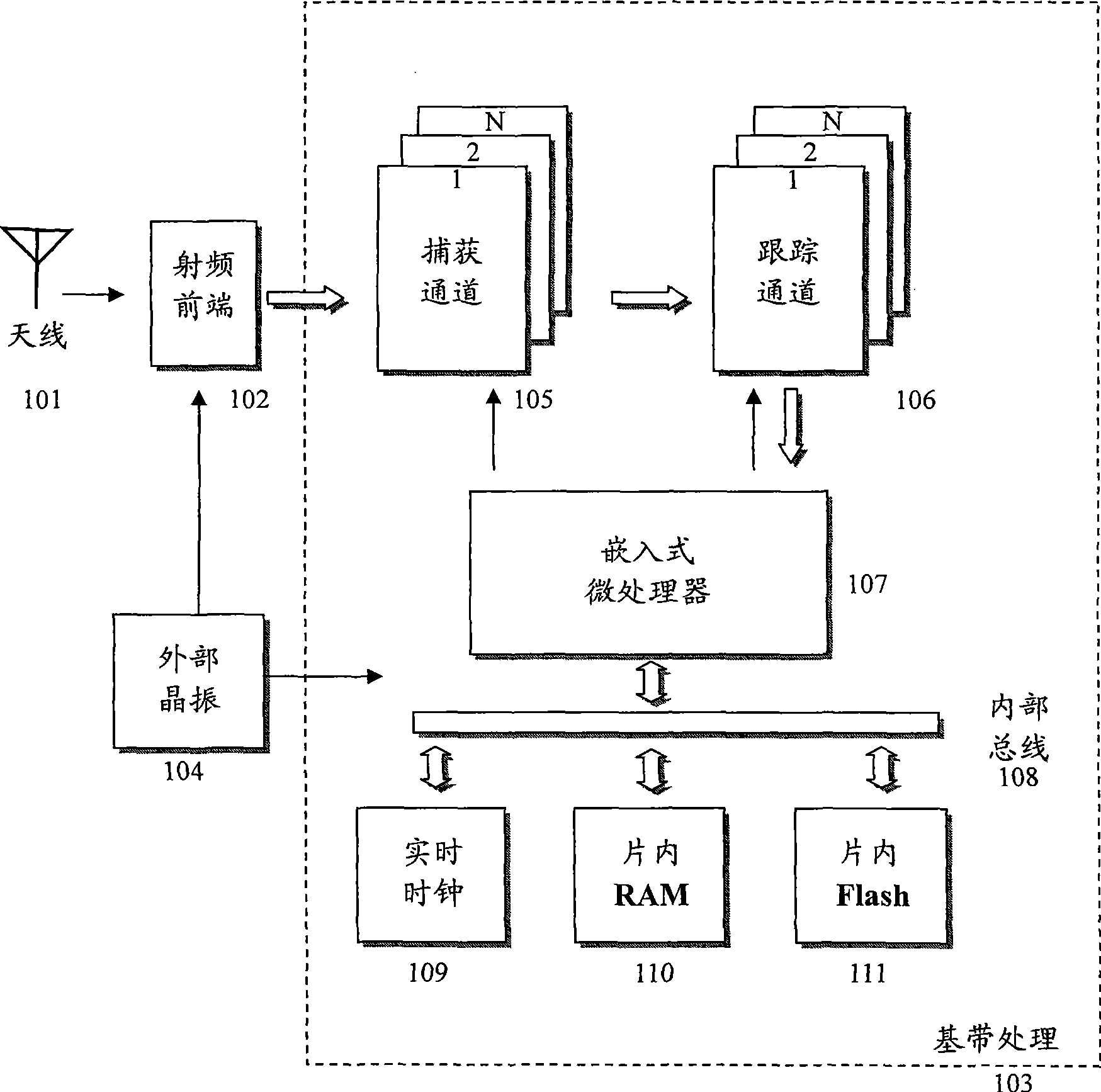

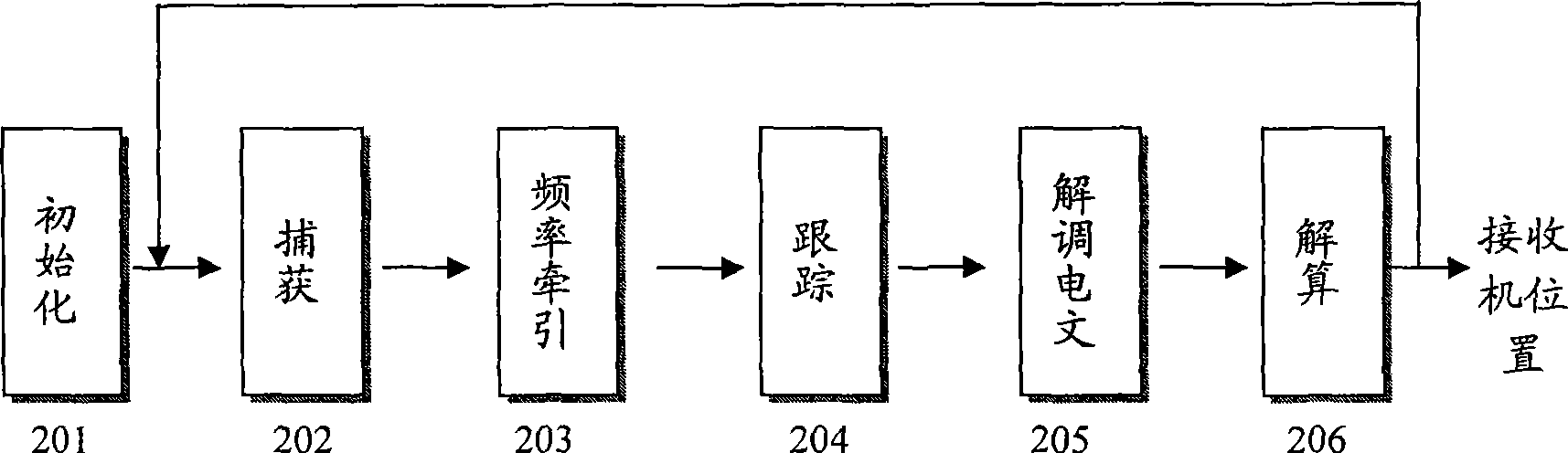

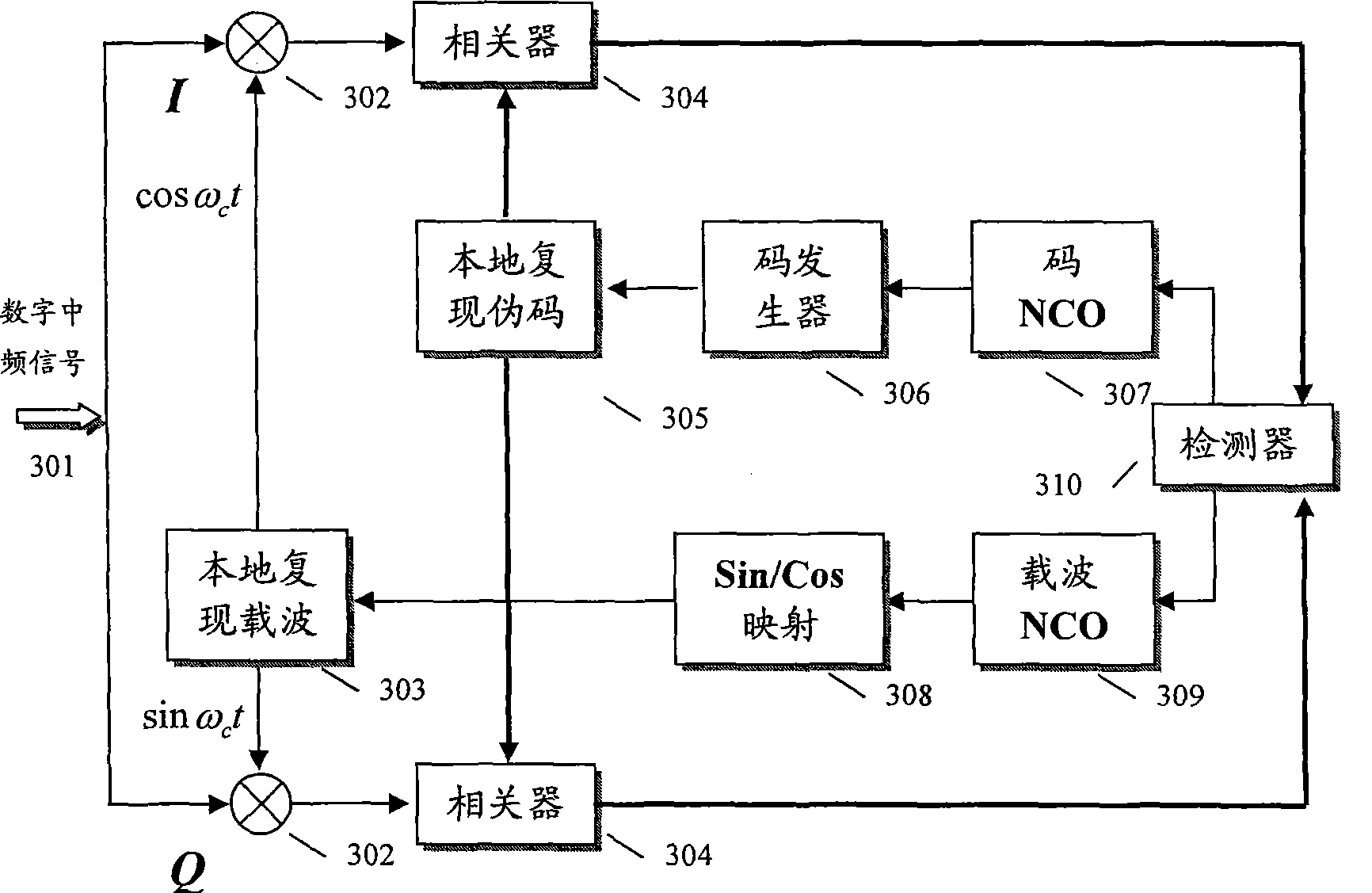

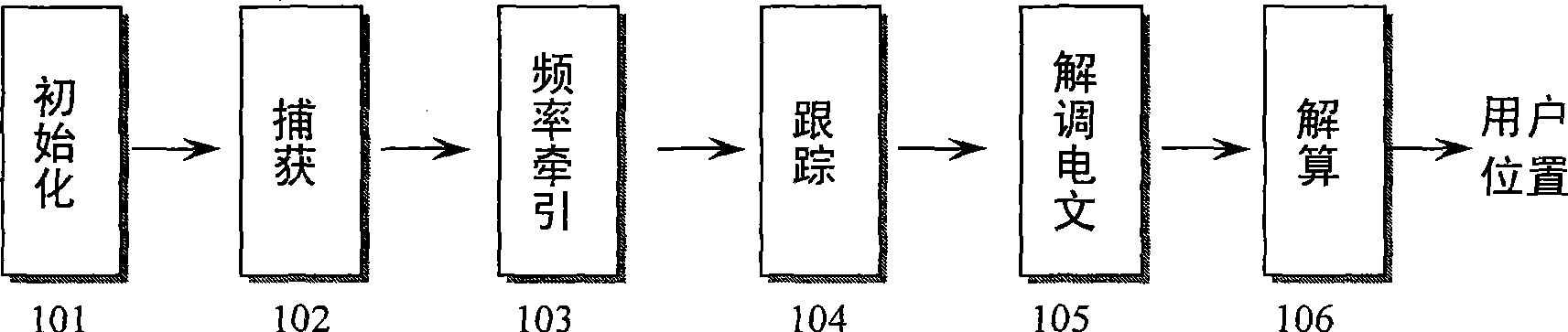

Rapidly recapturing and positioning method under receiver signal deletion condition of global positioning system

ActiveCN101424731ASmall area overheadReduce overheadPosition fixationAntenna radiation diagramsGps receiverBusiness forecasting

The invention relates to a quick positioning method for realizing quick recapture under a GPS signal lacking condition, which belongs to the field of global satellite positioning and guidance, such as a GPS system. The quick recapture and the positioning are realized by different tactics according to signal lacking time, the satellitic continuous tracking and positioning of short signal lack such as less than 2 seconds is realized by using a false tracking ring, a recapture method which is based on the prior knowledge is used for the direct recapture of a satellite, the quick recapture and positioning of the longer signal lack such as a plurality of minutes is realized by using the mixing heat recapture based on forecasting, and the quick recapture under a plurality of signal lacking conditions can be realized by using the method. The quick recapture and positioning method is suitable for baseband processing chips of arbitrary types of GPS receivers, the starting and positioning speed can be greatly increased, the structure is simple, the area of the chips is small, the cost is low, and the transplantation is convenient.

Owner:北京中科微知识产权服务有限公司

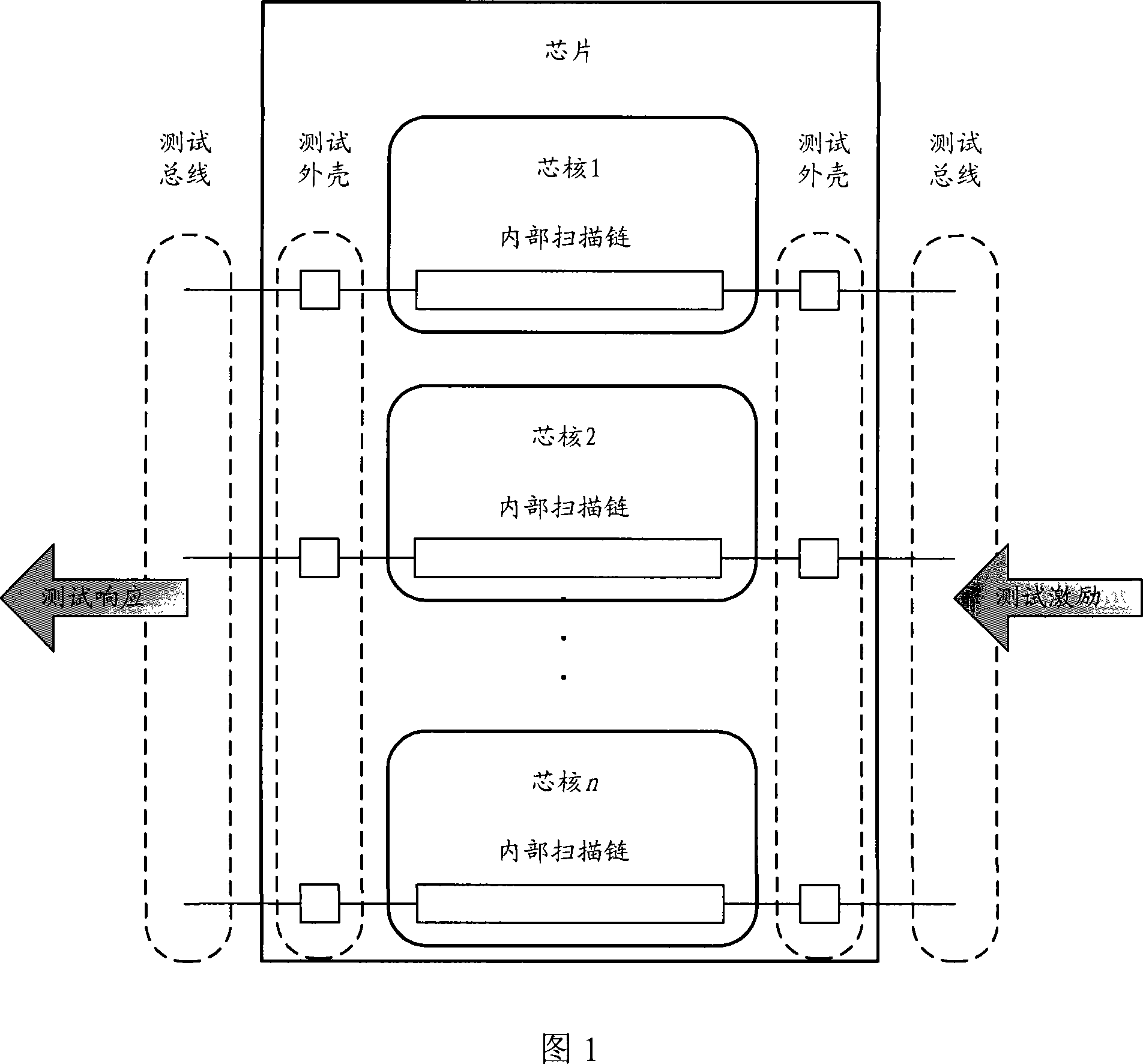

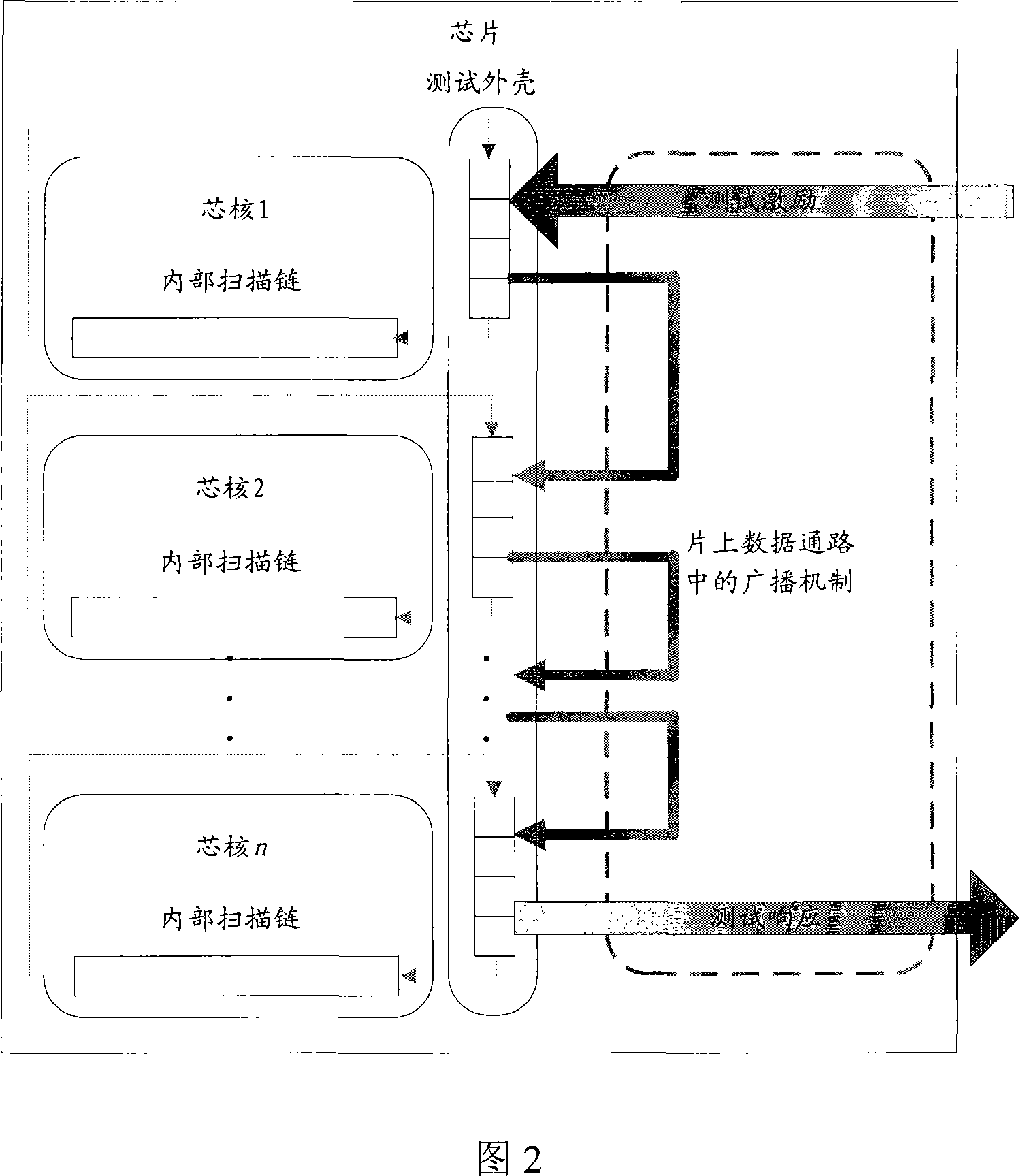

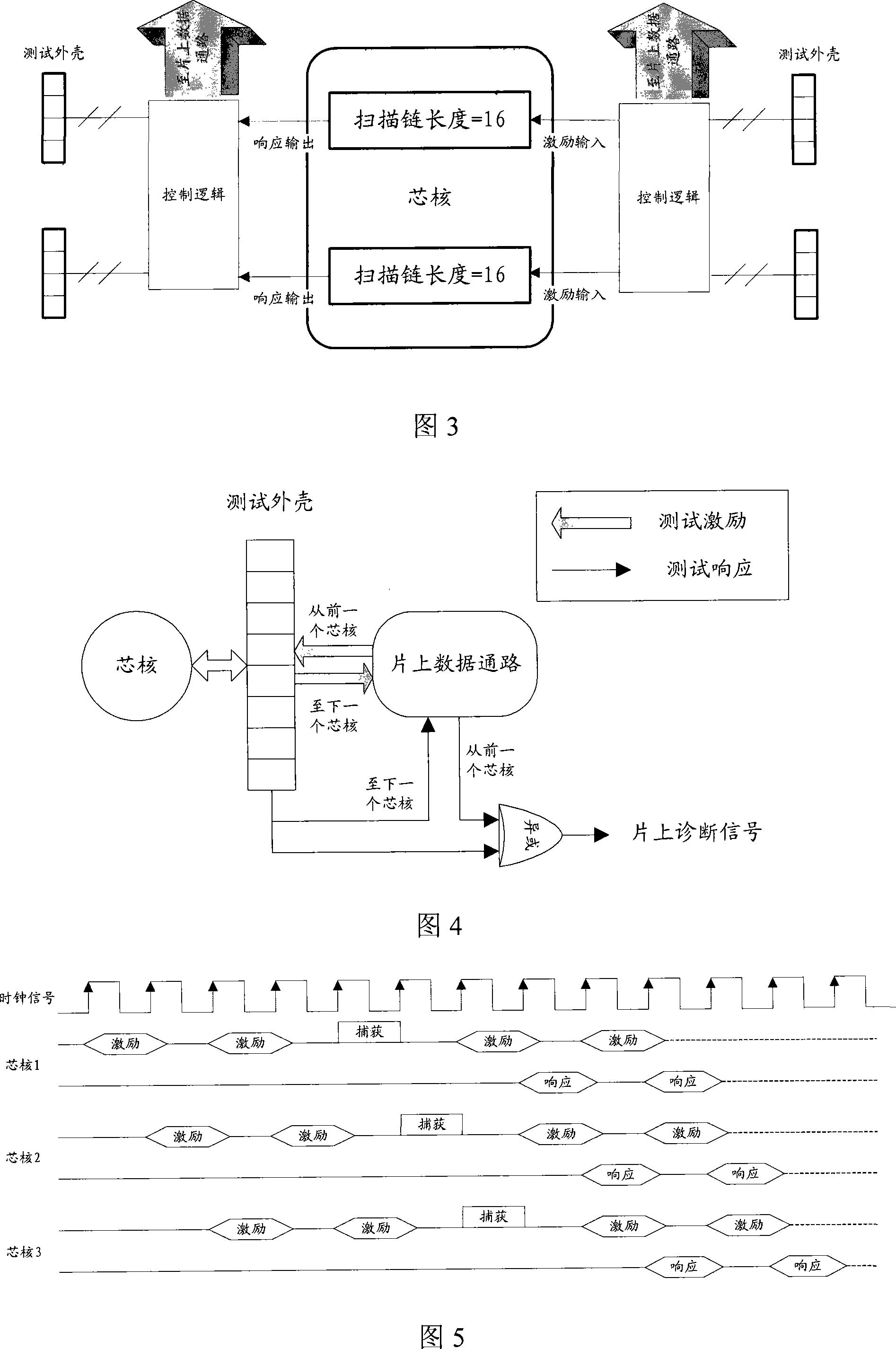

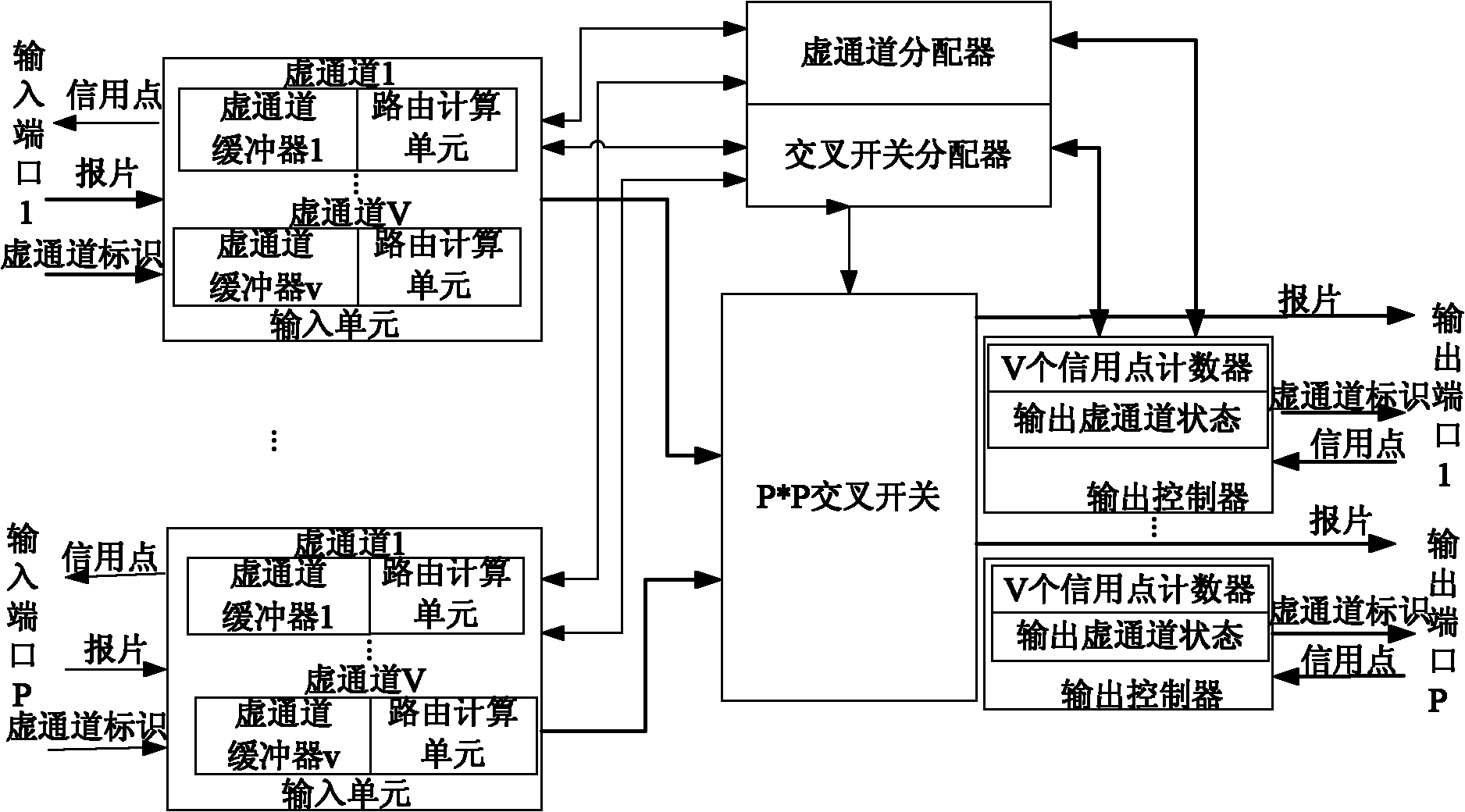

Test circuit of on-chip multicore processor and design method of testability

The present invention provides a testing circuit and a testability design method thereof for an on-chip multinuclear processor; wherein, the testing circuit comprises a testing shell register chain, a chip core connecting circuit waiting to be tested, an on-chip data path connecting circuit and a control logic circuit. The chip core connecting circuit waiting to be tested is an interconnection circuit, which is connected between the testing shell register chain and the chip core waiting to be tested. The on-chip data path connecting circuit is the interconnection circuit which is connected between the testing shell register chain and the on-chip data path. The control logic circuit controls the data flow direction of the chip core connecting circuit waiting to be tested and the on-chip data path connecting circuit. The present invention conducts an optimum design according to the characteristics of the on-chip multinuclear processor. The bandwidth of the on-chip data path is fully used. The testing cost is reduced and the amount of a transmission data packet in the on-chip data path is reduced. So an extra power spending caused by mass active data packet is greatly reduced and the testing time is greatly shortened.

Owner:INST OF COMPUTING TECHNOLOGY - CHINESE ACAD OF SCI

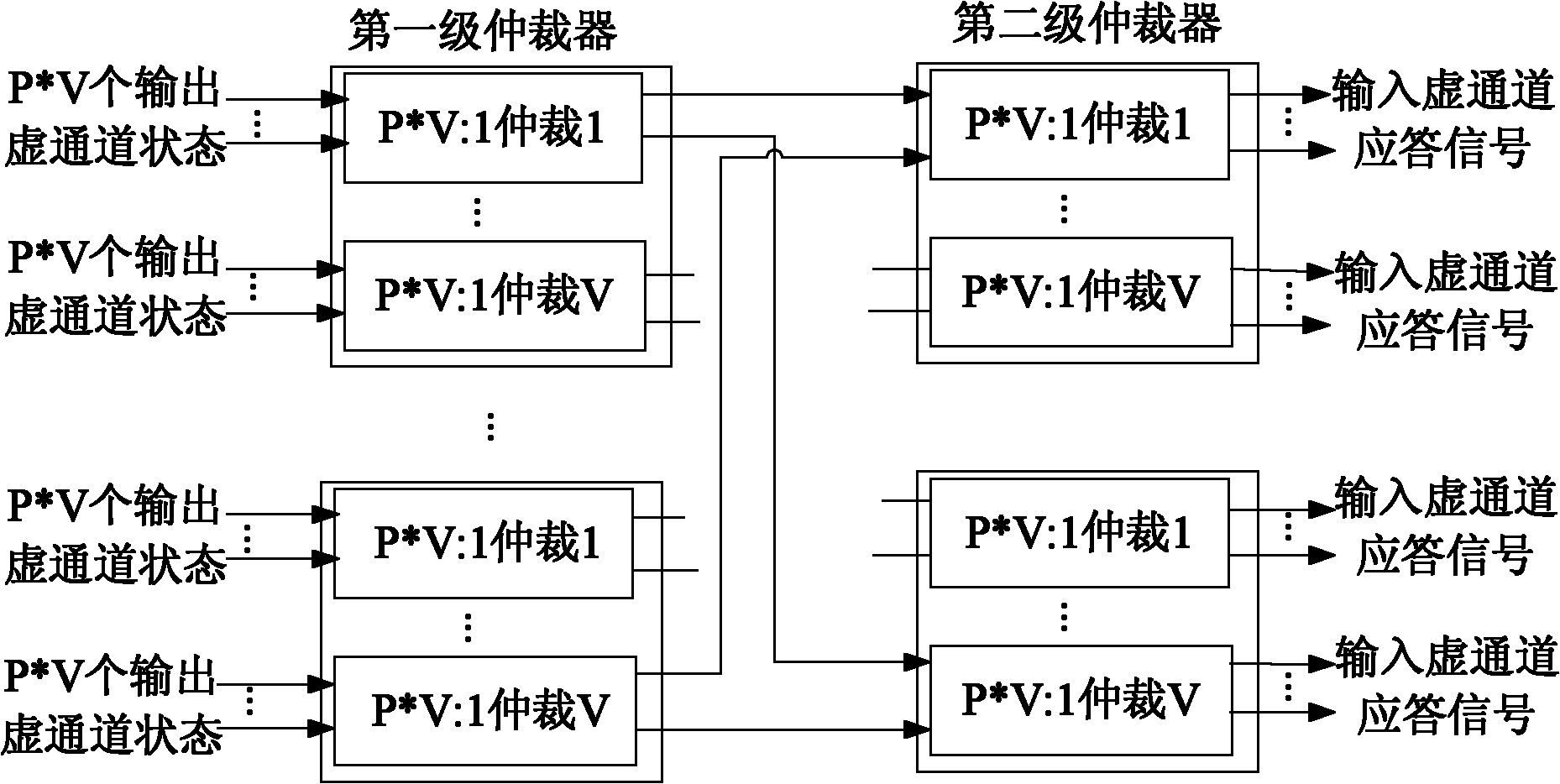

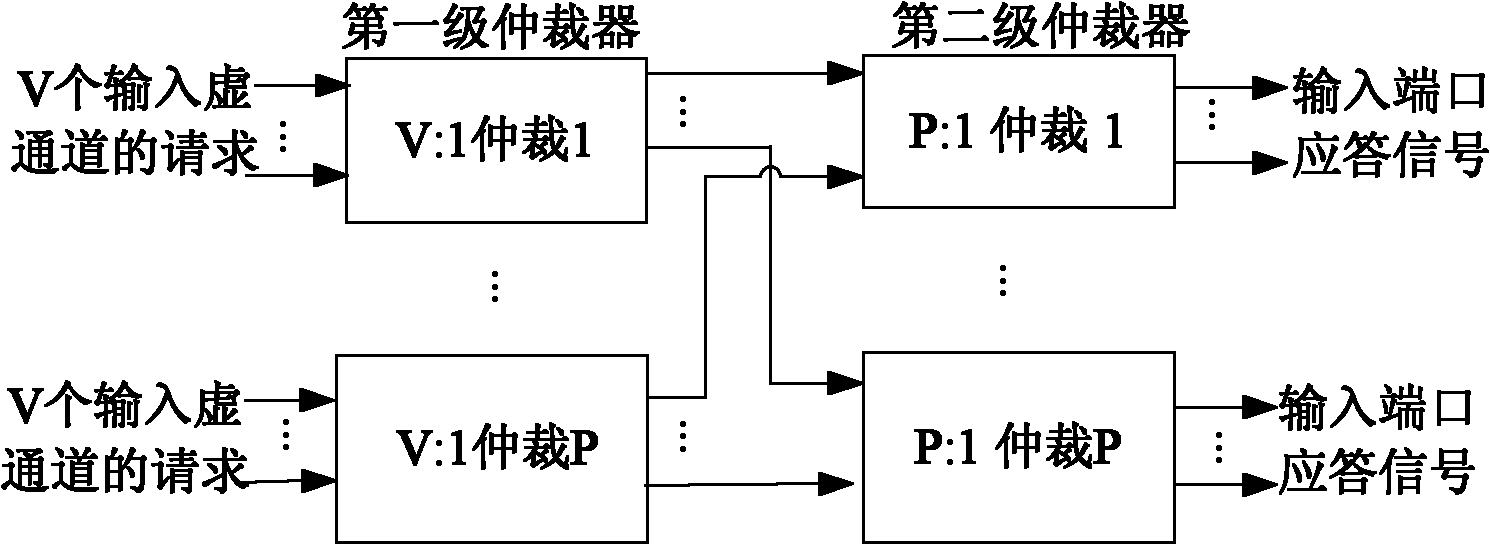

Network-on-chip oriented low delay router structure

The invention discloses a network-on-chip oriented low delay router structure, aiming to solve the problems that the existing router structure has relative large delay in forwarding fragments and can not make full use of storage resources in physical links. The invention consists of P numbered input units, P numbered output units and P numbered channel double buffer; each input unit consists of a buffer distributor, an input buffer and p numbered virtual output address queues; each output unit consists of a P:1 arbiter and a P:1 selector; the channel double buffer consists of a controller and a double buffer; the controller consists of a read pointer, a write pointer and a state machine; and the double buffer consists of two registers and a selector. The fragment transmission between routers adopts a ready-effective synchronous handshake protocol. By adopting the invention, both the delay in forwarding the fragments and the design complexity are reduced, the storage resources in the physical links are fully utilized, and the use ratio of the buffer of the input unit is improved.

Owner:NAT UNIV OF DEFENSE TECH

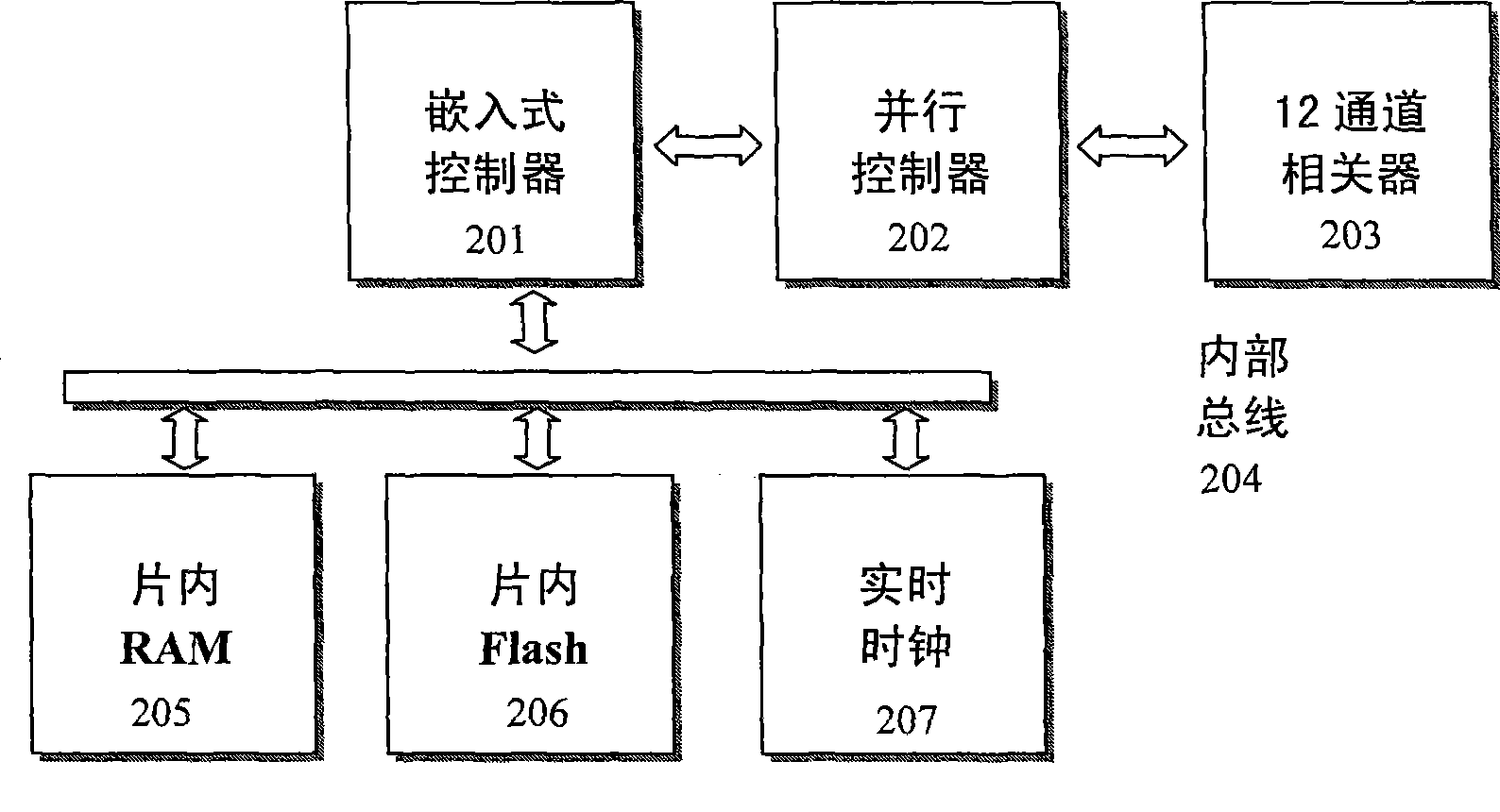

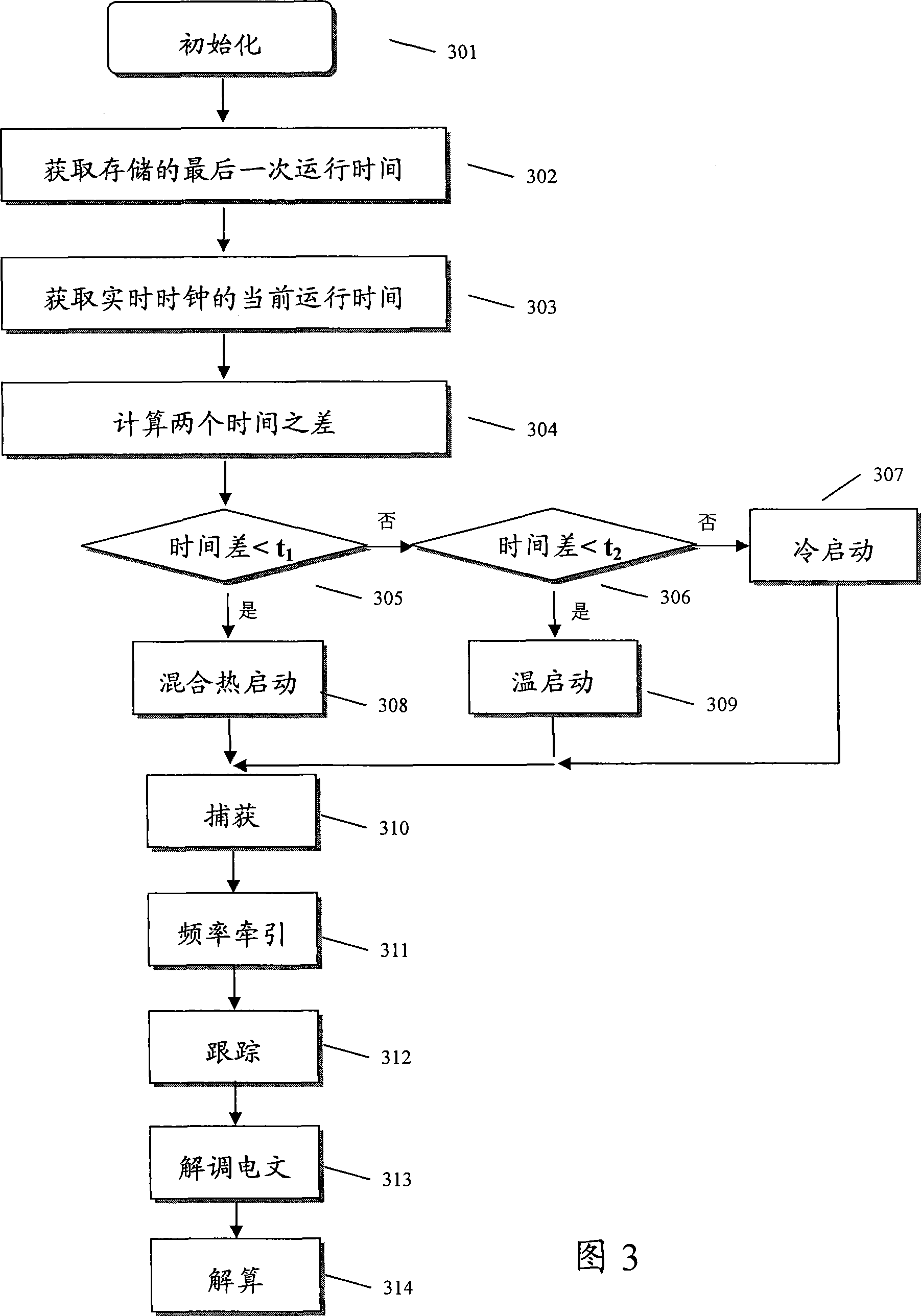

Receiver rapidly starting-up and positioning method in global positioning system

The invention provides a quick starting and positioning method of a receiver in a global positioning system, which relates to the field of global satellite positioning and navigation, such as a GPS system. The method comprises the steps that: the apriori information of the receiver is ensured, and the first time of the final running of the receiver is ensured and stored; when the receiver is restarted, and a second time from a real time clock is ensured. According to the difference of the first time and the second time, a starting method is selected from a hot starting and quick positioning method on the premise that the position of the receiver and the ephemeris of a GPS satellite are known, a warm starting method on the premise that the receiver position, the receiver time and the ephemeris of the GPS satellite are known, a quick starting method by mixing hot start and warm start, and a cold starting method.

Owner:中微智创(北京)软件技术有限公司

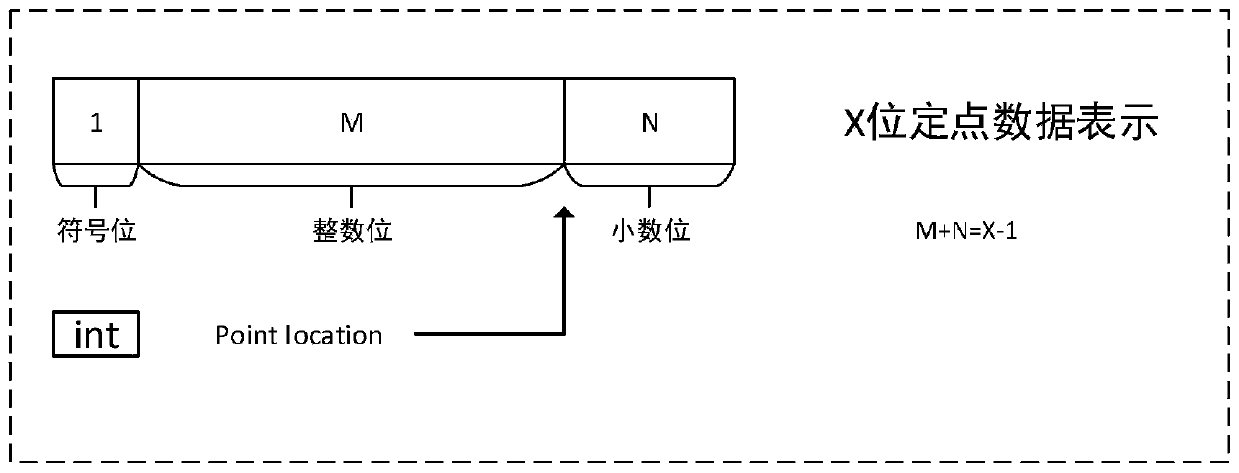

An apparatus and method for performing an artificial neural network forward operation

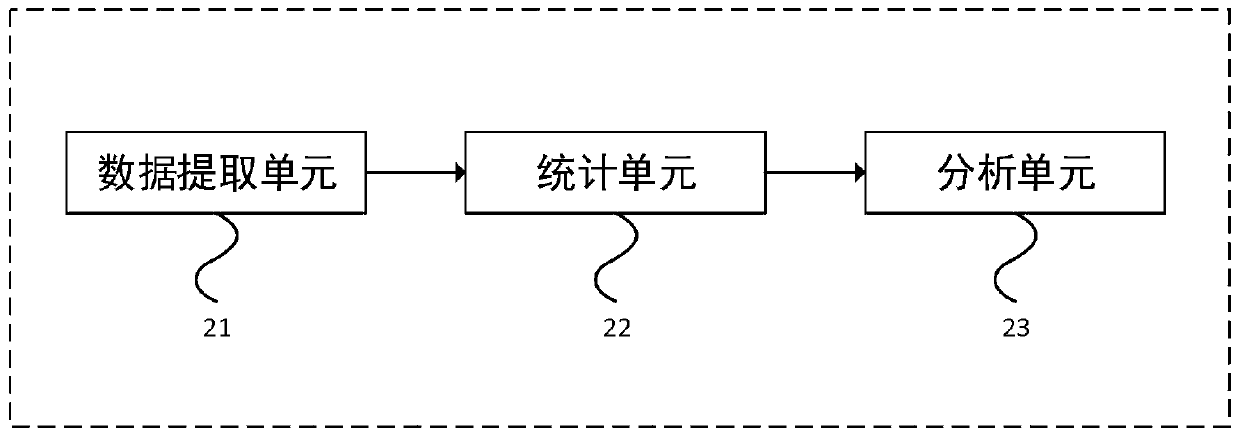

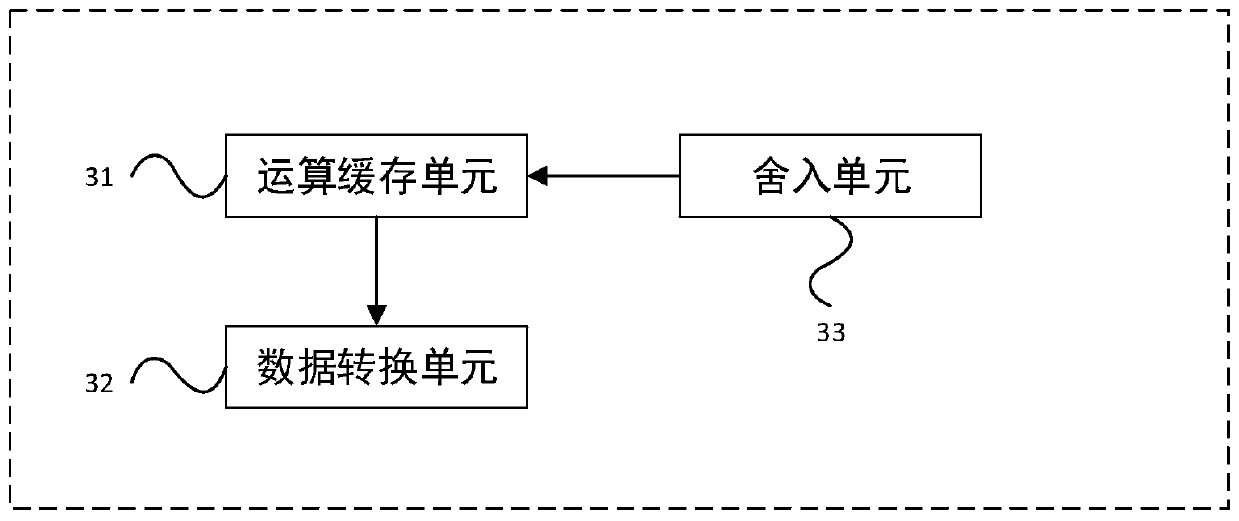

ActiveCN109934331ARealize forward operationSmall area overheadDigital data processing detailsCode conversionAlgorithmData operations

The invention discloses a device and a method for executing forward operation of an artificial neural network, and the device comprises a floating point data statistics module which is used for carrying out statistics analysis on various types of required data, and obtaining the decimal point position Point locality of fixed point data; a data conversion unit which is used for realizing conversionfrom the long-bit floating point data type to the short-bit fixed point data type according to the decimal point position of the fixed point data; And a fixed-point data operation module which is used for carrying out artificial neural network forward operation on the short-digit fixed-point data. According to the device disclosed by the invention, the data in the forward operation of the multilayer artificial neural network is represented by using the short-digit fixed points, and the corresponding fixed-point operation module is used, so that the short-digit fixed-point forward operation ofthe artificial neural network is realized, and the performance power consumption ratio of hardware is greatly improved.

Owner:CAMBRICON TECH CO LTD

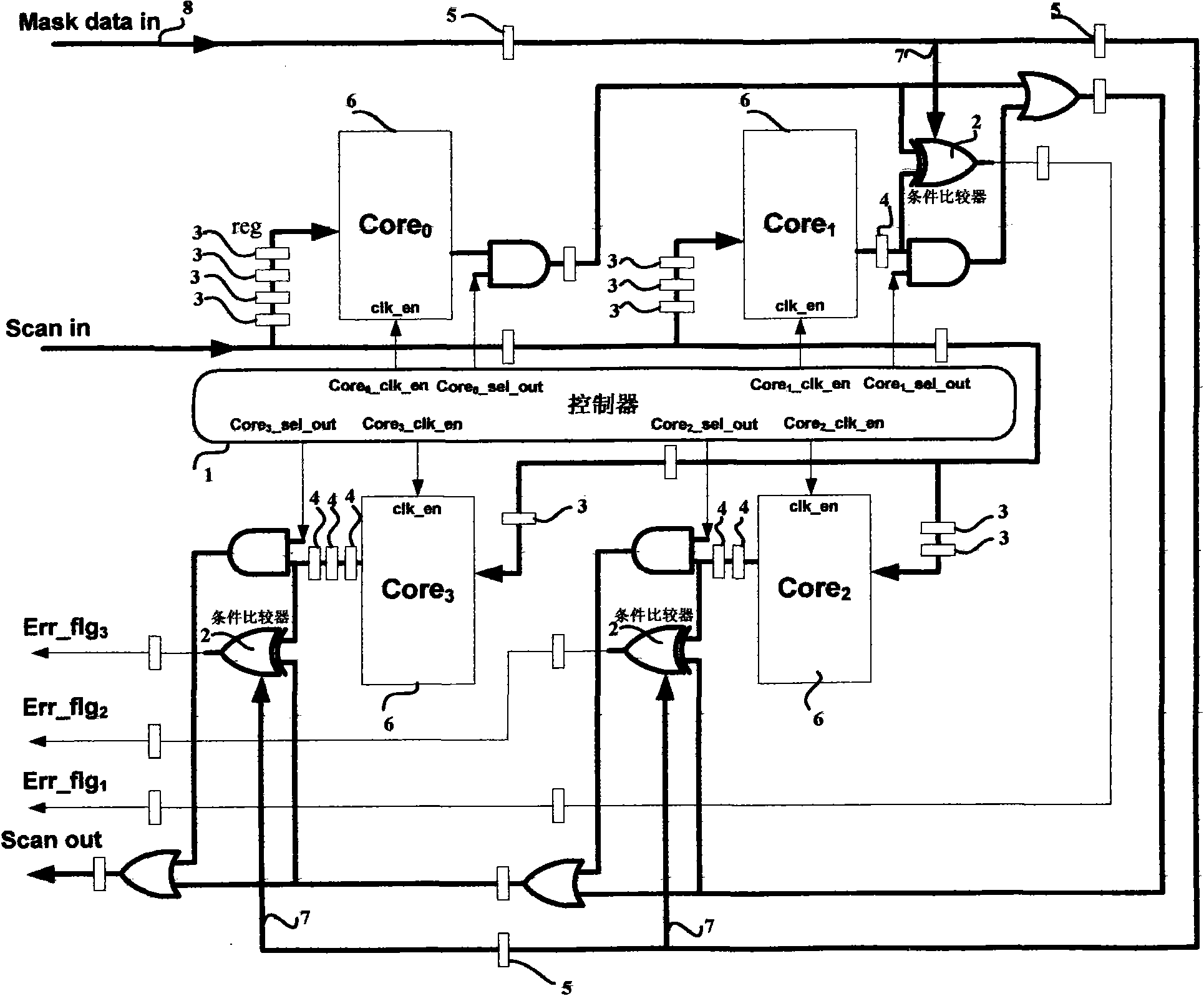

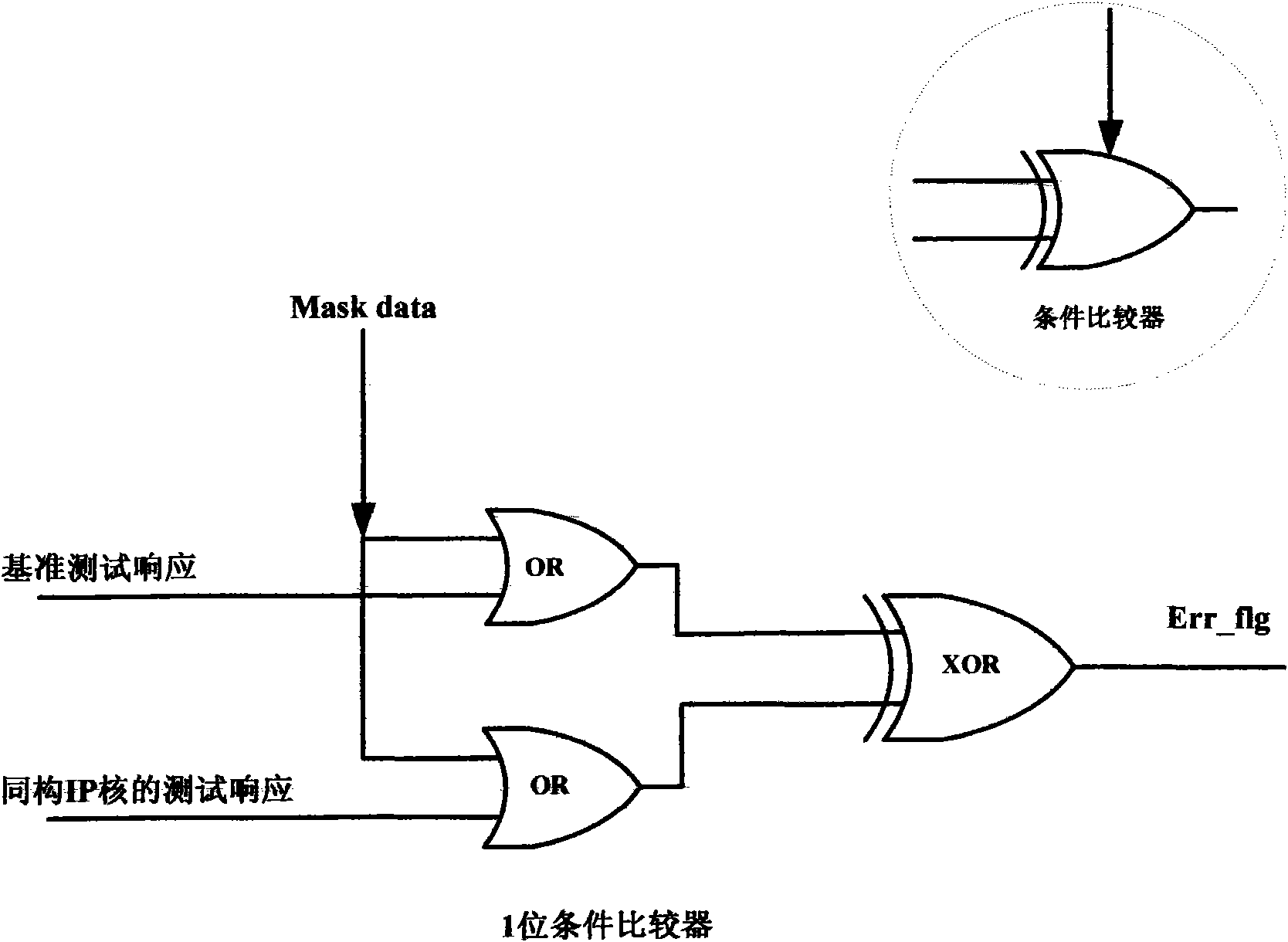

Device and method for testing system-on-chip chip with multiple isomorphic IP cores

ActiveCN101788644AReduced amount of test dataAvoid time costDigital circuit testingComputer hardwareReference test

The invention discloses a device and a method for testing a system-on-chip chip with a plurality of isomorphic IP cores. The device comprises a controller and a condition comparator, wherein the controller is provided with a plurality of control signal interfaces connected to each corresponding isomorphic IP core and is used for inputting a test control signal to each isomorphic IP core, controlling the test on one or more isomorphic IP cores, broadcasting the same test excitation data to the IP cores and simultaneously controlling the output of a test response of a certain IP core; the test response serves as a reference test response and is compared with the test responses of other IP cores; and the condition comparator is used for comparing the test response of a corresponding IP core with the reference test response and processing the comparison result to produce a one-bit error identification signal for identifying whether the comparison is accordant.

Owner:LOONGSON TECH CORP

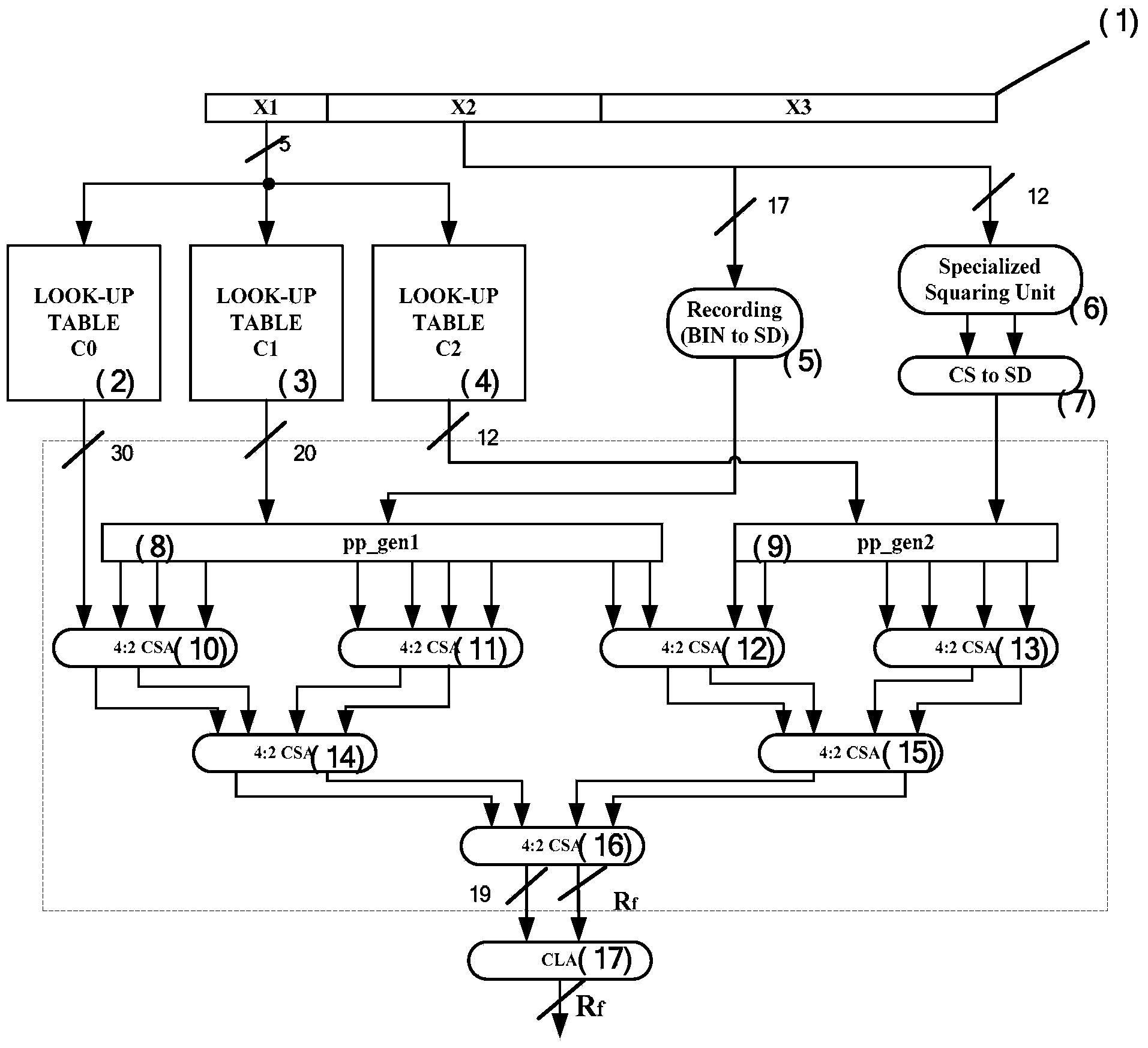

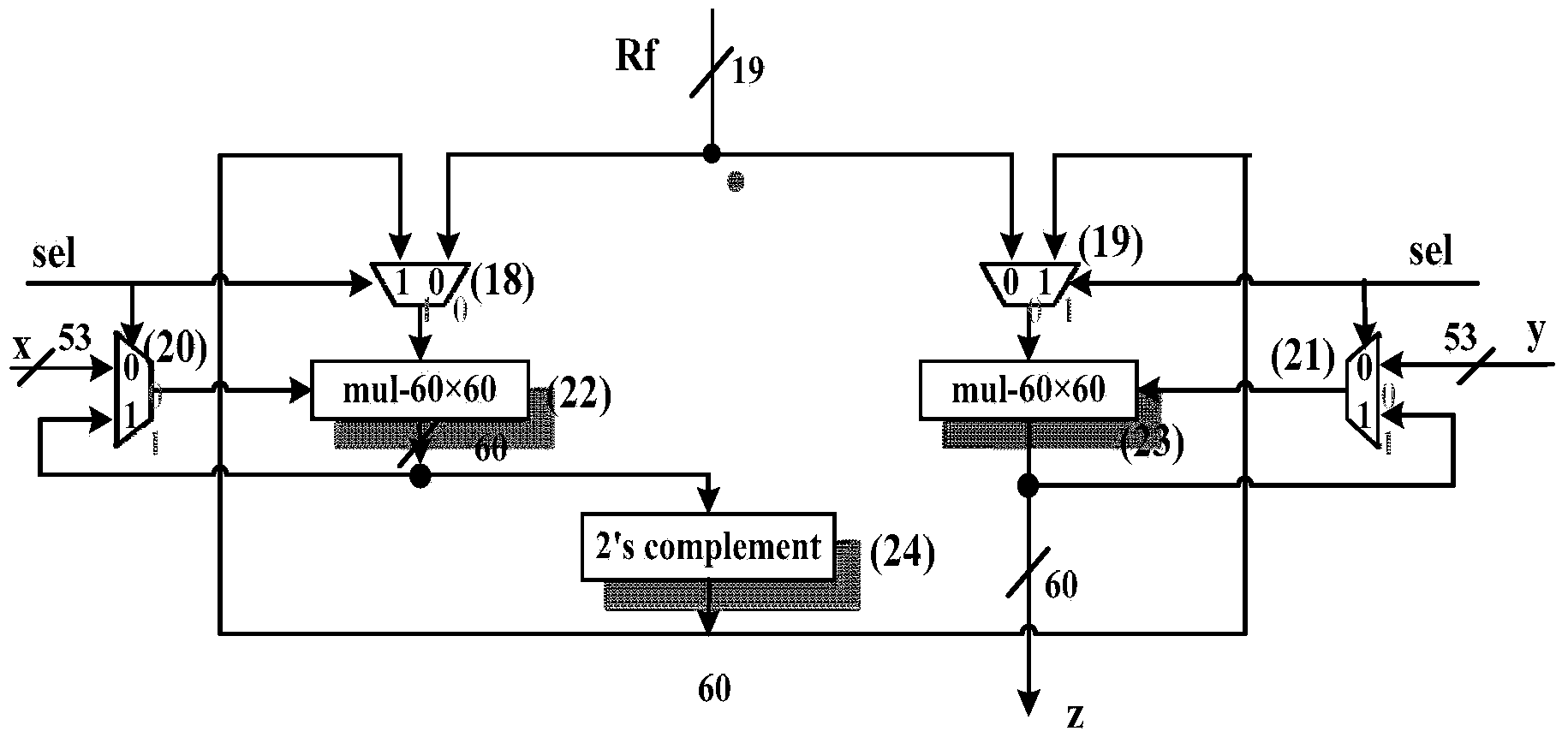

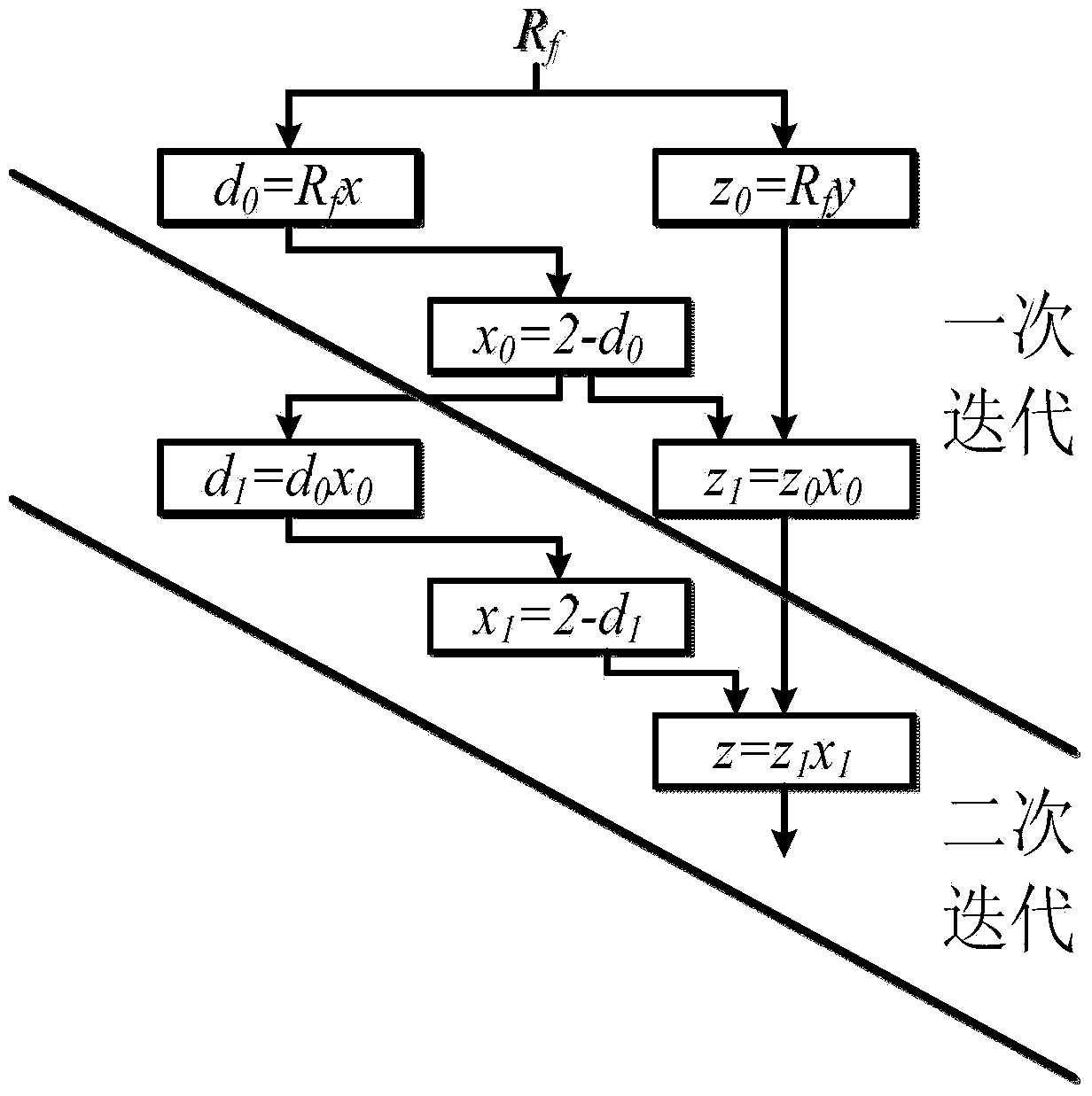

Design method of double-precision floating-point divider and divider

ActiveCN103809930AImprove performanceSmall area overheadDigital data processing detailsSpecial data processing applicationsDouble-precision floating-point formatDesign methods

The invention provides a design method of a double-precision floating-point divider and a divider. The method includes the steps that (1) a seed value Rf of a reciprocal function 1 / X is calculated in a min-max quadratic polynomial approach algorithm, wherein X is a 53-bit magnitude portion of a divisor; (2) on the basis of twice Goldschmidt iteration of a hardware multiplexing method, an ultimate precise result is obtained. The divider comprises a first portion used for calculating the seed value Rf of the reciprocal function 1 / X and a second portion connected with output of the first portion and used for calculating the ultimate precise result. The divider is high in performance and low in area overhead, by means of the hardware multiplexing method, under the condition that performance is seldom reduced, large area advantages are obtained, and the design method and the divider are especially suitable for being used in the field of embedment-type micro processors strict at area requirement.

Owner:PHYTIUM TECH CO LTD

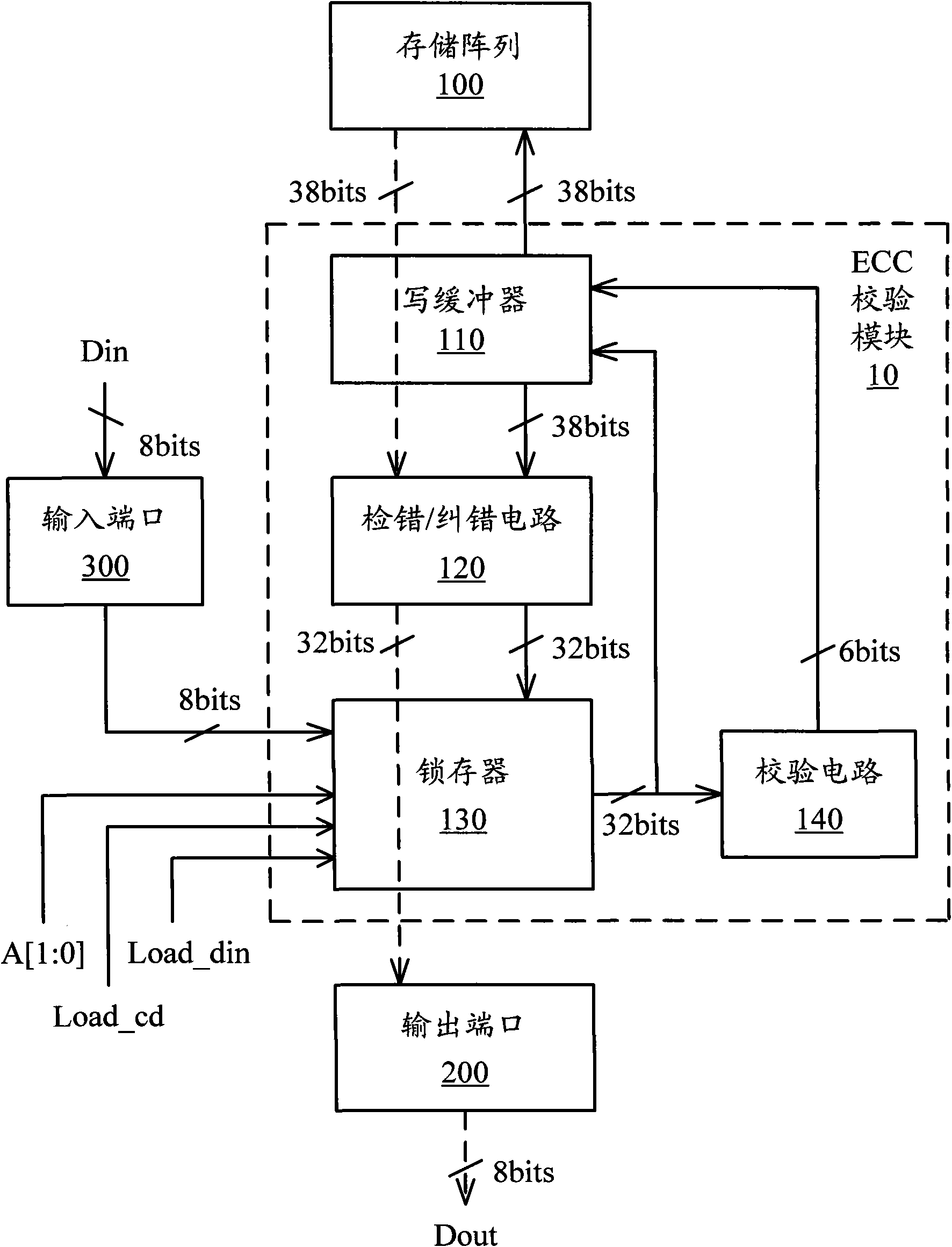

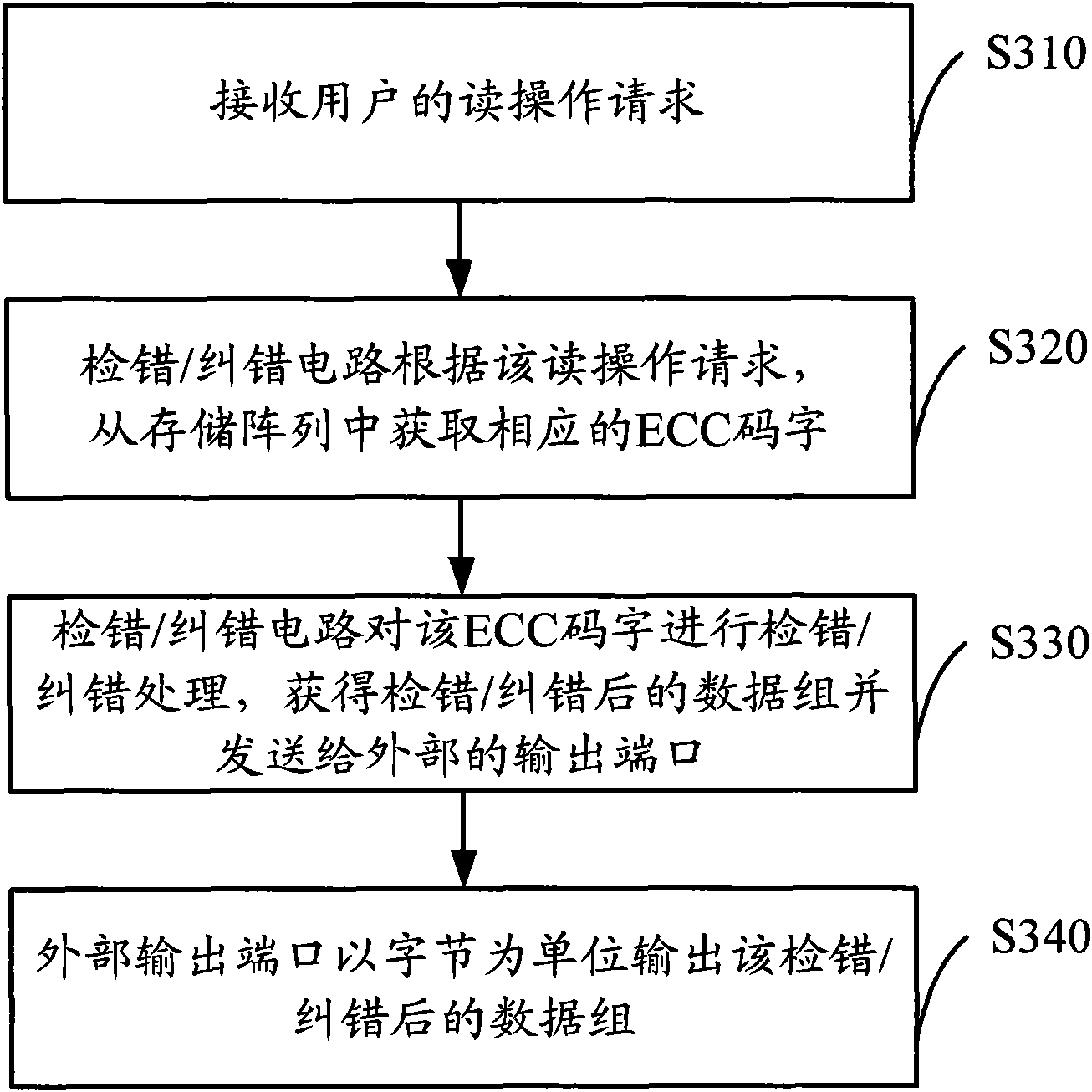

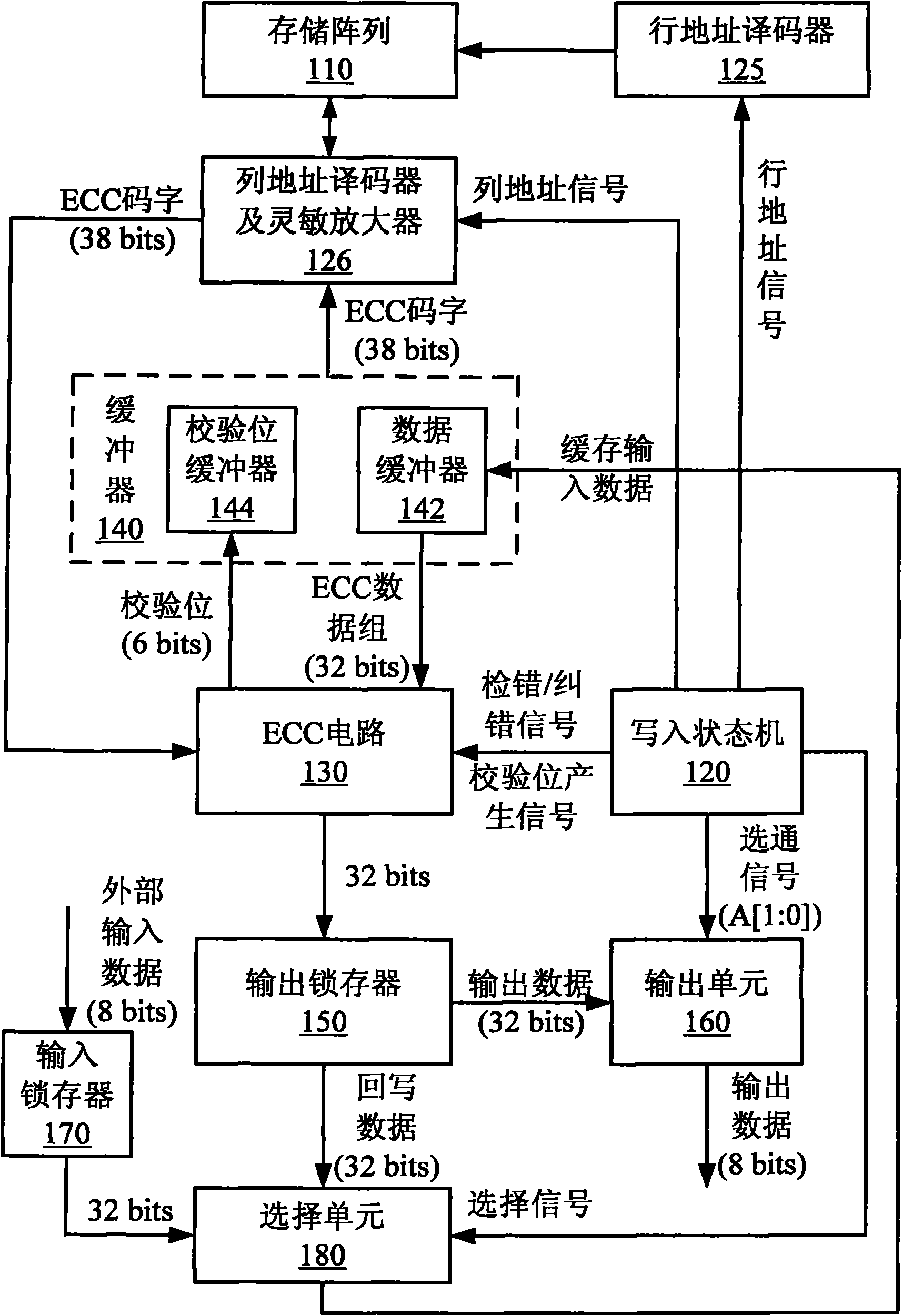

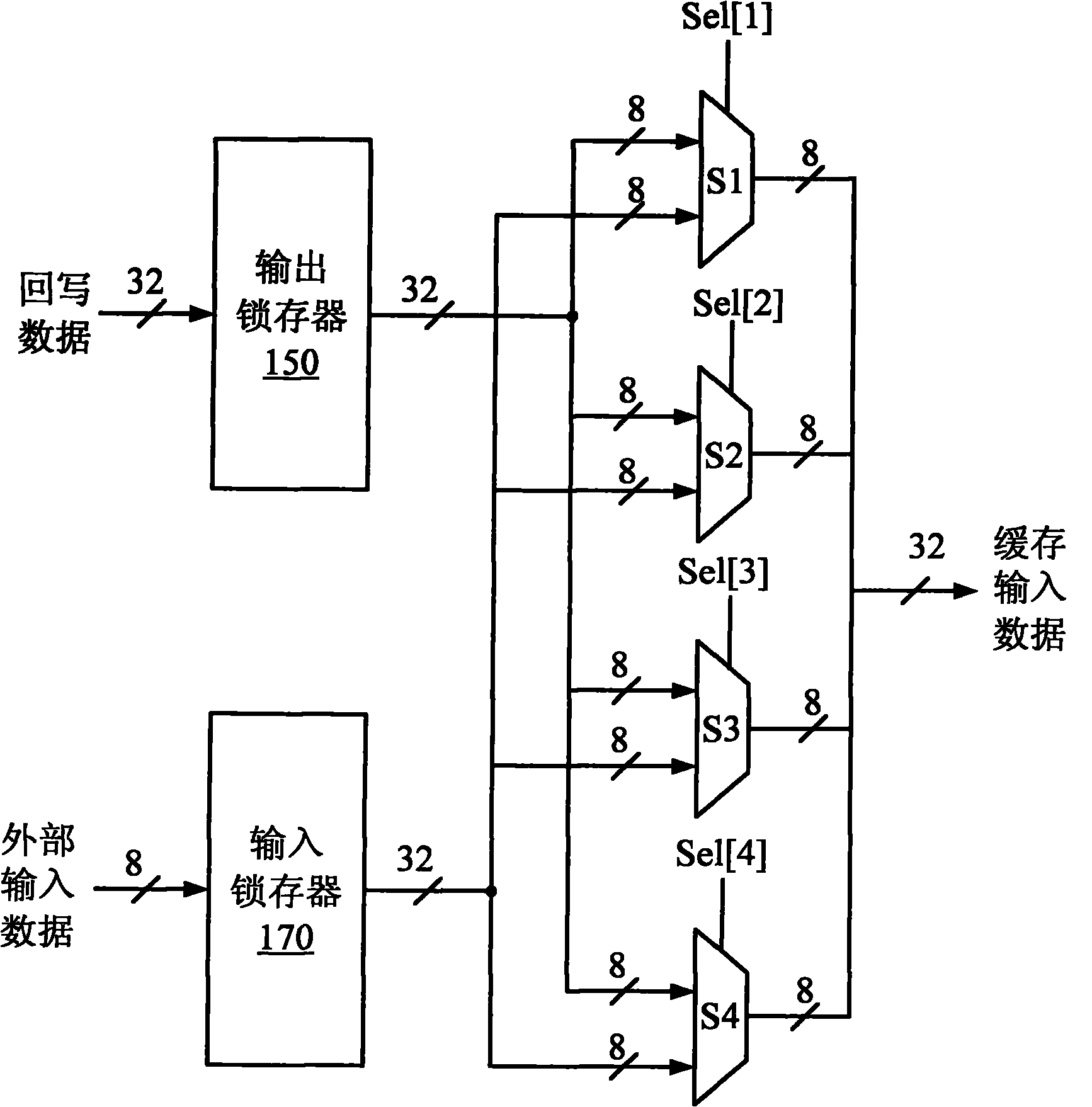

Error checking and correcting verification module and data reading-writing method thereof

The invention discloses an error checking and correcting (ECC) verification module and a data reading-writing method of the module, so as to solve the technical defect of low flexibility in present ECC verification modules. The verification module comprises: an ECC circuit used for ECC treatment of an ECC code word so as to obtain an error checked and corrected data set; a latch used for storing the error checked and corrected data set and updating the received input data to corresponding data positions in the checked and corrected data set, thus forming a data set to be written in; a verification circuit used for real-time verification of the data set to be written in and for generation of a verification bit corresponding to the data set to be written in; a write buffer used for writing the data set to be written in and a corresponding verification bit thereof into a storage medium. The embodiment of the invention realizes reading data from a main array or writing data into the main array in ECC code words, so that the control is easier and the data writing operation is speeded up.

Owner:GIGADEVICE SEMICON (BEIJING) INC

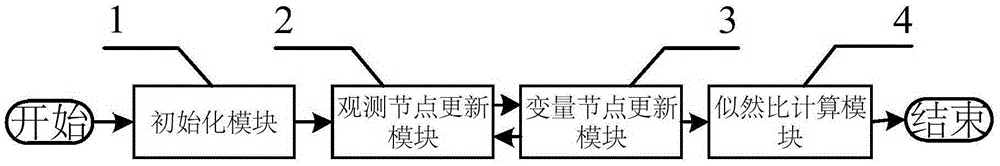

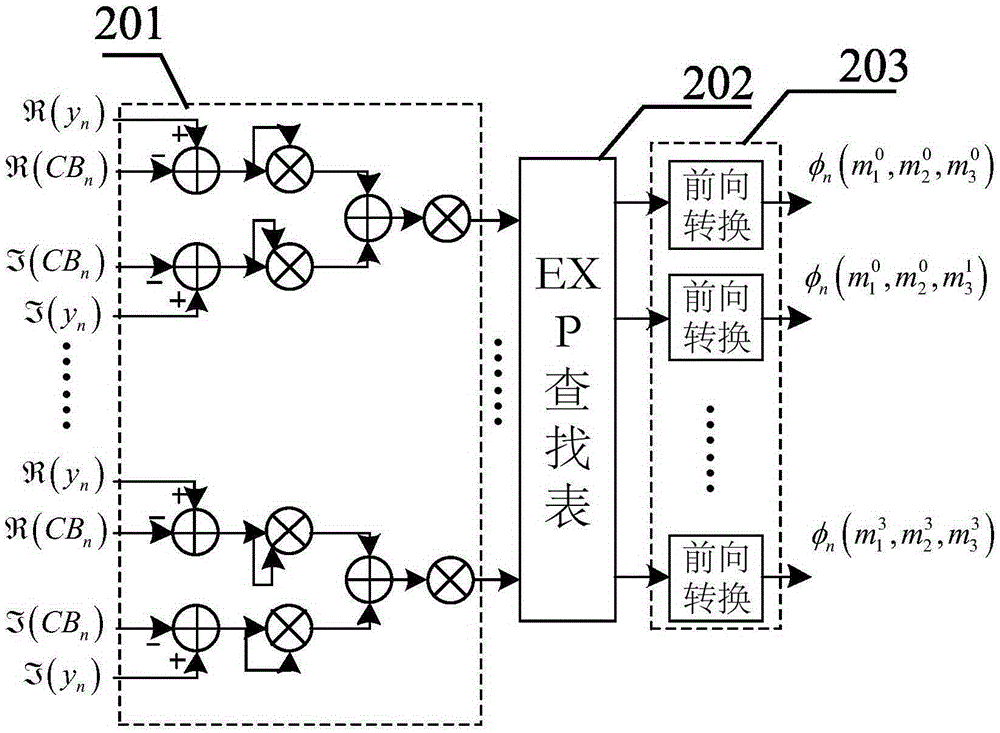

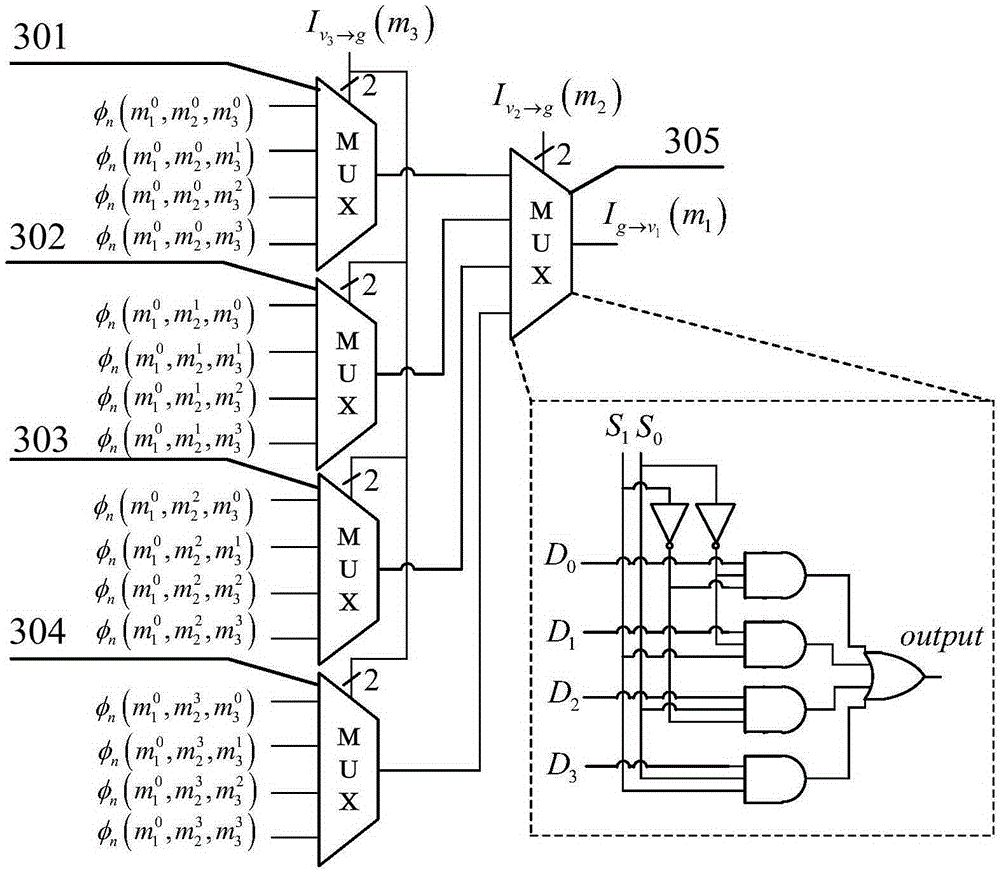

SCMA decoder based on probability calculation

ActiveCN105356971ASmall area overheadImprove throughputError preventionChannel parameterConditional probability

The invention discloses an SCMA decoder based on probability calculation. The SCMA decoder is characterized by comprising an initialization module, an observation node updating module, a variable node updating module and a likelihood ratio calculation module; the initialization module is connected to the observation node updating module and used for initializing a channel parameter and calculating the joint condition probability of all codewords possibly sent by a user born by each resource block; the observation node updating module is connected to the variable node updating module and used for calculating the edge condition probability according to the joint condition probability; the variable node updating module is connected to the likelihood ratio calculation module and used for calculating the posterior probability according to the edge condition probability, normalizing the posterior probability and returning the normalized posterior probability to the observation node updating module; and the likelihood ratio calculation module is used for calculating and outputting likelihood information according to the posterior probability. The SCMA decoder disclosed by the invention is low in area overhead and high in system throughput and calculation efficiency.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

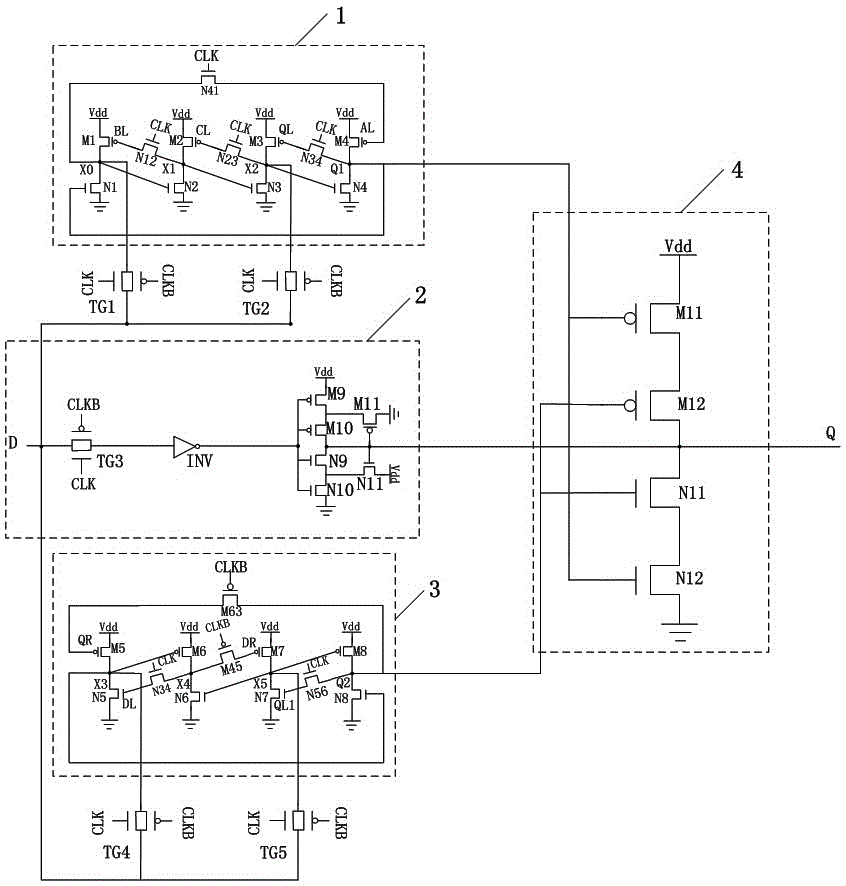

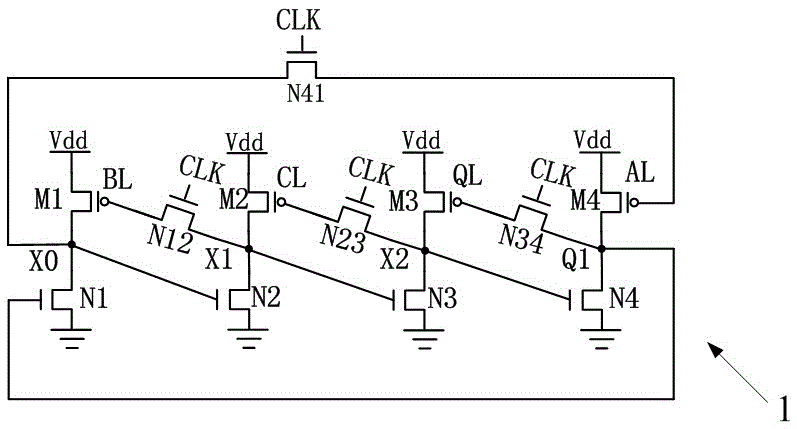

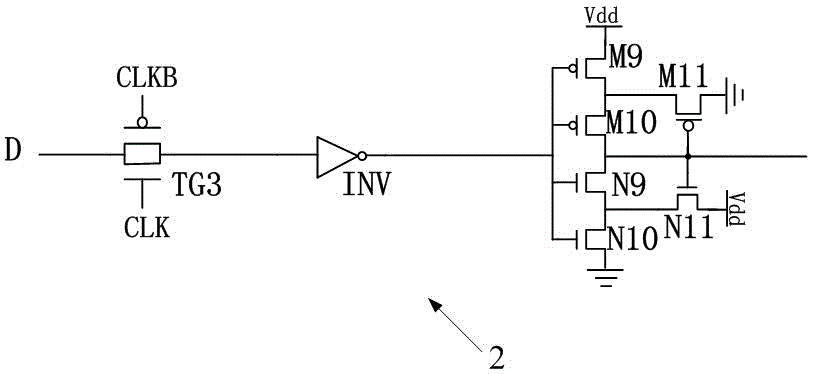

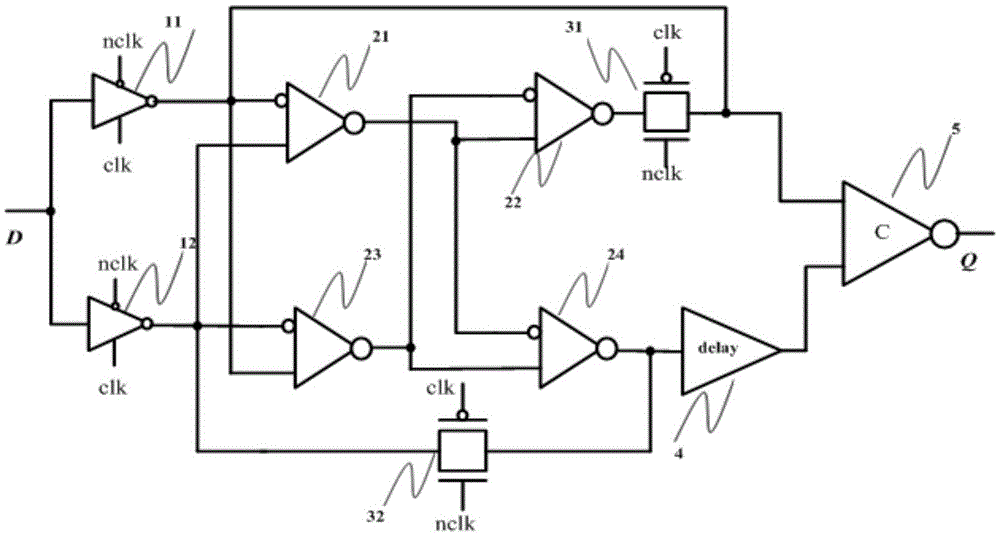

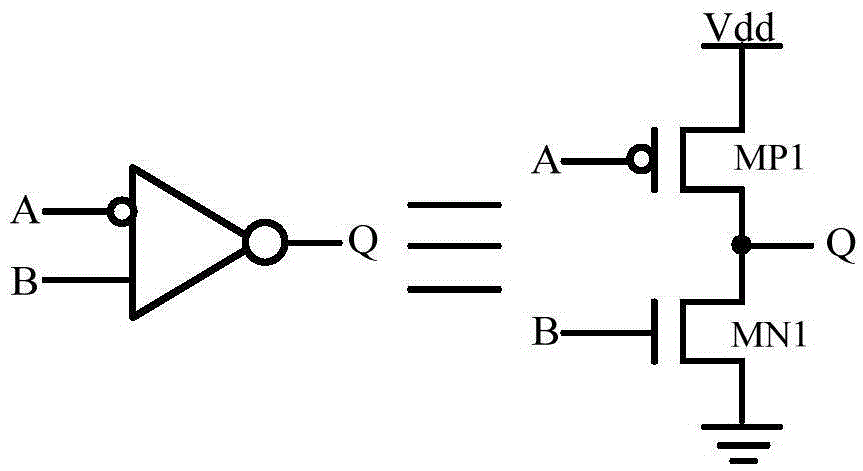

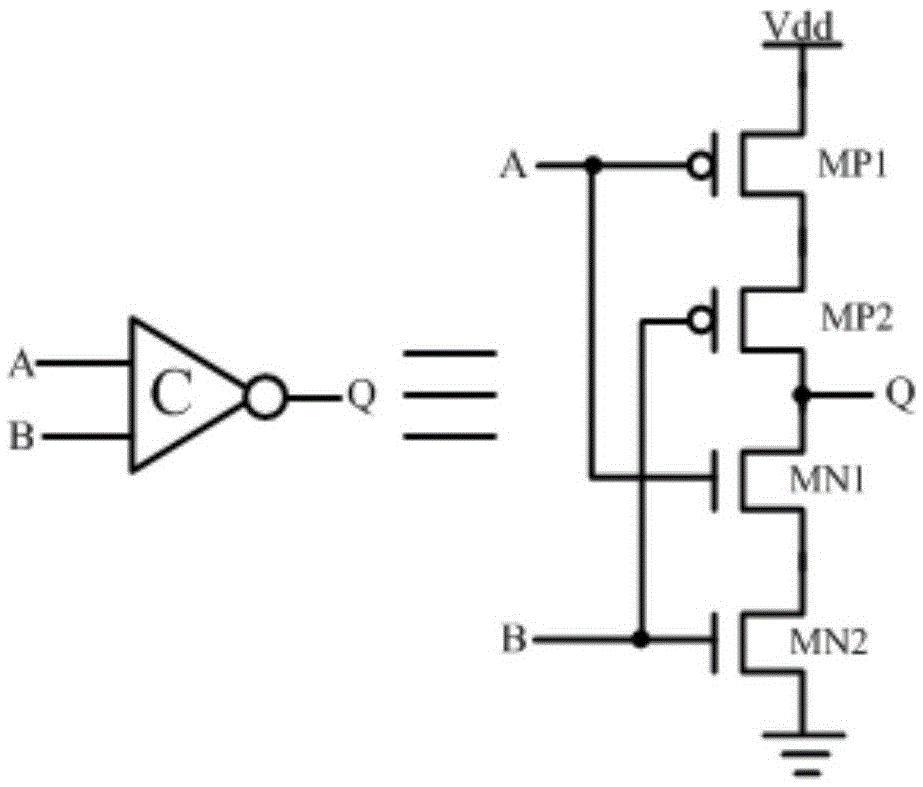

Radiation hardened latch based on heterogeneous double modular redundancy

ActiveCN106788379AReduce the numberImprove fault toleranceReliability increasing modificationsElectric pulse generatorFault toleranceSchmitt trigger

The invention relates to a radiation hardened latch based on a heterogeneous double modular redundancy. The radiation hardened latch comprises a first storage unit, a transmission unit, a second storage unit and a C unit; signal input ends of the first storage unit, the transmission unit and the second storage unit are all connected to an input signal D, a signal output end of the first storage unit is connected to a first signal input end of the C unit, a signal output end of the second storage unit is connected to a second signal input end of the C unit, a signal output end of the transmission unit is connected to a signal output end of the C unit, and the signal output end of the C unit serves as an output end of the radiation hardened latch. Because of the SET filtering function of a schmitt trigger, the latch filters a SET pulse in a transparency period; the first storage unit and the second storage unit used in the invention both have a capacity of tolerating single event upset and double node upset, and are combined with the C unit, so that the latch can tolerate the single event upset and multi-node upset, and has very good fault-tolerance performance.

Owner:HEFEI UNIV OF TECH

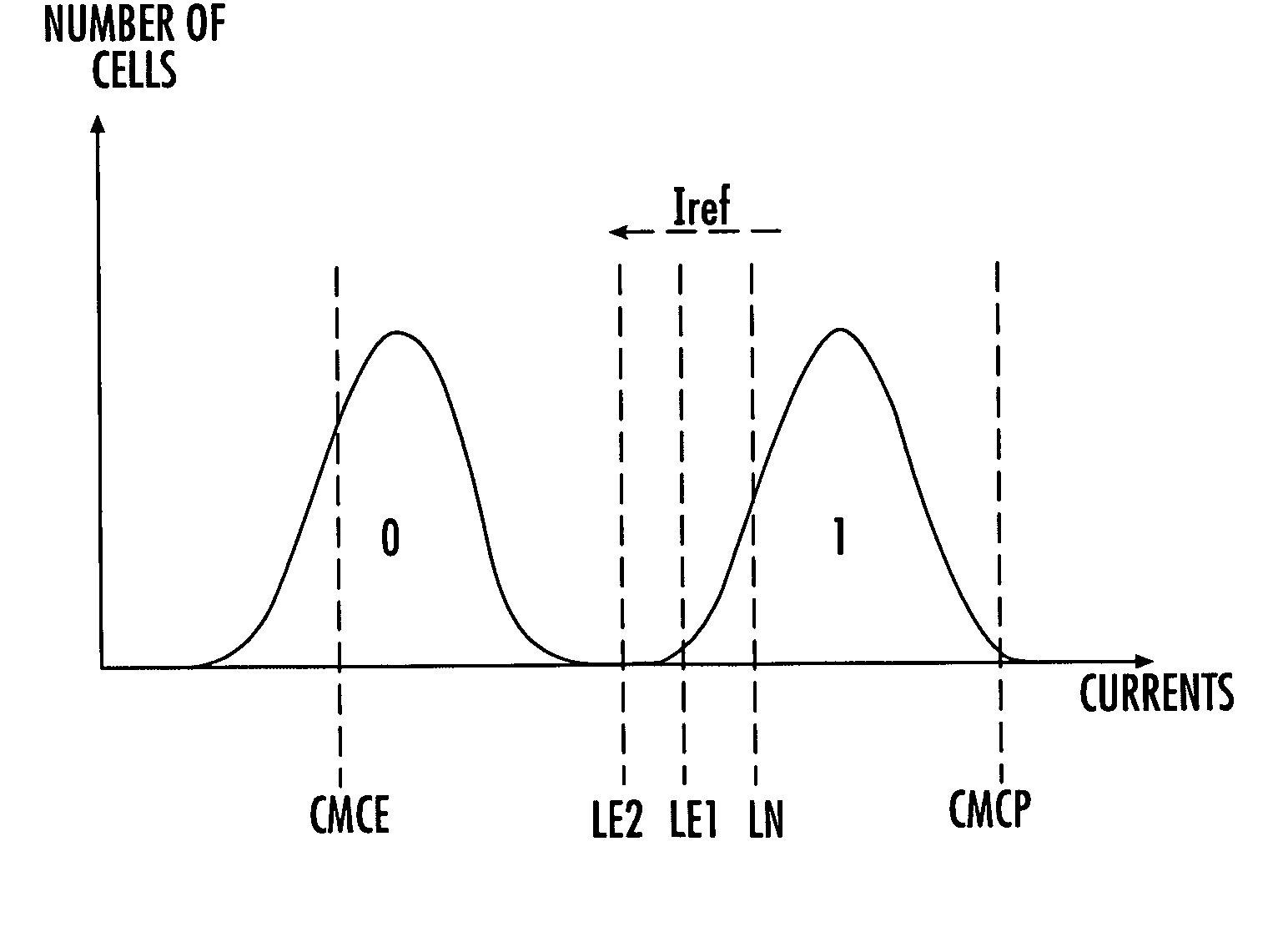

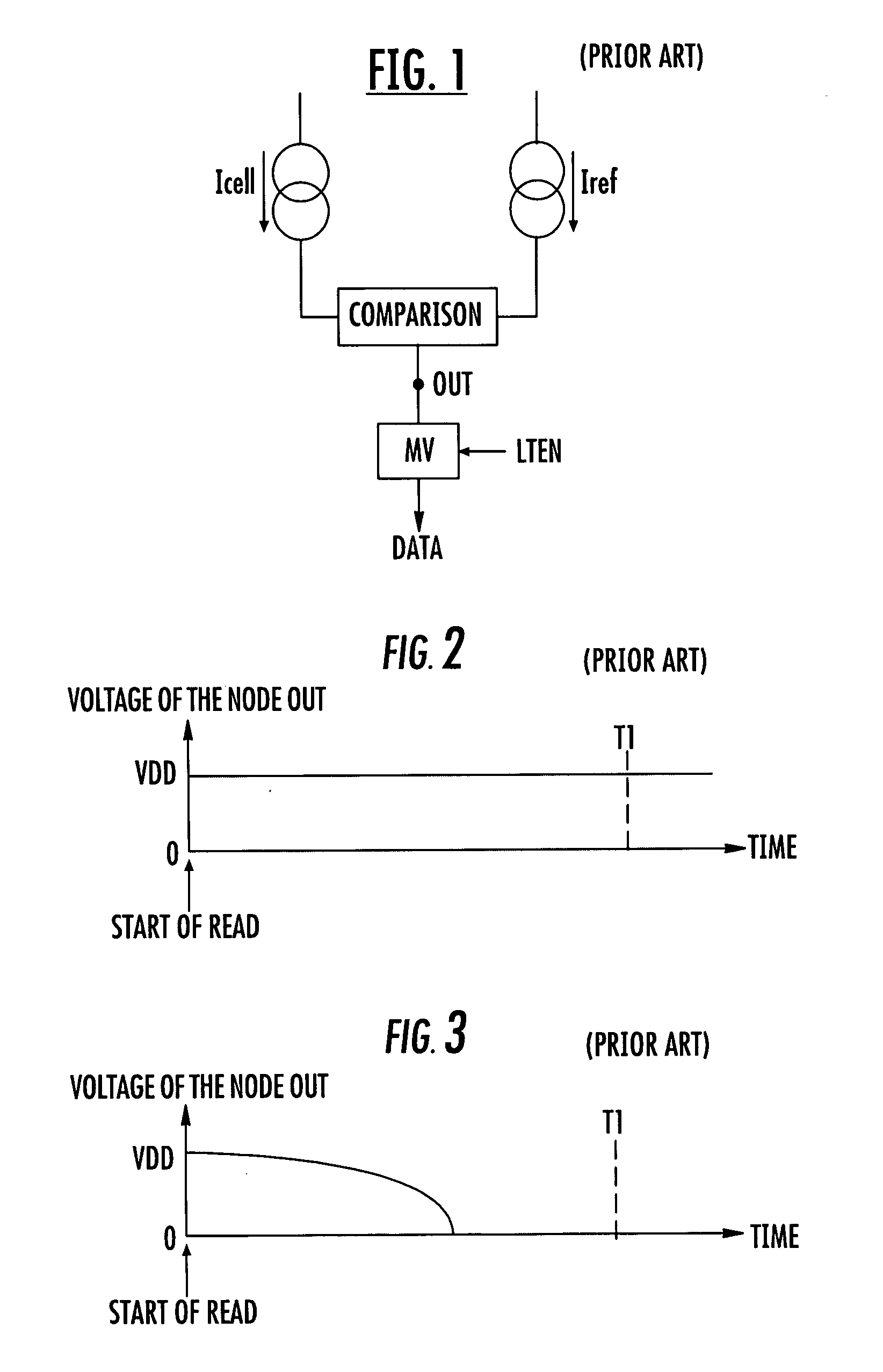

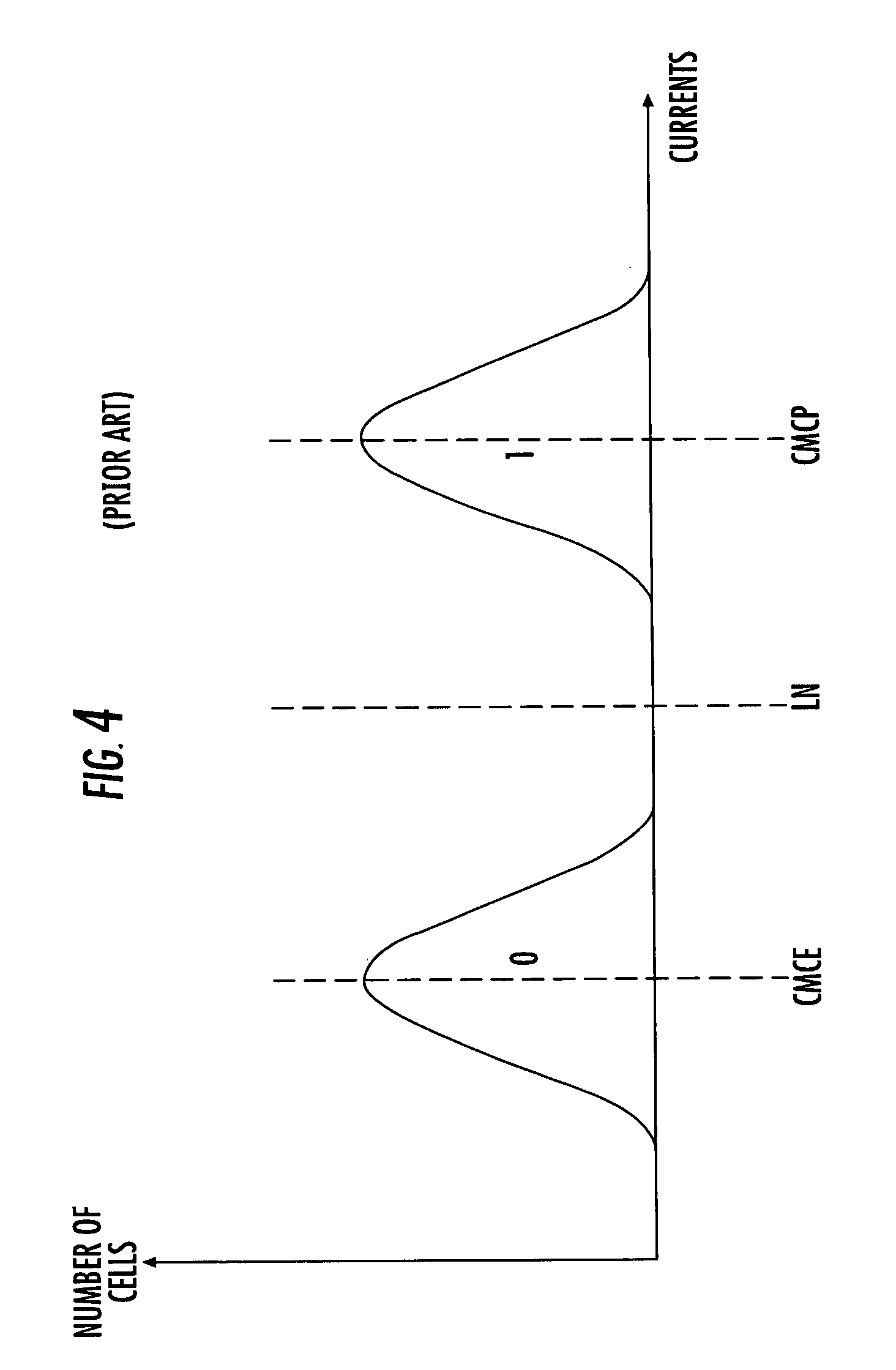

Method of detecting and correcting errors for a memory and corresponding integrated circuit

InactiveUS20060075320A1Increase the number ofSmall area overheadOther decoding techniquesUnequal/adaptive error protectionIntegrated circuitCoding block

A method is for detecting and correcting errors for a memory storing at least one code block including information data and control data. The method includes reading and decoding each element of the at least one code block to deliver an information item representative of a number of errors in the at least one code block. The method further includes, when the number of errors exceeds one, modifying a parameter of the read by a chosen value, and performing a reading and decoding of the at least one code block again to obtain a new error information item.

Owner:STMICROELECTRONICS SRL

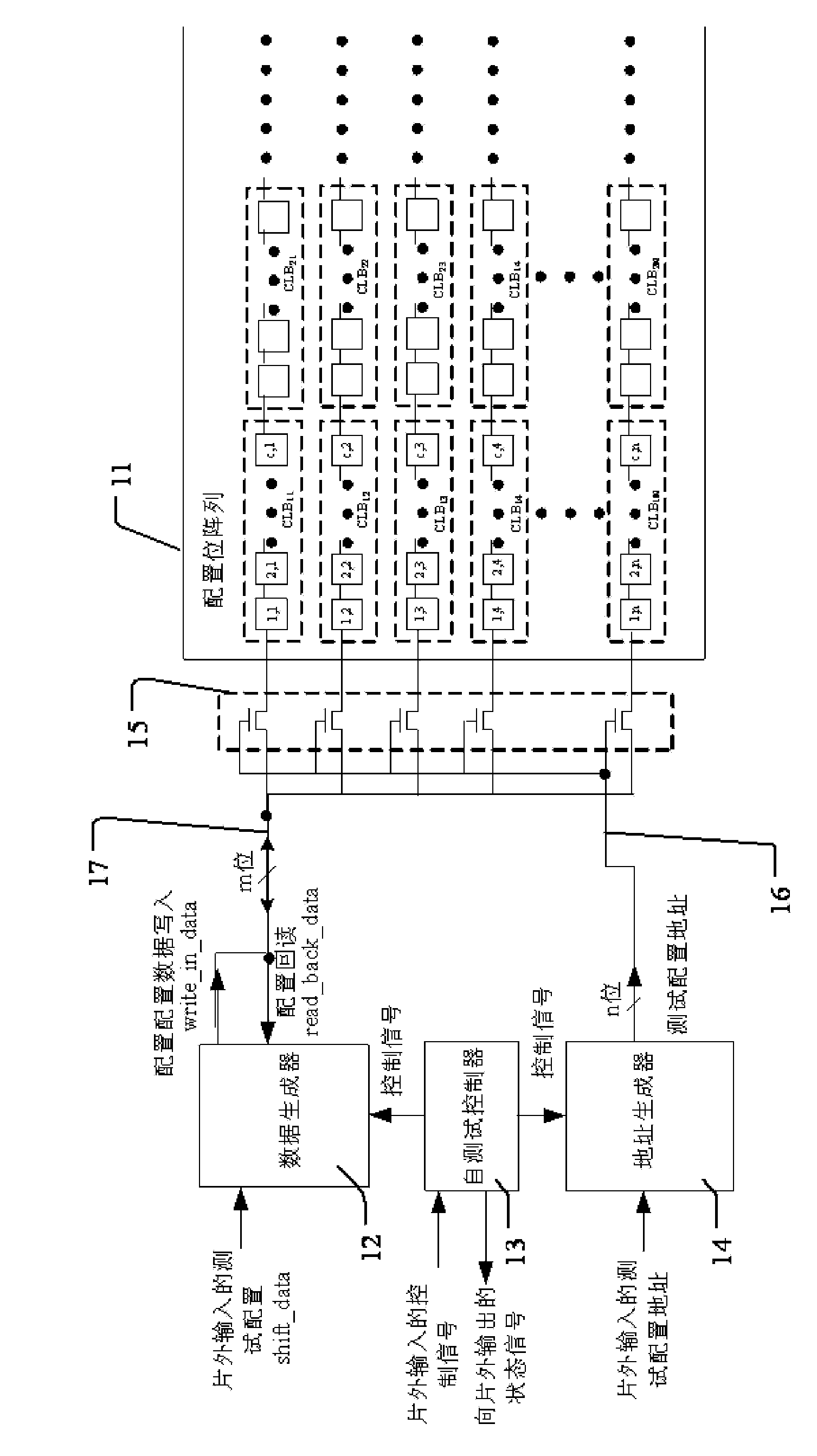

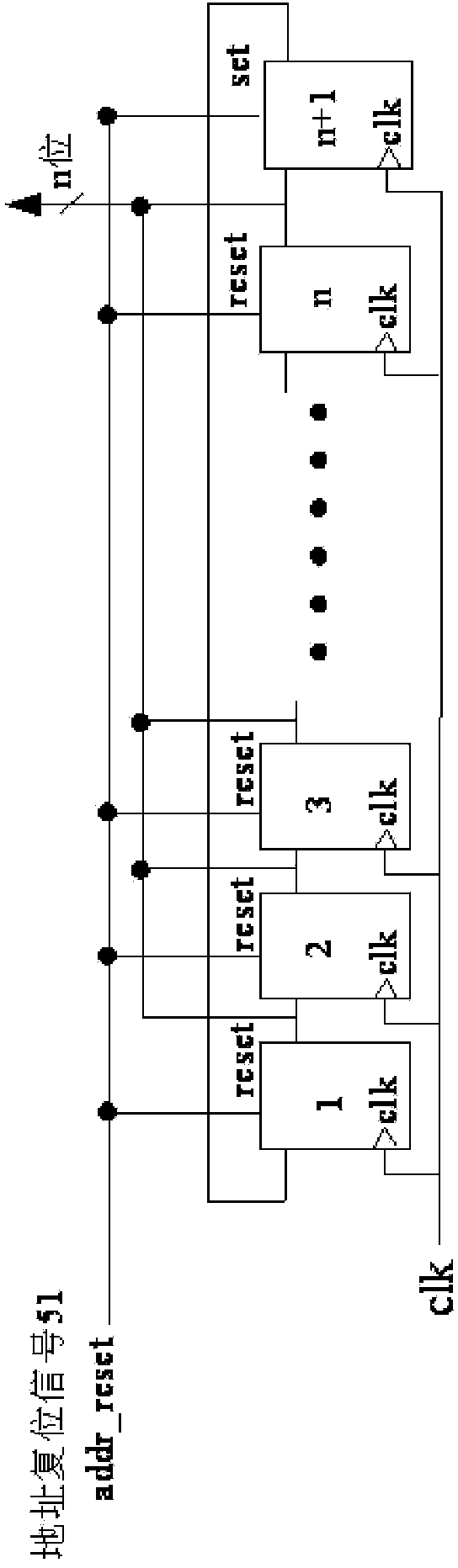

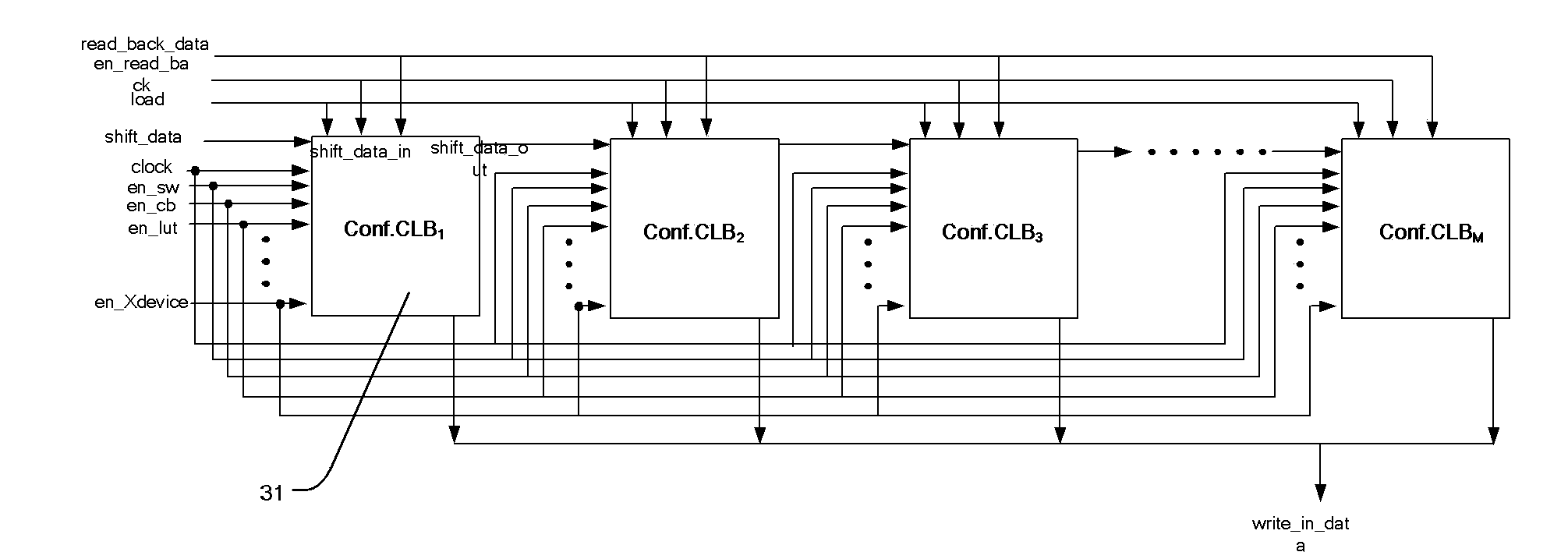

FPGA testing device and method

ActiveCN103792487AReduce the number of serial load test configurationsImprove test efficiencyDigital circuit testingTest efficiencyAddress generator

The invention provides a FPGA testing device and method. The FPGA testing device is disposed in a FPGA chip and comprises a self-testing controller, an address generator, and a data generator. The self-testing controller is used for generating an address generating signal and backward read enabling signal according to a preset time sequence. The address generator is used for generating addresses containing a tested FPGA configuration array under the driving of the address generating signal, and enabling the FPGA configuration array corresponding to the addresses in a corresponding read-write state. The data generator is used for firstly reading configuration data from the FPGA configuration array and converting the configuration data into a set of new testing configuration data according to each address provided by the address generator under the effect of the backward read enabling signal, and then rewriting the newly-generated testing configuration data in the address of the FPGA configuration array. The FPGA testing device and method decrease the times of externally loading testing configuration in series of a chip, increase testing efficiency, and reduce testing cost.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

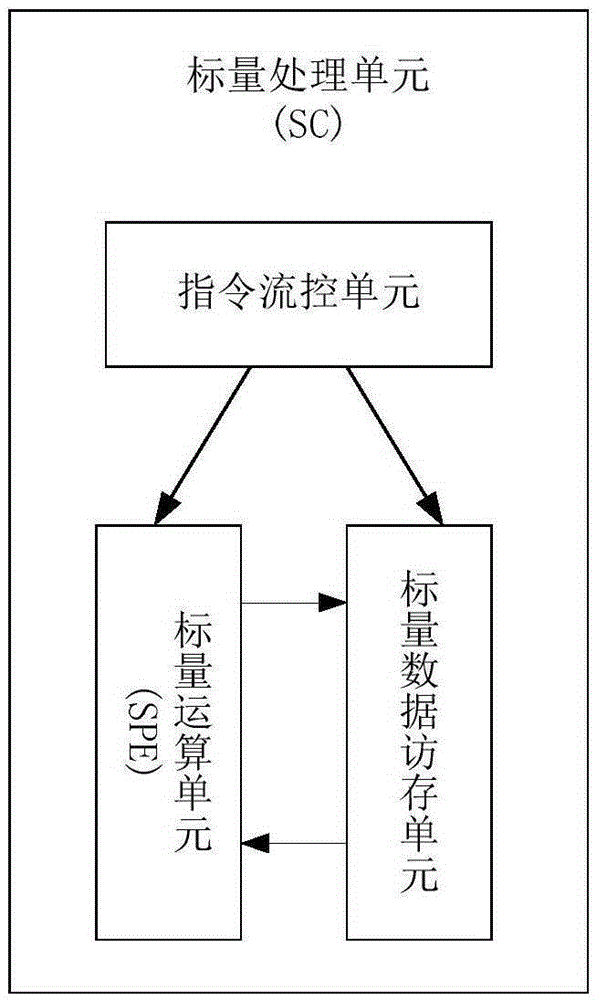

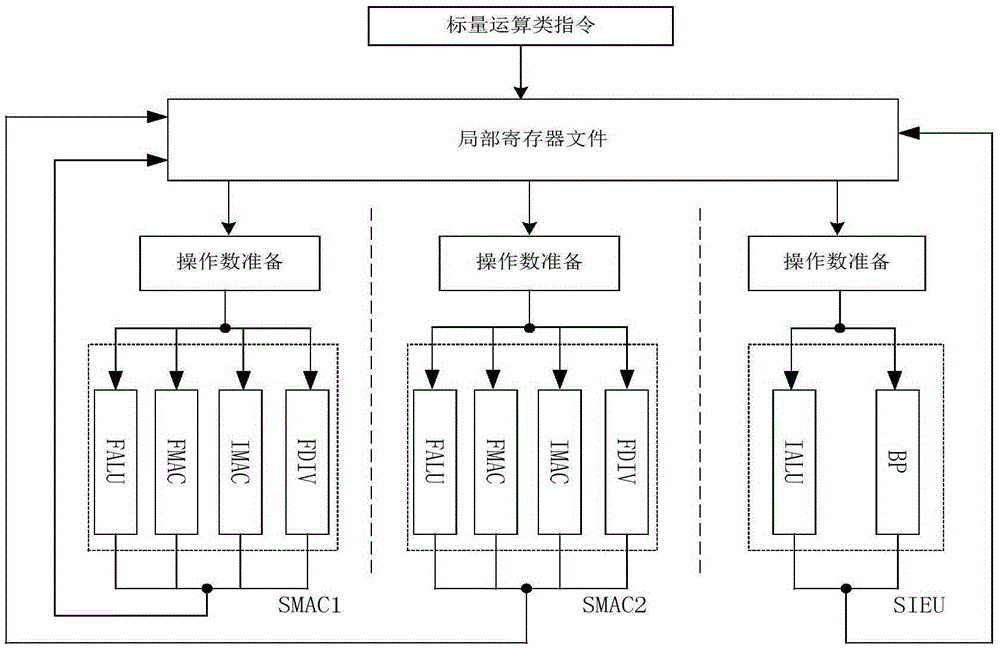

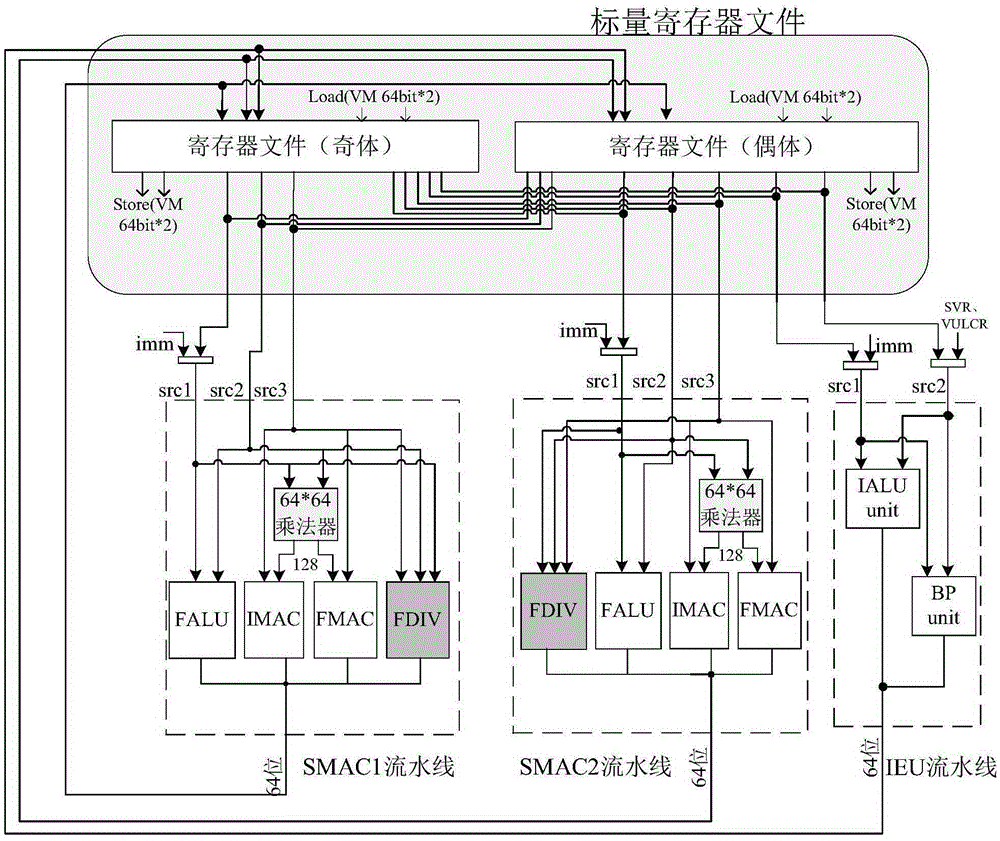

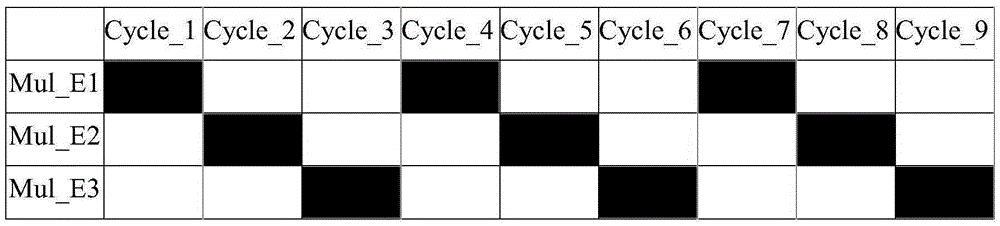

Scalar operation unit structure supporting floating-point division method in GPDSP

InactiveCN105335127AFewer instruction execution cyclesLower latencyComputation using non-contact making devicesConcurrent instruction executionParallel computingFloating point

The invention discloses a scalar operation unit structure supporting a floating-point division method in a GPDSP. The scalar operation unit structure comprises a first component SMAC1, a second component SMAC2 and a third component SIEU, which are used as scalar calculation components and are used for supporting the scalar basic calculation; each scalar calculation component corresponds to one scalar instruction in a VLIW execute packet. The scalar operation unit structure has the advantages that the instruction execution periods are few; the delay is small; the structure is simple; the feasibility is high, and the like.

Owner:NAT UNIV OF DEFENSE TECH

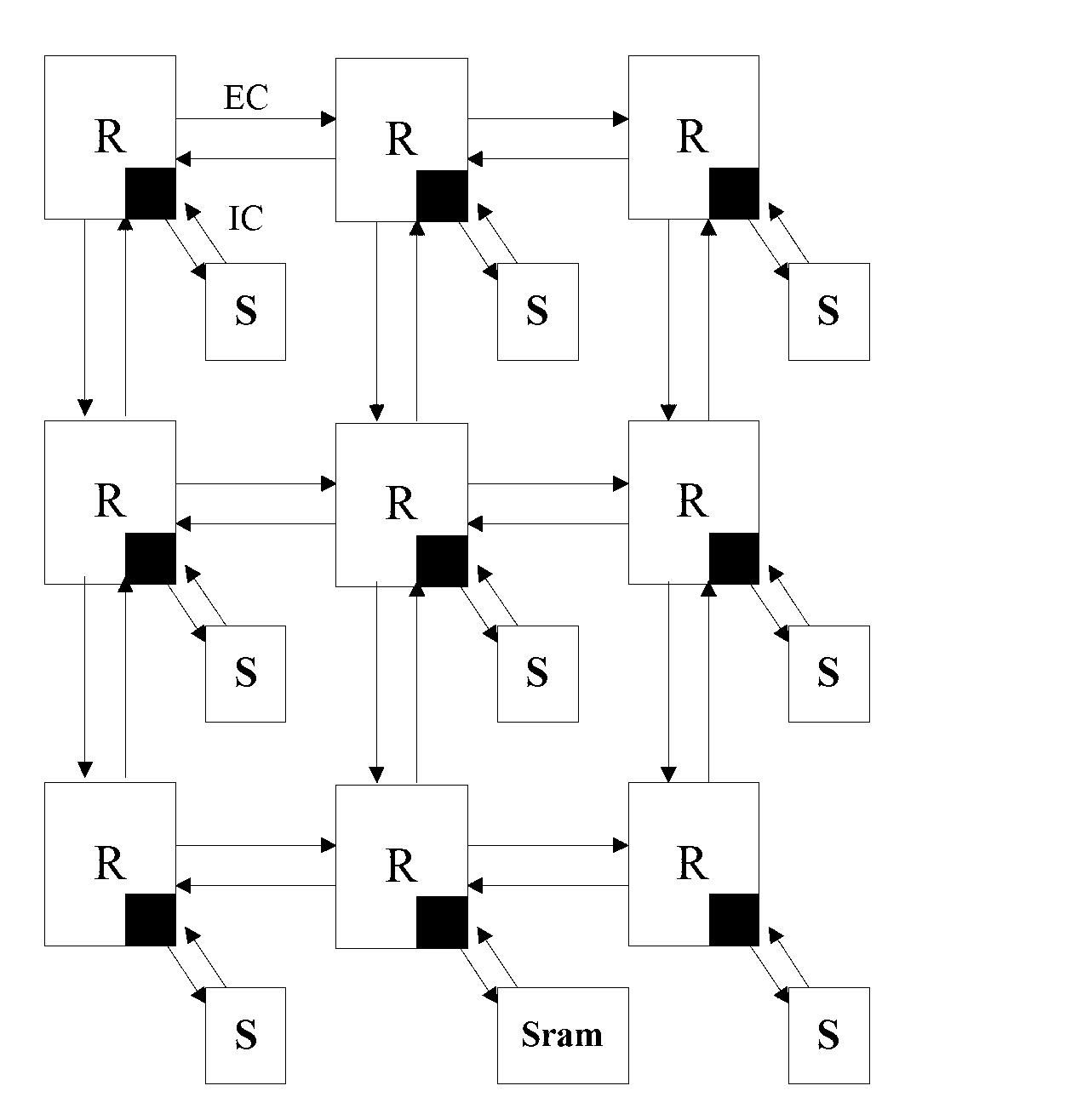

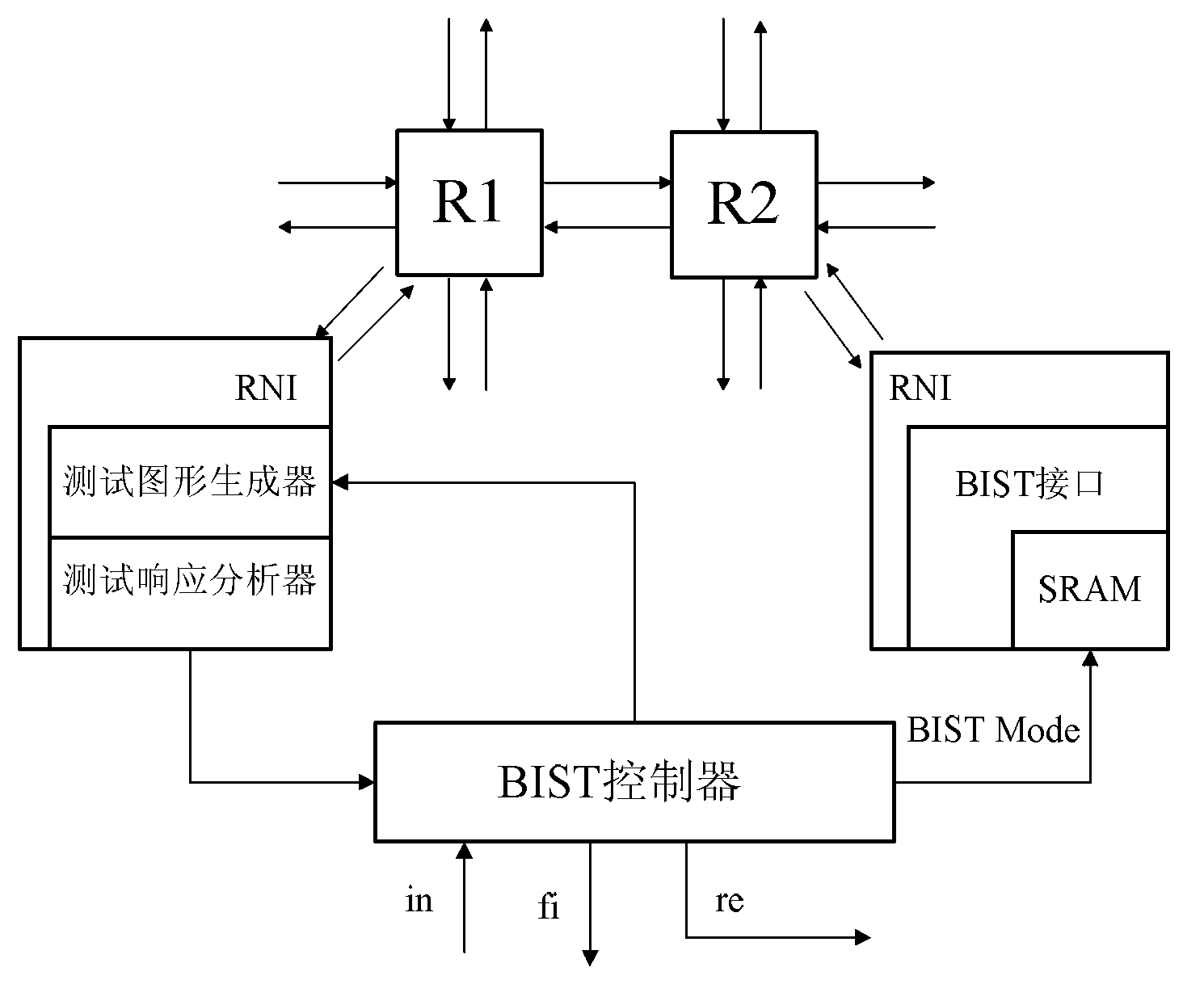

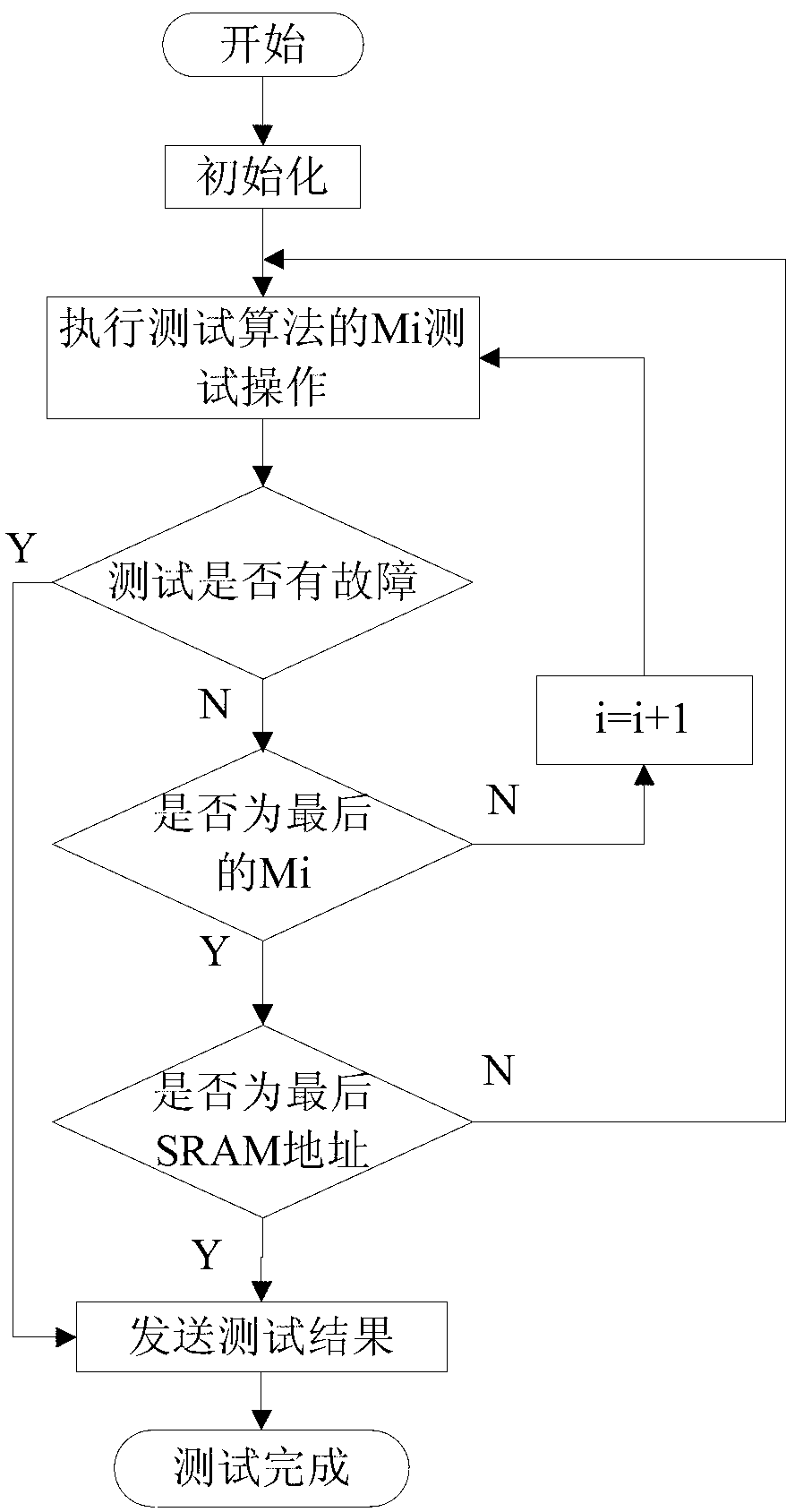

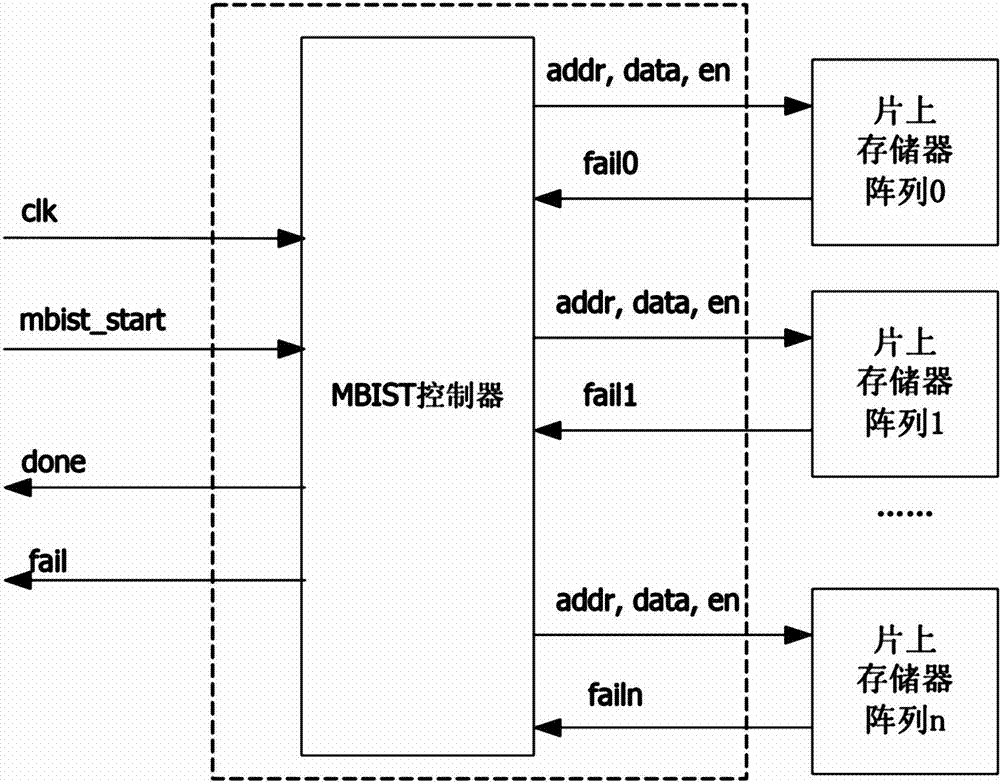

Built-in self-test structure and method for on-chip network resource node storage device

ActiveCN103310850AReduce areaSmall area overheadStatic storageStatic random-access memoryTest algorithm

The invention discloses a built-in self-test structure and method for an on-chip network resource node storage device. The built-in self-test structure comprises a built-in self-test (BIST) controller arranged on a field programmable gate array (FPGA) chip, a resource network interface and a BIST interface which are embedded into corresponding routers, a test pattern generator and a test response analyzer, wherein the BIST controller is connected with external test equipment through an external interface. The built-in self-test method comprises the following steps that: the external test equipment sends an instruction start test program to the BIST controller; the BIST controller sends an enabling signal and a state selection signal to each test module according to a March C+ test algorithm program, performs read-write operation on each address of a static random access memory (SRAM) under each test state, and stops sending the signals if failures are found out. A test result is sent to the external test equipment. According to the built-in self-test structure and method, the test time is reduced by 50 percent; a routing network of a network operation center (NoC) is reused as a test data route; data transmission is reliable and safe; a chip area is low in expense; the failure coverage rate is high.

Owner:GUILIN UNIV OF ELECTRONIC TECH

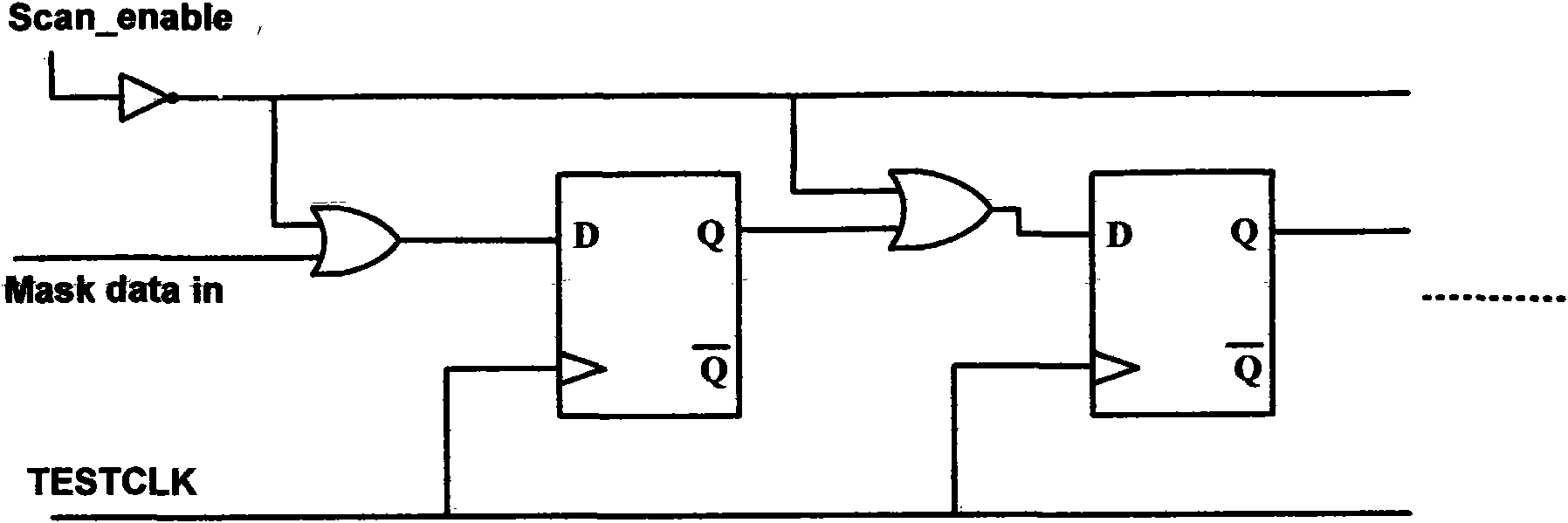

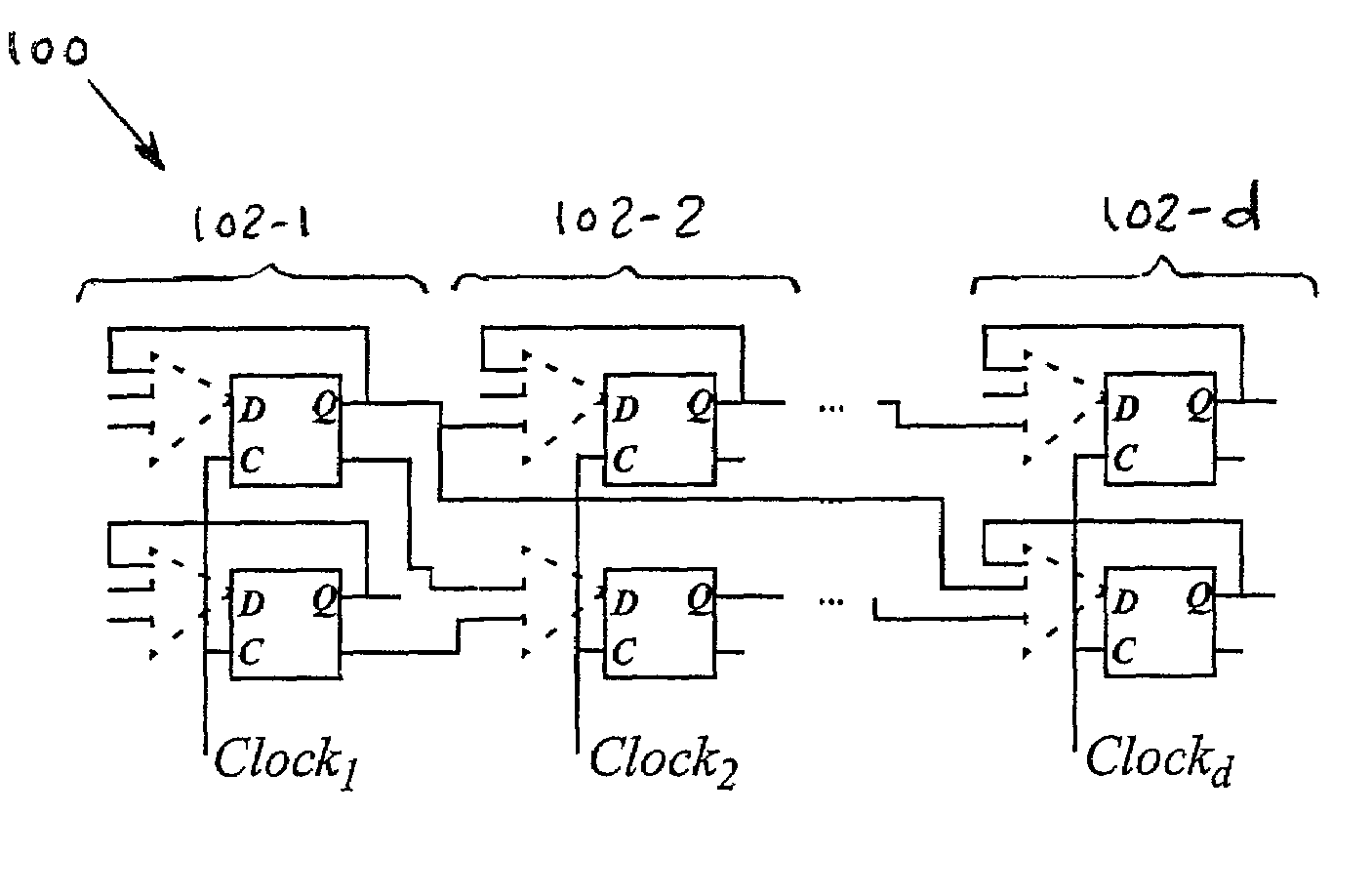

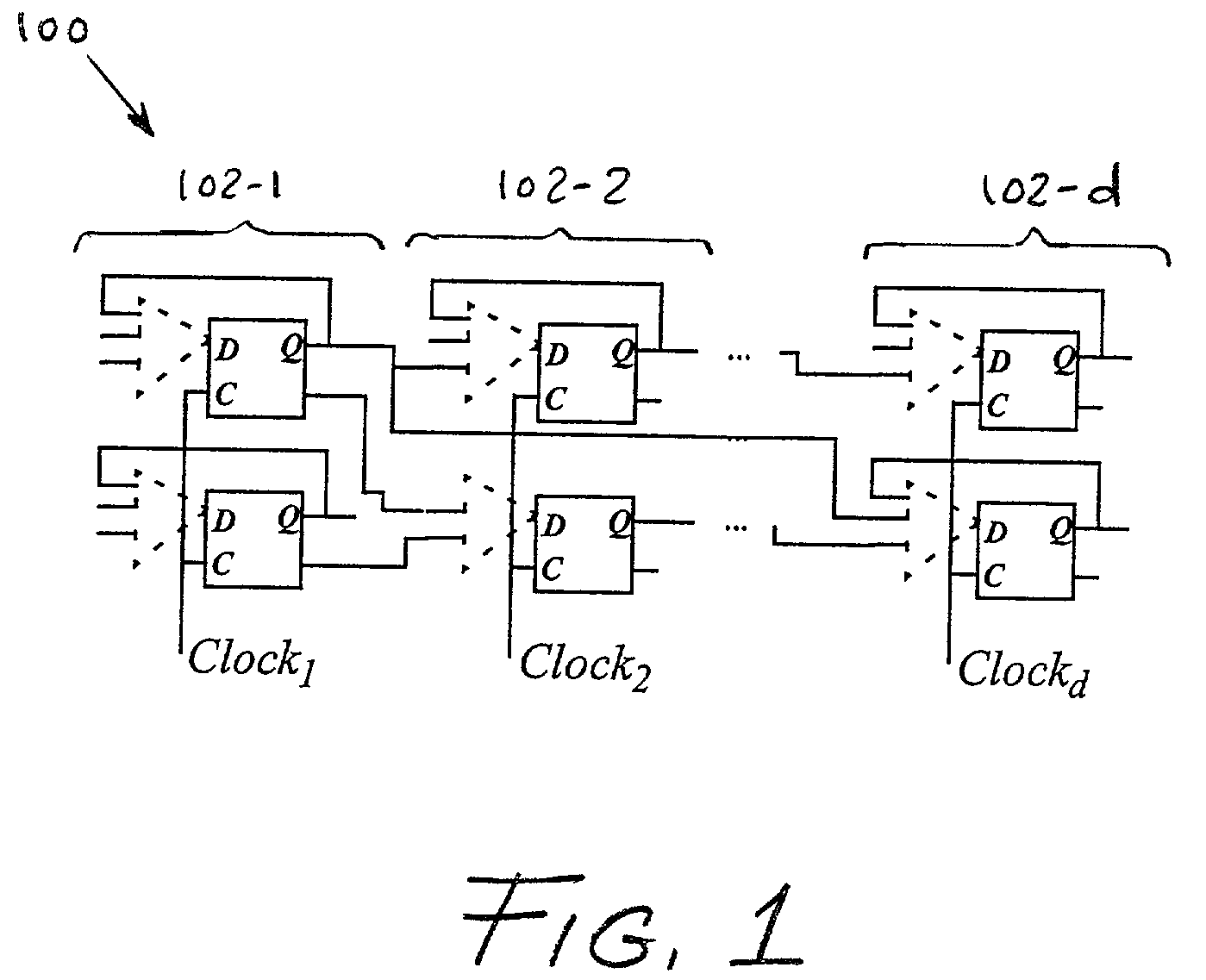

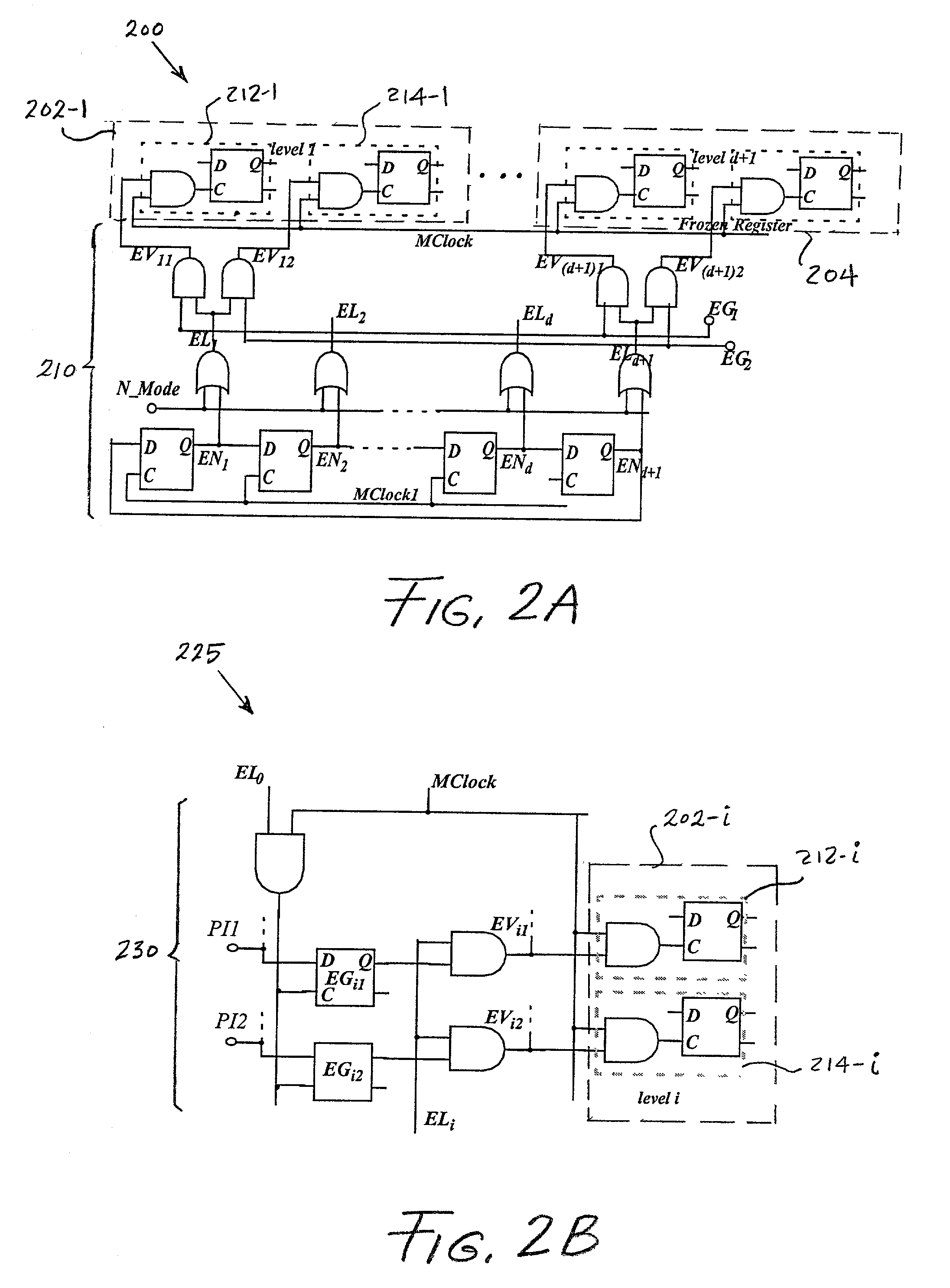

Sequential test pattern generation using clock-control design for testability structures

InactiveUS7017096B2No delay penaltiesSmall area overheadDigital circuit testingError detection/correctionProcessor registerPattern generation

Techniques for testing a sequential circuit comprising a plurality of flip-flops or other types of registers. The circuit is first configured such that substantially all feedback loops associated with the registers, other than one or more self-loops each associated with a corresponding one of the registers, are broken. Test patterns are then generated for application to the circuit. The test patterns are applied to the circuit in conjunction with partitioned clock signals each of which is associated with a corresponding level of the circuit containing at least one of the self-loops.

Owner:BELL SEMICON LLC

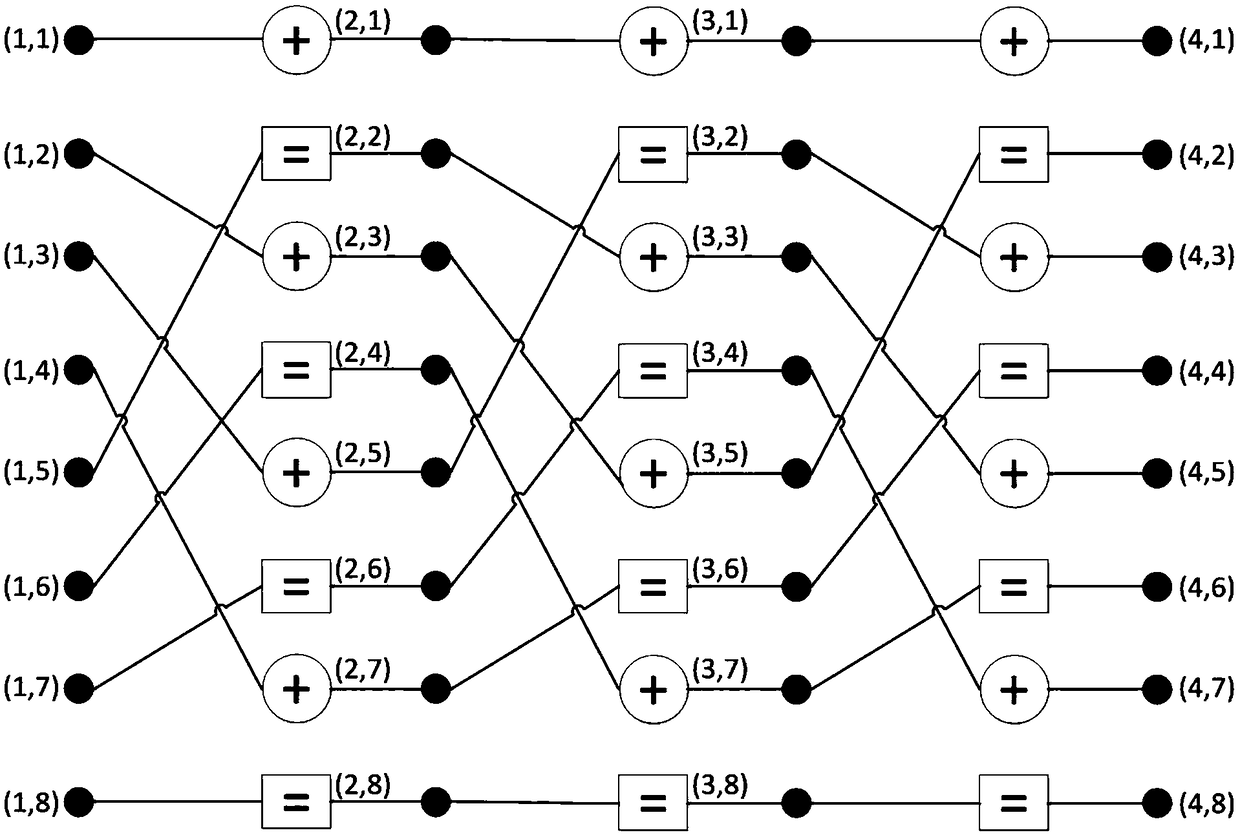

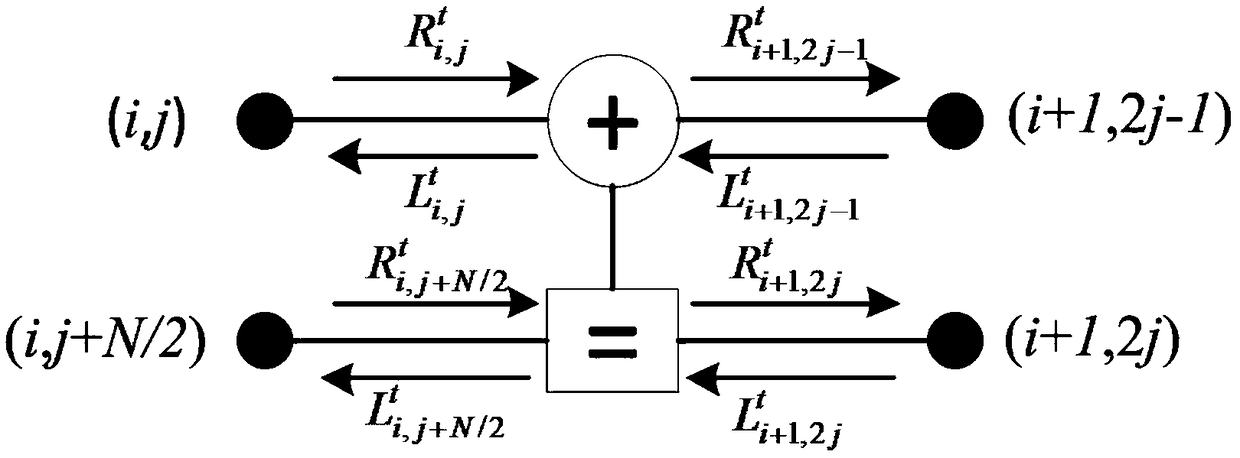

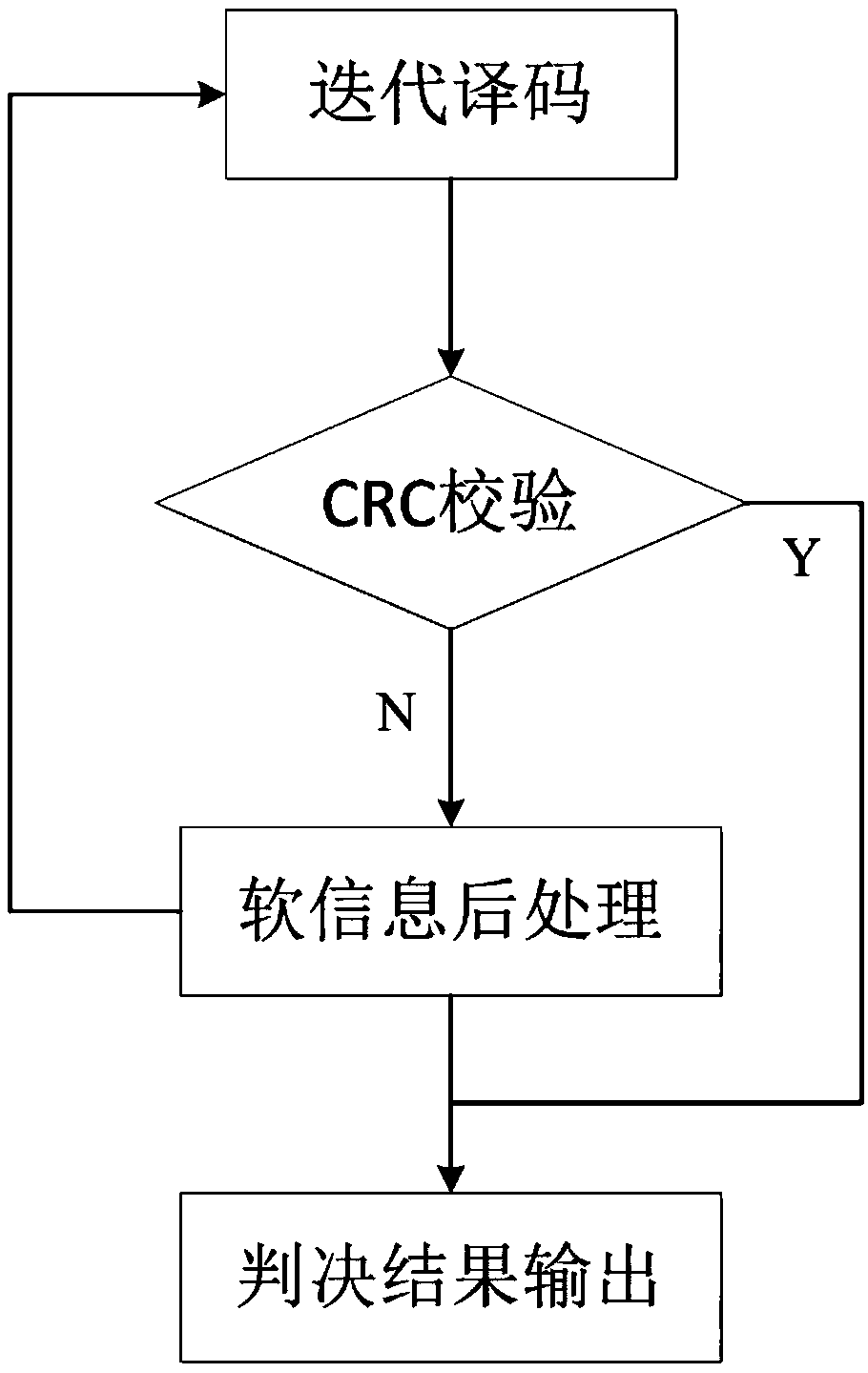

BP decoding algorithm for polarization code based on information postprocessing

ActiveCN108847848AIncrease decoding gainSmall area overheadError correction/detection using multiple parity bitsCode conversionComputer scienceSoft information

The invention discloses a BP decoding algorithm for a polarization code based on information postprocessing. According to the algorithm, a soft information postprocessing step is added based on the traditional BP algorithm, when the number of iterations of iterative decoding reaches the maximum number of iterations and a CRC check is not passed, at least one piece of estimated bit information arranged near the front is selected from an absolute value ascending sort arrangement of estimated bit information to be turned over, a symbol after the selected estimated bit information is turned over is used as the symbol of initial freezing bit information on a corresponding position, and then iterative decoding is performed once again according to the adjusted initial freezing bit information andreceived channel information. Therefore, according to the BP decoding algorithm for the polarization code based on information postprocessing provided by the invention, although the number of turn-over and the number of iterations are increased, the decoding gains can be significantly enhanced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

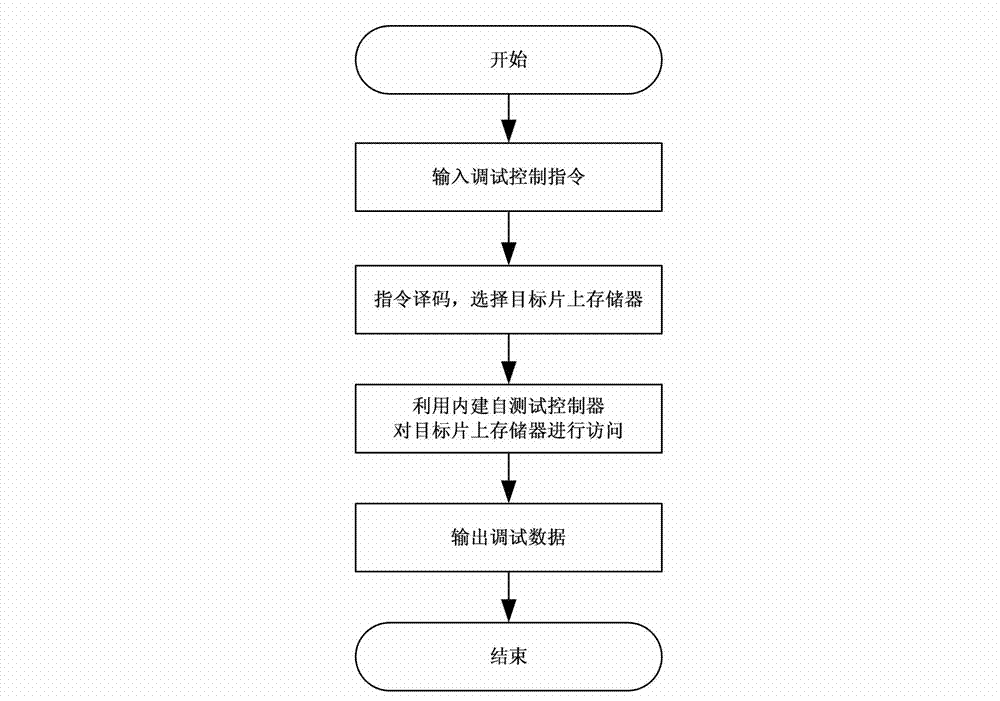

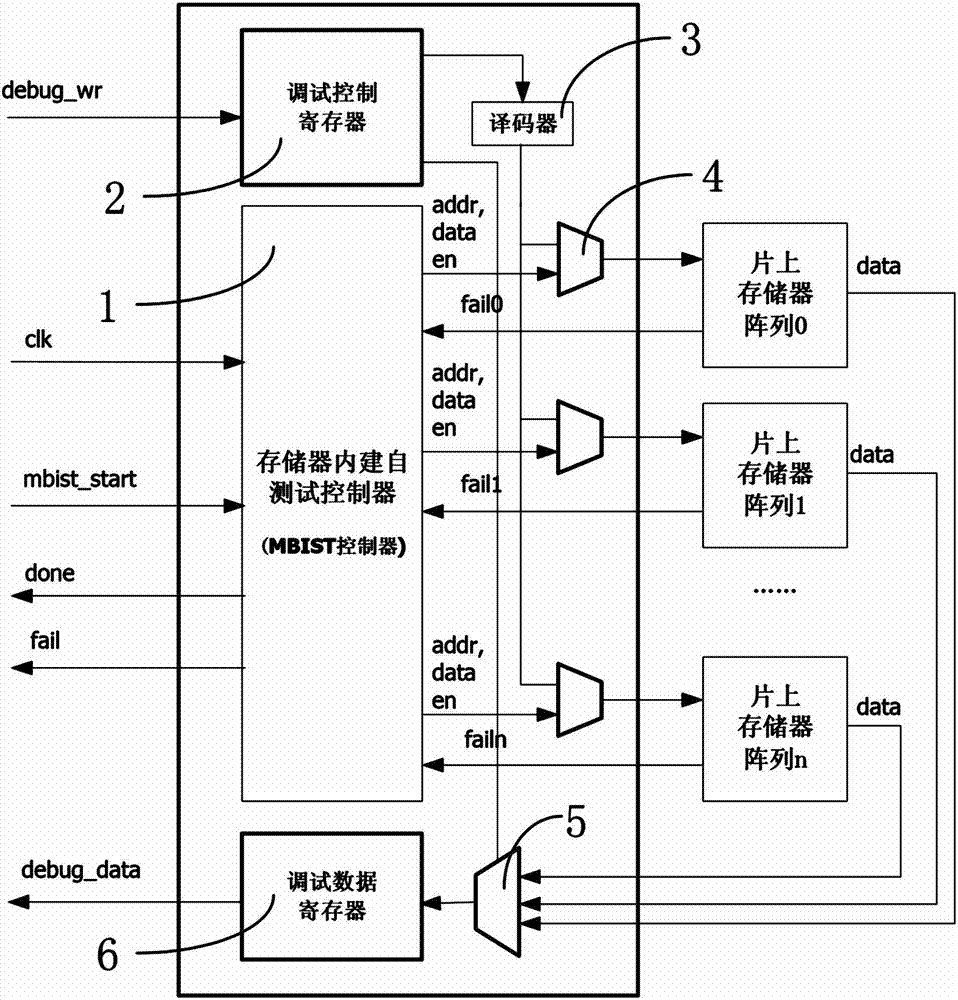

On-chip memory debugging method and device based on memory built-in self-test

InactiveCN102969027AReduced commissioning timeIncrease success rateStatic storageBuilt-in self-testInput selection

The invention discloses an on-chip memory debugging method and a device based on memory built-in self-test. The method comprises the following steps: 1) inputting a debugging control instruction, and starting memory debugging; 2) decoding the debugging control instruction, and selecting a target on-chip memory according to a decoding signal; 3) accessing the selected target on-chip memory according to a to-be-debugged reading area of the debugging control instruction under the control of a memory built-in self-test controller; and 4) caching the reading data of the target on-chip memory to a debugging data register, and taking the data of the debugging data register as debugging result data output of the debugging control instruction. The device comprises a memory built-in self-test controller, a debugging control register, a decoder, an input selector, an output selector and a debugging data register. The memory debugging data can be accessed on the basis of the memory built-in self-test, and the on-chip memory debugging method has the advantages of low hardware overhead, low area overhead and high cost performance.

Owner:NAT UNIV OF DEFENSE TECH

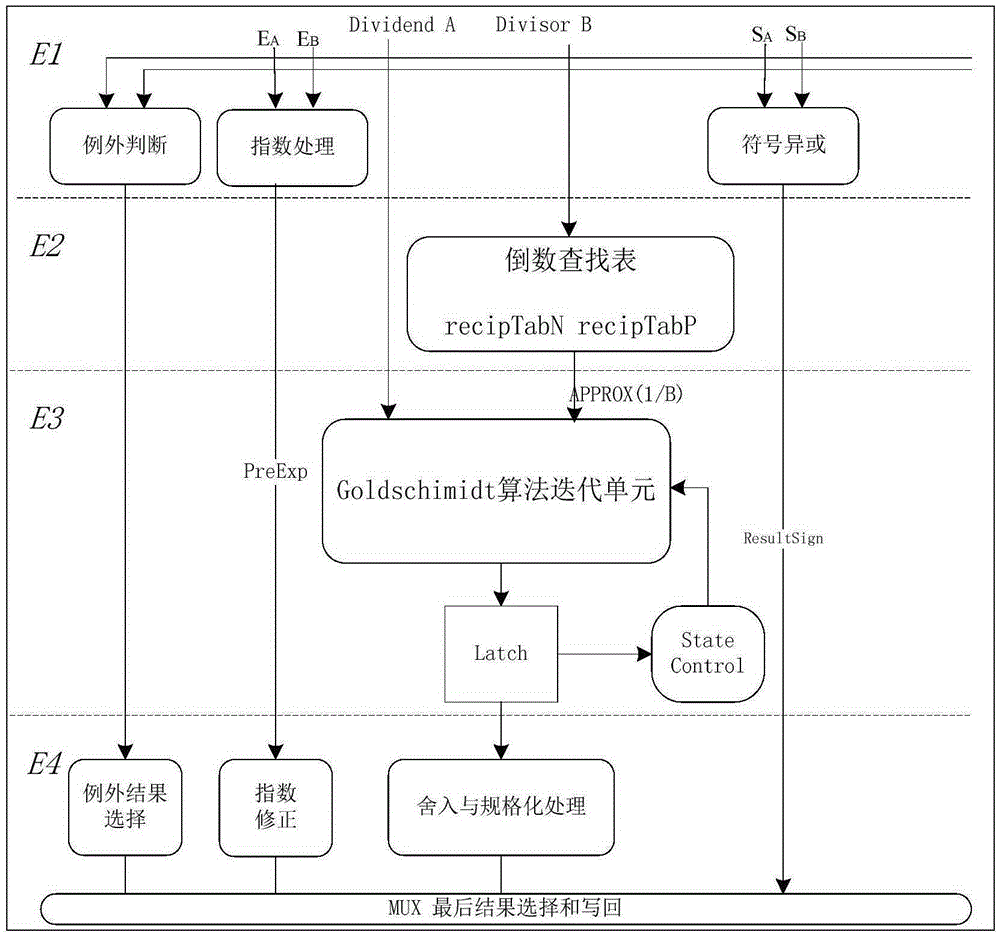

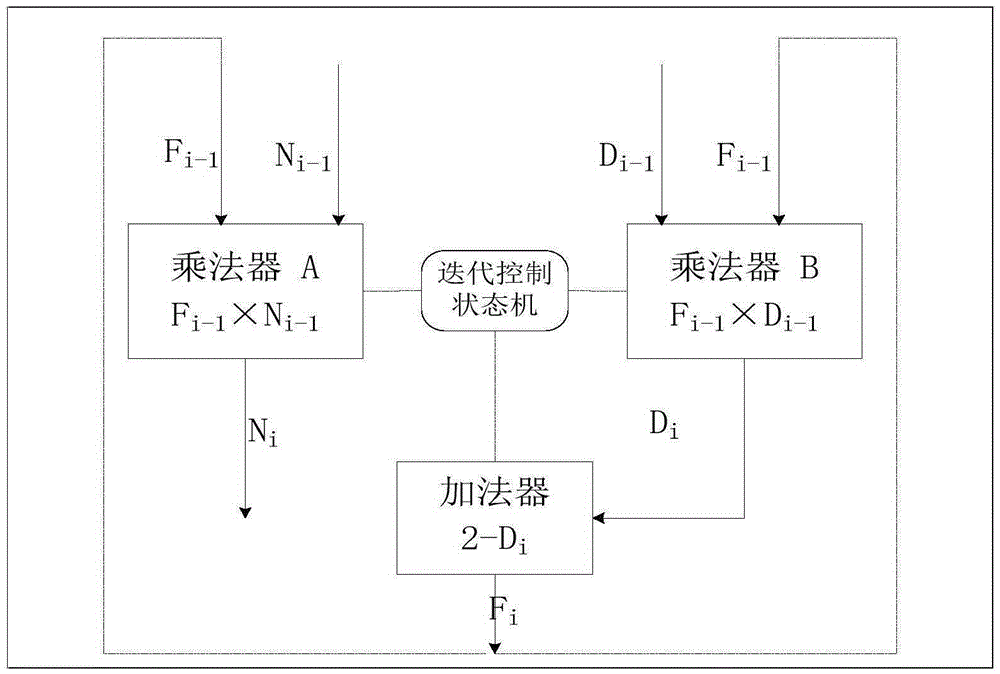

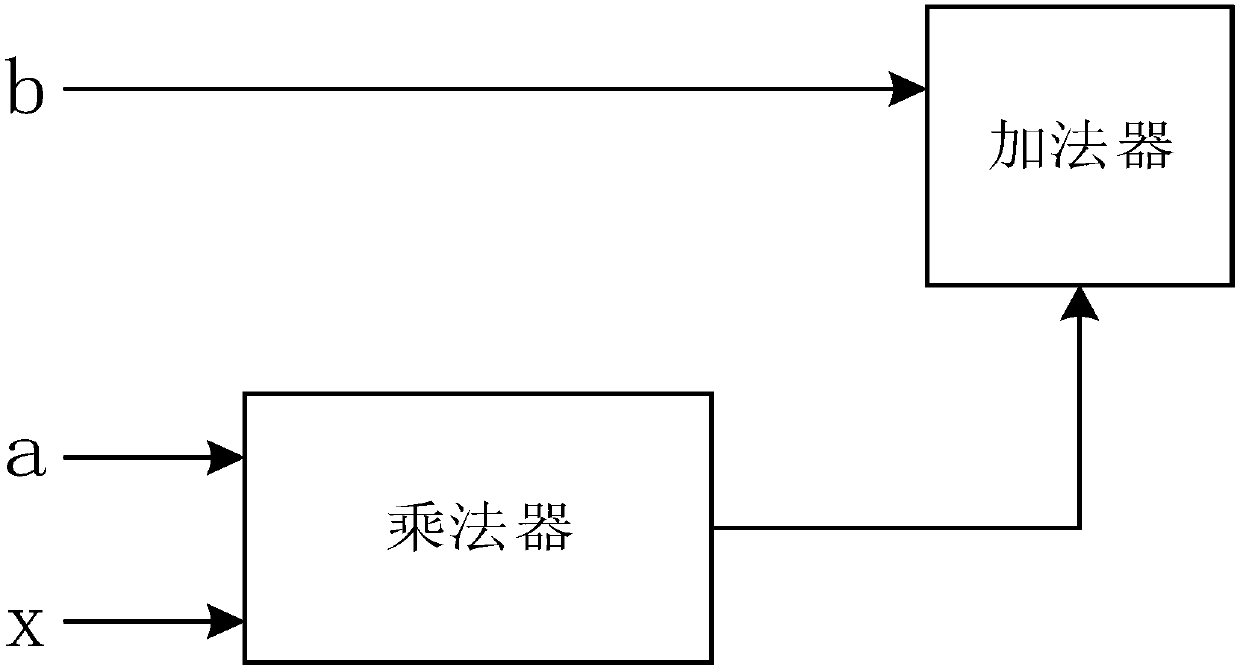

Goldschmidt algorithm-based floating-point divider

InactiveCN105389157AShort cycleAchieve precisionDigital data processing detailsBinary multiplierFloating point

The present invention discloses a Goldschmidt algorithm-based floating-point divider. The Goldschmidt algorithm-based floating-point divider comprises: an iterative initial value generator for generating an approximate value of a reciprocal of a mantissa of a divisor, wherein the approximate value is accurate to 14 bits; a Goldschmidt algorithm iteration module comprising two multipliers, one adder and one iterative control state machine, wherein the iterative control state machine is used for controlling a Goldschmidt algorithm iteration process, and filling a multiplier pipeline station by scheduling three continuous division instructions; and a normalization processing module for performing floating-point number exception determination and sign bit, exponent and mantissa specification, and normalizing a quotient result with different operation accuracy of a dual-accuracy floating-point division or single-accuracy floating-point division. The Goldschmidt algorithm-based floating-point divider disclosed by the present invention has the advantages of short instruction execution period, short delay, simple structure, high feasibility and the like.

Owner:NAT UNIV OF DEFENSE TECH

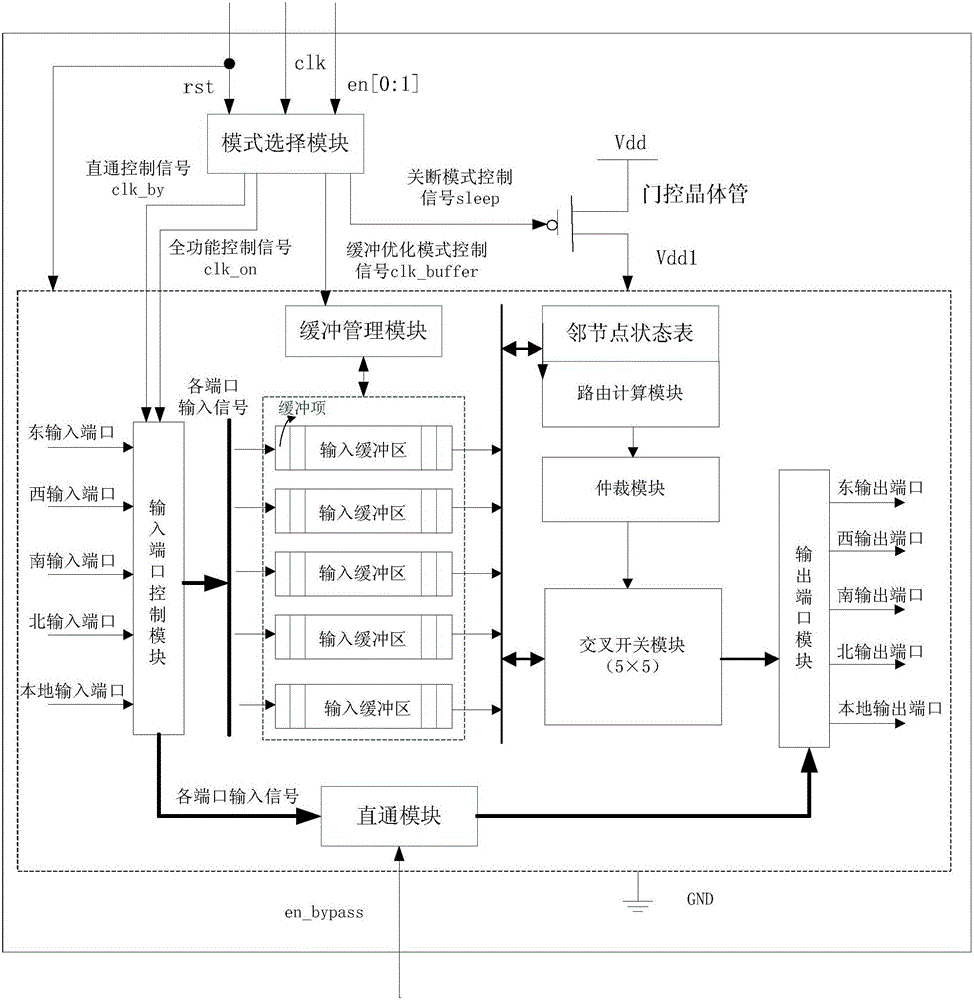

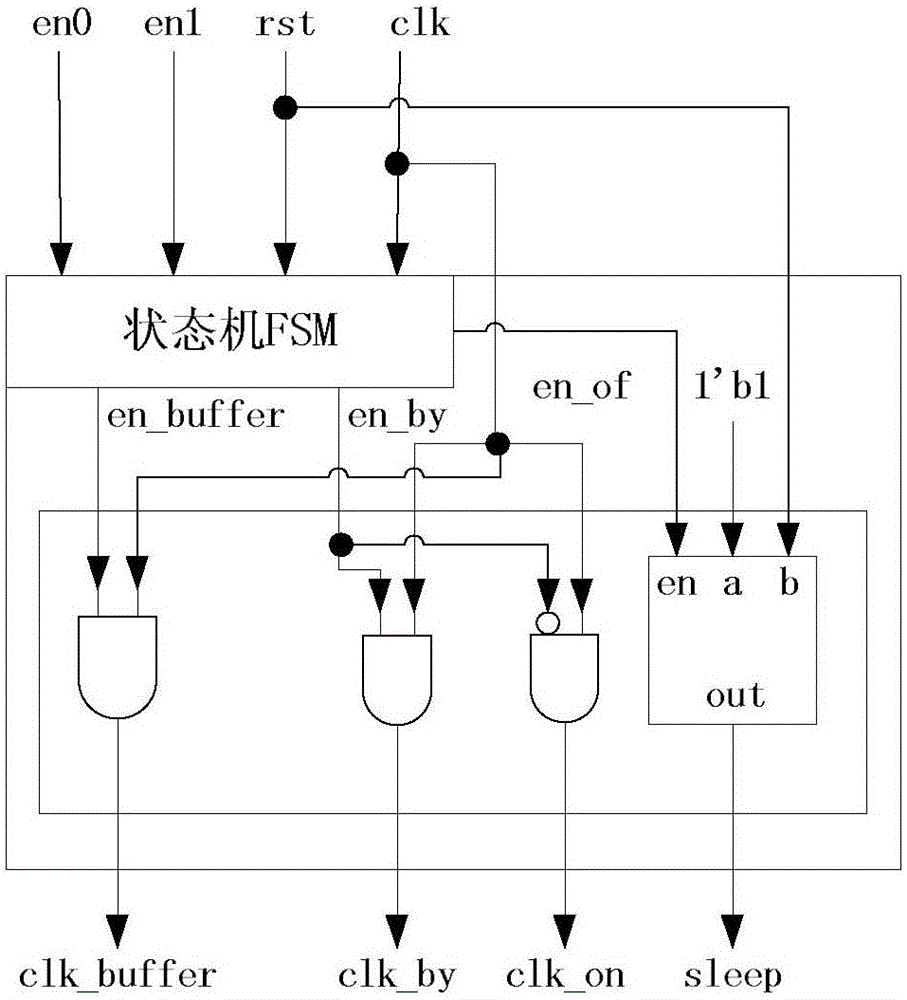

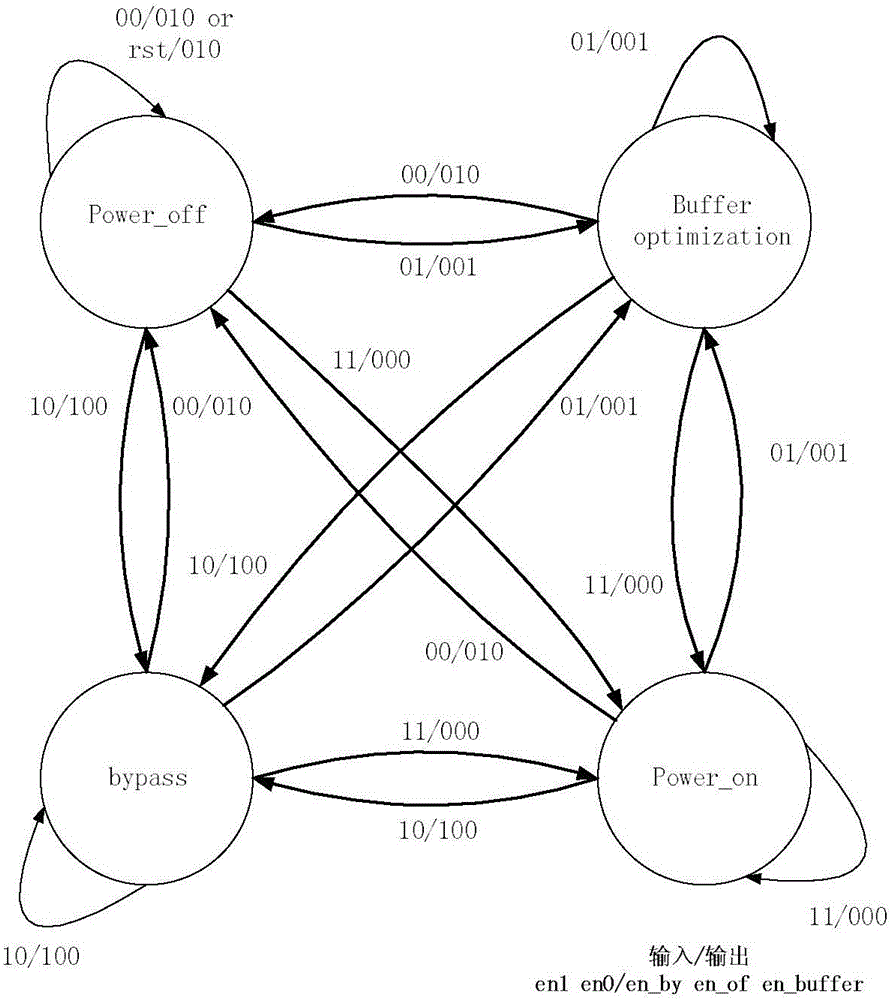

On-chip network router and routing method with various working modes

ActiveCN106302163ASmall area overheadReduce power consumptionData switching networksCrossover switchMode selection

The invention discloses an on-chip network router with various working modes. The on-chip network router with various working modes comprises a mode selecting module, a switch-off module and a routing module. The routing module comprises input ports, an input port control module, a buffer management module, buffer zones, a routing calculation module, an arbitration module, a cross switch module, a straight-through module and output ports. The input ports comprise the east input port, the west input port, the south input port, the north input port and the local input port. The output ports comprise the east output port, the west output port, the south output port, the north output port and the local output port. The buffer zones comprise multiple input buffer zones. The invention further discloses an on-chip network routing method with various working modes. Compared with a router of a basic structure, power consumption of the router is effectively reduced through mode switching on the premise that small-area expenses are increased, and accordingly the purpose of optimizing power consumption of a multi-core system is realized in case of dark silicon.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

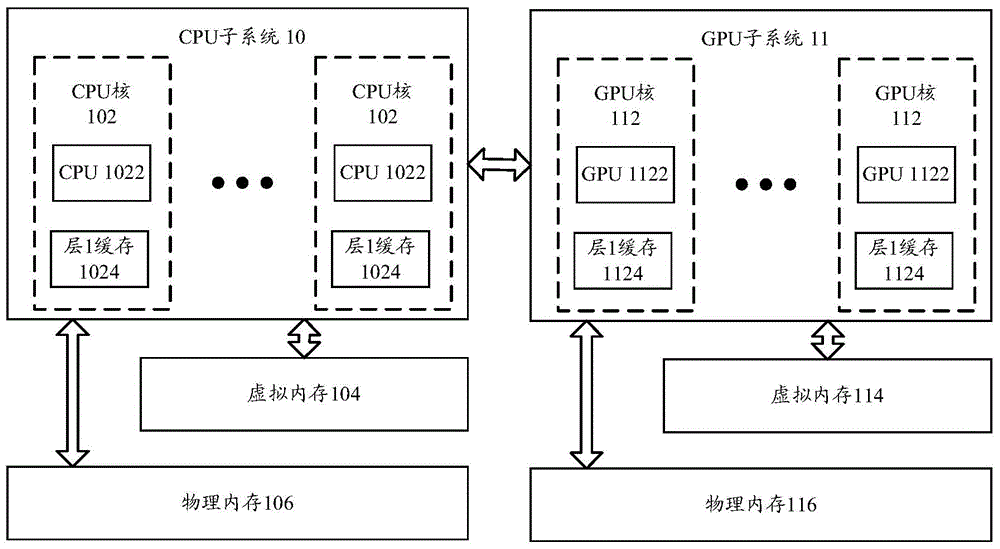

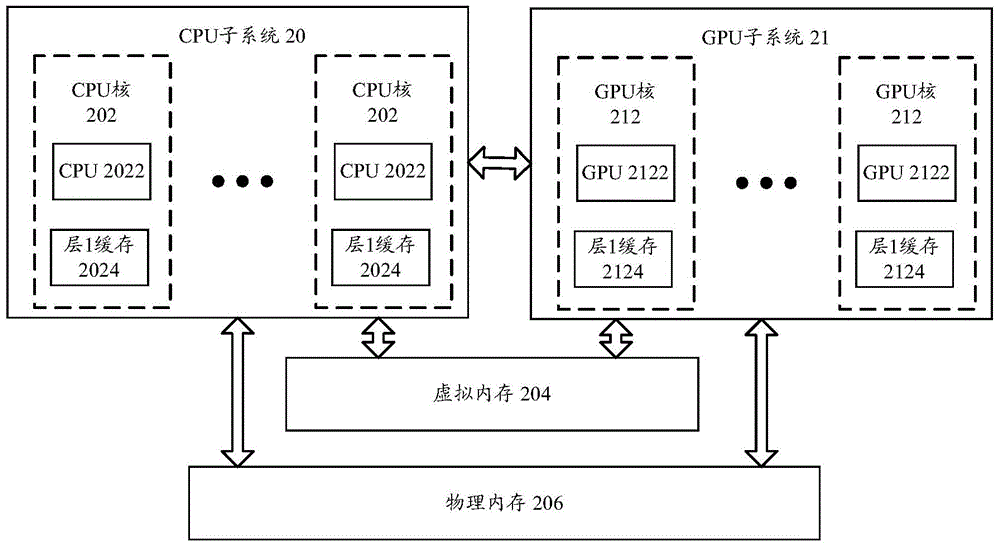

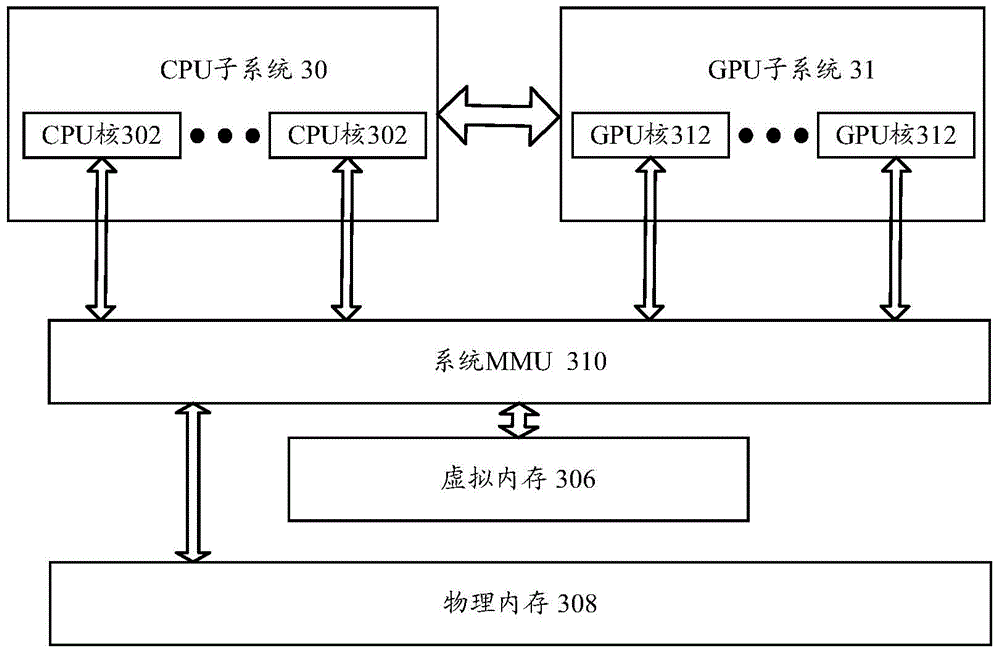

System on chip and memory access management method thereof

InactiveCN105302765ASmall footprintSmall area overheadMemory adressing/allocation/relocationDigital computer detailsMemory sharingAccess management

The invention provides a system on chip SOC and a memory access management method thereof, and aims at realizing the memory sharing of different processor subsystems in the SOC, and carrying out consistency management on a shared memory among the processor subsystems, so as to reduce the area and the power consumption of the SOC and realize the uniform management of the shared memory. The system on chip comprises the processor subsystems, the shared memory and a system memory management unit MMU, wherein the system MMU is connected between the processor subsystems and the shared memory and used for managing the access from the processor subsystems to the shared memory.

Owner:CHINA ACAD OF TELECOMM TECH

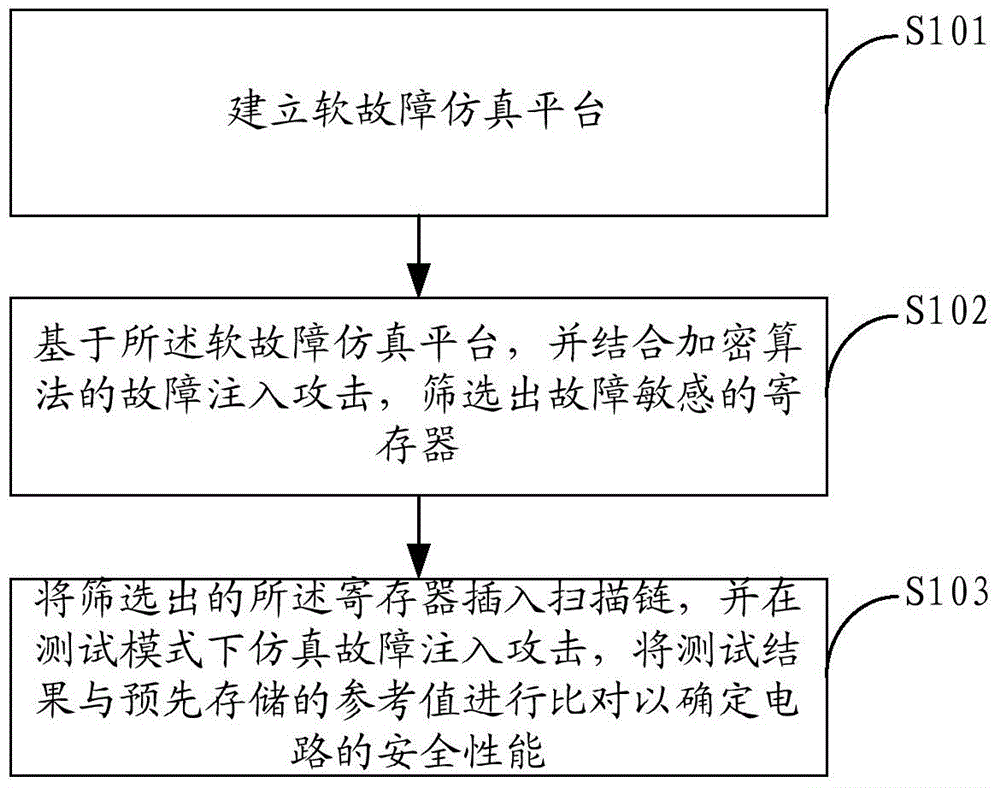

Security testing method and system

ActiveCN104660466ASuitable for batch testingImprove securityData switching networksComputer hardwareProcessor register

The invention relates to the technical field of information security, and provides a security testing method and a security testing system. The security testing method comprises the following steps: establishing a soft fault simulation platform; based on the soft fault simulation platform and with the combination of fault injection attack of an encryption algorithm, screening a register with fault sensitivity; inserting the screened register into a scanning chain, simulating fault injection attack in a testing mode, and comparing the testing result with a pre-stored reference value to determine the security property of a circuit. The security testing method and the security testing system are applicable to in-batch testing on crypto chips, and the security property of the crypto chips can be effectively improved.

Owner:南方电网互联网服务有限公司

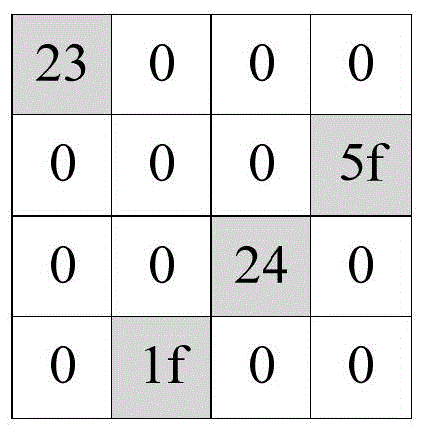

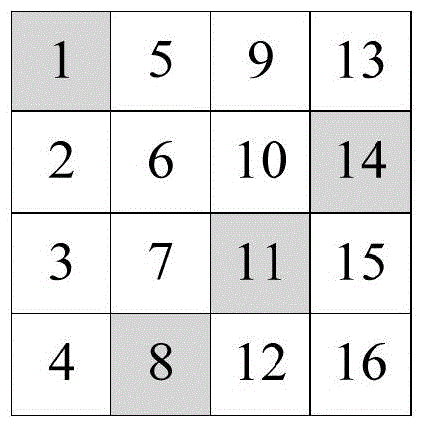

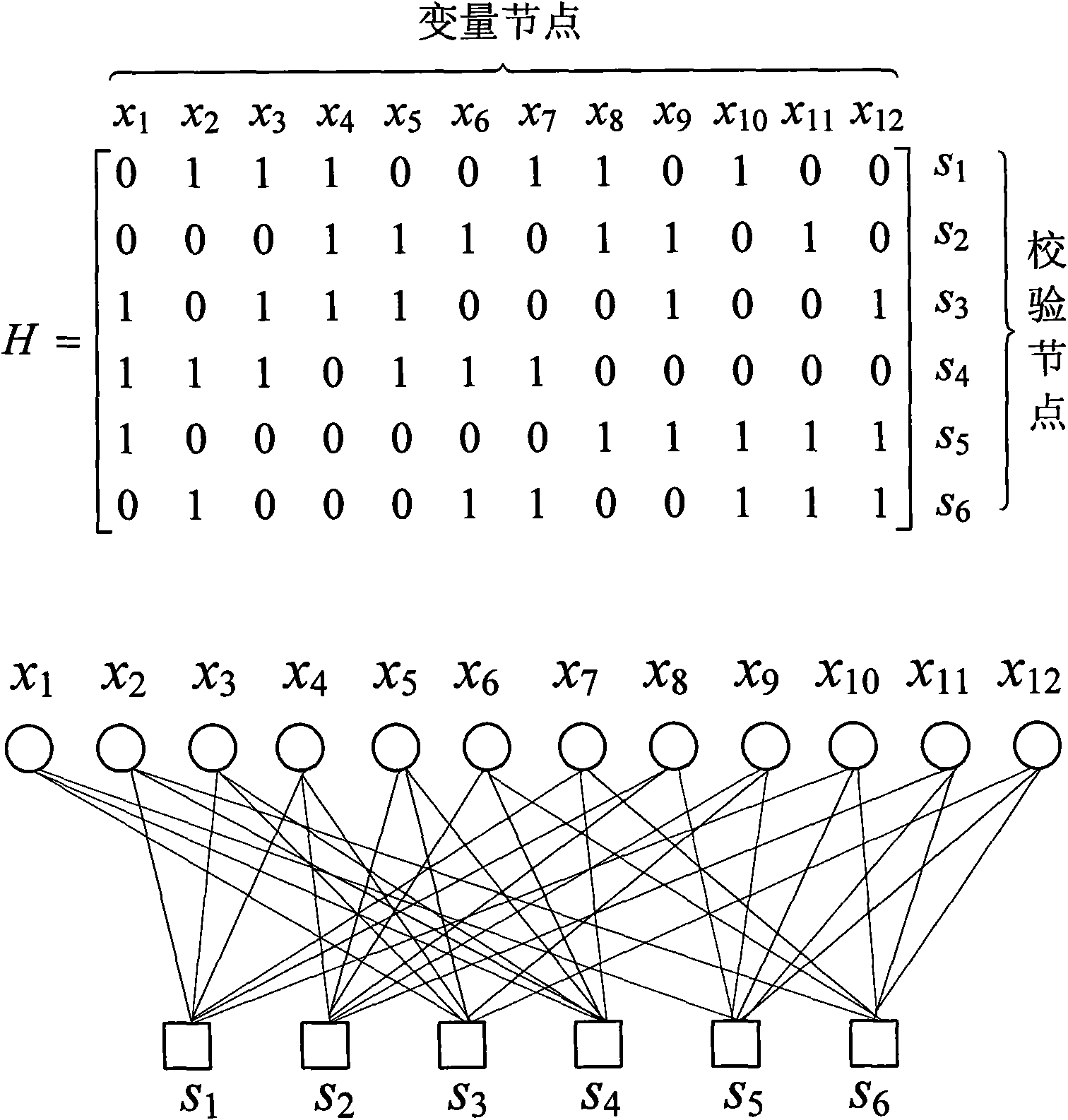

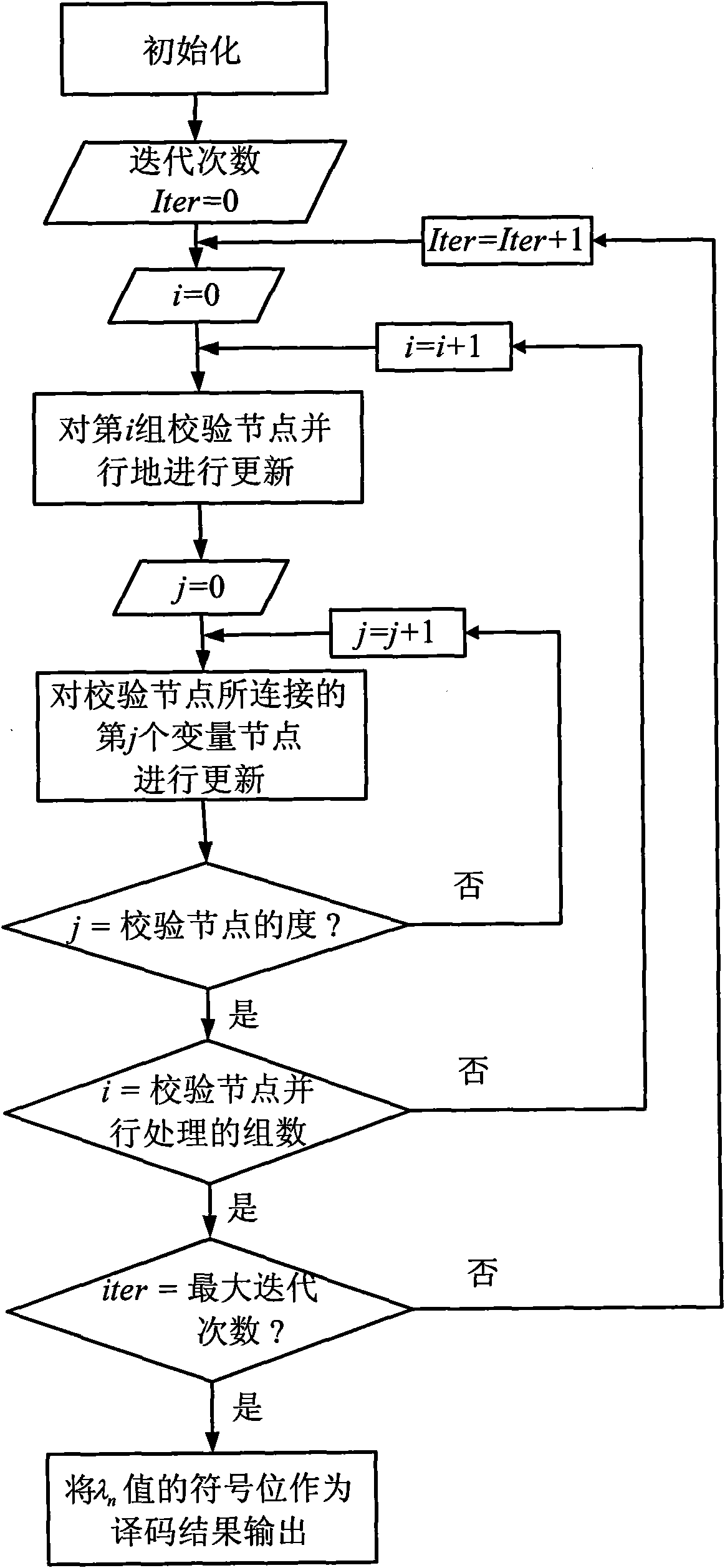

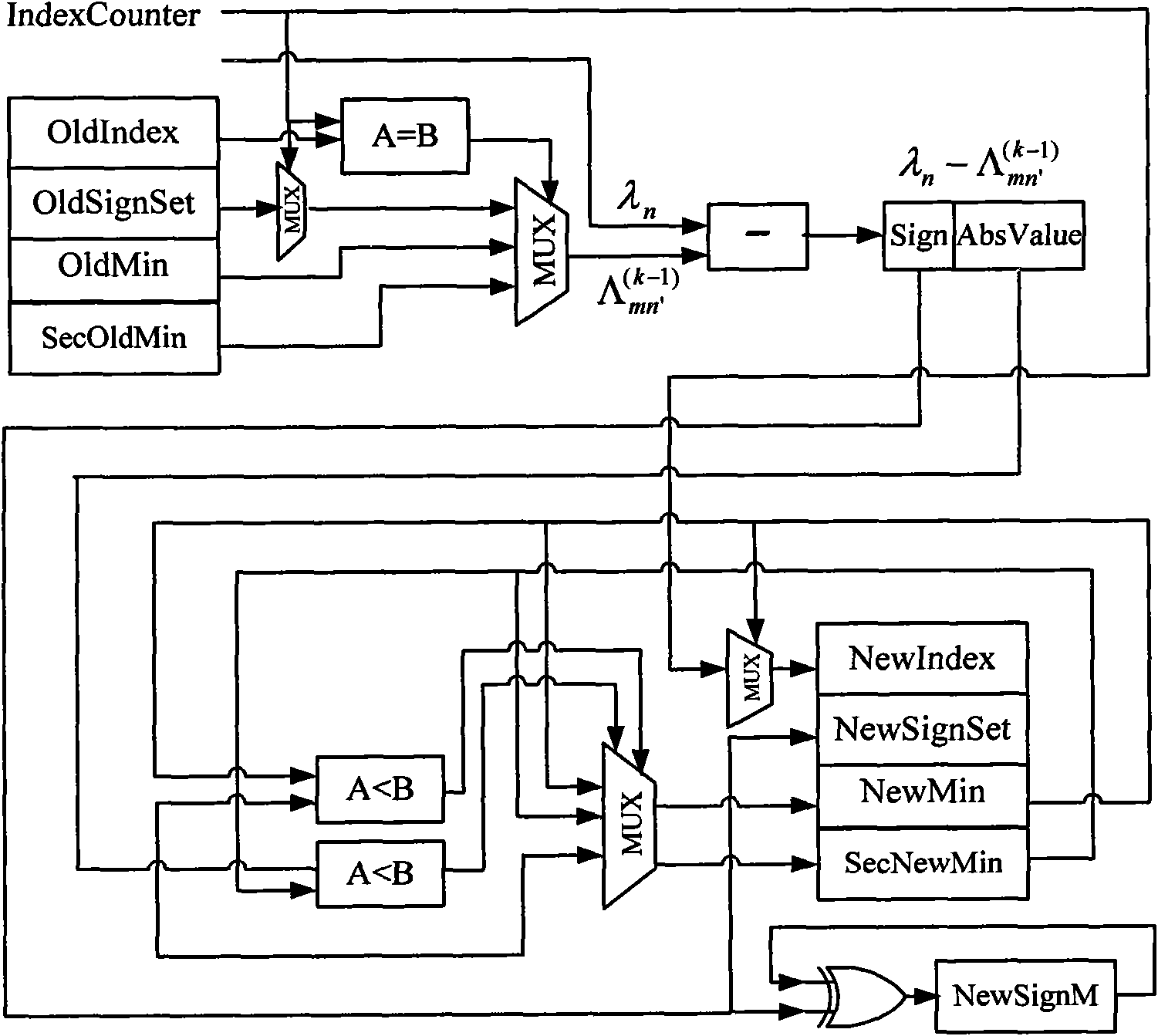

Structured LDPC code decoding method and device for system on explicit memory chip

ActiveCN101777921AReduce combinatorial logic areaReduce hardware implementation complexityError correction/detection using multiple parity bitsParty-line systemsCoding decodingExplicit memory

The invention relates to a structured LDPC code decoding method and a device for a system on an explicit memory chip; the method comprises the following steps that: (1)decoding initialization: the initialization process comprises the steps that the LLR is stored to a variable node storage block in a special storage method, the value of an initialization calibration node storage block is 0, and a maximum iteration is preset; (2) iterative process: an iteration counter Iter is started, and iteration operation is carried out; and (3) decoding result outputting: when the iteration counter Iter reaches the maximum iteration and the decoding operation of the last calibration node is completed, decoding is stopped and decoding results are output; and otherwise, go to step (2) to continue the iteration. The decoding device comprises a code rate reconfigurable storage management controller, a decoding controller and a processing array unit. The invention has the advantages of simple and compact structure, low cost, convenient operation, capability of reducing the hardware complexity and supporting various code rate and the like.

Owner:NAT UNIV OF DEFENSE TECH

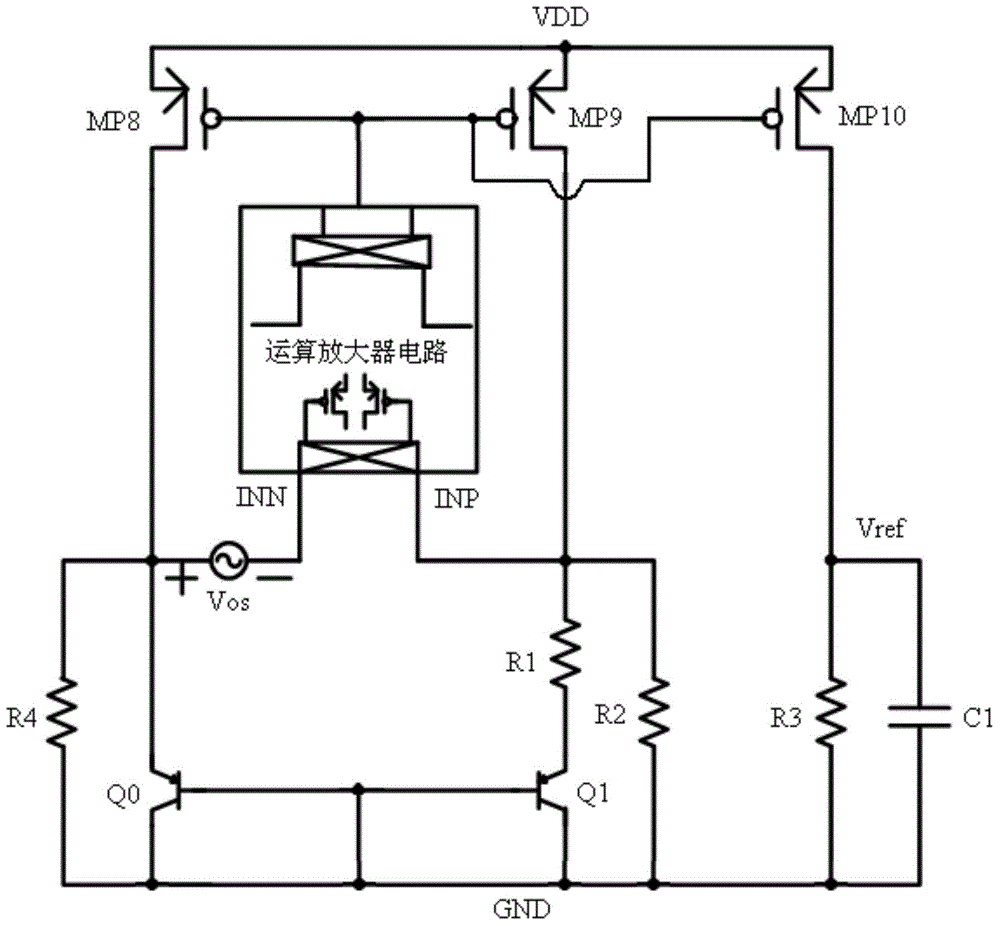

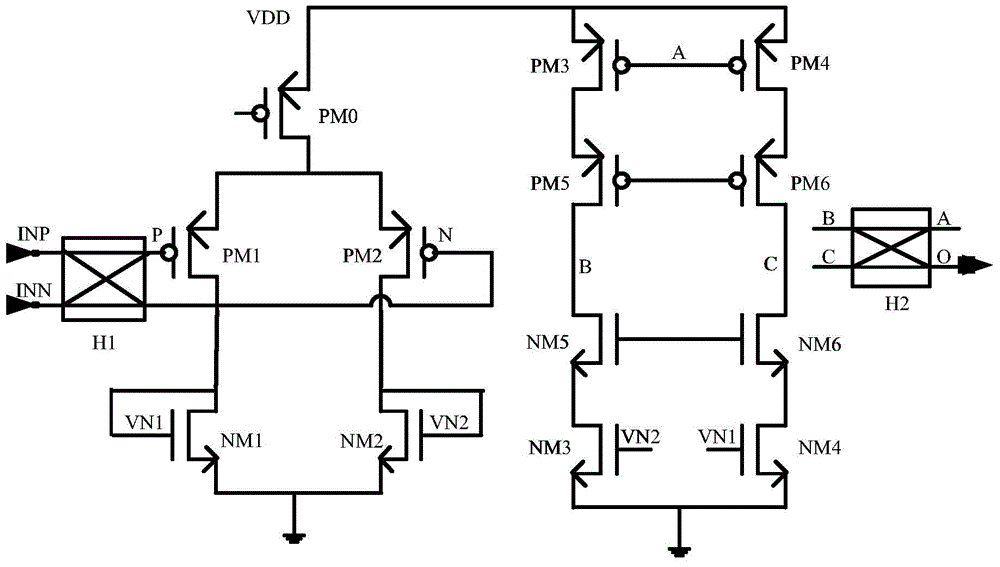

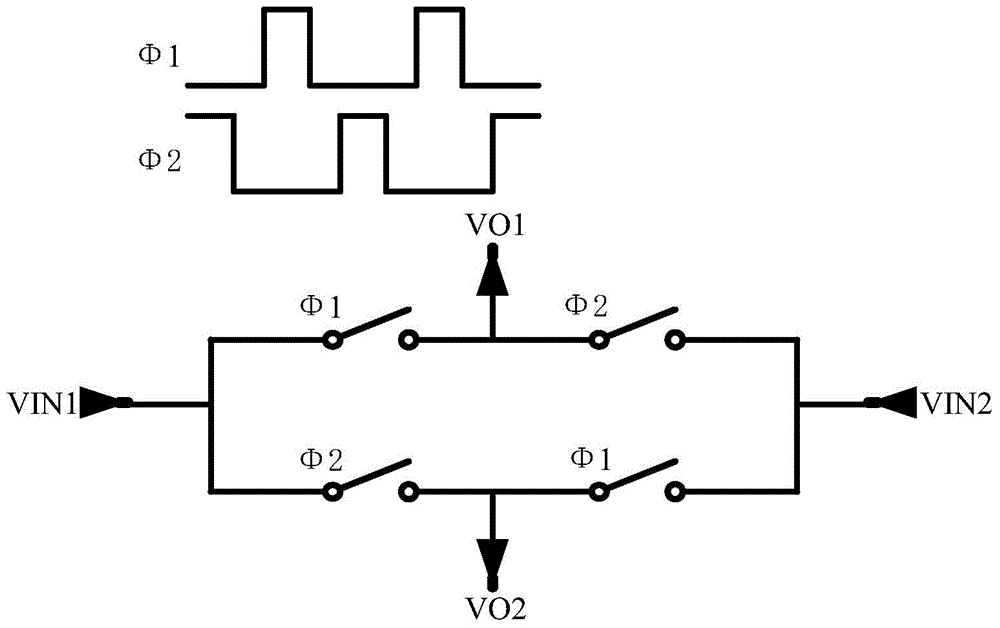

Operational amplifier circuit and reference voltage generating circuit module

InactiveCN104601127AHigh precisionCancel offset voltageDifferential amplifiersElectric variable regulationPower flowAudio power amplifier

The invention discloses an operational amplifier circuit. The operational amplifier circuit comprises an operational amplifier and a chopping offset elimination circuit for eliminating an offset signal and flicker noise of the operational amplifier. The invention further discloses a reference voltage generating circuit module. The reference voltage generating circuit module comprises a reference voltage generating circuit, an operational amplifier, a chopping offset elimination circuit and a filtering circuit, wherein the reference voltage generating circuit is used for generating voltage with a zero temperature coefficient and current with a zero temperature coefficient; the operational amplifier is used for providing feedback for the reference voltage generating circuit in order that the output of the reference voltage generating circuit is stabilized at a required working point; the chopping offset elimination circuit is used for modulating the inherent offset voltage and the low-frequency flicker noise of the operational amplifier in order to modulate the influence of the offset of the operational amplifier on a reference voltage generated by the reference voltage generating circuit; and the filtering circuit is used for filtering the offset signal modulated by the offset elimination circuit and keeping a useful reference voltage signal. Through adoption of the operational amplifier circuit and the reference voltage generating circuit module, the offset and the flicker noise of the operational amplifier can be eliminated, and the accuracy is increased.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

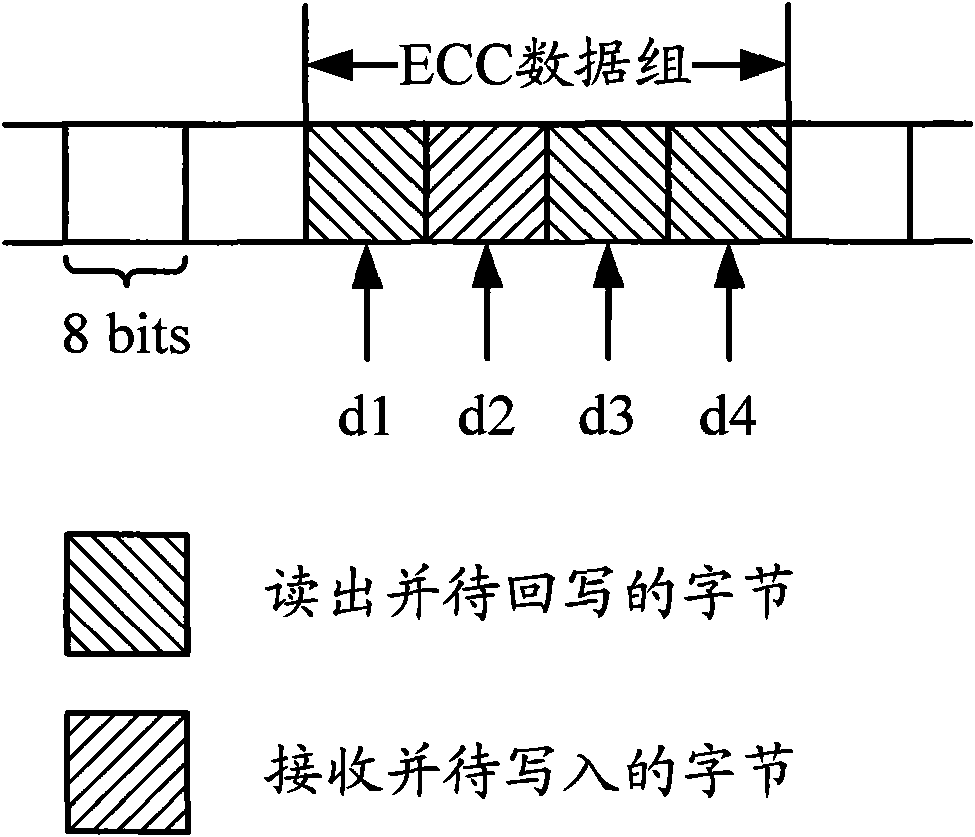

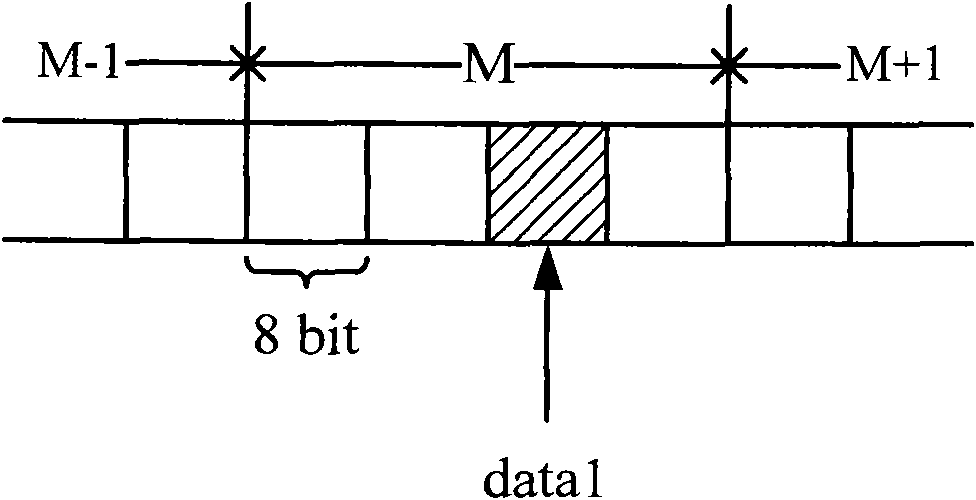

Non-volatile memory with error checking/correcting circuit and methods thereof for reading and writing data

The invention discloses a non-volatile memory with an error checking / correcting (ECC) circuit and methods thereof for reading and writing data. Read-write operations are carried inside the memory, with ECC code words as the unit. The method for writing the data comprises the following steps: acquiring the head address and the end address of external input data and buffering the external input data; acquiring the bytes which are unnecessary to be replaced, namely write-back data, from a memory array of the non-volatile memory if part of the bytes in an ECC data set in which the external input data are included is unnecessary to be replaced; forming a new ECC data set with the external input data or the external input data and the write-back data and buffering the new ECC data set; generating a corresponding check bit for the new ECC data set; and writing the new ECC data set and the corresponding check bit into the memory array. The invention only erases the corresponding ECC code words during writing data and improves the memory flexibility and the utilization efficiency of the memory space.

Owner:GIGADEVICE SEMICON (BEIJING) INC

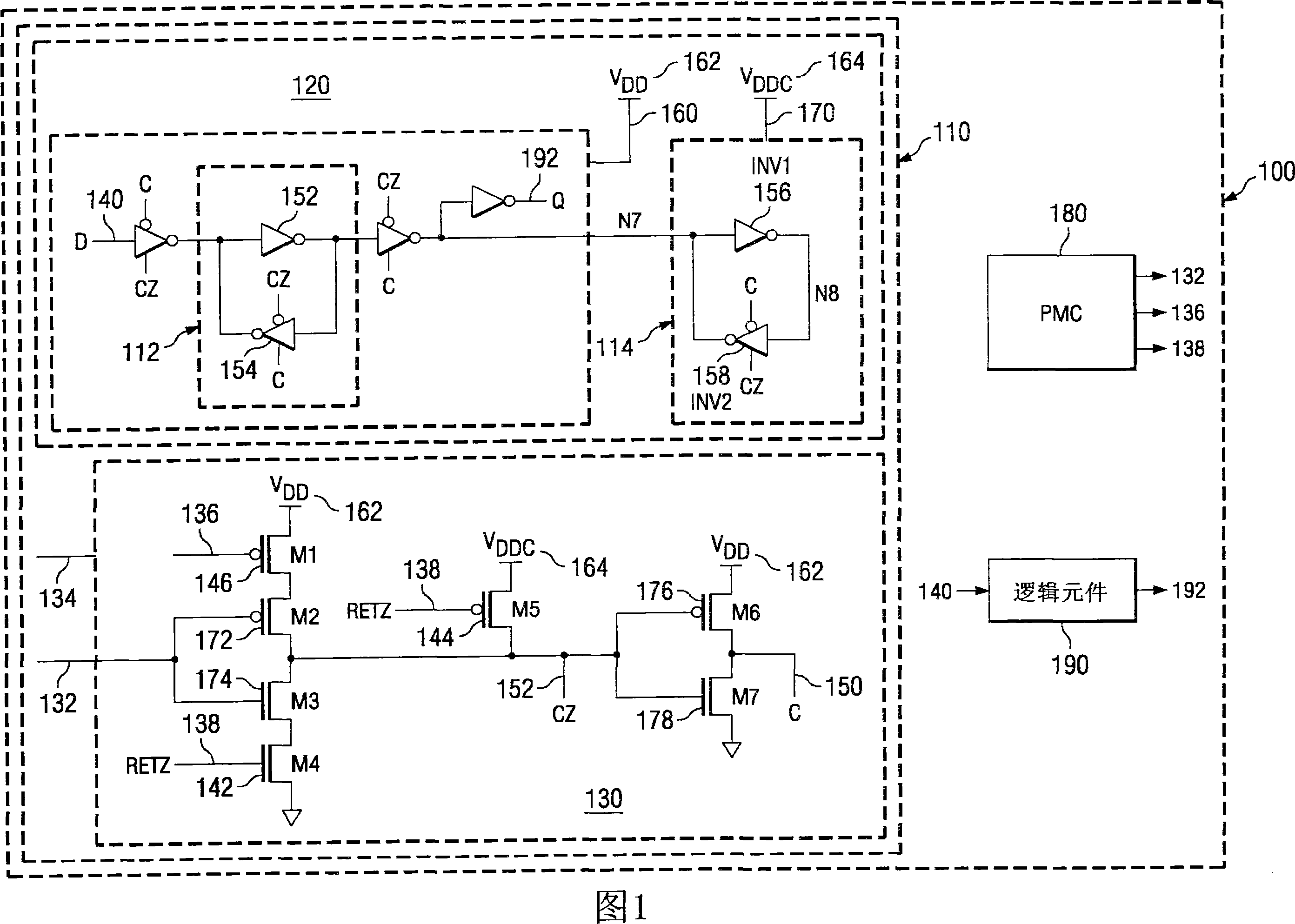

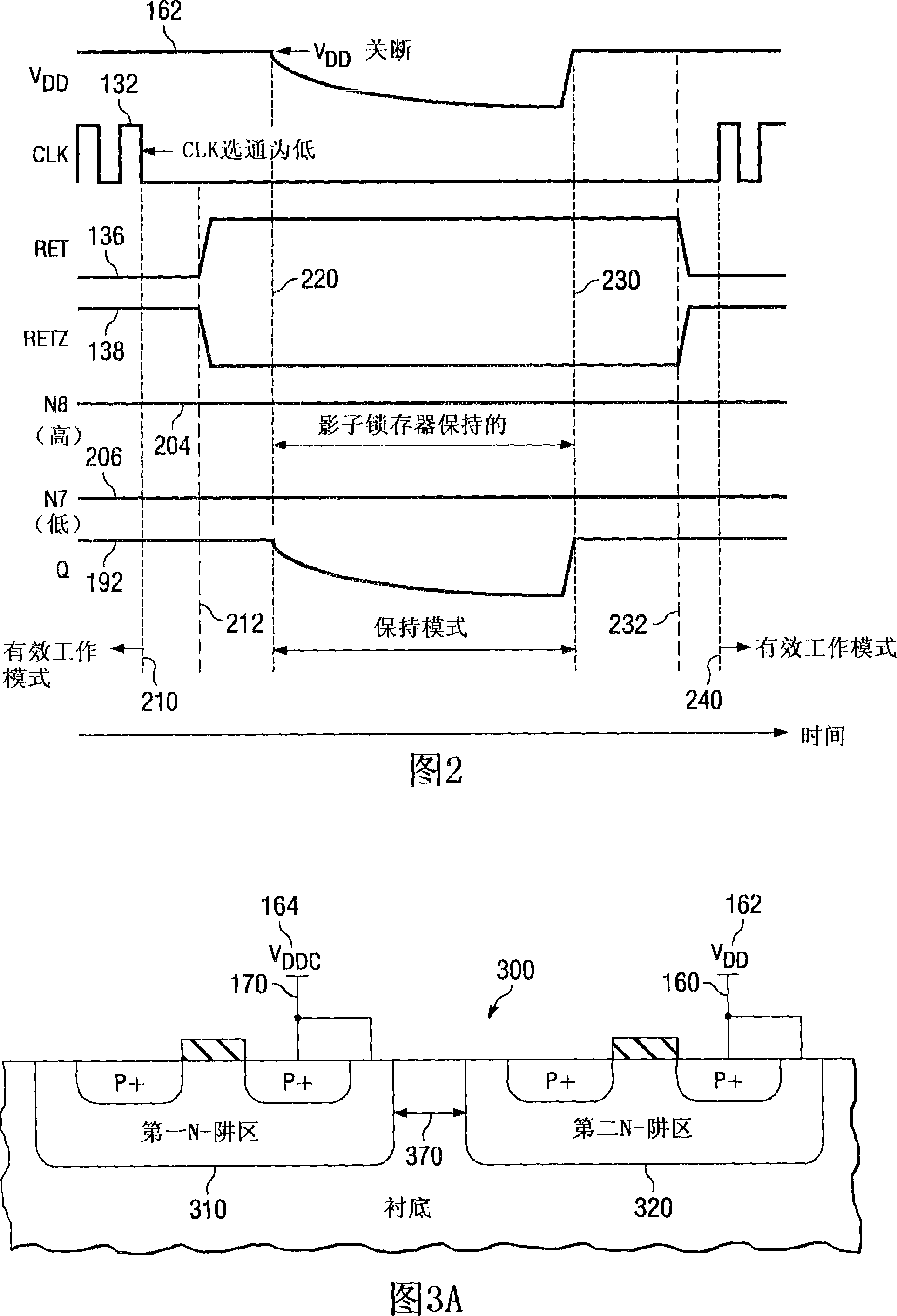

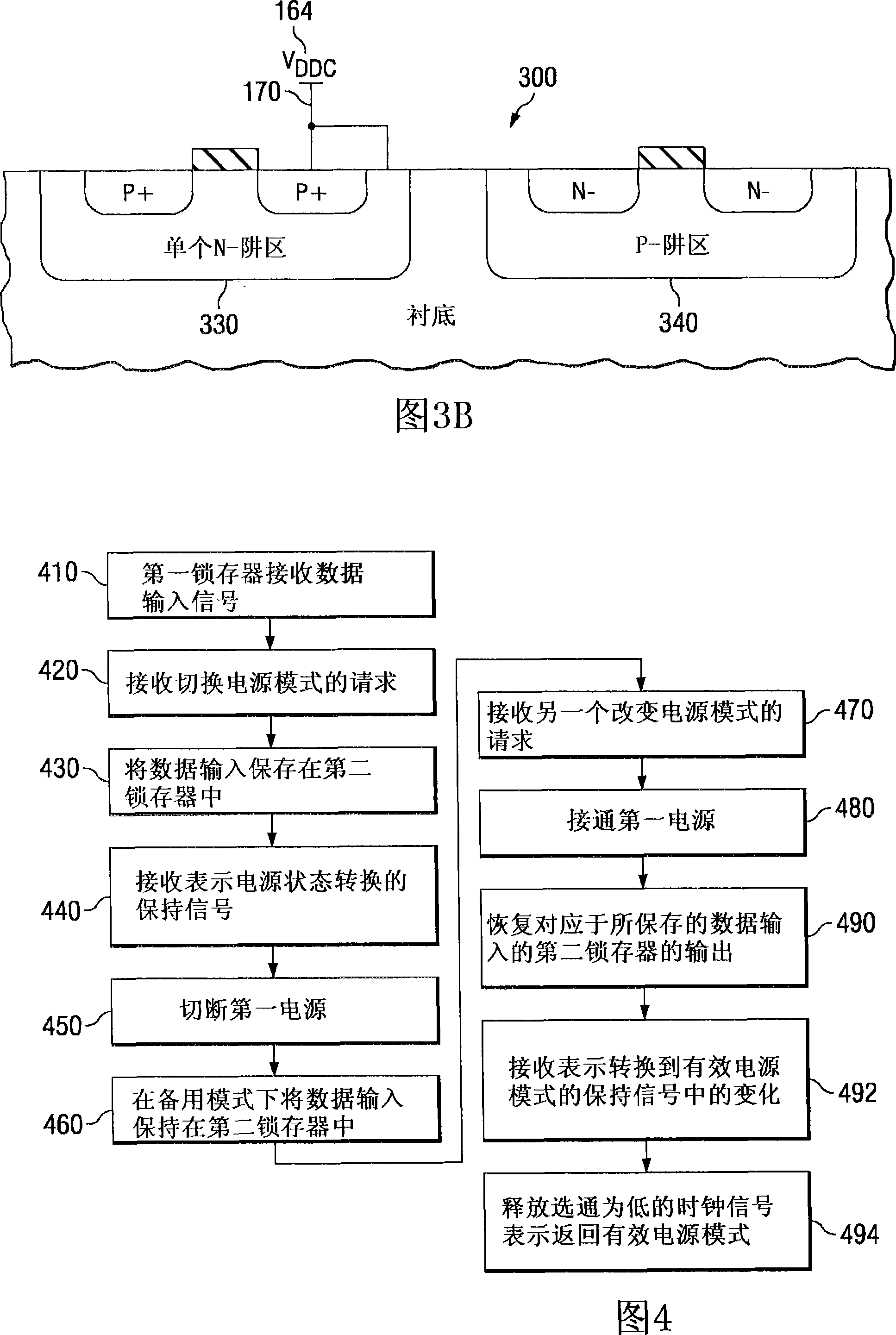

Data retention device for power-down applications and method

InactiveCN101233687ADie size reductionExtend battery lifePower managementElectric pulse generatorElectricityStandby power

In a method and system for data retention, a data input is latched by a first latch. A second latch coupled to the first latch receives the data input for retention while the first latch is inoperative in a standby power mode. The first latch receives power from a first power line that is switched off during the standby power mode. The second latch receives power from a second power line. A controller receives a clock input and a retention signal and provides a clock output to the first latch and the second latch. A change in the retention signal is indicative of a transition to the standby power mode. The controller continues to hold the clock output at a predefined voltage level and the second latch continues to receive power from the second power line in the standby power mode, thereby retaining the data input.

Owner:TEXAS INSTR INC

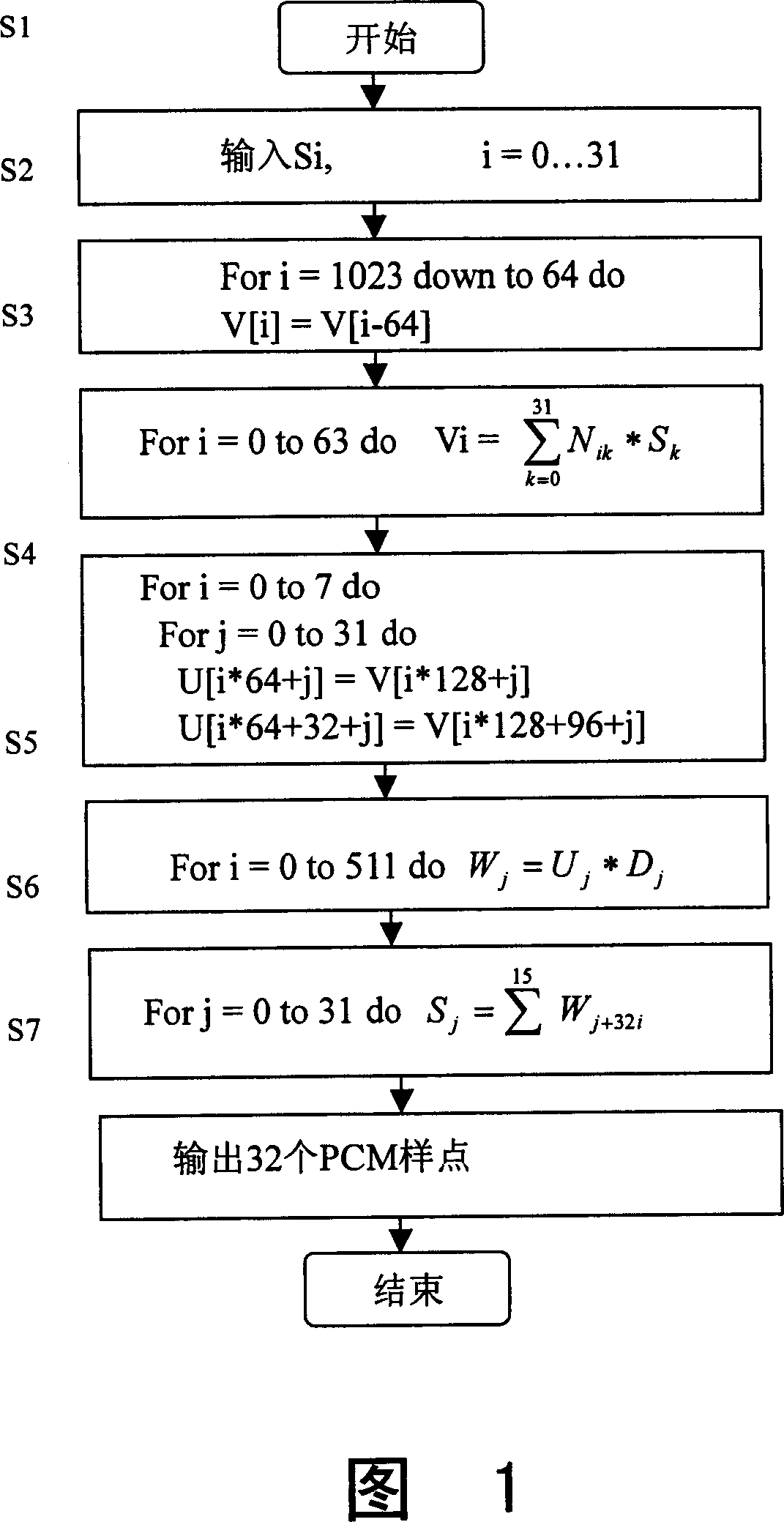

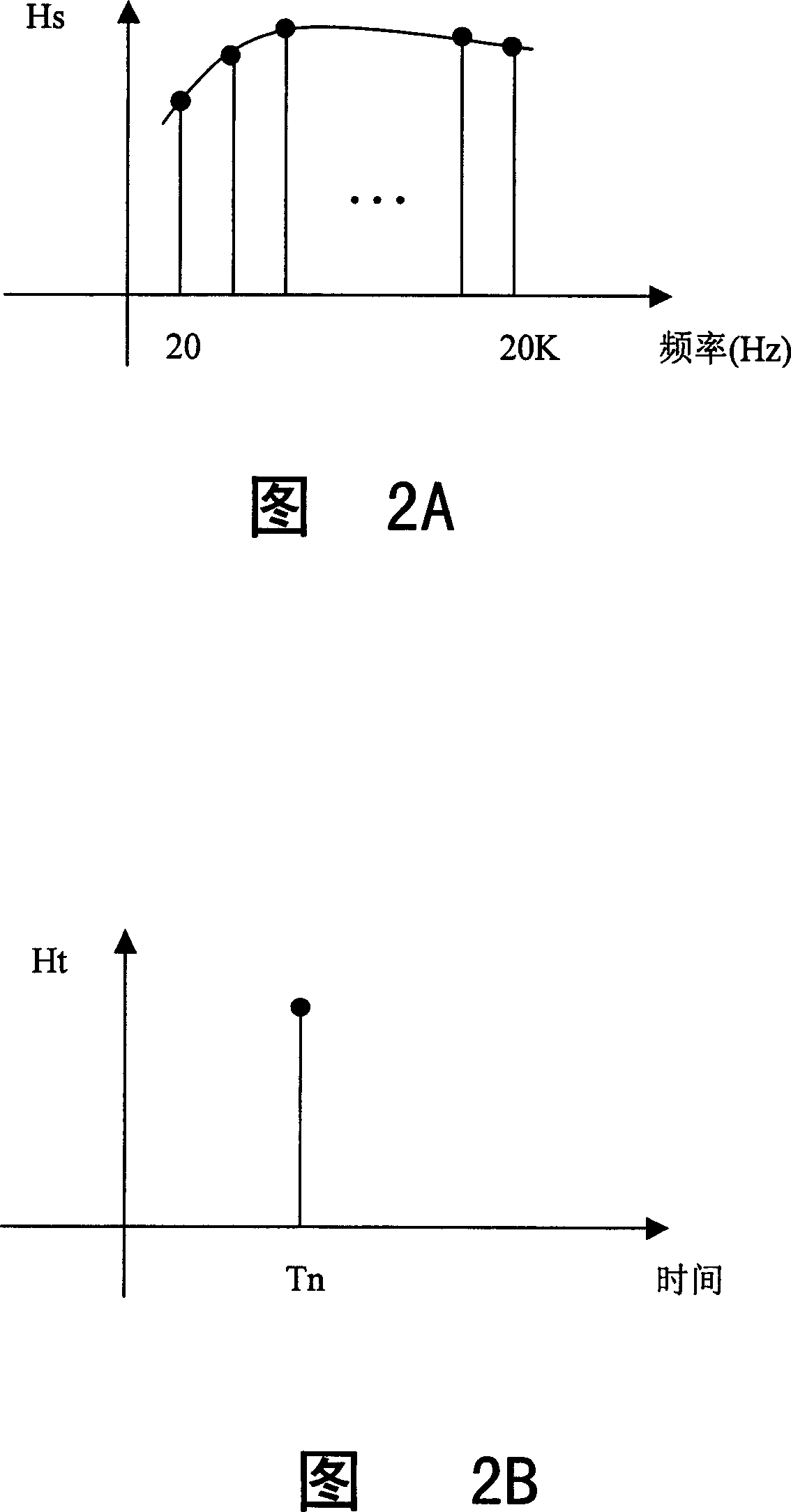

Synthetic sub-band filtering method for audio decoding and synthetic sub-band filter

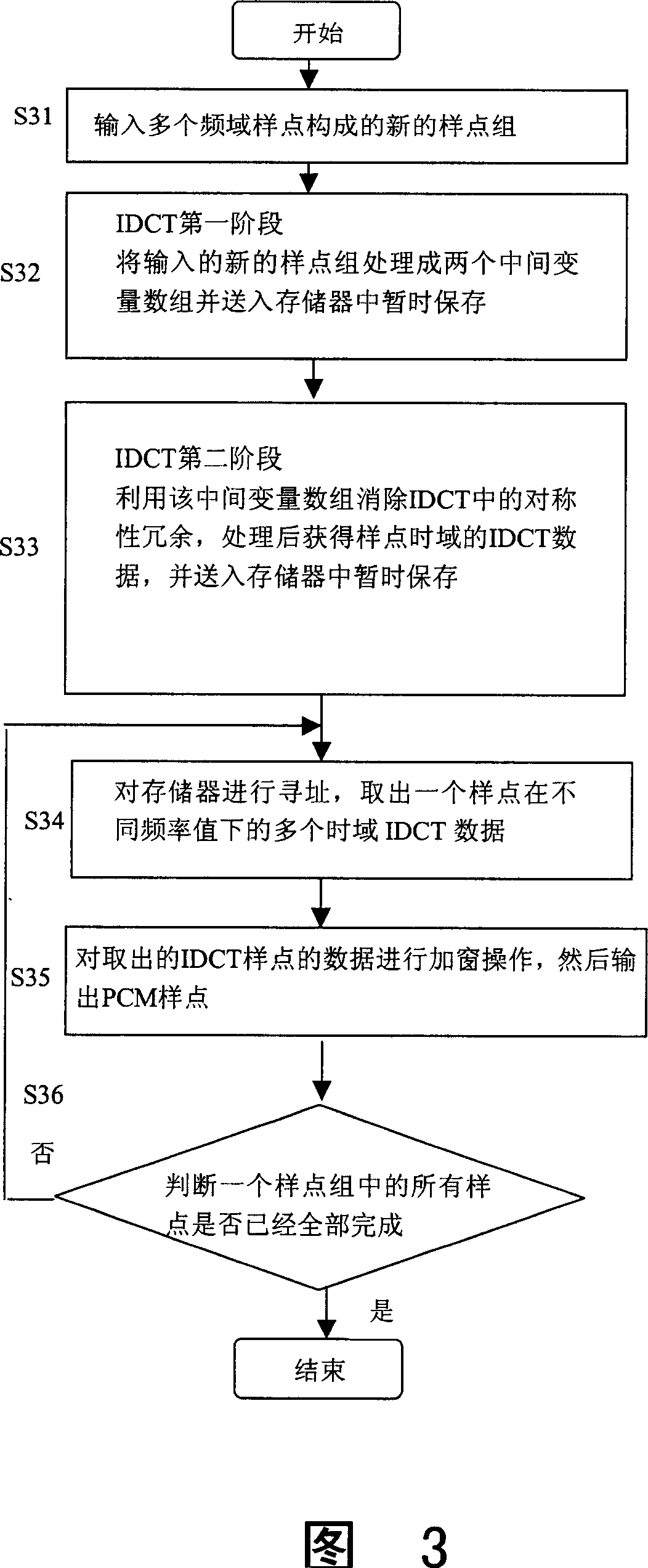

InactiveCN101025919ASave computing resources and storage resourcesSmall area overheadSpeech analysisIntermediate variableArray data structure

The invention relates to a synthesis subband filtering method and a synthesis subband filter during the audio decoding process, which includes: (a) It inputs a number of frequency-domain samples to form a new point group. (b) During the first stage of IDCT, it converts the new samples group into two intermediate variable arrays and puts them into memory for temporary preservation. (c) During the second stage of IDCT, it gets the intermediate variable arrays from the memory and eliminates redundant IDCT of symmetry by using of the intermediate variables arrays to obtain the IDCT data of time domain samples and puts them into the memory for temporary preservation. (d) It addresses the memory and takes out a number of time domain IDCT data of different frequency of a point sample. (e) It adds window for the IDCT sample data, then it outputs the PCM samples. (f) It repeats step (d) and (e) till it completes all the window-adding about a point sample group.

Owner:SHANGHAI MAGIMA DIGITAL INFORMATION

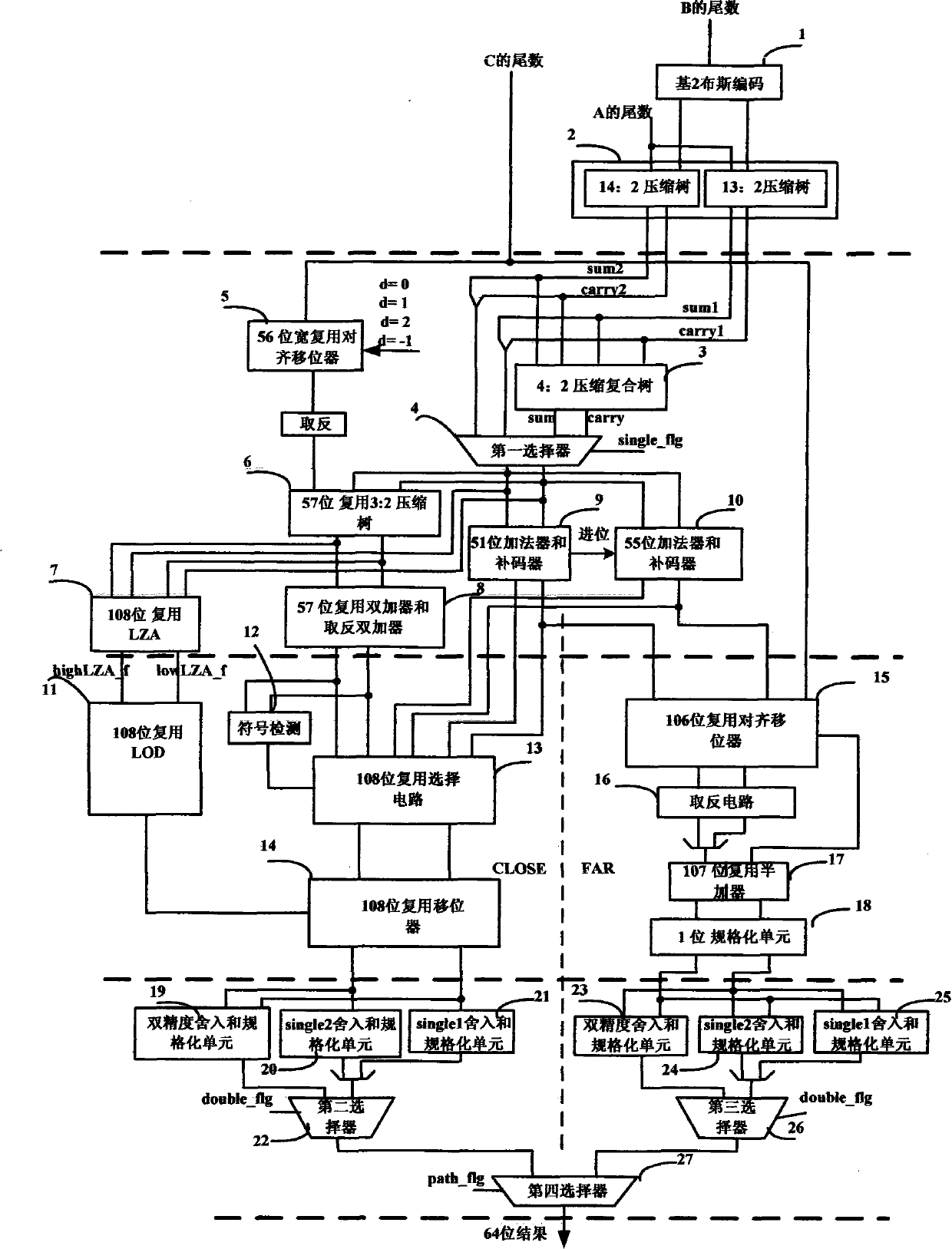

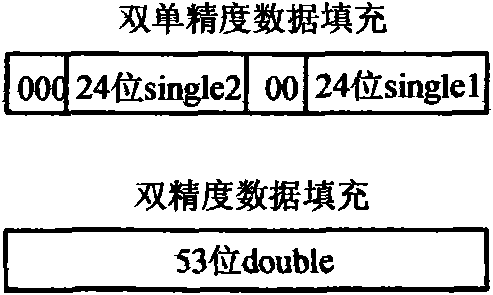

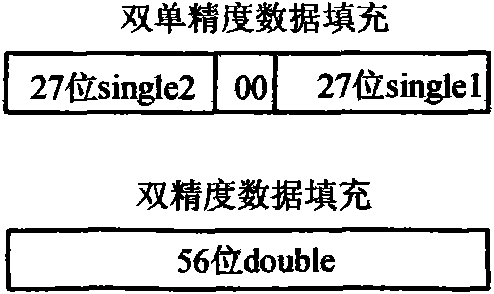

Floating-point multiply-add fused unit compatible with double-precision and double-single-precision and compatibility processing method thereof

ActiveCN101770355AIncreased area overheadSmall area overheadDigital data processing detailsFloating pointParallel processing

The invention discloses a floating-point multiply-add fused unit compatible with double-precision and double-single-precision and a compatibility processing method thereof. The floating-point multiply-add fused unit comprises a multiplication tree, a shifter, an LZA, an LOD and an adder, which can respectively carry out both the operation of two single-precision and the operation of a double-precision. Two sections are formed as much as possible or the input data is compatibly processed so as to achieve the purpose of parallel processing of double-precision and single-precision. The technique ensures the compatible operation of double-precision and single-precision under the conditions of minimizing or minimally increasing the areas of the floating-point multiply-add fused components, thereby improving the performance of the single-precision operation of the floating-point multiply-add fused unit under the condition of lesser area overhead.

Owner:LOONGSON TECH CORP

Self-recovery single particle resistance latch register structure based on time-delay unit

InactiveCN105577160AWith self-recovery functionSimple structureReliability increase in field effect transistorsSelf recoveryDual mode

The invention discloses a self-recovery single particle resistance latch register structure based on a time-delay unit, comprising two clock-control inverter structures, four dual-input inverter structures, two transmission gate structures, one time delay unit and a C unit structure; the four dual-input inverter structures constitute a dual-mode interlocking structure to realize self-recovery of the single event upset (SEU); the time delay unit structure and an C unit constitute a filtering structure to block the single event transient (SET) coming from the combination logic circuit. The invention can tolerate the SEU happened in the latch register structure and the SET transmitted from the logic circuit, has the self-recovery function, has a simple circuit, reduces the consumption of the area, reduces the power consumption and improves the system reliability.

Owner:HEFEI UNIV OF TECH

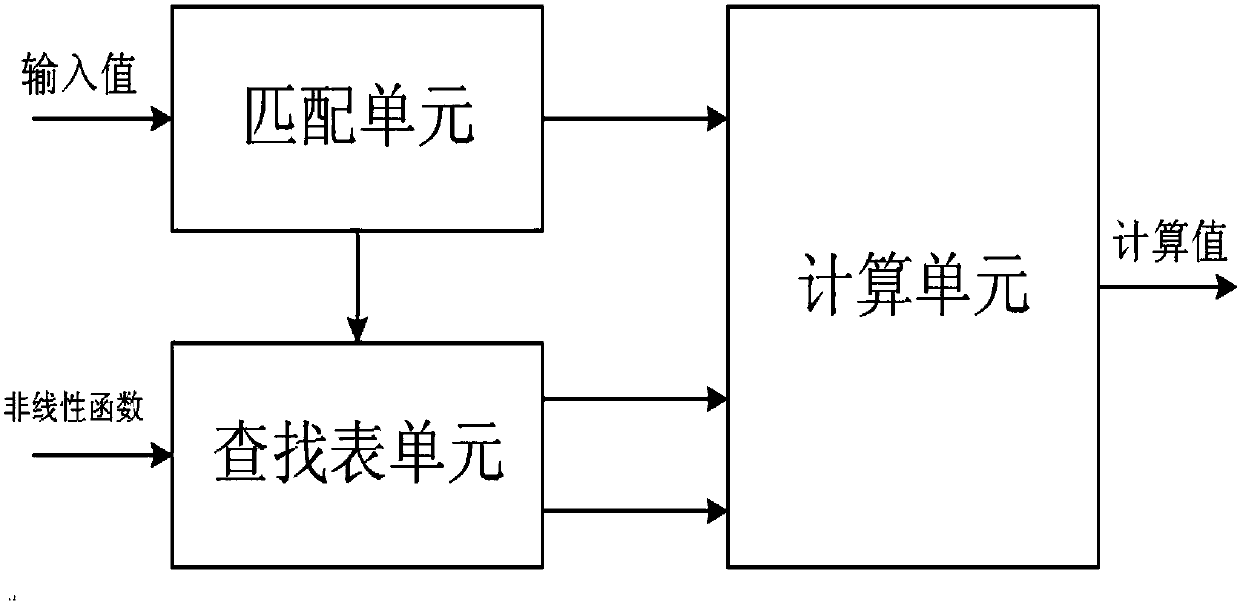

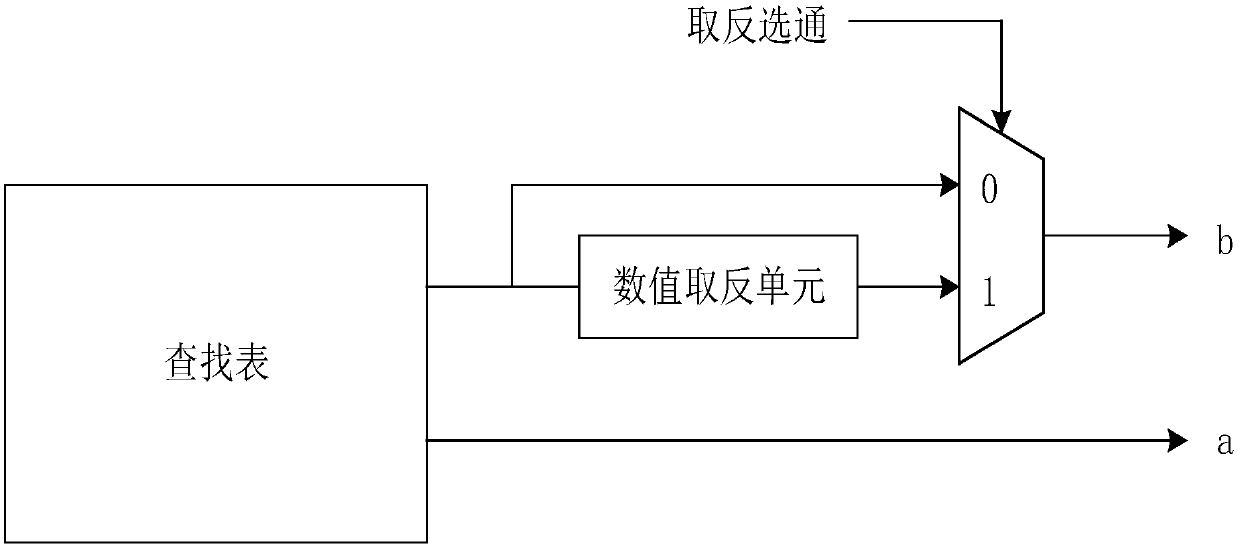

Calculation device and method of non-linear function

InactiveCN107589935ACalculation speedSave circuit area overhead and energy consumptionDigital data processing detailsNon linear functionsNon linearity

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI