Built-in self-test structure and method for on-chip network resource node storage device

A technology of built-in self-test and resource node, applied in the field of built-in self-test structure of on-chip network resource node memory, can solve problems such as the number of users cannot exceed one pair, the bus structure address space is limited, and the communication efficiency is low, so as to save The effect of test cost, shortened test time, and high fault coverage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] Embodiment of built-in self-test structure of on-chip network resource node memory

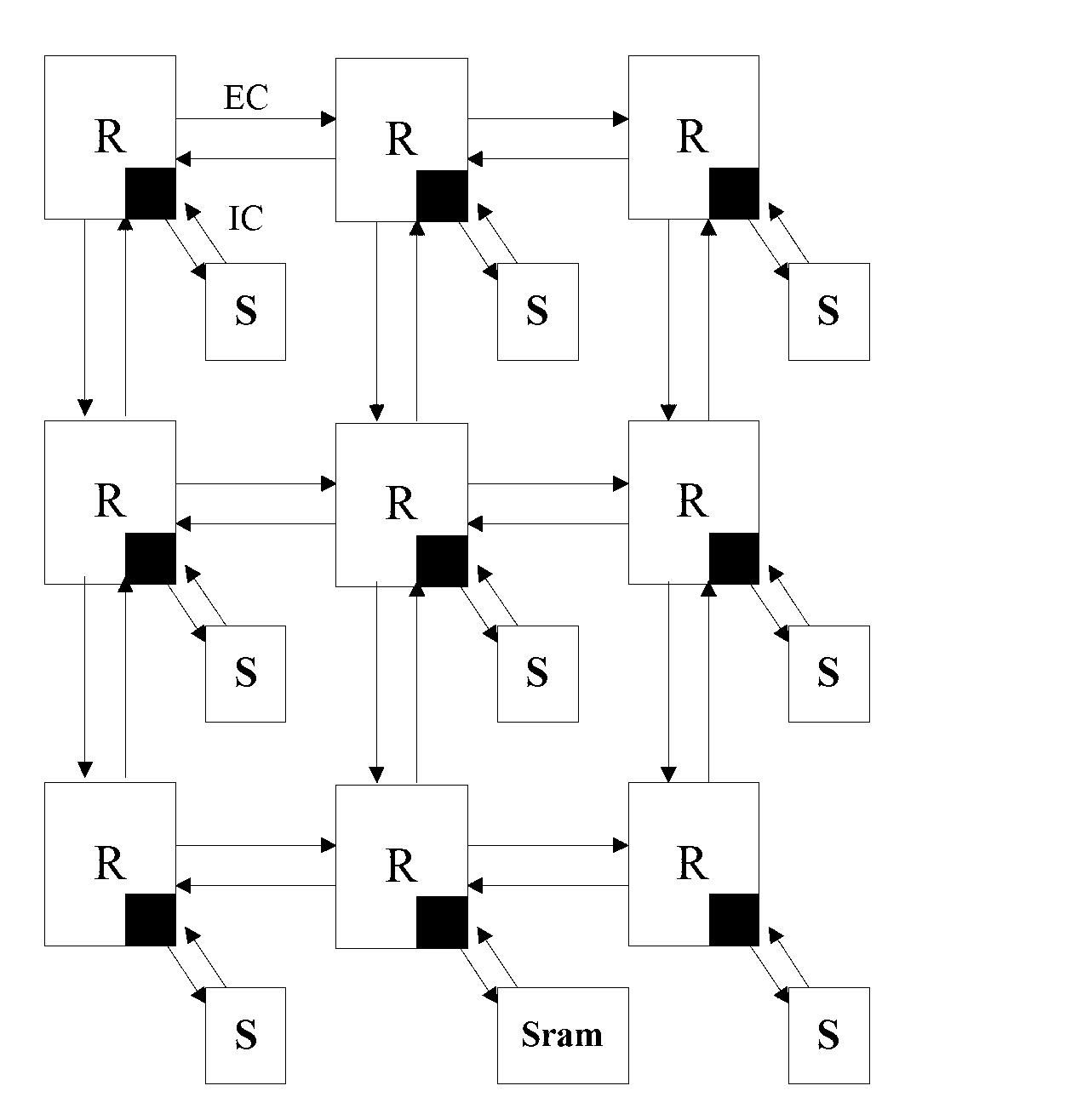

[0051] The on-chip network used in the built-in self-test structure embodiment of this on-chip network resource node memory is based on FPGA chips, such as figure 1 As shown, 3×3 routers R are connected to each other by external channels EC, forming a router network with a regular 2-dimensional grid (2D-Mesh) topology. The routers in the NoC adopt a wormhole data exchange mechanism based on virtual channel technology. The algorithm adopts the source routing algorithm. Each router is connected to the resource node through the resource network interface. The off-chip general-purpose memory SRAM connected to one router R2 through the resource network interface is the resource node memory to be tested. The resource node memory to be tested is represented by SRAM below. The resource network interface is a bidirectional data flow interface.

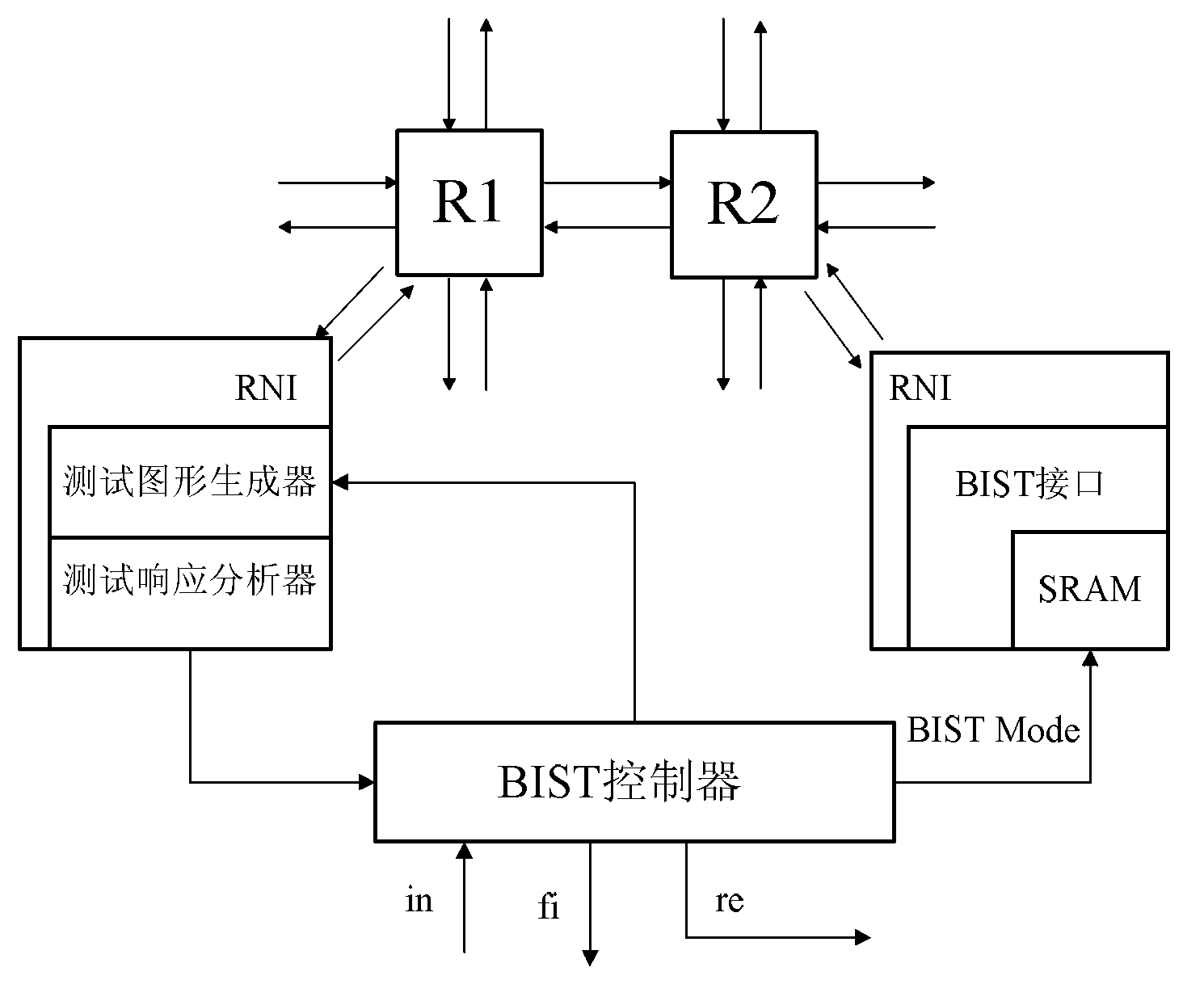

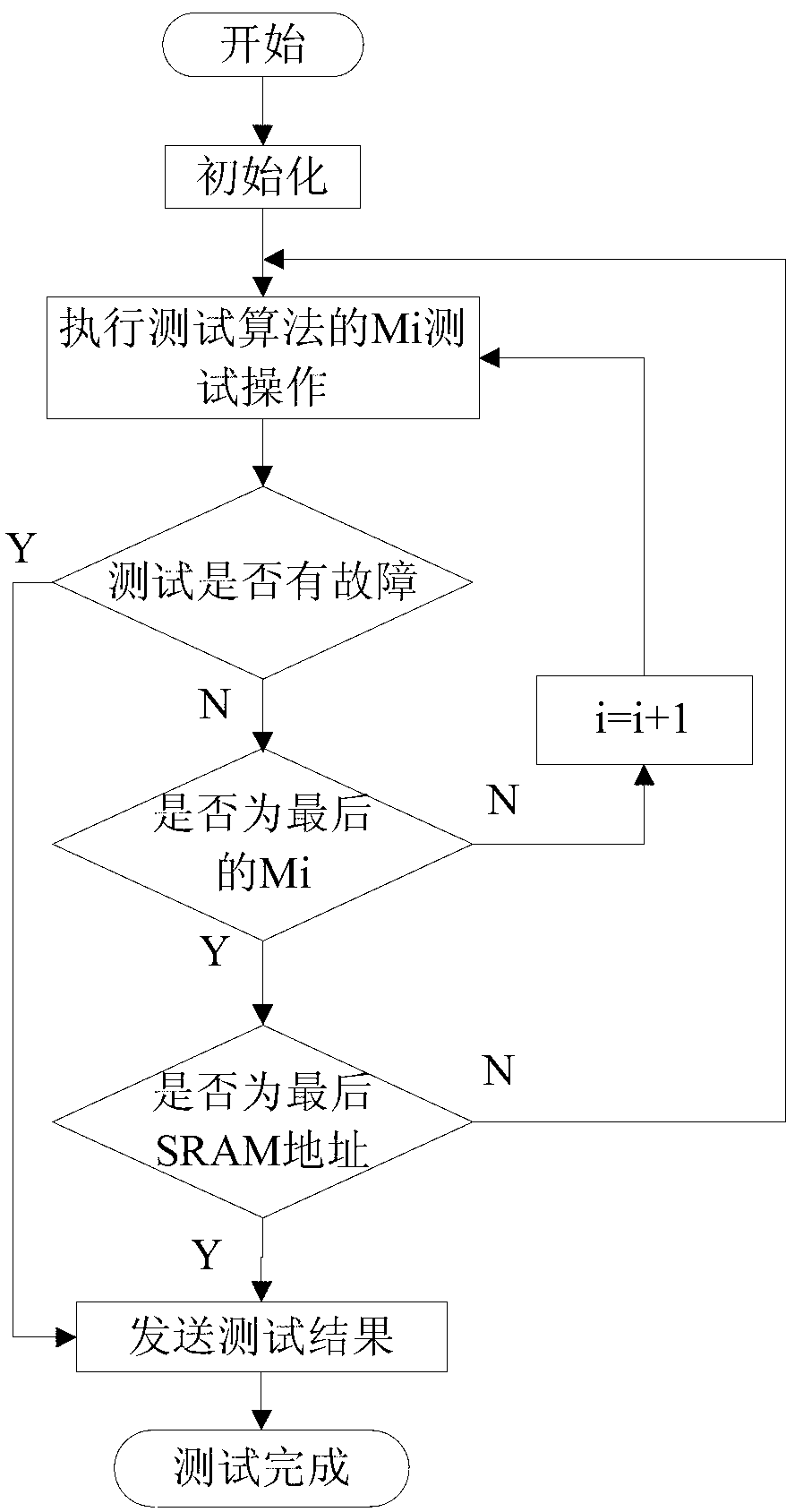

[0052] The built-in self-test structure of the re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More